Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

577 results about "Indium phosphide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Indium phosphide (InP) is a binary semiconductor composed of indium and phosphorus. It has a face-centered cubic ("zincblende") crystal structure, identical to that of GaAs and most of the III-V semiconductors.

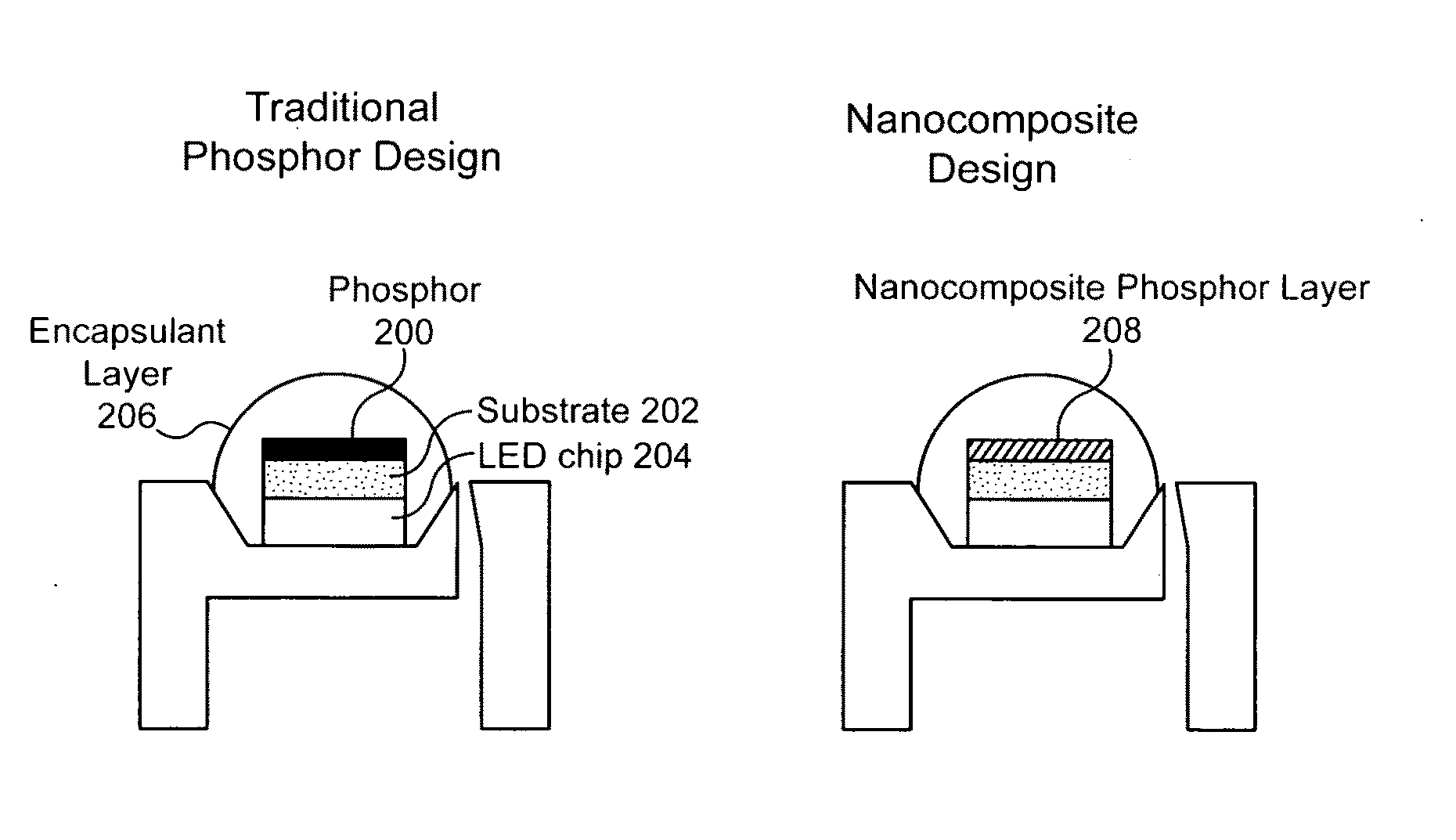

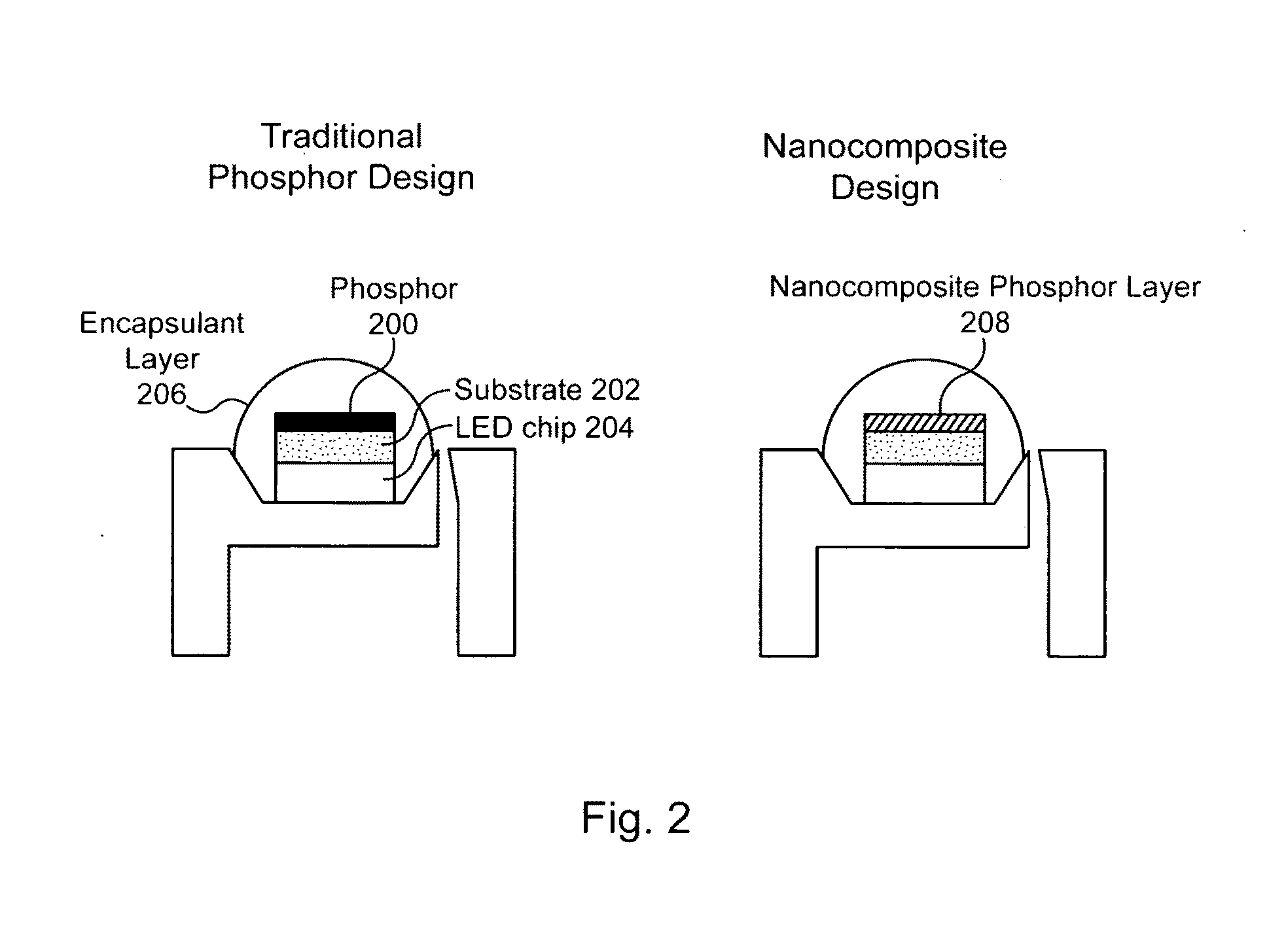

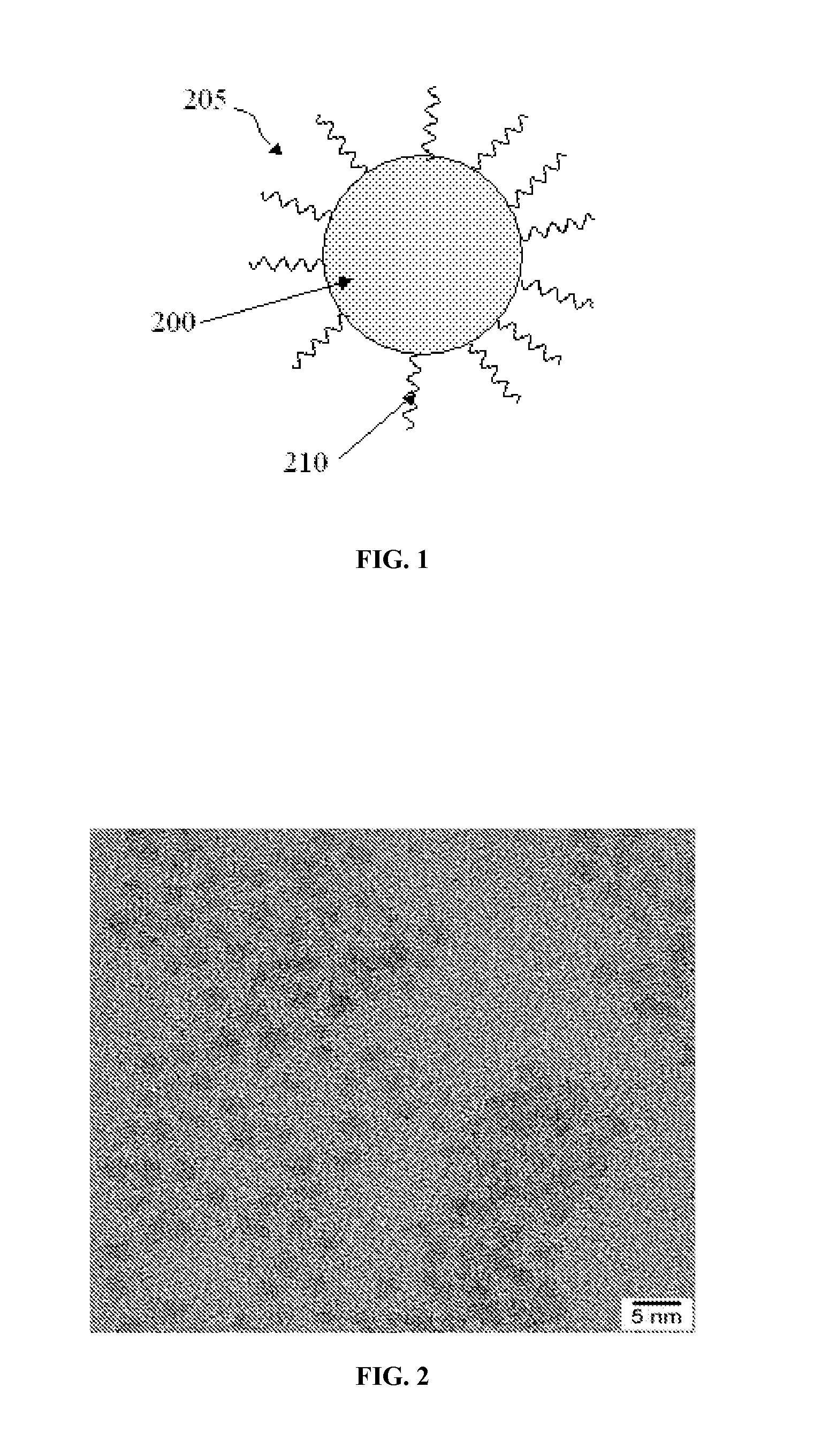

Nanocrystal doped matrixes

ActiveUS20070034833A1Good miscibilityInhibit aggregationMaterial nanotechnologyIndividual molecule manipulationAnti-reflective coatingSemiconductor nanocrystals

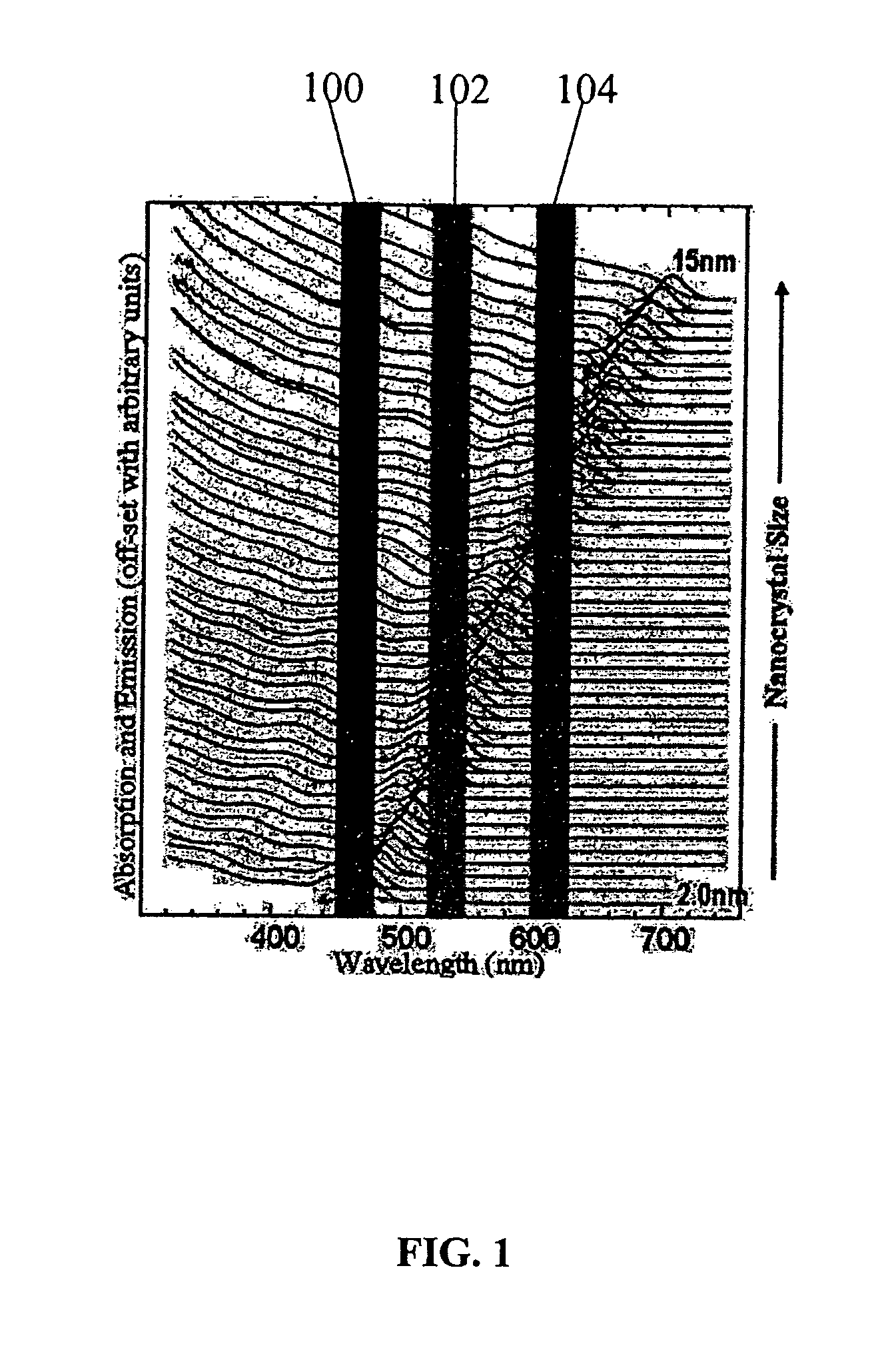

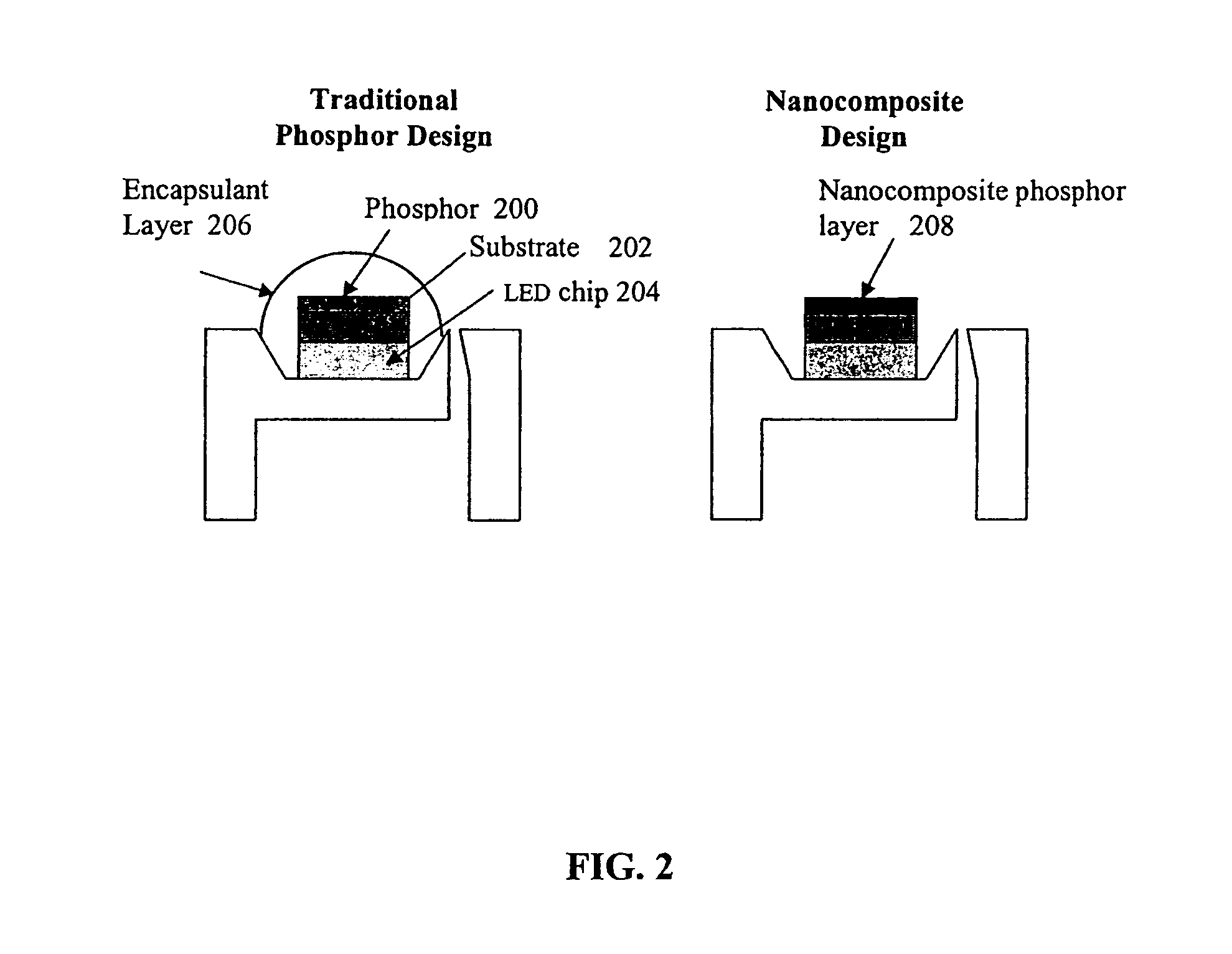

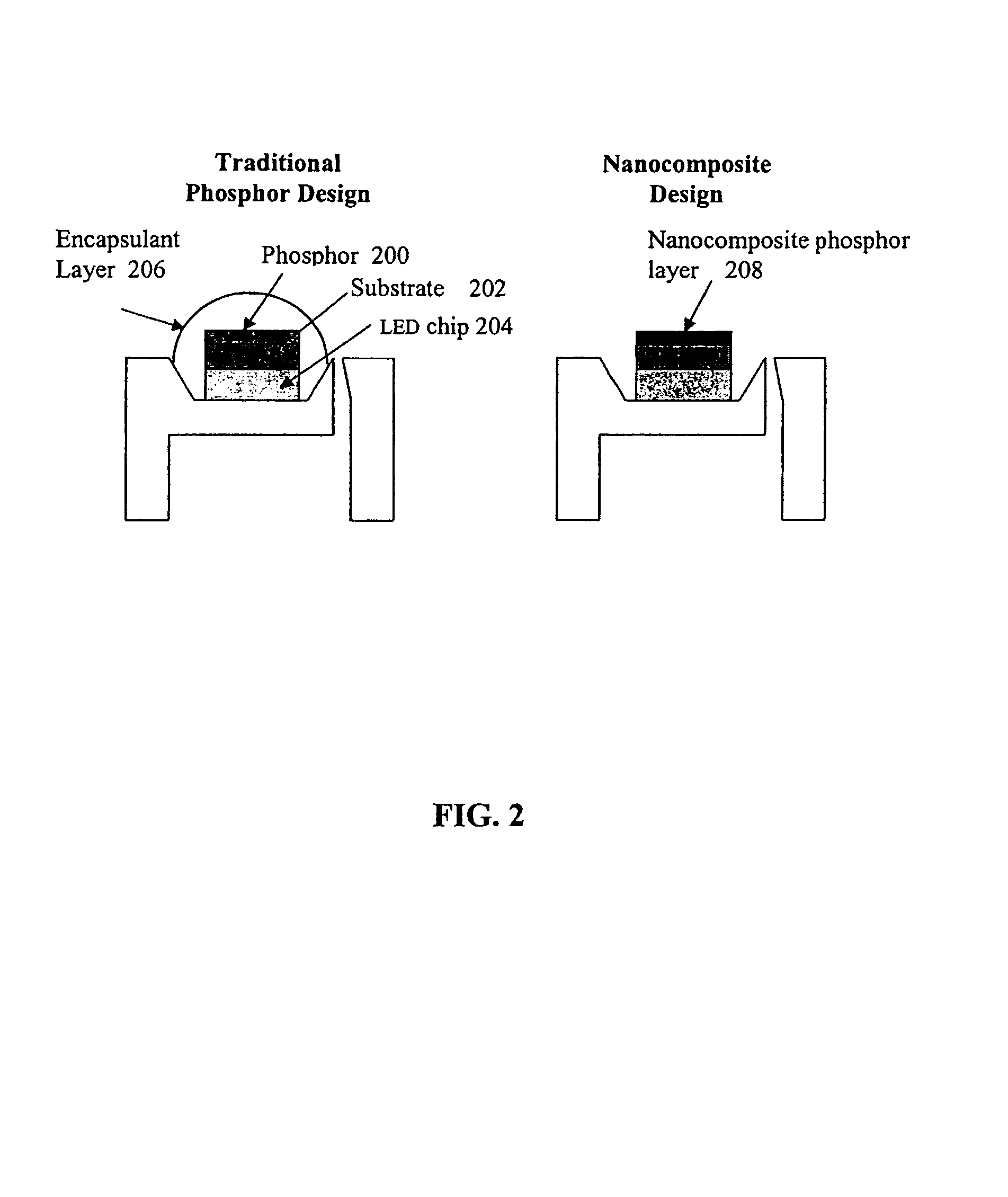

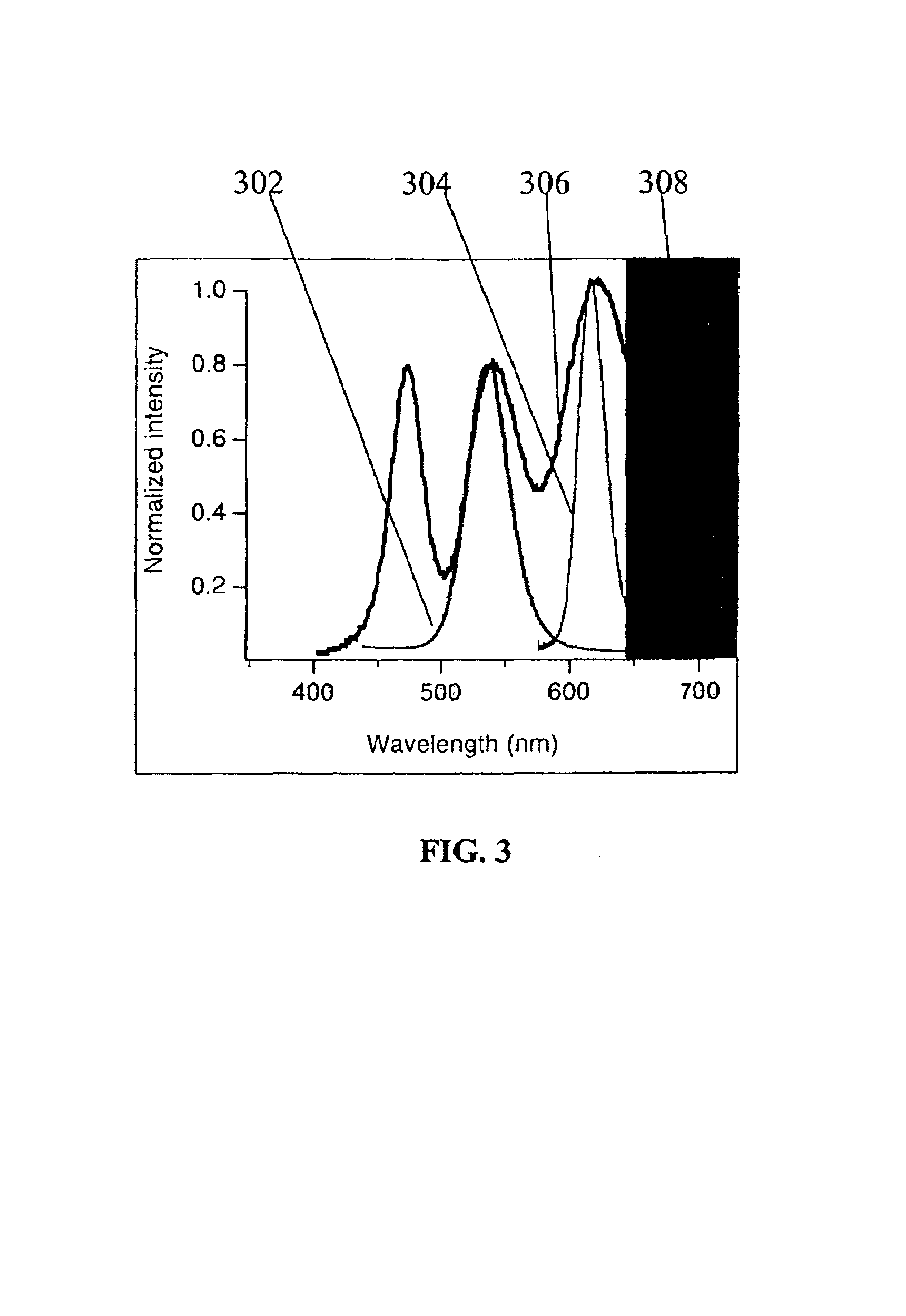

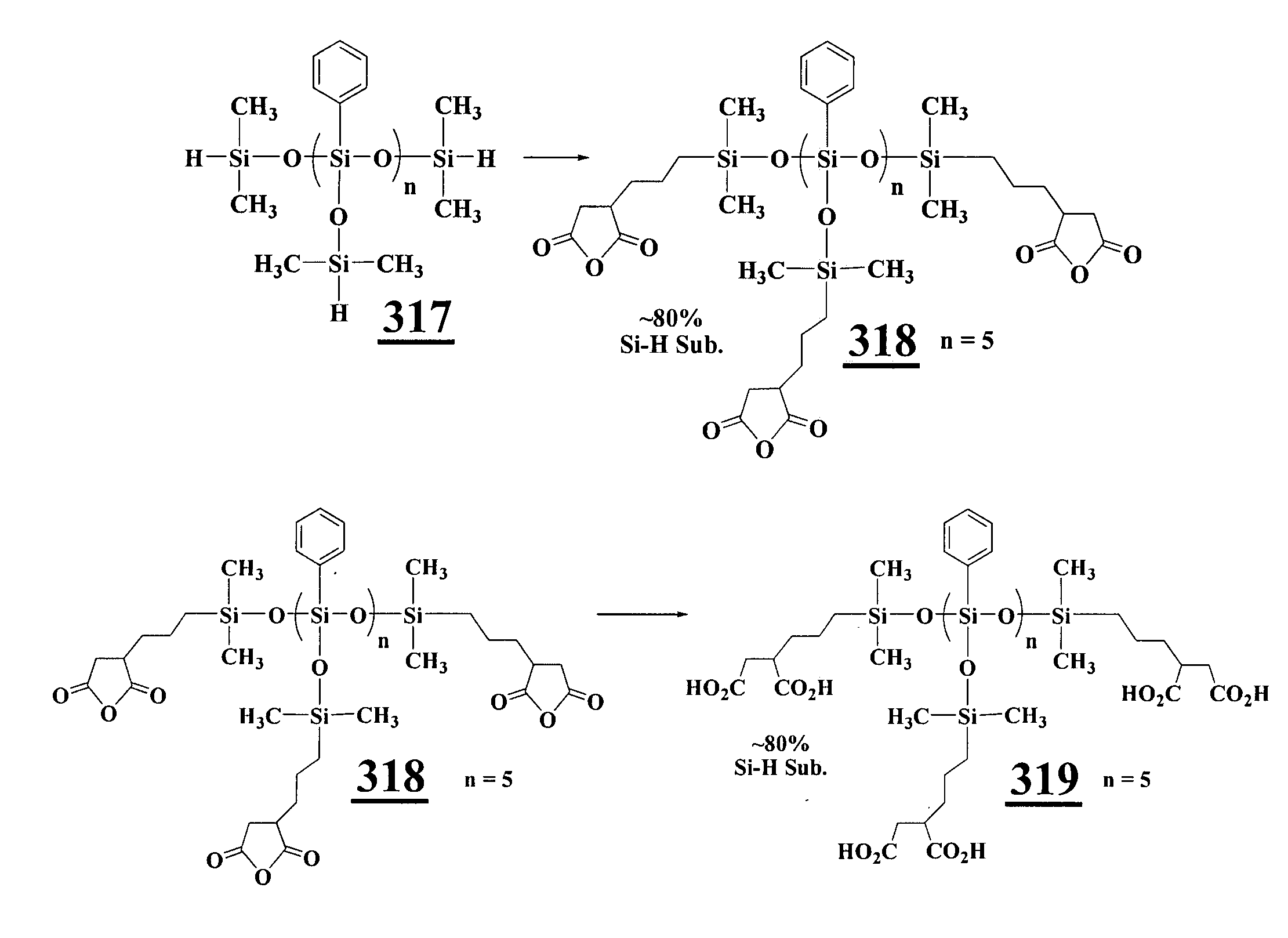

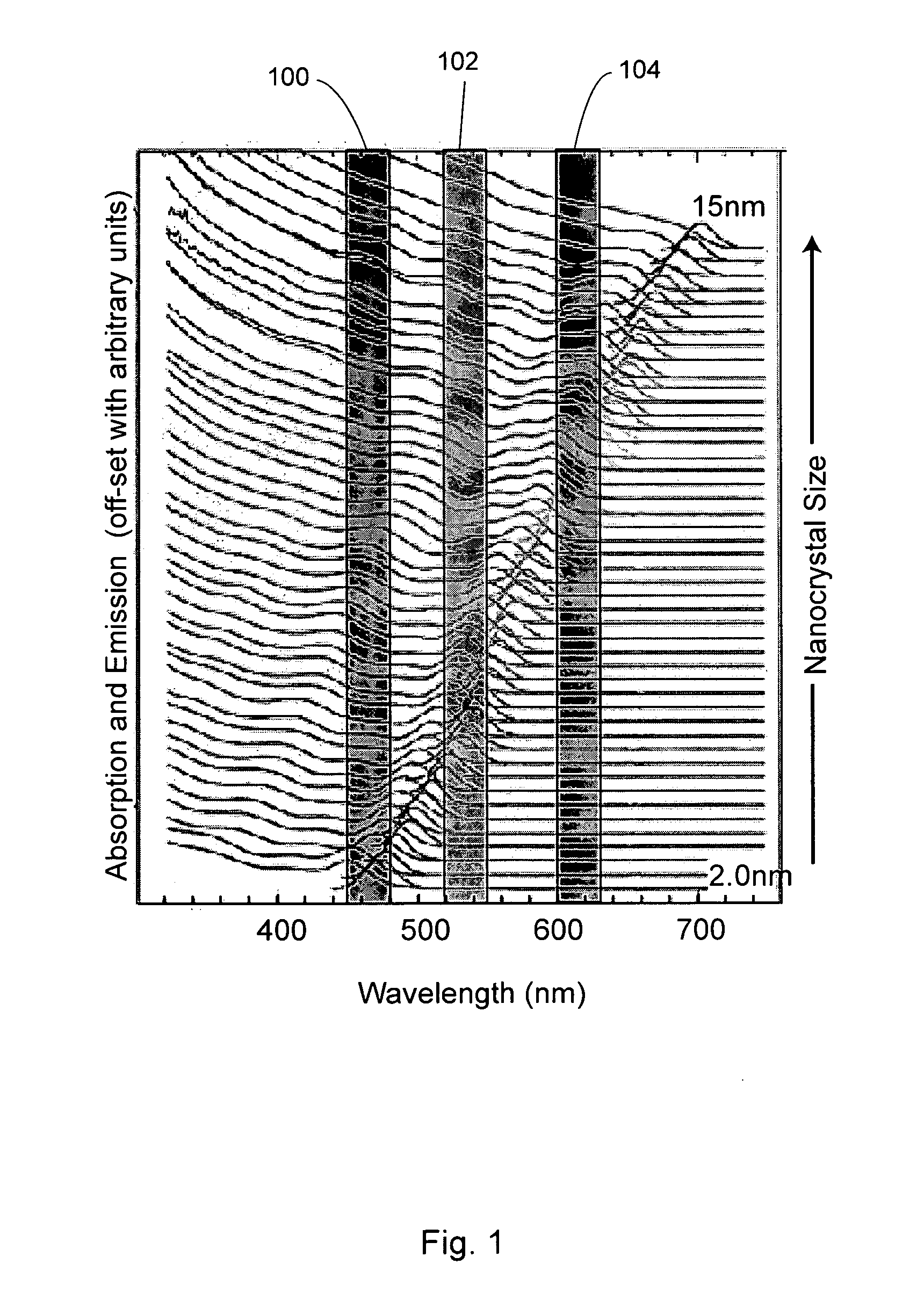

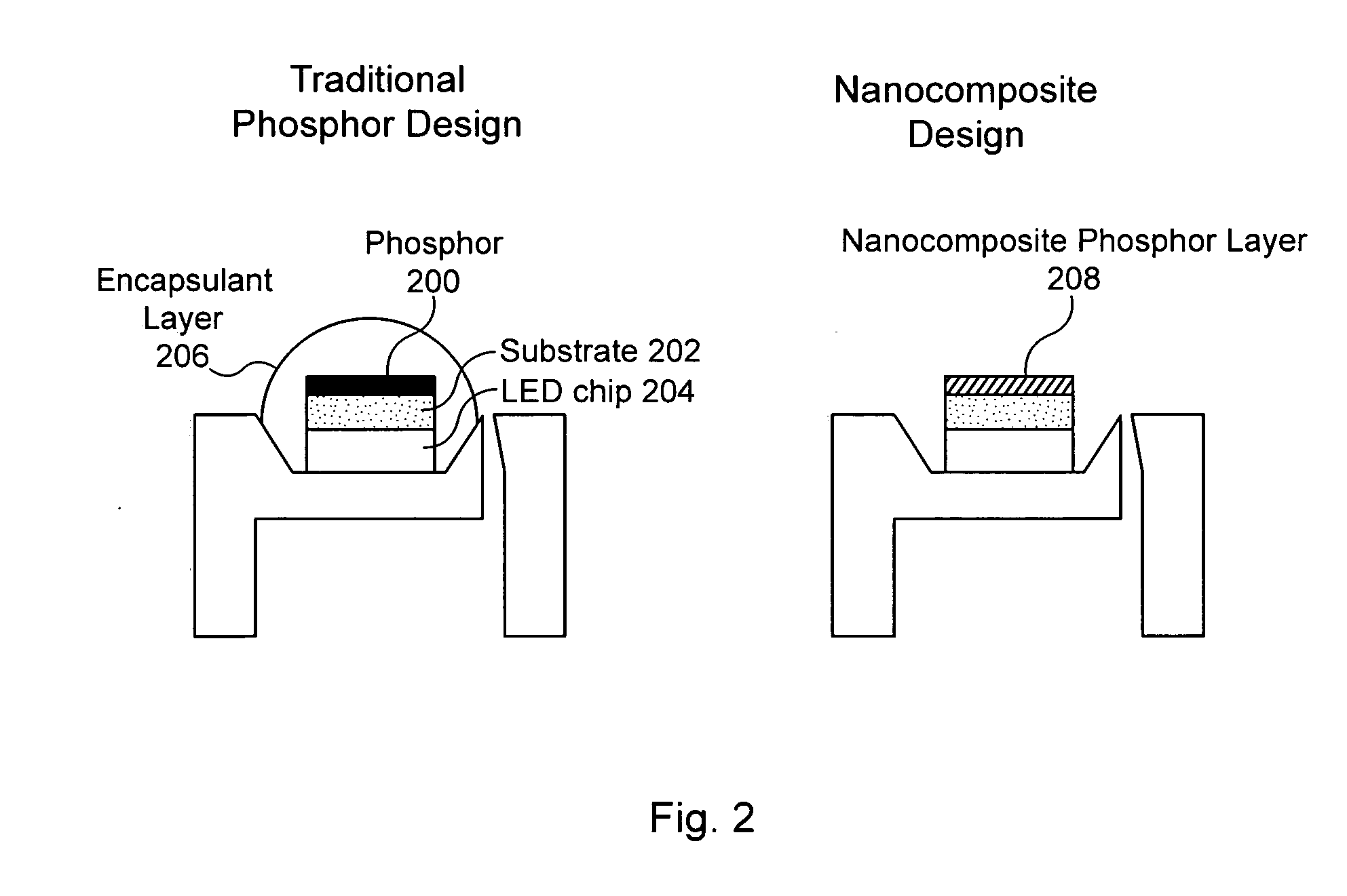

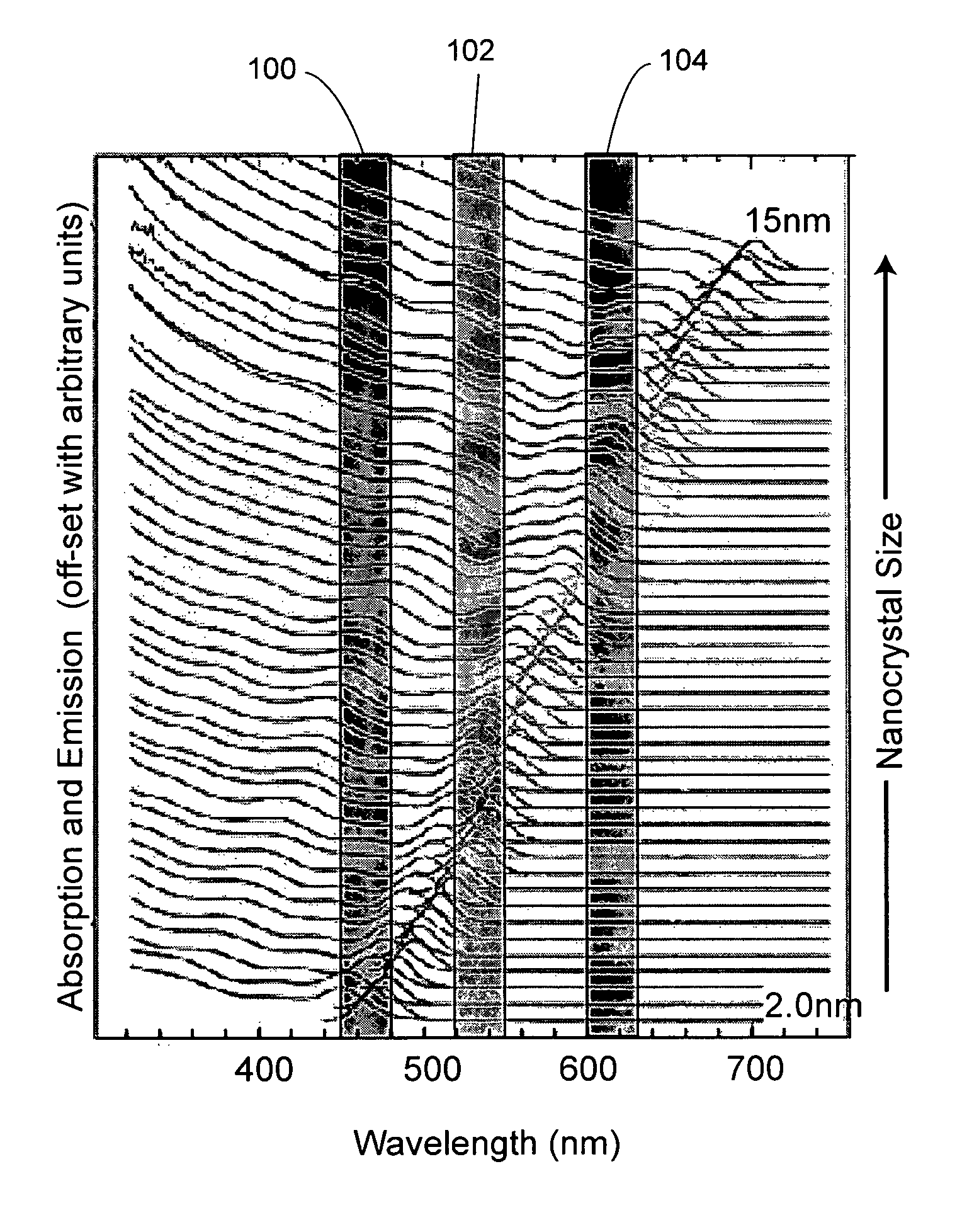

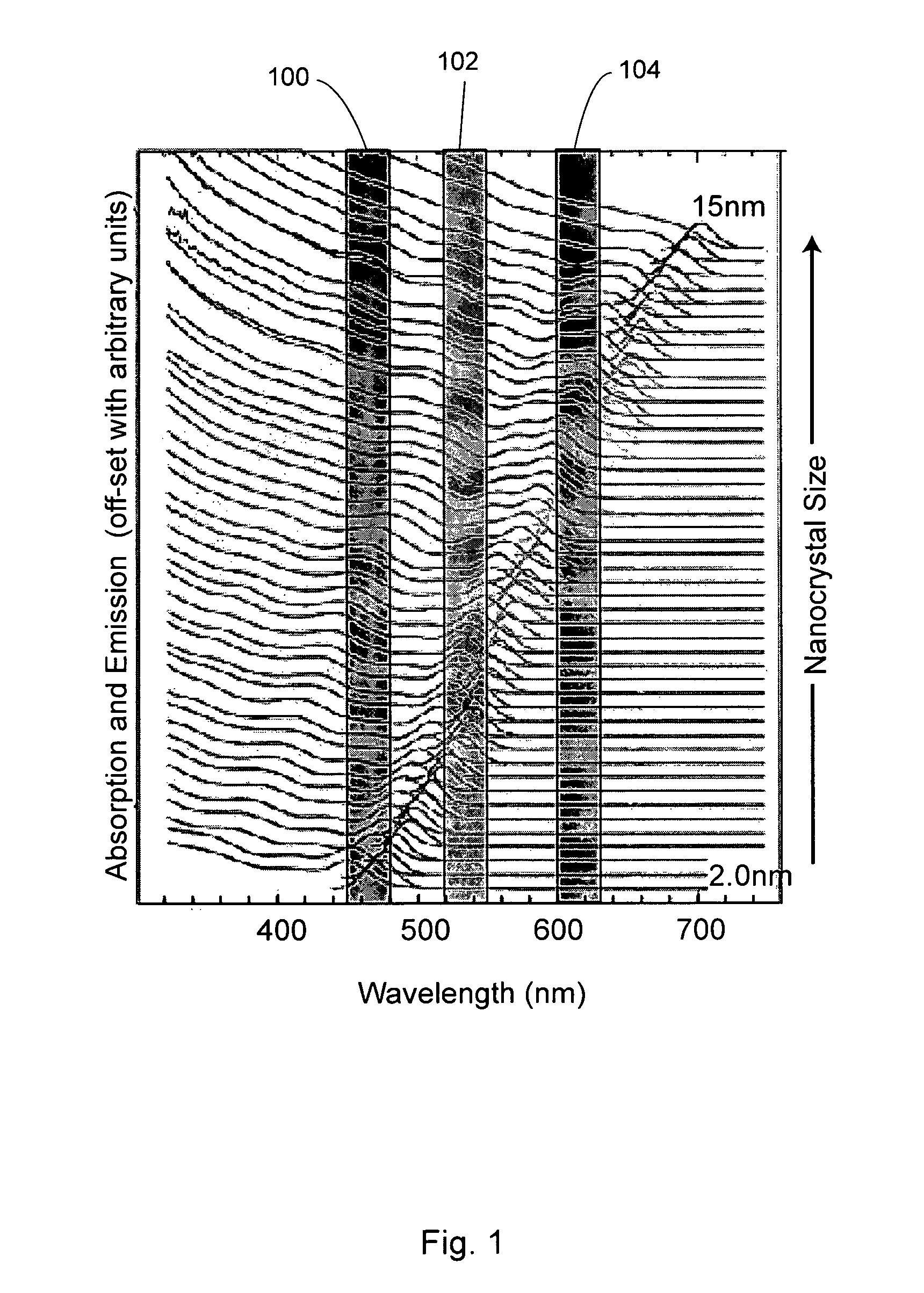

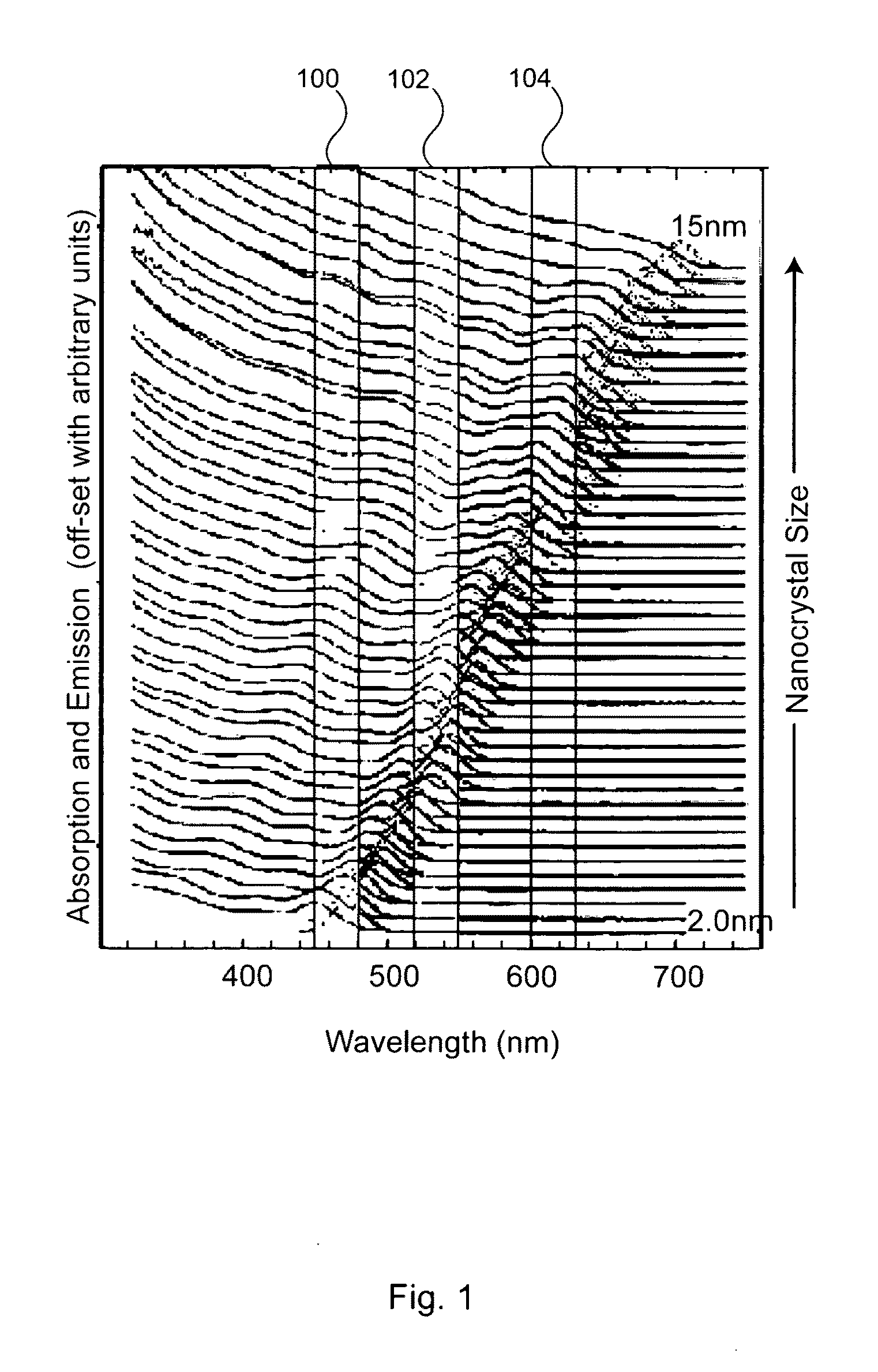

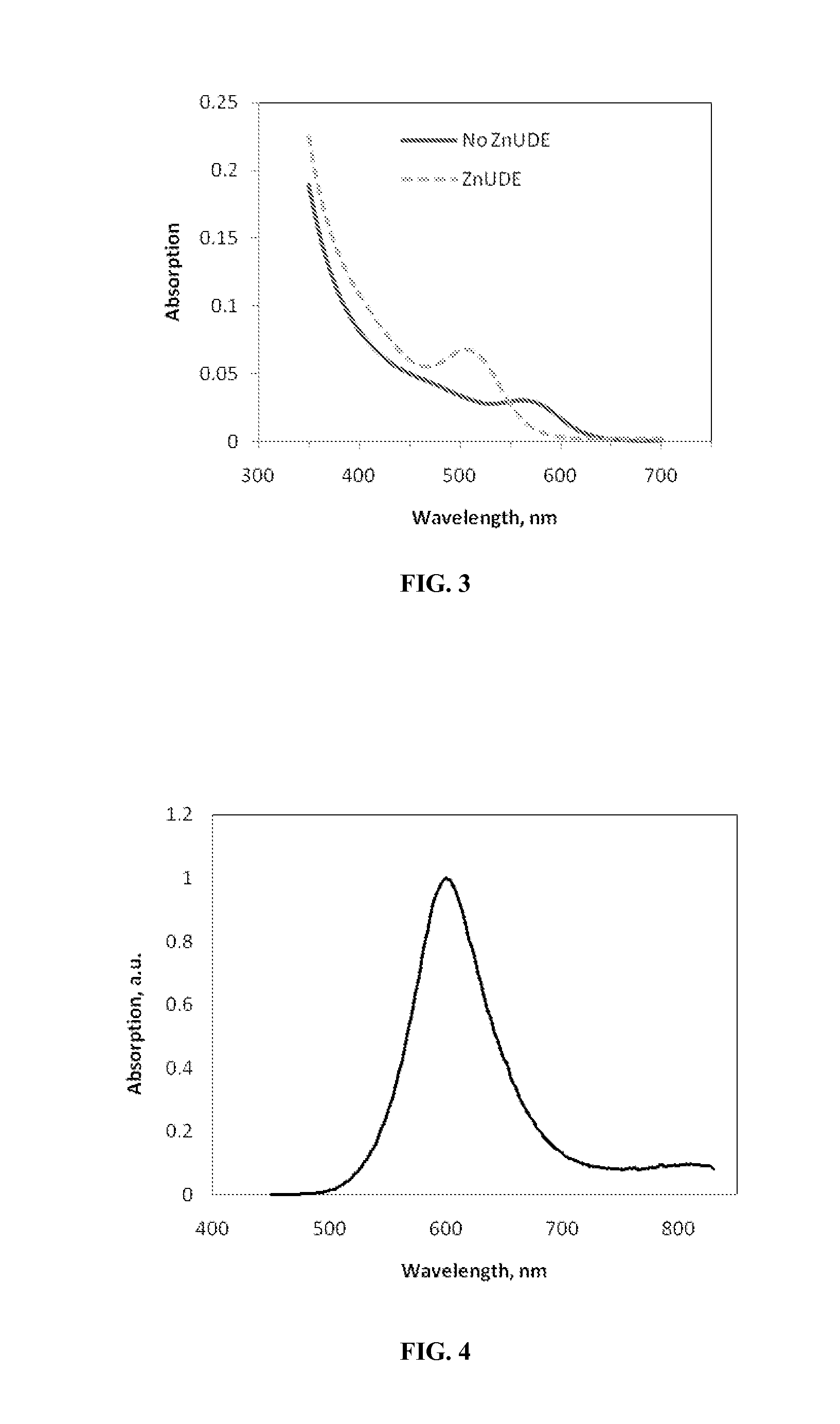

Matrixes doped with semiconductor nanocrystals are provided. In certain embodiments, the semiconductor nanocrystals have a size and composition such that they absorb or emit light at particular wavelengths. The nanocrystals can comprise ligands that allow for mixing with various matrix materials, including polymers, such that a minimal portion of light is scattered by the matrixes. The matrixes of the present invention can also be utilized in refractive index matching applications. In other embodiments, semiconductor nanocrystals are embedded within matrixes to form a nanocrystal density gradient, thereby creating an effective refractive index gradient. The matrixes of the present invention can also be used as filters and antireflective coatings on optical devices and as down-converting layers. Processes for producing matrixes comprising semiconductor nanocrystals are also provided. Nanostructures having high quantum efficiency, small size, and / or a narrow size distribution are also described, as are methods of producing indium phosphide nanostructures and core-shell nanostructures with Group II-VI shells.

Owner:SAMSUNG ELECTRONICS CO LTD

Nanocrystal doped matrixes

ActiveUS7645397B2Good miscibilityInhibit aggregationMaterial nanotechnologyIndividual molecule manipulationAnti-reflective coatingQuantum efficiency

Owner:SAMSUNG ELECTRONICS CO LTD

Functionalized matrixes for dispersion of nanostructures

ActiveUS20100276638A1High quantum yieldFacilitate device fabricationMaterial nanotechnologyGroup 4/14 element organic compoundsAnti-reflective coatingVolumetric Mass Density

Matrixes doped with semiconductor nanocrystals are provided. In certain embodiments, the semiconductor nanocrystals have a size and composition such that they absorb or emit light at particular wavelengths. The nanocrystals can comprise ligands that allow for mixing with various matrix materials, including polymers, such that a minimal portion of light is scattered by the matrixes. The matrixes are optionally formed from the ligands. The matrixes of the present invention can also be utilized in refractive index matching applications. In other embodiments, semiconductor nanocrystals are embedded within matrixes to form a nanocrystal density gradient, thereby creating an effective refractive index gradient. The matrixes of the present invention can also be used as filters and antireflective coatings on optical devices and as down-converting layers. Processes for producing matrixes comprising semiconductor nanocrystals are also provided. Nanostructures having high quantum efficiency, small size, and / or a narrow size distribution are also described, as are methods of producing indium phosphide nanostructures and core-shell nanostructures with Group II-VI shells.

Owner:NANOSYS INC

Functionalized matrices for dispersion of nanostructures

ActiveUS8283412B2Good miscibilityInhibit aggregationMaterial nanotechnologyGroup 4/14 element organic compoundsAnti-reflective coatingSemiconductor nanocrystals

Matrixes doped with semiconductor nanocrystals are provided. In certain embodiments, the semiconductor nanocrystals have a size and composition such that they absorb or emit light at particular wavelengths. The nanocrystals can comprise ligands that allow for mixing with various matrix materials, including polymers, such that a minimal portion of light is scattered by the matrixes. The matrixes are optionally formed from the ligands. The matrixes of the present invention can also be utilized in refractive index matching applications. In other embodiments, semiconductor nanocrystals are embedded within matrixes to form a nanocrystal density gradient, thereby creating an effective refractive index gradient. The matrixes of the present invention can also be used as filters and antireflective coatings on optical devices and as down-converting layers. Processes for producing matrixes comprising semiconductor nanocrystals are also provided. Nanostructures having high quantum efficiency, small size, and / or a narrow size distribution are also described, as are methods of producing indium phosphide nanostructures and core-shell nanostructures with Group II-VI shells.

Owner:SHOEI CHEM IND CO LTD

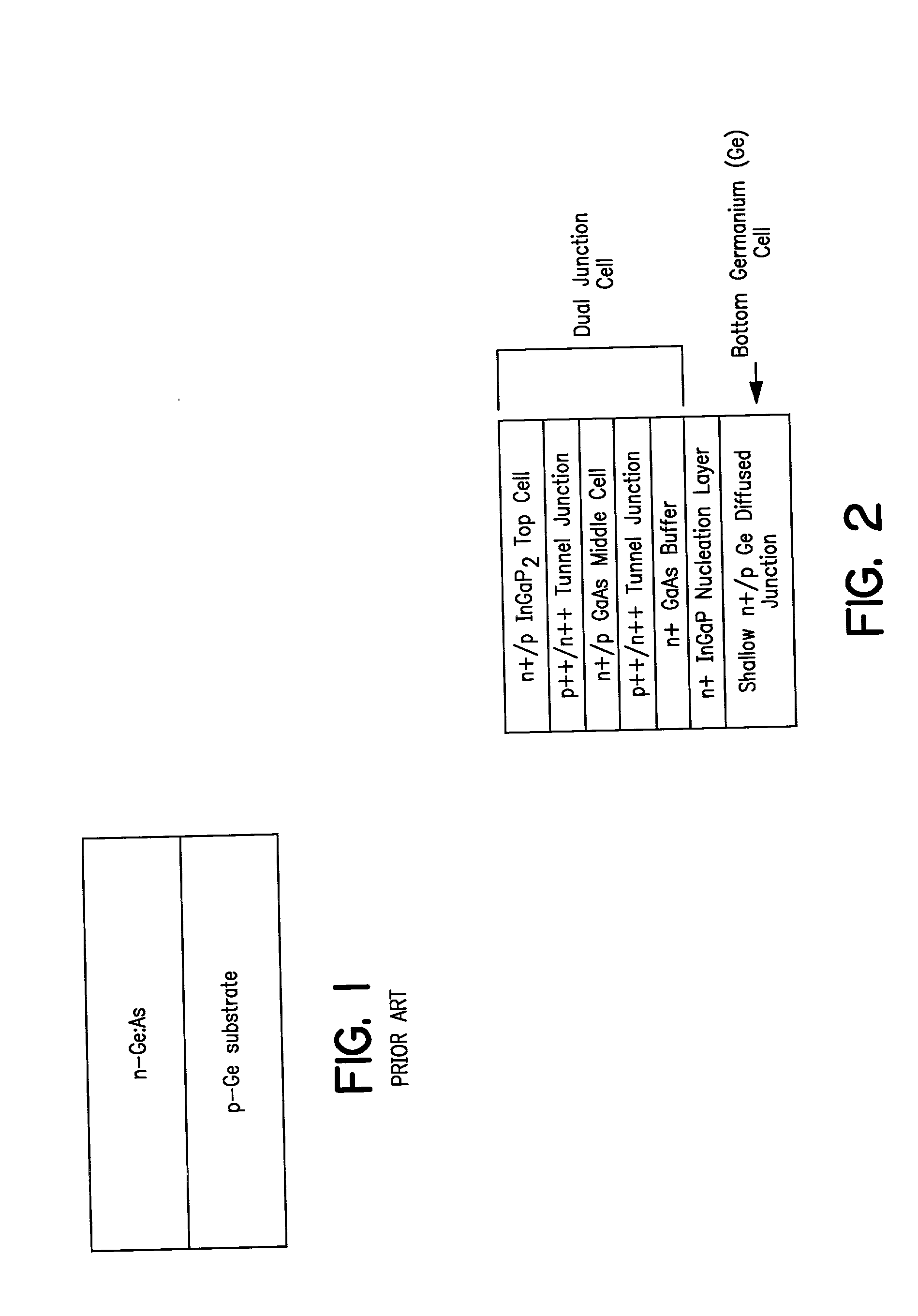

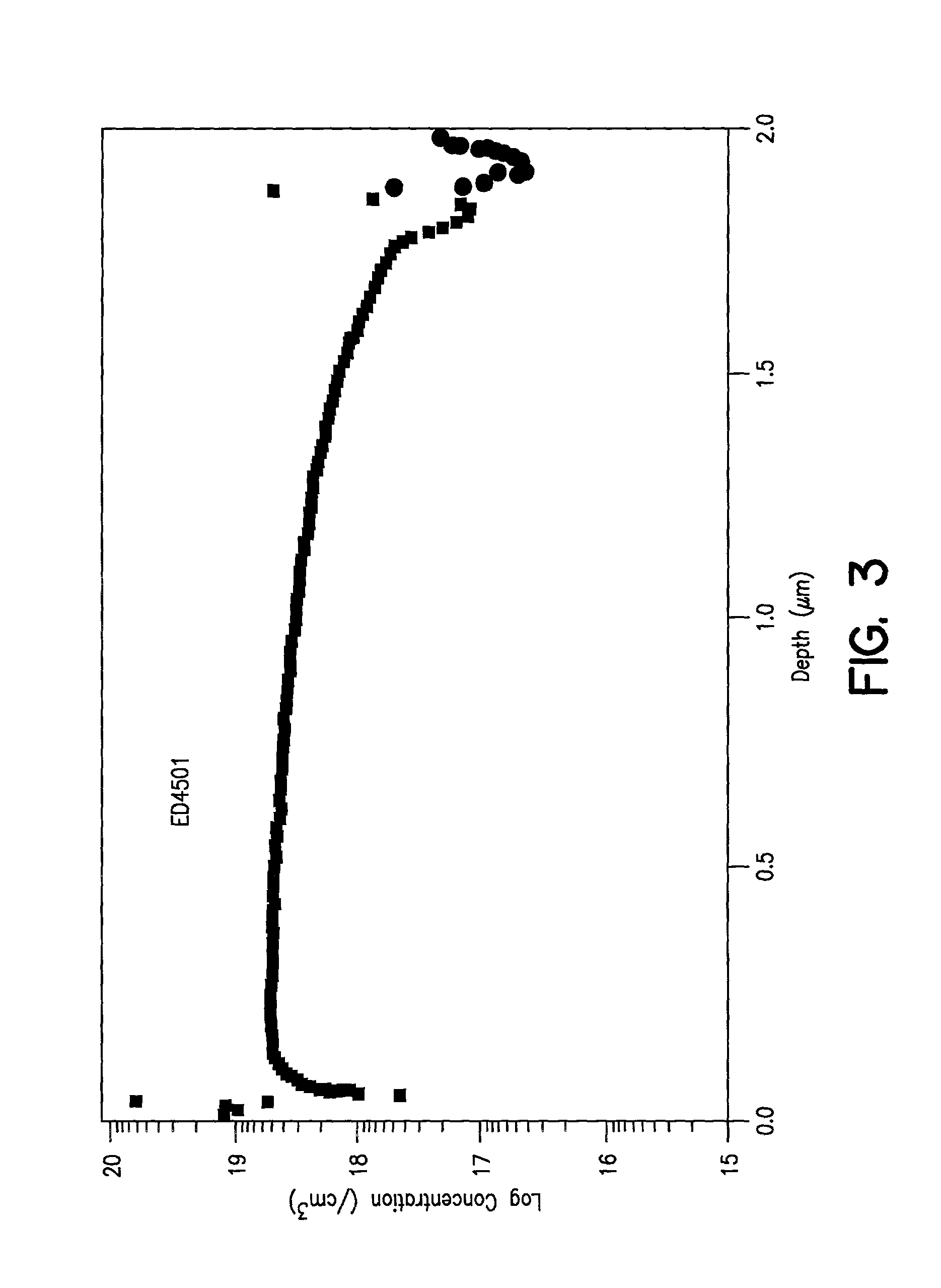

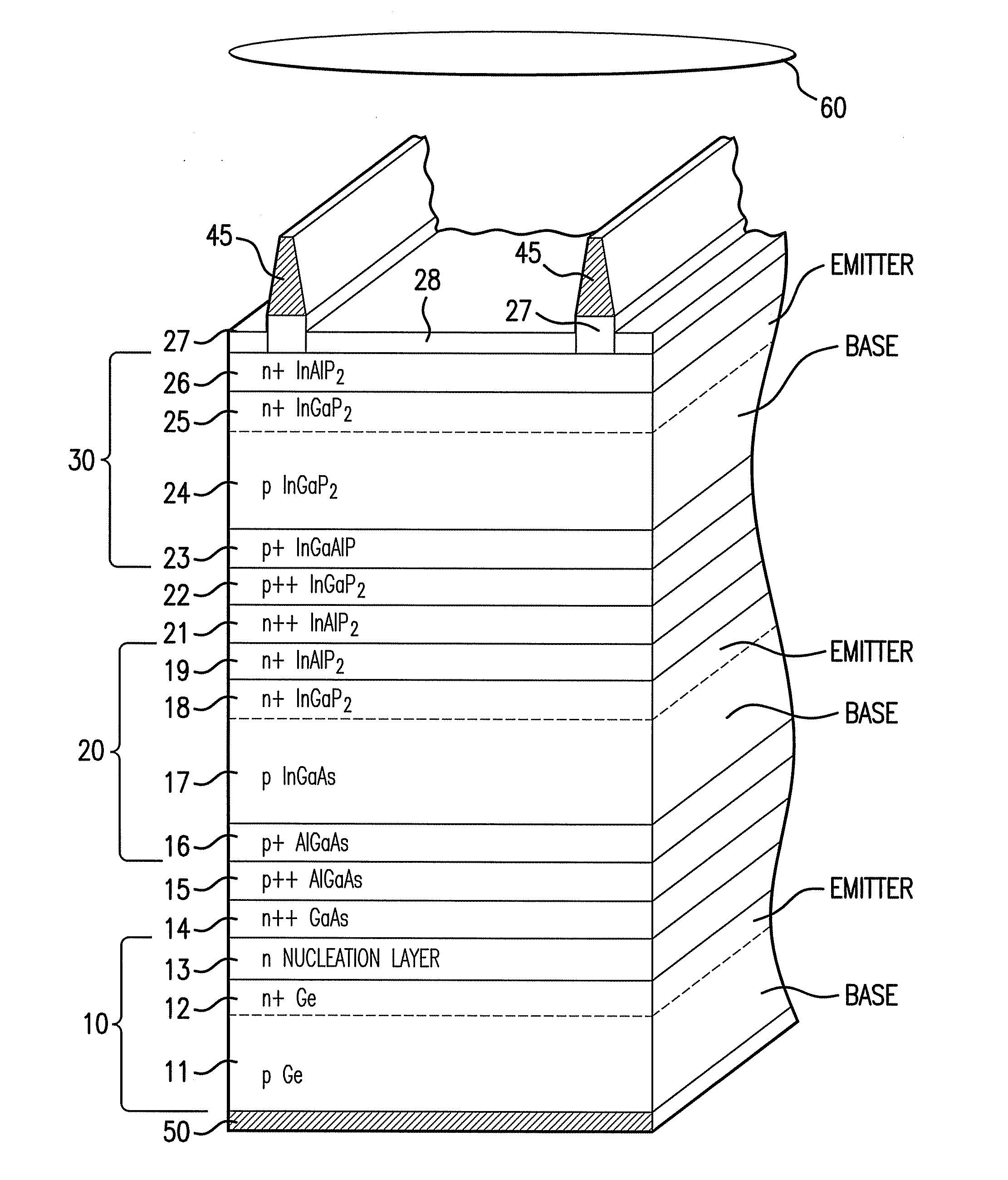

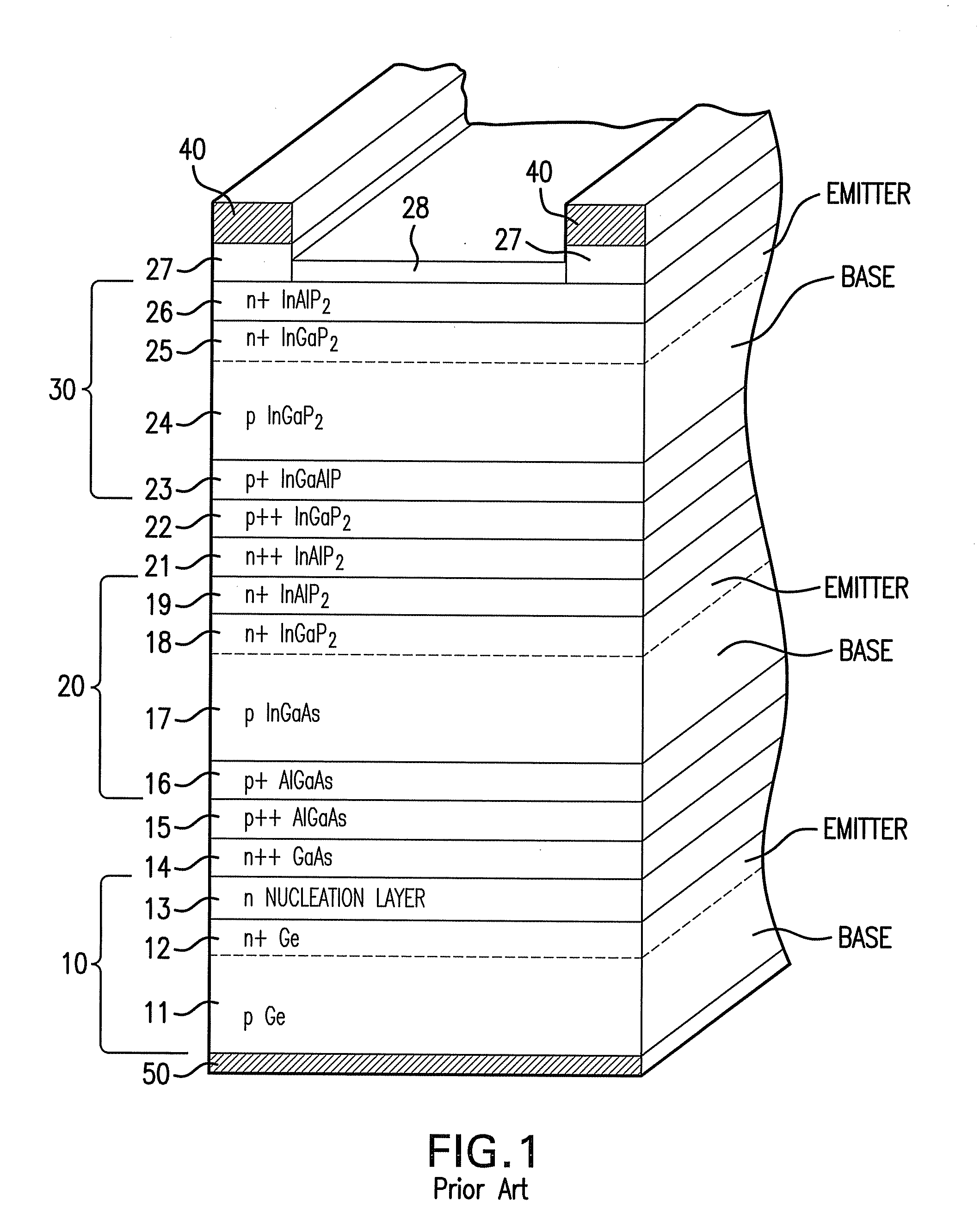

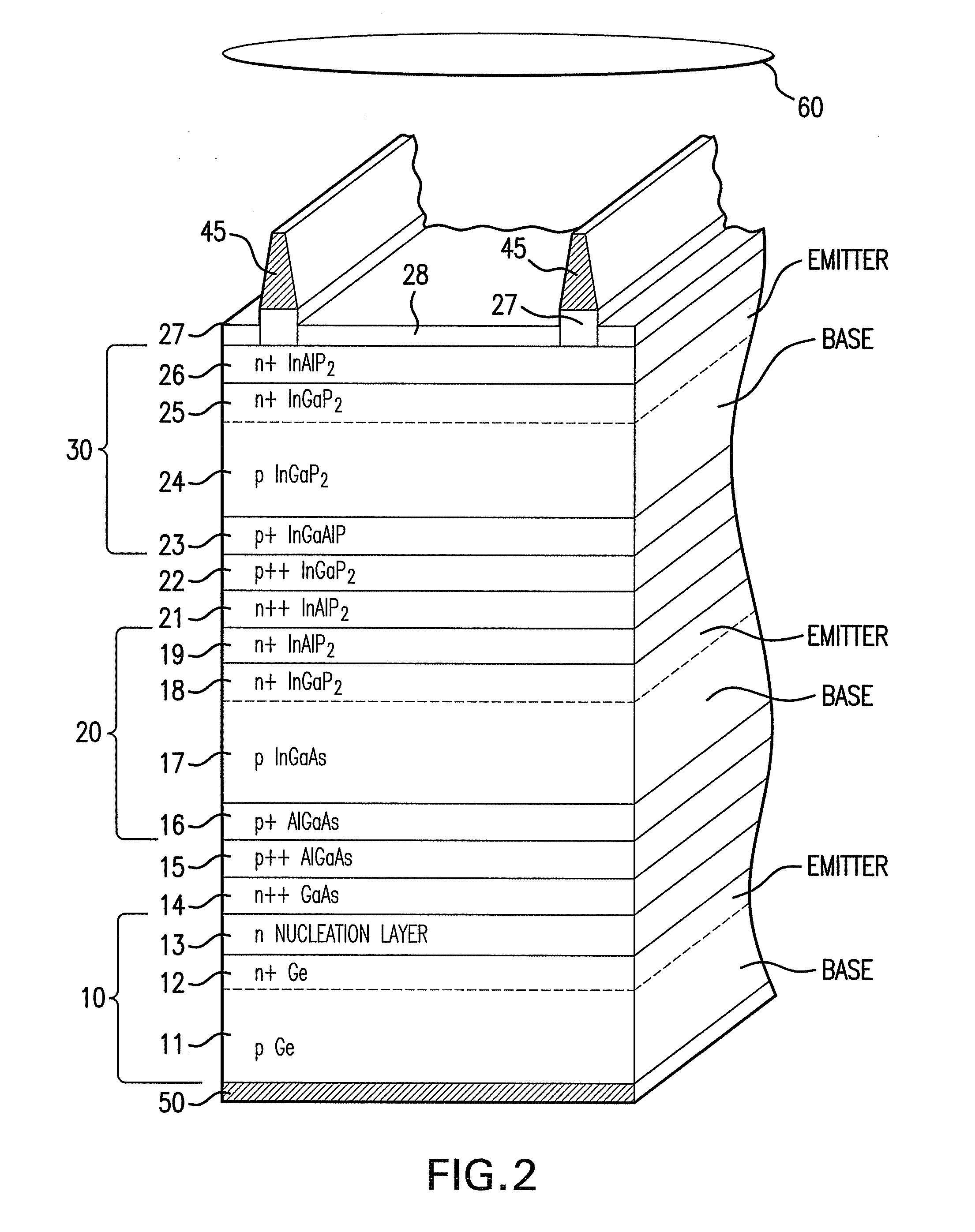

Apparatus and method for optimizing the efficiency of germanium junctions in multi-junction solar cells

InactiveUS20020040727A1PV power plantsSemiconductor/solid-state device manufacturingDopantDiffusion barrier

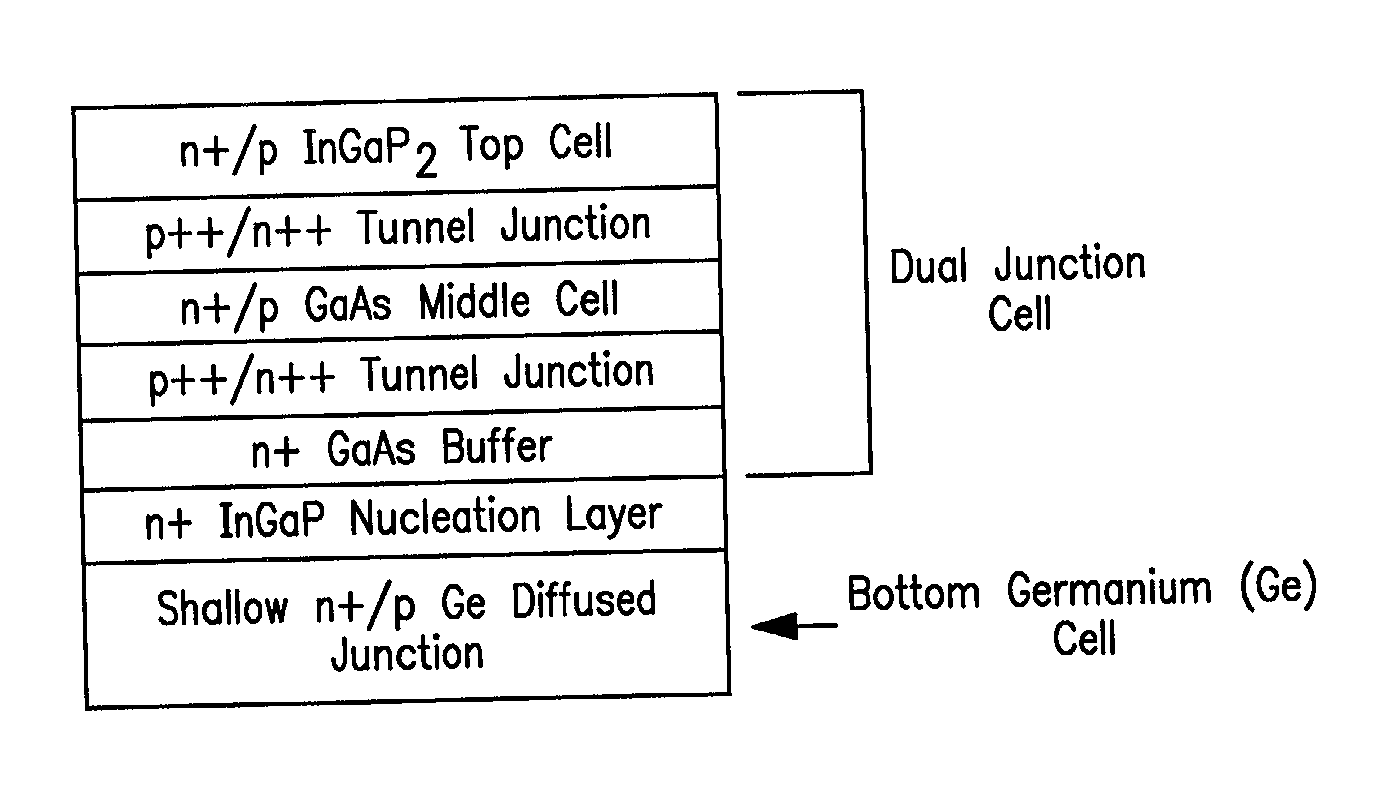

Apparatus and Method for Optimizing the Efficiency of Germanium Junctions in Multi-Junction Solar Cells. In a preferred embodiment, an indium gallium phosphide (InGaP) nucleation layer is disposed between the germanium (Ge) substrate and the overlying dual-junction epilayers for controlling the diffusion depth of the n-doping in the germanium junction. Specifically, by acting as a diffusion barrier to arsenic (As) contained in the overlying epilayers and as a source of n-type dopant for forming the germanium junction, the nucleation layer enables the growth time and temperature in the epilayer device process to be minimized without compromising the integrity of the dual-junction epilayer structure. This in turn allows the arsenic diffusion into the germanium substrate to be optimally controlled by varying the thickness of the nucleation layer. An active germanium junction formed in accordance with the present invention has a typical diffused junction depth that is ⅕ to ½ of that achievable in prior art devices. Furthermore, triple-junction solar cells incorporating a shallow n-p germanium junction of the present invention can attain 1 sun AM0 efficiencies in excess of 26%.

Owner:SOLAERO TECH CORP

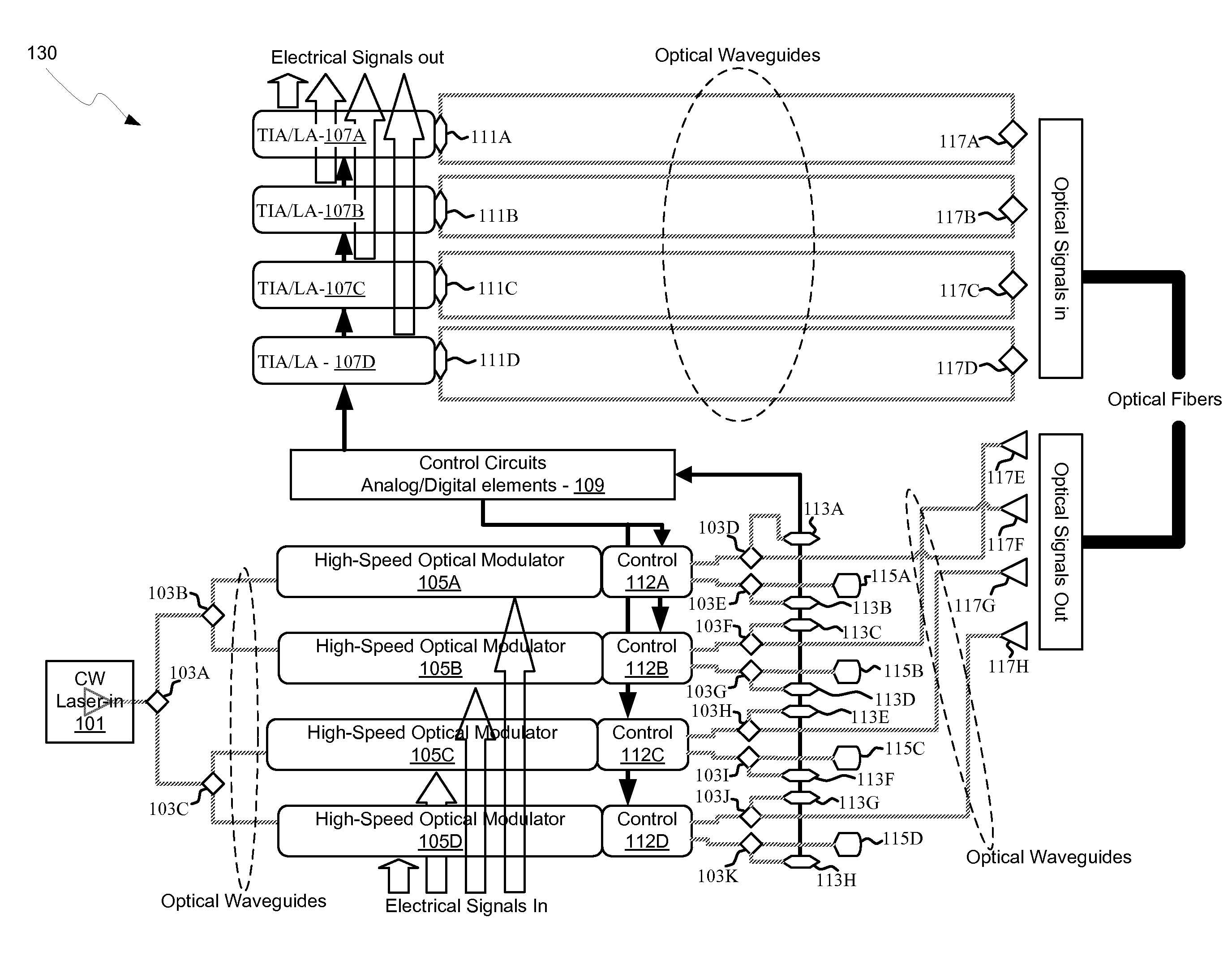

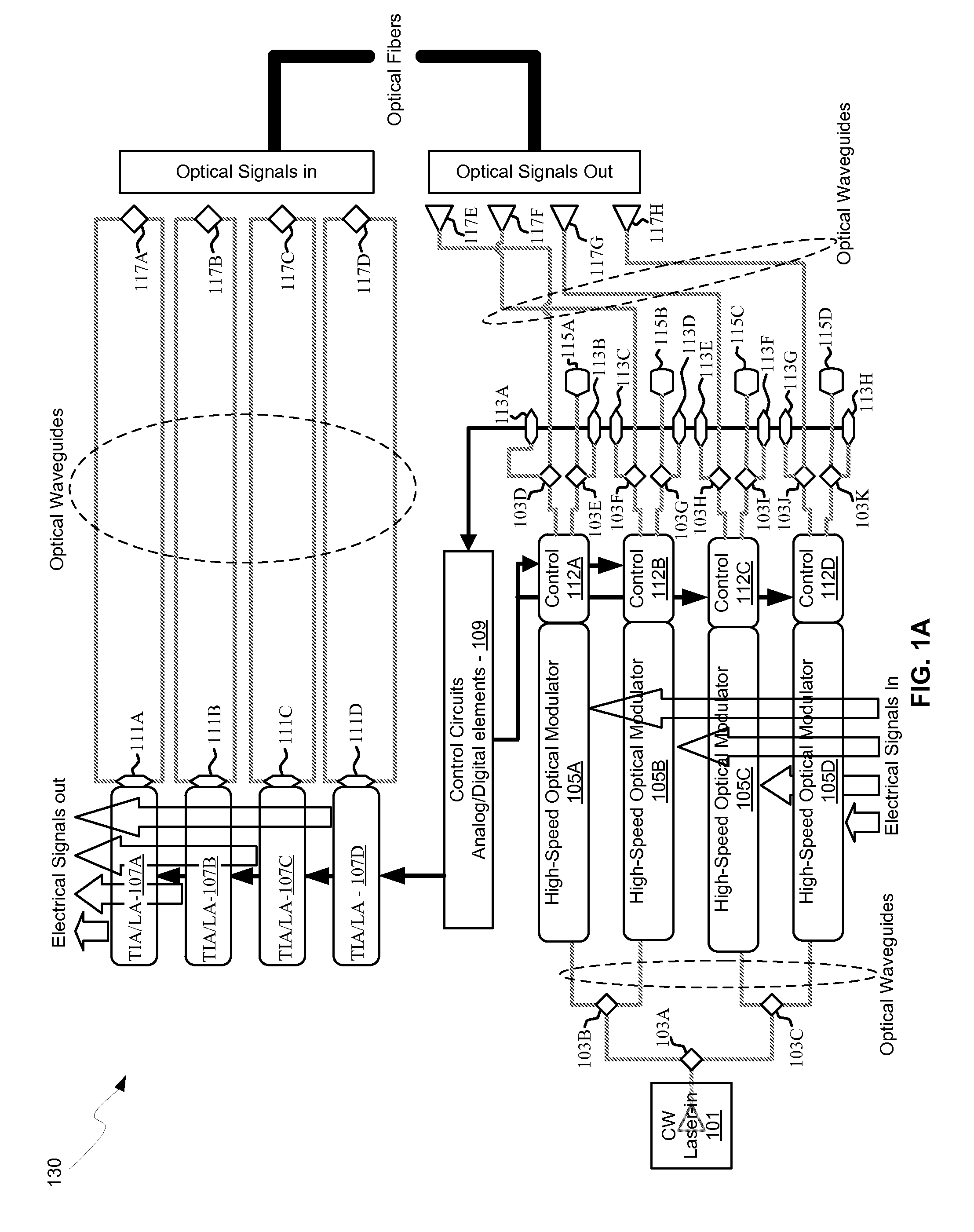

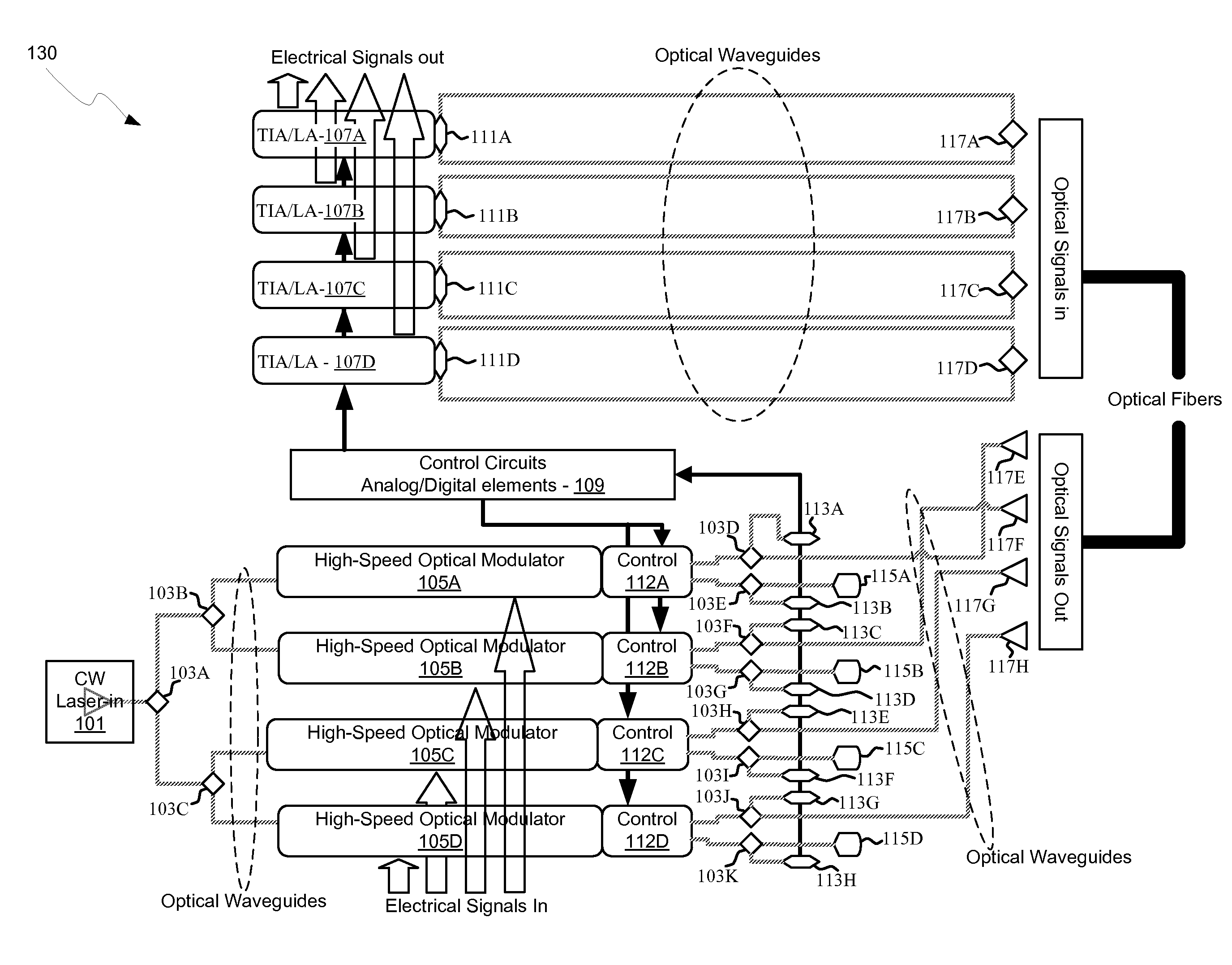

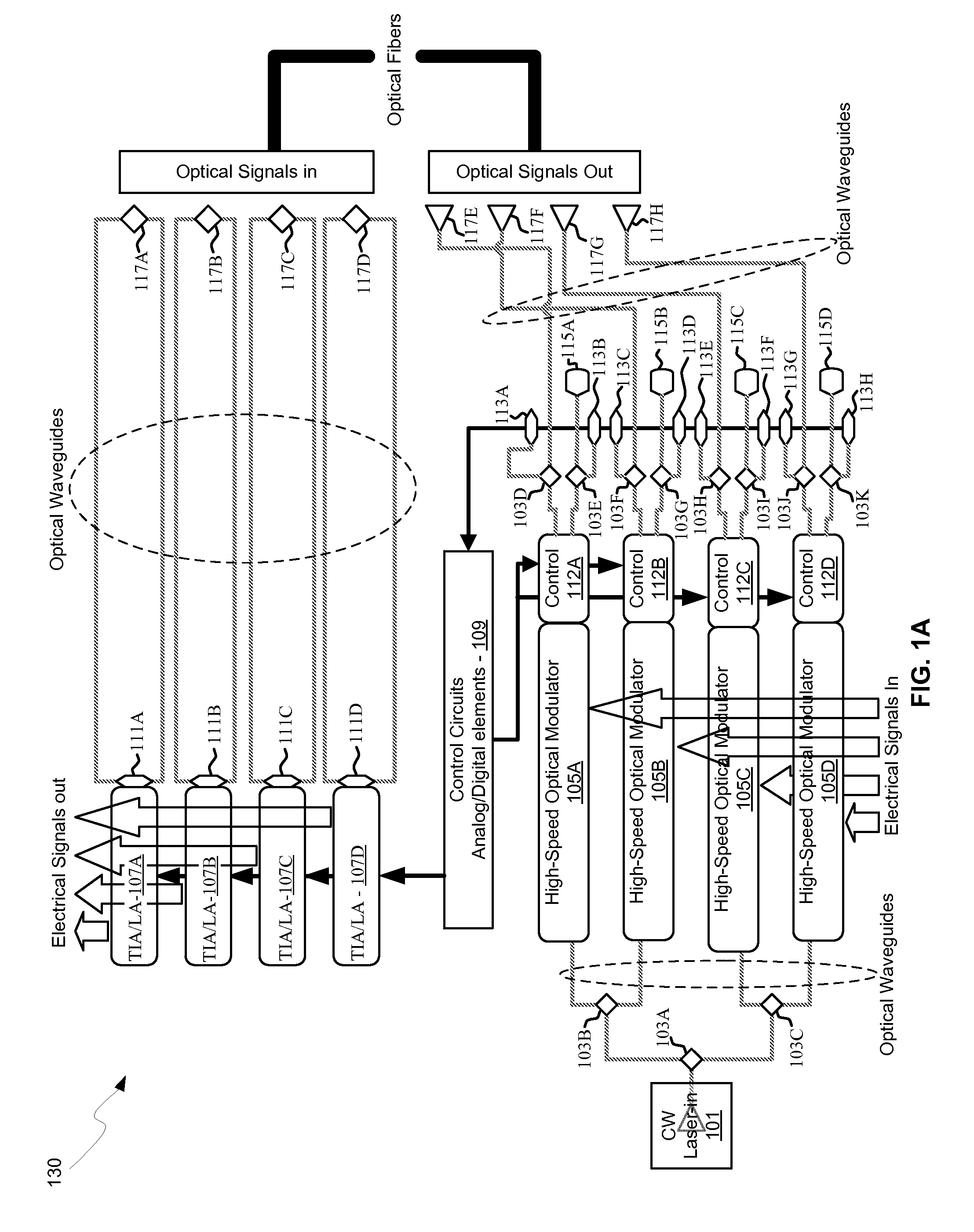

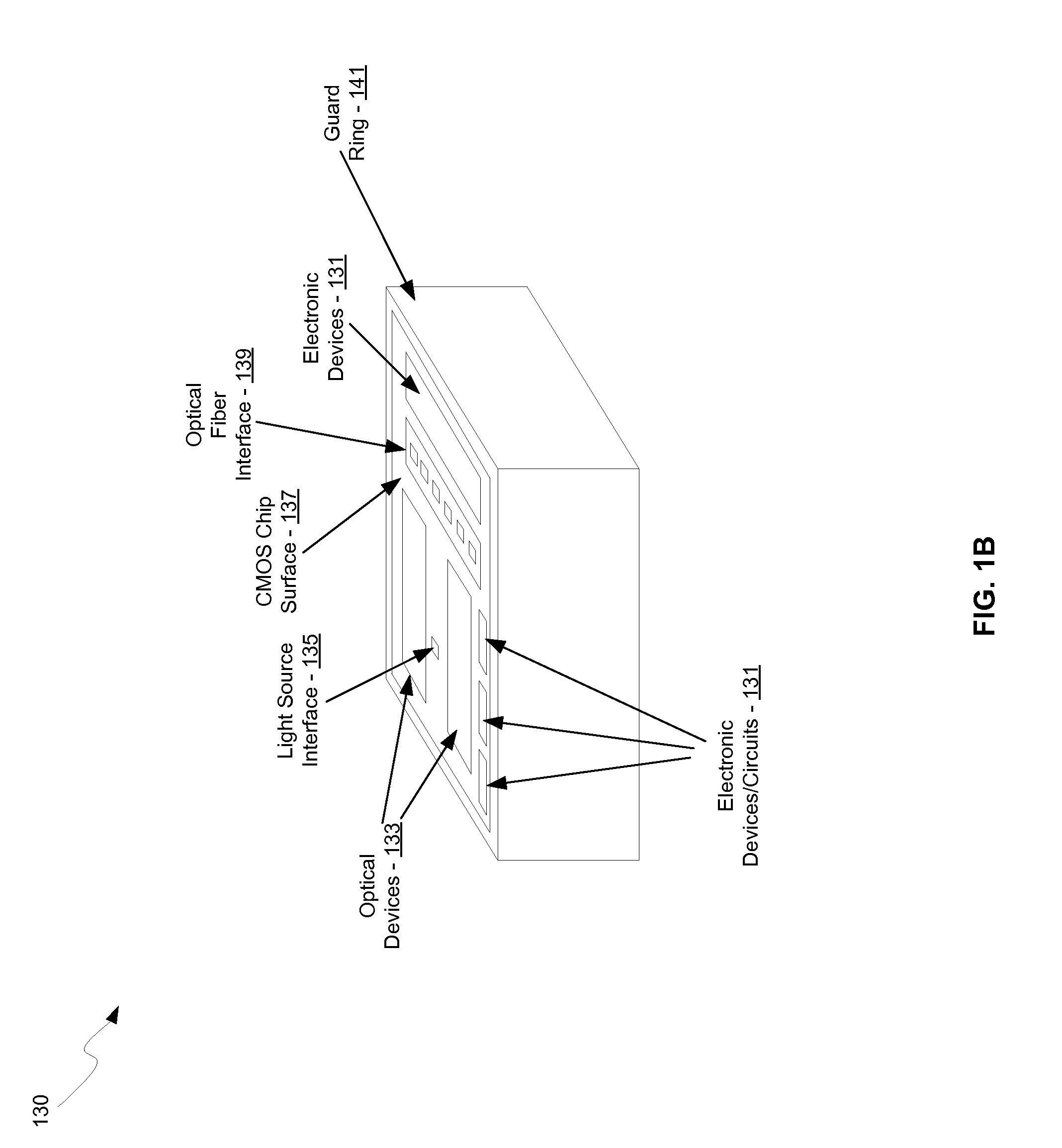

Method and circuit for encoding multi-level pulse amplitude modulated signals using integrated optoelectronic devices

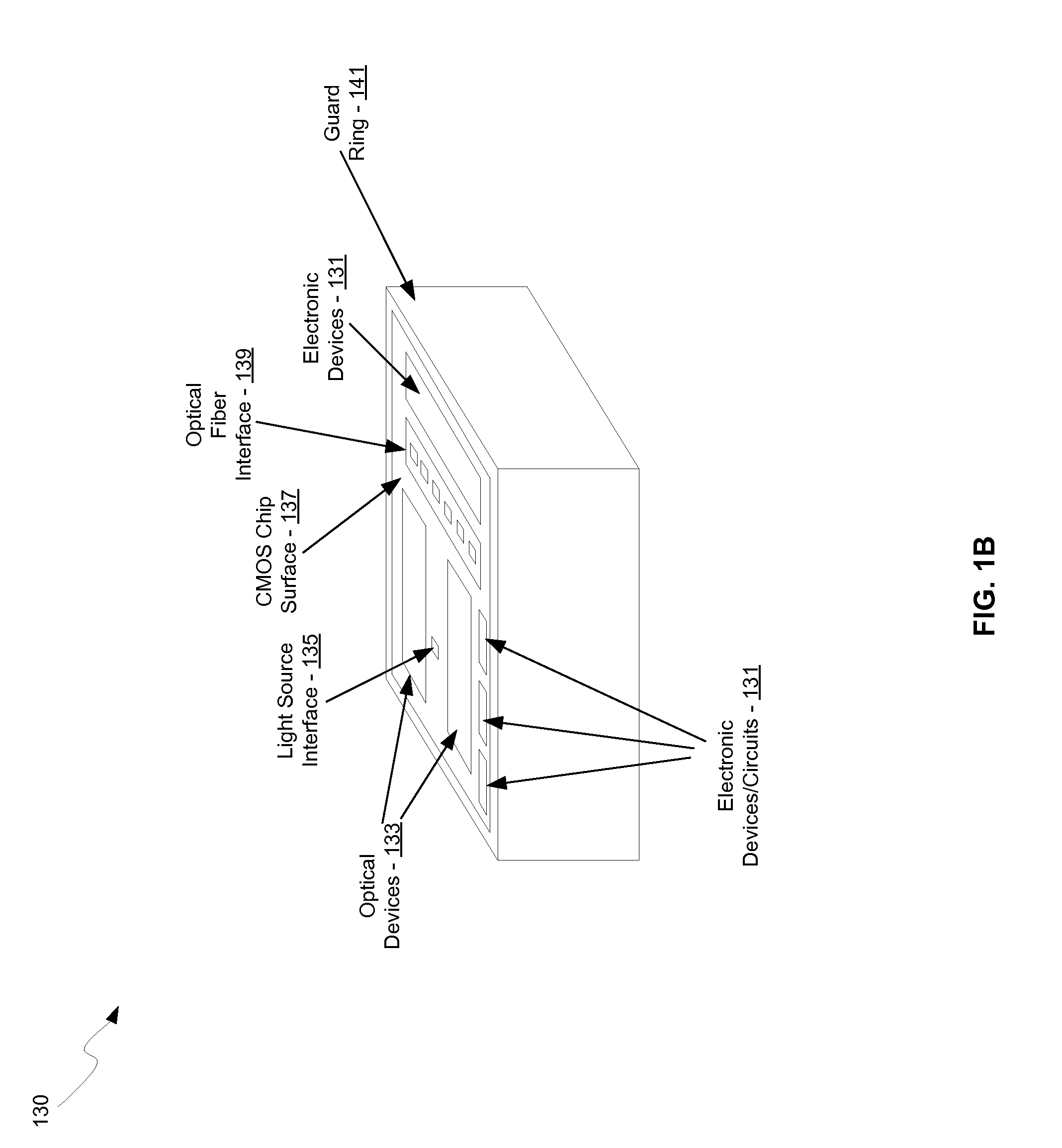

ActiveUS20100060972A1Electromagnetic transmissionNon-linear opticsMach–Zehnder interferometerEngineering

Methods and systems for encoding multi-level pulse amplitude modulated signals using integrated optoelectronics are disclosed and may include generating a multi-level, amplitude-modulated optical signal utilizing an optical modulator driven by two or more electrical input signals. The optical modulator may include optical modulator elements coupled in series and configured into groups. The number of optical modular elements and groups may configure the number of levels in the multi-level amplitude modulated optical signal. Unit drivers may be coupled to each of the groups. The electrical input signals may be synchronized before communicating them to the unit drivers utilizing flip-flops. Phase addition may be synchronized utilizing one or more electrical delay lines. The optical modulator may be integrated on a single substrate, which may include one of: silicon, gallium arsenide, germanium, indium gallium arsenide, polymers, or indium phosphide. The optical modulator may include a Mach-Zehnder interferometer or one or more ring modulators.

Owner:CISCO TECH INC

Ultraviolet laser ablative patterning of microstructures in semiconductors

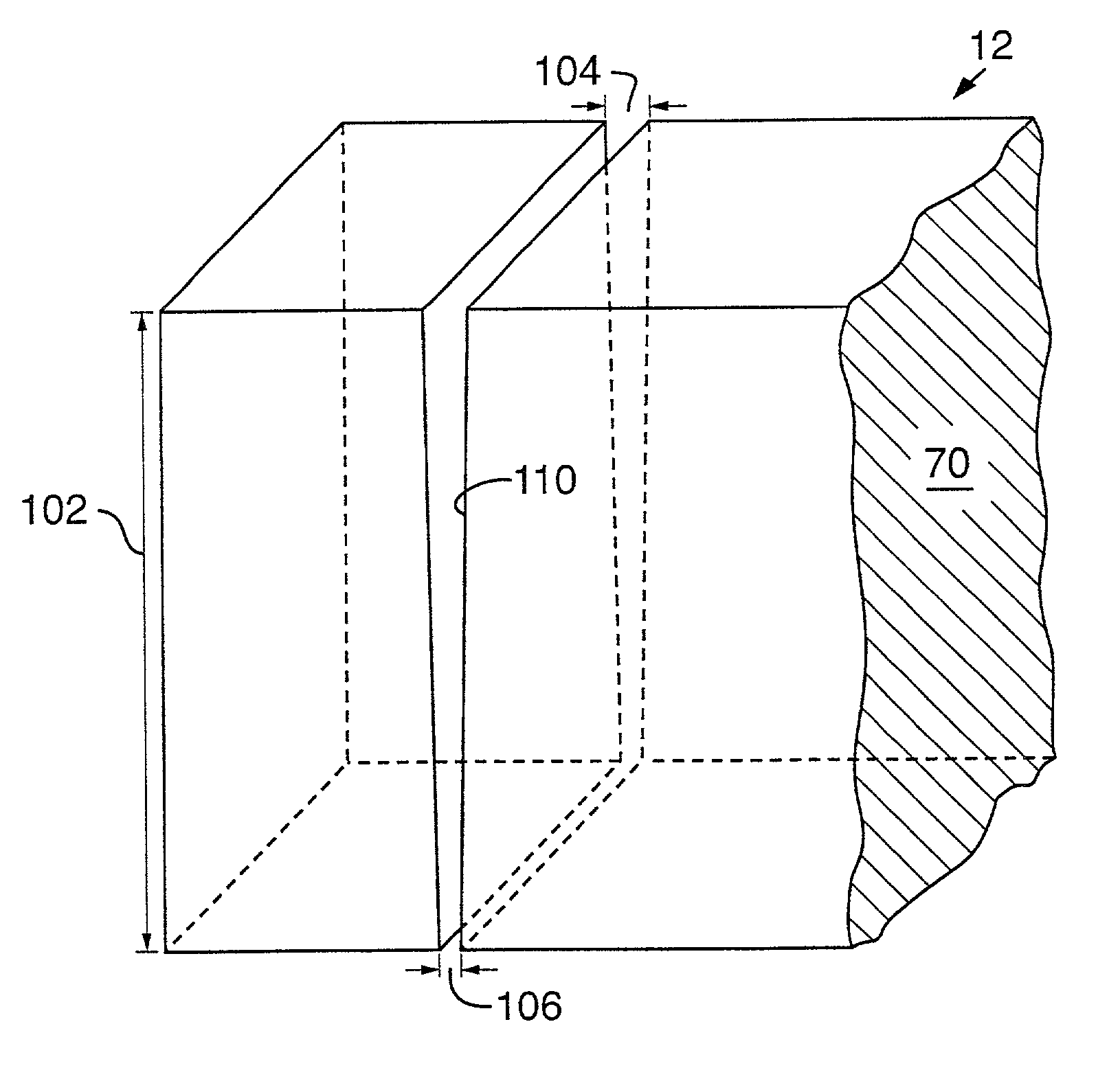

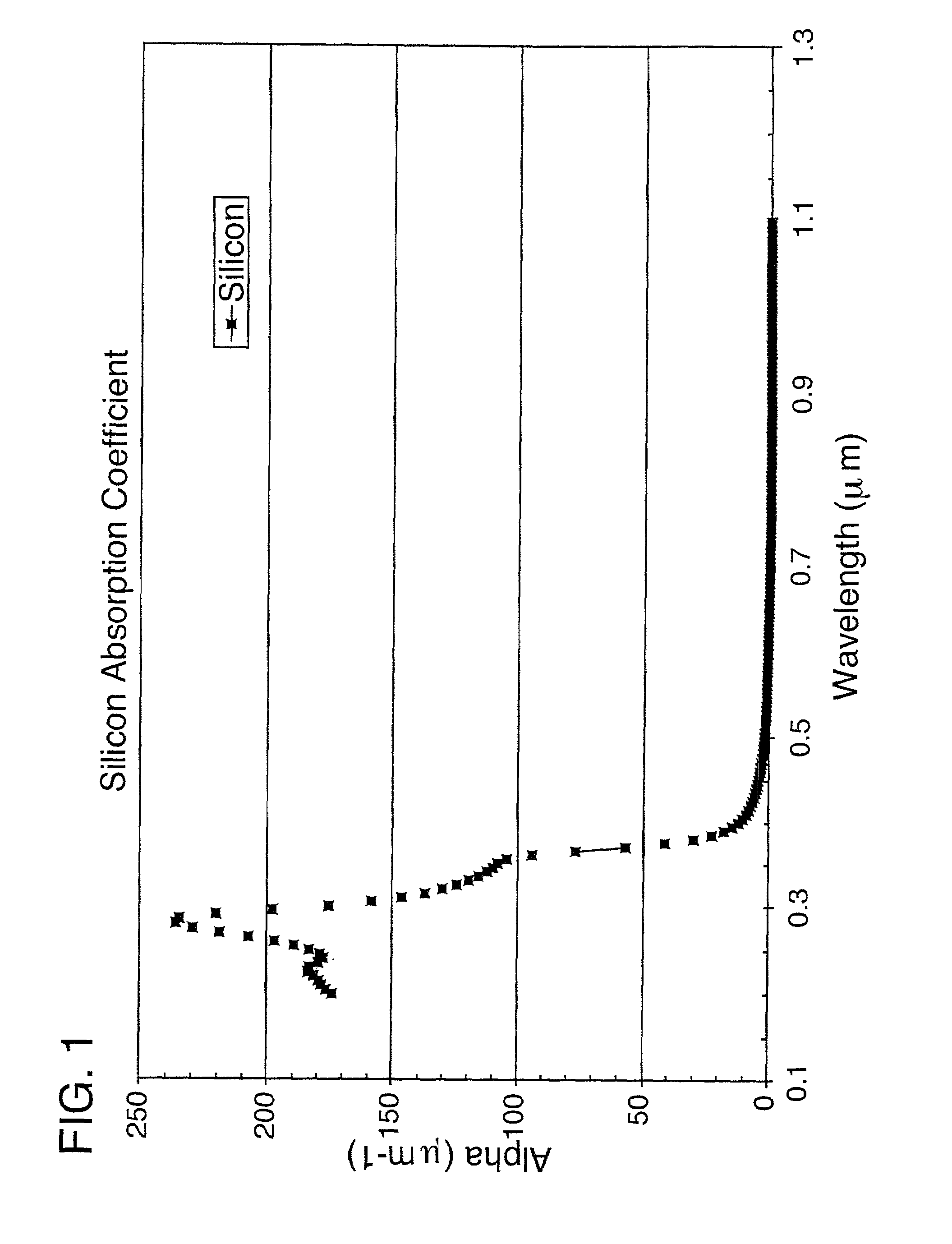

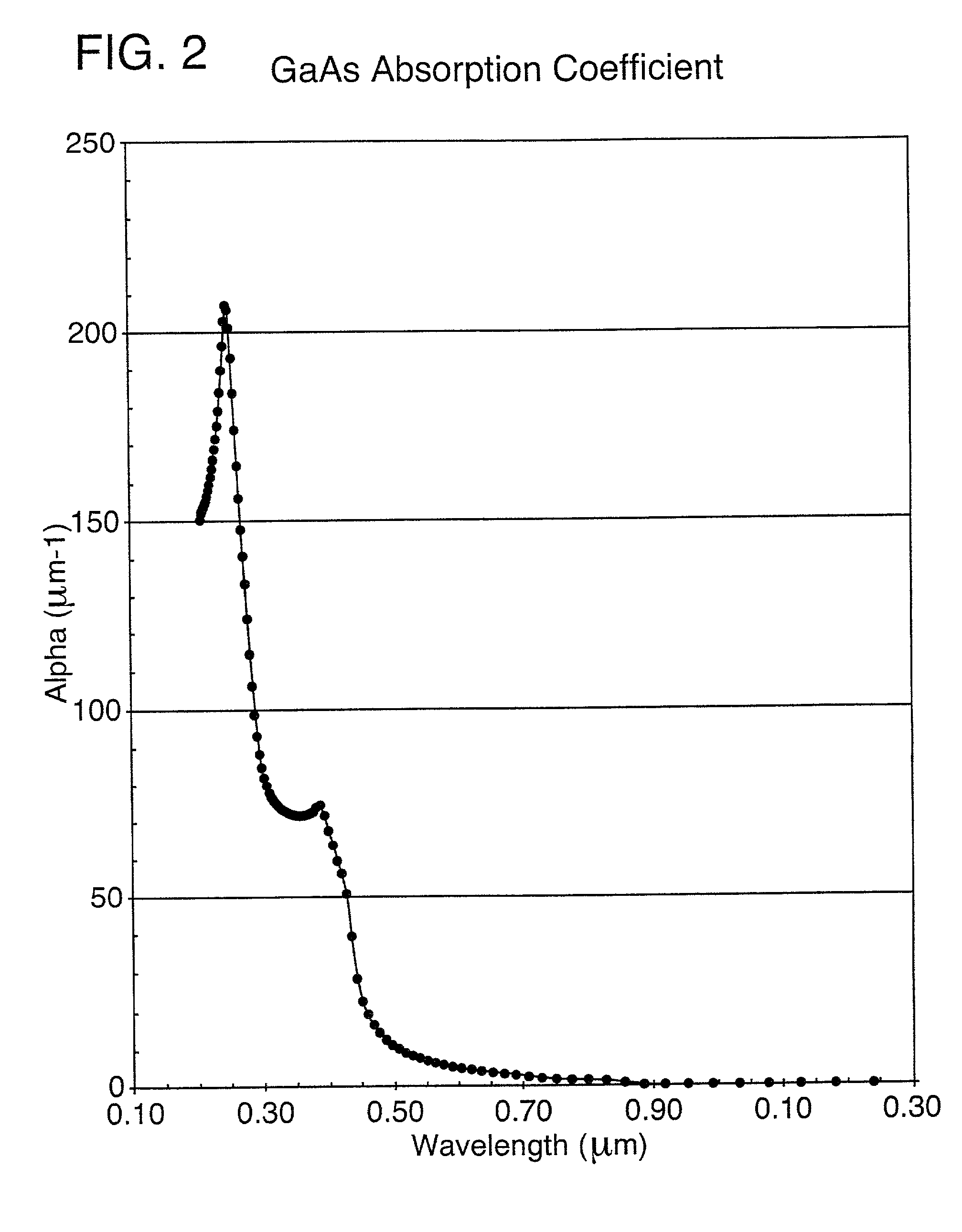

InactiveUS7157038B2High aspect ratioGreat depth of focusSemiconductor/solid-state device manufacturingWelding/soldering/cutting articlesUltravioletSingle crystal

Patterns with feature sizes of less than 50 microns are rapidly formed directly in semiconductors, particularly silicon, GaAs, indium phosphide, or single crystalline sapphire, using ultraviolet laser ablation. These patterns include very high aspect ratio cylindrical through-hole openings for integrated circuit connections; singulation of processed die contained on semiconductor wafers; and microtab cutting to separate microcircuit workpieces from a parent semiconductor wafer. Laser output pulses (32) from a diode-pumped, Q-switched frequency-tripled Nd:YAG, Nd:YVO4, or Nd:YLF is directed to the workpiece (12) with high speed precision using a compound beam positioner. The optical system produces a Gaussian spot size, or top hat beam profile, of about 10 microns. The pulse energy used for high-speed ablative processing of semiconductors using this focused spot size is greater than 200 μJ per pulse at pulse repetition frequencies greater than 5 kHz and preferably above 15 kHz. The laser pulsewidth measured at the full width half-maximum points is preferably less than 80 ns.

Owner:ELECTRO SCI IND INC

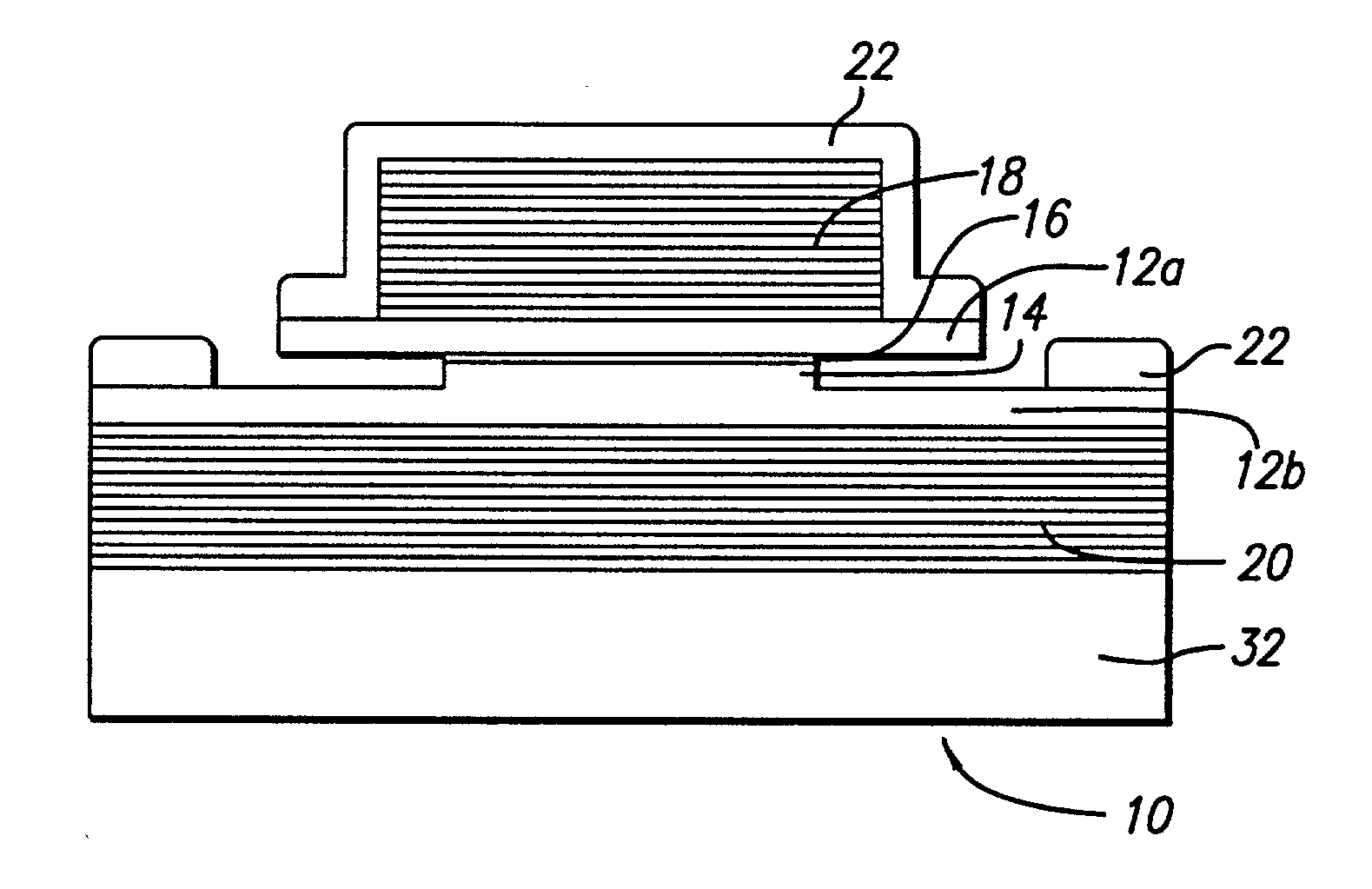

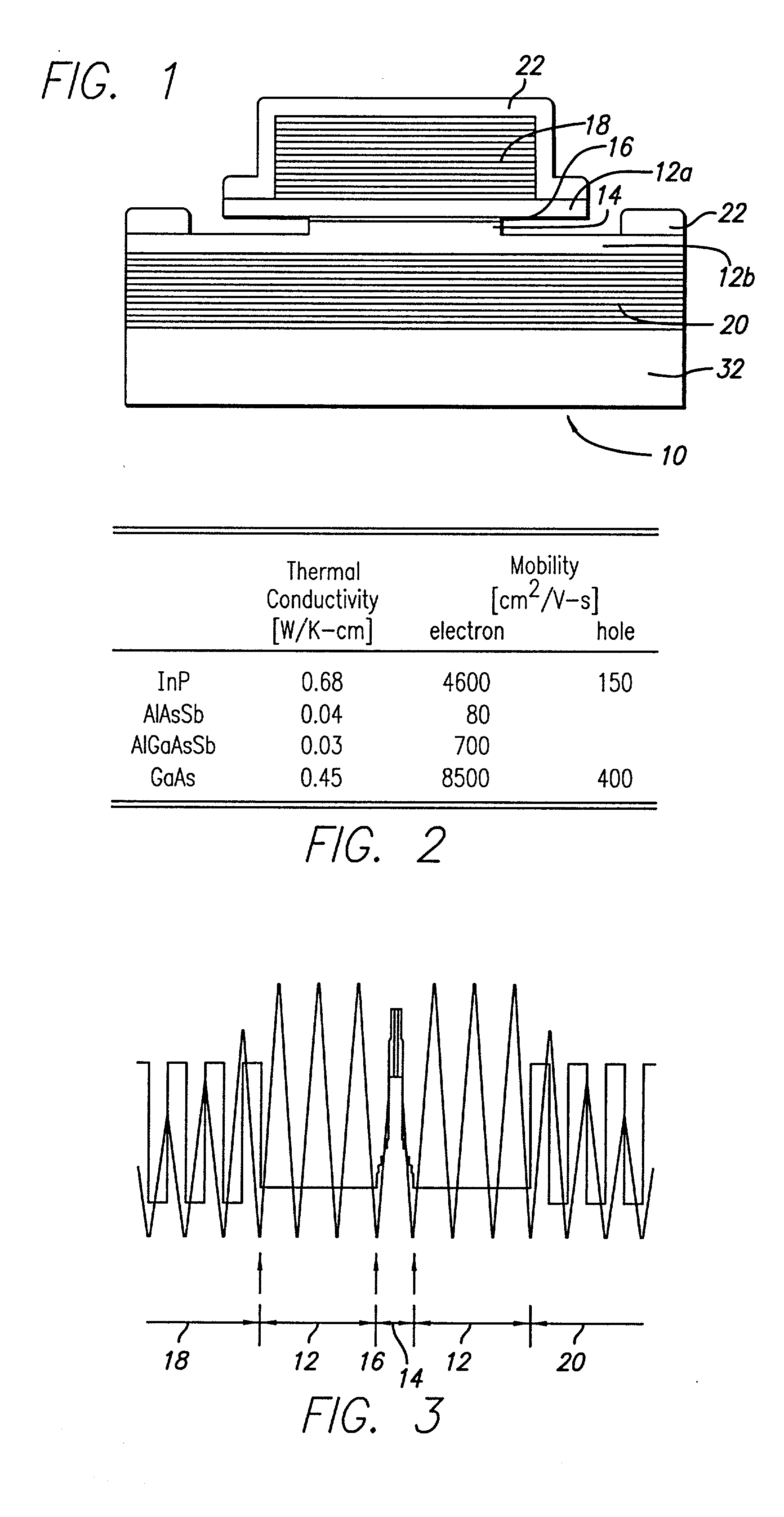

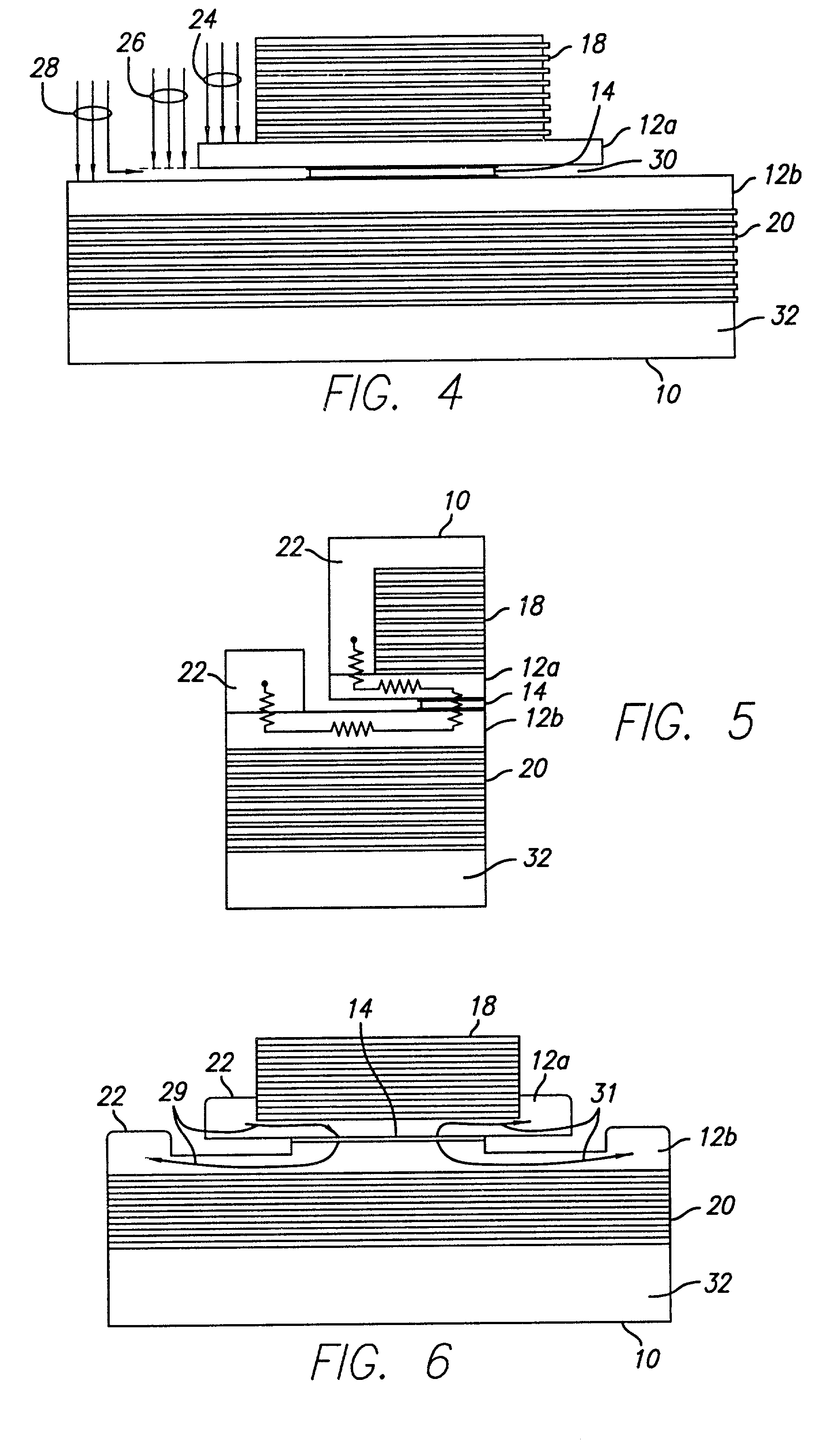

Contact scheme for intracavity-contacted vertical-cavity surface-emitting laser

InactiveUS20020071464A1Improve featuresTotal current dropLaser active region structureRussian swingsVertical-cavity surface-emitting laserTunnel junction

A vertical cavity surface emitting laser (VCSEL) includes a semiconductor device having a pair of mirror portions, an active region, a tunnel junction, a pair of cladding layers and a substrate. Heat generated by the VCSEL dissipates through the cladding layers, which utilize an indium phosphide material. The VCSEL also includes selective etches that are used to aperture the active region to allow electric current to be injected into the active region.

Owner:RGT UNIV OF CALIFORNIA

Method and circuit for encoding multi-level pulse amplitude modulated signals using integrated optoelectronic devices

ActiveUS8238014B2Electromagnetic transmissionNon-linear opticsMach–Zehnder interferometerEngineering

Methods and systems for encoding multi-level pulse amplitude modulated signals using integrated optoelectronics are disclosed and may include generating a multi-level, amplitude-modulated optical signal utilizing an optical modulator driven by two or more electrical input signals. The optical modulator may include optical modulator elements coupled in series and configured into groups. The number of optical modular elements and groups may configure the number of levels in the multi-level amplitude modulated optical signal. Unit drivers may be coupled to each of the groups. The electrical input signals may be synchronized before communicating them to the unit drivers utilizing flip-flops. Phase addition may be synchronized utilizing one or more electrical delay lines. The optical modulator may be integrated on a single substrate, which may include one of: silicon, gallium arsenide, germanium, indium gallium arsenide, polymers, or indium phosphide. The optical modulator may include a Mach-Zehnder interferometer or one or more ring modulators.

Owner:CISCO TECH INC

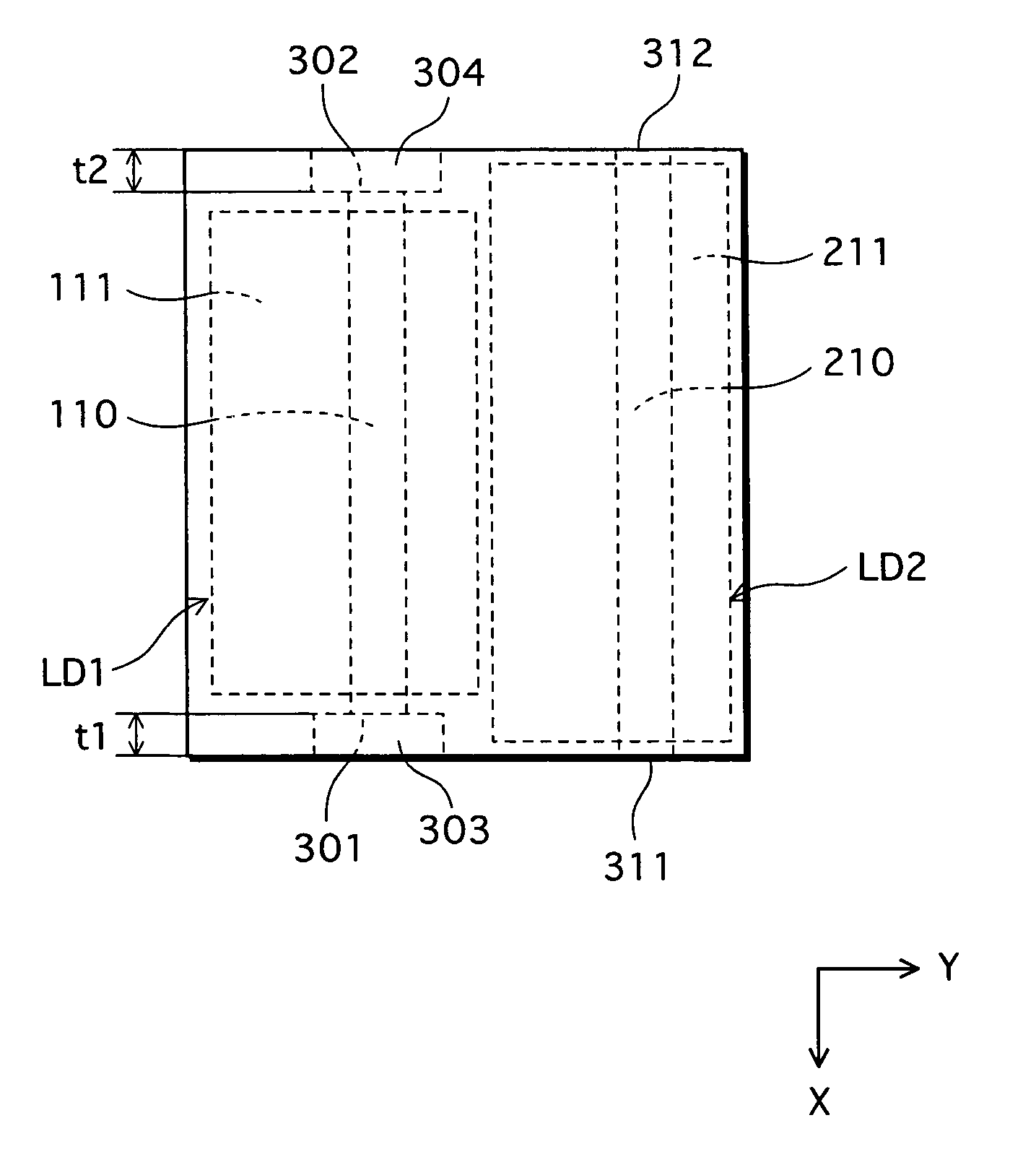

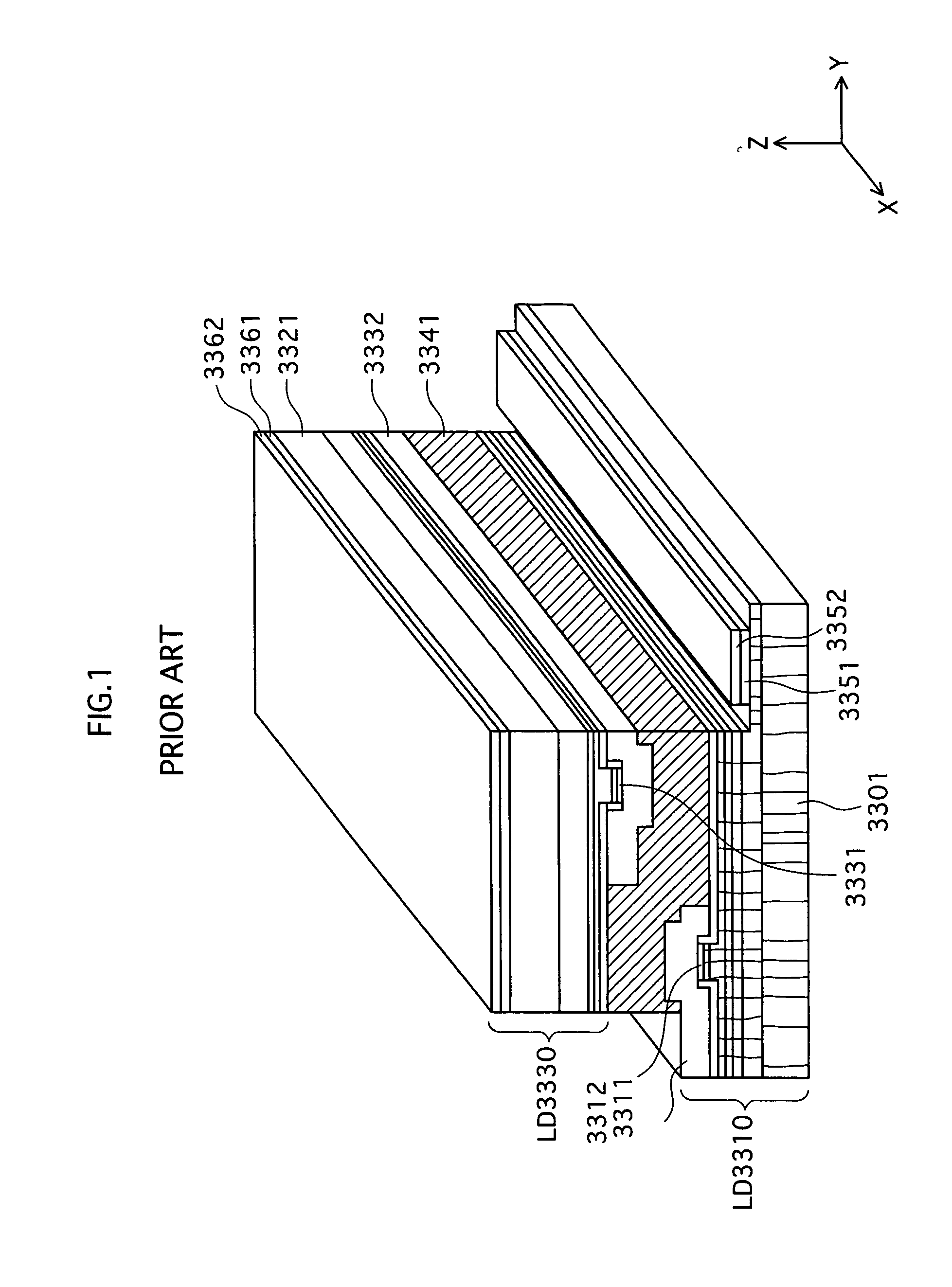

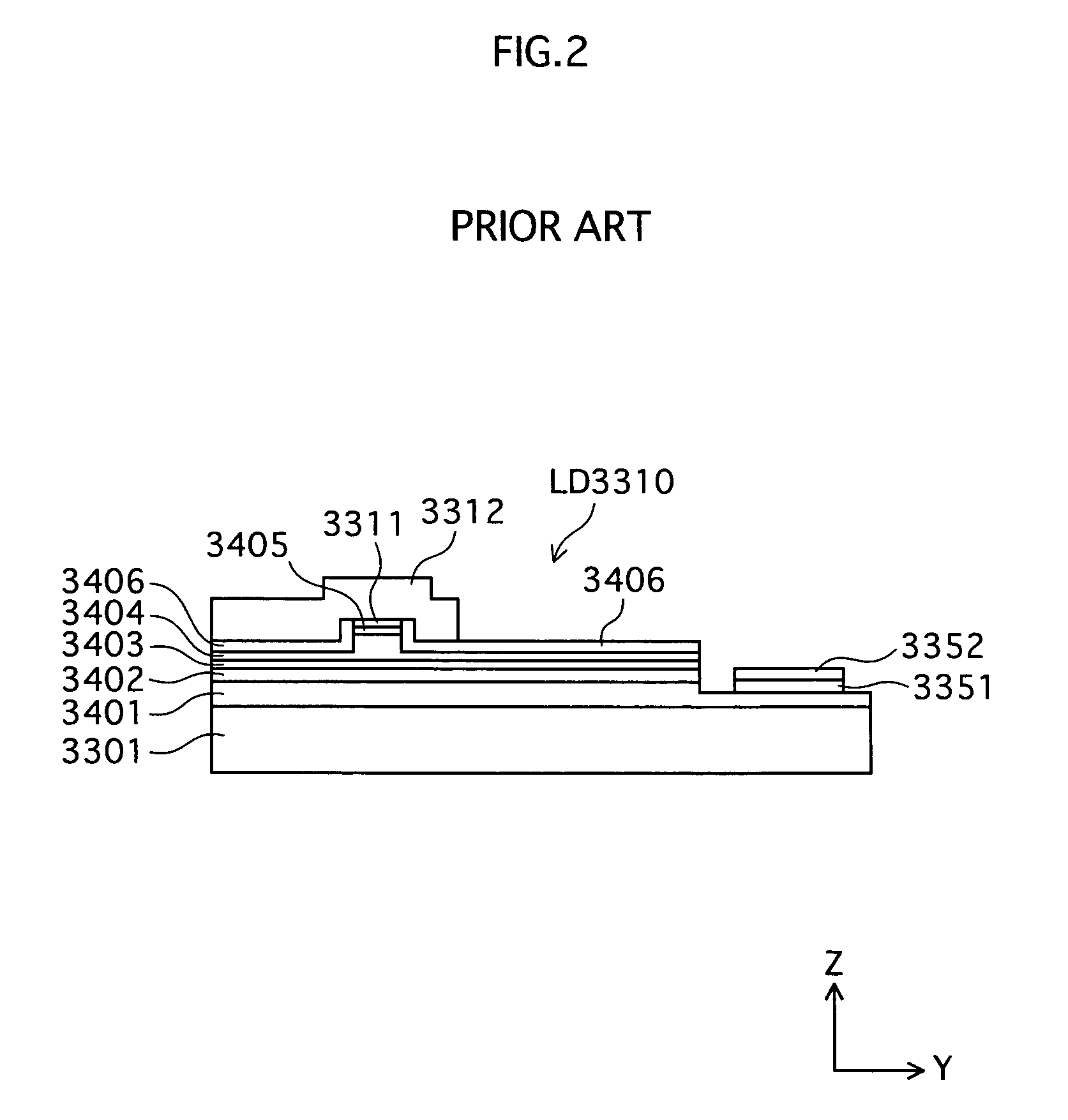

Integrated semiconductor laser diode module and manufacturing method of the same

InactiveUS20050232327A1Improve production yieldSuppression of distortionOptical wave guidanceLaser optical resonator constructionSemiconductor structureAluminium gallium indium phosphide

Improving the lifetime of an integrated semiconductor laser diode module into which a GaN semiconductor laser diode and a GaP semiconductor laser diode are integrated, and the lasing properties of the laser diodes. Prior to a joining step of an LD 1 wafer that is made of a nitride semiconductor structure formed on a GaN substrate and an LD 2 wafer that is made of an aluminum gallium indium phosphide semiconductor structure, a facet of a resonator of the nitride semiconductor structure is formed by etching A facet of a resonator of the aluminum gallium indium phosphide semiconductor structure is formed, after the joining step, by cleaving. The wafers are joined so that the facets of the resonators of the nitride semiconductor structure and aluminum gallium indium phosphide semiconductor structure are out of alignment in a lengthwise direction of the resonators.

Owner:SANYO ELECTRIC CO LTD

Nanocrystal doped matrixes

ActiveUS20100140551A1Good miscibilityInhibit aggregationMaterial nanotechnologyLiquid surface applicatorsAnti-reflective coatingSemiconductor nanocrystals

Matrixes doped with semiconductor nanocrystals are provided. In certain embodiments, the semiconductor nanocrystals have a size and composition such that they absorb or emit light at particular wavelengths. The nanocrystals can comprise ligands that allow for mixing with various matrix materials, including polymers, such that a minimal portion of light is scattered by the matrixes. The matrixes of the present invention can also be utilized in refractive index matching applications. In other embodiments, semiconductor nanocrystals are embedded within matrixes to form a nanocrystal density gradient, thereby creating an effective refractive index gradient. The matrixes of the present invention can also be used as filters and antireflective coatings on optical devices and as down-converting layers. Processes for producing matrixes comprising semiconductor nanocrystals are also provided. Nanostructures having high quantum efficiency, small size, and / or a narrow size distribution are also described, as are methods of producing indium phosphide nanostructures and core-shell nanostructures with Group II-VI shells.

Owner:SAMSUNG ELECTRONICS CO LTD

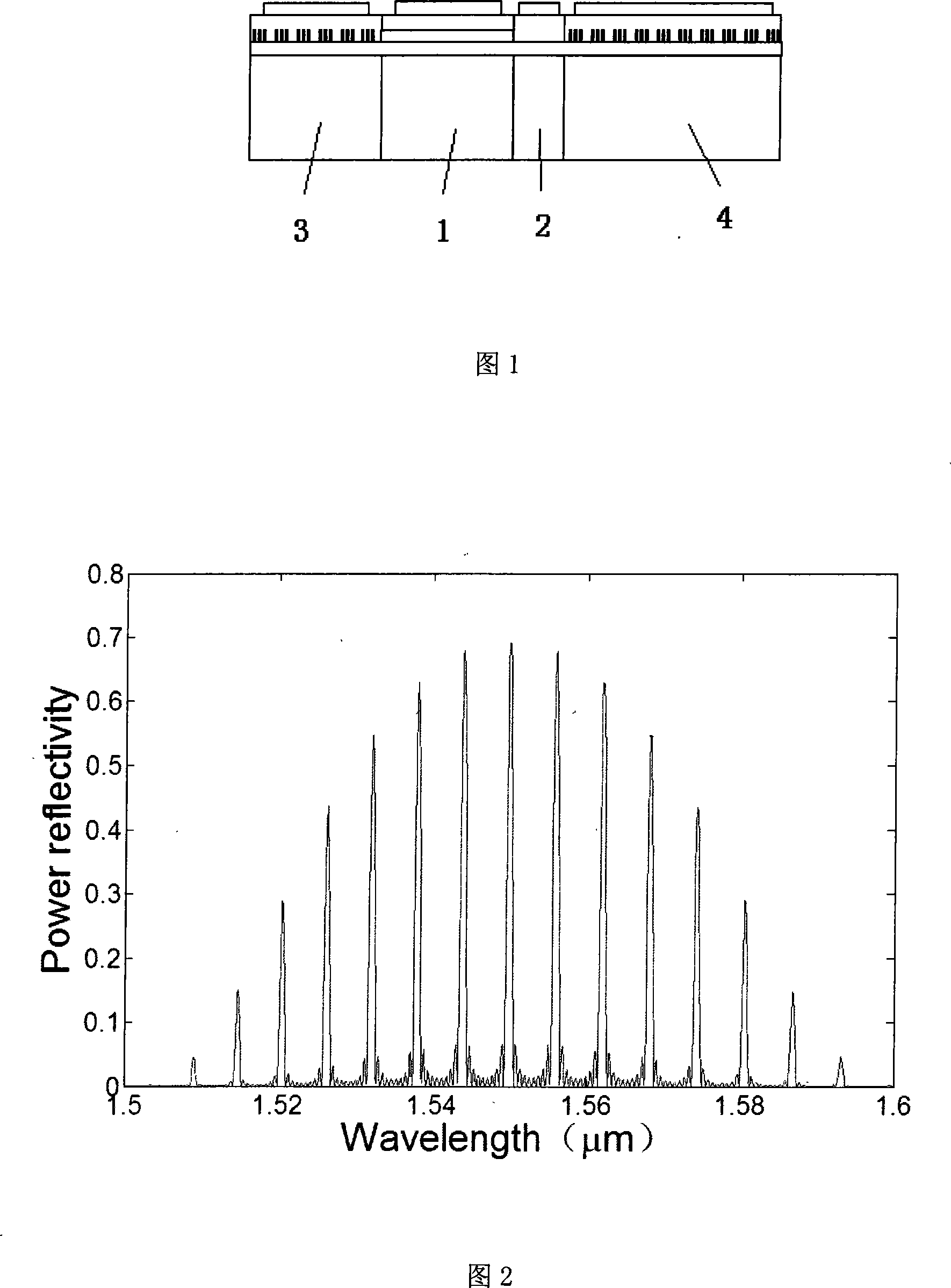

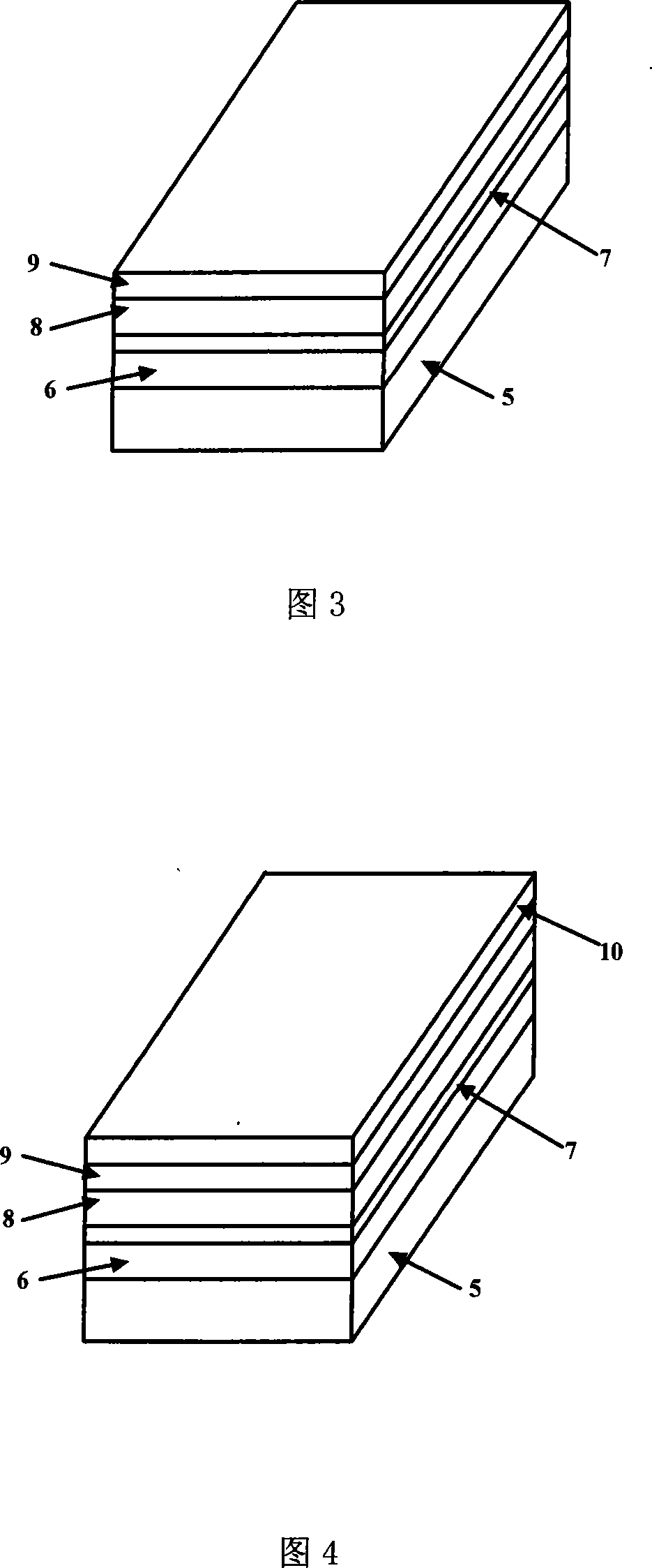

Manufacturing method of tunable semiconductor laser and tunable semiconductor laser

ActiveCN101227061AIncrease investmentShorten the development cycleOptical wave guidanceLaser detailsGratingWaveguide

Provided is a making method of a tunable semiconductor laser and a tunable semiconductor laser, wherein the making method comprises the following procedures: growing lower waveguide layer, multiple quantum trap structure, upper waveguide layer and indium phosphide layer epitaxially and sequentially on the n type substrate; growing earth silicon dielectric membrane on the epitaxial layer; dividing into active waveguide region and raster region; butting passive waveguide portion; removing earth silicon dielectric membrane and indium phosphide layer on the surface of the active waveguide region; growing ridge waveguide indium phosphide material and low resistivity InGaAs ternary layer sequentially; growing earth silicon dielectric membrane; making raster graphic of the ridge waveguide and the ridge waveguide on the raster region; etching raster of the ridge waveguide and the ridge waveguide on the raster region; growing earth silicon dielectric membrane continuously; opening the window separately on active waveguide region and raster region in order to make electrode isolation ditch; making P face and N face electrode of laser. The invention has good product property and high automation degree of the product making, which simplifies the technology process and has good product ratio.

Owner:GUANGXUN SCI & TECH WUHAN

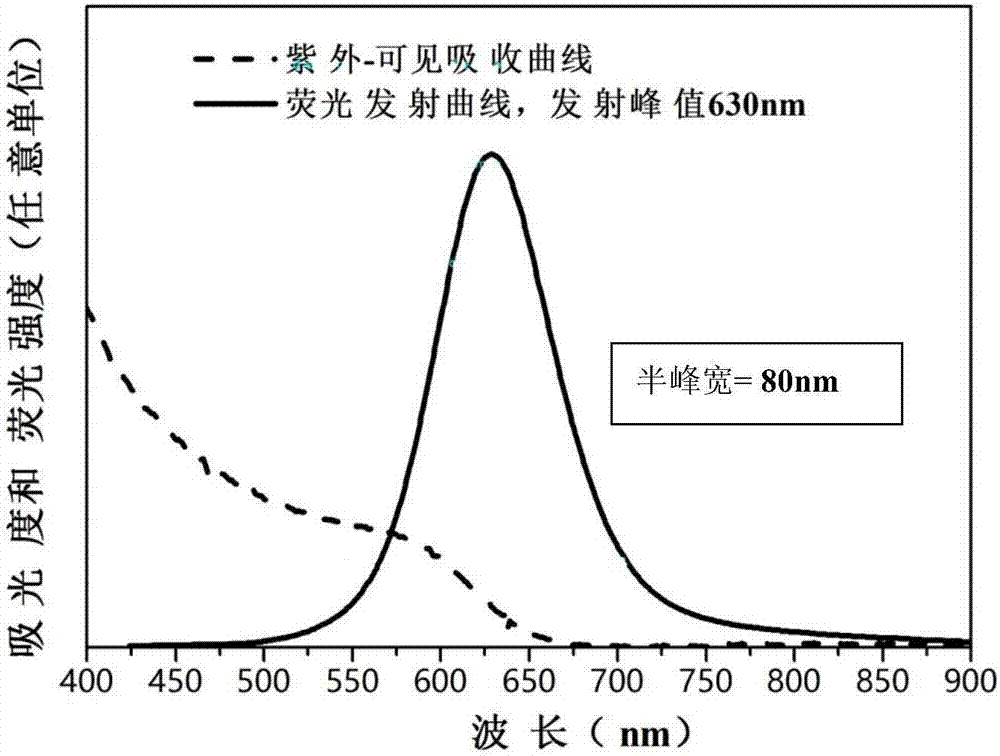

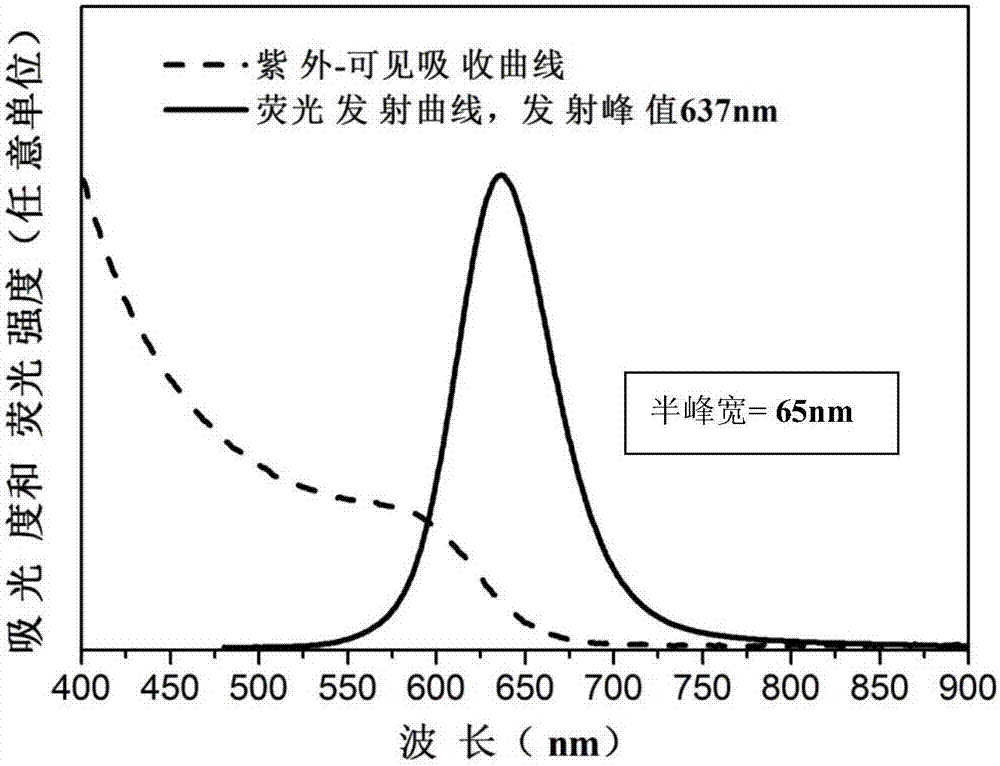

Preparation method of indium phosphide quantum dots

InactiveCN107098324AUniform size distributionGood optical performanceLuminescent compositionsPhosphidesIndiumSurface oxidation

The invention provides a preparation method of indium phosphide quantum dots. The preparation method comprises the following steps: firstly mixing an indium precursor, an acid ligand and a non-coordinating solvent and preparing a uniform indium precursor solution; then adding hydrogen phosphide at a temperature of 100-130 DEG C, raising the temperature to a second temperature and keeping for a period of time; finally regulating the solution to a third temperature and adding a precursor substance required by a synthetic shell to obtain the shell-coated indium phosphide quantum dots. The indium phosphide quantum dots with nuclear shell structures are synthesized by adopting the method of low-temperature nucleating, raised temperature-curing and high-temperature shell-coating; the nucleation and growth processes of indium phosphide nano crystalline nucleuses can be controlled at a low temperature, so that the synthesized quantum dots are uniform in size distribution; meanwhile, the risk of surface oxidation of the indium phosphide nano crystalline nucleuses can also be effectively avoided at a low temperature, so that the optical performance of the indium phosphide quantum dots are improved to a certain degree.

Owner:SUZHOU XINGSHUO NANOTECH CO LTD

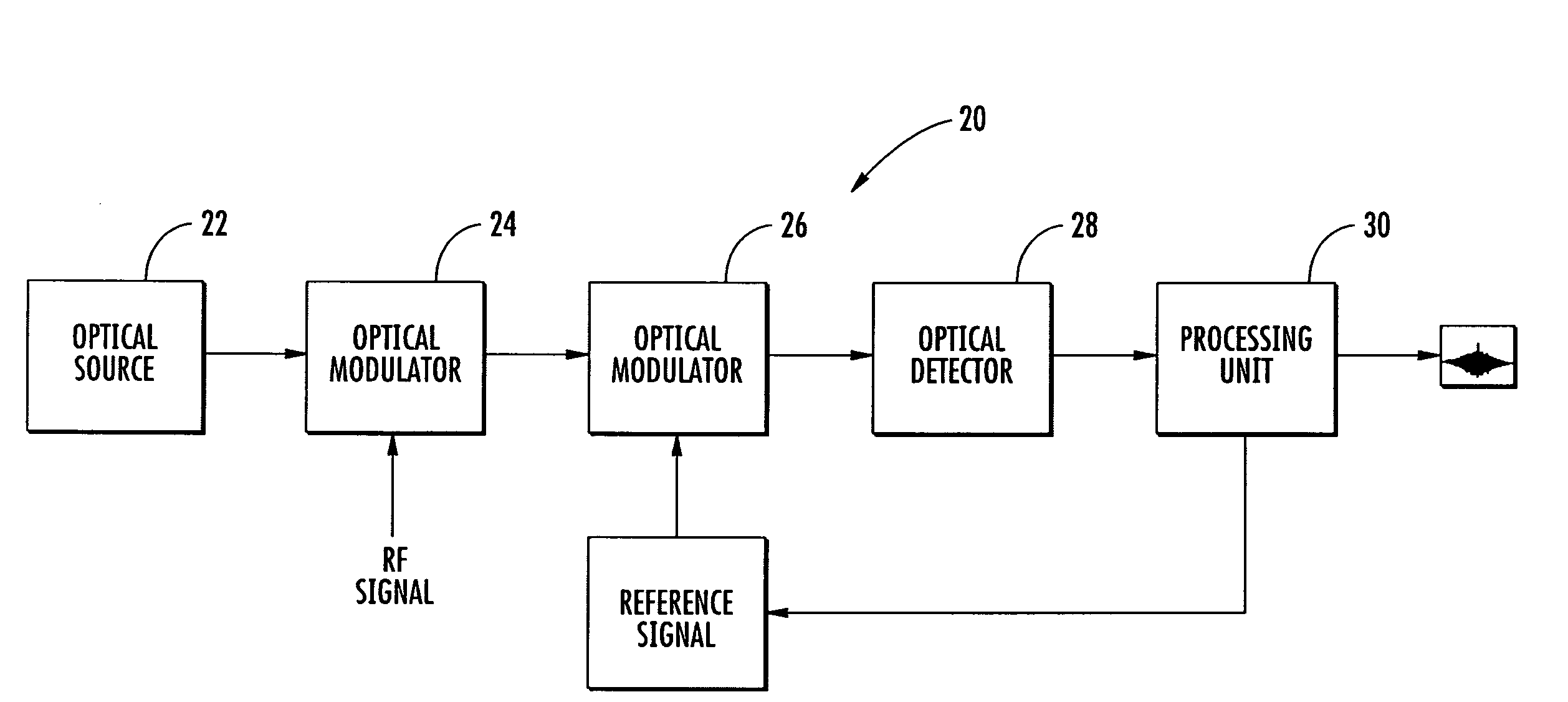

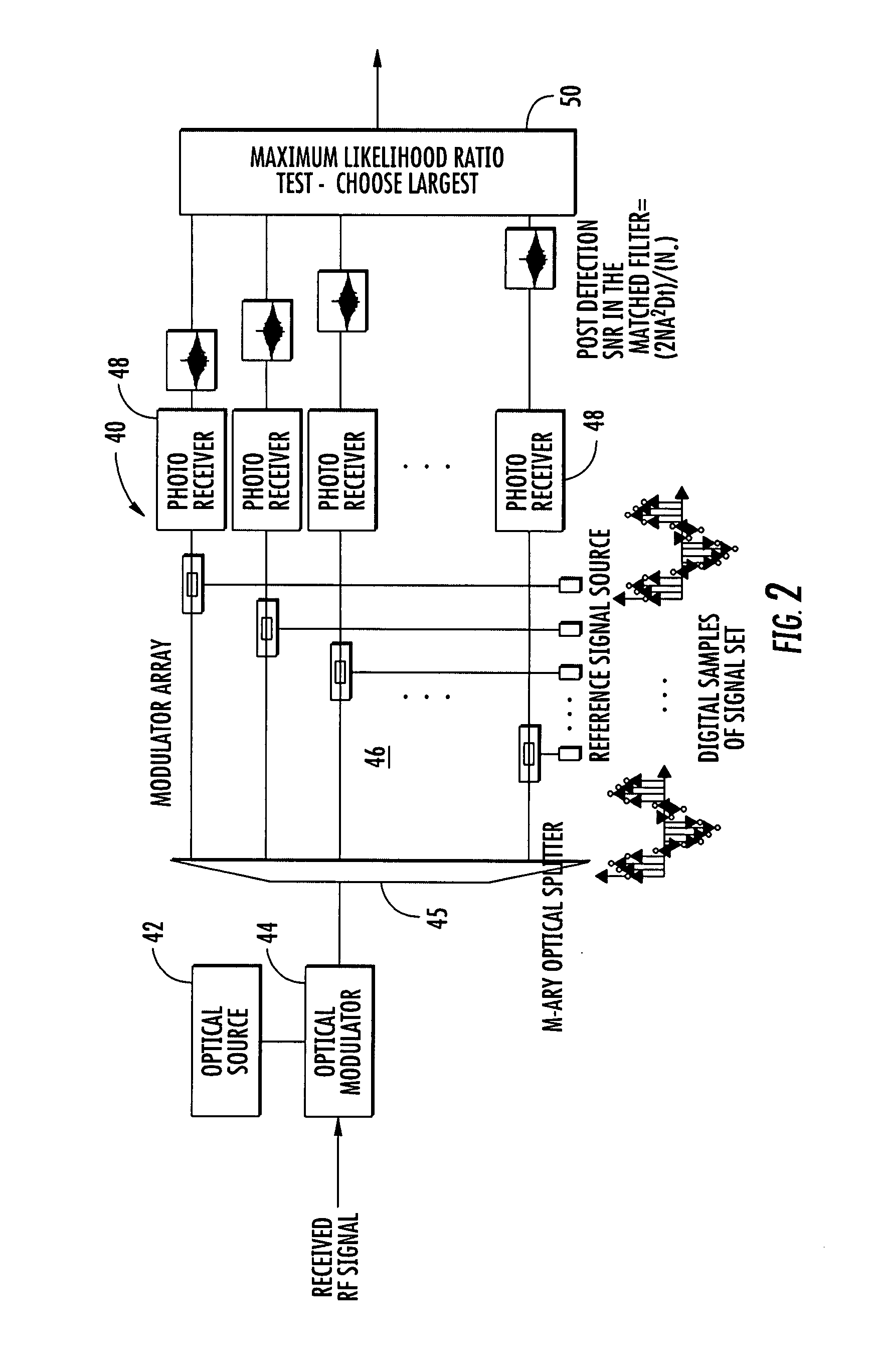

Radio frequency (RF) signal receiver using optical processing and associated methods

ActiveUS20070280704A1Reduced sampling rate requirementsIncrease data rateAmplitude-modulated carrier systemsAmplitude demodulationOptical processingRadio frequency

A signal receiver, such as an RF-matched filter receiver, includes an optical source (e.g. a mode-locked laser) providing an optical signal, and a first optical modulator to modulate the optical signal with a received RF signal and provide a modulated optical signal. A second optical modulator modulates the modulated optical signal with a reference signal and provides a twice modulated optical signal. The modulators may be Mach-Zehnder Modulators (MZM) and / or Indium Phosphide (InP) modulators. An optical detector receives the twice modulated optical signal and provides a detected signal, and a processing unit receives the detected signal and extracts or measures cross-correlation between the received RF signal and the reference signal.

Owner:ALCATEL LUCENT SAS +2

Indium phosphide colloidal nanocrystals

InactiveUS20120205586A1High crystallinityNarrow size distributionPolycrystalline material growthLiquid surface applicatorsSemiconductor nanocrystalsSolvent

A method of making a colloidal solution of indium phosphide semiconductor nanocrystals, includes forming a first solution by combining solvents and ligands; and heating the first solution to a temperature equal to or higher than 290° C. and, while heating, adding to the first solution, a second solution containing trialkylindium, a phosphorus precursor and solvents and ligands so that a reaction takes place that forms a colloidal solution of indium phosphide semiconductor nanocrystals. The method further includes forming core shell indium phosphide semiconductor nanocrystals by forming semiconducting shells on the nanocrystals.

Owner:EASTMAN KODAK CO

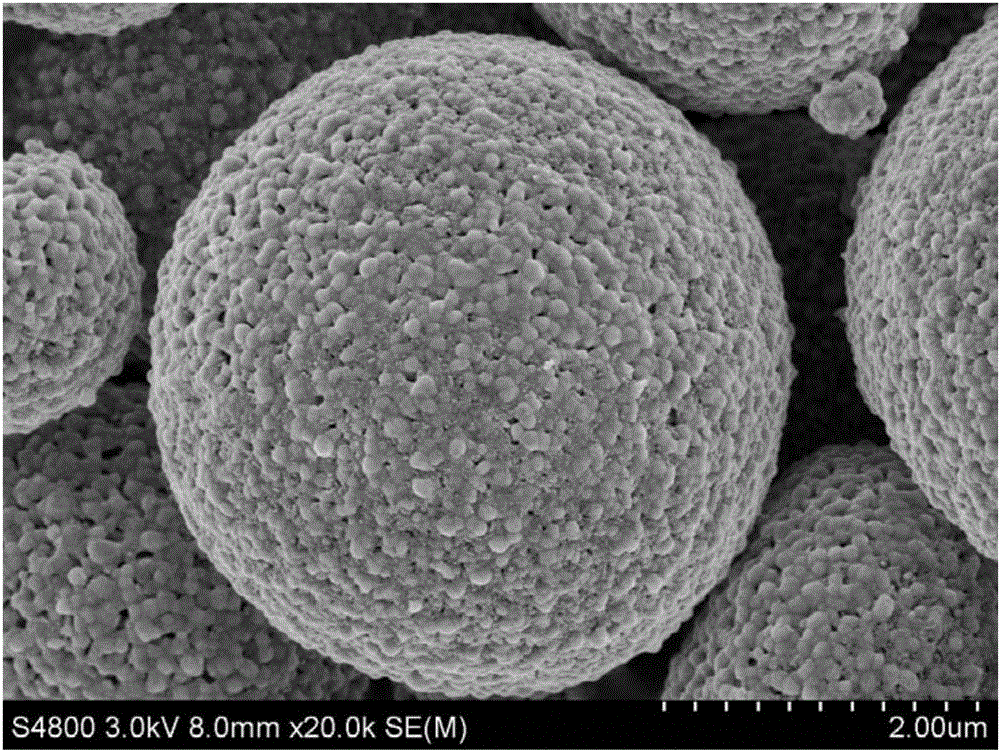

High density spherical nano lithium iron phosphate material, a preparation method thereof, and lithium ion battery containing same

ActiveCN106229505ATightly boundImprove liquidityCell electrodesSecondary cellsSodium-ion batteryLithium-ion battery

A high density spherical nano lithium iron phosphate material, a preparation method thereof, and a lithium ion battery containing the same are provided. The preparation method comprises the following steps: (1) pre-sintering a lithium resource, iron phosphides, adulterant, and a carbon source with protective gas after dry mixing; (2) mixing a pre-sintering material, dispersant, and deionized water, and performing ultra fine grinding; (3) performing spray drying on a sizing agent obtained by ultra fine grinding, to obtain a spherical nano lithium iron phosphate precursor; and (4) performing chemical vapor deposition coating on the spherical nano lithium iron phosphate precursor obtained in step (3), to prepare the high density spherical nano lithium iron phosphate material. A primary particle size of the lithium iron phosphate material prepared in the present invention is not large, and a powder conductivity may reach 10.1 S / cm, so that a material capacity, low temperature, rate performance, and fabrication and cycling performance may be well balanced.

Owner:江苏贝特瑞纳米科技有限公司

Polishing Composition and Polishing Method Using The Same

InactiveUS20110223840A1Improve polishing ratePigmenting treatmentOther chemical processesZeta potentialIndium

Owner:FUJIMI INCORPORATED

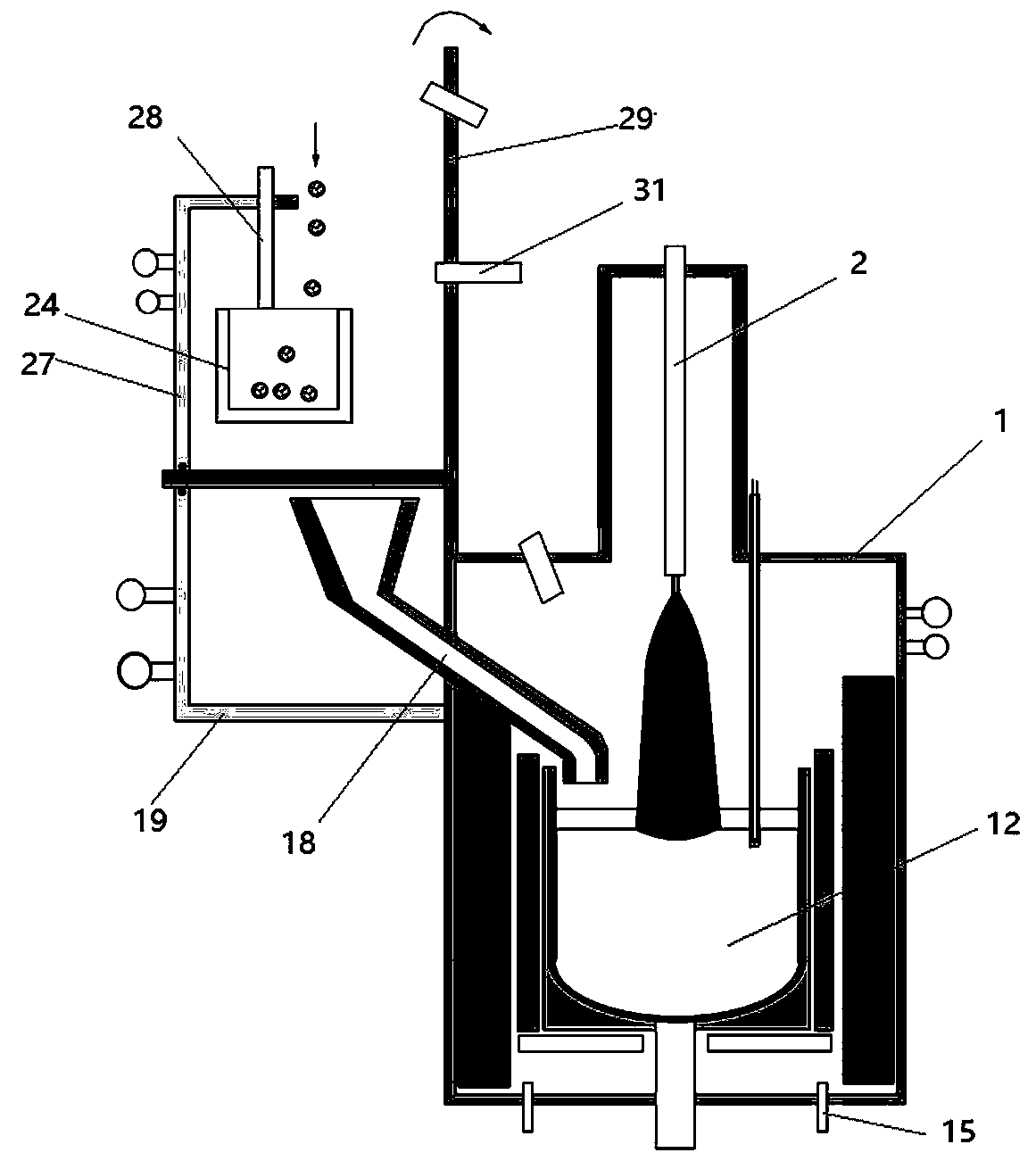

Method for manufacturing double diffusion type optical avalanche diode with incident light on back surface by adopting epitaxial equipment

The invention relates to a method for manufacturing a double diffusion type optical avalanche diode with incident light on a back surface by adopting epitaxial equipment. MOCVD epitaxial equipment is used for carrying out epitaxial treatment once on an avalanche photodiode on an indium phosphide substrate; a double diffusion method of the MOCVD epitaxial equipment is used for doping; a sputtering method is used for manufacturing a P-surface electrode; the substrate is thinned and polished; a wet corrosion method is used for manufacturing a light incidence window and an anti-reflection layer; the sputtering method is used for manufacturing a N-surface electrode; and the N-surface electrode is alloyed. By using the double diffusion method, in the diffusion process, the invention realizes gradient doping of different regions and different concentration by controlling the flow rate of a diffusion source; and an abrupt junction is formed in diffusion. The invention has good diffusion uniformity and high rate of finished products of pieces; and the manufactured avalanche photodiode with incident light on the back surface has the characteristics of small dark current, high sensitivity, small series resistance, high reliability and the like.

Owner:WUHAN HUAGONG GENUINE OPTICS TECH

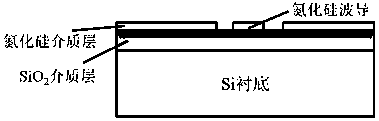

Silicon nitride optical waveguide device and graphene detector integrated chip and manufacturing method thereof

ActiveCN108231803AReconfigurable optical signal processing functionBroad light absorption wavelength rangeDiodeEnergy conversion devicesGratingElectrical bandwidth

The invention discloses a silicon nitride optical waveguide device and graphene detector integrated chip and a manufacturing method thereof. The integrated chip structurally comprises a silicon nitride vertical coupling optical grating, a silicon nitride optical waveguide device and a graphene detector, wherein the silicon nitride vertical coupling optical grating is an optical signal input port,and is connected to the silicon nitride vertical coupling optical grating; the silicon nitride optical waveguide device is used for processing an optical signal, the processed optical signal is connected and transmitted to the graphene detector, and the graphene detector is used for carrying out photovoltaic conversion on the processed optical signal. The integrated chip has the advantages that firstly, various reconfigurable optical signal processing functions can be realized by designing the silicon nitride optical waveguide device with different structure; secondly, compared with a traditional indium phosphide based detector, the graphene detector has boarder optical absorption wavelength range and wider electrical bandwidth; and thirdly, the device is simple in structure, and an optical signal processing function unit and a chip of on-chip monolithic integration can be realized.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Grid design for iii-v compound semiconductor cell

InactiveUS20120285519A1Final product manufacturePhotovoltaic energy generationEngineeringGrid design

A photovoltaic solar cell for producing energy from the sun including a germanium substrate including a first photoactive junction and forming a bottom solar subcell; a gallium arsenide middle cell disposed on said substrate; an indium gallium phosphide top cell disposed over the middle cell; and a surface grid including a plurality of spaced apart grid lines, wherein the grid lines have a thickness greater than 7 microns, and each grid line has a cross-section in the shape of a trapezoid with a cross-sectional area between 45 and 55 square microns.

Owner:SOLAERO TECH CORP

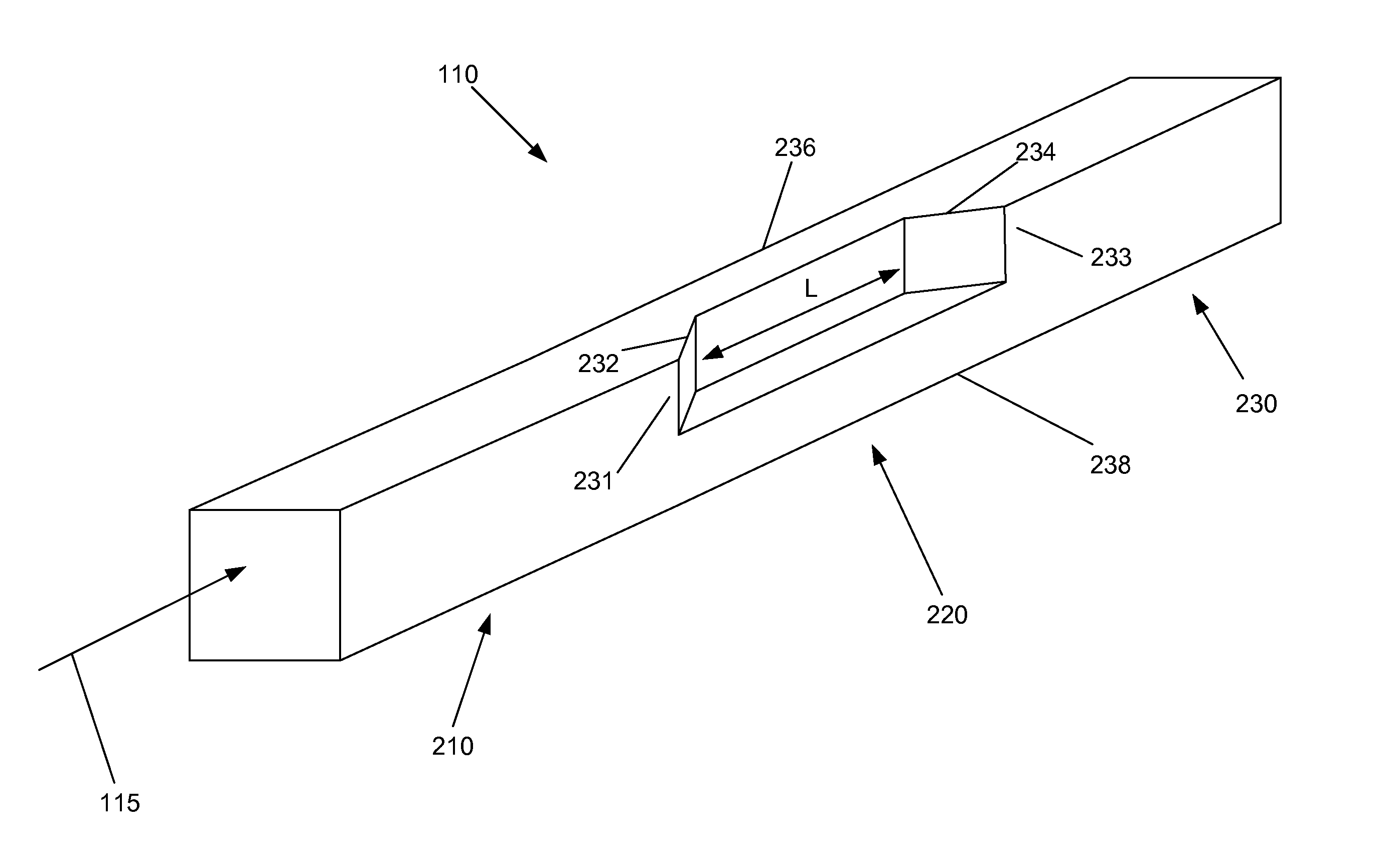

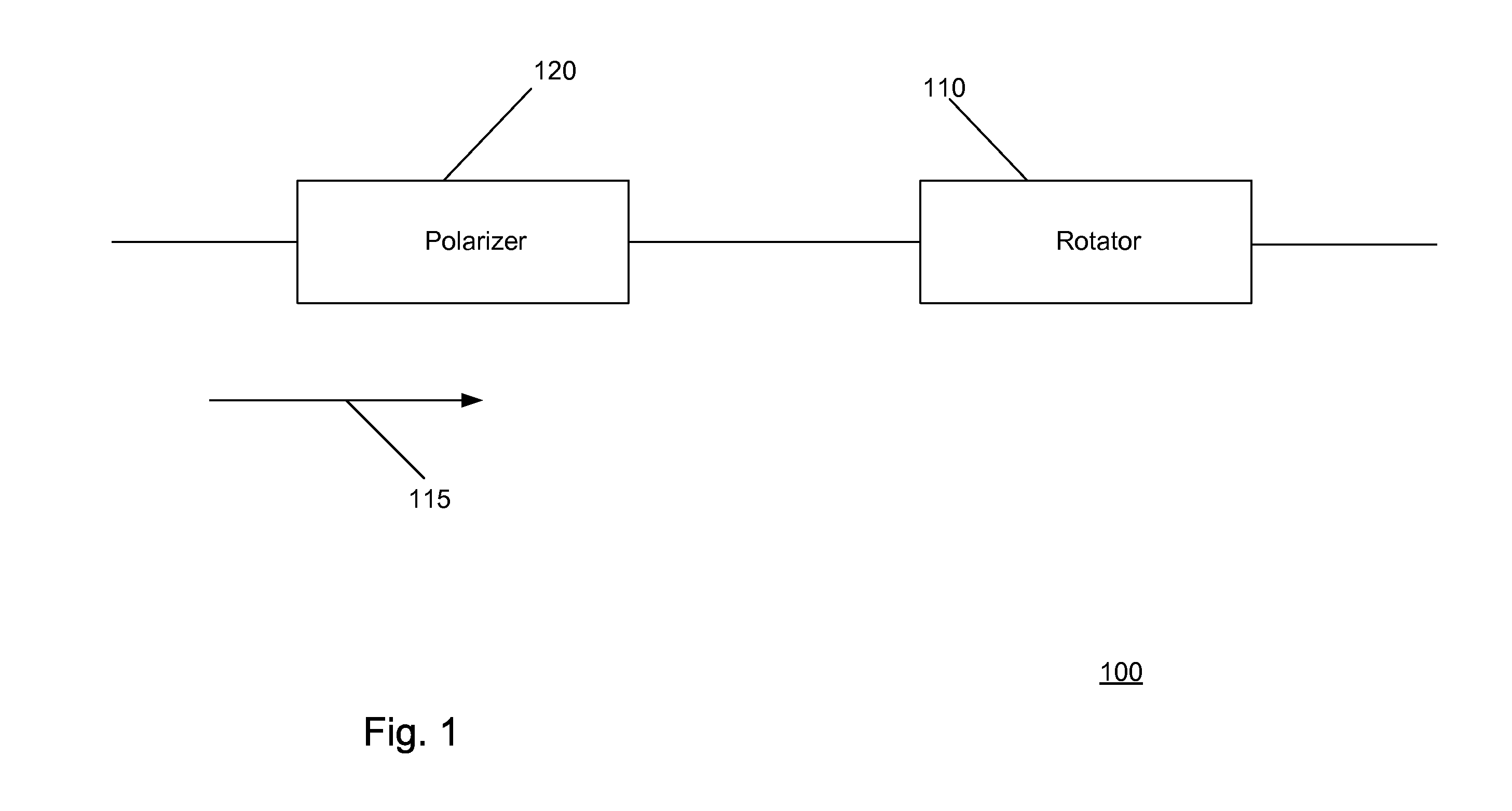

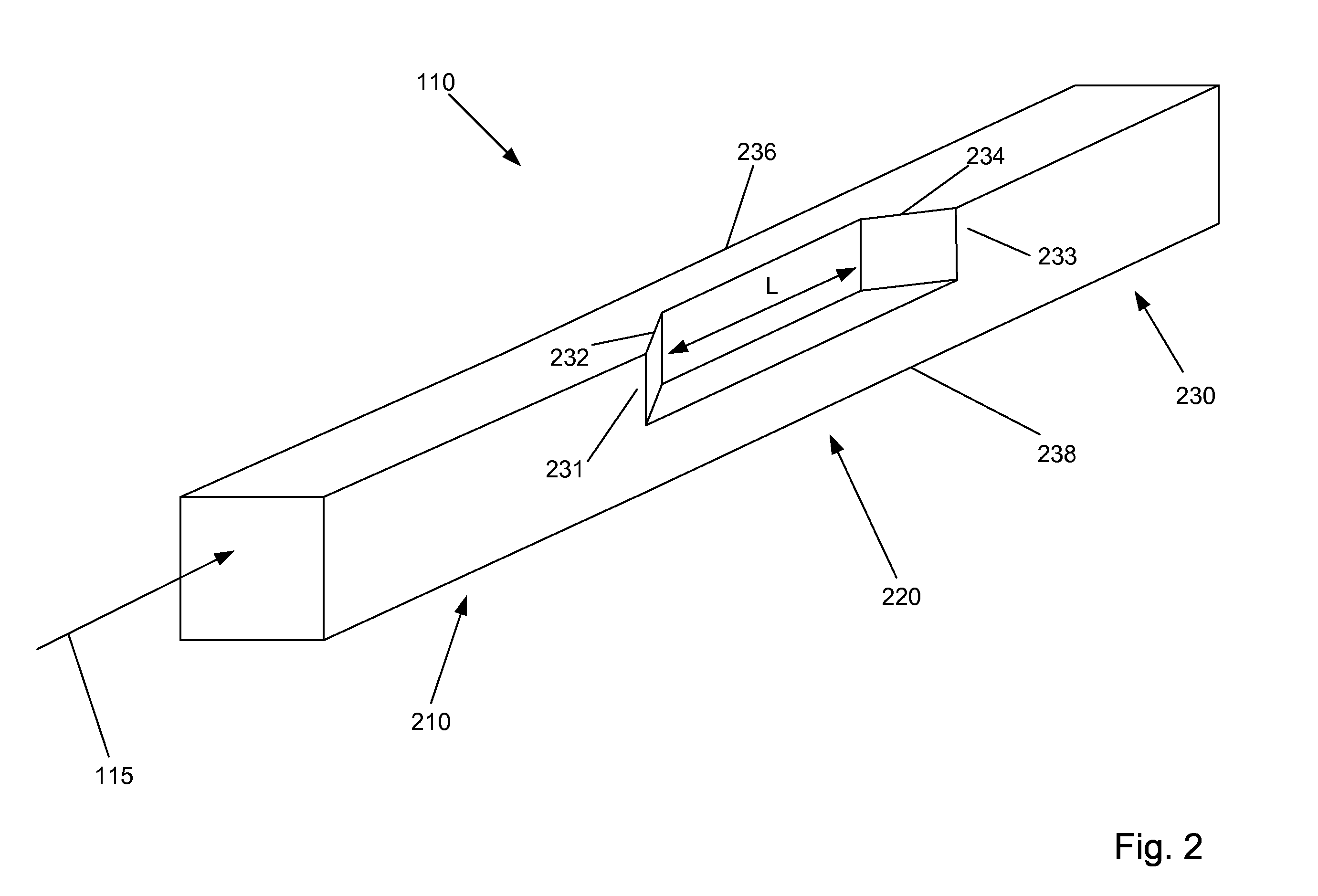

Optical integrated circuit

ActiveUS20110150384A1Coupling light guidesOptical waveguide light guideSemiconductor materialsPolarizer

Consistent with the present disclosure, a non-adiabatic polarization rotator is provided that can rotate the polarization of an incoming over a relatively short length. Light is supplied to the polarization rotator via a polarizer, which insures that the optical input to the polarization polarization rotator has a desired polarization. Preferably, the polarization rotator has a structure that is readily implemented with semiconductor materials and can be fabricated with known processing techniques. In addition, the polarization rotator and polarizer may include similar materials and / or layers, such that both may be readily integrated on a common substrate, such as an indium phosphide (InP) substrate.

Owner:INFINERA CORP

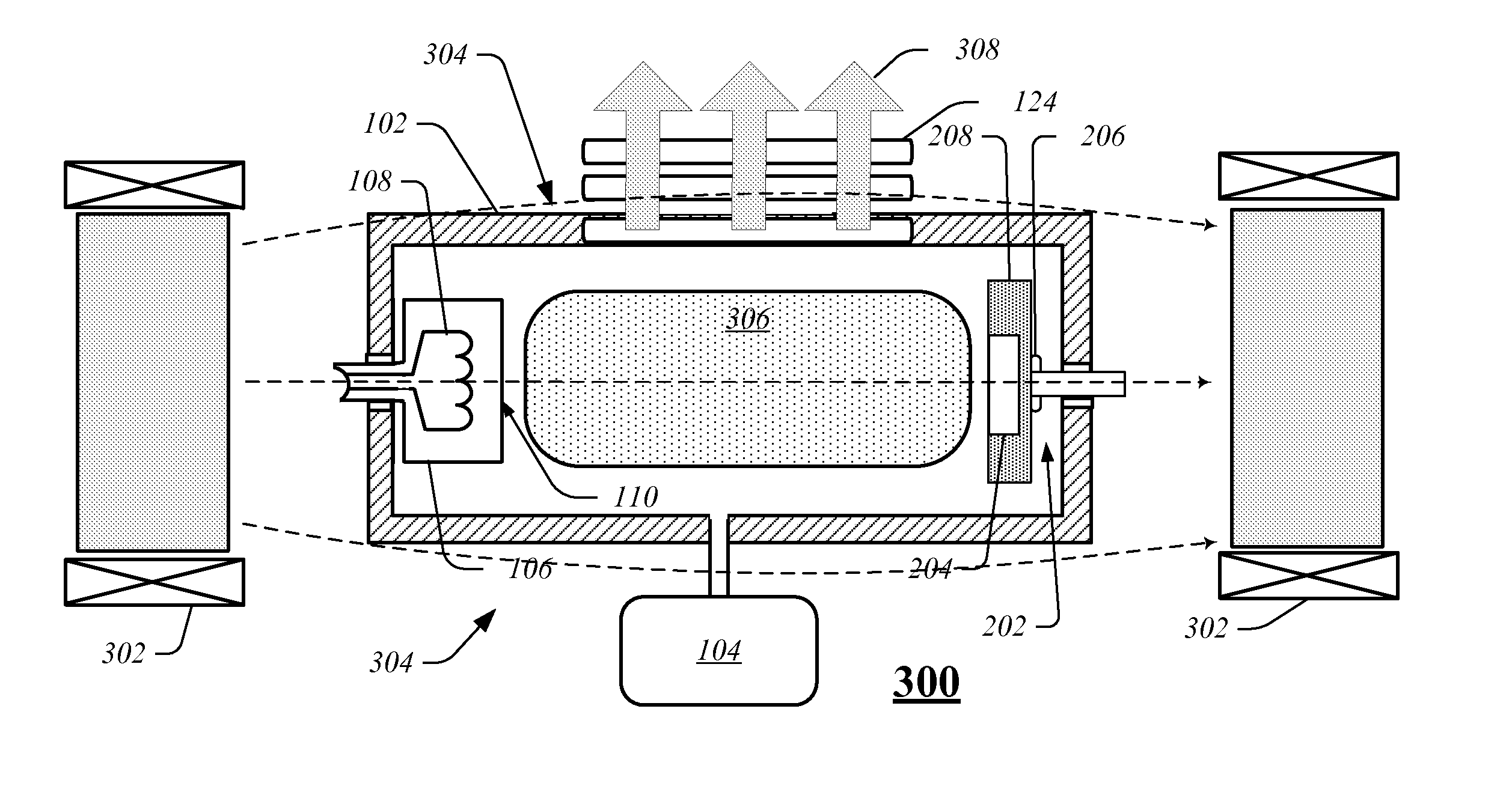

Lifetime ion source

InactiveUS20150034837A1Improve performanceMaterial analysis by optical meansIon beam tubesGas phaseAluminum phosphide

An ion source includes an ion source chamber, a gas source to provide a fluorine-containing gas species to the ion source chamber and a cathode disposed in the ion source chamber configured to emit electrons to generate a plasma within the ion source chamber. The ion source chamber and cathode are comprised of a refractory metal. A phosphide insert is disposed within the ion source chamber and presents an exposed surface area that is configured to generate gas phase phosphorous species when the plasma is present in the ion source chamber, wherein the phosphide component is one of boron phosphide, tungsten phosphide, aluminum phosphide, nickel phosphide, calcium phosphide and indium phosphide.

Owner:VARIAN SEMICON EQUIP ASSOC INC

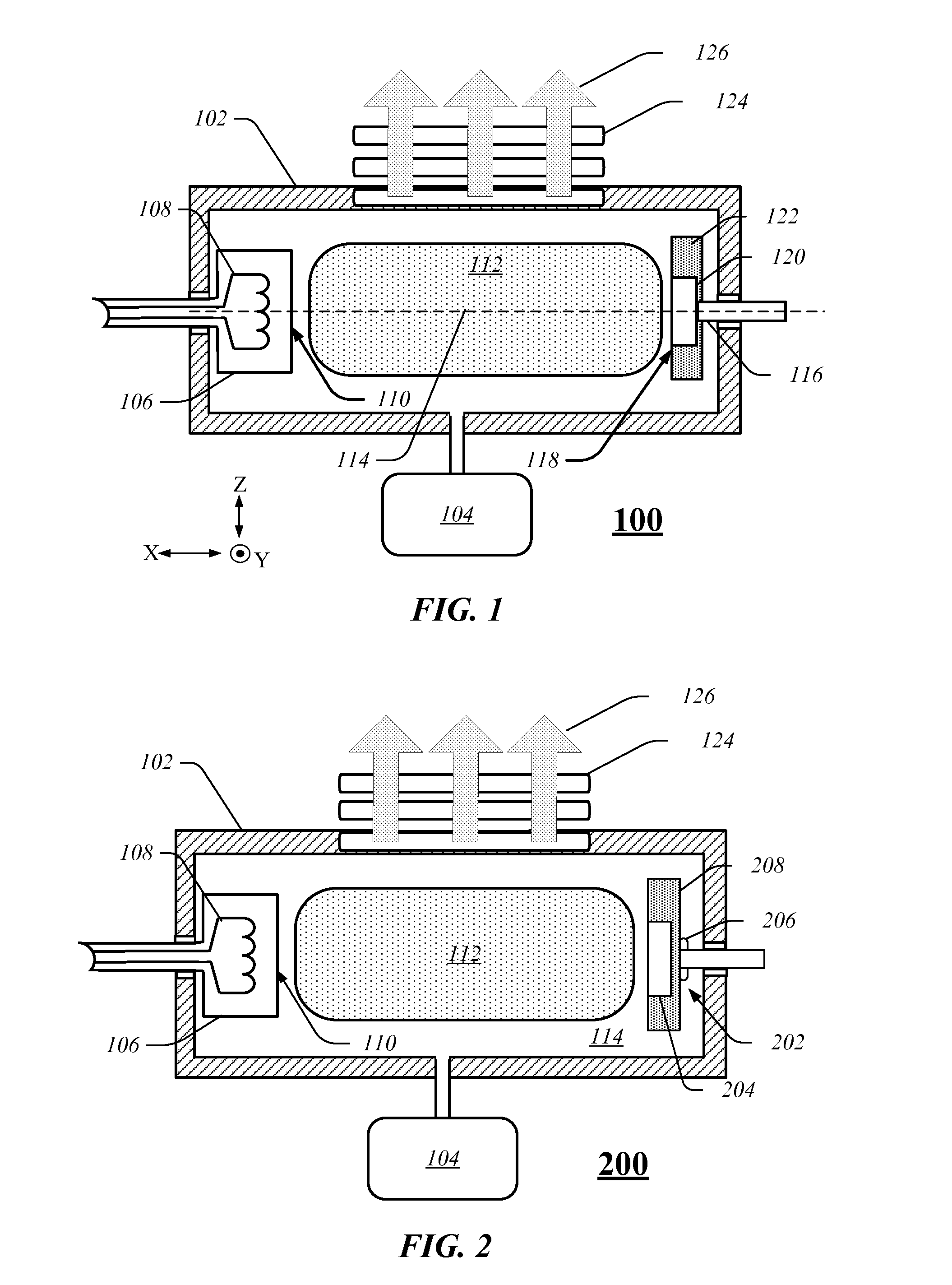

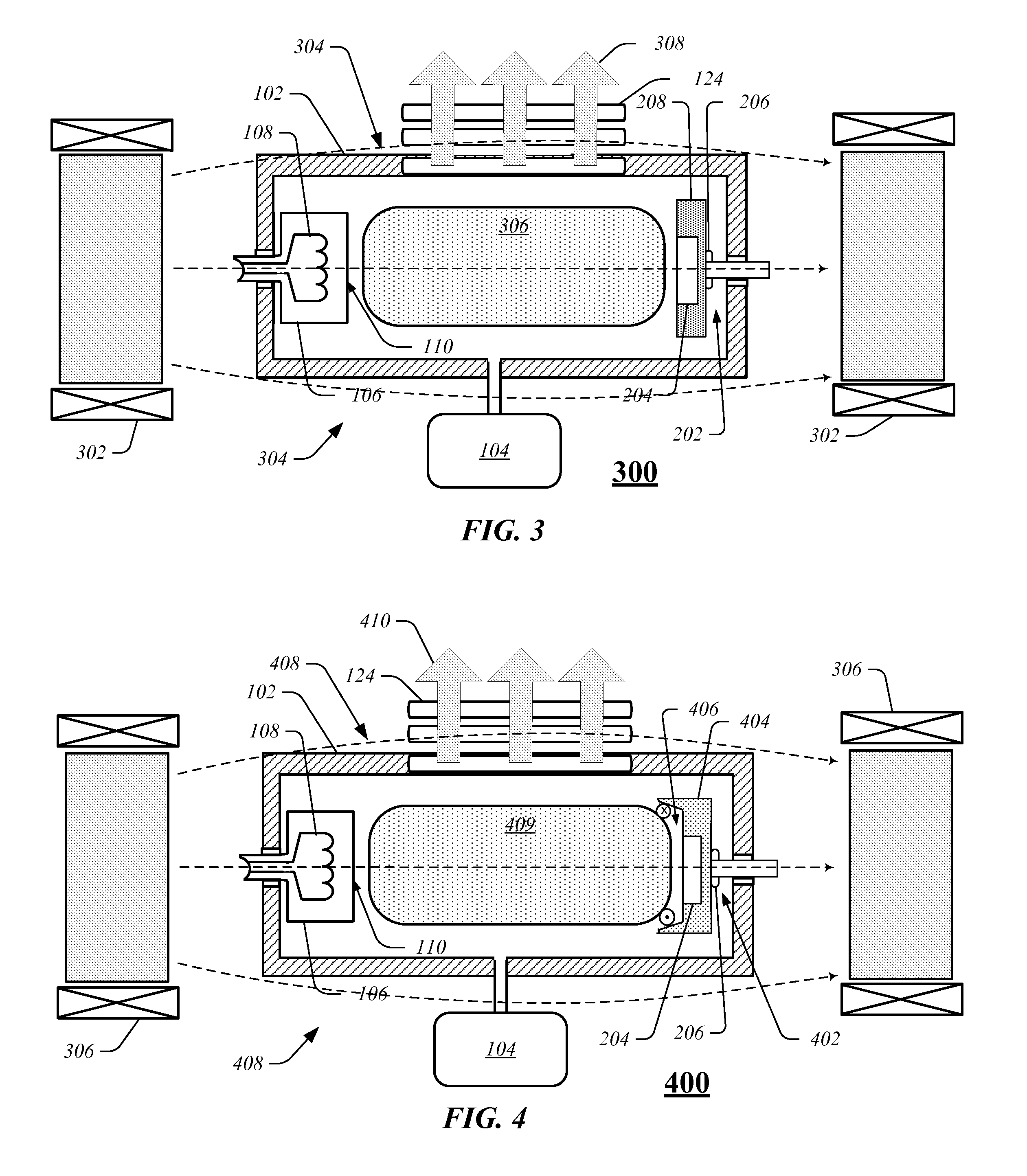

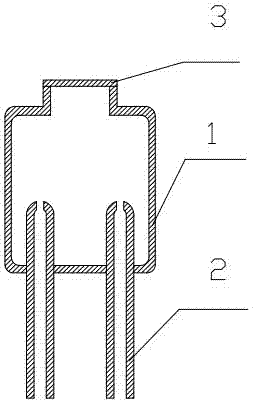

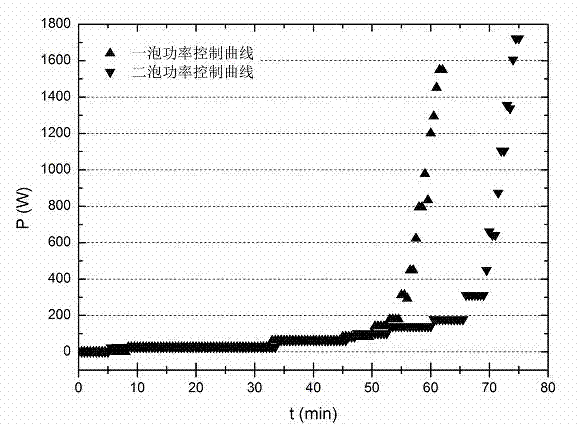

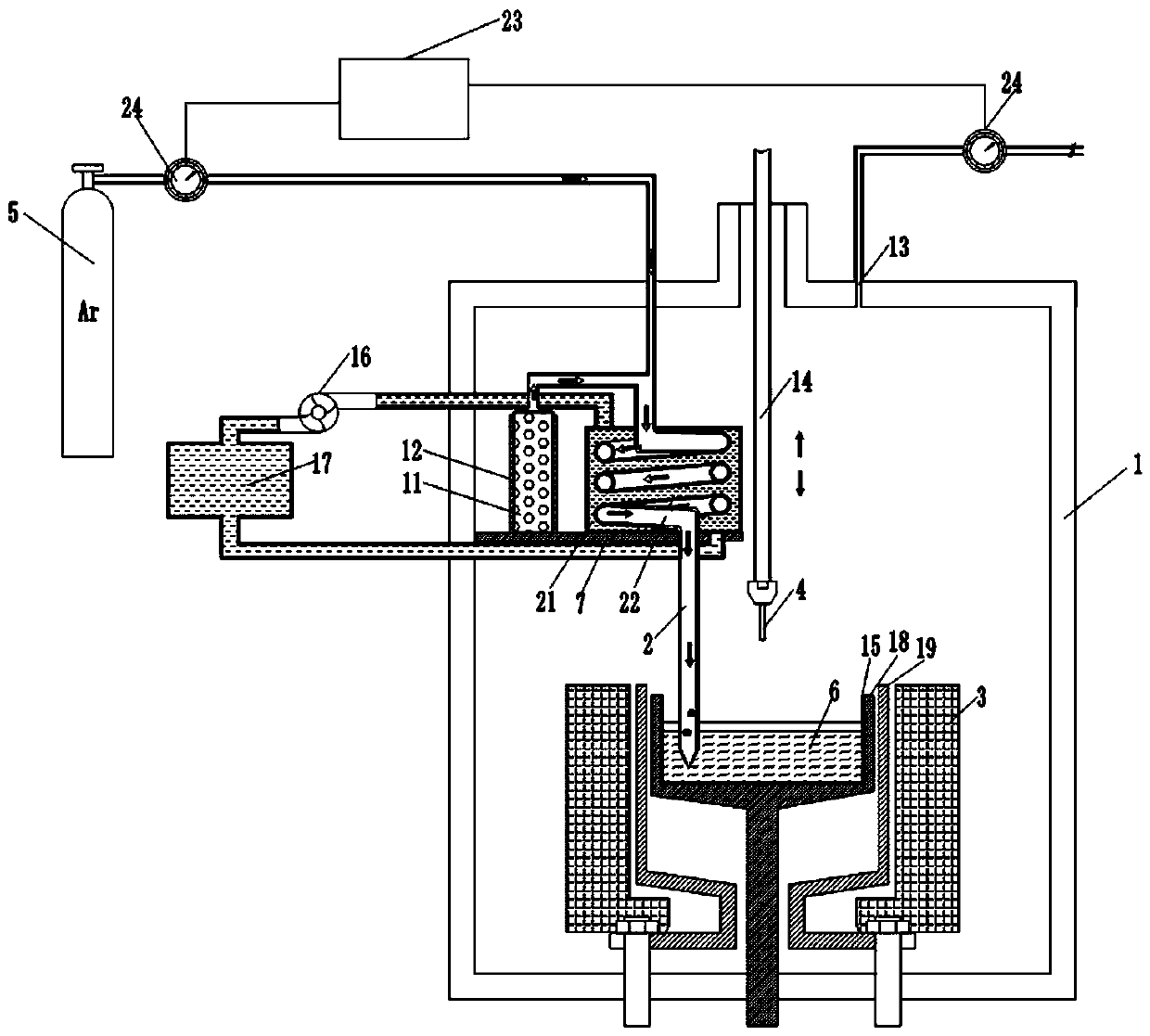

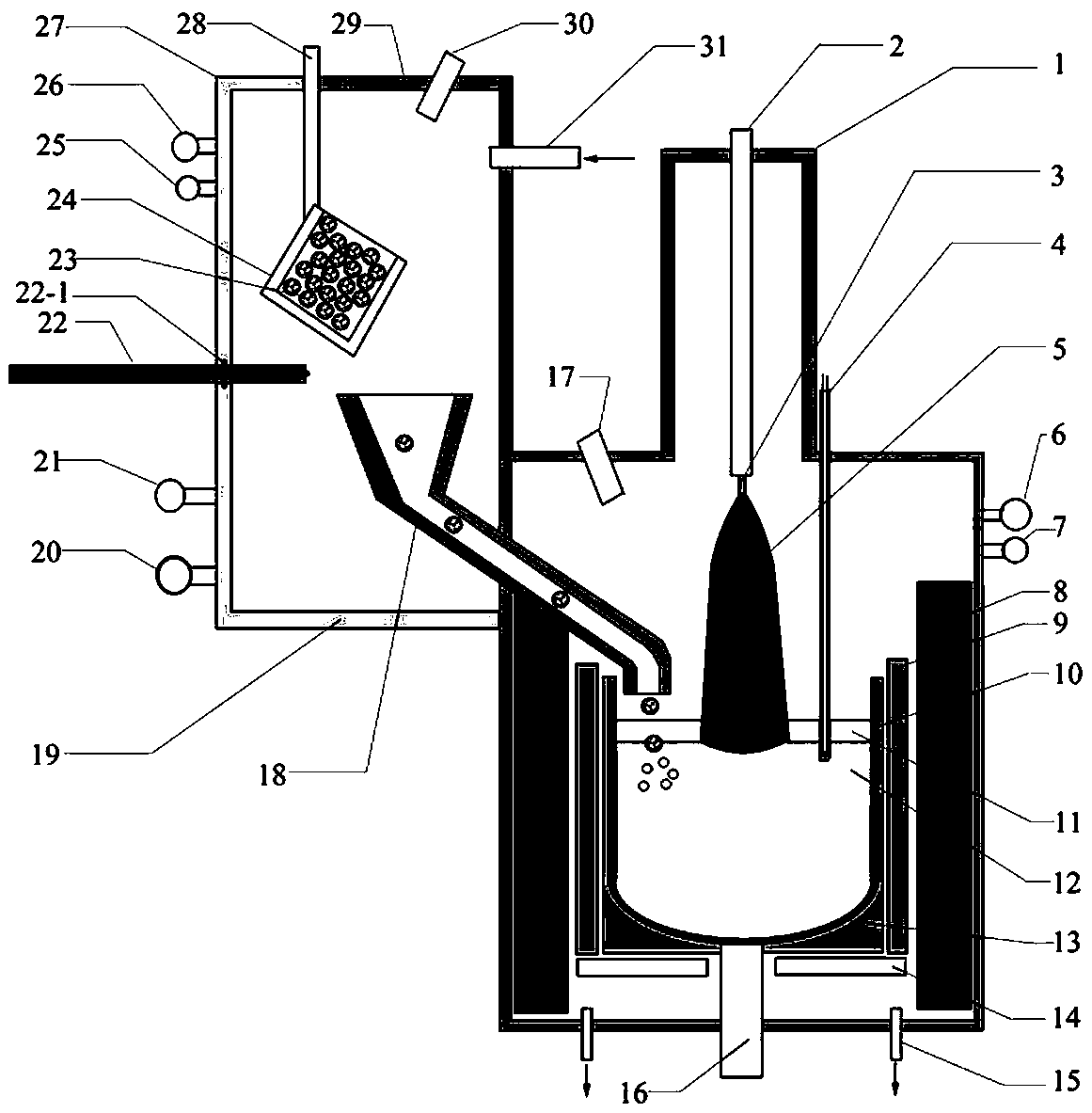

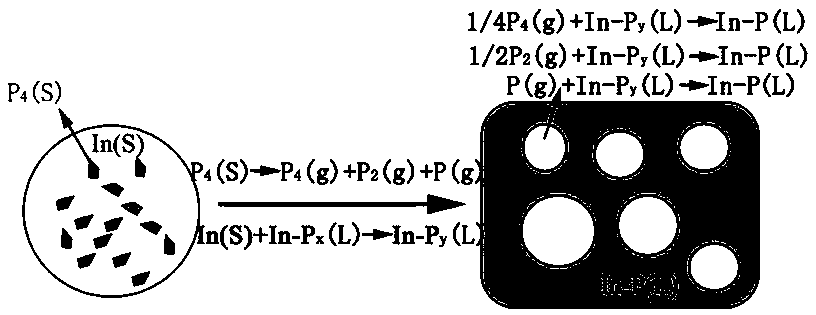

Rapid synthesis method of indium phosphide polycrystalline material and multi-tubular quartz phosphorus bubble thereof

InactiveCN102965734ASynthetic high purityContinuous growthPolycrystalline material growthSingle crystal growth detailsIndiumSynthesis methods

The invention discloses a rapid synthesis method of an indium phosphide polycrystalline material, which comprises the following steps of: (I) performing surface cleaning treatment on indium; (II) placing a multi-tubular quartz phosphorus bubble with phosphorus into a phosphorus source furnace; (III) placing the pre-designed thermal insulation system, heater, crucible with indium, phosphorus source furnace and seed crystal and B2O3 into a high-pressure single-crystal furnace hearth; (IV) vacuumizing the inside of the furnace and filling high-purity argon; (V) heating to vaporize phosphorus in the phosphorus bubble and injecting into indium melt, and reacting to generate indium phosphide; and (VI) growing crystal. The multi-tubular quartz phosphorus bubble comprises a quartz phosphorus container, at least two quartz phosphorus bubble tubes and a quartz cover. By adopting a multi-tubular quartz phosphorus bubble, the method disclosed by the invention realizes a rapid multi-tubular phosphorus injection synthesis technology, solves the problems of long synthesis time, non-uniform melt proportioning, impurity pollution and the like in the original technology, realizes rapid, efficient and high-purity synthesis of the indium phosphide material, and performs InP single crystal growth more easily.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

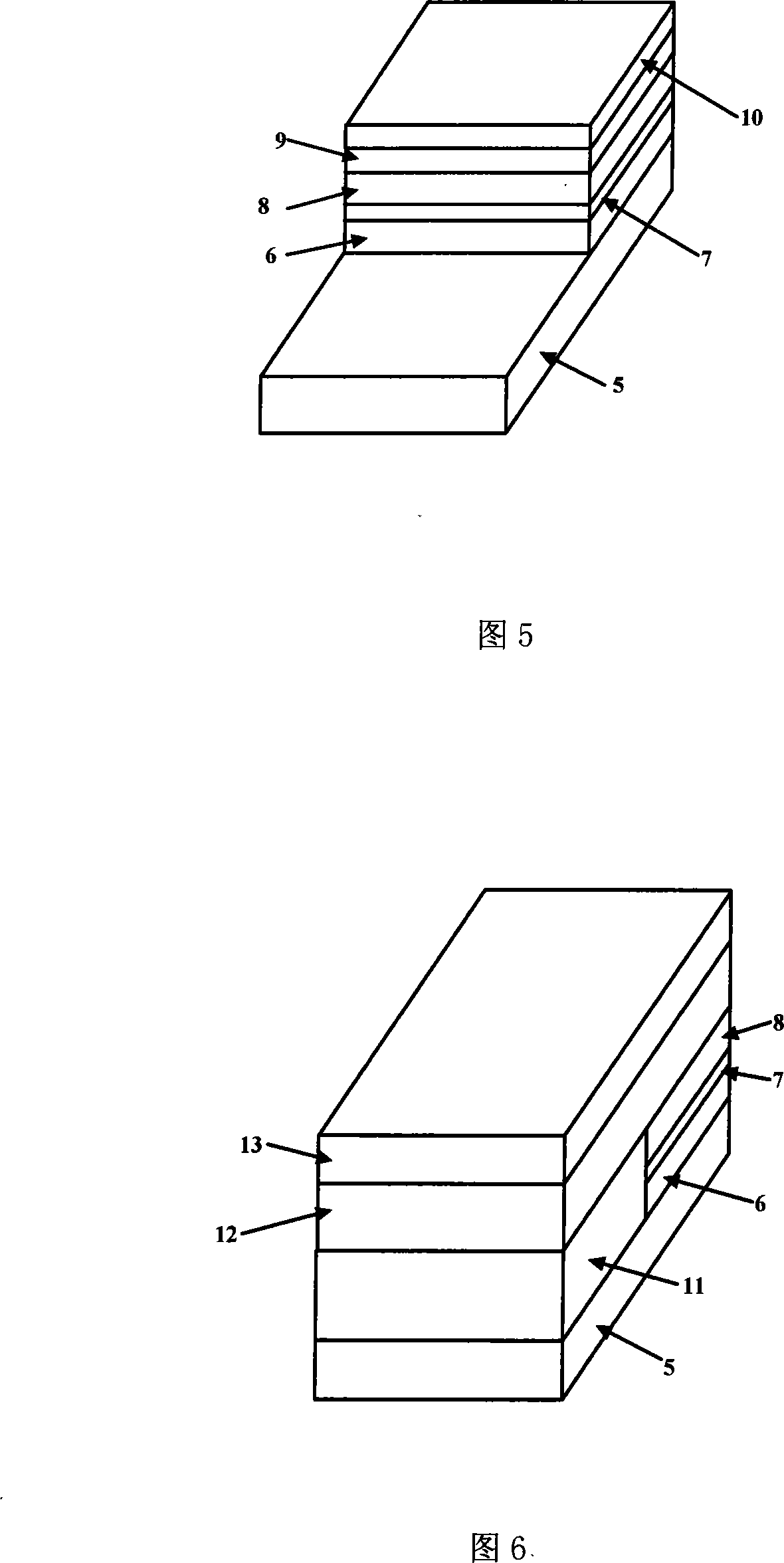

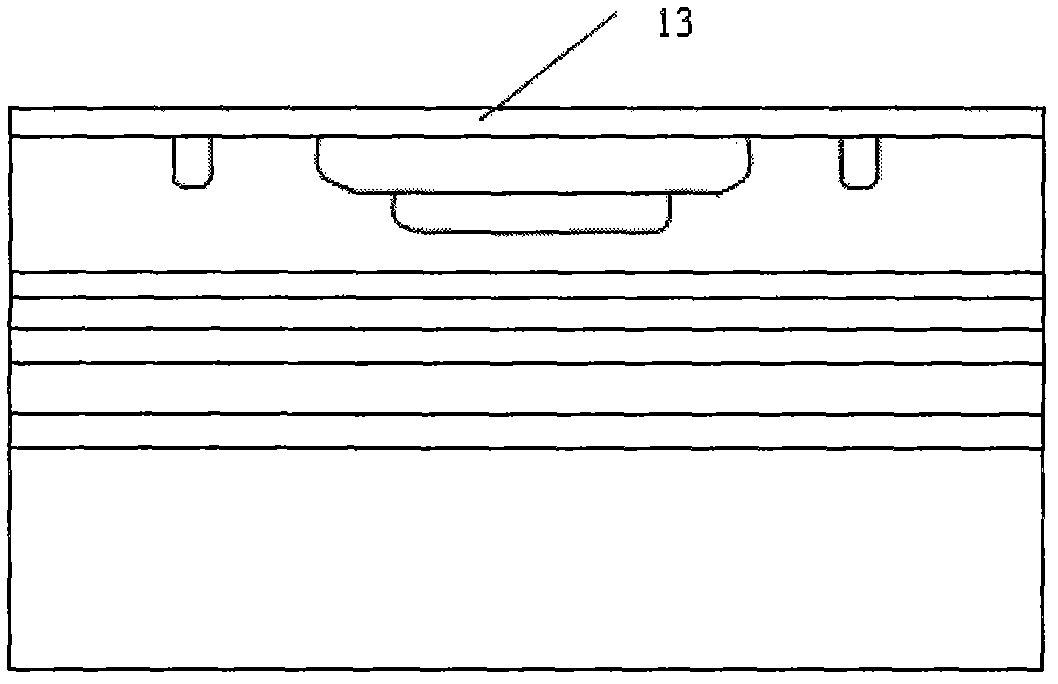

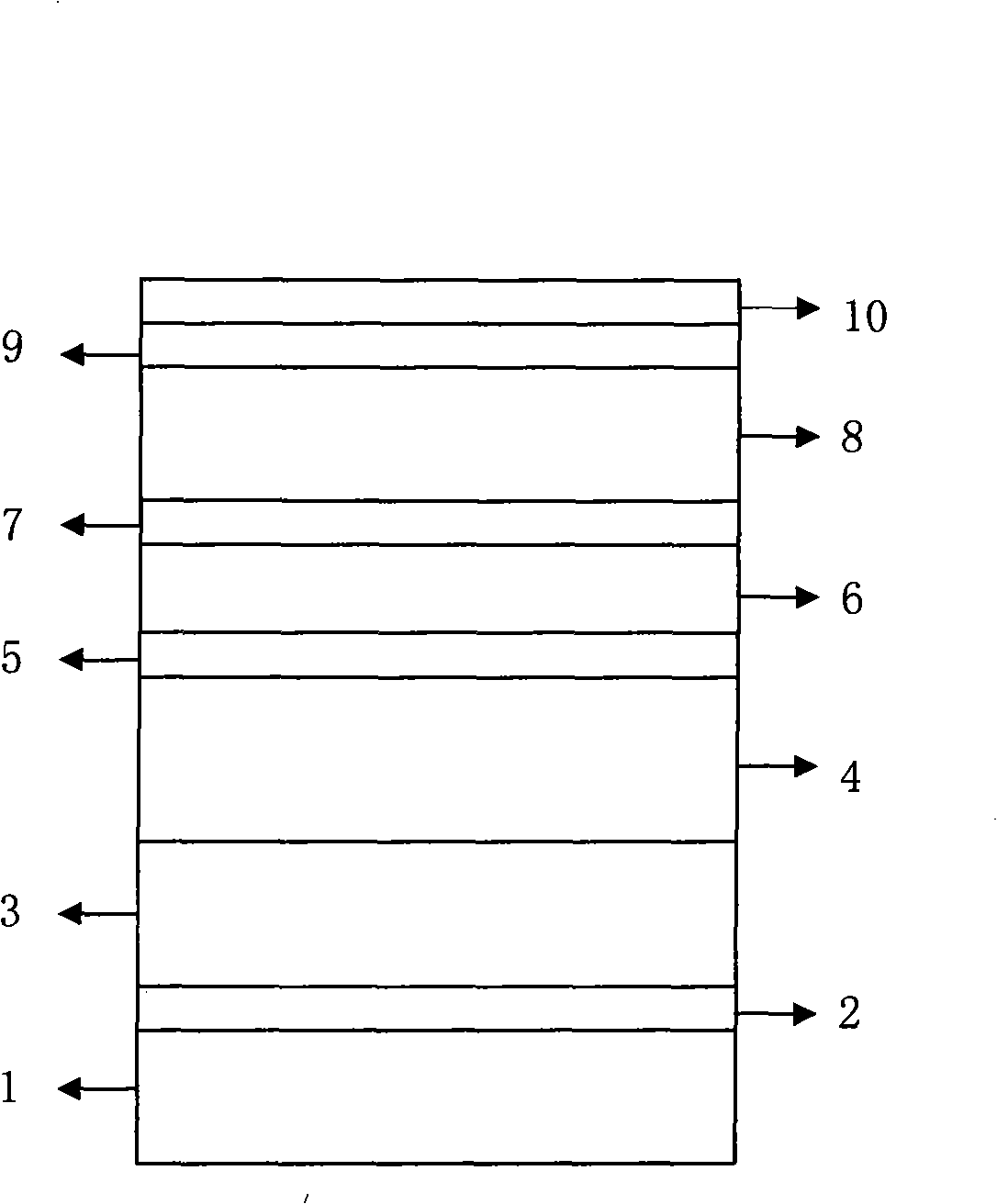

Silicon-based InGaAs PIN photoelectric detector based on heterogeneous integration and vertical optical coupling

ActiveCN102779892AAchieve vertical couplingSimple structureCoupling light guidesSemiconductor devicesGratingBonding process

The invention discloses a silicon-based InGaAs PIN photoelectric detector based on heterogeneous integration and vertical optical coupling. The silicon-based InGaAs PIN photoelectric detector comprises a silicon-on-insulator (SOI) substrate, a vertical coupling grating, a benzocyclobutene (BCB) bonding layer, an anti-reflecting layer, a first conductivity type indium phosphide layer, an intrinsic InGaAs layer and a second conductivity type indium phosphide layer, wherein the vertical coupling grating is produced in top silicon of the SOI substrate, the BCB bonding layer is covered on the vertical coupling grating, the anti-reflecting layer is located above the BCB bonding layer, the first conductivity type indium phosphide layer is located above the anti-reflecting layer, the intrinsic InGaAs layer is located above the first conductivity type indium phosphide layer, the second conductivity type indium phosphide layer is located above the intrinsic InGaAs layer, the vertical coupling grating is produced by etching the top silicon of the SOI substrate, the etching depth is 70-110 nm, the grating period is 600-680 nm, and the refractive index of the anti-reflecting layer is between refractive indexes of the BCB bonding layer and the first conductivity type indium phosphide layer. According to the silicon-based InGaAs PIN photoelectric detector, by means of an adhesiveness bonding process, InP / InGaAs / InP stack material layers are adhered to the grating which is etched on the SOI substrate, so that light and the InP / InGaAs / InP layers are vertically coupled, and suitable designs and prioritization schemes are provided for specific applications of the silicon-based InGaAs PIN photoelectric detector.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Growing method and growing device for indium phosphide single crystal

ActiveCN104911690AReduce dosageSimple processPolycrystalline material growthFrom frozen solutionsDopantVertical gradient

The invention provides a growing method for an indium phosphide single crystal. The method comprises the following steps: using a vertical gradient freeze method for heating indium phosphide seed, indium phosphide polycrystal, diboron trioxide and red phosphorus, and growing crystals to obtain the indium phosphide single crystal, wherein the red phosphorus takes up 0.05-0.1% of the total mass of the indium phosphide polycrystal, the diboron trioxide and the red phosphorus. By the provided growing method, the indium phosphide single crystal with substantially lower dislocation density can be obtained without adding dopant such as ferrum or sulfur, thereby simplifying the technology and saving the cost; moreover, the few red phosphorus (only one tenth of the dosage of the red phosphorus in the prior art) is used in the preparation method, thereby reducing the danger during the production. It is shown by experiments that the average dislocation density of the indium phosphide single crystal obtained by the provided growing method is 2000-4000 / cm2, with the local dislocation density being less than 500 / cm2. The invention further provides a growing device of the indium phosphide single crystal.

Owner:威科赛乐微电子股份有限公司

Method for synthesizing indium phosphide by liquid phosphorus injection method

ActiveCN111424310ASolve synthetic regurgitationSolve the bubble problemPolycrystalline material growthBy pulling from meltIndiumPhysical chemistry

The invention discloses a method for synthesizing indium phosphide by a liquid phosphorus injection method, and belongs to the technical field of semiconductors; according to the method, gaseous phosphorus is converted into liquid phosphorus through a condenser; liquid phosphorus is injected into an indium solution, and meanwhile, phosphorus gasification is prevented by virtue of flowing of low-temperature inert gas, so that the liquid phosphorus and the liquid indium solution instantaneously react, the indium phosphide solution can be synthesized in a high-capacity manner at a relatively lowtemperature and a high-efficiency and high-purity ratio, the growth of phosphorus-rich indium phosphide polycrystals is facilitated, and the growth of indium phosphide single crystals is facilitated.The method comprises the steps of indium cleaning, phosphorus loading, furnace loading, condenser communication, synthesis, crystal preparation and the like.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

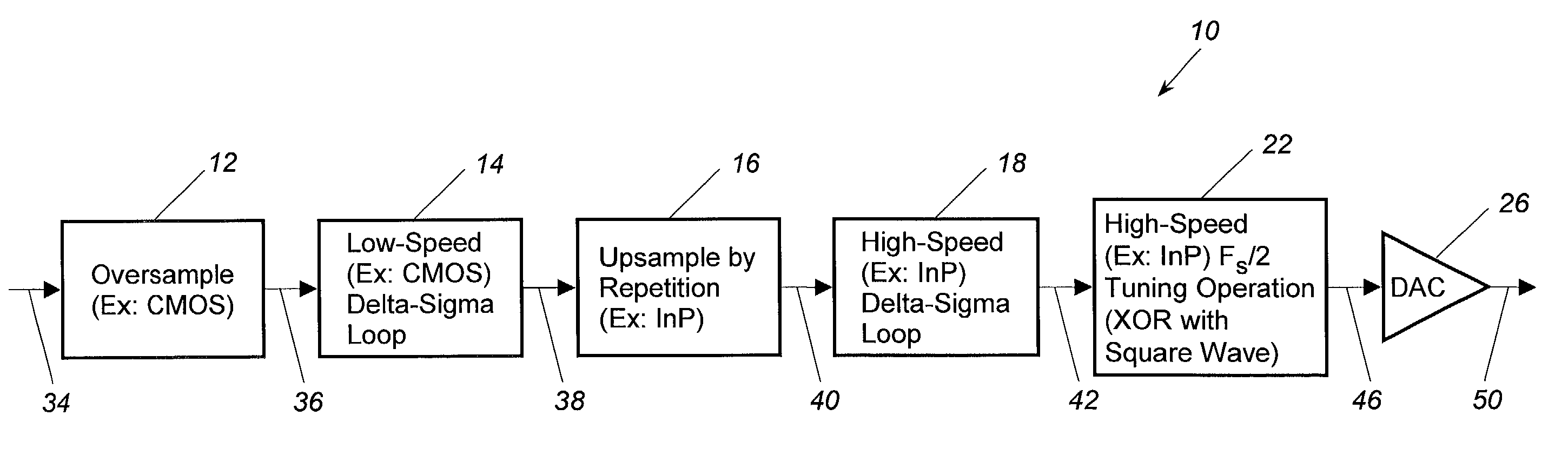

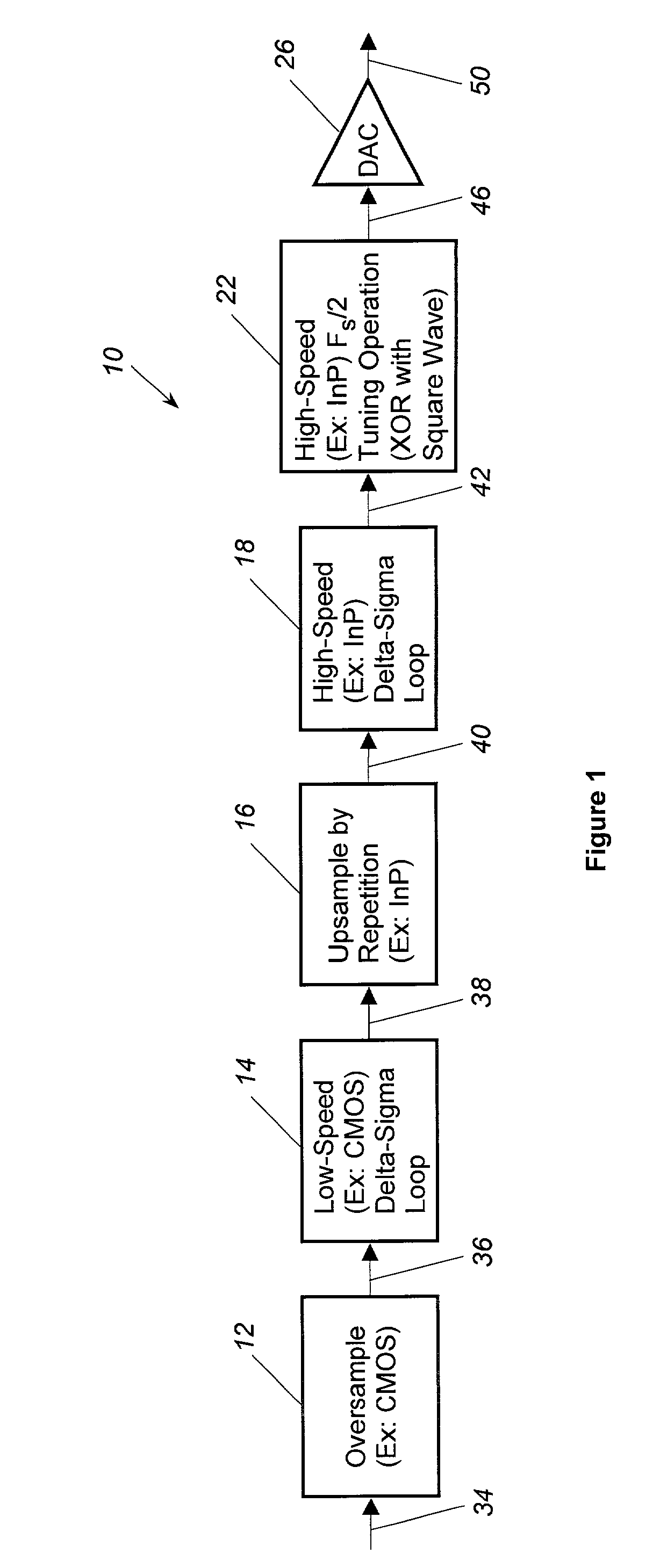

Apparatus and methods for digital-to-analog conversion

ActiveUS7031395B2Reduced word lengthLess circuit “ real estate ”Analogue/digital conversionElectric signal transmission systemsCarrier signalEngineering

An apparatus for converting a digital input signal to an analog signal for transmission. The input signal can include more than one carrier signal. A plurality of delta-sigma modulation loop circuits are connected in an increasing order of operating frequency so as to reduce a word length of the input signal. A tuning circuit adjusts the signal frequency to a transmitting frequency for conversion to analog by a digital-to-analog converter. A first loop circuit is implemented using CMOS gates, and a second loop circuit and the tuning circuit are implemented using indium phosphide gates. The apparatus allows a high-resolution, wide-band RF multiple-carrier signal to be re-quantized to a lower-resolution signal while an acceptable signal-to-noise ratio is maintained.

Owner:NORTHROP GRUMMAN SYST CORP

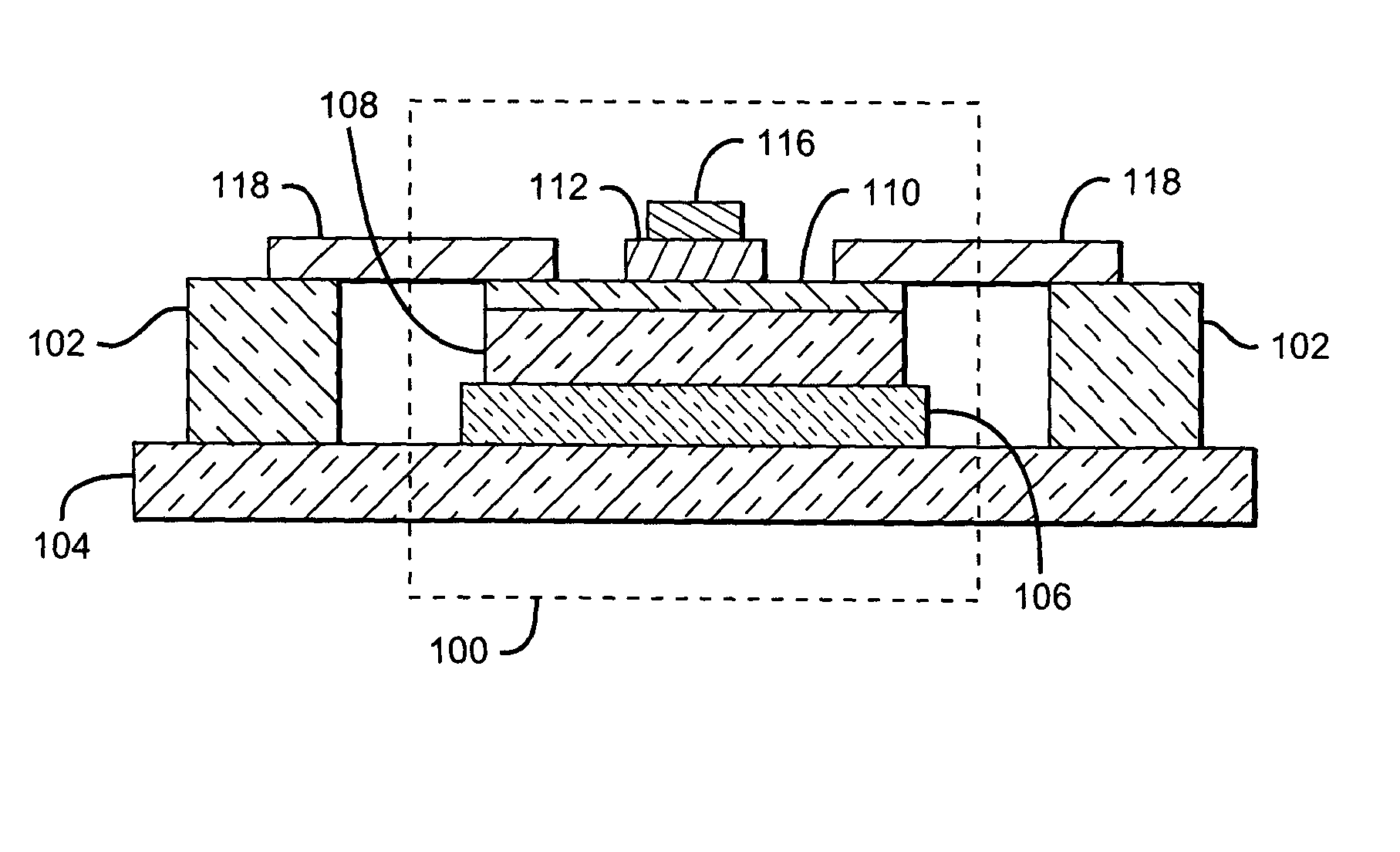

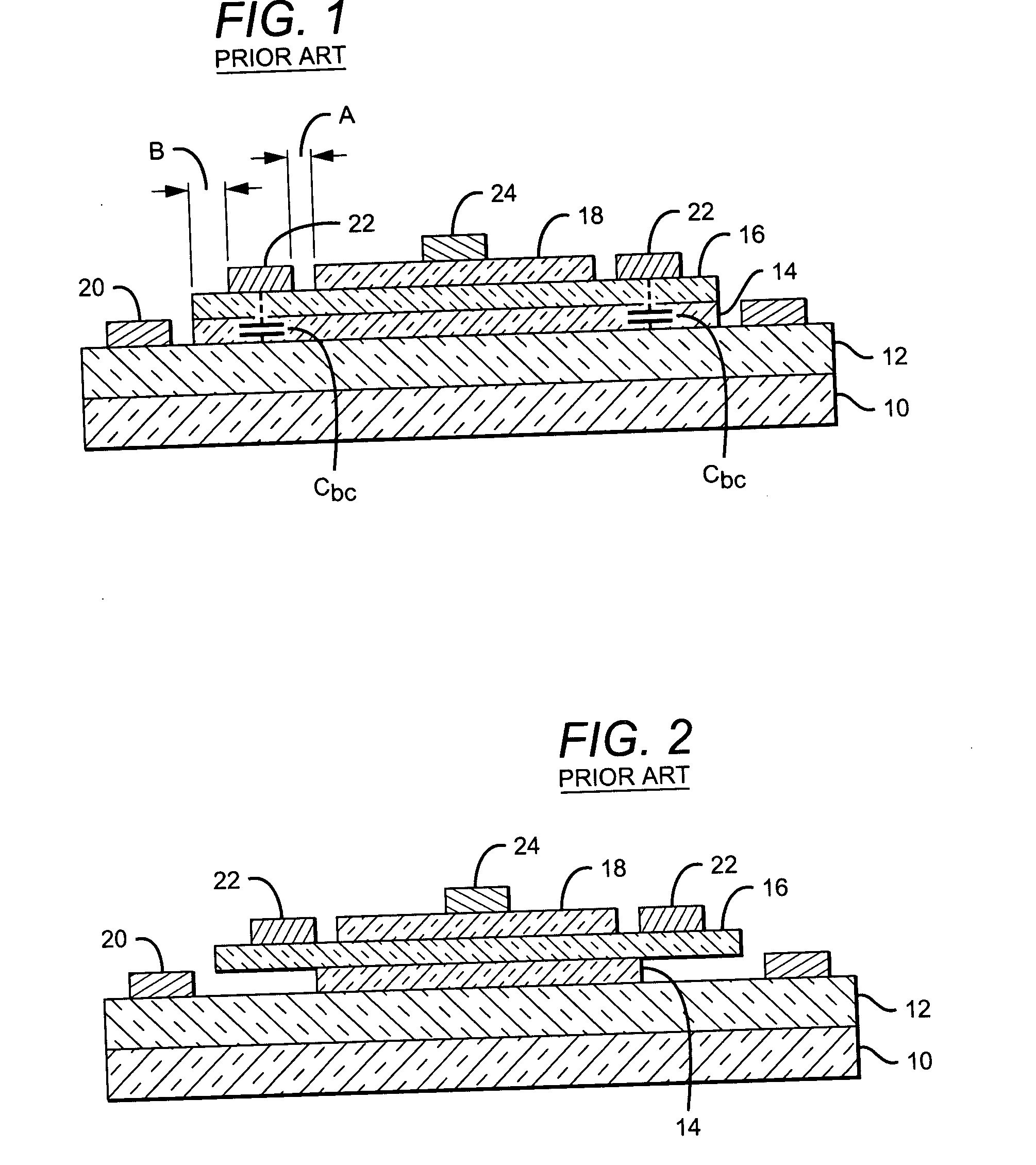

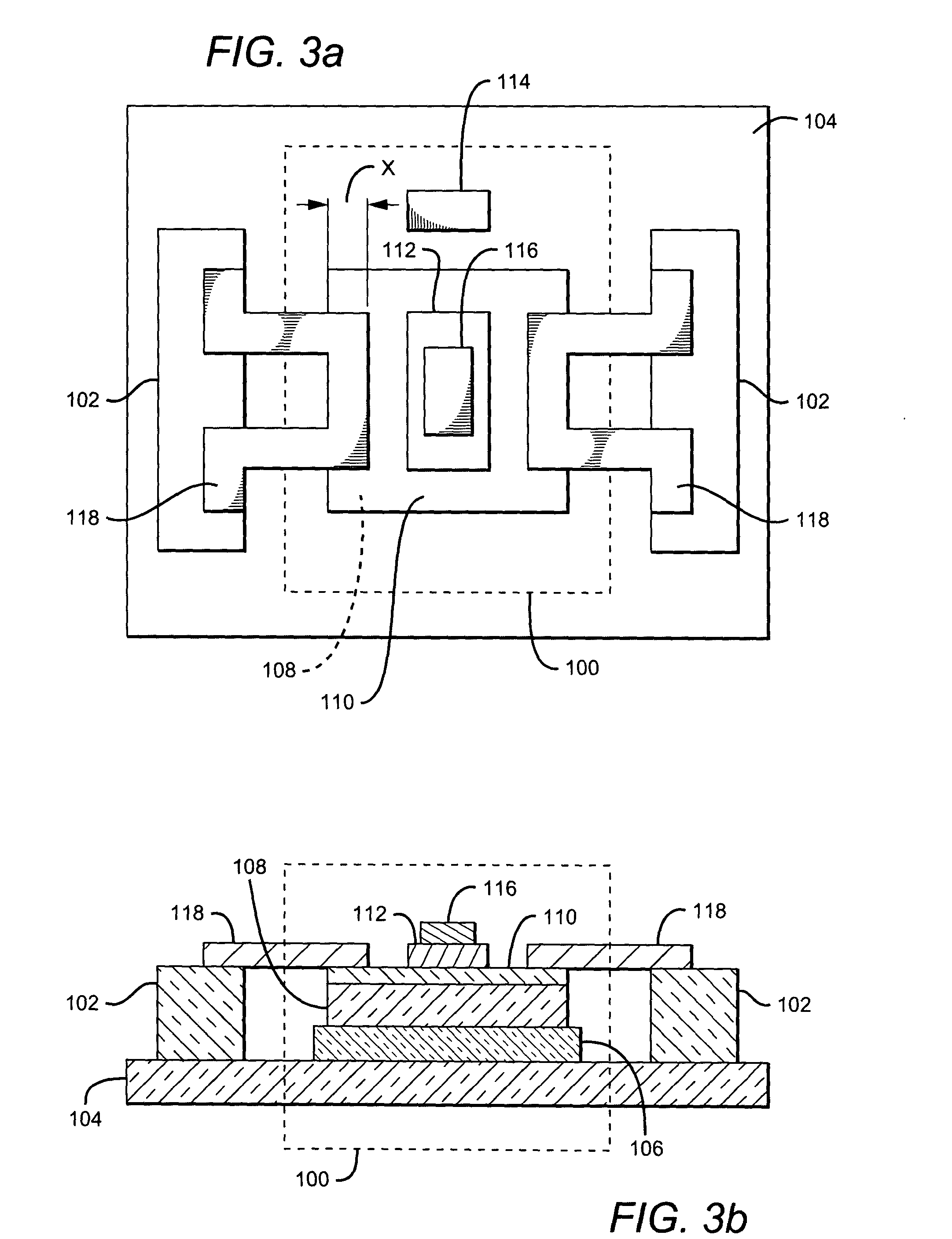

Mechanically-stable BJT with reduced base-collector capacitance

ActiveUS20050023643A1Maintain mechanical stabilityReduce capacitanceTransistorSemiconductor/solid-state device detailsHeterojunctionCapacitance

A bipolar junction transistor (BJT) requires the fabrication of a BJT structure and of a support post which is adjacent to, but physically and electrically isolated from, the BJT structure. The BJT structure includes a semi-insulating substrate, a subcollector, a collector, a base, and an emitter. Metal contacts are formed on the subcollector and emitter to provide collector and emitter terminals. Contact to the structure's base is accomplished with a metal contact which extends from the top of the support post to the edge of the base nearest the support post. The contact bridges the physical and electrical separation between the support post and the base and provides a base terminal for the device. The base contact need extend over the edge of the base by no more than the transfer length associated with the fabrication process. This results in the smaller base contact area over the collector than would otherwise be necessary, and a consequent reduction in base-collector capacitance. The invention is particularly useful when forming heterojunction bipolar transistors (HBTs), built on a compound semiconductor substrate such as indium phosphide (InP).

Owner:TELEDYNE SCI & IMAGING

Method for preparing indium phosphide crystals by utilizing indium-phosphorus mixture

ActiveCN110760932AReduce volatilityHigh purityPolycrystalline material growthFinal product manufactureIndiumPhysical chemistry

The invention relates to a method for preparing indium phosphide crystals by using an indium-phosphorus mixture, and belongs to the technical field of semiconductors, and the method comprises the following steps of: preparing indium-phosphorus mixed balls, charging, keeping blast furnace pressure and low temperature of the indium-phosphorus mixed balls, melting a covering agent, feeding, synthesizing and growing the crystals. The proportioned indium-phosphorus mixed balls are directly melted to synthesize the indium phosphide crystals. Indium powder and phosphorus powder are uniformly mixed and pressed into spherical indium-phosphorus mixed particles, then a mixture of the indium-phosphorus mixed balls and boron oxide powder is put into a melt with a boron oxide covering agent, and crystalgrowth is carried out in situ after synthesis. The method has the advantages of being short in reaction time, high in efficiency and capable of saving raw materials, effectively reducing the risk that the materials are contaminated, saving procedures and reducing the material preparation cost.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

808nm large-power quantum well laser in non-aluminum active region of asymmetric structure

ActiveCN101340060AIncreased light confinement factorReduce leakageOptical wave guidanceLaser detailsIndium arsenideWaveguide

The invention provides an aluminum-free active region 808nm high-power quantum-well laser with asymmetric structure. From the bottom to the top, the structure of the laser sequentially comprises a substrate, a buffer layer, an N-type lower limiting layer, a lower waveguide layer, a quantum-well layer, an upper waveguide layer, a potential barrier limiting layer, a P-type upper limiting layer, a transition layer and an ohmic contact layer, wherein, the upper waveguide layer and the lower waveguide layer are made of aluminum-free material Indium gallium phosphide, the quantum-well layer made of gallium indium arsenide phosphide material, the waveguide layer and the quantum-well layer form the aluminum-free active region, and one layer potential barrier limiting layer which is made of P-type aluminum gallium indium phosphide material and 50nm-150nm thick and has a band gap wider than that of the upper limiting layer is arranged between the upper limiting layer and the upper waveguide layer. The laser of the invention can increase the optical limiting factor of the P-type material region, reduce the optical leakage towards the P-type material region, reduce optical absorption loss of a current carrier at the highly doped area, and improve the work efficiency of the laser; the structure of the invention also improves the limiting effect of the active region on the carrier, reduce the leakage of the carrier and is favorable to the decrease of the threshold current.

Owner:Shandong Huaguang Optoelectronics Co. Ltd.

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com