Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

14716 results about "CMOS" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Complementary metal–oxide–semiconductor (CMOS), also known as complementary-symmetry metal–oxide–semiconductor (COS-MOS), is a type of MOSFET (metal–oxide–semiconductor field-effect transistor) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFETs for logic functions. CMOS technology is used for constructing integrated circuits (ICs), including microprocessors, microcontrollers, memory chips (including CMOS BIOS), and other digital logic circuits. CMOS technology is also used for analog circuits such as image sensors (CMOS sensors), data converters, RF circuits (RF CMOS), and highly integrated transceivers for many types of communication.

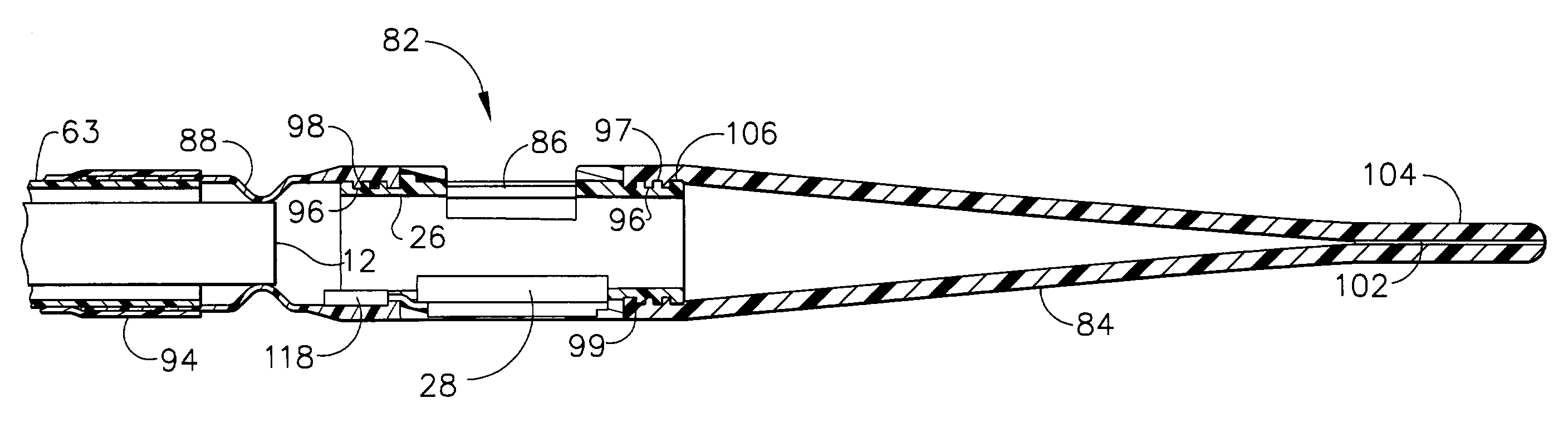

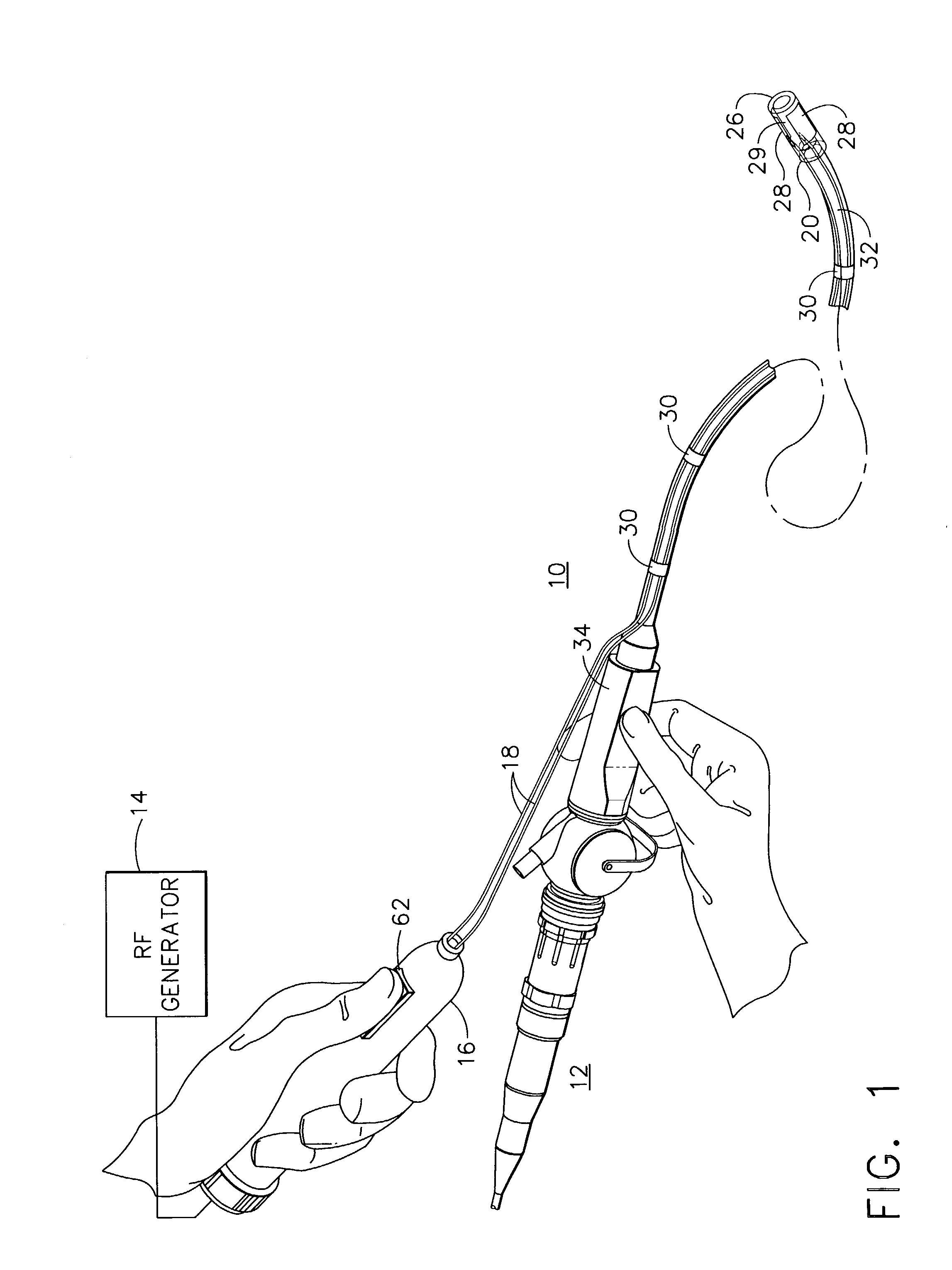

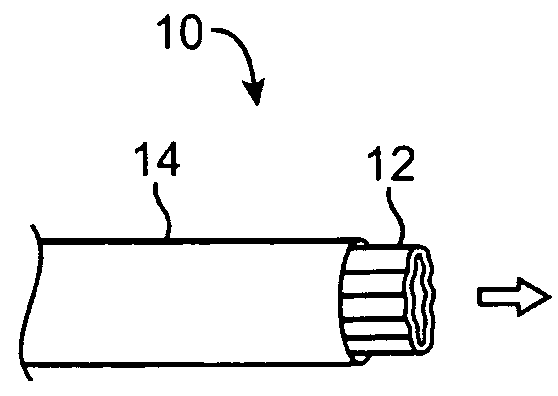

Endoscopic ablation system with a distally mounted image sensor

A tissue ablation system is described. The tissue ablation system can include a plurality of electrodes, a viewing window between adjacent electrodes, illuminating elements, and an image sensor. The image sensor can be a CMOS device.

Owner:ETHICON ENDO SURGERY INC

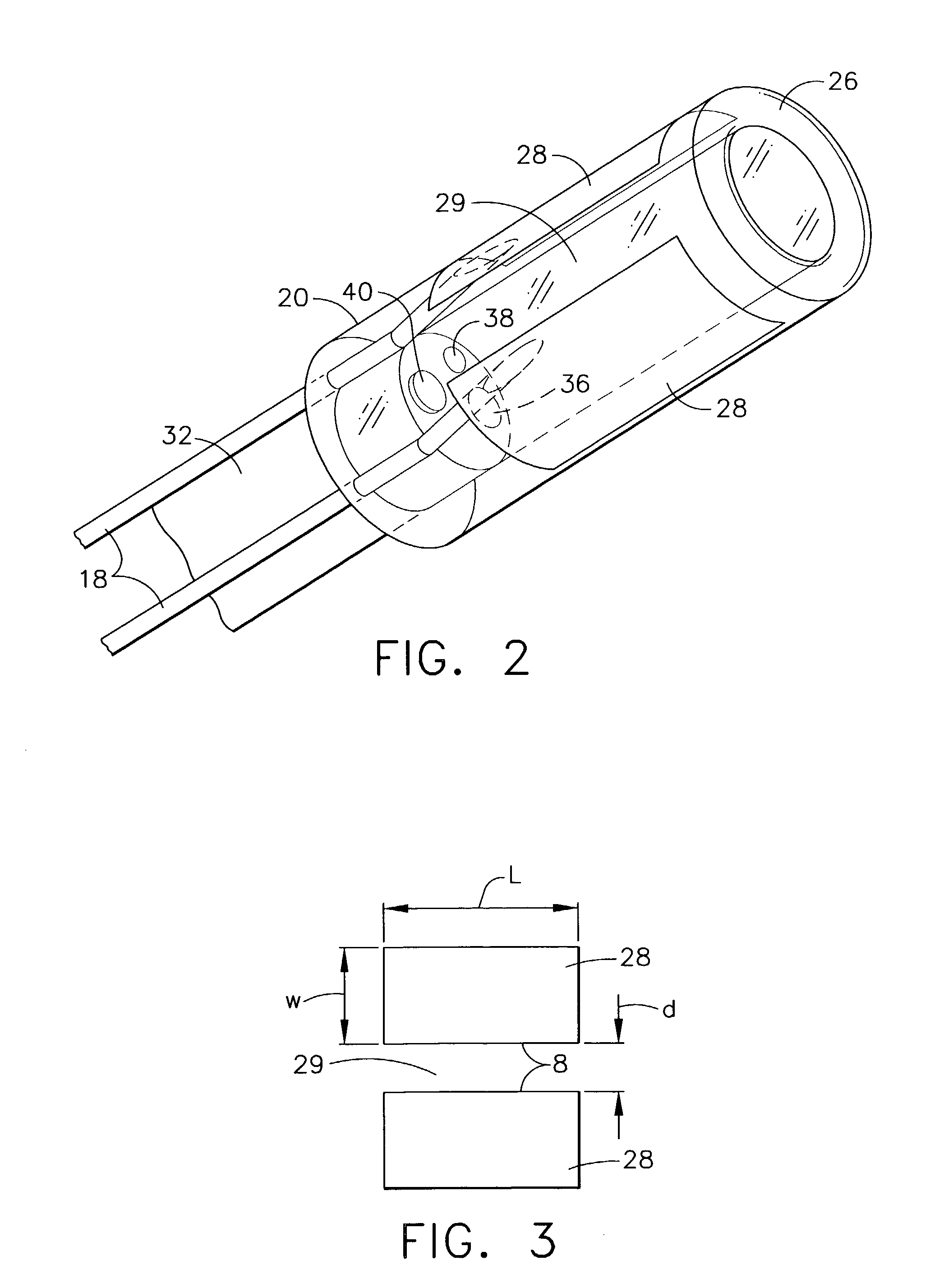

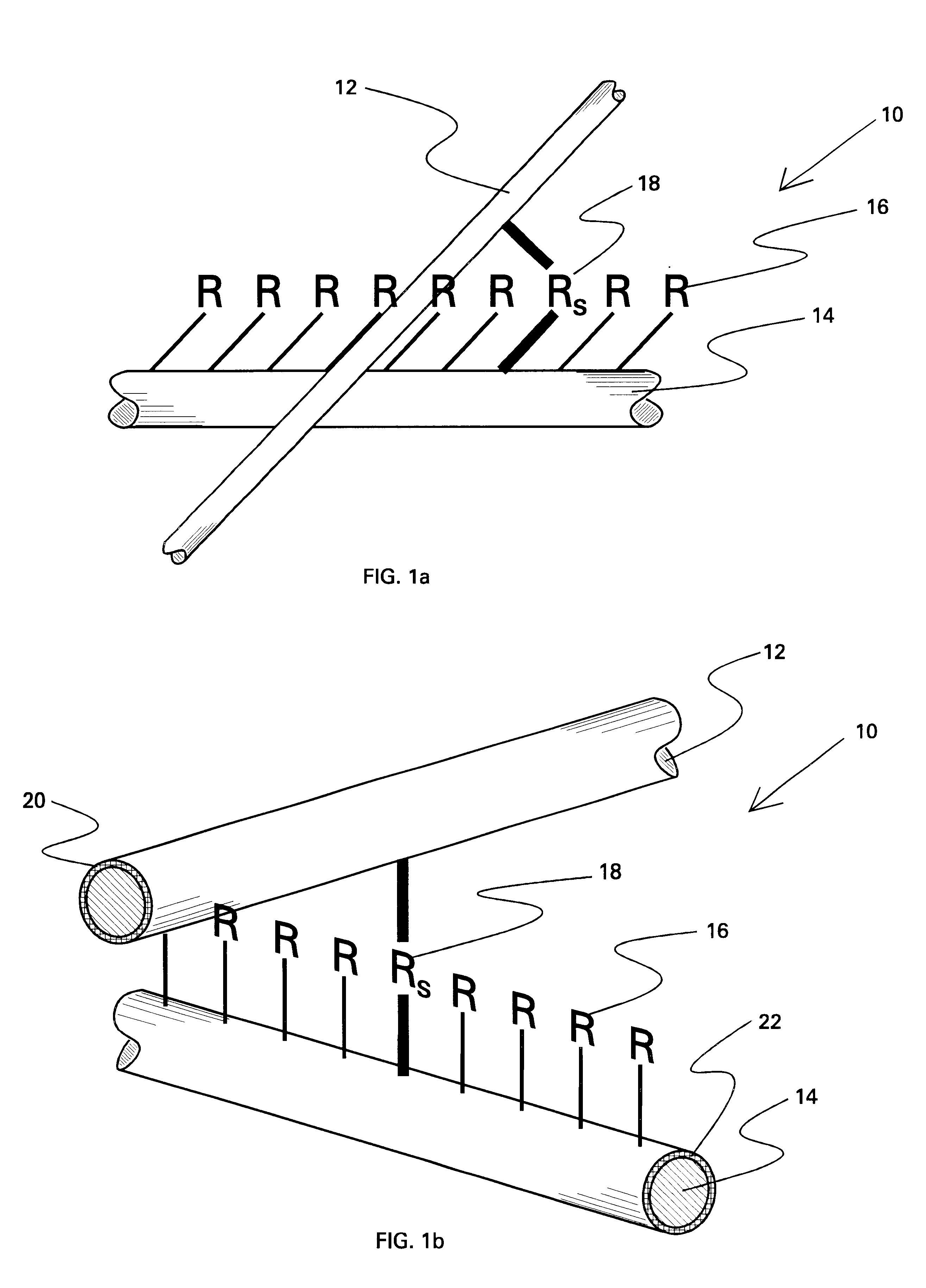

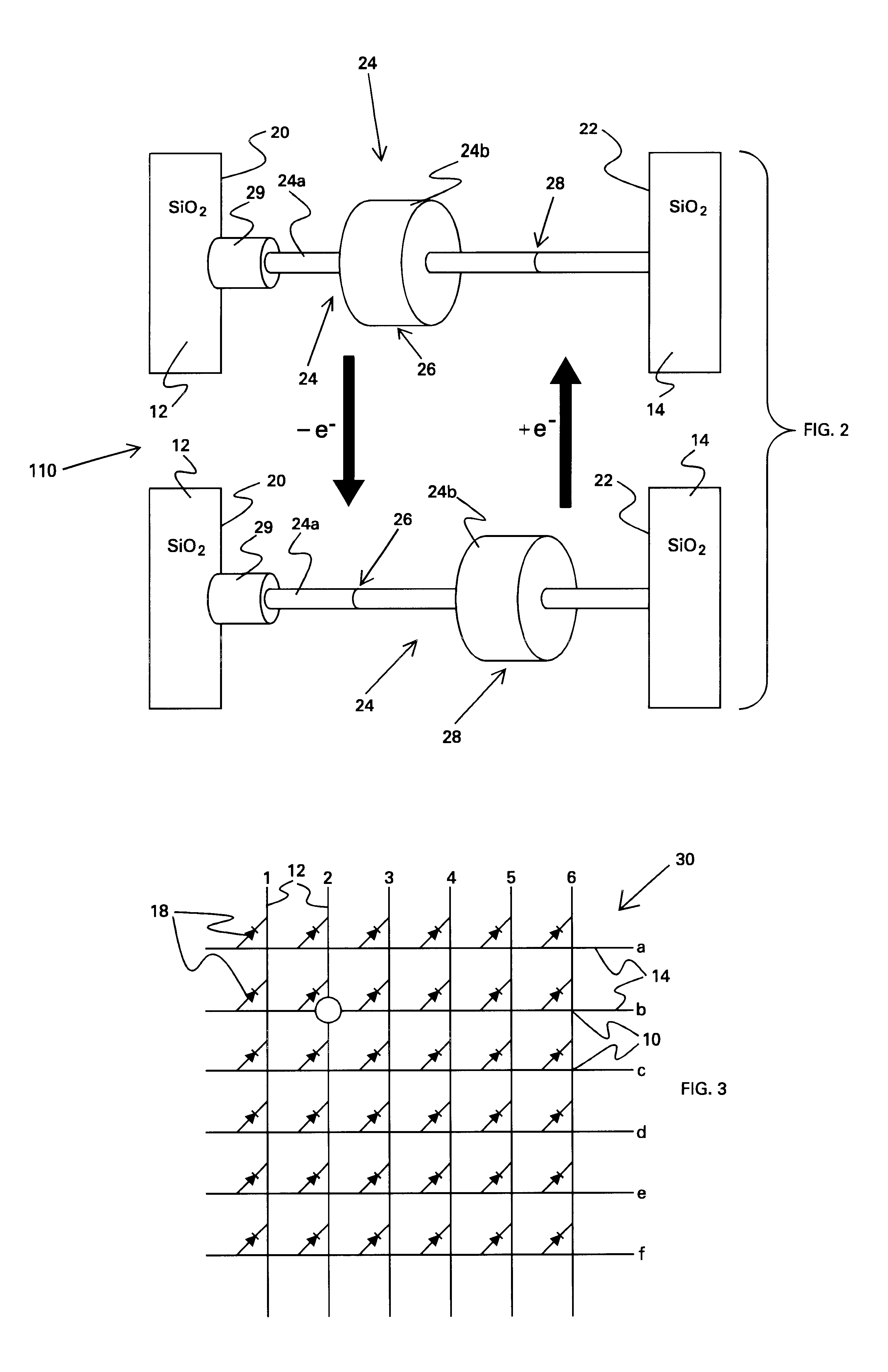

Demultiplexer for a molecular wire crossbar network (MWCN DEMUX)

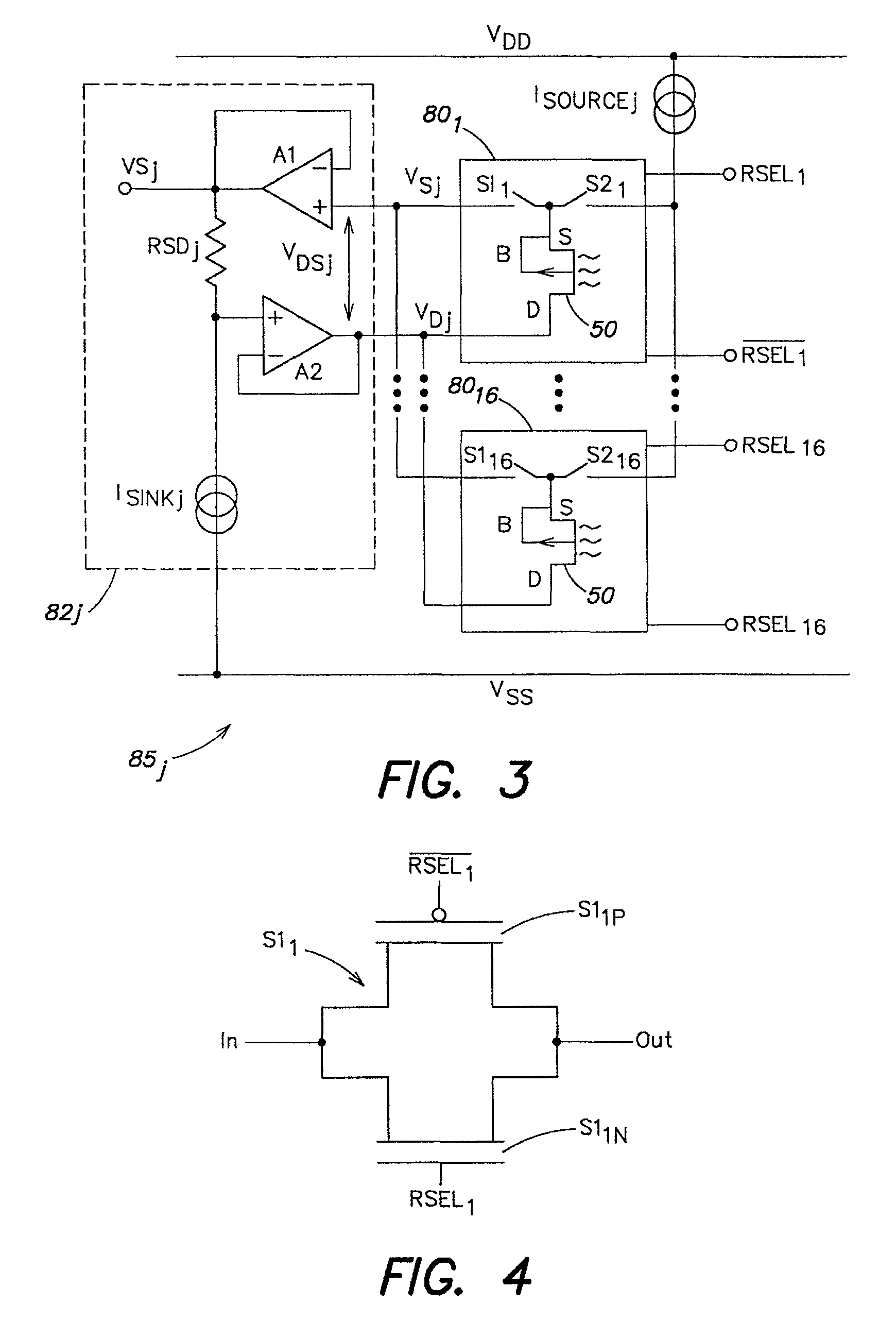

A demultiplexer for a two-dimensional array of a plurality of nanometer-scale switches (molecular wire crossbar network) is disclosed. Each switch comprises a pair of crossed wires which form a junction where one wire crosses another and at least one connector species connecting said pair of crossed wires in said junction. The connector species comprises a bi-stable molecule. The demultiplexer comprises a plurality of address lines accessed by a first set of wires in the two-dimensional array by randomly forming contacts between each wire in the first set of wires to at least one of the address lines. The first set of wires crosses a second set of wires to form the junctions. The demultiplexer solves both the problems of data input and output to a molecular electronic system and also bridges the size gap between CMOS and molecules with an architecture that can scale up to extraordinarily large numbers of molecular devices. Further, the demultiplexer is very defect tolerant, and can work despite a large number of defects in the system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

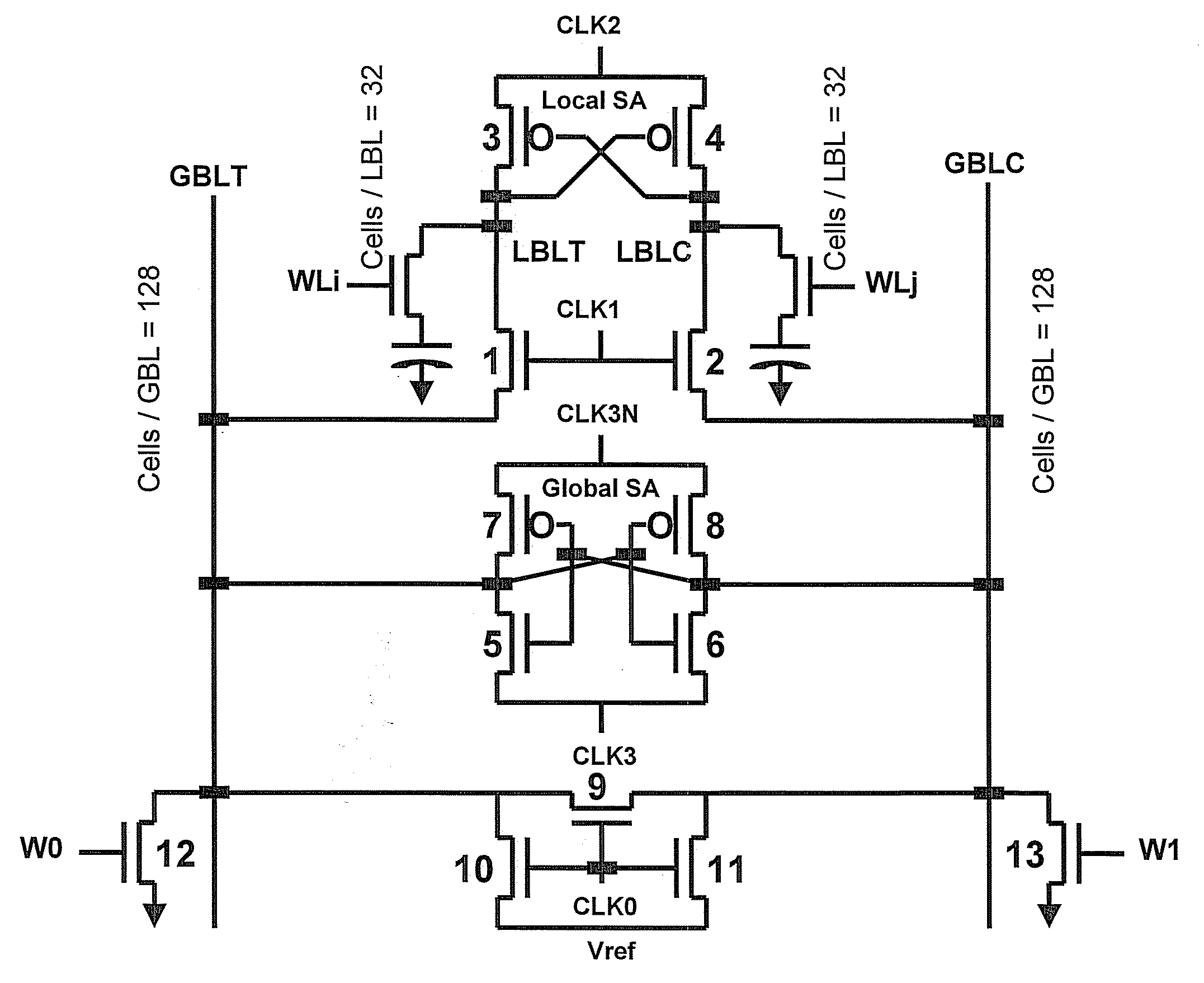

Methods and apparatus for measuring analytes using large scale FET arrays

ActiveUS7948015B2Reduce porosityHigh densityTransistorMicrobiological testing/measurementCMOSOrganismal Process

Methods and apparatus relating to very large scale FET arrays for analyte measurements. ChemFET (e.g., ISFET) arrays may be fabricated using conventional CMOS processing techniques based on improved FET pixel and array designs that increase measurement sensitivity and accuracy, and at the same time facilitate significantly small pixel sizes and dense arrays. Improved array control techniques provide for rapid data acquisition from large and dense arrays. Such arrays may be employed to detect a presence and / or concentration changes of various analyte types in a wide variety of chemical and / or biological processes. In one example, chemFET arrays facilitate DNA sequencing techniques based on monitoring changes in hydrogen ion concentration (pH), changes in other analyte concentration, and / or binding events associated with chemical processes relating to DNA synthesis.

Owner:LIFE TECH CORP

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

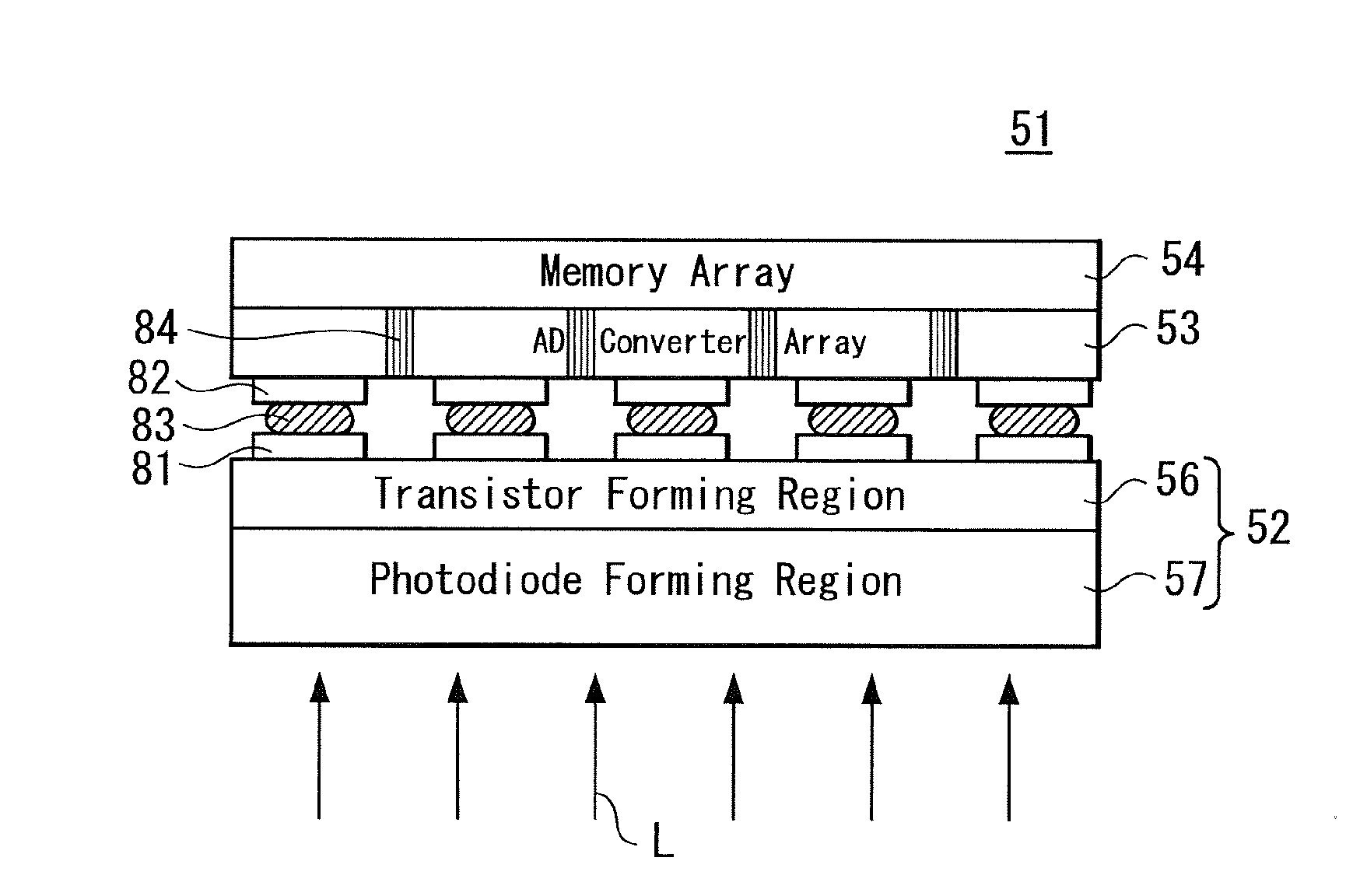

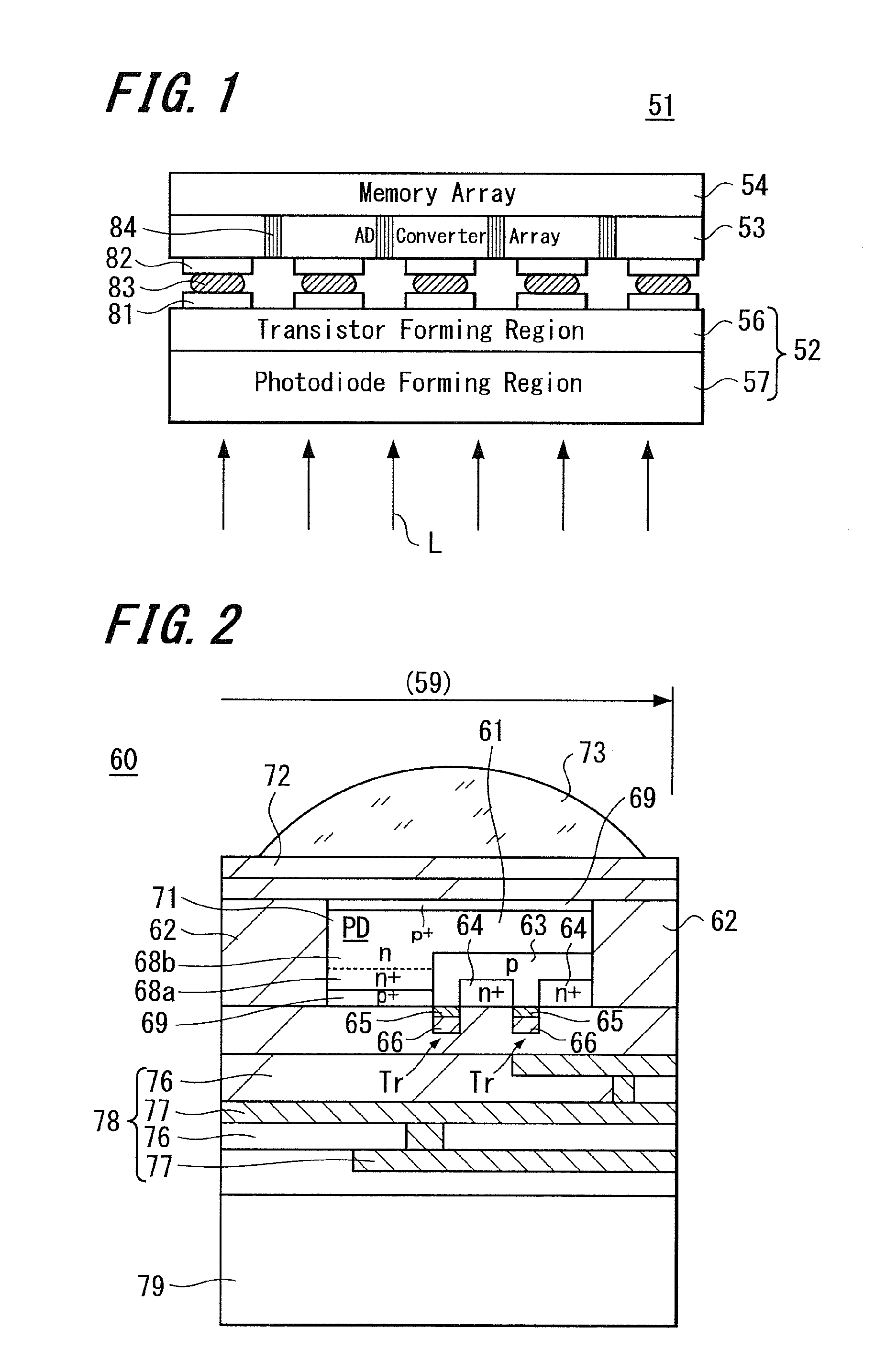

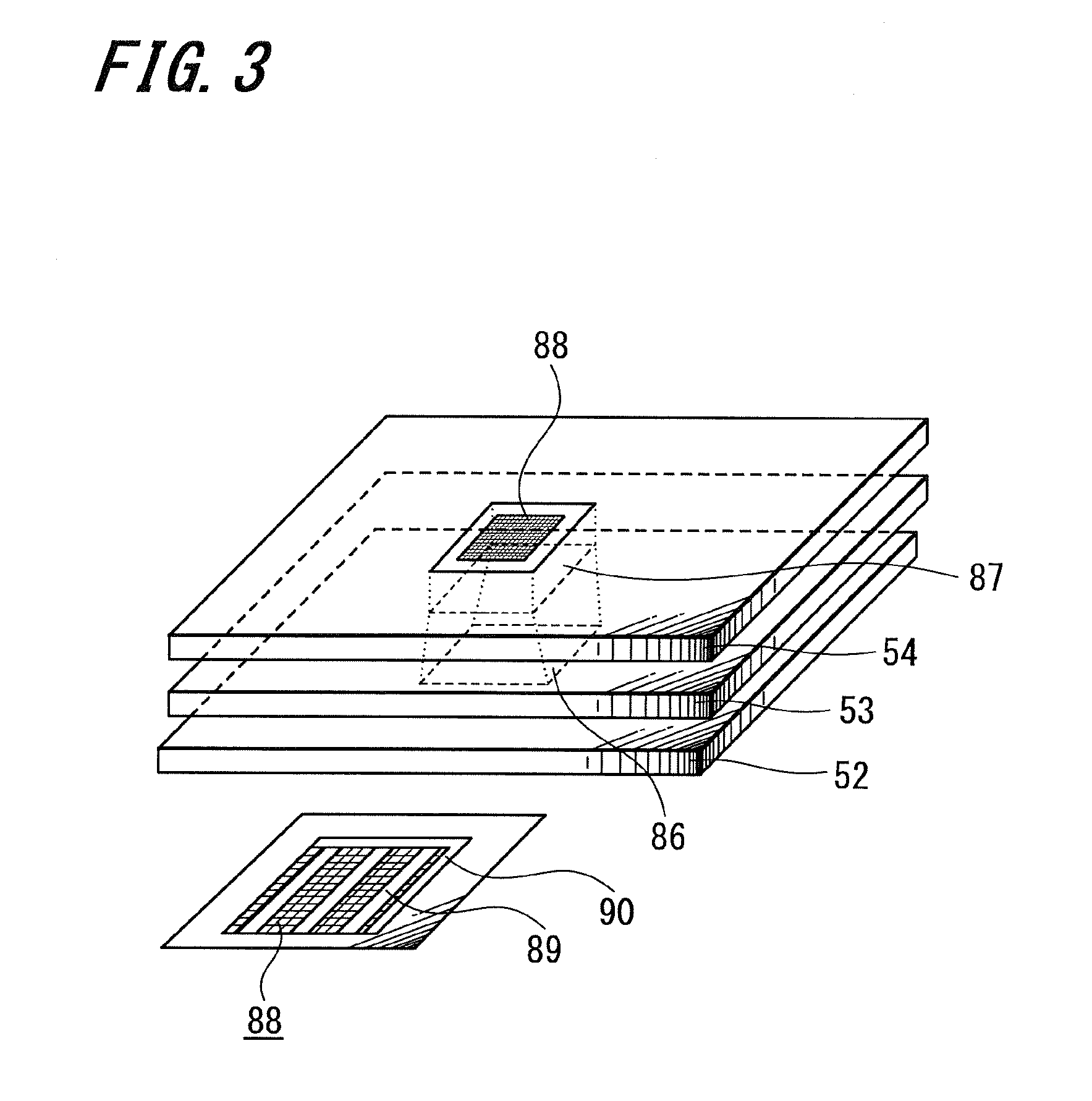

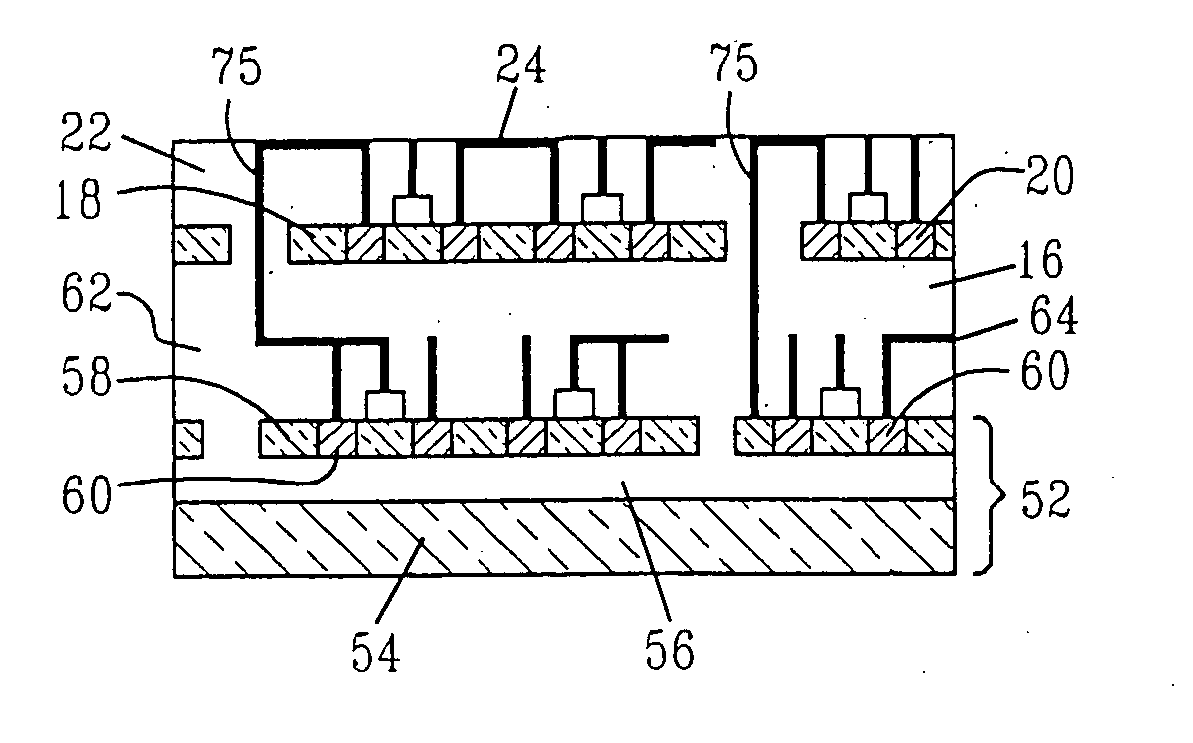

Semiconductor image sensor module and method of manufacturing the same

ActiveUS20100276572A1Increase the aperture ratioIncrease profitTransistorTelevision system detailsCMOSSemiconductor chip

A CMOS type semiconductor image sensor module wherein a pixel aperture ratio is improved, chip use efficiency is improved and furthermore, simultaneous shutter operation by all the pixels is made possible, and a method for manufacturing such semiconductor image sensor module are provided. The semiconductor image sensor module is provided by stacking a first semiconductor chip, which has an image sensor wherein a plurality of pixels composed of a photoelectric conversion element and a transistor are arranged, and a second semiconductor chip, which has an A / D converter array. Preferably, the semiconductor image sensor module is provided by stacking a third semiconductor chip having a memory element array. Furthermore, the semiconductor image sensor module is provided by stacking the first semiconductor chip having the image sensor and a fourth semiconductor chip having an analog nonvolatile memory array.

Owner:SONY CORP

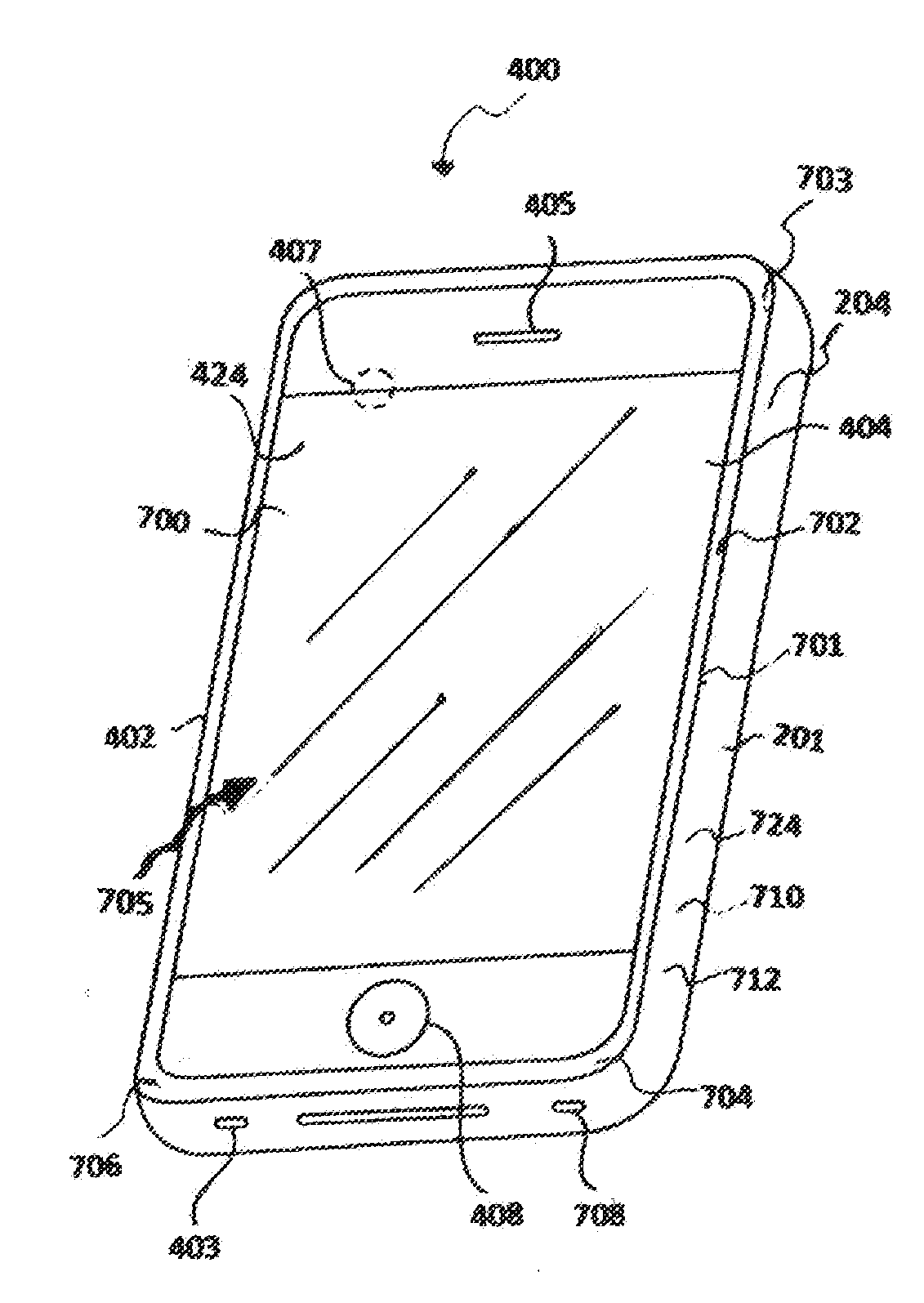

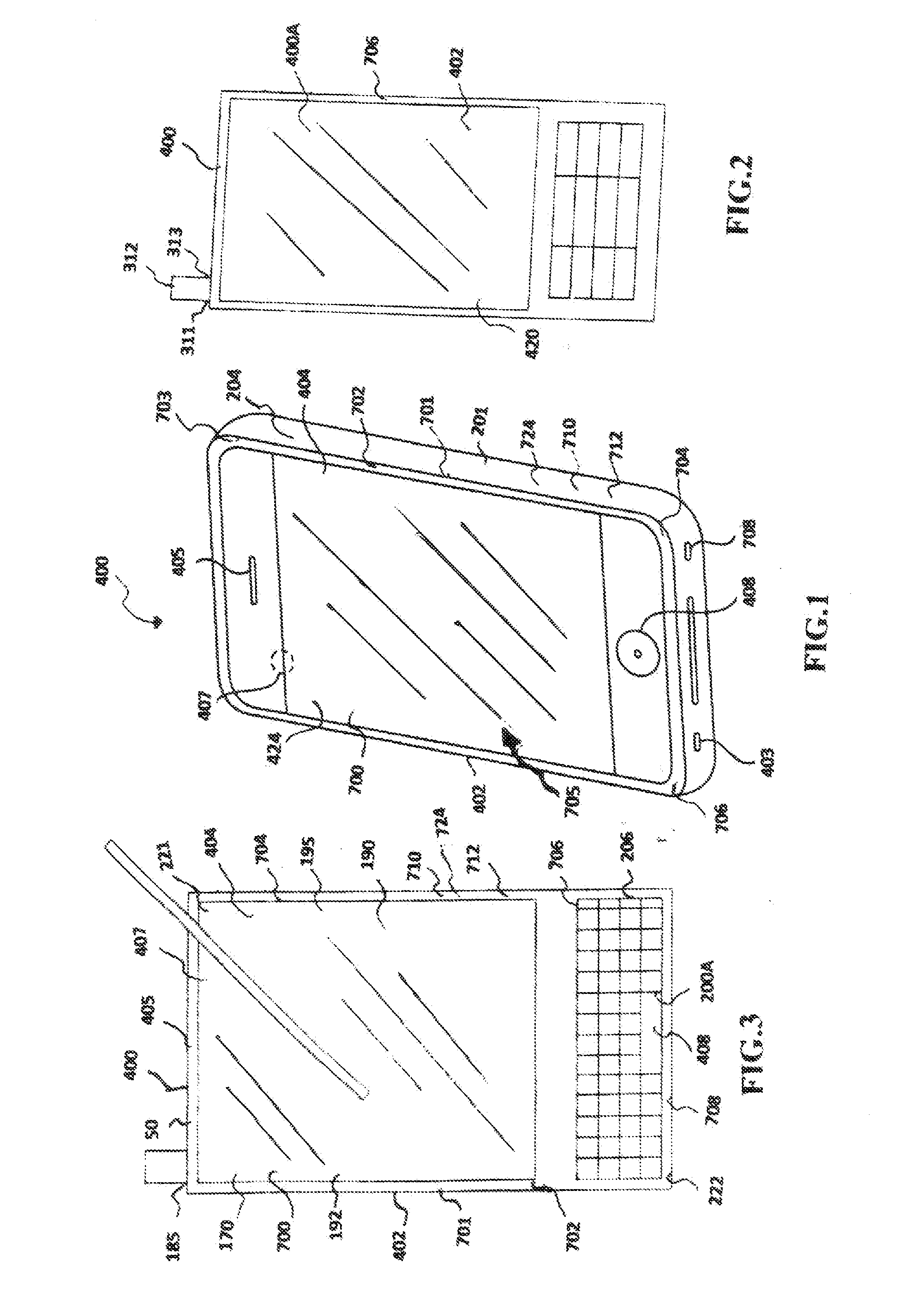

Energy harvesting computer device in association with a communication device configured with apparatus for boosting signal reception

ActiveUS20130157729A1Improve consumer electronics hybrid consumer electronics performanceLow densityMaterial nanotechnologyEnergy efficient ICTCellular telephoneCommunication device

Disclosed embodiments comprise an energy harvesting computer device in association with a communication device comprising interactive user interface operatively configured with CMOS multiple antennas on chip for boosting signal receptions and for providing faster data transmission speed. Disclosed embodiment encompasses three modes of communications—the Cell phone, wireless Internet applications, and Global communication and media information. Embodiments provide communication apparatus operable to enhance mobile communication efficiency with touch sensitive display comprising energy harvesting platform in communication with a charging circuit board configured with memories, processors, sensors, and modules. Embodiments further provide a gaming device, a wireless media device configured with touch pads comprising sensors being embedded in silicon substrate and fused in nano-fiber / microfiber material having excellent electrical characteristics. Certain embodiments provide communication apparatus configured for voice enabled applications comprising human voice auditory operable to convert text into voice auditory and / or voice auditory into text applications.

Owner:TABE JOSEPH AKWO

Semiconductor structure and device and methods of forming same using selective epitaxial process

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both n-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

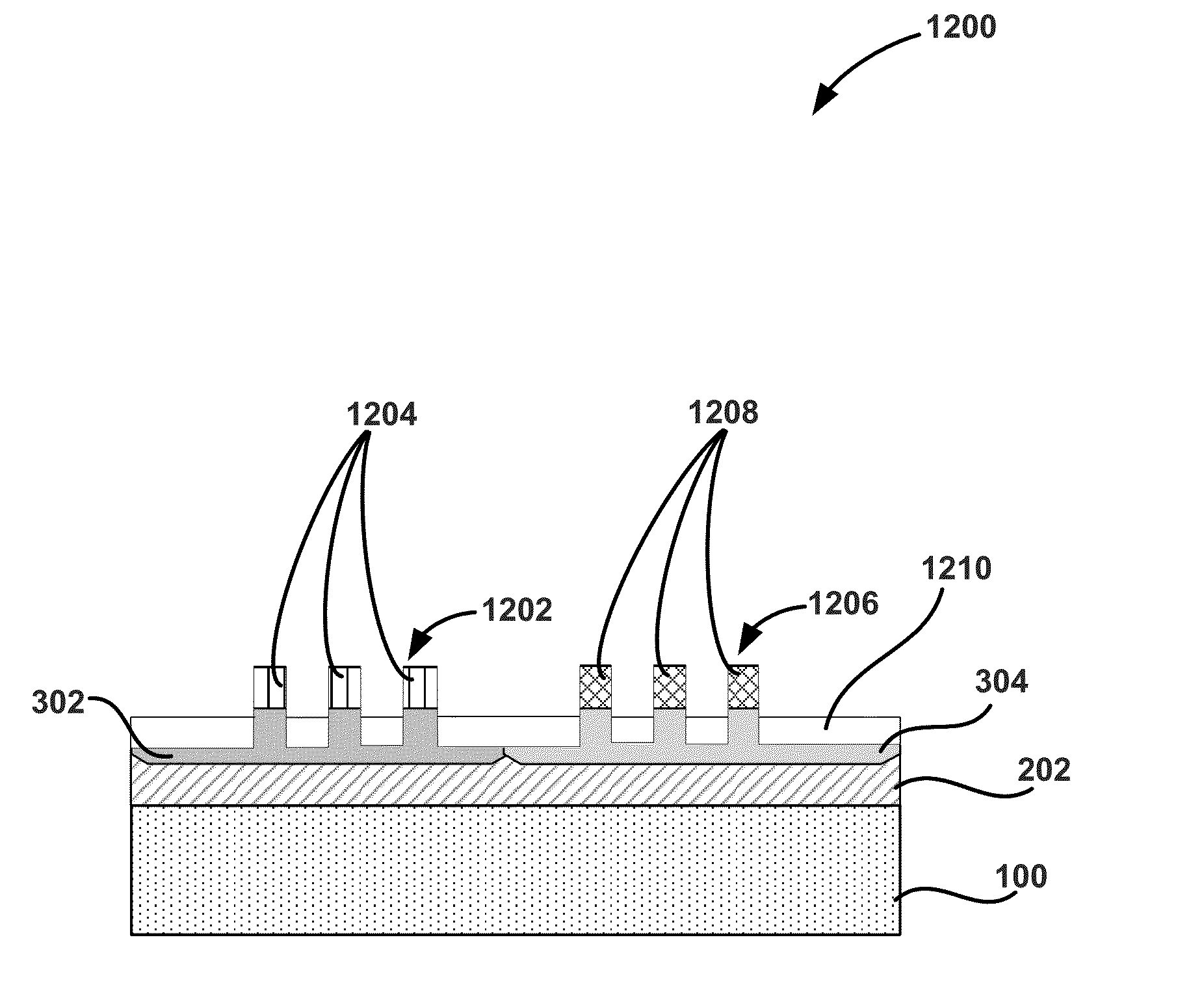

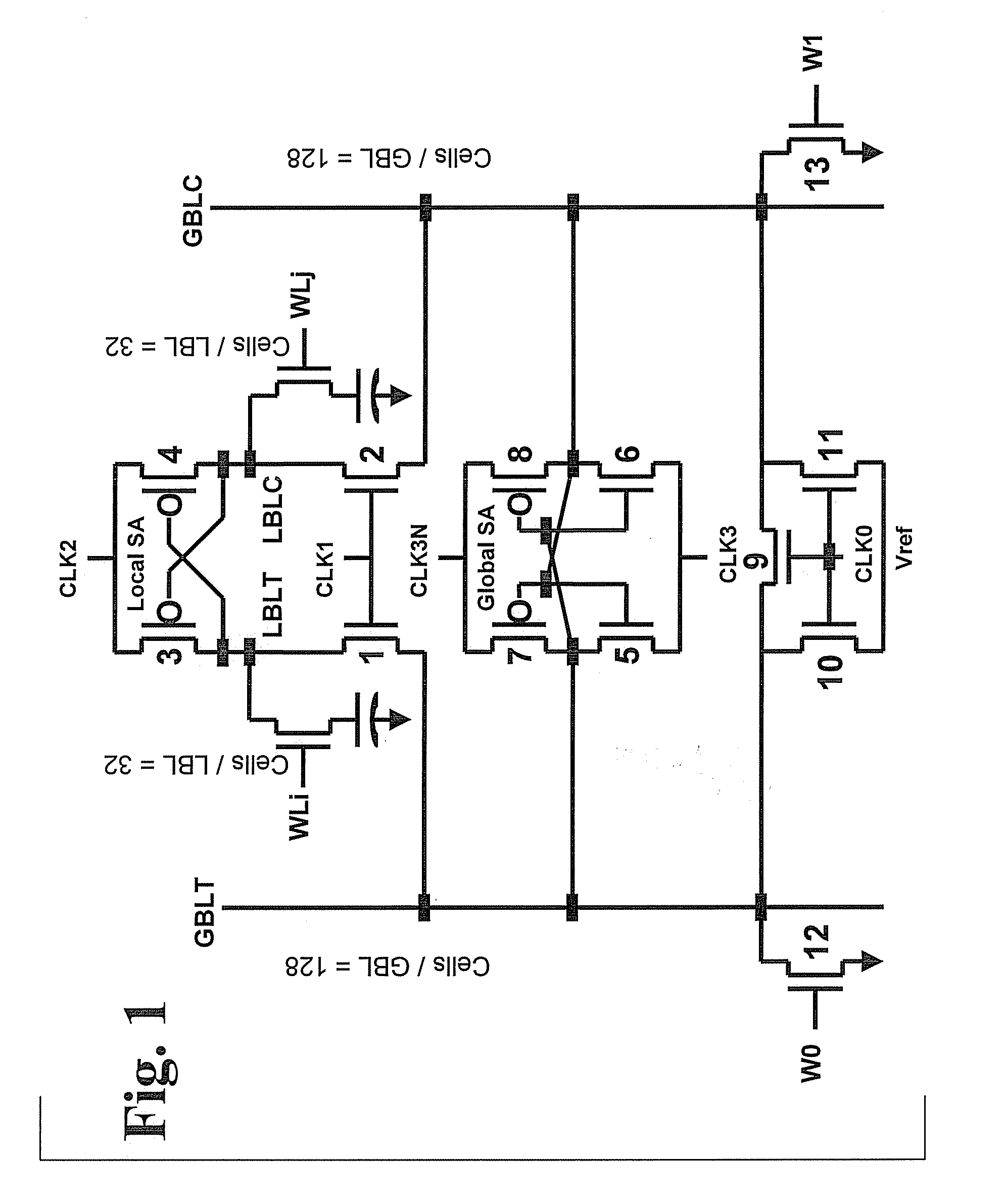

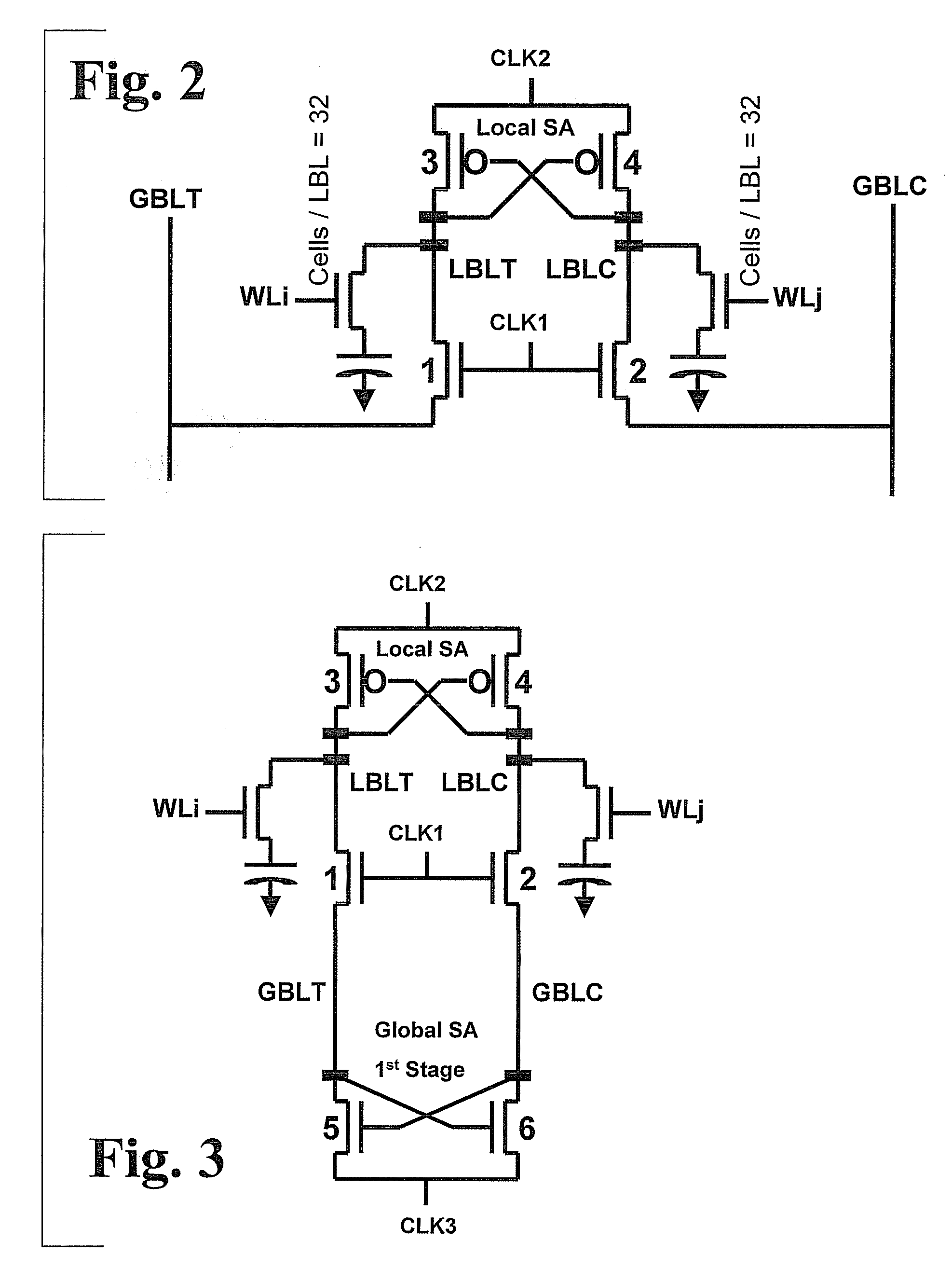

eDRAM HIERARCHICAL DIFFERENTIAL SENSE AMP

In an embodiment of the present invention, a hierarchical differential sensing approach is effectuated wherein an array of 1T DRAM cells are organized in rows and columns in which the rows represent words and the columns represent bits of the word, each bit column having more than one pair of balanced, true and complement local bit lines, the local bit lines being connected to a pair of balanced, true and complement global bit lines by way of CMOS transistor switches.

Owner:GLOBALFOUNDRIES INC

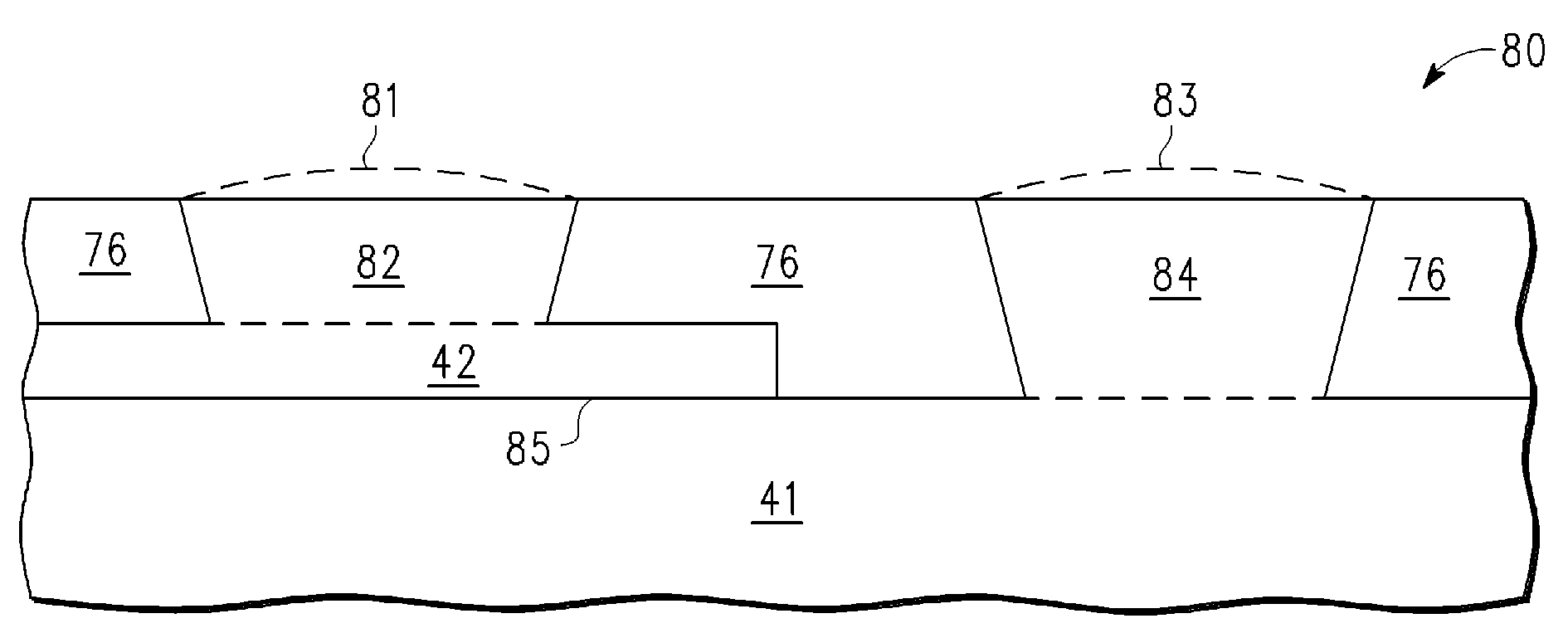

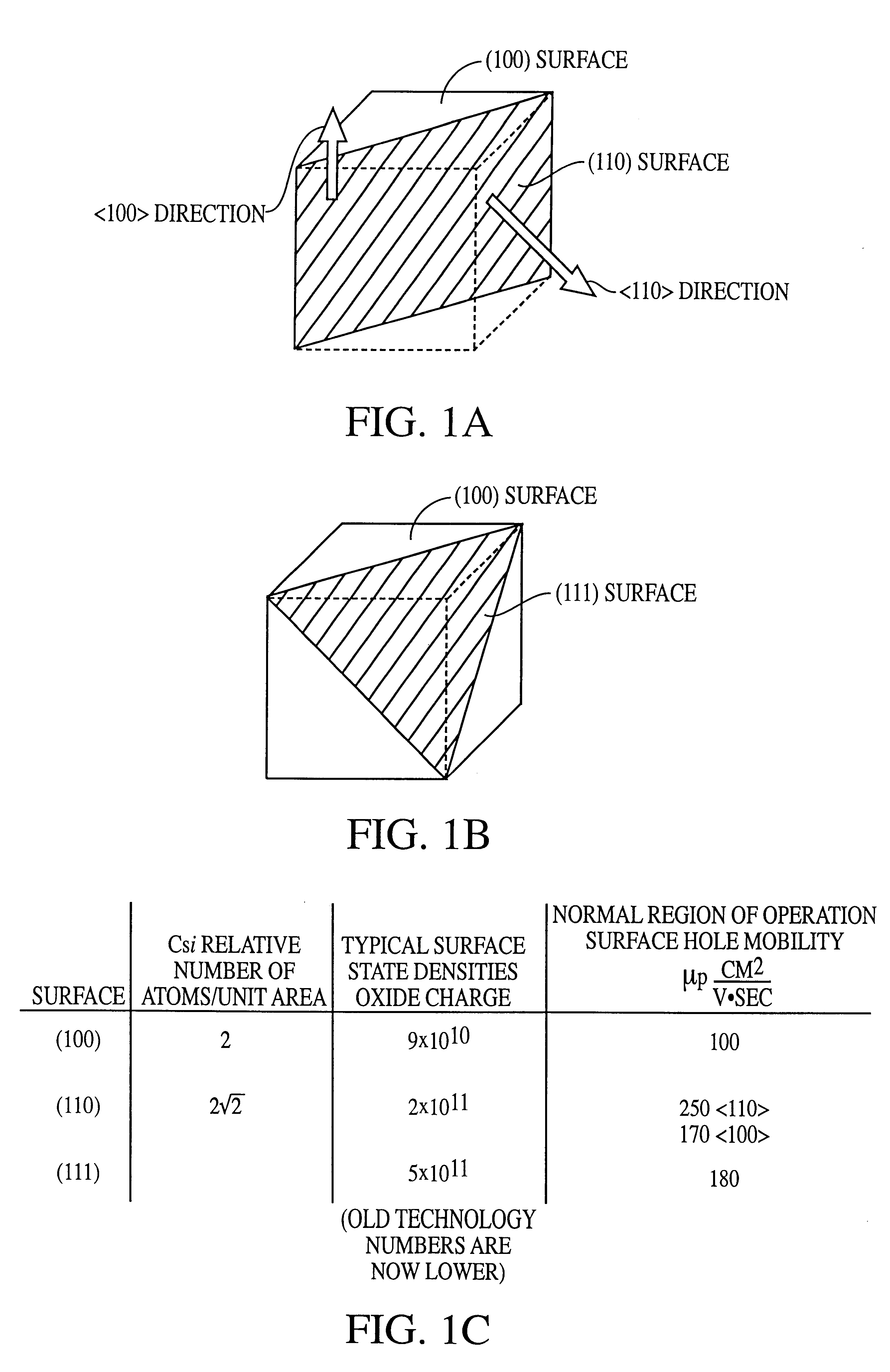

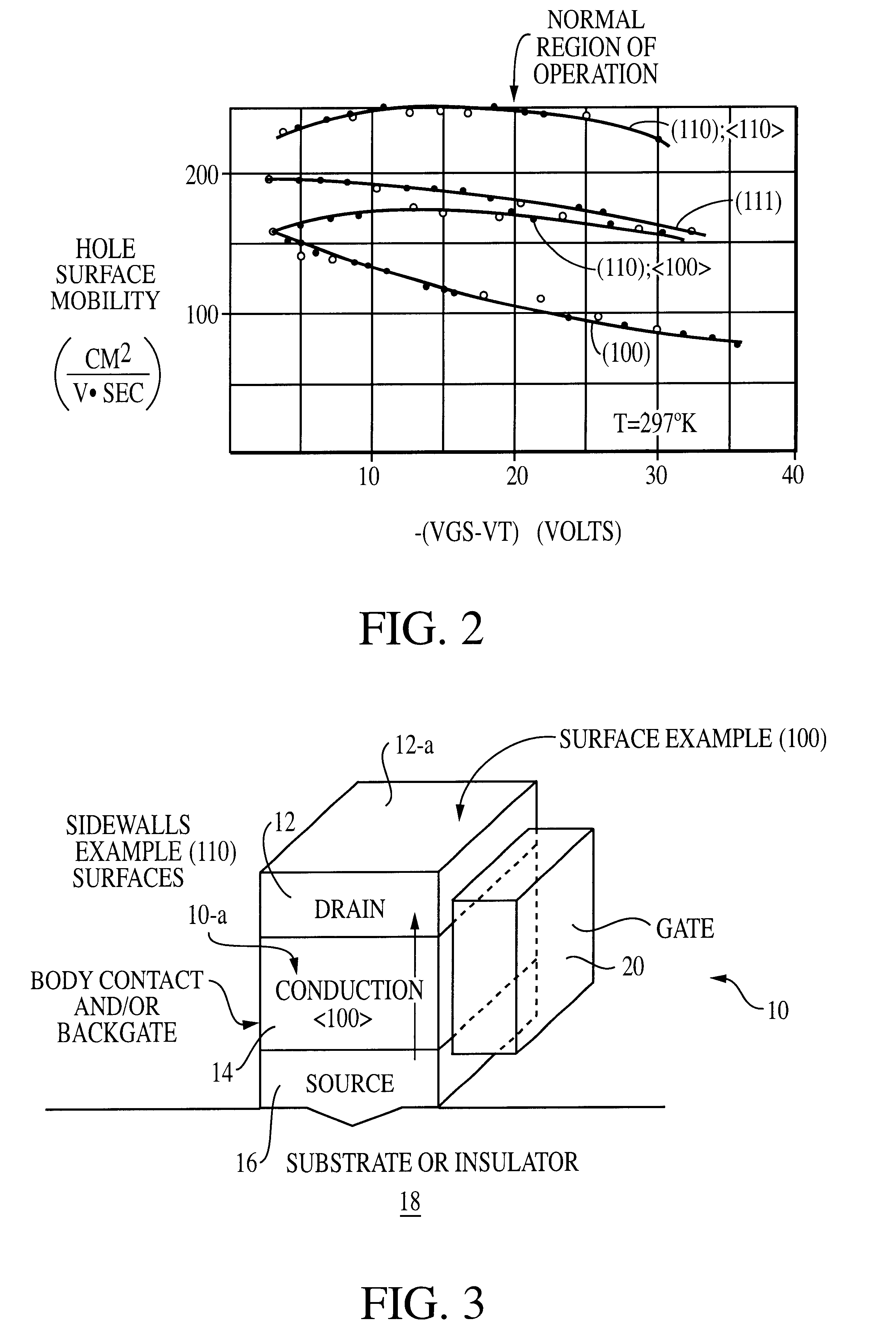

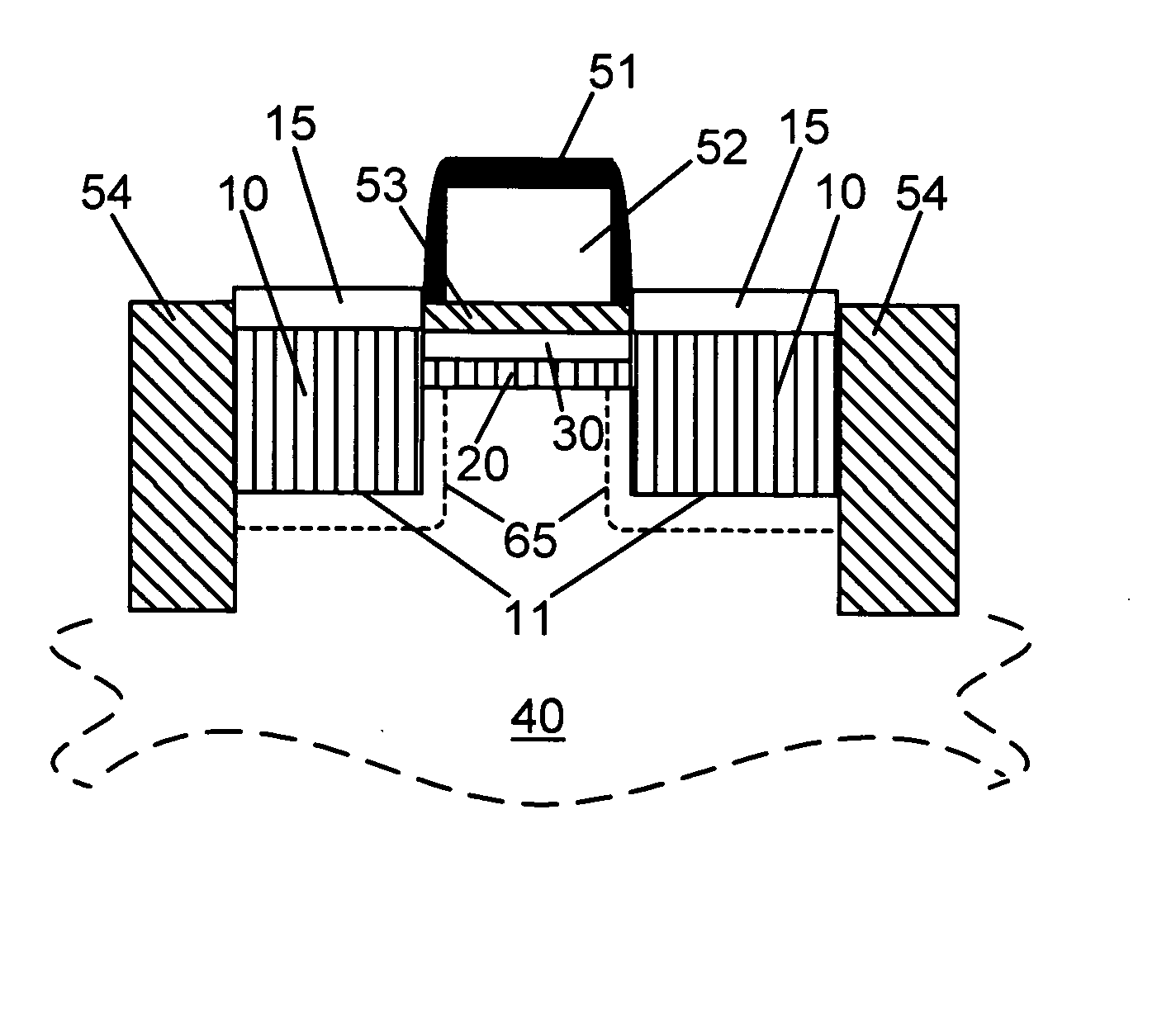

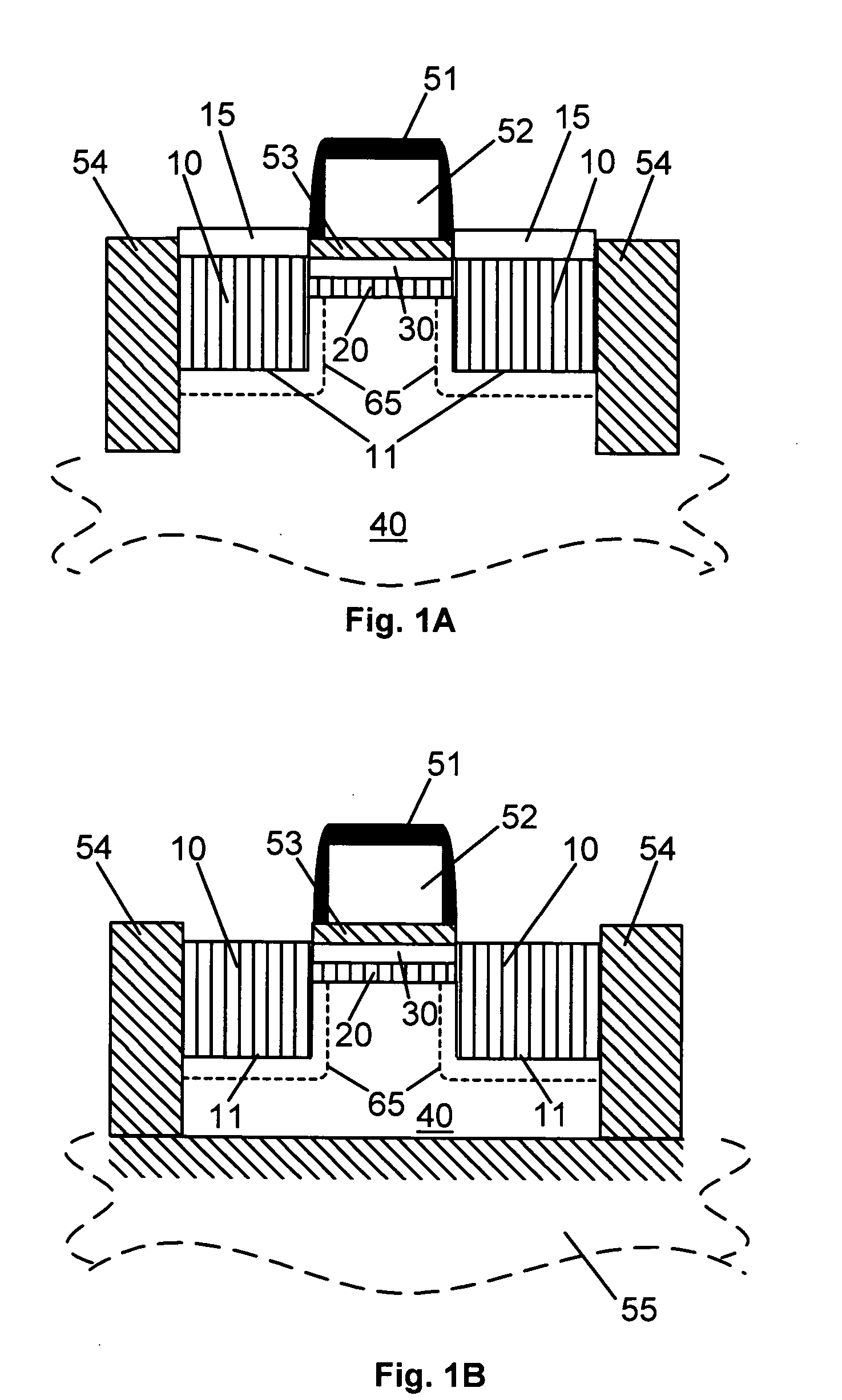

Inverse slope isolation and dual surface orientation integration

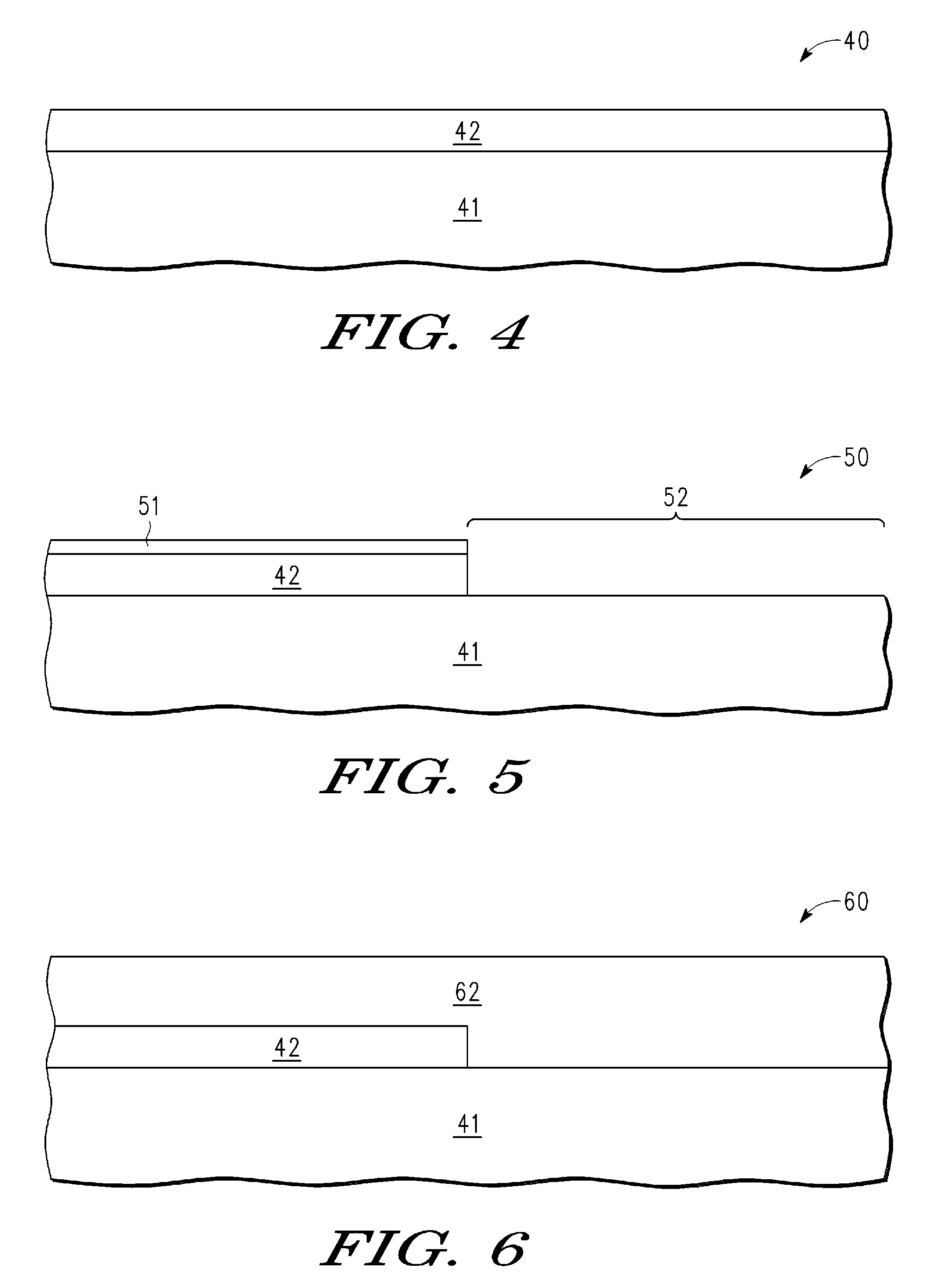

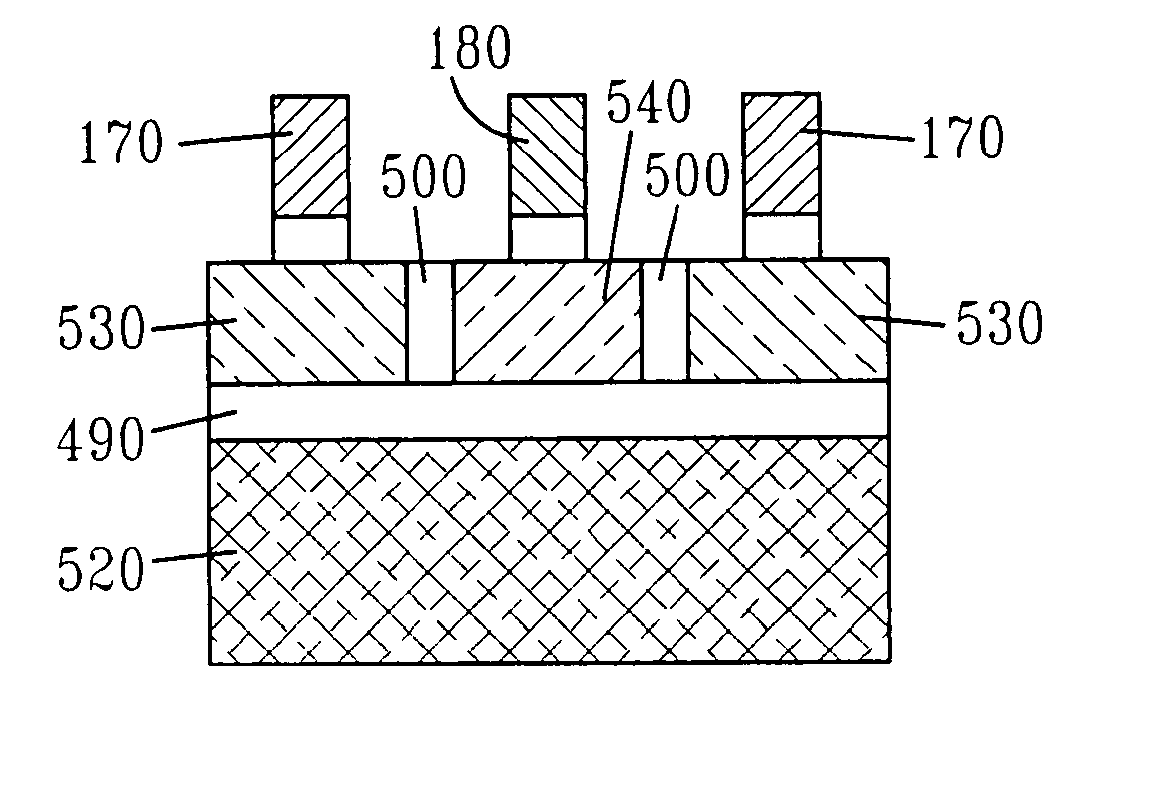

A semiconductor process and apparatus provide a high performance CMOS devices (108, 109) with hybrid or dual substrates by etching a deposited oxide layer (62) using inverse slope isolation techniques to form tapered isolation regions (76) and expose underlying semiconductor layers (41, 42) in a bulk wafer structure prior to epitaxially growing the first and second substrates (84, 82) having different surface orientations that may be planarized with a single CMP process. By forming first gate electrodes (104) over a first substrate (84) that is formed by epitaxially growing (100) silicon and forming second gate electrodes (103) over a second substrate (82) that is formed by epitaxially growing (110) silicon, a high performance CMOS device is obtained which includes high-k metal PMOS gate electrodes having improved hole mobility.

Owner:NXP USA INC

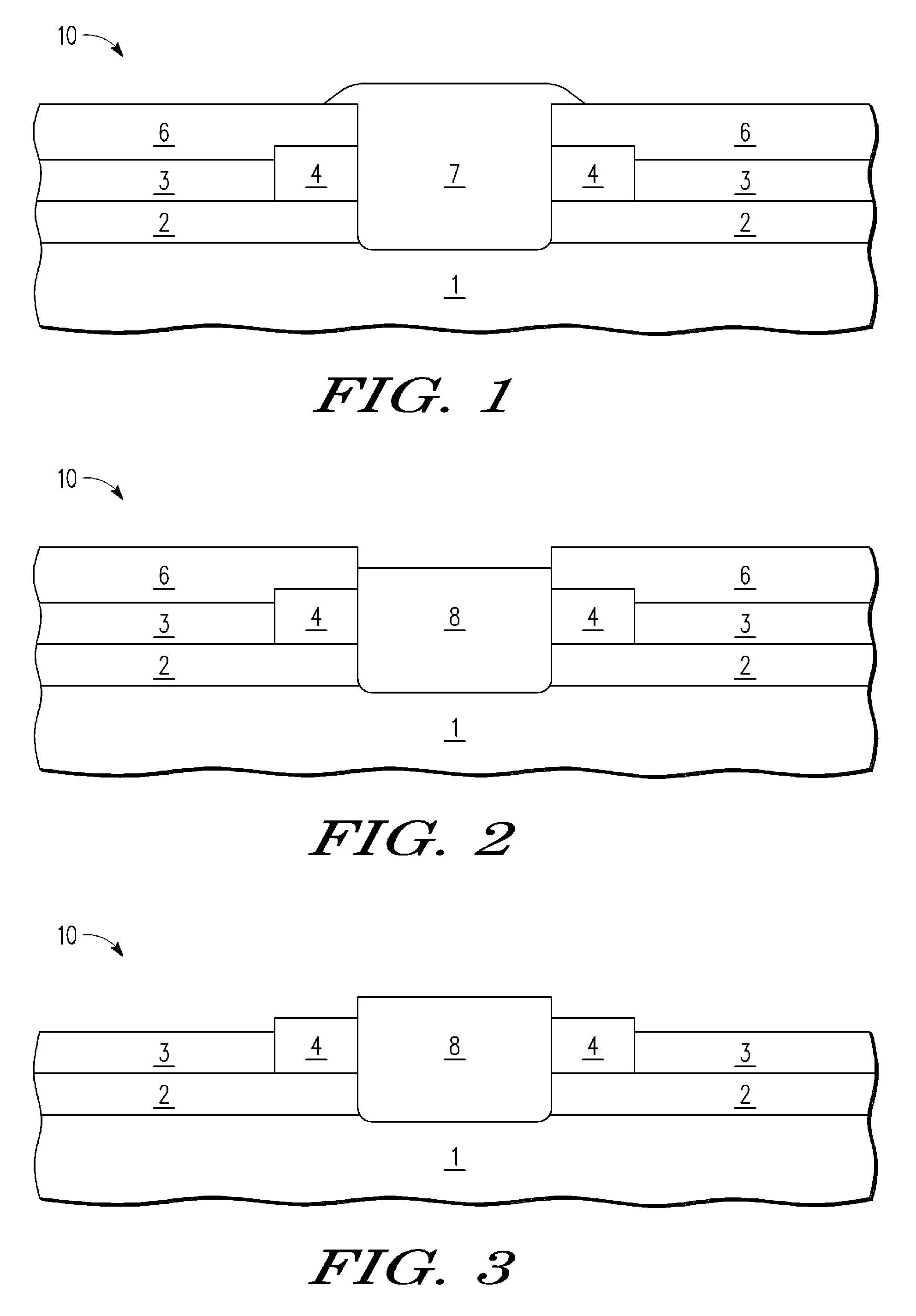

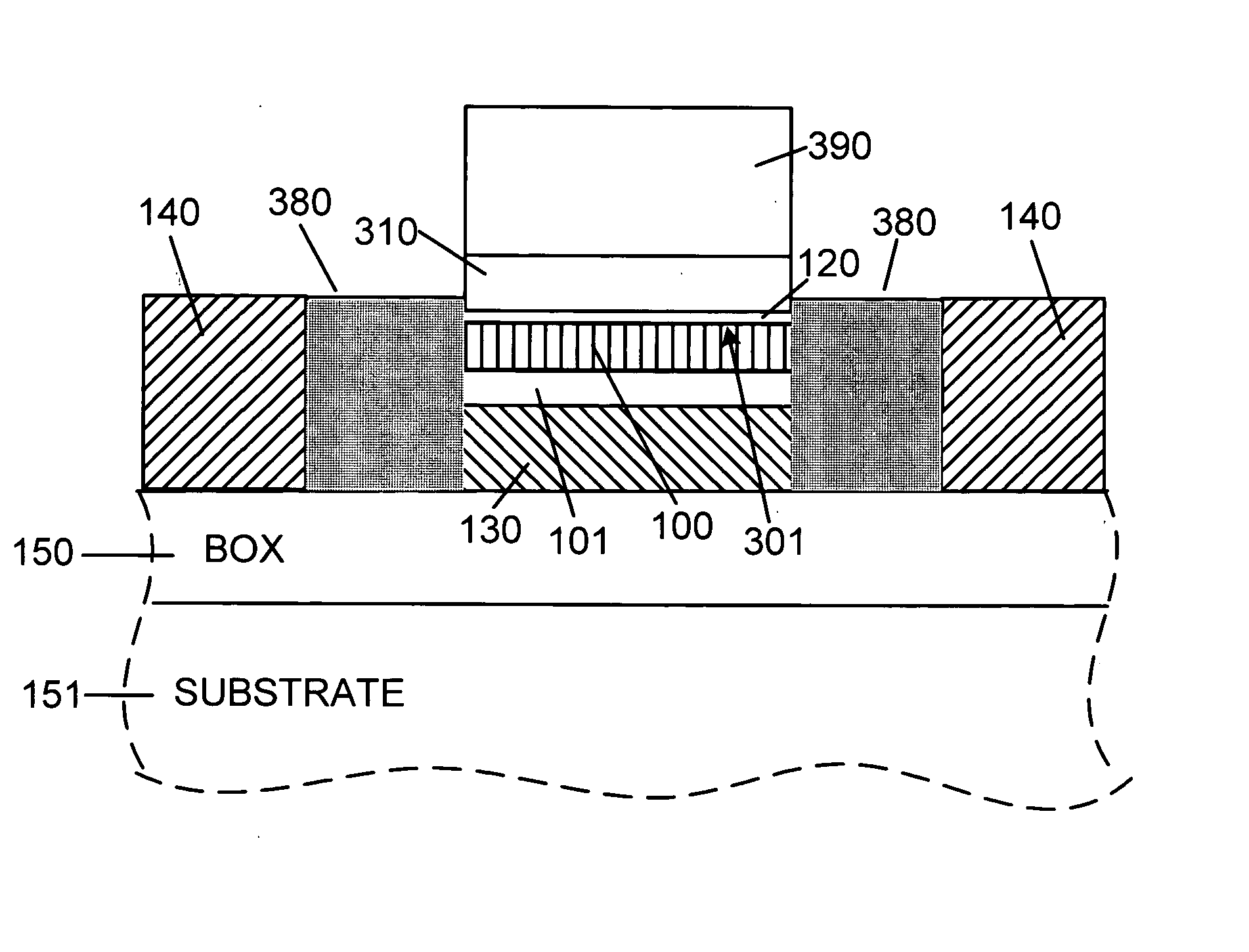

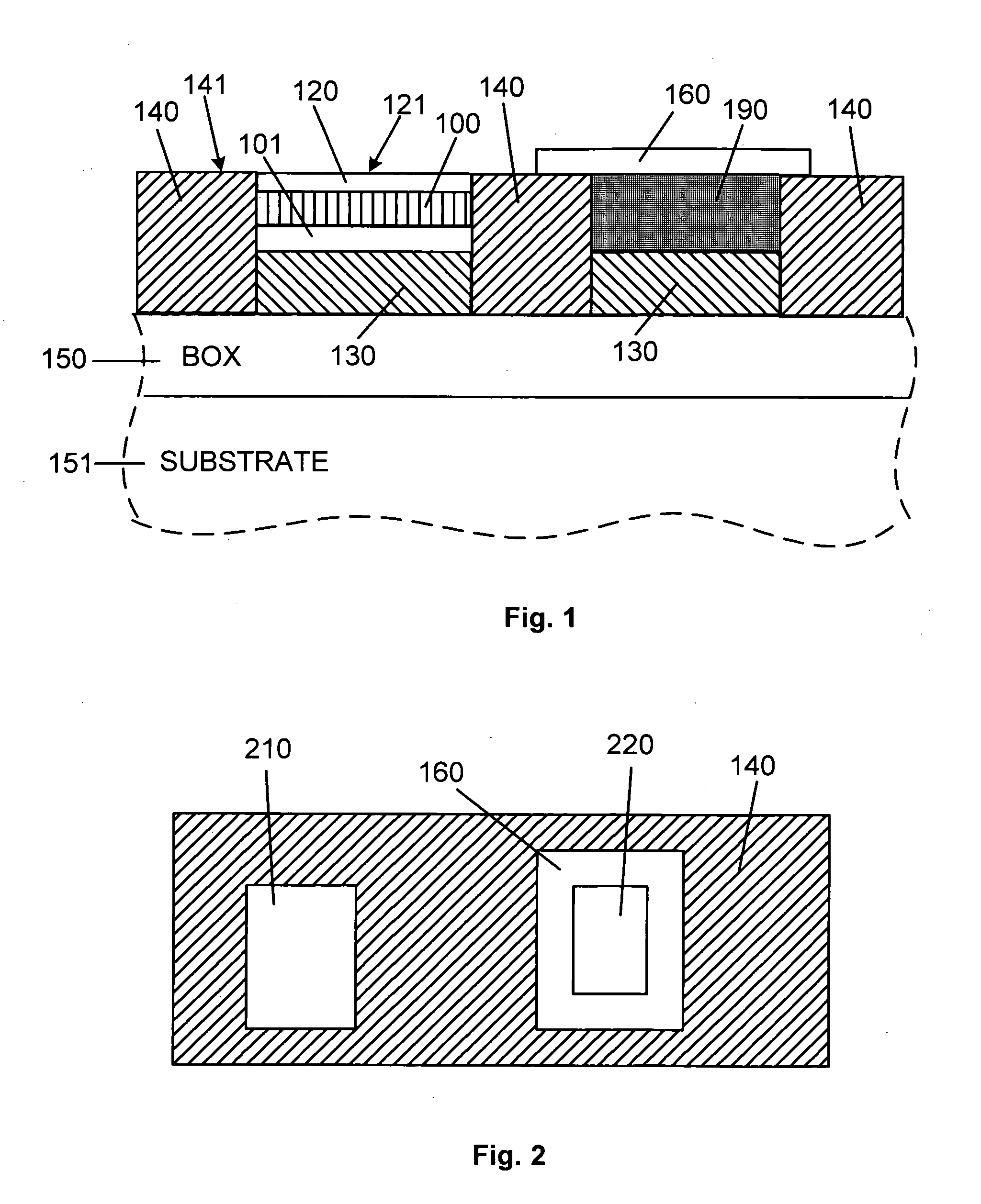

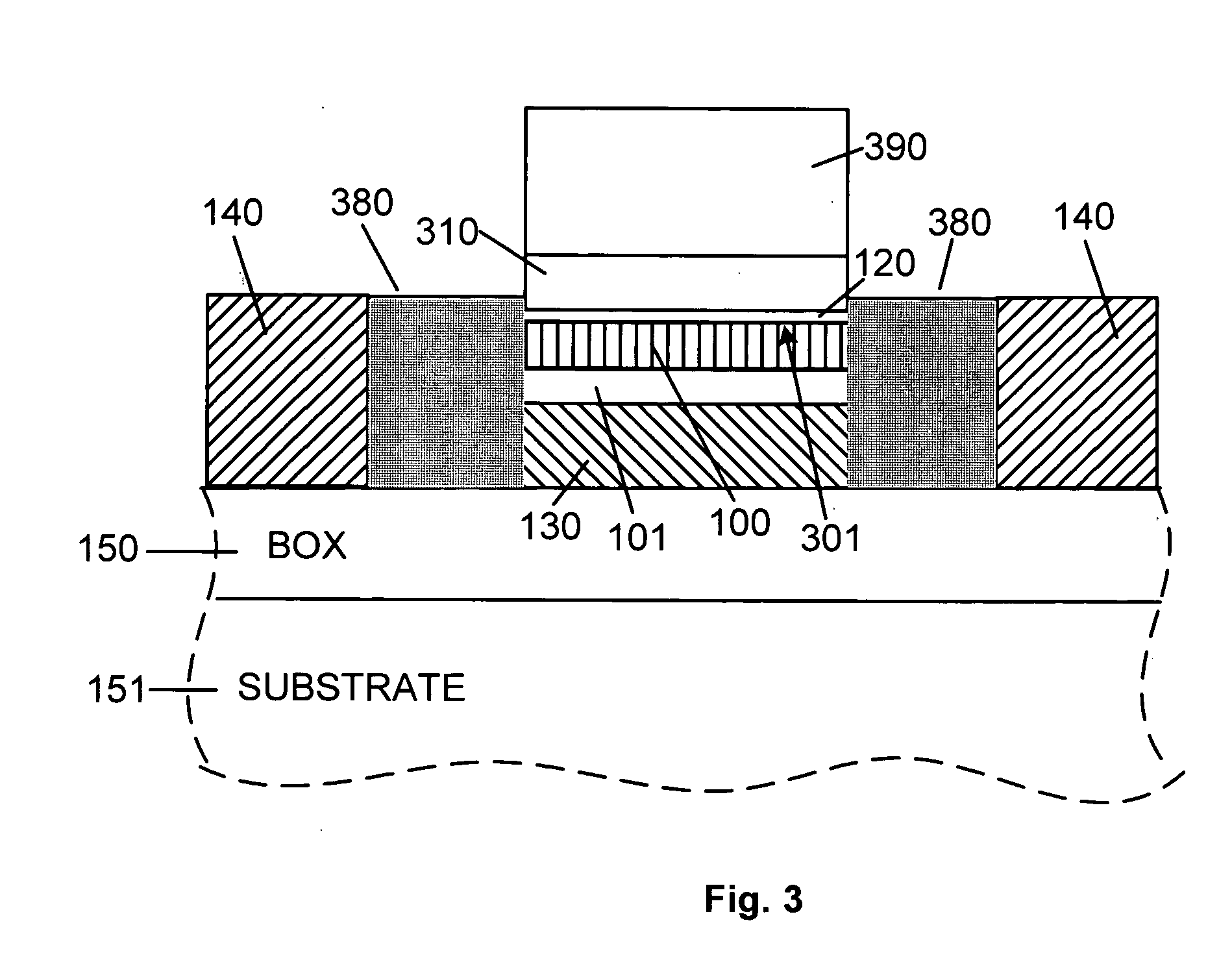

Planar substrate with selected semiconductor crystal orientations formed by localized amorphization and recrystallization of stacked template layers

A method utilizing localized amorphization and recrystallization of stacked template layers is provided for making a planar substrate having semiconductor layers of different crystallographic orientations. Also provided are hybrid-orientation semiconductor substrate structures built with the methods of the invention, as well as such structures integrated with various CMOS circuits comprising at least two semiconductor devices disposed on different surface orientations for enhanced device performance.

Owner:GLOBALFOUNDRIES INC

Semiconductor structure and device and methods of forming same using selective epitaxial process

Semiconductor structures, devices, and methods of forming the structures and device are disclosed. Exemplary structures include multi-gate or FinFET structures that can include both re-channel MOS (NMOS) and p-channel MOS (PMOS) devices to form CMOS structures and devices on a substrate. The devices can be formed using selective epitaxy and shallow trench isolation techniques.

Owner:ASM IP HLDG BV

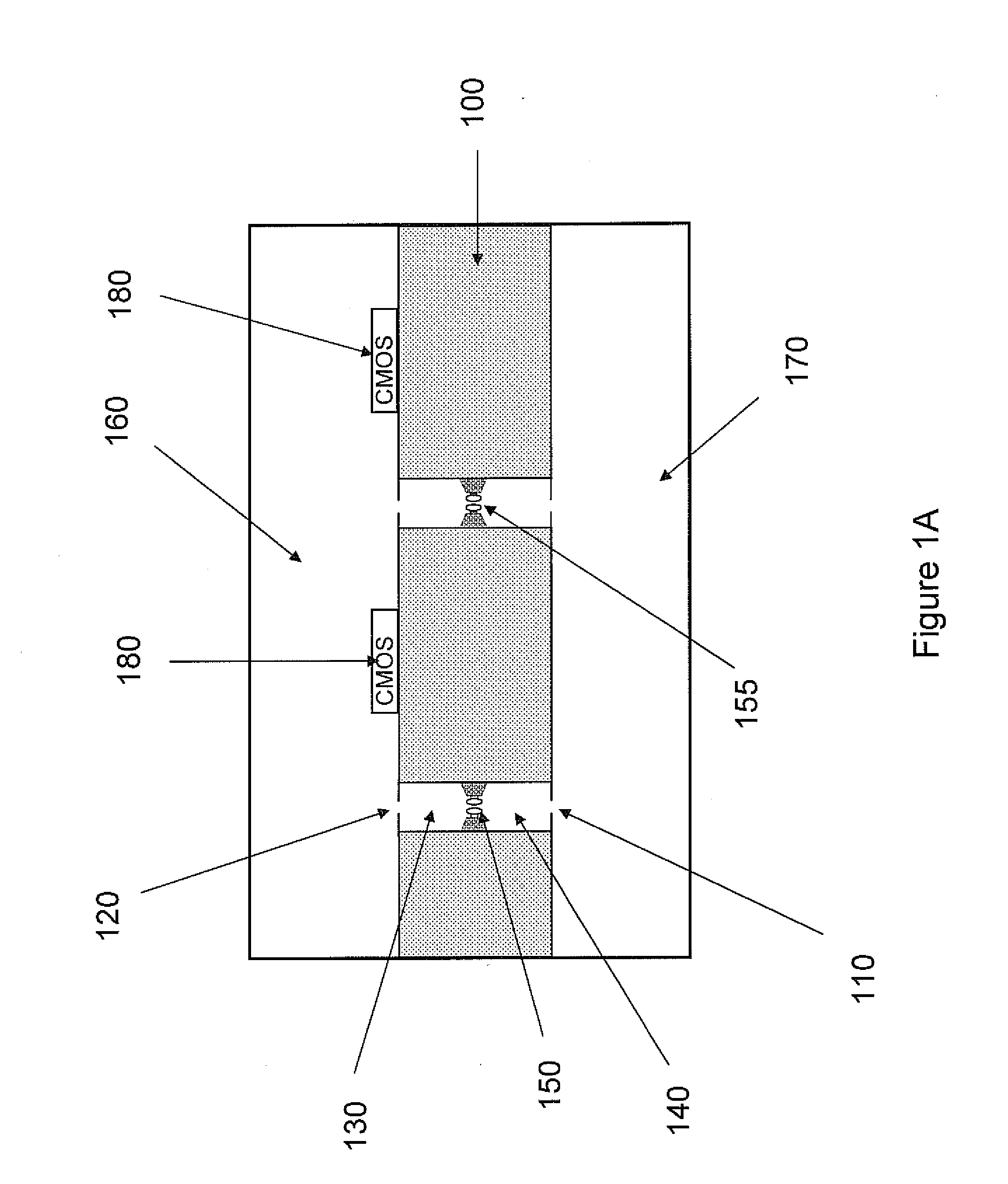

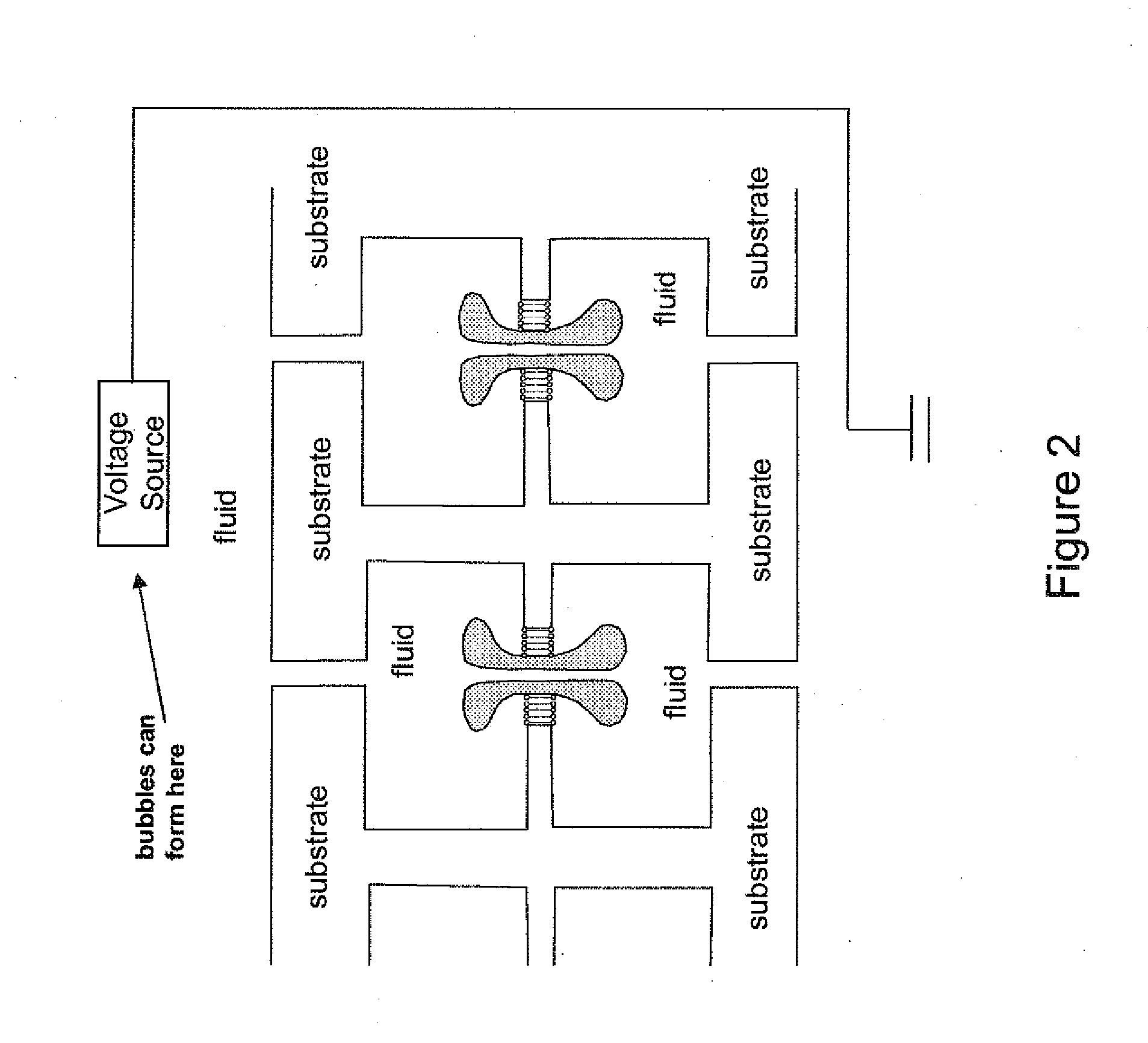

Nanopore sequencing devices and methods

ActiveUS20100331194A1Microbiological testing/measurementMaterial analysis by electric/magnetic meansCMOSElectrical resistance and conductance

The invention relates to devices and methods for nanopore sequencing. The invention includes arrays of nanopores having incorporated electronic circuits, for example, in CMOS. In some cases, the arrays of nanopores comprise resistive openings for isolating the electronic signals for improved sequencing. Methods for controlling translocation of through the nanopore are disclosed.

Owner:PACIFIC BIOSCIENCES

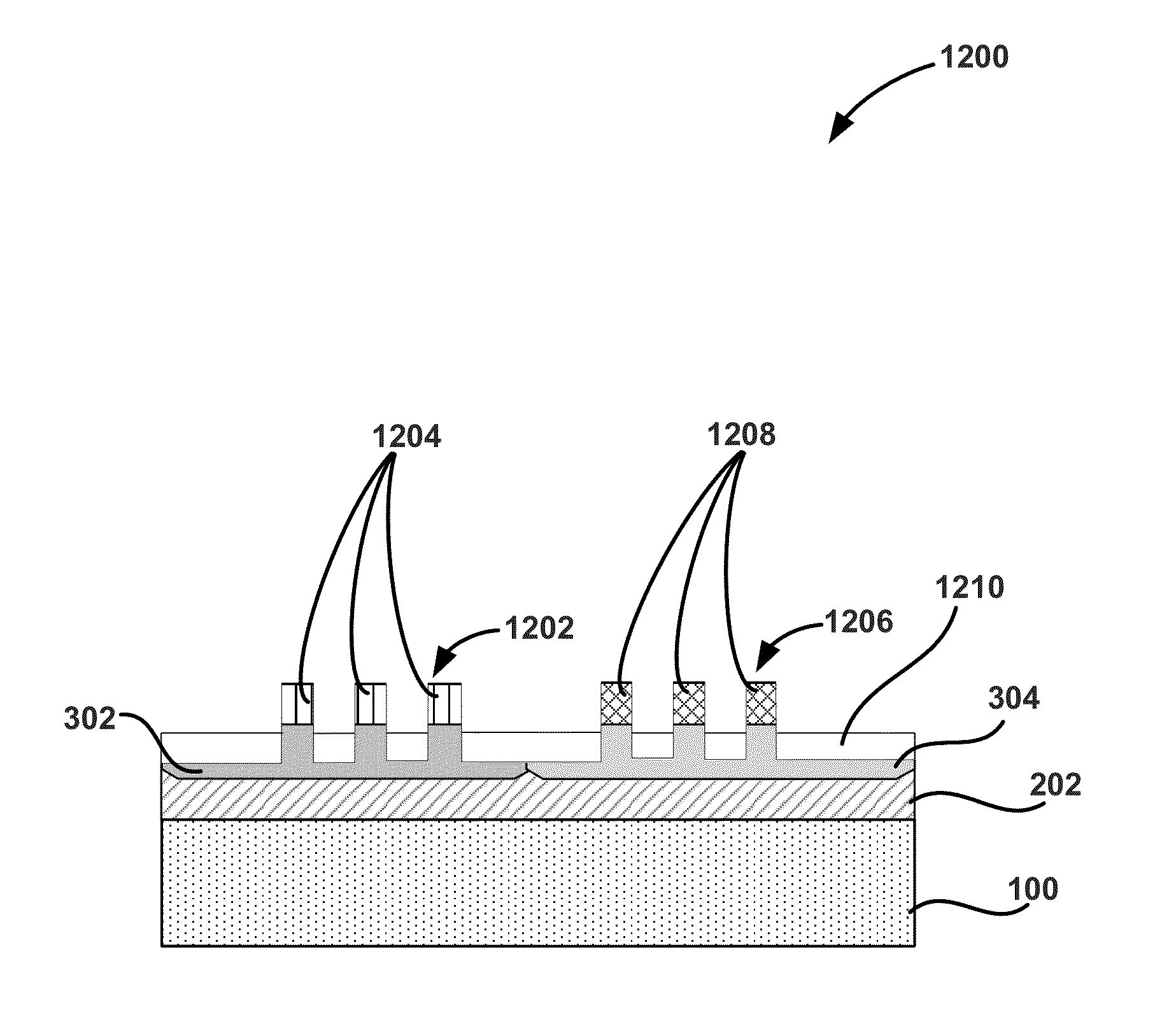

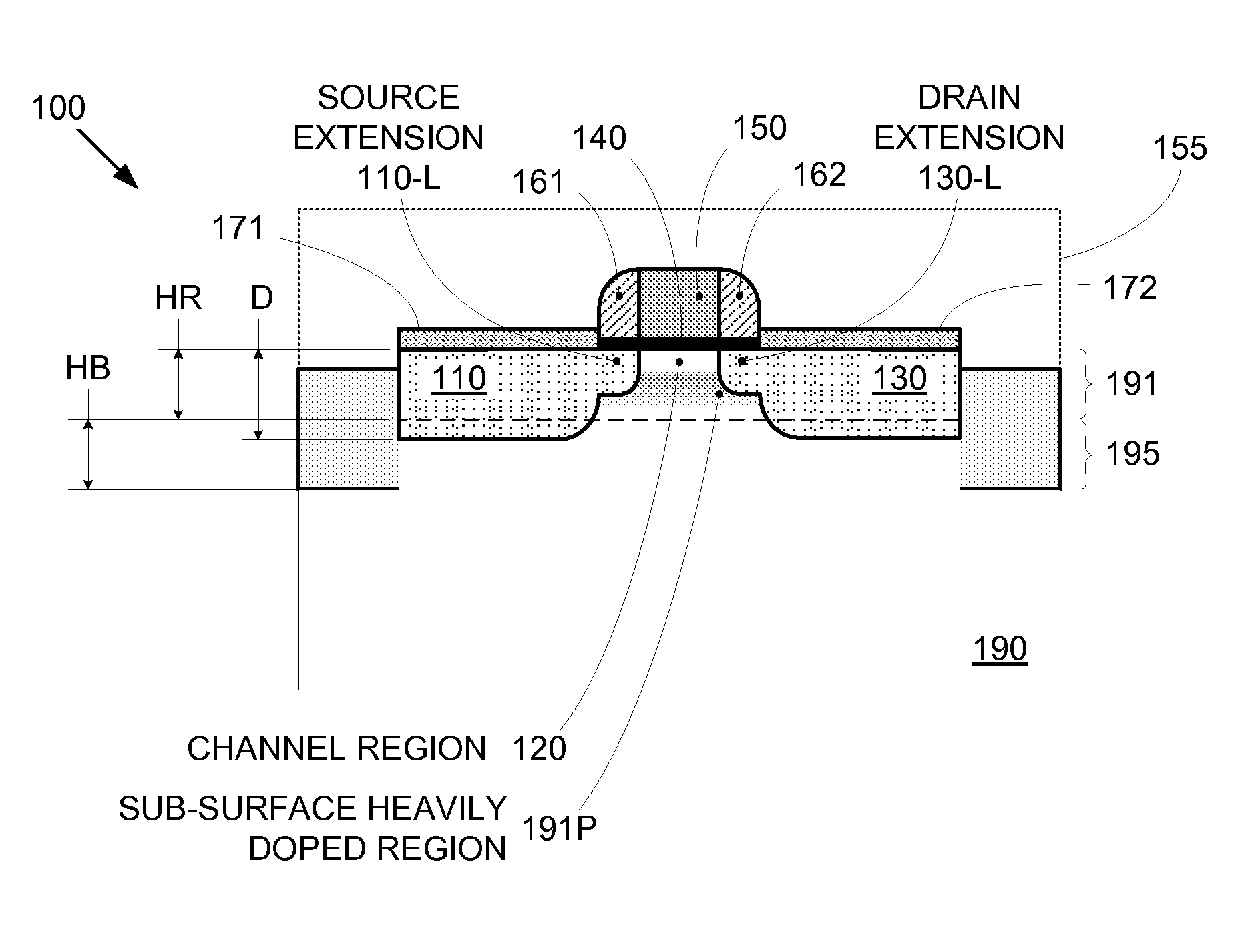

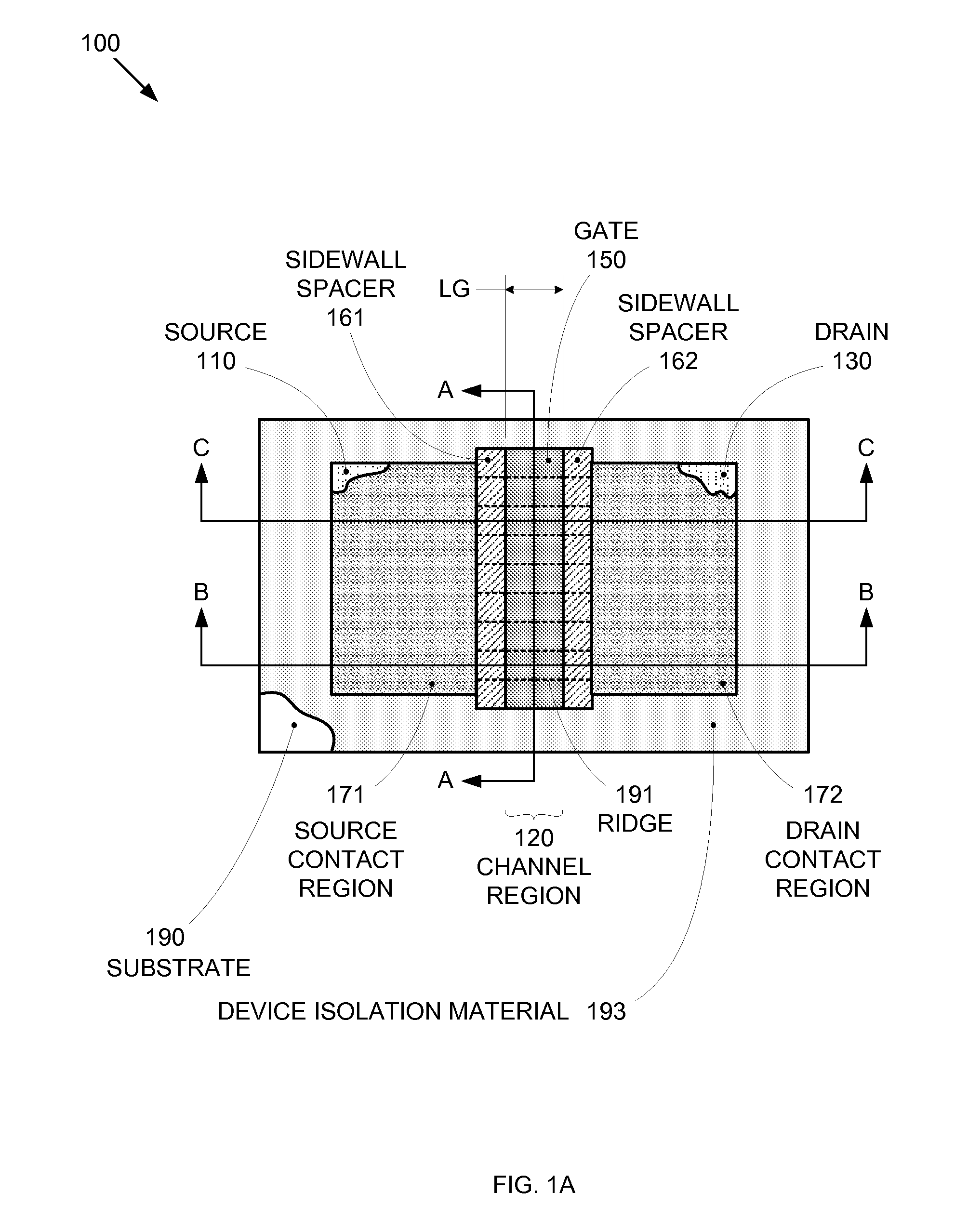

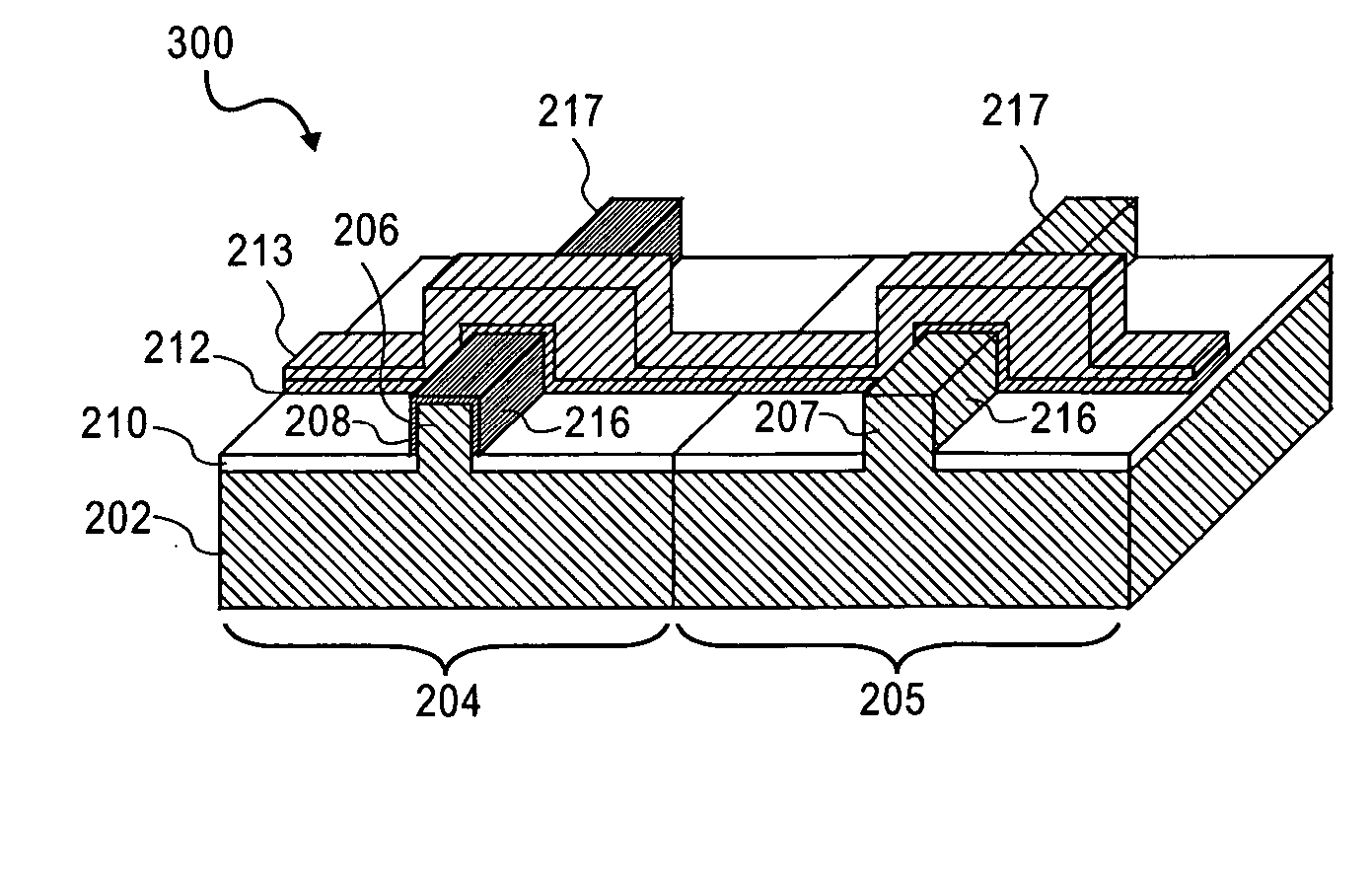

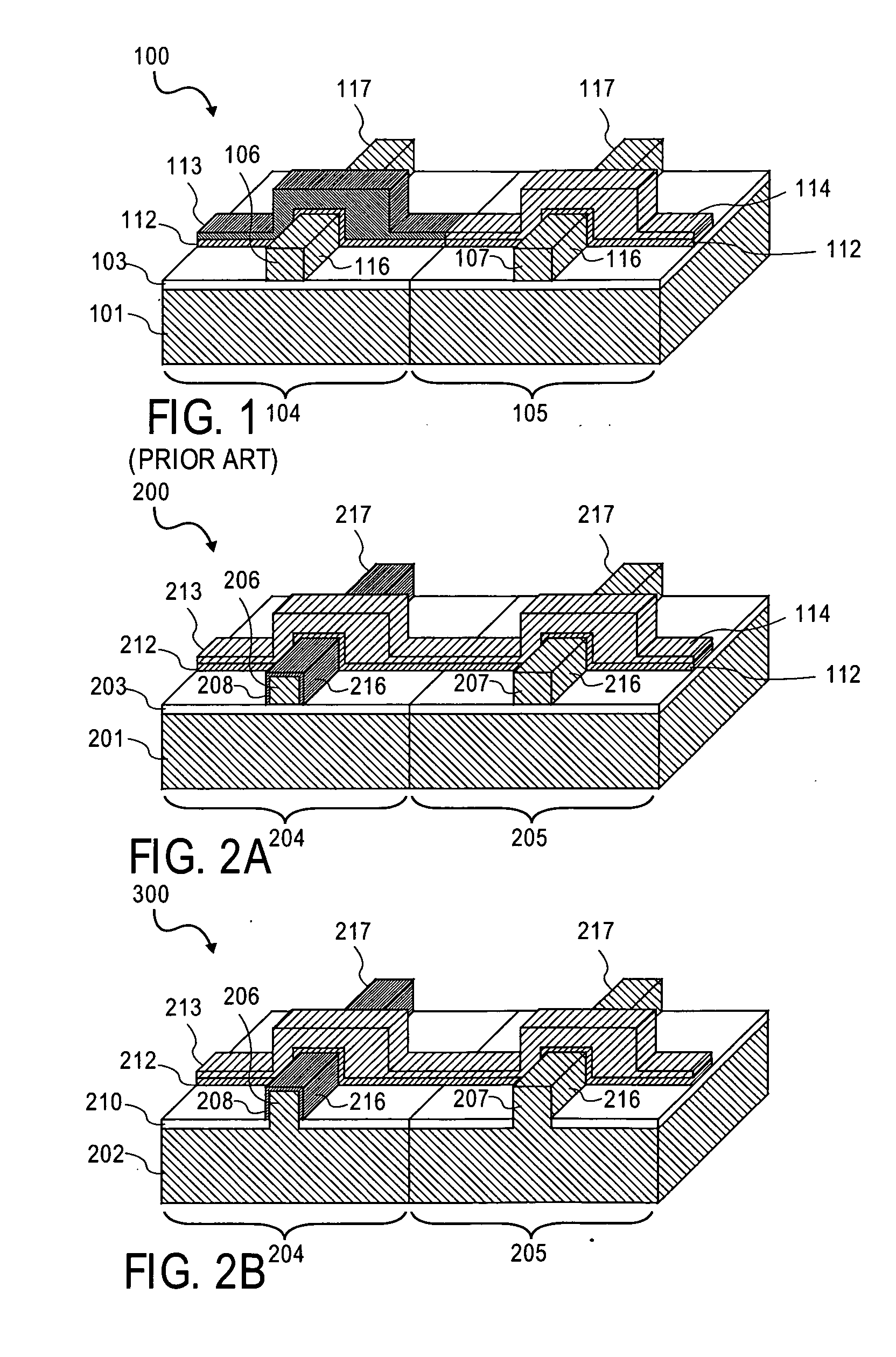

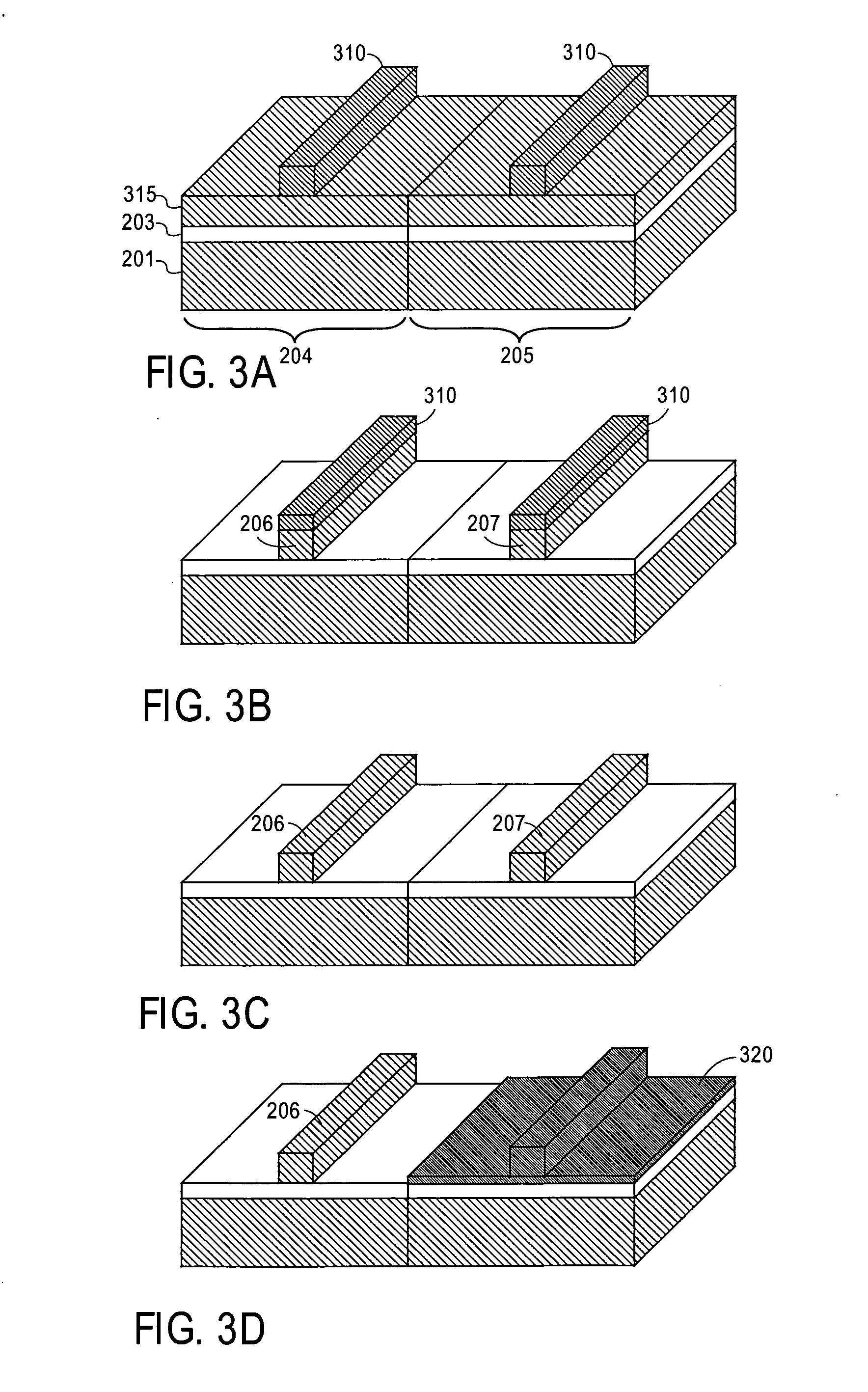

Sequential Selective Epitaxial Growth

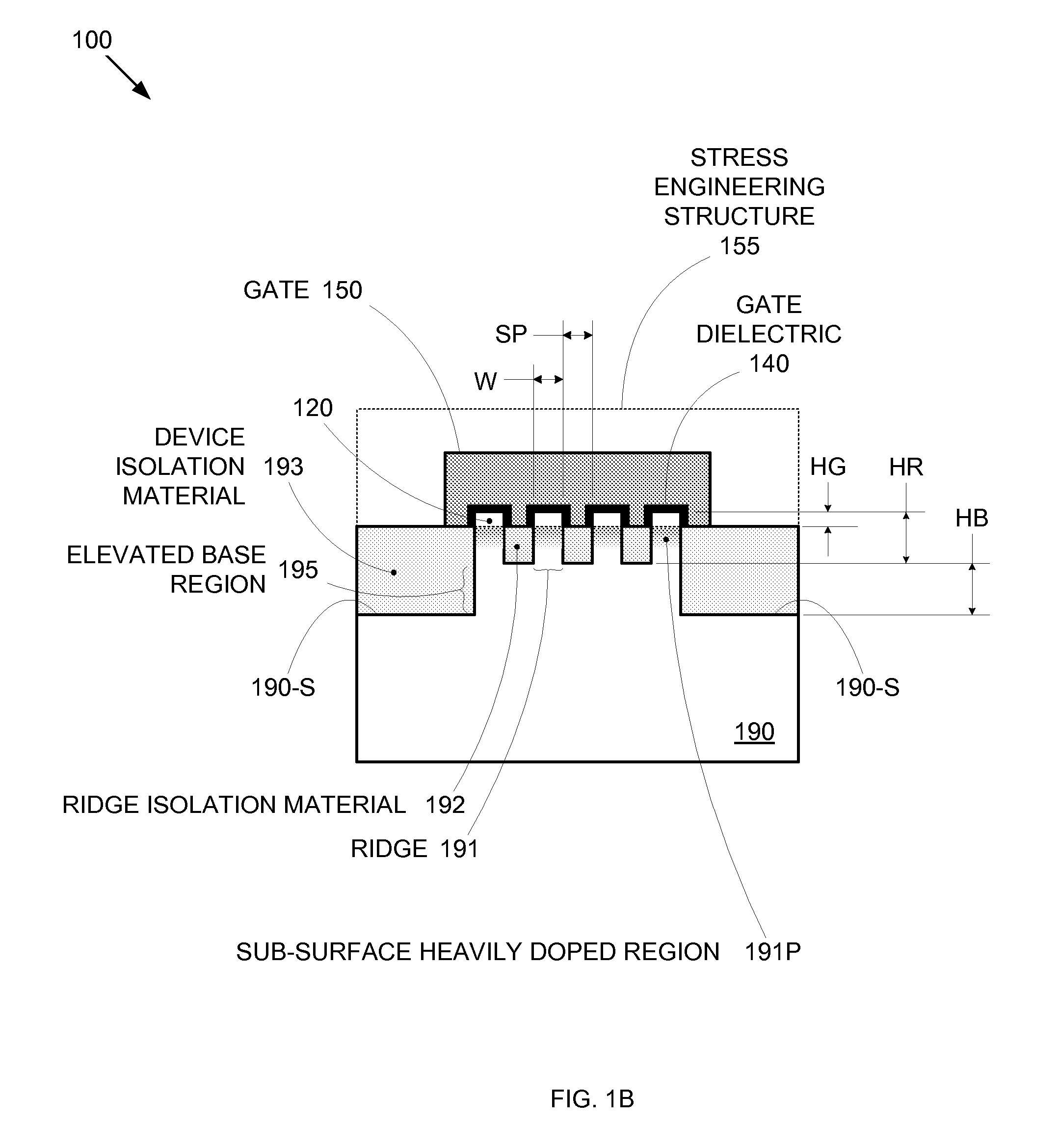

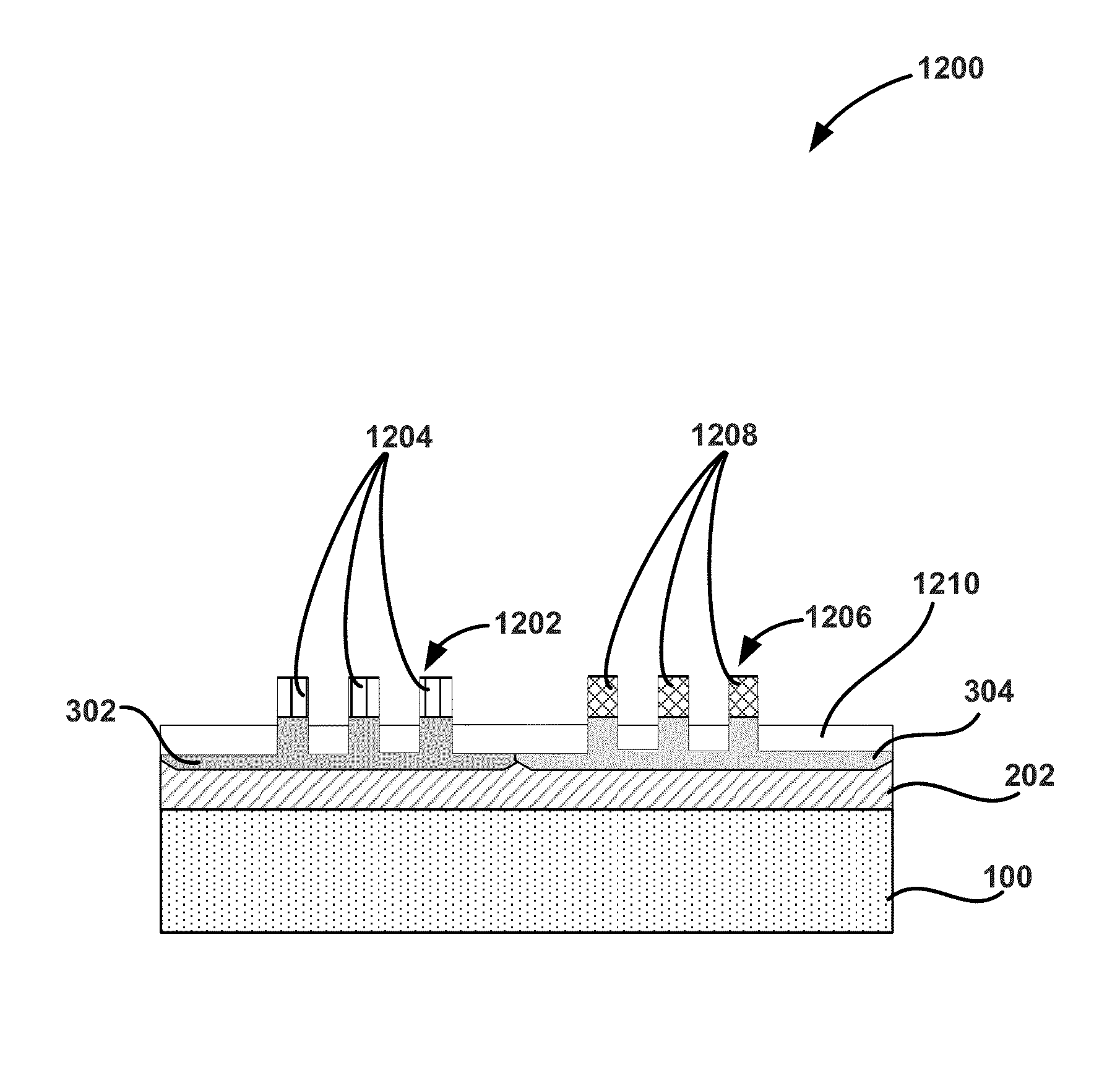

ActiveUS20070122954A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETCMOS

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. A multi step epitaxial process can be used to extend the ridges with different dopant types, high mobility semiconductor, and or advanced multi-layer strutures. For CMOS integrated circuits a capping layer is formed over the a first region. Epitaxial layers are formed in a second region. Then the capping layer is removed from the first region and a capping layer is formed over the second region. Epitaxial layers can than be formed in the first region.

Owner:SYNOPSYS INC

Semiconductor structure and device and methods of forming same using selective epitaxial process

Owner:ASM IP HLDG BV

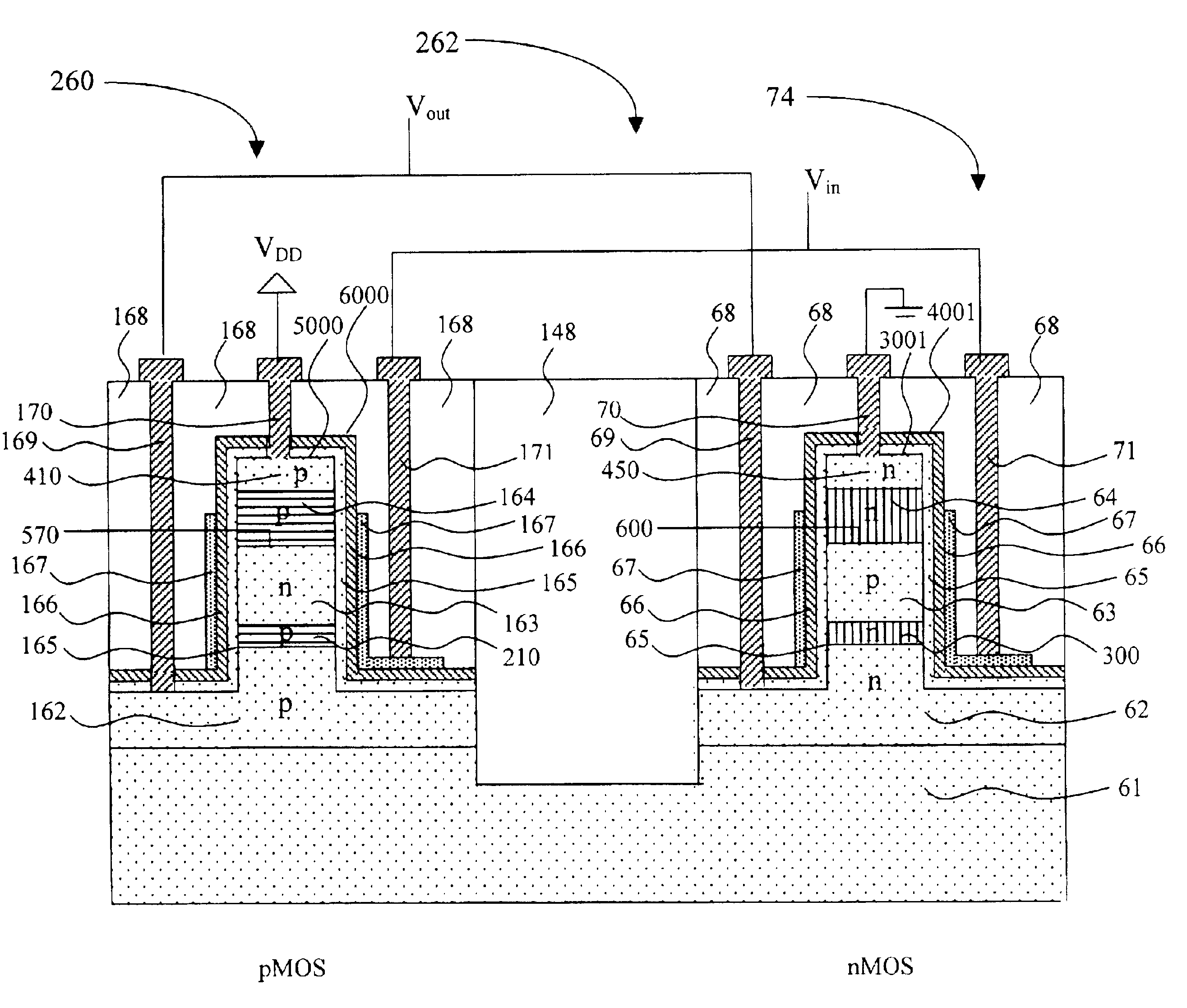

CMOS devices with a single work function gate electrode and method of fabrication

InactiveUS20070090416A1Lower threshold voltageEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingCMOSDevice form

Described herein are a device utilizing a gate electrode material with a single work function for both the pMOS and nMOS transistors where the magnitude of the transistor threshold voltages is modified by semiconductor band engineering and article made thereby. Further described herein are methods of fabricating a device formed of complementary (pMOS and nMOS) transistors having semiconductor channel regions which have been band gap engineered to achieve a low threshold voltage.

Owner:TAHOE RES LTD

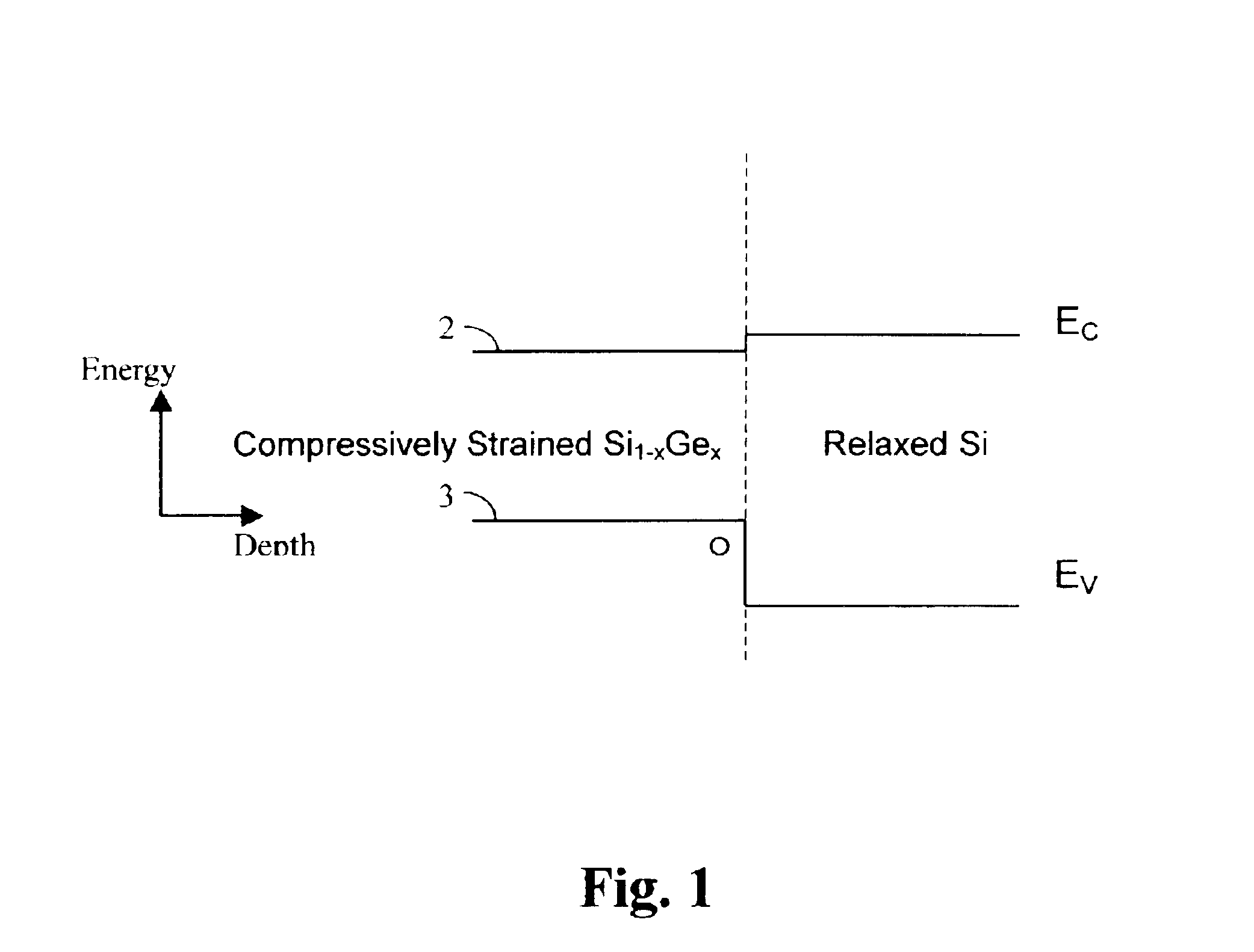

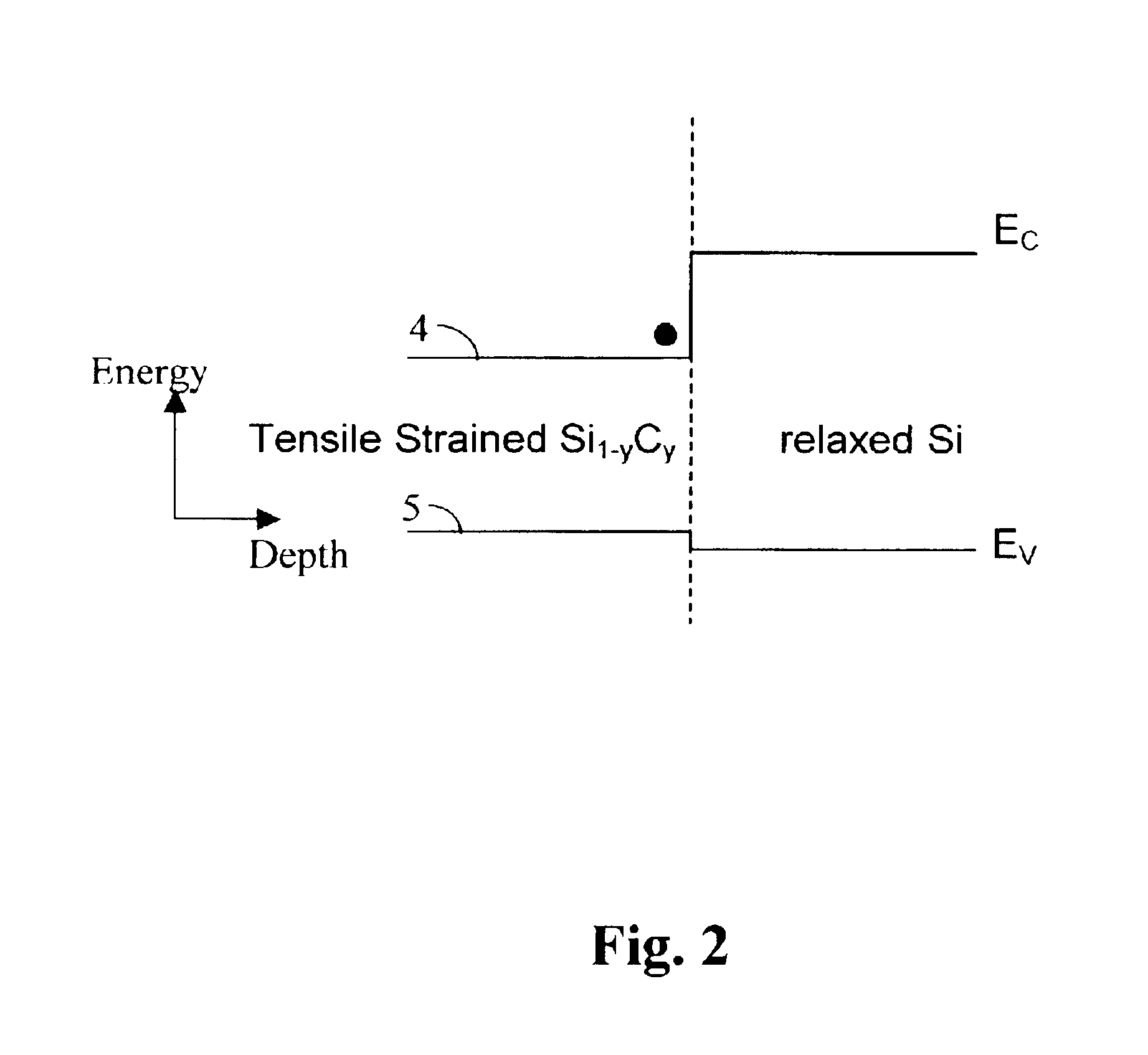

Integration of strained Ge into advanced CMOS technology

InactiveUS20050285097A1Improve mobilityImprove scalabilitySolid-state devicesSemiconductor/solid-state device manufacturingCMOSEngineering

A structure and method of fabrication for PFET devices in a compressively strained Ge layer is disclosed. The fabrication method of such devices is compatible with standard CMOS technology and it is fully scalable. The processing includes selective epitaxial depositions of an over 50% Ge content buffer layer, a pure Ge layer, and a SiGe top layer. Fabricated buried channel PMOS devices hosted in the compressively strained Ge layer show superior device characteristics relative to similar Si devices.

Owner:GLOBALFOUNDRIES INC

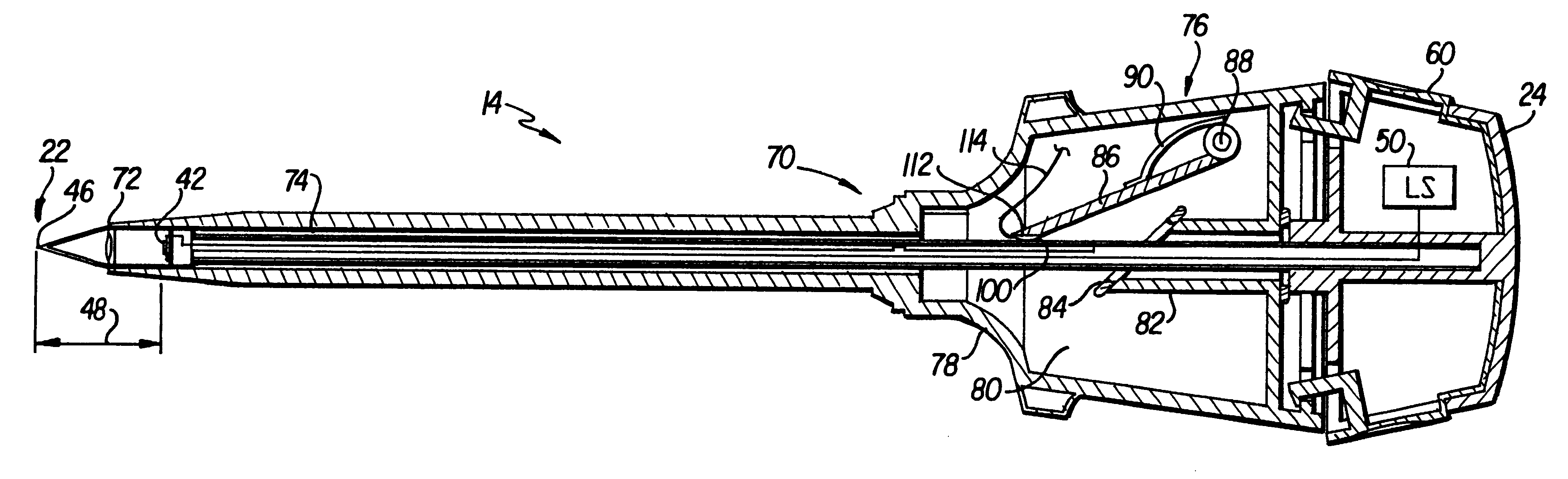

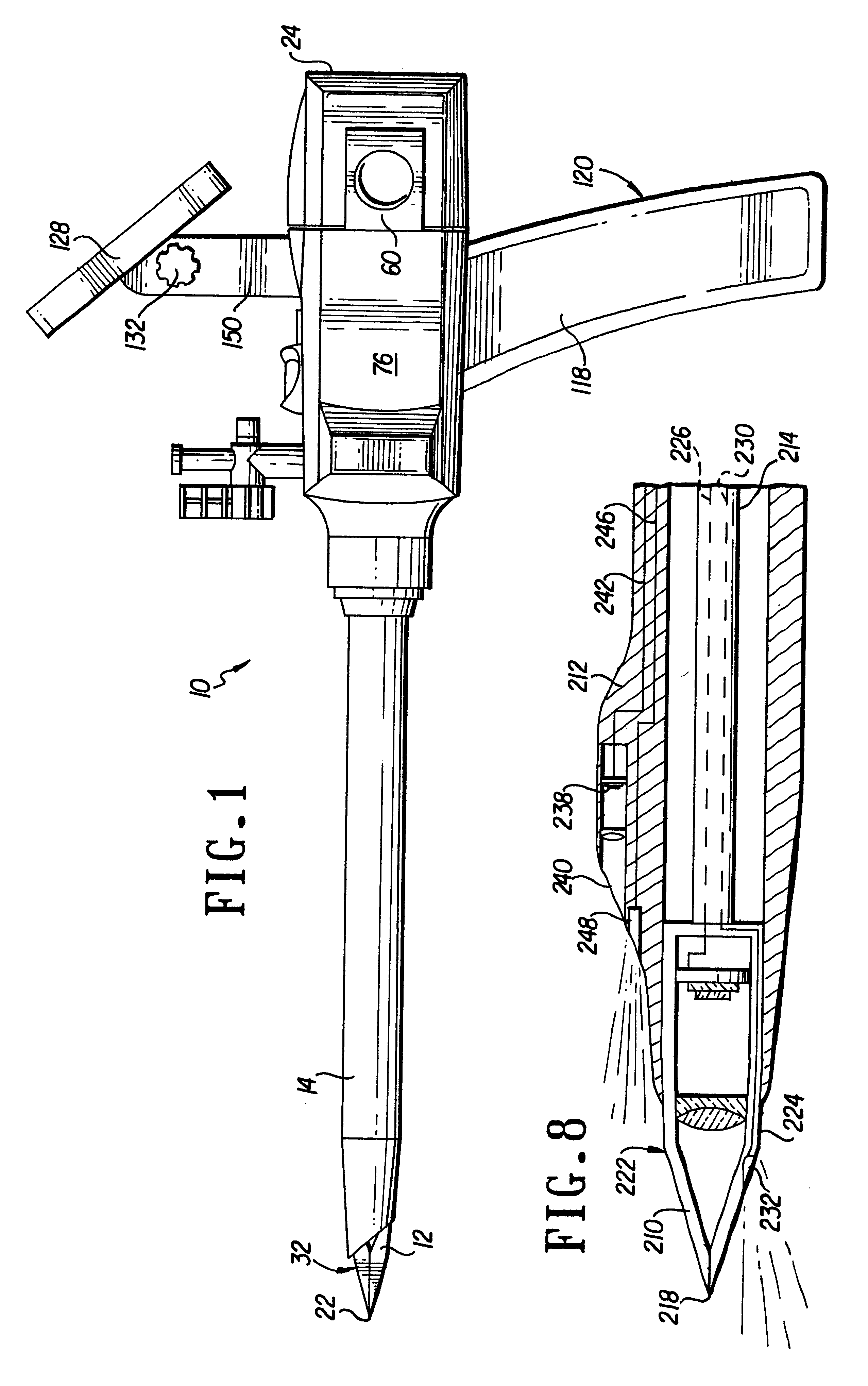

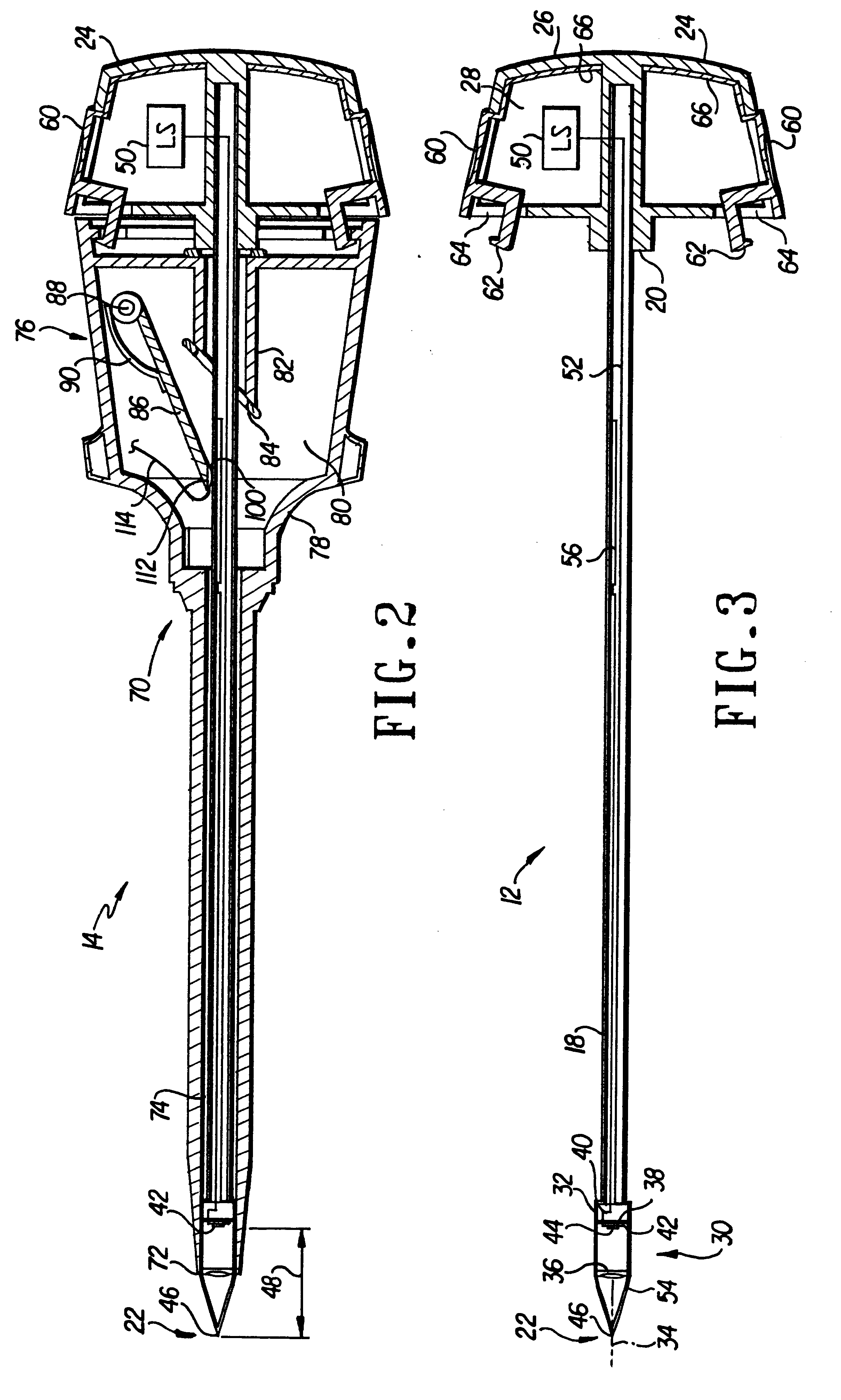

Penetrating endoscope and endoscopic surgical instrument with CMOS image sensor and display

A penetrating endoscope provides visualization of organ or tissue structures or foreign objects in a body. The penetrating endoscope includes an elongate penetrating member, a complementary metal dioxide semiconductor (CMOS) image sensor and an objective lens. The CMOS image sensor is substantially planar and includes a plurality of pixels with a pixel signal processing circuit for generating a color image ready signal. The CMOS image sensor converts image light energy into electrical color image ready signal energy for transmission out of the body. The color image ready signal is viewed on a color image display. The CMOS image sensor is carried on the elongate penetrating member adjacent a distal end of the elongate penetrating member. The objective lens is also carried on the distal end of the elongate penetrating member on an optical axis and focuses an image corresponding to an endoscope field of view at an image plane intersecting the optical axis. The CMOS image sensor is mounted with the CMOS image sensor pixels disposed substantially in the image plane and on the optical axis. The penetrating endoscope may include end effectors such as cutters and forceps.

Owner:YOON INBAE

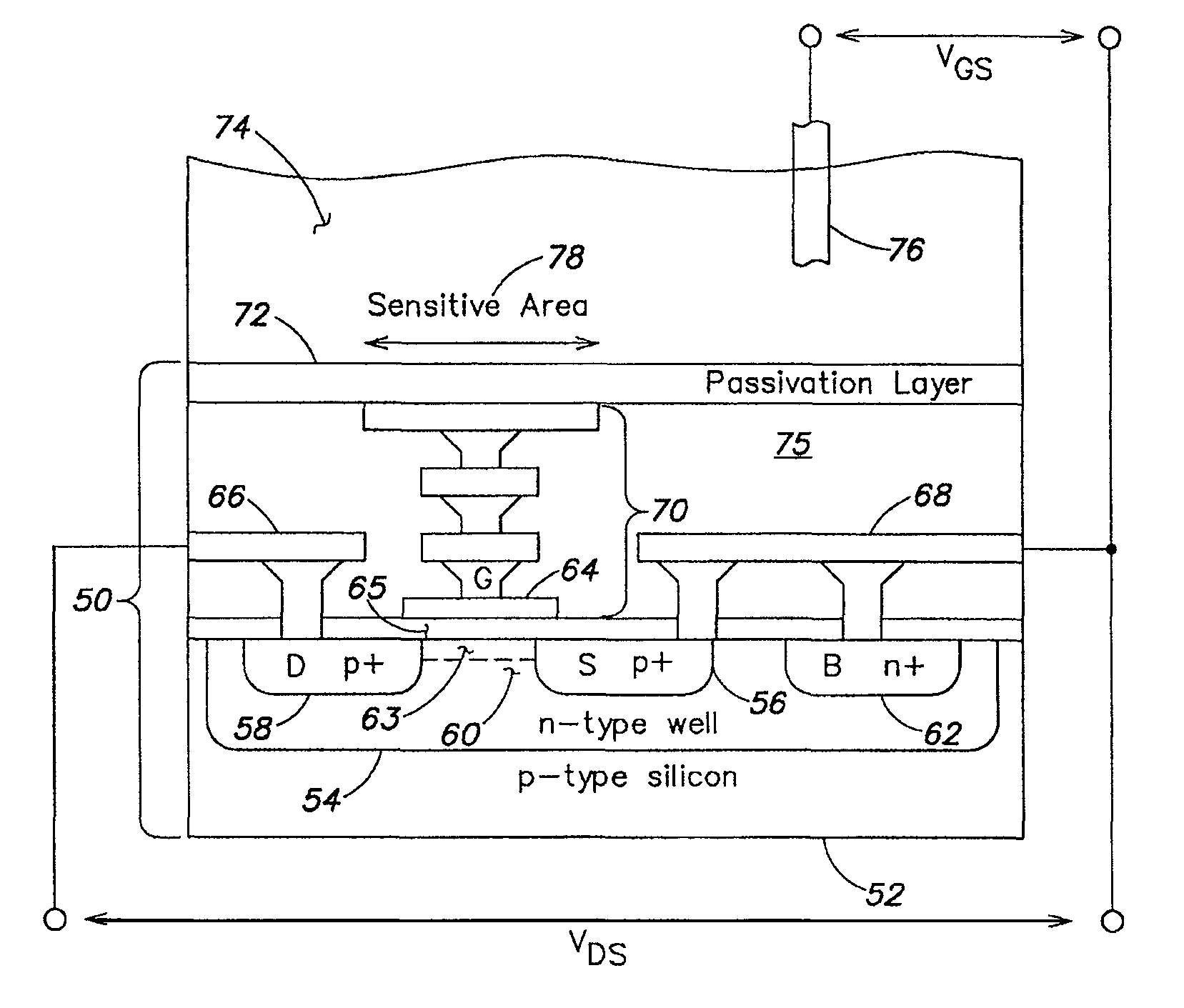

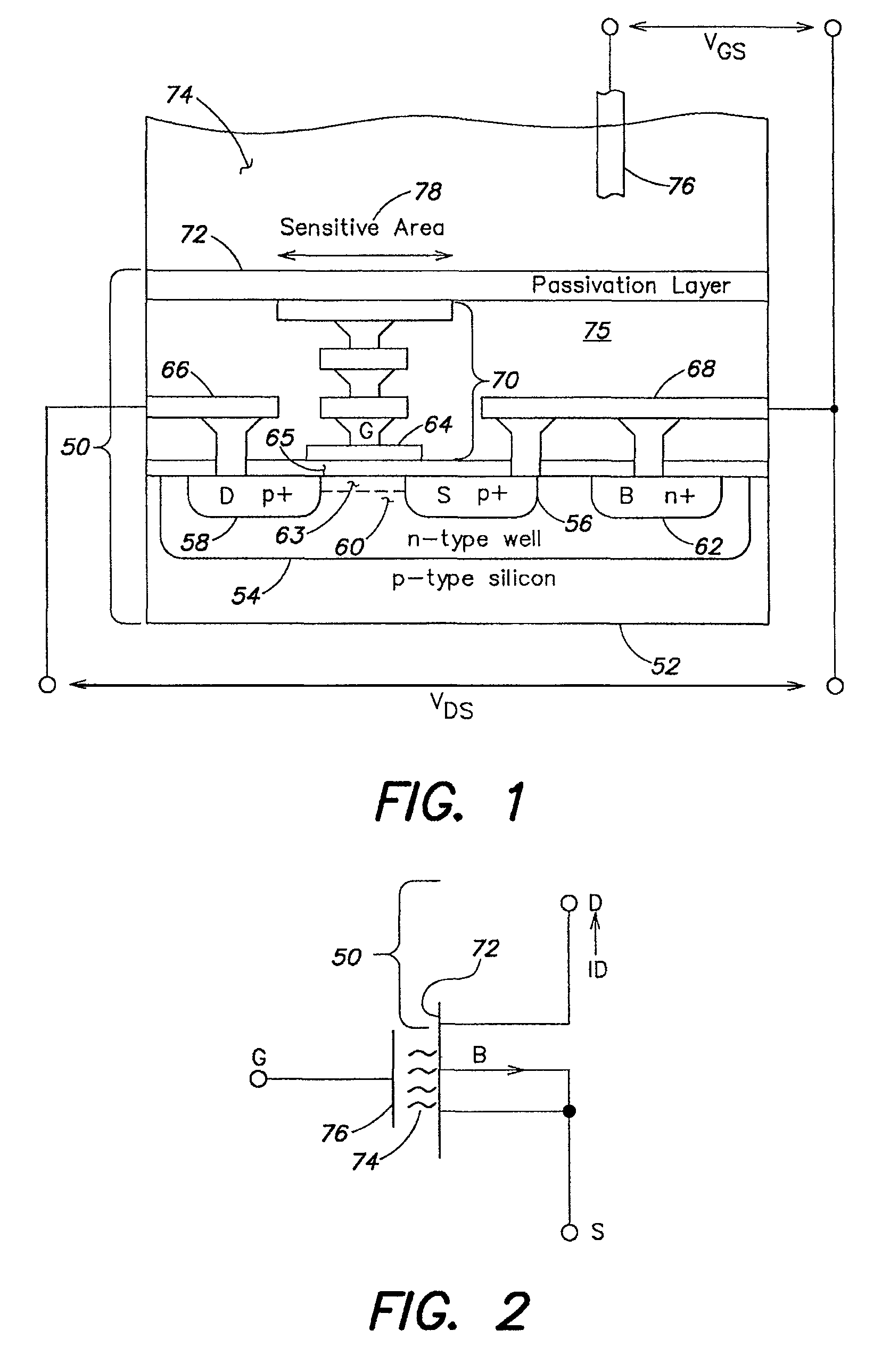

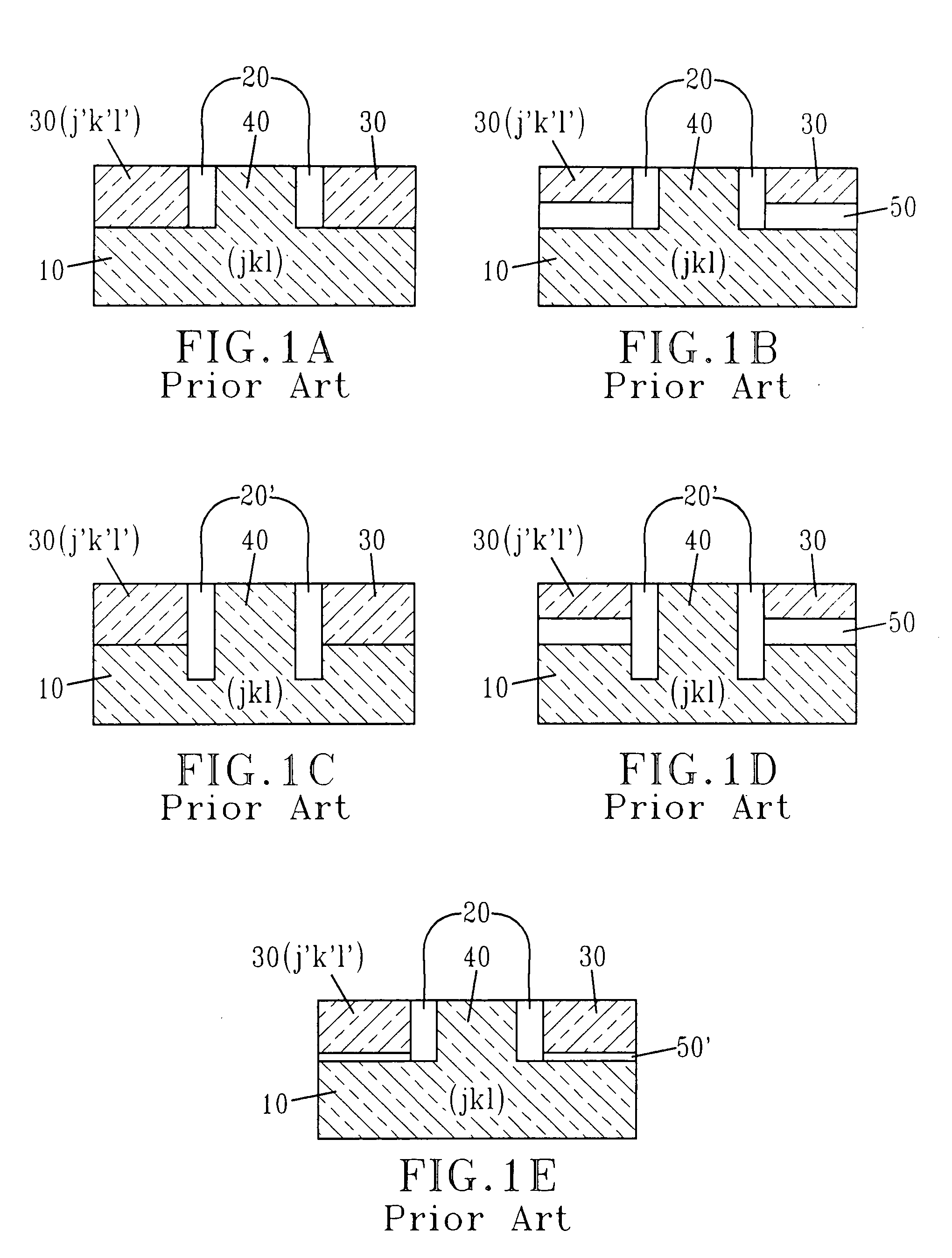

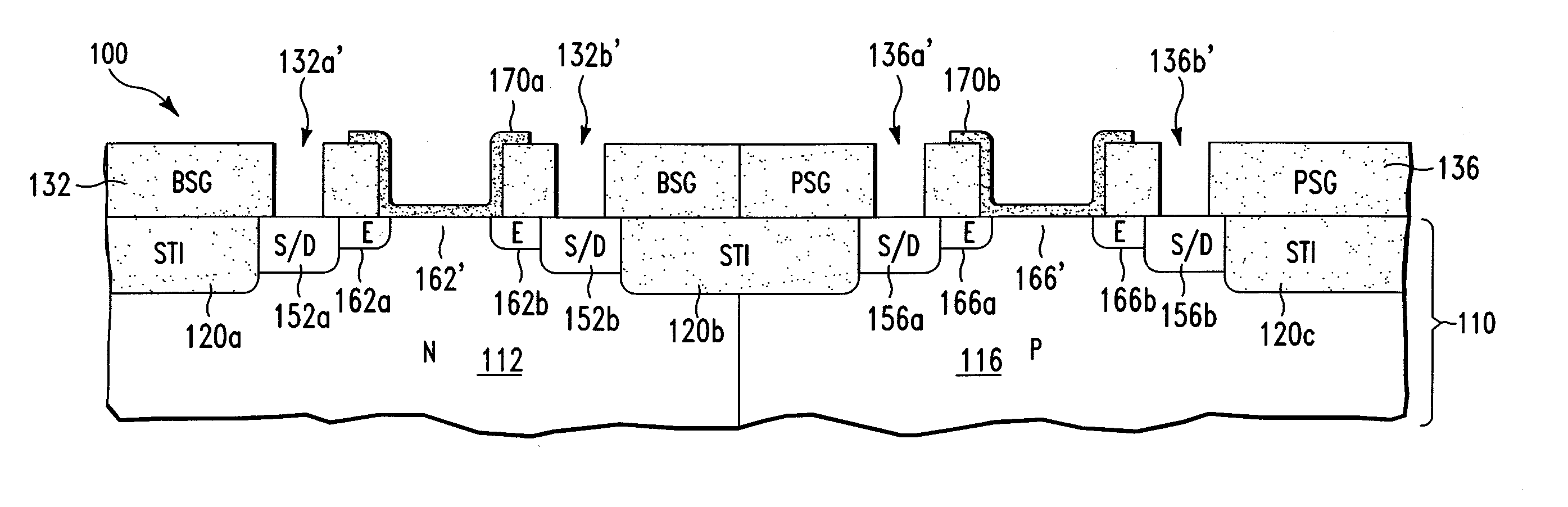

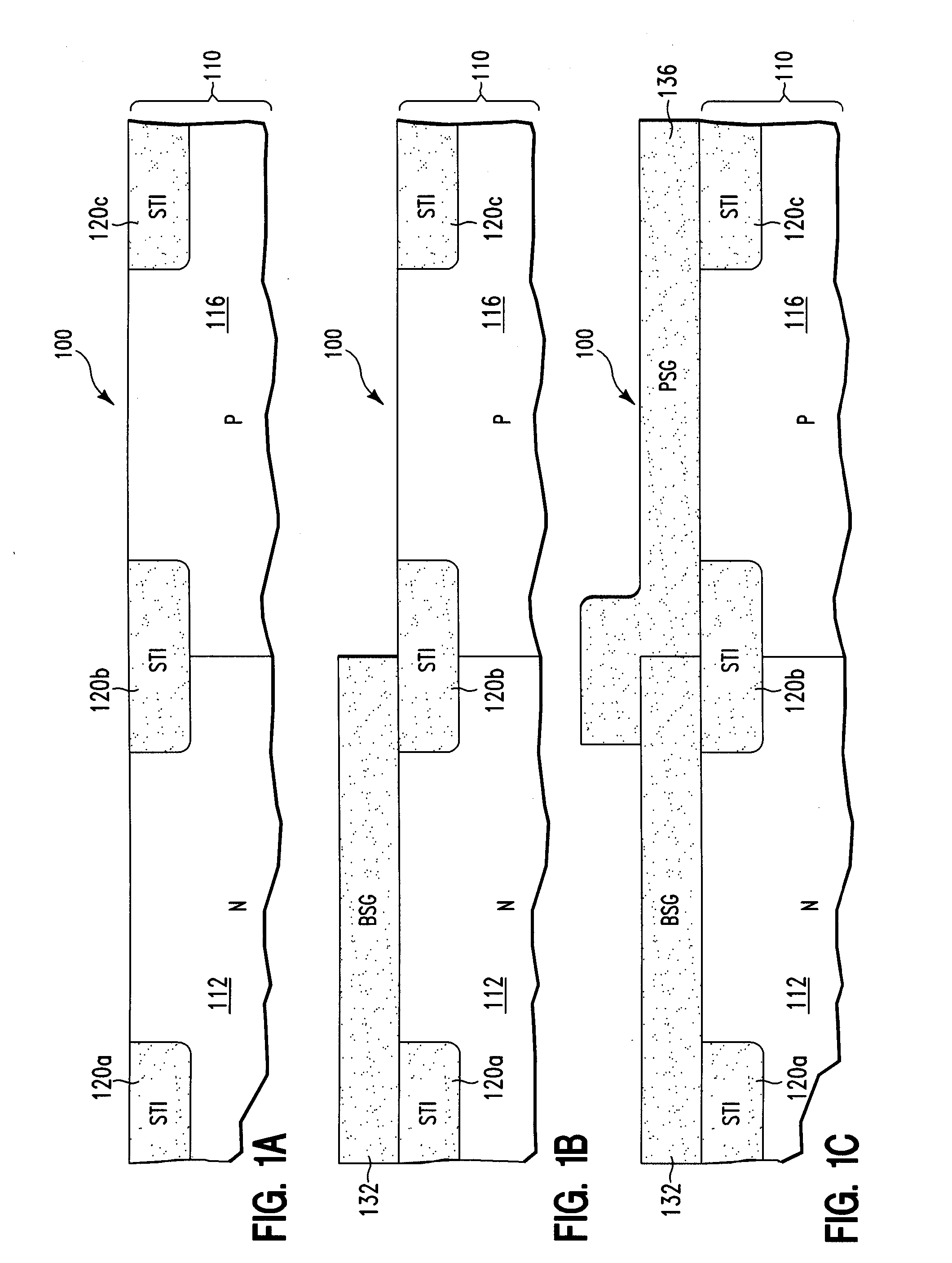

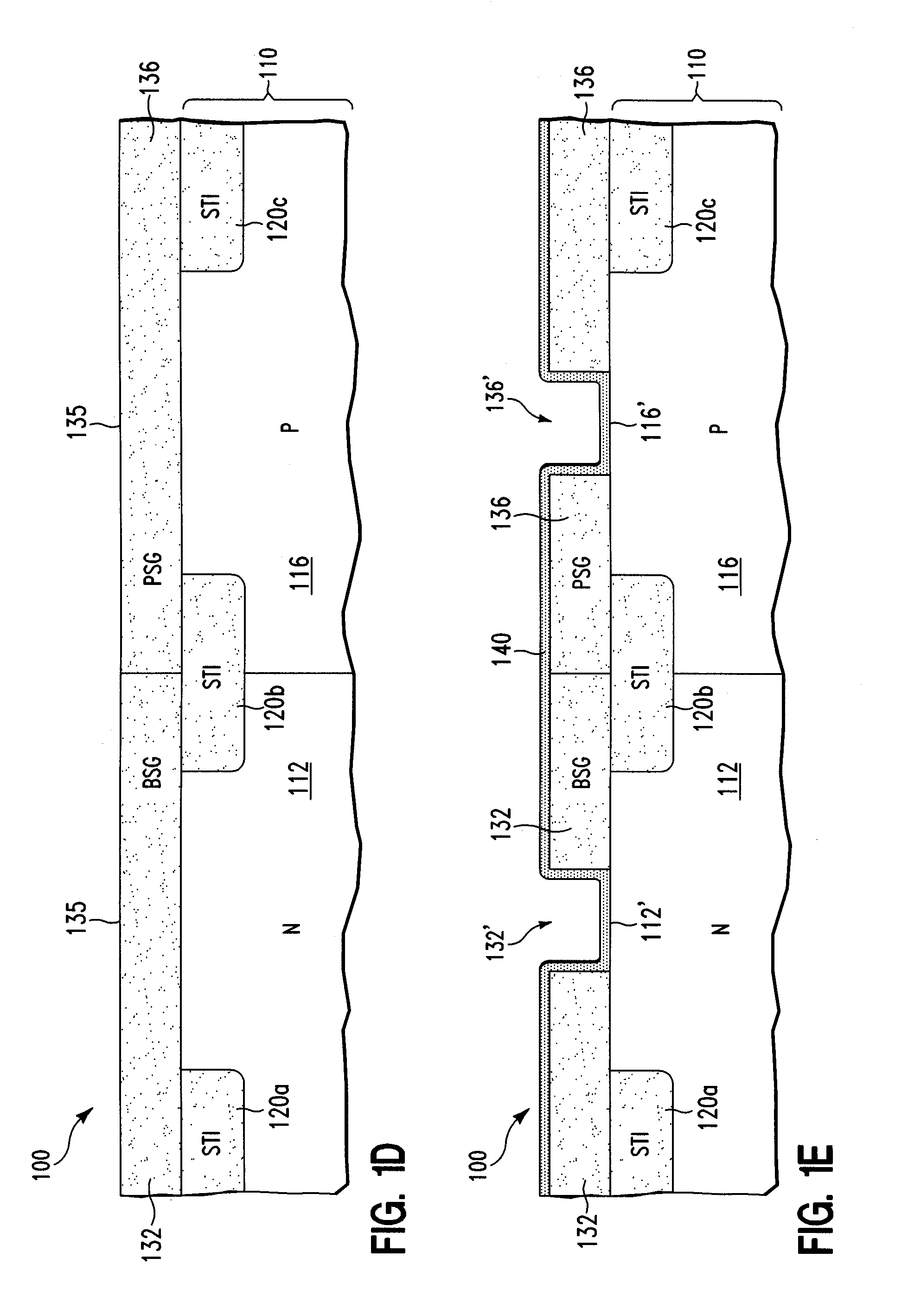

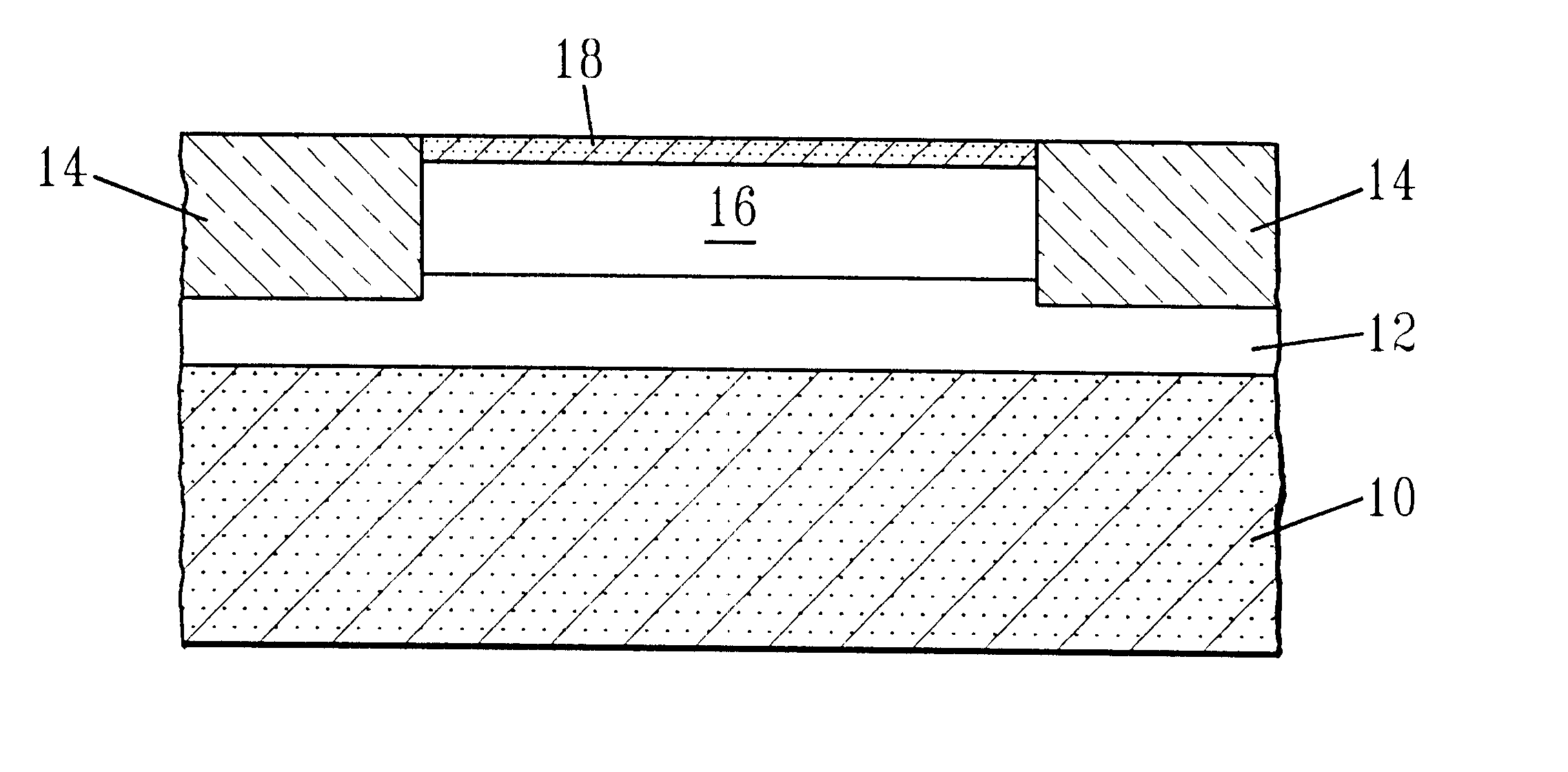

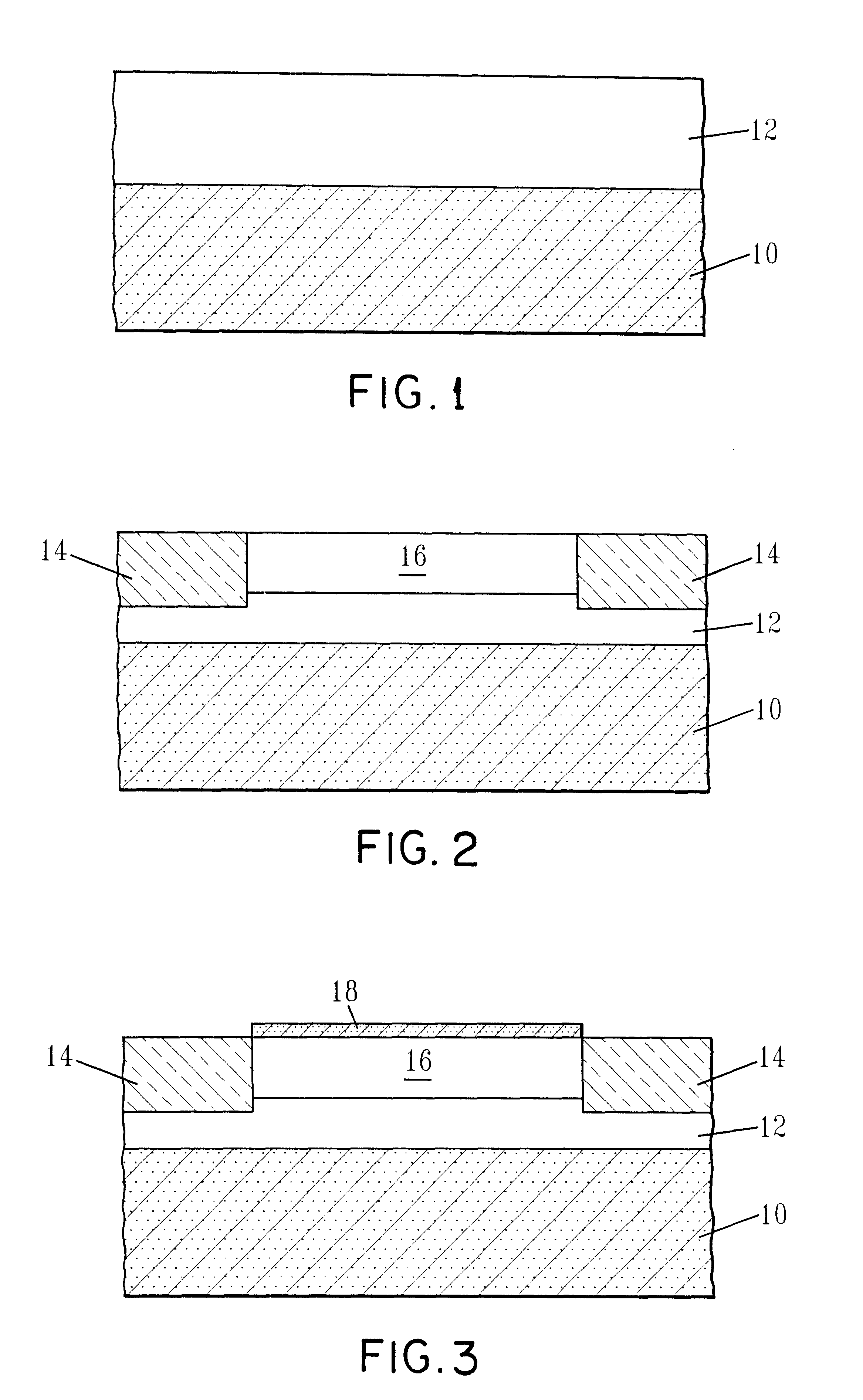

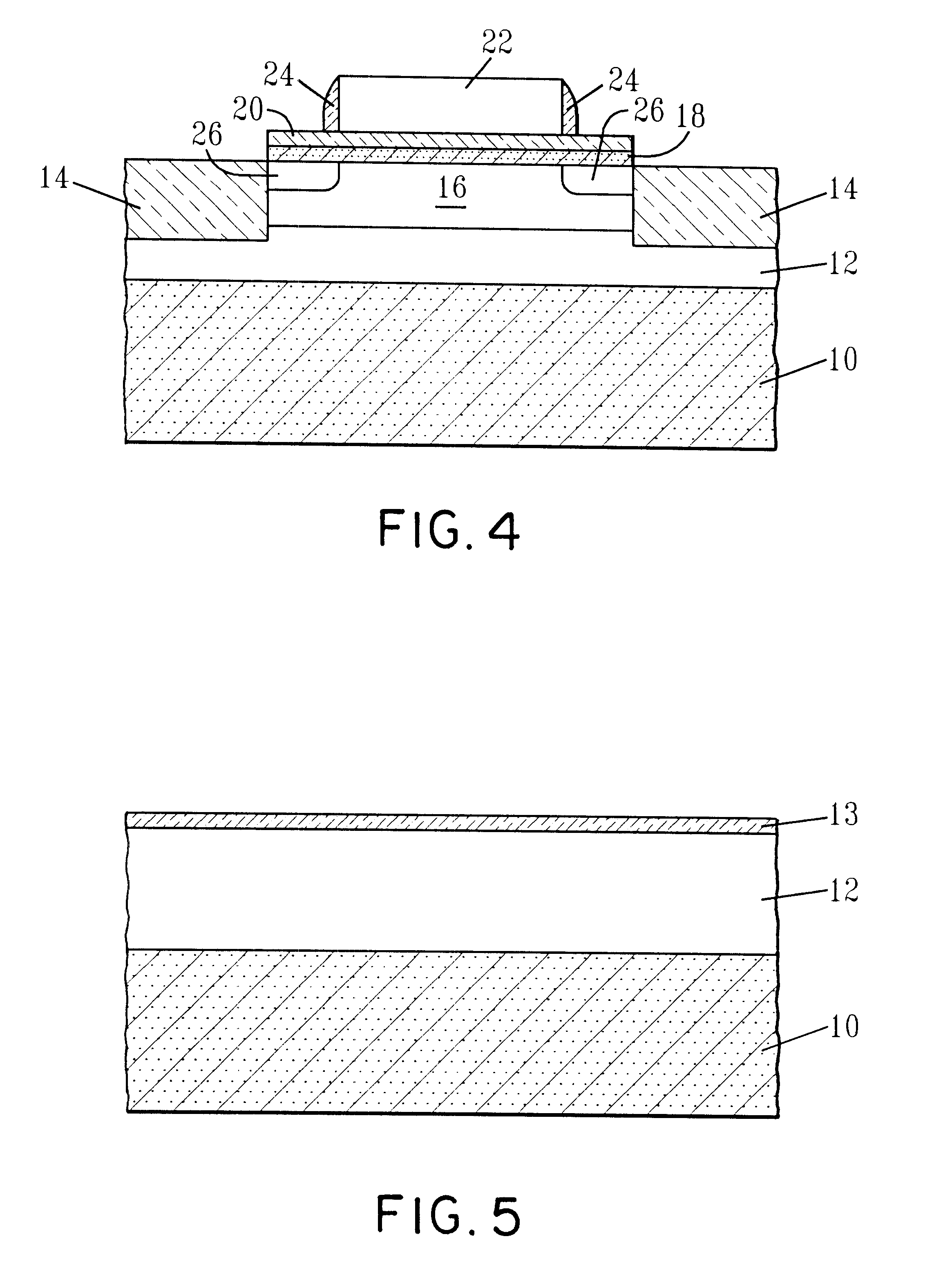

IMPROVED CMOS (Complementary Metal Oxide Semiconductor) TECHNOLOGY

InactiveUS20070020830A1Leakage problemSemiconductor/solid-state device manufacturingSemiconductor devicesDopantCMOS

A method for forming semiconductor transistor. The method comprises providing a structure including (a) a semiconductor region, and (b) first and second dopant source regions on and in direct physical contact with the semiconductor region, wherein each region of the first and second dopant source regions comprises a dielectric material which contains dopants; causing the dopants to diffuse from the first and second dopant source regions into the semiconductor region so as to form first and second source / drain extension regions, respectively, wherein the first and second source / drain extension regions define a channel region disposed between; forming a gate dielectric region on a channel region; and forming a gate region on the gate dielectric region, wherein the gate dielectric region electrically insulates the gate region from the channel region.

Owner:IBM CORP

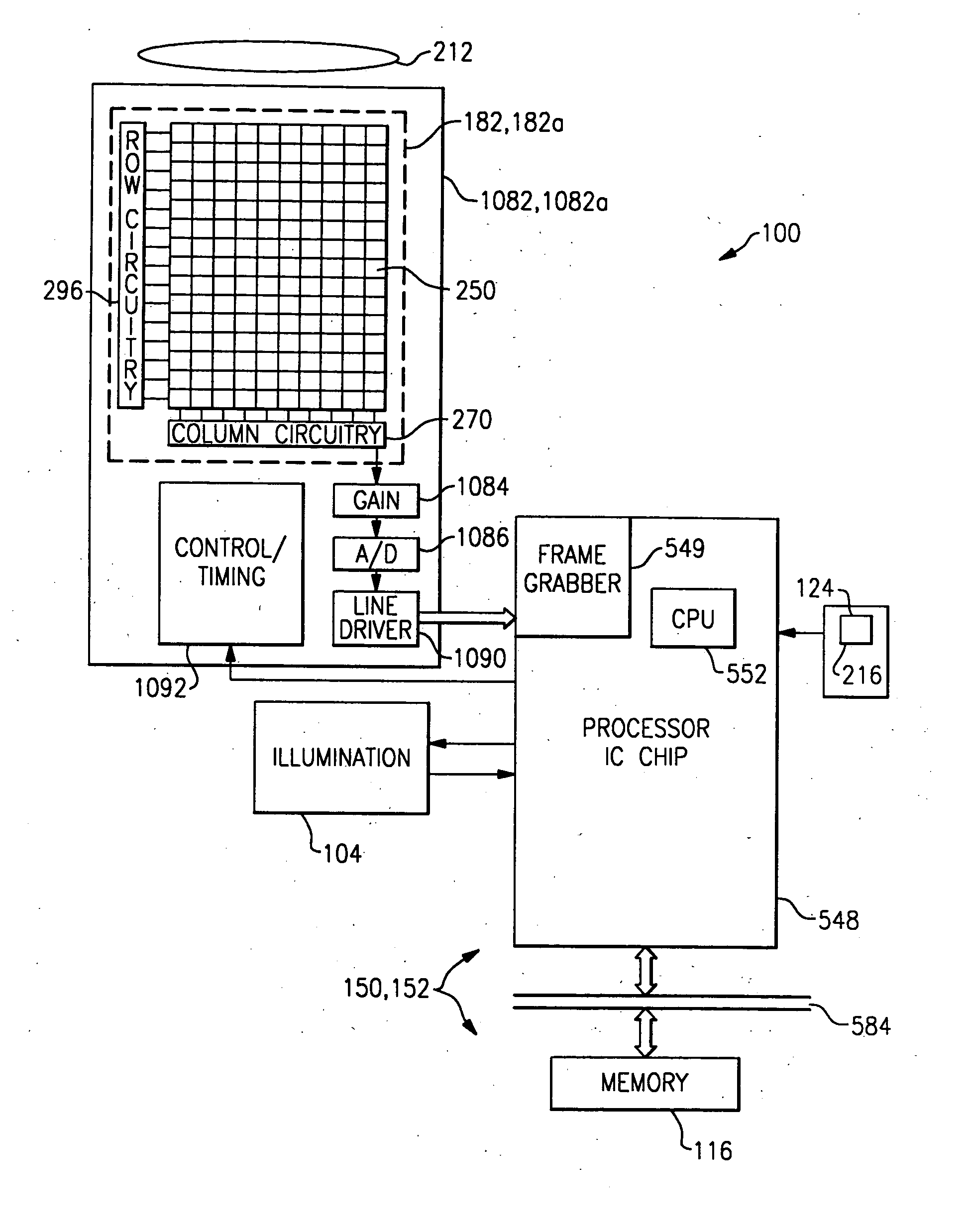

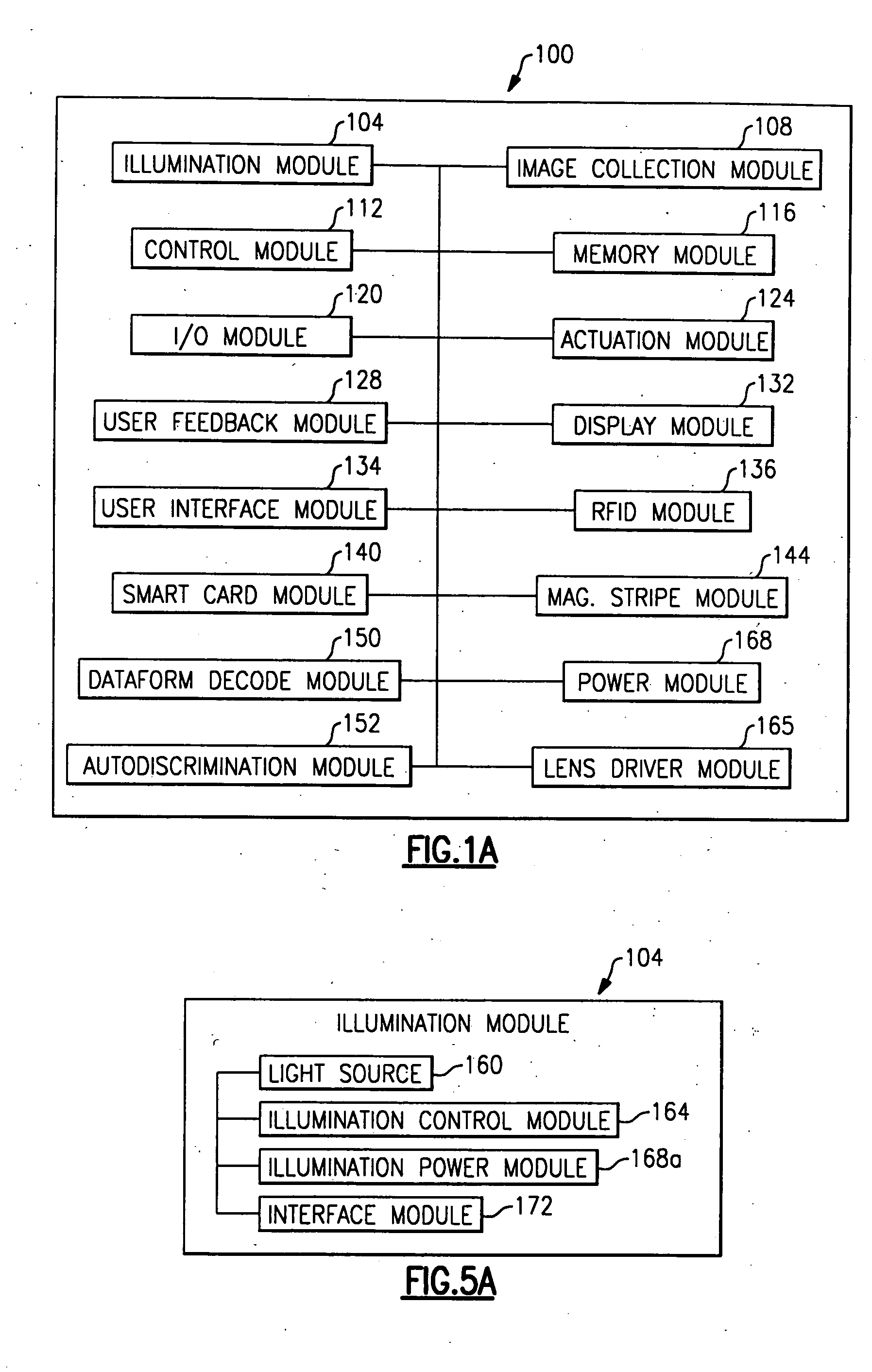

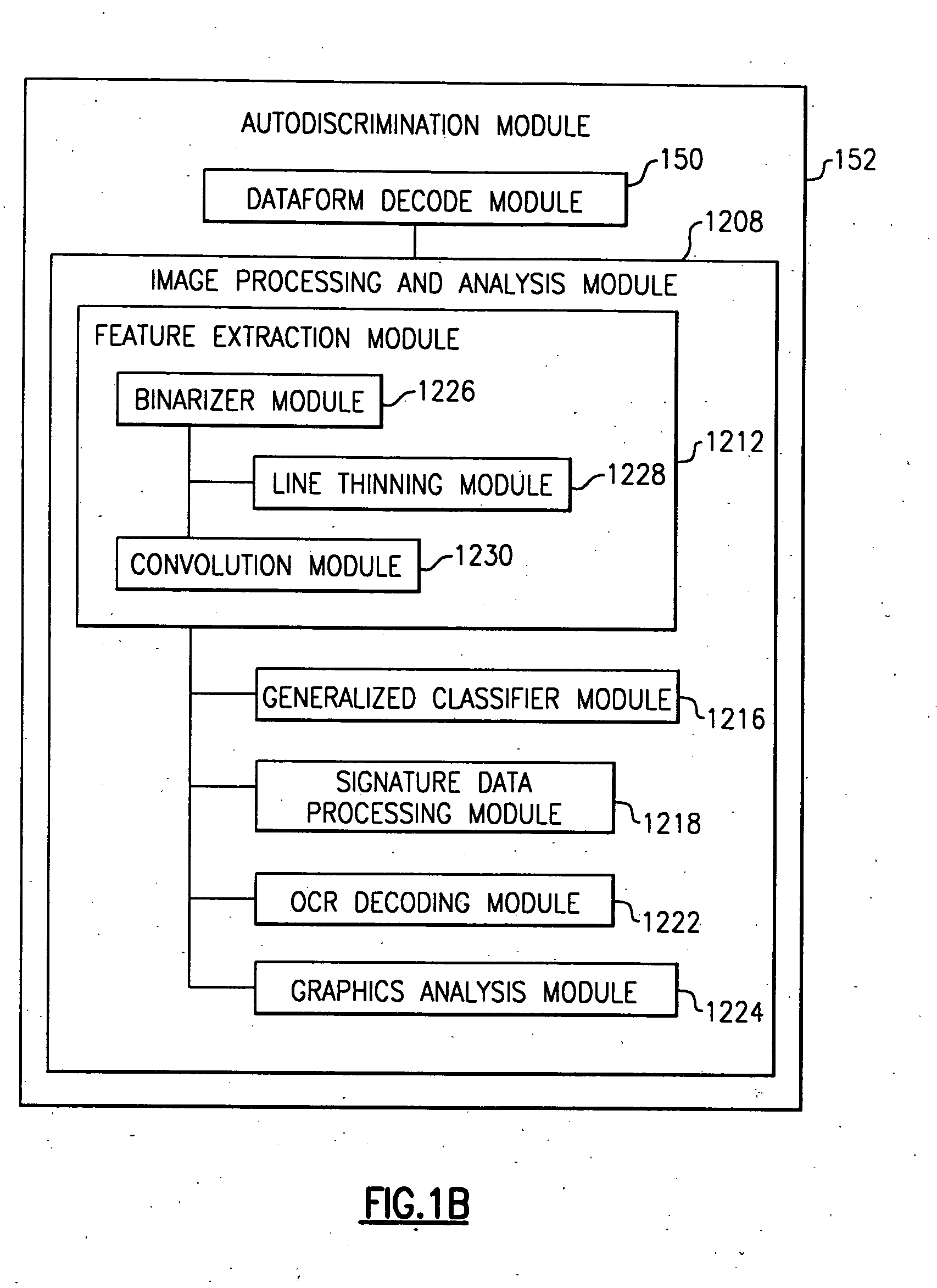

Bar code reading device with global electronic shutter control

ActiveUS20060202036A1Minimize degradationTelevision system detailsTransmission systemsSensor arrayElectronic shutter

The invention features an image reader and a corresponding method for capturing a sharp distortion free image of a target, such as a one or two-dimensional bar code. In one embodiment, the image reader comprises a two-dimensional CMOS based image sensor array, a timing module, an illumination module, and a control module. The time during which the target is illuminated is referred to as the illumination period. The capture of the image by the image sensor array is driven by the timing module that, in one embodiment, is able to simultaneously expose substantially all of the pixels in the array. The time during which the pixels are collectively activated to photo-convert incident light into charge defines the exposure period for the sensor array. In one embodiment, at least a portion of the exposure period occurs during the illumination period.

Owner:HAND HELD PRODS

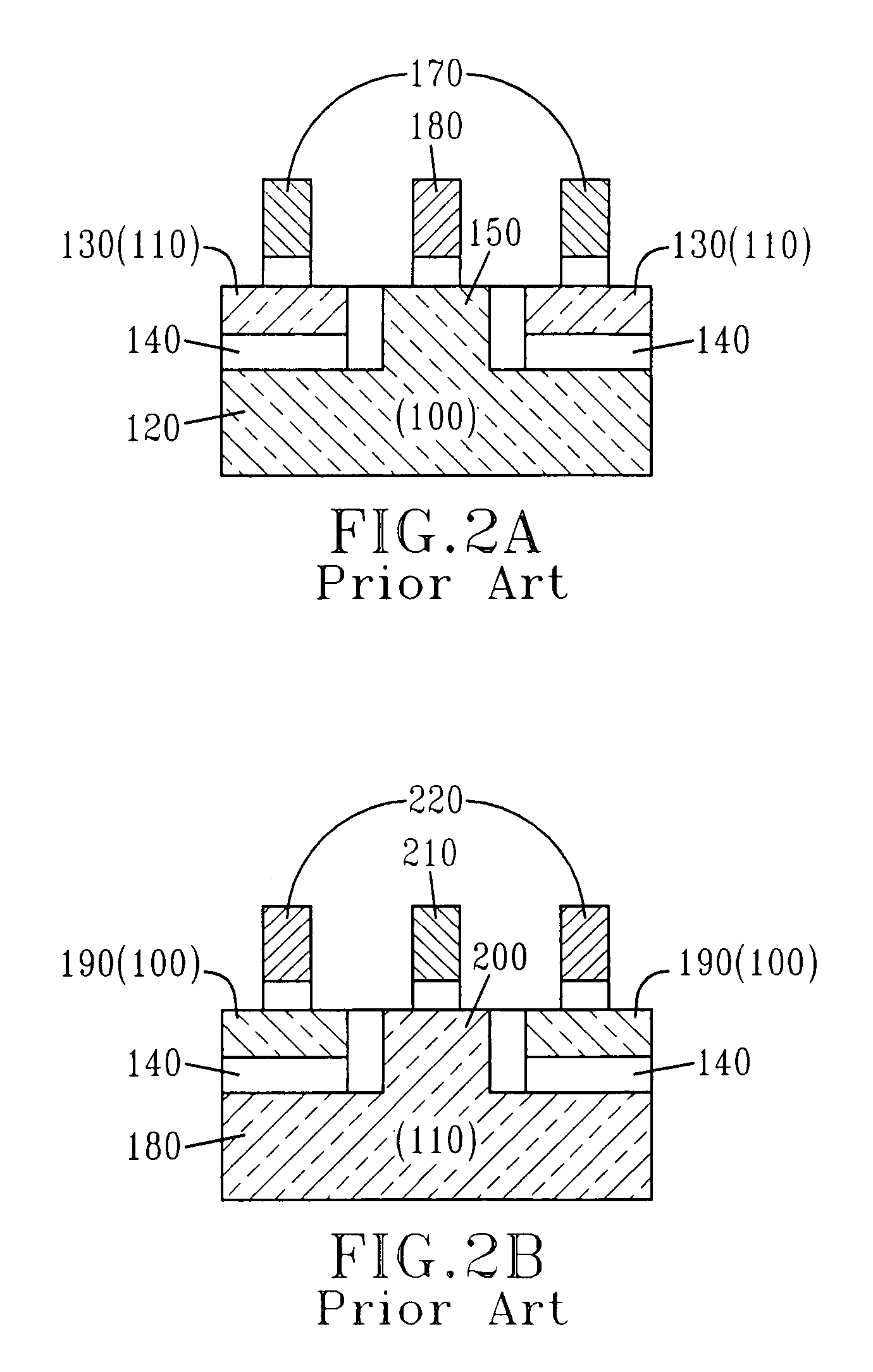

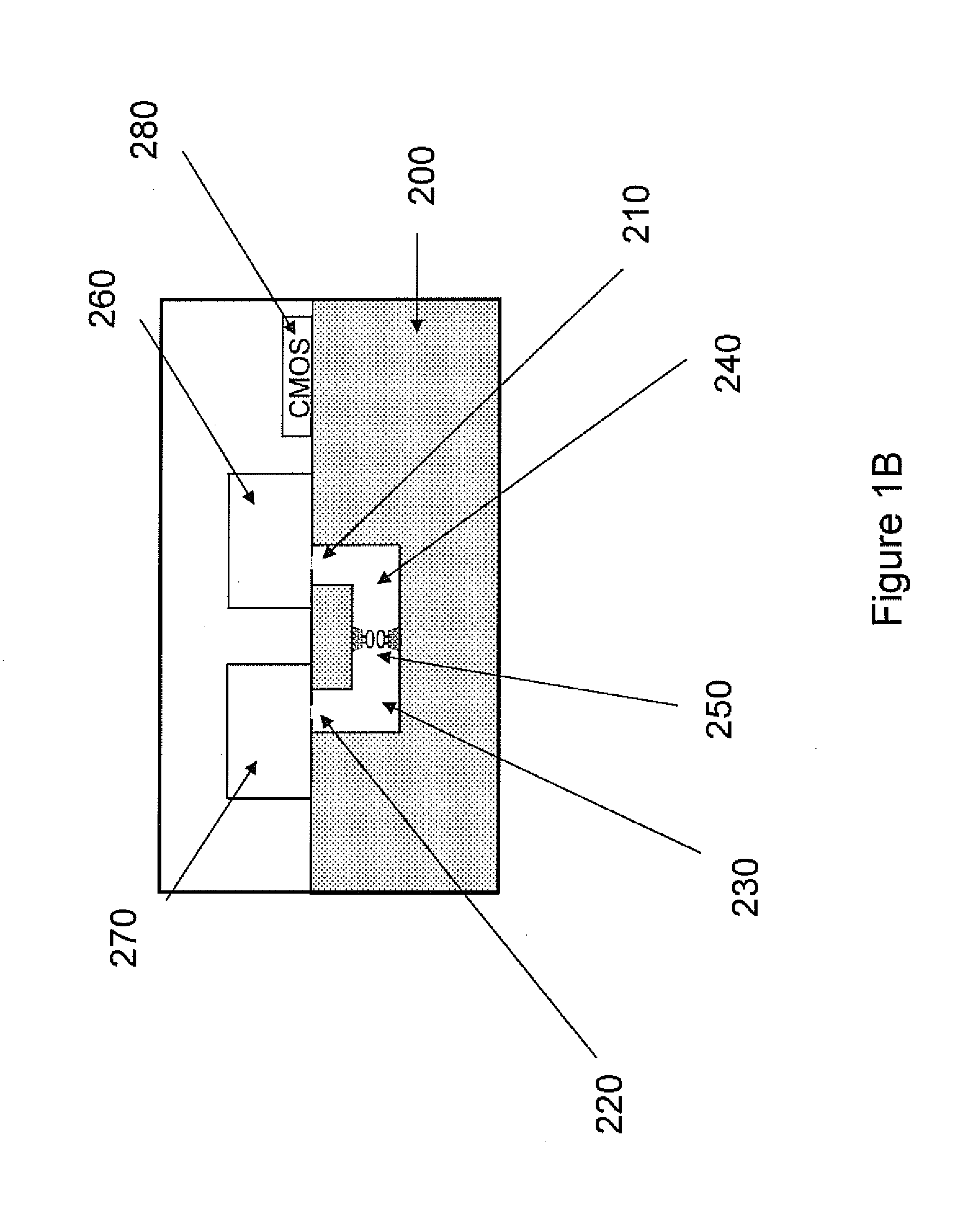

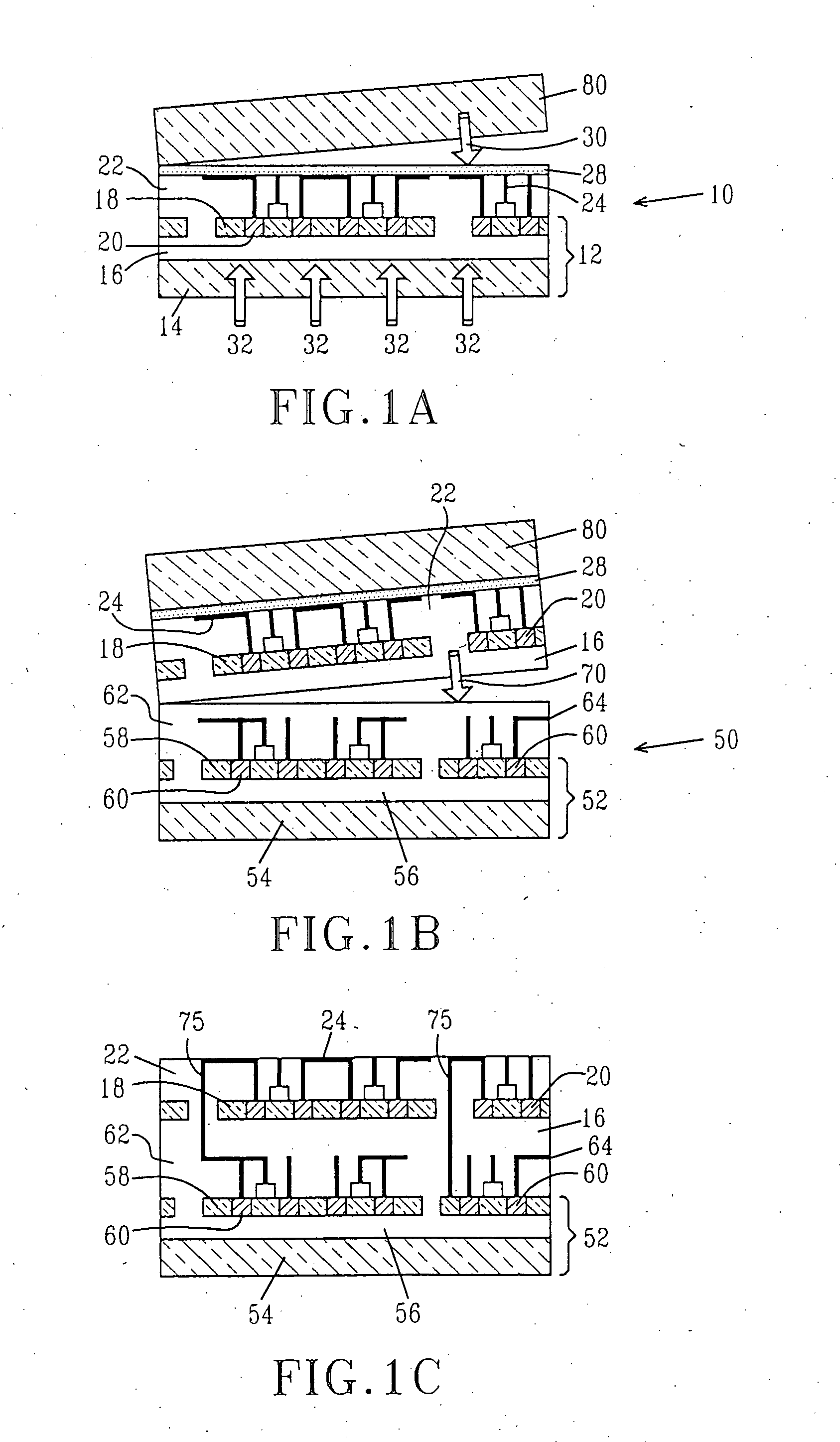

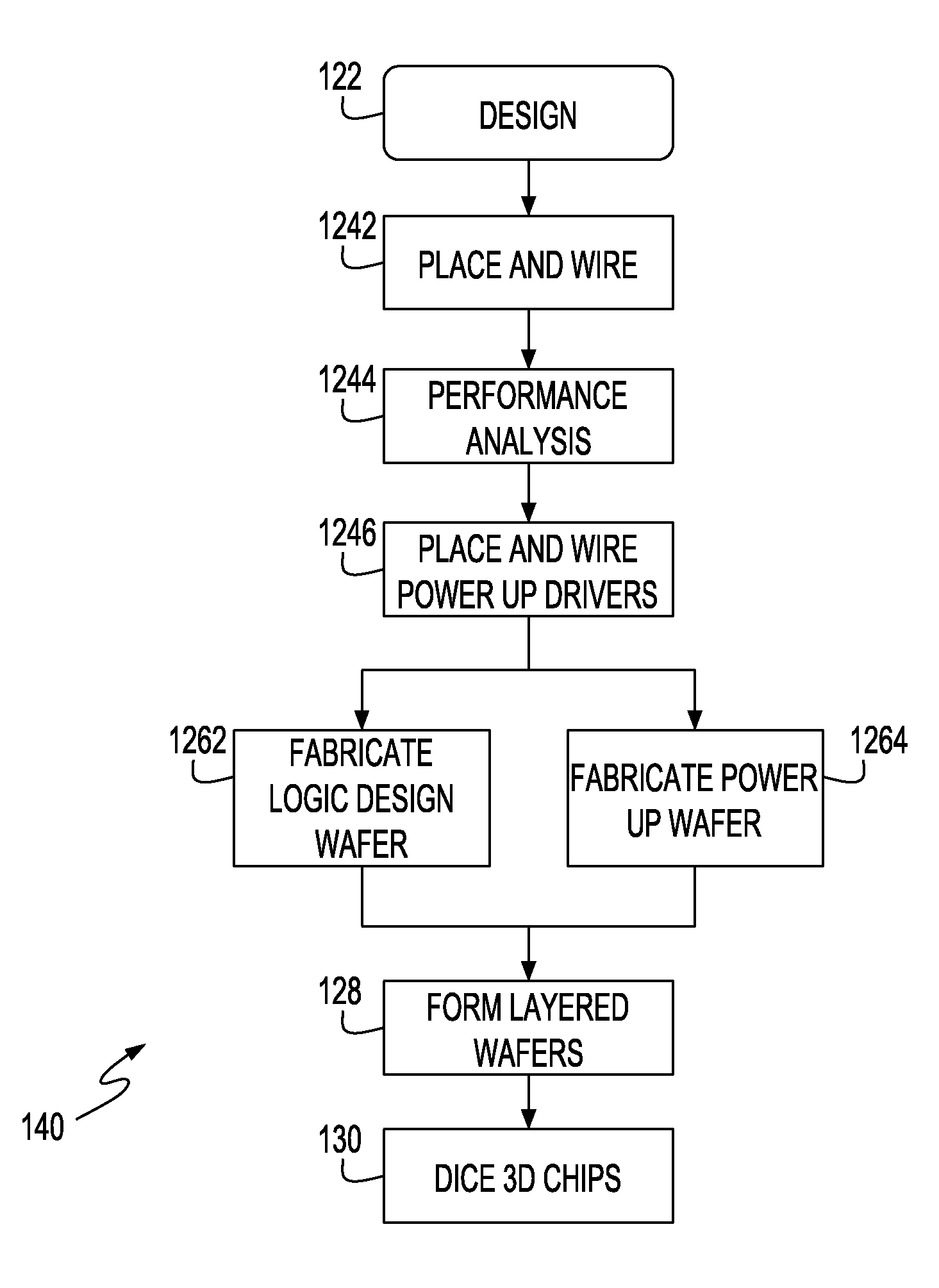

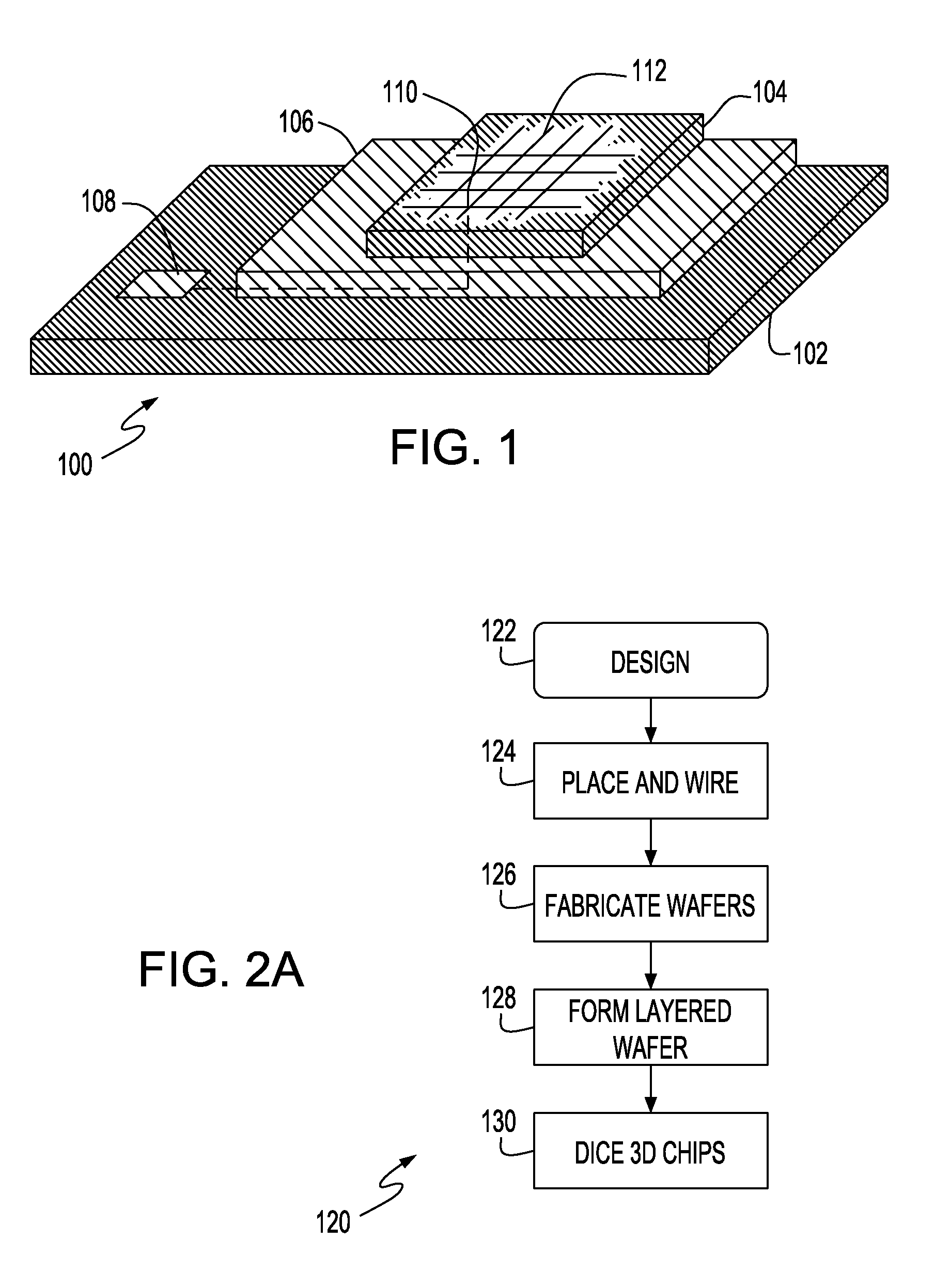

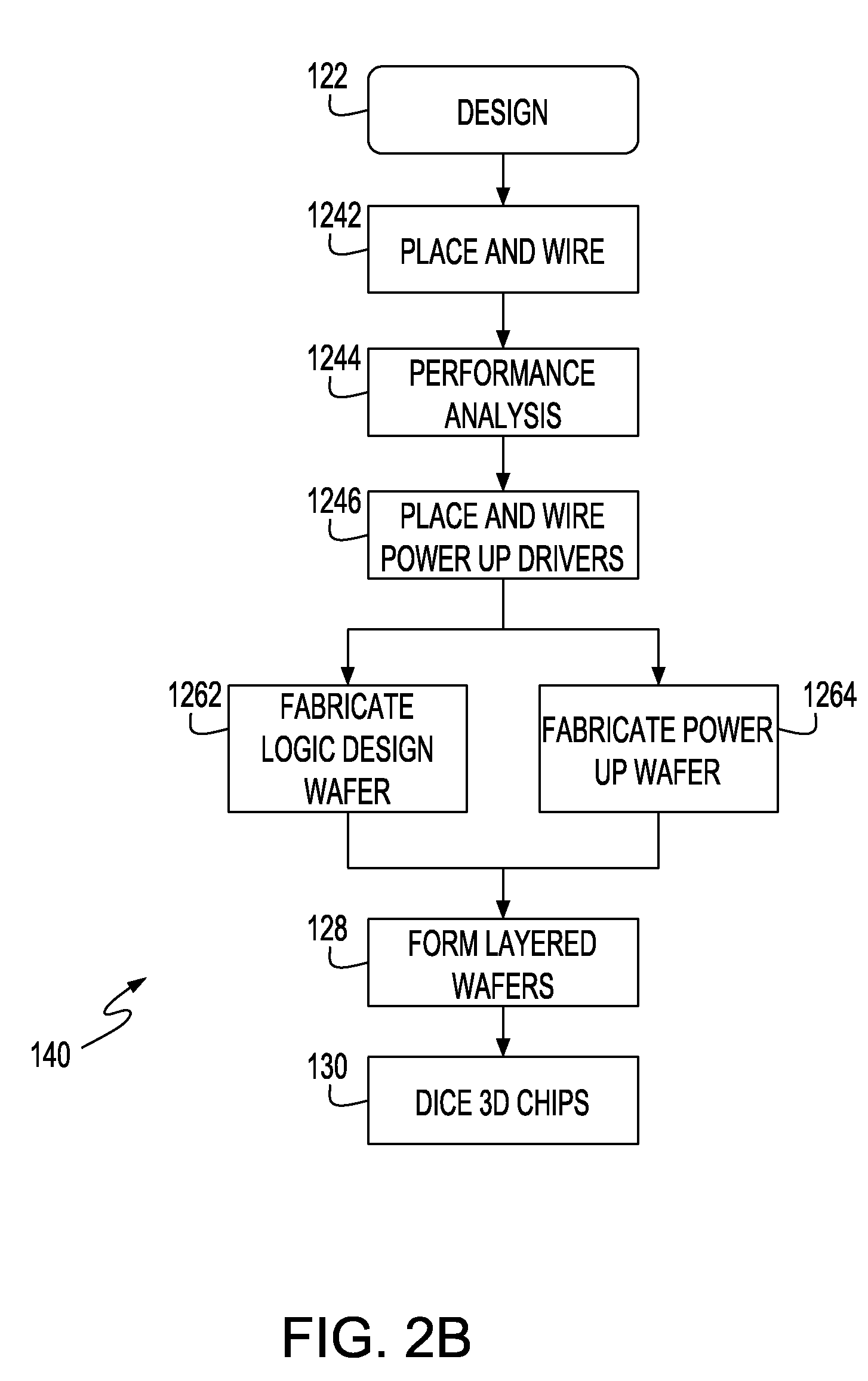

Three dimensional CMOS integrated circuits having device layers built on different crystal oriented wafers

InactiveUS20050067620A1High bulk densityReduce chip footprintTransistorSemiconductor/solid-state device details3d integrated circuitCMOS

Three-dimensional (3D) integration schemes of fabricating a 3D integrated circuit in which the pFETs are located on an optimal crystallographic surface for that device and the nFETs are located on a optimal crystallographic surface for that type of device are provided. In accordance with a first 3D integration scheme of the present invention, first semiconductor devices are pre-built on a semiconductor surface of a first silicon-on-insulator (SOI) substrate and second semiconductor devices are pre-built on a semiconductor surface of a second SOI substrate. After pre-building those two structures, the structure are bonded together and interconnect through wafer-via through vias. In a second 3D integration scheme, a blanket silicon-on-insulator (SOI) substrate having a first SOI layer of a first crystallographic orientation is bonded to a surface of a pre-fabricating wafer having second semiconductor devices on a second SOI layer that has a different crystallographic orientation than the first SOI layer; and forming first semiconductor device on the first SOI layer.

Owner:GLOBALFOUNDRIES INC

Method to fabricate a strained Si CMOS structure using selective epitaxial deposition of Si after device isolation formation

InactiveUS6429061B1Thickness minimizationTransistorSemiconductor/solid-state device manufacturingCMOSMOSFET

A strained Si CMOS structure is formed by steps which include forming a relaxed SiGe layer on a surface of a substrate; forming isolation regions and well implant regions in said relaxed SiGe layer; and forming a strained Si layer on said relaxed SiGe layer. These processing steps may be used in conjunction with conventional gate processing steps in forming a strained MOSFET structure.

Owner:SAMSUNG ELECTRONICS CO LTD

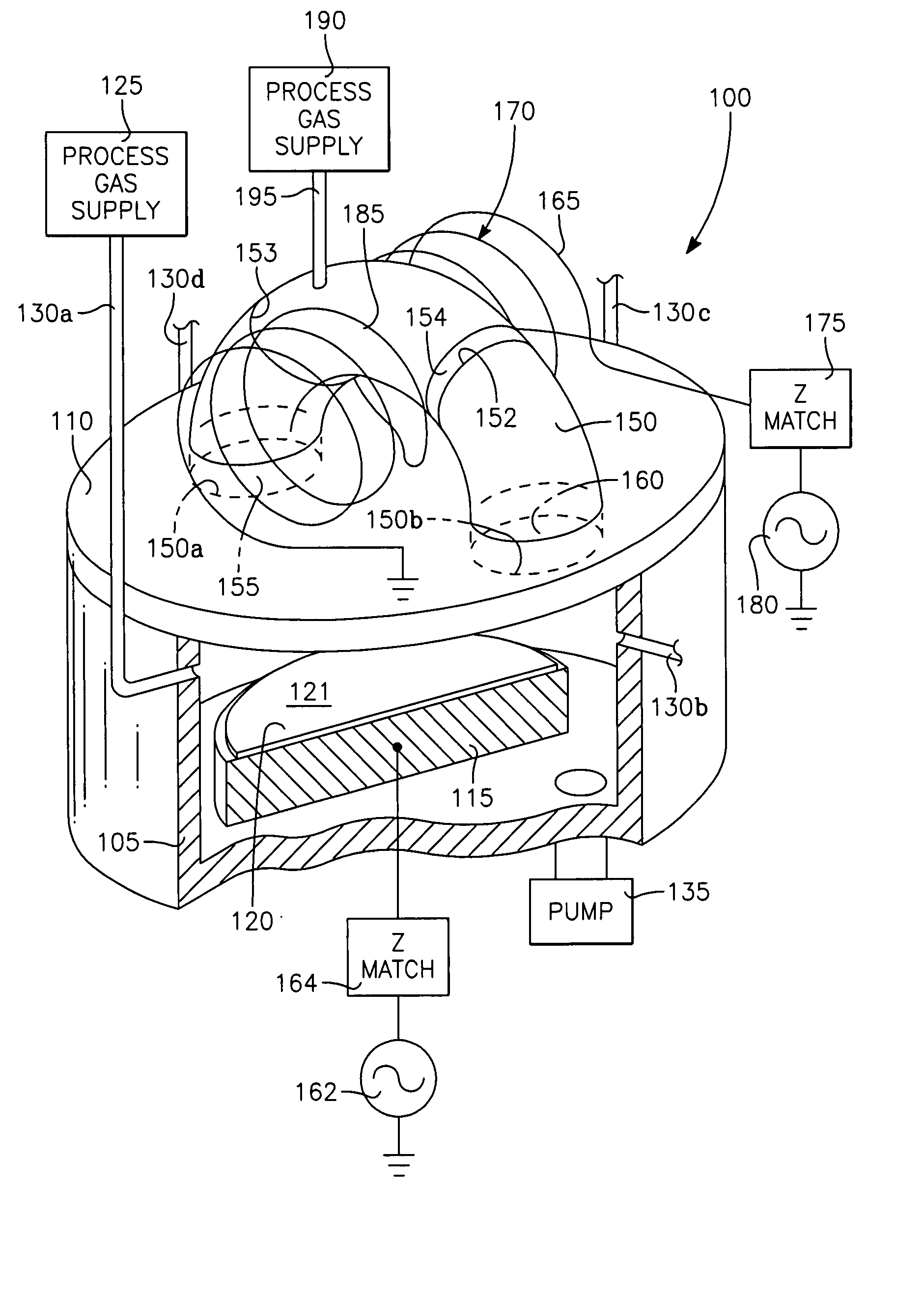

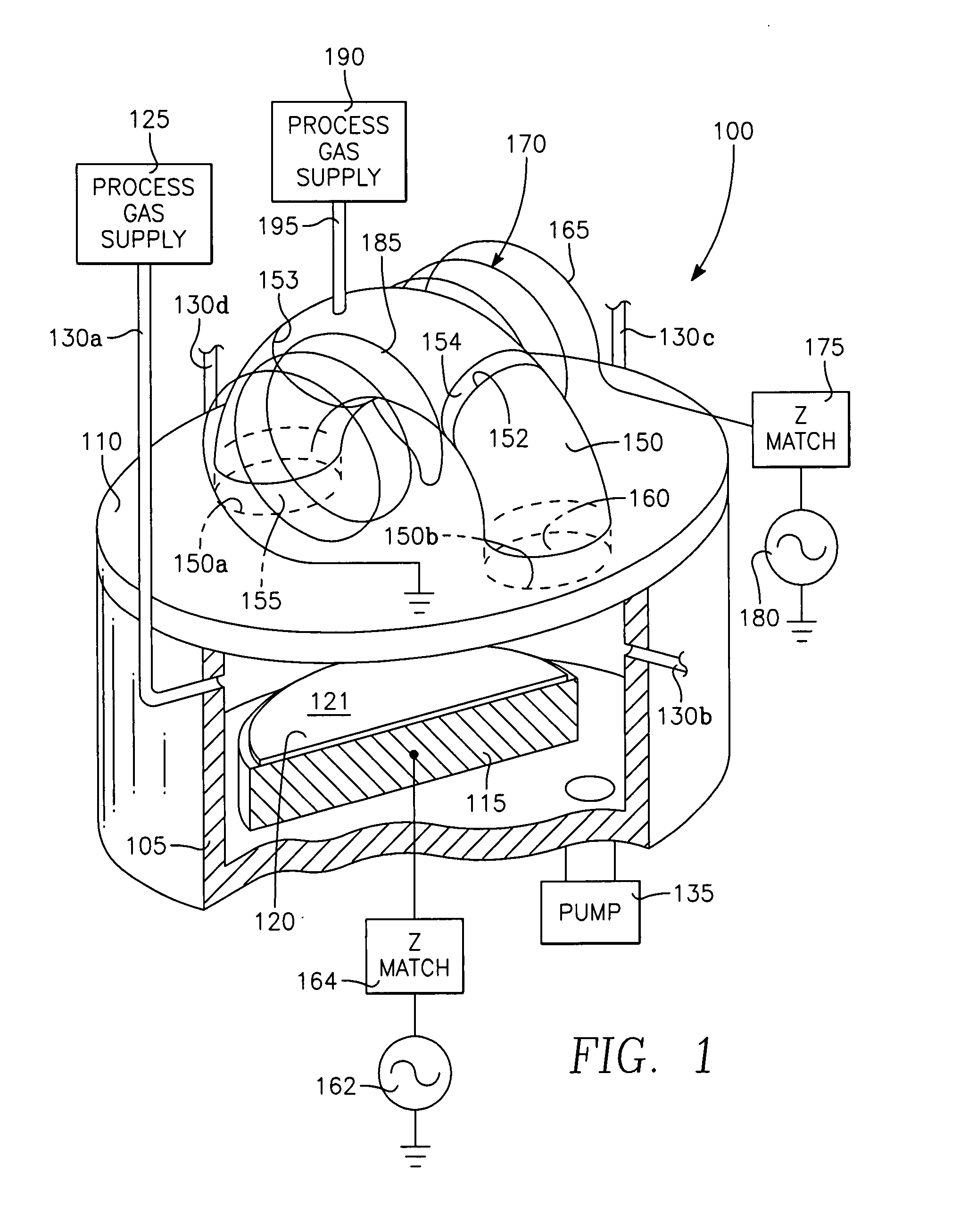

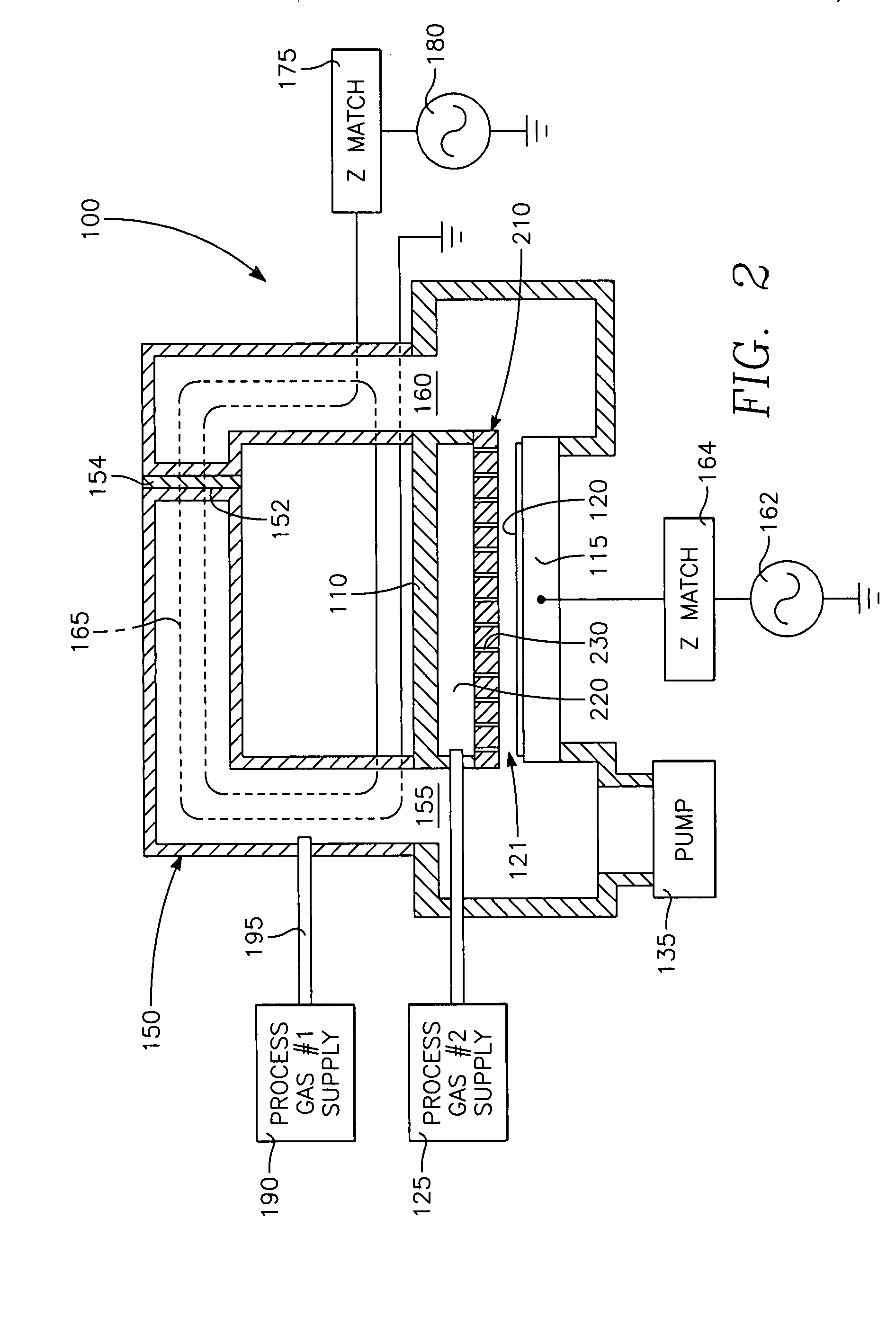

Low temperature CVD process with selected stress of the CVD layer on CMOS devices

Device-enhancing coatings are deposited on CMOS devices by successively masking with photoresist each one of the sets of N-channel and P-channel devices while unmasking or leaving unmasked the other set, and after each step of successively masking one of the sets of devices, carrying out low temperature CVD steps with a toroidal RF plasma current while applying an RF plasma bias voltage. The temperature of the workpiece is held below a threshold photoresist removal temperature. The RF bias voltage is held at a level at which the coating is deposited with a first stress when the unmasked set consists of the P-channel devices and with a second stress when the unmasked set consists of N-channel devices.

Owner:APPLIED MATERIALS INC

Vertical sub-micron CMOS transistors on (110), (111), (311), (511), and higher order surfaces of bulk, SOI and thin film structures and method of forming same

A method for forming NMOS and PMOS transistors that includes cutting a substrate along a higher order orientation and fabricating deep sub-micron NMOS and PMOS transistors on the vertical surfaces thereof. The complementary NMOS and PMOS transistors form a CMOS transistor pair. The transistors are preferably used in structures such as memory circuits, e.g., DRAMs, which are, in turn, used in a processor-based system. Ideally, the deep sub-micron NMOS and PMOS transistors are operated in velocity saturation for optimal switching operation.

Owner:APTINA IMAGING CORP

High mobility heterojunction complementary field effect transistors and methods thereof

ActiveUS20050093021A1Minimal toleranceHigh hole mobilityTransistorSolid-state devicesHeterojunctionCMOS

A structure, and method of fabrication, for high performance field effect devices is disclosed. The MOS structures include a crystalline Si body of one conductivity type, a strained SiGe layer epitaxially grown on the Si body serving as a buried channel for holes, a Si layer epitaxially grown on the SiGe layer serving as a surface channel for electrons, and a source and a drain containing an epitaxially deposited, strained SiGe of opposing conductivity type than the Si body. The SiGe source / drain forms a heterojunction and a metallurgical junction with the Si body that coincide with each other with a tolerance of less than about 10 nm, and preferably less than about 5 nm. The heterostructure source / drain is instrumental in reducing short channel effects. These structures are especially advantageous for PMOS due to increased hole mobility in the compressively strained SiGe channel. Representative embodiments include CMOS structures on bulk and on SOI.

Owner:GLOBALFOUNDRIES US INC

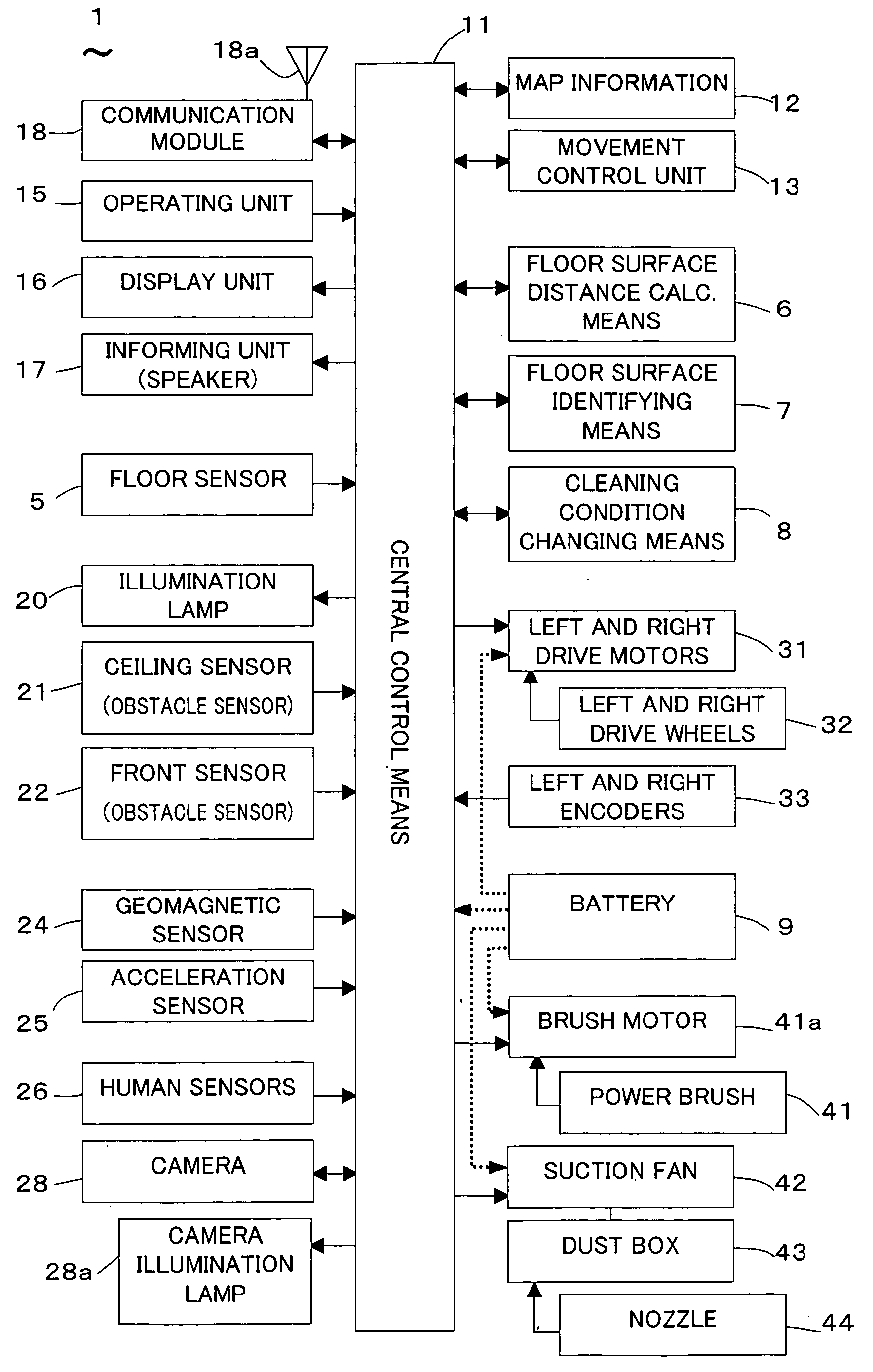

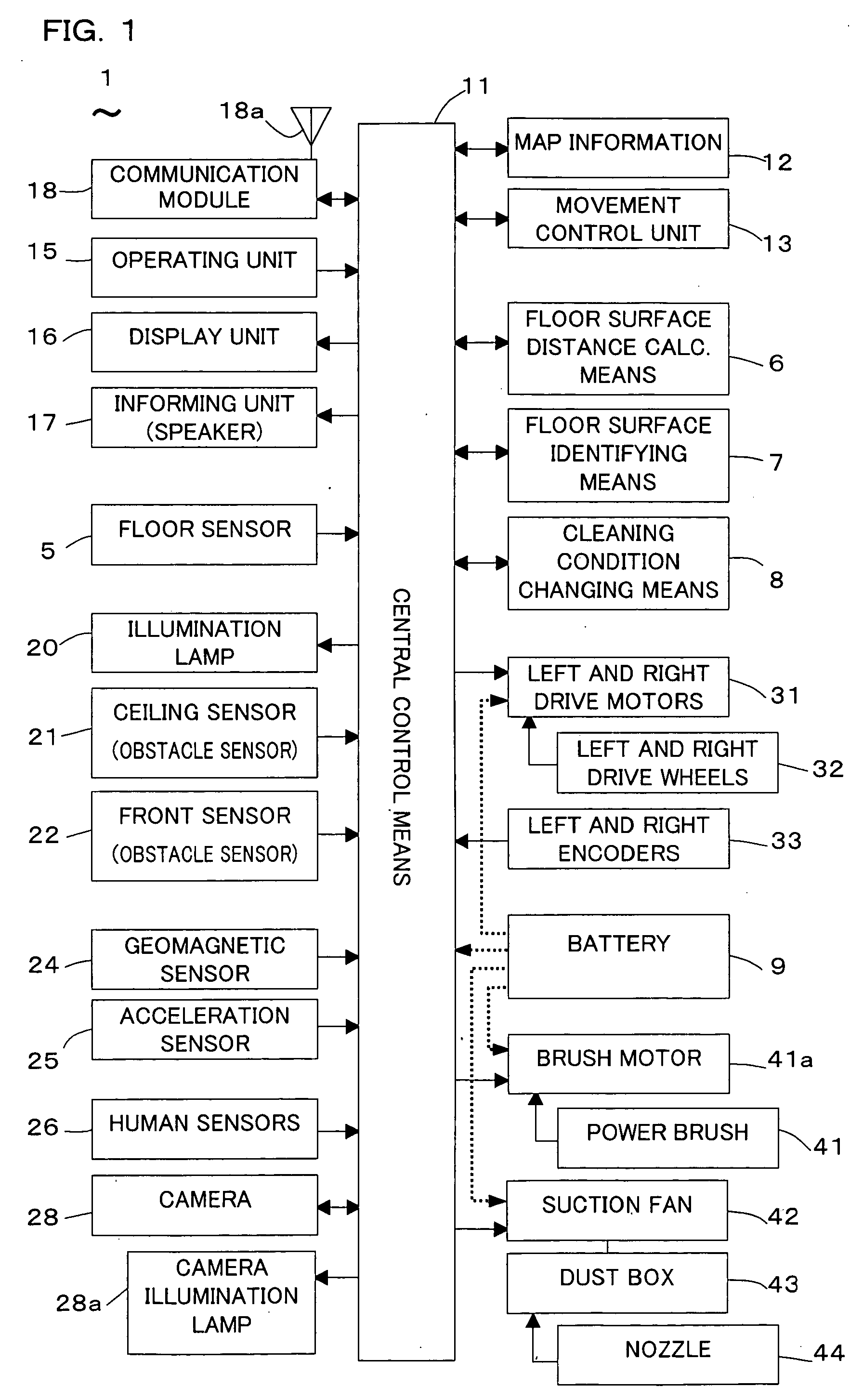

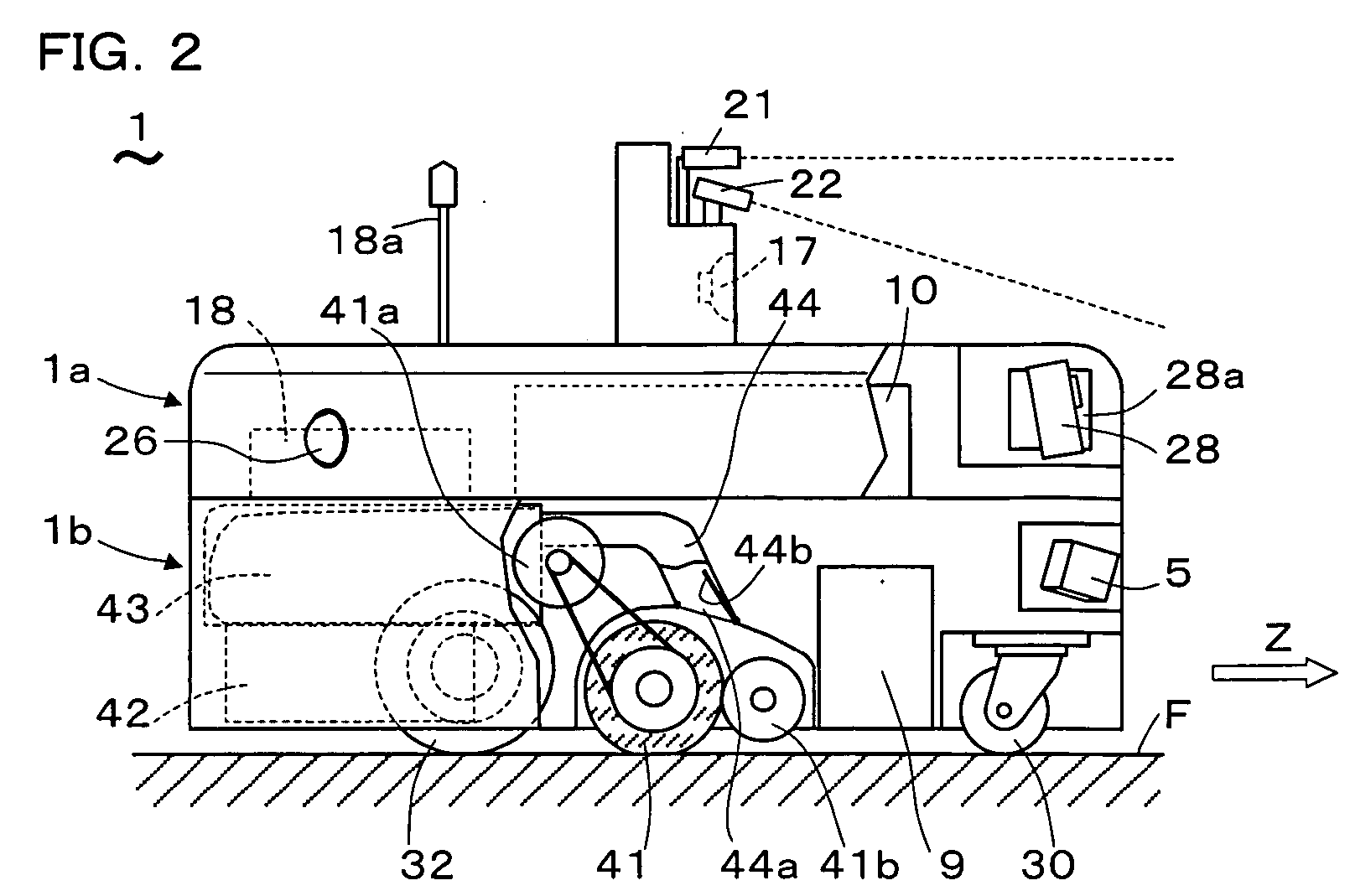

Autonomous vacuum cleaner

InactiveUS20050166354A1Accurate materialsHigh resolutionAutomatic obstacle detectionTravelling automatic controlCMOSLine sensor

An autonomous vacuum cleaner comprises: obstacle detection sensors; moving means; a cleaning means including a power brush, a suction fan and a nozzle for sucking up dust on a floor surface; floor surface sensors each comprising a passive-type CMOS line sensor to receive light from the floor surface for detecting floor surface conditions. It performs cleaning while autonomously moving. Based on received light signals of the floor surface sensors, distance distributions to floor surface areas within the viewing angle of each sensor are derived. Detection of a step on the floor surface and identification of the material of the floor surface (polished floorboard, tatami or carpet) are performed by analyzing spatial frequency in the distance distribution. Based on the identification, cleaning conditions including at least the moving speed, the dust suction force of the suction fan or the brushing strength of the power brush are changed. With simple structure using one same floor sensor, this autonomous vacuum cleaner can detect a step on a floor surface and can more accurately identify the material of the floor surface, thereby enabling meticulous cleaning.

Owner:FUNAI ELECTRIC CO LTD

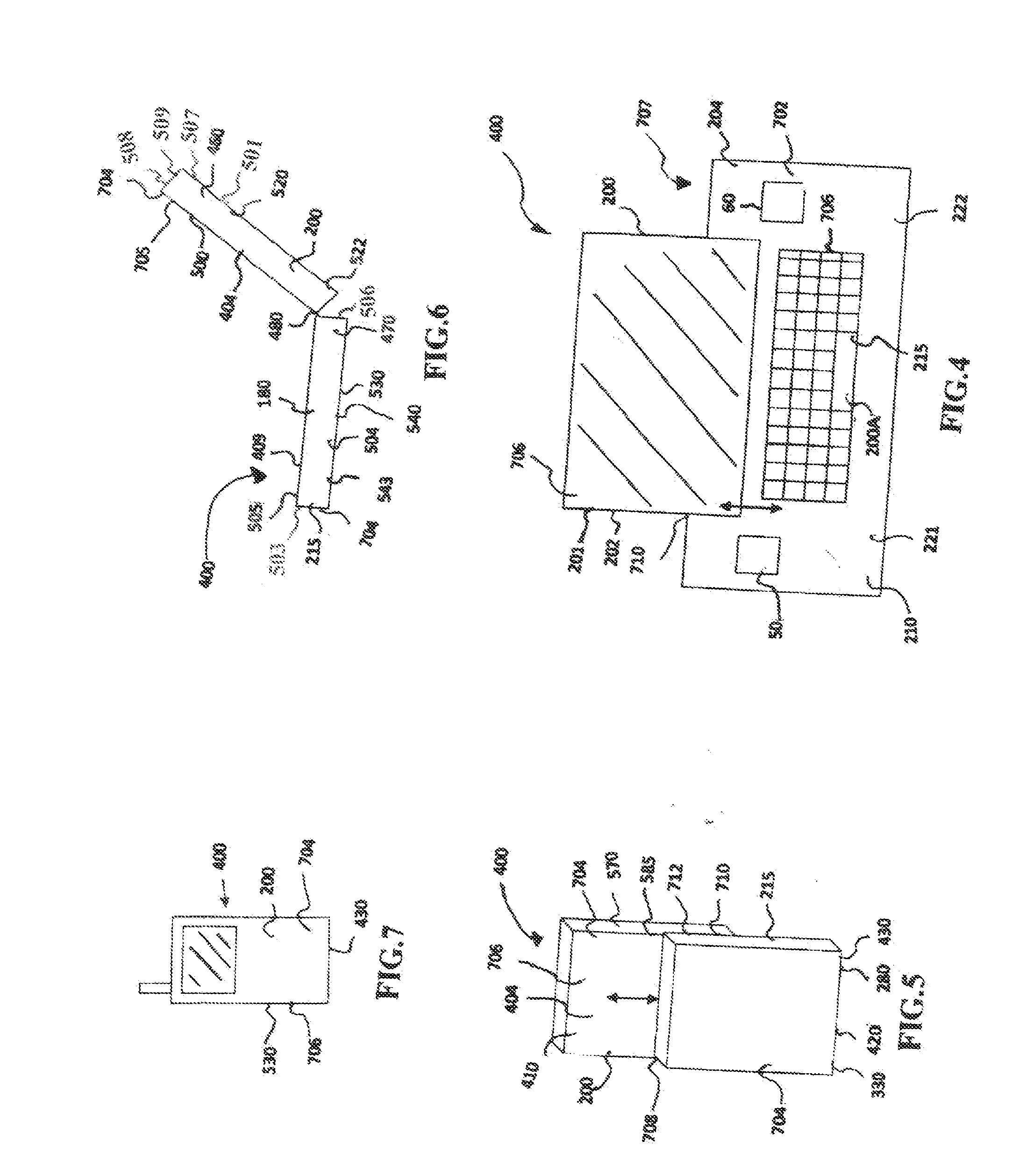

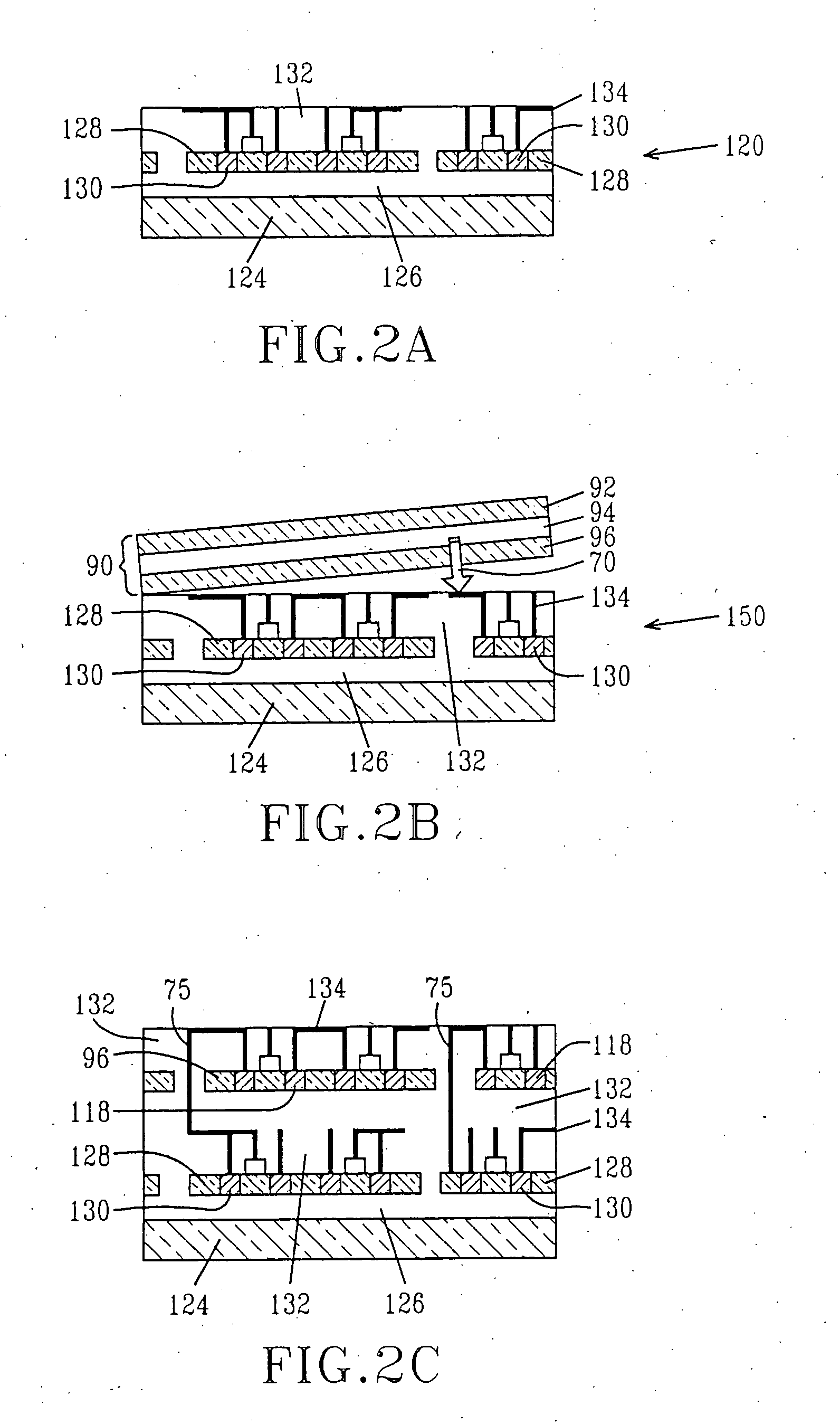

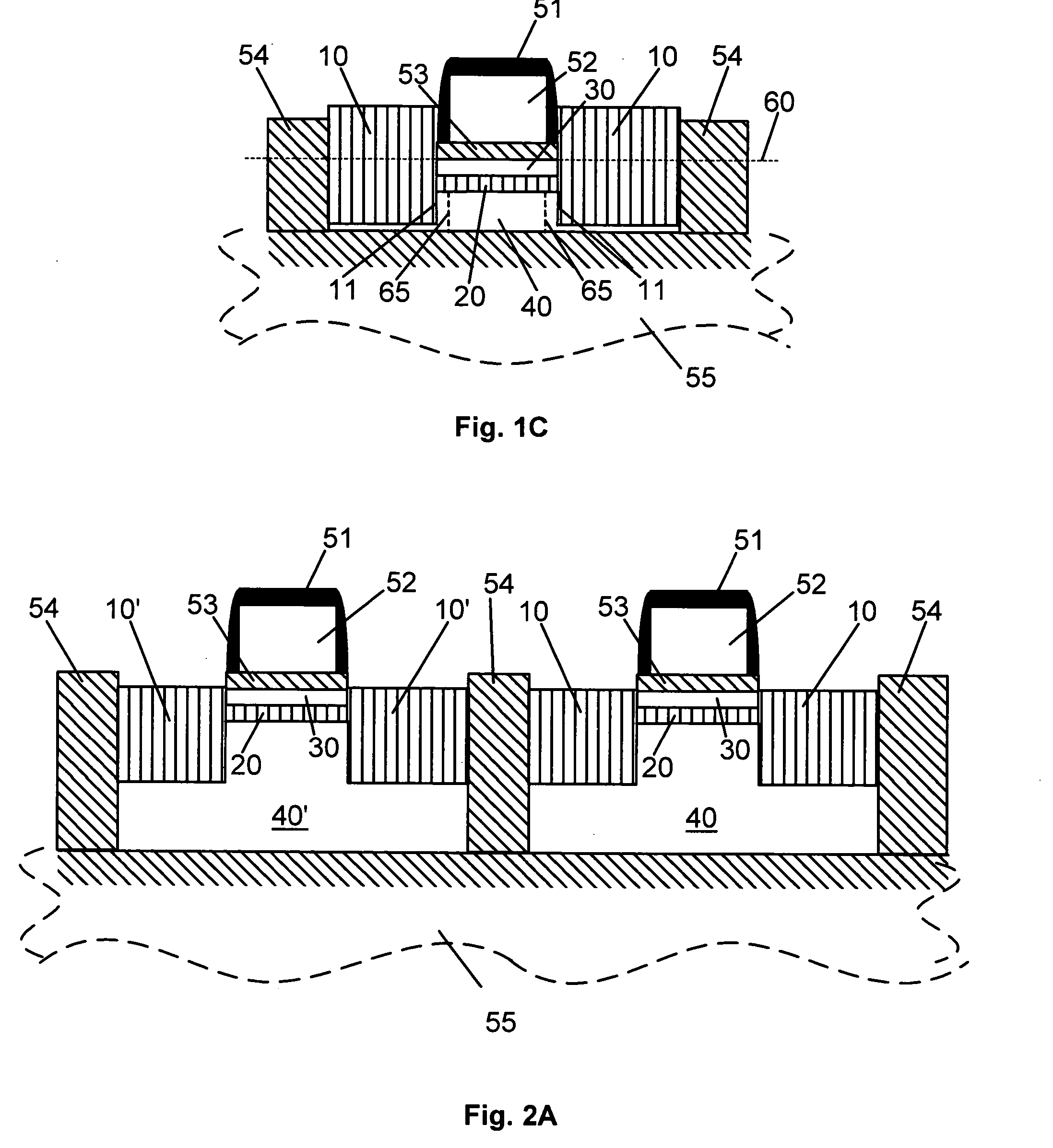

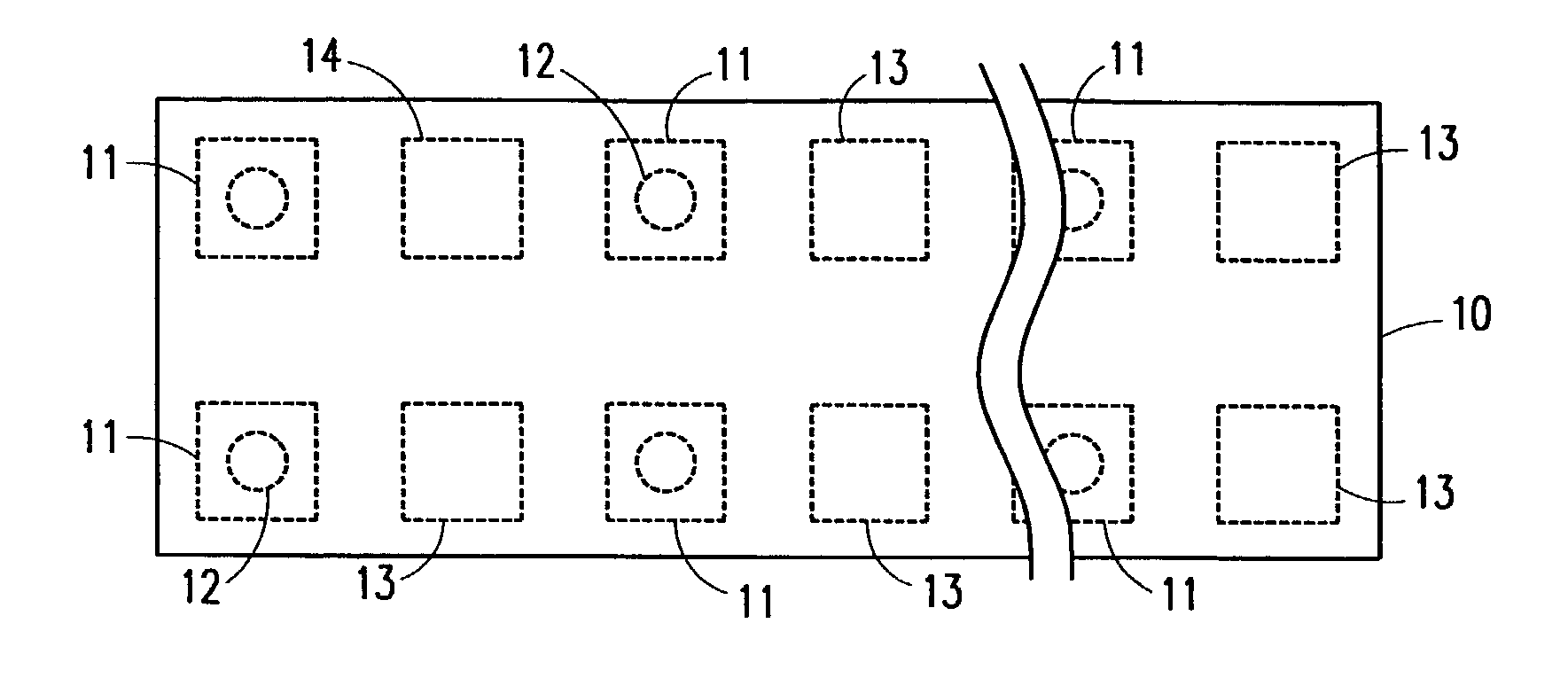

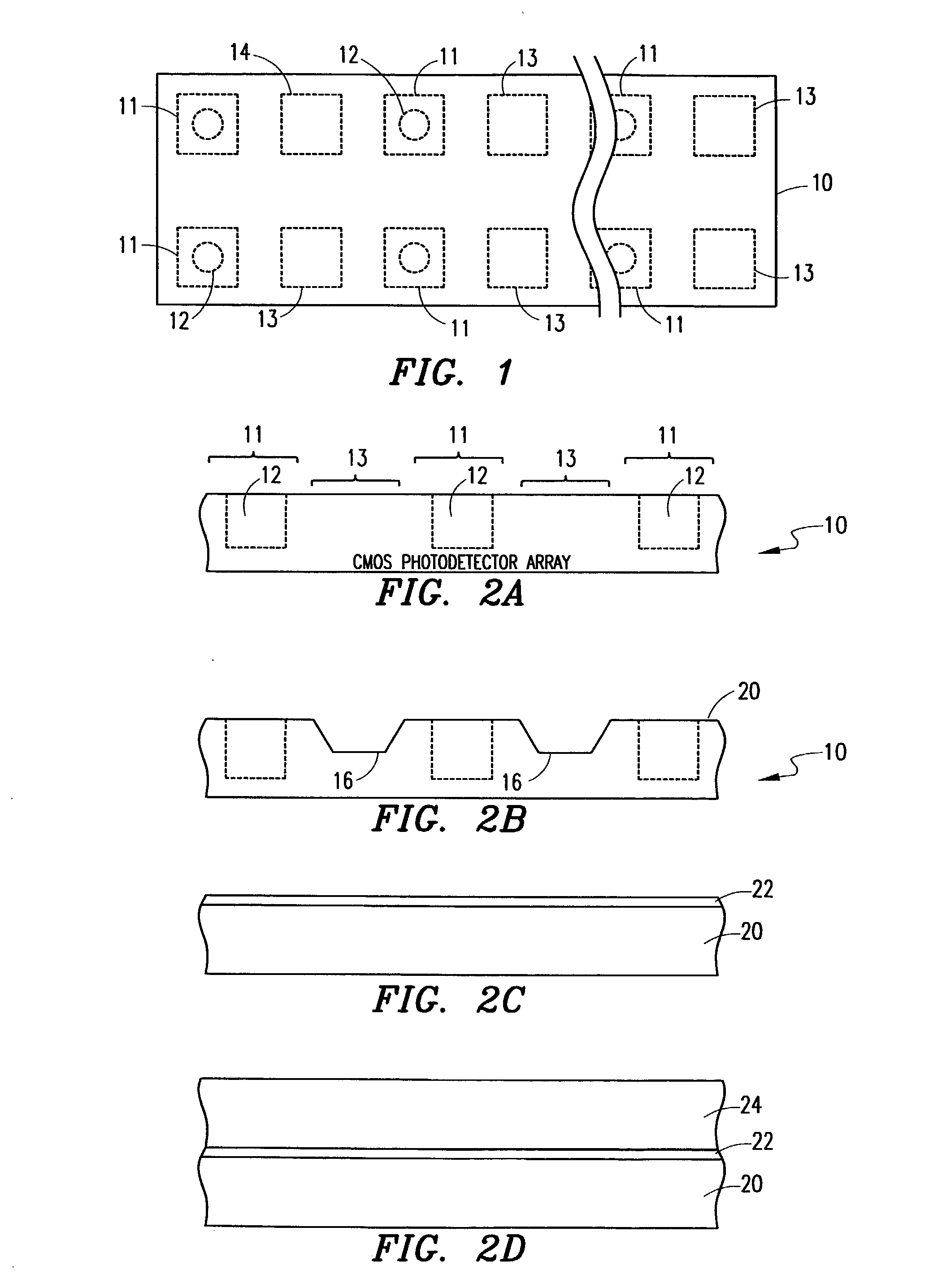

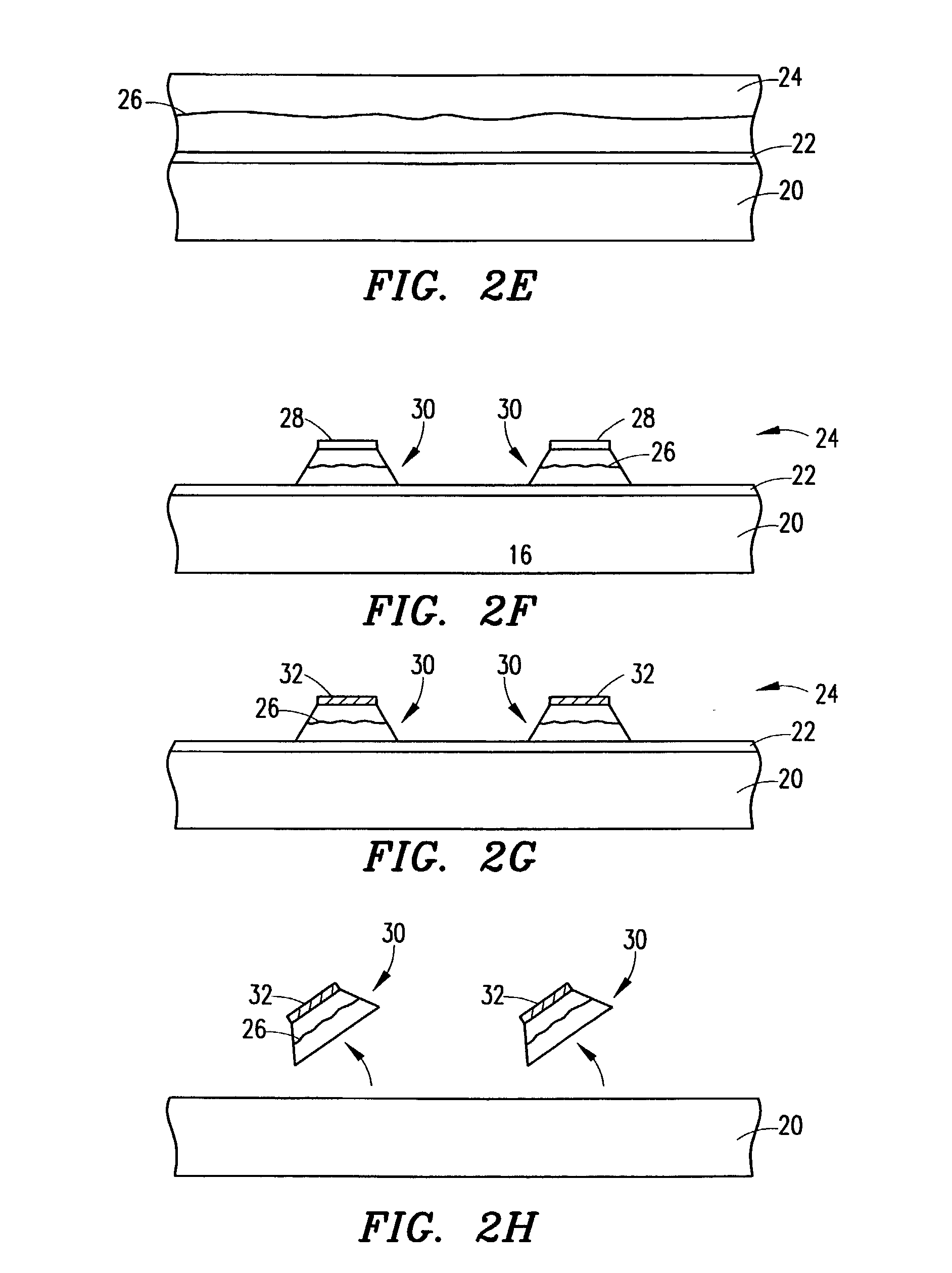

Optical excitation/detection device and method for making same using fluidic self-assembly techniques

InactiveUS20040222357A1Solid-state devicesMaterial analysis by optical meansCMOSPhotovoltaic detectors

The disclosure is directed toward an optical excitation / detection device that includes an arrayed plurality of photodetectors and separately formed photoemitters, as well as a method for making such a device. A CMOS fabricated photodetector array including a plurality of individual photoreceptors is selectively etched back between photoreceptor locations to reveal a plurality of recessed regions having a certain geographic profile. A plurality of semiconductor blocks, each having light emitting capability and each having a certain geometric profile that is complementary in size and shape to the certain geometric profile of the recessed regions, are separately fabricated. These blocks are included within a fluid to form a slurry. The slurry is then flowed over the CMOS fabricated photodetector array in accordance with a fluidic self-assembly technique, and the included semiconductor blocks are individually deposited within each of the plurality of recessed regions in the CMOS fabricated photodetector array. The deposited blocks are then attached within the recessed regions to form the optical excitation / detection device from an arrayed plurality of photodetectors and separately formed photoemitters.

Owner:SANOFI AVENTIS DEUT GMBH

Three dimensional integrated circuit and method of design

InactiveUS20070287224A1Function increaseSimple designFluid pressure measurement by electric/magnetic elementsSolid-state devicesCMOSEngineering

A three dimensional (3D) integrated circuit (IC), 3D IC chip and method of fabricating a 3D IC chip. The chip includes multiple layers of circuits, e.g., silicon insulator (SOI) CMOS IC layers, each including circuit elements. The layers may be formed in parallel and one layer attached to another to form a laminated 3D chip.

Owner:GLOBALFOUNDRIES INC

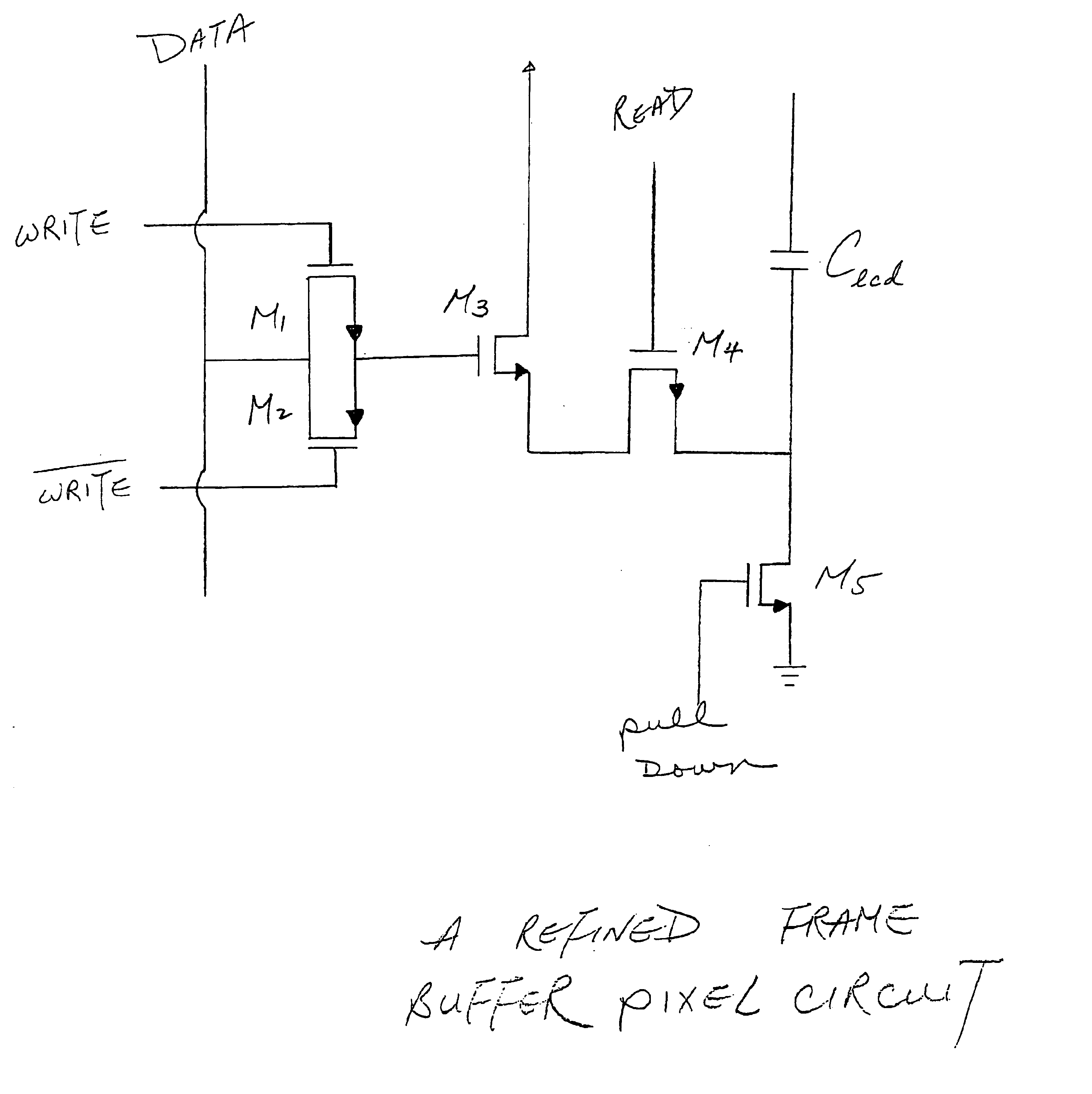

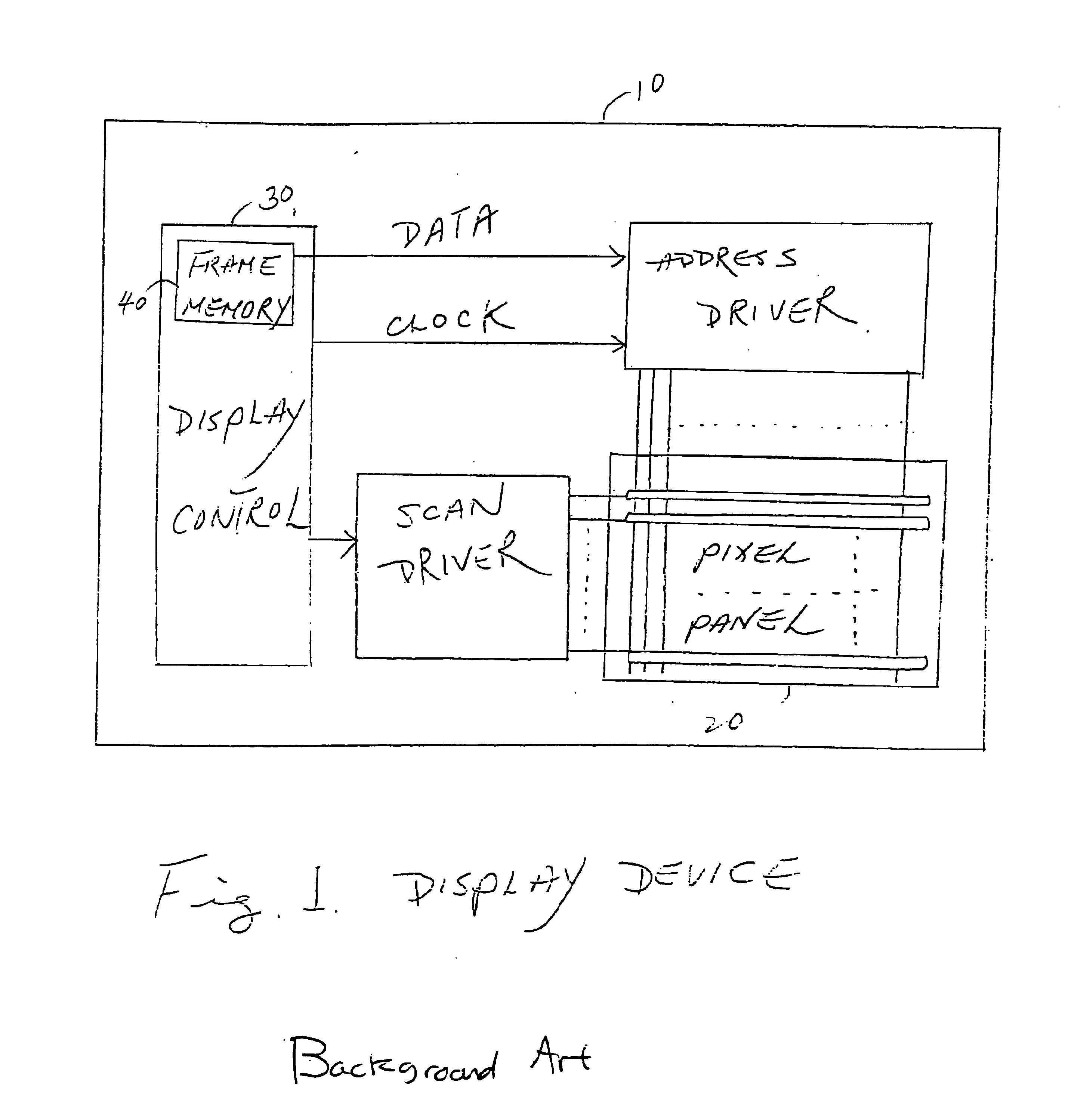

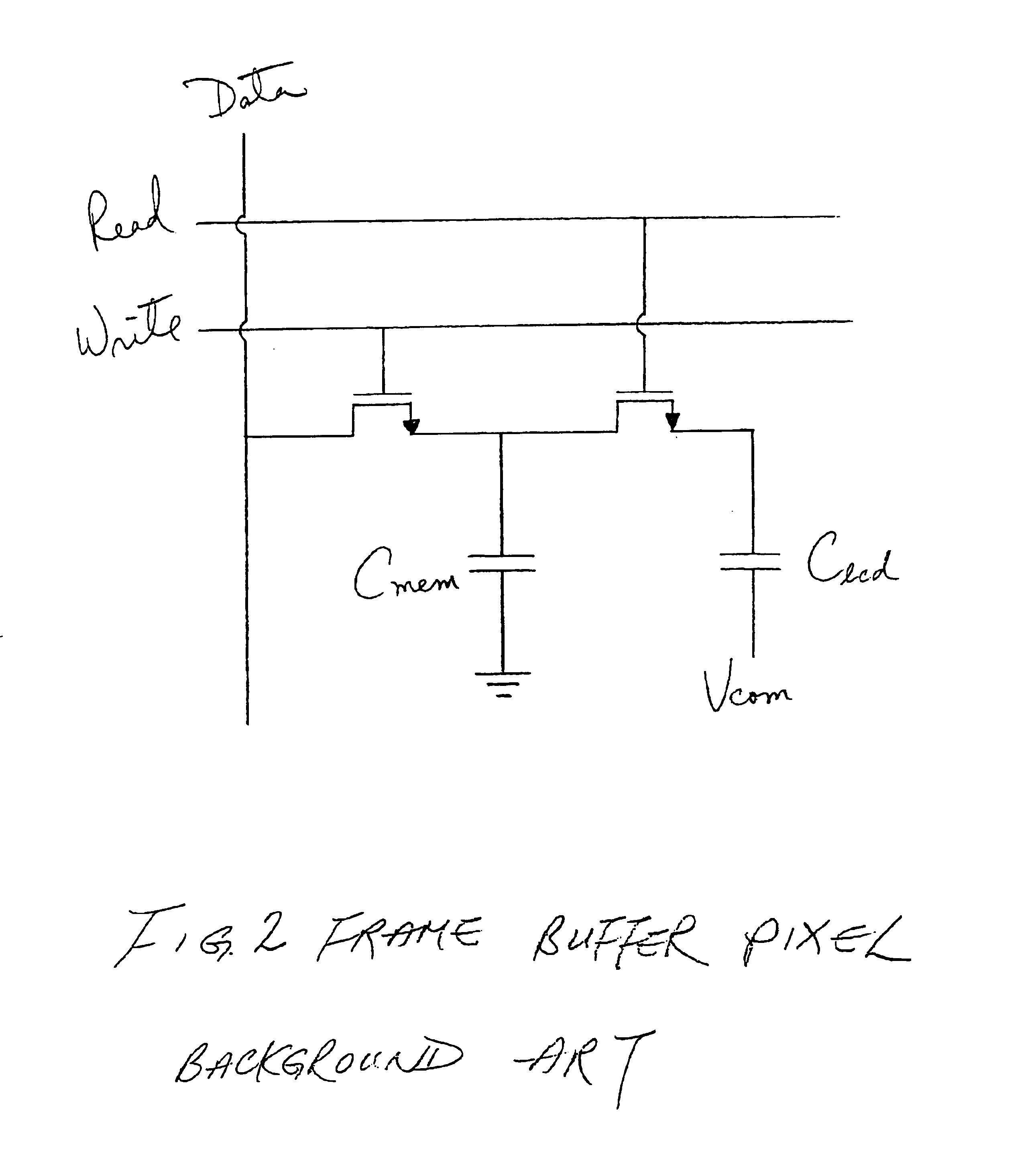

Frame buffer pixel circuit for liquid crystal display

InactiveUS6911964B2Enhanced frame buffer pixelIncrease contrastStatic indicating devicesNon-linear opticsCMOSLiquid-crystal display

An enhanced frame buffer pixel circuit with two control transistors and a separate capacitor put in as a memory capacitor before the memory transistor yields a high contrast ratio by removing induced charge and solving a charge sharing problem between the memory capacitor and the liquid crystal display (LCD) capacitor. The memory transistor may be made of either CMOS or PMOS. The frame buffer pixel can be used to drive binary displays which expresses ON and OFF only if a comparator is put in after the pixel electrode circuit to represent gray levels with reduced sub-frame frequency.

Owner:DUKE UNIV +1

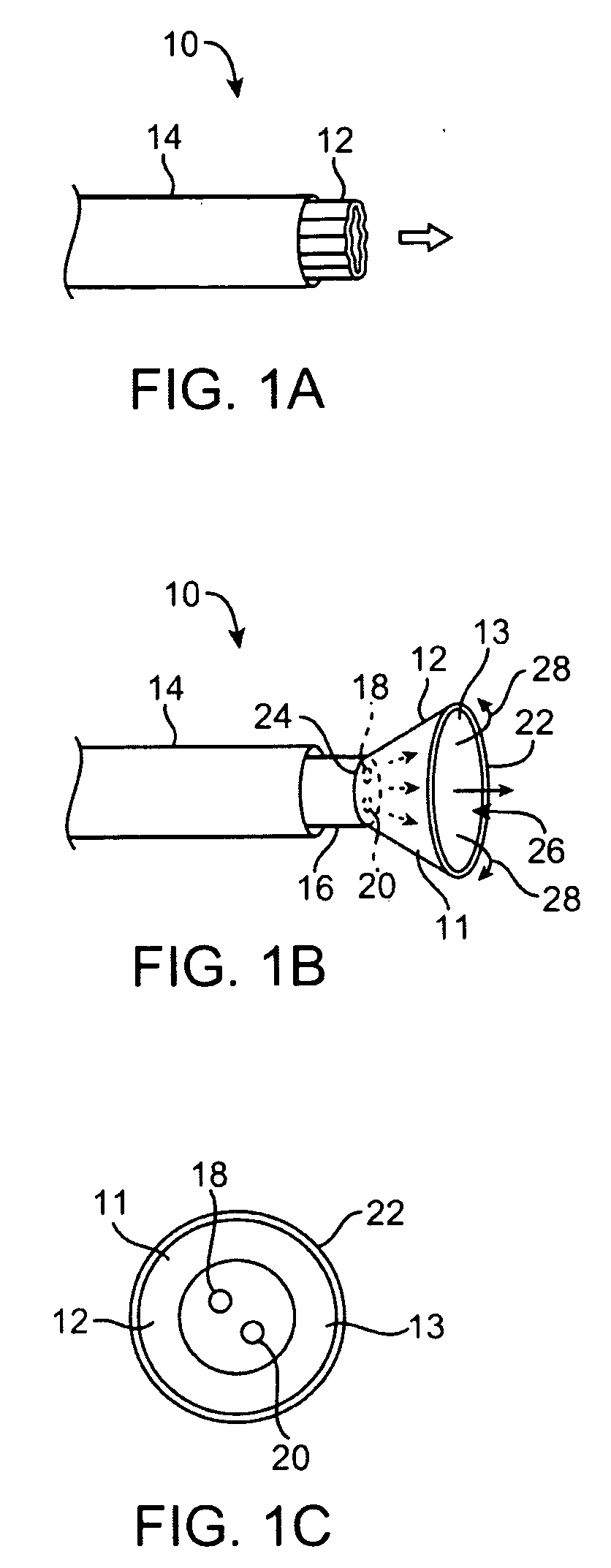

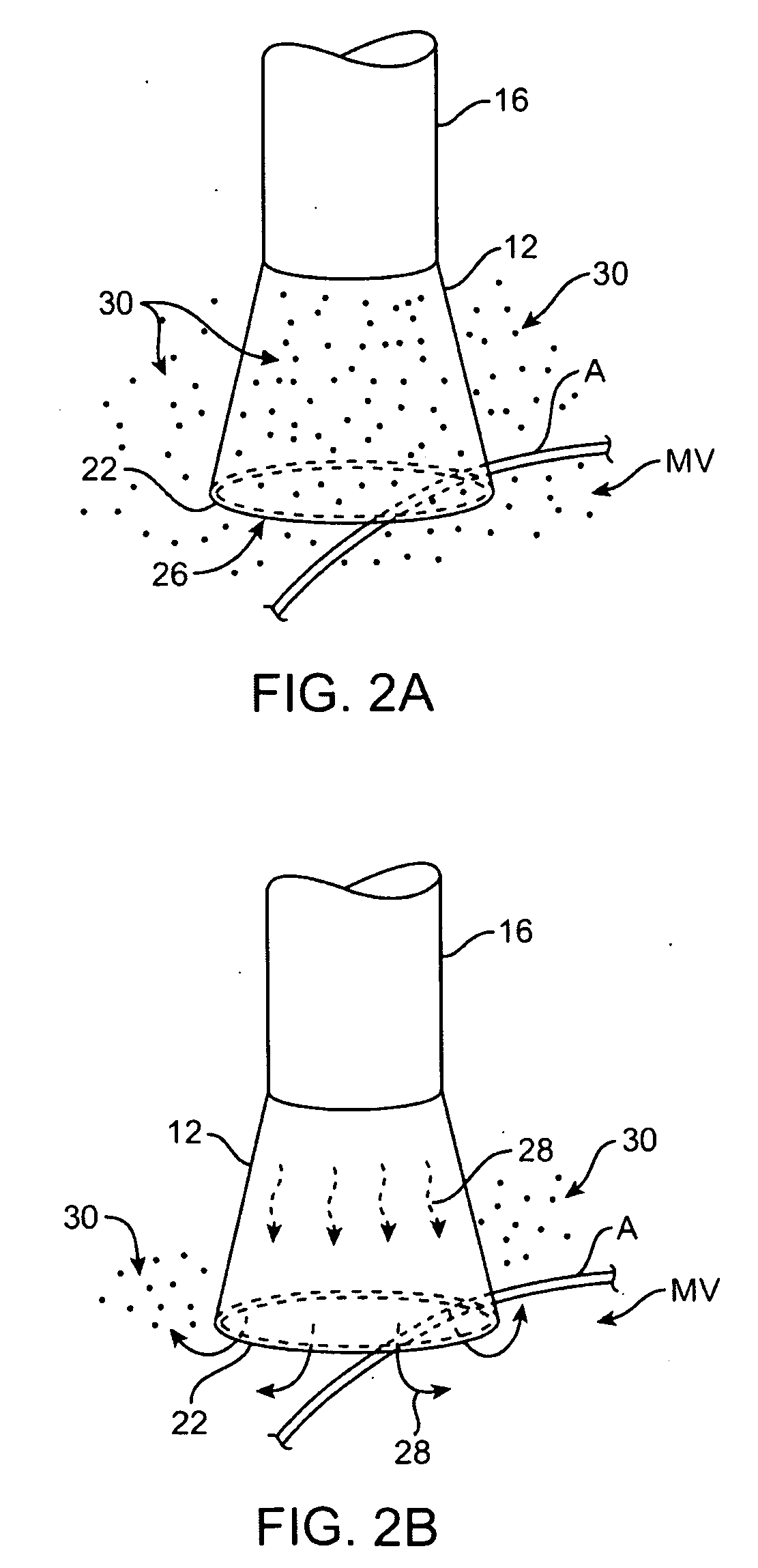

Combination imaging and treatment assemblies

Combination imaging and treatment assemblies are described herein which may utilize a deployment catheter in combination with an endoscopic system. The combined system comprises an open architecture to modularly incorporate any number of imaging devices (such as optical fiber, CMOS or CCD endoscopes) to provide high resolution optical images of tissue within an opaque environment. Additional variations may include an imaging hood or balloon member incorporated upon an endoscope or advanced through an endoscope working channel to visualize and treat tissue through blood.

Owner:INTUITIVE SURGICAL OPERATIONS INC

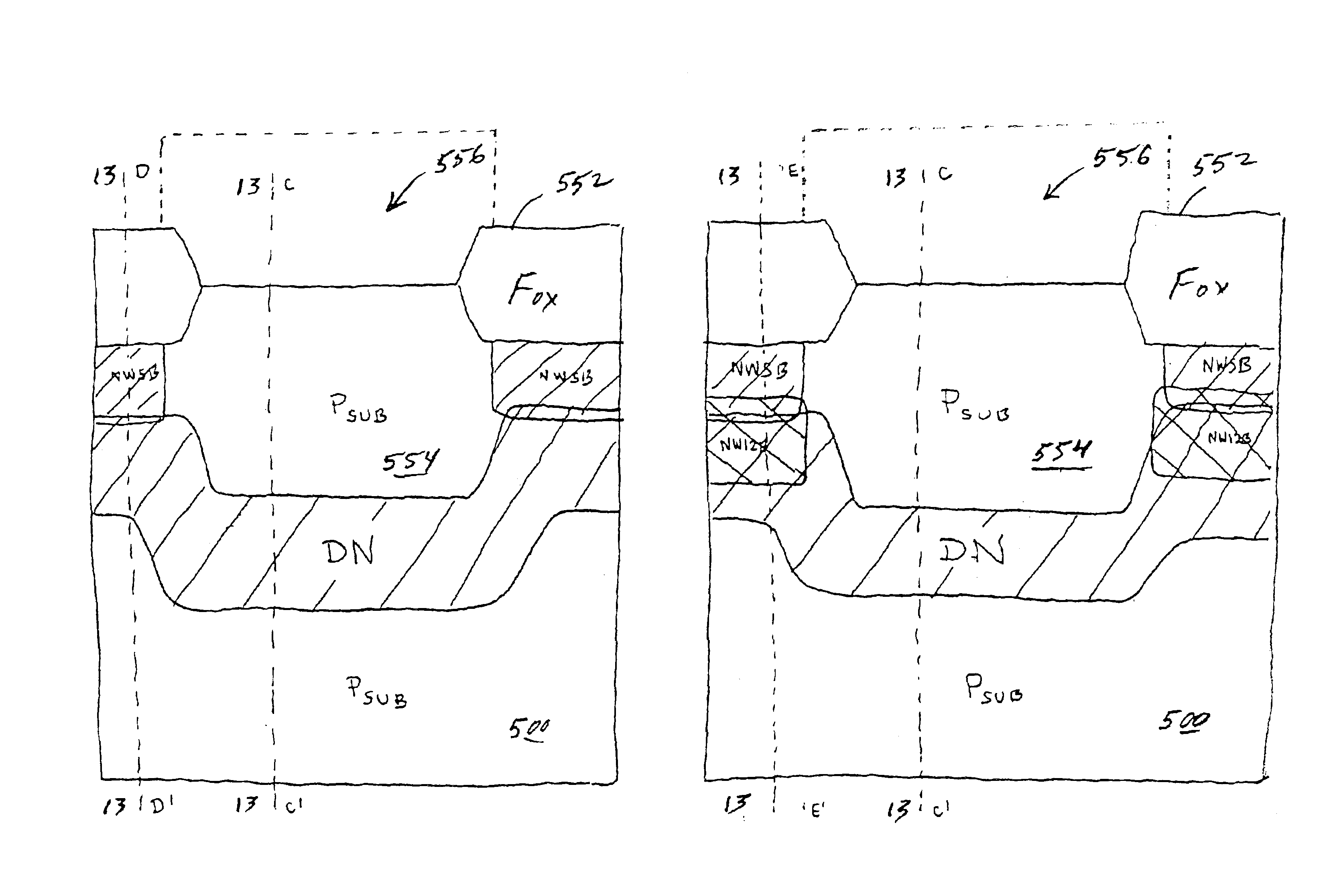

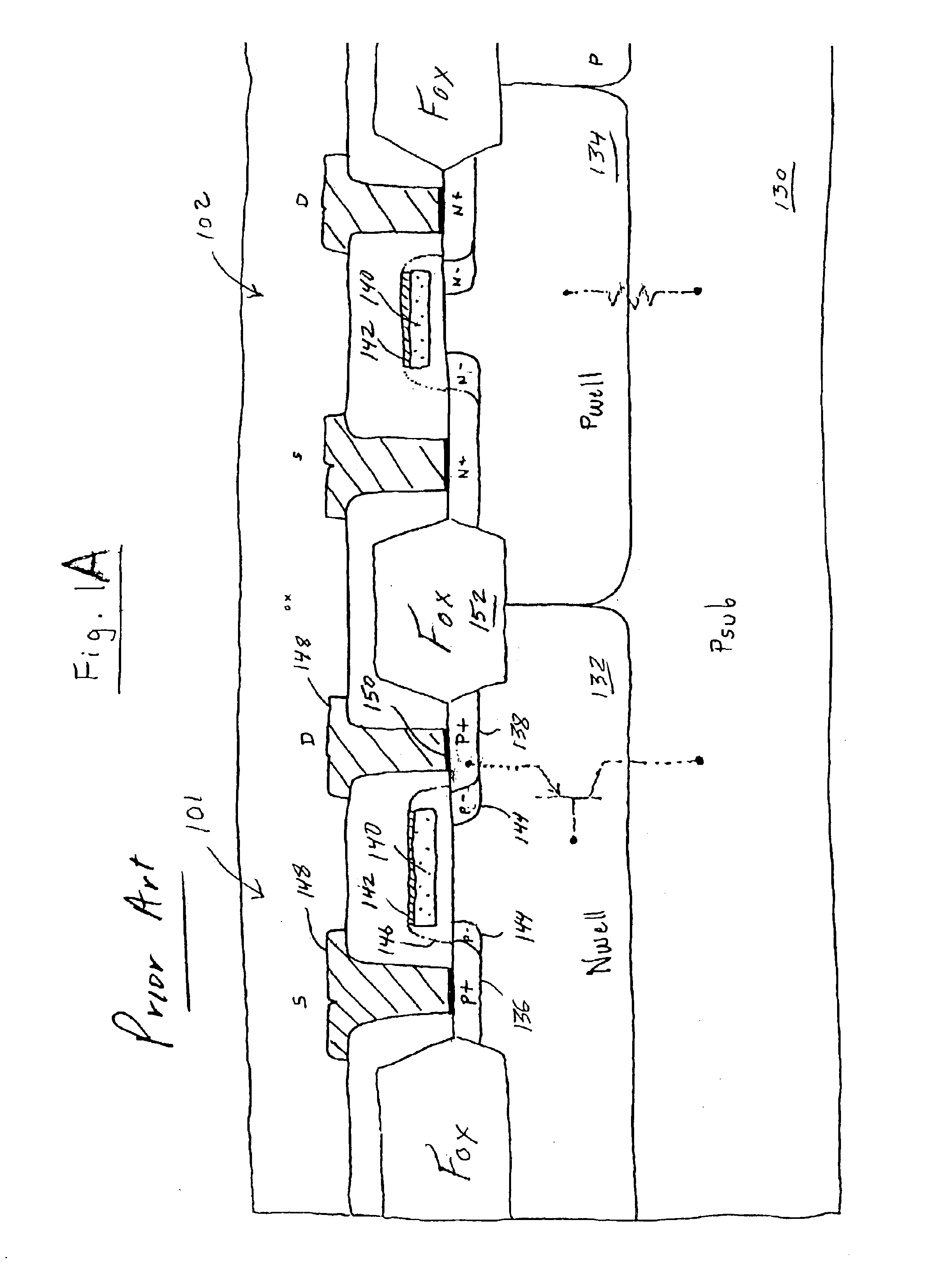

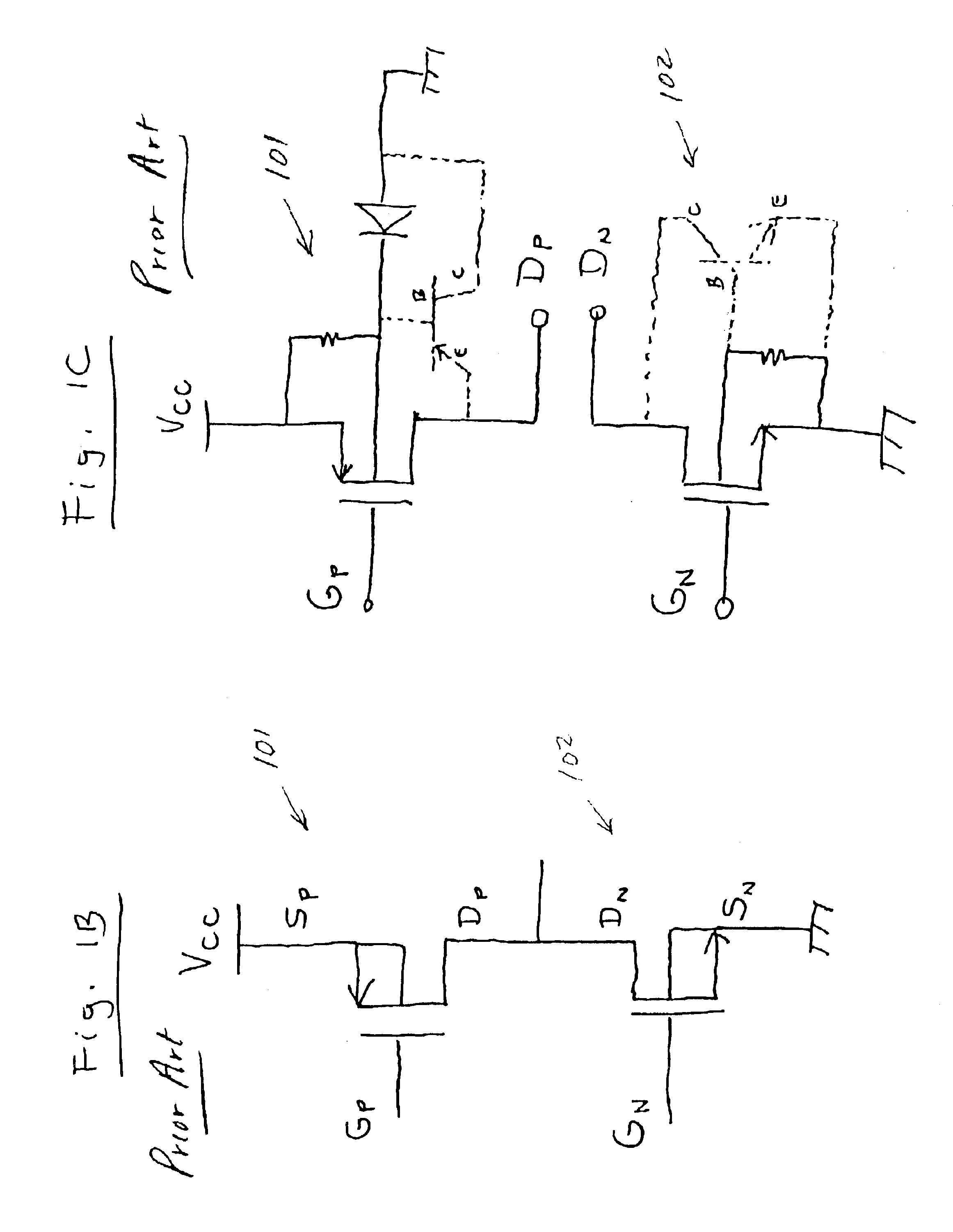

Modular bipolar-CMOS-DMOS analog integrated circuit & power transistor technology

A family of semiconductor devices is formed in a substrate that contains no epitaxial layer. In one embodiment the family includes a 5V CMOS pair, a 12V CMOS pair, a 5V NPN, a 5V PNP, several forms of a lateral trench MOSFET, and a 30V lateral N-channel DMOS. Each of the devices is extremely compact, both laterally and vertically, and can be fully isolated from all other devices in the substrate.

Owner:ADVANCED ANALOGIC TECH (HONG KONG) LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com