Three dimensional CMOS integrated circuits having device layers built on different crystal oriented wafers

a technology of integrated circuits and crystal oriented wafers, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of reducing the orientation of nfet devices, reducing the efficiency of nfet devices, and undesirable pfets having larger widths, etc., to achieve improved transistor packing density, reduced chip footprint, and increased packing density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

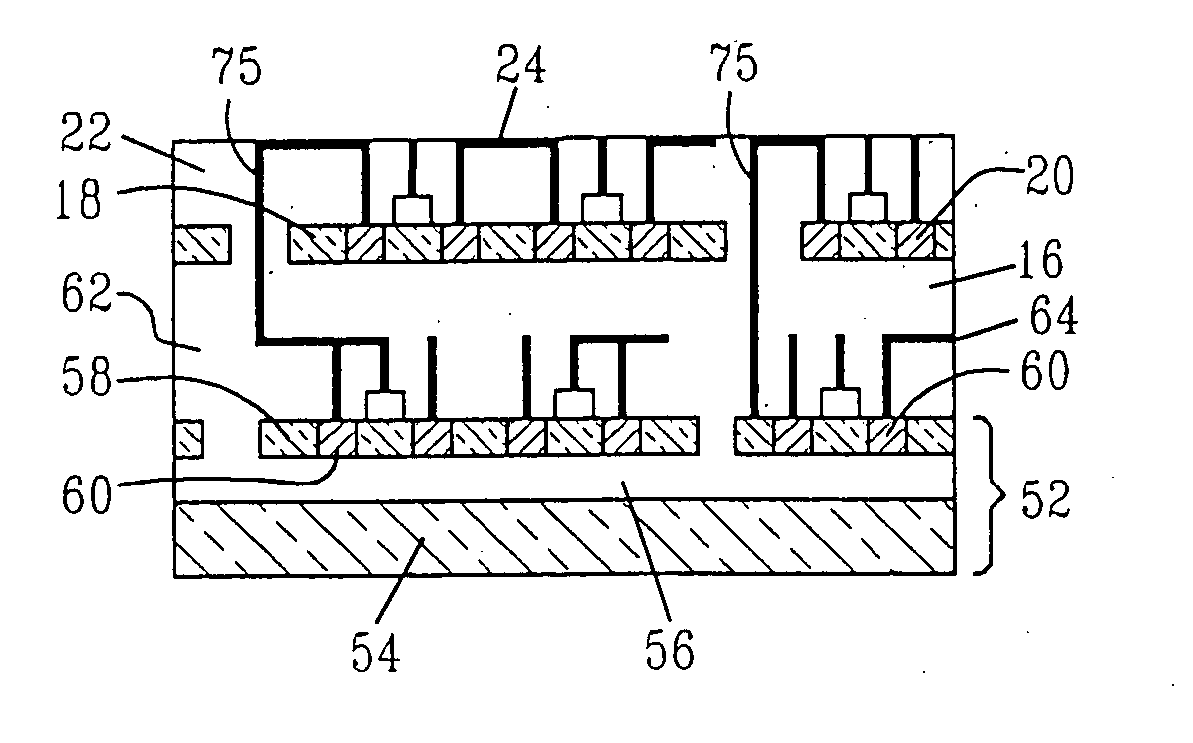

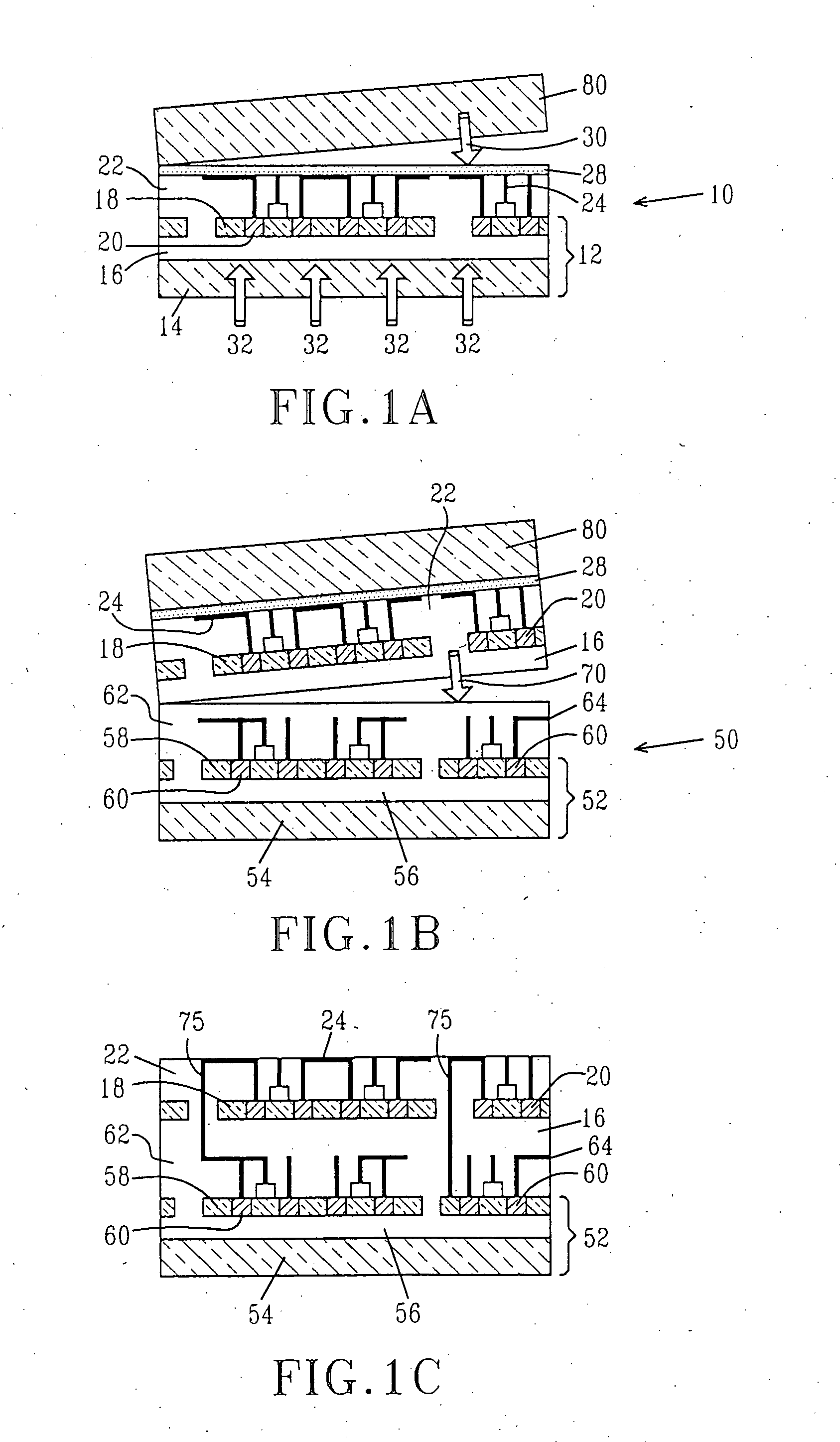

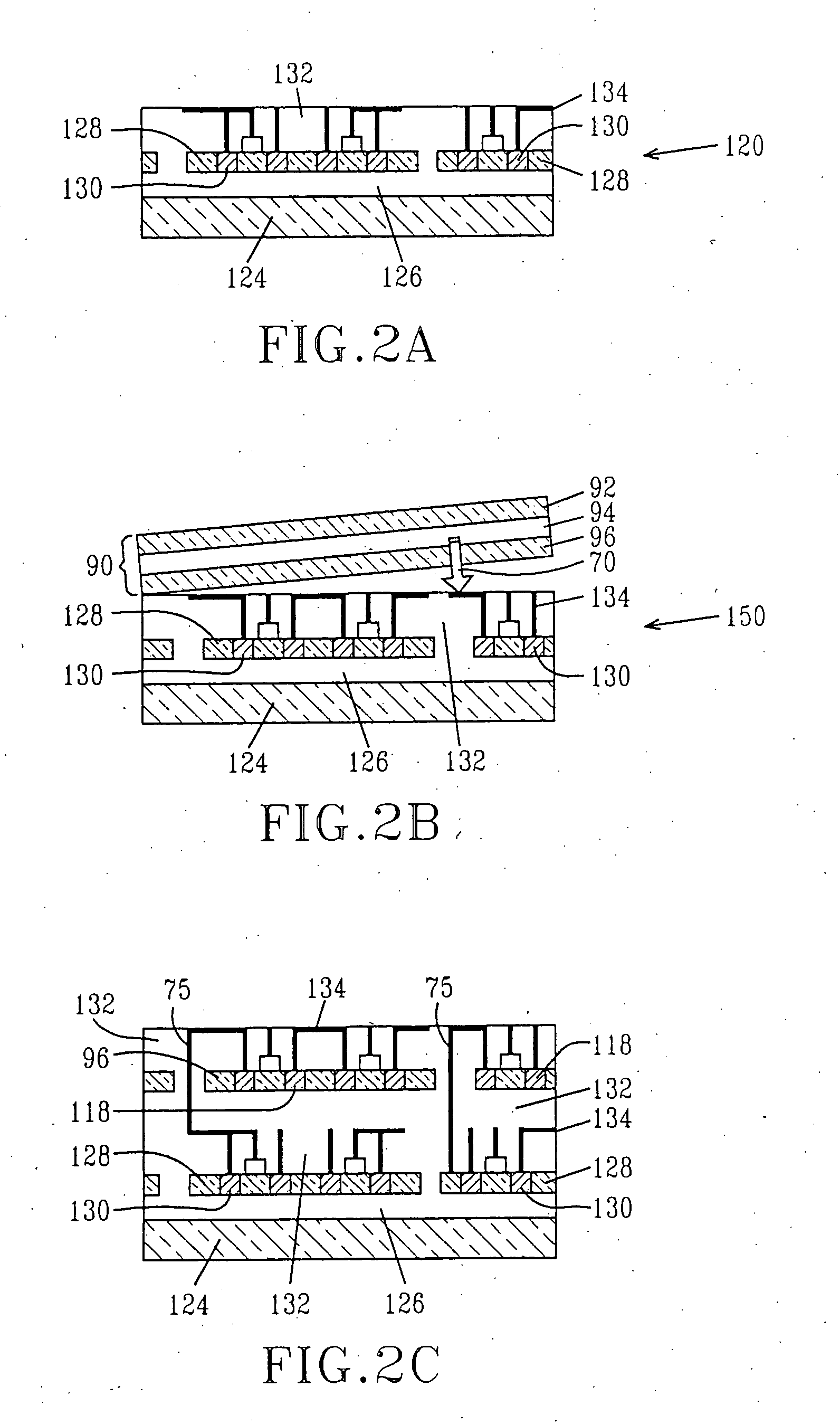

[0031] The present invention, which provides 3D integration schemes for forming a 3D CMOS integrated circuit having device layers built on different crystal oriented SOI wafers, will now be described in greater detail by referring to the drawings that accompany the present invention. In the accompanying drawings, like and / or corresponding elements are referred to by like reference numerals.

[0032] In the present invention, the terms “silicon-on-insulator” or “SOI” wafer (the term ‘substrate’ can interchangeable used with the term ‘wafer’) are used to define a semiconductor structure in which a buried insulating layer, such as a buried oxide layer, separates a top Si-containing layer (also referred to as the SOI layer or the device layer) from a bottom Si-containing substrate layer. The term “Si-containing” is used in the present invention to denote a semiconductor material that includes silicon. Illustrative examples of such Si-containing materials include, but are not limited to: S...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com