Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

680 results about "Performance enhancement" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

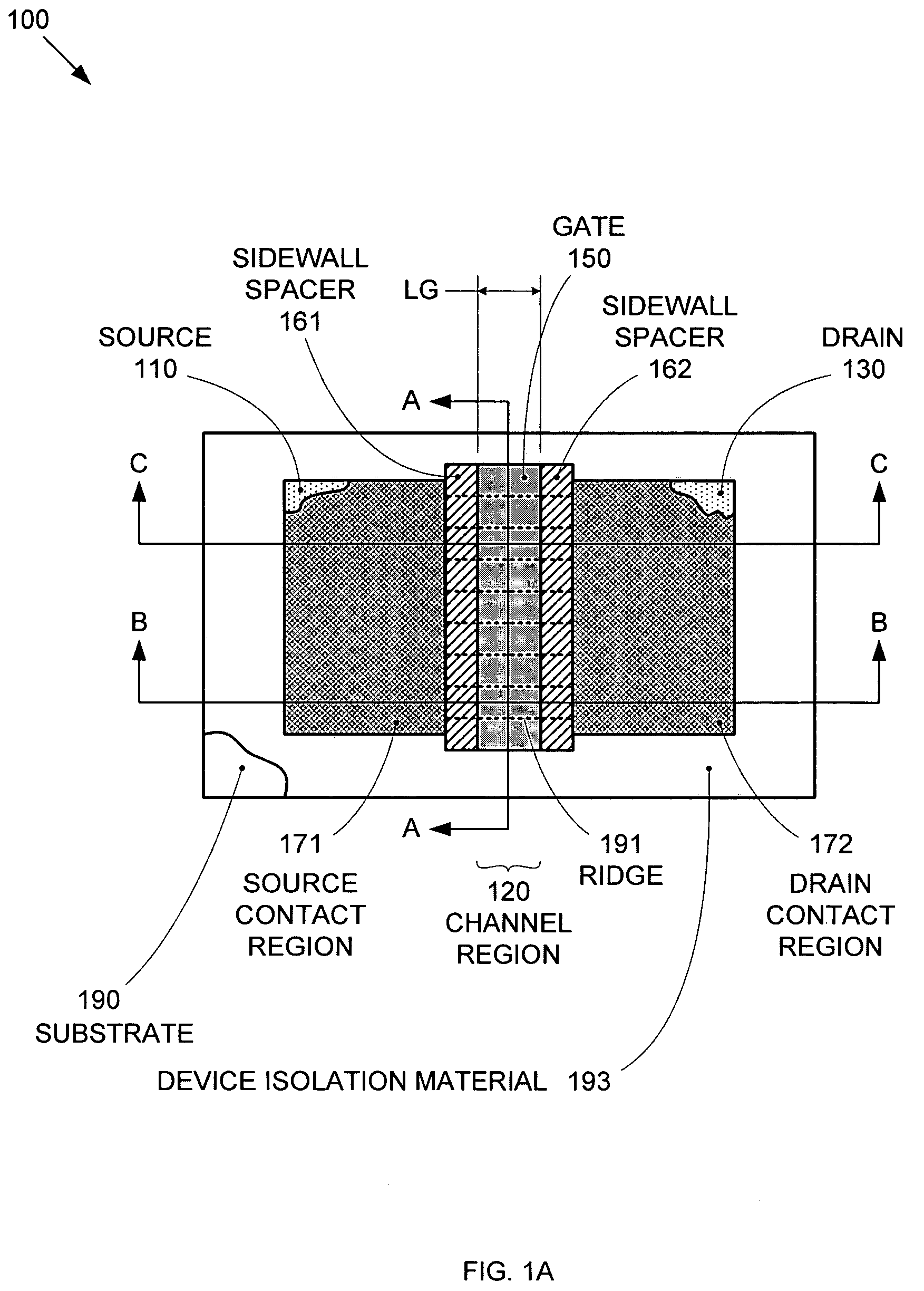

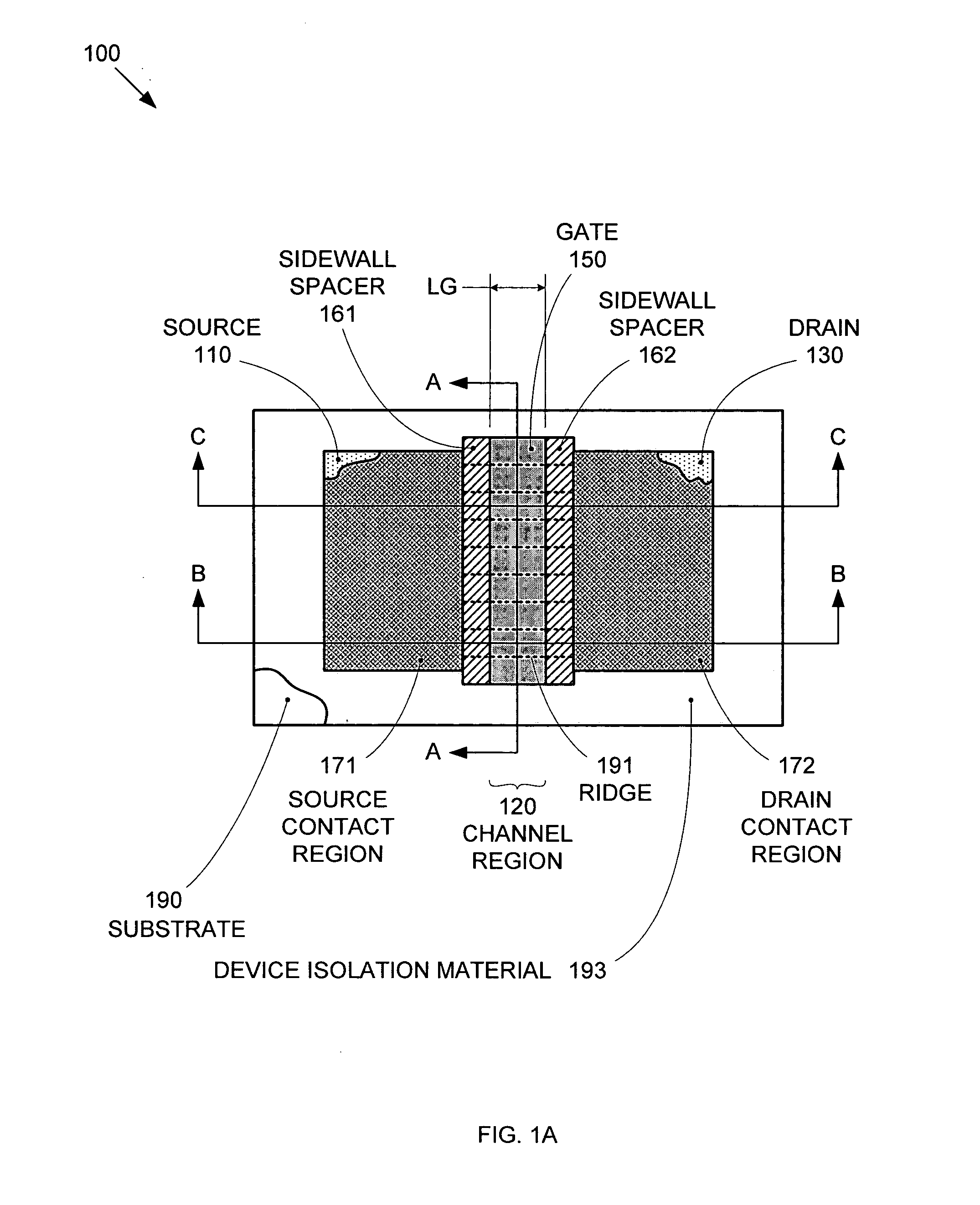

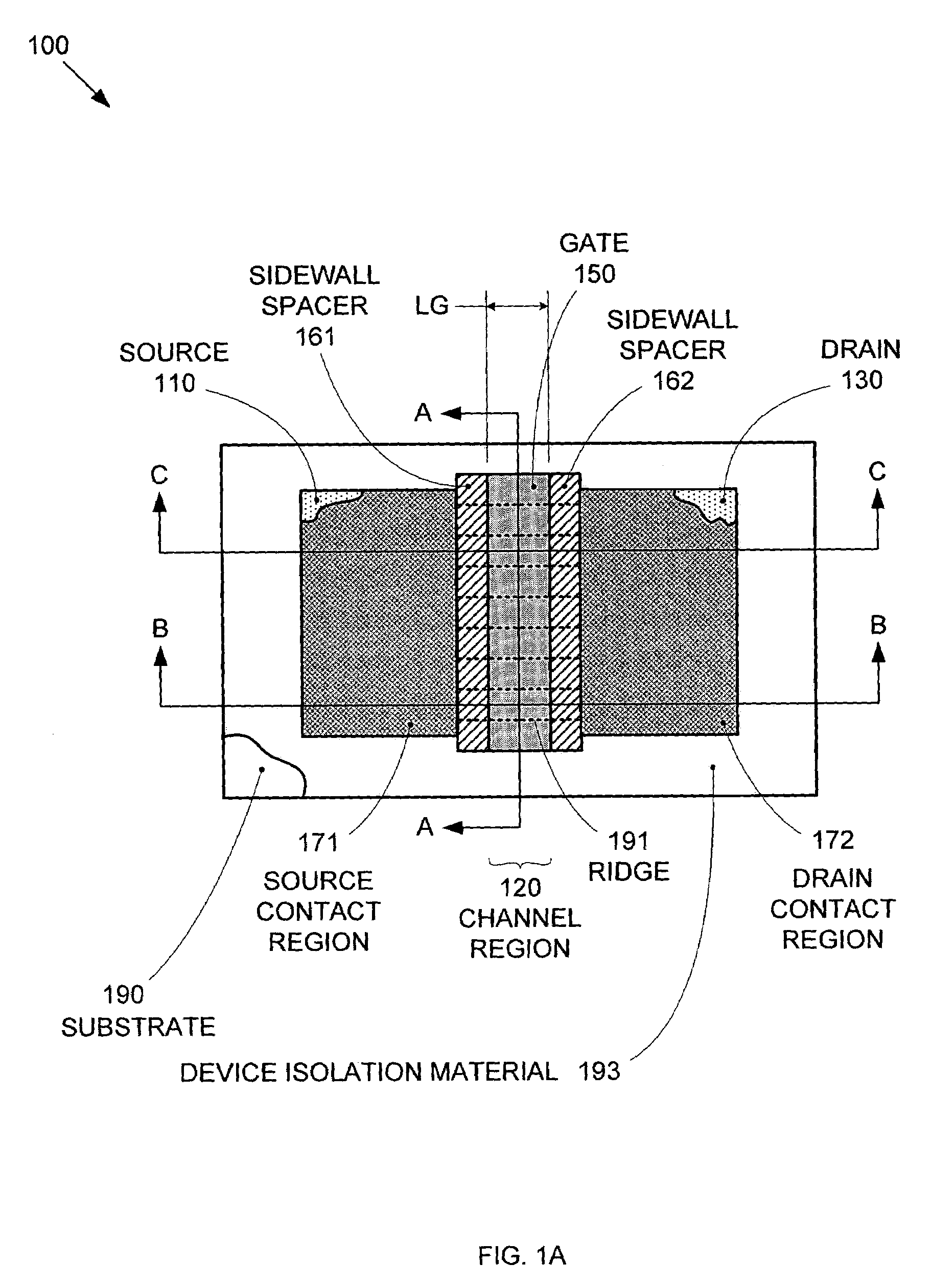

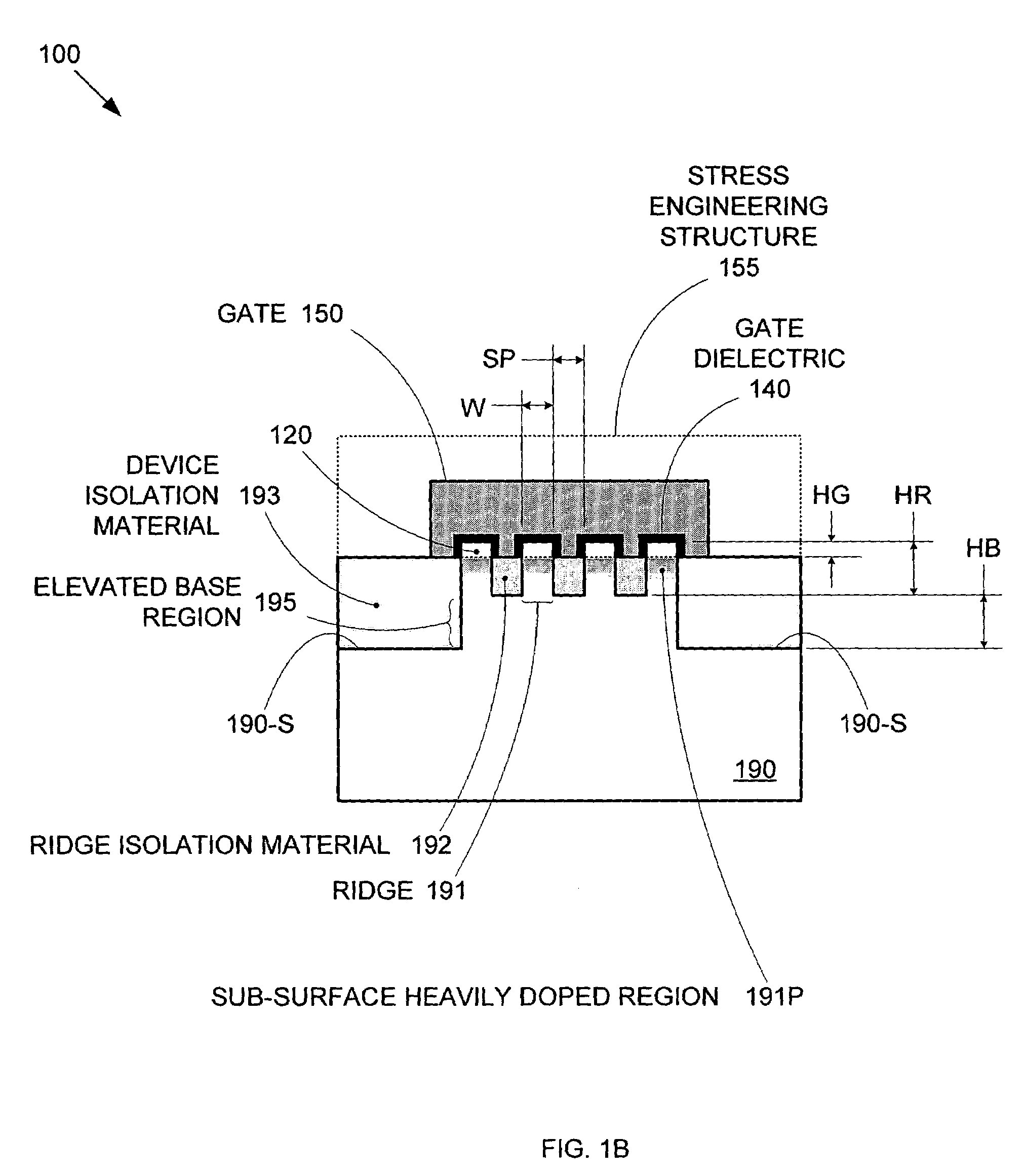

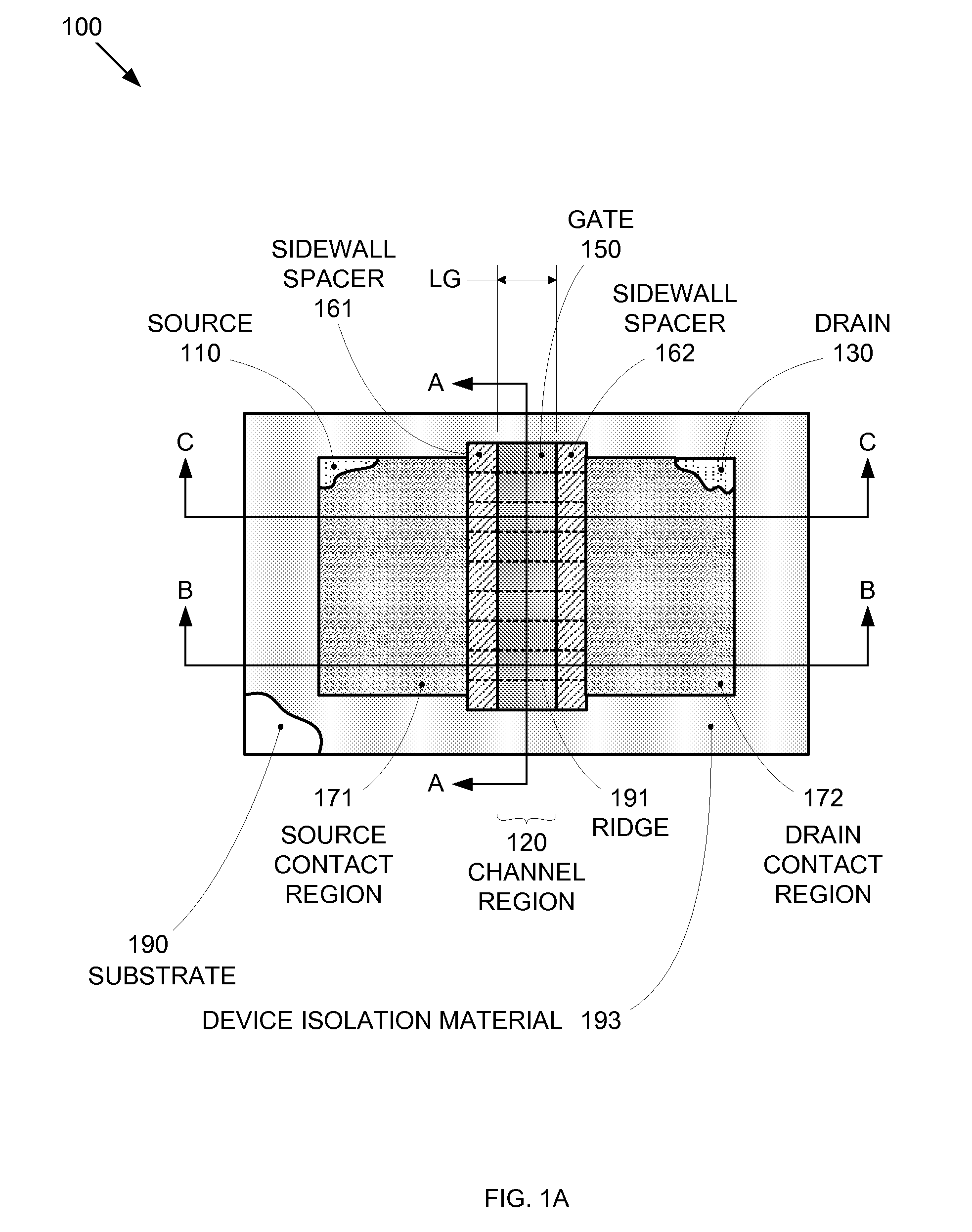

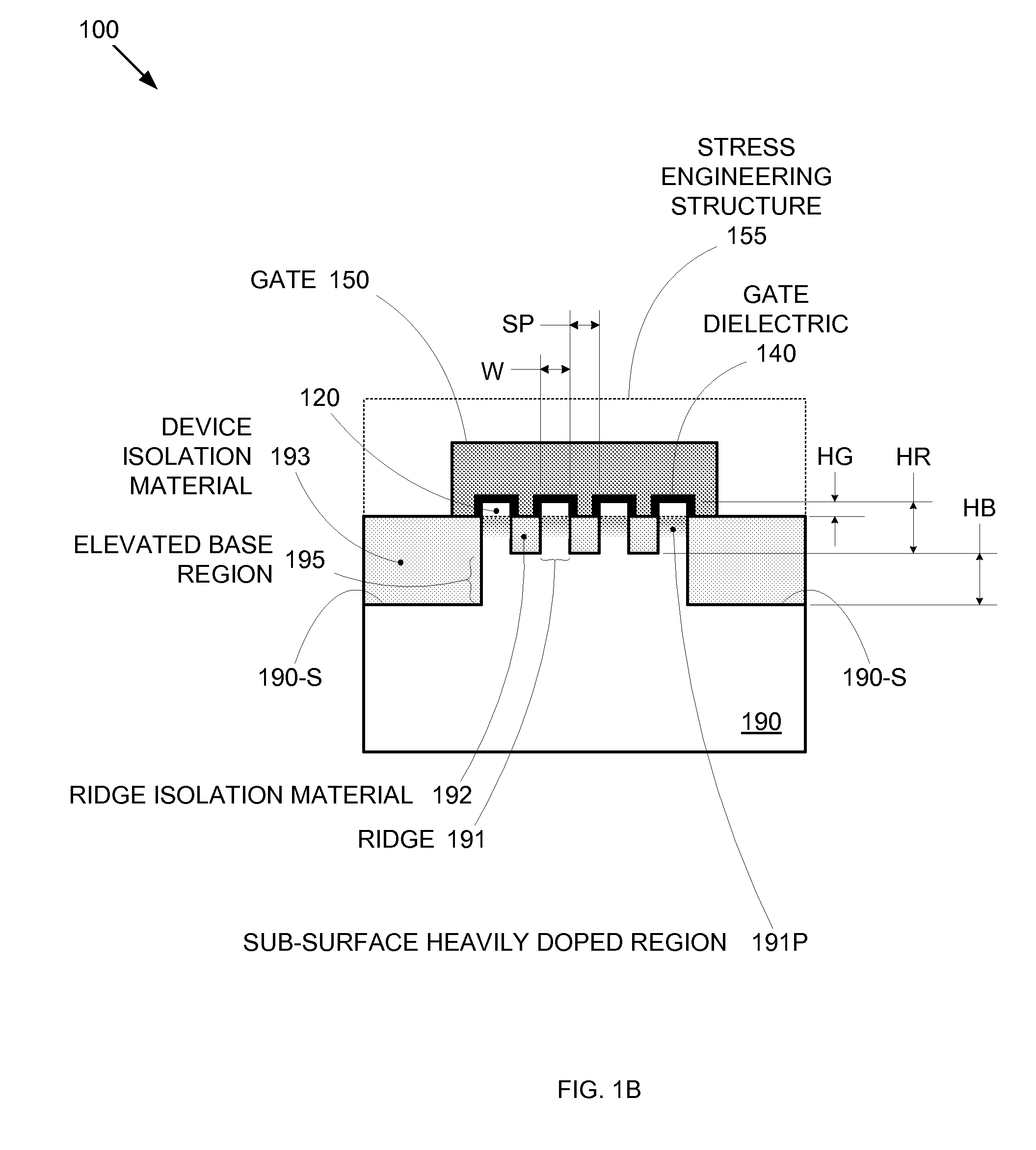

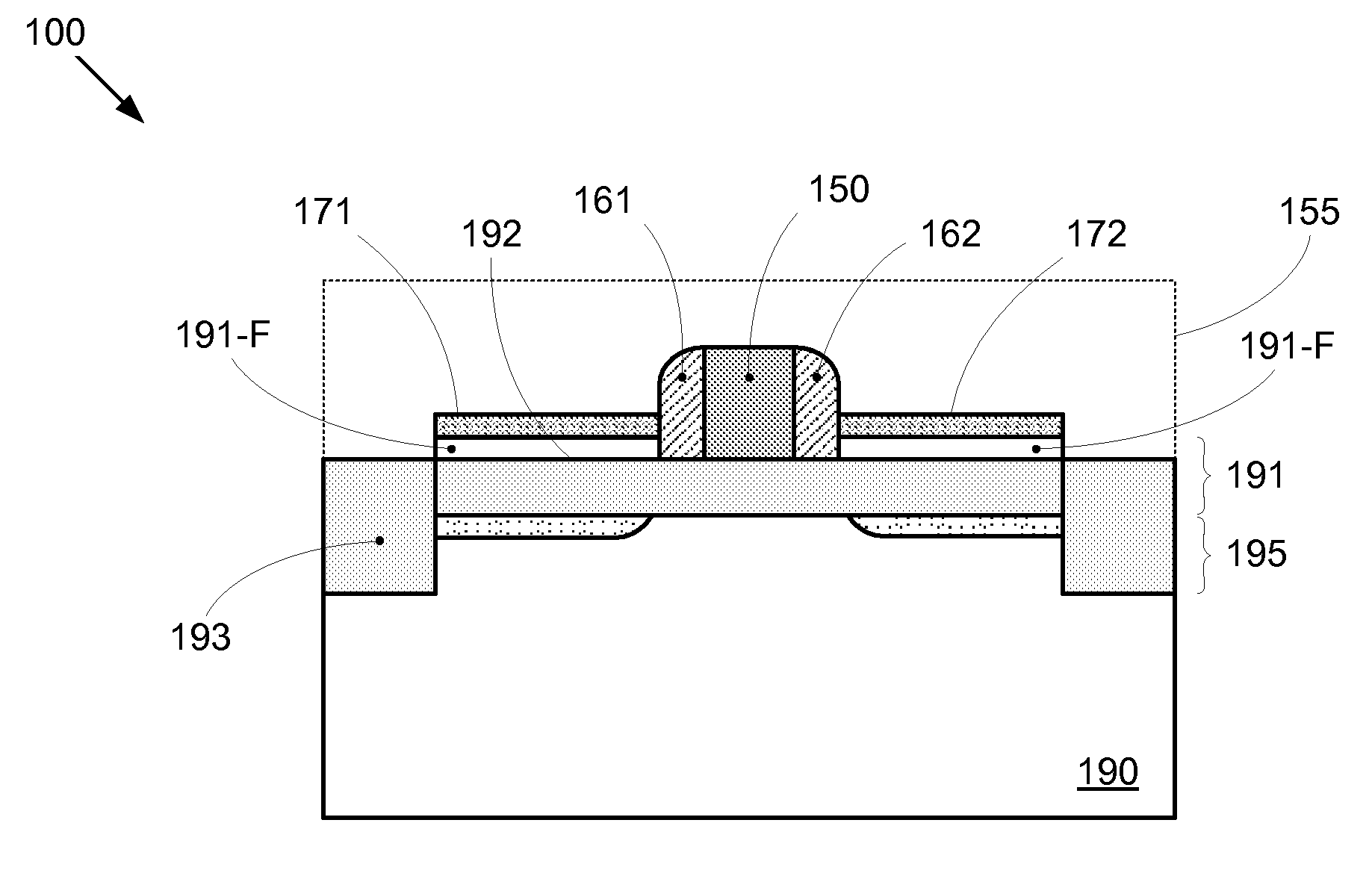

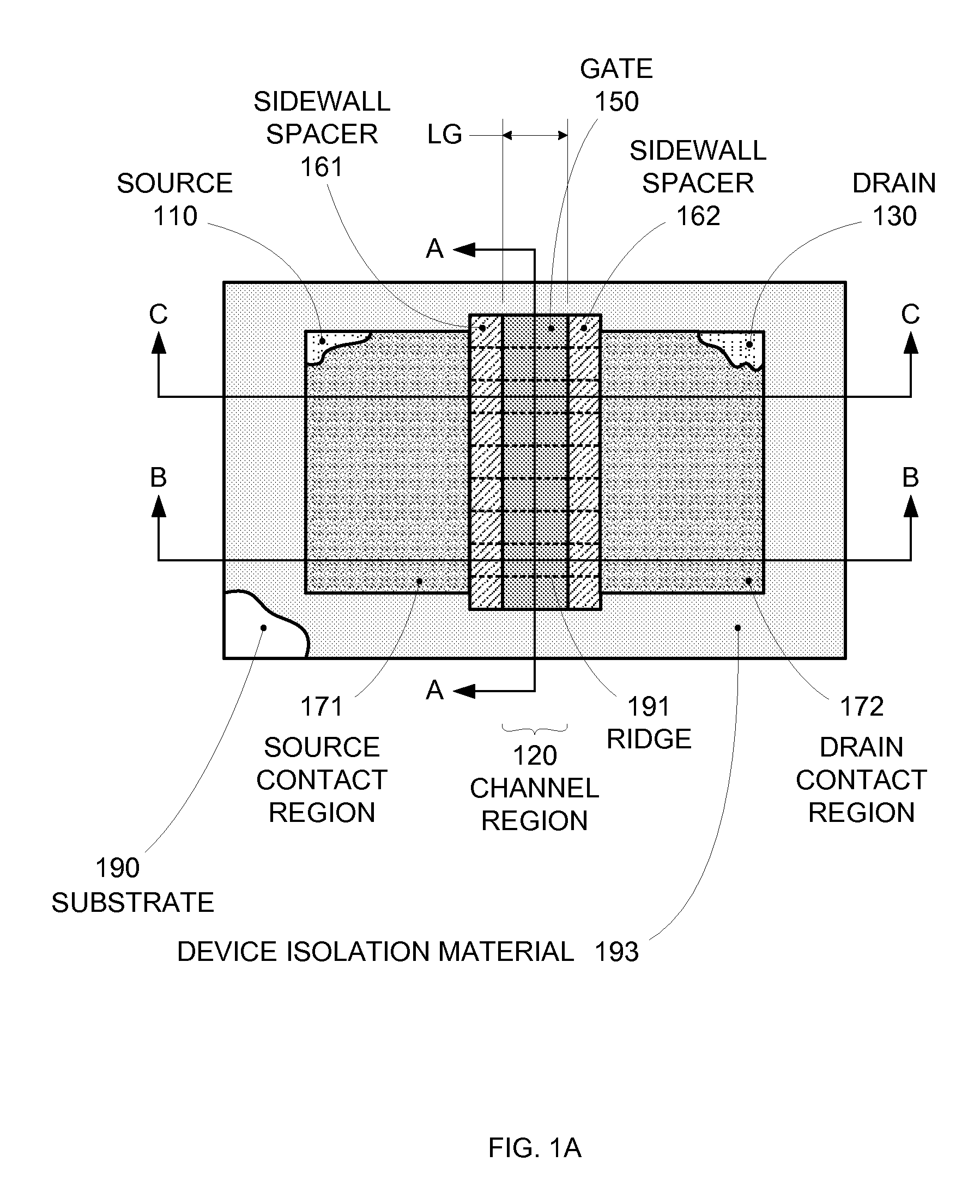

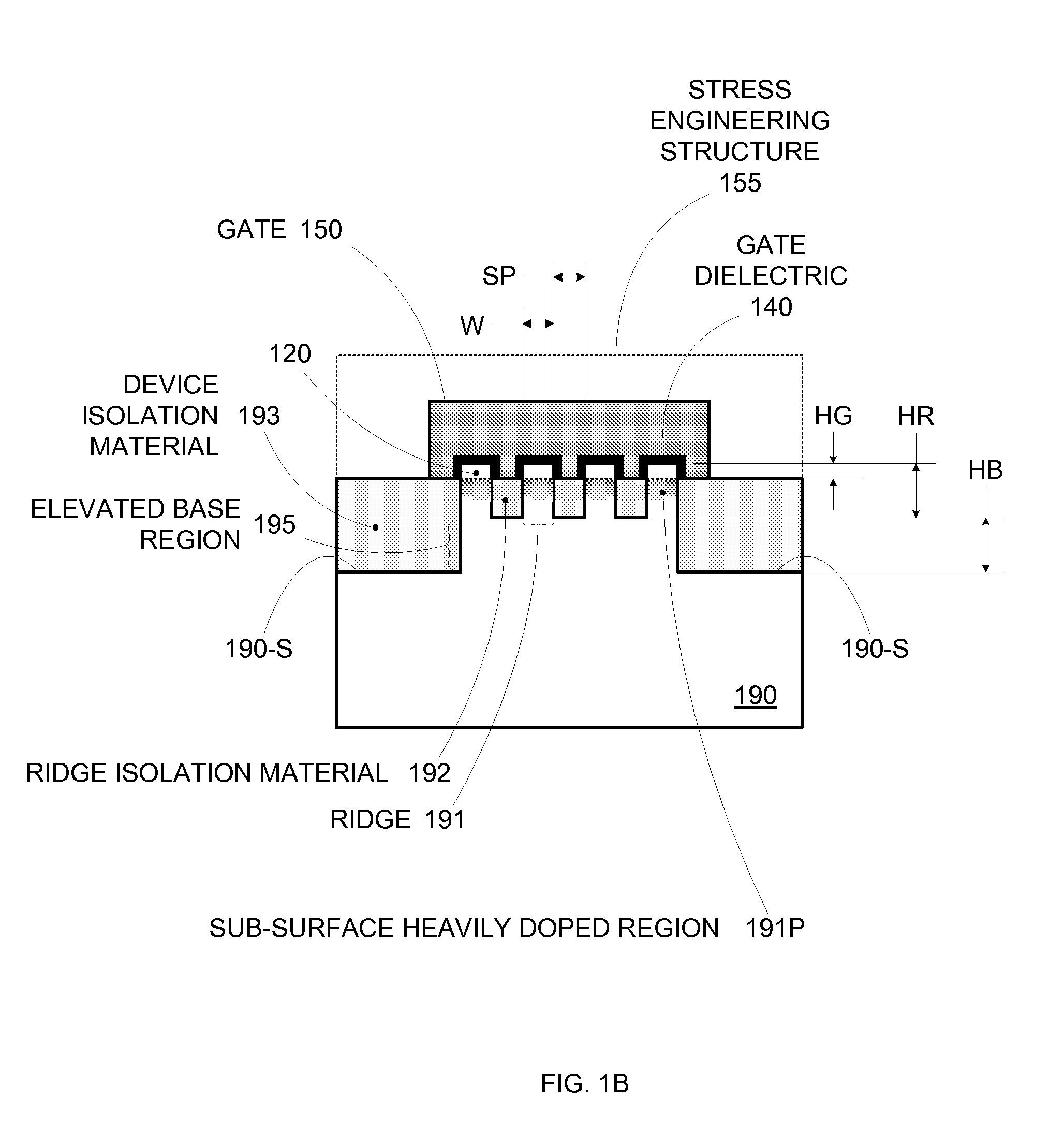

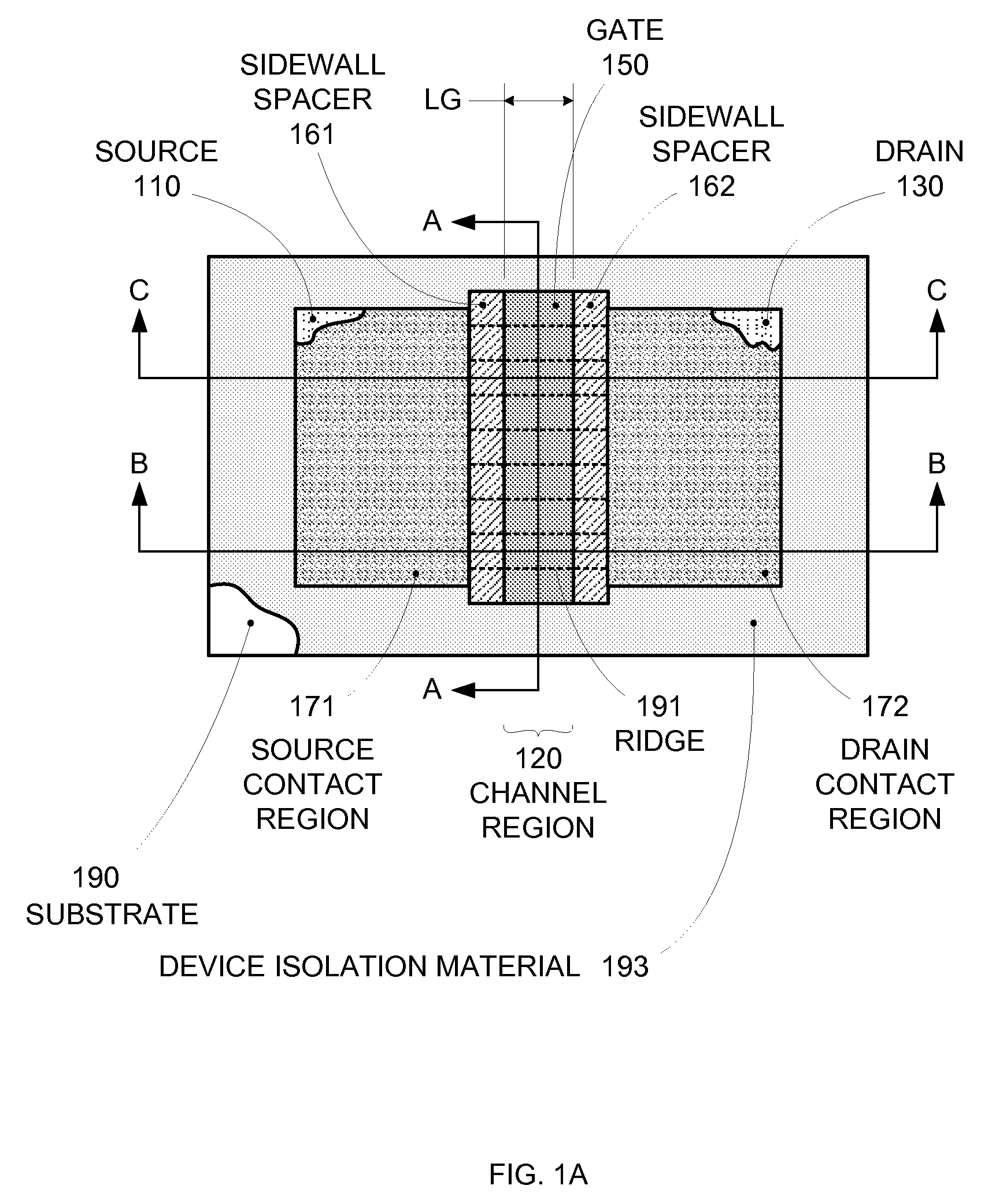

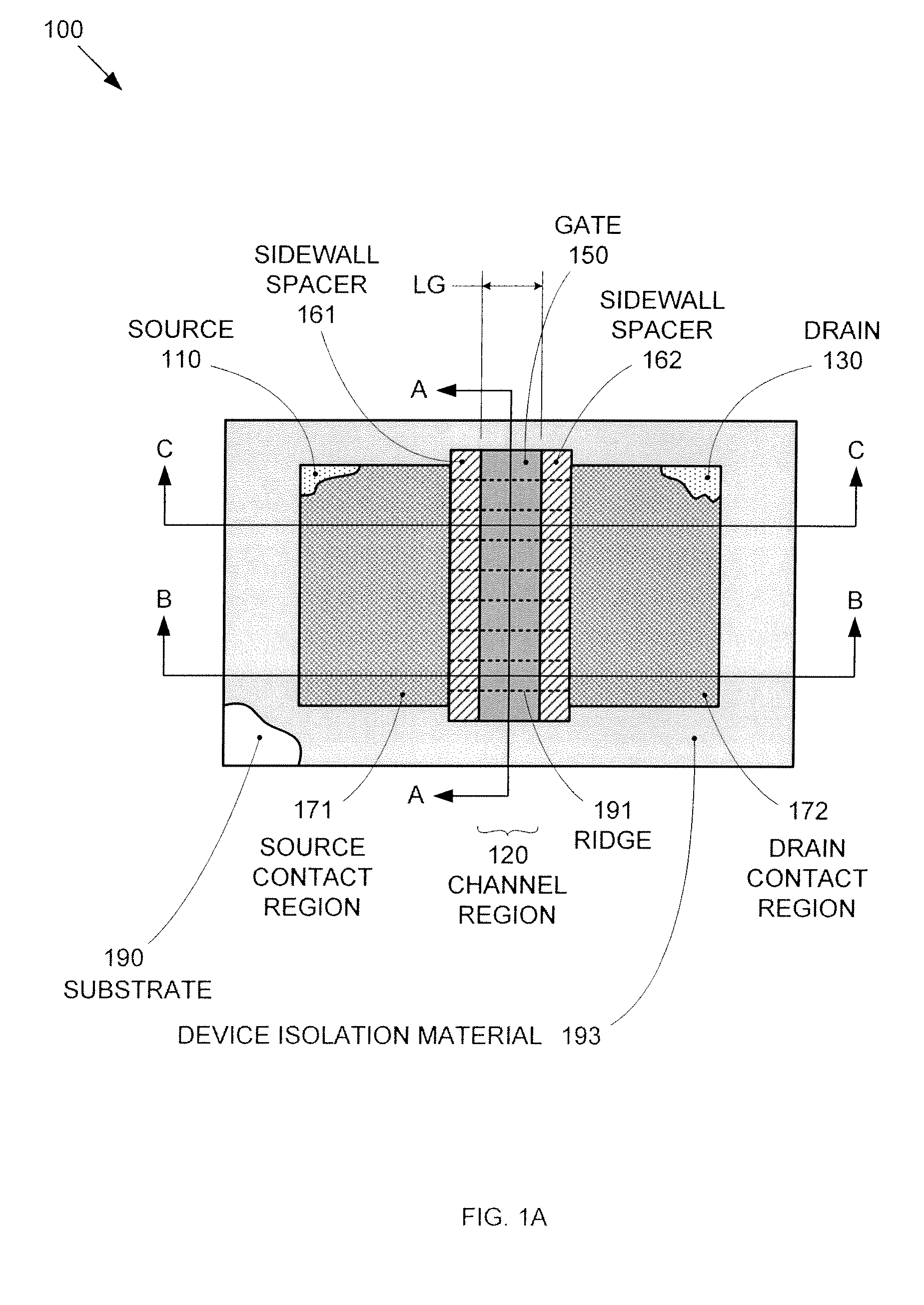

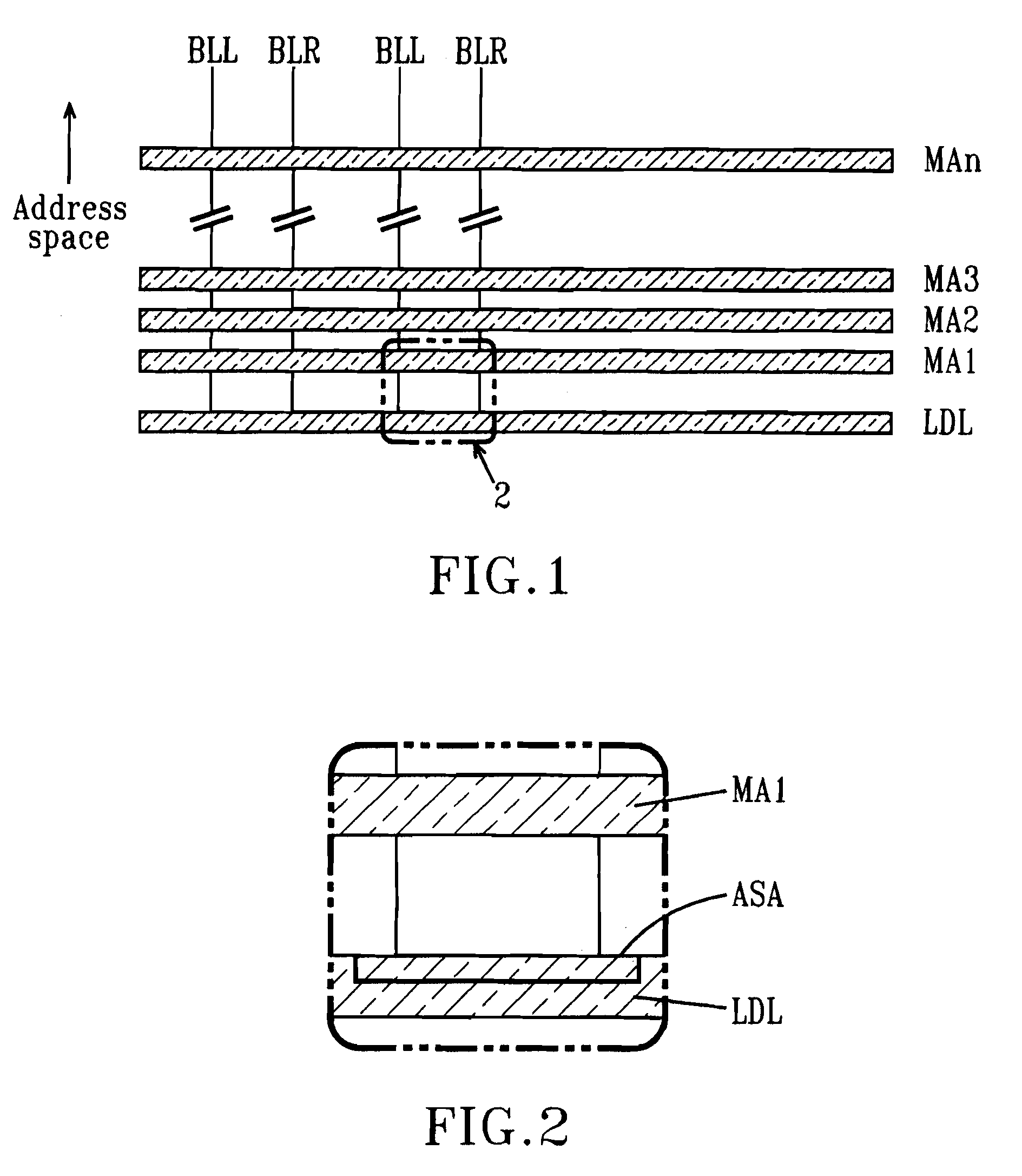

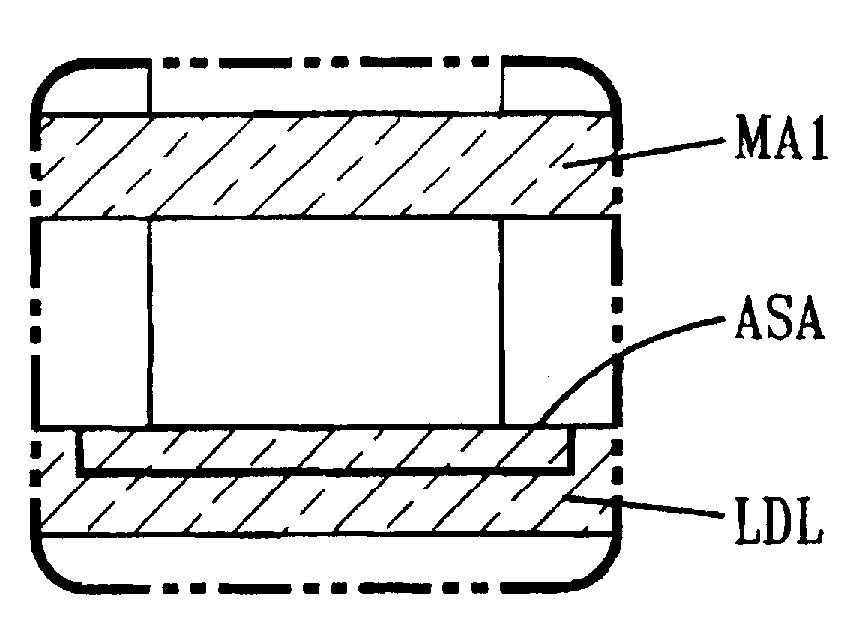

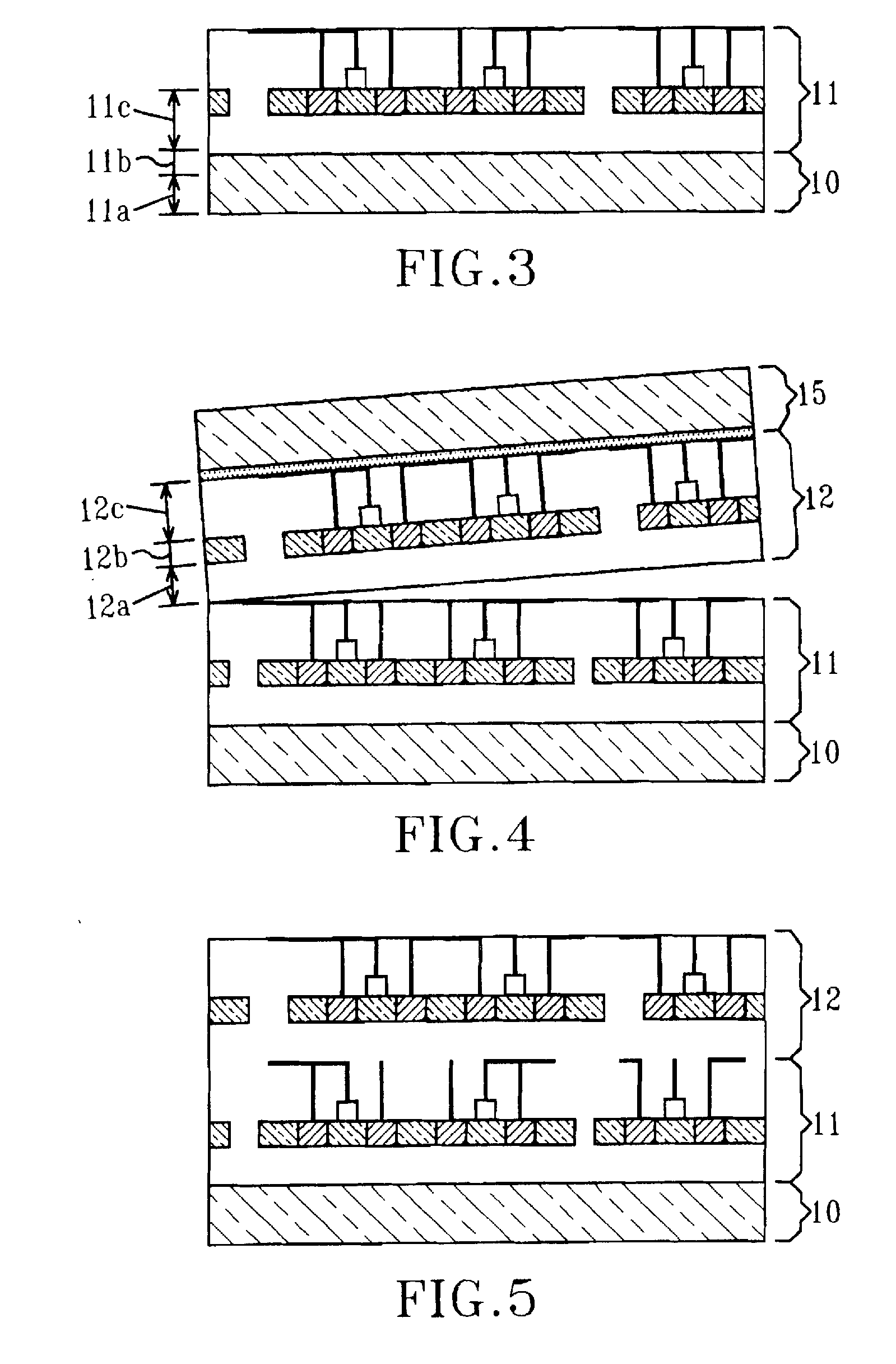

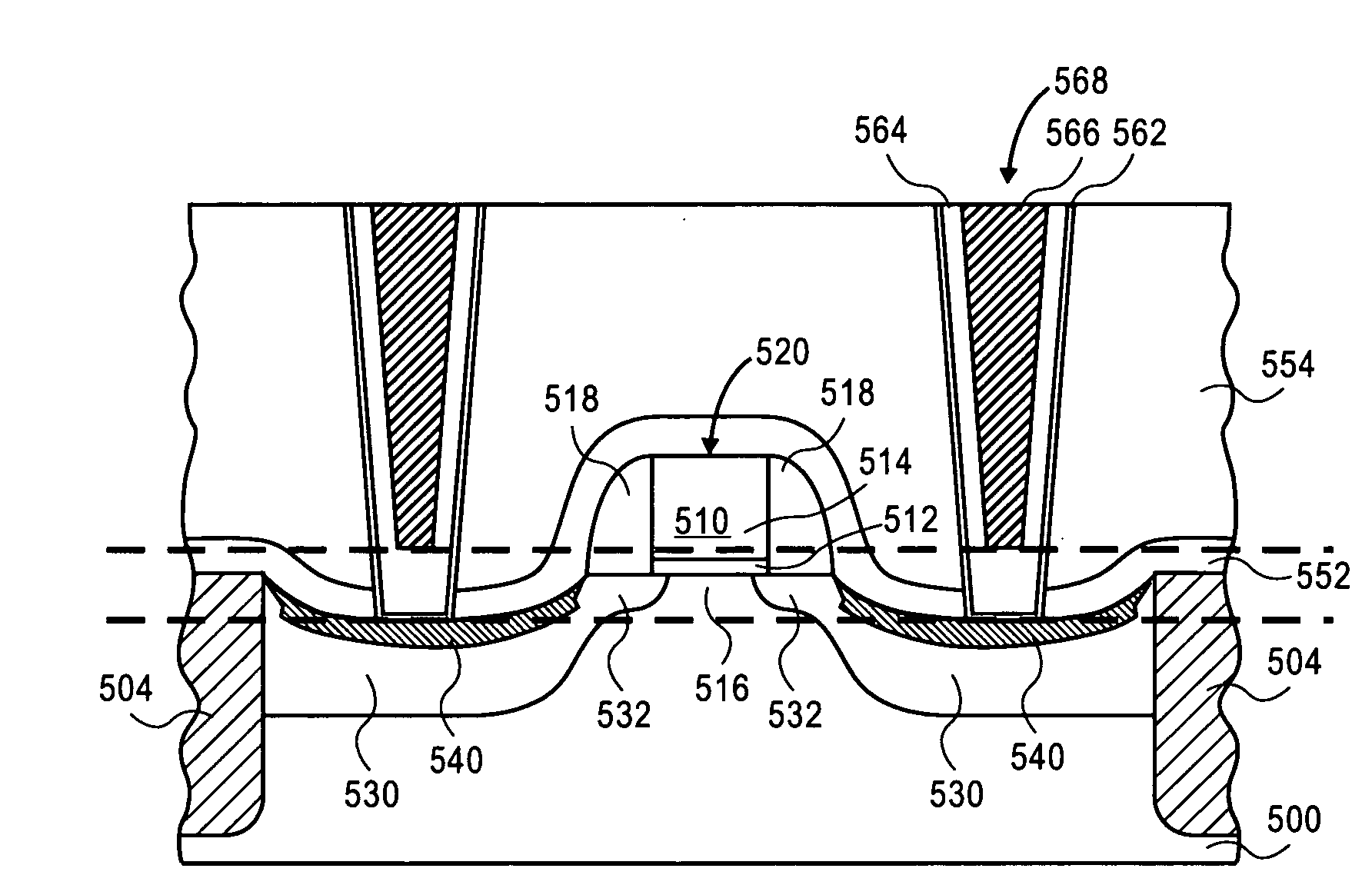

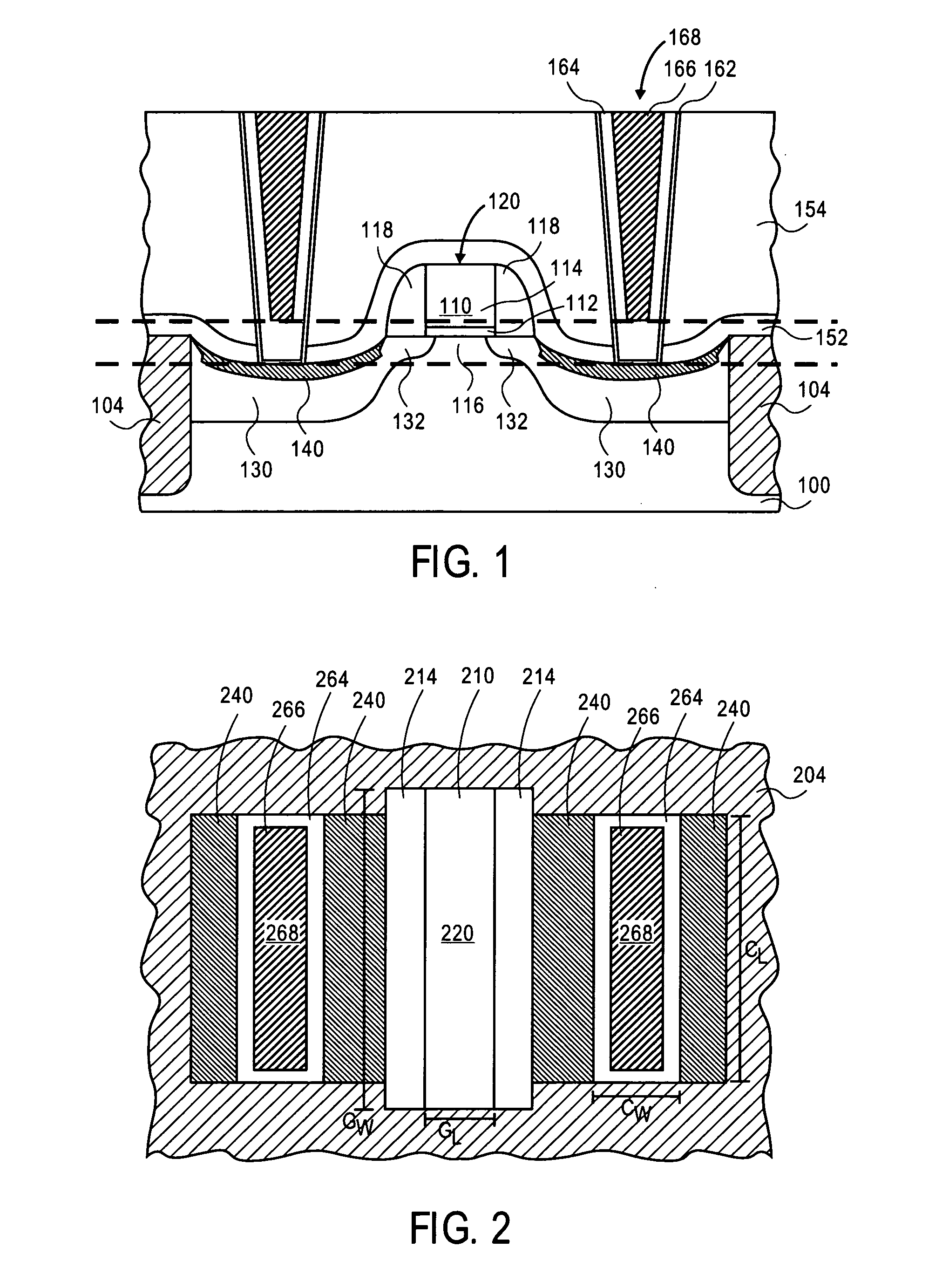

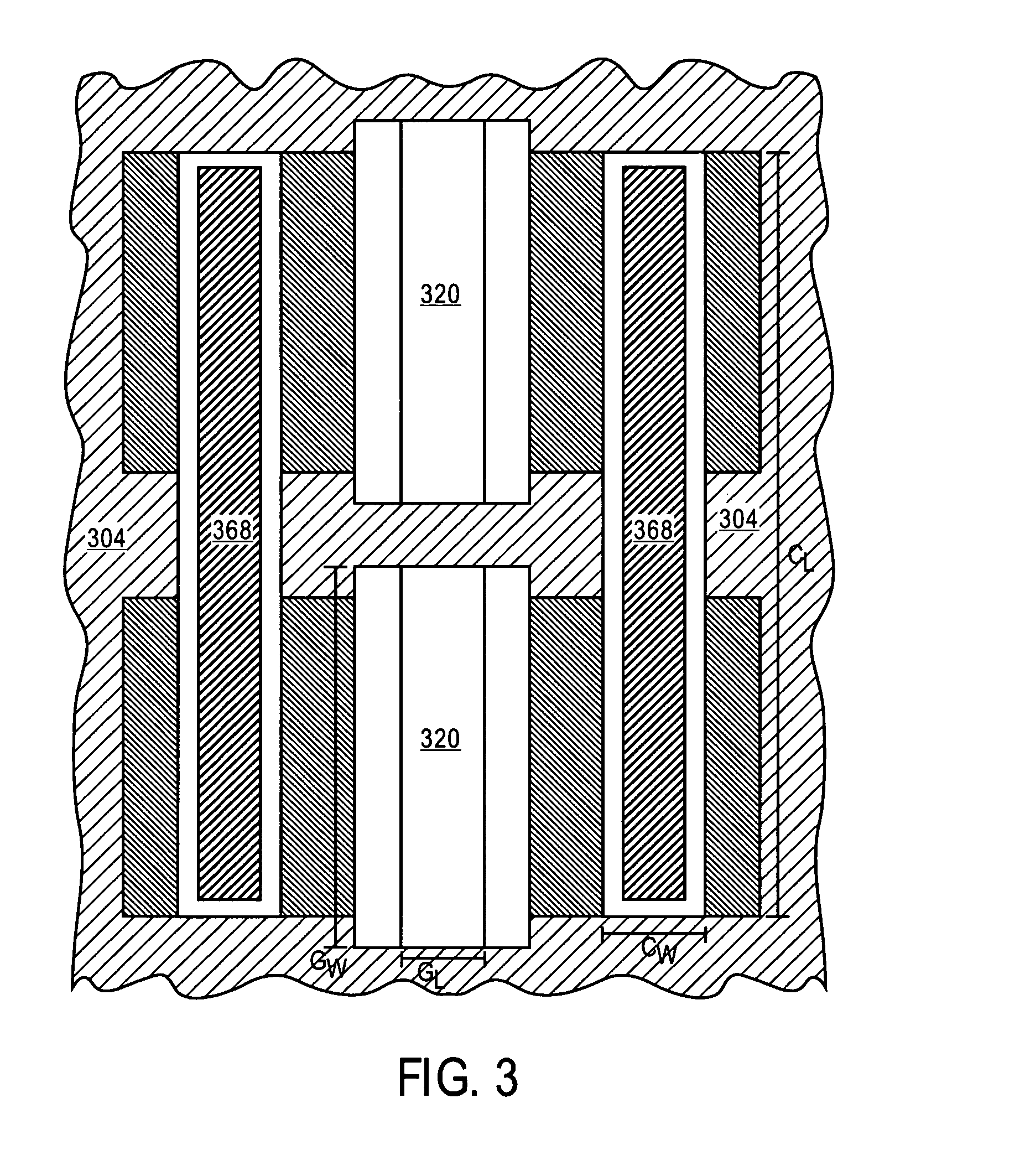

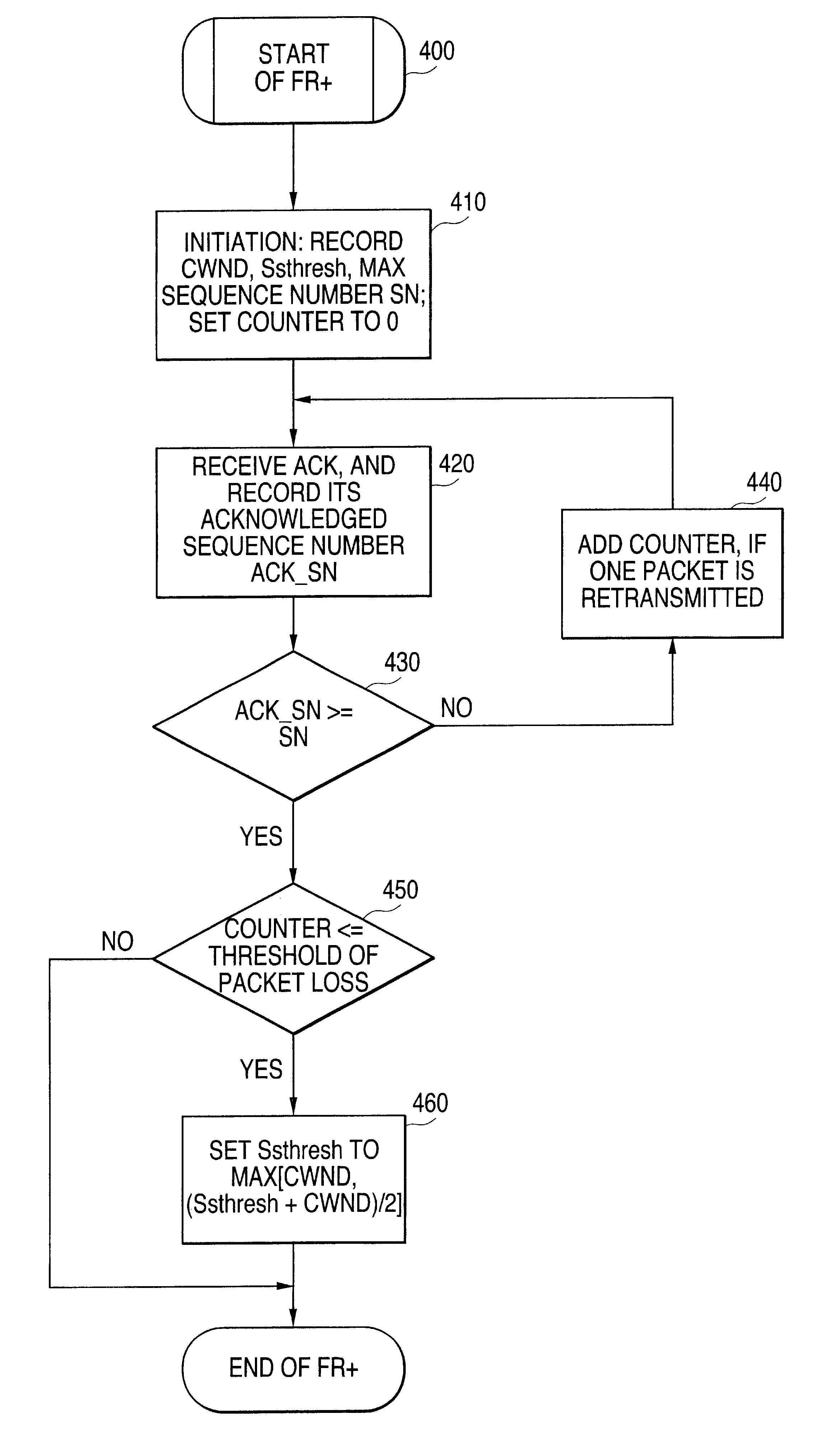

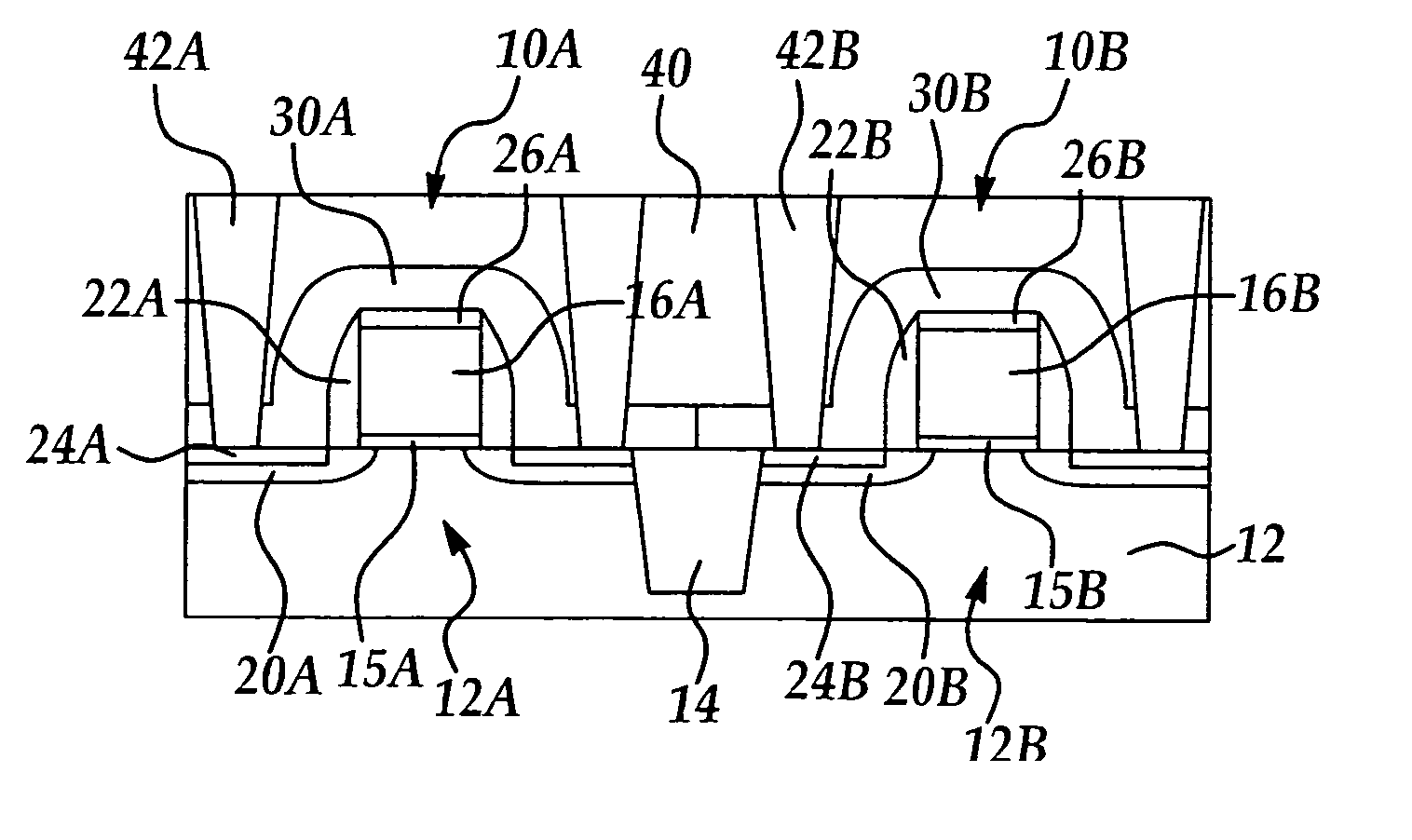

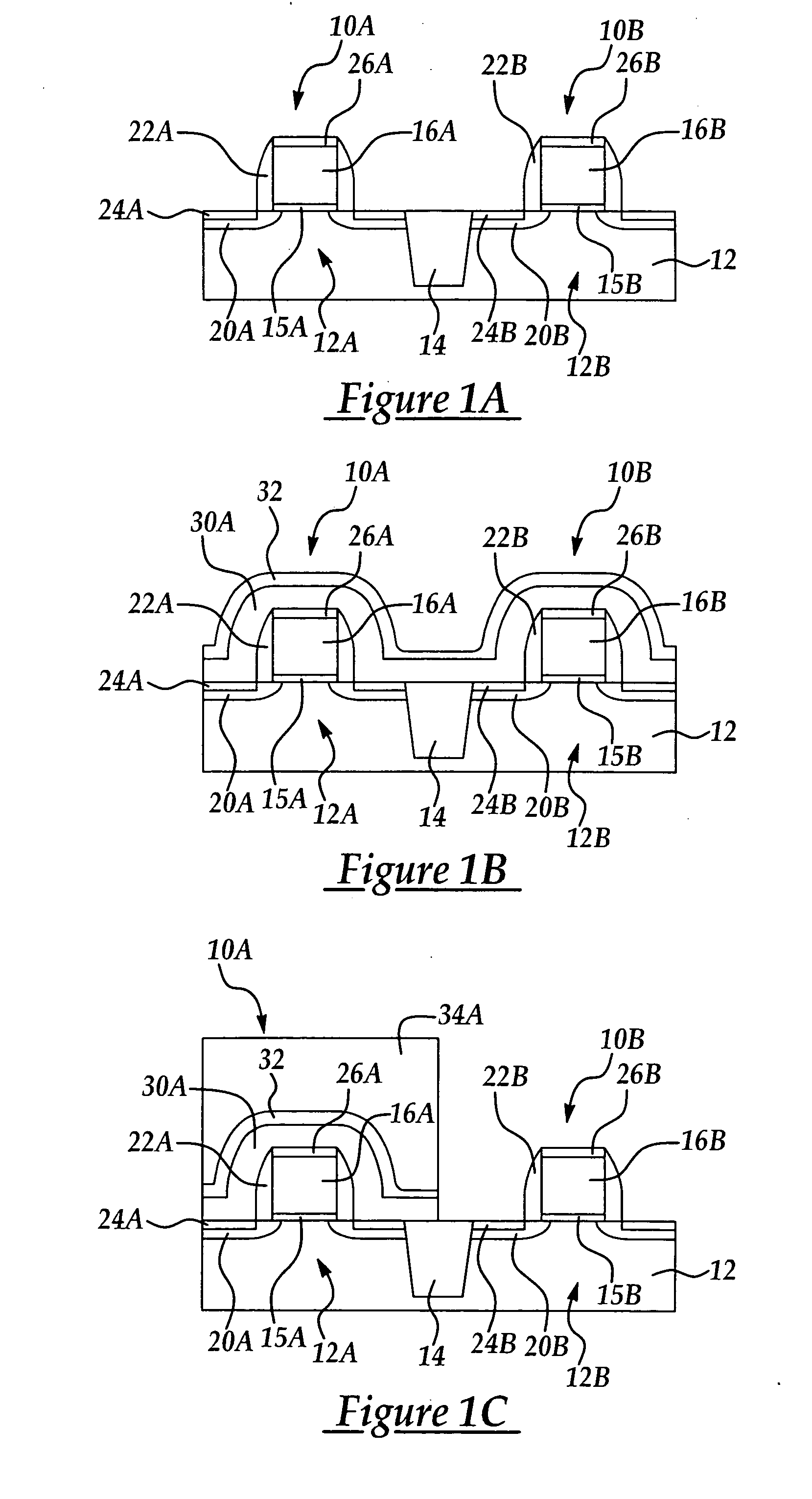

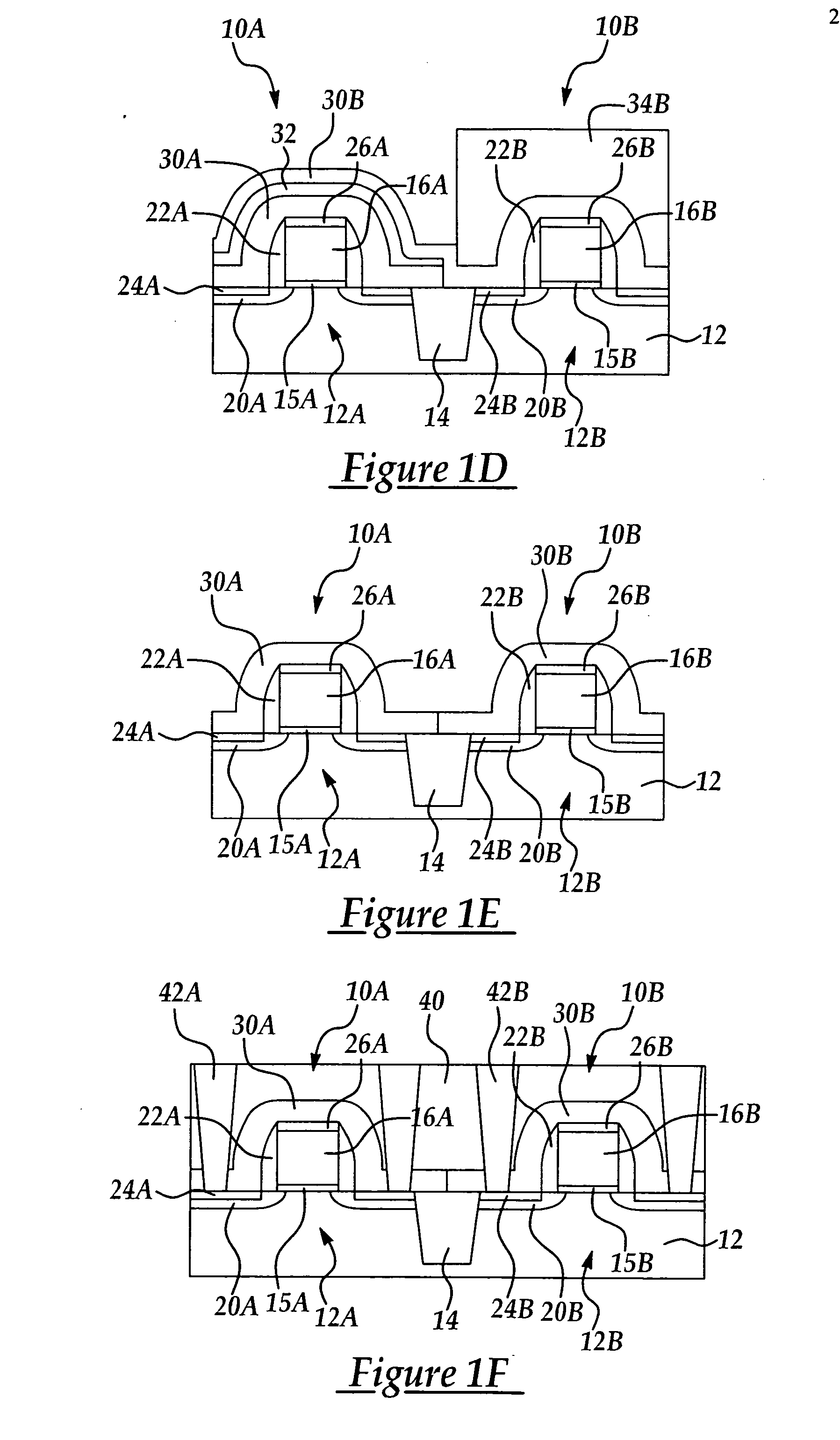

Segmented channel MOS transistor

ActiveUS7247887B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETLithographic artist

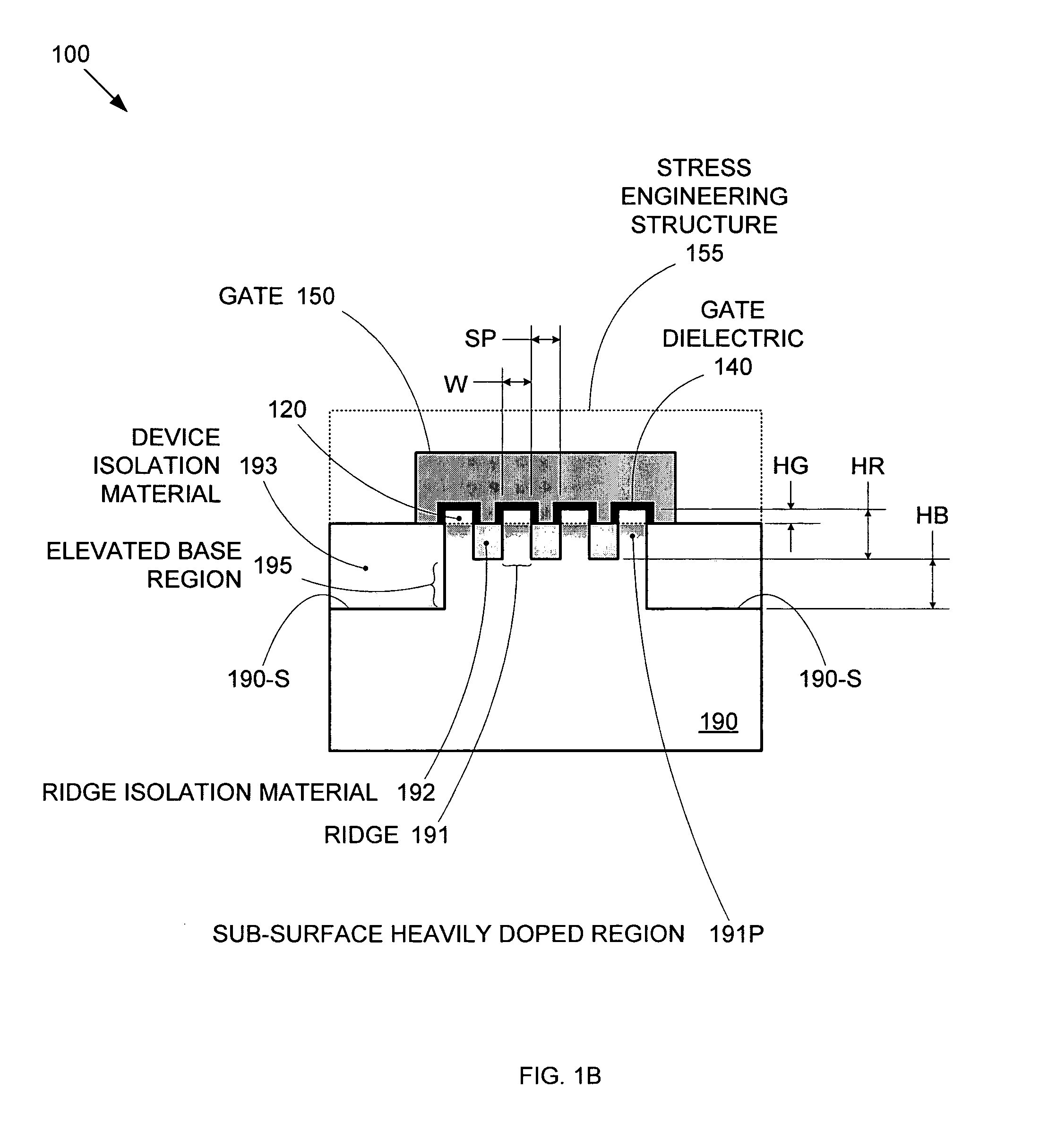

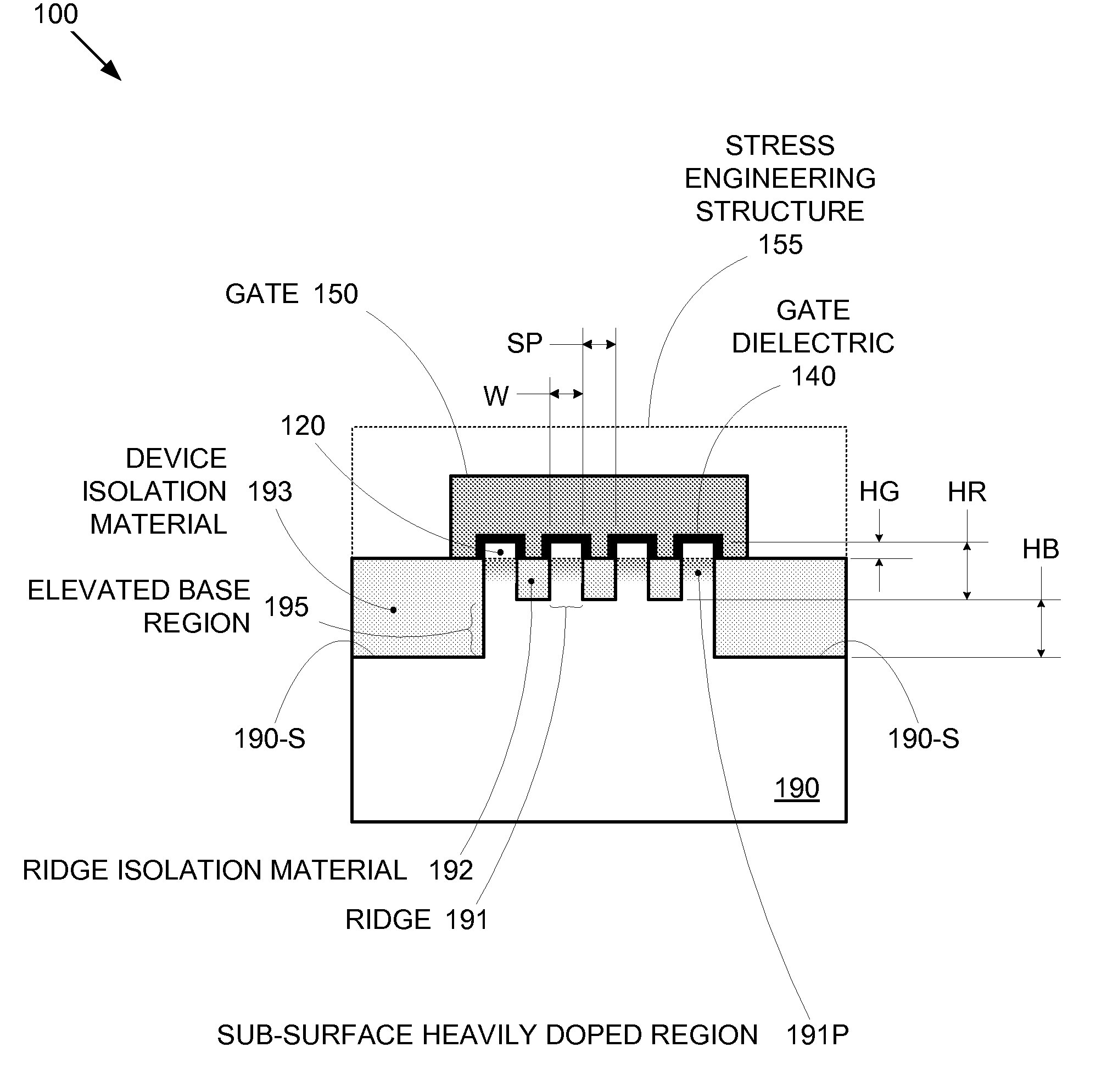

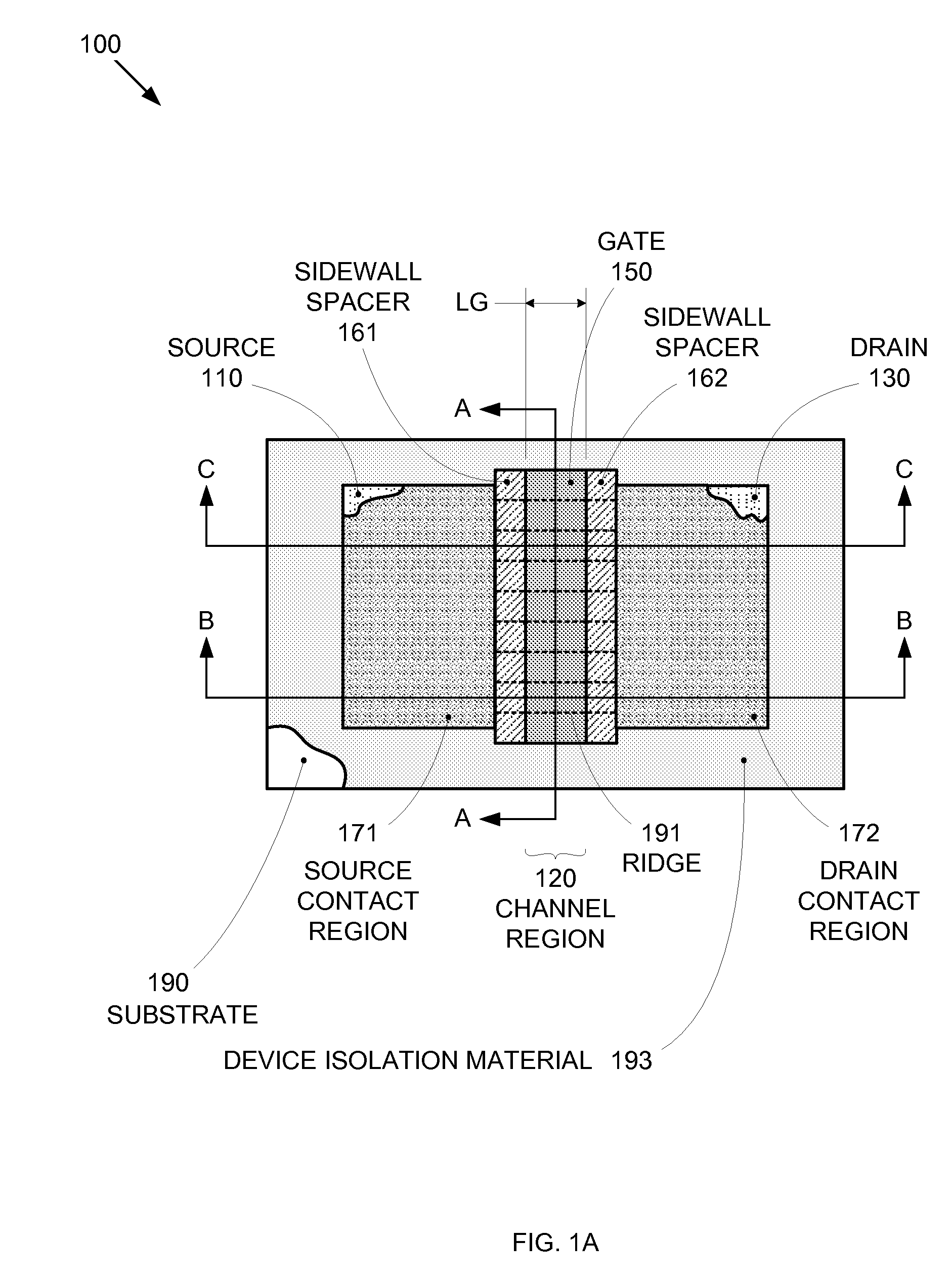

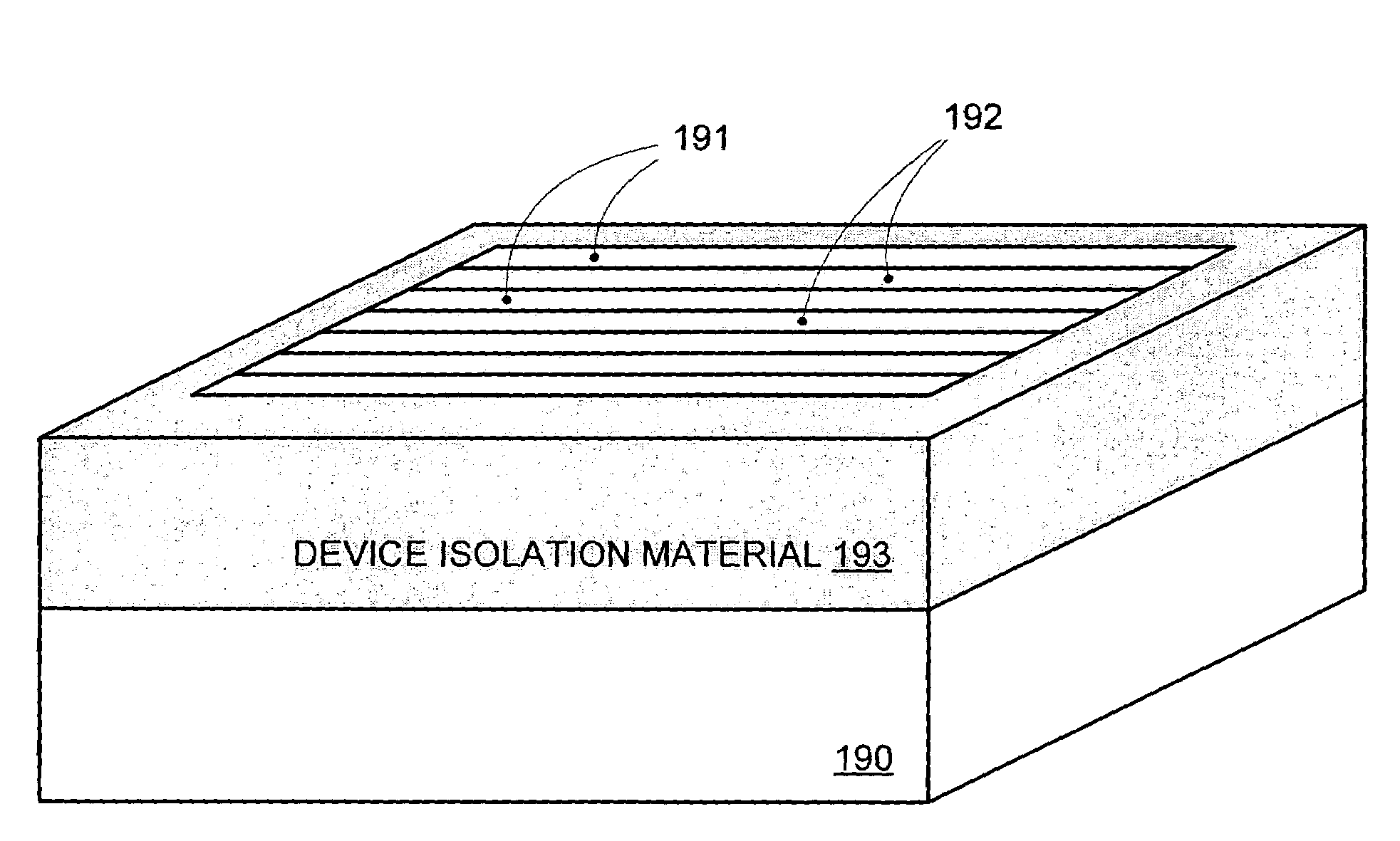

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

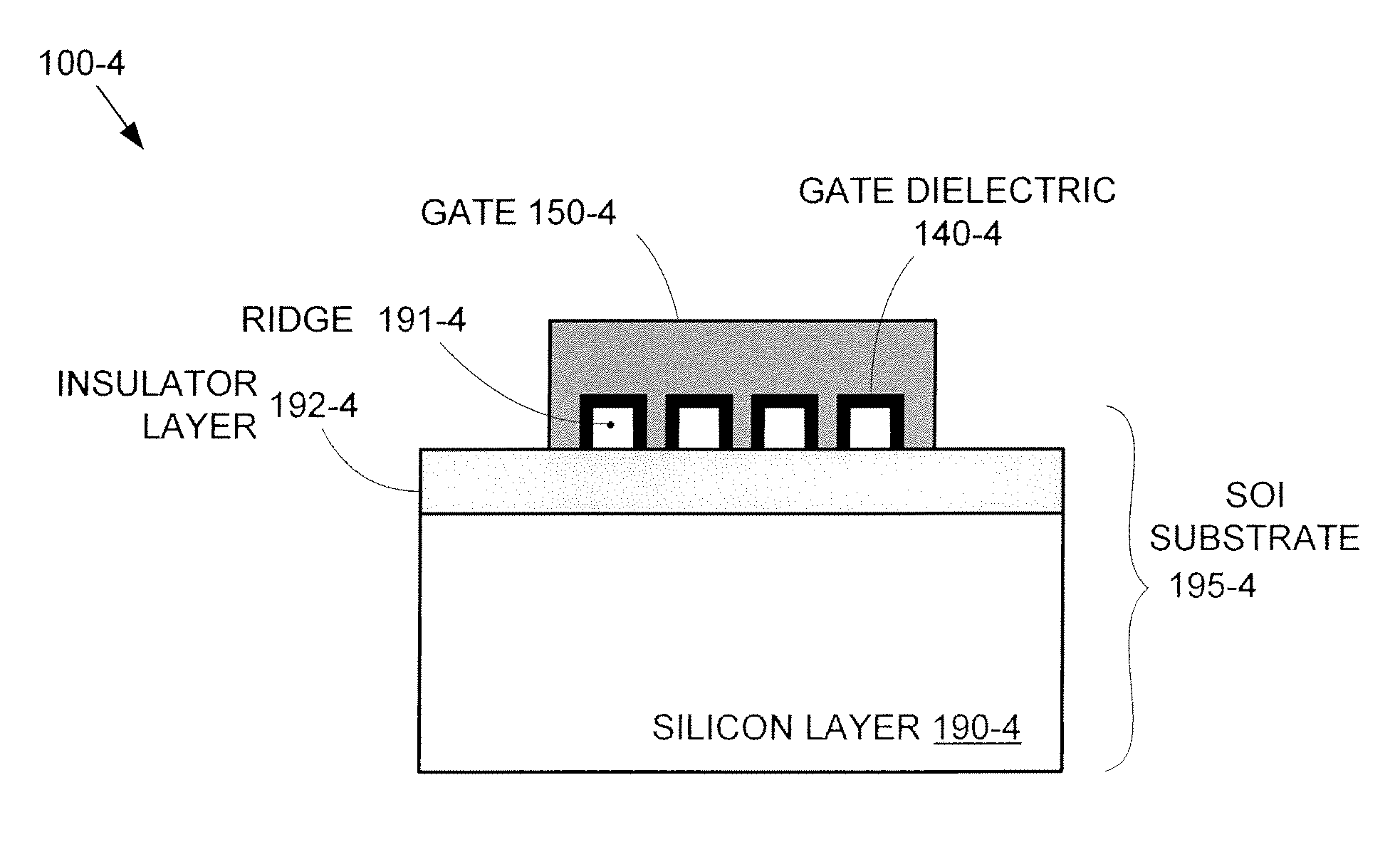

Integrated circuit on corrugated substrate

ActiveUS7190050B2Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

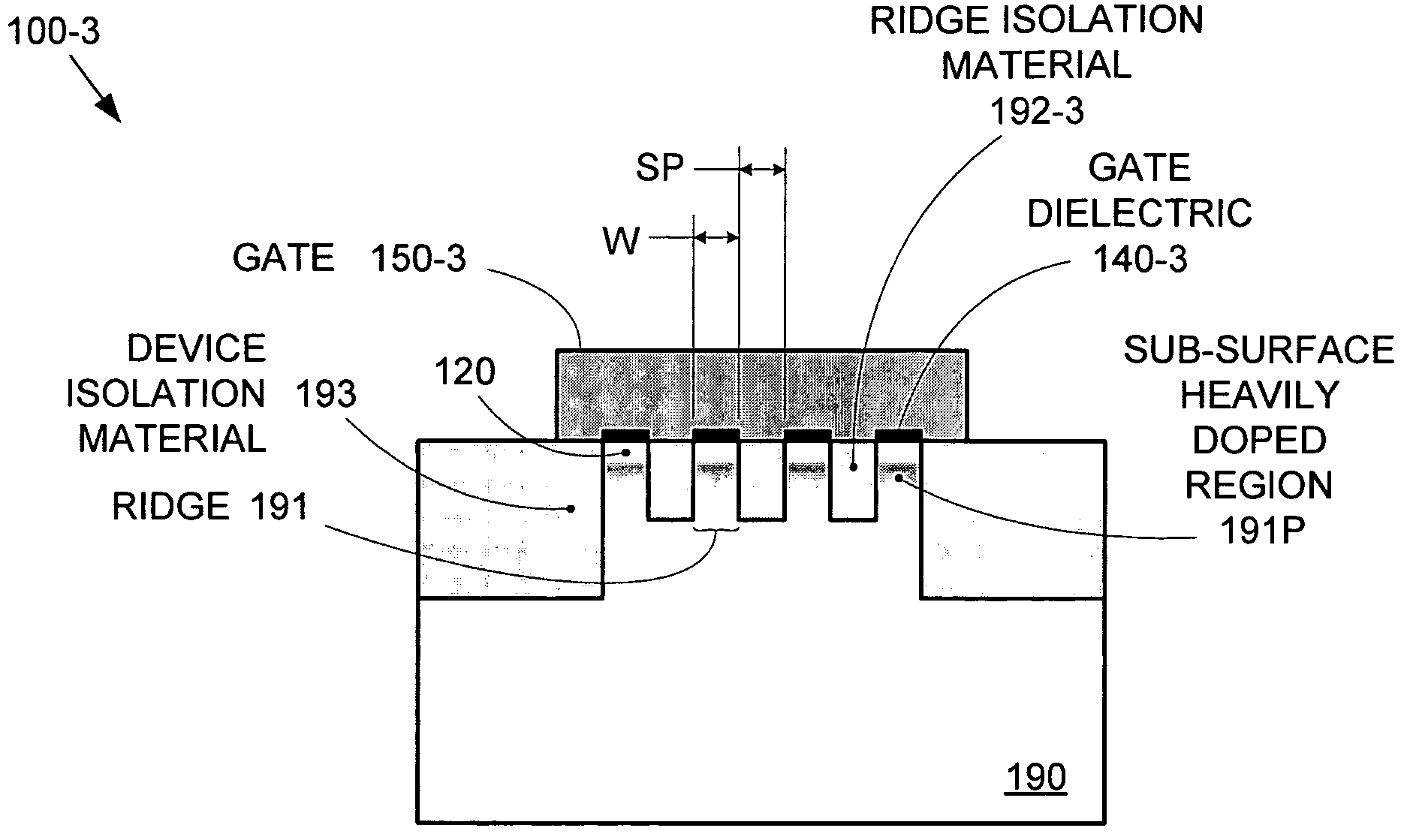

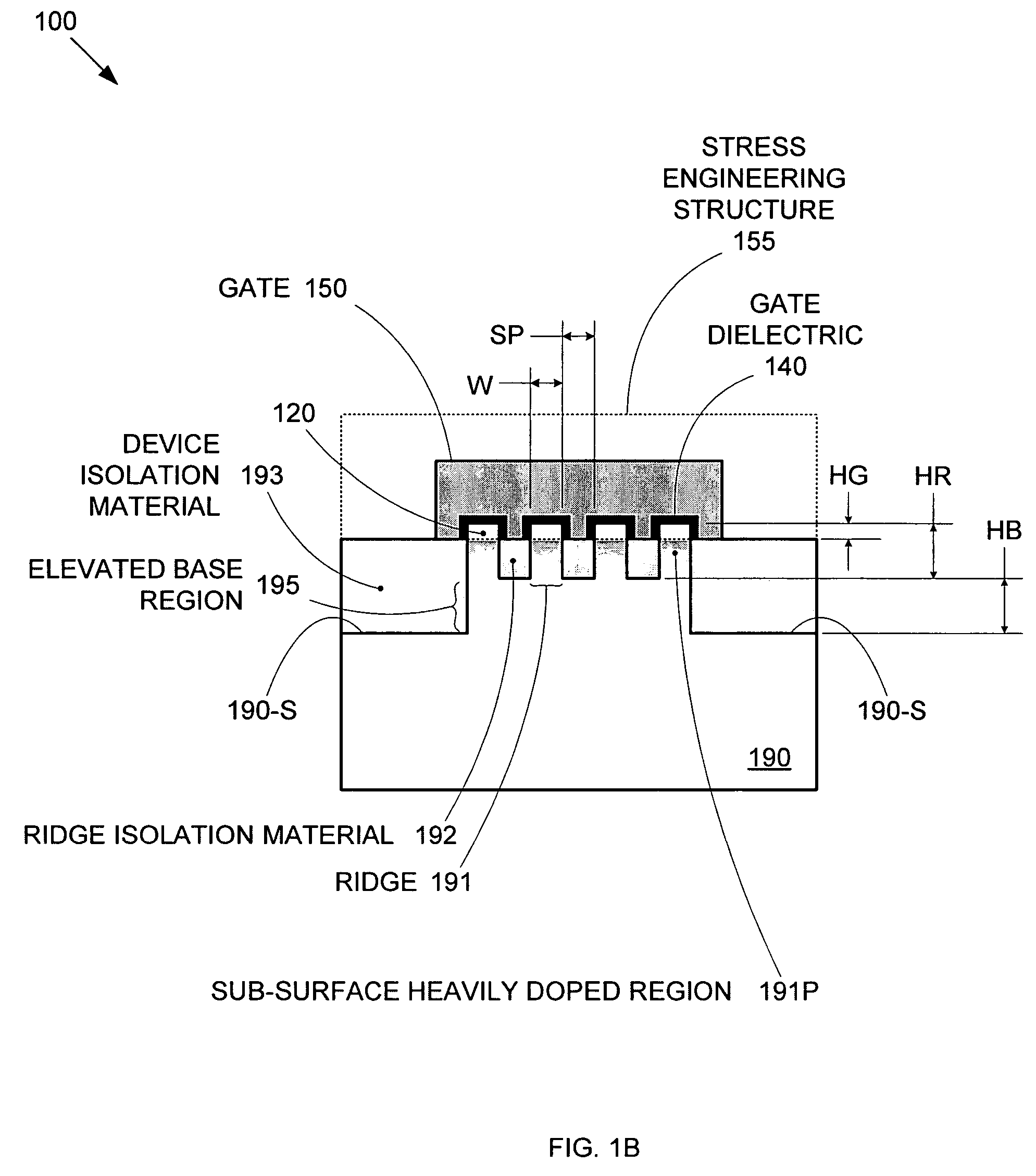

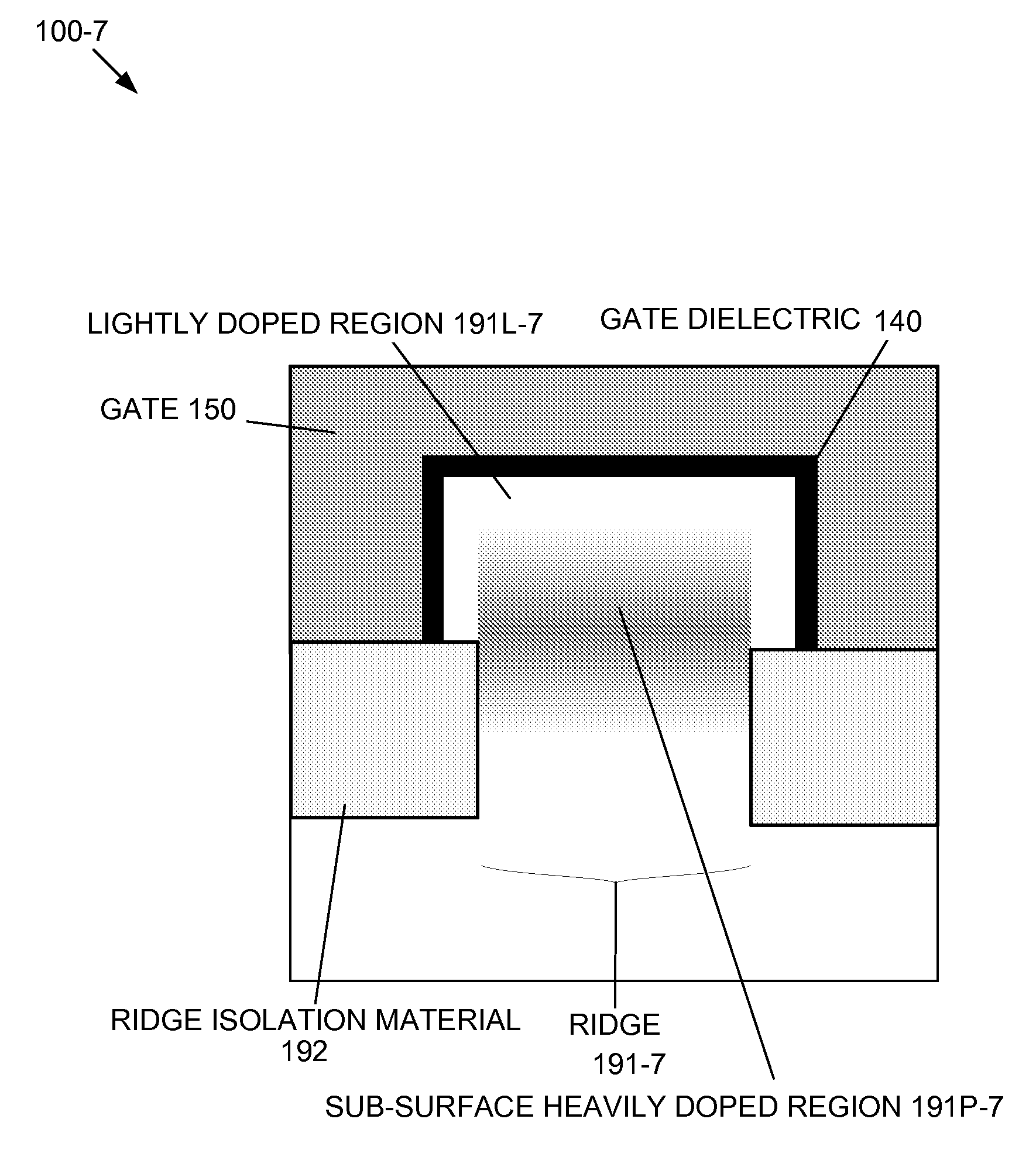

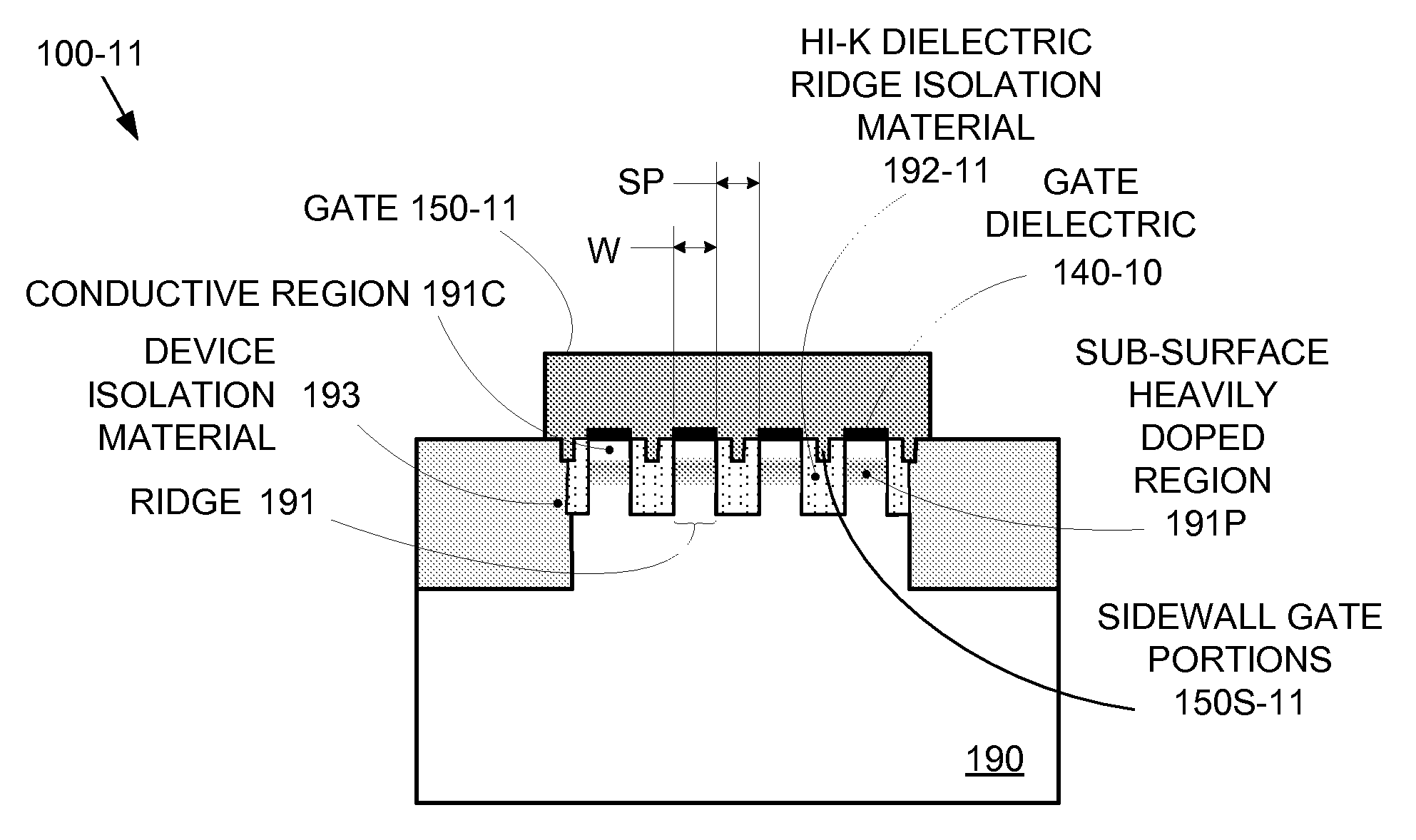

Enhanced Segmented Channel MOS Transistor with Multi Layer Regions

ActiveUS20070120156A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Method of IC production using corrugated substrate

ActiveUS7265008B2Improve performance consistencyImprove performanceLaser detailsSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

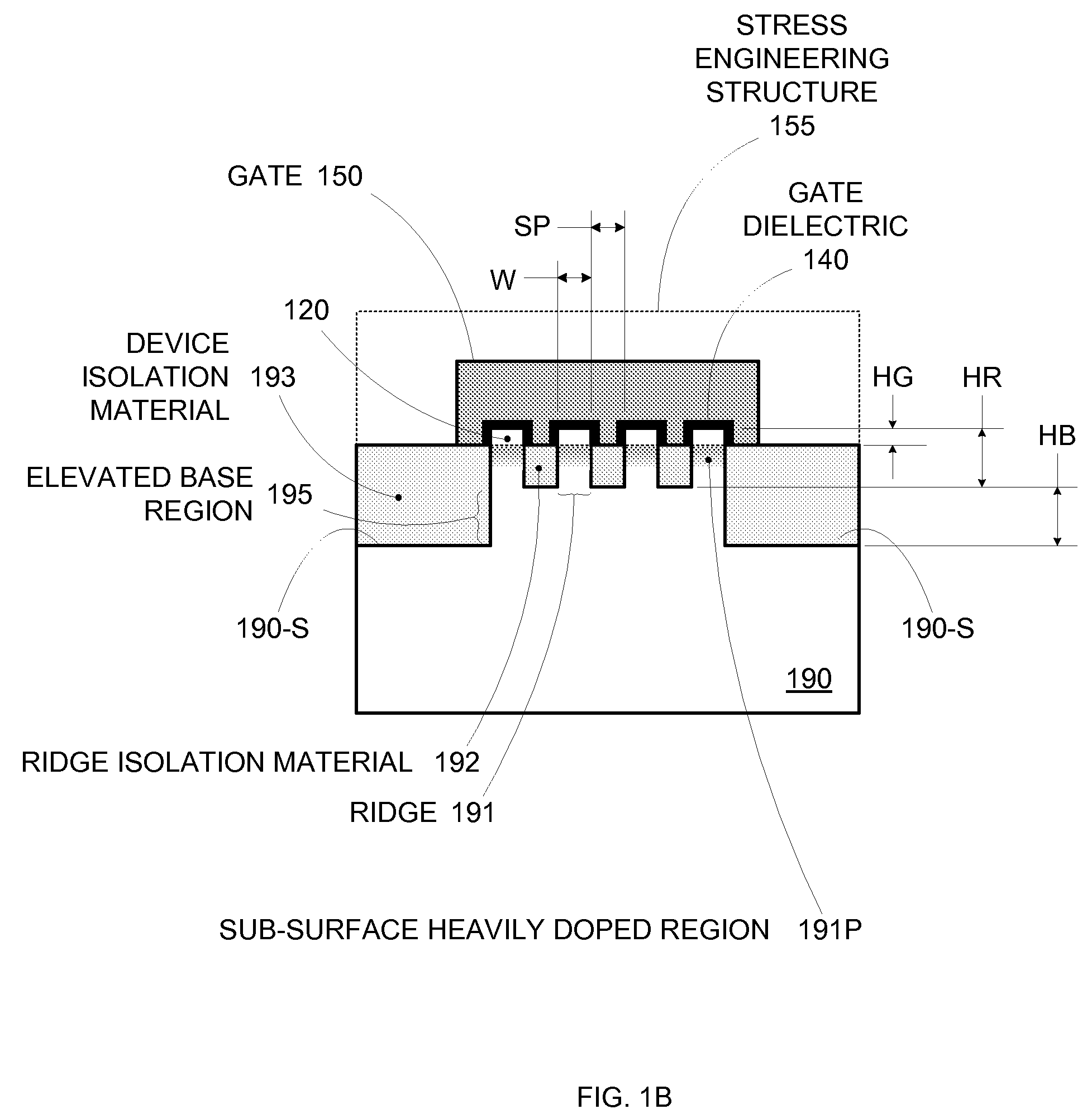

Enhanced segmented channel MOS transistor with narrowed base regions

ActiveUS7508031B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably produced. Ridges on the corrugated substrate can be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials, high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced Segmented Channel MOS Transistor with High-Permittivity Dielectric Isolation Material

ActiveUS20070122953A1Increase costImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with high-permittivity dielectric isolation material

ActiveUS7605449B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Integrated Circuit On Corrugated Substrate

ActiveUS20070132053A1Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETSemiconductor materials

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

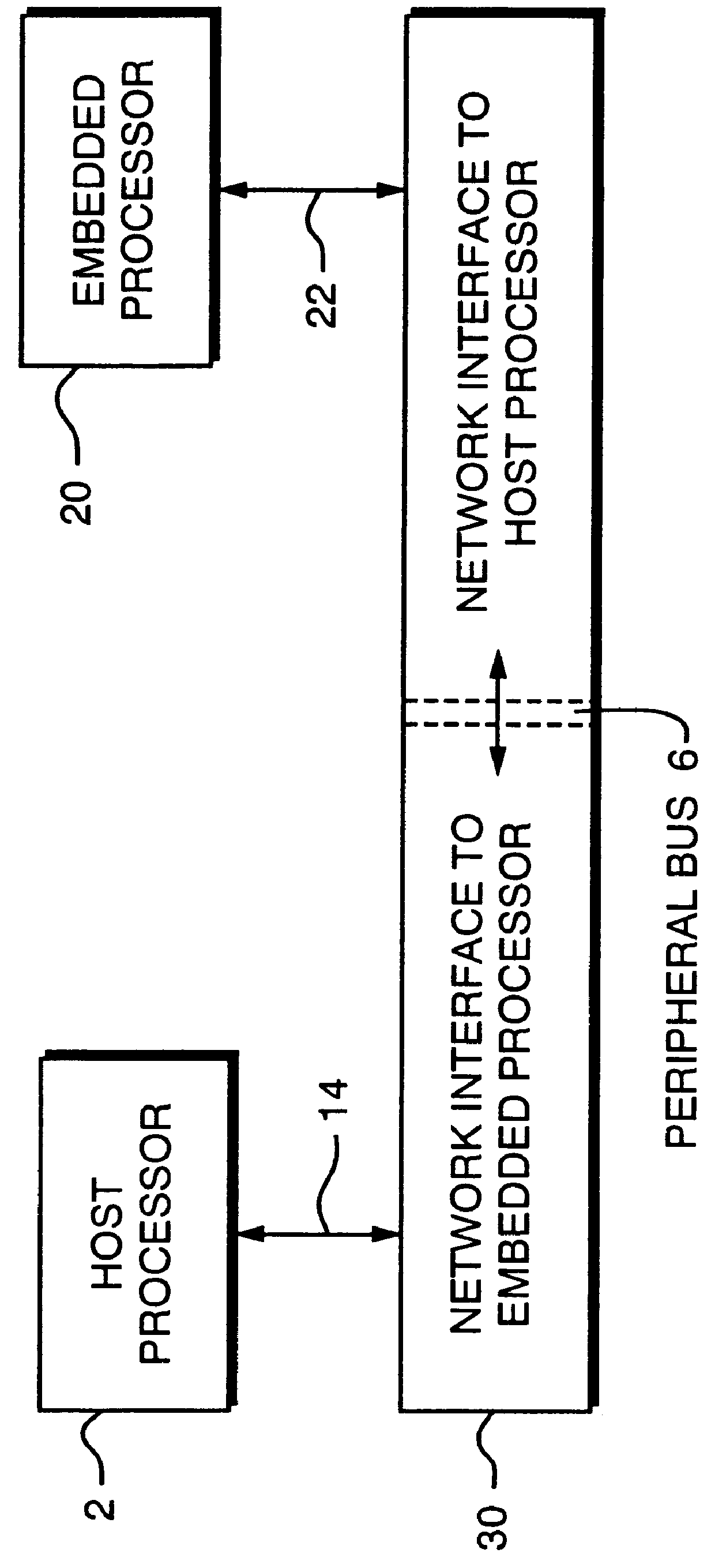

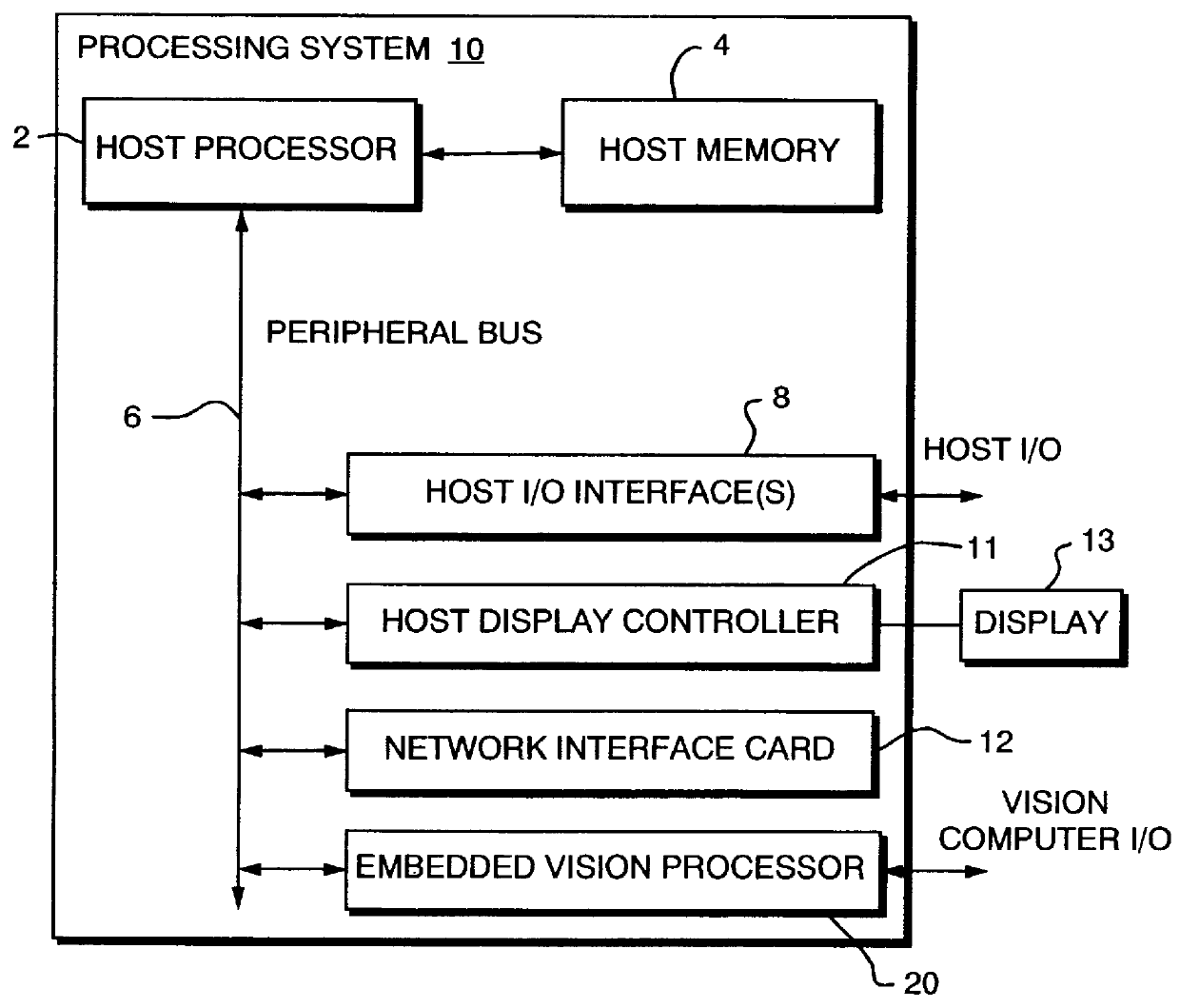

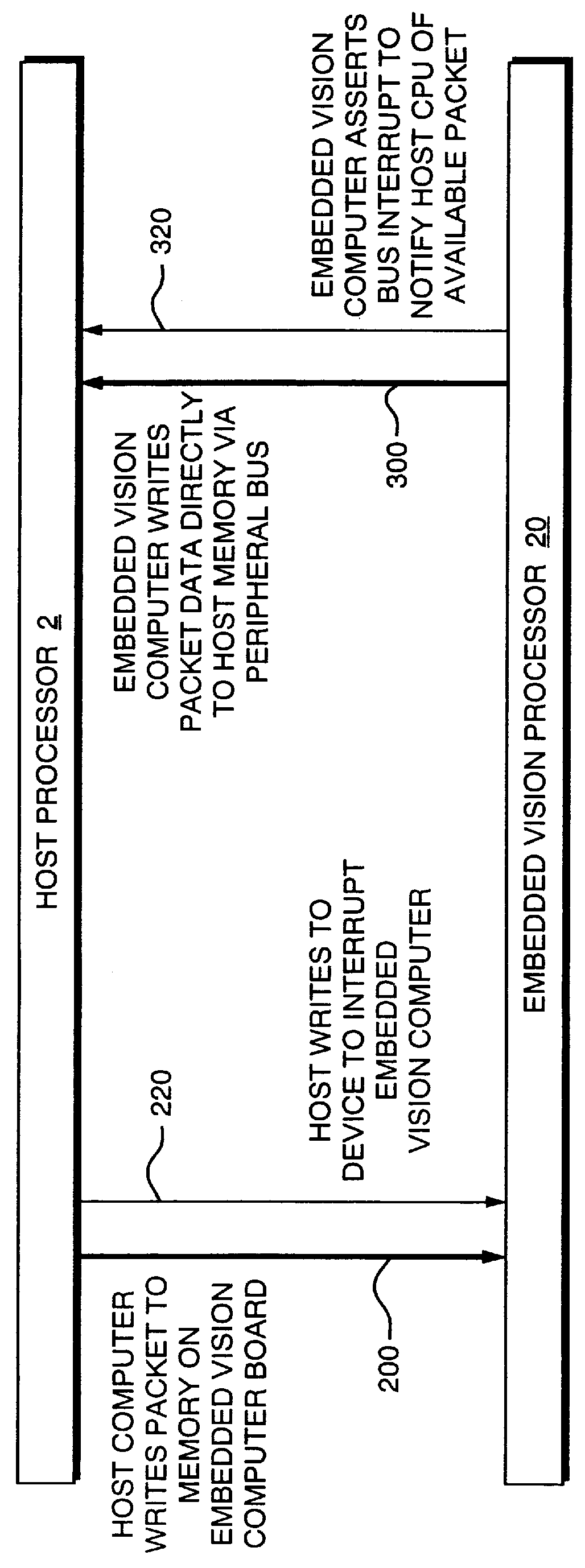

Apparent network interface for and between embedded and host processors

InactiveUS6058434ASignificant comprehensive benefitsMultiple digital computer combinationsElectric digital data processingPerformance enhancementWeb service

An apparent network interface permits one processor such as a processor embedded within a larger processing system (an embedded processor) to communicate to a host processor or other processors and devices on the network to which the embedded processor is attached, using standard network communication mechanisms / protocols such as TCP / IP, NFS, FTP, HTTP, etc. The web server protocol HTTP is particularly useful because it permits the embedded computer to publish a user interface for remote monitoring and remote control using a standard web browser application. The invention provides the host computer with an apparent network interface that appears to be a standard network device, such as an Ethernet interface card. This apparent interface communicates directly with the embedded processor, which appears to be a device on this apparent network. Significant cost savings and performance enhancements are realized by implementing the communication directly over the host computer's peripheral bus rather than using standard network hardware such as Ethernet hardware.

Owner:MICROSCAN SYSTEMS

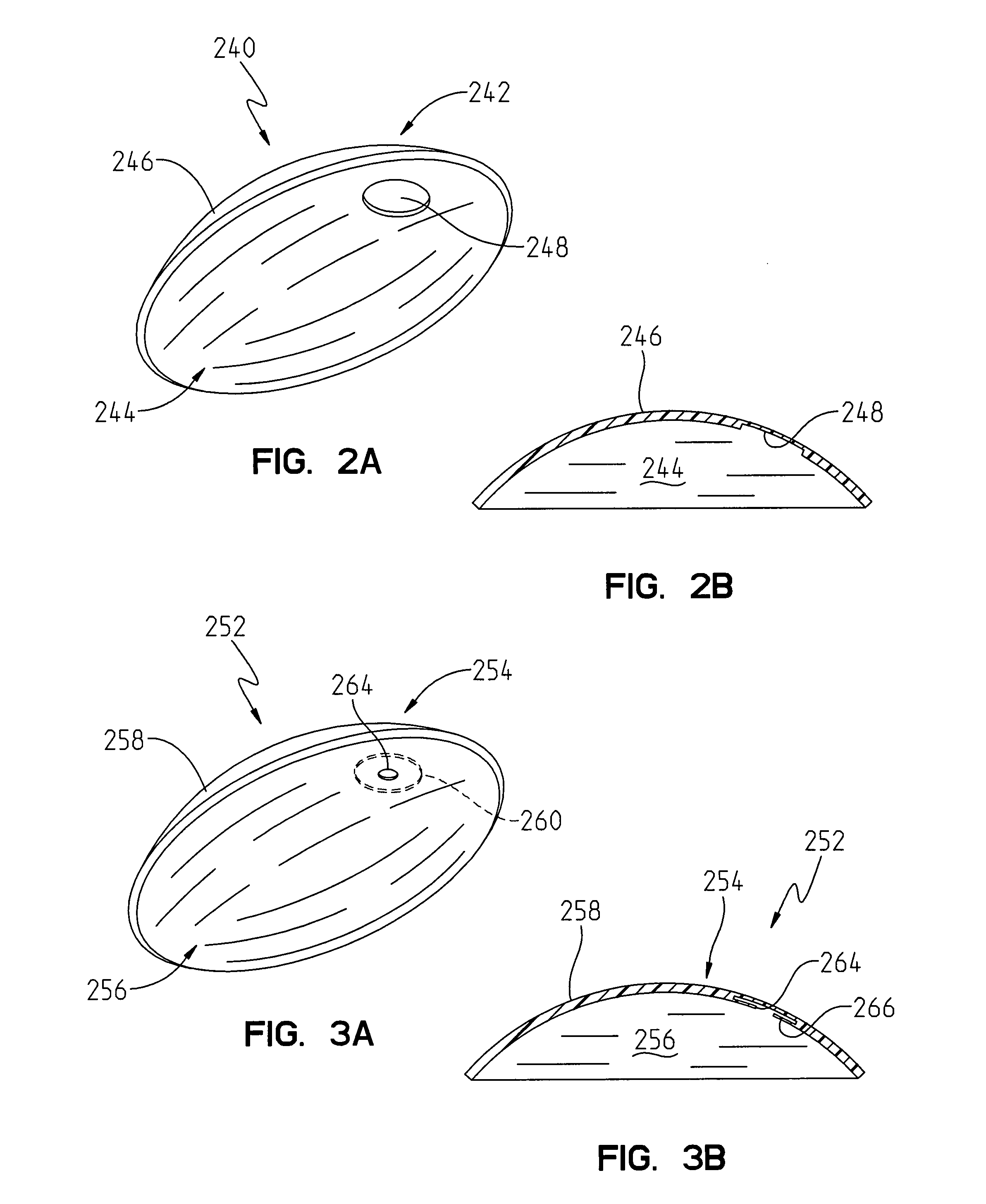

Acoustic resonator performance enhancement using alternating frame structure

ActiveUS7388454B2Impedence networksPiezoelectric/electrostriction/magnetostriction machinesPerformance enhancementAcoustics

Disclosed is an acoustic resonator that includes a substrate, a first electrode, a layer of piezoelectric material, a second electrode, and an alternating frame region. The first electrode is adjacent the substrate, and the first electrode has an outer perimeter. The piezoelectric layer is adjacent the first electrode. The second electrode is adjacent the piezoelectric layer and the second electrode has an outer perimeter. The alternating frame region is on one of the first and second electrodes.

Owner:AVAGO TECH INT SALES PTE LTD

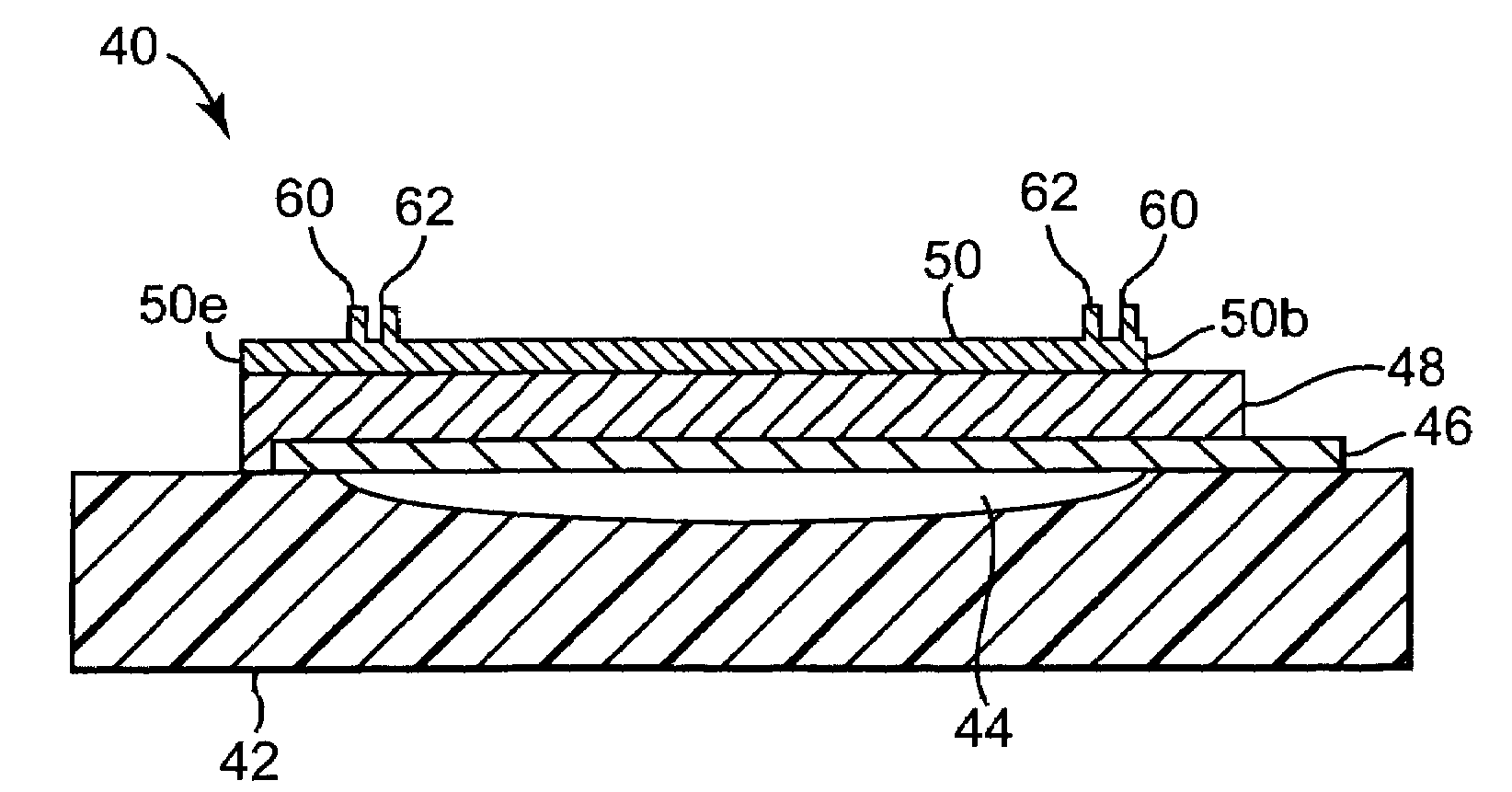

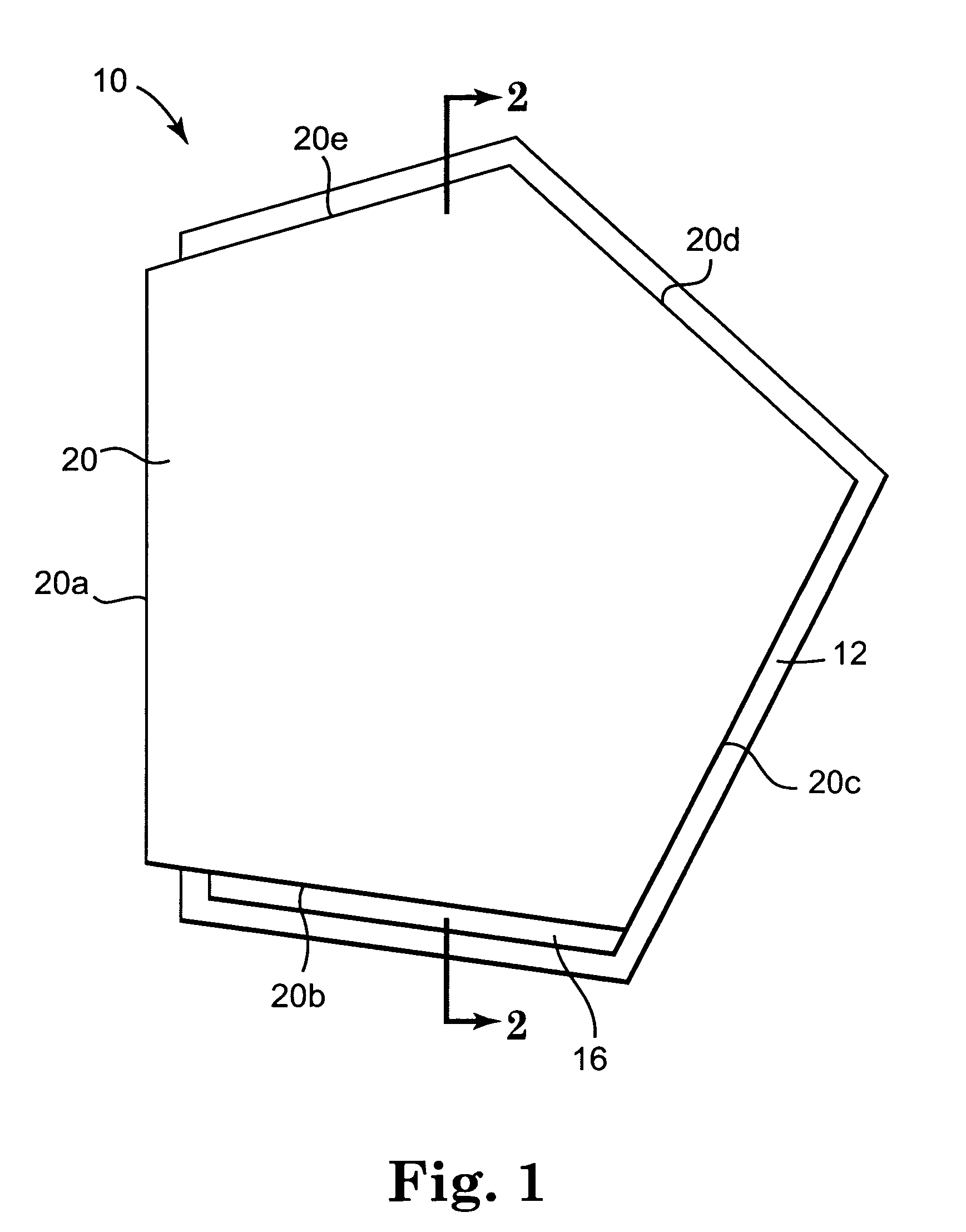

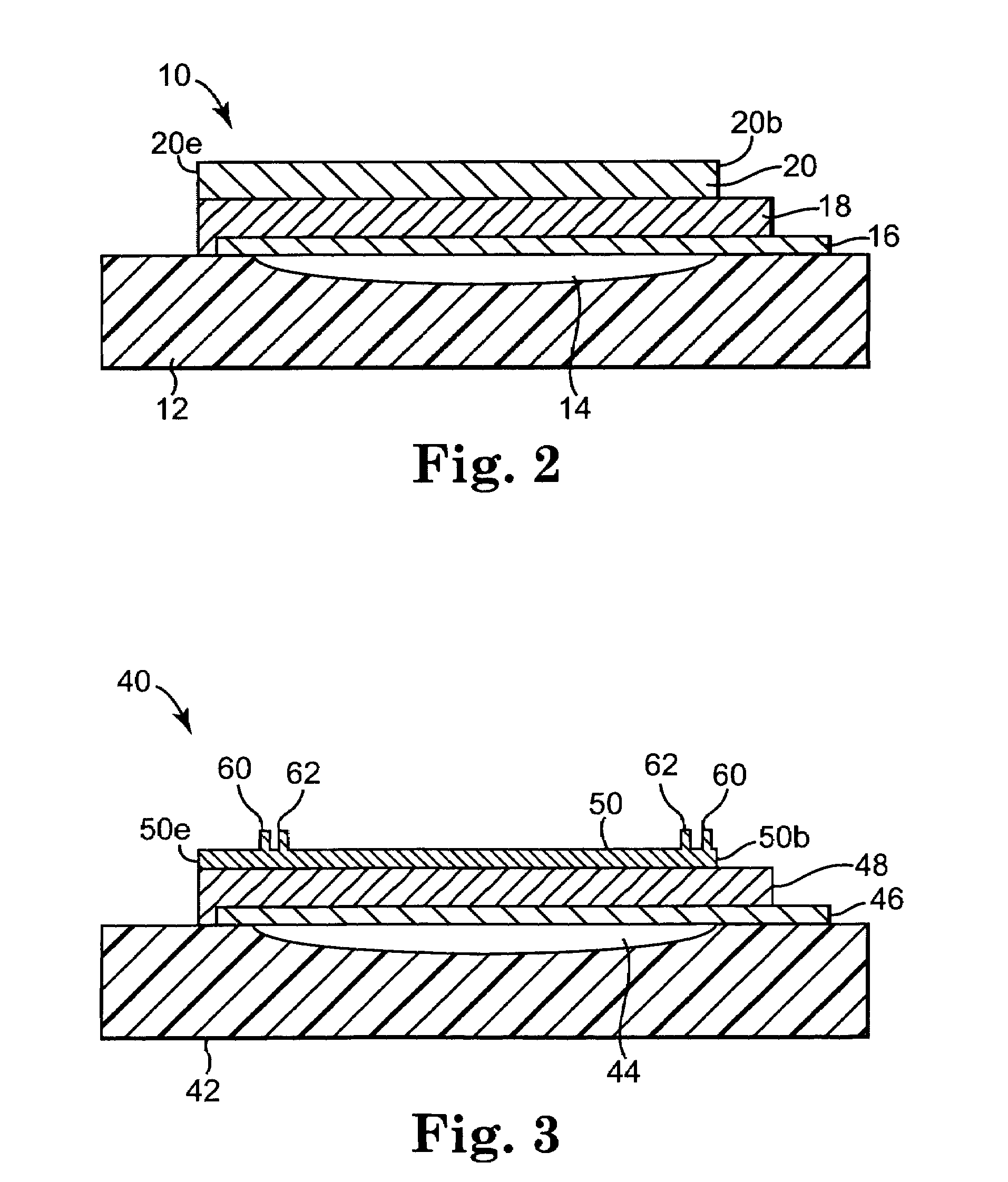

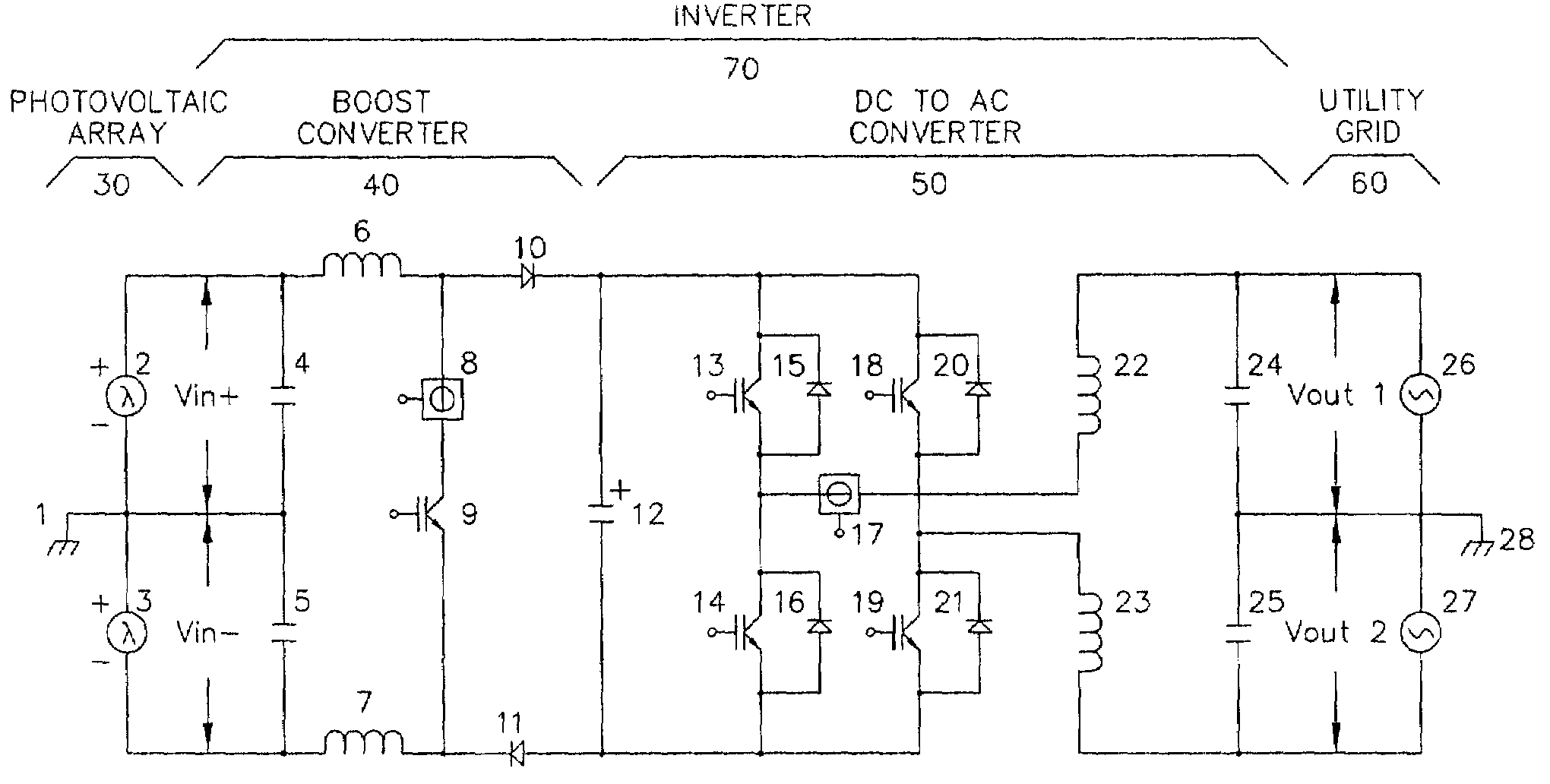

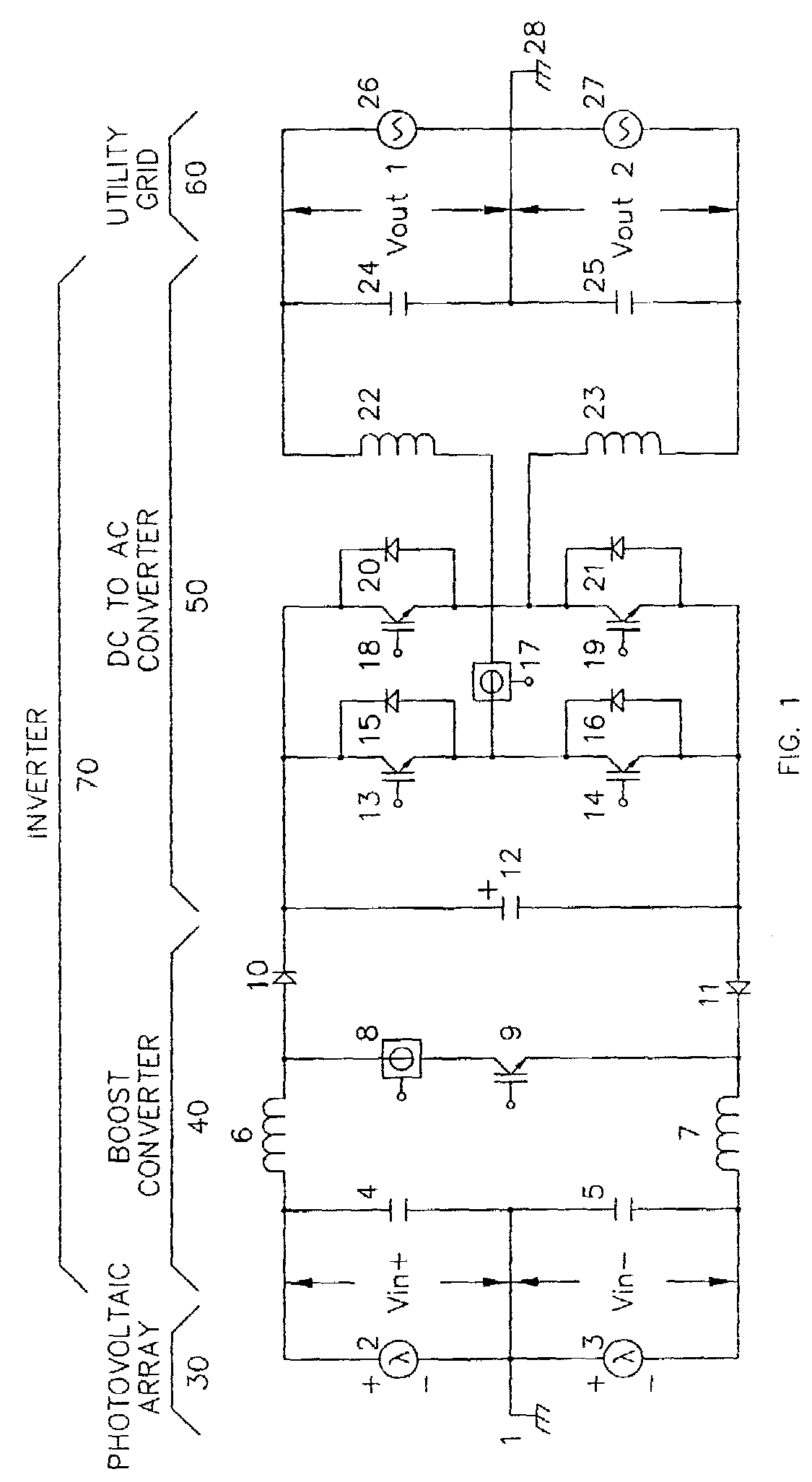

DC to AC inverter with single-switch bipolar boost circuit

InactiveUS7099169B2Conversion with intermediate conversion to dcEmergency protective circuit arrangementsPower inverterPerformance enhancement

This invention improves the performance and lowers the cost of DC to AC inverters and the systems where these inverters are used. The performance enhancements are most valuable in renewable and distributed energy applications where high power conversion efficiencies are critical. The invention allows a variety of DC sources to provide power thru the inverter to the utility grid or directly to loads without a transformer and at very high power conversion efficiencies. The enabling technology is a novel boost converter stage that regulates the voltage for a following DC to AC converter stage and uses a single semiconductor switching device. The AC inverter output configuration is either single-phase or three-phase.

Owner:SCHNEIDER ELECTRIC SOLAR INVERTERS USA

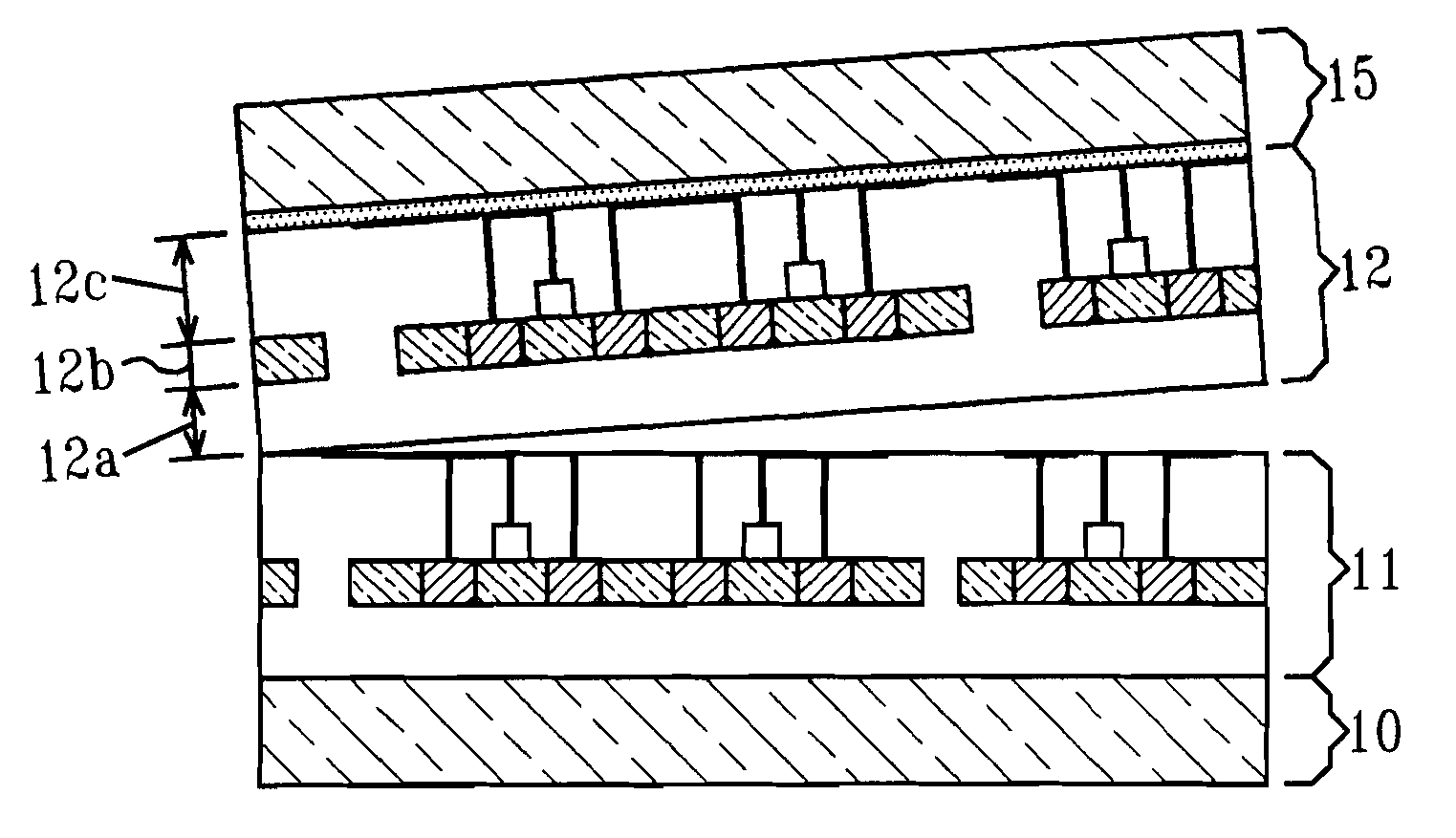

3-dimensional integrated circuit architecture, structure and method for fabrication thereof

ActiveUS20070228383A1Solid-state devicesSemiconductor/solid-state device manufacturingPerformance enhancementAudio power amplifier

An integrated circuit design, structure and method for fabrication thereof includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

Structure comprising 3-dimensional integrated circuit architecture, circuit structure, and instructions for fabrication thereof

ActiveUS20070283298A1Allow optimizationSolid-state devicesSemiconductor/solid-state device manufacturingAudio power amplifierPerformance enhancement

A design structure comprising an integrated circuit architecture, circuit structure, and / or instructions for fabrication thereof. The circuit structure includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

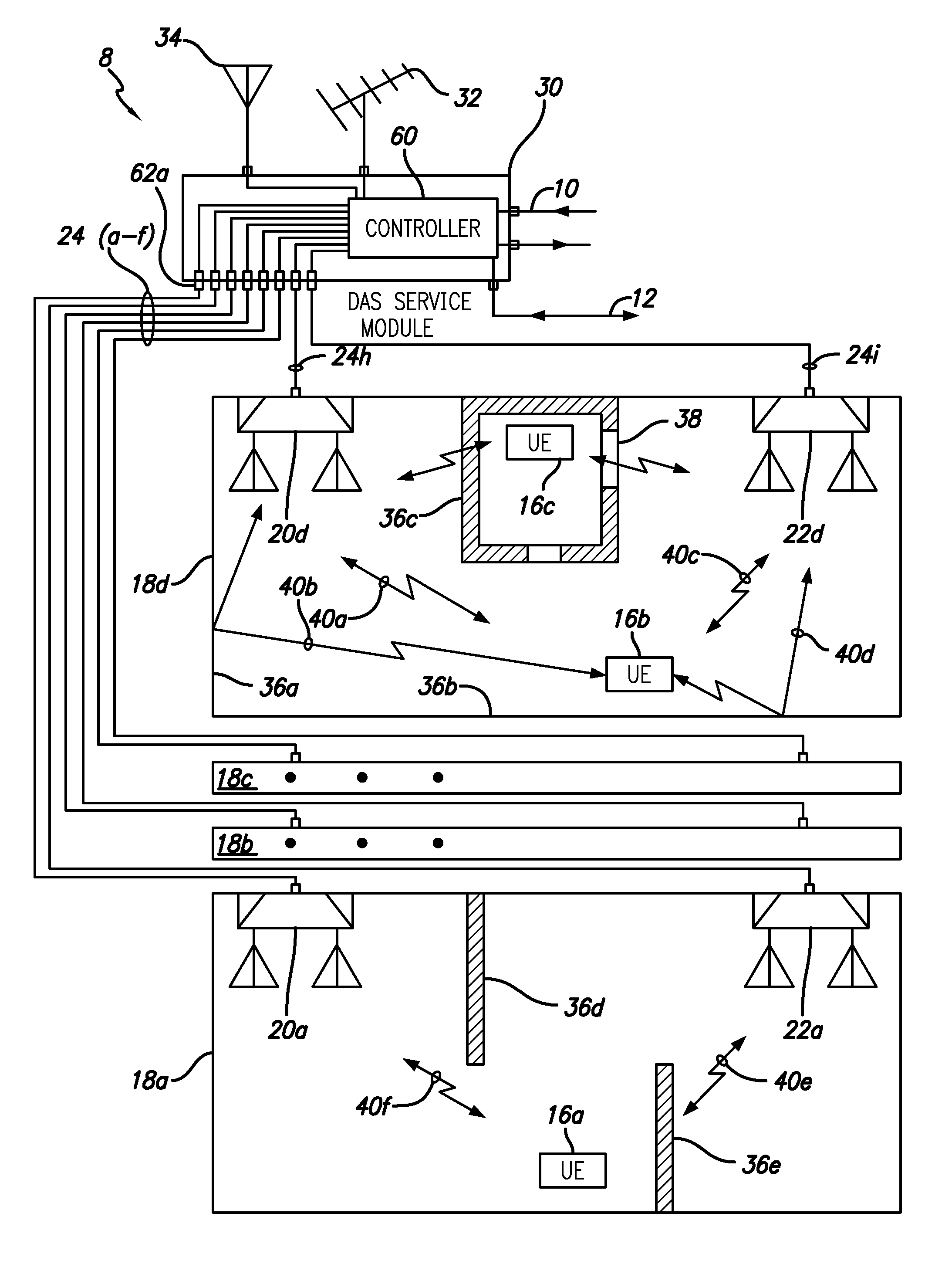

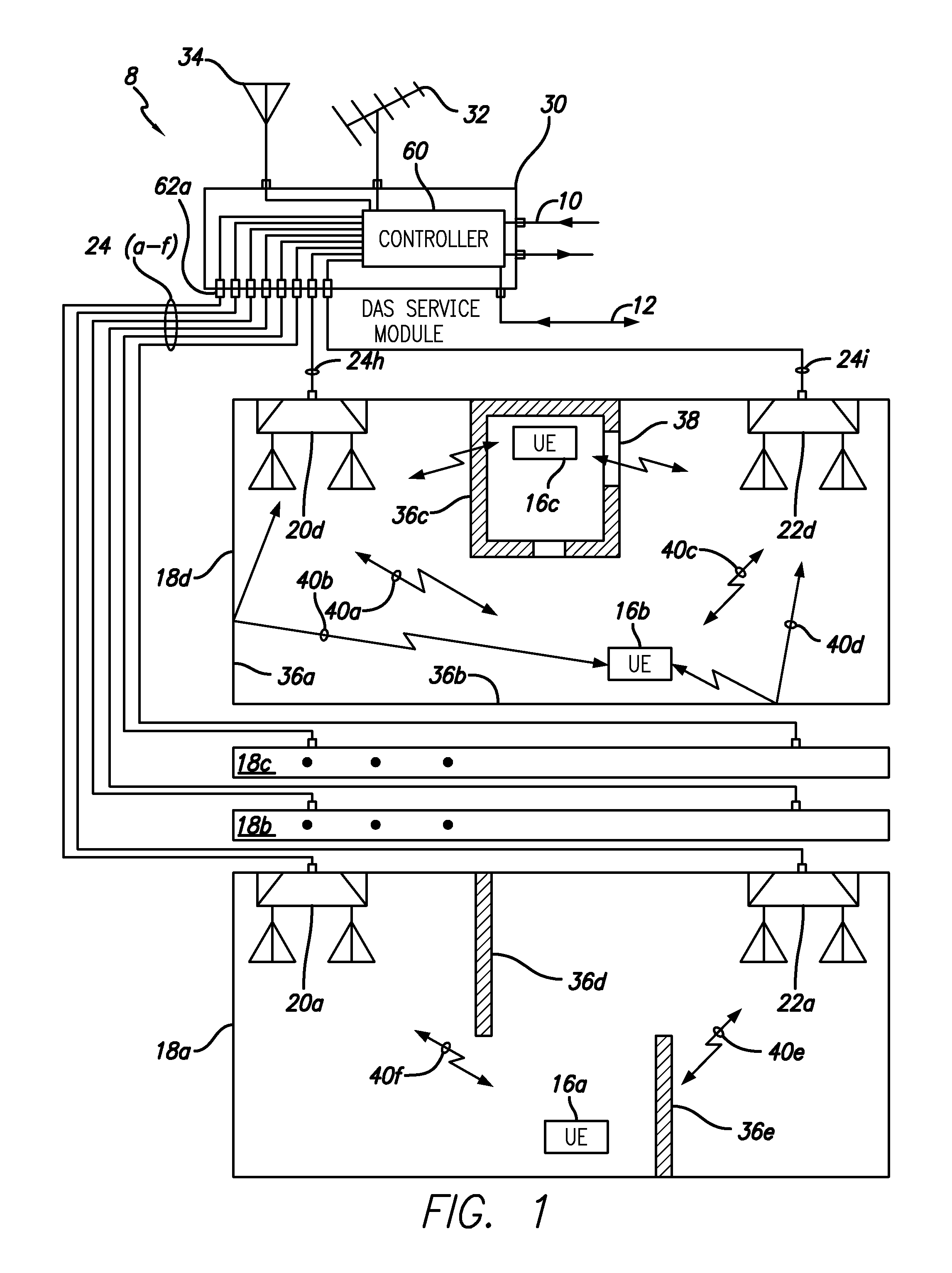

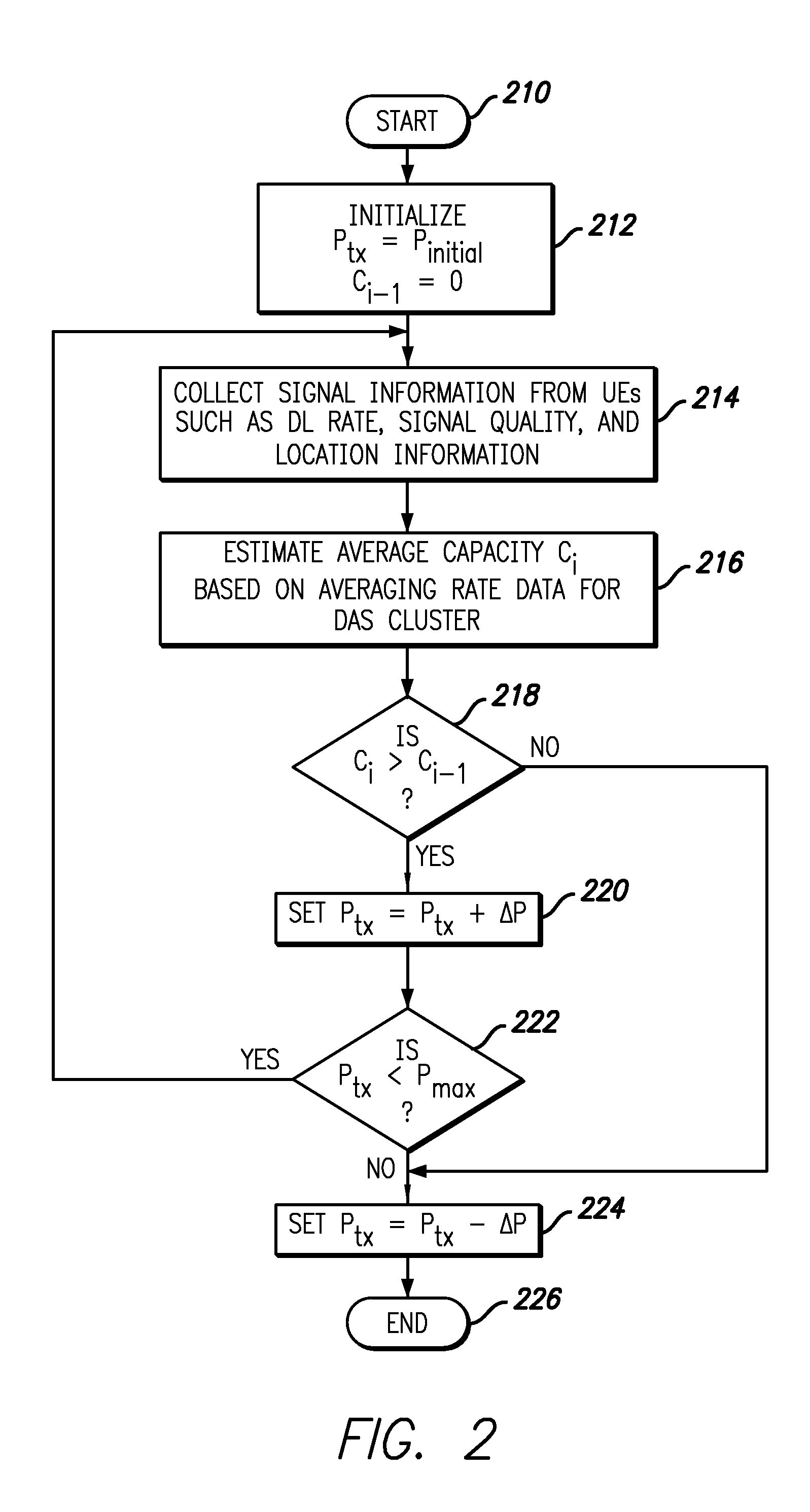

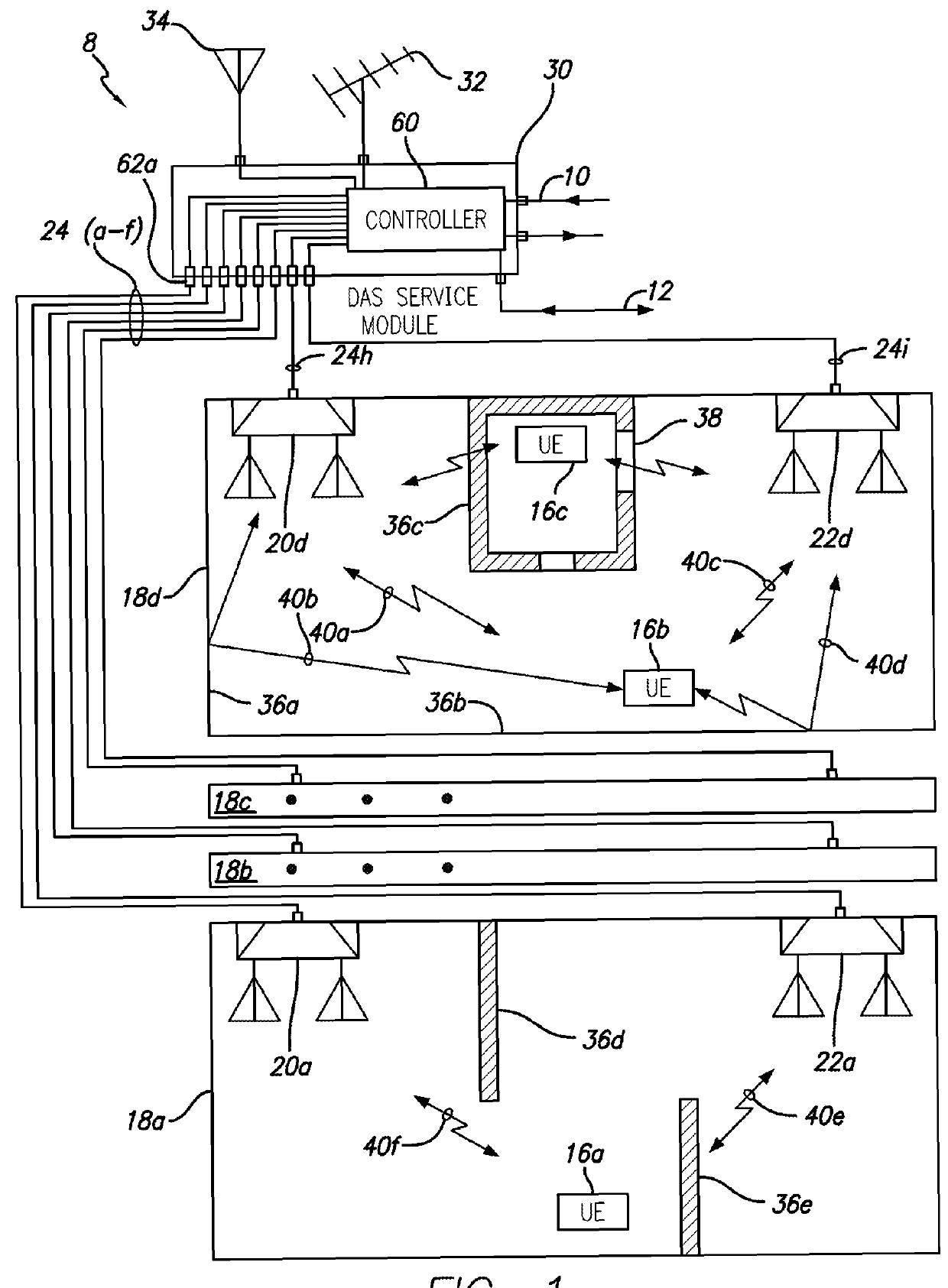

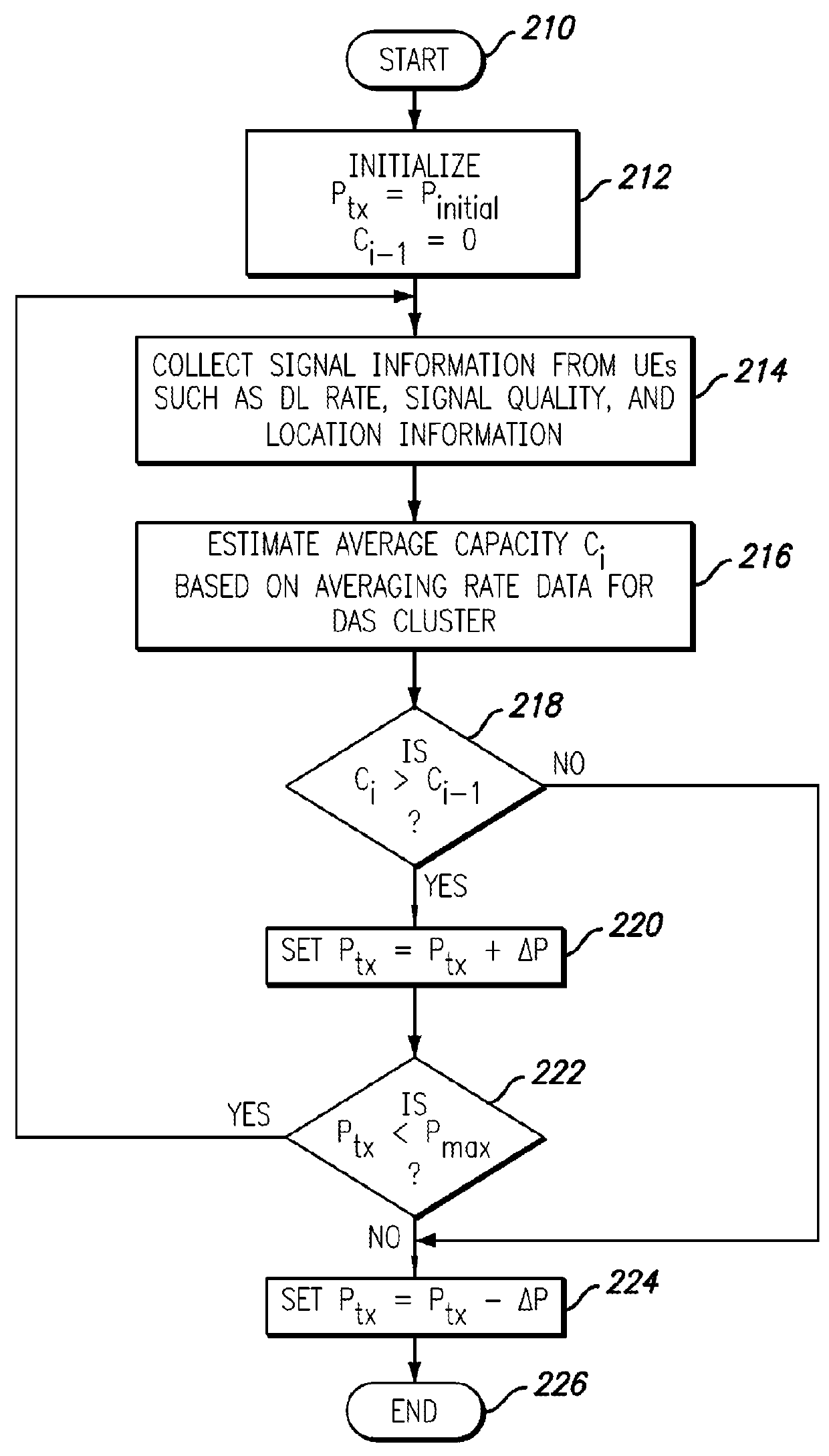

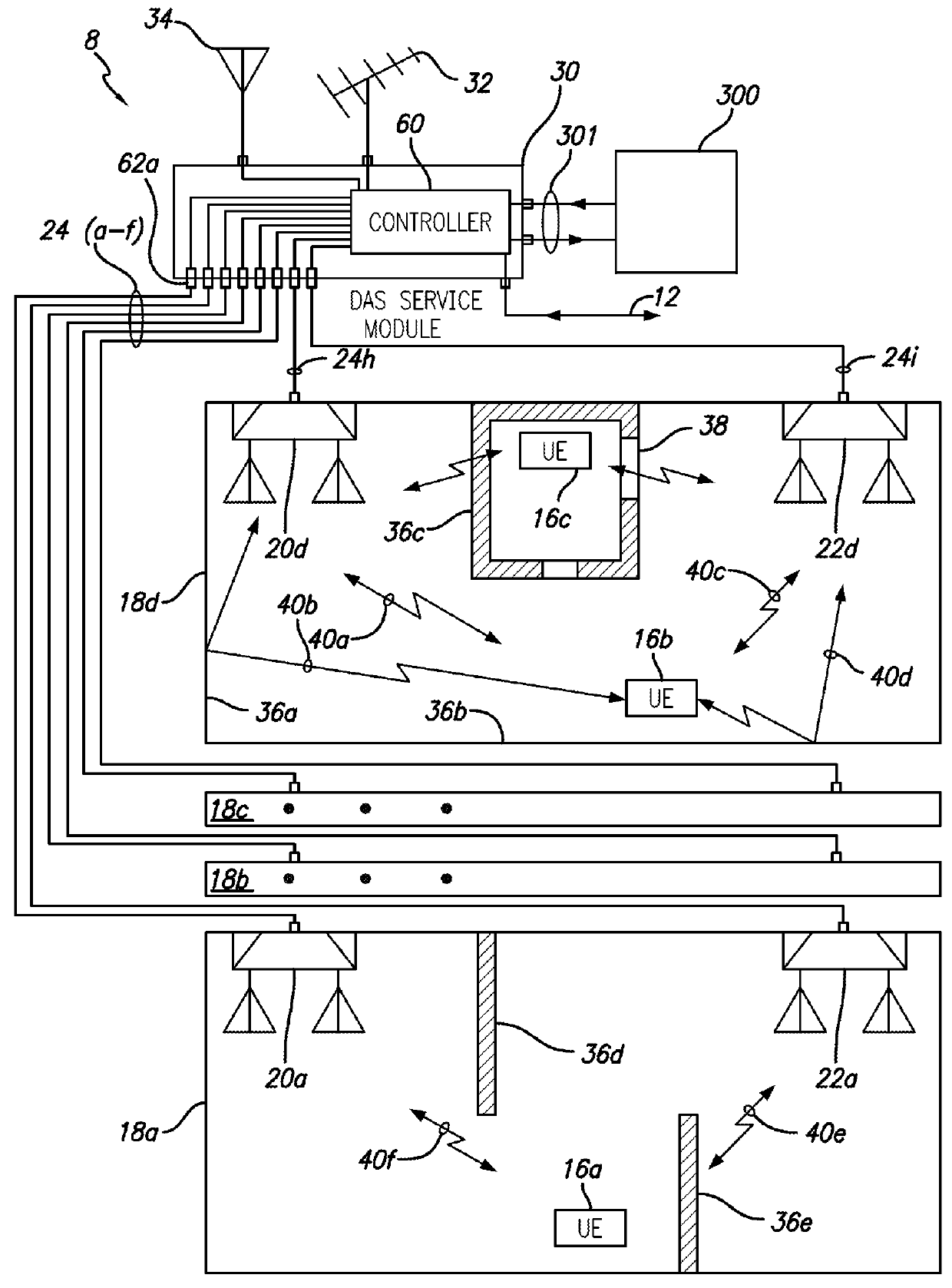

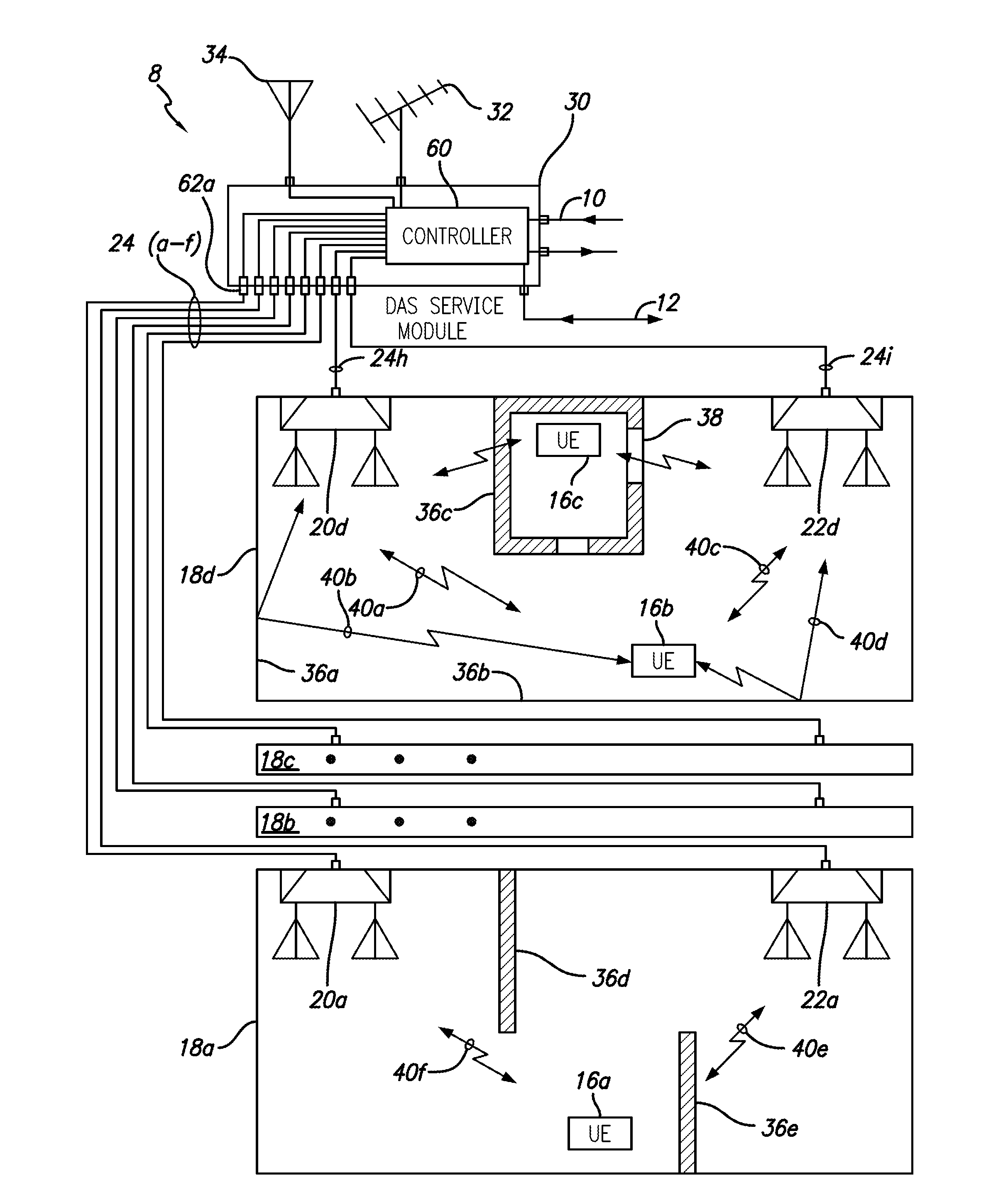

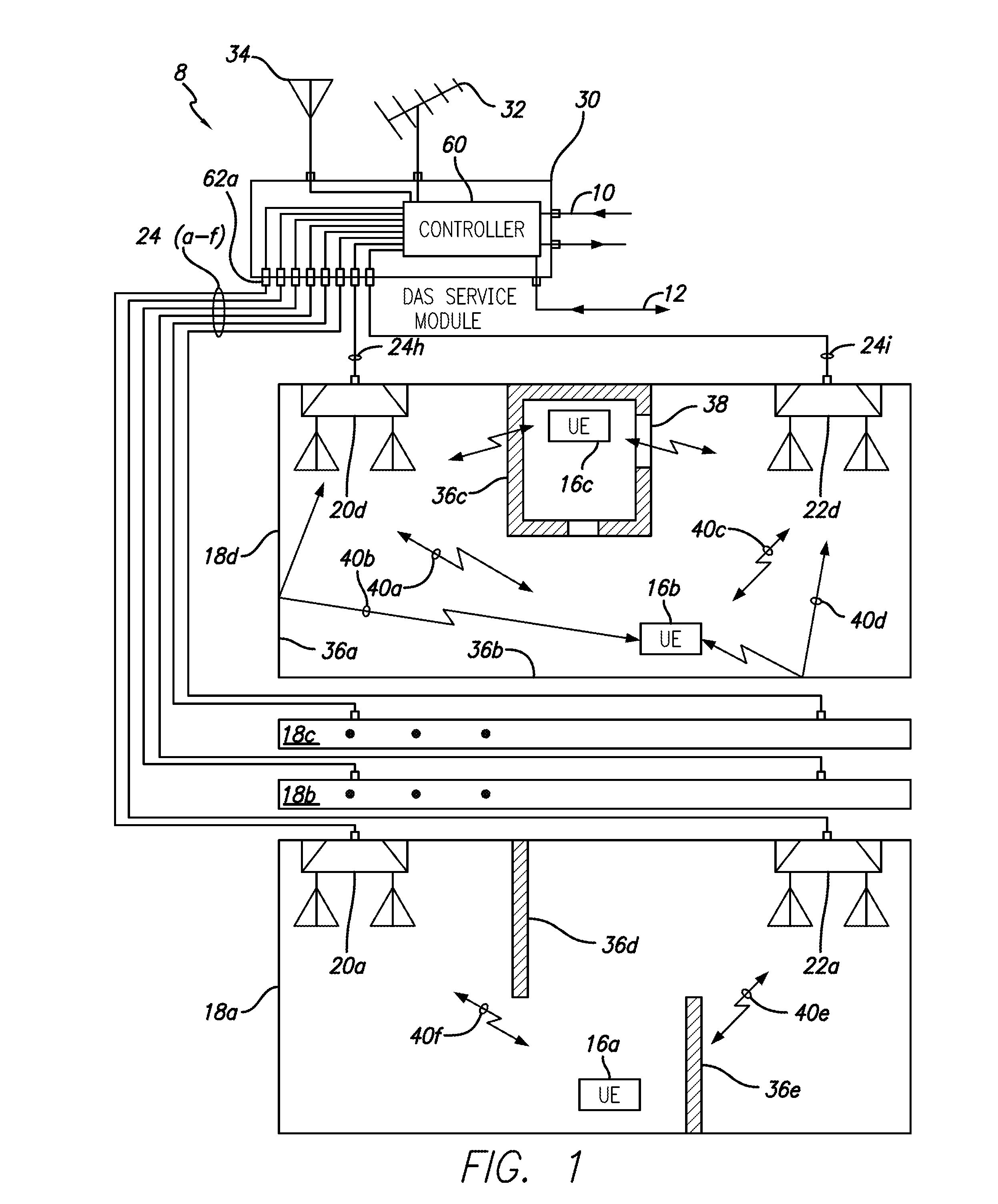

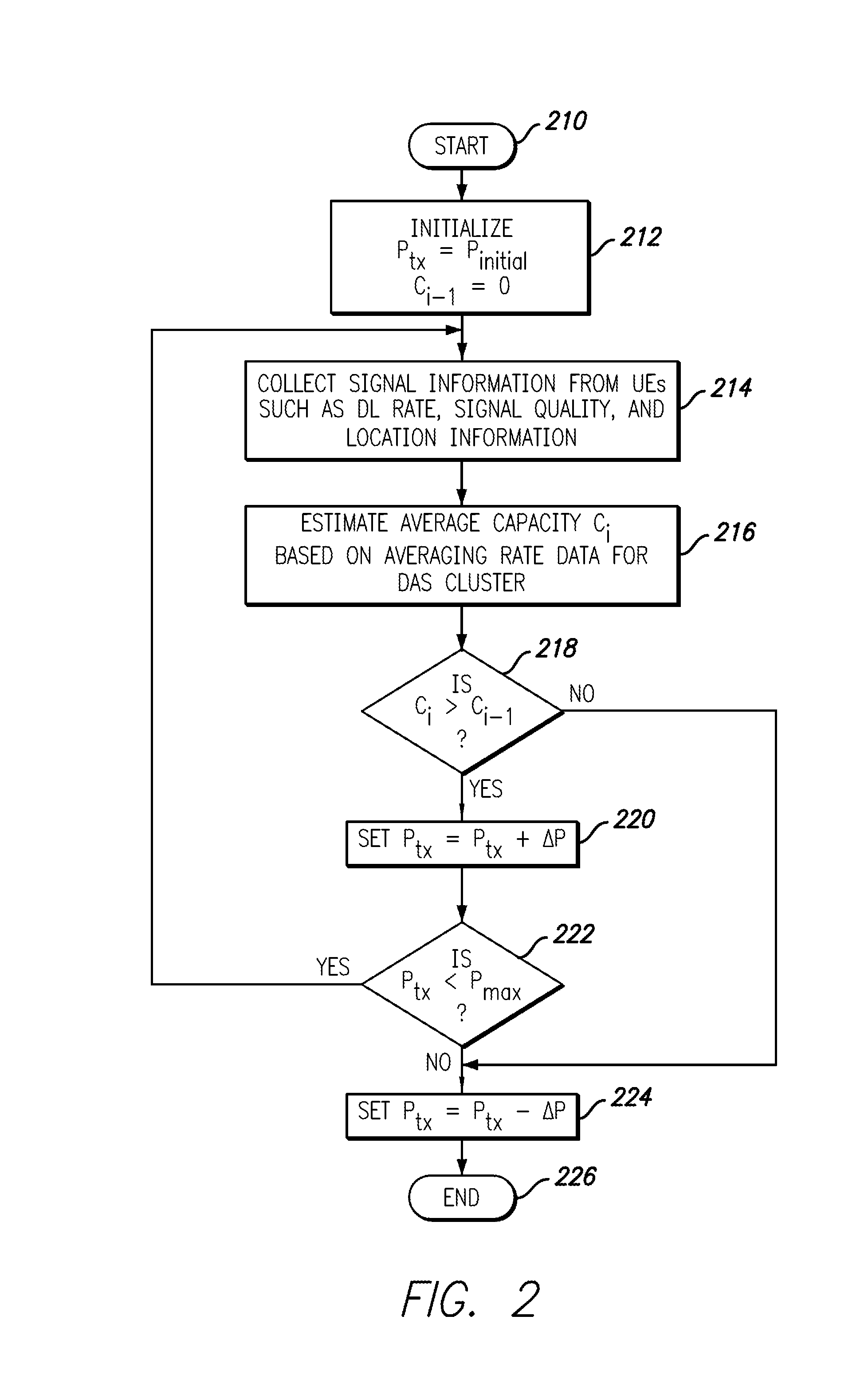

System and method for performance enhancement in heterogeneous wireless access network employing distributed antenna system

ActiveUS9020555B2Power optimizationImprove system performancePower managementFrequency-division multiplex detailsAccess networkPerformance enhancement

A system and method for dynamically optimizing the performance of indoor distributed antenna systems communicate to user equipment is disclosed. The user equipment measures information describing the downlink signals such as the downlink data rates, the quality of the received signal, and the location of the user equipment. A service module collects this information and determines an optimized power level for each of the antenna units. The service module may optimize only one antenna unit power level or a subset of the antenna units within the distributed antenna system in a preferred embodiment. One or more of the antenna units then transmits downlink signals with the optimized power levels. The optimized power level may be less than the initial power level in a preferred embodiment. As a result, the performance of the indoor distributed antenna systems is enhanced.

Owner:INTEL CORP

System and method for performance enhancement in heterogeneous wireless access network employing band selective power management

A system and method for enhancing the performance in heterogeneous wireless access networks employing a distributed antenna system is disclosed. A control unit comprises a distributed antenna system management server which collects load information from each of the carriers. The control unit further comprises a power management decision engine which determines the optimal downlink transmission power level for the carriers based on the collected load information and a set of parameters related to the power for the carriers. Power levels may decrease to baseline parameters when the load on carriers decreases.

Owner:INTEL CORP

Stressed barrier plug slot contact structure for transistor performance enhancement

ActiveUS20080157208A1TransistorSemiconductor/solid-state device detailsStress inducedPerformance enhancement

A method for forming a slot contact structure for transistor performance enhancement. A contact opening is formed to expose a contact region, and a slot contact is disposed within the contact opening in order to induce a stress on an adjacent channel region. In an embodiment, a stress inducing barrier plug is disposed within a portion of the contact opening and the remainder of the contact opening is filled with a lower resistivity contact metal. By selecting the proper materials and deposition parameters, the slot contact can be tuned to induce a tensile or compressive stress on the adjacent channel region, thus being applicable for both p-type and n-type devices.

Owner:INTEL CORP

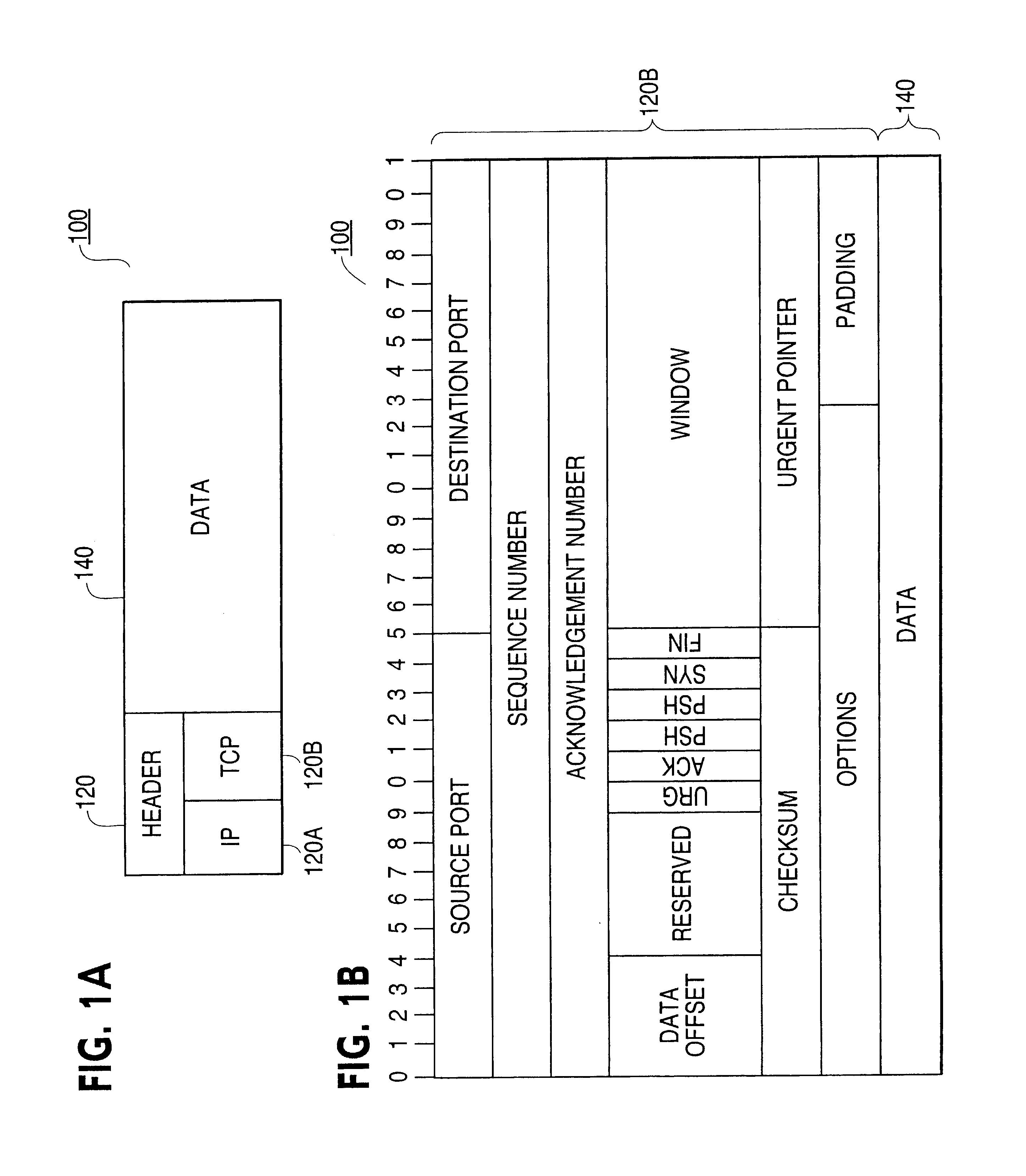

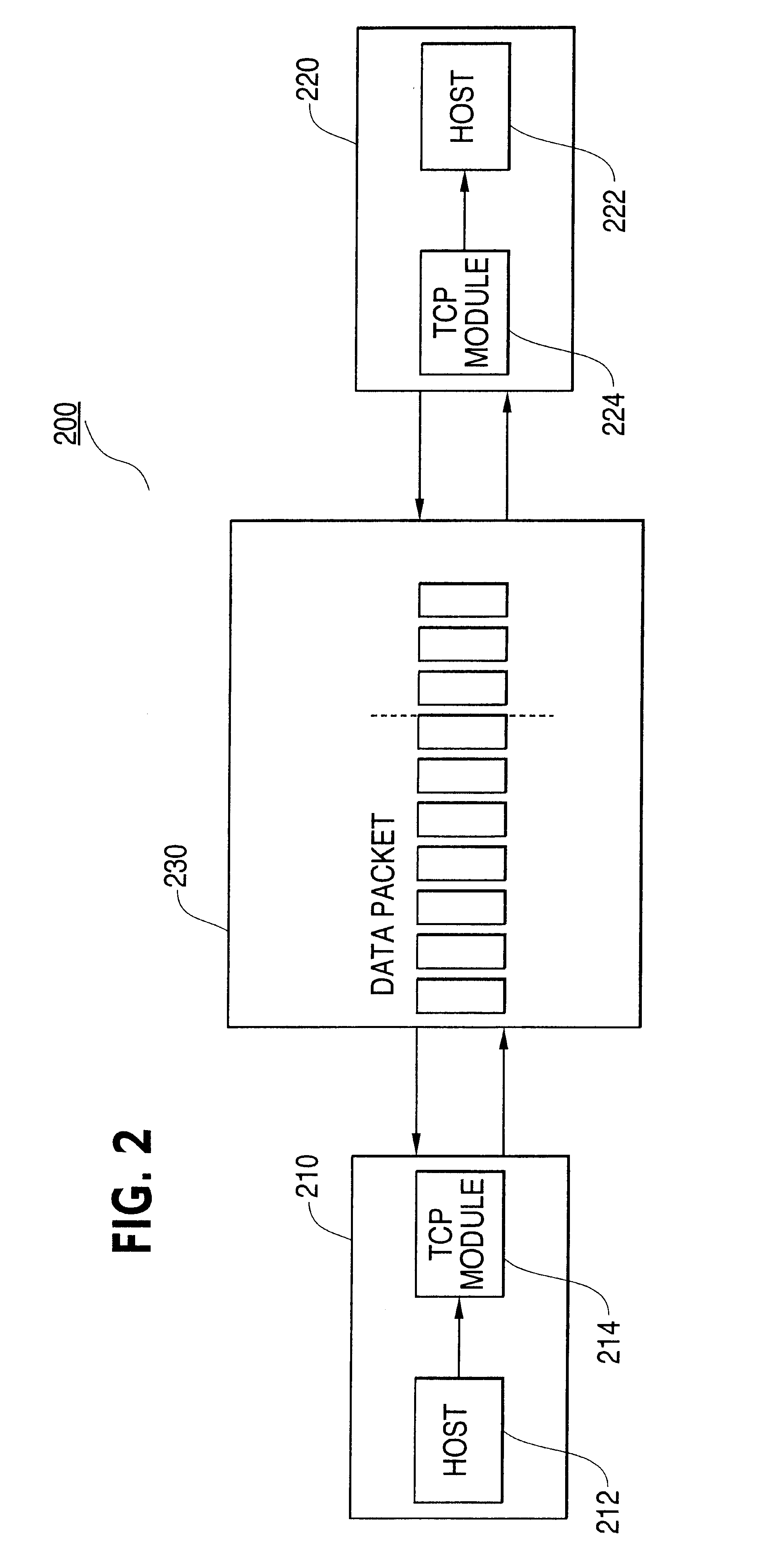

Performance enhancement of transmission control protocol (TCP) for wireless network applications

InactiveUS6757248B1Error prevention/detection by using return channelNetwork traffic/resource managementPerformance enhancementData stream

A new Fast Recovery Plus (FR+) mechanism, and associated method, for wireless and / or mobile network applications to control data flow and avoid network congestion in a TCP / IP packet-switched network.

Owner:NOKIA INTERNET COMM

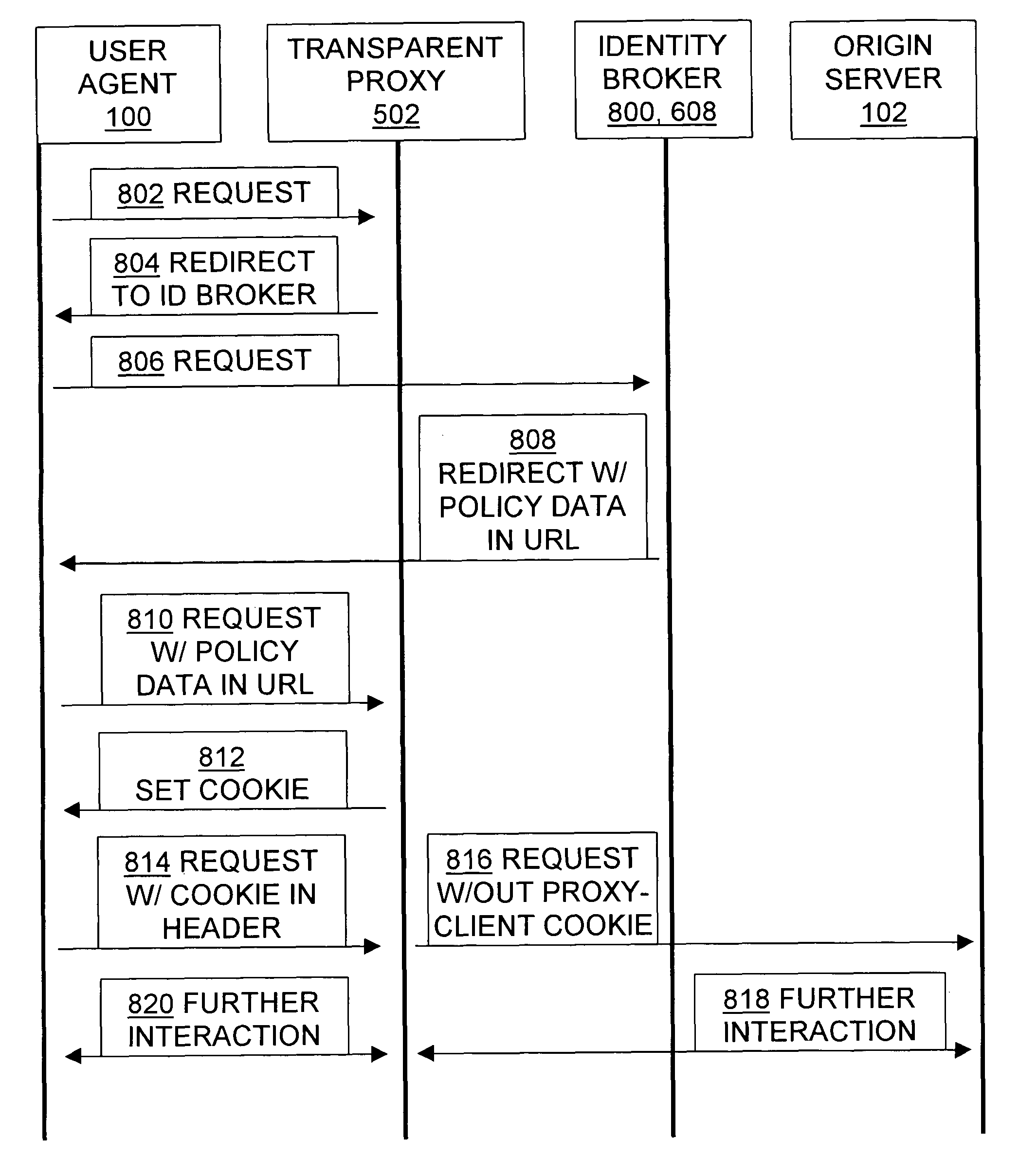

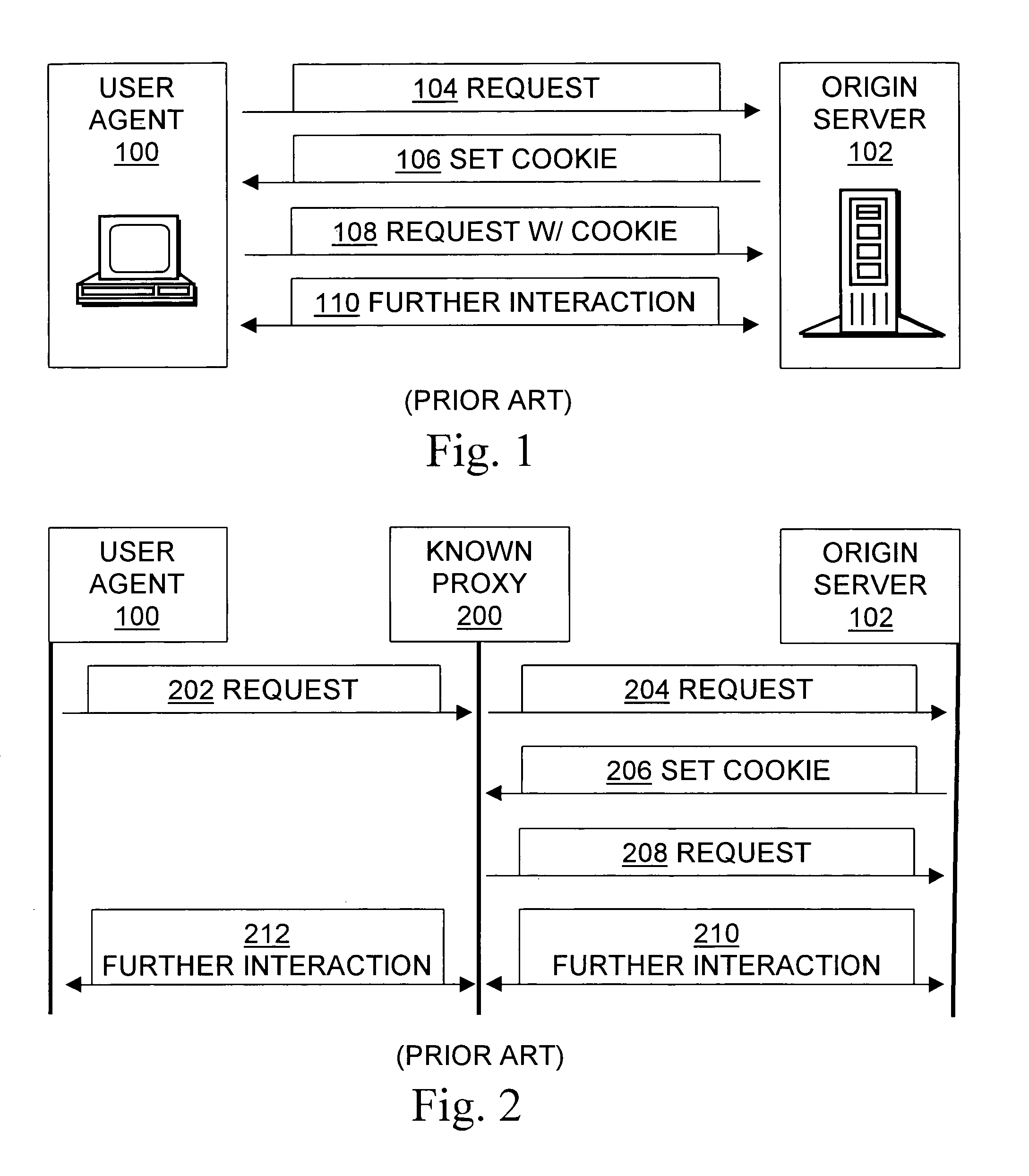

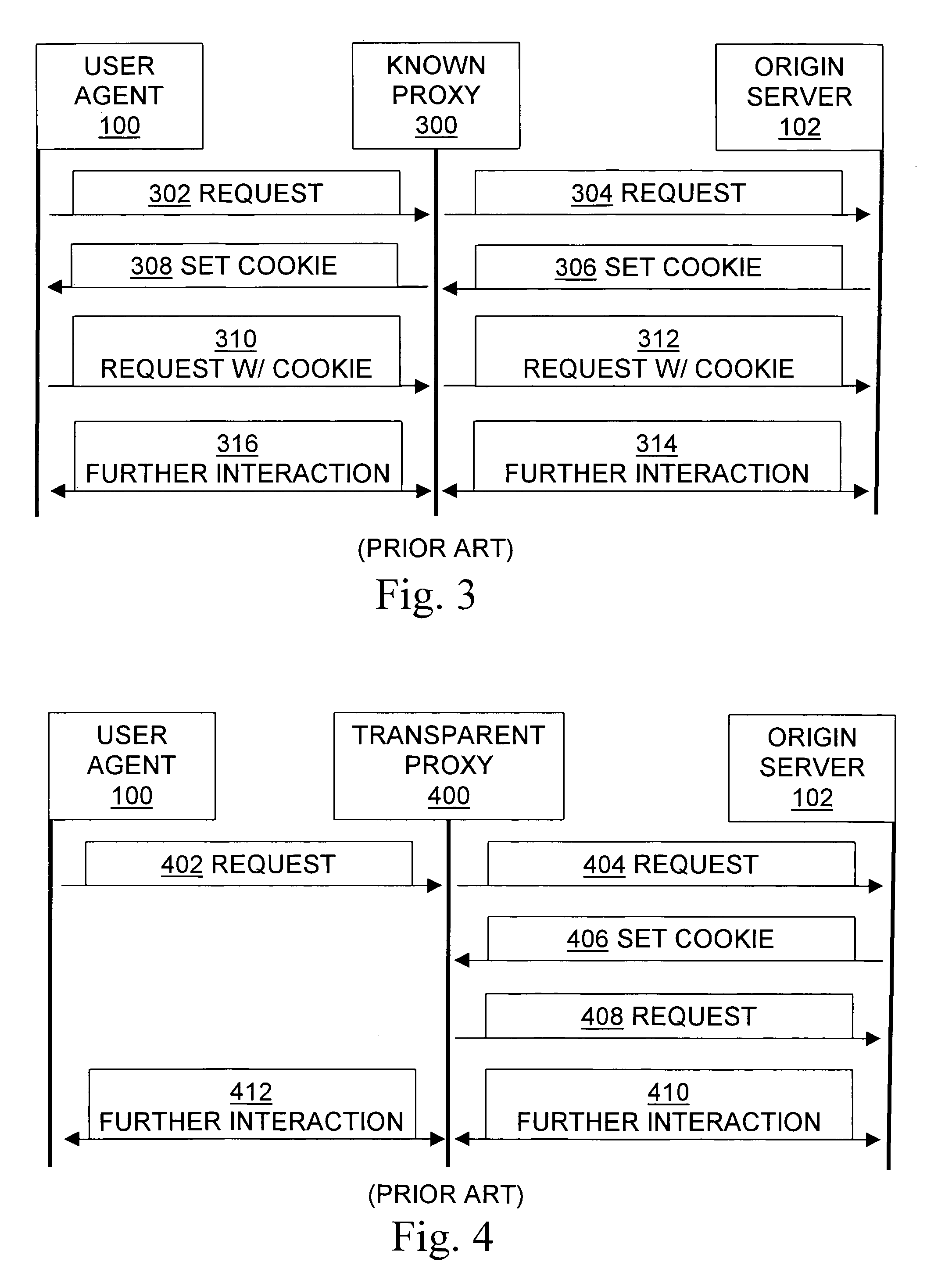

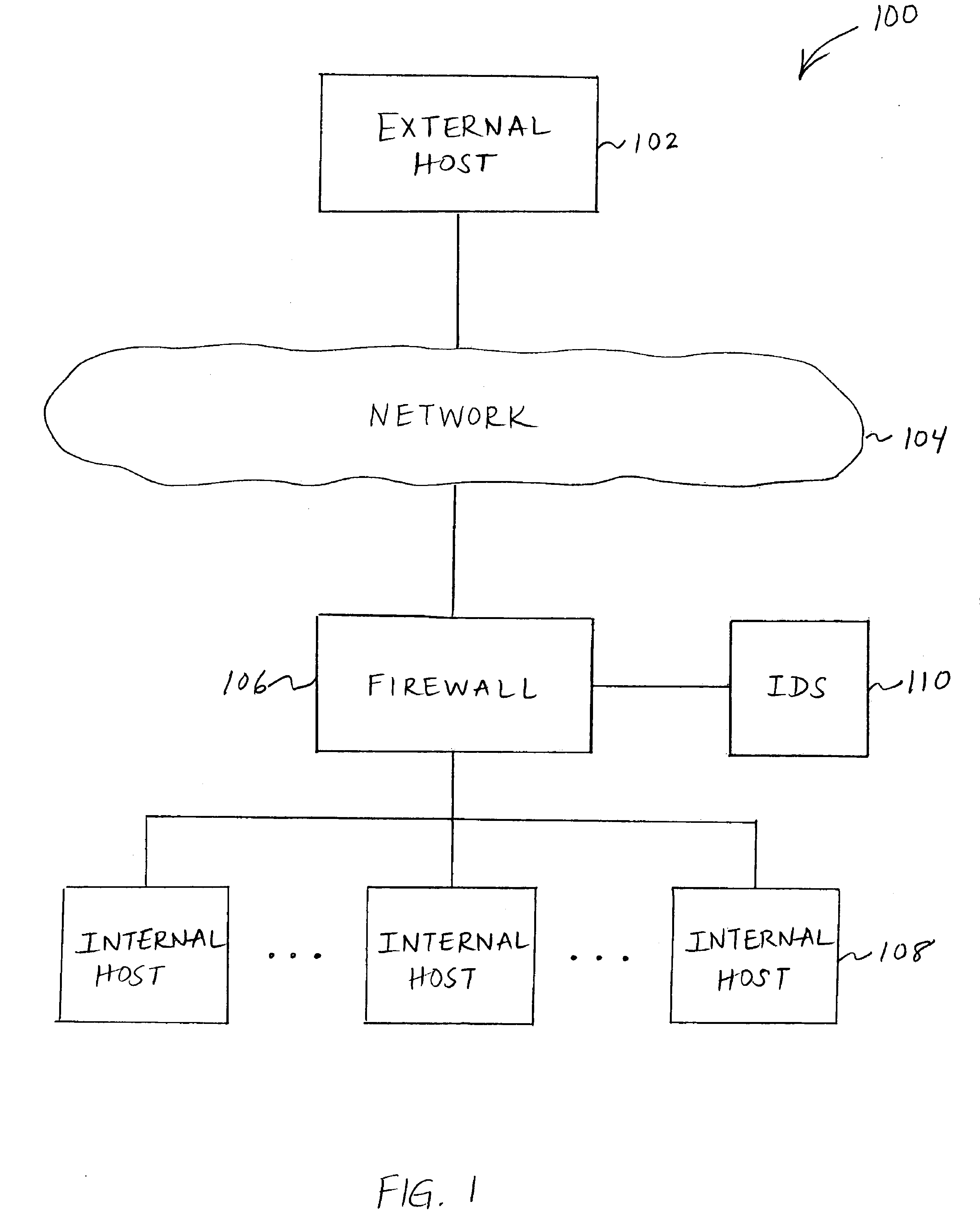

Brokering state information and identity among user agents, origin servers, and proxies

InactiveUS7954144B1Easy to useGuaranteed to continue to useDigital data processing detailsUser identity/authority verificationPerformance enhancementClient-side

Methods, signals, devices, and systems are provided for using proxy servers to transparently forward messages between clients and origin servers if, and only if doing so does not violate network policies. In some systems, a transparent proxy uses a combination of standard-format HTTP commands, embedding auxiliary information in URLs and other tools and techniques to redirect an initial client request to one or more policy modules, such as a login server or an identity broker or an access control server. The policy module authenticates the request, and uses HTTP redirection to have the client transmit authorization data to the proxy. The proxy extracts the authorization data, directs the client to use a corresponding cookie, and subsequently provides the implicitly requested proxy services to the client in response to the client's subsequently providing the authorization data in a cookie. This is accomplished without requiring installation of any invention-specific software or hardware on either the client or the origin server, and also works with proxy servers that are known to the client. Unless the client request violates network policy, a person using the client will generally perceive no reduction of services, and will instead benefit from the proxy's caching and / or other performance enhancements.

Owner:RPX CORP

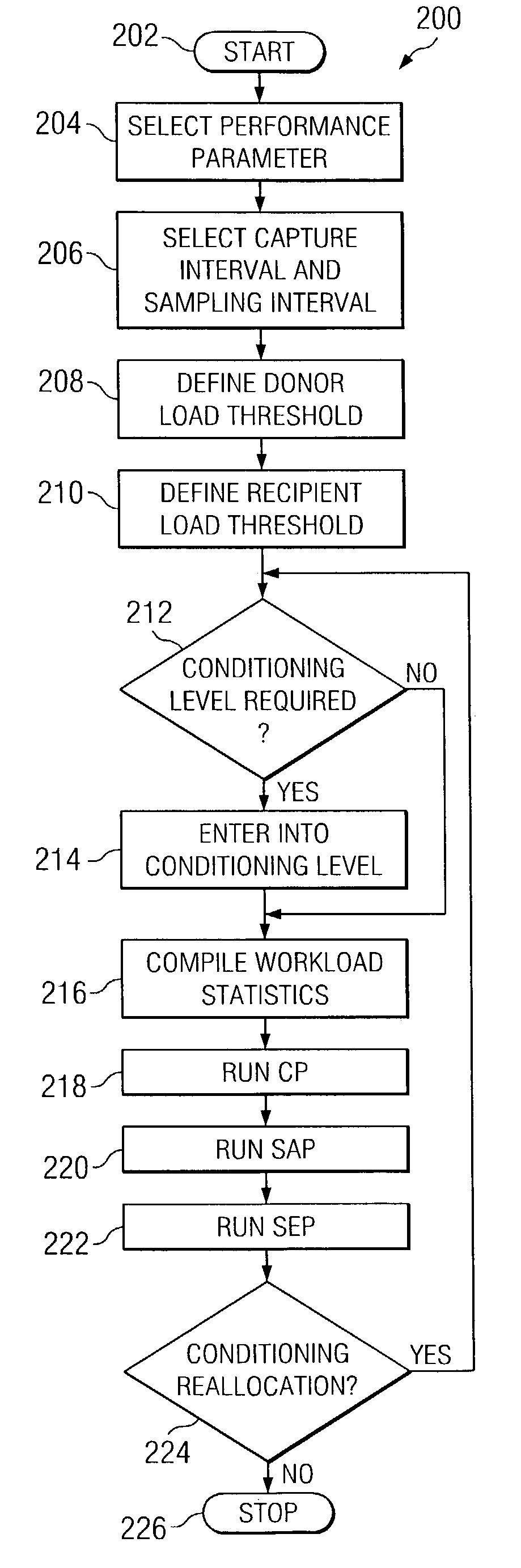

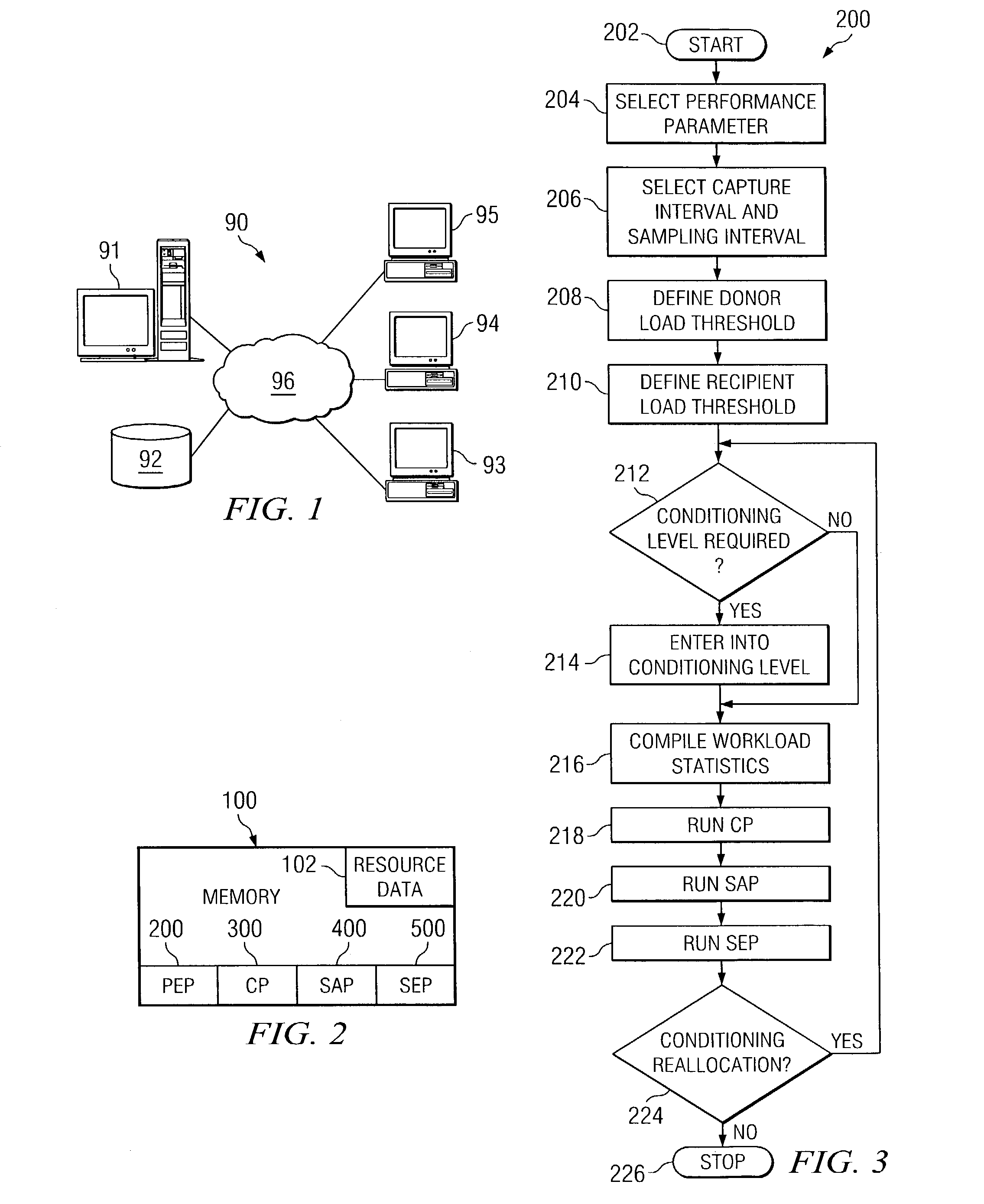

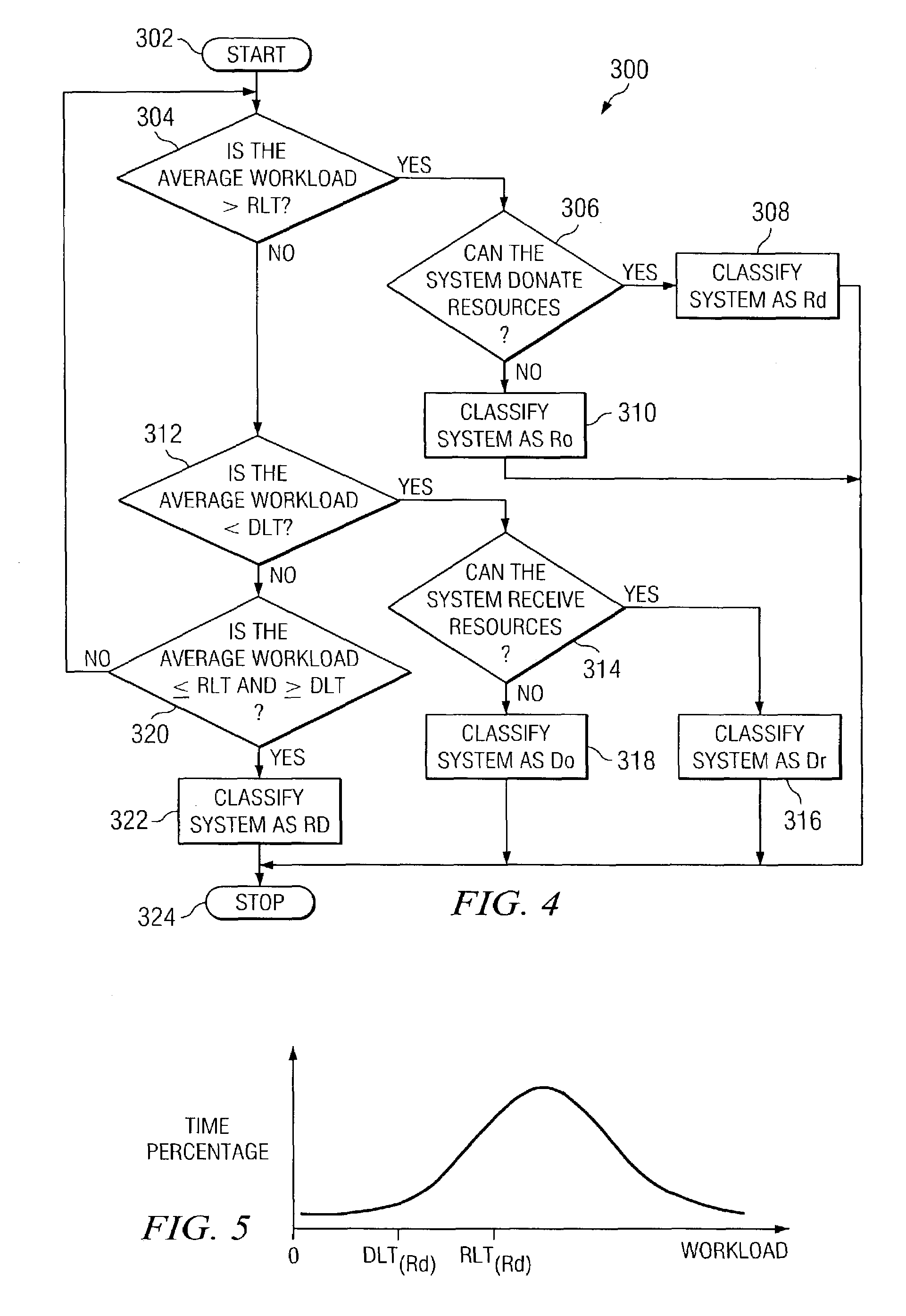

Reciprocity and stabilization in dynamic resource reallocation among logically partitioned systems

InactiveUS7313796B2Easy to switchResource allocationSoftware simulation/interpretation/emulationPerformance enhancementDifferentiator

A method and system for achieving stability while reallocating resources in a logically partitioned environment. The present invention comprises Performance Enhancement Program (PEP), Classification Program (CP), System Analysis Program (SAP), and System Evaluation Program (SEP). PEP allows a user to enter several performance parameters. CP classifies each of the virtual systems in the managed system based on their workload. SAP analyses the managed system to determine the configuration of the managed system. Managed systems configurations are classified according to the reciprocity of resource allocation and the overall symmetry of the managed systems. SEP evaluates the configuration of the managed system and recommends alterations for improved performance of the managed system. The managed system will be optimized when the functional differentiator (FD) of the virtual systems is small enough to allow reallocation of resources without an unacceptable sacrifice in managed system stability.

Owner:GOOGLE LLC

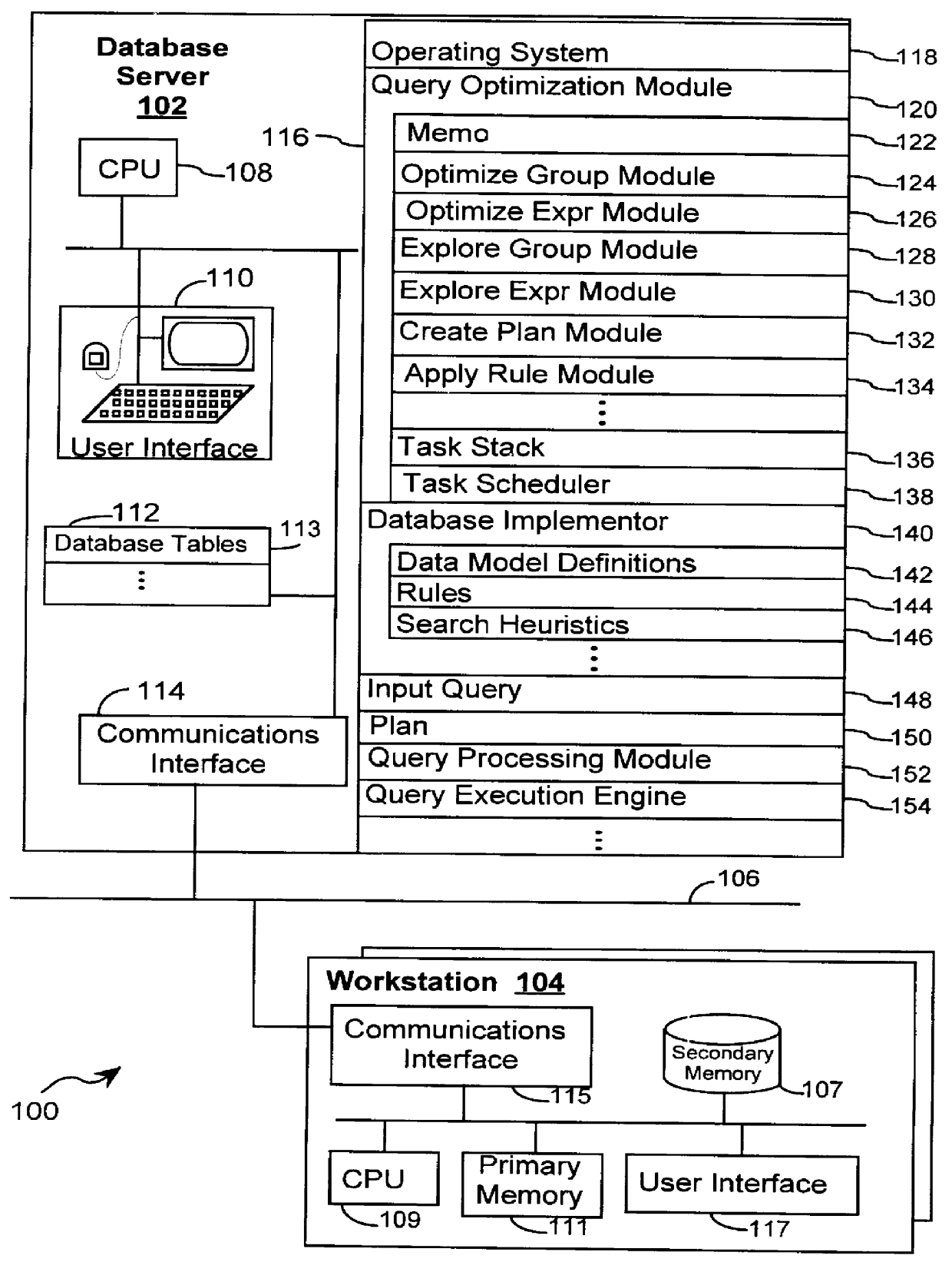

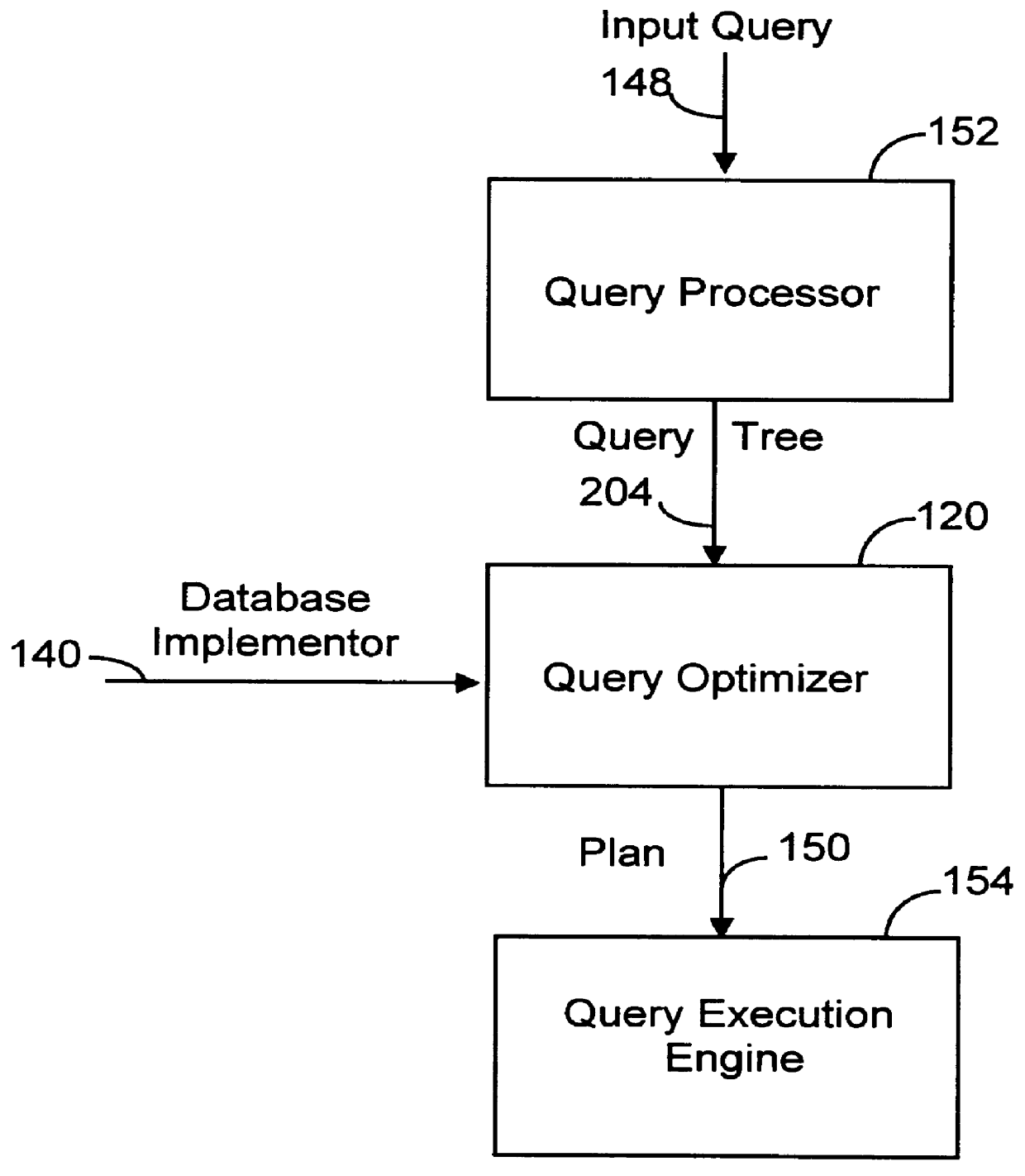

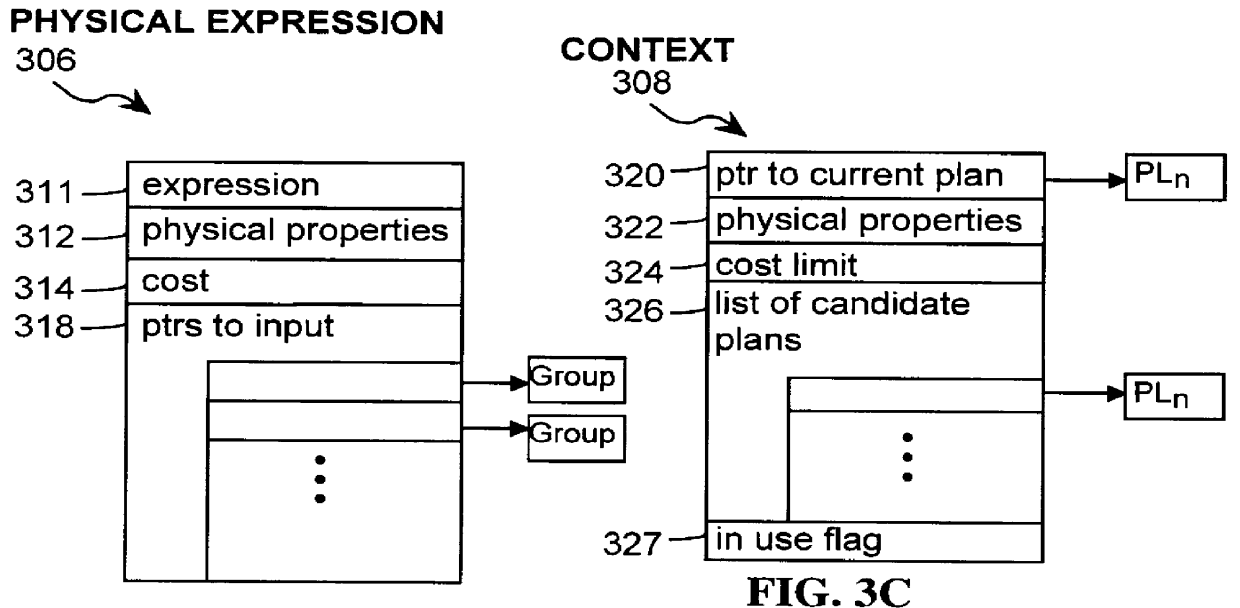

System and method for optimizing database queries with improved performance enhancements

InactiveUS6021405AEffective trackingEfficient searchDigital data information retrievalData processing applicationsExecution planPerformance enhancement

A system and method for optimizing a database query with improved performance enhancements is herein disclosed. The database query consists of one or more logical expressions. Through the repeated application of one or more rules, the logical expressions are transformed into execution plans. The query optimizer partitions the database query into one or more subproblems with each subproblem consisting of one or more logical expressions. A plan is obtained for each subproblem with the plan for the database query including the plans for each subproblem. The query optimizer is cost-based and uses rules including transformation and implementation rules that are used to perform transformations on the logical expressions in a subproblem in order to produce a plan. The rules are classified into context-free and context-sensitive in order to avoid generating duplicate expressions. Context-free rules are applied once for each logical expression and context-sensitive rules are applied once for each logical expression for a particular optimization goal. In a preferred embodiment, the query optimizer performs several optimization passes over the database query in order to obtain an optimal plan. For each pass, if no optimal plan exists for the requested optimization goal, existing plans having the same optimization goal are utilized with each input reoptimized for a more cost effective plan.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

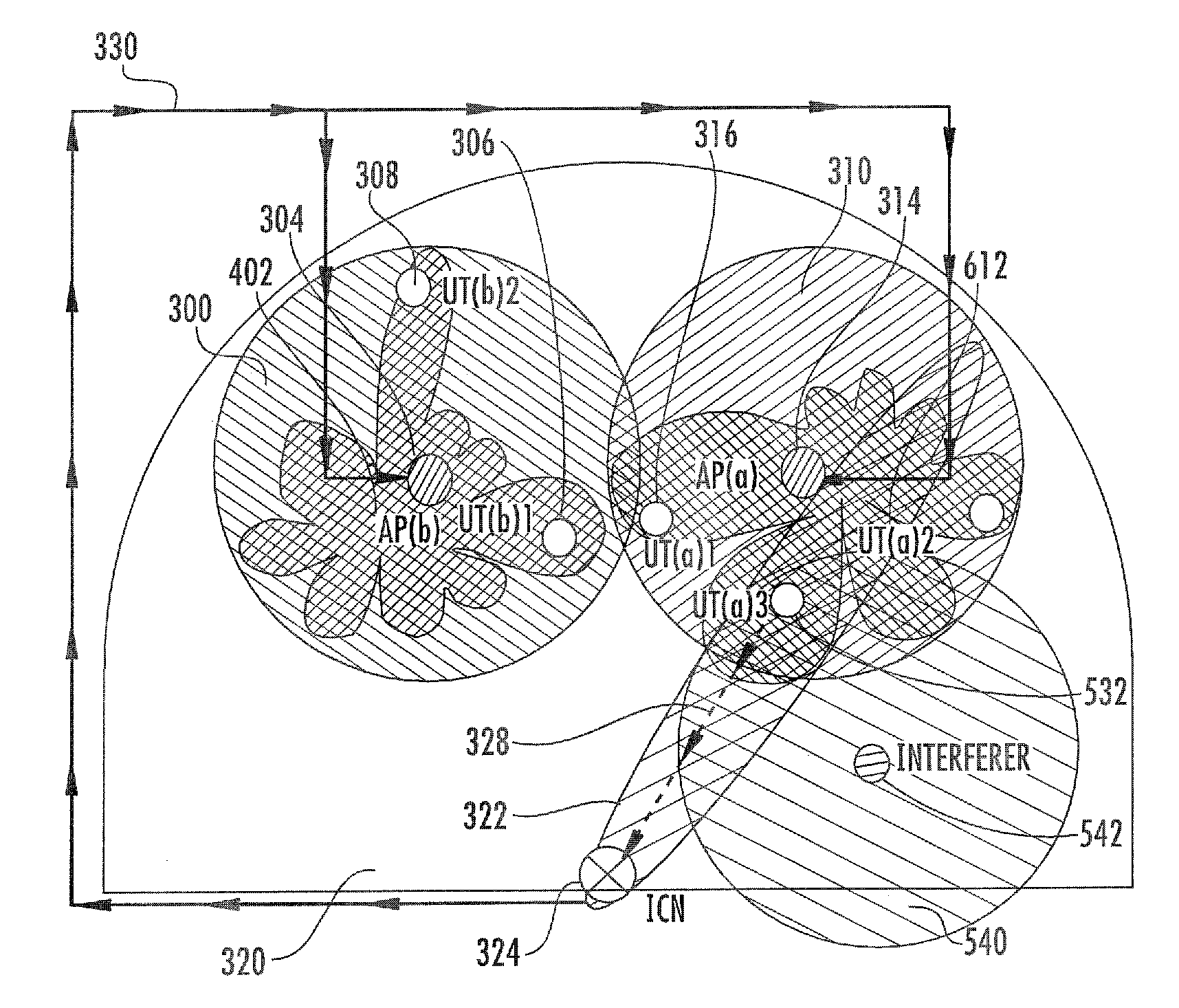

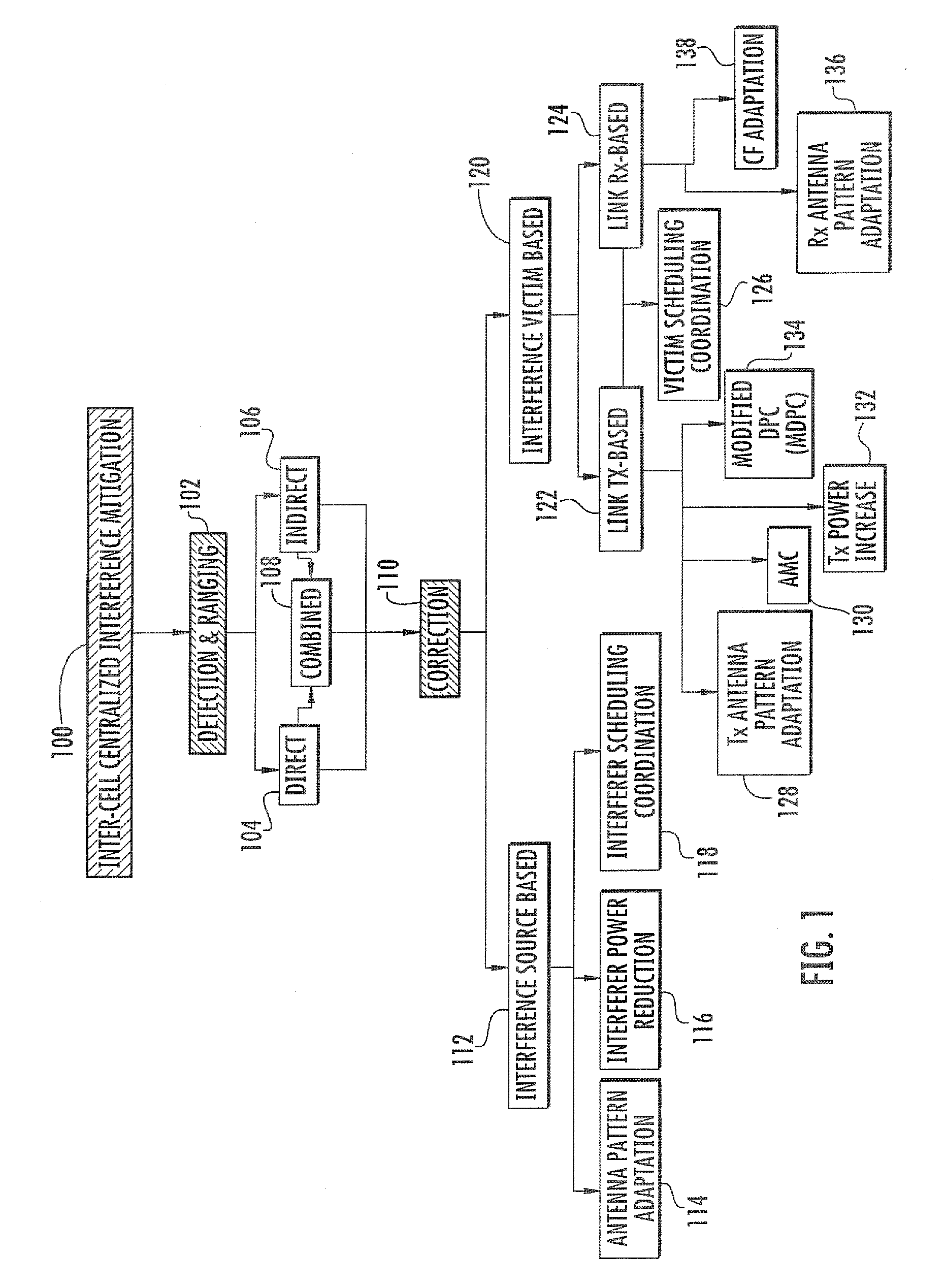

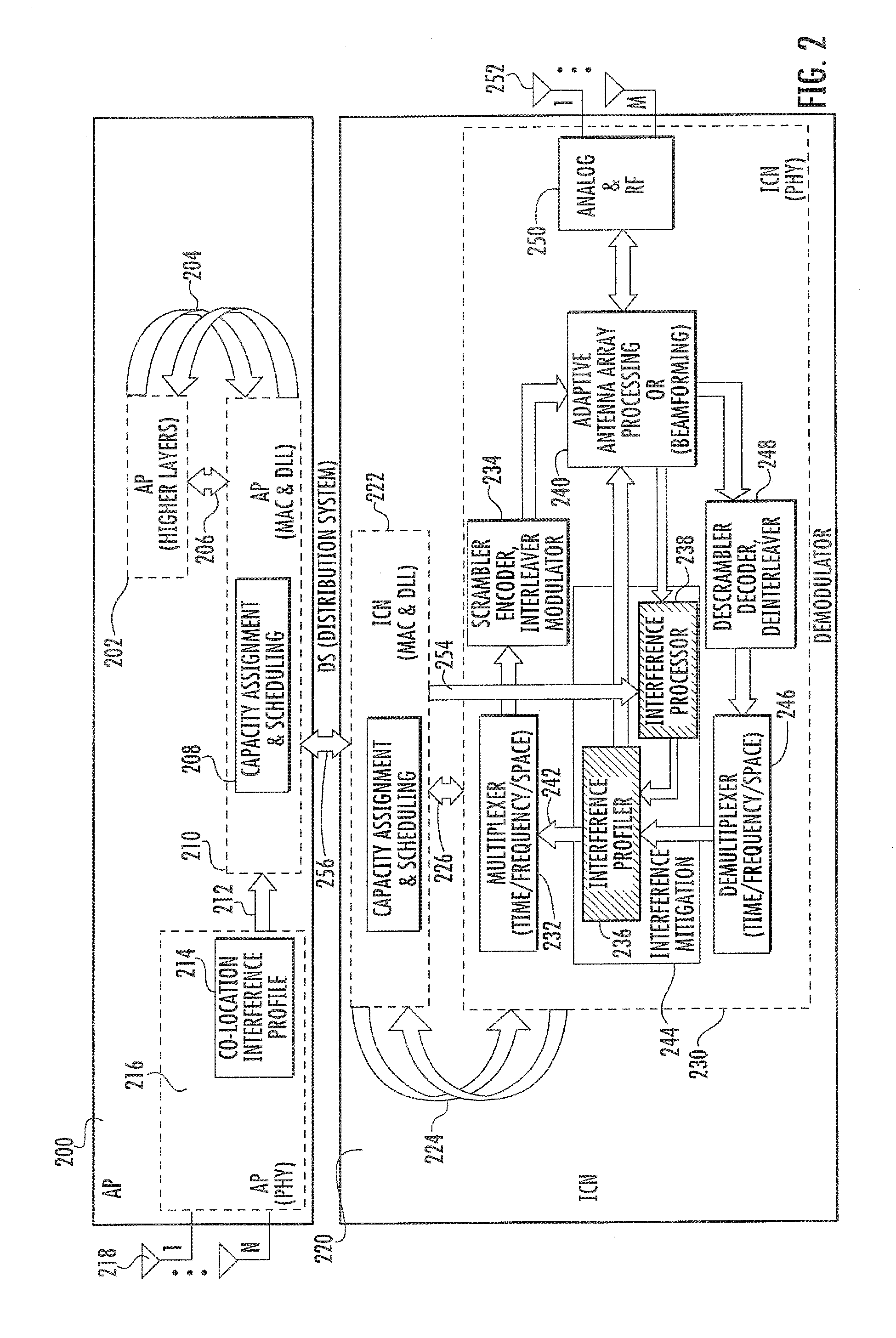

Methods and apparatus for centralized and coordinated interference mitigation in a WLAN network

InactiveUS20110090885A1Facilitate communicationEasy to interferePower managementNetwork topologiesBroadcast channelsPrecoding

Method and apparatus for interference mitigation in wireless local area networks (such as WLANs). In one embodiment, a centralized interference measurement and mitigation method is disclosed. The method may involve spectral sensing, beamforming, MIMO, power control, MAC scheduling using a cross-layer approach, and / or broadcast channel precoding, employed towards performance enhancement of WLAN networks in presence of interference. In one variant, different actions at interference mitigation are selected based on the source of the interference (e.g., inter-network or intra-network).

Owner:SAFAVI SAEID

System and method for performance enhancement in heterogeneous wireless access network employing band selective power management

A system and method for enhancing the performance in heterogeneous wireless access networks employing a distributed antenna system is disclosed. A control unit comprises a distributed antenna system management server which collects load information from each of the carriers. The control unit further comprises a power management decision engine which determines the optimal downlink transmission power level for the carriers based on the collected load information and a set of parameters related to the power for the carriers. Power levels may decrease to baseline parameters when the load on carriers decreases.

Owner:INTEL CORP

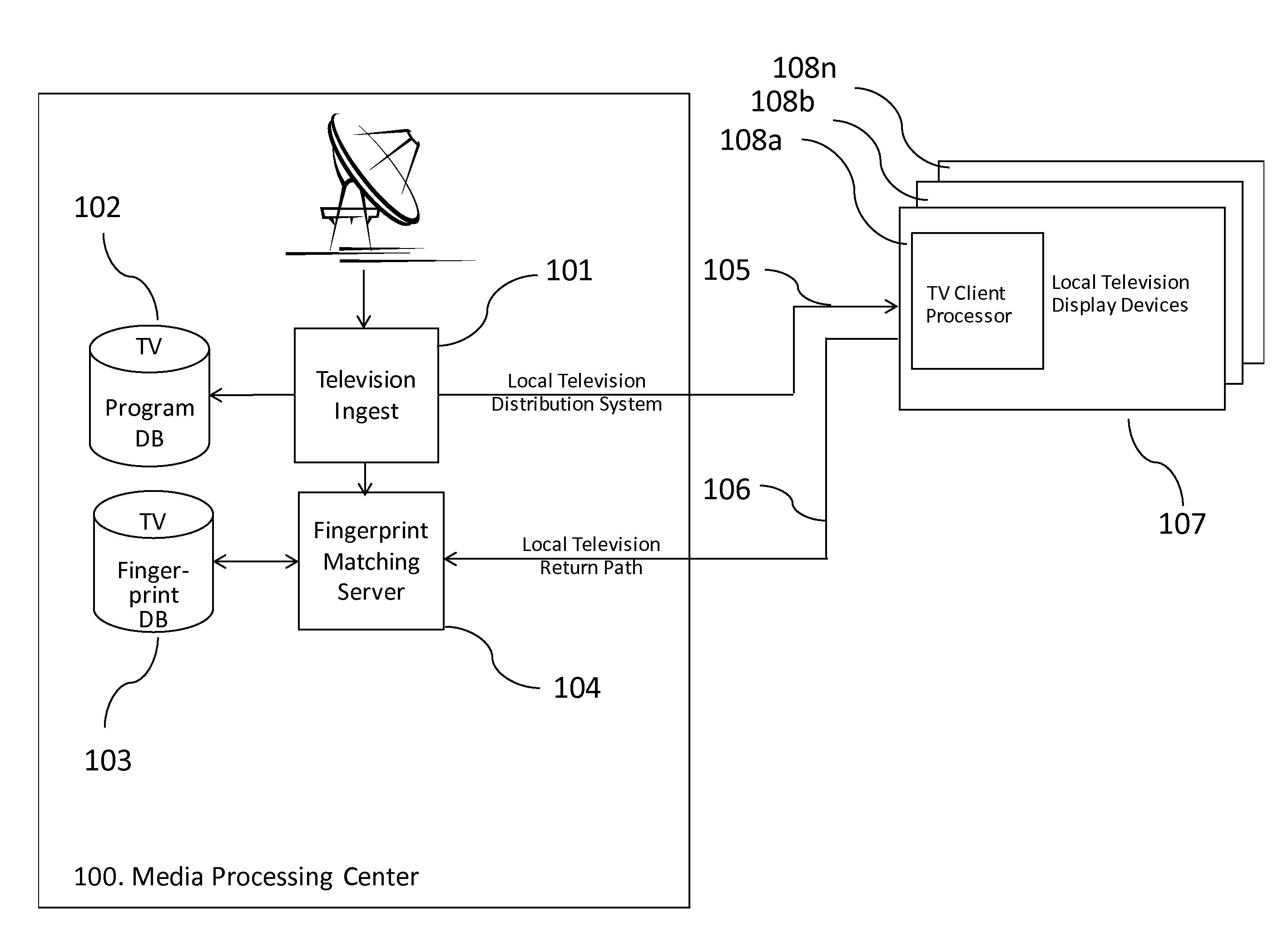

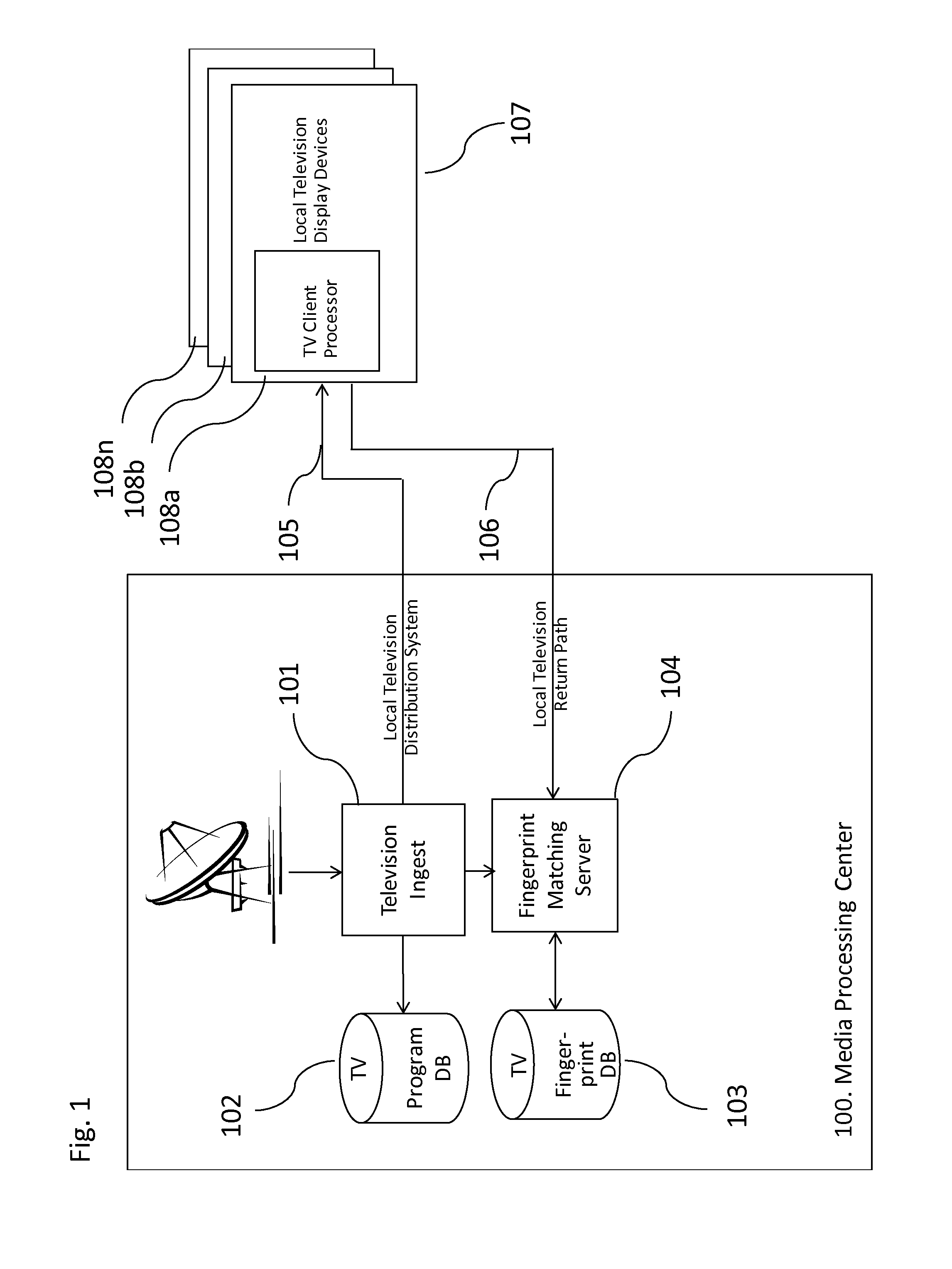

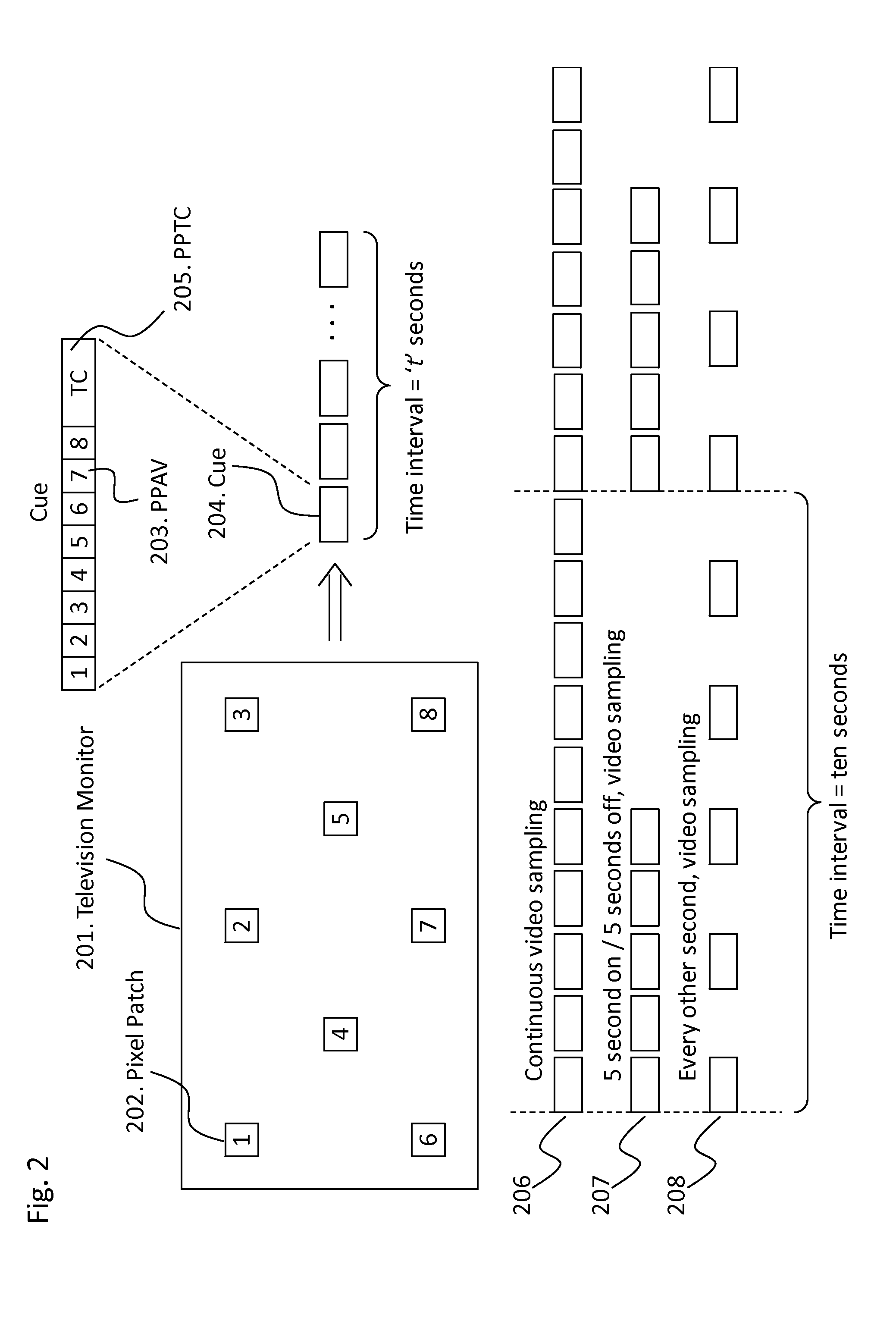

Systems and methods for improving server and client performance in fingerprint acr systems

ActiveUS20140201787A1Improving serverImproving client performanceTelevision system detailsMultimedia data retrievalPerformance enhancementDigital content

A system and method are disclosed that improve the efficiency and performance of an Automatic Content Recognition (ACR) system. Several approaches are described that may be used alone or in combination to reduce total system computational costs related to the manner in which such an ACR means takes samples, called “fingerprints,” of digital content being played by a television display device and transmits said fingerprints to a remote server to be compared to a database of fingerprints from known programming. Methods are described for implementing such system performance enhancement including varying sampling rates and other resolution metrics during the process of creating such fingerprints and transmitting them to the database server. The system and method disclosed also describes how to reduce the probability that, when compared to samples from already-identified programming, such fingerprints are incorrectly identified as being of programming other than that which they are in fact derived from.

Owner:INSCAPE DATA INC

Contact lens materials, designs, substances, and methods

InactiveUS7878650B2Improve performanceReduce the possibilityOptical partsPerformance enhancementReduced size

A contact lens is provided that is capable of being worn by a user. The lens includes a contact lens body having an eye-engaging surface placeable against a surface of an eye and an outer surface. Microphobic features are provided in the lens for eliminating microbes from the eye-engaging surface. Preferably, these microphobic features are chosen from a group consisting of electrical charge inducing agents, magnetic field inducing agents, chemical agents and textural features. In another embodiment of the present invention, a contact lens is provided that can include a reservoir portion capable of holding a performance enhancement agent for enhancing the performance of the lens. The performance enhancement agent can include such thins as sealant solutions, protective agents, therapeutic agents, anti-microbial agents, medications and reduced size transparent portions. In other embodiments, a wide variety of designs, materials and substances are disclosed for use with contact lenses.

Owner:DOMESTIC ASSET LLP

Local stress control for CMOS performance enhancement

InactiveUS20050214998A1Increase charge mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesCMOSPerformance enhancement

A semiconductor device and method for forming the same for improving charge mobility in NMOS and PMOS devices simultaneously, the method including forming a first dielectric layer including a stress type selected from the group consisting of tensile stress and compressive stress over the respective PMOS and NMOS device regions; removing a portion of the first dielectric layer overlying one of the PMOS and NMOS device regions; forming a second dielectric layer including a stress type opposite from the first dielectric layer stress type over the respective PMOS and NMOS device regions; and, removing a portion of the second dielectric layer overlying one of the PMOS and NMOS device regions having an underlying first dielectric layer to form a compressive stress dielectric layer over the PMOS device region and a tensile stress dielectric layer over the NMOS device region.

Owner:TAIWAN SEMICON MFG CO LTD

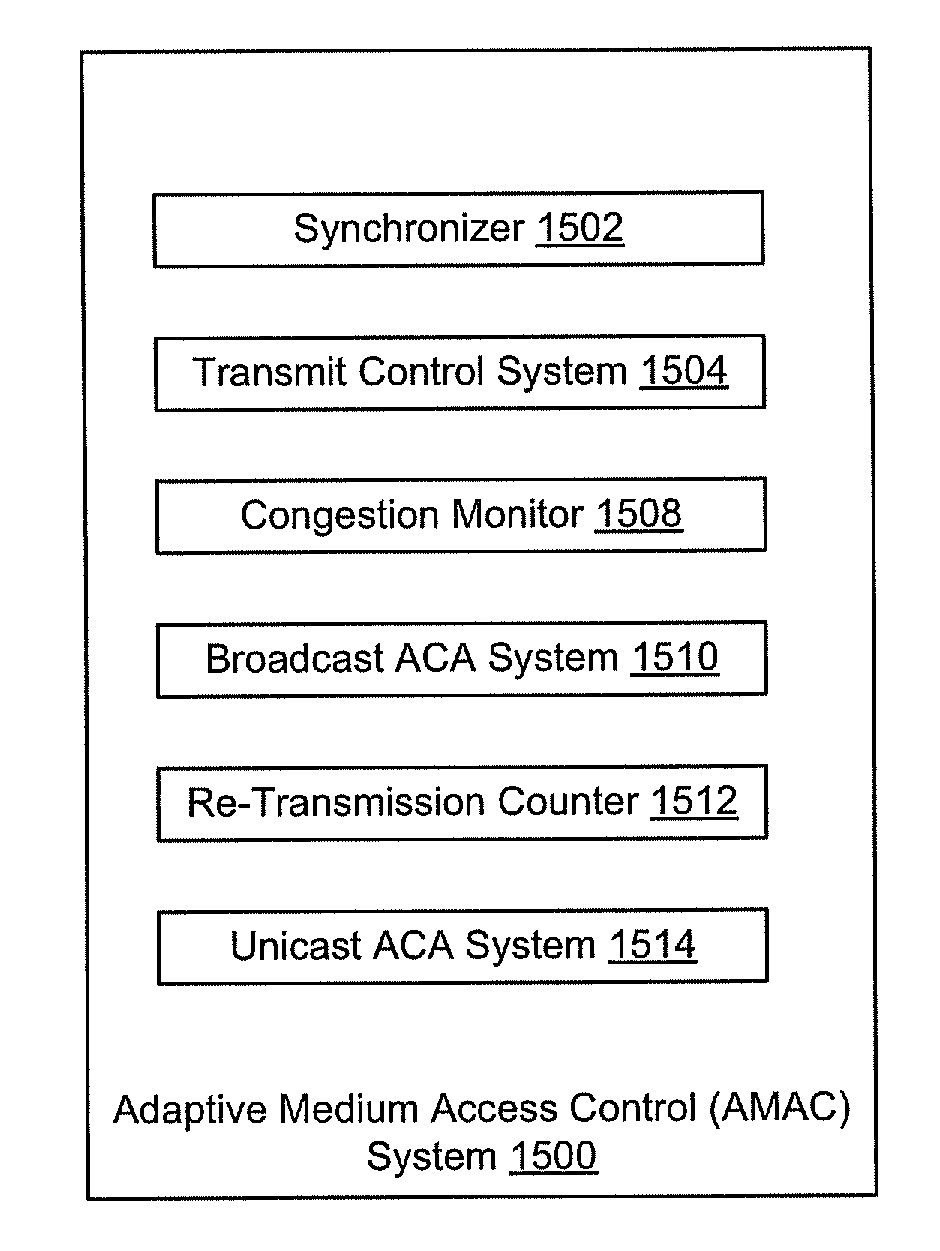

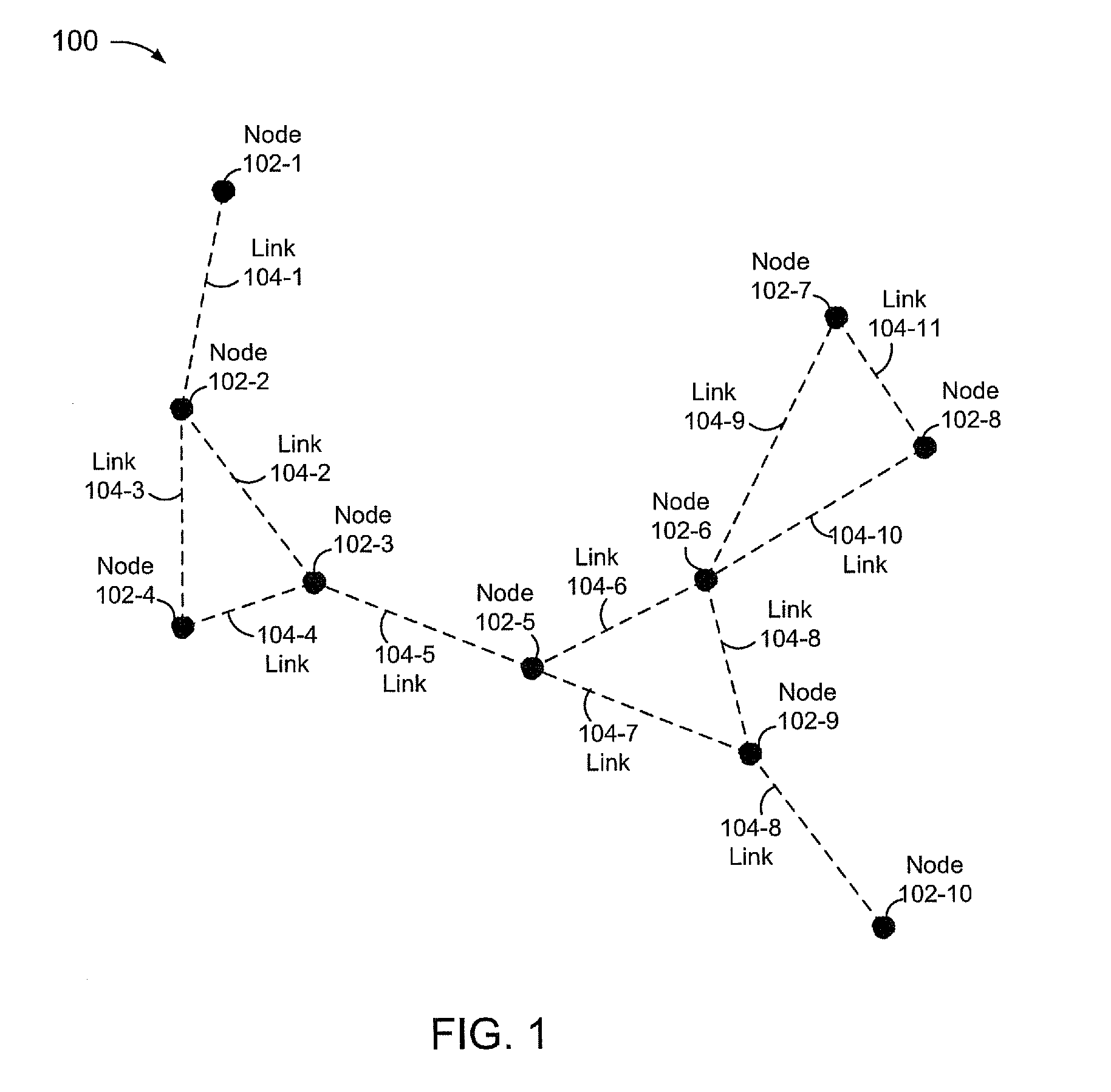

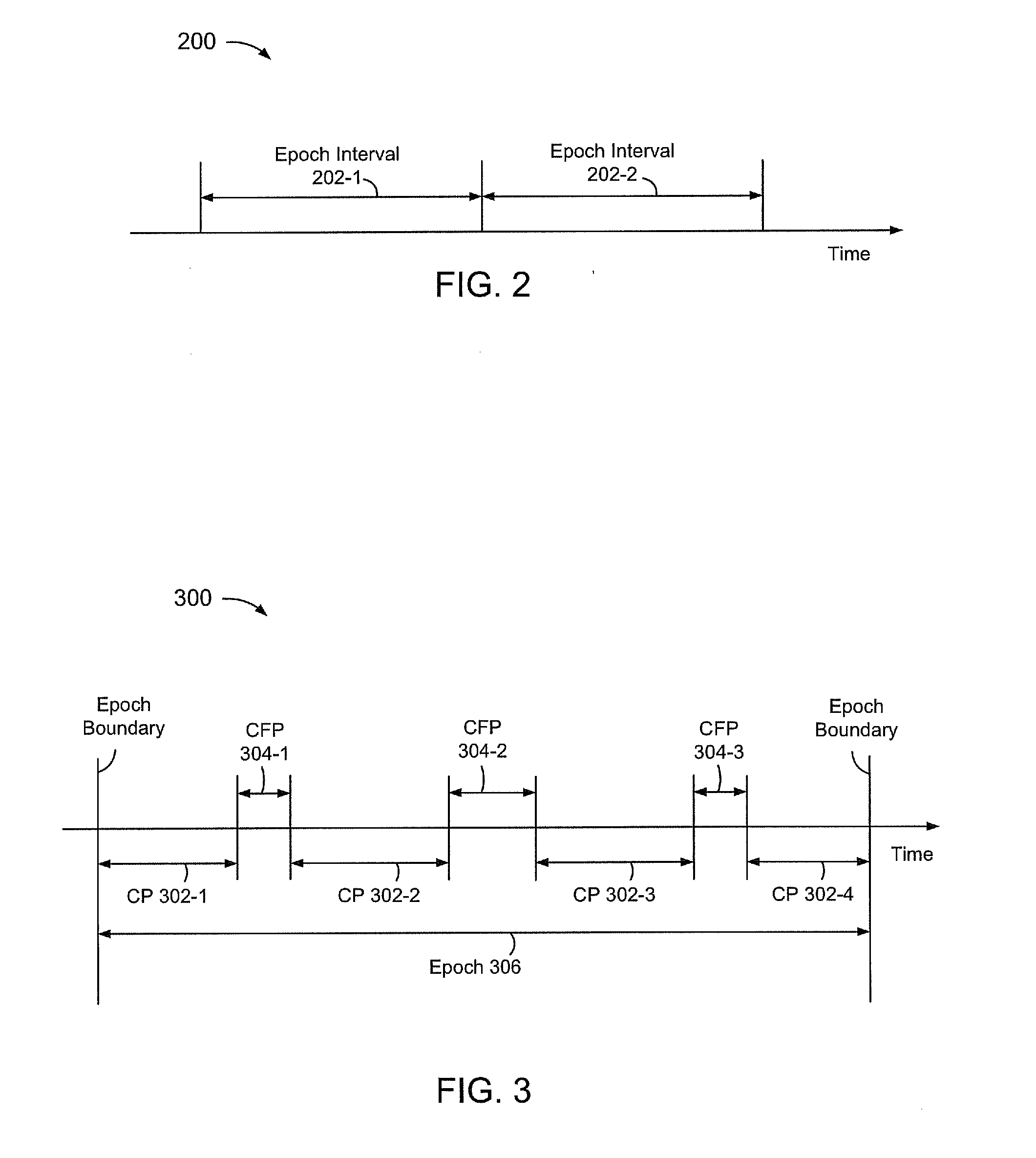

Adaptive Medium Access Control

ActiveUS20120182867A1Controlling the riskError preventionTransmission systemsPerformance enhancementTraffic flow

Bandwidth allocation configuration and fully decentralized adaptive medium access control (AMAC) systems and methods with support for time critical applications, spectrum efficiency, scalability enhancements, and fair allocation of bandwidth among nodes sharing a common channel. The methods fully integrate TDMA and CSMA / CA channel access approaches and incorporate adaptive congestion and collisions avoidance scheme to reduce bandwidth wastage and diminish adverse cross layers interactions. AMAC improves support for multi-media traffic while allowing higher transmission incidents from large number of transmitting devices sharing a common channel, with fair distribution of the available bandwidth, to enable improved multi-level-security connectivity over a common multi-hop wireless network, provide end-to-end performance enhancement for constant bit rate traffic, variable bit rate traffic, and distribute bandwidth fairly amongst competing TCP traffic flows that traverse varying length paths in multi-hop ad-hoc wireless networks.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

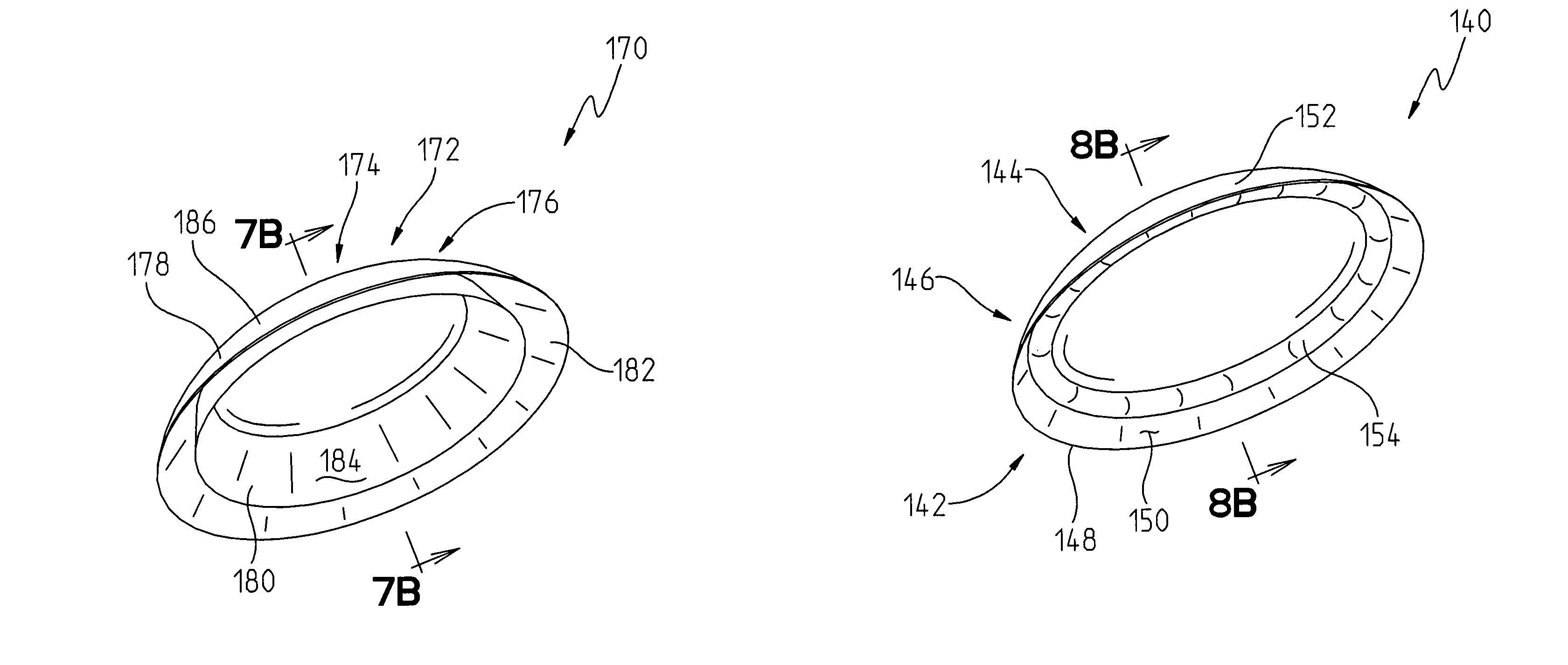

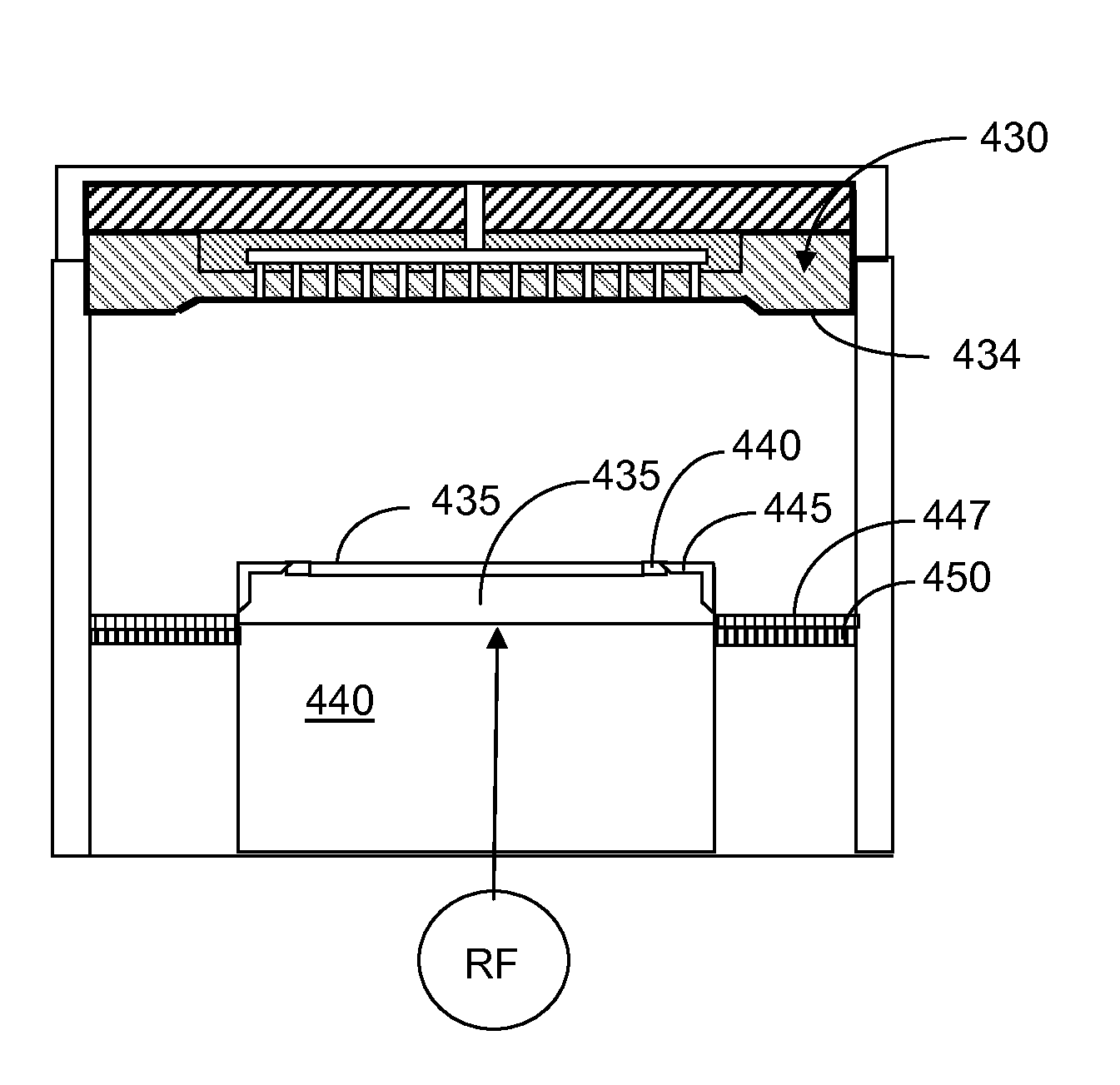

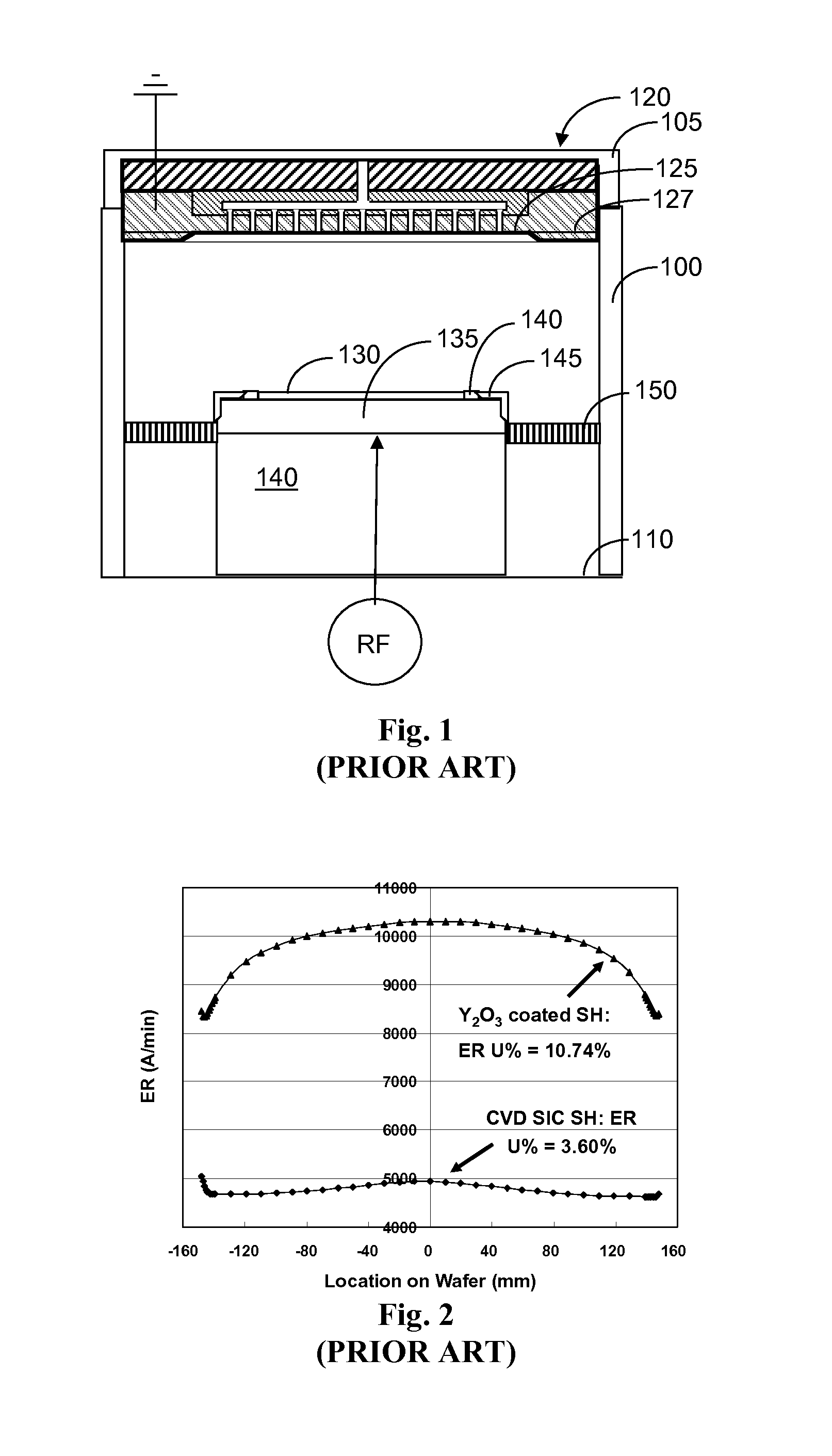

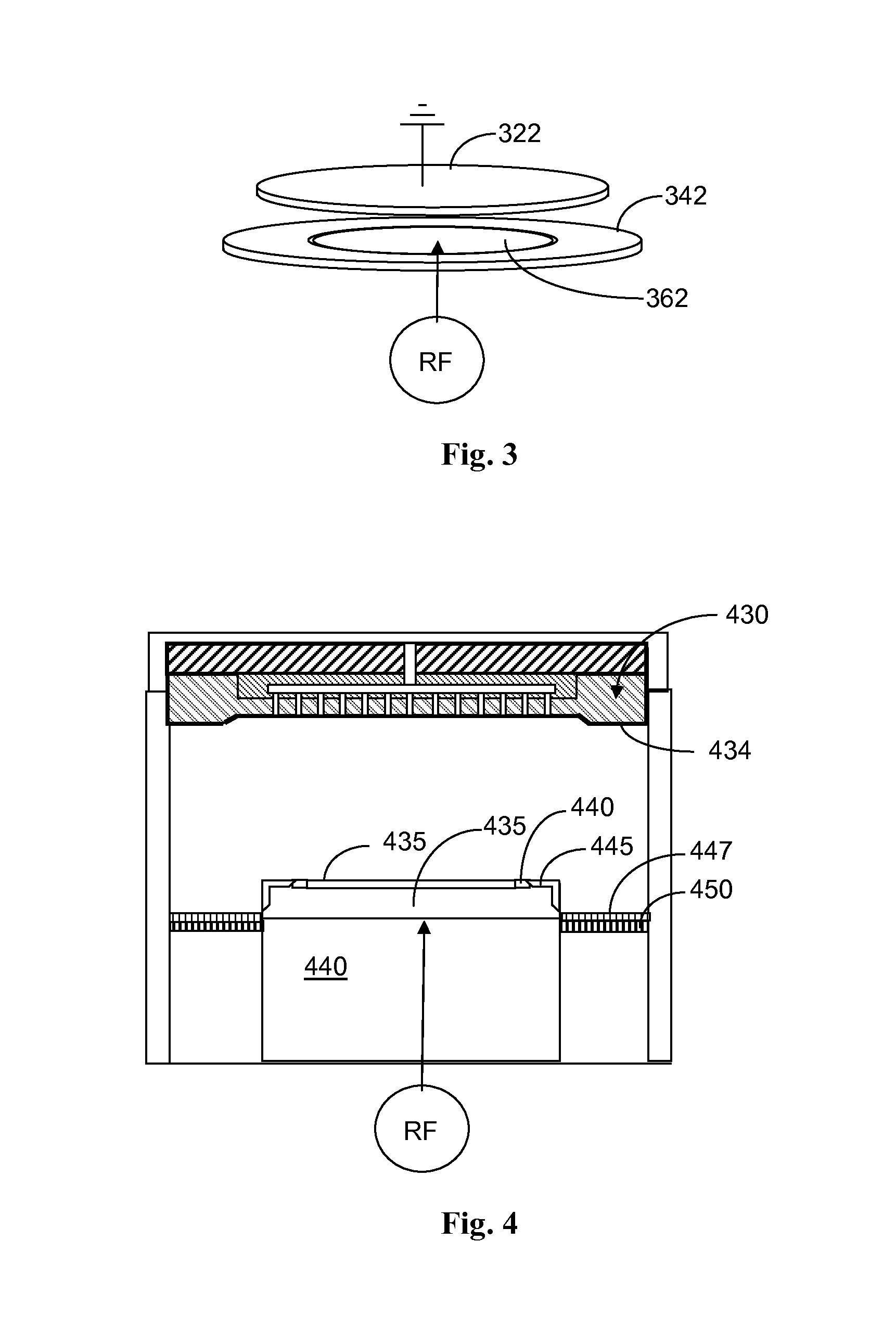

Coating for performance enhancement of semiconductor apparatus

InactiveUS20140116338A1Improve performanceImprove stabilityElectric discharge tubesVacuum evaporation coatingPerformance enhancementPlasma coating

A plasma processing chamber having advanced coating for the showerhead and for an extended bottom electrode. The extended bottom electrode can be formed by one or more of the focus ring, cover ring, and plasma confinement ring. The extended electrode can be formed using a one-piece composite cover ring. The composite cover ring may be made of Al2O3 and include a Y2O3 plasma resistant coating. The plasma confinement ring may include a flow equalization ion shield that may also be provided with the plasma resistant coating. The plasma resistant coating of the extended electrode may have elements matching that of the showerhead.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

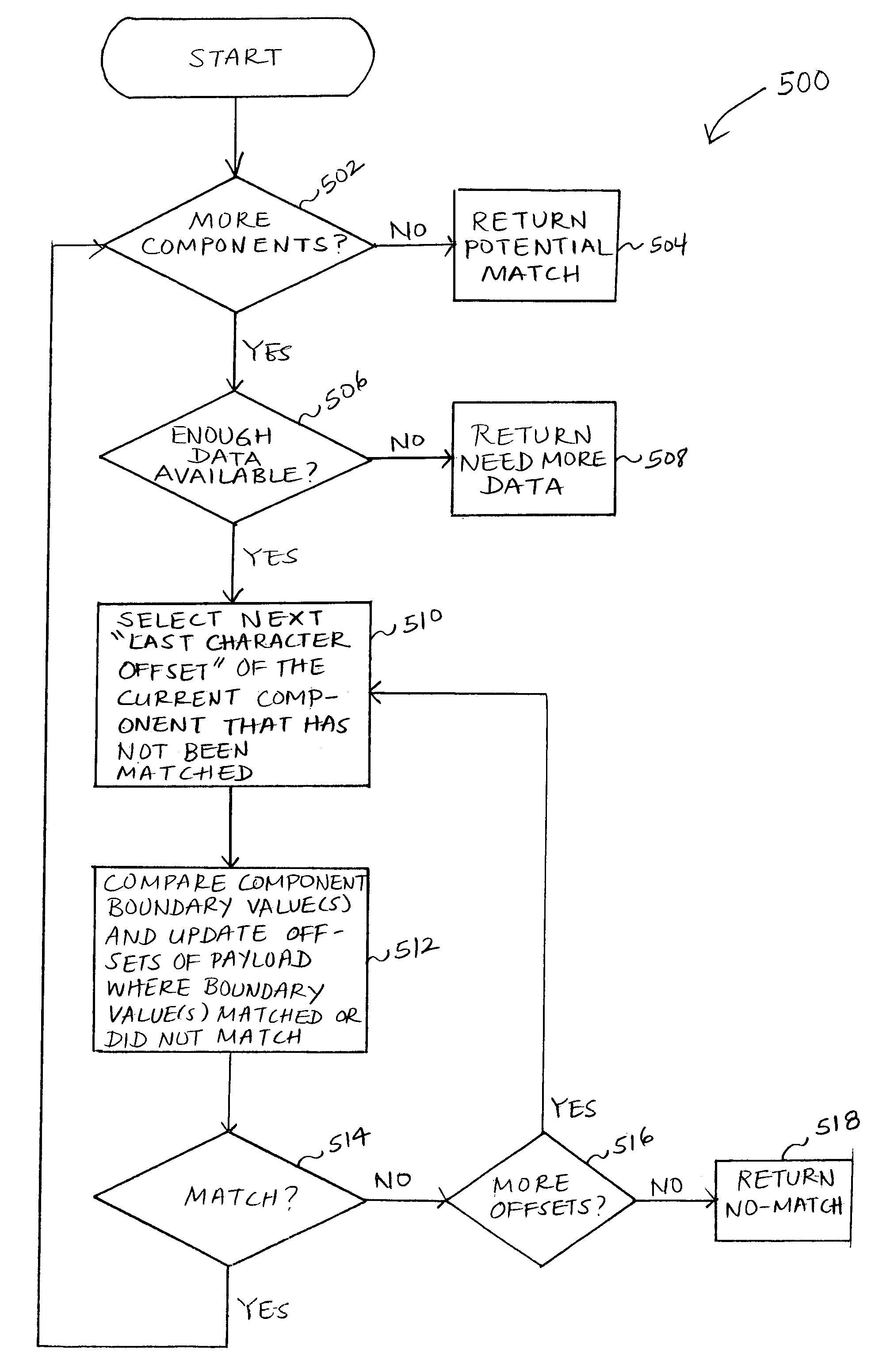

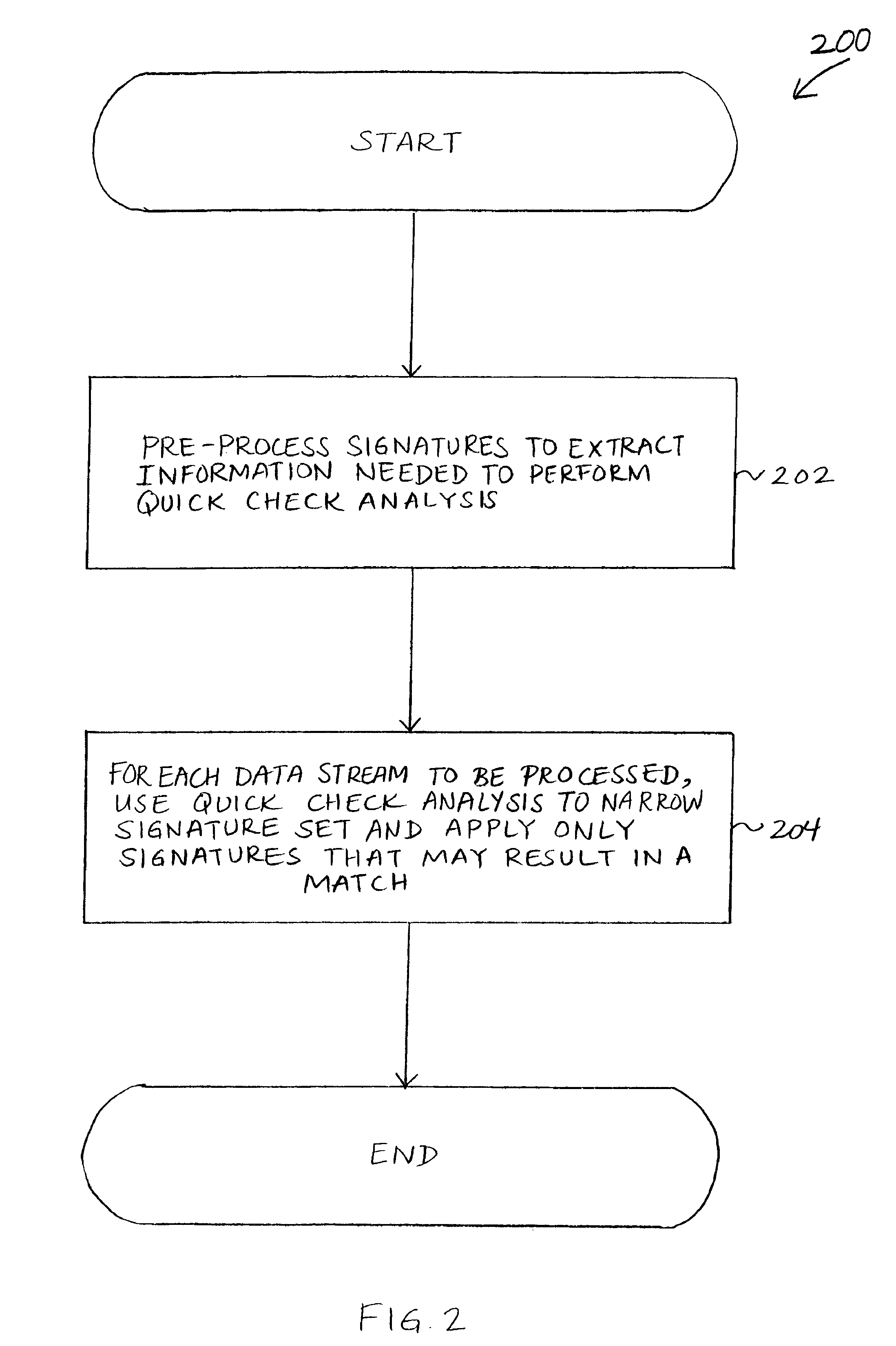

Performance enhancement for signature based pattern matching

InactiveUS7810155B1Memory loss protectionError detection/correctionData streamPerformance enhancement

Performance enhancement for signature based pattern matching may include one or more signature preprocessing steps. The signatures in the signature set may be preprocessed prior to performing pattern matching, including by breaking each signature broken down into one or more components. For at least one of the one or more components, boundary values as well as possible offsets of the boundary values may be identified and matched against a data stream to determine whether the data stream does not match a particular signature, thereby allowing a quick narrowing of the set of signatures to be applied fully to the data stream.

Owner:CA TECH INC

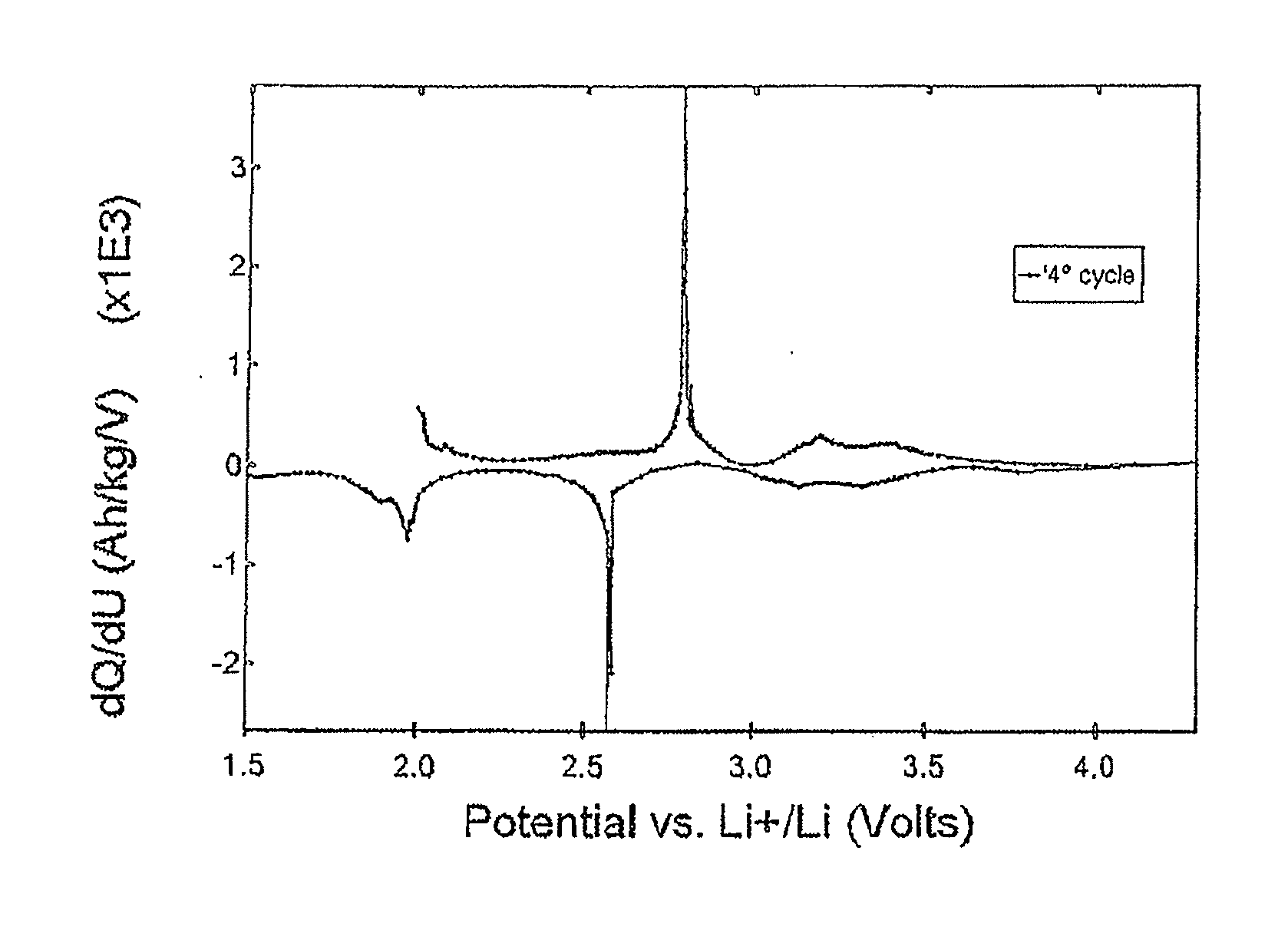

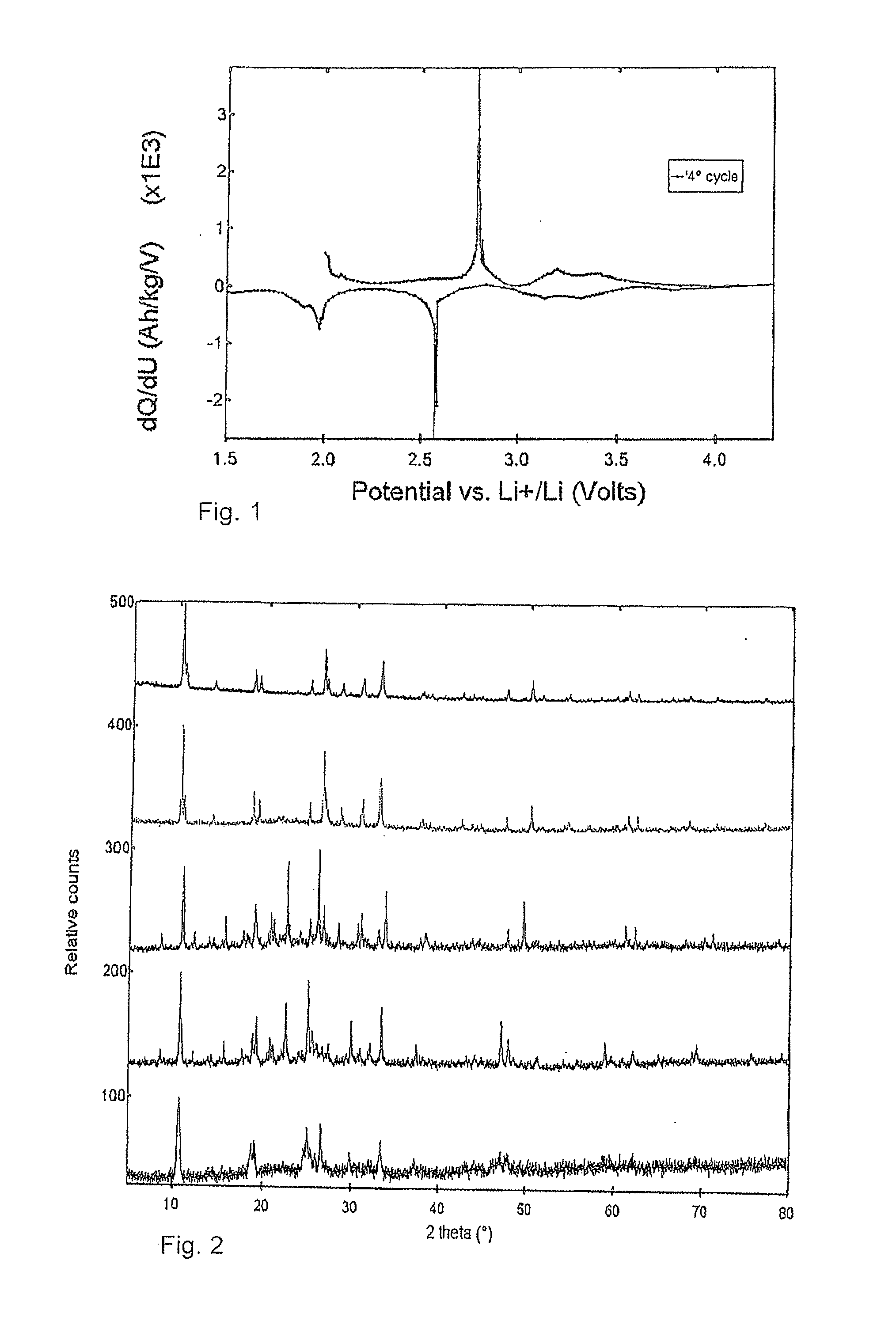

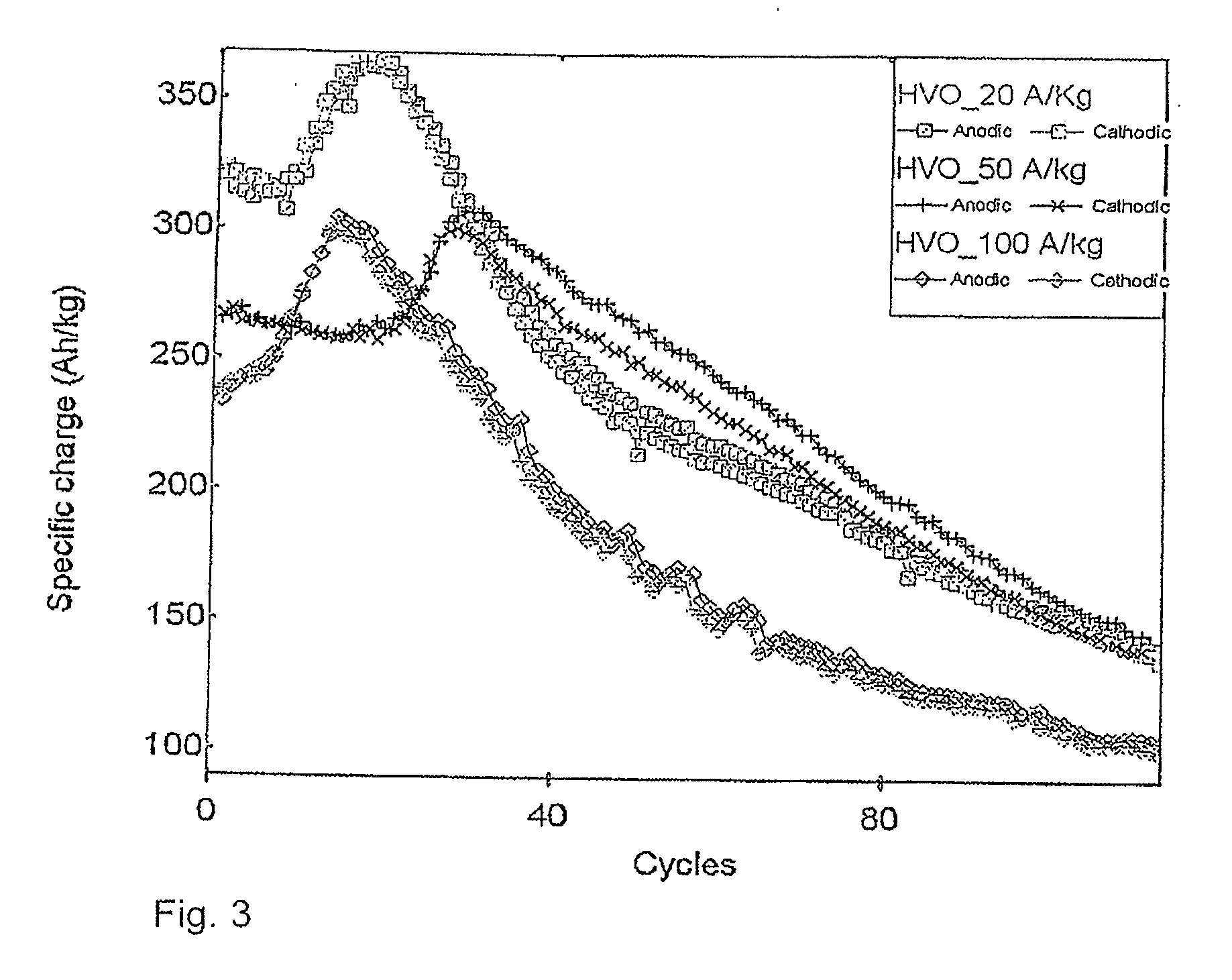

Electrode (anode and cathode) performance enhancement by composite formation with graphene oxide

ActiveUS20120100402A1Low and reduced matrix contentHigh matrix conductivityMaterial nanotechnologyBatteries circuit arrangementsFiberPerformance enhancement

Described is an electrode comprising and preferably consisting of electronically active material (EAM) in nanoparticulate form and a matrix, said matrix consisting of a pyrolization product with therein incorporated graphene flakes and optionally an ionic lithium source. Also described are methods for producing a particle based, especially a fiber based, electrode material comprising a matrix formed from pyrolized material incorporating graphene flakes and rechargeable batteries comprising such electrodes.

Owner:BELENOS CLEAN POWER HLDG

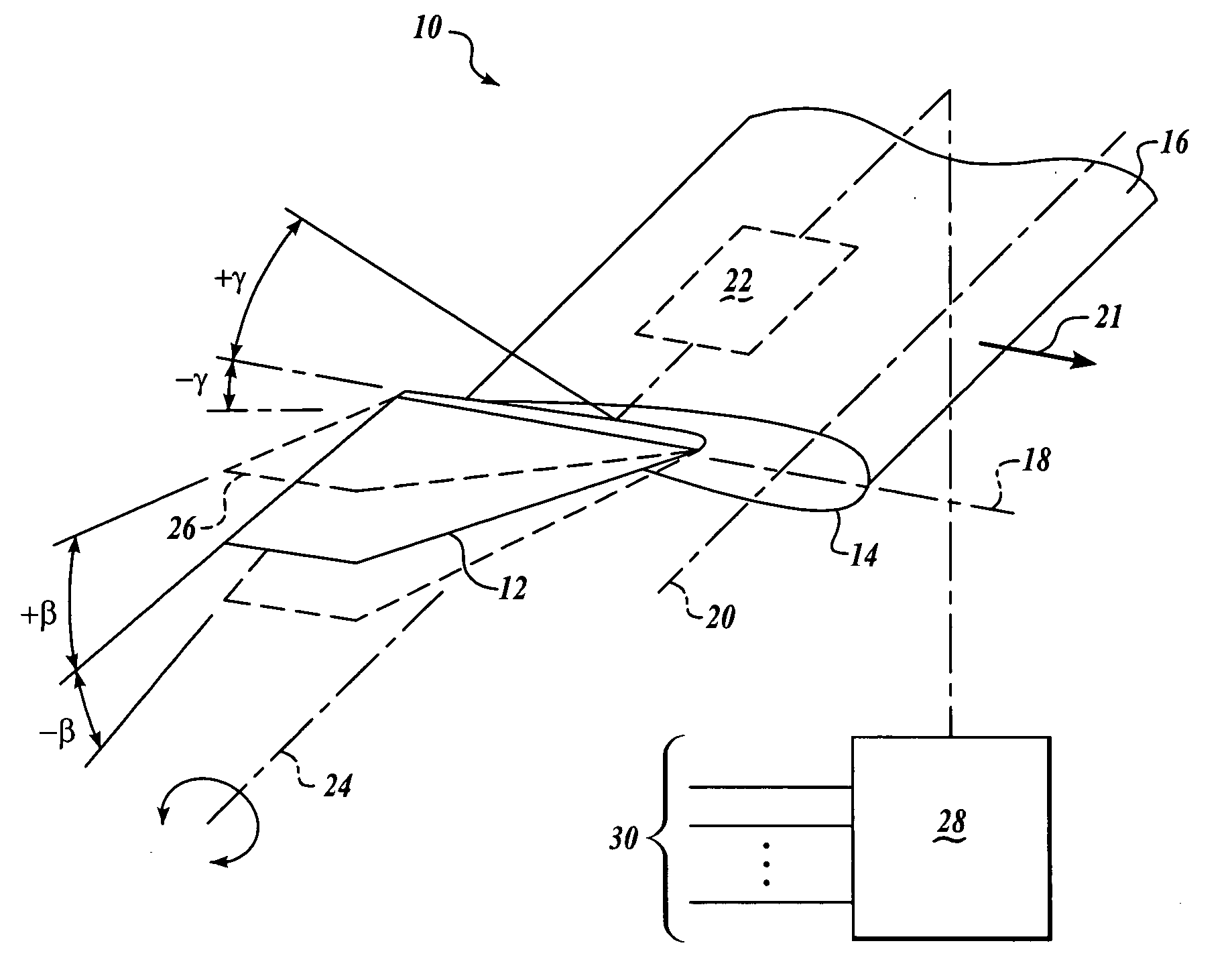

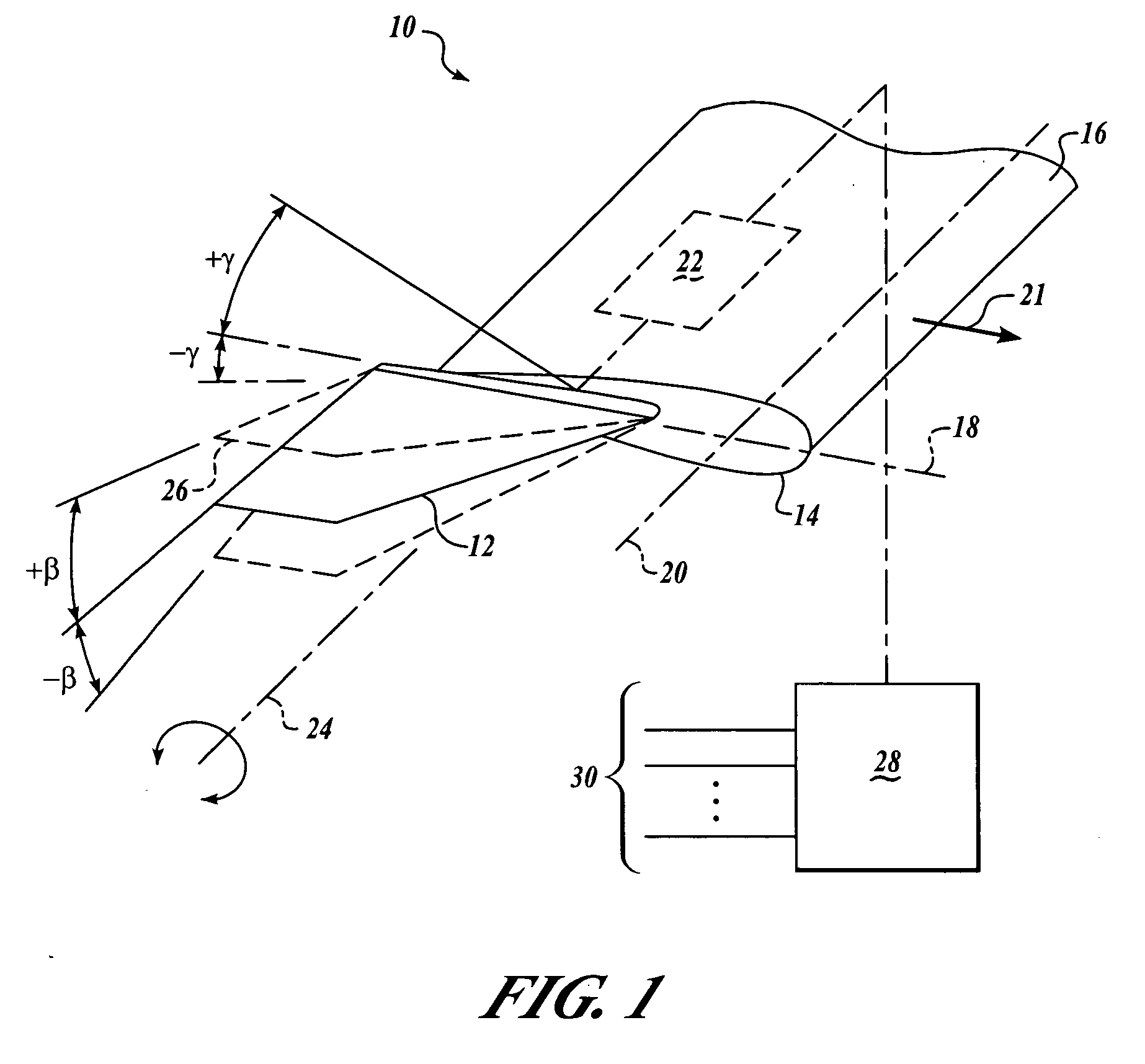

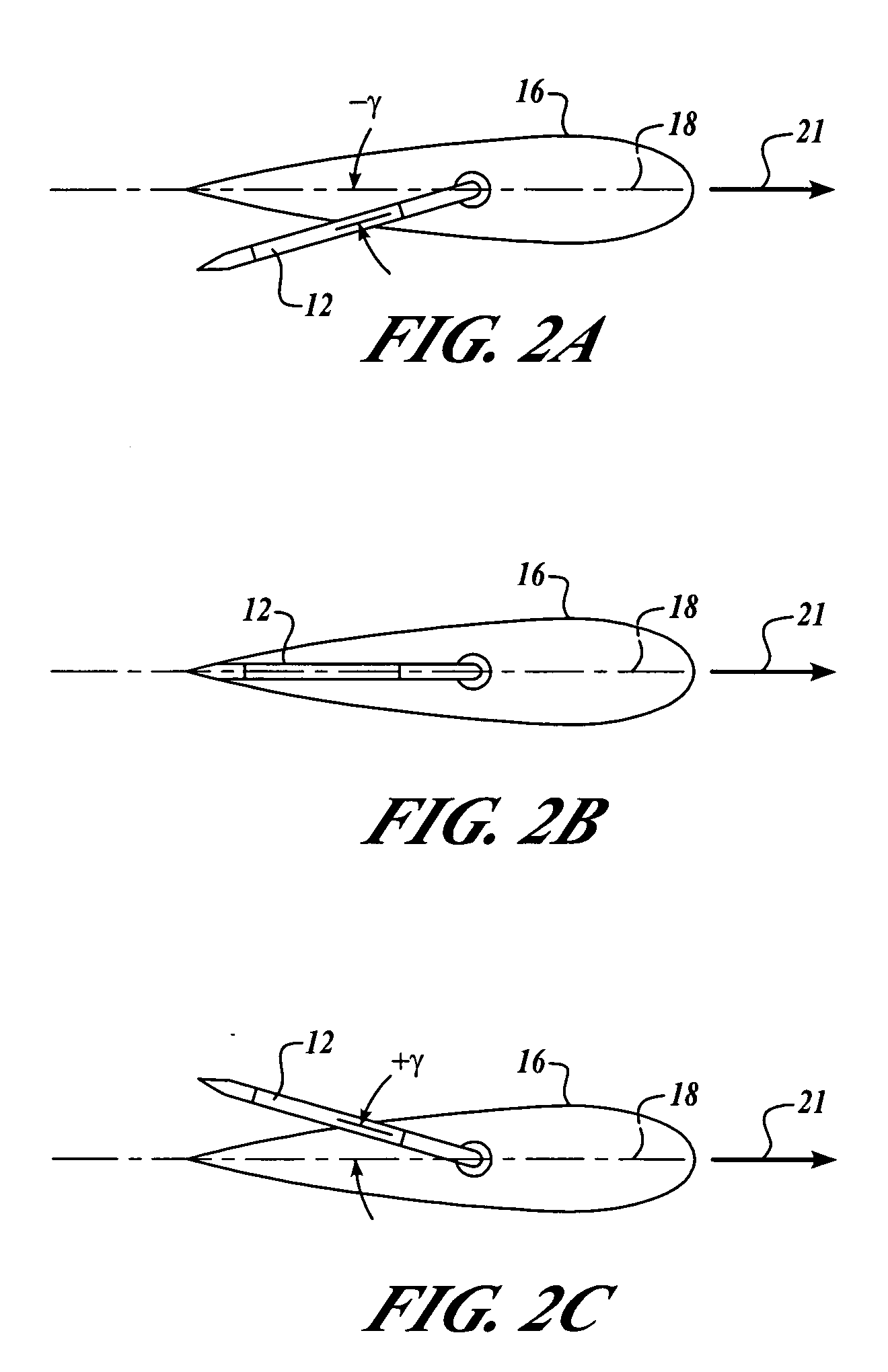

System and method for improved rotor tip performance

InactiveUS20060027703A1Improve performancePropellersPump componentsPerformance enhancementControl system

The present invention discloses systems and methods for the performance enhancement of rotary wing aircraft through reduced torque, noise and vibration. In one embodiment, a system includes a sail having an aerodynamic shape positioned proximate to a tip of the rotor blade. An actuator may be configured to rotate the sail relative to the blade tip. a A control system receives information from a rotorcraft system and commands the actuator to rotate the sail to a predetermined favorable rotor blade operating condition. In another embodiment, a method includes configuring the rotorcraft in a selected flight condition, communicating input signals to a control system operable to position sails coupled to tips of blades of a rotor assembly, processing the input signals according to a constraint condition to generate sail positional information, and transferring the sail positional information to the sail.

Owner:THE BOEING CO

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com