Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

706 results about "Circuit performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method of maximizing integrated circuit manufacturing yield with fabrication process simulation driven layout optimization

InactiveUS20080046846A1Maximizing manufacturing yieldYield maximizationCAD circuit designSoftware simulation/interpretation/emulationIntegrated circuit manufacturingEngineering

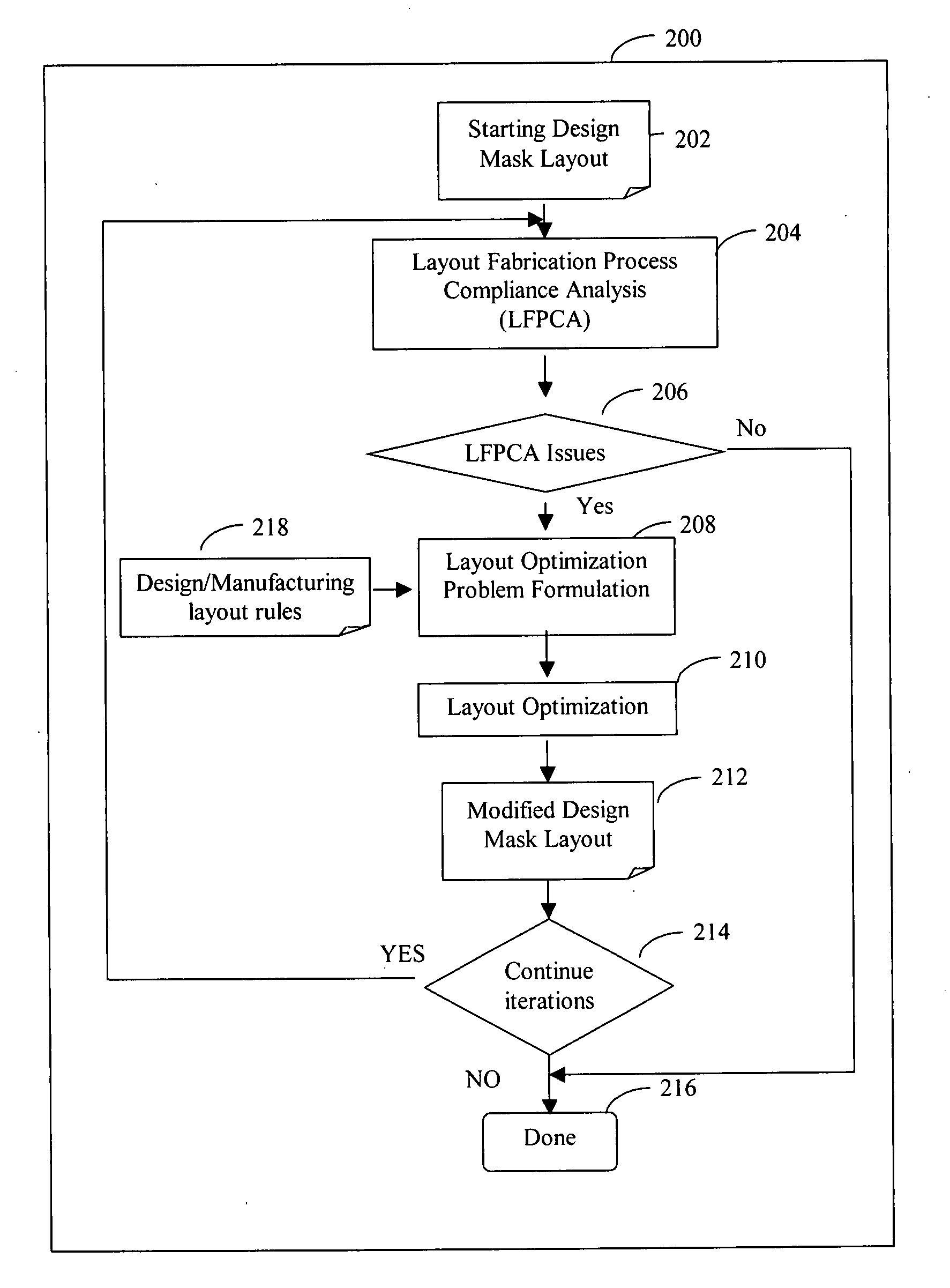

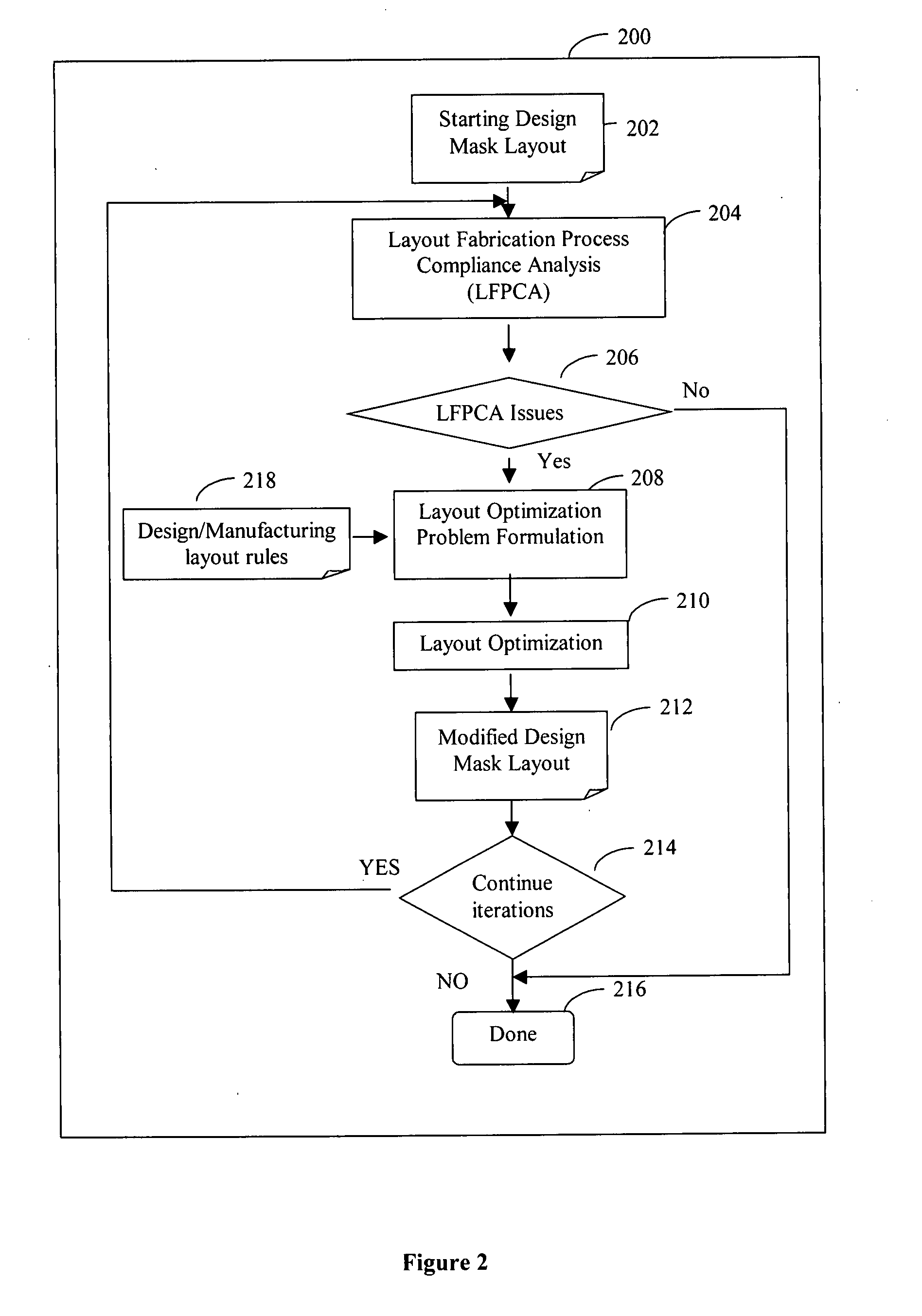

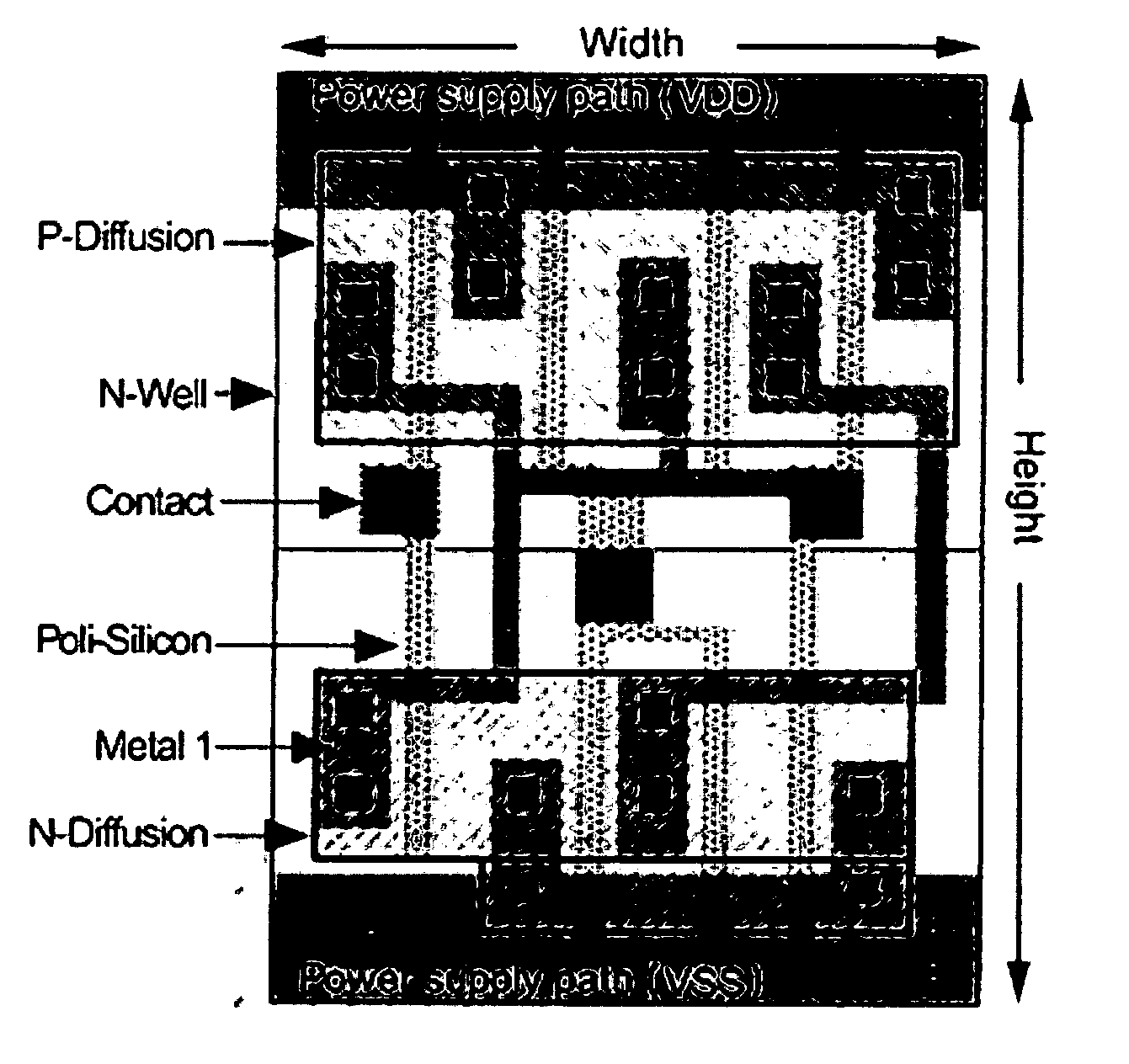

A system and a method of maximizing the manufacturing yield of integrated circuit (“IC”) design using IC fabrication process simulation driven layout optimization is described. An IC design layout is automatically modified through formulation of a layout optimization problem utilizing the results of layout fabrication process compliance analysis tools. The modification of layout is performed adaptively and iteratively to make an IC layout less susceptible to yield issues while maintaining design rule correctness and minimal circuit performance impact.

Owner:CHEW MARKO P +1

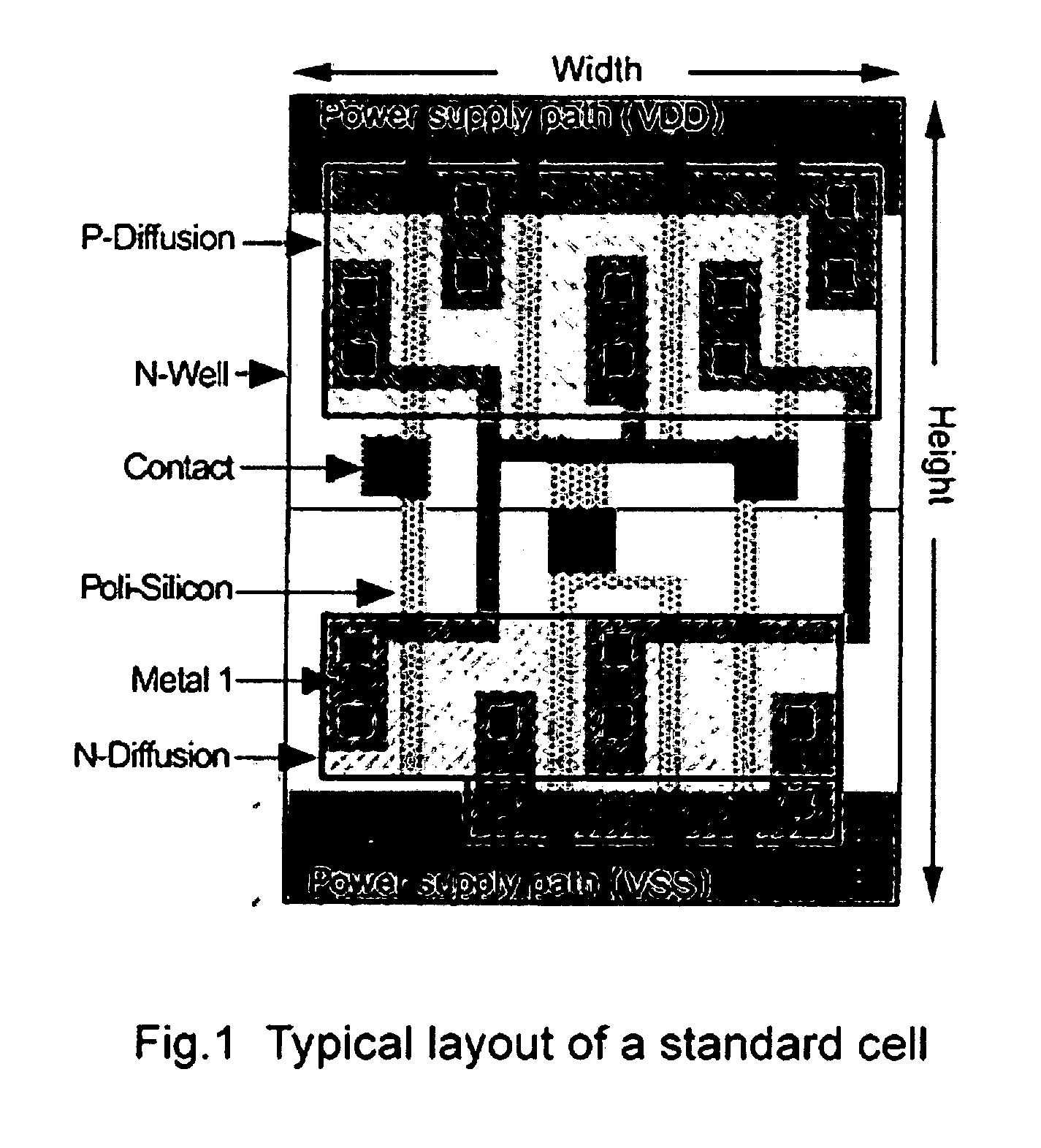

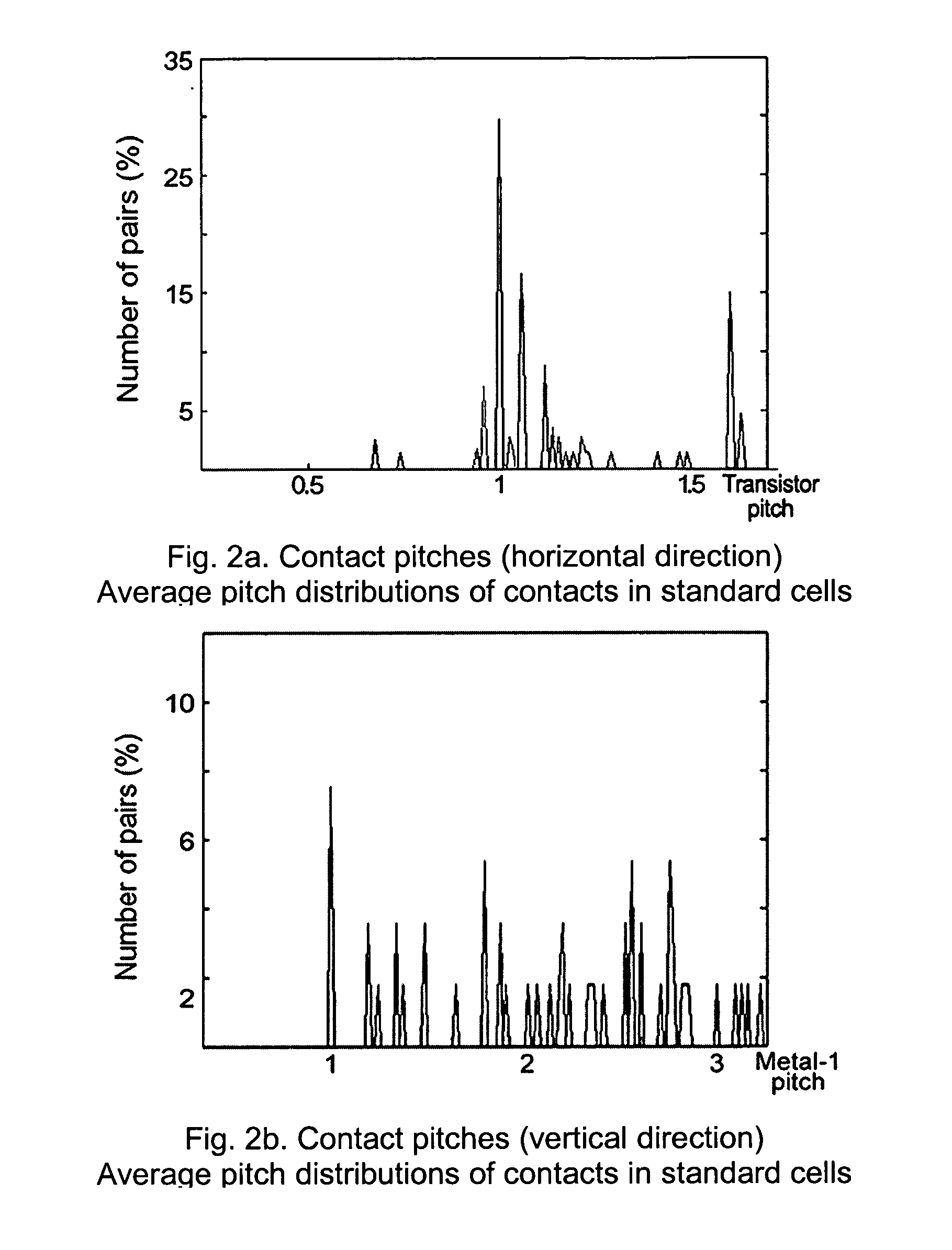

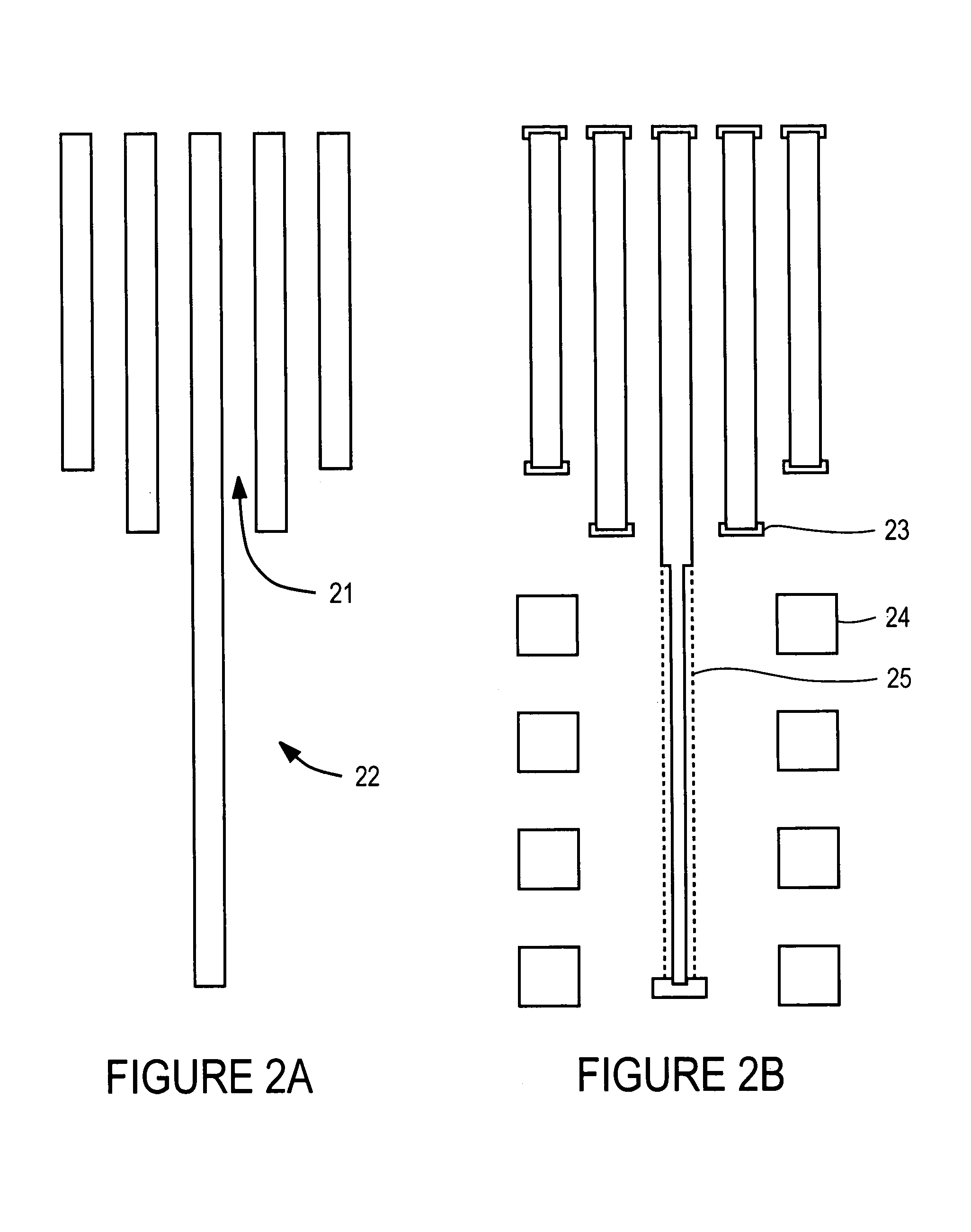

Rectangular contact lithography for circuit performance improvement and manufacture cost reduction

ActiveUS20050196685A1Reduce manufacturing costLot of restrictionPhoto-taking processesSemiconductor/solid-state device manufacturingManufacturing cost reductionEngineering

An optical lithography method is disclosed that uses double exposure of a reusable template mask and a trim mask to fabricate regularly-placed rectangular contacts in standard cells of application-specific integrated circuits (ASICs). A first exposure of the reusable template mask with periodic patterns forms periodic dark lines on a wafer and a second exposure of an application-specific trim mask remove the unwanted part of the dark lines and the small cuts of the dark lines left form the rectangular regularly-placed contacts. All contacts are placed regularly in one direction while unrestrictedly in the perpendicular direction. The regular placement of patterns on the template mask enable more effective use of resolution enhancement technologies, which in turn allows a decrease in manufacturing cost and the minimum contact size and pitch. Since there is no extra application-specific mask needed comparing with the conventional lithography method for unrestrictedly-placed contacts, the extra cost is kept to the lowest. The method of the invention can be used in the fabrication of standard cells in application-specific integrated circuits (ASICs) to improve circuit performance and decrease circuit area and manufacturing cost.

Owner:THE UNIVERSITY OF HONG KONG

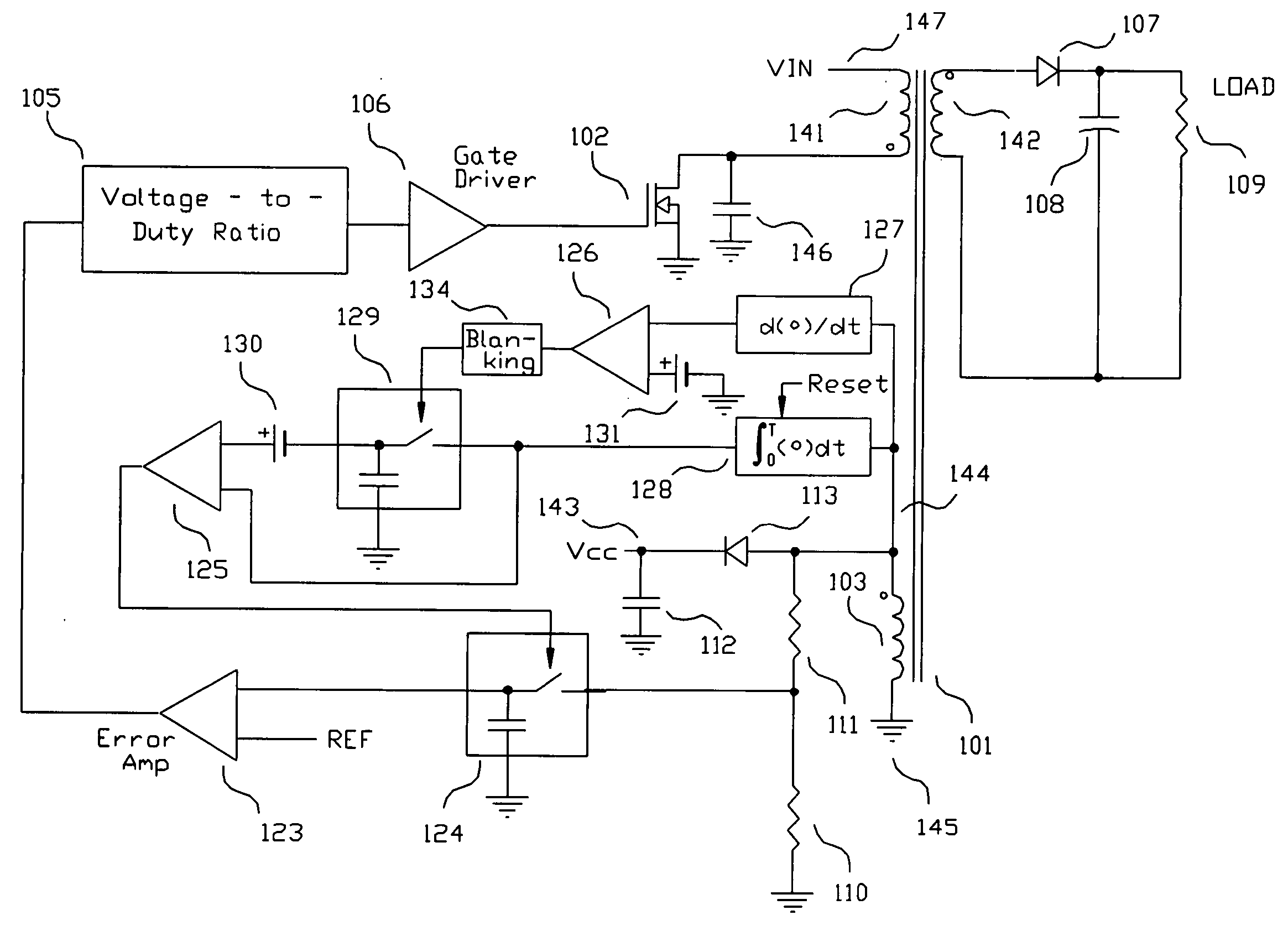

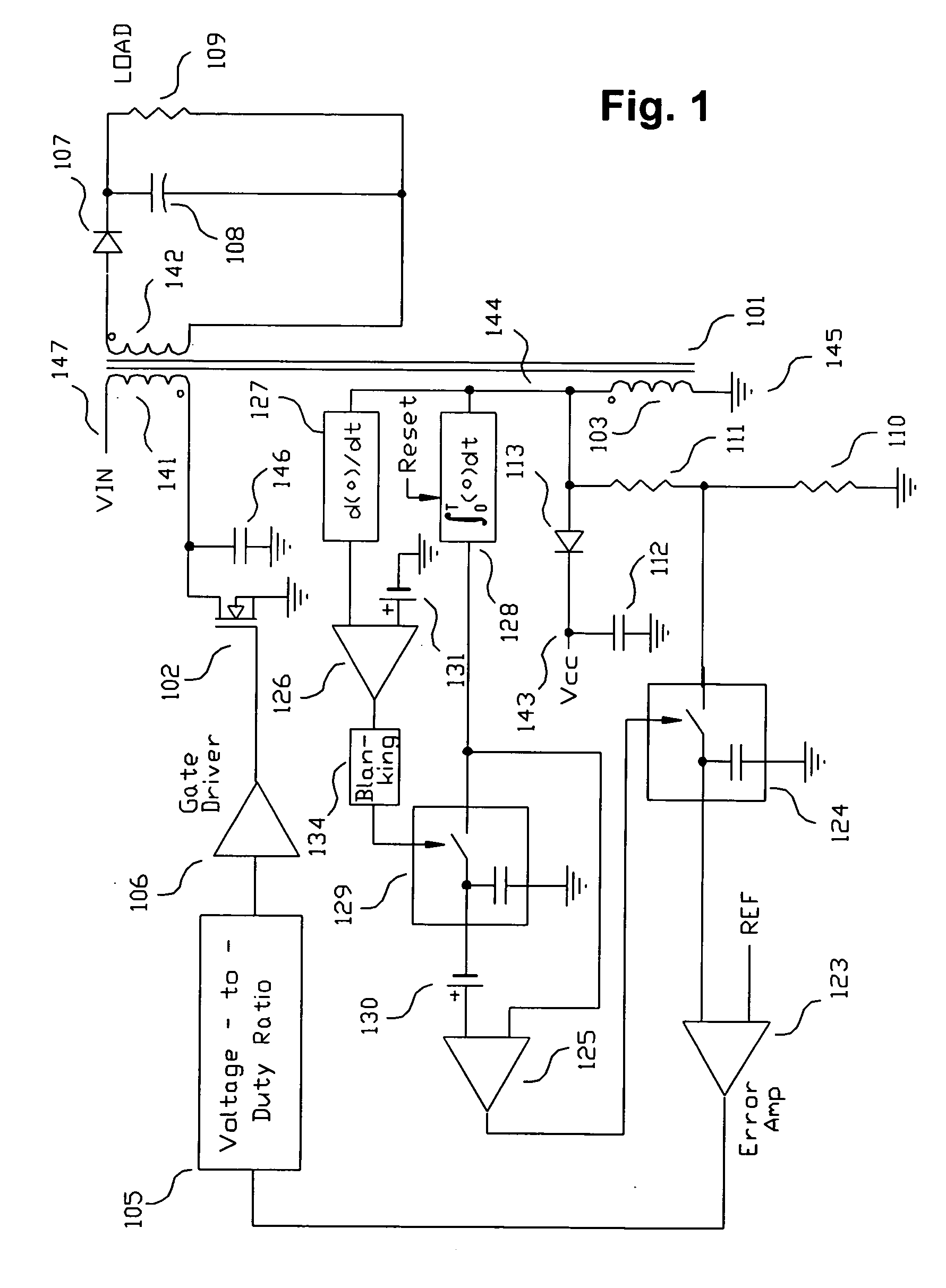

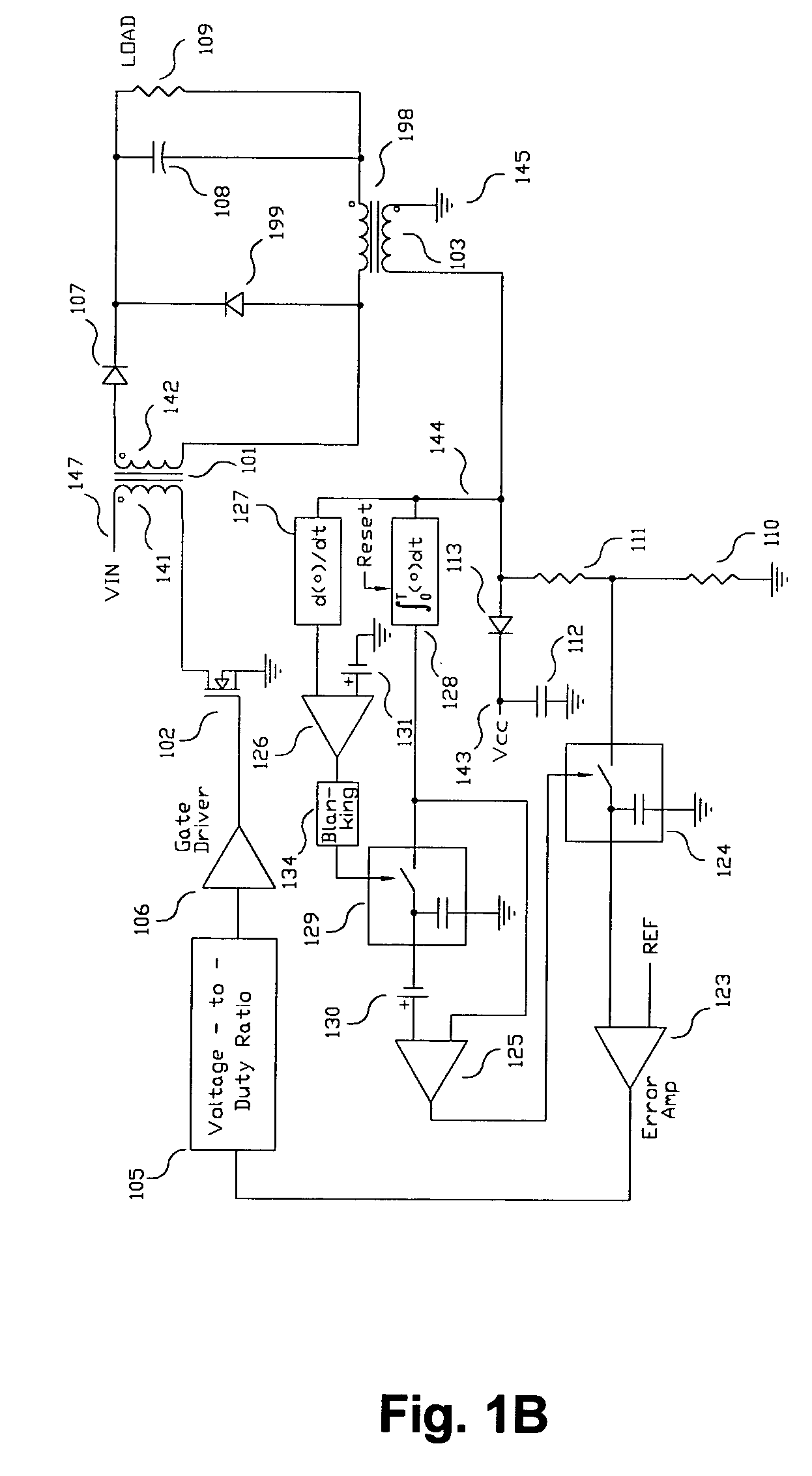

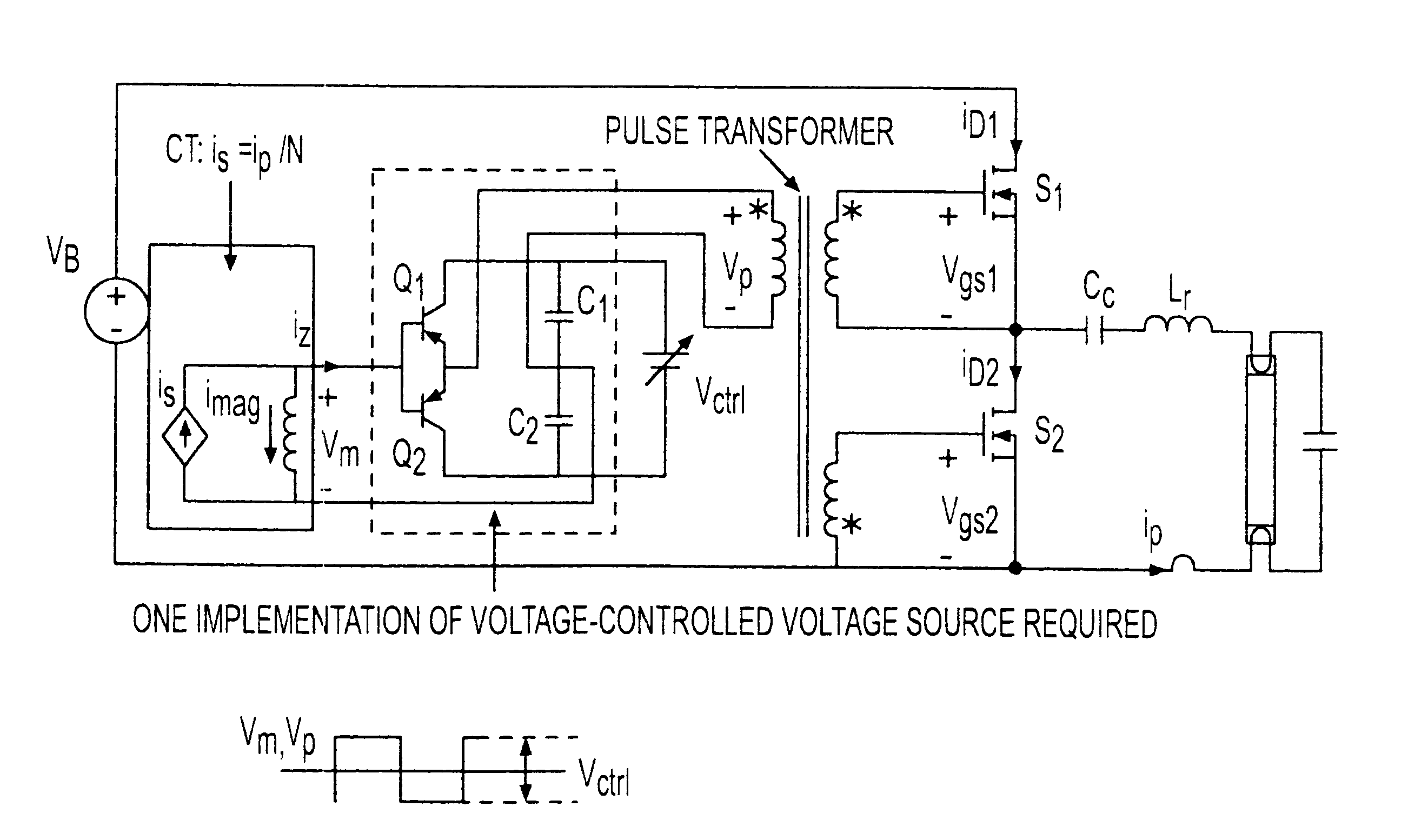

Switching power converter and method of controlling output voltage thereof using predictive sensing of magnetic flux

ActiveUS20050073862A1Improve immunityDc-dc conversionElectric variable regulationIntegratorSwitching cycle

A switching power converter and method of controlling an output voltage thereof using predictive sensing of magnetic flux provides a low-cost switching power converter via primary-side control using a primary-side winding. The power converter has improved immunity to parasitic phenomena and other variations within the power converter components. An integrator is used to generate a voltage analog that represents magnetic flux within a power magnetic element via an integration of a voltage on a primary-side winding of the power magnetic element. A detection circuit detects the end of a half-cycle of post-conduction resonance that occurs in the power magnetic element subsequent to the energy level in the power magnetic element reaching zero. The voltage of the integrator is stored at the end of the post-conduction resonance half-cycle and is used to determine a sampling point prior to or equal to the start of post-conduction resonance in a subsequent switching cycle of the power converter (which is the predicted zero-energy storage point of the power magnetic element). The primary-side winding voltage is then sampled at the sampling point, providing an indication of the output voltage of the power converter. By predicting the zero-magnetic-energy storage point, the output voltage of a power converter operating in discontinuous or boundary conduction mode can be accurately controlled without being affected by parasitic phenomena or variations in circuit performance over time, input voltage and temperature.

Owner:MICROCHIP TECH INC

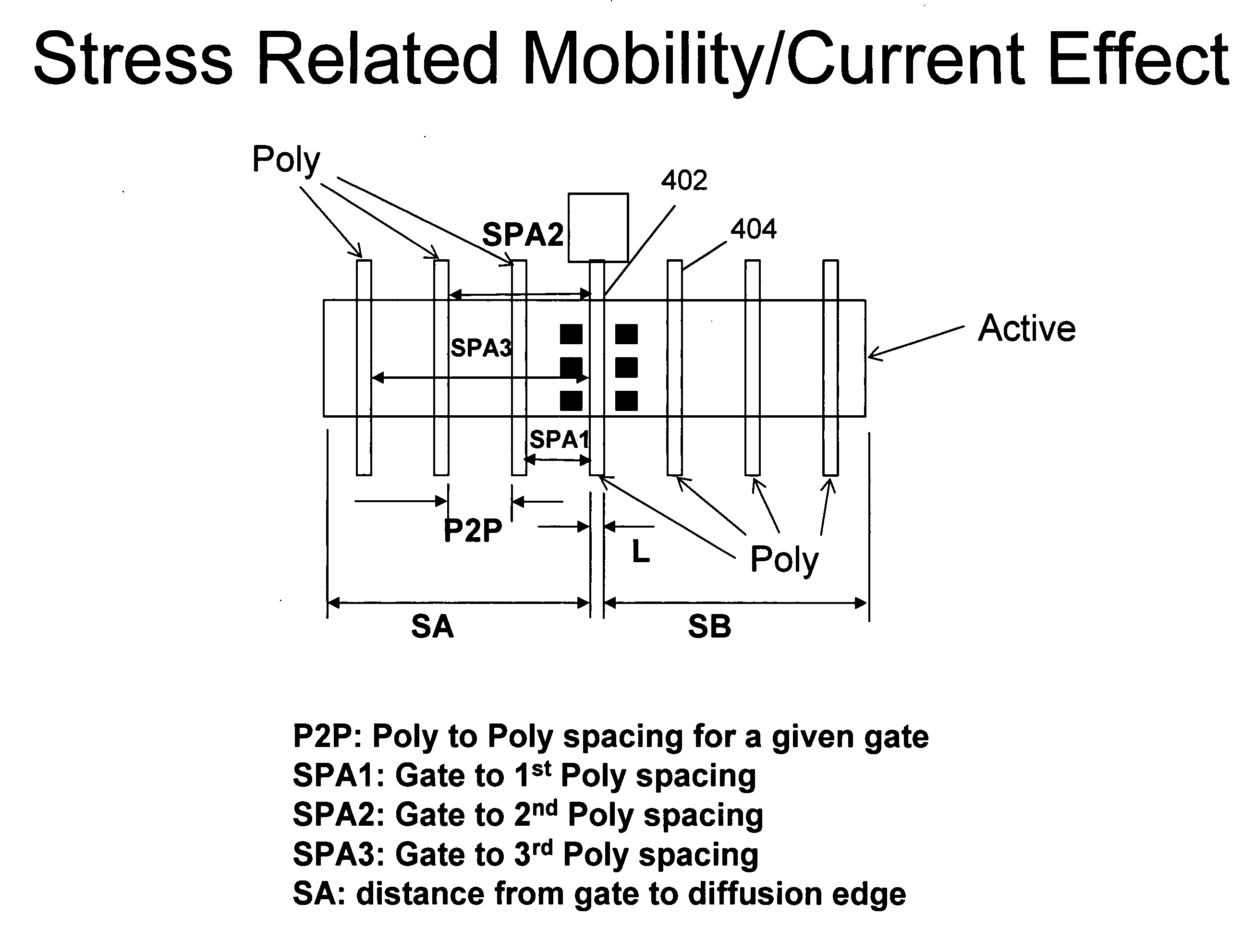

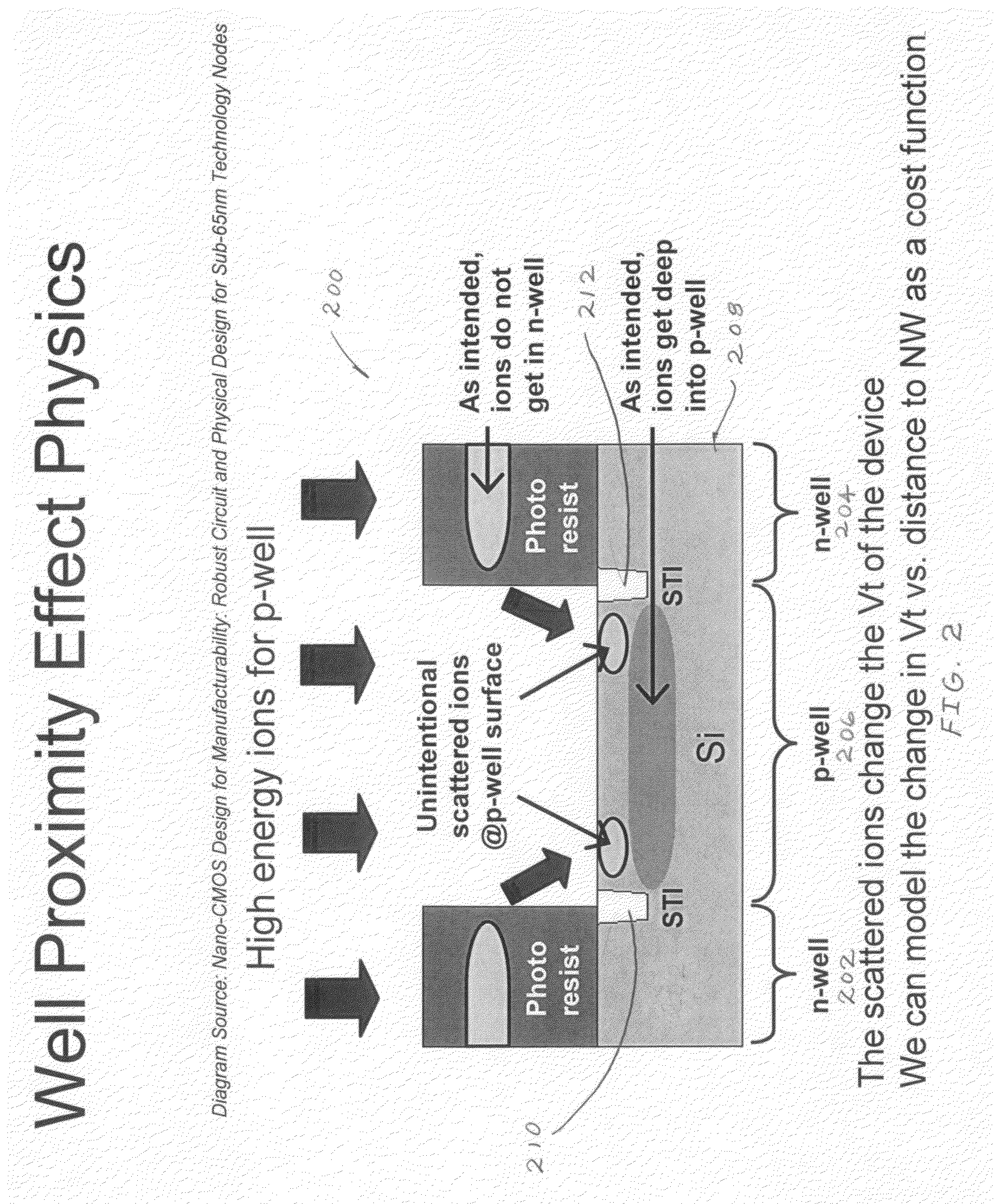

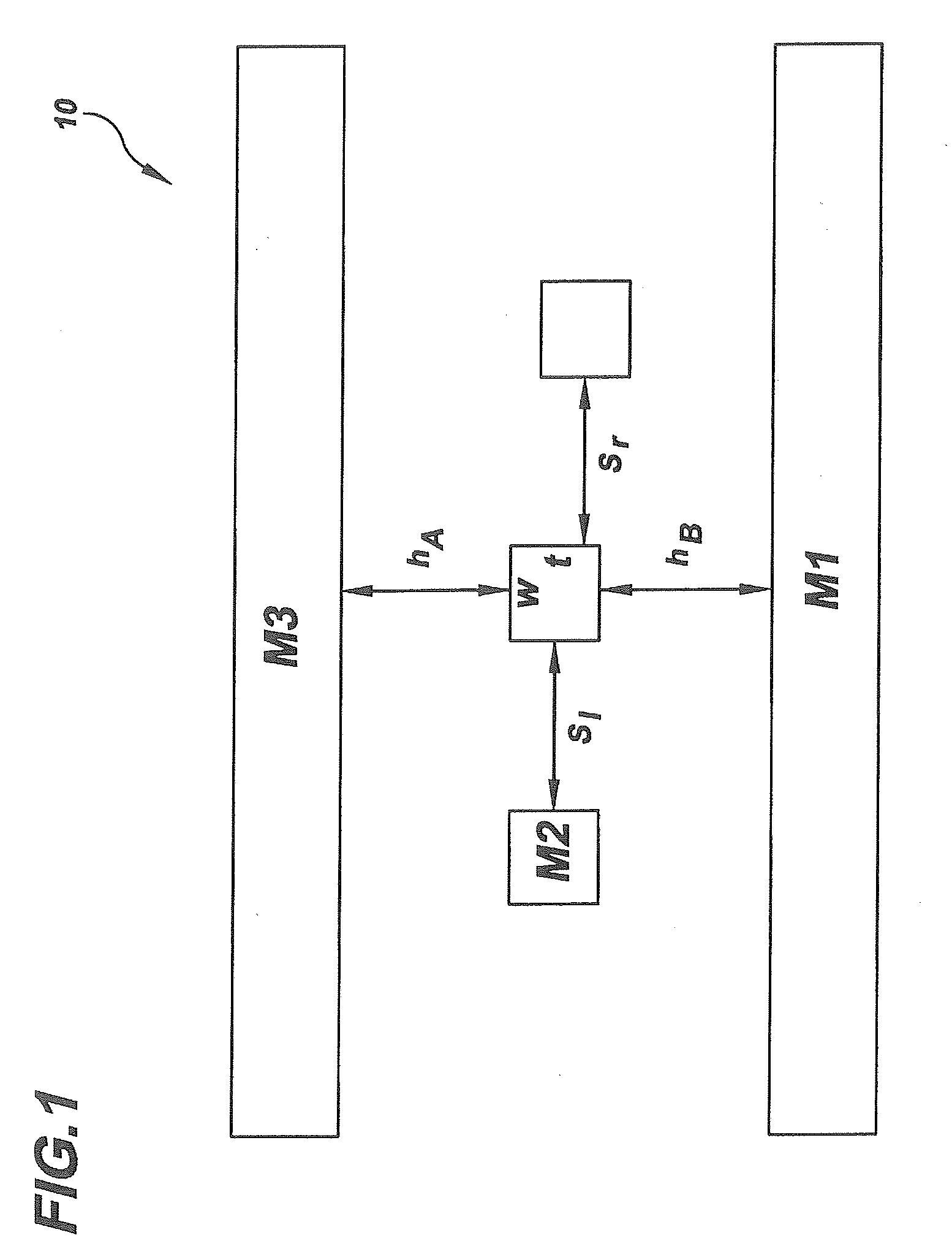

Automated optimization of an integrated circuit layout using cost functions associated with circuit performance characteristics

InactiveUS20100100856A1Low variabilityImprove performanceCAD circuit designMulti-objective optimisationLocal patternIntegrated circuit layout

An integrated circuit (IC) design system and method provide an optimization of a layout of an integrated circuit wherein an assessment is taken into account of the circuit performance characteristics and the layout of the IC design. The system and method assess associated circuit performance characteristics, each as a cost function of a local pattern of shapes in an initial circuit layout, aggregate cost functions of the associated circuit performance characteristics to derive an integral performance number associated to the initial global circuit layout, perturb the integral performance number by varying the global circuit layout, and select perturbations that optimize the performance number, so as to optimize the global circuit layout. Assessment is taken into account of the circuit performance characteristics based on the layout and the interdependence of the circuit performance characteristics for the IC design. The physical process related effects such as well proximity effect and stress / strain engineering and / or performance parameters such as the P-N transistor size ratio are taken into account to achieve optimization.

Owner:MITTAL ANURAG

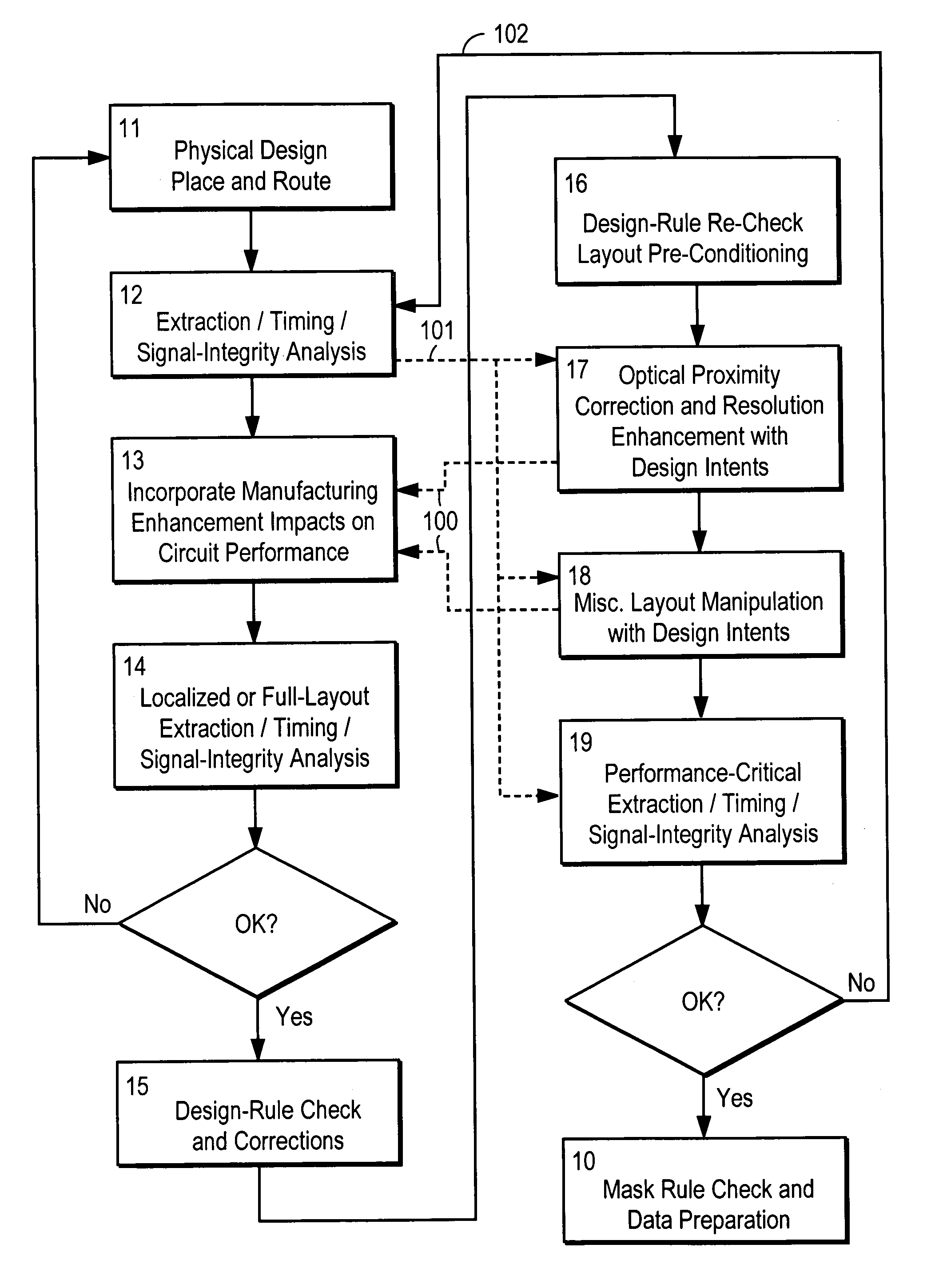

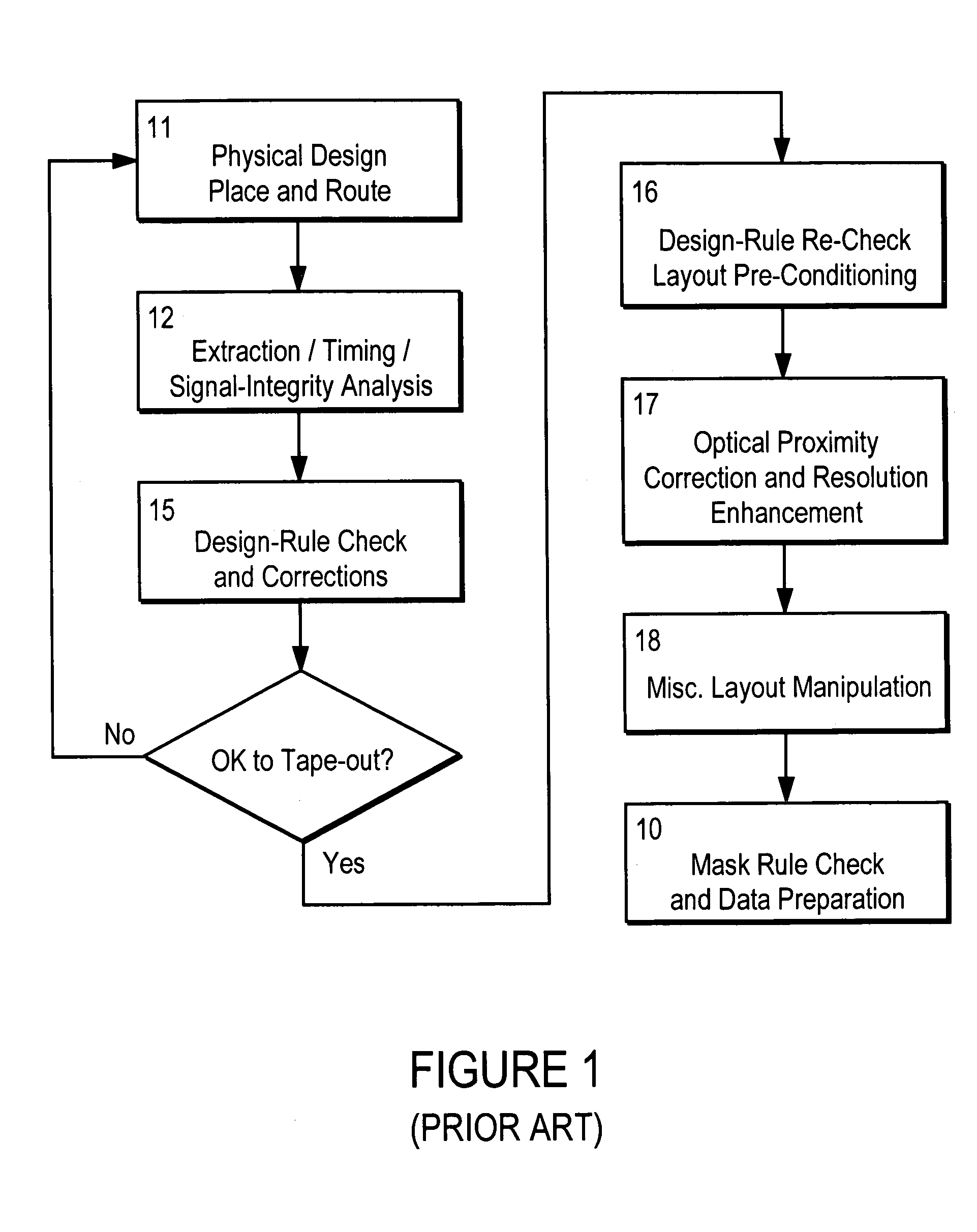

Method and platform for integrated physical verifications and manufacturing enhancements

InactiveUS20050044514A1High storageHigh memoryDigital computer detailsComputer aided designPhysical verificationEngineering

An automated design for manufacturability platform which provides integrated physical verification and manufacturing enhancement operations. The platform uses an efficient data structure capable of handling and manipulating both layout circuit and geometry characteristics, which permits a wide range of operations such as timing analysis, design-rule checking and optical proximity corrections on a single platform. This feature eliminates the need to translate layout representations between various tools without the requirement of using a common database. Moreover, the platform's common user interface enables encapsulated information exchange between the design and the manufacturing teams, permiting early consideration of manufacturing distortion or enhancement impact on circuit performance.

Owner:RPX CORP

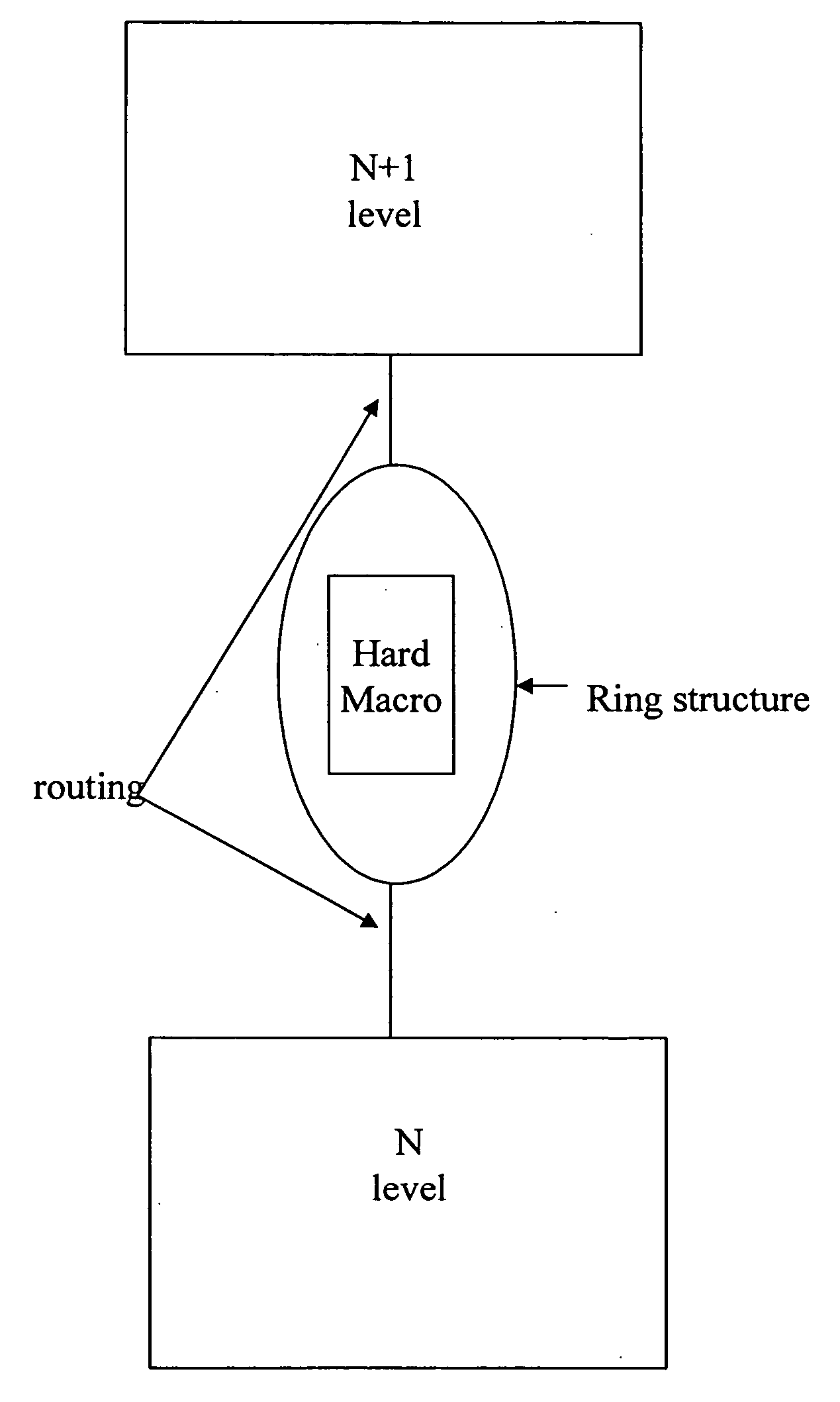

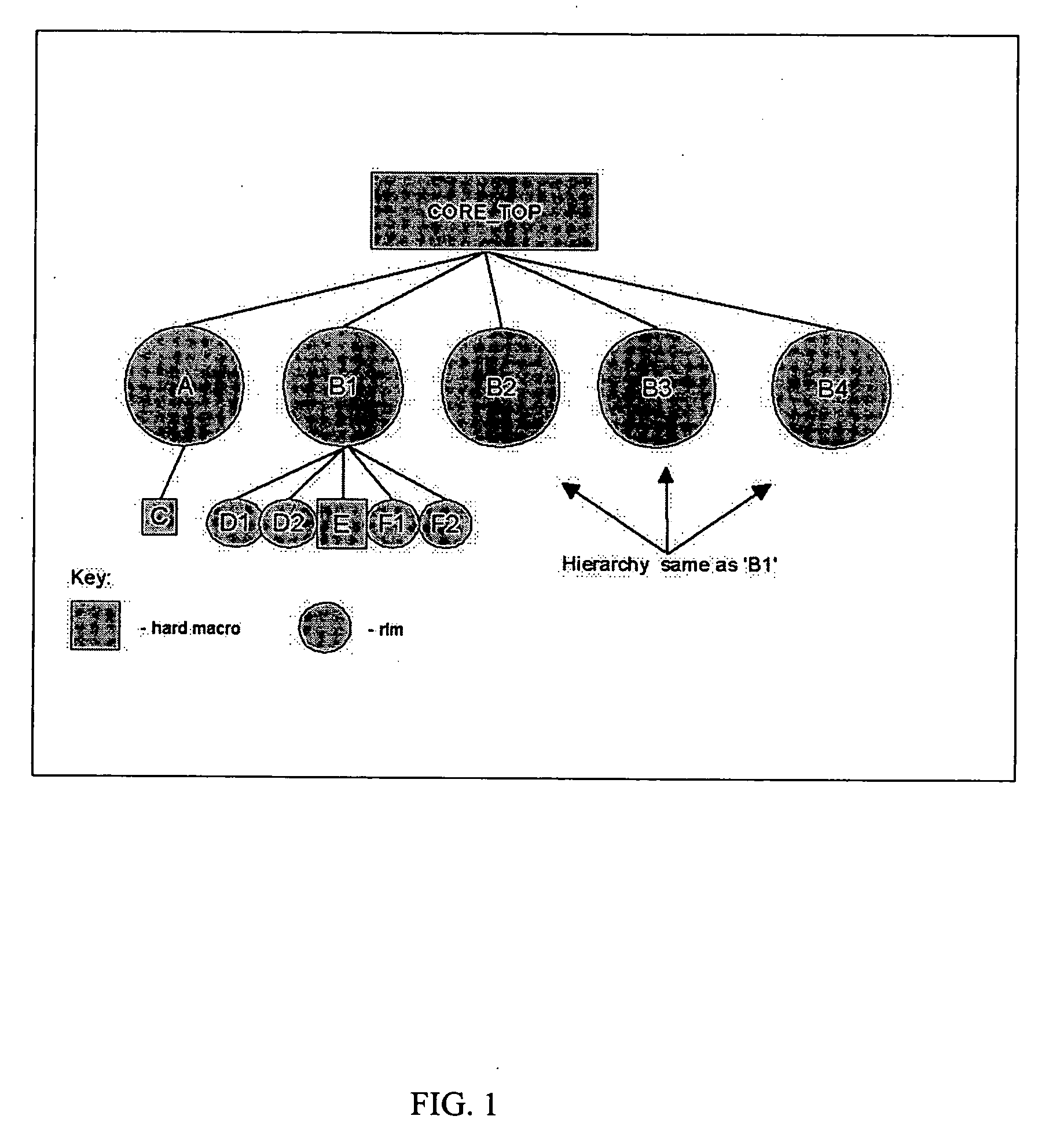

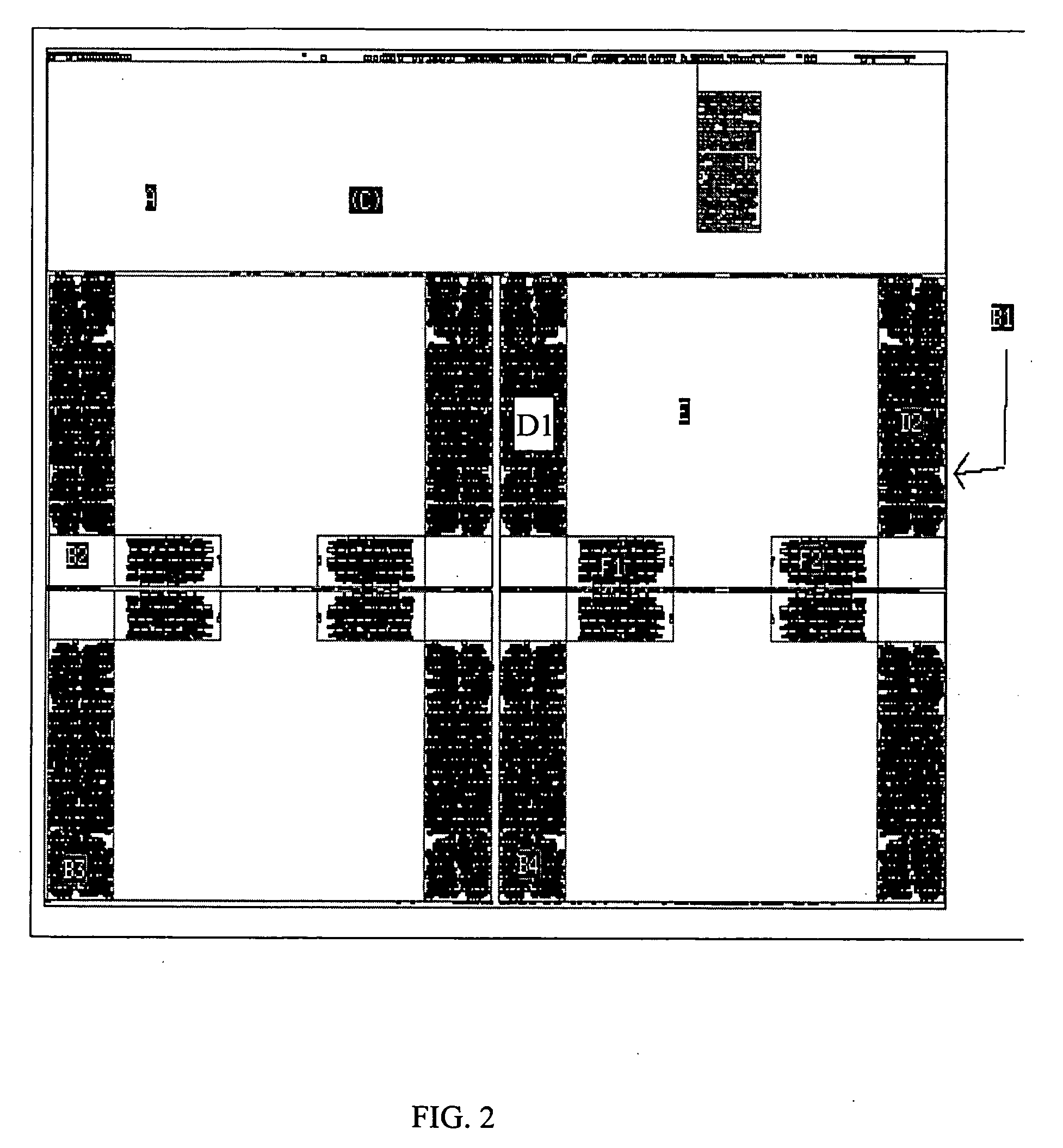

System and method to power route hierarchical designs that employ macro reuse

InactiveUS20070256044A1Computer aided designSpecial data processing applicationsHierarchical designLinearity

A method of routing a random logic macro (RLM) that is used multiple times in a hierarchical VLSI design without having to route each individual instantiation independently. Once an RLM has been routed and timed it can be copied and reused in a physical design as is, and does not require any wiring changes. This method is an advantage over existing art because it conserves area, improves wireability, and reduces the time required for routing and timing each RLM instance. Furthermore, each RLM possesses the same timing and power characteristics, which improves overall circuit performance.

Owner:IBM CORP

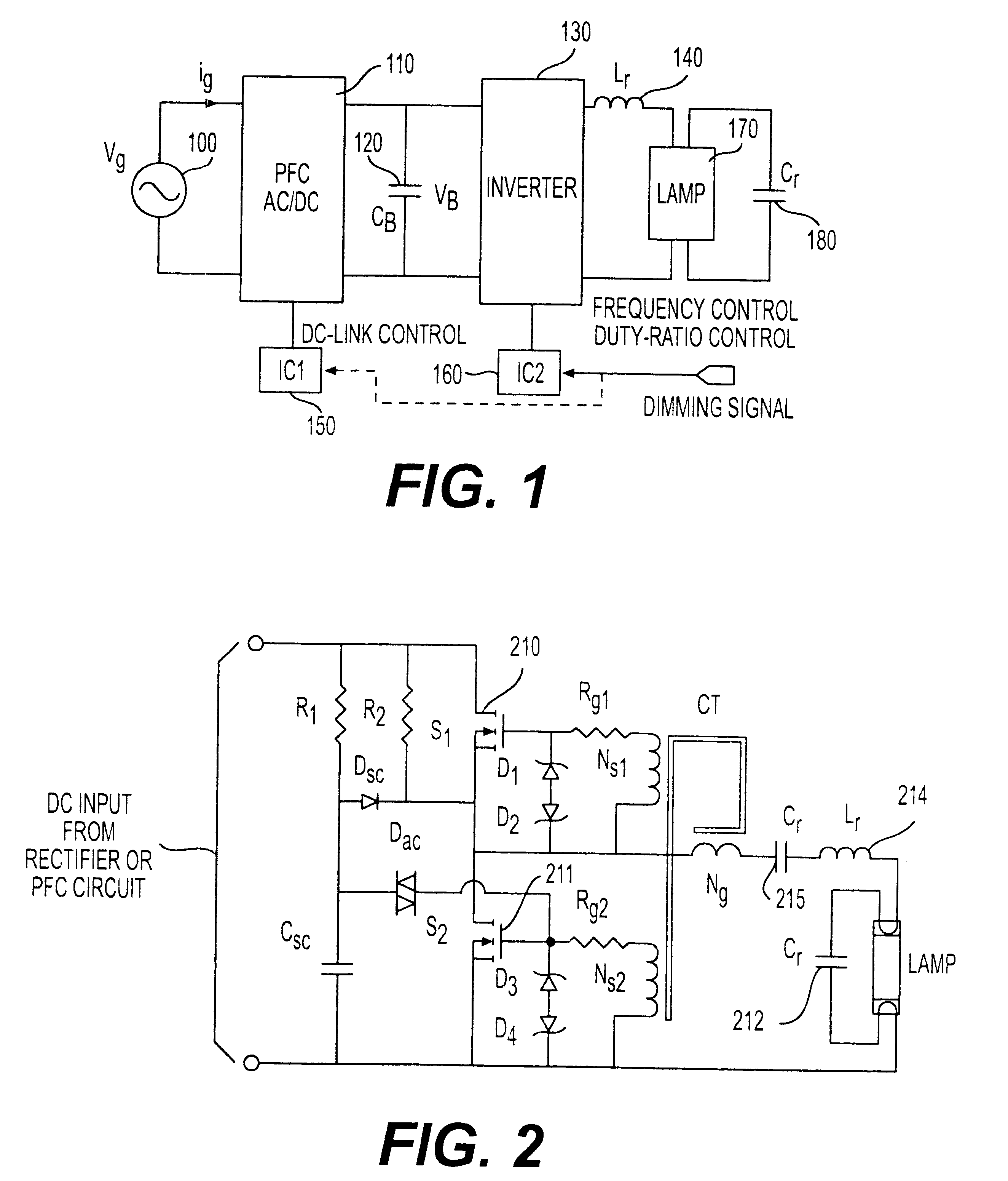

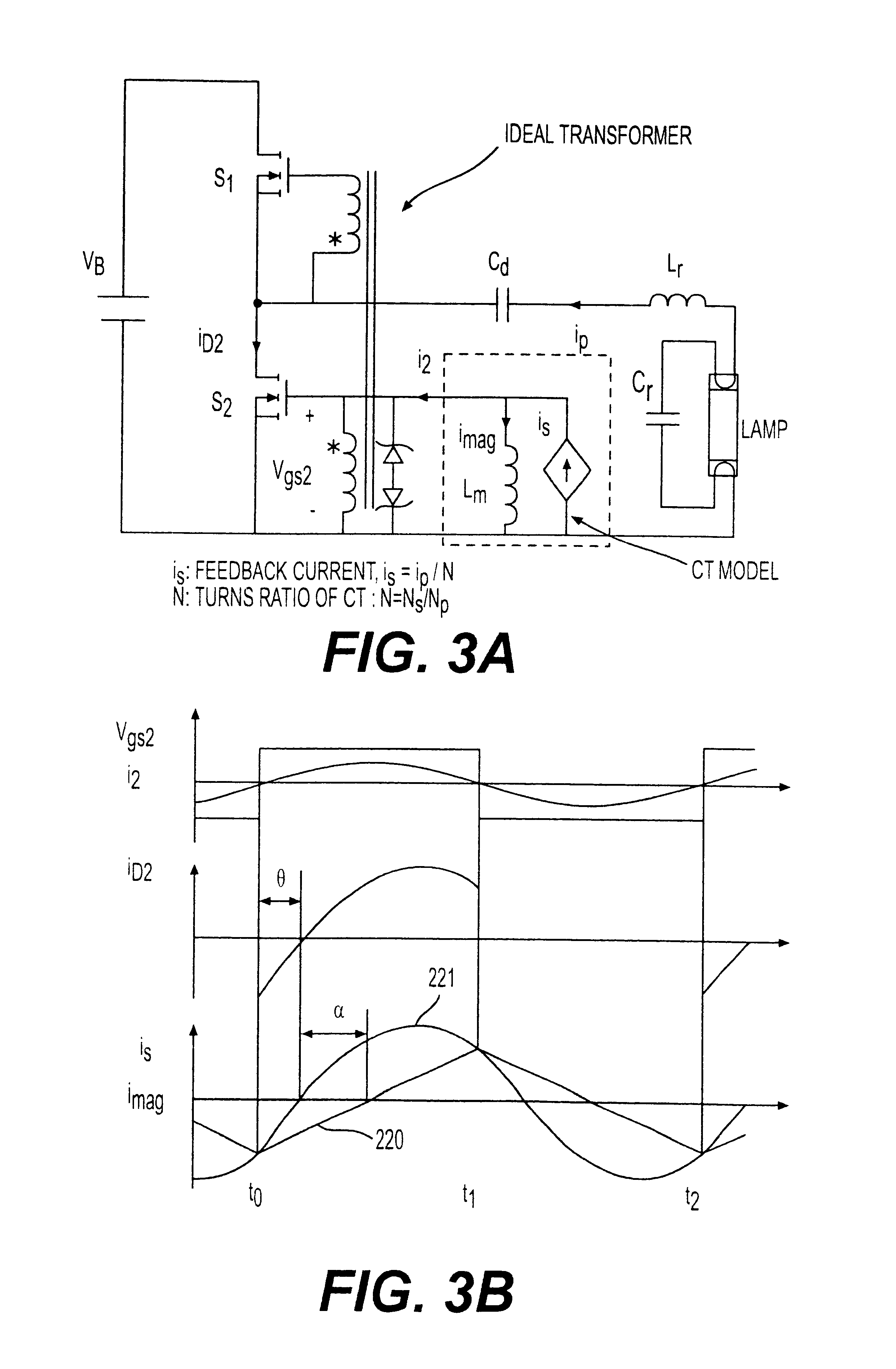

Self-oscillating electronic discharge lamp ballast with dimming control

InactiveUS6696803B2Improving crest factorTechnique is effectiveElectrical apparatusElectric light circuit arrangementCapacitanceModulation transformer

A simplified electronic ballast for a discharge lamp which provides dimming by control of inverter frequency through modulation of magnetizing current in a transformer such that the switching frequency is made substantially independent of the load presented. The principle of frequency control in a manner independent of the load is extendable to other types of loads and power supplies and converters to regulate power coupled to the load. Clamping capacitors are used to replace other clamping circuits in order to allow current injection to be controlled by a simple variable voltage while frequency control by current injection provides enhanced circuit performance.

Owner:VIRGINIA TECH INTPROP INC

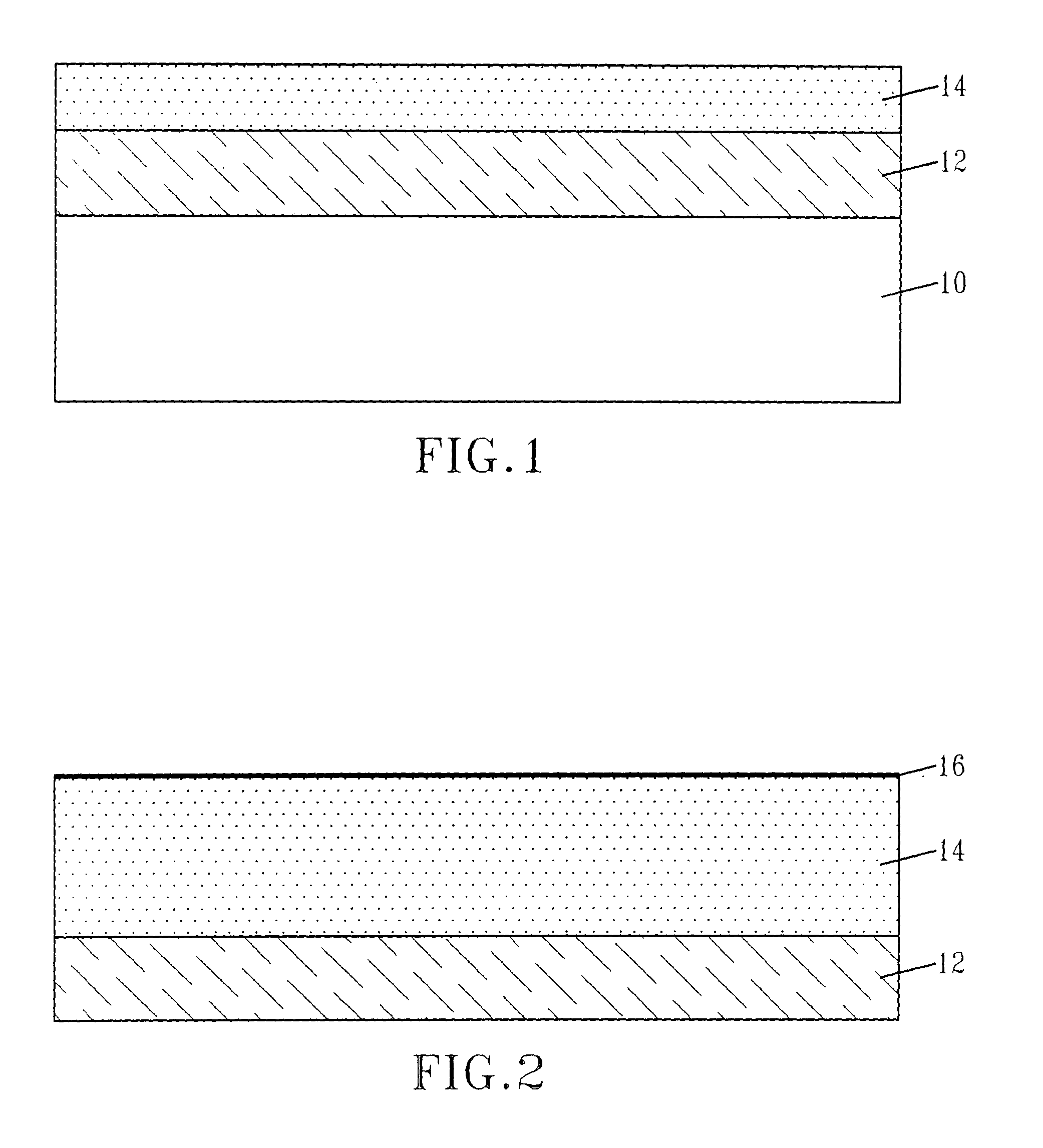

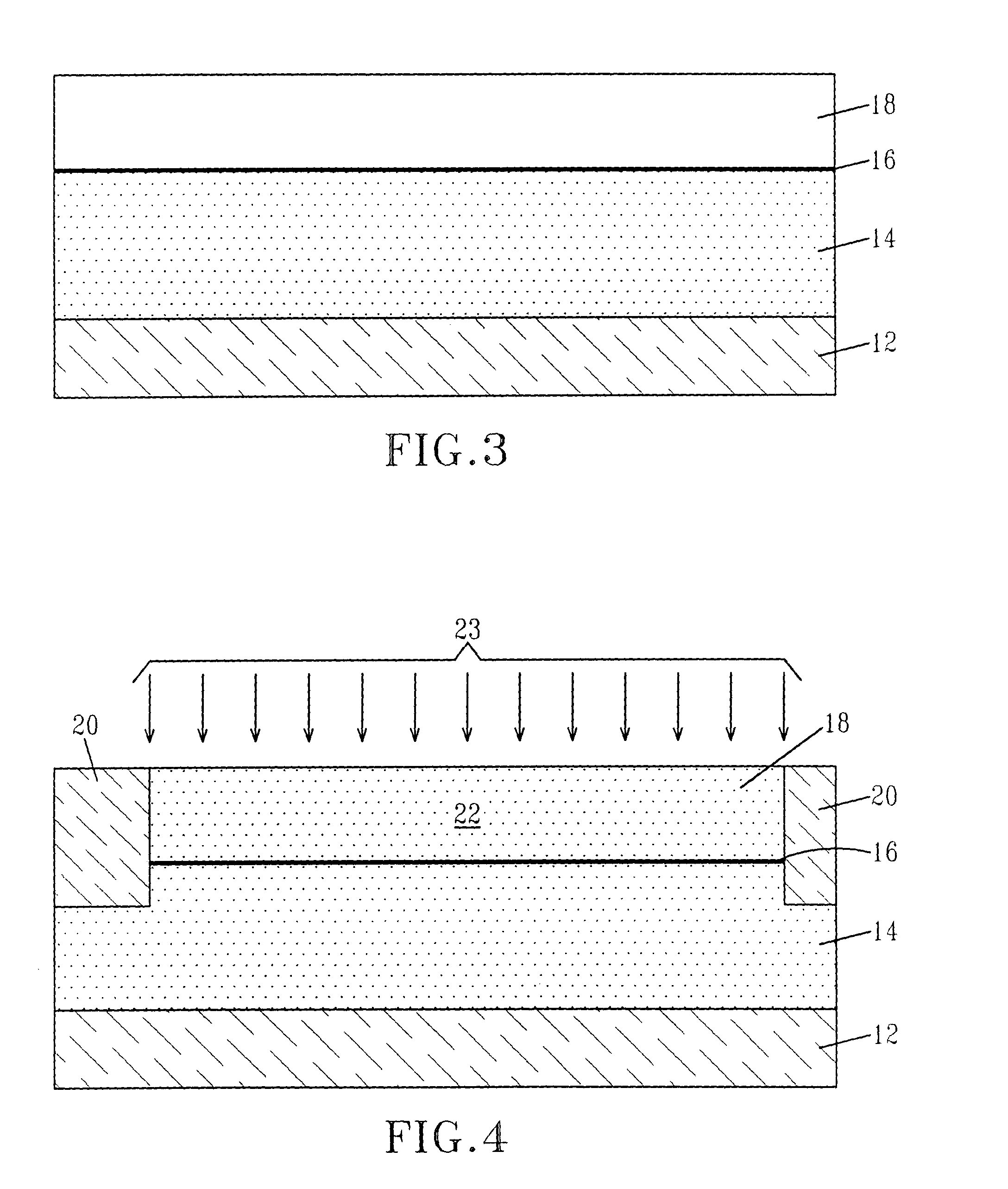

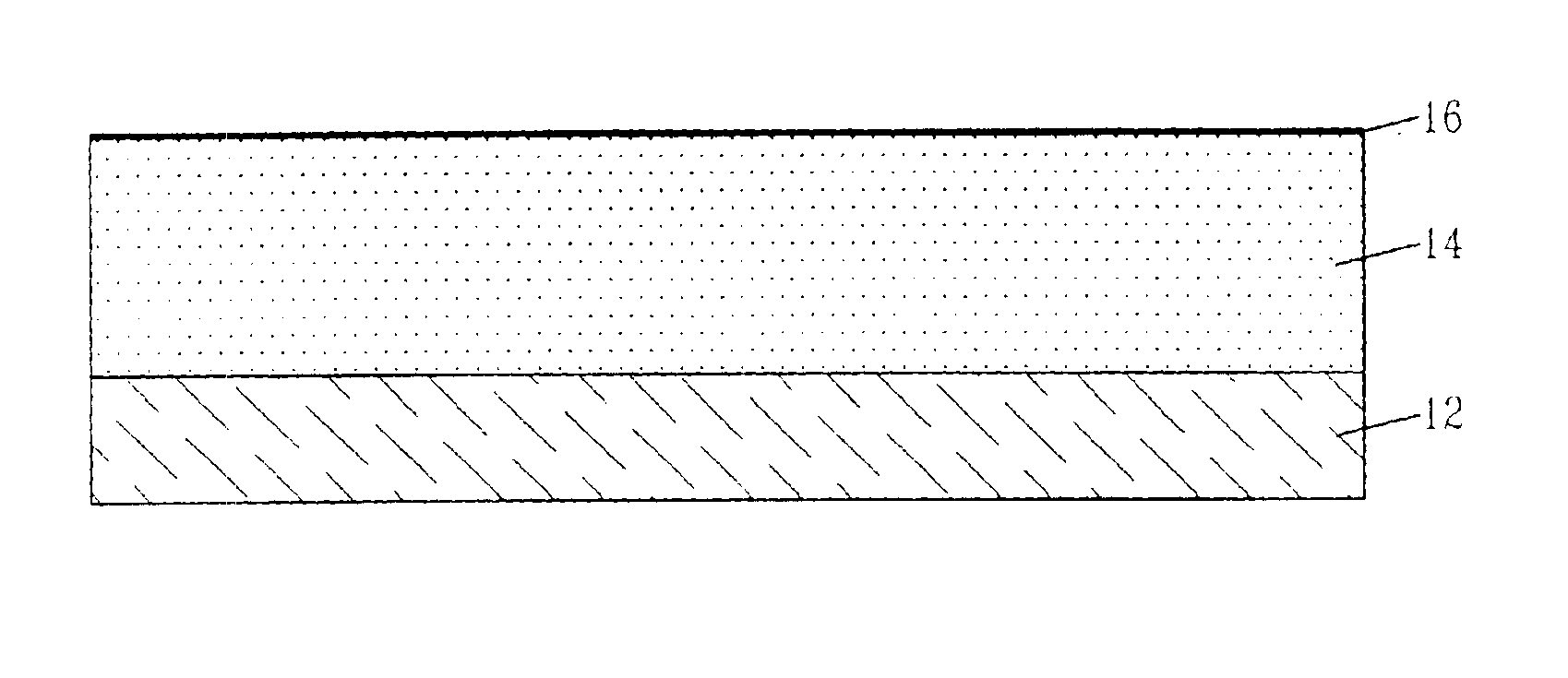

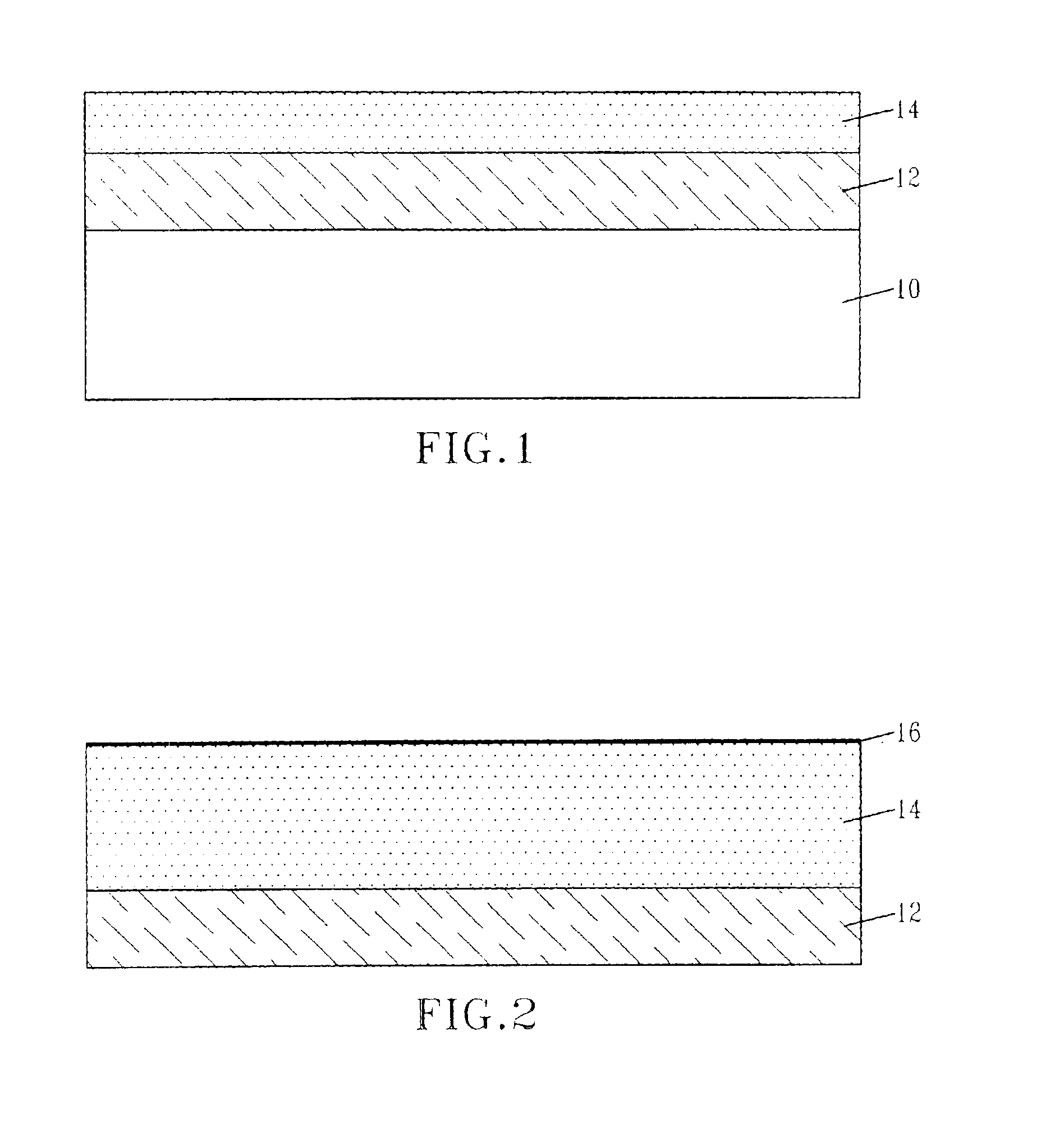

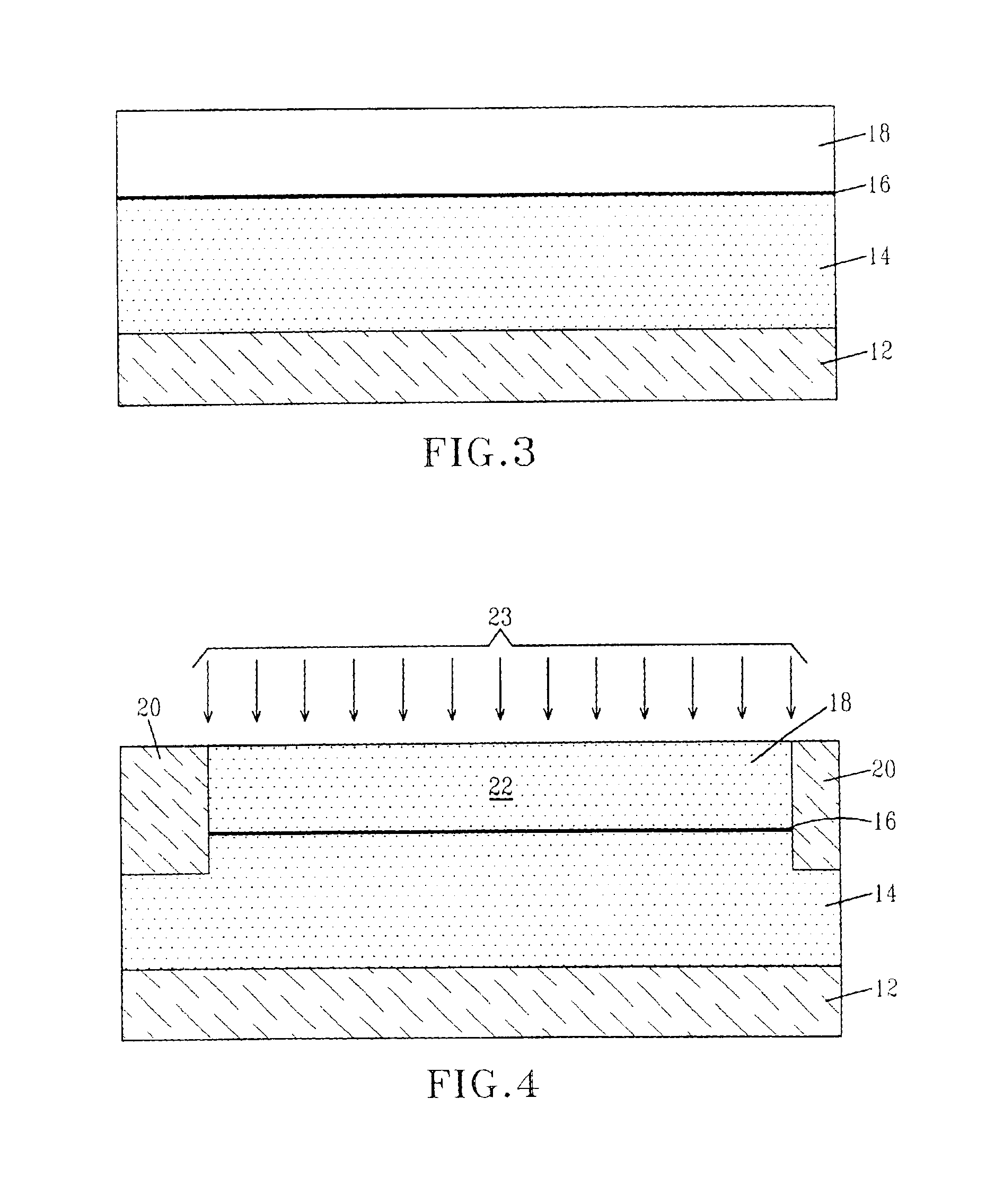

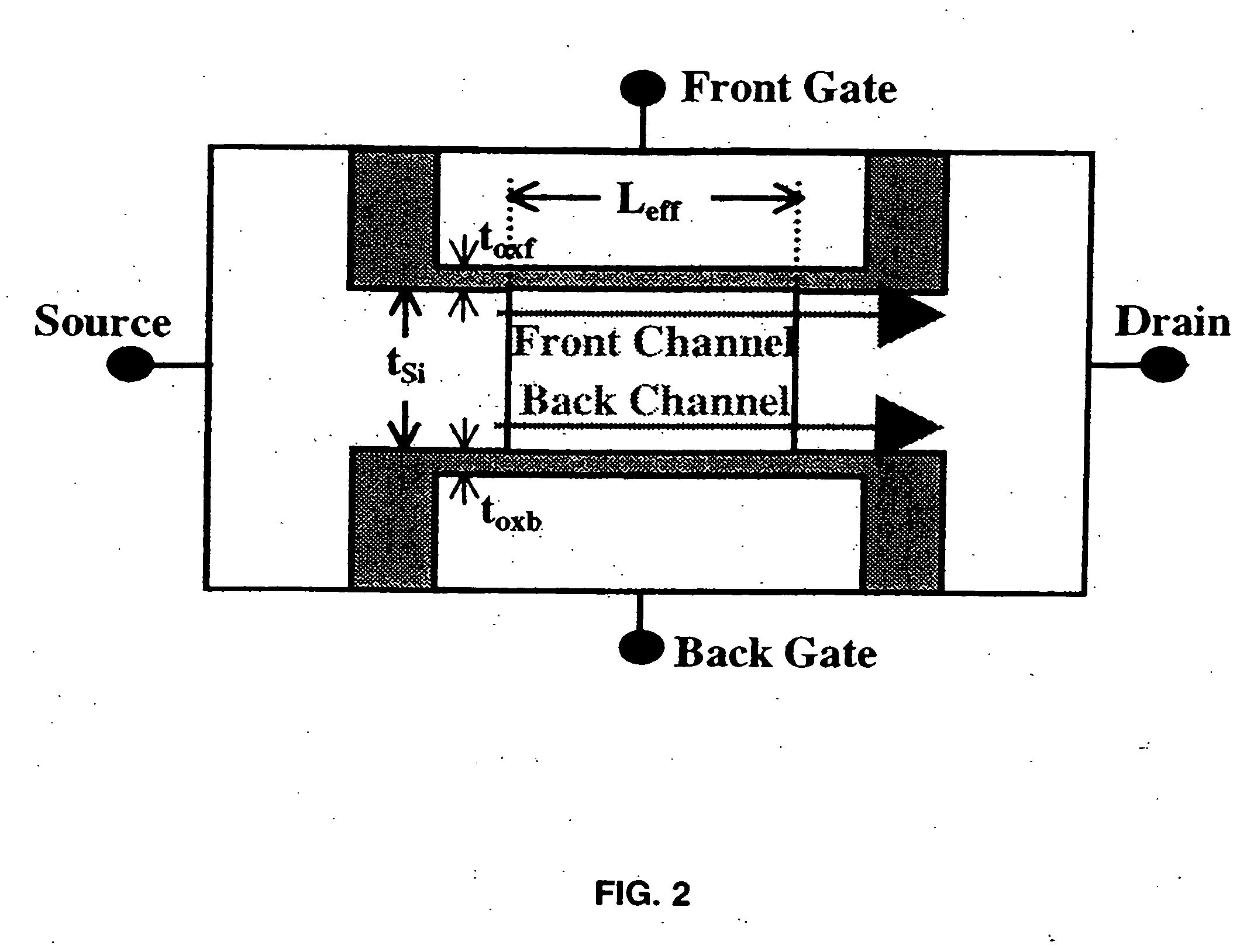

Device threshold control of front-gate silicon-on-insulator mosfet using a self-aligned back-gate

InactiveUS20050037582A1Minimize capacitanceImprove circuit performanceTransistorSemiconductor/solid-state device manufacturingCapacitanceMOSFET

The present invention provides SOI CMOS technology whereby a polysilicon back-gate is used to control the threshold voltage of the front-gate device, and the nMOS and pMOS back-gates are switched independently of each other and the front gates. Specifically, the present invention provides a method of fabricating a back-gated fully depleted CMOS device in which the device's back-gate is self-aligned to the device's front-gate as well as the source / drain extension. Such a structure minimizes the capacitance, while enhancing the device and circuit performance. The back-gated fully depleted CMOS device of the present invention is fabricated using existing SIMOX (separation by ion implantation of oxygen) or bonded SOI wafers, wafer bonding and thinning, polySi etching, low-pressure chemical vapor deposition and chemical-mechanical polishing.

Owner:GLOBALFOUNDRIES INC

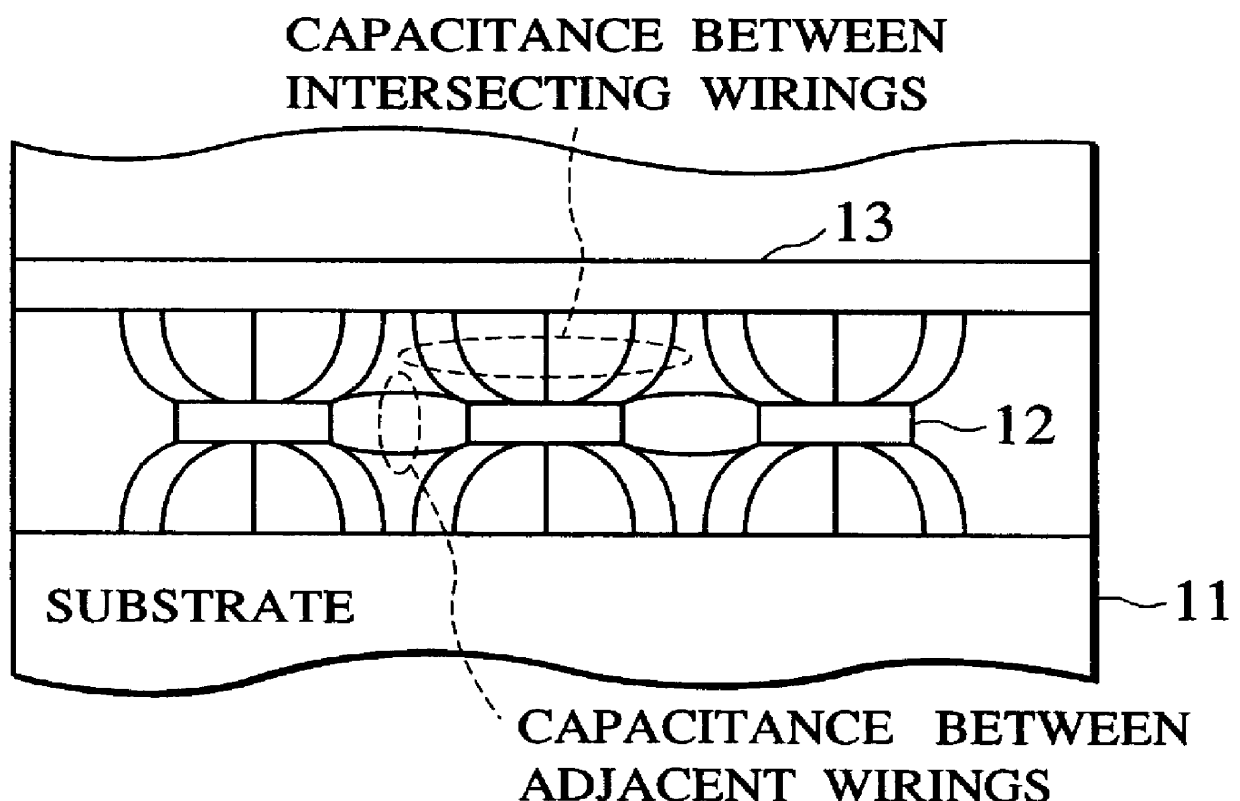

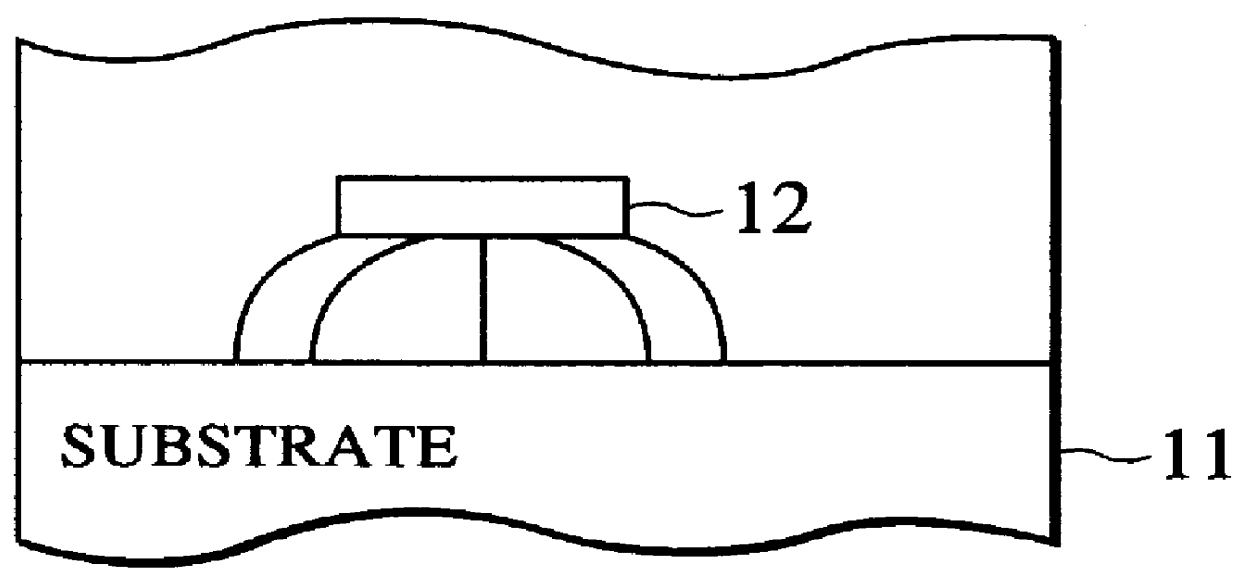

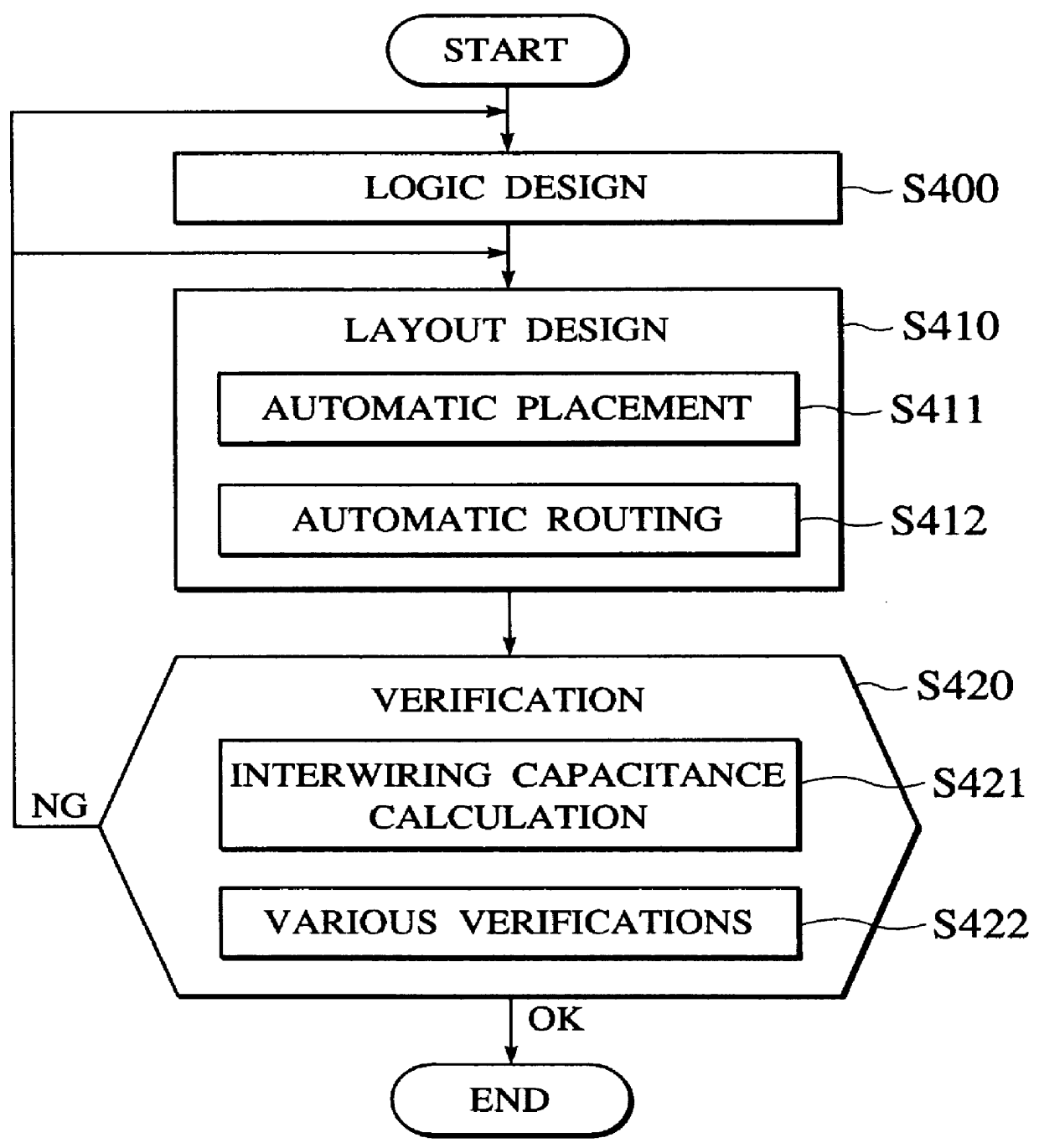

Layout design method and system for an improved place and route

InactiveUS6110222ASemiconductor/solid-state device manufacturingComputer aided designCapacitanceDesign methods

A layout design method and system for a semiconductor integrated circuit improves circuit performances related to operated frequency and power consumption by improved placement and routing. The method features an intersecting wiring predicting step that predicts the number of the intersecting wirings based on predicted wiring routes and an intersecting wiring capacitance calculating step that calculates the capacitances between the intersecting wirings.

Owner:KK TOSHIBA

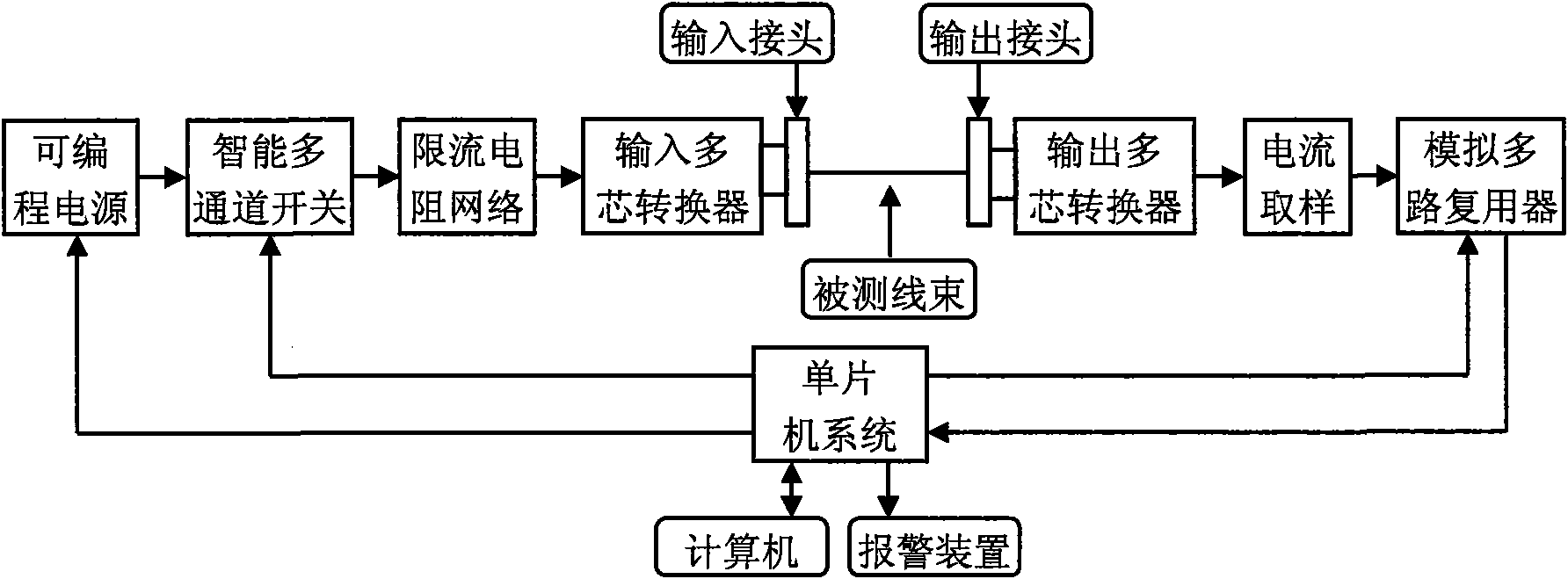

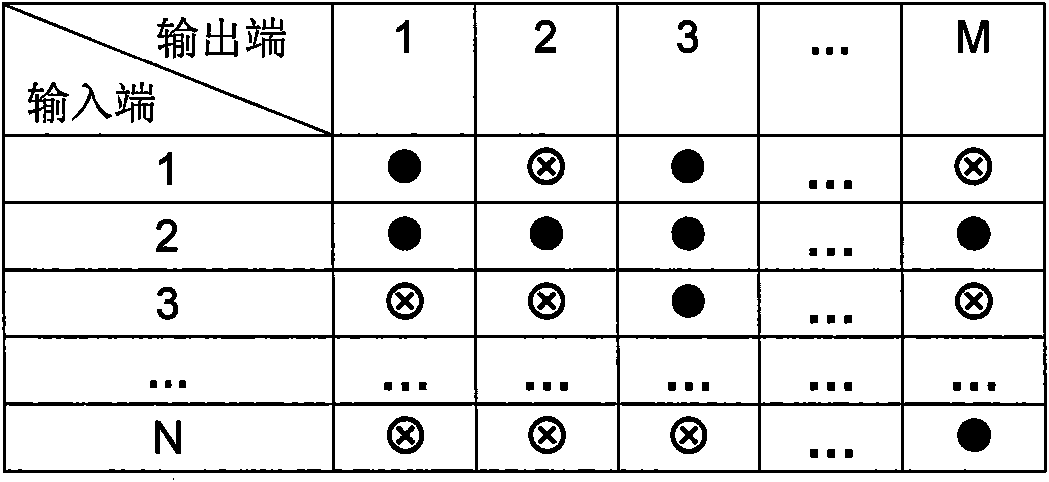

Intelligent multi-core cable harness detection device

InactiveCN101937038AEliminate disturbing effectsHigh measurement accuracyCurrent/voltage measurementElectrical testingExtensibilityEngineering

The invention relates to an intelligent multi-core cable harness detection device. The device consists of a programmable power supply, an intelligent multi-channel switch, a current-limiting resistor network, a multi-core converter, a current sampling module, an analog multiplexer, a single-chip, a computer and detection software. The device can automatically analyze short-circuit performance, open-circuit performance and conduction performance of a multi-core cable harness. A harness system state is determined through a harness performance testing matrix graphical detection result and by comparing the result with a pre-stored standard, and different fault types are indicated by colors; and meanwhile, a fault alarm can be sent by an alarm device with sound and changing light. The device has the characteristics of simple and convenient operation, high testing efficiency, high system extensibility and the like, and can be directly used for development of harness-related products, quality control and performance detection.

Owner:CHINA FIRST AUTOMOBILE

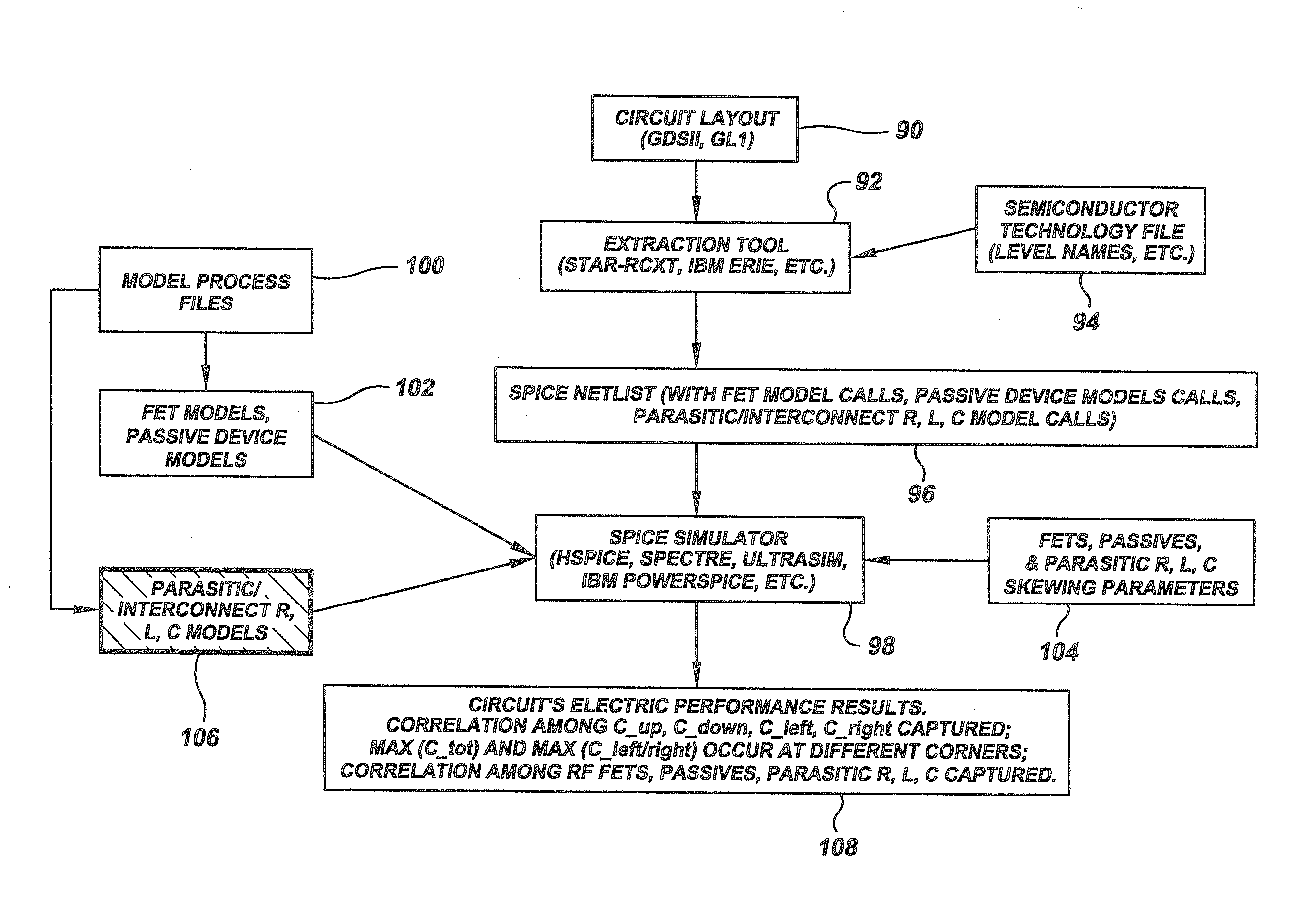

Method for treating parasitic resistance, capacitance, and inductance in the design flow of integrated circuit extraction, simulations, and analyses

InactiveUS20080028353A1Detecting faulty computer hardwareComputer aided designElectrical resistance and conductanceCapacitance

An extraction, simulation, and analysis combined method is employed to account for the parasitic couplings from interconnect wires. Variations of parasitic resistance, capacitance, and inductance are used in circuit analysis calculators, including considering the variations of the parasitics on worst case circuit performance, skewing, and statistical Monte Carlo analysis. Each parasitic element is modeled as a call-up function with associated process distributions. Circuit analysis, such as a SPICE analysis is performed on the selected models.

Owner:IBM CORP

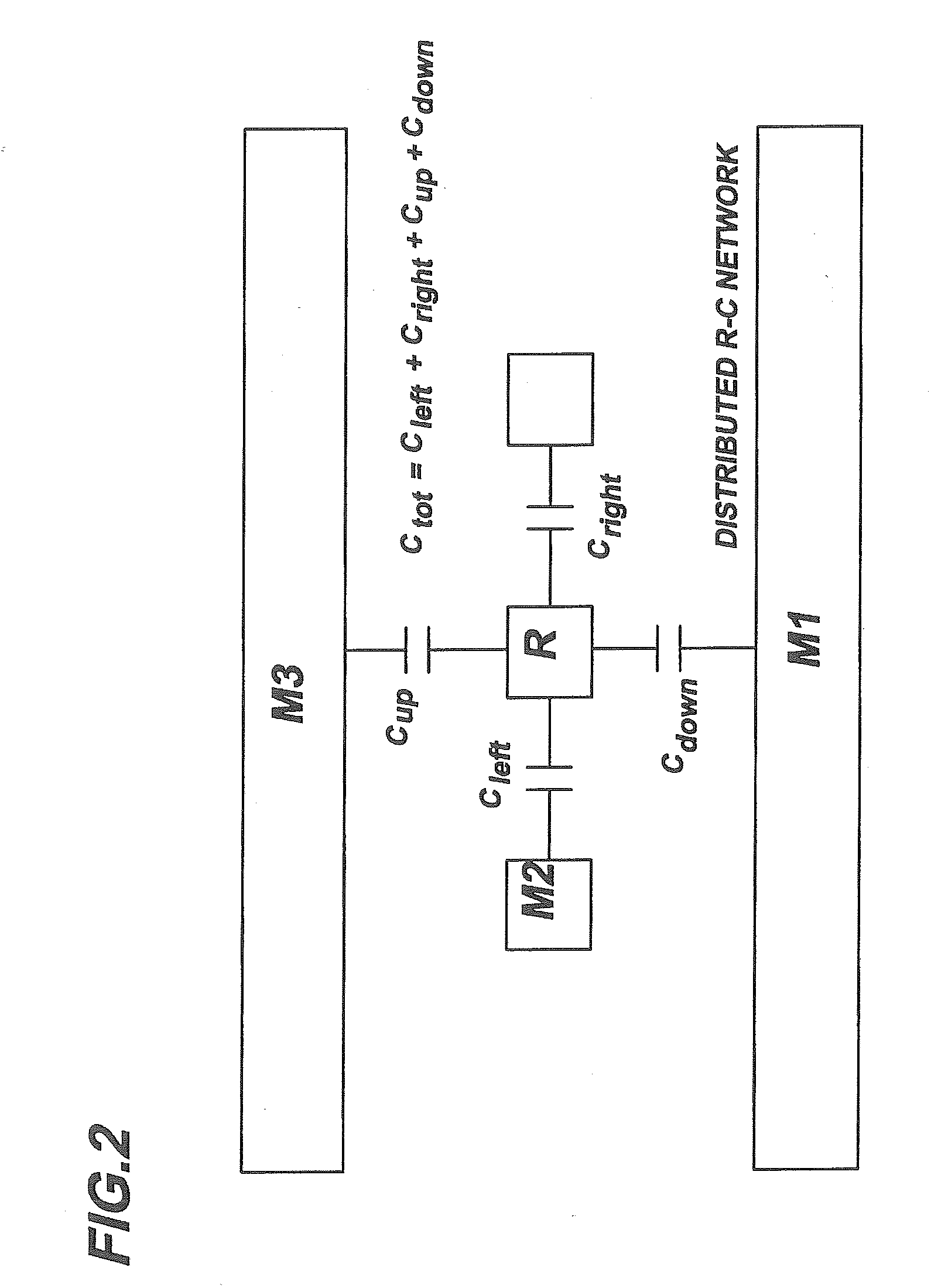

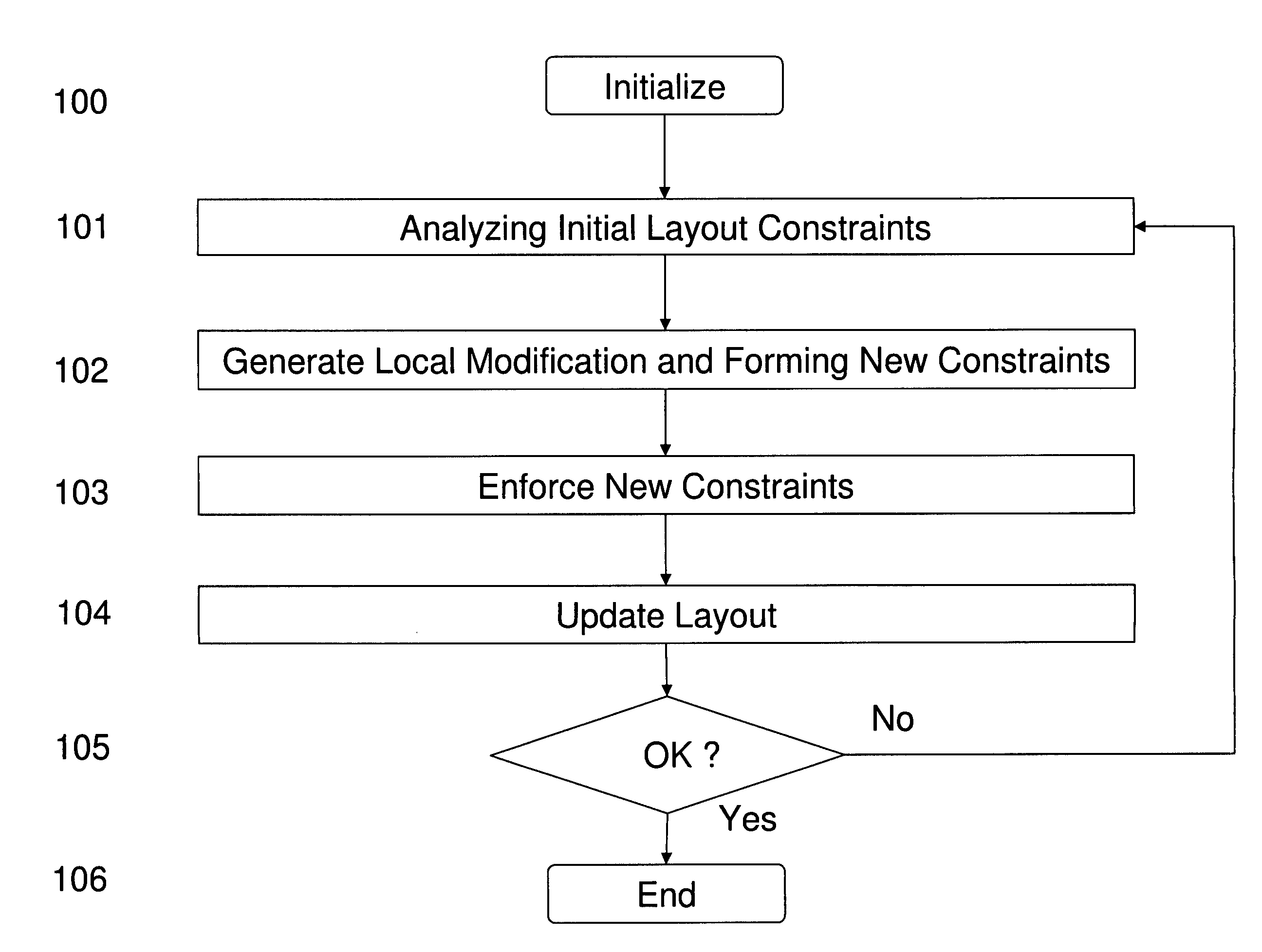

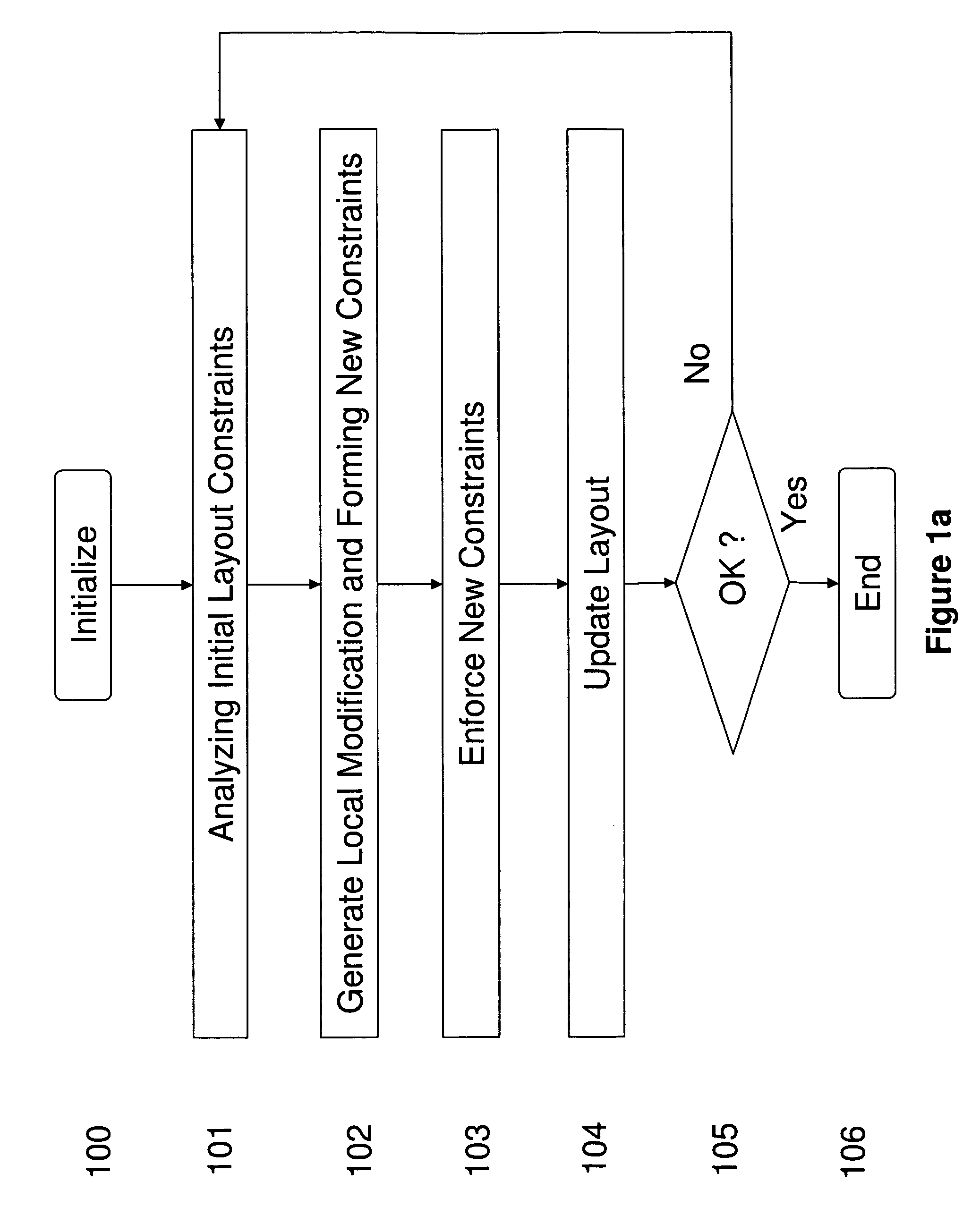

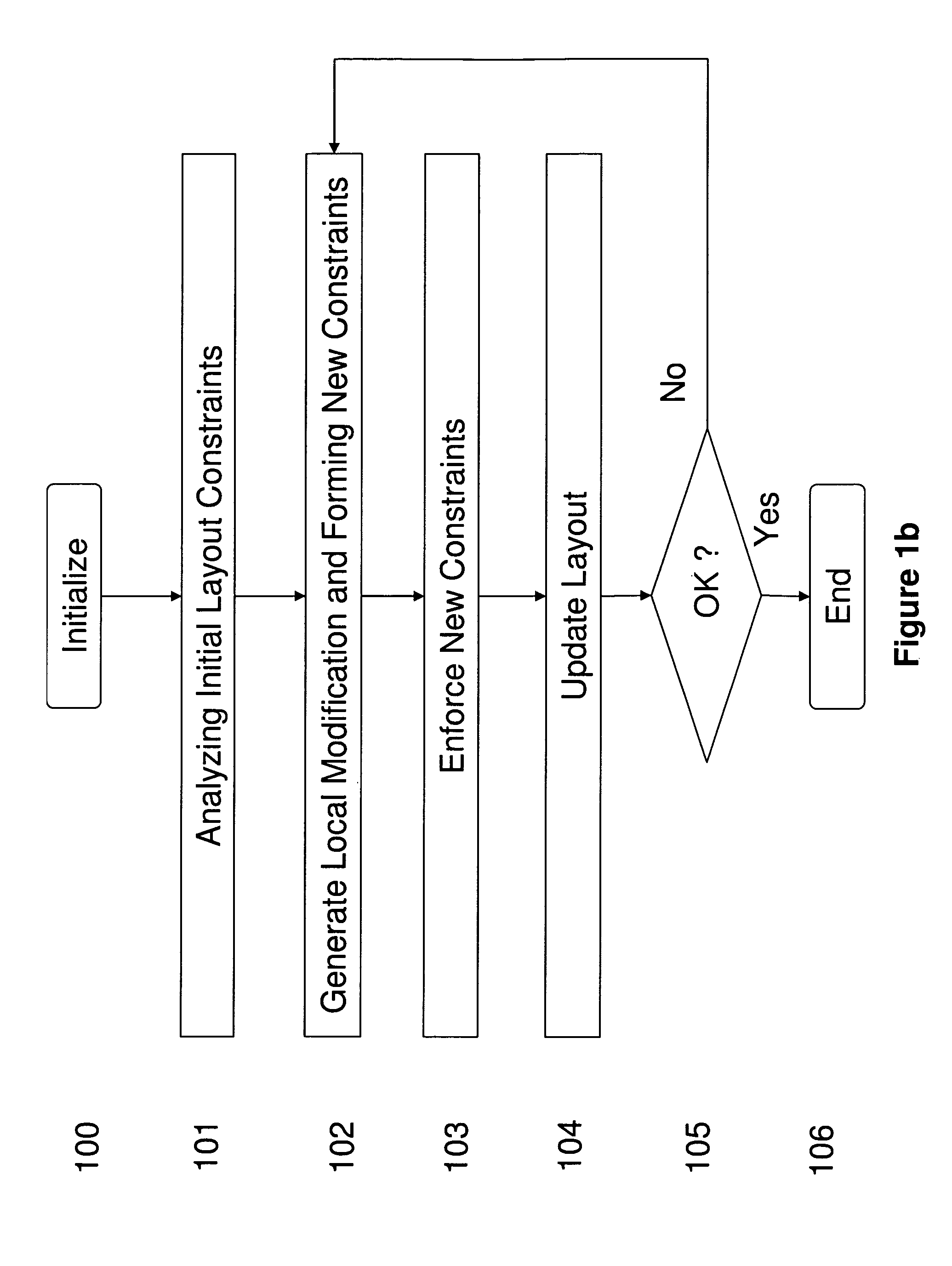

Method and system for optimizing integrated circuit layout

ActiveUS8176445B1Reduce sensitivityReduce in quantityCAD circuit designSpecial data processing applicationsComputer architectureIntegrated circuit layout

We disclose a method for optimizing integrated circuit layout which comprises analyzing constraint relationship among objects in an initial layout; constructing local modifications to the constraint relationship; forming new constraint relationships by combining initial constraint relationships with their local modifications; and producing a new layout by implementing the new constraint relationships. Local modification to constraints provides a framework for bringing detailed local information into the design process in a highly automated manner, which can be applied to a wide range of situations. We disclose preferred embodiments on improving lithography printability, reducing defect susceptibility, and improving circuit performance such as reducing layout variability and leakage.

Owner:IYM TECH

Method and apparatus for simulating manufacturing, electrical and physical characteristics of a semiconductor device

InactiveUS6826517B2Semiconductor/solid-state device detailsDetecting faulty computer hardwareElement modelMaterial Design

An electronic device simulator includes a three-dimensional lumped device model, a three-dimensional visco-elastic process simulation model and a material design model that are interlinked with each other. The three-dimensional lumped device element model comprises a Poisson's equation model, an electron continuity equation model, a hole continuity equation model, a Maxwell's equations model, an eddy current equation model, and an Ohm's law equation model. The simulator accounts for the three dimensional characteristics of the circuit to determine circuit performance.

Owner:KK TOSHIBA

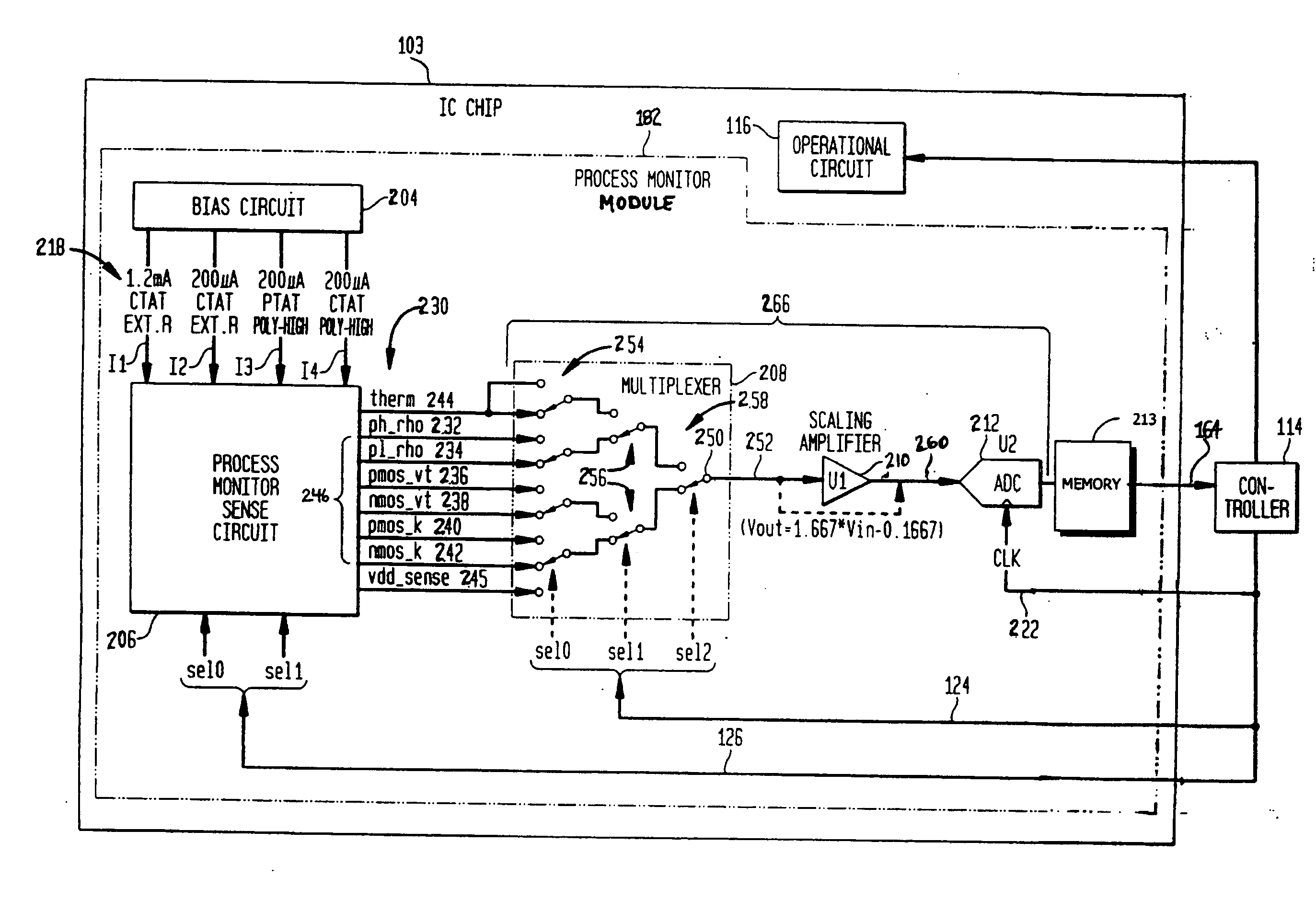

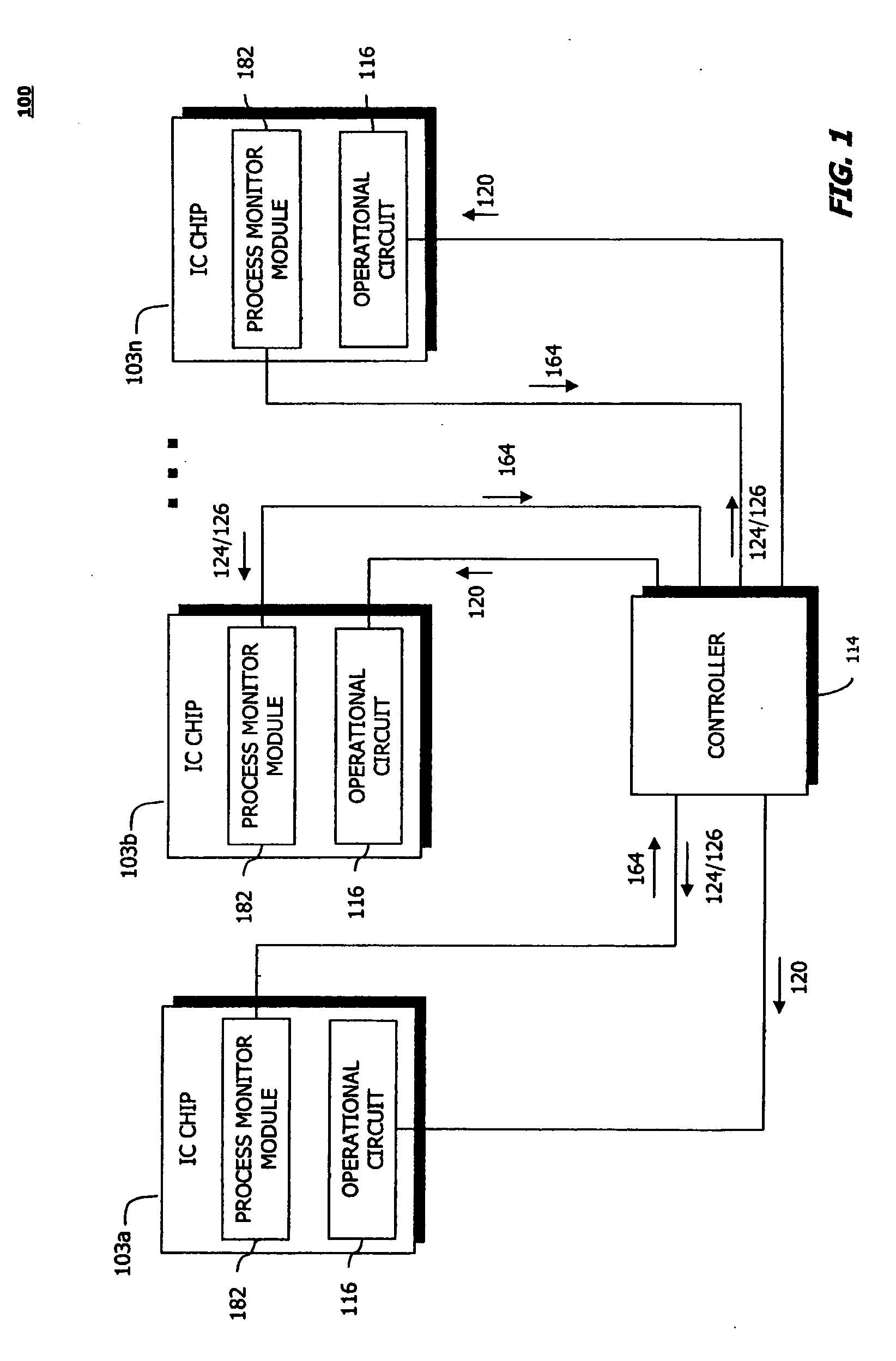

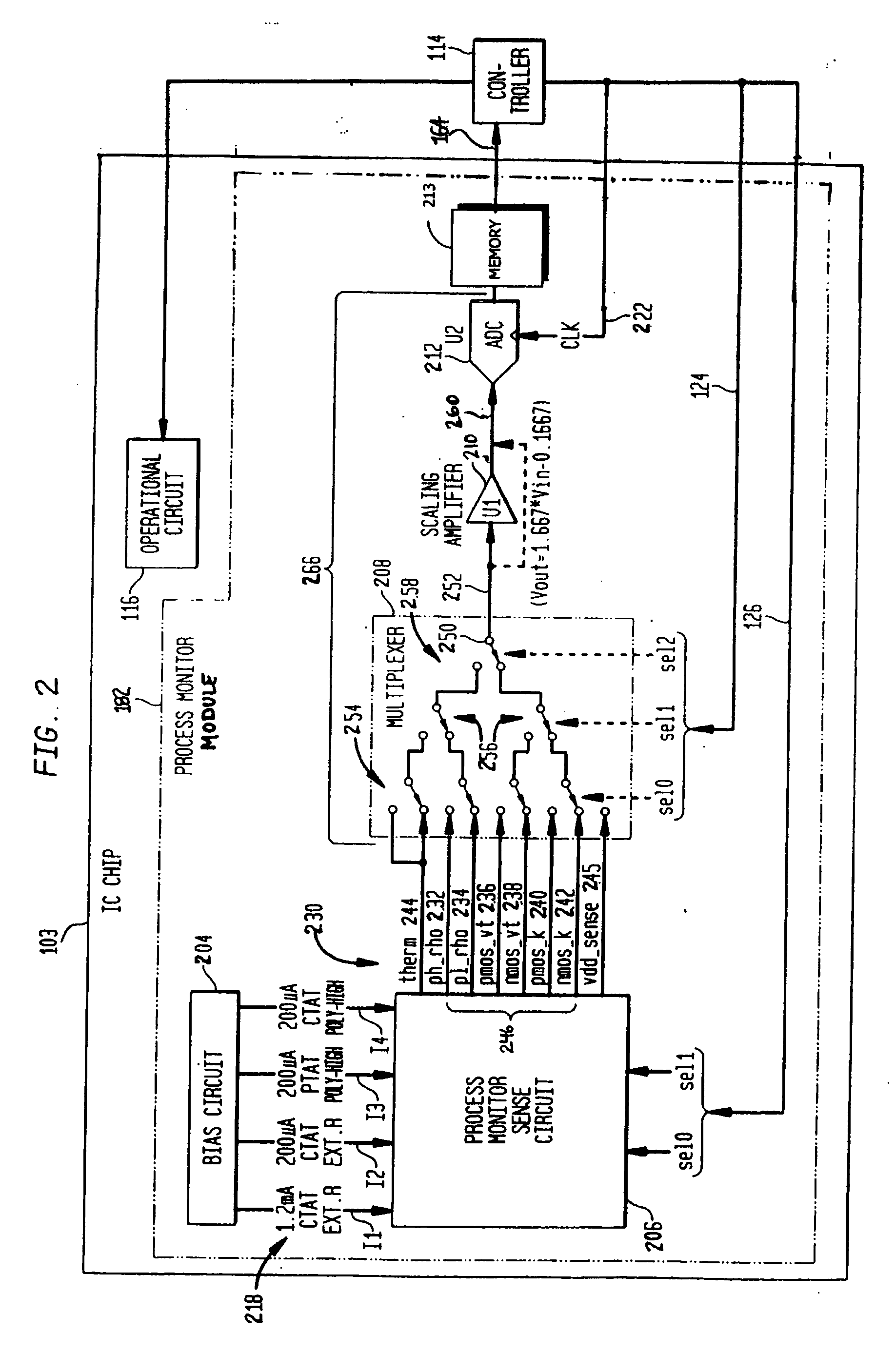

Process monitor for monitoring and compensating circuit performance

A method and system for monitoring and compensating the performance of an operational circuit is provided. The system includes one or more integrated circuit chips and a controller. Each integrated circuit chip includes one or more operational circuits, each operational circuit having at least one controllable circuit parameter. Each integrated circuit chip also includes a process monitor module at least partially constructed thereon. The controller is coupled to each process monitor module and to each operational circuit. The controller includes logic for evaluating the performance of an operational circuit based on data obtained from process monitor module and operational circuit related data stored in a memory. Based on the evaluation, the controller determines whether any deviations from desired or optimal performance of the circuit exist. If deviations exist, the controller generates a control signal to initiate adjustments to the operational circuit to compensate for the deviations.

Owner:AVAGO TECH INT SALES PTE LTD

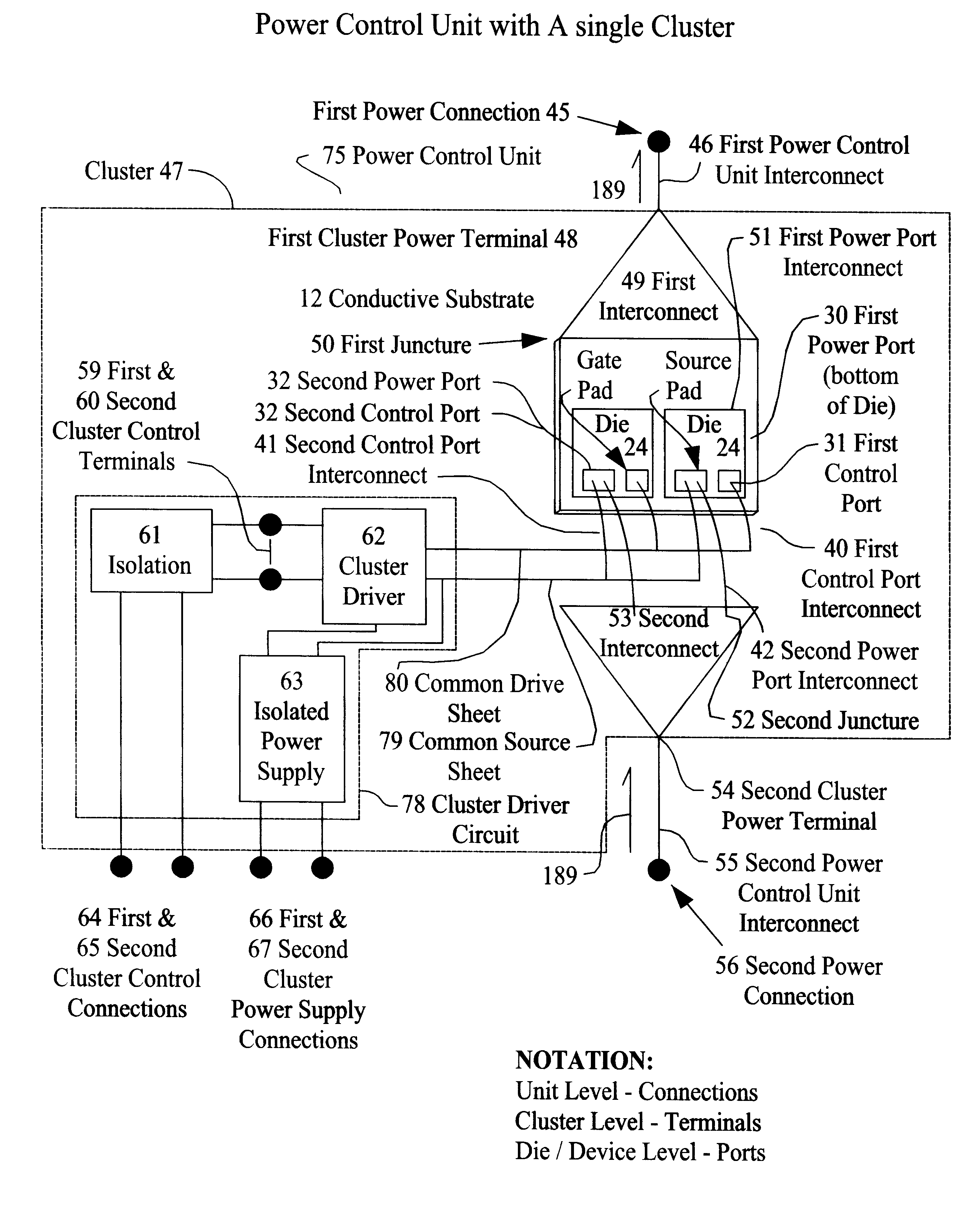

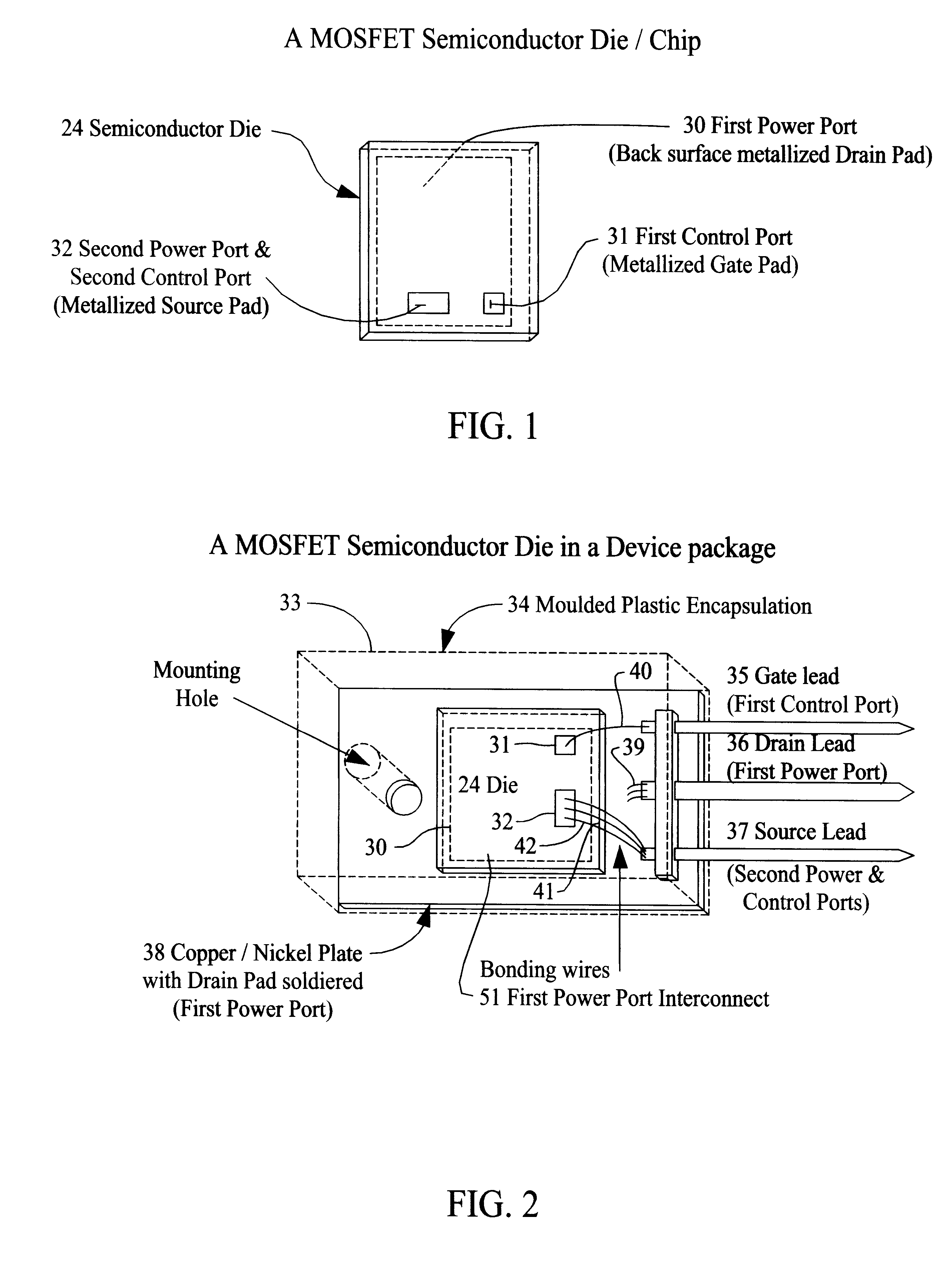

Power semiconductor packaging

InactiveUS6384492B1Reduce construction costsImprove efficiencyBatteries circuit arrangementsSemiconductor/solid-state device detailsCouplingEngineering

Power output switching circuit for use in high current and high frequency applications. The output circuit provides a series of geometrically symmetric, parallel spaced semiconductor converters arranged such that the voltage for each semiconductor output device is substantially equal and minimal for each device. In this way, each device exhibits substantially the same impedance, such that circuit performance is largely a function of intrinsic device characteristics, and substantially independent of cross coupling and other external influences.

Owner:SPINEL

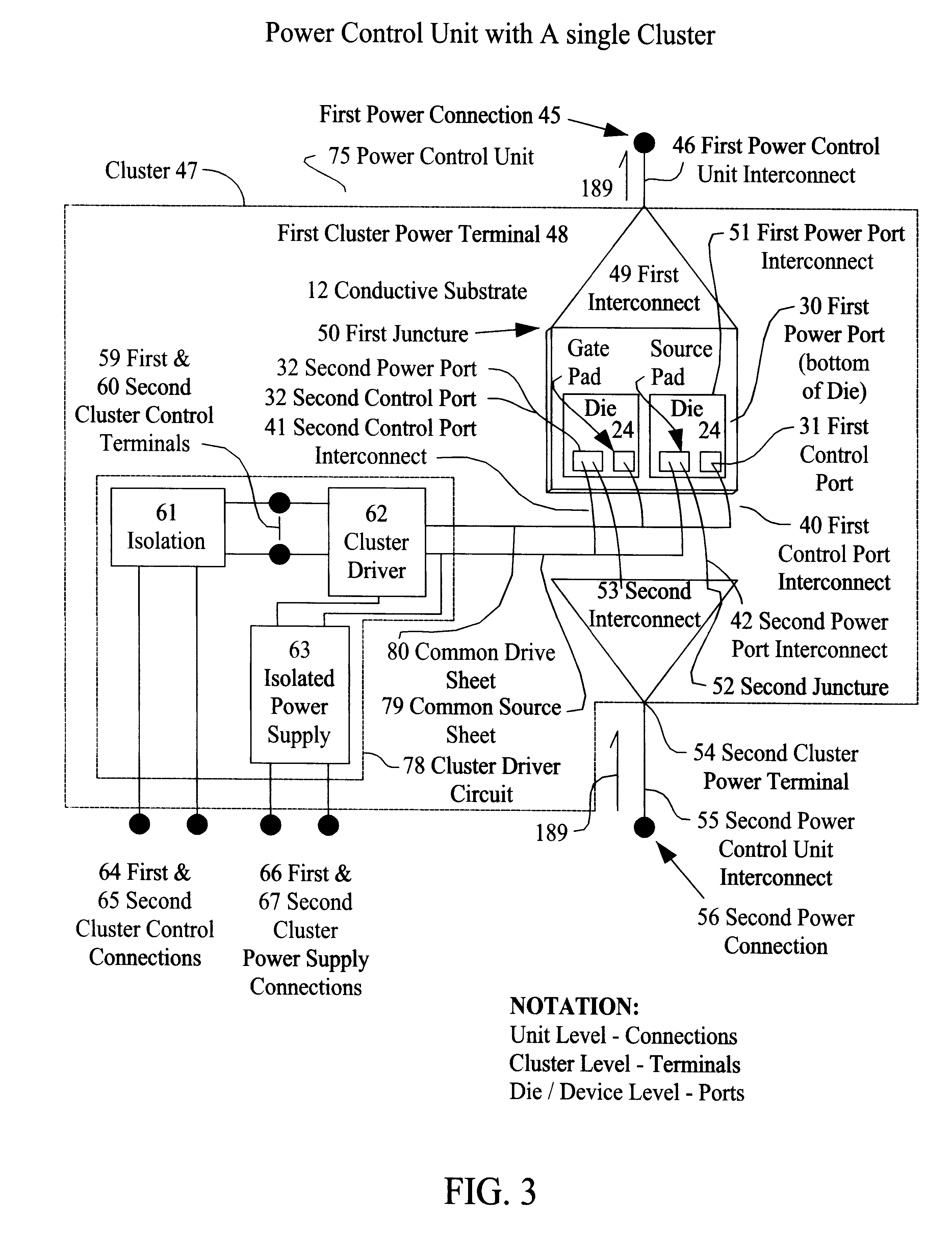

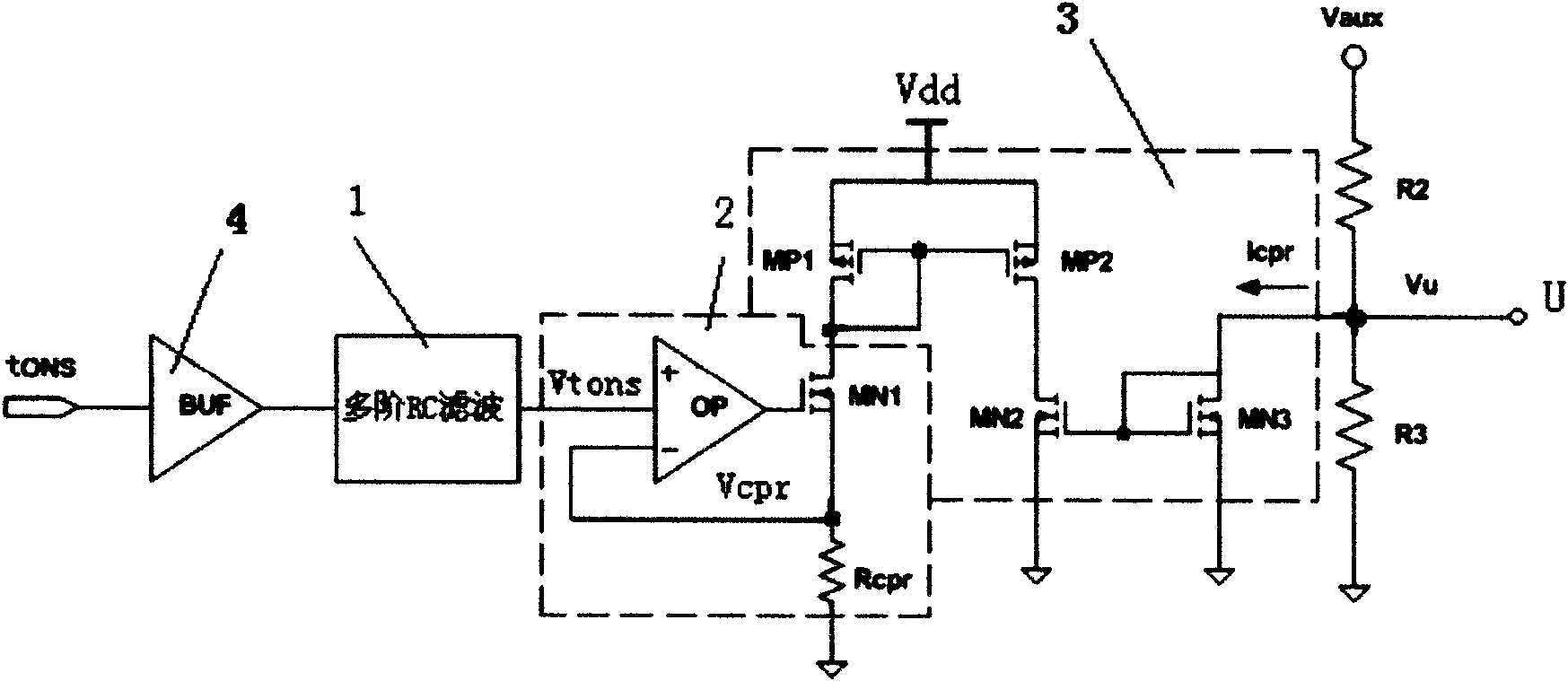

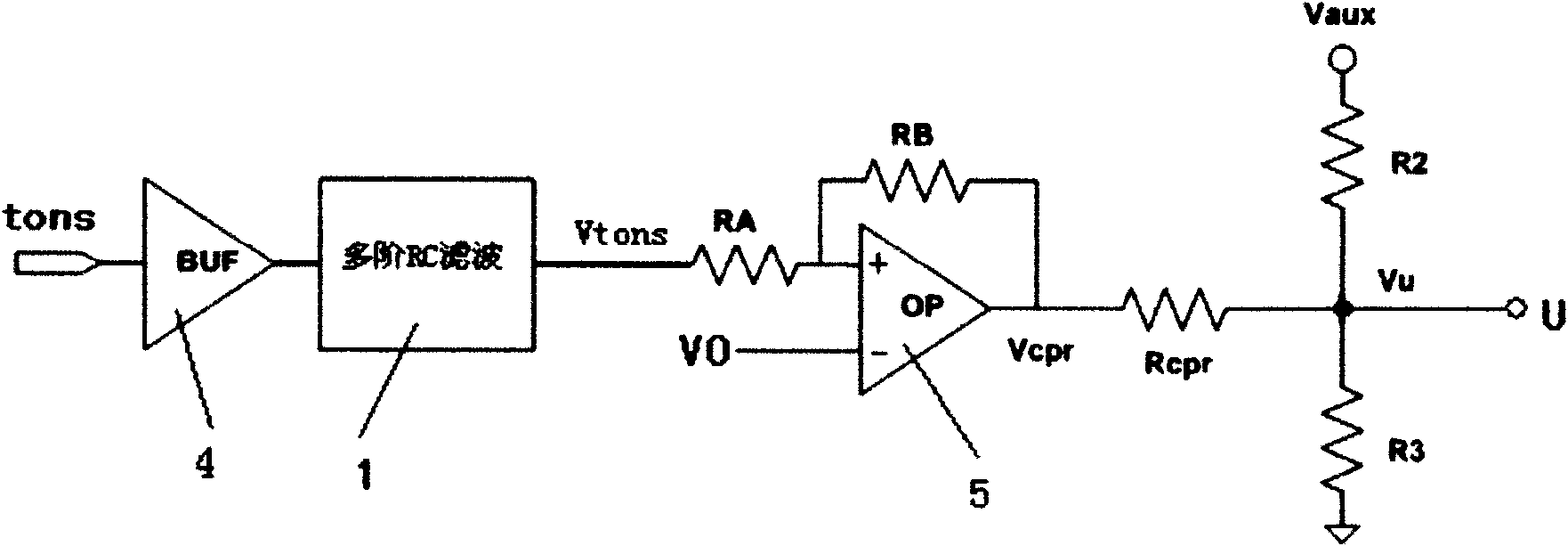

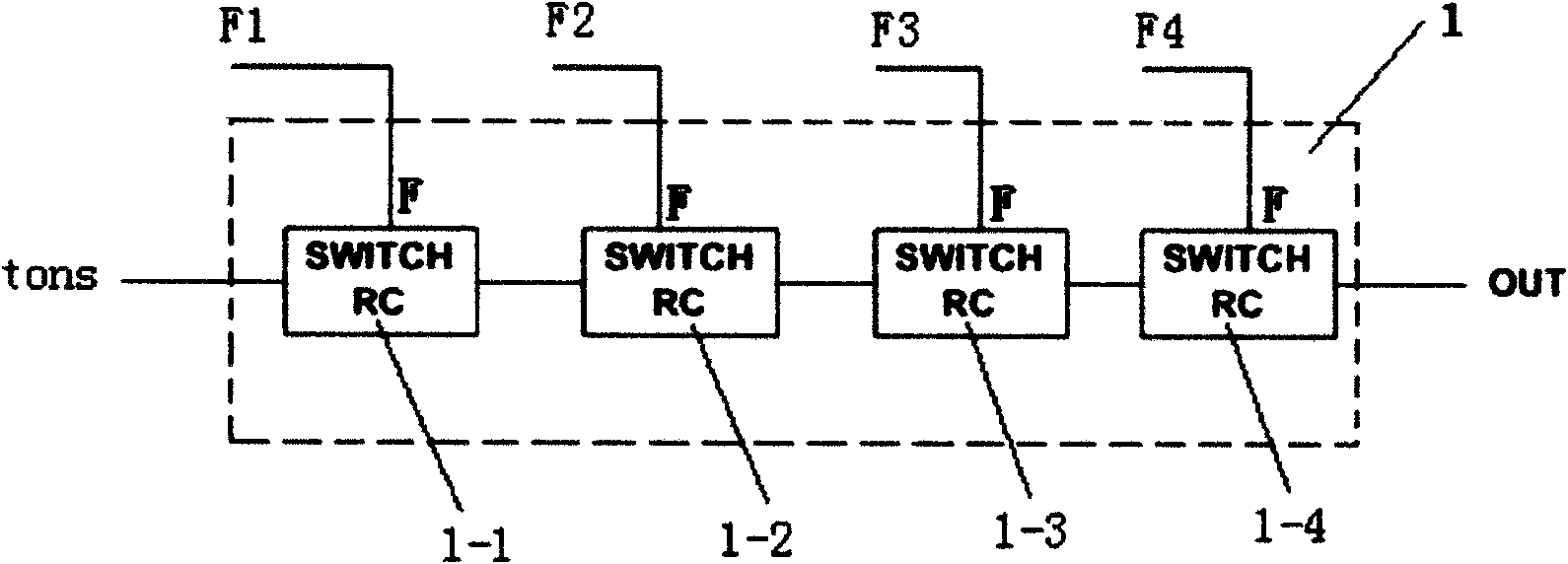

Line loss compensation circuit for switch power supply

InactiveCN101860243AImprove performanceSimple structureAc-dc conversionCapacitanceElectrical resistance and conductance

The invention relates to a line loss compensation circuit for a switch power supply, which is divided into a current-type line loss compensation circuit and a voltage-type line loss compensation circuit, wherein the current-type circuit comprises a multi-stage RC low pass filter, a voltage / current switching circuit and a current mirroring circuit, and the voltage-type circuit comprises a multi-stage RC low pass filter, a subtractor and a compensating resistance. The invention can produce a compensating current of Icpr or a compensating voltage of Vcpr which is proportionable to an output current of Iout, and the compensating current or the compensating voltage is used for offsetting voltage drop of an output wire caused by change of Iout, thereby recovering voltage stabilizing control function of a control loop to secure constant output. The invention has the advantages of skilful design idea and simple circuit and is easy to realize. The improvement of the invention is that: the switch RC filter is adopted to greatly reduce volume of an electric capacity of the RC filter, thereby facilitating integration, further improving circuit performance and simplifying circuit structure, and strengthening operation reliability of the switch power supply.

Owner:西安英洛华微电子有限公司

Method of making a device threshold control of front-gate silicon-on-insulator MOSFET using a self-aligned back-gate

InactiveUS7018873B2Minimize capacitanceImprove performanceTransistorSemiconductor/solid-state device manufacturingCapacitanceMOSFET

Owner:GLOBALFOUNDRIES INC

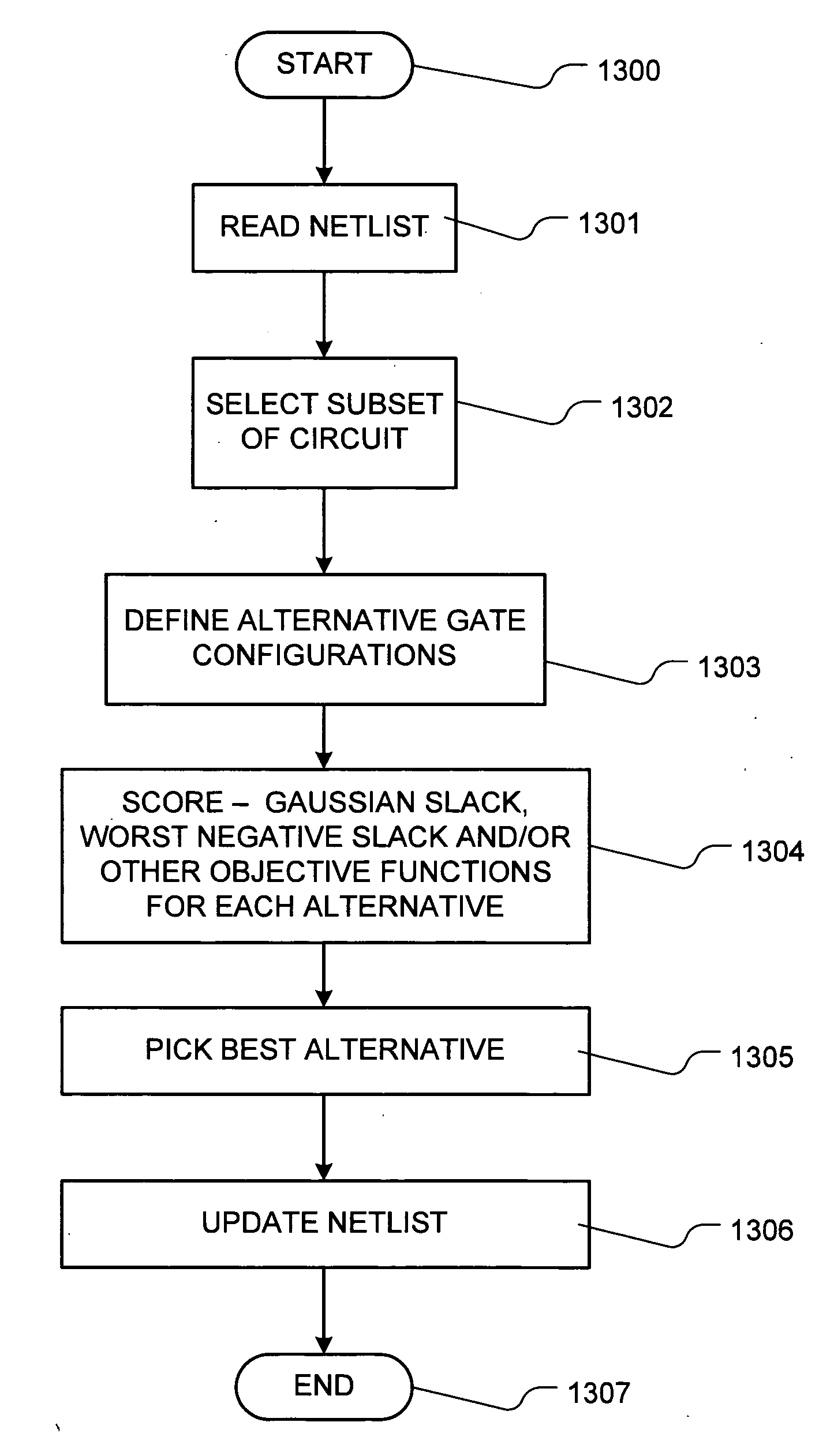

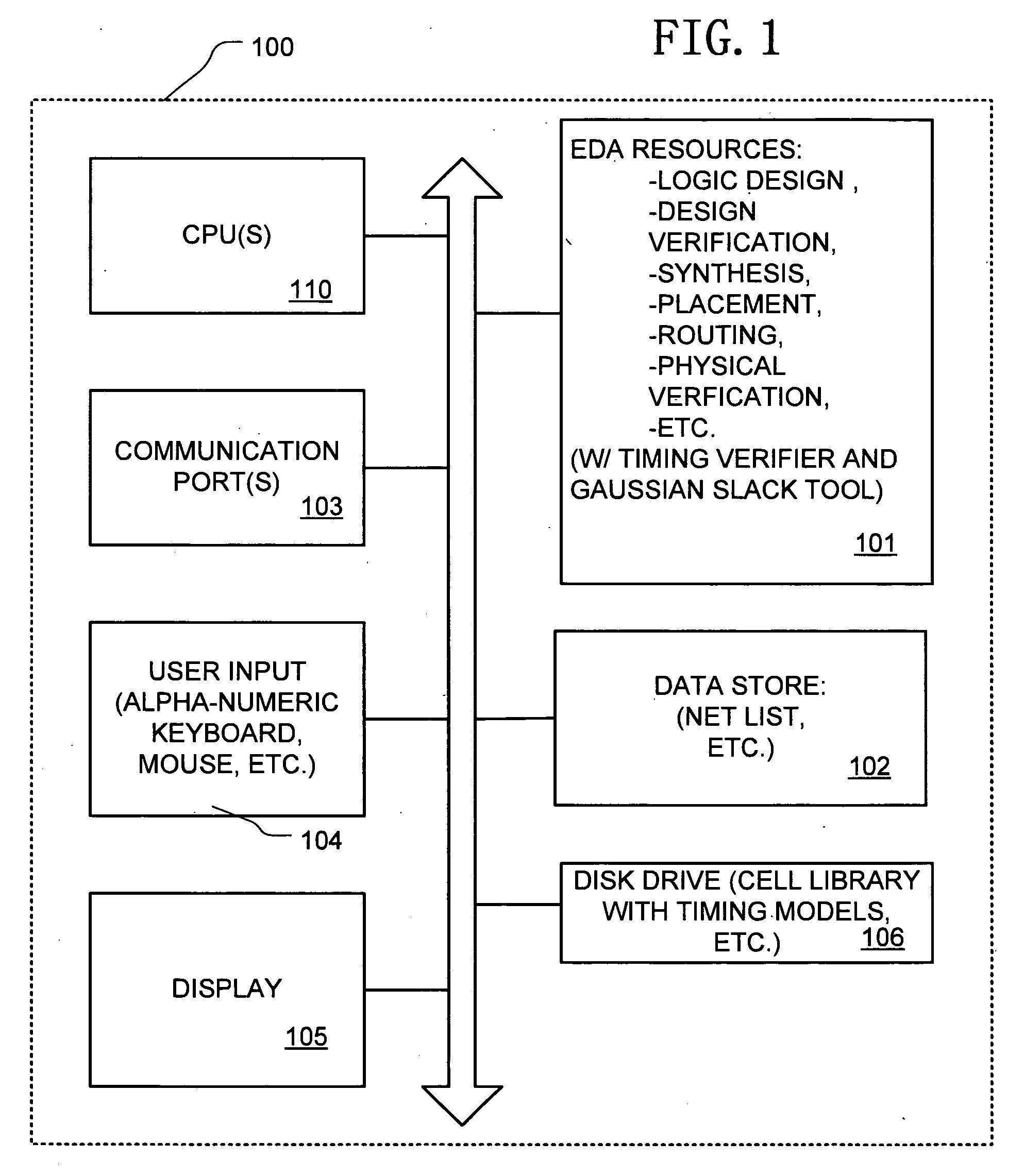

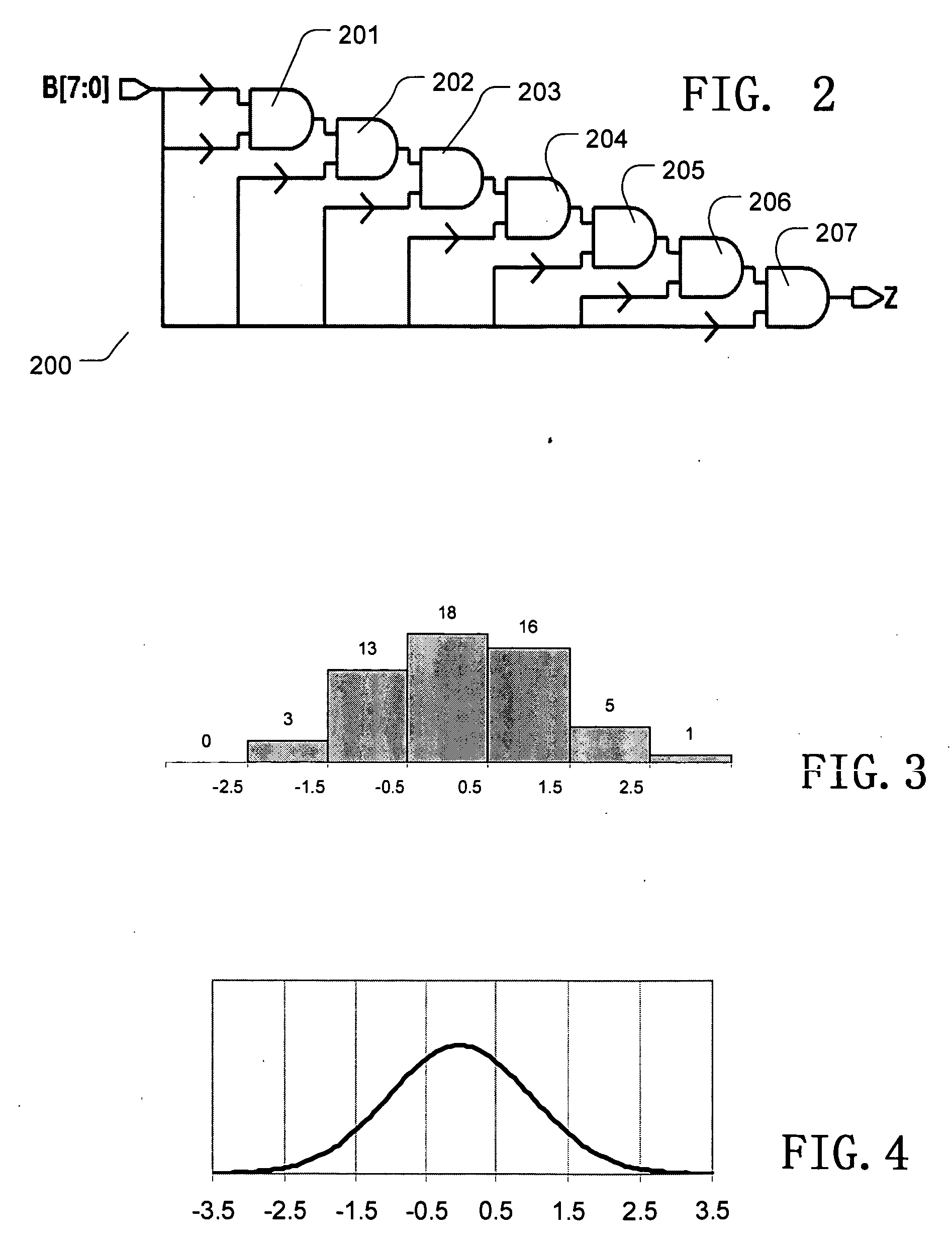

Automation method and system for assessing timing based on Gaussian slack

ActiveUS20070016881A1Analogue computers for electric apparatusComputation using non-denominational number representationAlgorithmArrival time

An automated design process using a computer system includes identifying a set of timing endpoints in a circuit defined by a machine-readable file. Values of slack in the estimated arrival times for the timing endpoints are assigned. Probability distribution functions, such as Gaussian distributions, are assigned for the respective values of slack, and are combined. The combination of probability distribution functions represents a measure of circuit performance. The measure is computed for alternative implementations of the circuit, and used to identify an alternative more likely to meet timing constraints.

Owner:SYNOPSYS INC

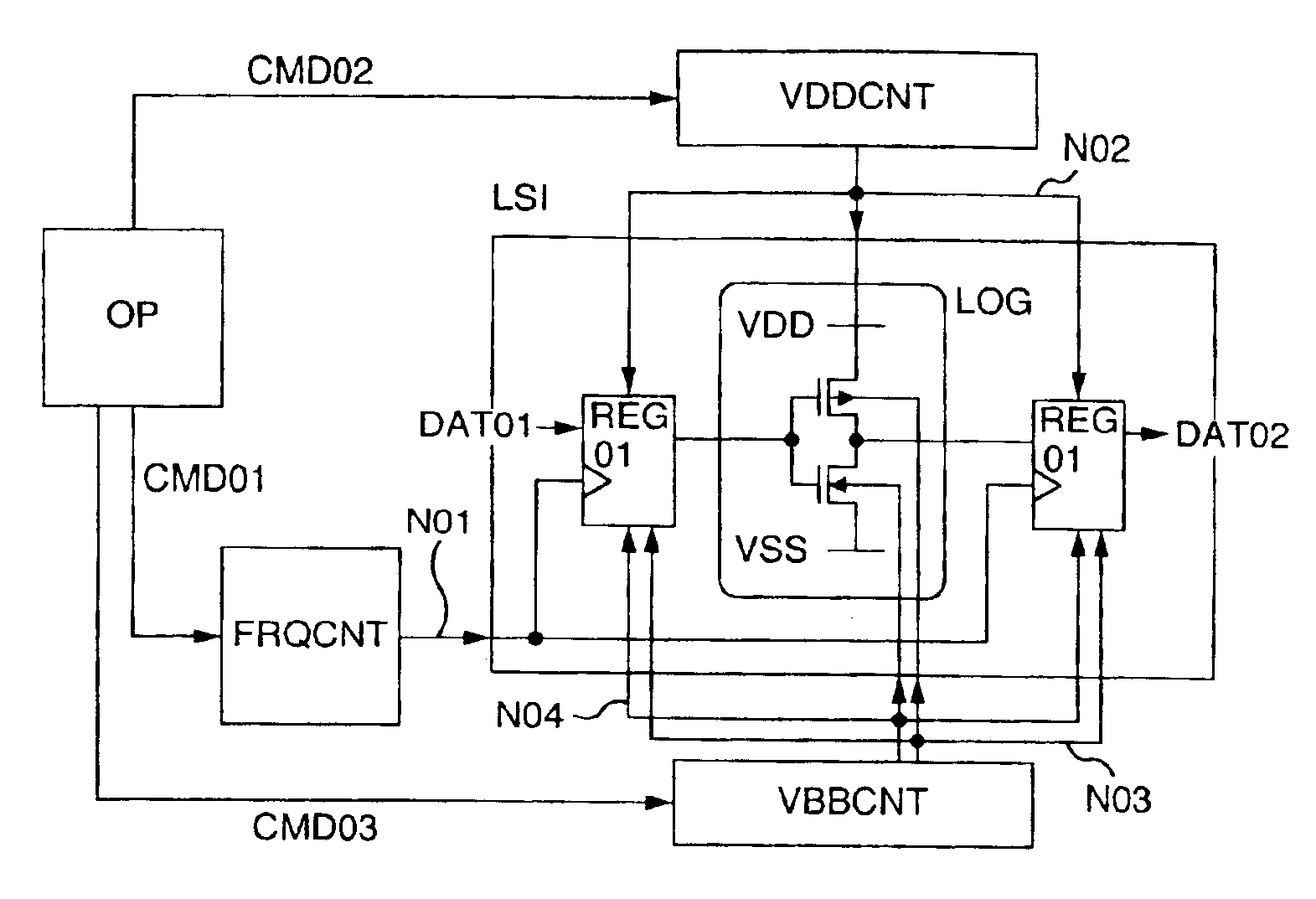

Semiconductor integrated circuit device in which operating frequency, supply voltage and substrate bias voltage are controllable to reduce power consumption

InactiveUS6943613B2Approximate performanceControl moreTransistorReliability increasing modificationsCMOSSubstrate bias voltage

A semiconductor integrated circuit device includes control circuits FRQCNT, VDDCNT and VBBCNT that generate the optimum clock signal, supply voltage and substrate bias respectively and then supply them to a main circuit LSI. This operation makes it possible to suppress the variations of a CMOS circuit characteristic, thereby improving the circuit performance. Further, the low power consumption is realized without degrading the operating speed of the CMOS circuit or increasing the power consumption of the CMOS circuit.

Owner:RENESAS ELECTRONICS CORP

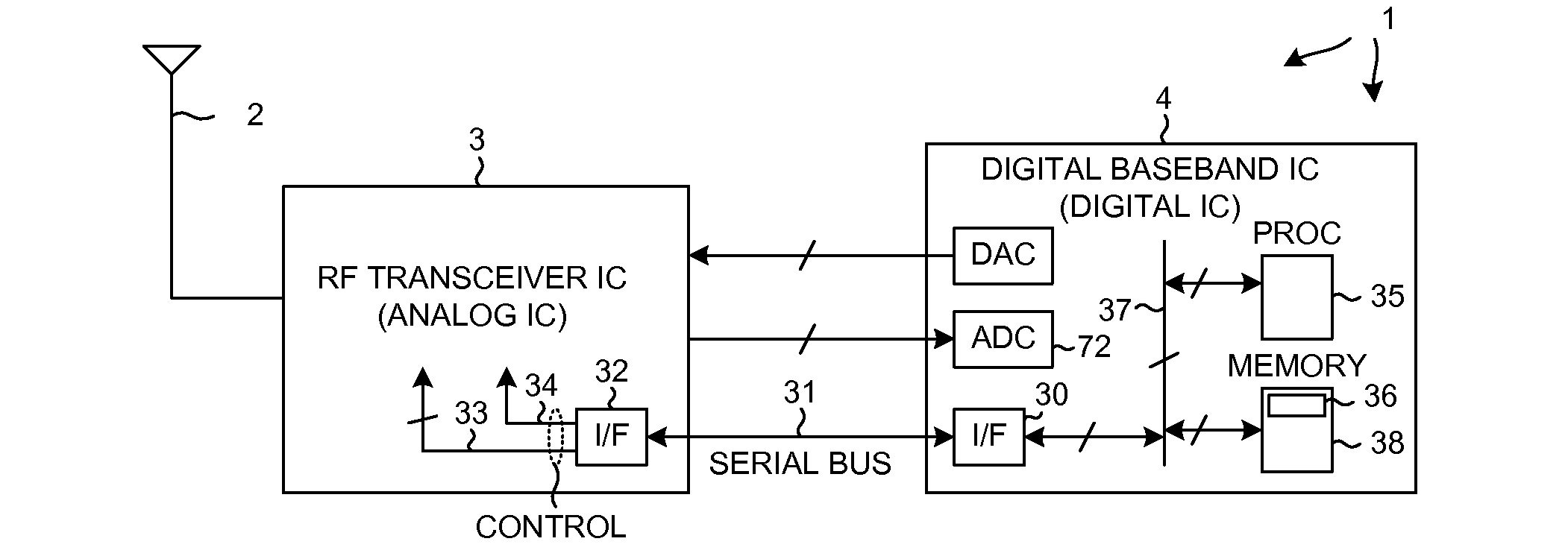

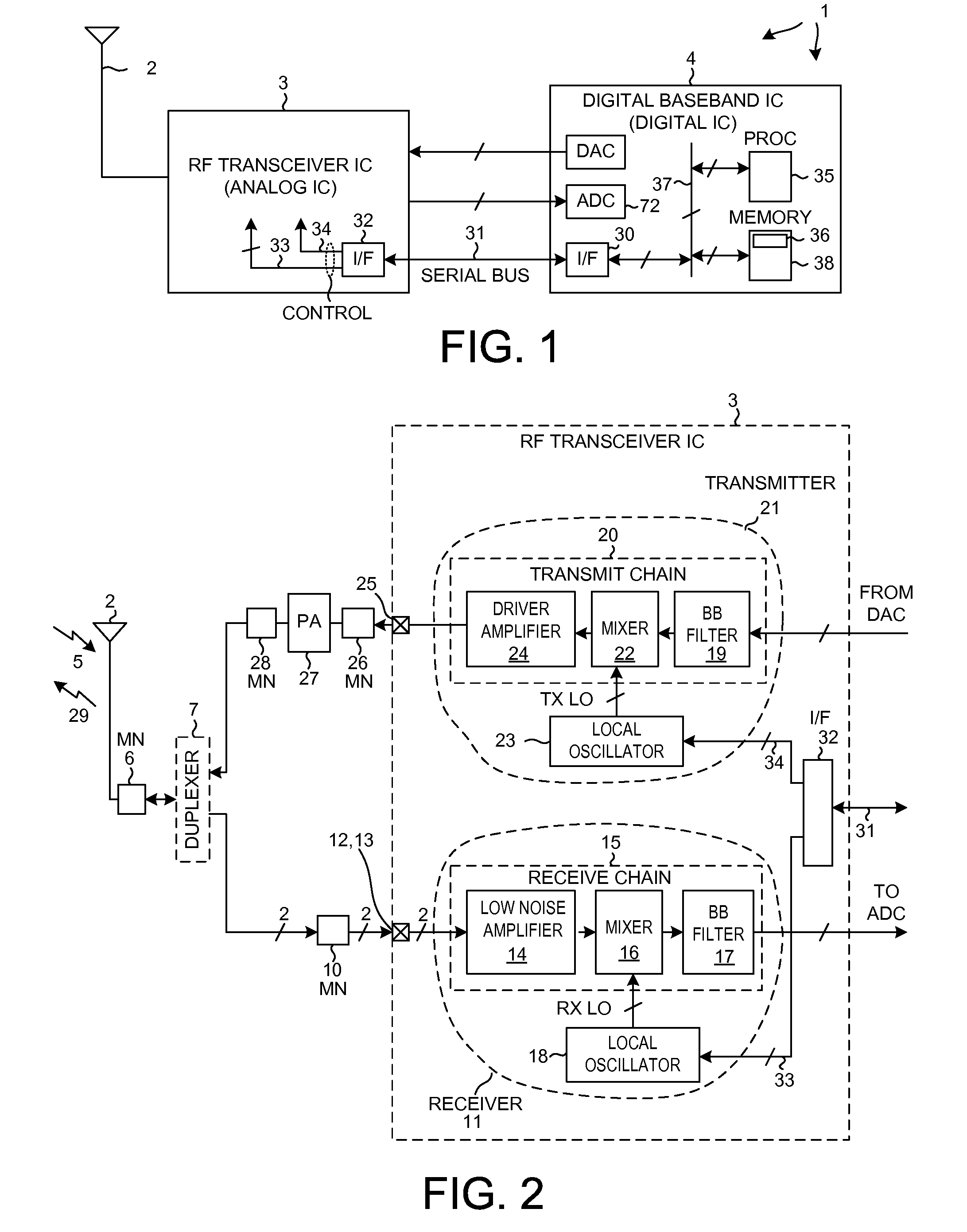

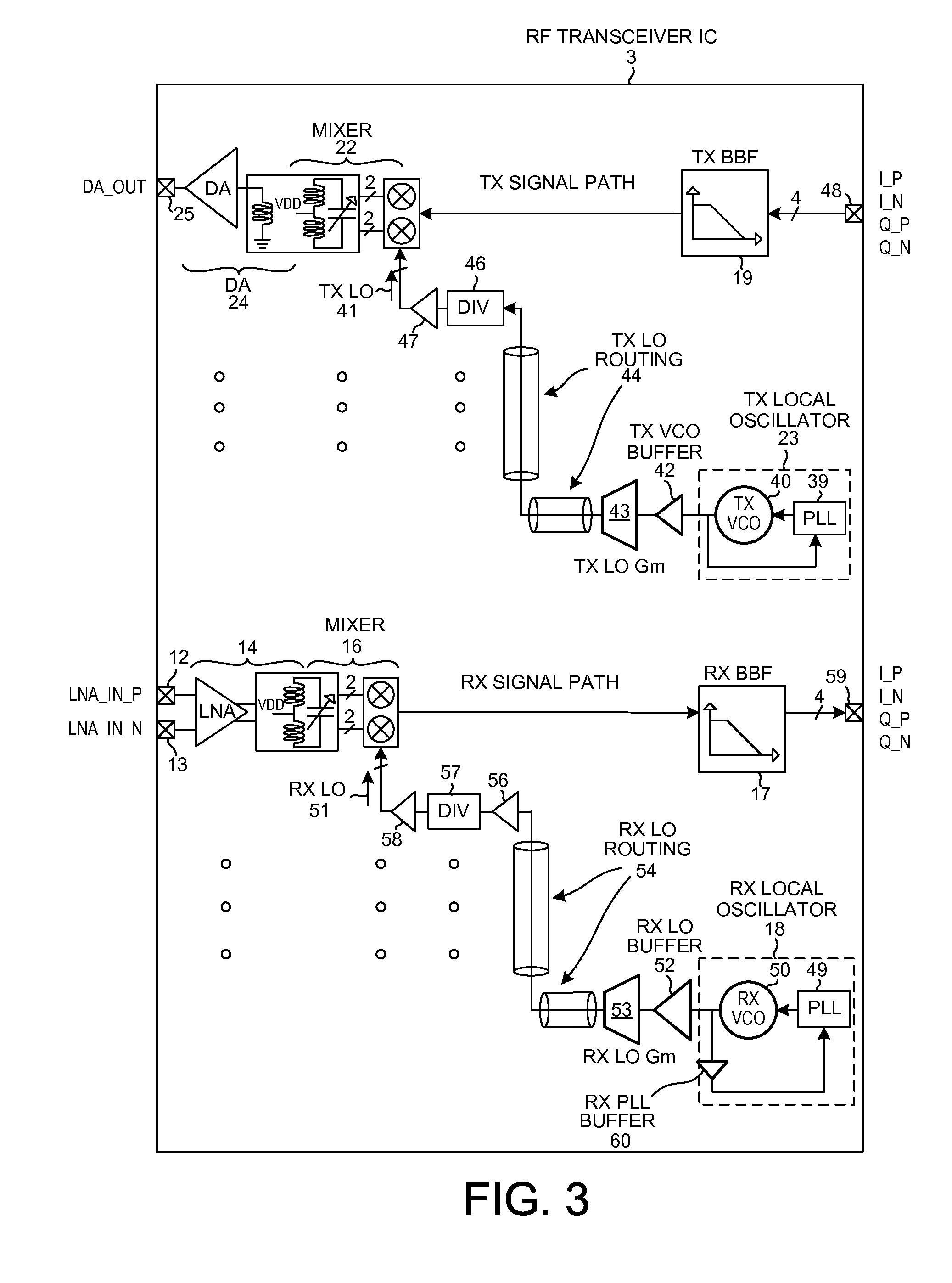

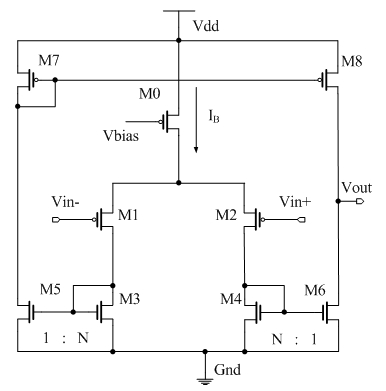

Reducing power consumption by taking advantage of superior in-circuit duplexer performance

Although the duplexer in a full-duplex transceiver circuit may only be guaranteed by the duplexer manufacturer to have a transmit band rejection from its TX port to its RX port of a certain amount, and may only be guaranteed to have a receive band rejection of another amount, the actual transmit band rejection and the actual receive band rejection of a particular instance of the duplexer may be better than specified. Rather than consuming excess power in the receiver and / or transmitter in order to meet performance requirements assuming the duplexer only performs as well as specified, the duplexer's in-circuit performance is measured as part of a transmitter-to-receiver isolation determination. Transmitter and / or receiver power settings are reduced where possible to take advantage of the measured better-than-specified in-circuit duplexer performance, while still meeting transceiver performance requirements. Power settings are not changed during normal transmit and receive mode operation.

Owner:QUALCOMM INC

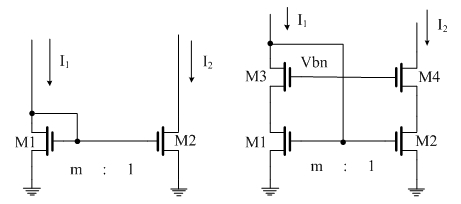

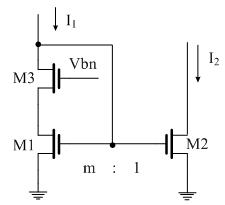

Low-power consumption broadband high-gain high-swing rate single-level operation transconductance amplifier

InactiveCN102045035AImprove performanceAddressing Inherent LimitationsDifferential amplifiersDc-amplifiers with dc-coupled stagesTransconductanceCircuit performance

The invention discloses a low-power consumption broadband high-gain high-slew rate single-stage operational transconductance amplifier, which is formed by successively connecting a constant current bias stage, a differential input stage and a load current mirror transmission output stage in series. The load current mirror transmission output stage comprises eight N type MOS (metal oxide semiconductor) transistors from NM1 to NM8. Through the invention, the inherent limit restraint in a linear operational amplifying circuit is thoroughly solved, and the circuit performance under static AC small signals and dynamic big signals is comprehensively improved and enhanced.

Owner:SOUTHEAST UNIV

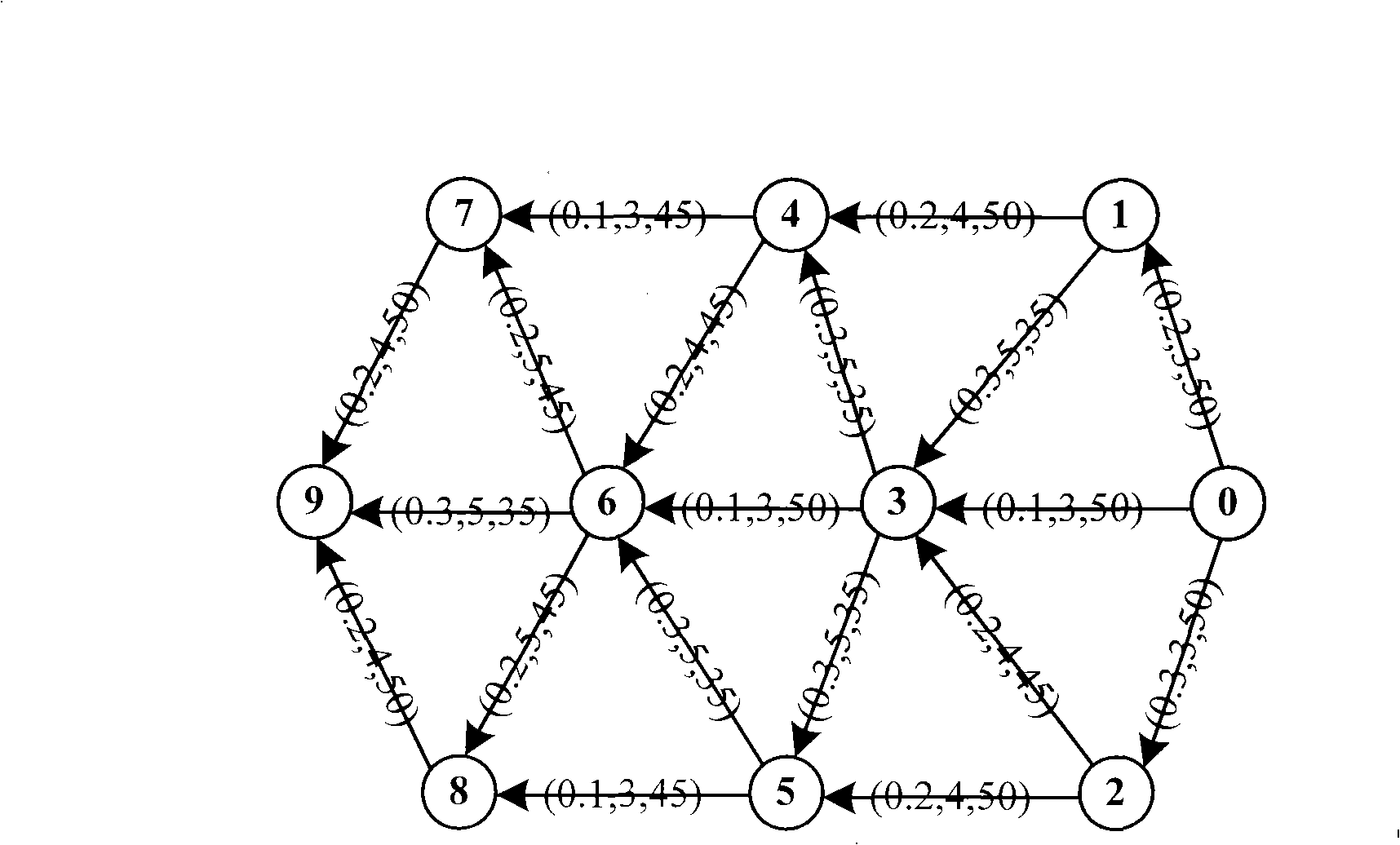

Method for establishing multi-path route based on link multiple characteristic values in wireless sensor network

InactiveCN101325544AExtend the life cycleImprove reliabilityNetwork traffic/resource managementNetwork topologiesWireless mesh networkTime delays

The invention relates to a multipath routing establishing method based on chain circuit multi-eigenvalue in a wireless sensor network. The method includes: upon transmitting 'interest' data packets from a destination node to an originating node, endowing a definite selection probability to each route according to three eigenvalues (energy consumption, time-delay and band-width) in network chain, thereby establishing a gradient table; upon transmitting detecting data packets from the originating node to the destination nods, selecting a neighbor node with highest probability every time as the node of next-hop, if the neighbor node with highest probability reject to receive data packets, selecting a neighbor node with next high probability as the node of next-hop, until reaching the destination node; finally the destination node transmitting strengthened signals with different grades to the originating node, thereby establishing multipath from the originating node onto the destination node, so that the data can always been transmitted in multipath with better chain circuit performance. The invention extends survival cycle of network, improves transmission reliability and realizes load proportion.

Owner:WUHAN UNIV OF TECH

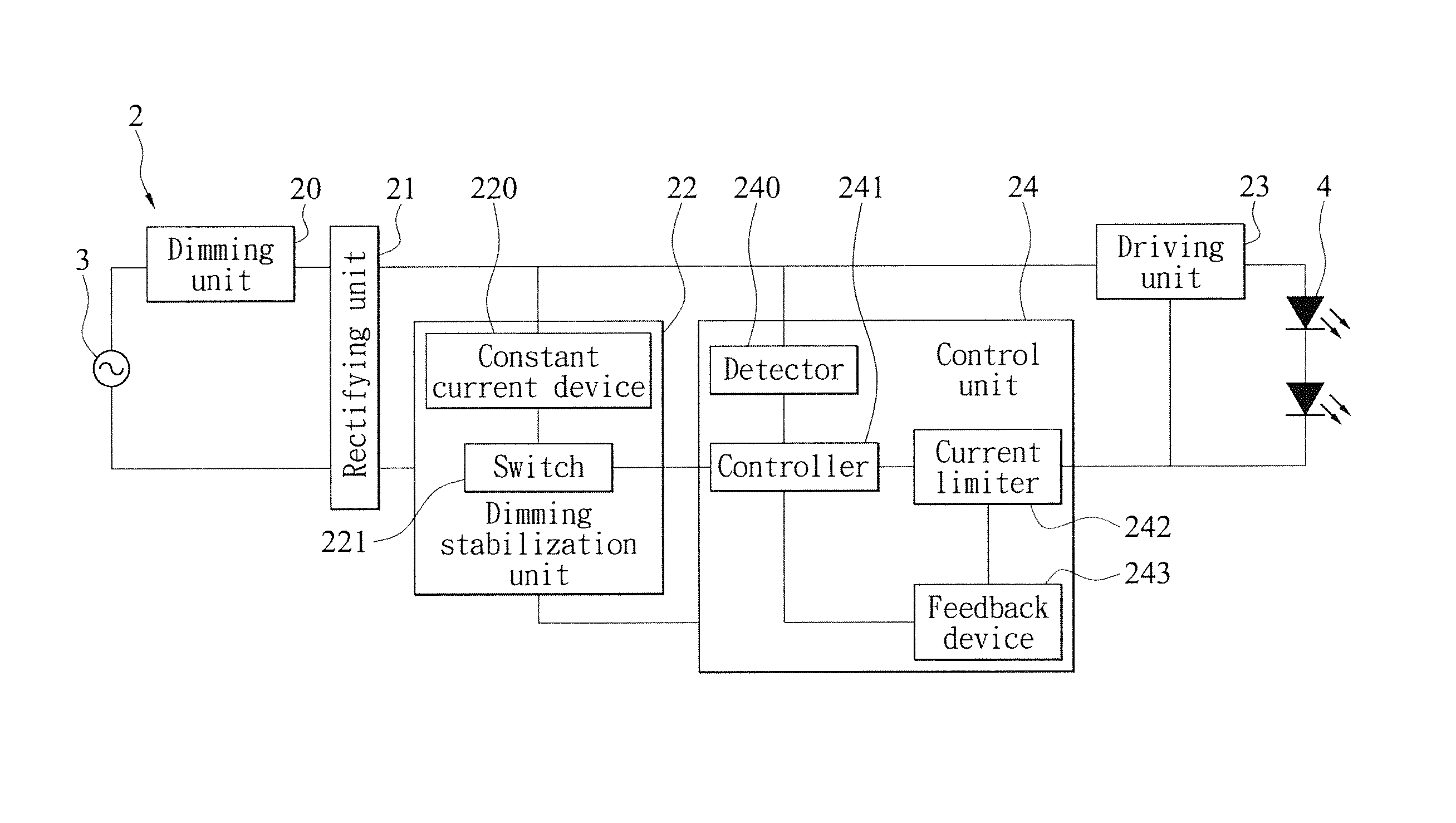

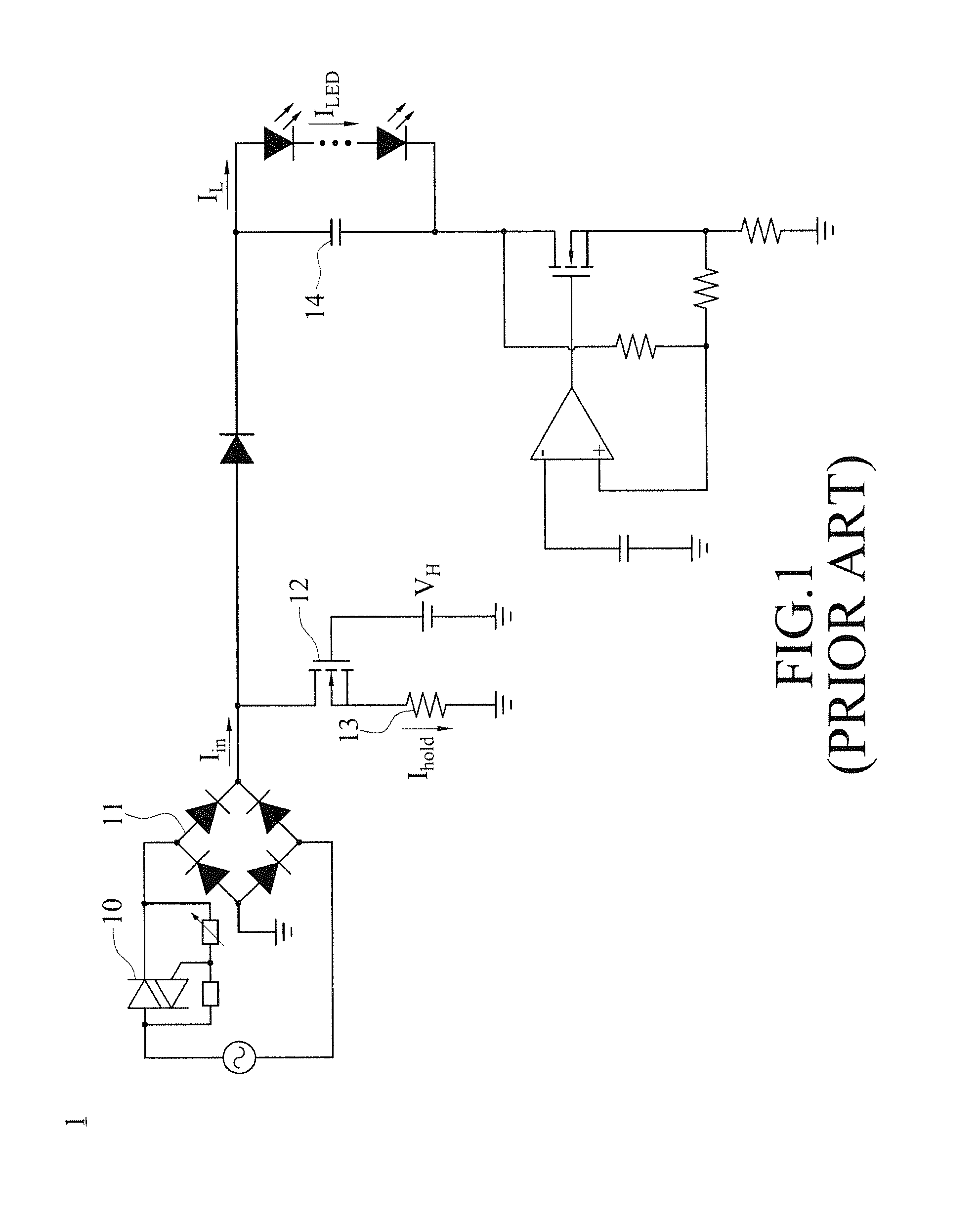

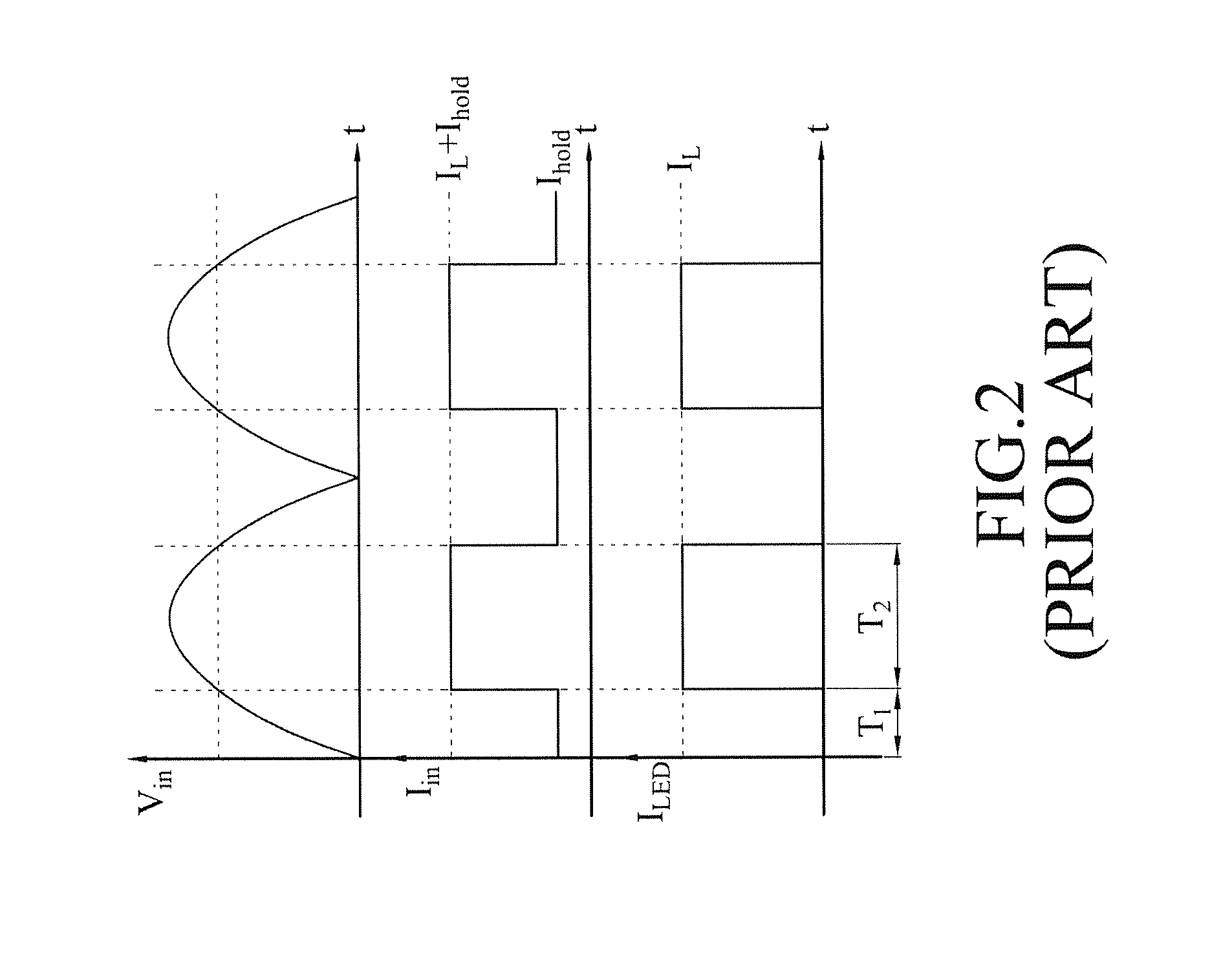

Variable power dimming control circuit

ActiveUS8941328B2Improve dimming stabilityReduce unnecessary power consumptionElectrical apparatusElectroluminescent light sourcesTRIACControl circuit

Disclosed is a variable power dimming control circuit for driving and linearly adjusting the illumination brightness of a plurality of light emitting diodes (LEDs), and the circuit includes a dimming stabilization unit and a control unit. The control unit is provided for detecting an input current of a circuit, and the dimming stabilization unit is driven for outputting a holding current when the input power is smaller than a standard, and stopping the output the holding current when the input power is greater than the standard. When the LEDs are dimmed to low luminance, a chip controls the operation of the dimming stabilization unit to assure the stability of the dimming operation of a TRIAC. When the LEDs are adjusted to high or full brightness, the chip stops the output of the holding current to reduce unnecessary power consumption and enhance the overall circuit performance effectively.

Owner:EPISTAR CORP

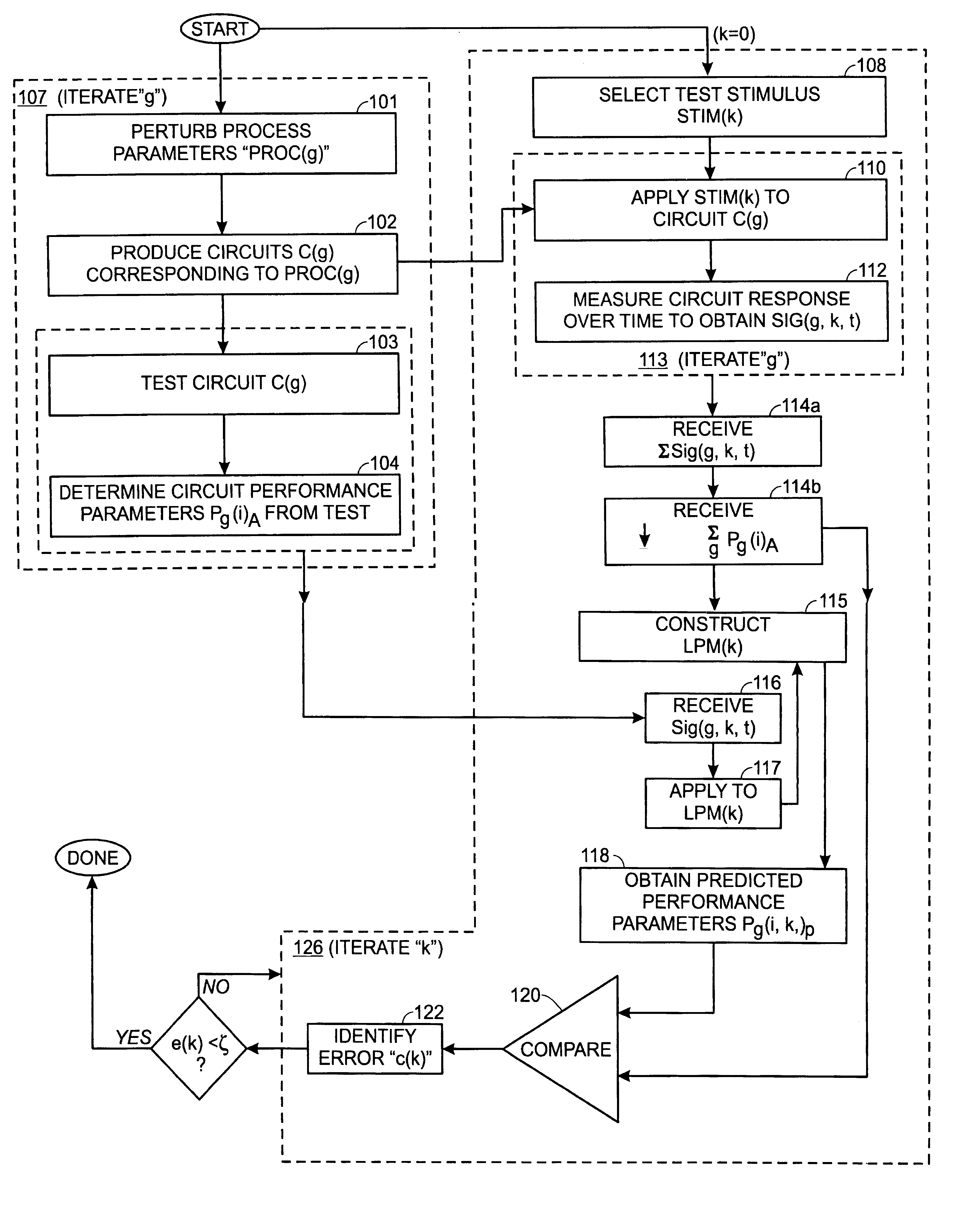

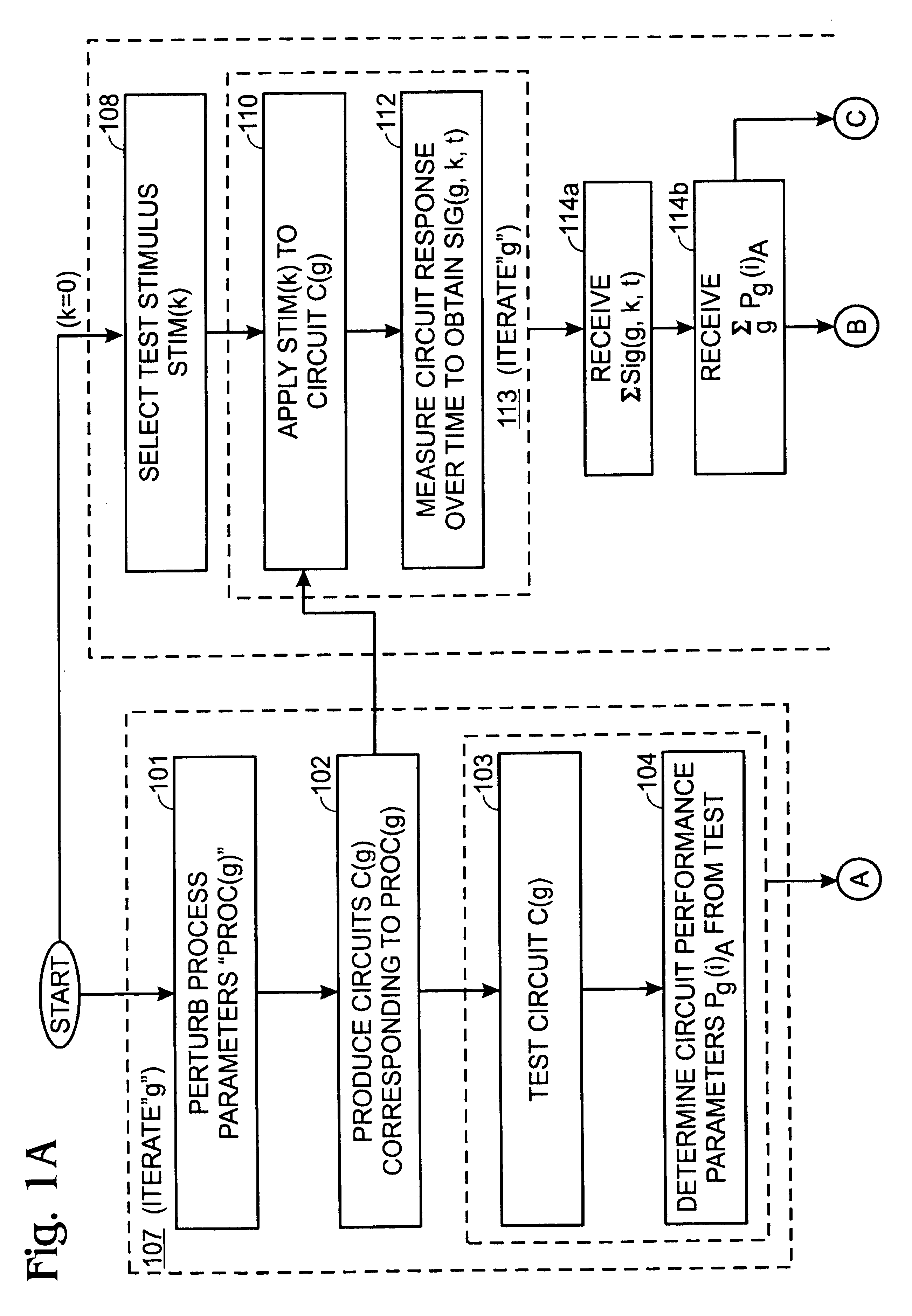

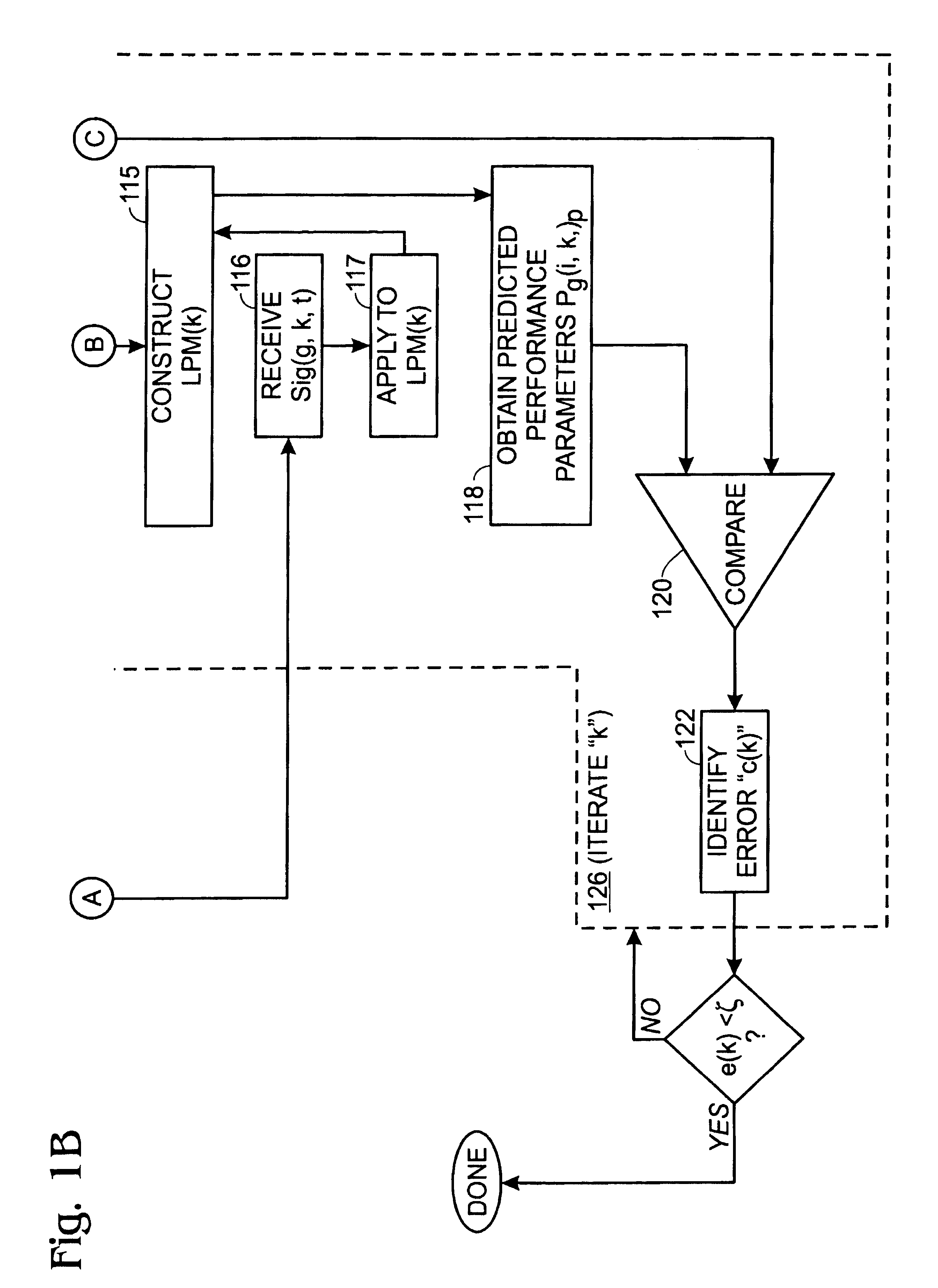

Method and apparatus for low cost signature testing for analog and RF circuits

InactiveUS7006939B2Error minimizationLow costResistance/reactance/impedenceElectronic circuit testingTest stimulusPredicting performance

A low cost signature test for RF and analog circuits. A model is provided to predict one or more performance parameters characterizing a first electronic circuit produced by a manufacturing process subject to process variation from the output of one or more second electronic circuits produced by the same process in response to a selected test stimulus, and iteratively varying the test stimulus to minimize the error between the predicted performance parameters and corresponding measured values for the performance parameters, for determining an optimized test stimulus. A non-linear model is preferably constructed for relating signature test results employing the optimized test stimulus in manufacturing testing to circuit performance parameters.

Owner:GEORGIA TECH RES CORP

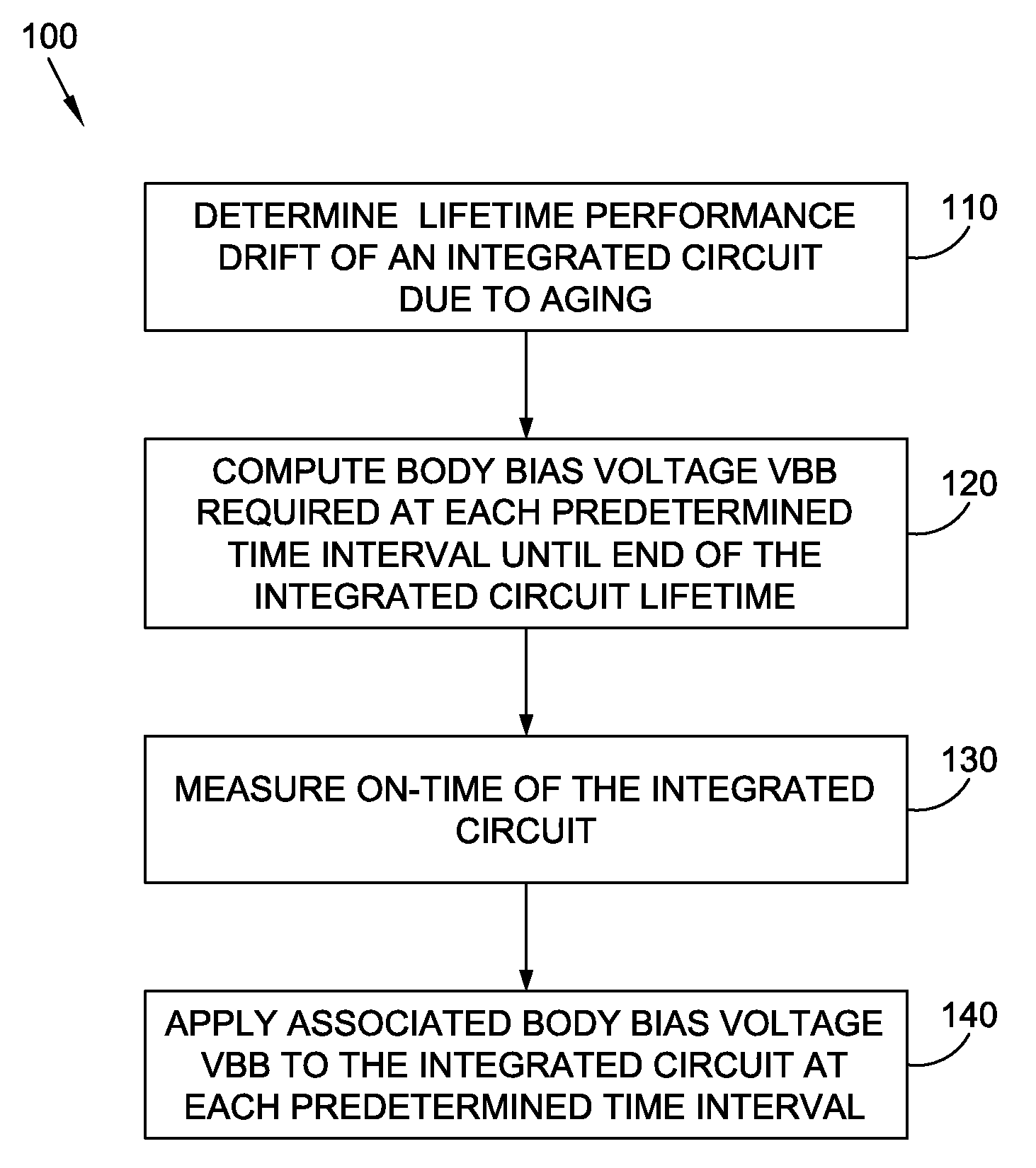

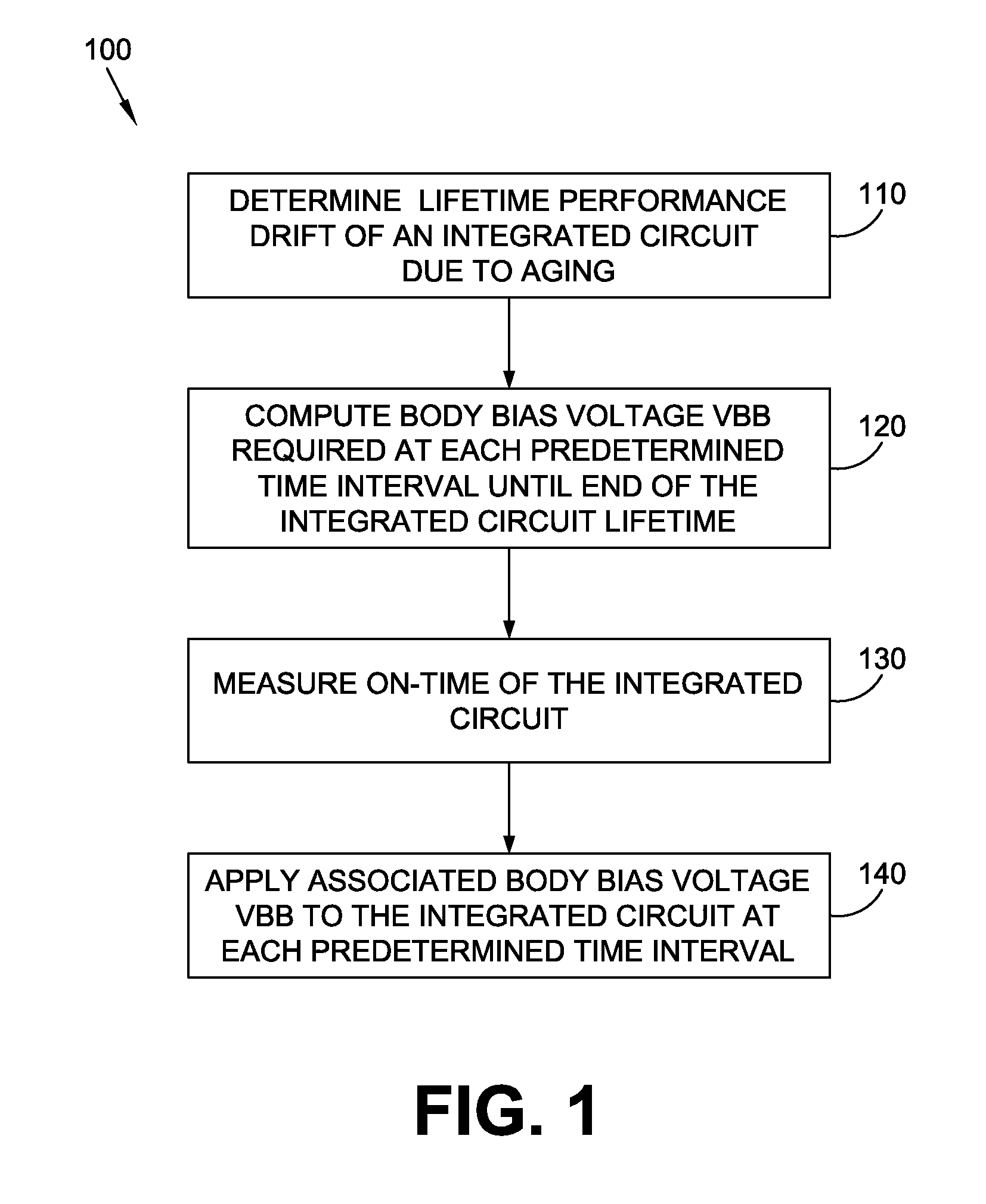

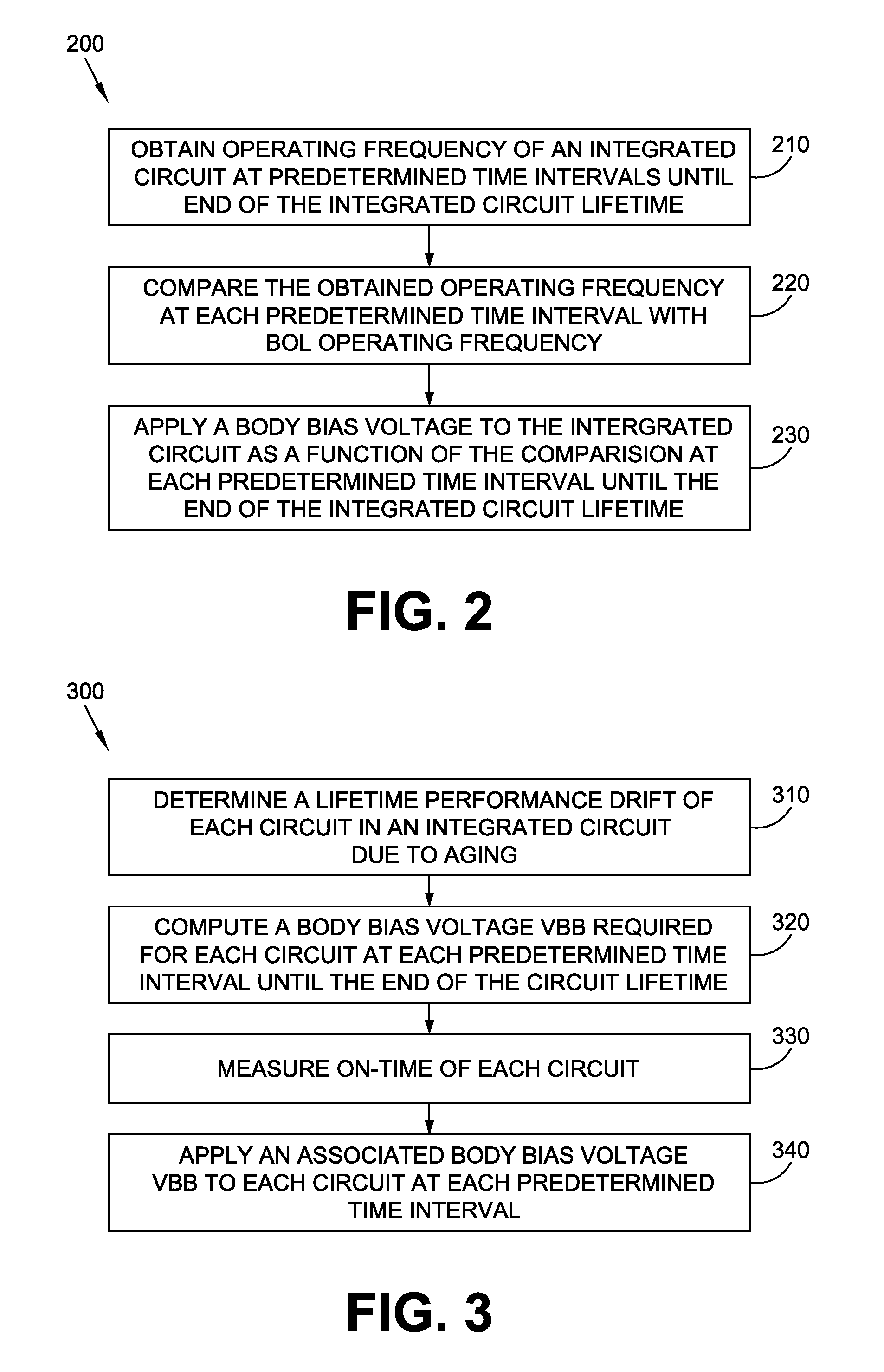

Technique for aging induced performance drift compensation in an integrated circuit

ActiveUS20080116455A1Resistance/reactance/impedenceSemiconductor/solid-state device detailsEngineeringLife time

An improved compensation circuit that compensates for lifetime performance drifts due to aging of integrated circuits to improve the circuit performance. In one example embodiment, this is achieved by applying a body bias voltage VBB to the integrated circuit to compensate for the lifetime performance drift due to hot carrier and NBTI induced aging

Owner:TEXAS INSTR INC

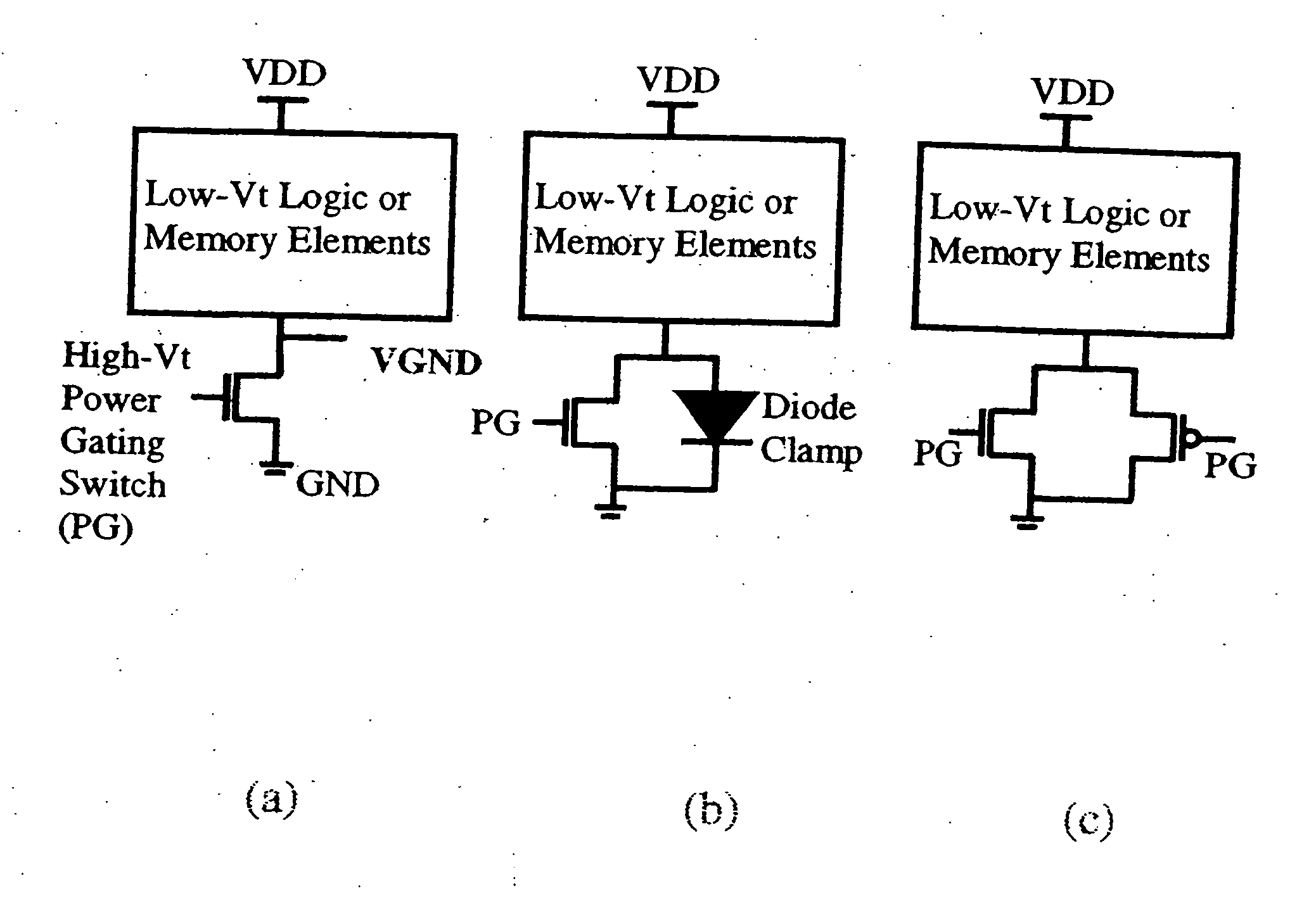

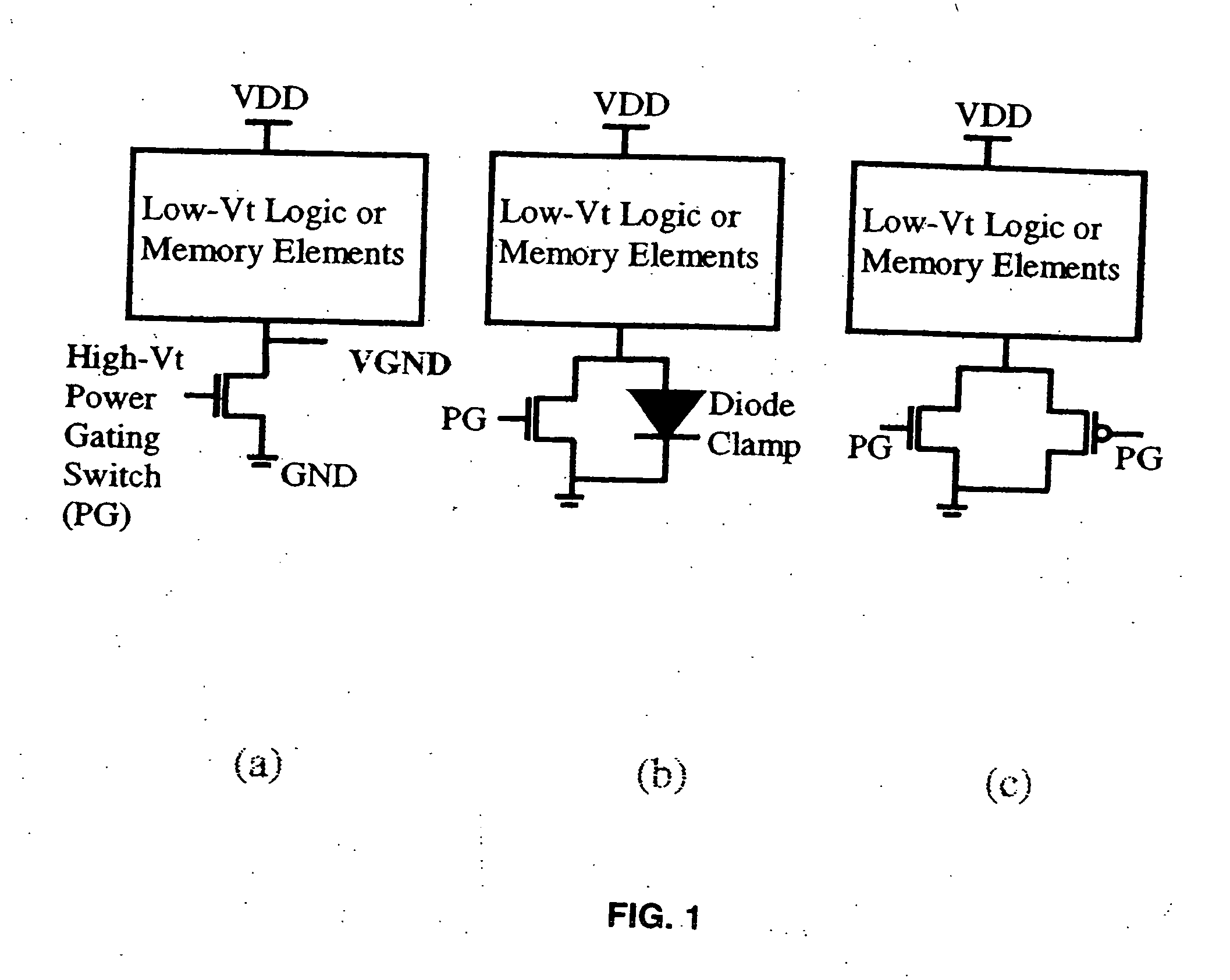

High-density low-power data retention power gating with double-gate devices

A new power gating structure with robust data retention capability using only one single double-gate device to provide both power gating switch and virtual supply / ground diode clamp functions. The scheme reduces the transistor count, area, and capacitance of the power gating structure, thus improving circuit performance, power, and leakage. The scheme is compared with the conventional power gating structure via mixed-mode physics-based two-dimensional numerical simulations. Analysis of virtual supply / ground bounce for the proposed scheme is also presented.

Owner:GLOBALFOUNDRIES US INC

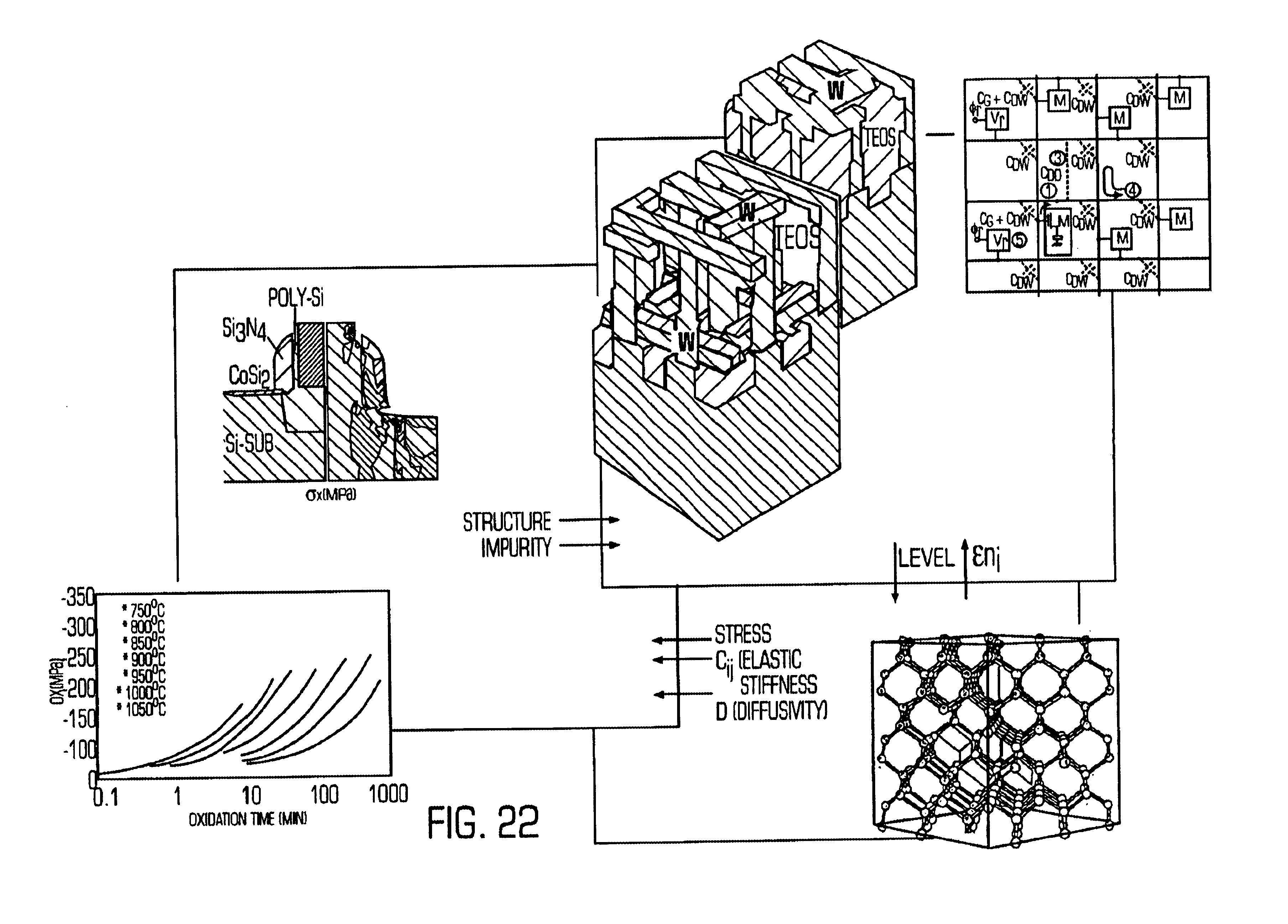

Method and apparatus for simulating manufacturing, electrical and physical characteristics of a semiconductor device

InactiveUS20020123872A1Semiconductor/solid-state device detailsSolid-state devicesElement modelMaterial Design

An electronic device simulator includes a three-dimensional lumped device model, a three-dimensional visco-elastic process simulation model and a material design model that are interlinked with each other. The three-dimensional lumped device element model comprises a Poisson's equation model, an electron continuity equation model, a hole continuity equation model, a Maxwell's equations model, an eddy current equation model, and an Ohm's law equation model. The simulator accounts for the three dimensional characteristics of the circuit to determine circuit performance.

Owner:KK TOSHIBA

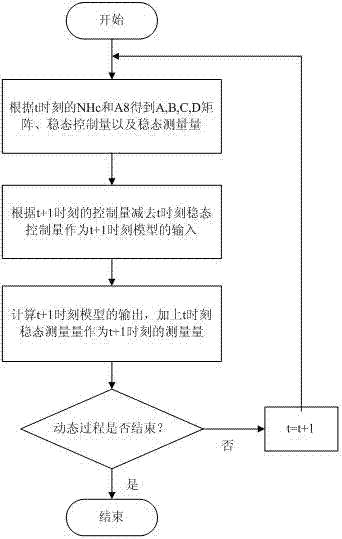

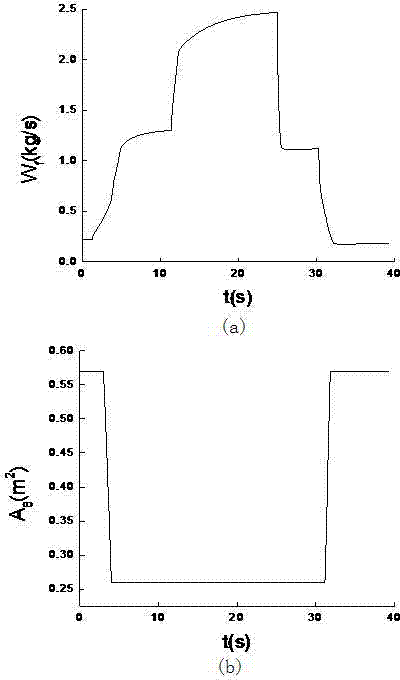

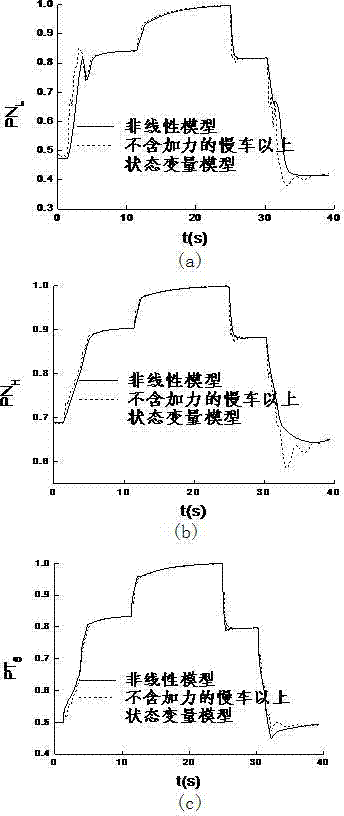

Method for building covered wire inner full-state turbofan engine vehicle-mounted real-time model

InactiveCN103942357AMeet real-time requirementsReduce computing timeSpecial data processing applicationsAdaptive controlKaiman filterIdle speed

The invention discloses a method for building a covered wire inner full-state turbofan engine vehicle-mounted real-time model. The method comprises the steps of firstly building a vehicle-mounted real-time dynamic model, indicating an applied force-included and above-idle-speed state, of a turbofan engine, then, building a starting simplified model of the turbofan engine, finally, utilizing a Kalman filter for estimating gas circuit performance characteristic parameters of the turbofan engine, and building a vehicle-mounted self-adaptation real-time model indicating the applied force-included and above-idle-speed state. The method can meet the requirement of a covered wire full-state general model of the turbofan engine for precision and vehicle-mounted real-time performance, the strong adaptive capacity for model mismatch caused by the engine individual difference and performance degradation is obtained, model foundation is provided for experimental verification of a modern control theory and a fault-tolerant control method, and the method plays a positive and promotion role in shortening the preparation time, reducing test risk and cost.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Integrated scheme for yield improvement by self-consistent minimization of IC design and process interactions

InactiveUS20050114822A1Improve performanceHigh yieldCAD circuit designOriginals for photomechanical treatmentEngineeringSensitivity analyses

A method for performing self-consistent minimization of IC design and process interactions is disclosed. This method is based on calculating the amount of design-process interaction based on the information derived from circuit sensitivity analysis and process characterization. Optical proximity correction is subsequently performed in such a way that a) ensures that desired circuit performance is achieved in a given manufacturing environment if at all possible and b) also limits the increase in mask complexity to a realistic minimum.

Owner:AXELRAD VALERY +2

Method and platform for integrated physical verifications and manufacturing enhancements

InactiveUS7100134B2Optimize circuit designDigital computer detailsComputer aided designPhysical verificationEngineering

An automated design for manufacturability platform which provides integrated physical verification and manufacturing enhancement operations. The platform uses an efficient data structure capable of handling and manipulating both layout circuit and geometry characteristics, which permits a wide range of operations such as timing analysis, design-rule checking and optical proximity corrections on a single platform. This feature eliminates the need to translate layout representations between various tools without the requirement of using a common database. Moreover, the platform's common user interface enables encapsulated information exchange between the design and the manufacturing teams, permiting early consideration of manufacturing distortion or enhancement impact on circuit performance.

Owner:RPX CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com