Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

223results about How to "Improve circuit performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

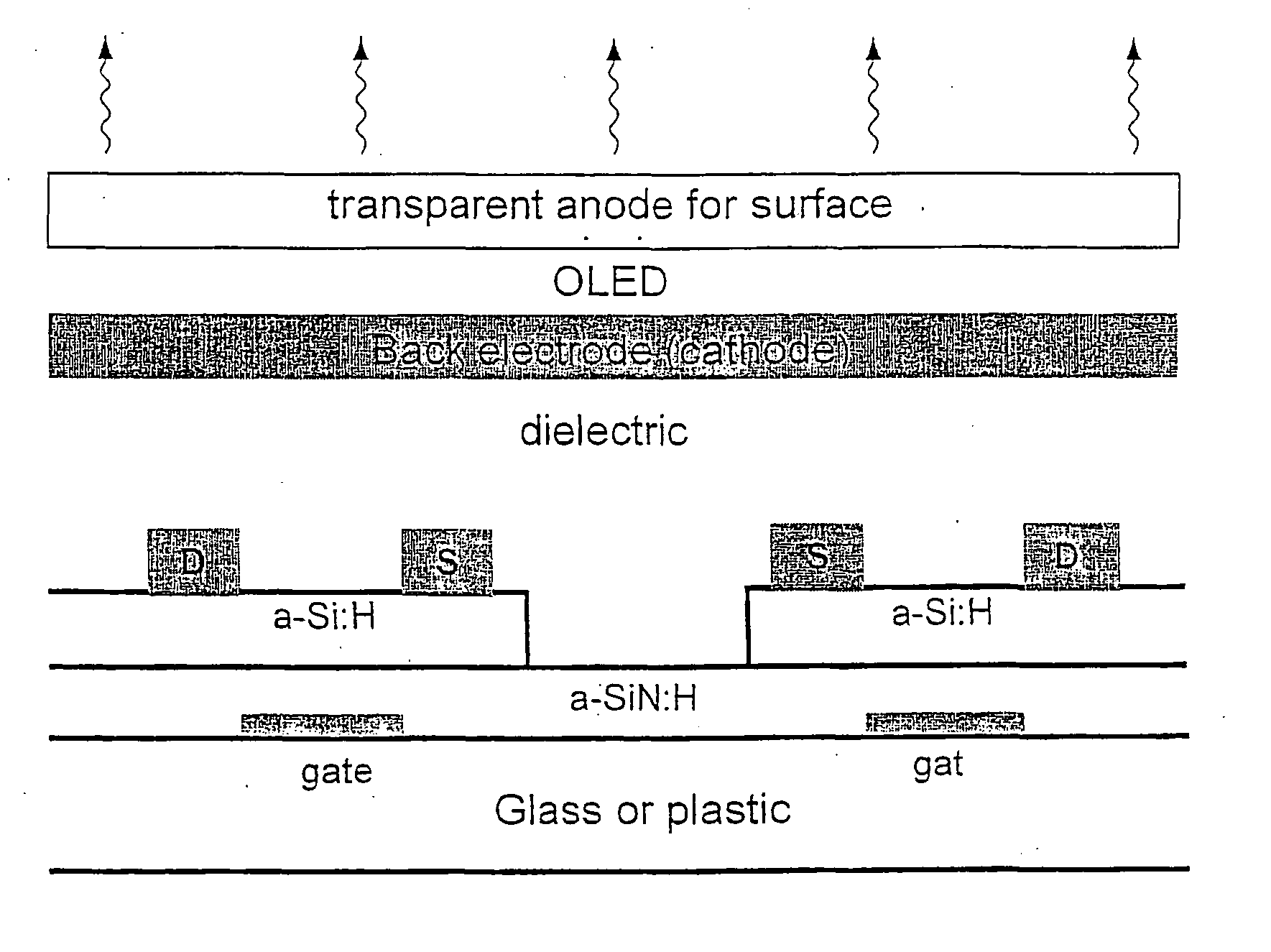

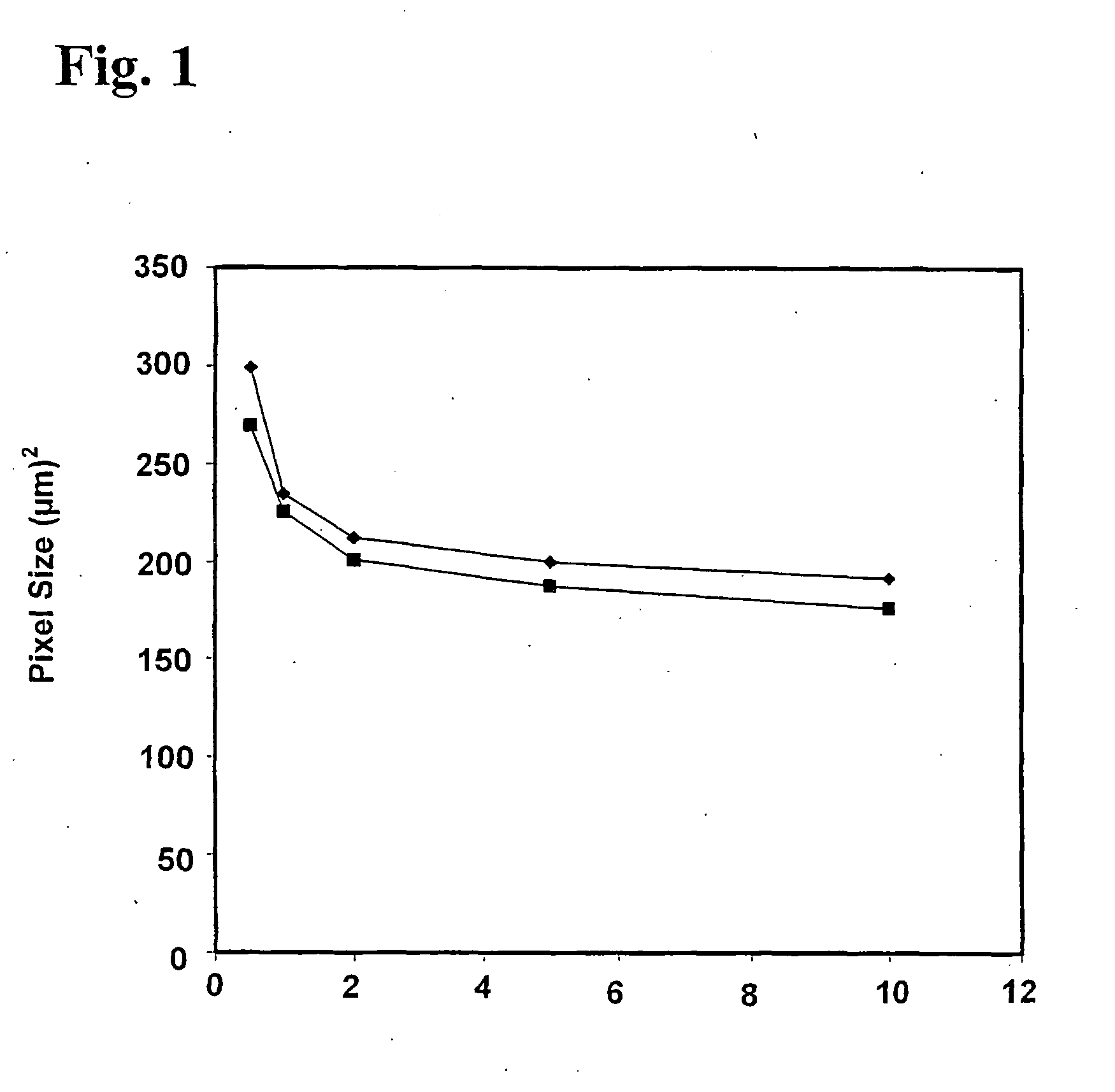

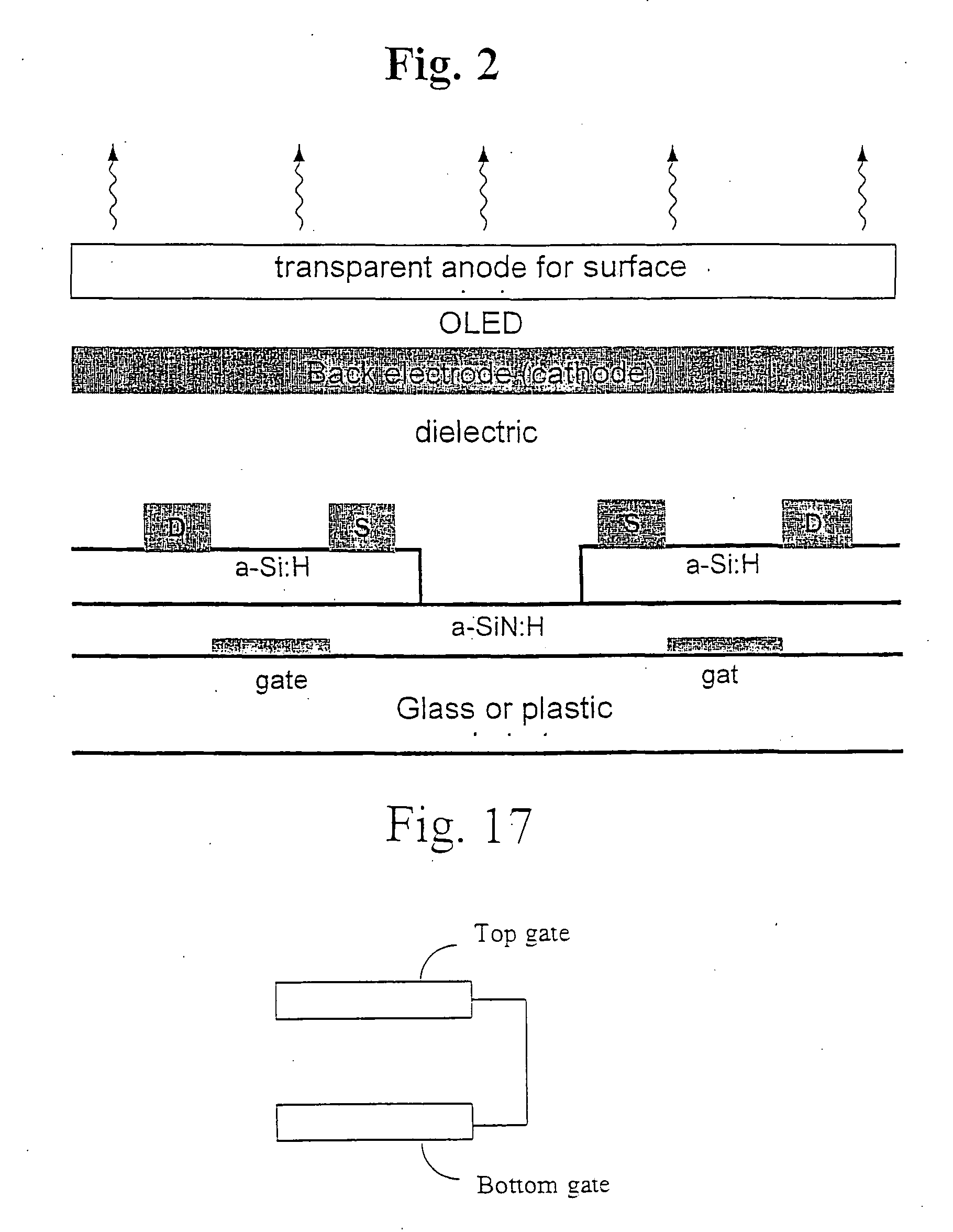

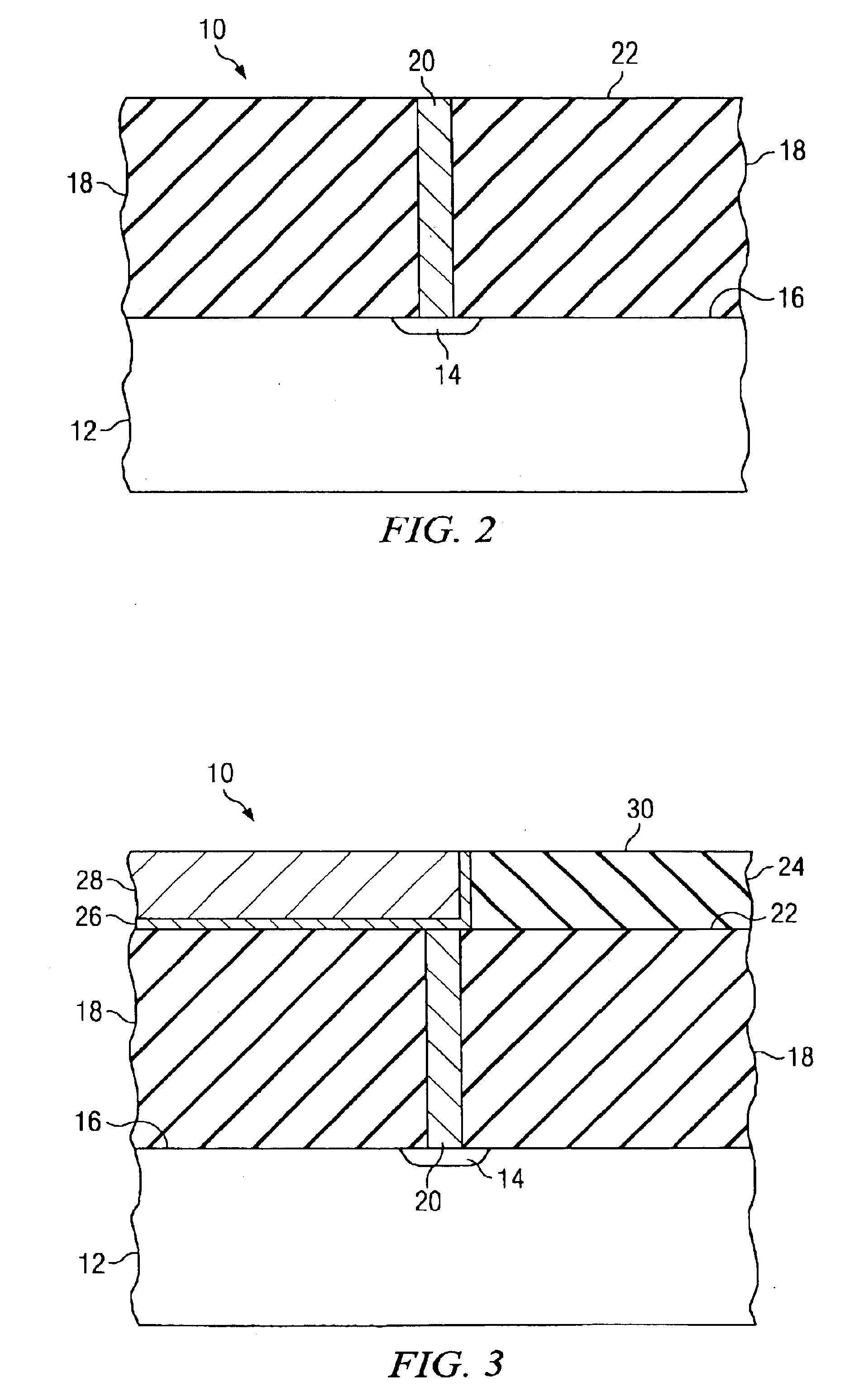

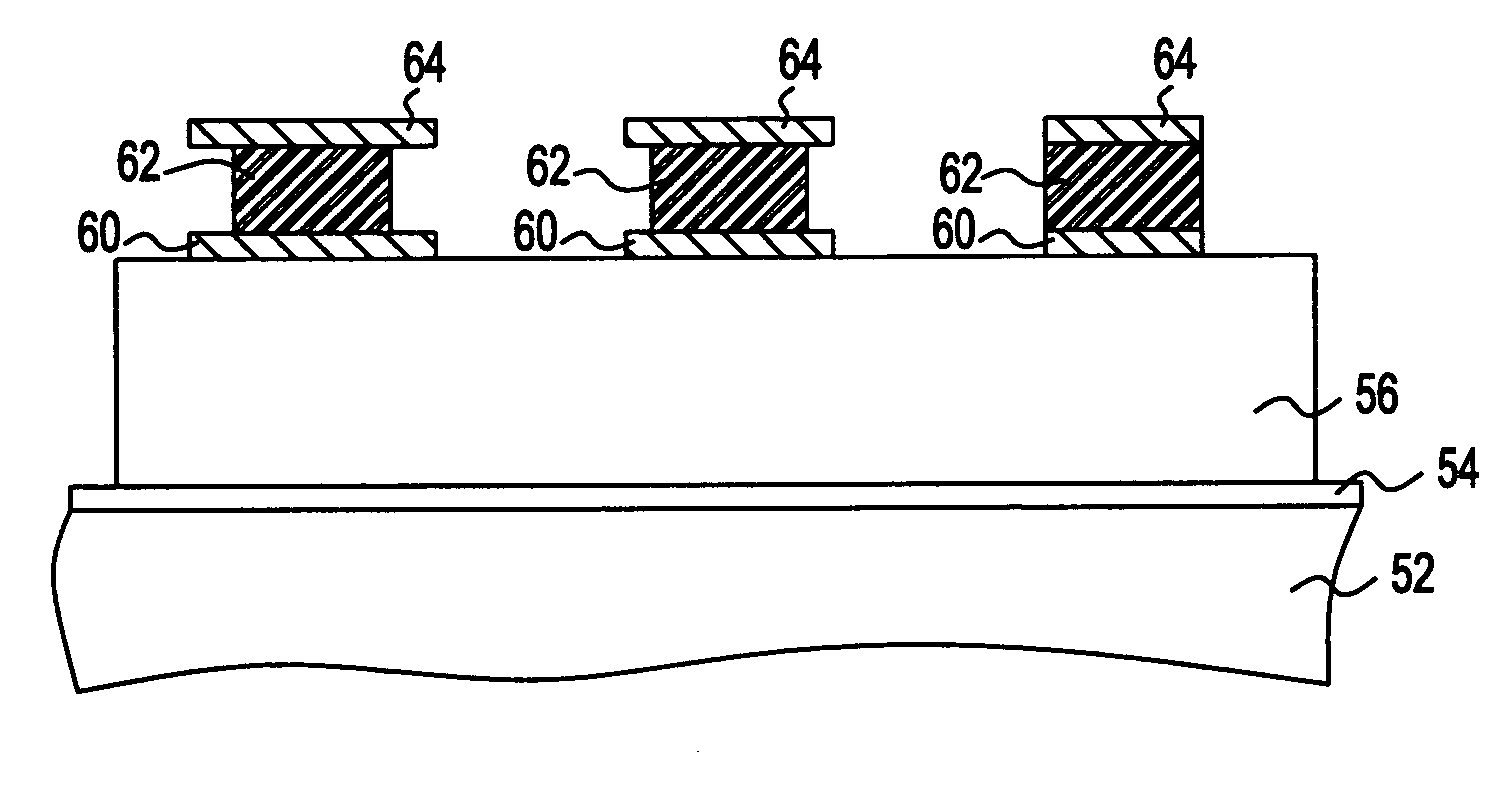

Pixel current driver for organic light emitting diode displays

InactiveUS20060027807A1Improve circuit performanceMinimize chargeTransistorStatic indicating devicesBottom gateDisplay device

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed ΔVT-compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for δVT. The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

Owner:IGNIS INNOVATION

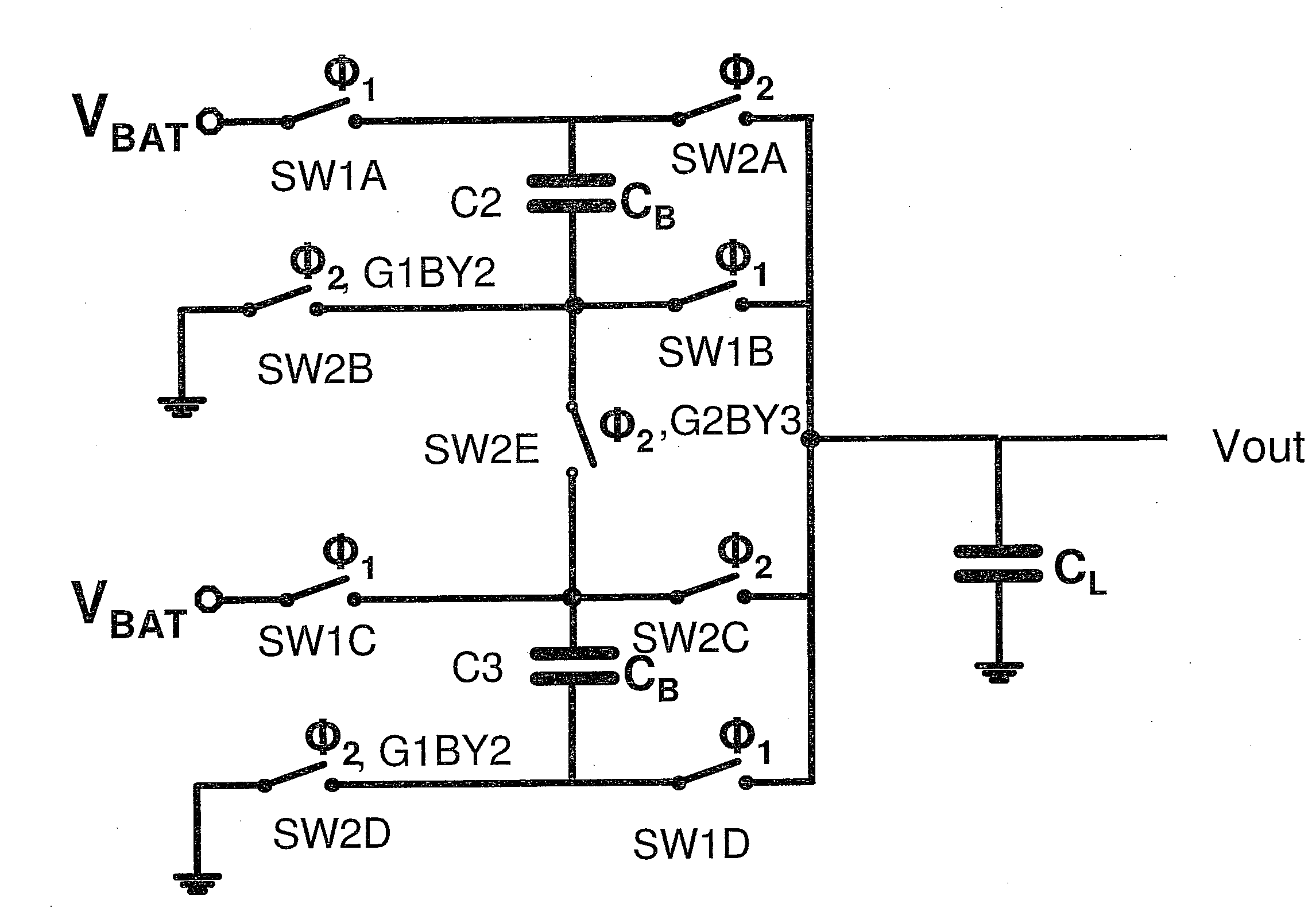

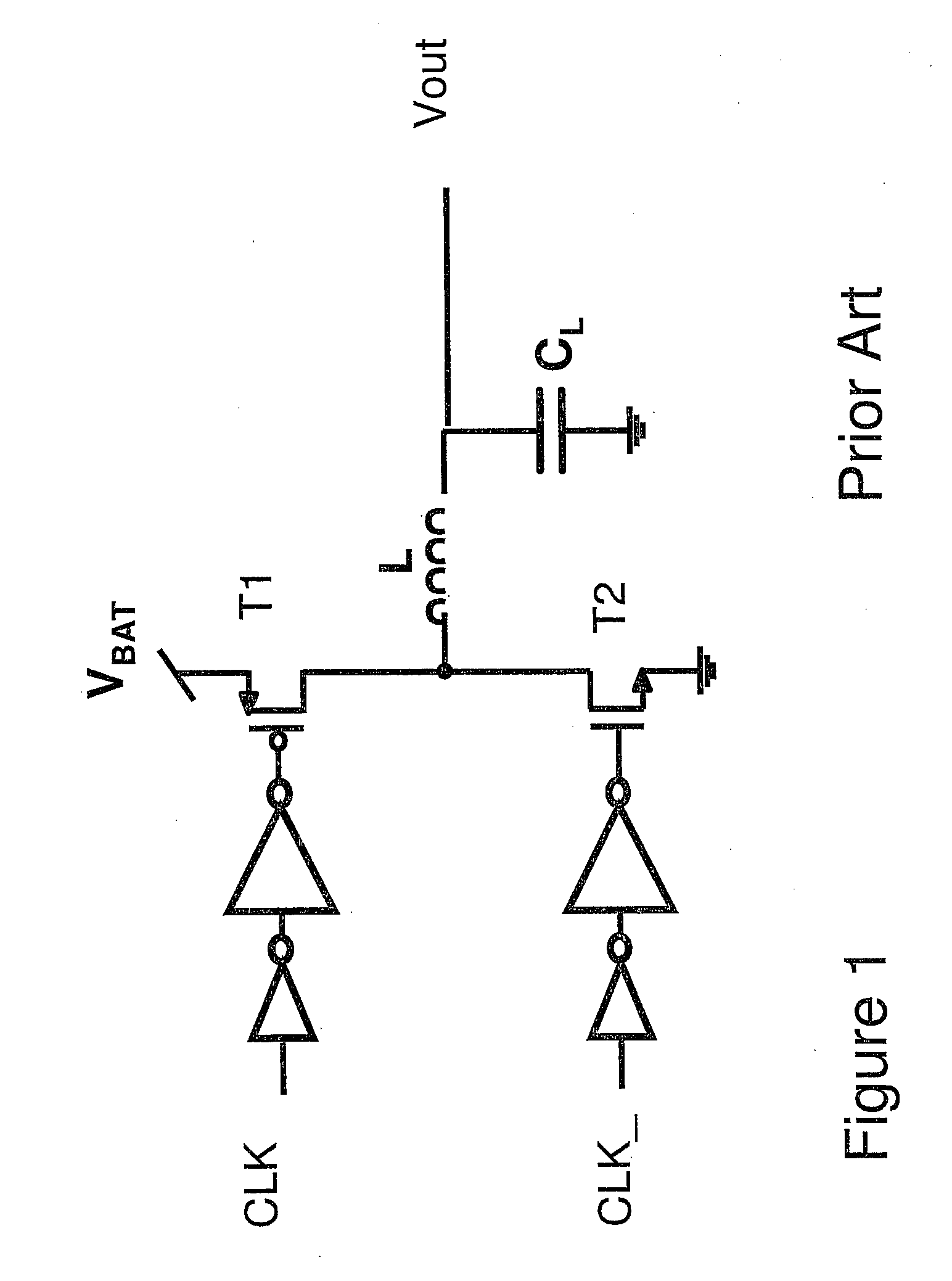

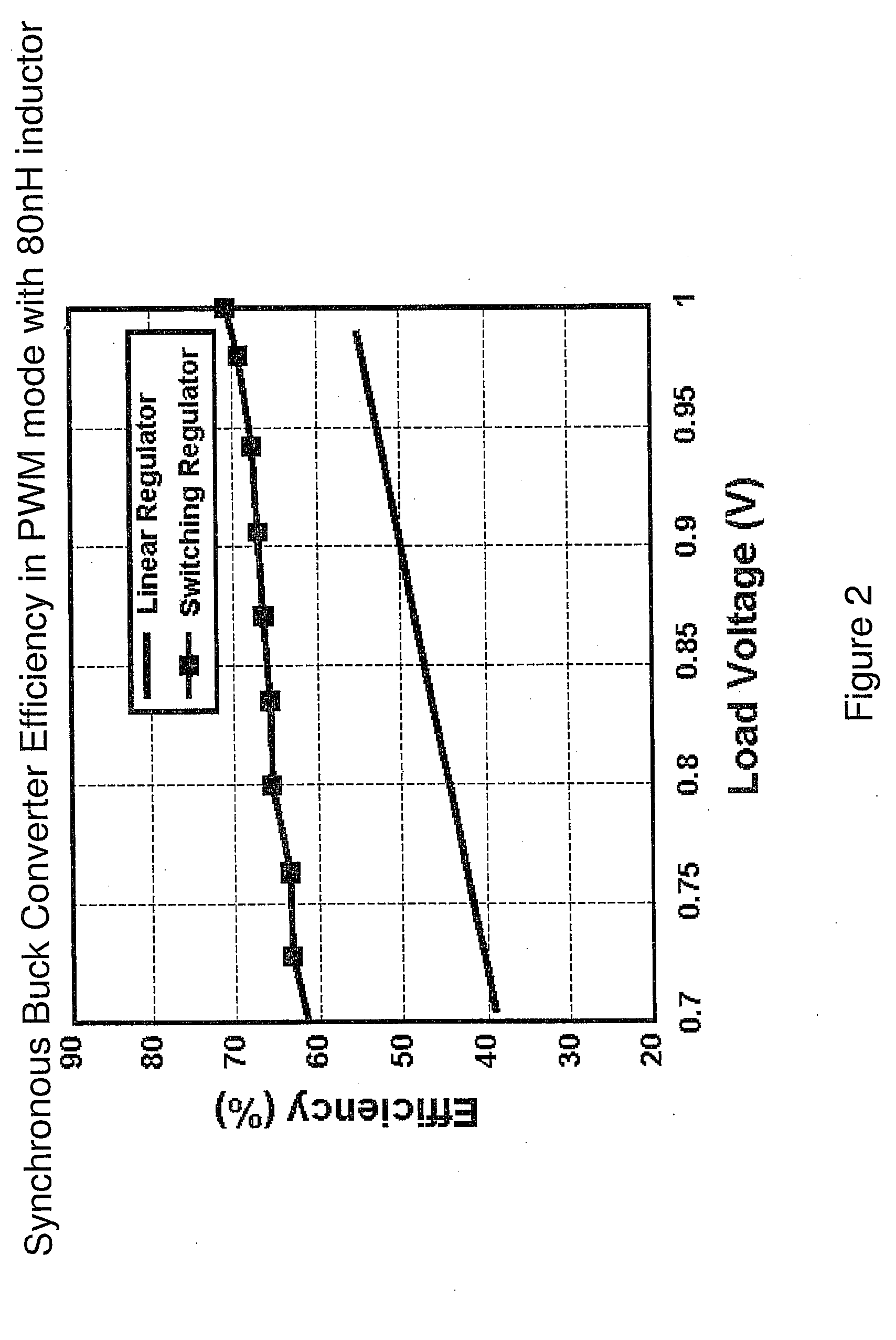

Circuit and Method for a Fully Integrated Switched-Capacitor Step-Down Power Converter

ActiveUS20090072800A1Efficiently regulateLow loadAc-dc conversionApparatus without intermediate ac conversionCapacitanceFixed frequency

A circuit and method for providing a fully integrated DC-DC converter using on-chip switched capacitors is disclosed. A switched capacitor matrix is coupled as a digitally controlled transfer capacitor. A pair of non-overlapping, fixed frequency clock signals is provided to a switched capacitor circuit including the switched capacitor matrix and a load capacitor coupled to the output terminal. A DC input voltage supply is provided. A hysteretic feedback loop is used to control the voltage at the output as a stepped-down voltage from the input by digitally modulating the transfer capacitor using switches in the switch matrix to couple more, or fewer, transfer capacitors to the output terminal during a clock cycle. A coarse and a fine adjustment circuit are provided to improve the regulation during rapid changes in load power. A method of operating the regulator is disclosed.

Owner:TEXAS INSTR INC

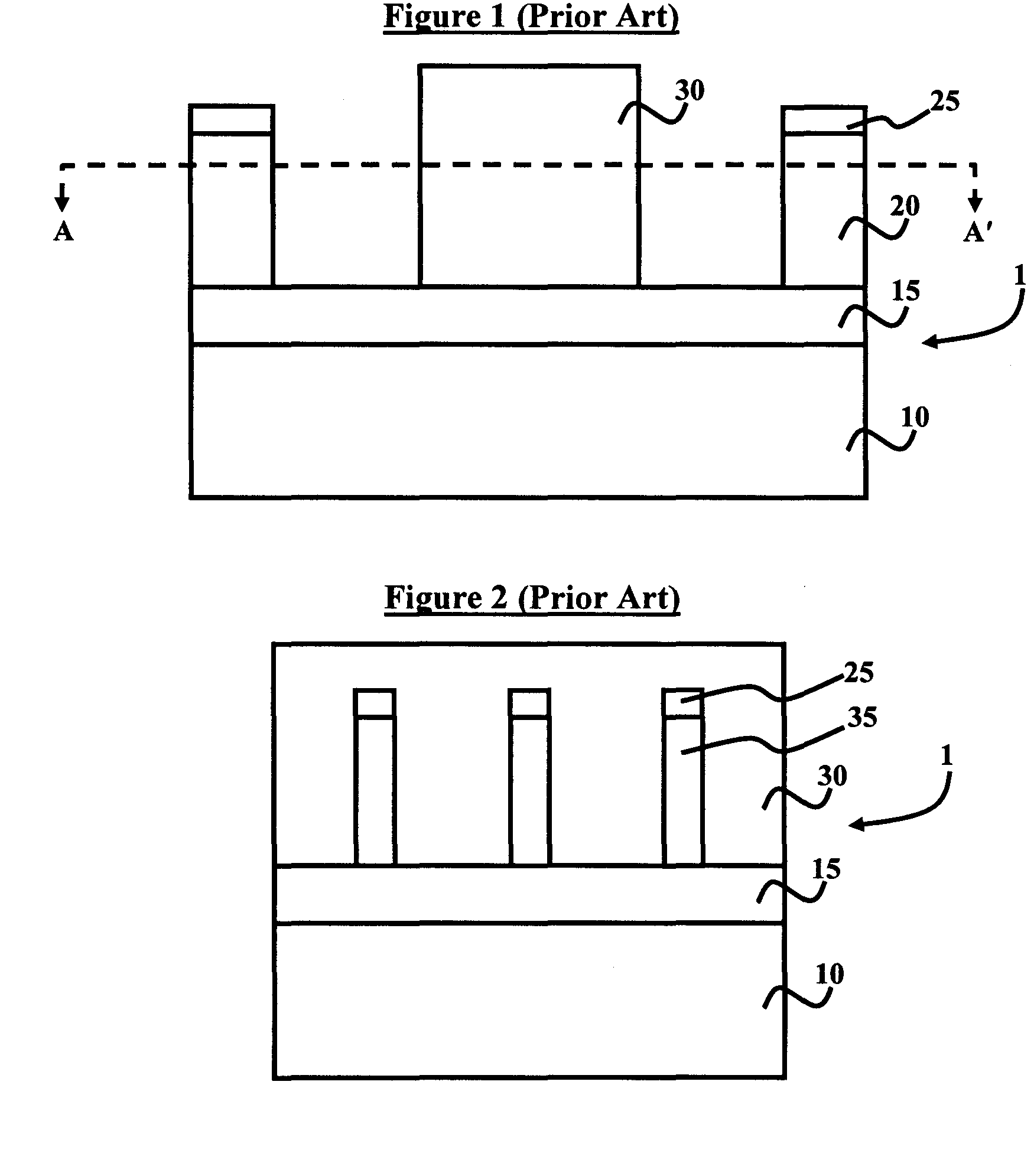

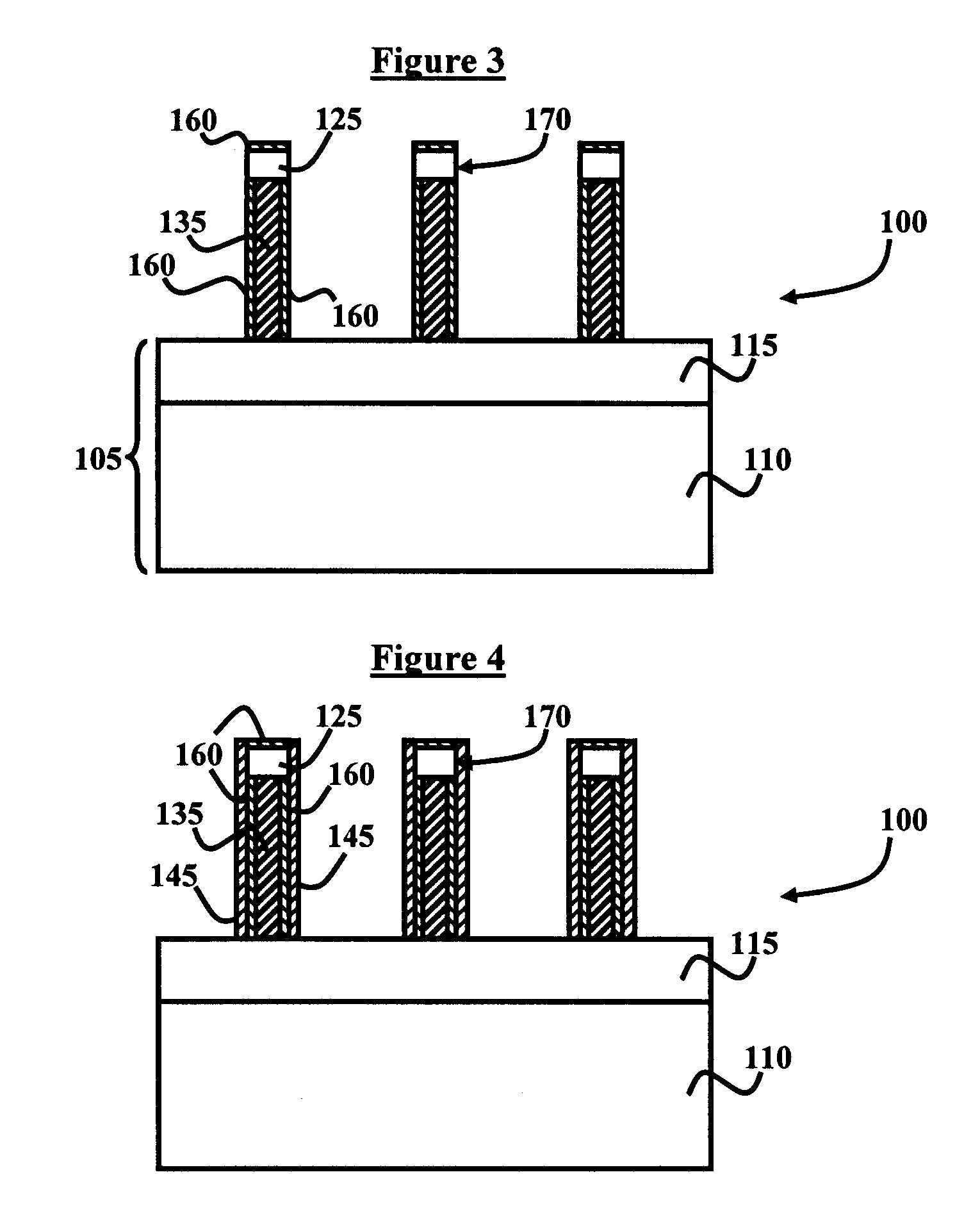

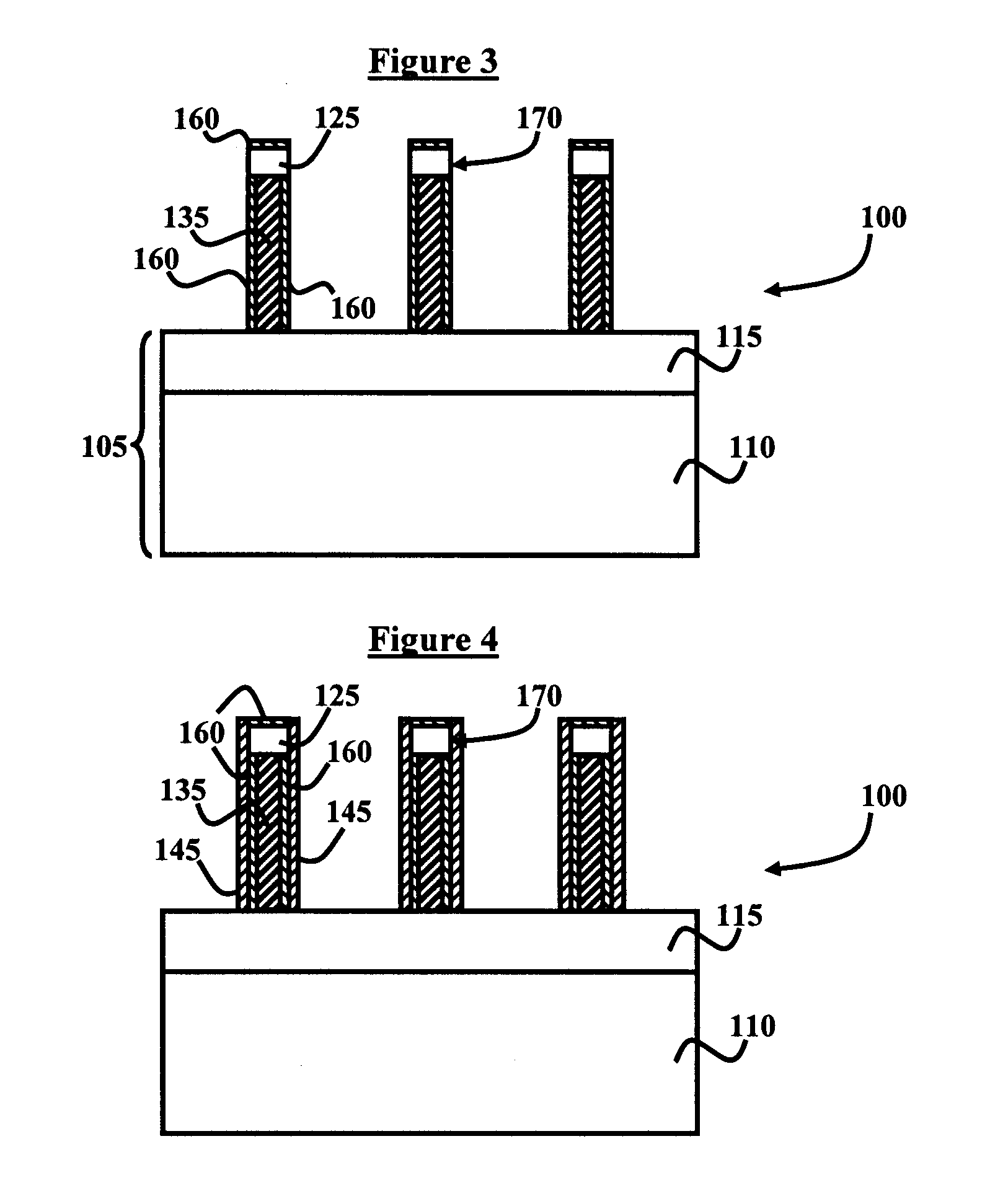

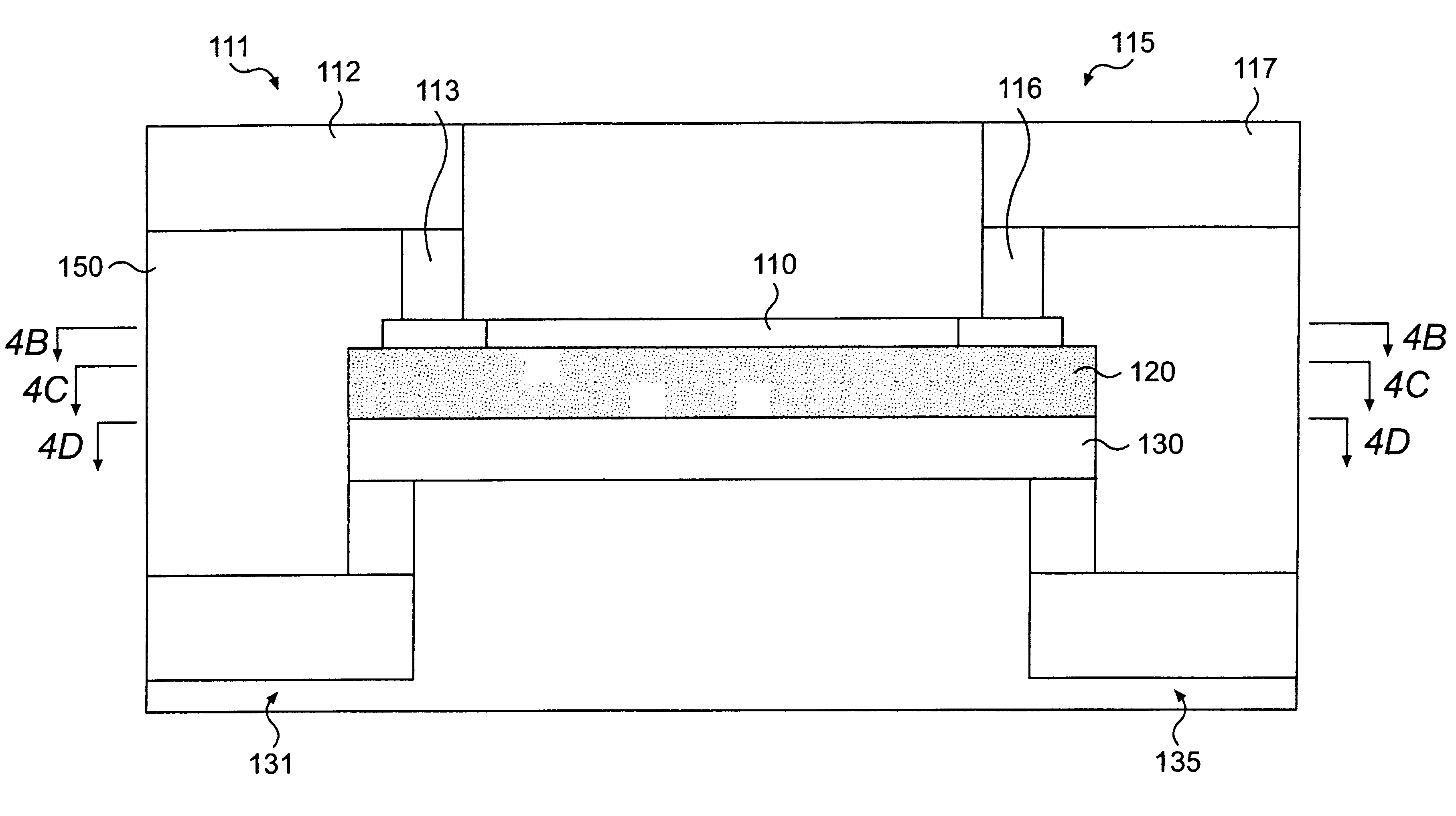

FinFET with low gate capacitance and low extrinsic resistance

ActiveUS7105934B2Reduce gate capacitanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceGate insulator

A FinFET device and a method of lowering a gate capacitance and extrinsic resistance in a field effect transistor, wherein the method comprises forming an isolation layer comprising a BOX layer over a substrate, configuring source / drain regions above the isolation layer, forming a fin structure over the isolation layer, configuring a first gate electrode adjacent to the fin structure, disposing a gate insulator between the first gate electrode and the fin structure, positioning a second gate electrode transverse to the first gate electrode, and depositing a third gate electrode on the fin structure, the first gate electrode, and the second gate electrode, wherein the isolation layer is formed beneath the insulator, the first gate electrode, and the fin structure. The method further comprises sandwiching the second gate electrode with a dielectric material. The fin structure is formed by depositing an oxide layer over a silicon layer.

Owner:MICROSOFT TECH LICENSING LLC

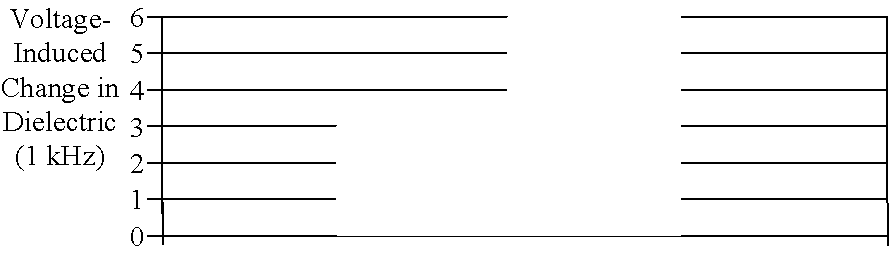

Nanoparticle-enhanced liquid crystal radio frequency phase shifter

InactiveUS20140022029A1Improve circuit performanceMinimal insertion lossNanoopticsDelay linesNanoparticleGround plane

A nanoparticle-enhanced liquid crystal phase shifter is provided including a first substrate layer, a plurality of electrodes attached to the substrate layer, a ground plane layer attached to a second substrate layer, and a liquid crystal layer between the ground plane layer and the first substrate layer, including a suspension of a liquid crystal material and highly polarizable nanoparticles having specific shape and size characteristics.

Owner:UNIV OF COLORADO THE REGENTS OF

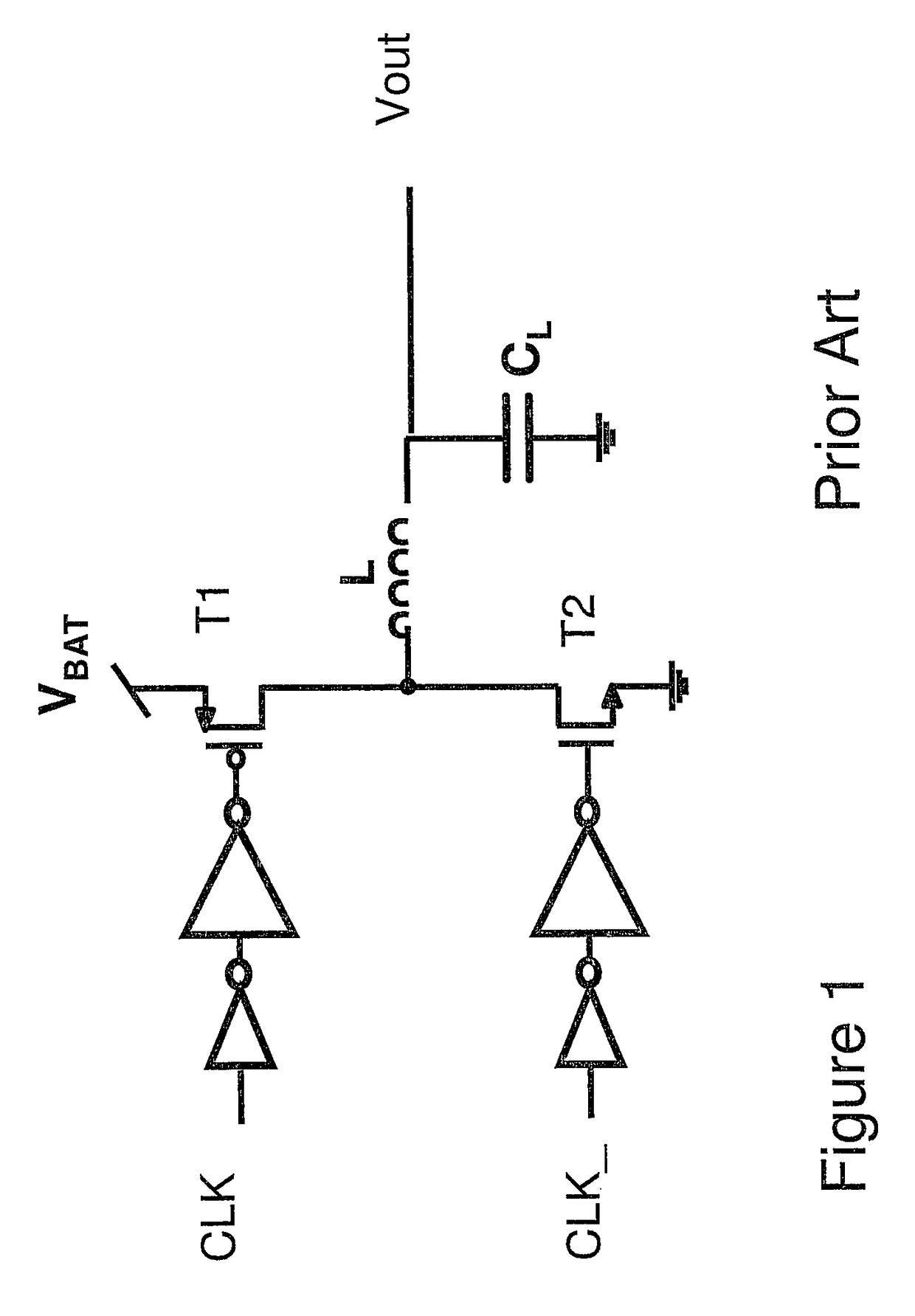

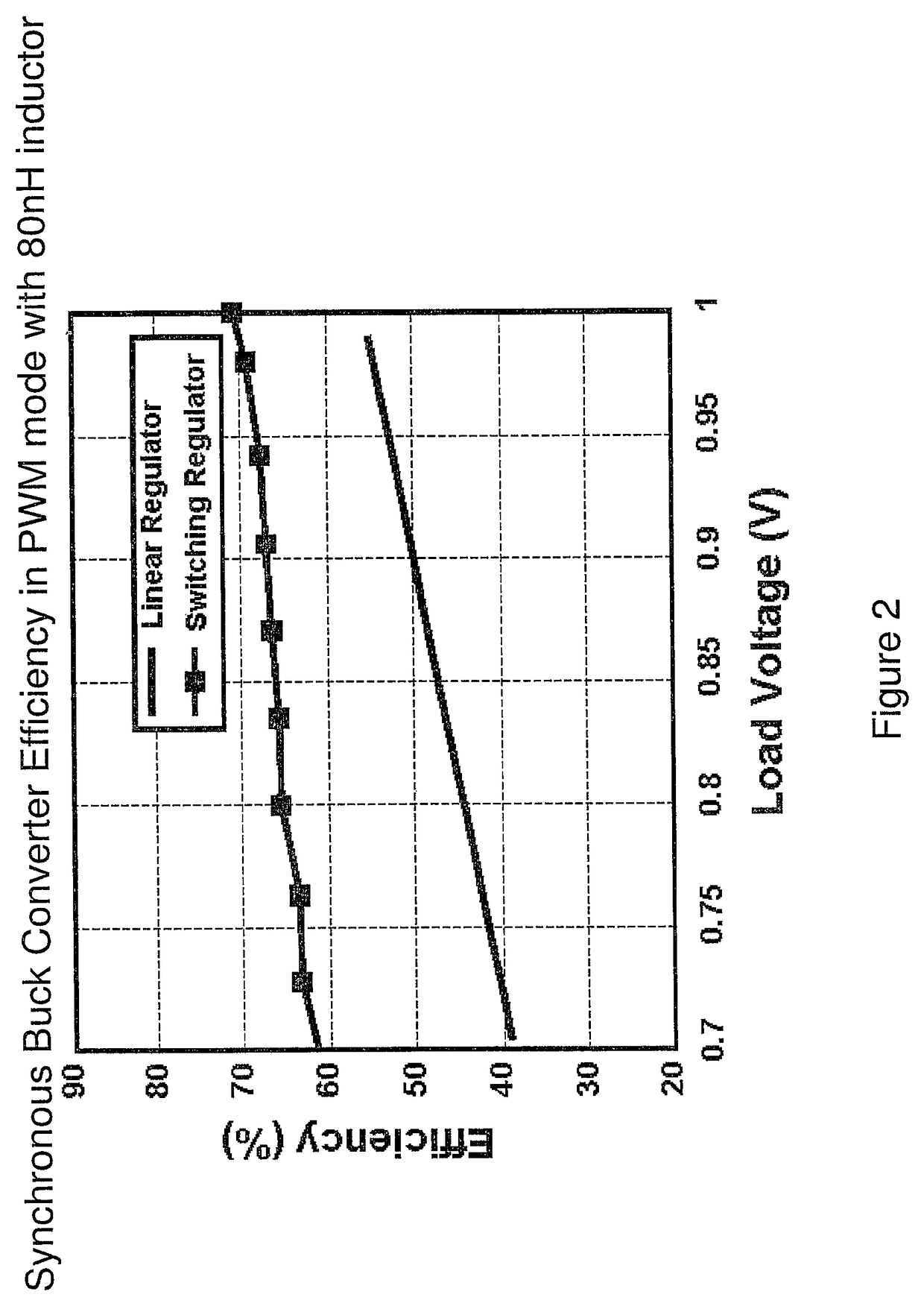

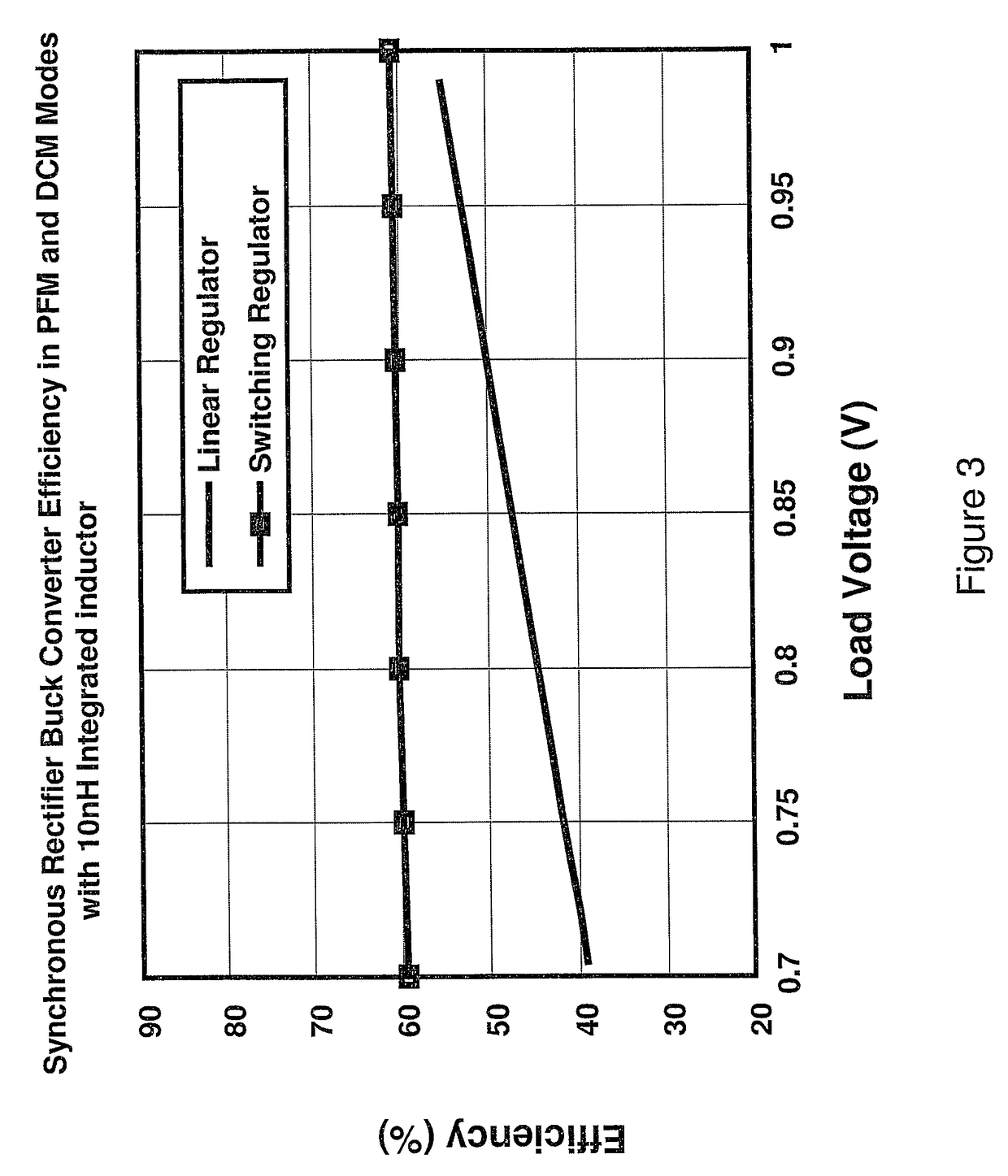

Circuit and method for a fully integrated switched-capacitor step-down power converter

ActiveUS7907429B2Effective regulationEasy to adjustAc-dc conversionApparatus without intermediate ac conversionDc dc converterVoltage control

A circuit and method for providing a fully integrated DC-DC converter using on-chip switched capacitors is disclosed. A switched capacitor matrix is coupled as a digitally controlled transfer capacitor. A pair of non-overlapping, fixed frequency clock signals is provided to a switched capacitor circuit including the switched capacitor matrix and a load capacitor coupled to the output terminal. A DC input voltage supply is provided. A hysteretic feedback loop is used to control the voltage at the output as a stepped-down voltage from the input by digitally modulating the transfer capacitor using switches in the switch matrix to couple more, or fewer, transfer capacitors to the output terminal during a clock cycle. A coarse and a fine adjustment circuit are provided to improve the regulation during rapid changes in load power. A method of operating the regulator is disclosed.

Owner:TEXAS INSTR INC

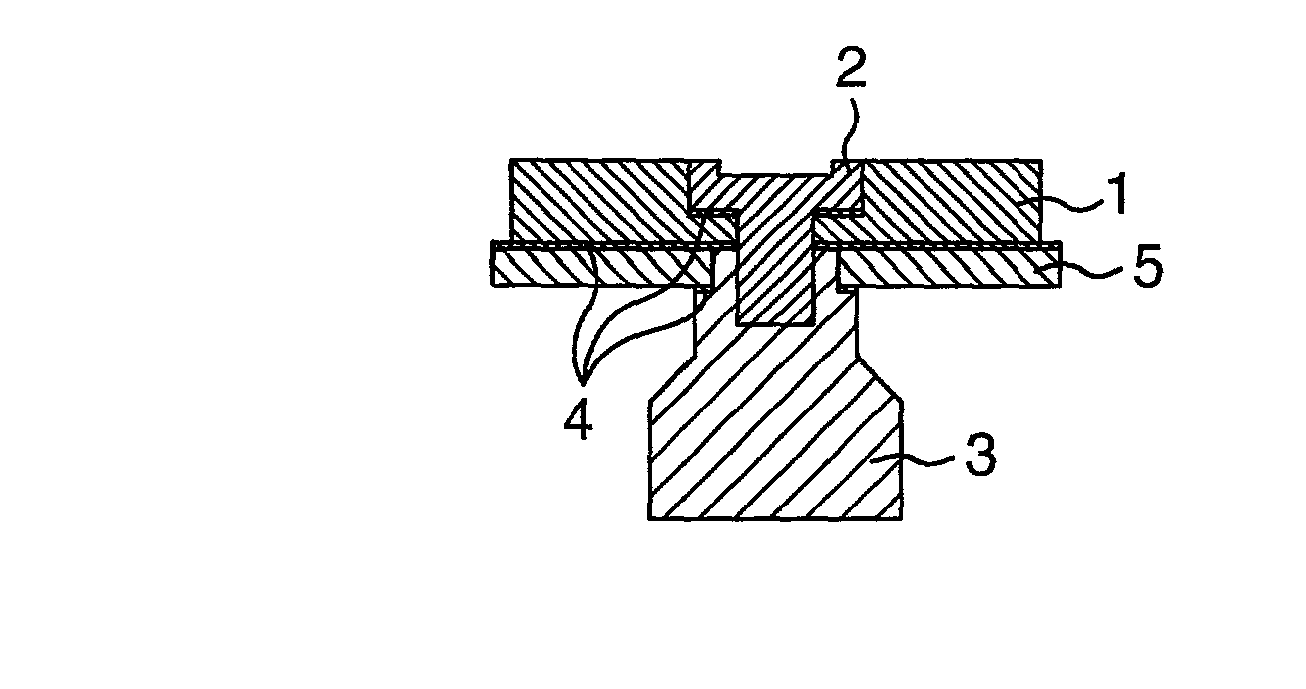

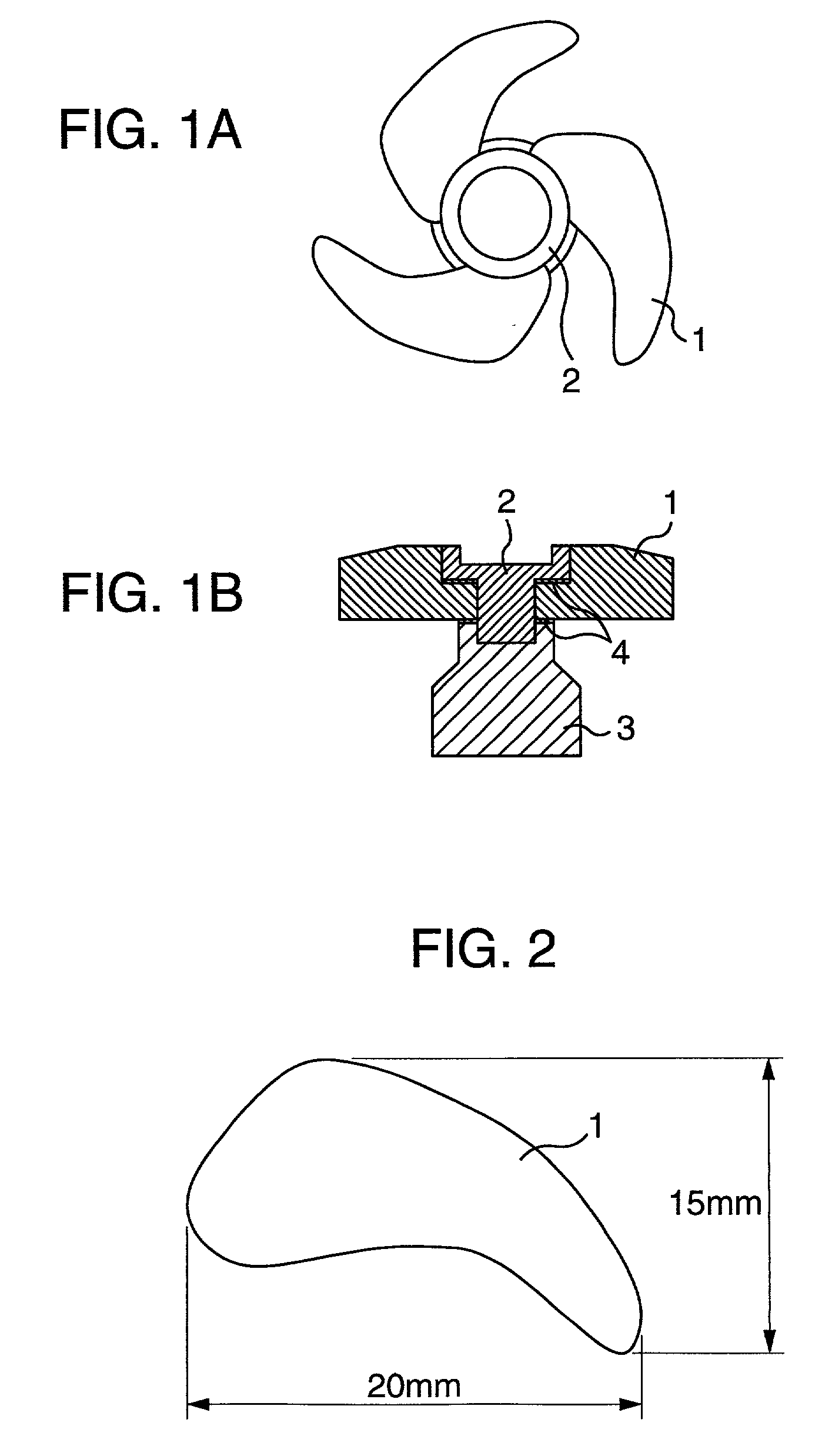

Electrode of a vacuum valve, a producing method thereof, a vacuum valve, a vacuum circuit-breaker and a contact point of the electrode

InactiveUS20020144977A1Improve circuit performanceWell formedContact materialsContact member manufacturingHigh conductivityMetal

The inventive electric contact point of a vacuum valve is made of a sintered alloy containing a heat-resistant metal and a high-conductivity metal. The contact point has at least three slit grooves which extend from the central region to the peripheral region of the contact point, and is soldered to an electrode rod which is connected to the contact point. The contact point includes at least three radially extending vane type contact point members each made of a sintered alloy containing a heat-resistant metal and a high-conductivity metal, and soldered to the electrode rod.

Owner:HITACHI LTD

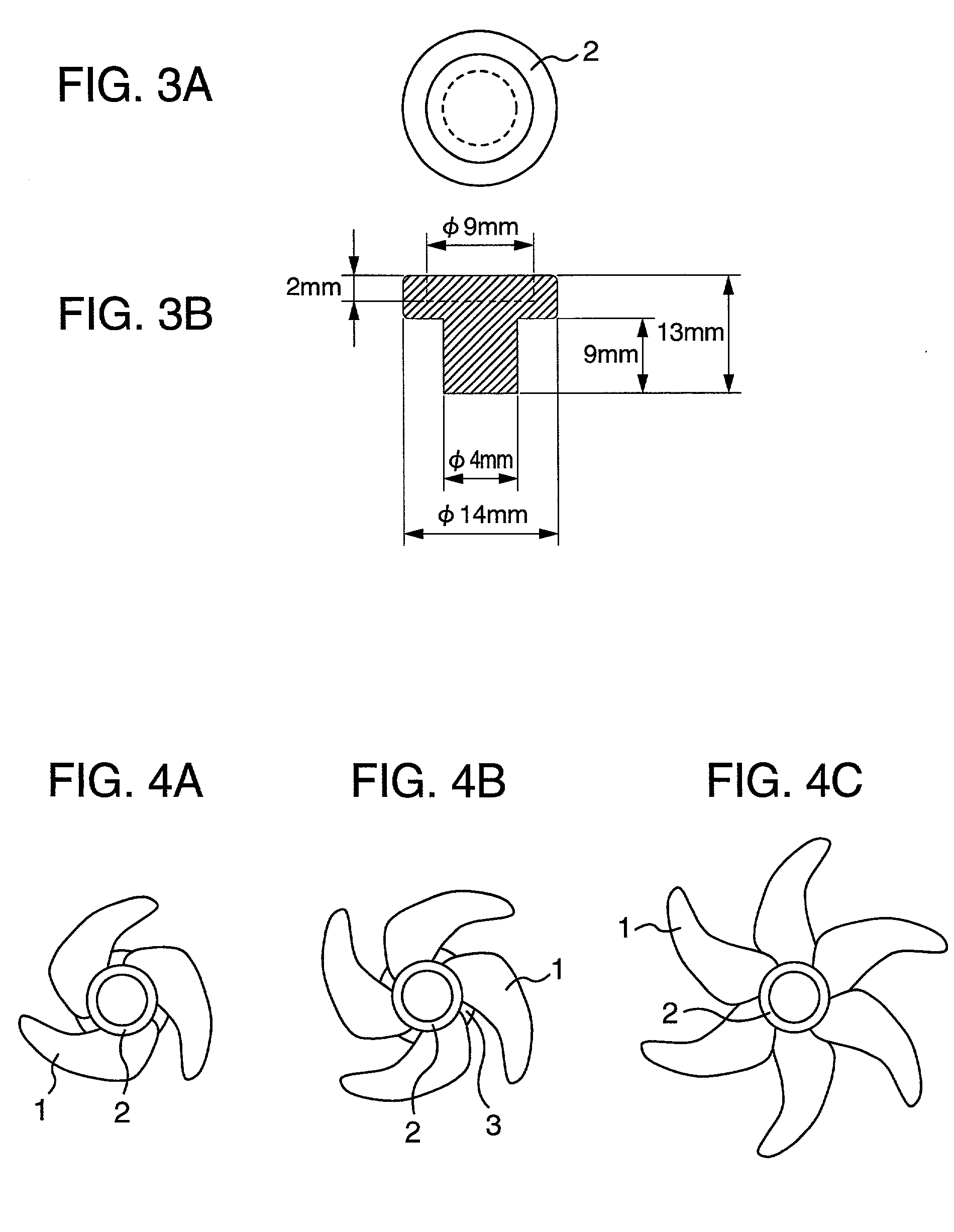

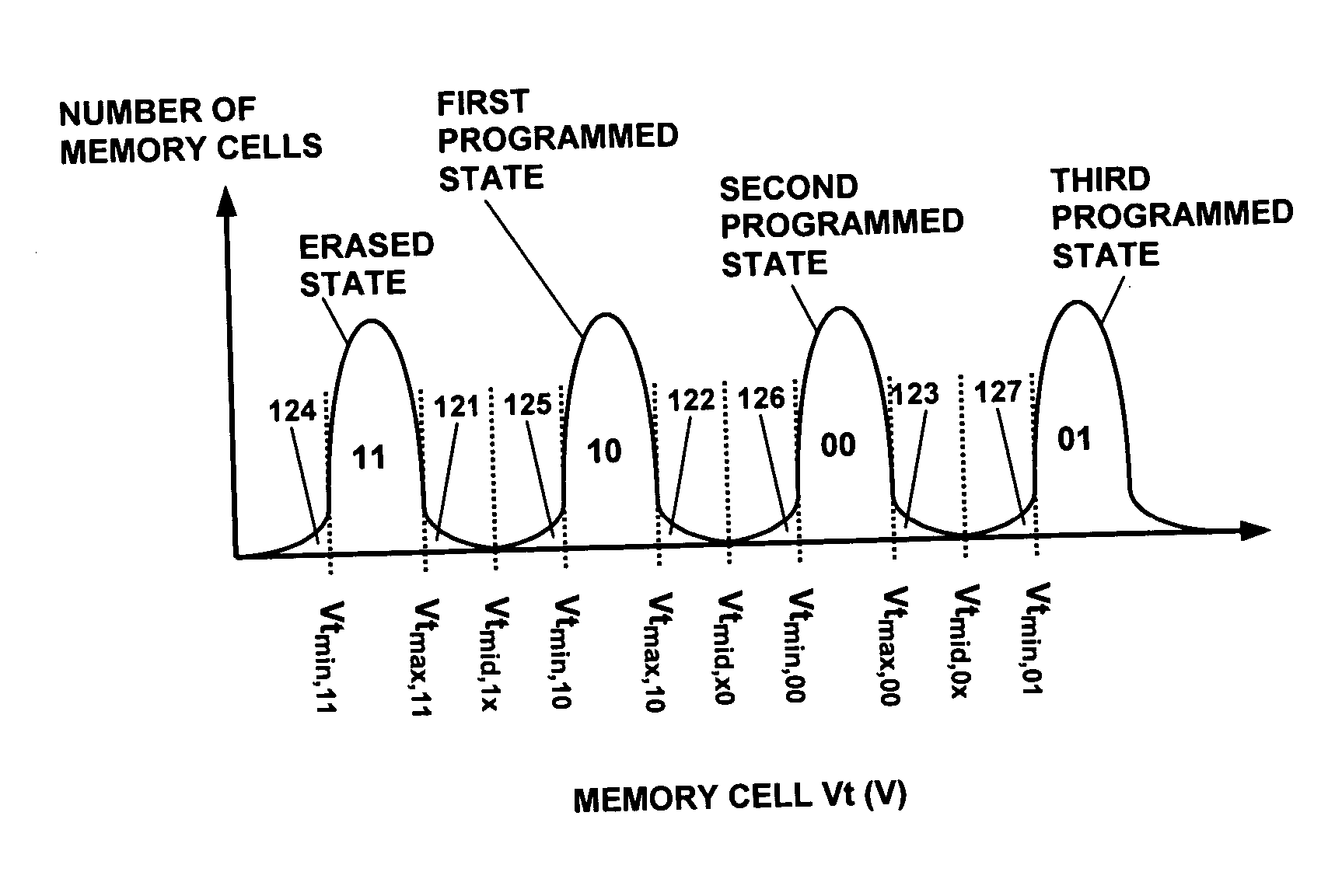

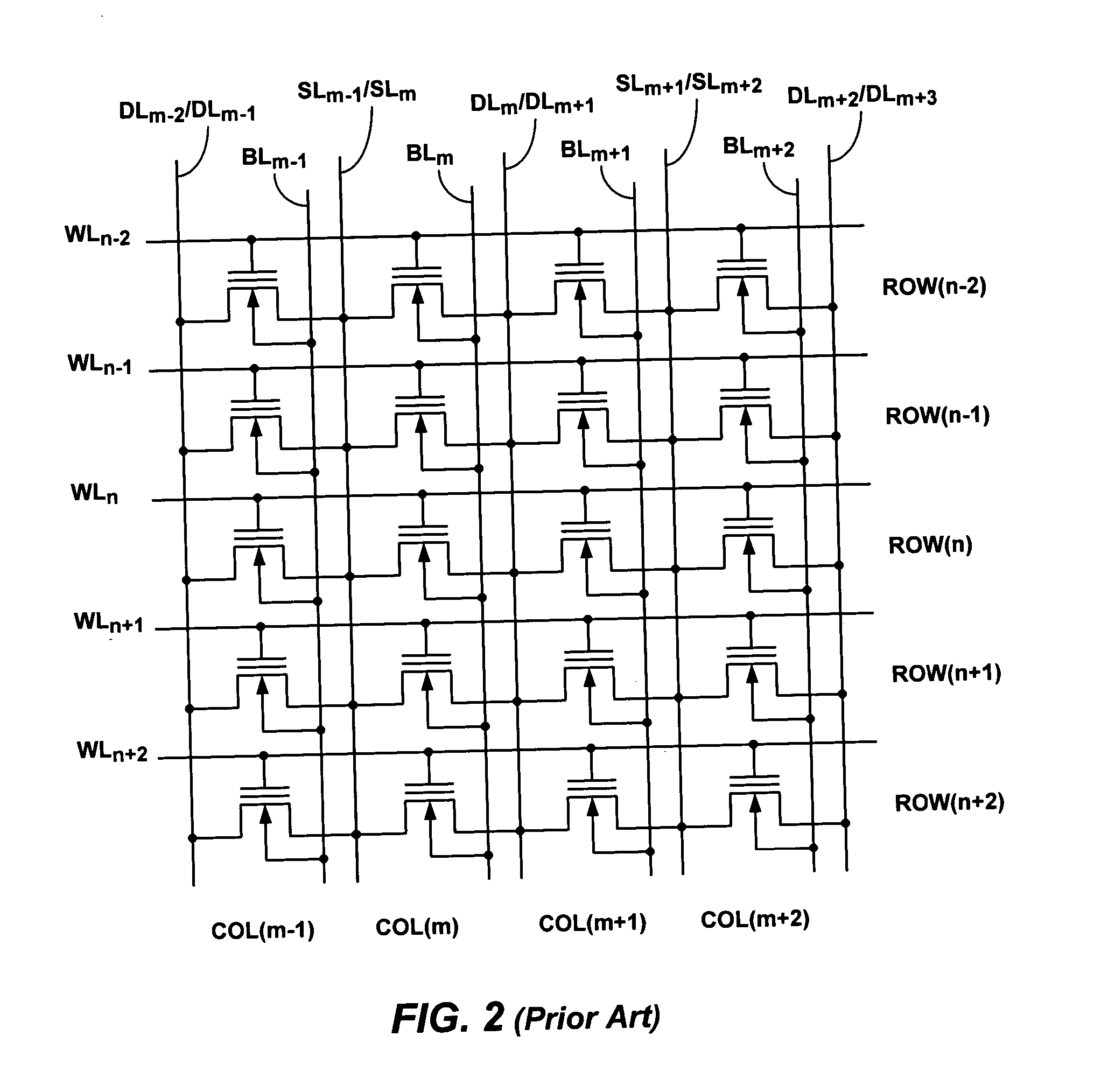

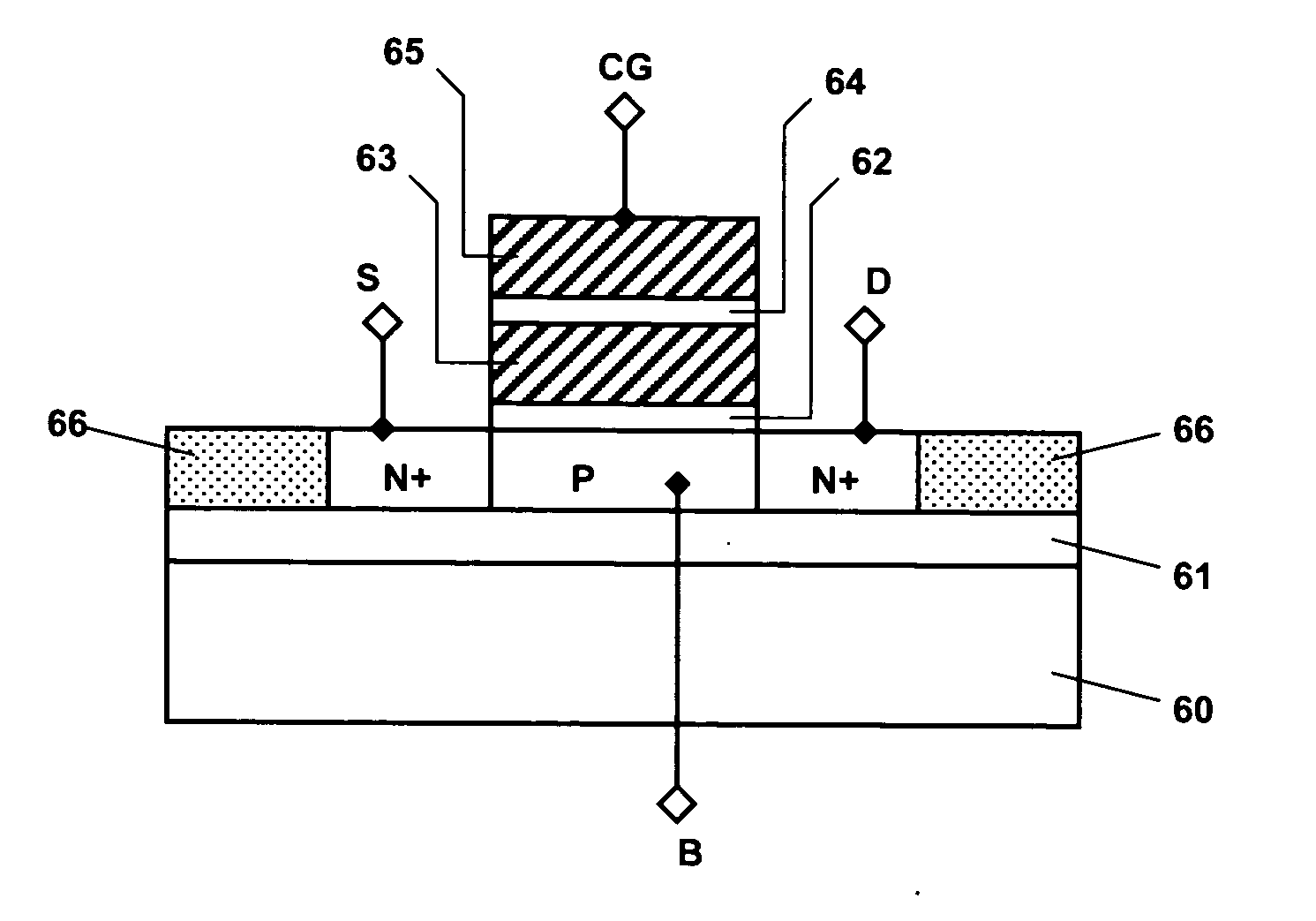

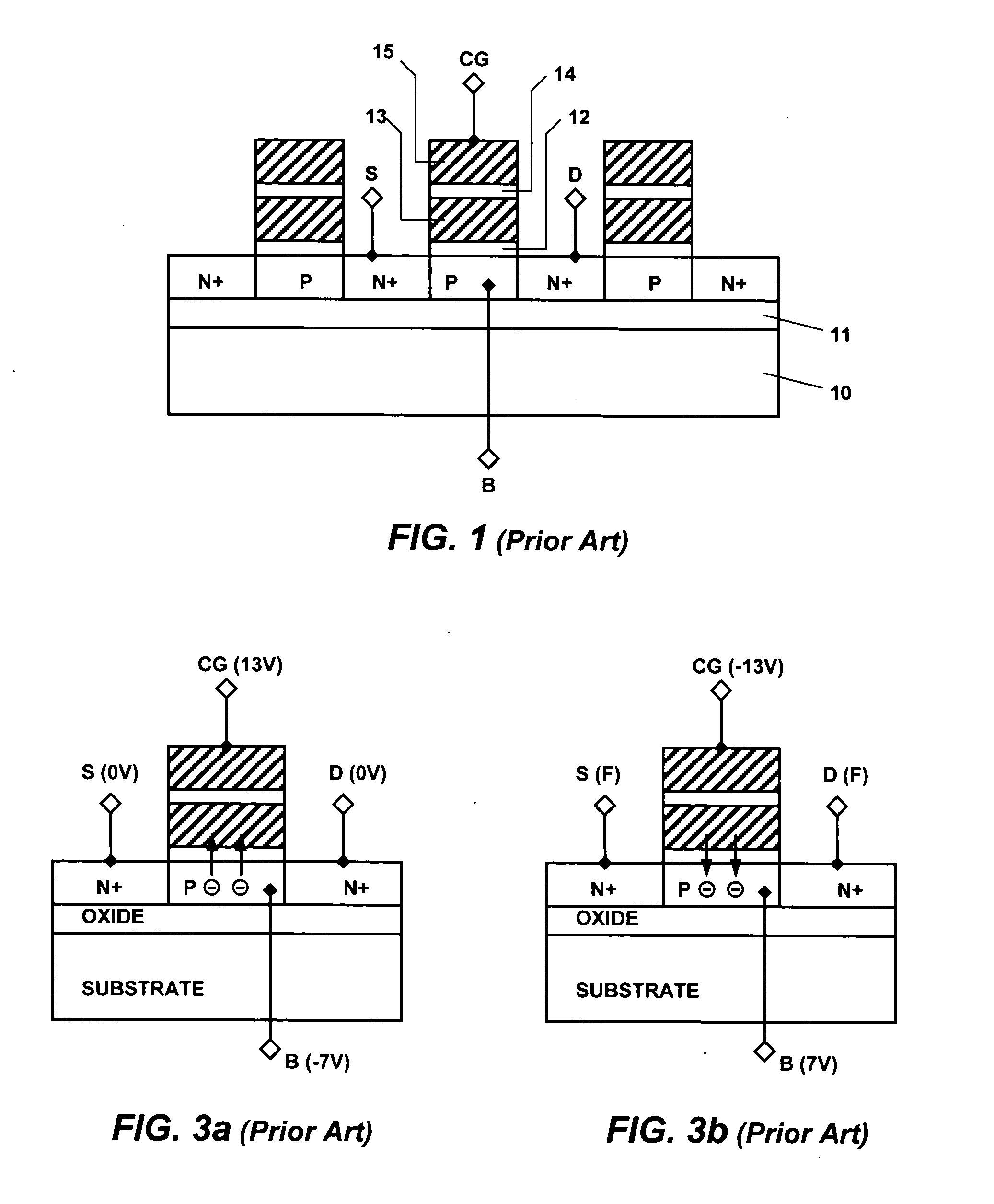

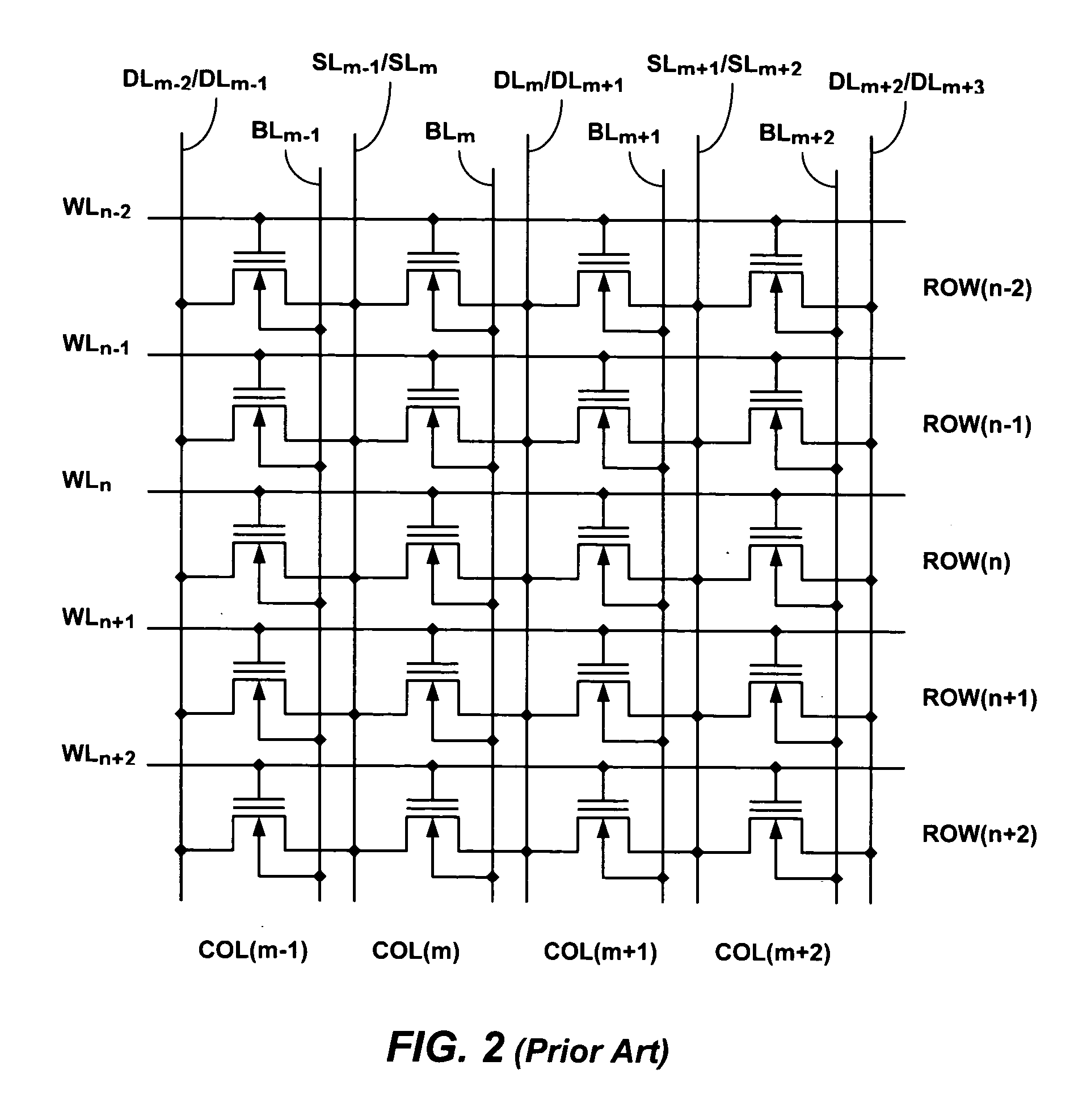

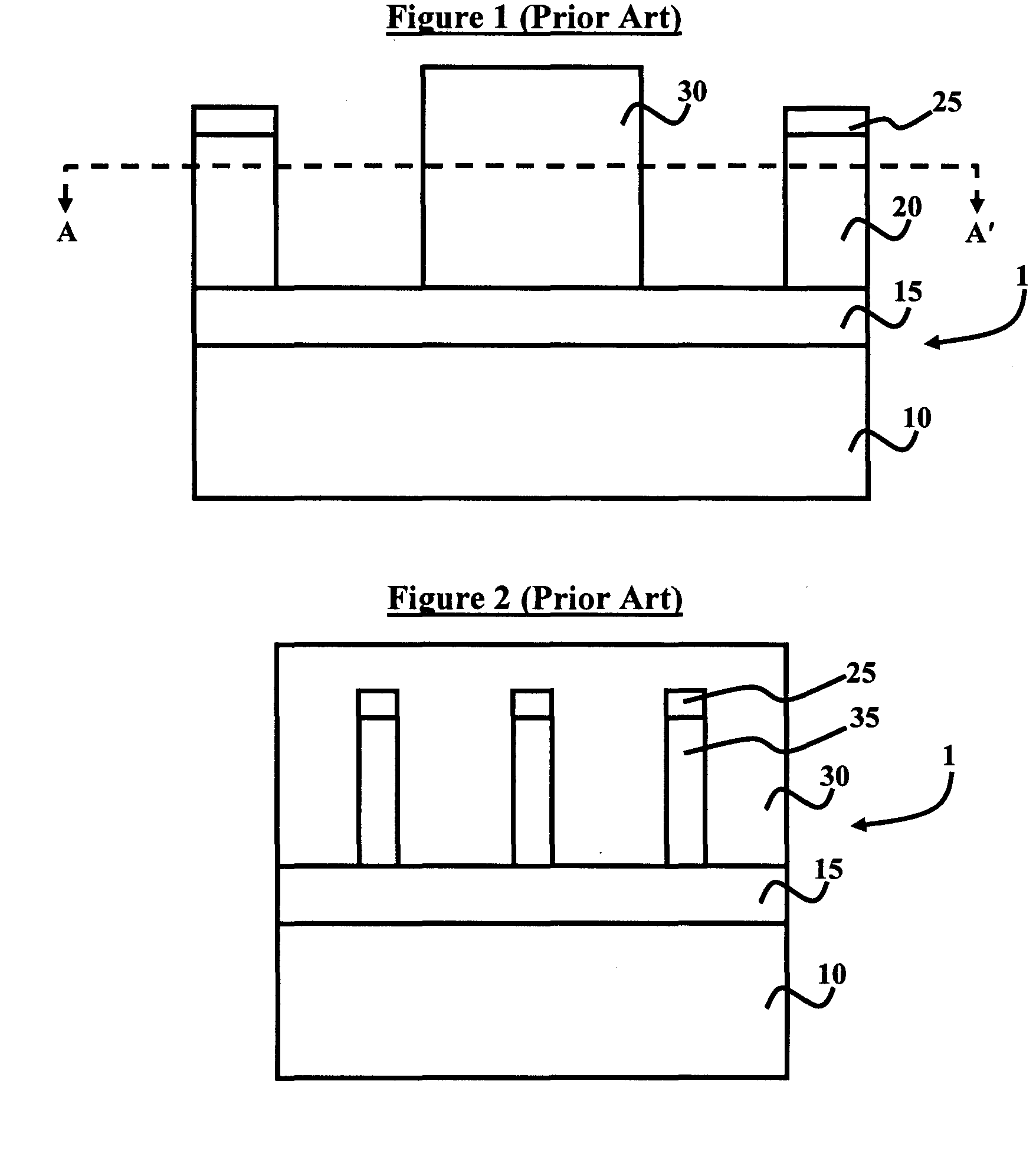

Nor-type channel-program channel-erase contactless flash memory on SOI

InactiveUS20060018164A1Improve good performanceImprove circuit performanceTransistorSolid-state devicesProgrammable read-only memoryDevice material

A semiconductor device having an electrically erasable programmable read only memory (EEPROM) comprises a contactless array of EEPROM memory cells disposed in rows and columns and constructed over a silicon-on-insulator wafer. Each EEPROM memory cell comprises a drain region, a source region, a gate region, and a body region. The semiconductor device further comprises a plurality of gate lines each connecting the gate regions of a row of EEPROM memory cells, a plurality of body lines each connecting the body regions of a column of EEPROM memory cells, a plurality of source lines each connecting the source regions of a column of EEPROM memory cells, and a plurality of drain lines each connecting the drain regions of a column of EEPROM memory cells. The source lines and the drain lines are buried lines, and the source regions and the drain regions of a column of EEPROM memory cells are insulated from the source regions and the drain regions of the adjacent columns of EEPROM memory cells.

Owner:WU KOUCHENG

Nor-type channel-program channel-erase contactless flash memory on SOI

InactiveUS20050179079A1Improve good performanceImprove circuit performanceTransistorSolid-state devicesProgrammable read-only memoryDevice material

A semiconductor device having an electrically erasable programmable read only memory (EEPROM) comprises a contactless array of EEPROM memory cells disposed in rows and columns and constructed over a silicon-on-insulator wafer. Each EEPROM memory cell comprises a drain region, a source region, a gate region, and a body region. The semiconductor device further comprises a plurality of gate lines each connecting the gate regions of a row of EEPROM memory cells, a plurality of body lines each connecting the body regions of a column of EEPROM memory cells, a plurality of source lines each connecting the source regions of a column of EEPROM memory cells, and a plurality of drain lines each connecting the drain regions of a column of EEPROM memory cells. The source lines and the drain lines are buried lines, and the source regions and the drain regions of a column of EEPROM memory cells are insulated from the source regions and the drain regions of the adjacent columns of EEPROM memory cells.

Owner:WU KOUCHENG

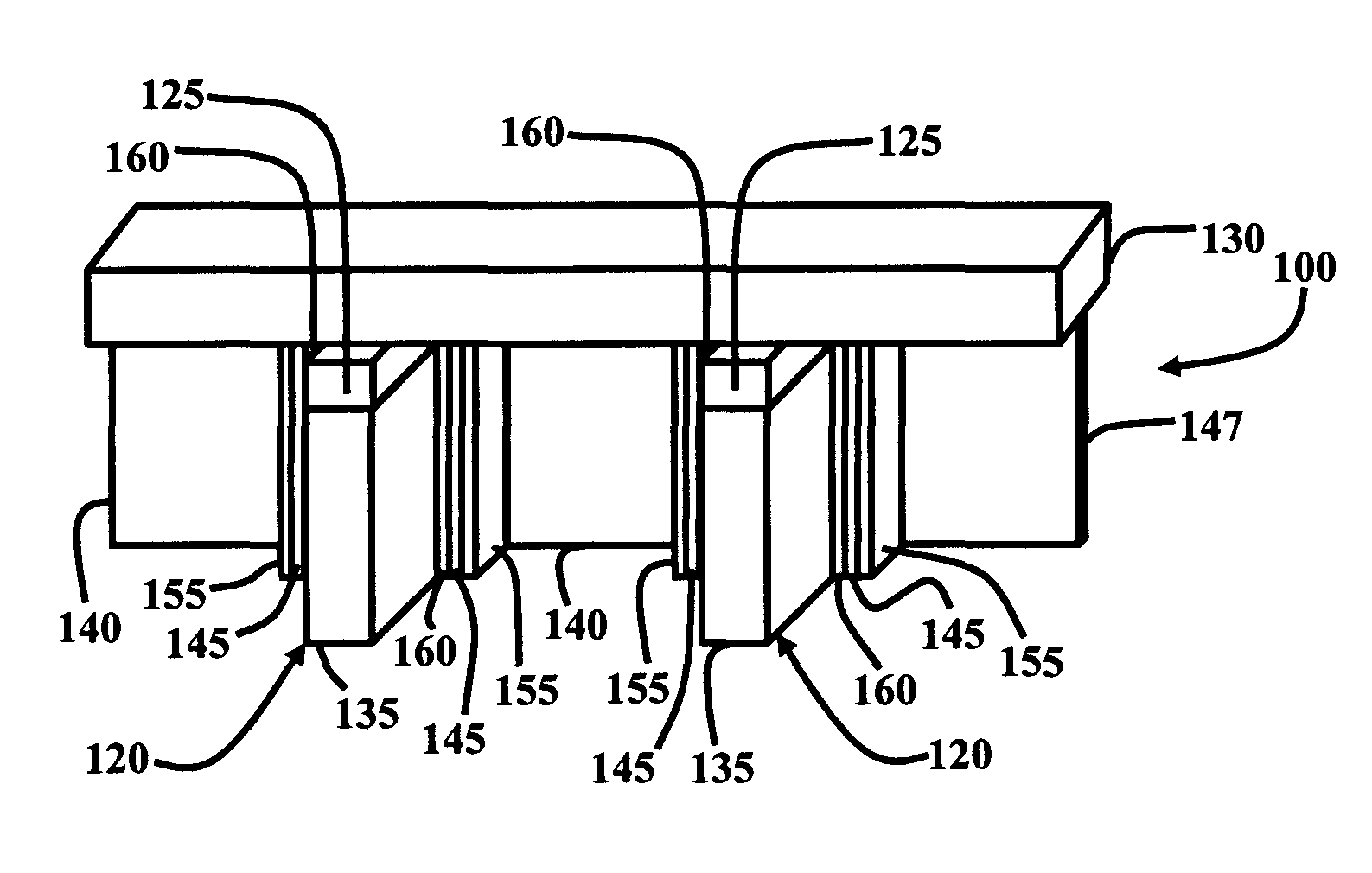

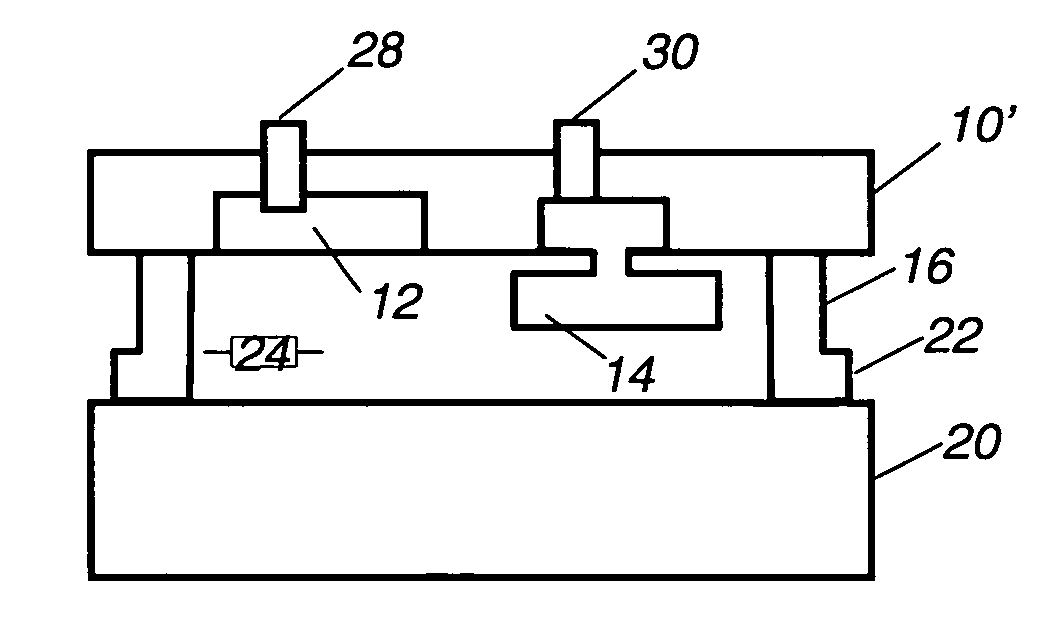

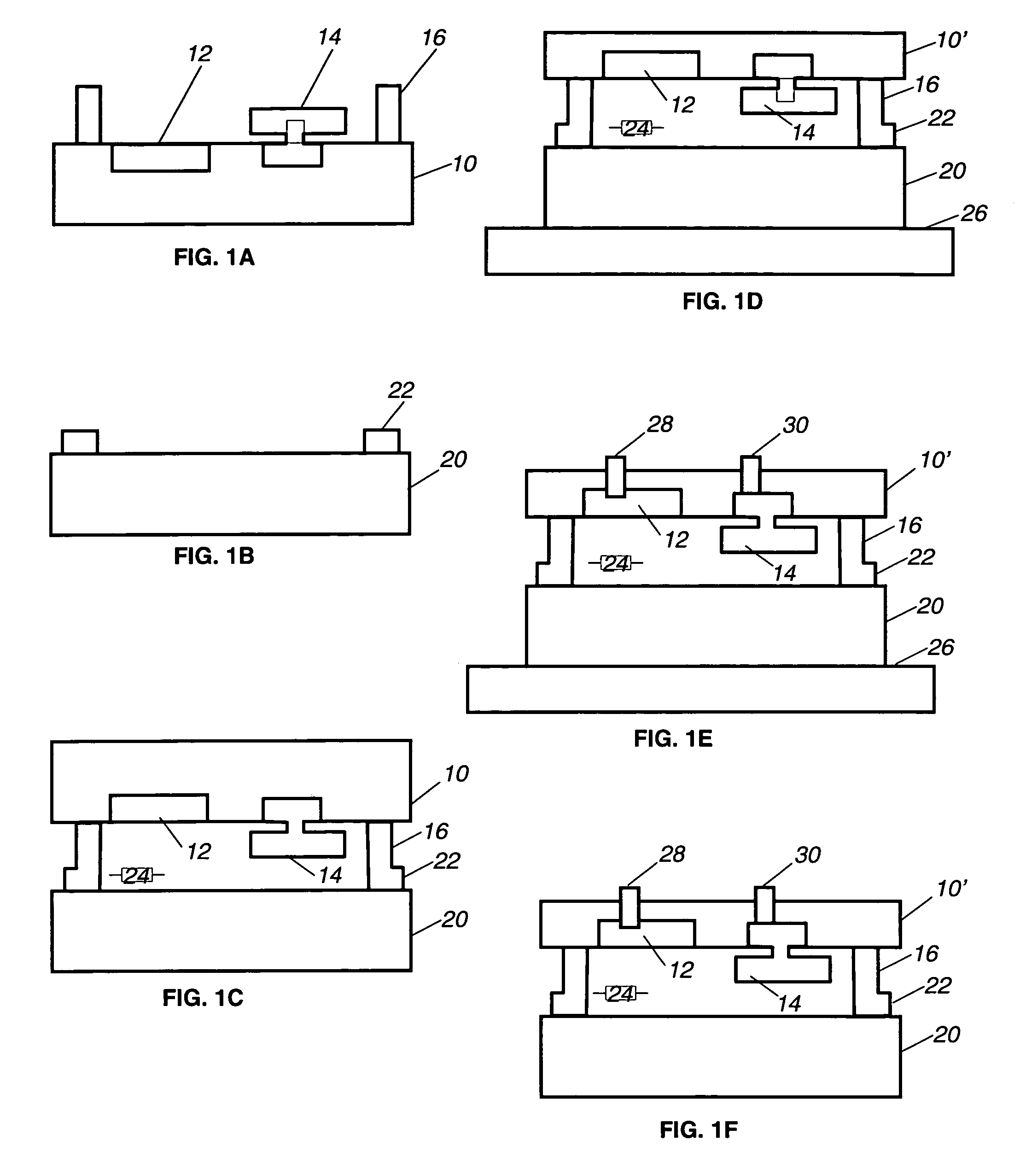

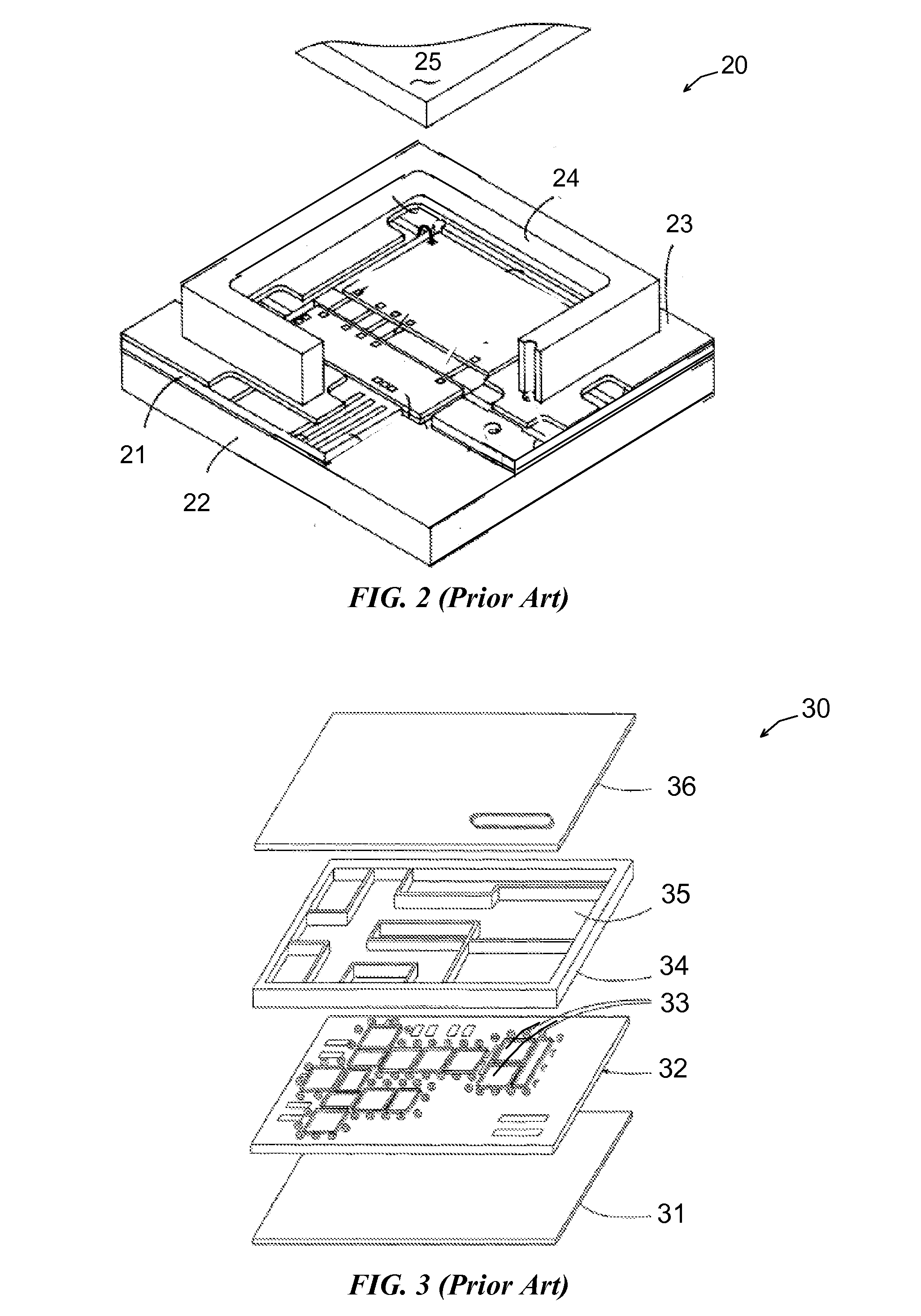

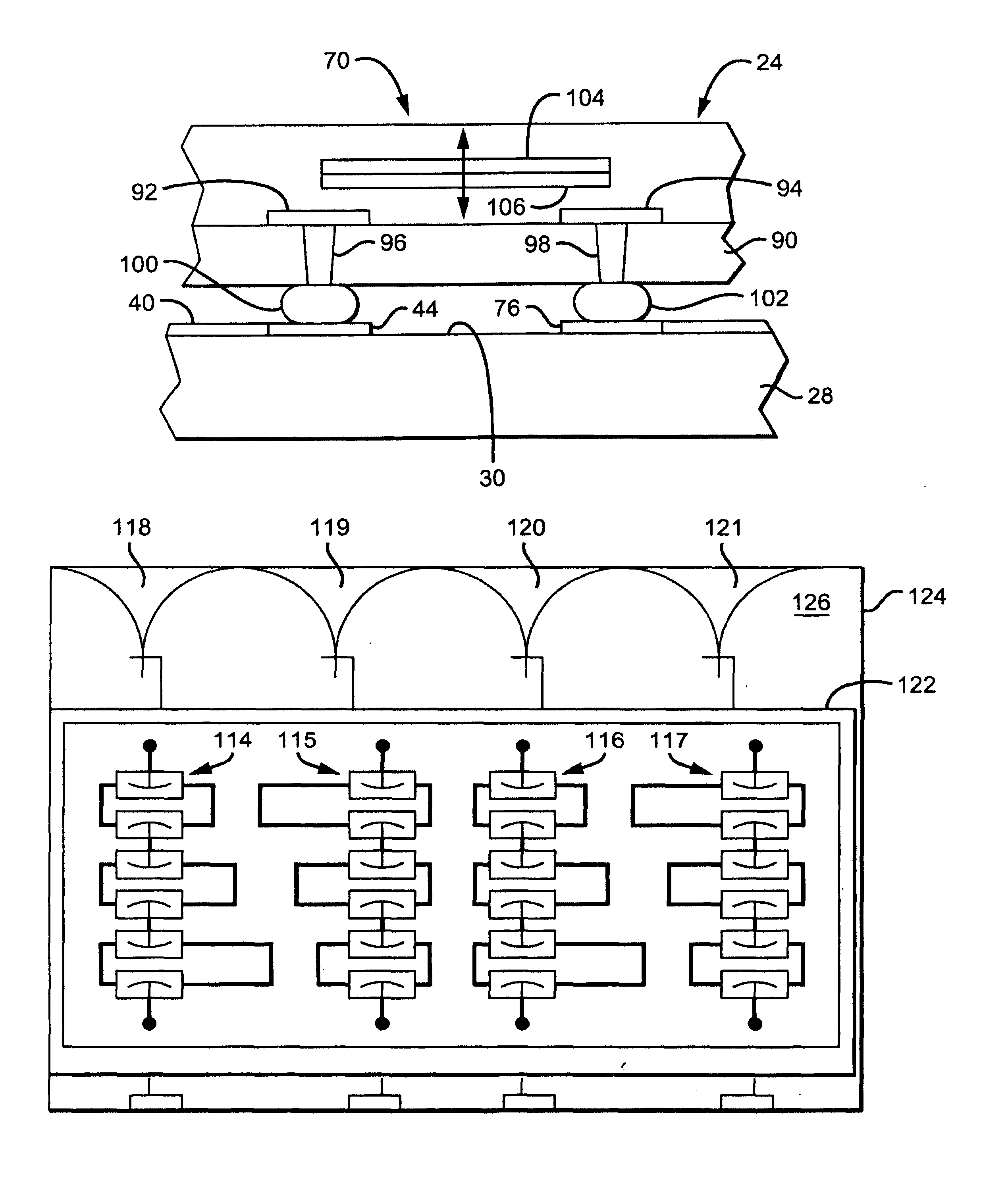

Method of fabricating high yield wafer level packages integrating MMIC and MEMS components

ActiveUS7067397B1Improve circuit performanceHigh product yieldSemiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

Monolithic microwave integrated circuit (MMIC) components and micro electromechanical systems (MEMS) components are integrated onto a single substrate at a wafer scale, by first performing MMIC and MEMS fabrication on a front face of a thick substrate wafer, bonding the substrate wafer to a cover wafer, thinning the back face of the substrate wafer and, finally, completing MMIC and MEMS fabrication on the back face of the thinned substrate wafer. The fabrication process is facilitated by use of a guard ring between the wafers to provide additional mechanical support to the substrate wafer and to protect the devices while the MMIC / MEMS fabrication is completed, and by a low temperature bonding process to join the substrate wafer and the cover wafer at multiple device cavity seal rings.

Owner:NORTHROP GRUMMAN SYST CORP

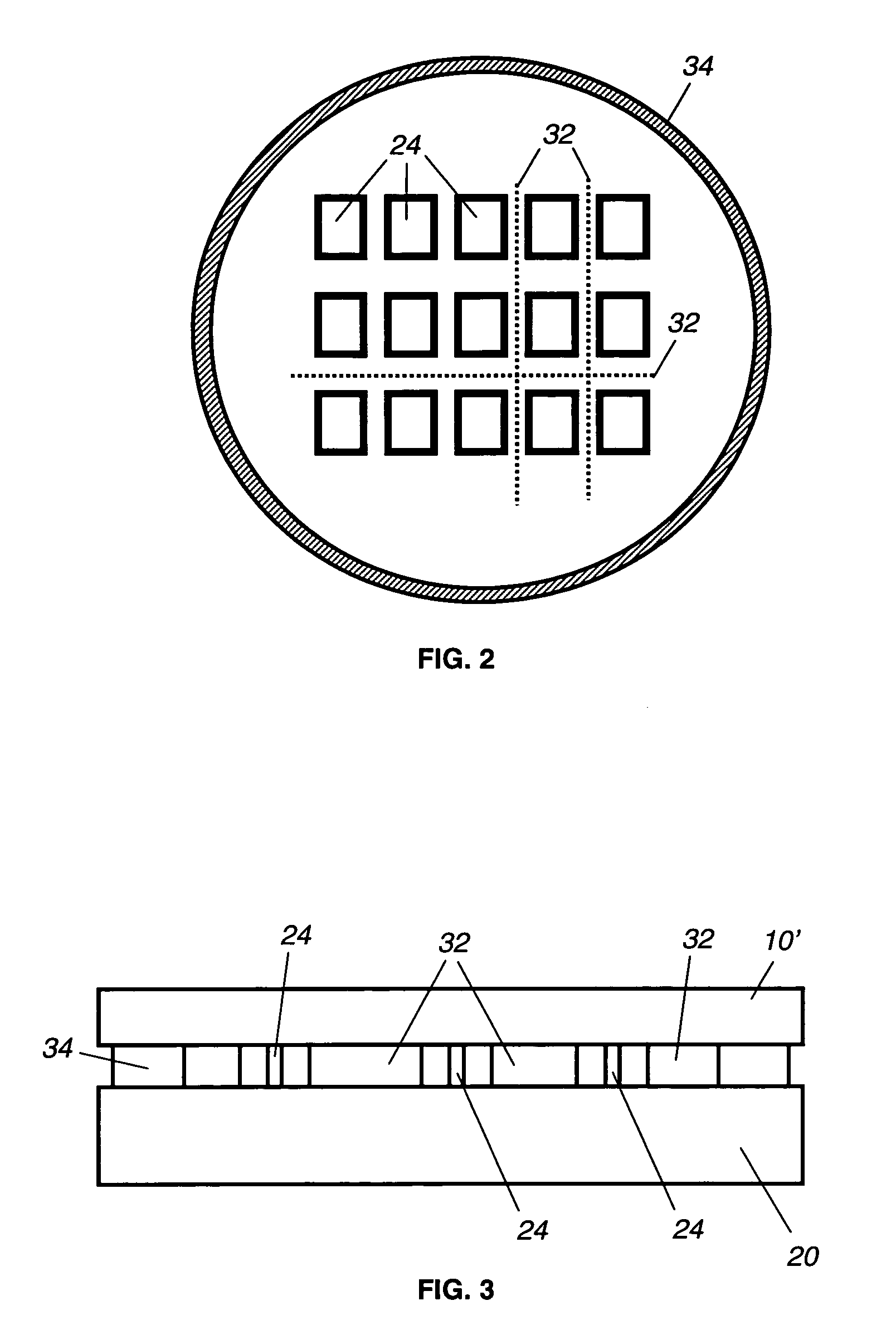

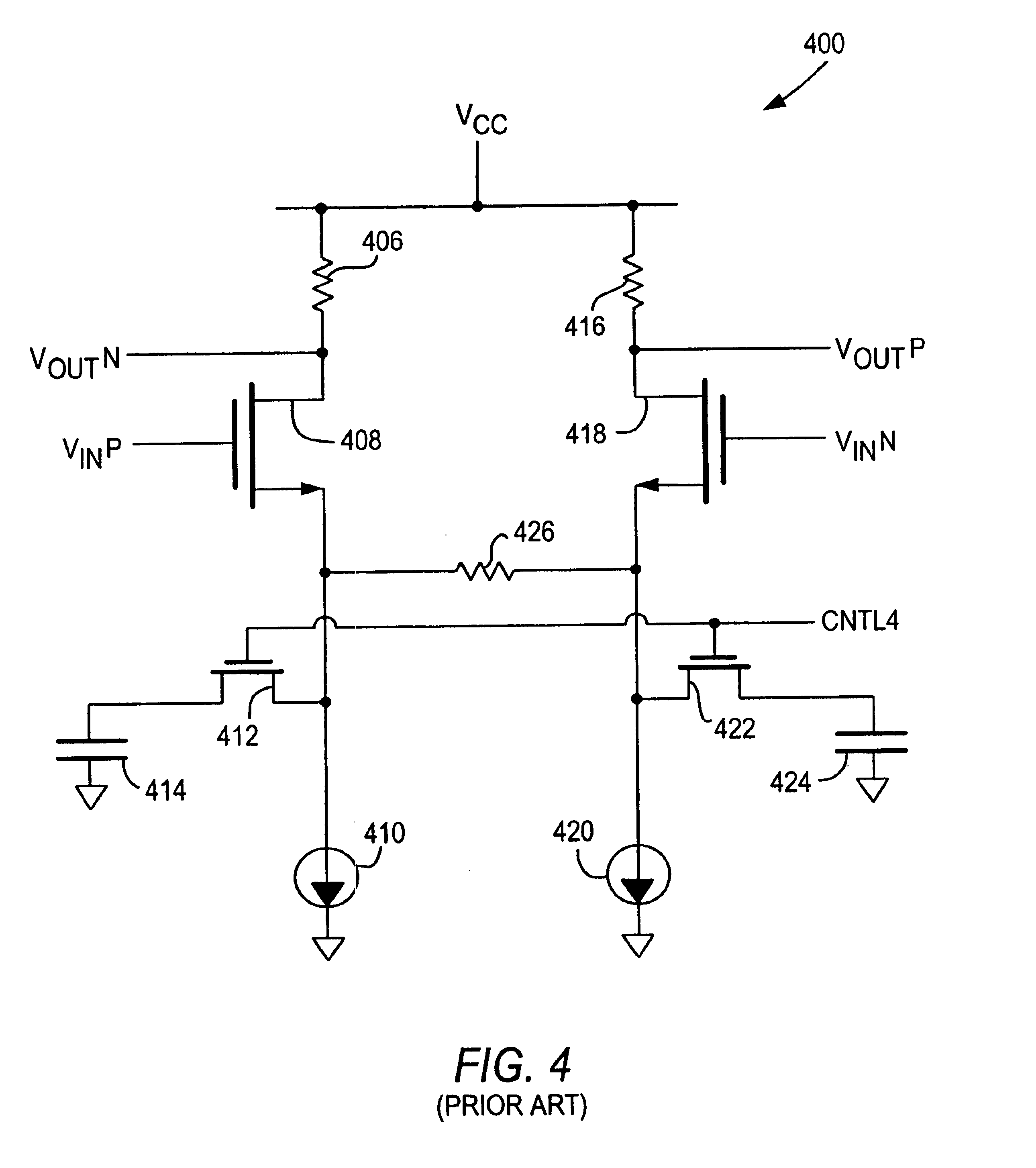

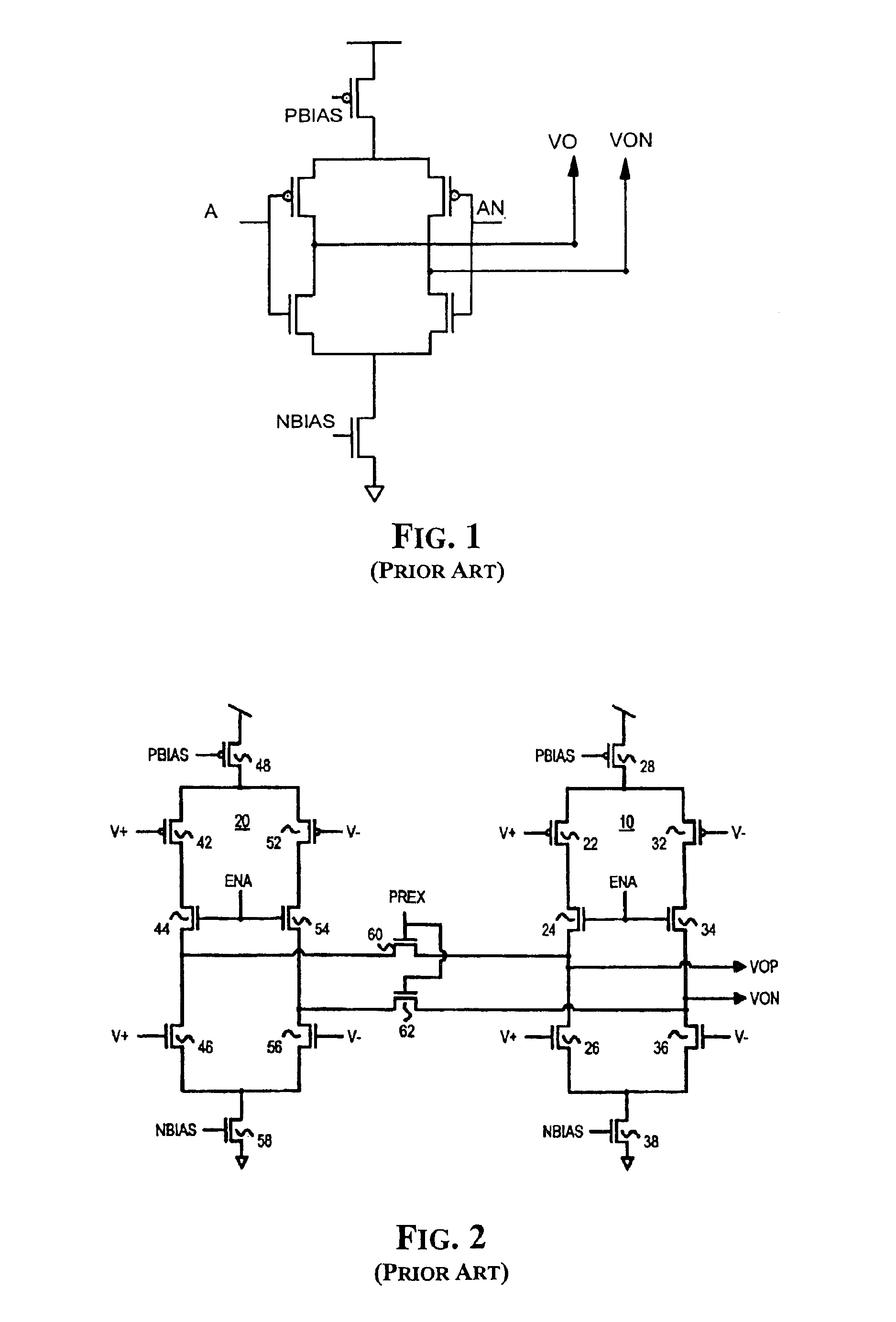

Programmable differential capacitors for equalization circuits

InactiveUS6870404B1Improve circuit performanceCommon noise rejectionMultiple input and output pulse circuitsElectric pulse generatorCapacitanceDifferential signaling

Programmable differential capacitance is implemented in equalization circuits. The programmable differential capacitance improves the common mode rejection ratio of circuits processing differential signals of various frequencies and voltage swings. Multiple capacitance devices provide the programmable capacitance, which provides an equalization circuit with different, selectable (i.e., programmable) values of capacitance for boosting the transition speed and strength of differential signals processed by the equalization circuit.

Owner:ALTERA CORP

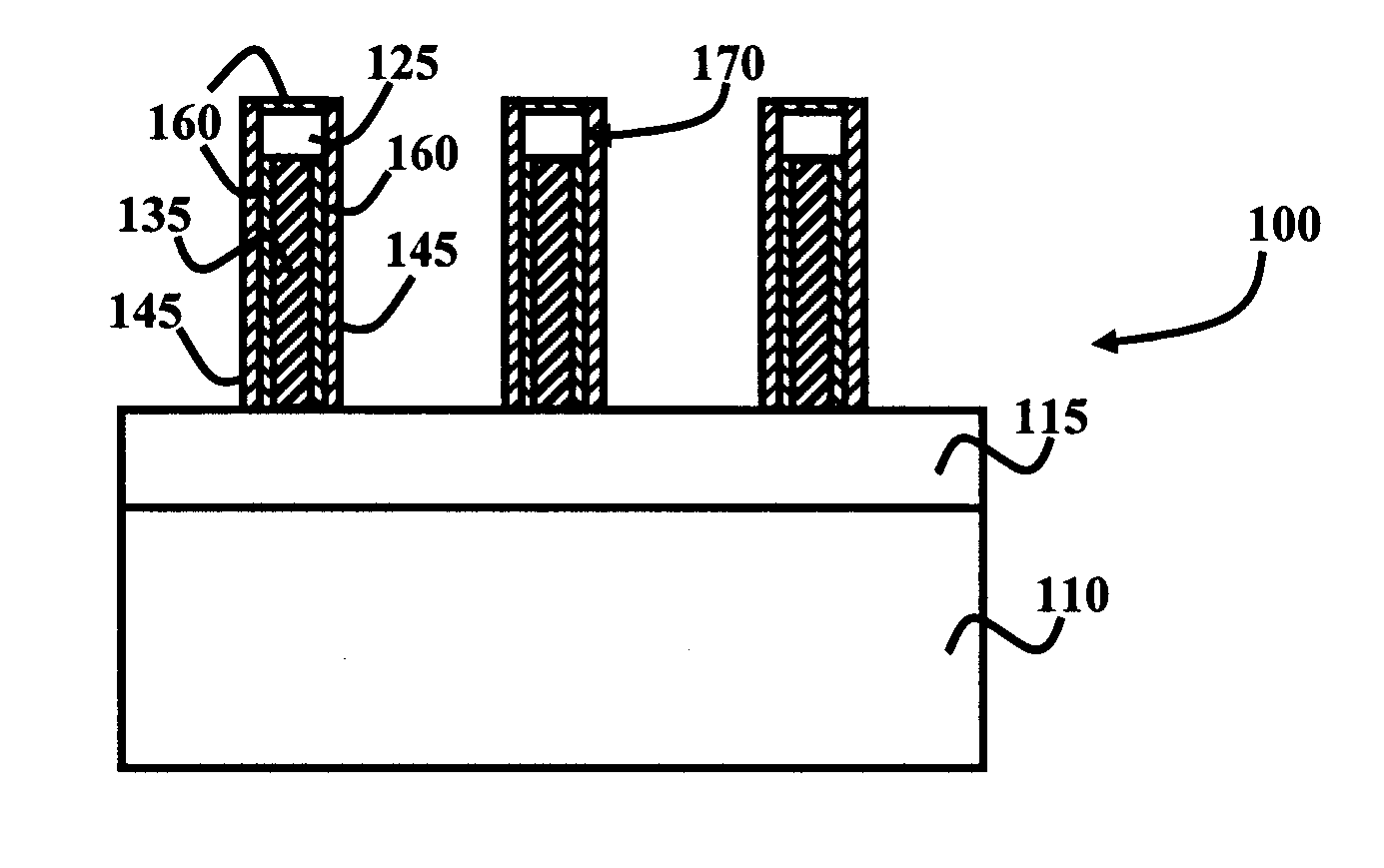

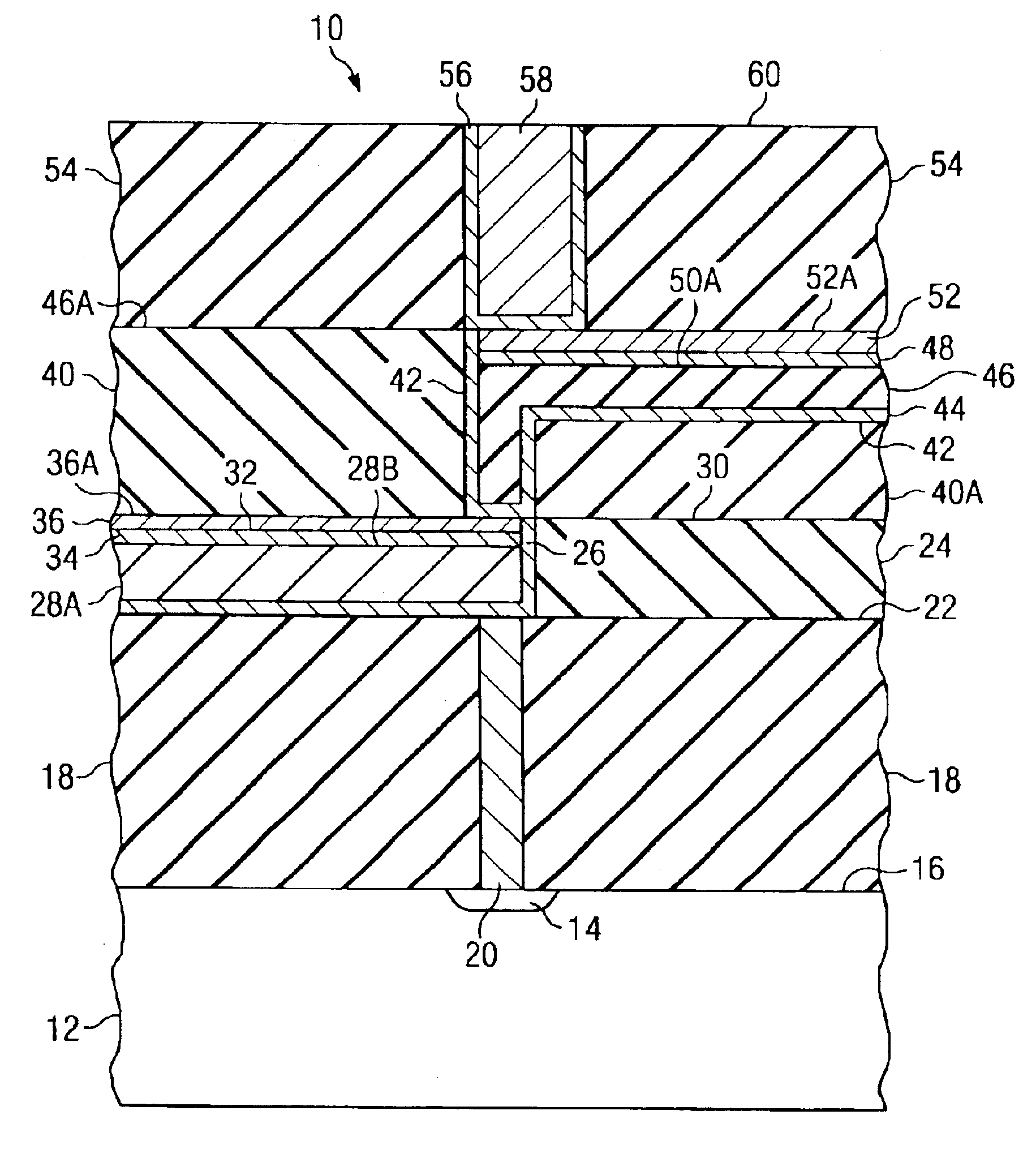

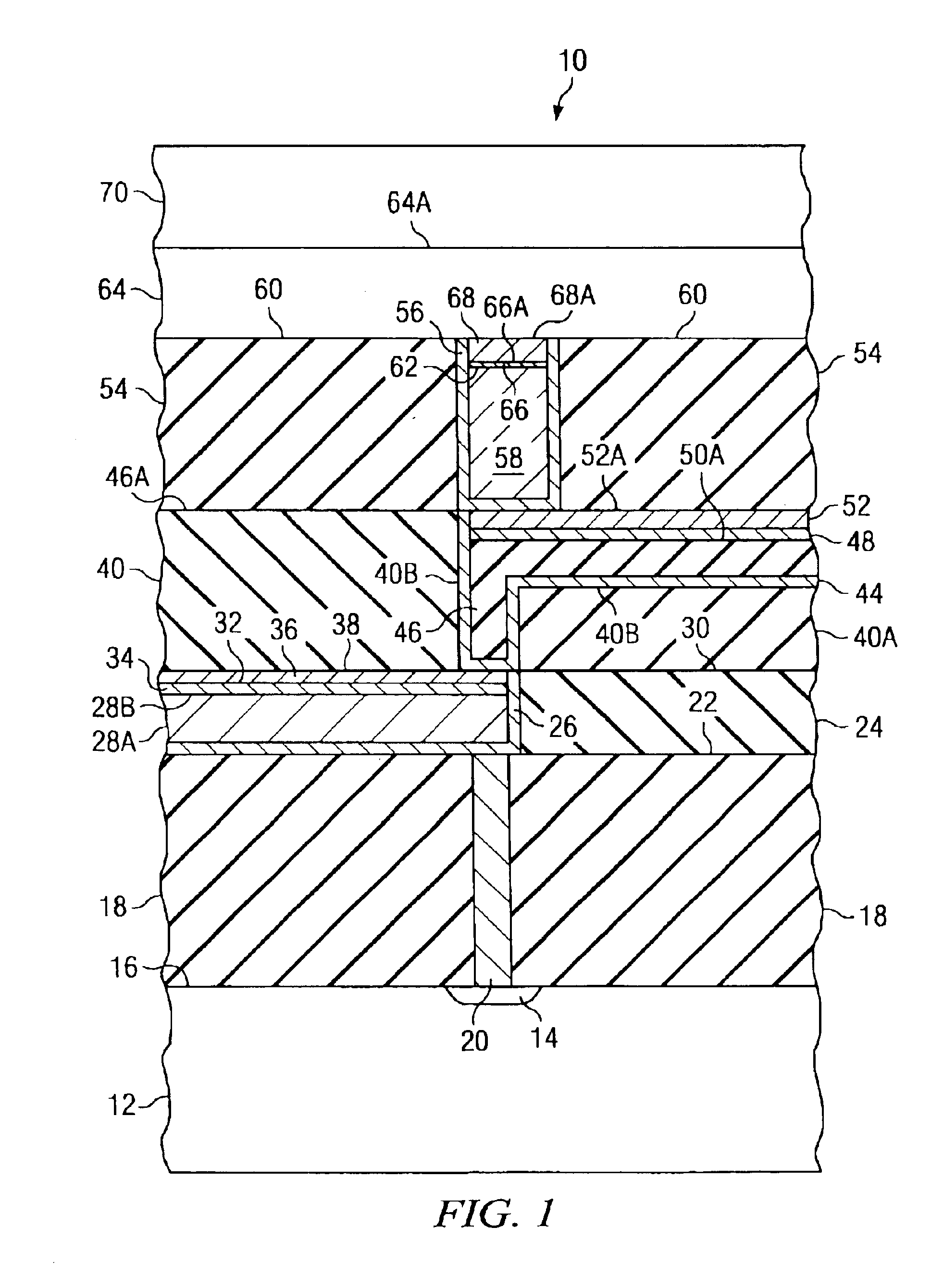

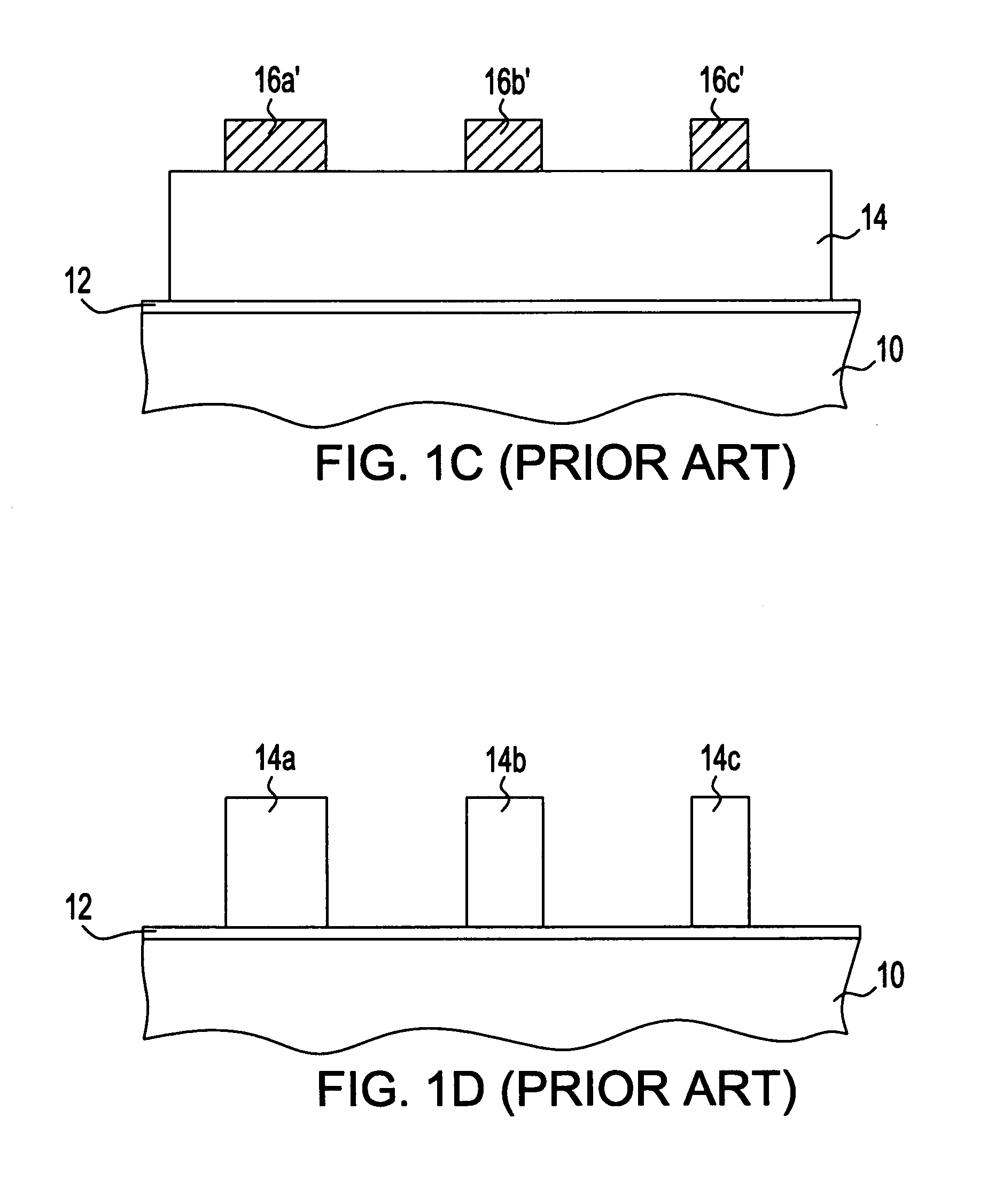

Finfet with low gate capacitance and low extrinsic resistance

ActiveUS20060043616A1Reduce gate capacitanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceGate insulator

A FinFET device and a method of lowering a gate capacitance and extrinsic resistance in a field effect transistor, wherein the method comprises forming an isolation layer comprising a BOX layer over a substrate, configuring source / drain regions above the isolation layer, forming a fin structure over the isolation layer, configuring a first gate electrode adjacent to the fin structure, disposing a gate insulator between the first gate electrode and the fin structure, positioning a second gate electrode transverse to the first gate electrode, and depositing a third gate electrode on the fin structure, the first gate electrode, and the second gate electrode, wherein the isolation layer is formed beneath the insulator, the first gate electrode, and the fin structure. The method further comprises sandwiching the second gate electrode with a dielectric material. The fin structure is formed by depositing an oxide layer over a silicon layer.

Owner:MICROSOFT TECH LICENSING LLC

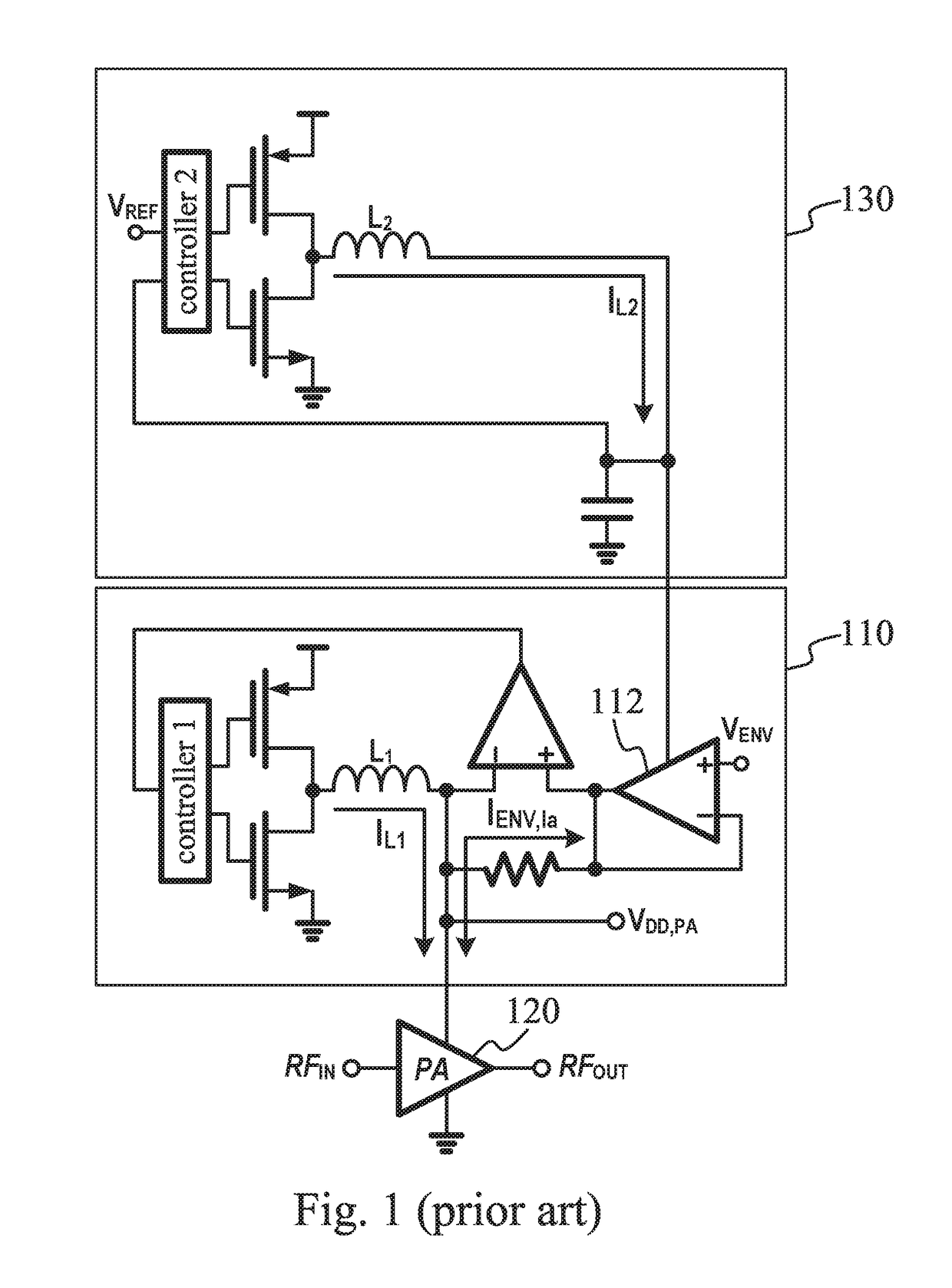

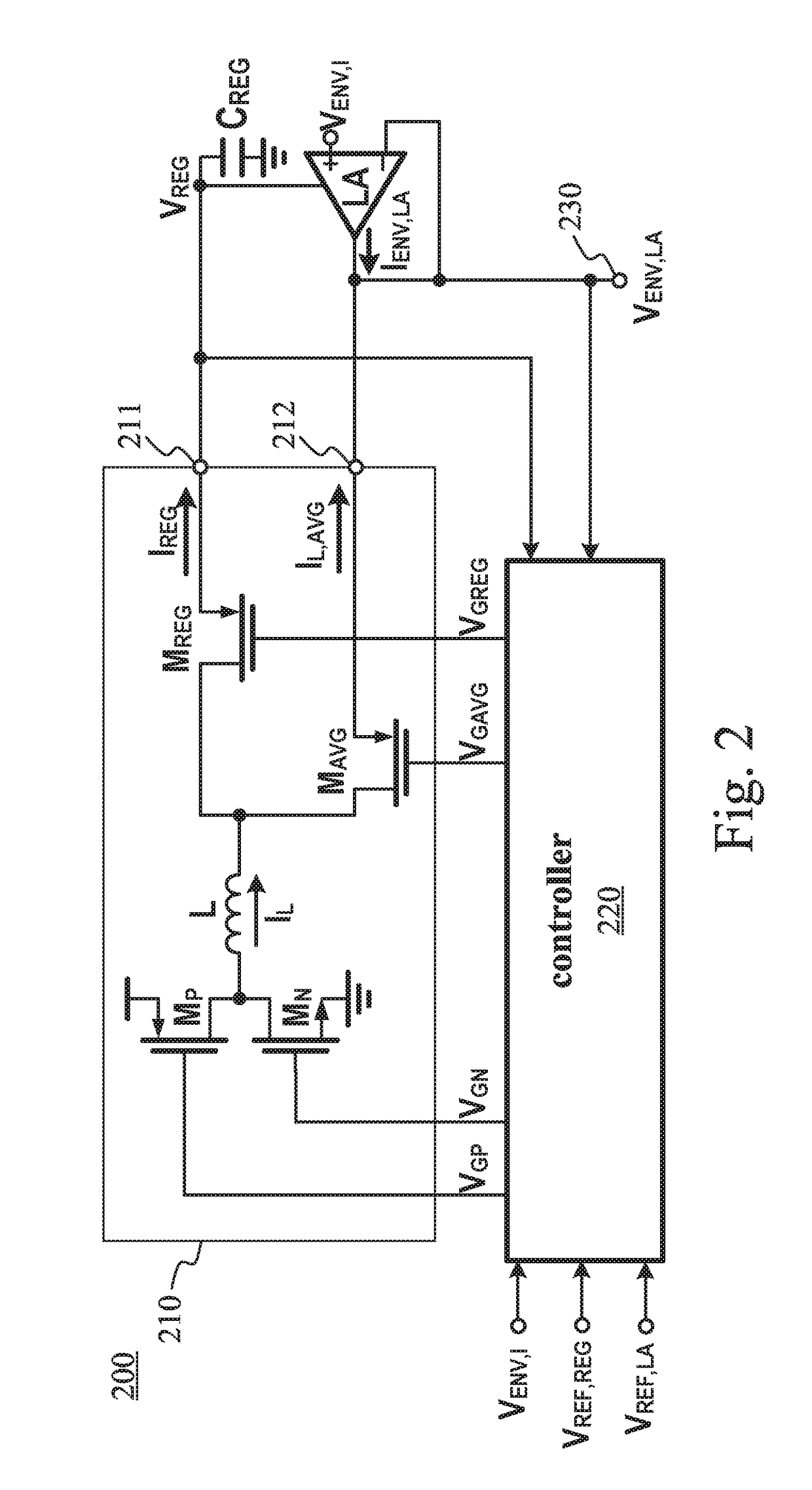

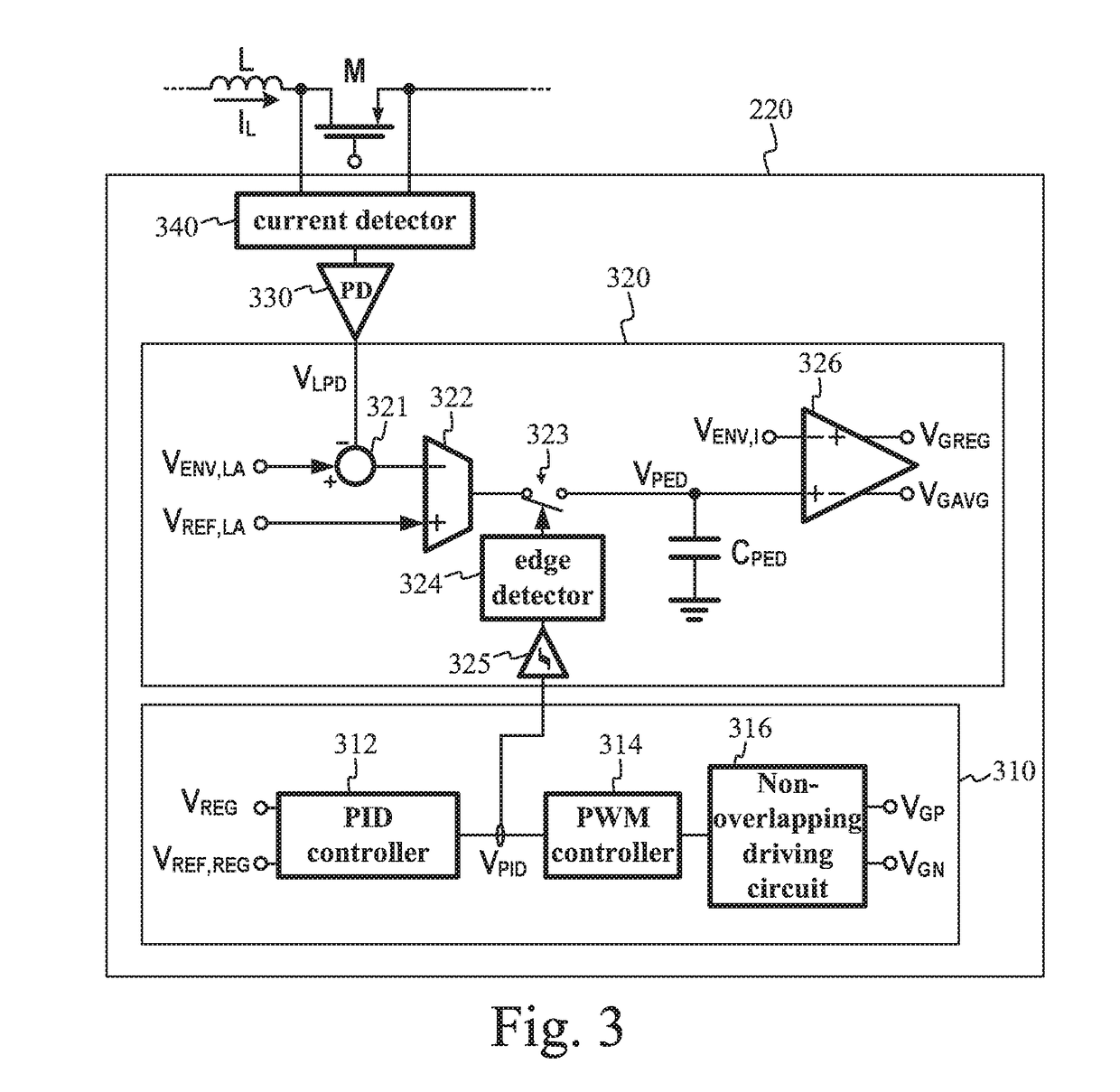

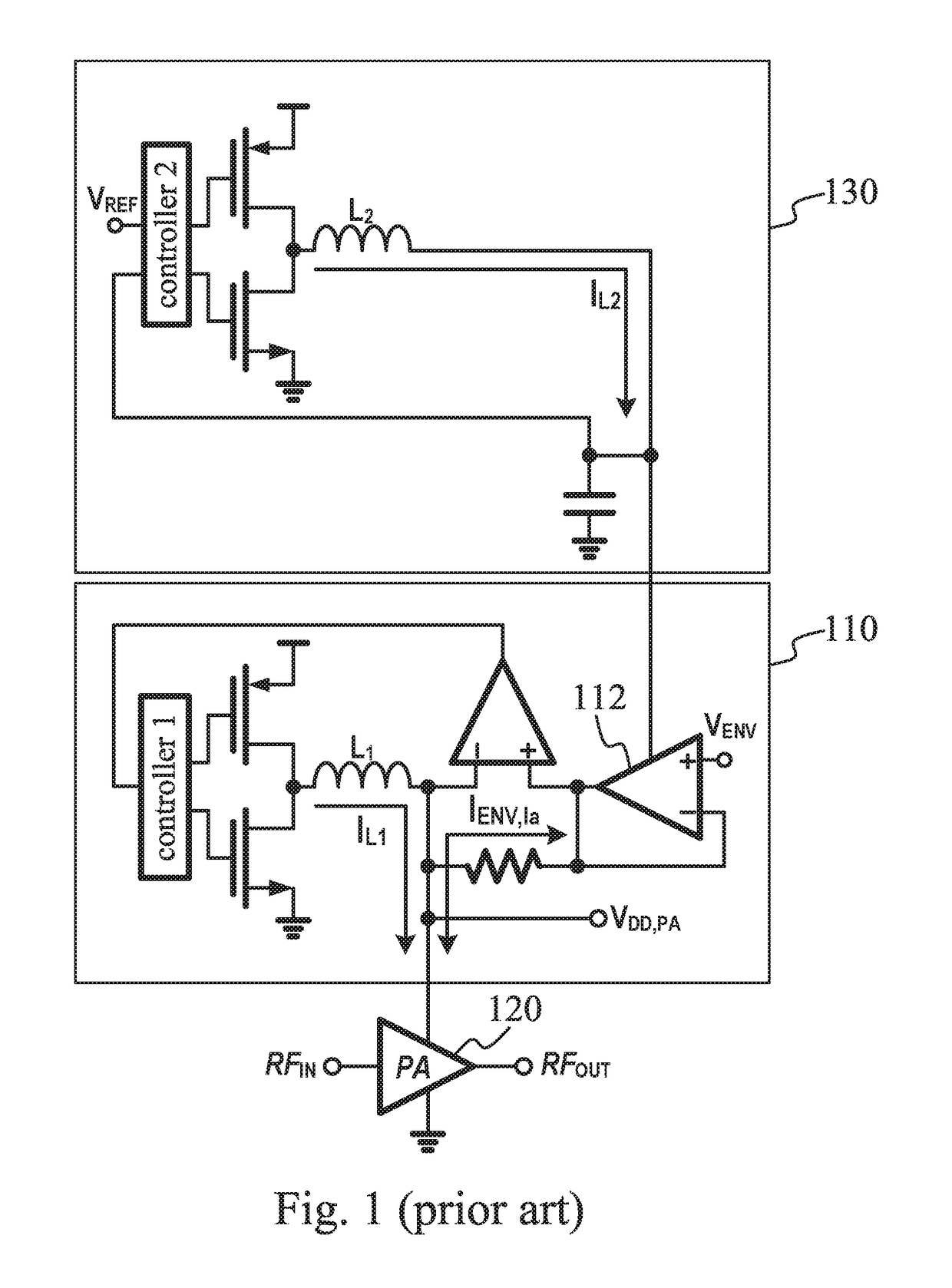

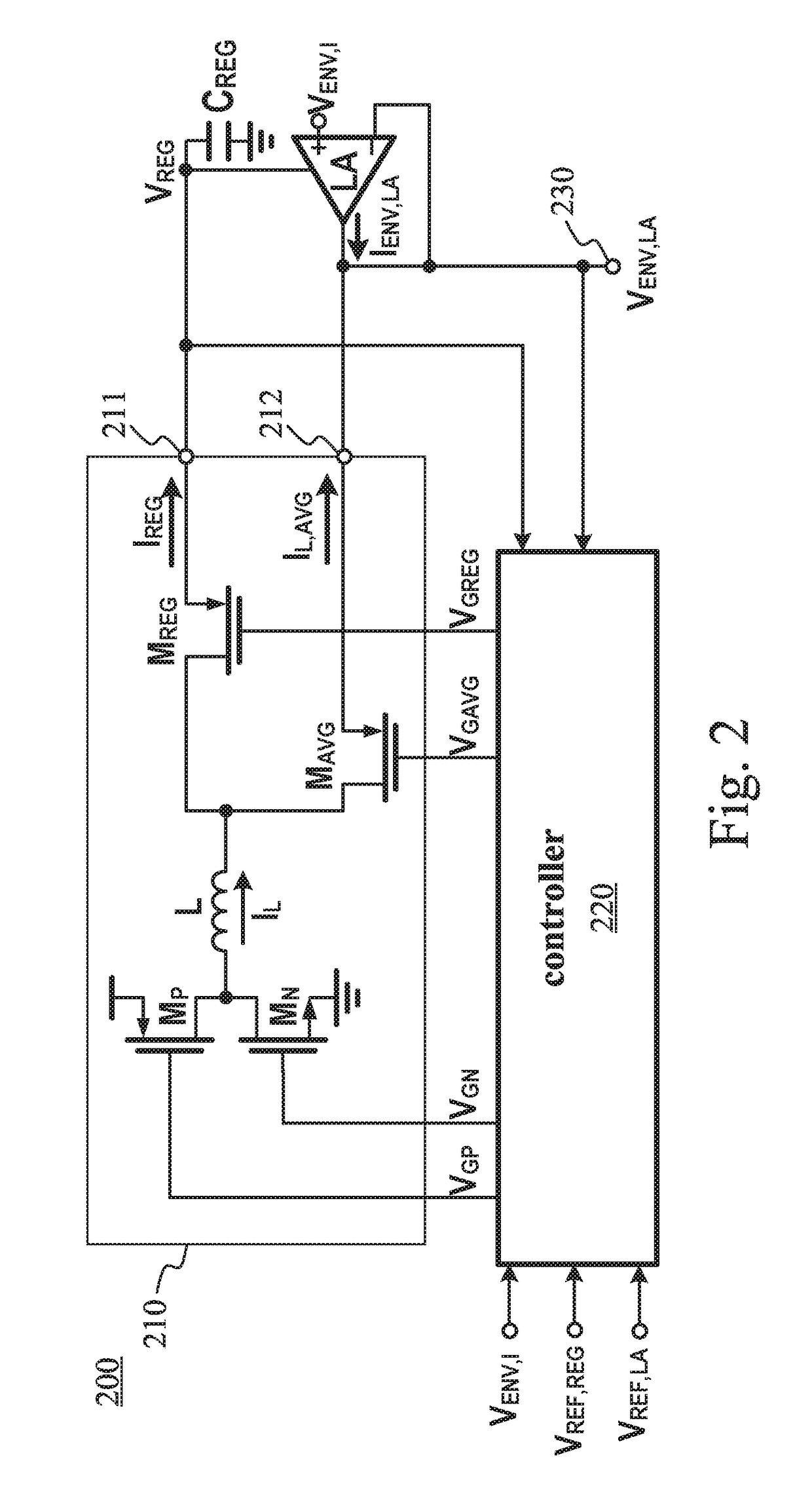

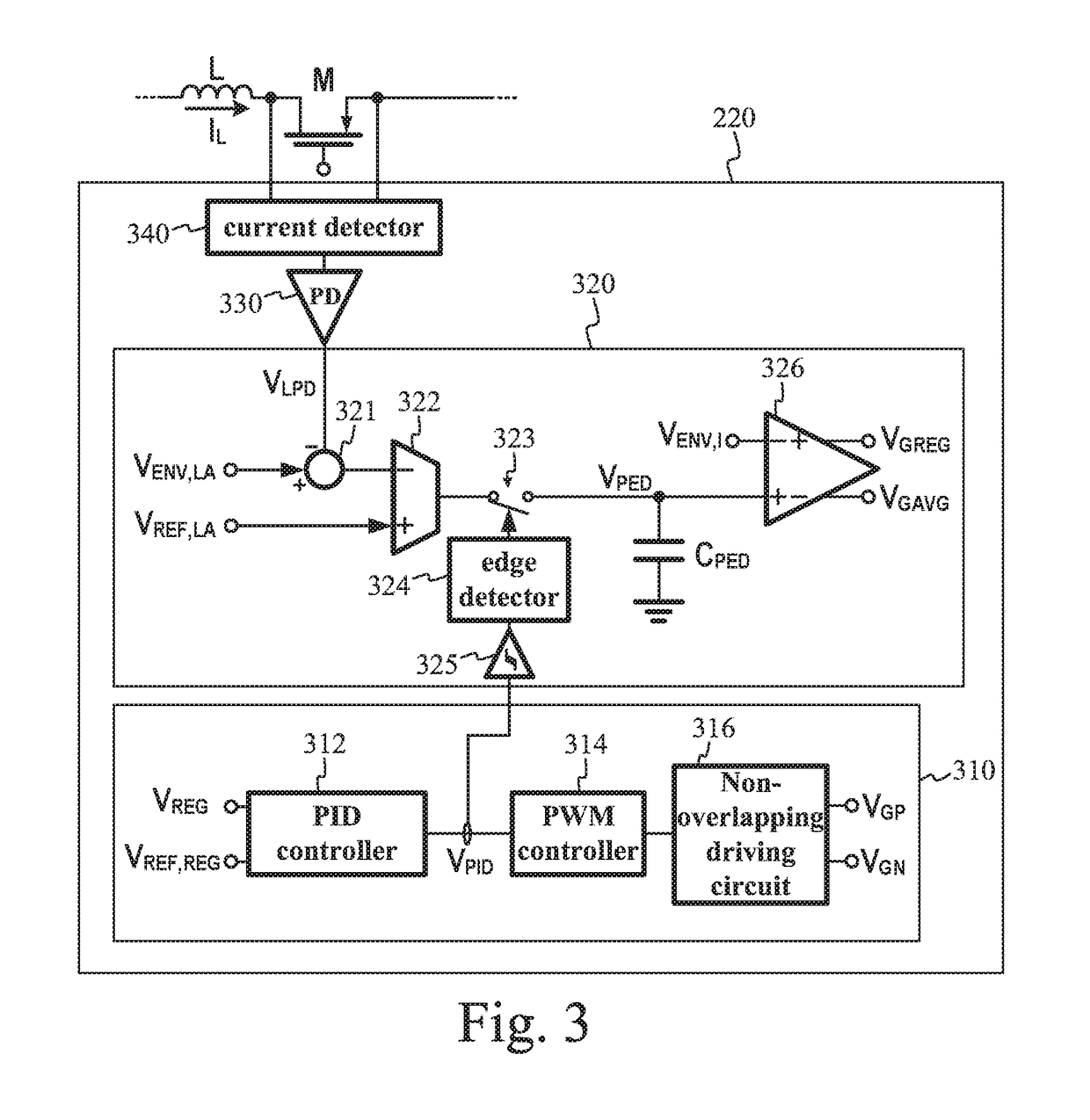

Envelope-tracking power supply modulator

ActiveUS20180367101A1Reduce hardware costsAvoid energy wasteHigh frequency amplifiersPower amplifiersAudio power amplifierEngineering

An envelope-tracking power supply modulator (ETSM) supplies power to a radio frequency power amplifier (RFPA) of a radio frequency (RF) circuit according to a baseband envelope signal. The ETSM includes a linear amplifier, a capacitor, a single inductor multiple output (SIMO) switch-mode converter, and a controller. The linear amplifier receives the baseband envelope signal, and has its output terminal coupled to a power input of the RFPA. One terminal of the capacitor is coupled to a reference voltage, and the other terminal is coupled to a power input of the linear amplifier. The SIMO switch-mode converter includes two output terminals. One of the output terminals is coupled to the capacitor and the power input of the linear amplifier, and the other of the output terminals is coupled to the output terminal of the linear amplifier and the power input of the RFPA. The controller controls the SUMO switch-mode converter.

Owner:REALTEK SEMICON CORP

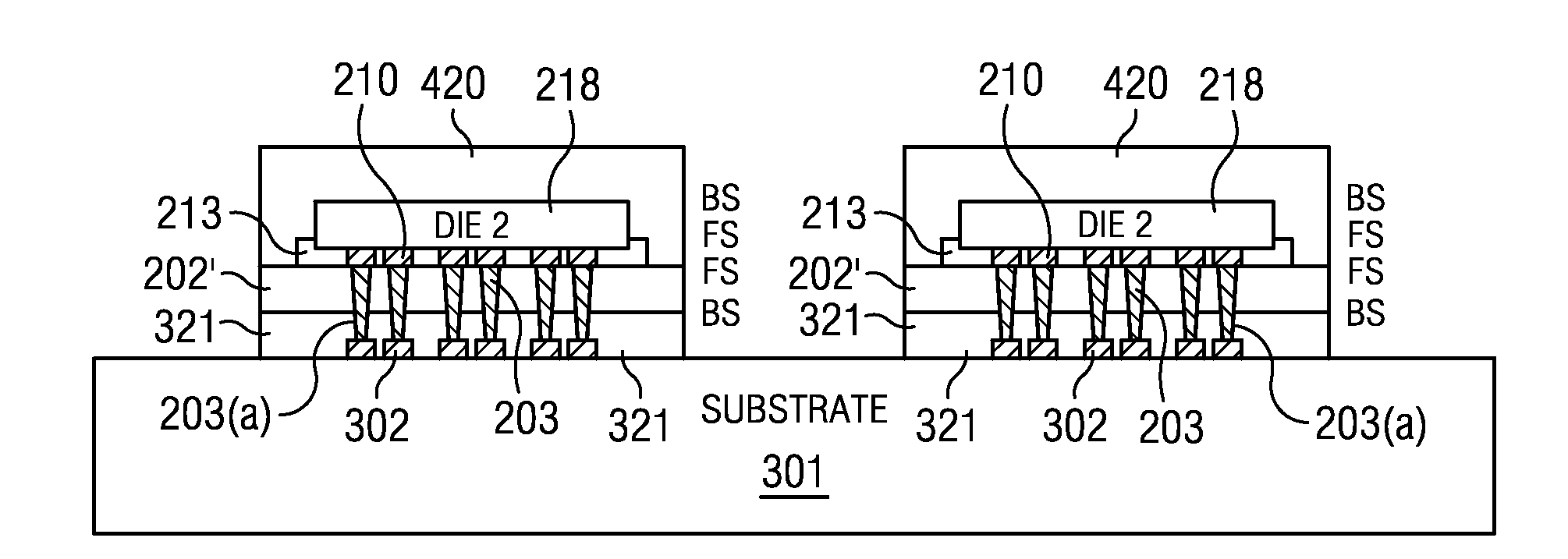

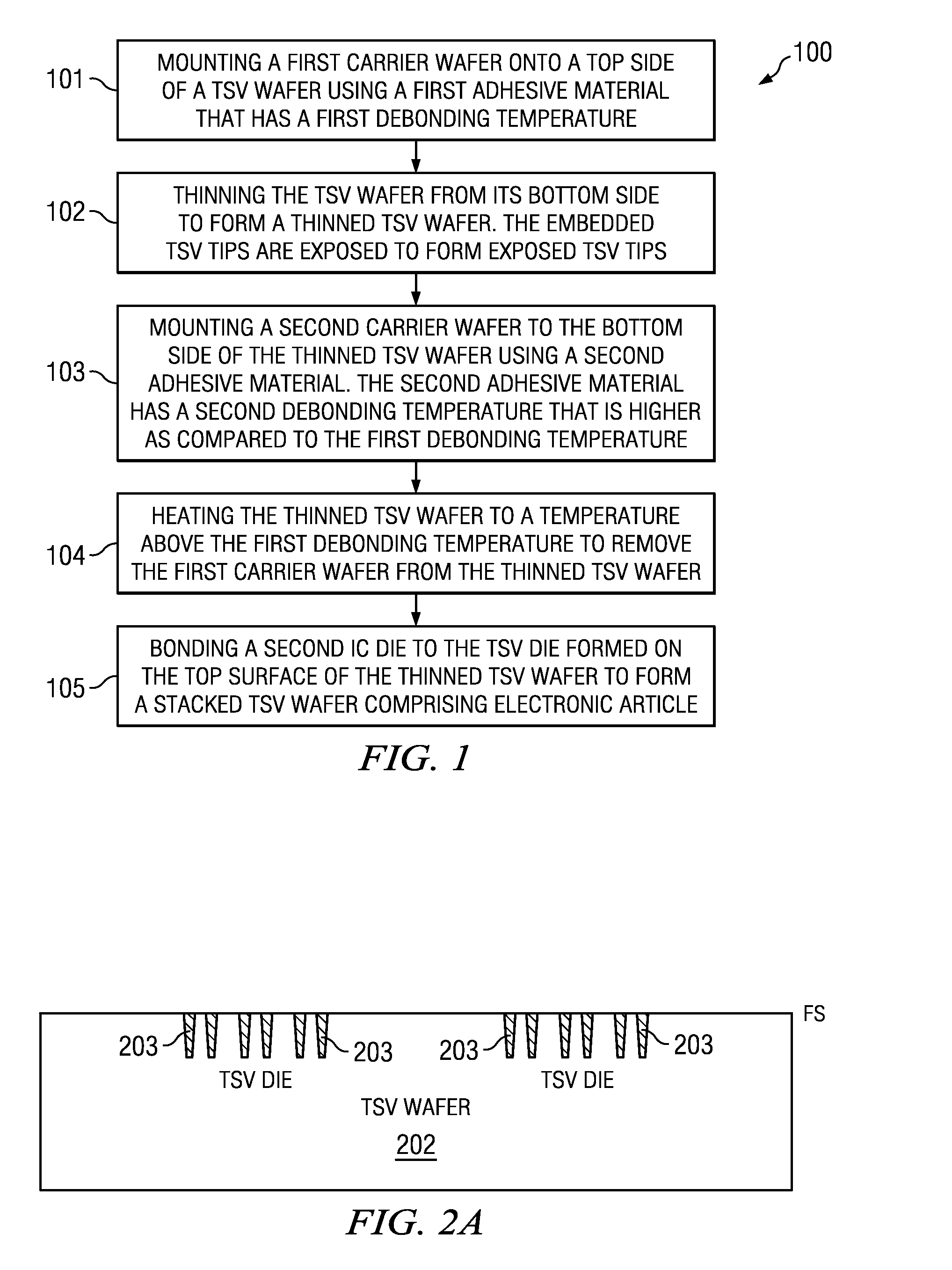

Dual carrier for joining IC die or wafers to TSV wafers

ActiveUS20110183464A1Reduce contact resistanceImprove circuit performanceSolid-state devicesAdhesive processes with adhesive heatingWaferingEngineering

A method of forming stacked electronic articles using a through substrate via (TSV) wafer includes mounting a first carrier wafer to a top side of the TSV wafer using a first adhesive material that has a first debonding temperature. The TSV wafer is thinned from a bottom side of the TSV wafer to form a thinned TSV wafer. A second carrier wafer is mounted to the bottom side of the TSV wafer using a second adhesive material that has a second debonding temperature that is higher as compared to the first debonding temperature. The thinned TSV wafer is heated to a temperature above the first debonding temperature to remove the first carrier wafer from the thinned TSV wafer. At least one singulated IC die is bonded to TSV die formed on the top surface of the thinned TSV wafer to form the stacked electronic article.

Owner:TEXAS INSTR INC

Method to form selective cap layers on metal features with narrow spaces

InactiveUS6893959B2Improve circuit performanceEliminate needSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorRandom access memory

Interconnect layers on a semiconductor device containing logic circuits (microprocessors, Asics of others) or random access memory cells (DRAM's) are formed in a manner to significantly reduce the number of shorts between adjacent conductor / vias with narrow separations in technologies having feature sizes of 0.18 microns or smaller. This is accomplished by etching to form recessed copper top surfaces on each layer after a chemical-mechanical polishing process has been completed. The thickness of a selectively formed barrier layer on the recessed copper surfaces, is controlled to be essentially co-planar with the surrounding insulator surfaces. Because the barrier layers are recessed, shorting of adjacent conductive lines is prevented.

Owner:INFINEON TECH AG

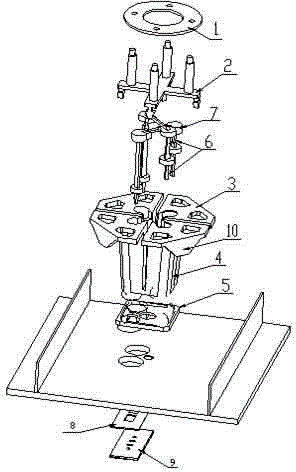

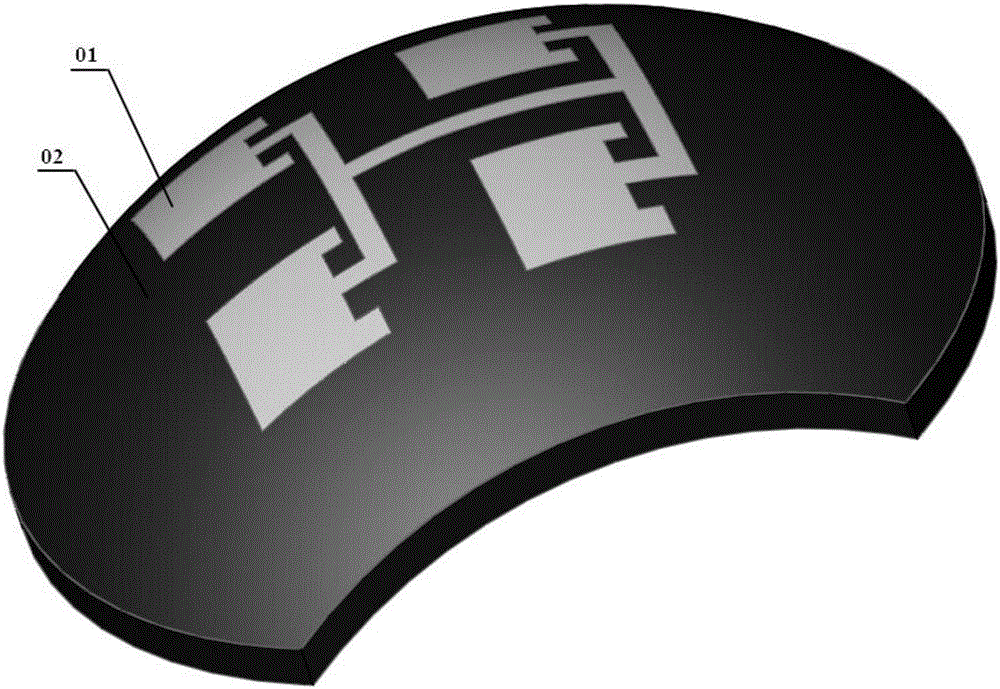

Broadband radiating unit and antenna array

ActiveCN104900987AImprove circuit performanceImprove stabilitySimultaneous aerial operationsRadiating elements structural formsDielectricBroadband

The invention provides a broadband radiating unit and an antenna array. The broadband radiating unit comprises a support Balun, a radiation arm, a feeding core, a positioning dielectric block, a positioning support snap, a parasitic radiation sheet and an oscillator pad. The radiation arm is above the support Balun, and an oscillator body is formed by the support Balun and the radiation arm. The feeding core is in the cylindrical hole of the support Balun and is coated and positioned by the positioning dielectric block. The oscillator pad is under the oscillator body. The parasitic radiation sheet is fixed above the positioning support snap which is fixed above the radiation arm. In antenna array, a PCB protruding column is arranged under the support Balun of each radiation unit, the PCB protruding column goes through a reflection plate and a PCB and then is welded to a microstrip grounding block, one end of the feeding core is connected to the oscillator body by using the mode of coupling feed, and the other end goes through the reflection plate and the PCB and then is welded to a microstrip line. The radiating unit of the invention has the advantage of simple assembly, few solders, flexible wire running of a back PCB, and higher intermodulation stability.

Owner:WUHAN HONGXIN TELECOMM TECH CO LTD

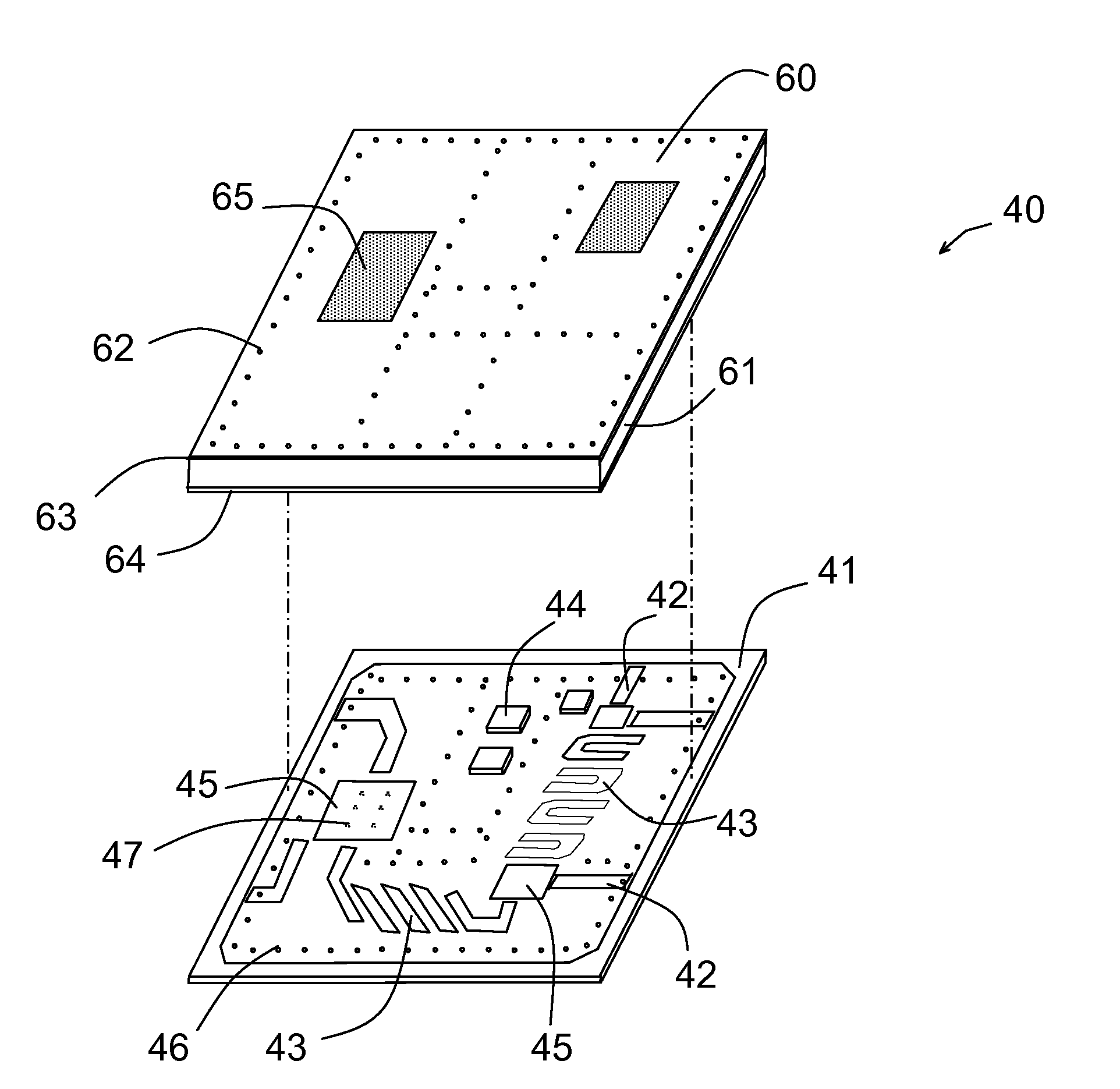

Highly Integrated Miniature Radio Frequency Module

ActiveUS20110051375A1Low costHighly integratedLine/current collector detailsSemiconductor/solid-state device detailsElectricityDielectric substrate

A highly integrated miniature RF module includes a dielectric base board with opposing top and bottom metal layers and having interconnects traces, radio frequency (RF) circuits and semiconductor chips at the top metal layer and ground and signal pads at the bottom metal layer. Metalized vias extending through the dielectric material connect the top and bottom layers. A top cover made out of laminate material, such as FR-4, with opposing top and bottom metal layers and having machined compartments and channels, surrounded with arrays of metal plated vias extending through the laminate material, protects the RF circuits and chips and provide the required isolation and wave propagation.

Owner:VU SYST LLC

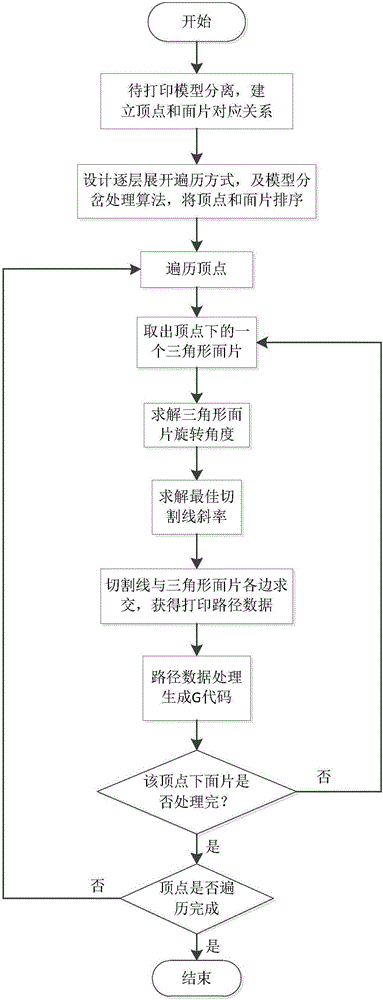

Slicing treatment method for surface model surface ink jet printing

ActiveCN106738864AImprove connectivityImprove qualityAdditive manufacturing apparatus3D object support structuresSurface modeData treatment

The invention discloses a slicing treatment method for surface model surface ink jet printing. The method comprises the following steps: a surface model to be printed is separated from a computer, and is preserved as a STL format for data processing to remove redundant data; a corresponding relation between a peak and a facet is built; a layer-by-layer unfolding traversal mode of the peak of the STL model and a fork processing algorithm are designed; the peak and the facet are arranged by a certain sequence; the peak is traversed; the facet included under the peak is read; an angle of rotating the facet to be printed to the horizontal position and an optimal cutting line slope are calculated; a printing error is reduced; a layering tangent line and each edge of the triangular facet are intersected to obtain printing path data; and all peaks and facets are traversed to obtain a complete G code of the model to be printed. The slicing treatment method can prevent the step effect of the forming surface of the surface model and the precision problem caused by ink flowing, and can improve the surface overall connectivity and the printing precision.

Owner:XIDIAN UNIV

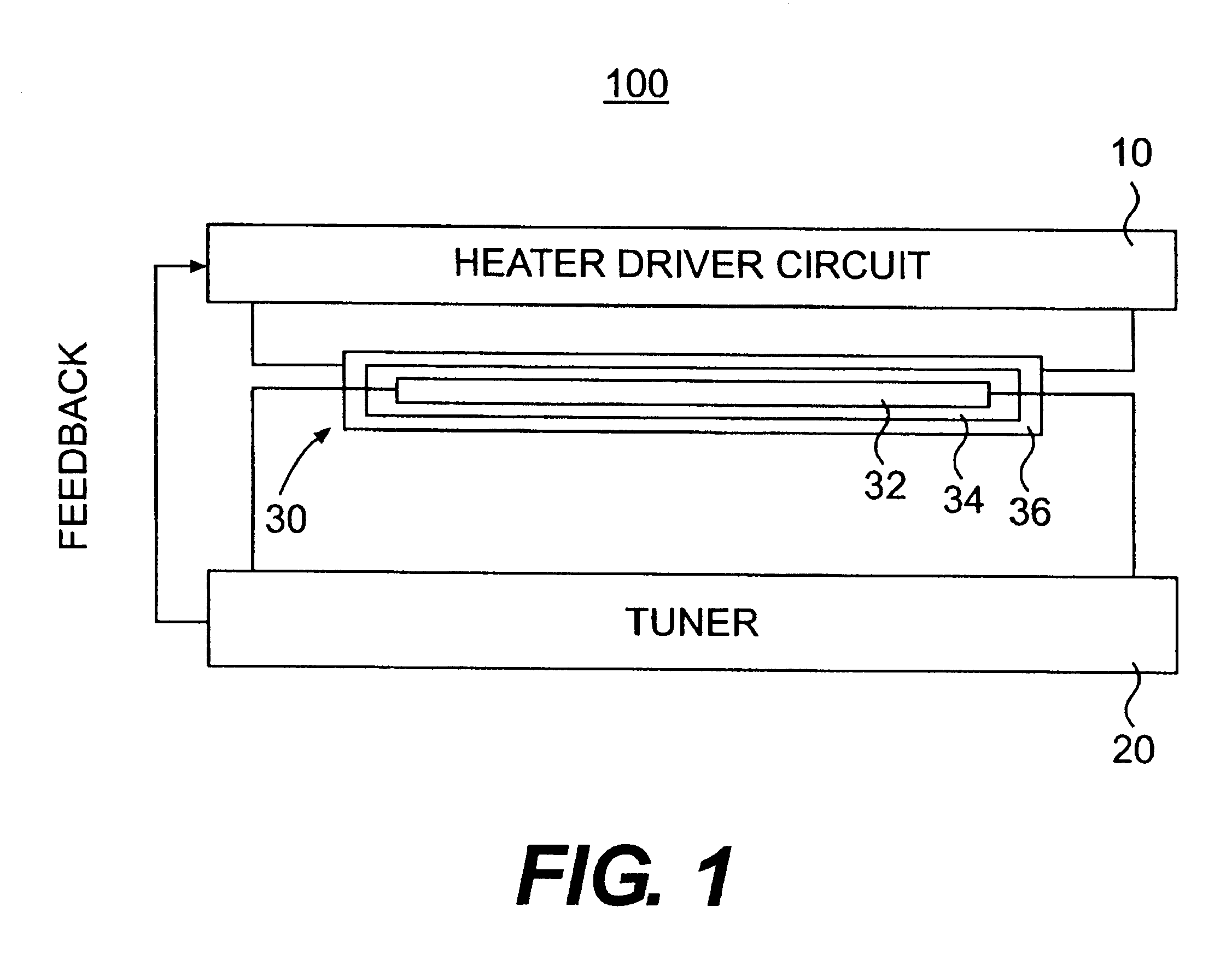

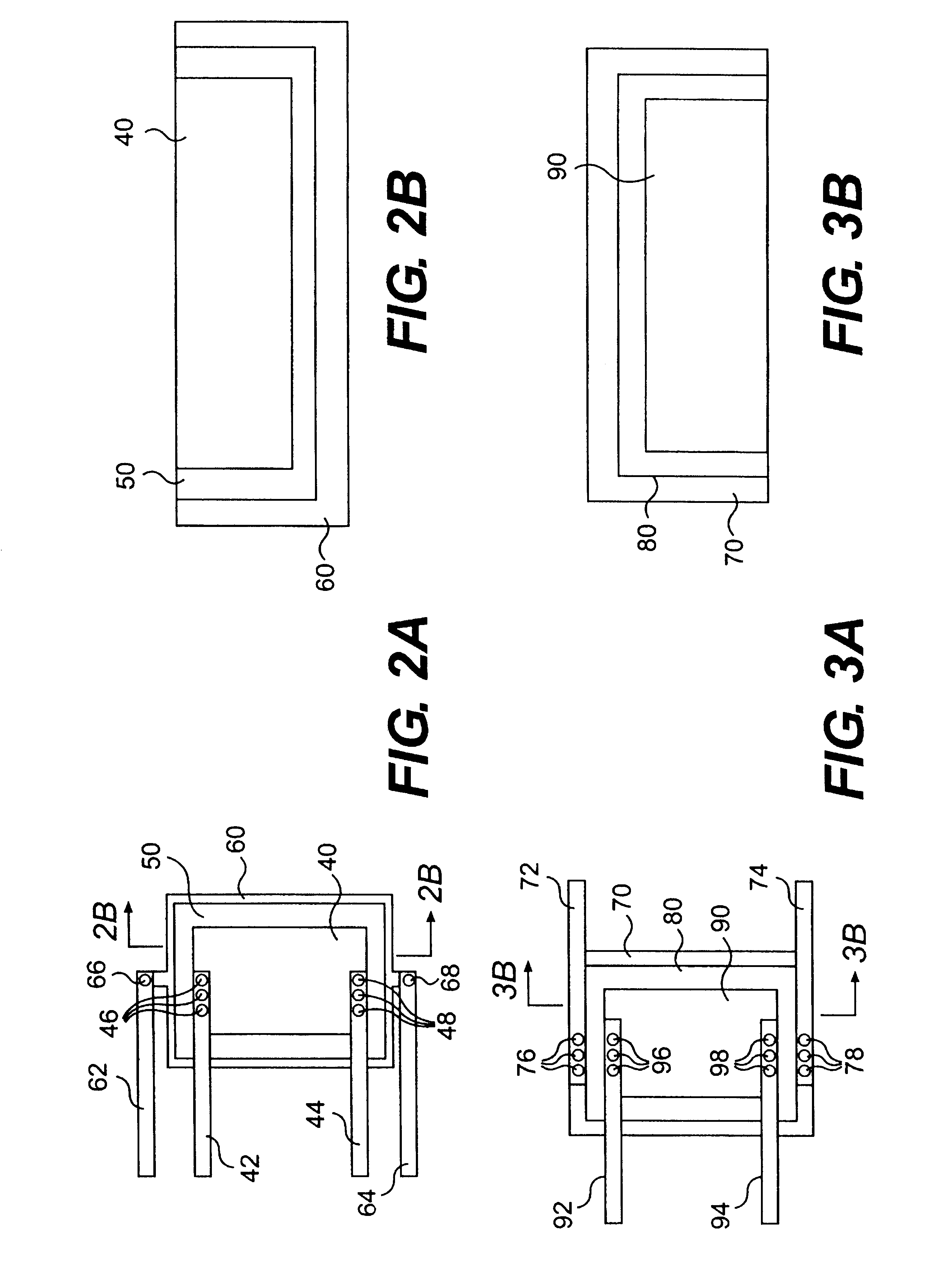

Electrically tunable on-chip resistor

InactiveUS6960744B2Improve circuit performanceResistance of the resistorElectric heatingCurrent responsive resistorsElectrical resistance and conductanceEngineering

A device having a resistor and a heater disposed proximate to the resistor and capable of raising the temperature of the resistor. The device further includes a dieletric disposed between the heater and the resistor and a tuner electrically coupled to the resistor. The heater adjusts the resistance of the resistor in response to the tuner.

Owner:INT BUSINESS MASCH CORP

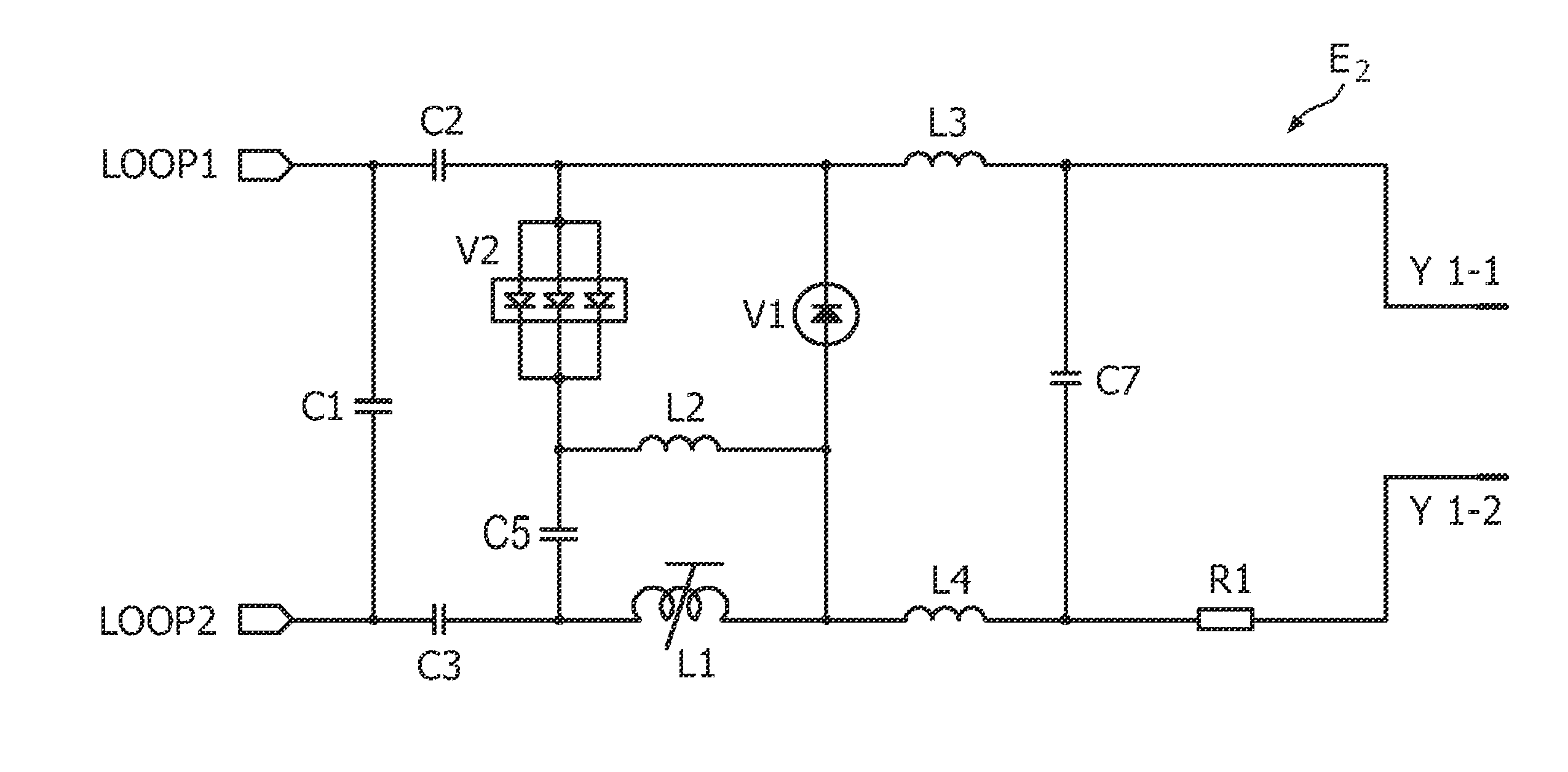

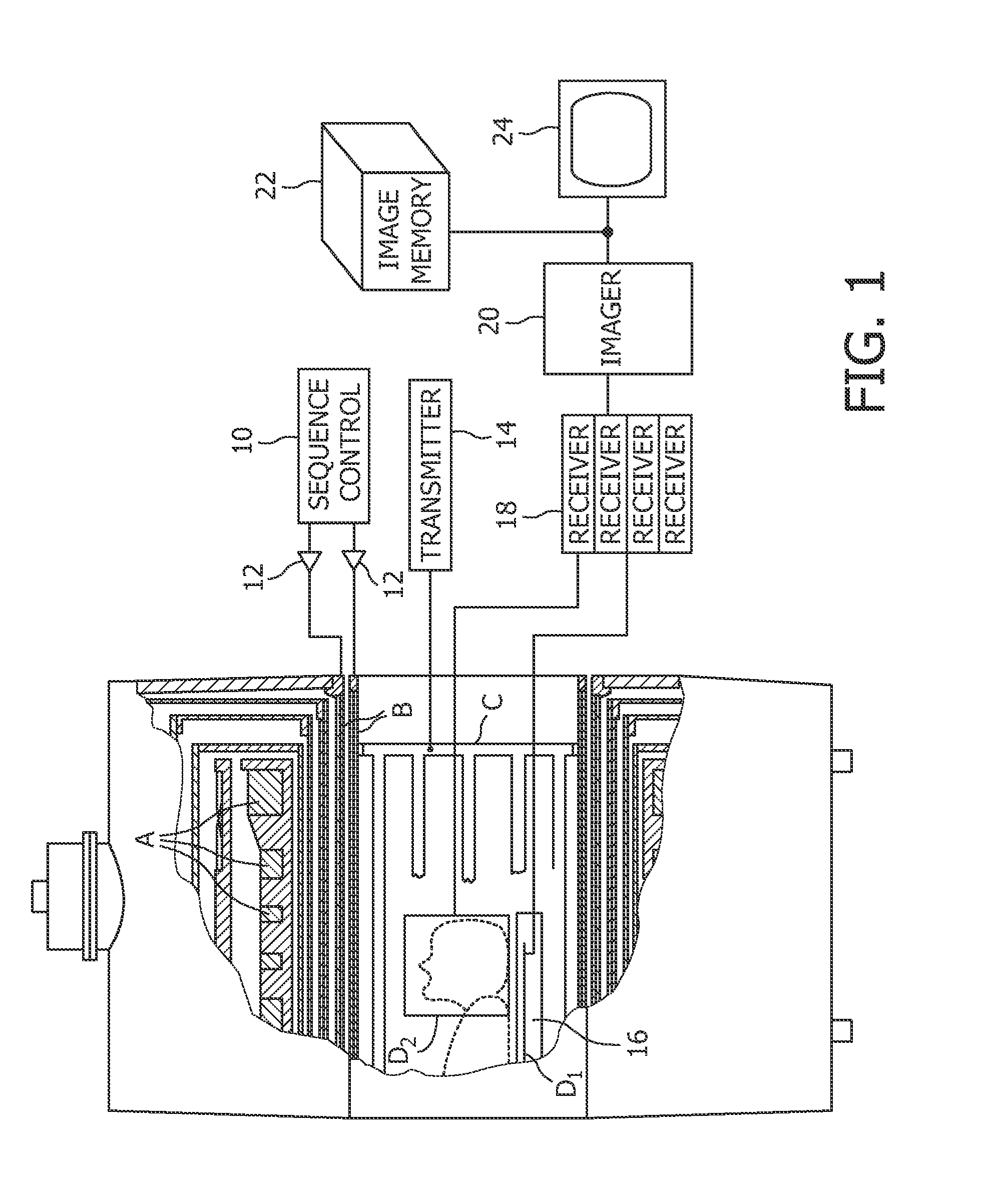

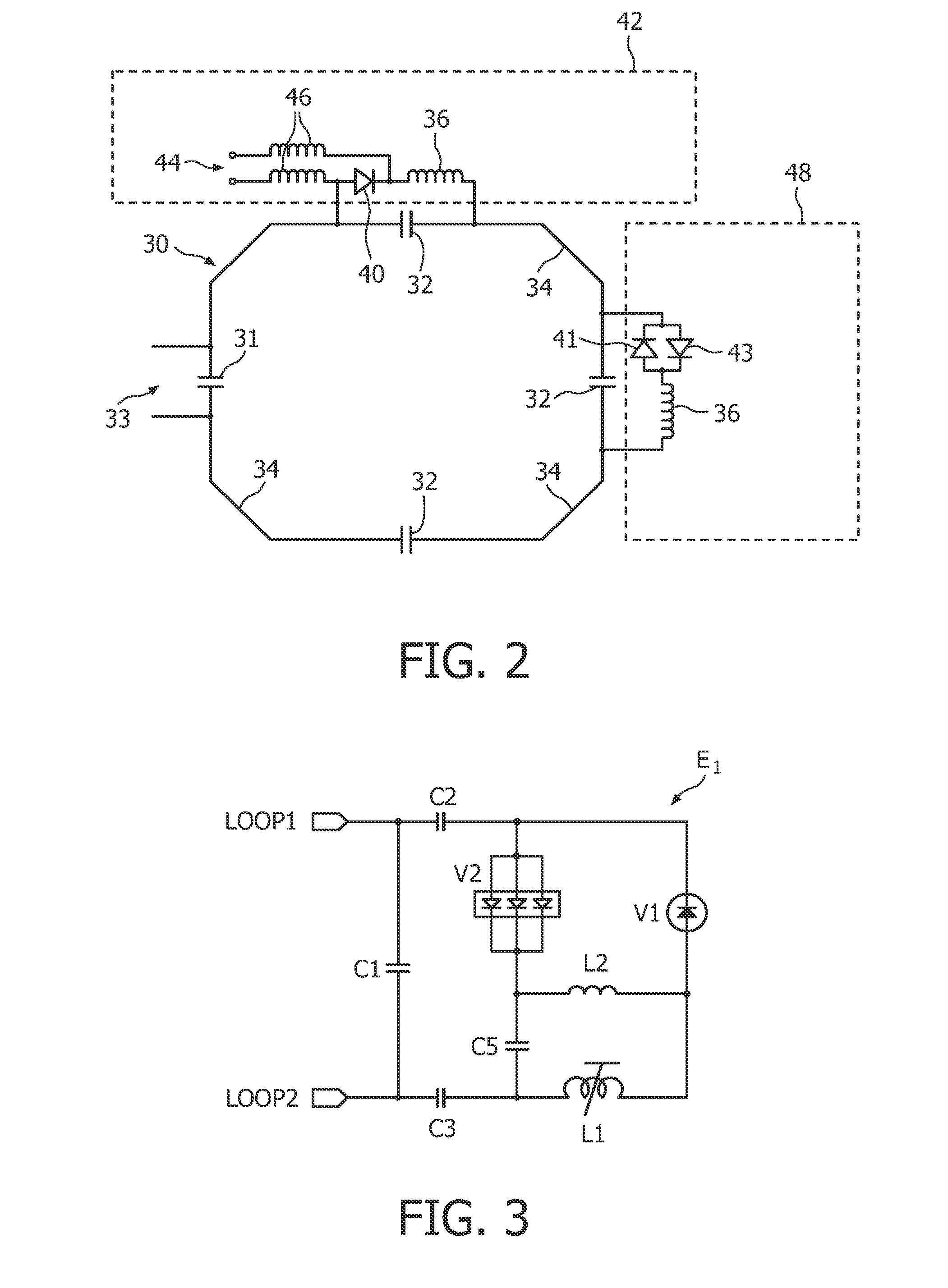

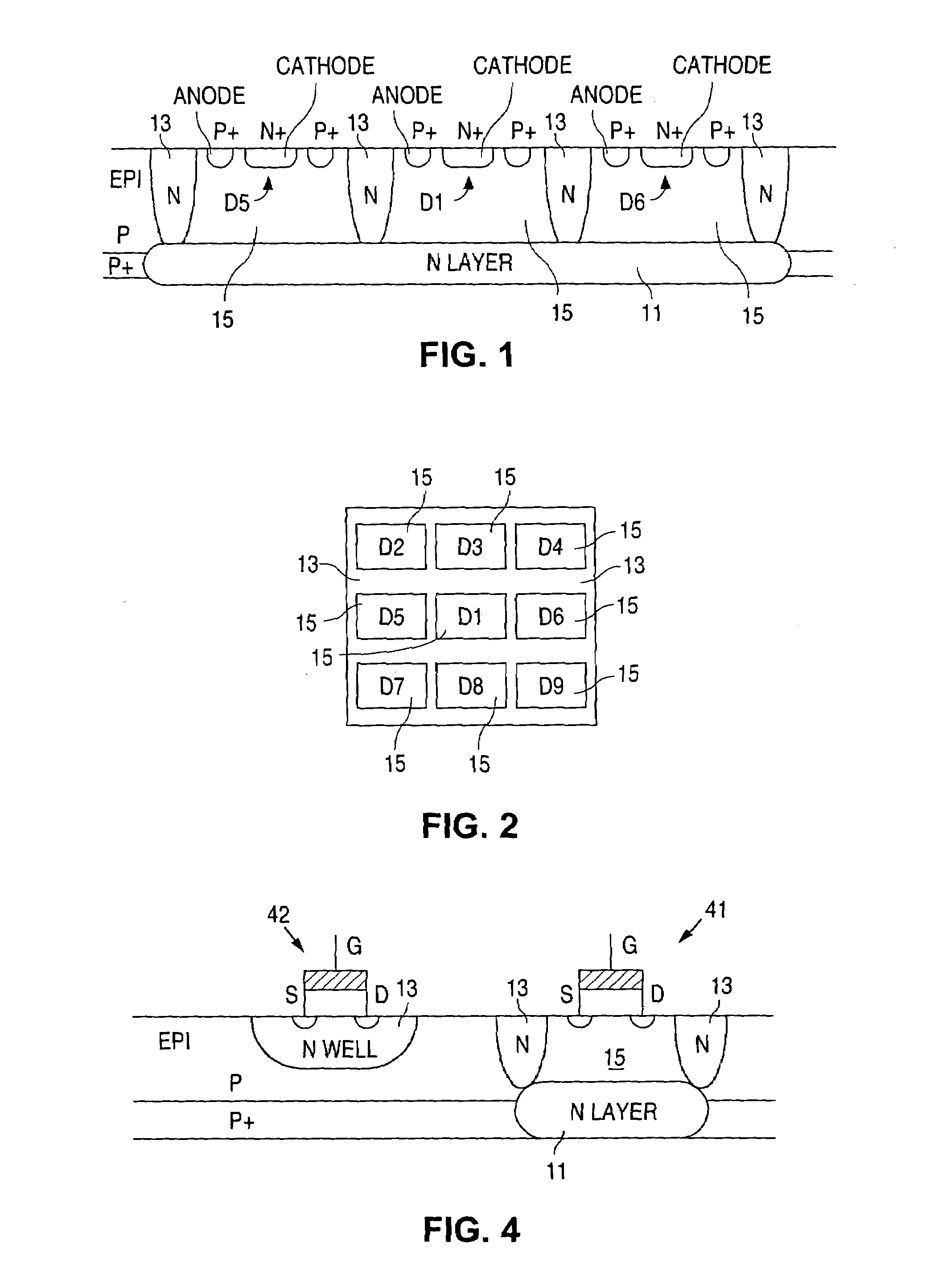

Detuning circuit and detuning method for an MRI system

InactiveUS8013609B2Sufficient deliveryRobustMagnetic measurementsElectric/magnetic detectionDc currentHigh field mri

The present invention relates to a magnetic resonance imaging system and a corresponding method having a transmit phase and a receive phase. Further, the present invention relates to a detuning circuit and a corresponding detuning method for detuning an RF receive coil during the transmit phase in such a magnetic resonance imaging system. In high-field MRI systems the transmit mode operating frequency is higher than normal high breakdown voltage rectifiers can handle when they are used to forward bias a passive detuning circuit PIN diode switch. The proposed circuit uses a current-limiting capacitor (C5) in series with a fast (e.g. schottky) rectifier diode (V2) with a reverse breakdown voltage of e.g. 20 volts and a fast reverse recovery time to generate a DC current. The rectifying circuit is isolated from the PIN diode (V1) with a relatively high-value inductor (L2), which ensures that no harmful transient current spikes can flow from the PIN diode anode to the rectifying circuit. The inductor (L2) still passes and maintains the DC current generated by the rectifying circuit through the PIN diode, thus enabling the robust forward-biasing of the PIN-diode during transmit mode. The use of a fast (and thus low-power) rectifier results in less dissipation on the detuning circuit, and helps in fulfilling the surface temperature limits posed on receiver coils.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

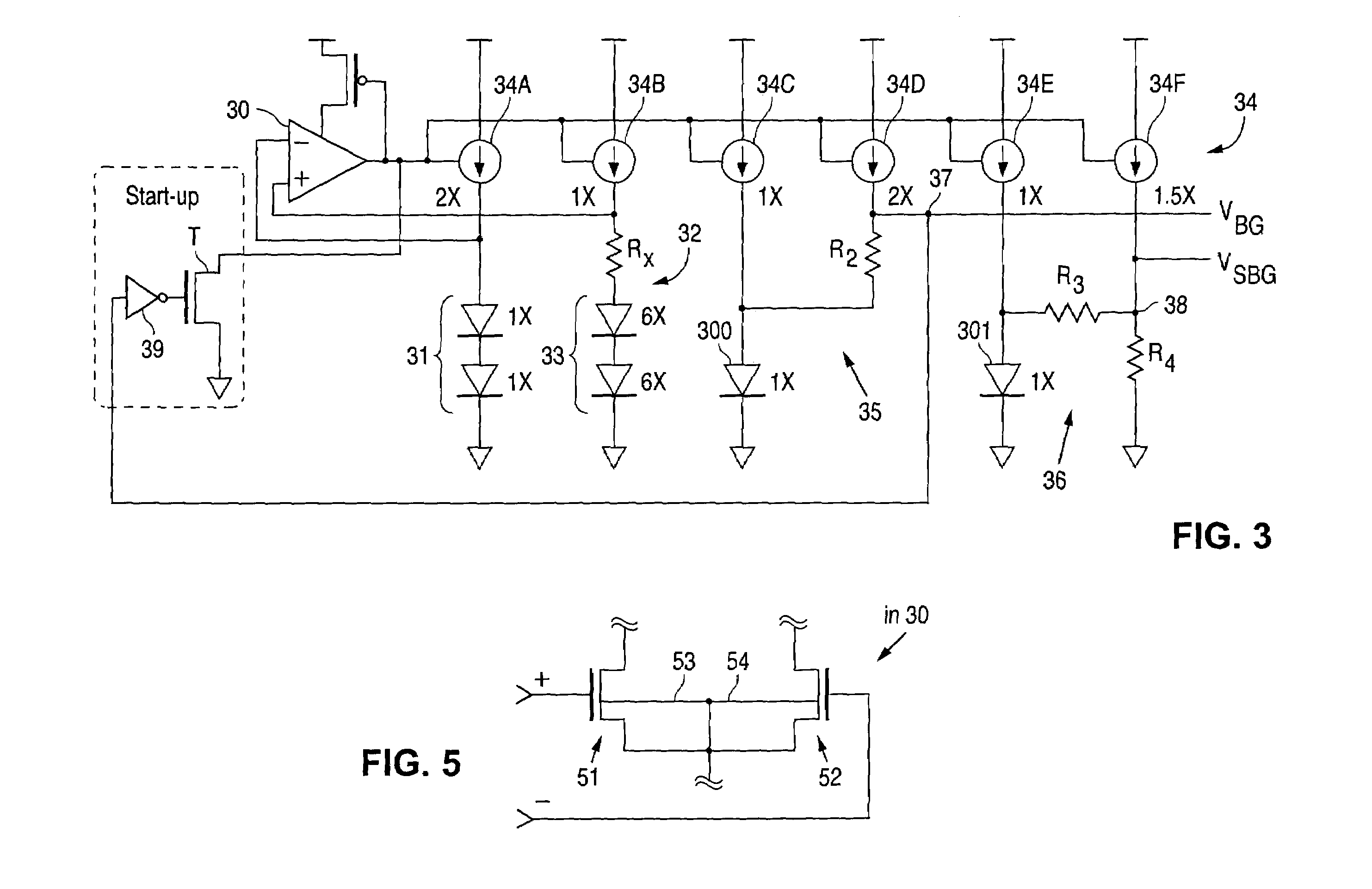

Bandgap reference designs with stacked diodes, integrated current source and integrated sub-bandgap reference

ActiveUS7253598B1Improve bandgap reference circuit performanceLower input sensitivityElectric variable regulationAudio power amplifierReference design

The performance of a bandgap reference circuit is improved by increasing the ΔVBE, and thereby correspondingly decreasing the input sensitivity of the error amplifier in the control loop. The ΔVBE can be increased by presenting stacked diode configurations at the amplifier inputs, by increasing the diode ratio presented at the amplifier inputs, and by providing a higher current in the CTAT leg than in the PTAT leg. The stacked diode configuration is achieved by producing isolated diodes with a triple well CMOS process. The stacked diode configuration and the triple well CMOS process also permit the input stage of the amplifier to use N-channel transistors operating in the threshold region.

Owner:NAT SEMICON CORP

Design method and architecture for power gate switch placement

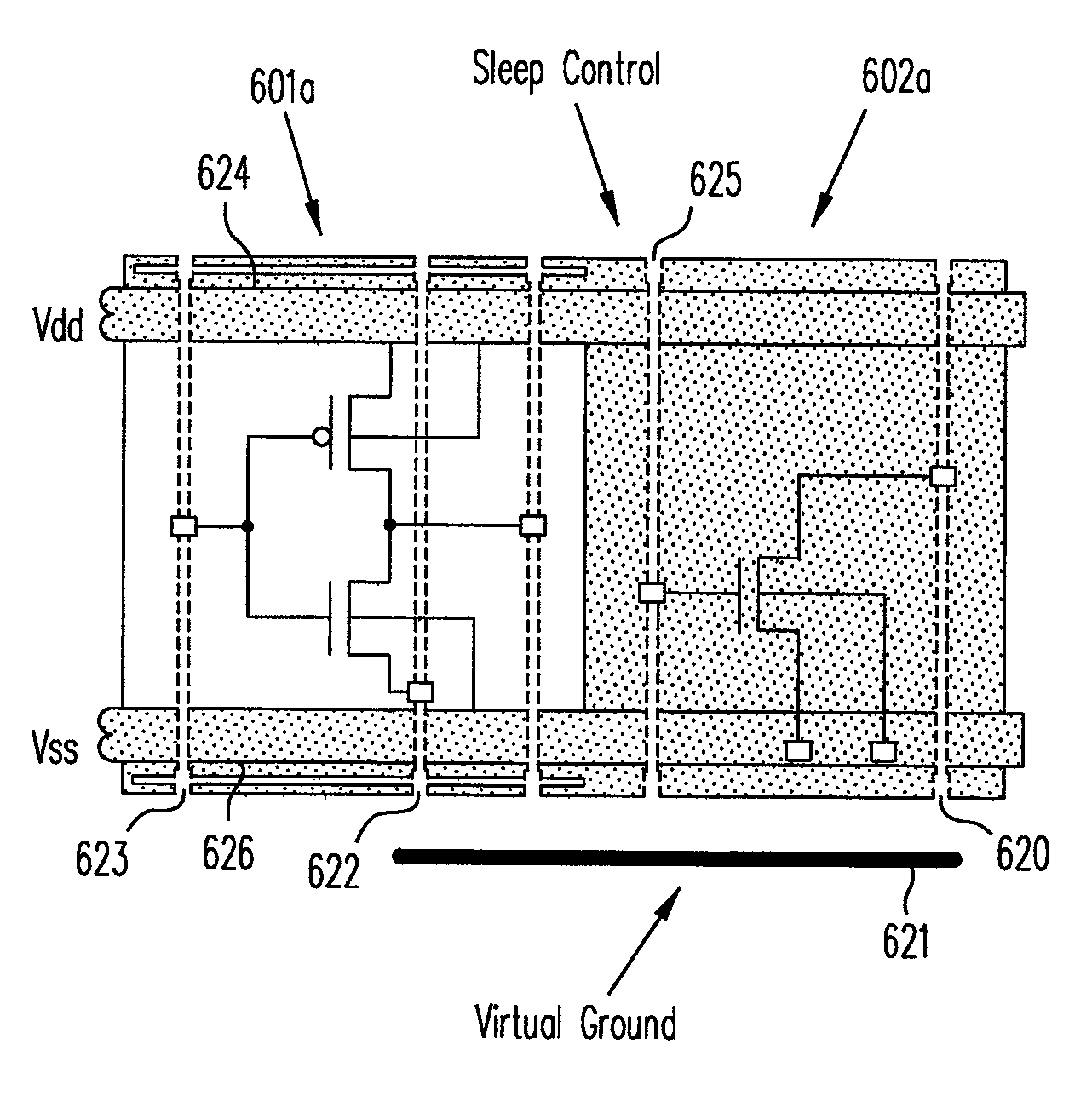

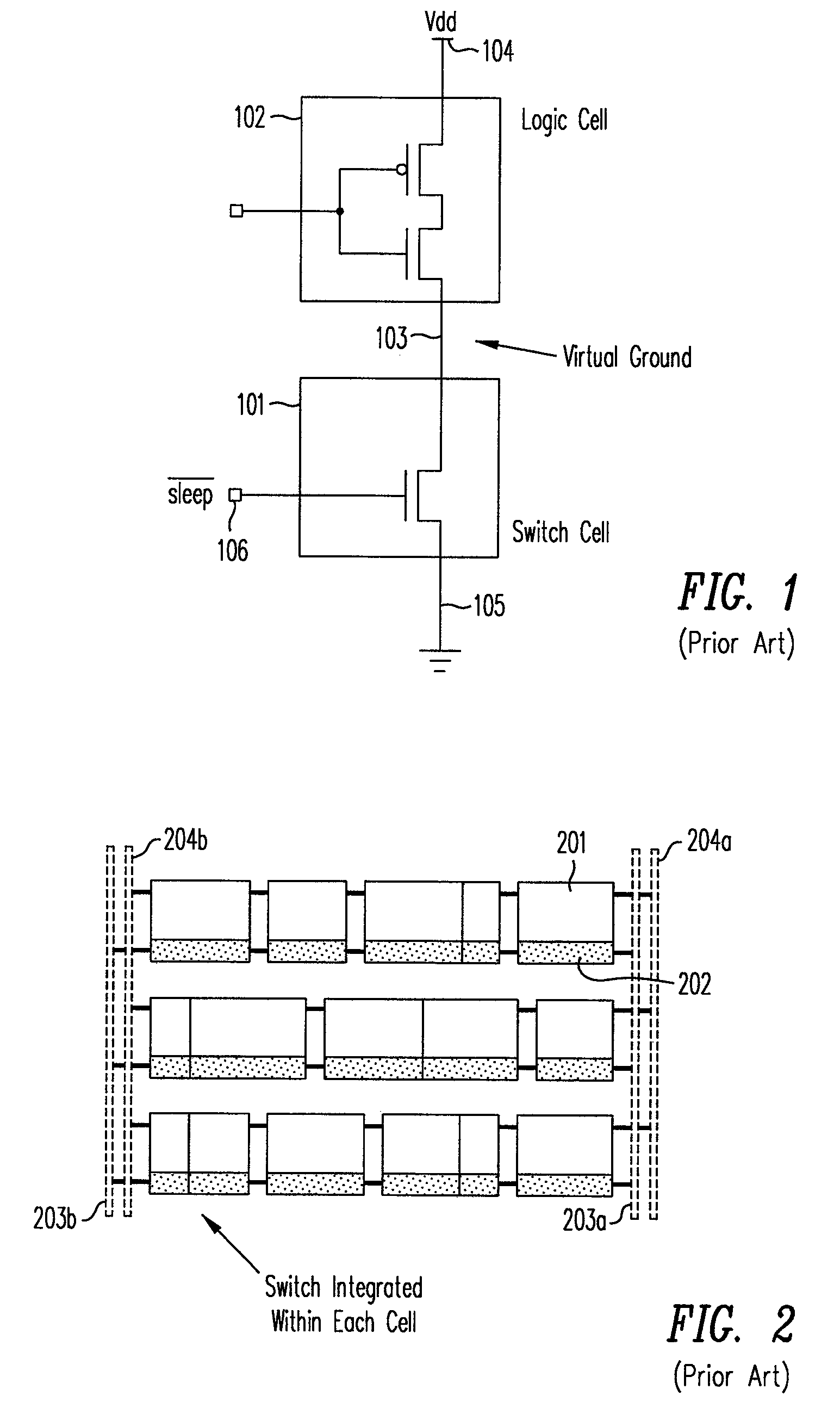

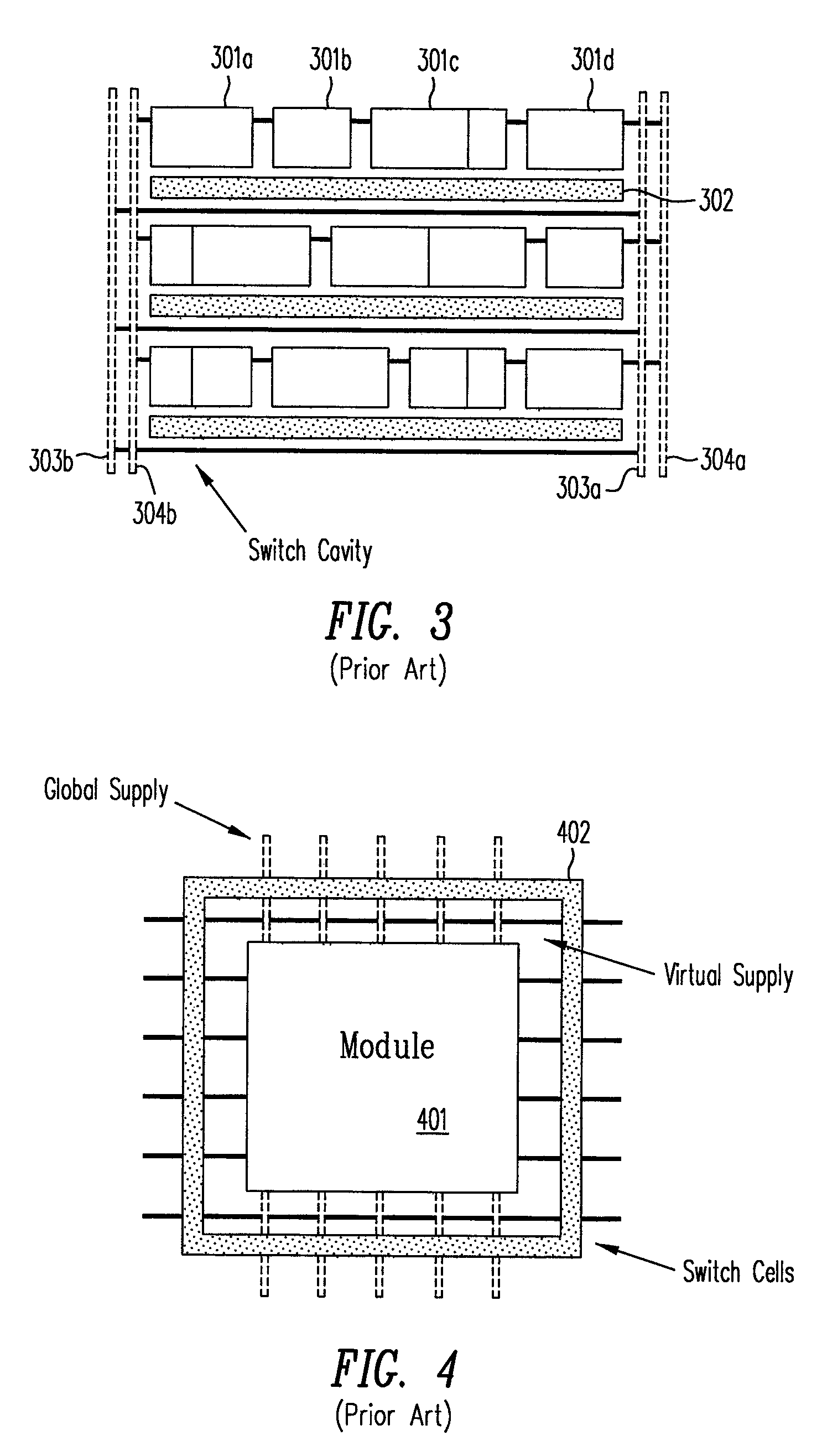

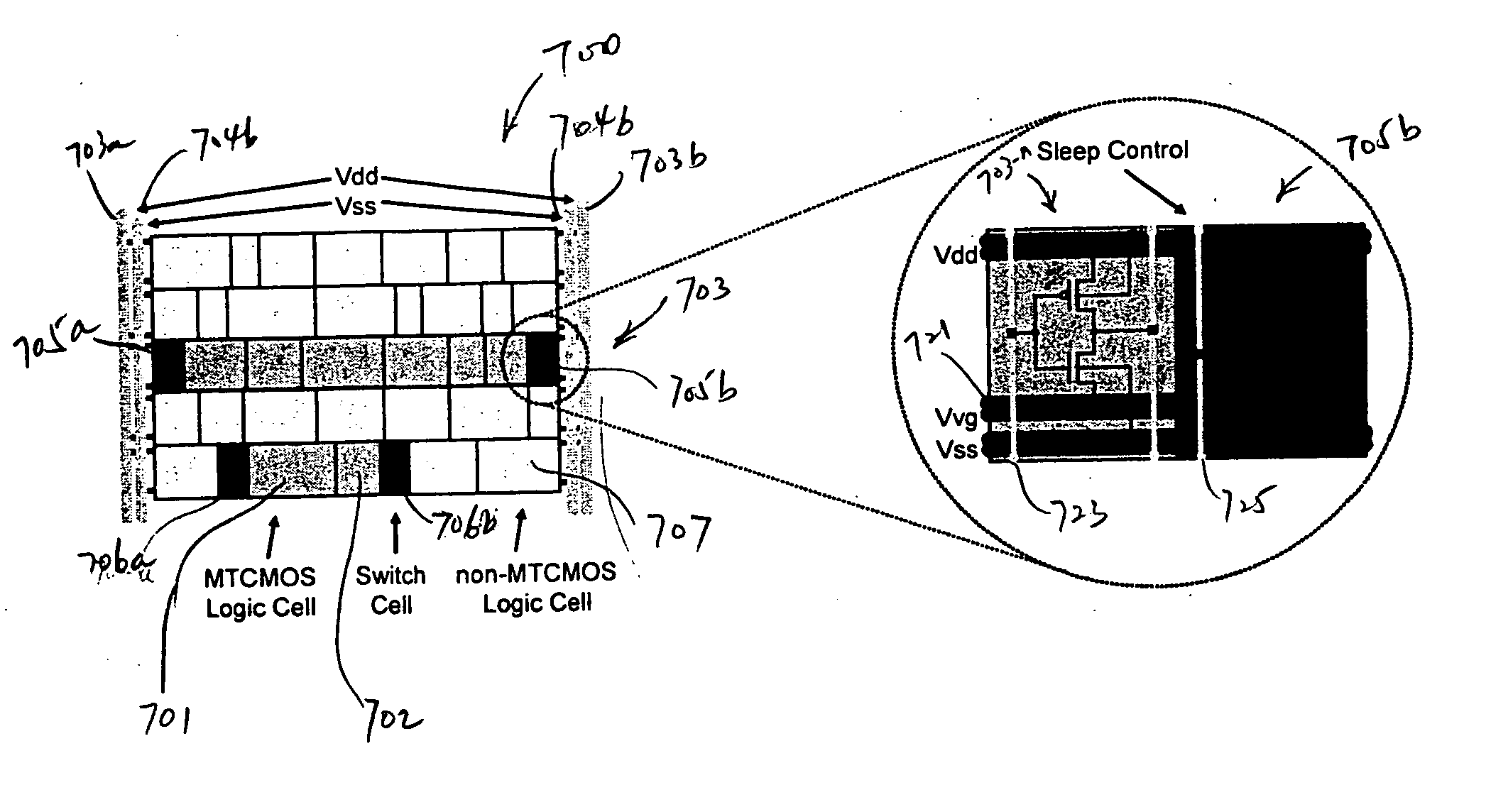

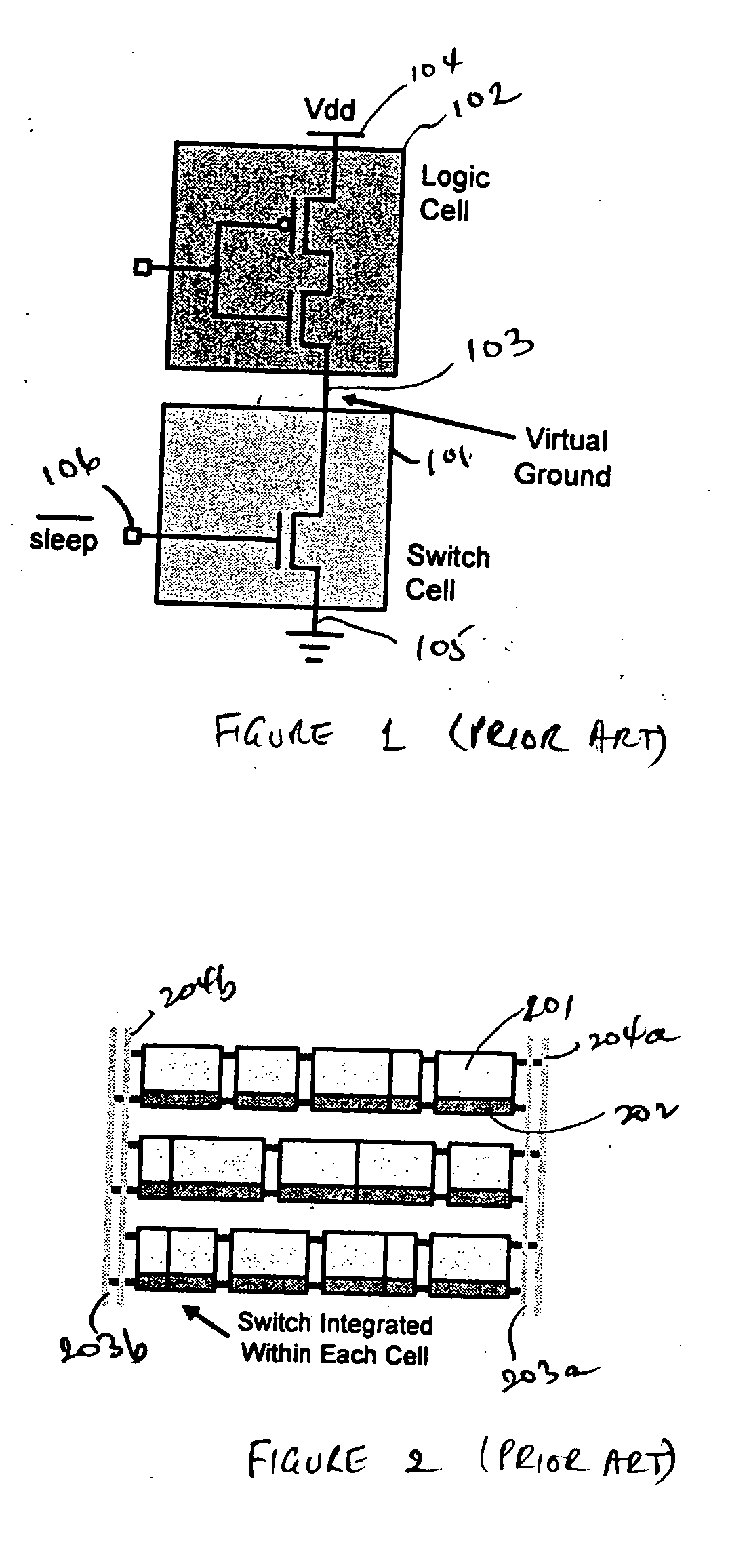

ActiveUS7590962B2Improve circuit performanceReduce violationsReliability increasing modificationsPower reduction by control/clock signalLogic cellEngineering

A design method places power gates or switch cells using unoccupied locations of logic cell rows. Two types of such switch cells, filler switches and sealer switches, may be provided using the unoccupied locations. In one embodiment, virtual ground voltage references to the logic cells are routed to their associated switch cells. Because conventional standard cell design and placement techniques achieve only a placement density or utilization between 70-80% (i.e., unoccupied space constitutes between 20 to 30% of the available space in each row of logic cells), by placing the power gate cells in the unoccupied space, the method does not increase the silicon real estate requirement even though the power gate cells are introduced into the design. Optimization techniques may be applied to achieve proper sizing and distribution of power gate cells, so as to avoid a performance penalty due to the power gate cells. In one embodiment, fine-grained power gating is achieved by selectively providing non-power-gated logic cells among power-gated logic cells.

Owner:ANSYS INC

Design method and architecture for power gate switch placement

ActiveUS20060114025A1Improve circuit performanceReduce violationsMajority/minority circuitsPower reduction by control/clock signalLogic cellVoltage reference

A design method places power gates or switch cells using unoccupied locations of logic cell rows. Two types of such switch cells, filler switches and sealer switches, may be provided using the unoccupied locations. In one embodiment, virtual ground voltage references to the logic cells are routed to their associated switch cells. Because conventional standard cell design and placement techniques achieve only a placement density or utilization between 70-80% (i.e., unoccupied space constitutes between 20 to 30% of the available space in each row of logic cells), by placing the power gate cells in the unoccupied space, the method does not increase the silicon real estate requirement even though the power gate cells are introduced into the design. Optimization techniques may be applied to achieve proper sizing and distribution of power gate cells, so as to avoid a performance penalty due to the power gate cells. In one embodiment, fine-grained power gating is achieved by selectively providing non-power-gated logic cells among power-gated logic cells.

Owner:ANSYS

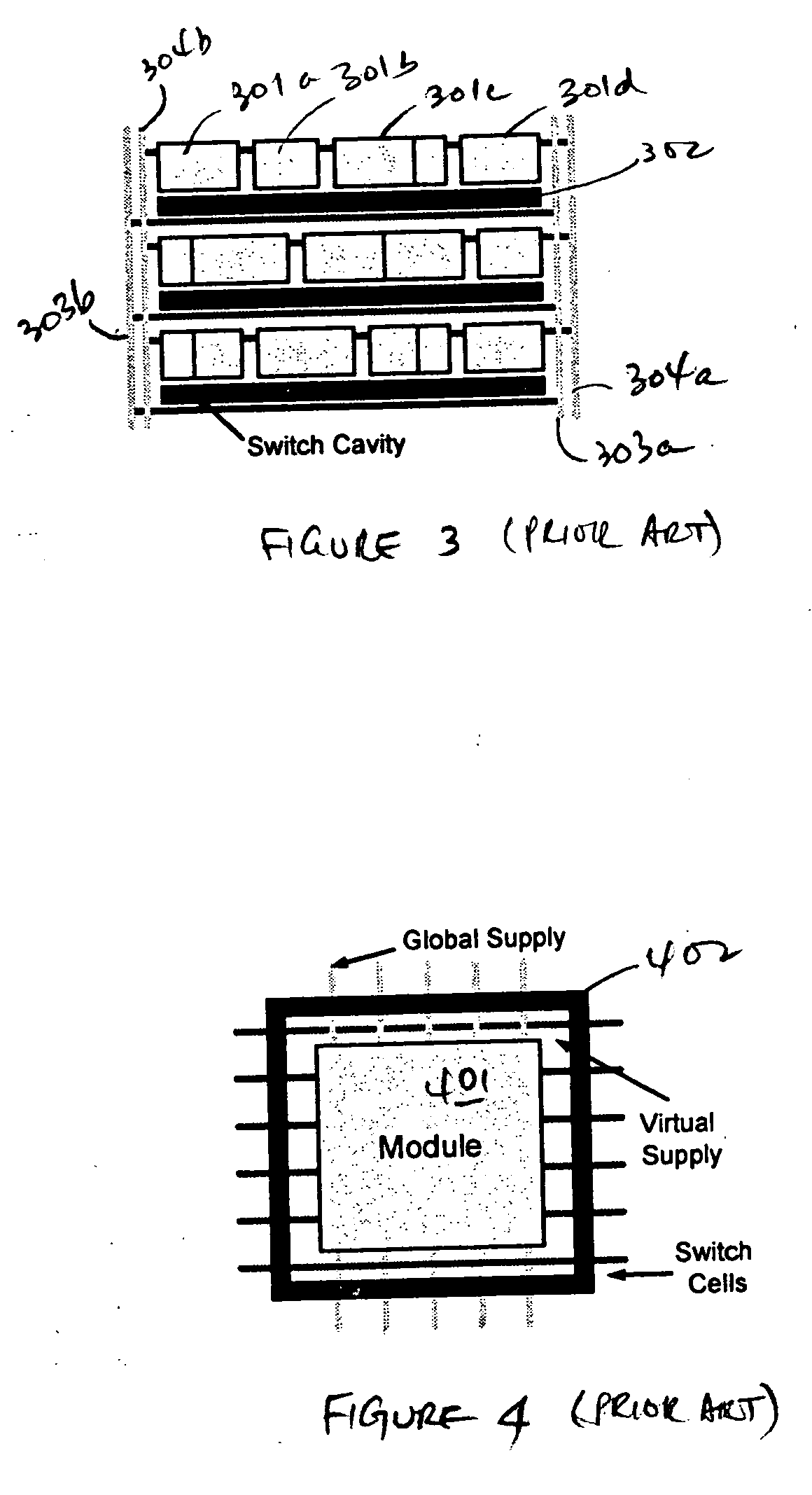

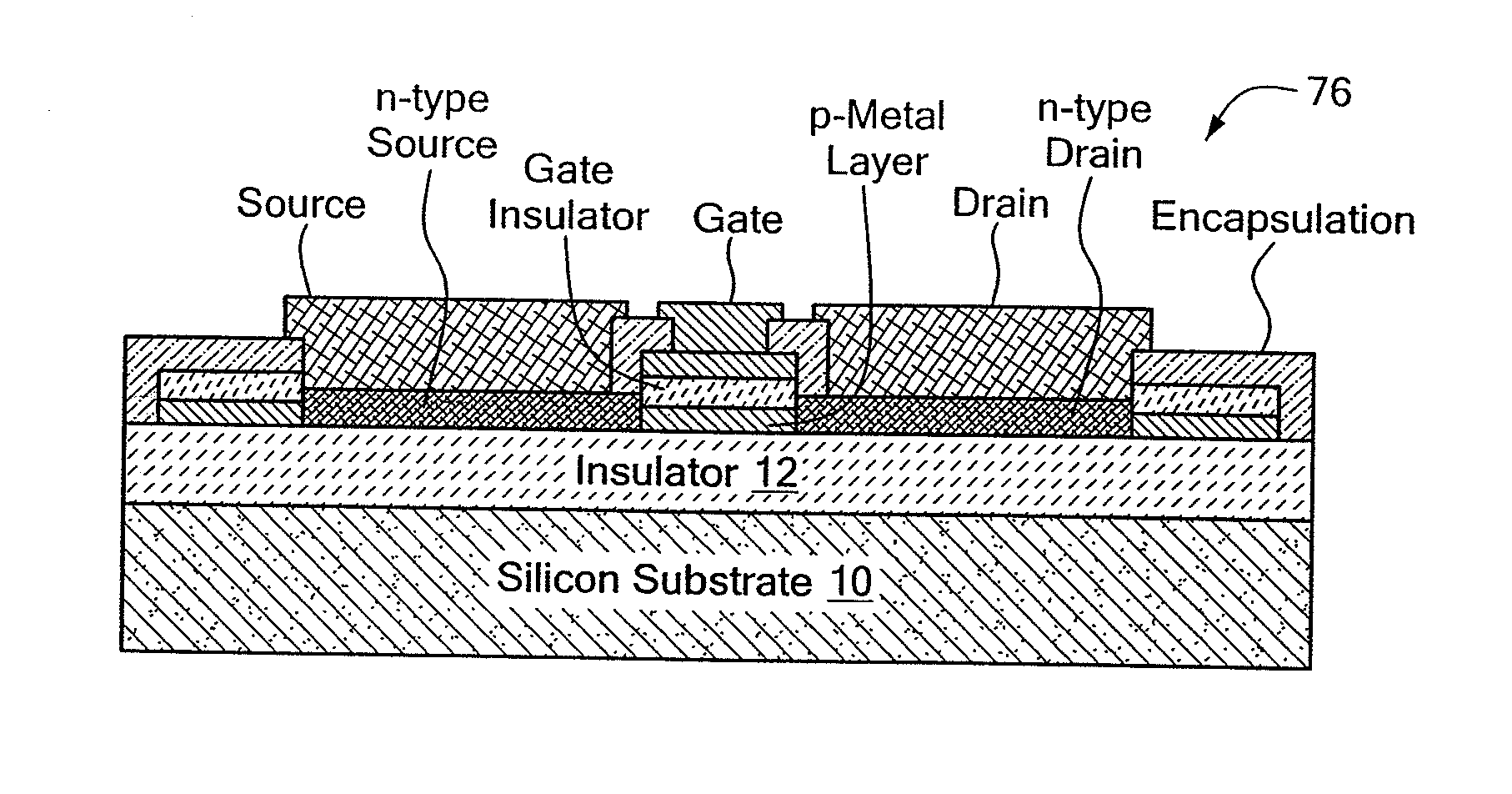

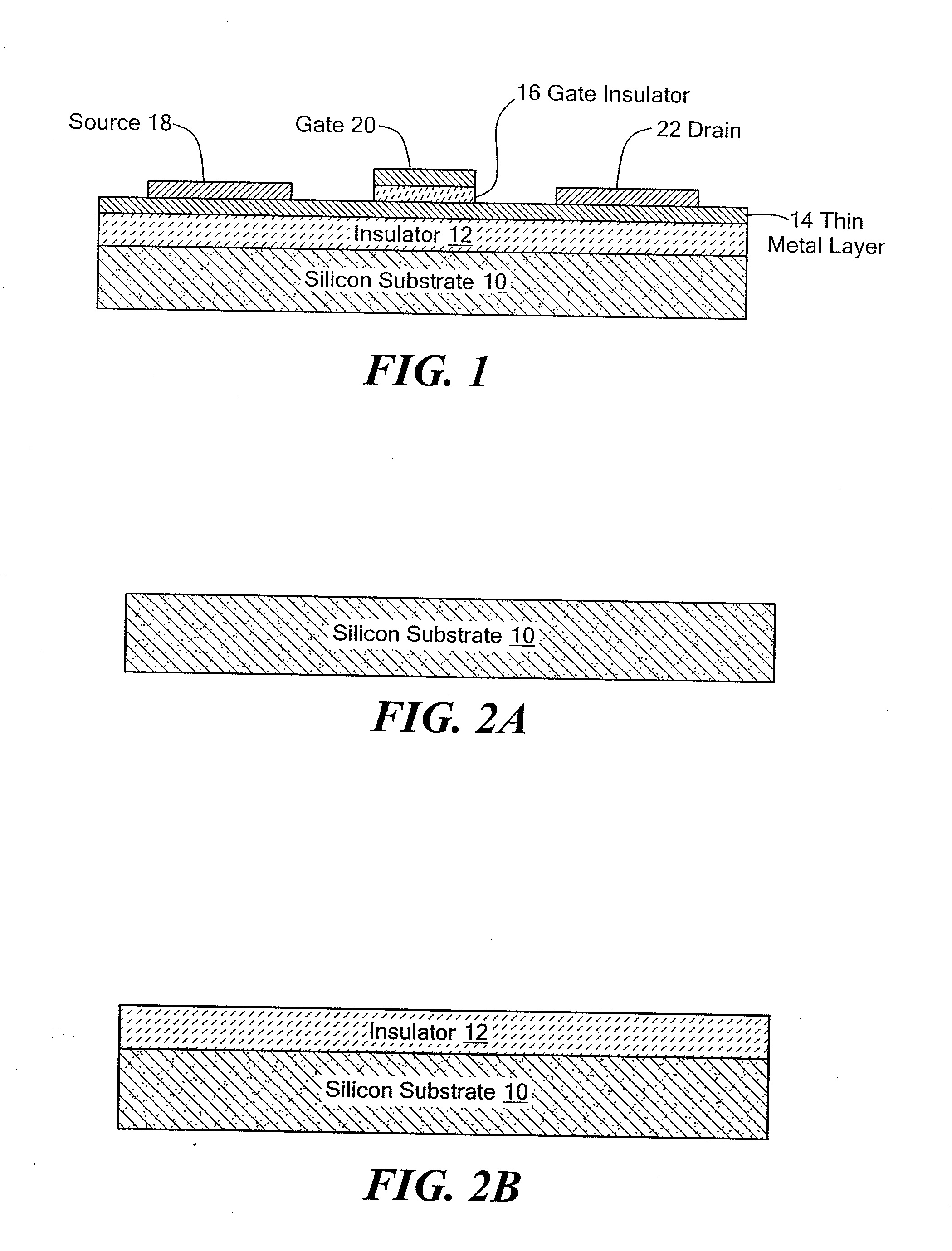

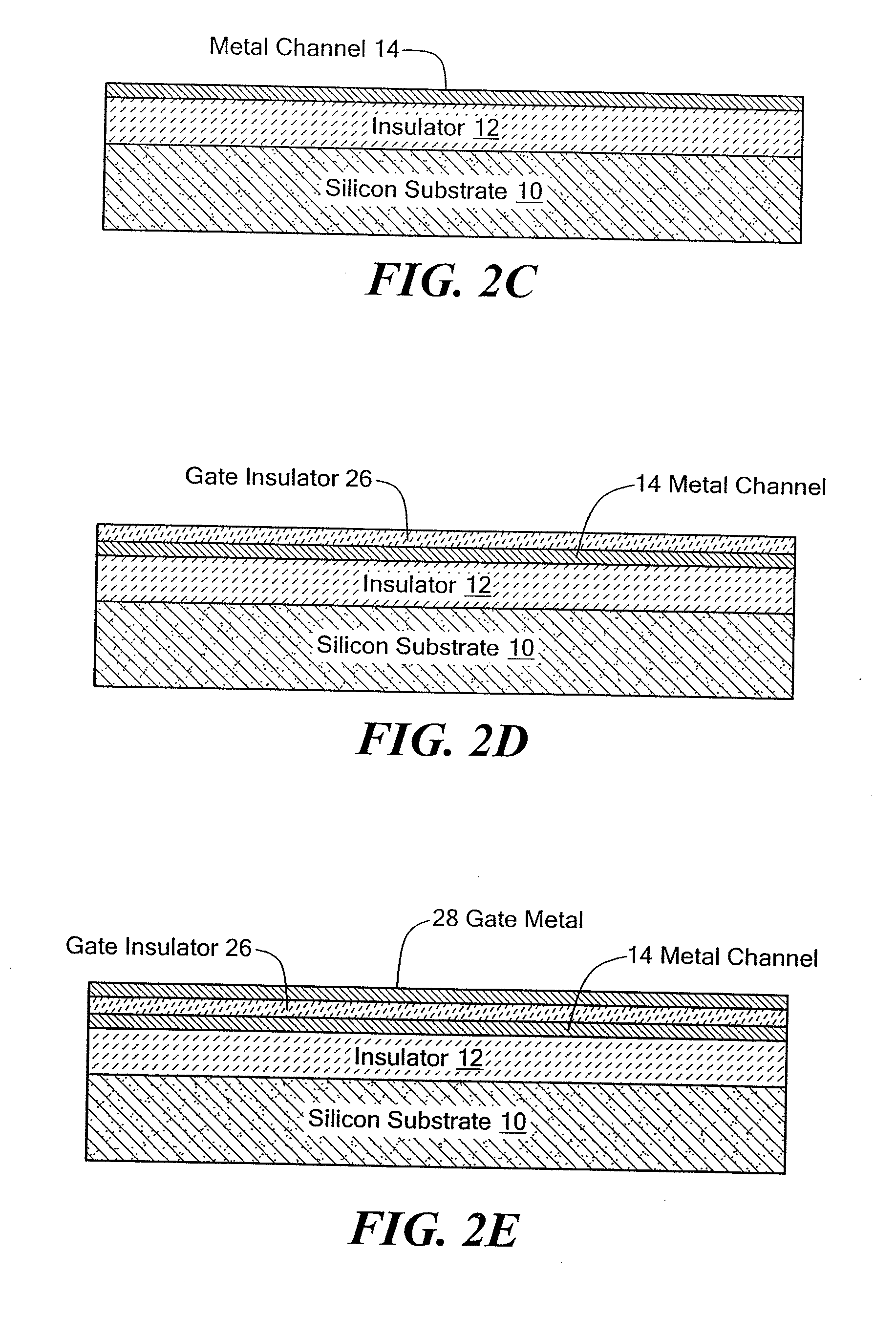

Metal transistor device

ActiveUS20110180867A1Small sizeImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMaterials scienceMetal

The present invention is related to a depletion or enhancement mode metal transistor in which the channel regions of a transistor device comprises a thin film metal or metal composite layer formed over an insulating substrate.

Owner:TSANG DEAN Z

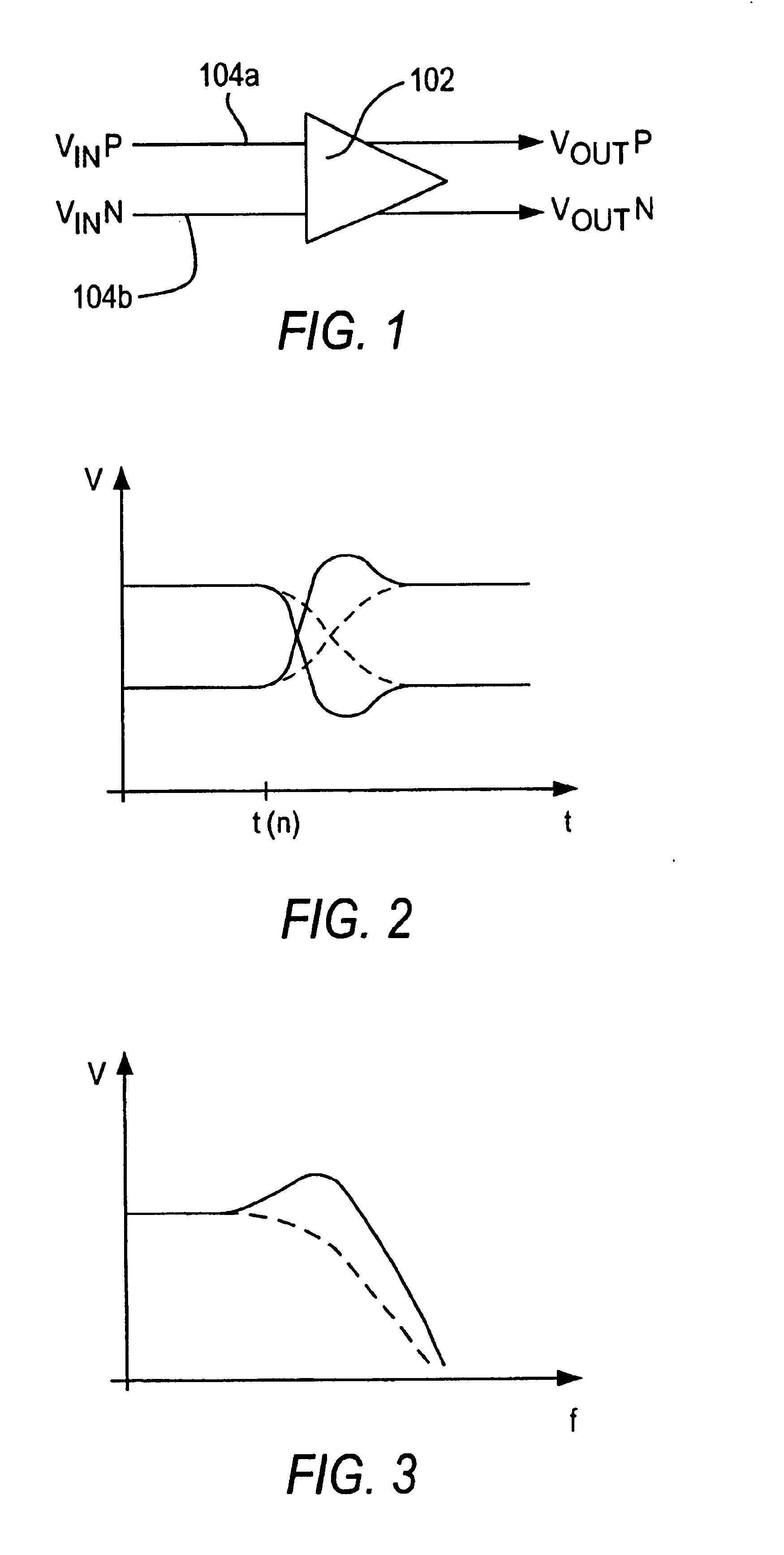

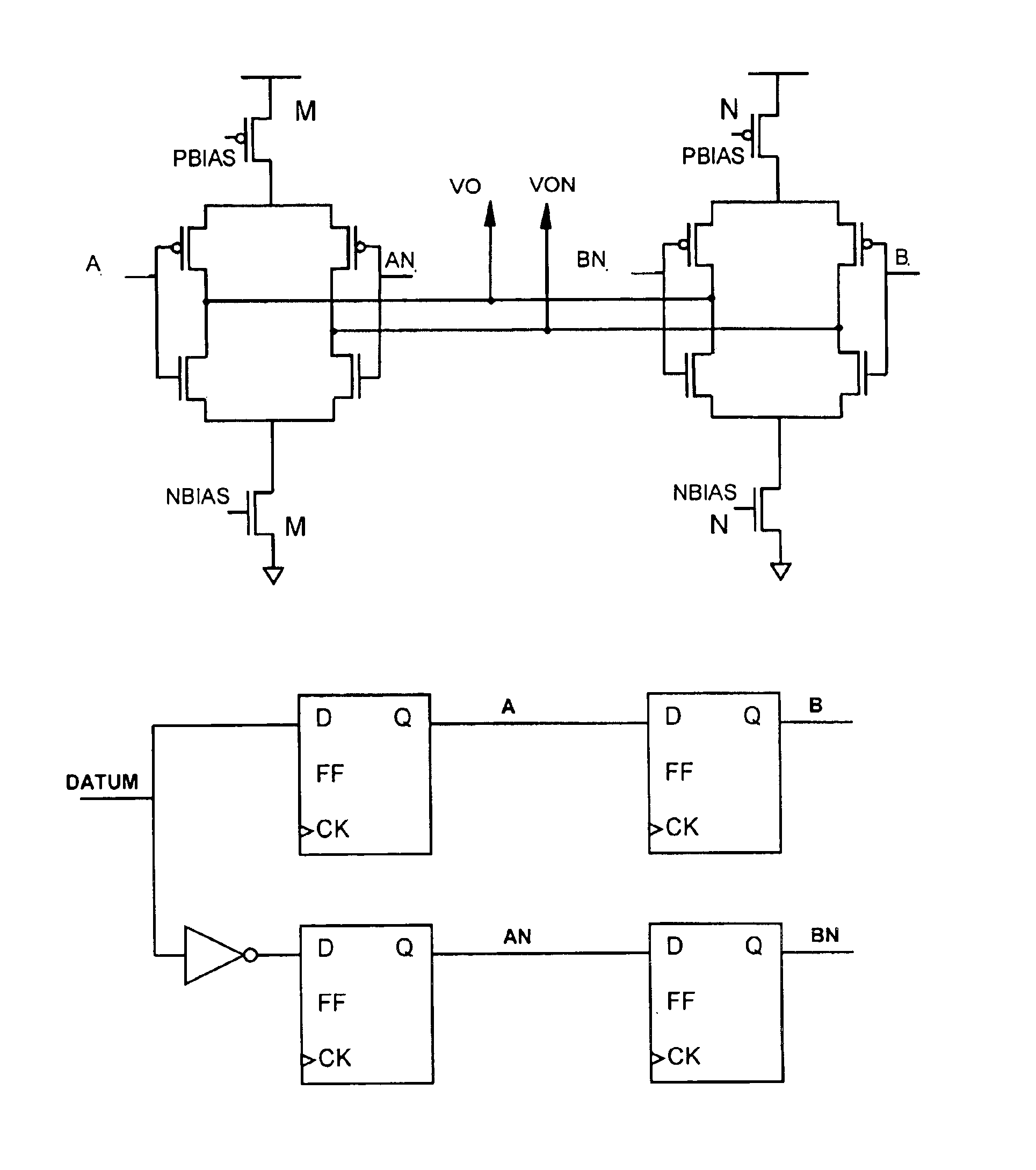

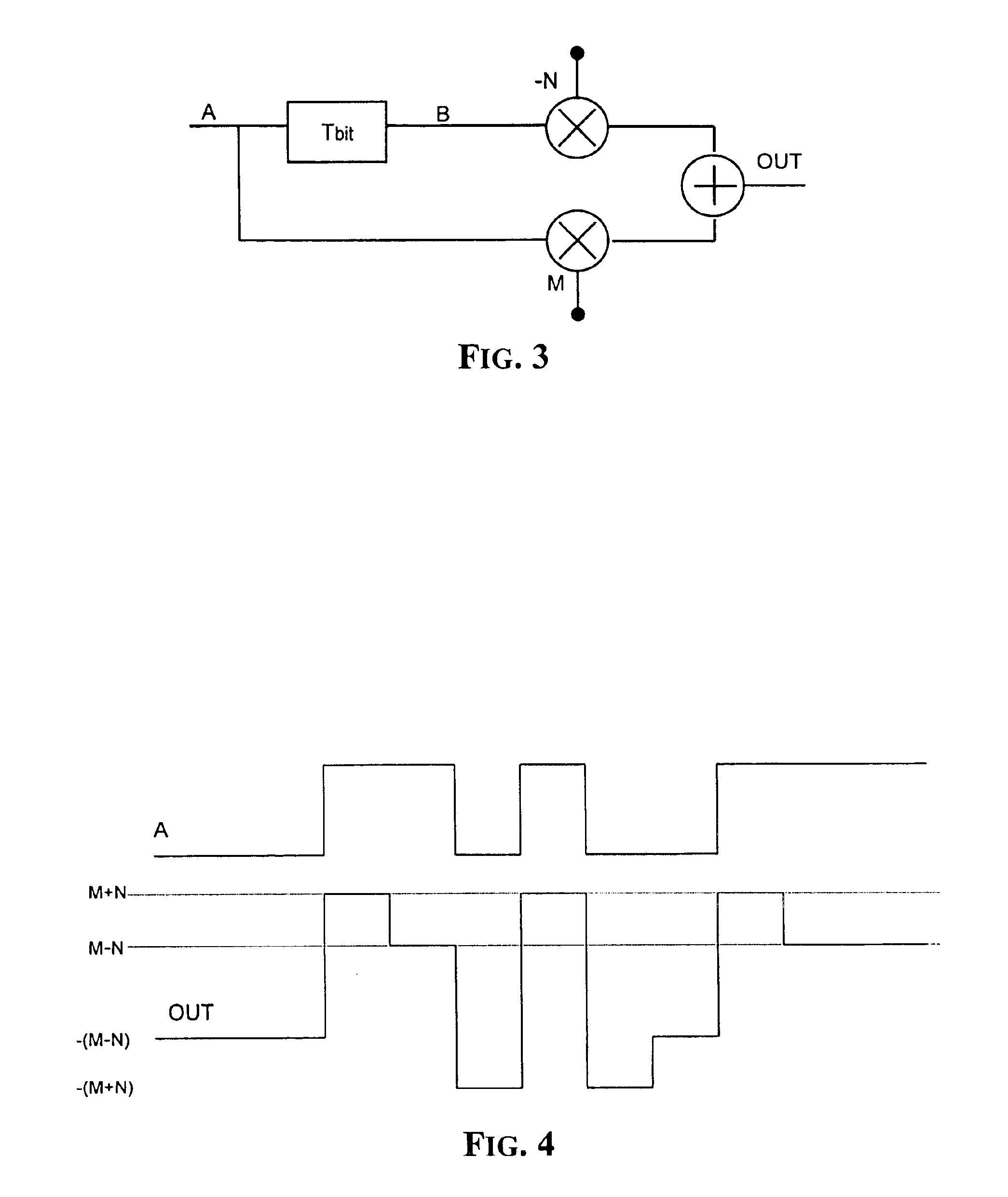

Method and amplification circuit with pre-emphasis

InactiveUS6853220B2Improve circuit performanceHigh gainMultiple input and output pulse circuitsBaseband system detailsEngineeringLine driver

A method for amplifying a digital signal representative of data to be transmitted by a line driver with pre-emphasis over an output line is provided. The gain of the line driver is varied between an upper value to coincide with switching of the digital signal and a lower value in absence of the digital signal switching. In particular, the varying includes amplifying the digital signal with a first gain for generating an amplified digital signal, delaying the digital signal with a predetermined delay for generating a delayed digital signal, and amplifying the delayed digital signal with a second gain for generating a delayed and amplified digital signal. An ouput signal corresponding to a difference between the amplified digital signal and the delayed and amplified digital signal is output over the output line.

Owner:STMICROELECTRONICS SRL

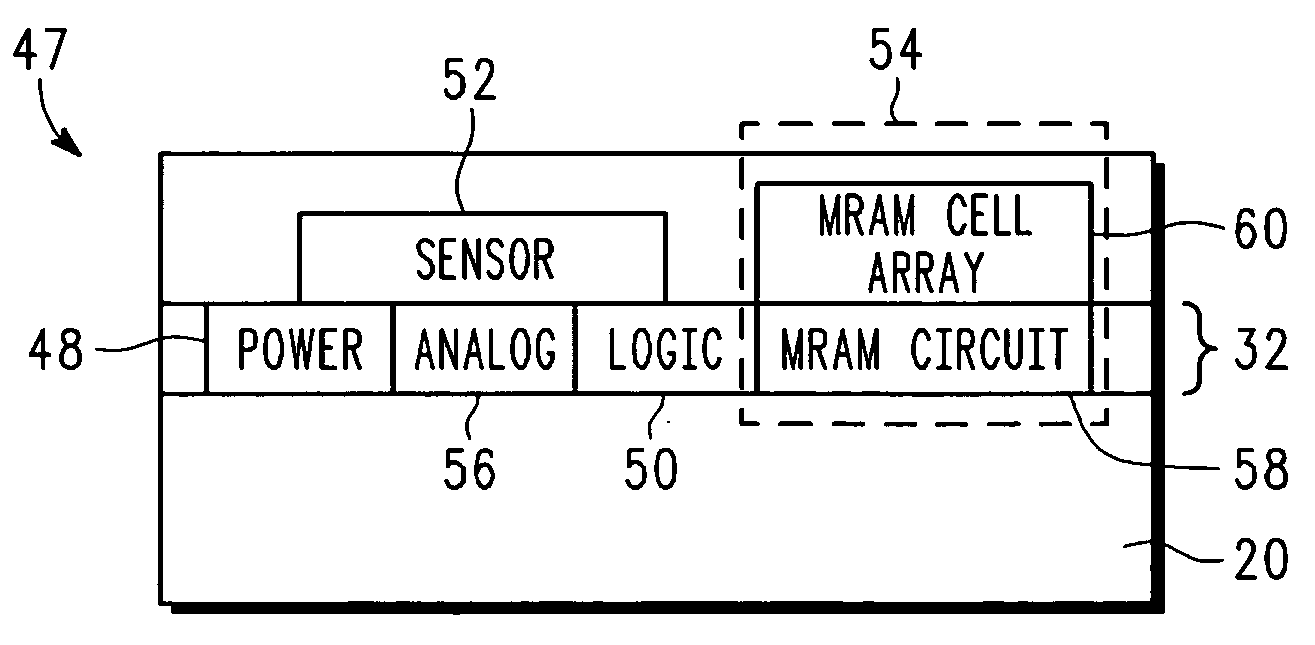

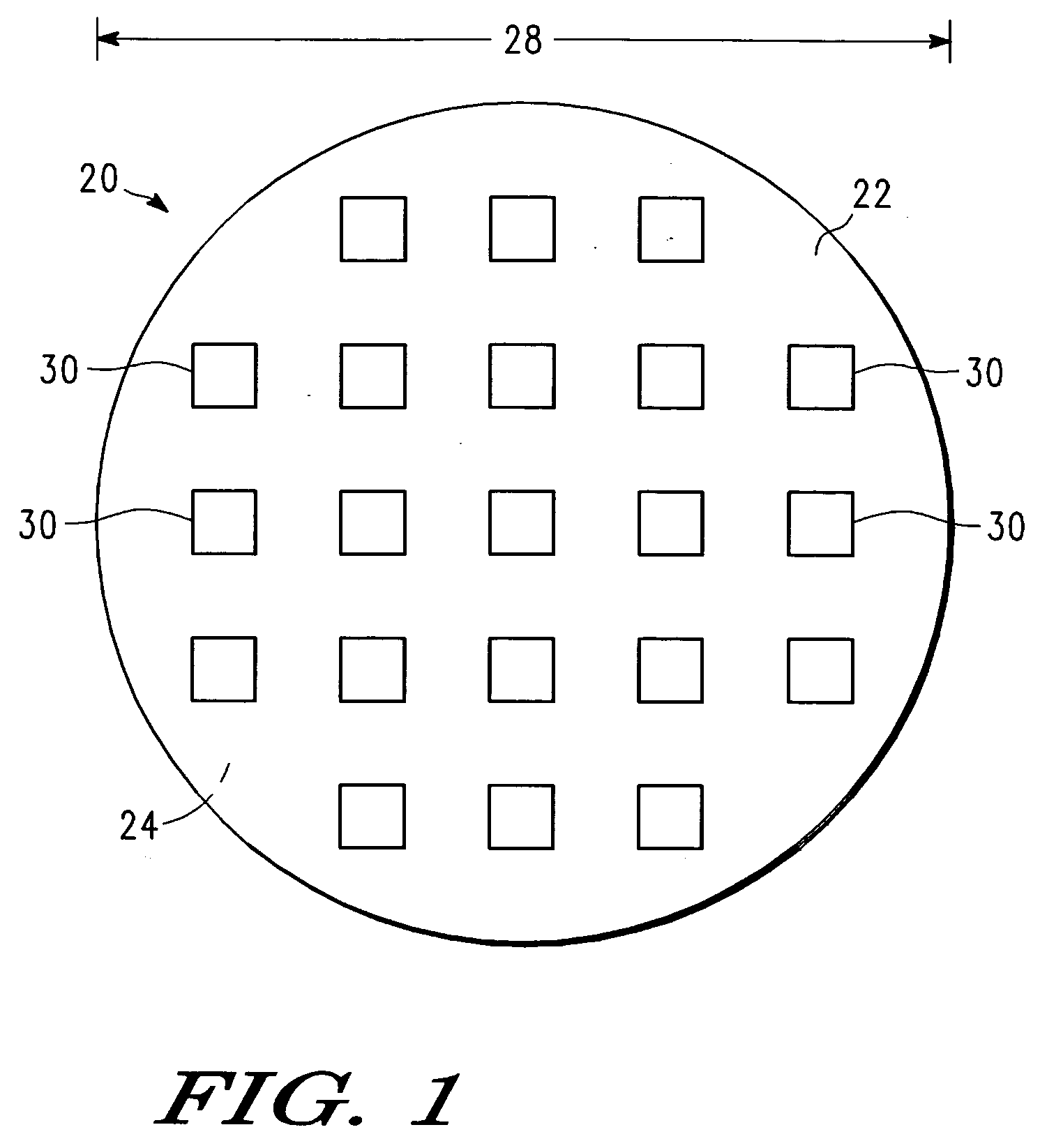

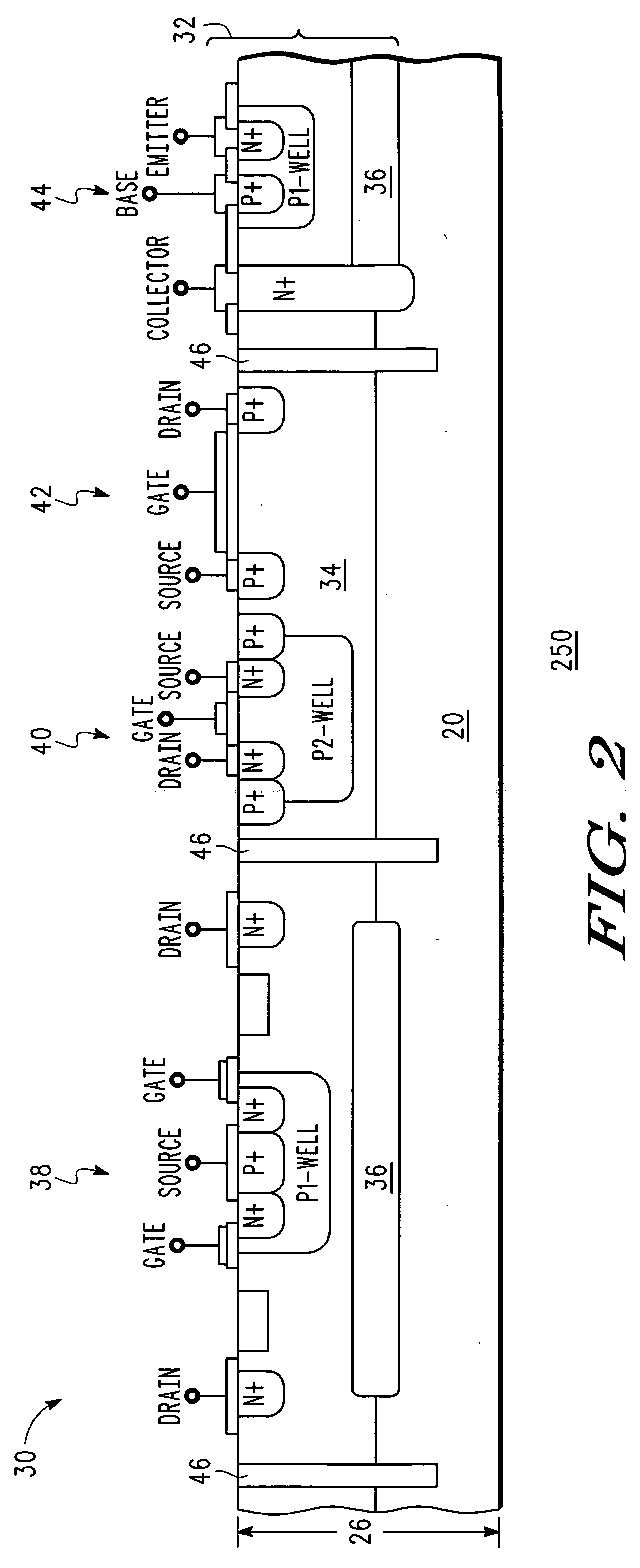

Electronic assembly having magnetic tunnel junction voltage sensors and method for forming the same

InactiveUS20080112214A1Improve stabilityPromote growthTransistorNanomagnetismElectricityMagnetic reluctance

A method and assembly for sensing a voltage with a memory cell (88) is provided. The memory cell includes first and second electrodes (96,112), first and second ferromagnetic bodies (104,108) positioned between the first and second electrodes and an insulating body (94) positioned between the first and second ferromagnetic bodies. The first electrode is electrically connected to a first portion of a microelectronic assembly (47). The second electrode is electrically connected to a second portion of the microelectronic assembly. The voltage across the first and second portions of the microelectronic assembly is determined based on an electrical resistance of the memory cell. The memory cell may be a magnetoresistive random access memory (MRAM) cell. In one embodiment, the memory cell is a magnetic tunnel junction (MTJ) memory cell.

Owner:EVERSPIN TECHNOLOGIES

Envelope-tracking power supply modulator

ActiveUS10171038B1Low hardware costReduce circuit areaHigh frequency amplifiersPower amplifiersAudio power amplifierVoltage reference

An envelope-tracking power supply modulator (ETSM) supplies power to a radio frequency power amplifier (RFPA) of a radio frequency (RF) circuit according to a baseband envelope signal. The ETSM includes a linear amplifier, a capacitor, a single inductor multiple output (SIMO) switch-mode converter, and a controller. The linear amplifier receives the baseband envelope signal, and has its output terminal coupled to a power input of the RFPA. One terminal of the capacitor is coupled to a reference voltage, and the other terminal is coupled to a power input of the linear amplifier. The SIMO switch-mode converter includes two output terminals. One of the output terminals is coupled to the capacitor and the power input of the linear amplifier, and the other of the output terminals is coupled to the output terminal of the linear amplifier and the power input of the RFPA. The controller controls the SUMO switch-mode converter.

Owner:REALTEK SEMICON CORP

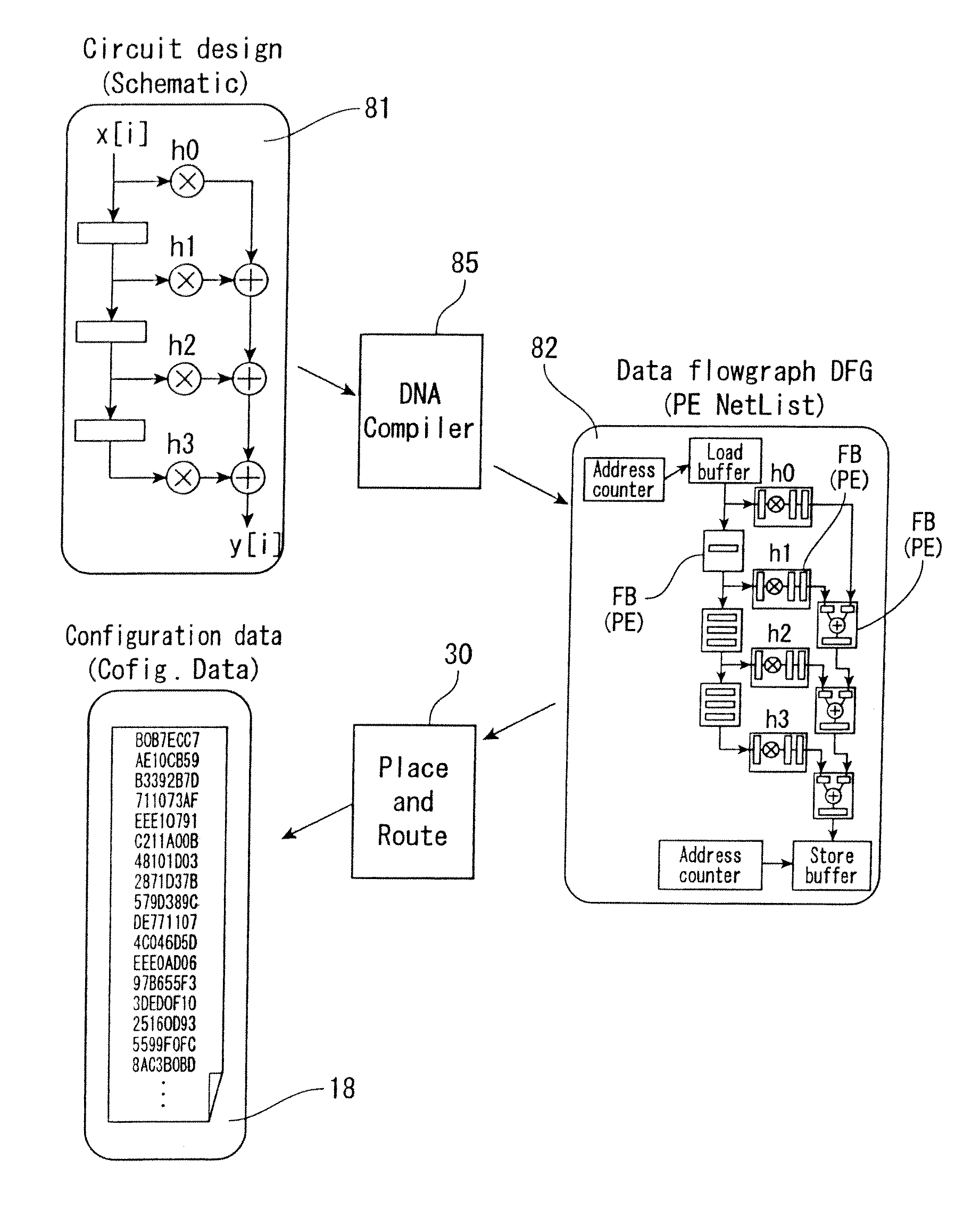

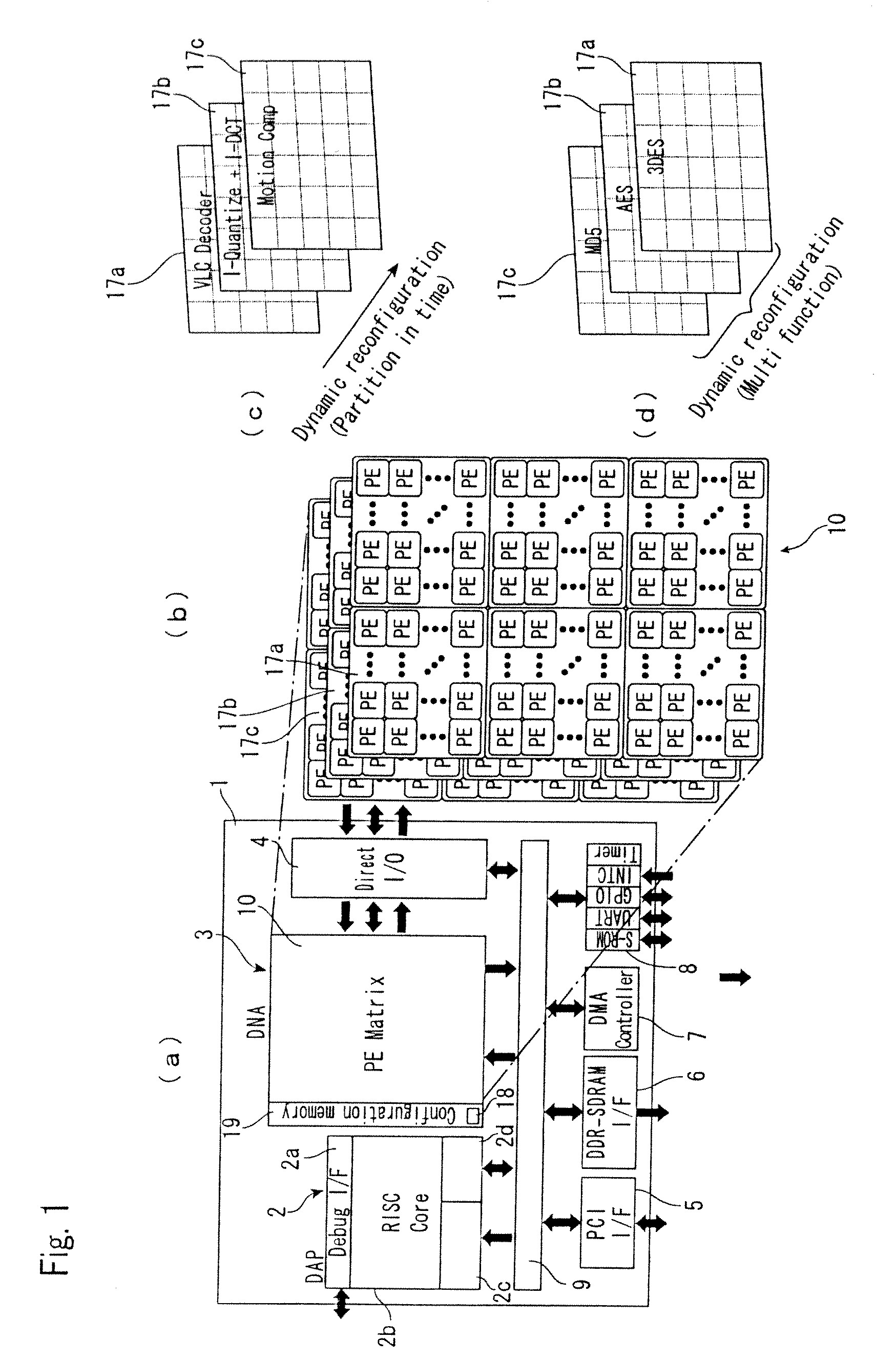

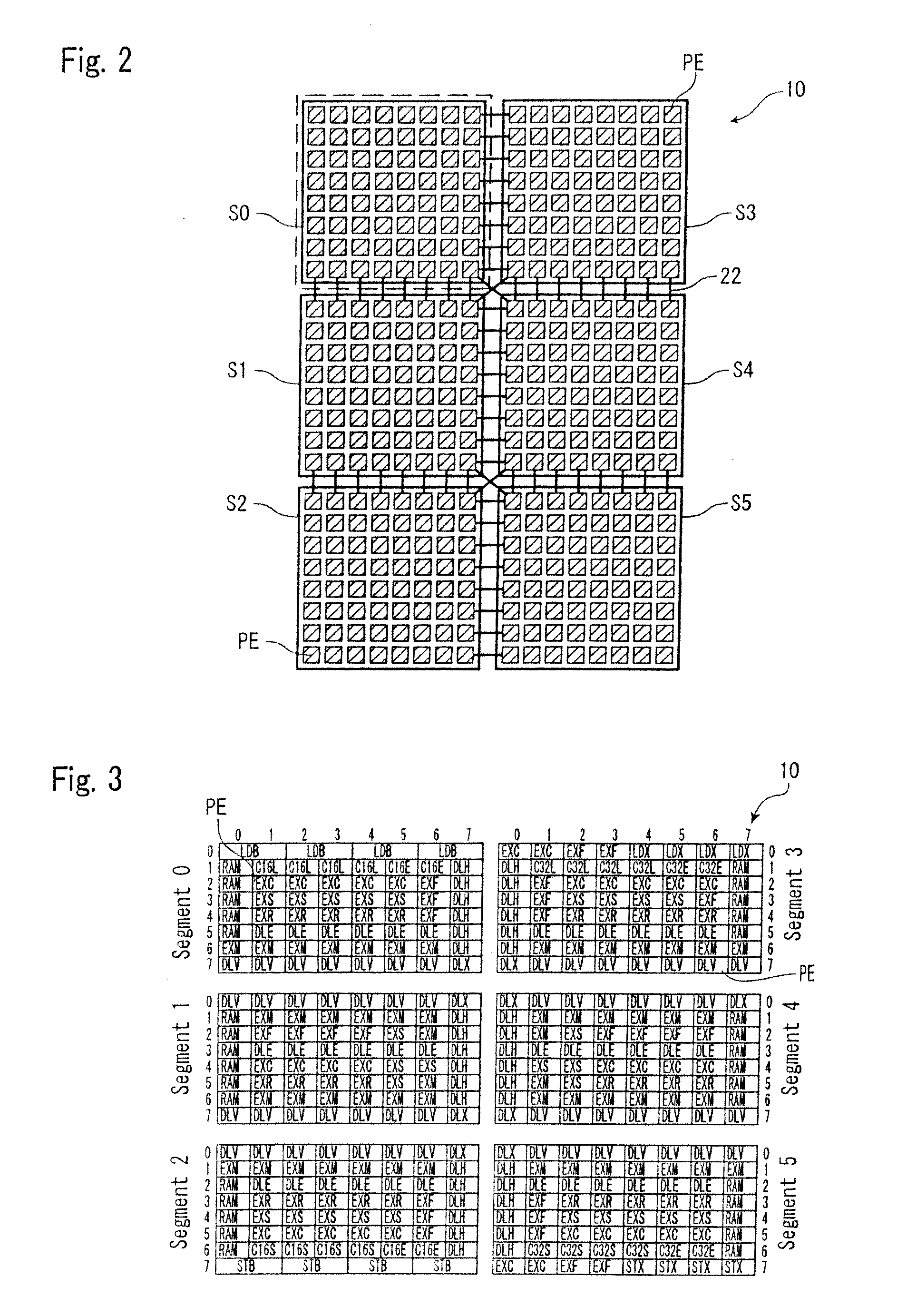

Method and system for mounting circuit design on reconfigurable device

InactiveUS20100017774A1Minimize cost functionMinimizing useCAD circuit designSoftware simulation/interpretation/emulationEngineeringComputer hardware

There is provided a system for generating configuration data for implementing a circuit design in a segmented reconfigurable device. A placement and routing design aiding system (30) includes a database (31) for storing hardware information (89) including data of PEs included in each segment and data of a first-level and second-level routing matrix and an apparatus (33) for mapping the circuit design onto the PEs. The mapping apparatus (33) generates mappings of the circuit design onto the PEs by carrying out an iterative algorithm that minimizes a cost function based on the hardware information (89). The cost function includes an item that minimizes usage of the second-level routing matrix (22) that connects between the segments.

Owner:FUJIFILM BUSINESS INNOVATION CORP

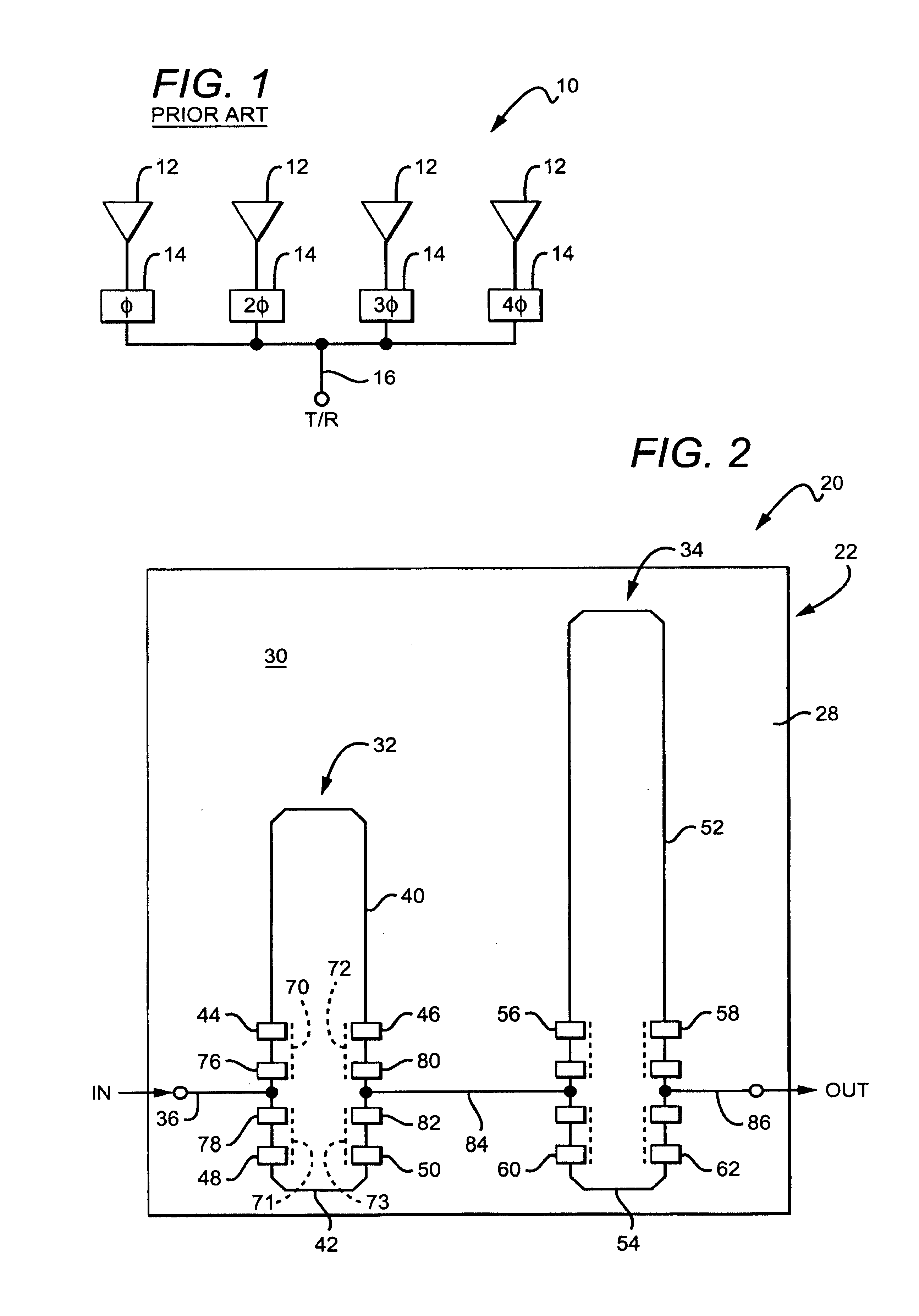

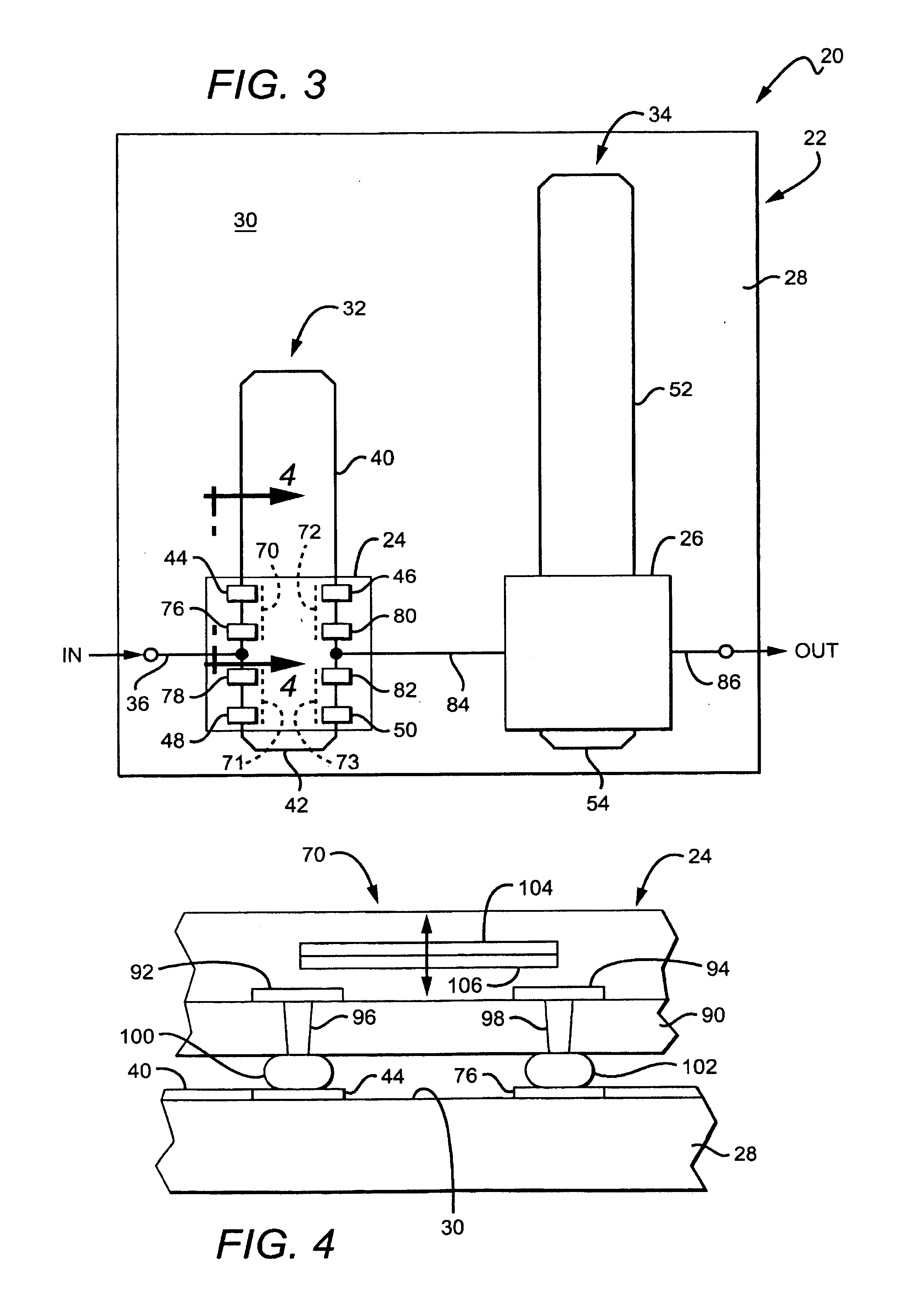

Low loss RF phase shifter with flip-chip mounted MEMS interconnection

ActiveUS7068220B2Reduce lossAvoid incompatibilitiesDelay linesWaveguidesFlip chip interconnectComputer module

Owner:TELEDYNE SCI & IMAGING

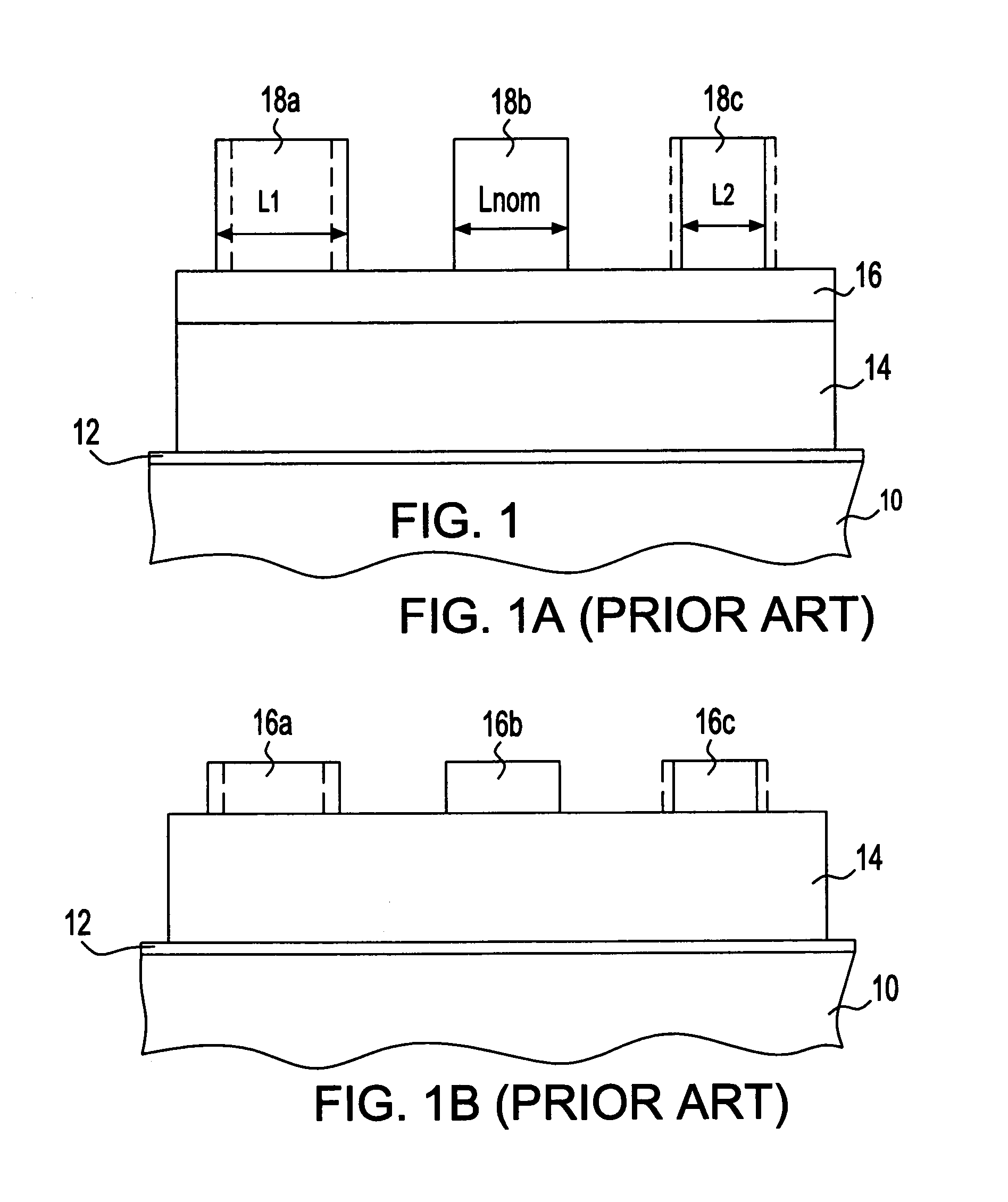

Nanocircuit and self-correcting etching method for fabricating same

InactiveUS7026247B2Reduced feature requirementsProduce some attenuationSemiconductor/solid-state device manufacturingSemiconductor devicesNanostructureCritical dimension

A self-correcting etching (SCORE) process for fabricating microstructure is provided. The SCORE process of the present invention is particularly useful for reducing preselected features of a hard mask without degrading the variation of the critical dimension (CD) within each wafer. Alternatively, the CD variation of the hard mask features' produced during printing can be substantially reduced by applying SCORE. Hence, ultra-sub-lithographic features (e.g., nanostructures) can be reliably fabricated. Consequently, the method of the present invention can be used to increase the circuit performance, while improving the manufacturing yield.

Owner:INT BUSINESS MASCH CORP

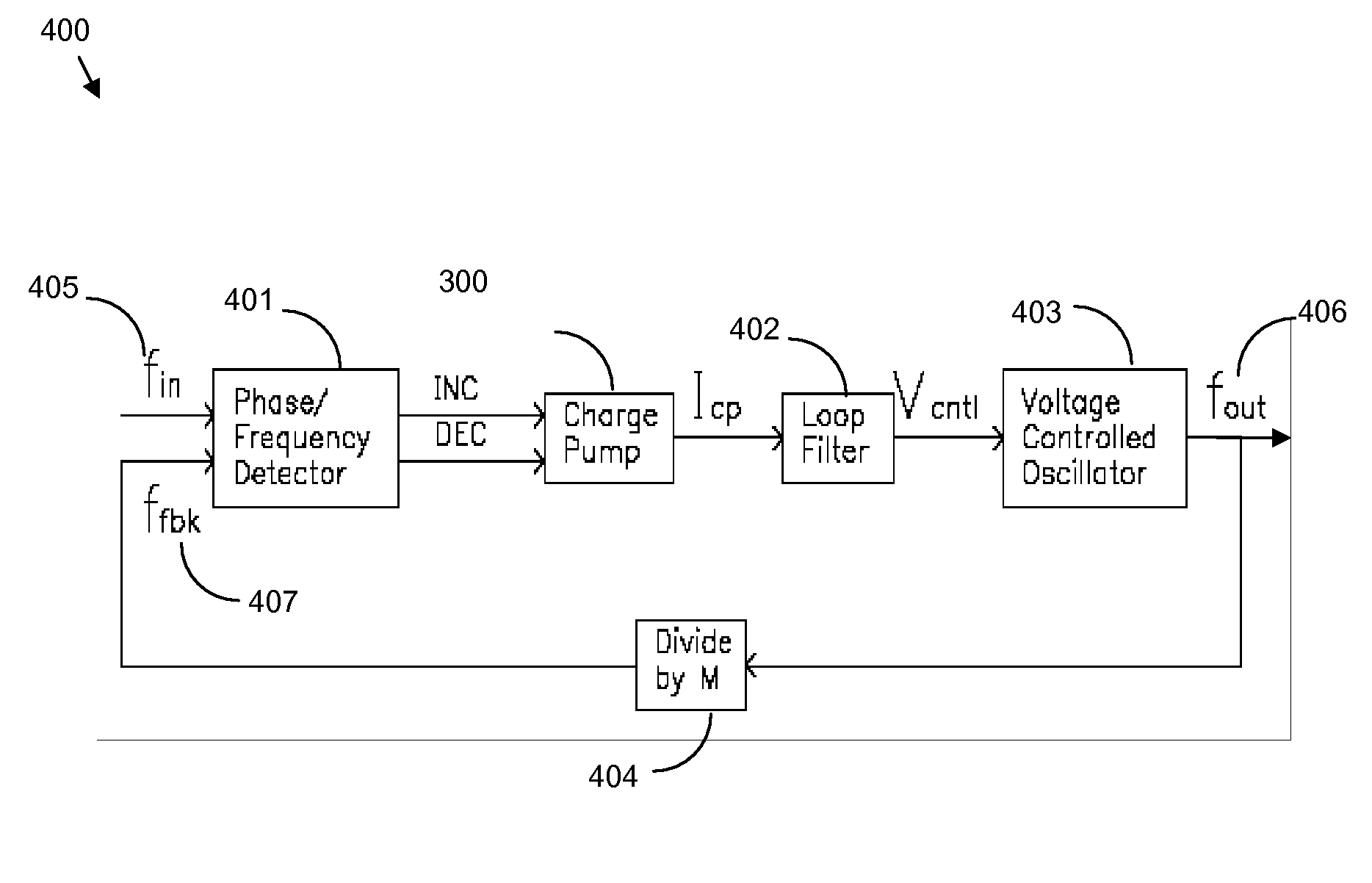

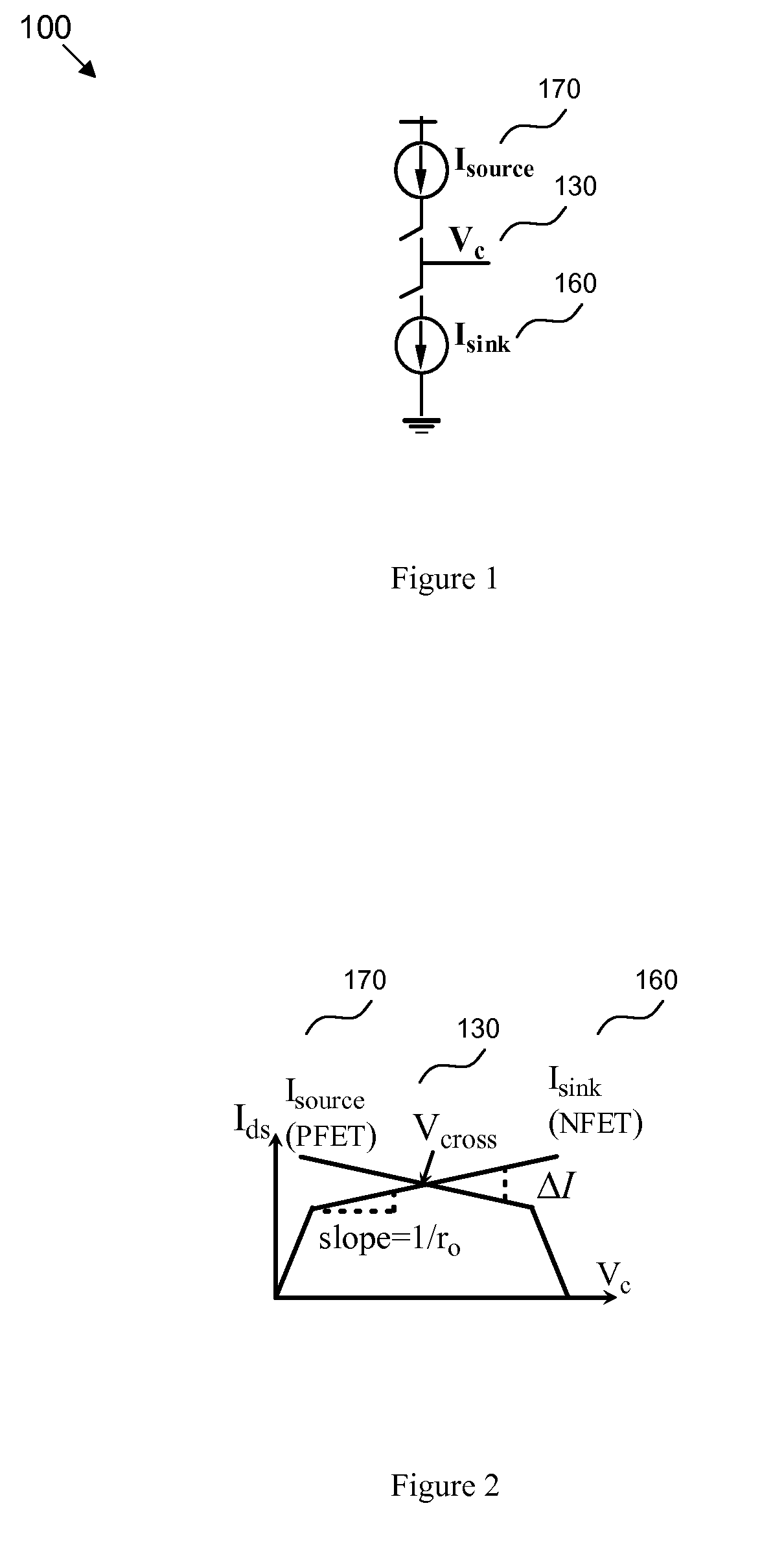

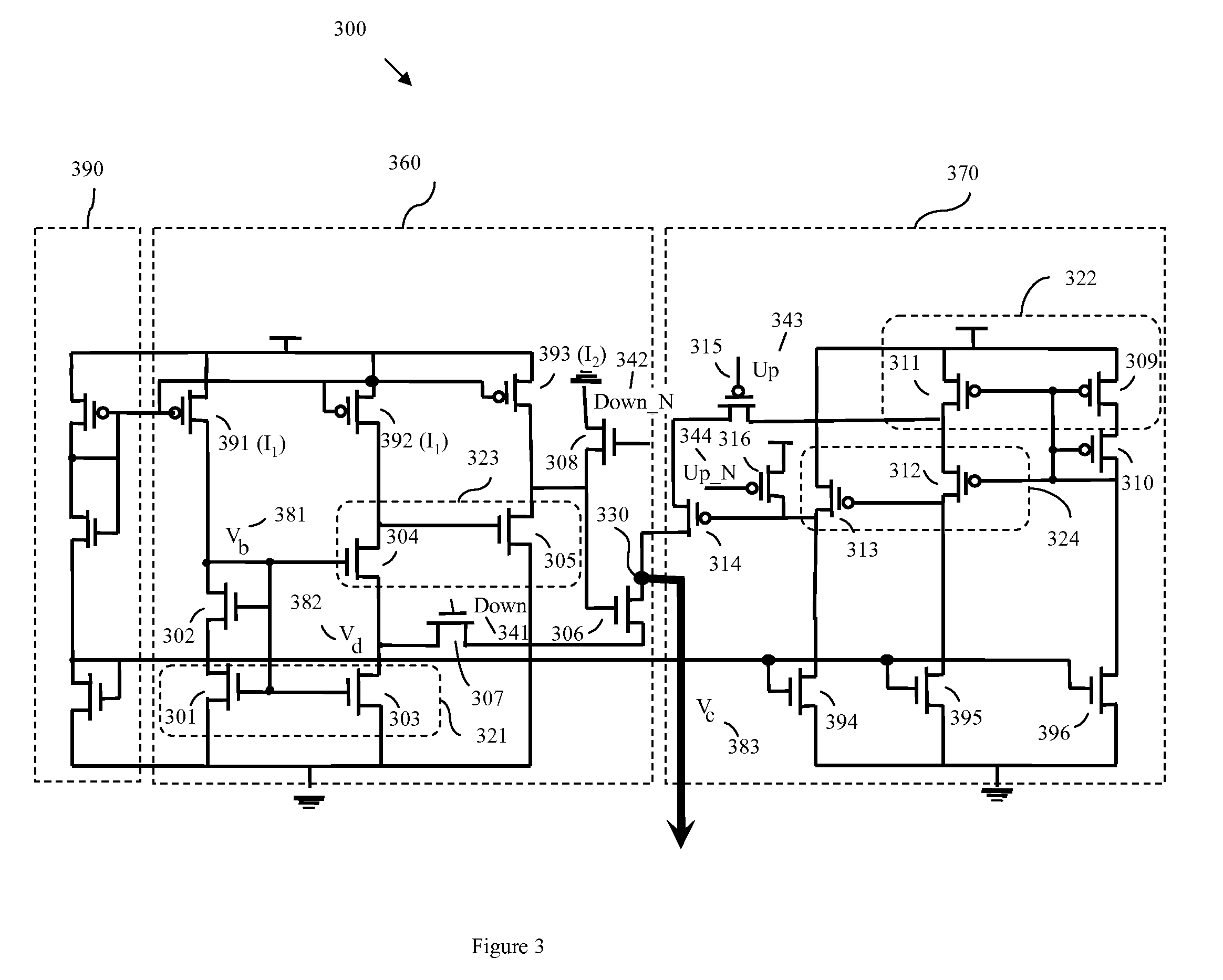

High output resistance, wide swing charge pump

InactiveUS20090033383A1Increase the output resistanceWide operating voltage rangePulse automatic controlApparatus without intermediate ac conversionAudio power amplifierVoltage range

Disclosed are current sink and source circuits, a charge pump that incorporates them, and a phase locked loop that incorporates the charge pump. The current sink and source circuits each have a current mirror that biases a transistor connected to an output node. These circuits each further have a two-stage feedback amplifier to sense the current mirror drain voltage and to control the transistor gate voltage in order to stabilize the current mirror drain voltage independent of output voltage at the output node. The amplifier also increases output resistance at the output node. This configuration allows for a wide operation voltage range and ensures good circuit performance under a very low power supply. A charge pump that incorporates these circuits generates highly matched charging and discharging currents. A PLL that incorporates this charge pump exhibits minimal bandwidth shifts and minimal locking speed and jitter performance degradation.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com