Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4003 results about "Gate voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

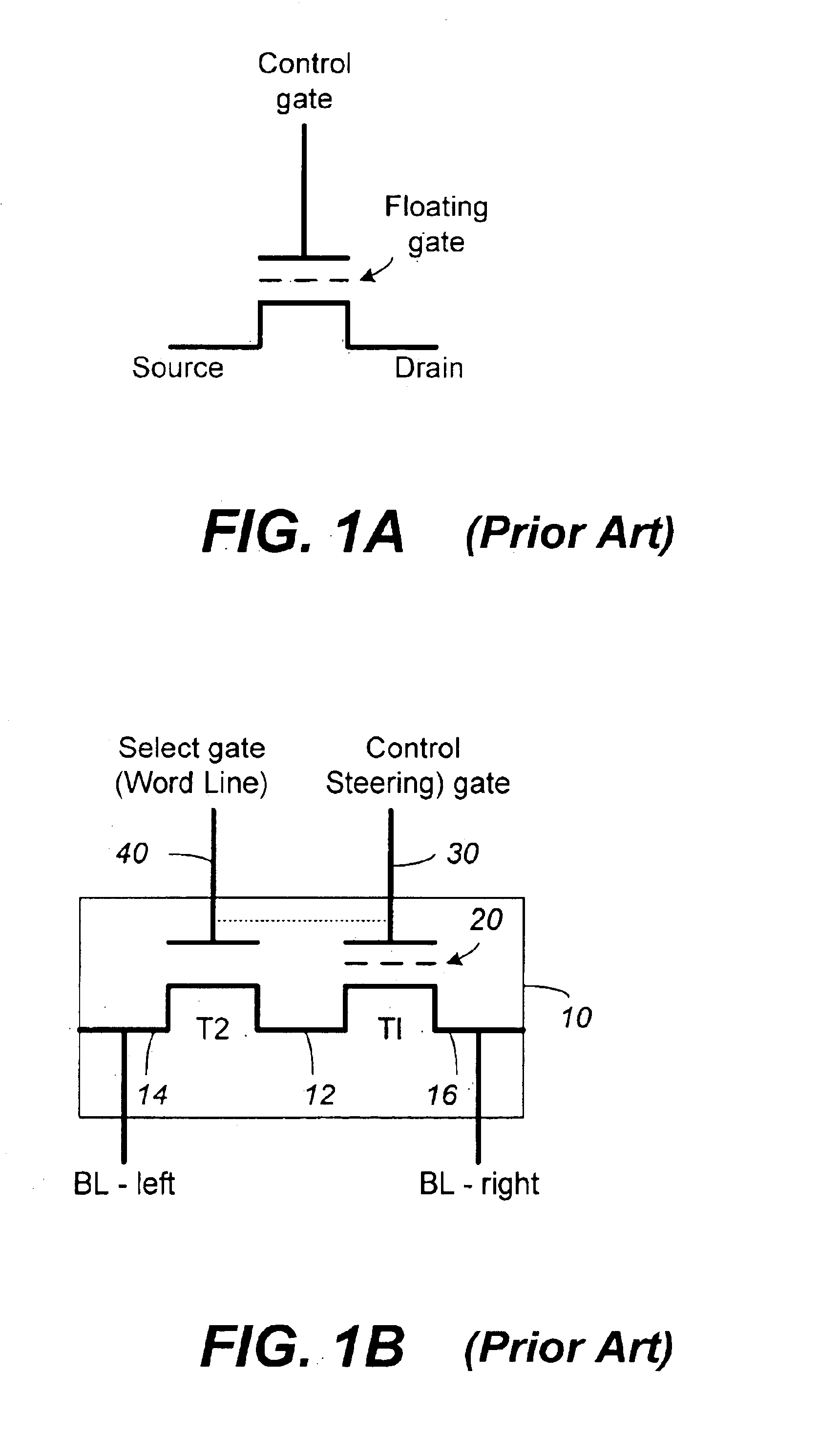

The gate-source voltage, VGS, of a FET transistor is the voltage that falls across the gate-source terminal of the transistor, as shown above. The gate-source voltage, VGS, is a very important voltage because it is the voltage which is responsible for turning off a JFET or a depletion MOSFET transistor.

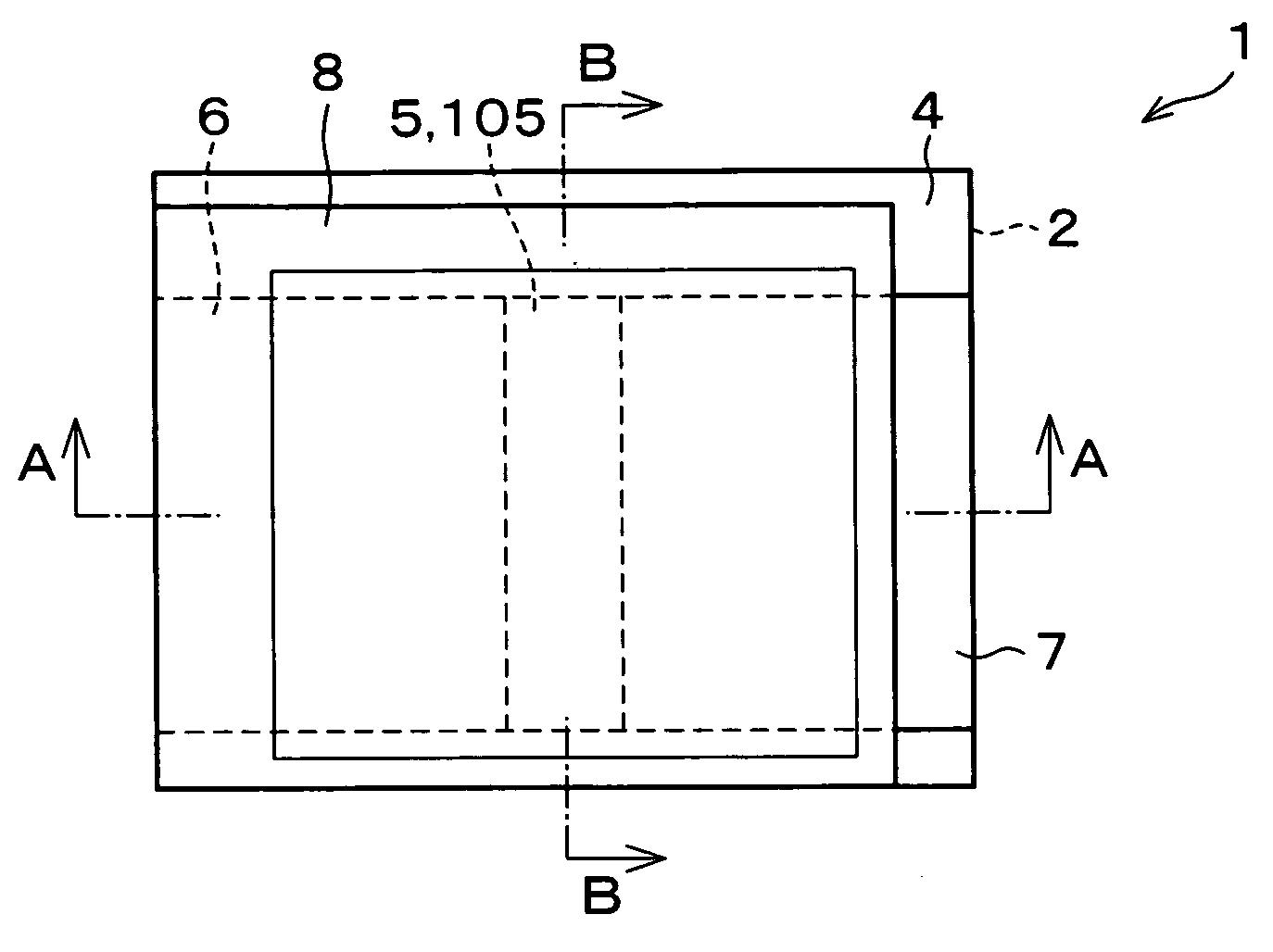

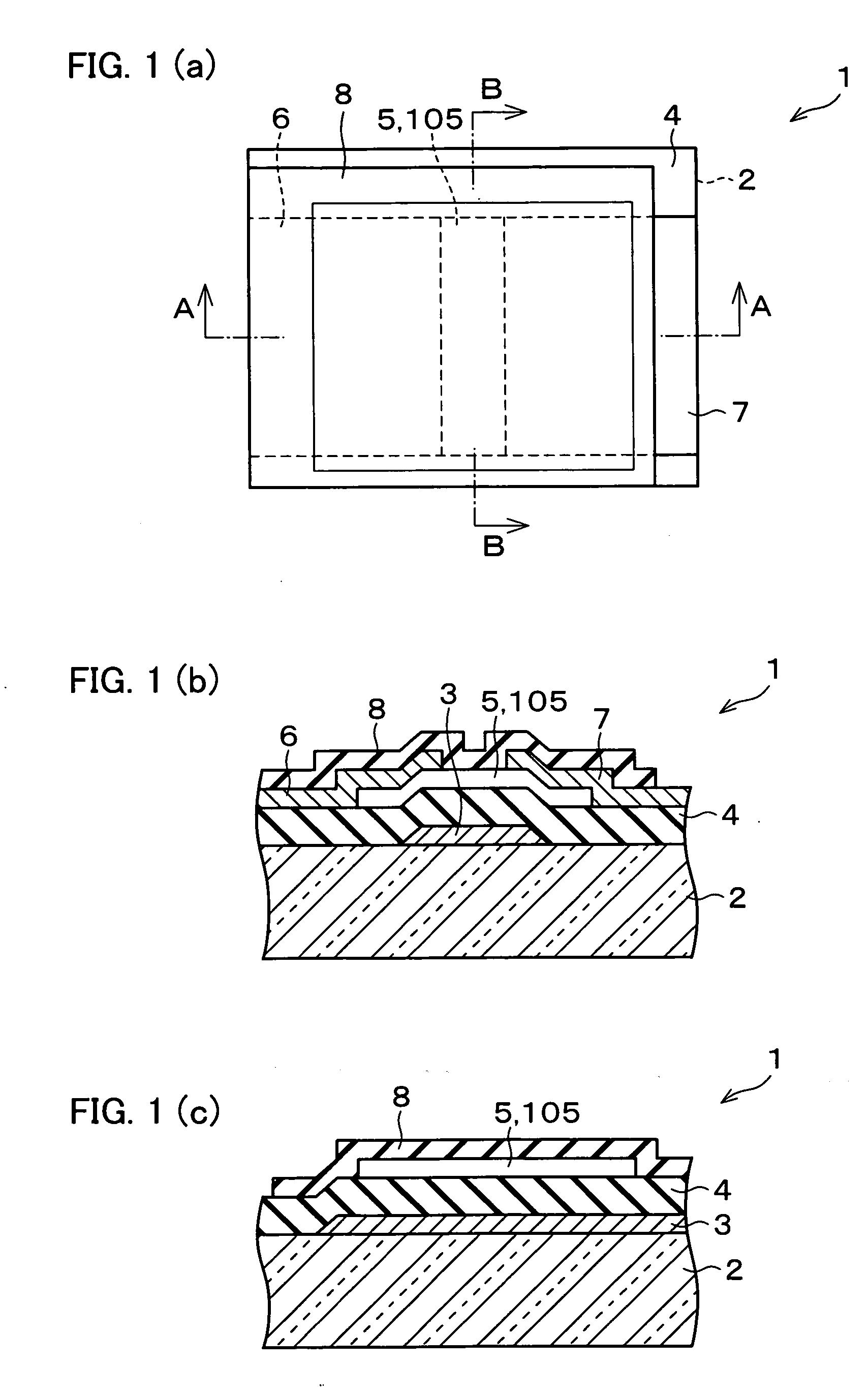

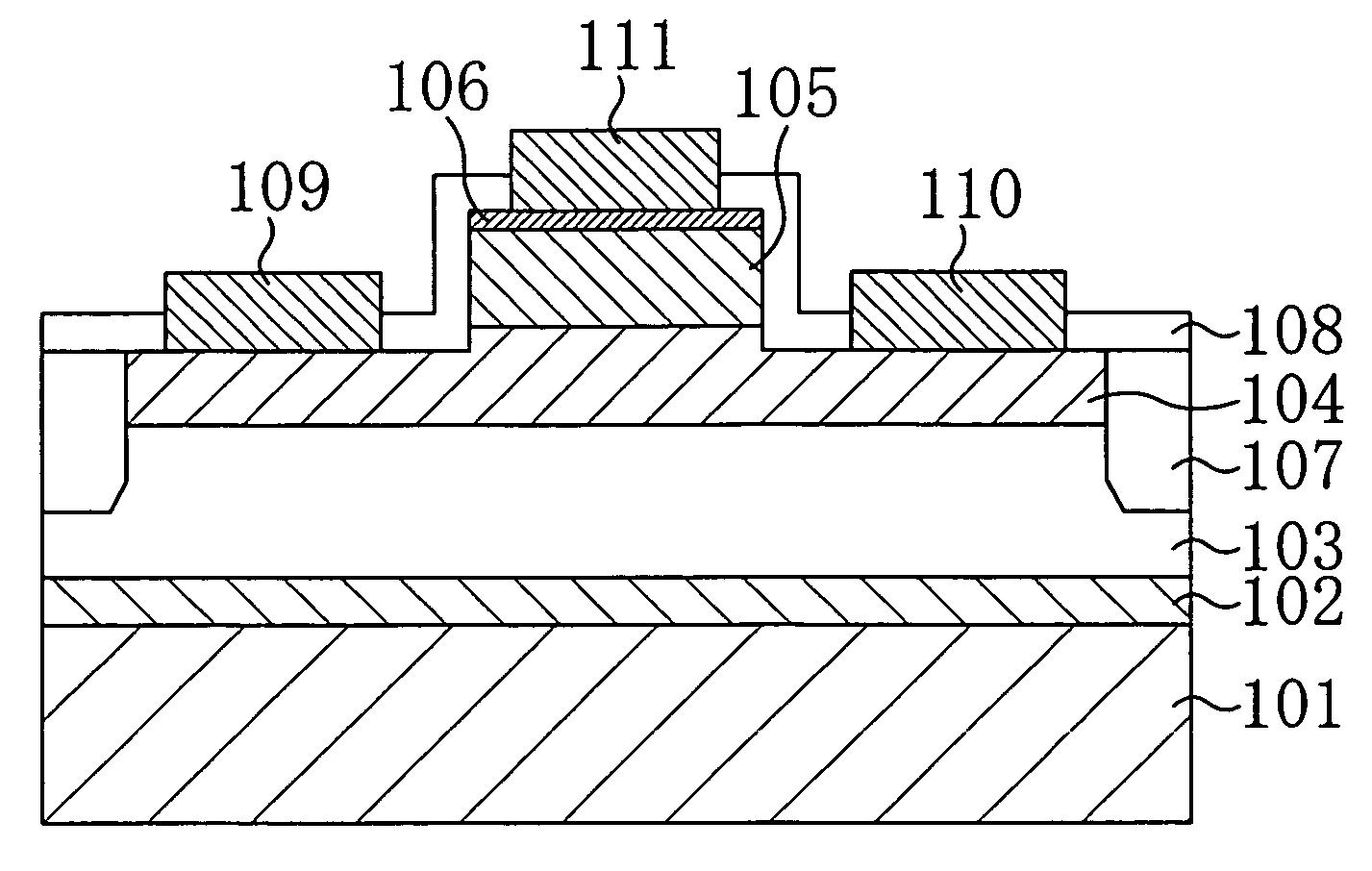

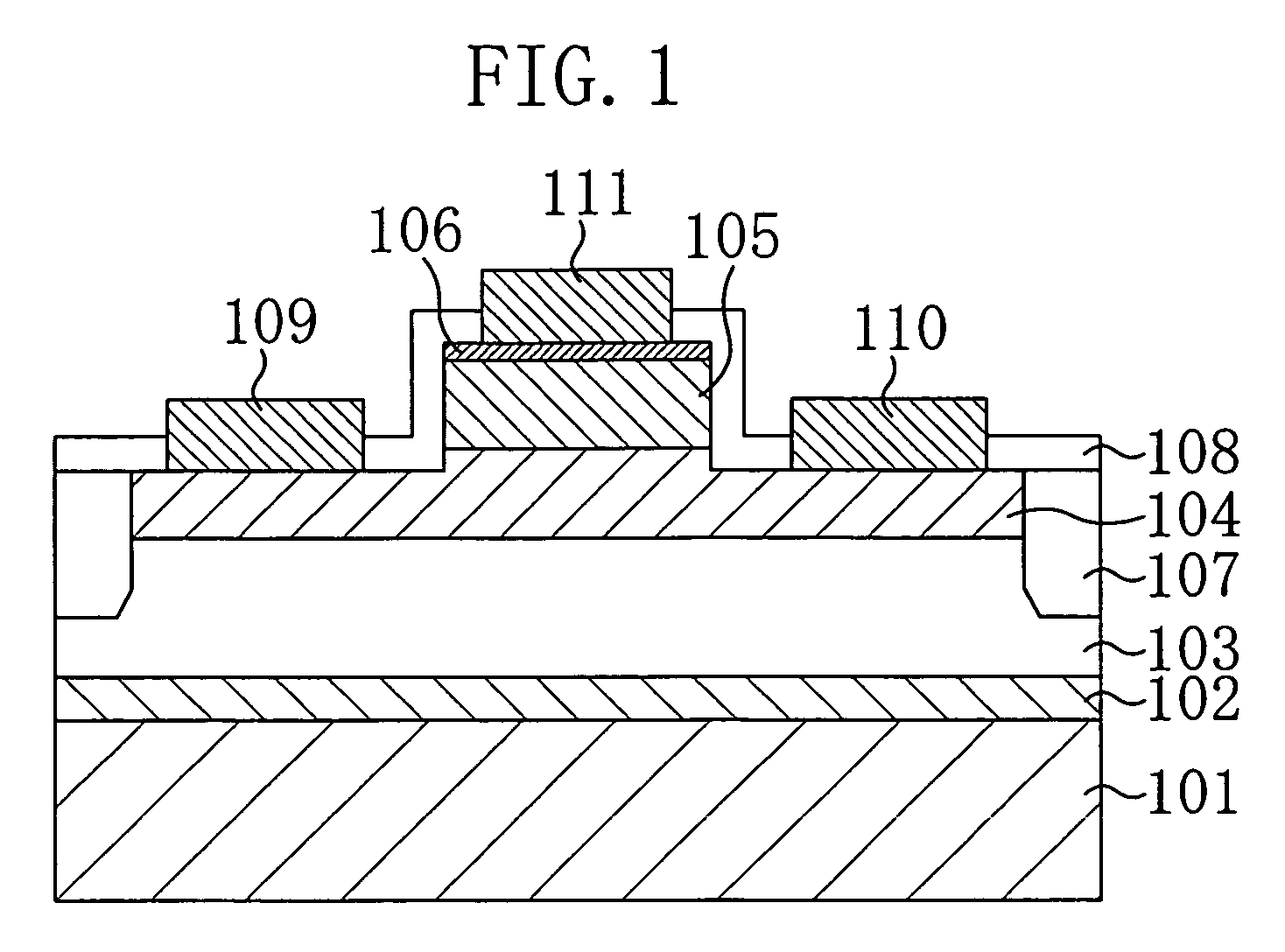

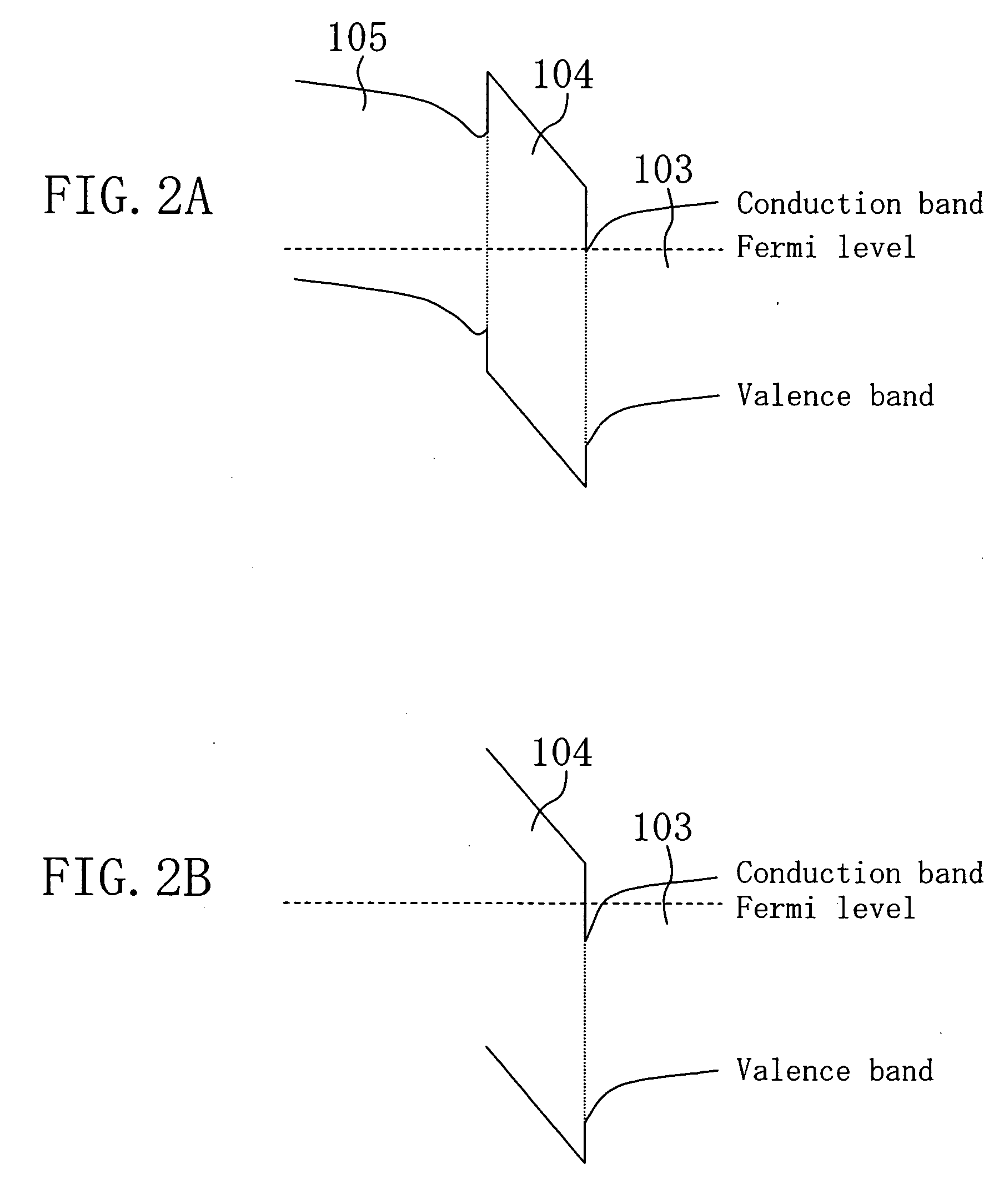

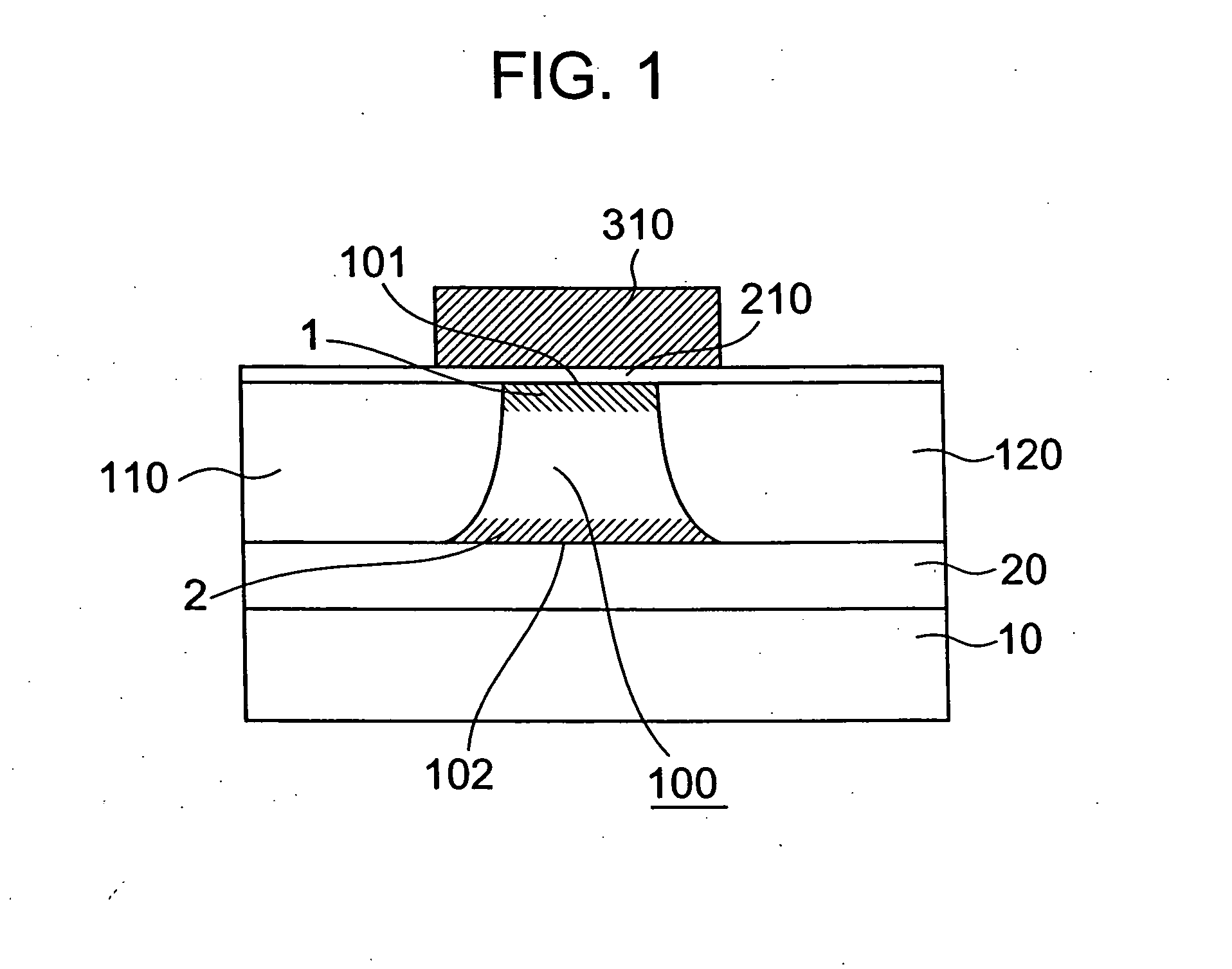

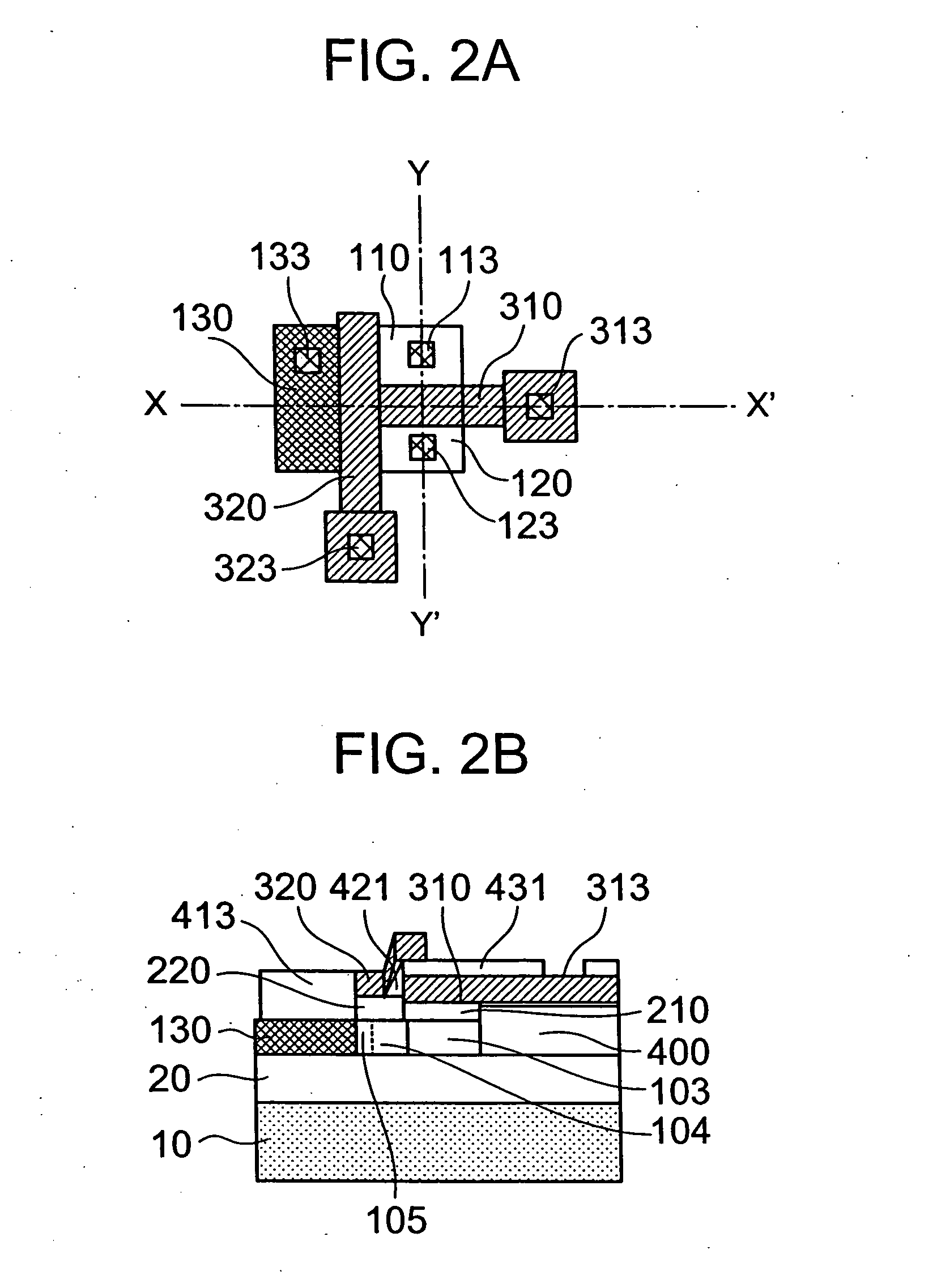

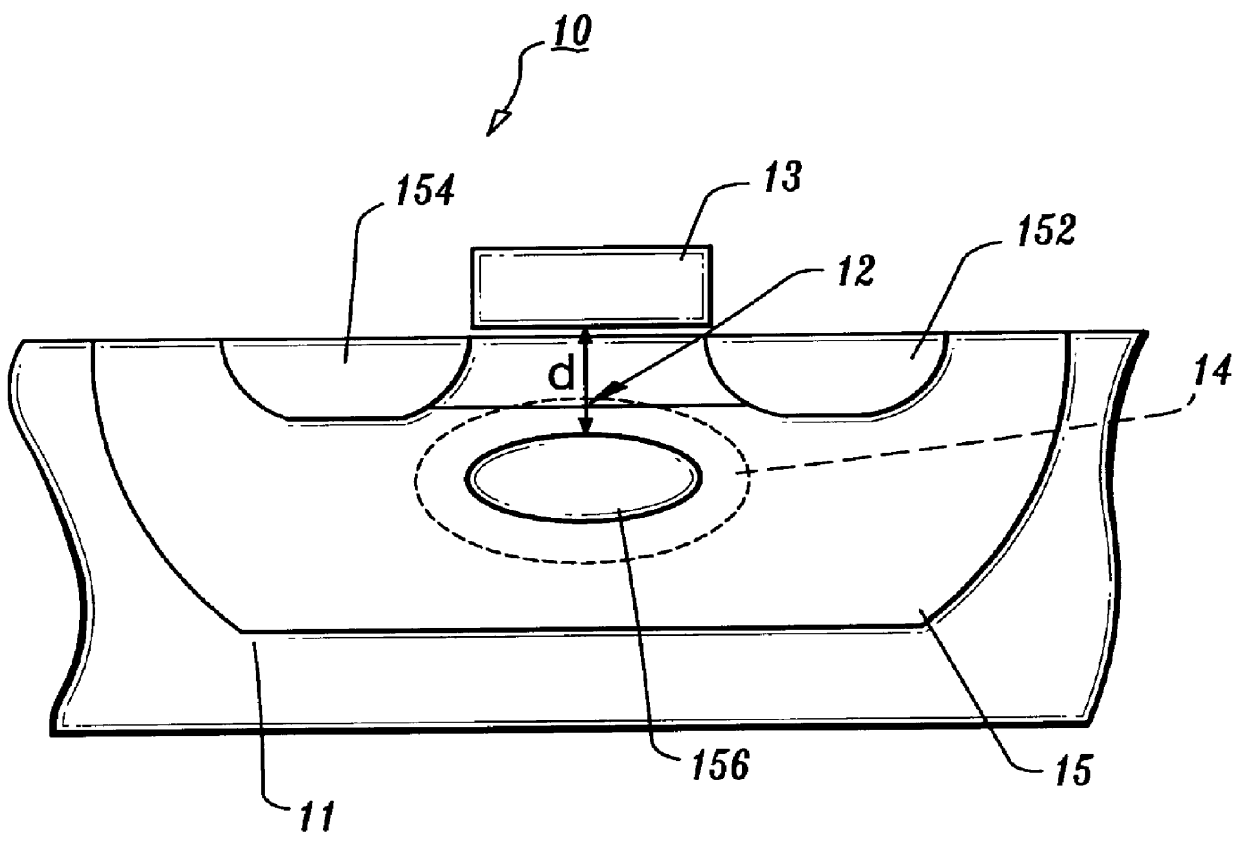

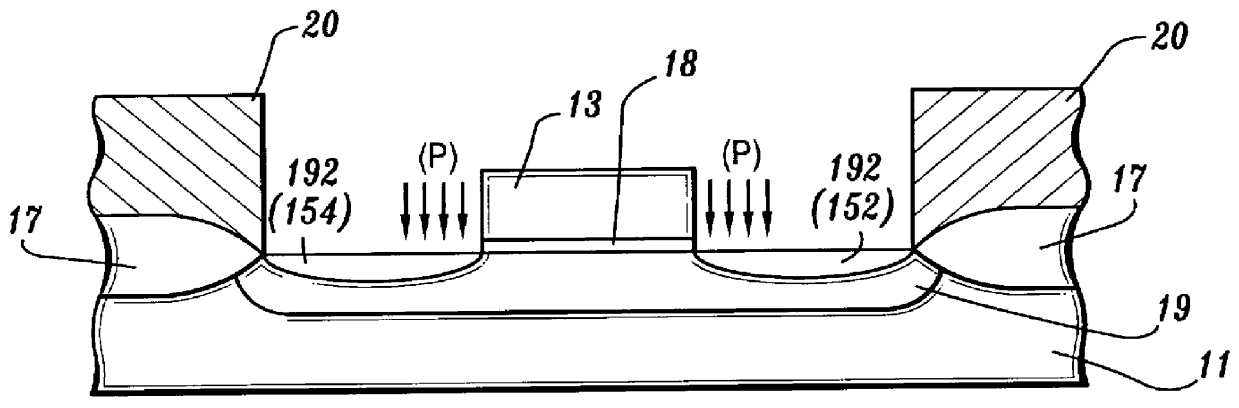

Semiconductor device, manufacturing method, and electronic device

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

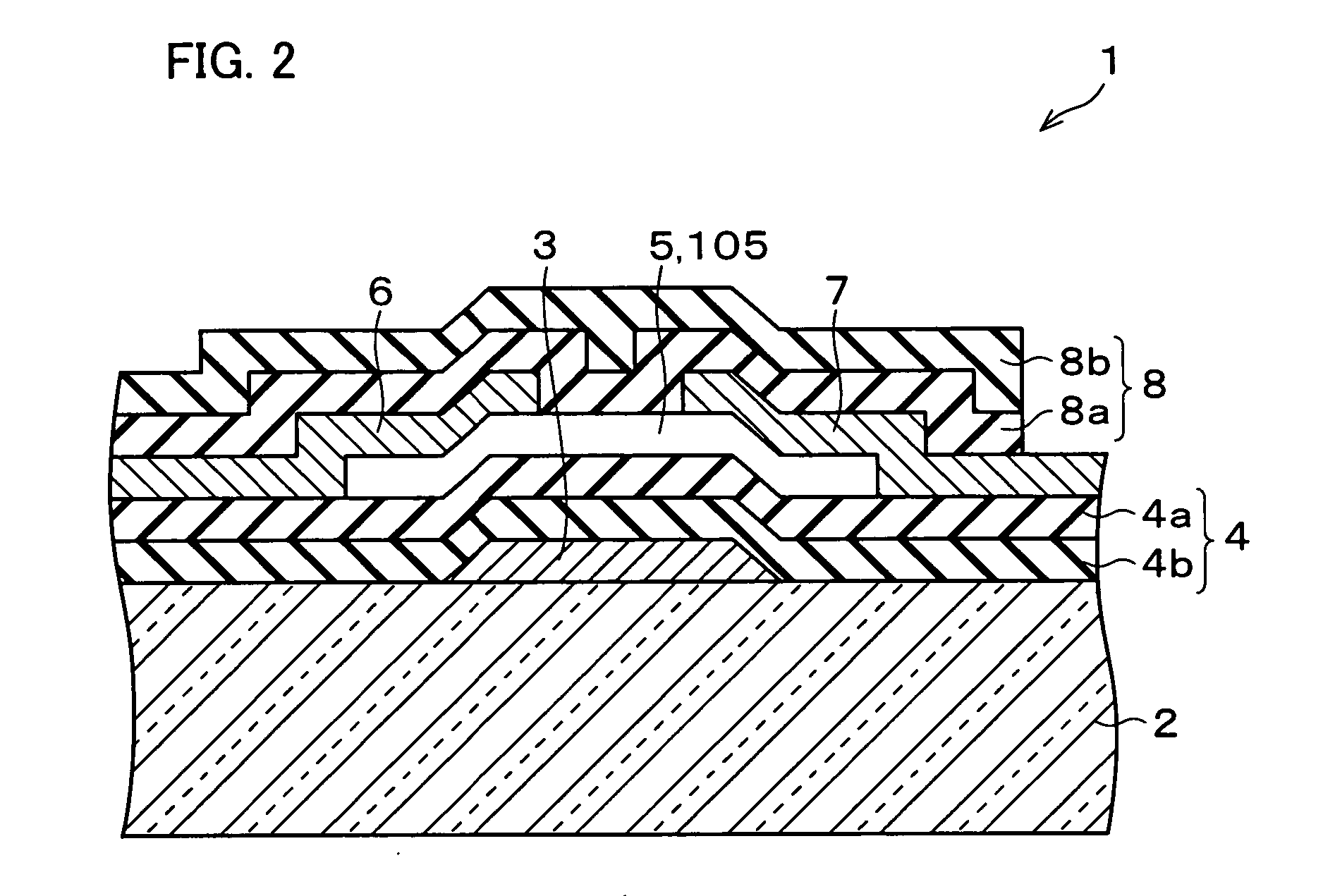

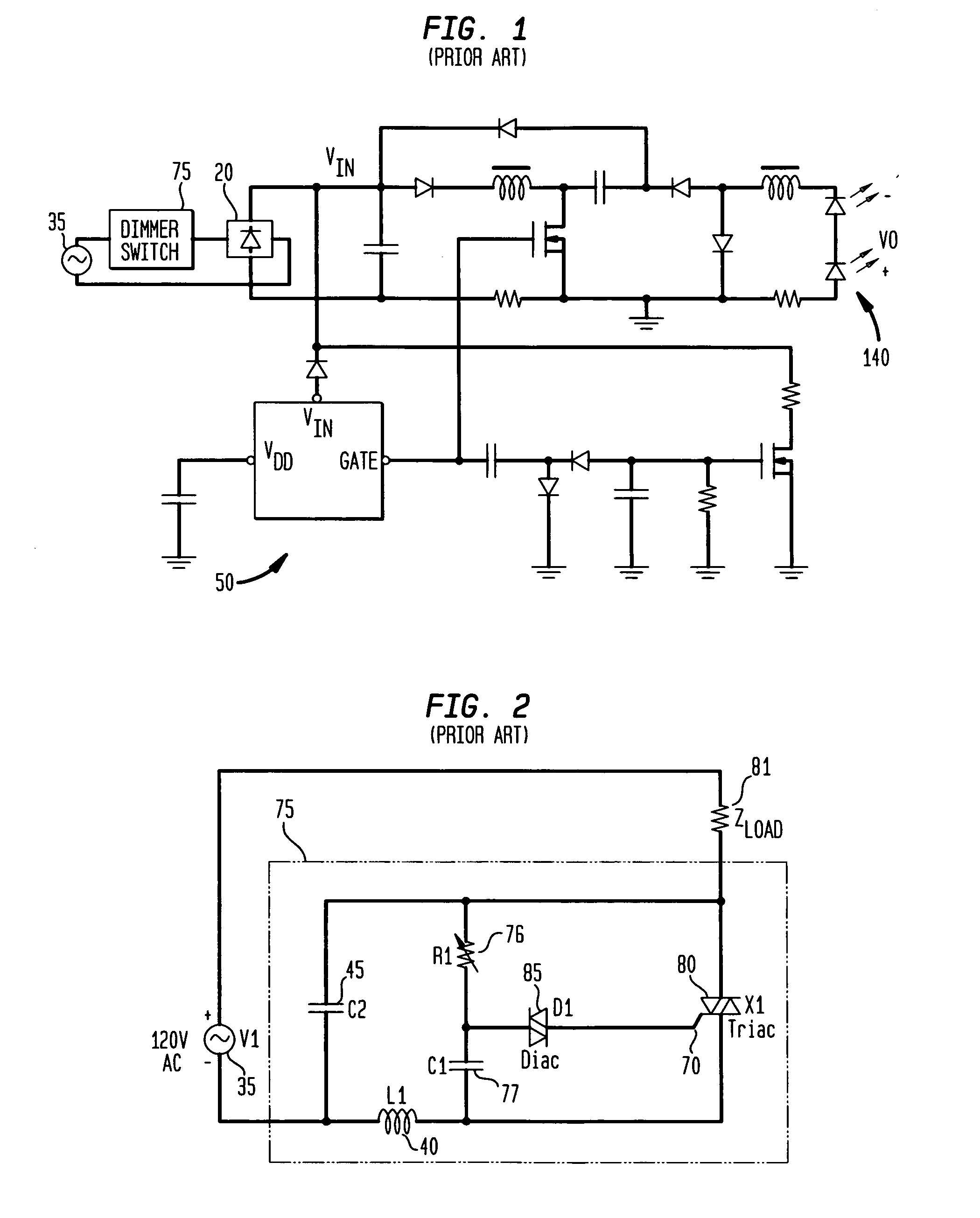

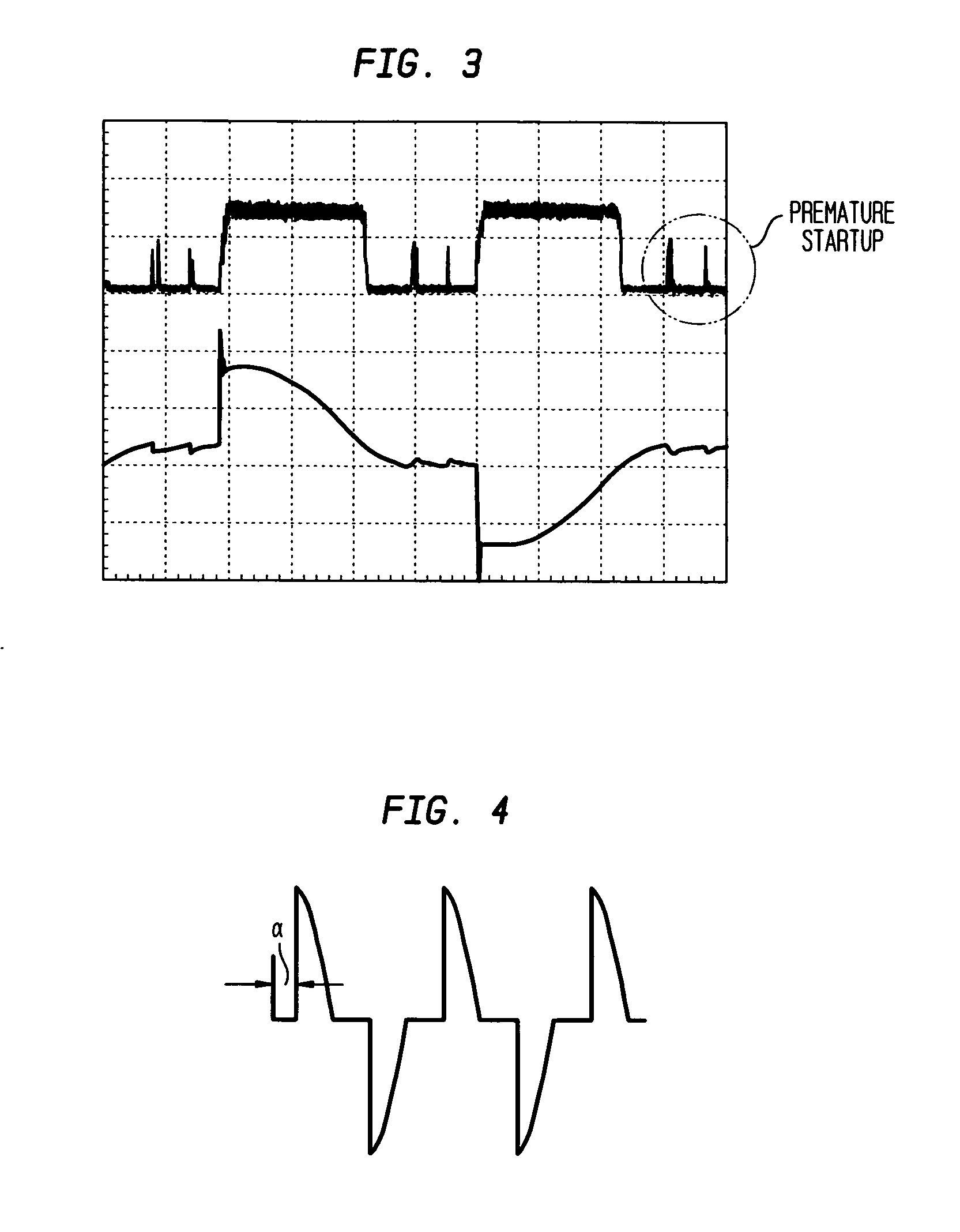

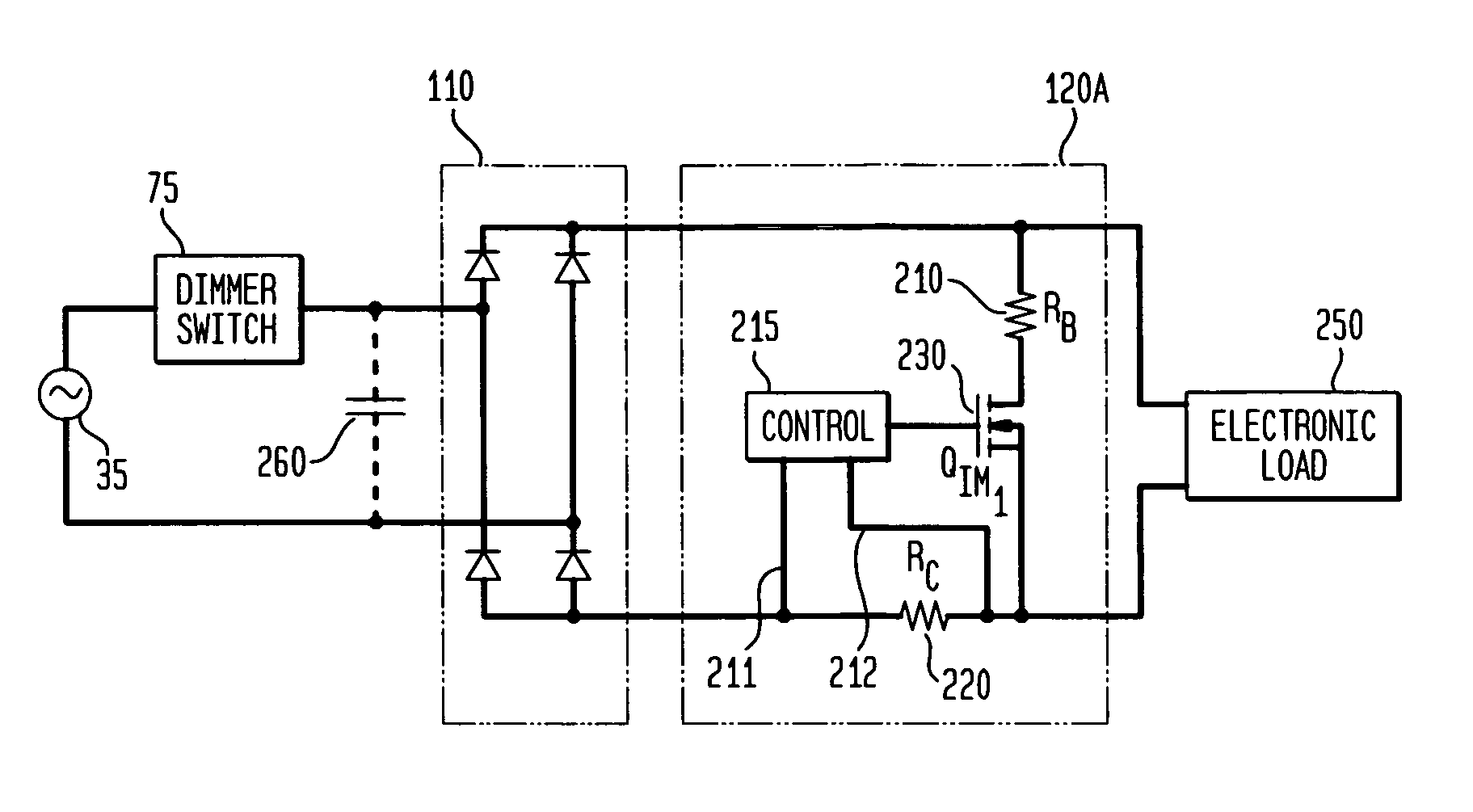

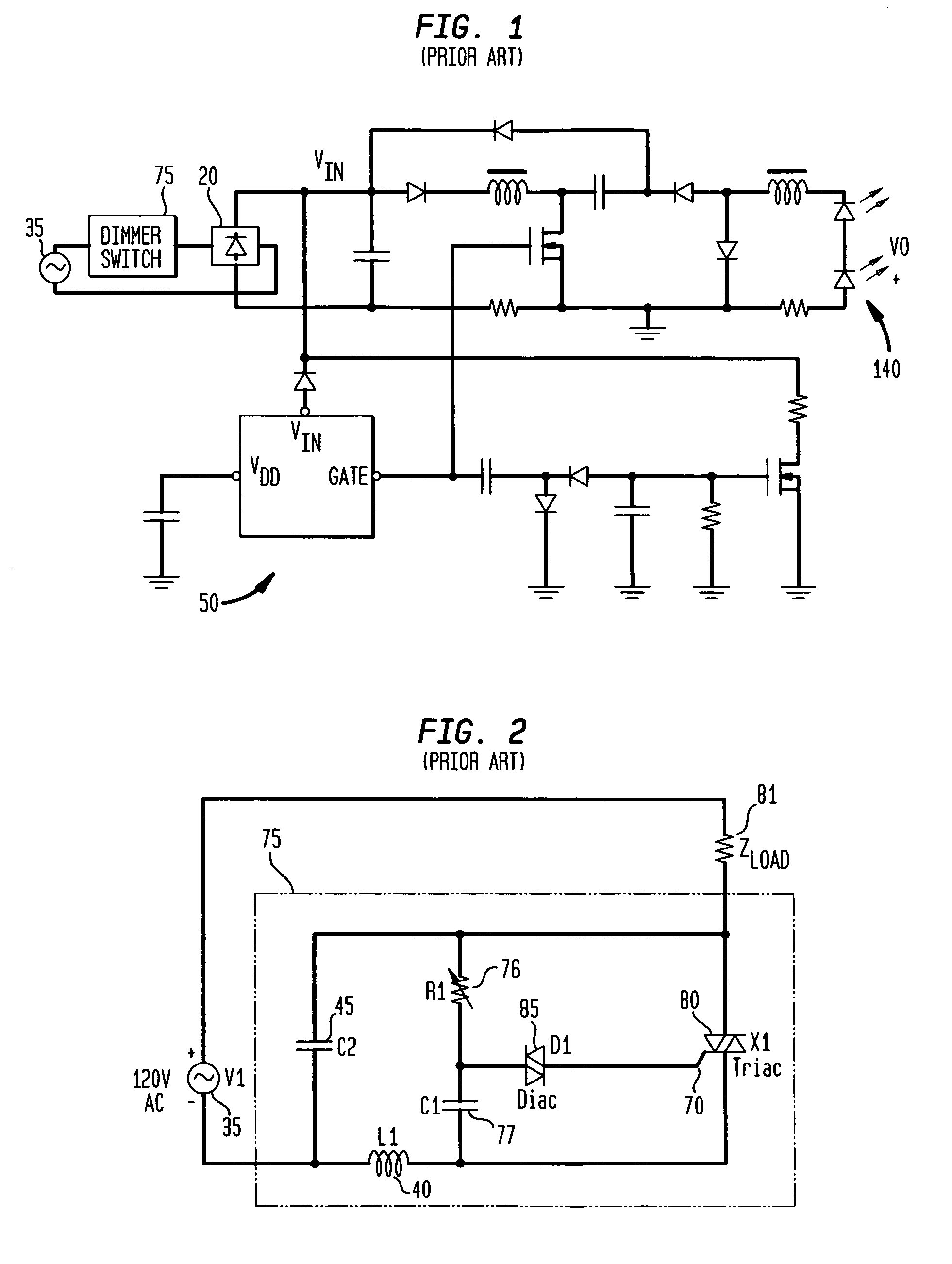

Impedance matching circuit for current regulation of solid state lighting

ActiveUS20070182347A1Low component requirementsElectrical apparatusElectroluminescent light sourcesSilicon-controlled rectifierElectrical resistance and conductance

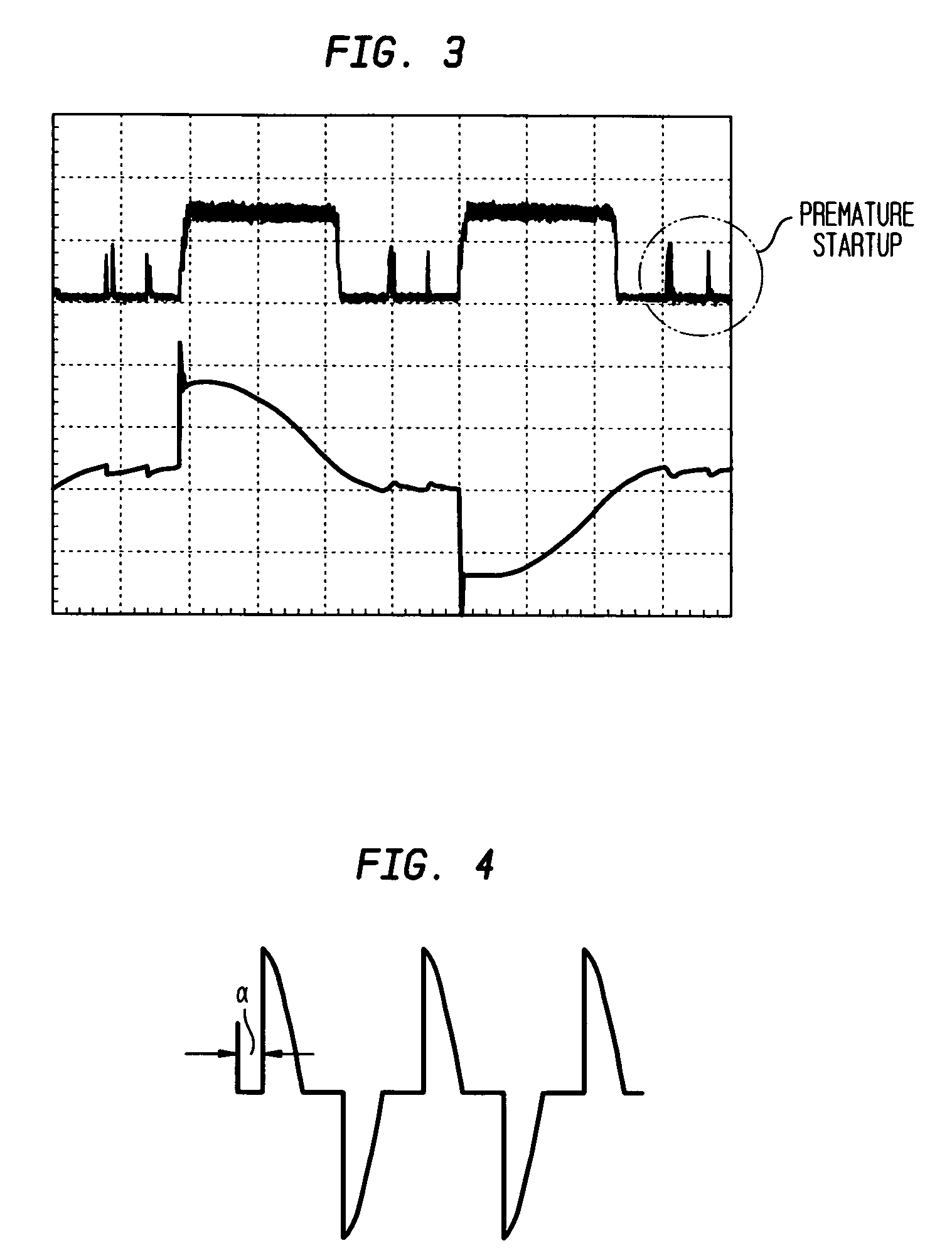

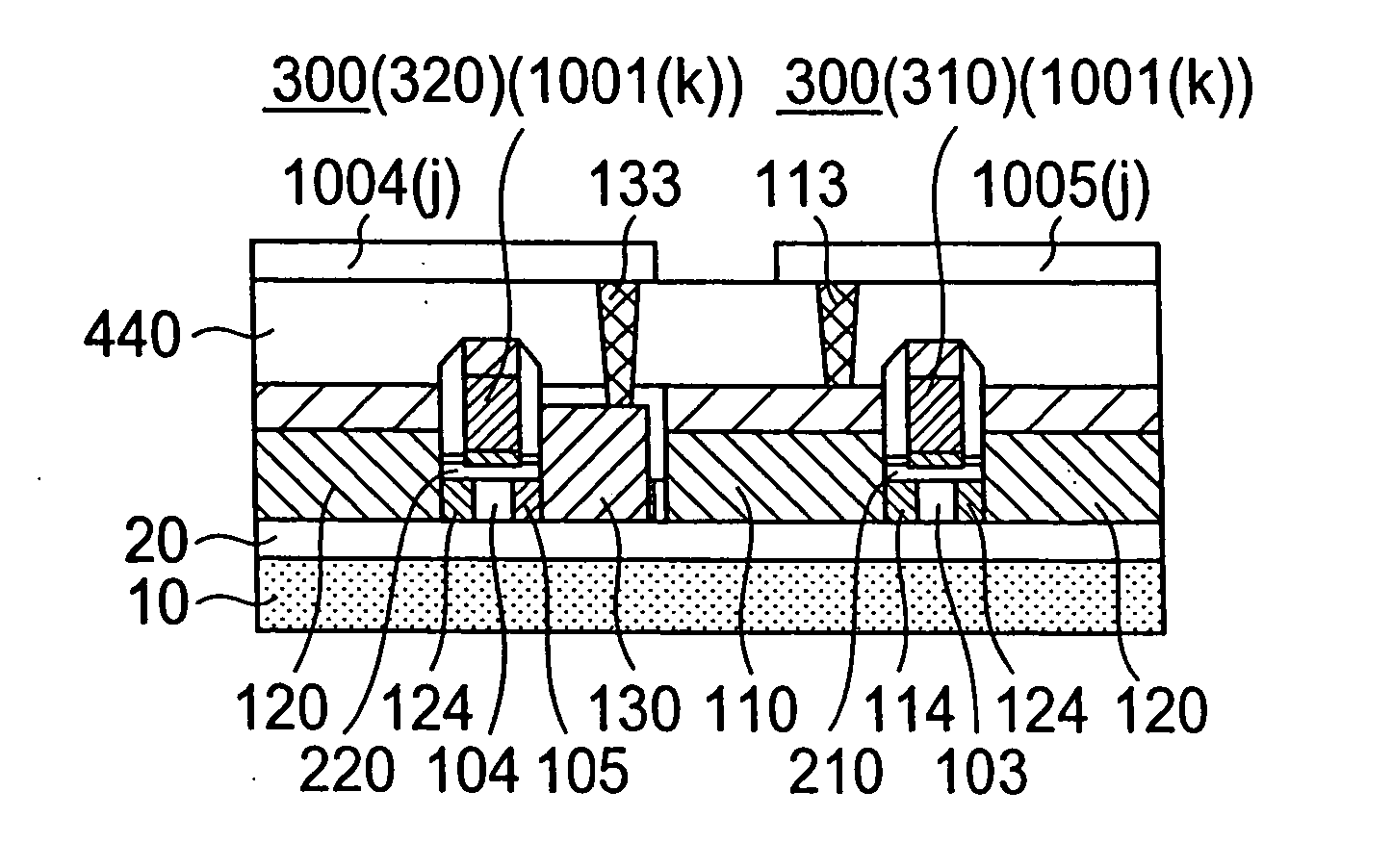

Exemplary embodiments provide an impedance matching circuit for providing variable power from a dimmer switch having a triac to a switching power supply couplable to solid-state lighting. An exemplary impedance matching circuit includes a first resistor coupled to receive a first current from the switching power supply; a second resistor; and a transistor coupled in series to the second resistor, with the transistor responsive to a gate voltage to modulate a second current through the second resistor in response to a detected level of the first current through the first resistor.

Owner:CHEMTRON RES

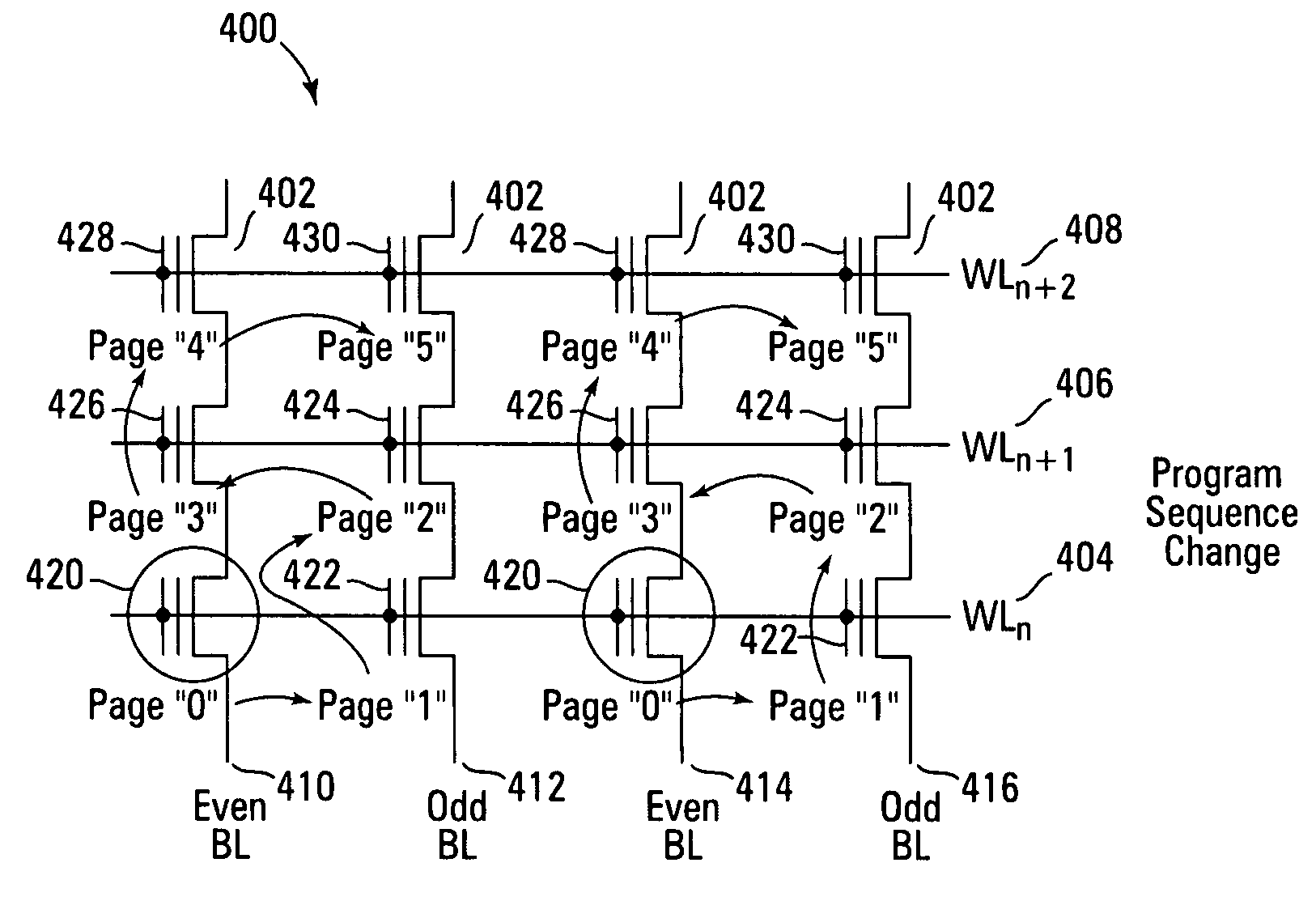

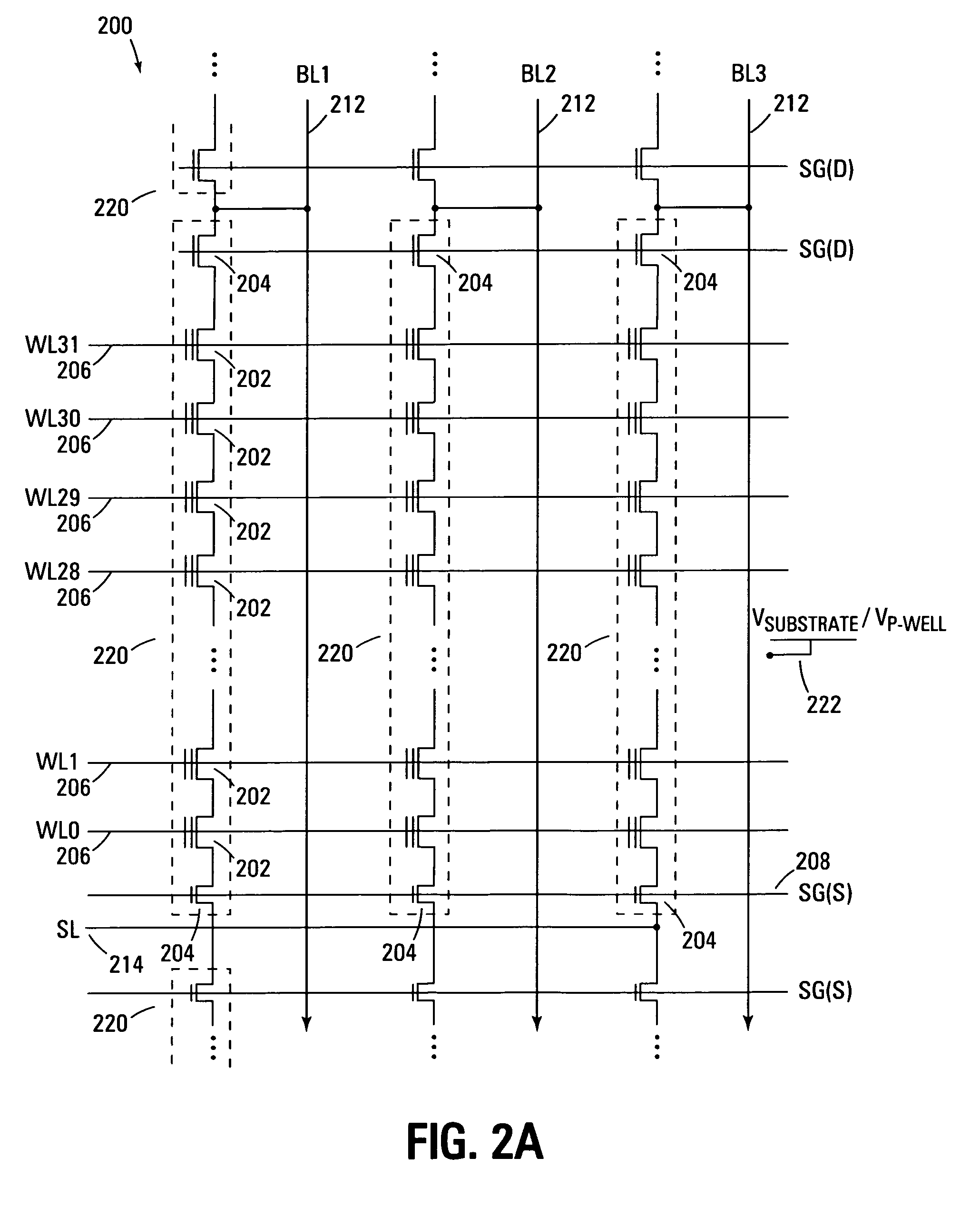

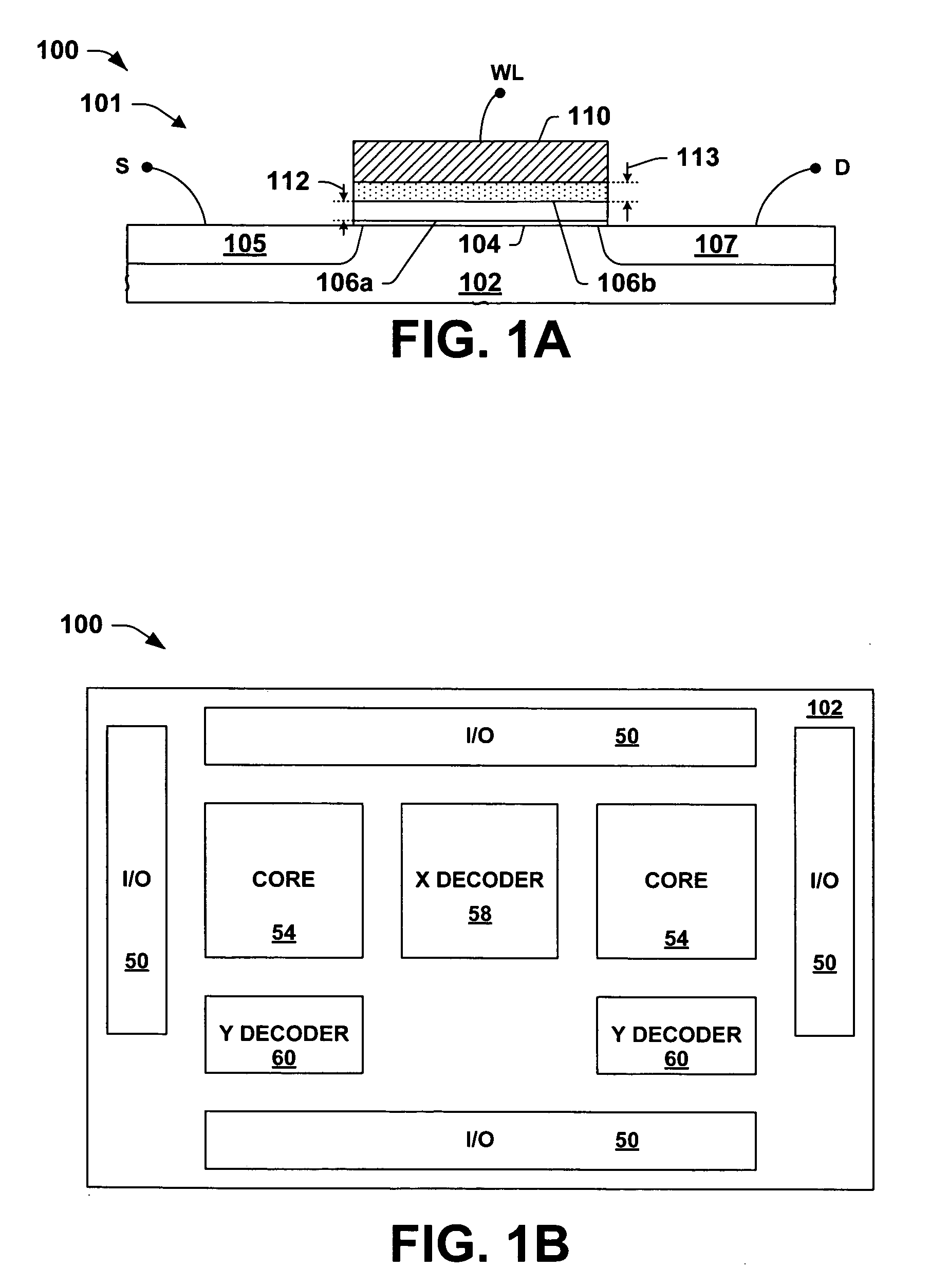

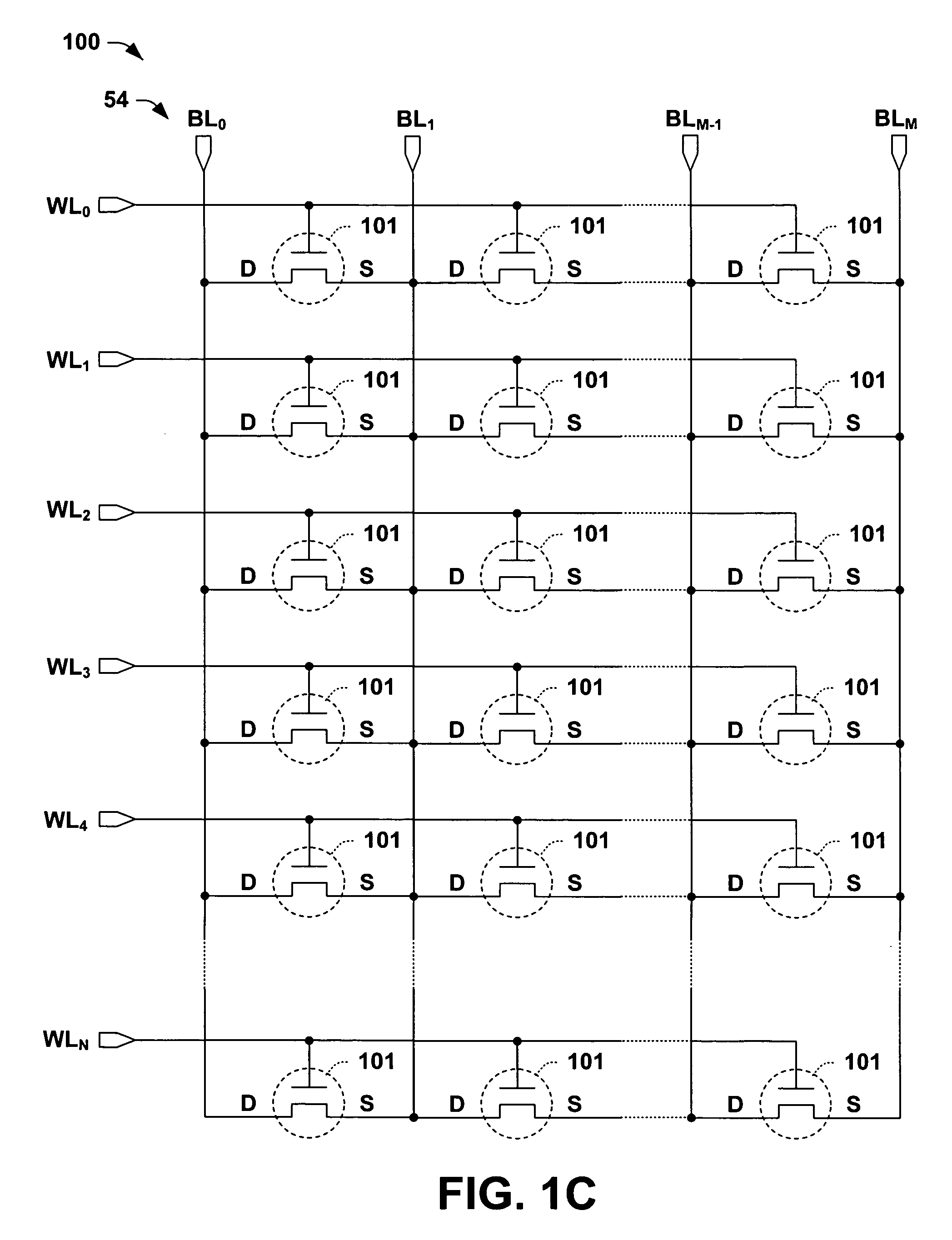

Programming method to reduce gate coupling interference for non-volatile memory

Owner:MICRON TECH INC

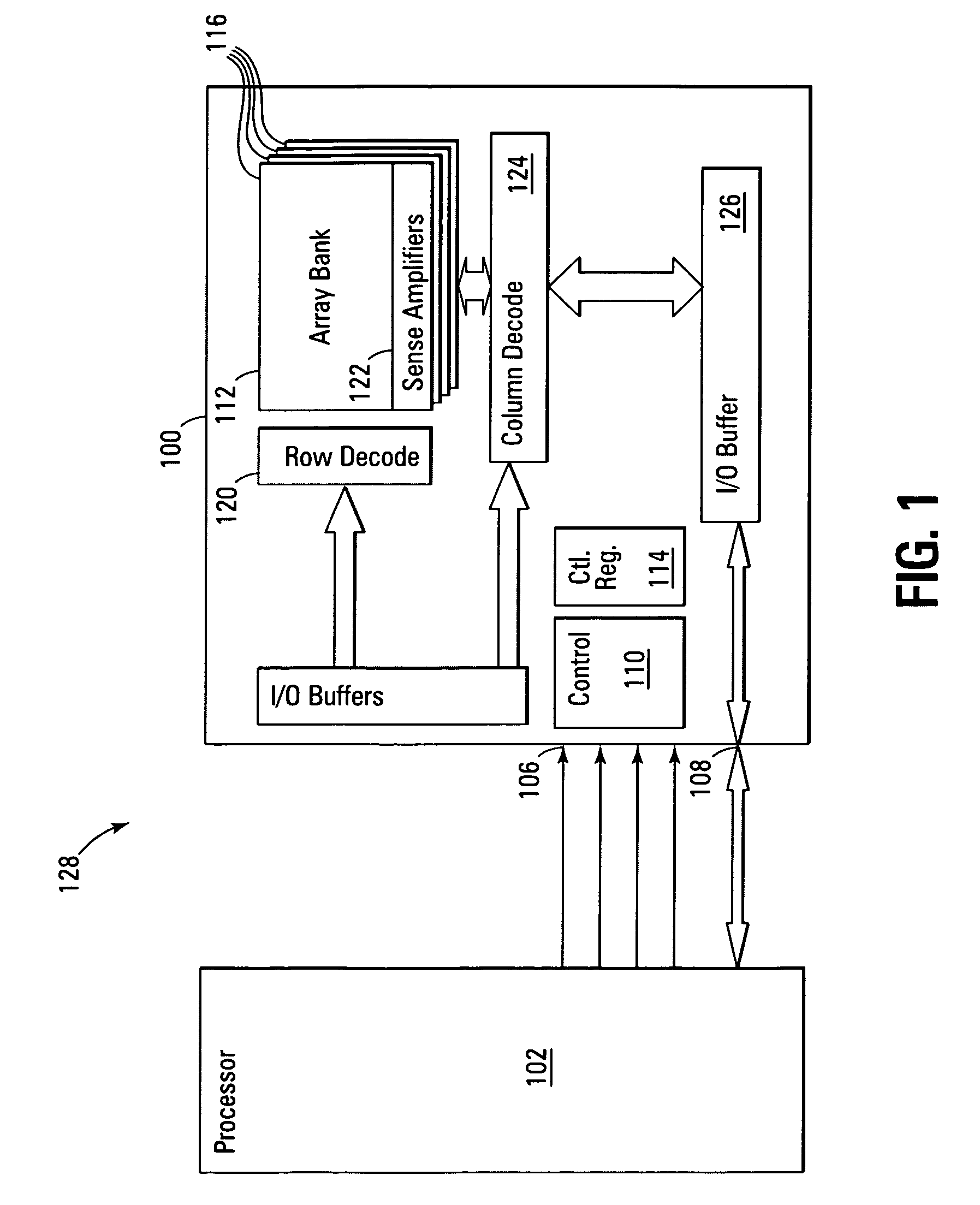

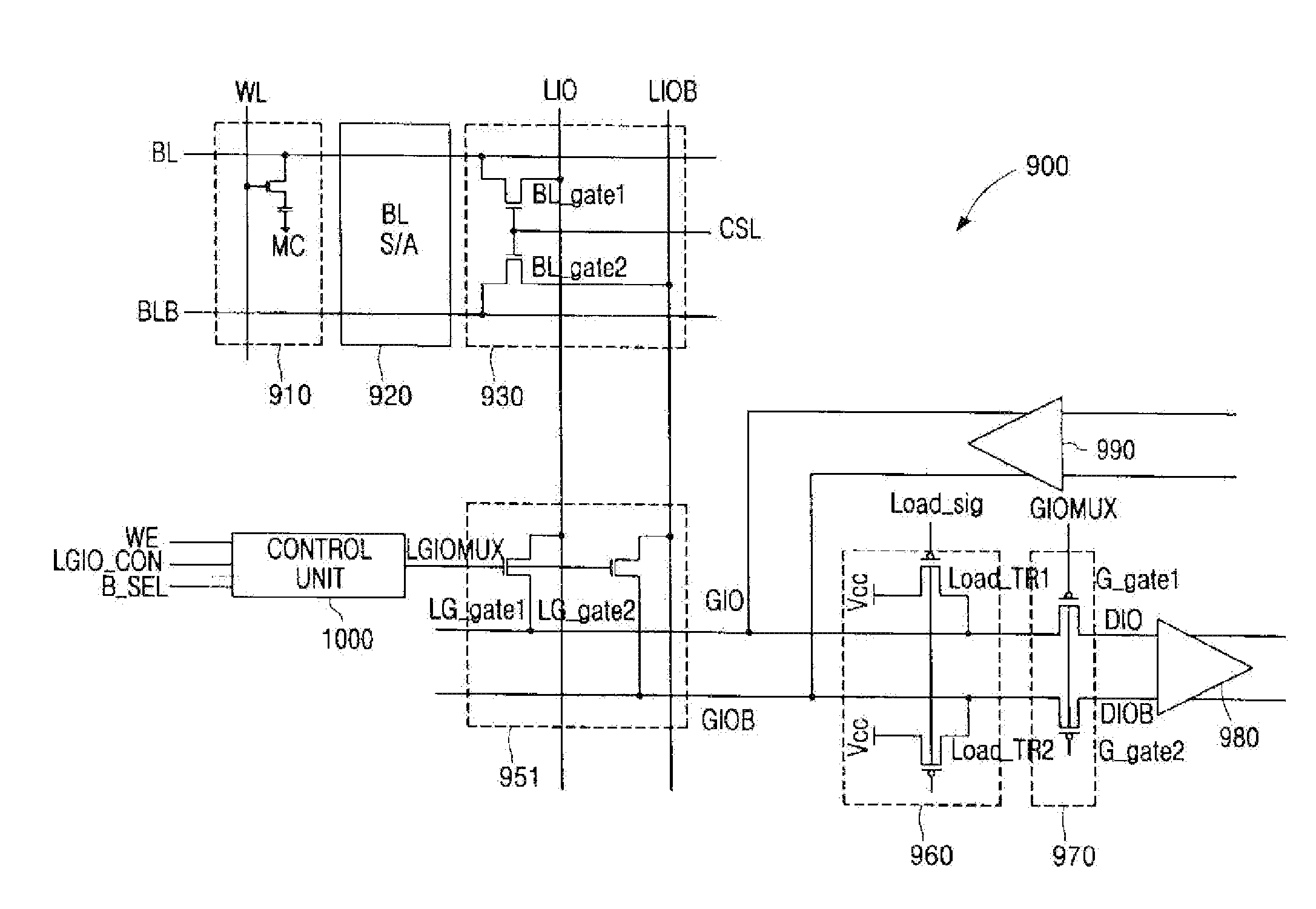

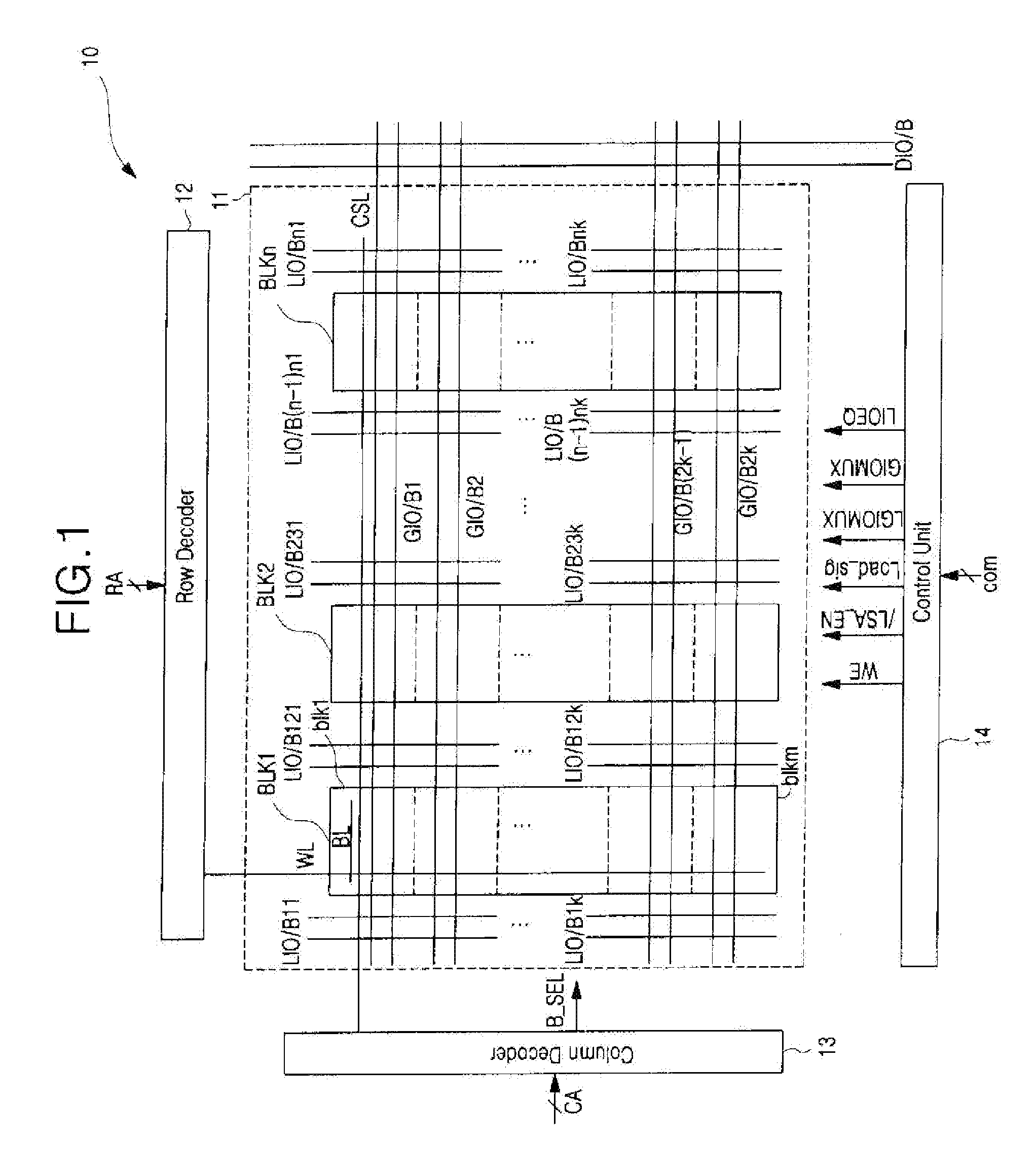

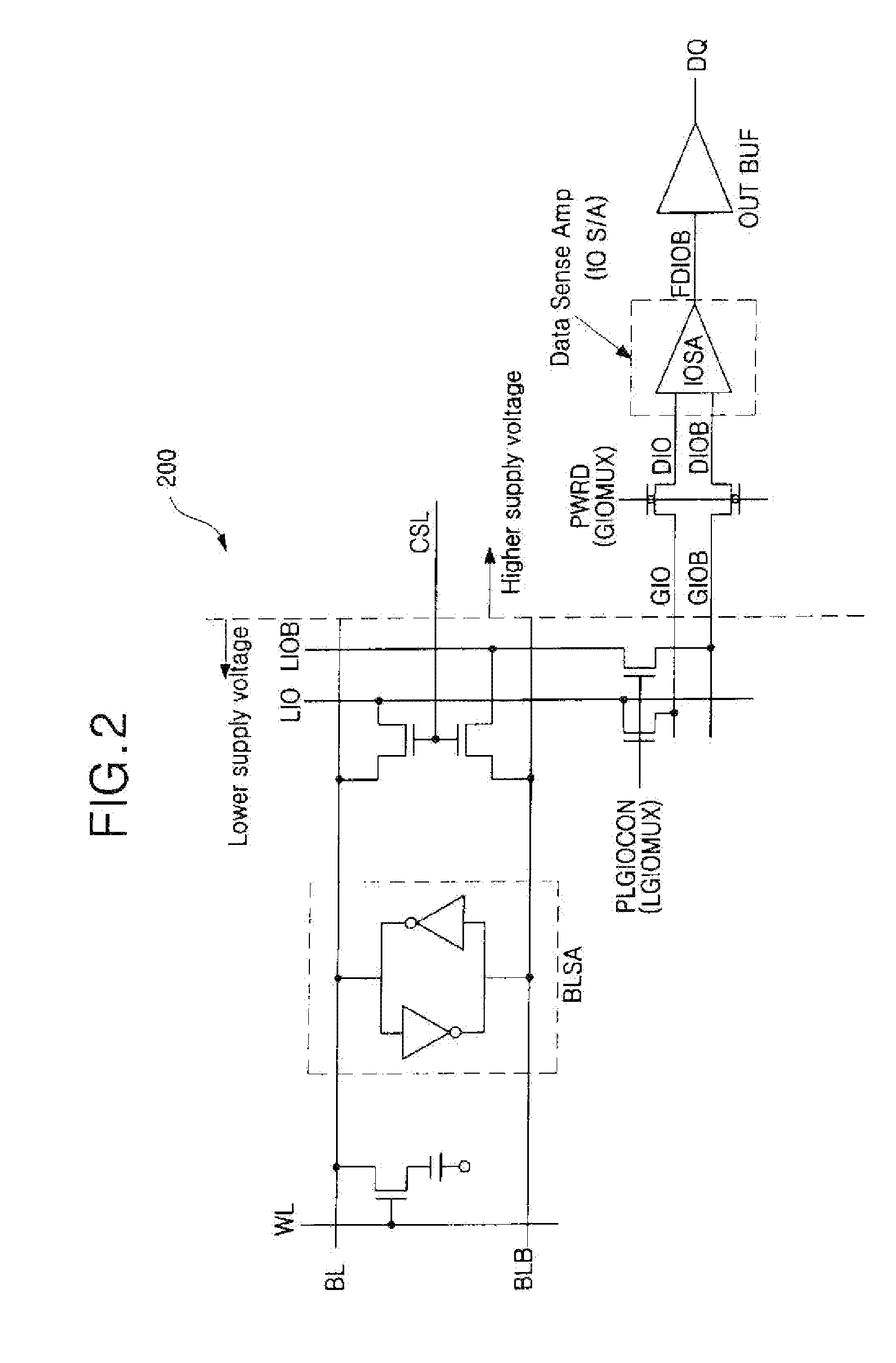

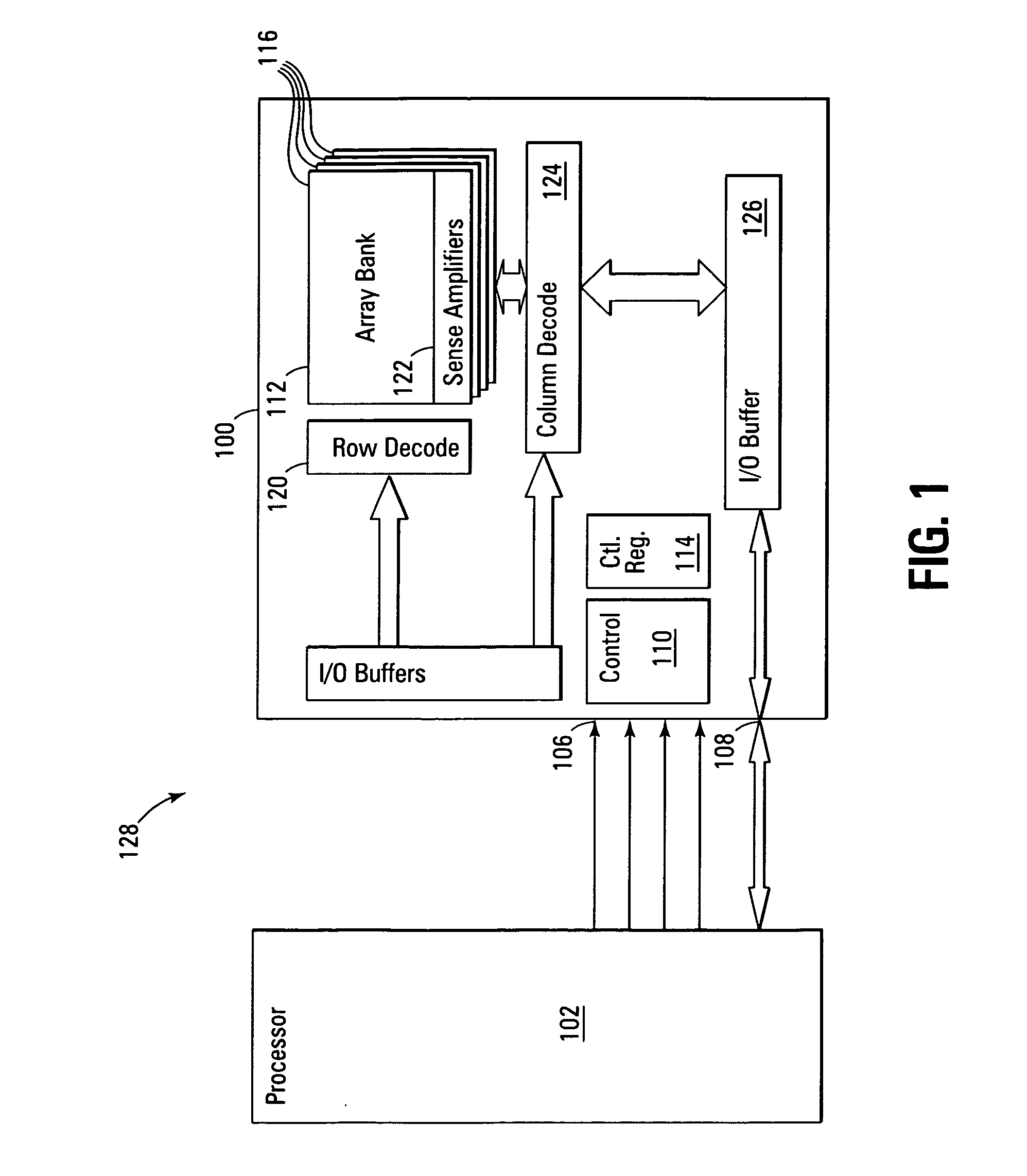

Memory device with separate read and write gate voltage controls

A circuit and method are provided for controlling the gate voltage of a transistor acting between local and global input / output lines of a memory device, the circuit including a local input / output line, a local from / to global input / output multiplexer in signal communication with the local input / output line, a global input / output line in signal communication with the local from / to global input / output multiplexer, and a local from / to global input / output controller having an input node and an output node, the input node disposed for receiving a signal indicative of an input or output operation, and the output node in signal communication with a gate of the local from / to global input / output multiplexer for providing a gate signal of a first or second level in the presence of the output operation, and a gate signal of a third level in the presence of the input operation.

Owner:SAMSUNG ELECTRONICS CO LTD

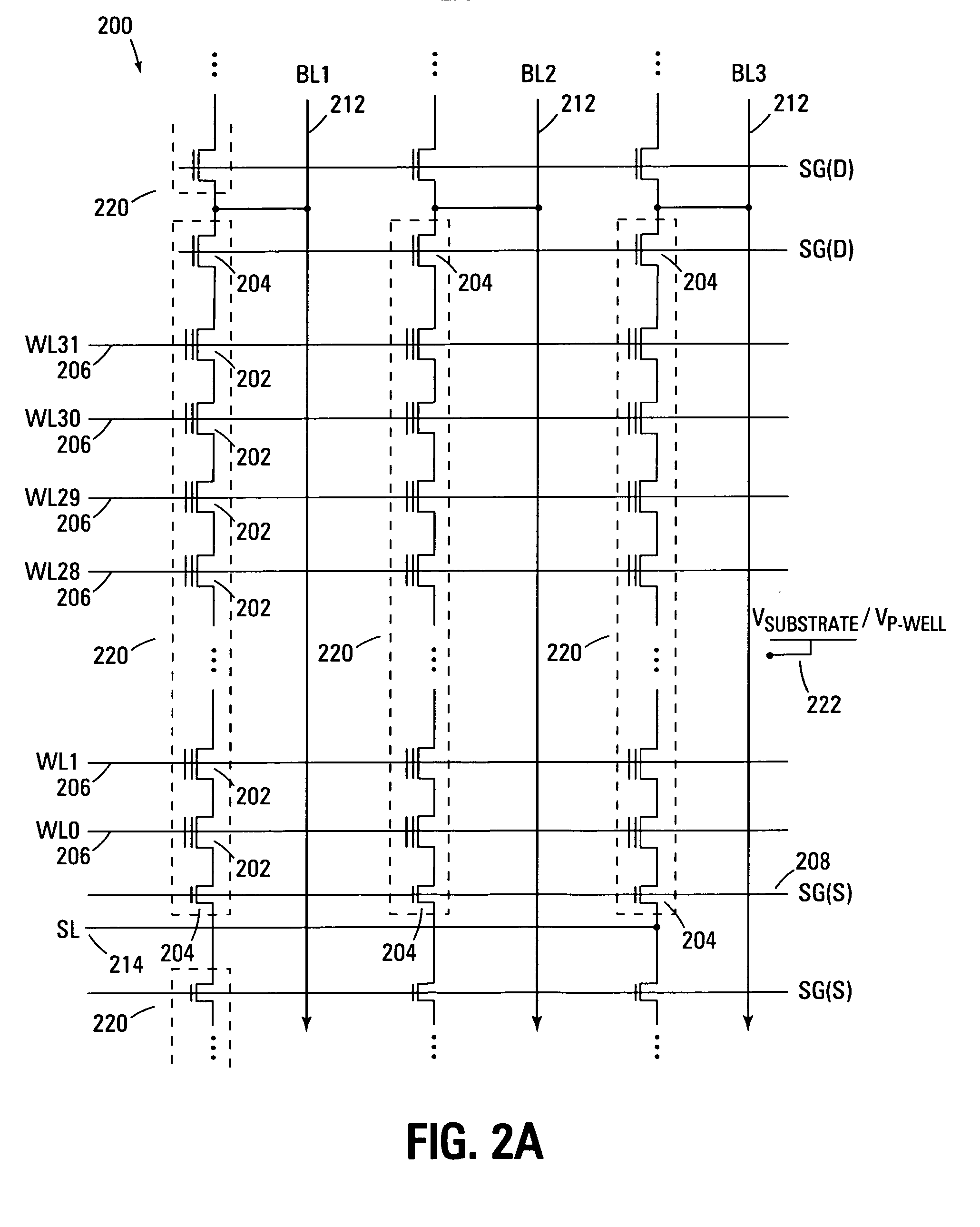

Flash memory cell and methods for programming and erasing

ActiveUS20060291282A1Facilitate device scaling effortsMitigates and avoids interface damageRead-only memoriesSemiconductor/solid-state device manufacturingElectricityElectrical battery

Owner:MONTEREY RES LLC

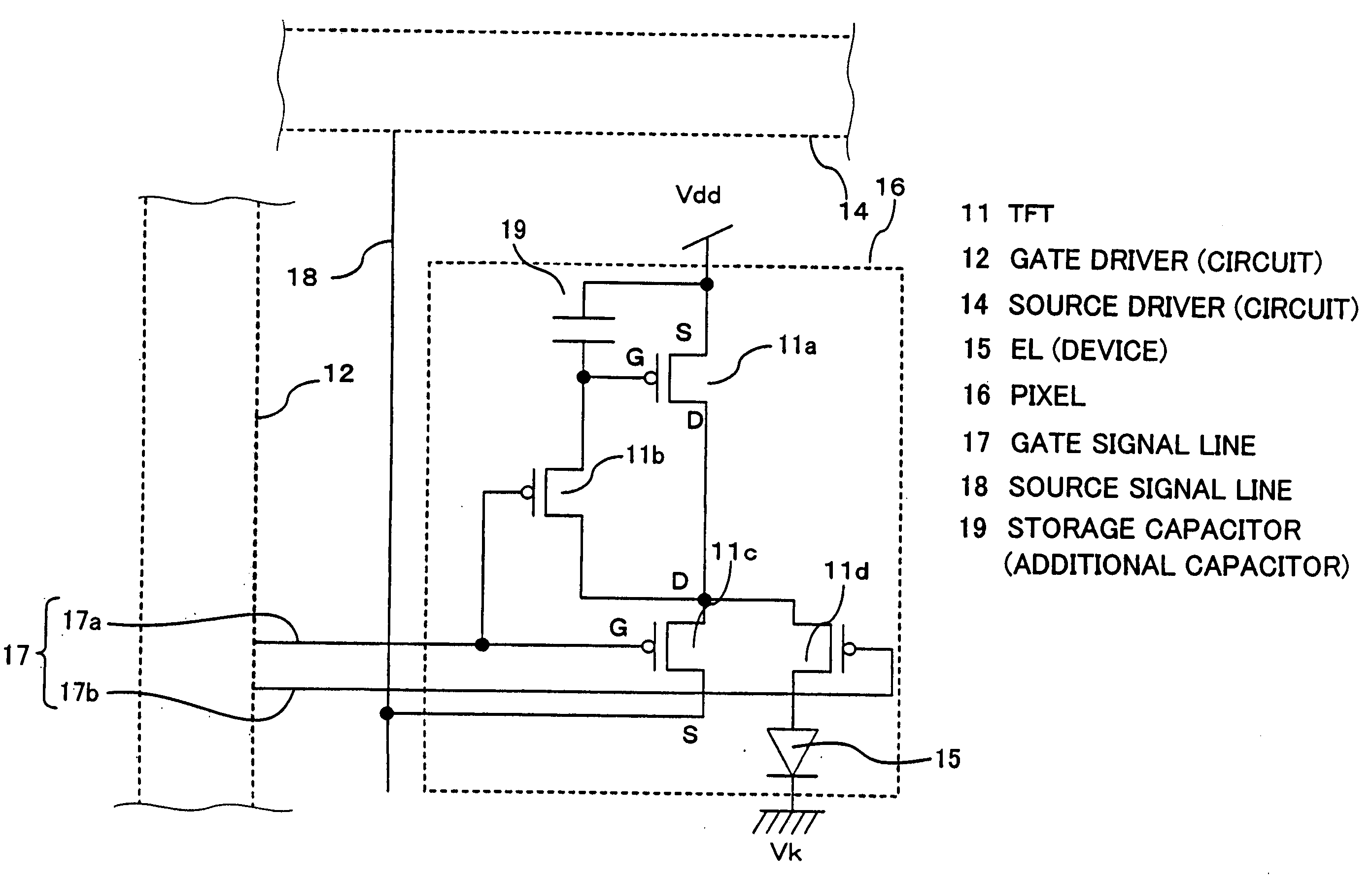

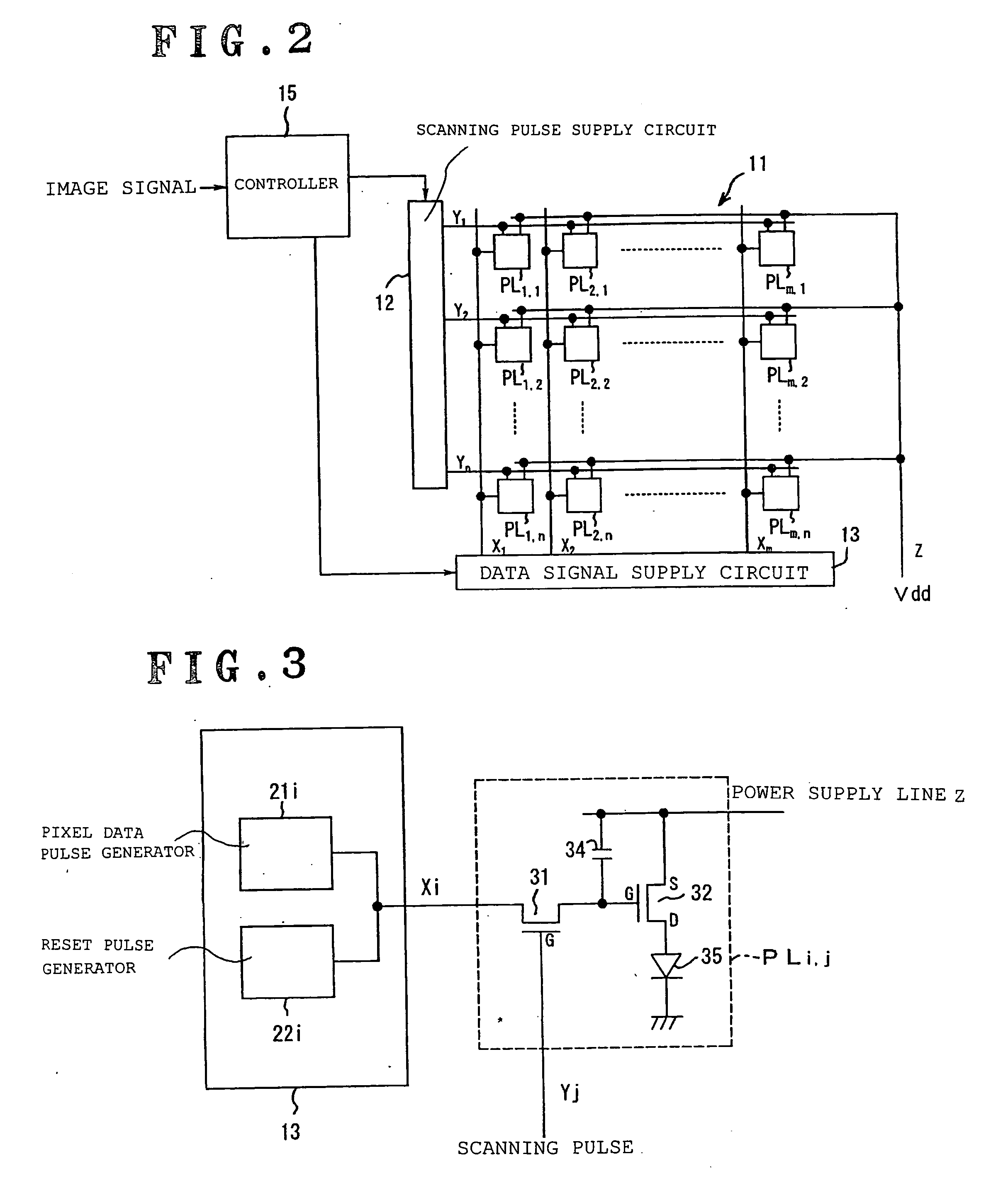

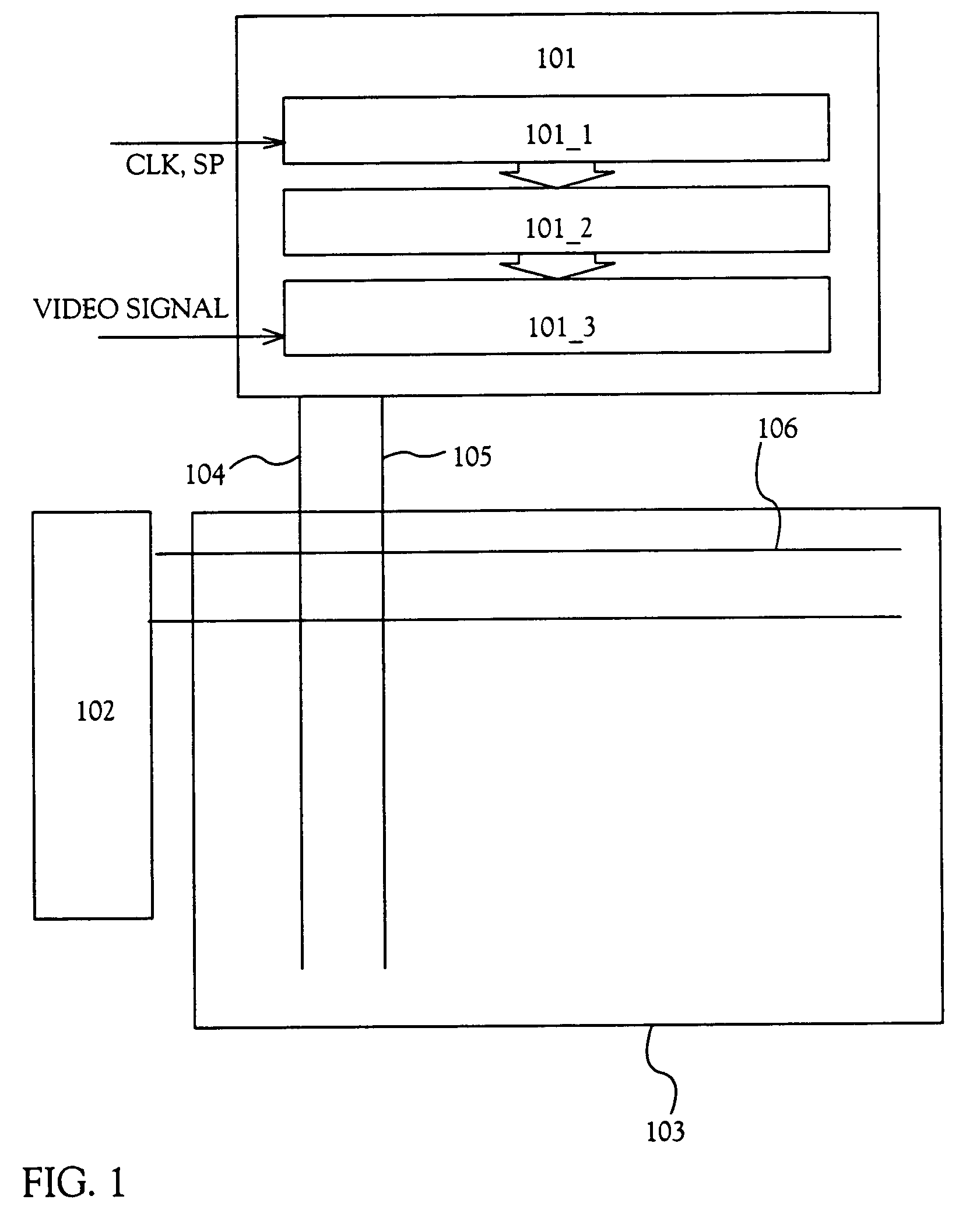

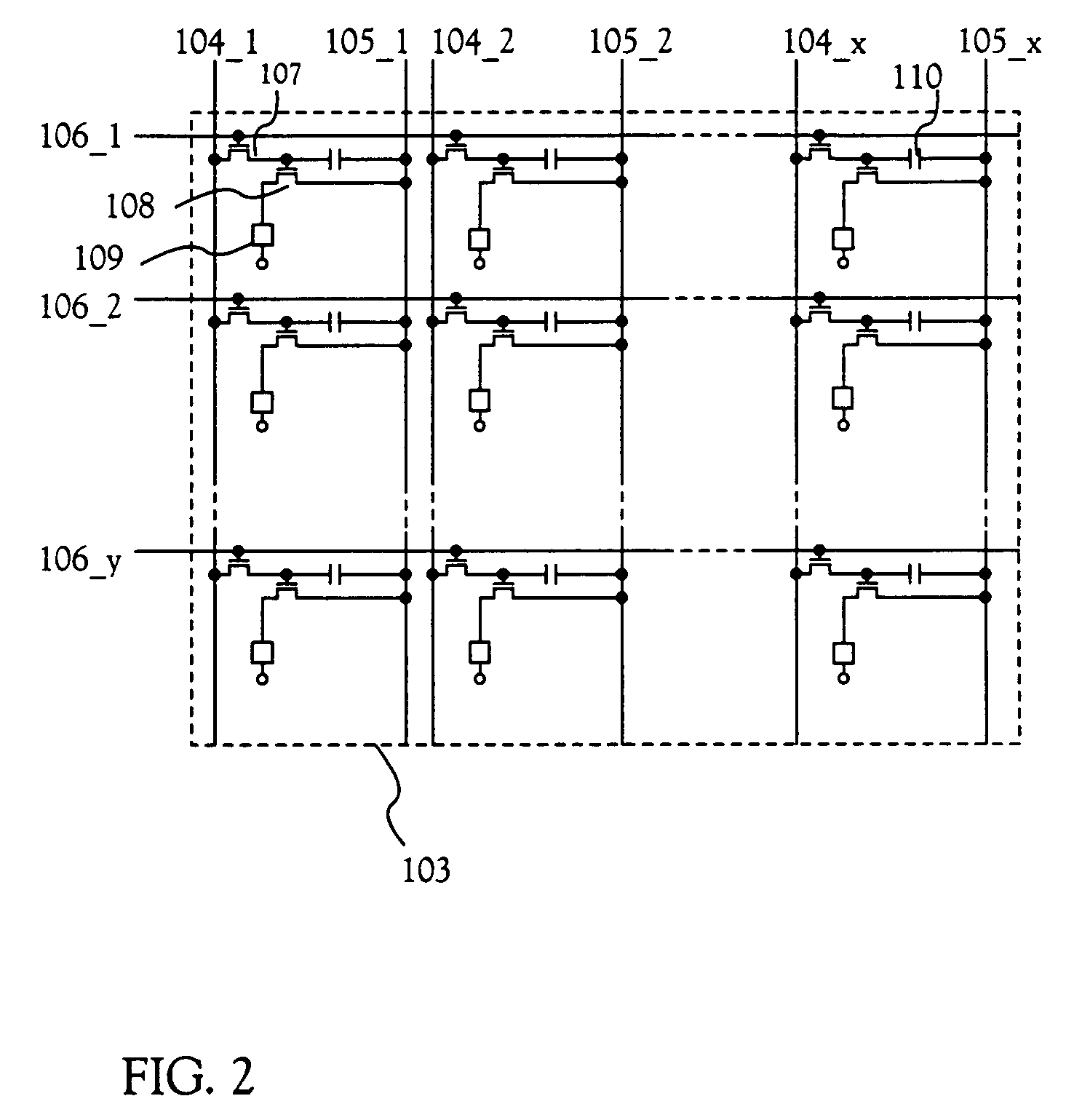

El display panel and el display apparatus comprising it

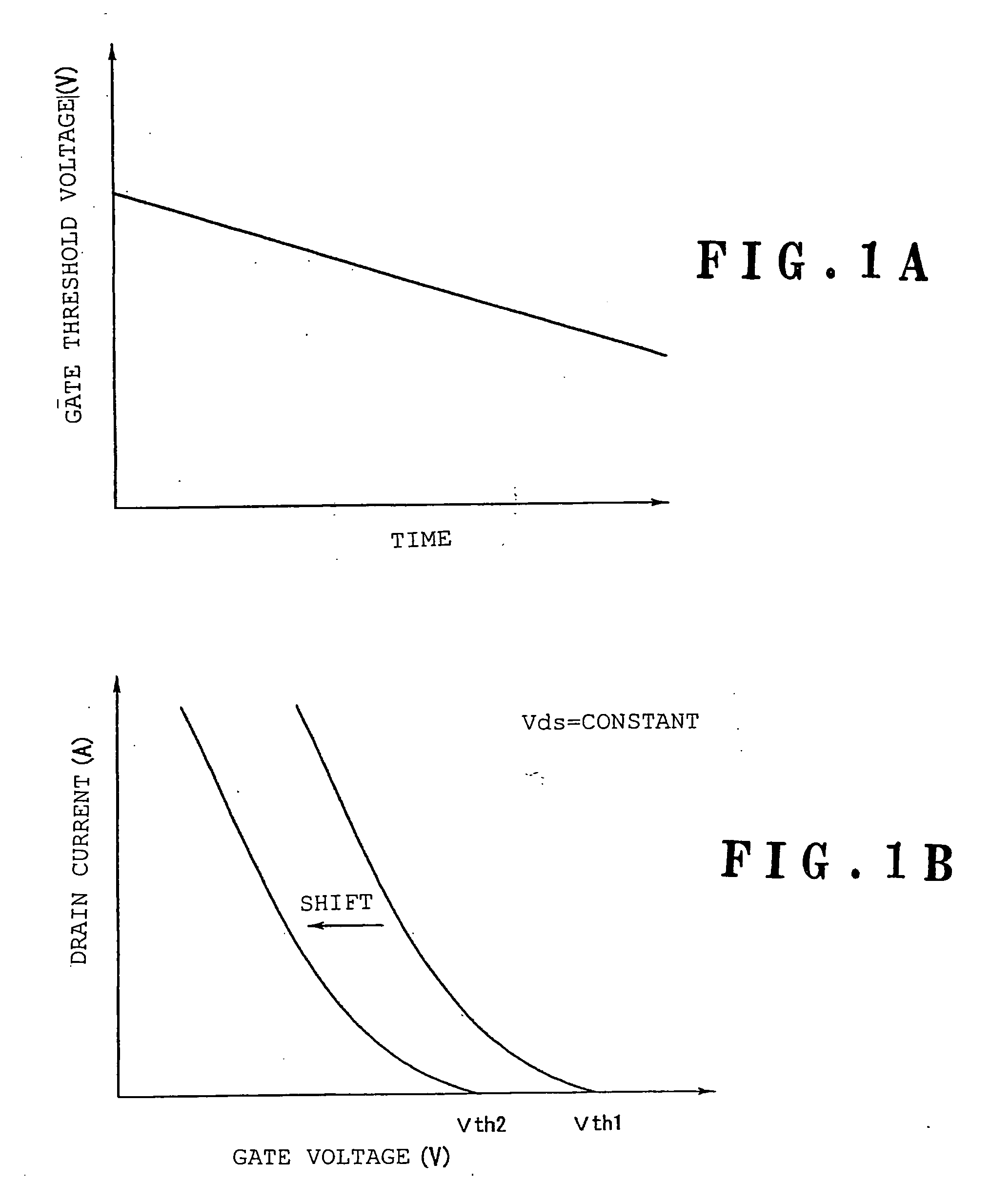

InactiveUS20050057580A1Quality improvementSuppress mutationSolid-state devicesCathode-ray tube indicatorsDisplay deviceGate voltage

In a source driver (14) provided in an electroluminescent (EL) display device of the present invention, the gate voltage of a first-stage current source formed by a transistor (631) is applied to the gate of a transistor (632a) which is a second-stage current source situated next to the transistor (631) and, as a result, a current flowing through the transistor (632a) is transferred to a transistor (632b) which is a second-stage current source. In addition, the gate voltage of the transistor (632b) is applied to the gate of a transistor (633a) which is a third-stage current source situated next to the transistor (632b) and, as a result, a current flowing through the transistor (633a) is transferred to a transistor (633b) which is a third-stage current source. The gate of the transistor (633b) is provided with a large number of current sources (634) corresponding to the number of bits required.

Owner:PANASONIC CORP

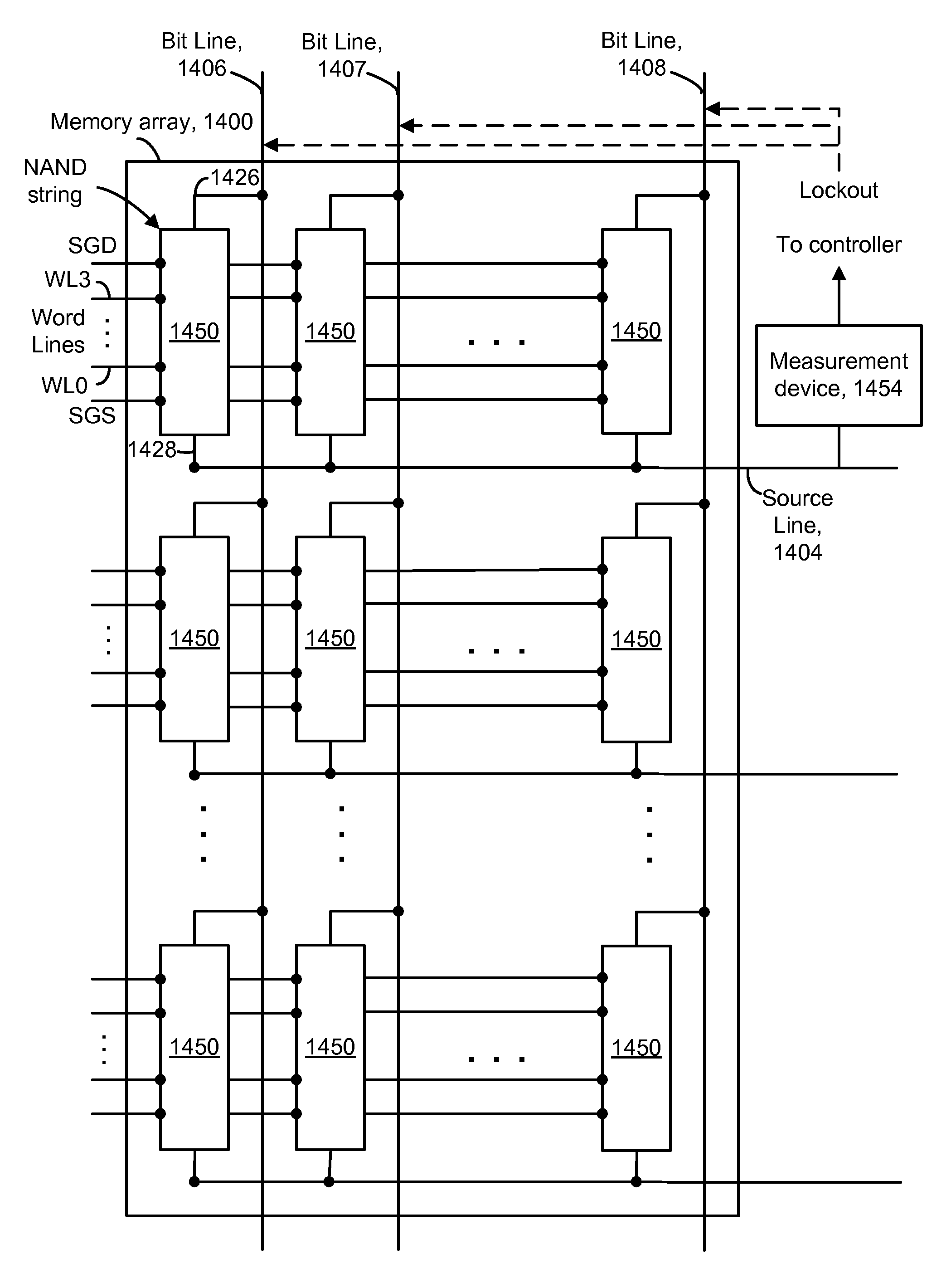

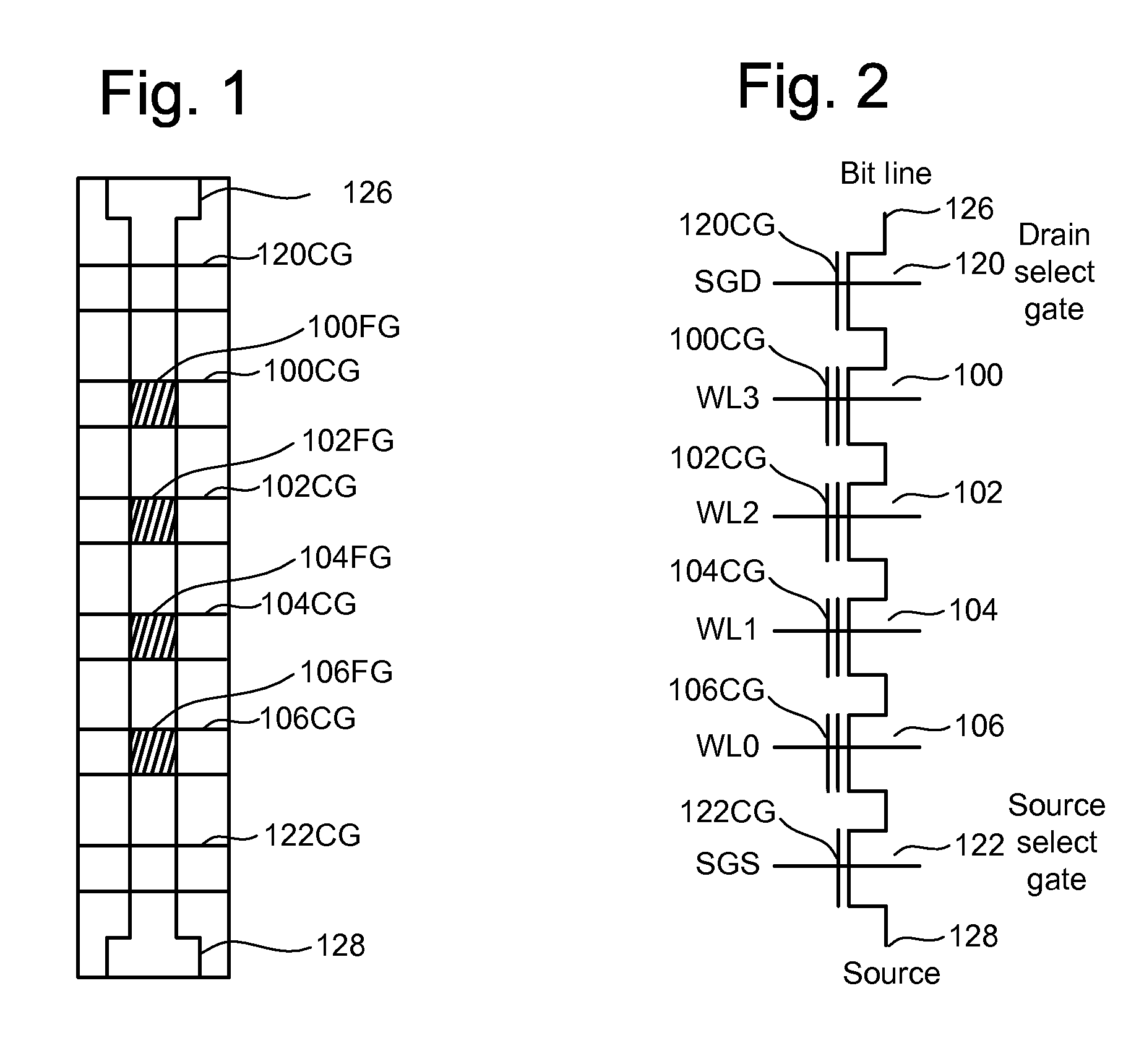

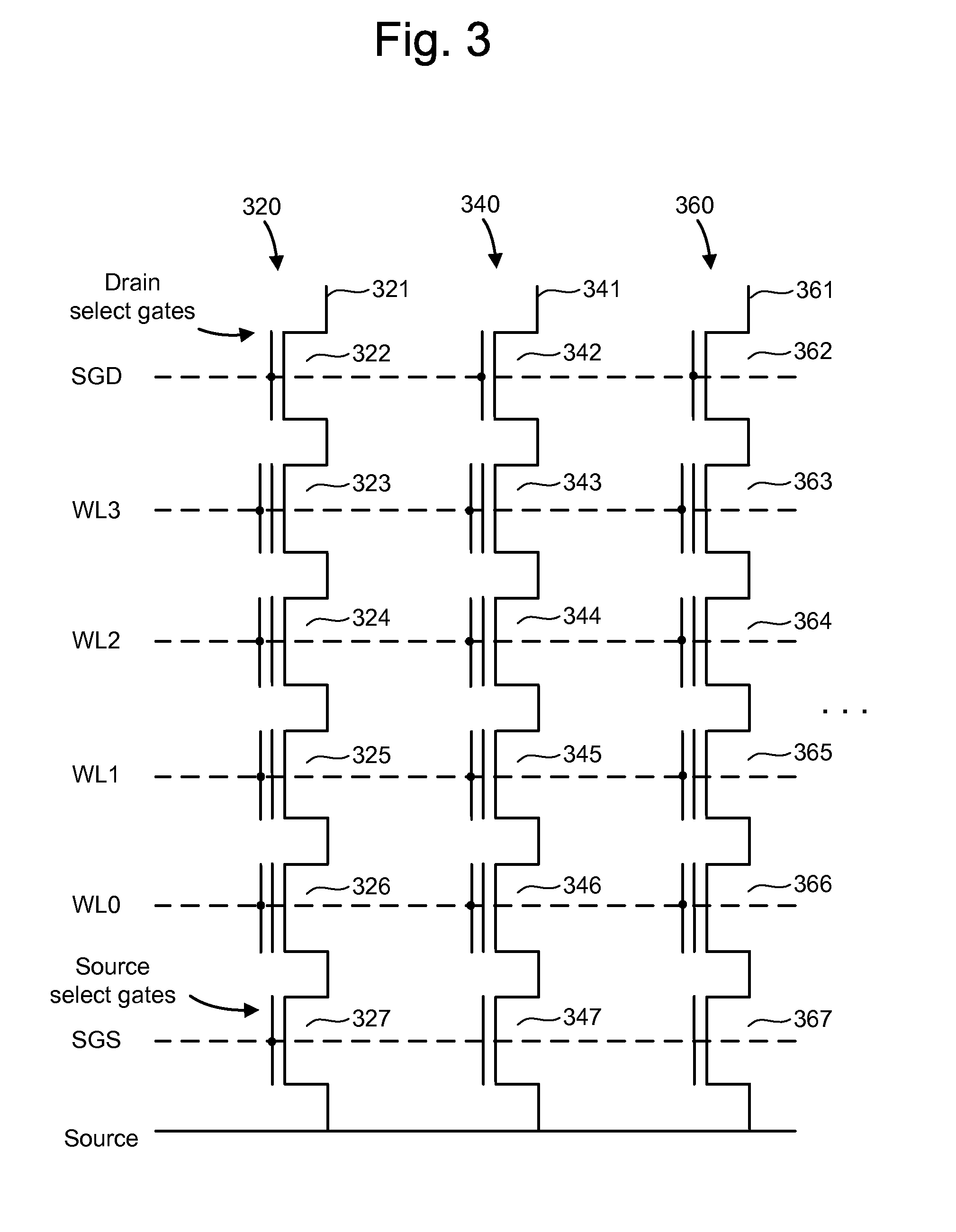

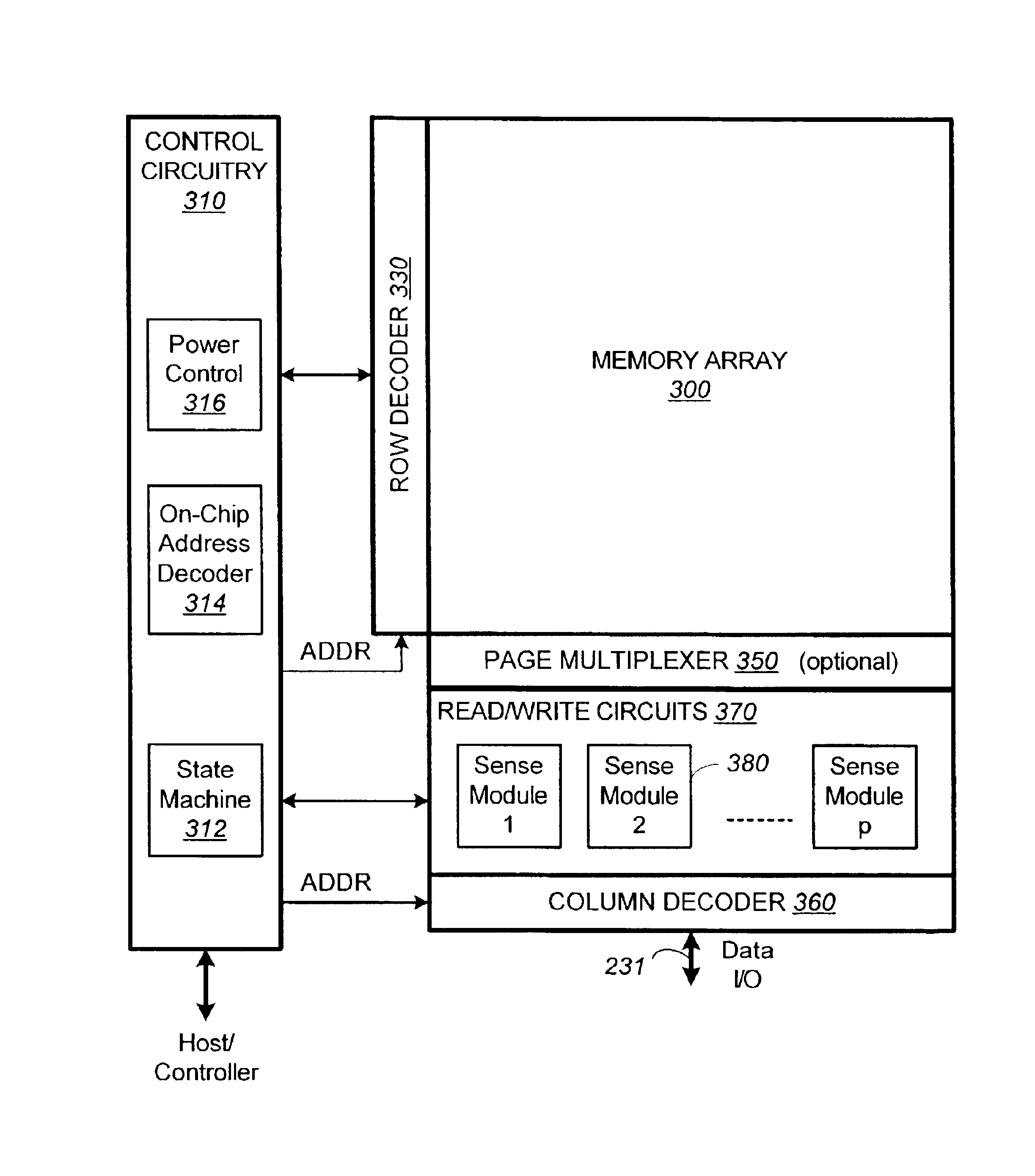

Measuring threshold voltage distribution in memory using an aggregate characteristic

ActiveUS20080285351A1Reduce errorsResistance/reactance/impedenceRead-only memoriesBit lineCapacitance

A threshold voltage distribution of a set of storage elements in a memory device is measured by sweeping a control gate voltage while measuring a characteristic of the set of storage elements as a whole. The characteristic indicates how many of the storage elements meet a given condition, such as being in a conductive state. For example, the characteristic may be a combined current, voltage or capacitance of the set which is measured at a common source of the set. The control gate voltage can be generated internally within a memory die. Similarly, the threshold voltage distribution can be determined internally within the memory die. Optionally, storage elements which become conductive can be locked out, such as by changing a bit line voltage, so they no longer contribute to the characteristic. New read reference voltages are determined based on the threshold voltage distribution to reduce errors in future read operations.

Owner:SANDISK CORP +1

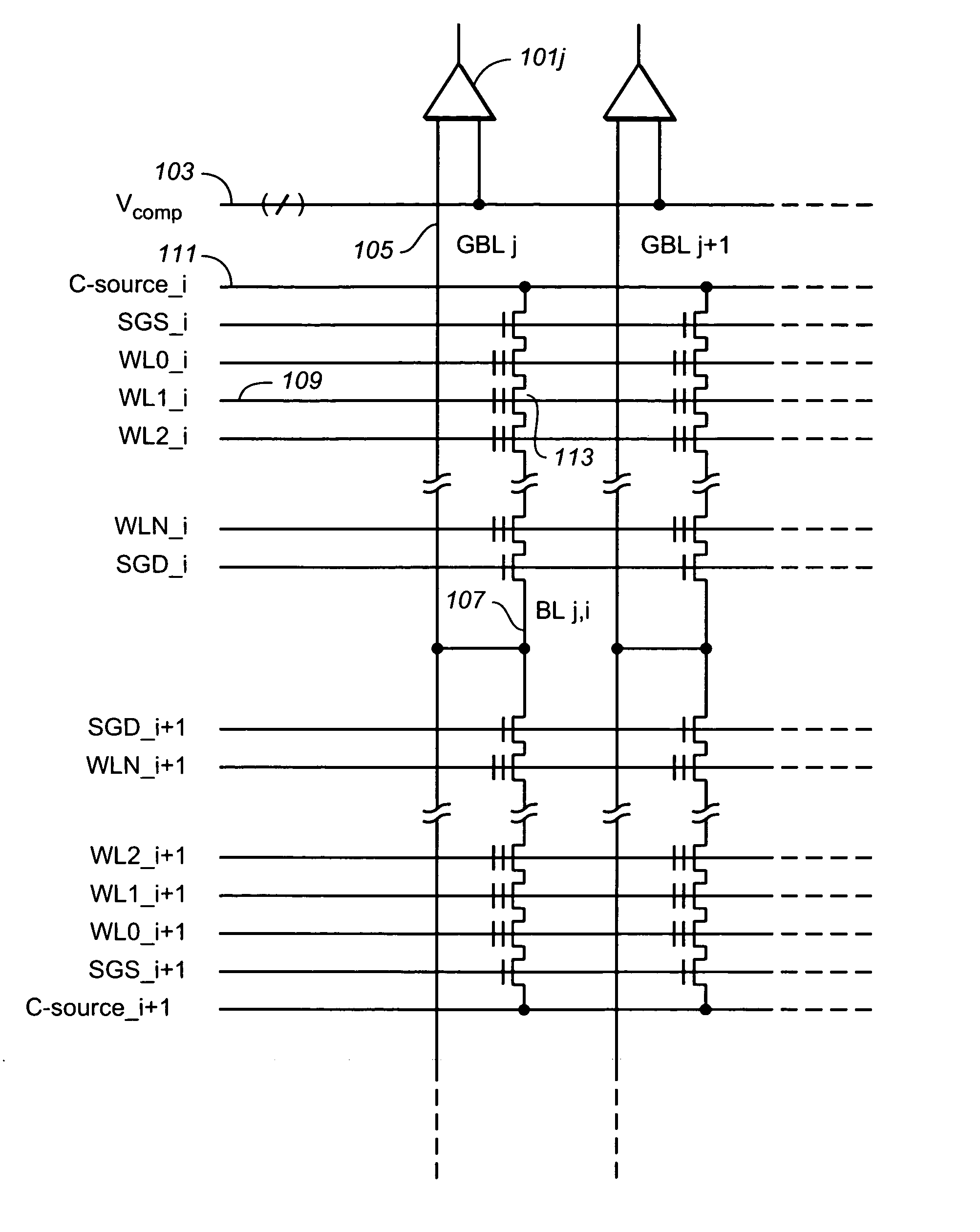

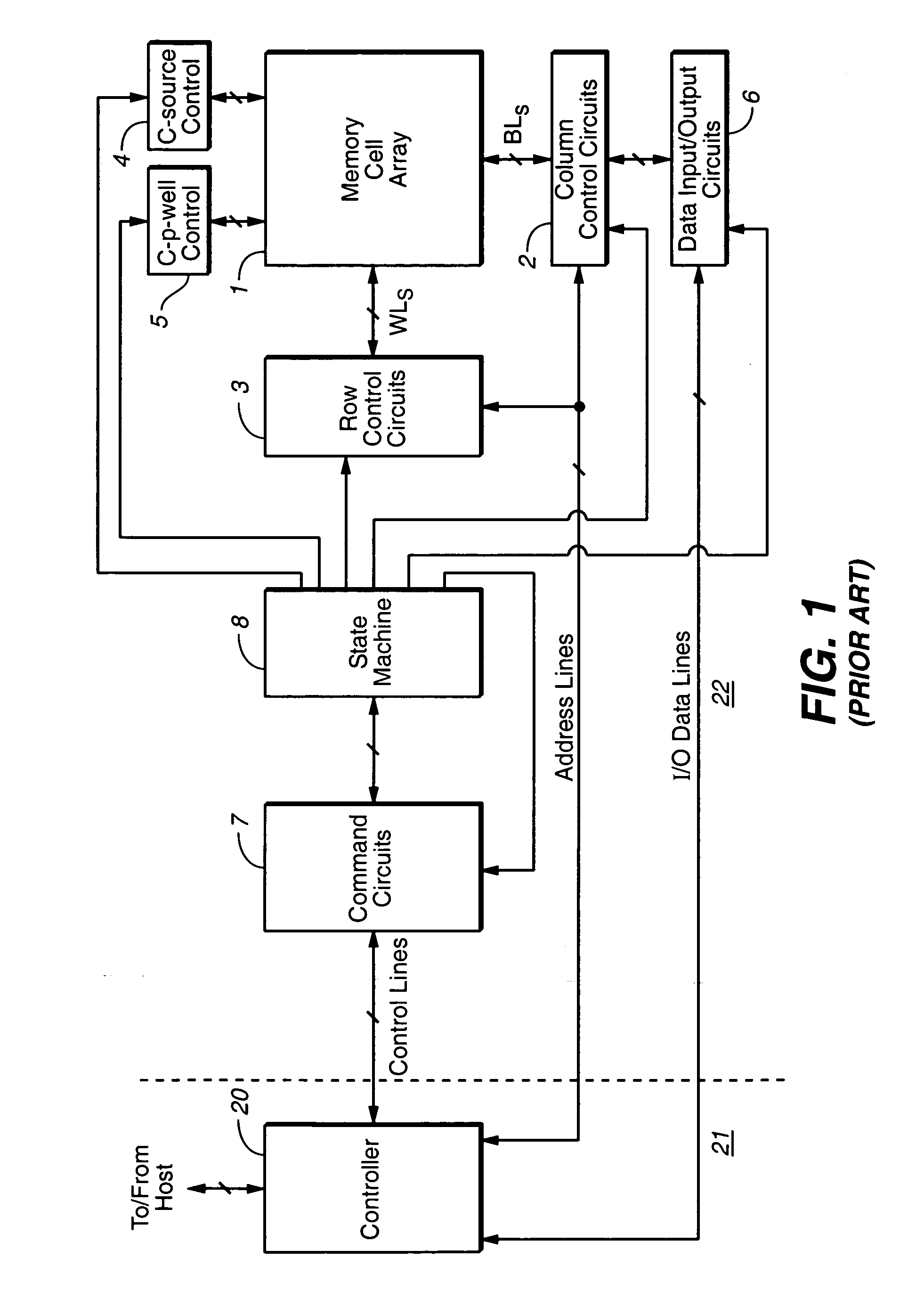

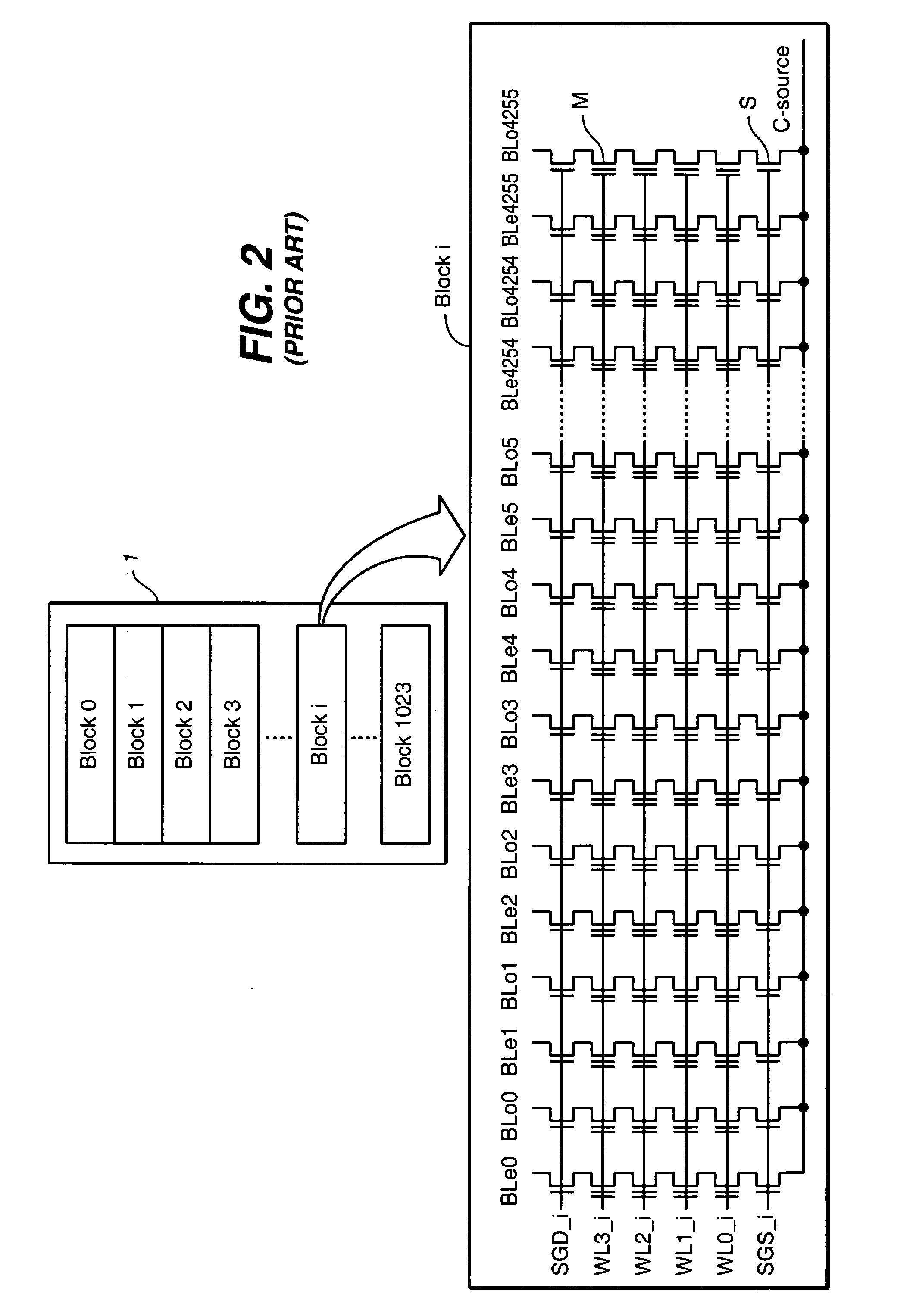

Non-volatile memory and method with reduced source line bias errors

ActiveUS7196931B2Large capacityImprove performanceRead-only memoriesDigital storageVoltage dropEngineering

Source line bias is an error introduced by a non-zero resistance in the ground loop of the read / write circuits. During sensing the control gate voltage of a memory cell is erroneously biased by a voltage drop across the resistance. This error is minimized when the current flowing though the ground loop is reduced. A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In this way, sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells.

Owner:SANDISK TECH LLC

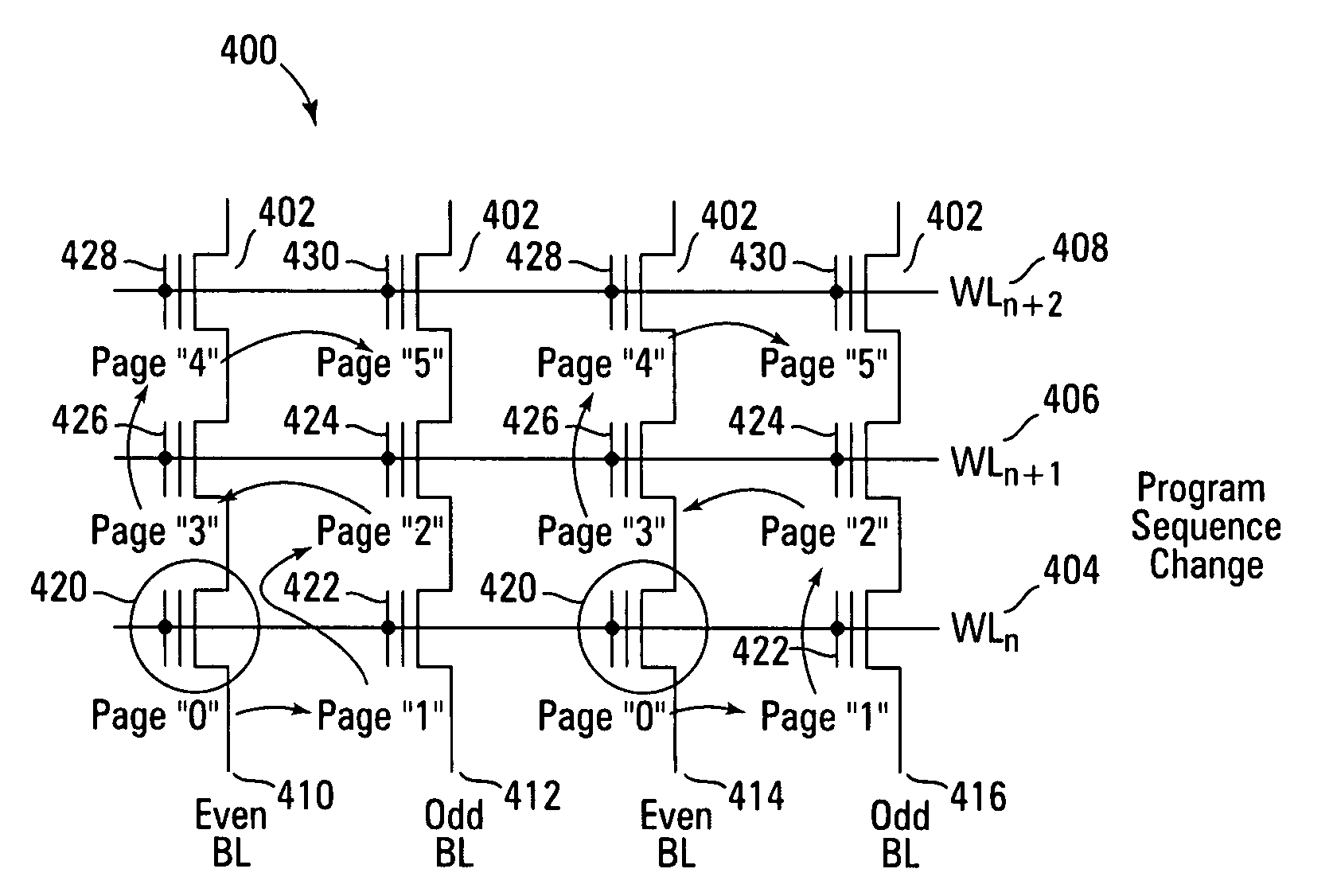

Programming method to reduce gate coupling interference for non-volatile memory

ActiveUS20070189073A1Reduce the impactReduce impactRead-only memoriesDigital storageGoal programmingEngineering

A non-volatile memory device and programming process is described that compensates for coupling effects on threshold gate voltages of adjacent floating gate or non-conductive floating node memory cells by adjusting the threshold voltage level programmed in view of the data being programmed on a following programming cycle into adjacent memory cells, so that the coupling effect results in the desired target threshold voltages for the cells. In one embodiment of the present invention, memory cell coupling is compensated for by adjusting programming level of one or more memory cells of a first page a memory array to a higher or lower threshold verify target voltage given the data / programming level to be written to directly adjacent memory cells of a second page, so that coupling between the directly adjacent memory cells of the first and second pages brings the memory cells of first page to their final target programming level.

Owner:MICRON TECH INC

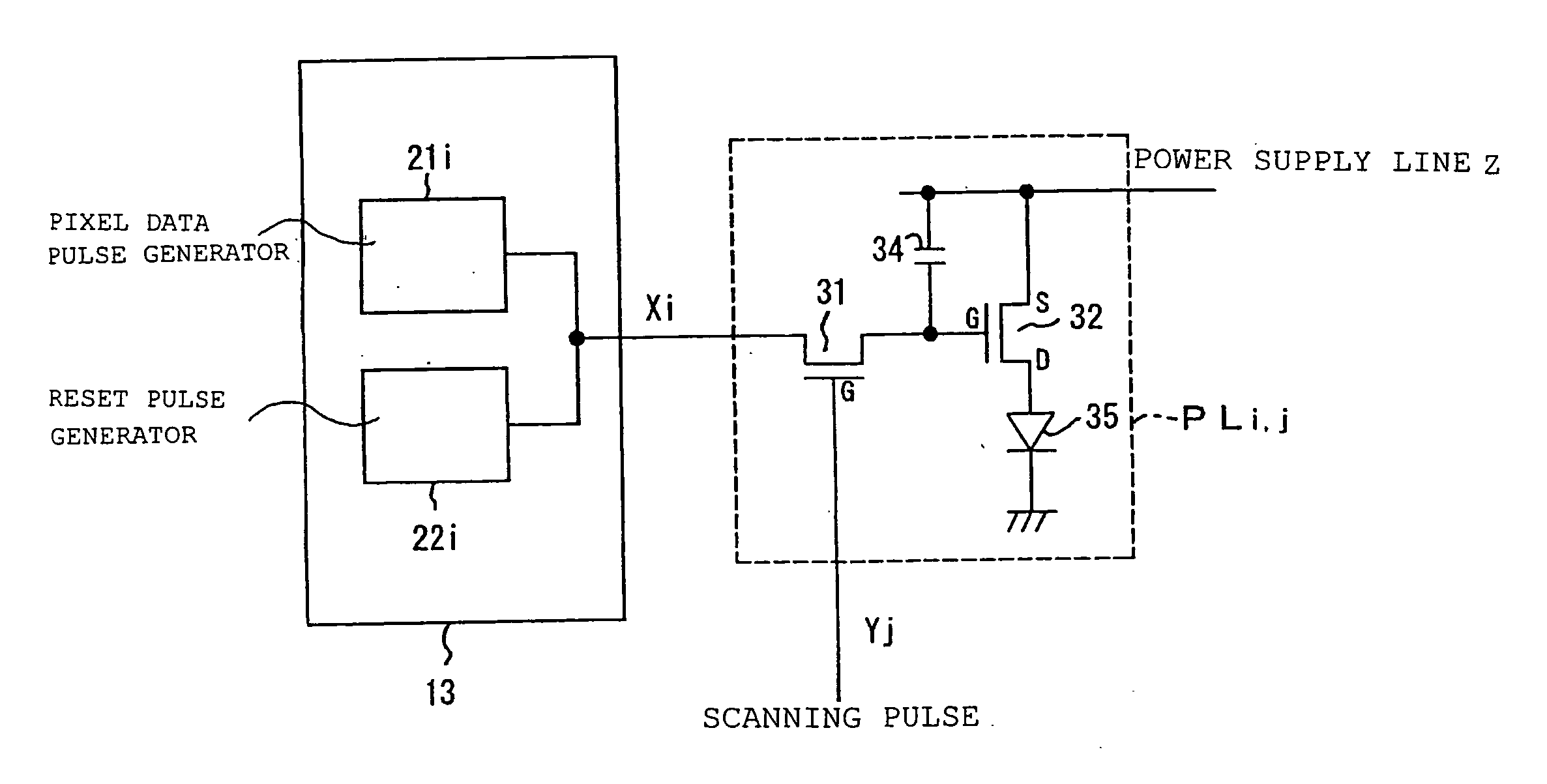

Display apparatus with active matrix display panel, and method for driving same

InactiveUS20070080906A1Suppressing gate stressPrevent display quality degradationStatic indicating devicesActive matrixElectrical polarity

A display apparatus with an active matrix display panel which can suppress gate stress to prevent a degradation of the display quality. Specified at least one pixel section having a light emitting element to driven for light emission in one row is supplied with a data pulse indicative of a first gate voltage of a thin film transistor upon supply of a display scanning pulse. Subsequently, each pixel in the one row is supplied with a reset scanning pulse, and when supplying a reset scanning pulse, the at least one pixel section is supplied with a reset pulse indicative of a second gate voltage of the thin film transistor for making the polarity of agate-to-source voltage or gate-to-drain voltage of the thin film transistor reverse to that during light emission driving.

Owner:PIONEER CORP

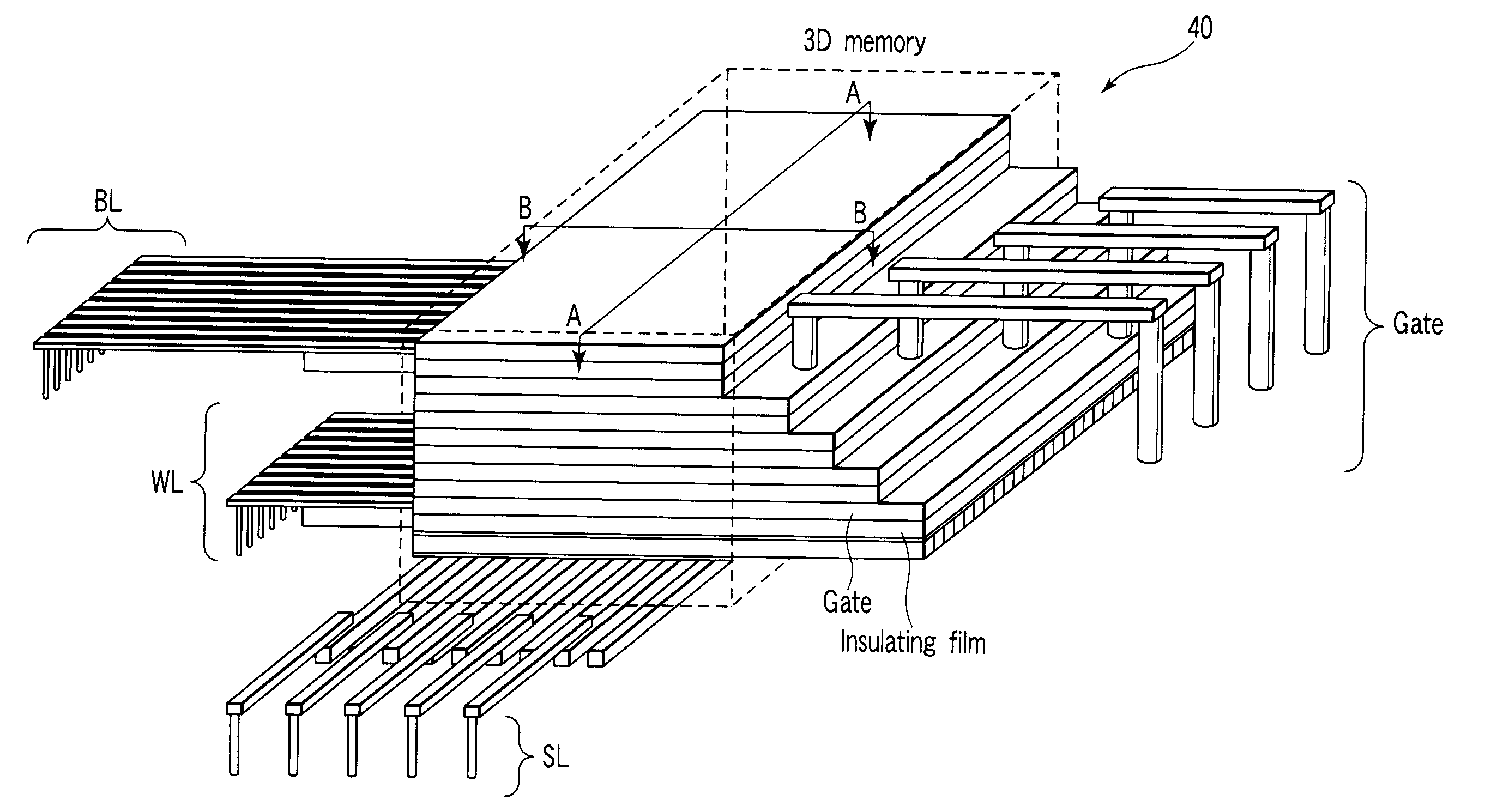

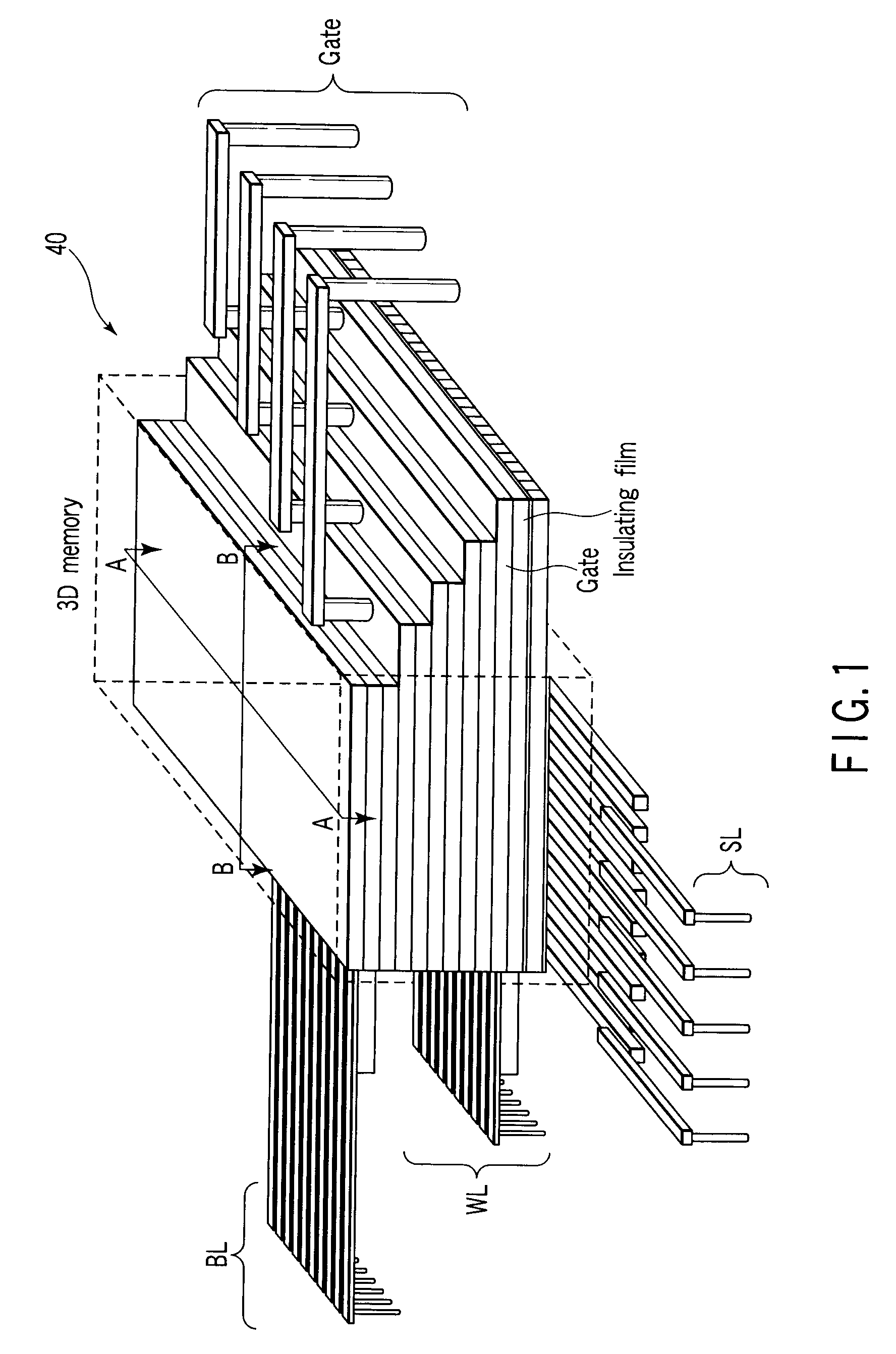

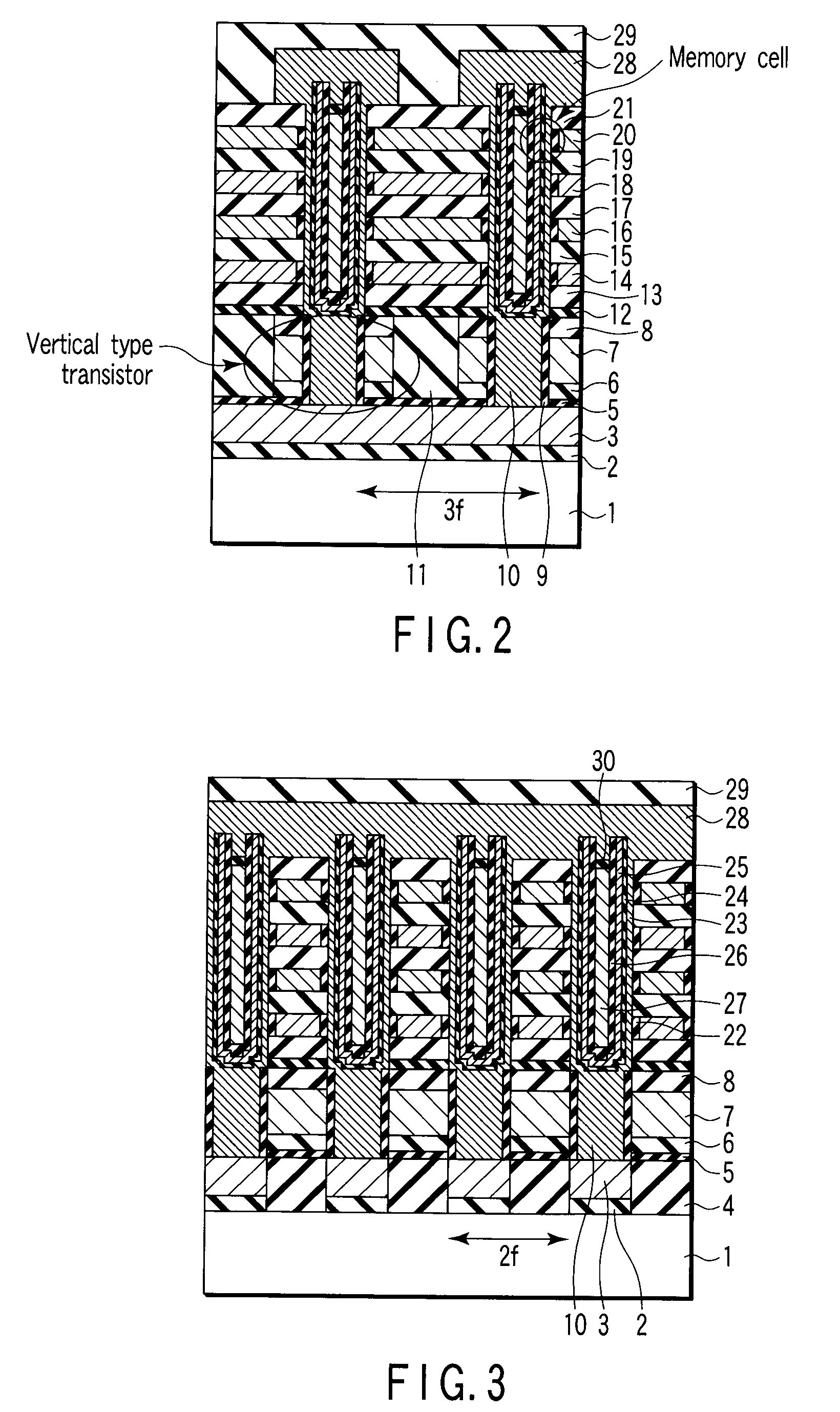

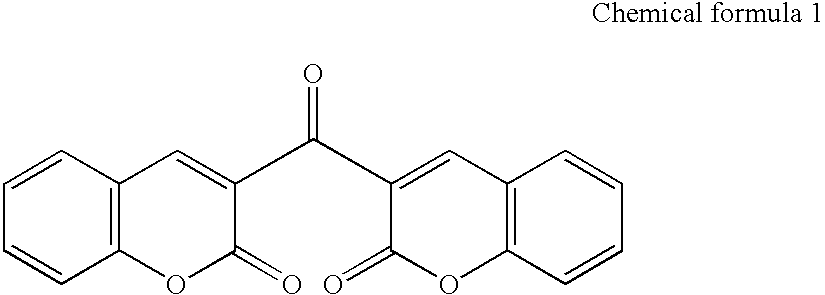

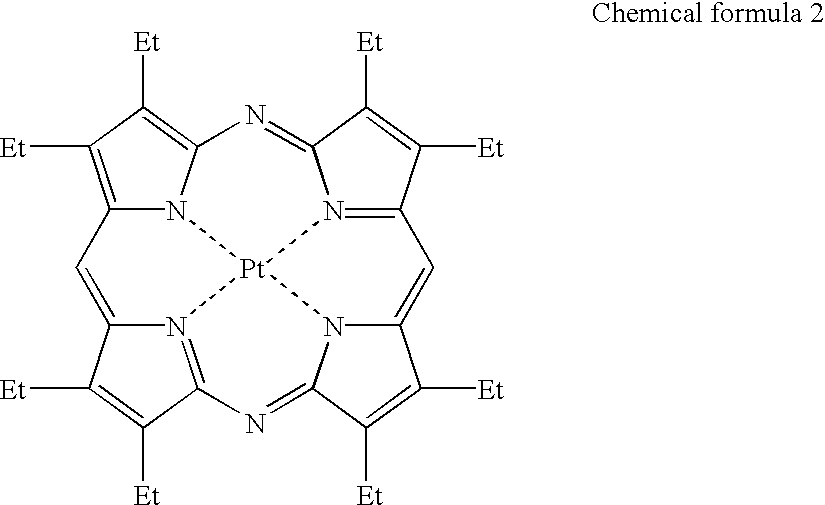

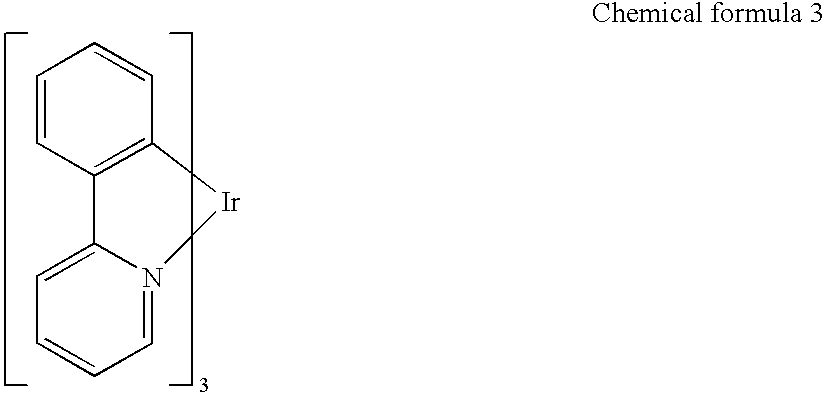

Semiconductor memory device and method of manufacturing the same

InactiveUS20080149913A1Solid-state devicesSemiconductor/solid-state device manufacturingGate voltageSemiconductor

A semiconductor memory device is disclosed, which includes a first memory cell array formed on a semiconductor substrate and composed of a plurality of memory cells stacked in layers each having a characteristic change element and a vertical type memory cell transistor connected in parallel to each other, a plurality of second memory cell arrays formed on the semiconductor substrate and having the same structure as the first memory cell array, and arranged in an X direction with respect to the first memory cell array, and a plurality of third memory cell arrays formed on the semiconductor substrate and having the same structure as the first memory cell array, and arranged in a Y direction with respect to the first memory cell array, wherein a gate voltage is applied to gates of the vertical type memory cell transistors of the first to third memory cell arrays in a same layer.

Owner:KK TOSHIBA

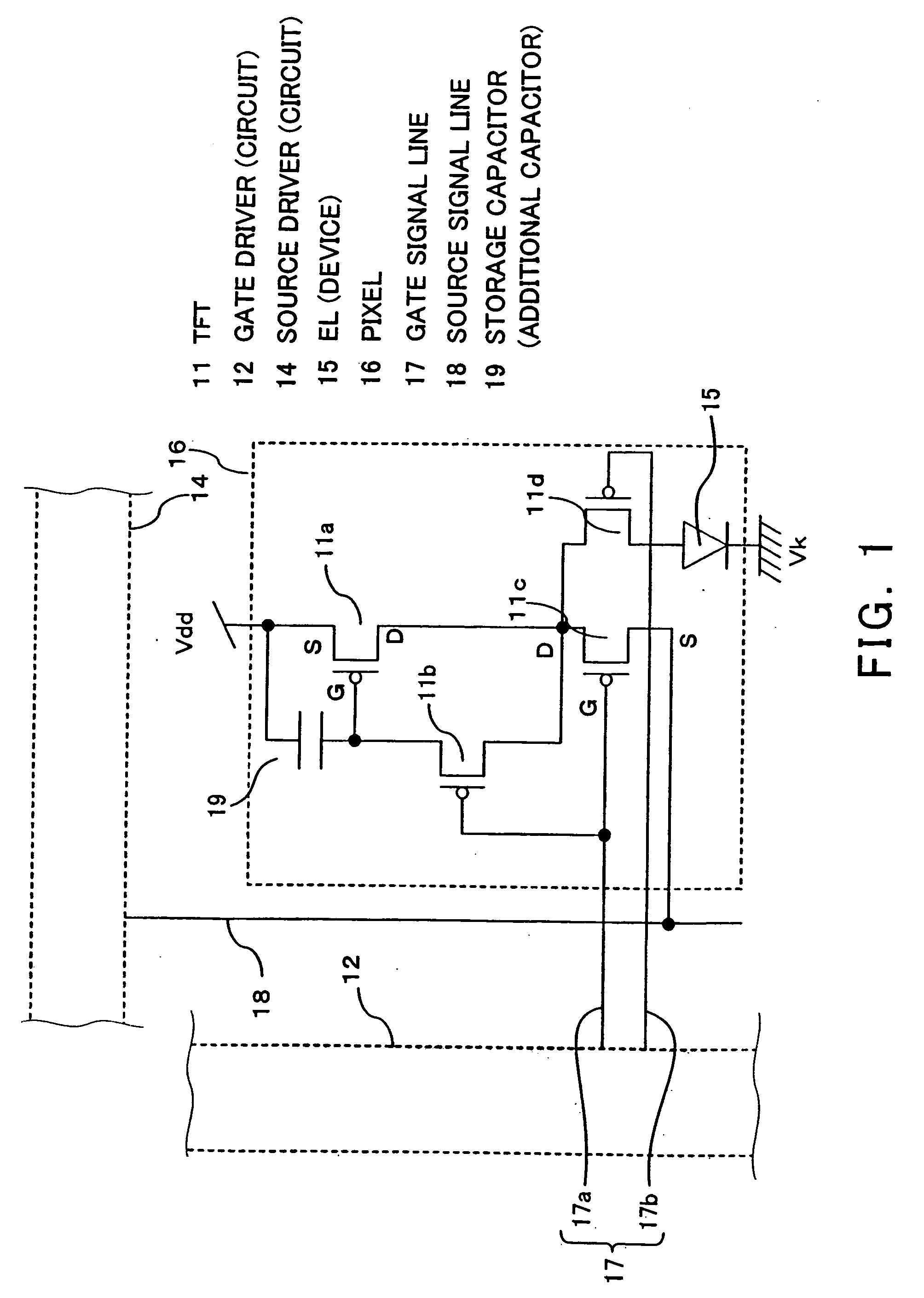

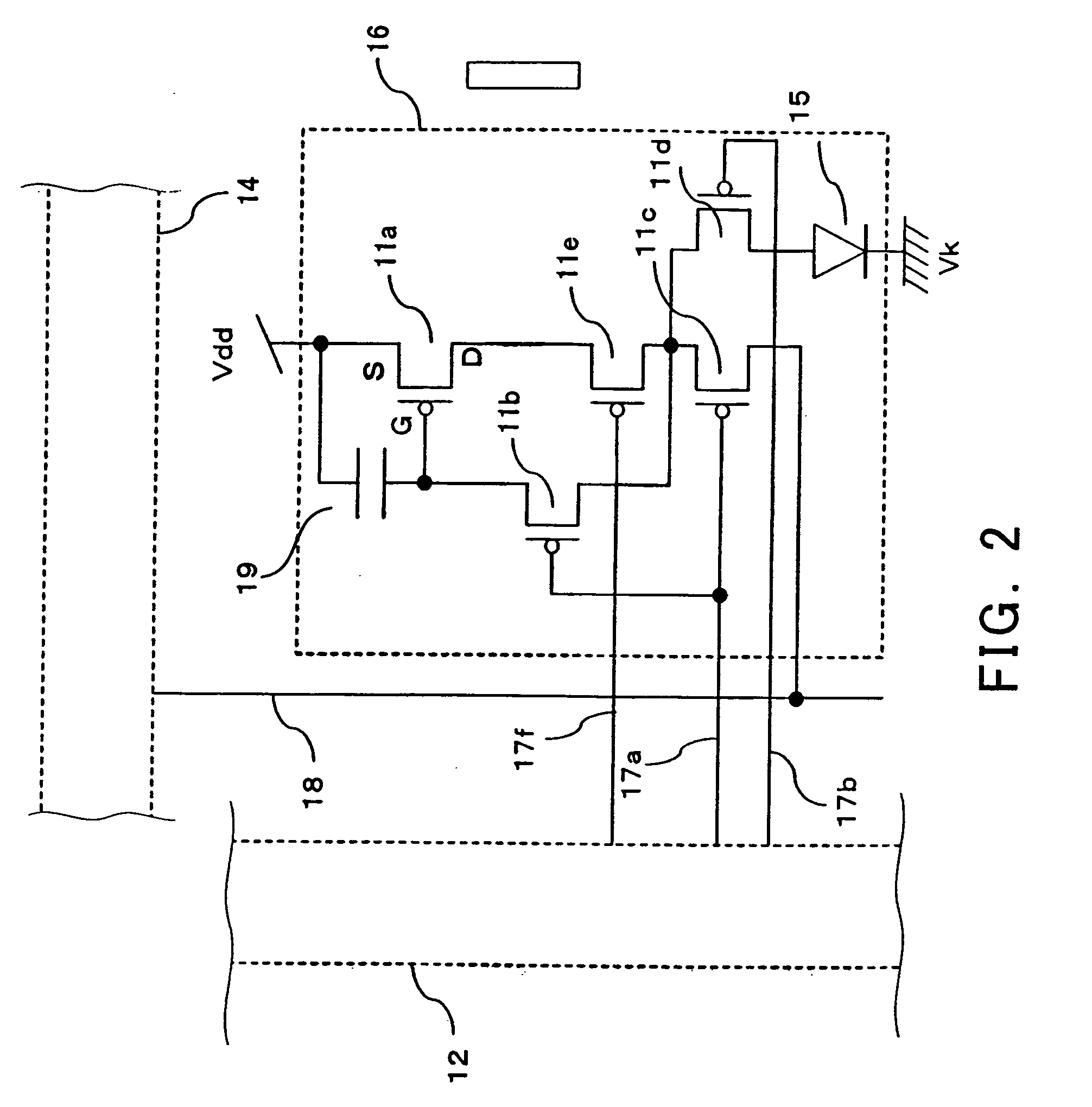

Light emitting device

InactiveUS20020104995A1Solid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

A light emitting device is provided which can prevent a change in gate voltage due to leakage or other causes and at the same time can prevent the aperture ratio from lowering. A capacitor storage is formed from a connection wiring line, an insulating film, and a capacitance wiring line. The connection wiring line is formed over a gate electrode and an active layer of a TFT of a pixel, and is connected to the active layer. The insulating film is formed on the connection wiring line. The capacitance wiring tine is formed on the insulating film. This structure enables the capacitor storage to overlap the TFT, thereby increasing the capacity of the capacitor storage while keeping the aperture ratio from lowering. Accordingly, a change in gate voltage due to leakage or other causes can be avoided to prevent a change in luminance of an OLED and flickering of screen in analog driving.

Owner:SEMICON ENERGY LAB CO LTD

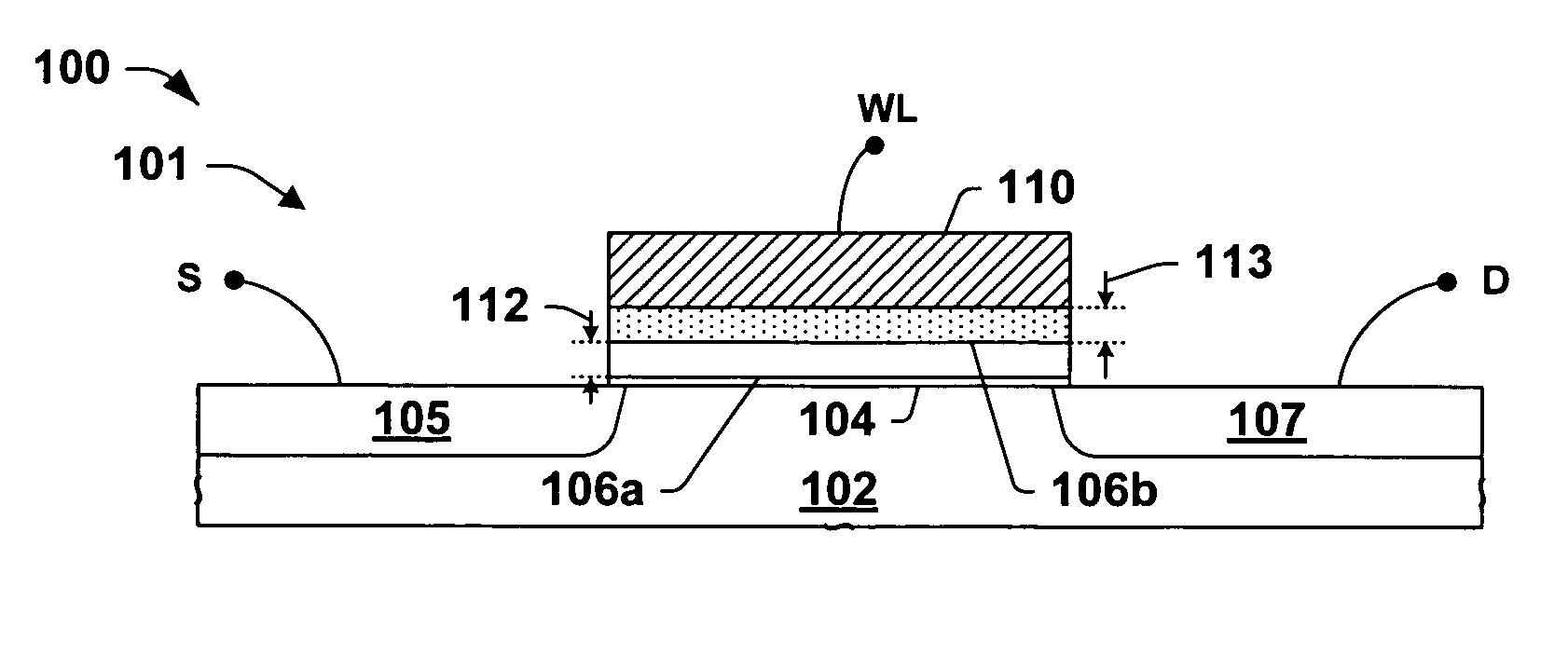

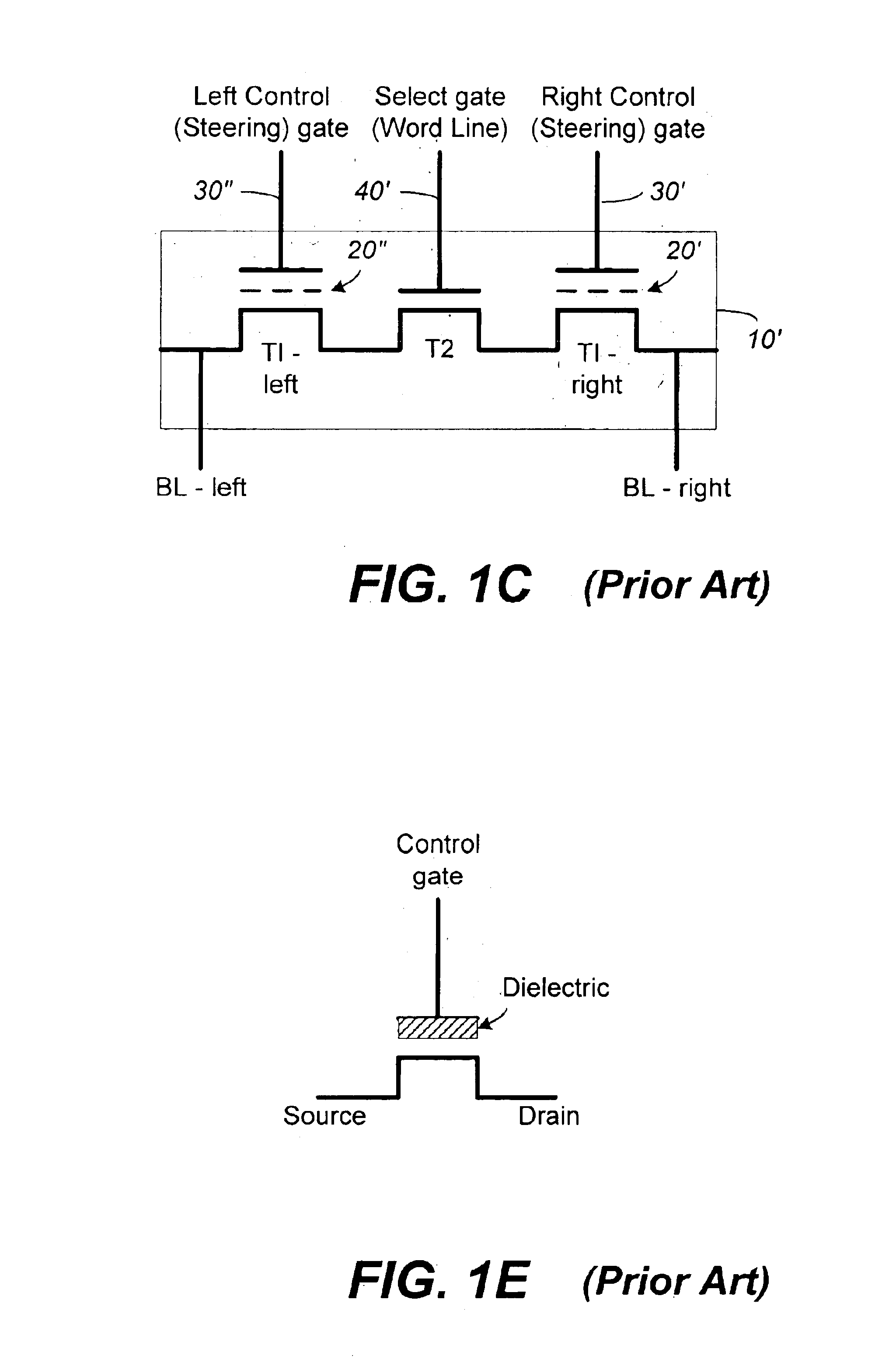

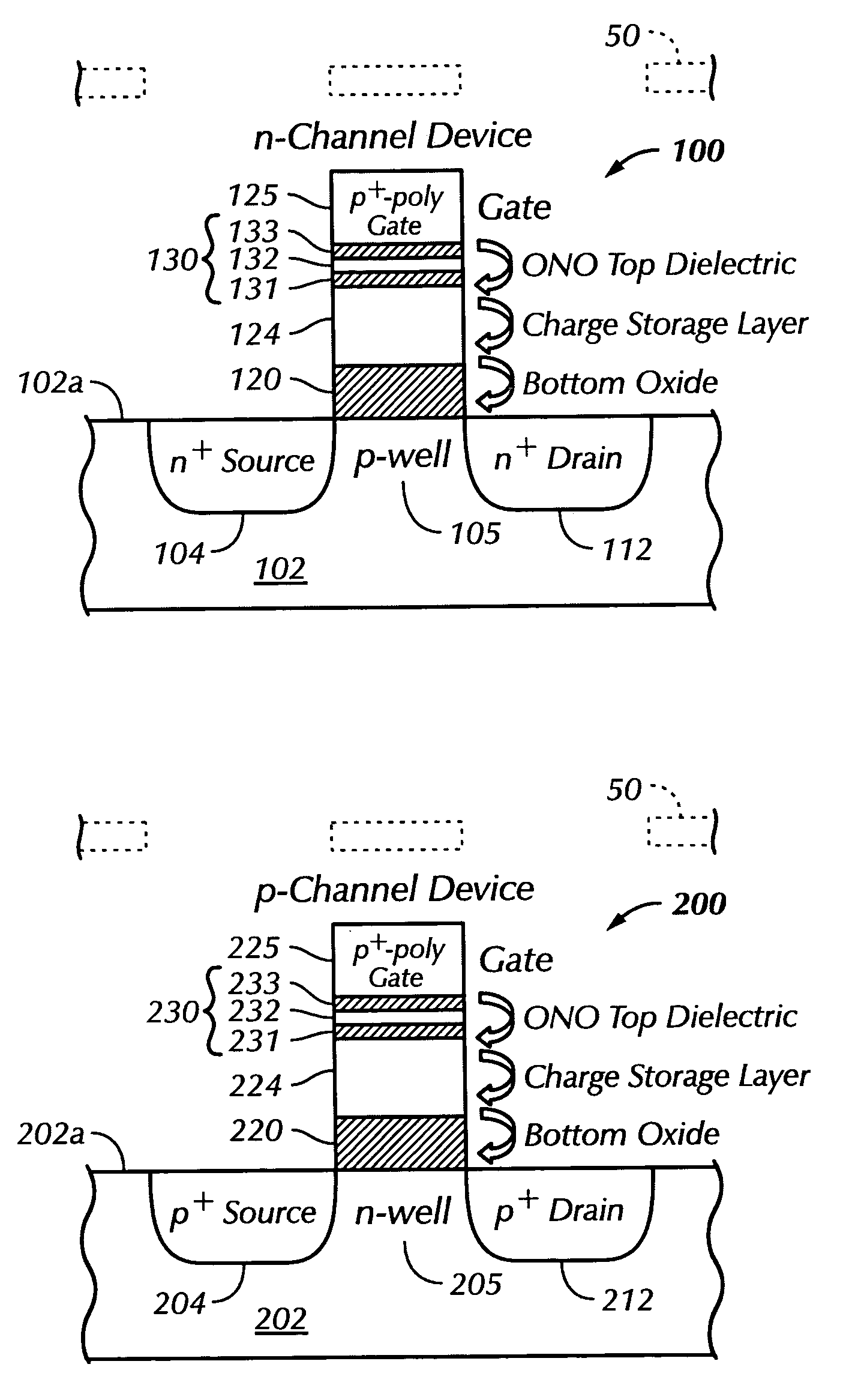

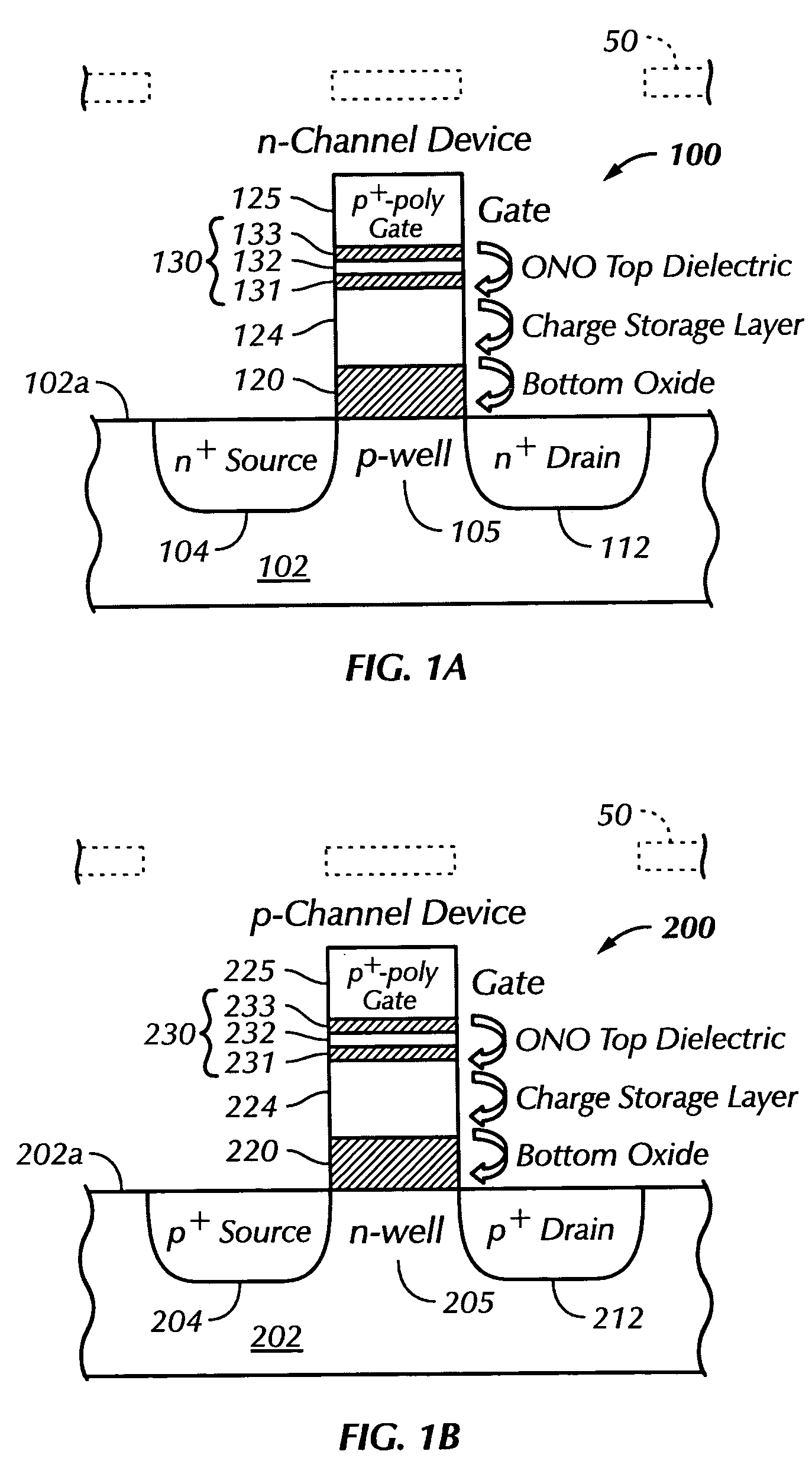

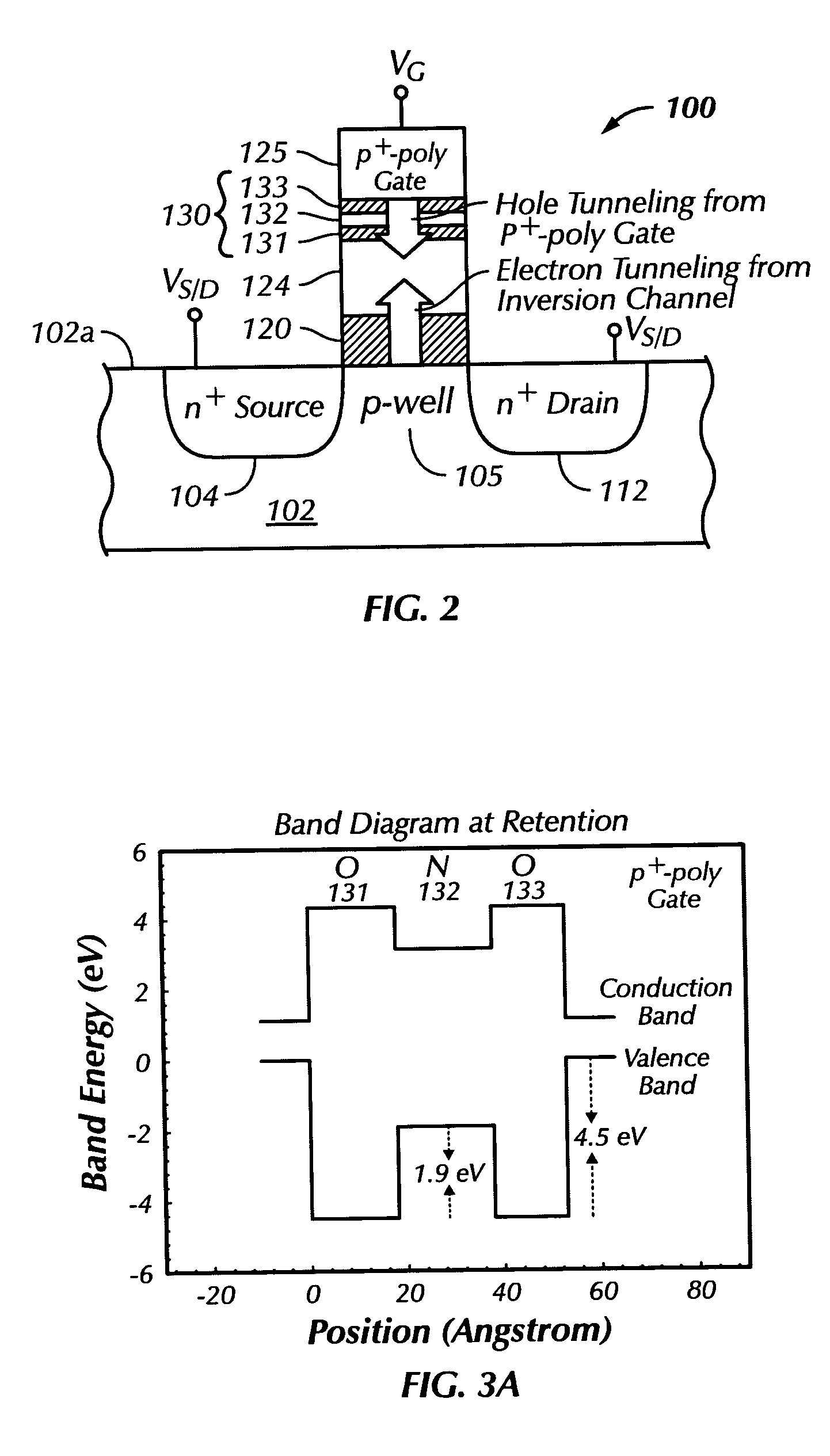

Non-volatile memory semiconductor device having an oxide-nitride-oxide (ONO) top dielectric layer

ActiveUS20070029625A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialGate voltage

A non-volatile memory (NVM) cell includes a silicon substrate having a main surface, a source region in a portion of the silicon substrate, a drain region in a portion of the silicon substrate, and a well region disposed in a portion of the silicon substrate between the source and drain regions The cell includes a bottom oxide layer formed on the main surface of the substrate. The bottom oxide layer is disposed on a portion of the main surface proximate the well region. The cell includes a charge storage layer disposed above the bottom oxide layer, a dielectric tunneling layer disposed above the charge storage layer and a control gate formed above the dielectric tunneling layer. The dielectric tunneling layer includes a first oxide layer, a nitride layer and a second oxide layer. Erasing the NVM cell includes applying a positive gate voltage to inject holes from the gate.

Owner:MACRONIX INT CO LTD

Field-effect transistor and method for fabricating the same

ActiveUS20060273347A1Small gateHigh currentSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactOptoelectronics

An AlN buffer layer, an undoped GaN layer, an undoped AlGaN layer, a p-type GaN layer and a heavily doped p-type GaN layer are formed in this order. A gate electrode forms an Ohmic contact with the heavily doped p-type GaN layer. A source electrode and a drain electrode are provided on the undoped AlGaN layer. A pn junction is formed in a gate region by a two dimensional electron gas generated at an interface between the undoped AlGaN layer and the undoped GaN layer and the p-type GaN layer, so that a gate voltage can be increased.

Owner:PANASONIC CORP

Impedance matching circuit for current regulation of solid state lighting

ActiveUS7656103B2Low component requirementsElectrical apparatusElectroluminescent light sourcesElectrical resistance and conductanceTRIAC

Owner:CHEMTRON RES

Thin film memory, array, and operation method and manufacture method therefor

A memory cell which is formed on a fully depleted SOI or other semiconductor thin film and which operates at low voltage without needing a conventional large capacitor is provided as well as a memory cell array. The semiconductor thin film is sandwiched between first and second semiconductor regions which face each other across the semiconductor thin film and which have a first conductivity type. A third semiconductor region having the opposite conductivity type is provided in an extended portion of the semiconductor thin film. From the third semiconductor region, carriers of the opposite conductivity type are supplied to and accumulated in the semiconductor thin film portion to change the gate threshold voltage of a first conductivity type channel that is induced by a first conductive gate voltage in the semiconductor thin film between the first and second semiconductor regions through an insulating film.

Owner:HAYASHI YUTAKA +1

Alternate sensing techniques for non-volatile memories

ActiveUS20070147113A1Improve performanceHigh voltageRead-only memoriesDigital storageElectricityBit line

The present invention presents a scheme for sensing memory cells. Selected memory cells are discharged through their channels to ground and then have a voltage level placed on the traditional source and another voltage level placed on the control gate, and allowing the cell bit line to charge up. The bit line of the memory cell will then charge up until the bit line voltage becomes sufficiently high to shut off any further cell conduction. The rise of the bit line voltage will occur at a rate and to a level dependent upon the data state of the cell, and the cell will then shut off when the bit line reaches a high enough level such that the body effect affected memory cell threshold is reached, at which point the current essentially shuts off. A particular embodiment performs multiple such sensing sub-operations, each with a different control gate voltage, but with multiple states being sensed in each operation by charging the previously discharged cells up through their source.

Owner:WODEN TECH INC

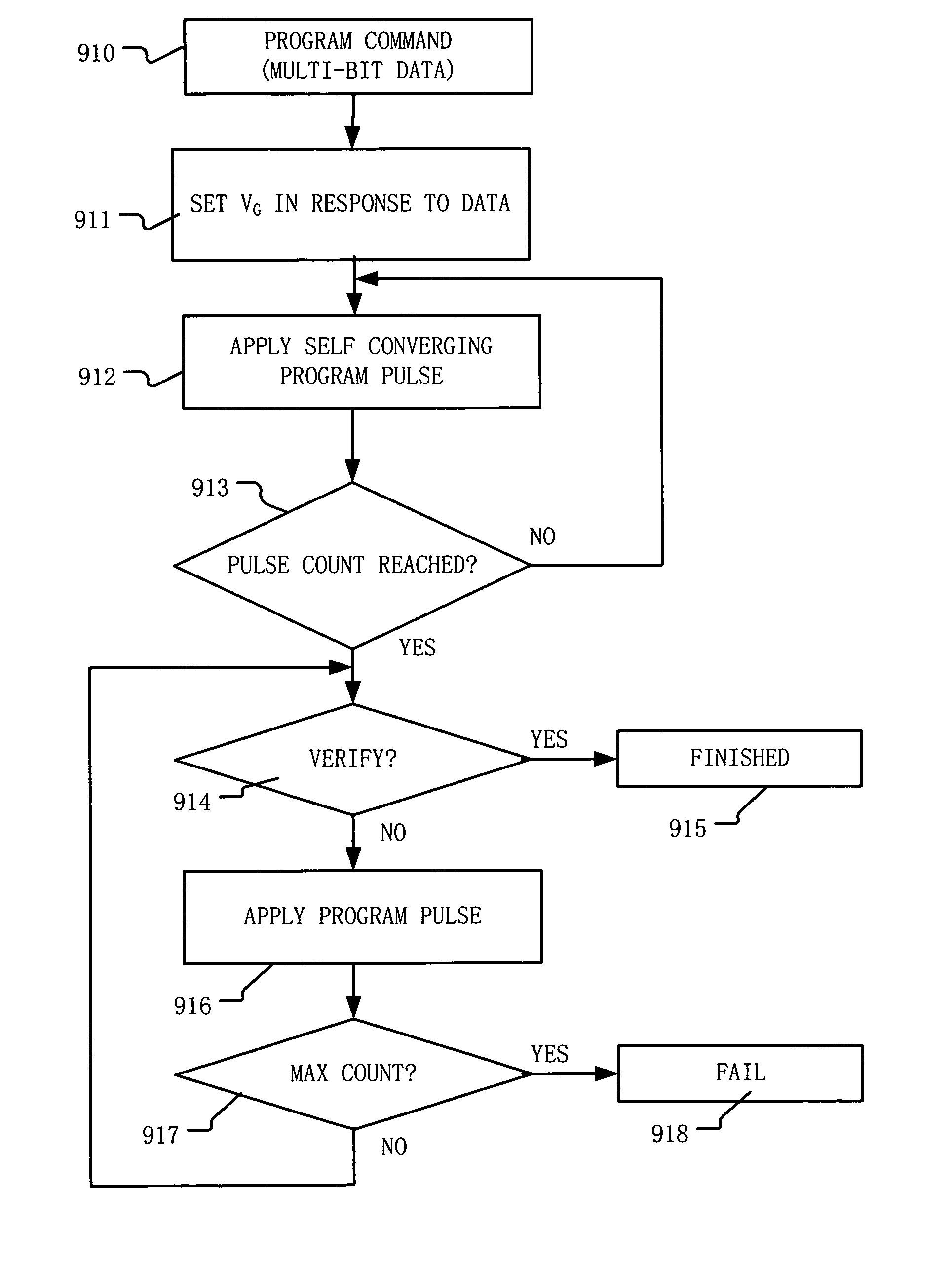

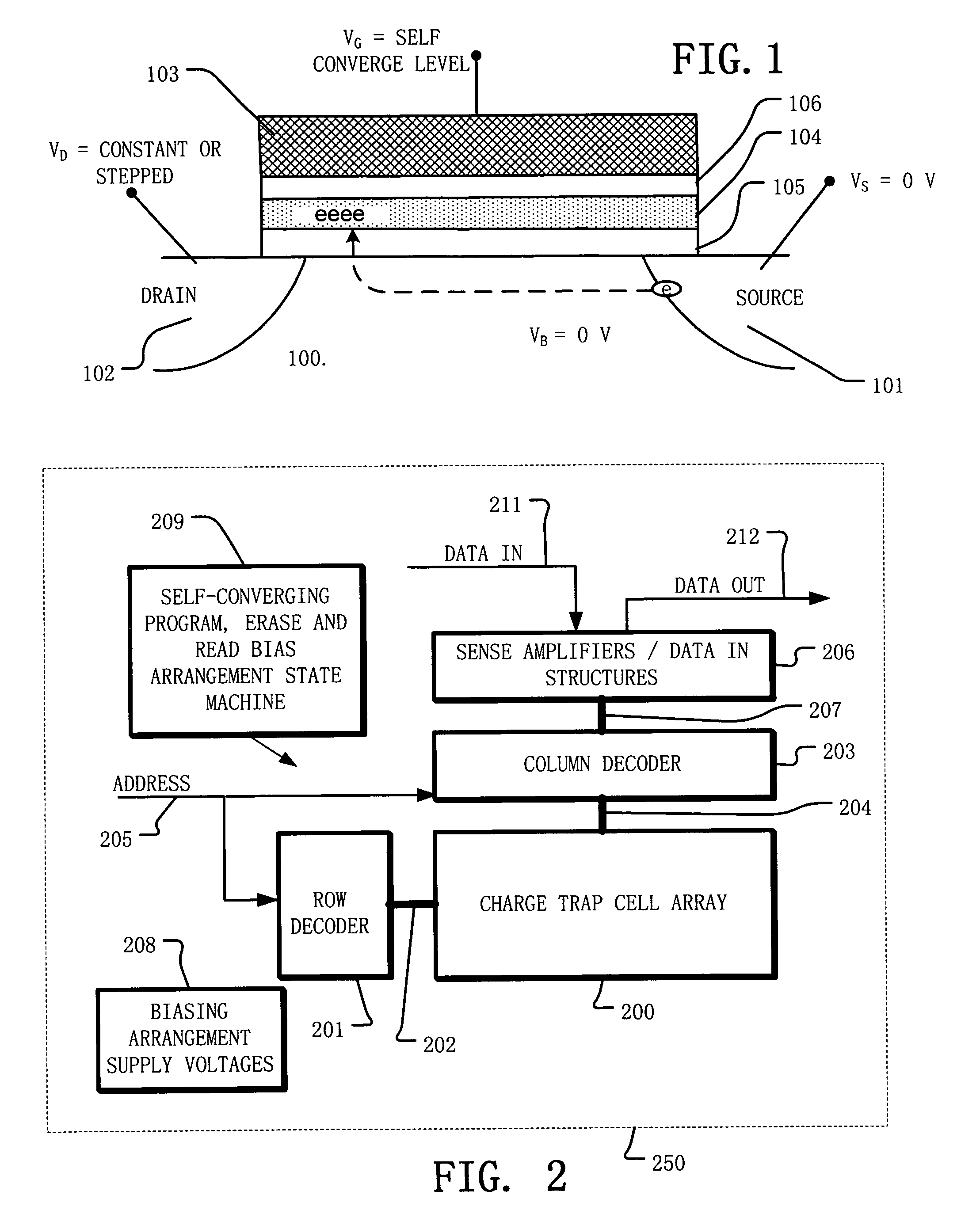

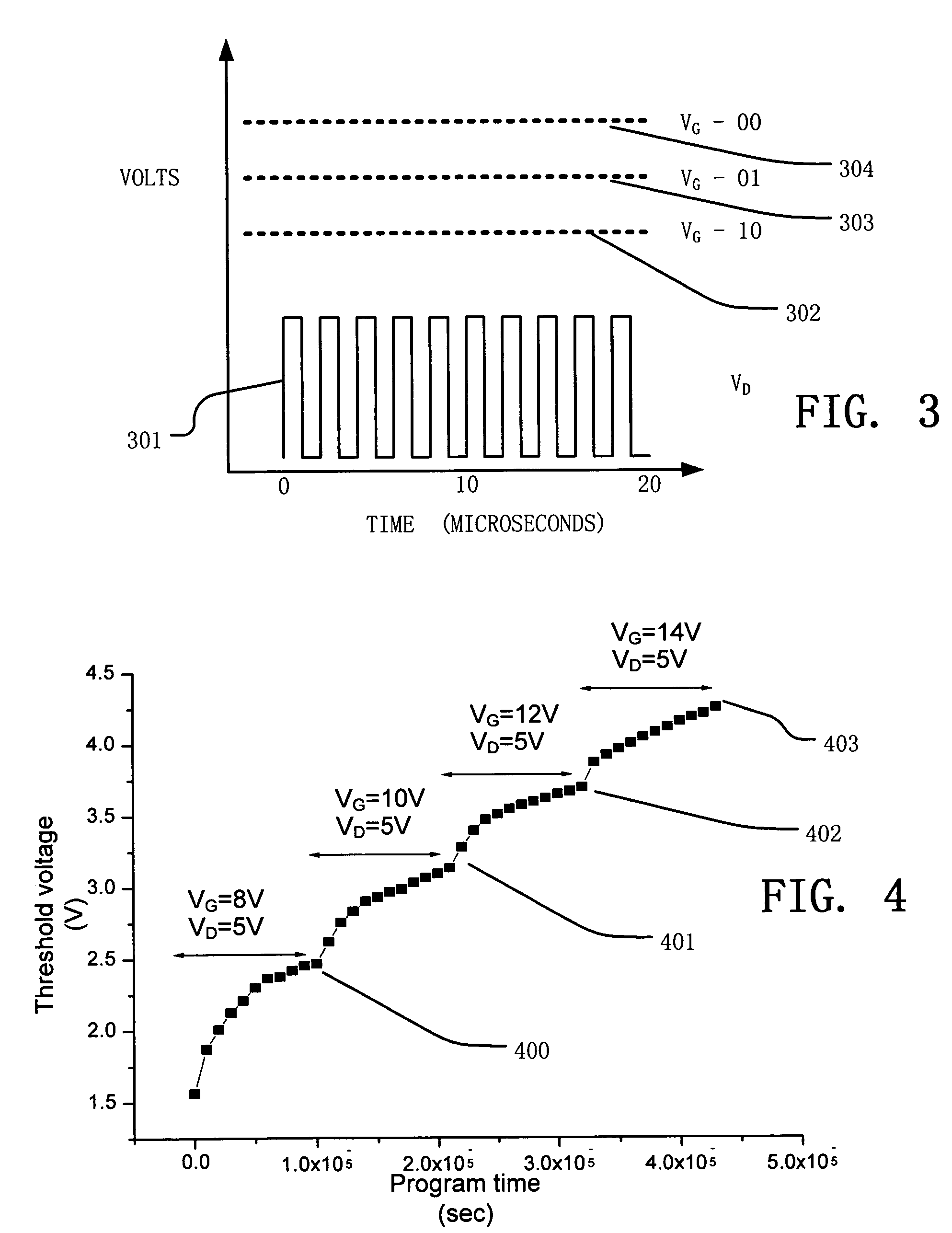

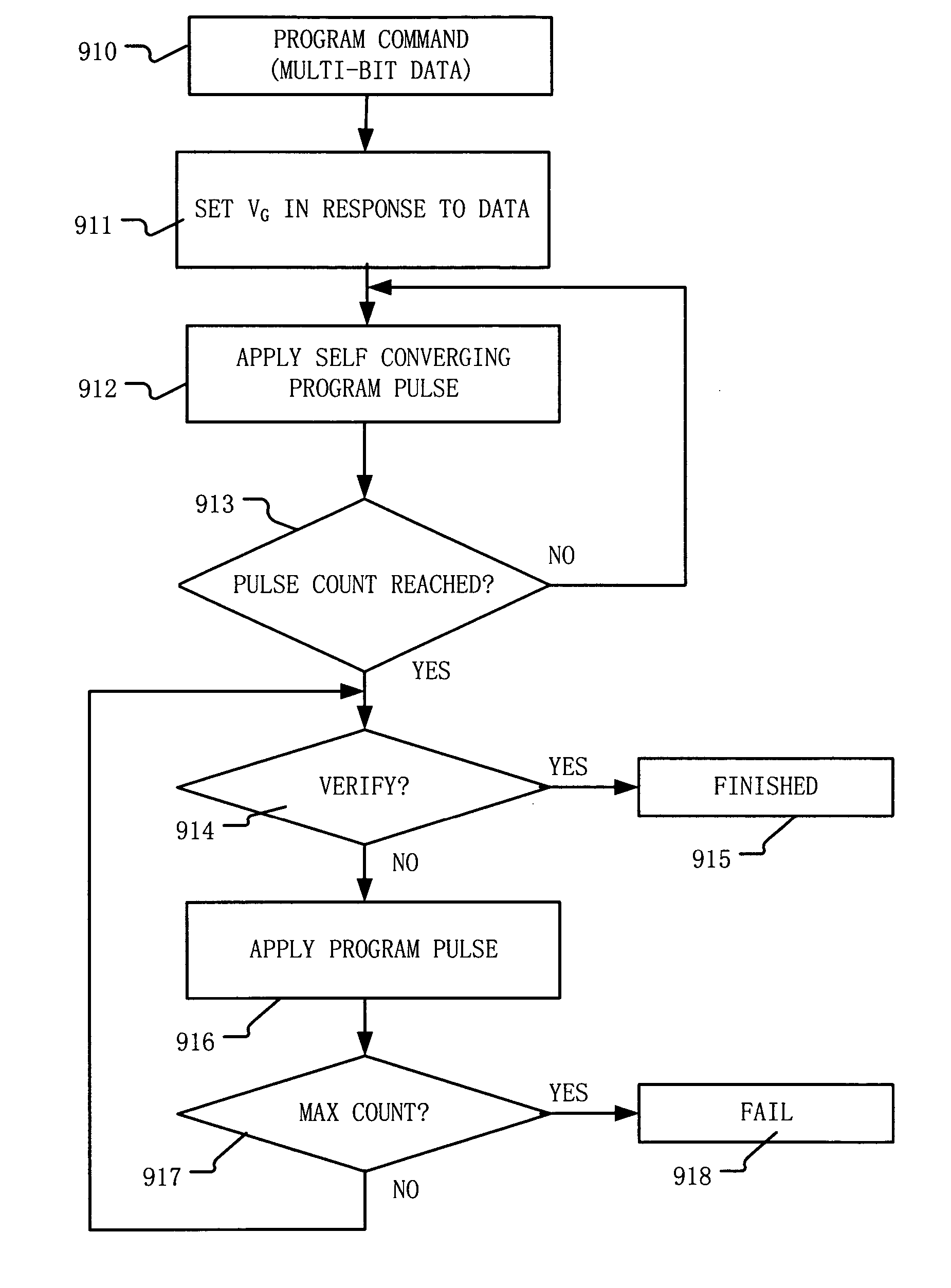

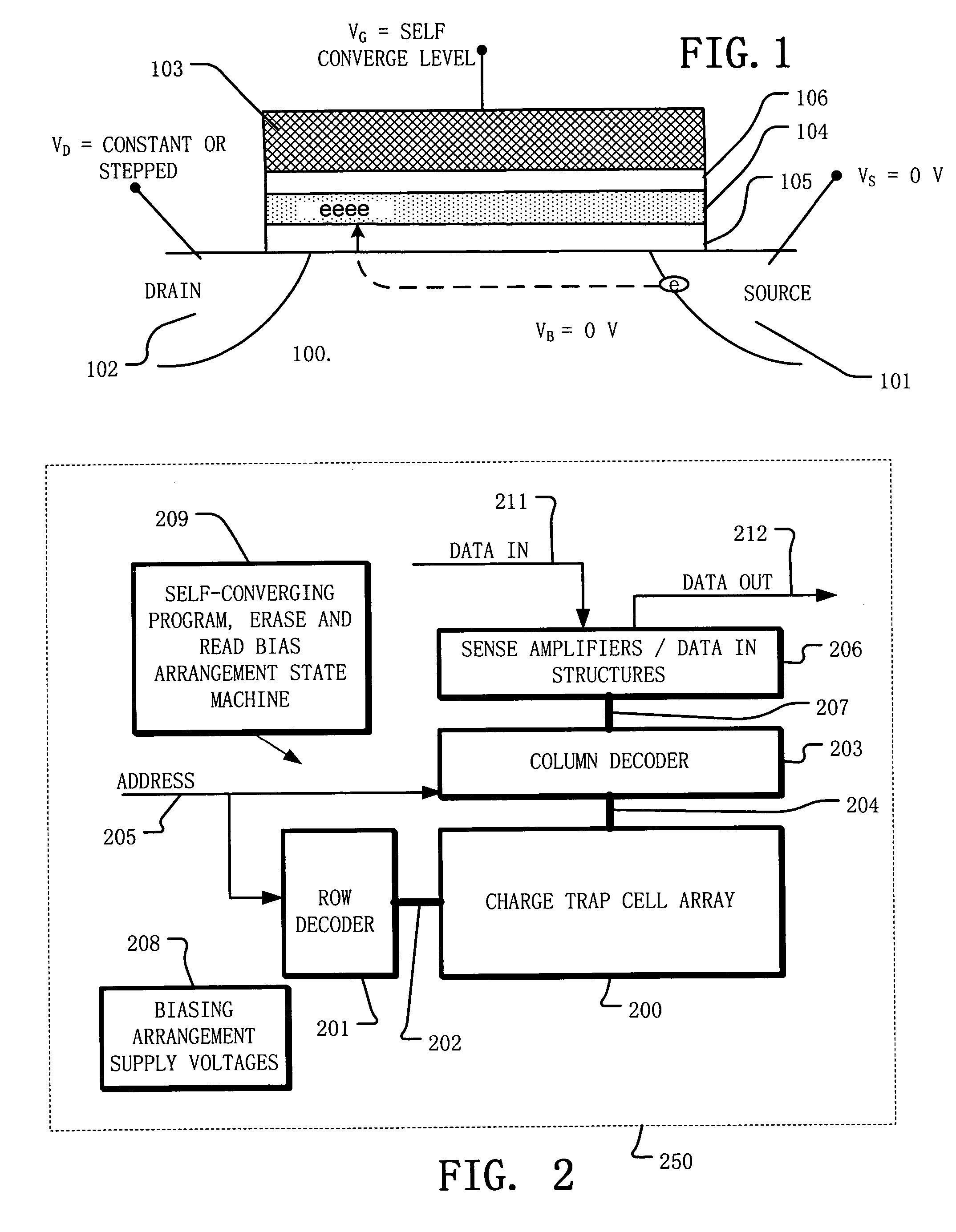

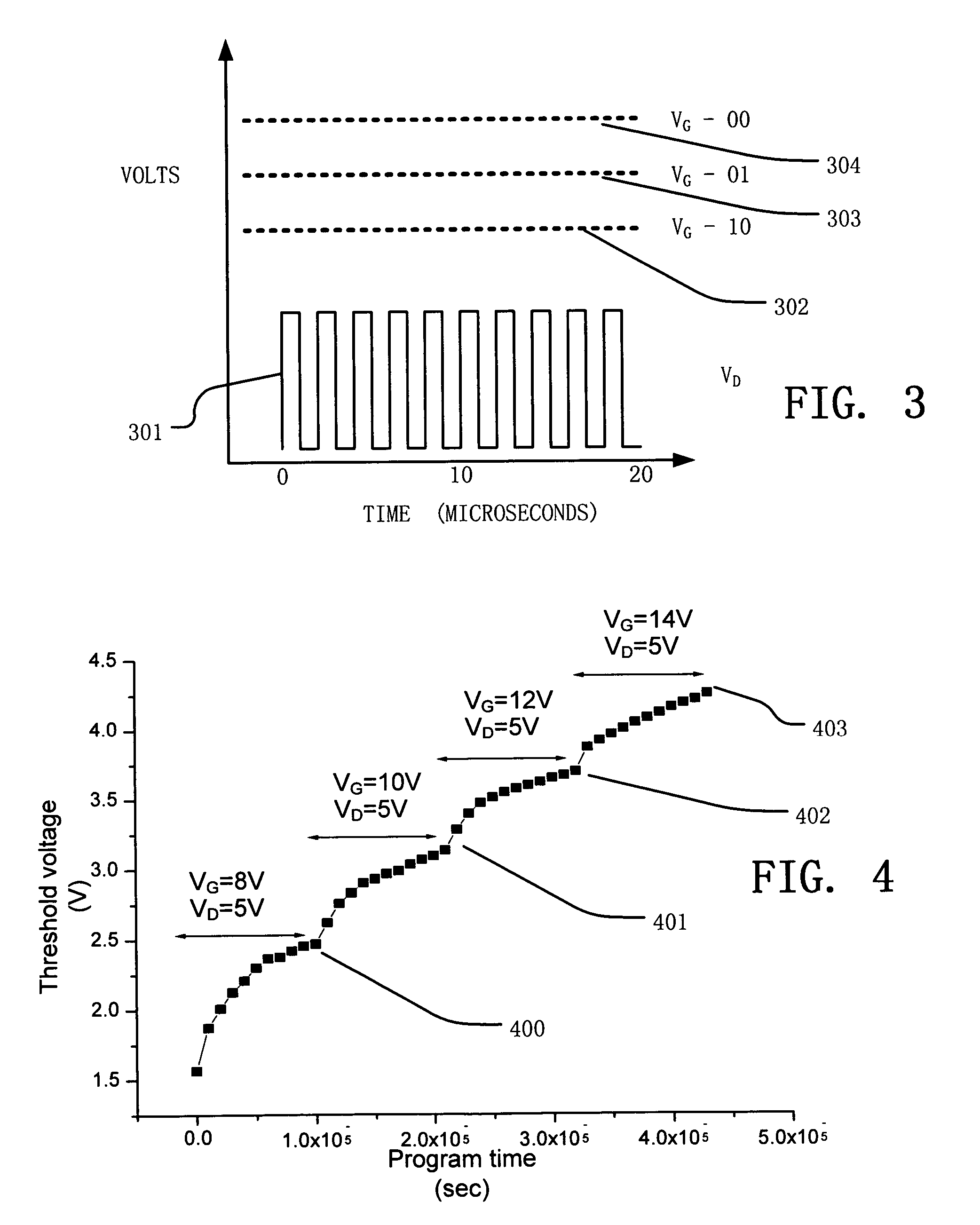

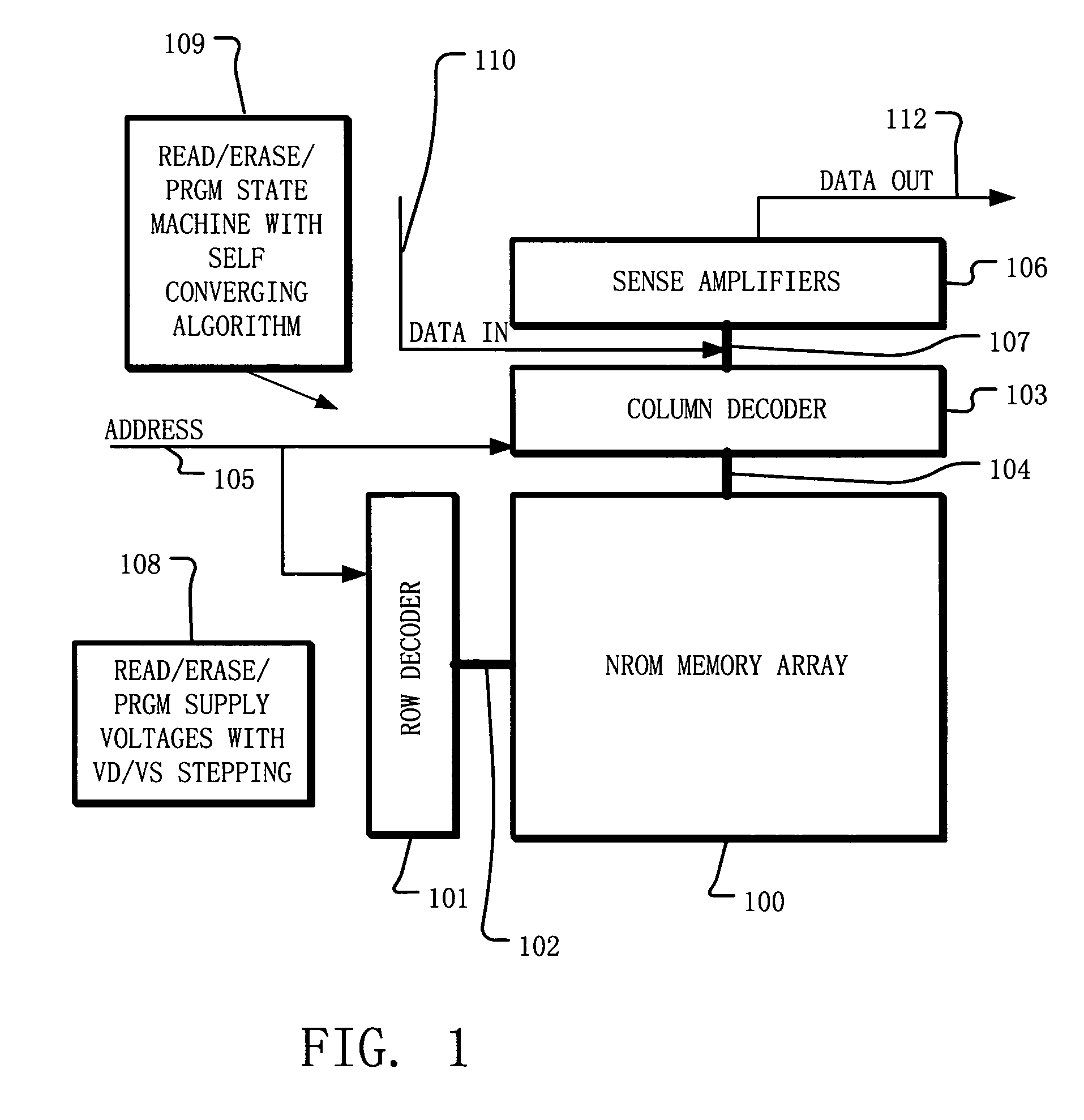

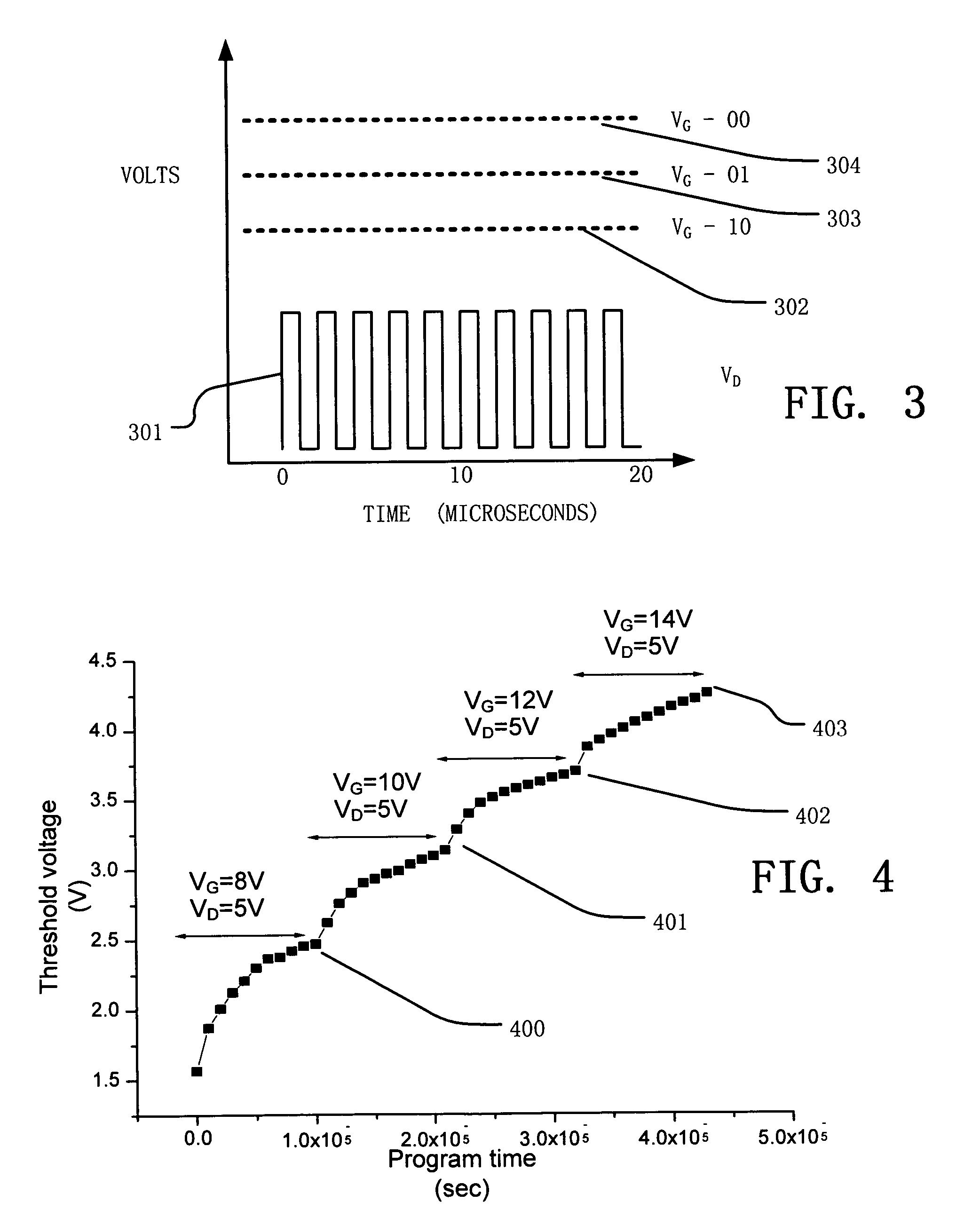

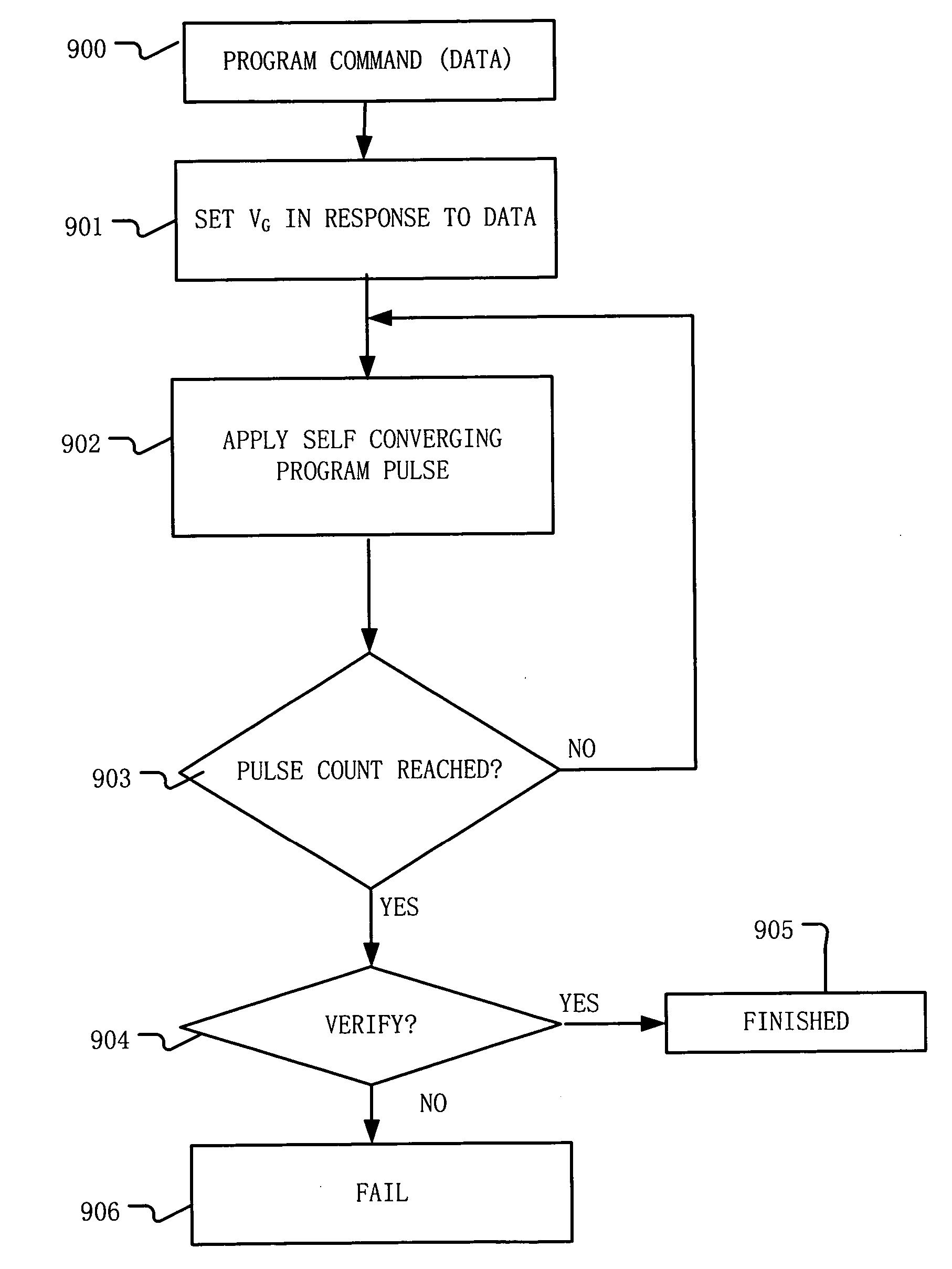

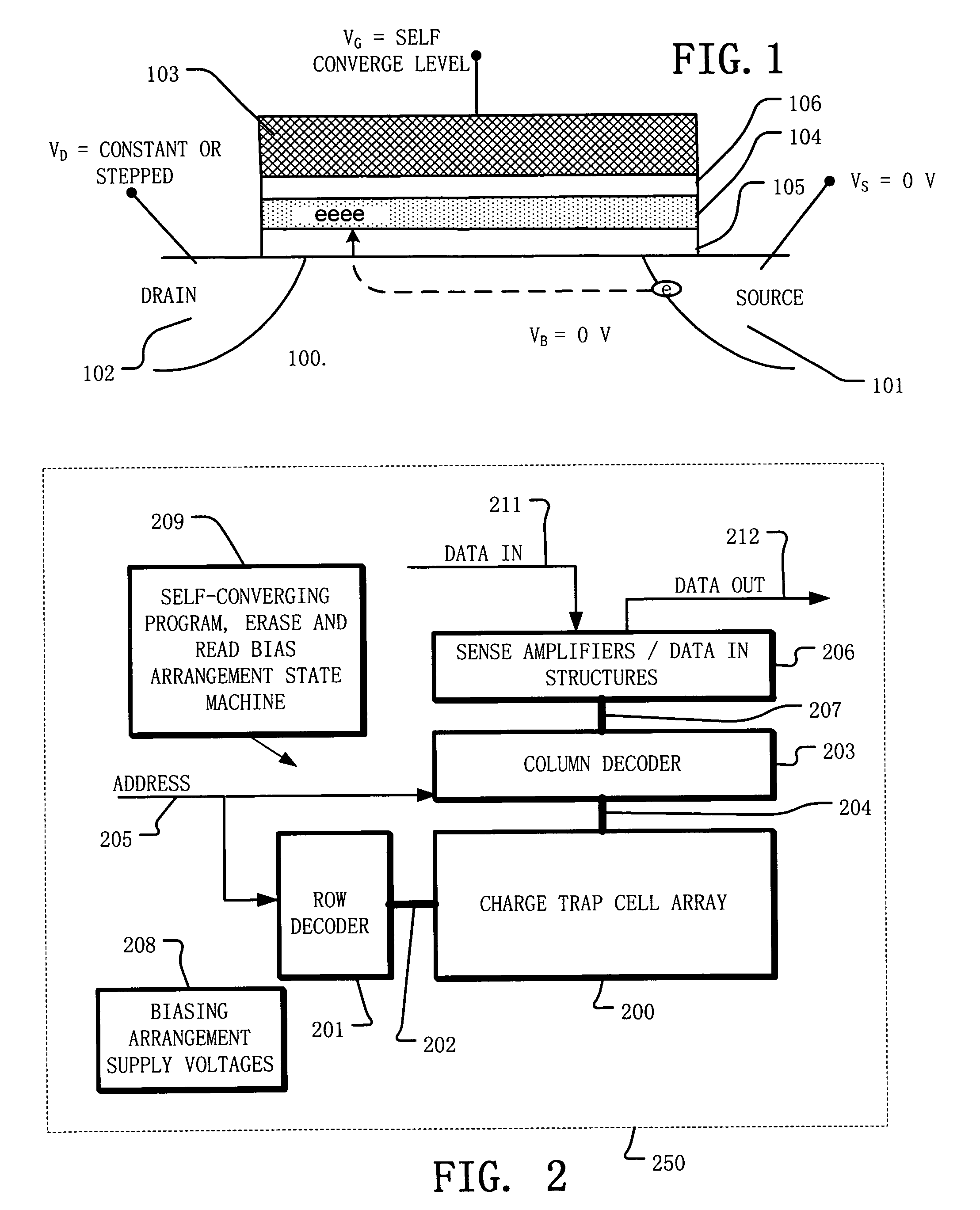

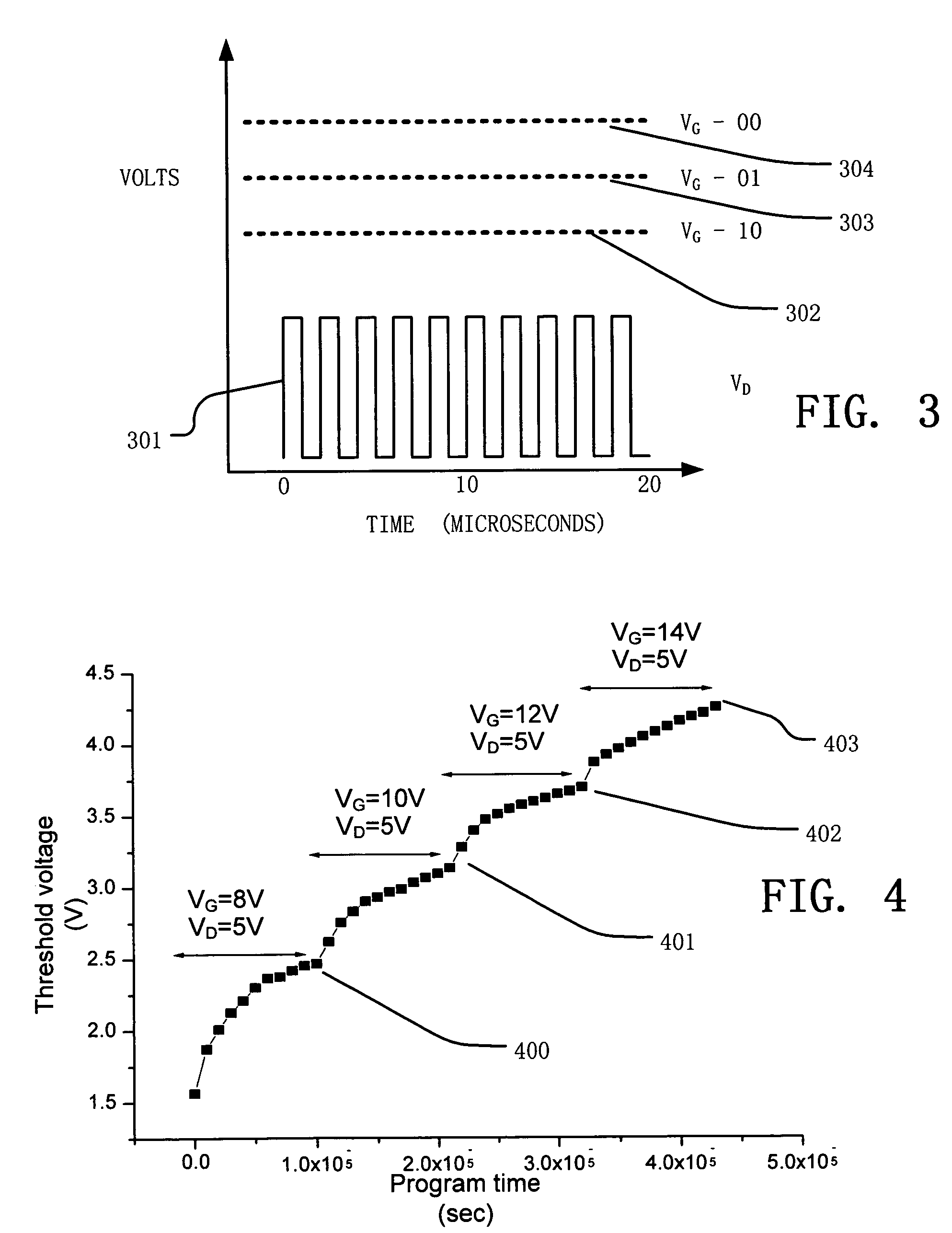

Operation scheme for programming charge trapping non-volatile memory

ActiveUS7151692B2Verify operation is reduced and eliminatedShorten the timeRead-only memoriesDigital storageEngineeringGate voltage

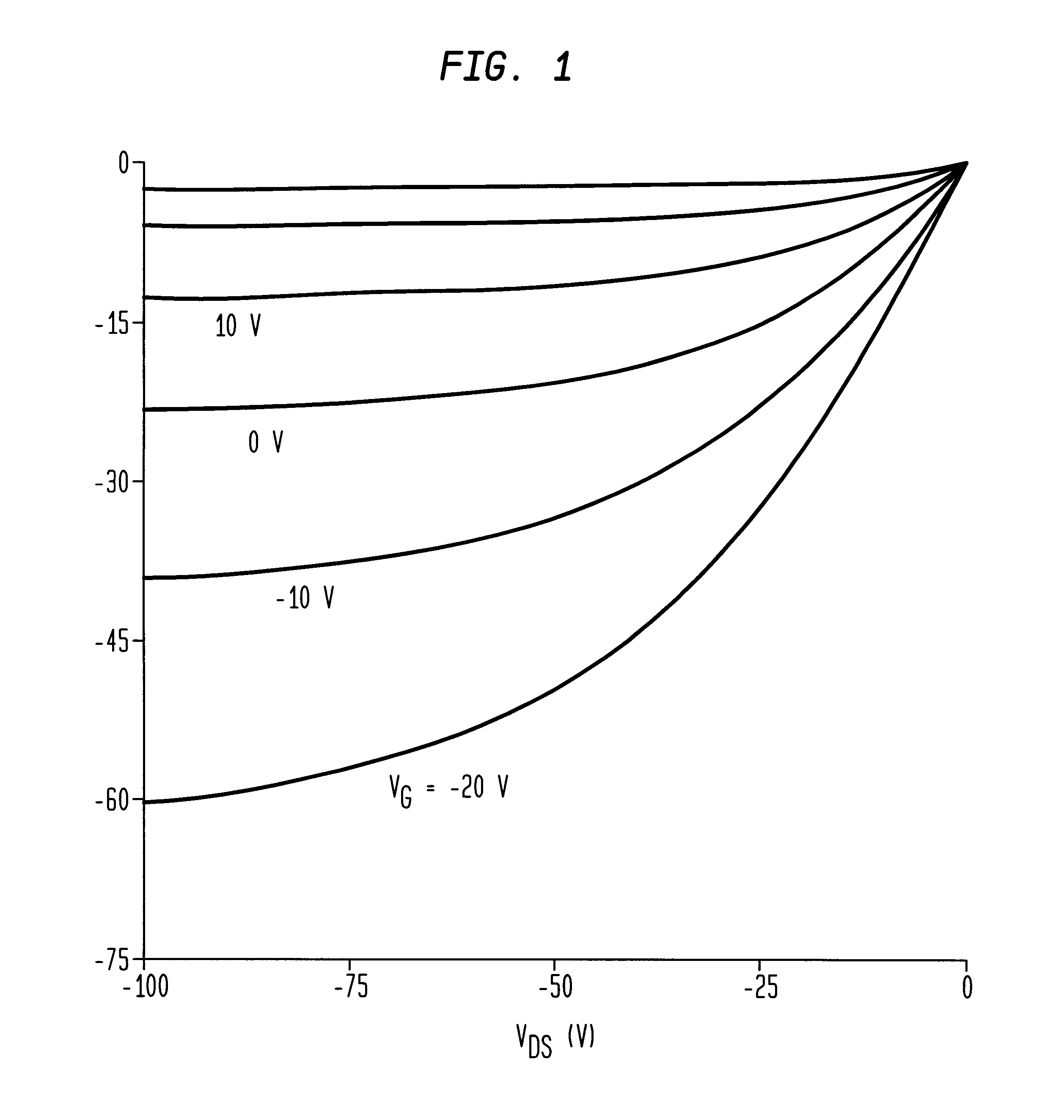

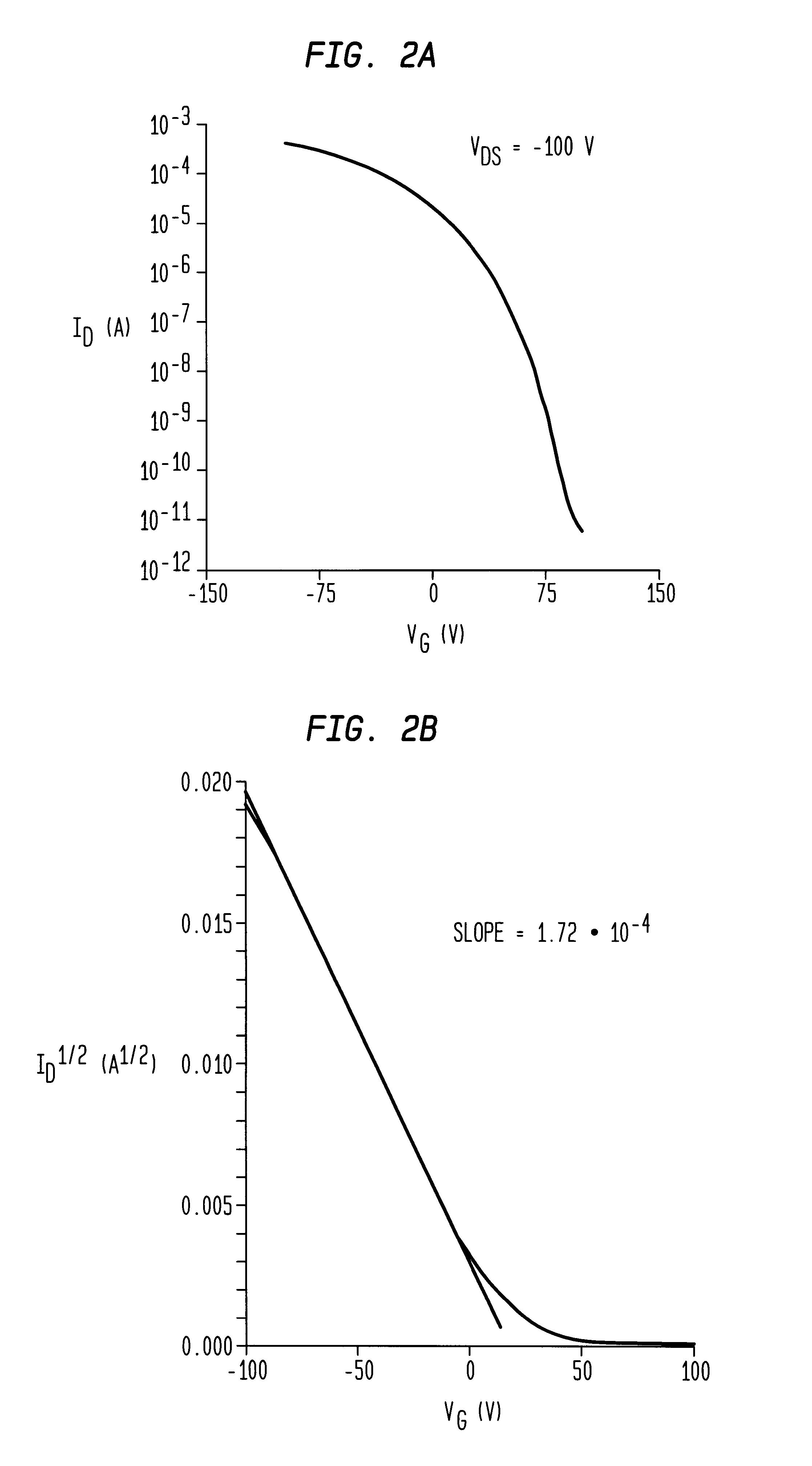

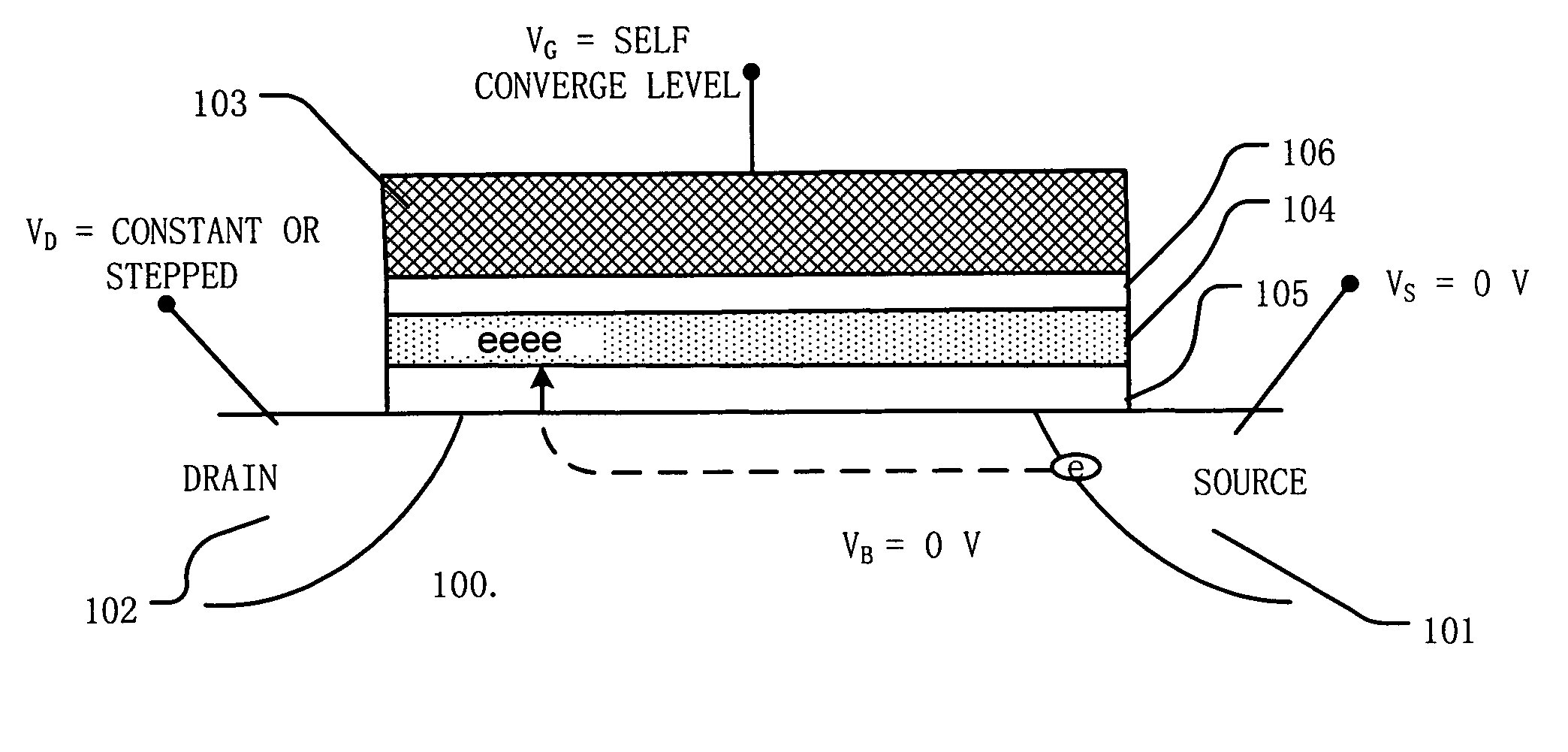

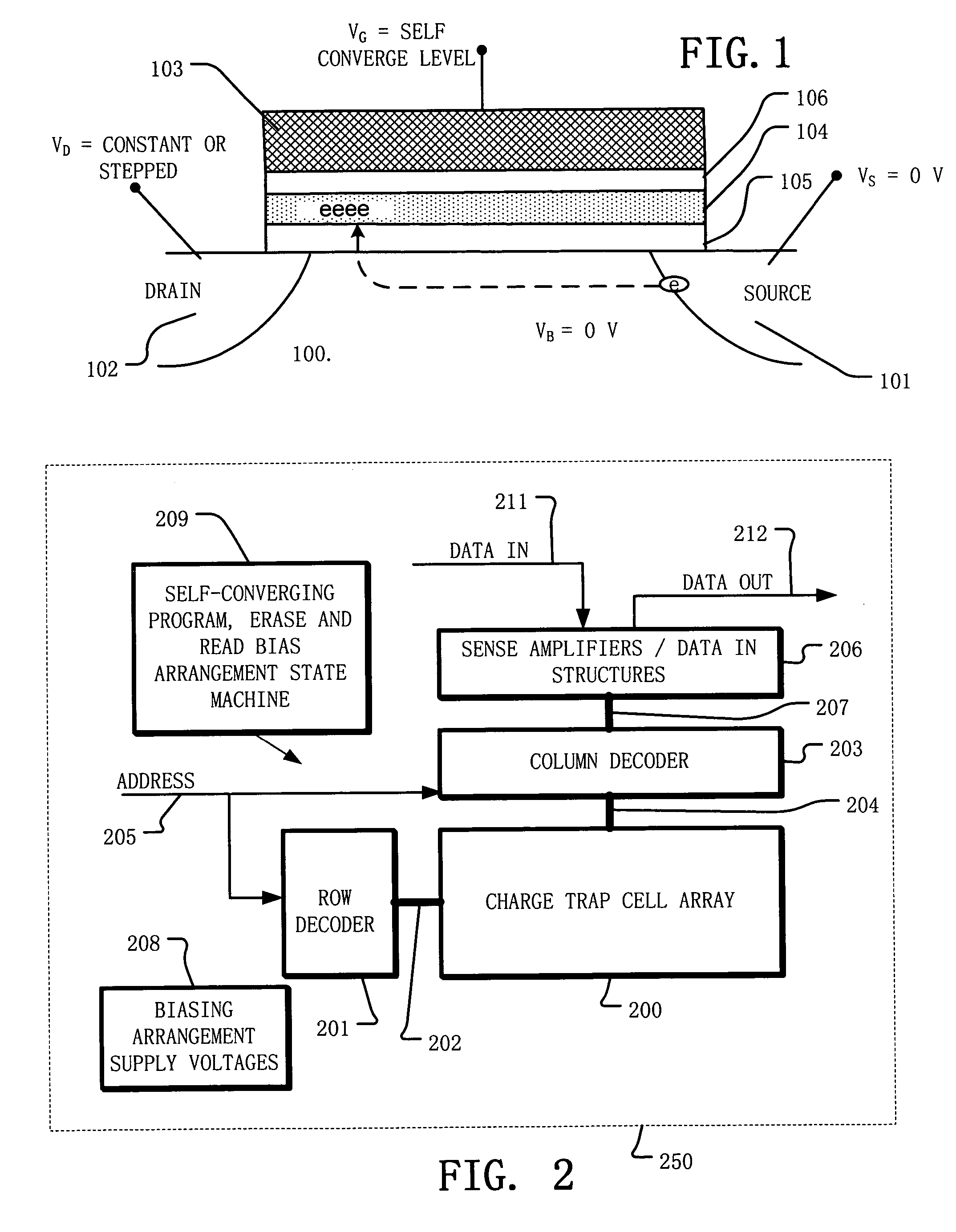

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash. The method includes determining a data value from one of more than two data values to be stored in the memory cell, and applying a gate voltage to the control gate at one of a predetermined set of gate voltage levels selected in response to the determined data value. Programming parameters are controlled to establish a self-converging threshold state that is determined by the selected gate voltage. In this manner, the threshold voltage converges on a target threshold corresponding with the determined data value for the memory cell. Program verify operations are reduced or eliminated in various embodiments, reducing the overall time required for the program operation, and improving device performance. A second portion of the program operation can include verify operations to improve threshold margins across the array.

Owner:MACRONIX INT CO LTD

Operation scheme for programming charge trapping non-volatile memory

ActiveUS7190614B2Verify operation is reduced and eliminatedShorten the timeRead-only memoriesDigital storageHemt circuitsEngineering

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash. The method includes determining a data value from one of more than two data values to be stored in the memory cell, and applying a gate voltage to the control gate at one of a predetermined set of gate voltage levels selected in response to the determined data value. Programming parameters are controlled to establish a self-converging threshold state that is determined by the selected gate voltage. In this manner, the threshold voltage converges on a target threshold corresponding with the determined data value for the memory cell. Program verify operations are reduced or eliminated in various embodiments, reducing the overall time required for the program operation, and improving device performance. A second portion of the program operation can include verify operations to improve threshold margins across the array.

Owner:MACRONIX INT CO LTD

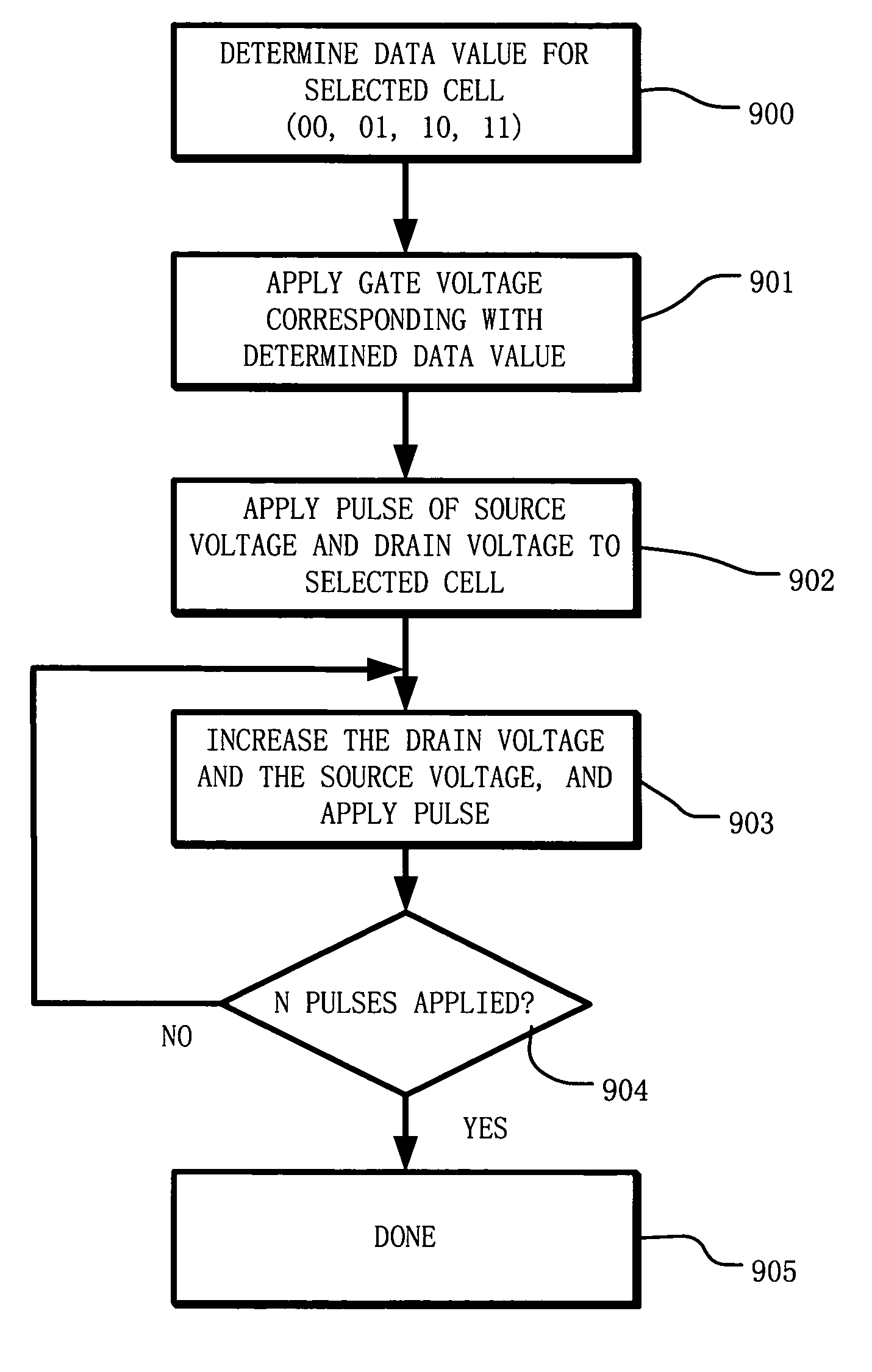

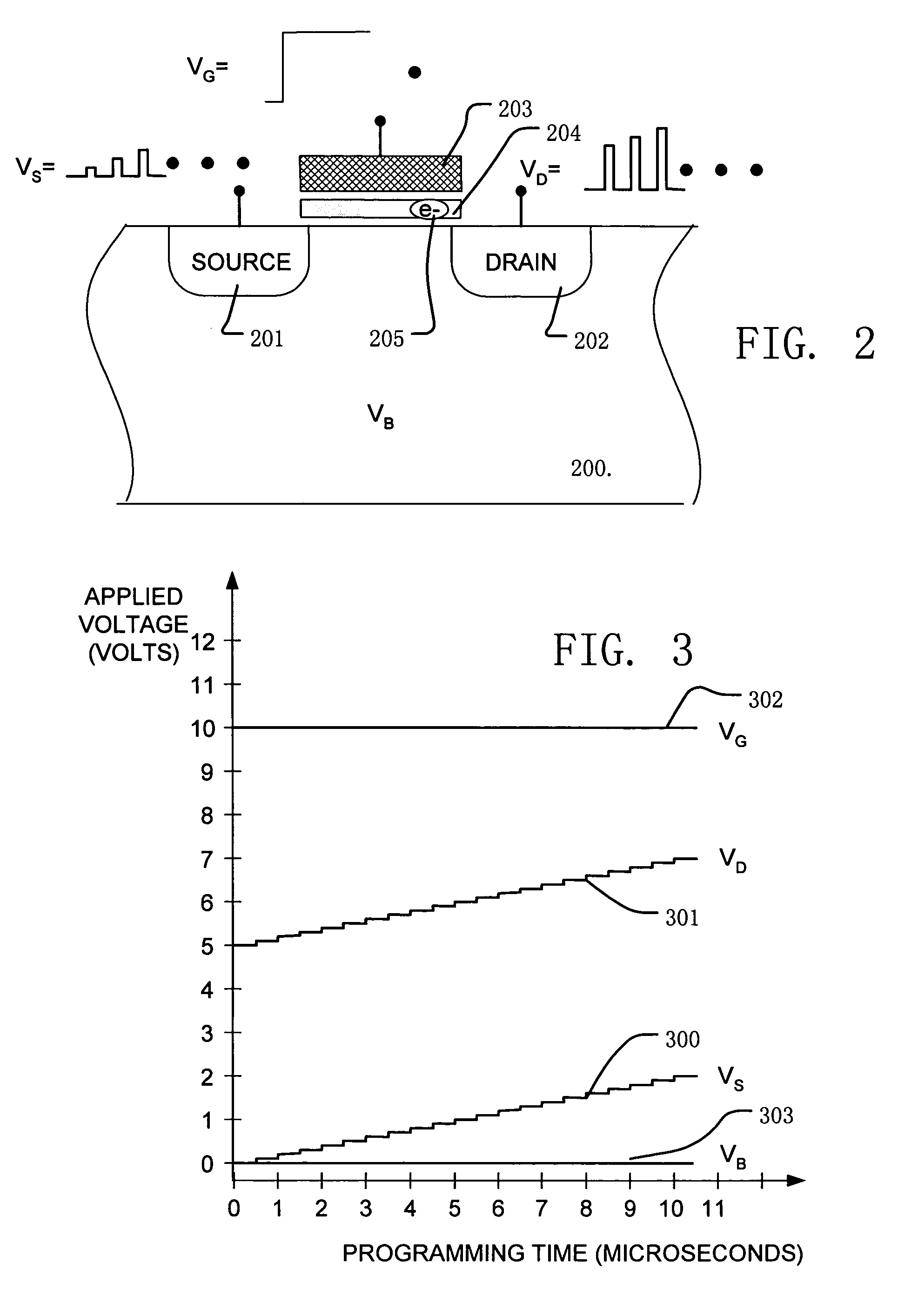

Circuit and method for programming charge storage memory cells

ActiveUS6937511B2Increases the effective thresholdHot electron injection efficiencySolid-state devicesRead-only memoriesEngineeringGate voltage

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash, having a source and a drain in a substrate, a charge storage element and a control gate. The method includes applying source voltage, inducing a body effect that increases the effective threshold, and increasing the source voltage along with the drain voltage to moderate hot electron injection efficiency during the program operation, at least during a portion of the program operation in which convergence on a target threshold occurs. A selected gate voltage is applied during the operation to establish the target threshold voltage. In multiple bit cells, the gate voltage is set according to the data values to be stored, enabling self-convergence at more than one target threshold.

Owner:MACRONIX INT CO LTD

Light-emitting device

InactiveUS7129917B2Drop in opening ratioSuppression of uneven brightnessTransistorDischarge tube luminescnet screensDisplay deviceEngineering

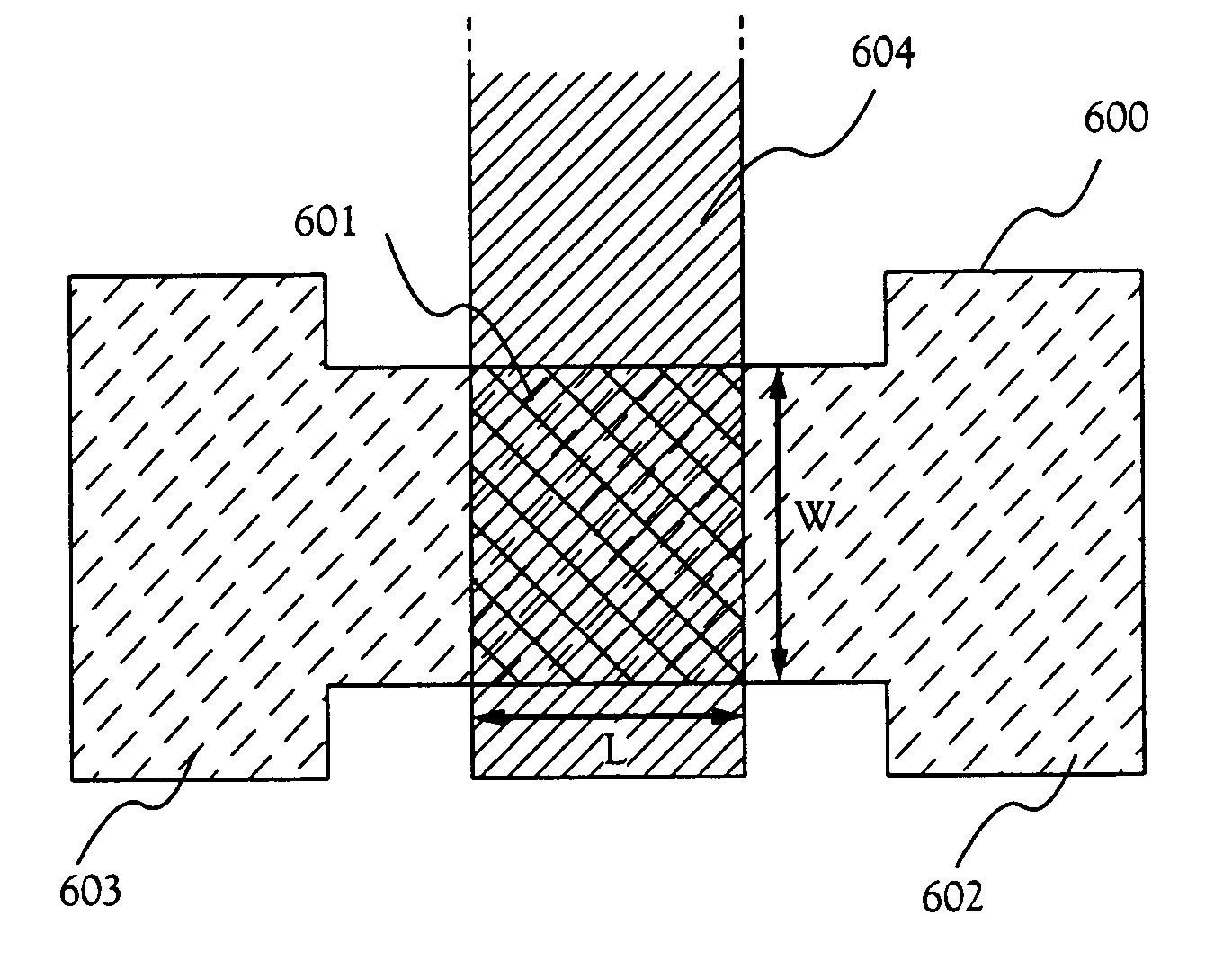

There is provided an EL light-emitting device with less uneven brightness. When a drain current of a plurality of current controlling TFTs is Id, a mobility is μ, a gate capacitance per unit area is Co, a maximum gate voltage is Vgs(max), a channel width is W, a channel length is L, an average value of a threshold voltage is Vth, a deviation from the average value of the threshold voltage is ΔVth, and a difference in emission brightness of a plurality of EL elements is within a range of ±n %, a semiconductor display device is characterized in thatA=2Idμ*C0A(Vgs(max)-Vth)2≦WL≦(1+n100-1)2*AΔVth2ΔVth≦(1+n100-1)*A*L / W

Owner:SEMICON ENERGY LAB CO LTD

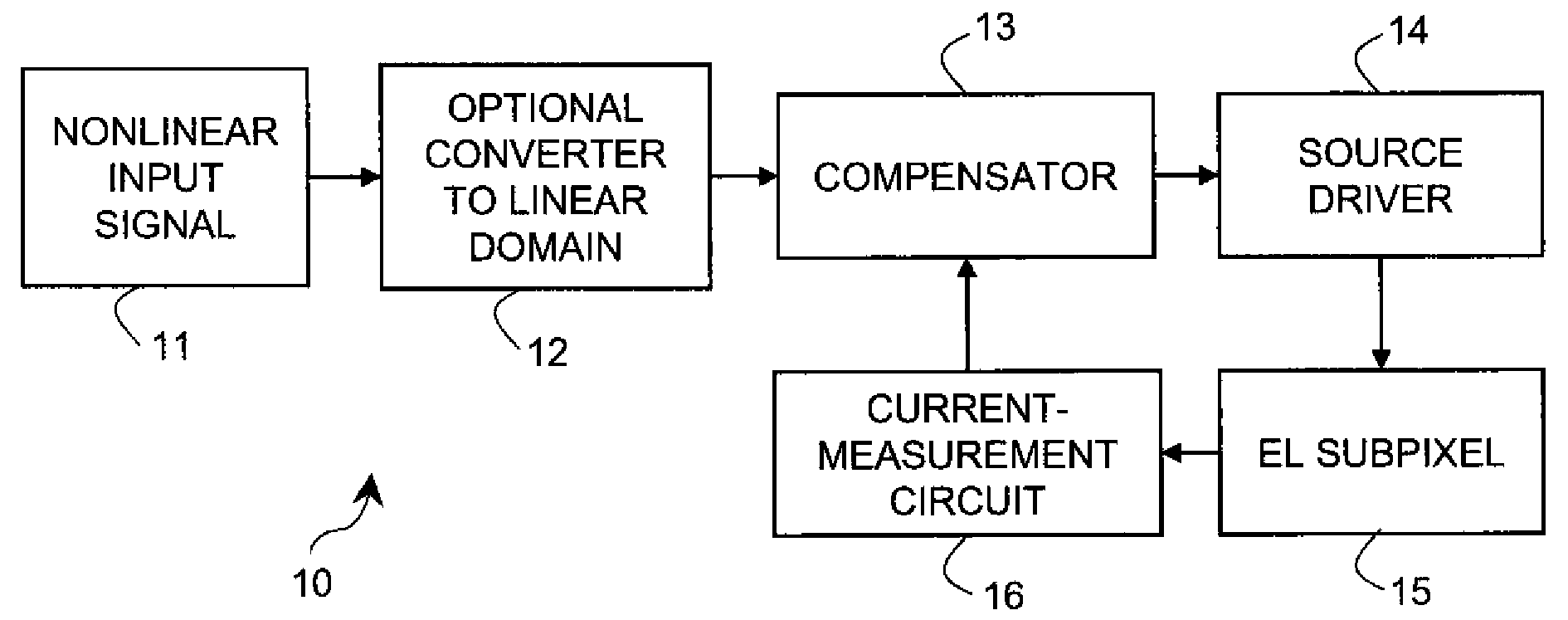

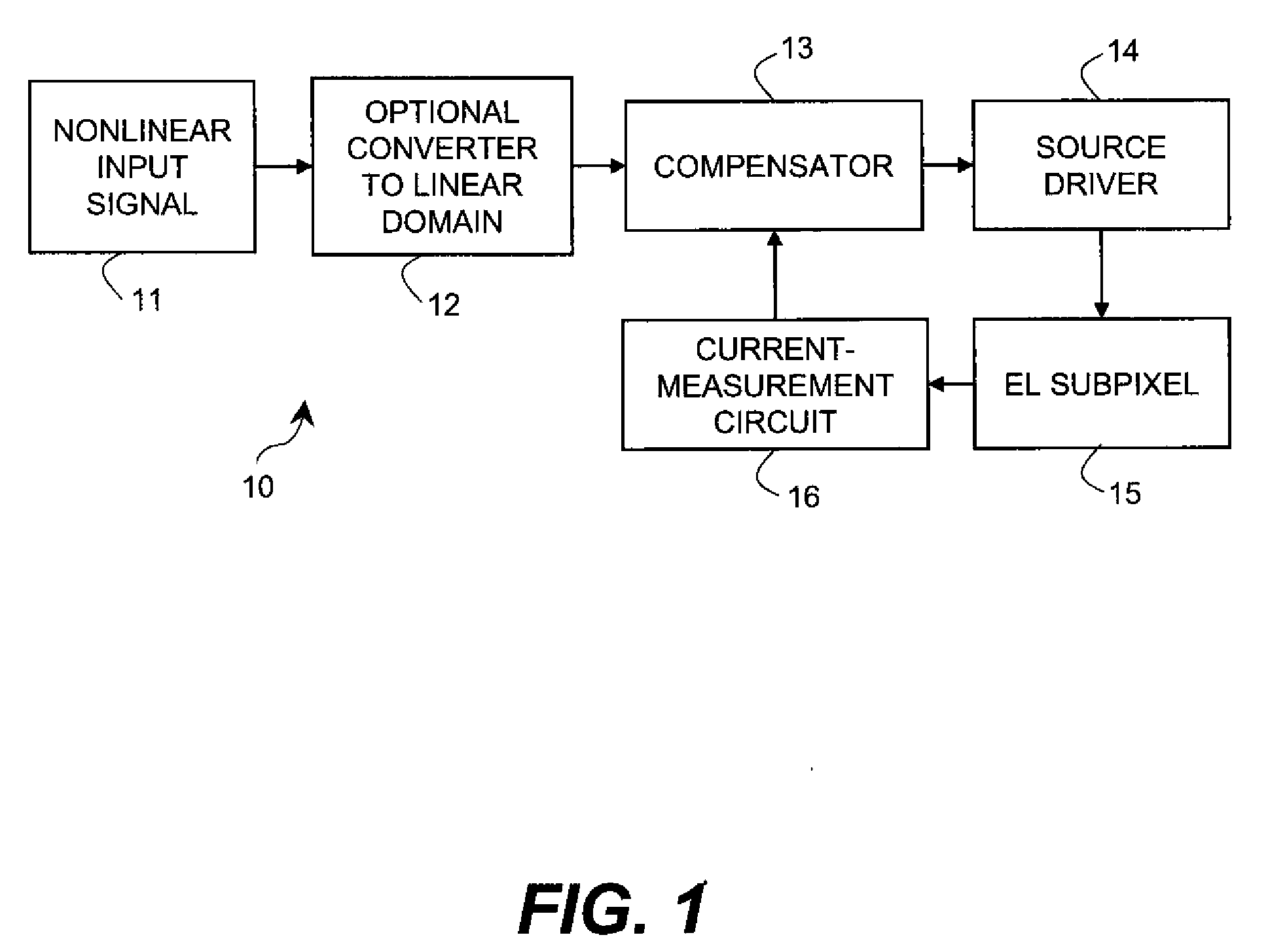

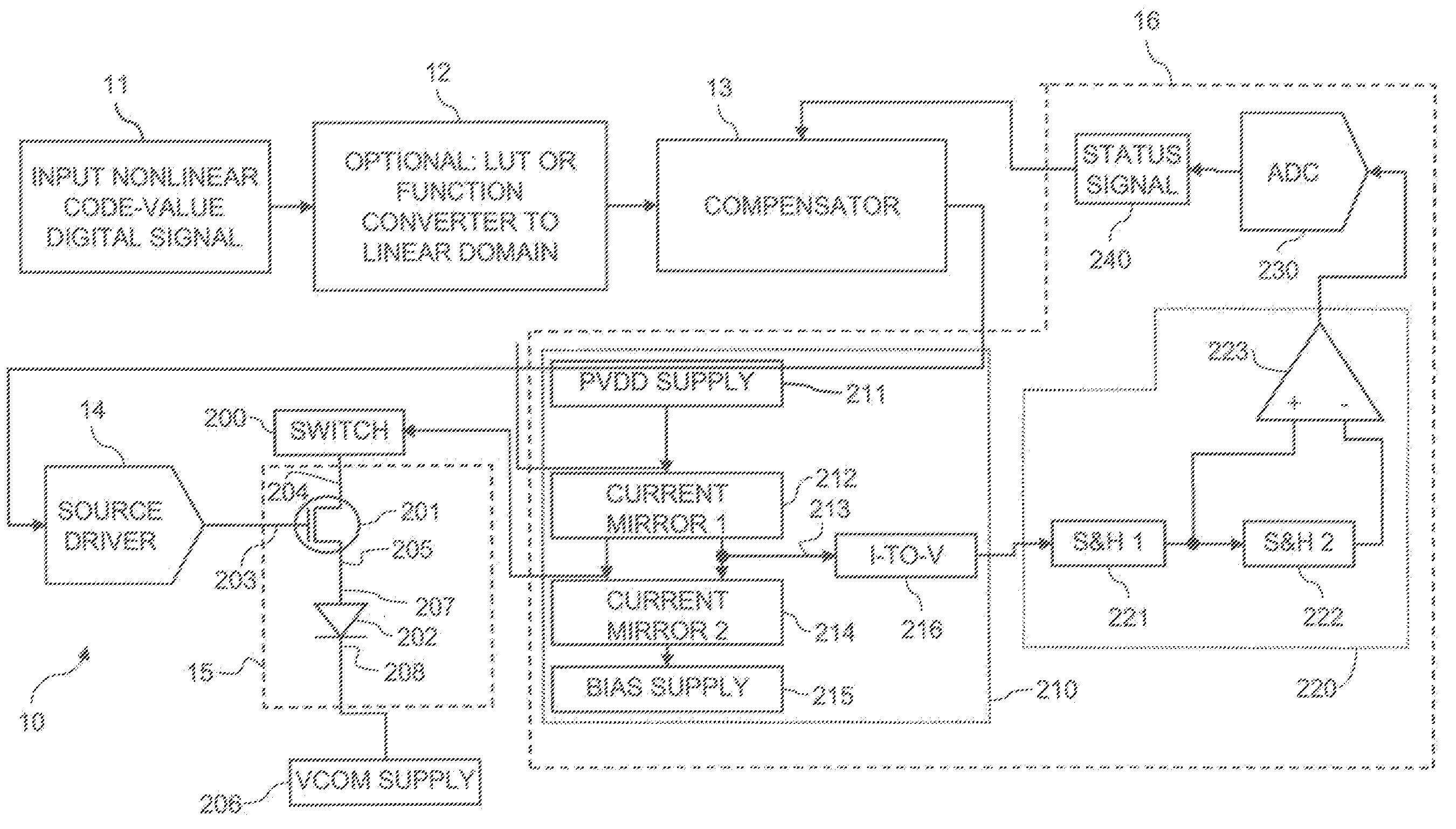

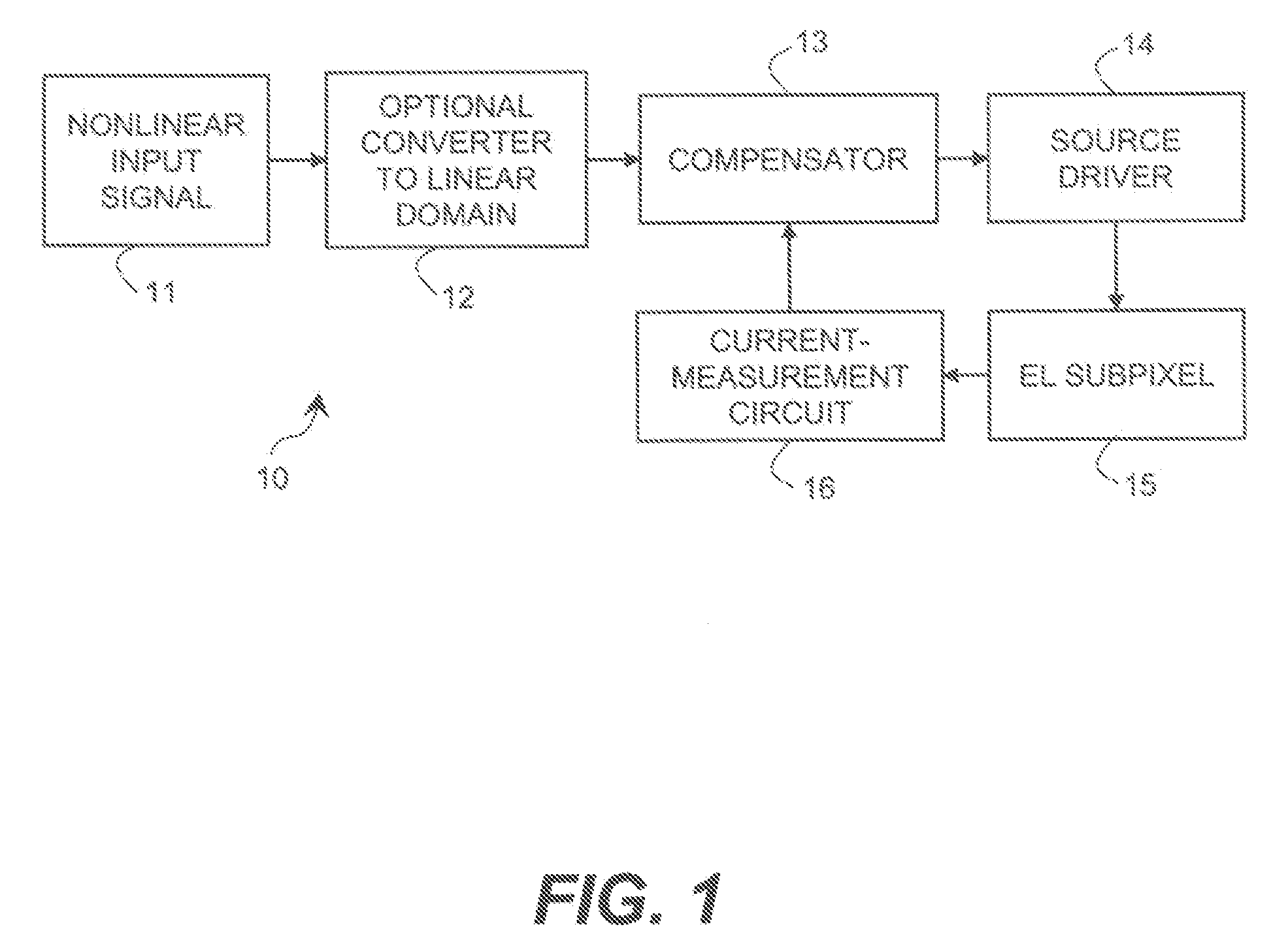

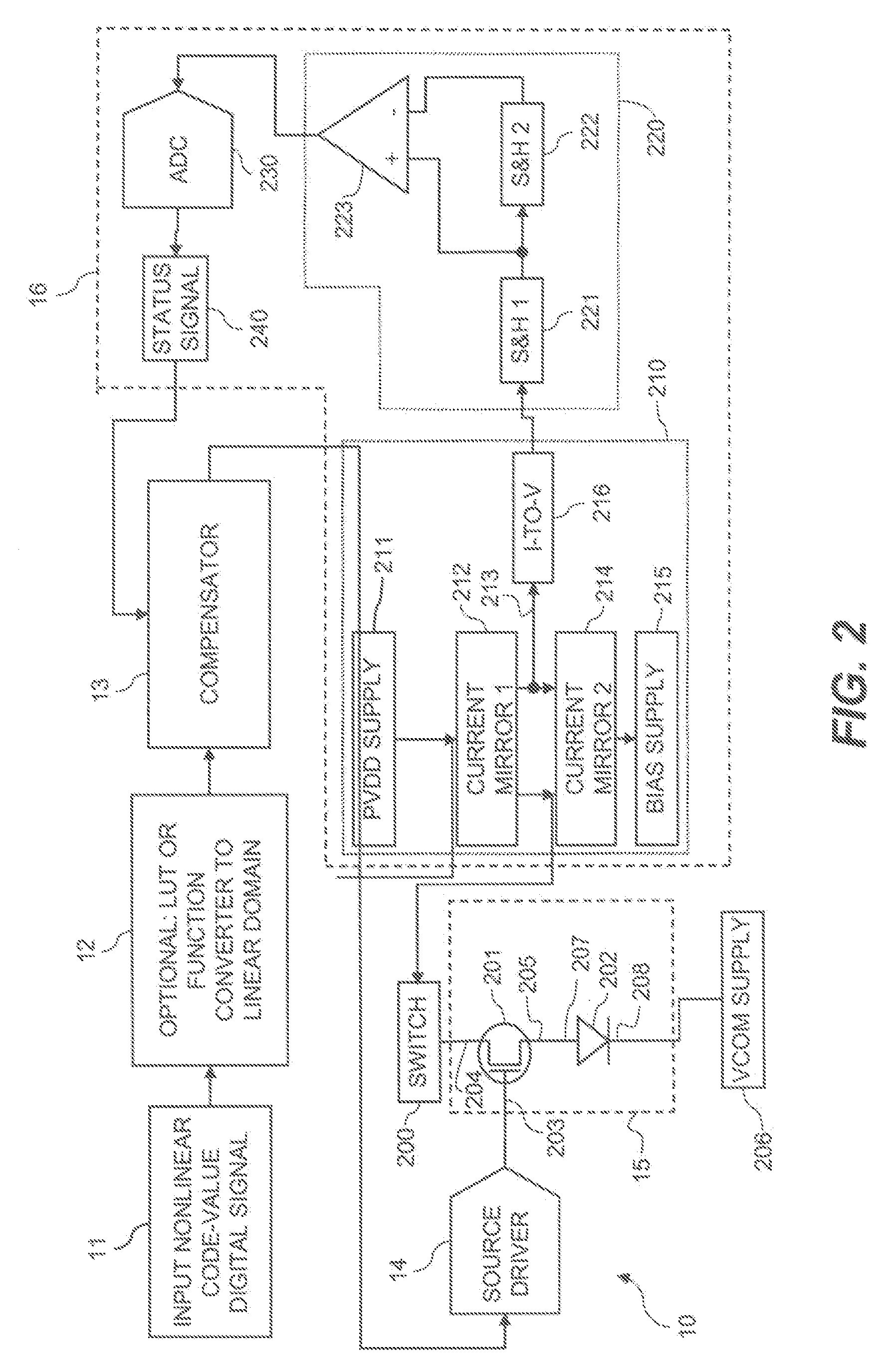

Electroluminescent subpixel compensated drive signal

ActiveUS20100225630A1Increase the aperture ratioImprove signal-to-noise ratioCathode-ray tube indicatorsInput/output processes for data processingSignal-to-noise ratio (imaging)Gate voltage

An electroluminescent (EL) subpixel, such as an organic light-emitting diode (OLED) subpixel, is compensated for aging effects such as threshold voltage Vth shift, EL voltage Voled shift, and OLED efficiency loss. The drive current of the subpixel is measured at one or more measurement reference gate voltages to form a status signal representing the characteristics of the drive transistor and EL emitter of the subpixel. Current measurements are taken in the linear region of drive transistor operation to improve signal-to-noise ratio in systems such as modern LTPS PMOS OLED displays, which have relatively small Voled shift over their lifetimes and thus relatively small current change due to channel-length modulation. Various sources of noise are also suppressed to further increase signal-to-noise ratio.

Owner:GLOBAL OLED TECH

Electroluminescent display compensated drive signal

ActiveUS20100225634A1Increase the aperture ratioIncrease productionCathode-ray tube indicatorsInput/output processes for data processingChannel length modulationDriving current

Subpixels on an electroluminescent (EL) display panel, such as an organic light-emitting diode (OLED) panel, are compensated for initial nonuniformity (“mura”) and for aging effects such as threshold voltage Vth shift, EL voltage Voled shift, and OLED efficiency loss. The drive current of each subpixel is measured at one or more measurement reference gate voltages to form status signals representing the characteristics of the drive transistor and EL emitter of those subpixels. Current measurements are taken in the linear region of drive transistor operation to improve signal-to-noise ratio in systems such as modern LTPS PMOS OLED displays, which have relatively small Voled shift over their lifetimes and thus relatively small current change due to channel-length modulation. Various sources of noise are also suppressed to further increase signal-to-noise ratio.

Owner:GLOBAL OLED TECH

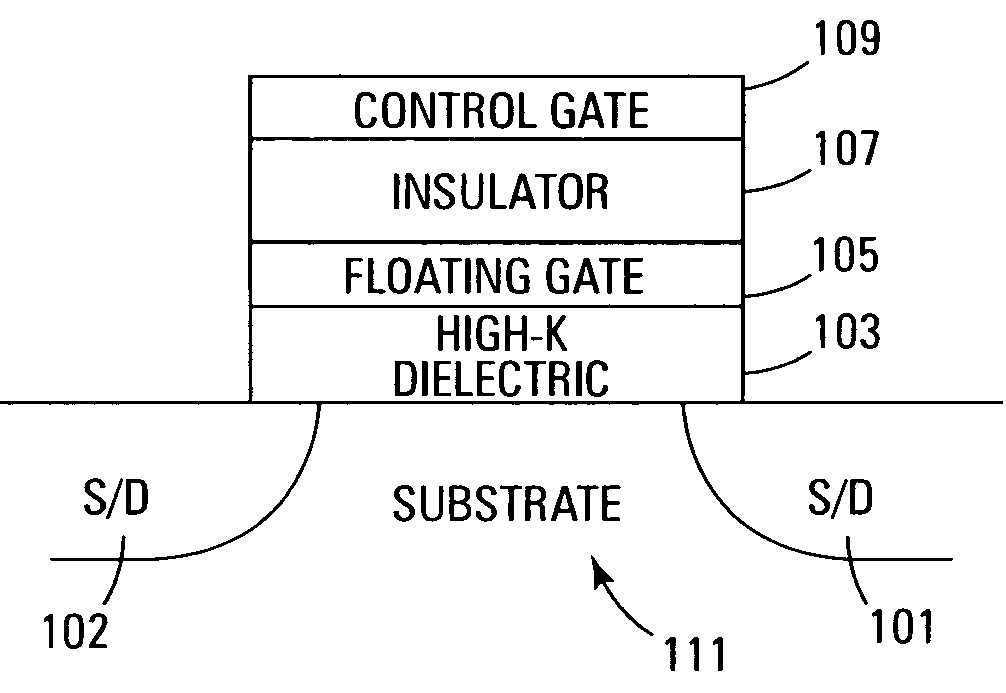

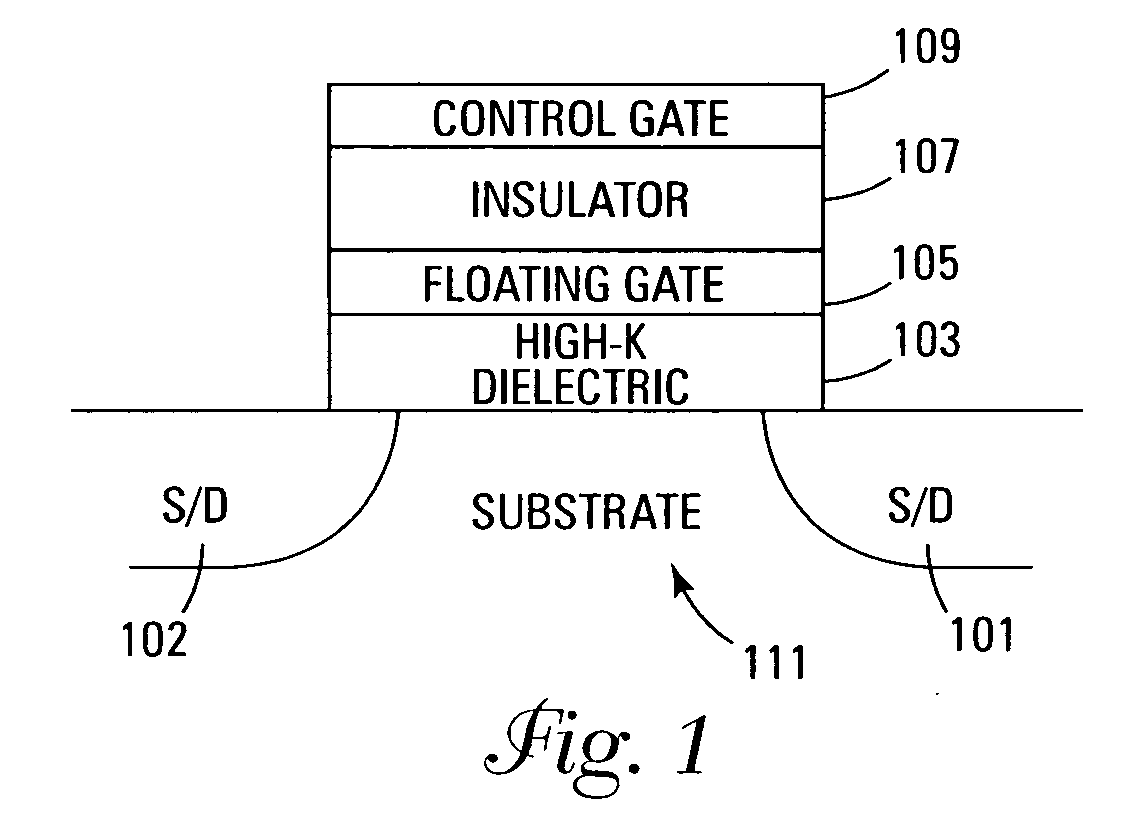

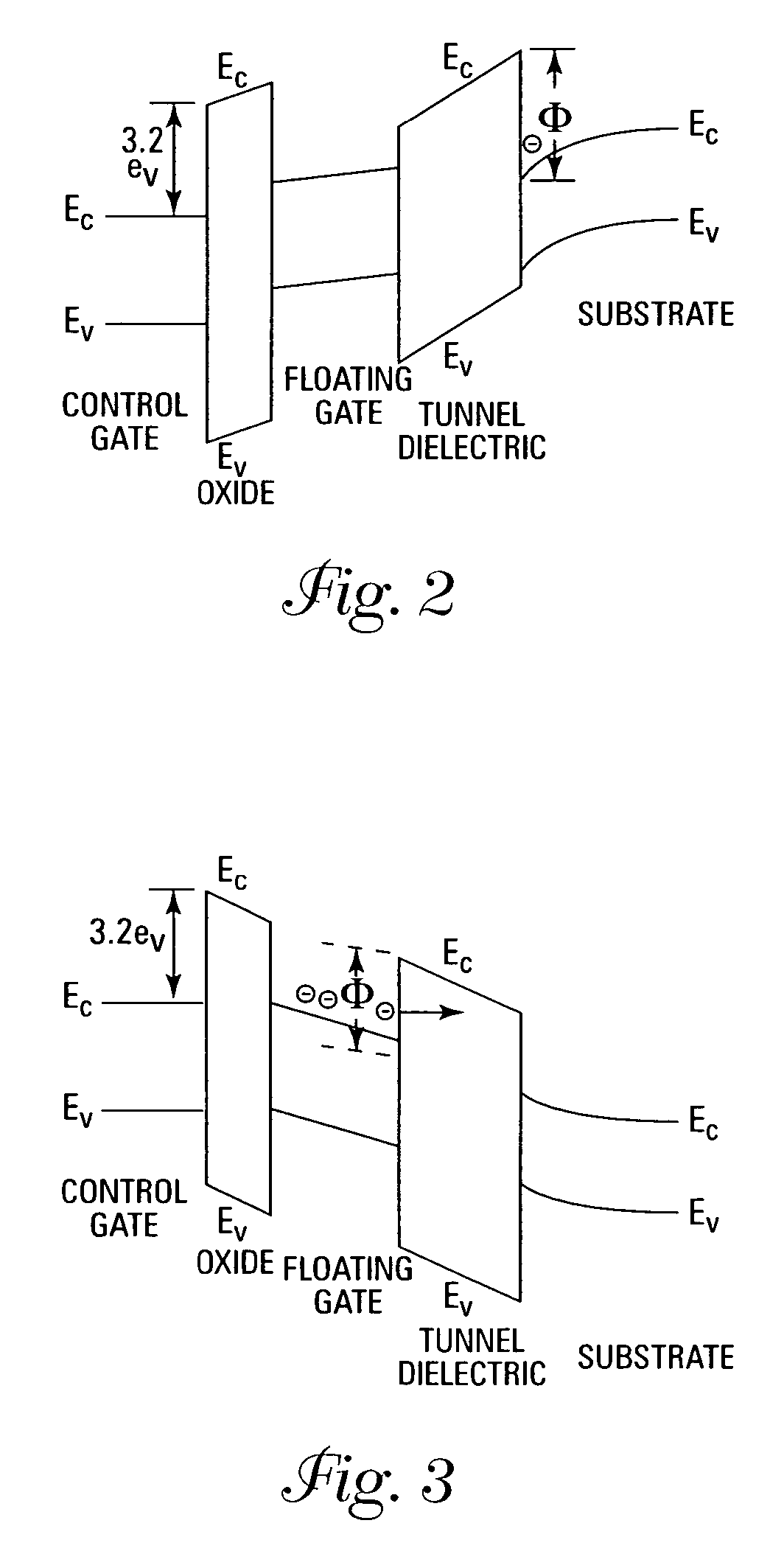

Flash memory having a high-permittivity tunnel dielectric

A high permittivity tunneling dielectric is used in a flash memory cell to provide greater tunneling current into the floating gate with smaller gate voltages. The flash memory cell has a substrate with source / drain regions. The high-k tunneling dielectric is formed above the substrate. The high-k tunneling dielectric can be deposited using evaporation techniques or atomic layer deposition techniques. The floating gate is formed on top of the high-k dielectric layer with an oxide gate insulator on top of that. A polysilicon control gate is formed on the top gate insulator.

Owner:MICRON TECH INC

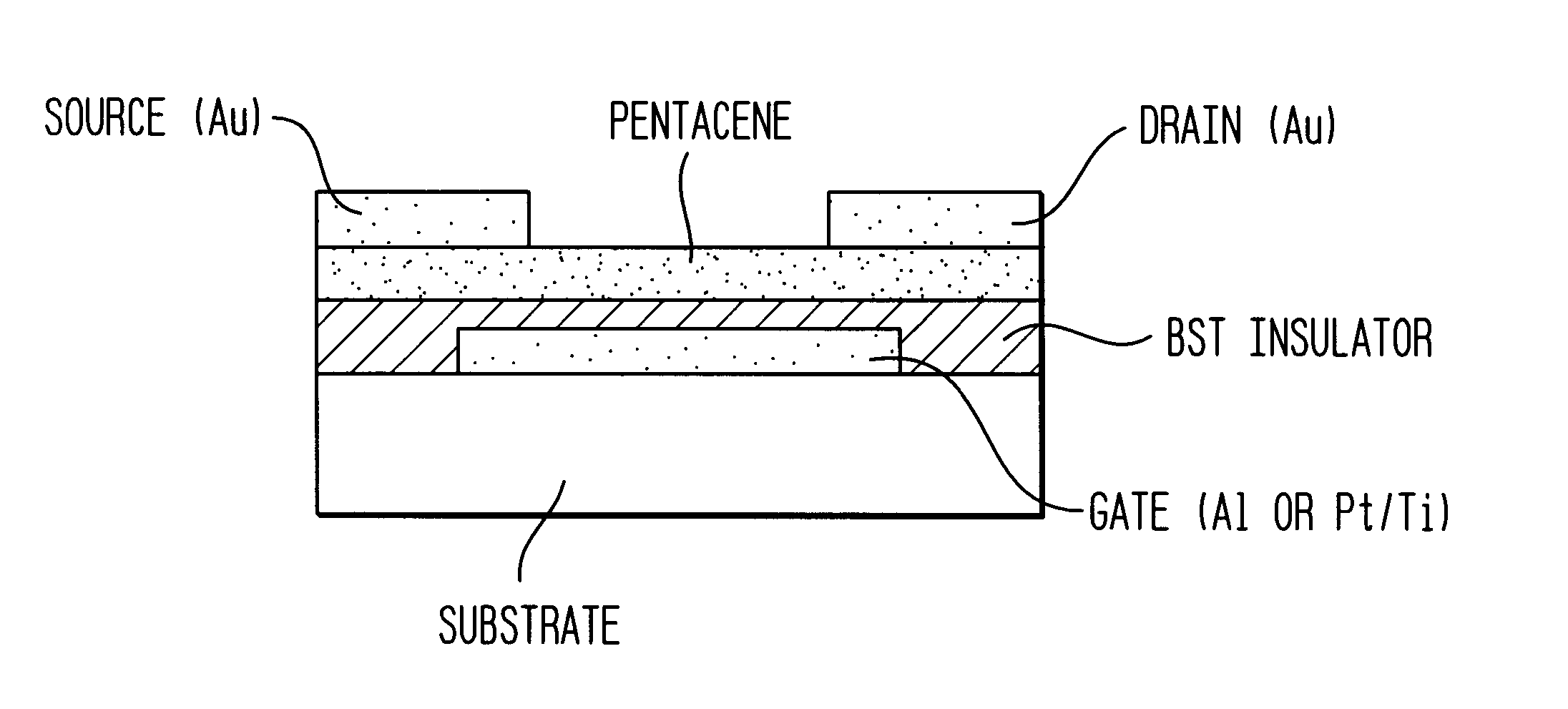

Thin-film field-effect transistor with organic semiconductor requiring low operating voltages

InactiveUS6344660B1Reduce thicknessImprove mobilityTransistorSolid-state devicesDisplay deviceFlat panel display

A thin film transistor (TFT) device structure based on an organic semiconductor material, that exhibits a high field effect mobility, high current modulation and a low sub-threshold slope at lower operating voltages than the current state of the art organic TFT devices. The structure comprises a suitable substrate disposed with he following sequence of features: a set of conducting gate electrodes covered with a high dielectric constant insulator, a layer of the organic semiconductor, sets of electrically conducting source and drain electrodes corresponding to each of the gate lines, and an optional passivation layer that can overcoat and protect the device structure. Use of high dielectric constant gate insulators exploits the unexpected gate voltage dependence of the organic semiconductor to achieve high field effect mobility levels at very low operating voltages. Judicious combinations of the choice of this insulator material and the means to integrate it into the TFT structure are taught that would enable easy fabrication on glass or plastic substrates and the use of such devices in flat panel display applications.

Owner:GLOBALFOUNDRIES INC

Operation scheme for programming charge trapping non-volatile memory

ActiveUS20050281085A1Shorten the timeImprove device performanceRead-only memoriesDigital storageHemt circuitsEngineering

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash. The method includes determining a data value from one of more than two data values to be stored in the memory cell, and applying a gate voltage to the control gate at one of a predetermined set of gate voltage levels selected in response to the determined data value. Programming parameters are controlled to establish a self-converging threshold state that is determined by the selected gate voltage. In this manner, the threshold voltage converges on a target threshold corresponding with the determined data value for the memory cell. Program verify operations are reduced or eliminated in various embodiments, reducing the overall time required for the program operation, and improving device performance. A second portion of the program operation can include verify operations to improve threshold margins across the array.

Owner:MACRONIX INT CO LTD

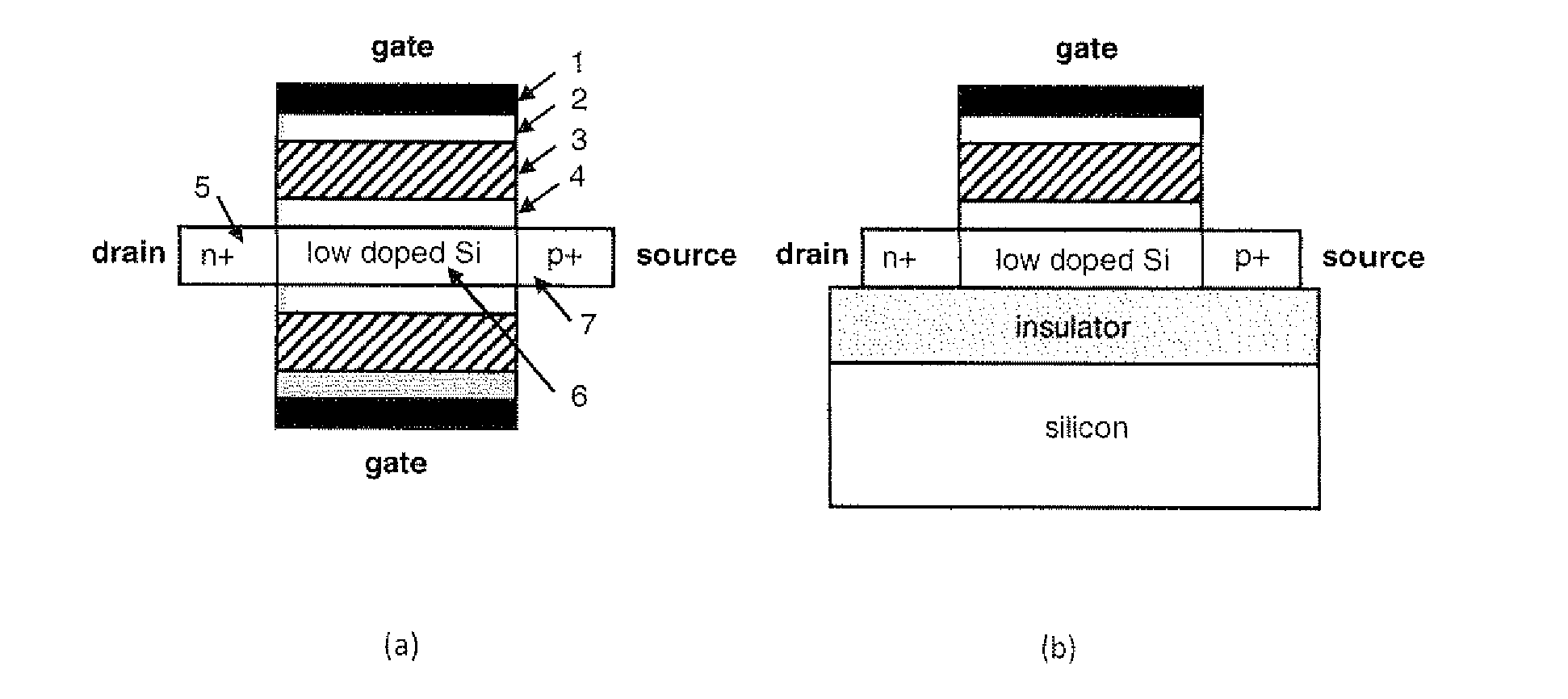

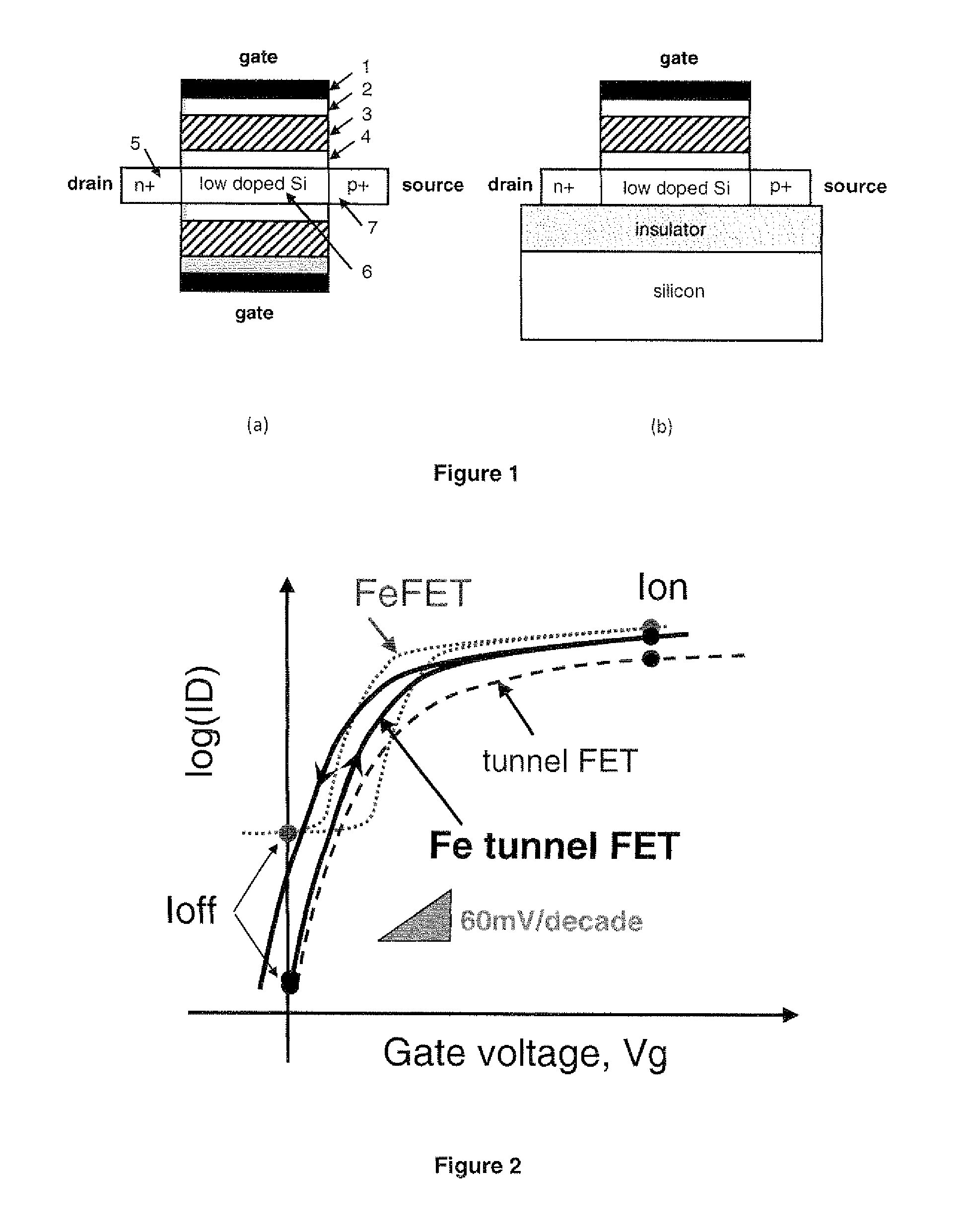

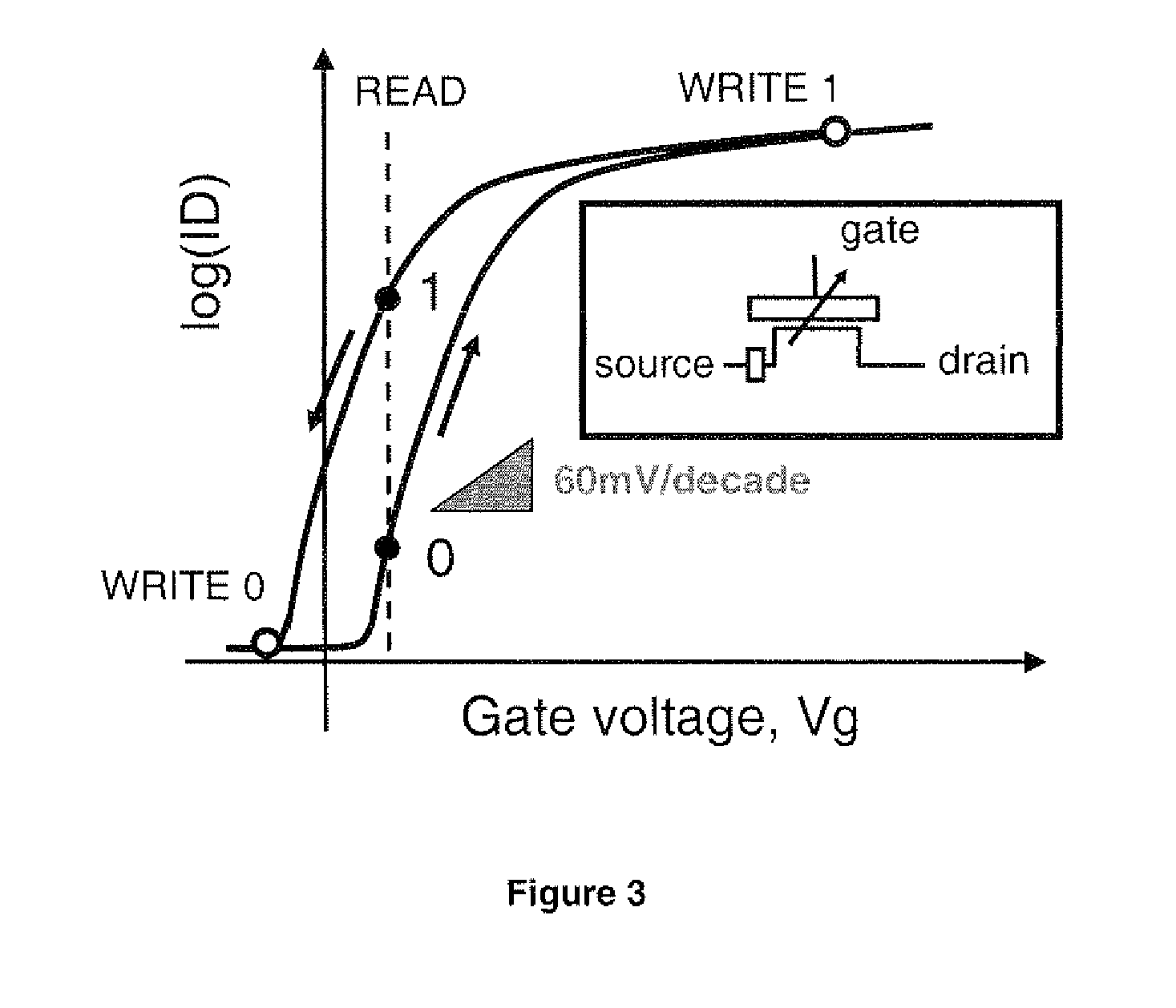

Ferroelectric tunnel fet switch and memory

ActiveUS20100140589A1Reduce power consumptionLimited successMaterial nanotechnologySemiconductor/solid-state device detailsCapacitanceSubthreshold swing

A Ferroelectric tunnel FET switch as ultra-steep (abrupt) switch with subthreshold swing better than the MOSFET limit of 60 mV / decade at room temperature combining two key principles: ferroelectric gate stack and band-to-band tunneling in gated p-i-n junction, wherein the ferroelectric material included in the gate stack creates, due to dipole polarization with increasing gate voltage, a positive feedback in the capacitive coupling that controls the band-to-band (BTB) tunneling at the source junction of a silicon p-i-n reversed bias structure, wherein the combined effect of BTB tunneling and ferroelectric negative capacitance offers more abrupt off-on and on-off transitions in the present proposed Ferroelectric tunnel FET than for any reported tunnel FET or any reported ferroelectric FET.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

Operation scheme for programming charge trapping non-volatile memory

ActiveUS20050219906A1Shorten the timeImprove device performanceRead-only memoriesDigital storageEngineeringGate voltage

A circuit and method for self-converging programming of a charge storage memory cell, such as NROM or floating gate flash. The method includes determining a data value from one of more than two data values to be stored in the memory cell, and applying a gate voltage to the control gate at one of a predetermined set of gate voltage levels selected in response to the determined data value. Programming parameters are controlled to establish a self-converging threshold state that is determined by the selected gate voltage. In this manner, the threshold voltage converges on a target threshold corresponding with the determined data value for the memory cell. Program verify operations are reduced or eliminated in various embodiments, reducing the overall time required for the program operation, and improving device performance. A second portion of the program operation can include verify operations to improve threshold margins across the array.

Owner:MACRONIX INT CO LTD

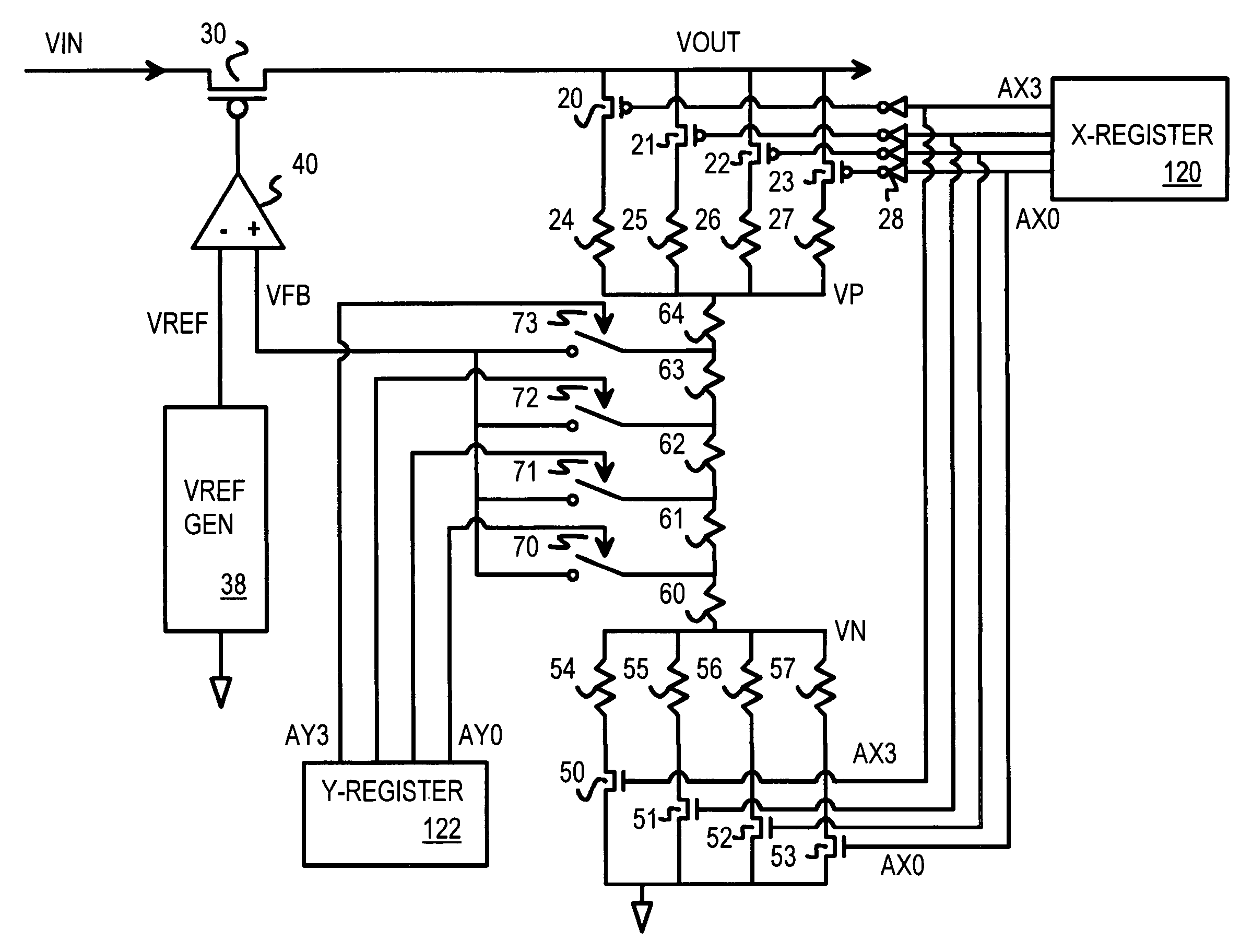

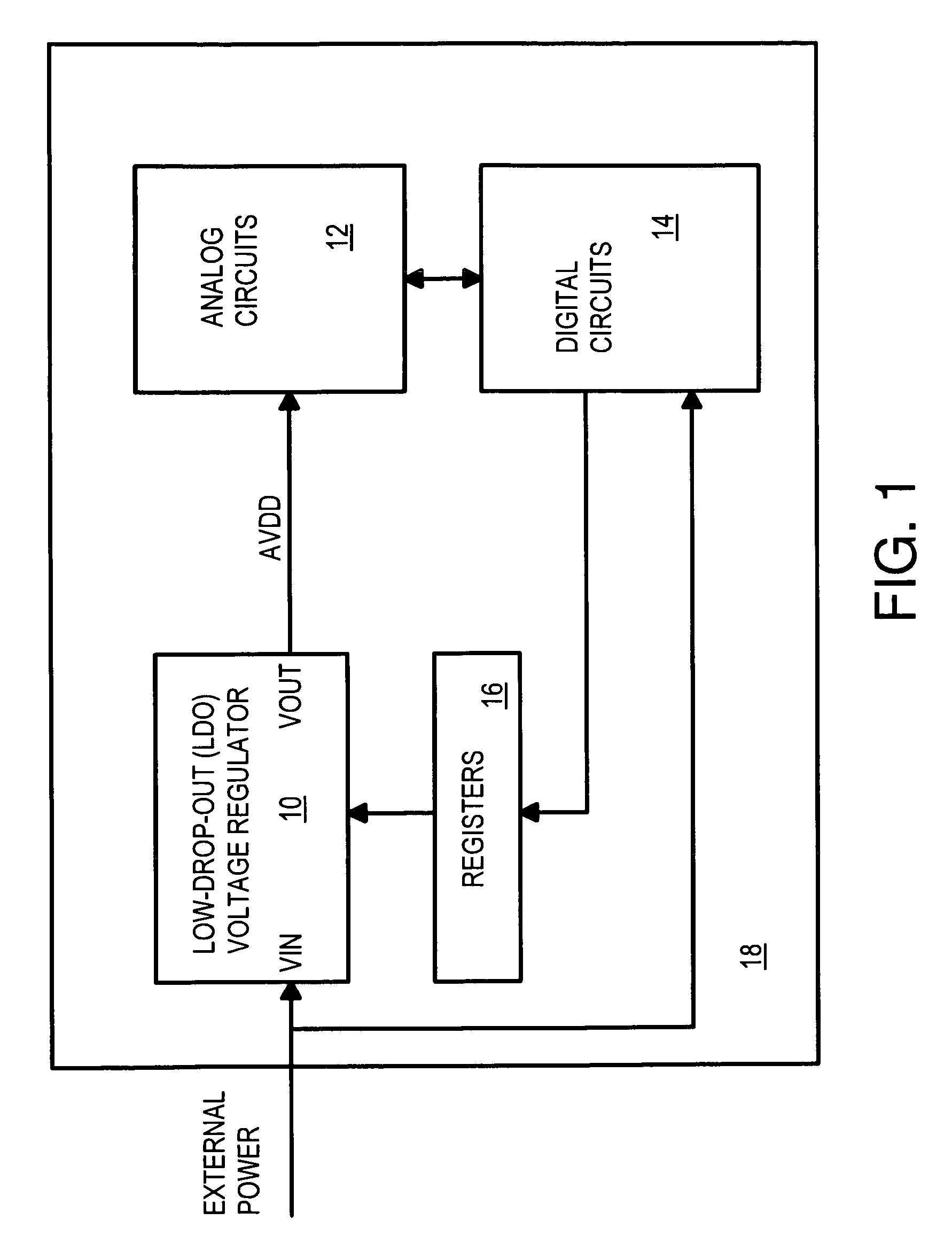

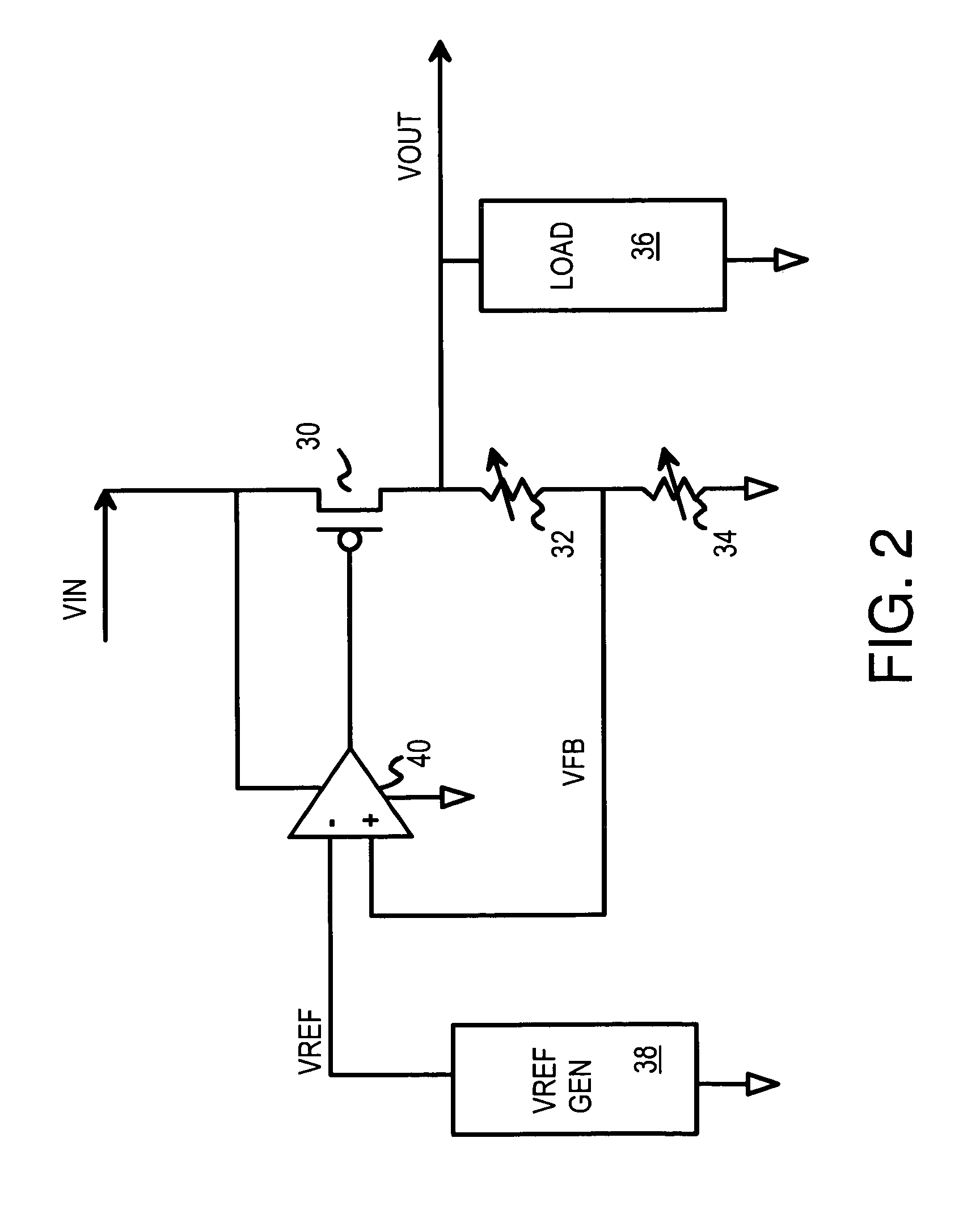

Low dropout voltage regulator with programmable on-chip output voltage for mixed signal embedded applications

ActiveUS7619402B1Multiple-port networksOne-port networksElectrical resistance and conductanceVoltage generator

A programmable voltage generator has software-programmable registers that may be decoded to generate control bits that turn on select transistors that control a variable resistor network. An external power voltage is input to a regulator transistor, which has a channel resistance controlled by a gate voltage. The channel resistance of the regulator transistor produces a regulated voltage as an output. An op amp compares a reference voltage to a feedback voltage to generate the gate voltage. The feedback voltage is taken from a tap within the variable resistor network. The variable resistor network has select transistors that select one resistor between the regulated voltage and an upper node, and that select one resistor between a lower node and ground. Switches select a tap within a series of resistors between the upper and lower nodes. Y (fine) control bits select the tap while X (coarse) control bits enable select transistors.

Owner:HONG KONG APPLIED SCI & TECH RES INST

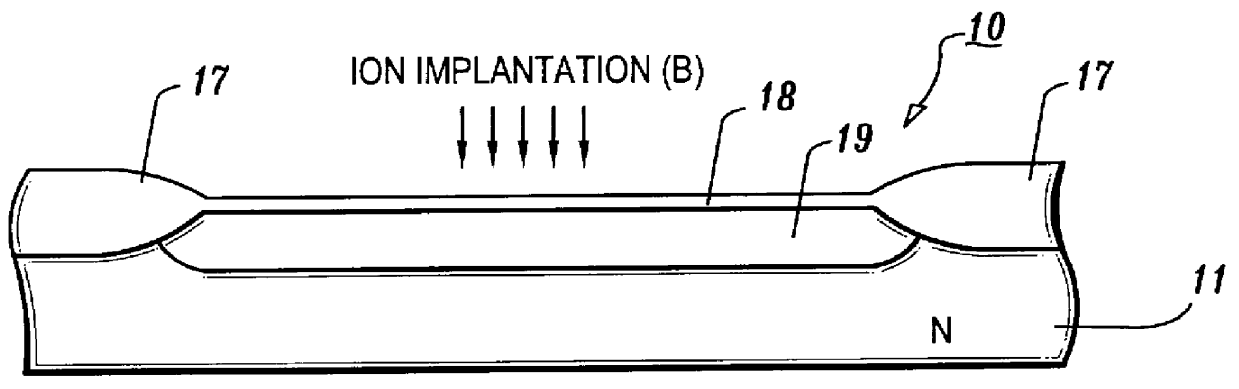

Semiconductor device having opposite-polarity region under channel

InactiveUS6163053ASemiconductor/solid-state device manufacturingSemiconductor devicesElectrical polarityEngineering

A semiconductor device and fabrication method thereof are provided, which include an opposite-polarity region formed in a predetermined location under a gate channel region, having a conductive property opposite to that of a surrounding well region. The gate voltage is controlled so that a second depleted layer region is induced concurrently with the opposite-polarity region by the applied gate voltage and can be coupled with a first depleted region which is formed under the channel region and is controllable by the applied gate voltage. In this structure of the semiconductor device, drain current of the device is rendered more responsive to the applied gate voltage, and leakage currents at a certain applied drain voltage and at zero gate voltage are reduced, thereby reducing the standby currents of the semiconductor device.

Owner:RICOH KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com