Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

703 results about "Conduction current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

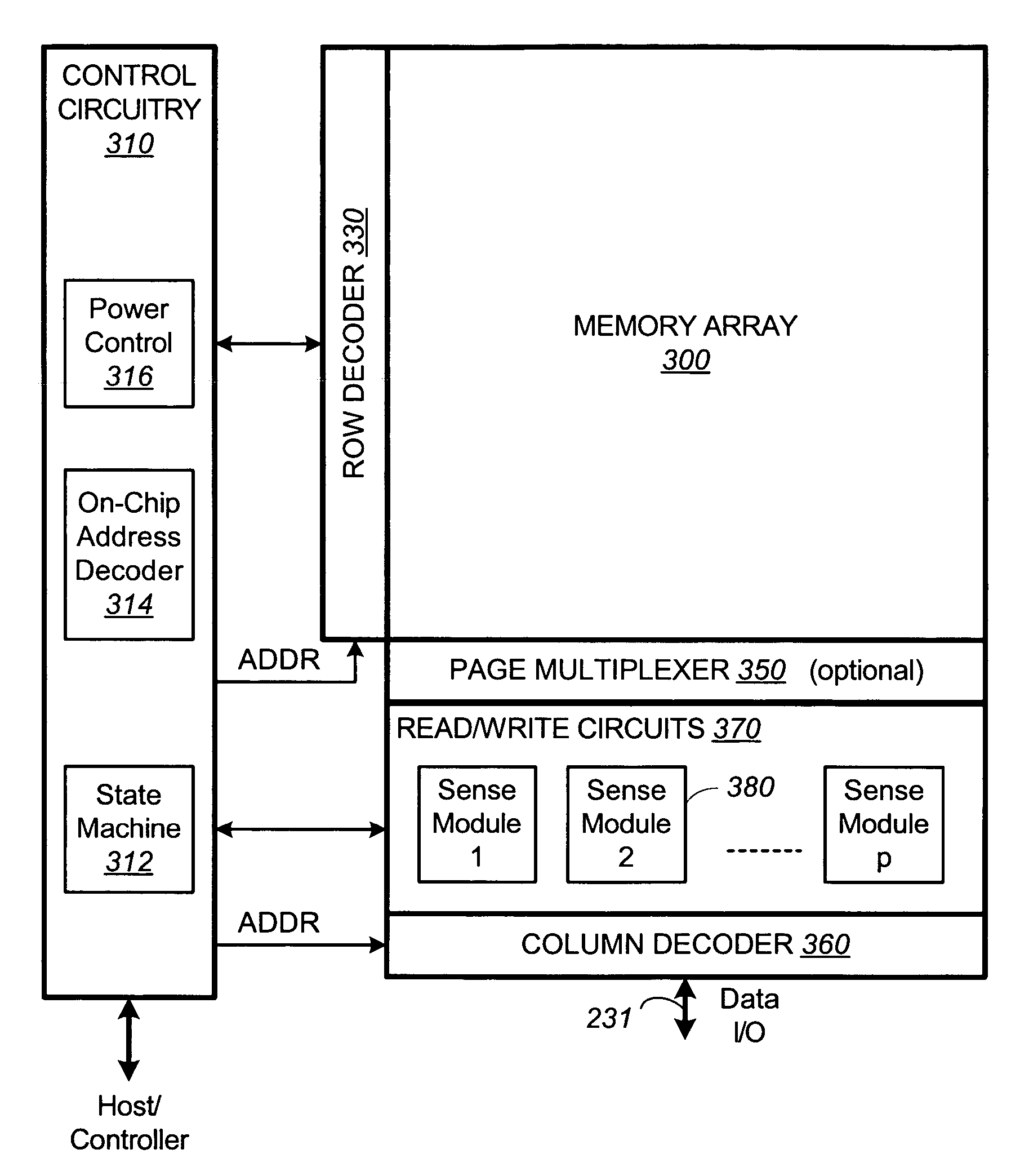

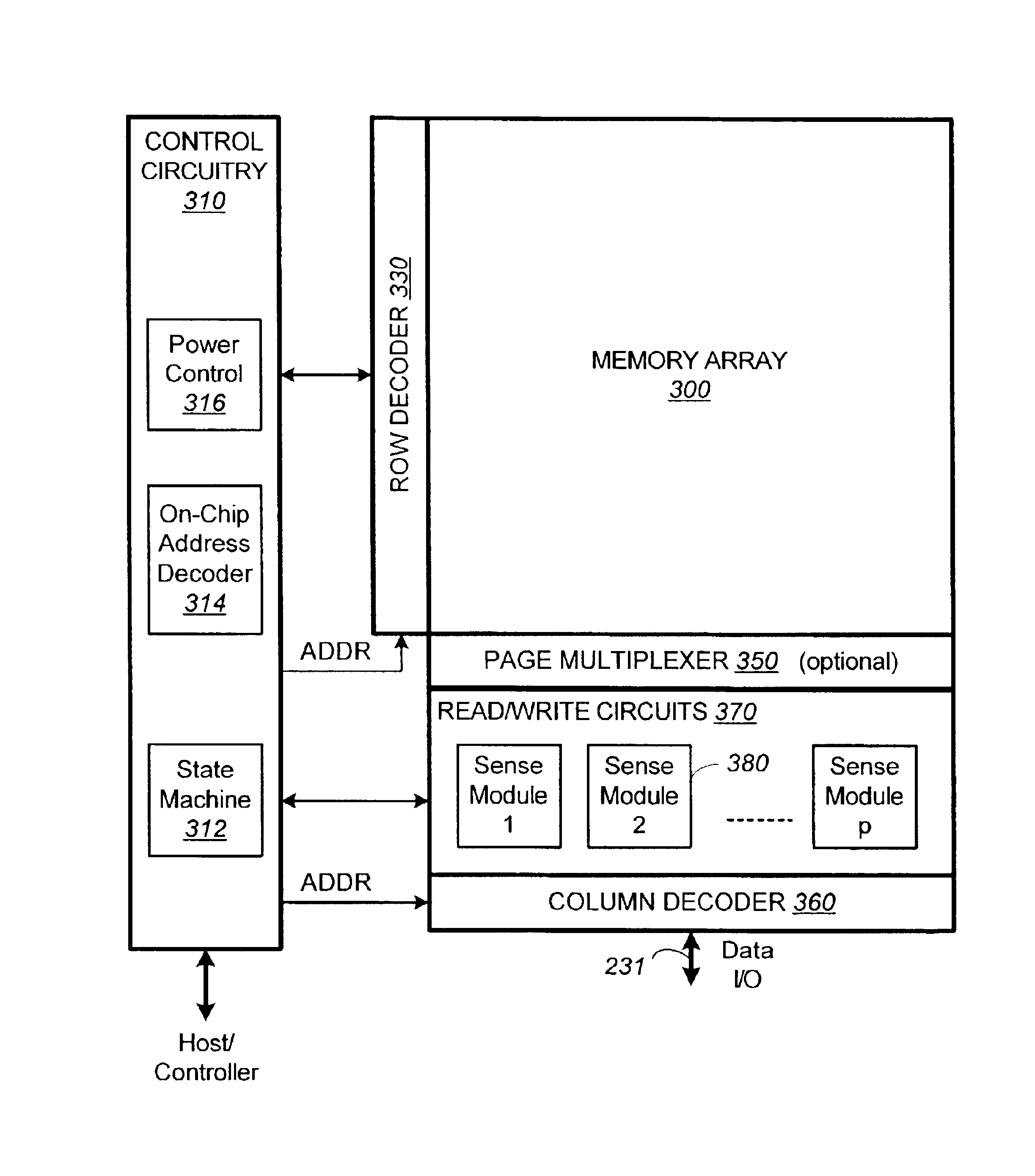

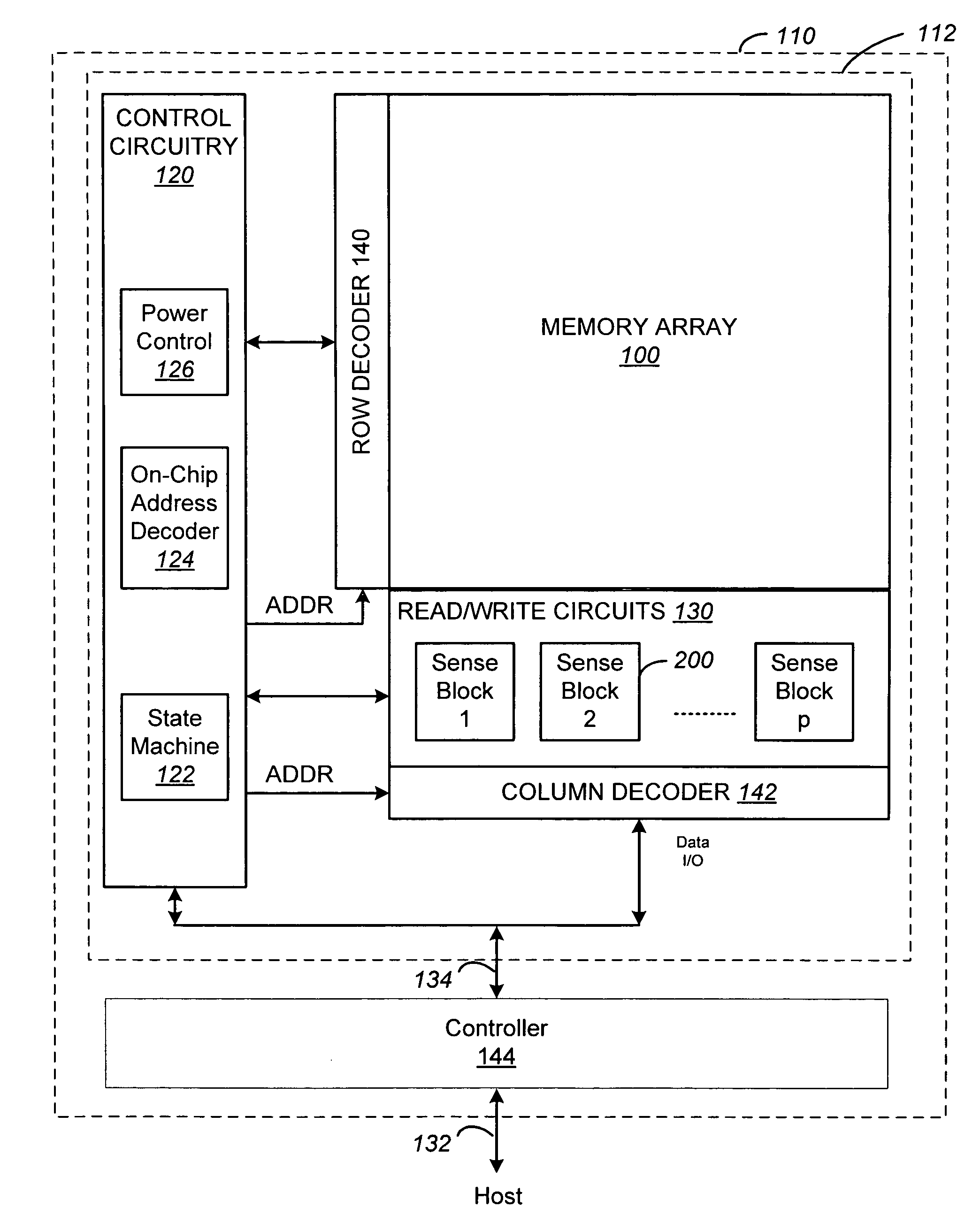

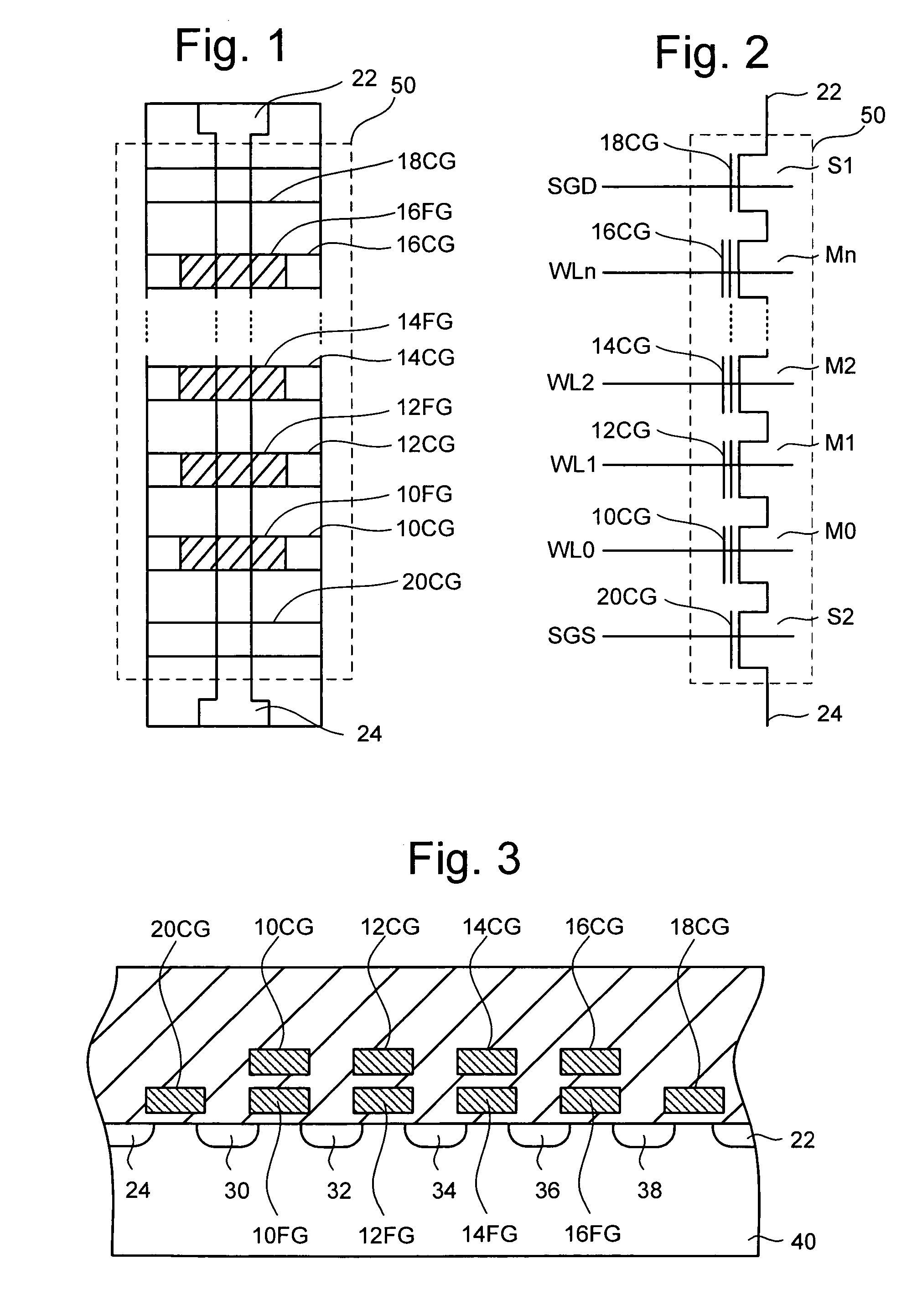

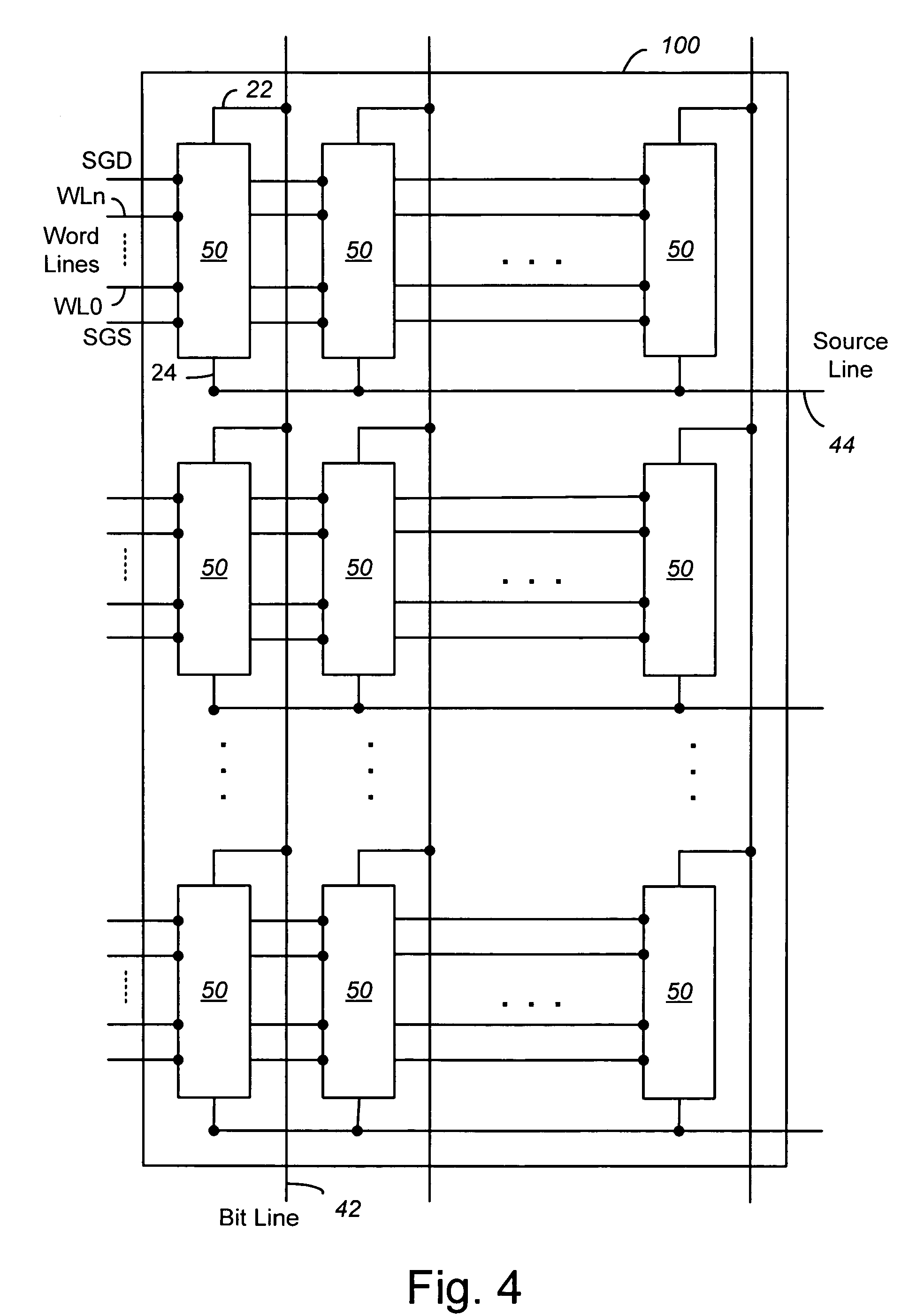

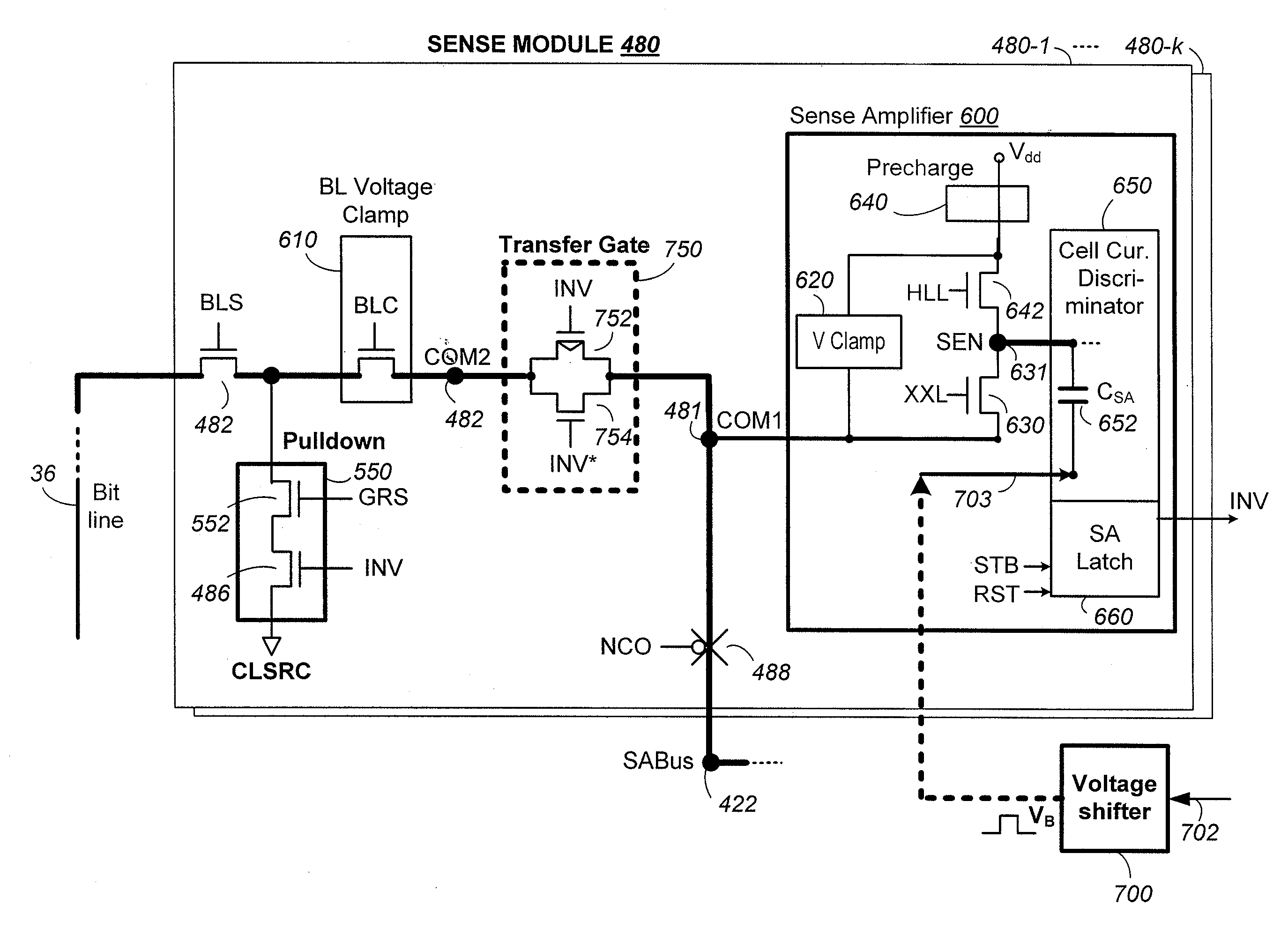

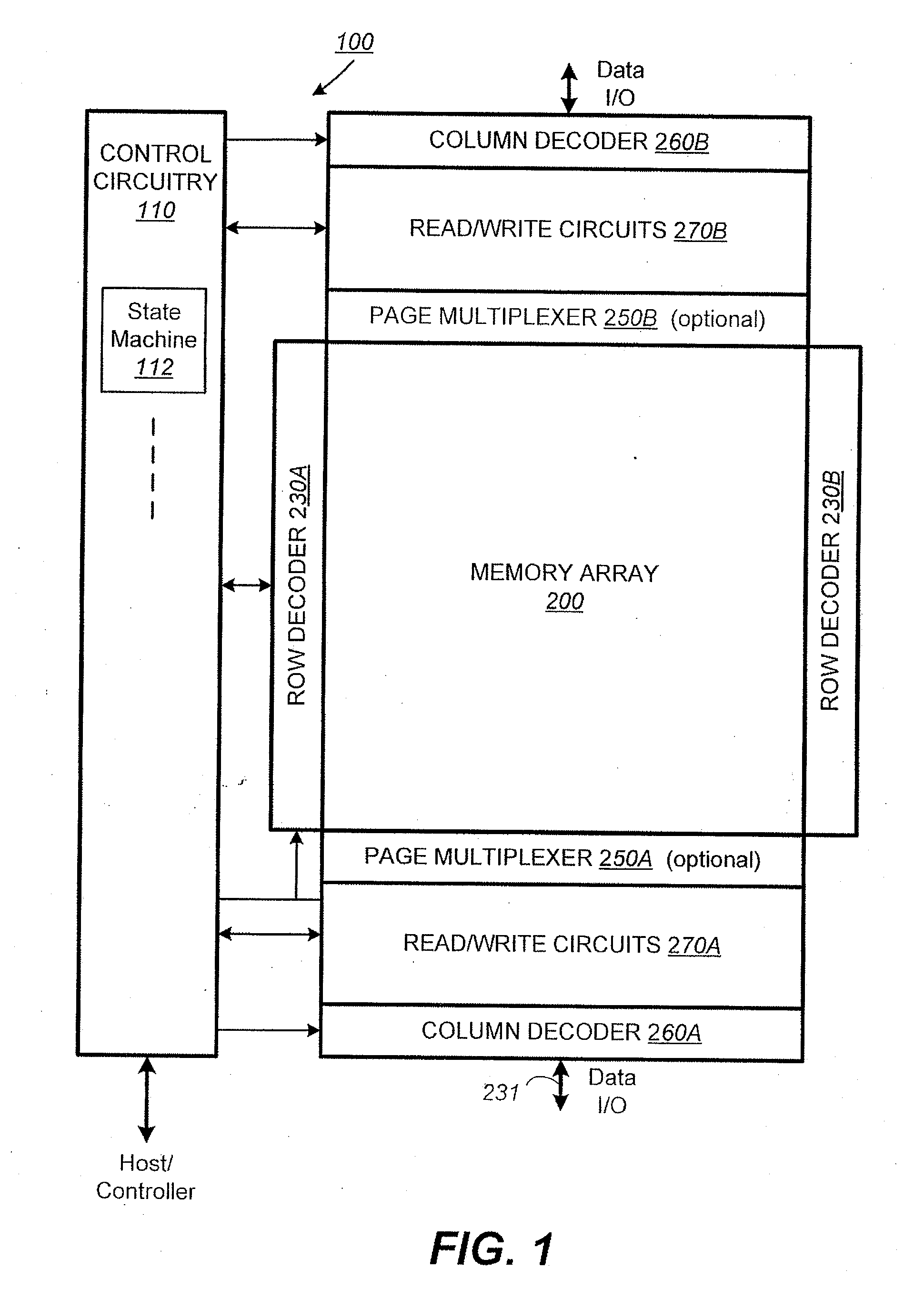

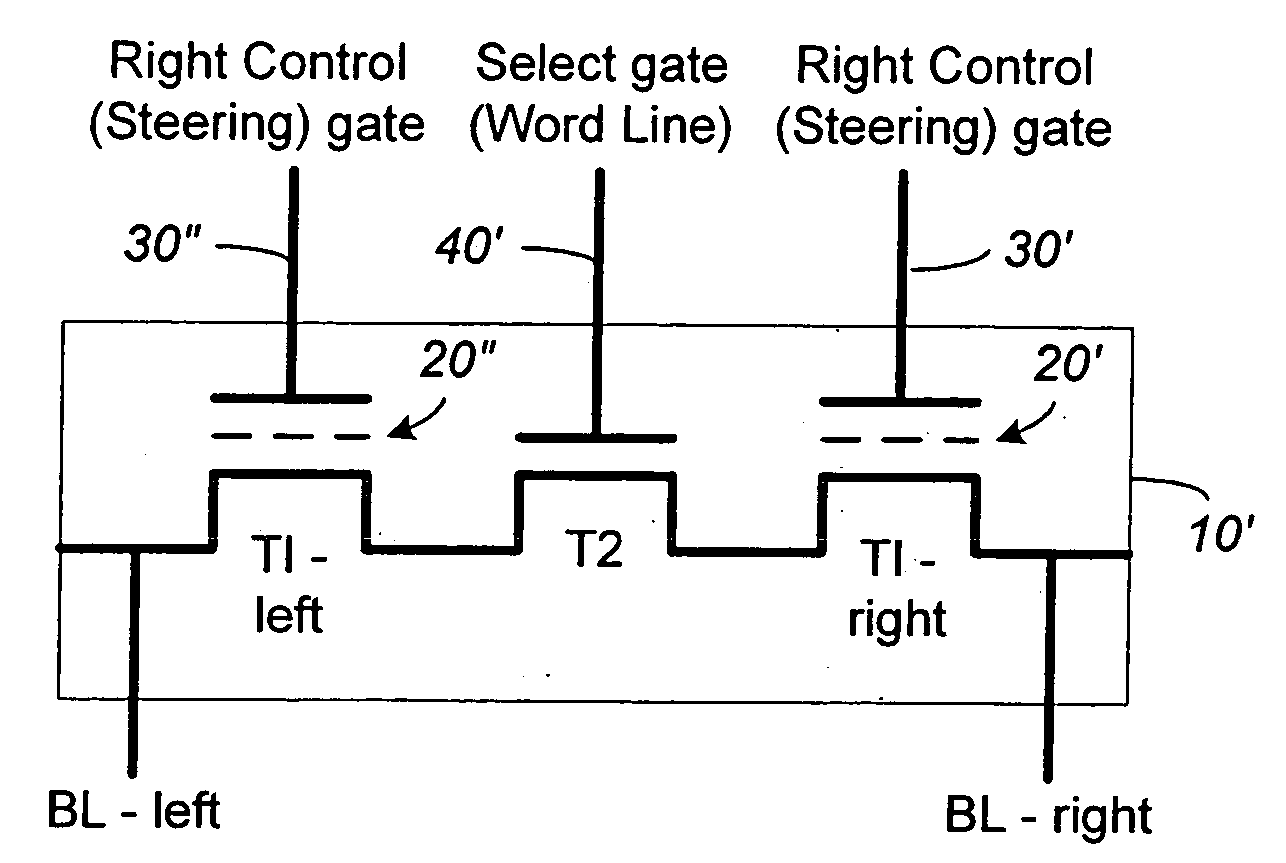

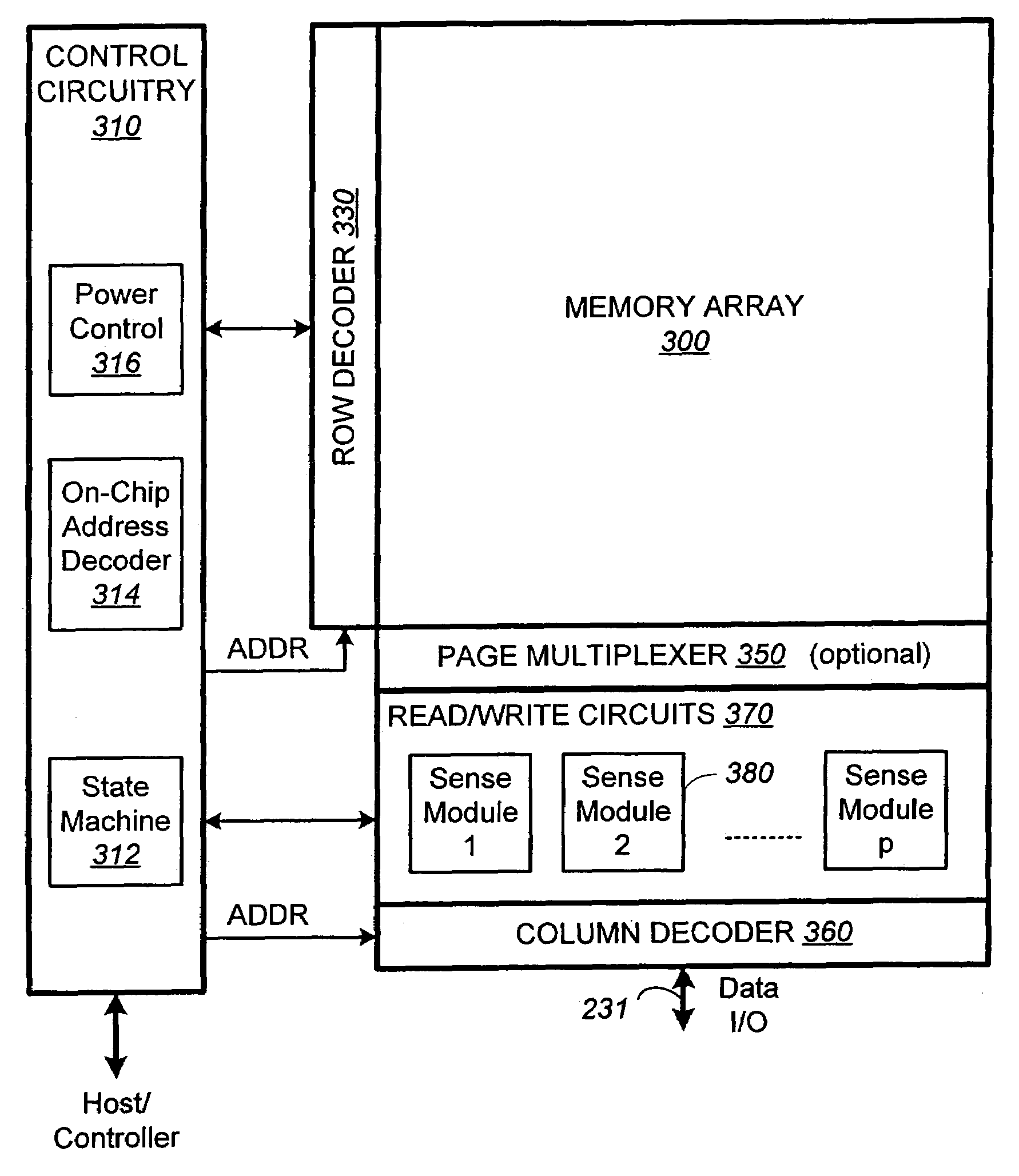

Memory sensing circuit and method for low voltage operation

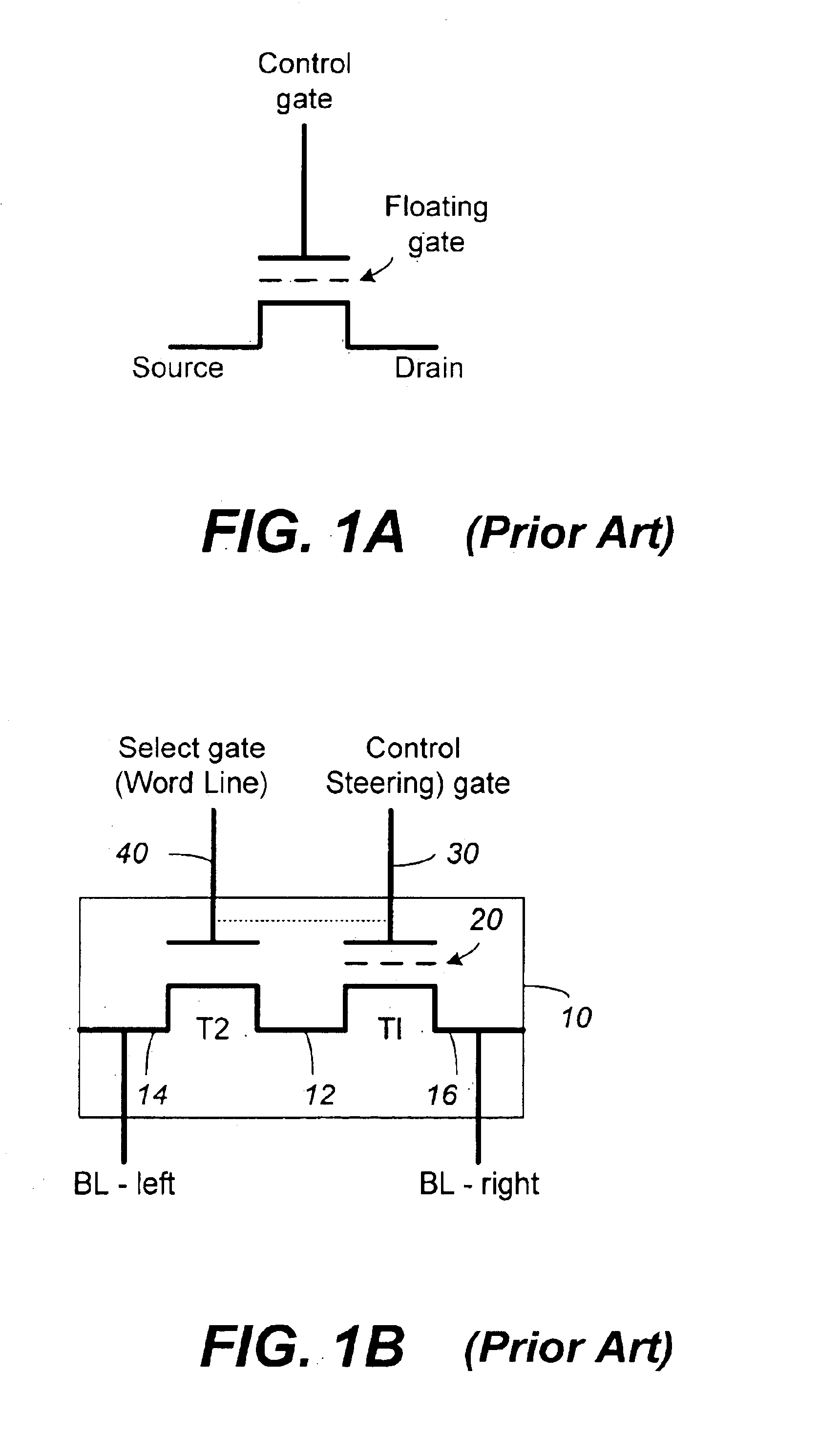

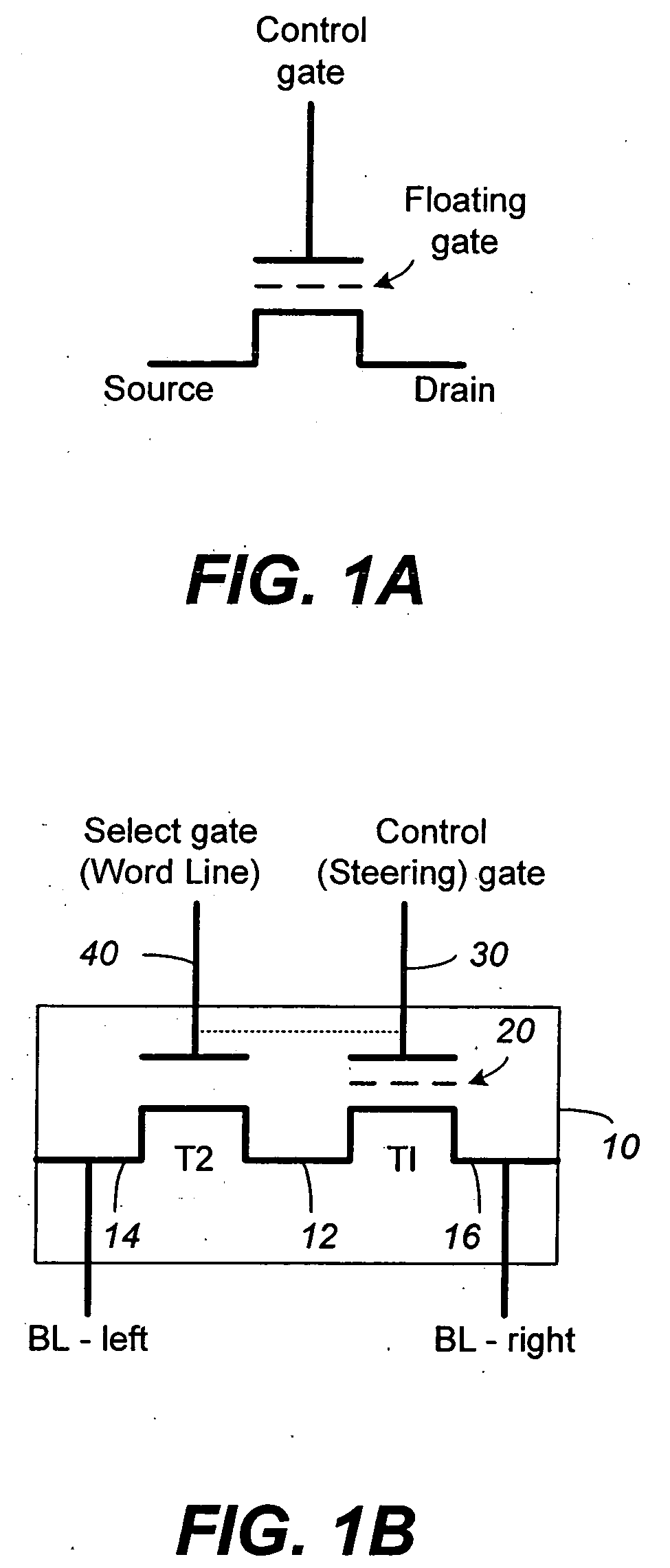

InactiveUS20050169082A1Large capacityImprove performanceRead-only memoriesDigital storageConduction currentConstant voltage

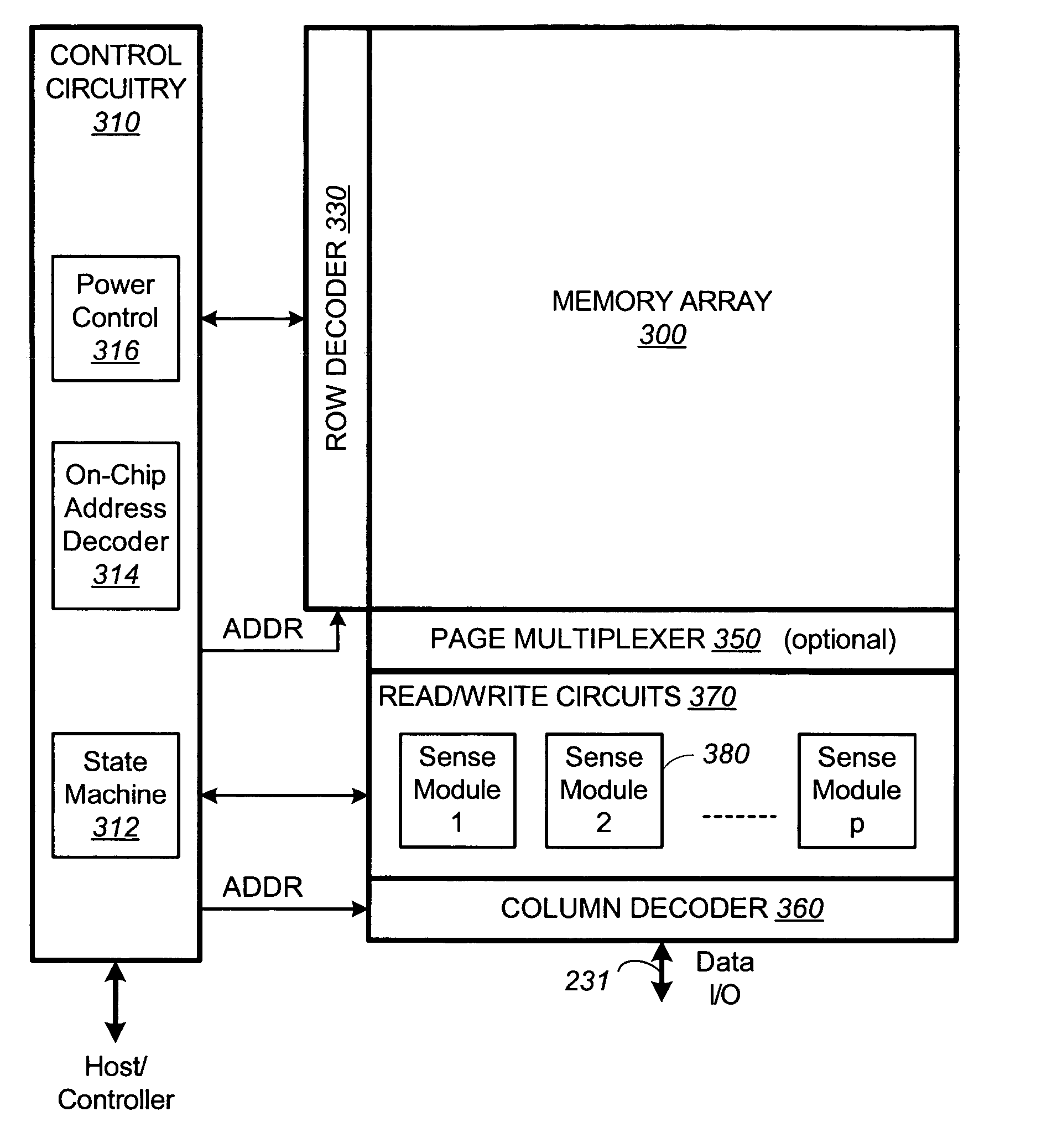

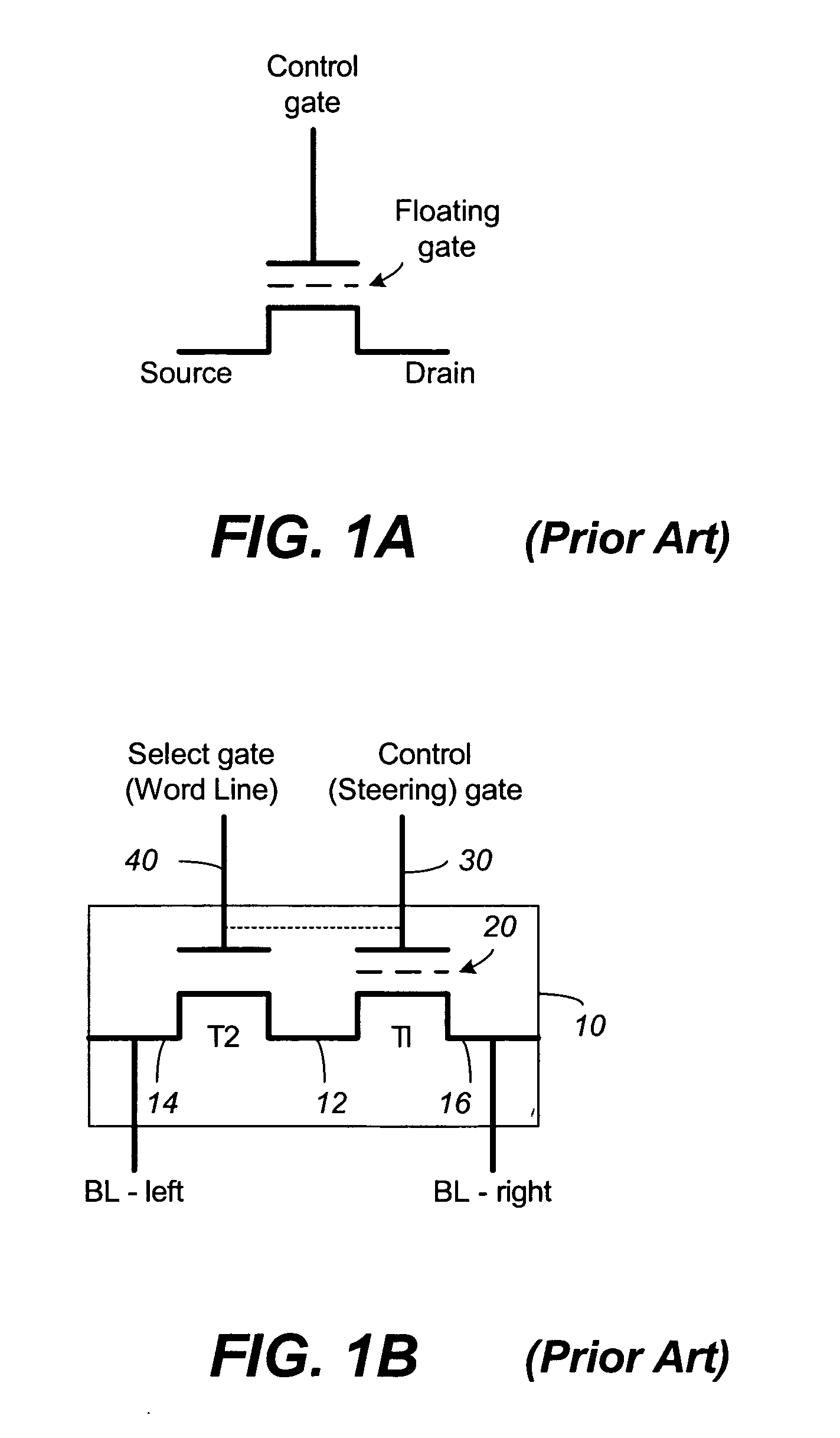

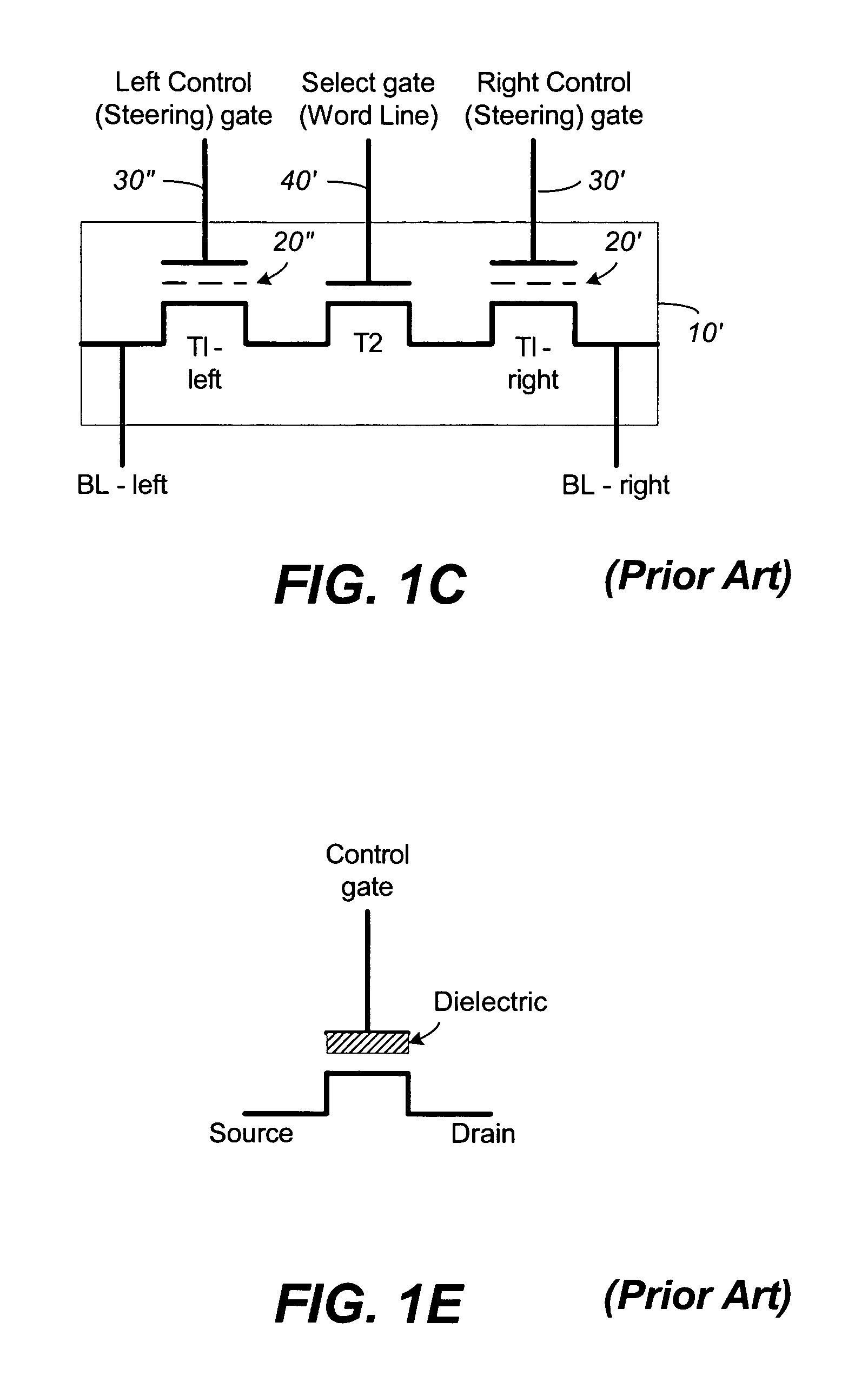

A sensing module operates with a sense amplifier sensing a conduction current of a memory cell via a coupled bit line under constant voltage condition in order to minimize bit-line to bit-line coupling. The rate of discharge of a dedicated capacitor as measured by a change in the voltage drop there across in a predetermined period is used to indicate the magnitude of the conduction current. The voltage cannot drop below a minimum level imposed by a circuit for maintaining the constant voltage condition on the bit line. A voltage shifter is used to boost the voltage during the discharge and to unboost the voltage after the discharge, so that the change in voltage drop properly reflects the rate of discharge without running into the minimum level.

Owner:SANDISK TECH LLC

Reference sense amplifier for non-volatile memory

InactiveUS20060158947A1Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierReference current

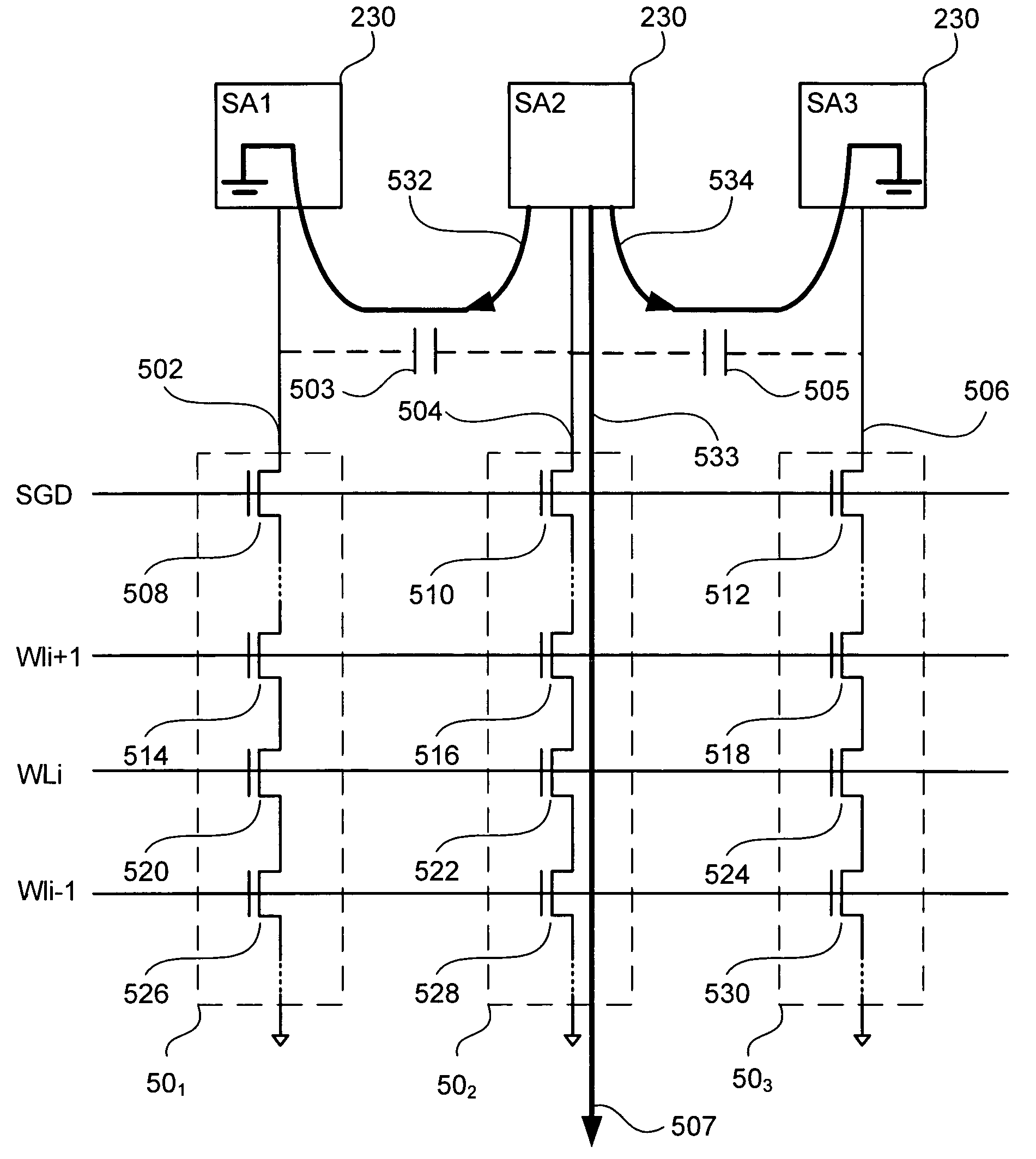

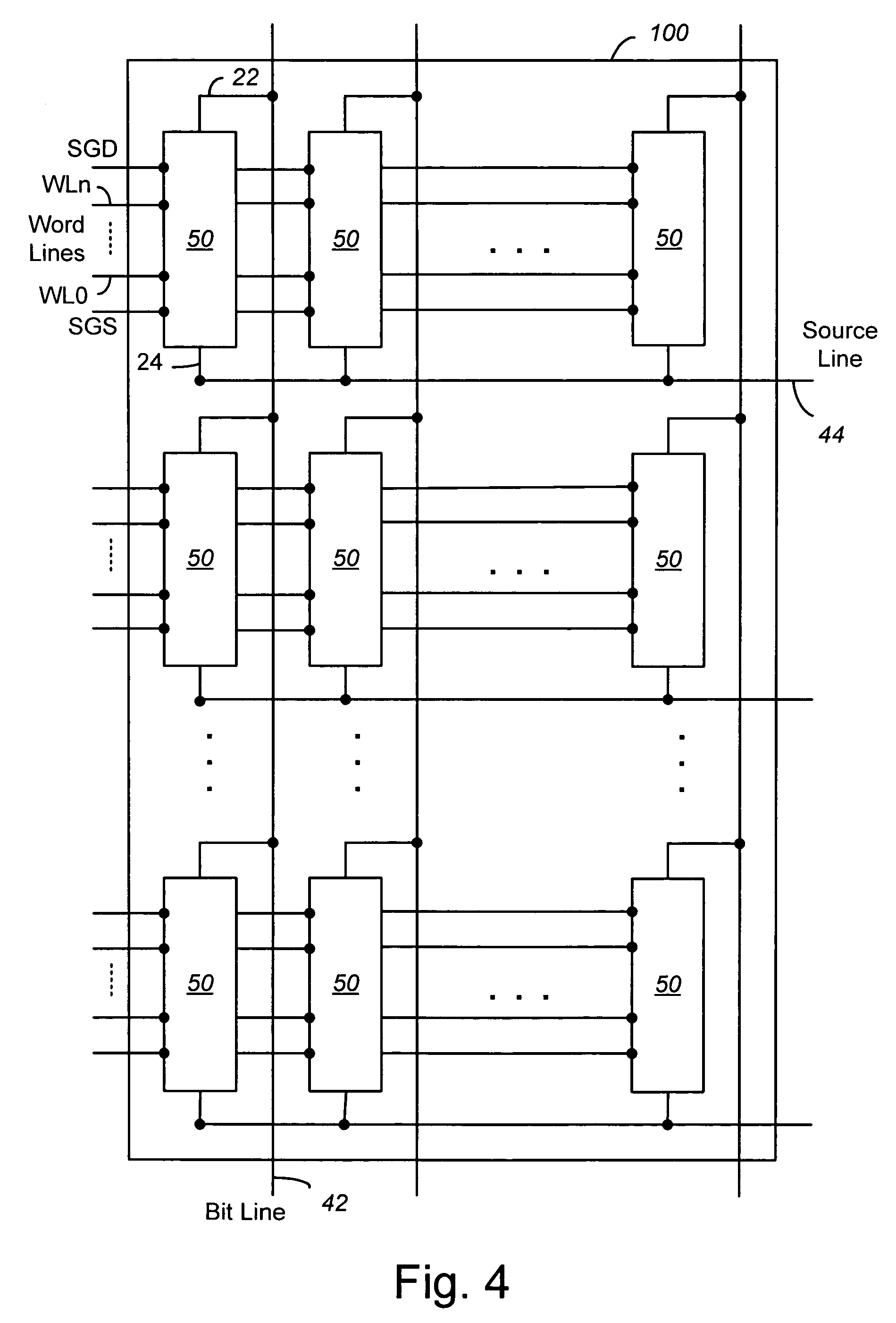

One or more sense amplifiers for sensing the conduction current of non-volatile memory is controlled by signals that are timed by a reference sense amplifier having similar characteristics and operating conditions. In one aspect, a sensing period is determined by when the reference sense amplifier sensing a reference current detects an expected state. In another aspect, an integration period for an amplified output is determined by when the reference sense amplifier outputs an expected state. When these determined timings are used to control the one or more sense amplifiers, environment and systemic variations are tracked.

Owner:SANDISK TECH LLC

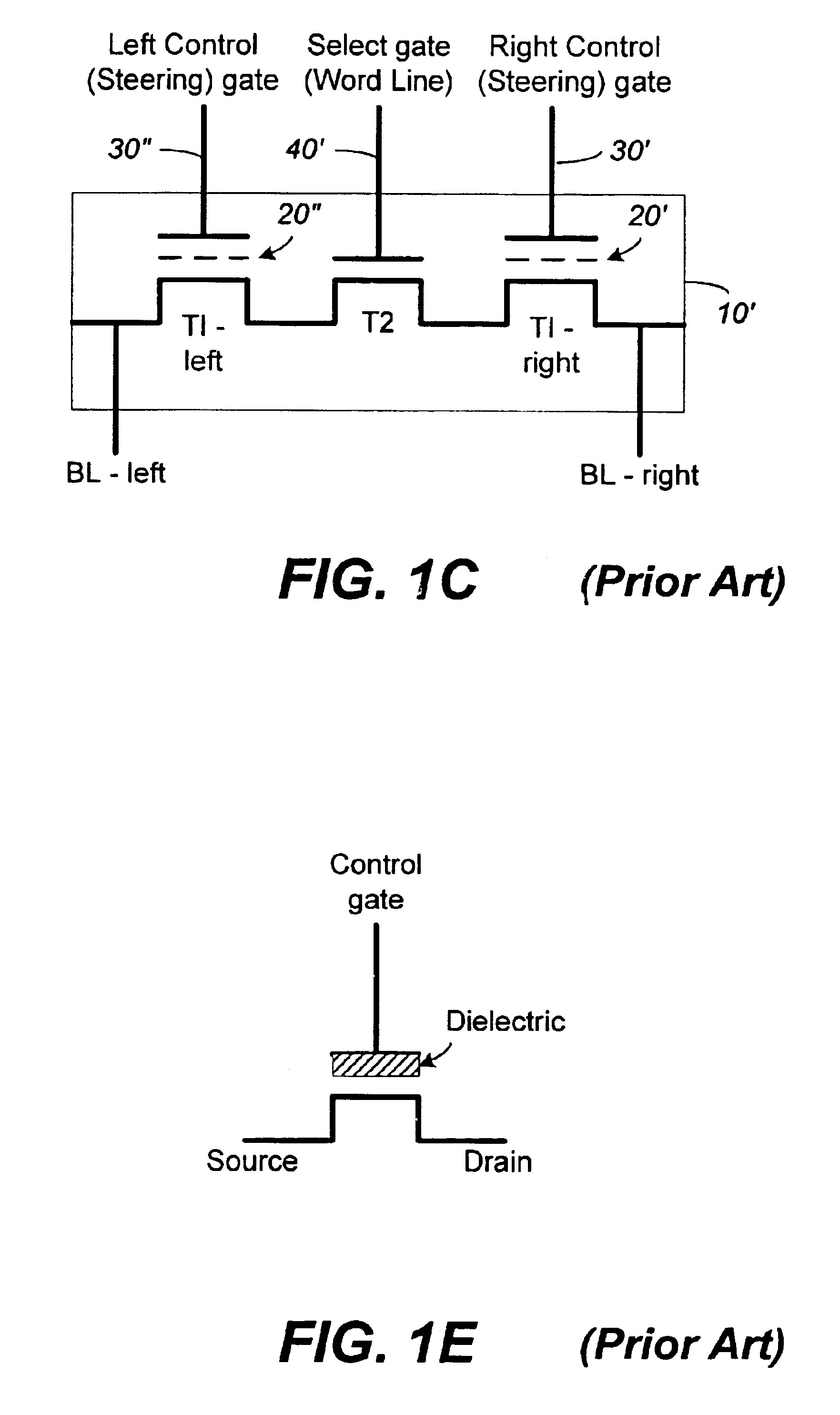

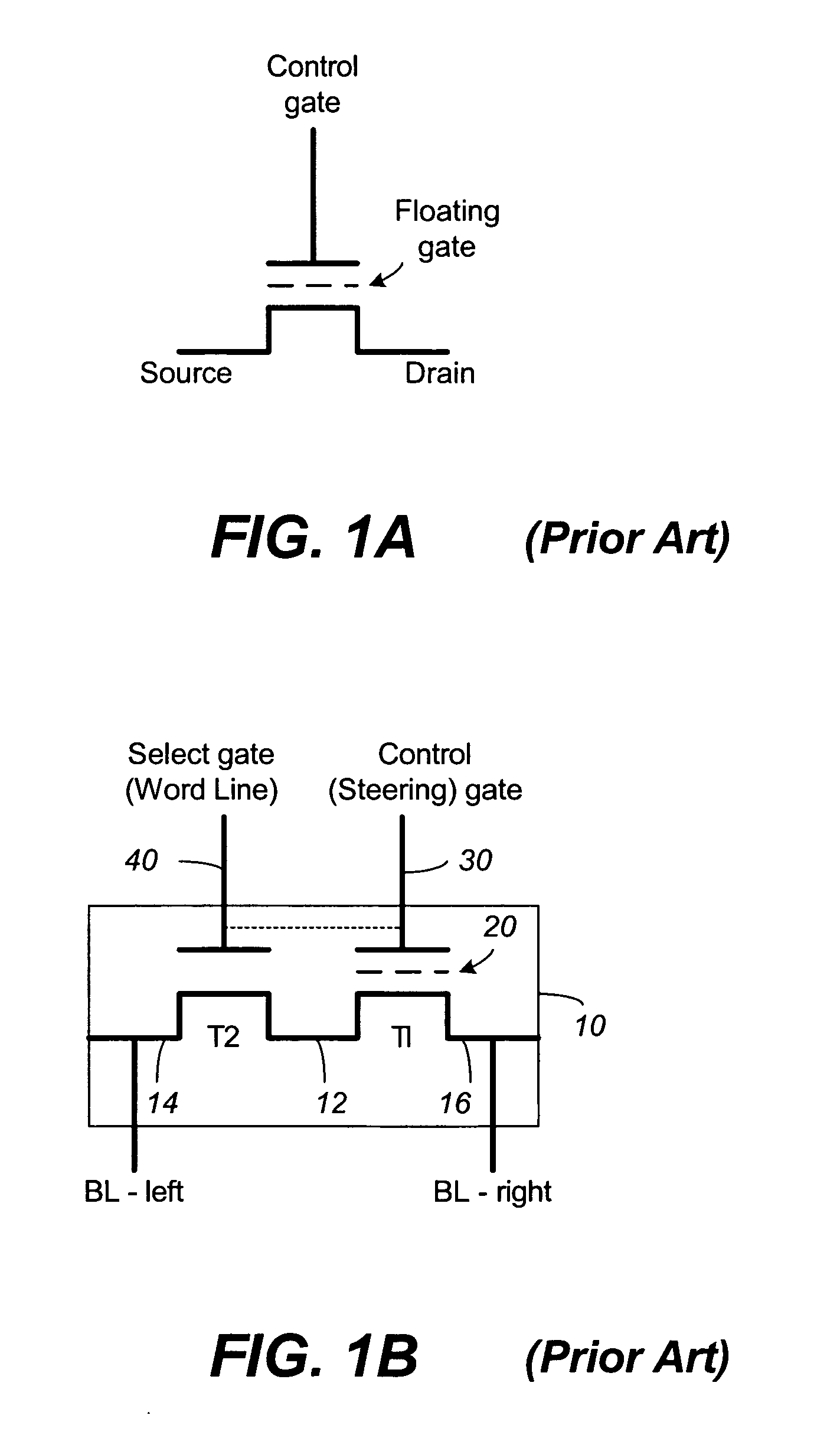

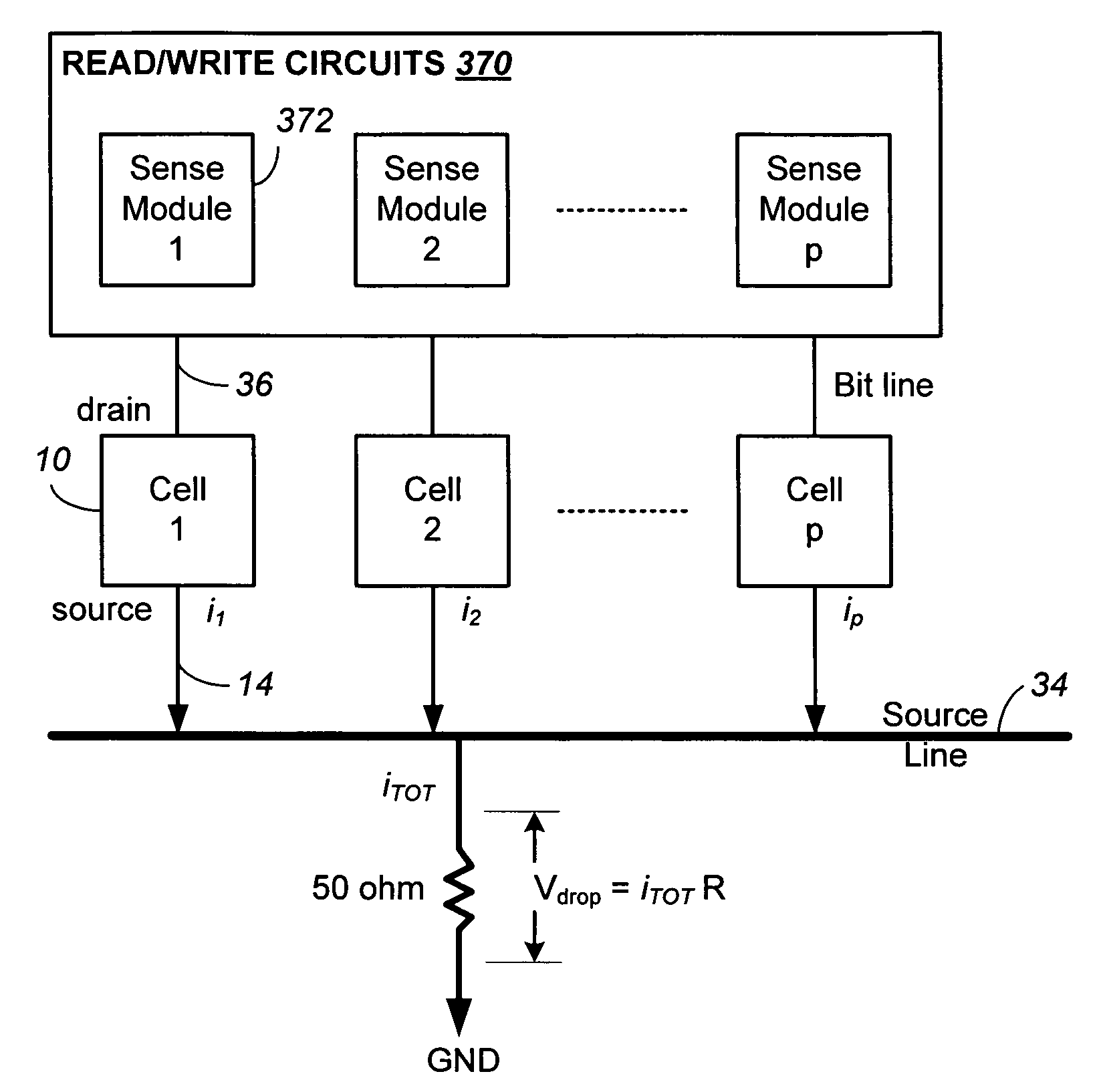

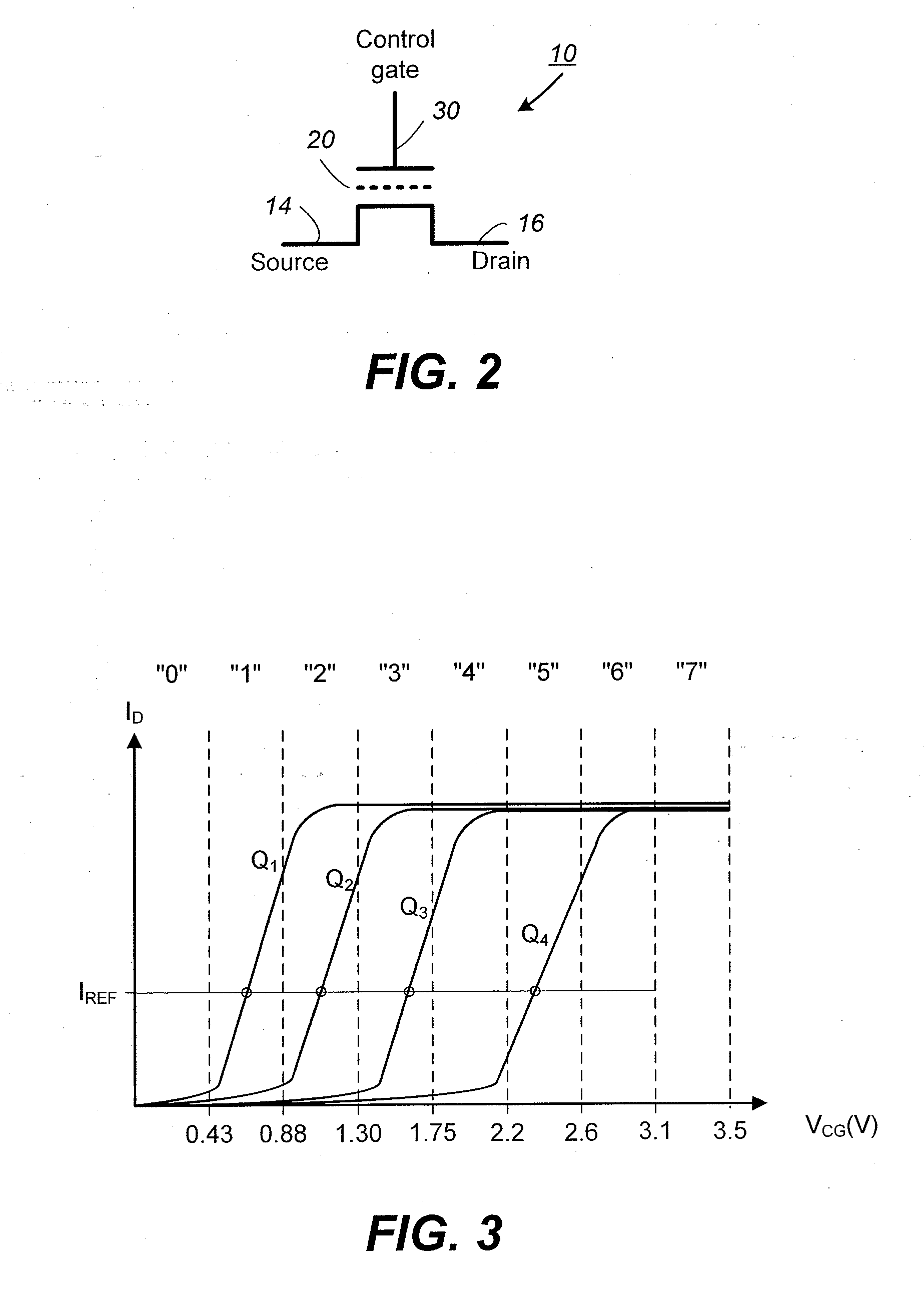

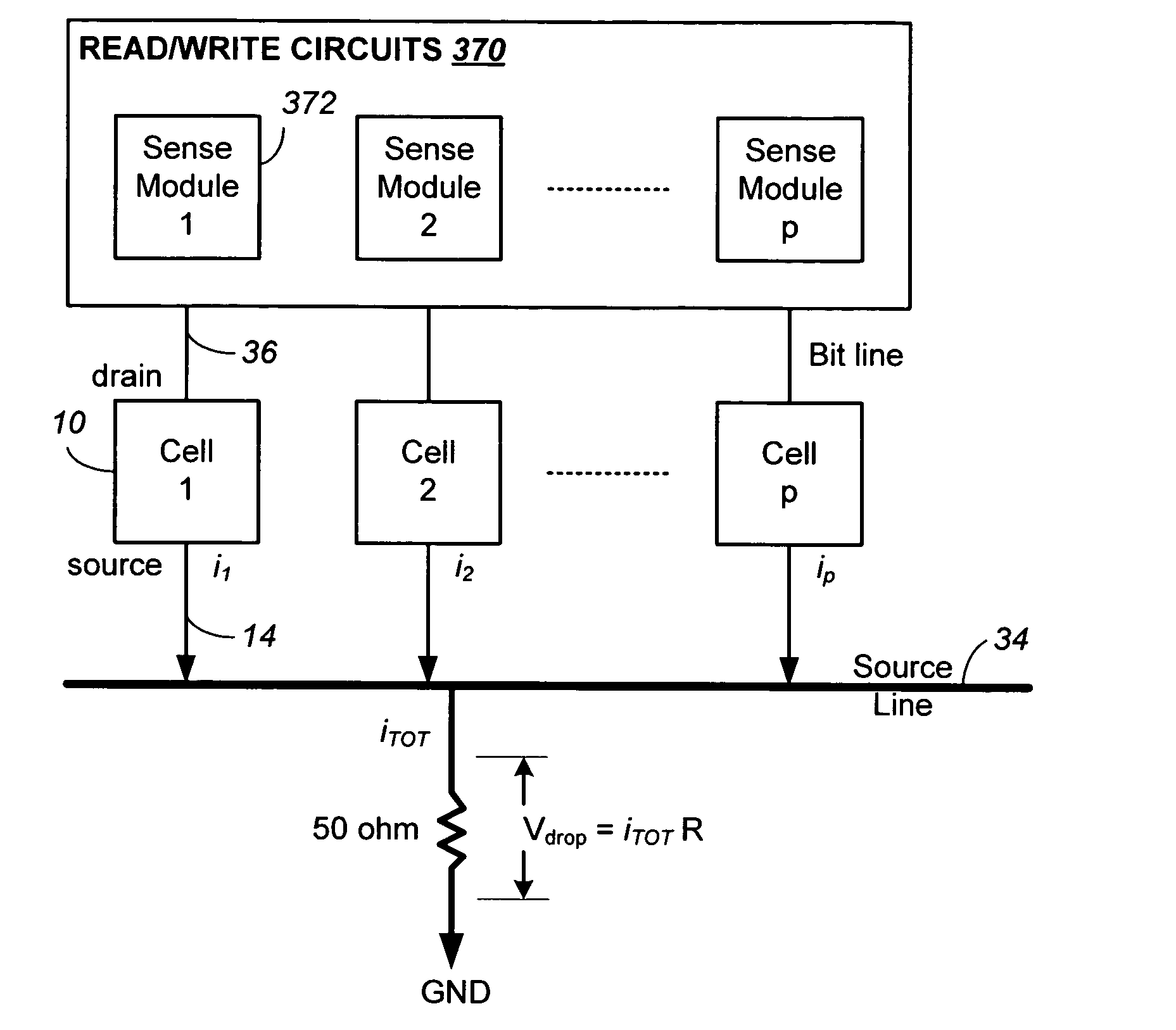

Non-volatile memory and method with improved sensing

InactiveUS7023736B2Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierMultiple pass

A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In particular, the identified memory cells are shut down after all sensing in the current pass have been completed. In this way the shutting down operation does not disturb the sensing operation. Sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells. In another aspect of sensing improvement, a reference sense amplifier is employed to control multiple sense amplifiers to reduce their dependence on power supply and environmental variations.

Owner:SANDISK TECH LLC

Memory sensing circuit and method for low voltage operation

InactiveUS7046568B2Large capacityImprove performanceRead-only memoriesDigital storageBit lineAudio power amplifier

A sensing module operates with a sense amplifier sensing a conduction current of a memory cell via a coupled bit line under constant voltage condition in order to minimize bit-line to bit-line coupling. The rate of discharge of a dedicated capacitor as measured by a change in the voltage drop there across in a predetermined period is used to indicate the magnitude of the conduction current. The voltage cannot drop below a minimum level imposed by a circuit for maintaining the constant voltage condition on the bit line. A voltage shifter is used to boost the voltage during the discharge and to unboost the voltage after the discharge, so that the change in voltage drop properly reflects the rate of discharge without running into the minimum level.

Owner:SANDISK TECH LLC

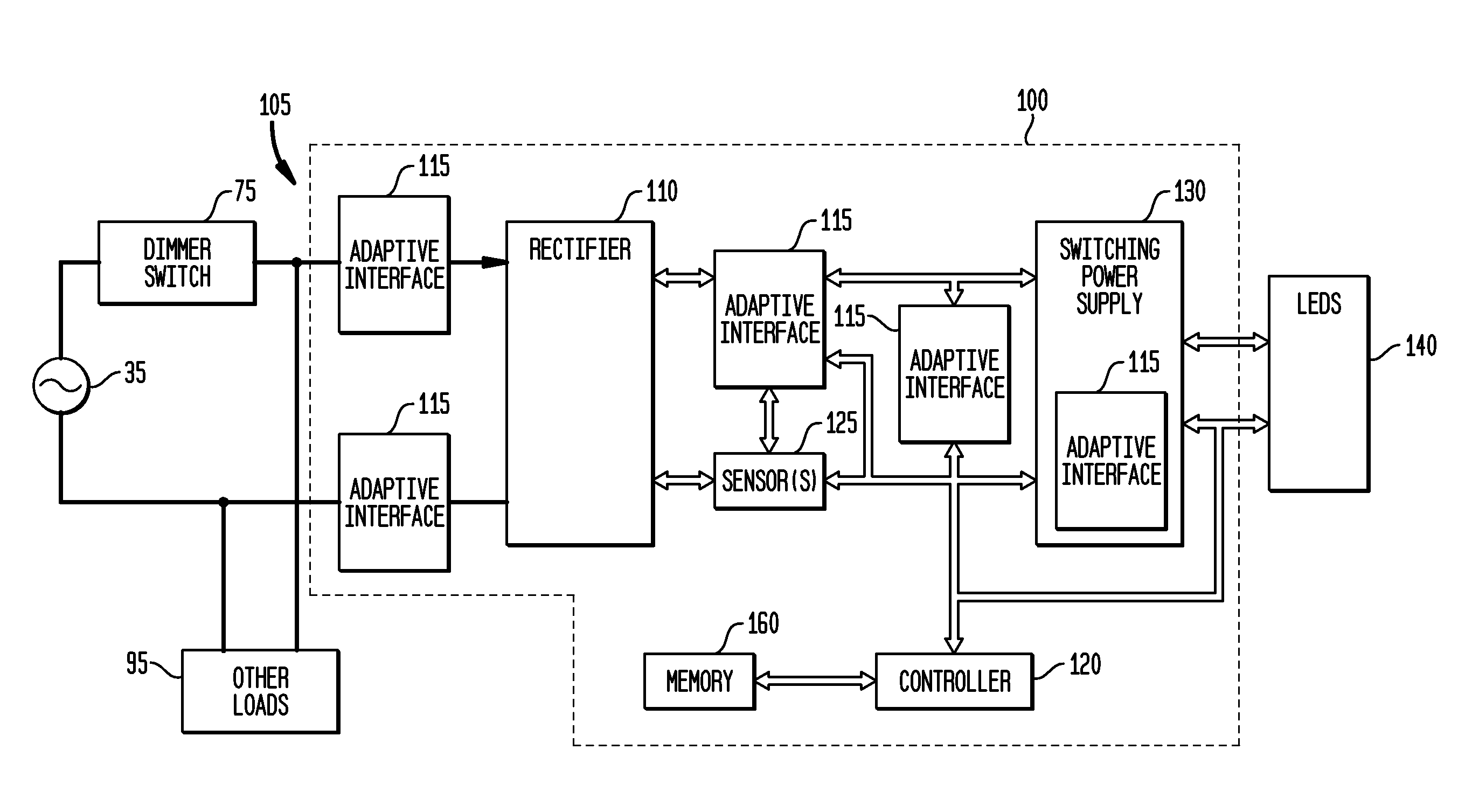

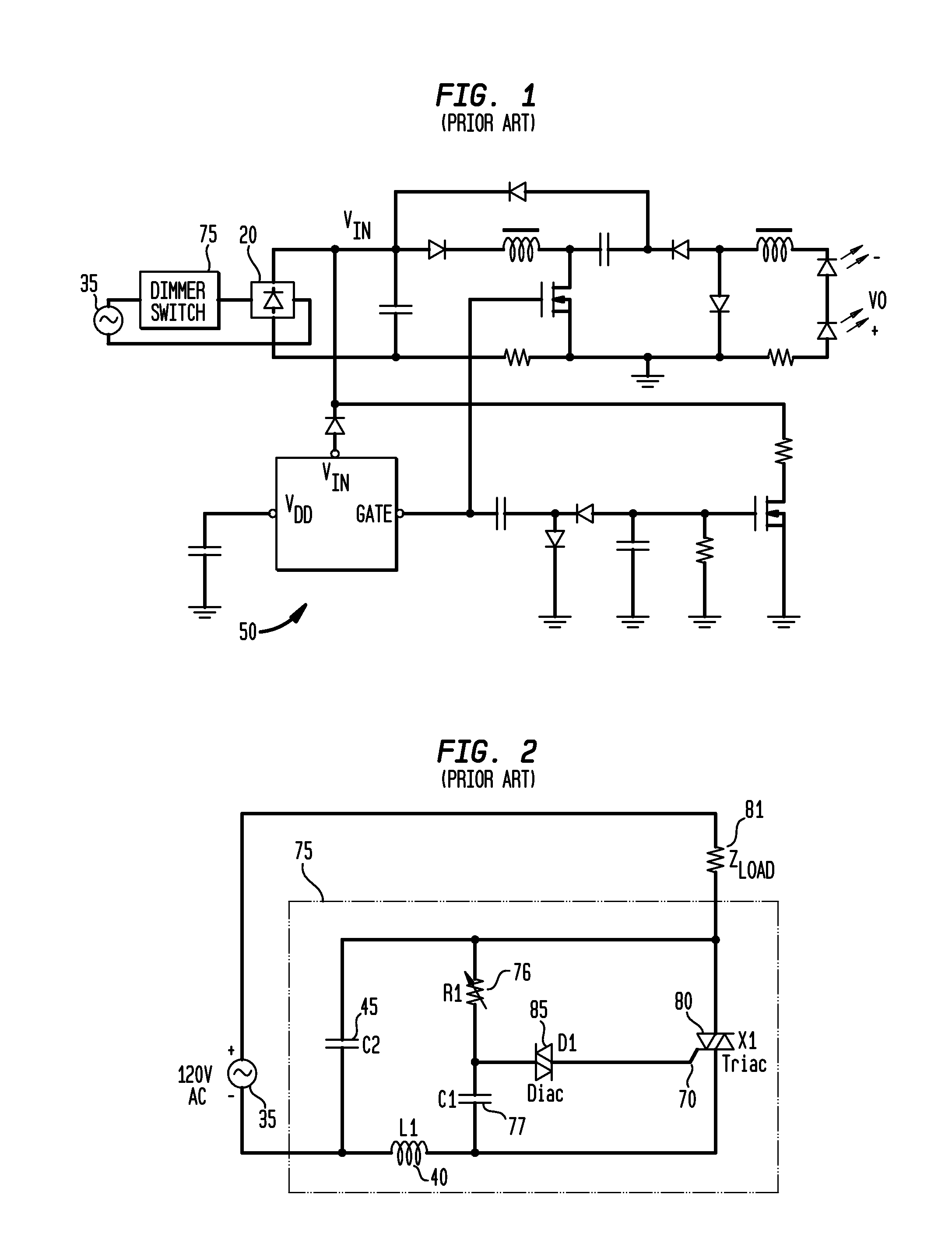

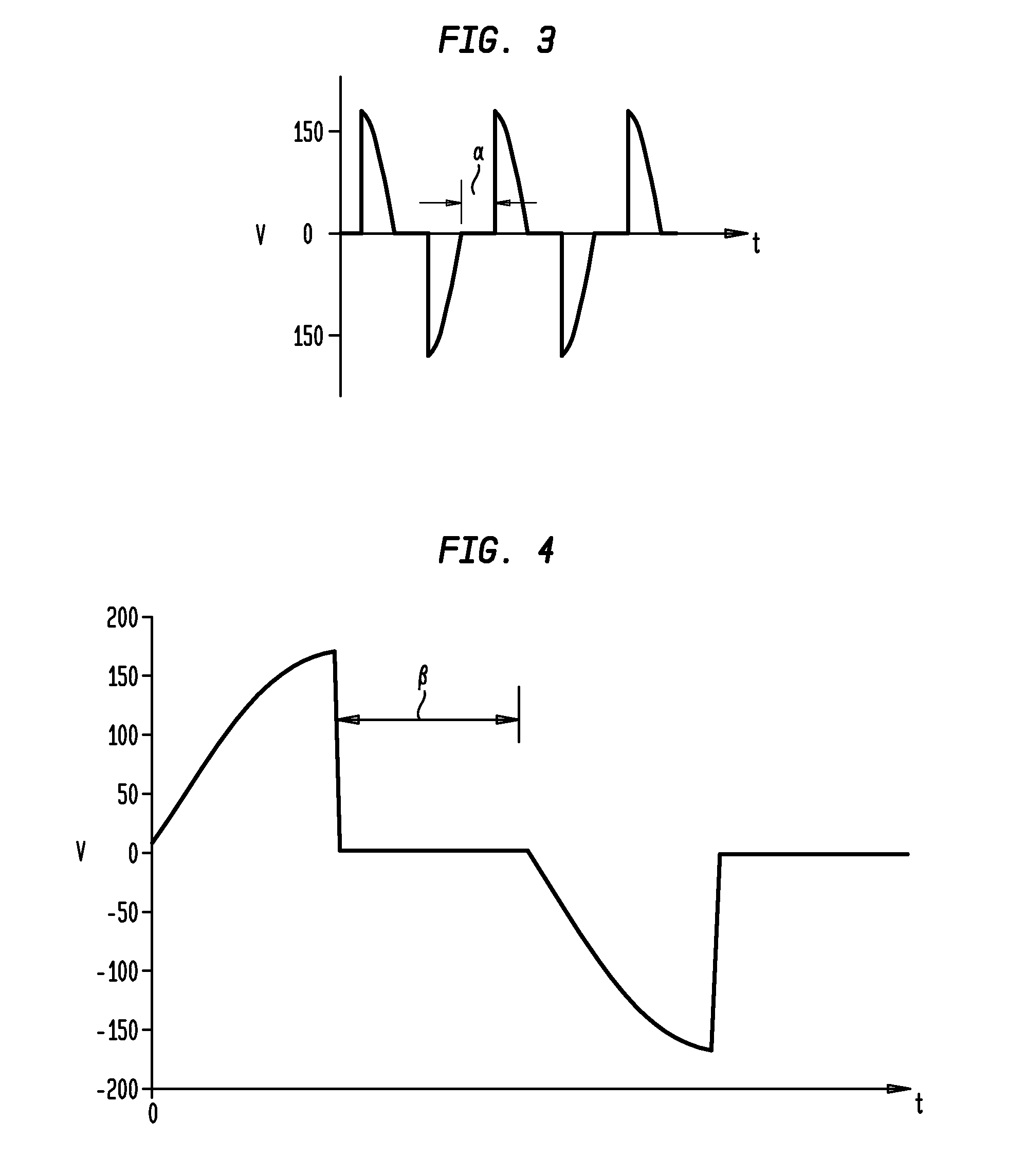

Adaptive Current Regulation for Solid State Lighting

ActiveUS20100213859A1Low component requirementsSeamless and stable operationElectrical apparatusElectroluminescent light sourcesDimmerEngineering

Exemplary embodiments provide an apparatus, system and method for power conversion to provide power to solid state lighting, and which may be coupled to a first switch, such as a dimmer switch. An exemplary system for power conversion comprises: a switching power supply comprising a second, power switch; solid state lighting coupled to the switching power supply; a voltage sensor; a current sensor; a memory; a first adaptive interface circuit to provide a resistive impedance to the first switch and conduct current from the first switch in a default mode; a second adaptive interface circuit to create a resonant process when the first switch turns on; and a controller to modulate the second adaptive interface circuit when the first switch turns on to provide a current path during the resonant process of the switching power supply.

Owner:CHEMTRON RES

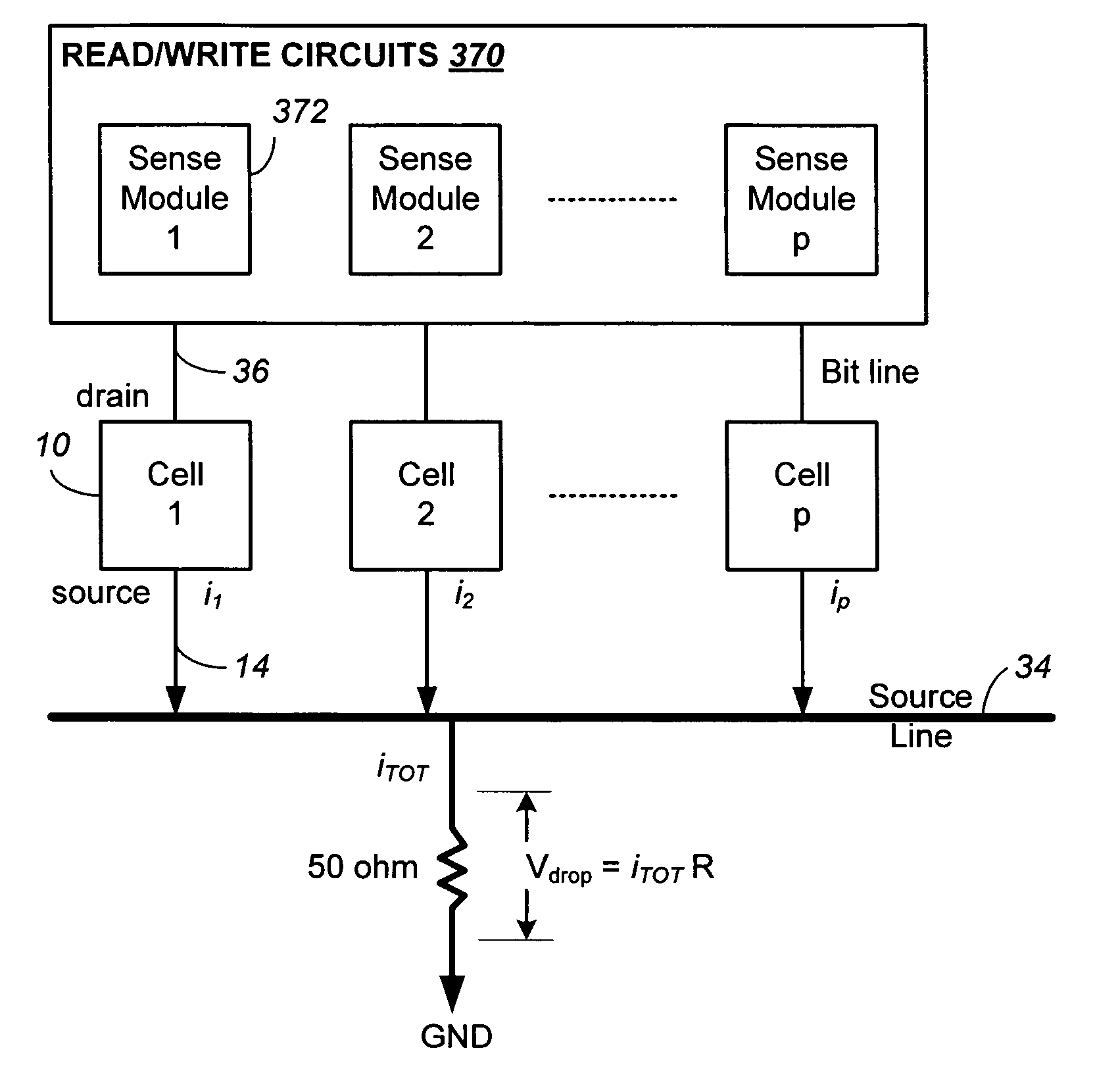

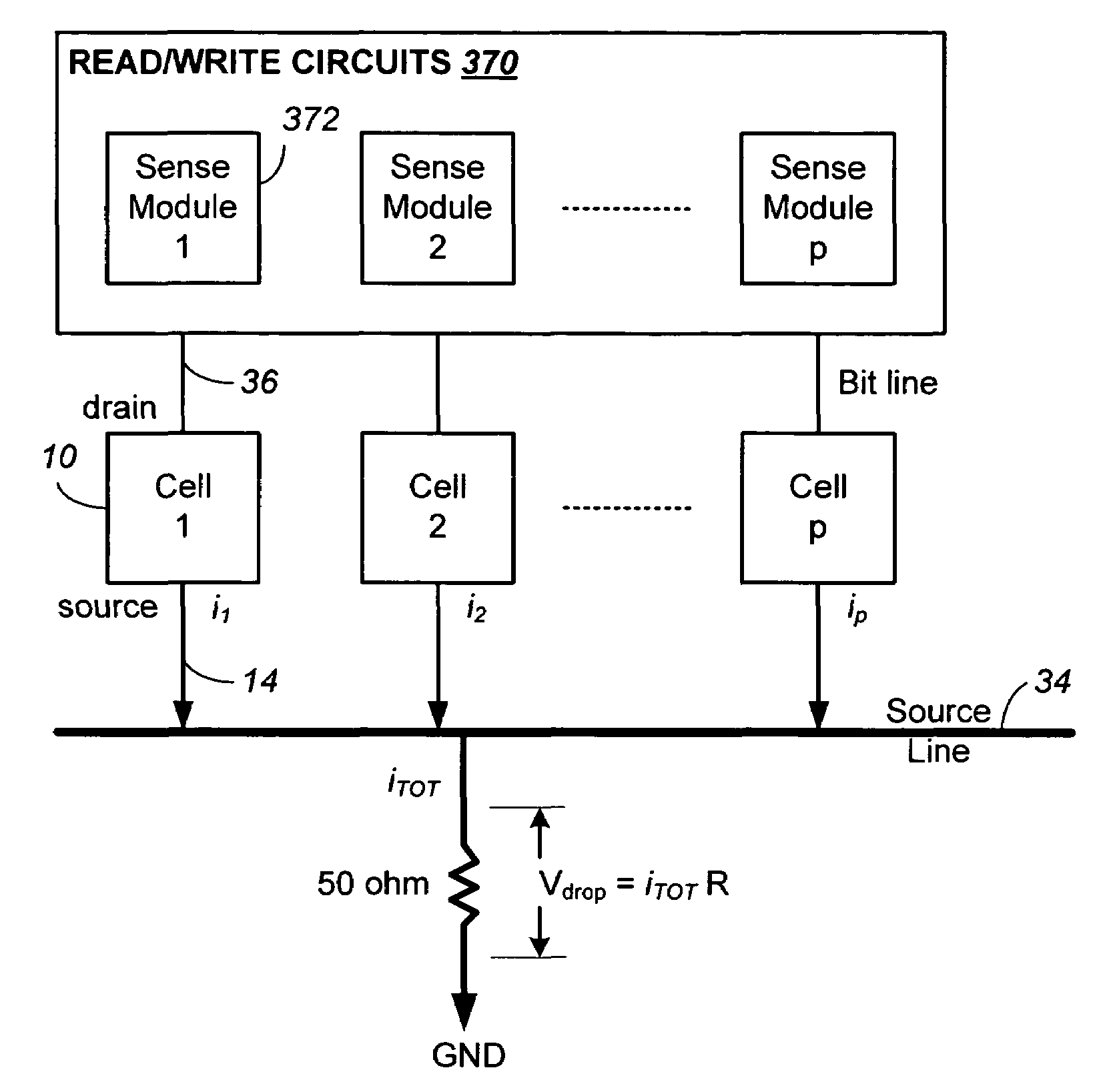

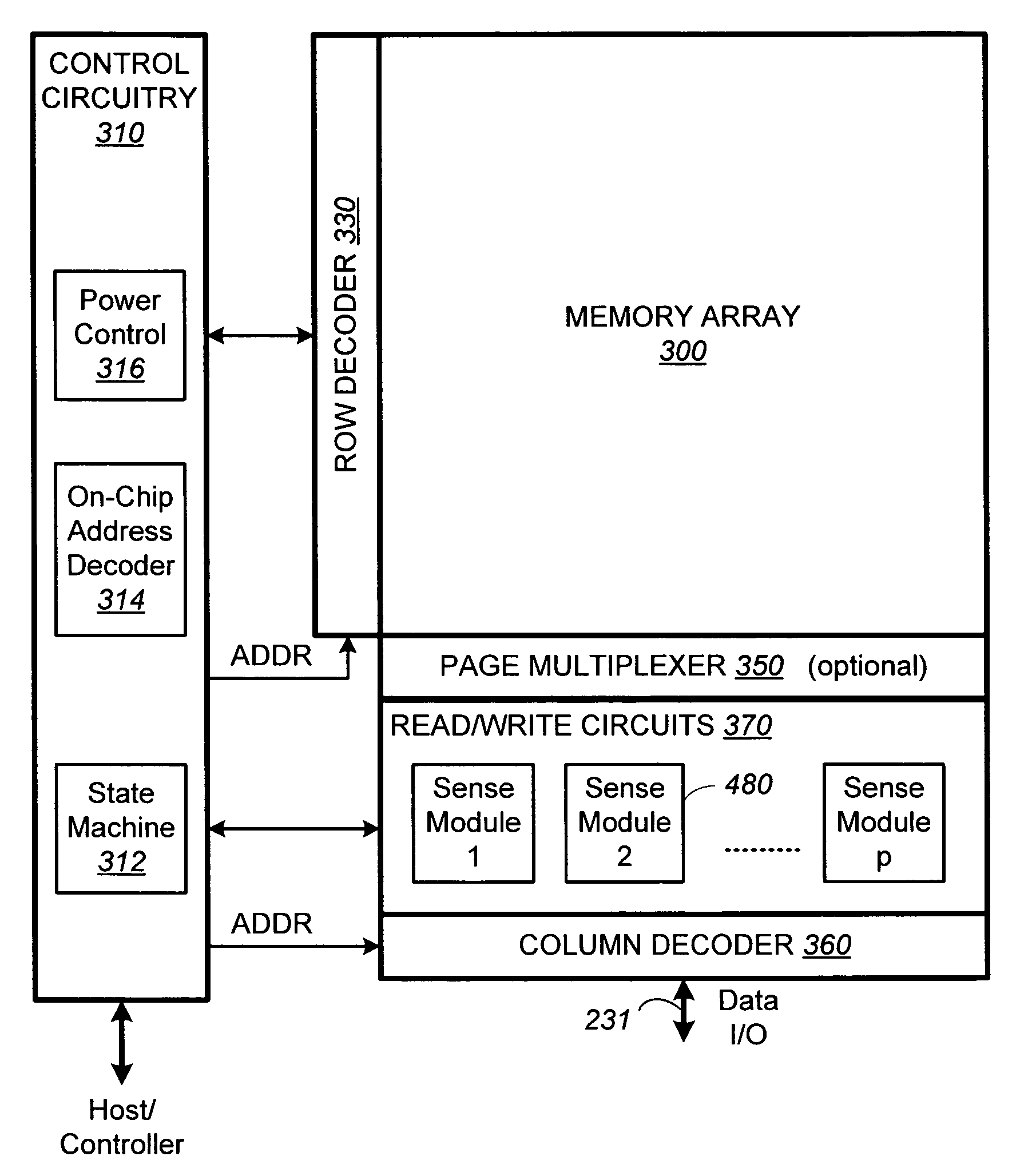

Non-volatile memory and method with reduced source line bias errors

ActiveUS7196931B2Large capacityImprove performanceRead-only memoriesDigital storageVoltage dropEngineering

Source line bias is an error introduced by a non-zero resistance in the ground loop of the read / write circuits. During sensing the control gate voltage of a memory cell is erroneously biased by a voltage drop across the resistance. This error is minimized when the current flowing though the ground loop is reduced. A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In this way, sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells.

Owner:SANDISK TECH LLC

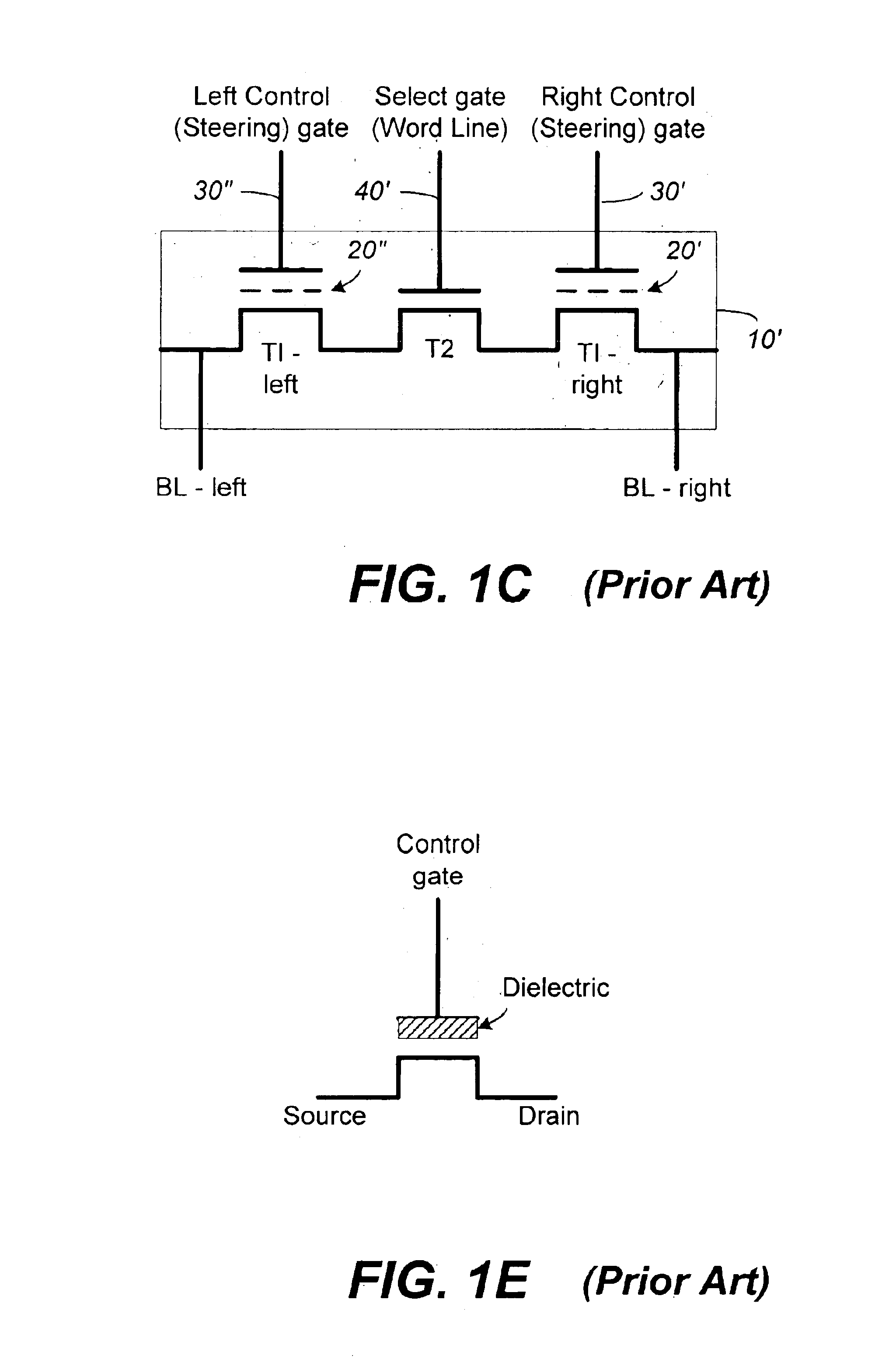

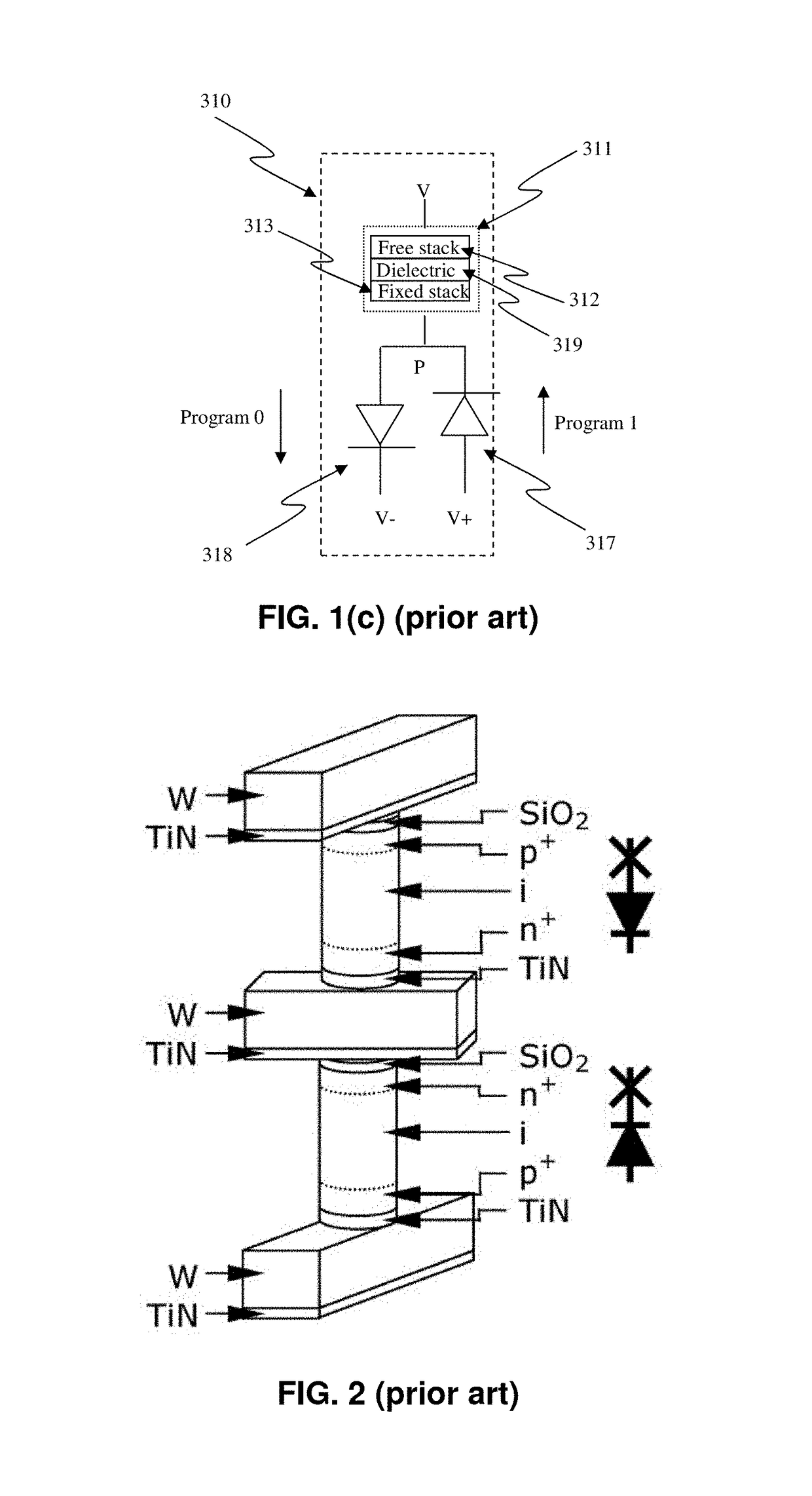

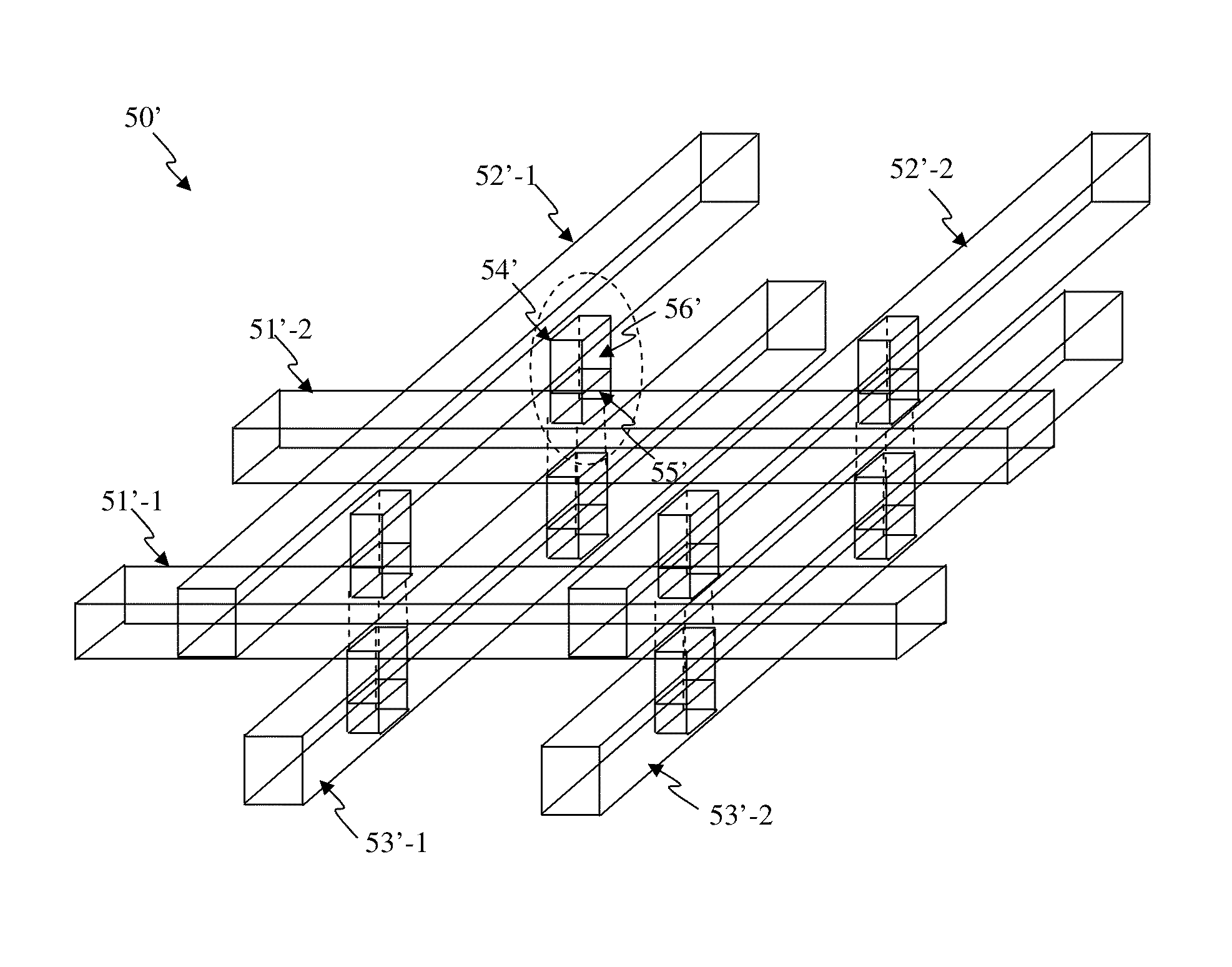

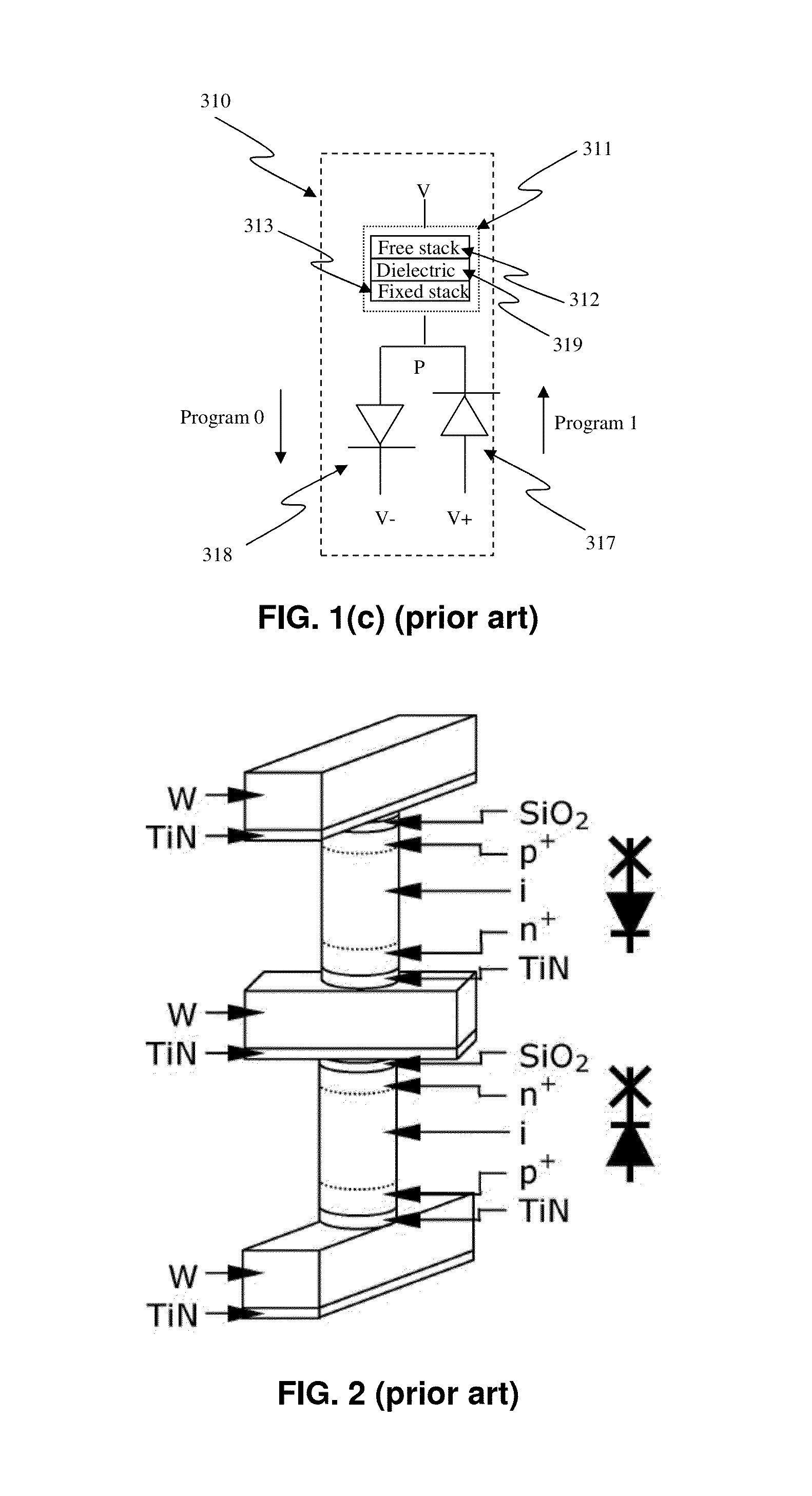

Programmable resistive device and memory using diode as selector

Building programmable resistive devices in contact holes at the crossover of a plurality of conductor lines in more than two vertical layers is disclosed. There are plurality of first conductor lines and another plurality of second conductor lines that can be substantially perpendicular to each other, though in two different vertical layers. A diode and / or a programmable resistive element can be fabricated in the contact hole between the first and second conductor lines. The programmable resistive element can be coupled to another programmable resistive device or shared between two programmable devices whose diodes conducting currents in opposite directions and / or coupled to a common conductor line. The programmable resistive memory can be configured to be programmable by applying voltages to conduct current flowing through the programmable resistive element to change its resistance for a different logic state.

Owner:ATTOPSEMI TECH CO LTD

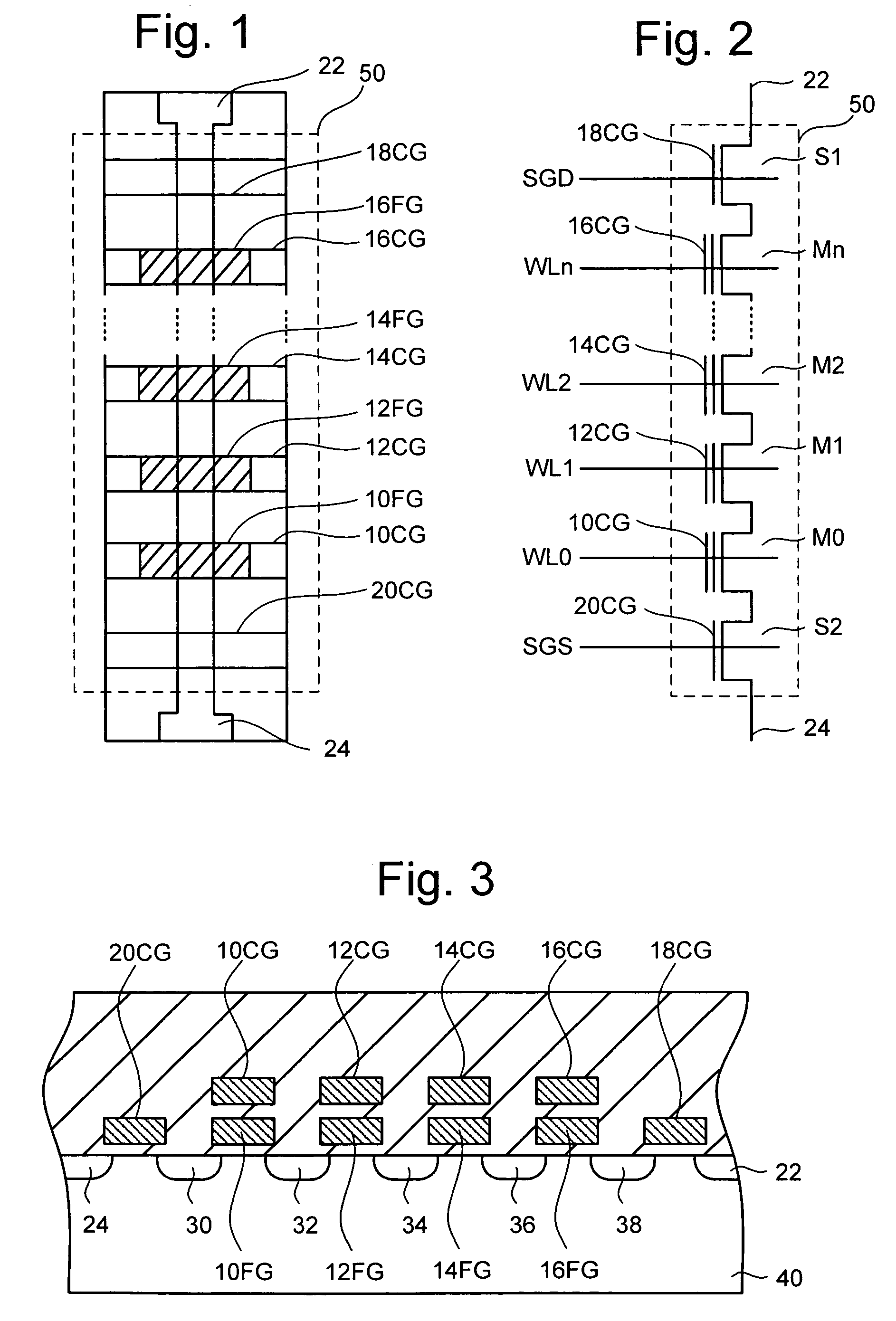

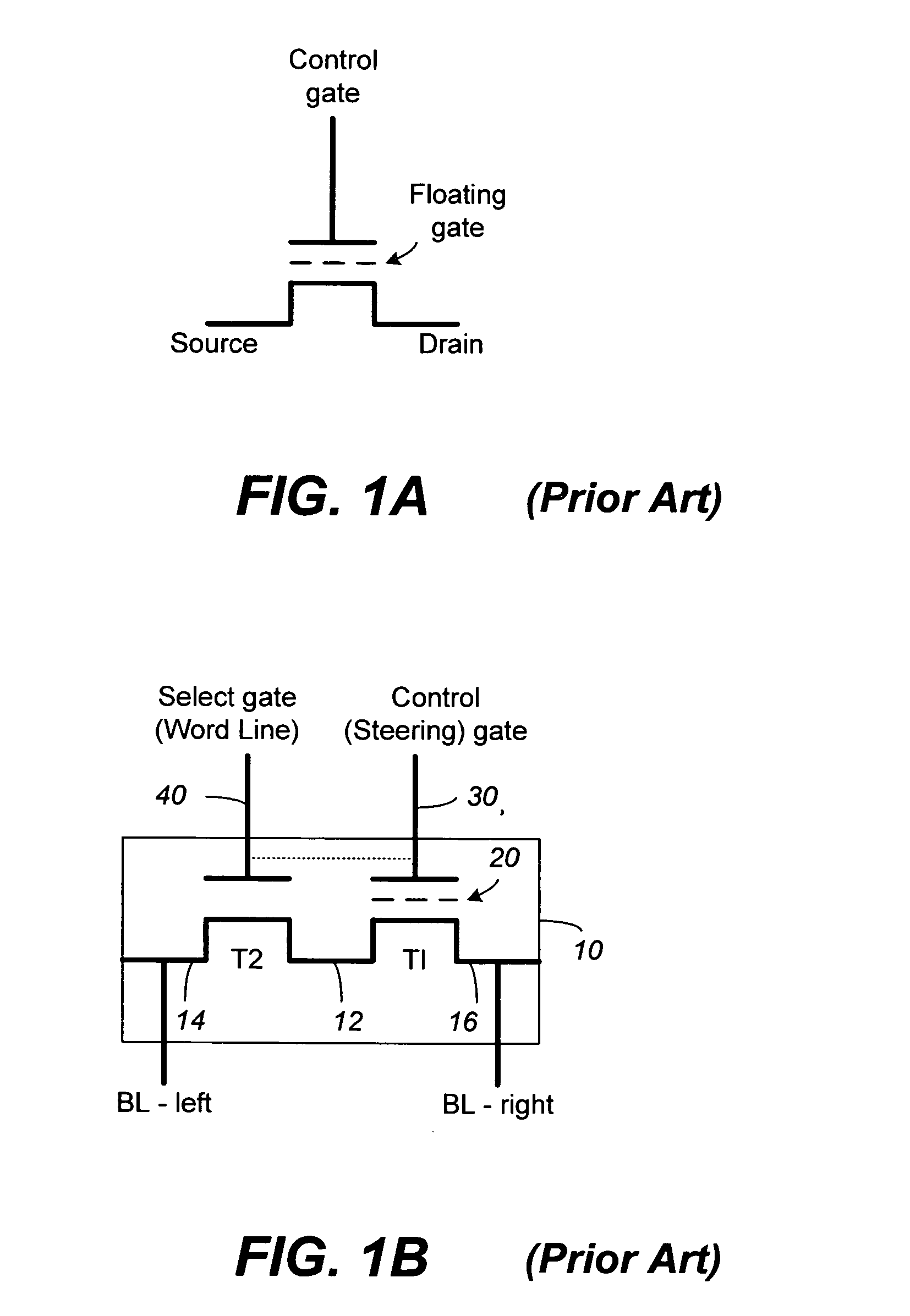

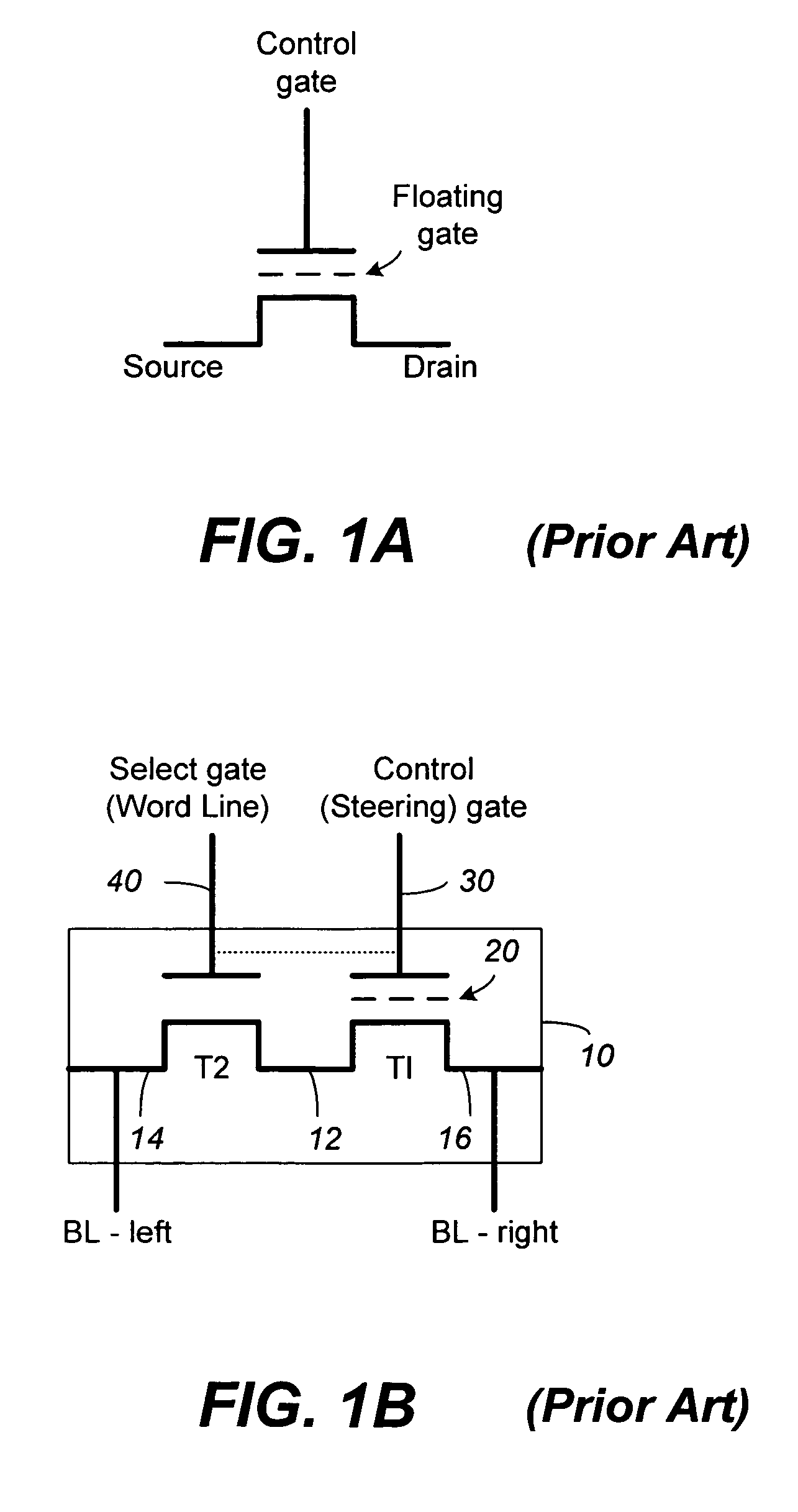

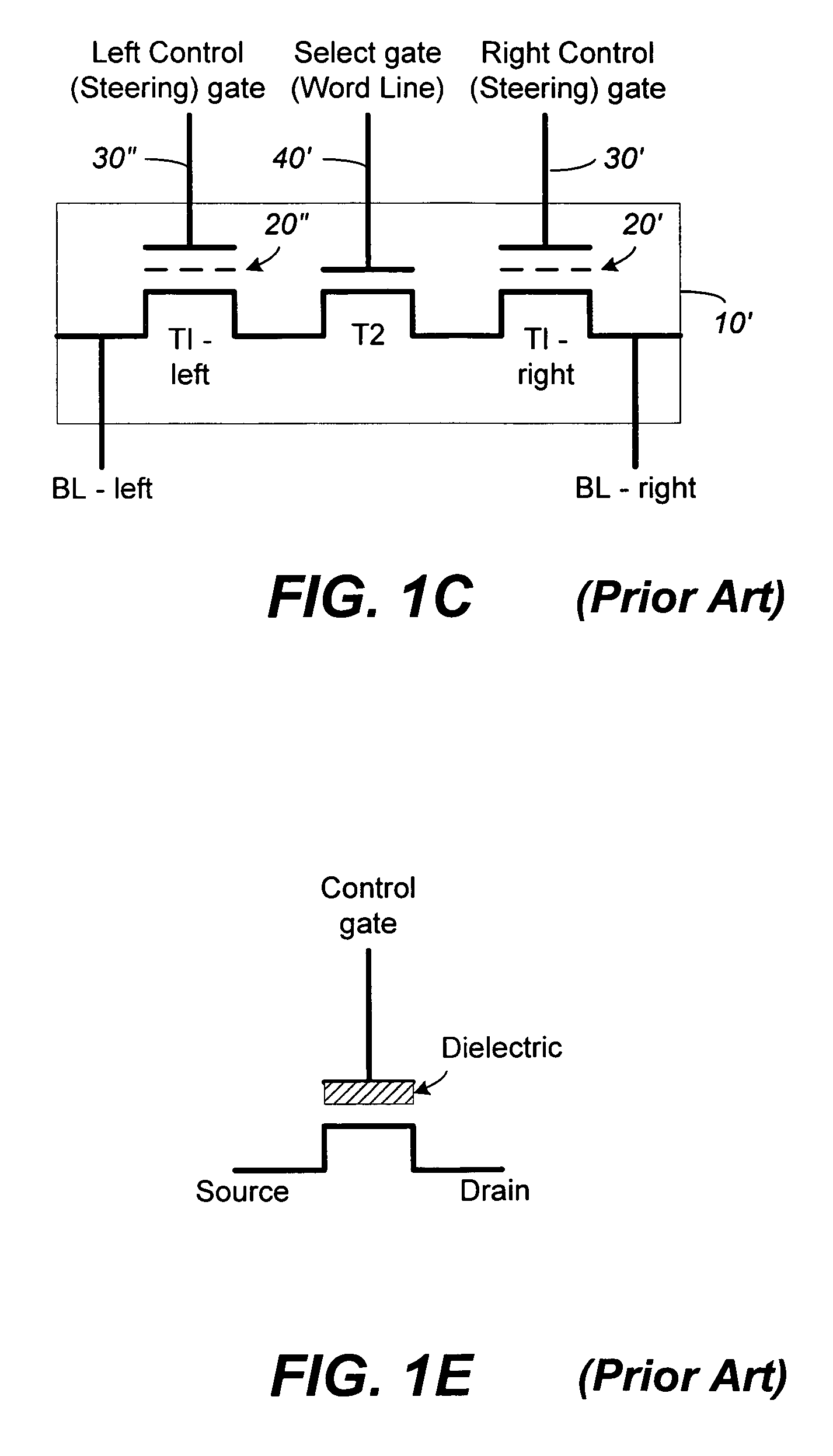

Compensation currents in non-volatile memory read operations

Shifts in the apparent charge stored on a floating gate of a non-volatile memory cell can occur because of coupling of an electric field based on the charge stored in adjacent floating gates. The shift in apparent charge can lead to erroneous readings by raising the apparent threshold voltage, and consequently, lowering the sensed conduction current of a memory cell. The read process for a selected memory cell takes into account the state of one or more adjacent memory cells. If an adjacent memory cell is in one or more of a predetermined set of programmed states, a compensation current can be provided to increase the apparent conduction current of the selected memory cell. An initialization voltage is provided to the bit line of the programmed adjacent memory cell to induce a compensation current between the bit line of the programmed adjacent memory cell and the bit line of the selected memory cell.

Owner:SANDISK TECH LLC

Method for compensated sensing in non-volatile memory

InactiveUS7324393B2Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierReference current

Owner:SANDISK TECH LLC

Non-volatile memory and method with power-saving read and program-verify operations

ActiveUS20060209592A1More powerAverage power consumptionRead-only memoriesDigital storageBit lineComputer science

A non-volatile memory device capable of reading and writing a large number of memory cells with multiple read / write circuits in parallel has features to reduce power consumption during read, and program / verify operations. A read or program verify operation includes one or more sensing cycles relative to one or more demarcation threshold voltages to determine a memory state. In one aspect, selective memory cells among the group being sensed in parallel have their conduction currents turned off when they are determined to be in a state not relevant to the current sensing cycle. In another aspect, a power-consuming period is minimized by preemptively starting any operations that would prolong the period. In a program / verify operation cells not to be programmed have their bit lines charged up in the program phase. Power is saved when a set of these bit lines avoids re-charging at every passing of a program phase.

Owner:SANDISK TECH LLC

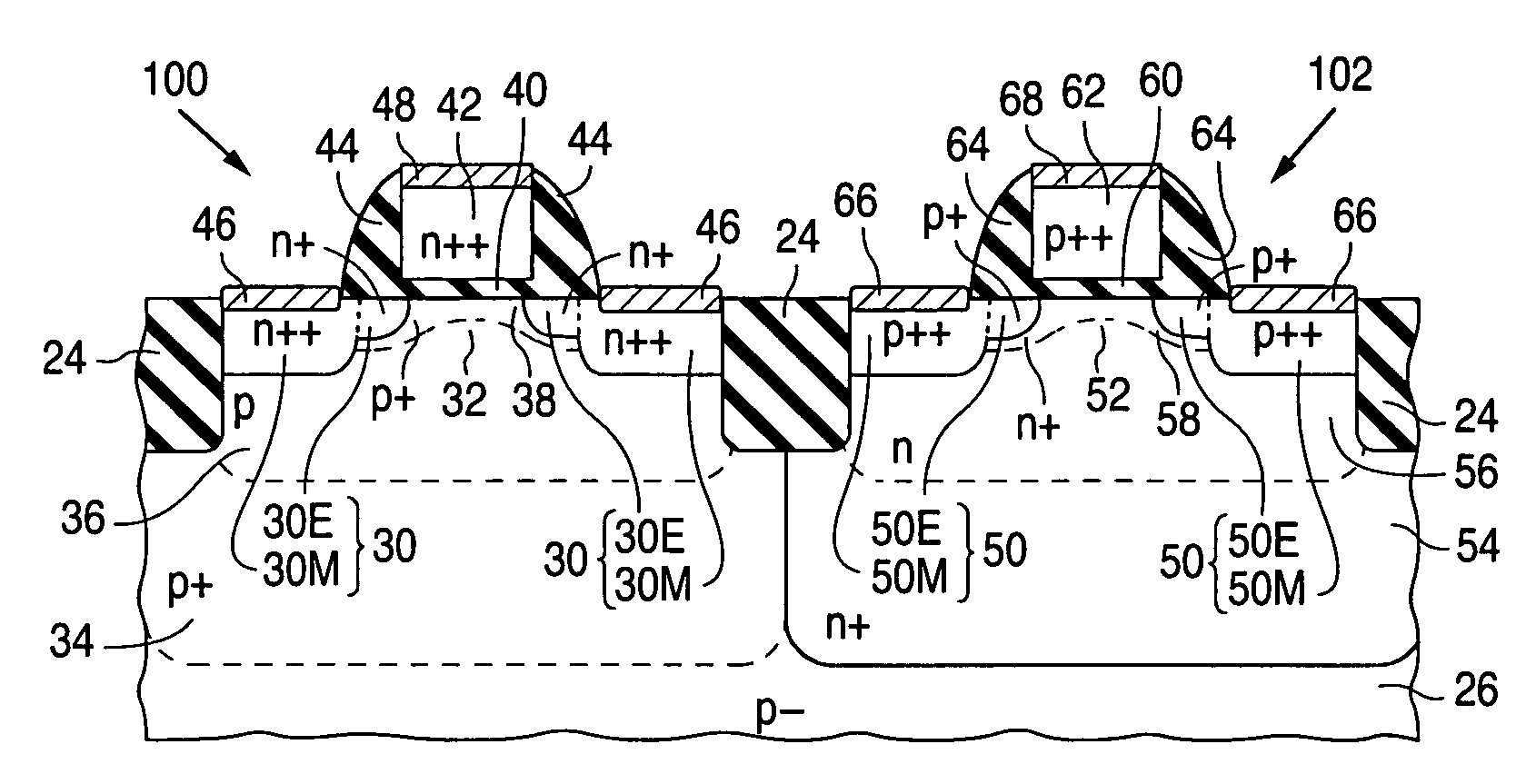

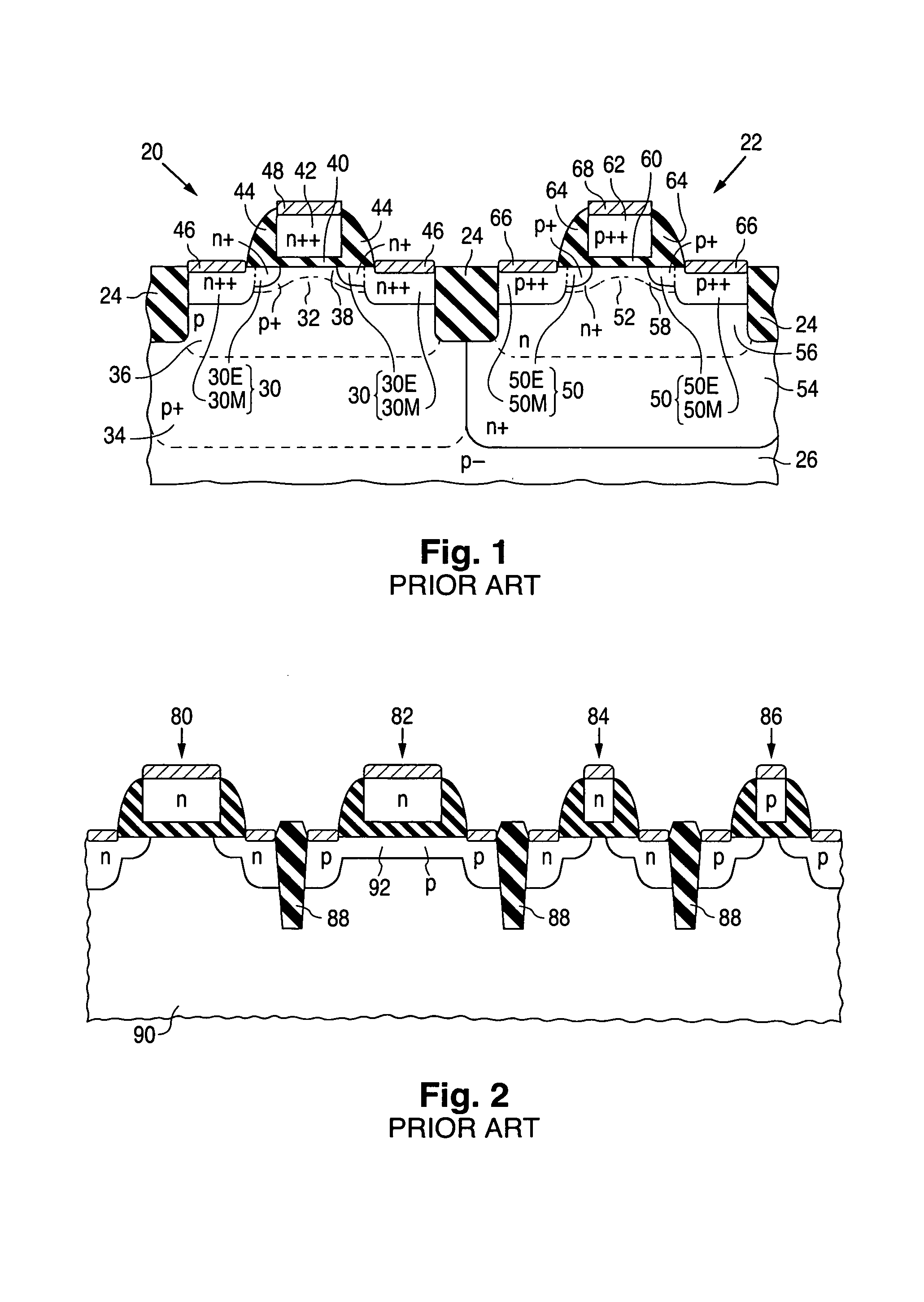

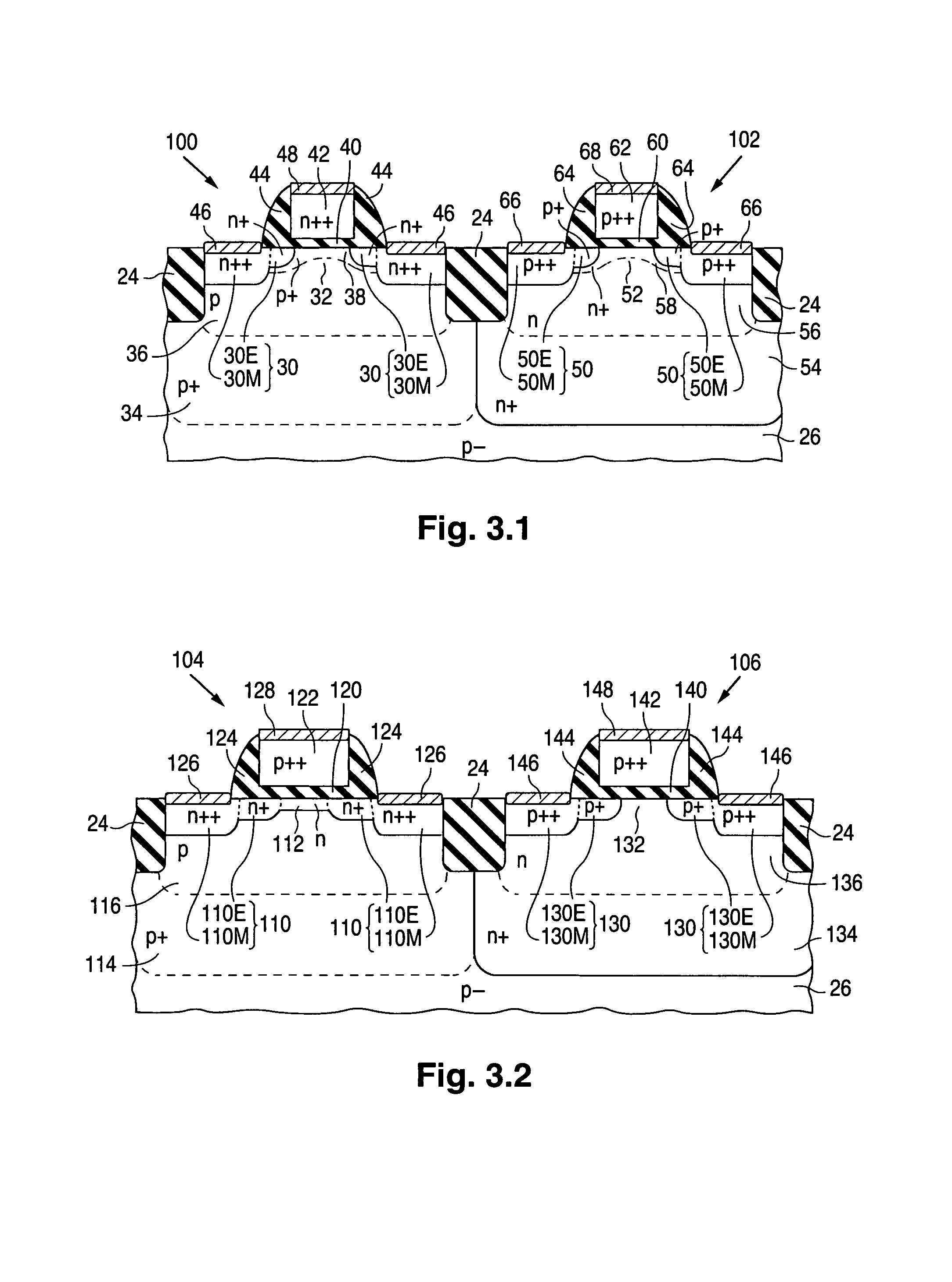

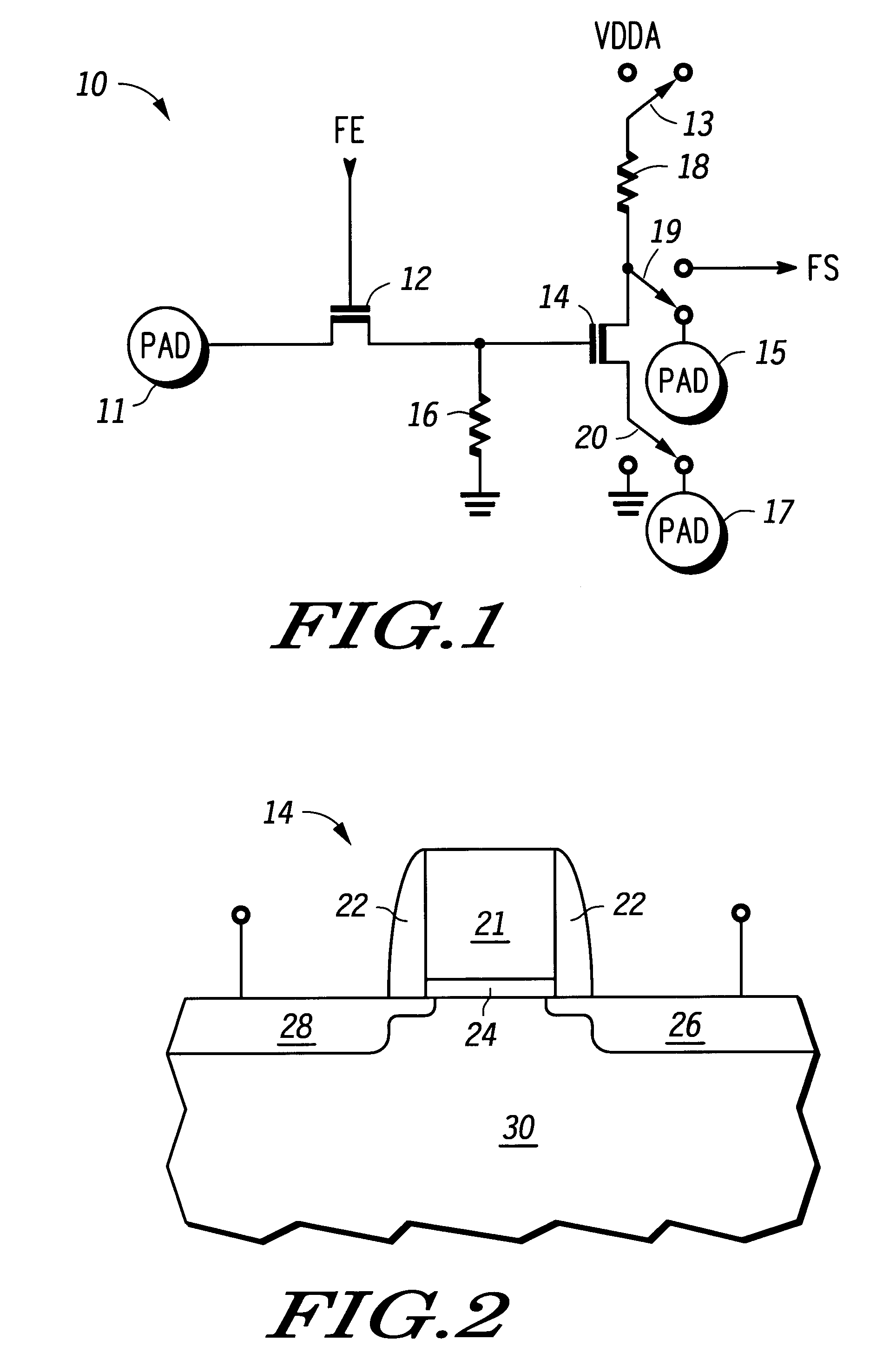

Semiconductor structure having n-channel channel-junction field-effect transistor

ActiveUS7176530B1Large noise reductionEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

A semiconductor technology combines a normally off n-channel channel-junction insulated-gate field-effect transistor (“IGFET”) (104) and an n-channel surface-channel IGFET (100 or 160) to reduce low-frequency 1 / f noise. The channel-junction IGFET is normally of materially greater gate dielectric thickness than the surface-channel IGFET so as to operate across a greater voltage range than the surface-channel IGFET. Alternatively or additionally, the channel-junction IGFET may conduct current through a field-induced surface channel. A p-channel surface-channel IGFET (102 or 162), which is typically of approximately the same gate-dielectric thickness as the n-channel surface-channel IGFET, is preferably combined with the two n-channel IGFETs to produce a complementary-IGFET structure. A further p-channel IGFET (106, 180, 184, or 192), which is typically of approximately the same gate dielectric thickness as the n-channel channel-junction IGFET, is also preferably included. The further p-channel IGFET can be a surface-channel or channel-junction device.

Owner:NAT SEMICON CORP

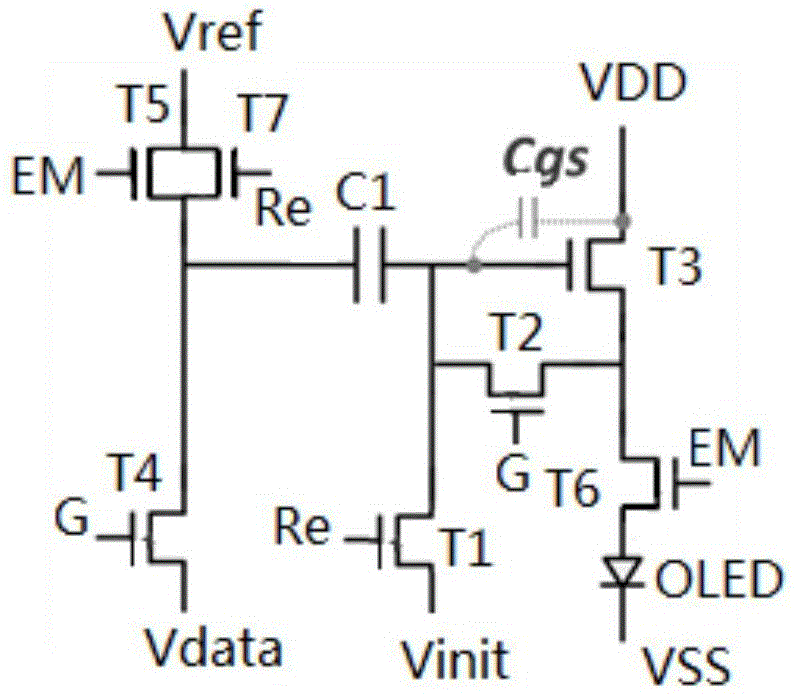

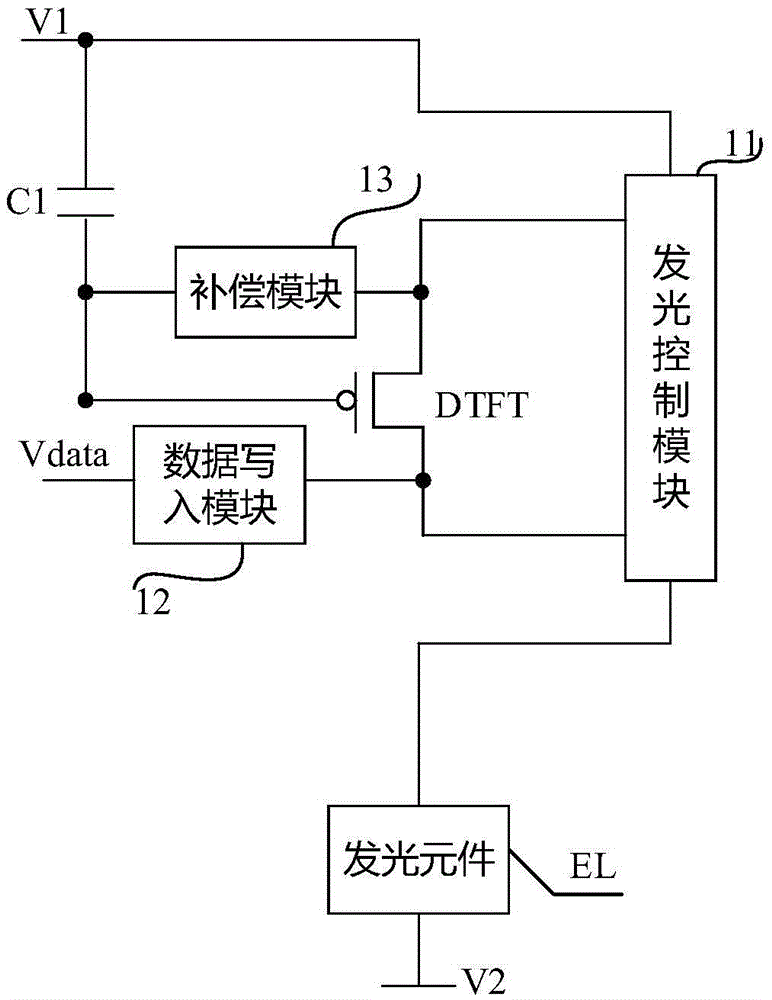

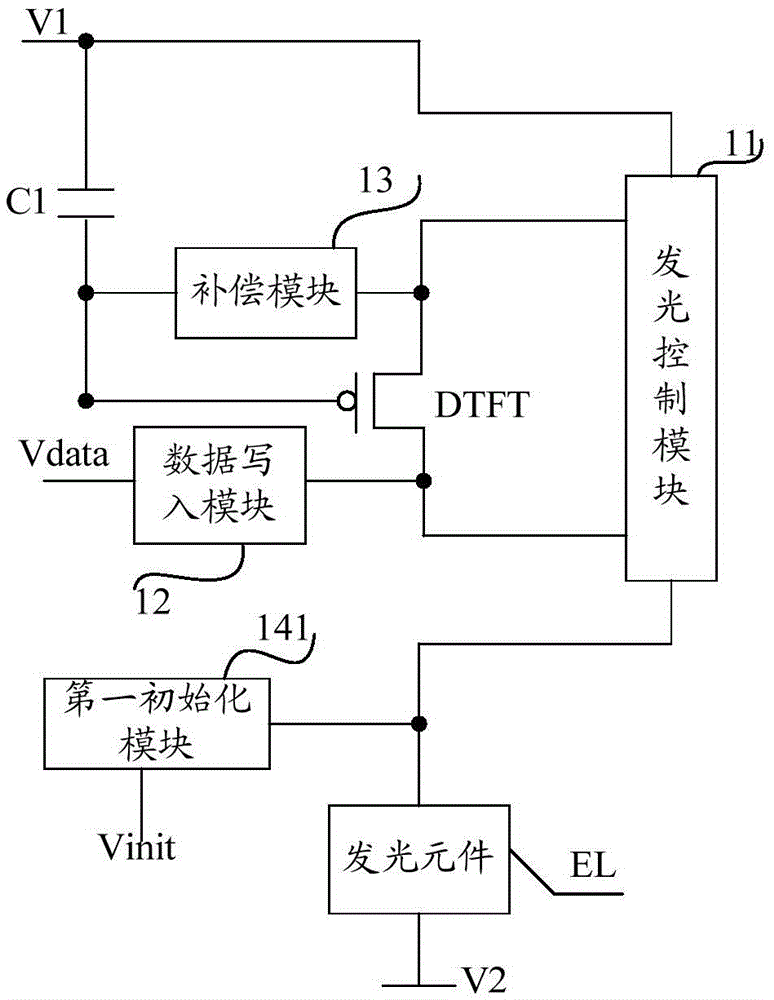

Pixel circuit and driving method thereof, array substrate, display panel and display device

ActiveCN105679236ASolve for uniformityReduce the reference voltage lineStatic indicating devicesCapacitanceDisplay device

The invention provides a pixel circuit and a driving method thereof, an array substrate, a display panel and a display device. The pixel circuit comprises a light-emitting component, a driving transistor, a first storage capacitor, a light-emitting control module, a data write-in module and a compensation module. The data write-in module controls data voltage Vdata to be written into a second pole of the driving transistor in the compensation stage; and the compensation module controls a first pole of the driving transistor to be connected with the grid electrode of the driving transistor in the compensation stage to control the driving transistor to be conducted and control the conduction current of the driving transistor to flow from the second pole of the driving transistor to the first pole of the driving transistor until the electric potential of the grid electrode of the driving transistor is Vdata+Vth, wherein the Vth is a threshold voltage of the driving transistor. The problem that the threshold voltage of the driving transistor cannot be compensated in the light-emitting stage, and thus uniformity of brightness of the display panel is poor in the prior art is solved.

Owner:BOE TECH GRP CO LTD +1

Reference sense amplifier for non-volatile memory

InactiveUS7327619B2Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierReference current

One or more sense amplifiers for sensing the conduction current of non-volatile memory is controlled by signals that are timed by a reference sense amplifier having similar characteristics and operating conditions. In one aspect, a sensing period is determined by when the reference sense amplifier sensing a reference current detects an expected state. In another aspect, an integration period for an amplified output is determined by when the reference sense amplifier outputs an expected state. When these determined timings are used to control the one or more sense amplifiers, environment and systemic variations are tracked.

Owner:SANDISK TECH LLC

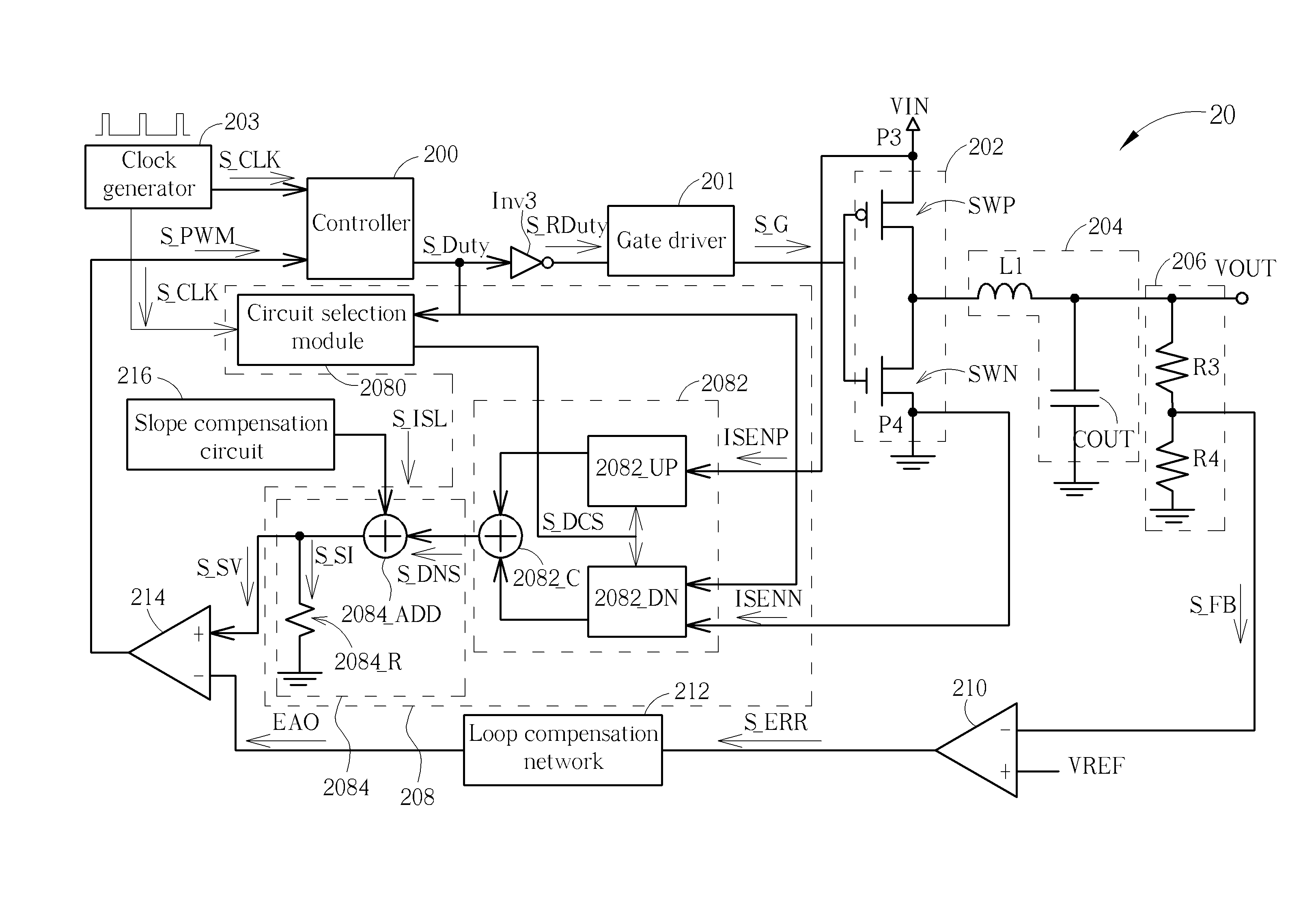

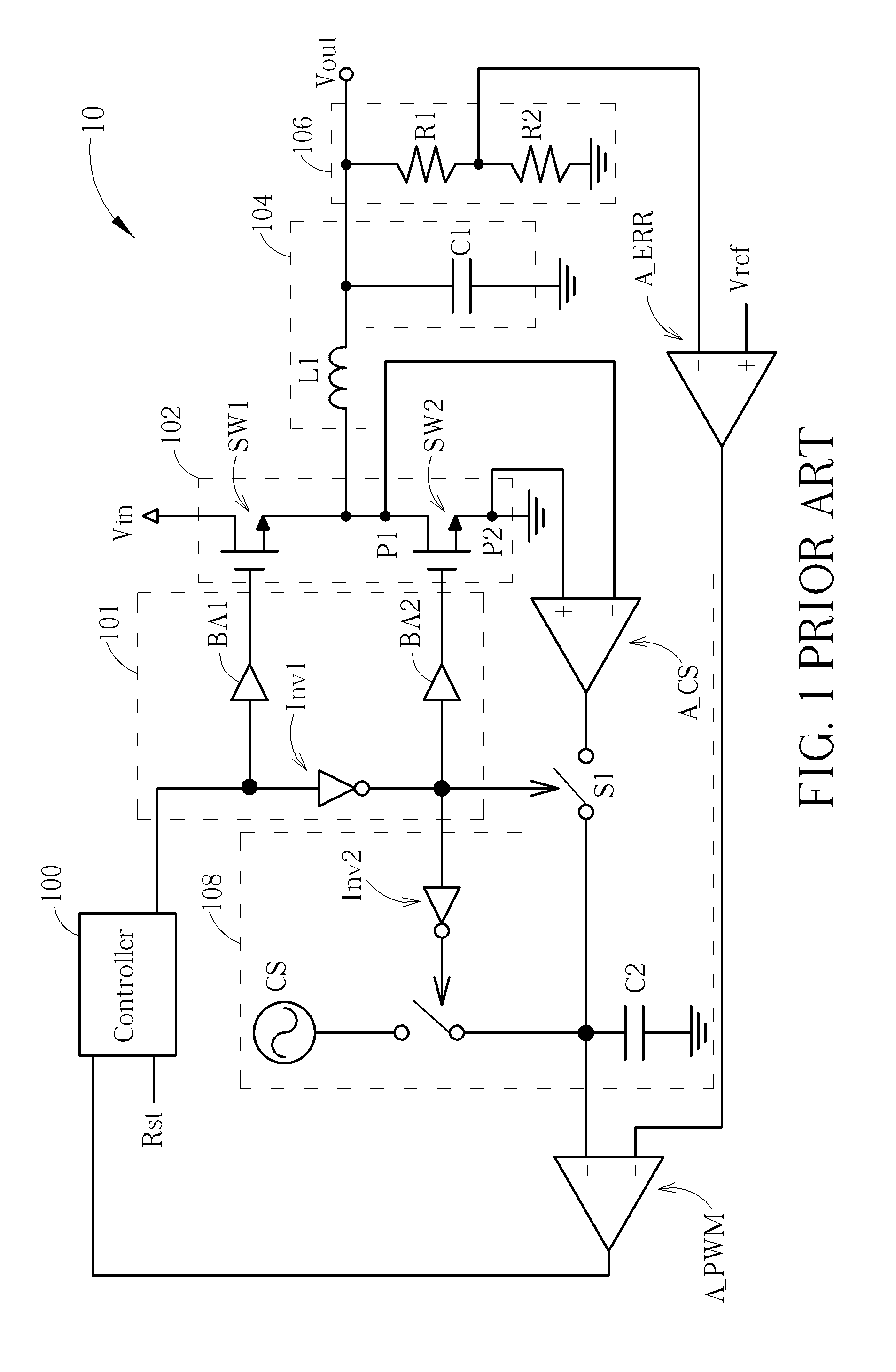

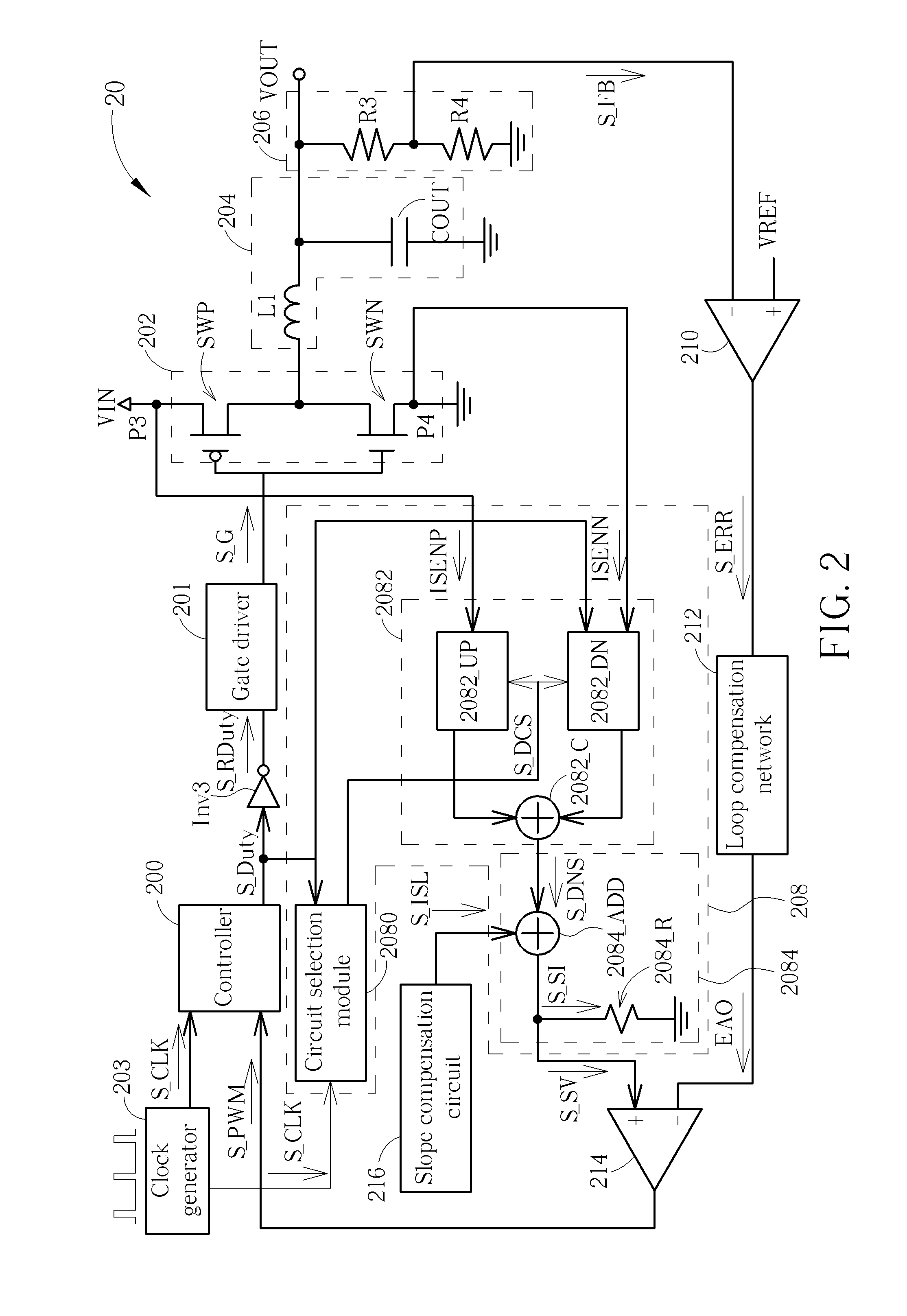

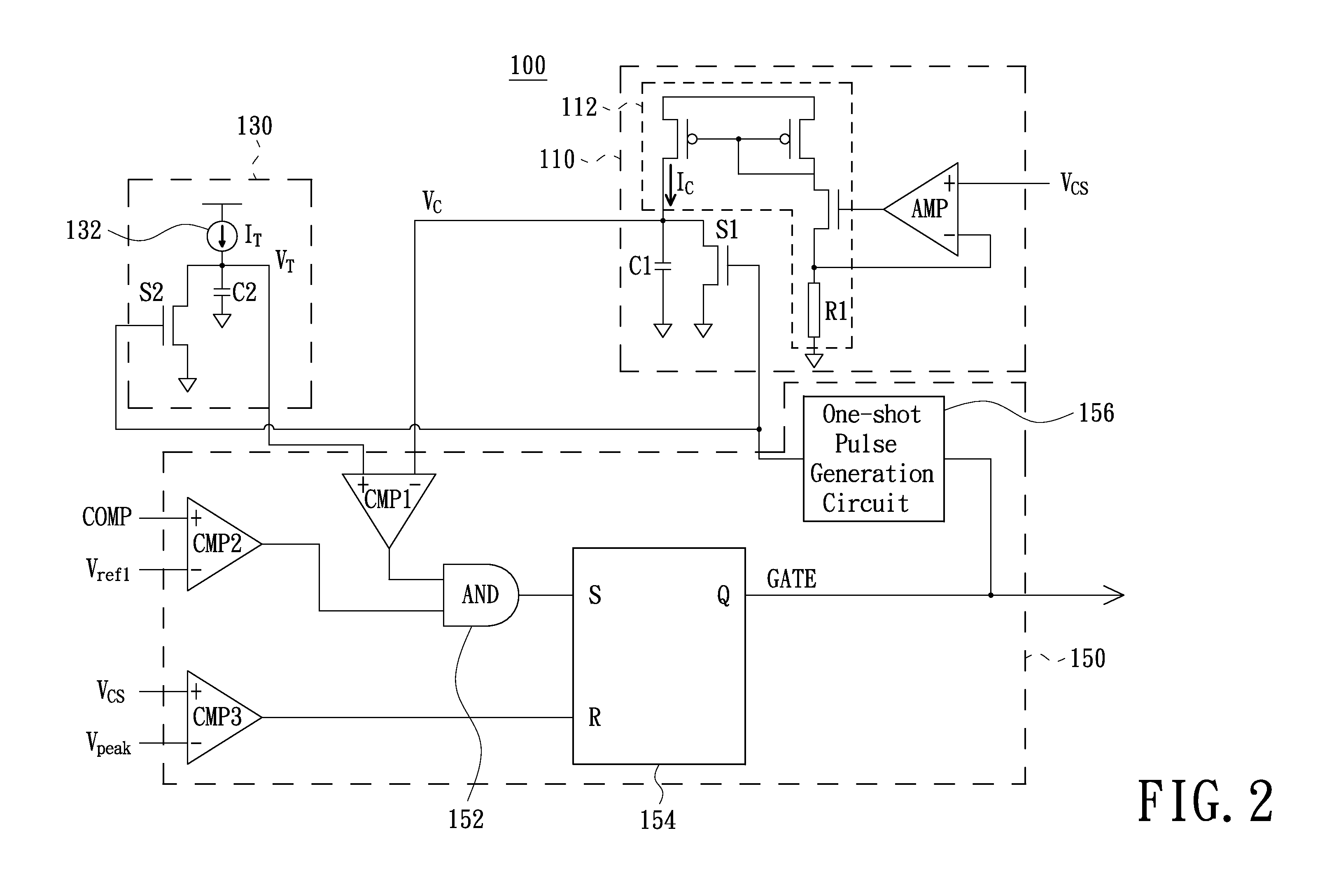

Method and Apparatus for All Duty Current Sensing in Current Mode Converter

ActiveUS20130293211A1Efficient power electronics conversionDc-dc conversionVoltage converterCurrent mode

A current sensing apparatus for a voltage converter apparatus includes a circuit selection module for generating a circuit selection result according to a clock signal and a duty cycle signal; a current sensing module coupled to the circuit selection module, an up-bridge circuit and a down-bridge circuit of the voltage converter apparatus for measuring an up-bridge conduction current and a down-bridge conduction current according to the circuit selection result; and a current generation module coupled to the current sensing module and a slope compensation circuit of the voltage converter apparatus for generating a sensing voltage according to a slope compensation current, the up-bridge conduction current or the down-bridge conduction current, so as to adjust the duty cycle signal of the controller. The current sensing apparatus utilizes the duty cycle signal to drive the voltage converter apparatus.

Owner:ANPEC ELECTRONICS CORPORATION

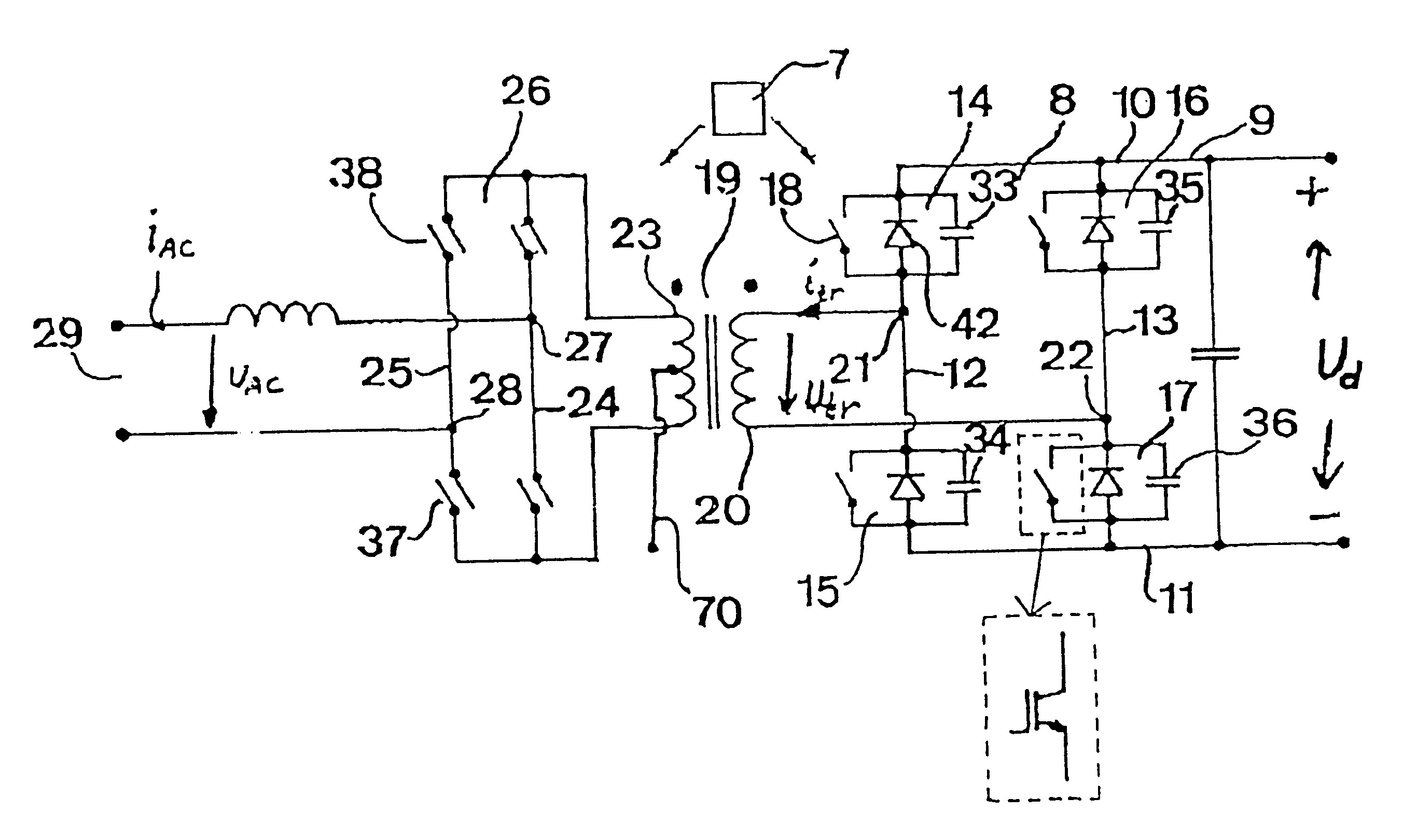

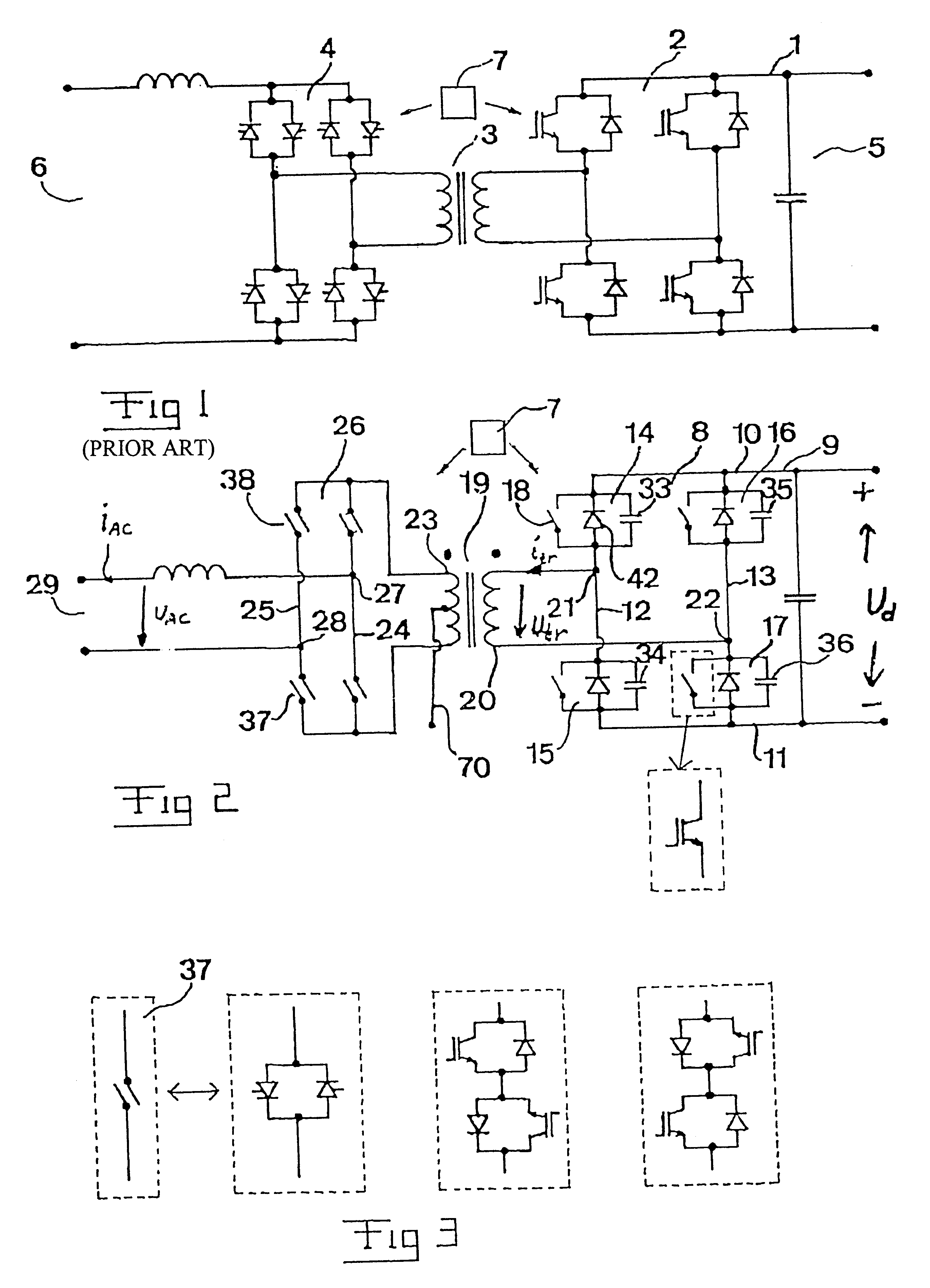

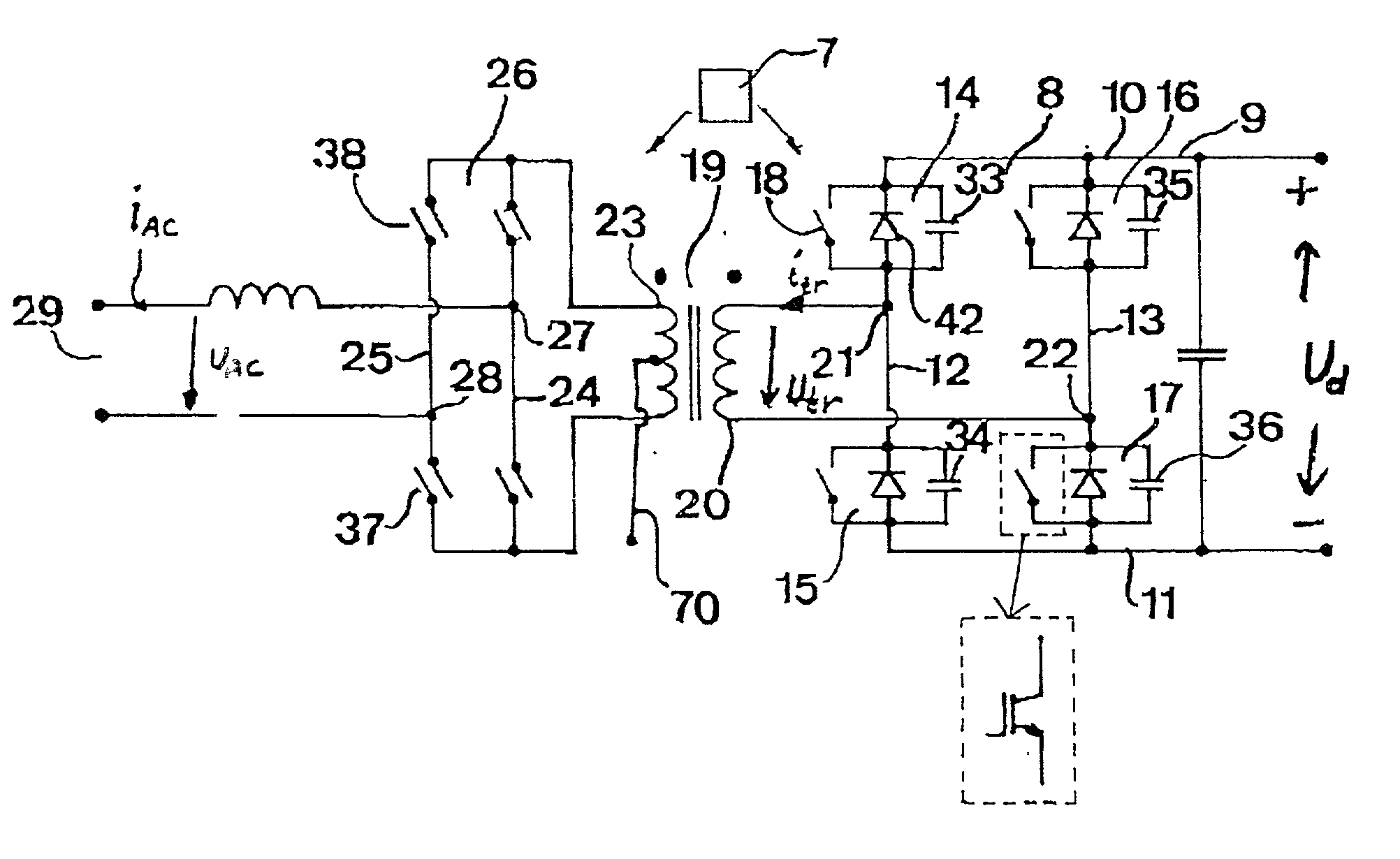

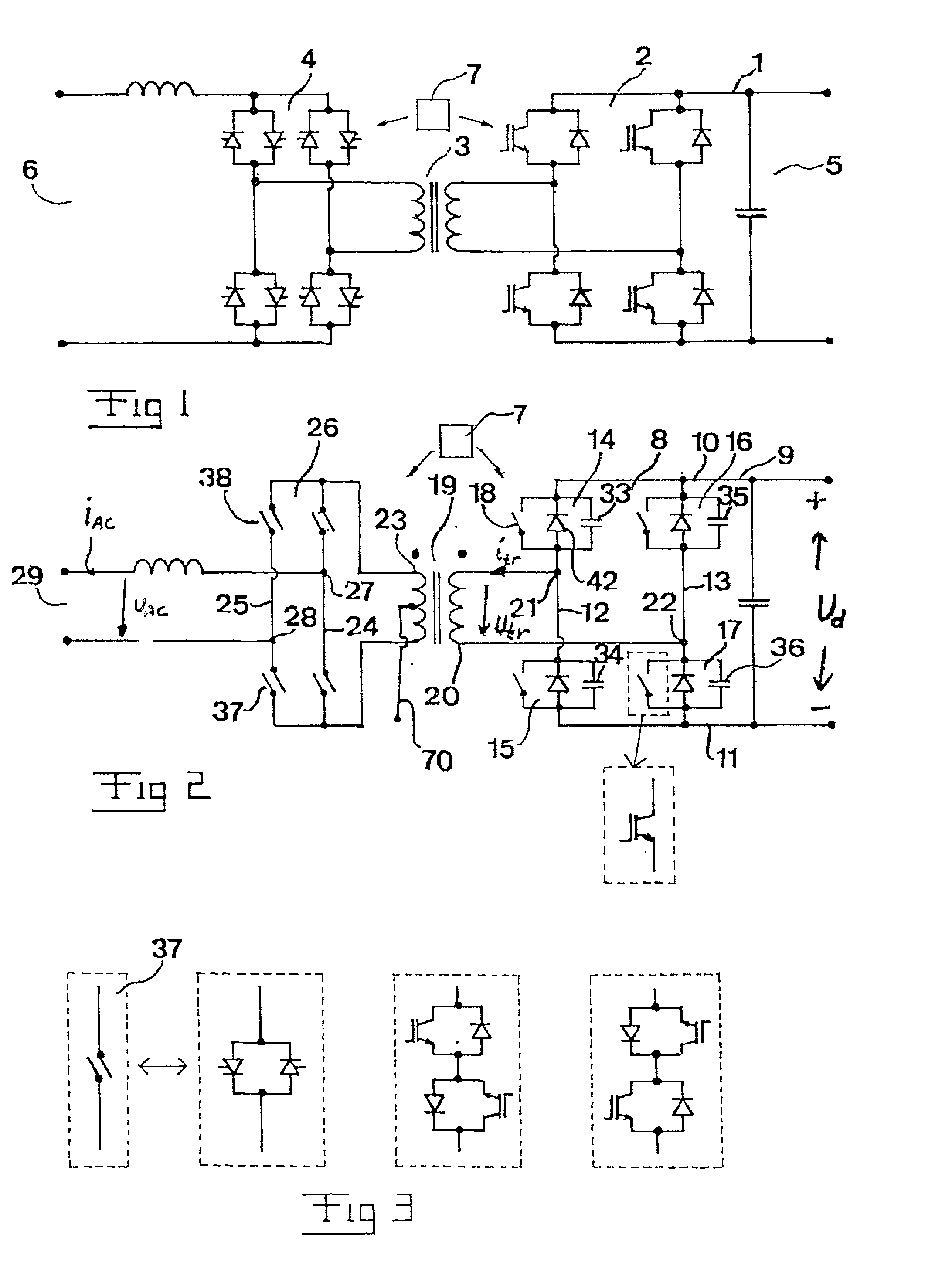

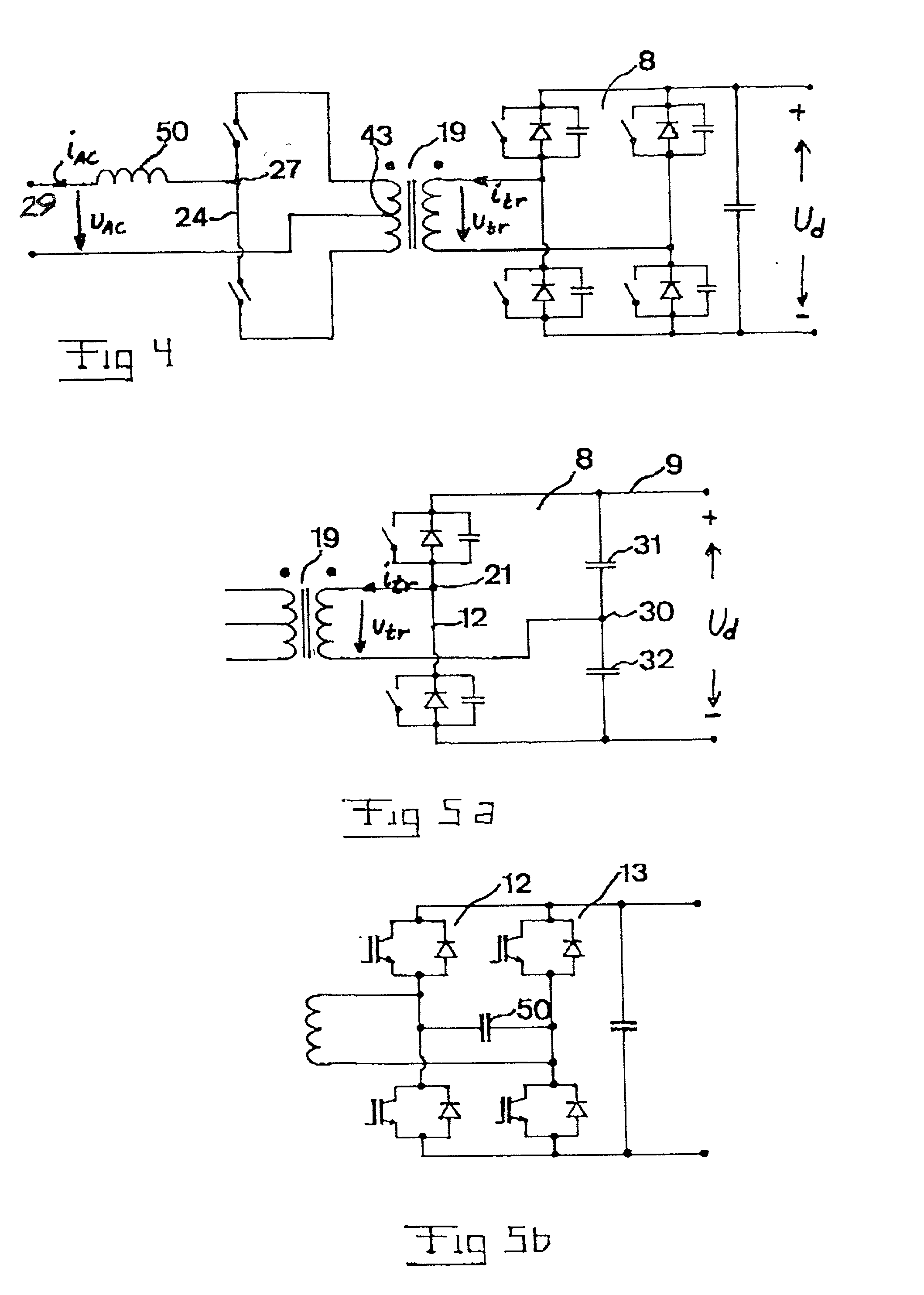

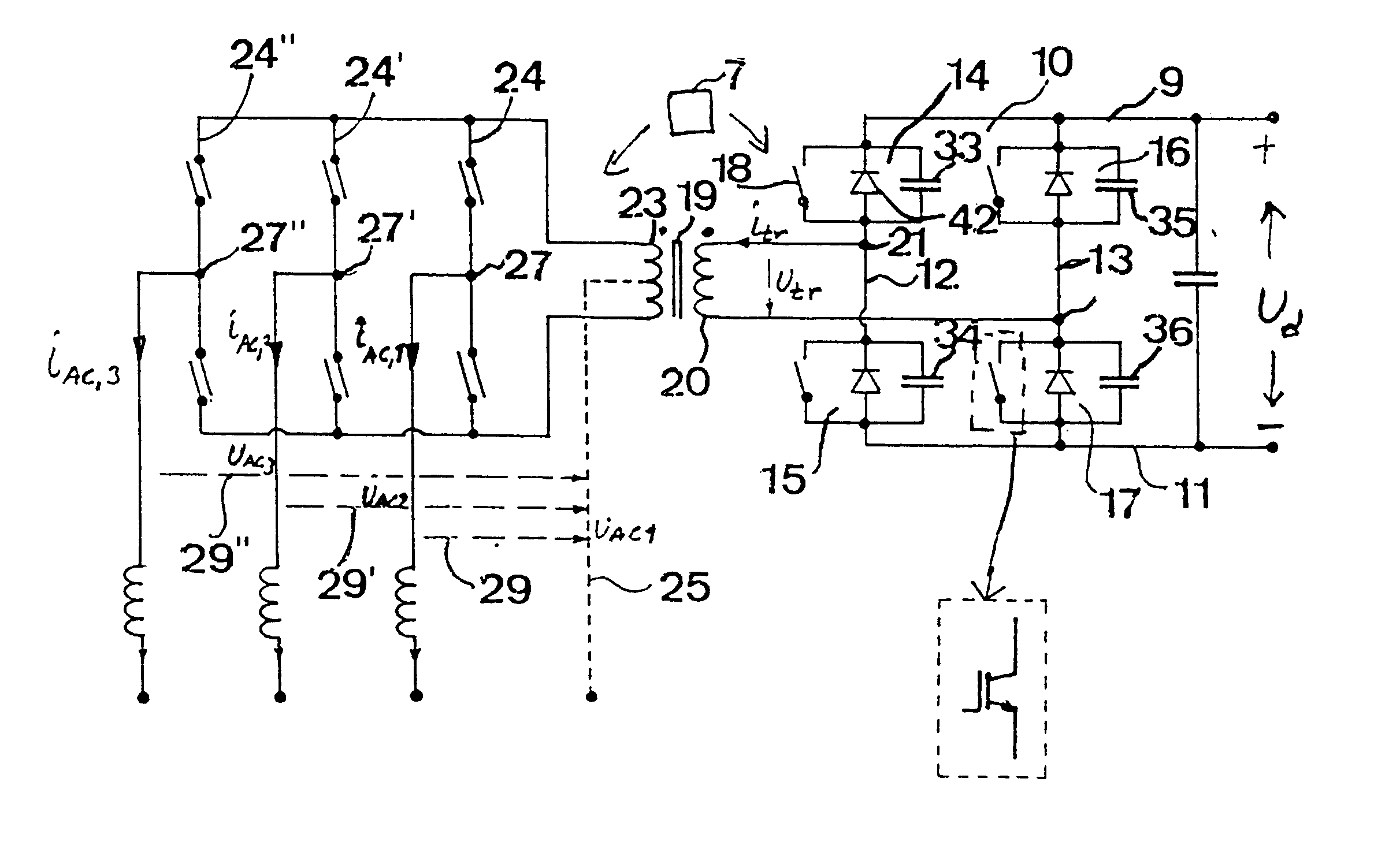

Apparatus and a method for voltage conversion

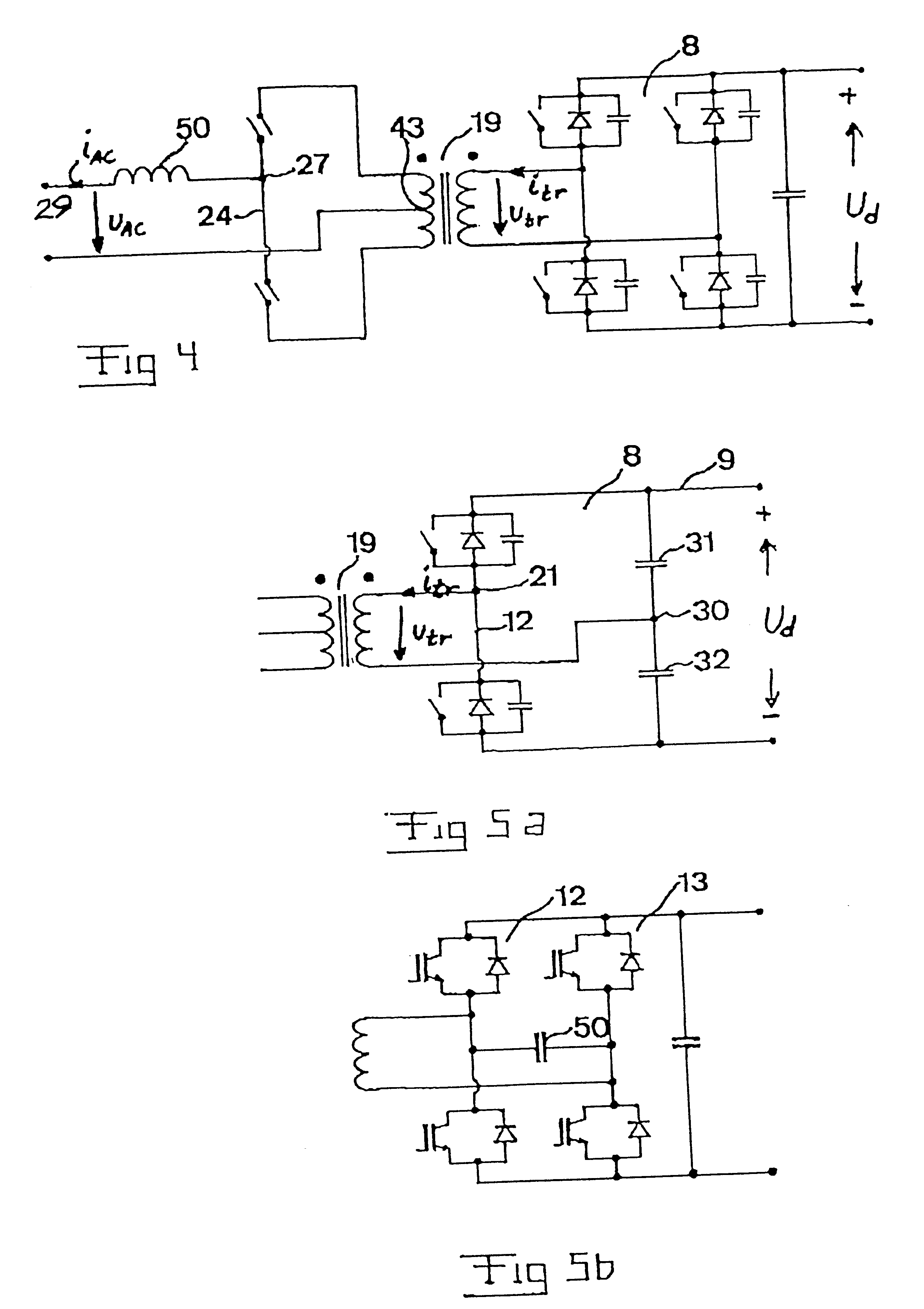

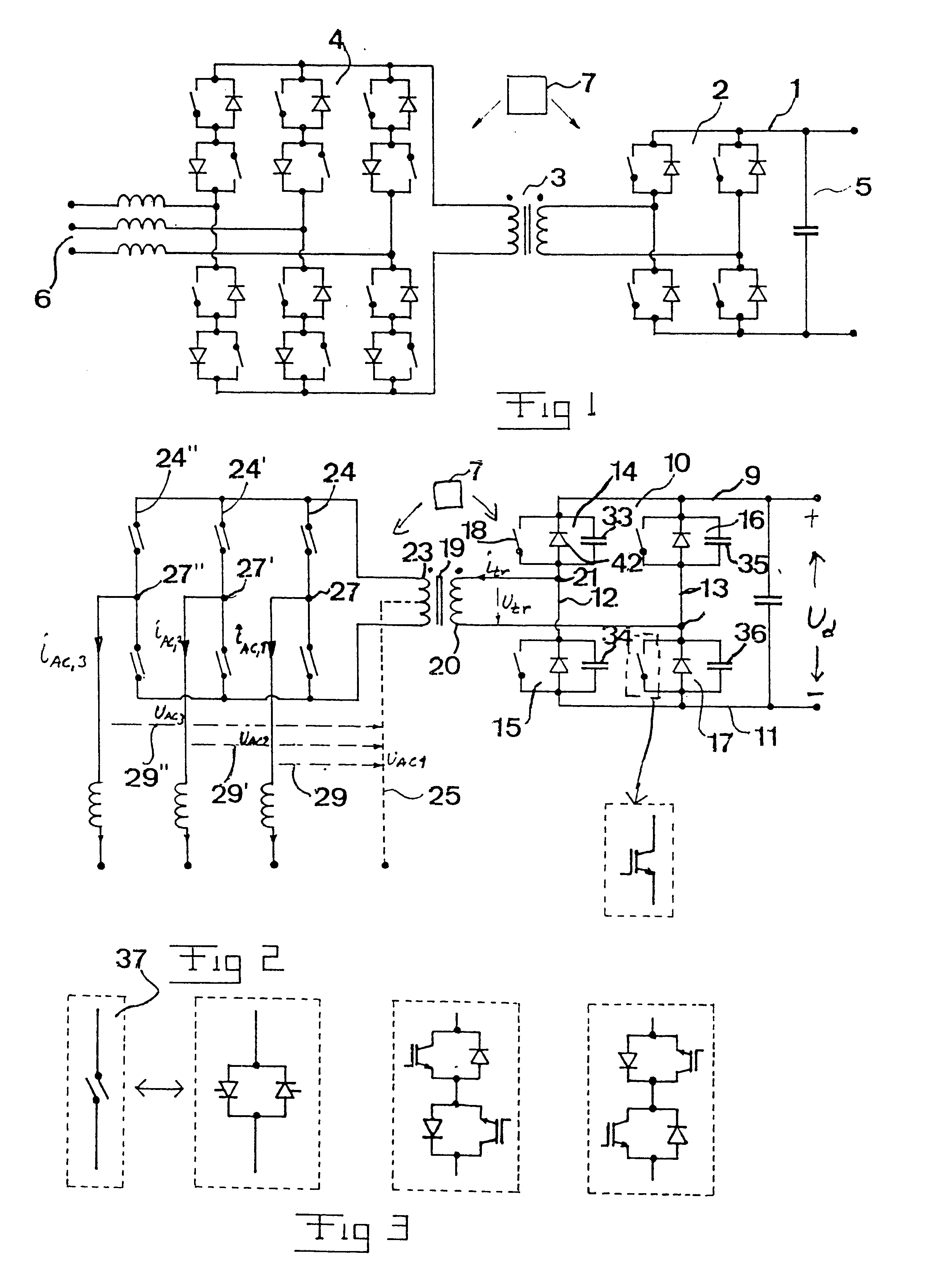

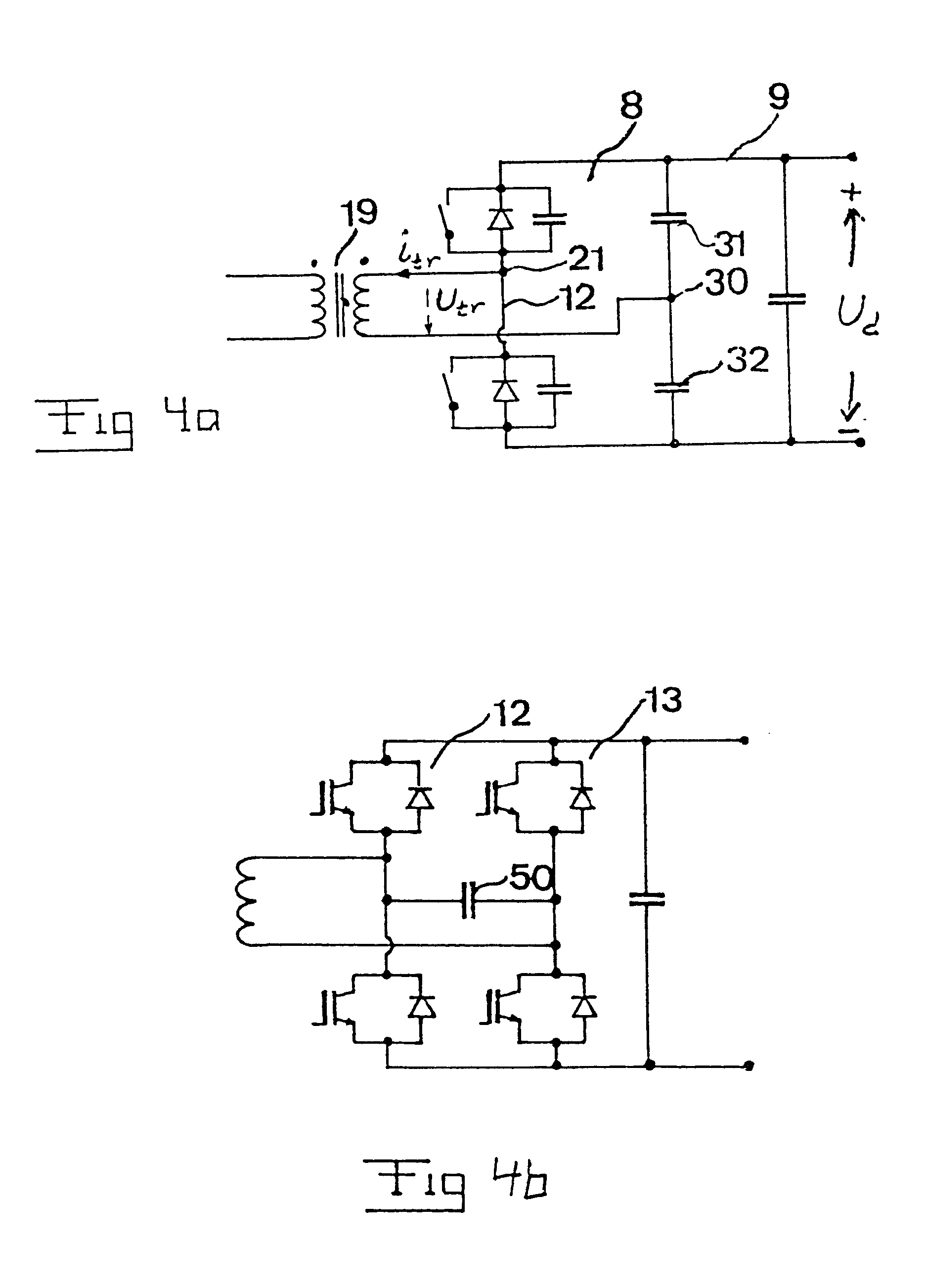

An apparatus for converting direct voltage into alternating voltage and conversely comprises a VSC-converter (8) having a direct voltage intermediate link (9) and at least one phase leg (12, 13). Each current valve (14-17) of the phase legs has at least one semiconductor device of turn-off type and a rectifying member connected in anti-parallel therewith. A transformer (19) has two opposite ends of a first winding (20) thereof connected to an output (21, 22) each of the VSC-converter and a second winding (23) connected to a direct converter having at least one phase leg. Each of the current valves of the direct converter being able to conduct current and block voltage in both directions and to turn on by gate control. A midpoint (27) of the phase leg of the direct converter is provided with a phase output for forming a terminal for the alternating phase voltage between this output and a further phase output (28).

Owner:ABB (SCHWEIZ) AG

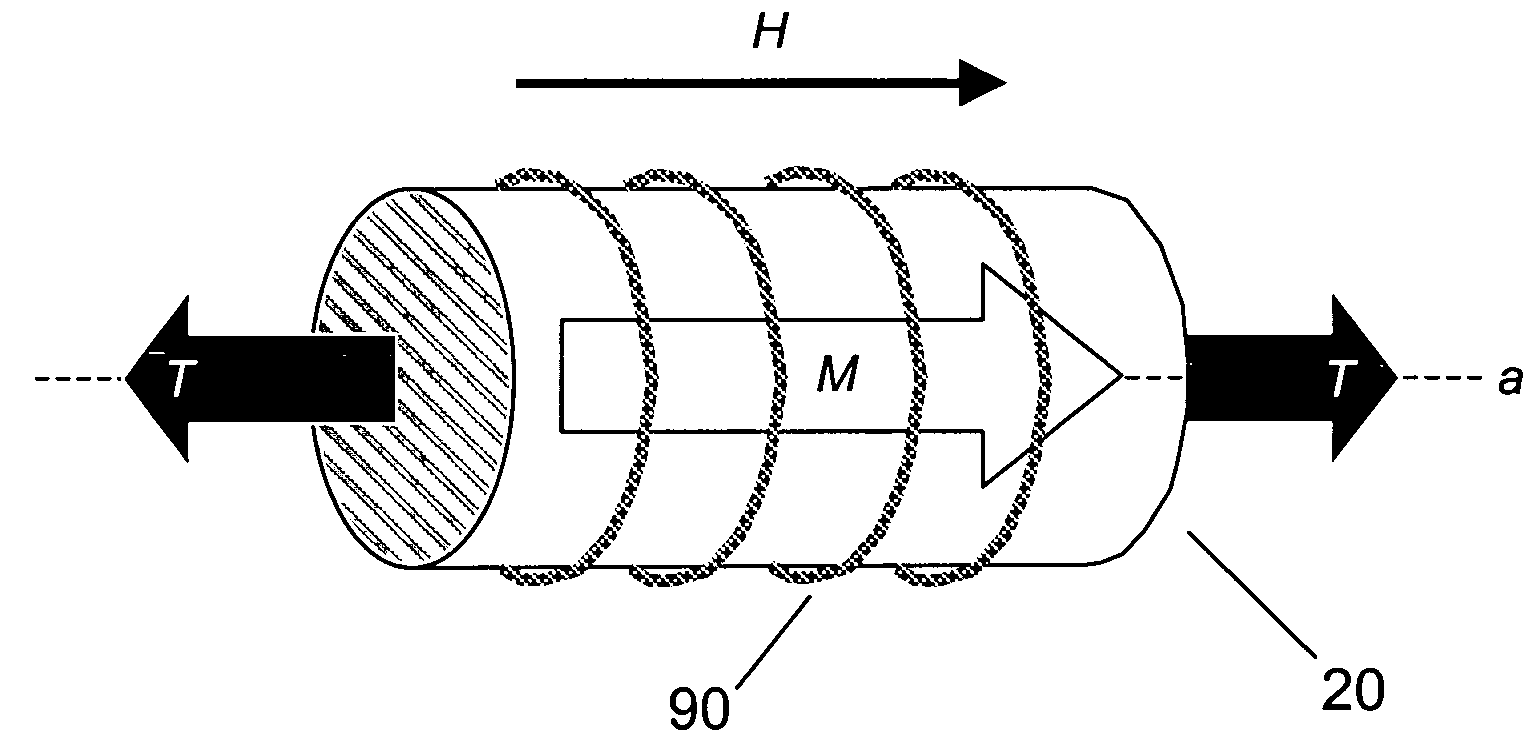

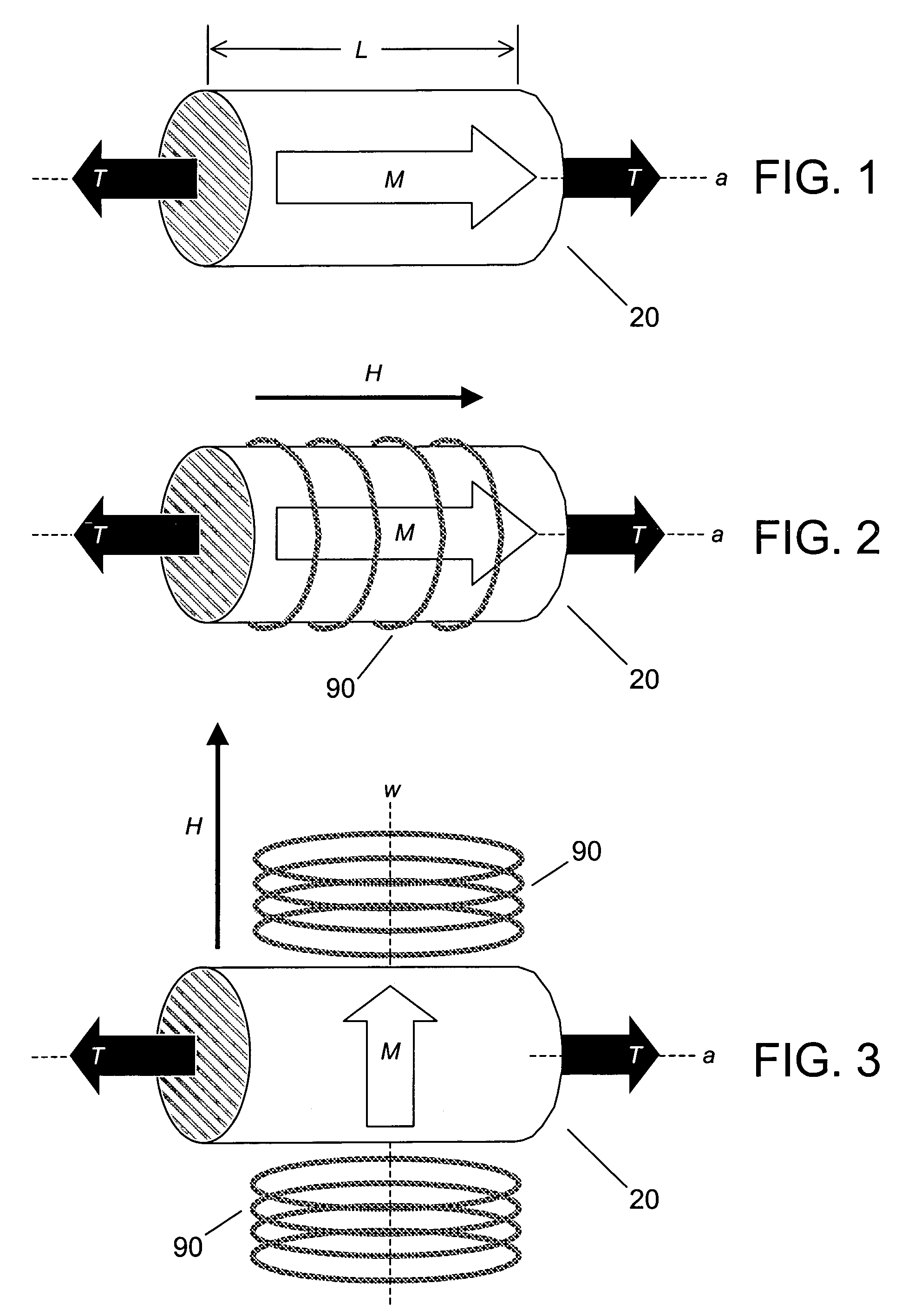

High magnetostriction of positive magnetostrictive materials under tensile load

InactiveUS7564152B1Magnetostrictive device manufacture/assemblyPiezoelectric/electrostriction/magnetostriction machinesElectrical conductorMagnetization

An elongate structure having a magnetostrictive material composition is subjected to tensile stress in the longitudinal-axial direction, thereby generally orienting the magnetization of the elongate structure in the longitudinal-axial direction. Electrical current is conducted through the elongate structure and / or through at least one adjacent elongate conductor, thereby generally orienting the magnetization of the elongate structure in the transverse direction, generally in parallel with the transverse direction of the magnetic field concomitant the conduction of current through the elongate structure. The elongate structure magnetostrictively contracts due to the (generally 90°) repositioning of the magnetization of the elongate structure. Examples of inventive configurational variants include: (i) an elongate structure itself conducting current; (ii) a hollow elongate structure accommodating placement therethrough of at least one elongate conductor; (iii) an elongate structure flanked by a pair of elongate conductors conducting current in opposite directions; (iv) plural elongate structures bordering a centralized elongate conductor.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

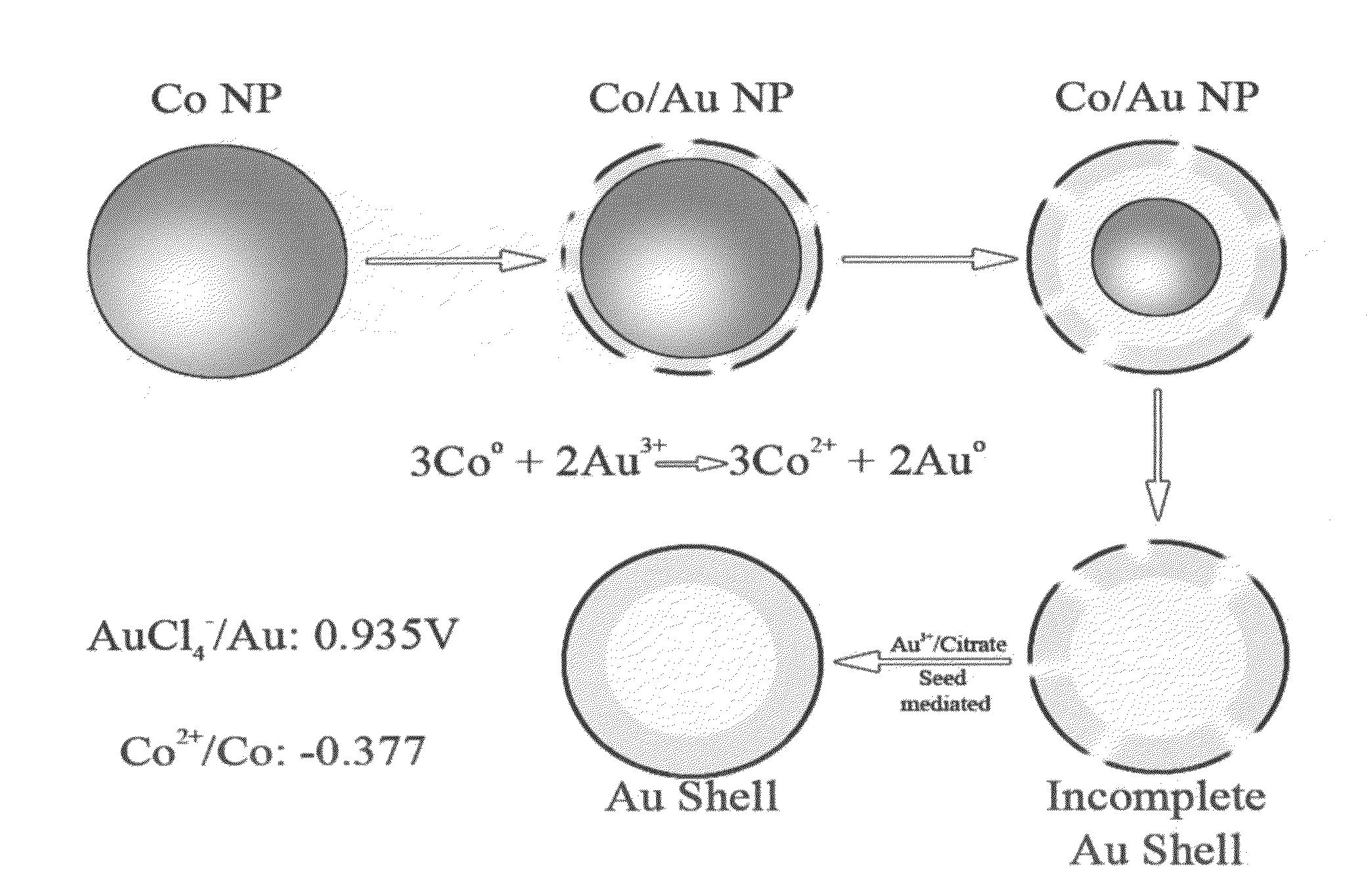

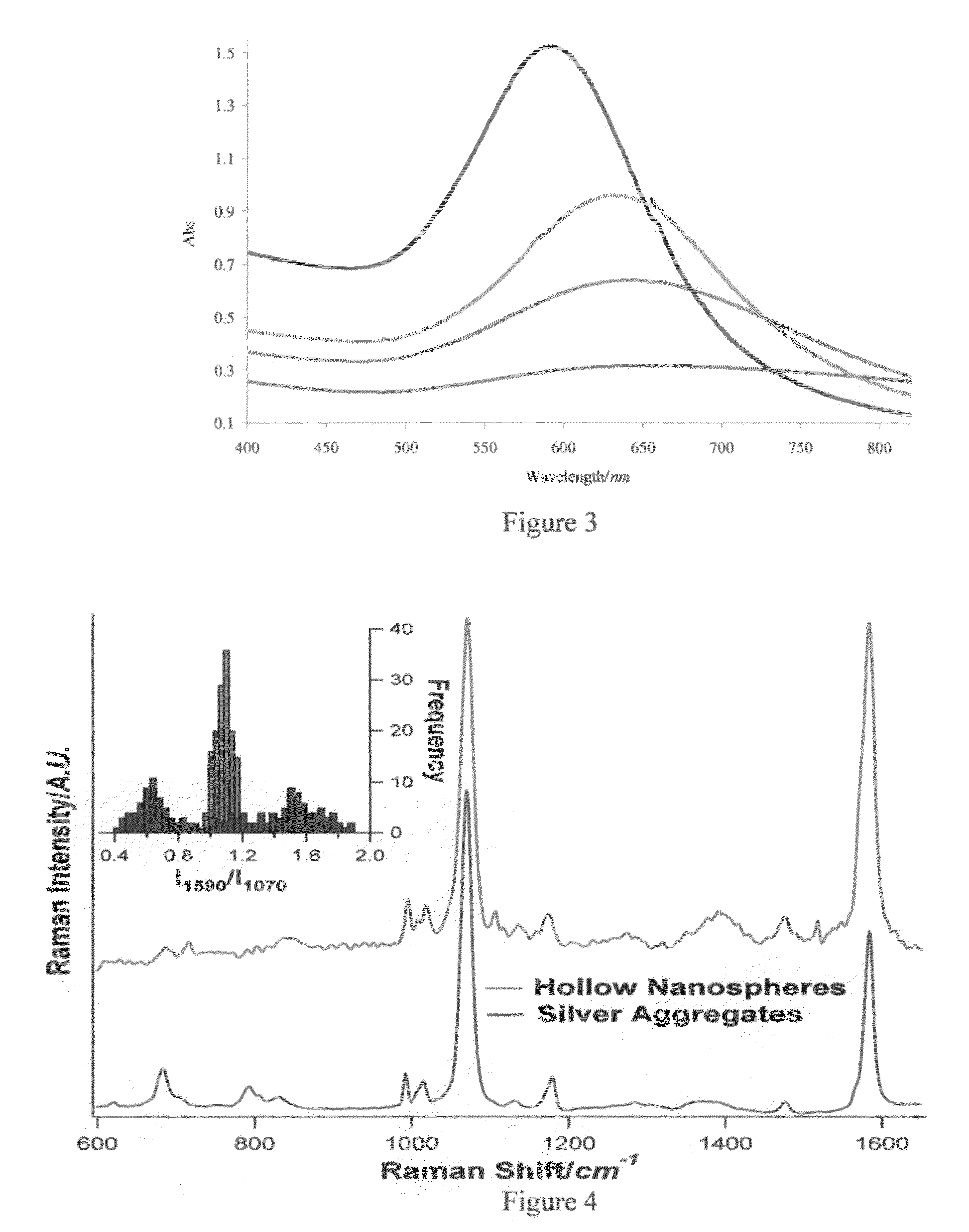

Novel gold nanostructures and methods of use

ActiveUS20100009338A1Material nanotechnologyNon-insulated conductorsElectrical conductorNanostructure

Owner:RGT UNIV OF CALIFORNIA

Programmable Resistive Device and Memory Using Diode as Selector

Building programmable resistive devices in contact holes at the crossover of a plurality of conductor lines in more than two vertical layers is disclosed. There are plurality of first conductor lines and another plurality of second conductor lines that can be substantially perpendicular to each other, though in two different vertical layers. A diode and / or a programmable resistive element can be fabricated in the contact hole between the first and second conductor lines. The programmable resistive element can be coupled to another programmable resistive device or shared between two programmable devices whose diodes conducting currents in opposite directions and / or coupled to a common conductor line. The programmable resistive memory can be configured to be programmable by applying voltages to conduct current flowing through the programmable resistive element to change its resistance for a different logic state.

Owner:ATTOPSEMI TECH CO LTD

Apparatus and a method for voltage conversion

An apparatus for converting direct voltage into alternating voltage and conversely comprises a VSC-converter (8) having a direct voltage intermediate link (9) and at least one phase leg (12, 13). Each current valve (14-17) of the phase legs has at least one semiconductor device of turn-off type and a rectifying member connected in anti-parallel therewith. A transformer (19) has two opposite ends of a first winding (20) thereof connected to an output (21, 22) each of the VSC-converter and a second winding (23) connected to a direct converter having at least one phase leg. Each of the current valves of the direct converter being able to conduct current and block voltage in both directions and to turn on by gate control. A midpoint (27) of the phase leg of the direct converter is provided with a phase output for forming a terminal for the alternating phase voltage between this output and a further phase output (28).

Owner:ABB (SCHWEIZ) AG

Compensation currents in non-volatile memory read operations

ActiveUS20060285391A1Increase apparent conduction currentRead-only memoriesDigital storageBit lineCoupling

Shifts in the apparent charge stored on a floating gate of a non-volatile memory cell can occur because of coupling of an electric field based on the charge stored in adjacent floating gates. The shift in apparent charge can lead to erroneous readings by raising the apparent threshold voltage, and consequently, lowering the sensed conduction current of a memory cell. The read process for a selected memory cell takes into account the state of one or more adjacent memory cells. If an adjacent memory cell is in one or more of a predetermined set of programmed states, a compensation current can be provided to increase the apparent conduction current of the selected memory cell. An initialization voltage is provided to the bit line of the programmed adjacent memory cell to induce a compensation current between the bit line of the programmed adjacent memory cell and the bit line of the selected memory cell.

Owner:SANDISK TECH LLC

Apparatus and a method for voltage conversion

InactiveUS6603675B1Efficient power electronics conversionConversion without intermediate conversion to dcConvertersDevice material

An apparatus for converting direct voltage into three-phase alternating voltage and conversely comprises a VSC-converter (8) having a direct voltage intermediate link (9) and at least one phase leg (12, 13). Each current valve (14-17) of the phase legs has at least one semiconductor device of turn-off type and a rectifying member connected in anti-parallel therewith. A transformer (19) has two opposite ends of a first winding (20) thereof connected to an output (21, 22) each of the VSC-converter and a second winding (23) connected to a direct converter having at least three phase legs. Each of the current valves of the direct converter being able to conduct current and block voltage in both directions and to turn on by gate control. The midpoints (27, 27', 27'') of the phase legs of the direct converters are provided with phase outputs for forming a terminal for the alternating phase voltage between these phase outputs.

Owner:ABB (SCHWEIZ) AG

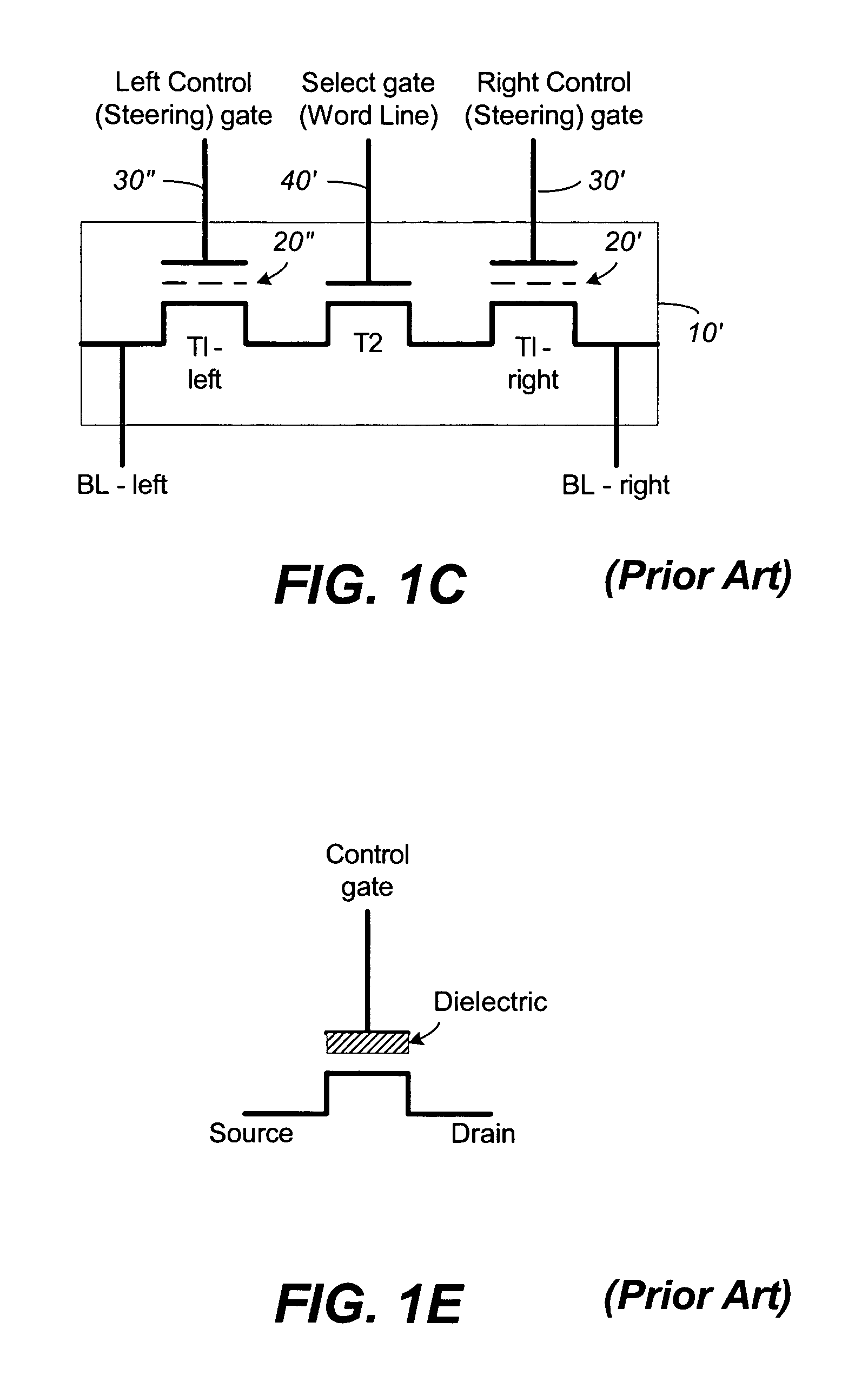

Anti-fuse circuit and method of operation

InactiveUS6597234B2Semiconductor/solid-state device detailsSolid-state devicesElectricityGate dielectric

An anti-fuse useful in implementing redundancy in a memory utilizes a normal transistor characteristic that is generally considered undesirable in order to provide two easily detected states. The un-programmed state, which is the high impedance state, is achieved simply with a normal transistor in its non-conductive state. The programmed state, which is the low impedance state, is achieved by forcing a normal transistor to conduct current through its gate. This causes the gate dielectric to become permanently conductive. This programmed transistor then is conductive between its source and drain that is easily differentiated from the transistor that is held in its non-conductive state. The result is a fuse technology using an anti-fuse that provides for easily distinguishable programmed and un-programmed states achieved by electrical programming rather than by laser programming.

Owner:FREESCALE SEMICON INC

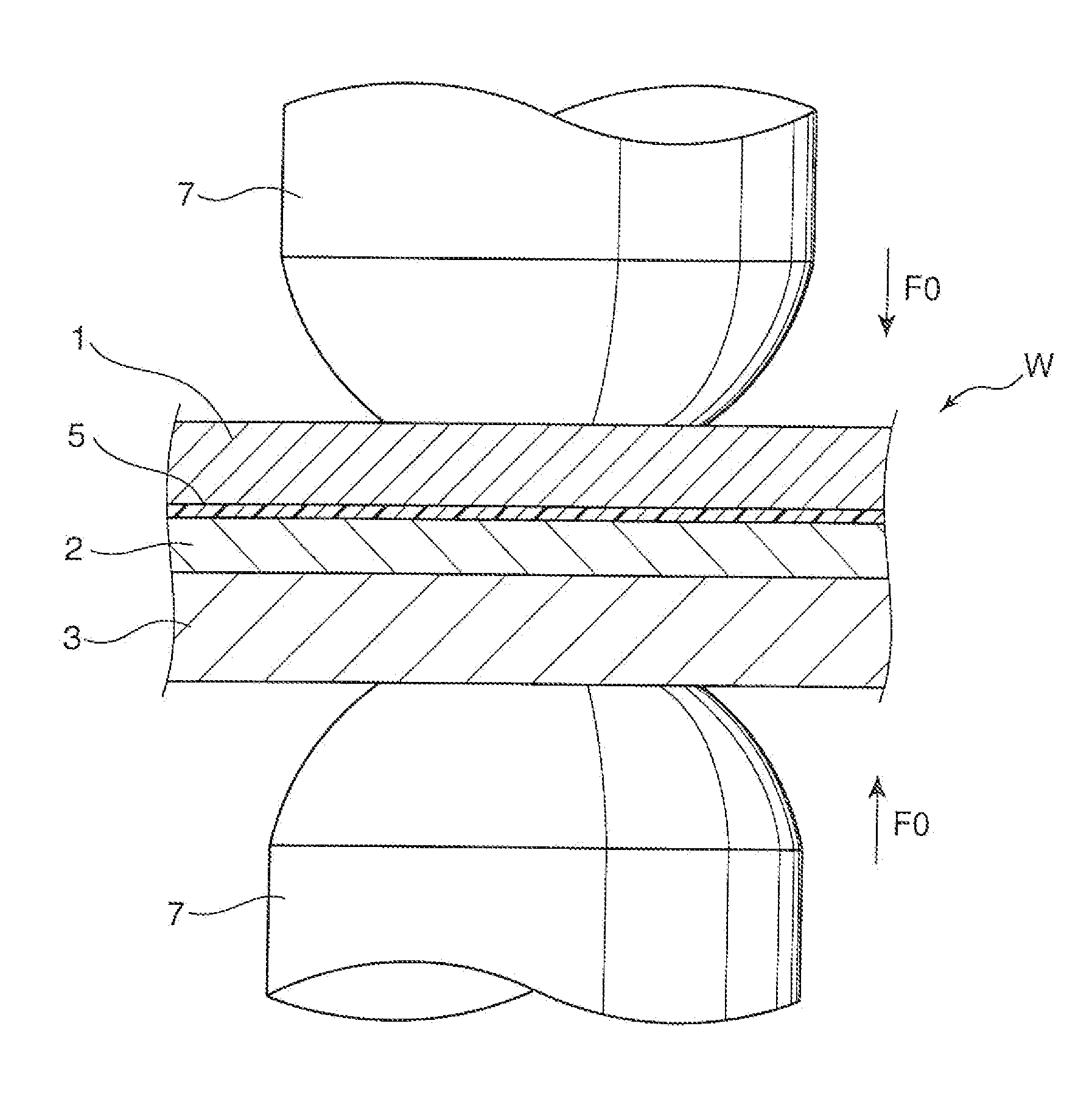

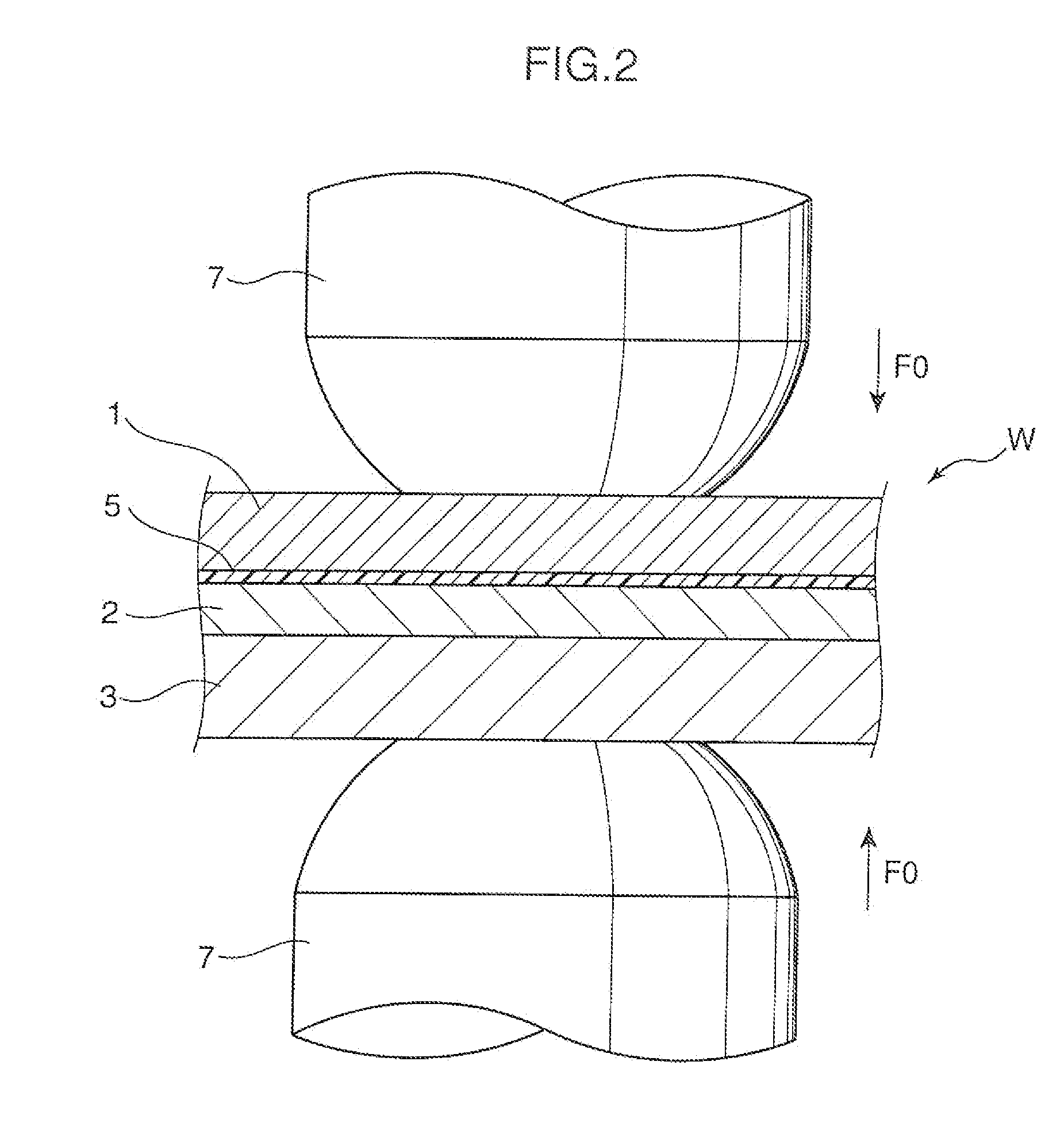

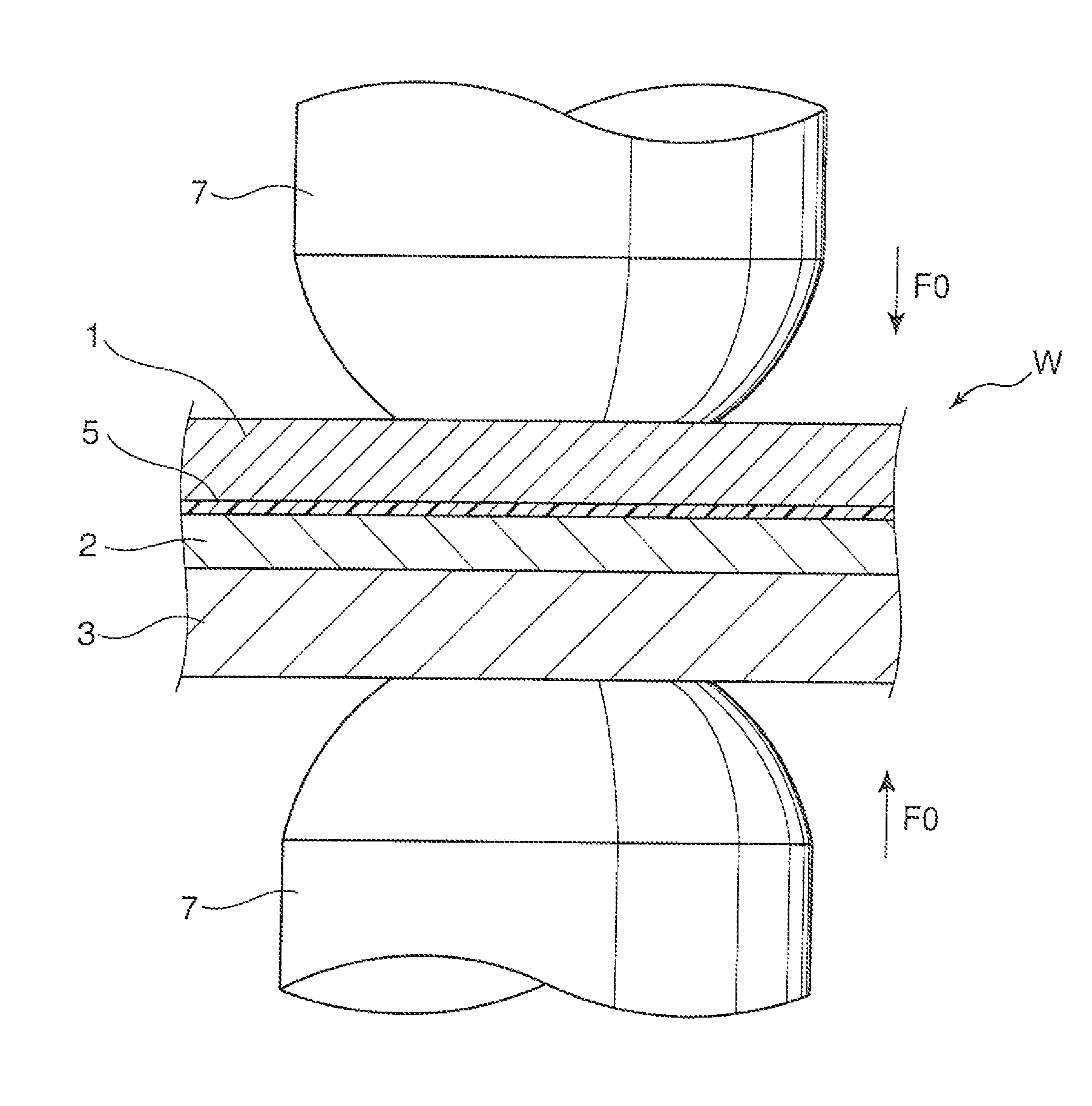

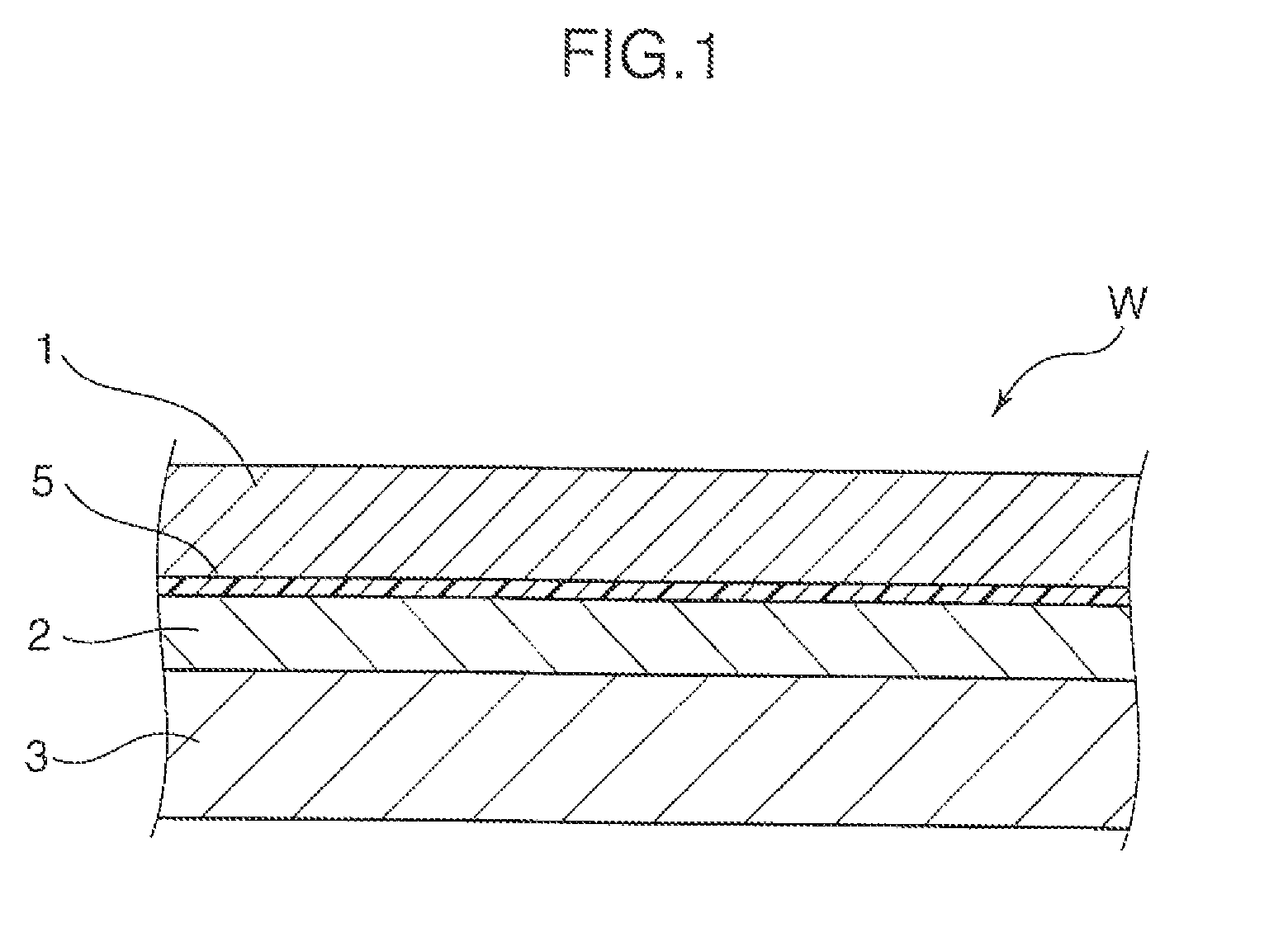

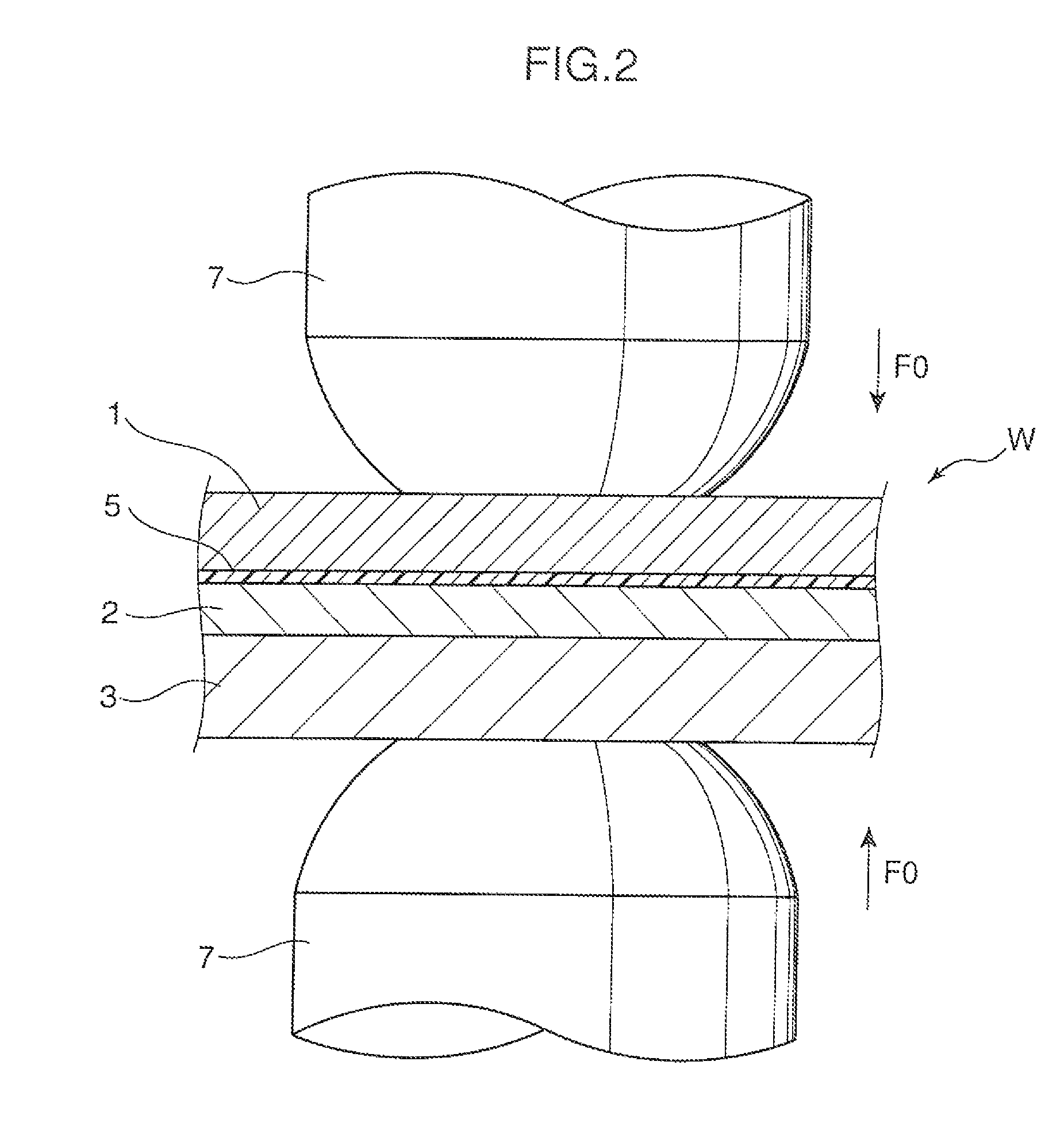

Joining method of dissimilar metal plates and dissimilar metal joined body

ActiveUS20110097594A1Improve joint strengthWelding electric supplyArc welding apparatusPower flowAdhesive

The joining method of the present invention includes a lapping step of lapping the aluminum alloy plate (1) and the plated steel plate (2) via the adhesive (5), a pre-heating step of clamping both of the metal plates (1, 2) that have been lapped in the lapping step between a pair of electrodes (7, 7) for spot welding and applying pressure thereto, and applying a current between the pair of electrodes (7, 7), a cooling step of pressurizing, after the pre-heating step, both of the metal plates (1, 2) at a pressing force which is higher than that at the start of the pre-heating step in a state where conduction between the electrodes (7, 7) is stopped, and continuing this pressurization over a predetermined cooling time, and a welding step of pressurizing, after the cooling step, both of the metal plates (1, 2) at a pressing force which is higher than that at the start of the pre-heating step, and welding both of the metal plates (1, 2) by applying a current which is higher than the conduction current value in the pre-heating step between the pair of electrodes (7, 7). It is thereby possible to firmly join the dissimilar metal plates (1, 2) by combining adhesion due to an adhesive and spot welding.

Owner:MAZDA MOTOR CORP +1

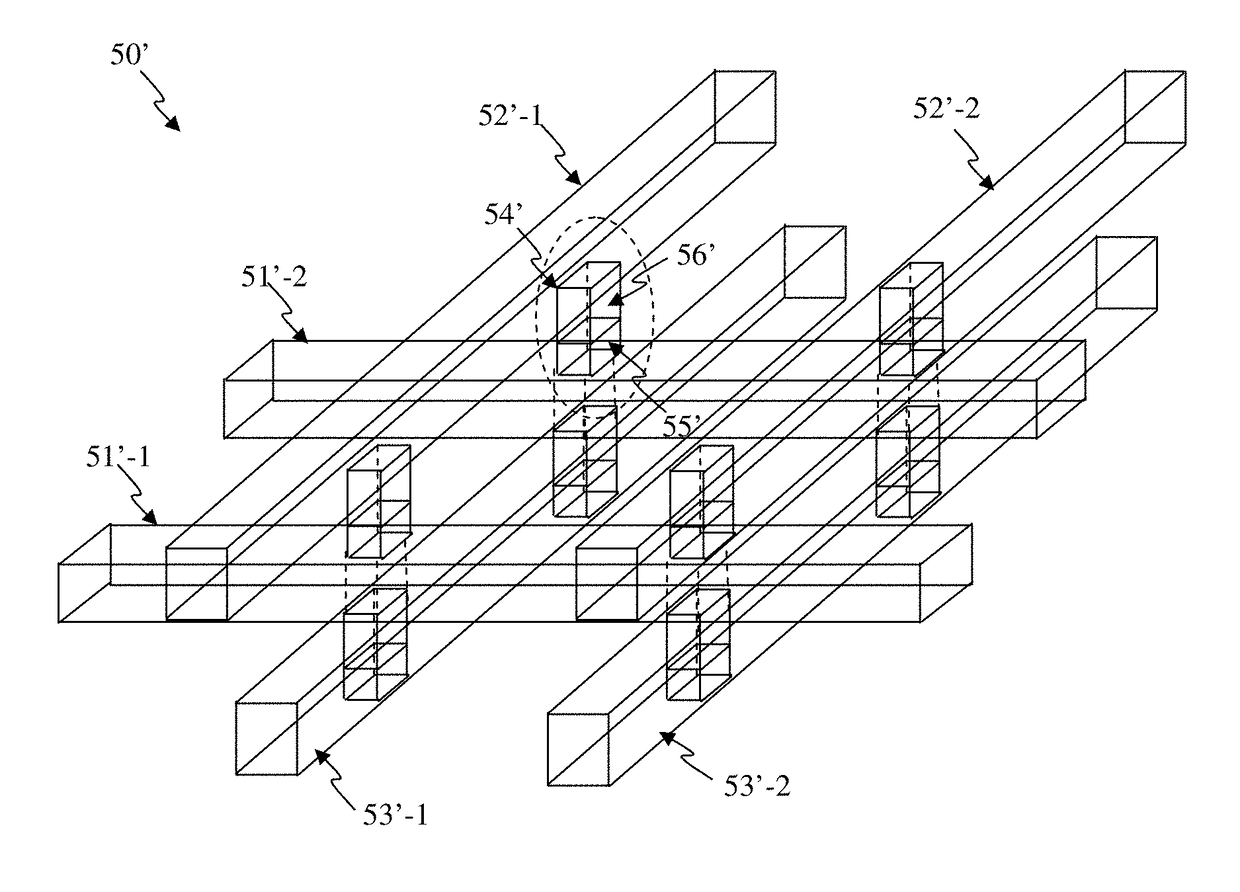

High Speed Sense Amplifier Array and Method for Nonvolatile Memory

ActiveUS20090296488A1Reduce noiseRead-only memoriesDigital storageAudio power amplifierComparators circuits

Sensing circuits for sensing a conduction current of a memory cell among a group of non-volatile memory cells being sensed in parallel and providing the result thereof to a data bus are presented. A precharge circuit is coupled to a node for charging the node to an initial voltage. An intermediate circuit is also coupled to the node and connectable to the memory cell, whereby current from the precharge circuit can be supplied to the memory cell. The circuit also includes a comparator circuit to perform a determination the conduction current by a rate of discharge at the node; a data latch coupled to the comparator circuit to hold the result of said determination; and a transfer gate coupled to the data latch to supply a result latched therein to the data bus independently of the node. This arrangement improves sensing performance and can help to eliminate noise on the analog sensing path during sensing and reduce switching current.

Owner:SANDISK TECH LLC

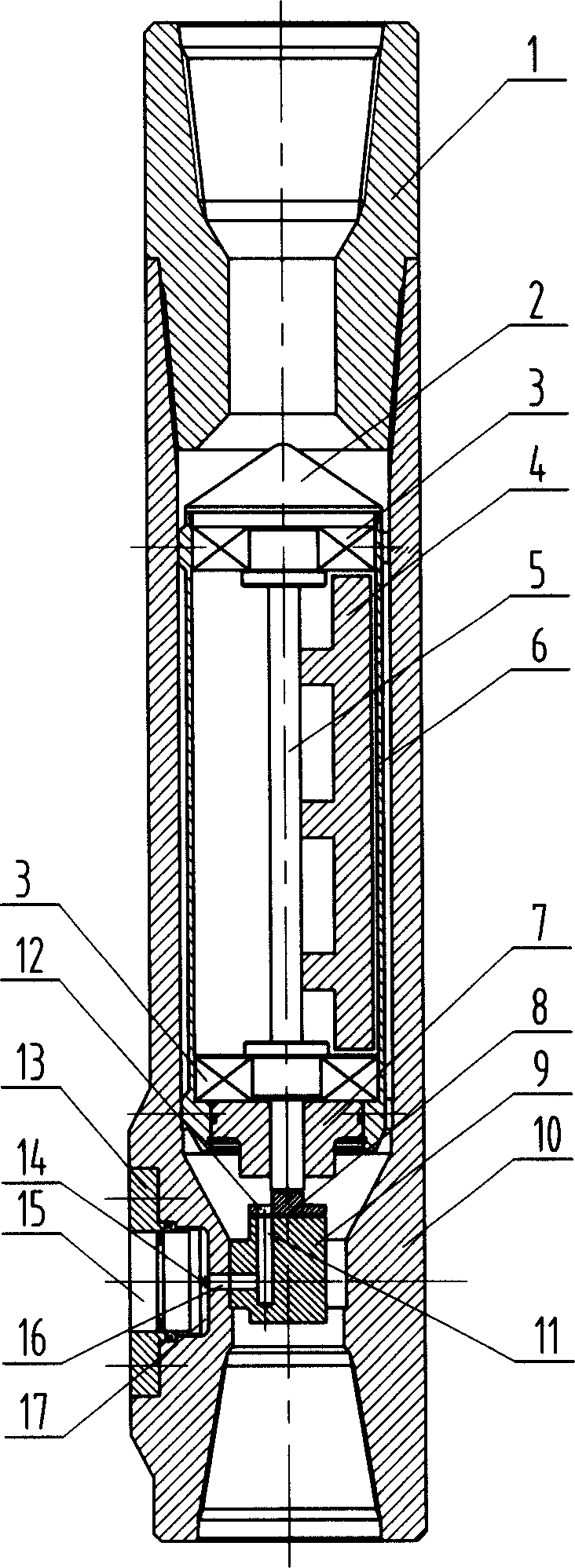

Mechanical automatic vertical drilling tool

InactiveCN1676862AIncrease drilling speedShorten the purification processDirectional drillingWell drillingDifferential pressure

One kind of mechanical type automatic vertically well-drilling tool, including turner, the conduction current head, the bearing, the counterweight, the spindle, in-tube, the back plate, above plate-valve, gets down plate-value, the shell, the piston cylinder back plate and the piston, its principle is at the right moment induces the well slanting gravity signal, by the gravity-actuates in the organization, the establishment drills inside and out the column high-low pressure channel between the fluid, uses two between the differential pressure, actuates the piston at the right moment to push depends on the wall of a well is high side, the wall of a well reacting force then pushes the drill bit to is low side, but in well-eye other positions, the piston does not push depends on the wall of a well, drills the column revolves, this process circulation reciprocation, the well is slanting namely is unceasingly induced and the revision, this invention realization is initiative, At the right moment guards against slanting at the same time, but also can effectively liberate distilling, largely enhances drills fast and well-eye the quality, reduces the construction risk, this invention has the structure is simple, reliable, is suitable to the many kinds of well drilling platform, the processing makes the maintenance cost is low and so on the characteristic.

Owner:SHENGLI PETROLEUM ADMINISTRATION BUREAU DRILLING TECH ACAD SINOPEC

Method for compensated sensing in non-volatile memory

InactiveUS20060158935A1Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierReference current

One or more sense amplifiers for sensing the conduction current of non-volatile memory is controlled by signals that are timed by a reference sense amplifier having similar characteristics and operating conditions. In one aspect, a sensing period is determined by when the reference sense amplifier sensing a reference current detects an expected state. In another aspect, an integration period for an amplified output is determined by when the reference sense amplifier outputs an expected state. When these determined timings are used to control the one or more sense amplifiers, environment and systemic variations are tracked.

Owner:SANDISK TECH LLC

Joining method of dissimilar metal plates and dissimilar metal joined body

The joining method includes a step of lapping the aluminum alloy plate and the plated steel plate via adhesive, a pre-heating step of clamping both metal plates lapped in the lapping step between a pair of electrodes for spot welding and applying pressure thereto, and applying a current between the pair of electrodes, a cooling step of pressurizing both metal plates at a pressing force higher than that at the start of the pre-heating step in a state where conduction between the electrodes is stopped, and continuing this pressurization over a predetermined cooling time, and a welding step of pressurizing both metal plates at a pressing force higher than that at the start of the pre-heating step, and welding both of the metal plates by applying a current higher than the conduction current value in the pre-heating step between the pair of electrodes.

Owner:MAZDA MOTOR CORP +1

Non-volatile memory and method with improved sensing

InactiveUS20060050562A1Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierVoltage drop

Source line bias is an error introduced by a non-zero resistance in the ground loop of the read / write circuits. During sensing the control gate voltage of a memory cell is erroneously biased by a voltage drop across the resistance. This error is minimized when the current flowing though the ground loop is reduced. A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In particular, the identified memory cells are shut down after all sensing in the current pass have been completed. In this way the shutting down operation does not disturb the sensing operation. Sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells. In another aspect of sensing improvement, a reference sense amplifier is employed to control multiple sense amplifiers to reduce their dependence on power supply and environmental variations.

Owner:SANDISK TECH LLC

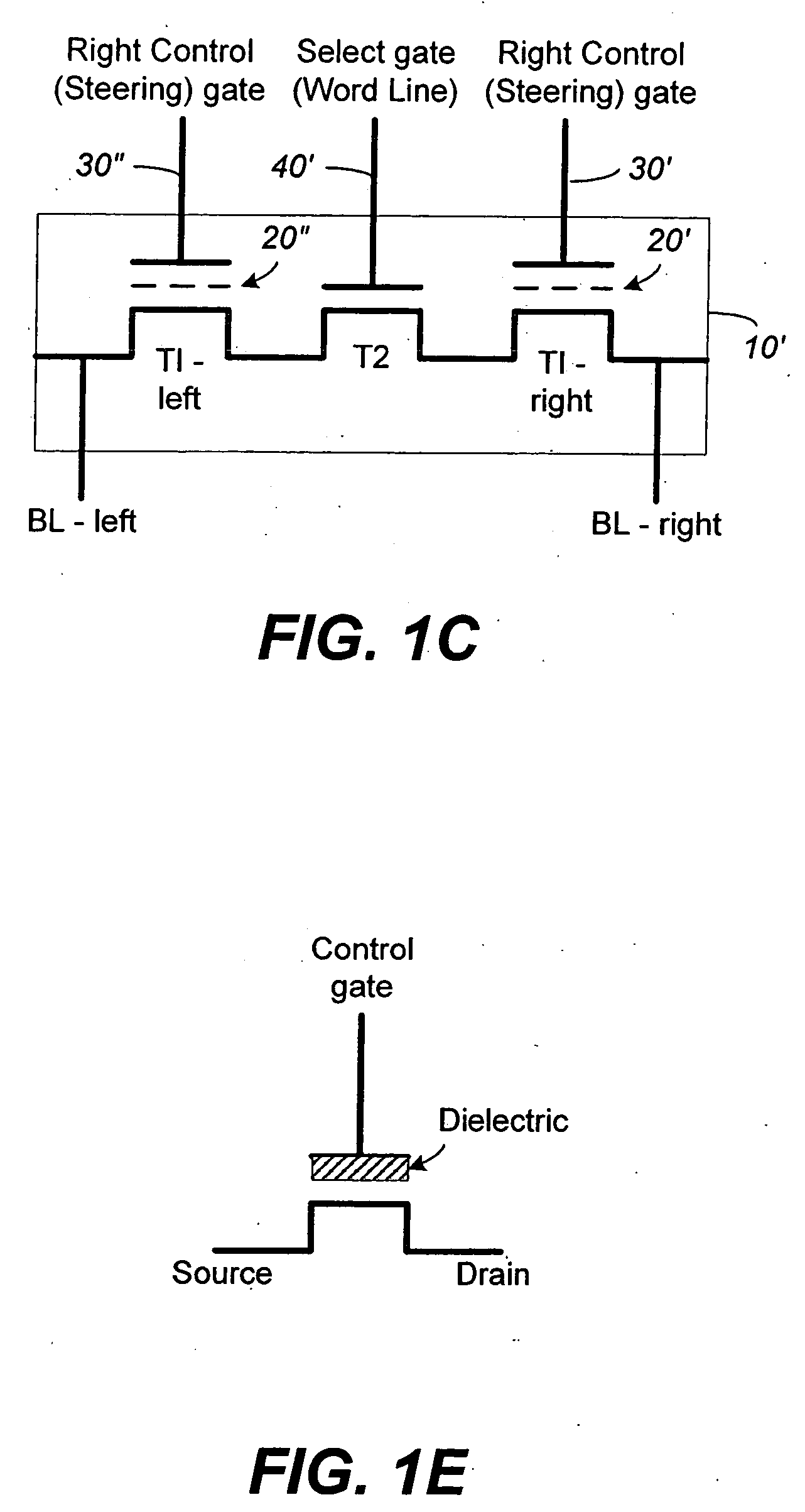

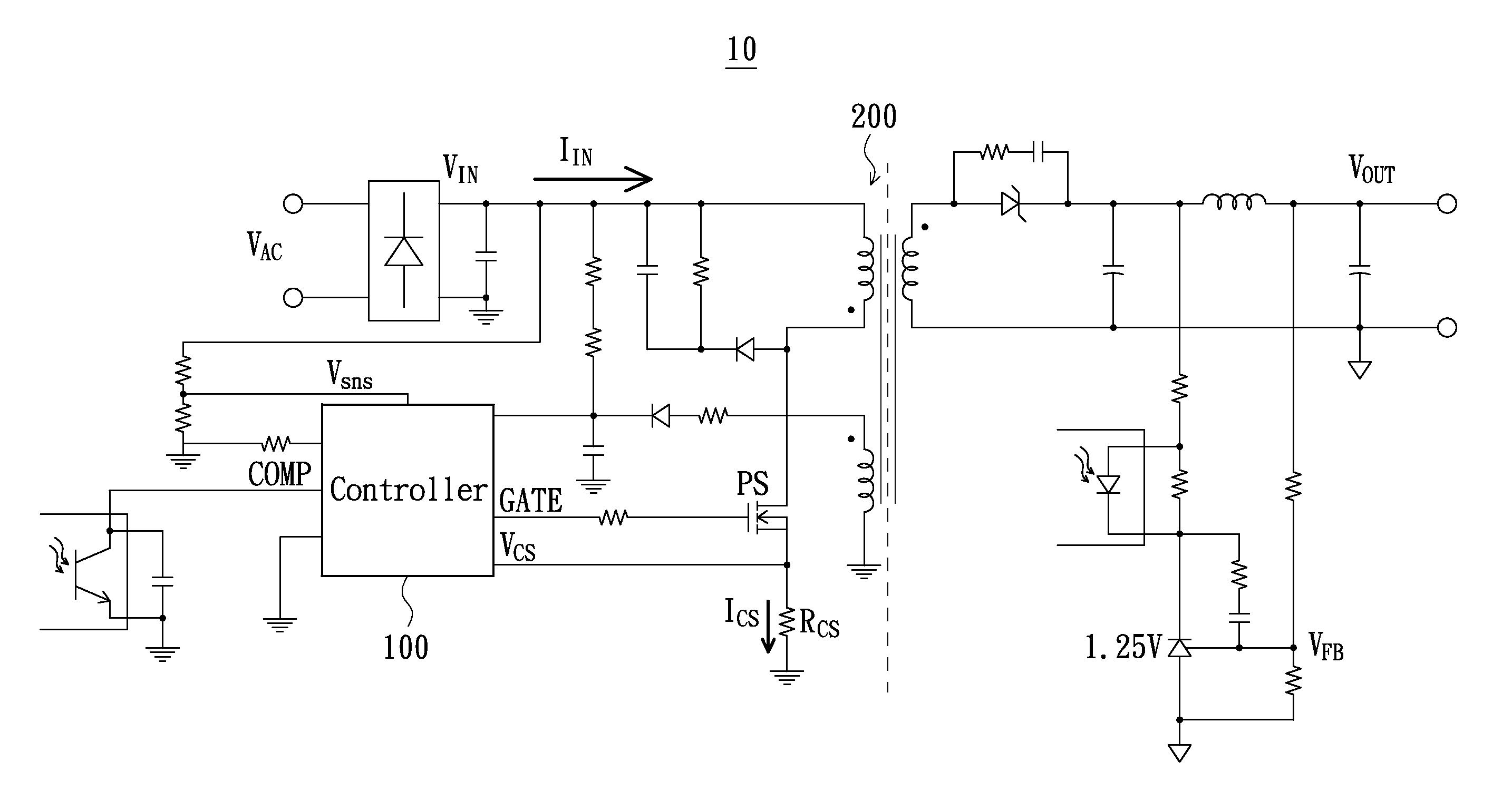

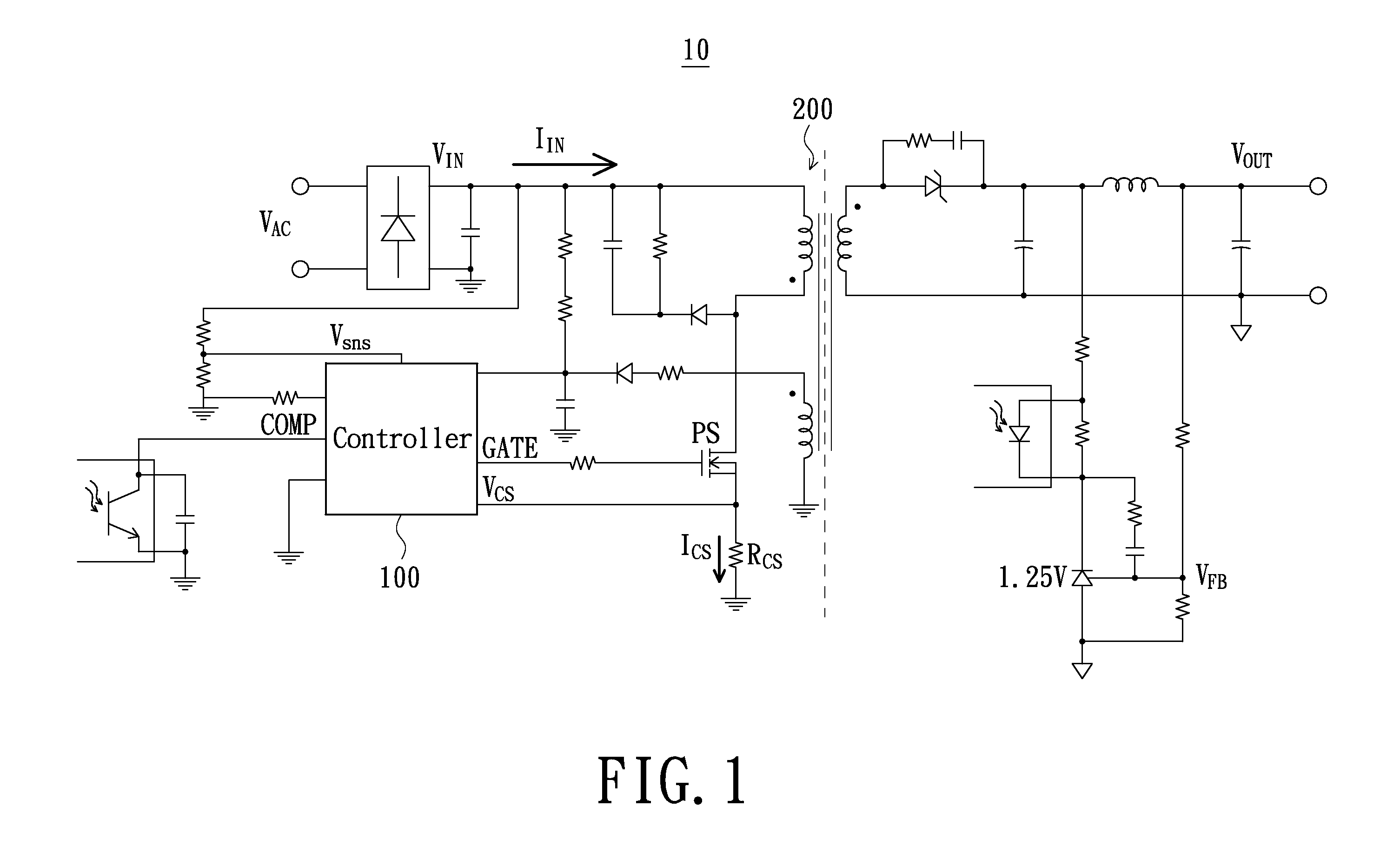

Controller and controlling method for power converter

InactiveUS20120155122A1Efficient mechanismDc-dc conversionElectric variable regulationRelative magnitudeReference current

A controller for a power converter is provided. The controller includes a sense current integrating circuit, a reference current integrating circuit and a drive signal generation circuit. The sense current integrating circuit performs an integrating operation to a sense current representative of a conduction current flowing through a power switch of the power converter and thereby outputs a first integrating result. The reference current integrating circuit performs another integrating operation to a reference current and thereby outputs a second integrating result. The drive signal generation circuit determines a switching period of the power switch according to a status of an output voltage of the power converter cooperative with a relative magnitude relationship between the first integrating result and the second integrating circuit. Furthermore, a controlling method for such power converter also is provided.

Owner:RICHTEK TECH

Non-volatile memory and method with improved sensing

InactiveUS7212445B2Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierEnvironmental variation

A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In particular, the identified memory cells are shut down after all sensing in the current pass have been completed. In this way the shutting down operation does not disturb the sensing operation. Sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells. In another aspect of sensing improvement, a reference sense amplifier is employed to control multiple sense amplifiers to reduce their dependence on power supply and environmental variations.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com