Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

310results about How to "Small cell size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

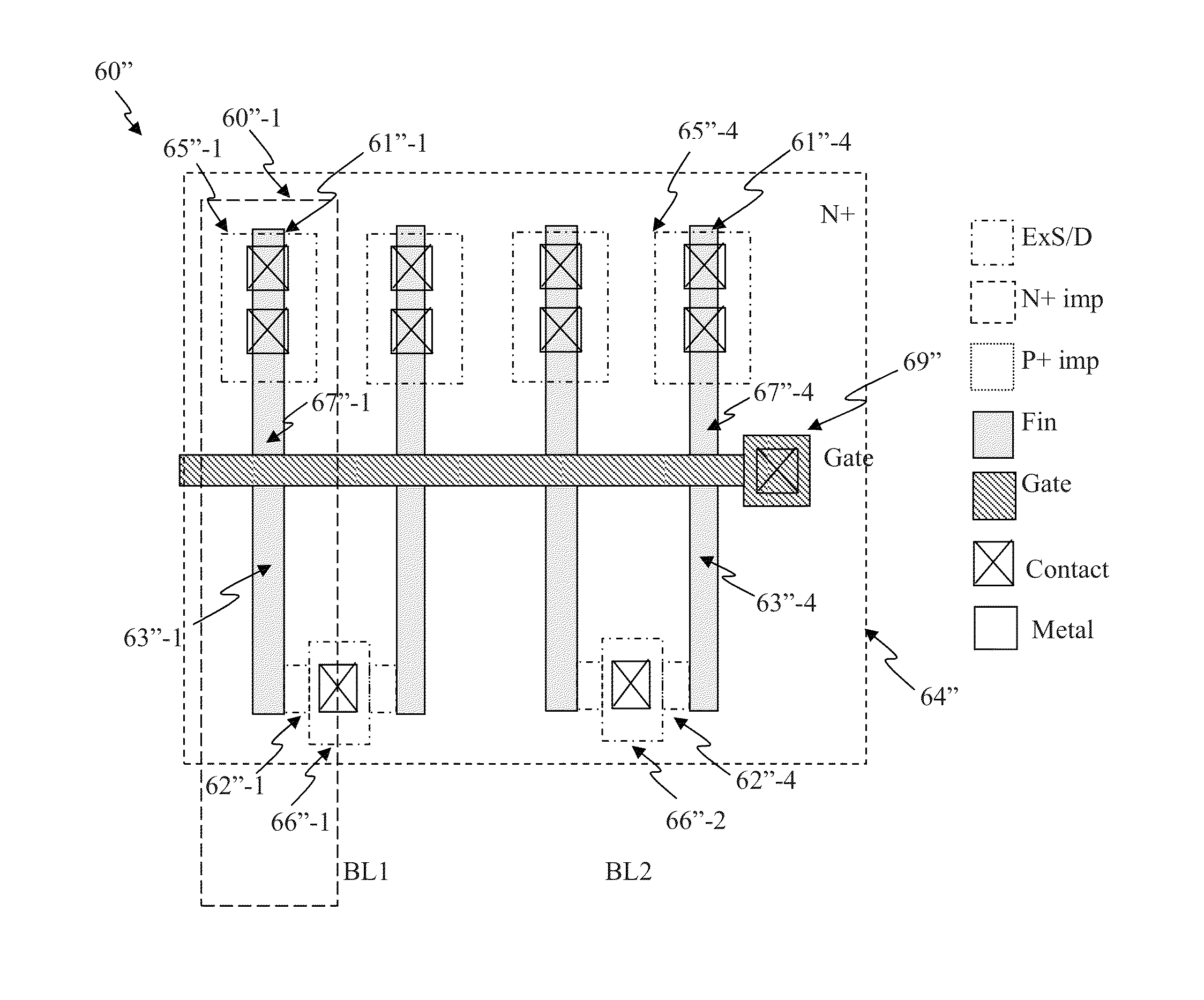

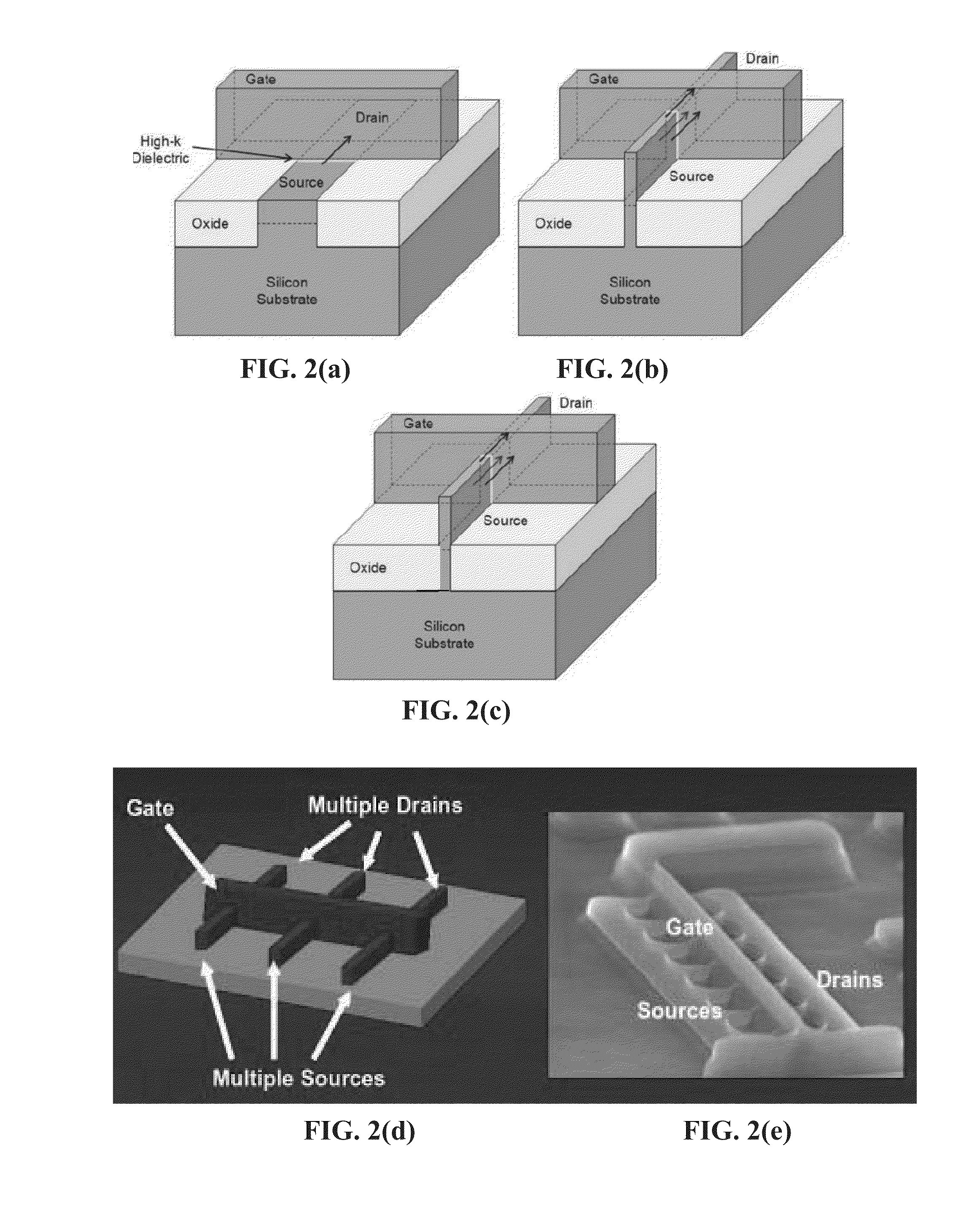

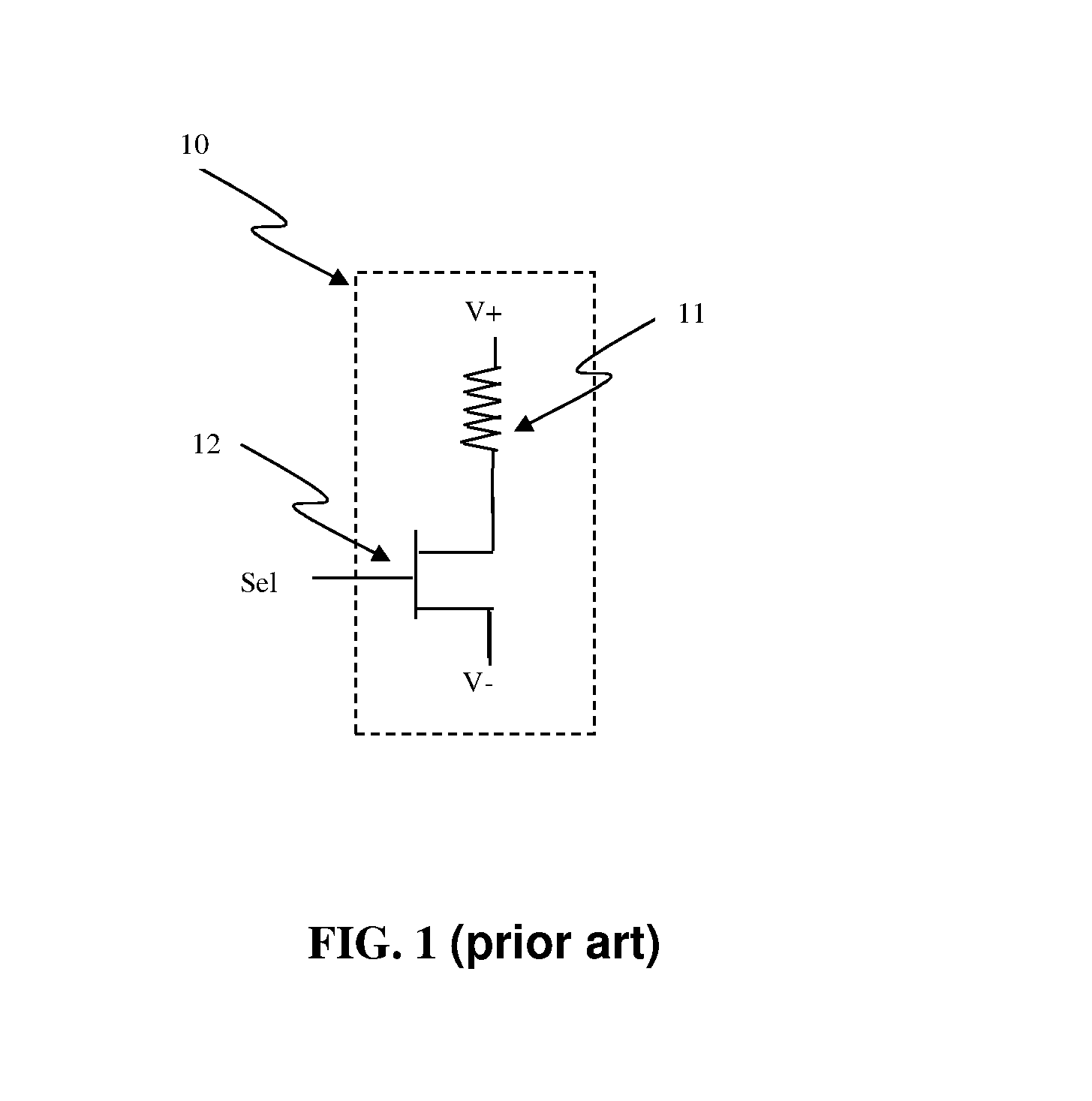

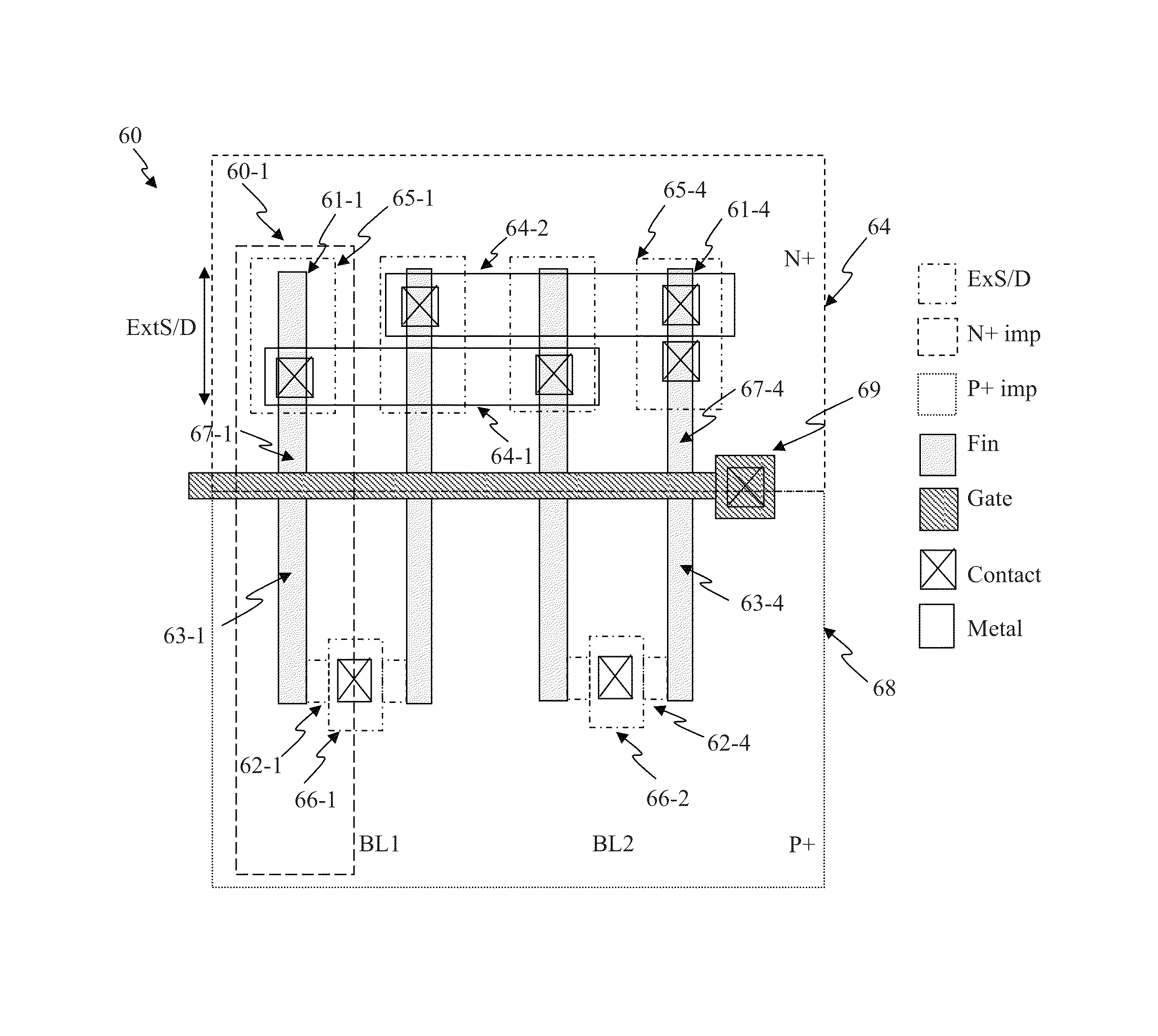

Circuit and system of using finfet for building programmable resistive devices

ActiveUS20130148409A1Small cell sizeLow costSolid-state devicesRead-only memoriesHemt circuitsEngineering

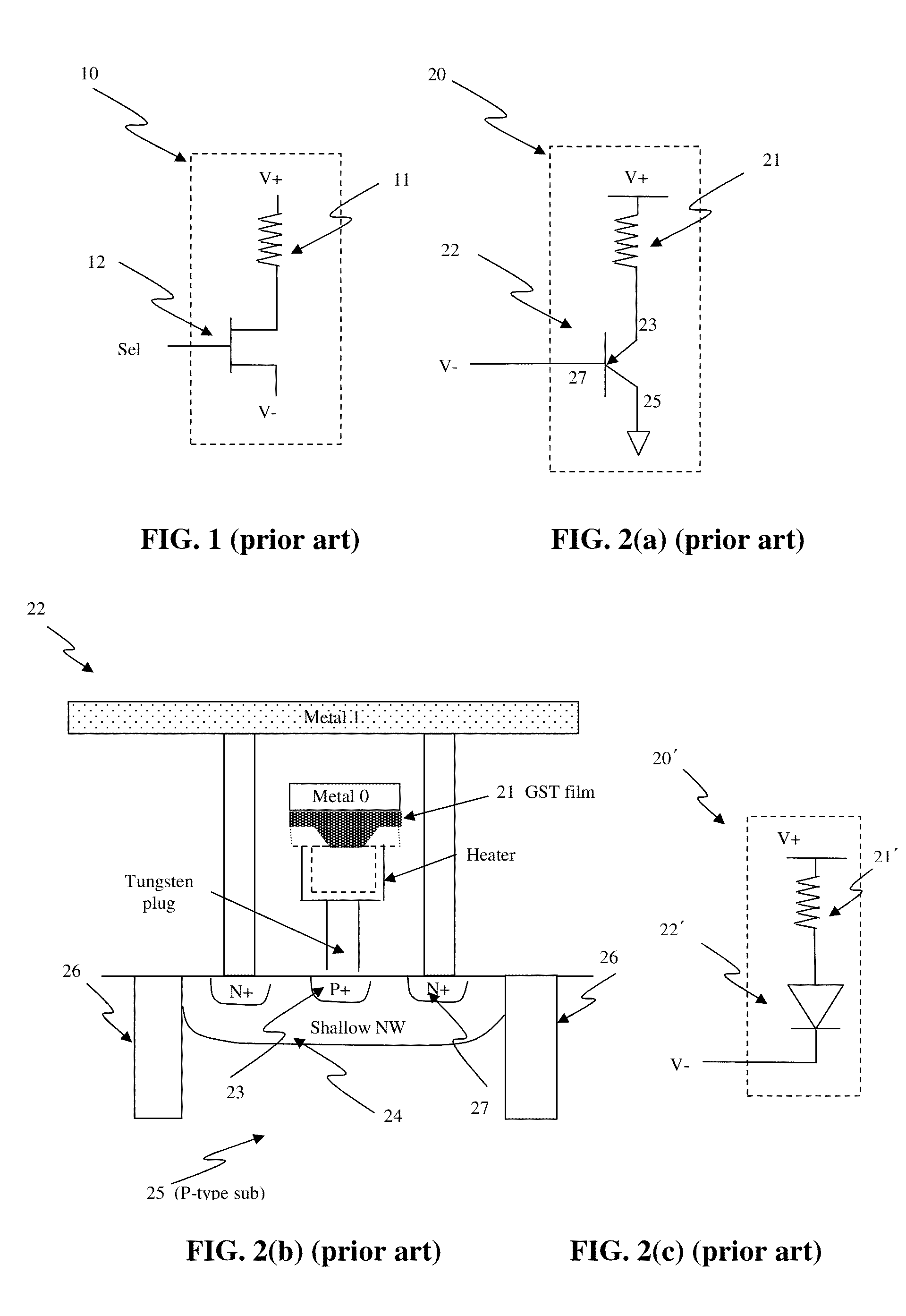

Junction diodes or MOS devices fabricated in standard FinFET technologies can be used as program selectors or One-Time Programmable (OTP) element in a programmable resistive device, such as interconnect fuse, contact / via fuse, anti-fuse, or emerging nonvolatile memory such as MRAM, PCRAM, CBRAM, or RRAM. The MOS or diode can be built on at least one fin structure or at least one active region that has at least one first active region and a second active region. The first and the second active regions can be isolated by a dummy MOS gate or silicide block layer (SBL) to construct a diode.

Owner:ATTOPSEMI TECH CO LTD

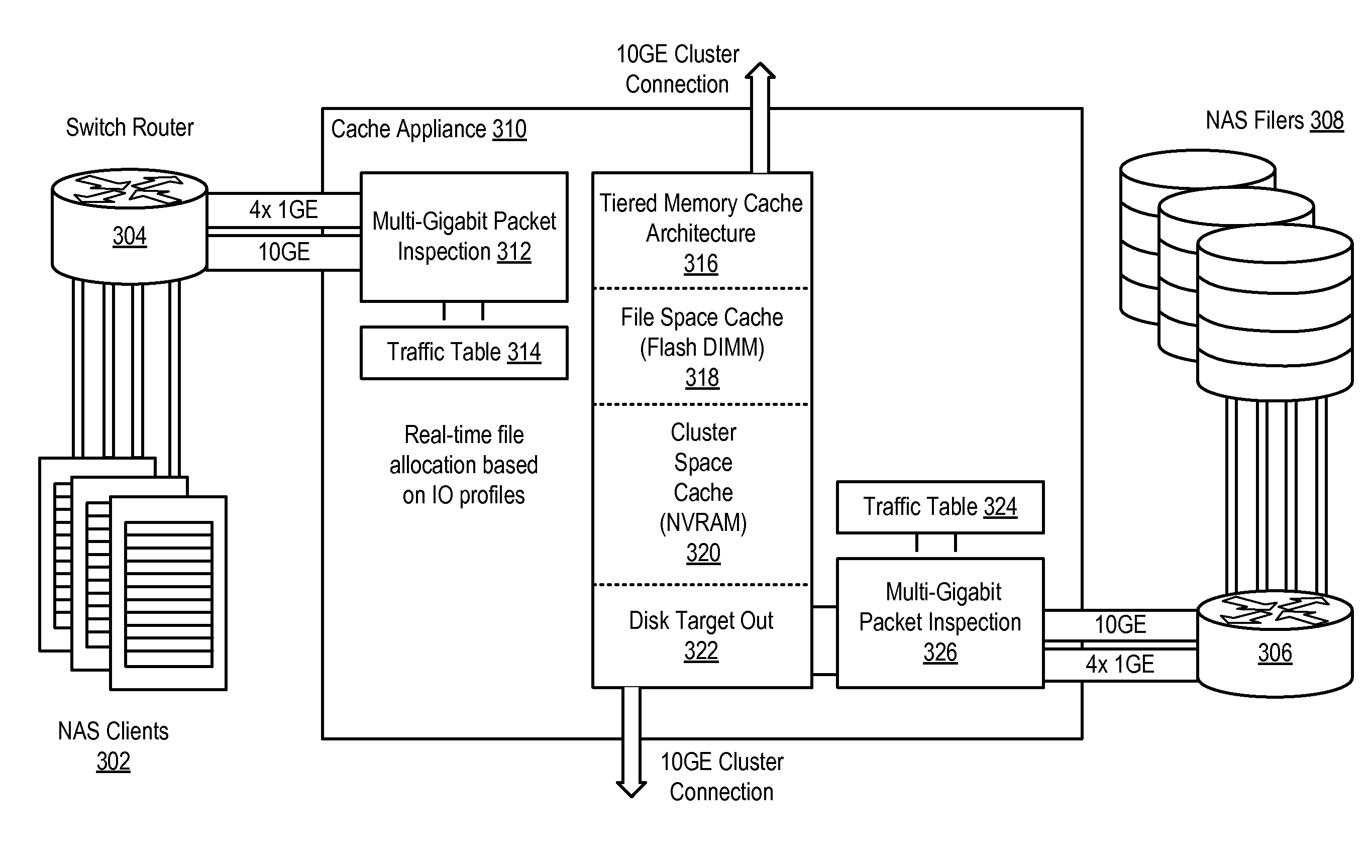

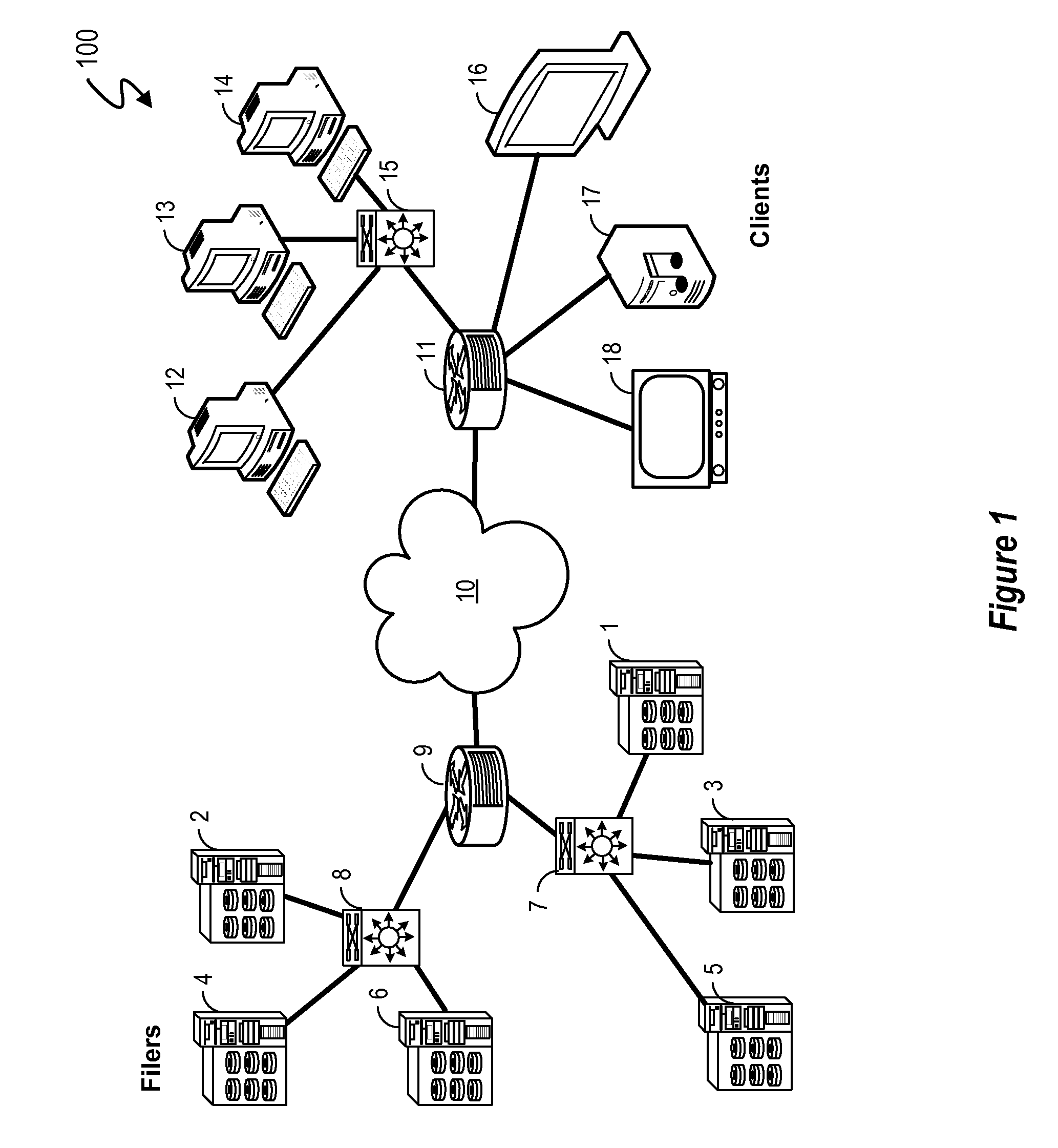

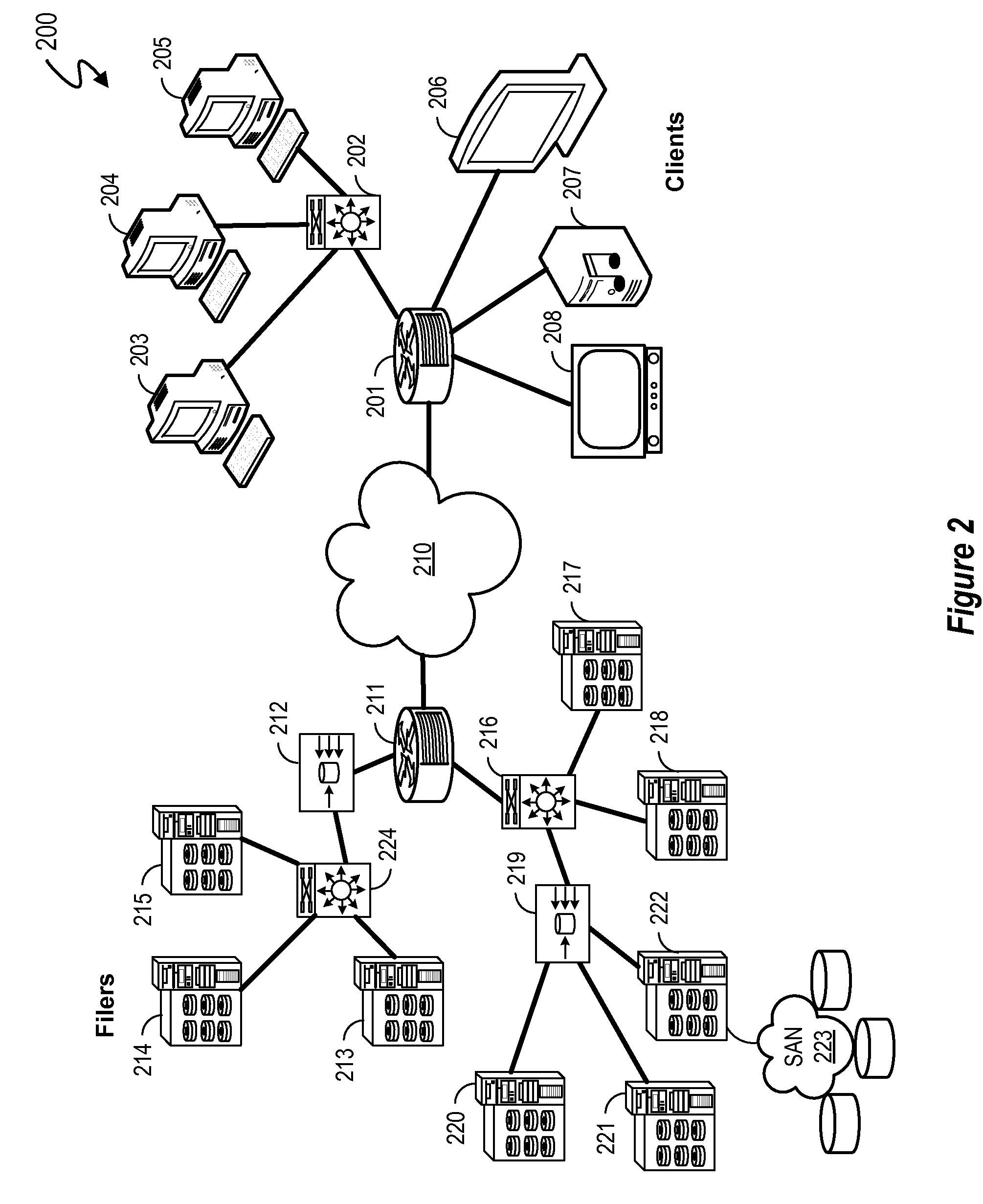

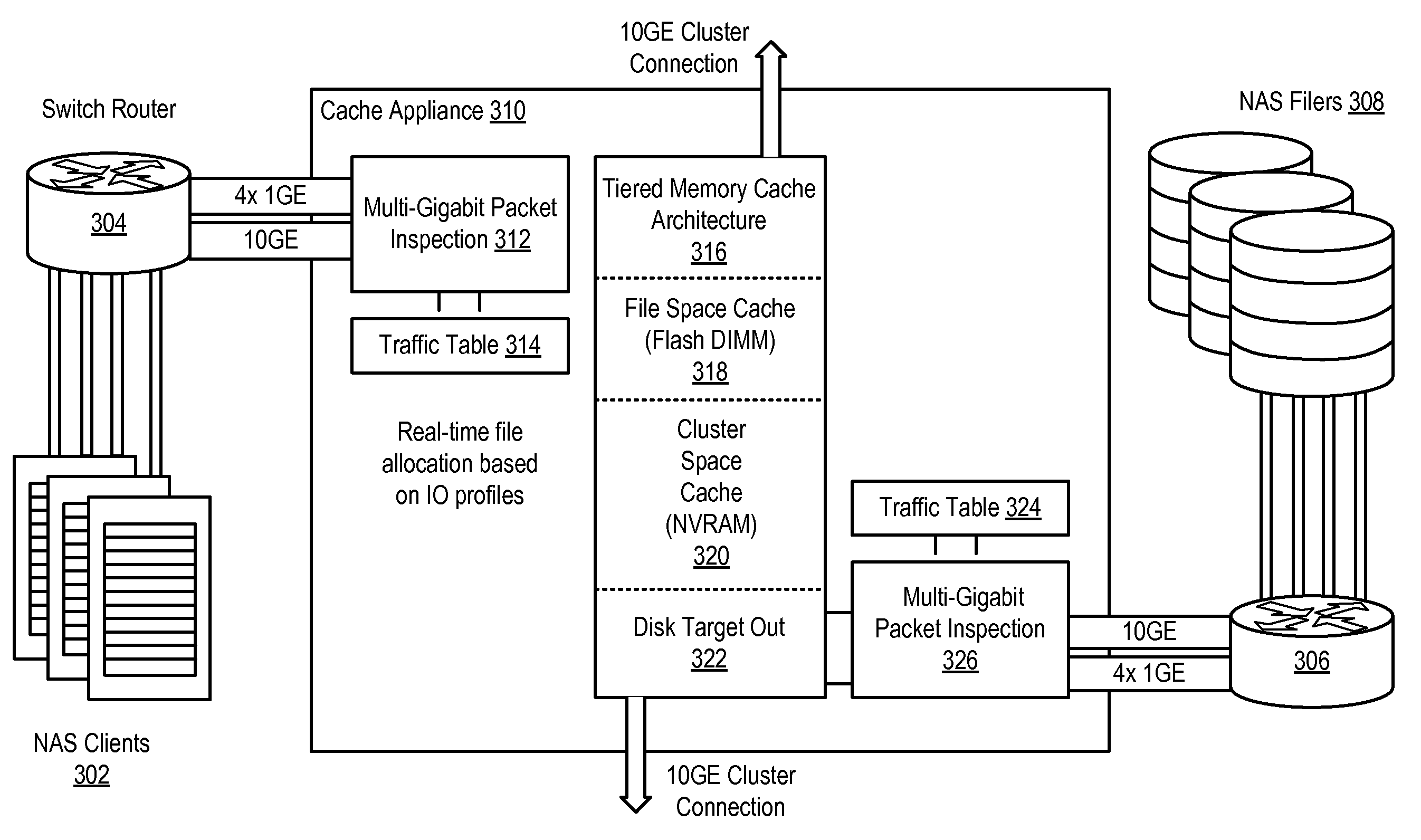

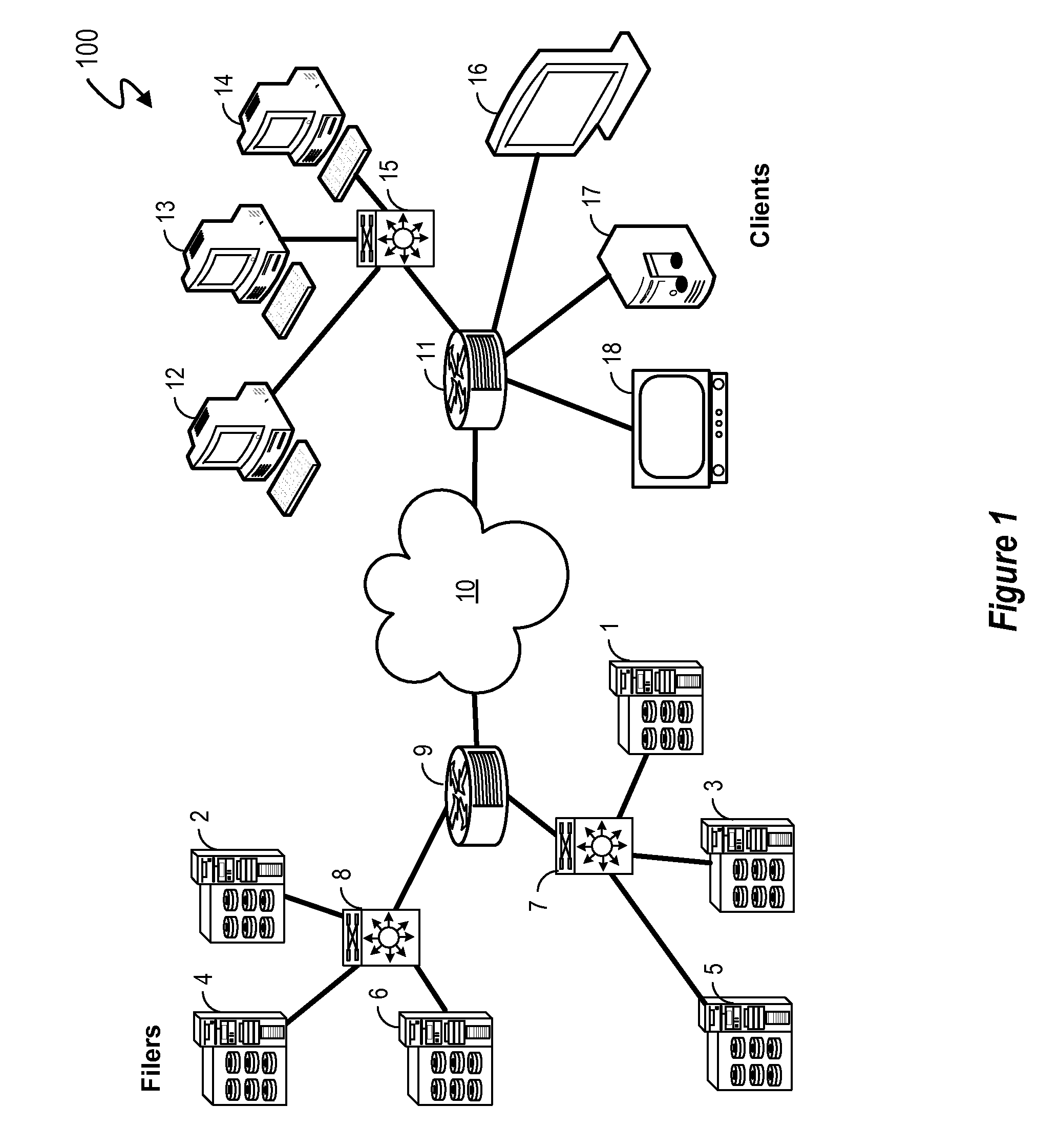

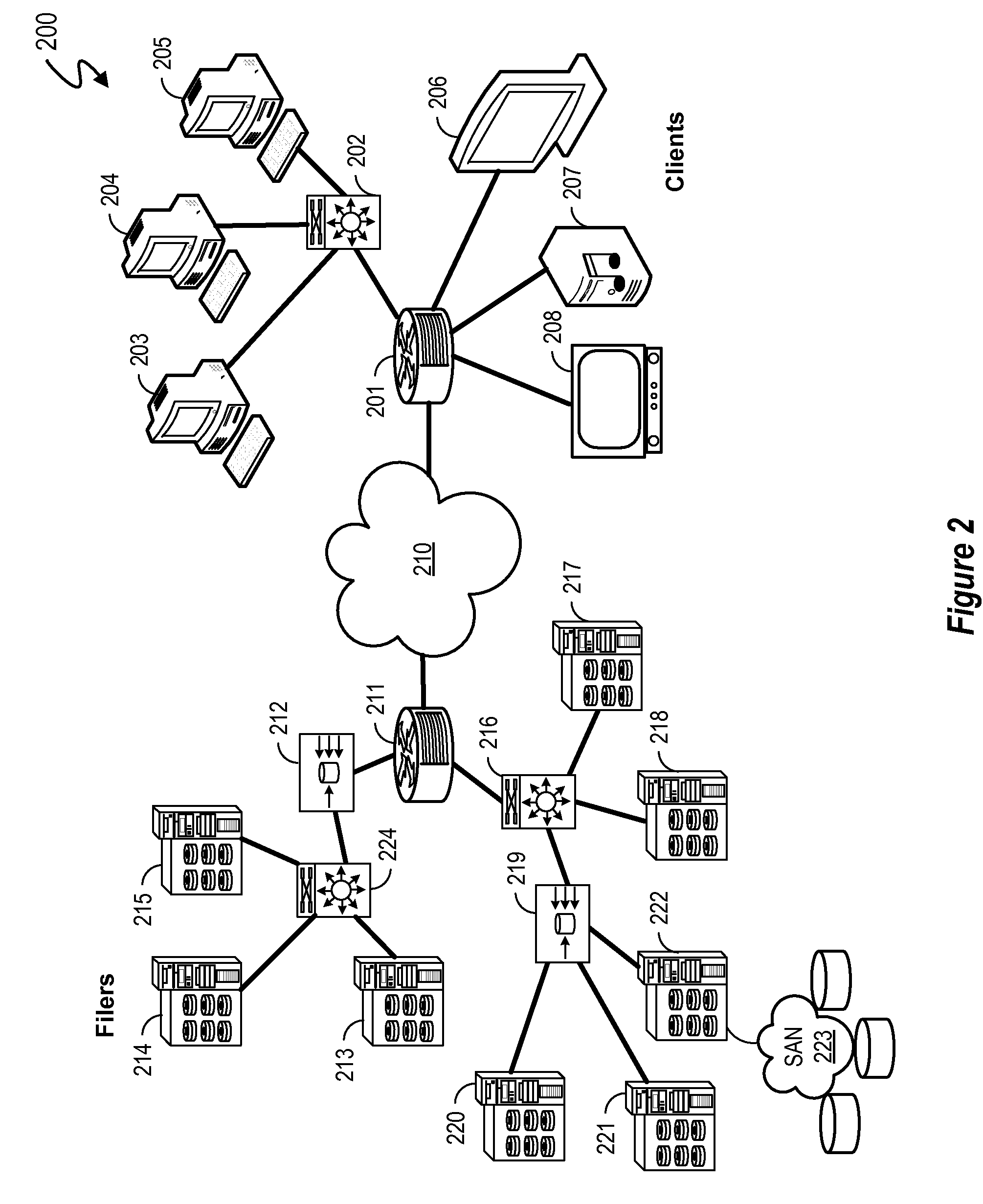

Flash DIMM in a Standalone Cache Appliance System and Methodology

InactiveUS20100023674A1Low costLess power consumptionMemory architecture accessing/allocationMemory adressing/allocation/relocationDIMMClient-side

A method, system and program are disclosed for accelerating data storage in a cache appliance cluster that transparently monitors NFS and CIFS traffic between clients and NAS subsystems and caches files in a multi-rank flash DIMM cache memory by pipelining multiple page write and page program operations to different flash memory ranks, thereby improving write speeds to the flash DIMM cache memory.

Owner:NETWORK APPLIANCE INC

Flash DIMM in a standalone cache appliance system and methodology

InactiveUS7941591B2Low costLess power consumptionMemory architecture accessing/allocationTransmissionDIMMClient-side

Owner:NETWORK APPLIANCE INC

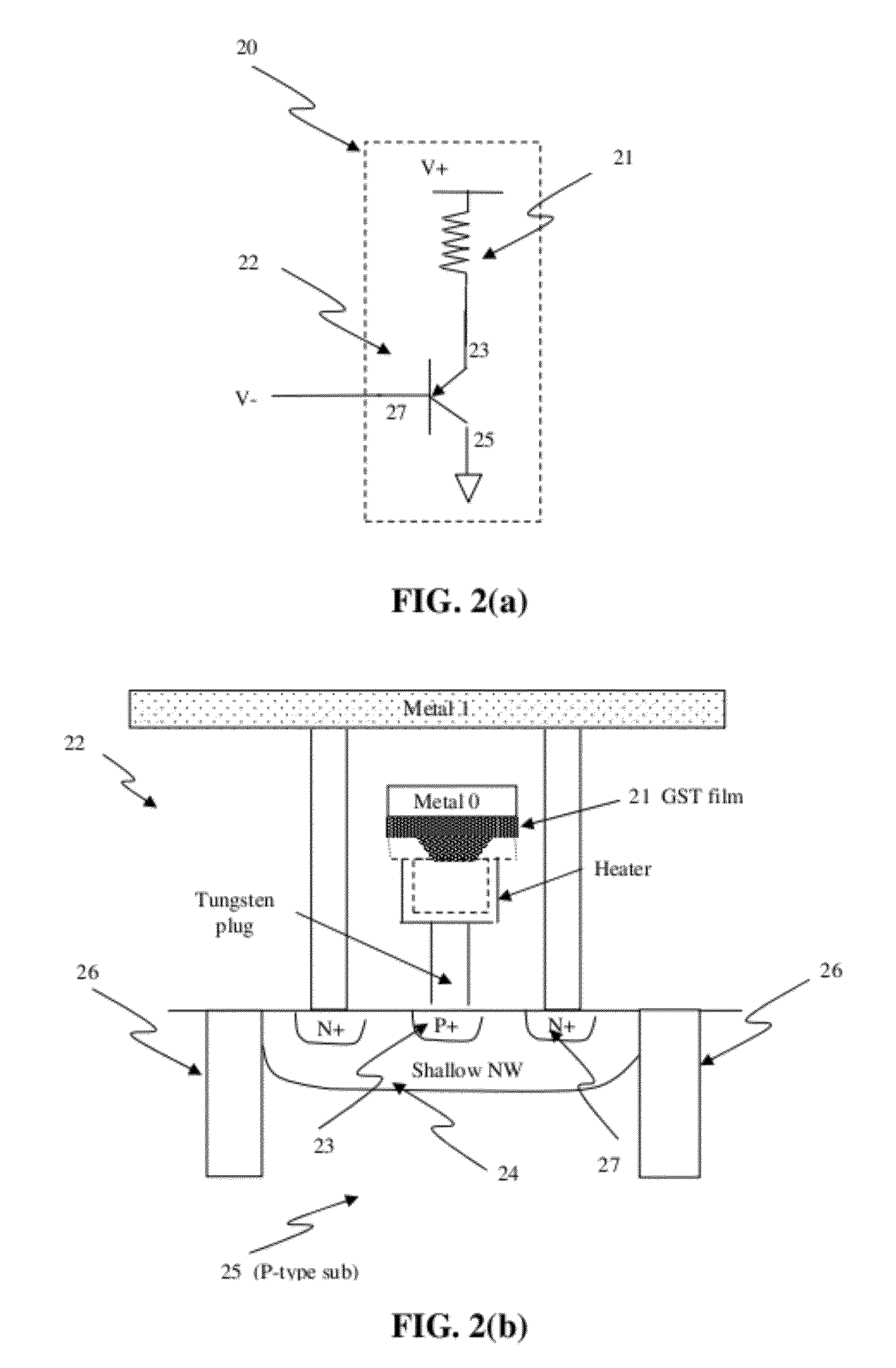

Multiple-Bit Programmable Resistive Memory Using Diode as Program Selector

ActiveUS20120314472A1Small cell sizeLow costRead-only memoriesDigital storageResistive elementPolycrystalline silicon

A method and system for multiple-bit programmable resistive cells having a multiple-bit programmable resistive element and using diode as program selector are disclosed. The first and second terminals of the diode having a first and second types of dopants can be fabricated from source / drain of MOS in a well for MOS devices or fabricated on the same polysilicon structure. If a multiple-bit programmable resistive cell has 2n (n>1) distinct resistance levels to store n-bit data, at least 2n−1 reference resistance levels can be designated to differential resistances between two adjacent states. Programming multiple-bit programmable resistive elements can start by applying a program pulse with initial program voltage (or current) and duration. A read verification cycle can follow to determine if the desirable resistance level is reached. If the desired resistance level has not been reached, additional program pulses can be applied.

Owner:ATTOPSEMI TECH CO LTD

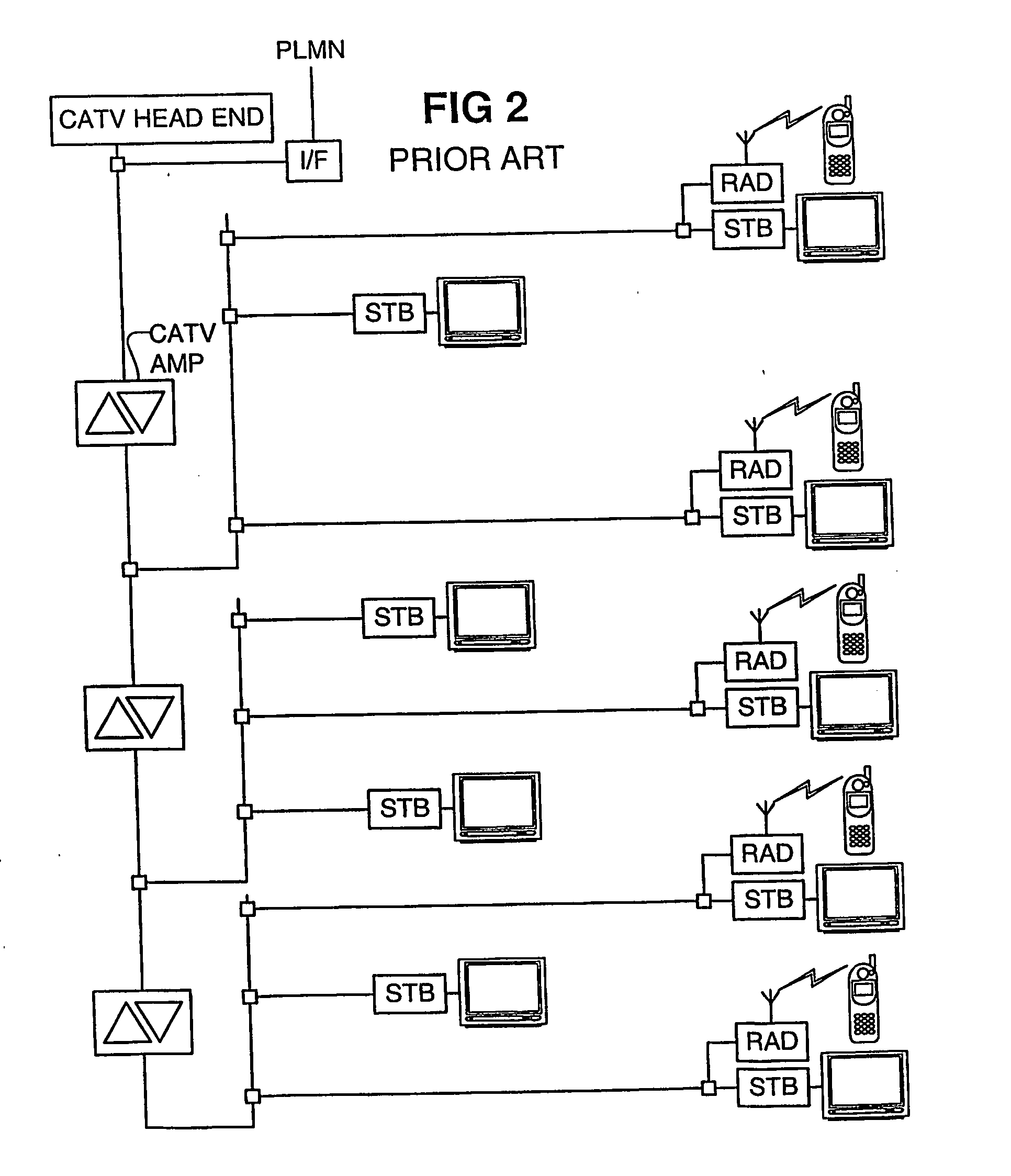

Wireless provider monitoring of catv segment

InactiveUS20050144647A1Reduce disadvantagesSmall cell sizeAccounting/billing servicesInformation formatAudio power amplifierInformation support

A monitor enabled amplifier in the CATV segment of a wireless network includes a cellular interface communicating with a network control center to provide status information pertaining to the CATV network. A monitor enabled cable Mount cellular antenna with a twin mode cellular interface provide status and location correlation information to the network control center. The location correlation information supports an emergency response system and differential billing.

Owner:ZUSN MORDECHAI +3

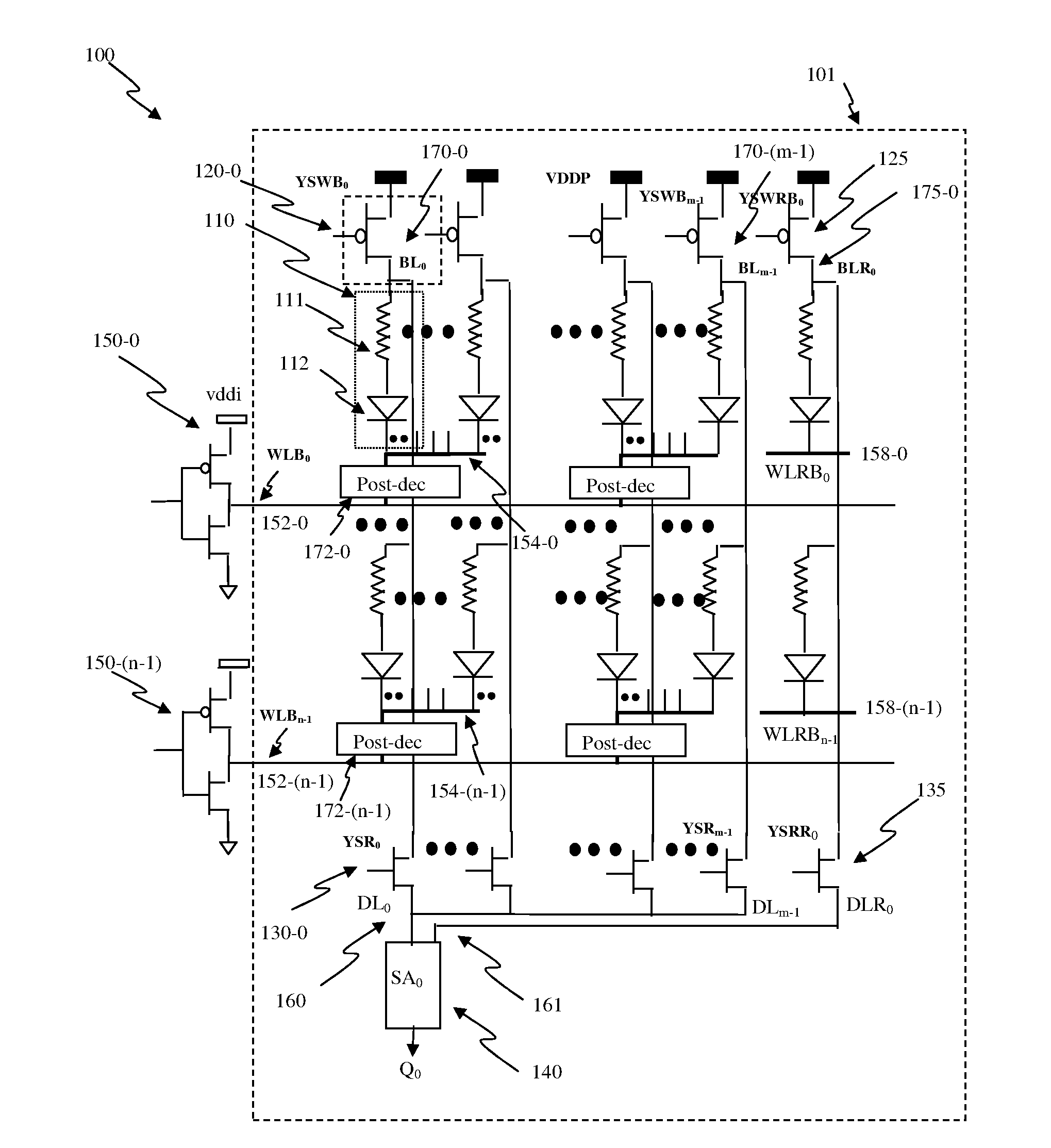

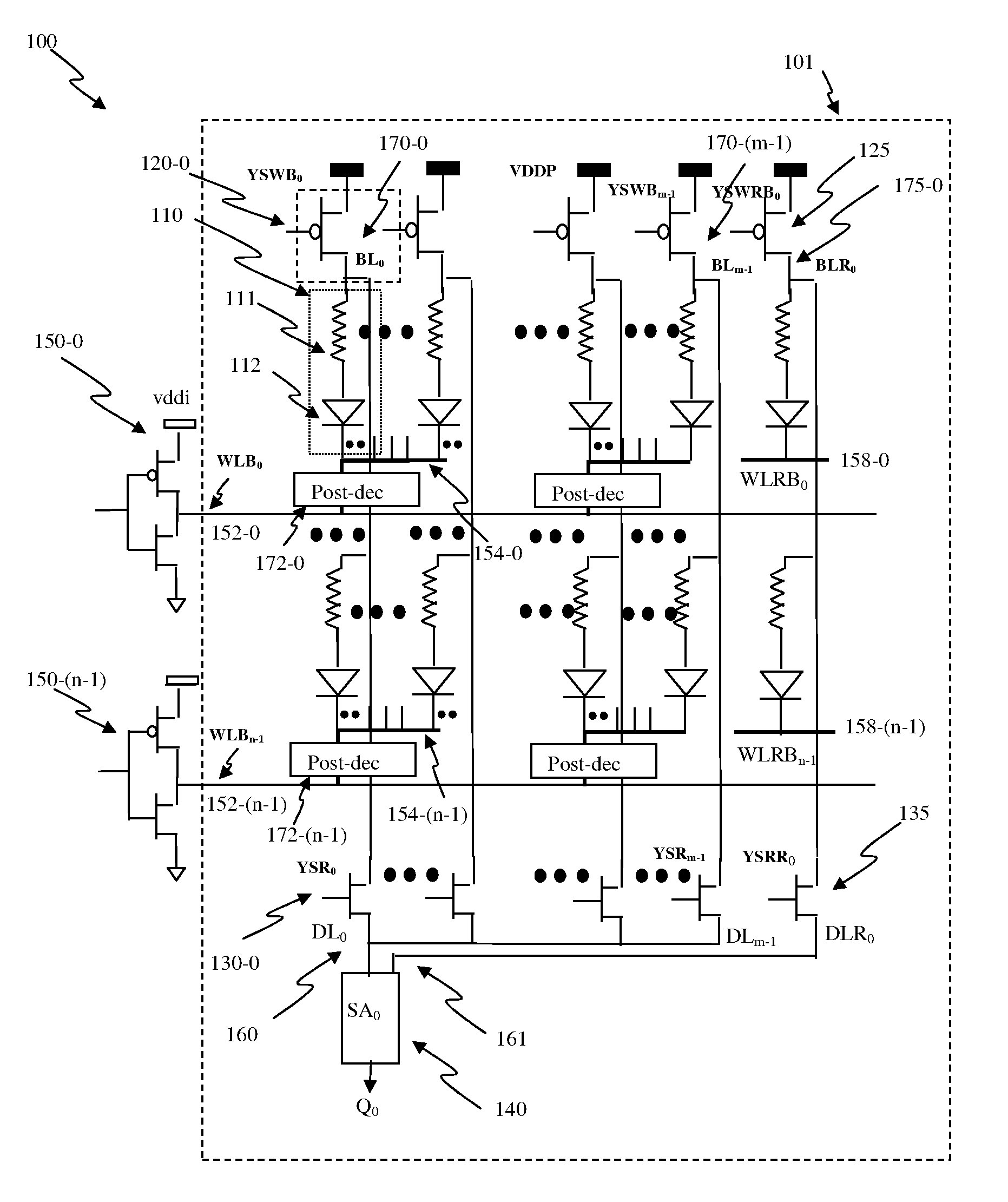

Programmable Resistive Memory Unit with Data and Reference Cells

A method and system of a programmable resistive memory having a plurality of programmable resistive memory units is disclosed. At least one of the programmable resistive memory units has at least one data cell and at least one reference cell. The data cell can have one programmable resistive element coupled to at least one diode as a program selector and also coupled to a bitline (BL). The reference cell can have a reference resistive element coupled to at least one reference diode as reference program selector and also coupled to a reference bitline (BLR). In one embodiment, the reference resistive element can have substantially the same material, structure, or shape of the programmable resistive element. In one embodiment, the reference diode can have the same material, structure, or shape of the diode serving as the program selector diode.

Owner:ATTOPSEMI TECH CO LTD

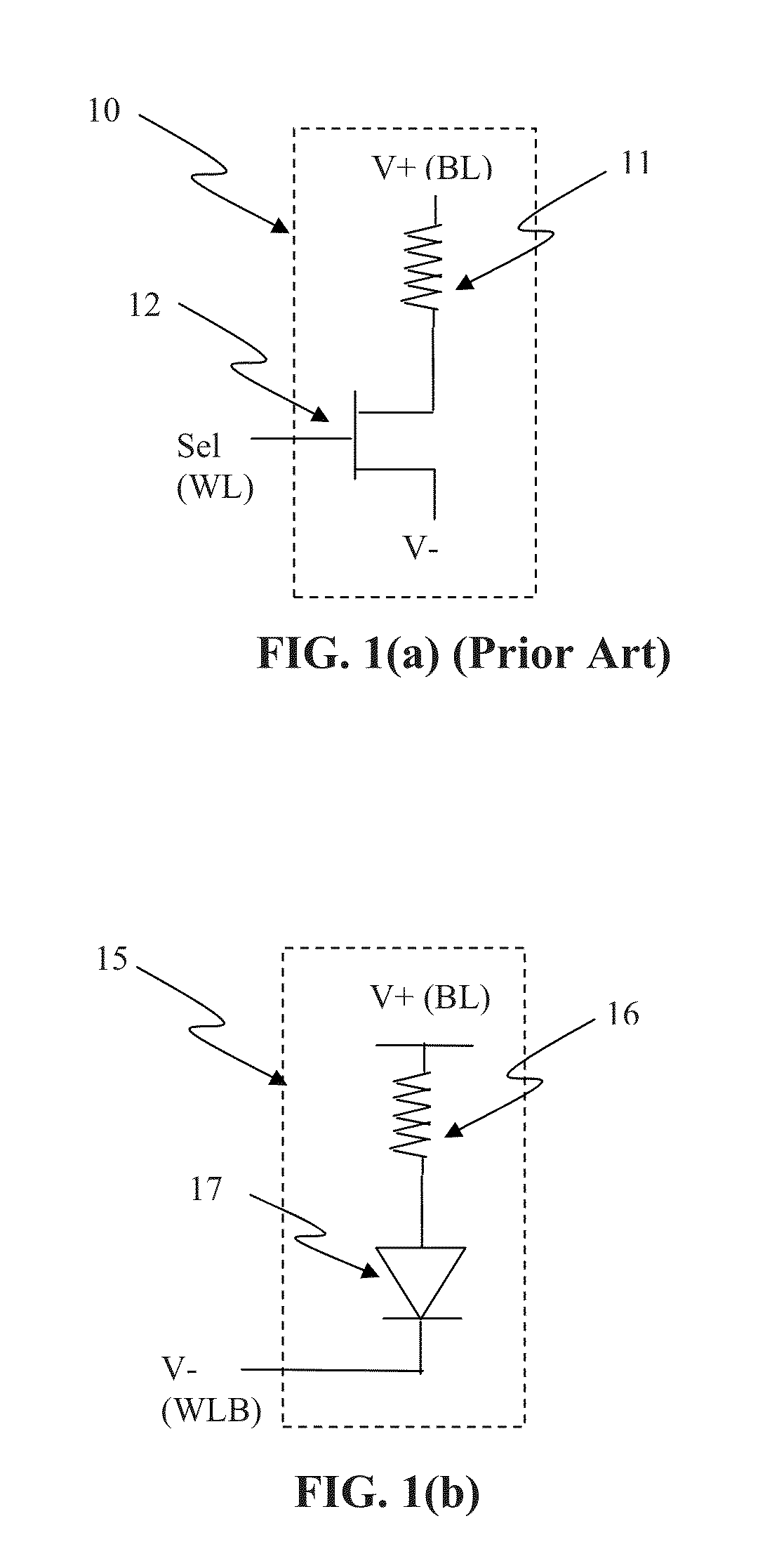

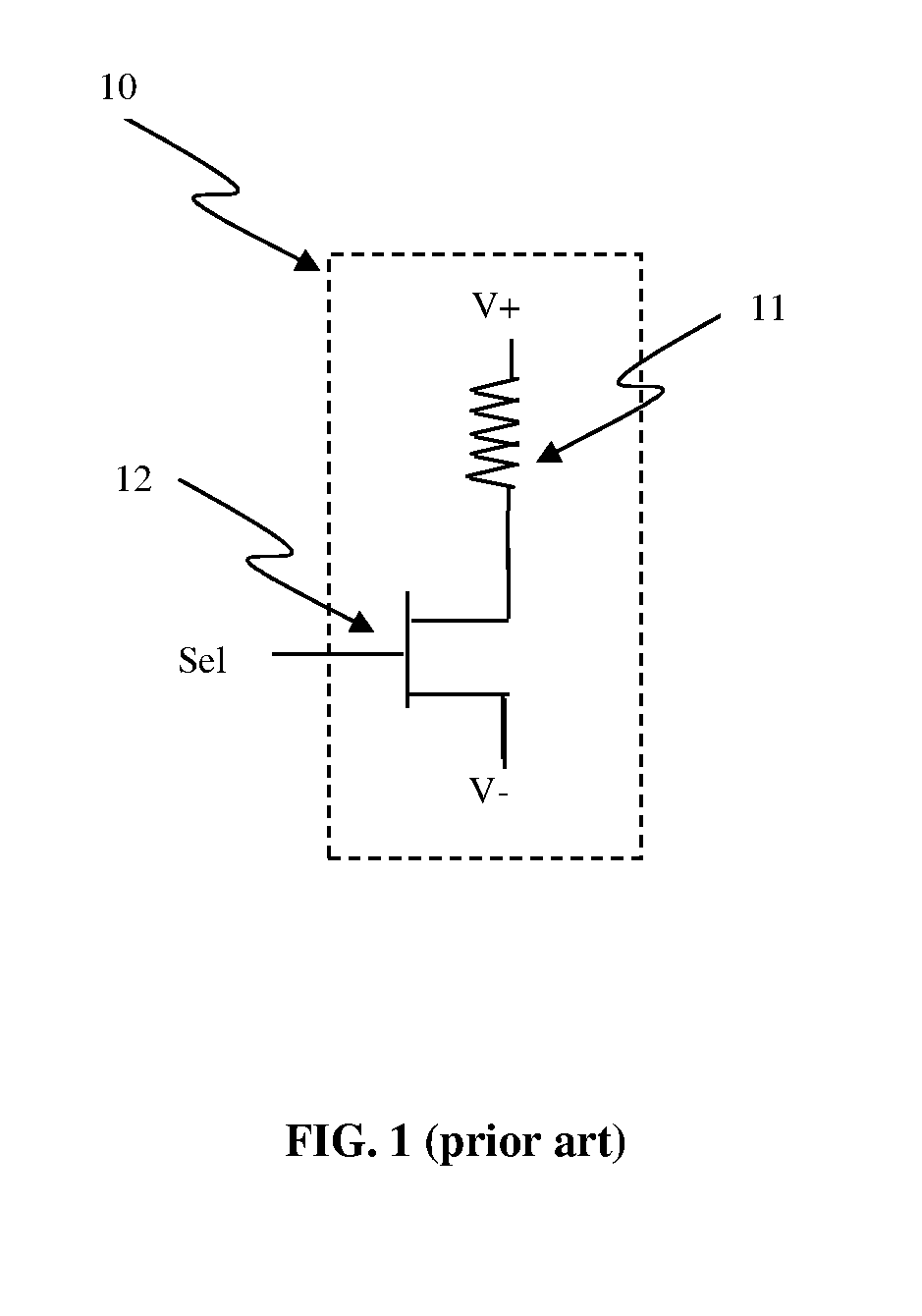

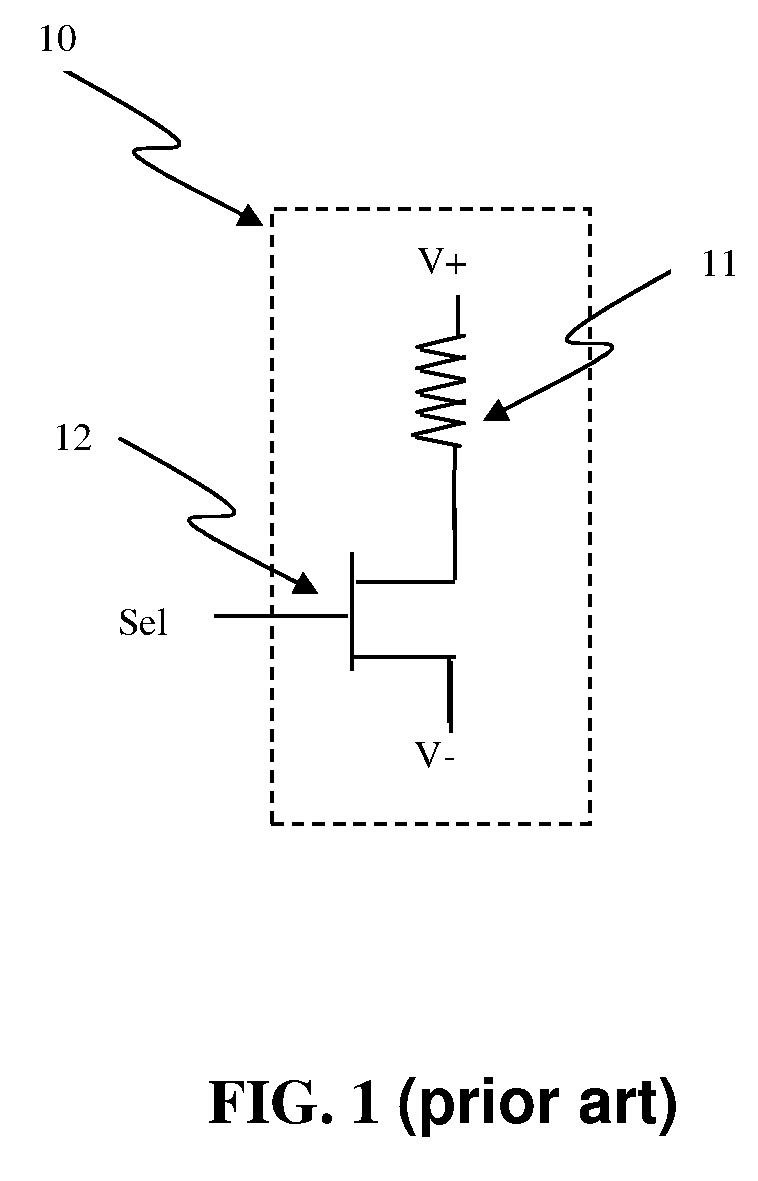

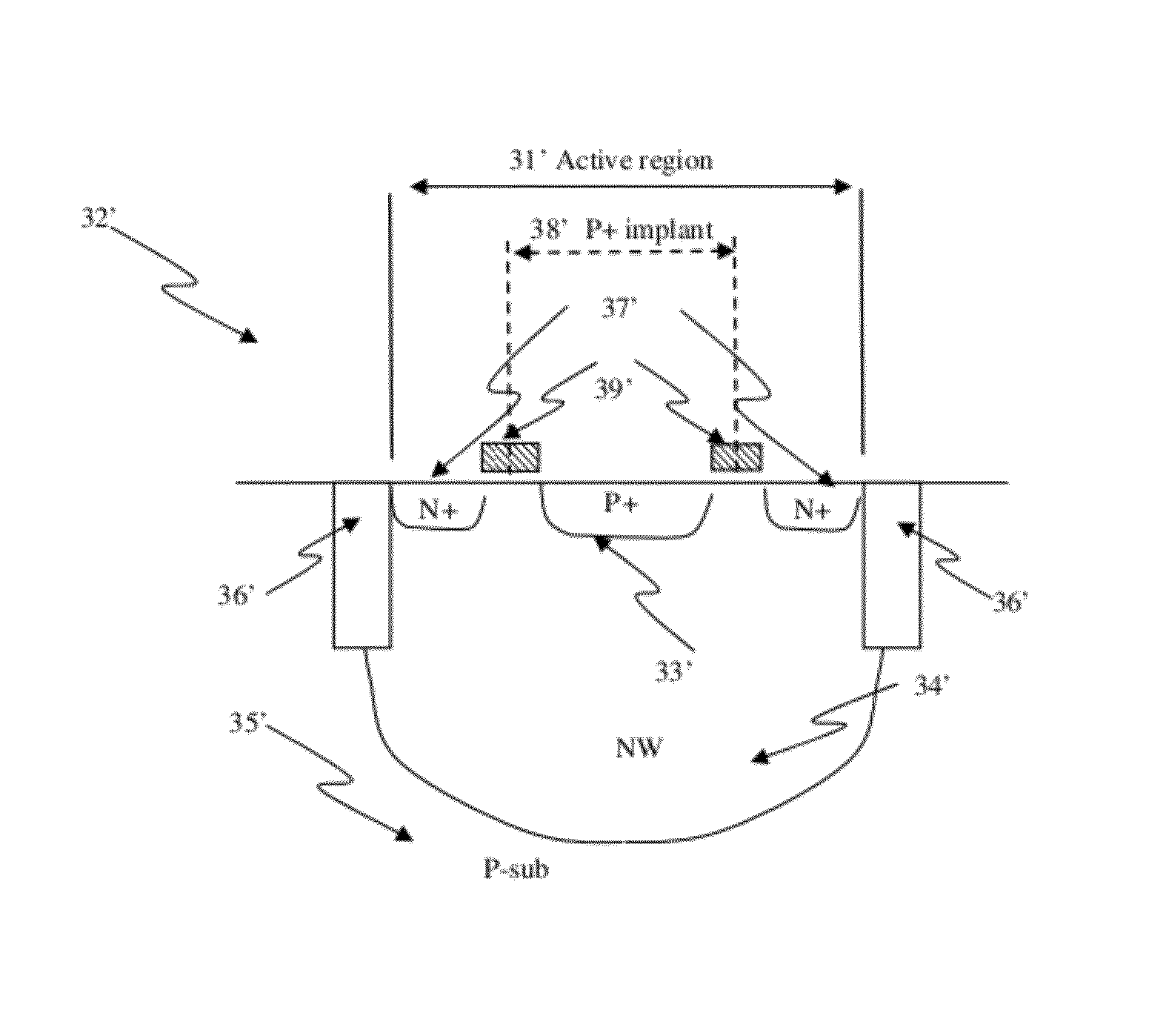

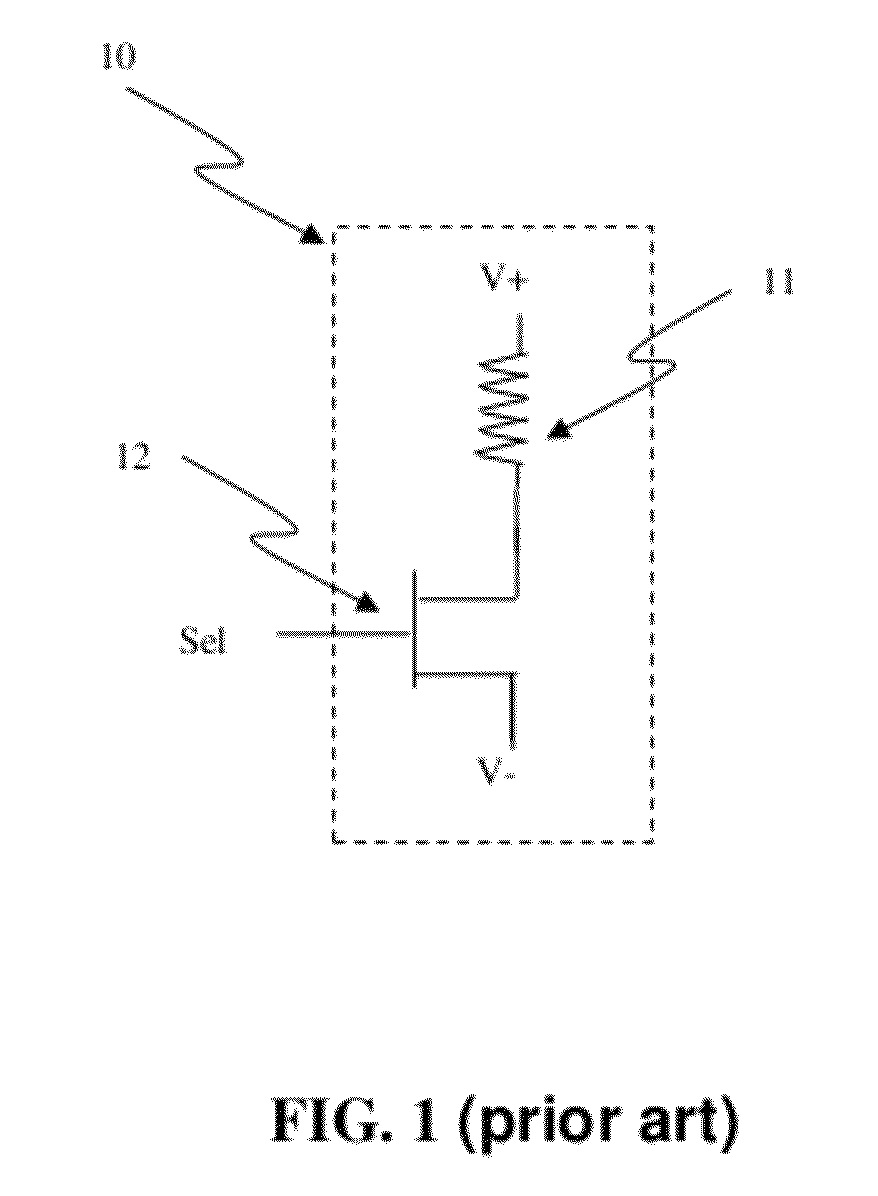

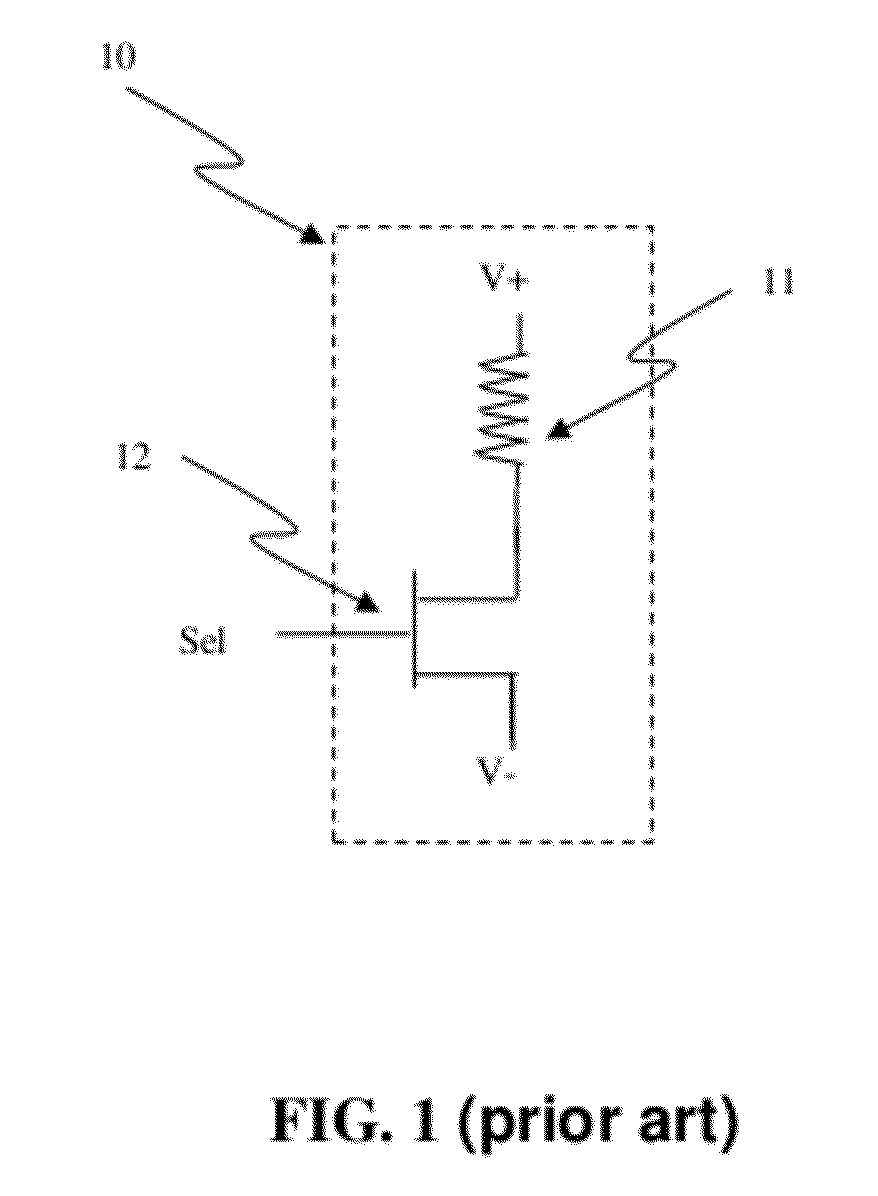

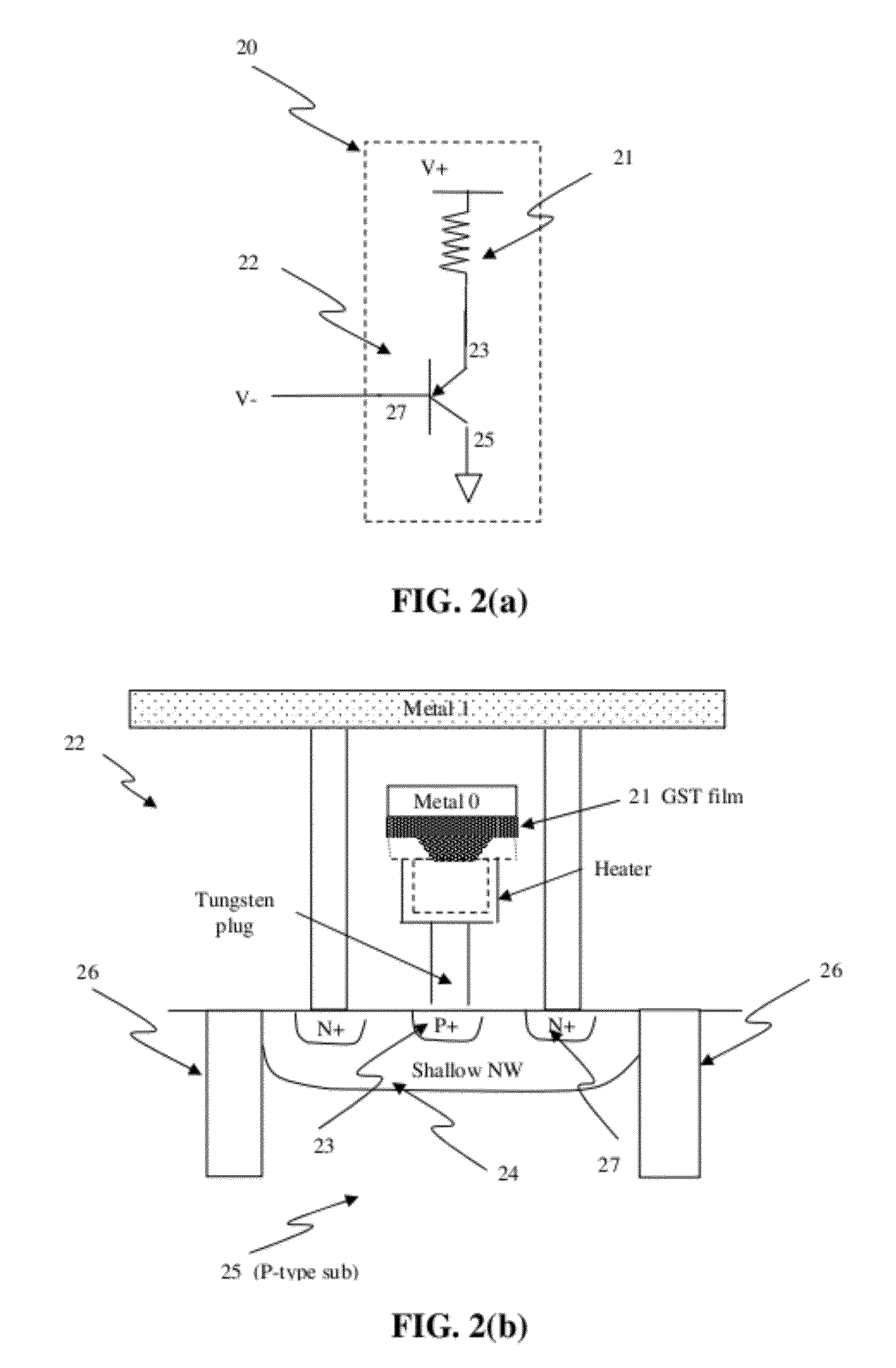

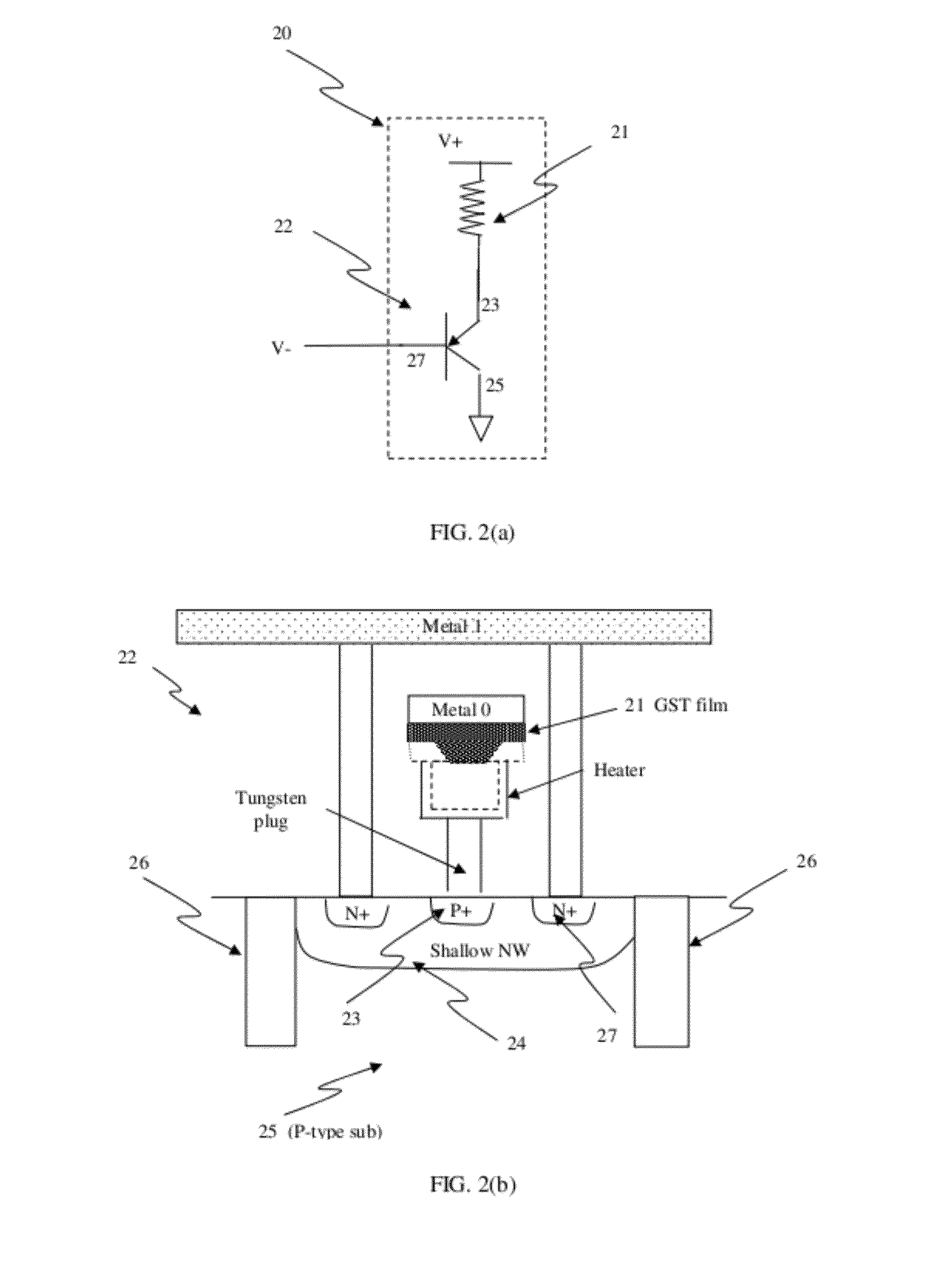

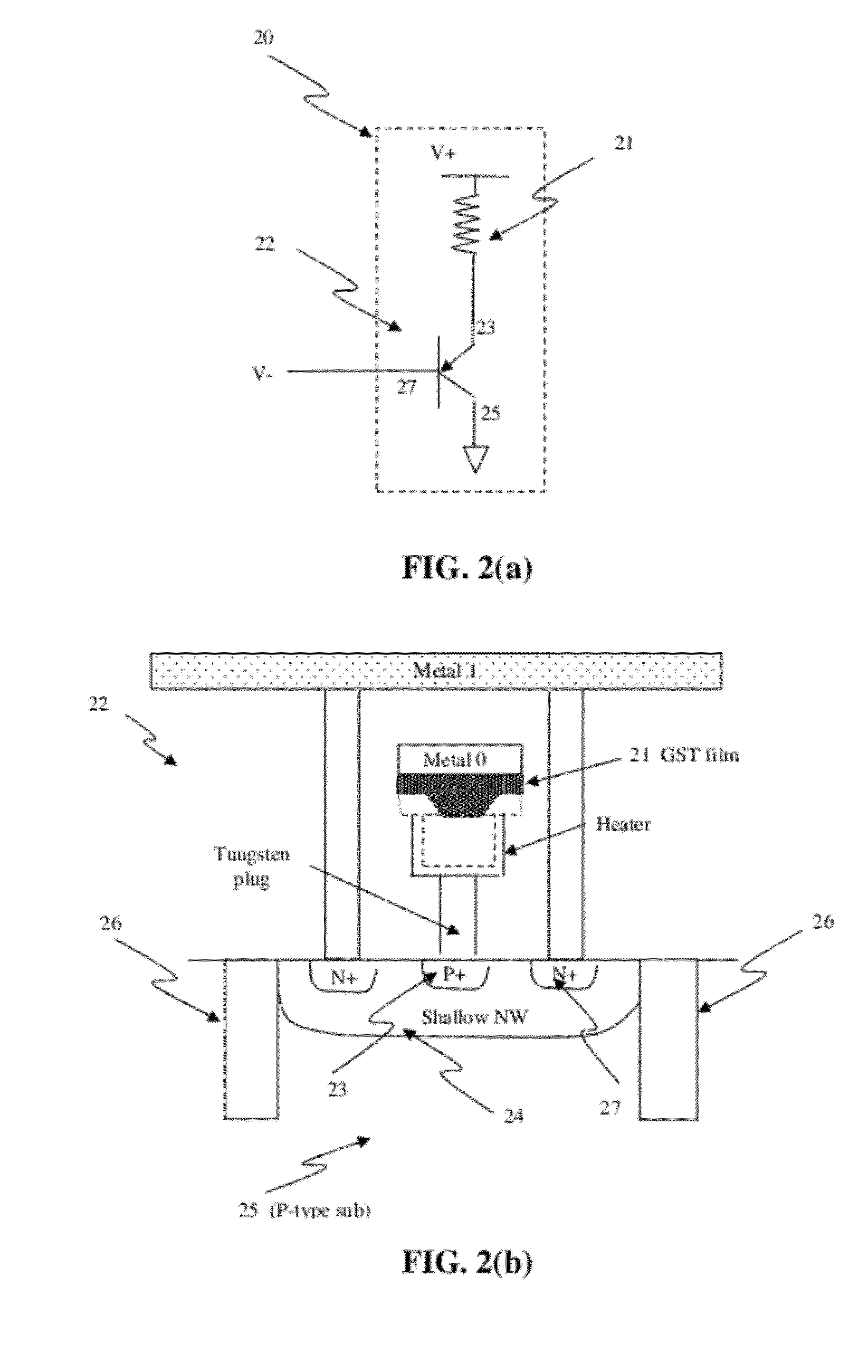

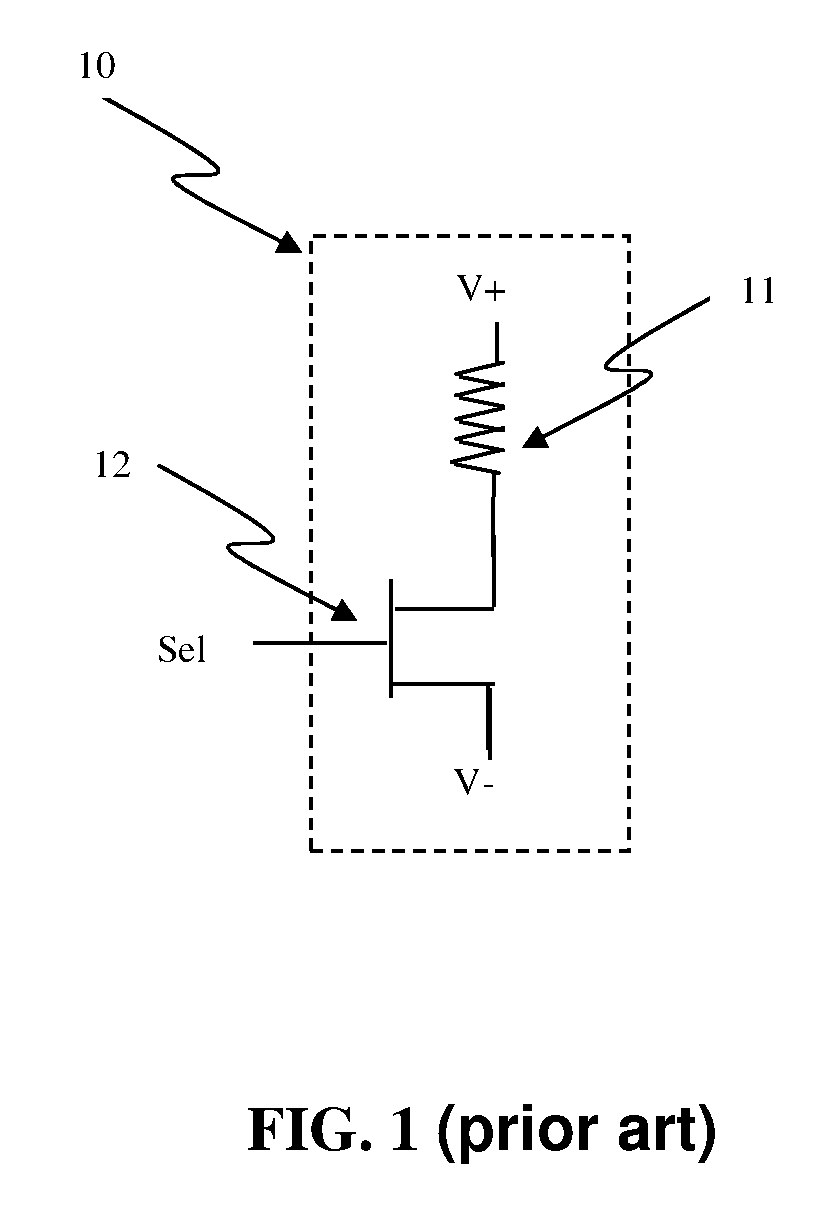

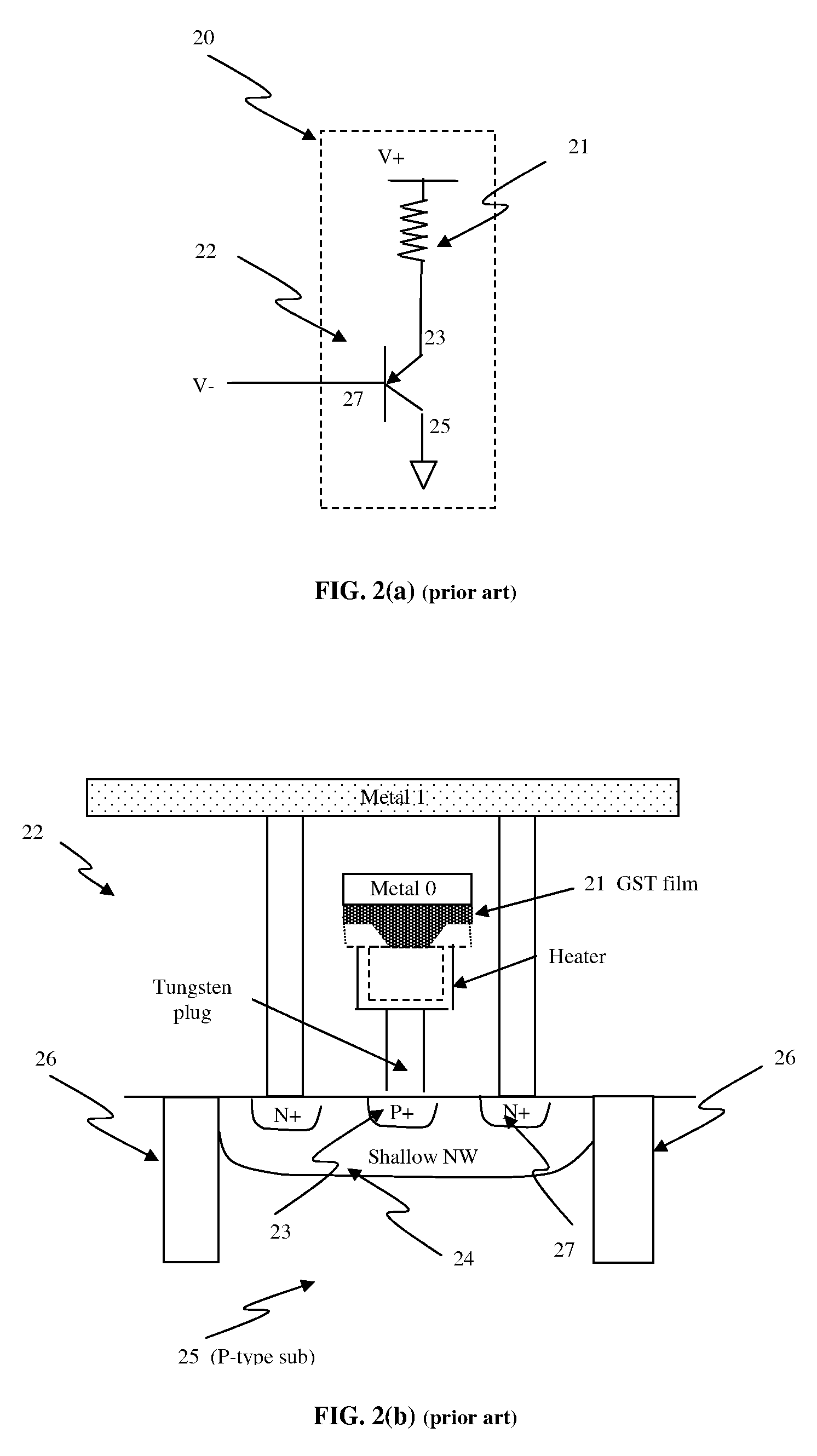

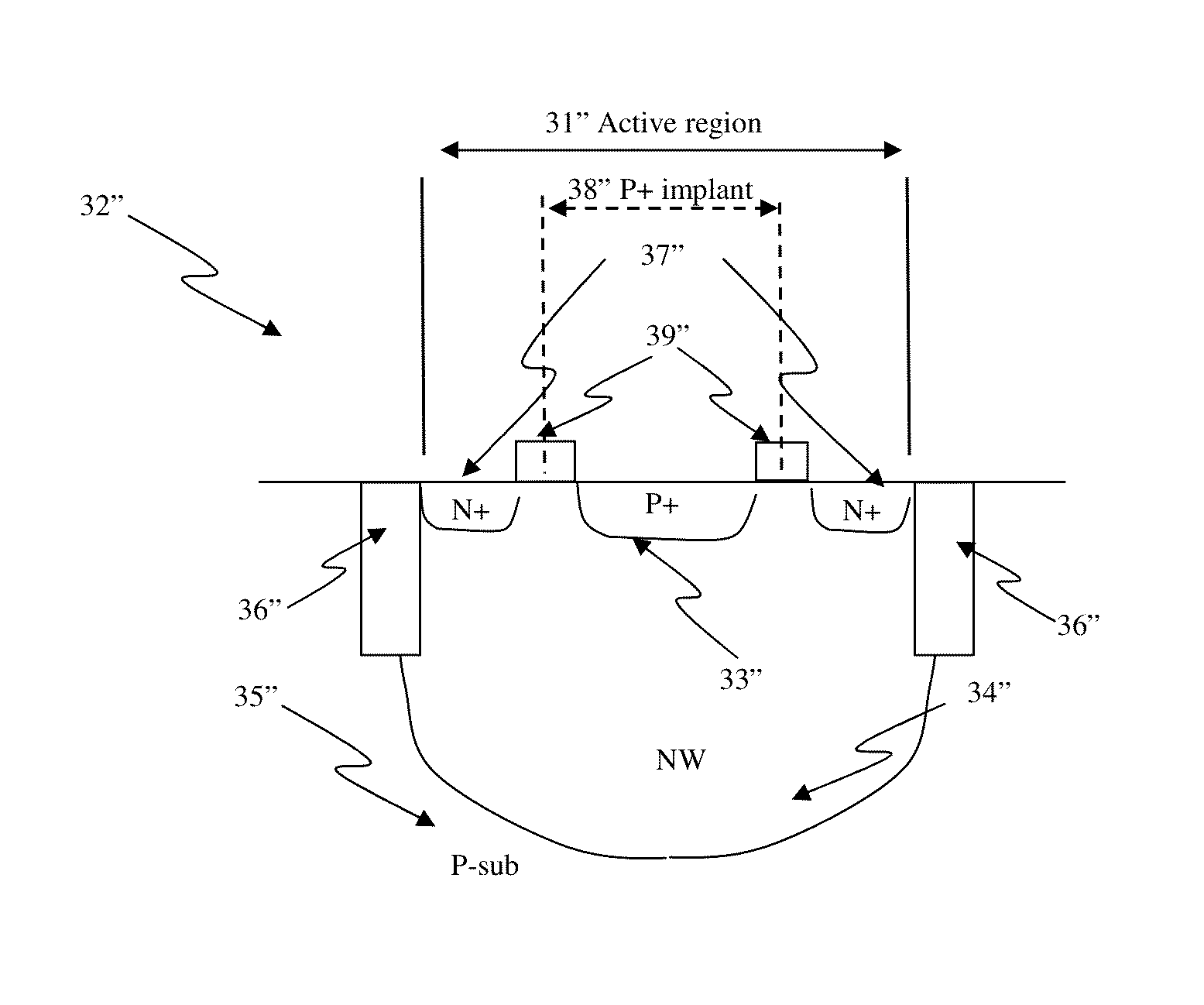

Circuit and system of using a junction diode as program selector for resistive devices

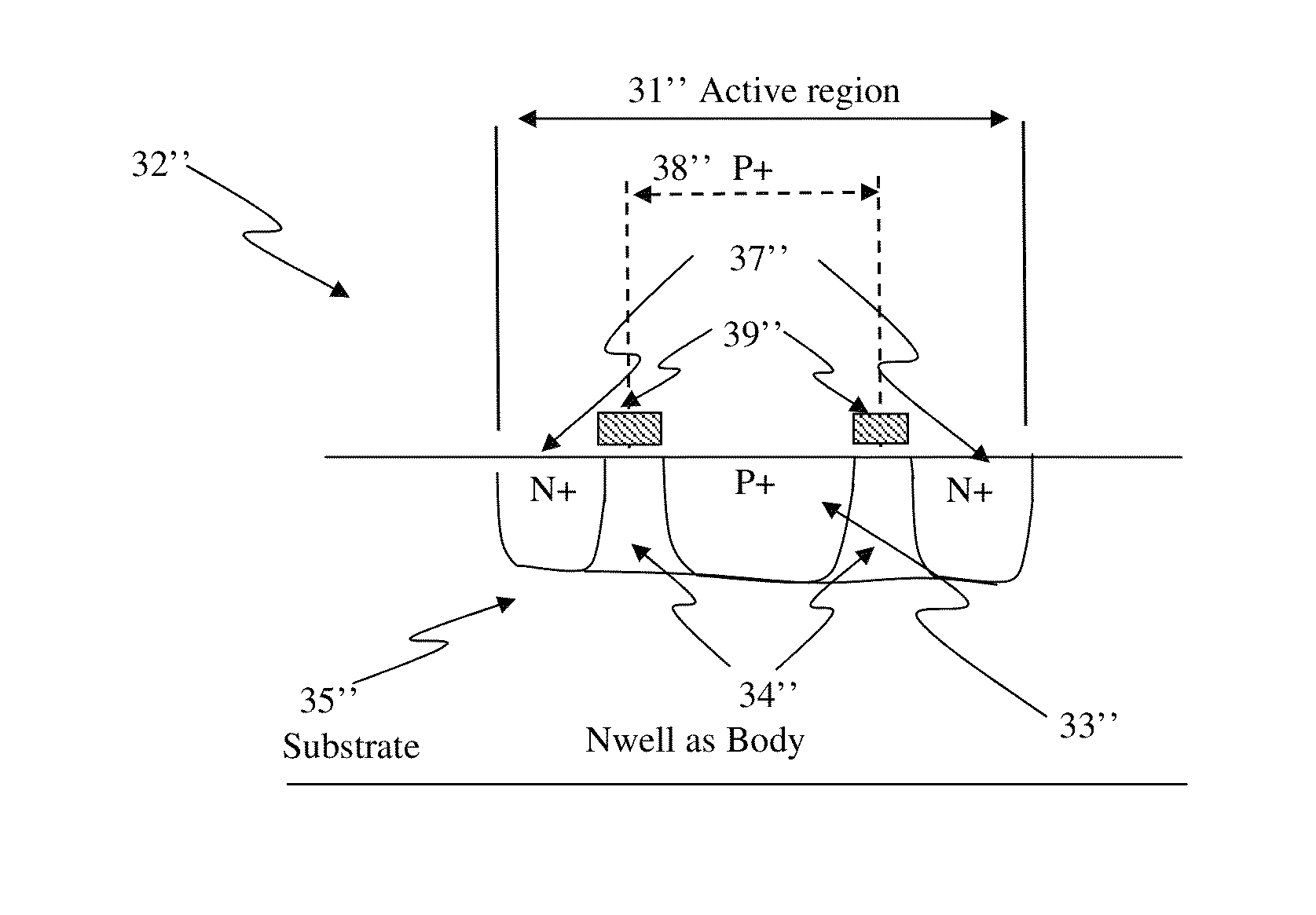

ActiveUS20120044746A1Low costSmall sizeSolid-state devicesRead-only memoriesCMOSElectrical resistance and conductance

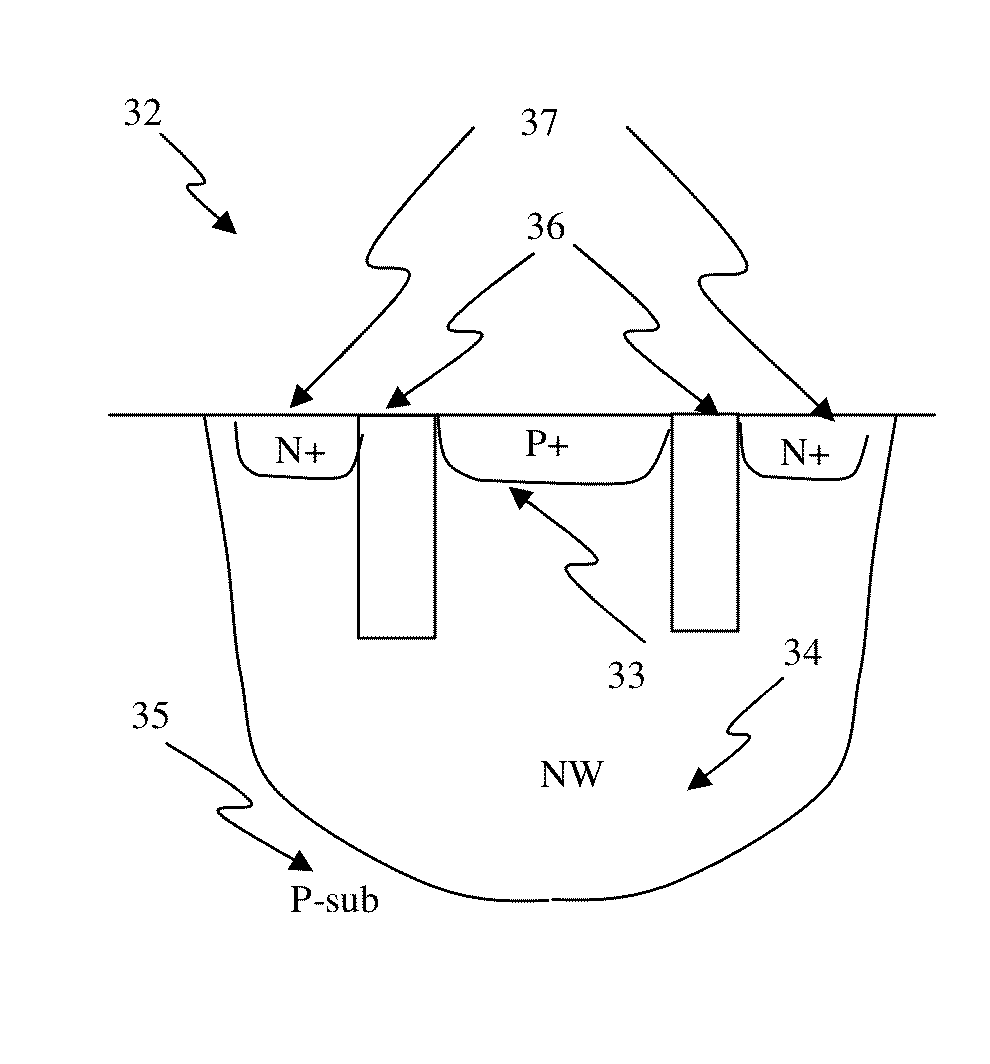

Junction diodes fabricated in standard CMOS logic technologies can be used as program selectors for a programmable resistive device, such as electrical fuse, contact / via fuse, anti-fuse, or emerging nonvolatile memory such as MRAM, PCM, CBRAM, or RRAM. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. By applying a high voltage to the P terminal of a diode and switching the N terminal of a diode to a low voltage for proper duration of time, a current flows through a resistive element in series with the program selector may change the resistance state. The P+ active region of the diode can be isolated from the N+ active region in the N well by using dummy MOS gate, SBL, or STI isolations. If the resistive element is an interconnect fuse based on CMOS gate material, the resistive element can be coupled to the P+ active region by an abutted contact such that the element, active region, and metal can be connected in a single rectangular contact.

Owner:ATTOPSEMI TECH CO LTD

Circuit and system of using junction diode as program selector for one-time programmable devices

ActiveUS8488359B2Low costSmall sizeMagnetic-field-controlled resistorsSolid-state devicesCMOSMetal alloy

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has at least one OTP element coupled to at least one diode in a memory cell. The diode can be constructed by P+ and N+ active regions in a CMOS N well, or on an isolated active region as the P and N terminals of the diode. The isolation between P+ and the N+ active regions of the diode in a cell or between cells can be provided by dummy MOS gate, SBL, or STI / LOCOS isolations. The OTP element can be polysilicon, silicided polysilicon, silicide, metal, metal alloy, local interconnect, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

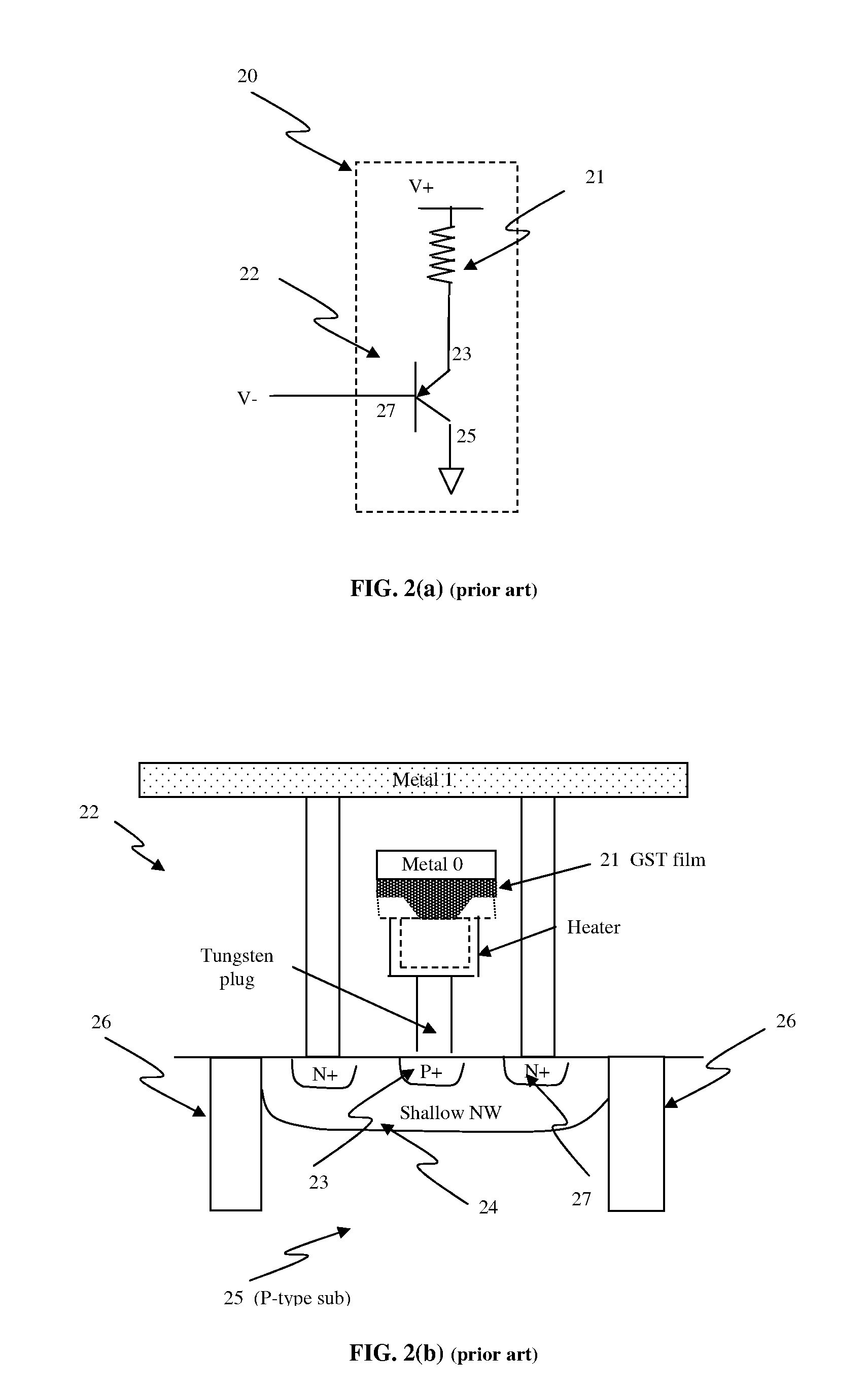

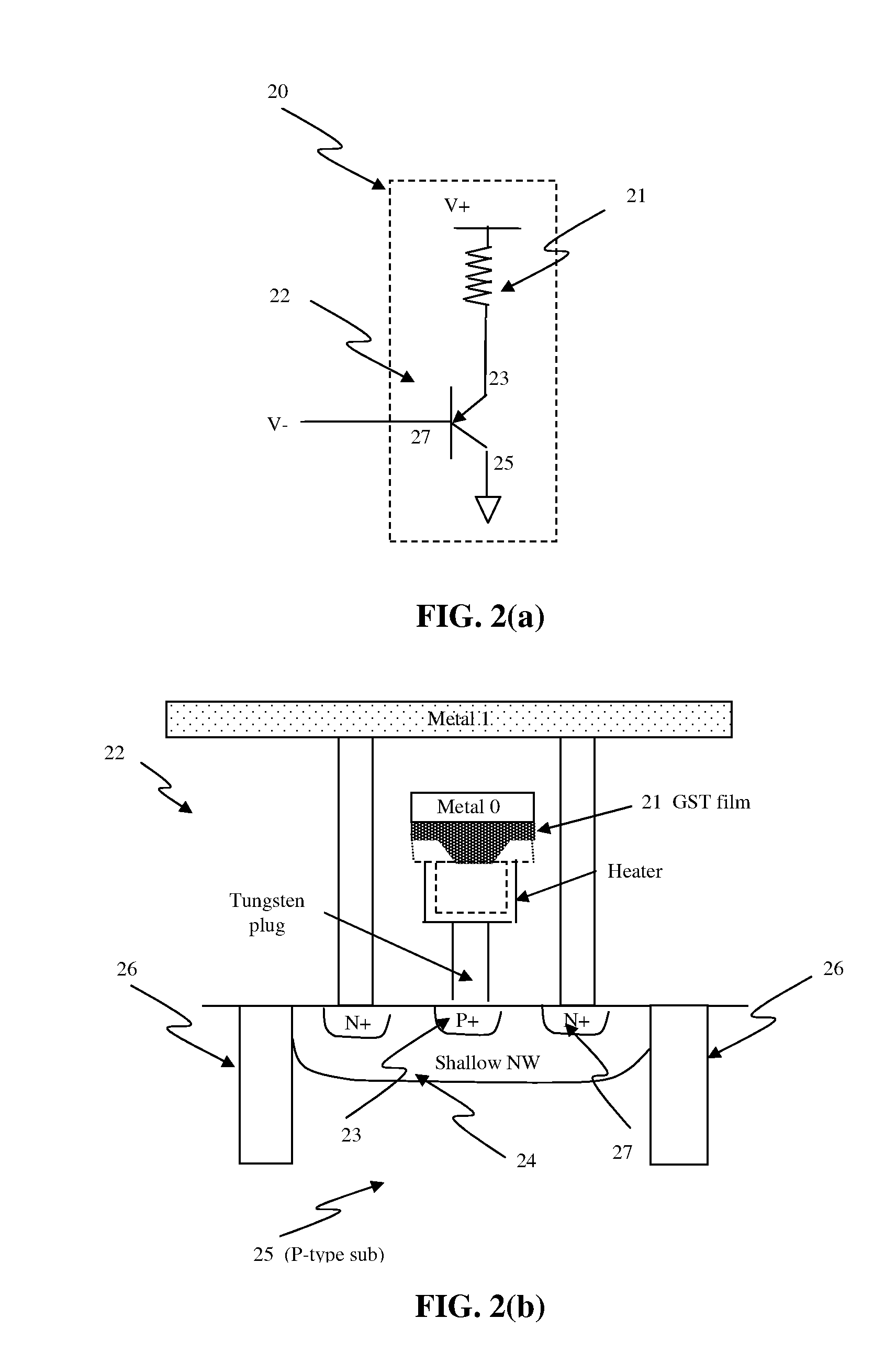

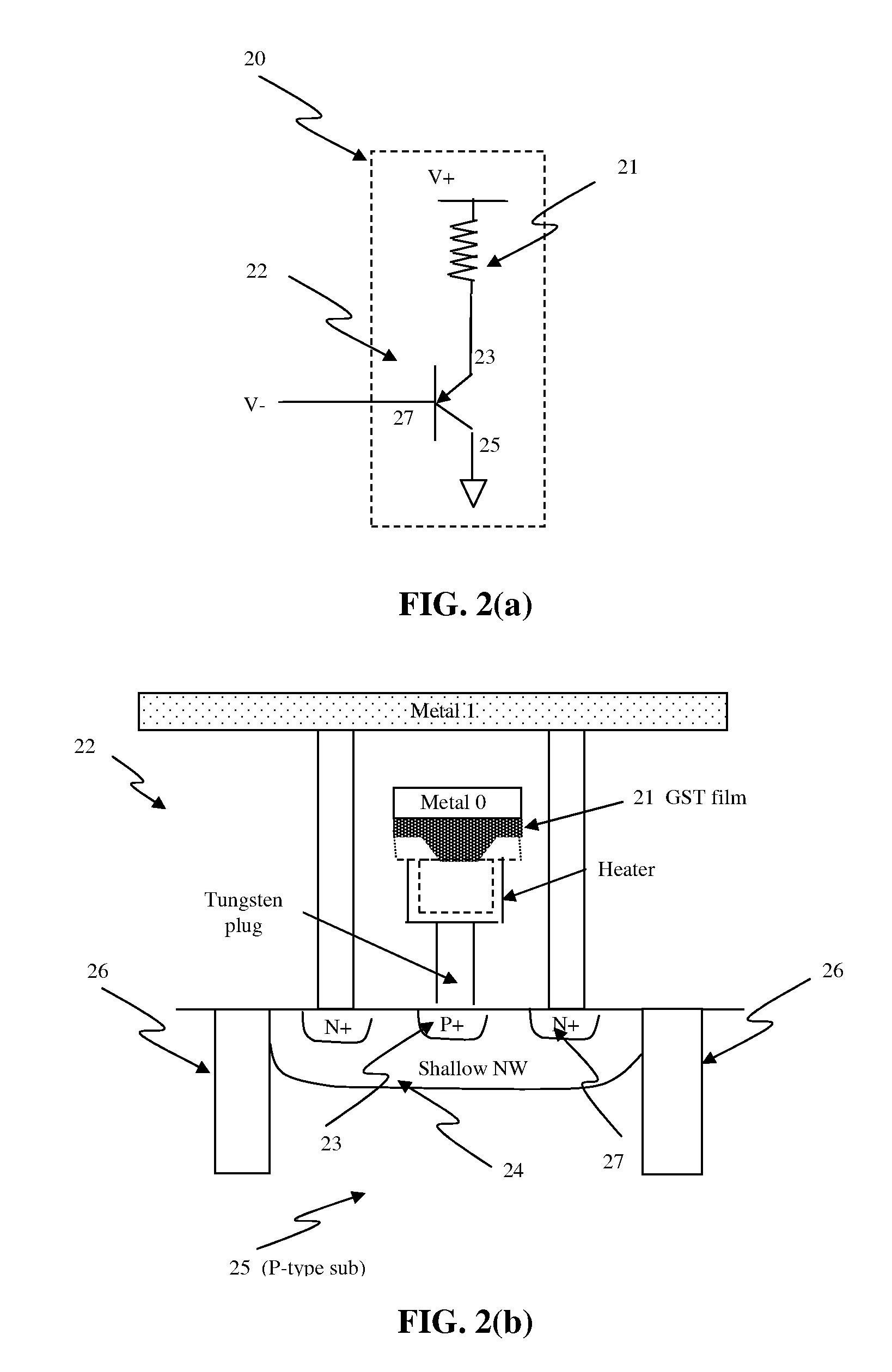

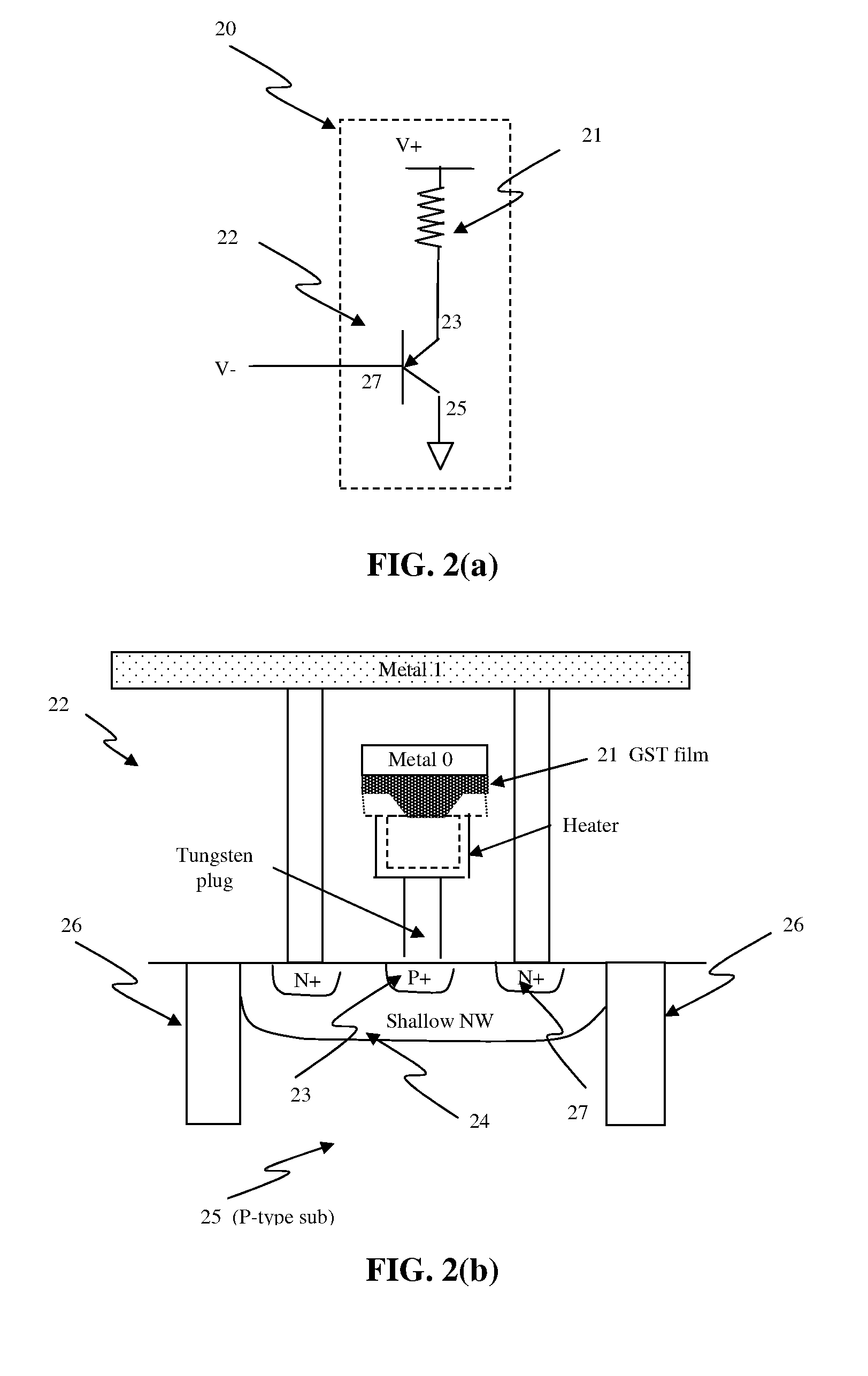

Circuit and System of Using Junction Diode as Porgram Selector for One-Time Programmable Devices with Heat Sink

ActiveUS20130215663A1Small cell sizeLow costTransistorSemiconductor/solid-state device detailsLocos isolationCMOS

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors with at least one heat sink or heater to assist programming for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The heat sink can be at least one thin oxide area, extended OTP element area, or other conductors coupled to the OTP element to assist programming. A heater can be at least one high resistance area such as an unsilicided polysilicon, unsilicided active region, contact, via, or combined in serial, or interconnect to generate heat to assist programming. The OTP device has at least one OTP element coupled to at least one diode in a memory cell. The diode can be constructed by P+ and N+ active regions in a CMOS N well, or on an isolated active region as the P and N terminals of the diode. The isolation between P+ and the N+ active regions of the diode in a cell or between cells can be provided by dummy MOS gate, SBL, or STI / LOCOS isolations. The OTP element can be polysilicon, silicided polysilicon, silicide, polymetal, metal, metal alloy, local interconnect, metal-0, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

Circuit and System of Using Junction Diode as Program Selector for One-Time Programmable Devices

ActiveUS20120224406A1Small cell sizeLow costMagnetic-field-controlled resistorsSolid-state devicesHemt circuitsEngineering

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has at least one OTP element coupled to at least one diode in a memory cell. The diode can be constructed by P+ and N+ active regions in a CMOS N well, or on an isolated active region as the P and N terminals of the diode. The isolation between P+ and the N+ active regions of the diode in a cell or between cells can be provided by dummy MOS gate, SBL, or STI / LOCOS isolations. The OTP element can be polysilicon, silicided polysilicon, silicide, metal, metal alloy, local interconnect, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

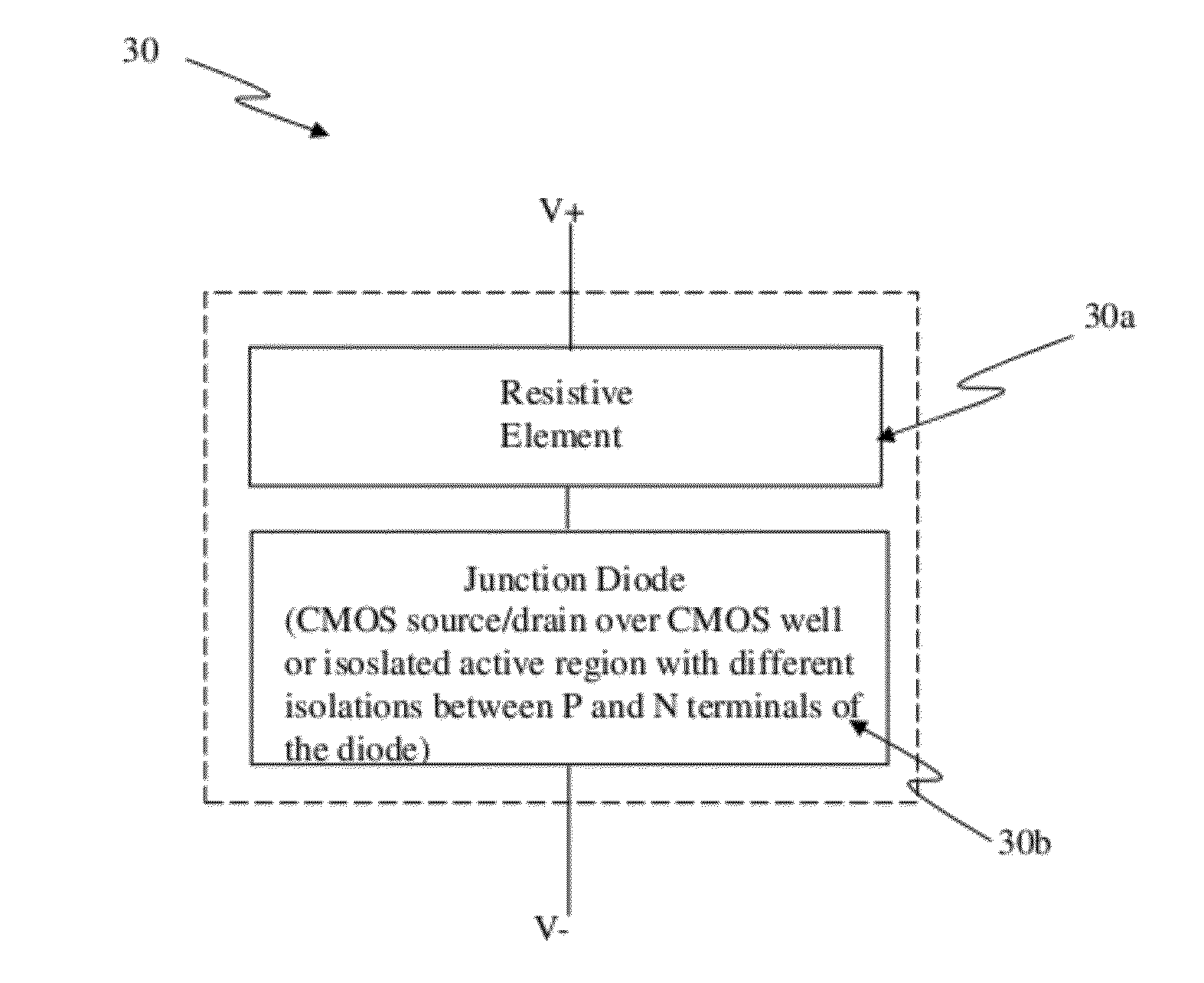

Programmably reversible resistive device cells using CMOS logic processes

ActiveUS20120044753A1Small cell sizeLow costSolid-state devicesRead-only memoriesCMOSCurrent limiting

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for reversible resistive devices, such as PCM, RRAM, CBRAM, or other memory cells. The reversible resistive devices have a reversible resistive element coupled to a diode. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. By applying a voltage or a current between a reversible resistive element and the N terminal of a diode, the reversible resistive device can be programmed into different states based on magnitude, duration, voltage-limit, or current-limit in a reversible manner. The P+ active region of the diode can be isolated from the N+ active region in the N well by using dummy MOS gate, SBL, or STI / LOCOS isolations.

Owner:ATTOPSEMI TECH CO LTD

Sensing Circuit For Programmable Resistive Device Using Diode as Program Selector

ActiveUS20120044748A1Low costSmall sizeSolid-state devicesRead-only memoriesHemt circuitsEngineering

A sensing circuit for programmable resistive device using diode as program selector is disclosed. The sensing circuit can have a reference and a sensing branch. In one embodiment, each branch can have a first type of MOS with the source coupled to a first supply voltage, the drain coupled to the drain of a second type of MOS, which can have the gate coupled to a bias supply voltage. The sources of the second type of MOS in the reference and sensing branches can be coupled to a reference resistor and a programmable resistance element, respectively, and they are further coupled to a second supply voltage through their diodes. The gate of the first type of MOS in the sensing branch can be coupled to the gate of the first type of MOS in the reference branch, which can have the drain coupled to the gate. The resistance difference between the reference resistor and the programmable resistive element can be sensed through the drain of the first type of MOS in the sensing branch into a logic level.

Owner:ATTOPSEMI TECH CO LTD

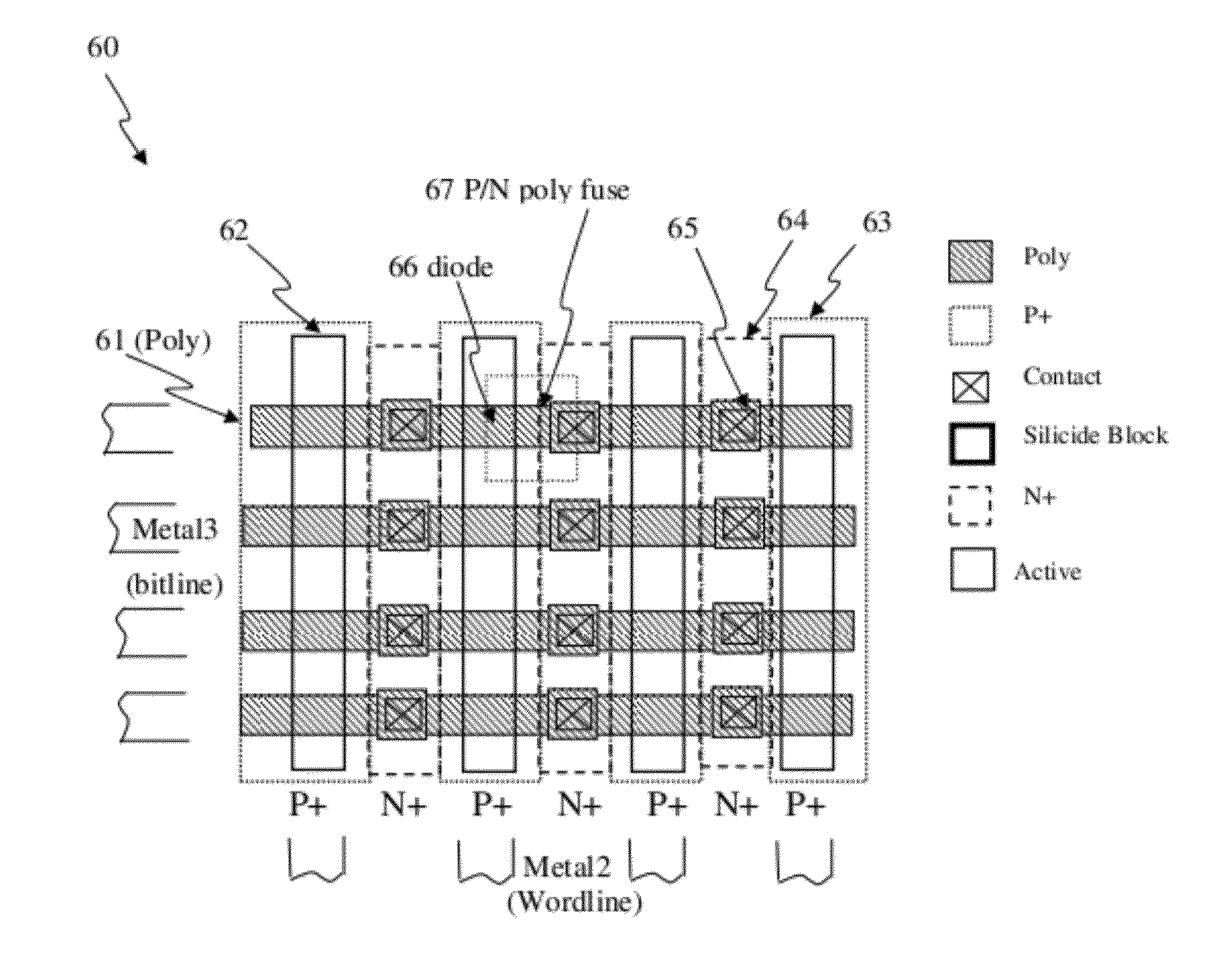

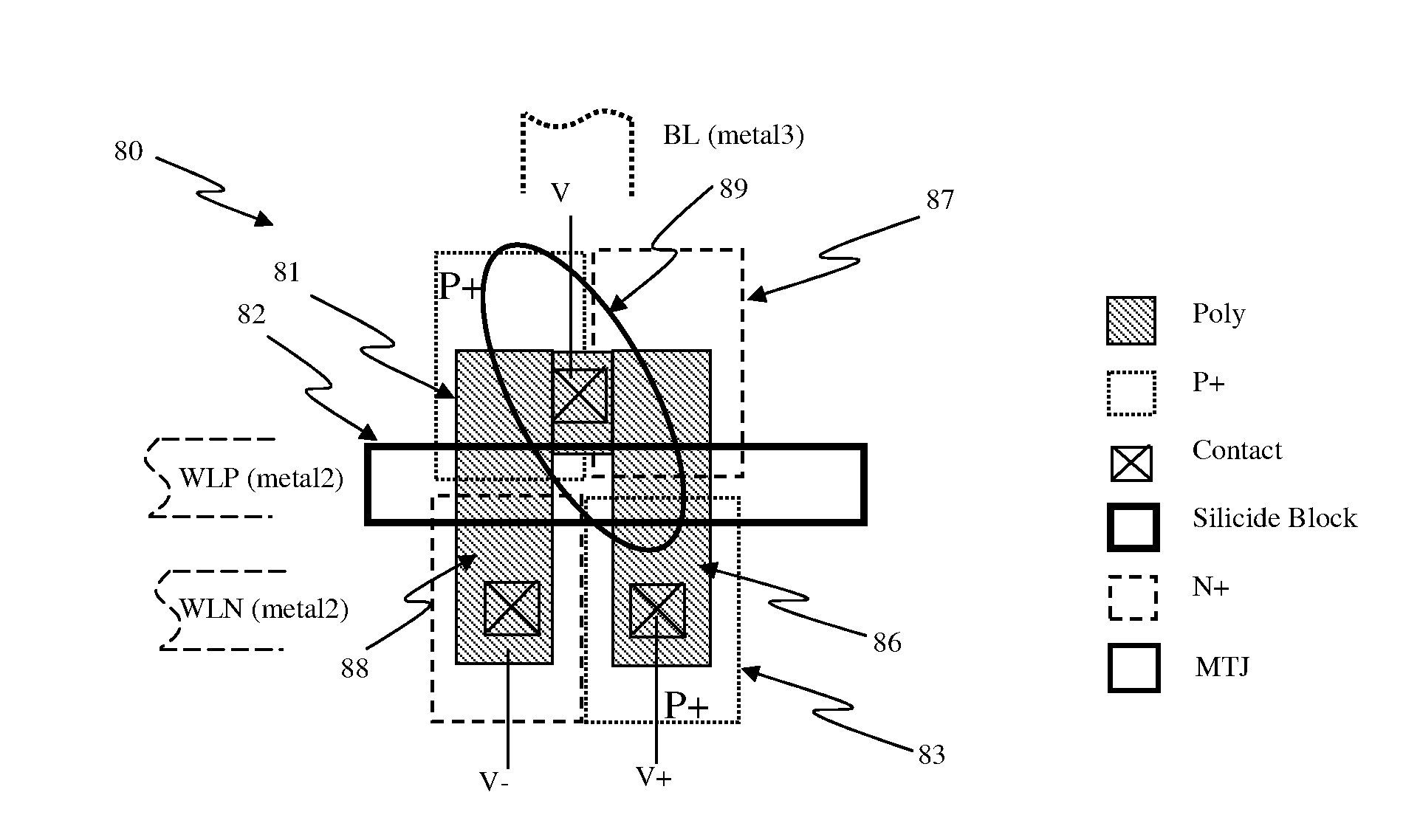

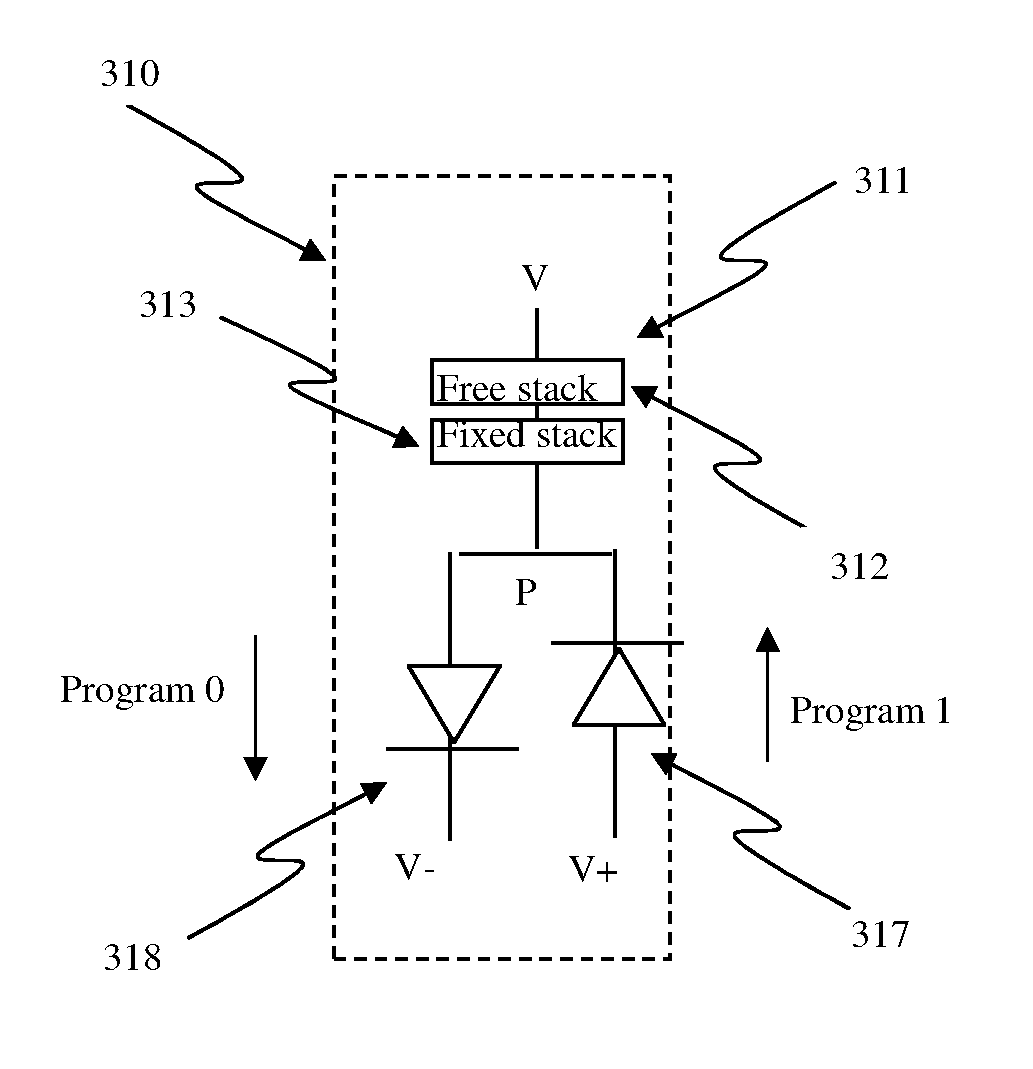

Circuit and system of using at least one junction diode as program selector for memories

ActiveUS20120044758A1Small cell sizeLow costSolid-state devicesRead-only memoriesCMOSElectrical resistance and conductance

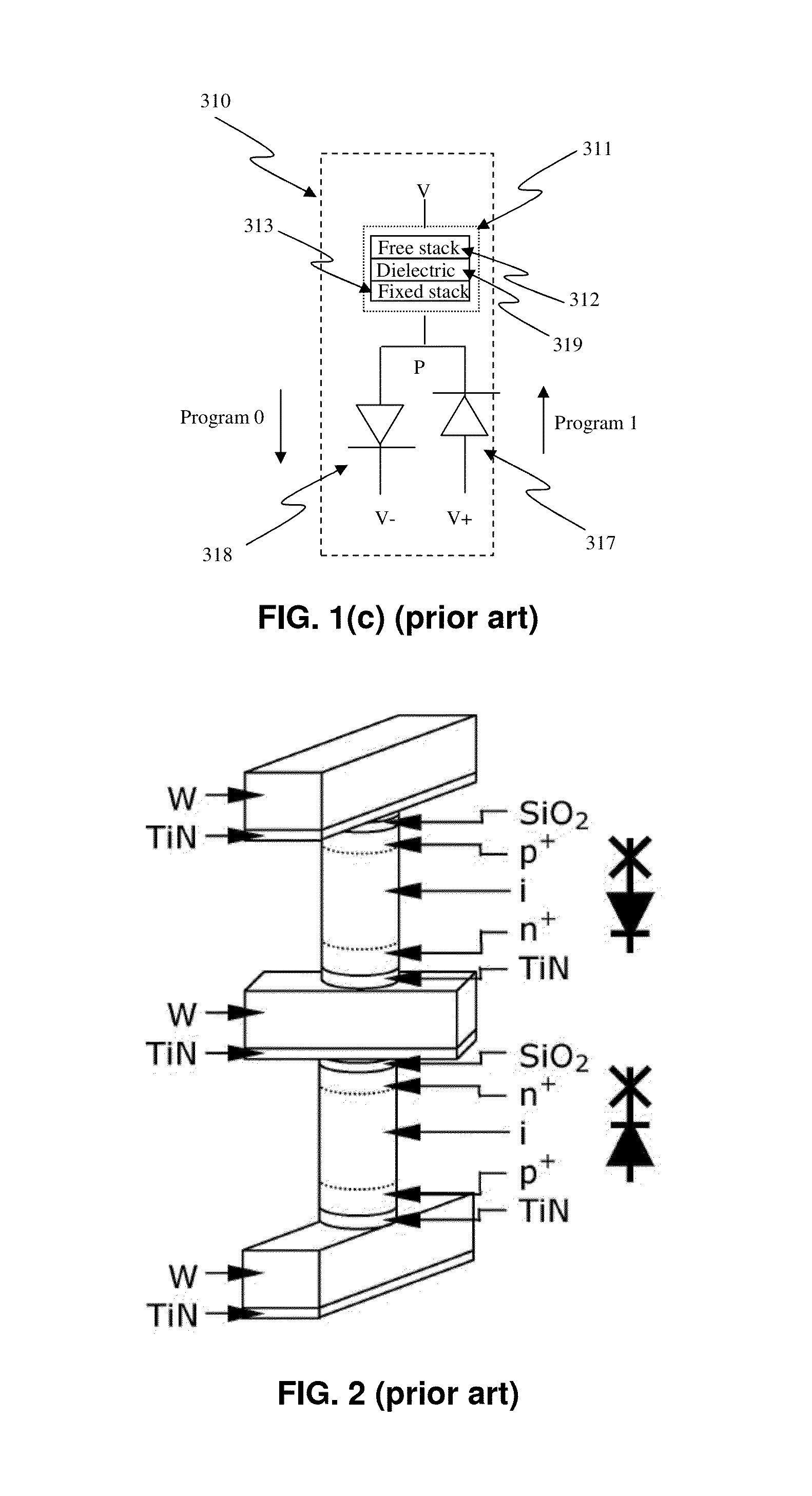

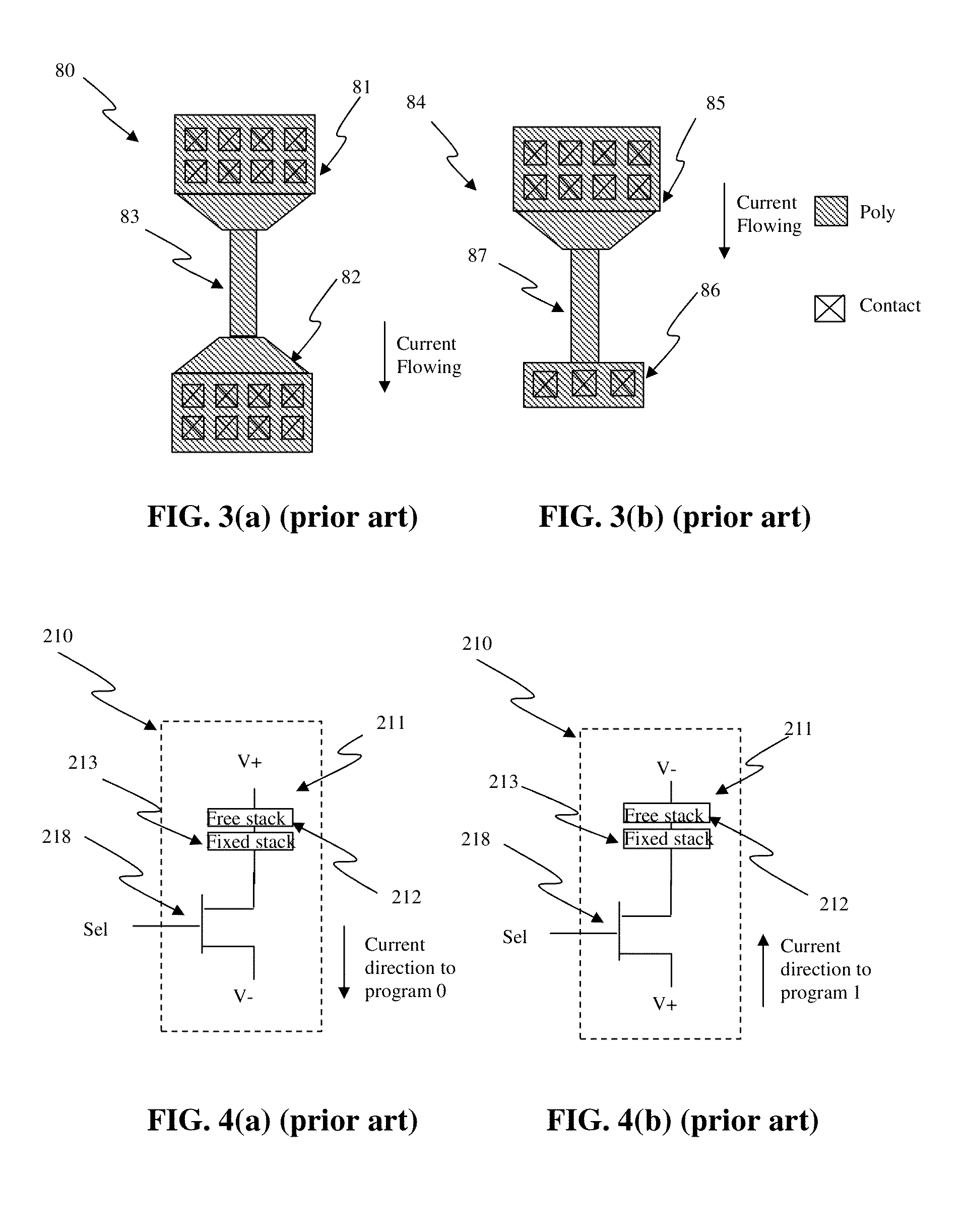

At least one junction diode fabricated in standard CMOS logic processes can be used as program selectors for memory cells that can be programmed based on direction of current flow. These cells are MRAM, RRAM, CBRAM, or other memory cells that have a programmable resistive element coupled to a P terminal of a first diode and to an N terminal of a second diode. The diodes can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diodes. The memory cells can be used to construct a two-dimensional memory array with the N terminals of the first diodes and the P terminals of the second diodes in a row connected as wordline(s) and the resistive elements in a column connected as a bitline. By applying a high voltage to a selected bitline and a low voltage to a selected wordline to turn on the first diode while disabling the second diode, a selected cell can be programmed into one state. Similarly, by applying a low voltage to a selected bitline and a high voltage to a selected wordline to turn on the second diode while disabling the first diode, a selected cell can be programmed into another state. The data in the resistive memory cell can also be read by turning on a selected wordline to couple a selected bitline to a sense amplifier. The wordlines may have high-resistivity local wordlines coupled to low-resistivity global wordlines through conductive contact(s) or via(s).

Owner:ATTOPSEMI TECH CO LTD

Memory using a plurality of diodes as program selectors with at least one being a polysilicon diode

ActiveUS20120044757A1Small cell sizeLow costSolid-state devicesRead-only memoriesBit lineElectrical current

Embodiments of programmable memory cells using a plurality of diodes as program selectors are disclosed for those memory cells that can be programmed based on direction of current flow. These memory cells are MRAM, RRAM, CBRAM, or other memory cells that have a programmable resistive element coupled to the P-terminal of a first diode and to the N-terminal of a second diode. At least one of the diodes can be a polysilicon diode fabricated using standard CMOS processes with P+ and N+ implants in two ends. The polysilicon diode can be constructed by P+ / N+ implants on a polysilicon substrate as a program selector. The memory cells can be used to construct a two-dimensional memory array with the N-terminals of the first diodes and the P-terminals of the second diodes in a row connected as wordline(s) and the resistive elements in a column connected as a bitline.

Owner:ATTOPSEMI TECH CO LTD

Memory devices using a plurality of diodes as program selectors with at least one being a polysilicon diode

ActiveUS20120044756A1Avoid shortingSmall cell sizeSolid-state devicesRead-only memoriesLow voltageBlocking layer

Embodiments of programmable memory cells using a plurality of diodes as program selectors are disclosed for those memory cells that can be programmed based on direction of current flow. These memory cells are MRAM, RRAM, CBRAM, or other memory cells that have a programmable resistive element coupled to the P-terminal of a first diode and to the N-terminal of a second diode. At least one of the diodes can be a polysilicon diode fabricated using standard CMOS processes. The polysilicon diode can be constructed by P+ / N+ implants on a polysilicon substrate as a program selector. The polysilicon diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. By applying a high voltage to a resistive element and switching the N-terminal of the first diode to a low voltage while disabling the second diode, a current flowing through the memory cell can change the resistance into one state. Similarly, by applying a low voltage to a resistive element and switching the P-terminal of the second diode to a high voltage while disabling the first diode, a current flowing through the memory cell can change the resistance into another state. On the polysilicon diode, the spacing and doping level of a gap between the P- and N-implants can be controlled for different breakdown voltages and leakage currents. A Silicide Block Layer (SBL) can be used to block silicide formation on the top of polysilicon to prevent shorting.

Owner:ATTOPSEMI TECH CO LTD

Memory devices using a plurality of diodes as program selectors with at least one being a polysilicon diode

ActiveUS8482972B2Avoid shortingSmall cell sizeSolid-state devicesRead-only memoriesPower flowCmos process

Embodiments of programmable memory cells using a plurality of diodes as program selectors are disclosed for memory cells that can be programmed based on direction of current flow. These memory cells are MRAM, RRAM, CBRAM, or other memory cells that have a programmable resistive element coupled to the P-terminal of a first diode and to the N-terminal of a second diode. At least one of the diodes can be a polysilicon diode fabricated using standard CMOS processes. The polysilicon diode can be constructed by P+ / N+ implants on a polysilicon substrate as a program selector.

Owner:ATTOPSEMI TECH CO LTD

One-time programmable memories using polysilicon diodes as program selectors

ActiveUS20120044738A1Small cell sizeCost reductionSolid-state devicesRead-only memoriesSense amplifierHigh resistivity

Polysilicon diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, using electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse etc. as OTP element The diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. The OTP device has an OTP element coupled to a polysilicon diode. The OTP devices can be used to construct a two-dimensional OTP memory with the N-terminals of the diodes in a row connected as a wordline and the OTP elements in a column connected as a bitline. By applying a high voltage between a selected bitline and a selected wordline to turn on a diode in a selected cell for suitable duration of time, a current flows through an OTP element may change the resistance state. The cell data in the OTP memory can also be read by turning on a selected wordline and to couple a selected bitline to a sense amplifier. The wordlines may have high-resistivity local wordlines coupled to low-resistivity global wordlines through conductive contact(s) or via(s).

Owner:ATTOPSEMI TECH CO LTD

Circuit and system of using FinFET for building programmable resistive devices

Junction diodes or MOS devices fabricated in standard FinFET technologies can be used as program selectors or One-Time Programmable (OTP) element in a programmable resistive device, such as interconnect fuse, contact / via fuse, anti-fuse, or emerging nonvolatile memory such as MRAM, PCRAM, CBRAM, or RRAM. The MOS or diode can be built on at least one fin structure or at least one active region that has at least one first active region and a second active region. The first and the second active regions can be isolated by a dummy MOS gate or silicide block layer (SBL) to construct a diode.

Owner:ATTOPSEMI TECH CO LTD

Circuit and system of using junction diode as program selector and MOS as read selector for one-time programmable devices

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has at least one OTP element coupled to at least one diode in a memory cell. The diode can be constructed by P+ and N+ active regions in a CMOS N well, or on an isolated active region as the P and N terminals of the diode. The isolation between P+ and the N+ active regions of the diode in a cell or between cells can be provided by dummy MOS gate, SBL, or STI / LOCOS isolations. The OTP cell can have a MOS in series with the OTP element as a read selector. The OTP element can be polysilicon, silicided polysilicon, silicide, polymetal, metal-0, metal, metal alloy, local interconnect, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

Fat retraction apparatus and method for using same

InactiveUS20090125013A1Small cell sizeReduce contentSurgical instruments for heatingSurgical instruments using microwavesDiseaseIntact skin

The present invention provides a method and apparatus for non-invasive reduction of excessive fat tissue by externally applying radio frequency (RF) electromagnetic (EM) waves adjusted to specific fat cells absorption frequency and electromagnetic propagation mode. Based on the performed experiments described further, the method and working apparatus has been invented that reduces fat layers without any medication, non-invasively through the intact skin. The invented method and apparatus facilitates the safe fat removal, and may lead to reduction and eradication of obesity and obesity associated diseases.

Owner:SYPNIEWSKI ROZA +1

System for optimizing the performance and reliability of a storage controller cache offload circuit

InactiveUS20080126700A1Improve performanceOptimizing reliabilityVolume/mass flow measurementHardware monitoringRAIDControl store

A method for offloading a cache memory is disclosed. The method generally includes the steps of (A) reading all of a plurality of cache lines from the cache memory in response to an assertion of a signal to offload of the cache memory, (B) generating a plurality of blocks by dividing the cache lines in accordance with a RAID configuration and (C) writing the blocks among a plurality of nonvolatile memories in the RAID configuration, wherein each of the nonvolatile memories has a write bandwidth less than a read bandwidth of the cache memory.

Owner:AVAGO TECH INT SALES PTE LTD

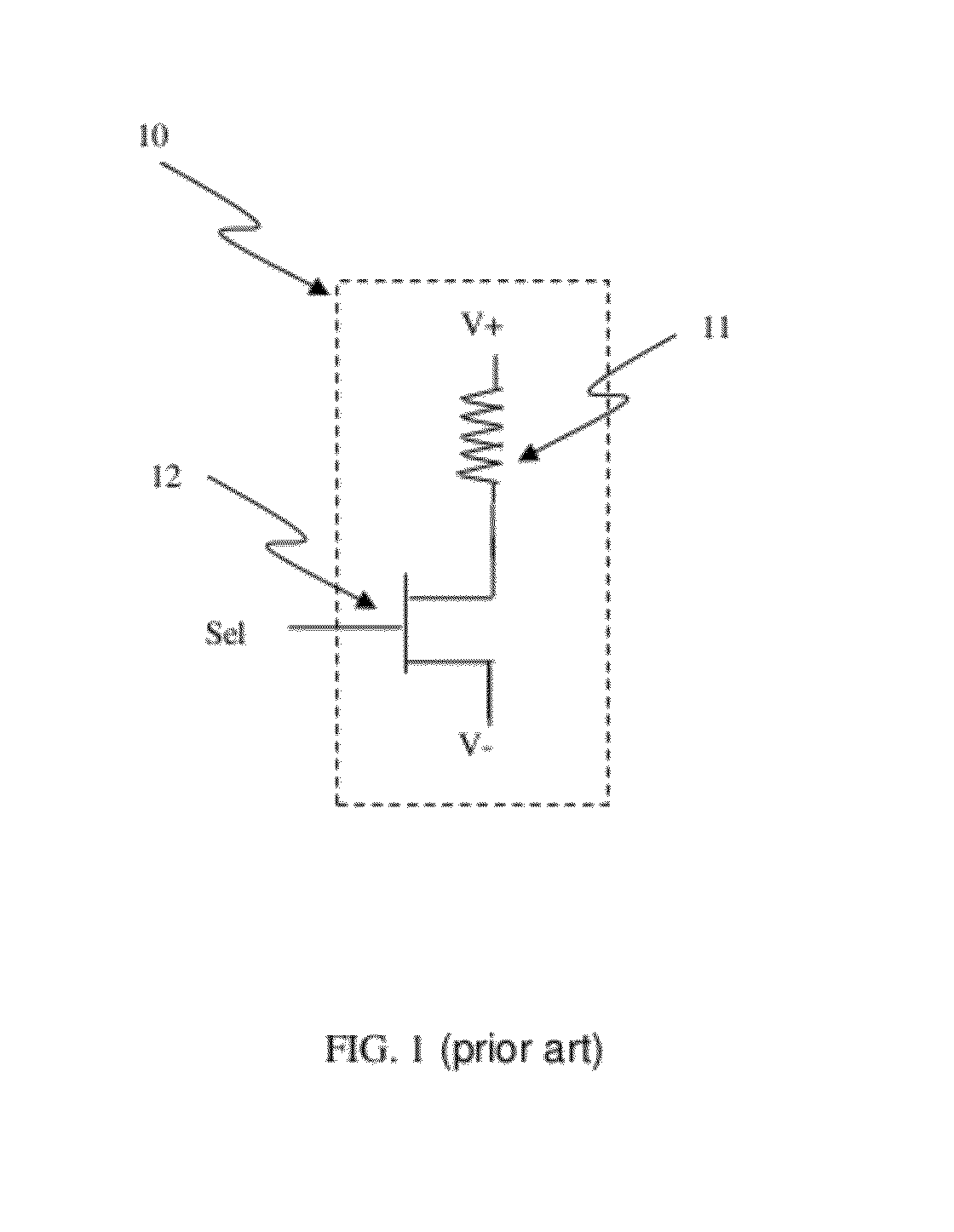

Programmable Resistive Device and Memory Using Diode as Selector

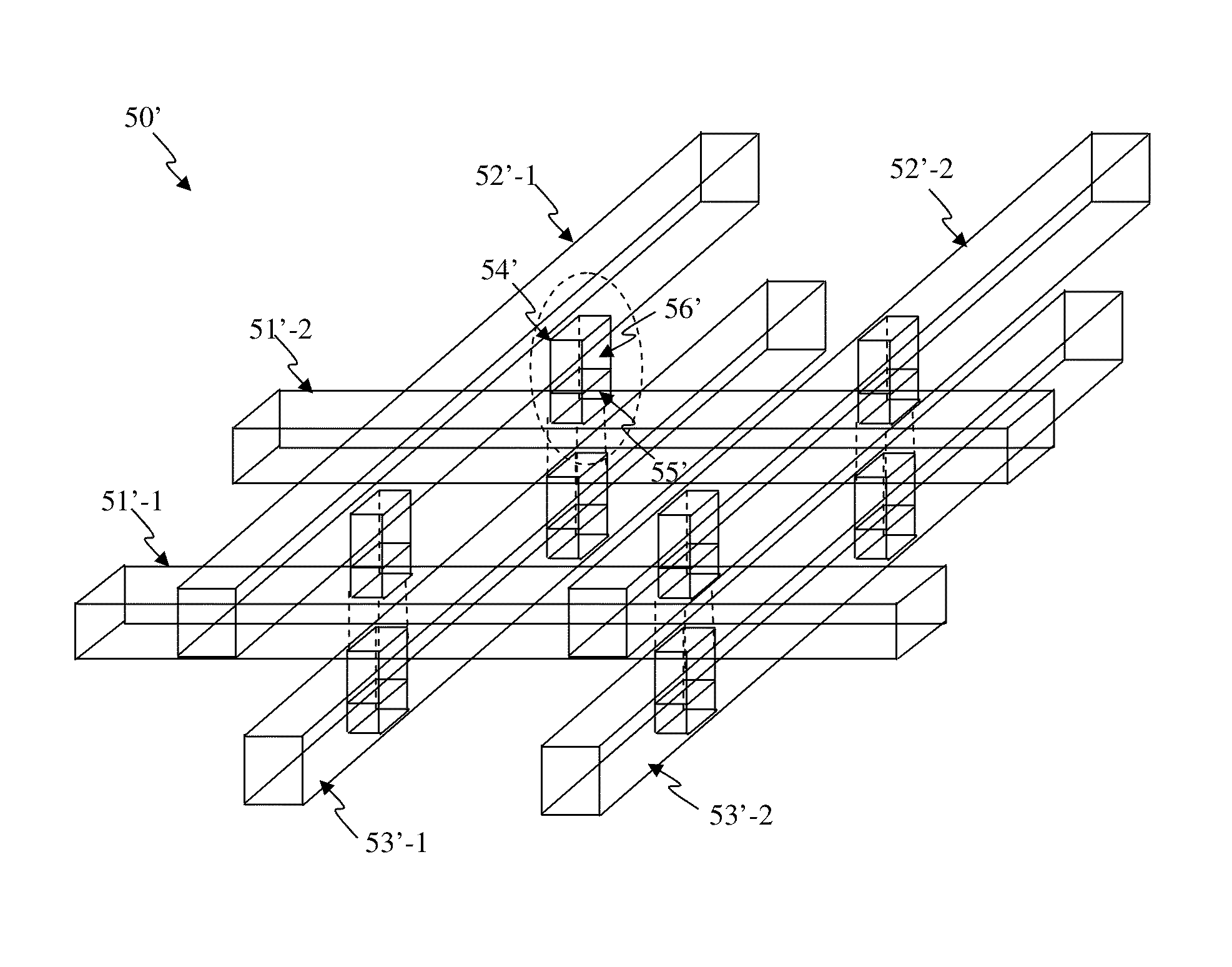

Building programmable resistive devices in contact holes at the crossover of a plurality of conductor lines in more than two vertical layers is disclosed. There are plurality of first conductor lines and another plurality of second conductor lines that can be substantially perpendicular to each other, though in two different vertical layers. A diode and / or a programmable resistive element can be fabricated in the contact hole between the first and second conductor lines. The programmable resistive element can be coupled to another programmable resistive device or shared between two programmable devices whose diodes conducting currents in opposite directions and / or coupled to a common conductor line. The programmable resistive memory can be configured to be programmable by applying voltages to conduct current flowing through the programmable resistive element to change its resistance for a different logic state.

Owner:ATTOPSEMI TECH CO LTD

Method and structure for reliable electrical fuse programming

ActiveUS20150003142A1Small cell sizeLow costMagnetic-field-controlled resistorsSolid-state devicesElectrical resistance and conductanceAlgorithm

A method of programming electrical fuses reliably is disclosed. If a programming current exceeds a critical current, disruptive mechanisms such as rupture, thermal runaway, decomposition, or melt, can be a dominant programming mechanism such that programming is not be very reliable. Advantageously, by controlled programming where programming current is maintained below the critical current, electromigration can be the sole programming mechanism and, as a result, programming can be deterministic and very reliable. In this method, fuses can be programmed in multiple shots with progressive resistance changes to determine a lower bound that all fuses can be programmed satisfactorily and an upper bound that at least one fuse can be determined failed. If programming within the lower and upper bounds, defects due to programming can be almost zero and, therefore, defects are essentially determined by pre-program defects.

Owner:ATTOPSEMI TECH CO LTD

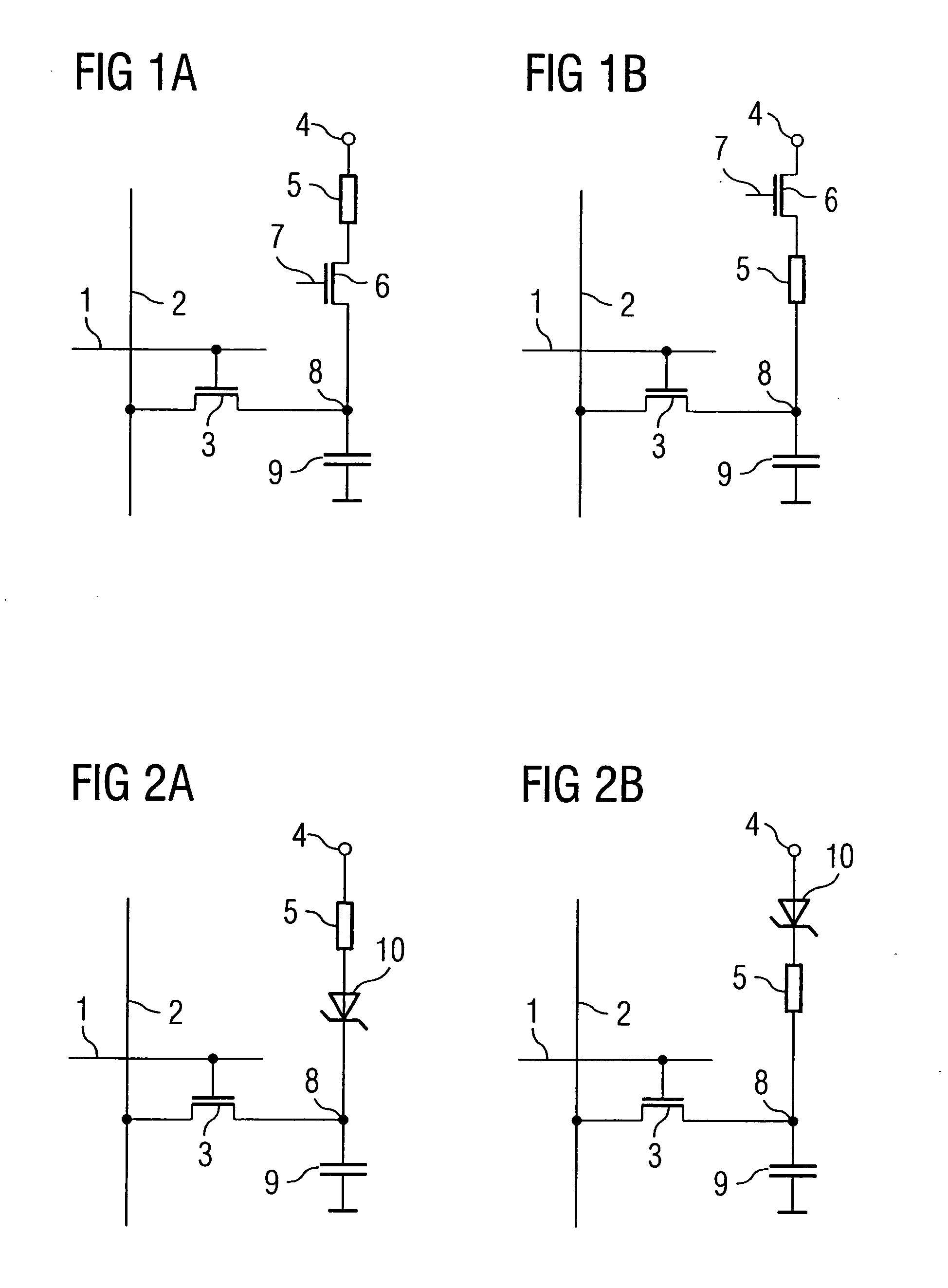

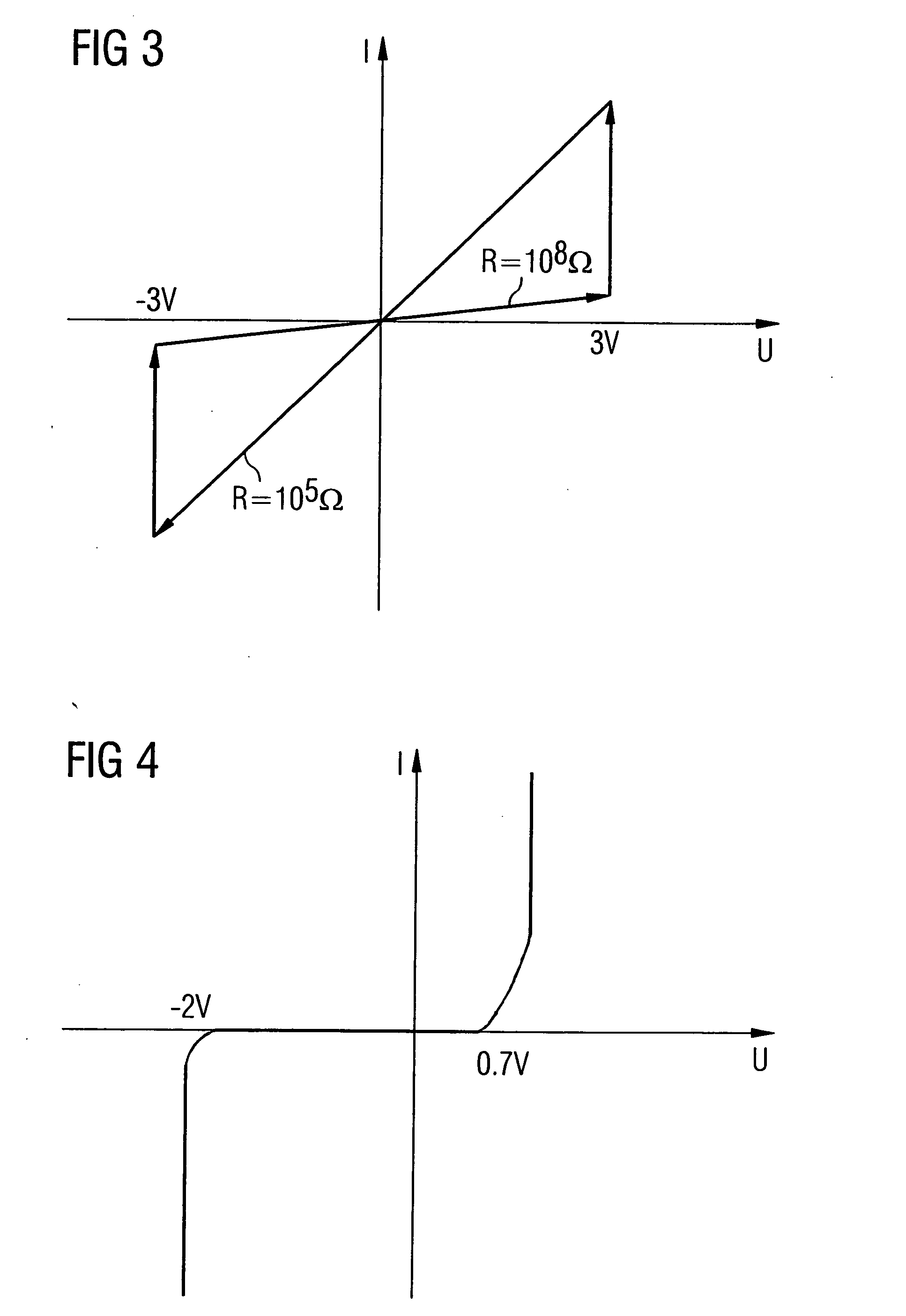

Semiconductor memory with volatile and non-volatile memory cells

InactiveUS20060120138A1Easy to operateReduce the voltage valueNanoinformaticsSolid-state devicesDram memorySemiconductor

The present invention relates to a semiconductor memory with a volatile memory device, in particular a DRAM memory device, and with a non-volatile memory device. The volatile memory device is electrically coupled with the non-volatile memory device, and the non-volatile memory device has a polymer memory device adapted to be switched between two states of information.

Owner:INFINEON TECH AG

Circuit and System of Using Junction Diode of MOS as Program Selector for Programmable Resistive Devices

ActiveUS20150029777A1Reduce cell size and costLow costRead-only memoriesDigital storageResistive elementEngineering

A programmable resistive device cell using at least one MOS device as selector can be programmed or read by turning on a source junction diode of the MOS or a channel of the MOS. A programmable resistive device cell can include at least one programmable resistive element and at least one MOS device. The programmable resistive element can be coupled to a first supply voltage line. The MOS can have a source coupled to the programmable resistive element, a bulk coupled to a drain, a drain coupled to a second supply voltage line, and a gate coupled to a third supply voltage line. The programmable resistive element can be configured to be programmable or readable by applying voltages to the first, second, and / or third supply voltage lines to turn on the source junction of the MOS and / or to turn on the channel of the MOS.

Owner:ATTOPSEMI TECH CO LTD

Multiple-state one-time programmable (OTP) memory to function as multi-time programmable (MTP) memory

ActiveUS9019742B2Low costSmall sizeRead-only memoriesDigital storageOne time programmableComputer science

Owner:ATTOPSEMI TECH CO LTD

One-time programmable devices using junction diode as program selector for electrical fuses with extended area

ActiveUS20150003143A1Small cell sizeLow costMagnetic-field-controlled resistorsSolid-state devicesCMOSOne time programmable

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuses. At least one portion of the electrical fuse can have at least one extended area to accelerate programming. An extended area is an extension of the fuse element beyond contact or via longer than required by design rules. The extended area also has reduced or substantially no current flowing through. The program selector can be at least one MOS. The OTP device can have the at least one OTP element coupled to at least one diode in a memory cell.

Owner:ATTOPSEMI TECH CO LTD

Programmable resistive memory unit with data and reference cells

InactiveUS9025357B2Low costSmall sizeRead-only memoriesDigital storageComputer scienceResistive element

A method and system of a programmable resistive memory having a plurality of programmable resistive memory units. At least one of the programmable resistive memory units has at least one data cell and at least one reference cell. The data cell can have one programmable resistive element coupled to at least one diode as a program selector and also coupled to a bitline (BL). The reference cell can have a reference resistive element coupled to at least one reference diode as reference program selector and also coupled to a reference bitline (BLR). In one embodiment, the reference resistive element can have substantially the same material, structure, or shape of the programmable resistive element. In one embodiment, the reference diode can have the same material, structure, or shape of the diode serving as the program selector diode.

Owner:ATTOPSEMI TECH CO LTD

System for optimizing the performance and reliability of a storage controller cache offload circuit

InactiveUS7904647B2Optimizing performance and reliabilityCapacity expansionHardware monitoringPower supply for data processingRAIDControl store

A method for offloading a cache memory is disclosed. The method generally includes the steps of (A) reading all of a plurality of cache lines from the cache memory in response to an assertion of a signal to offload of the cache memory, (B) generating a plurality of blocks by dividing the cache lines in accordance with a RAID configuration and (C) writing the blocks among a plurality of nonvolatile memories in the RAID configuration, wherein each of the nonvolatile memories has a write bandwidth less than a read bandwidth of the cache memory.

Owner:AVAGO TECH INT SALES PTE LTD

Thermoplastic polyurethane elastomer foam bead and preparation method thereof

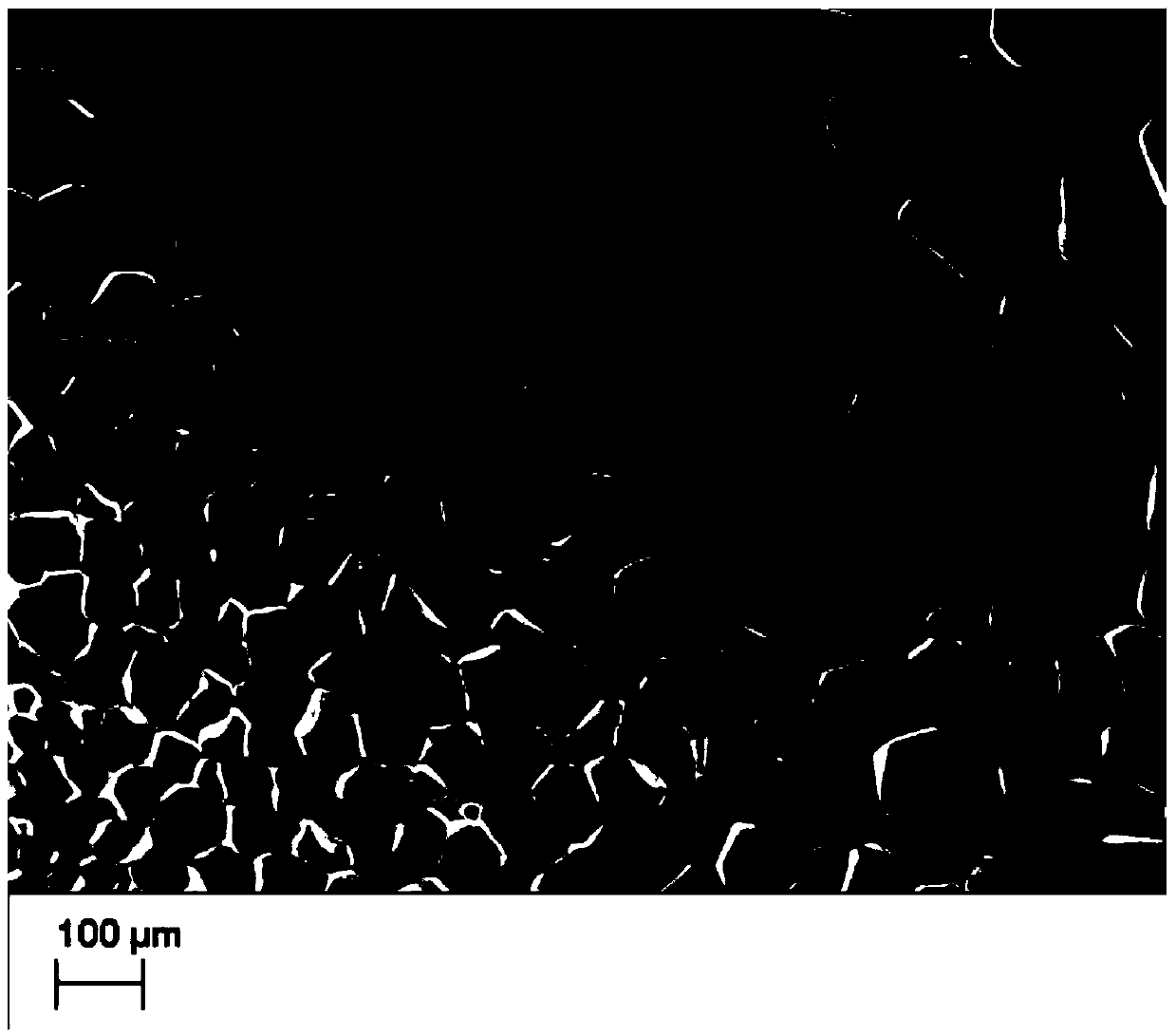

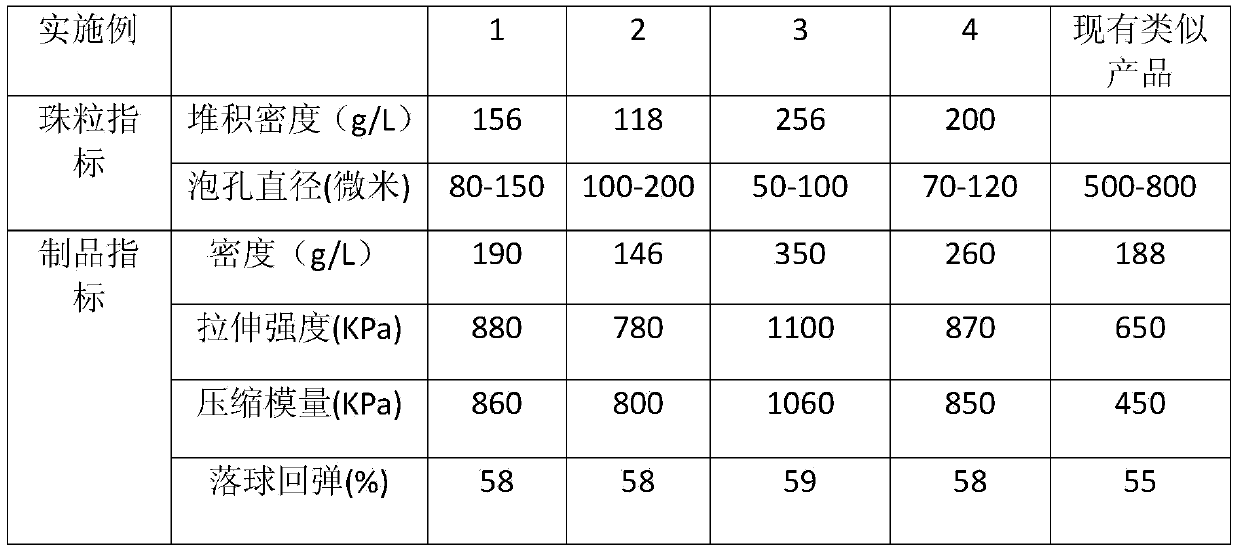

The invention discloses a thermoplastic polyurethane elastomer foam bead and a preparation method thereof. The method comprises the following steps: firstly, adding thermoplastic polyurethane particles and water to a reaction kettle according to the mass ratio of 1 to (0.8-4); adding liquid carbon dioxide to the reaction kettle, and controlling the intensity of pressure and the temperature in the reaction kettle, so that the carbon dioxide in the reaction kettle is in a super-critical state; raising the temperature inside the reaction kettle to 90-140 DEG C; carrying out heat preservation; putting the materials in the kettle into a pressure tank, maintaining pressure, and cooling to below 70 DEG C; foaming the thermoplastic polyurethane elastomer particles once, and controlling the volume ratio of the reaction pressure to the pressure tank to be 1 to (15-30); putting the disposable foam particles into a storage tank, and carrying out secondary normal pressure foaming to obtain thermoplastic polyurethane elastomer foam beads; and removing the surface moisture of the foam beads, and curing the foam beads at normal pressure and normal temperature for over 48 hours, so as to obtain the product. The product disclosed by the invention has the characteristics of even and compact cells, small size, high percentage of closed area, high molding product strength, good rebound resilience and the like.

Owner:新辉新材料(常州)有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com