Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

246results about How to "Reduce memory size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Image processing method, image processing apparatus, and system

ActiveUS20090179824A1Increase speedReduce memory sizeCharacter and pattern recognitionCathode-ray tube indicatorsDistortionChromatic aberration

One of a plurality of color components which form pixels in an image that is influenced by chromatic aberrations caused by an optical system is selected as a reference color, and coordinates after conversion are calculated by applying conversion for correcting a distortion of the optical system with respect to the image to coordinates of pixels in association with the reference color. Correction values indicating amounts of color misregistration are calculated using the proportional relationship of difference values between the calculated coordinates and coordinates obtained by applying the conversion to coordinates of the image in association with remaining colors except for the reference color of the plurality of color components. Based on the calculated correction values, coordinates obtained by applying the conversion to coordinates of the image in association with the remaining colors are calculated.

Owner:CANON KK

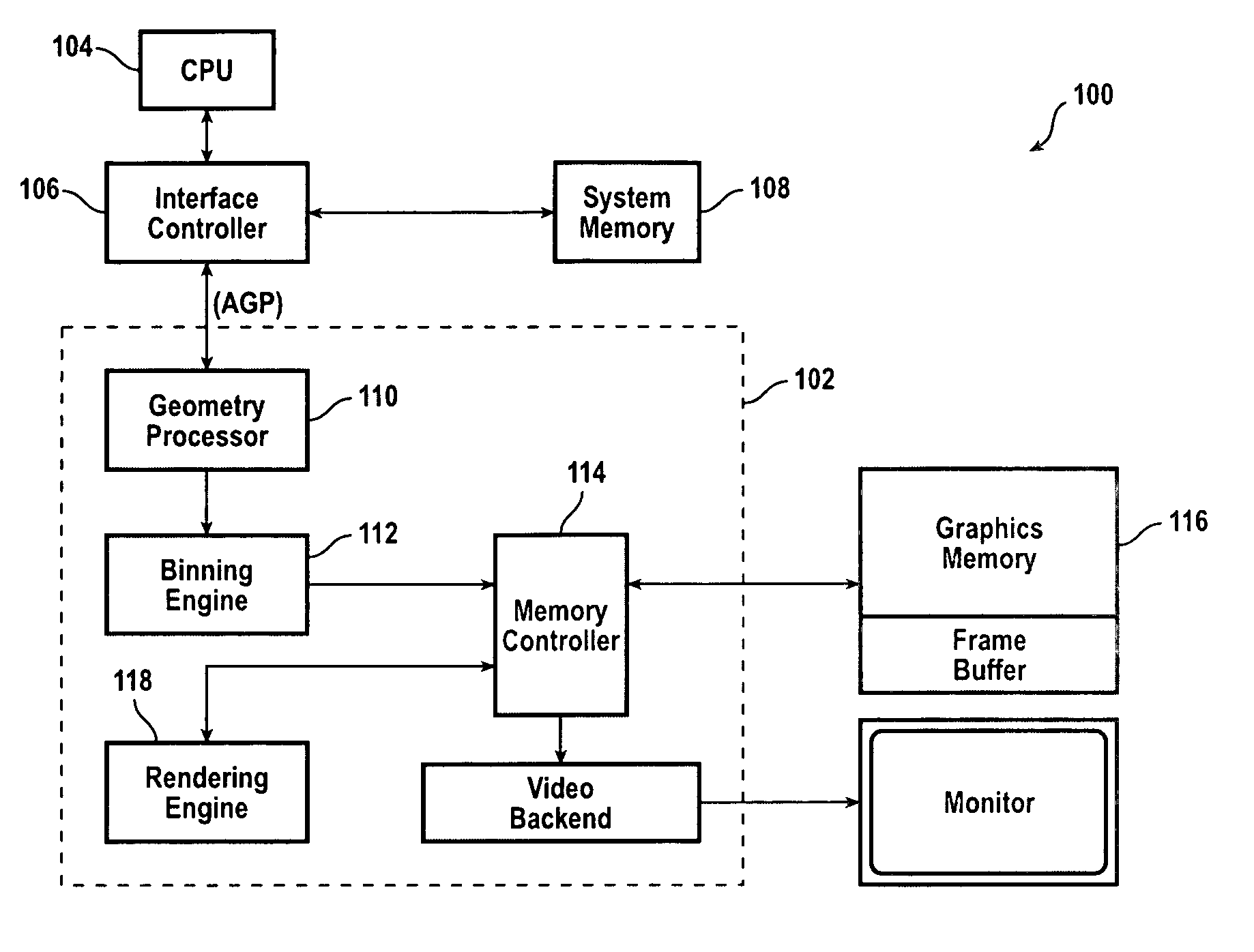

Demand-based memory system for graphics applications

InactiveUS7102646B1High resolutionSmall size of pageMemory adressing/allocation/relocationImage memory managementApplication softwareGraphics

A memory system and methods of operating the same that drastically increase the efficiency in memory use and allocation in graphics systems. In a graphics system using a tiled architecture, instead of pre-allocating a fixed amount of memory for each tile, the invention dynamically allocates varying amounts of memory per tile depending on the demand. In one embodiment all or a portion of the available memory is divided into smaller pages that are preferably equal in size. Memory allocation is done by page based on the amount of memory required for a given tile.

Owner:NVIDIA CORP

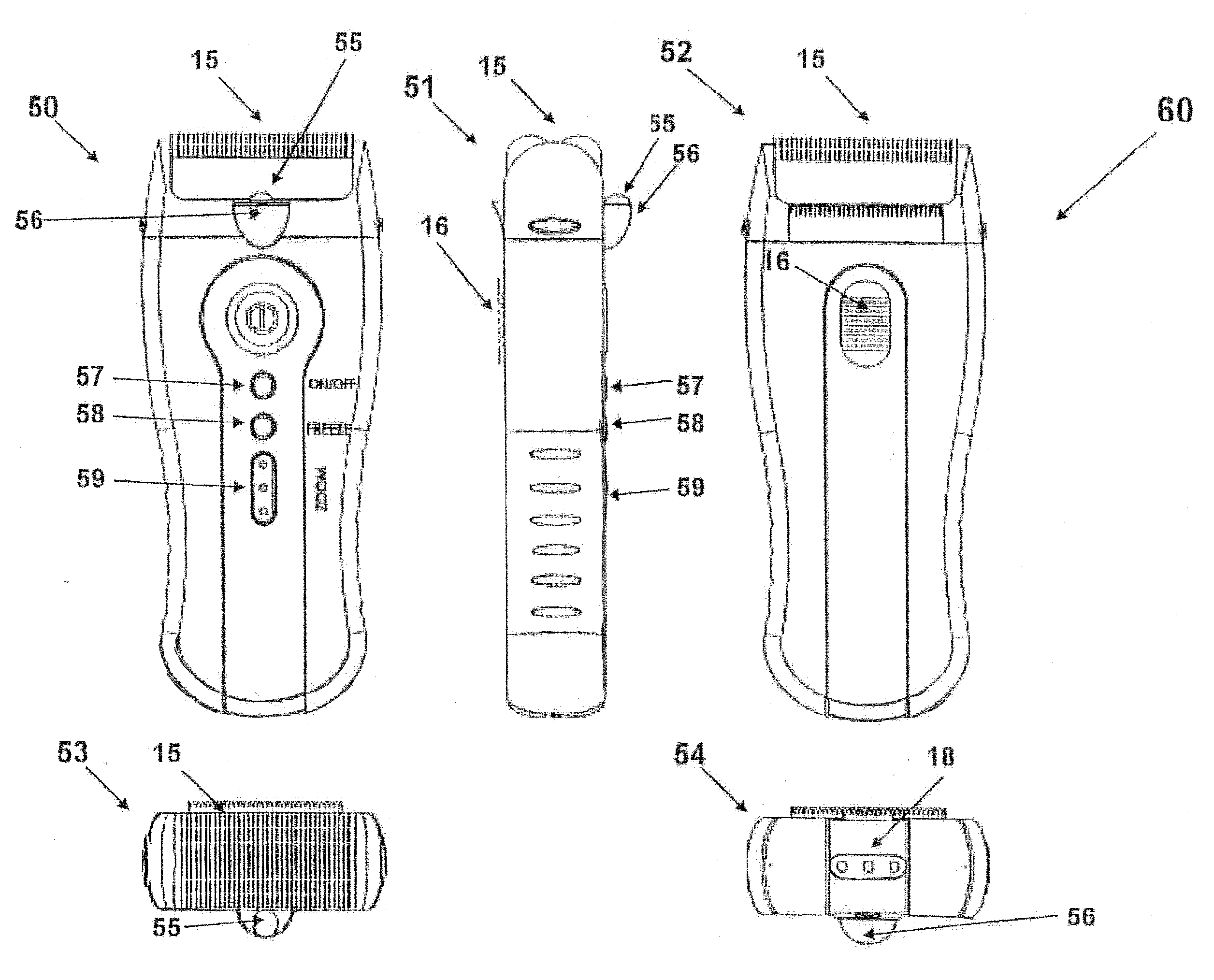

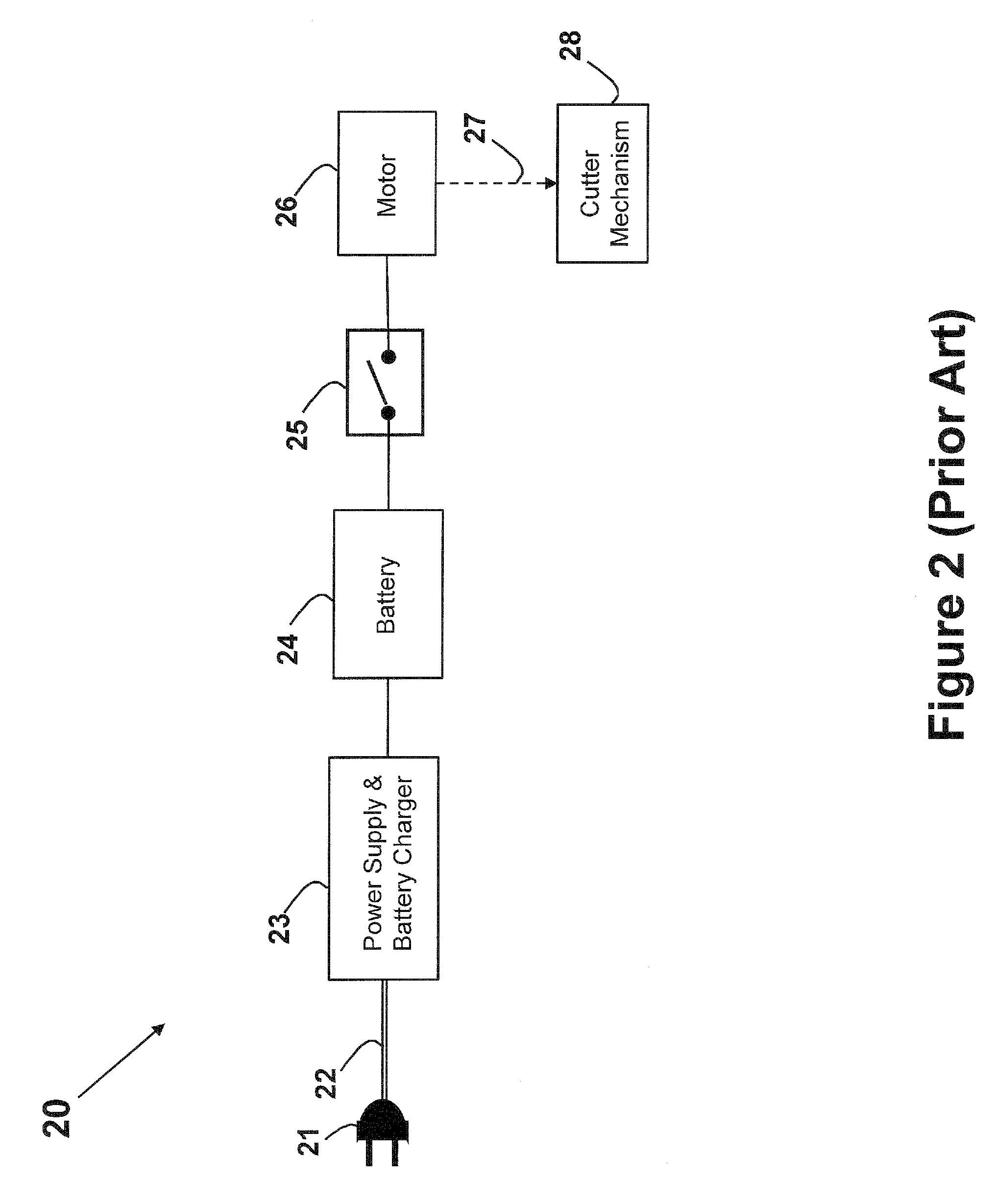

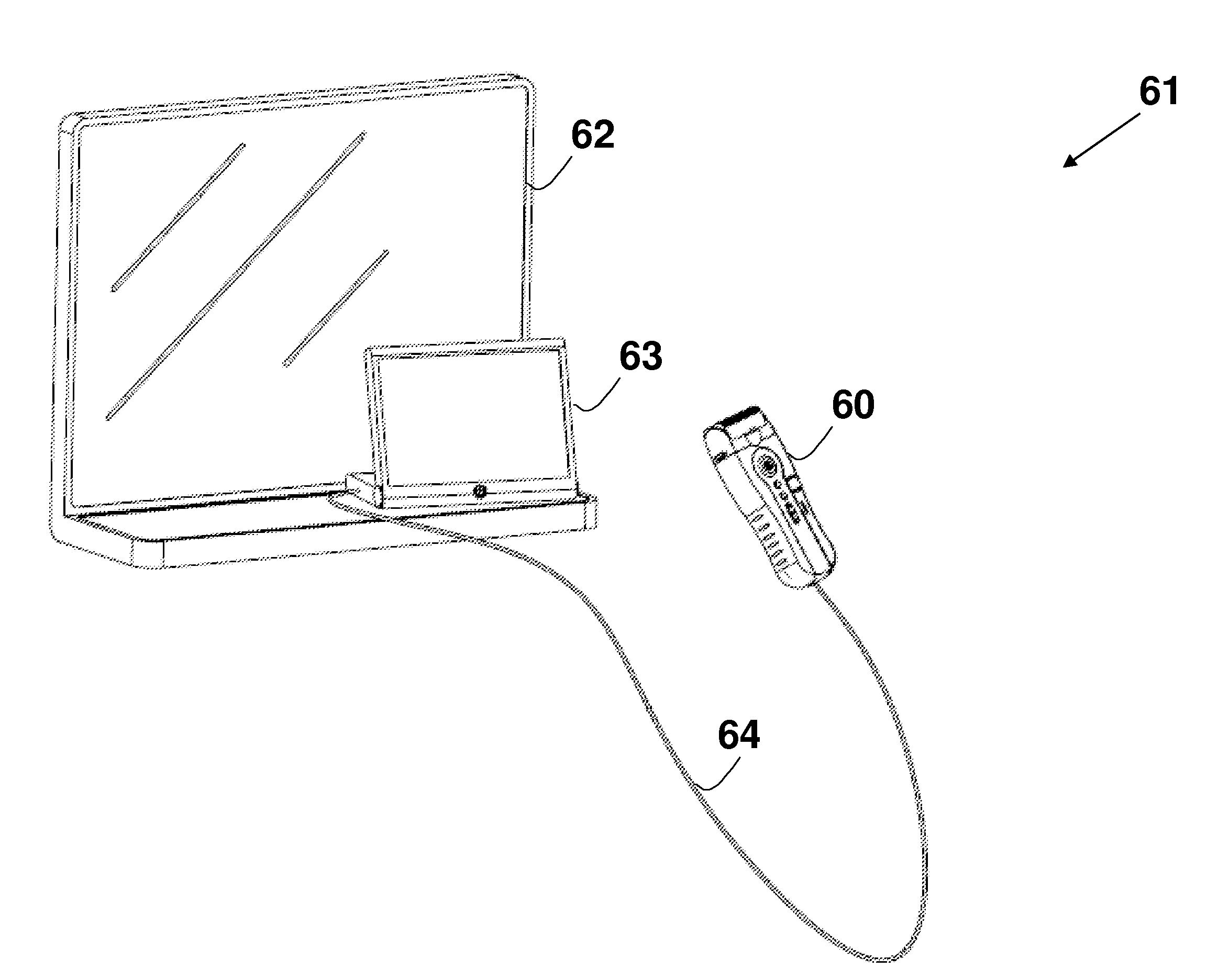

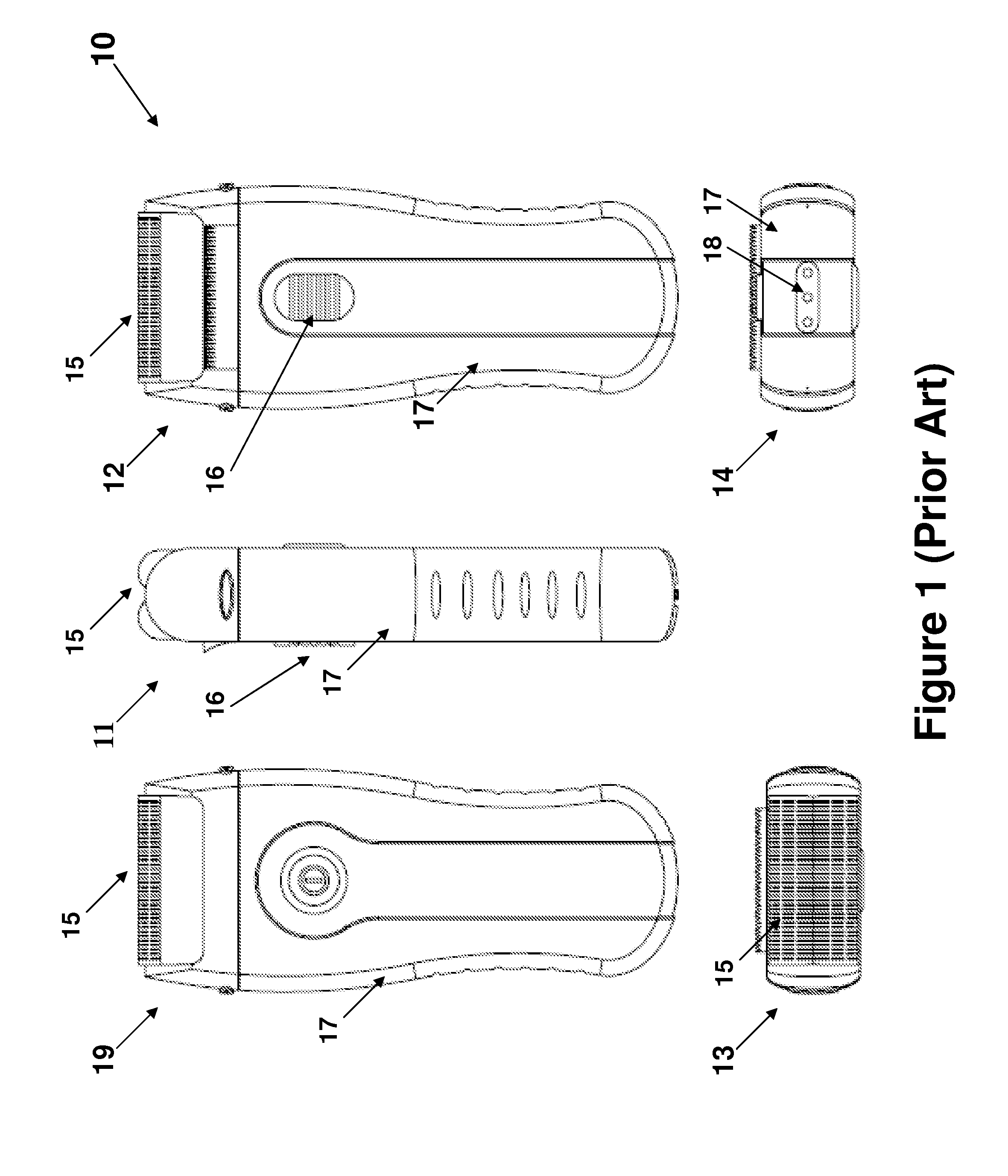

Electric shaver with imaging capability

InactiveUS20100186234A1Reduce memory sizeLow data rateTelevision system detailsHair-singeingVisibilityWired communication

System and method for improving the shaving experience by providing improved visibility of the skin shaving area. A digital camera is integrated with the electric shaver for close image capturing of shaving area, and displaying it on a display unit. The display unit can be integral part of the electric shaver casing, or housed in a separated device which receives the image via a communication channel. The communication channel can be wireless (using radio, audio or light) or wired, such as dedicated cabling or using powerline communication. A light source is used to better illuminate the shaving area. Video compression and digital image processing techniques are used for providing for improved shaving results. The wired communication medium can simultaneously be used also for carrying power from the electric shaver assembly to the display unit, or from the display unit to the electric shaver.

Owner:MAY PATENTS LTD

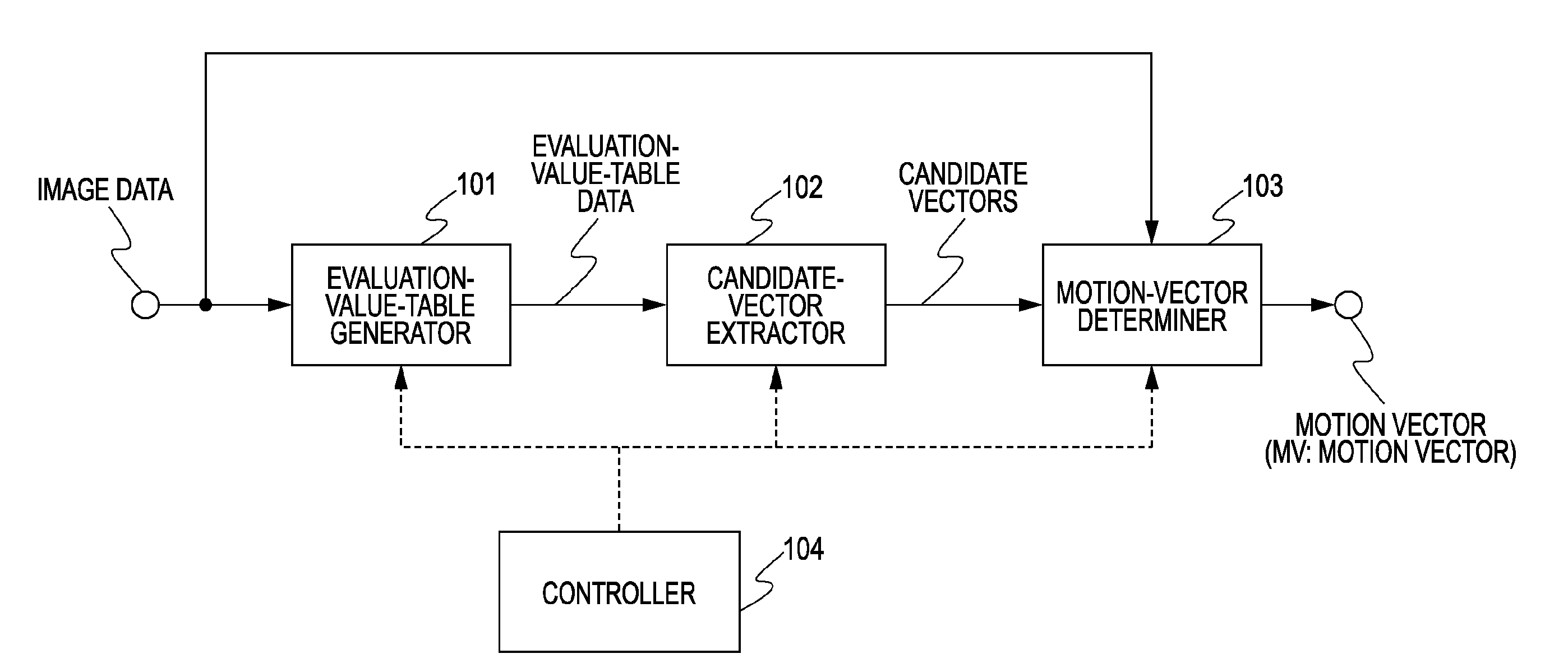

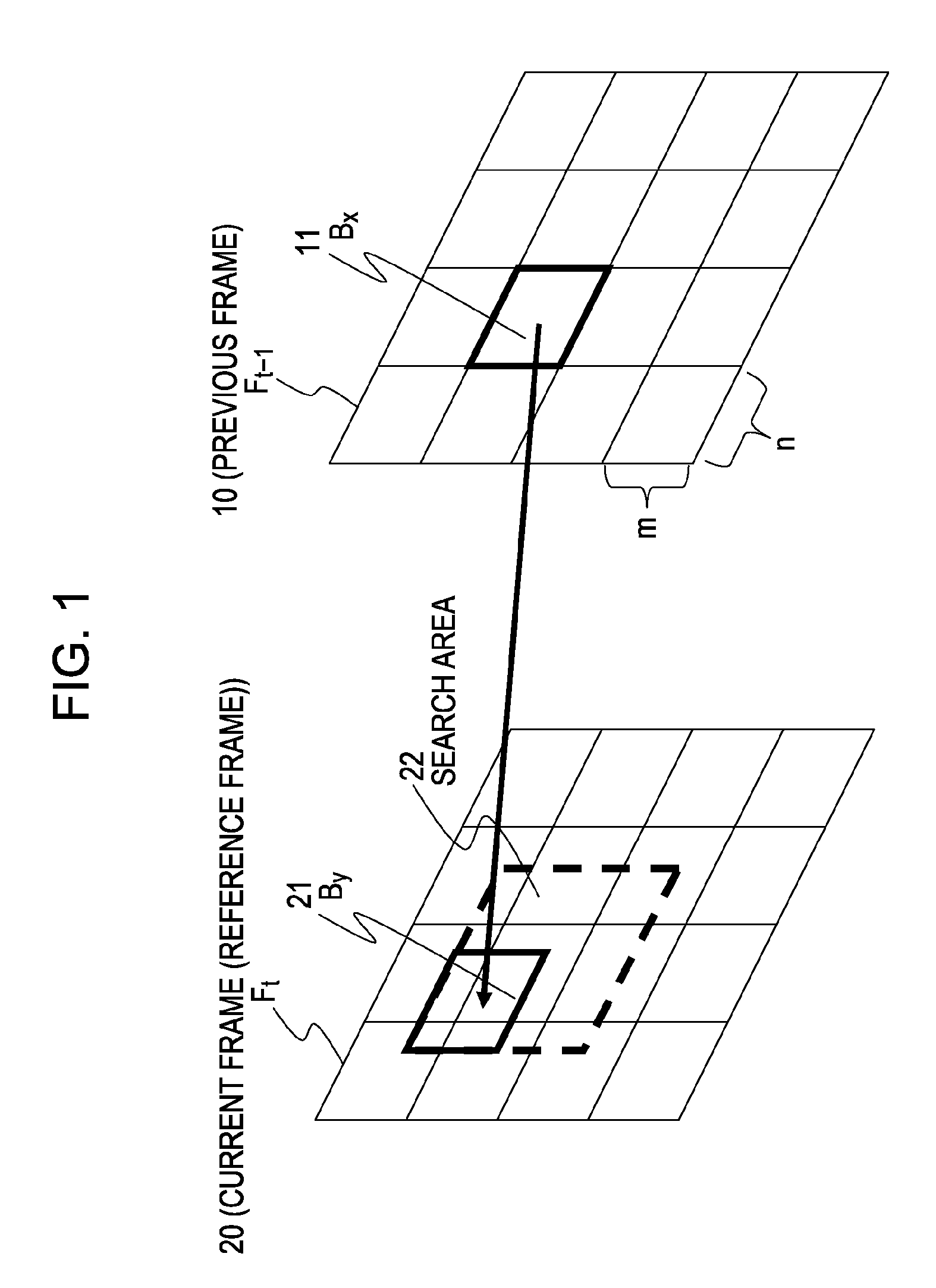

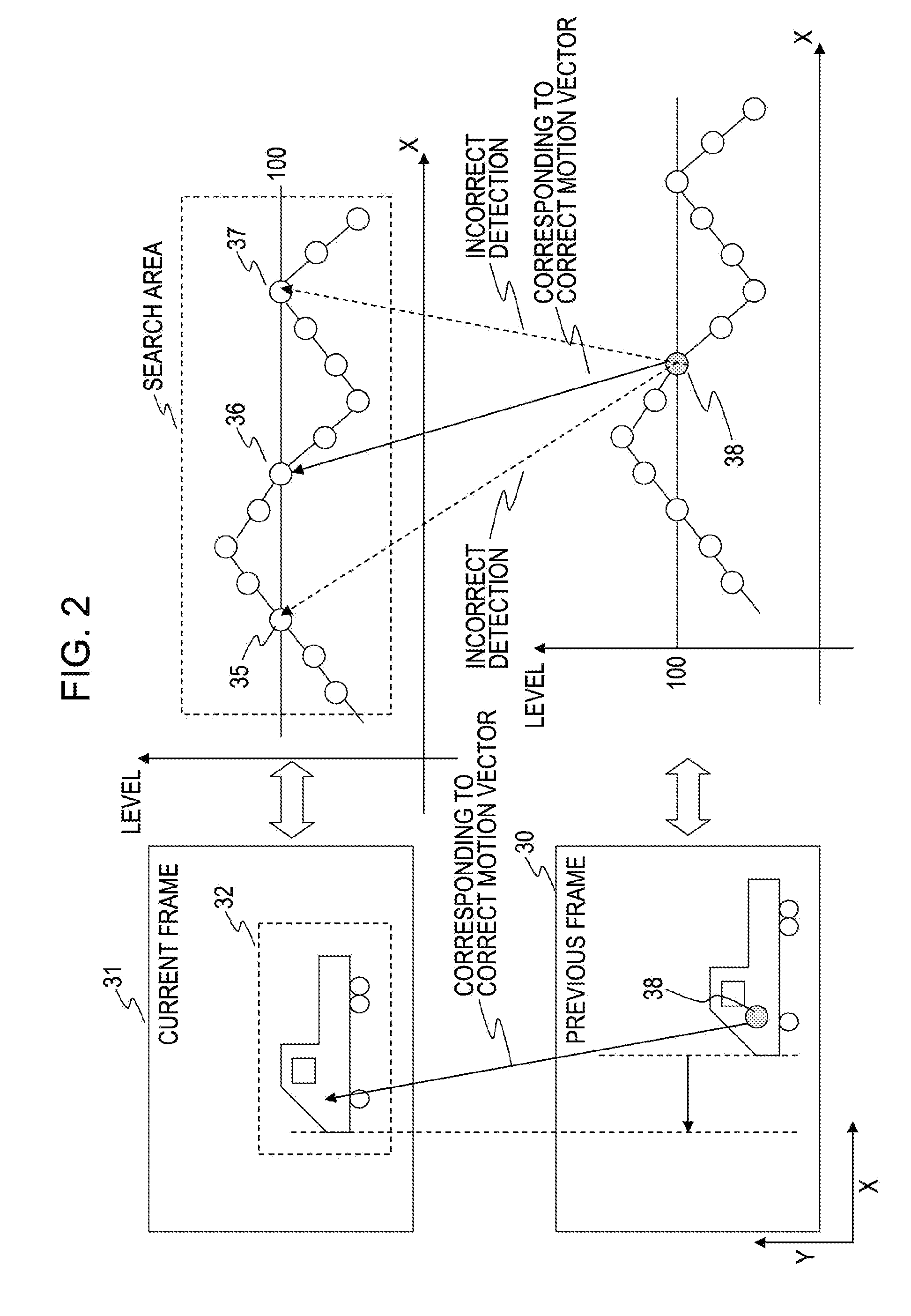

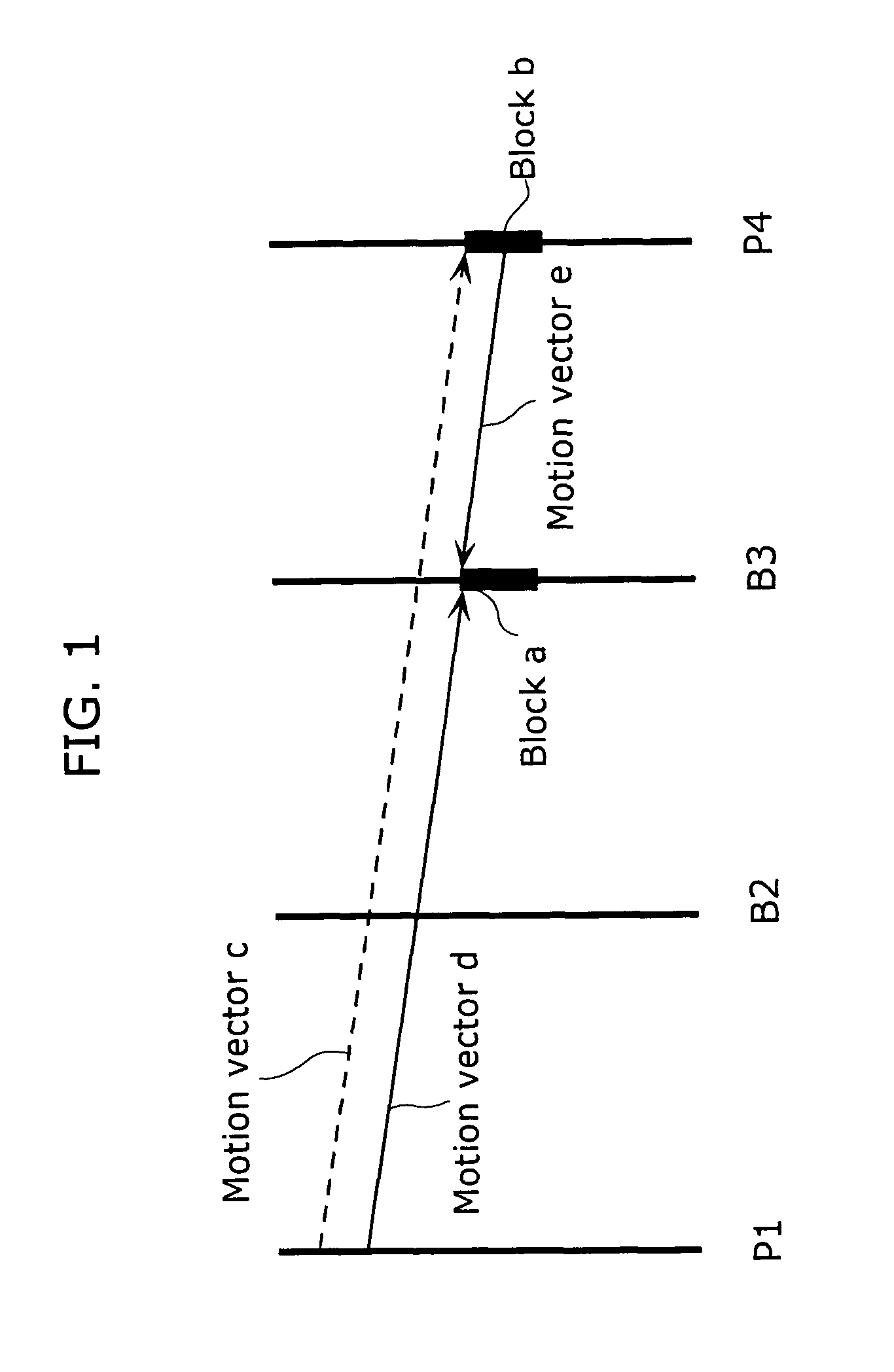

Motion-vector detecting device, motion-vector detecting method, and computer program

InactiveUS20060285596A1Accurate evaluation-value tableAccurate Motion DetectionColor television with pulse code modulationImage analysisPattern recognitionRelevant information

A device and method that serve to generate an accurate evaluation-value table and to detect a correct motion vector are provided. A weight coefficient W is calculated on the basis of correlation information of a representative-point pixel and flag-correlation information based on flag data corresponding to pixel-value difference data between a subject pixel and a pixel in a neighboring region of the subject pixel. A confidence index is generated on the basis of the weight coefficient W calculated and an activity A as an index of complexity of image data, or a confidence index is generated on the basis of similarity of motion between the representative point and a pixel neighboring the representative point, and an evaluation value corresponding to the confidence index is accumulated to generate an evaluation-value table. Furthermore, correlation is checked on the basis of positions or pixel values of feature pixels neighboring the subject pixel to determine a motion vector.

Owner:SONY CORP

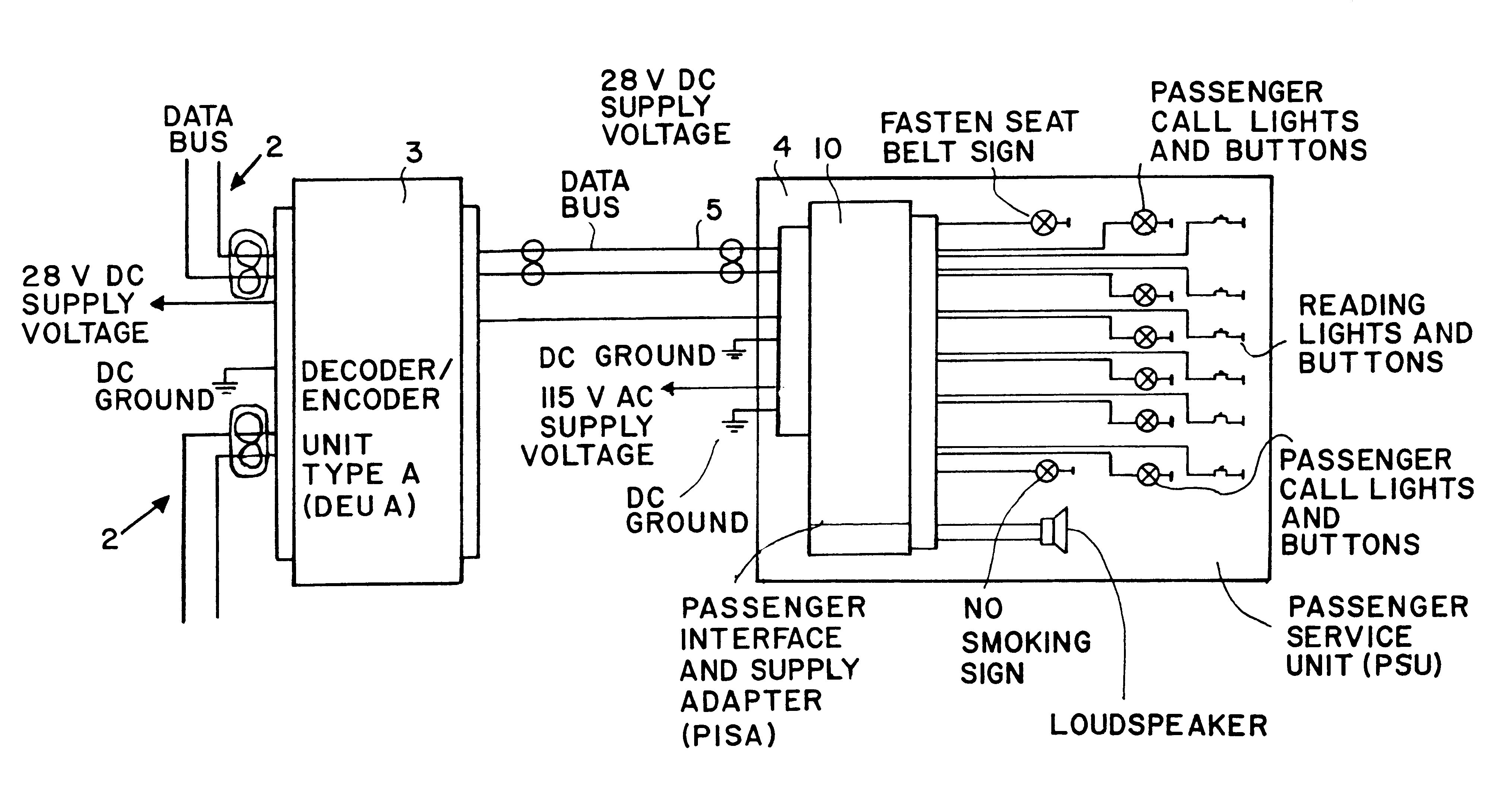

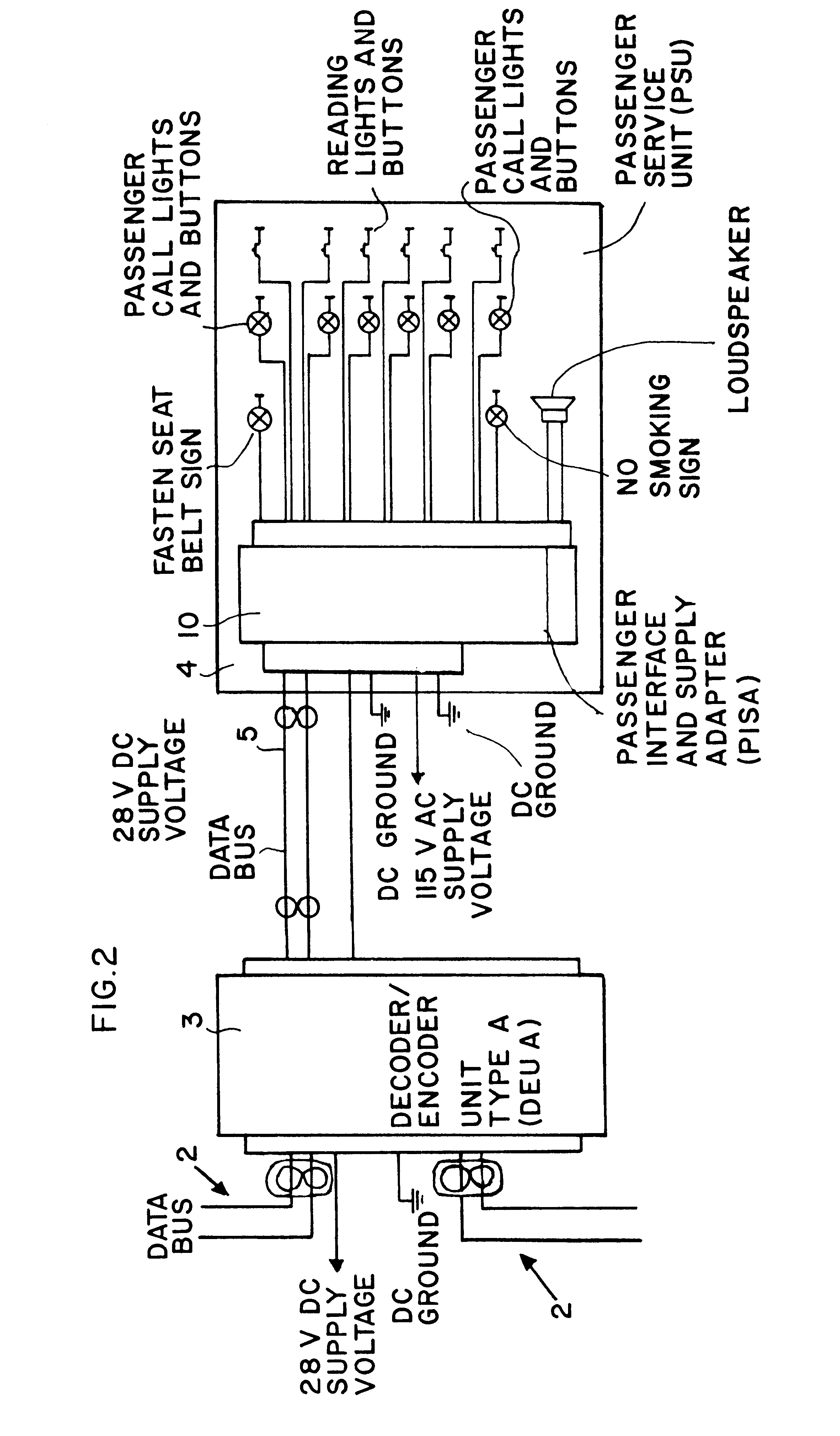

Passenger service unit and an aircraft cabin systems control with such service units

InactiveUS6393343B1Relieve and reduce operation and storageReduce wiring requirementDigital data processing detailsAir-treatment apparatus arrangementsFlight vehicleLighting system

Owner:AIRBUS OPERATIONS GMBH

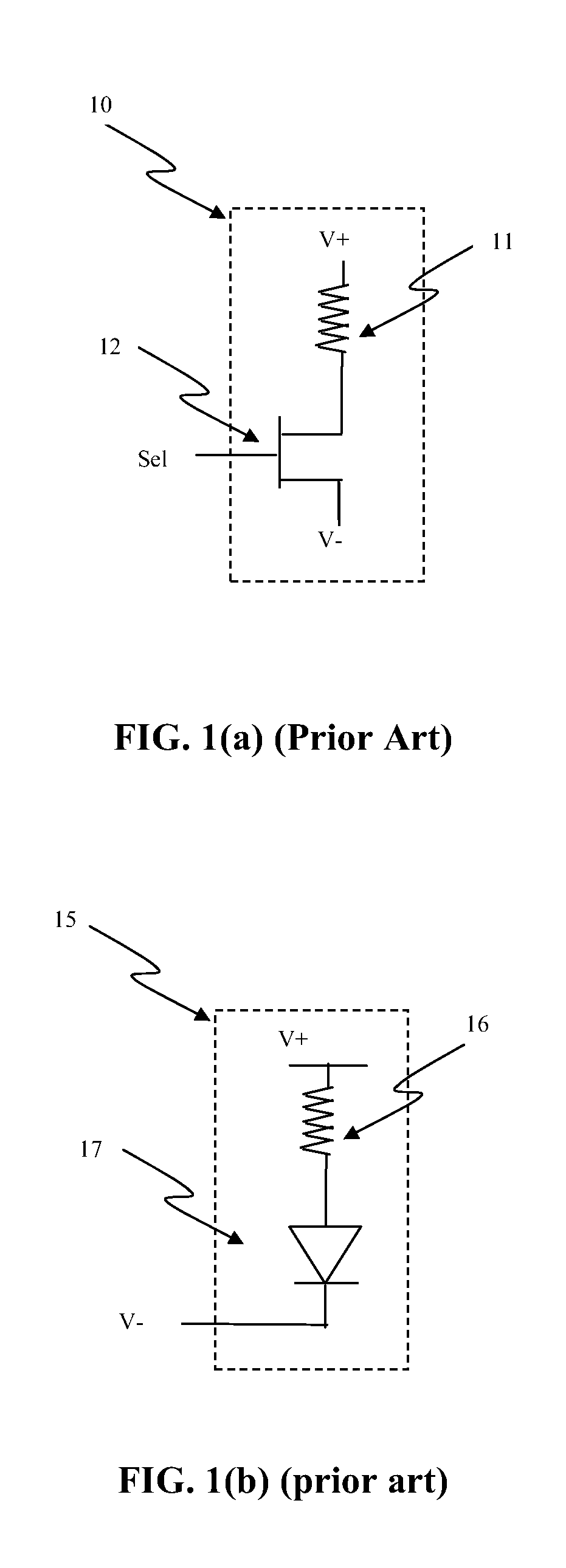

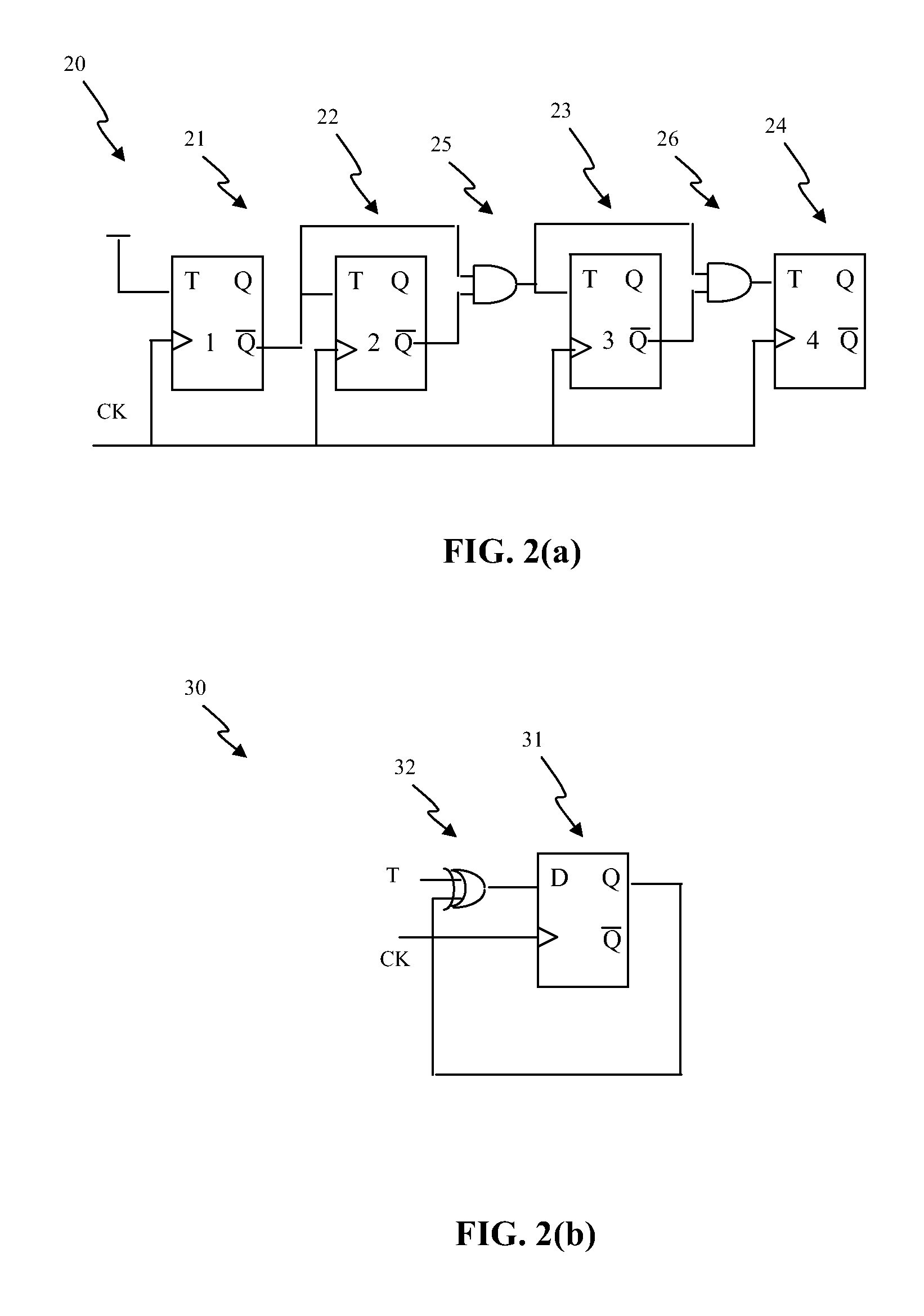

Circuit and System of a Low Density One-Time Programmable Memory

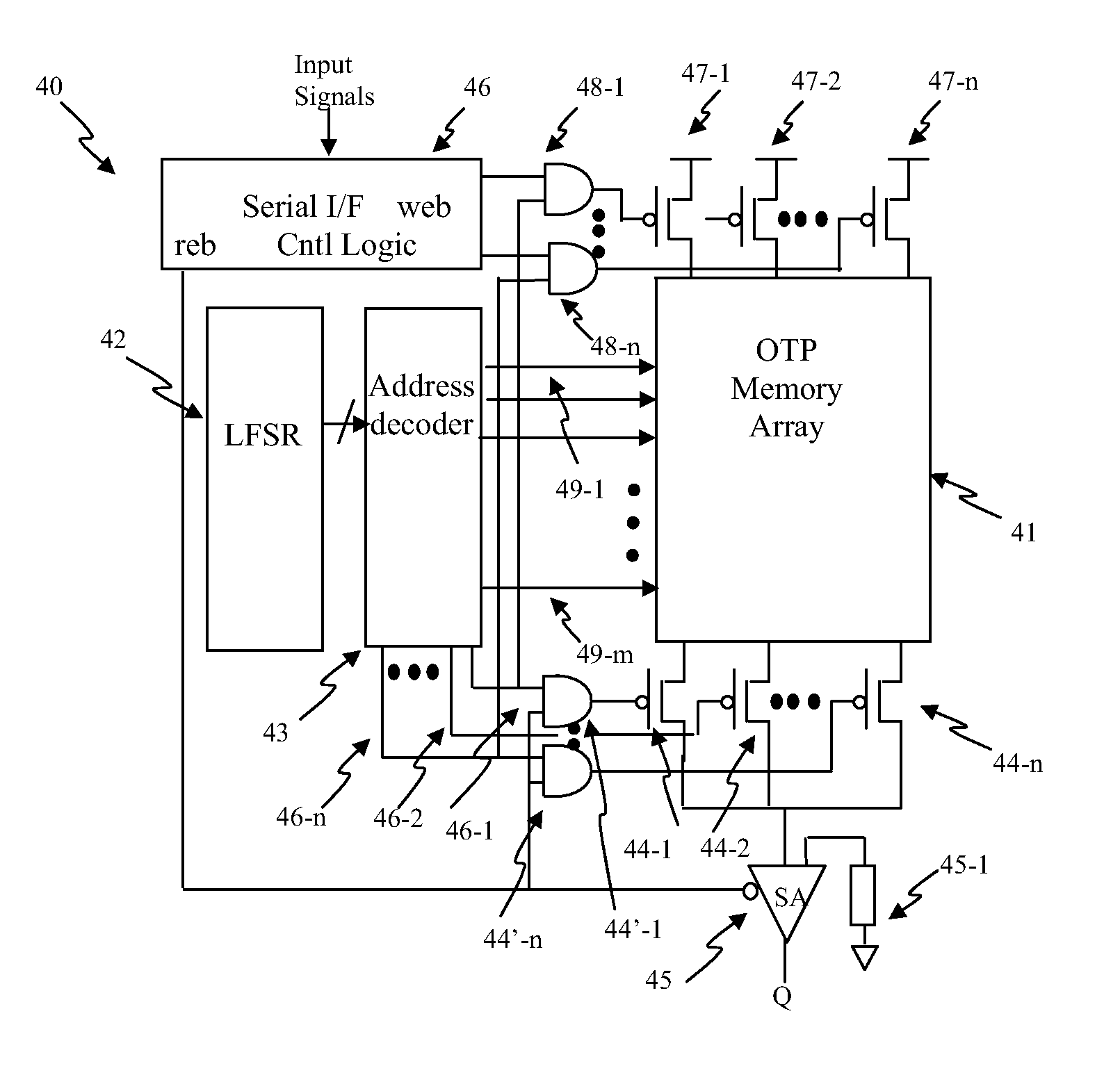

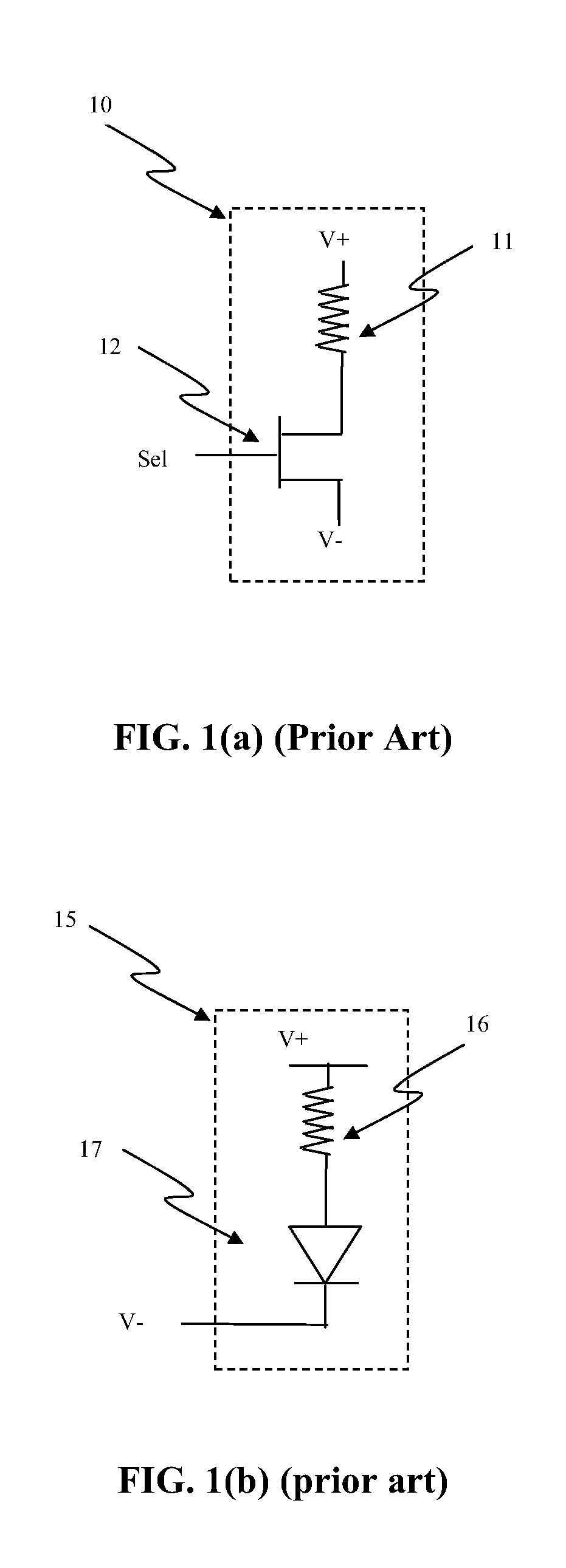

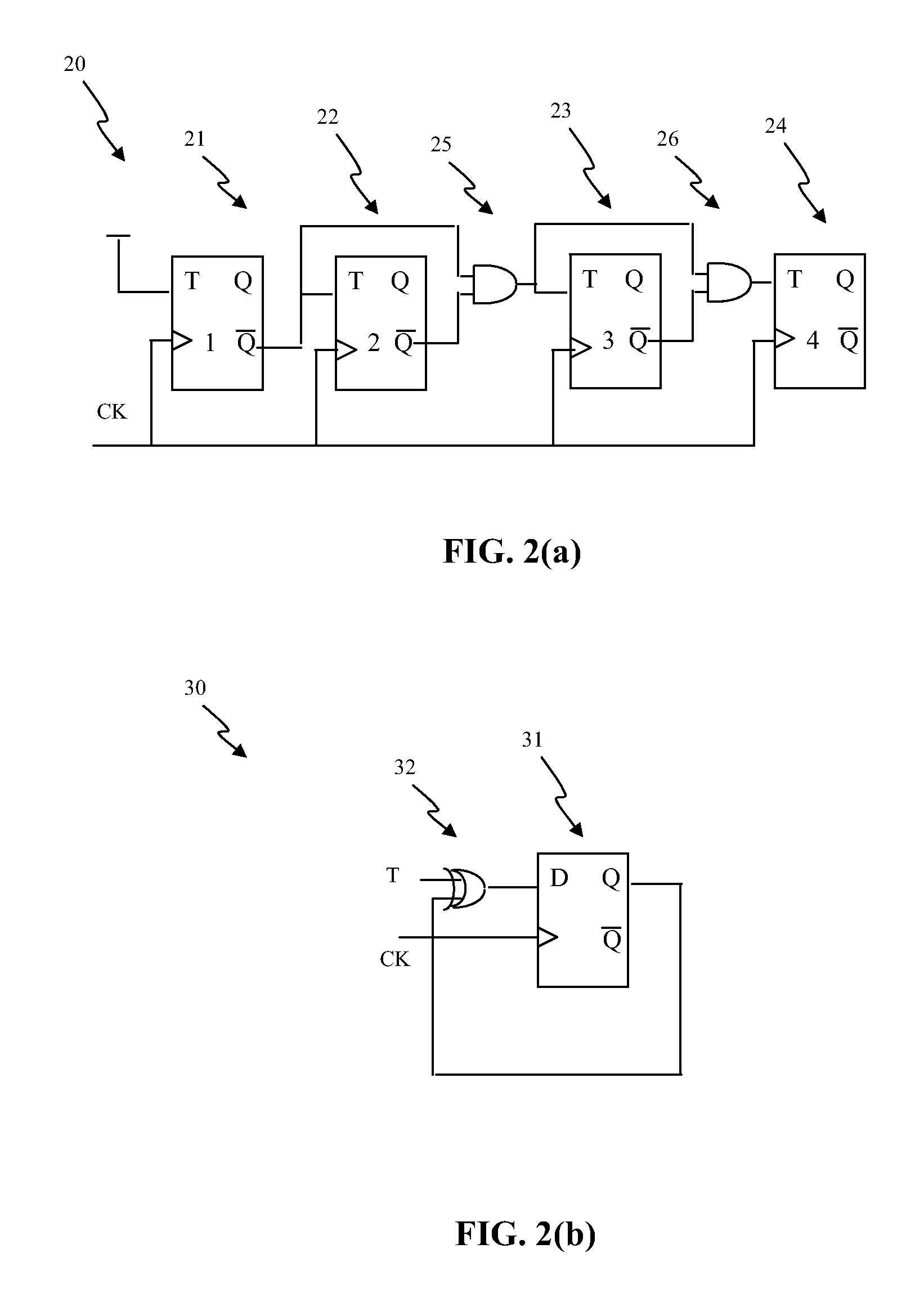

InactiveUS20130201745A1Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesAddress generatorHemt circuits

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

System and method for creating target byte code

InactiveUS7707547B2Efficient mappingSmaller and faster byte code of a second typeBinary to binaryDigital data processing detailsData elementByte

Owner:APPCELERATOR

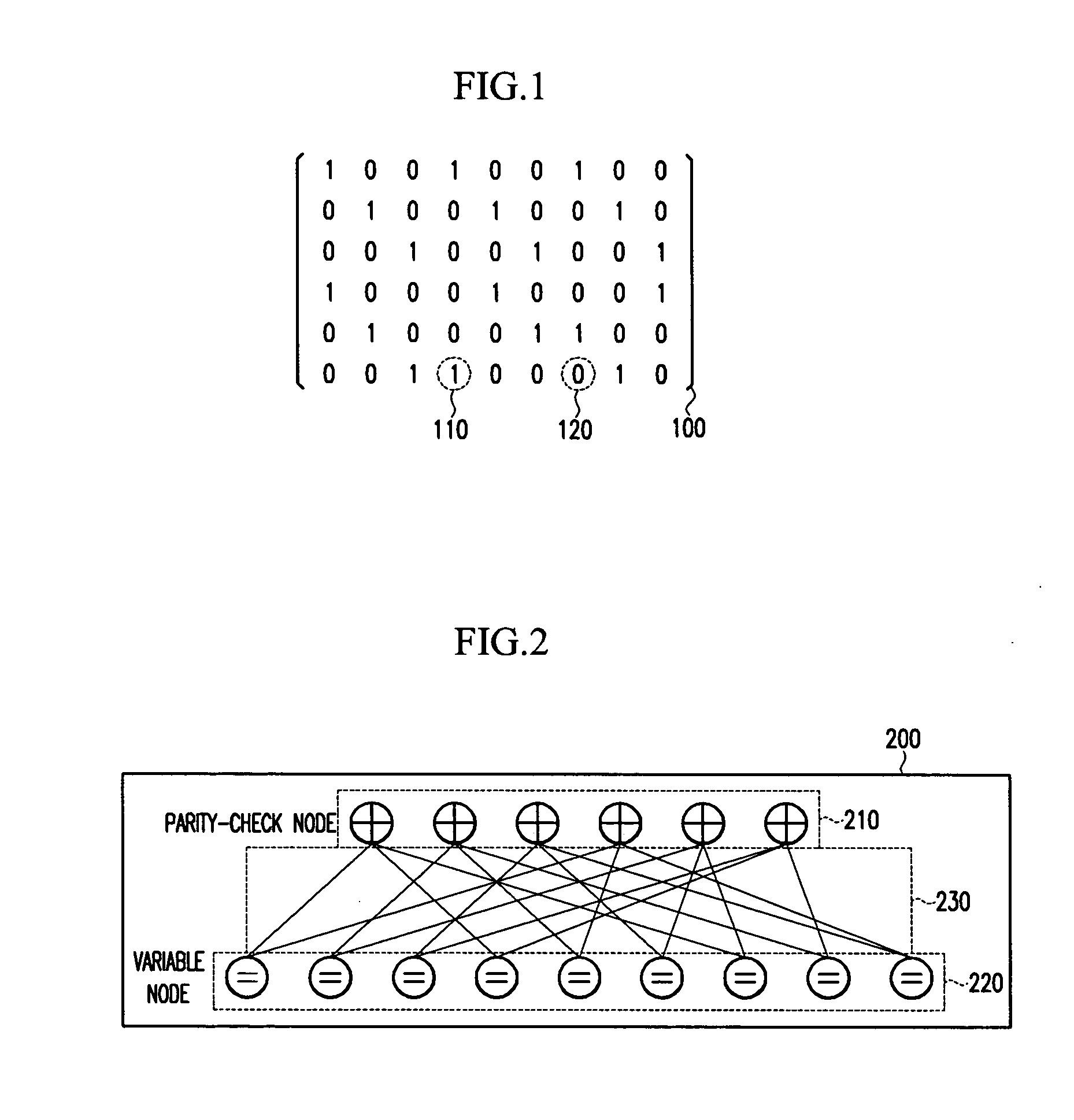

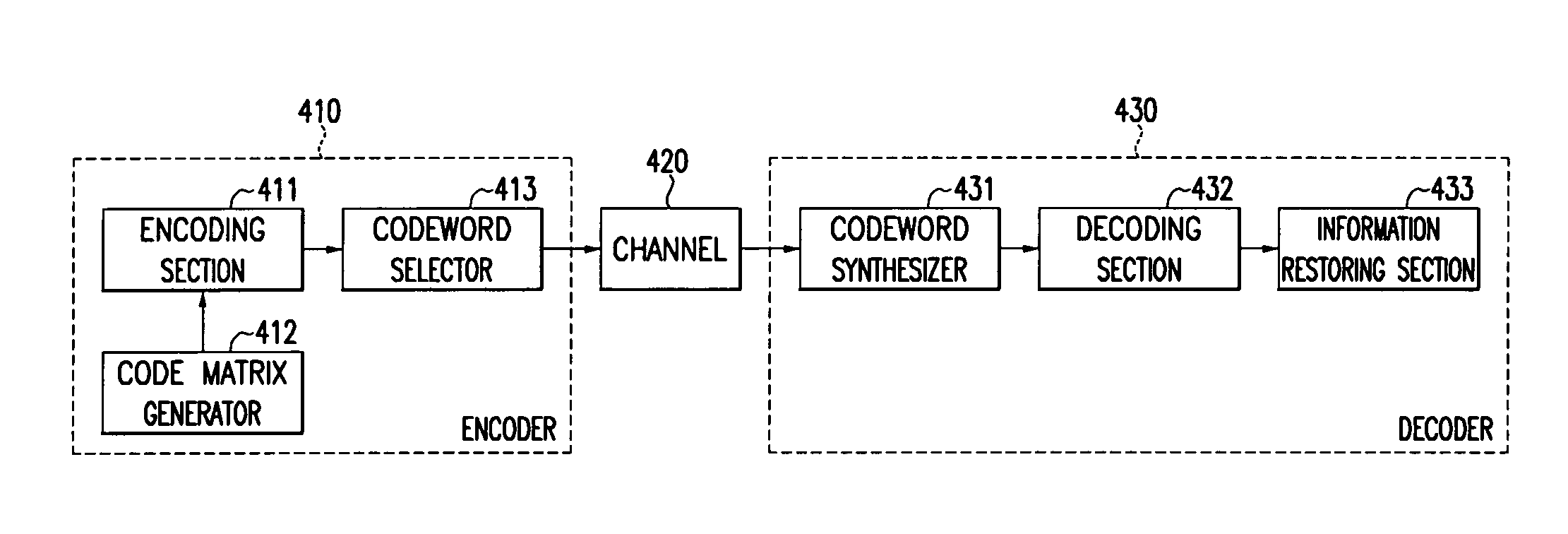

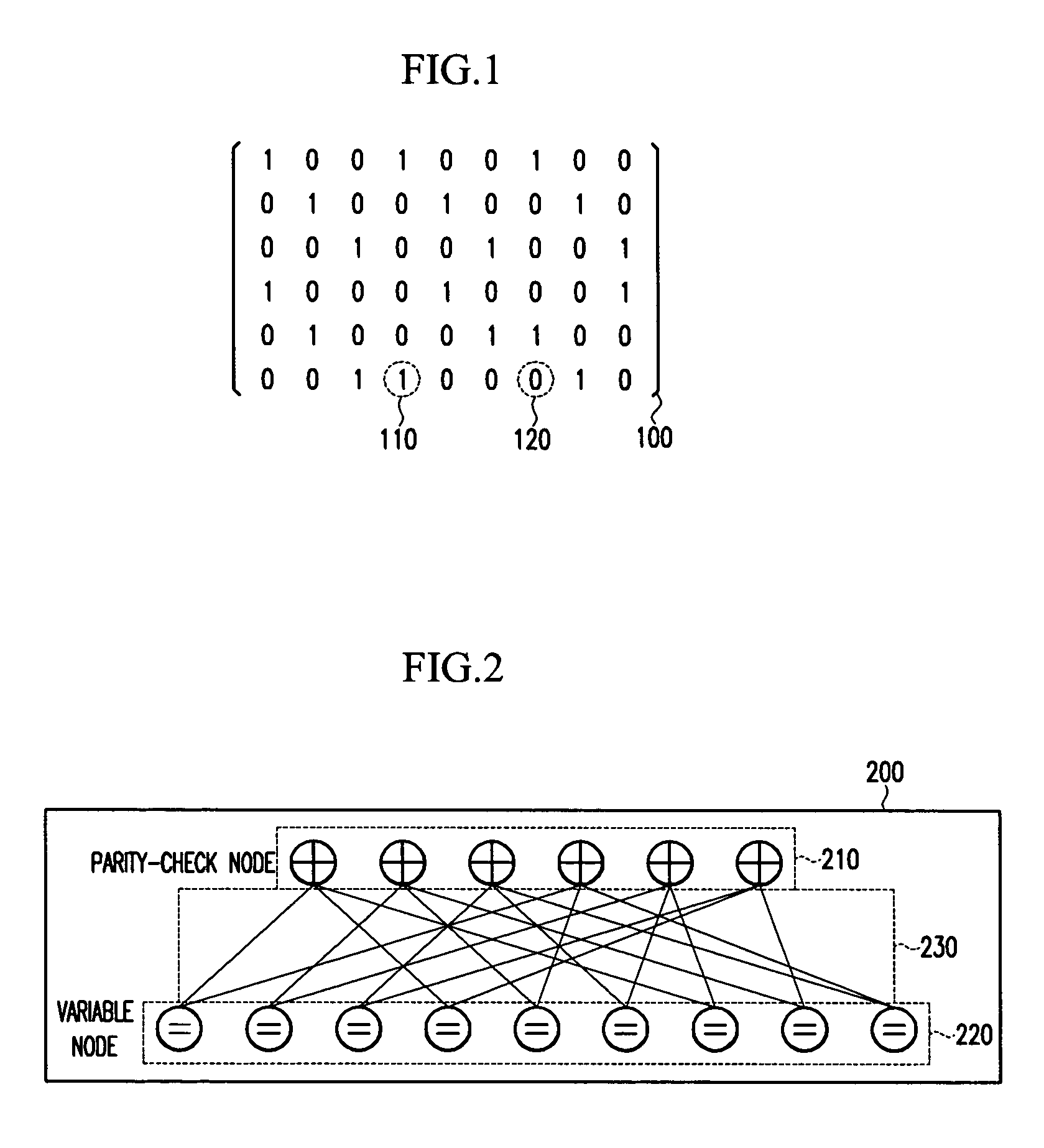

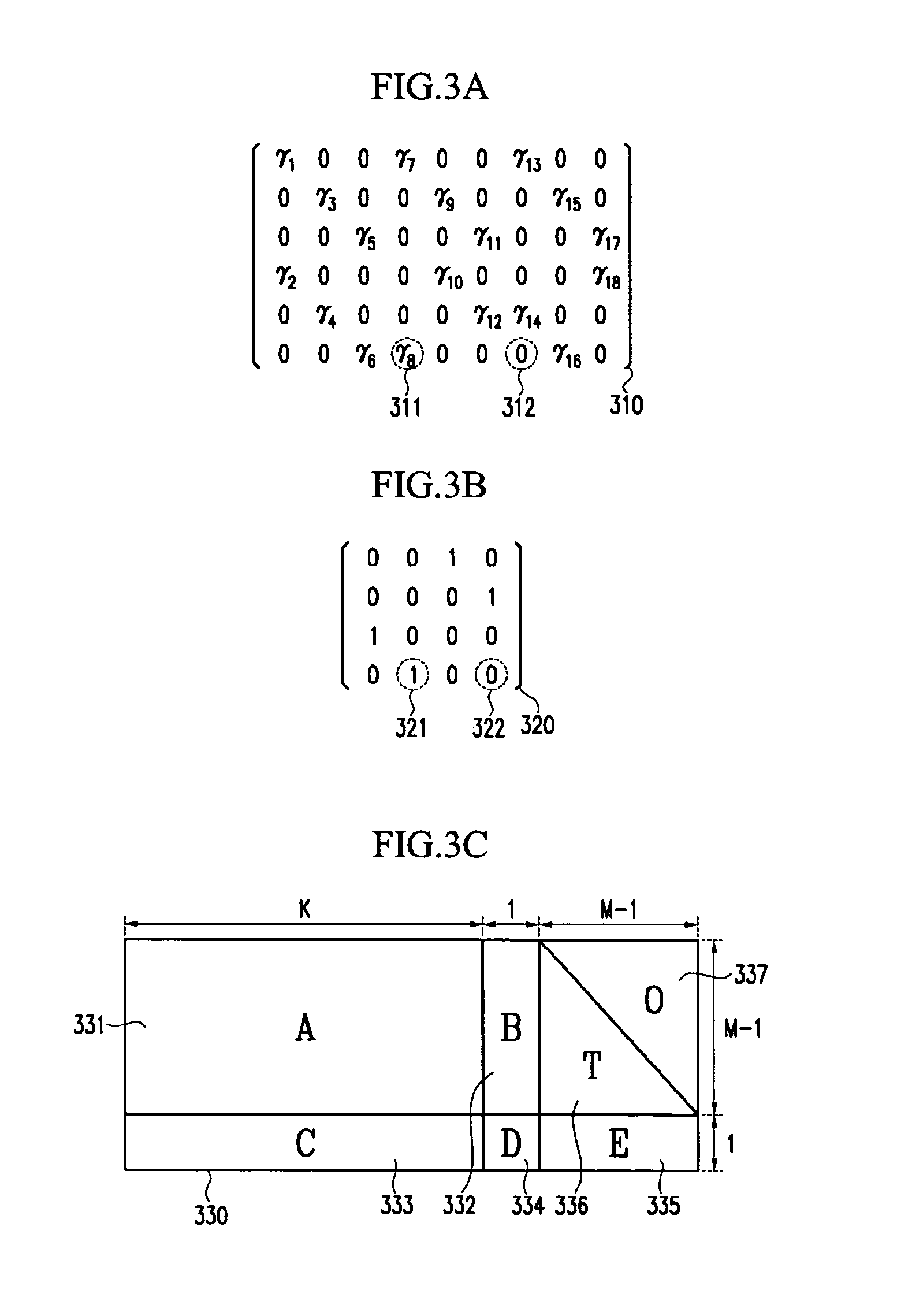

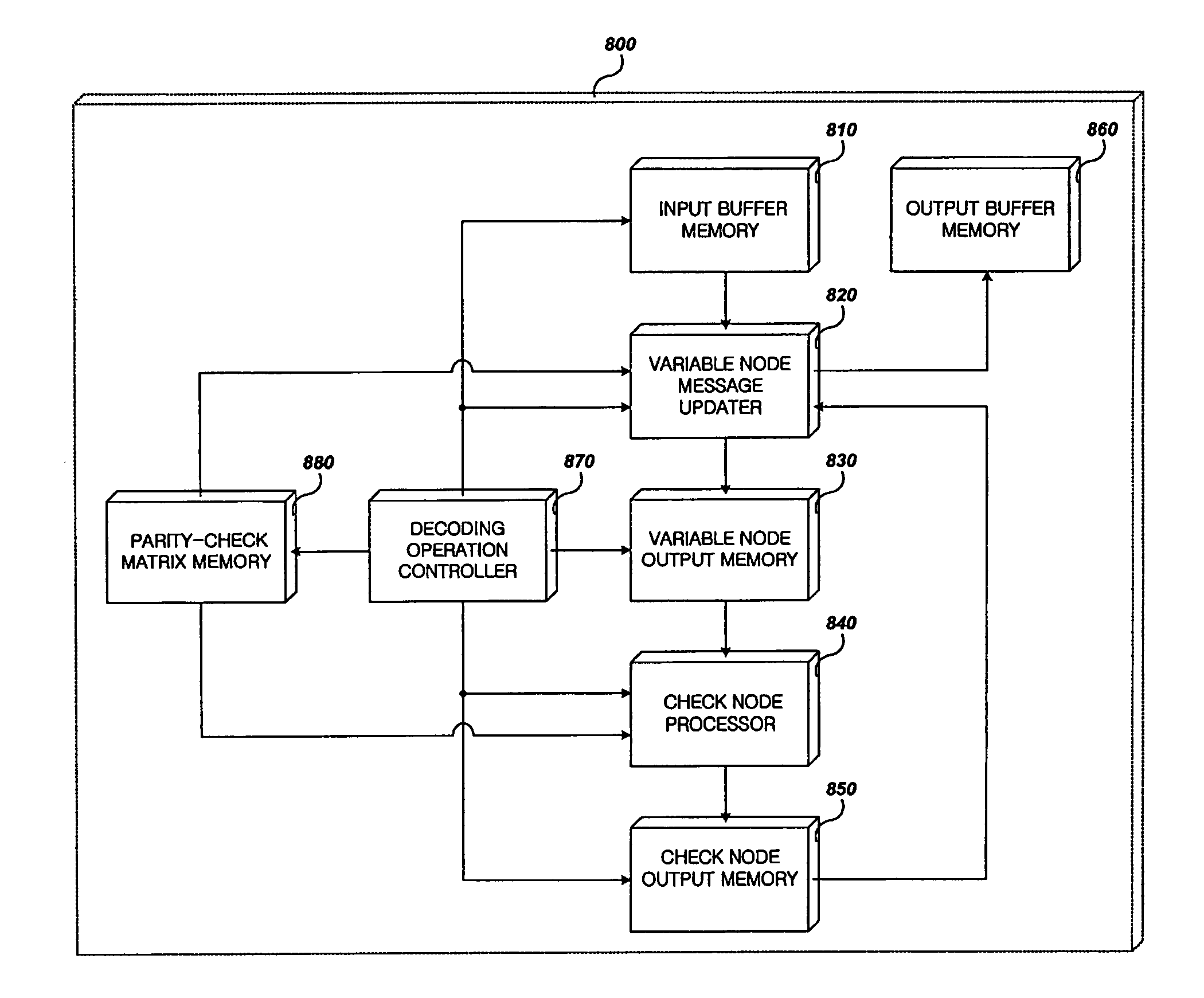

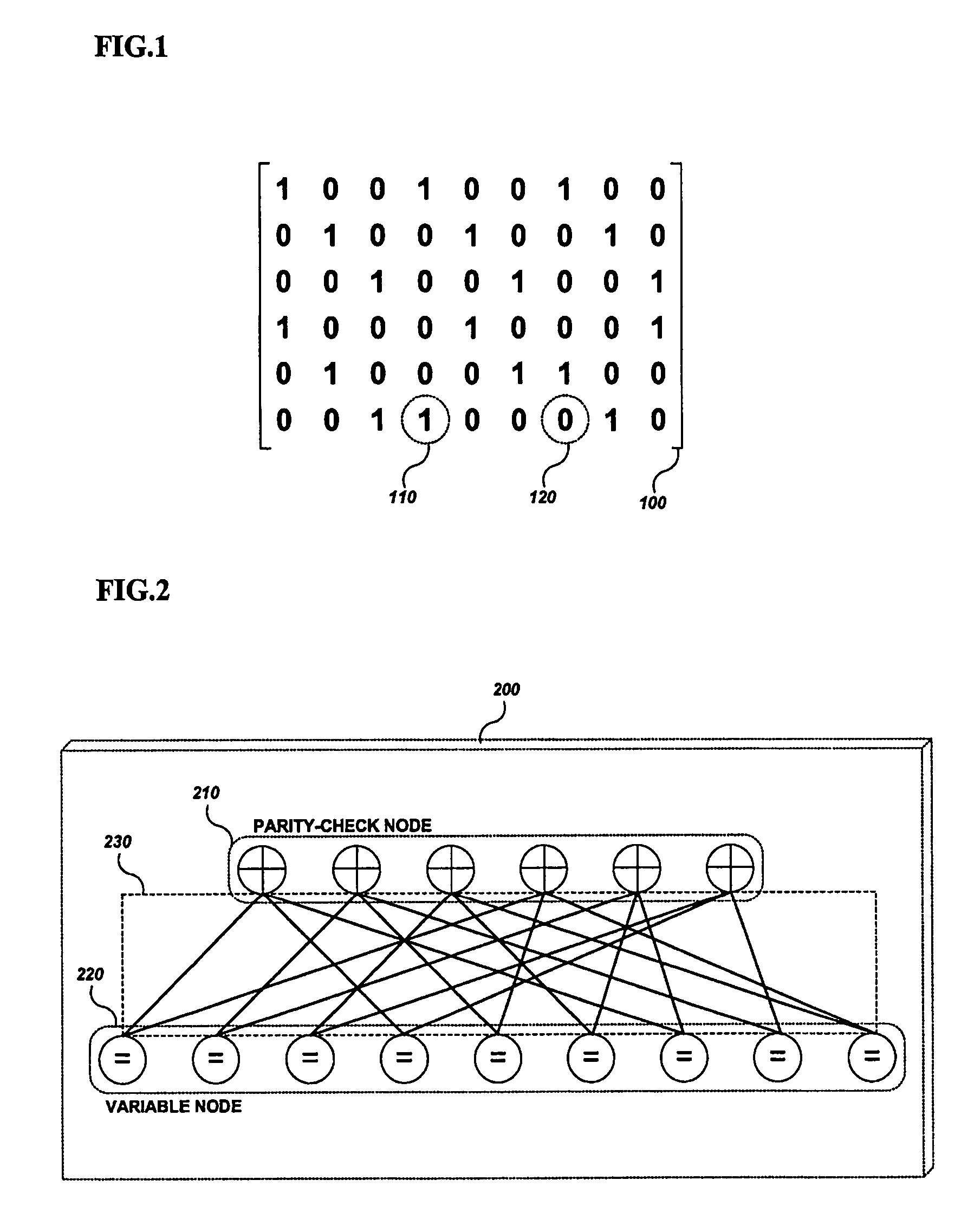

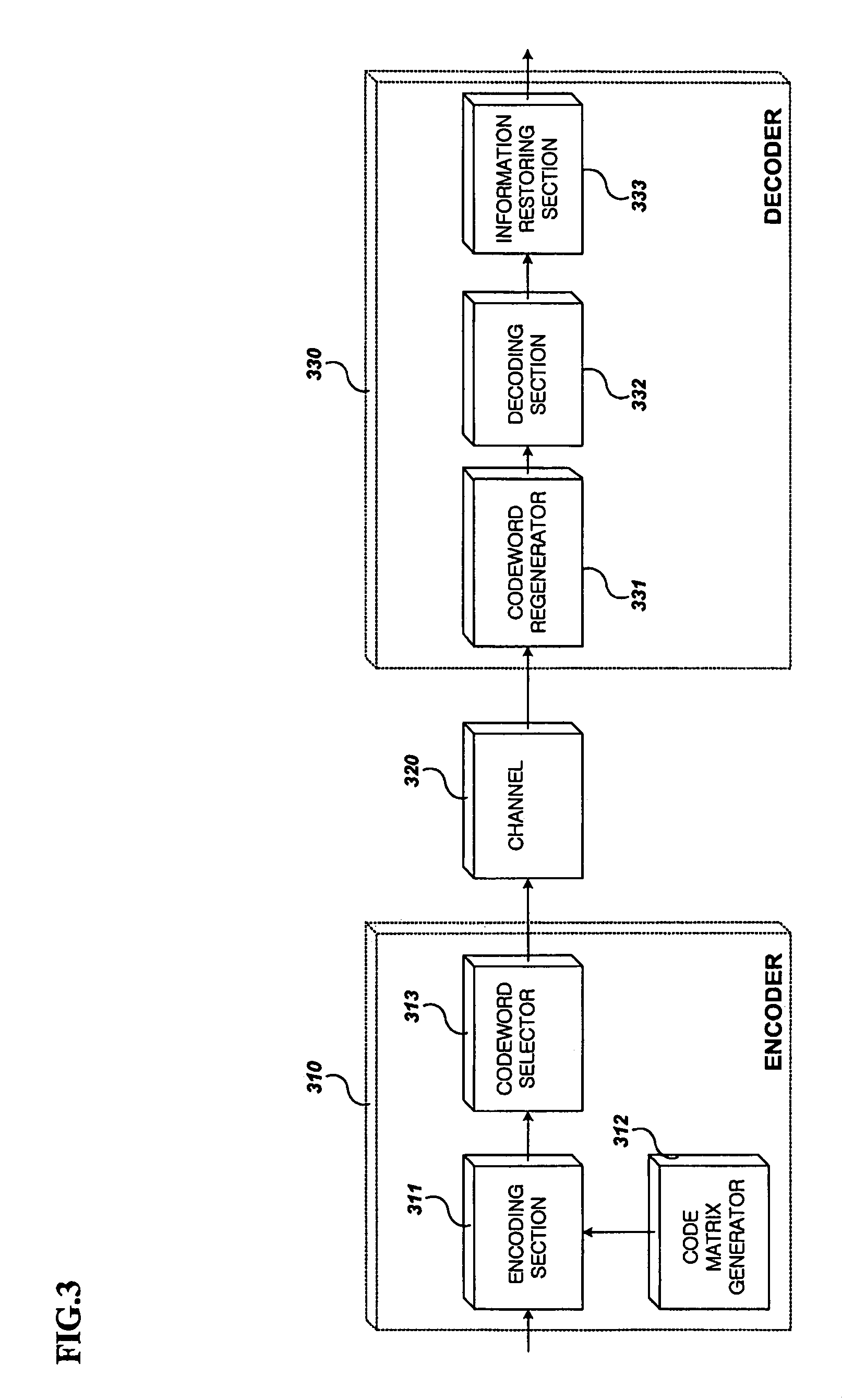

Apparatus for encoding and decoding of low-density parity-check codes, and method thereof

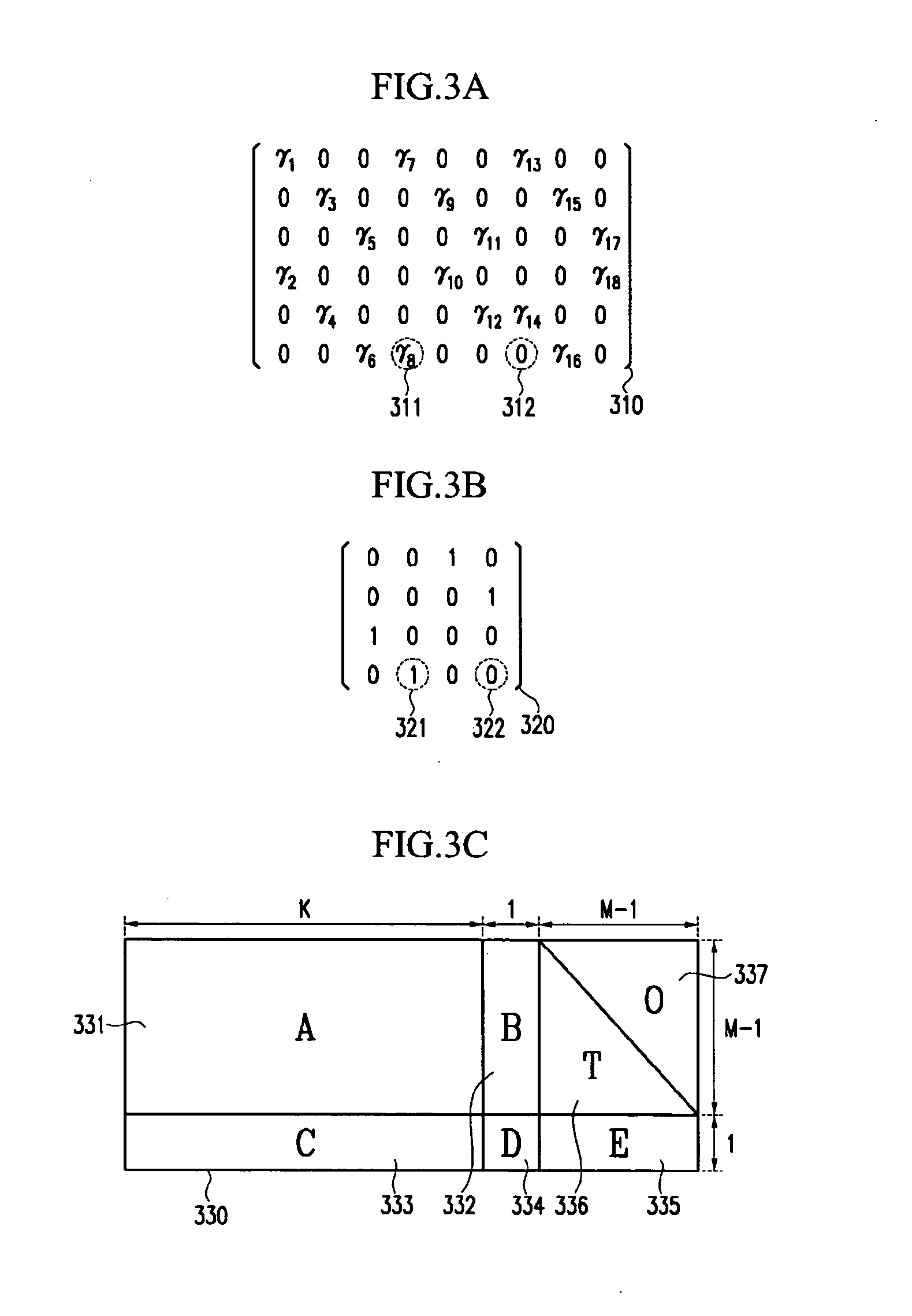

ActiveUS20050149840A1Reduce memory sizeHigh-speed and simple hardwareError detection/correctionError correction/detection using multiple parity bitsTanner graphAlgorithm

An LDPC code encoding apparatus includes: a code matrix generator for generating and transmitting a parity-check matrix comprising a combination of square matrices having a unique value on each row and column thereof; an encoding means encoding block LDPC codes according to the parity-check matrix received from the code matrix generator; and a codeword selector for puncturing the encoded result of the encoding means to generate an LDPC codeword. The code matrix generator divides an information word to be encoded into block matrices having a predetermined length to generate a vector information word. The encoding means encodes the block LDPC codes using the parity-check matrix divided into the block matrices and a Tanner graph divided into smaller graphs in correspondence to the parity-check matrix.

Owner:ELECTRONICS & TELECOMM RES INST

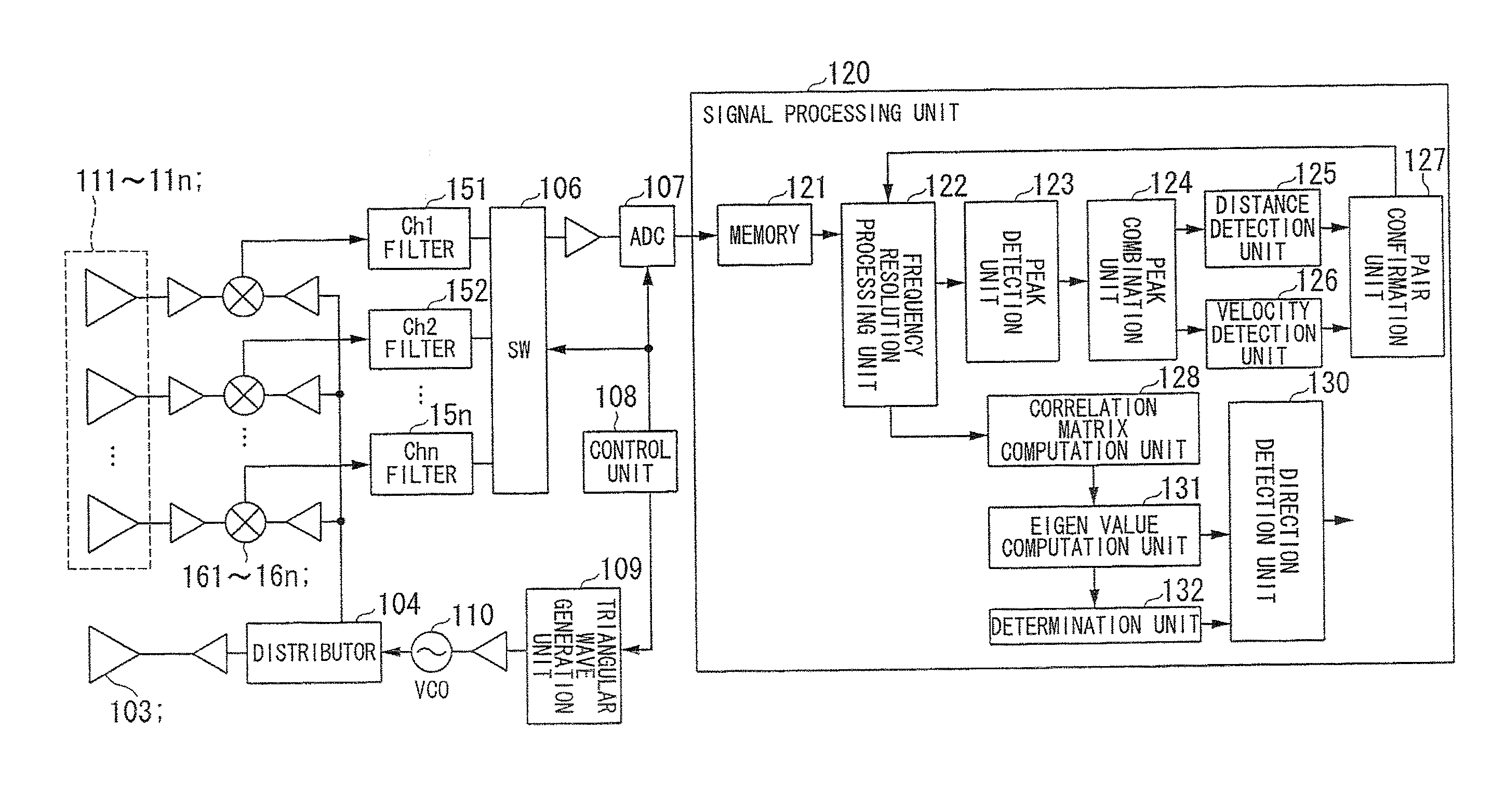

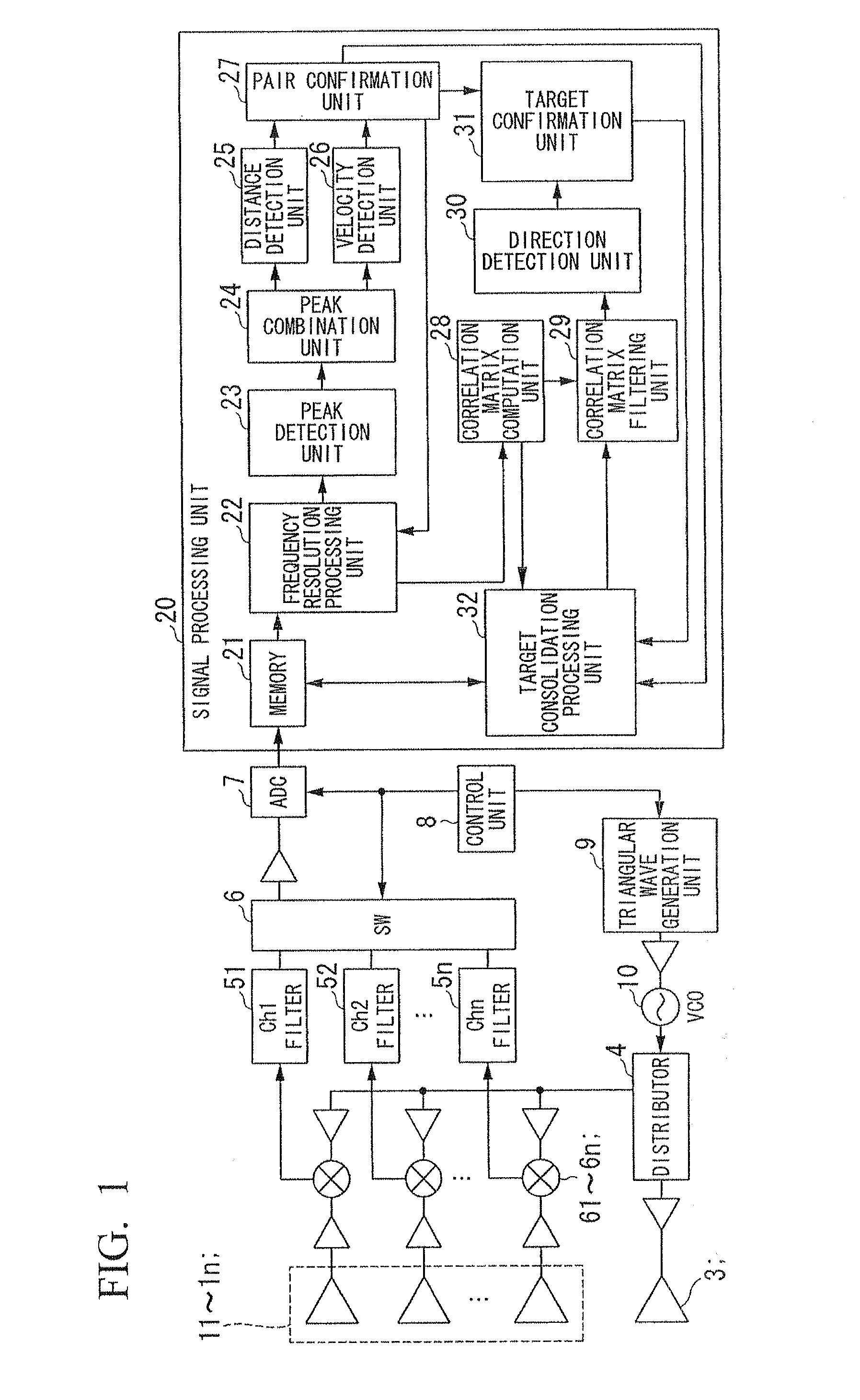

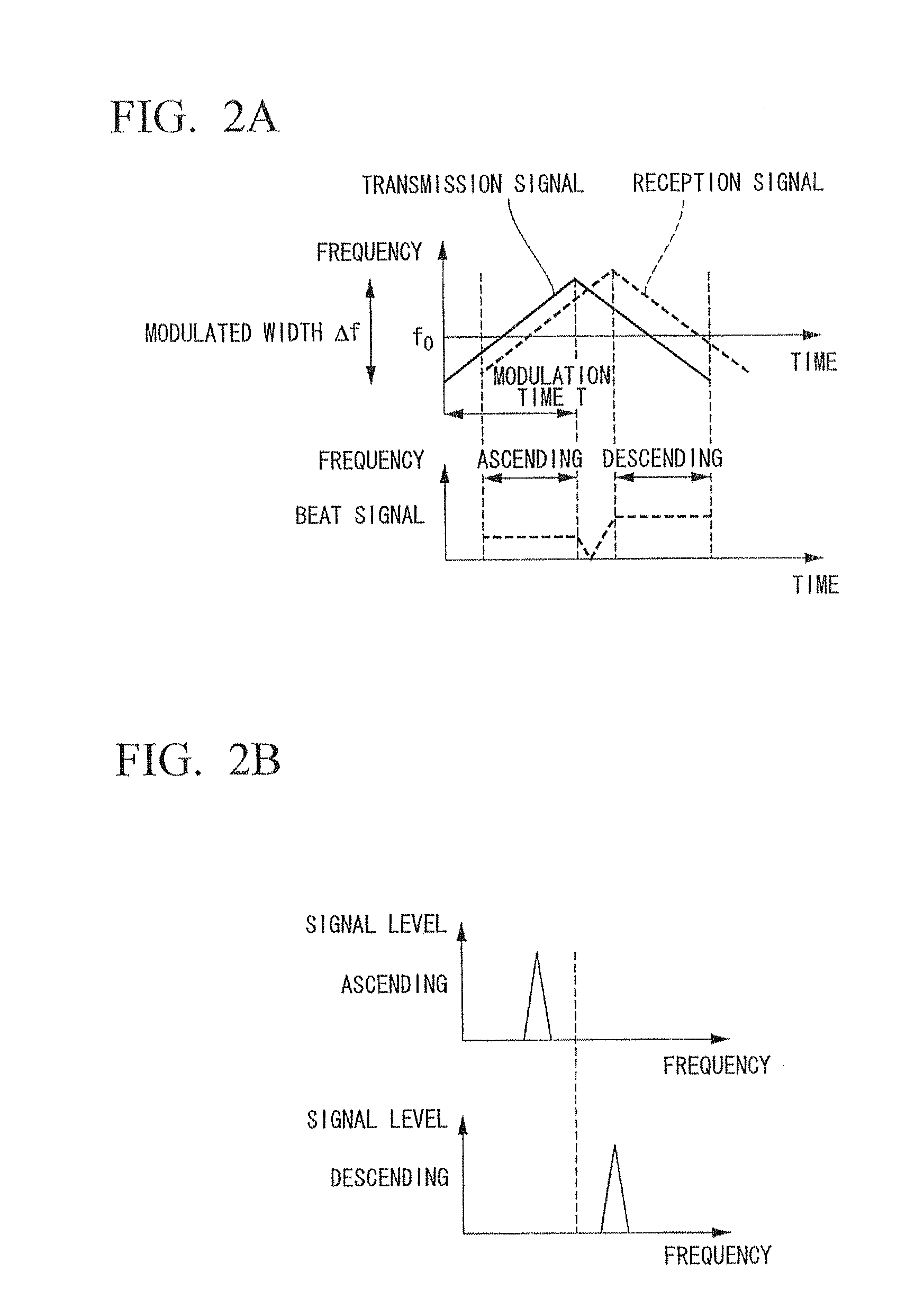

Electronic scanning type radar device, estimation method of direction of reception wave, and program estimating direction of reception wave

ActiveUS20100271254A1Easy to identifyEnsure correct executionMulti-channel direction-finding systems using radio wavesRadio wave reradiation/reflectionEstimation methodsImage resolution

An electronic scanning type radar device mounted on a moving body includes: a transmission unit transmitting a transmission wave; a reception unit comprising a plurality of antennas receiving a reflection wave of the transmission wave from a target; a beat signal generation unit generating a beat signal from the transmission wave and the reflection wave; a frequency resolution processing unit frequency computing a complex number data; a target detection unit detecting an existence of the target; a correlation matrix computation unit computing a correlation matrix from each of a complex number data of a detected beat frequency; a target consolidation processing unit linking the target in a present detection cycle and a past detection cycle; a correlation matrix filtering unit generating an averaged correlation matrix by weighted averaging a correlation matrix of a target in the present detection cycle and a correlation matrix of a related target in the past detection cycle; and a direction detection unit computing an arrival direction of the reflection wave based on the averaged correlation matrix.

Owner:HONDA ELESYS OF YBP HI TECH CENT

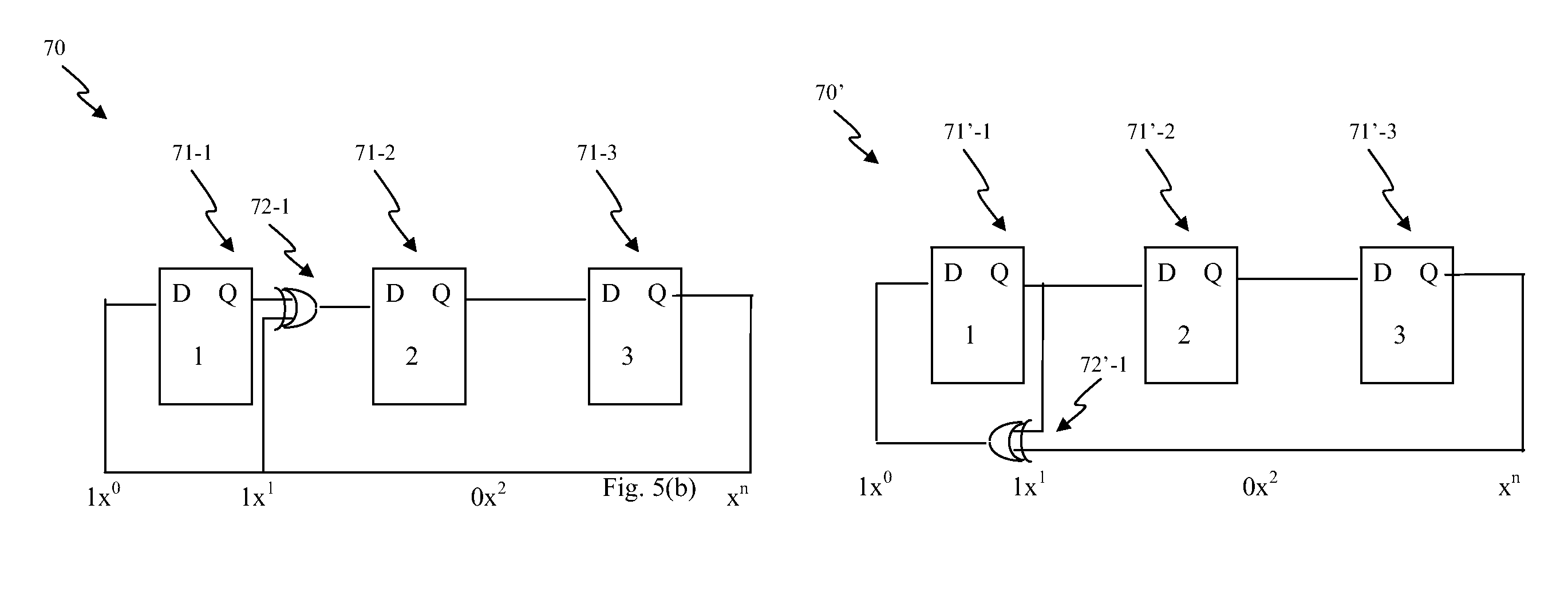

Circuit and system of a low density one-time programmable memory

InactiveUS8861249B2Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesIp addressAddress generator

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

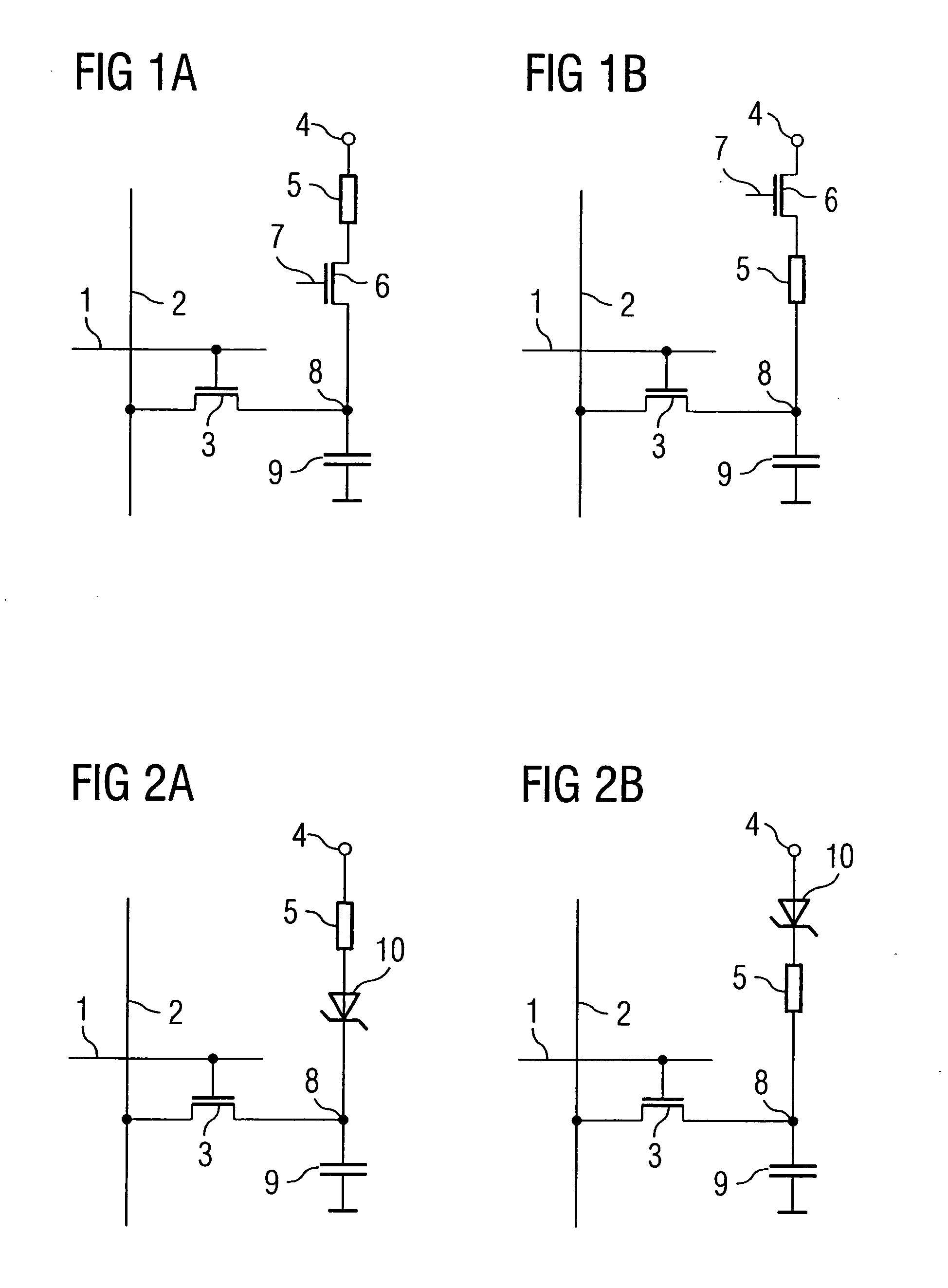

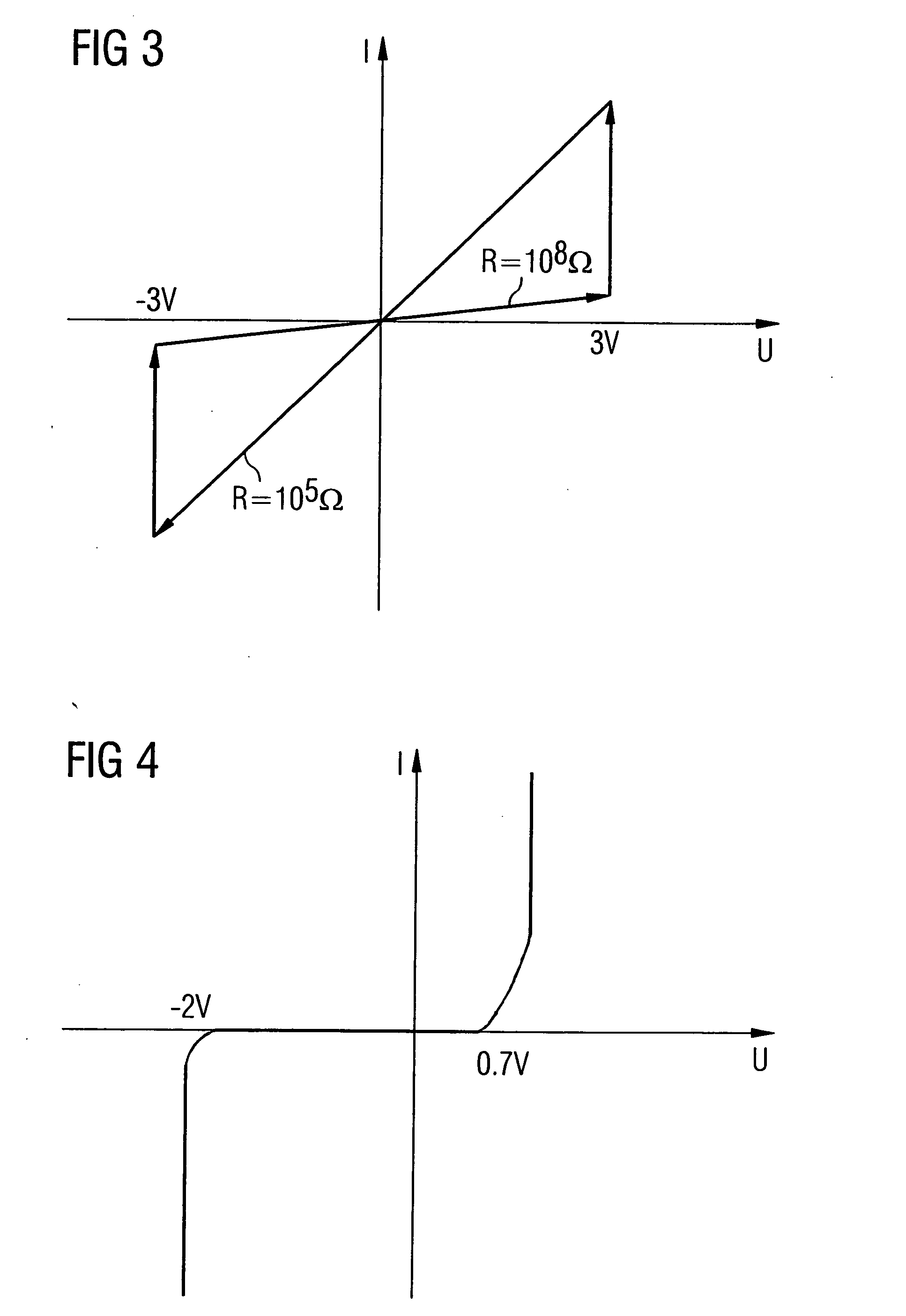

Semiconductor memory with volatile and non-volatile memory cells

InactiveUS20060120138A1Easy to operateReduce the voltage valueNanoinformaticsSolid-state devicesDram memorySemiconductor

The present invention relates to a semiconductor memory with a volatile memory device, in particular a DRAM memory device, and with a non-volatile memory device. The volatile memory device is electrically coupled with the non-volatile memory device, and the non-volatile memory device has a polymer memory device adapted to be switched between two states of information.

Owner:INFINEON TECH AG

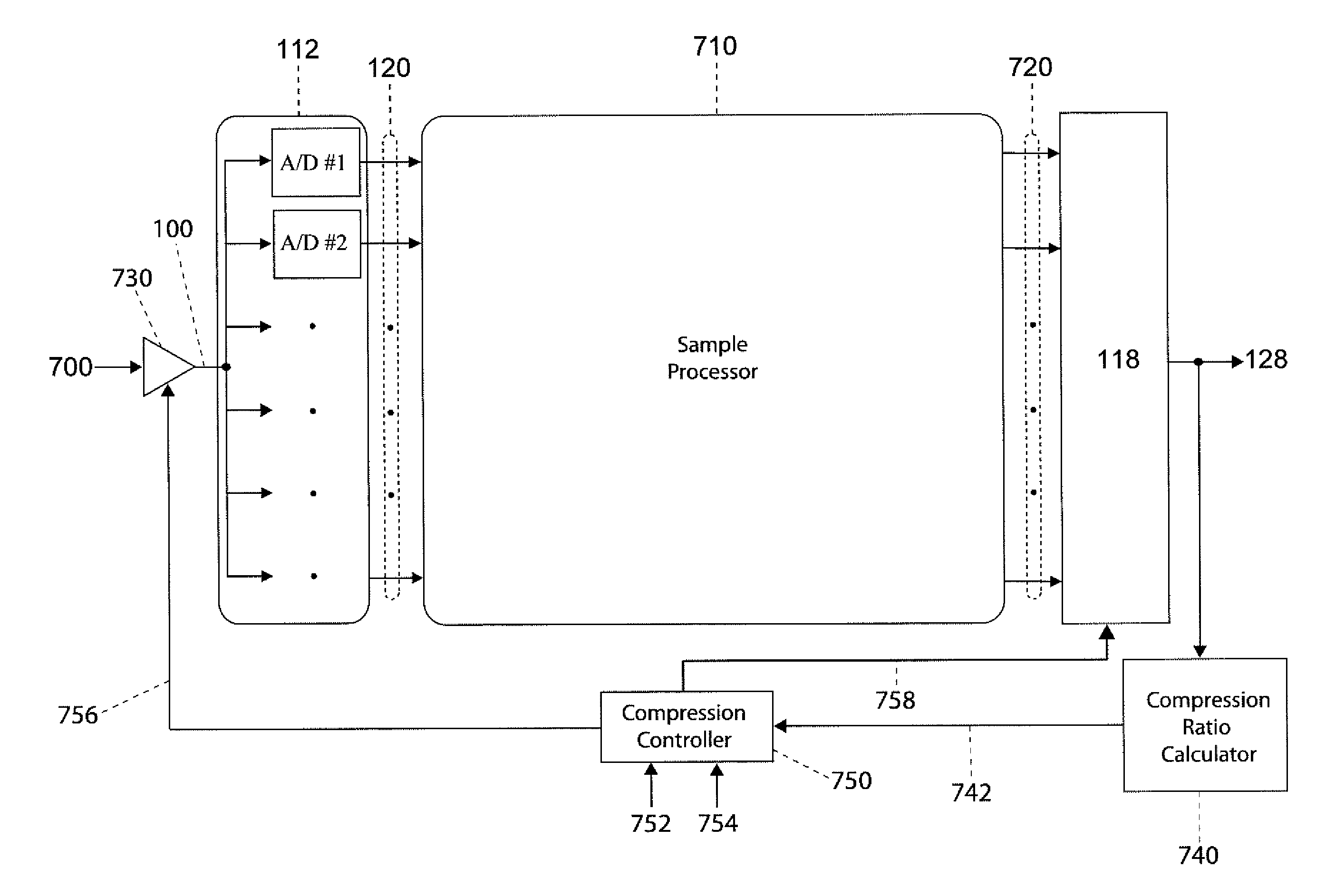

Enhanced Time-Interleaved A/D Conversion Using Compression

InactiveUS20080018502A1Increase the compression ratioDegrade signal qualityAnalogue/digital conversionBinary multiplierAnalog signal

Compression of signal samples output from a parallel, time-interleaved analog to digital converter (TIADC) for a baseband signal, includes calculating first or higher order differences of consecutive signal samples followed by lossless or lossy encoding of the difference samples to produce compressed samples. Compression of a TIADC output signal with a nonzero center frequency, includes calculating sums or differences of pairs of signal samples separated by an appropriate number of sampling intervals followed by lossless or lossy encoding. The sums or differences of the signal samples have lower magnitudes than the original samples, allowing more efficient compression. Lossy compression alternatives produce compressed data with a fixed bit rate or with a fixed quality in the decompressed samples. Alternatives for lossy compression include attenuating the analog signal before sampling by the TIADC, applying bit shifters or multipliers after sampling to reduce the magnitudes of the signal samples, and lossy encoding.

Owner:ALTERA CORP

System and method for creating target byte code

InactiveUS20060230070A1Improve developmentEfficient mappingBinary to binaryDigital data processing detailsSoftwareByte

A system and method for converting byte code of a first type into byte code of a second type. Byte code of a first type is received as input. The first byte code is converted into constituent byte code data elements that can comprise any logical unit or grouping of at least a portion of a software application. The first byte code data elements are mapped to data elements of a second byte code type. The second byte code data elements are assembled into a resulting second byte code.

Owner:APPCELERATOR

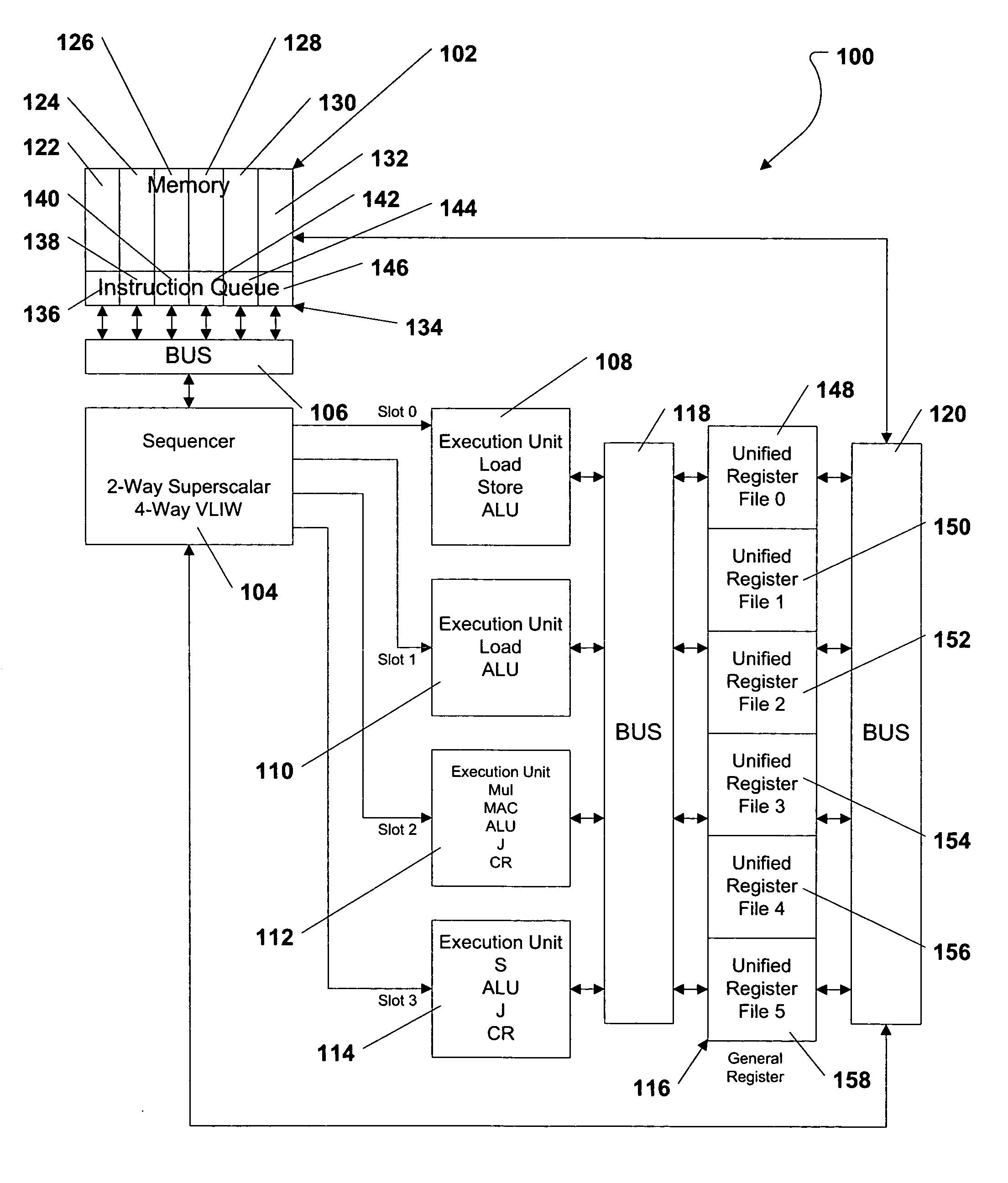

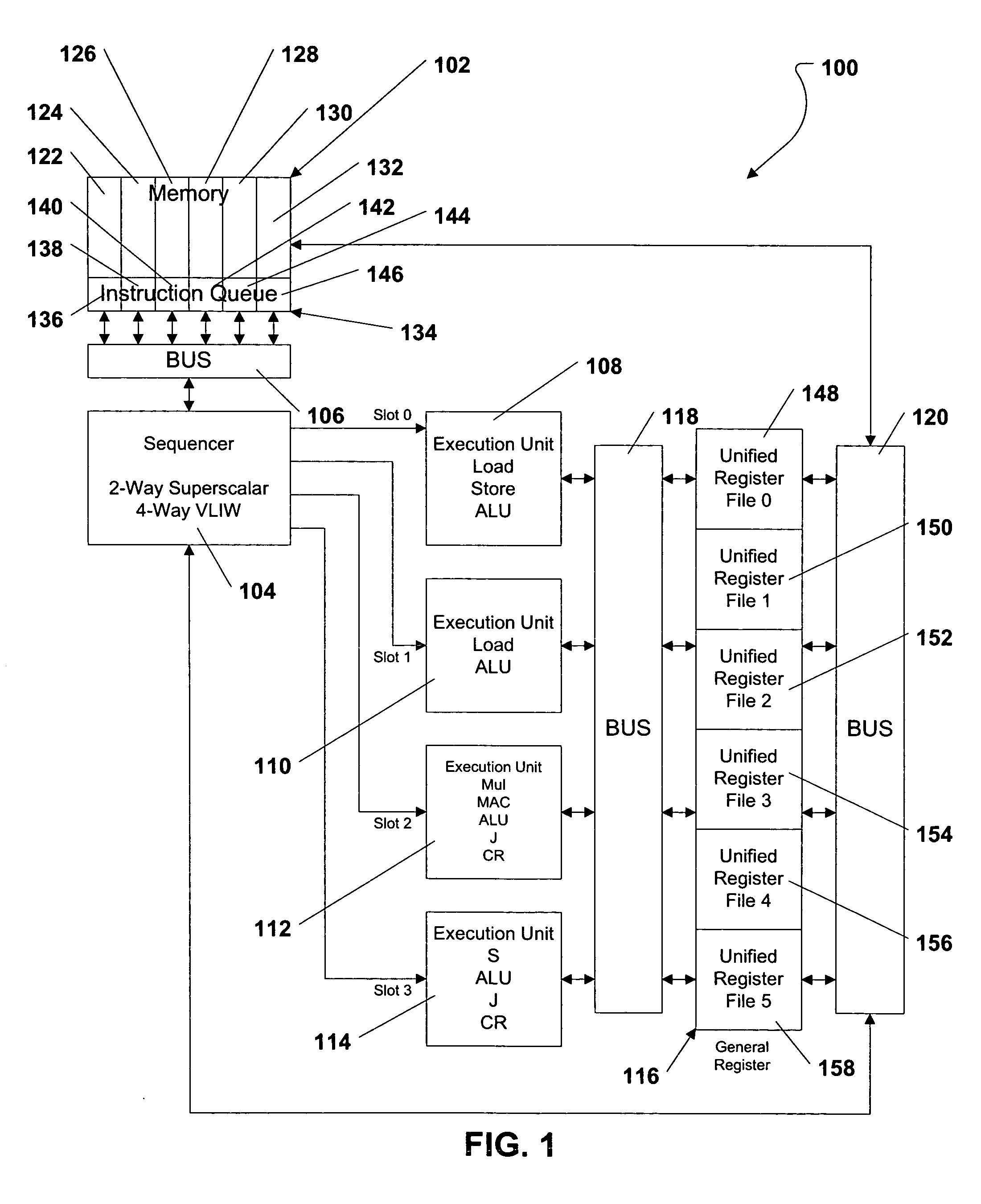

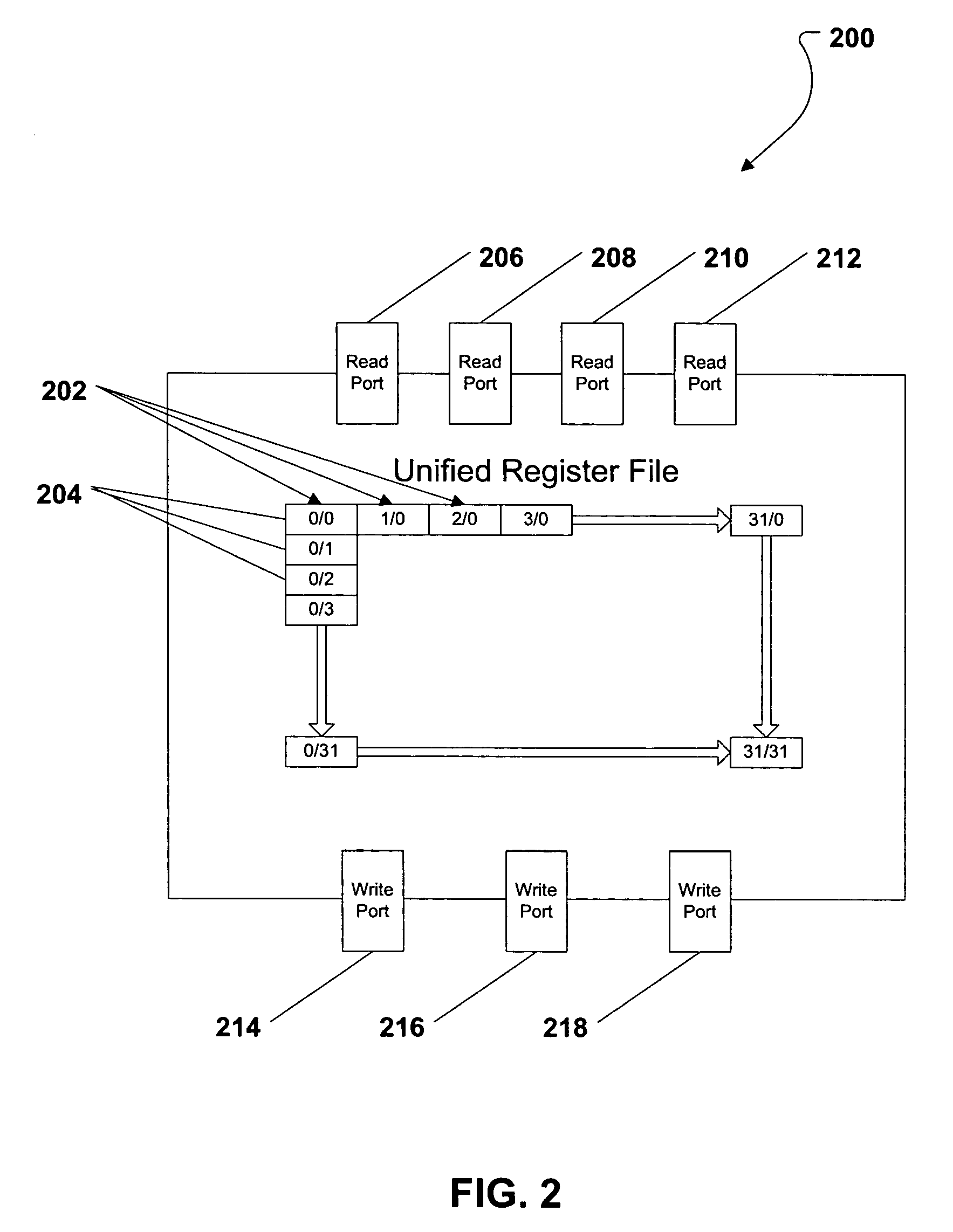

Register files for a digital signal processor operating in an interleaved multi-threaded environment

ActiveUS20060242384A1Reduce memory sizeLow costRegister arrangementsInstruction analysisOperandExecution unit

A processor device is disclosed and includes a memory and a sequencer that is responsive to the memory. The sequencer supports very long instruction word (VLIW) type instructions and at least one VLIW instruction packet uses a number of operands during execution. The processor device further includes a plurality of instruction execution units responsive to the sequencer and a plurality of register files. Each of the plurality of register files includes a plurality of registers and the plurality of register files are coupled to the plurality of instruction execution units. Further, each of the plurality of register files includes a number of data read ports and the number of data read ports of each of the plurality of register files is less than the number of operands used by the at least one VLIW instruction packet.

Owner:QUALCOMM INC

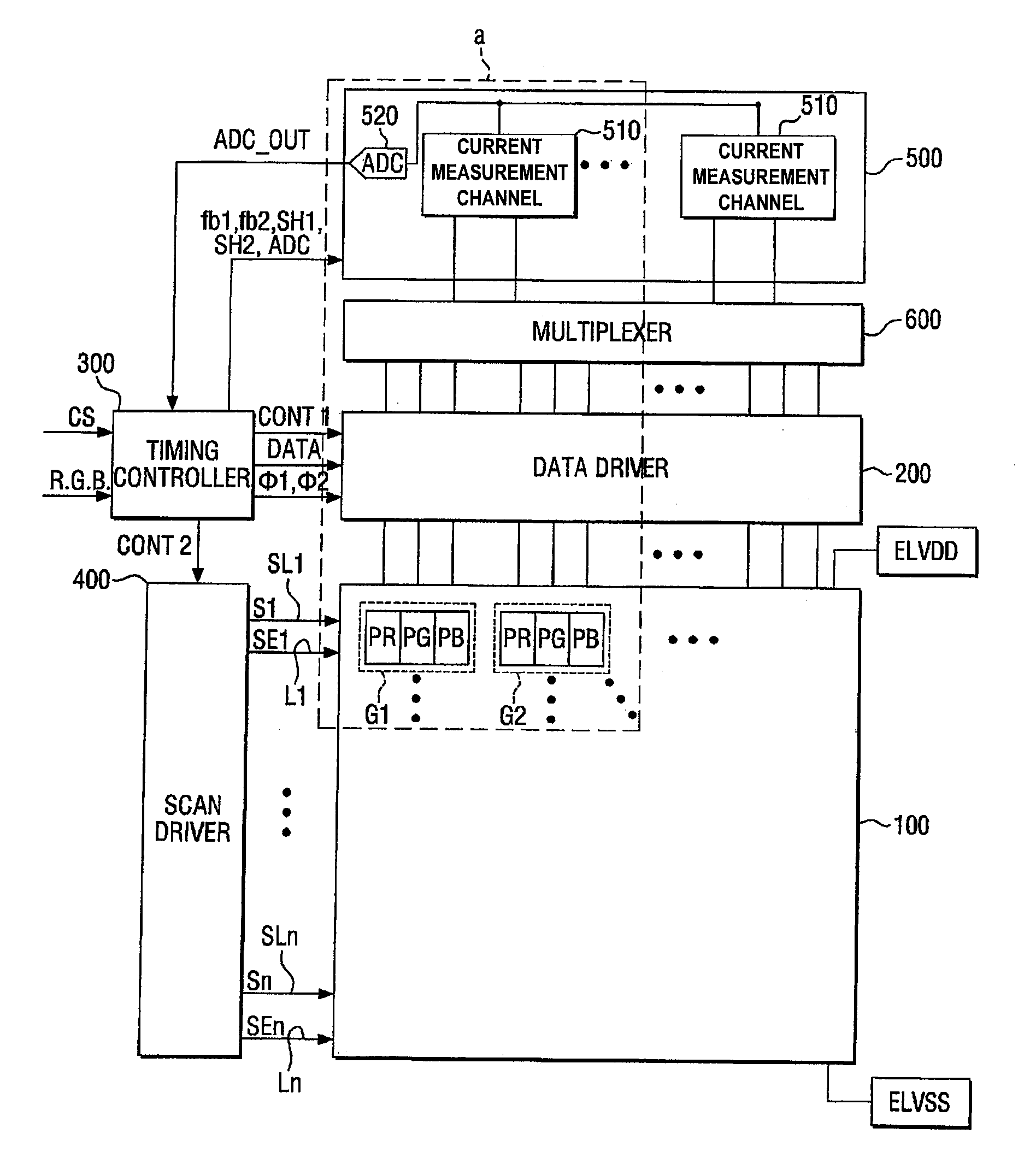

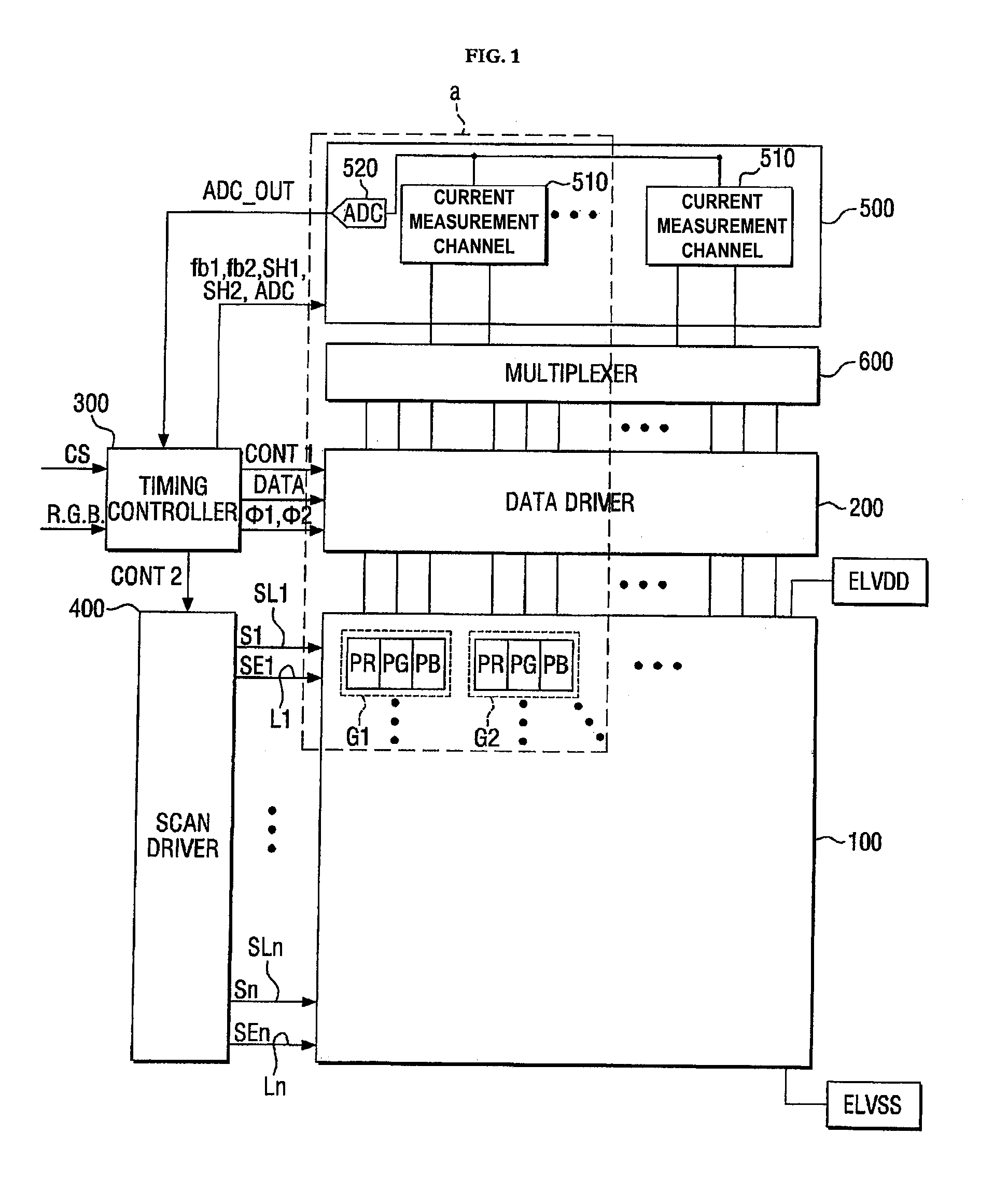

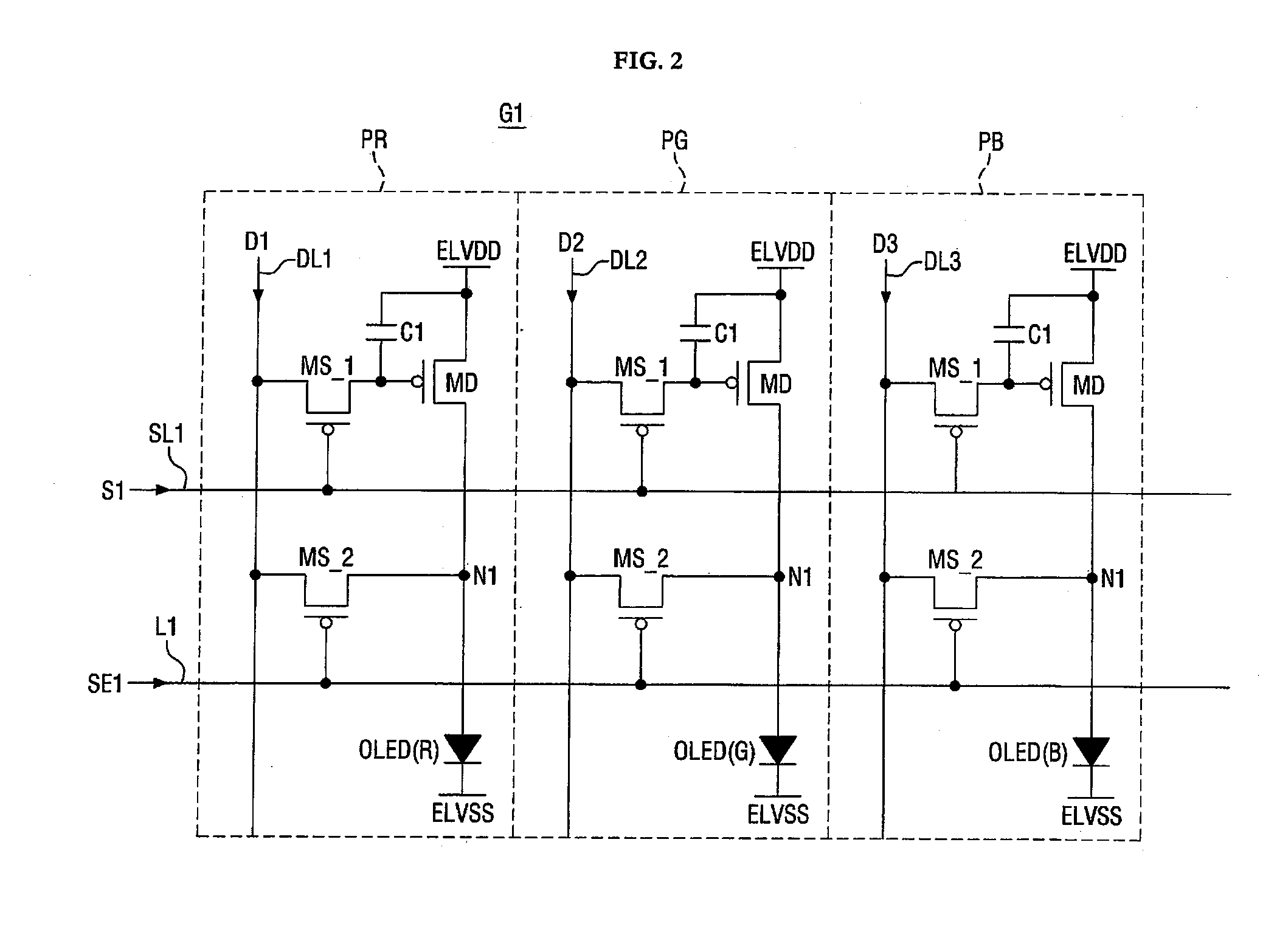

Organic light-emitting display and method of driving the same

InactiveUS20160163255A1Accurate currentSimple structureCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceElectrical current

An organic light-emitting display devices includes a display panel having first and second pixel groups, each group including first, second, and third pixels which emit light of different colors and a current measurement unit having a plurality of current measurement channels connected to the first and second pixel groups by data lines, wherein each of the current measurement channels includes a first measurement circuit connected to one of the first, second, and third pixels in the first pixel group and measures current characteristics of the connected one of the pixels and a second measurement circuit which measures current characteristics of one of the first, second, and third pixels, in the second pixel group, which emits light of the same color as that of light emitted from the one of the pixels connected to the first measurement circuit.

Owner:SAMSUNG DISPLAY CO LTD

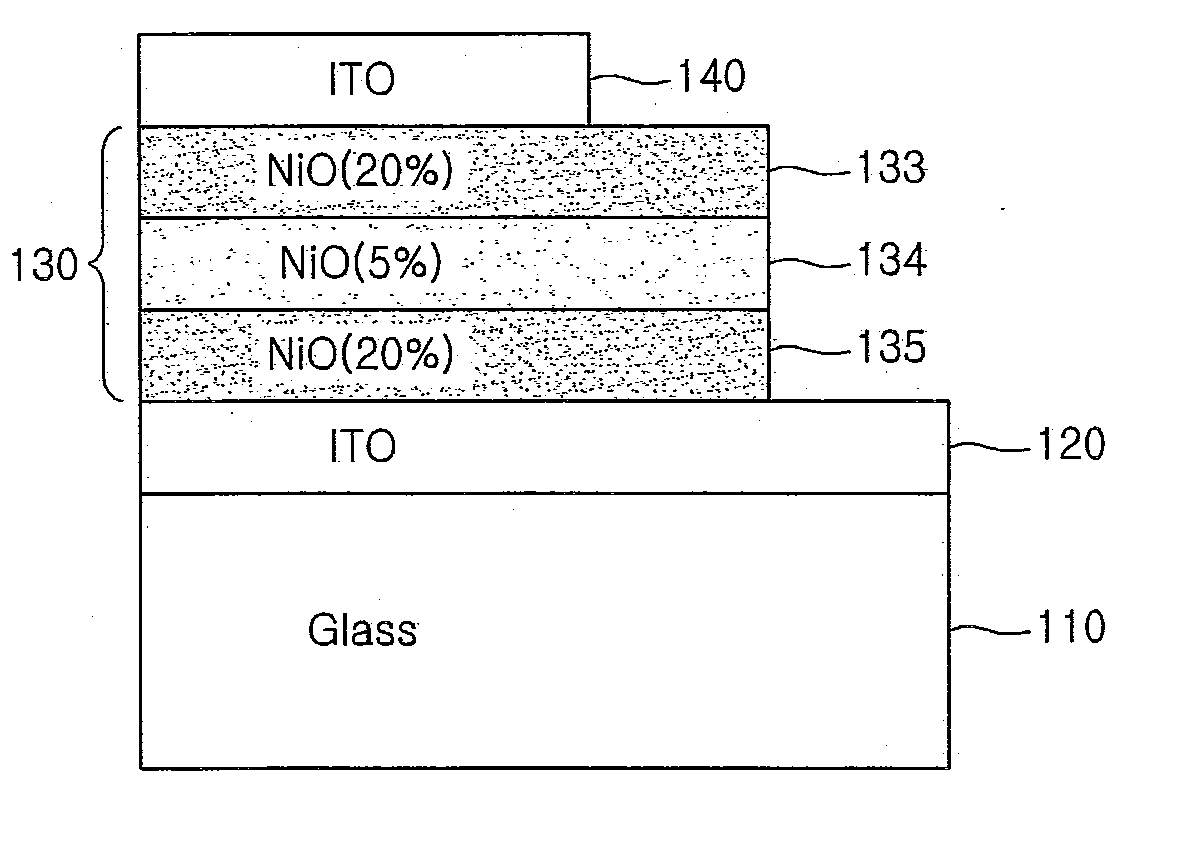

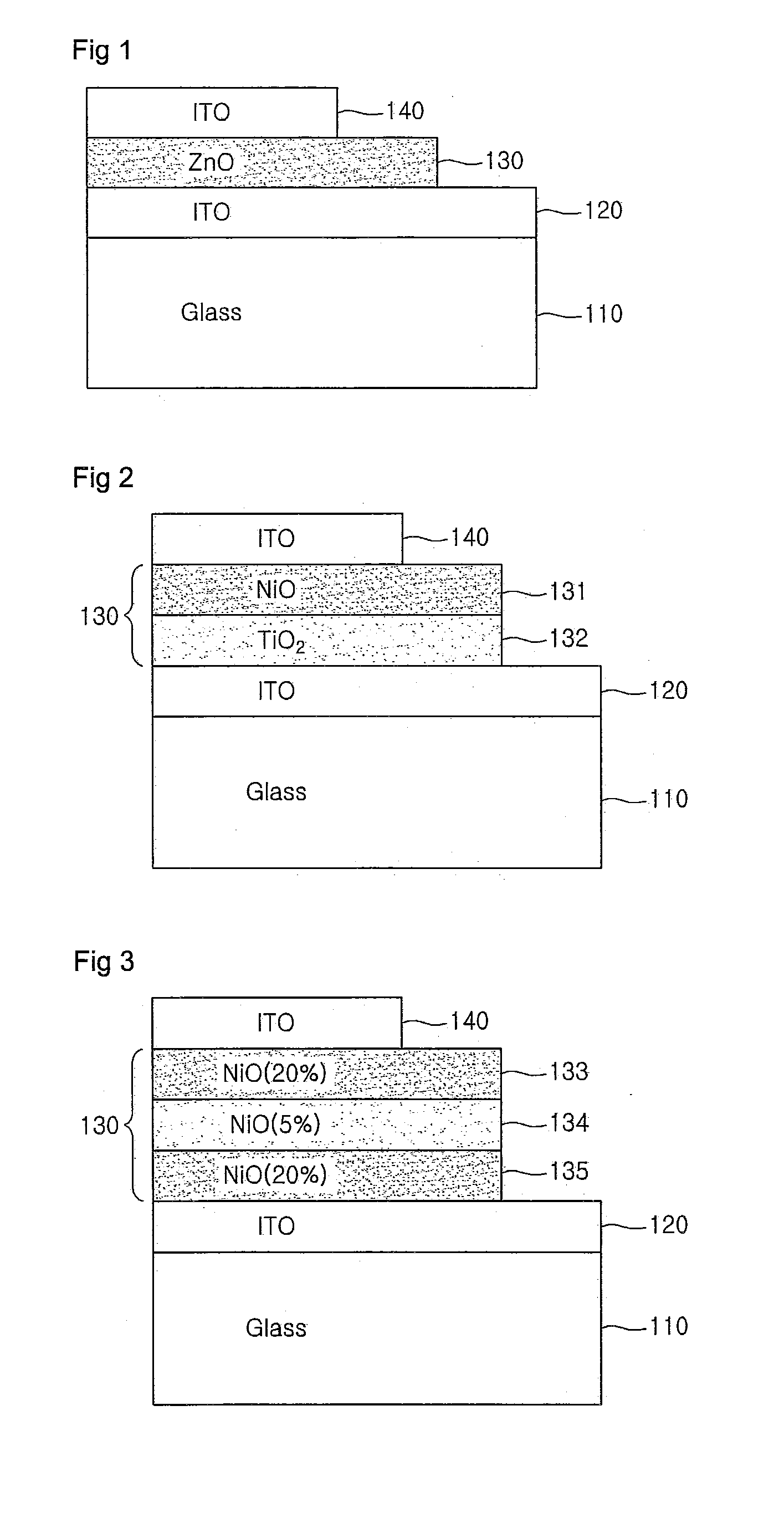

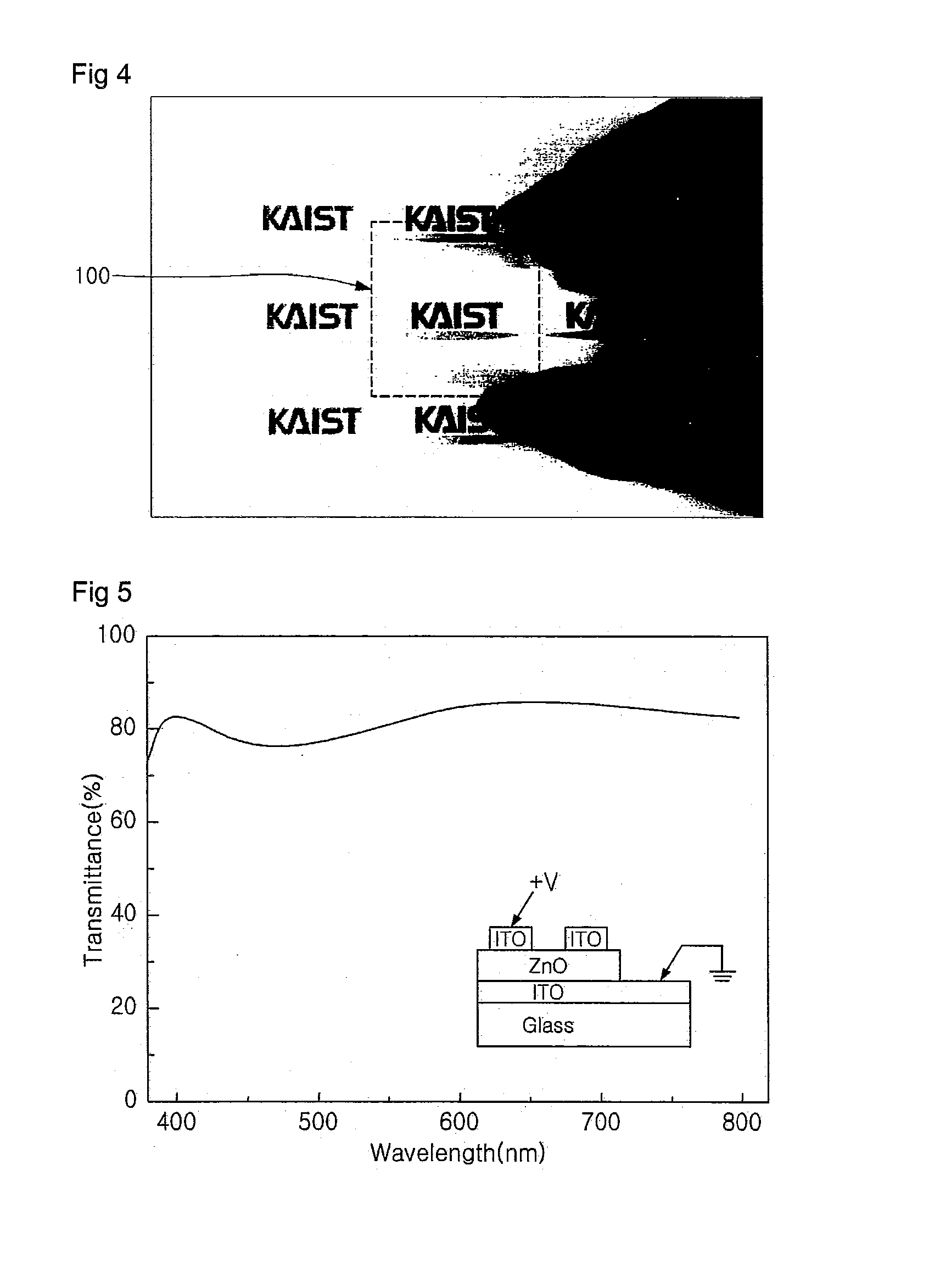

Transparent Memory for Transparent Electronic Device

InactiveUS20120132882A1High transparencyImprove switching characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingTransparent electronicsData store

The present invention relates to a transparent memory for a transparent electronic device. The transparent memory includes: a lower transparent electrode layer that is sequentially formed on a transparent substrate, and a data storage region and an upper transparent layer which are made of at least one transparent resistance-variable material layer. The transparent resistance-variable material layer has switching characteristics as a result of the resistance variance caused by the application of a certain voltage between the lower and upper transparent electrode layers. An optical band gap of the transparent resistance-variable material layer is 3 eV or more, and transmittivity of the material layer for visible rays is 80% or more. The invention provides transparent and resistance-variable memory that: has very high transparency and switching characteristics depending on resistance variation at a low switching voltage, and can maintain the switching characteristics thereof after a long time elapses.

Owner:KOREA ADVANCED INST OF SCI & TECH

Apparatus for encoding and decoding of low-density parity-check codes, and method thereof

ActiveUS7395494B2Reduce memory sizeHigh-speed and simple hardwareError detection/correctionError correction/detection using multiple parity bitsTanner graphParity-check matrix

An LDPC code encoding apparatus includes: a code matrix generator for generating and transmitting a parity-check matrix comprising a combination of square matrices having a unique value on each row and column thereof; an encoding means encoding block LDPC codes according to the parity-check matrix received from the code matrix generator; and a codeword selector for puncturing the encoded result of the encoding means to generate an LDPC codeword. The code matrix generator divides an information word to be encoded into block matrices having a predetermined length to generate a vector information word. The encoding means encodes the block LDPC codes using the parity-check matrix divided into the block matrices and a Tanner graph divided into smaller graphs in correspondence to the parity-check matrix.

Owner:ELECTRONICS & TELECOMM RES INST

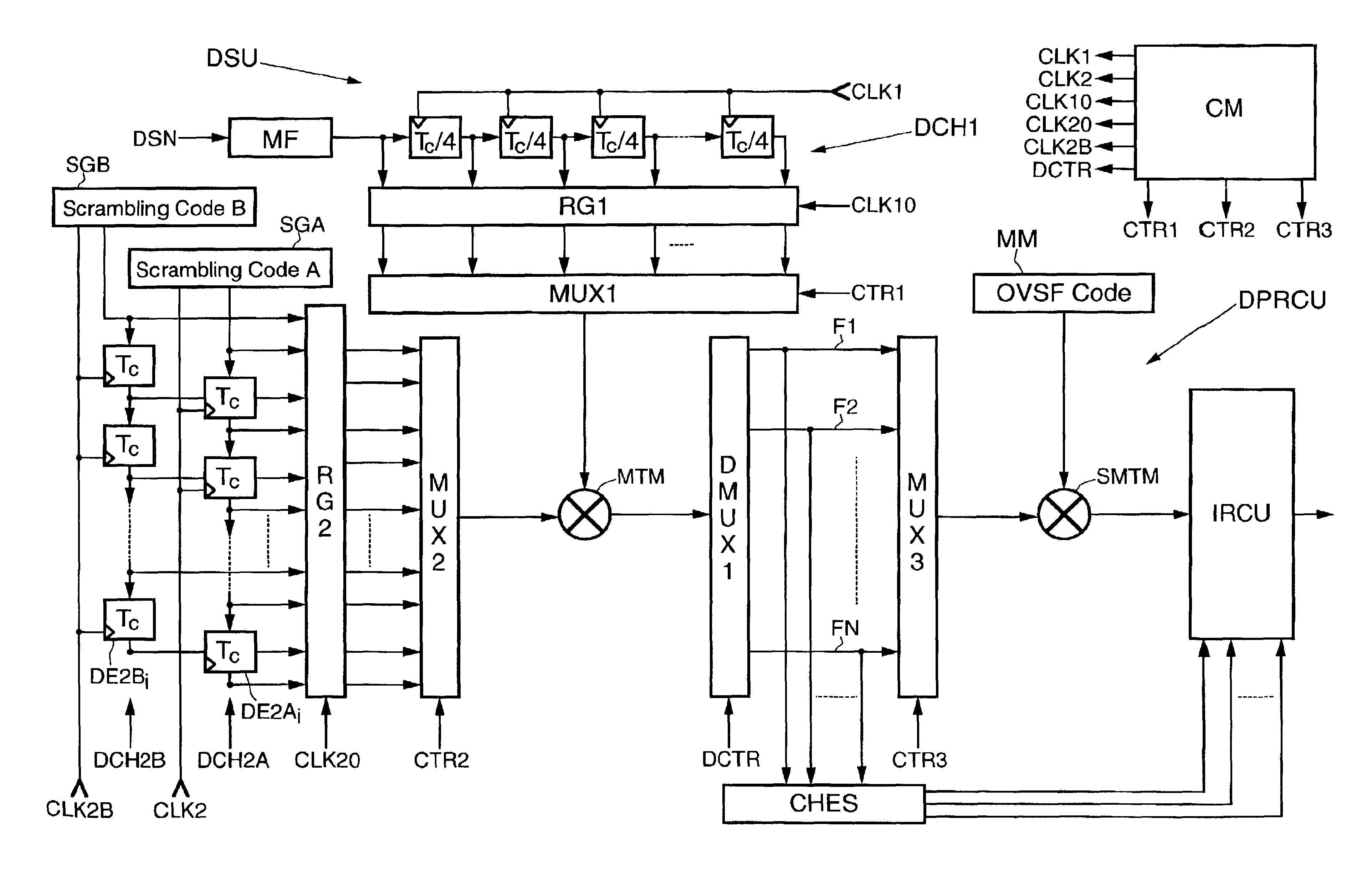

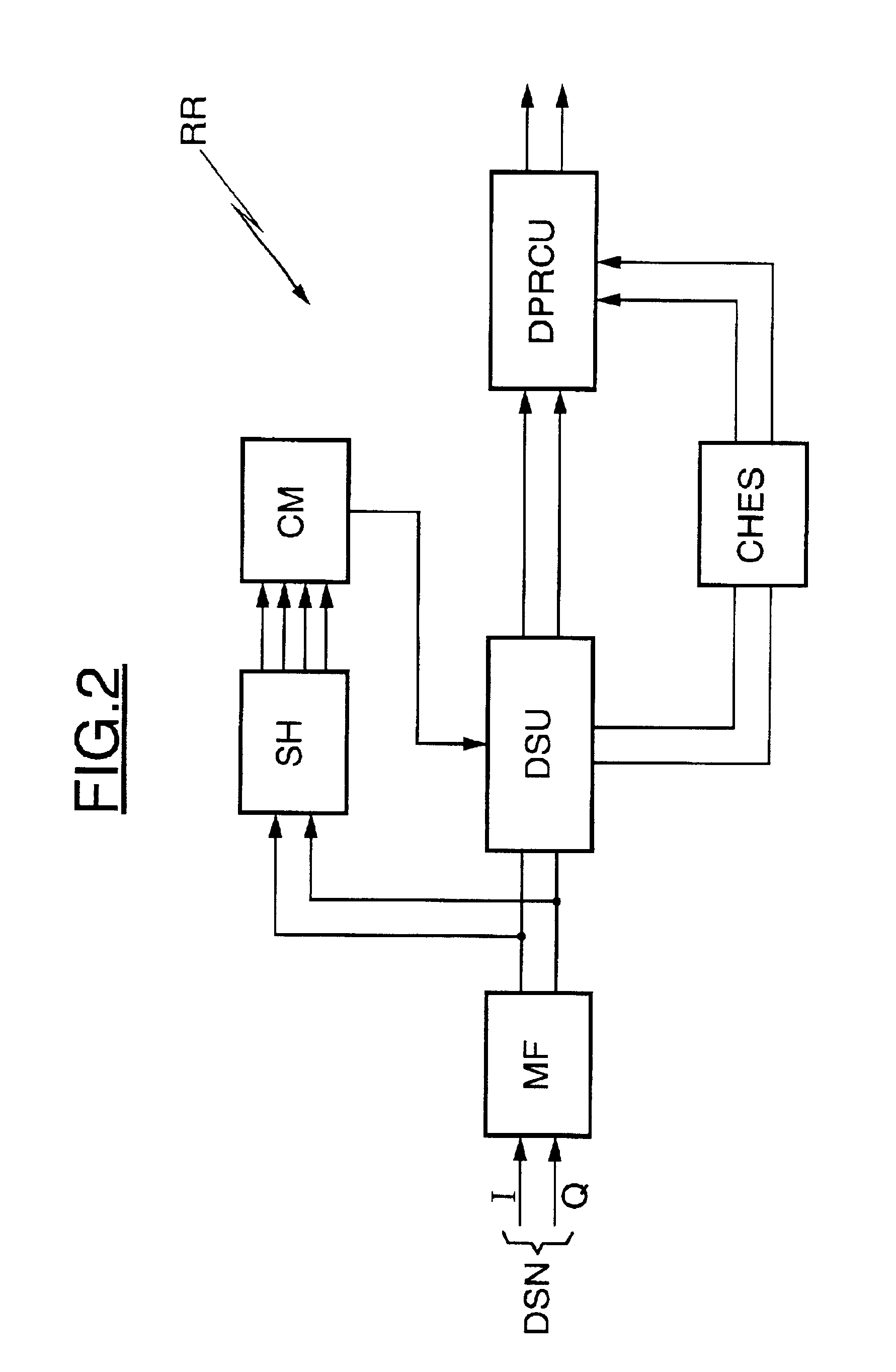

Rake receiver for a CDMA system, in particular incorporated in a cellular mobile phone

A rake receiver uses a delayed version of the received sequence and a delayed version of a scrambling code. The flexible hardware structure of the time-aligning and descrambling unit includes at least two delay chains and one multiplier. By controlling two multiplexers, the delayed versions of the received sequence can be multiplied with an arbitrary scrambling code having an arbitrary phase. During one chip period, one multiplication is performed for each path to be processed.

Owner:STMICROELECTRONICS SRL

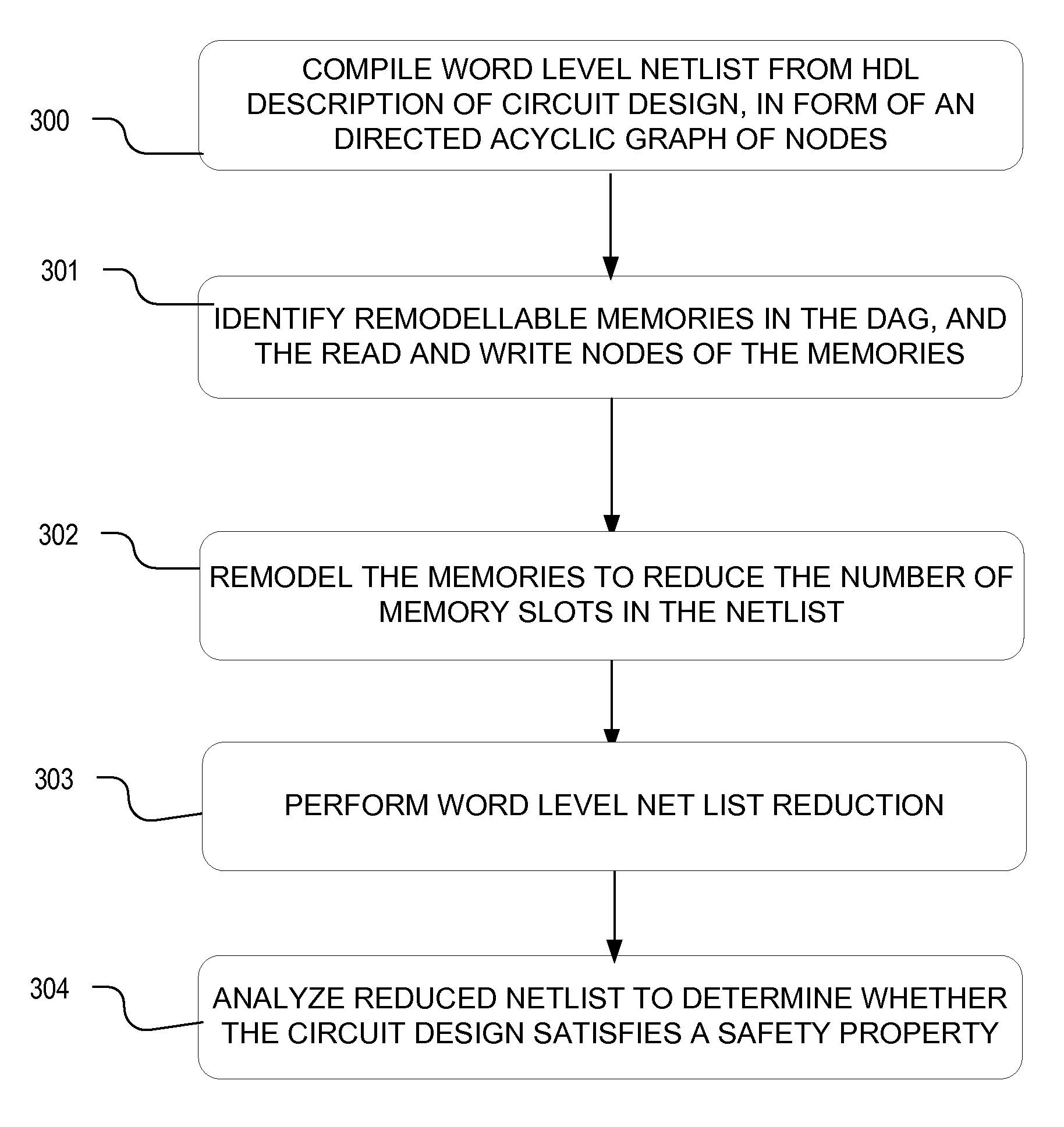

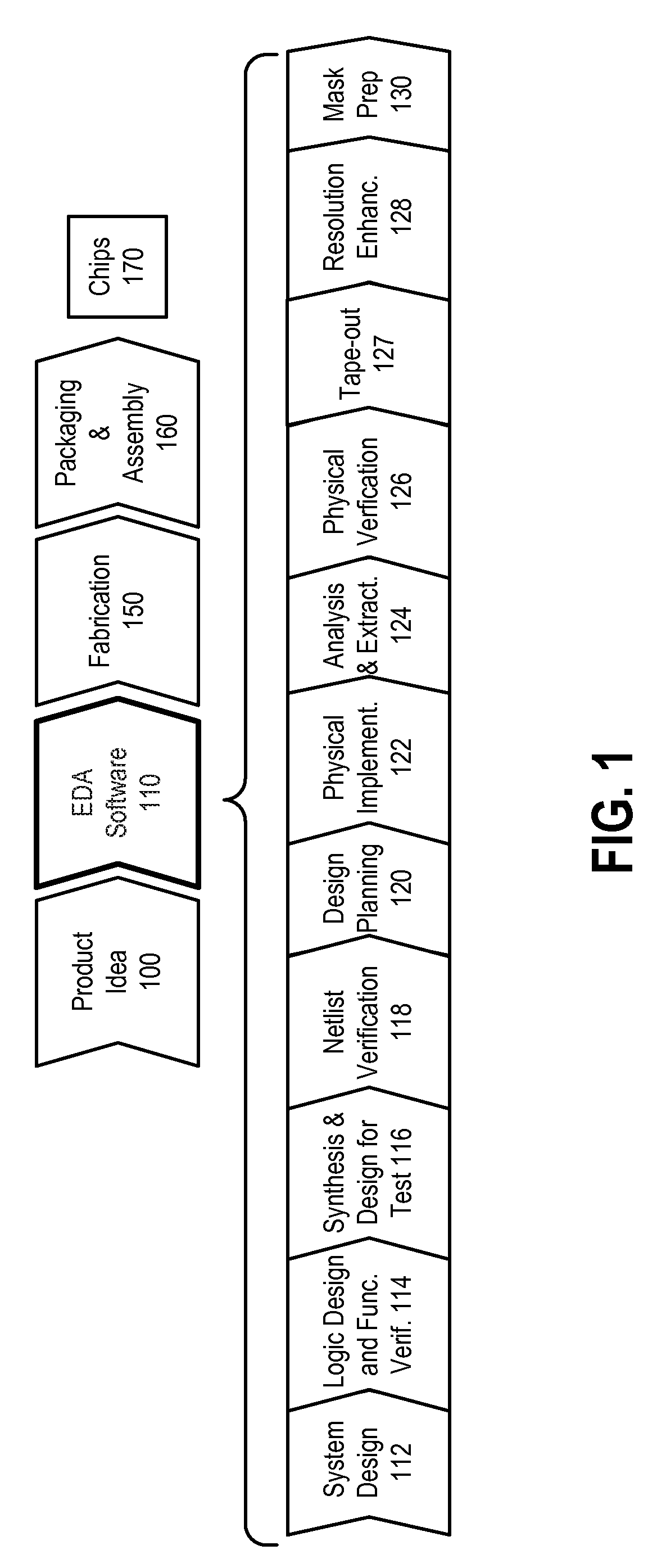

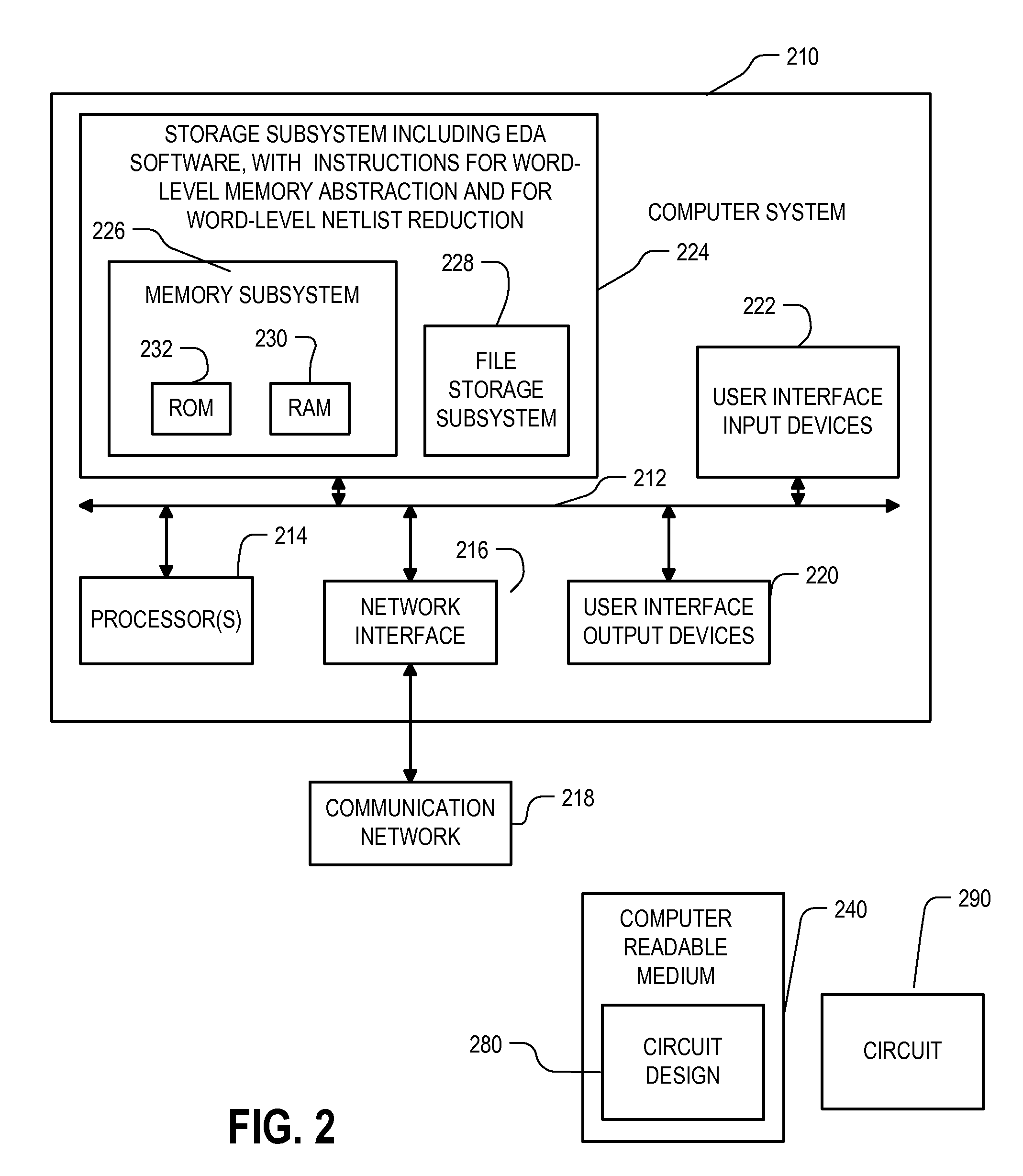

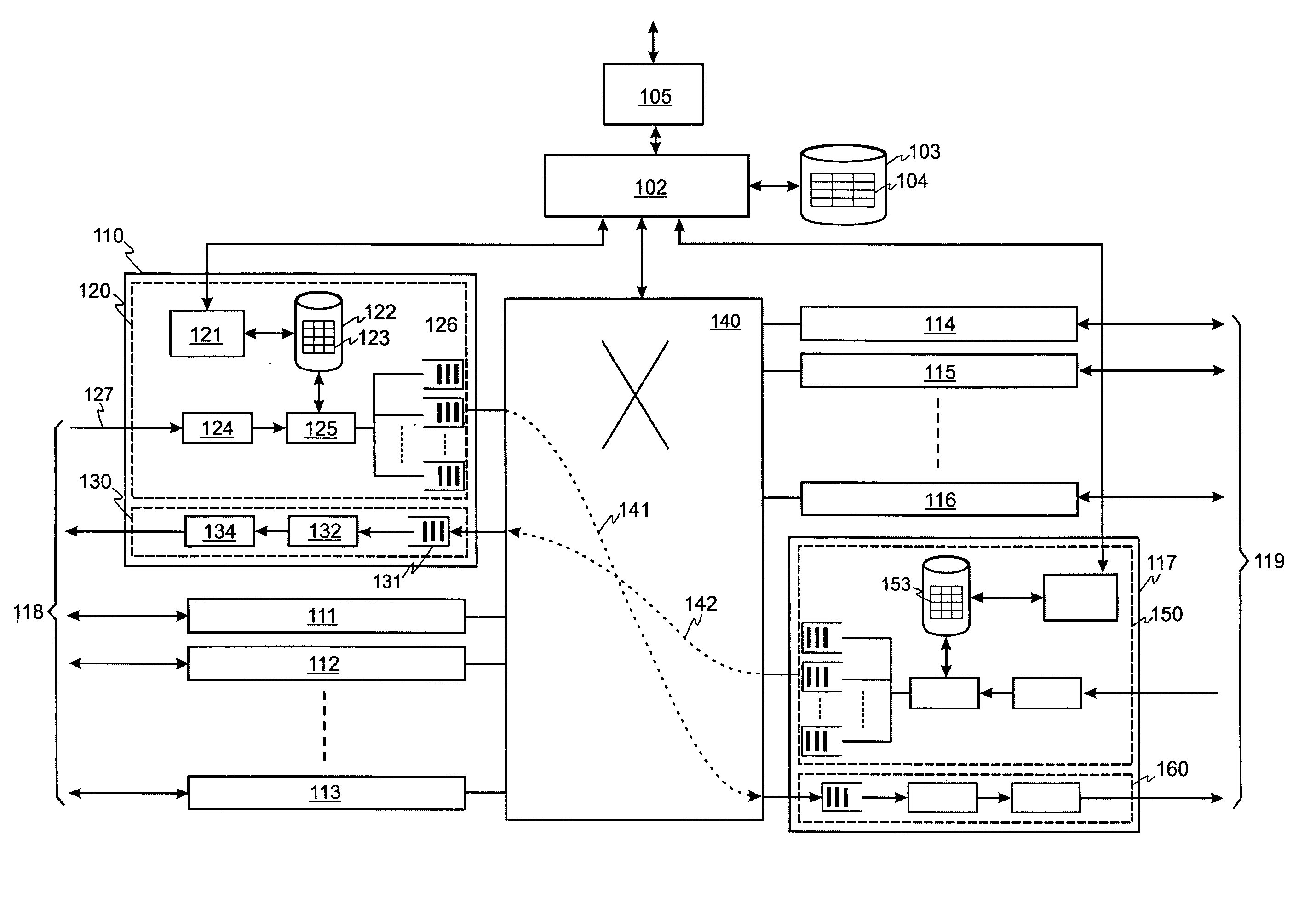

Method and apparatus for memory abstraction and for word level net list reduction and verification using same

ActiveUS20100107132A1Reduce decreaseReduced netlistComputer aided designSoftware simulation/interpretation/emulationNetlistCircuit design

A computer implemented representation of a circuit design including memory is abstracted to a smaller netlist by replacing memory with substitute nodes representing selected slots in the memory, segmenting word level nodes, including one or more of the substitute nodes, in the netlist into segmented nodes, finding reduced safe sizes for the segmented nodes and generating an updated data structure representing the circuit design using the reduced safe sizes of the segmented nodes. The correctness of such systems can require reasoning about a much smaller number of memory entries and using nodes having smaller bit widths than exist in the circuit design. As a result, the computational complexity of the verification problem is substantially reduced.

Owner:SYNOPSYS INC

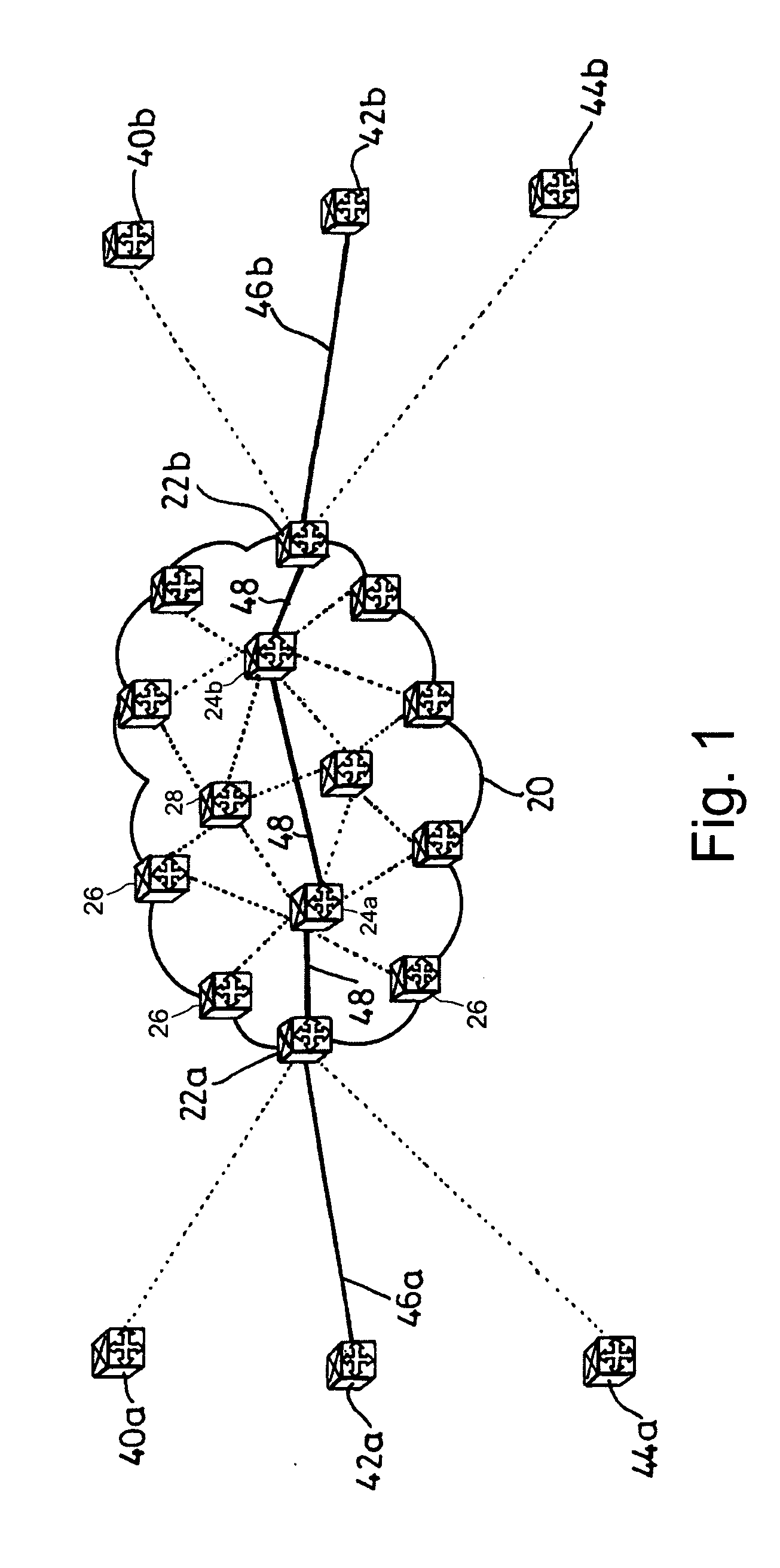

Forwarding table minimisation in Ethernet switches

InactiveUS20070047540A1Cost savingReduced memory sizeMultiplex system selection arrangementsData switching by path configurationInformation storageNetwork connection

An Ethernet switch for use in an Ethernet network comprises a set of ingress ports for receiving data frames and a set of egress ports. A memory is associated with each ingress port and stores forwarding information indicating one or more of the egress ports to which data frames received by that ingress port should be forwarded. A control or management interface receives information about a network connection established, or to be established, through the switch. A switch controller causes forwarding information to be stored in a memory associated with a first ingress port which the network connection will use, on the basis of the received information about a network connection. Forwarding information is not stored in a memory associated with a second of the set of ingress ports which the network connection will not use. Preferably, the switch controller causes forwarding information to be stored only in a memory associated with the first ingress port which the network connection will use and not to be stored in a memory associated with any of the other ingress ports.

Owner:RPX CLEARINGHOUSE

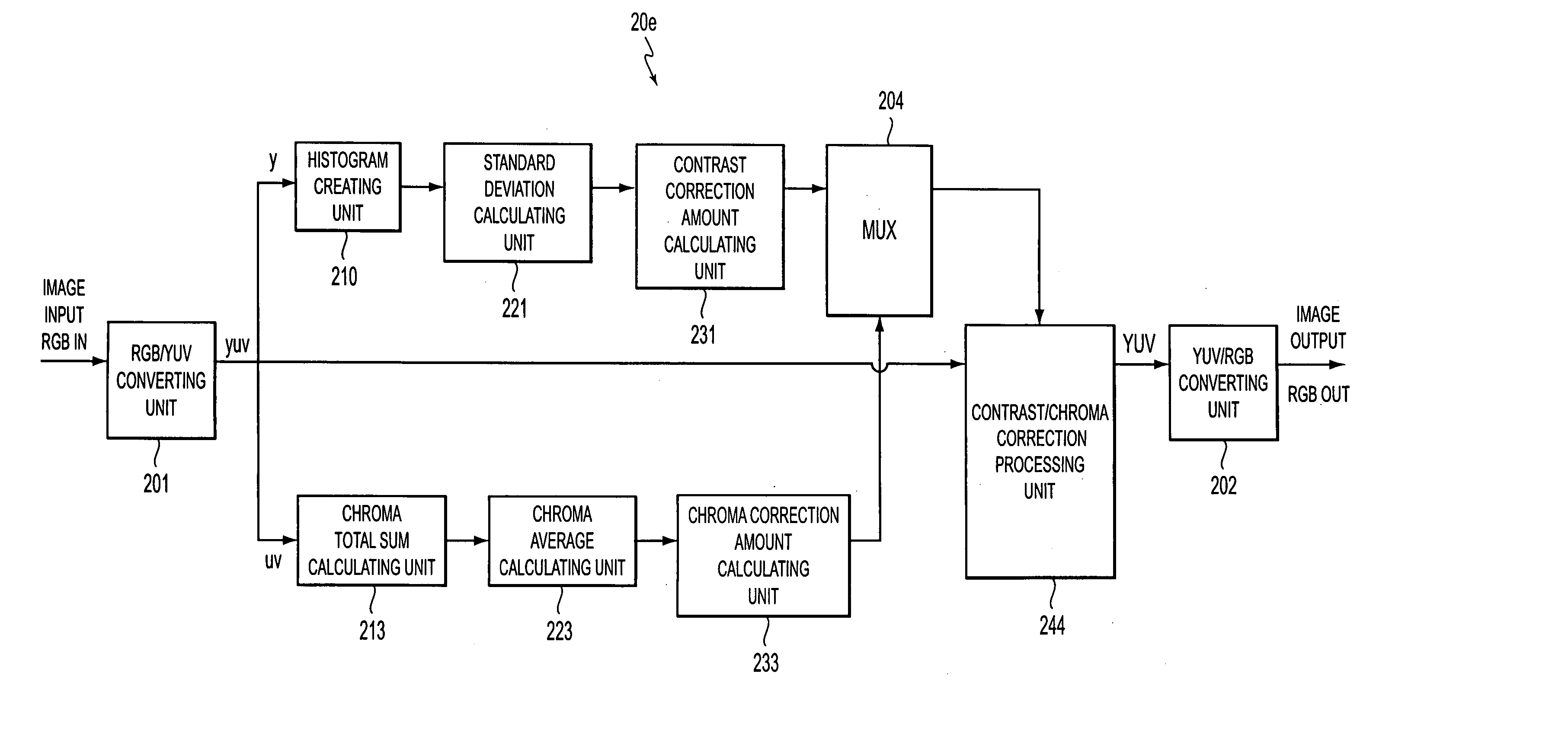

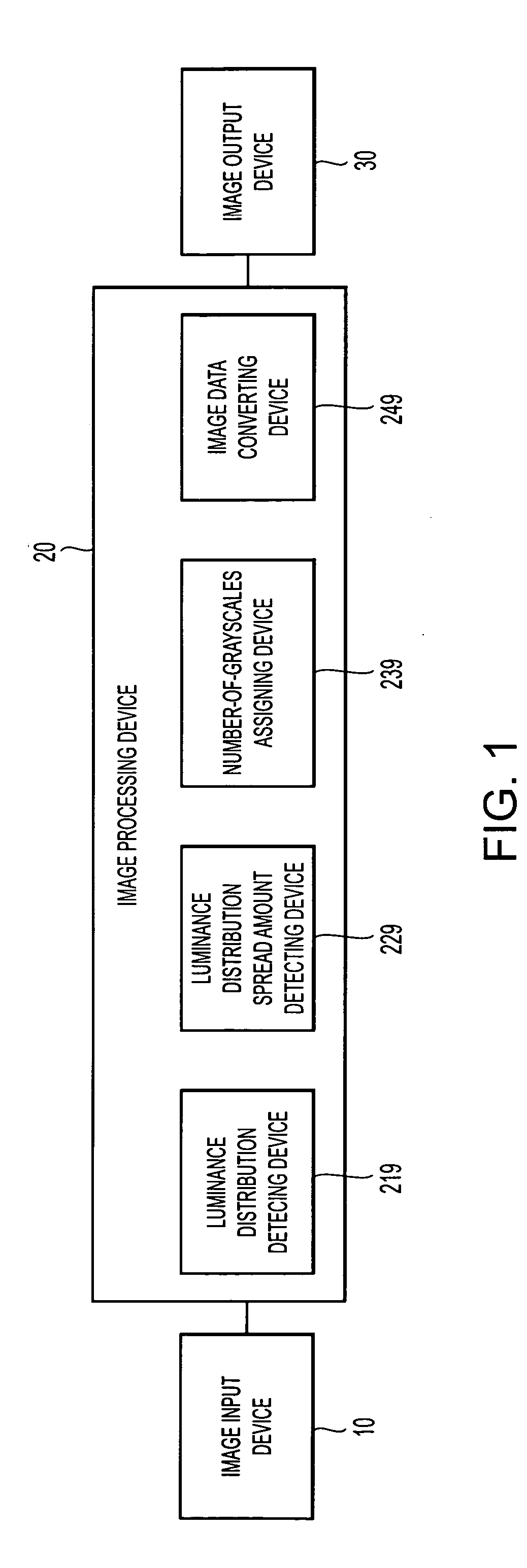

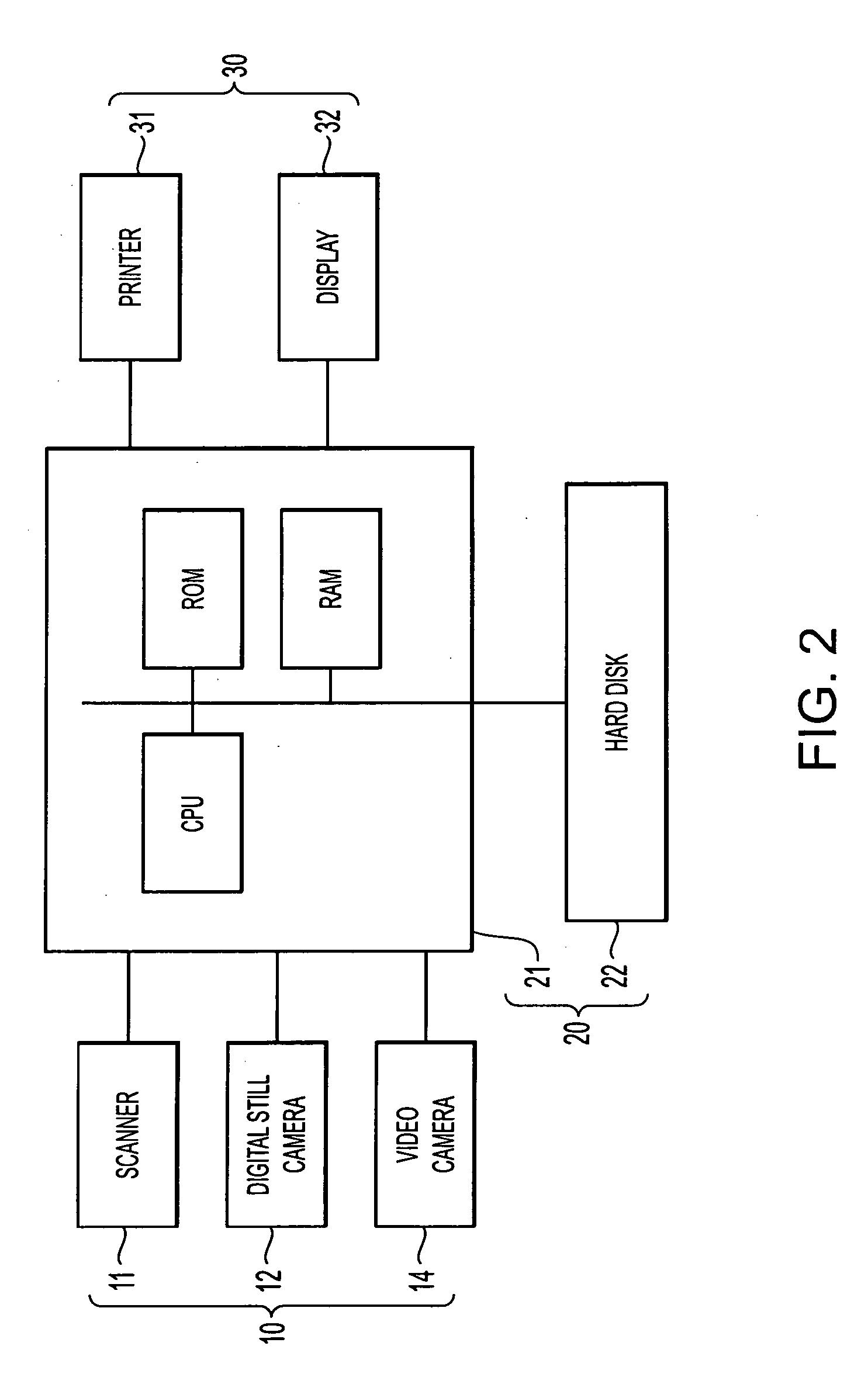

Image processor, image processing method, and recording medium on which image processing program is recorded

InactiveUS20040213457A1Reduce memory sizeTelevision system detailsImage enhancementImaging processingImage correction

To provide an image processor, an image processing method, and an image processing program which make it possible to perform high-speed image correction suitable for motion pictures while reducing a memory resource, etc., an image processor that corrects input image data having a predetermined grayscale range is provided. The image processor includes a coefficient holding device to hold correction coefficients of a correction curve that corresponds to the entire grayscale range or a portion of the grayscale range and includes one or more correction points and a combination portion that is formed of a combination of a plurality of specific curve pattern portions, a correction amount determination device to determine a correction amount based on statistical information of grayscale values of pixels in the image input data, and a correction device to correct the input image data by adding the product of the correction amount and the correction coefficients determined by the input image data to the input image data.

Owner:138 EAST LCD ADVANCEMENTS LTD

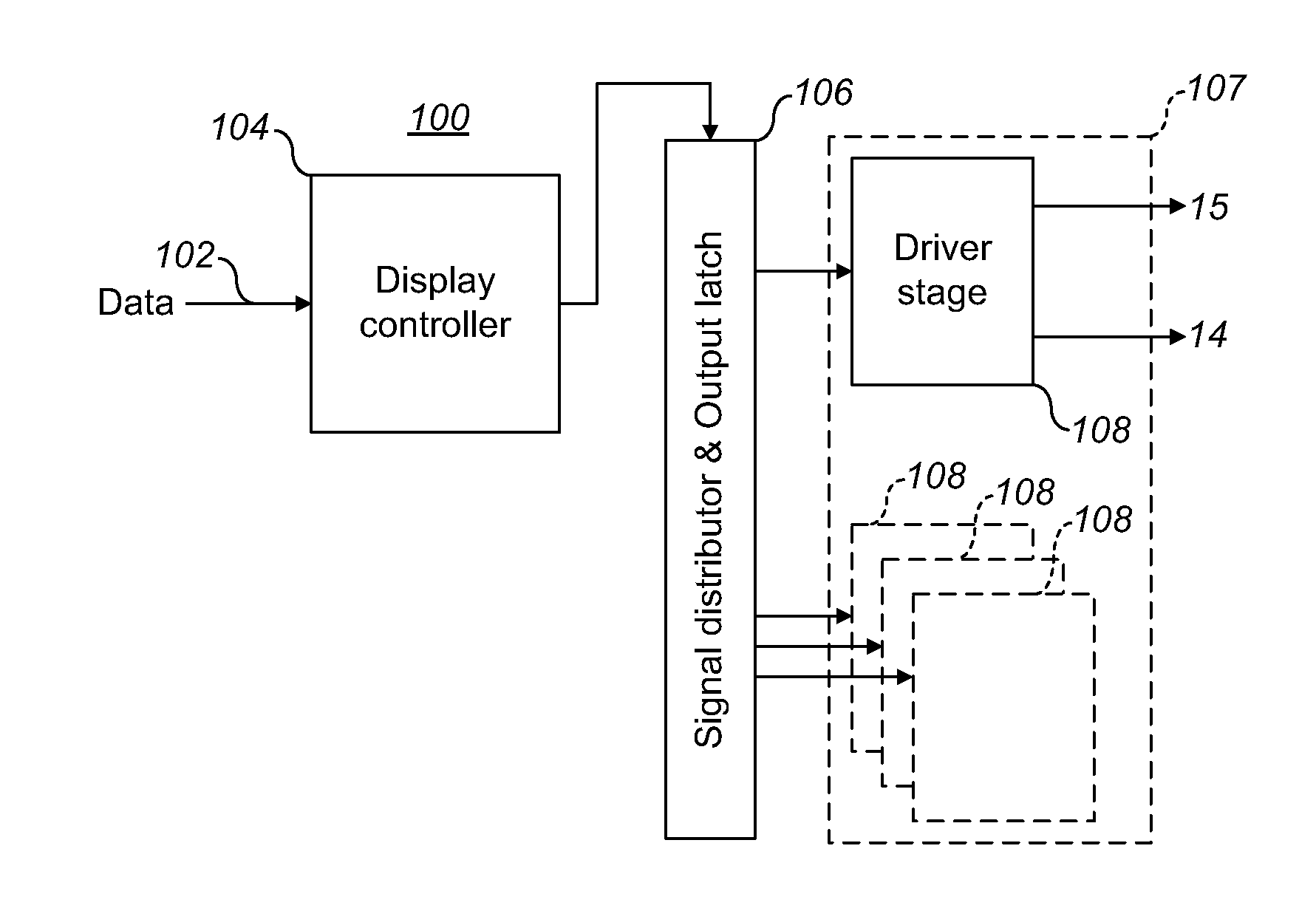

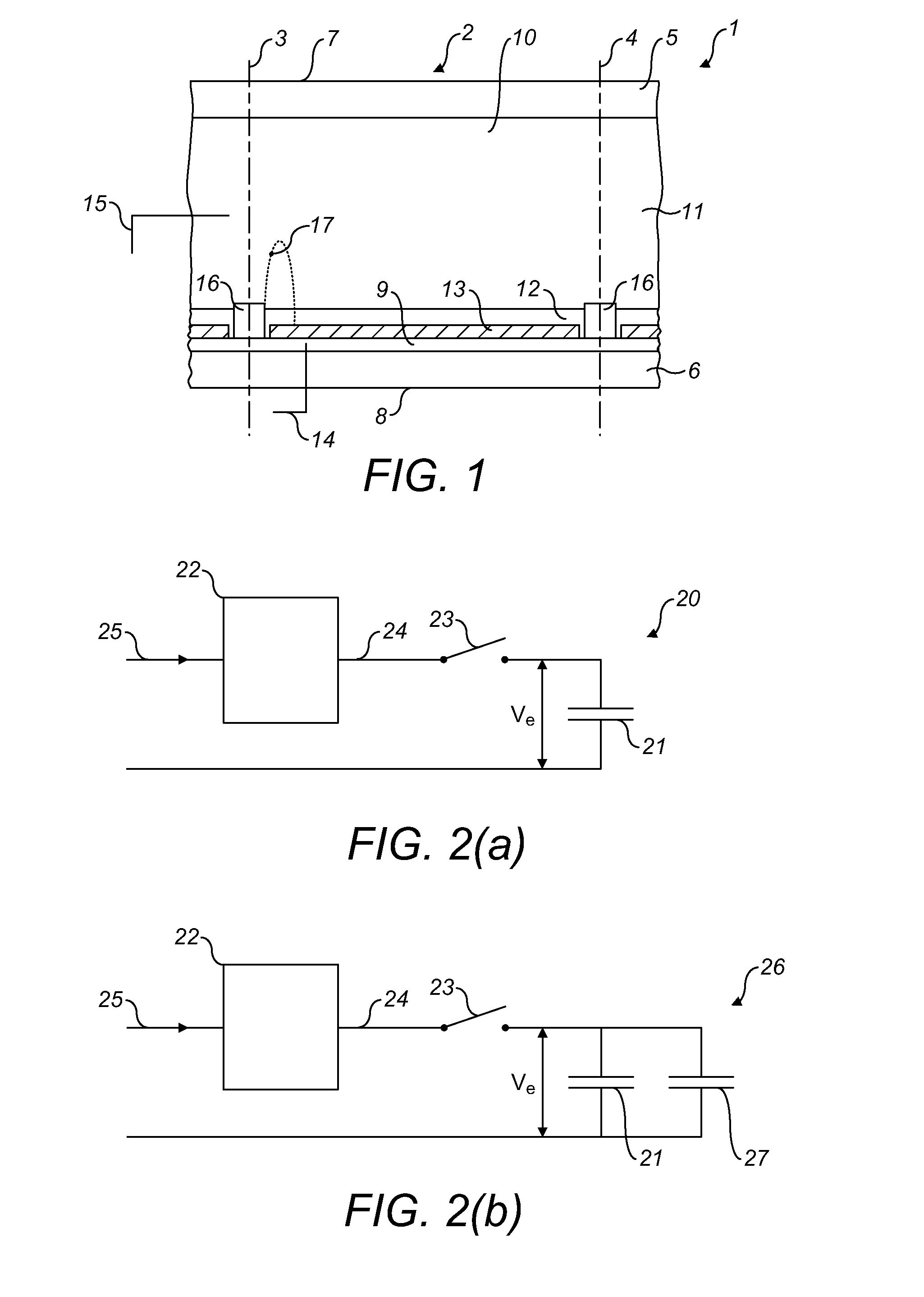

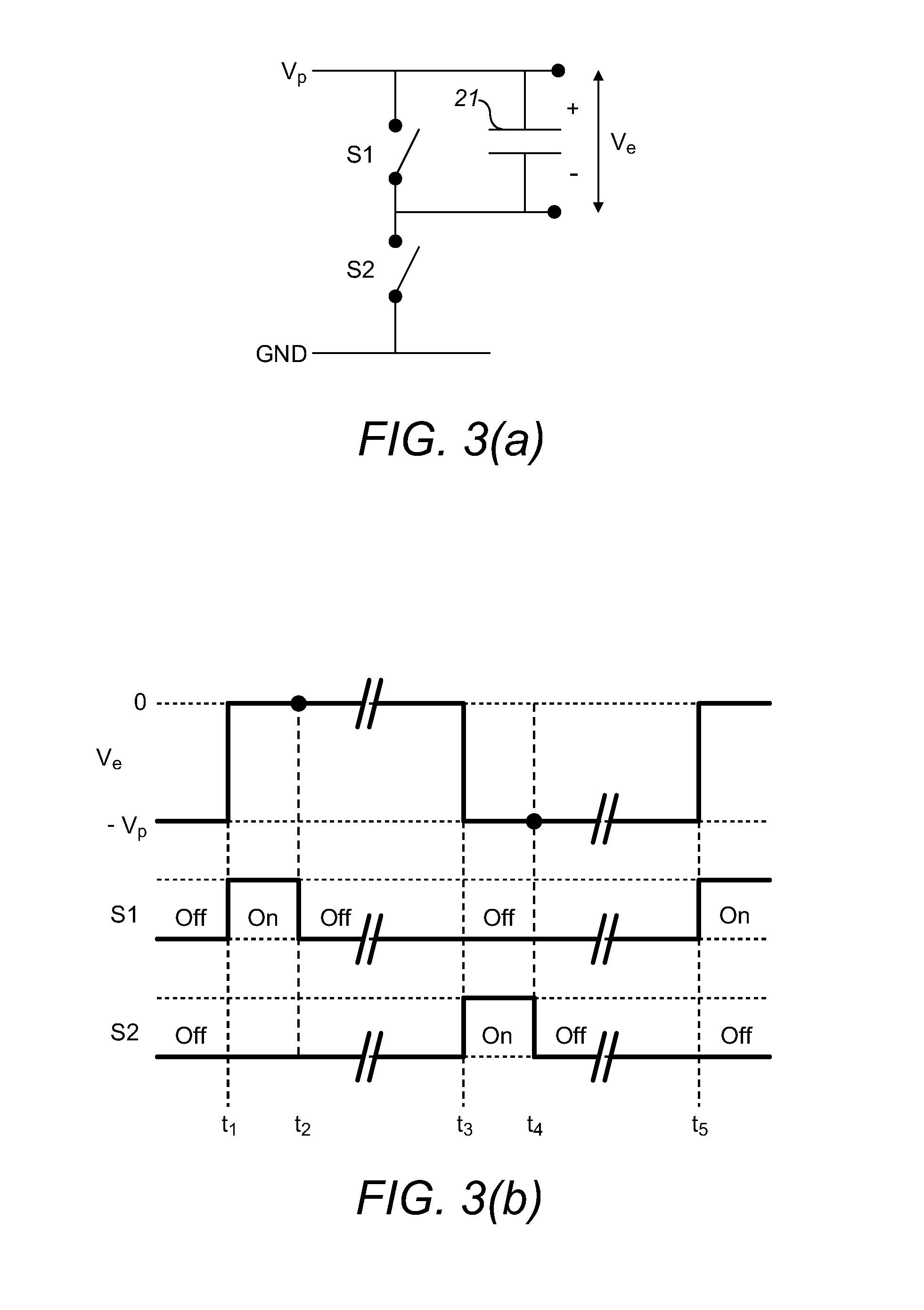

Electrowetting system

InactiveUS20110187696A1Reduce power consumptionReduce memory sizeCathode-ray tube indicatorsInput/output processes for data processingElectricityDisplay device

An electrowetting system including a display device having a plurality of electrowetting elements, including a first electrowetting element and a second electrowetting element, each being configurable in a plurality of different display states; and a display controller for electrical addressing of the plurality of electrowetting elements in order to switch the plurality of electrowetting elements between different display states. The display controller is arranged to address the first electrowetting element twice subsequently, separated by a first addressing interval, and to address the second electrowetting element twice subsequently, separated by a second addressing interval, the second addressing interval being longer than the first addressing interval. The present invention further relates to a display controller, a driver stage and a method of controlling a display device.

Owner:LIQUAVISTA BV

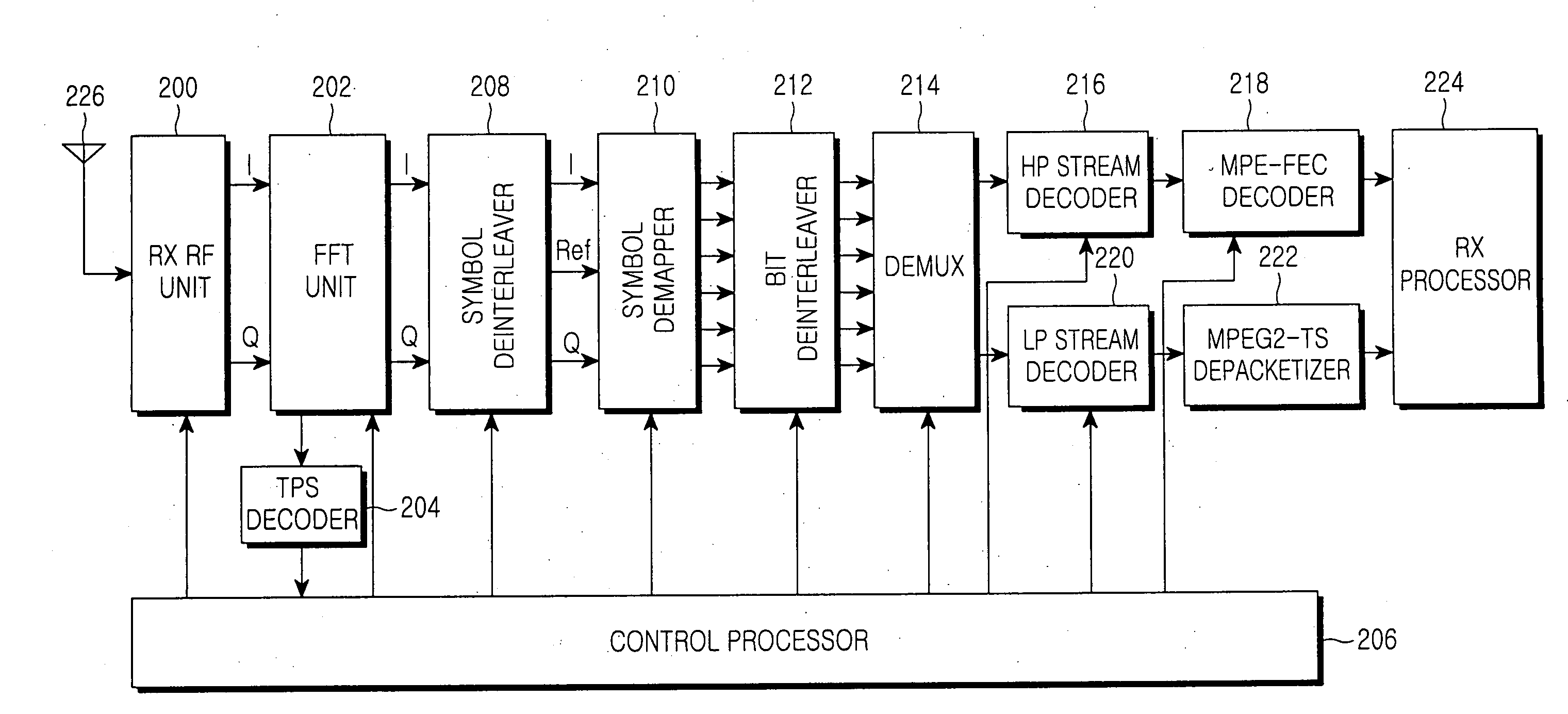

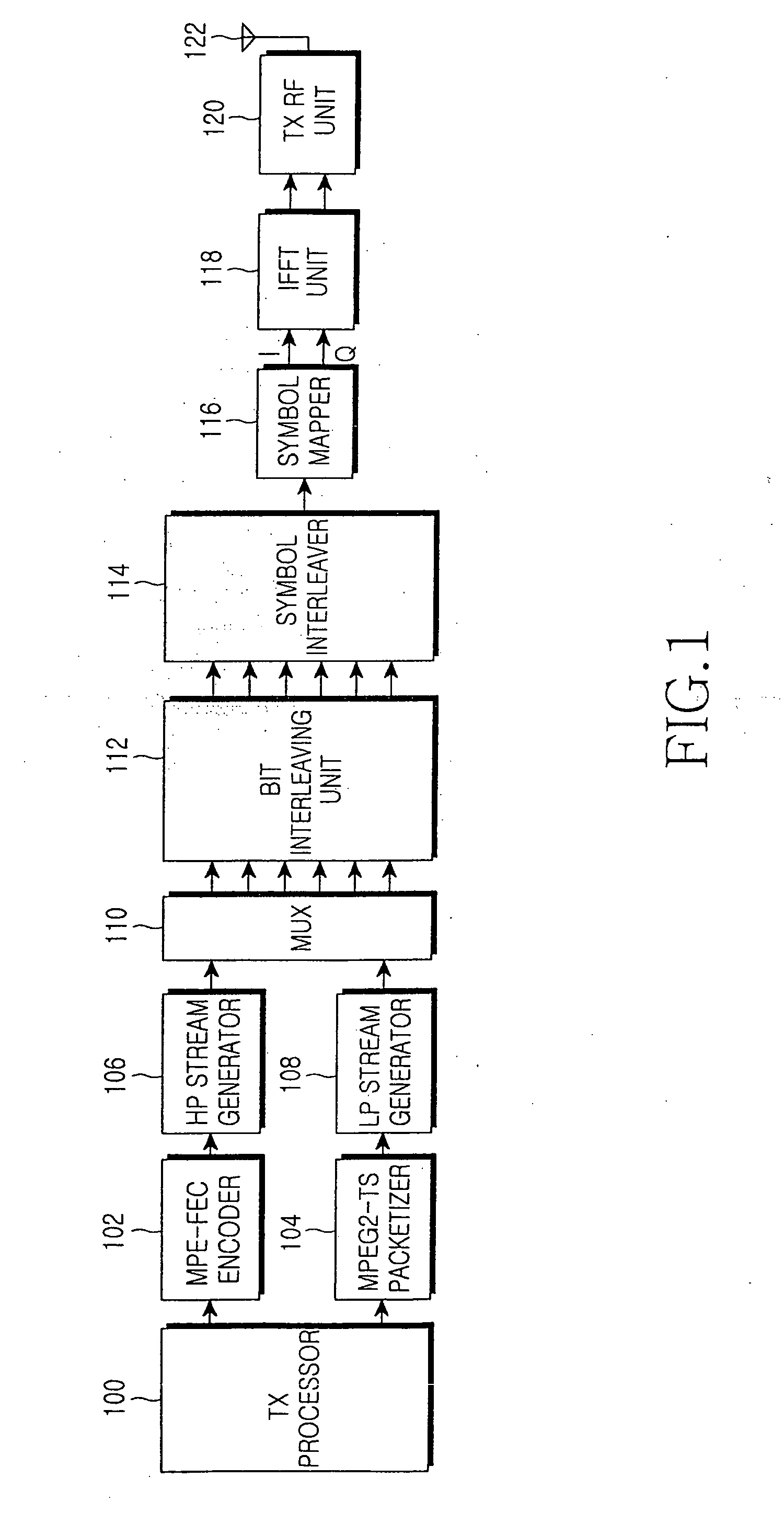

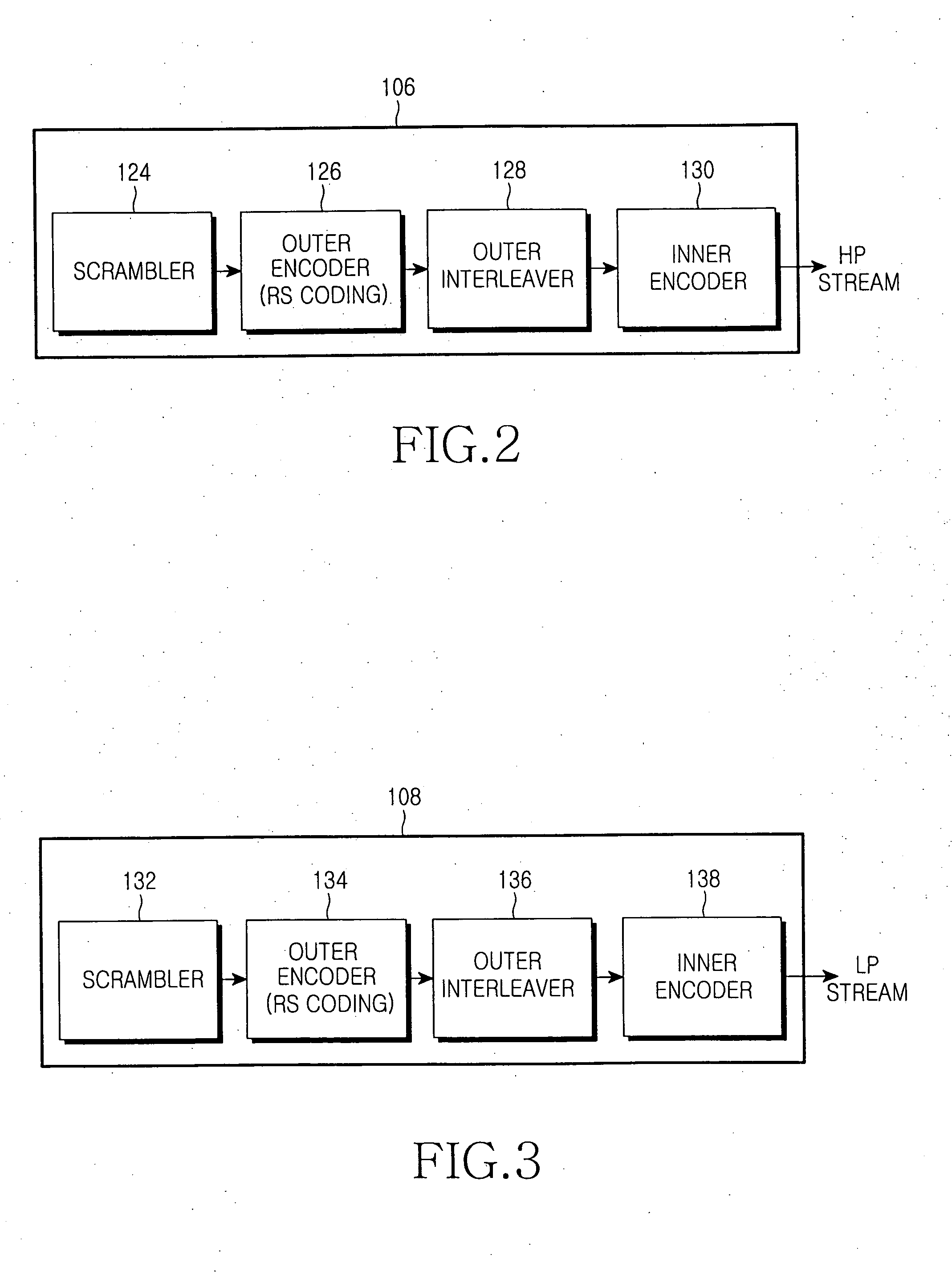

Apparatus and method for receiving data in a wireless communication system using bit interleaving, symbol interleaving and symbol mapping

InactiveUS20070165729A1Increase in hardware complexityIncrease power consumptionTime-division multiplexAmplitude-modulated carrier systemsFast Fourier transformCommunications system

An apparatus and method are provided for receiving data generated by sequentially performing bit interleaving, symbol interleaving and symbol mapping in a wireless communication system. A fast Fourier transform (FFT) processor receives in-phase / quadrature phase (I / Q) data of a radio channel generated by sequentially performing bit interleaving, symbol interleaving and symbol mapping, and performs an FFT process for the I / Q data. A symbol deinterleaver performs a process for symbol deinterleaving the FFT I / Q data and reference values to be used for symbol demapping of the I / Q data and outputs the symbol-deinterleaved I / Q data and reference values. A symbol demapper performs a process for symbol demapping the symbol-deinterleaved I / Q data according to the reference values. A bit deinterleaver performs a process for bit deinterleaving the symbol-demapped data. A demultiplexer demultiplexes the bit-deinterleaved data.

Owner:SAMSUNG ELECTRONICS CO LTD

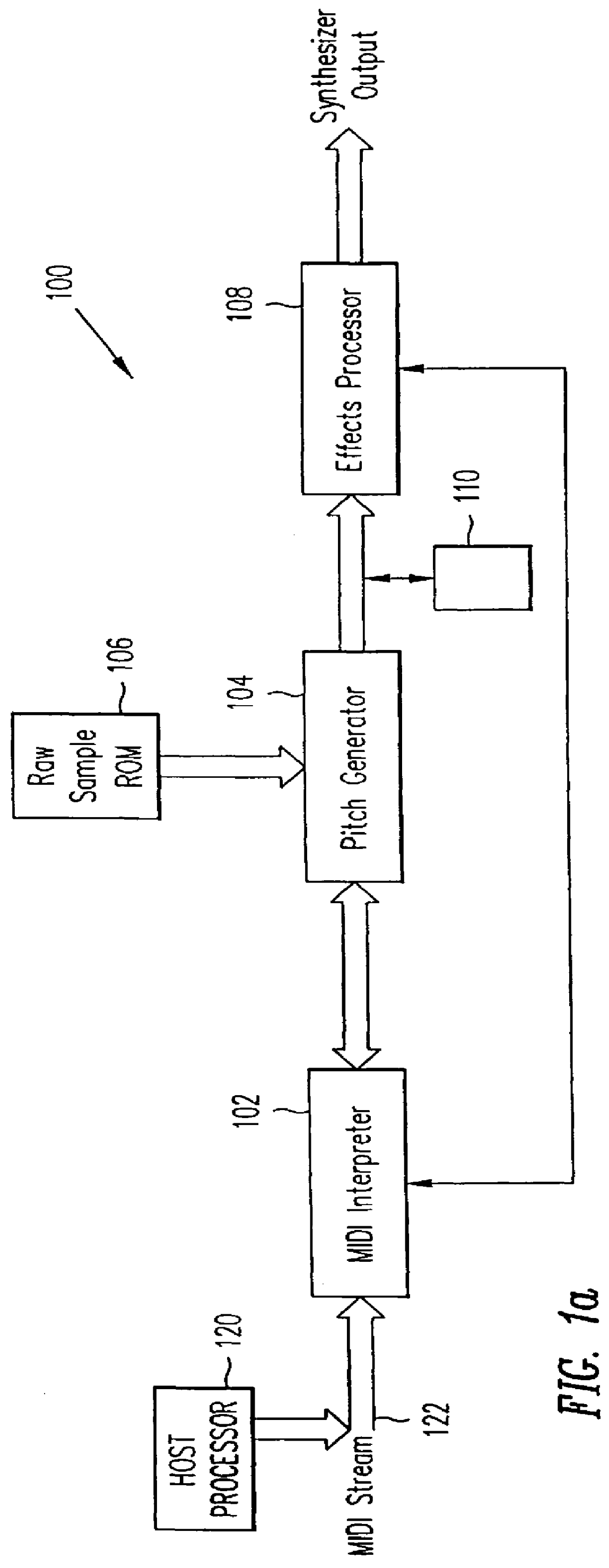

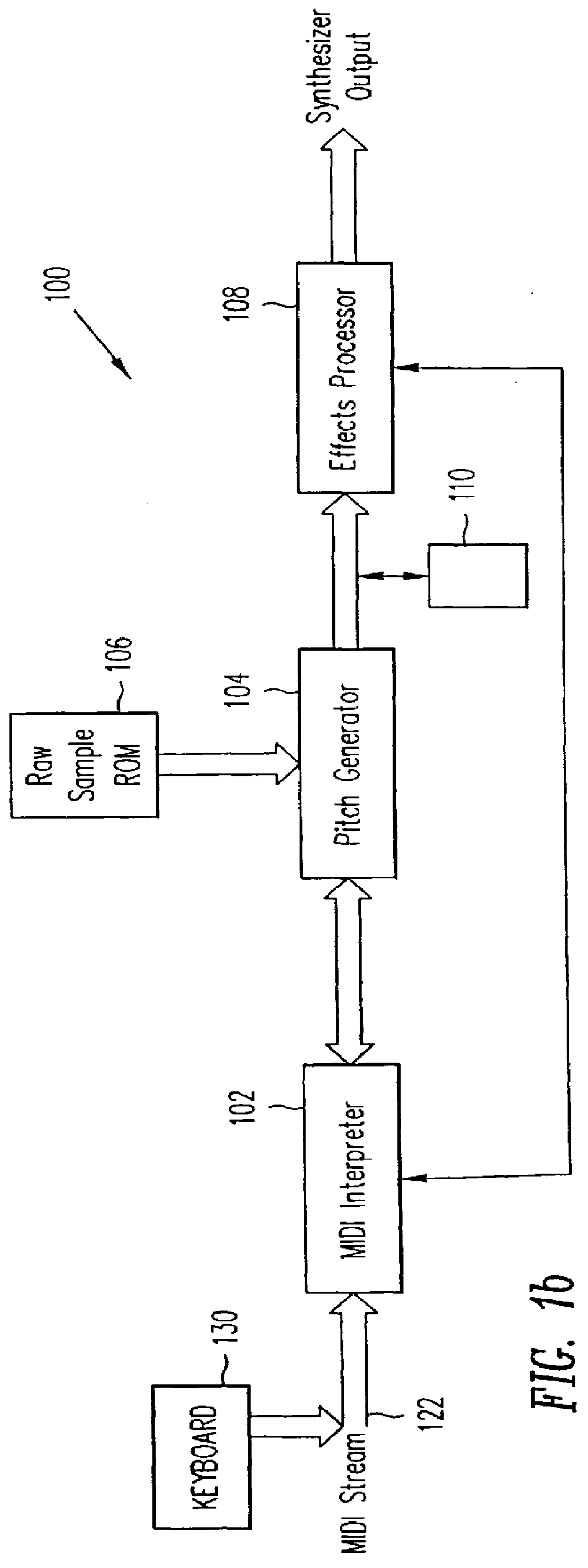

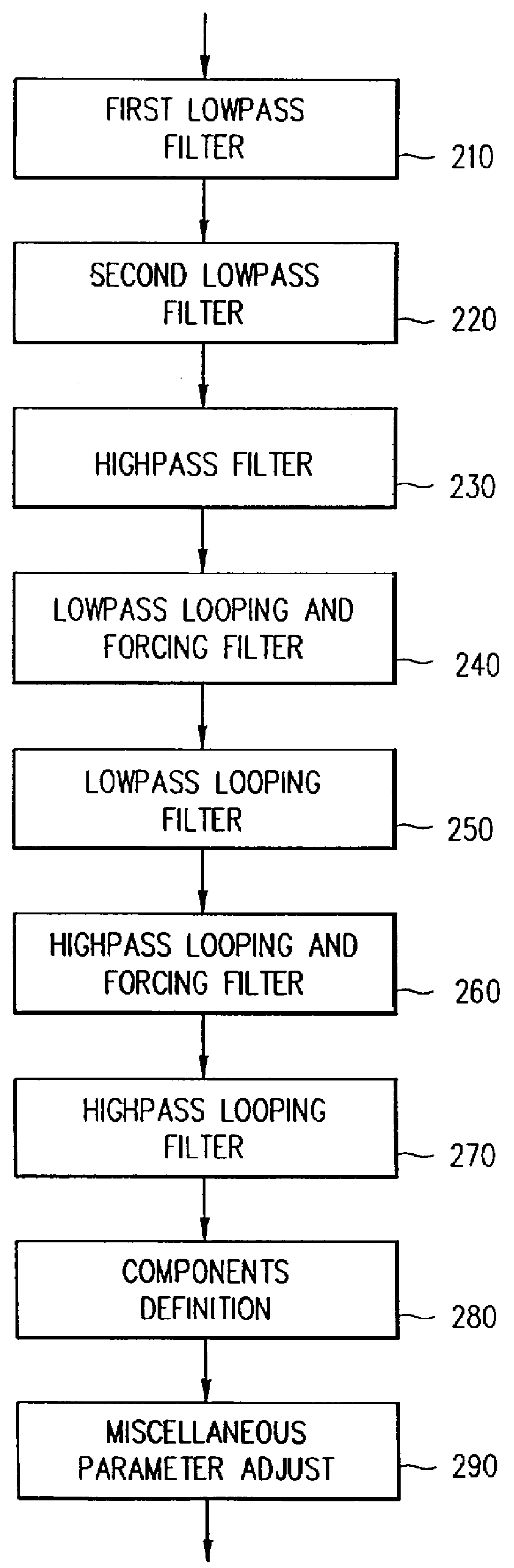

Period forcing filter for preprocessing sound samples for usage in a wavetable synthesizer

InactiveUS6096960ASmall sizeImprove fidelityElectrophonic musical instrumentsFrequency spectrumHarmonic

A nonperiodic waveform is forced to a periodic character to facilitate looping of the waveform without introducing audible, and thus objectionable, sound artifacts. Nonperiodic waveforms are typically nonperiodic due to the presence of nonharmonic high frequency spectral components. In time, the high frequency components decay faster than low frequency components and looping of the waveform is facilitated. A loop forcing process and loop forcing filter facilitate looping of a nonperiodic waveform by accelerating the removal of the nonperiodic high frequency components. A loop forcing filter accelerates the removal of nonperiodic high frequency components using a comb filter having a frequency selectivity that varies in time.

Owner:CRYSTAL SEMICON CORP

Decoding apparatus for low-density parity-check codes using sequential decoding, and method thereof

InactiveUS7590914B2Fast convergenceSmall sizeError preventionTransmission systemsComputer hardwareParity-check matrix

Disclosed is a decoding apparatus for LDPC (Low-Density Parity-Check) codes when receiving data encoded with LDPC codes on a channel having consecutive output values, and a method thereof. The decoding method for LDPC codes uses sequential decoding and includes the following steps: (a) the nodes are divided according to a parity-check matrix into check nodes for a parity-check message and variable nodes for a bit message; (b) the check nodes are divided into a predetermined number of subsets; (c) the LDPC codeword of each subset for all the check nodes is sequentially decoded; (d) an output message is generated for verifying validity of the decoding result; and (e) the steps (b), (c), and (d) are iteratively performed by a predetermined number of iterations.

Owner:ELECTRONICS & TELECOMM RES INST

Electric shaver with imaging capability

ActiveUS20120320180A1Reduce memory sizeLow data rateTelevision system detailsHair-singeingVisibilityWired communication

Owner:MAY PATENTS LTD

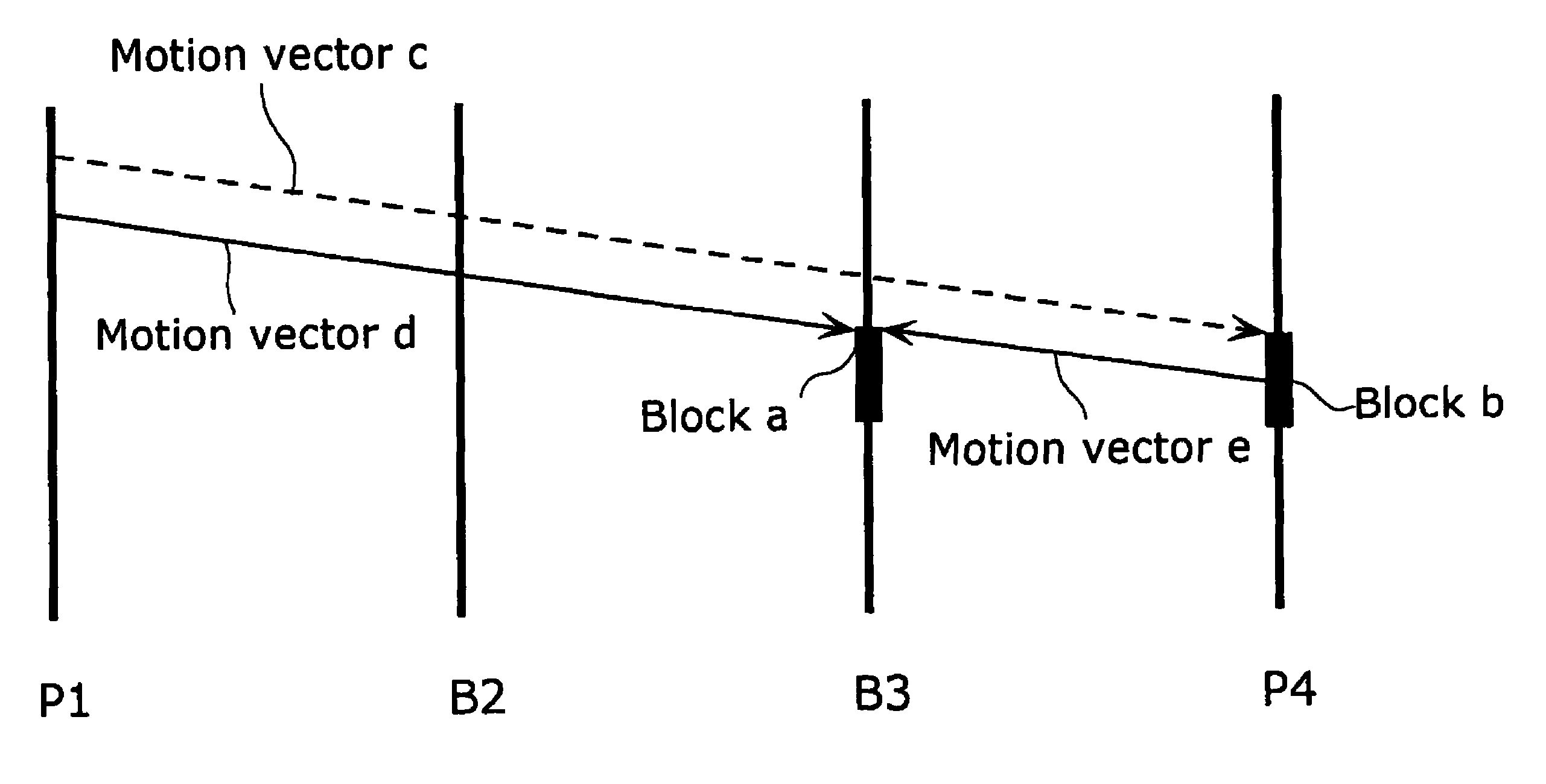

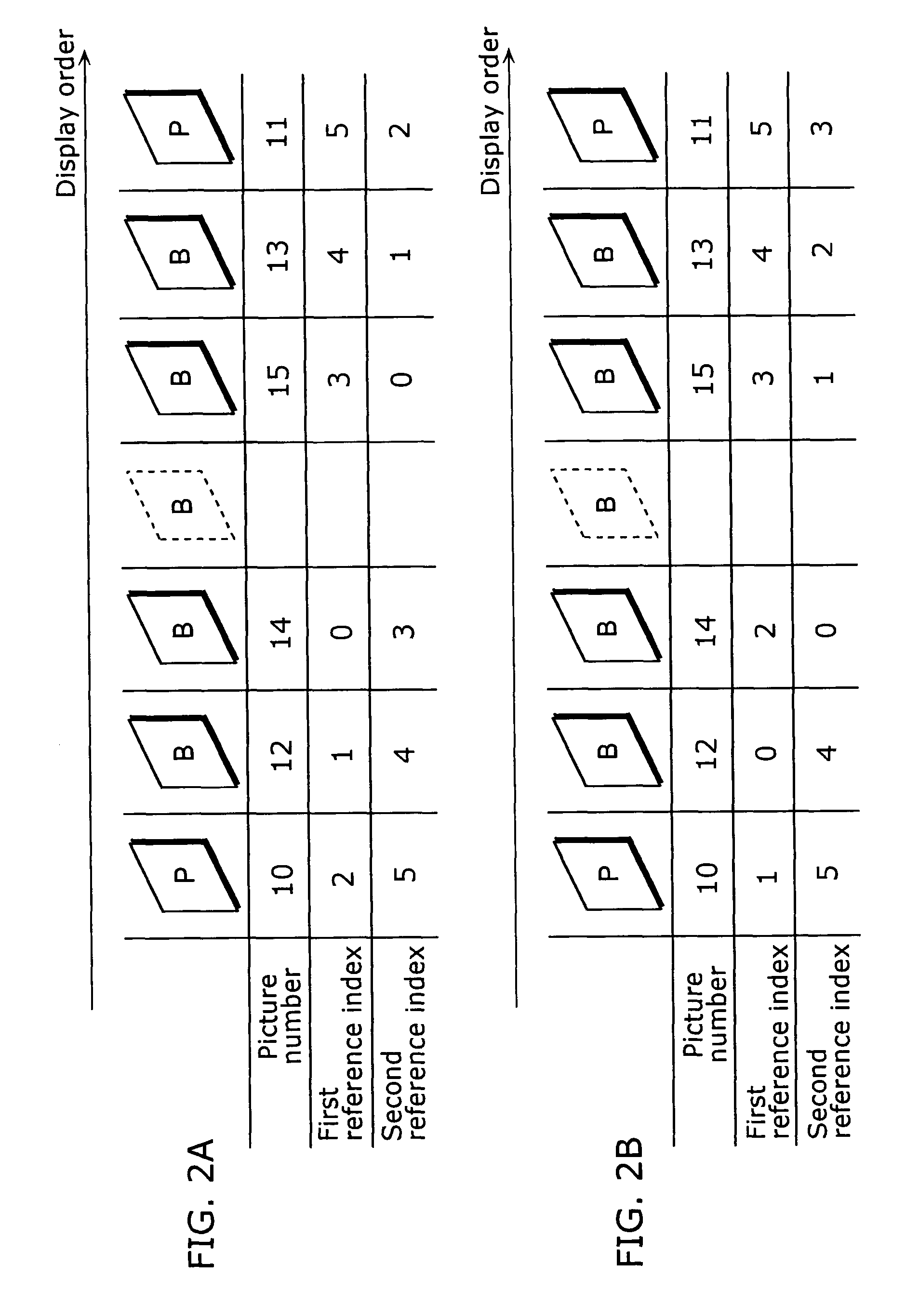

Moving picture encoding method, moving picture decoding method, and recording medium

InactiveUS7822120B2Improve coding efficiencyReduce memory sizeColor television with pulse code modulationColor television with bandwidth reductionMotion vectorComputer graphics (images)

In coding a picture to be used as a reference picture by another picture, a motion vector used in inter picture predictive coding is stored into the motion vector storage unit (116). However, the storage of a motion vector is controlled by the coding control unit (110) in such a way that motion vectors of pictures, fewer in number than the number of reference pictures, are stored into the storage unit (116). In the case where direct mode is used in coding a B-picture, if the motion vector to be referred to in coding in direct mode is stored in the motion vector storage unit (116), coding is performed using such motion vector. Further, in the case where the motion vector is not stored in the storage unit (116), coding is performed with the motion vector as “0”, and using a motion vector of a neighboring block.

Owner:PANASONIC CORP

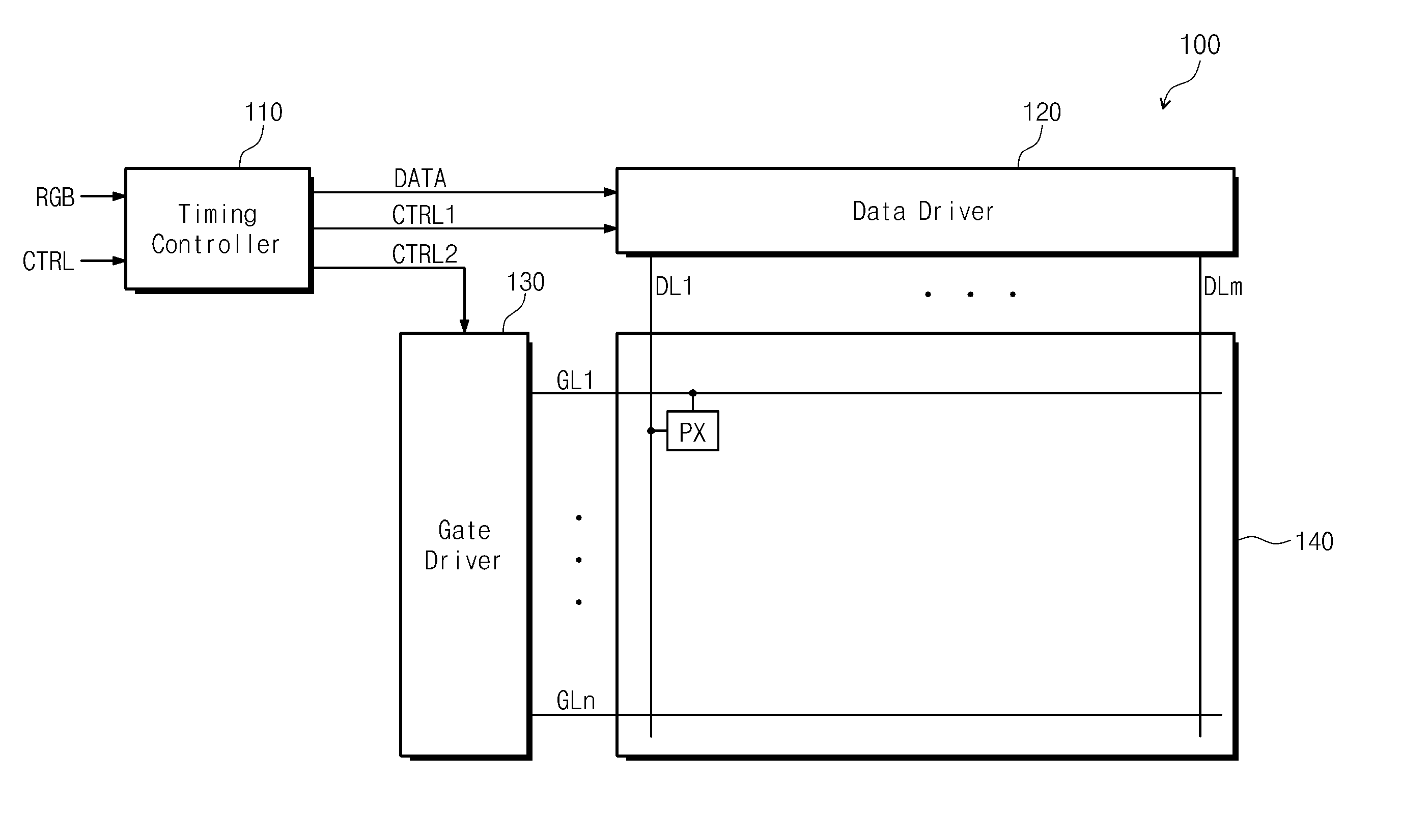

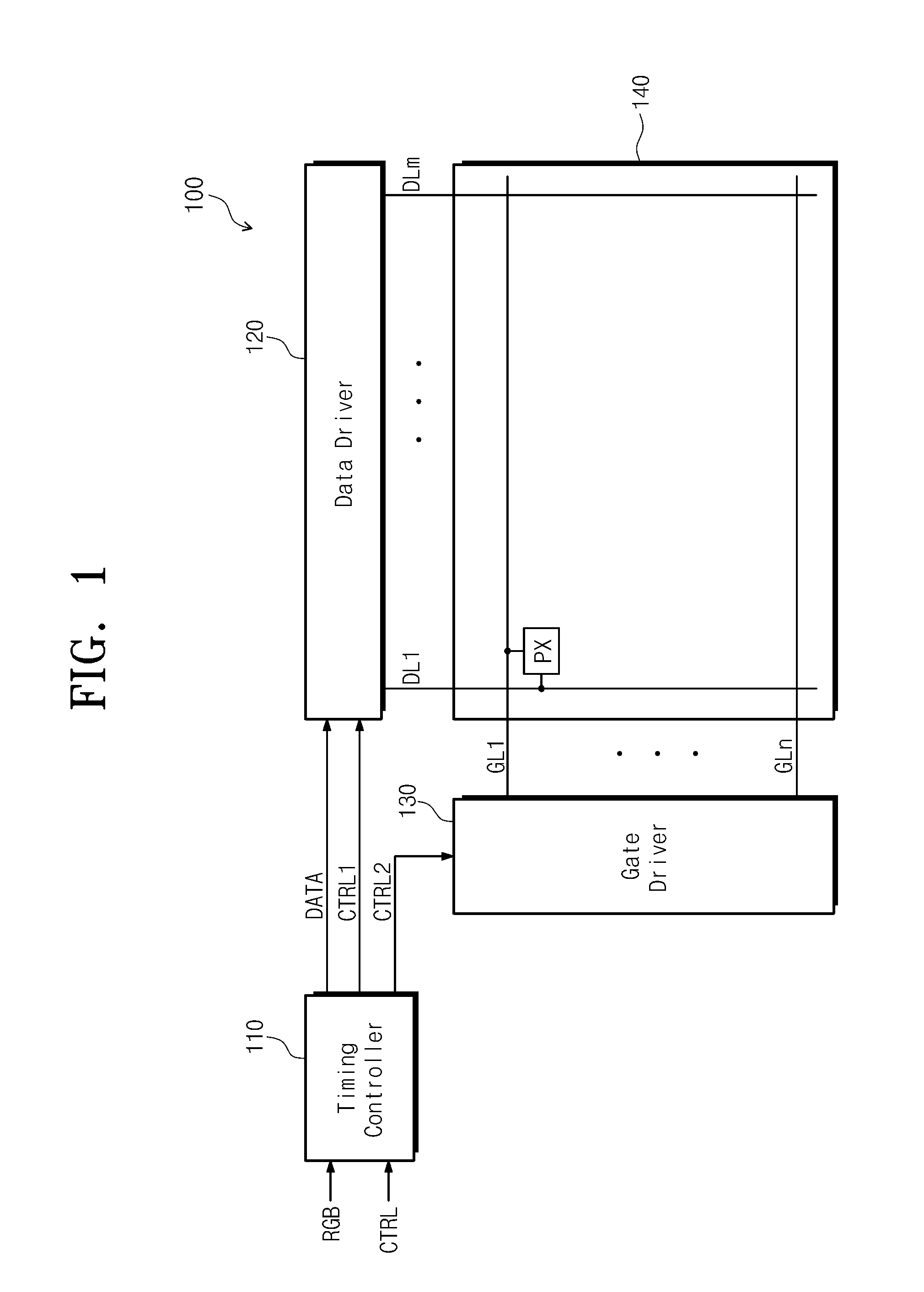

Display apparatus and method of driving the same

InactiveUS20150187303A1Reduced memory sizeImprove image qualityCathode-ray tube indicatorsInput/output processes for data processingTime signalImage signal

A display apparatus is provided. The display apparatus includes a display panel including a plurality of display blocks; a driving circuit configured to control an image to be displayed on the display panel; and a timing controller configured to control the driving circuit in response to an image signal and a control signal and to provide a data signal to the driving circuit, wherein the timing controller comprises a memory storing gamma correction values corresponding to gray scales of the image signal, and wherein the timing controller outputs the data signal, and the data signal is obtained by correcting the image signal using the gamma correction values.

Owner:SAMSUNG DISPLAY CO LTD

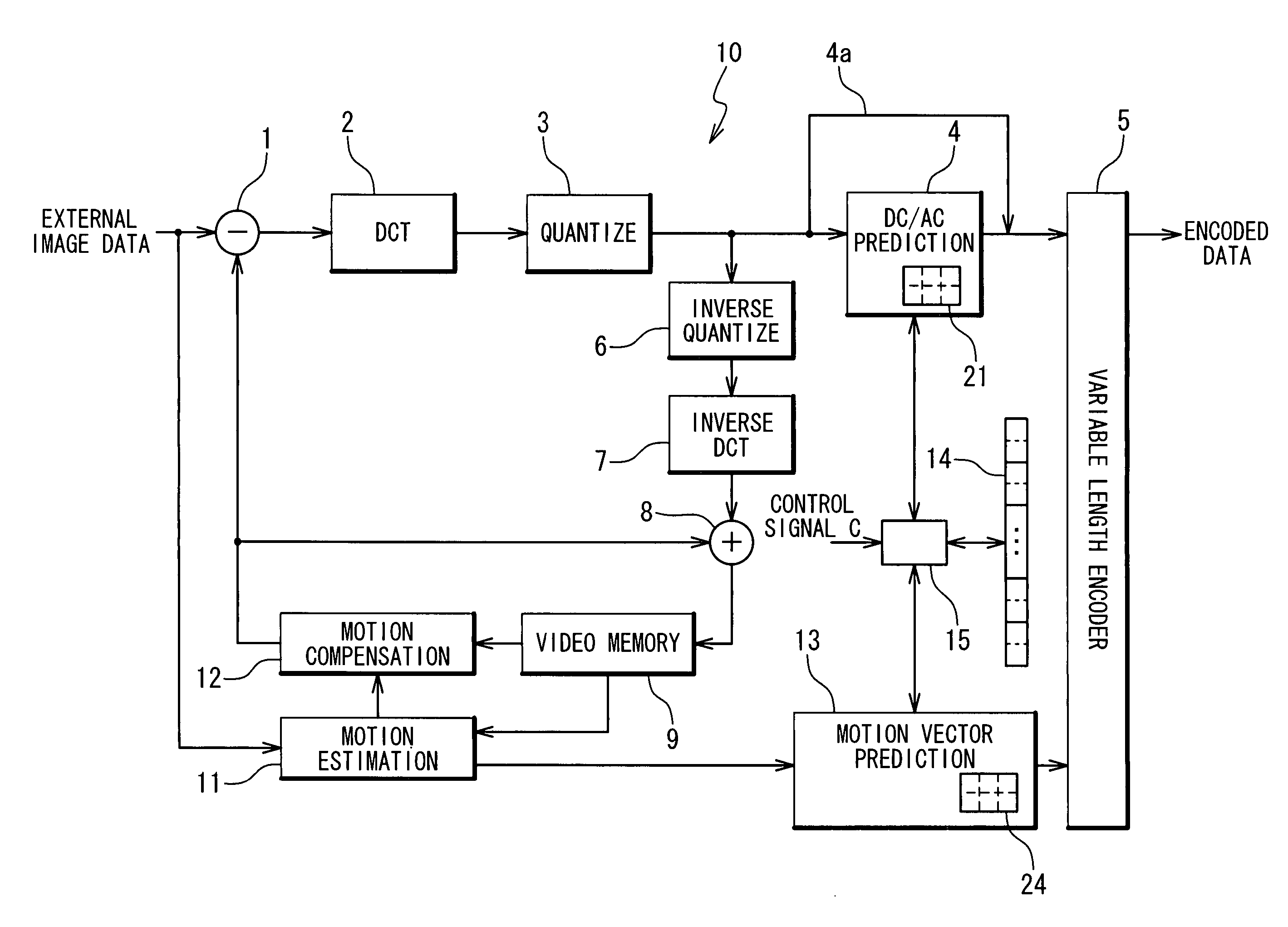

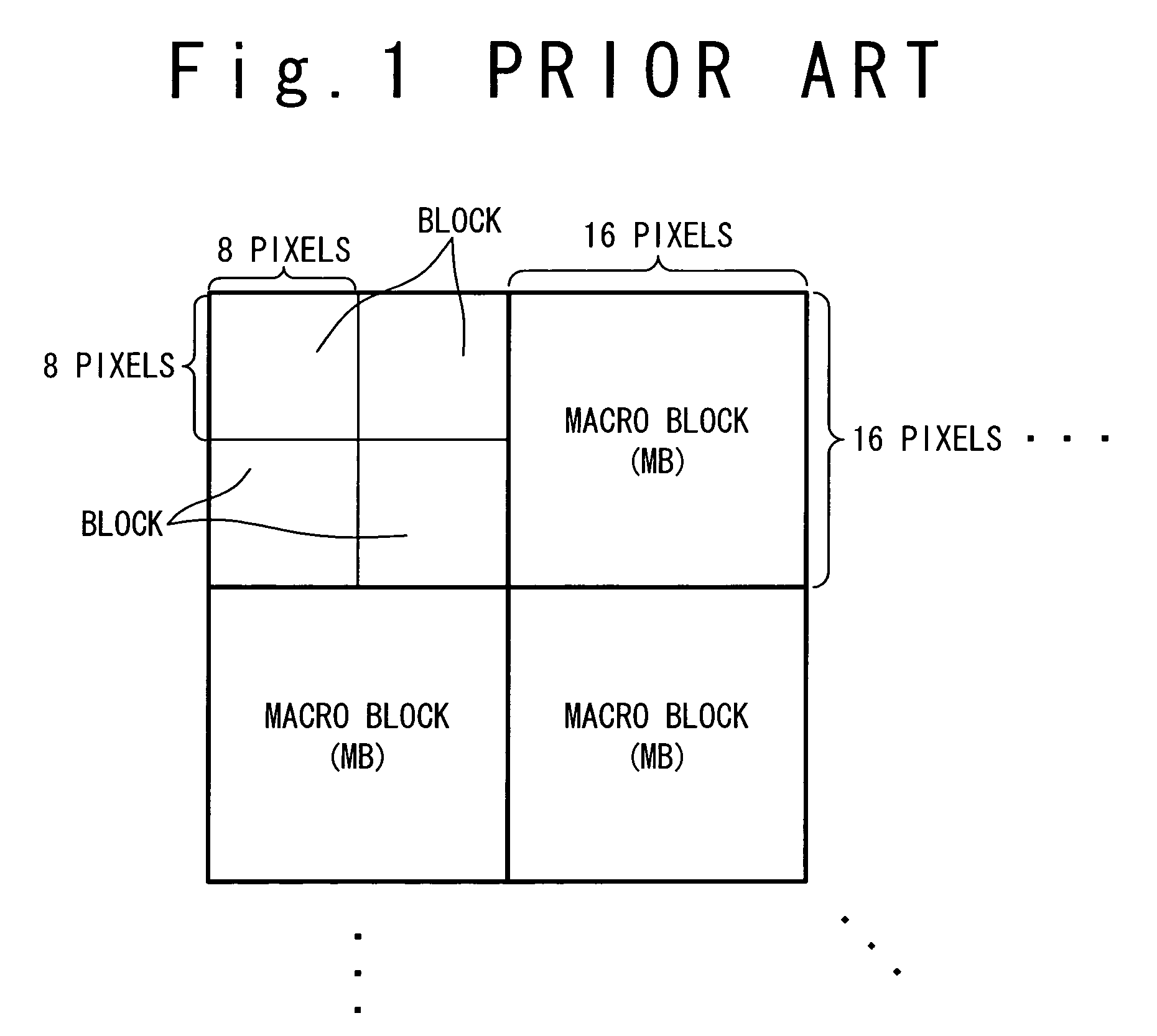

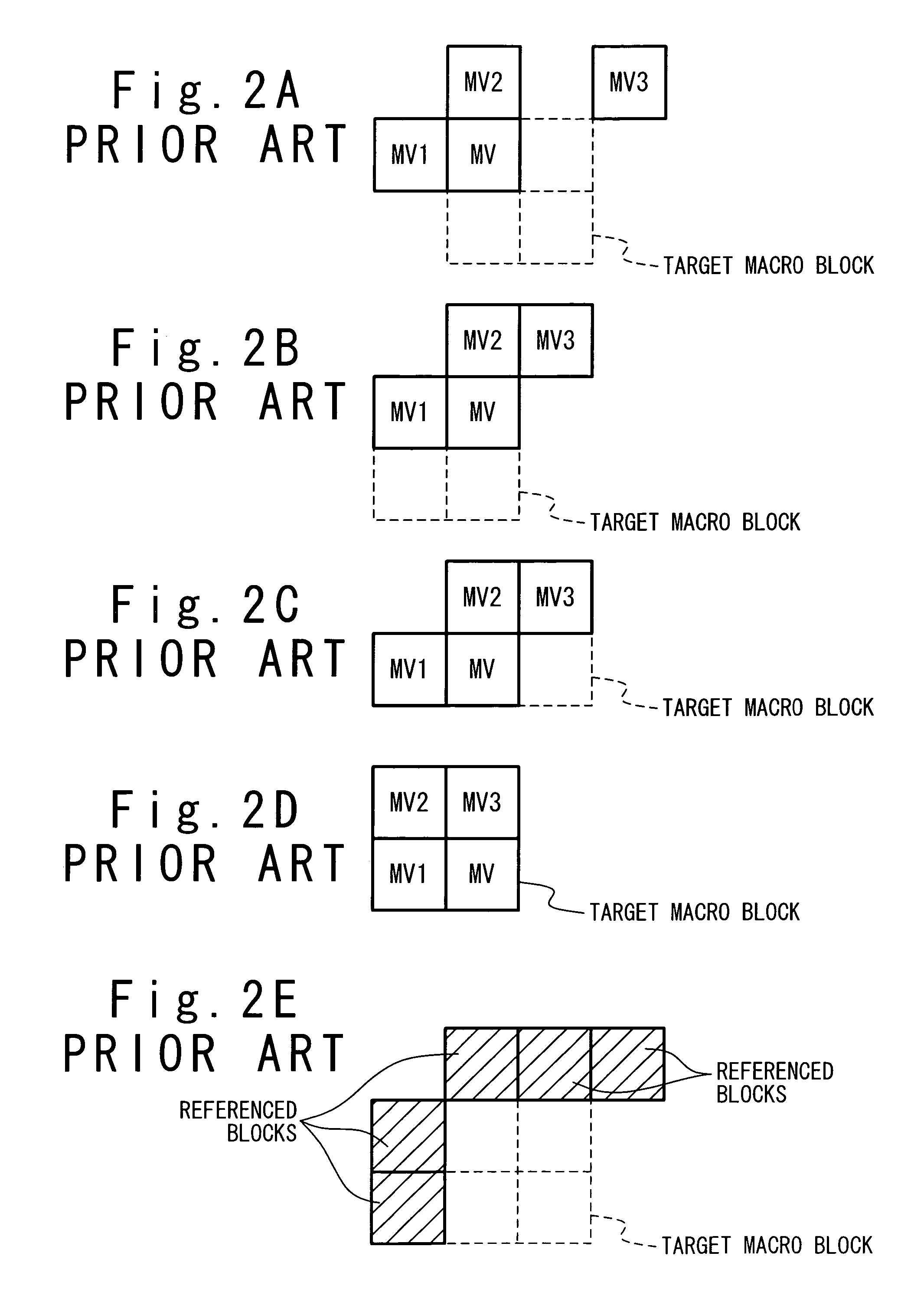

Video encoder and decoder for achieving inter-and intra-frame predictions with reduced memory resource

InactiveUS7876830B2Reduce memory capacityReduce capacityPicture reproducers using cathode ray tubesCode conversionVideo encodingMotion vector

Owner:RENESAS ELECTRONICS CORP

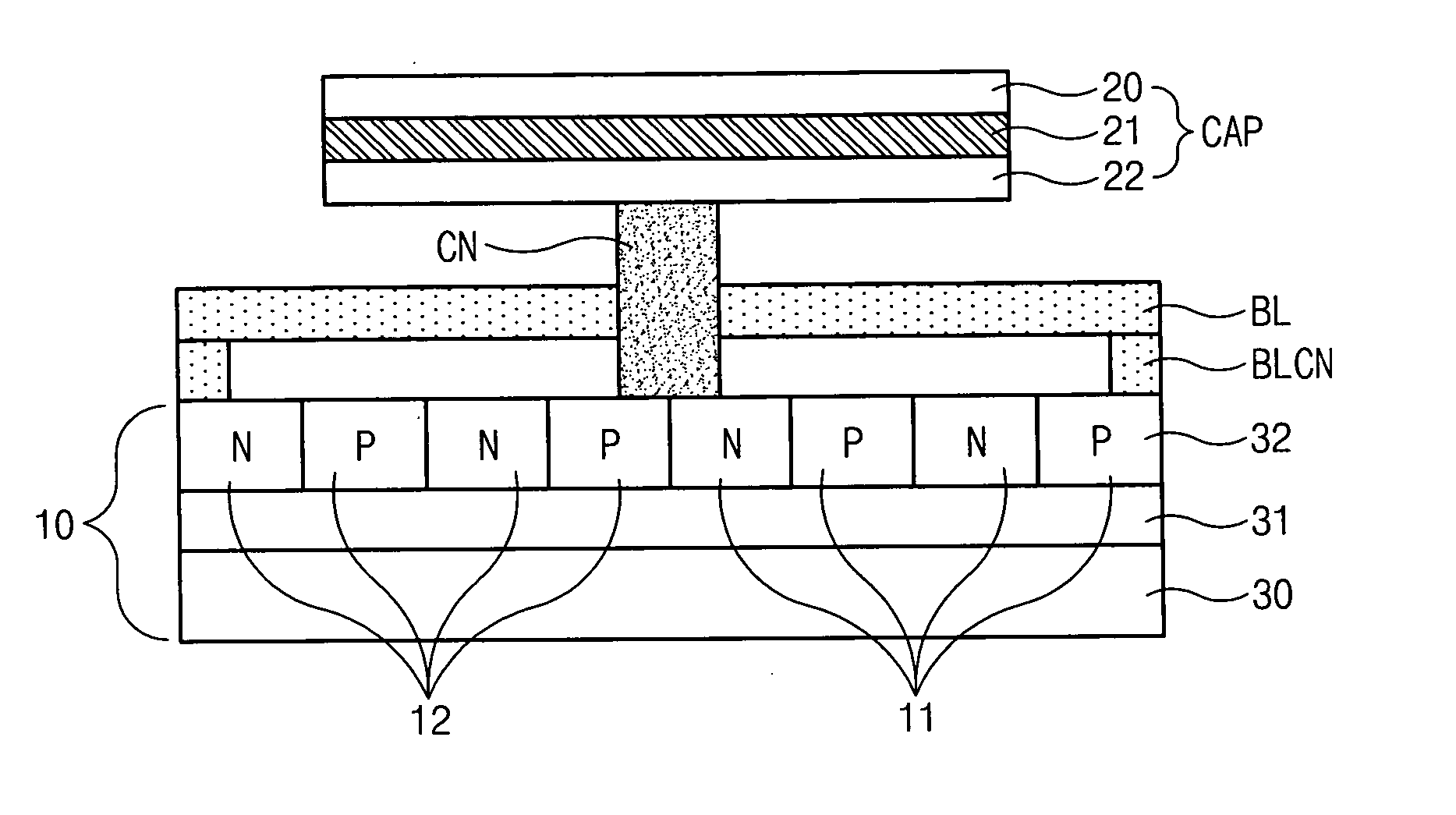

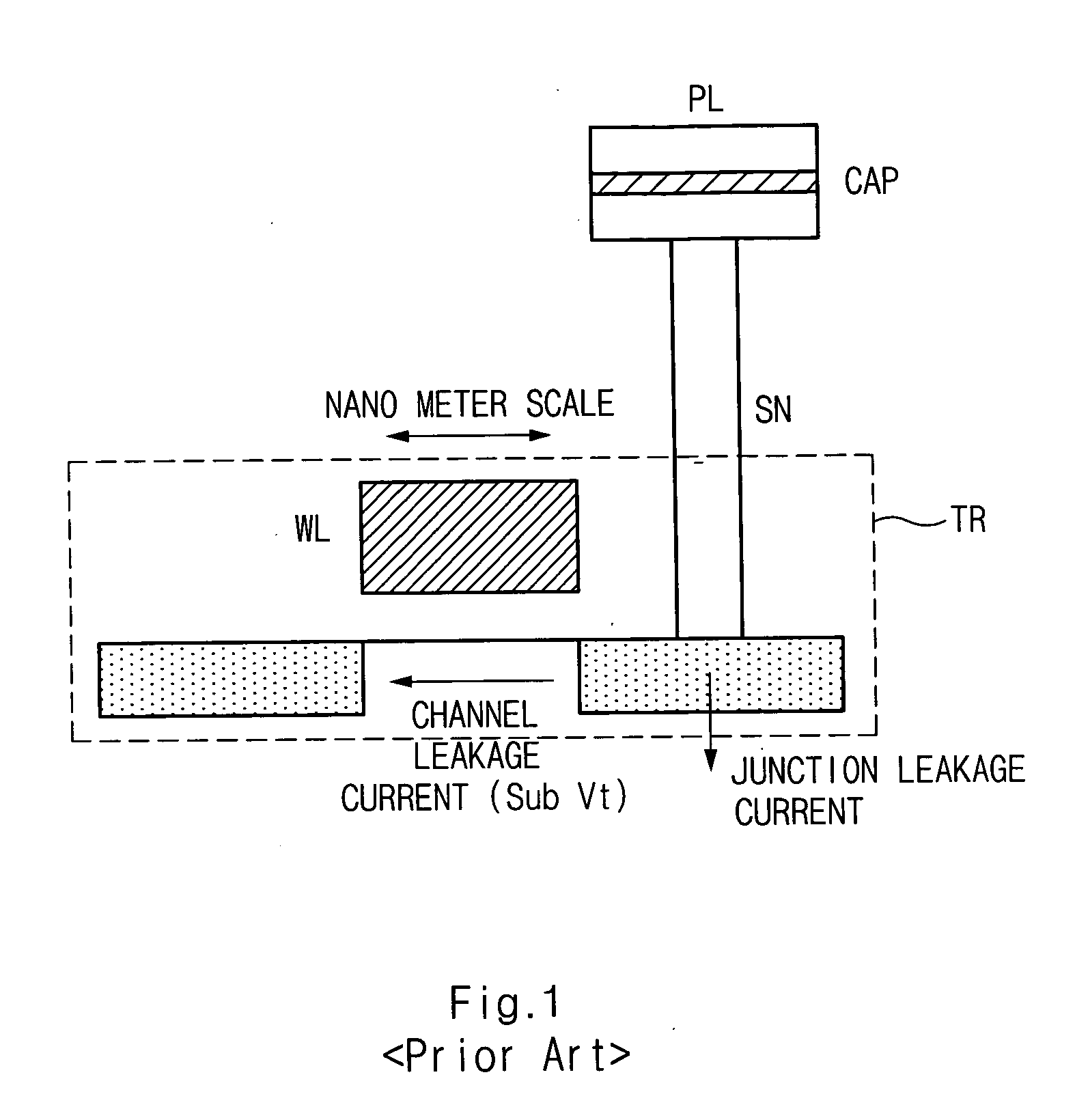

Nano tube cell and memory device using the same

InactiveUS20050180194A1Simple processReduce memory sizeTransistorAgricultural machinesBit lineChip size

A nano tube cell and a memory device using the same features a cross point cell using a capacitor and a PNPN nano tube switch to reduce the whole memory size. In the memory device, the unit nano tube cell comprising a capacitor and a PNPN nano tube switch which does not an additional gate control signal is located where a word line and a bit line are crossed, so that a cross point cell array is embodied. As a result, the whole chip size is reduced, and read and write operations are effectively improved.

Owner:SK HYNIX INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com