Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

683 results about "Address generator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

SIMD processor and addressing method

InactiveUS20060047937A1Without unduly consuming processor resourcesMemory adressing/allocation/relocationMicro-instruction address formationMemory addressProcessor register

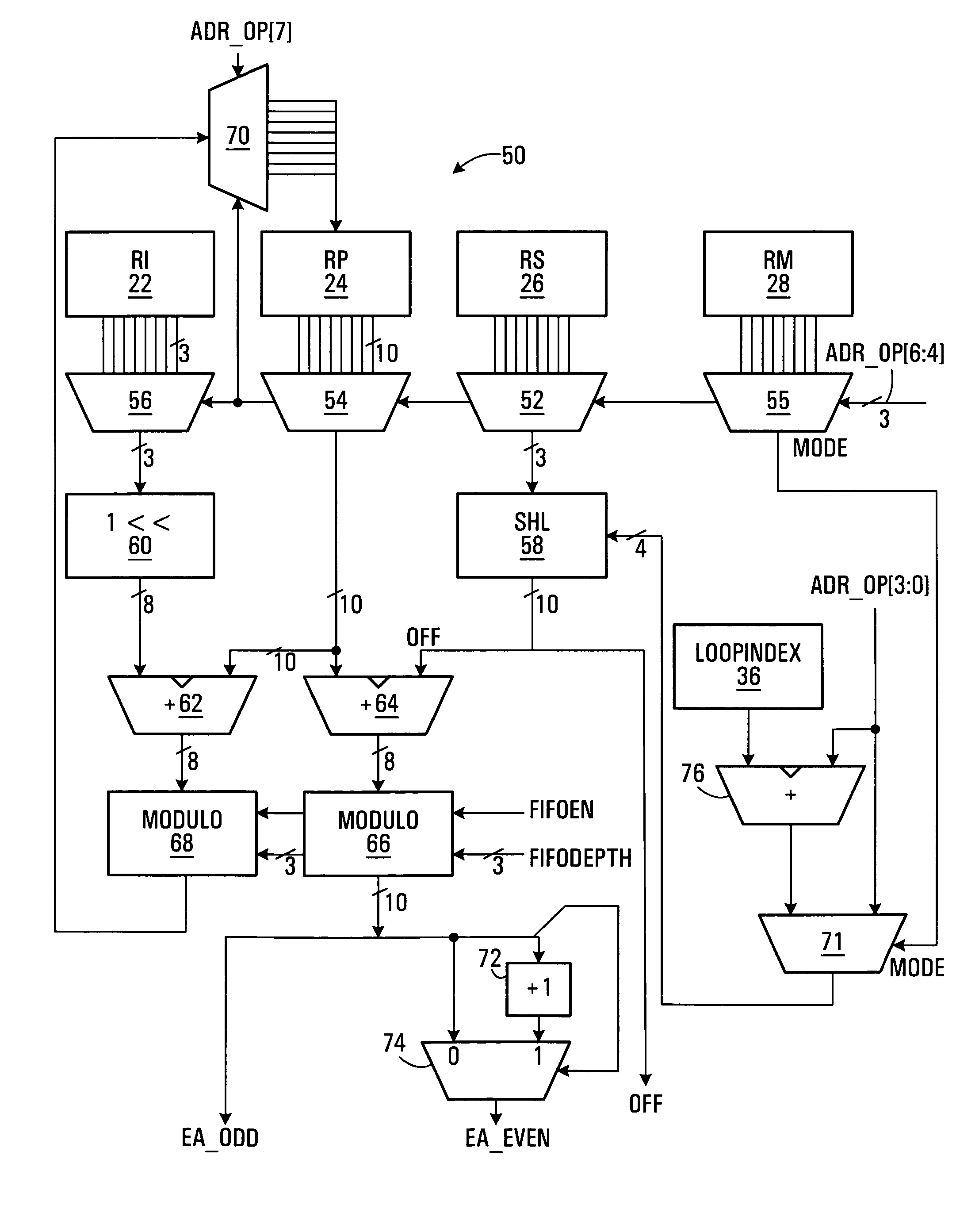

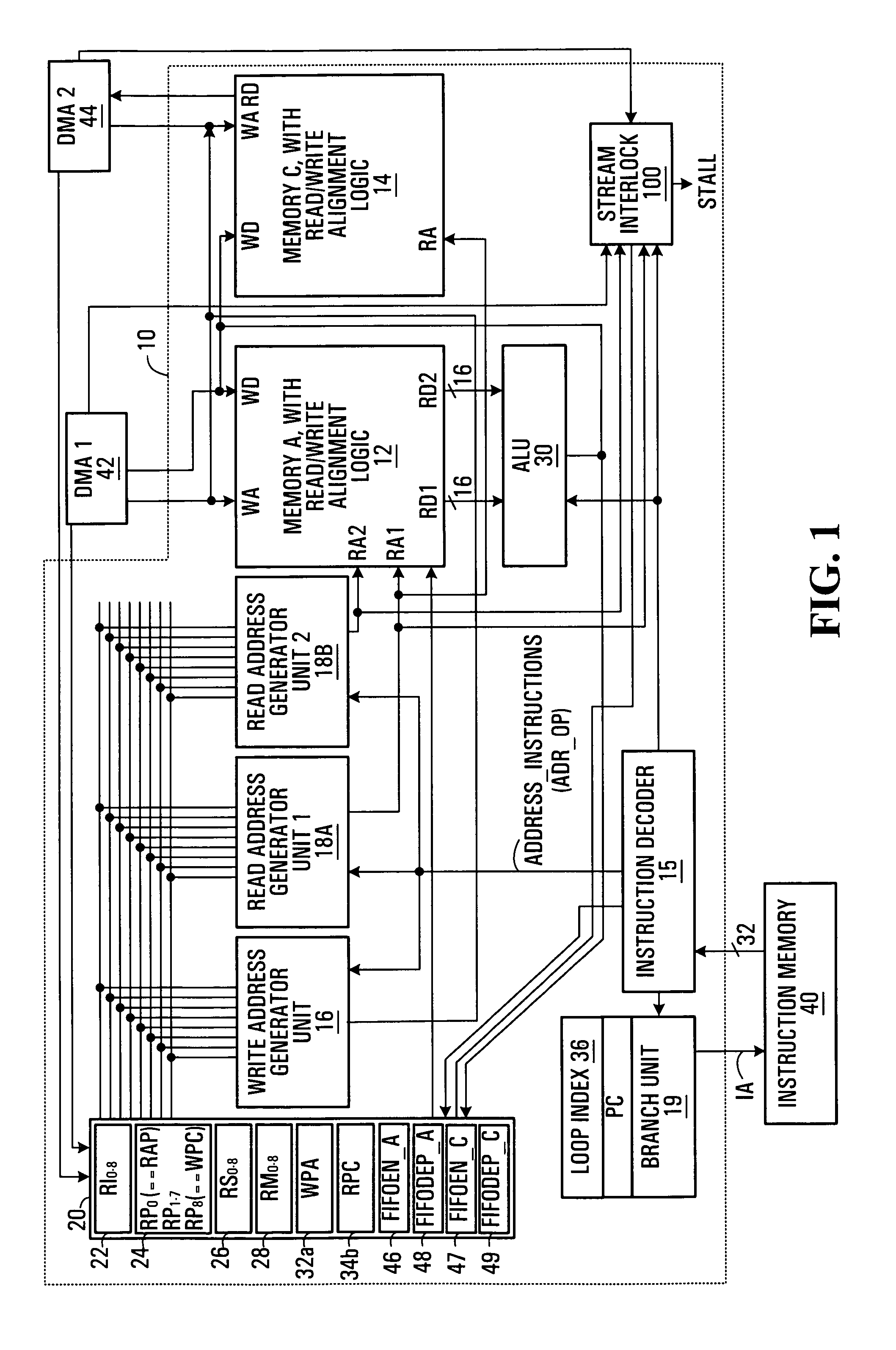

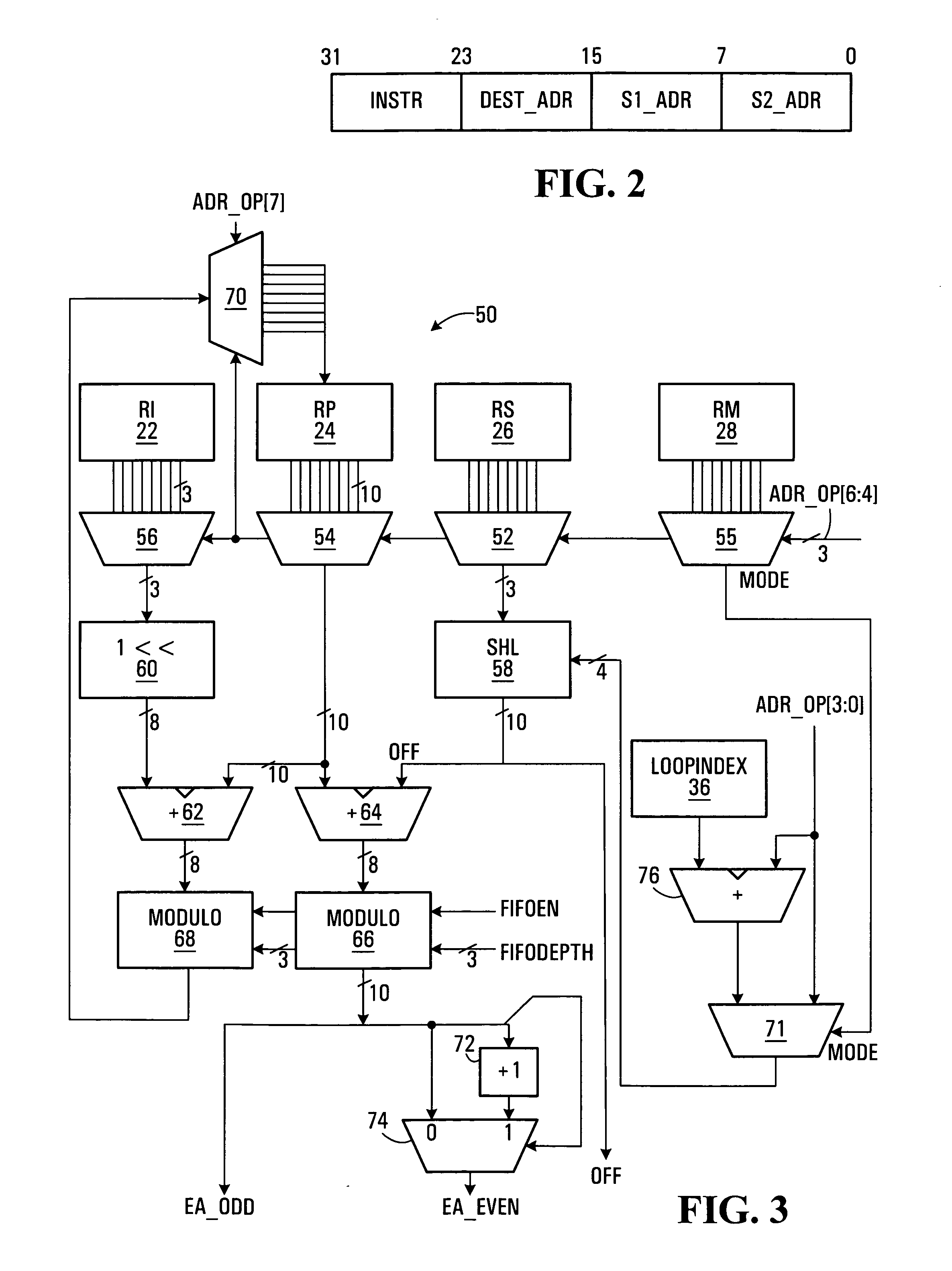

A single instruction, multiple data (SIMD) processor including a plurality of addressing register sets, used to flexibly calculate effective operand source and destination memory addresses is disclosed. Two or more address generators calculate effective addresses using the register sets. Each register set includes a pointer register, and a scale register. An address generator forms effective addresses from a selected register set's pointer register and scale register; and an offset. For example, the effective memory address may be formed by multiplying the scale value by an offset value and summing the pointer and the scale value multiplied by the offset value.

Owner:AVAGO TECH INT SALES PTE LTD

Data processing apparatus and method

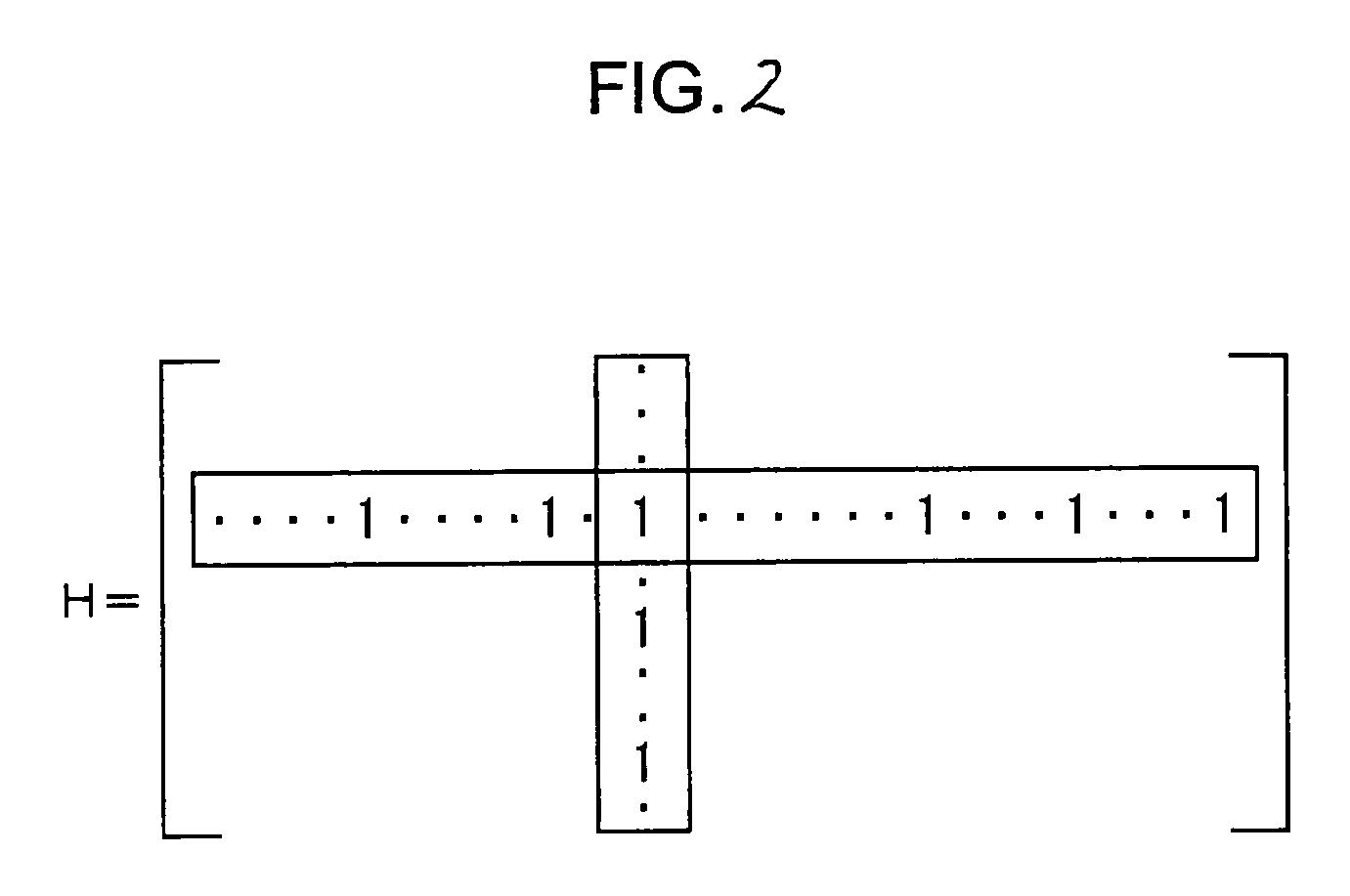

ActiveUS20090125780A1Improve performanceLow Density Parity Check (LDPCTransmission path divisionError detection/correctionCarrier signalTheoretical computer science

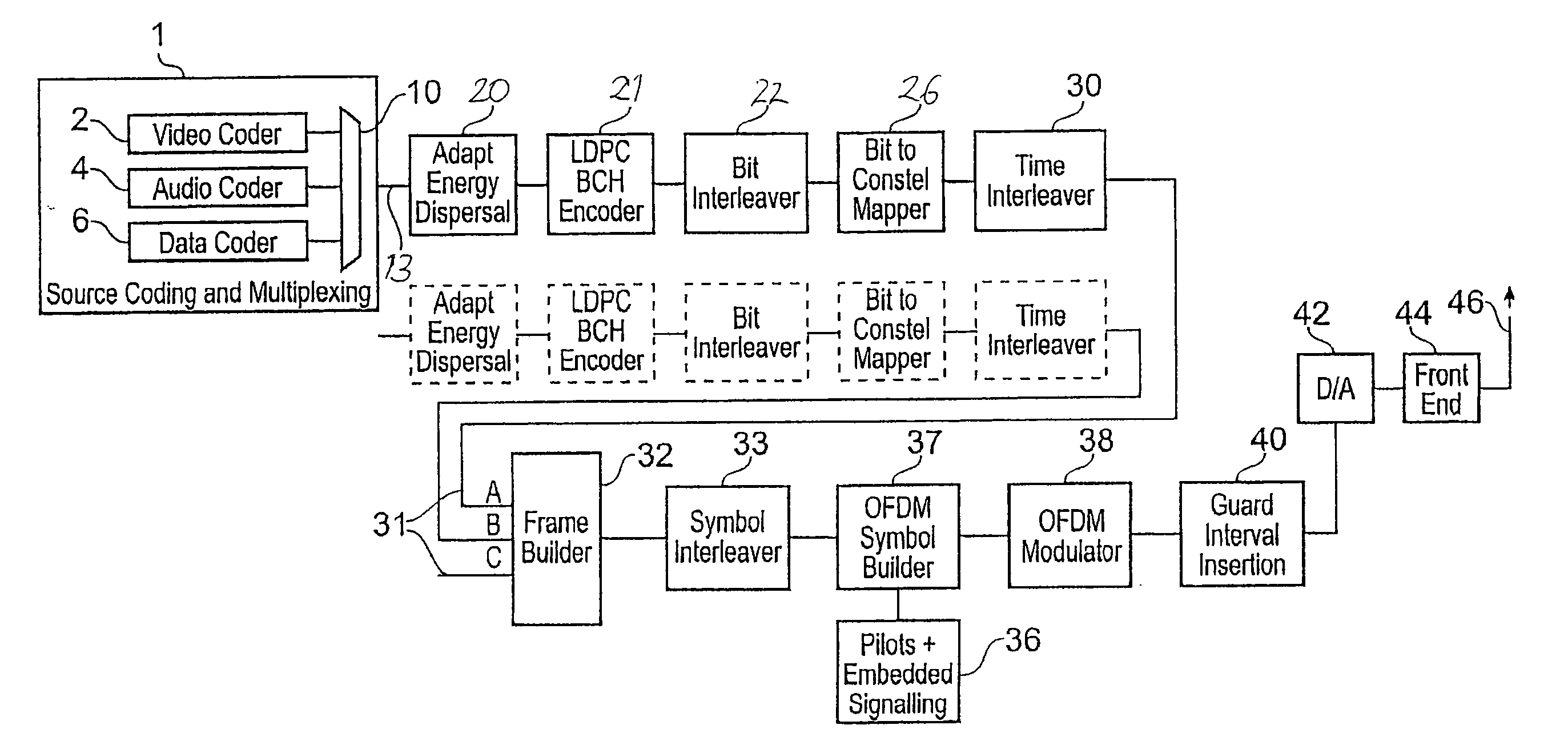

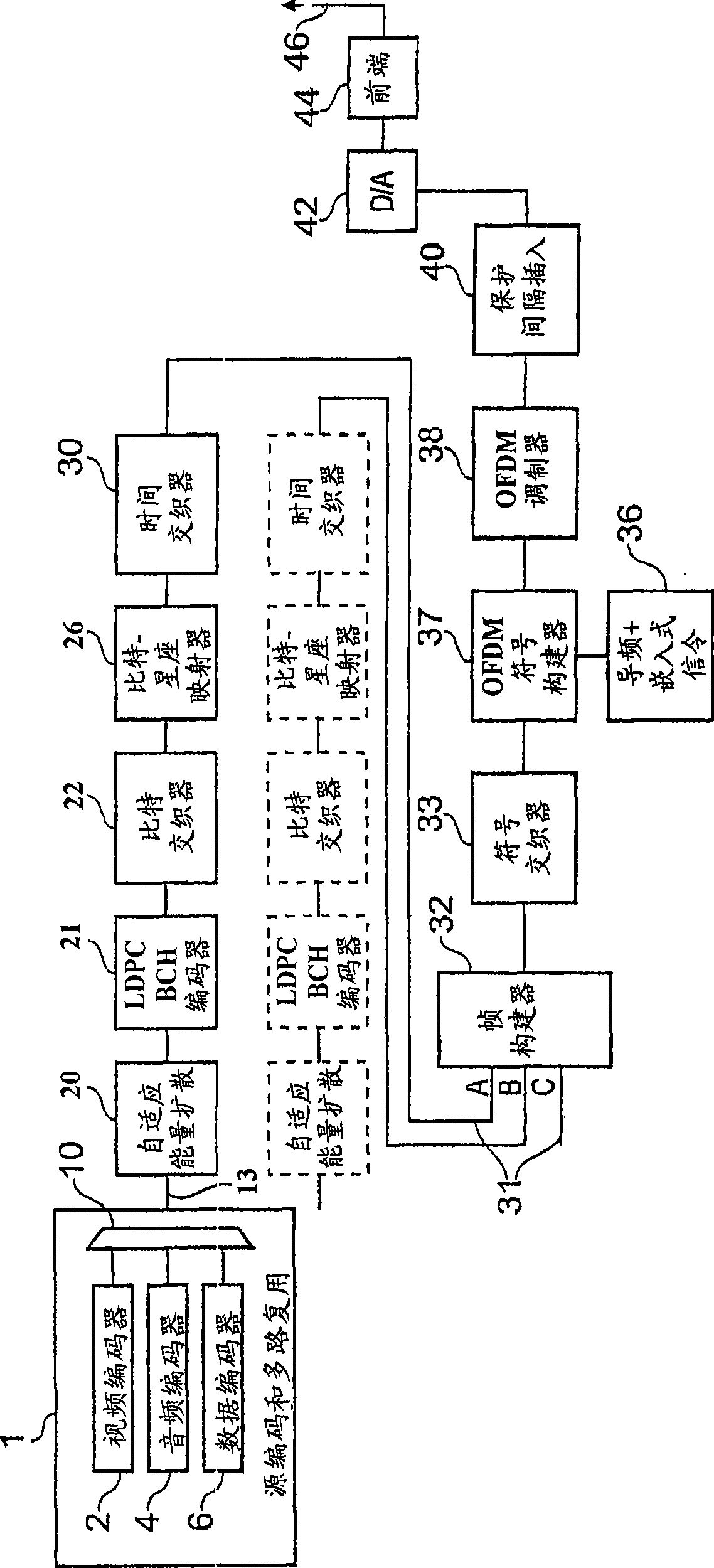

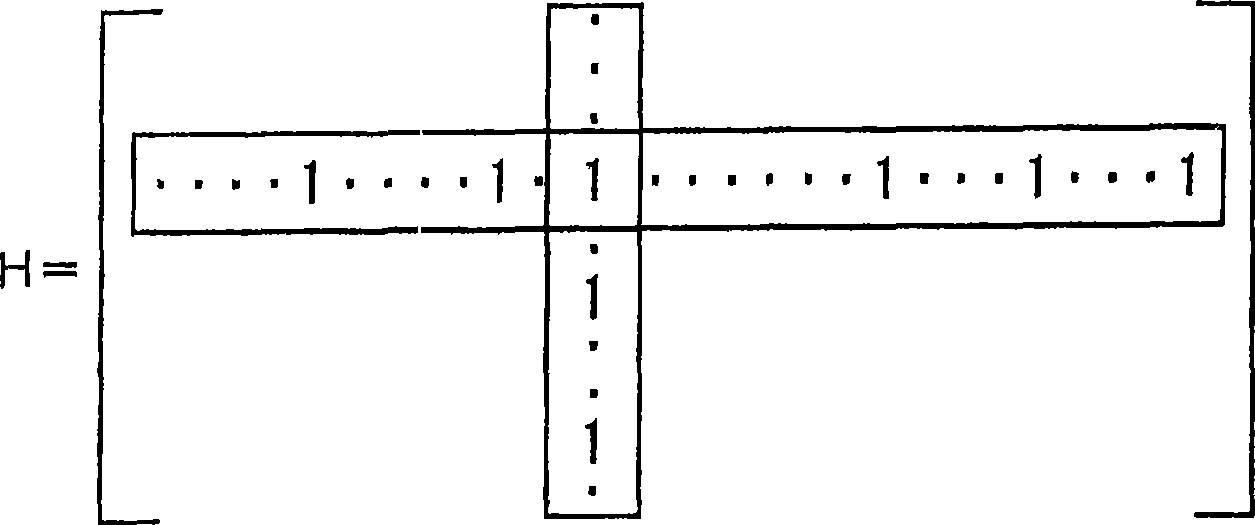

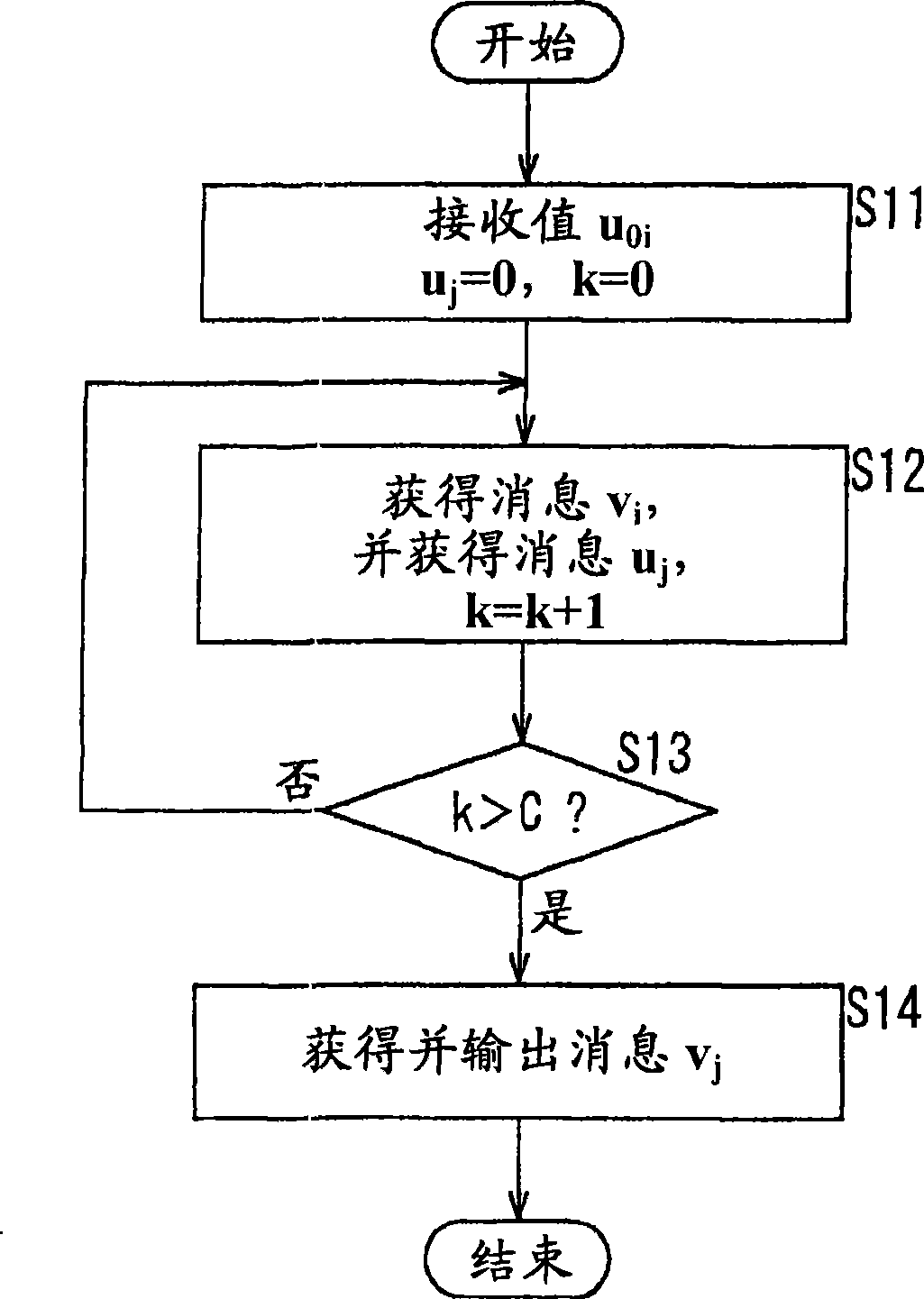

A data processing apparatus communicates data bits on a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processing apparatus comprises a parity interleaver operable to perform parity interleaving on Low Density Parity Check (LDPC) encoded data bits obtained by performing LDPC encoding according to a parity check matrix of an LDPC code including a parity matrix corresponding to parity bits of the LDPC code, the parity matrix having a stepwise structure, so that a parity bit of the LDPC encoded data bits is interleaved to a different parity bit position. A mapping unit maps the parity interleaved bits onto data symbols corresponding to modulation symbols of a modulation scheme of the OFDM sub-carrier signals. A symbol interleaver is arranged in operation to read-into a symbol interleaver memory the predetermined number of data symbols for mapping onto the OFDM sub-carrier signals, and to read-out of the interleaver memory the data symbols for the OFDM sub-carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on the sub-carrier signals. The set of addresses are generated by an address generator which has been optimised to interleave the data symbols on to the sub-carrier signals of the OFDM carrier signals for a given operating mode of the OFDM system, such as a 32K operating mode for DVB-T2 or DVB-C2.

Owner:SATURN LICENSING LLC

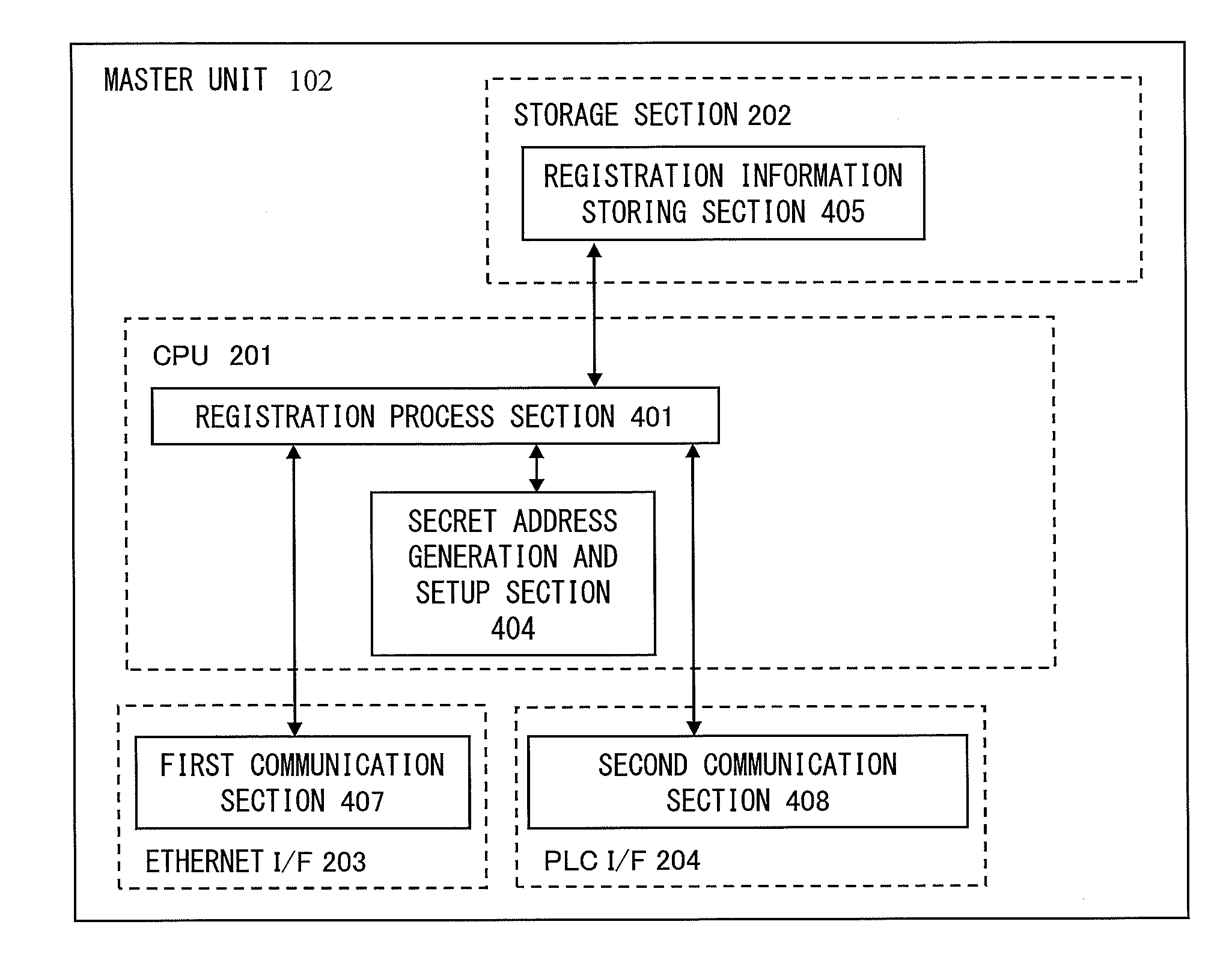

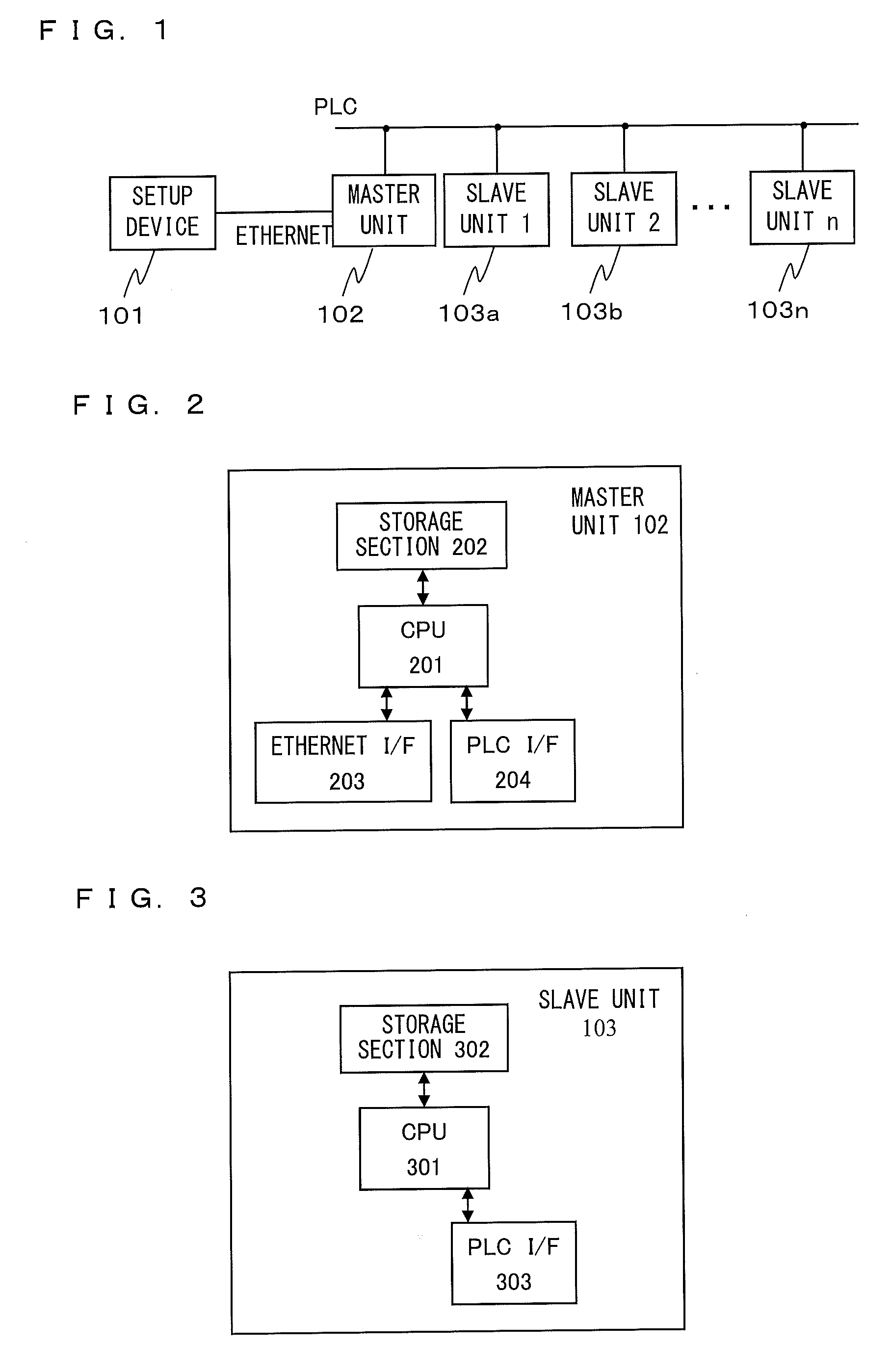

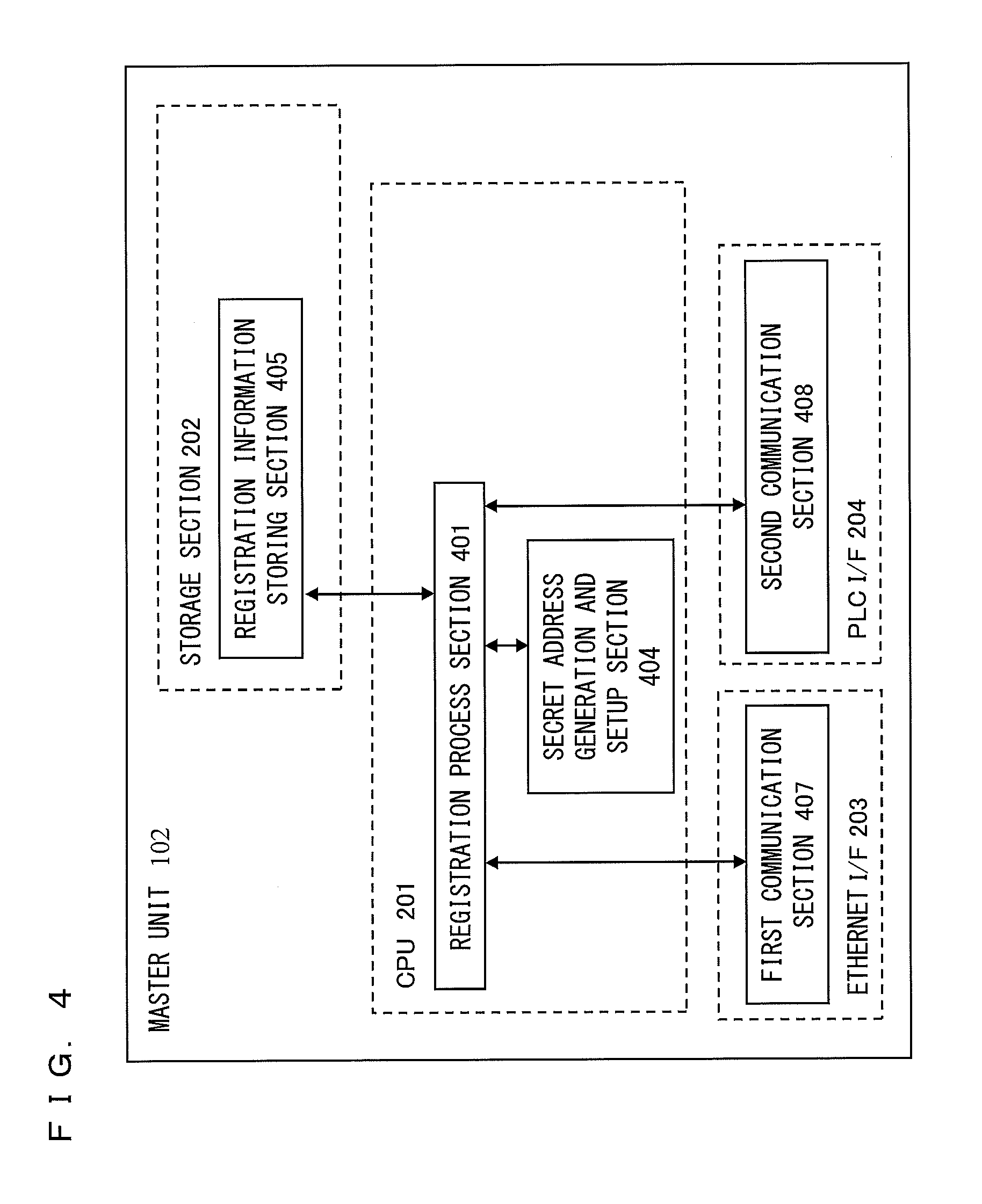

Master unit and slave unit

InactiveUS20110173447A1User identity/authority verificationDigital data authenticationAddress generatorKey generation

Provided is a communication device which securely registers a slave unit. A secret address generation and setup section generates a secret address generator, and a secret address of the slave unit used temporarily instead of a unique address of the slave unit based on the secret address generator and identification information of the slave unit. A second communication section transmits to the slave unit a registration start notice containing the secret address generator by broadcast. A registration process section generates a registration authentication key; generates a unique key of the slave unit by transmitting / receiving, to / from the slave unit, unique key generation information encrypted using the registration authentication key; receives, from the slave unit, the unique address of the slave unit encrypted using the registration authentication key; and stores the identification information in association with the unique address and the unique key of the slave unit in the registration information storing section.

Owner:PANASONIC CORP

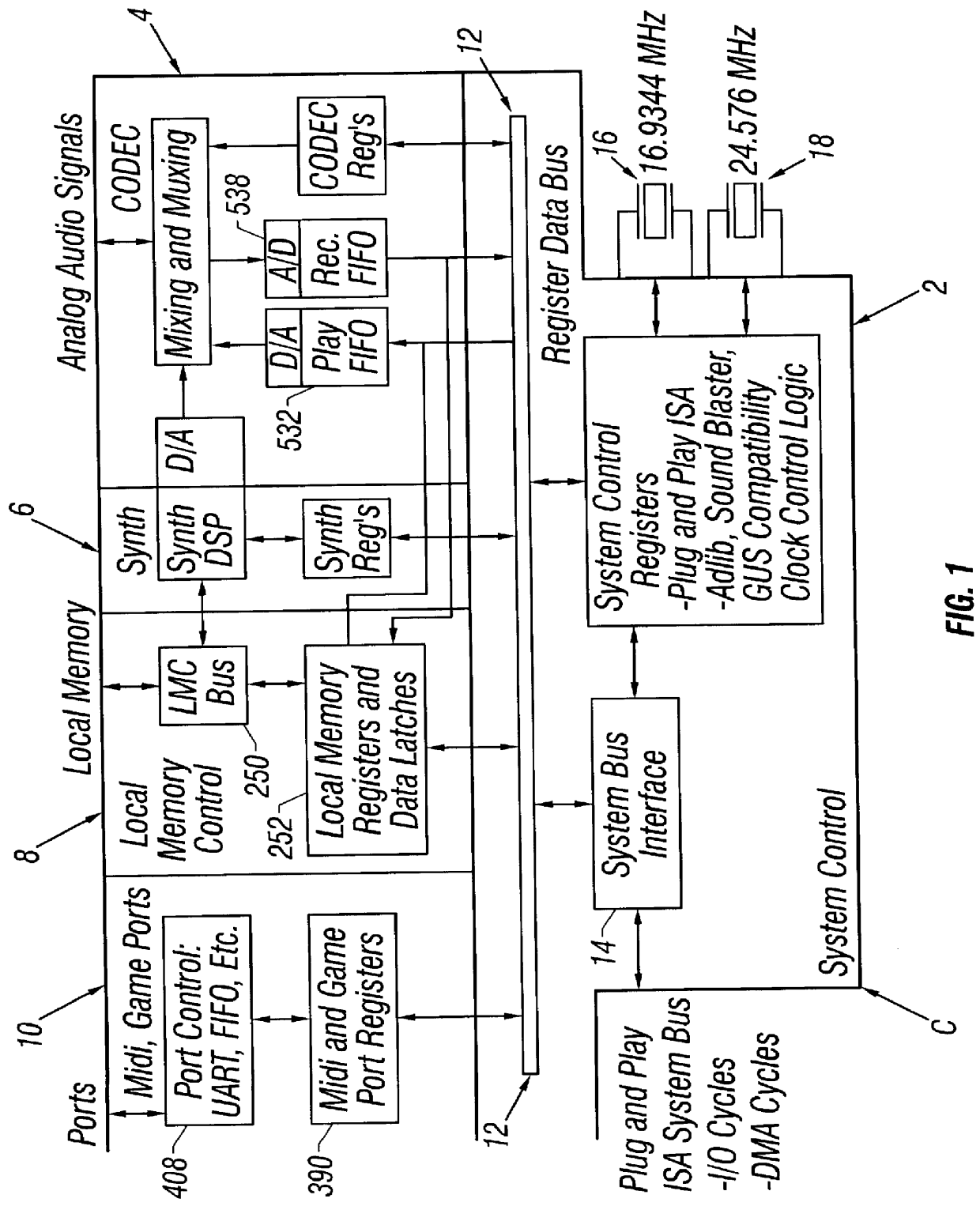

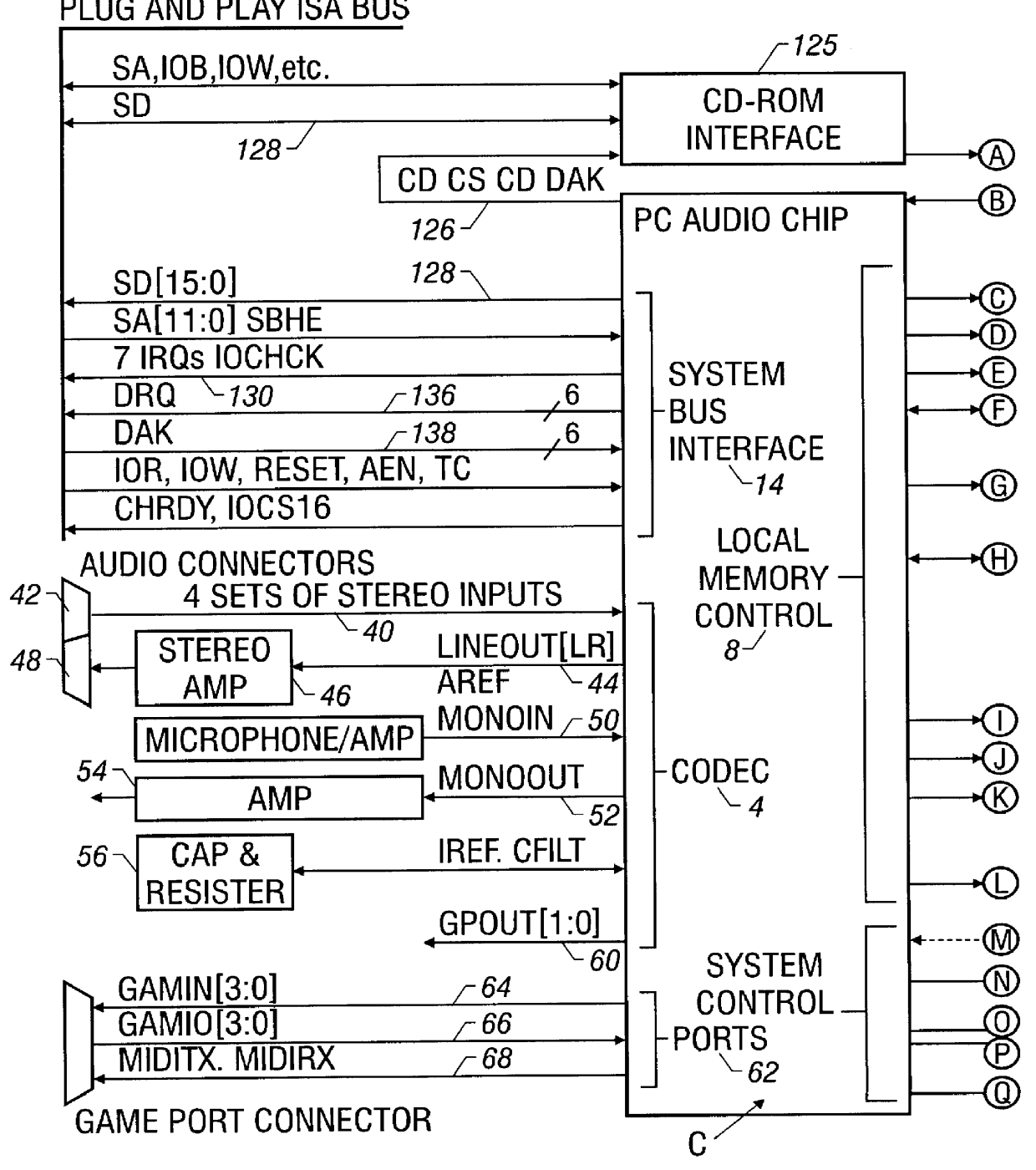

Digital wavetable audio synthesizer with delay-based effects processing

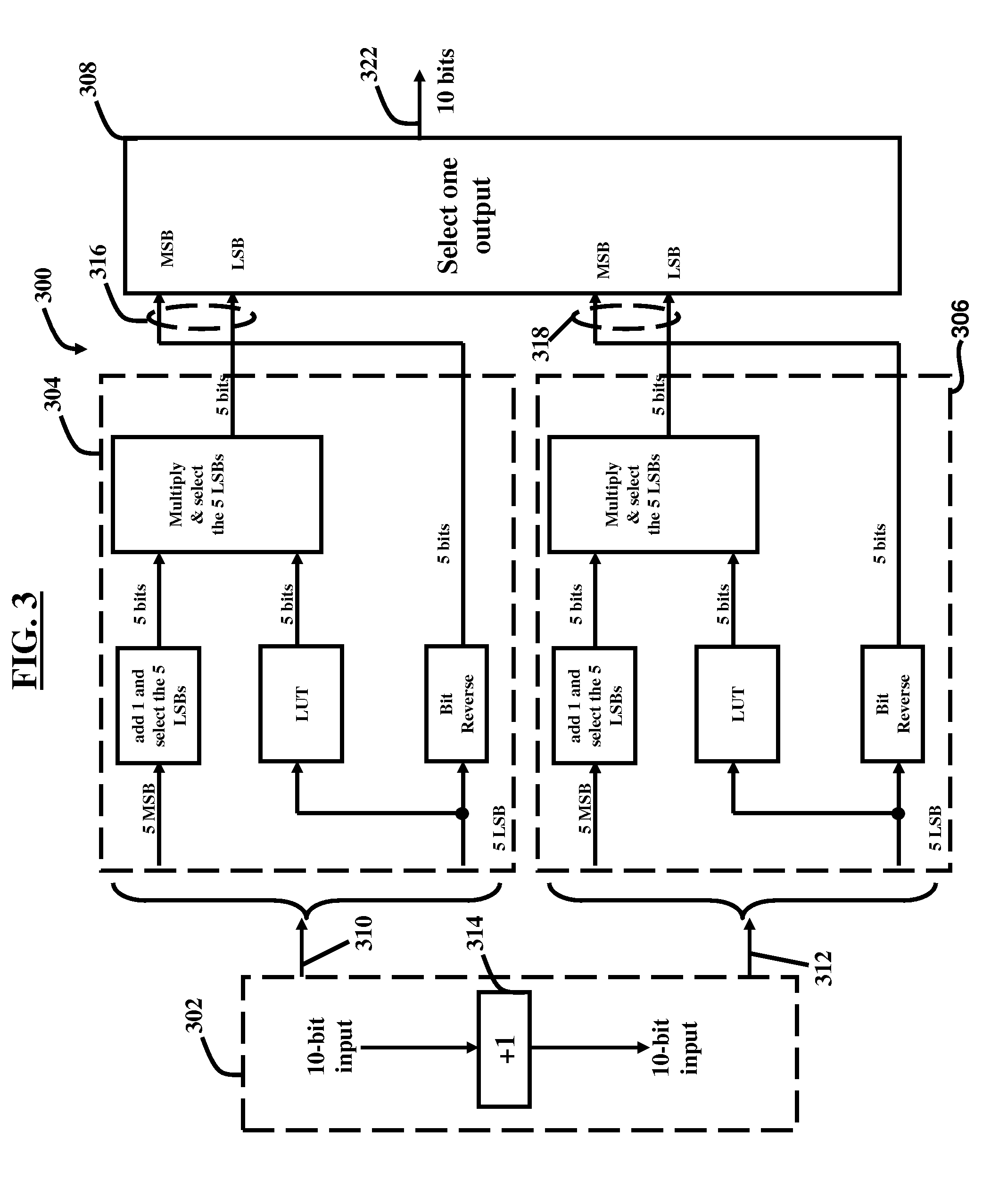

InactiveUS6047073AElectrophonic musical instrumentsCounting chain pulse countersAudio synthesisNoise

A digital wavetable audio synthesizer is described. The synthesizer can generate up to 32 high-quality audio digital signals or voices, including delay-based effects, at either a 44.1 KHz sample rate or at sample rates compatible with a prior art wavetable synthesizer. The synthesizer includes an address generator which has several modes of addressing wavetable data. The address generator's addressing rate controls the pitch of the synthesizer's output signal. The synthesizer performs a 10-bit interpolation, using the wavetable data addressed by the address generator, to interpolate additional data samples. When the address generator loops through a block of data, the signal path interpolates between the data at the end and start addresses of the block of data to prevent discontinuities in the generated signal. A synthesizer volume generator, which has several modes of controlling the volume, adds envelope, right offset, left offset, and effects volume to the data. The data can be placed in one of sixteen fixed stereo pan positions, or left and right offsets can be programmed to place the data anywhere in the stereo field. The left and right offset values can also be programmed to control the overall volume. Zipper noise is prevented by controlling the volume increment. A synthesizer LFO generator can add LFO variation to: (i) the wavetable data addressing rate, for creating a vibrato effect; and (ii) a voice's volume, for creating a tremolo effect. Generated data to be output from the synthesizer is stored in left and right accumulators. However, when creating delay-based effects, data is stored in one of several effects accumulators. This data is then written to a wavetable. The difference between the wavetable write and read addresses for this data provides a delay for echo and reverb effects. LFO variations added to the read address create chorus and flange effects. The volume of the delay-based effects data can be attenuated to provide volume decay for an echo effect. After the delay-based effects processing, the data can be provided with left and right offset volume components which determine how much of the effect is heard and its stereo position. The data is then stored in the left and right accumulators.

Owner:MICROSEMI SEMICON U S

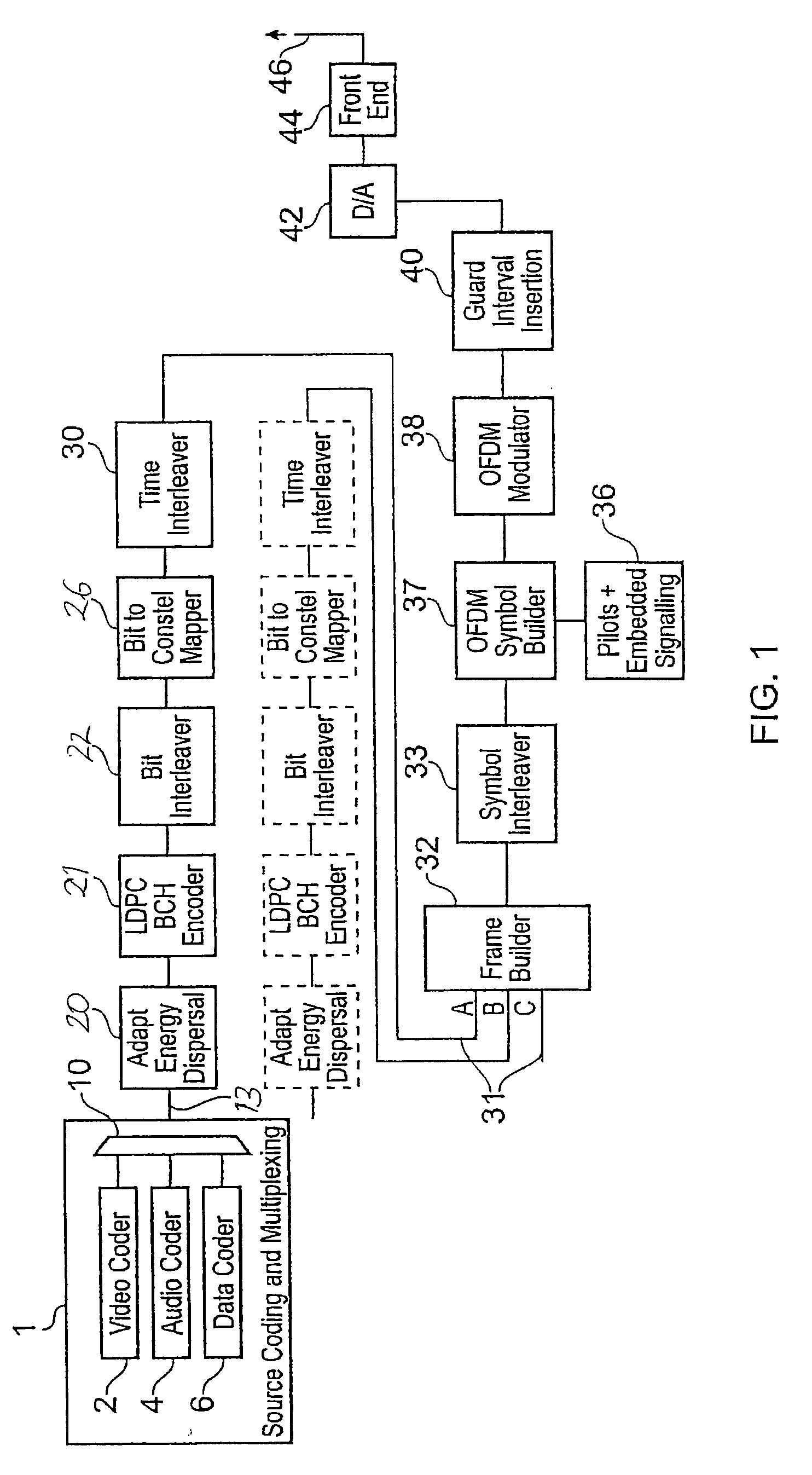

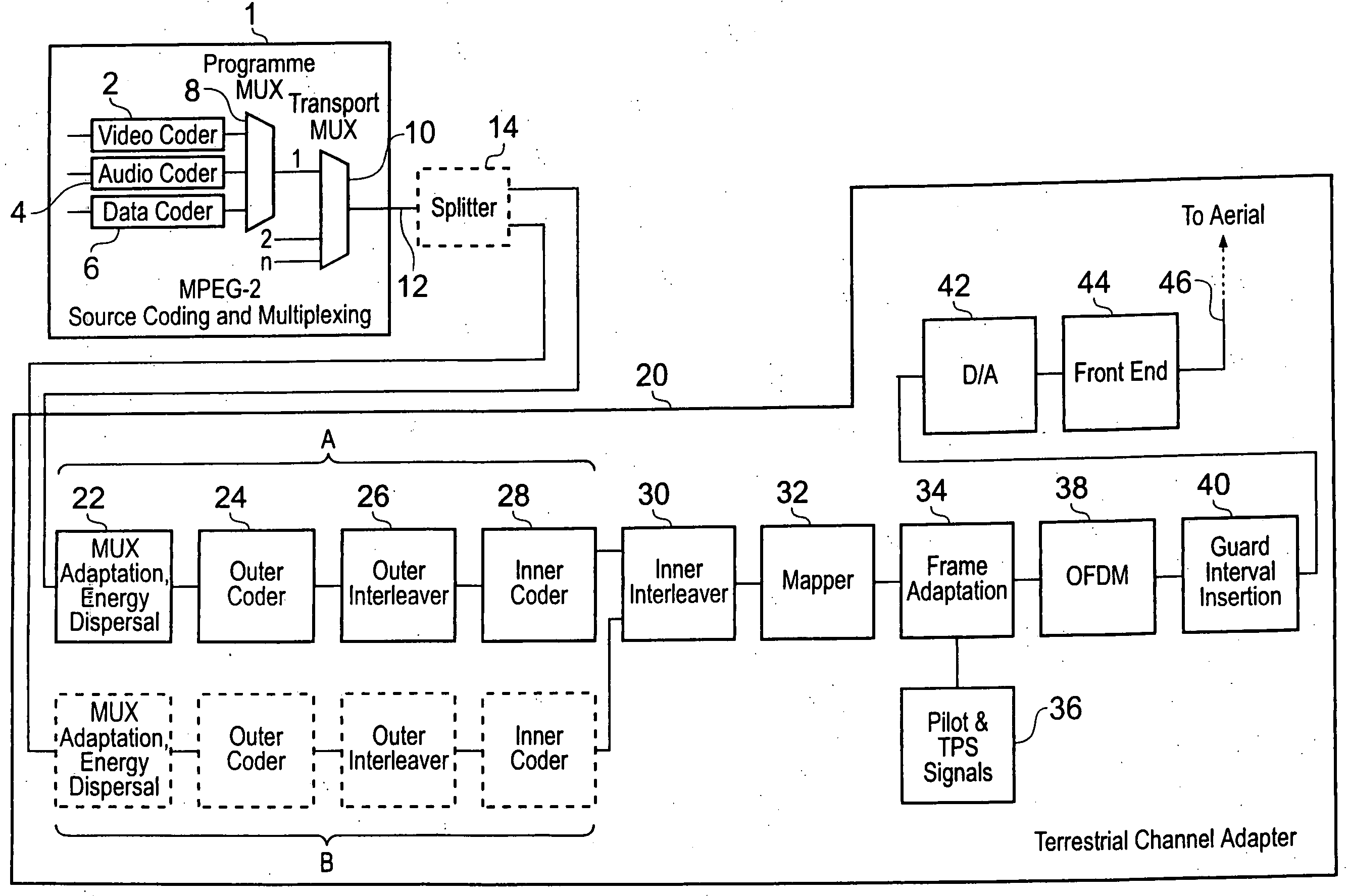

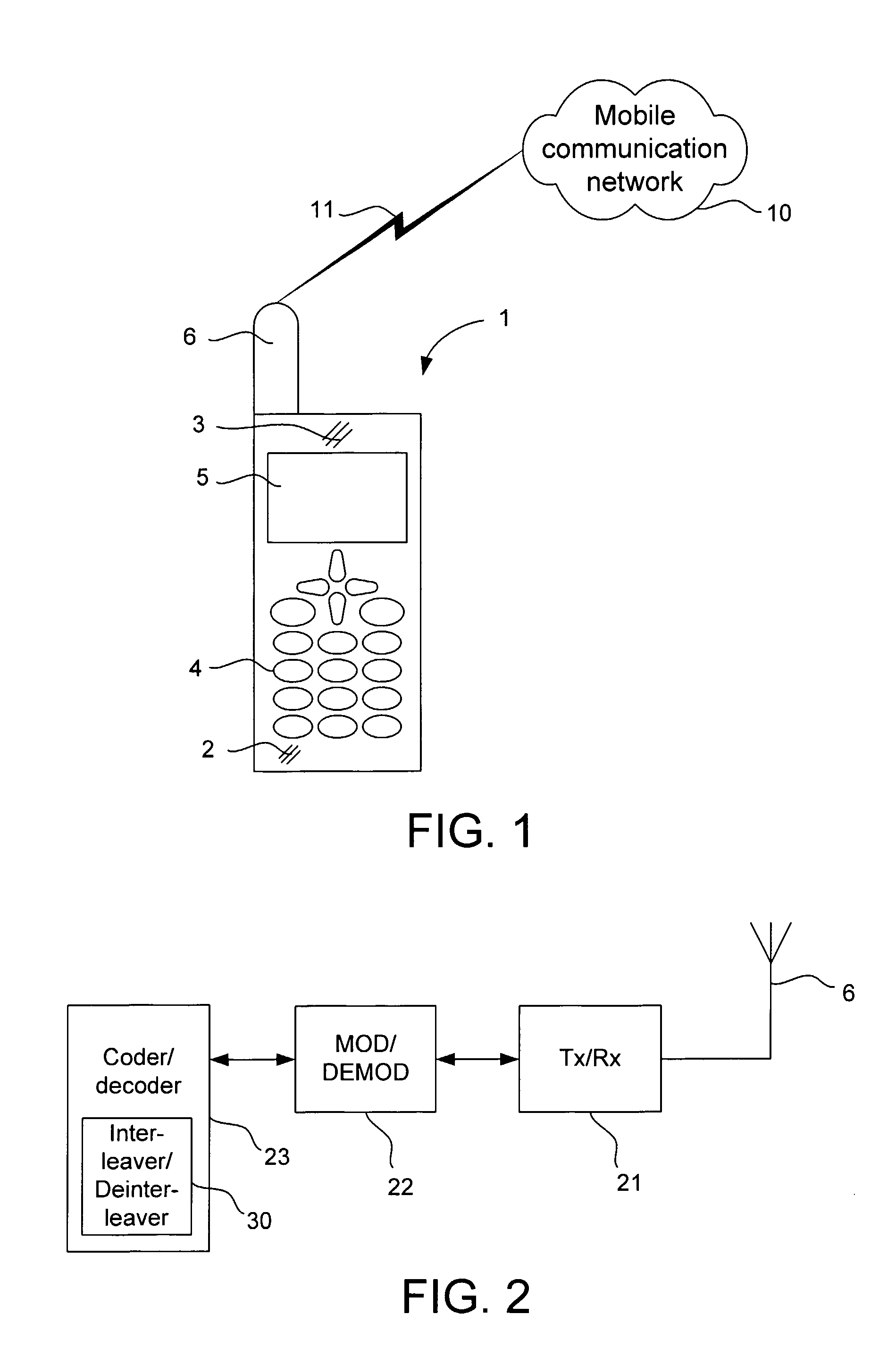

Data processing apparatus and method

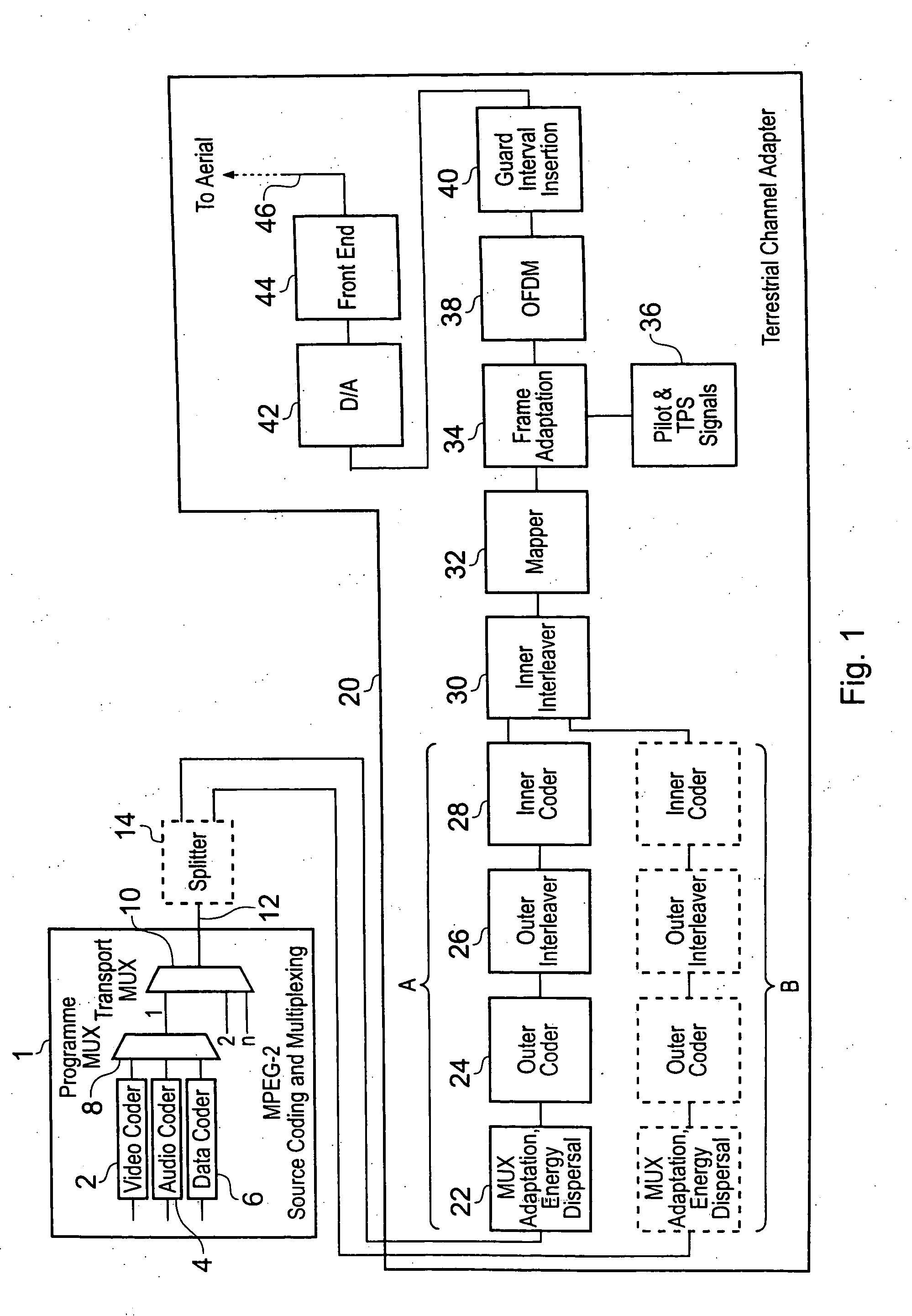

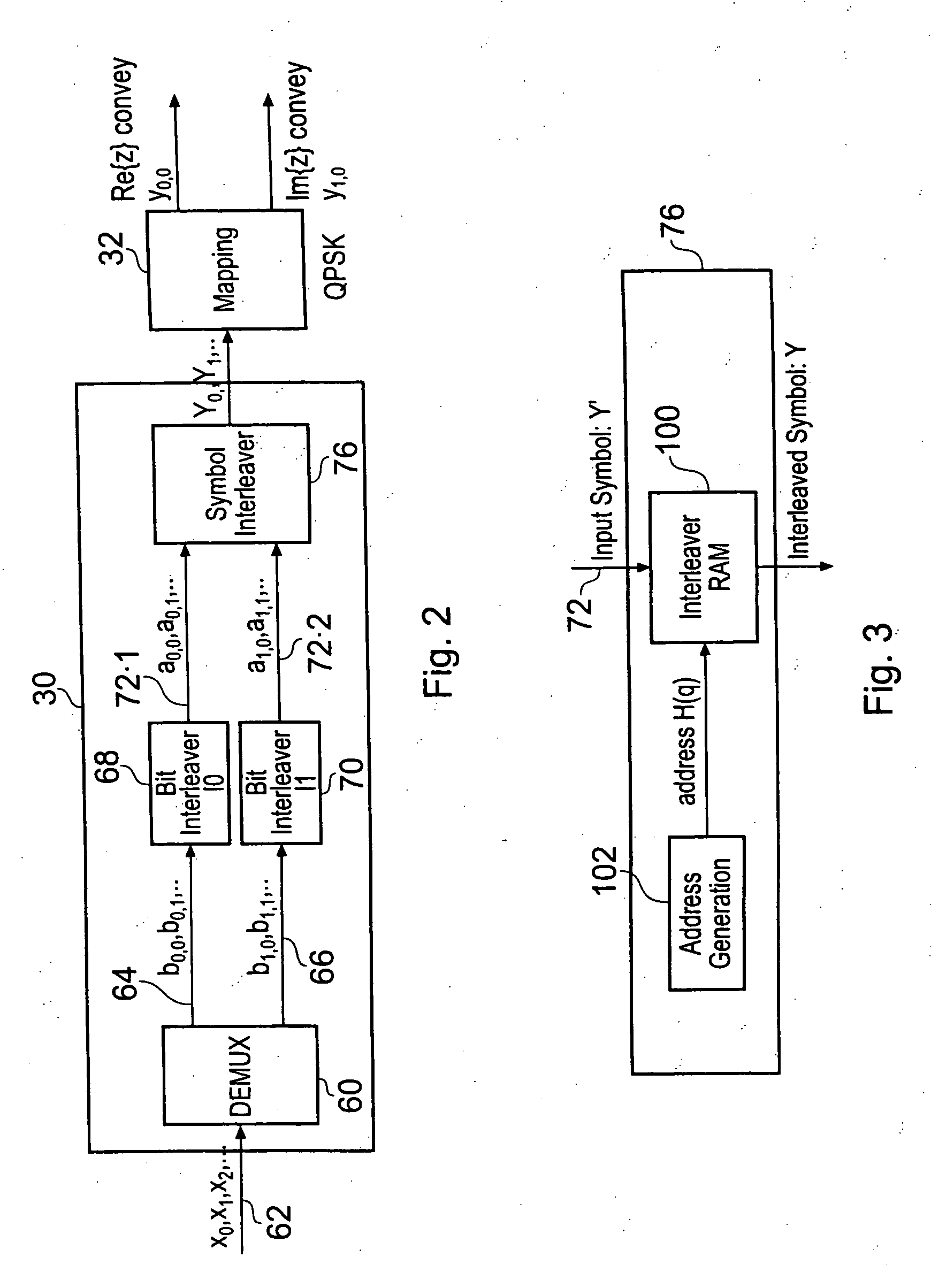

ActiveUS20040246888A1Easy to receiveTrack time variationTelevision system detailsCode conversionCarrier signalAddress generator

A data processing apparatus maps input symbols to be communicated onto a predetermined number of carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processor includes an interleaver memory which reads-in the predetermined number of data symbols for mapping onto the OFDM carrier signals. The interleaver memory reads-out the data symbols on to the OFDM carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on to the carrier signals. The set of addresses are generated from an address generator which comprises a linear feedback shift register and a permutation circuit. In order to provide a 4 k mode for an OFDM modulated system such as a Digital Video Broadcasting (DVB) standard such as DVB-Terrestrial (DVB-T) or DVB-Handheld (DVB-H) standards, a generator polynomial for the linear feedback shift register of Ri'[10]=Ri-1'[0]⊕Ri-1'[2] is provided with a permutation order which has been established by simulation analysis to optimise communication performance via typical radio channels.

Owner:SONY EUROPE BV

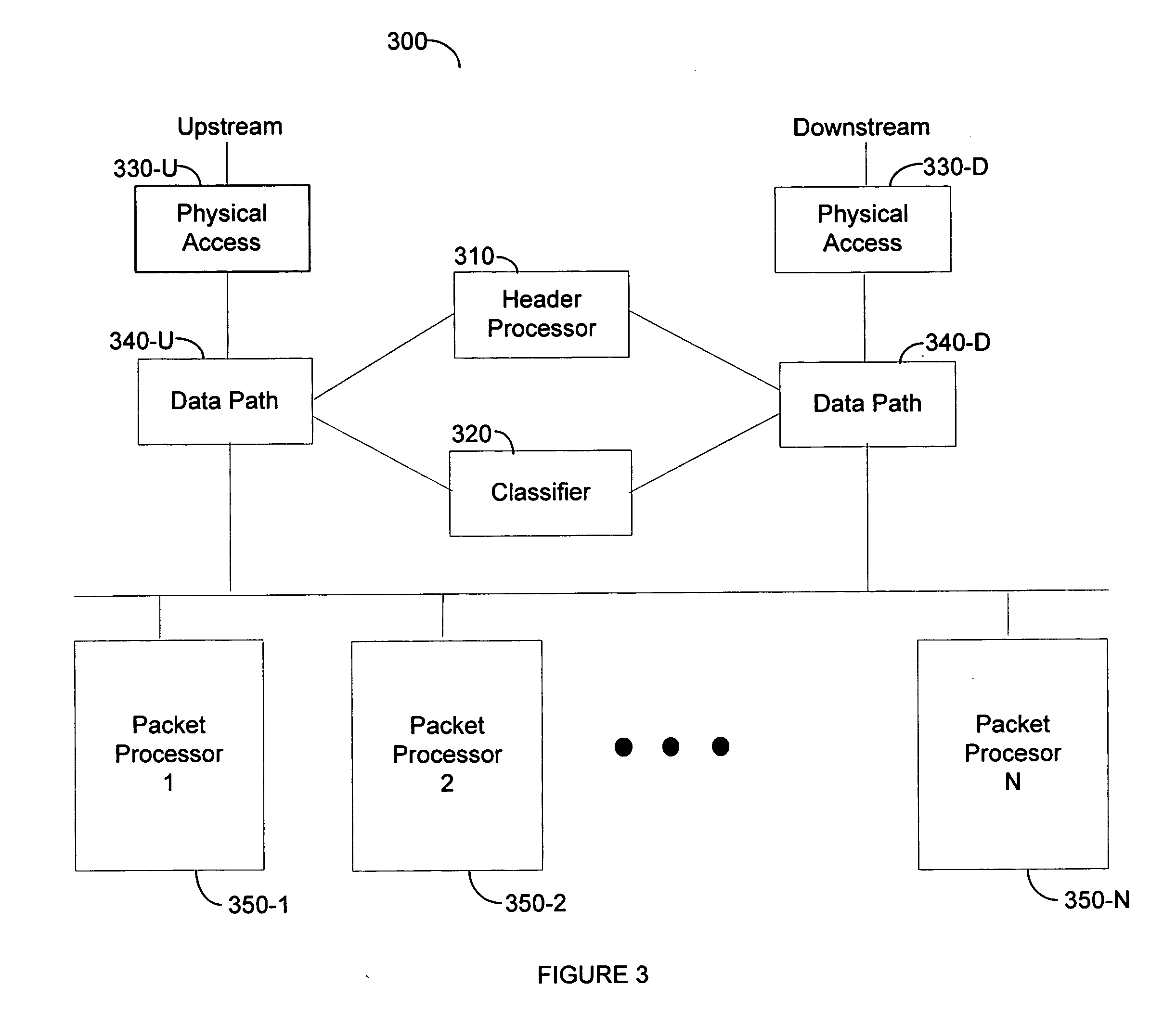

Method and apparatus for wire-speed application layer classification of upstream and downstream data packets

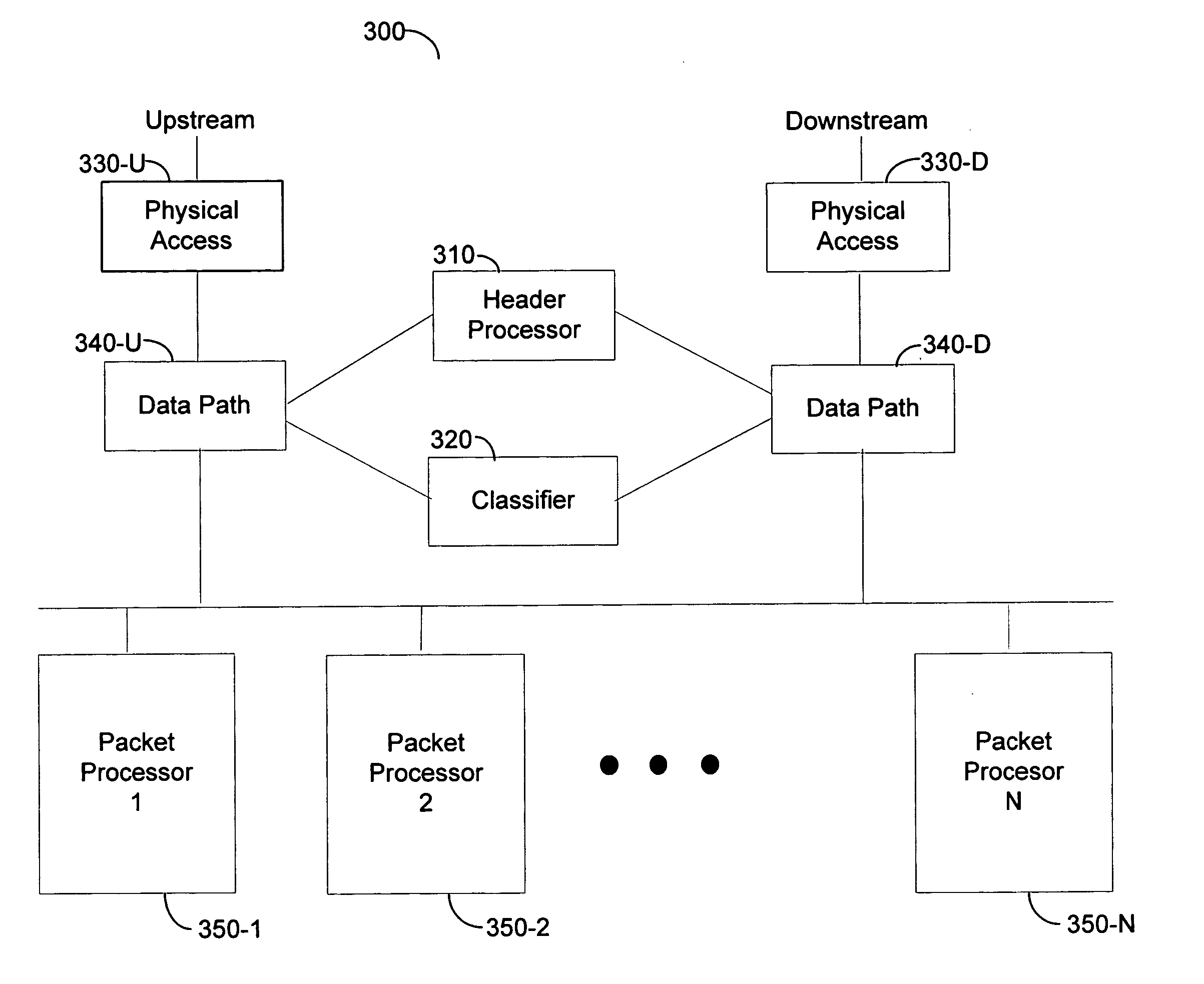

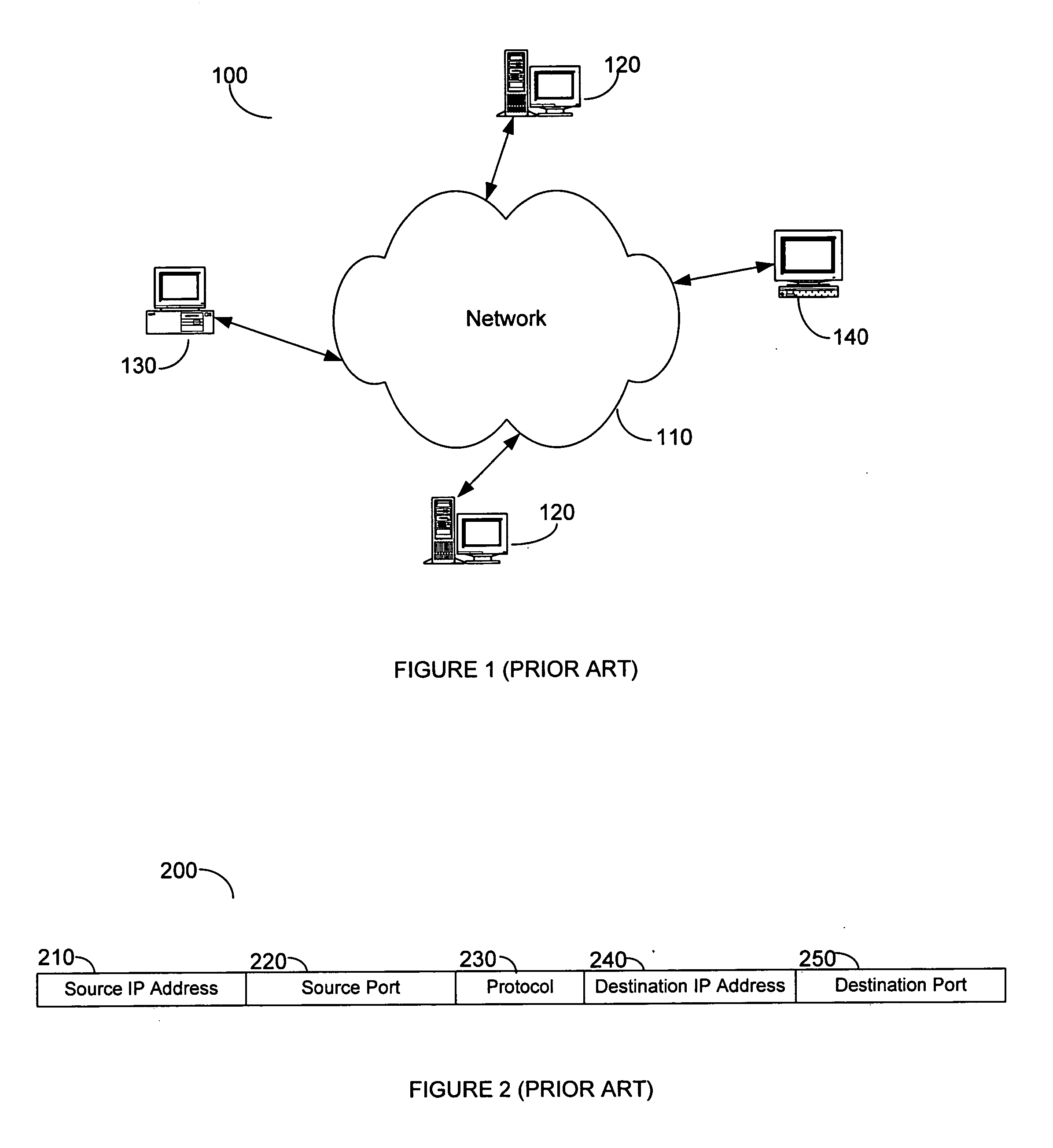

InactiveUS20050190694A1Efficient data processingError preventionFrequency-division multiplex detailsWire speedAddress generator

A data packet classifier to classify a plurality of N-bit input tuples, said classifier comprising a hash address, a memory and a comparison unit. The hash address generator generate a plurality of M-bit hash addresses from said plurality of N-bit input tuples, wherein M is significantly smaller than N. The memory has a plurality of memory entries and is addressable by said plurality of M-bit hash addresses, each such address corresponding to a plurality of memory entries, each of said plurality of memory entries capable of storing one of said plurality of N-bit tuples and an associated process flow information. The comparison unit determines if an incoming N-bit tuple can be matched with a stored N-bit tuple. The associated process flow information is output if a match is found and wherein a new entry is created in the memory for the incoming N-bit tuple if a match is not found.

Owner:CISCO SYST ISRAEL

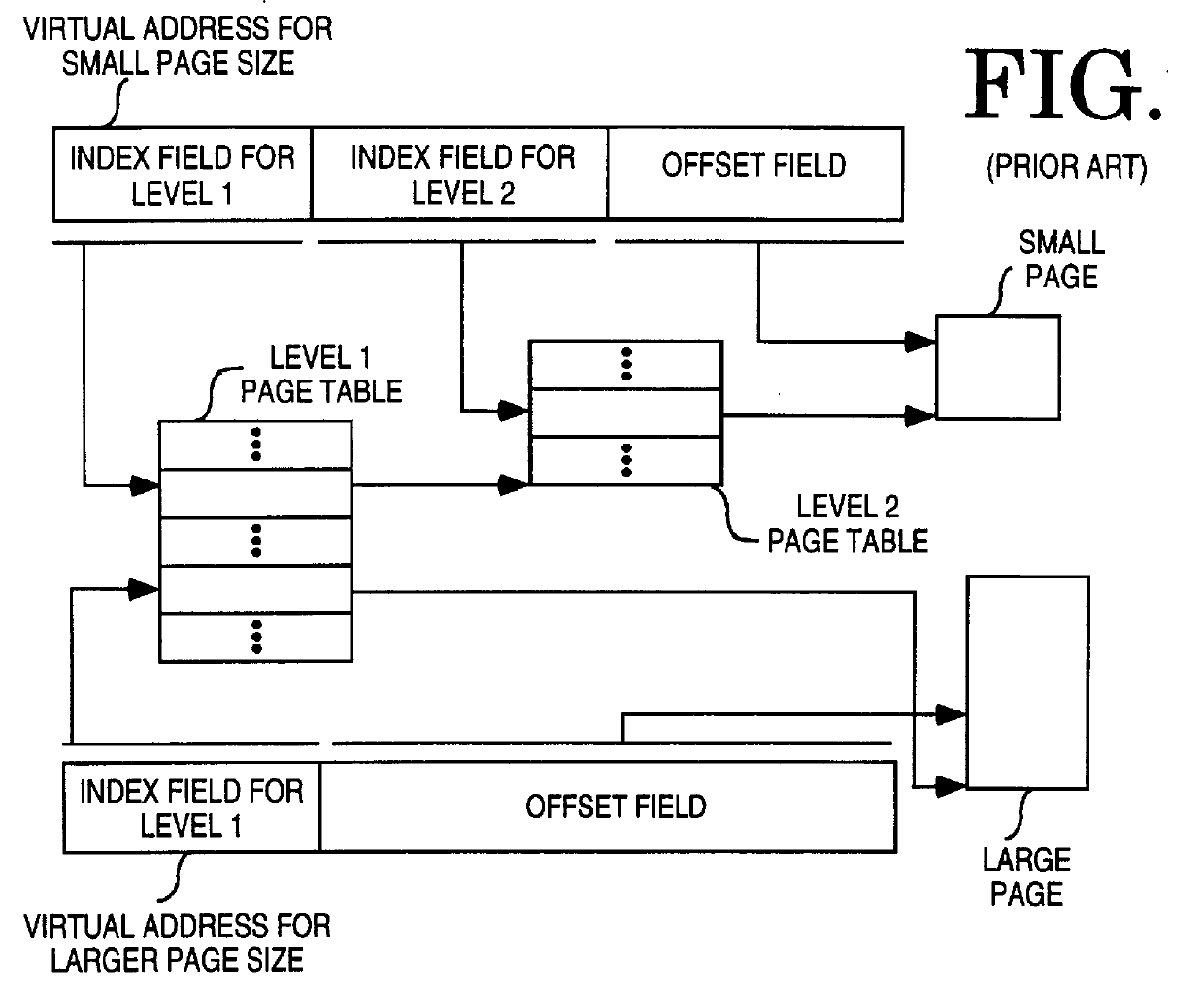

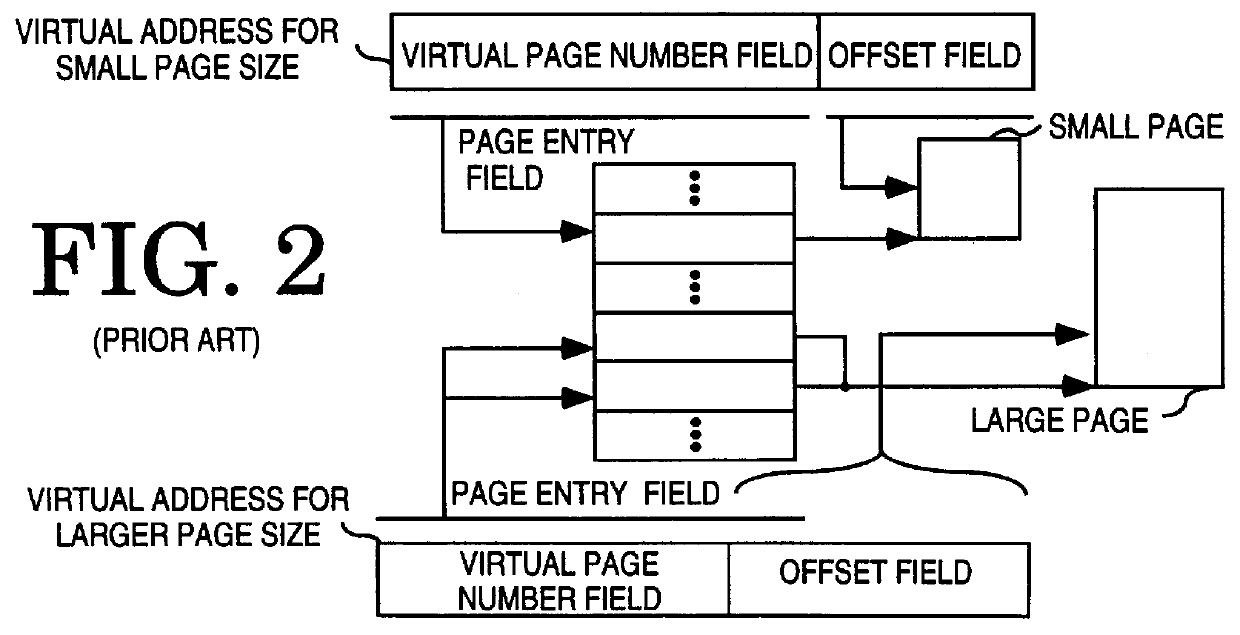

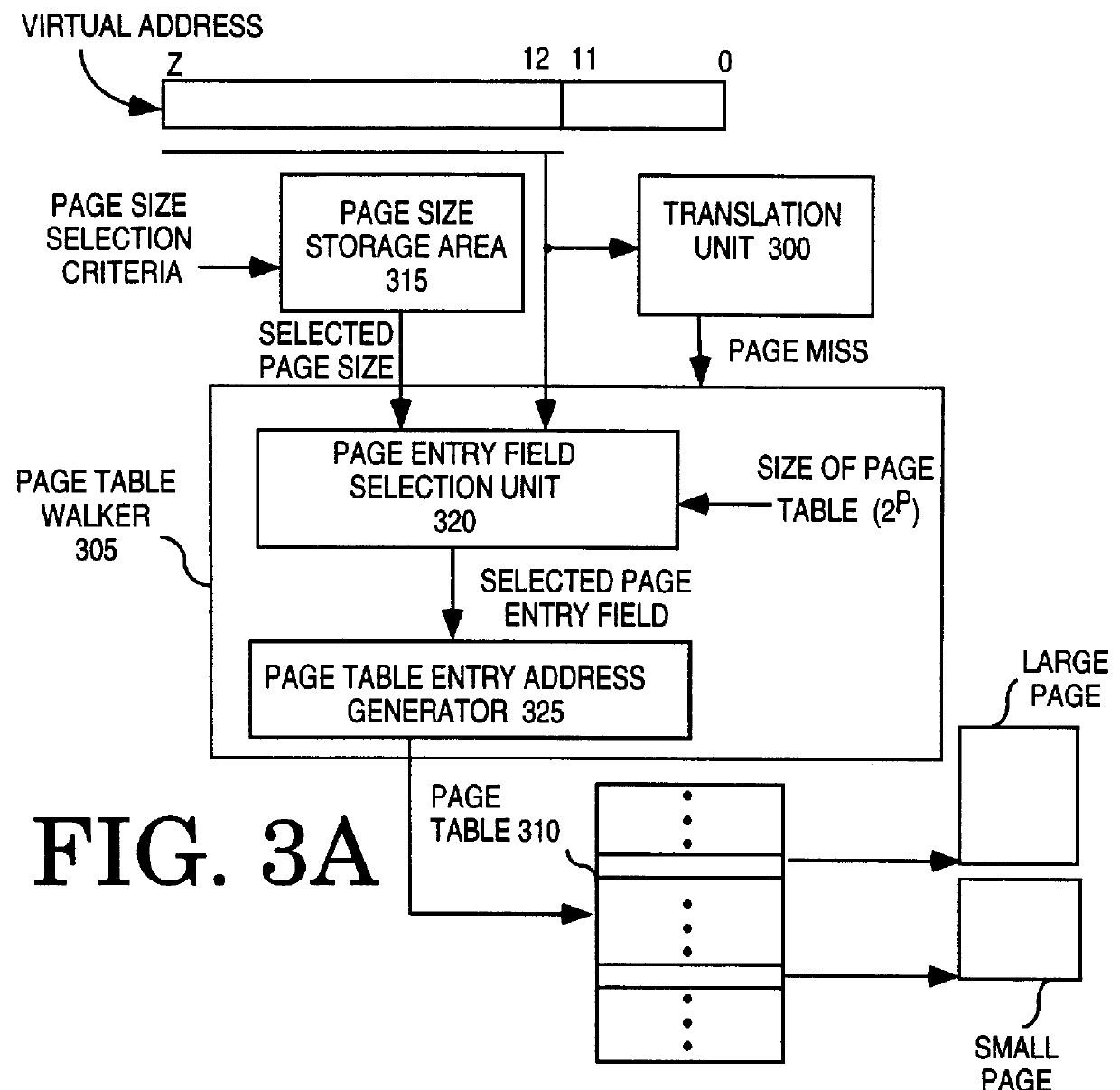

Page table walker that uses at least one of a default page size and a page size selected for a virtual address space to position a sliding field in a virtual address

InactiveUS6088780AMemory architecture accessing/allocationMemory adressing/allocation/relocationAddress generatorComputerized system

A method and apparatus for implementing a page table walker that uses at least one of a default page size and a page size selected for a virtual address space to position a sliding field in a virtual address. According to one aspect of the invention, an apparatus for use in a computer system is provided that includes a page size storage area and a page table walker. The page size storage area is used to store a number of page sizes each selected for translating a different set of virtual addresses. The page table walker includes a selection unit coupled to the page size storage area, as well as a page entry address generator coupled to the selection unit. For each of the virtual address received, the selection unit positions a field in that virtual address based on the page size selected for translating the set of virtual addresses to which that virtual address belongs. In response to receiving the bits in the field identified for each of the virtual addresses, the page entry address generator identifies an entry in a page table based on those bits.

Owner:INST FOR THE DEVMENT OF EMERGING ARCHITECTURES L L C

Data processing device and method

ActiveCN101510865APulse modulation television signal transmissionError preventionAddress generatorCarrier signal

A data processing device transmits the data bits on the predetermined quantity carrying wave signal of the OFDM sign. The data processing device comprises a parity interweaver for operating the pairs of LDPC coding data. The data bits are obtained by the parity matrix LDPC detecting with the LDPC code. The parity matrix has a ladder-type structure interweaving the LDPC code data to the different parity bit position. The mapping unit maps the parity interweaving bit to the data signs corresponding to the modulating signs of the solution. The sign interweaver reads the quantity signs to the sign interweaving store, carrying out the data sig of the sign interweaving store reading the order with different reading; the order address set is confirmed. The address set is generated by the address generator.

Owner:SONY CORP

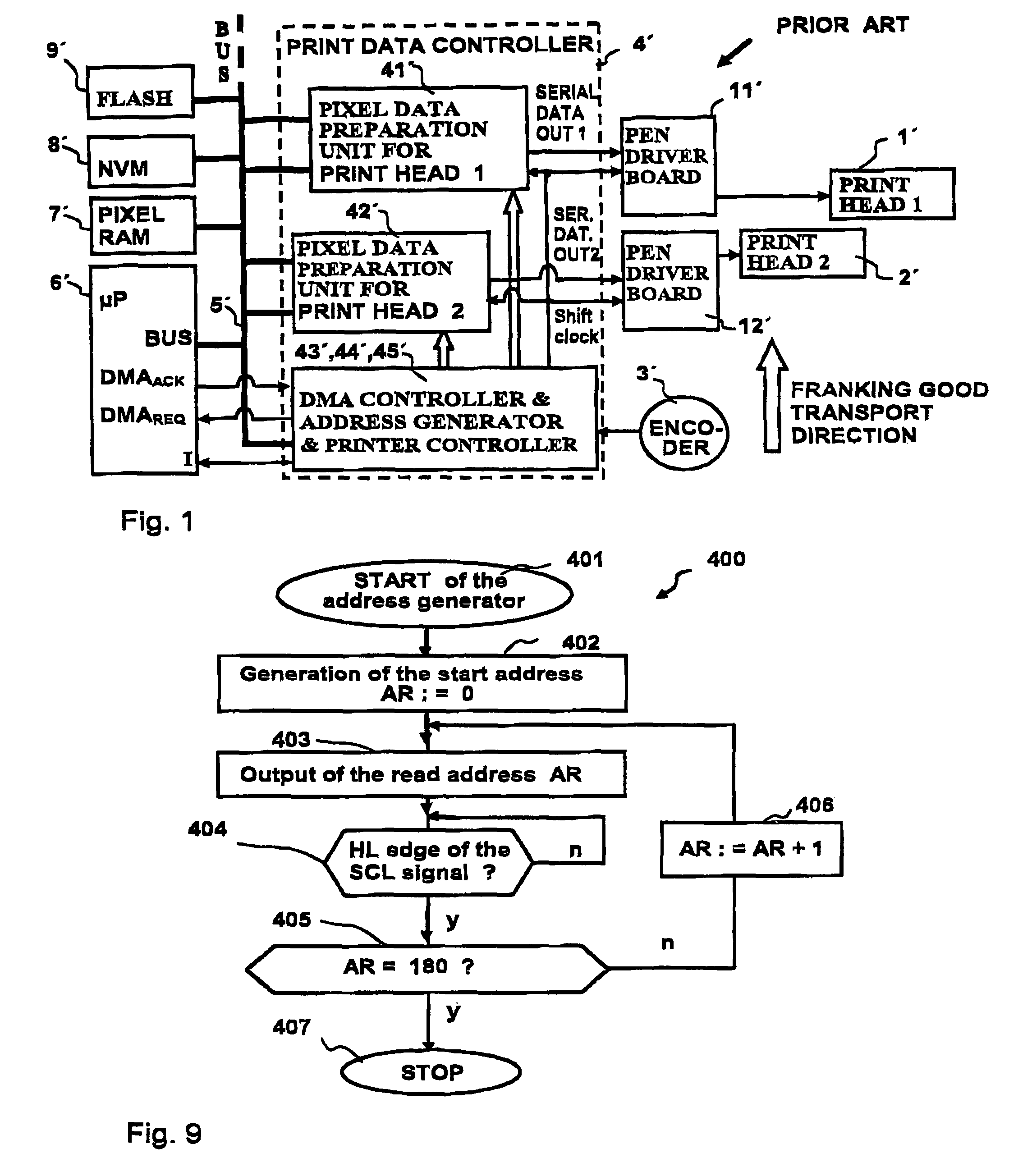

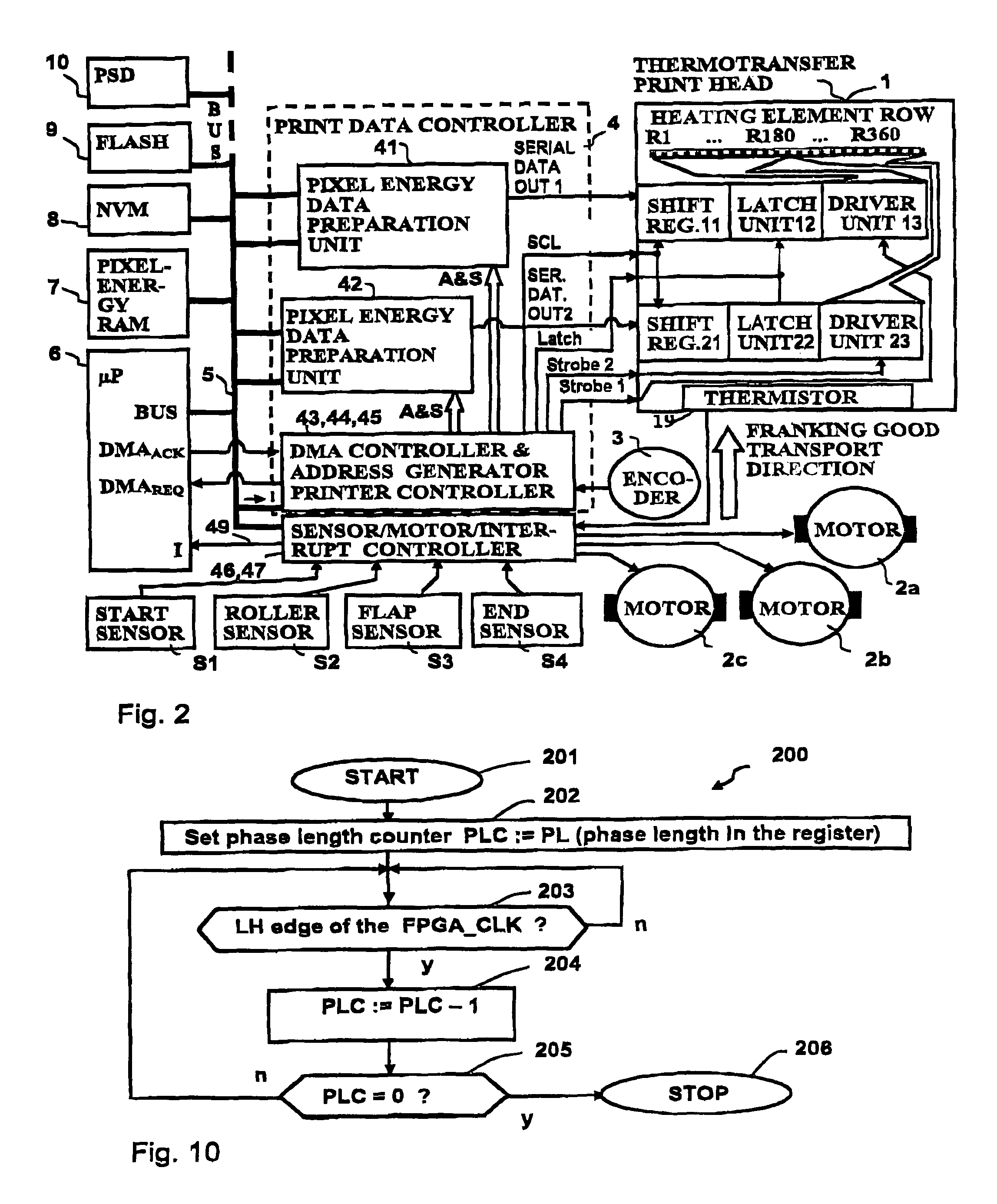

Method and arrangement for control of the printing of a thermotransfer printing device

InactiveUS7965308B2Improve throughputHigh resolutionRecording apparatusFranking apparatusShift registerData control

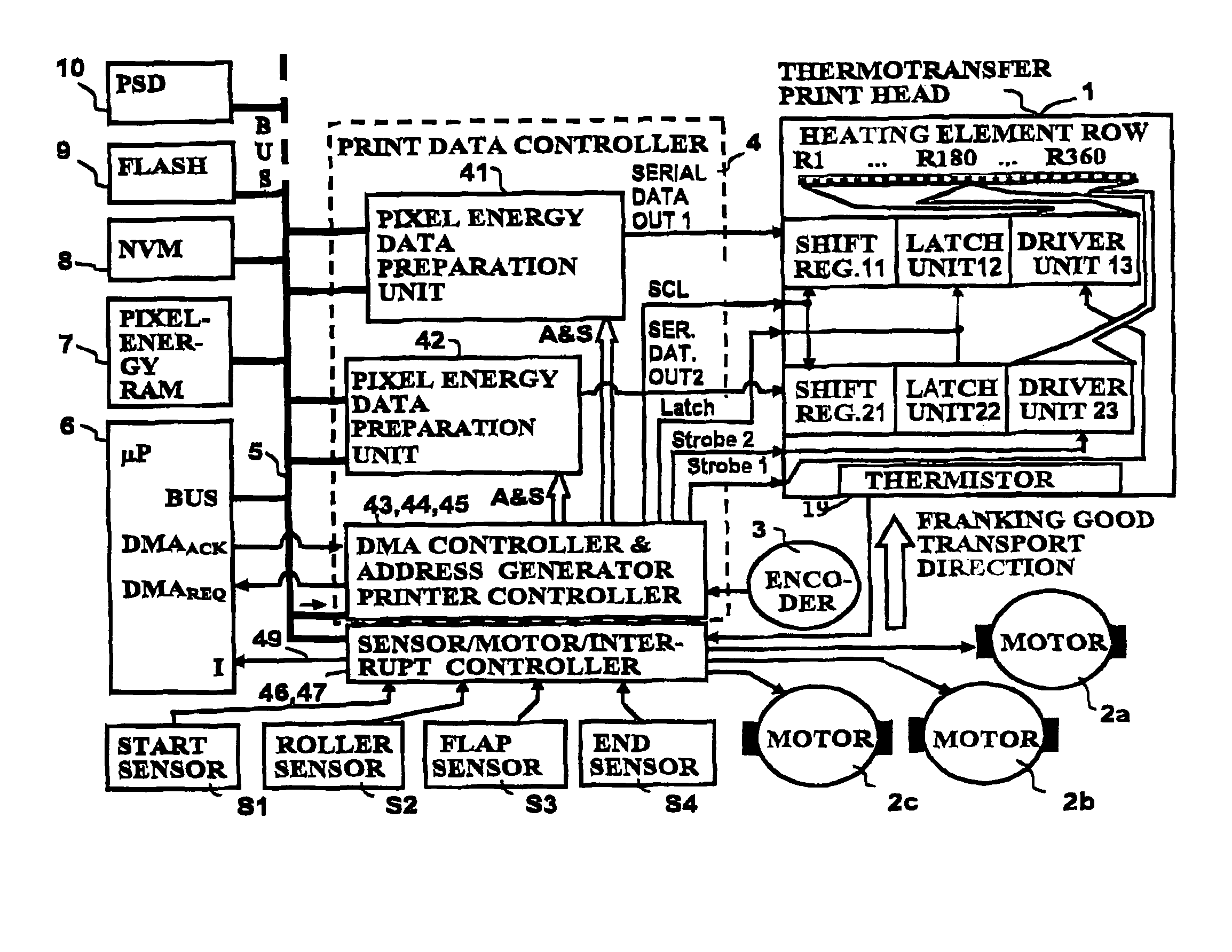

In a method and an arrangement for controlling printing by a thermotransfer printing apparatus with relative movement between a thermotransfer print head and a print medium, a microprocessor that provides pixel energy data to a pixel energy memory by making an energy value calculation and by coding, and a print data controller prepares the pixel energy data by decoding during the printing in a number (corresponding to the pixel energy value) of binary pixel data each with the same binary value. The print data controller includes at least one pixel energy data preparation unit, a DMA controller, an address generator, a printer controller and a phase counter. The DMA controller allows an access to the pixel energy data stored in the pixel energy memory as code in order to provide the pixel energy data in print columns to the at least one pixel energy data preparation unit. The address generator generates addresses for selection of the buffered code during each phase of a number of phases. The phase counter supplies a phase count value to a phase data preparation unit in which the code value A and phase count value B are compared in order to generated binary pixel data, which are serially supplied from the output D to at least one shift register of the thermotransfer print head.

Owner:FRANCOTYP POSTALIA

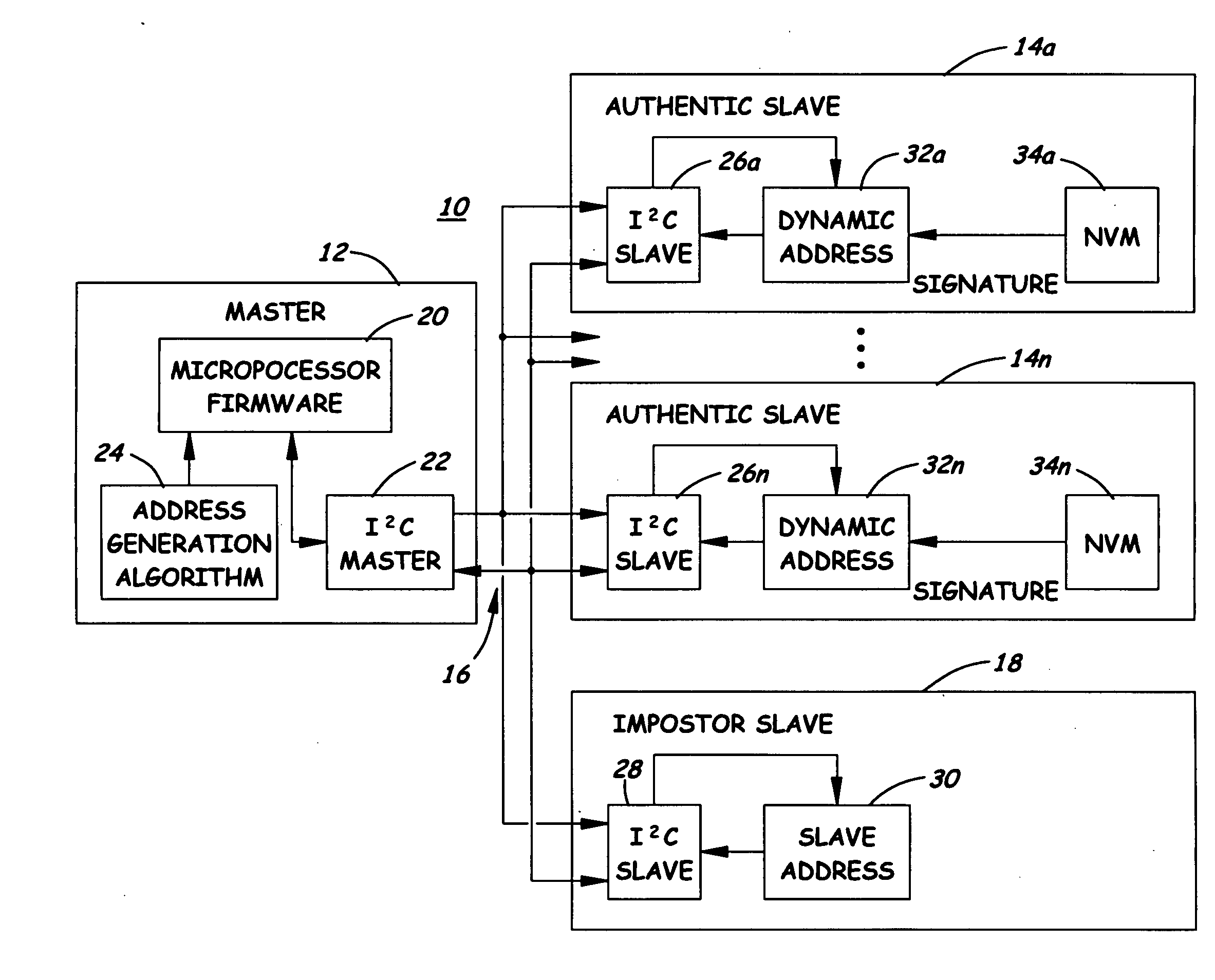

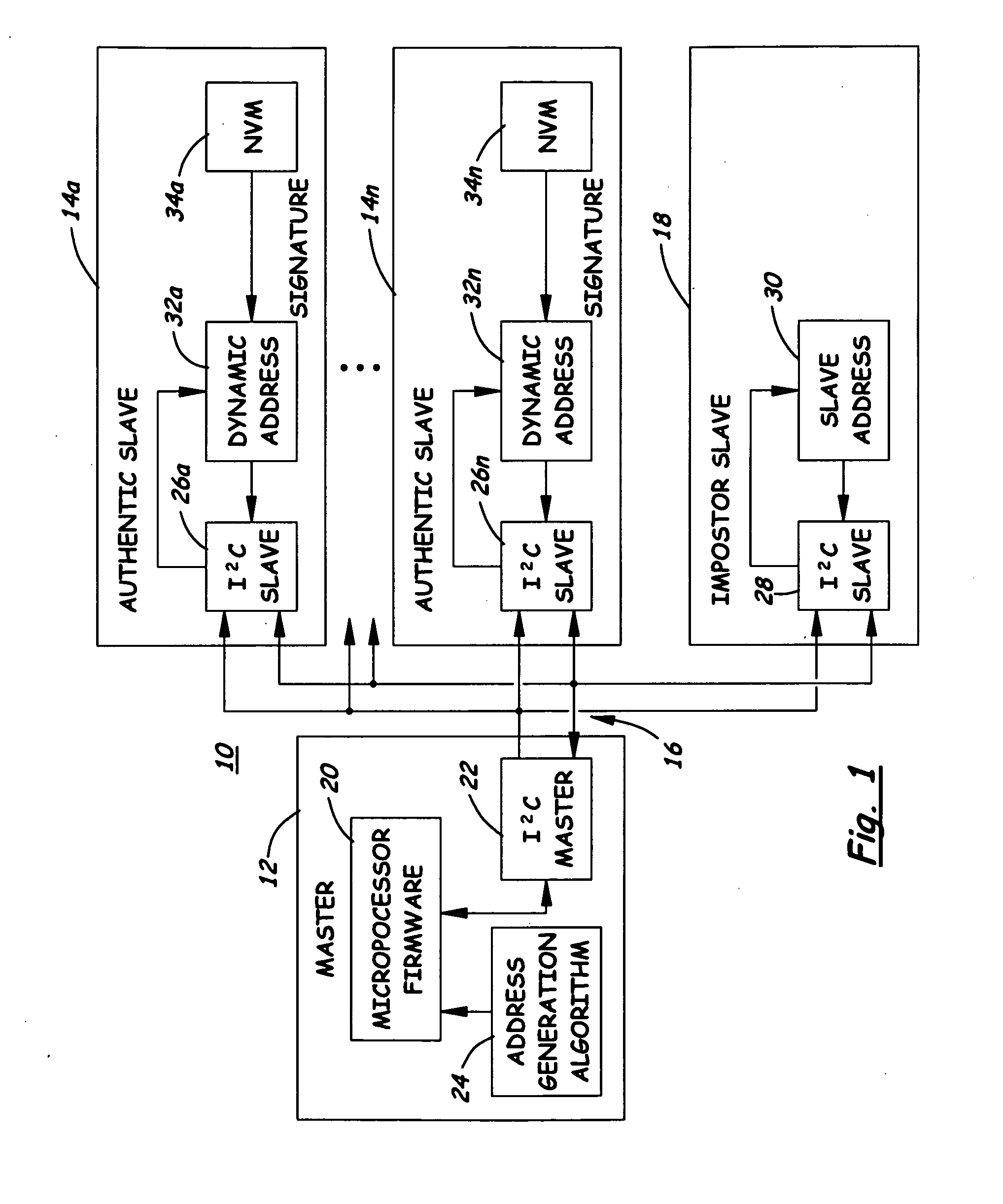

Dynamic Address Change for Slave Devices on a Shared Bus

ActiveUS20100306431A1Improve securityInput/output processes for data processingCommunications systemAddress generator

A master / slave data communication system in which a master device communicates with the slave devices by uniquely addressing each of the slave devices. In order to enhance the security of the data communication system, each slave device includes an address generator for generating unique addresses. Periodically, the master device requests that one or more slave device change its address. In response to the request, the addressed slave device increments its address generating algorithm to provide a new slave address. The master device also includes an algorithm that is synchronized with the slave address generating algorithm, whereby when the slave changes its address, it need not transmit the new slave address to the master device over the bus.

Owner:LEXMARK INT INC

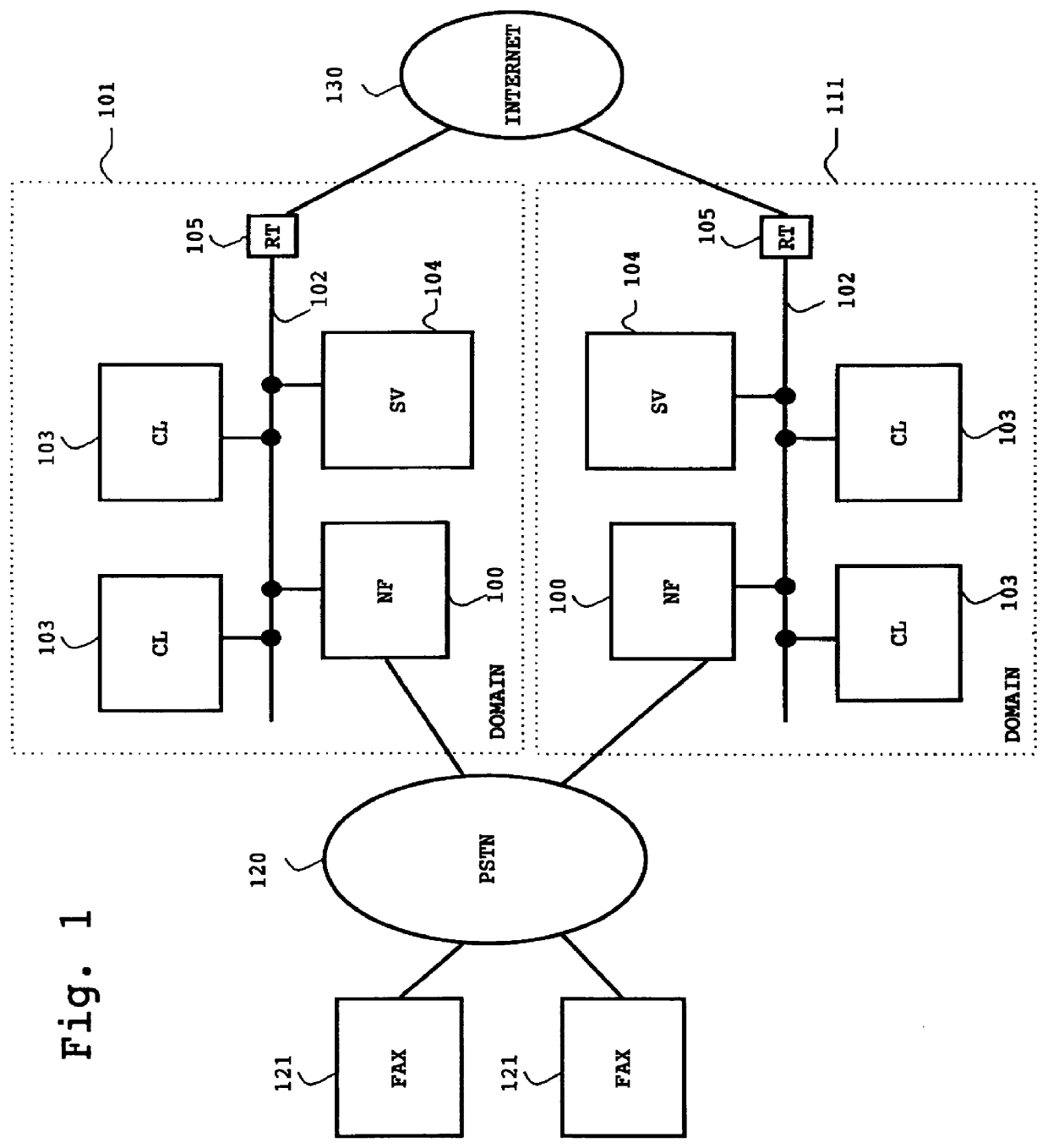

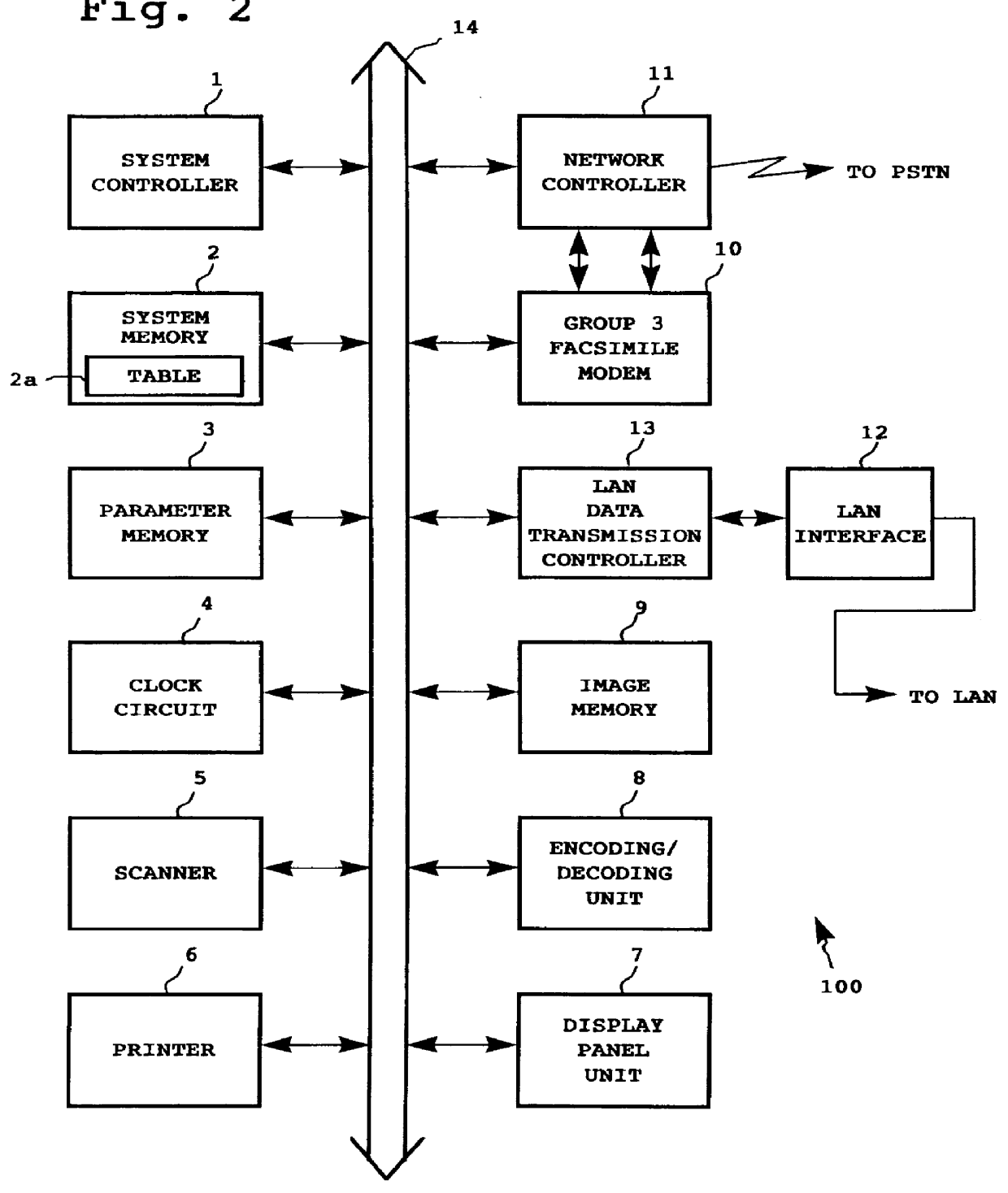

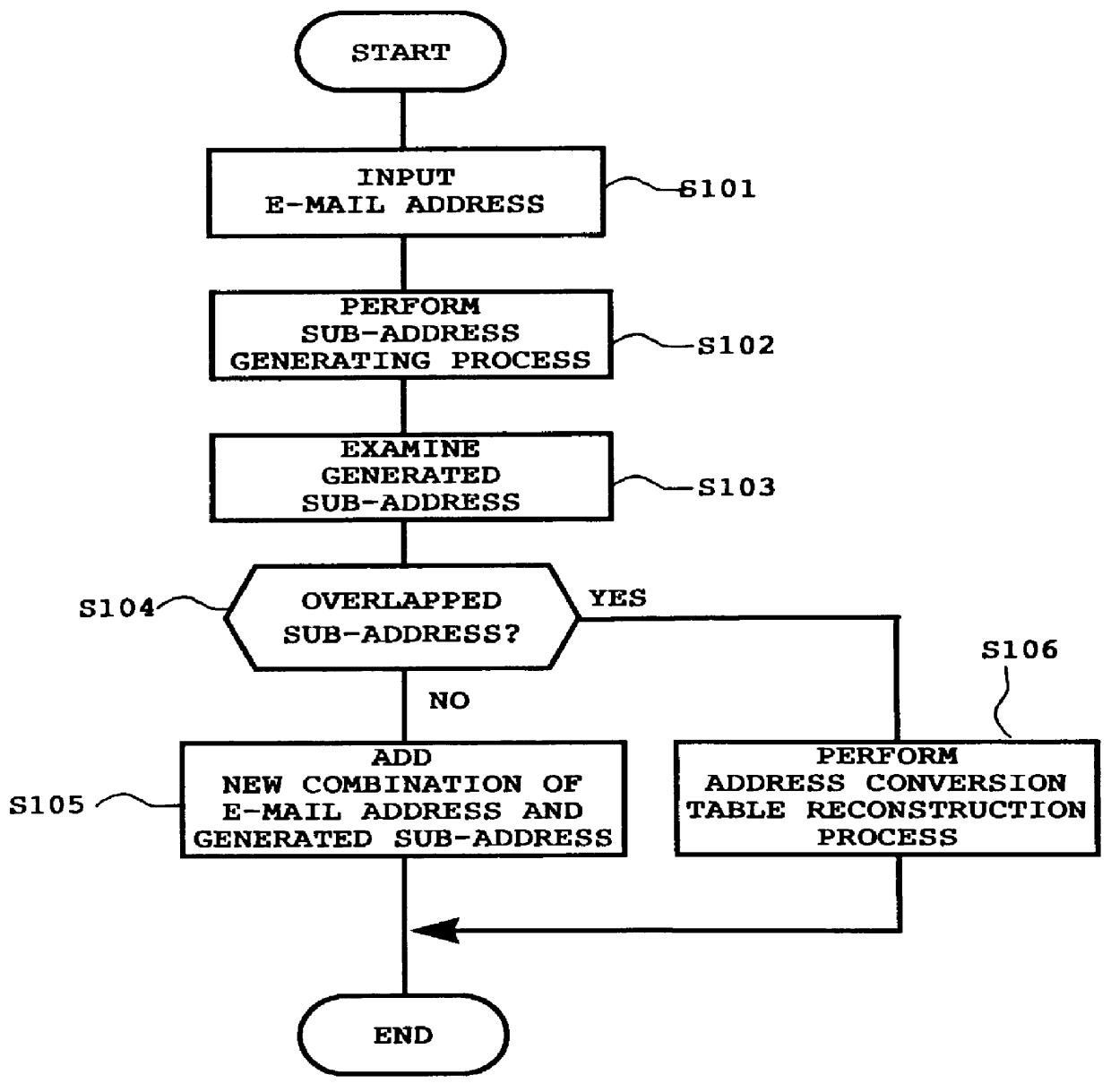

Network facsimile apparatus capable of E-mail communications

InactiveUS6097797AAvoid unnecessary operationsTelephonic communicationTransmissionData terminalEmail address

A data terminal which is coupled to an local area network and a public switched telephone network includes a sub-address generator that generates a sub-address based on an electronic mail address and a predetermined functional operation method. A data table generator generates an address conversion table correlating a plurality of sub-addresses to corresponding input electronic mail addresses. Each of the plurality of sub-addresses being uniquely coupled with a corresponding electronic mail address that is uniquely assigned to a single client terminal. The data terminal also includes memory to store the address conversion table and a terminal controller. The terminal controller checks an incoming call from a facsimile machine containing facsimile image information and a sub-address representing a destination client terminal, and upon receiving such incoming facsimile image information and sub-address, the controller determines an electronic mail address corresponding to the sub-address using the address conversion table. The controller then relays the facsimile image information to the destination client terminal at the determined appropriate electronic mail address.

Owner:RICOH KK

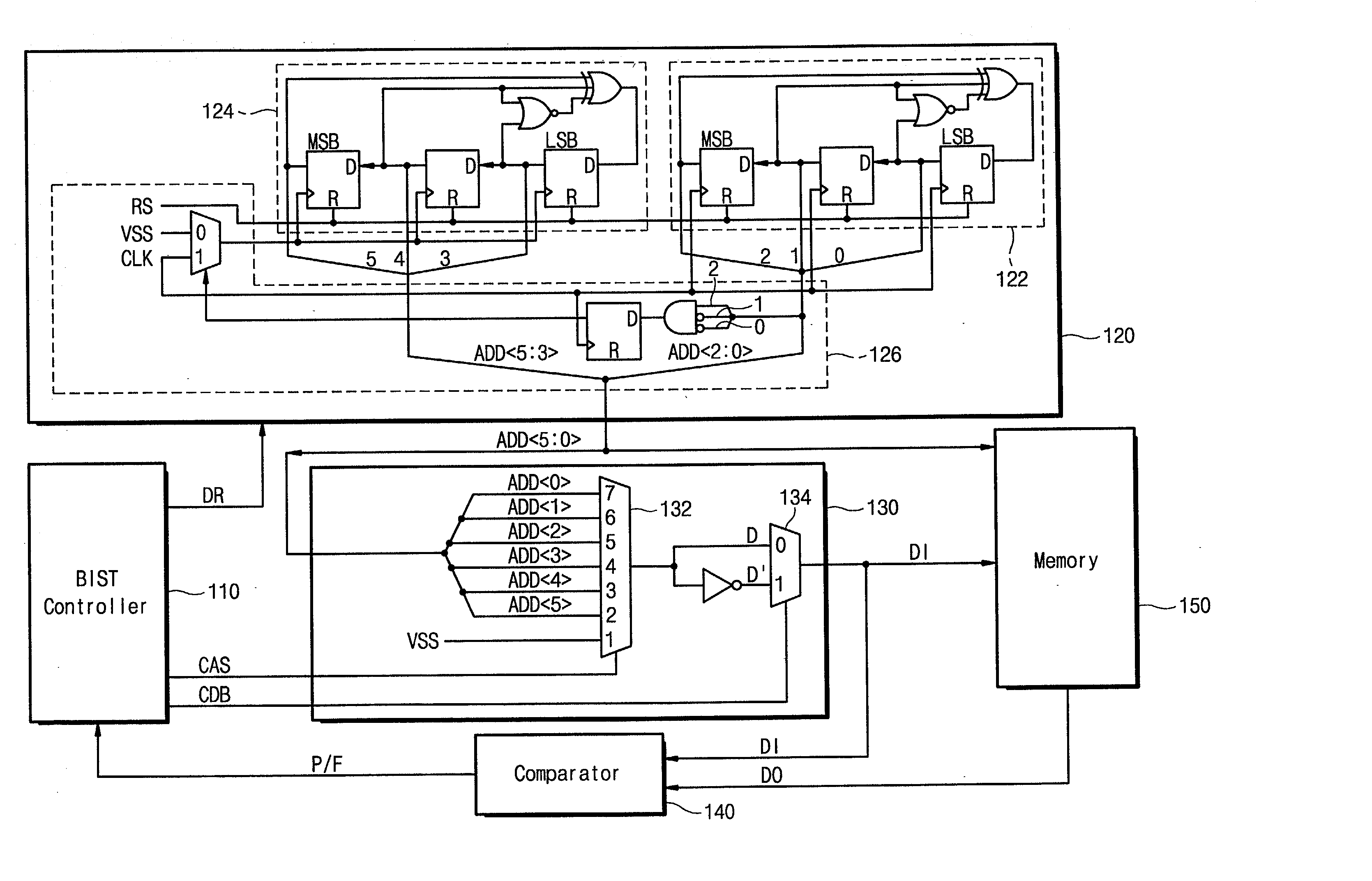

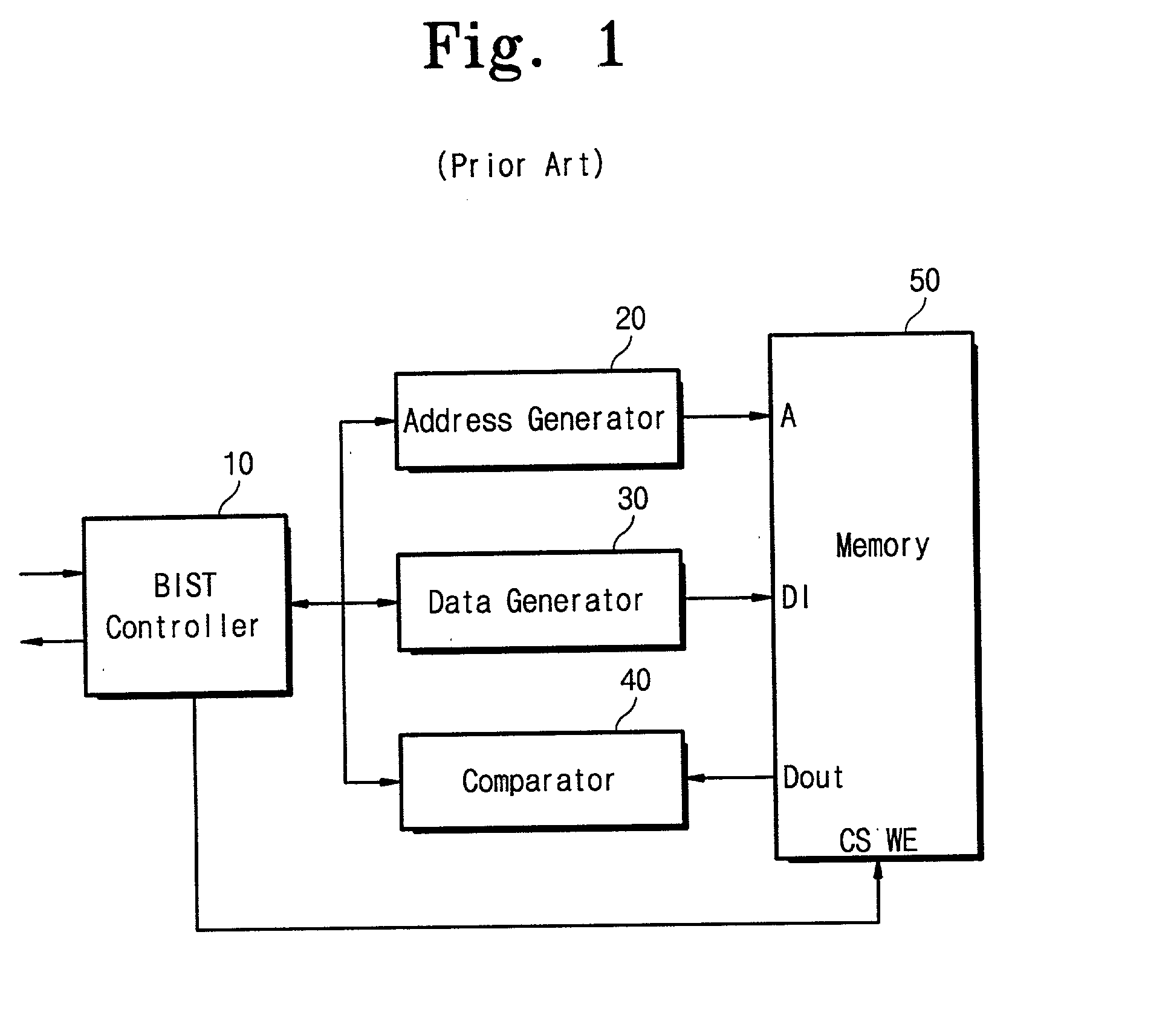

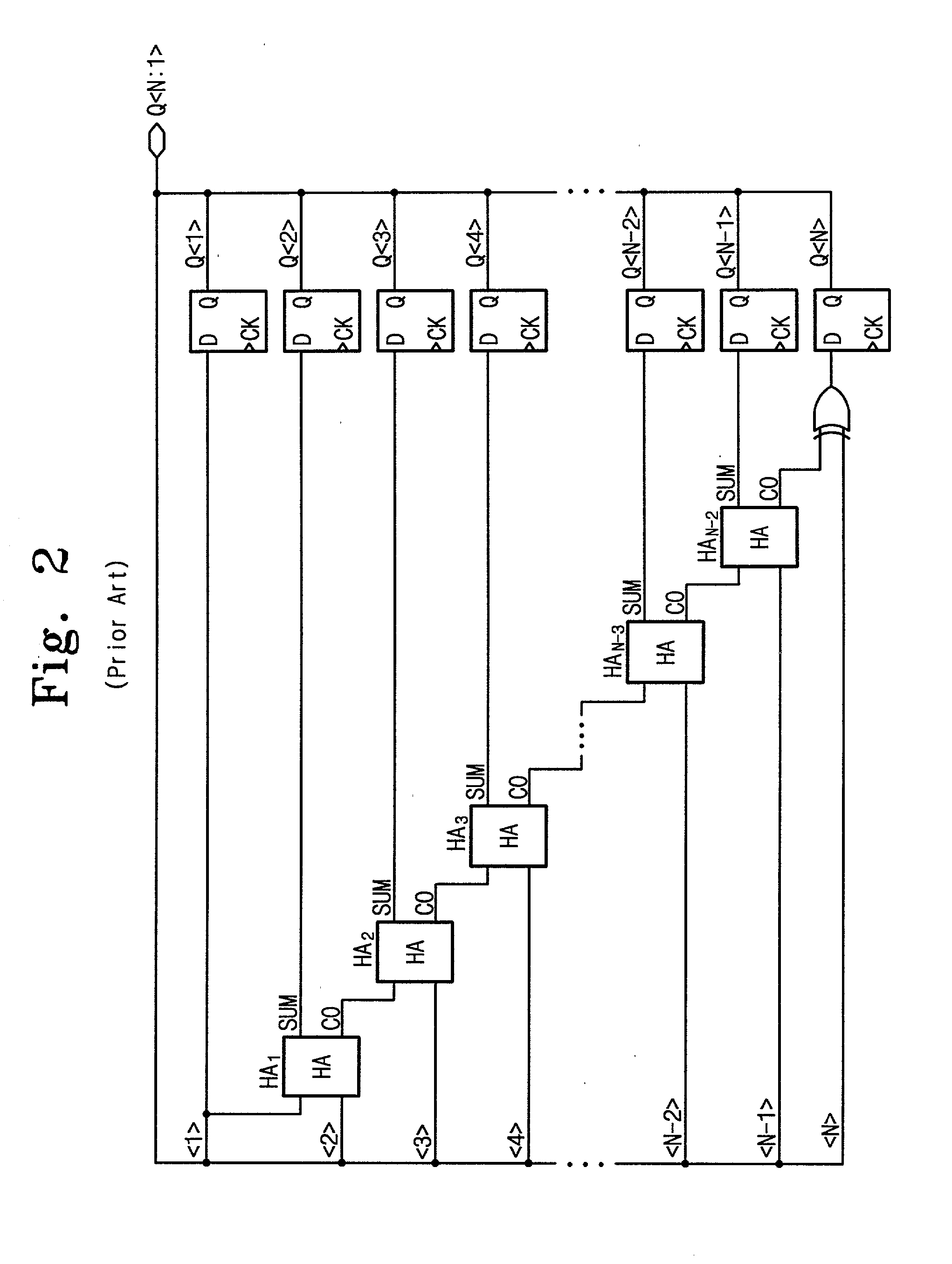

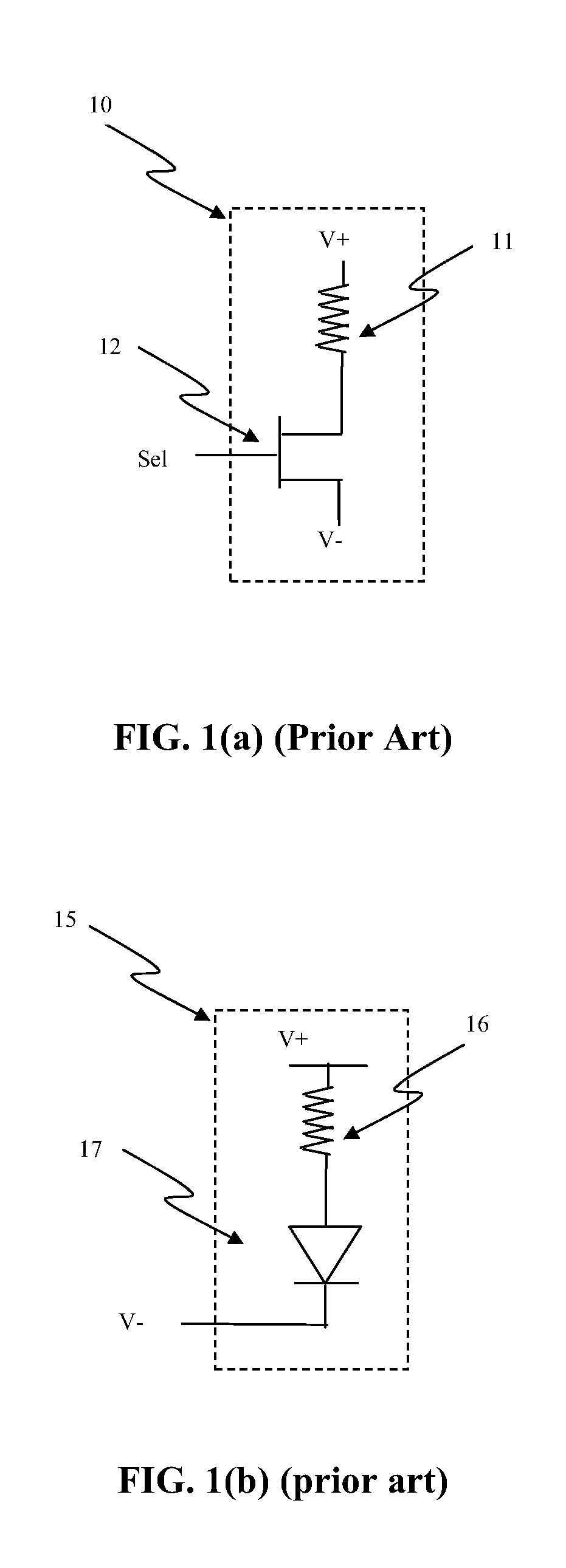

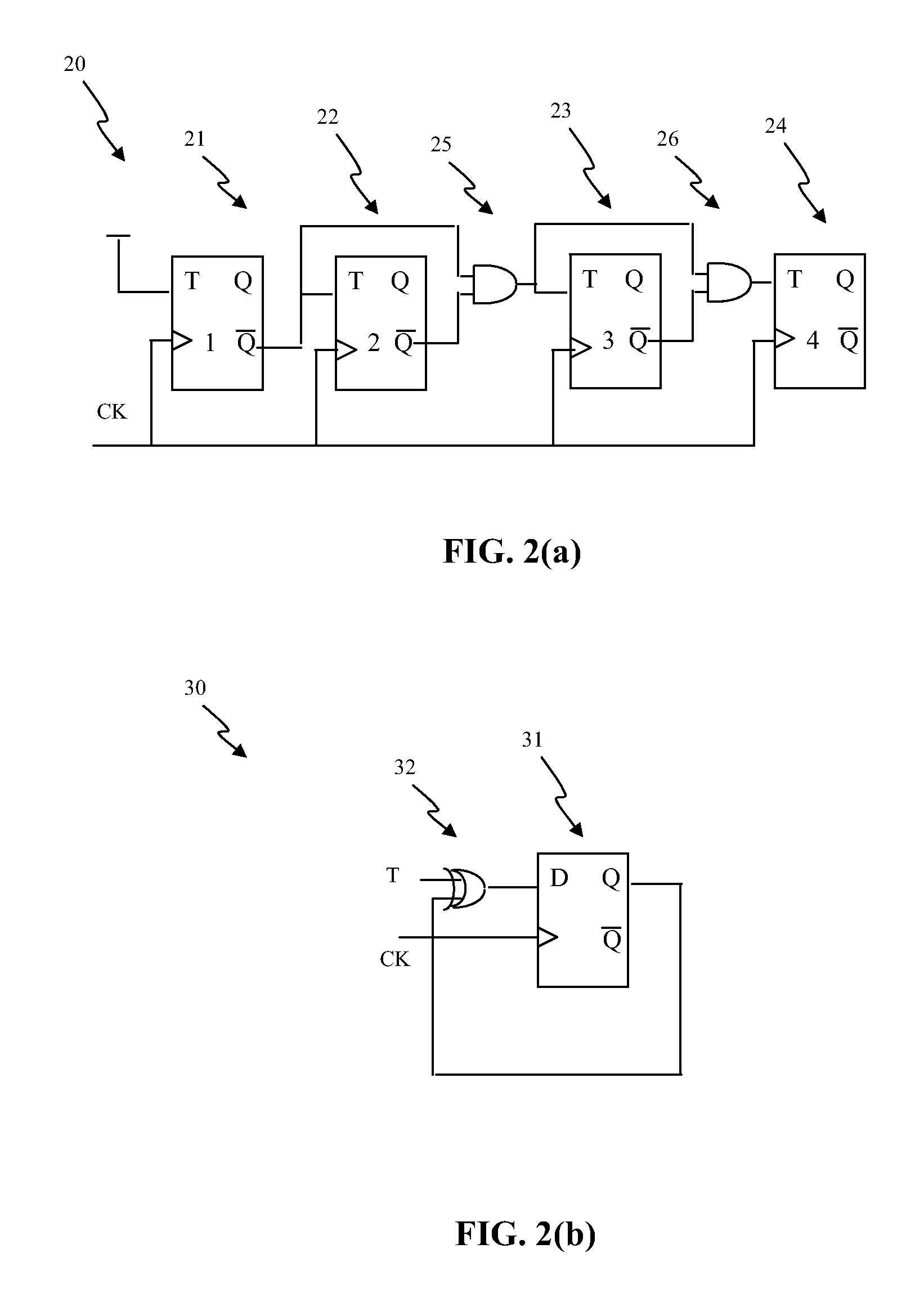

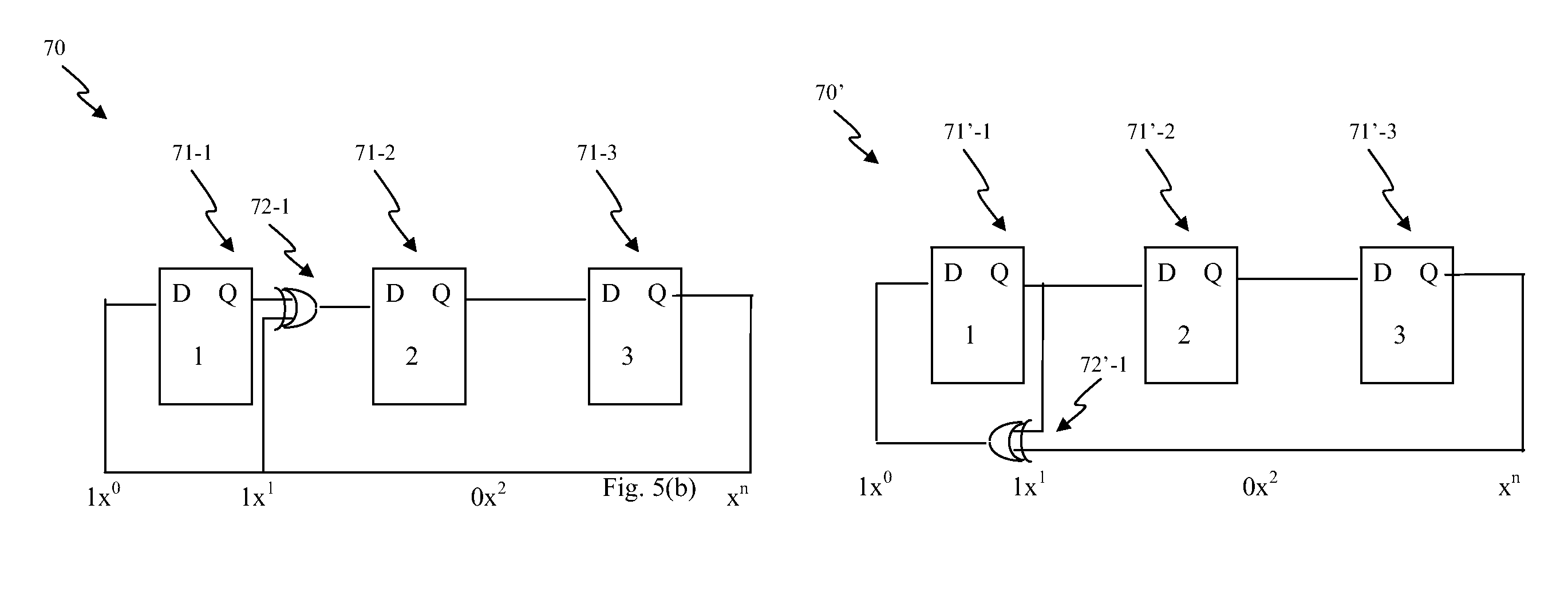

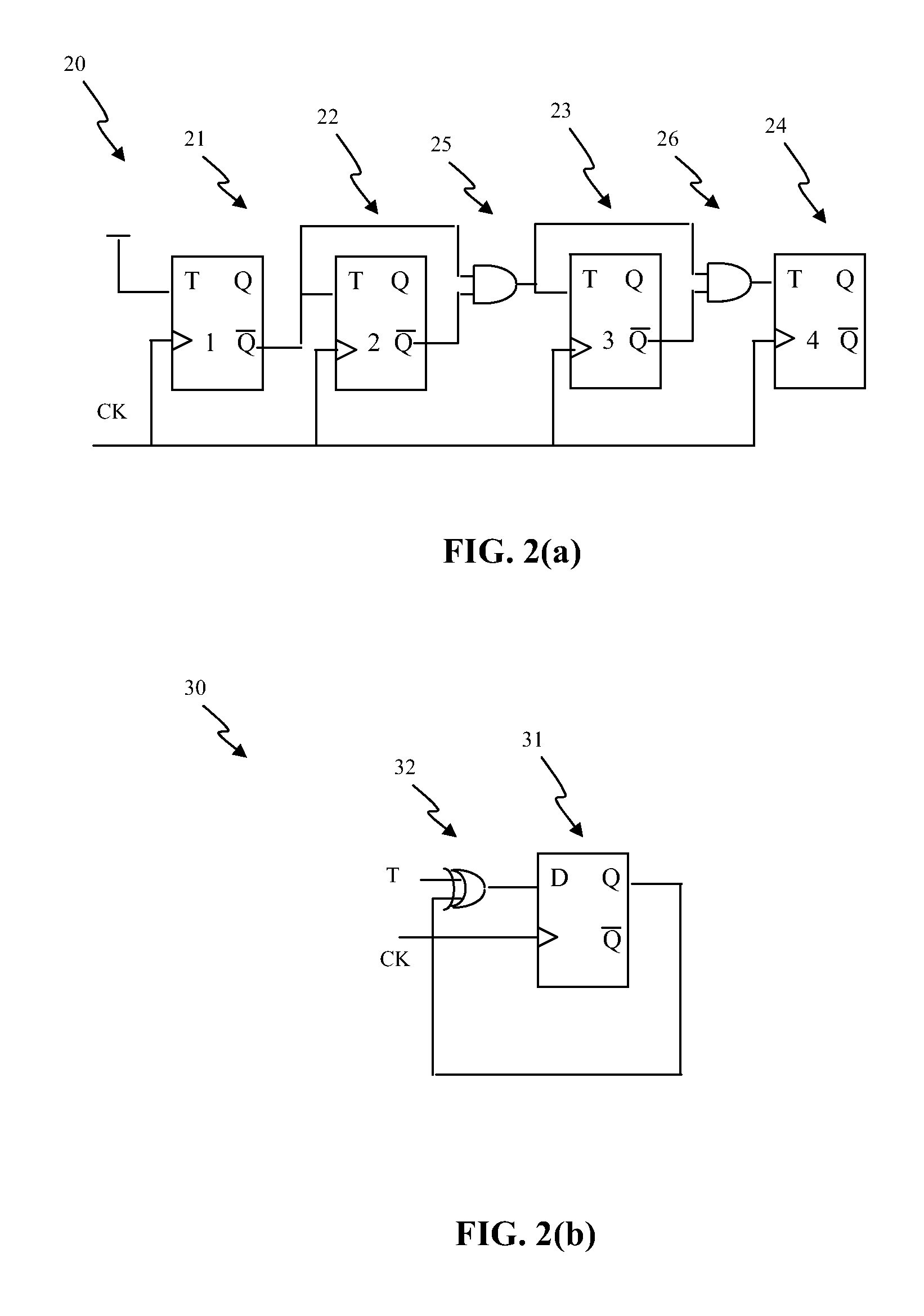

Built-in self test circuit using linear feedback shift register

A built-in self test (BIST) circuit comprising a linear feedback shift register is disclosed. The BIST circuit comprises a controller for controlling a self-testing operation of a memory chip embedded in an integrated circuit, an address generator for generating pseudo-random address patterns under control of the controller, a data generator for producing test data associated with data backgrounds of the address bits under the control of the controller, and a comparator for comparing the test data with memory data output from the memory chip to detect a defect, if any, of the memory chip. The pseudo-random random pattern comprises a single-random pseudo-random address pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

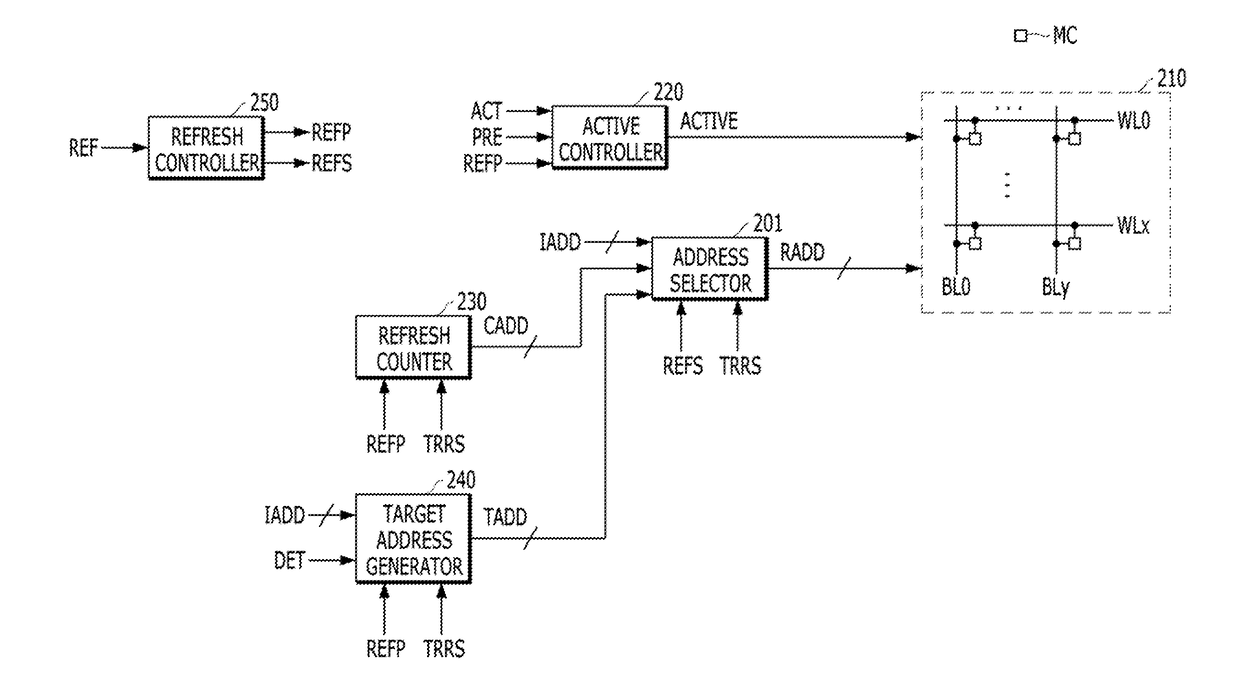

Memory device including refresh controller

ActiveUS9691466B1Ensure correct executionDigital storageEnergy efficient computingMemory bankAddress generator

A memory device may include: a target address generator suitable for storing one or more addresses for each time a refresh command is skipped, and for generating one or more target addresses for each of the stored addresses during a burst refresh operation; and a refresh controller suitable for refreshing a word line selected among a plurality of word lines of a memory bank based on the generated one or more target addresses during a target refresh operation.

Owner:SK HYNIX INC

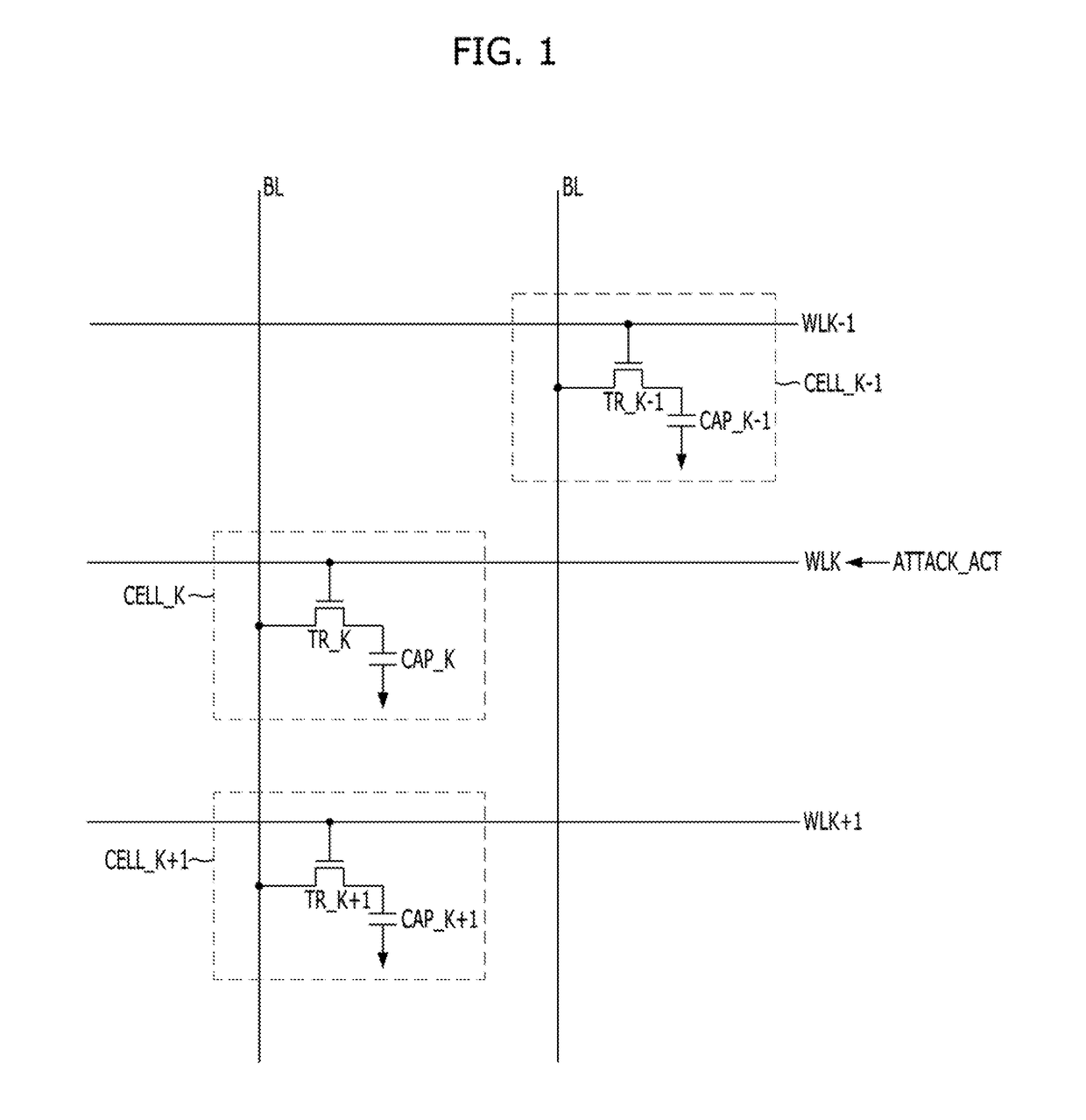

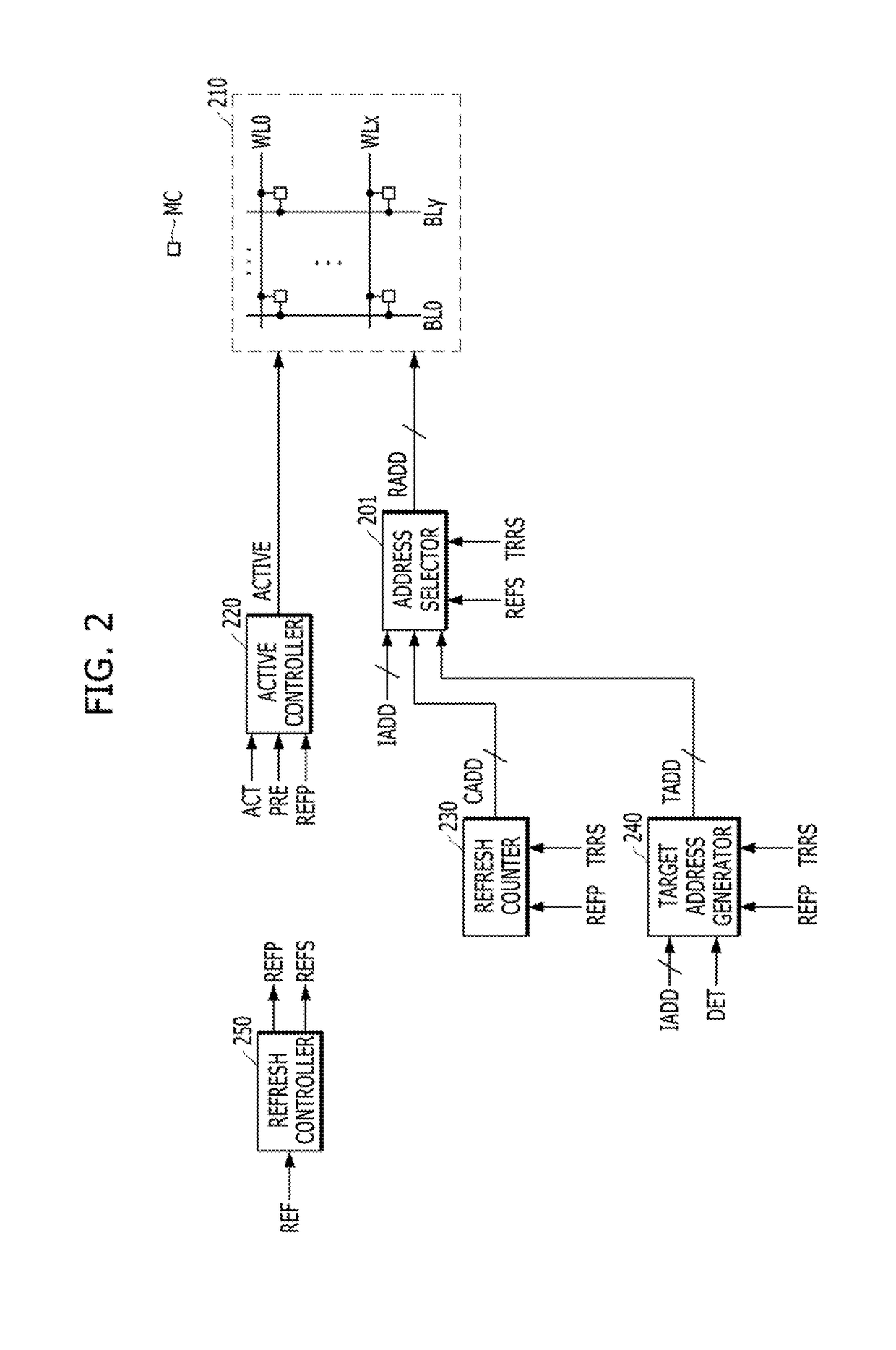

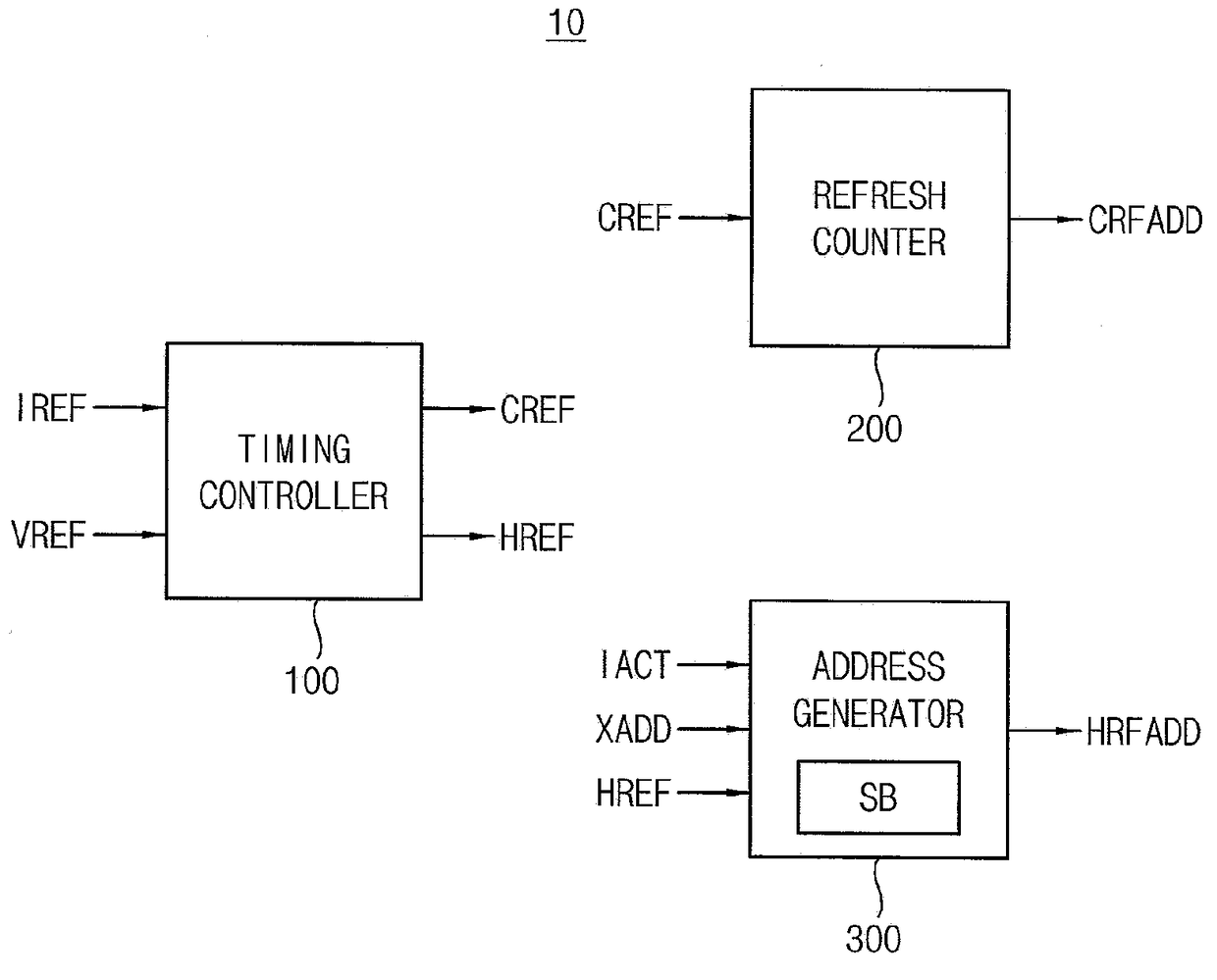

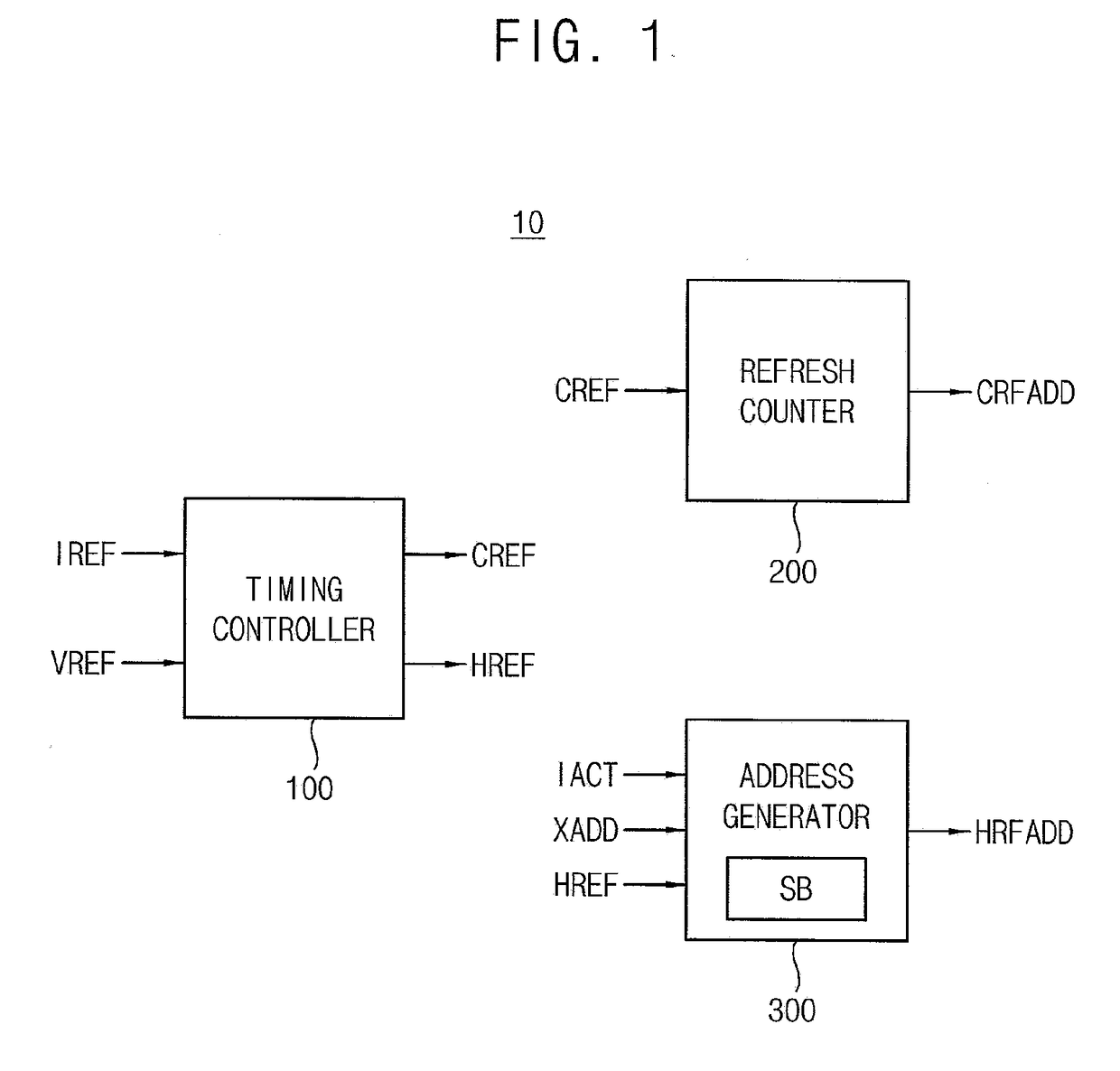

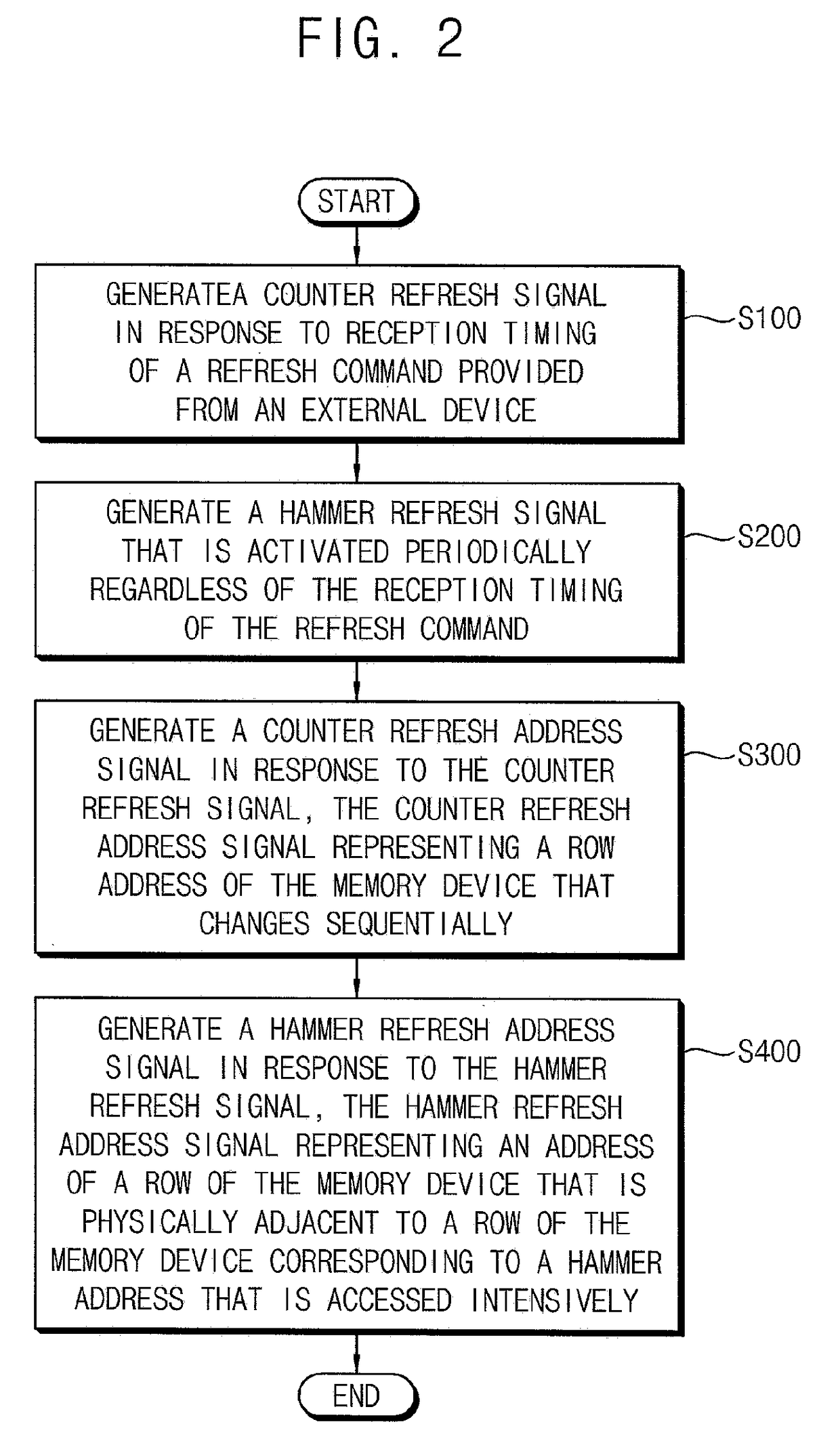

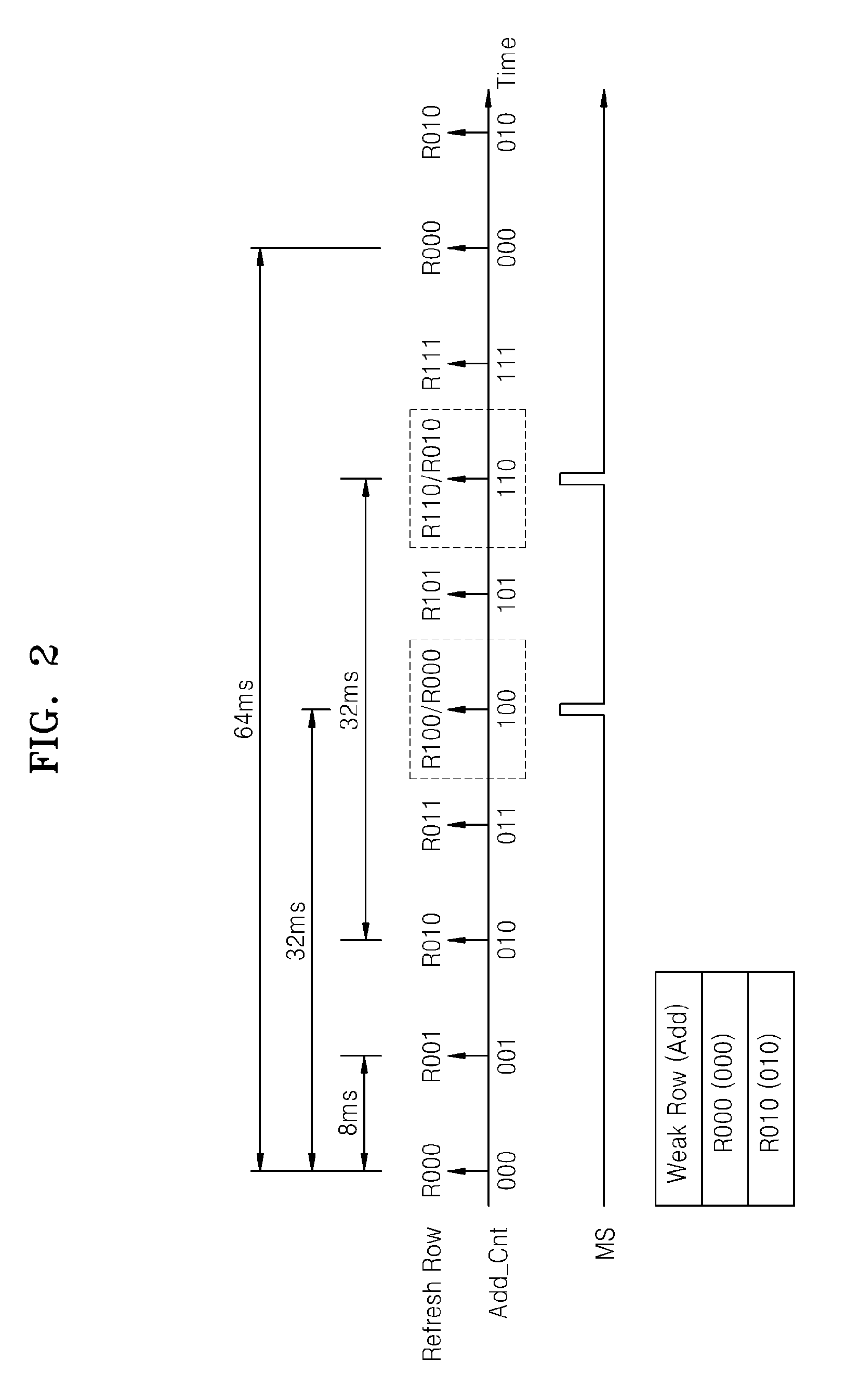

Refresh controller and memory device including the same

A refresh controller of a memory device may include a timing controller, a refresh counter and an address generator. The timing controller generates a counter refresh signal in response to receiving a refresh command provided from an external device, and generates a hammer refresh signal that is activated periodically. The refresh counter generates a counter refresh address signal in response to the counter refresh signal, such that the counter refresh address signal represents a row address, the refresh counter being configured sequentially change the counter refresh address signal. The address generator generates a hammer refresh address signal in response to the hammer refresh signal, the hammer refresh address signal representing an address of a row of the memory device that is physically adjacent to a row of the memory device corresponding to a hammer address that is accessed intensively.

Owner:SAMSUNG ELECTRONICS CO LTD

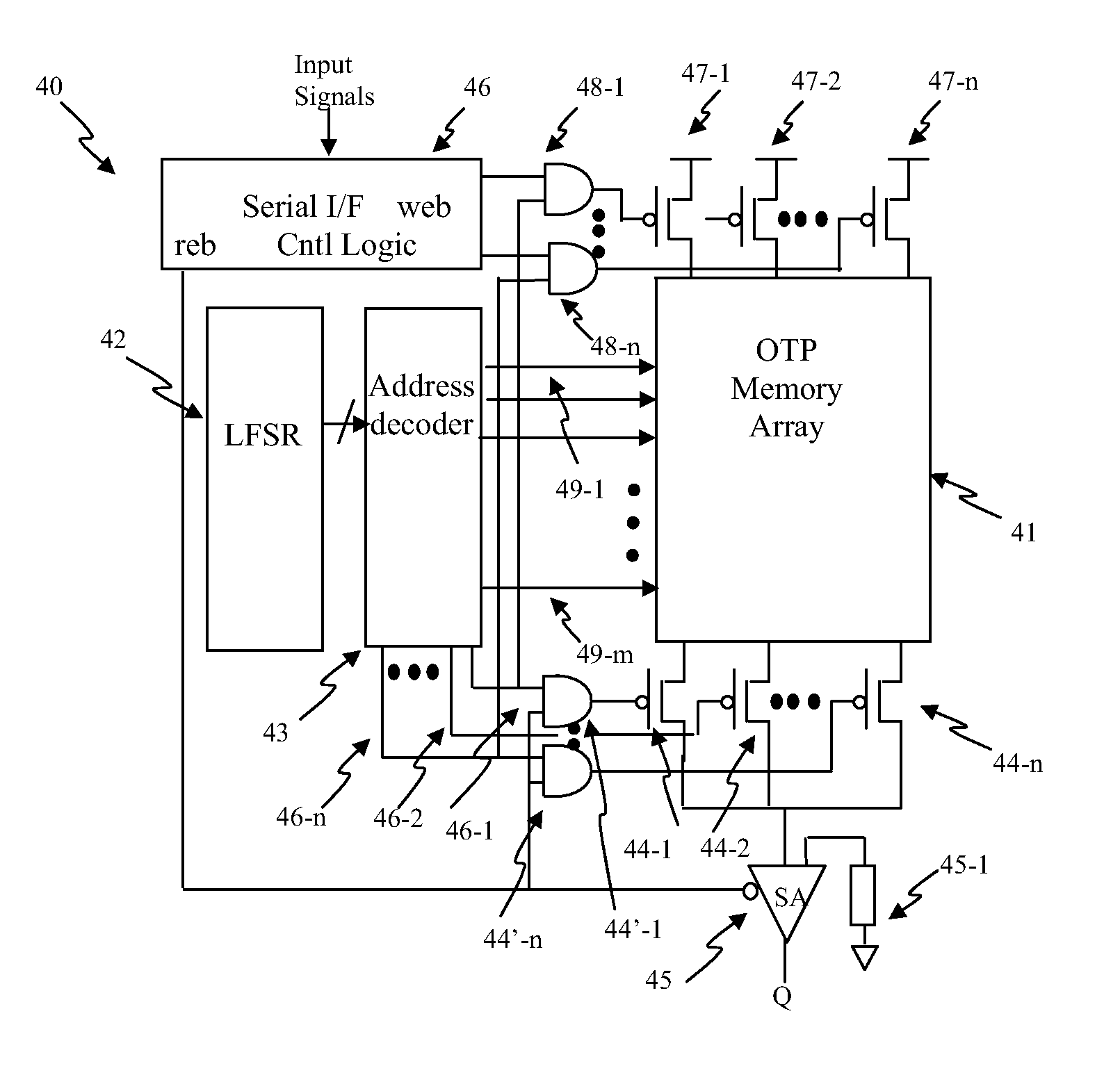

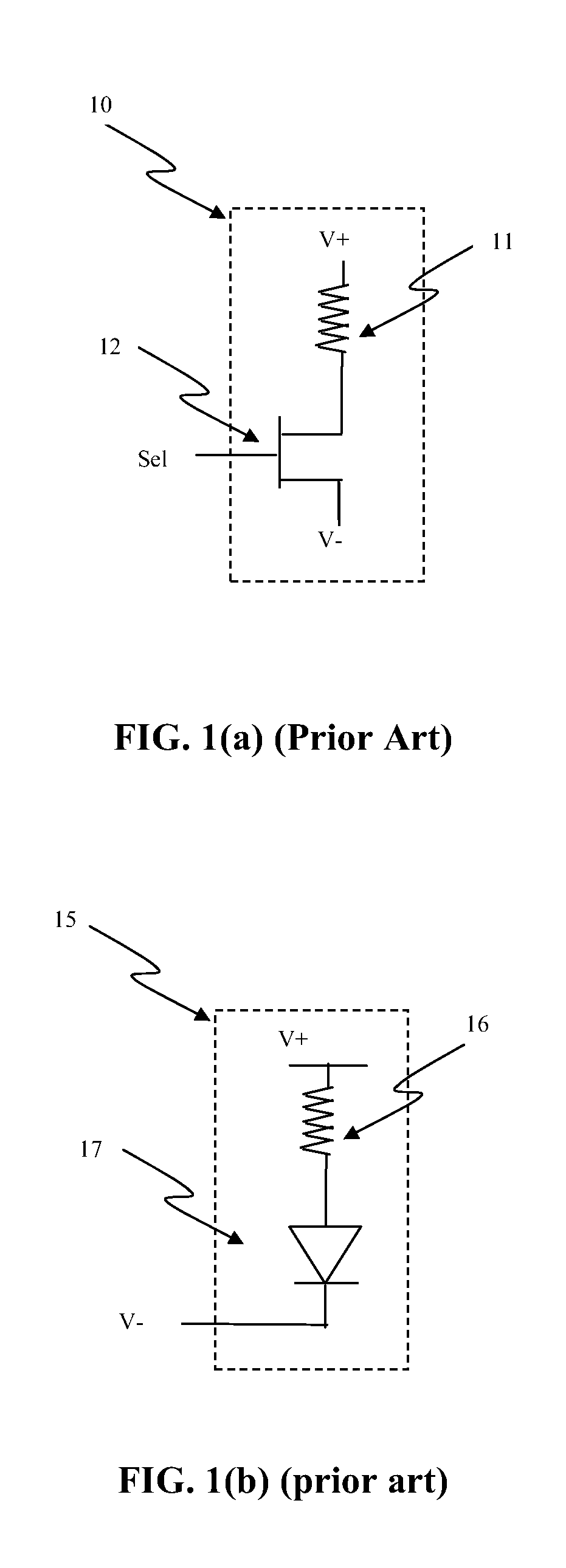

Circuit and System of a Low Density One-Time Programmable Memory

InactiveUS20130201745A1Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesAddress generatorHemt circuits

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

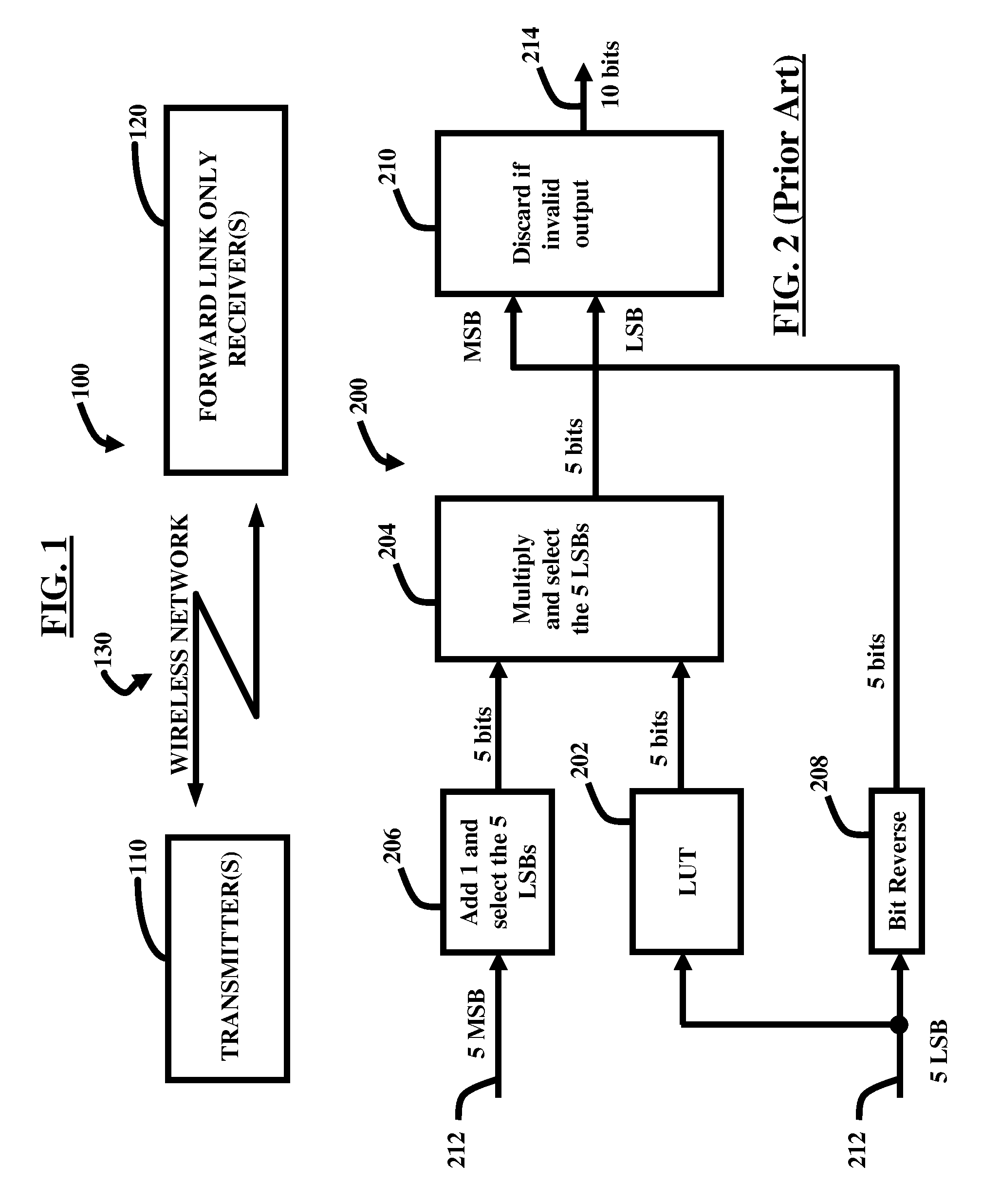

Interleaver address generation in turbo decoders for mobile multimedia multicast system communication systems

InactiveUS8102791B2Code conversionBroadcast transmission systemsCommunications systemAddress generator

Address generation for interleaving in a wireless communication system includes at least one input generation module to generate at least one input signal. A first address generator module and a second address generator module generate a first output address for interleaving and a second output address for interleaving. A selector module selects an address for interleaving from the first and the second output address based on predetermined criteria. At least one input translation module is receives an input signal and translate the received input signal to generate a nominal input signal based on a value of the received input signal. An address generation module generates an address for interleaving based on the nominal input signal.

Owner:ATMEL CORP

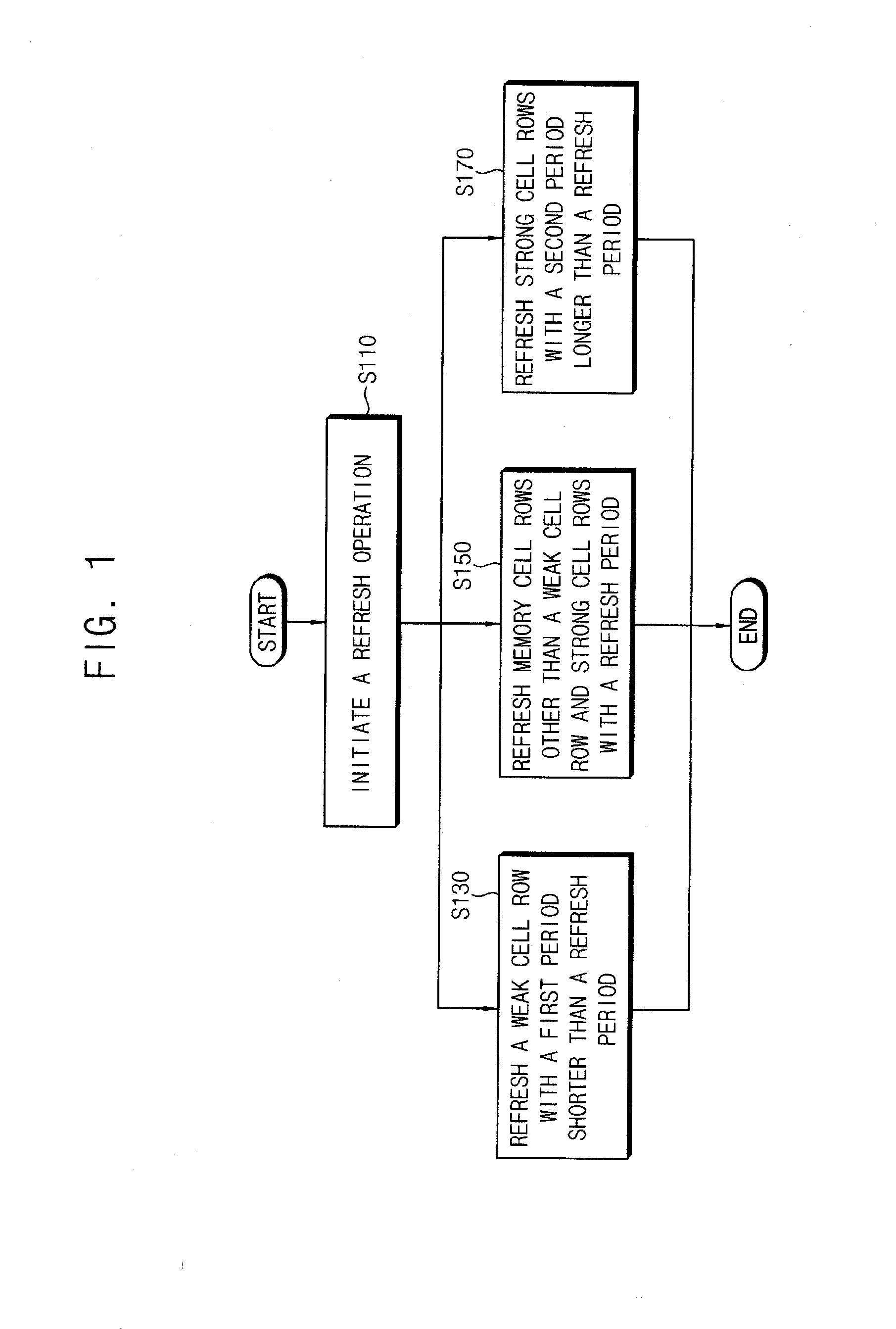

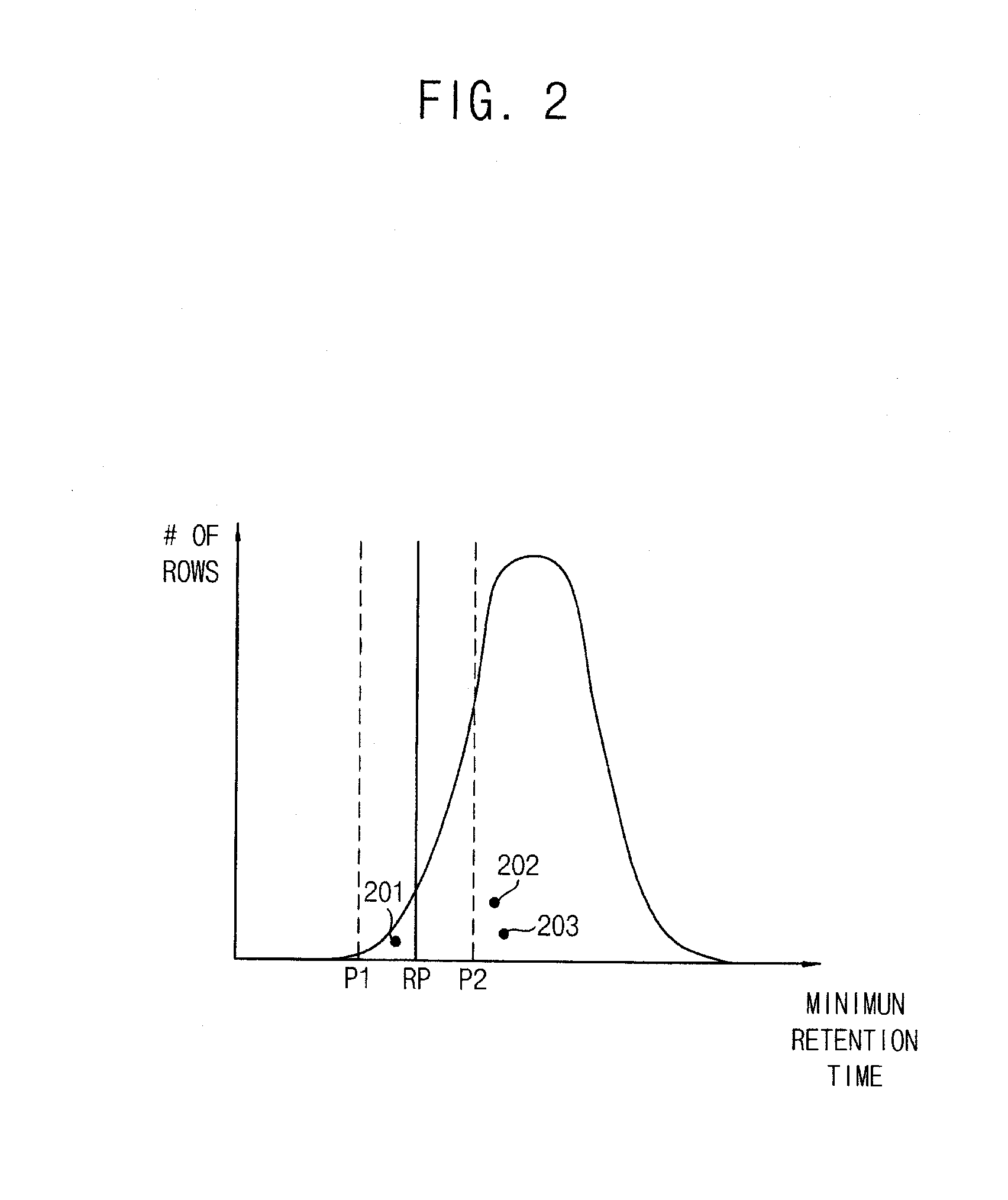

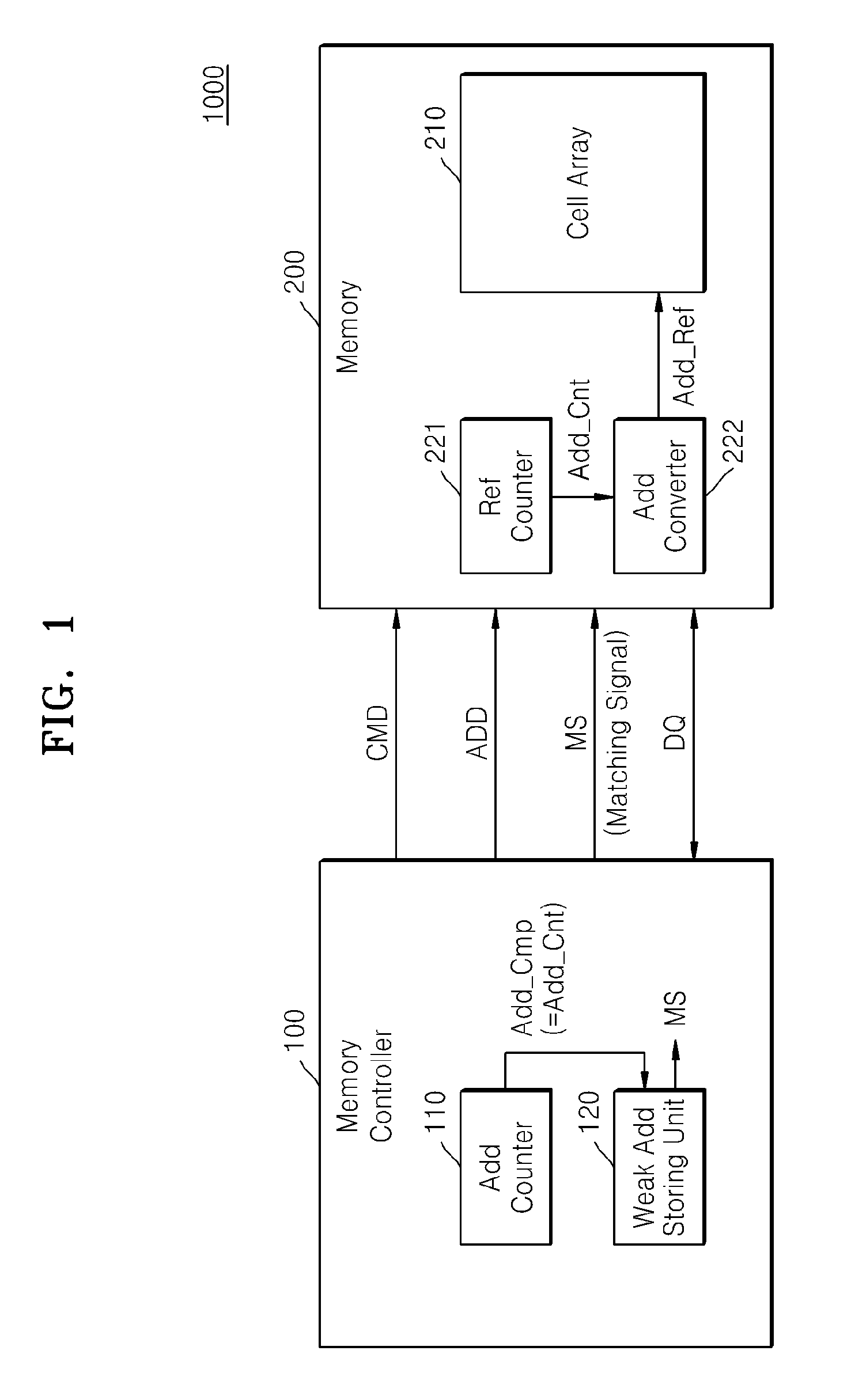

Method of Refreshing a Memory Device, Refresh Address Generator and Memory Device

A refresh address is generated with a refresh period for refreshing a memory device with refresh leveraging. A respective refresh is performed on a weak cell having a first address when the refresh address is a second address instead of on a first strong cell having the second address. A respective refresh is performed on one of the first strong cell or a second strong cell having a third address when the refresh address is the third address. Address information is stored for only one of the first, second, and third addresses such that memory capacity may be reduced. In alternative aspects, a respective refresh is performed on one of a weak cell, a first strong cell, or a second strong cell depending on a flag when the refresh address is any of at least one predetermined address to result in refresh leveraging.

Owner:SAMSUNG ELECTRONICS CO LTD

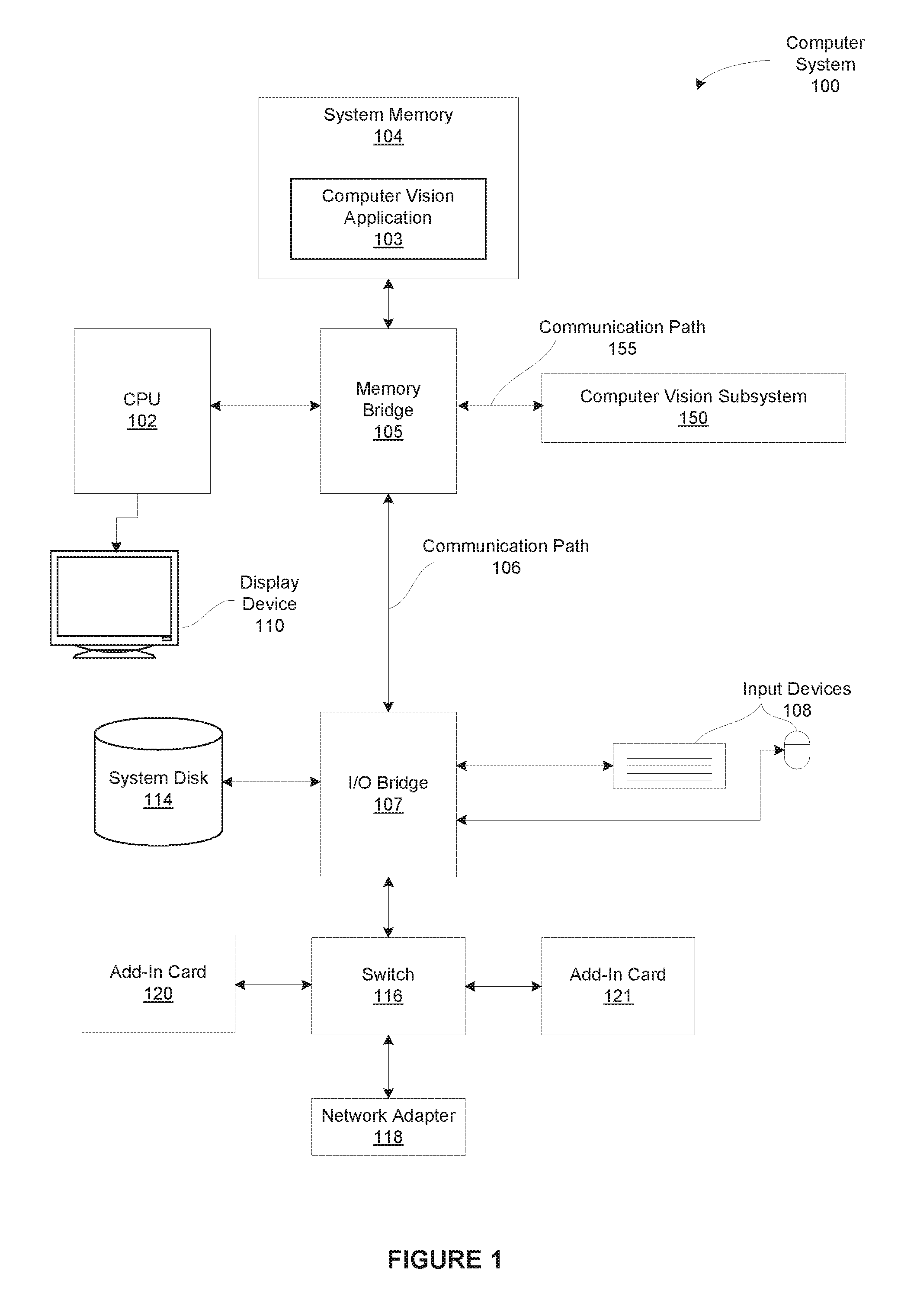

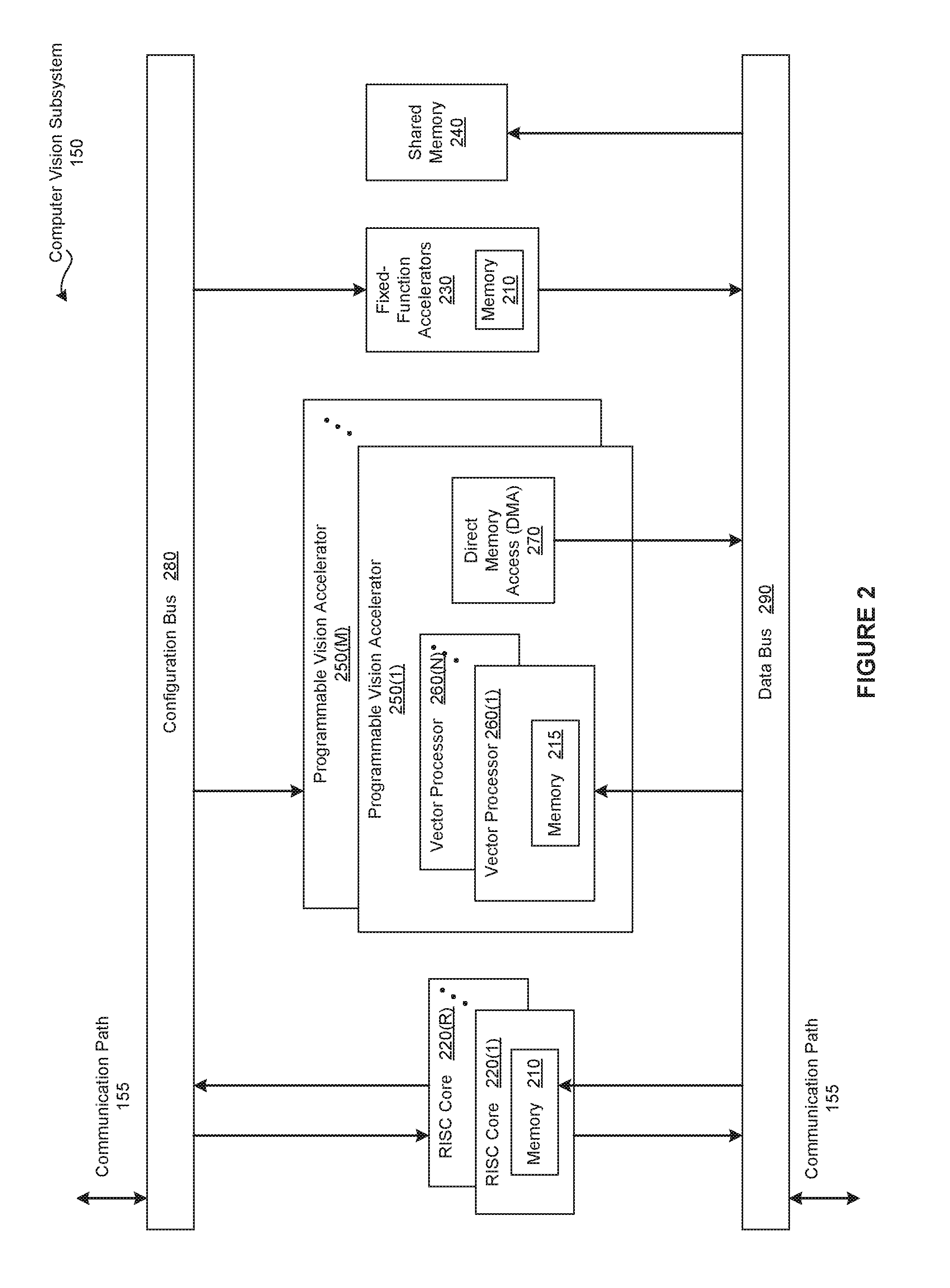

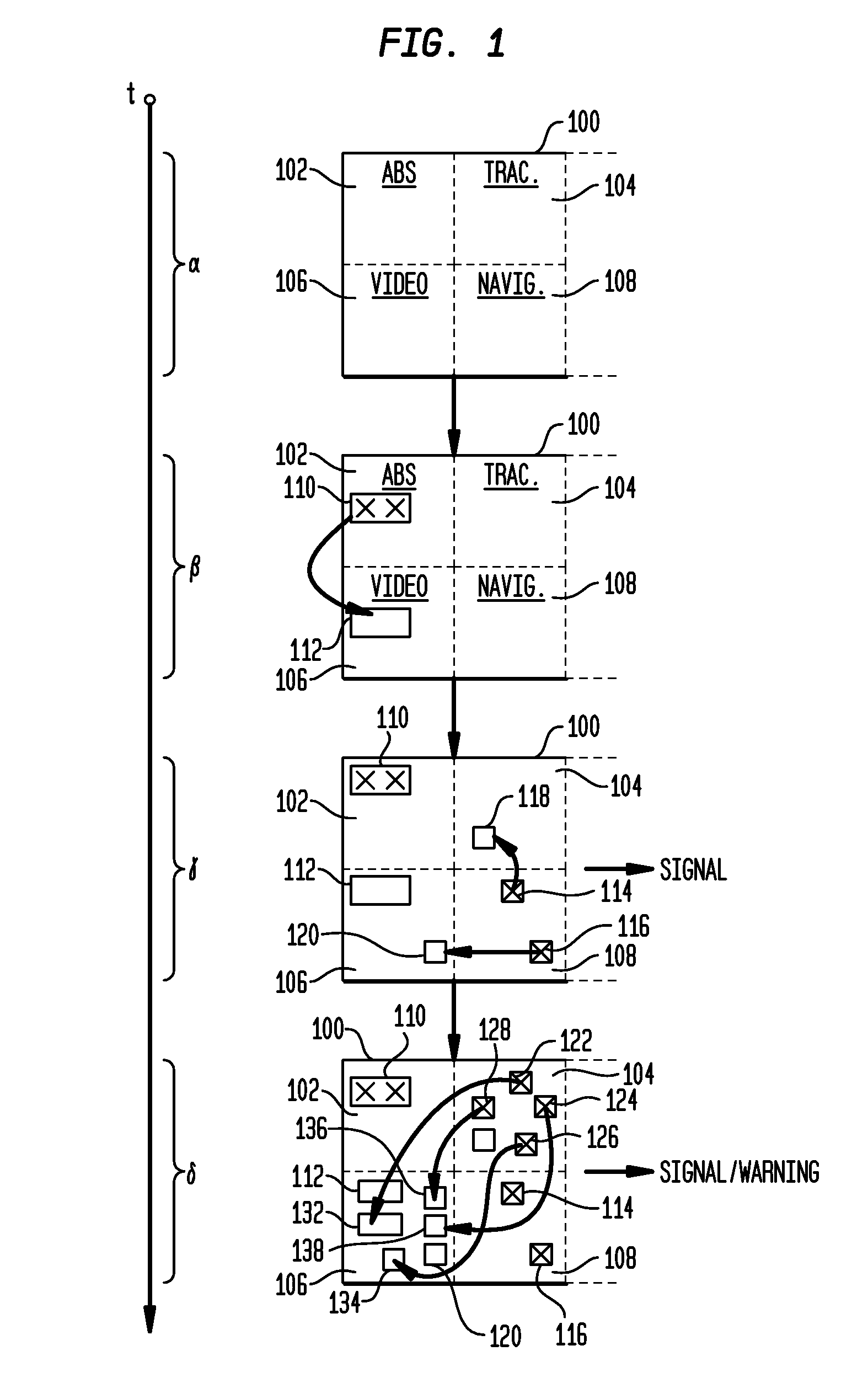

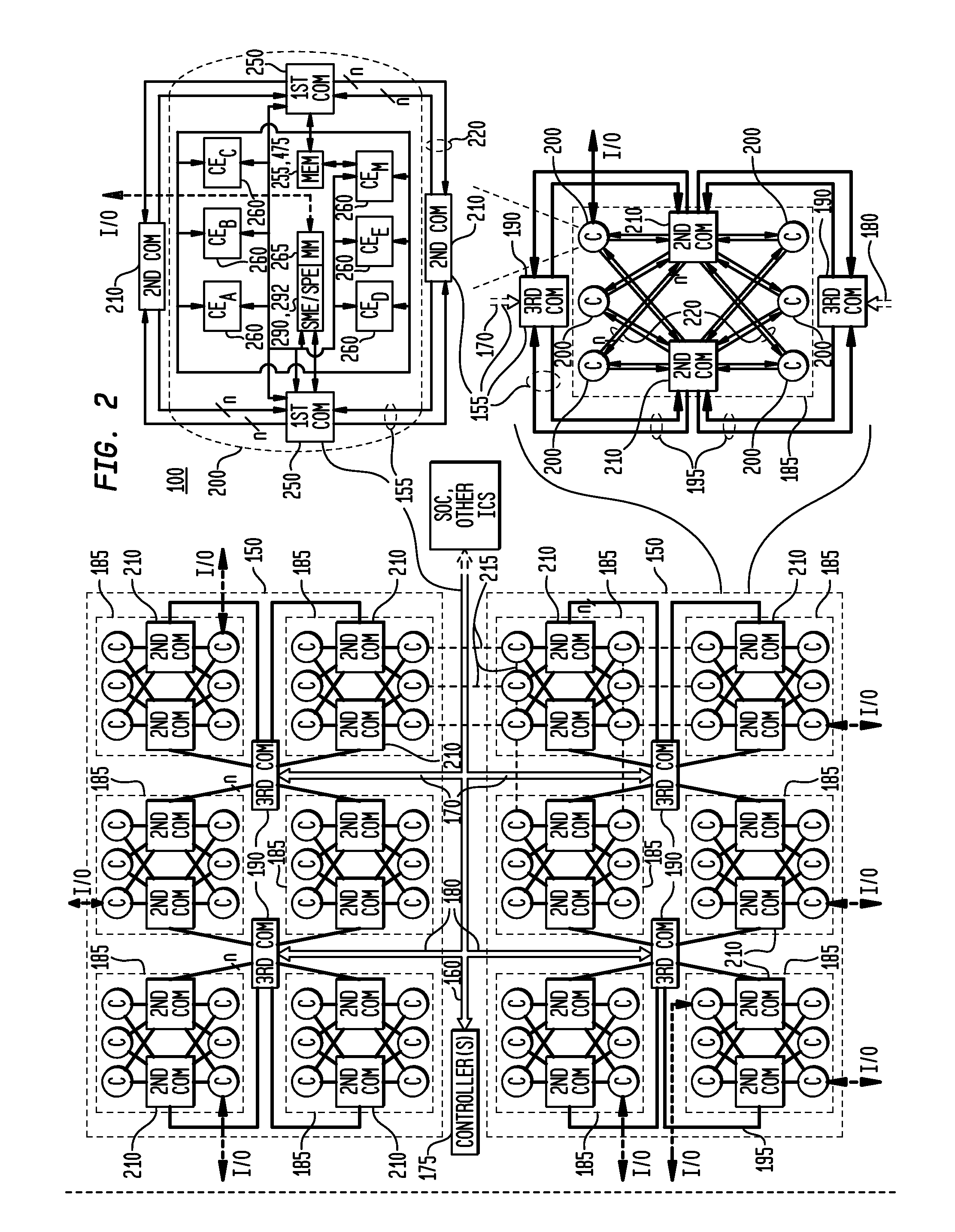

Programmable Vision Accelerator

ActiveUS20160321074A1Sacrificed flexibilitySacrificed performanceRegister arrangementsDigital computer detailsParallel computingAddress generator

In one embodiment of the present invention, a programmable vision accelerator enables applications to collapse multi-dimensional loops into one dimensional loops. In general, configurable components included in the programmable vision accelerator work together to facilitate such loop collapsing. The configurable elements include multi-dimensional address generators, vector units, and load / store units. Each multi-dimensional address generator generates a different address pattern. Each address pattern represents an overall addressing sequence associated with an object accessed within the collapsed loop. The vector units and the load store units provide execution functionality typically associated with multi-dimensional loops based on the address pattern. Advantageously, collapsing multi-dimensional loops in a flexible manner dramatically reduces the overhead associated with implementing a wide range of computer vision algorithms. Consequently, the overall performance of many computer vision applications may be optimized.

Owner:NVIDIA CORP

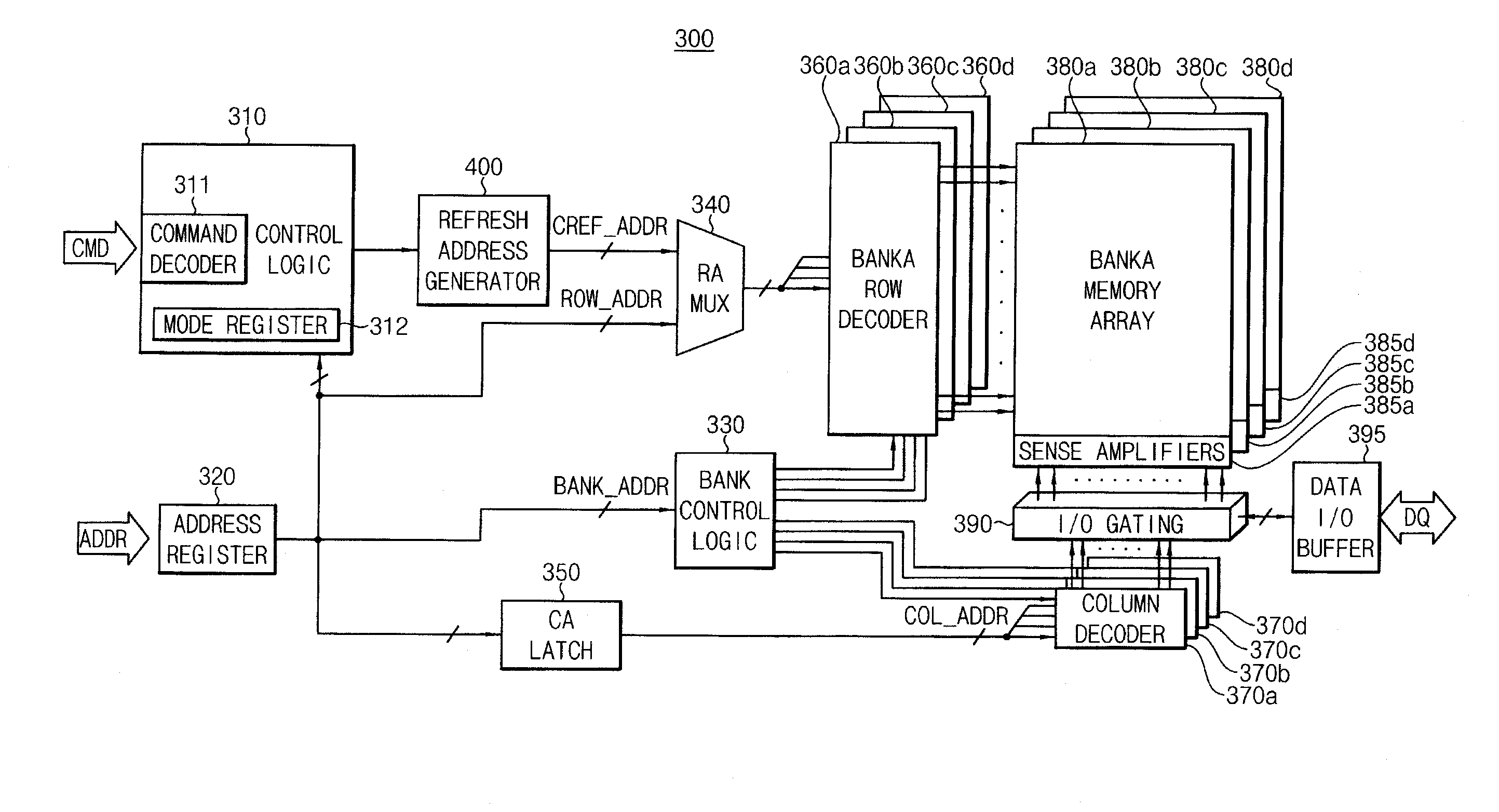

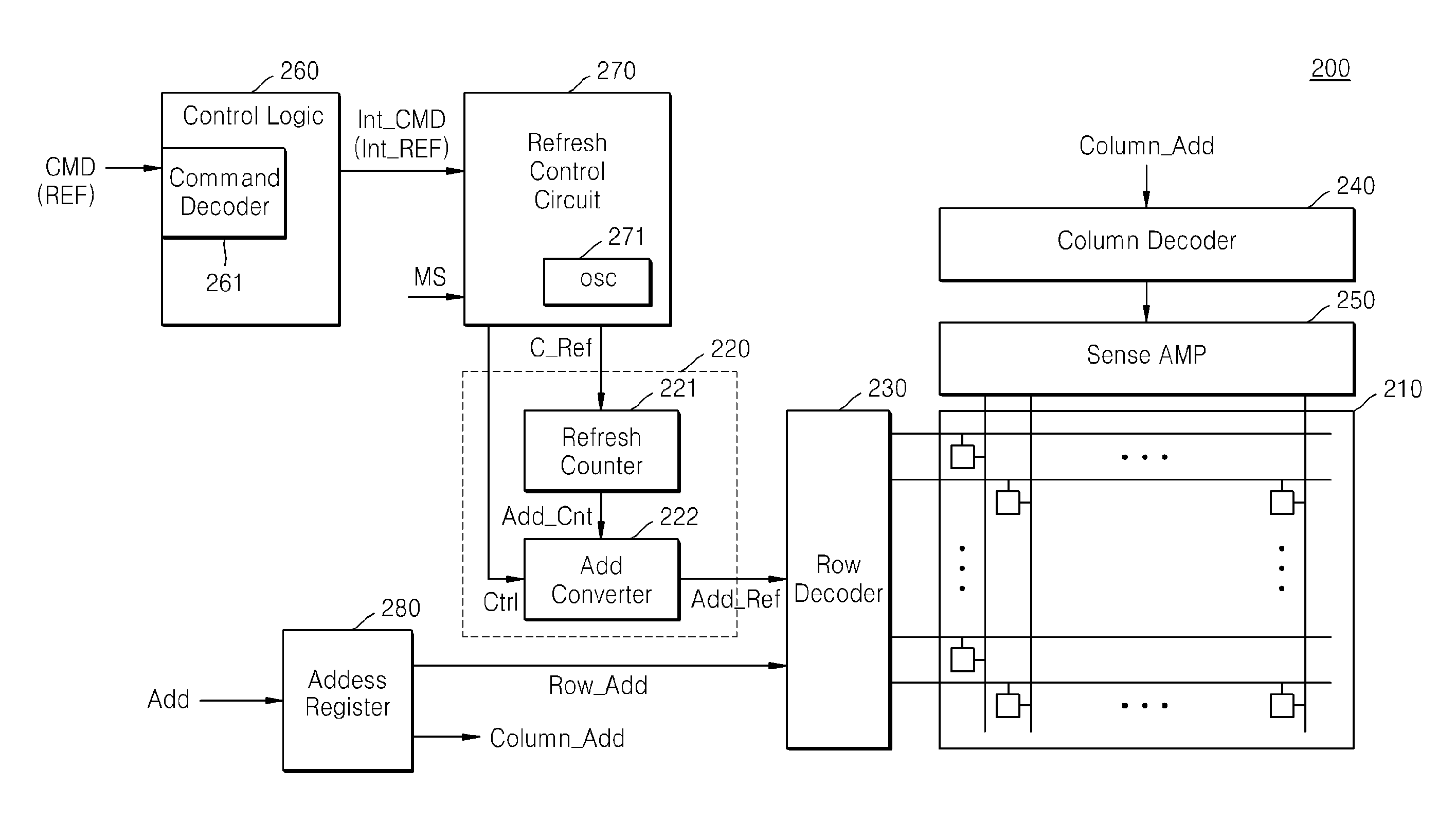

Semiconductor memory device having adjustable refresh period, memory system comprising same, and method of operating same

ActiveUS9153294B2Increase consumptionImprove reliabilityDigital storageMemory systemsControl signalCell region

A semiconductor memory device includes a cell array including a plurality of cell regions, a row decoder configured to drive rows corresponding to cell regions in which a refresh operation is to be performed, based on a counting address, and a refresh address generator configured to generate the counting address and a modified address in response to a control signal, wherein the modified address is generated by inverting at least one bit of the counting address, and wherein the semiconductor memory device performs concurrent refresh operations on a first cell region corresponding to the counting address and a second cell region corresponding to the modified address where the second cell region is determined to have weak cells.

Owner:SAMSUNG ELECTRONICS CO LTD

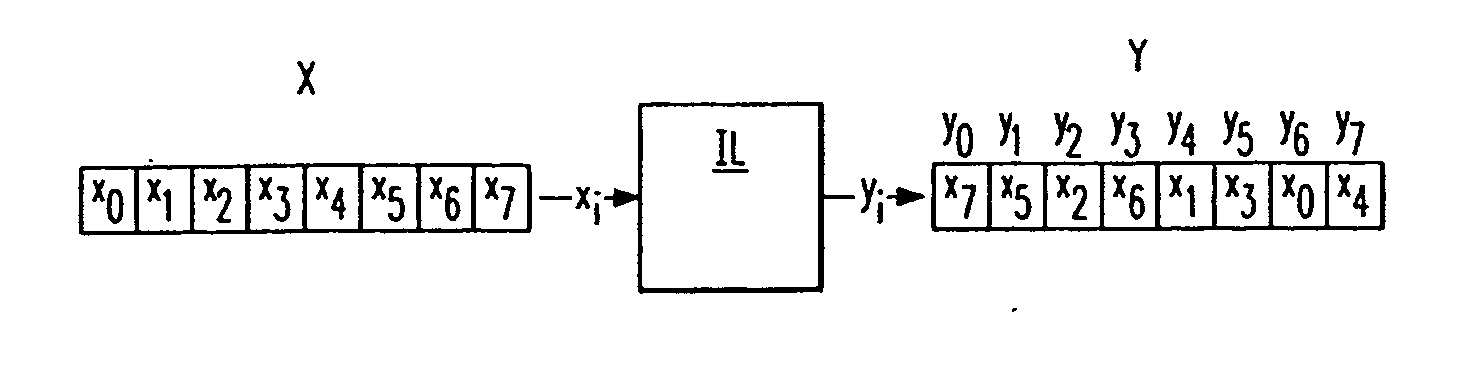

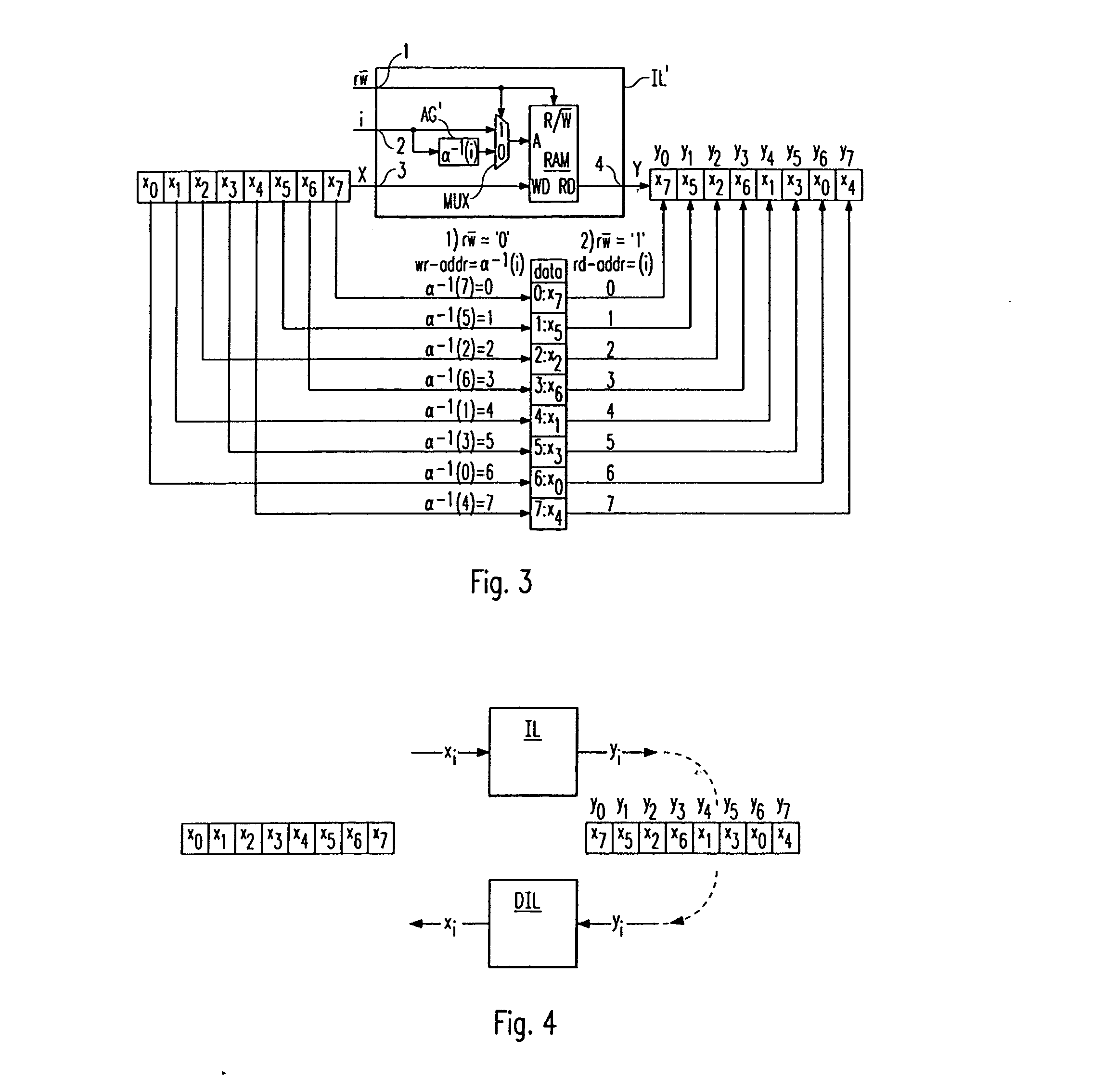

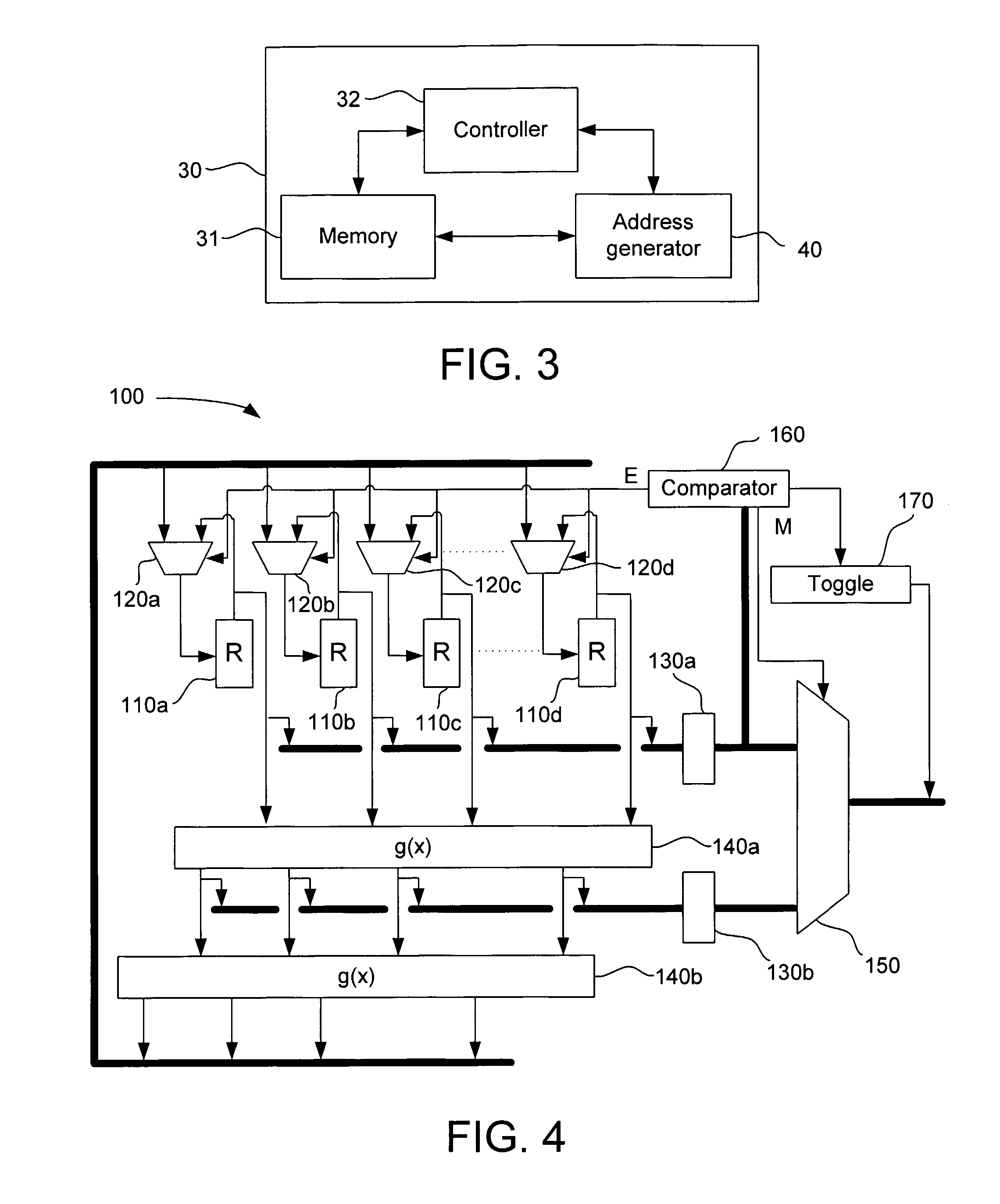

Combined interleaver and deinterleaver, and turbo decoder comprising a combined interleaver and deinterleaver

InactiveUS20050034046A1Reduce implementation complexityReduce complexityCode conversionError correction/detection by combining multiple code structuresAddress generatorData memory

Owner:INFINEON TECH AG

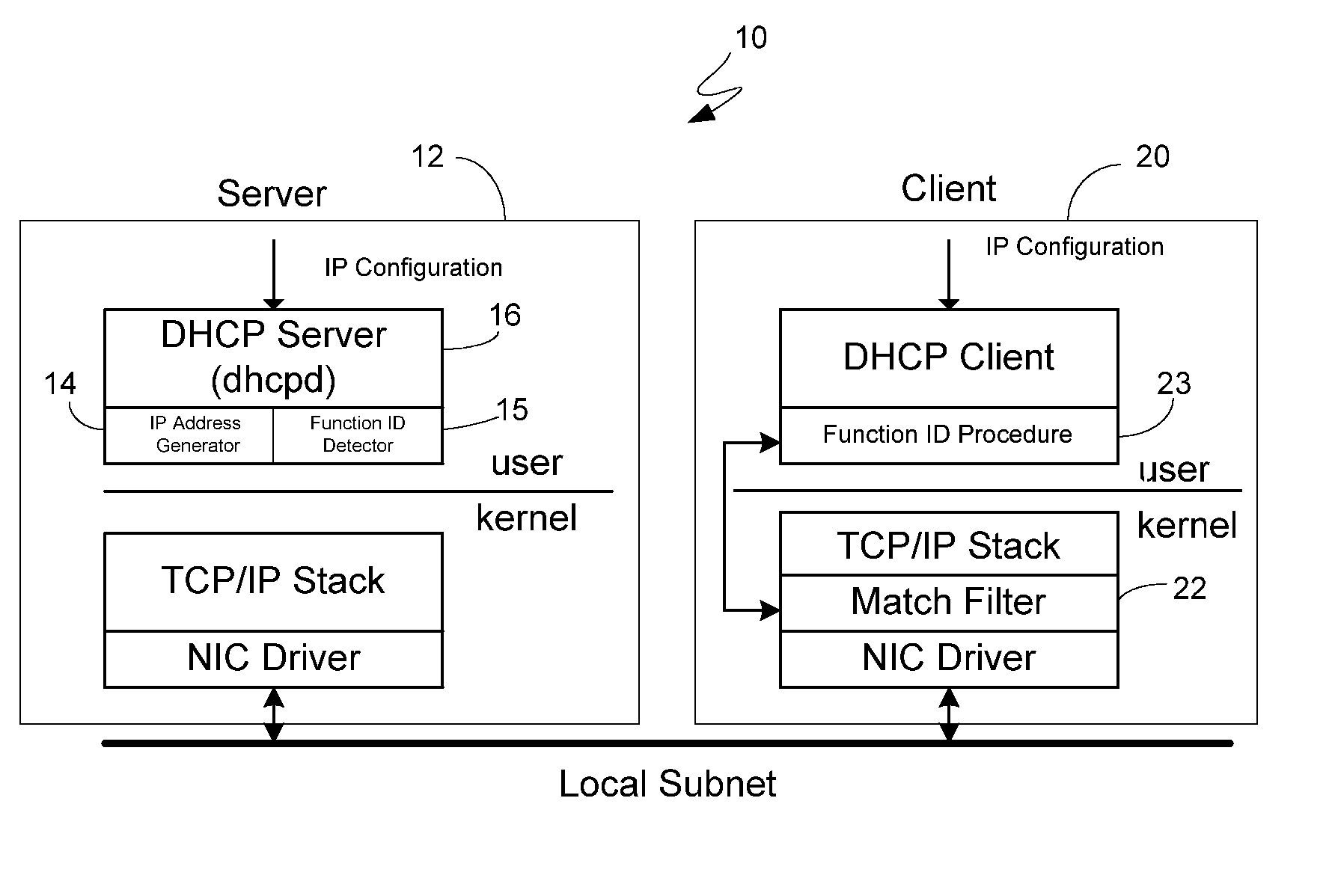

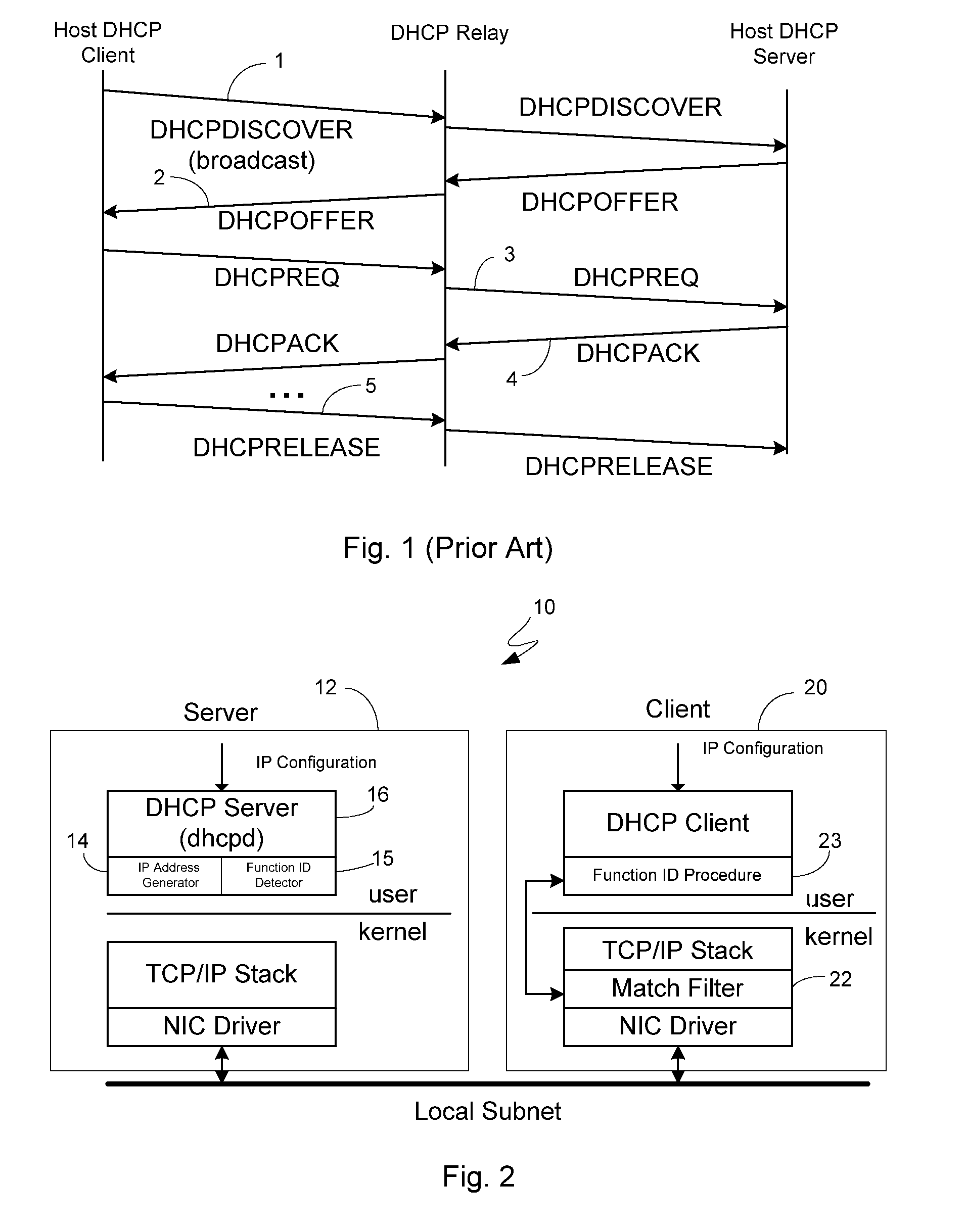

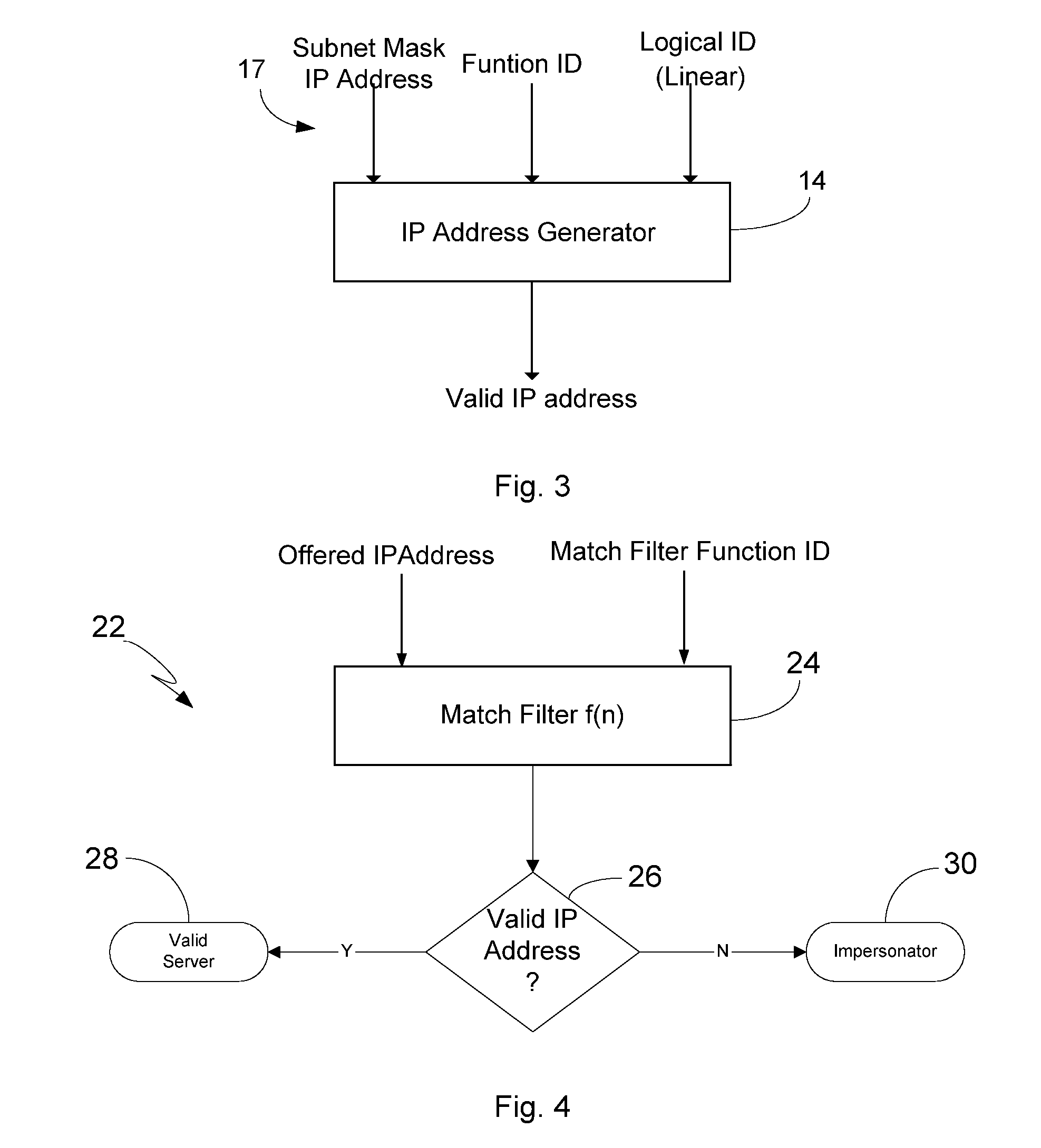

Security Enhanced Methods And System For IP Address Allocation

InactiveUS20060195610A1Easy to understandMultiple digital computer combinationsTransmissionAddress generatorSpamming

The present invention relates to methods and a system for enhancing DHCP to promote a more secure IP address allocation model. The invention advantageously accomplishes this through the utilization of an address generator which is compatible with the existing DHCP protocol, and which incorporates an algorithm for use in producing a selected IP address as one of a sub-set of allocable addresses that are non-sequentially distributed within an address pool. As such, the invention offers robust security and allows for the rapid detection of unauthorized activity such as network intrusion, worms, virus propagation, network scanners, and SPAM.

Owner:SYTEX

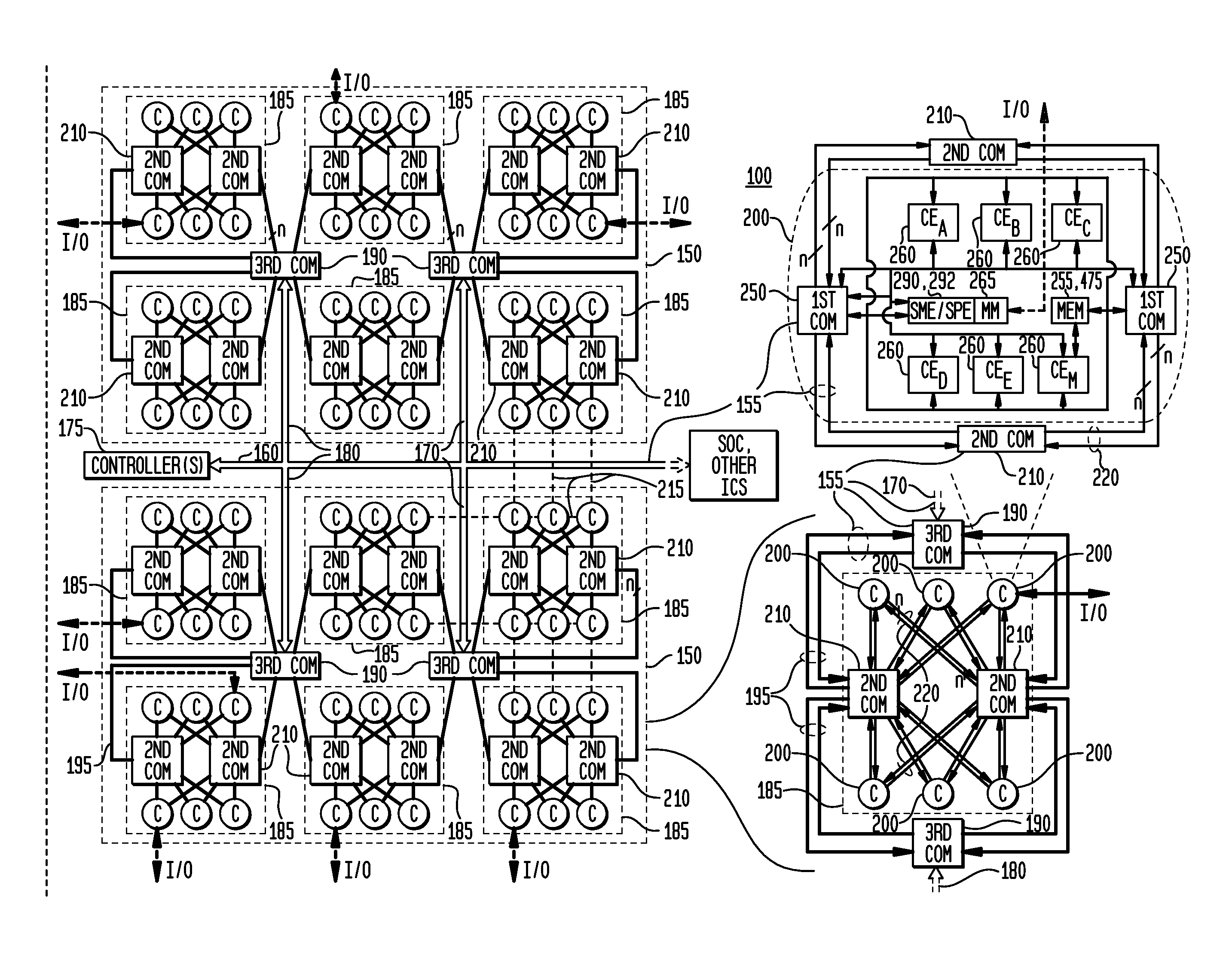

Multi-Context Configurable Memory Controller

InactiveUS20120131257A1Significant resiliencyFail-safe circuitsMemory adressing/allocation/relocationMultiple contextMemory address

The exemplary embodiments provide a multi-context configurable memory controller comprising: an input-output data port array comprising a plurality of input queues and a plurality of output queues; at least one configuration and control register to store, for each context of a plurality of contexts, a plurality of configuration bits; a configurable circuit element configurable for a plurality of data operations, each data operation corresponding to a context of a plurality of contexts, the plurality of data operations comprising memory address generation, memory write operations, and memory read operations, the configurable circuit element comprising a plurality of configurable address generators; and an element controller, the element controller comprising a port arbitration circuit to arbitrate among a plurality of contexts having a ready-to-run status, and the element controller to allow concurrent execution of multiple data operations for multiple contexts having the ready-to-run status.

Owner:ELEMENT CXI

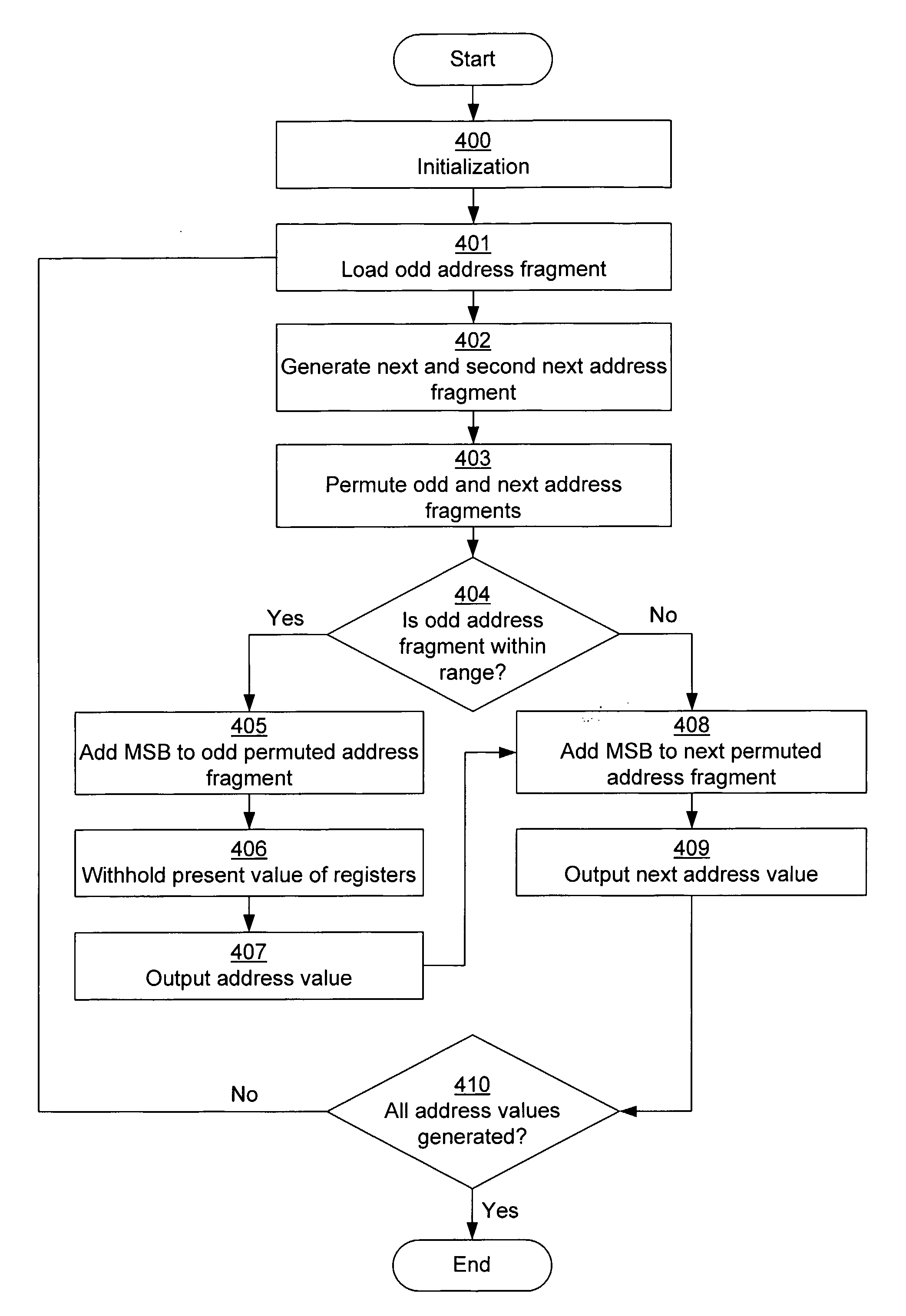

Address generator for an interleaver memory and a deinterleaver memory

InactiveUS20070139428A1Processing capabilitiesEnergeticMemory adressing/allocation/relocationCode conversionAddress generatorArtificial intelligence

Owner:TELEFON AB LM ERICSSON (PUBL)

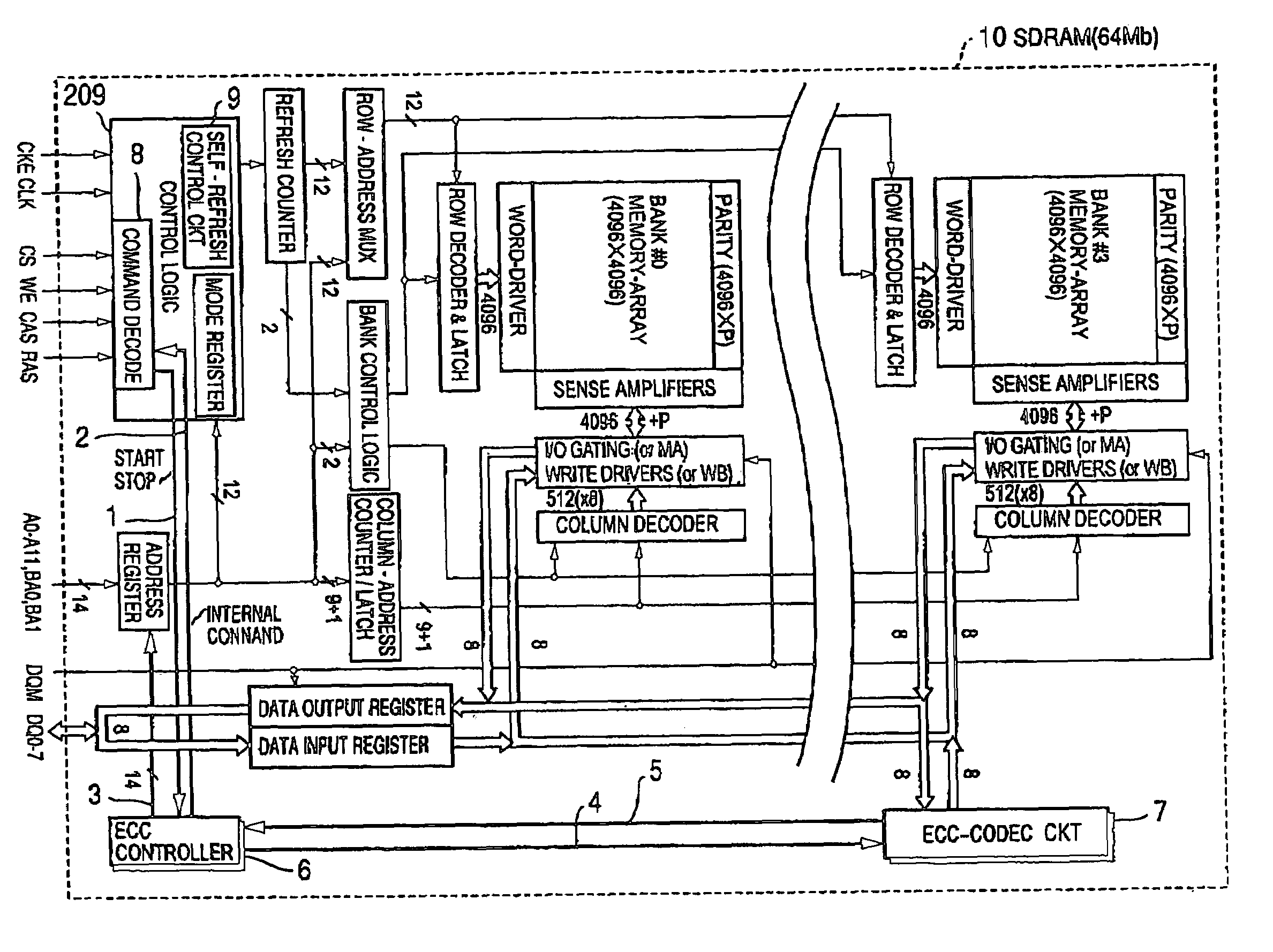

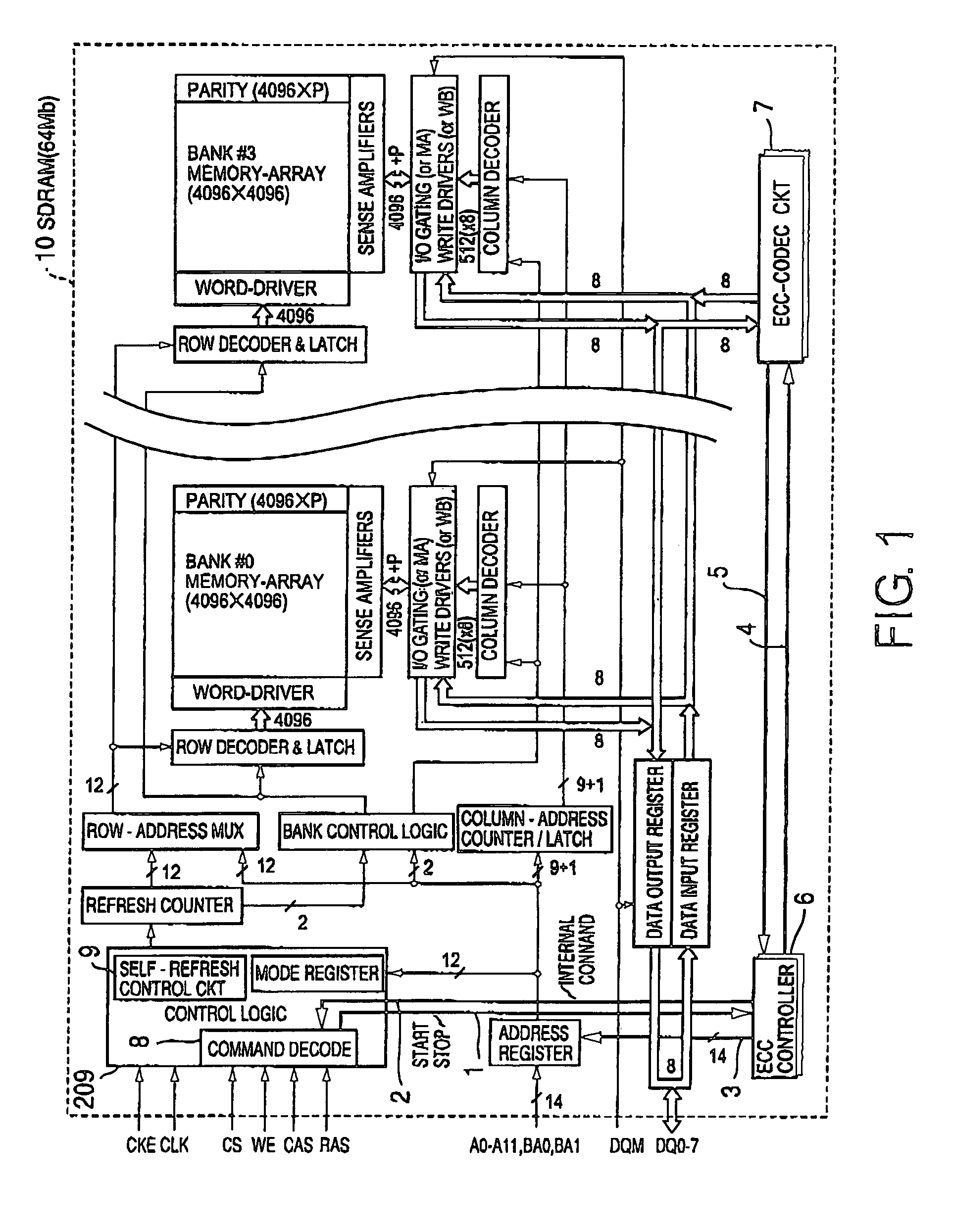

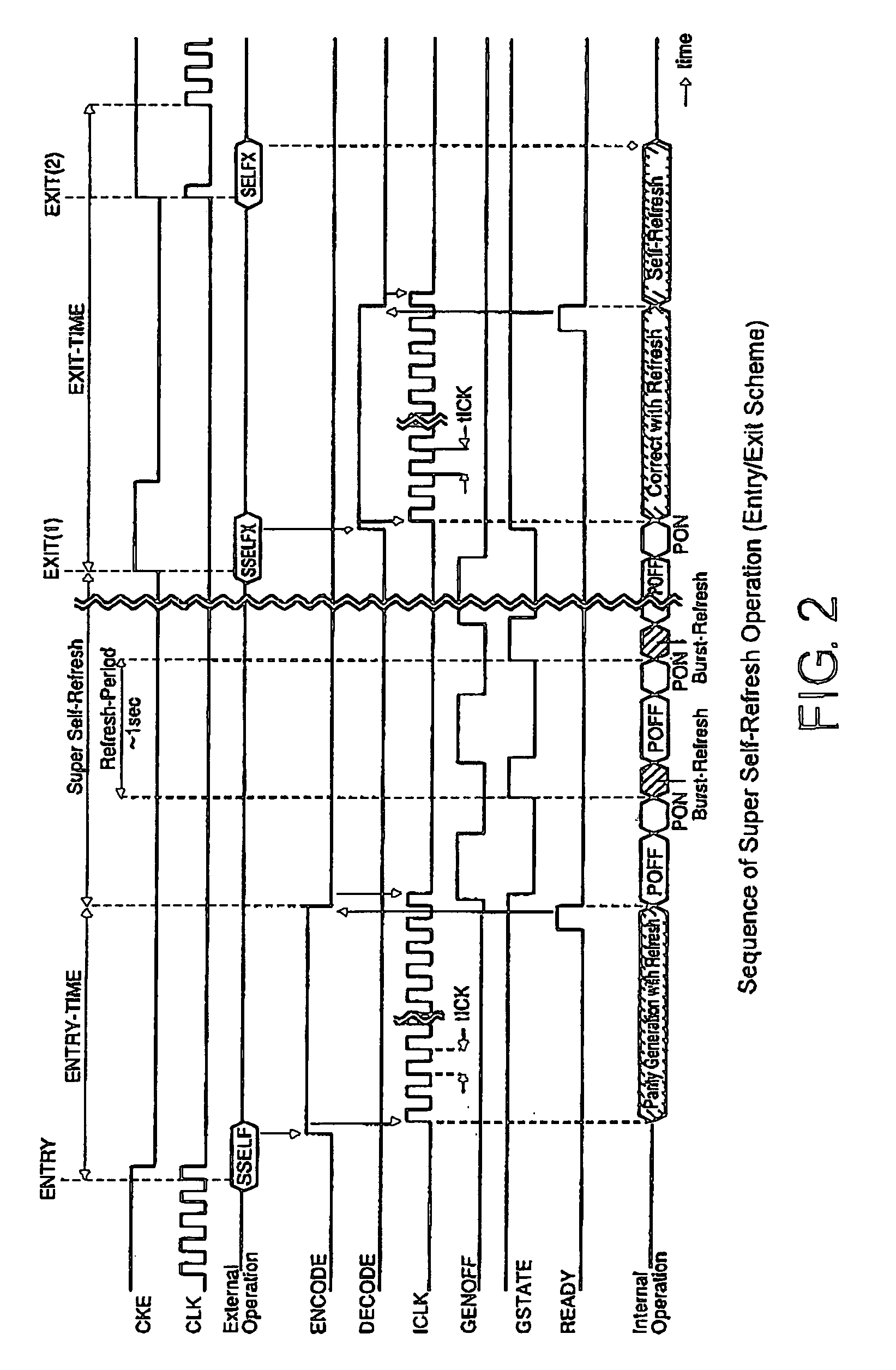

DRAM with super self-refresh and error correction for extended period between refresh operations

InactiveUS7216198B2Memory loss protectionError detection/correctionAddress generatorForward error correction

In a semiconductor integrated circuit device, a command decoder is adapted to receive not only an external command but also an internal command. An ECC controller has a command generator and an address generator. When the command decoder decodes an external entry command, the command generator instructs encoding to an ECC-CODEC circuit and the address generator sequentially produces addresses which are supplied to a memory array. The ECC-CODEC circuit produces check bits for error detection / correction with reference to information data of the memory array. Upon completion of an encoding operation of writing the check bits into a predetermined region of the memory array, the ECC controller delivers an end signal to the command decoder as the internal command to make a super self-refresh control circuit start a super self-refresh operation.

Owner:LONGITUDE LICENSING LTD

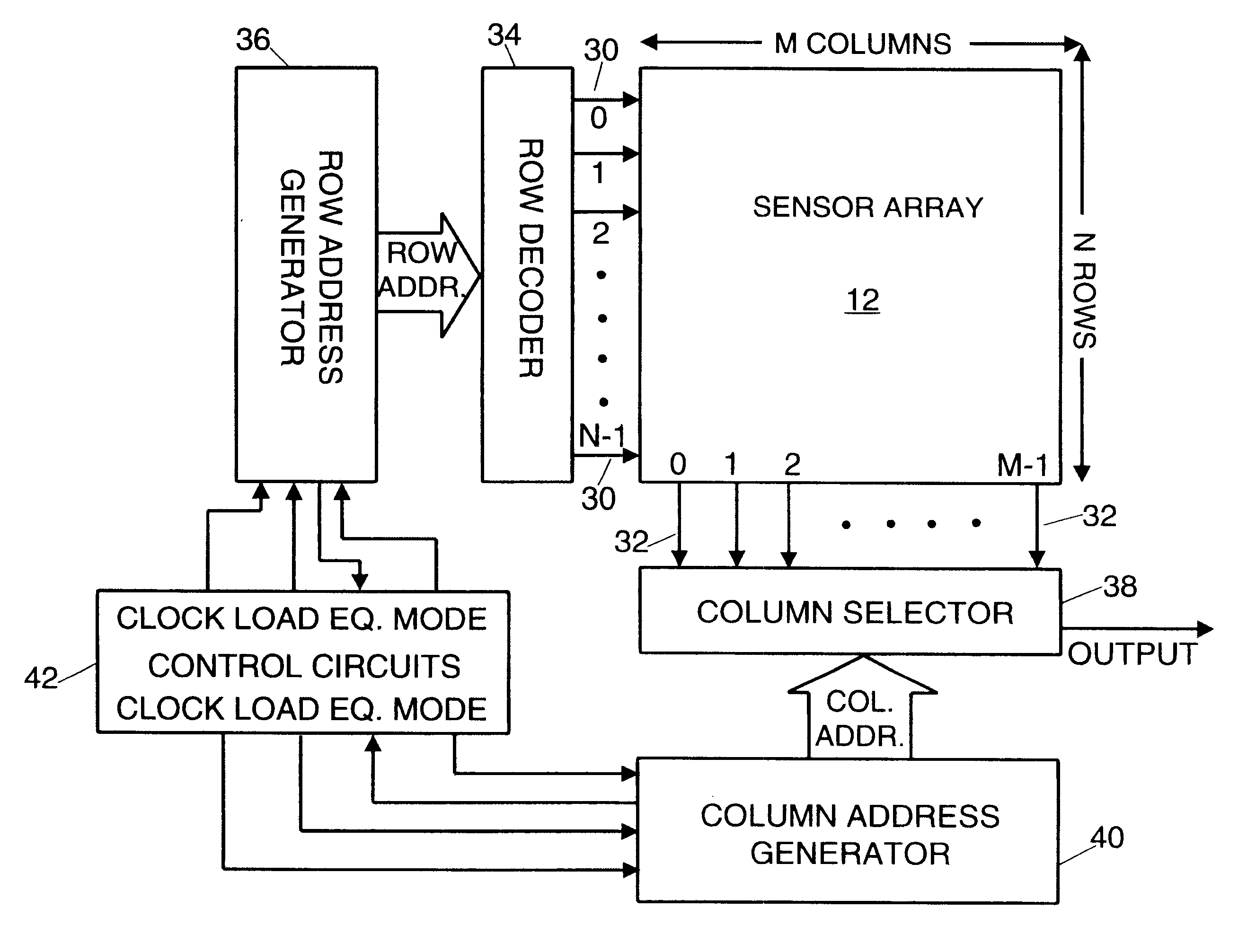

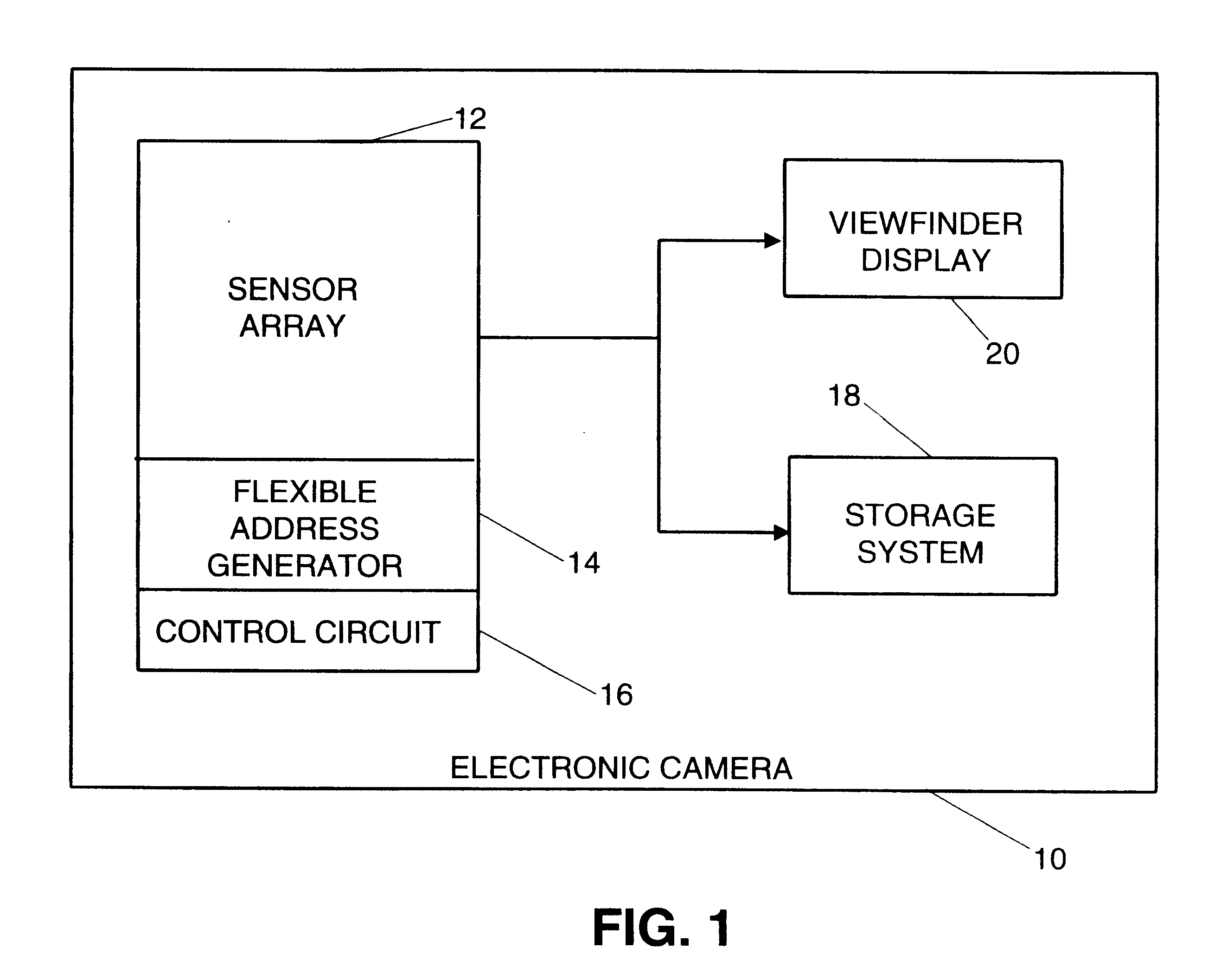

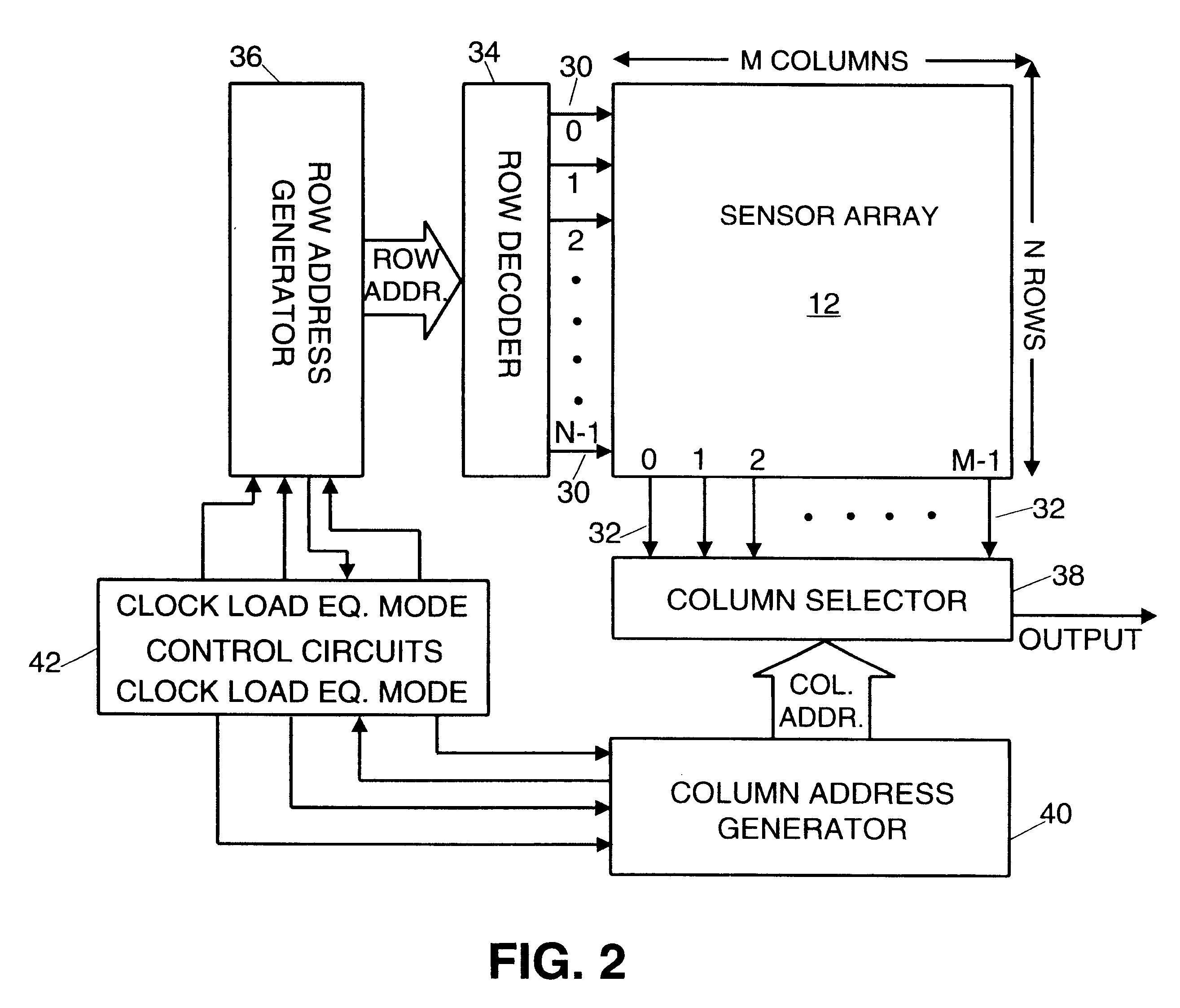

Image scanning circuitry with row and column addressing for use in electronic cameras

InactiveUS6512858B2Easy to controlTelevision system detailsTelevision system scanning detailsCMOS sensorAddress generator

A scanning circuit for use with an active pixel sensor array comprises a row-address generator configured to start at a selected row-start address, stop at a selected row-stop address, and increment row addresses by a factor K. A column-address generator is configured to start at a selected column-start address, stop at a selected column stop address, and increment column addresses by a factor K. Circuitry is coupled to the row address generator and the column address generator, for storing the row-start address, the row-stop address, the column-start address, the column-stop address and the factor K. A row decoder is coupled to the row-address generator and a column selector is coupled to the column-address generator. A plurality of row select lines are coupled to the row decoder, each one of the row select lines associated with a different row in the active pixel sensor array. A plurality of column output lines are coupled to the column selector, each one of the column output lines associated with a different column in the active pixel sensor array.

Owner:FOVEON

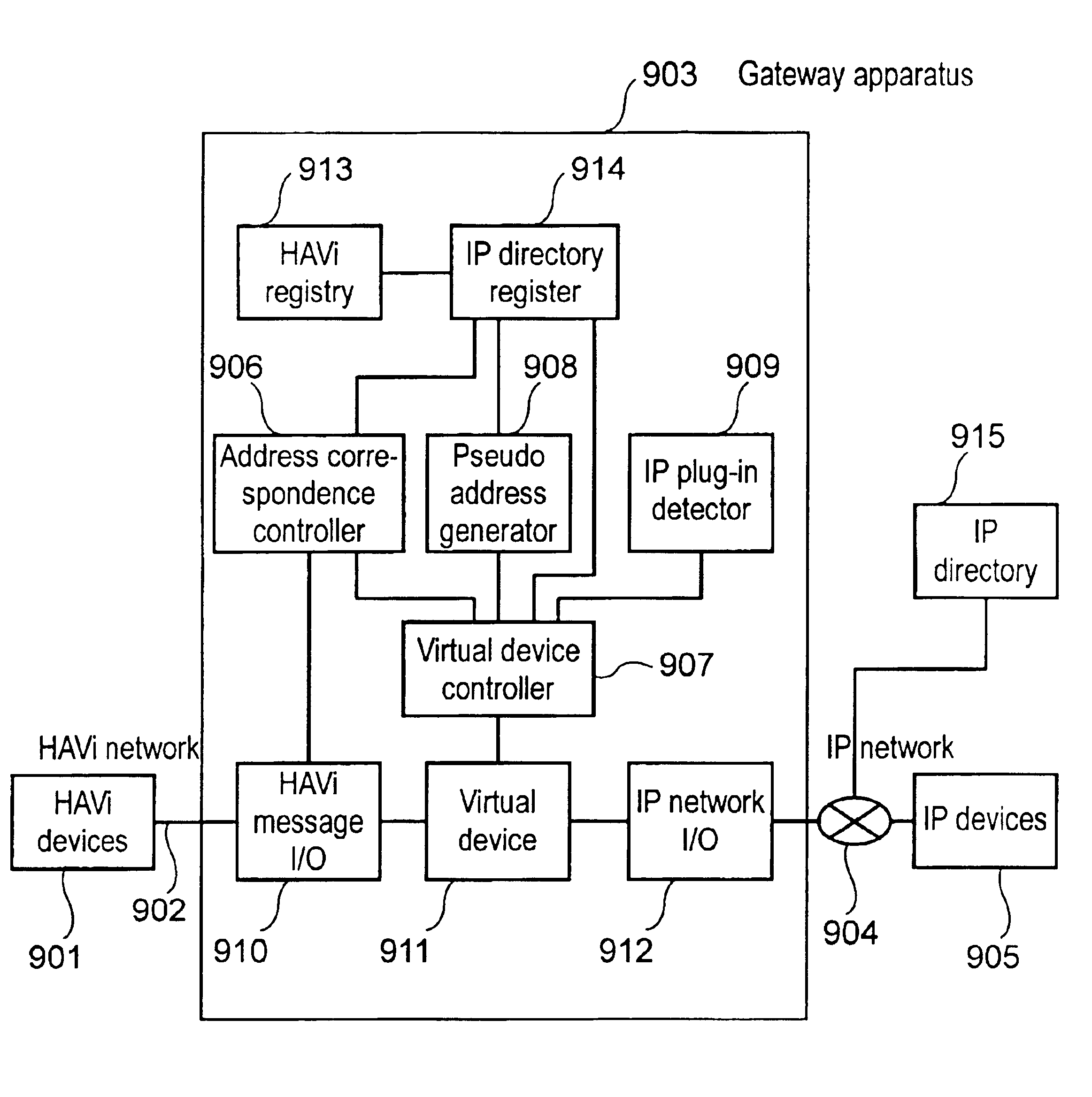

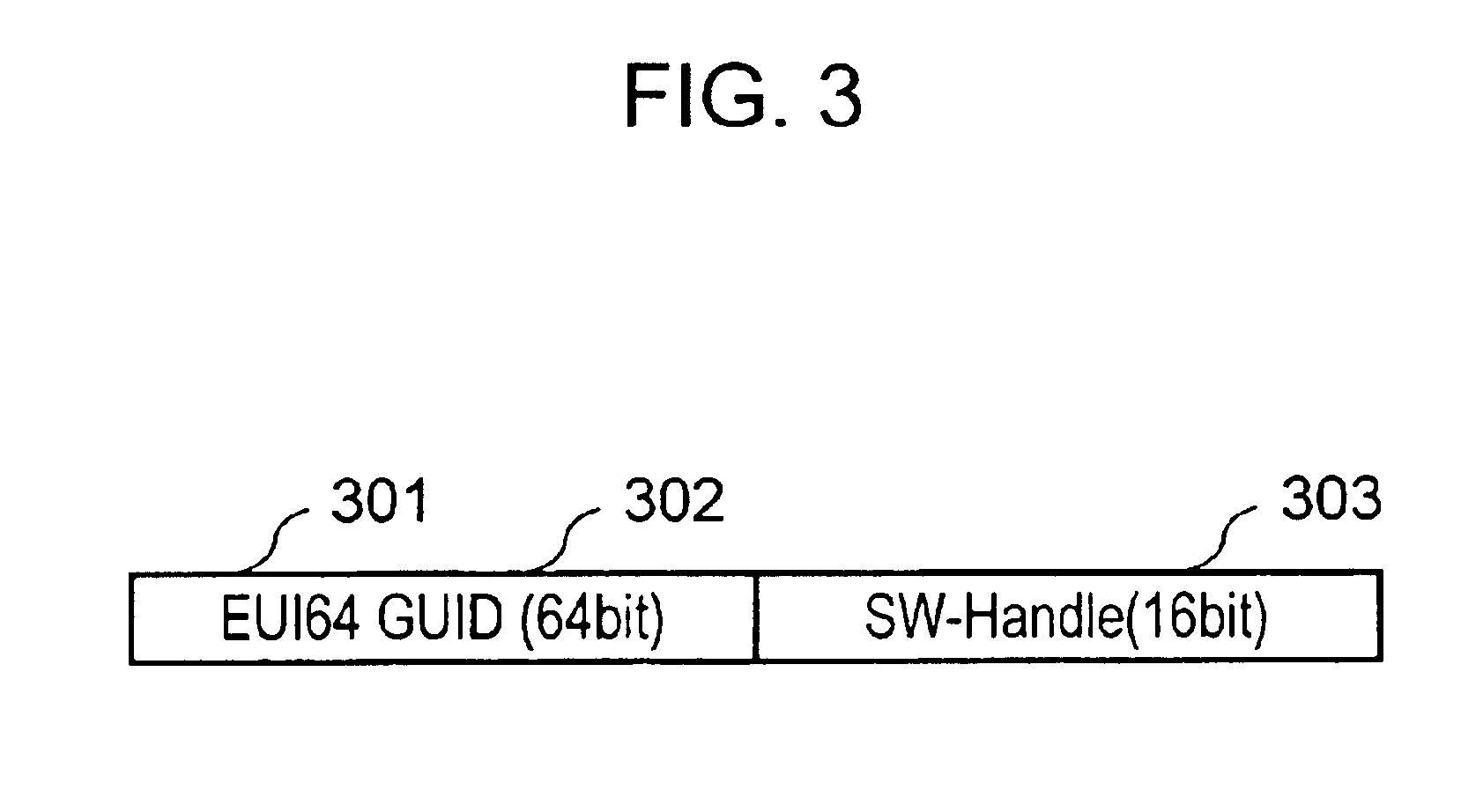

Gateway apparatus and the method thereof

InactiveUS6963925B1Multiple digital computer combinationsNetworks interconnectionComputer networkAddress generator

A gateway realizes a connection between a network where HAVi devices are hooked up and another network in accordance with a Play-and-Plug spec. (e.g. the internet protocol (IP)) other than the HAVi spec. An HAVi plug-in detector detects a plug-in of a device to the HAVi network. A virtual device functions as a gateway for accessing from a device plugged-in the IP network to the device plugged-in the HAVi network. A virtual device controller provides the virtual device with an IP identifier for accessing to the virtual device from the IP network, and turns the virtual device to a standby status waiting for connection. A pseudo address generator generates a pseudo address for the virtual device to communicate with the device in the HAVi network, and provides the virtual device with the pseudo address. An address-correspondence-controller controls the correspondence between an HAVi address and the IP identifier both provided to the virtual device.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

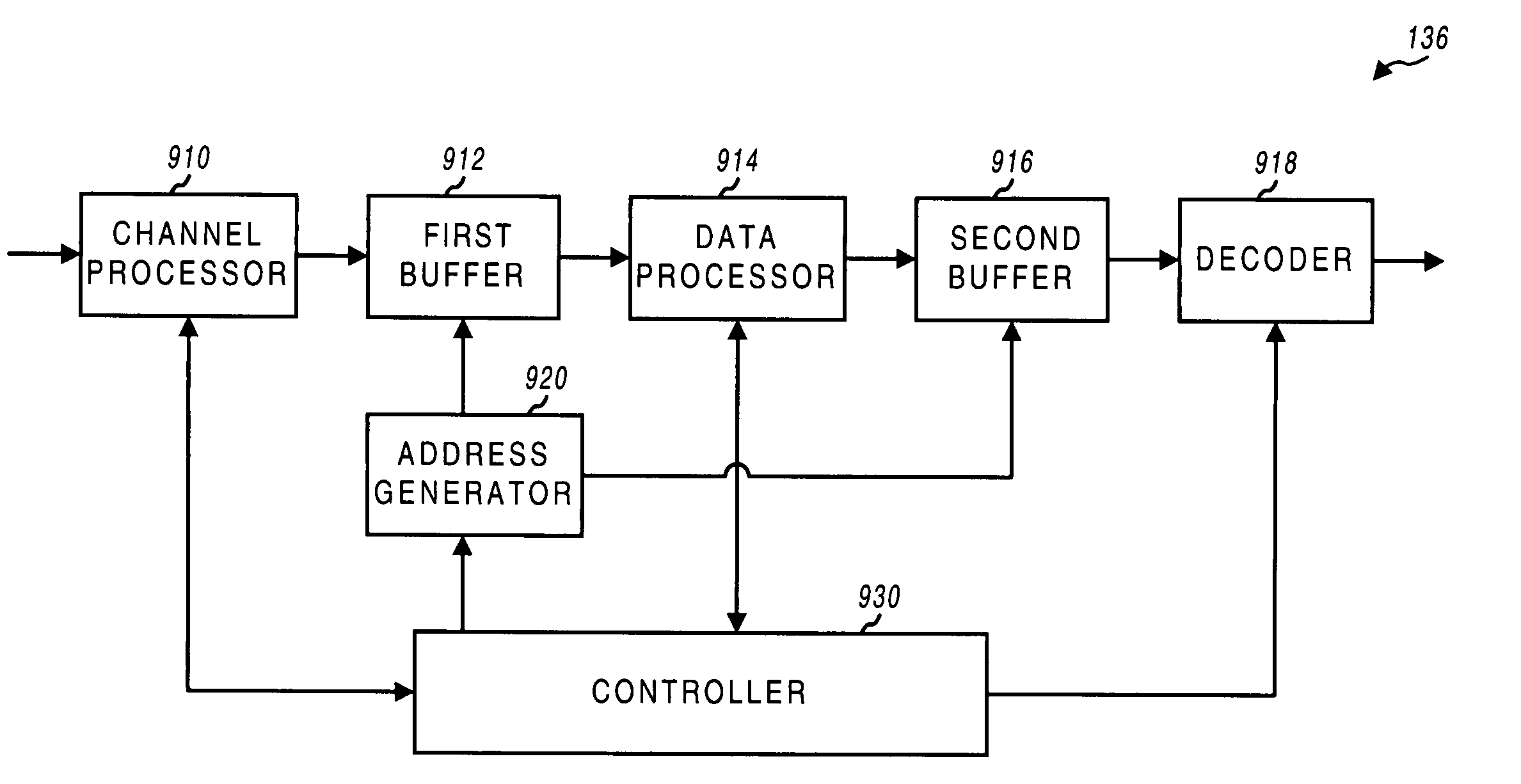

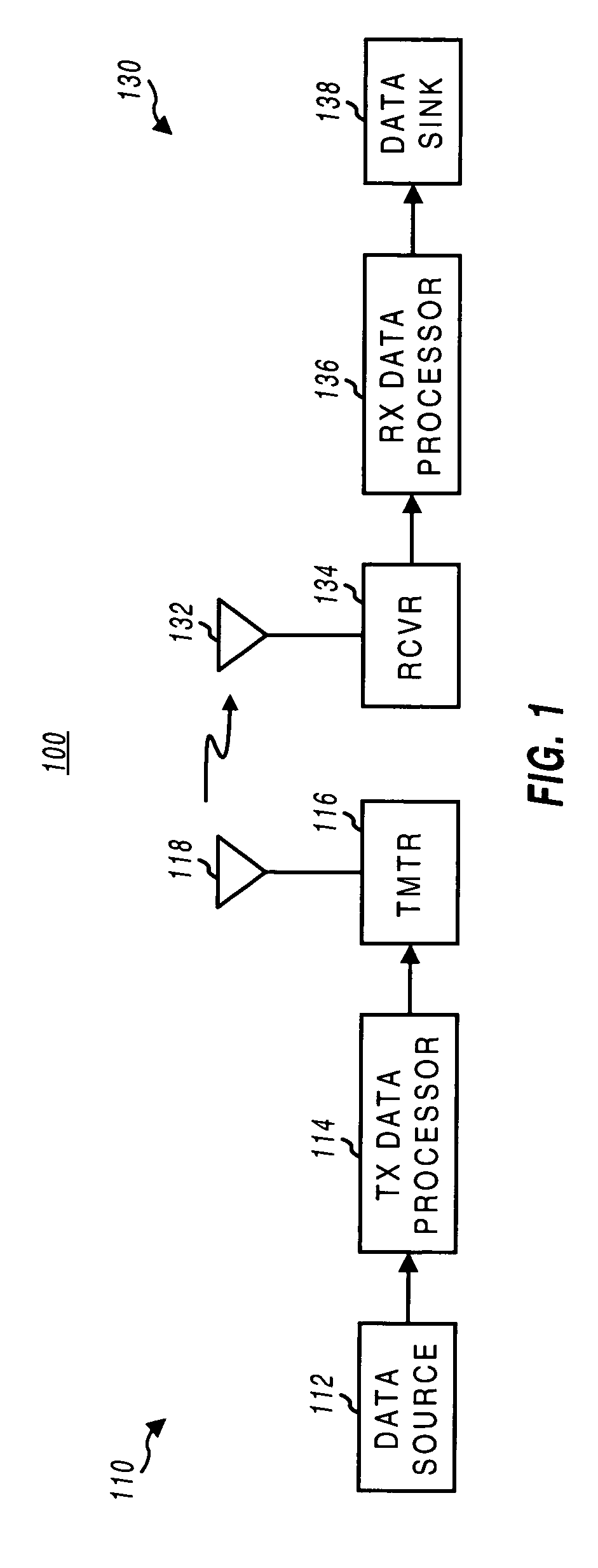

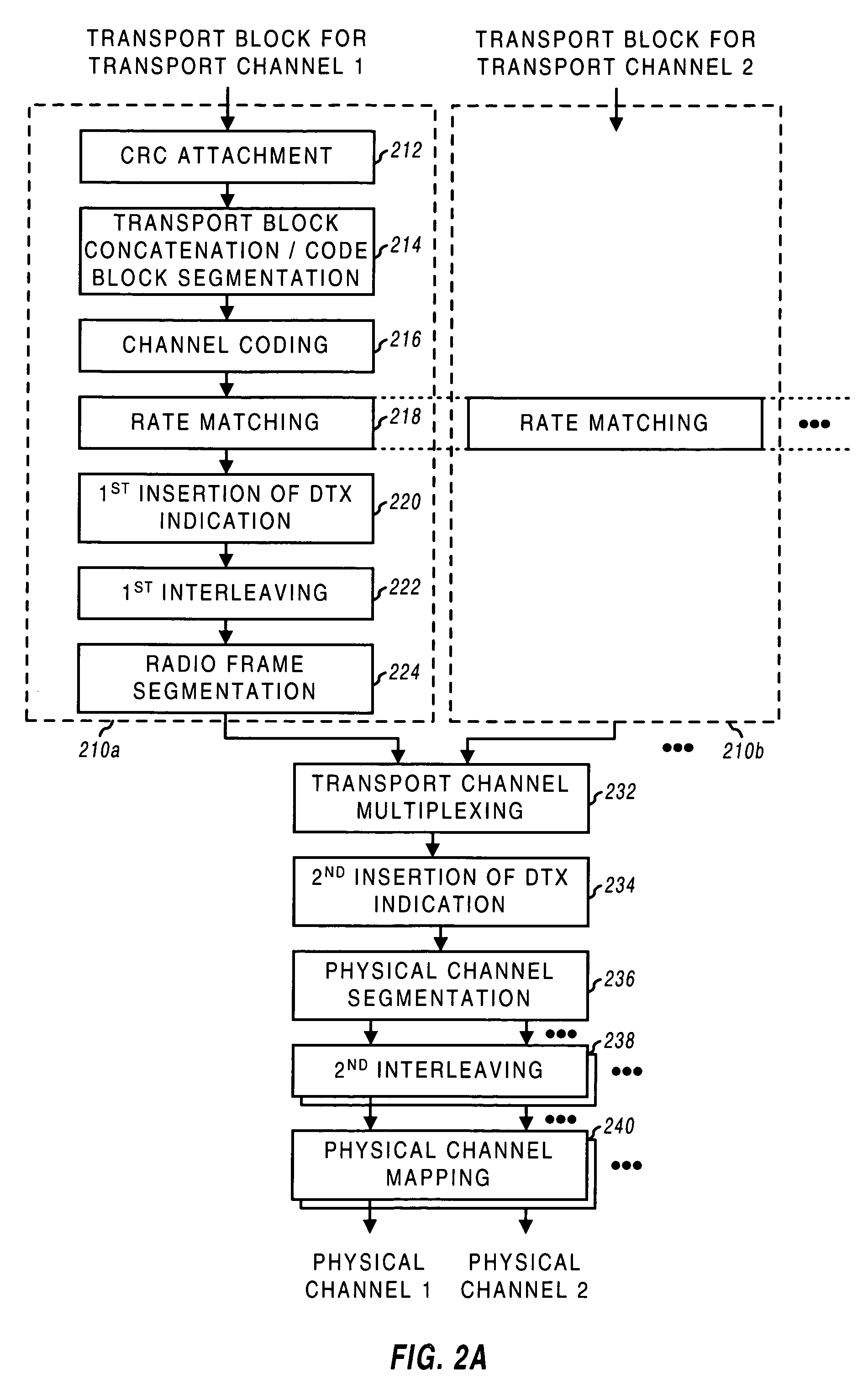

Data buffer structure for physical and transport channels in a CDMA system

InactiveUS7187708B1Efficient storageEasy maintenanceError preventionTransmission systemsAddress generatorCircular buffer

A buffer structure for storing symbols received via a number of (e.g., physical or transport) channels. Each channel is associated with a particular time interval (e.g., a radio frame period or a transmission time interval (TTI)) over which the received symbols are processed (e.g., interleaved). The buffer structure includes a buffer and an address generator. The buffer is partitioned into a number of sections. One section is assigned to each channel being processed. Each section can be operated as a circular buffer. The address generator provides addresses for writing symbols to the assigned sections. If the buffer structure is used for the transport channels, the sections can be assigned to the transport channels based on the associated TTIs (e.g., in descending order of TTIs). For each coded composite transport channel (CCTrCH), the transport channels in the CCTrCH can be assigned to sections defined starting from a respective initial location (e.g., the top or bottom of the buffer) and continuing along a respective direction of the buffer (e.g., downward or upward).

Owner:QUALCOMM INC

Circuit and system of a low density one-time programmable memory

InactiveUS8861249B2Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesIp addressAddress generator

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

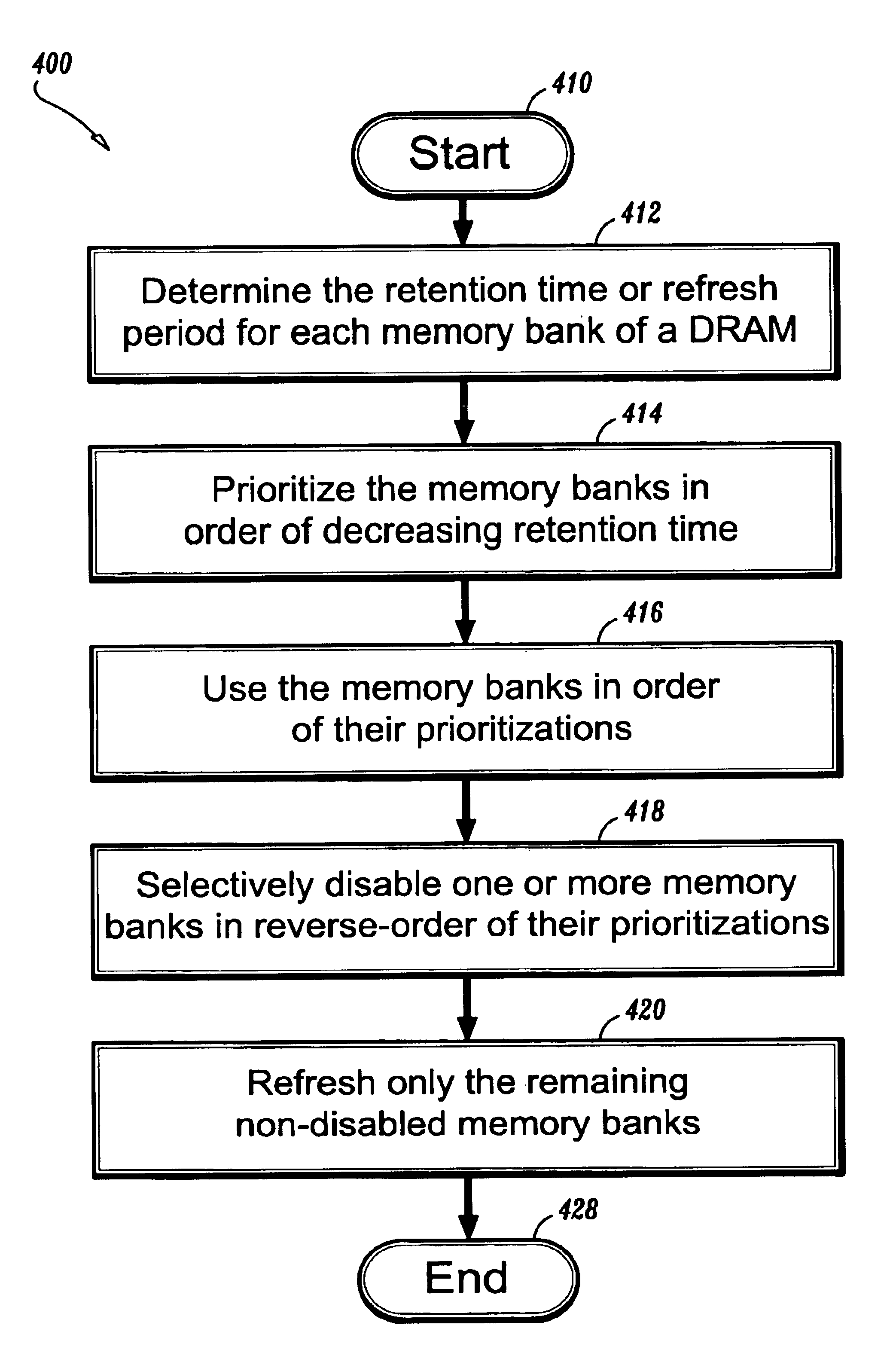

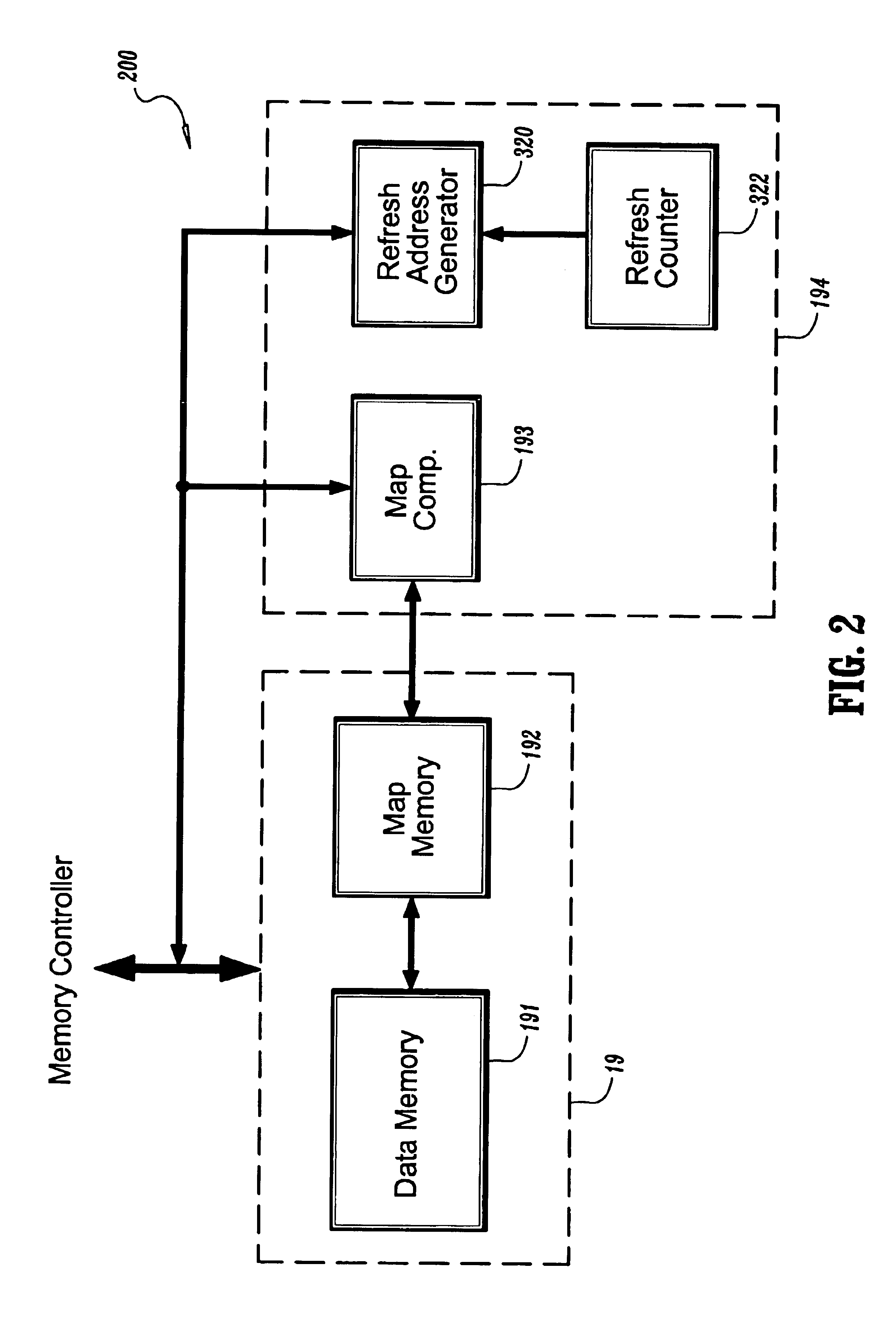

Bank address mapping according to bank retention time in dynamic random access memories

InactiveUS6920523B2Memory architecture accessing/allocationEnergy efficient ICTStatic random-access memoryRetention time

A system and method for refreshing data in a dynamic random access memory (“DRAM”) is provided, where the system includes a data memory having a plurality of memory banks, a map memory in signal communication with the data memory for translating an internal address of each of the plurality of memory banks into a corresponding external address, a map comparator in signal communication with the map memory for selectively enabling a memory bank in accordance with its external address, a refresh address generator in signal communication with the map comparator for selectively refreshing the enabled memory bank in accordance with its external address, and a refresh counter in signal communication with the refresh address generator for signaling a refresh in accordance with the maximum required refresh time of the enabled memory bank; and where the corresponding method includes determining the maximum required refresh period for each of the memory banks, respectively, prioritizing the memory banks in accordance with their respective refresh periods, utilizing the memory banks in order of their respective prioritizations, selectively disabling at least one of the memory banks in reverse-order of their respective prioritizations, and refreshing only the remaining non-disabled memory banks.

Owner:POLARIS INNOVATIONS LTD

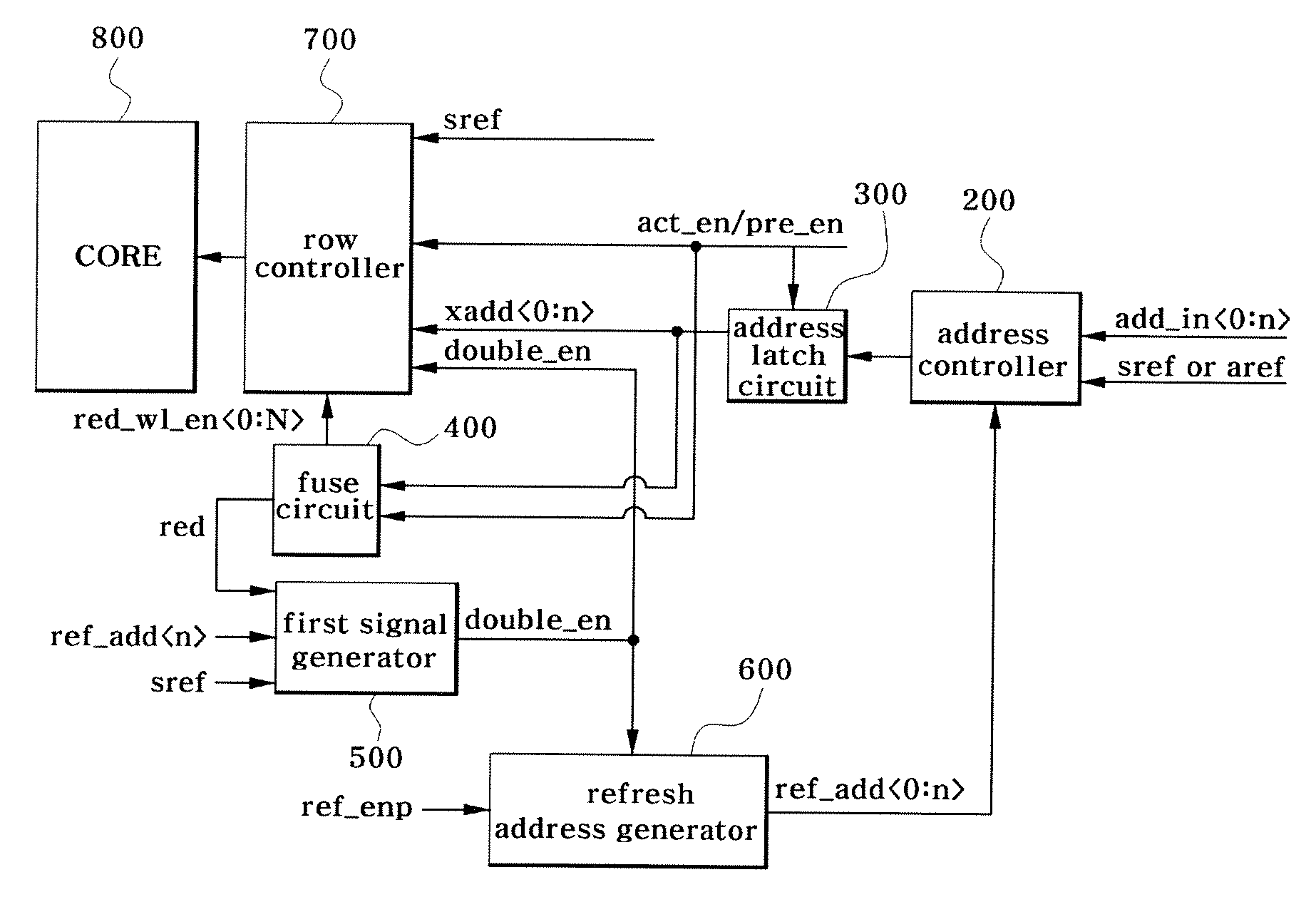

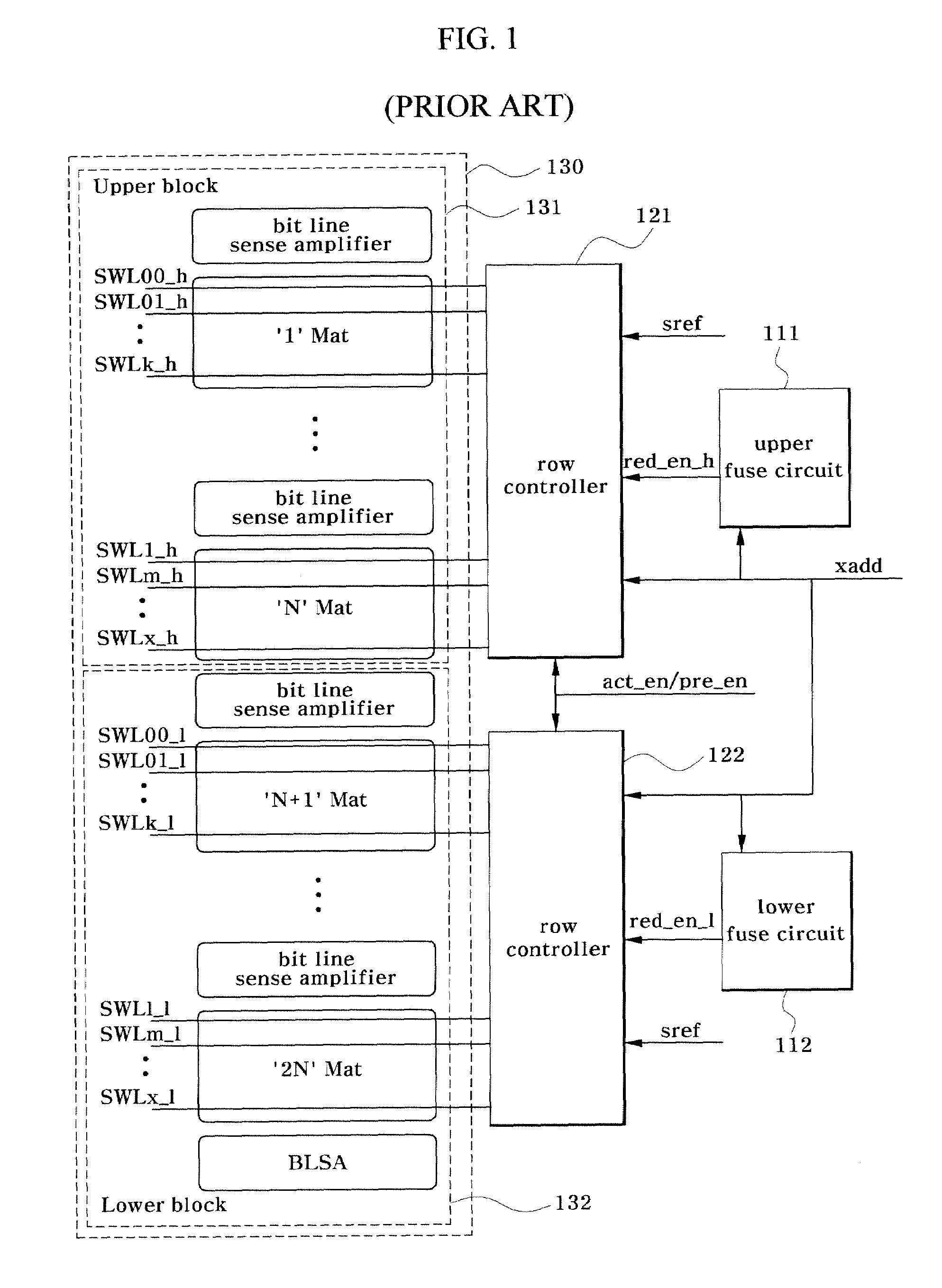

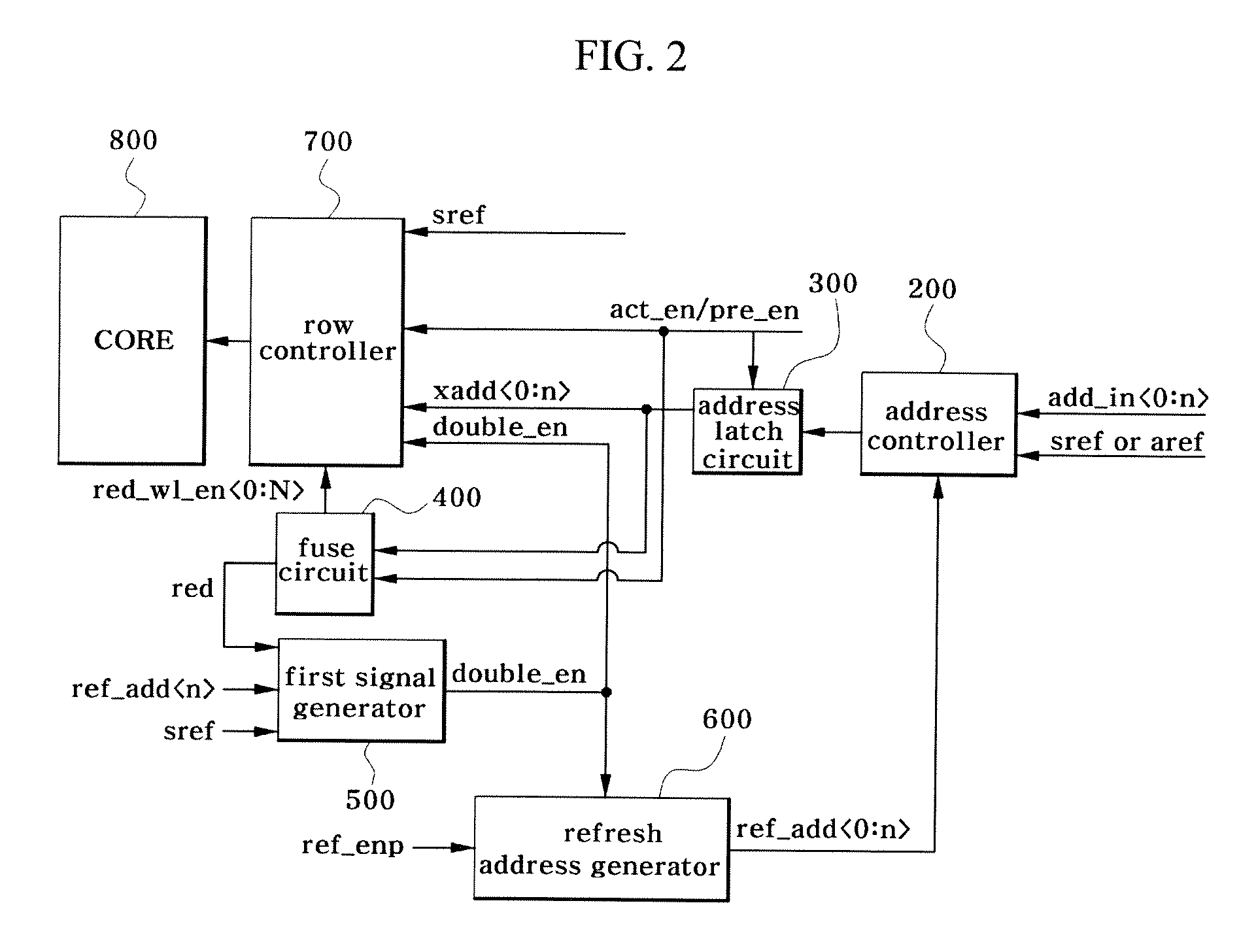

Semiconductor Device

InactiveUS20070147154A1Improve maintenance efficiencyReduce chip areaRead-only memoriesDigital storageAddress generatorSemiconductor

A multi-word line refresh-type semiconductor device may have a plurality of memory banks and performs a refresh operation simultaneously with respect to a plurality of word lines for each of the banks in a self-refresh mode. The semiconductor device includes an address controller for receiving a normal address and a refresh address and selectively outputting the received refresh address in a refresh mode, a fuse circuit for receiving the refresh address, determining whether the received refresh address corresponds to a word line to be repaired and outputting a redundancy word line enable signal and a first control signal according to a result of the determination, a first signal generator for, in response to a bit value for block selection of the refresh address and the first control signal, outputting a second control signal which defines a multi-word line refresh period, a refresh address generator for generating the refresh address in response to the second control signal, and a row controller for receiving the refresh address, second control signal and redundancy word line enable signal and controlling the refresh operation with respect to a memory core.

Owner:SK HYNIX INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com