Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

867 results about "Parity-check matrix" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

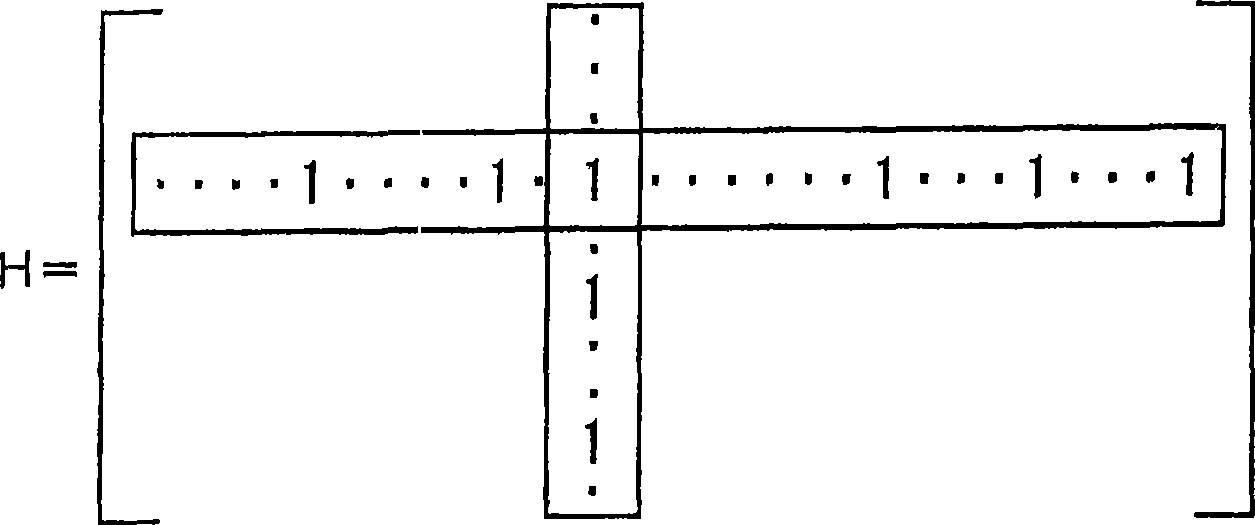

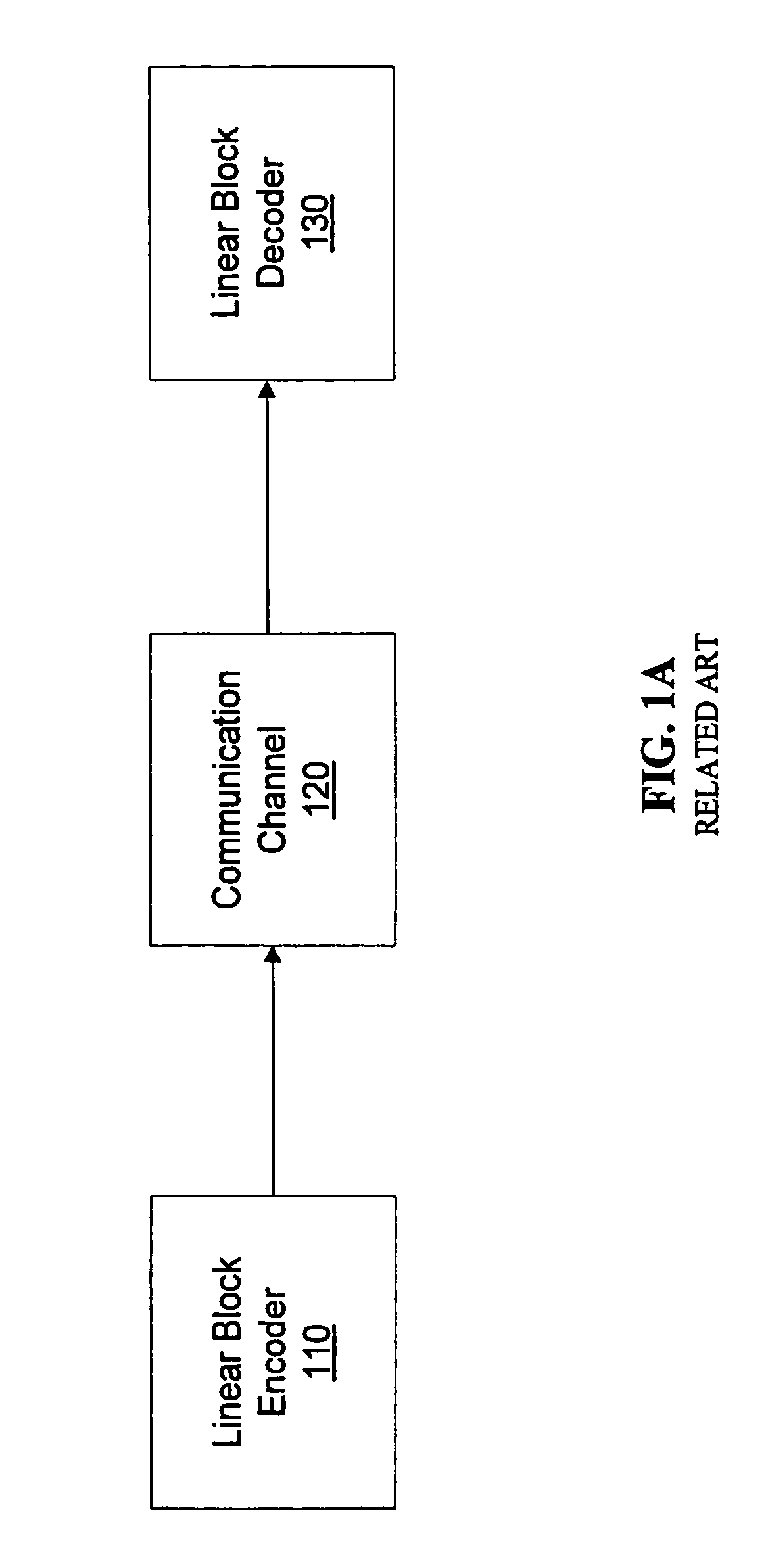

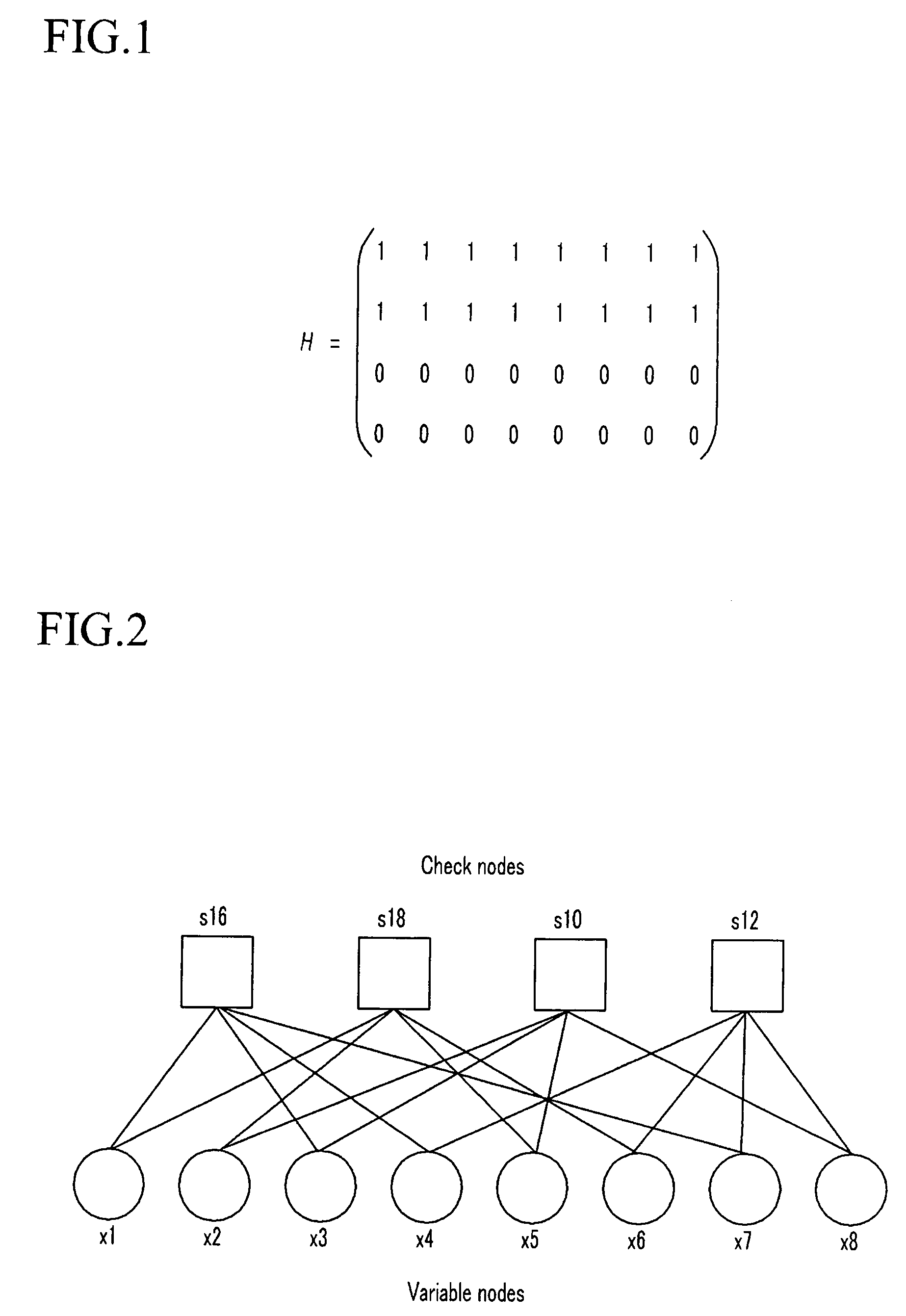

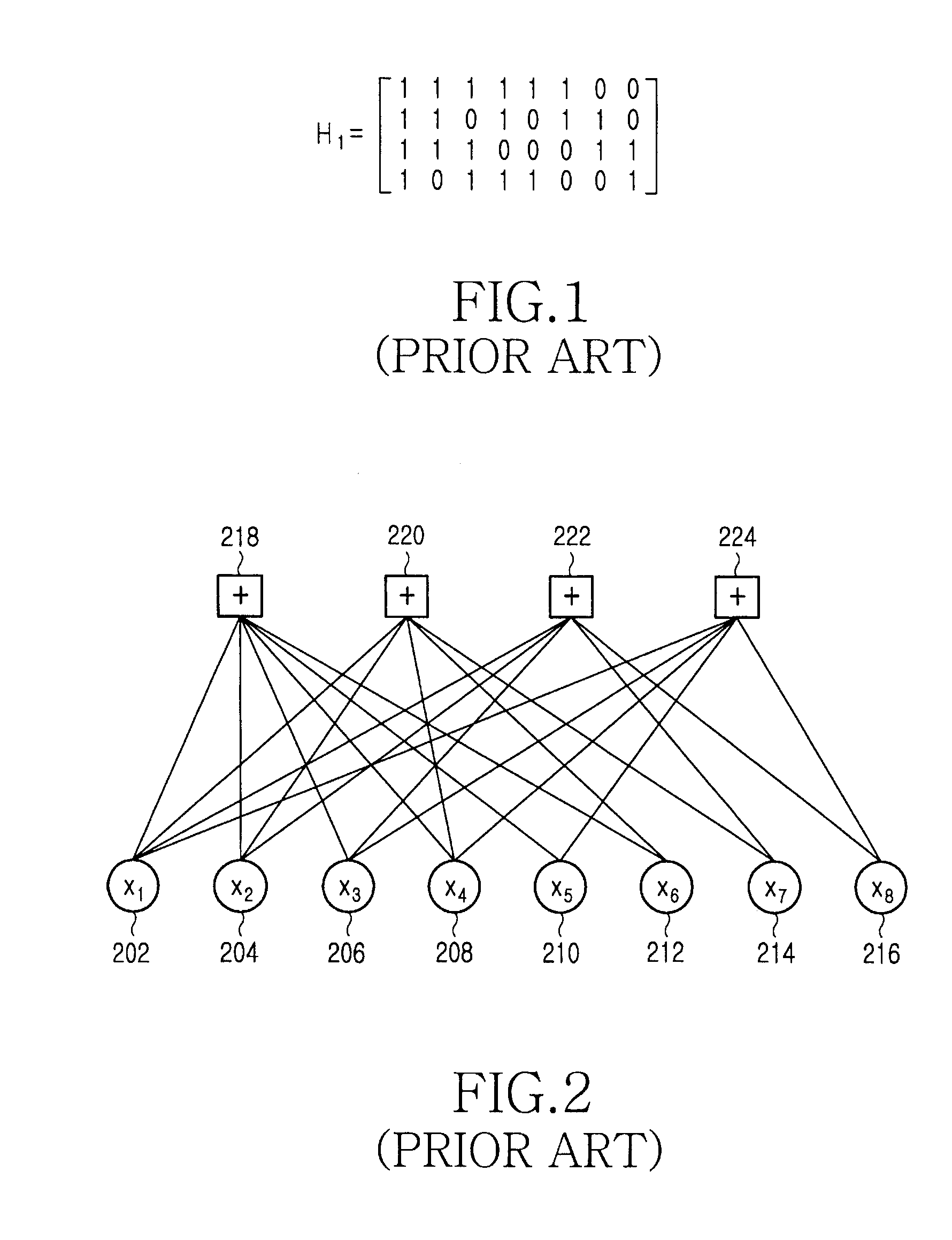

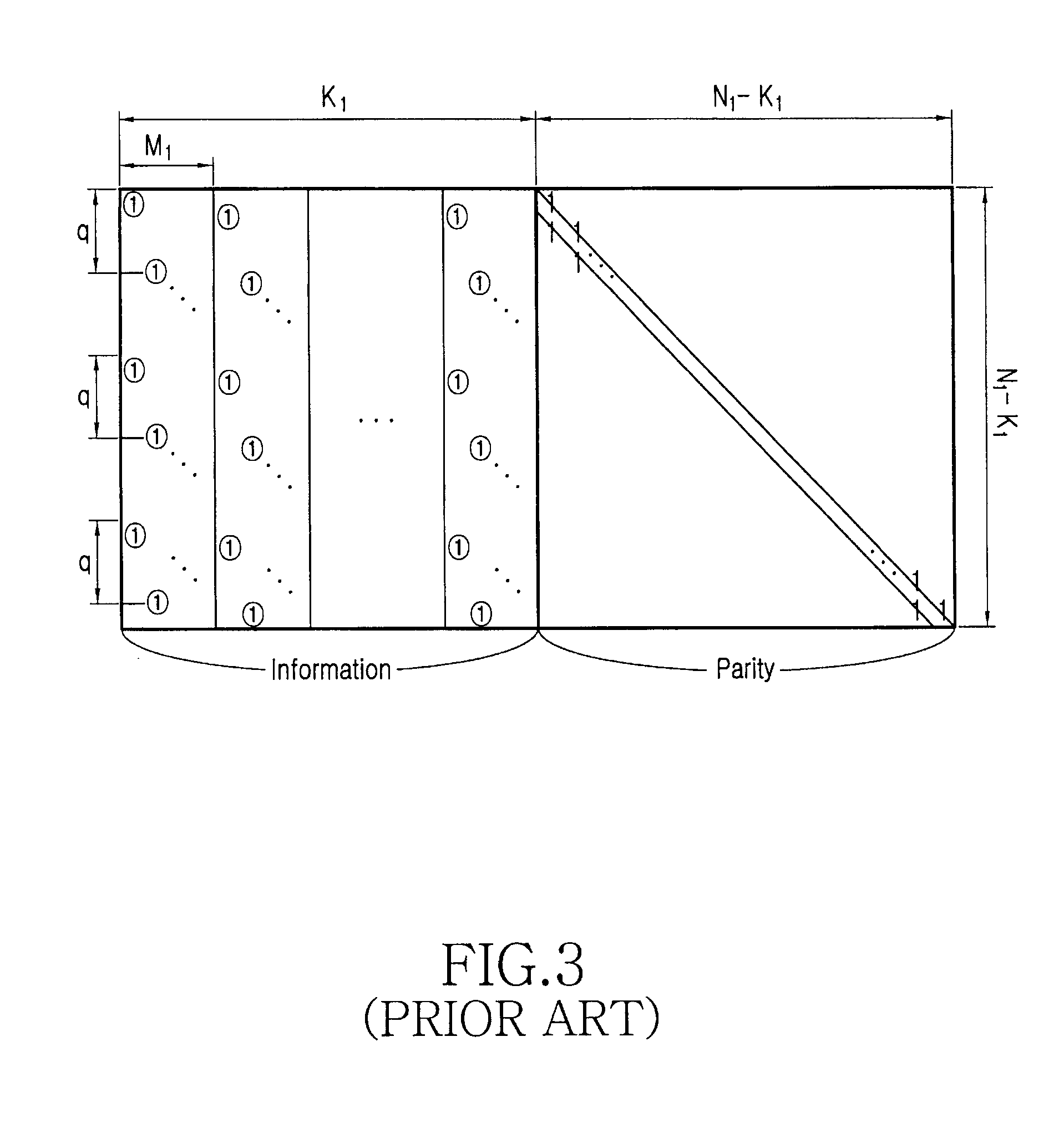

In coding theory, a parity-check matrix of a linear block code C is a matrix which describes the linear relations that the components of a codeword must satisfy. It can be used to decide whether a particular vector is a codeword and is also used in decoding algorithms.

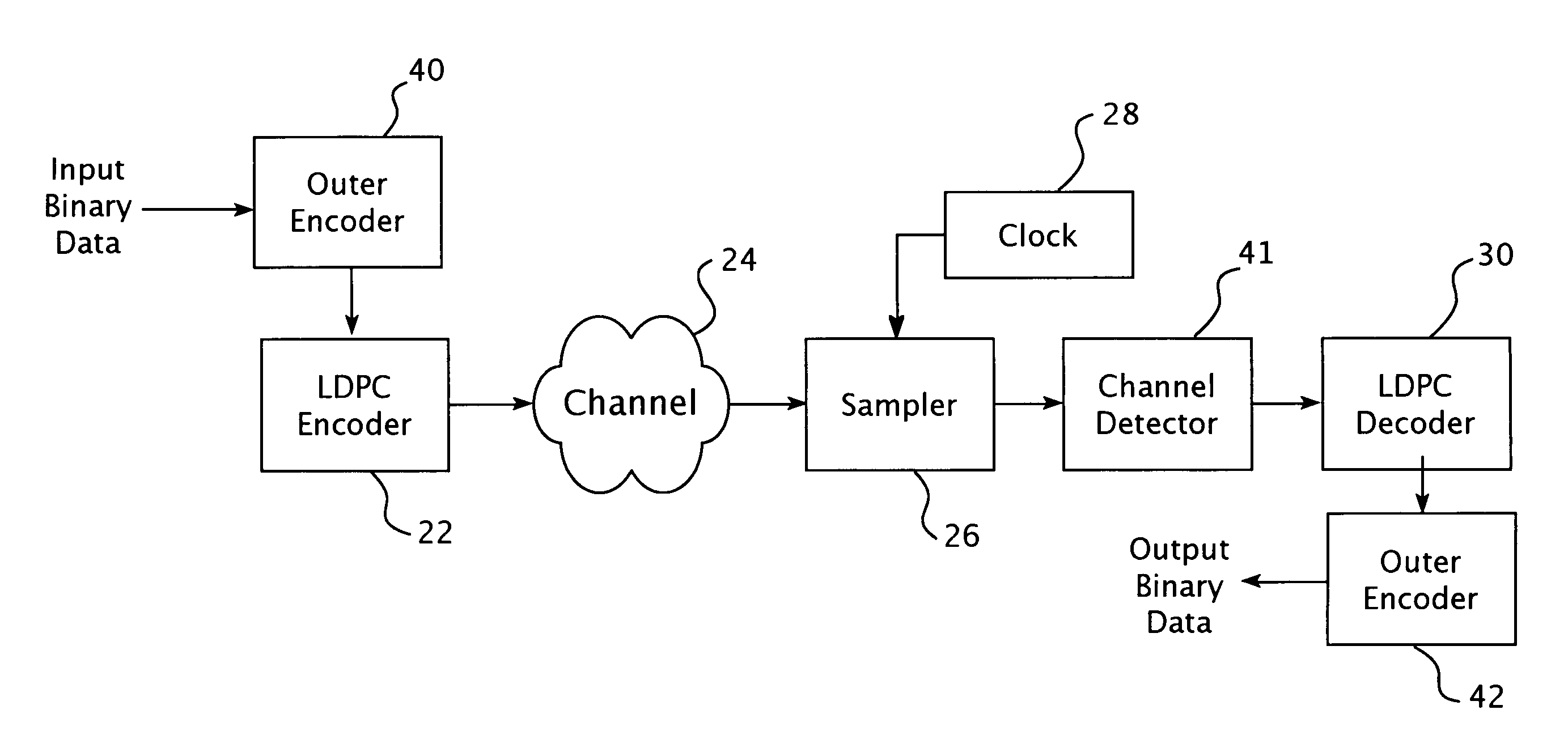

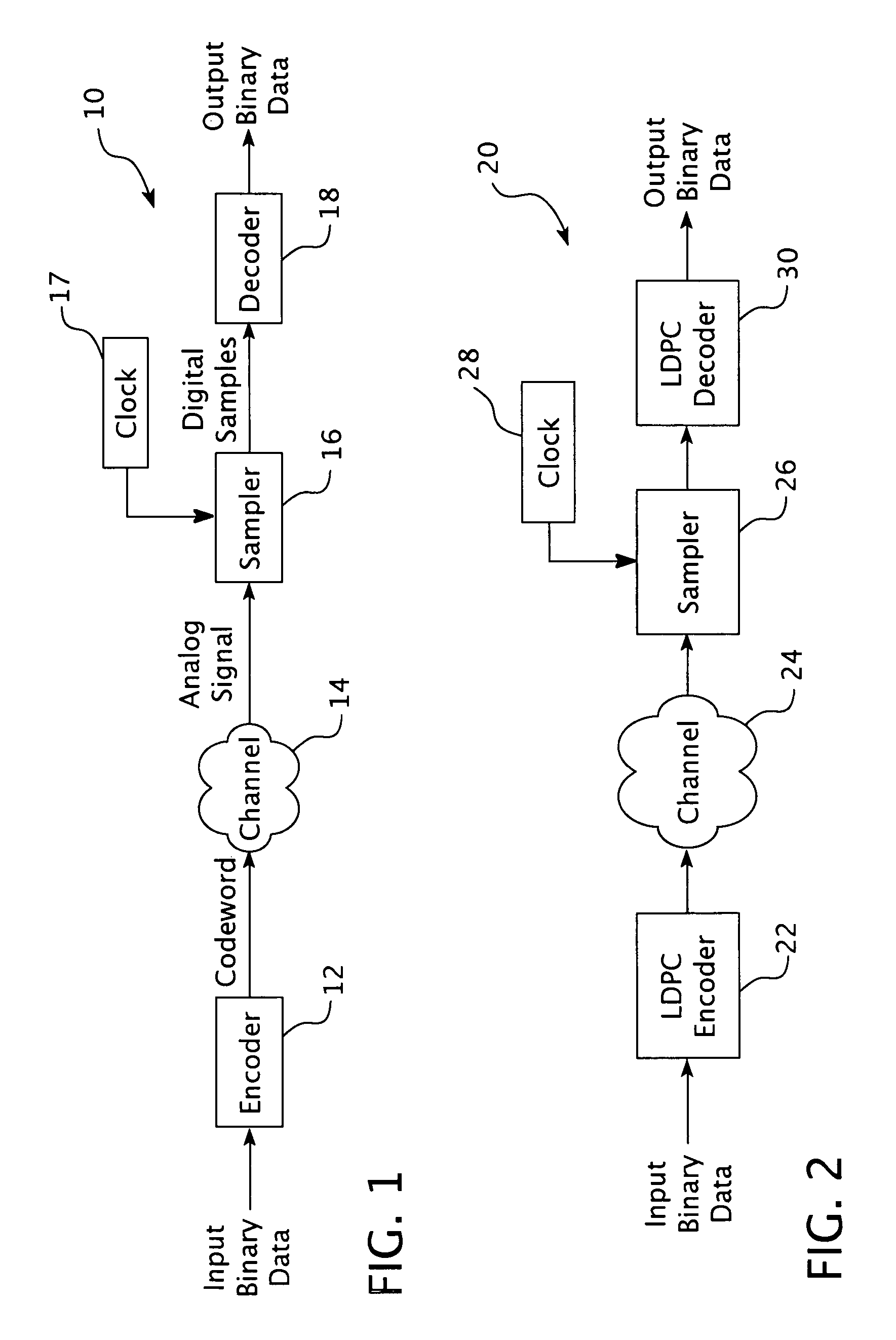

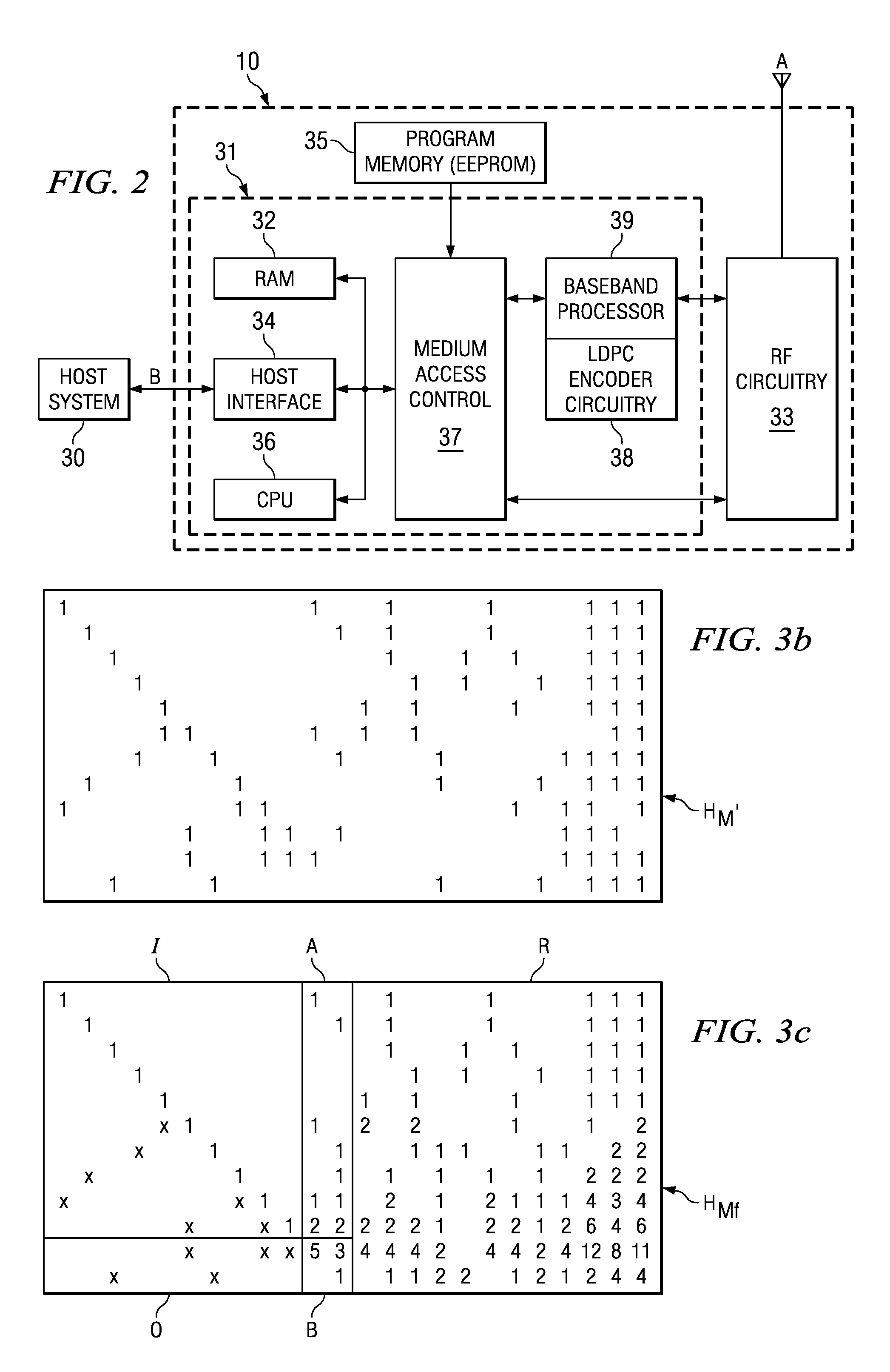

Method and apparatus for low density parity check encoding of data

InactiveUS6895547B2Improve performanceError preventionError detection/correctionTheoretical computer scienceParity-check matrix

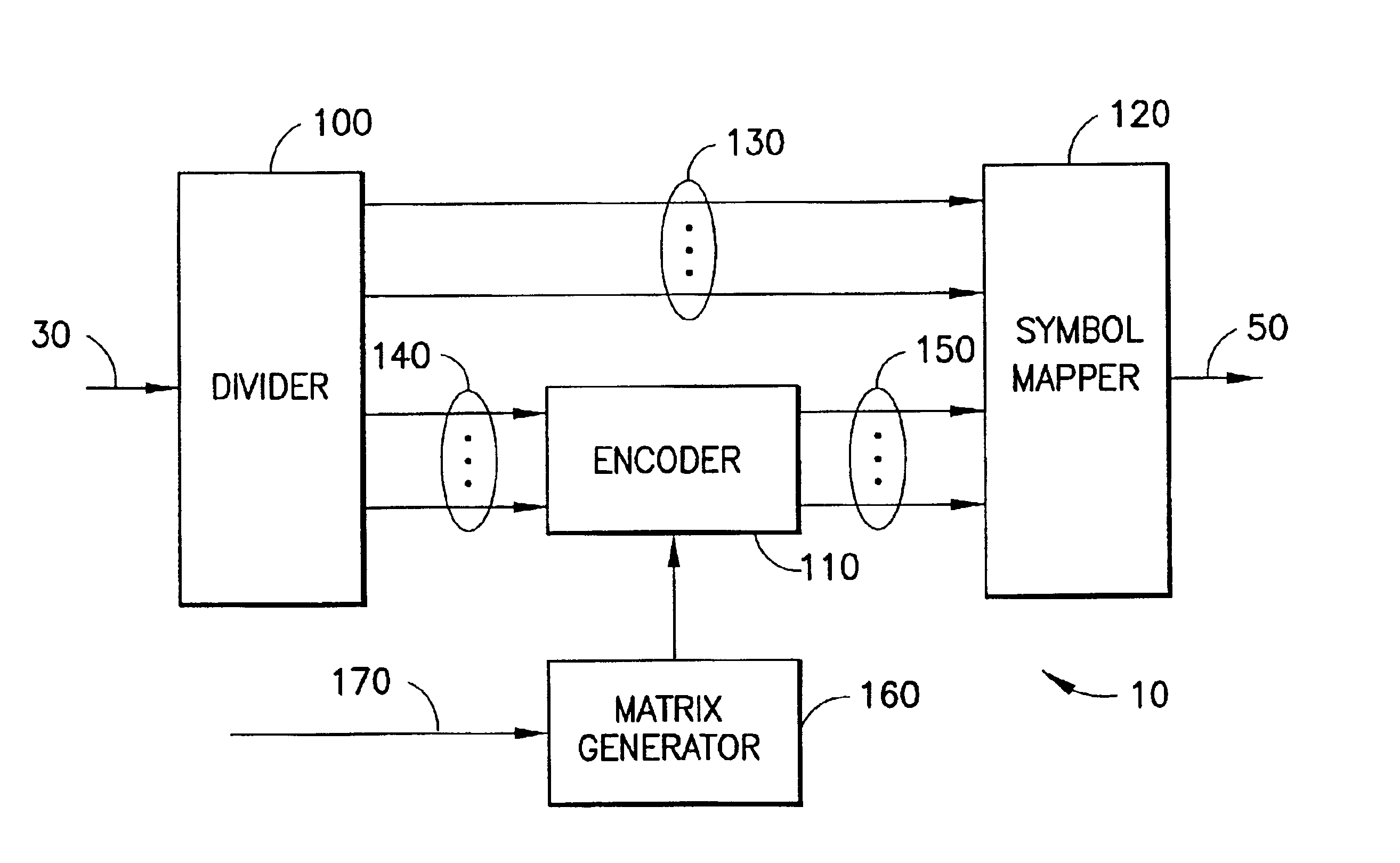

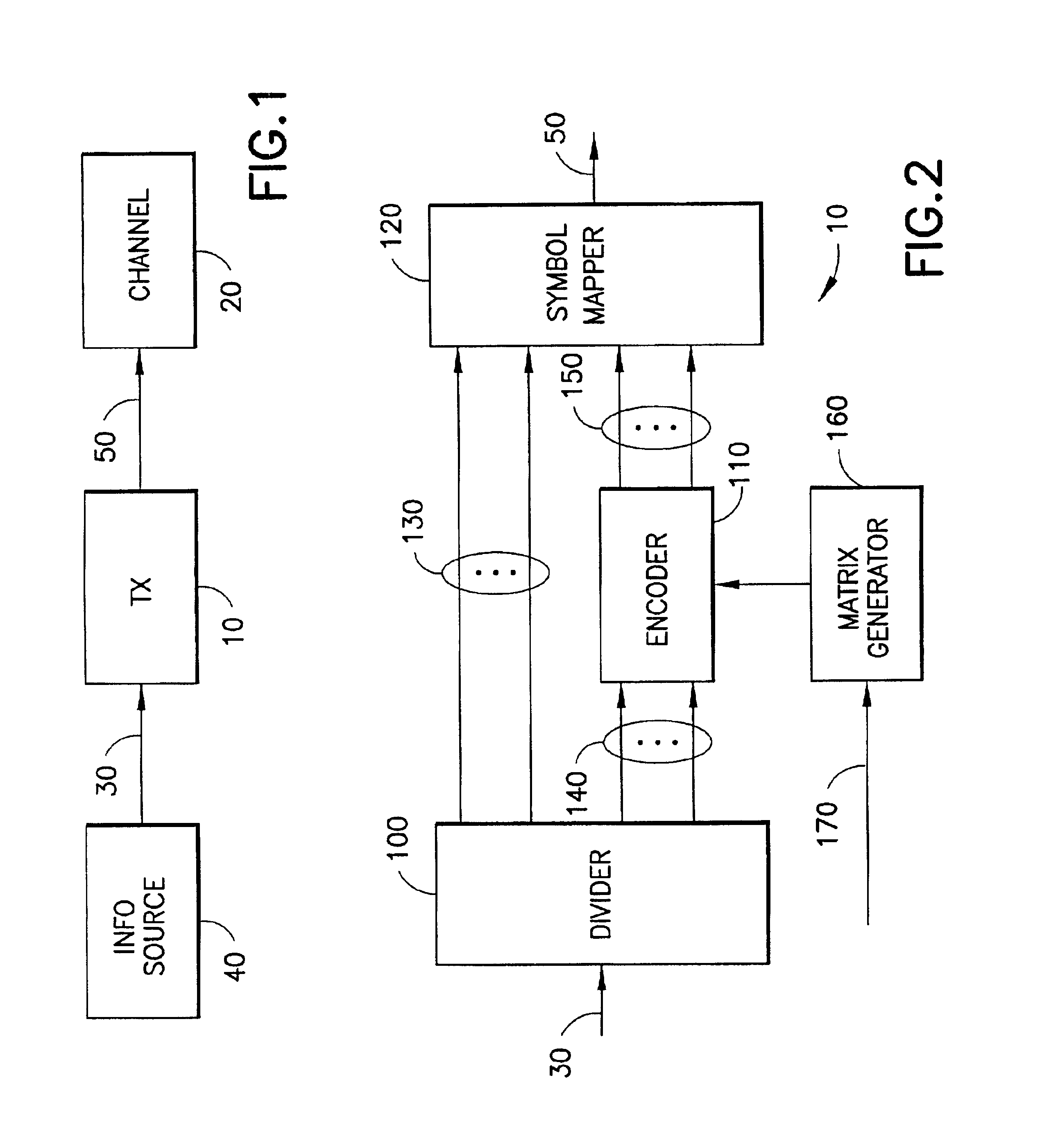

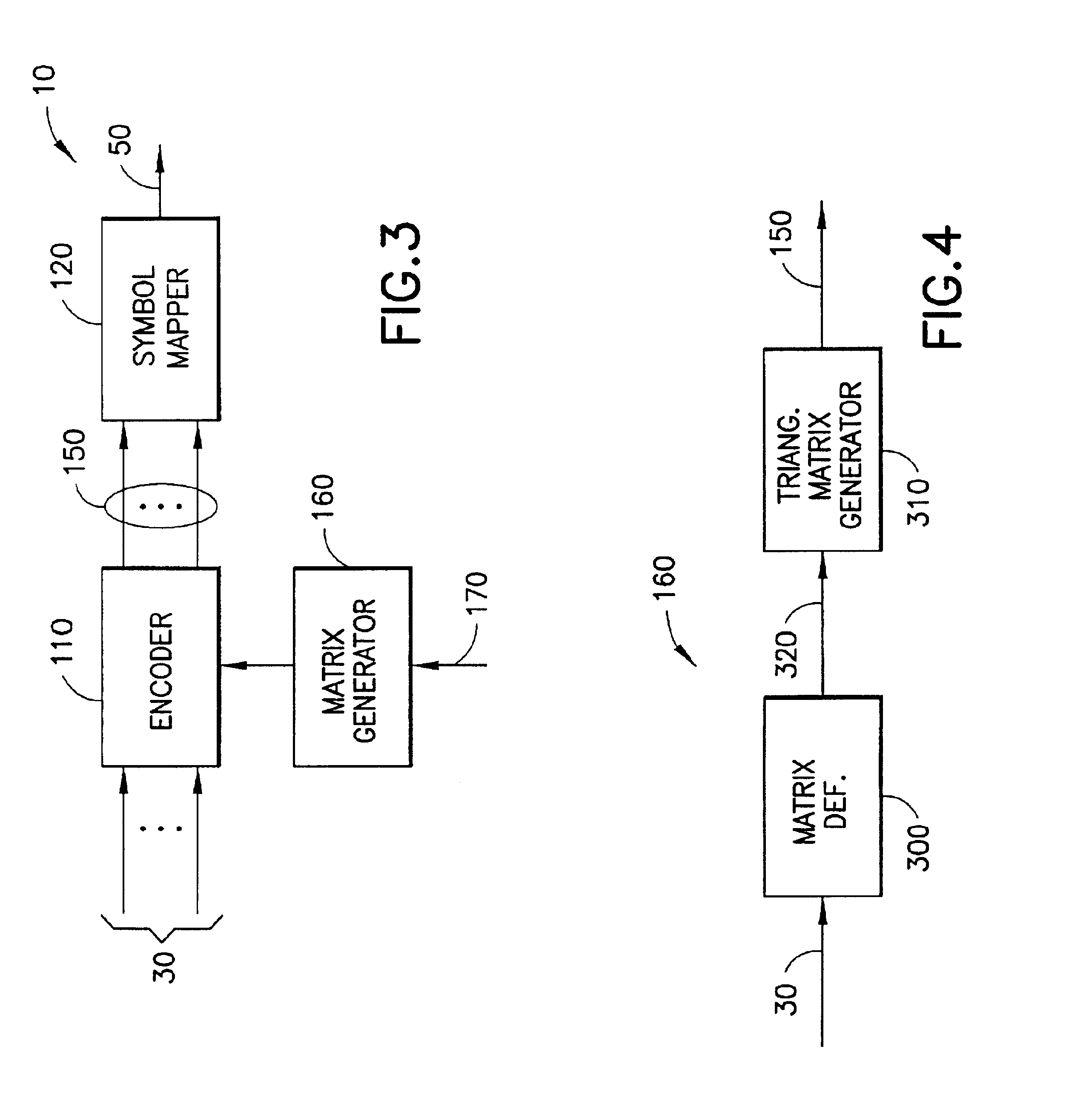

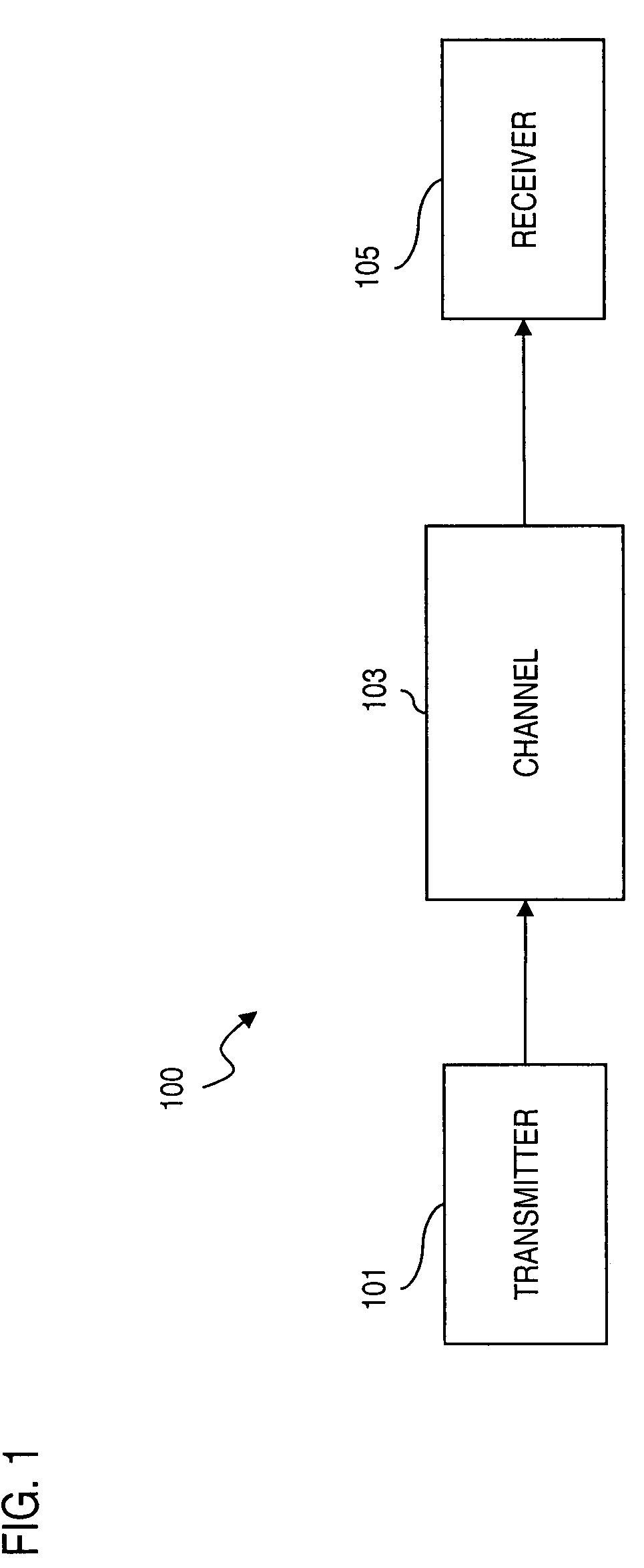

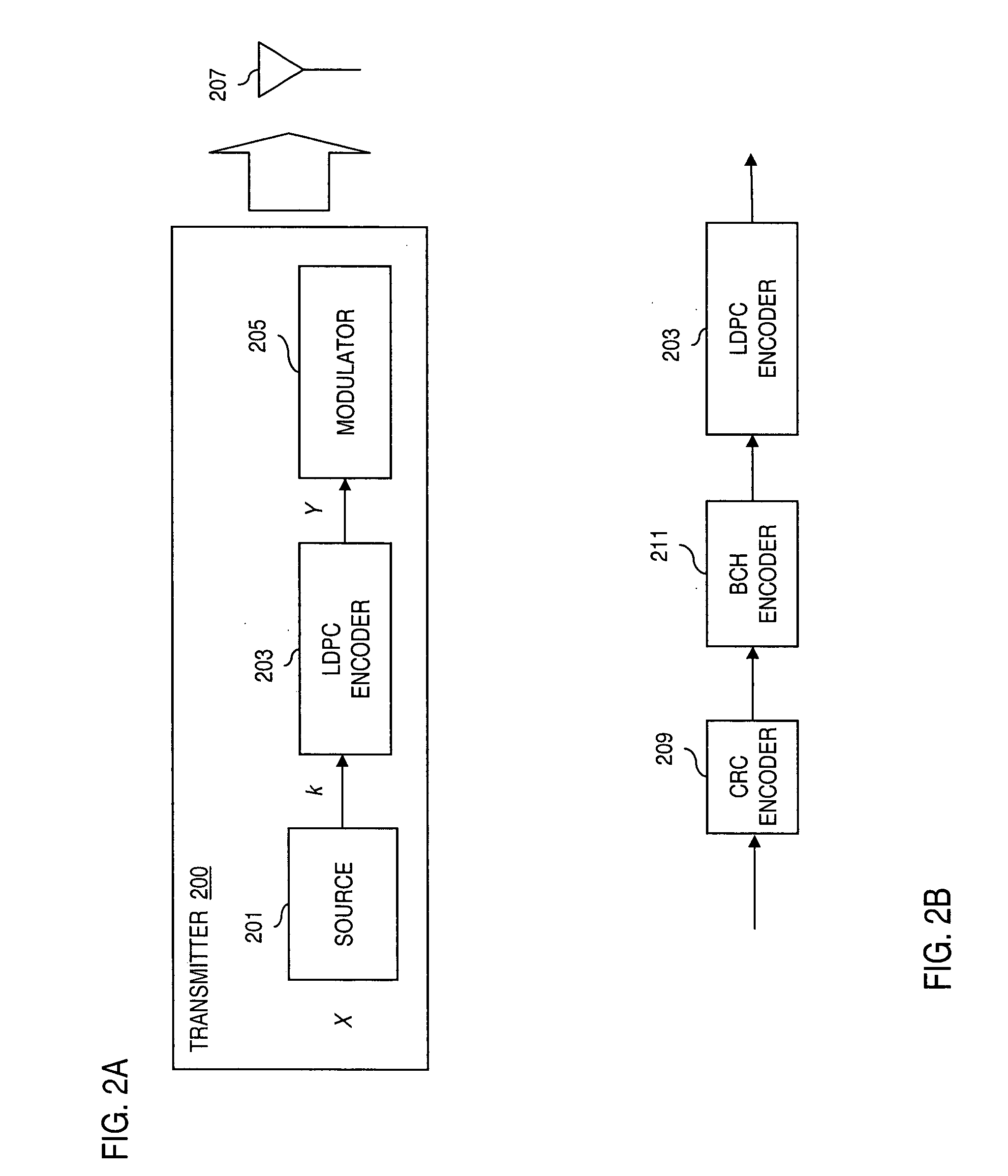

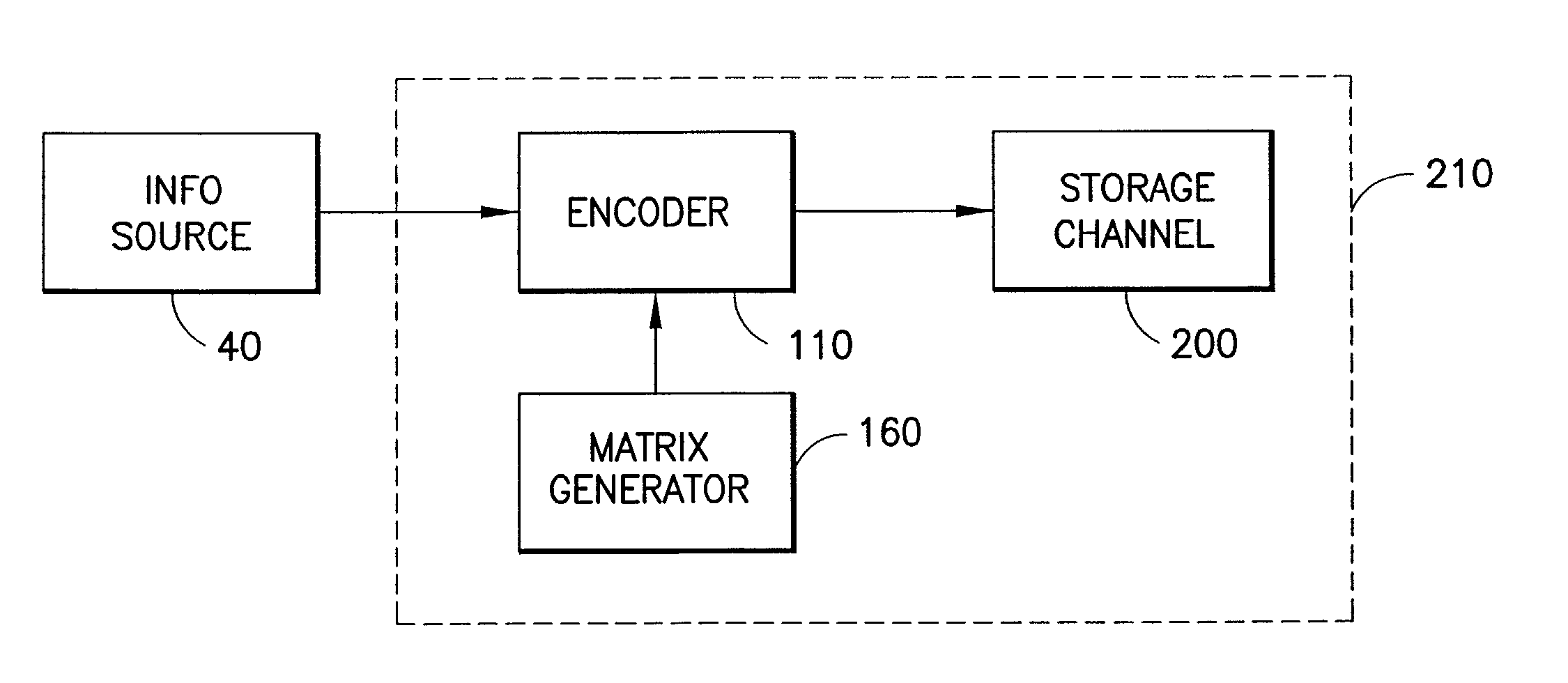

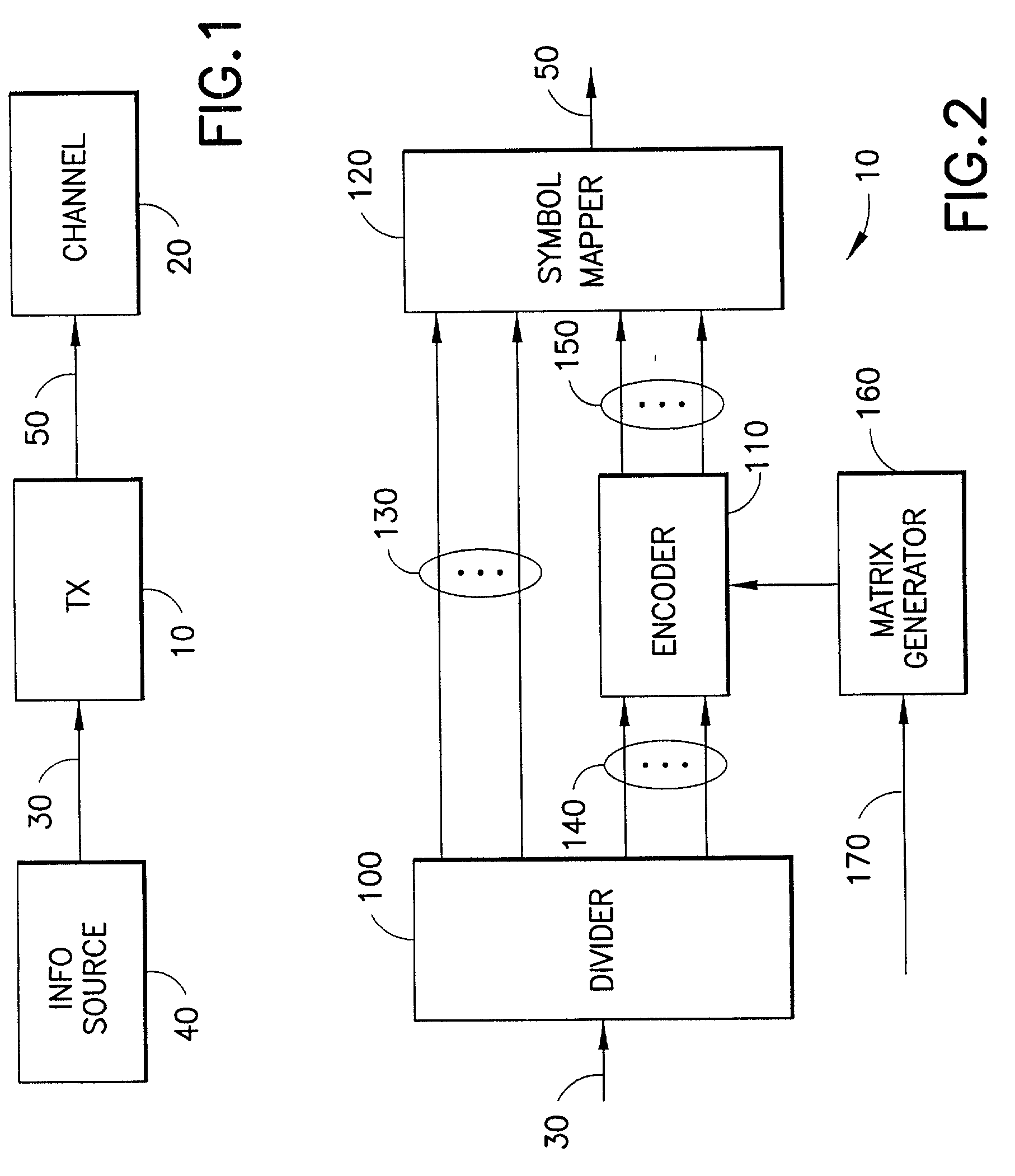

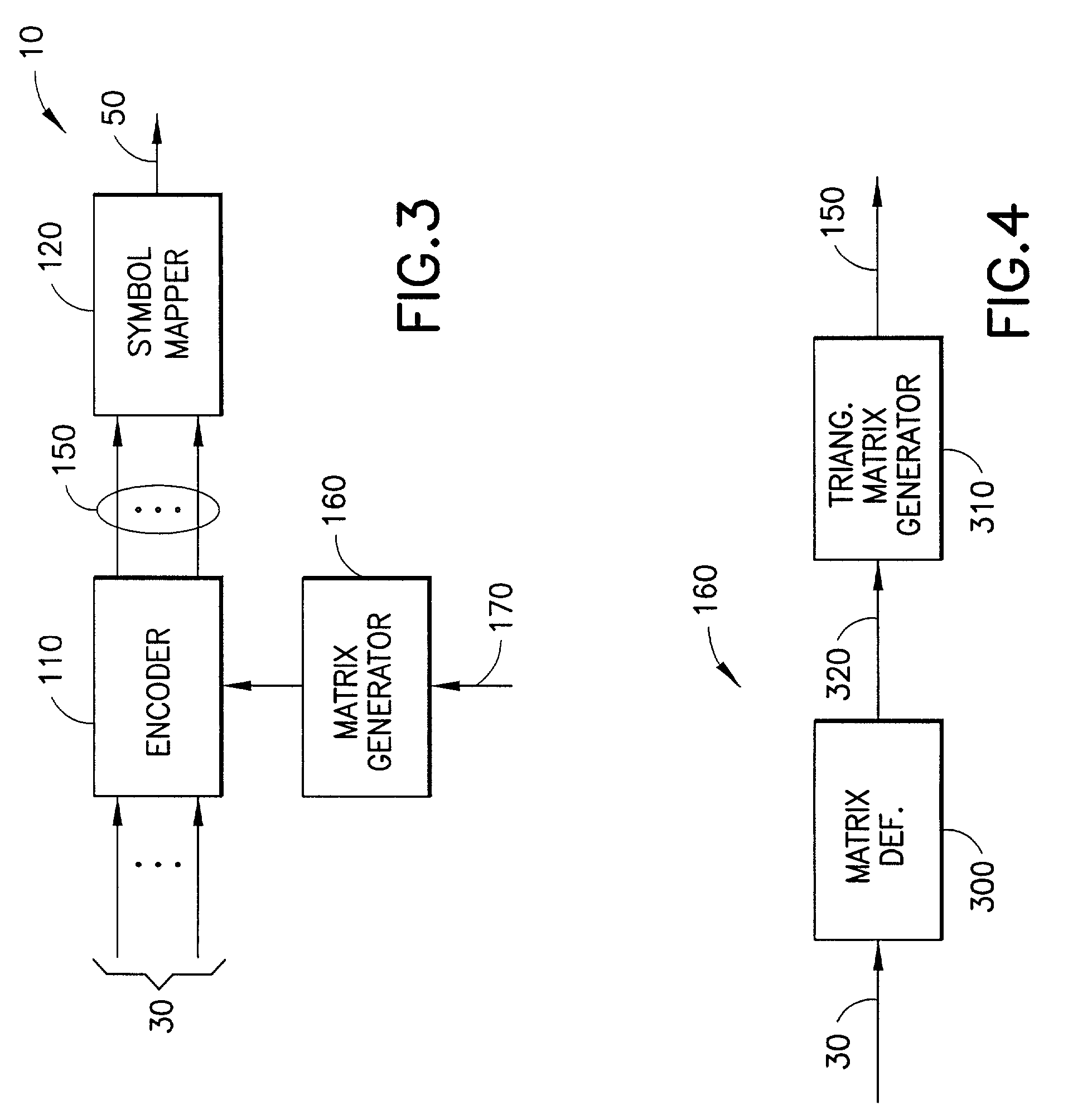

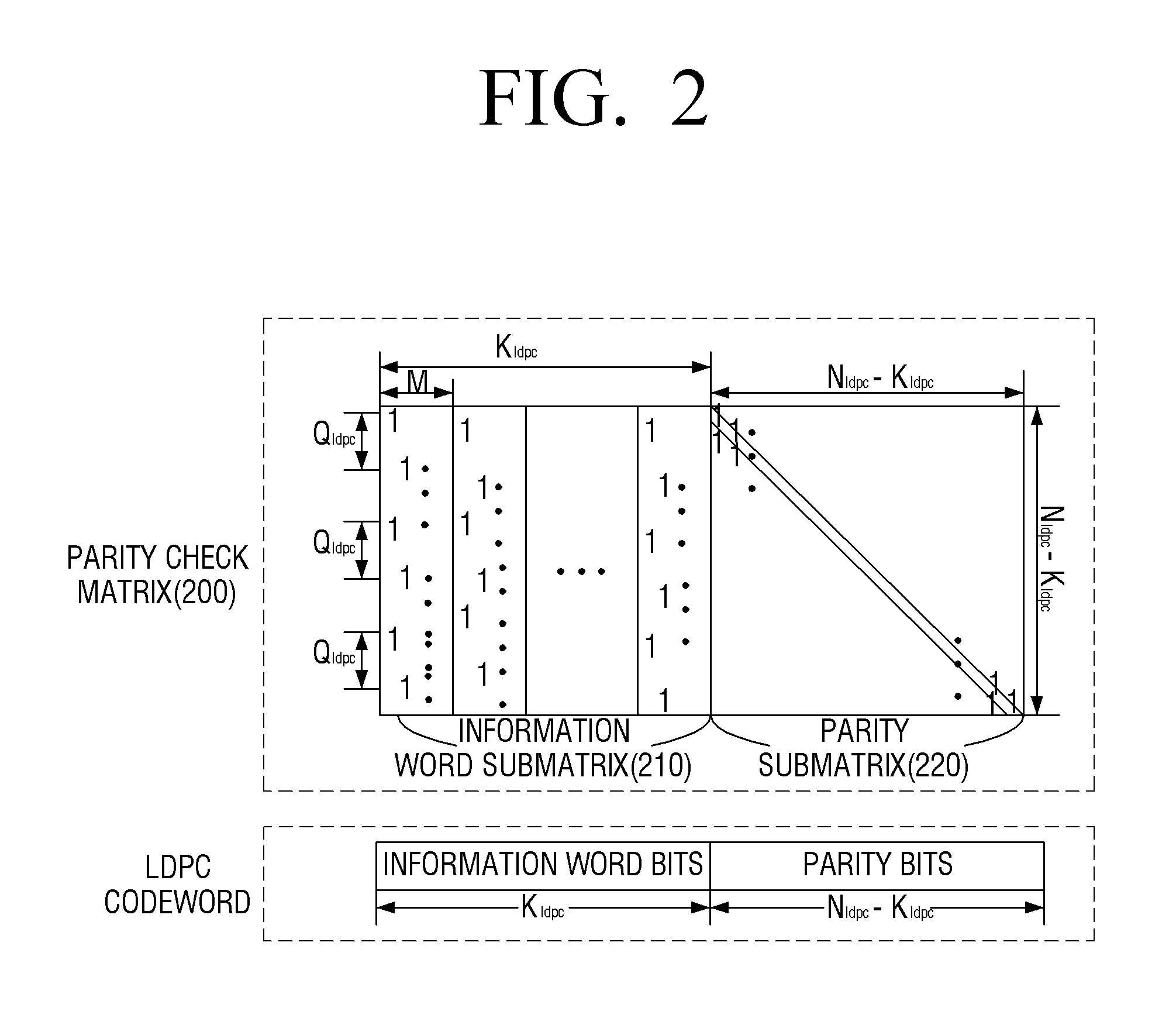

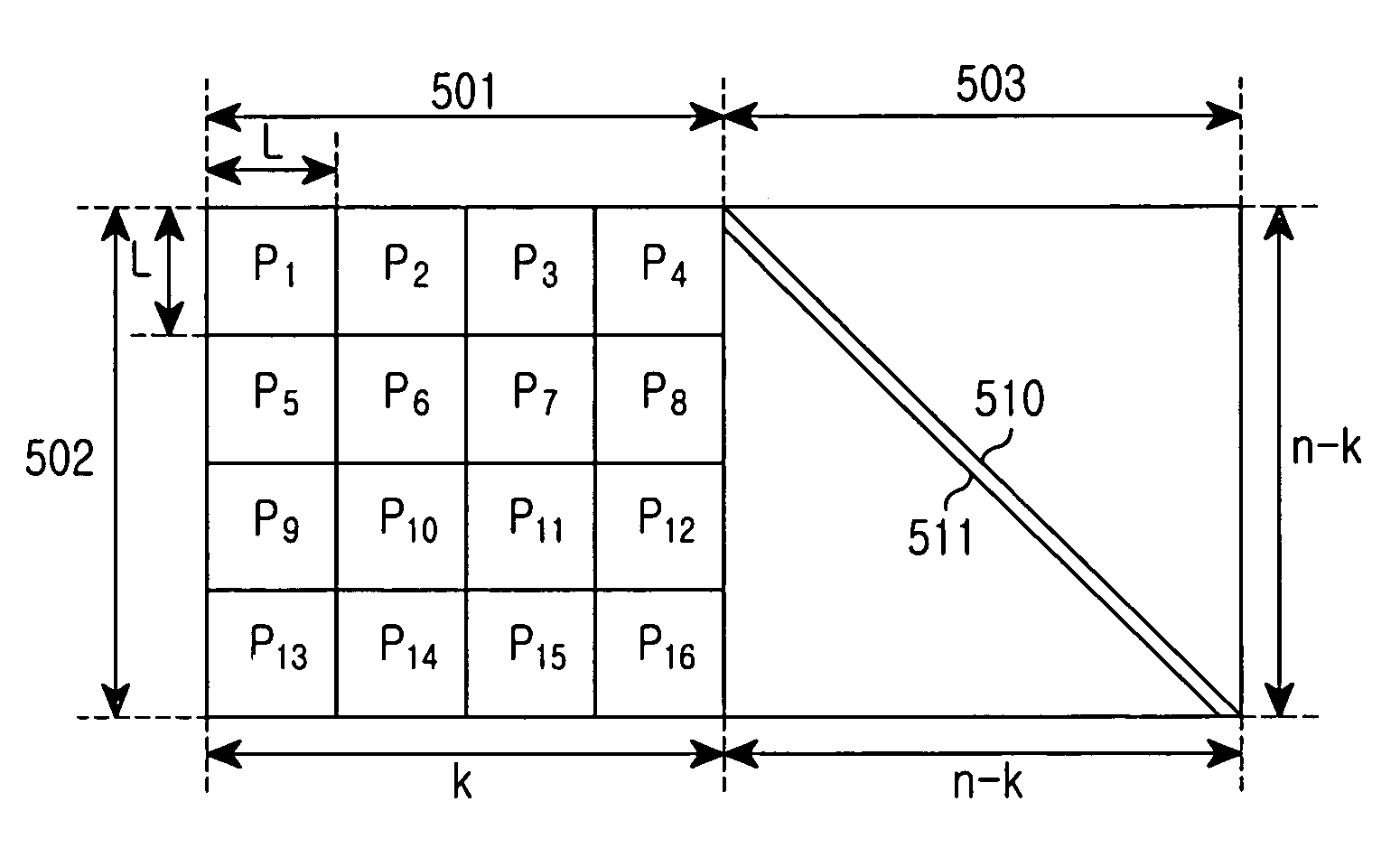

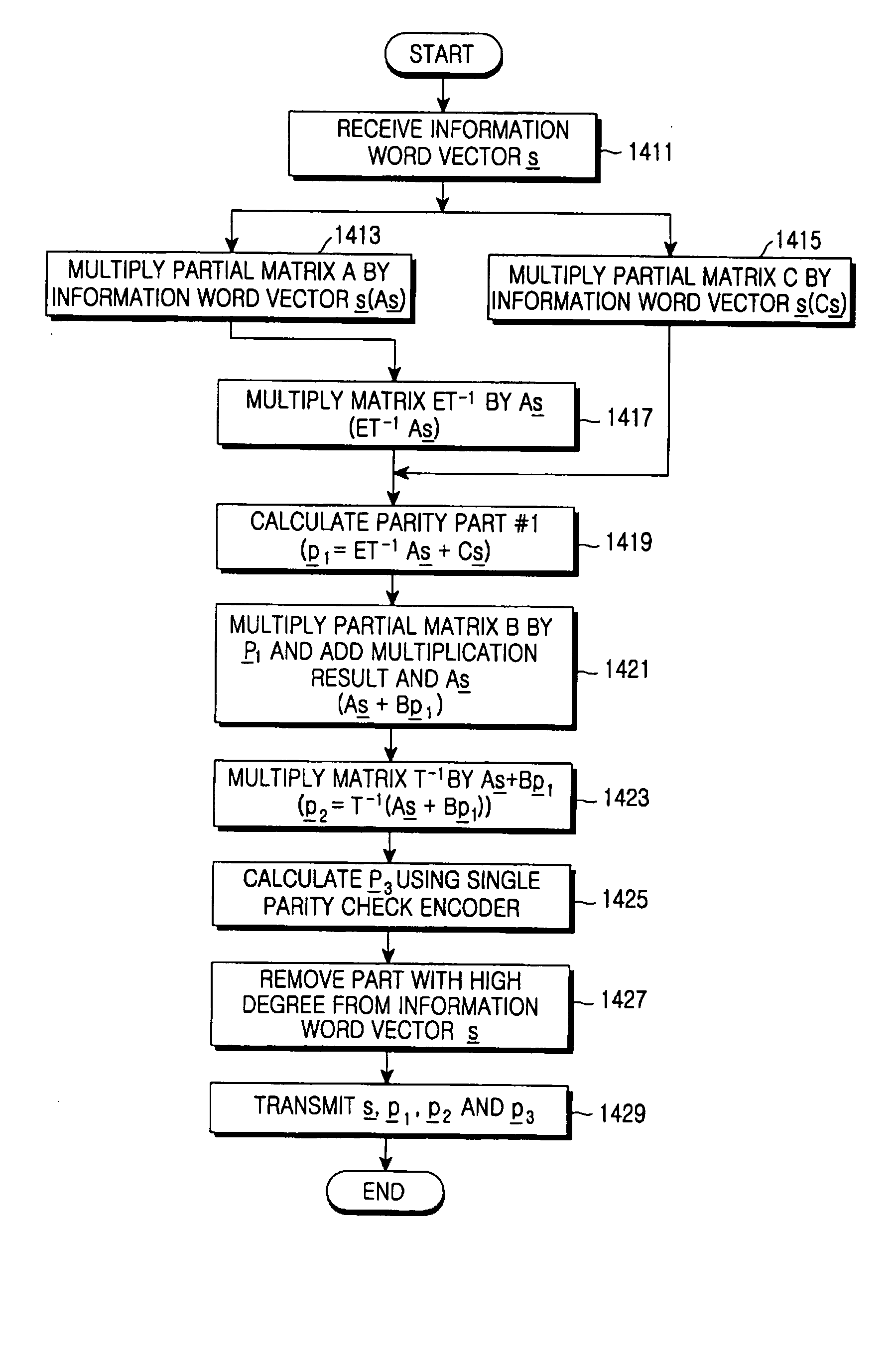

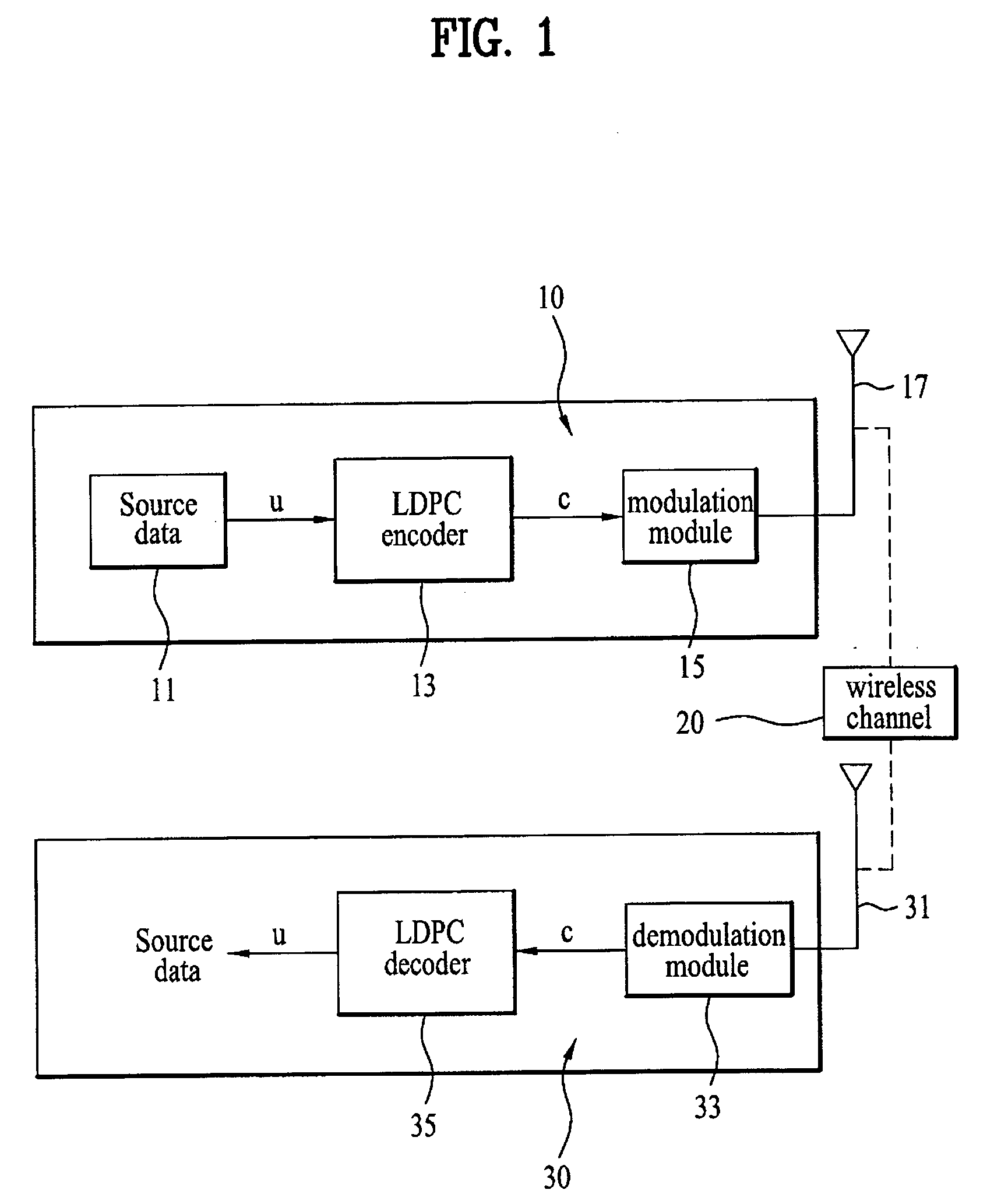

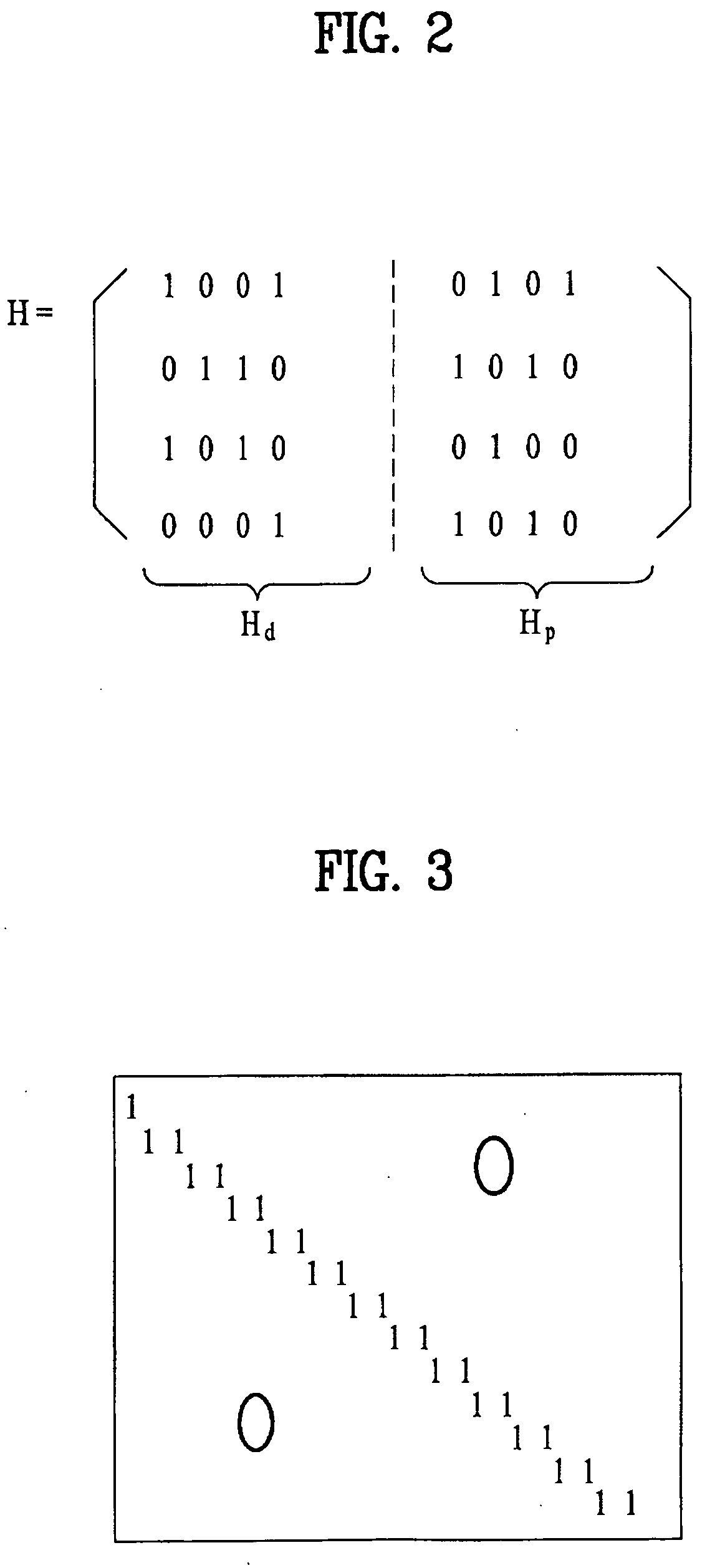

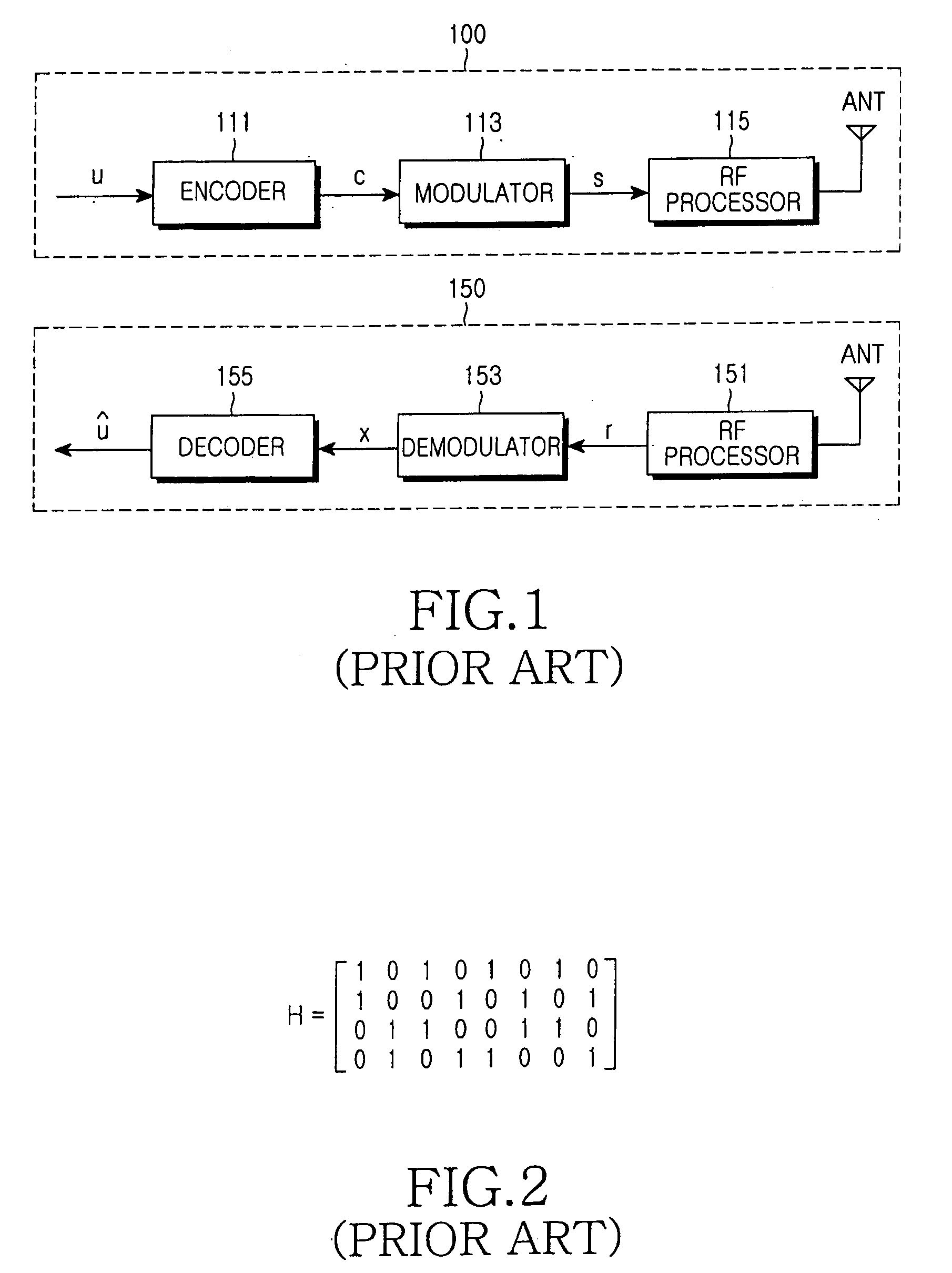

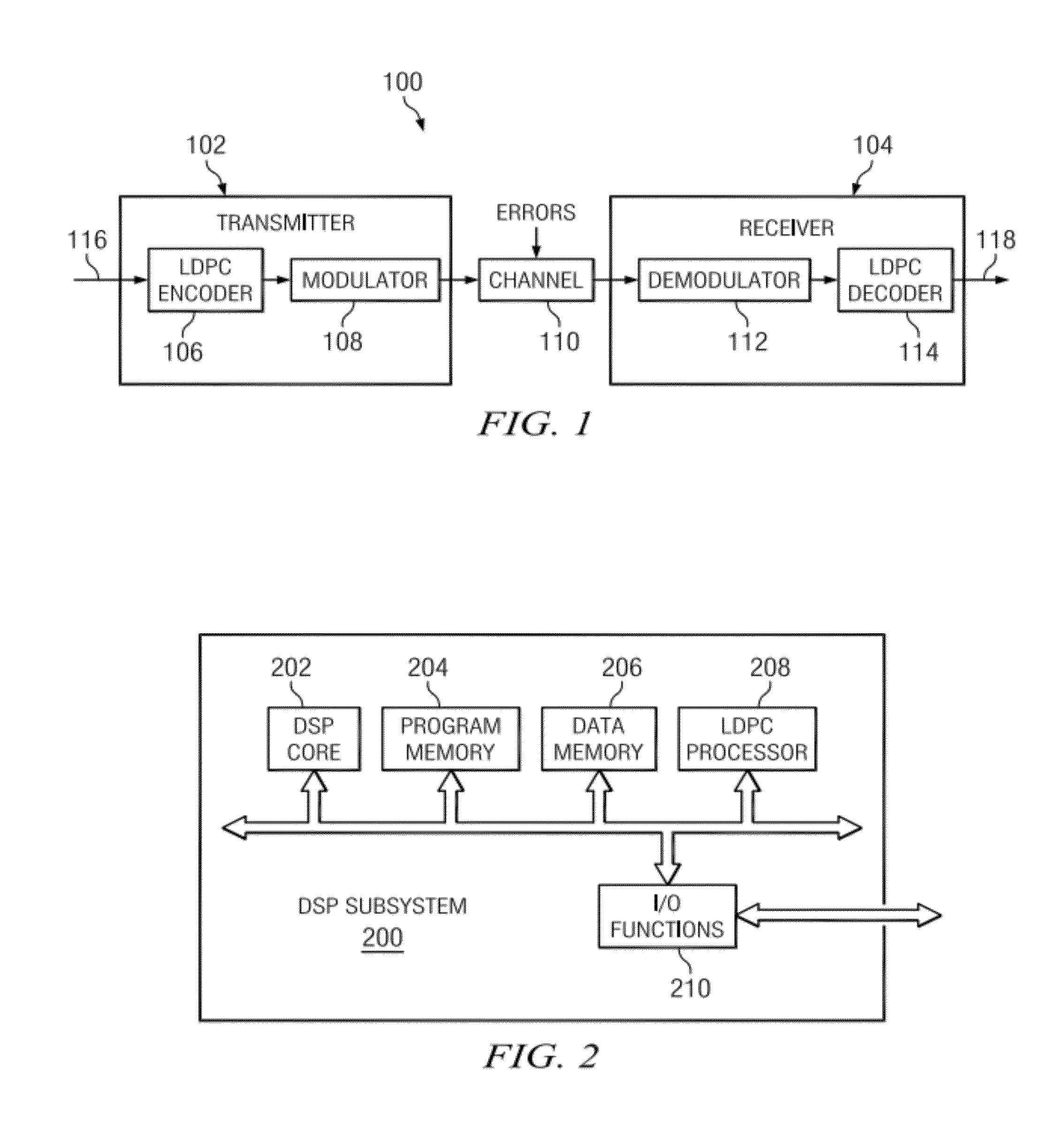

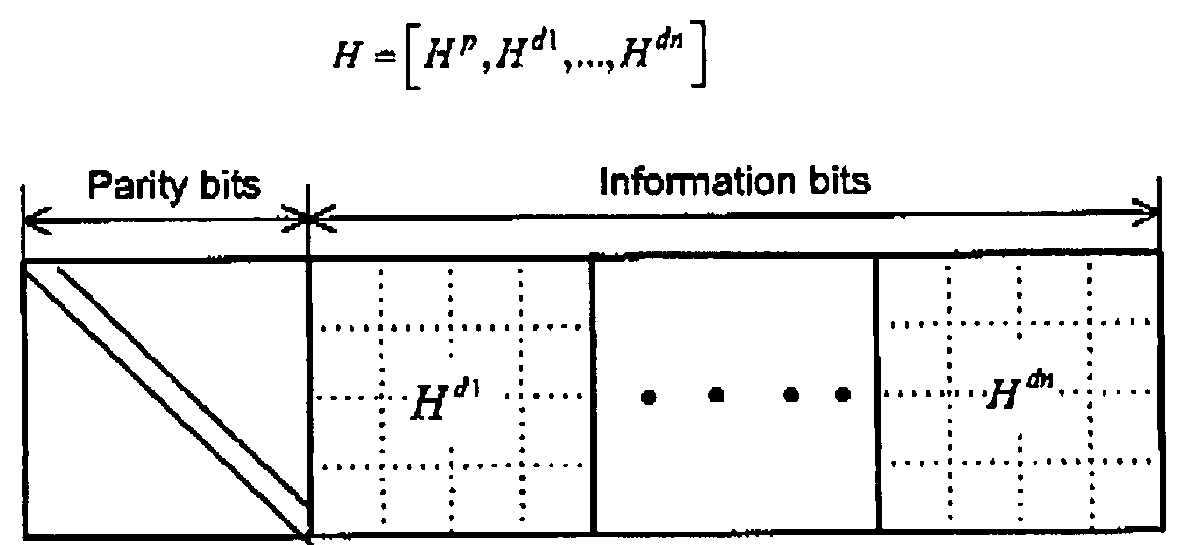

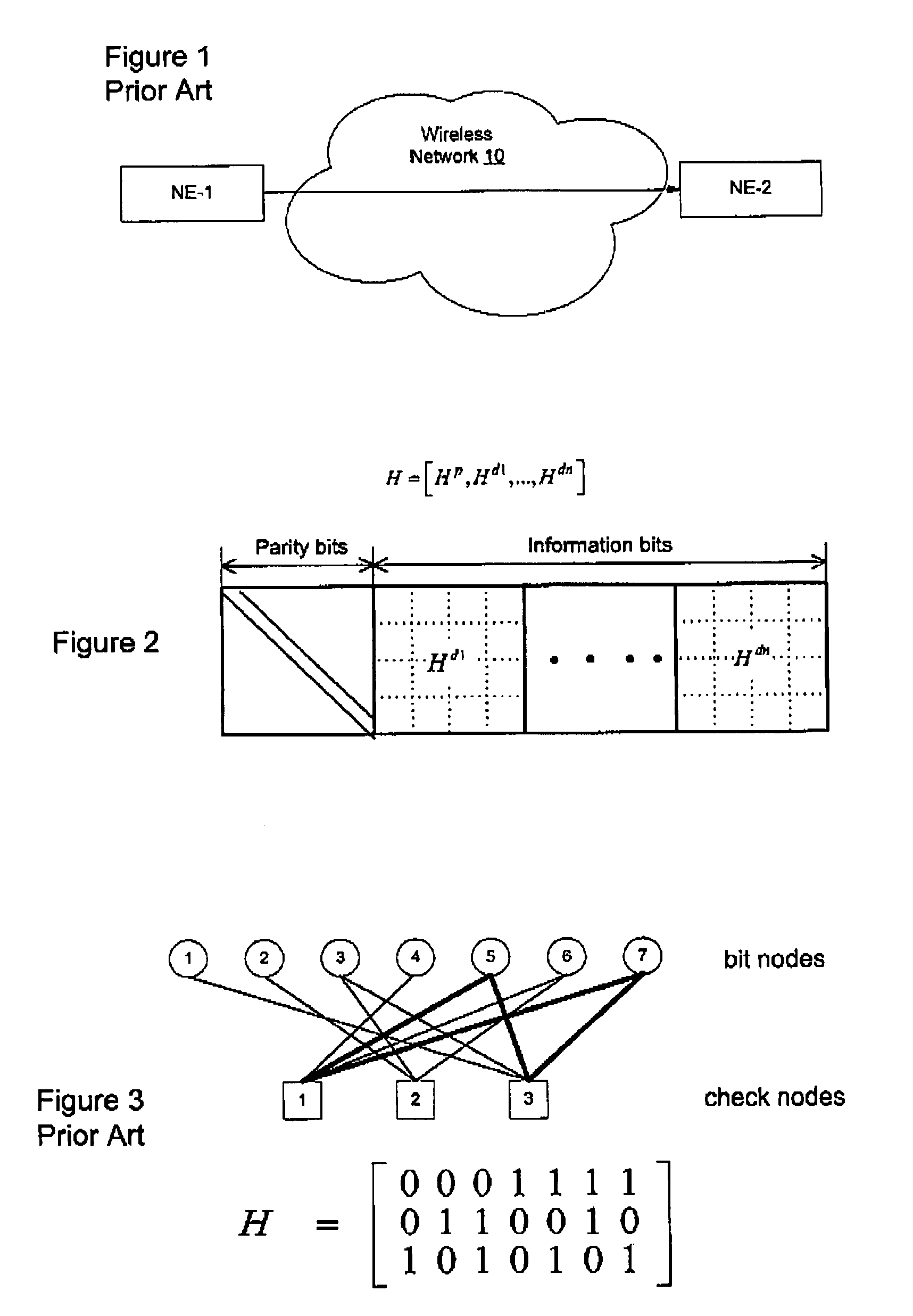

A method for low-density parity-check (LDPC) encoding of data comprises defining a first M×N parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an M×M triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

Method and system for providing low density parity check (LDPC) encoding

ActiveUS7191378B2Readily apparentInterconnection arrangementsError correction/detection using LDPC codesAlgorithmParity-check matrix

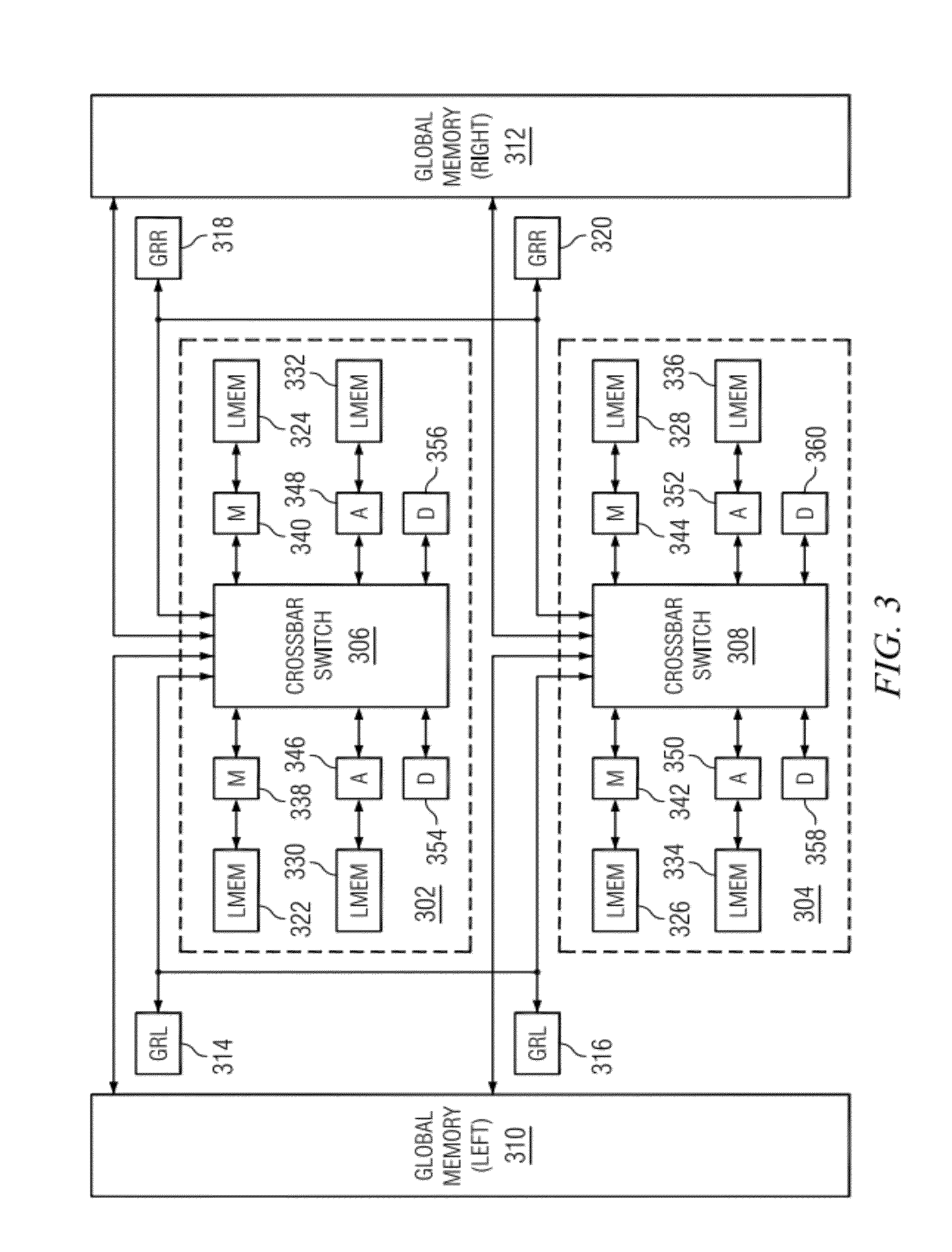

An approach is provided for a method of encoding structure Low Density Parity Check (LDPC) codes. Memory storing information representing a structured parity check matrix of Low Density Parity Check (LDPC) codes is accessed during the encoding process. The information is organized in tabular form, wherein each row represents occurrences of one values within a first column of a group of columns of the parity check matrix. The rows correspond to groups of columns of the parity check matrix, wherein subsequent columns within each of the groups are derived according to a predetermined operation. An LDPC coded signal is output based on the stored information representing the parity check matrix.

Owner:DTVG LICENSING INC

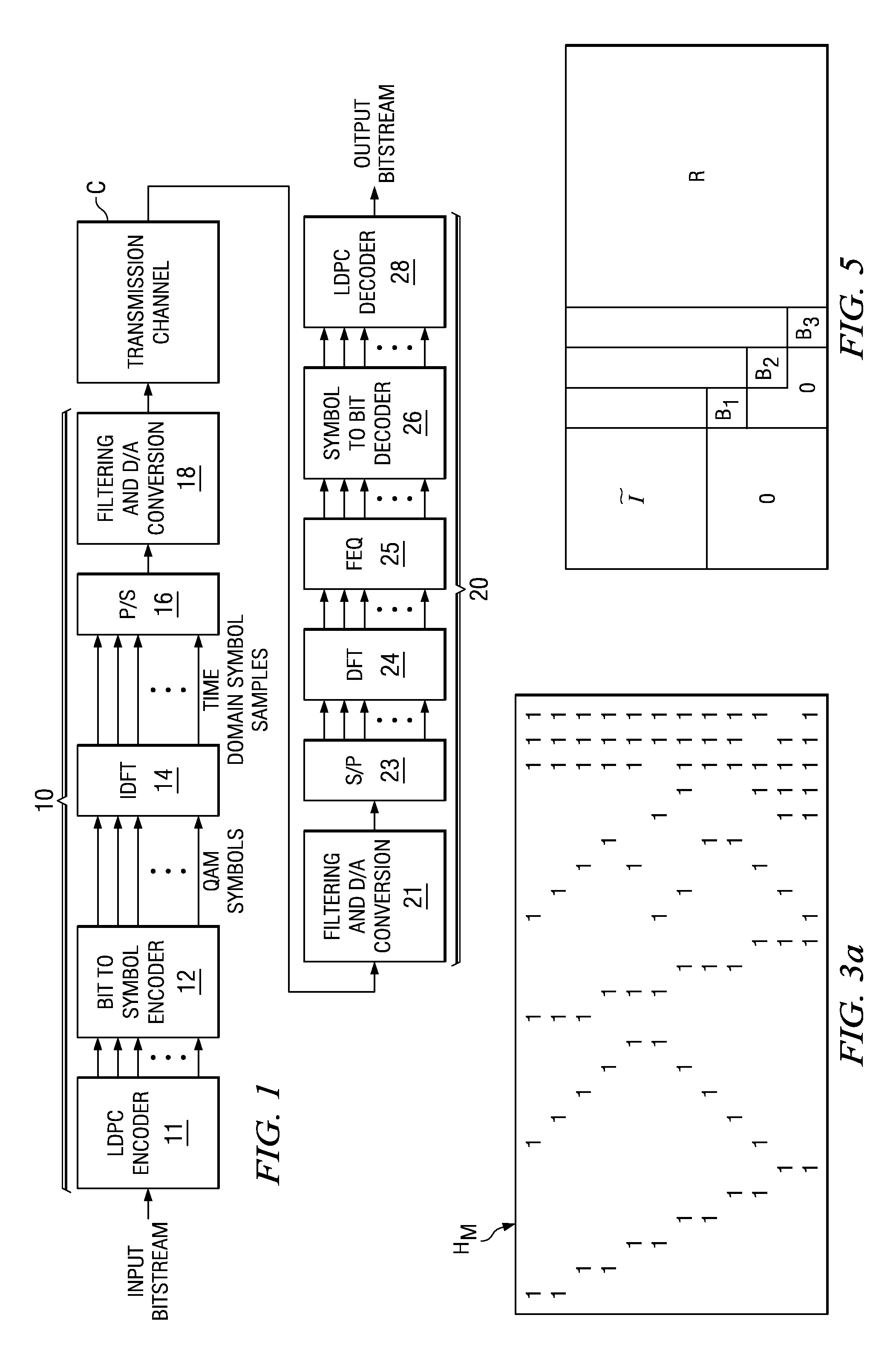

Data processing apparatus and method

ActiveUS20090125780A1Improve performanceLow Density Parity Check (LDPCTransmission path divisionError detection/correctionCarrier signalTheoretical computer science

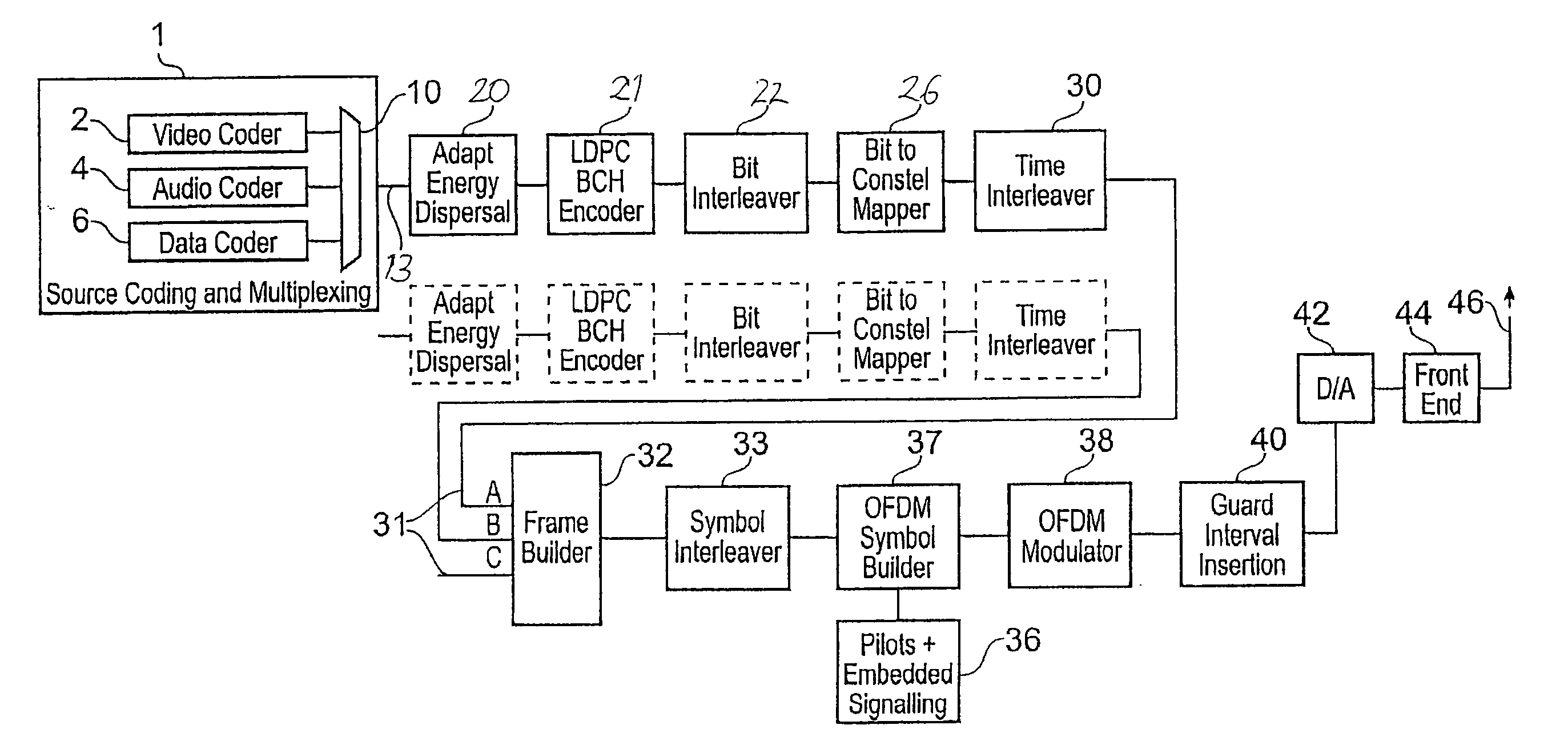

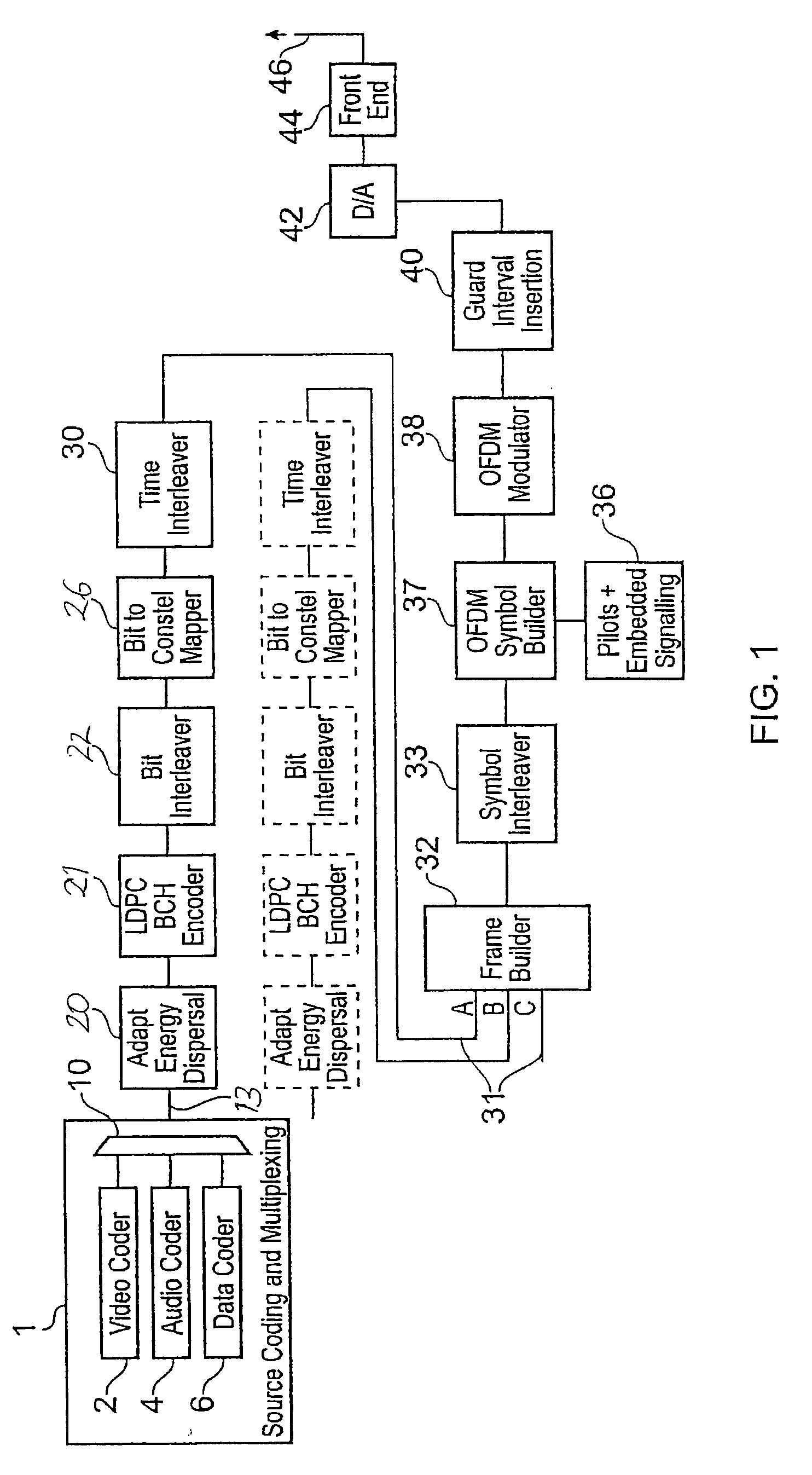

A data processing apparatus communicates data bits on a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processing apparatus comprises a parity interleaver operable to perform parity interleaving on Low Density Parity Check (LDPC) encoded data bits obtained by performing LDPC encoding according to a parity check matrix of an LDPC code including a parity matrix corresponding to parity bits of the LDPC code, the parity matrix having a stepwise structure, so that a parity bit of the LDPC encoded data bits is interleaved to a different parity bit position. A mapping unit maps the parity interleaved bits onto data symbols corresponding to modulation symbols of a modulation scheme of the OFDM sub-carrier signals. A symbol interleaver is arranged in operation to read-into a symbol interleaver memory the predetermined number of data symbols for mapping onto the OFDM sub-carrier signals, and to read-out of the interleaver memory the data symbols for the OFDM sub-carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on the sub-carrier signals. The set of addresses are generated by an address generator which has been optimised to interleave the data symbols on to the sub-carrier signals of the OFDM carrier signals for a given operating mode of the OFDM system, such as a 32K operating mode for DVB-T2 or DVB-C2.

Owner:SATURN LICENSING LLC

Encoding method using a low density parity check code with a column weight of two

ActiveUS7058873B2Facilitate the processOther decoding techniquesError correction/detection using multiple parity bitsTanner graphCommunications system

A method for communicating binary data and a digital communication system are presented. According to one embodiment, the method includes encoding a message word by multiplying the message word with a generator matrix, wherein the generator matrix multiplied by the transpose of a parity check matrix for a low density parity check code yields a null set, and wherein the parity check matrix has a column weight of two. Additionally disclosed is an encoding scheme based on a three-tier Tanner graph having a girth of twelve.

Owner:CARNEGIE MELLON UNIV

Method and apparatus for low density parity check encoding of data

InactiveUS20030037298A1Improve performanceError preventionError detection/correctionParity-check matrixTheoretical computer science

A method for low-density parity-check (LDPC) encoding of data comprises defining a first MxN parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an MxM triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

Set of irregular LDPC codes with random structure and low encoding complexity

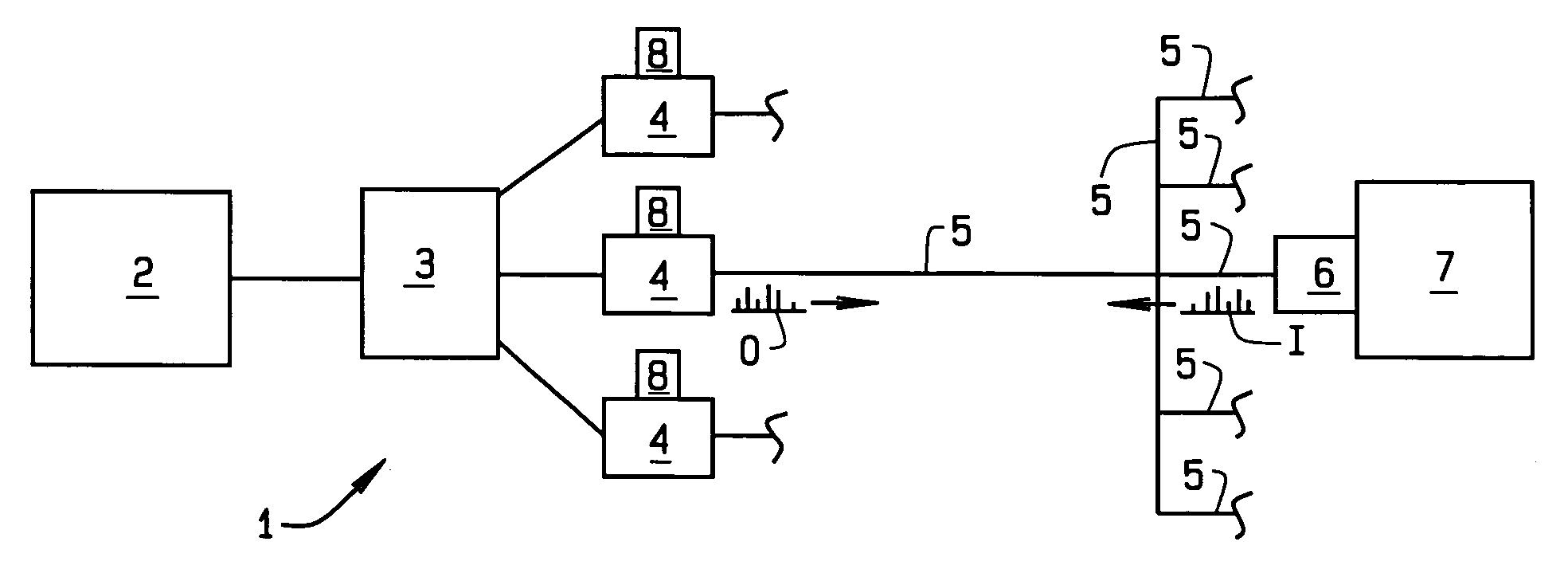

ActiveUS7523375B2Improve performanceEasy to controlError detection/correctionCode conversionParity-check matrixDistribution system

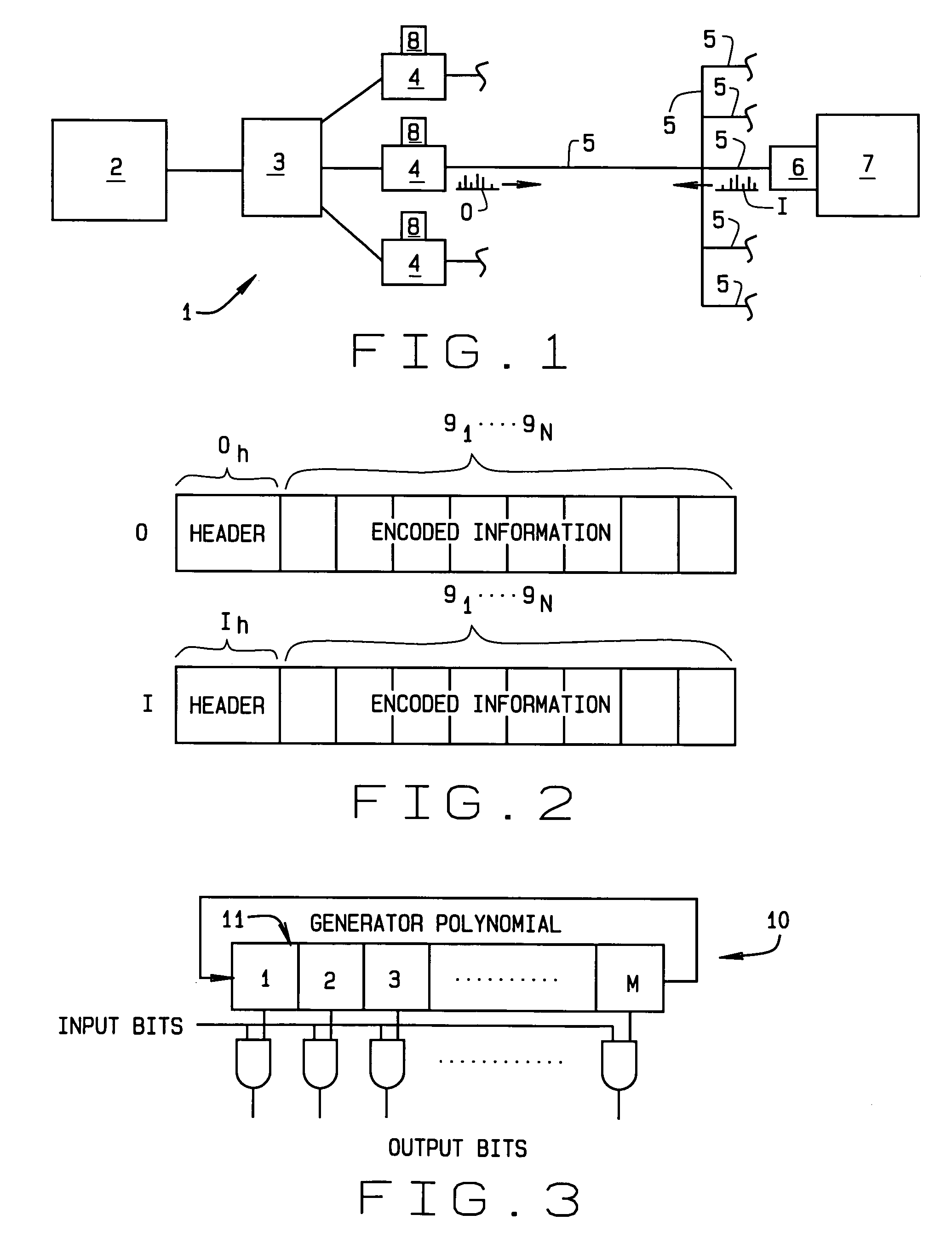

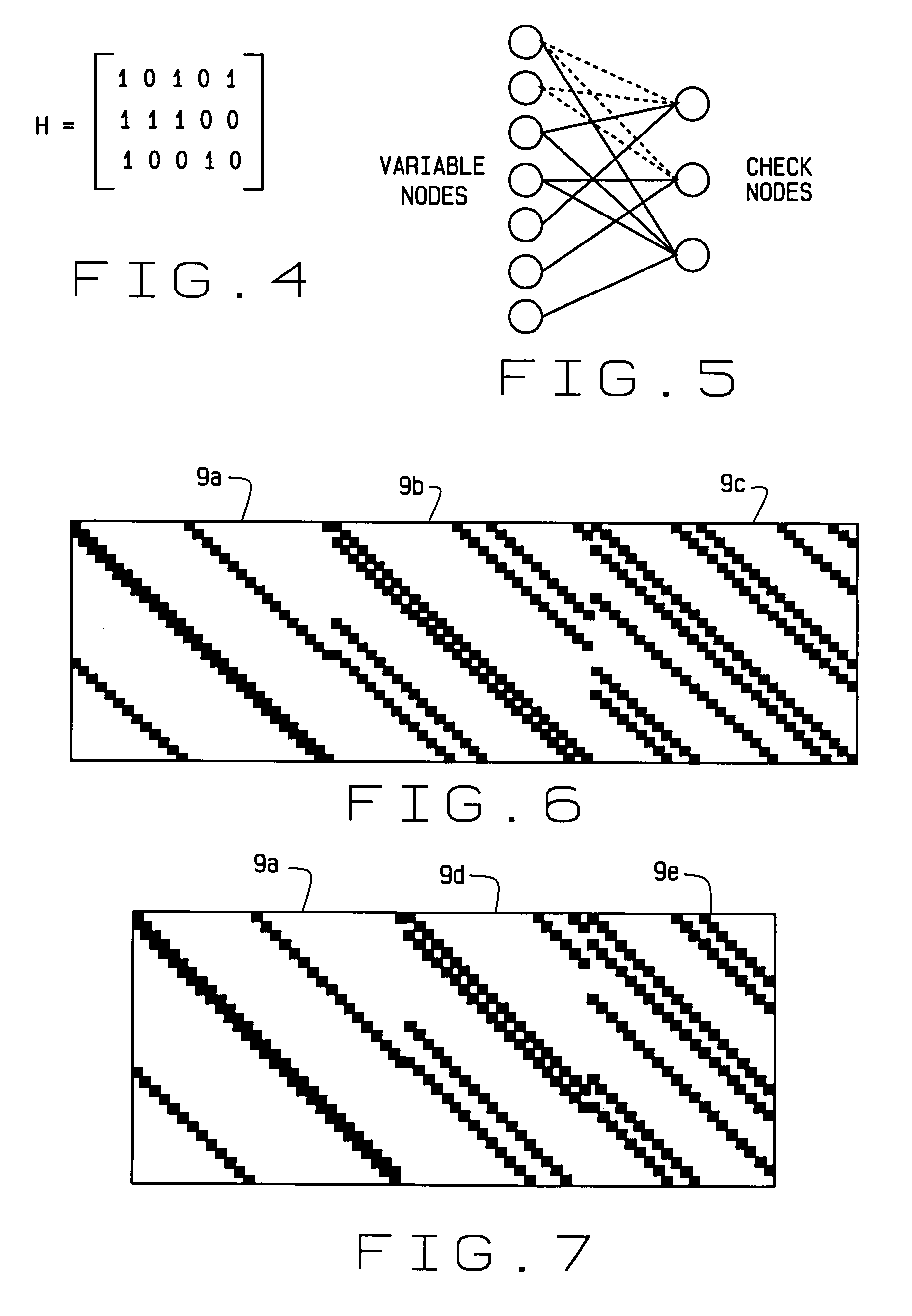

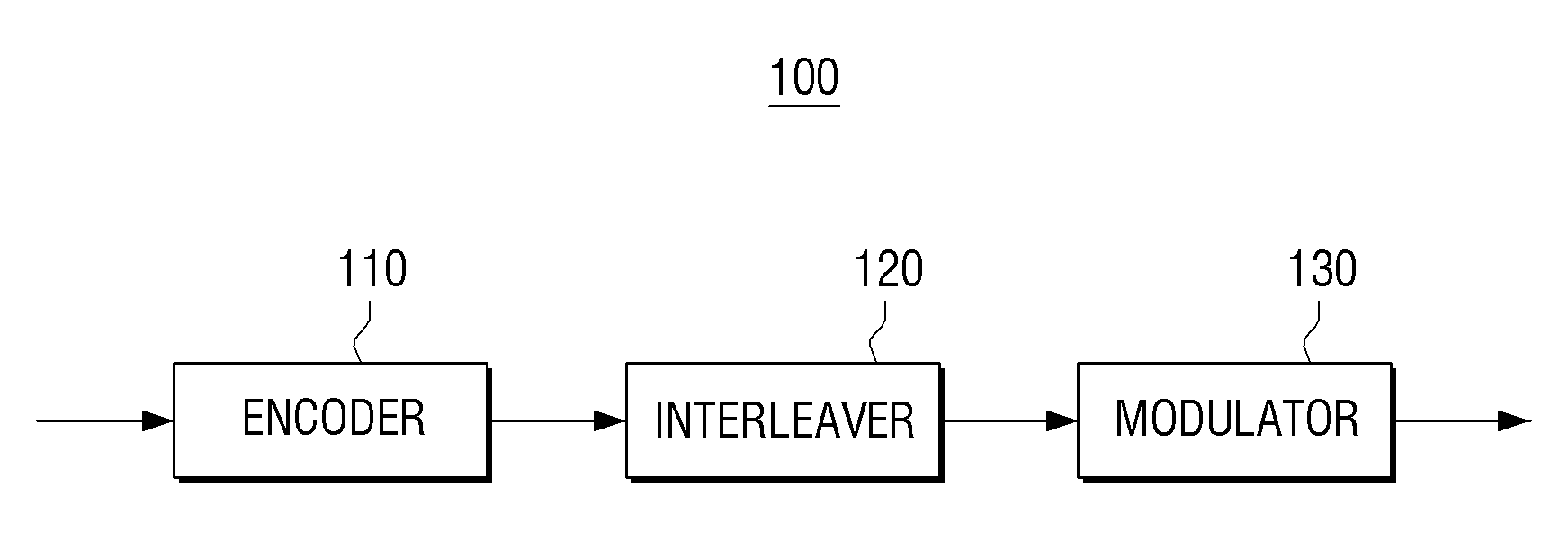

A set of irregular LDPC (Low Density Parity Check) codes having a pseudo-random structure and low encoding complexity. A block-cyclic LDPC code has an irregular row or an irregular column weight and includes a parity check matrix and an encoding matrix each of which has a pseudo-random structure. This allows the code to have the irregular row weight or irregular column weight together with an overall randomness to the code structure. Blocks within the code can be shortened, adjacent blocks of code can be overlapped, and adjacent columns within a block can be arbitrarily permuted so to change the weighting of rows and columns. The LDPC codes are particularly useful in two-way communications system for an electrical distribution system (1) to restore data lost or corrupted during its transmission.

Owner:ACLARA TECH LLC

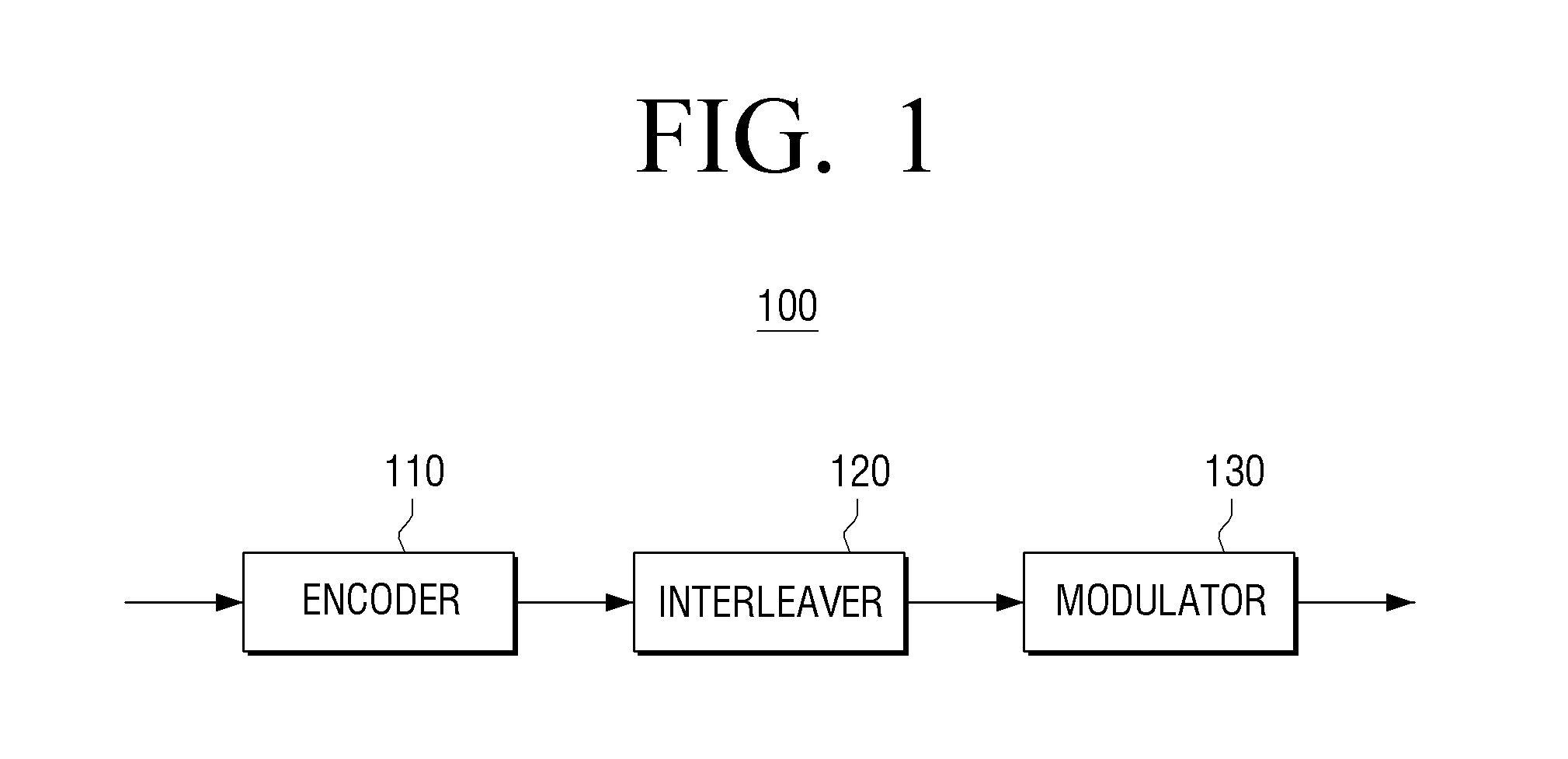

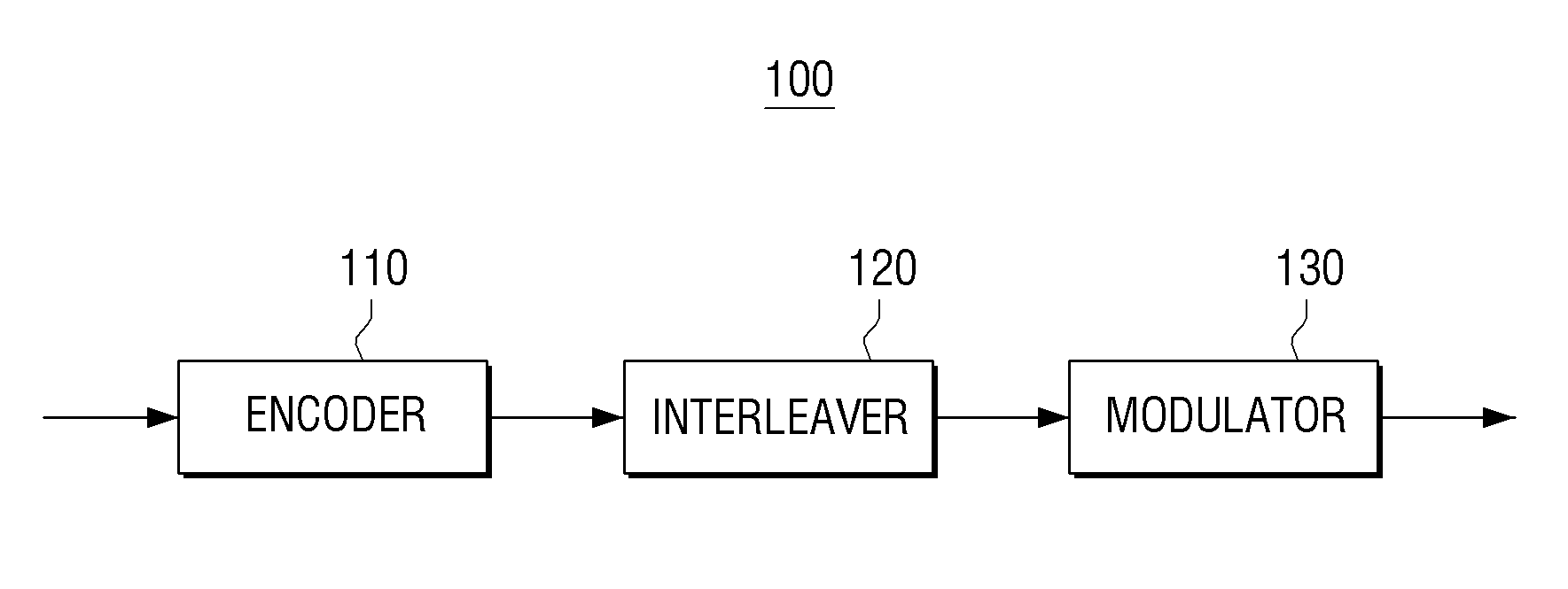

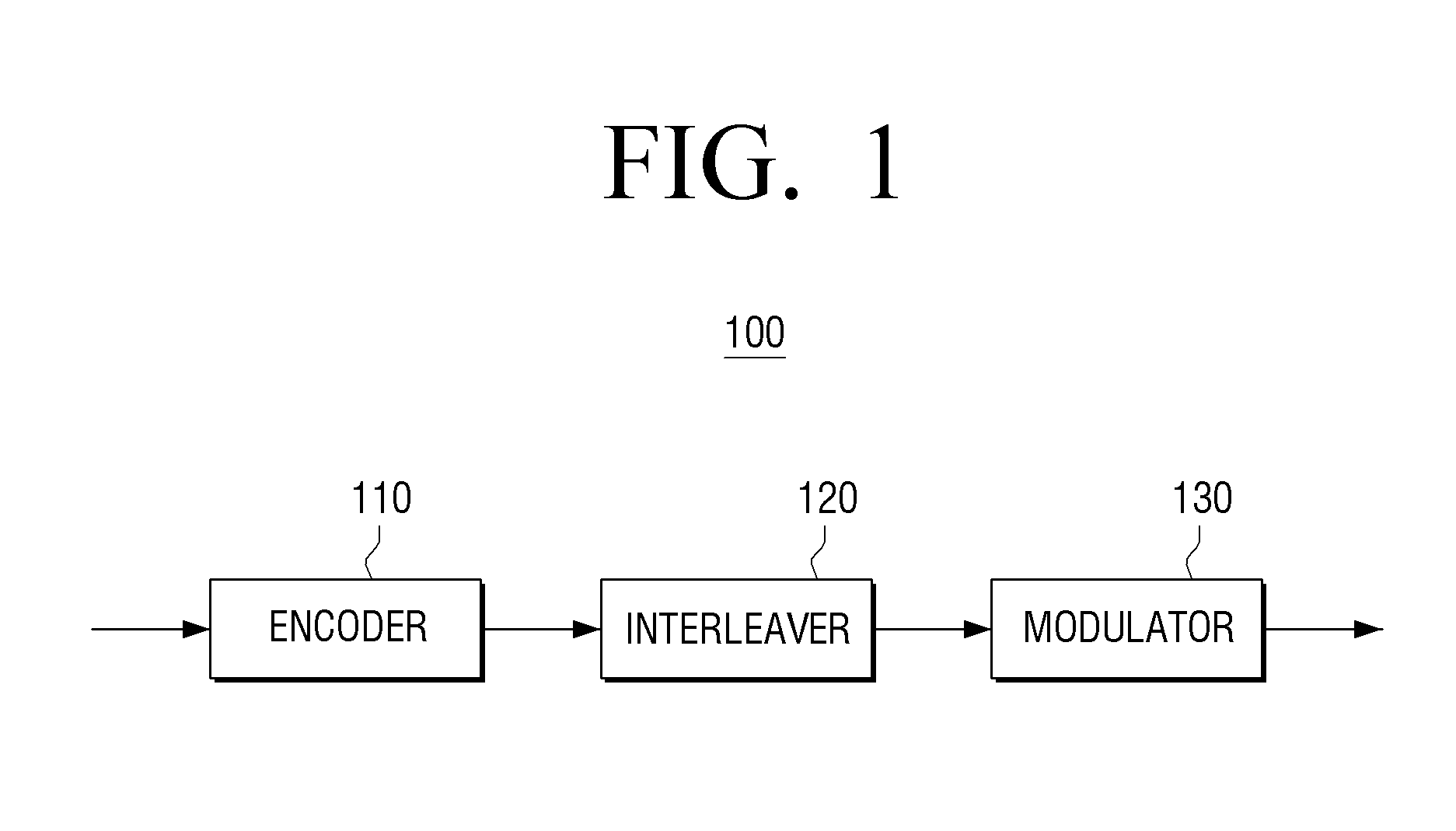

Transmitter apparatus and interleaving method thereof

ActiveUS20150236816A1Improve decoding performanceImprove reception performanceModulated-carrier systemsError correction/detection using LDPC codesComputer hardwareParity-check matrix

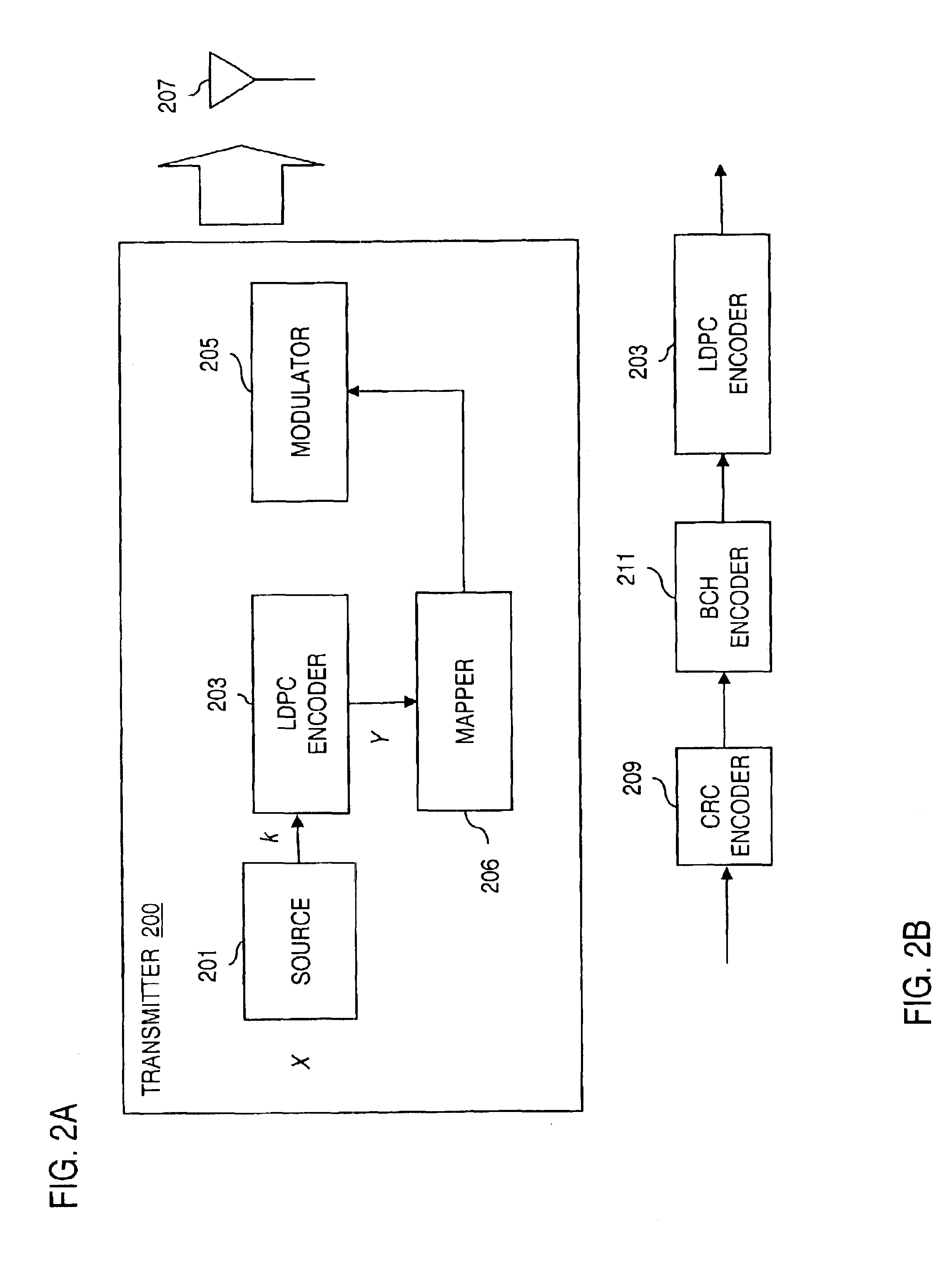

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding based on a parity check matrix; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Bit labeling for amplitude phase shift constellation used with low density parity check (LDPC) codes

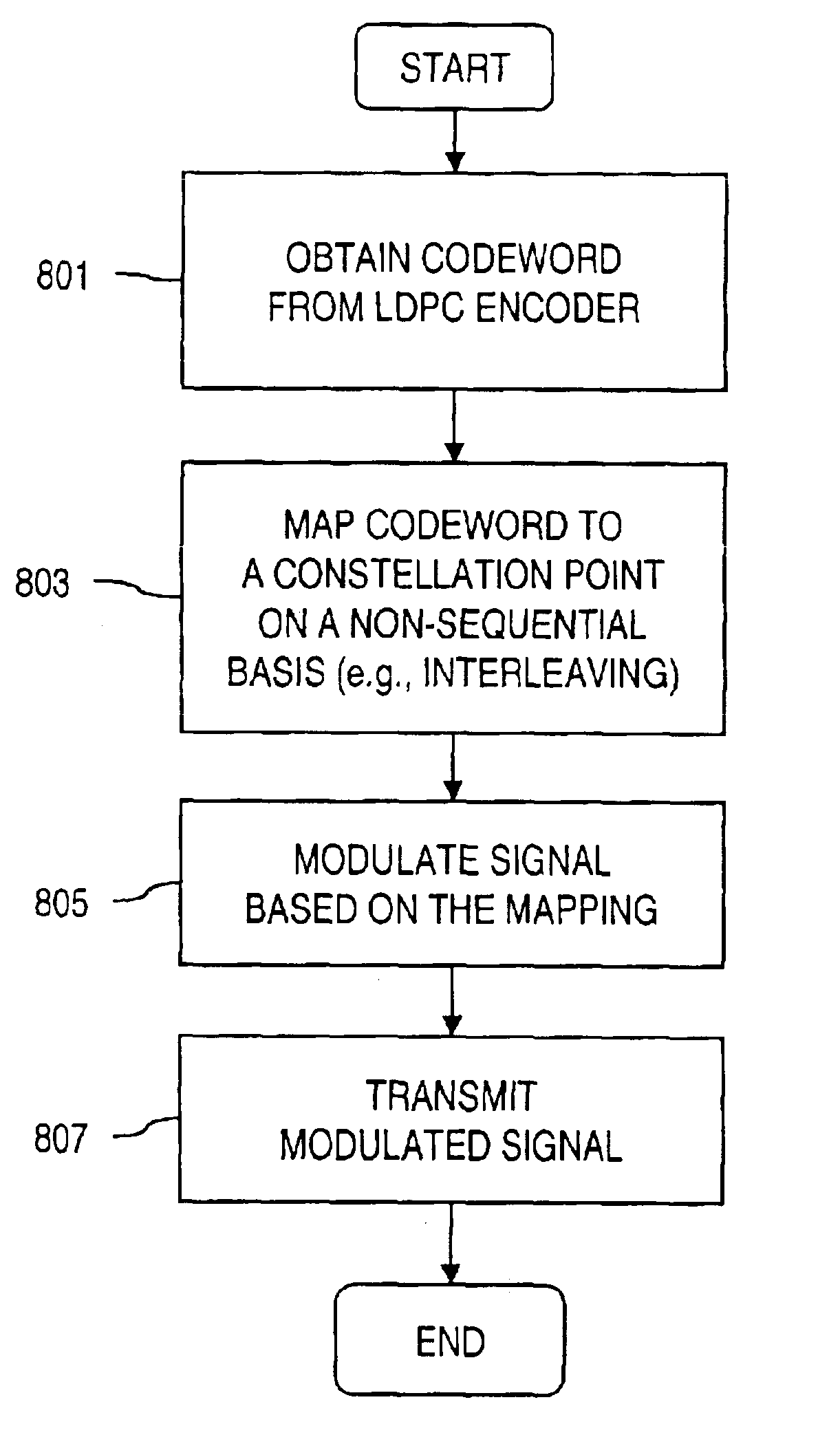

InactiveUS6963622B2Improve performanceError correction/detection using LDPC codesCode conversionParity-check matrixEngineering

An approach is provided for bit labeling of a signal constellation. A transmitter generates encoded signals using, according to one embodiment, a structured parity check matrix of a Low Density Parity Check (LDPC) code. The transmitter includes an encoder for transforming an input message into a codeword represented by a plurality of set of bits. The transmitter includes logic for mapping non-sequentially (e.g., interleaving) one set of bits into a higher order constellation (Quadrature Phase Shift Keying (QPSK), 8-PSK, 16-APSK (Amplitude Phase Shift Keying), 32-APSK, etc.), wherein a symbol of the higher order constellation corresponding to the one set of bits is output based on the mapping.

Owner:DTVG LICENSING INC

Hardware-efficient low density parity check code for digital communications

ActiveUS7178080B2Efficient implementationEfficient constructionError correction/detection using multiple parity bitsCode conversionMatrix groupParity-check matrix

Owner:TEXAS INSTR INC

Apparatus and method for encoding a low density parity check code

ActiveUS7178082B2Low Density Parity CheckEasy to calculateError detection/correctionError correction/detection using multiple parity bitsTheoretical computer scienceDiagonal matrix

An apparatus and method for generating an encoding matrix for a low density parity check (LDPC) code having a dual-diagonal matrix as a parity check matrix are disclosed. The apparatus and method construct an information sub-matrix of the encoding matrix with a predetermined number of square matrixes according to a predetermined code rate such that each of the square matrixes has columns and rows with a weight of 1 and has a different offset value, combine the square matrixes with the dual-diagonal matrix, and perform inter-row permutation on the information sub-matrix.

Owner:SAMSUNG ELECTRONICS CO LTD

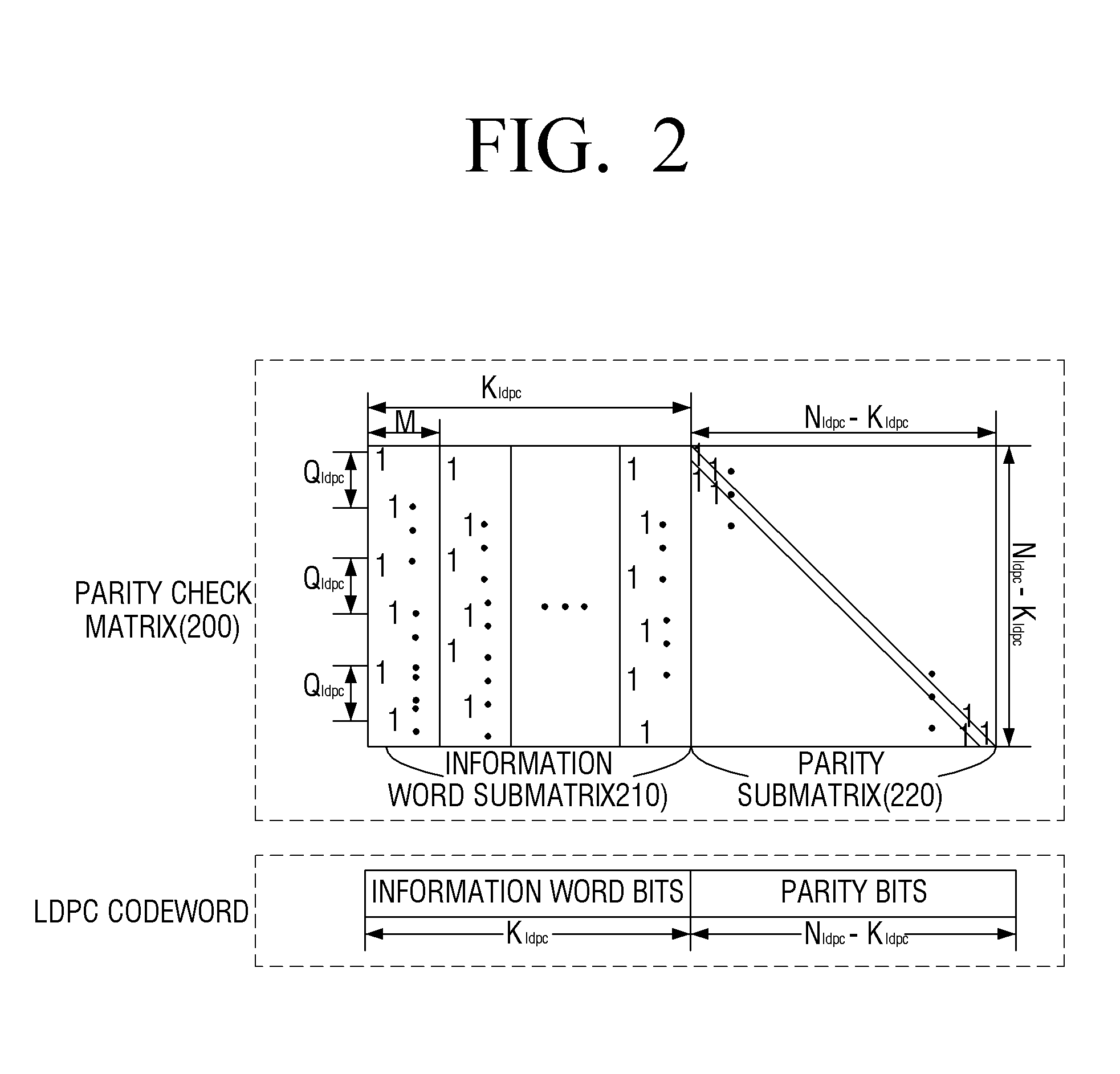

Transmitter apparatus and bit interleaving method thereof

ActiveUS20150341054A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError correction/detection using LDPC codesParity-check matrixCheck digit

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding of input bits based on a parity check matrix including information word bits and parity bits, the LDPC codeword including a plurality of bit groups each including a plurality of bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the interleaver is further configured to interleave the LDPC codeword such that a bit included in a predetermined bit group from among the plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Data processing device and method

ActiveCN101510865APulse modulation television signal transmissionError preventionAddress generatorCarrier signal

A data processing device transmits the data bits on the predetermined quantity carrying wave signal of the OFDM sign. The data processing device comprises a parity interweaver for operating the pairs of LDPC coding data. The data bits are obtained by the parity matrix LDPC detecting with the LDPC code. The parity matrix has a ladder-type structure interweaving the LDPC code data to the different parity bit position. The mapping unit maps the parity interweaving bit to the data signs corresponding to the modulating signs of the solution. The sign interweaver reads the quantity signs to the sign interweaving store, carrying out the data sig of the sign interweaving store reading the order with different reading; the order address set is confirmed. The address set is generated by the address generator.

Owner:SONY CORP

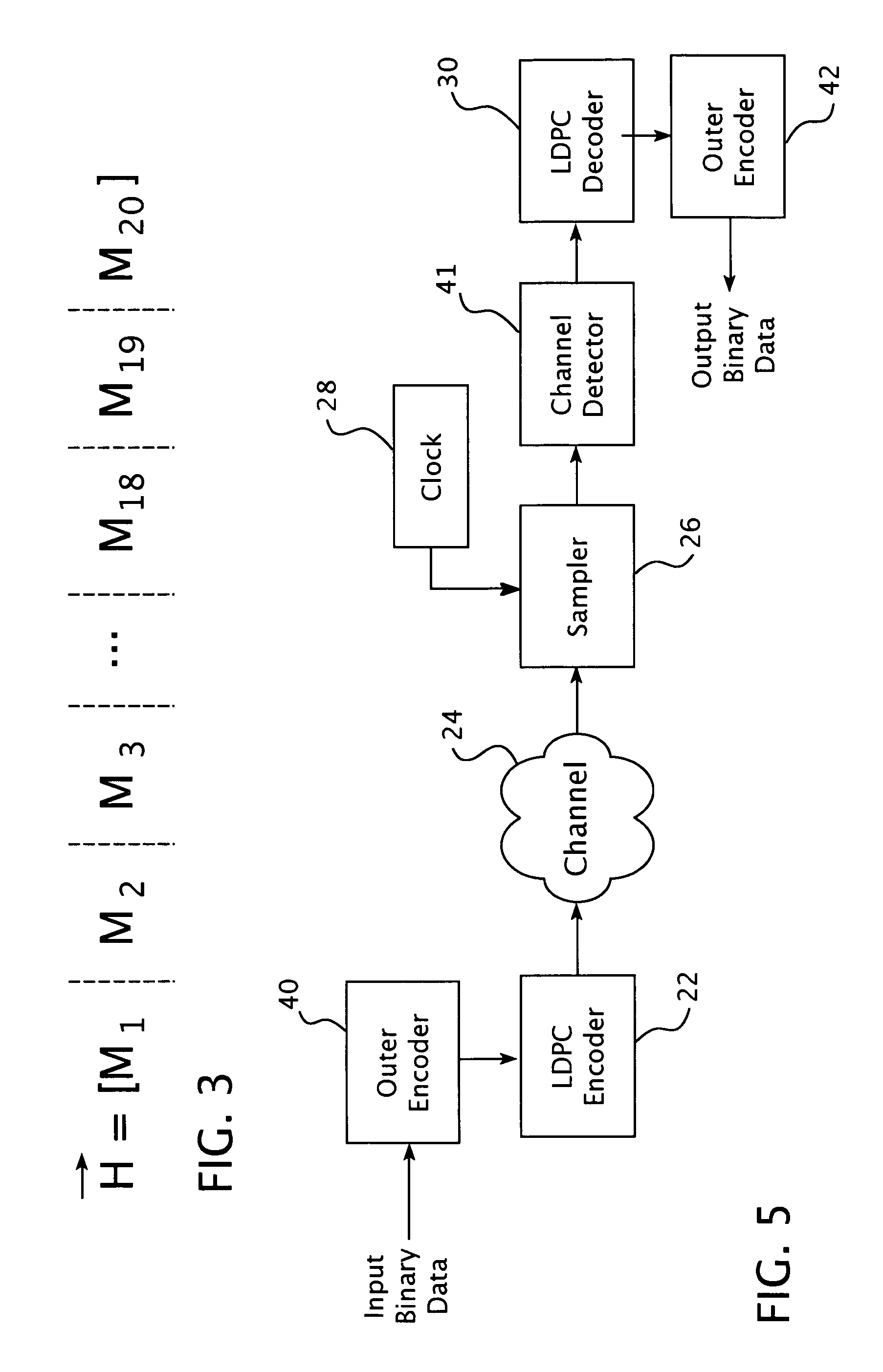

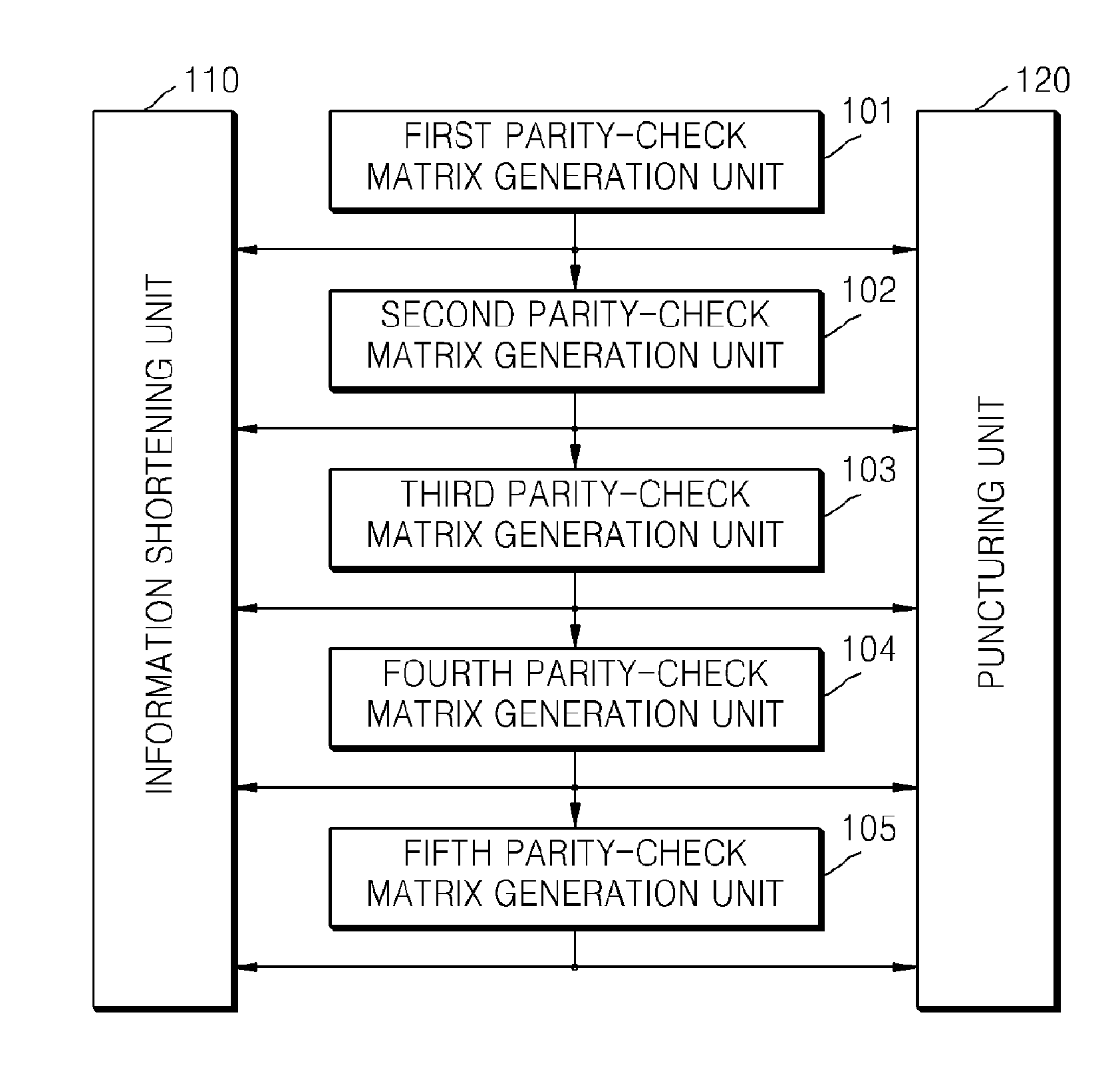

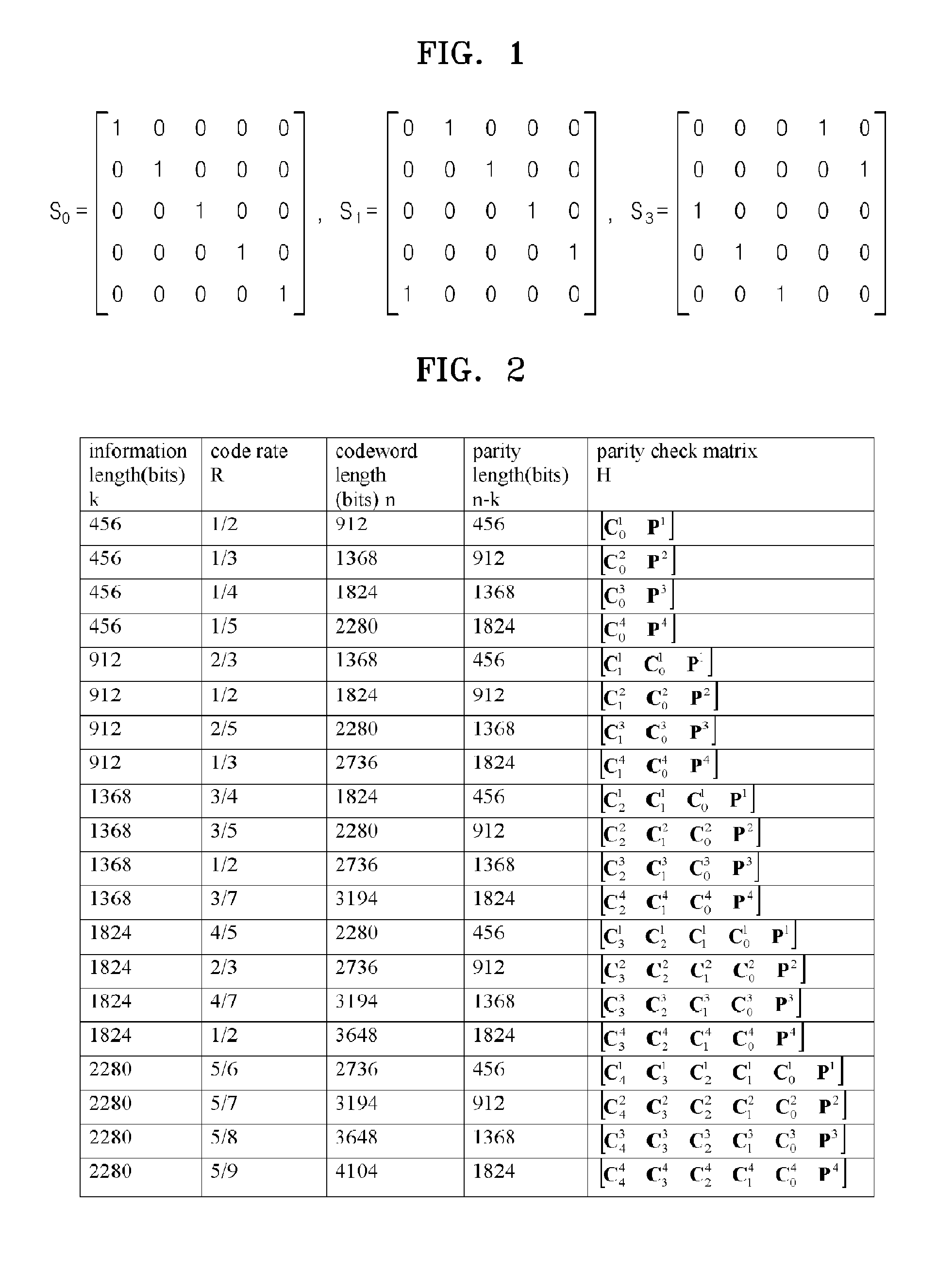

Method of generating parity-check matrix, encoding/decoding method for low density parity-check code with variable information length and variable code rate and apparatus using the same

InactiveUS20100325511A1Easily embodiedIncrease speedError correction/detection using multiple parity bitsCode conversionGeneration processParity-check matrix

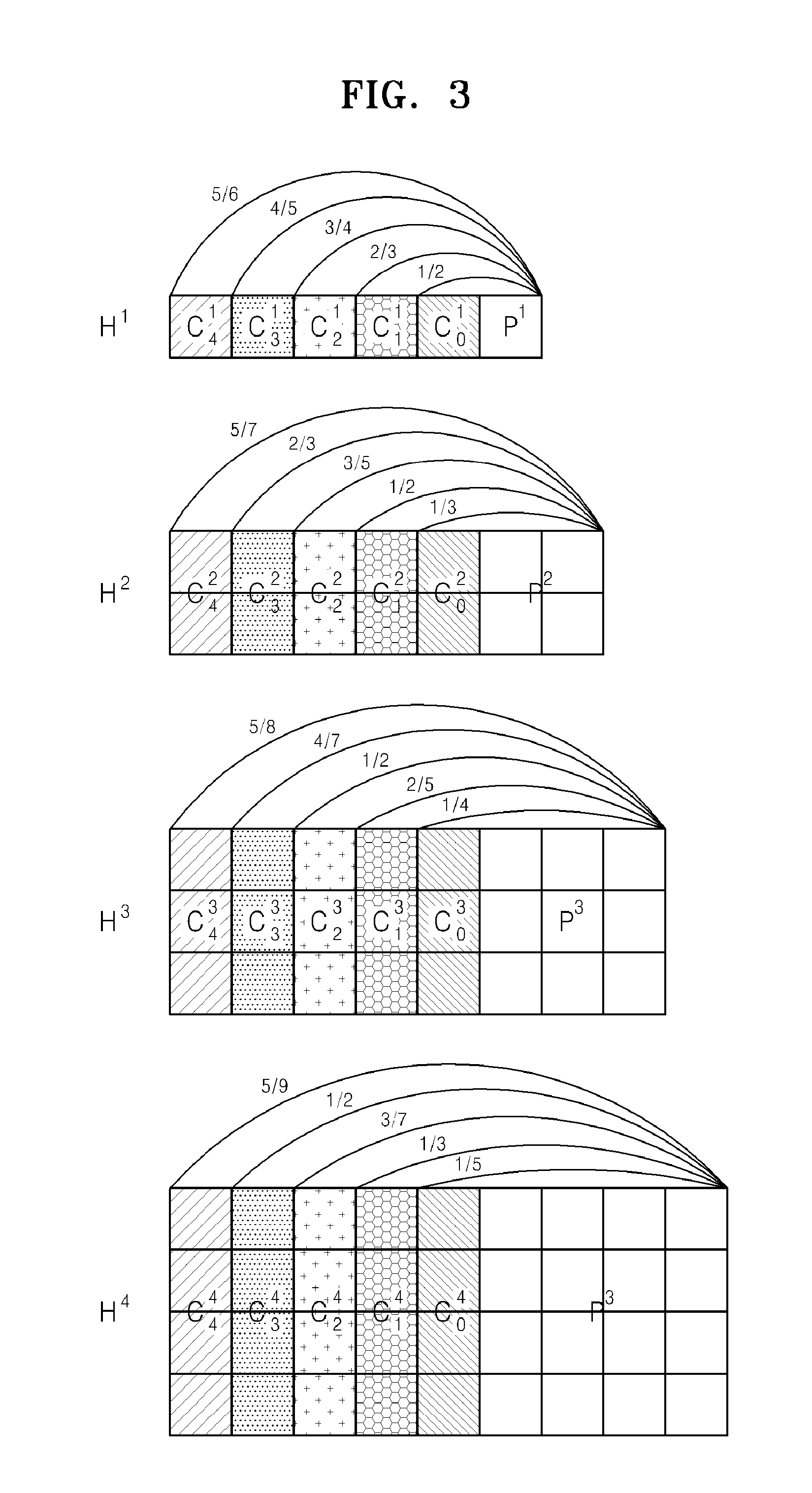

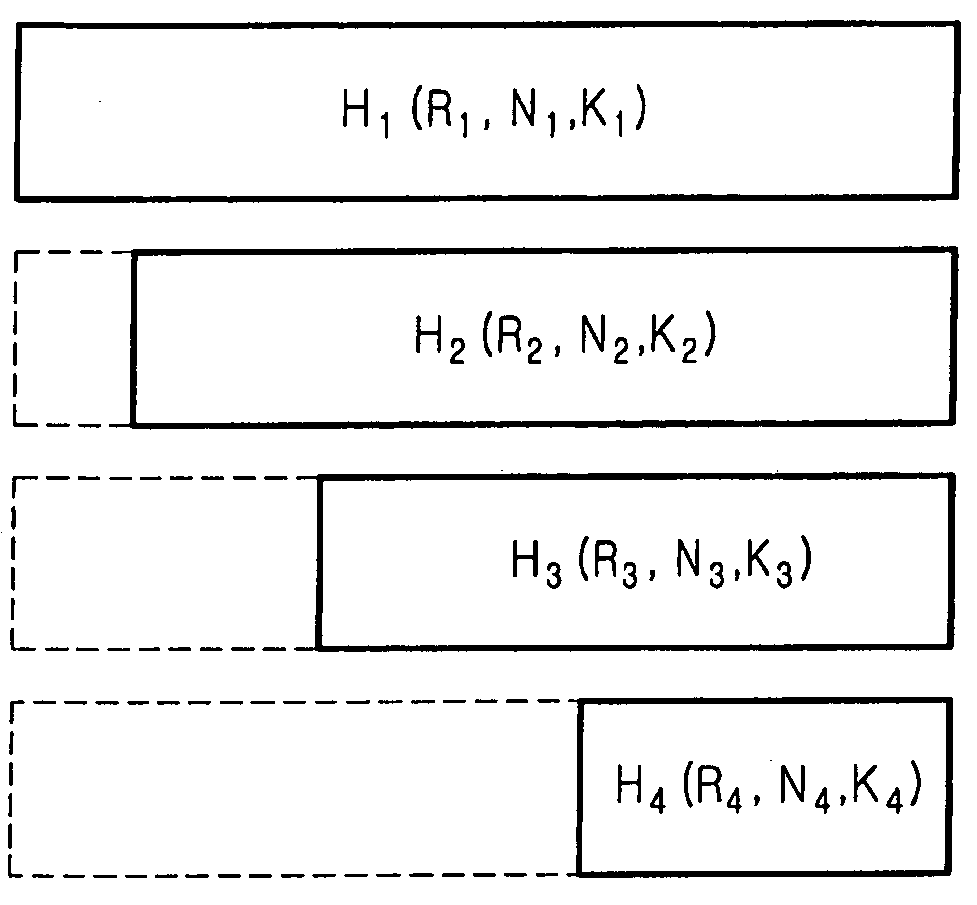

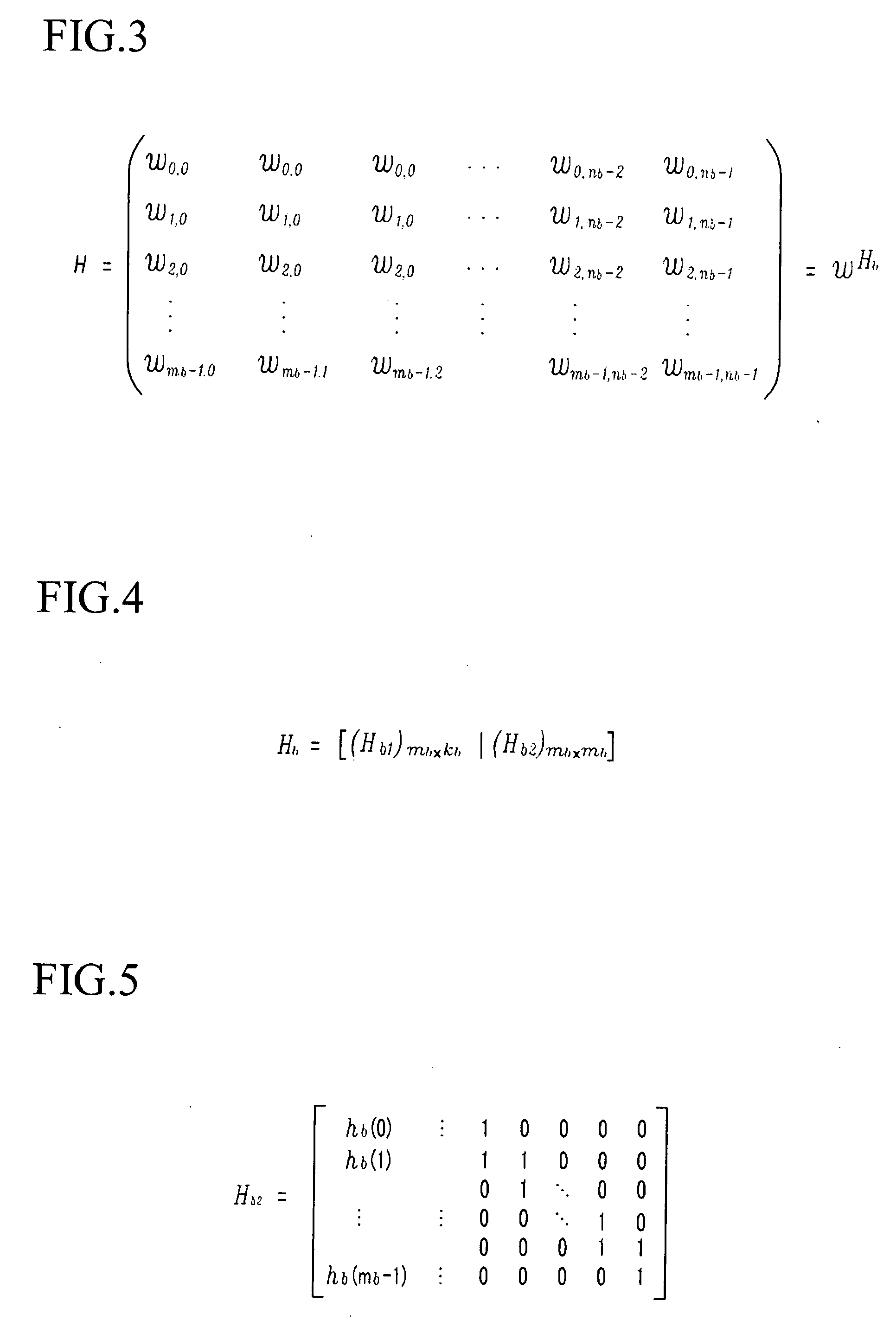

A method of generating a parity-check matrix of a low density parity-check (LDPC) code with a variable information length and a variable code rate, an encoding / decoding method, and an apparatus using the same are provided. The method of generating a parity-check matrix of an LDPC code includes: a first parity-check matrix generation process of generating a first parity-check matrix constructed with a first information block and a parity block; and an m-th parity-check matrix generation process of generating an m-th parity-check matrix by an m-th information block to a generated (m−1)-th parity-check matrix (1<m≦M, where M is a natural number equal to or greater than two). Accordingly, it is possible to provide an LDPC code with a variable information length and a variable code rate which has a low complexity for encoding / decoding and a high quality of correction and detection of errors.

Owner:ELECTRONICS & TELECOMM RES INST

Transmitting apparatus and interleaving method thereof

ActiveUS20150341052A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError detection/correctionParity-check matrixComputer engineering

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to perform a low-density parity check (LDPC) encoding on input bits using a parity check matrix to generate an LDPC codeword comprising information word bits and parity bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

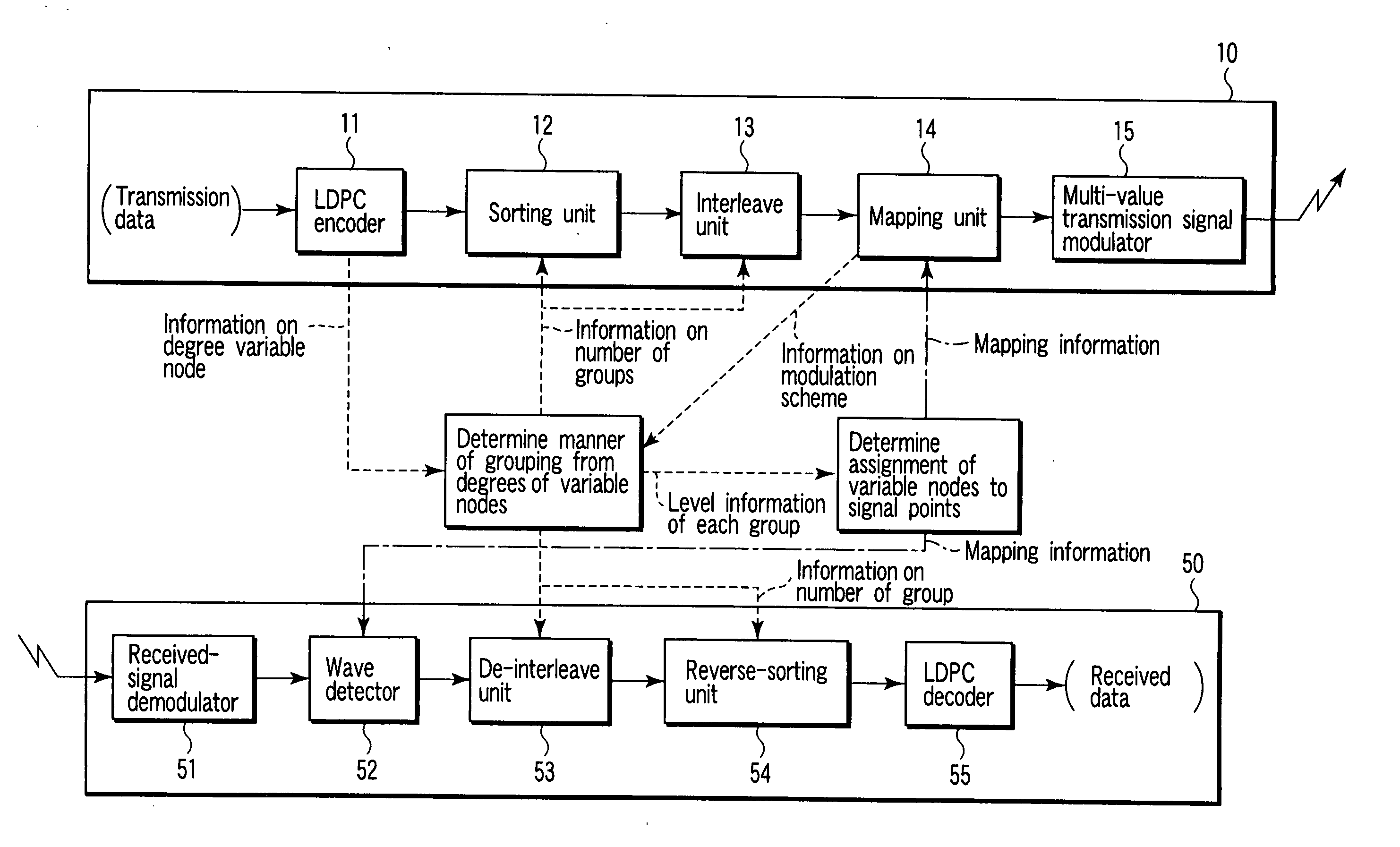

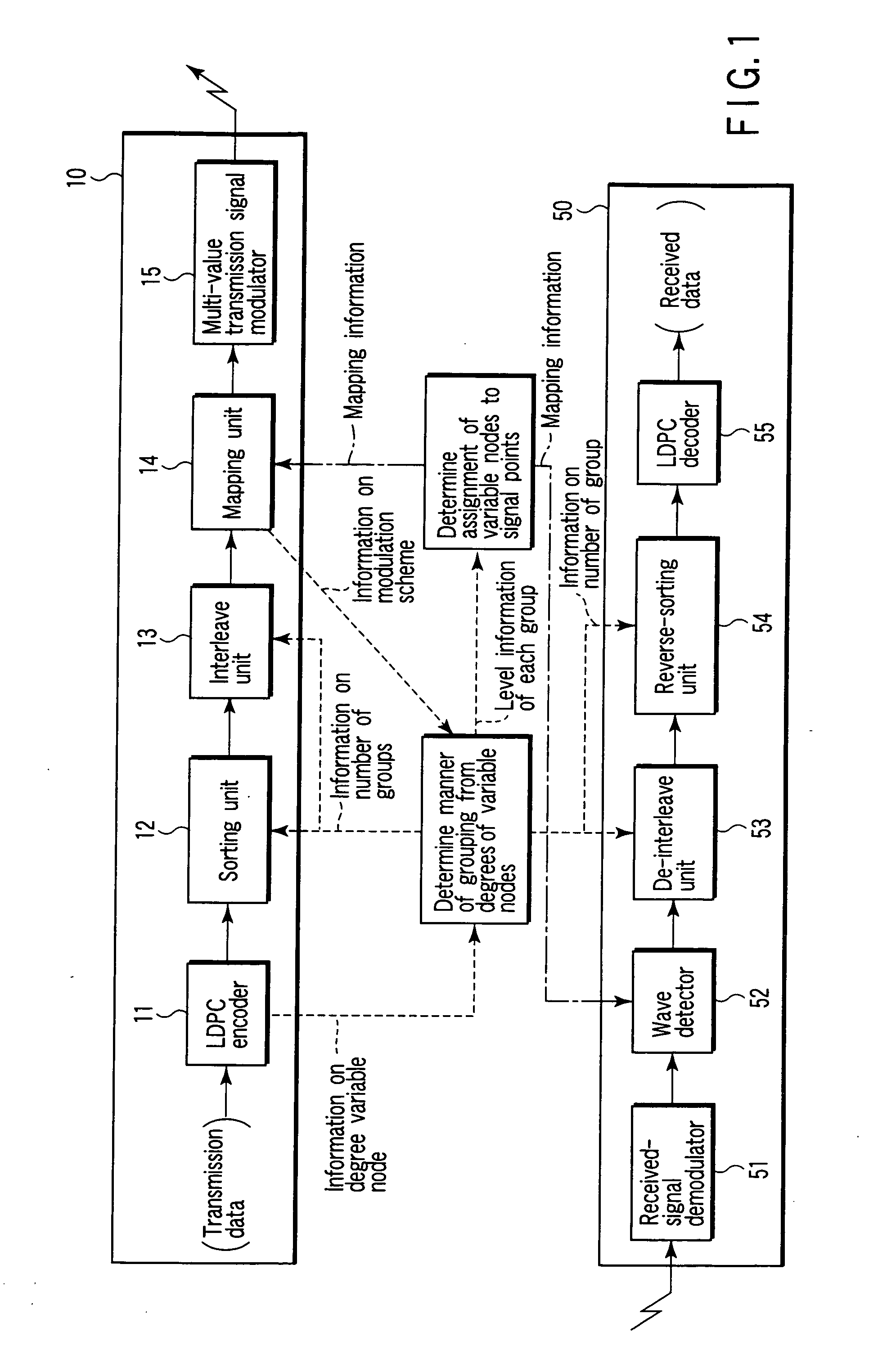

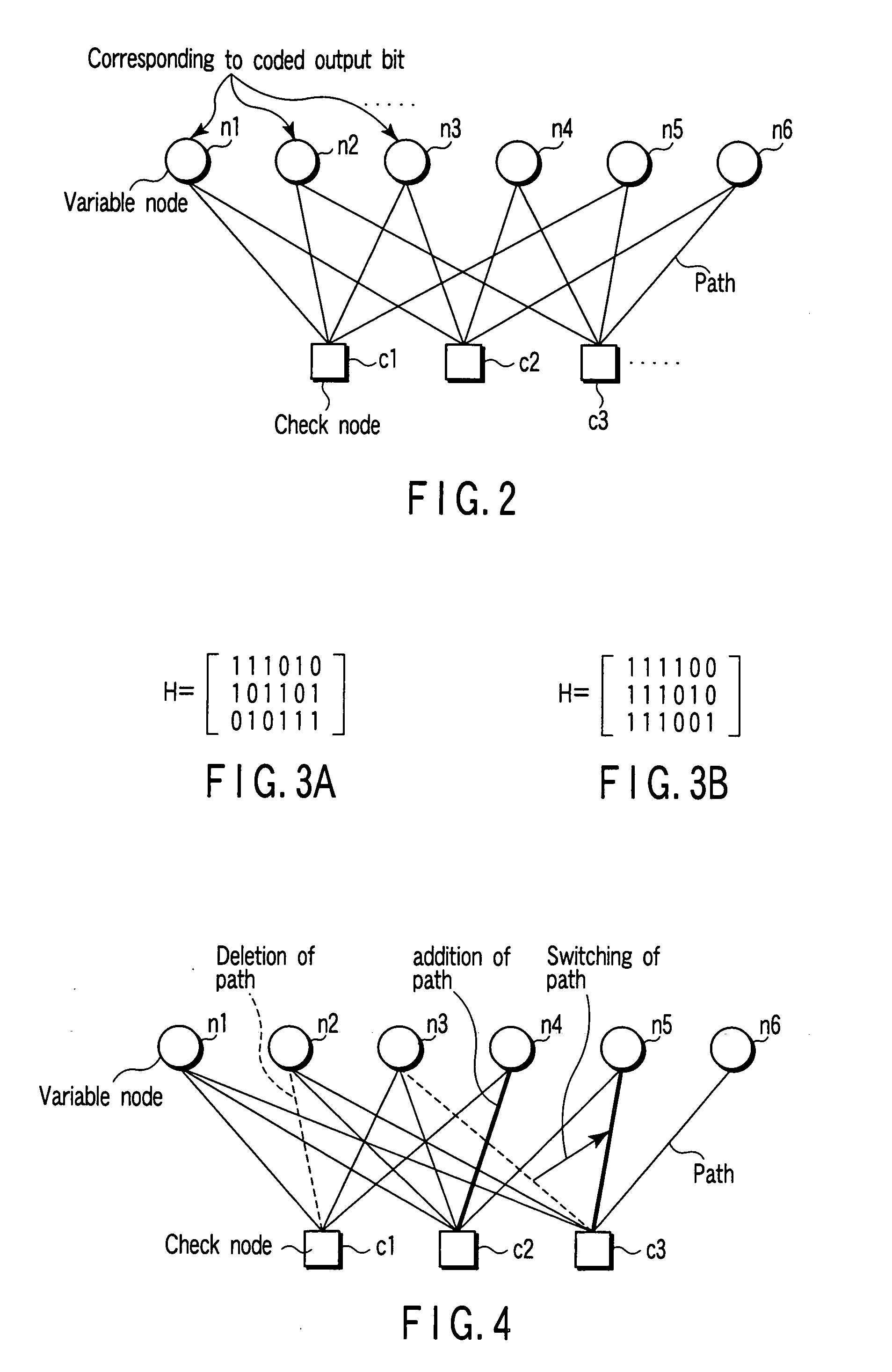

Mapping method for encoded bits using LDPC code, transmitting and receiving apparatuses employing this method, and program for executing this method

InactiveUS20050216821A1Transmission path divisionError correction/detection using LDPC codesTheoretical computer scienceParity-check matrix

A method for mapping of coded bits using a low density parity check (LDPC) code, comprises encoding information bits by using the LDPC code to generate coded bits, sorting the coded bits in accordance with degrees of variable nodes represented by a parity check matrix of the LDPC code, dividing the sorted coded bits into a plurality of groups in accordance with a using modulation scheme, and mapping the coded bits to respective modulation signal points by considering an error resistance of each of the groups and an error resistance of a corresponding one of the modulation signal points.

Owner:KK TOSHIBA

Transmitting apparatus and interleaving method thereof

ActiveUS20150236721A1Improve decoding performanceImprove reception performanceError correction/detection using LDPC codesError correction/detection using multiple parity bitsParity-check matrixLow density

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low density parity check (LDPC) codeword by LDPC encoding based on a parity check matrix; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

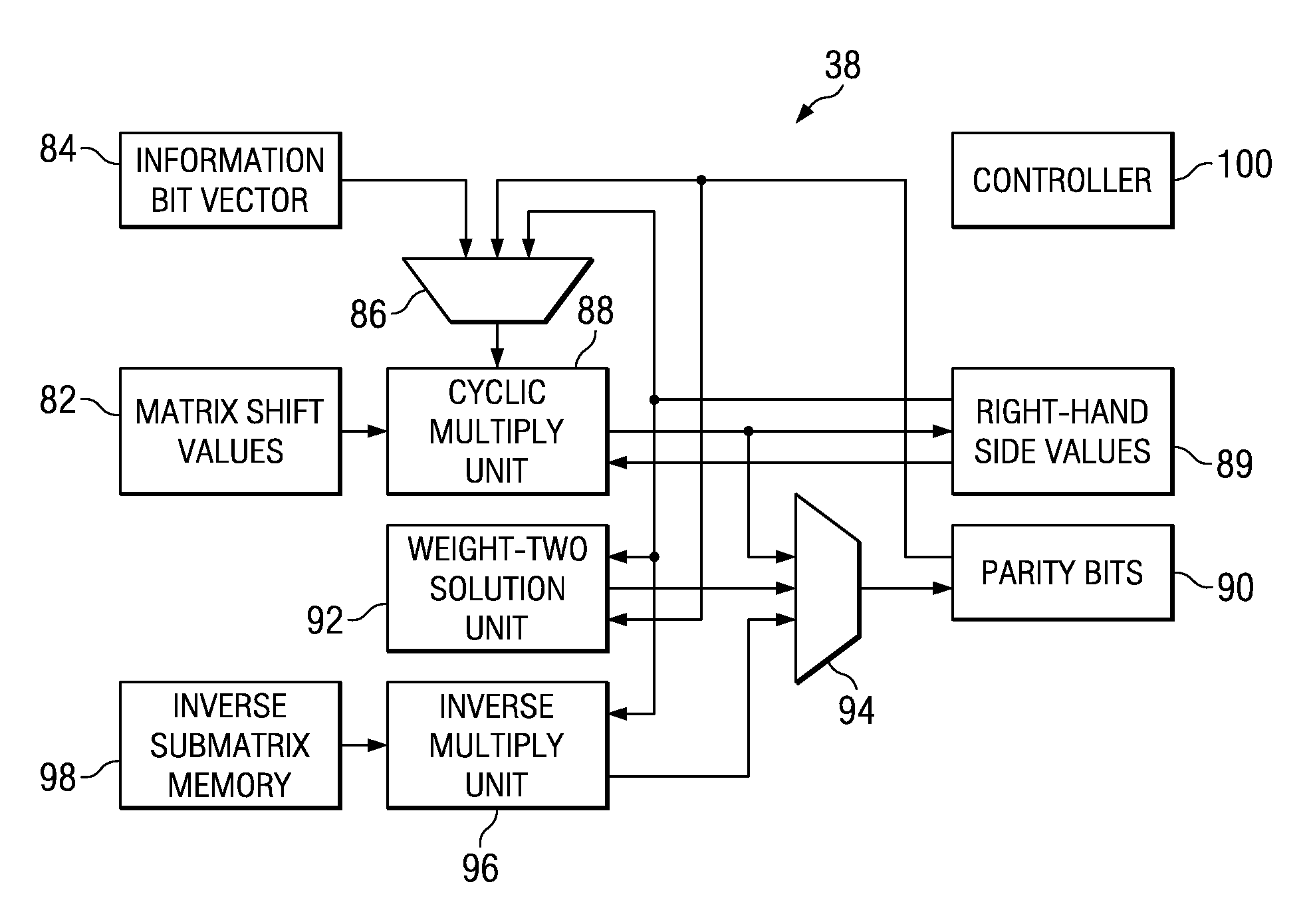

Efficient encoder for low-density-parity-check codes

ActiveUS7162684B2Improve efficiencyLow implementation costError detection/correctionError correction/detection using multiple parity bitsDiagonalParity-check matrix

Encoder circuitry for applying a low-density parity check (LDPC) code to information words is disclosed. The encoder circuitry takes advantage of a macro matrix arrangement of the LDPC parity check matrix in which a left-hand portion of the parity check matrix is arranged as an identity macro matrix, each entry of the macro matrix corresponding to a permutation matrix having zero or more circularly shifted diagonals. The encoder circuitry includes a cyclic multiply unit, which includes a circular shift unit for shifting a portion of the information word according to shift values stored in a shift value memory for the matrix entry, and a bitwise exclusive-OR function for combining the shifted entry with accumulated previous values for that matrix entry. Circuitry for solving parity bits for row rank deficient portions of the parity check matrix is also included in the encoder circuitry.

Owner:TEXAS INSTR INC

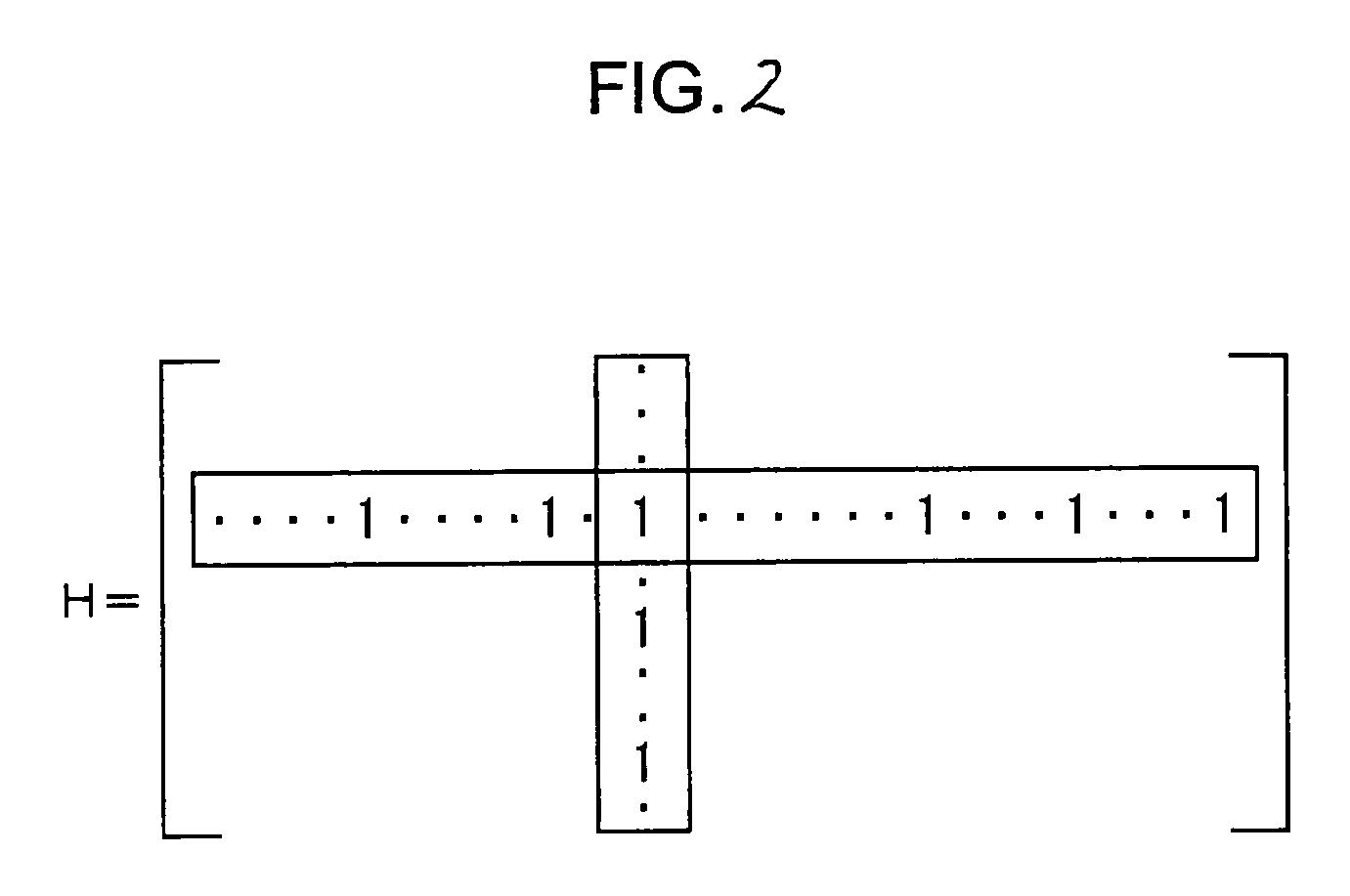

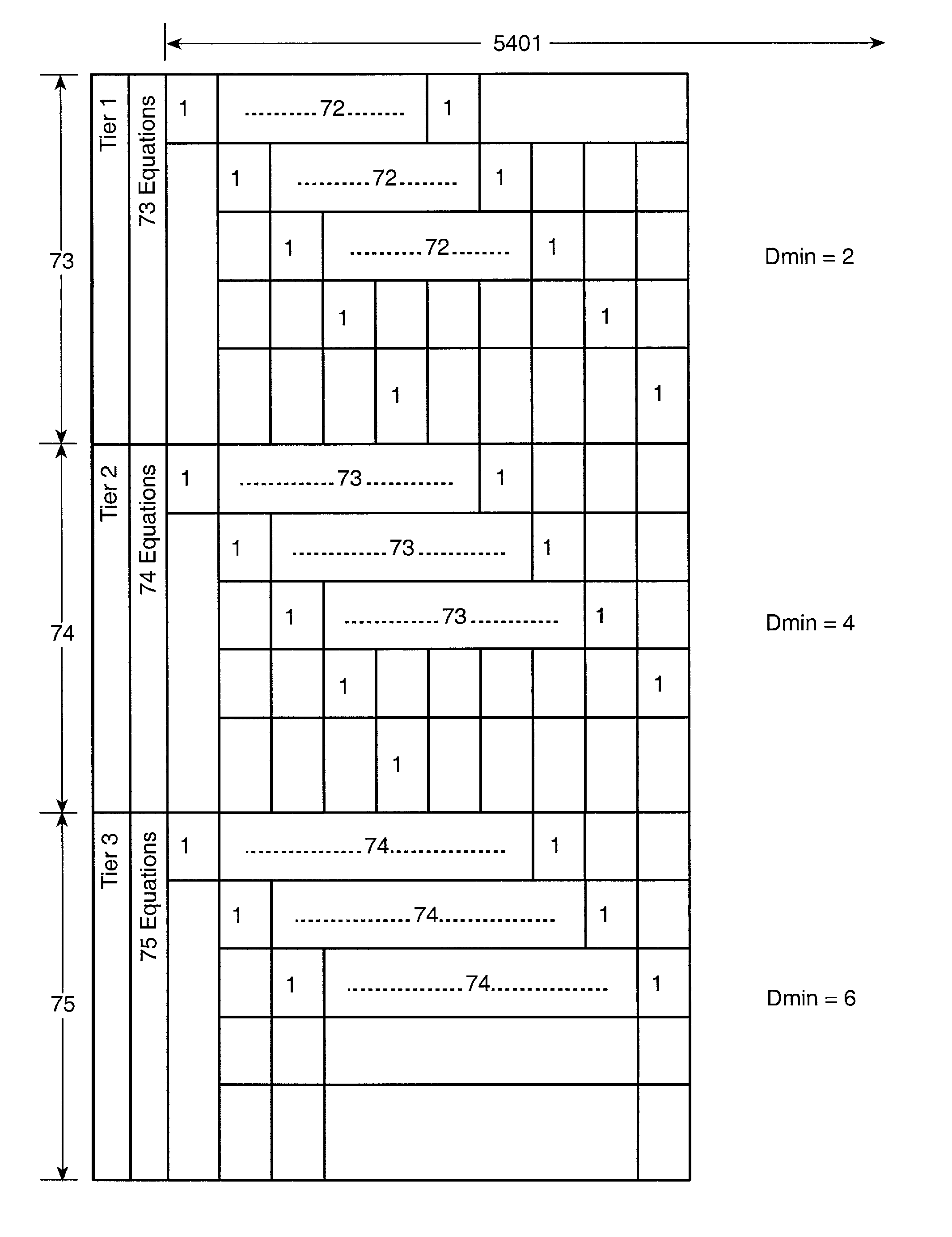

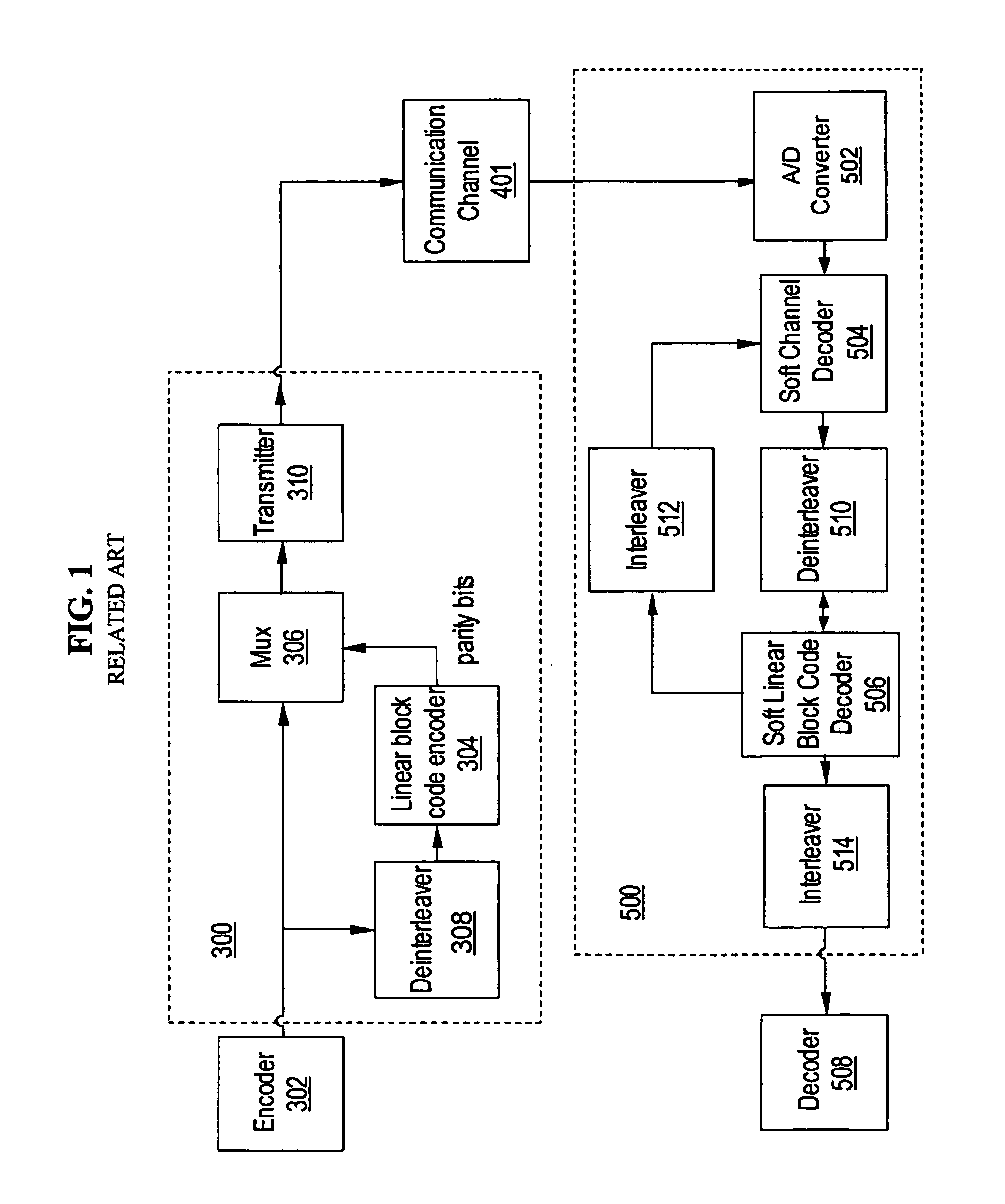

Parity check matrix and method of forming thereof

InactiveUS7000177B1Data representation error detection/correctionError detection/correctionTransfer systemBlock code

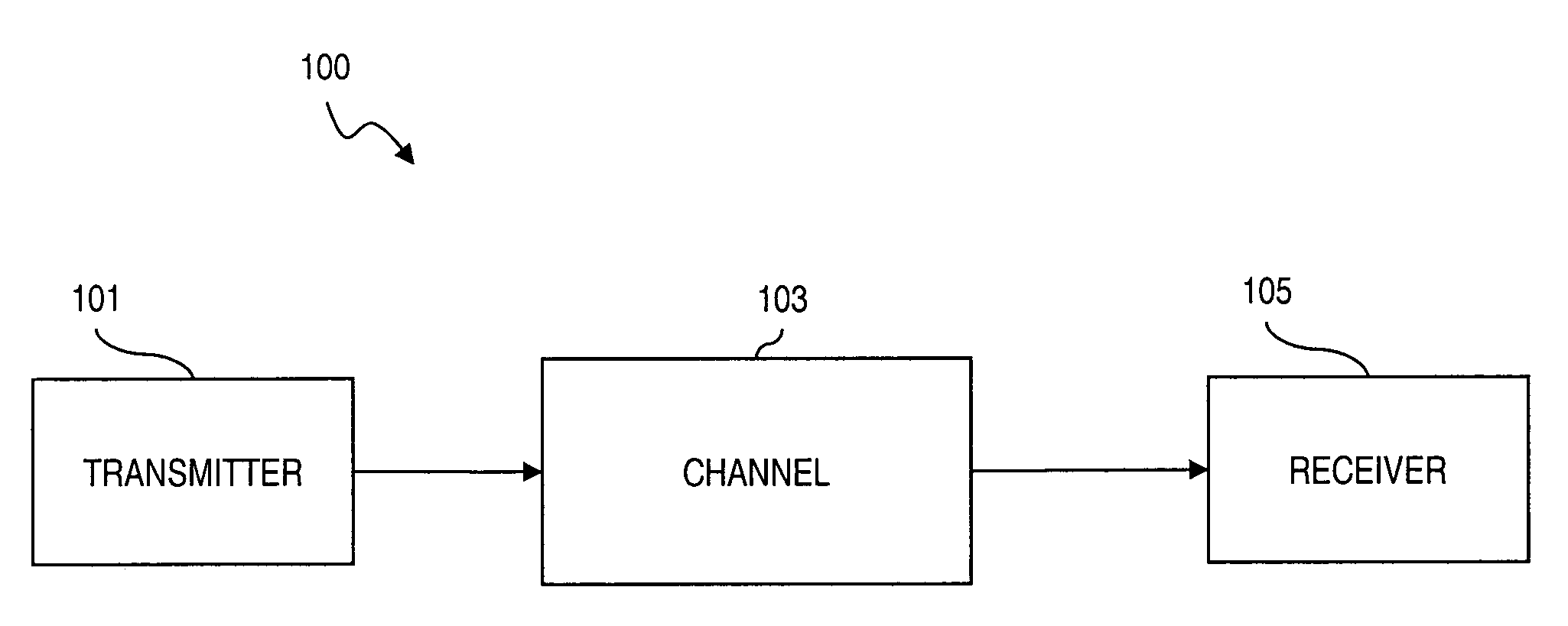

A data transmission system is provided for transmitting user data to and receiving data from a communication channel, including a parity check matrix having M tiers, wherein M≦2, Dmin=2*M for M=1 . . . 3 or 2*M≦Dmin≦6 for M>3, wherein Dmin is the minimum Hamming distance, tc=M, wherein tc is the column weight, and cycle−4=0. A linear block encoder encodes the user data in response to the parity check matrix, and a transmitter transmits an output of the linear block encoder to the communication channel. A soft channel decoder decodes data, and a soft linear block code decoder to decode data decoded by the soft channel decoder in response to the parity check matrix.

Owner:MARVELL ASIA PTE LTD

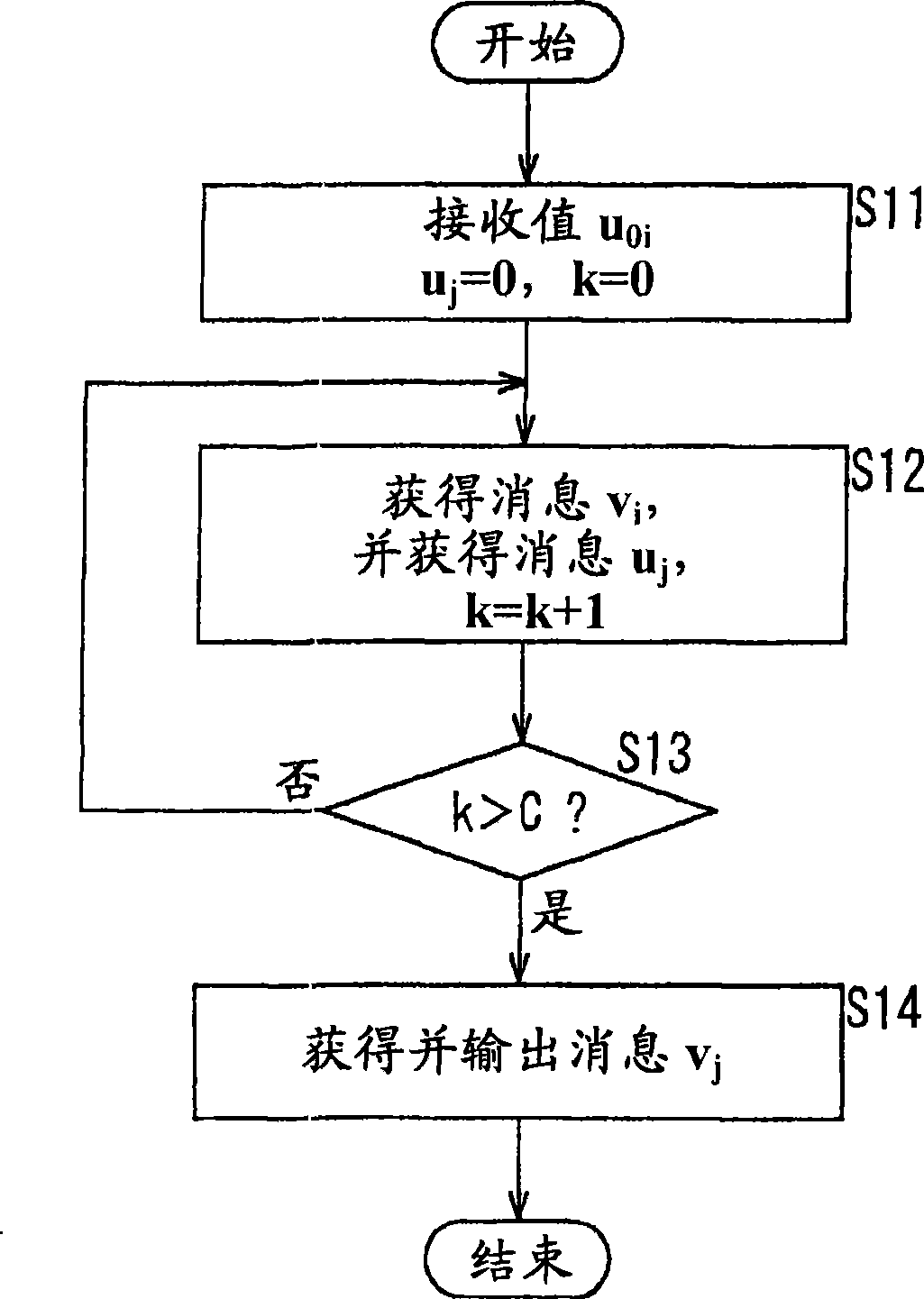

Decoding apparatus for low-density parity-check codes using sequential decoding, and method thereof

InactiveUS20050229087A1Fast convergenceImprove decoding performanceError preventionTransmission systemsComputer hardwareParity-check matrix

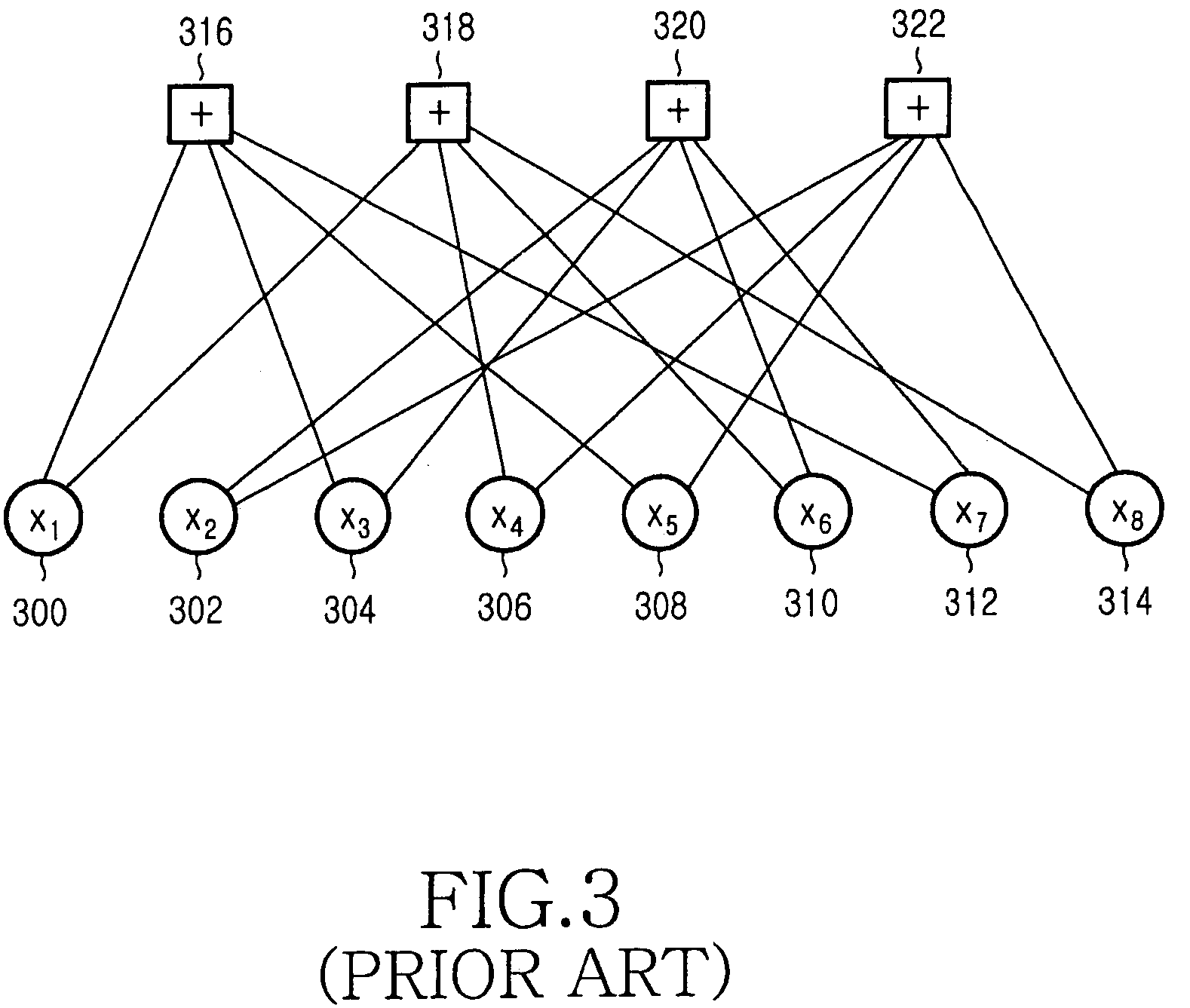

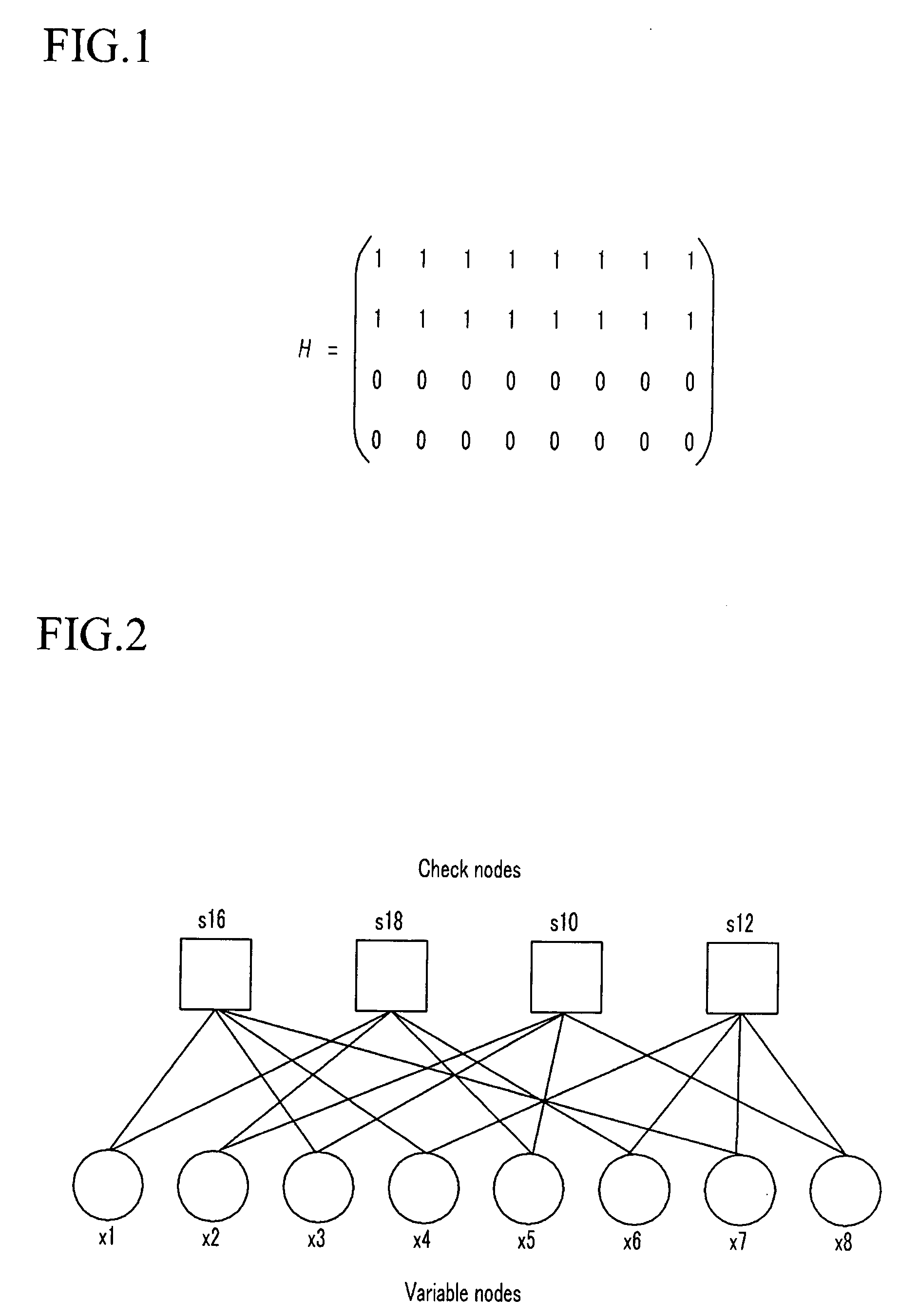

Disclosed is a decoding apparatus for LDPC (Low-Density Parity-Check) codes when receiving data encoded with LDPC codes on a channel having consecutive output values, and a method thereof. The decoding method for LDPC codes uses sequential decoding and includes: (a) dividing nodes into check nodes for a parity-check message and variable nodes for a bit message according to a parity-check matrix; (b) dividing the check nodes into a predetermined number of subsets; (c) sequentially decoding the LDPC codeword of each subset for all the check nodes; (d) generating an output message for verifying validity of the decoding result; and (e) iteratively performing the steps (b), (c), and (d) by a predetermined number of iterations.

Owner:ELECTRONICS & TELECOMM RES INST

Layered low density parity check decoding for digital communications

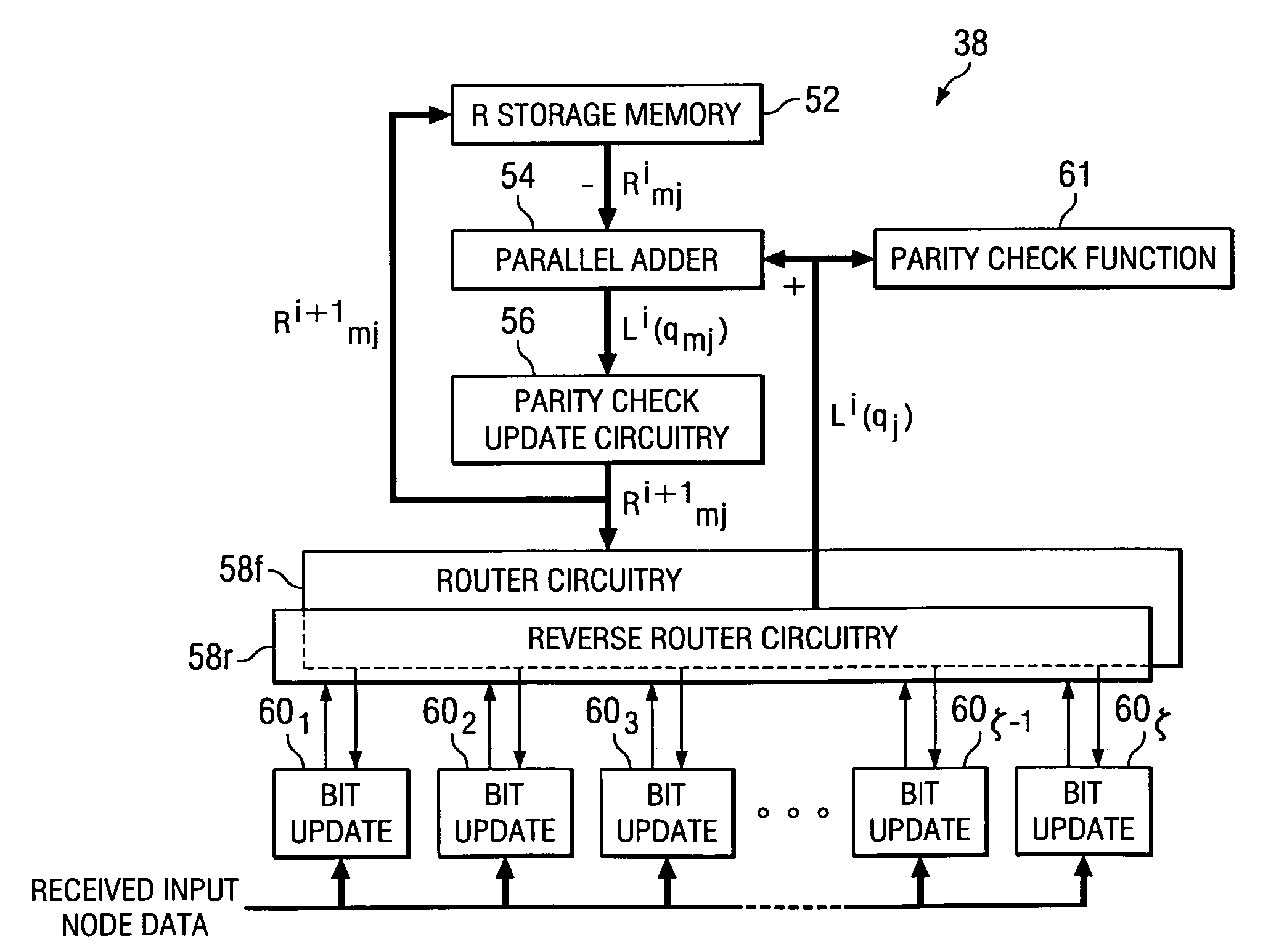

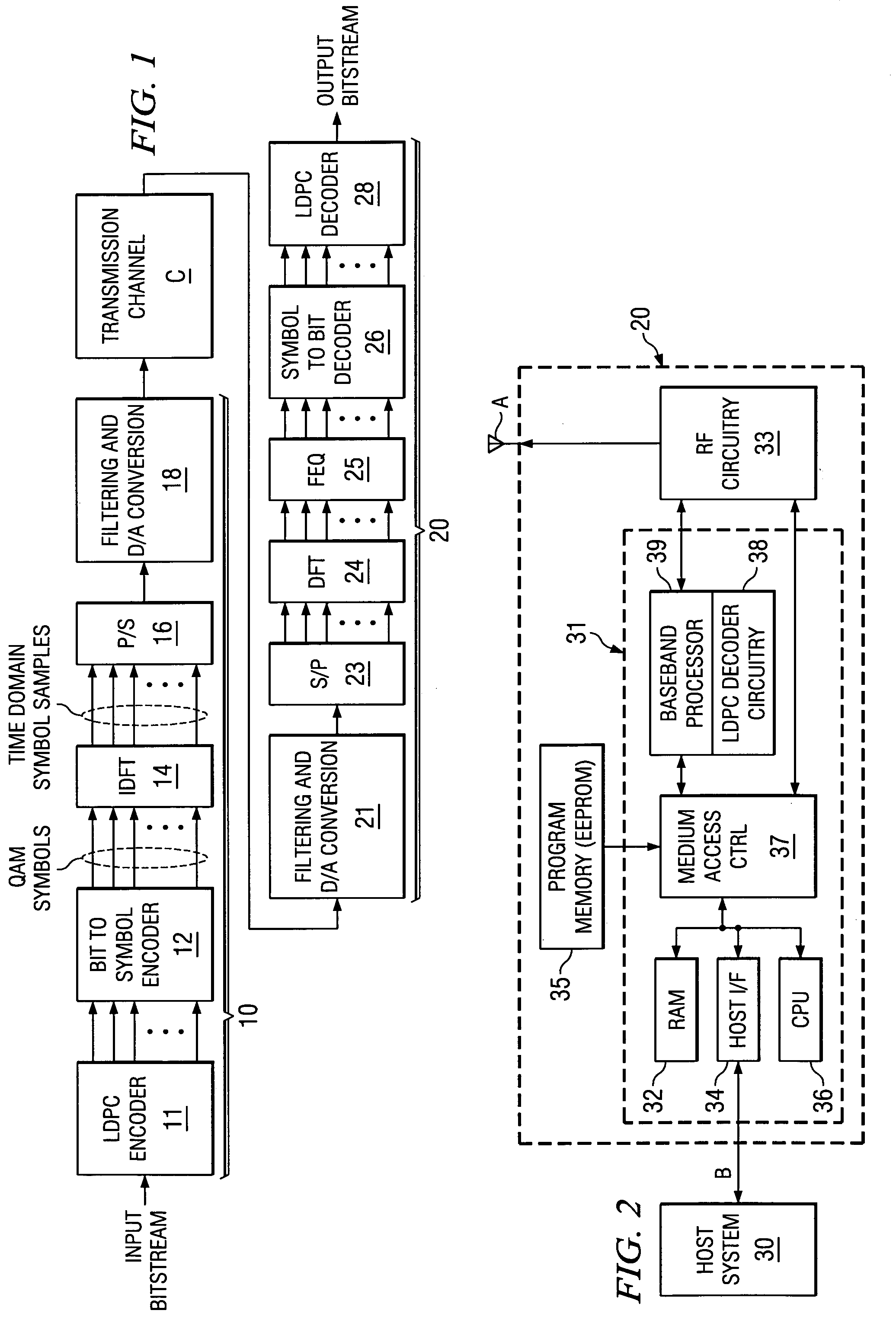

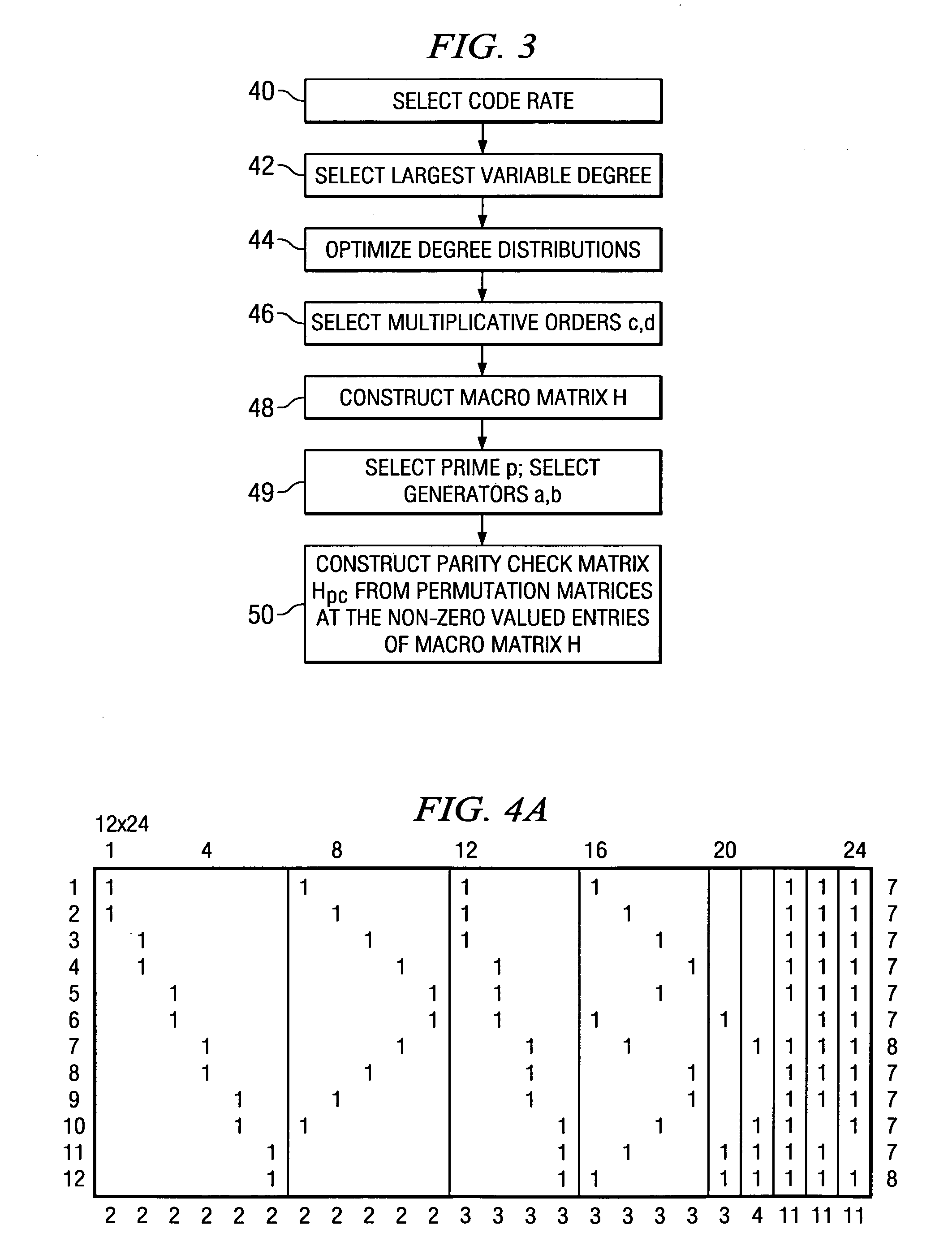

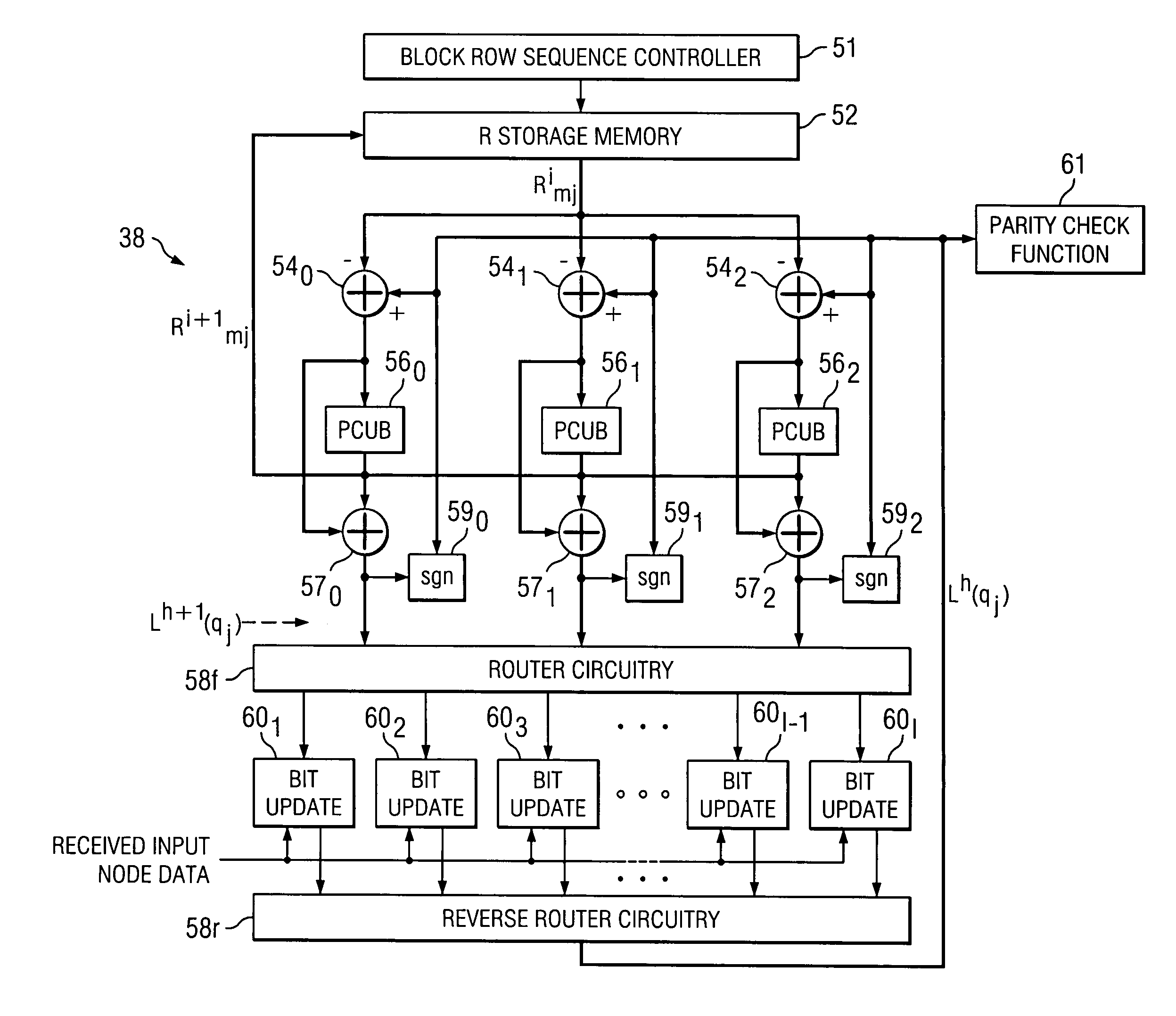

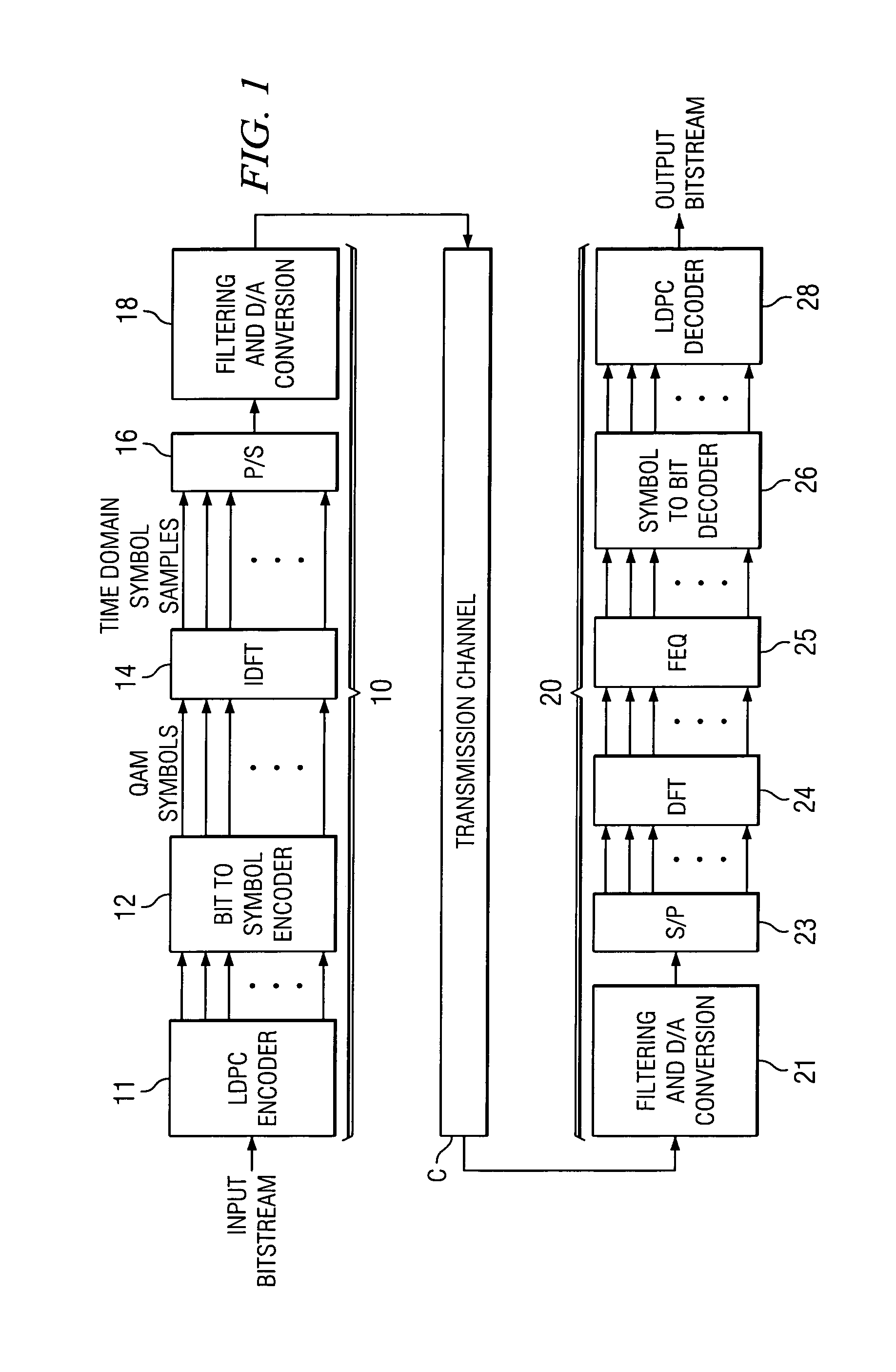

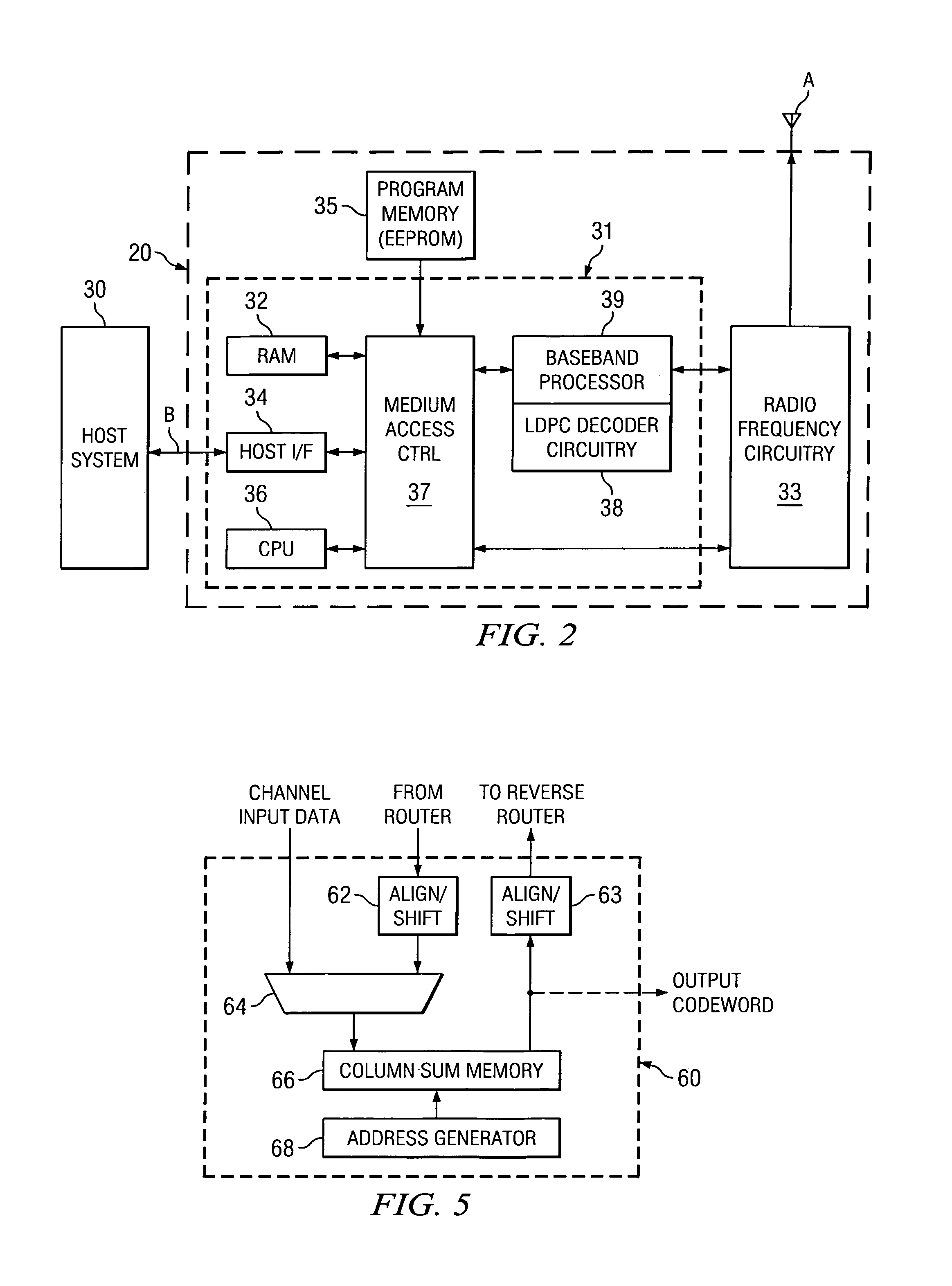

ActiveUS7139959B2Efficient implementationMost efficientError preventionError detection/correctionParity-check matrixTheoretical computer science

A low density parity check (LDPC) code that is particularly well adapted for hardware implementation of a belief propagation decoder circuit (38) is disclosed. The LDPC code is arranged as a parity check matrix (H) whose rows and columns represent check sums and input nodes, respectively. The parity check matrix is grouped into subsets of check sum rows, in which the column weight is a maximum of one. The decoder circuitry includes a parity check value estimate memory (52). Adders (54) generate extrinsic estimates, from immediately updated input node probability estimates, and the extrinsic estimates are applied to parity check update circuitry (56) for generating new parity check sum value estimates. These parity check sum value estimates are stored back into the memory (52), and after addition with the extrinsic estimates, are stored in a column sum memory (66) of a corresponding bit update circuit (60) as updated probability values for the input nodes.

Owner:TEXAS INSTR INC

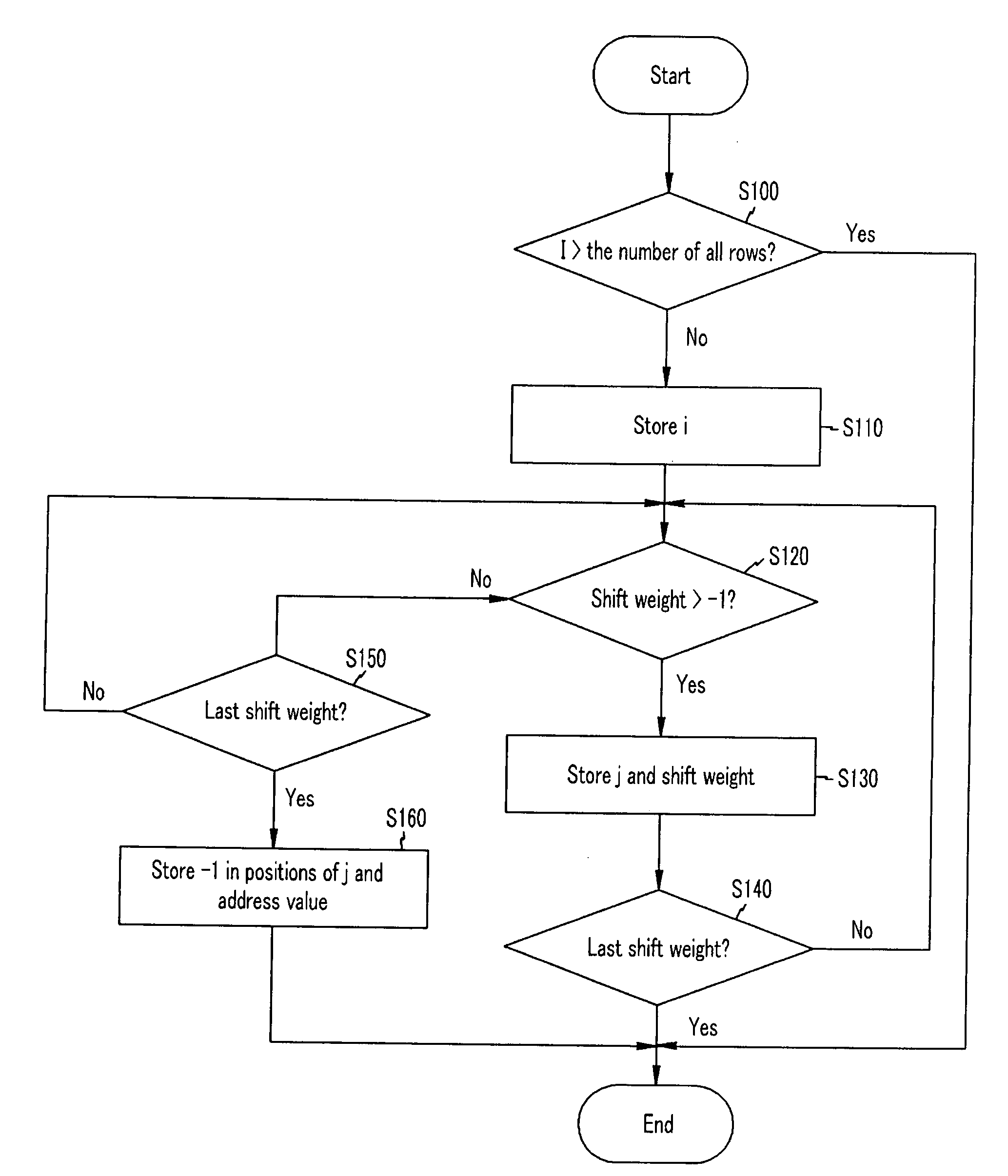

Parity check matrix storing method, block LDPC coding method, and apparatus using parity check matrix storing method

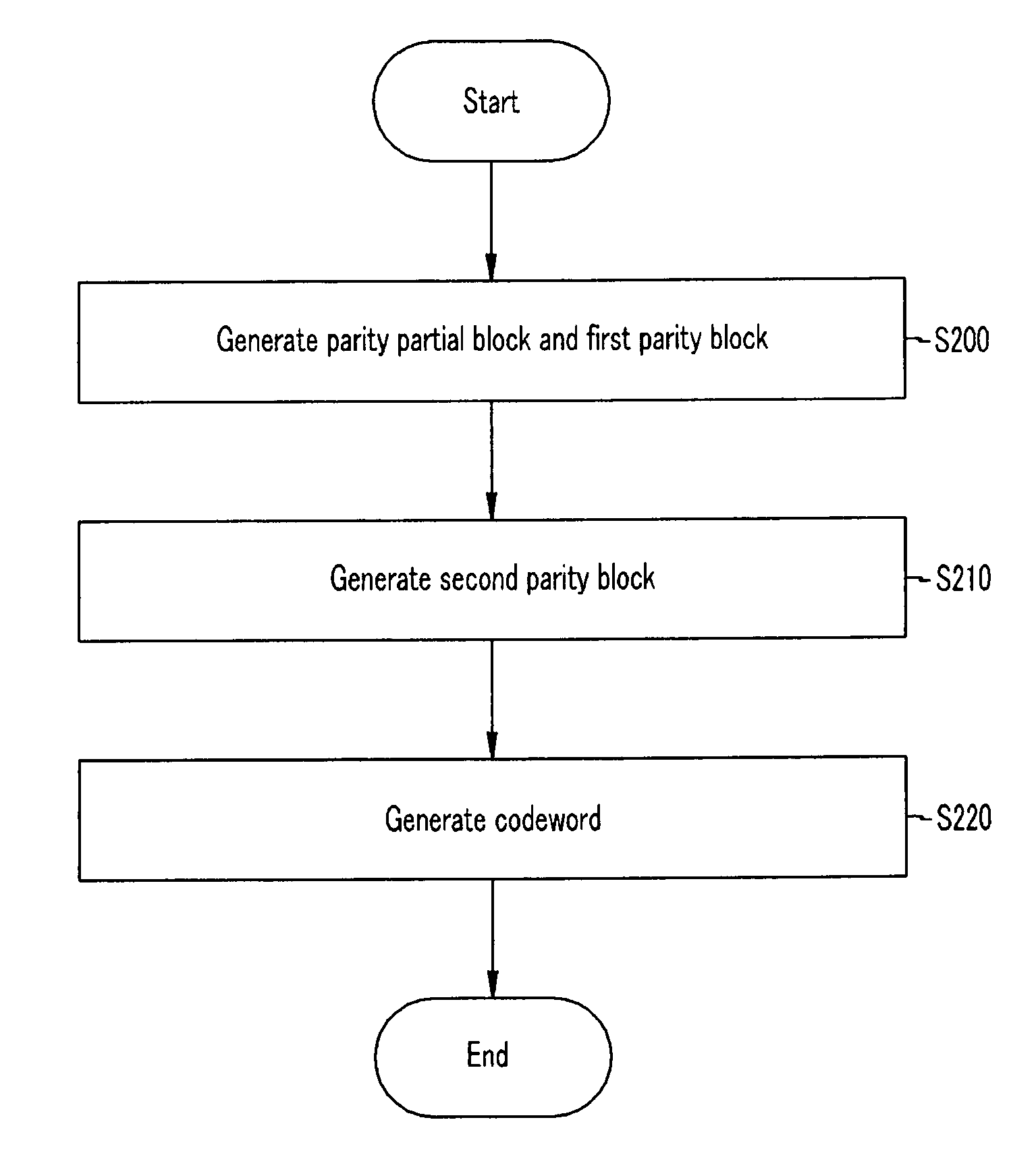

ActiveUS8190967B2Low density parity check (LDPC)Minimize complexityError detection/correctionError coding/decoding sychronisationParity-check matrixTheoretical computer science

The present invention relates to a low density parity check (LDPC) encoding method and an apparatus thereof. In the LDPC encoding method, a matrix multiplication corresponding to ET−1 and T−1 is eliminated according to a structural characteristic in an encoding process. Accordingly, shift weights that are not −1 among shift weights corresponding to partial blocks A, B, and C of a parity check matrix are used to perform an encoding operation, and a cyclic shift operation of an information unit block is performed in parallel so that a first parity block and a second parity block may be simultaneously generated.

Owner:ELECTRONICS & TELECOMM RES INST +1

Apparatus and method for coding and decoding semi-systematic block low density parity check codes

ActiveUS20050283709A1Coding complexityError preventionError detection/correctionParity-check matrixTheoretical computer science

An apparatus and method for coding a semi-systematic block low density parity check (LDPC) code in which an information word is received and coded into a codeword including the information word, a first parity, a second parity, and a third parity, based on one of a first parity check matrix and a second parity check matrix, depending on a size to be applied when generating the information word into a semi-systematic block LDPC code. A part having a degree being at least equal to a predetermined degree is punctured from the information word, generating the semi-systematic block LDPC code. The semi-systematic block LDPC code includes the information word, the part of which was punctured, the first parity, the second parity, and the third parity.

Owner:POSTECH ACAD IND FOUND

Method and apparatus of encoding and decoding data using low density parity check code in a wireless communication system

InactiveUS20050289437A1Error correction/detection using multiple parity bitsCode conversionCommunications systemParity-check matrix

A method of encoding data using low density parity check (LDPC) code defined by a m×n parity check matrix is disclosed. More specifically, the method includes encoding input source data using the parity check matrix, wherein the parity check matrix comprises a plurality of z×z sub-matrices of which row weights and column weights are ‘0’ or ‘1’.

Owner:LG ELECTRONICS INC

Apparatus and method for encoding and decoding block low density parity check codes with a variable coding rate

ActiveUS20050283708A1Coding complexityImprove resource efficiencyError correction/detection using multiple parity bitsCode conversionTheoretical computer scienceParity-check matrix

An apparatus and method for coding a block Low Density Parity Check (LDPC) code having a variable coding rate. The apparatus receives an information word and encodes the information word into a block LDPC code based on one of a first parity check matrix and a second parity check matrix, depending on a coding rate to be applied when generating the information word into the block LDPC code.

Owner:POSTECH ACAD IND FOUND

Parity check matrix storing method, block LDPC coding method, and apparatus using parity check matrix storing method

ActiveUS20080140686A1Minimize complexityReducing requiredDigital data processing detailsError detection/correctionTheoretical computer scienceParity-check matrix

The present invention relates to a low density parity check (LDPC) encoding method and an apparatus thereof. In the LDPC encoding method, a matrix multiplication corresponding to ET−1 and T−1 is eliminated according to a structural characteristic in an encoding process. Accordingly, shift weights that are not −1 among shift weights corresponding to partial blocks A, B, and C of a parity check matrix are used to perform an encoding operation, and a cyclic shift operation of an information unit block is performed in parallel so that a first parity block and a second parity block may be simultaneously generated.

Owner:ELECTRONICS & TELECOMM RES INST +1

Transmitting apparatus and interleaving method thereof

ActiveUS20150341053A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError correction/detection using LDPC codesParity-check matrixLow density

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding of input bits based on a parity check matrix including information word bits and parity bits, the LDPC codeword including a plurality of bit groups each including a plurality of bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the interleaver is further configured to interleave the LDPC codeword such that a bit included in a predetermined bit group from among the plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and system for decoding low density parity check codes

ActiveUS8392789B2Data representation error detection/correctionOther error detection/correction/protectionGraphicsData stream

A method for decoding a codeword in a data stream encoded according to a low density parity check (LDPC) code having an m×j parity check matrix H by initializing variable nodes with soft values based on symbols in the codeword, wherein a graph representation of H includes m check nodes and j variable nodes, and wherein a check node m provides a row value estimate to a variable node j and a variable node j provides a column value estimate to a check node m if H(m,j) contains a 1, computing row value estimates for each check node, wherein amplitudes of only a subset of column value estimates provided to the check node are computed, computing soft values for each variable node based on the computed row value estimates, determining whether the codeword is decoded based on the soft values, and terminating decoding when the codeword is decoded.

Owner:TEXAS INSTR INC

Method and apparatus for encoding and decoding channel in a communication system using low-density parity-check codes

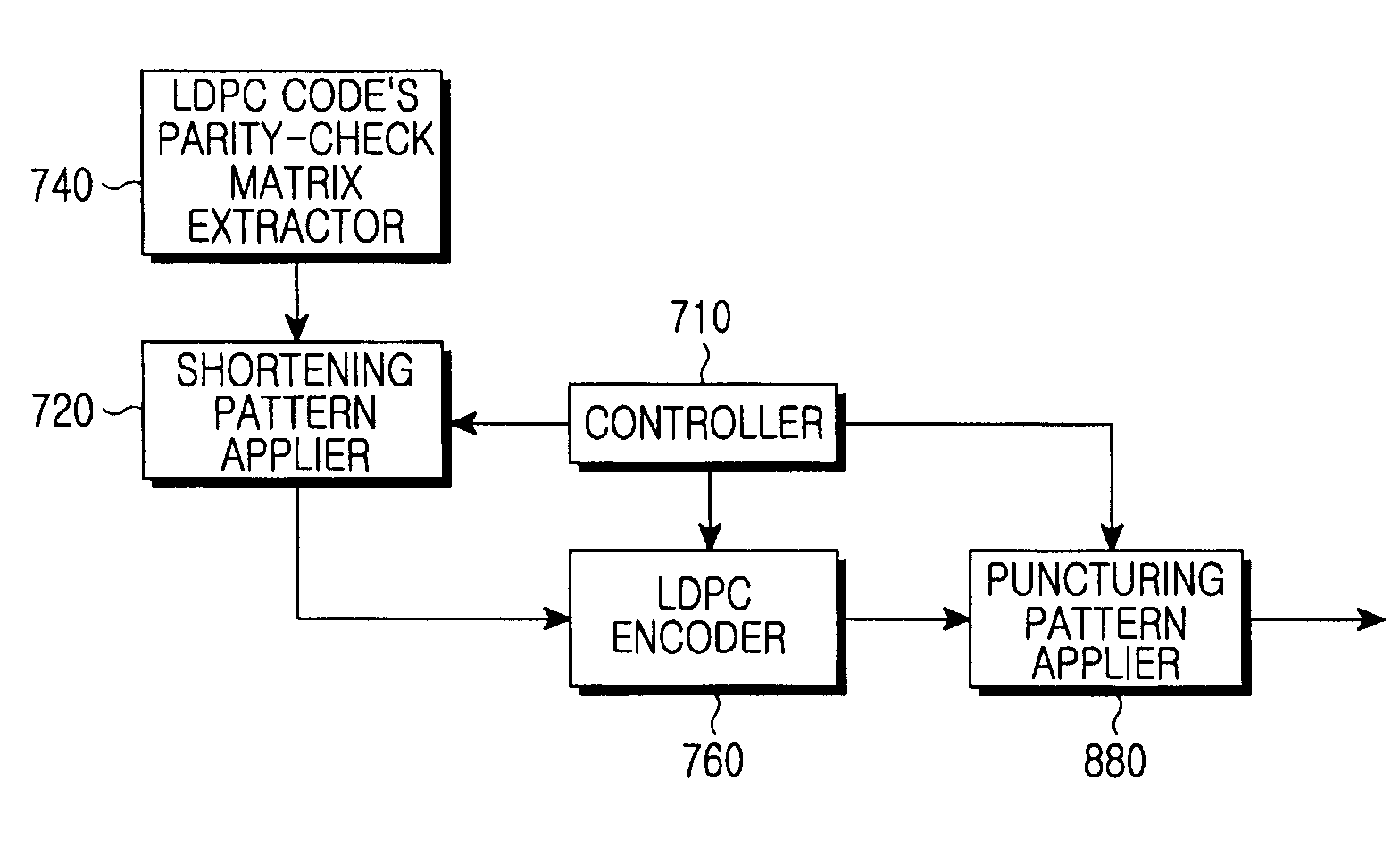

ActiveUS20090158129A1Improve performanceCode conversionCyclic codesCommunications systemParity-check matrix

A method for encoding a channel in a communication system using a Low-Density Parity-Check (LDPC) code. The method includes generating a plurality of column groups by grouping (categorizing) columns corresponding to an information word in a parity-check matrix of the LDPC code, and ordering the column groups; determining a range of an information word desired to be obtained by performing shortening; based on the determined range of the information word, performing column group-by-column group shortening on the column groups in order according to a predetermined shortening pattern; and LDPC encoding the shortened information word.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Algebraic low-density parity check code design for variable block sizes and code rates

InactiveUS7260763B2Readily implemented in hardwareHigher code rate parityError detection/correctionError correction/detection using multiple parity bitsVariable-length codeSignal-to-noise ratio (imaging)

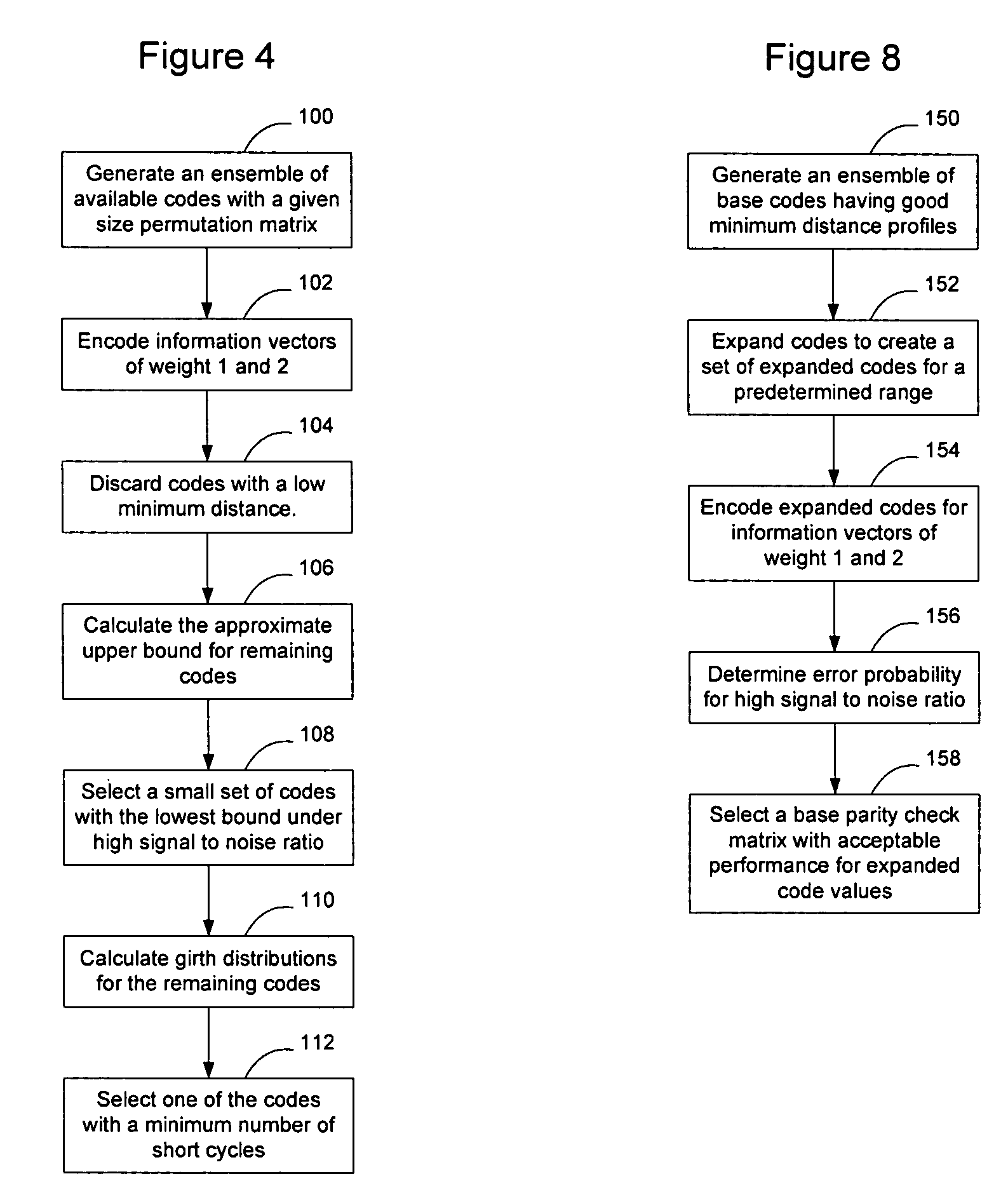

A higher code rate Low-Density Parity Check (LDPC) matrix may be designed by concatenating additional matrices to a π-rotation parity check matrix. The concatenated matrix may be selected such that the resultant LDPC matrix exhibits good expansion characteristics to enable the LDPC matrix to be used with variable block length codes. The codes may be designed by generating an ensemble of available codes, encoding them with information vectors of weight 1 and 2 and discarding codes with a low minimum distance. The approximate upper bounds for the remaining codes are then calculated and a small set of codes with the lowest bound under high signal to noise ratio is selected. The girth distributions for the remaining codes are then calculated and the code that has the minimum number of short cycles is selected. The selected code is concatenated to the original π-rotation parity check matrix.

Owner:MICROSOFT TECH LICENSING LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com