Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

634results about "Error correction/detection using LDPC codes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

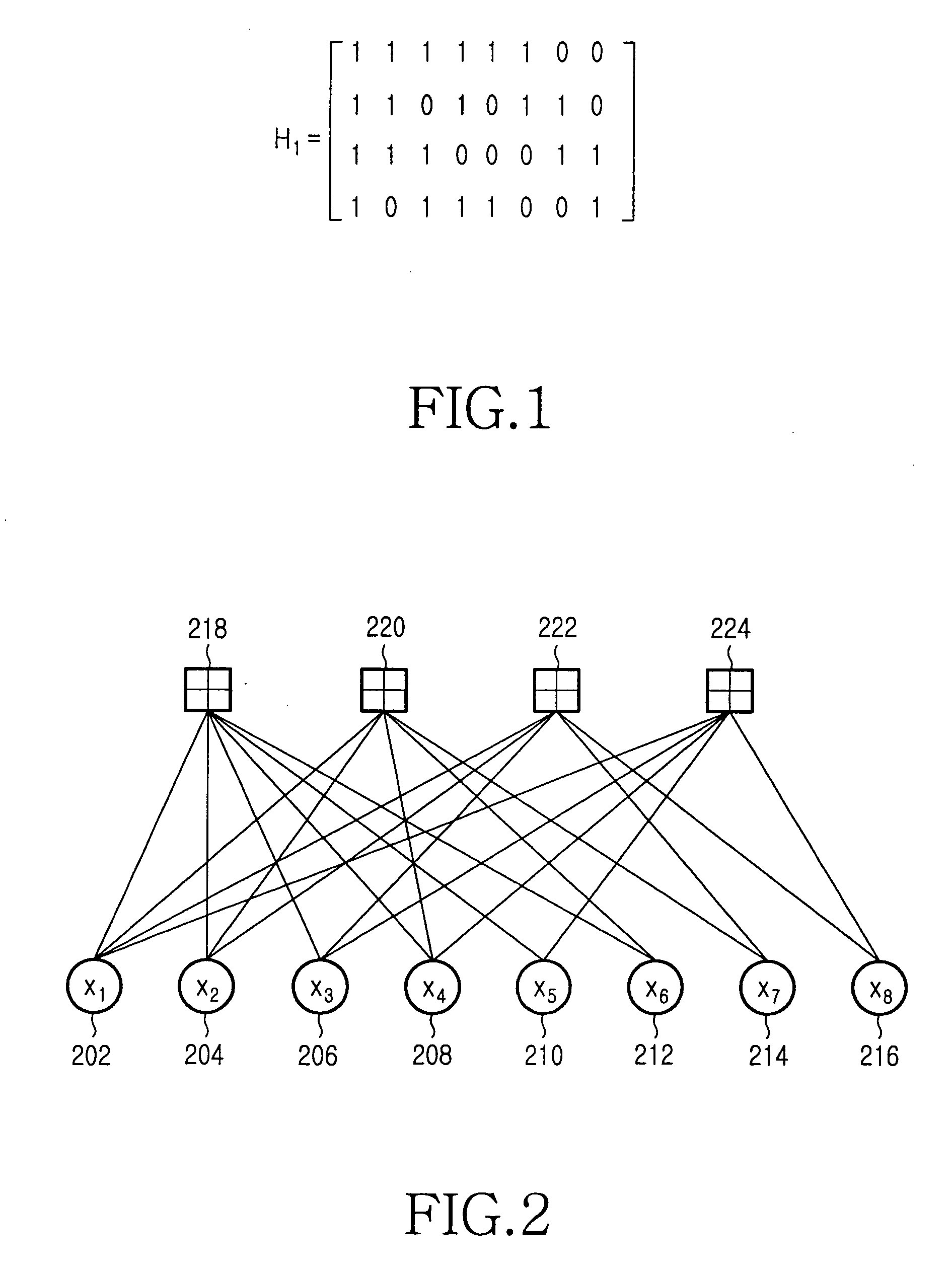

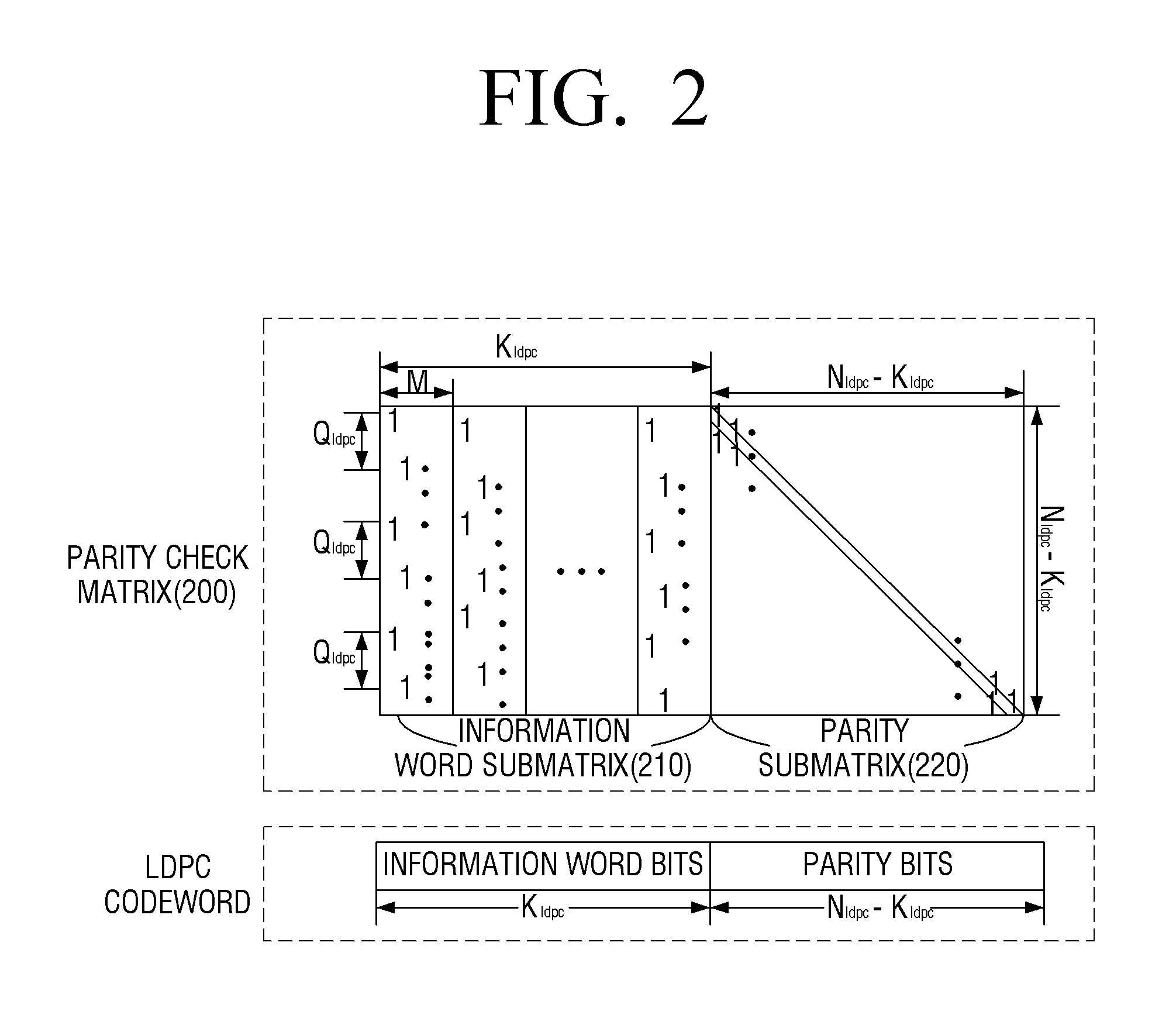

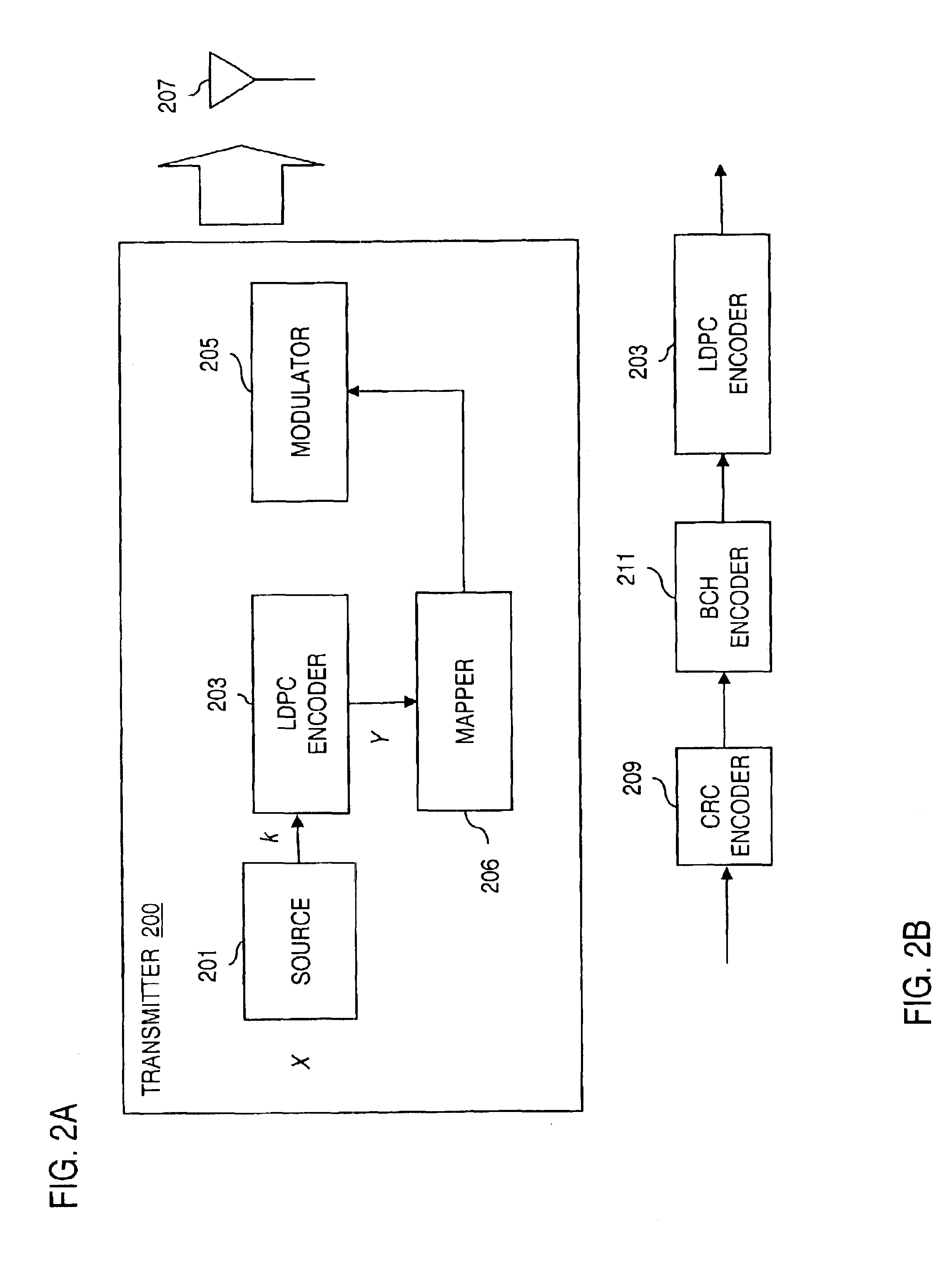

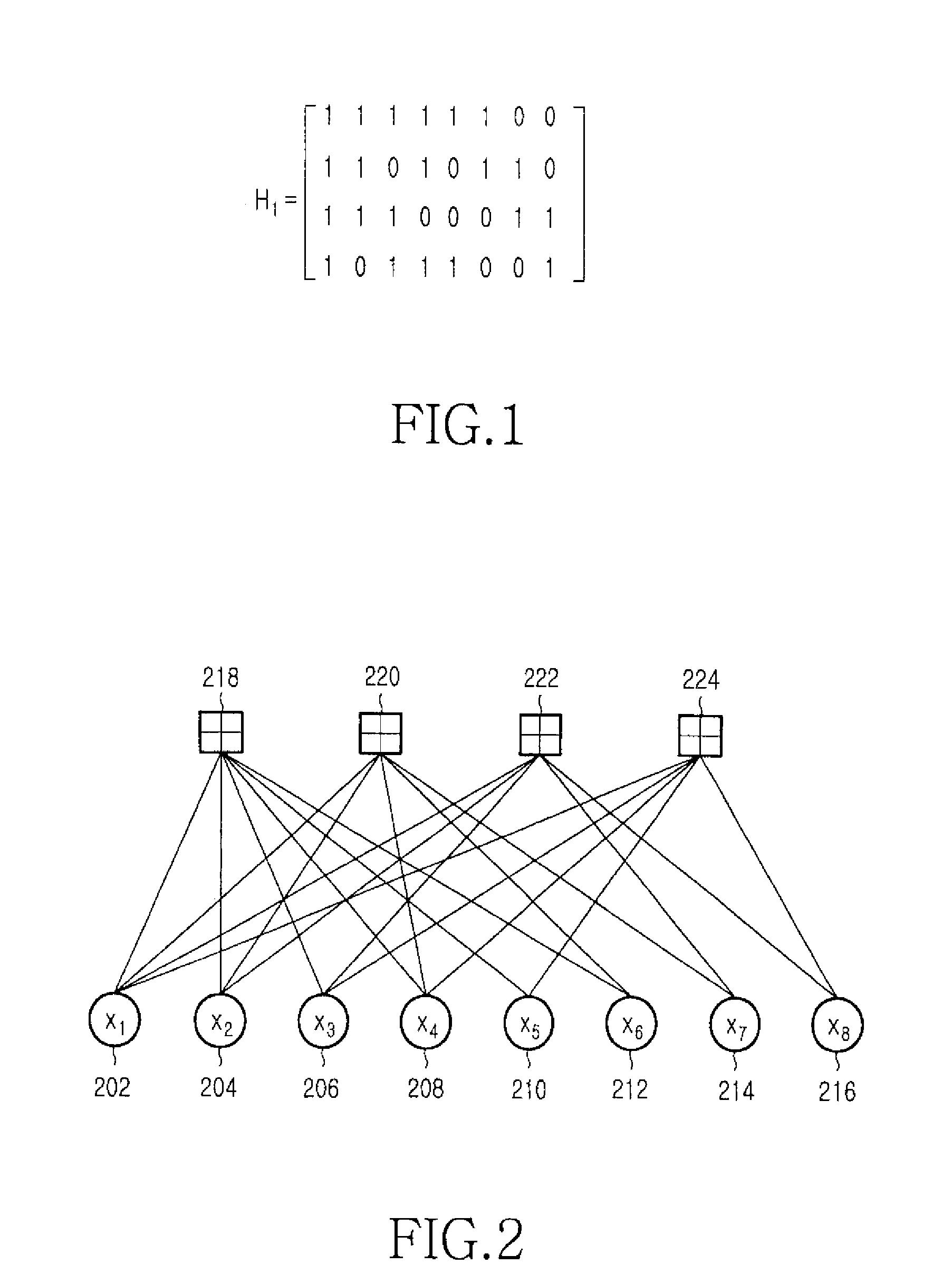

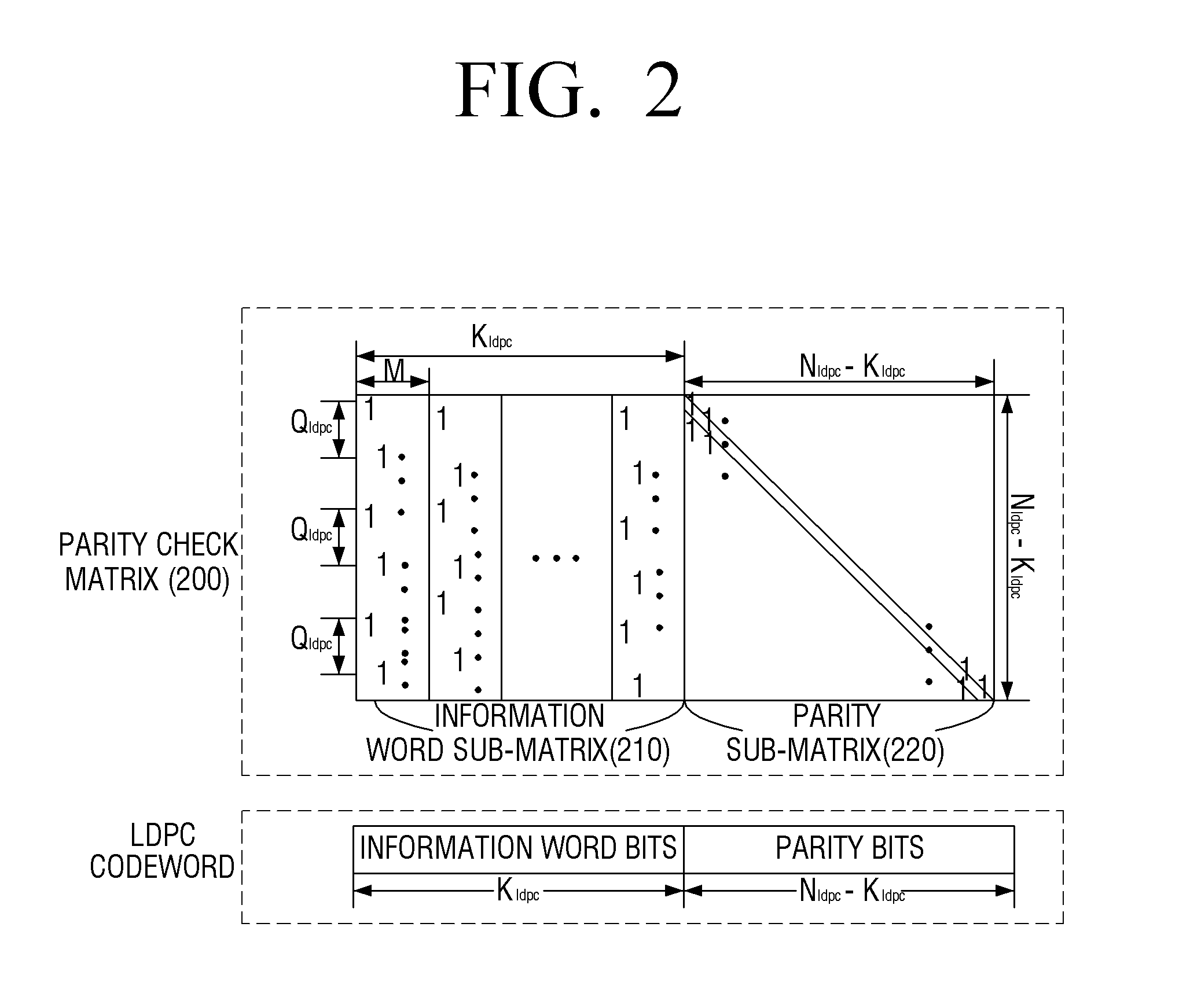

Method and apparatus for low density parity check encoding of data

InactiveUS6895547B2Improve performanceError preventionError detection/correctionTheoretical computer scienceParity-check matrix

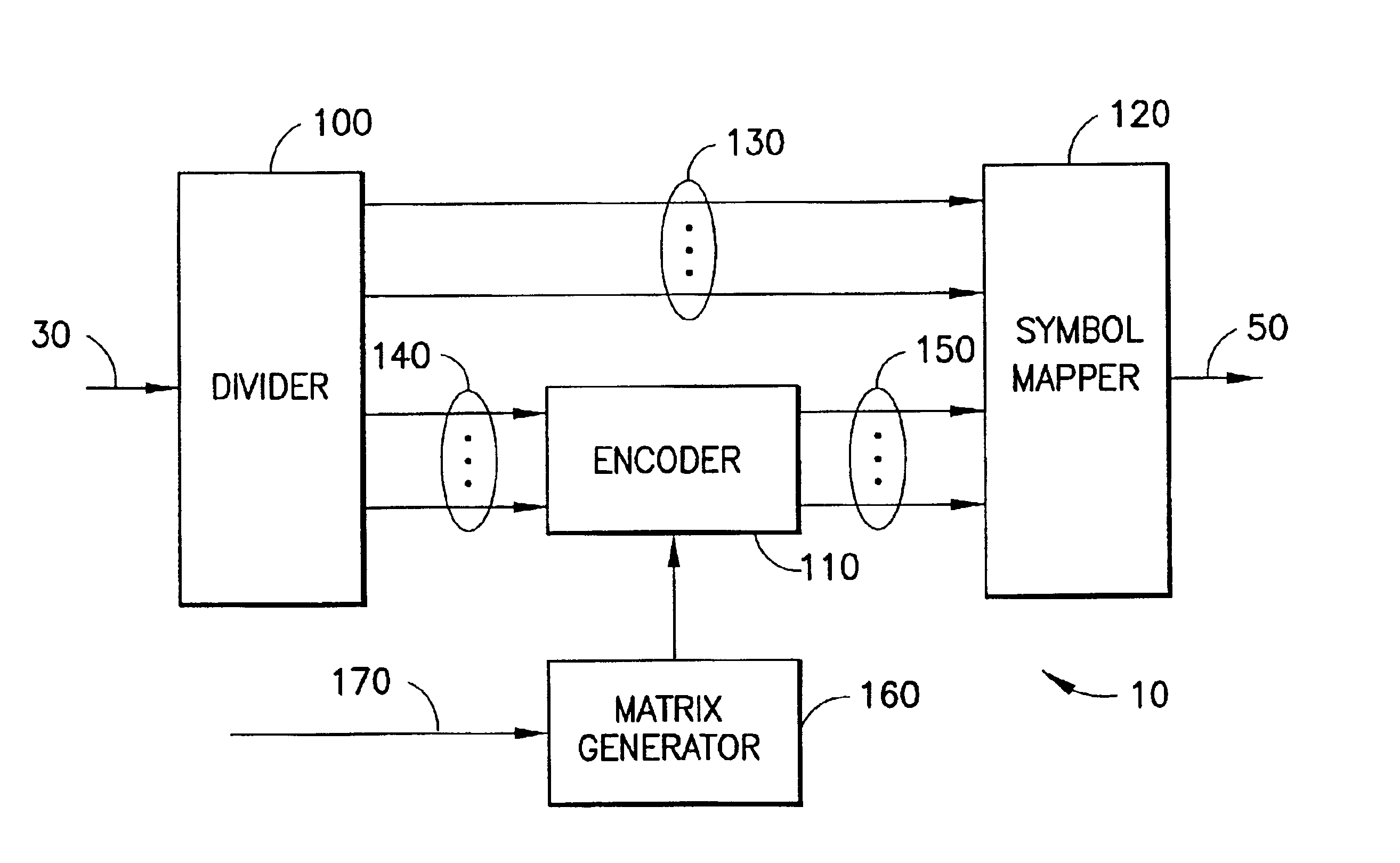

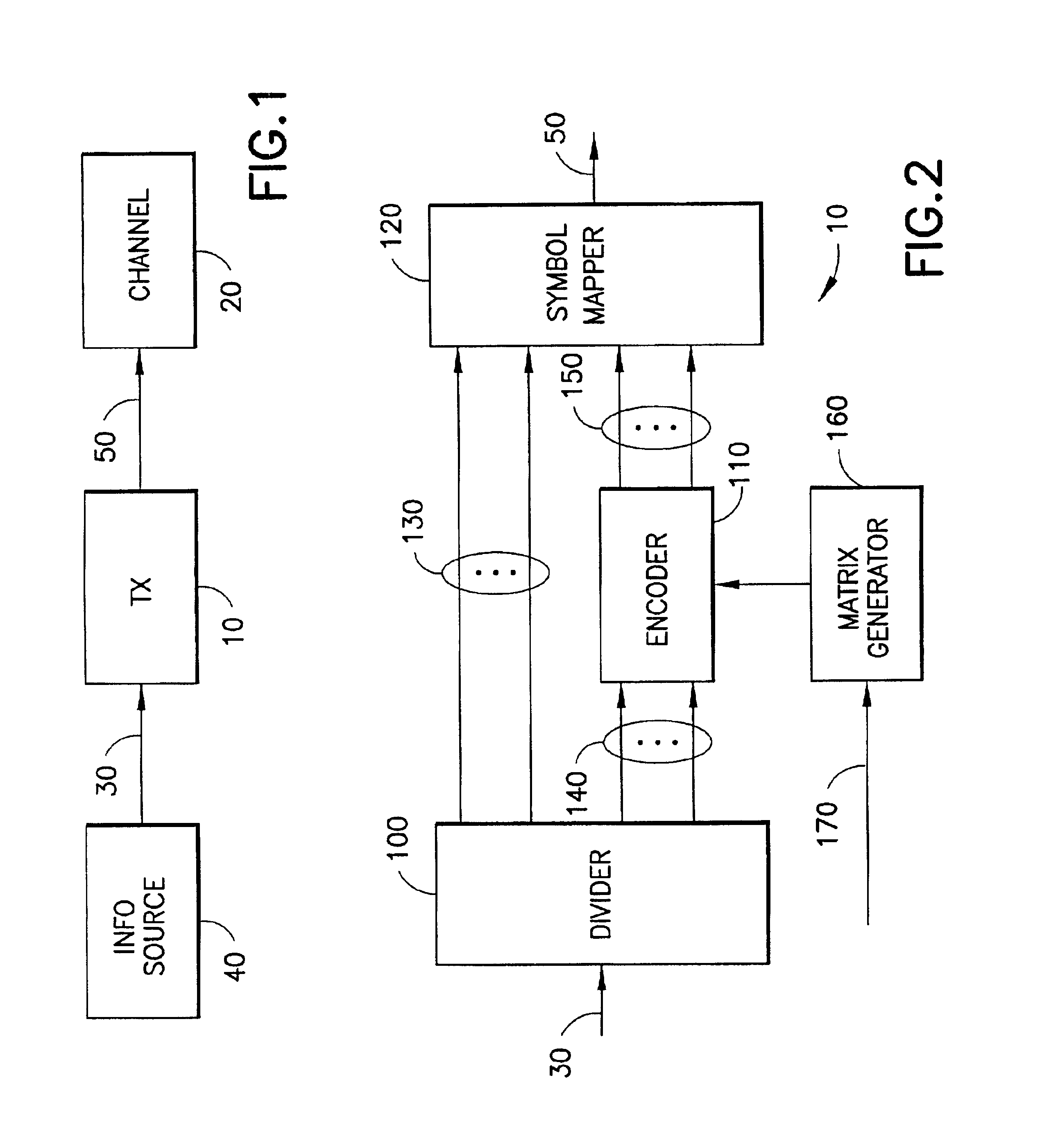

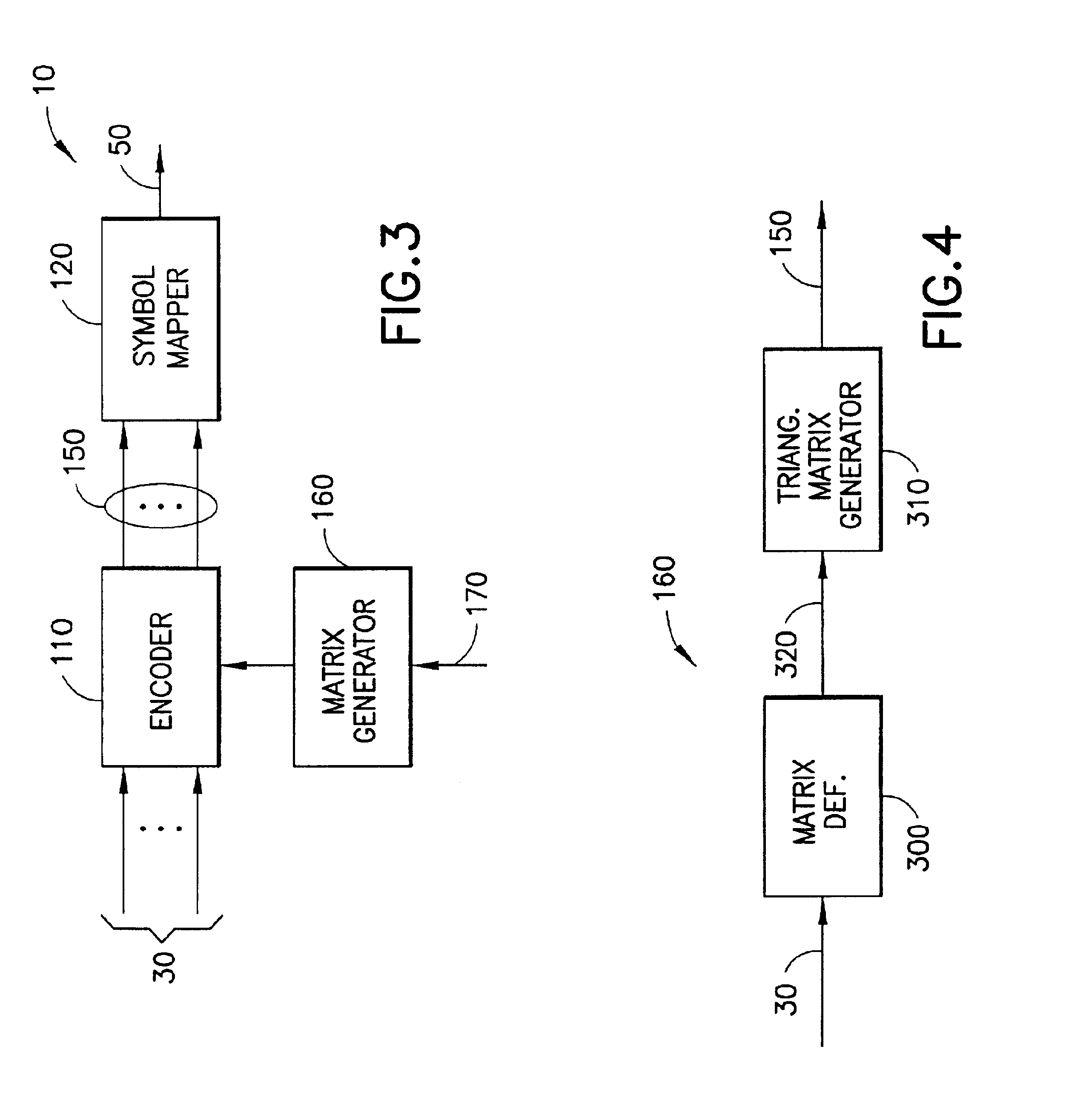

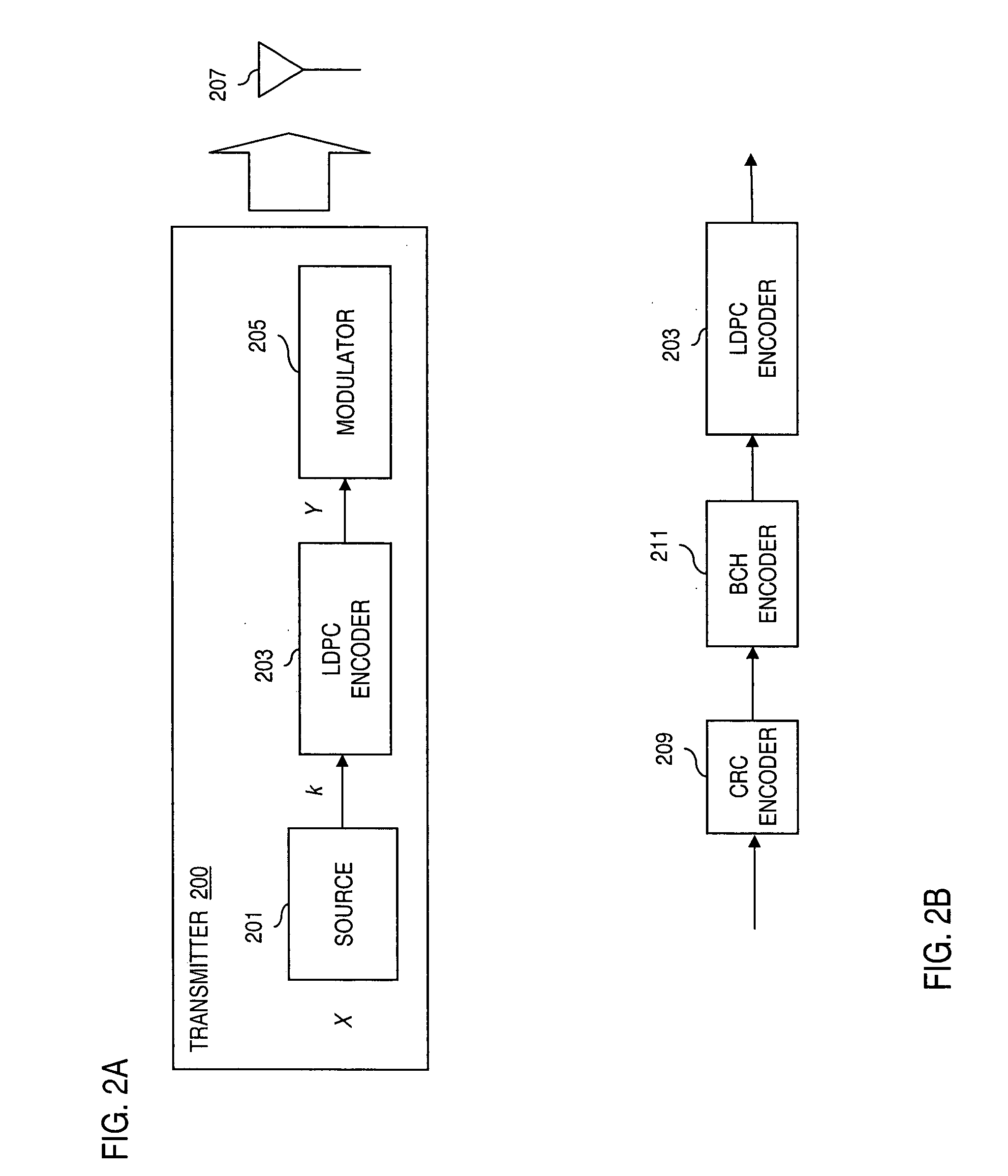

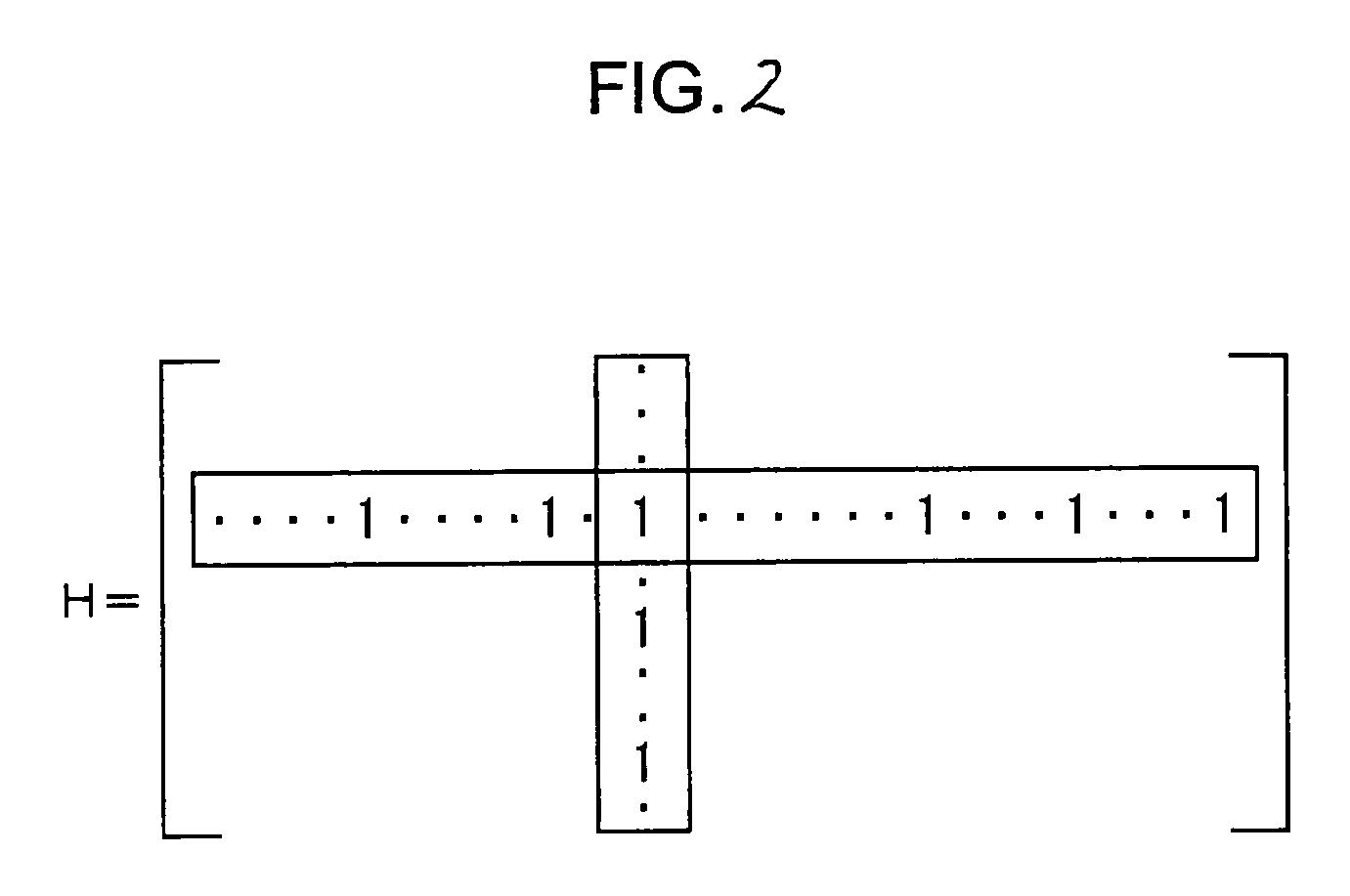

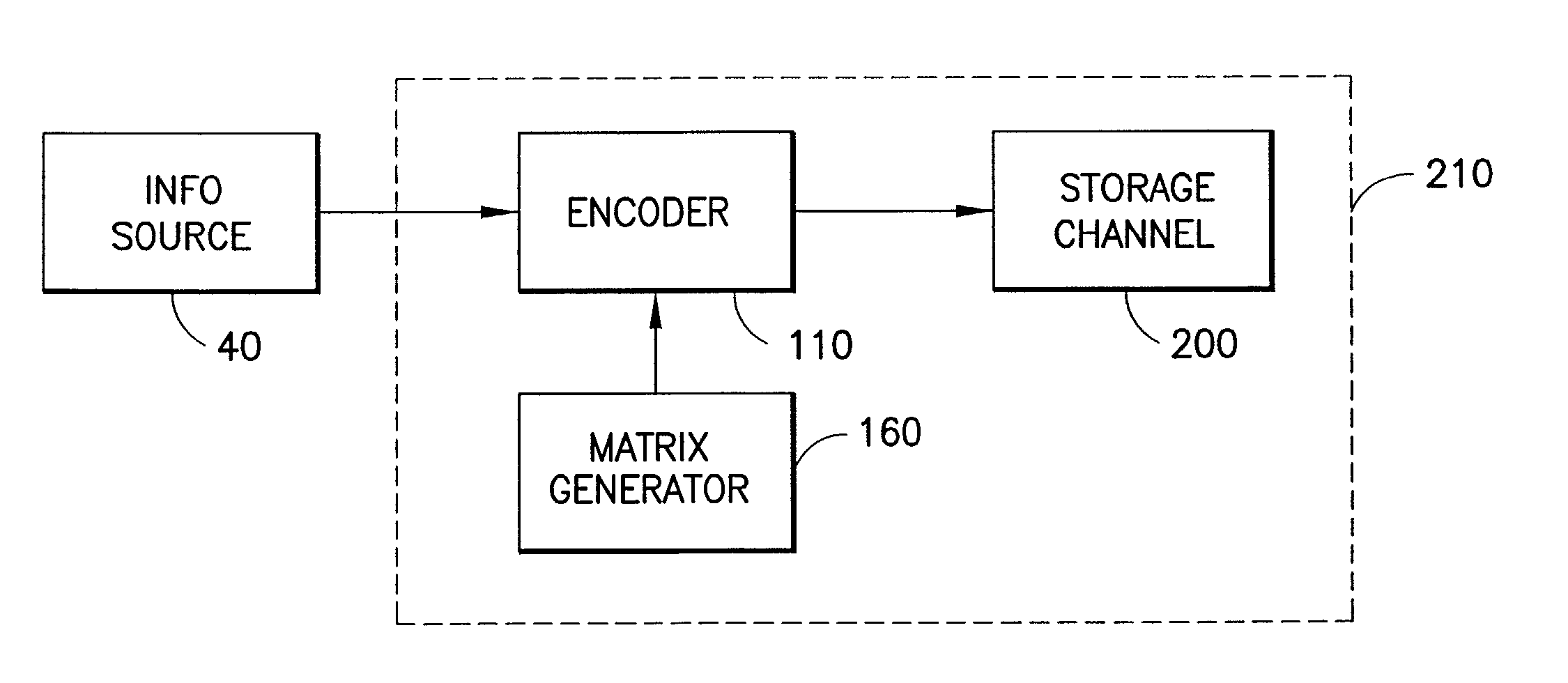

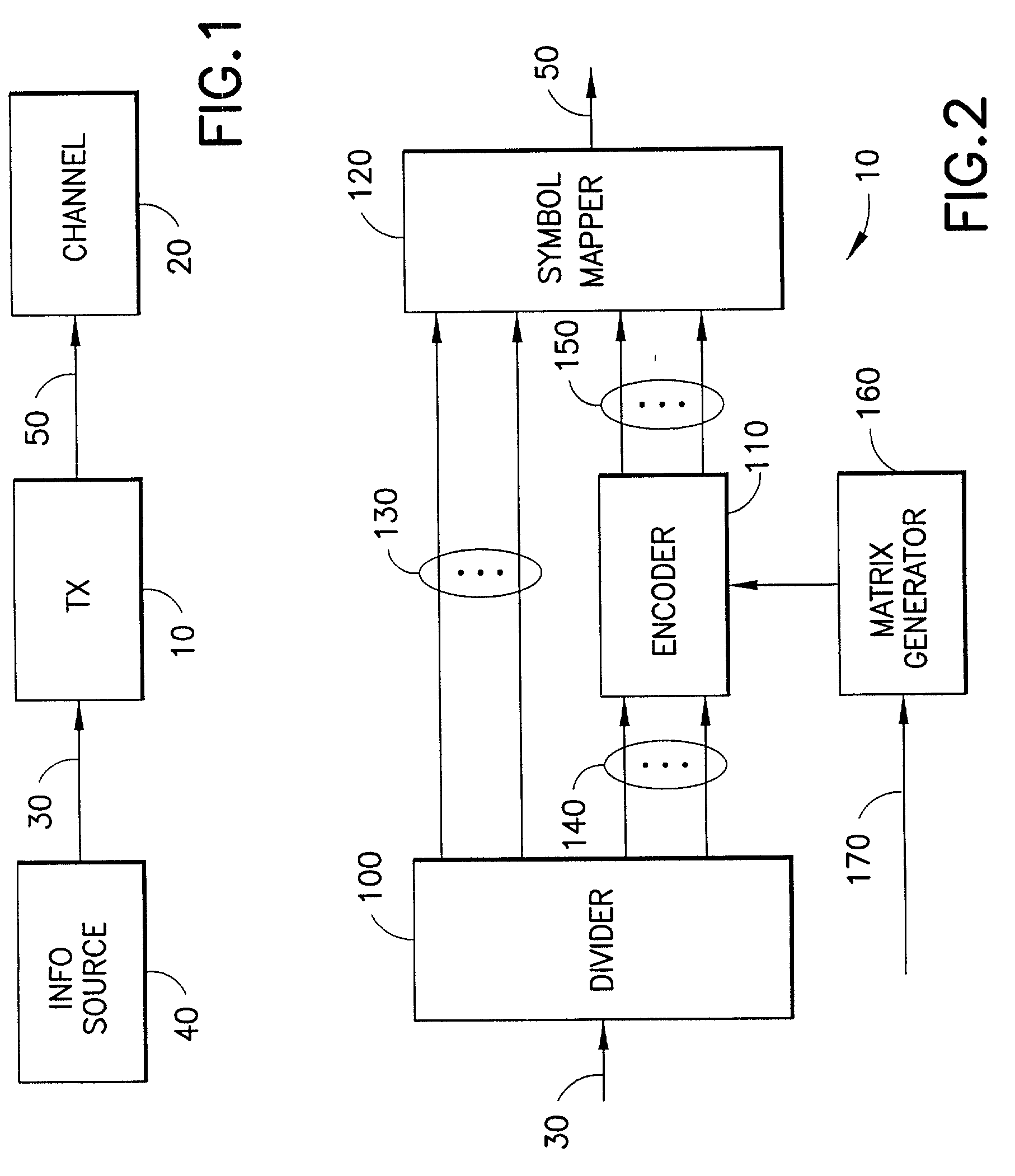

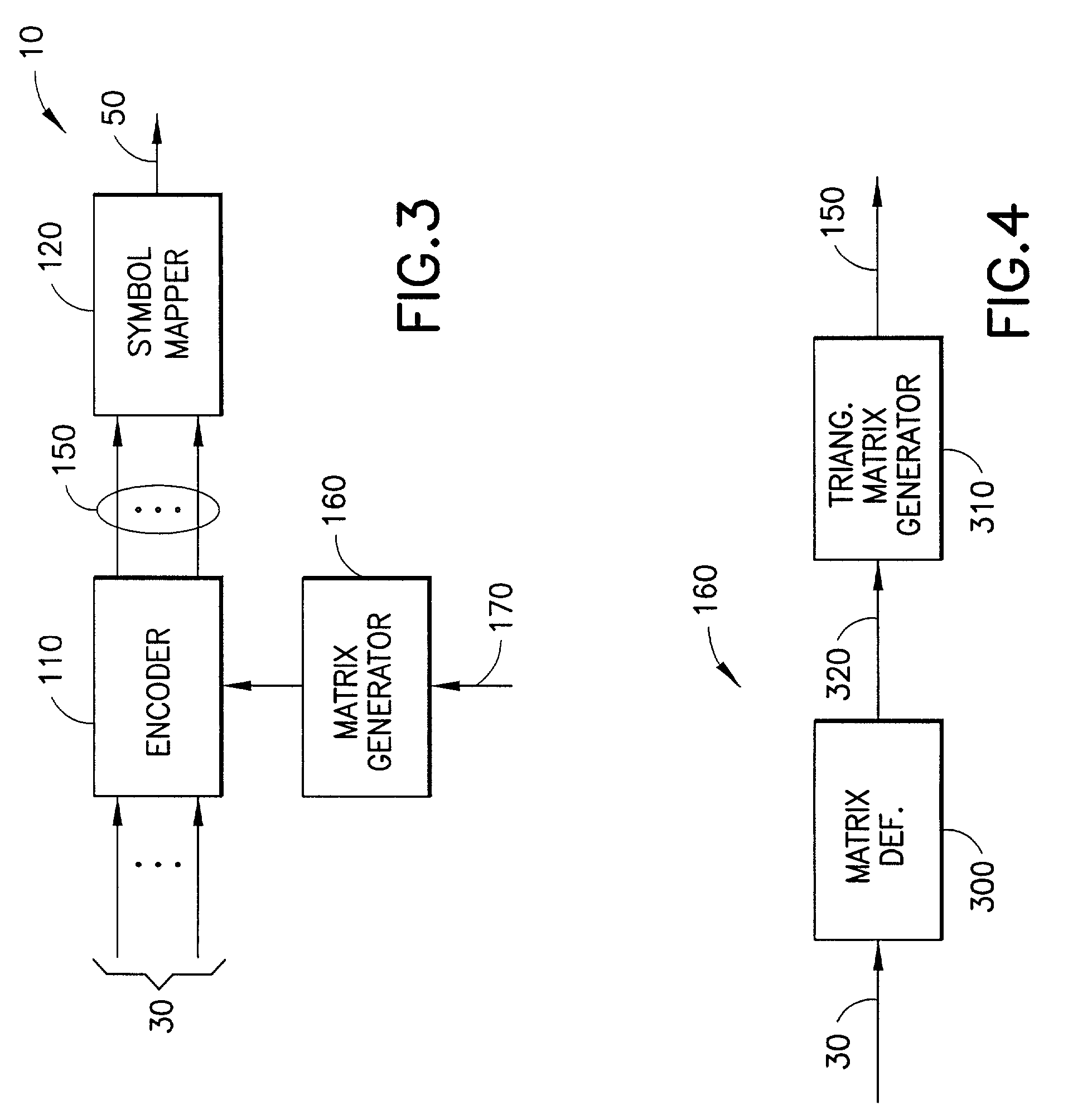

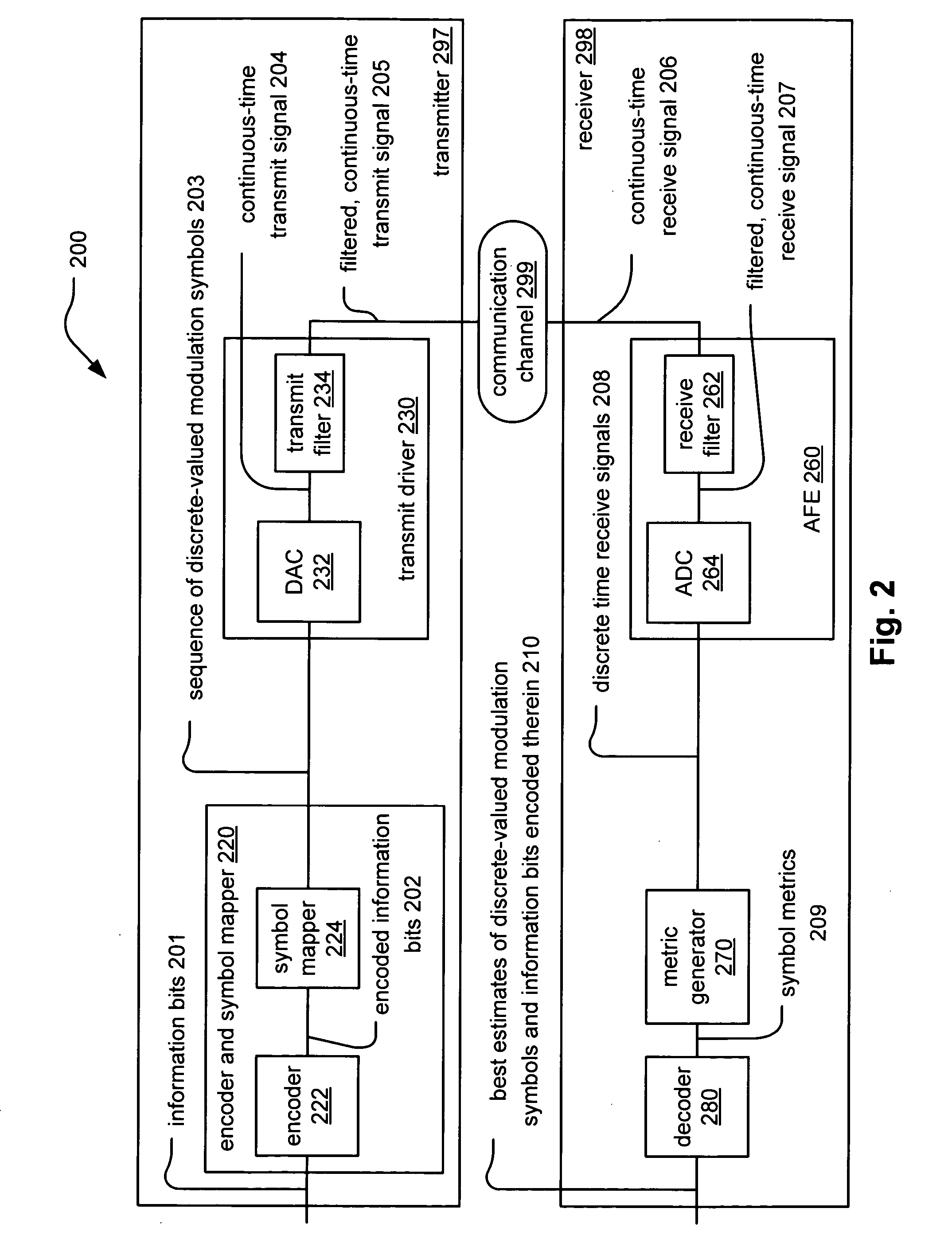

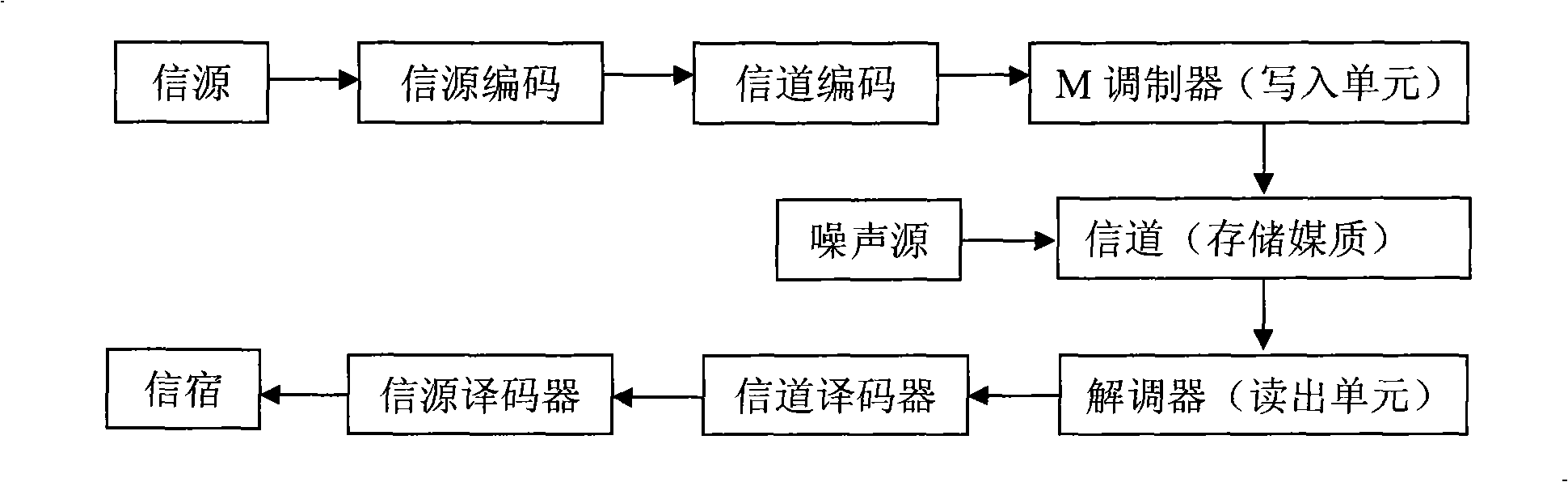

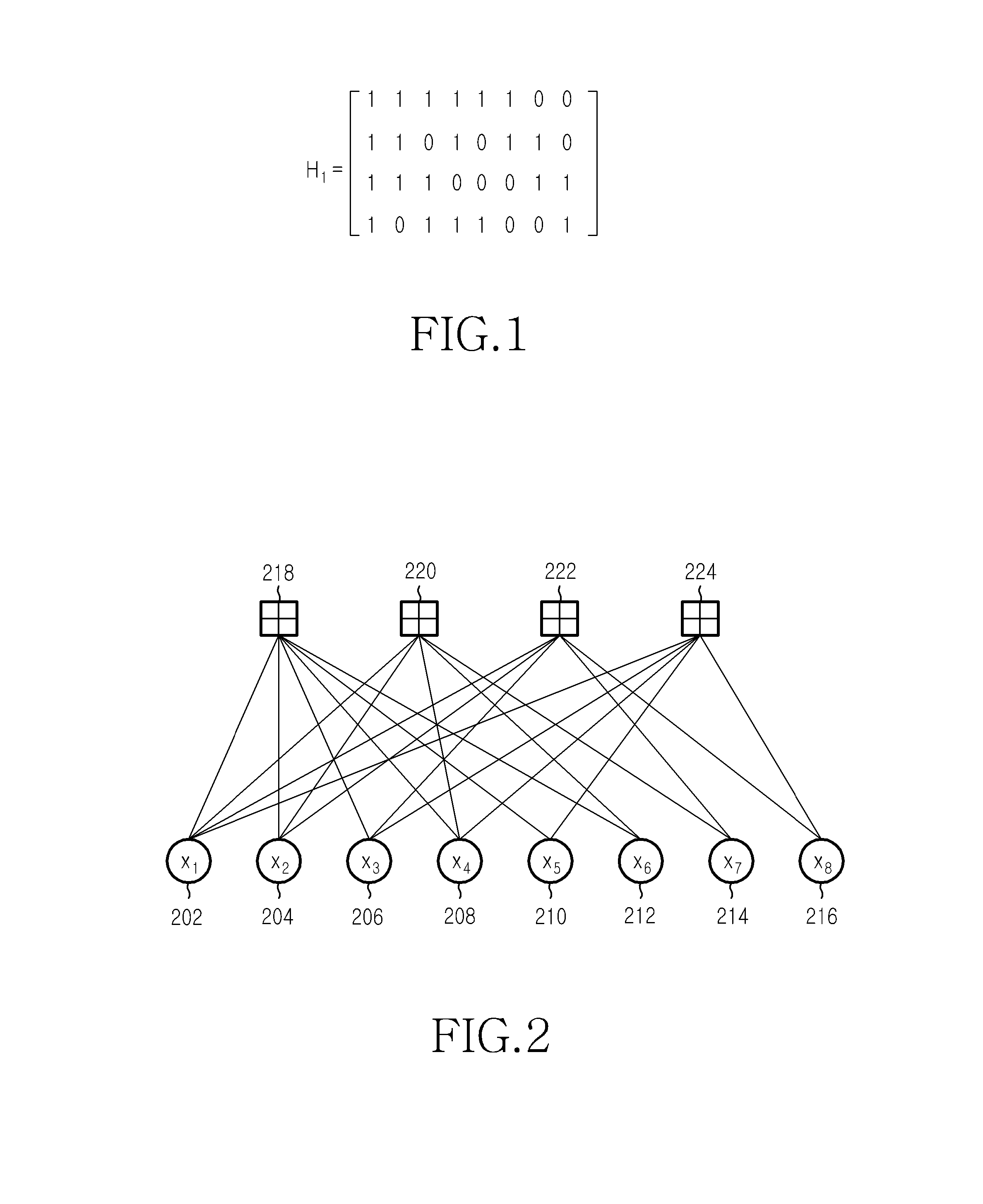

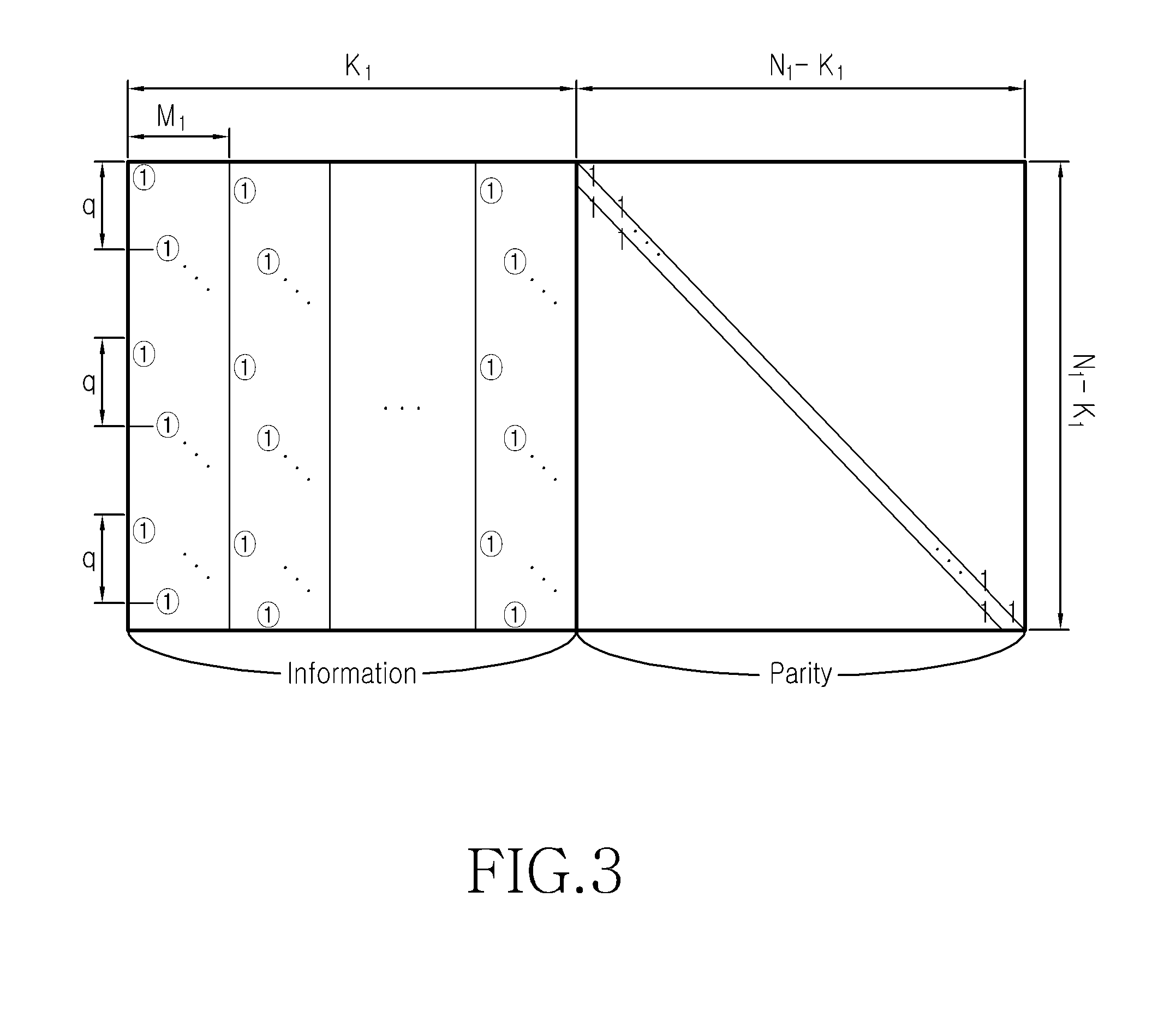

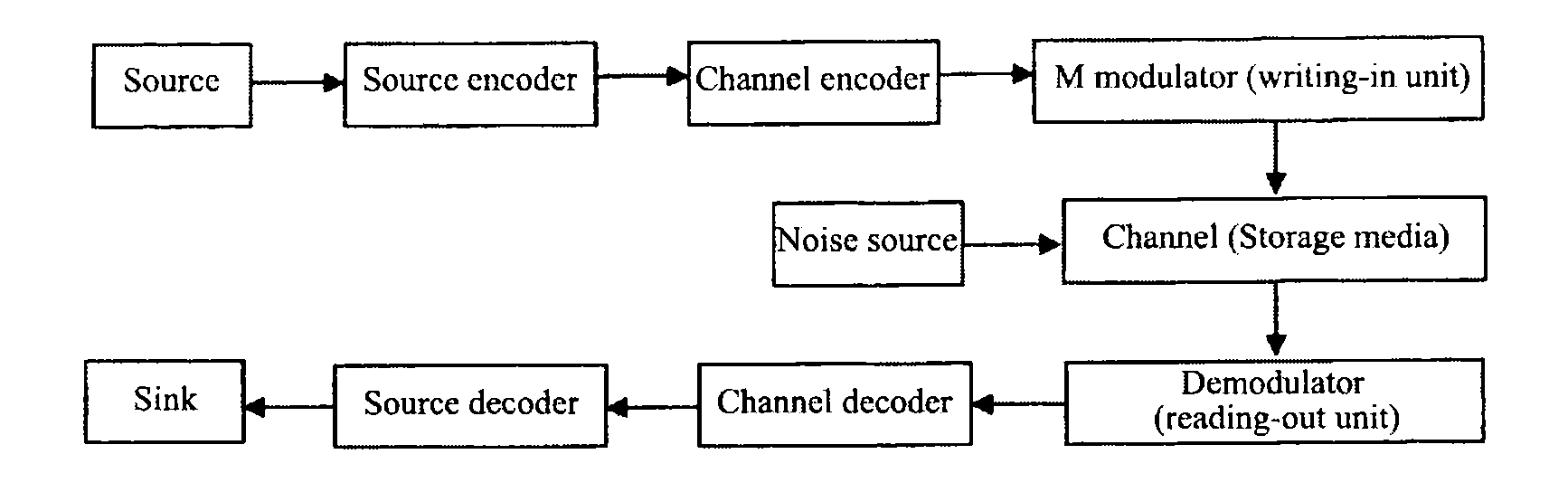

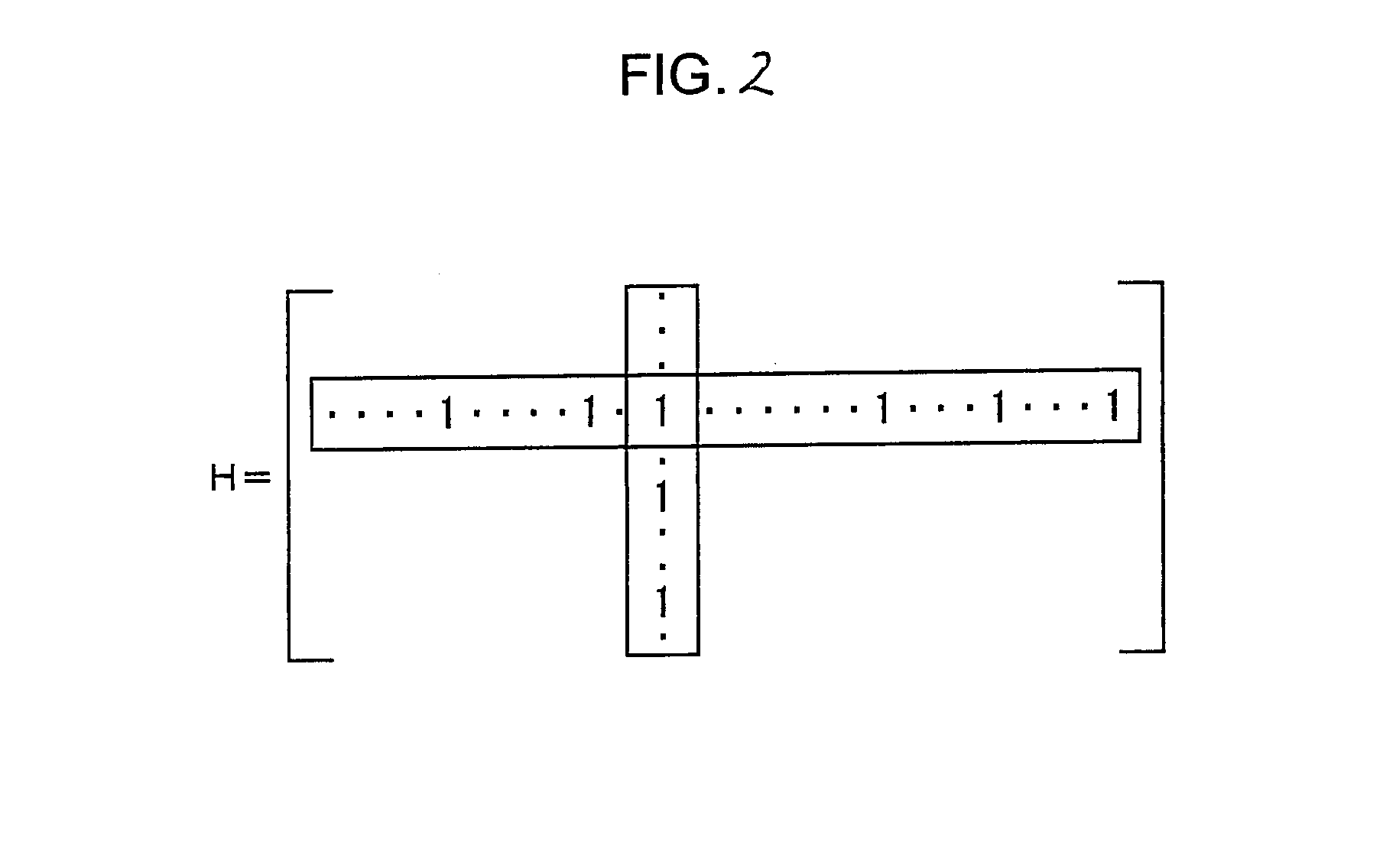

A method for low-density parity-check (LDPC) encoding of data comprises defining a first M×N parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an M×M triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

Method and system for providing low density parity check (LDPC) encoding

ActiveUS7191378B2Readily apparentInterconnection arrangementsError correction/detection using LDPC codesAlgorithmParity-check matrix

An approach is provided for a method of encoding structure Low Density Parity Check (LDPC) codes. Memory storing information representing a structured parity check matrix of Low Density Parity Check (LDPC) codes is accessed during the encoding process. The information is organized in tabular form, wherein each row represents occurrences of one values within a first column of a group of columns of the parity check matrix. The rows correspond to groups of columns of the parity check matrix, wherein subsequent columns within each of the groups are derived according to a predetermined operation. An LDPC coded signal is output based on the stored information representing the parity check matrix.

Owner:DTVG LICENSING INC

Data processing apparatus and method

ActiveUS20090125780A1Improve performanceLow Density Parity Check (LDPCTransmission path divisionError detection/correctionCarrier signalTheoretical computer science

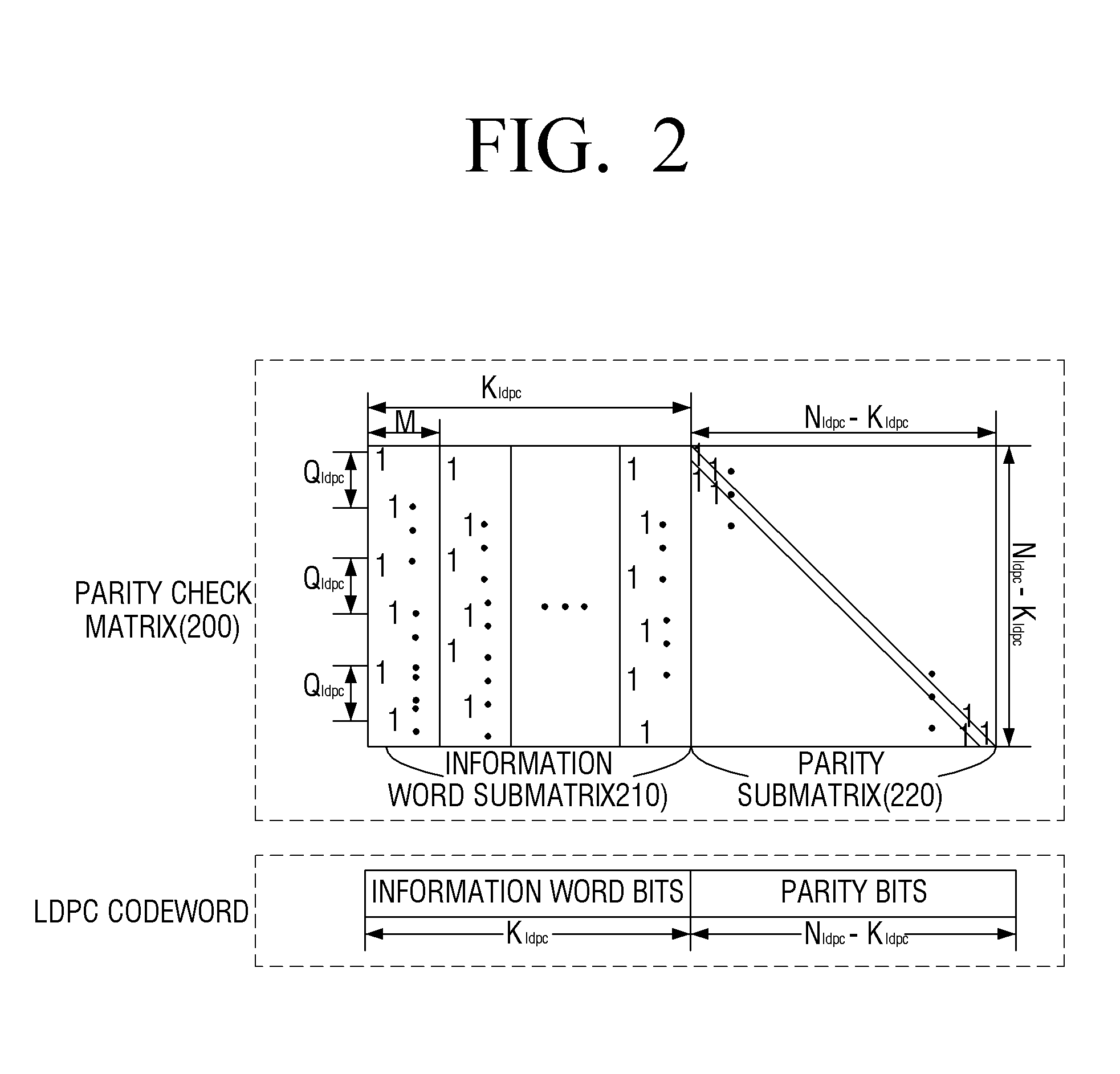

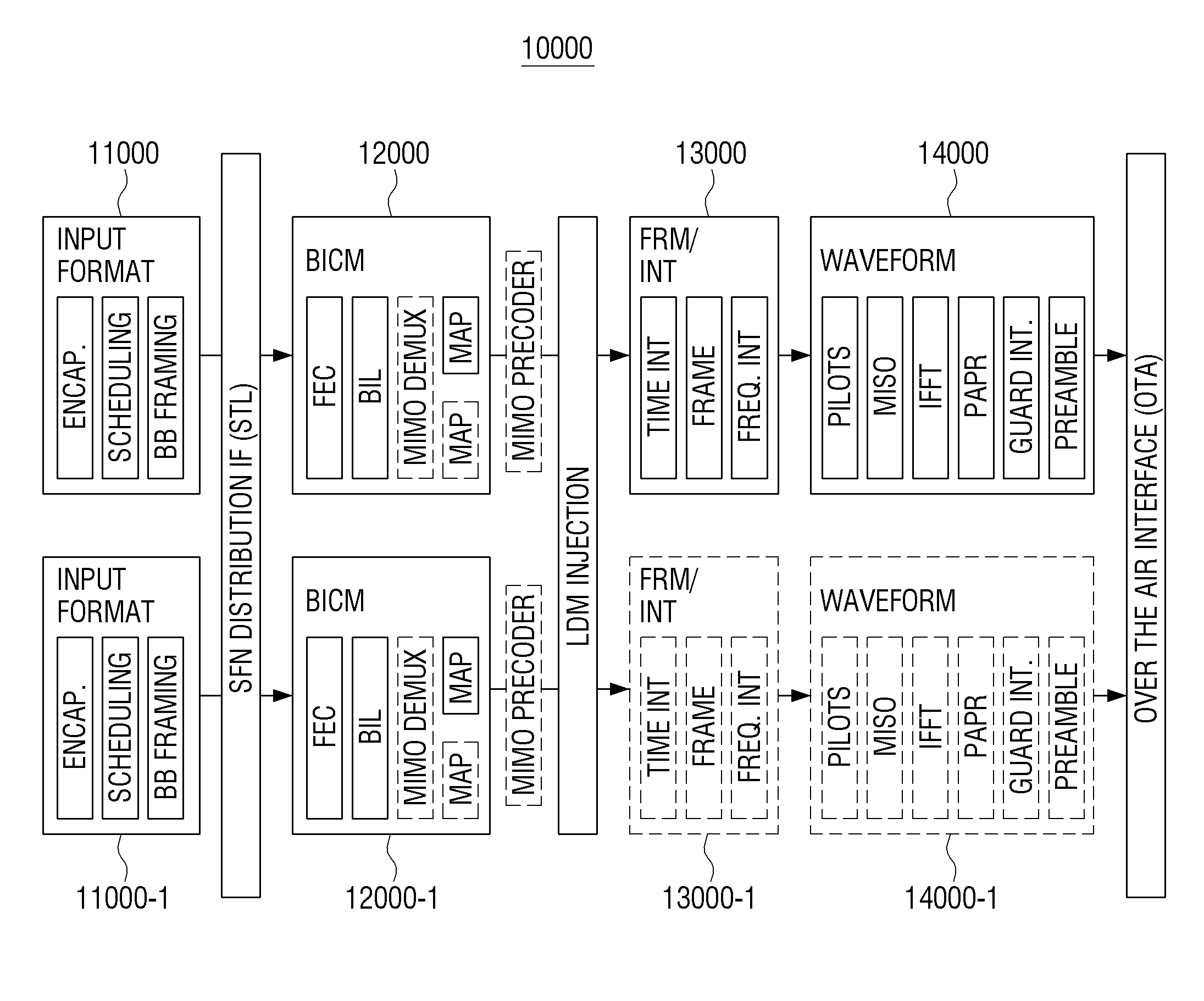

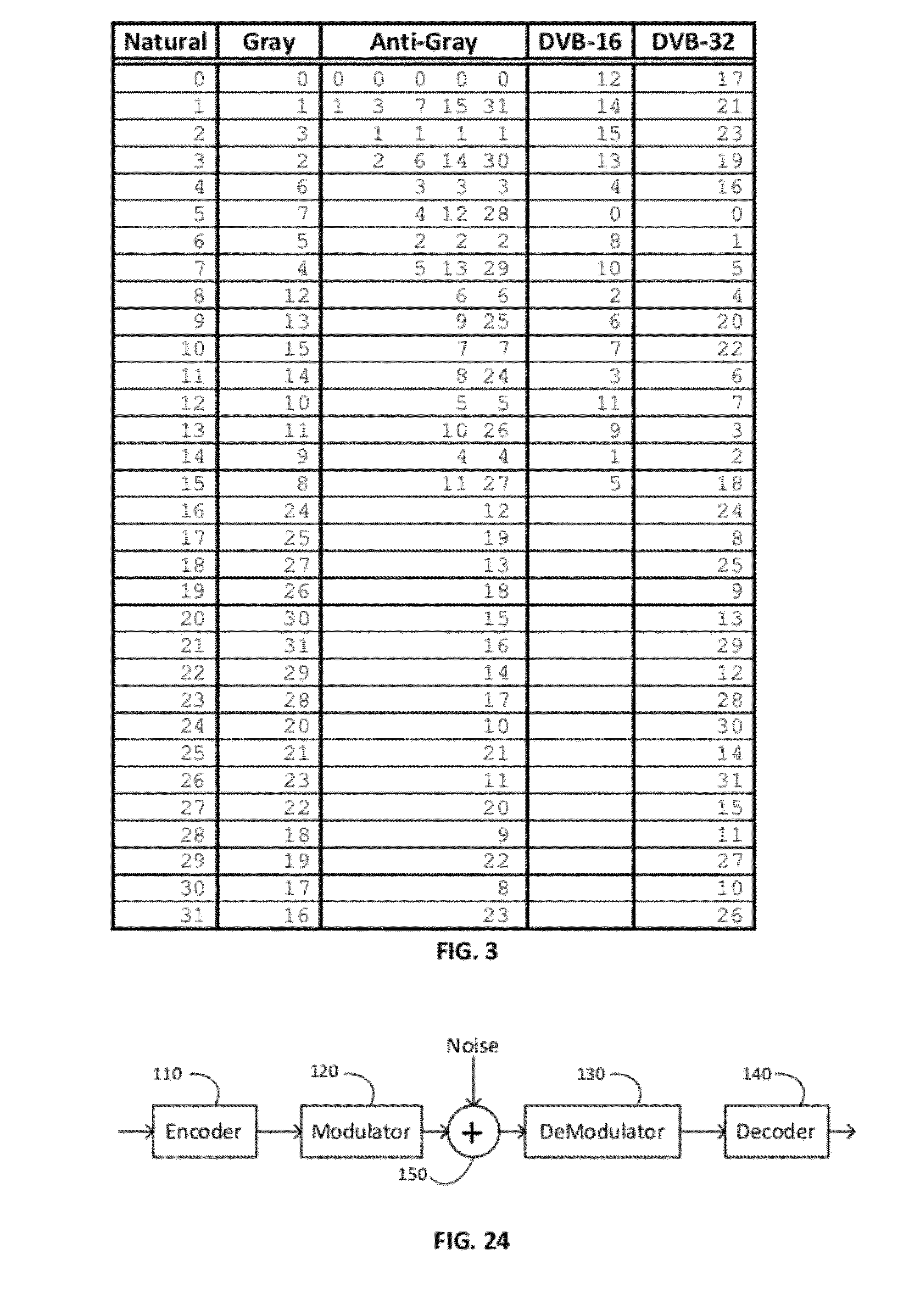

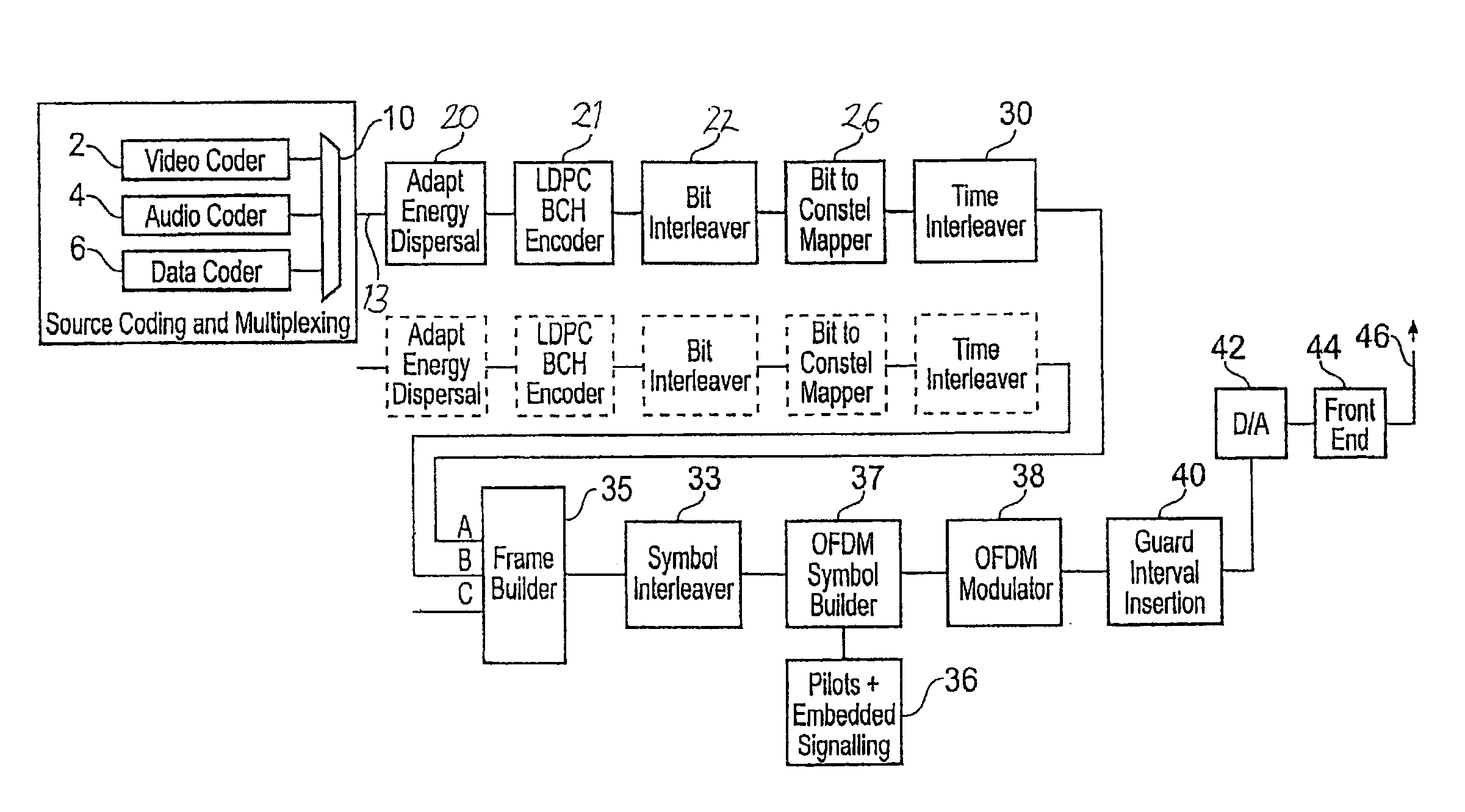

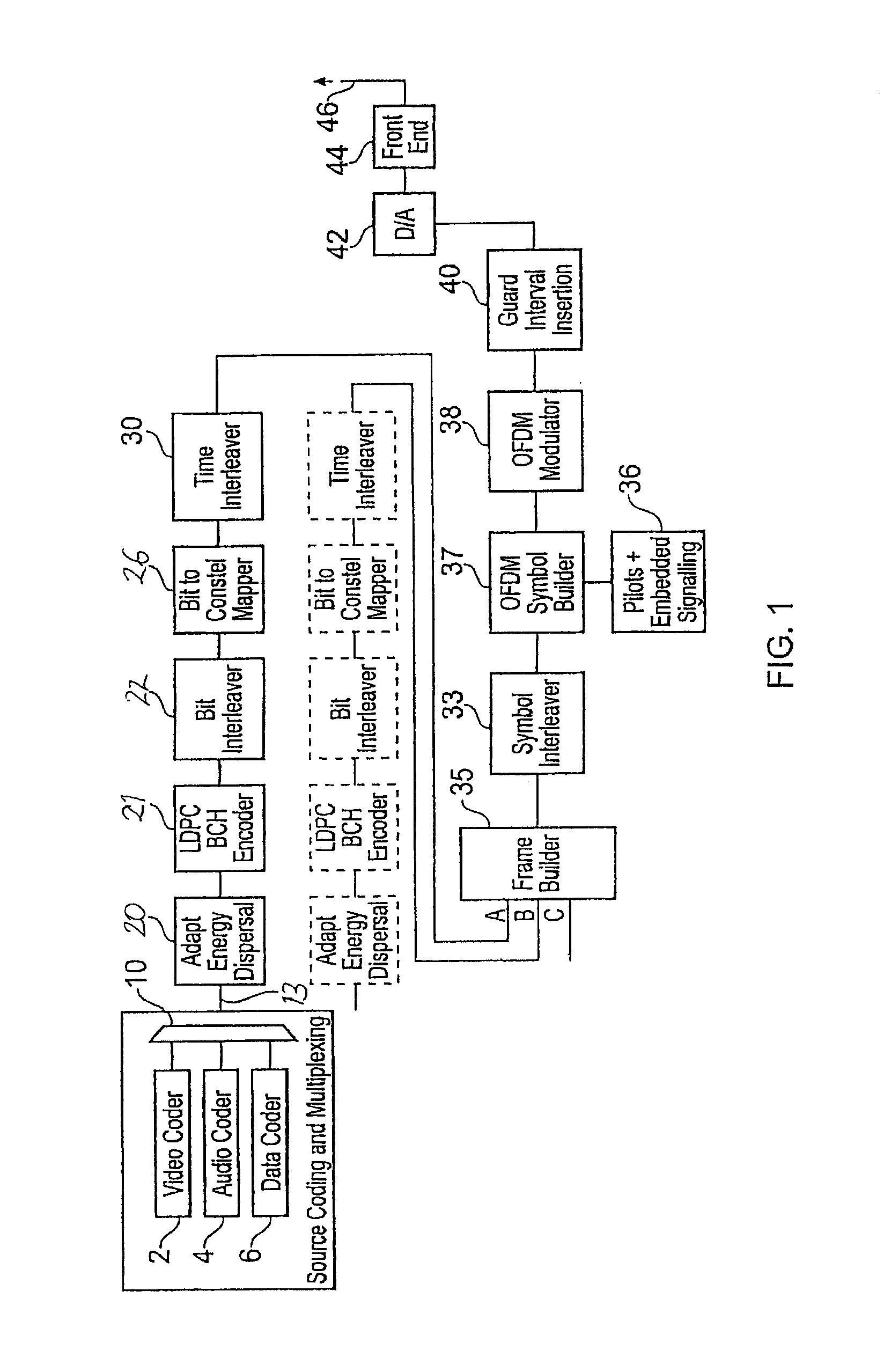

A data processing apparatus communicates data bits on a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processing apparatus comprises a parity interleaver operable to perform parity interleaving on Low Density Parity Check (LDPC) encoded data bits obtained by performing LDPC encoding according to a parity check matrix of an LDPC code including a parity matrix corresponding to parity bits of the LDPC code, the parity matrix having a stepwise structure, so that a parity bit of the LDPC encoded data bits is interleaved to a different parity bit position. A mapping unit maps the parity interleaved bits onto data symbols corresponding to modulation symbols of a modulation scheme of the OFDM sub-carrier signals. A symbol interleaver is arranged in operation to read-into a symbol interleaver memory the predetermined number of data symbols for mapping onto the OFDM sub-carrier signals, and to read-out of the interleaver memory the data symbols for the OFDM sub-carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on the sub-carrier signals. The set of addresses are generated by an address generator which has been optimised to interleave the data symbols on to the sub-carrier signals of the OFDM carrier signals for a given operating mode of the OFDM system, such as a 32K operating mode for DVB-T2 or DVB-C2.

Owner:SATURN LICENSING LLC

Interleaving method and deinterleaving method

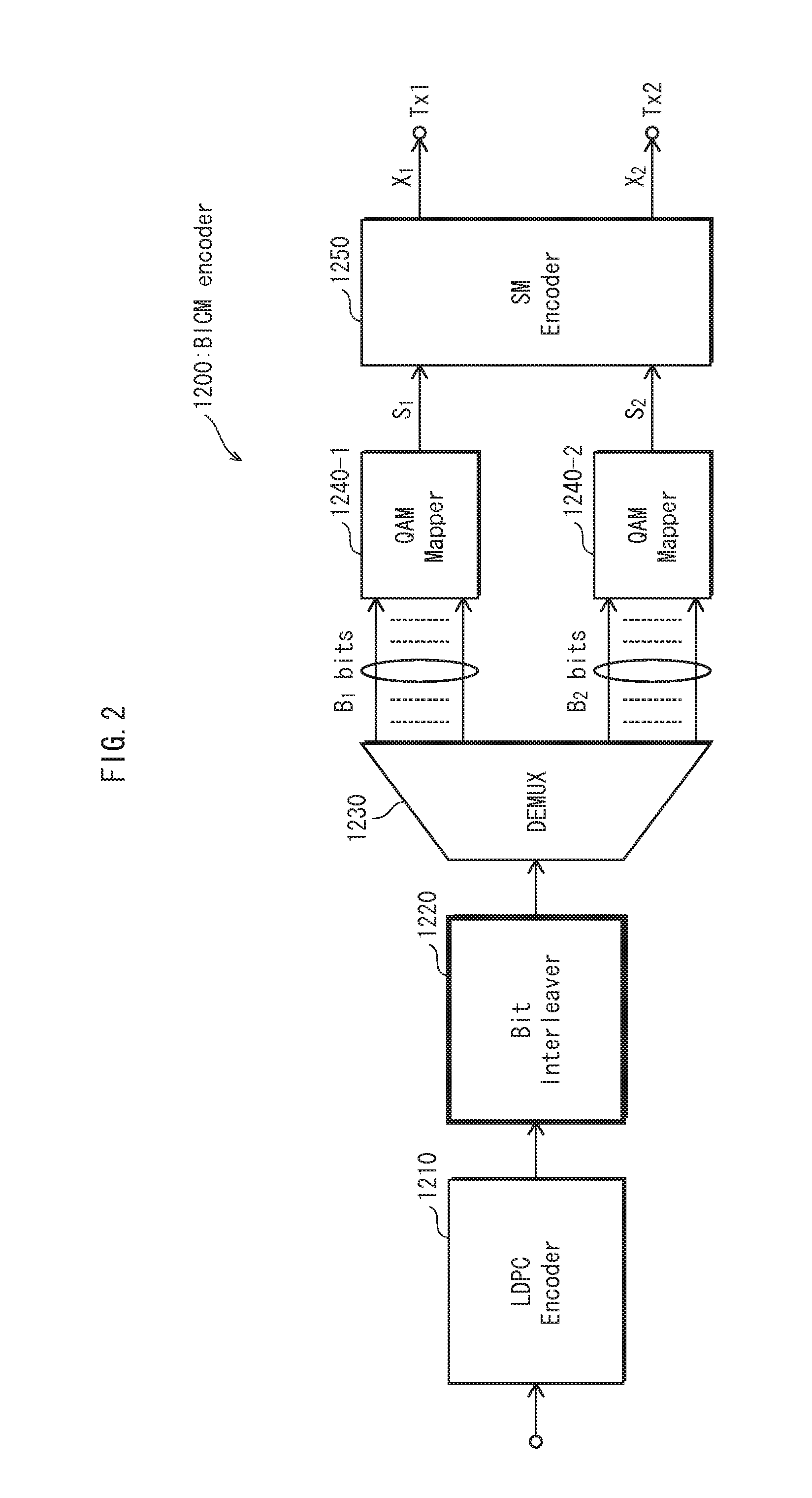

ActiveUS20130216001A1Improve reception performanceError correction/detection using LDPC codesChecking code calculationsCommunications systemLow-density parity-check code

An interleaving method performed by a transmitter for a communication system with quasi-cyclic low-density parity-check codes, spatial multiplexing, and T transmit antennas is used for applying permutation to N cyclic blocks of a codeword in order to map bits of the permutated cyclic blocks onto T constellation words constituting multiple spatial-multiplexing blocks from the codeword. Each cyclic block consists of Q bits.

Owner:SUN PATENT TRUST

Method and apparatus for low density parity check encoding of data

InactiveUS20030037298A1Improve performanceError preventionError detection/correctionParity-check matrixTheoretical computer science

A method for low-density parity-check (LDPC) encoding of data comprises defining a first MxN parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an MxM triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

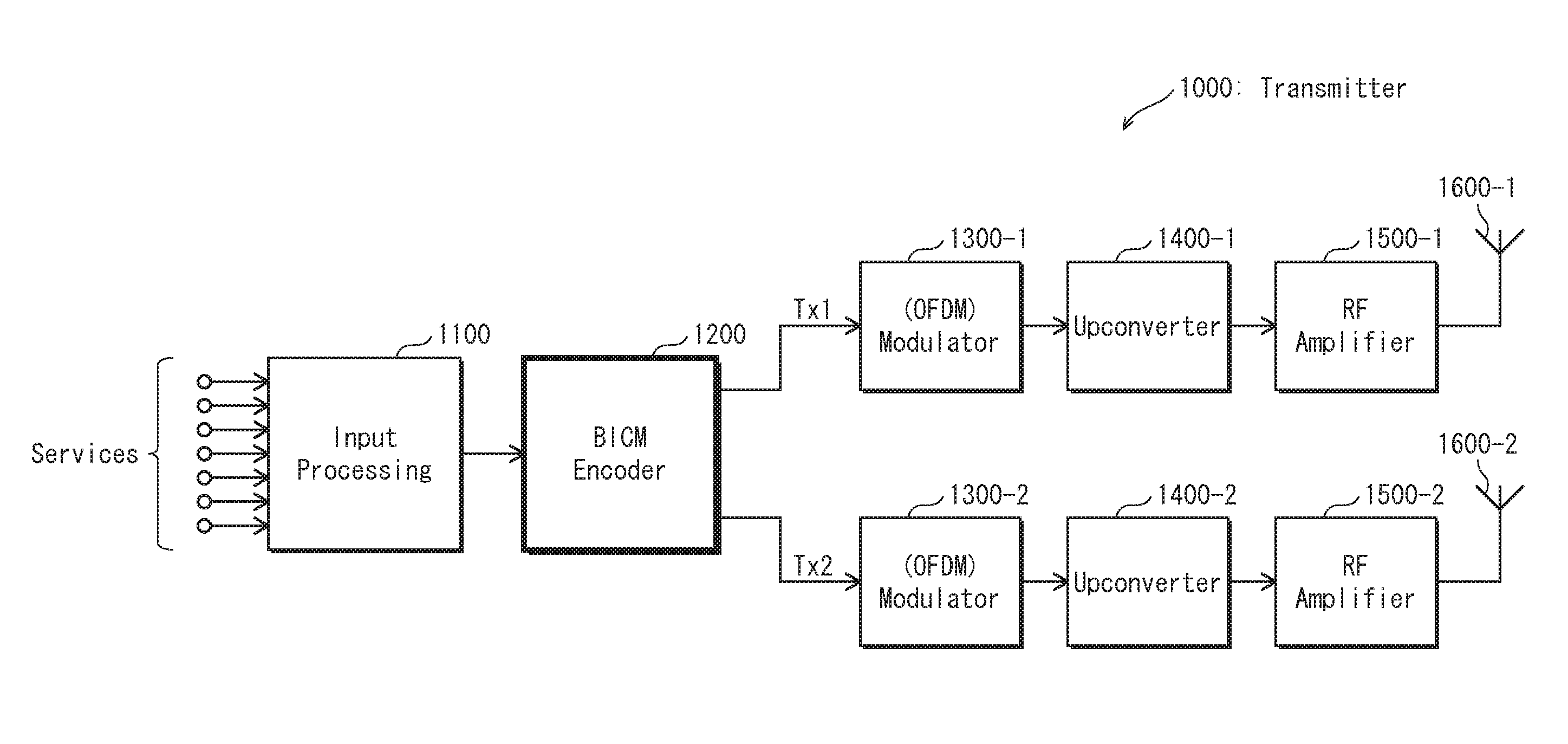

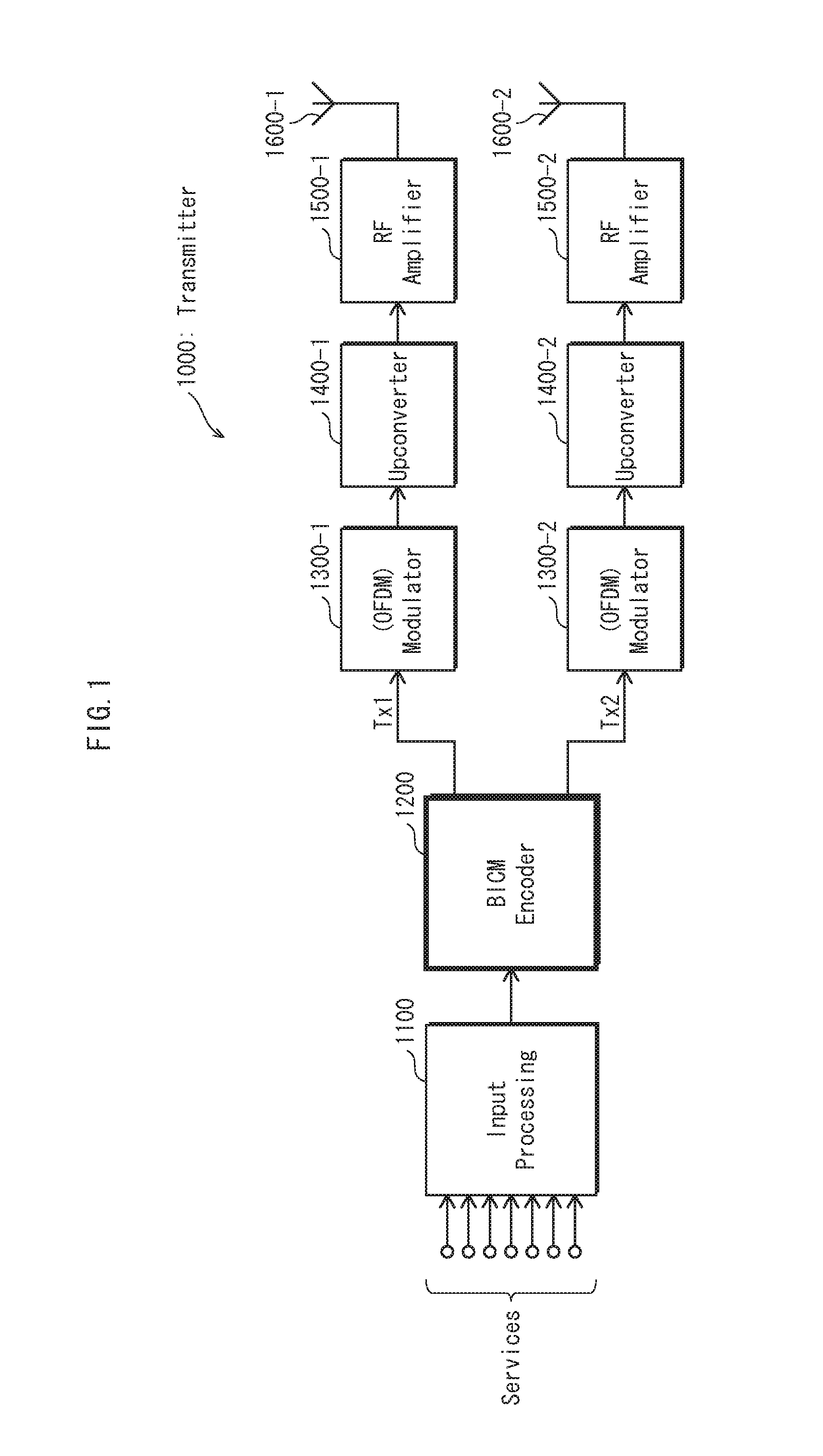

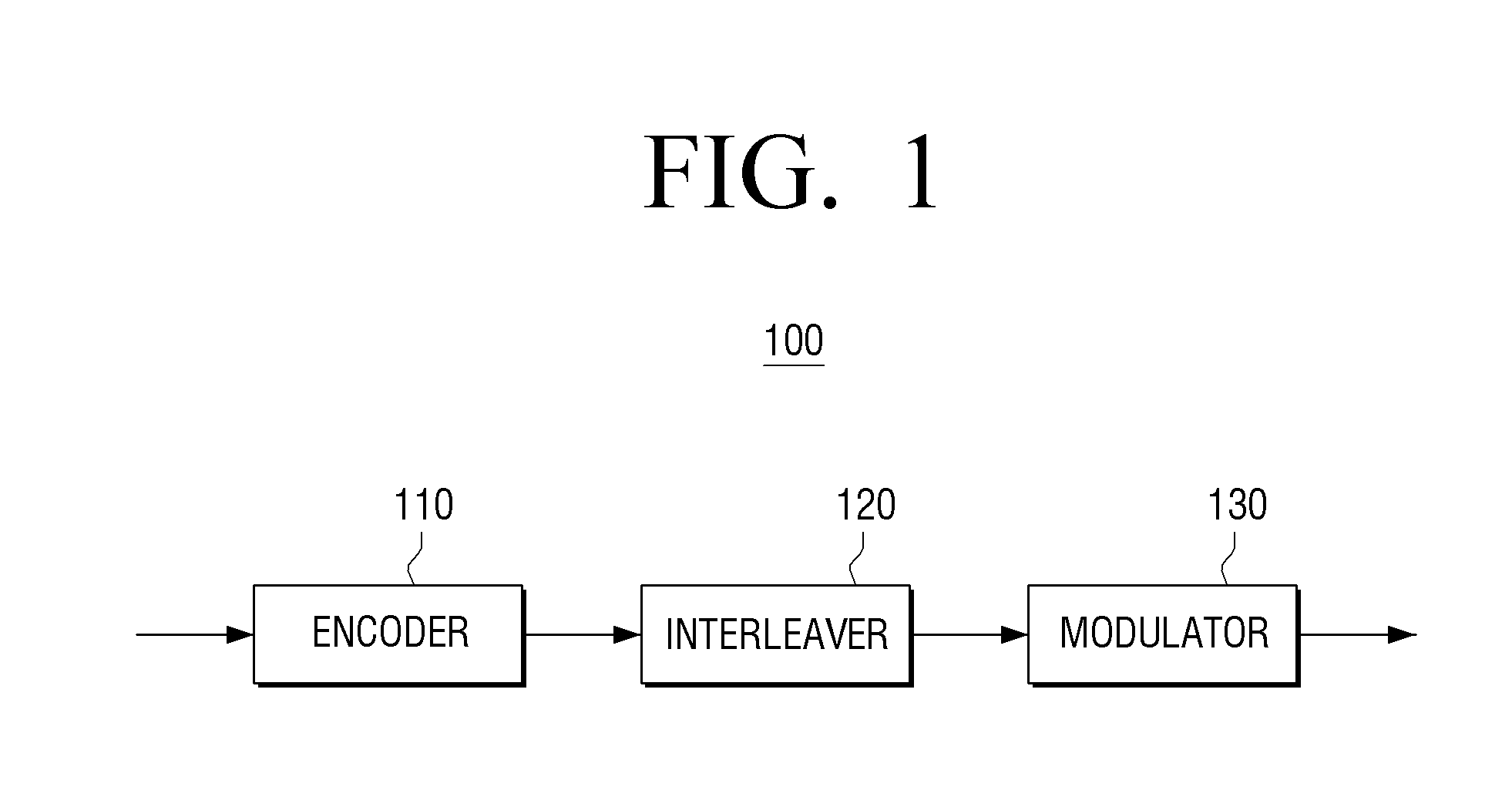

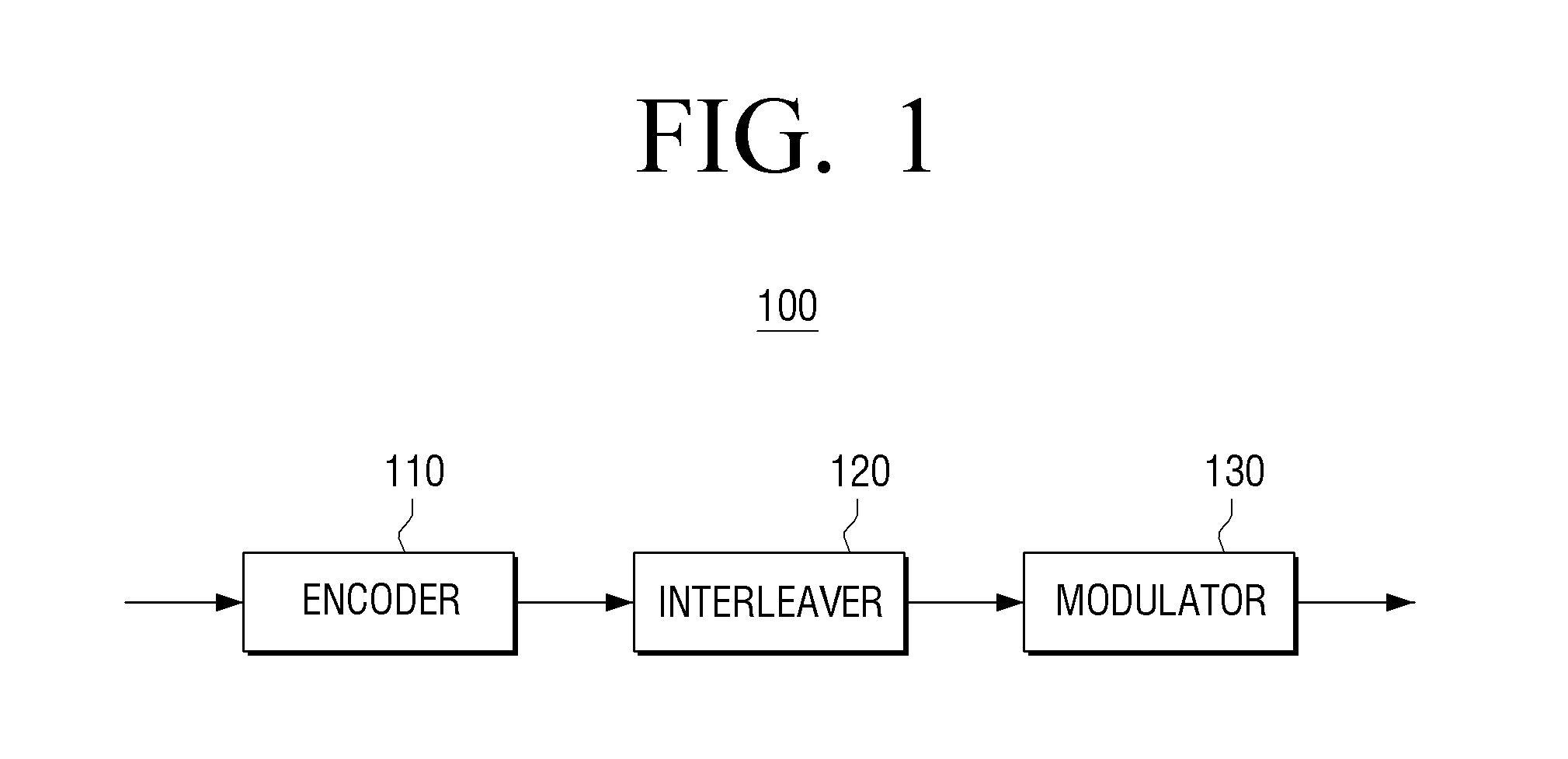

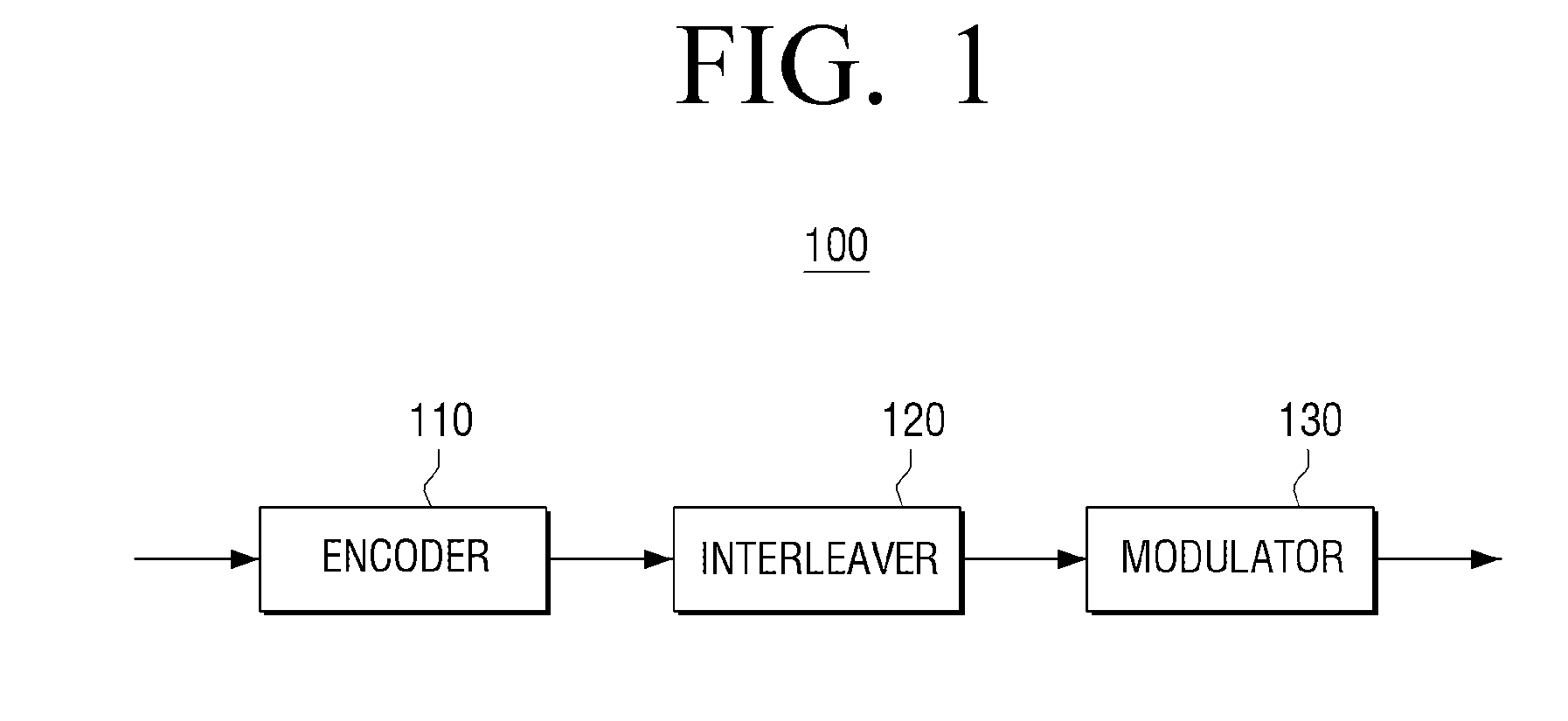

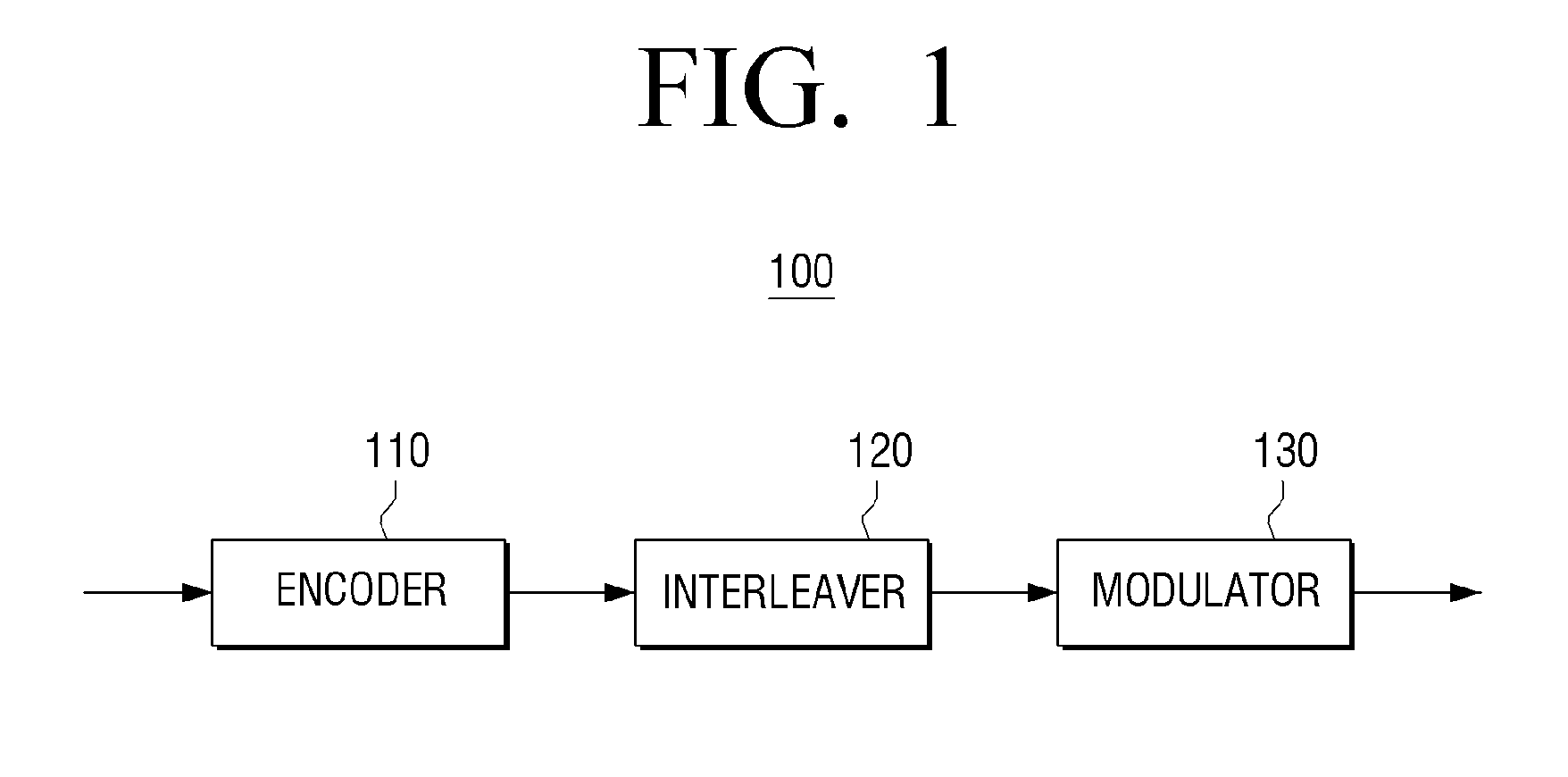

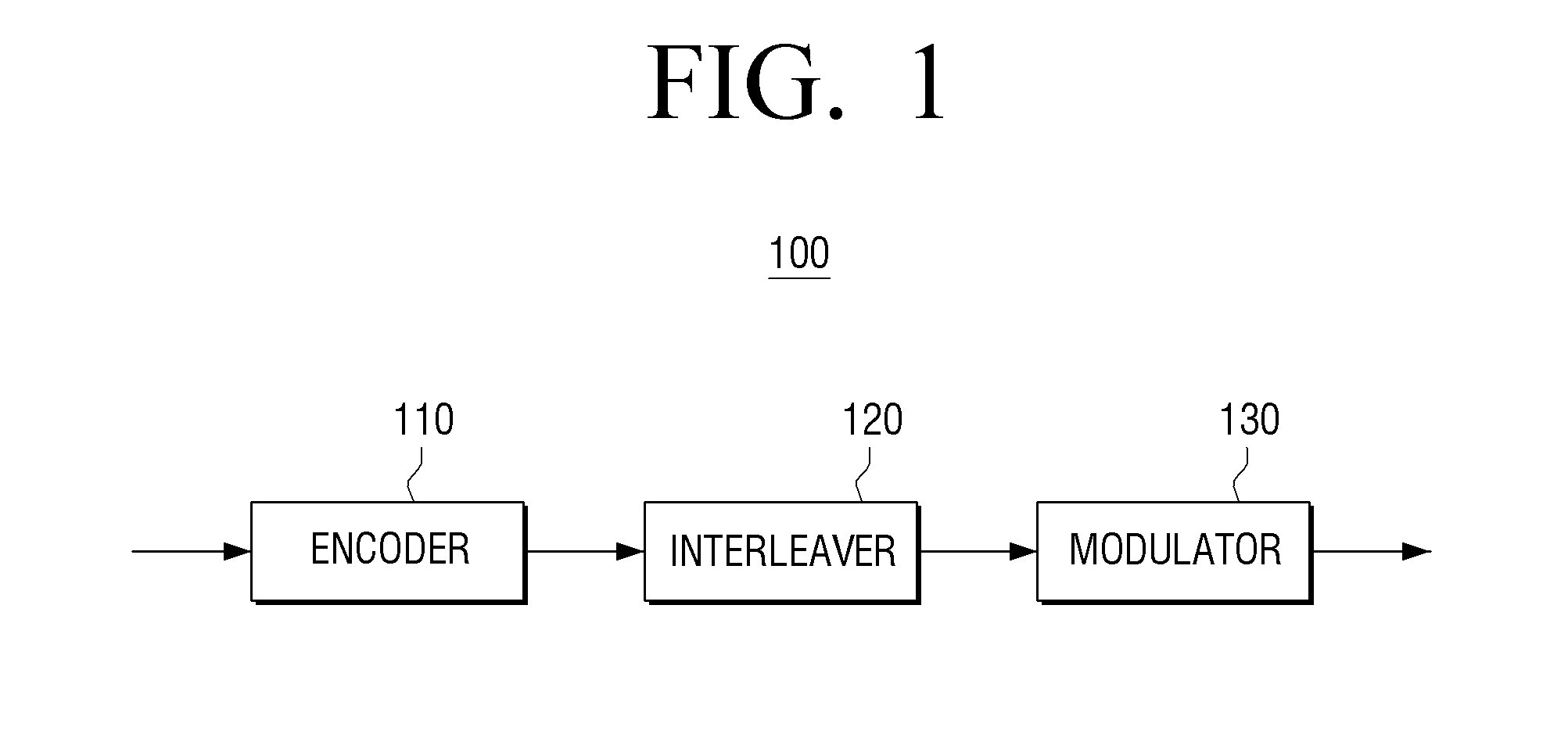

Transmitter apparatus and signal processing method thereof

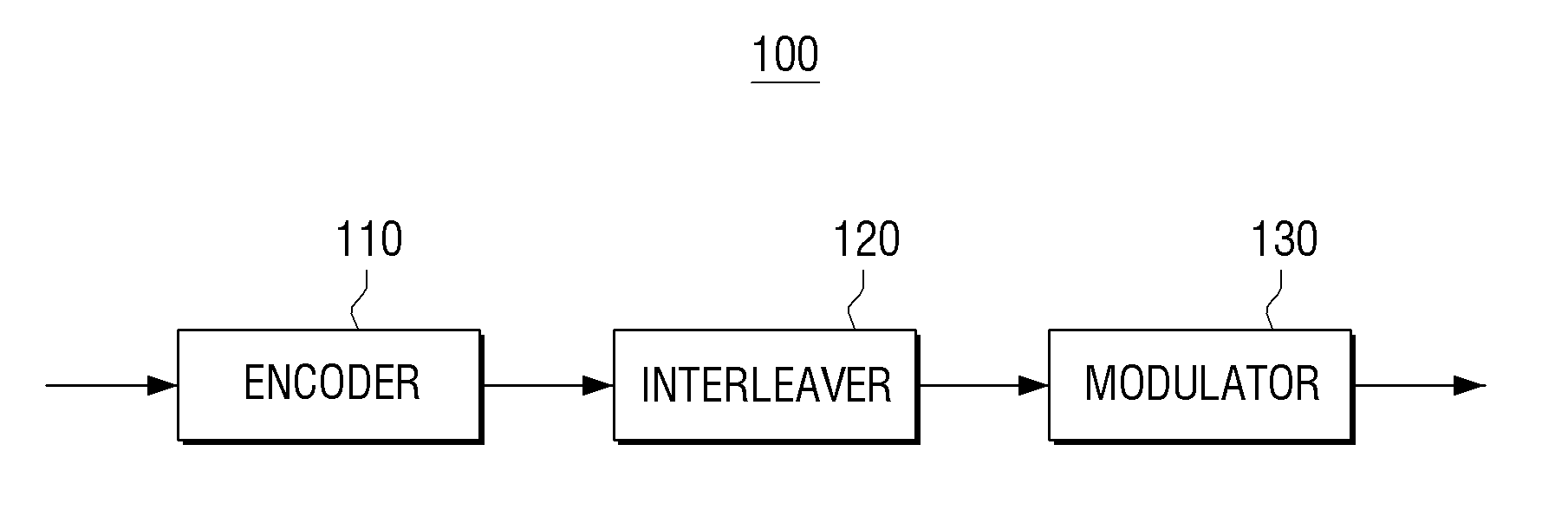

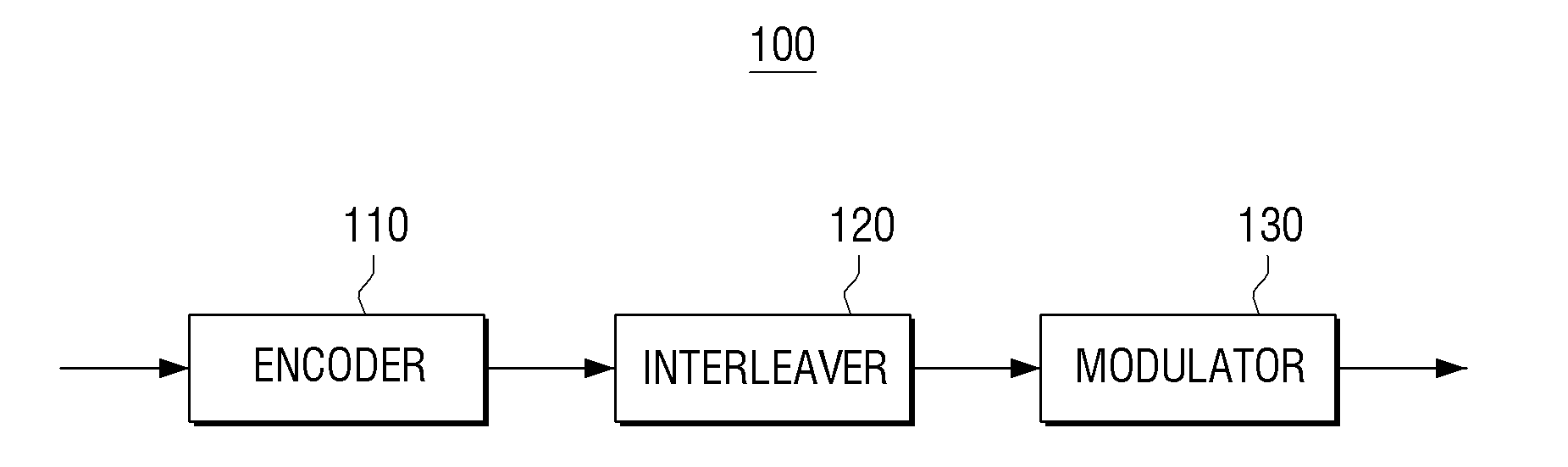

ActiveUS20150039973A1Improve decoding performanceImprove reception performanceError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow densityComputer science

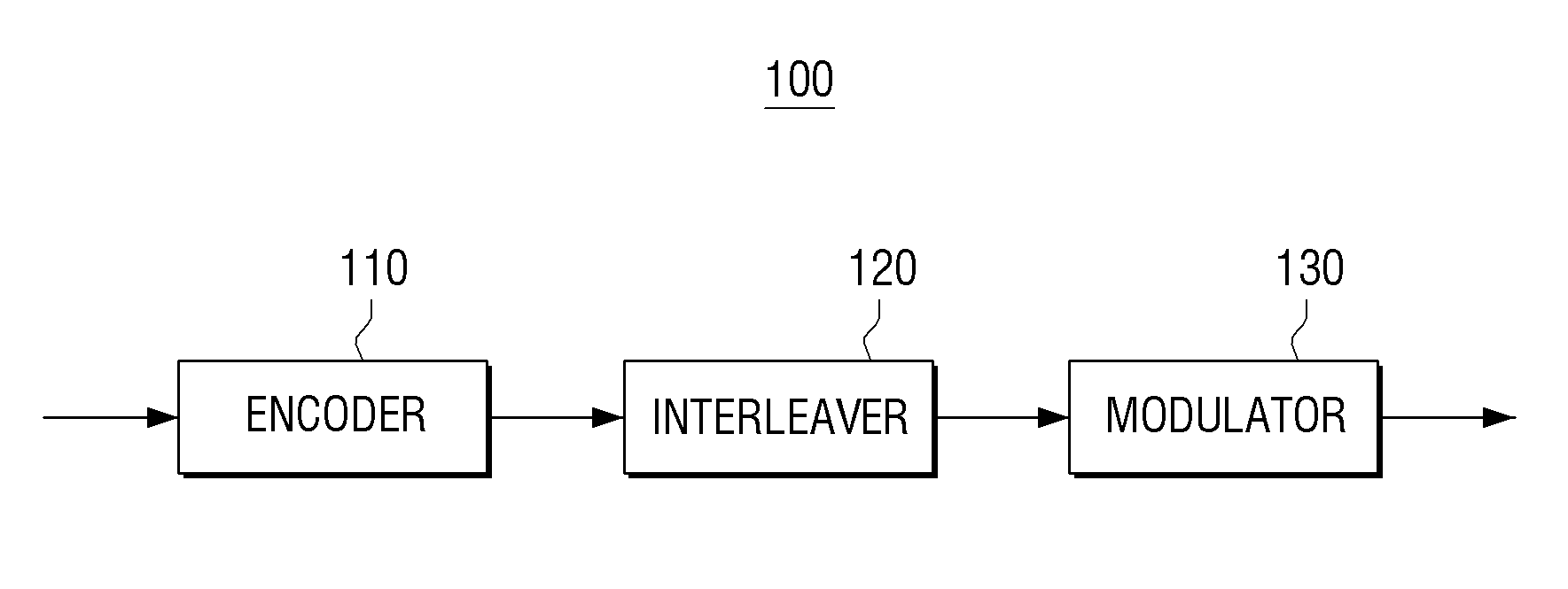

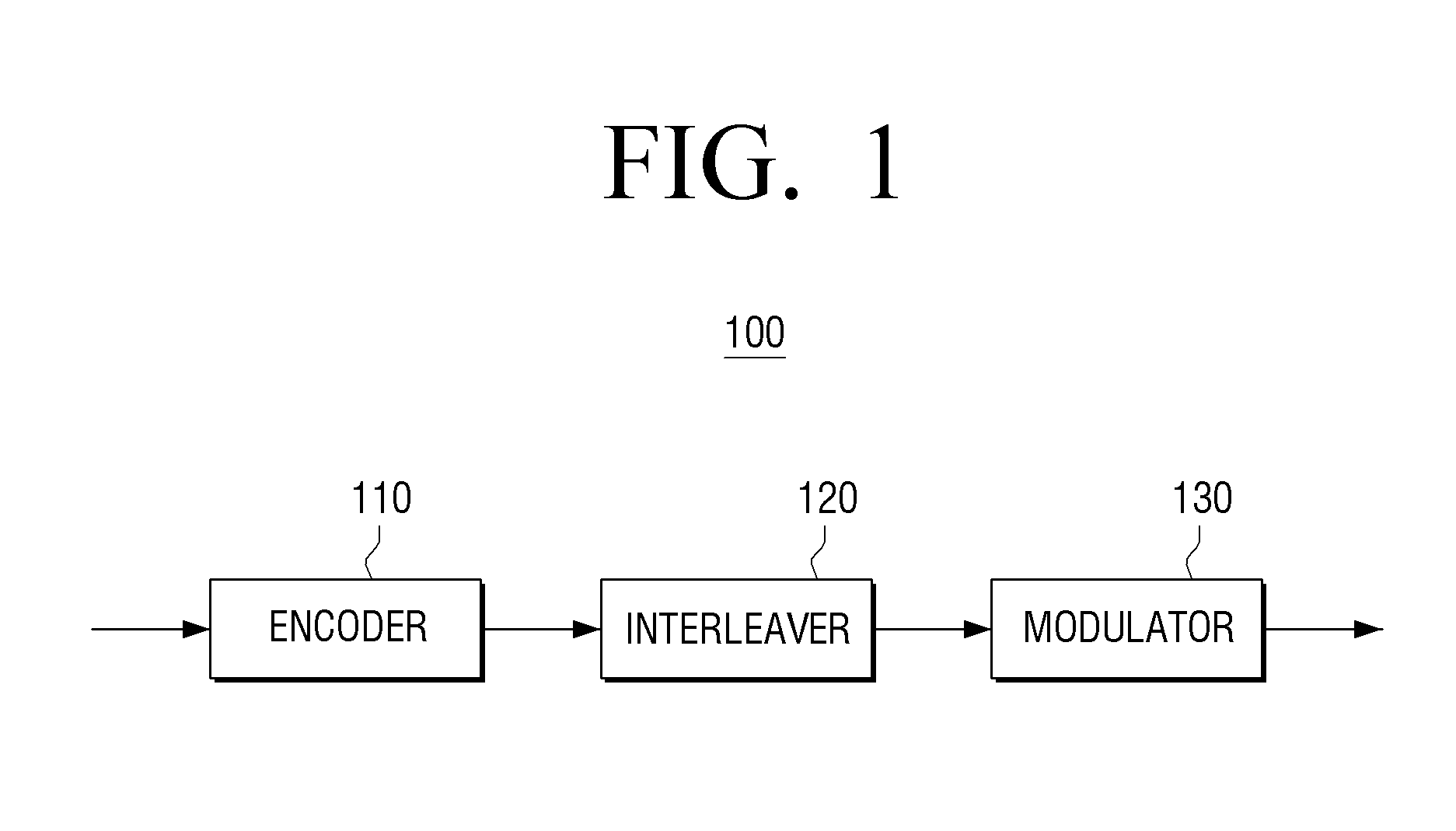

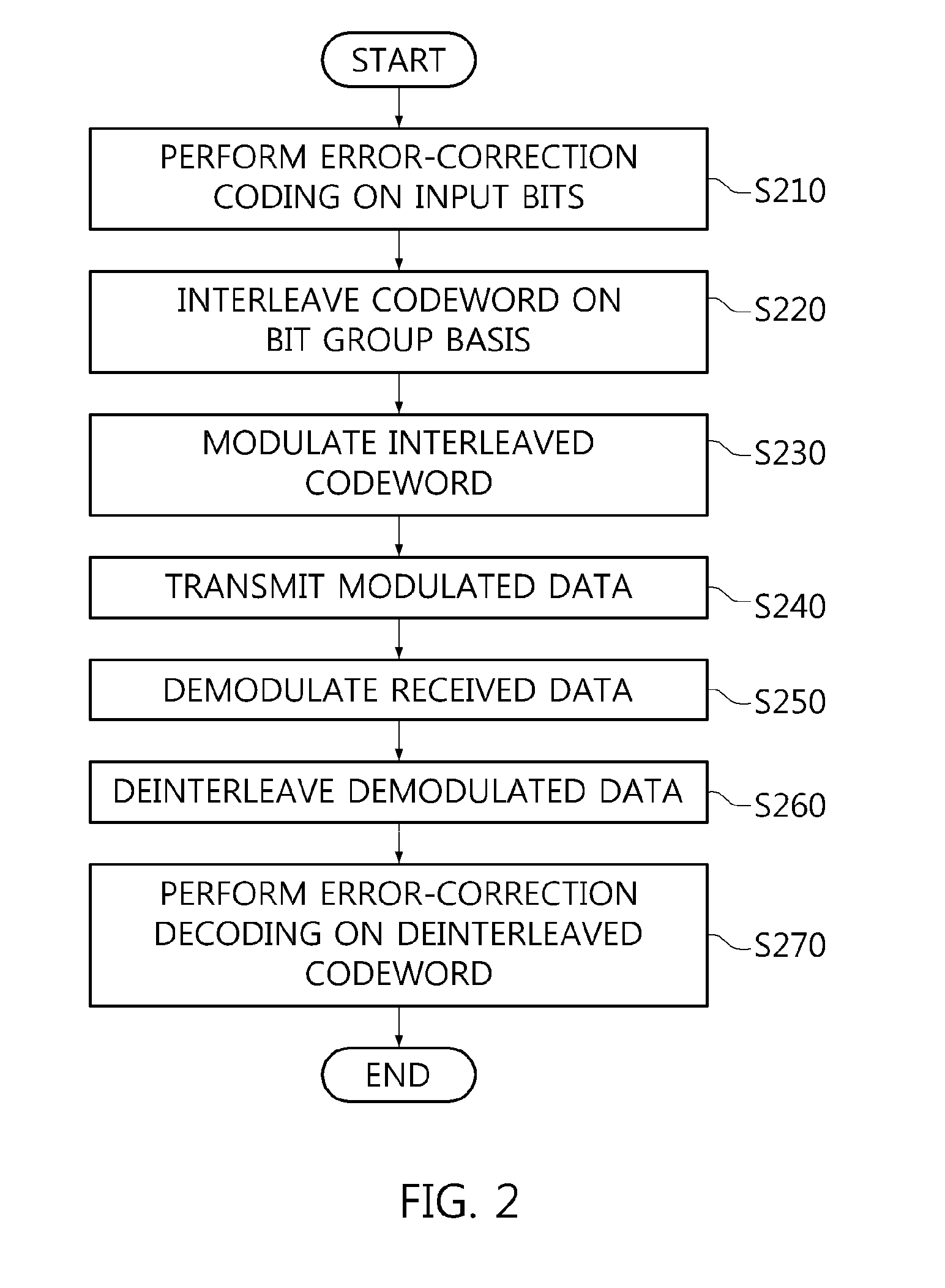

A transmitter apparatus and a receiver apparatus are provided. The transmitter apparatus includes: an encoder configured to generate a low density parity check (LDPC) by performing LDPC encoding; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol. The modulator maps a bit included in a predetermined group from among a plurality of groups constituting the LDPC codeword onto a predetermined bit in the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

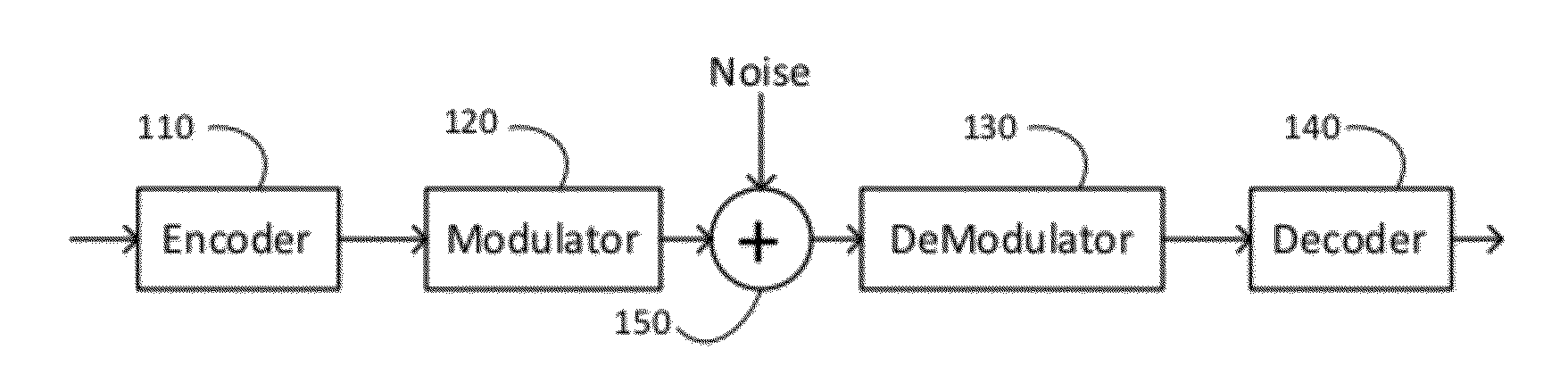

Apparatus and method for transmitting and receiving data in a communication system using low density parity check codes

ActiveUS20090063929A1Reduce signal distortionImprove performanceError prevention/detection by using return channelTransmission systemsCommunications systemLow-density parity-check code

An apparatus for transmitting data in a communication system using a Low Density Parity Check (LDPC) matrix is provided. The apparatus includes an interleaver for interleaving a descending bit-ordered codeword having a predetermined size and in accordance with a predetermined modulation scheme; and a bit mapper for mapping codeword bits constituting the interleaved codeword in accordance with a predetermined mapping scheme that takes into account degrees of the codeword bits and reliability characteristics of modulation symbol-constituting bits based on the predetermined modulation scheme.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitter apparatus and interleaving method thereof

ActiveUS20150236816A1Improve decoding performanceImprove reception performanceModulated-carrier systemsError correction/detection using LDPC codesComputer hardwareParity-check matrix

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding based on a parity check matrix; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

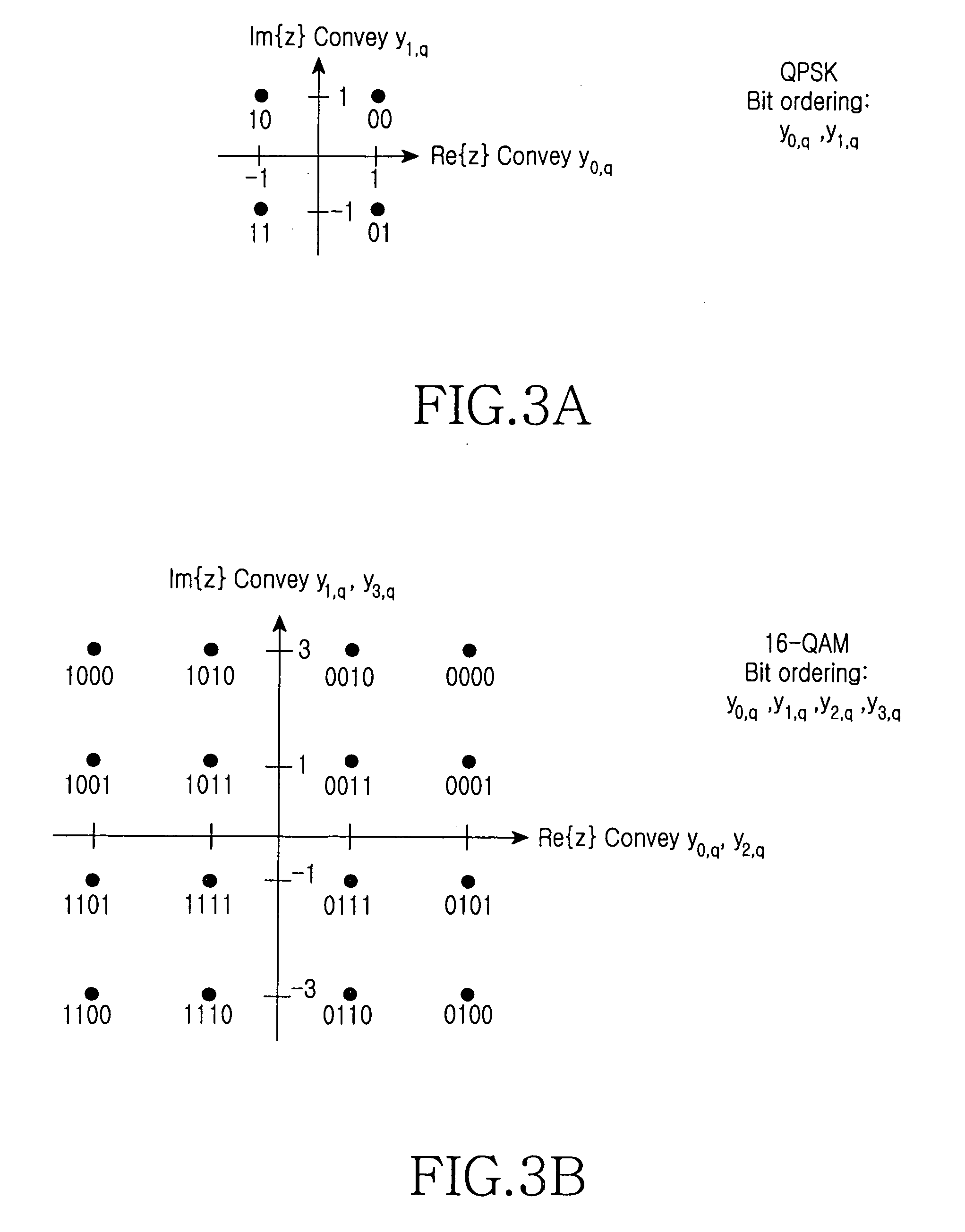

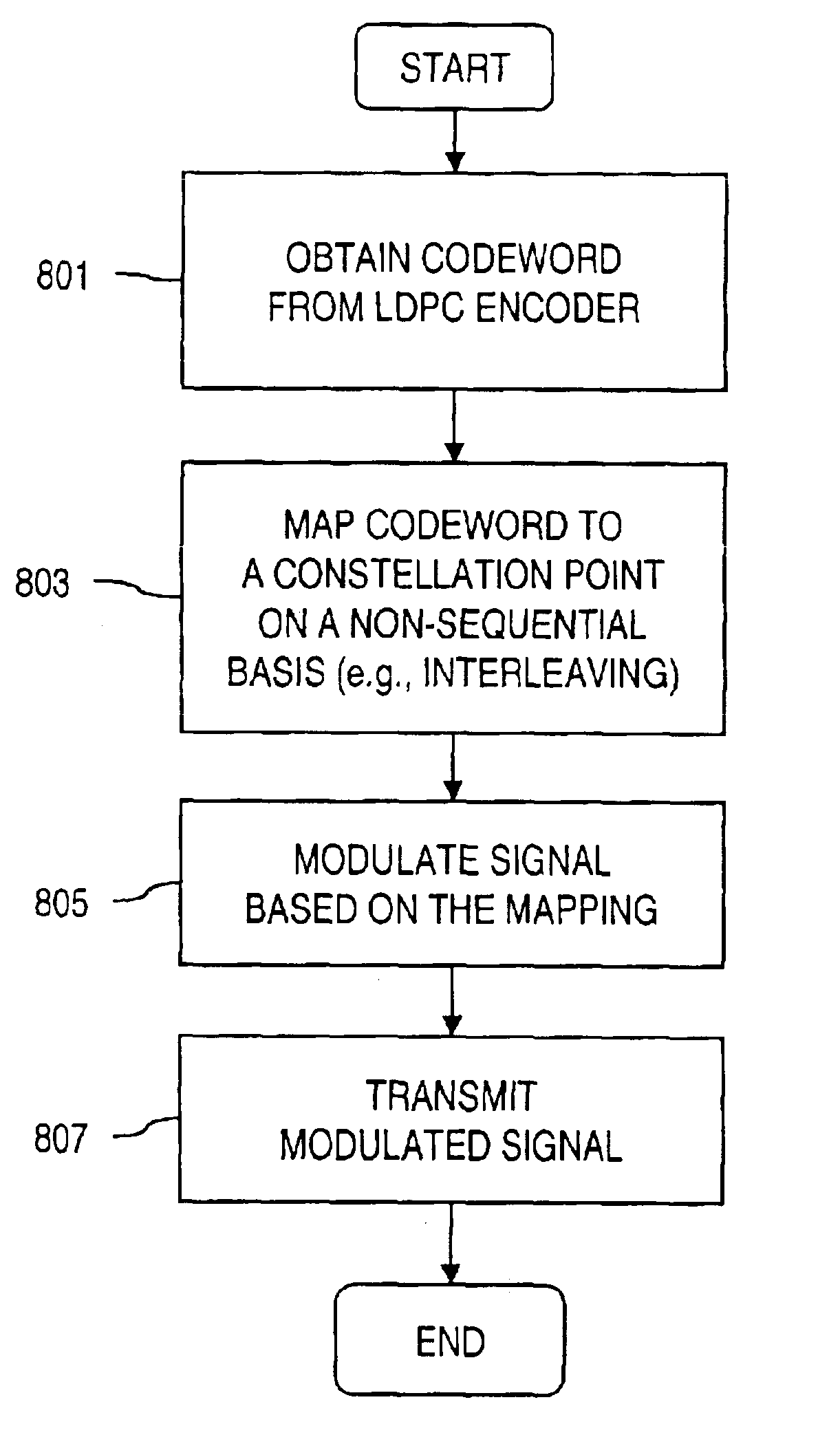

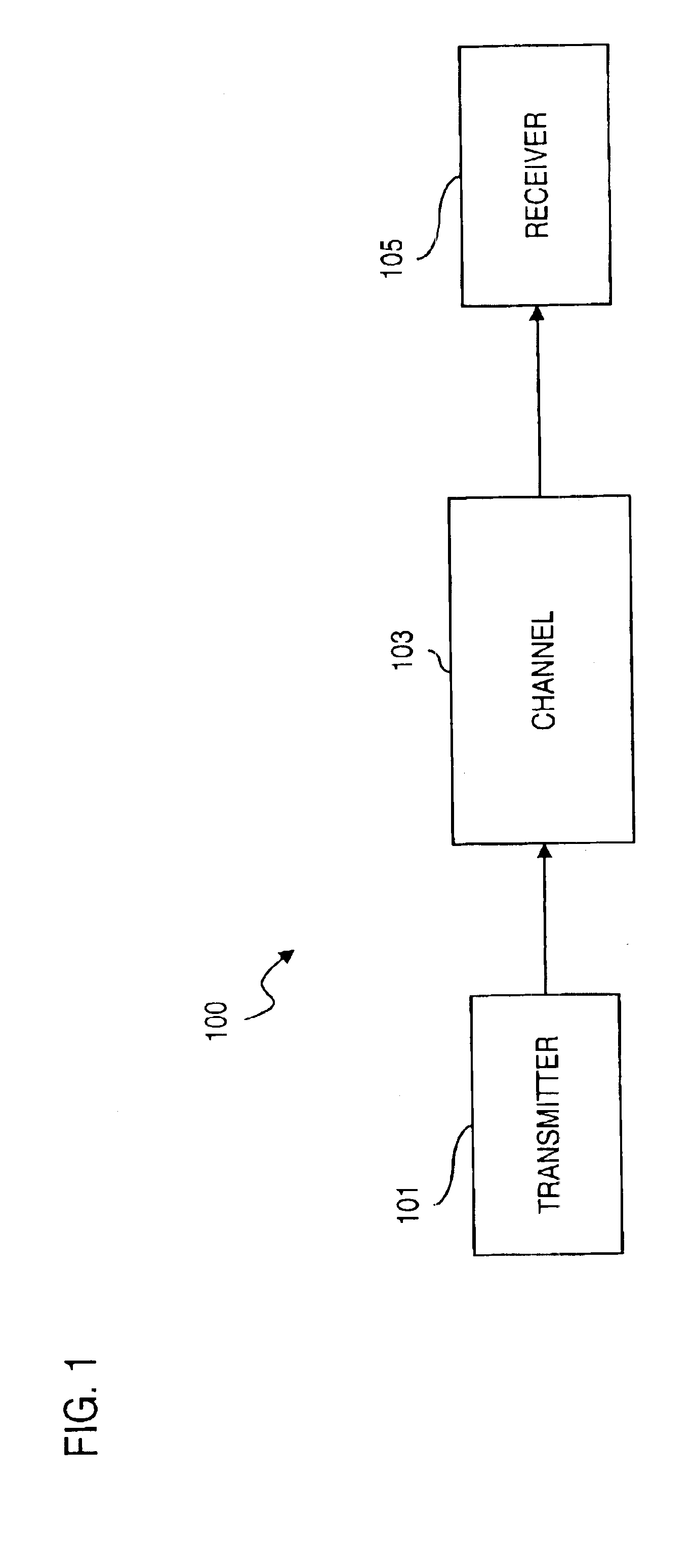

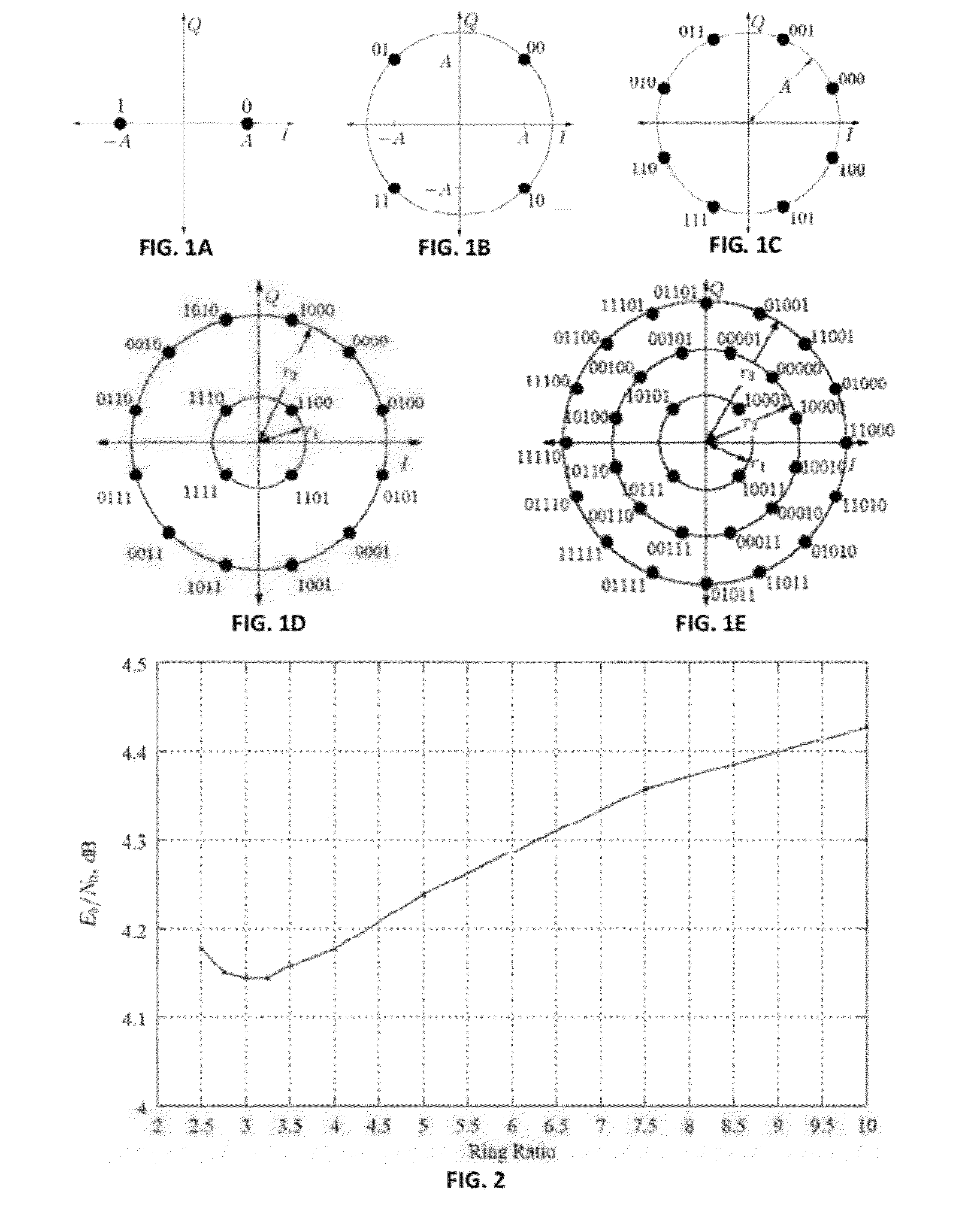

Bit labeling for amplitude phase shift constellation used with low density parity check (LDPC) codes

InactiveUS6963622B2Improve performanceError correction/detection using LDPC codesCode conversionParity-check matrixEngineering

An approach is provided for bit labeling of a signal constellation. A transmitter generates encoded signals using, according to one embodiment, a structured parity check matrix of a Low Density Parity Check (LDPC) code. The transmitter includes an encoder for transforming an input message into a codeword represented by a plurality of set of bits. The transmitter includes logic for mapping non-sequentially (e.g., interleaving) one set of bits into a higher order constellation (Quadrature Phase Shift Keying (QPSK), 8-PSK, 16-APSK (Amplitude Phase Shift Keying), 32-APSK, etc.), wherein a symbol of the higher order constellation corresponding to the one set of bits is output based on the mapping.

Owner:DTVG LICENSING INC

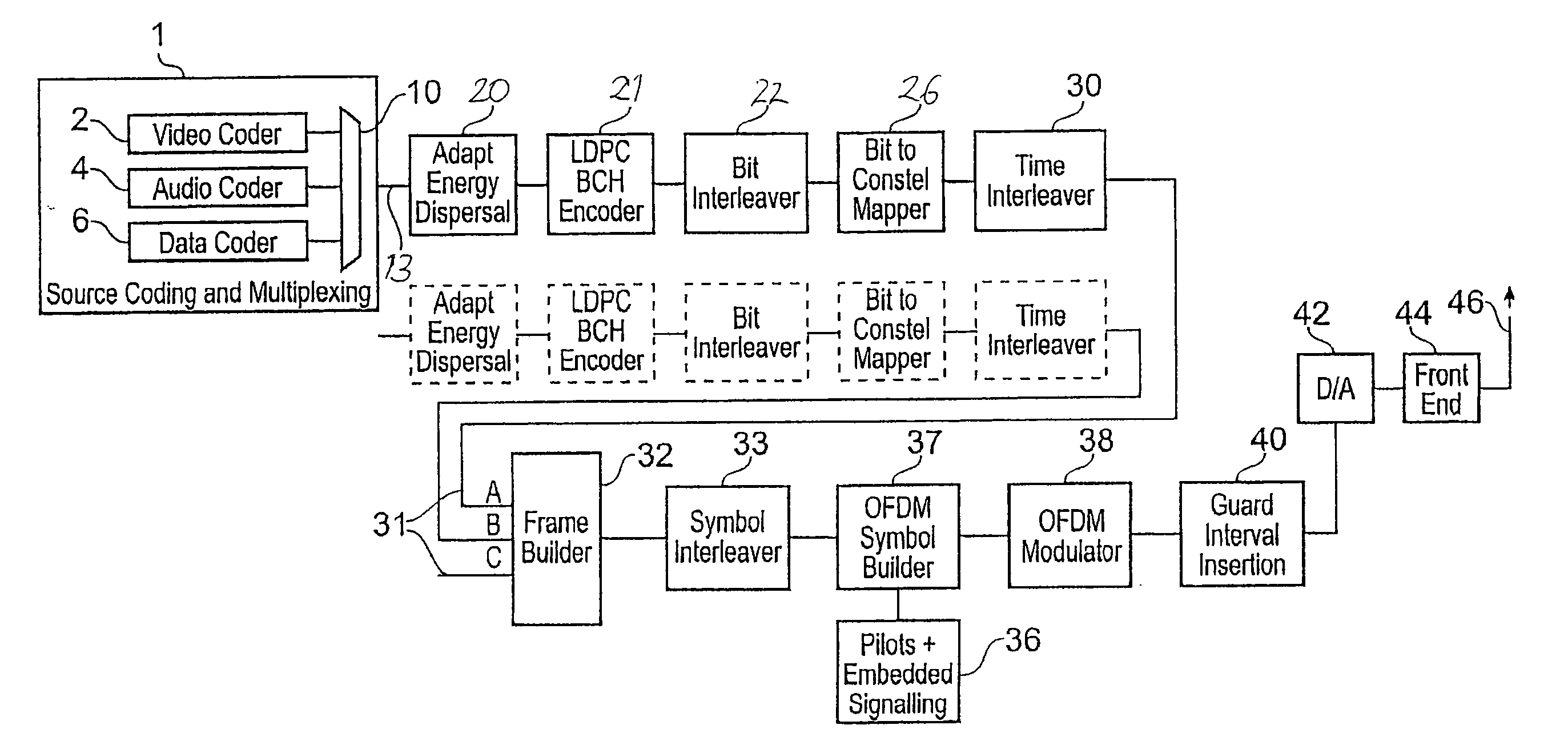

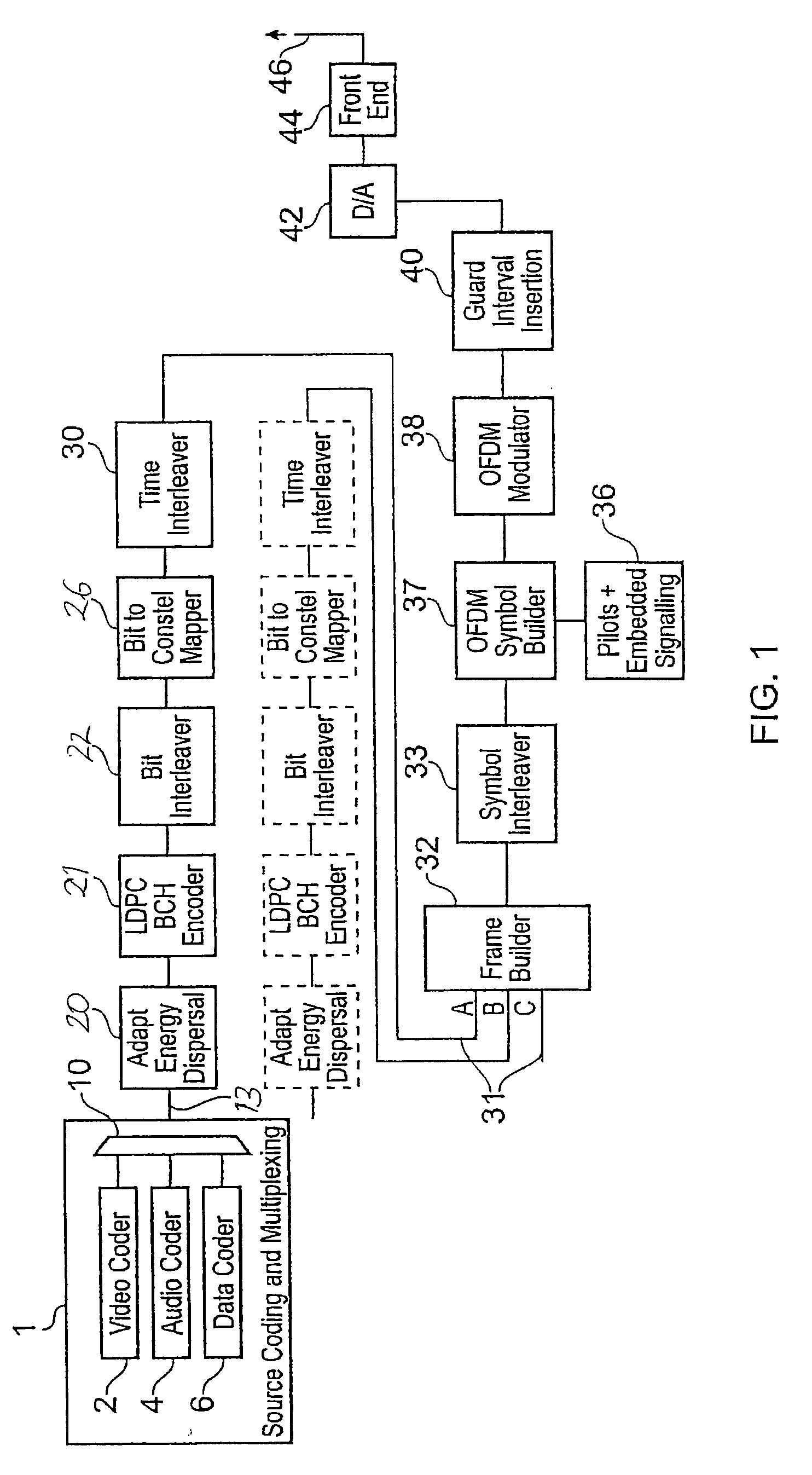

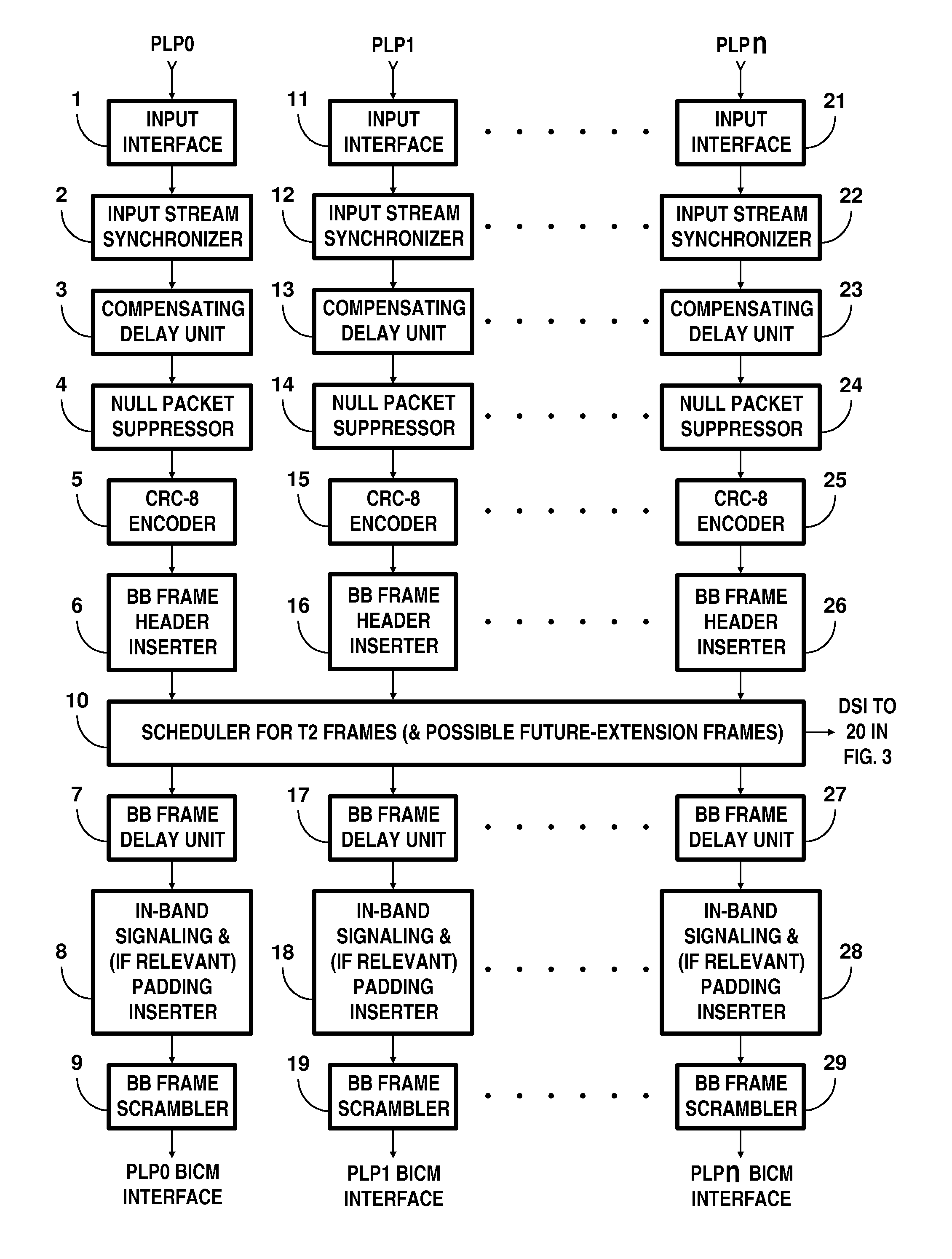

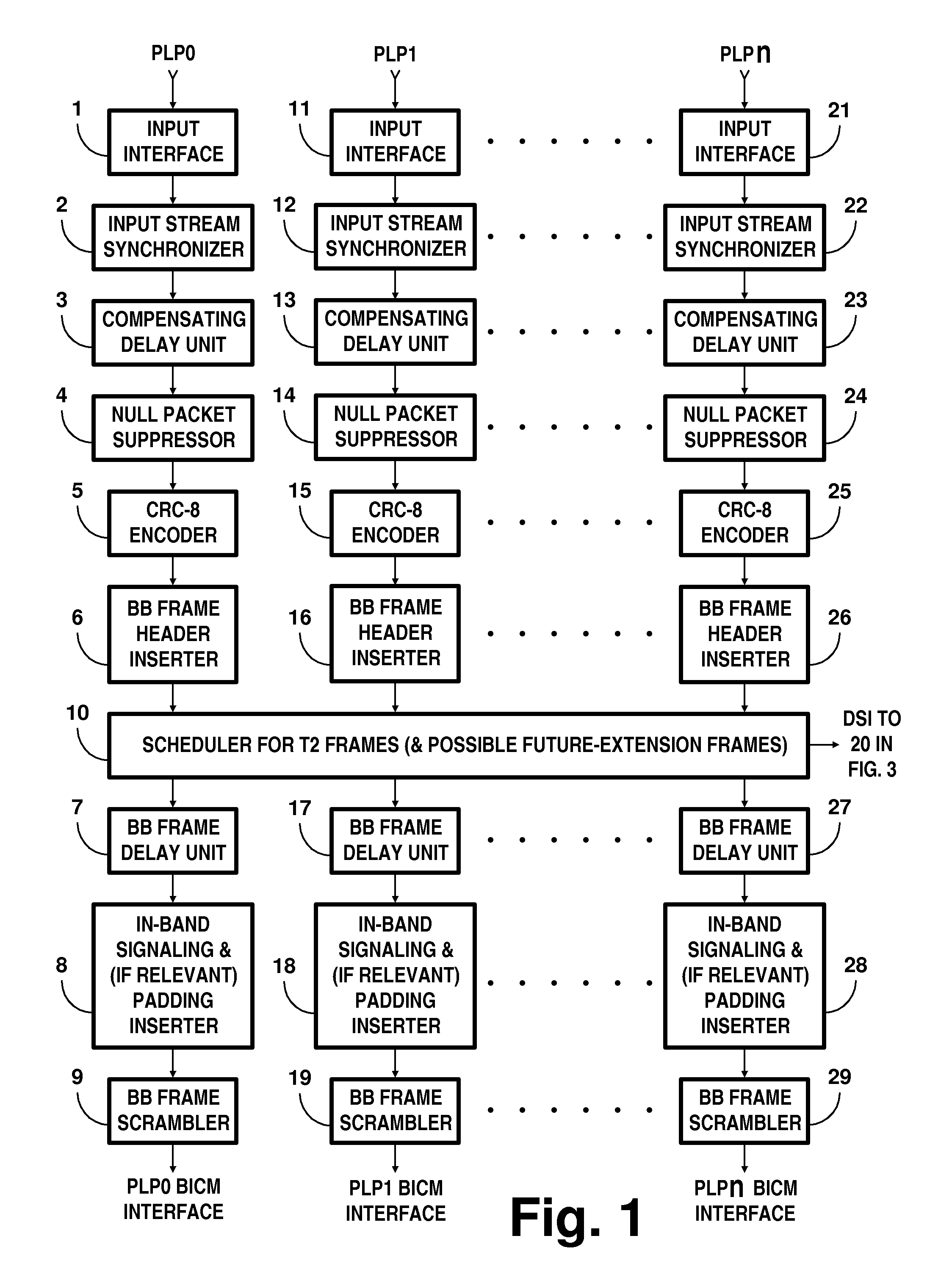

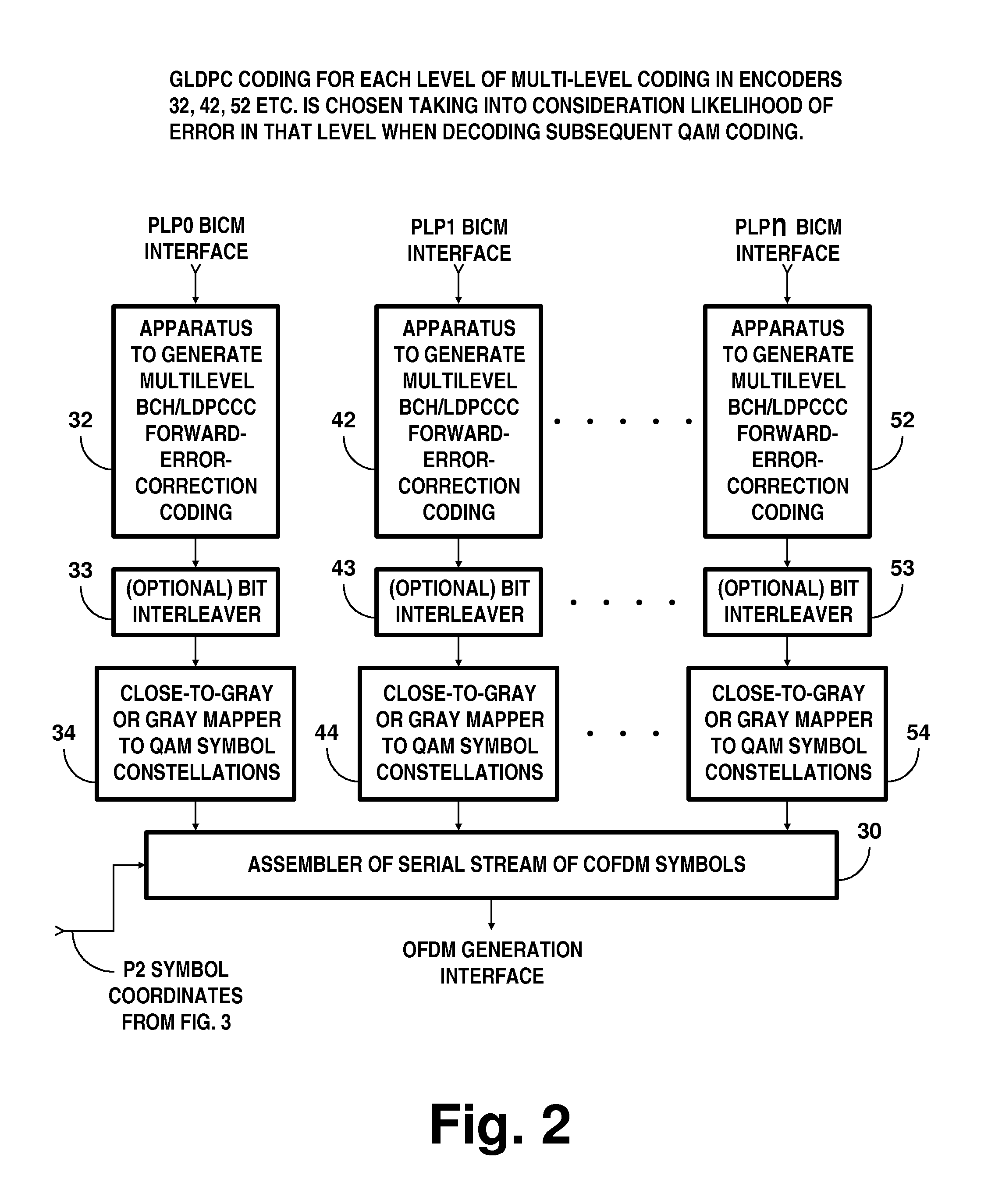

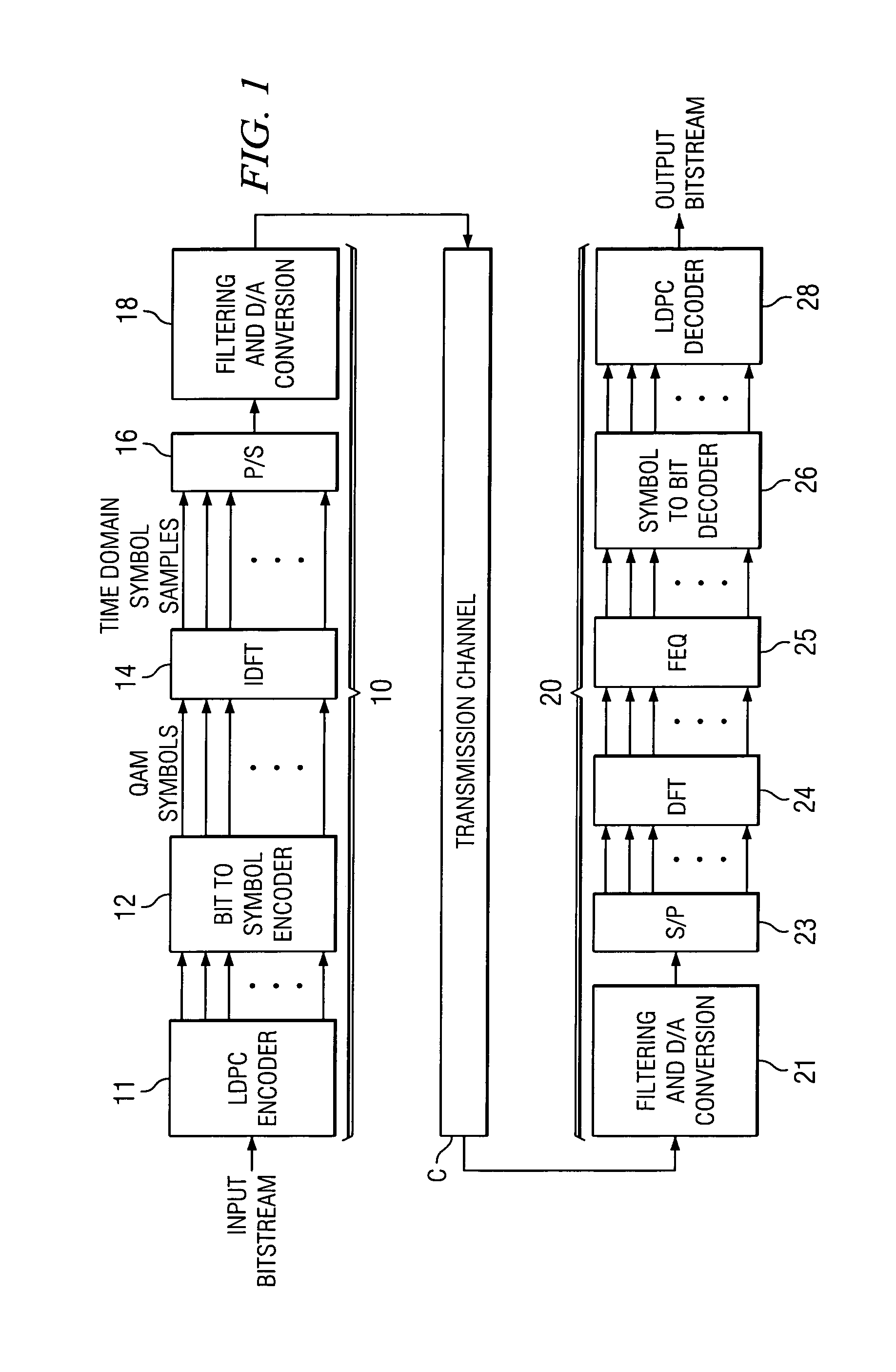

Digital television broadcasting system using coded orthogonal frequency-division modulation and multilevel LDPC convolutional coding

InactiveUS20150358648A1Facilitate parallel independent decodingError preventionError correction/detection using concatenated codesCarrier signalRadio frequency

In transmitter apparatus for a digital television (DTV) broadcasting system, internet-protocol (IP) packets of digital television information are subjected to multilevel concatenated Bose-Chaudhuri-Hocquenghem (BCH) coding and low-density parity-check convolutional coding (LDPCCC) before being bit-interleaved and mapped to quadrature-amplitude-modulation (QAM) constellations. The QAM constellations are used in coded orthogonal frequency-division modulation (COFDM) of plural carrier waves up-converted to a radio-frequency broadcast television channel. In receiver apparatus for the DTV broadcasting system the results of de-mapping QAM constellations recovered from demodulating the COFDM carrier waves are de-interleaved, and the constituent LDPCCC codewords are decoded to recover constituent BCH codewords of the multilevel BCH coding. The constituent BCH codewords are decoded to correct remnant bit errors in them. Then, IP packets of digital television information are reconstituted from the systematic data bits in those BCH codewords.

Owner:LIMBERG ALLEN LEROY

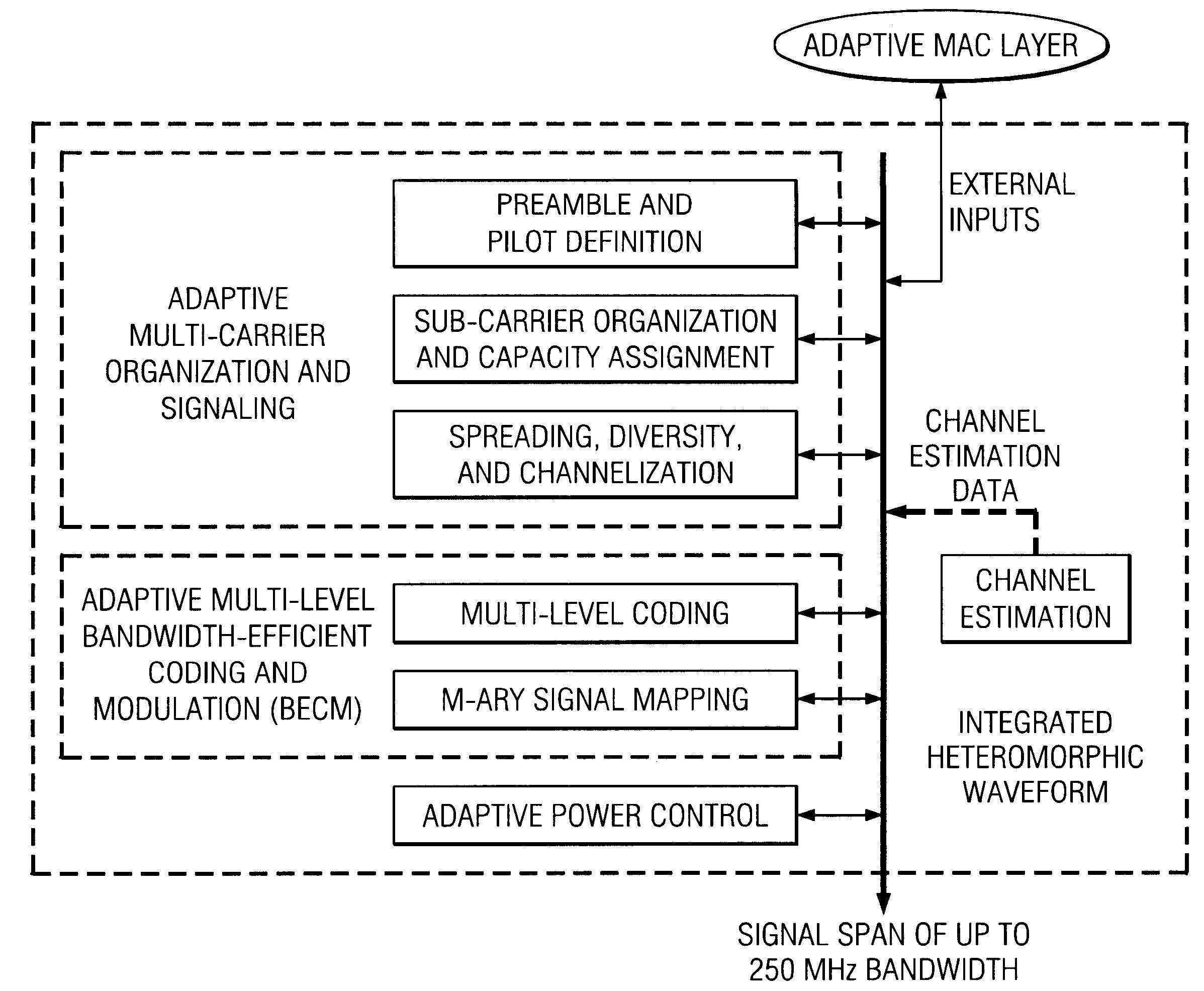

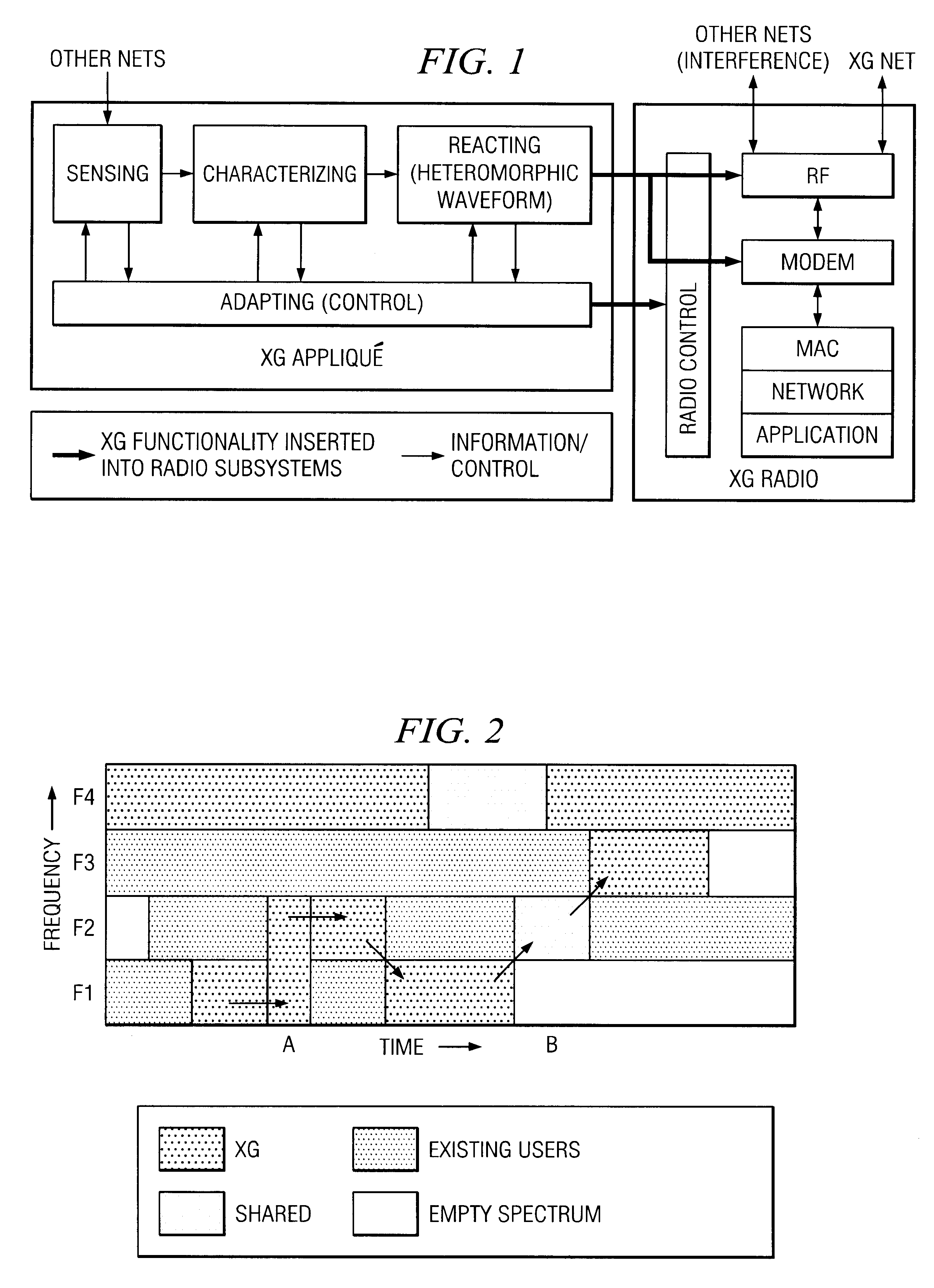

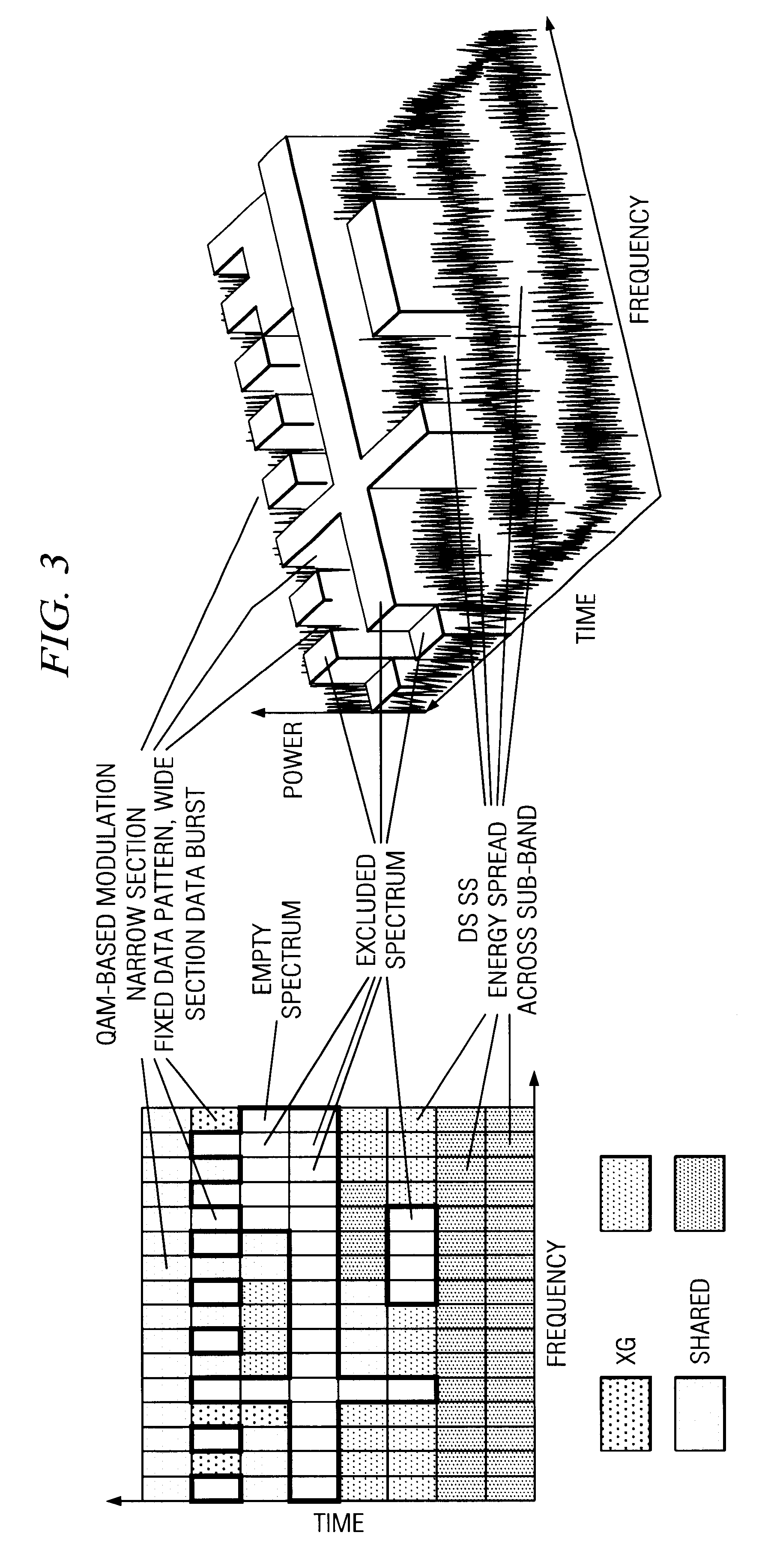

Adaptive air interface waveform

InactiveUS6847678B2Reduce and eliminate disadvantageReduce and eliminate and problemError correction/detection using LDPC codesCriteria allocationFrequency spectrumSpectral efficiency

In one embodiment, a method for generating an adaptive air interface waveform includes generating a waveform that includes a variable carrier frequency and variable bandwidth signal. The variable bandwidth signal includes one or more subcarriers that are dynamically placeable over a range of frequencies, and each subcarrier is separately modulated according to a direct sequence (DS) spread spectrum (SS) technique. The waveform has an embedded pilot usable to optimize one or more spectrum efficiencies of the waveform. A modulation constellation, a code rate, and a code length of the generated waveform are adapted according to an available spectrum and one or more sub-carrier conditions.

Owner:POWERWAVE COGNITION INC

Transmitter apparatus and bit interleaving method thereof

ActiveUS20150341054A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError correction/detection using LDPC codesParity-check matrixCheck digit

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding of input bits based on a parity check matrix including information word bits and parity bits, the LDPC codeword including a plurality of bit groups each including a plurality of bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the interleaver is further configured to interleave the LDPC codeword such that a bit included in a predetermined bit group from among the plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitting apparatus and interleaving method thereof

ActiveUS20150341052A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError detection/correctionParity-check matrixComputer engineering

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to perform a low-density parity check (LDPC) encoding on input bits using a parity check matrix to generate an LDPC codeword comprising information word bits and parity bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

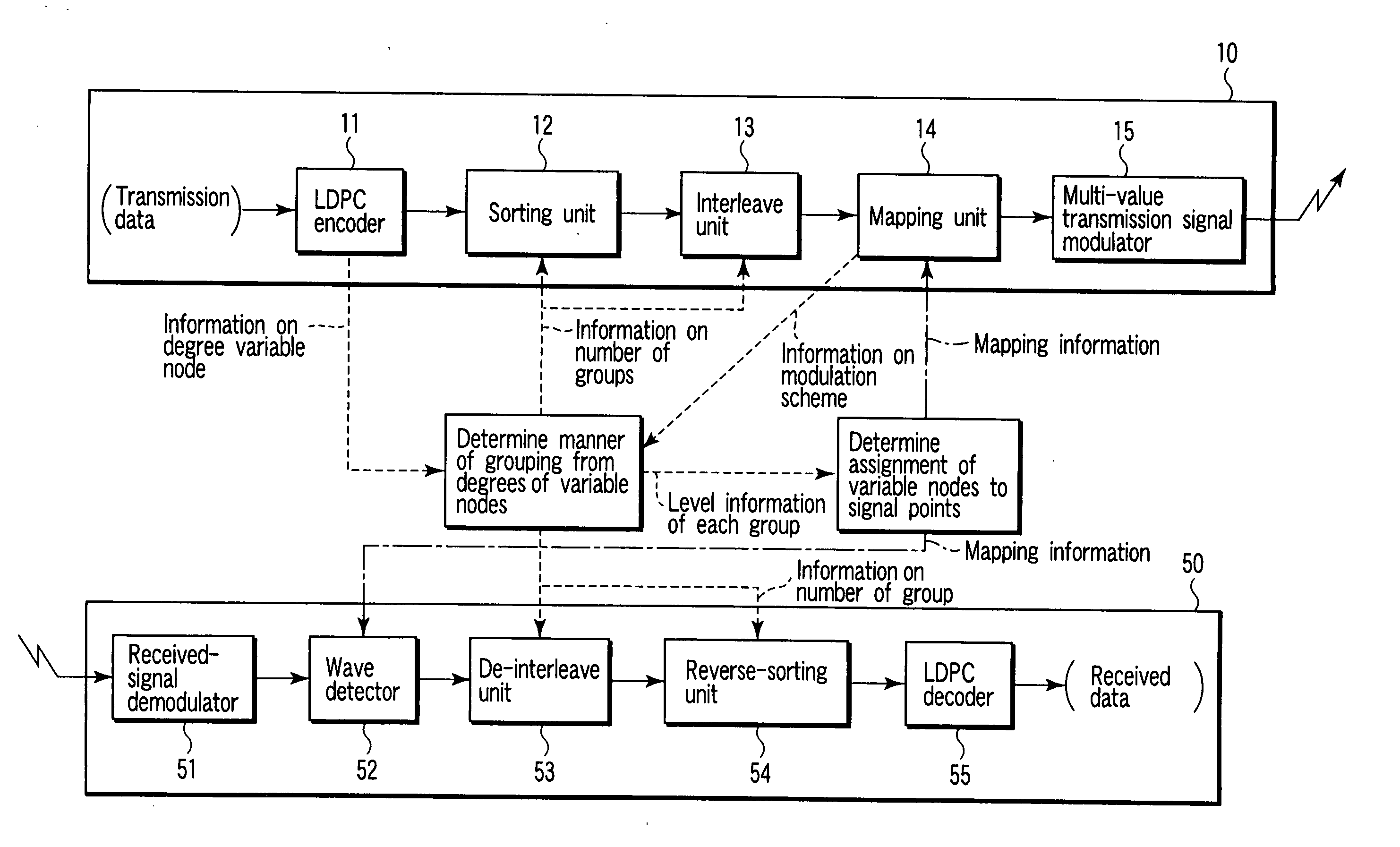

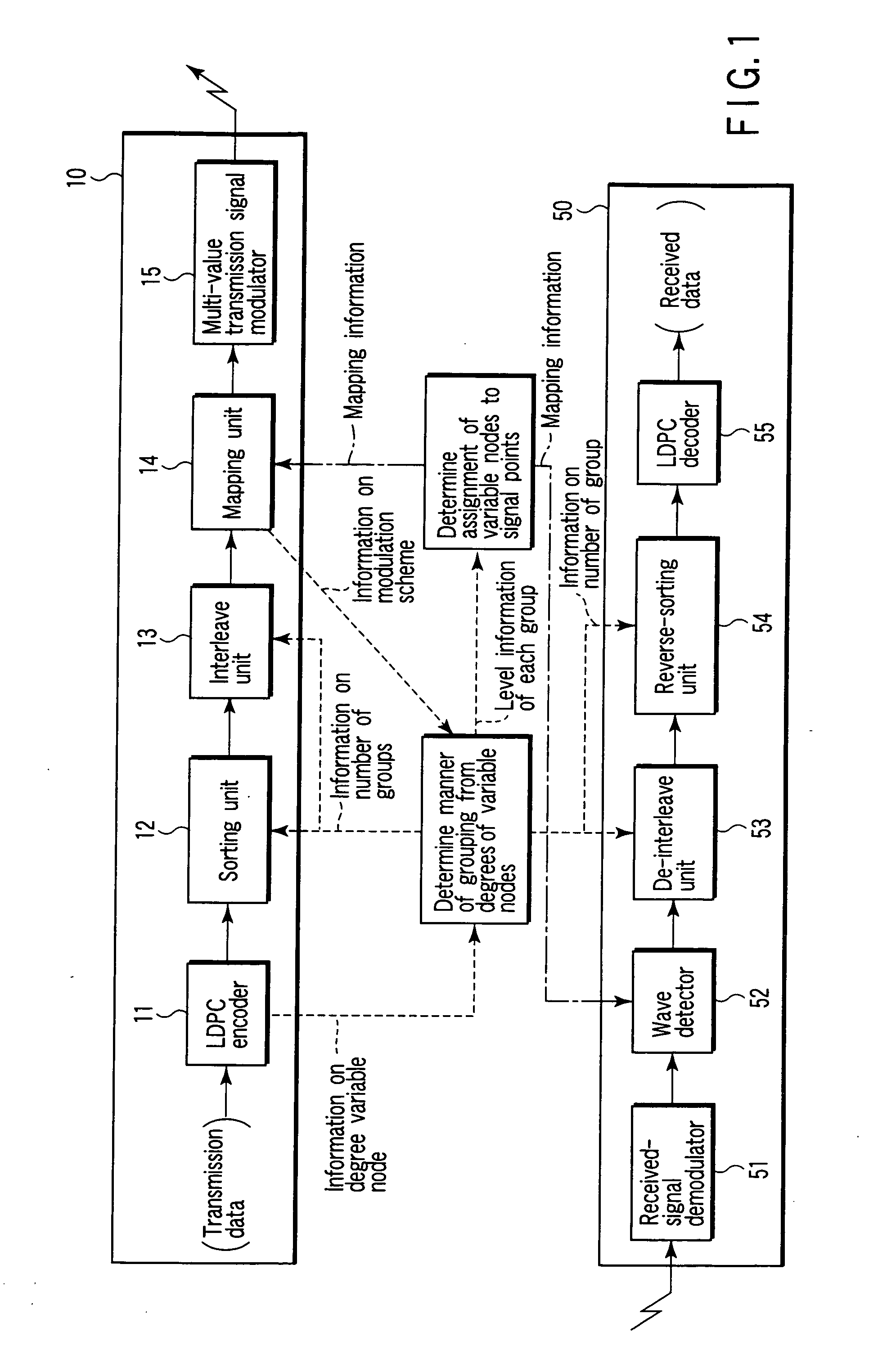

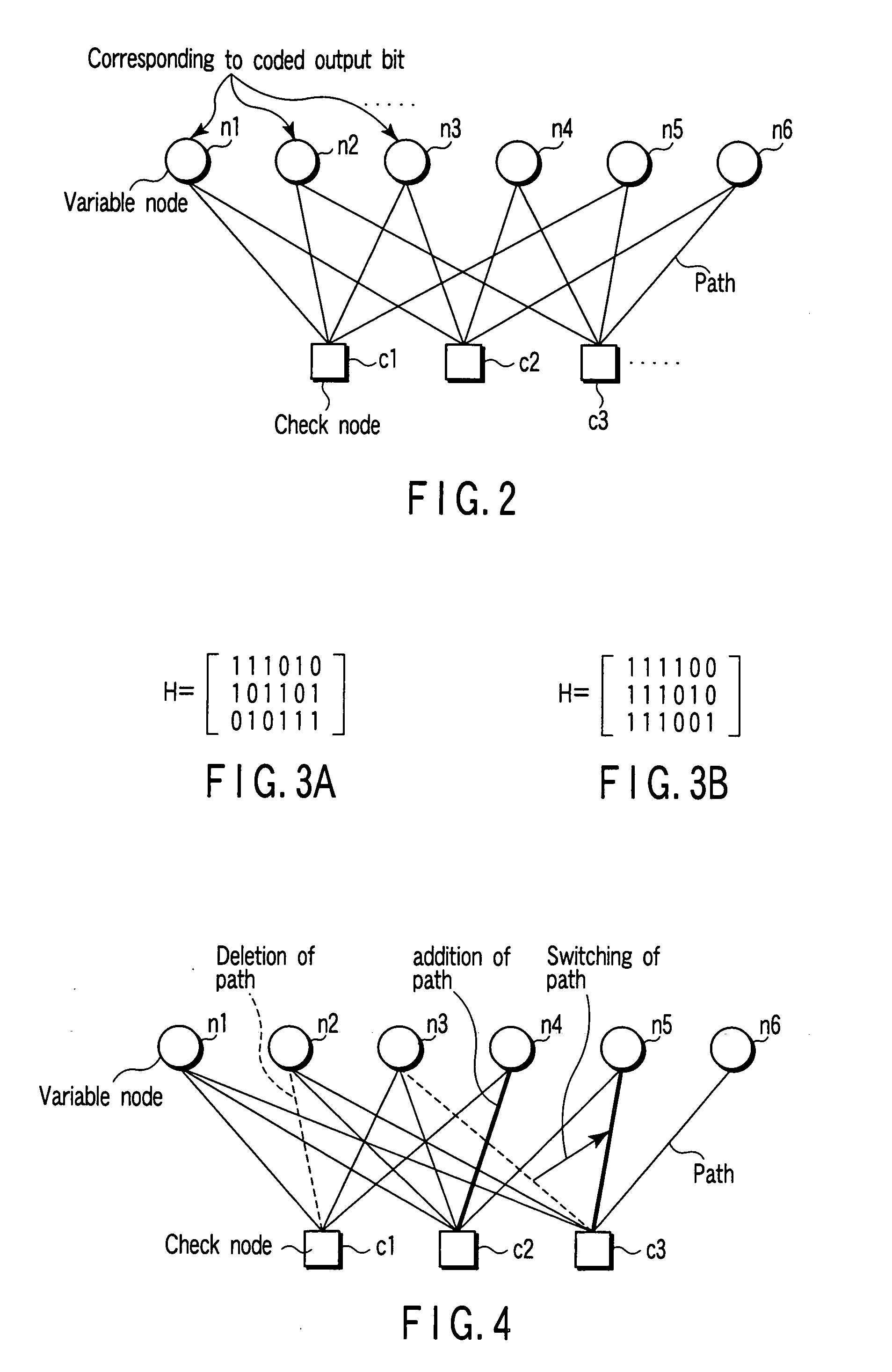

Mapping method for encoded bits using LDPC code, transmitting and receiving apparatuses employing this method, and program for executing this method

InactiveUS20050216821A1Transmission path divisionError correction/detection using LDPC codesTheoretical computer scienceParity-check matrix

A method for mapping of coded bits using a low density parity check (LDPC) code, comprises encoding information bits by using the LDPC code to generate coded bits, sorting the coded bits in accordance with degrees of variable nodes represented by a parity check matrix of the LDPC code, dividing the sorted coded bits into a plurality of groups in accordance with a using modulation scheme, and mapping the coded bits to respective modulation signal points by considering an error resistance of each of the groups and an error resistance of a corresponding one of the modulation signal points.

Owner:KK TOSHIBA

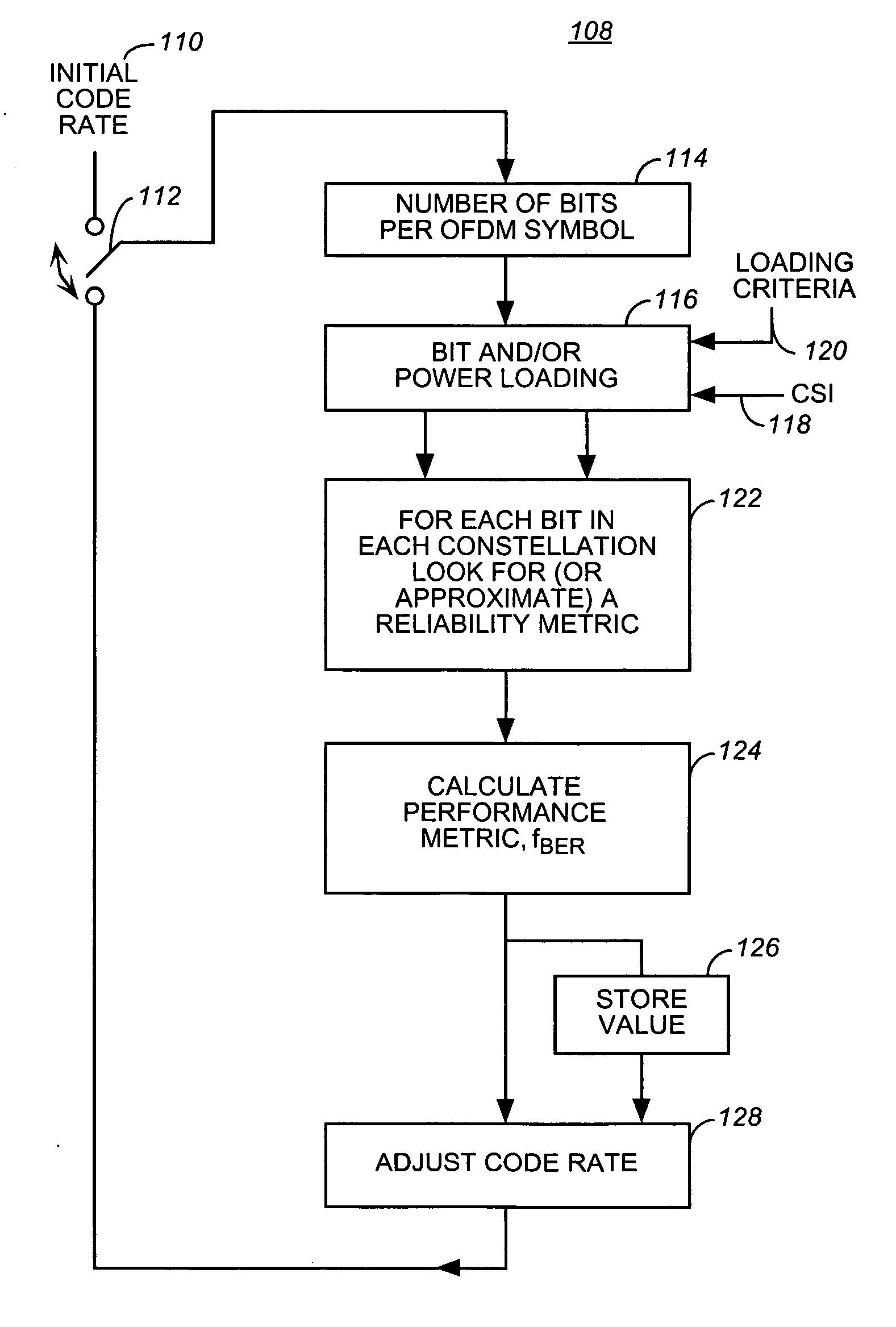

Apparatus, and associated method, for allocating communications in a multi-channel communication system

InactiveUS20060013181A1Transmission path divisionError correction/detection using LDPC codesCommunications systemSelf adaptive

Apparatus, and an associated method, for allocating communication data for communication in a multi-channel communication system, such as an OFDM system. An adaptive bit, power, and code rate scheme for a sending station that utilizes LDPC codes selects together bit, power, and code rates of data that are to be communicated upon different ones of the channels in manners that optimize a selected performance criteria.

Owner:NOKIA CORP

LDPC (Low Density Parity Check) coding and interleaving implemented in MIMO communication systems

ActiveUS20060156169A1Data representation error detection/correctionError correction/detection using LDPC codesCommunications systemSignal-to-noise ratio (imaging)

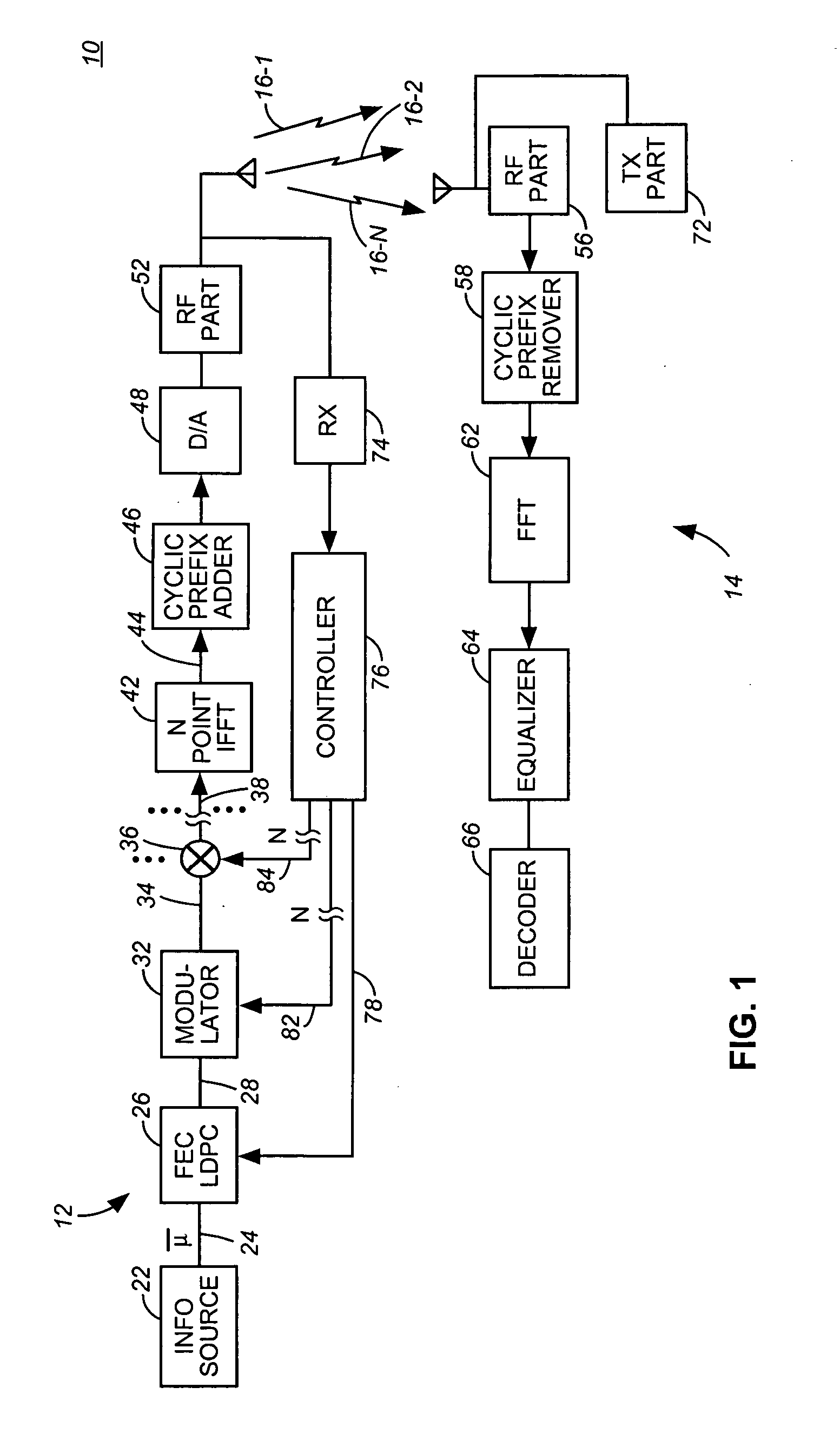

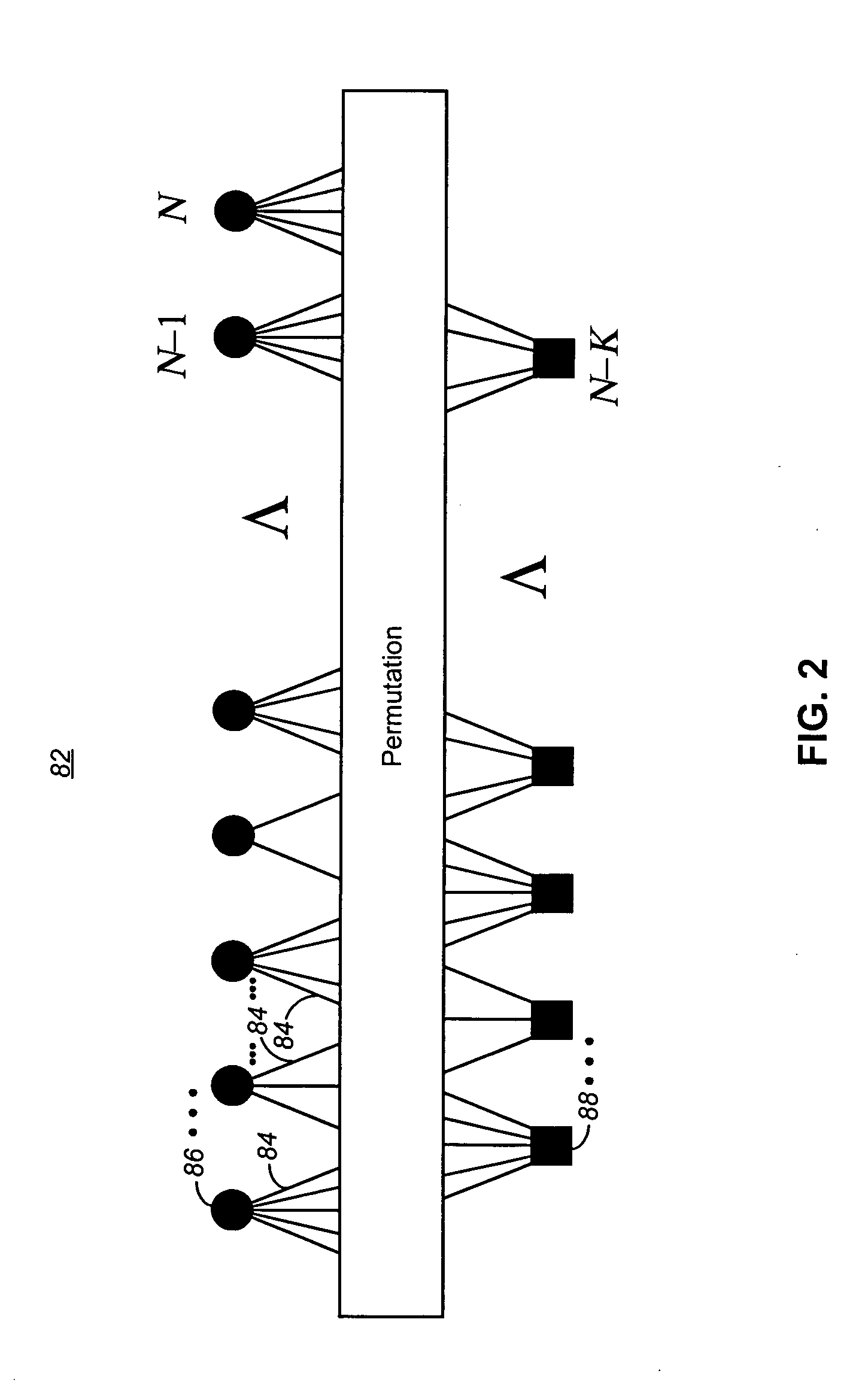

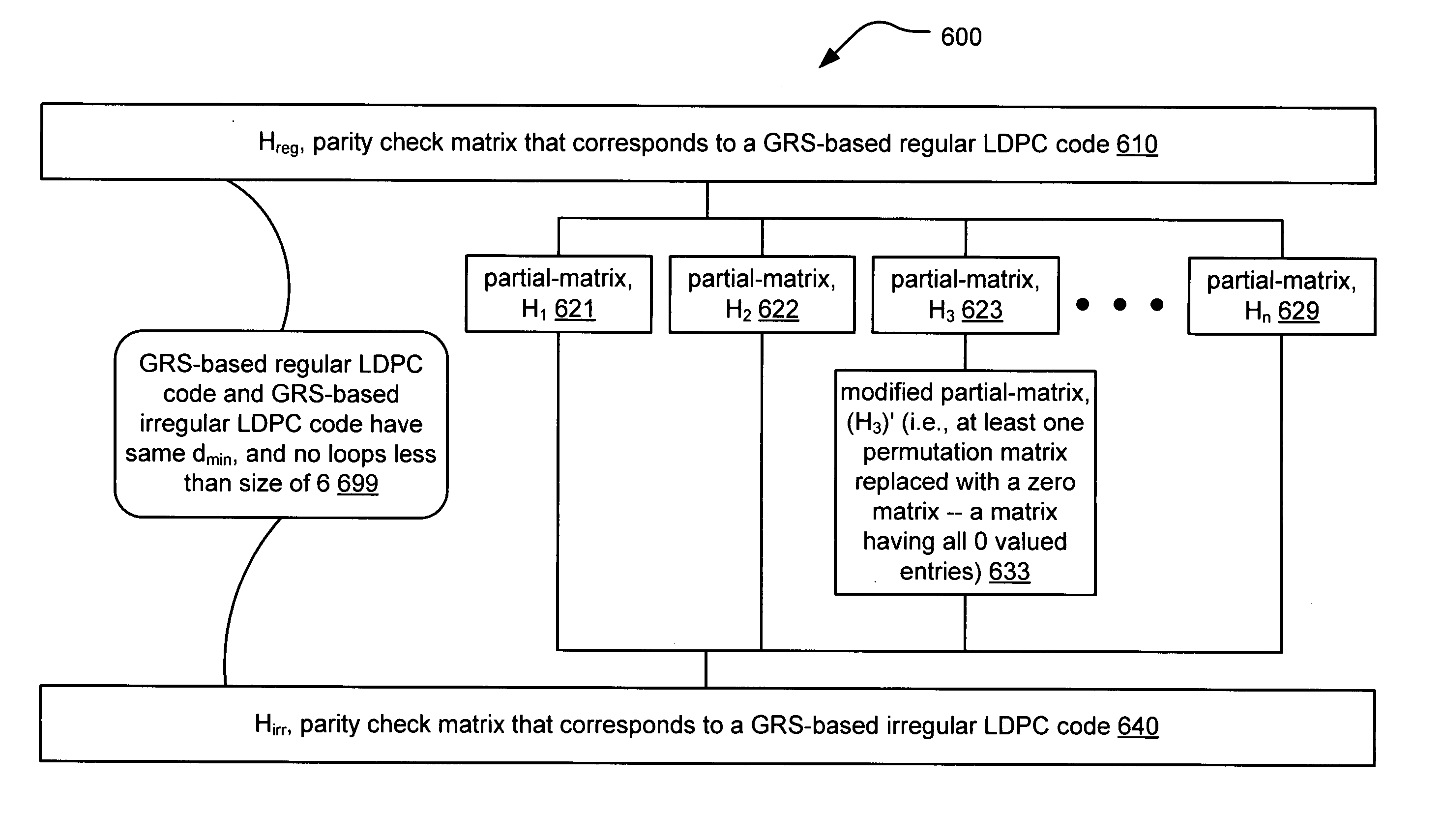

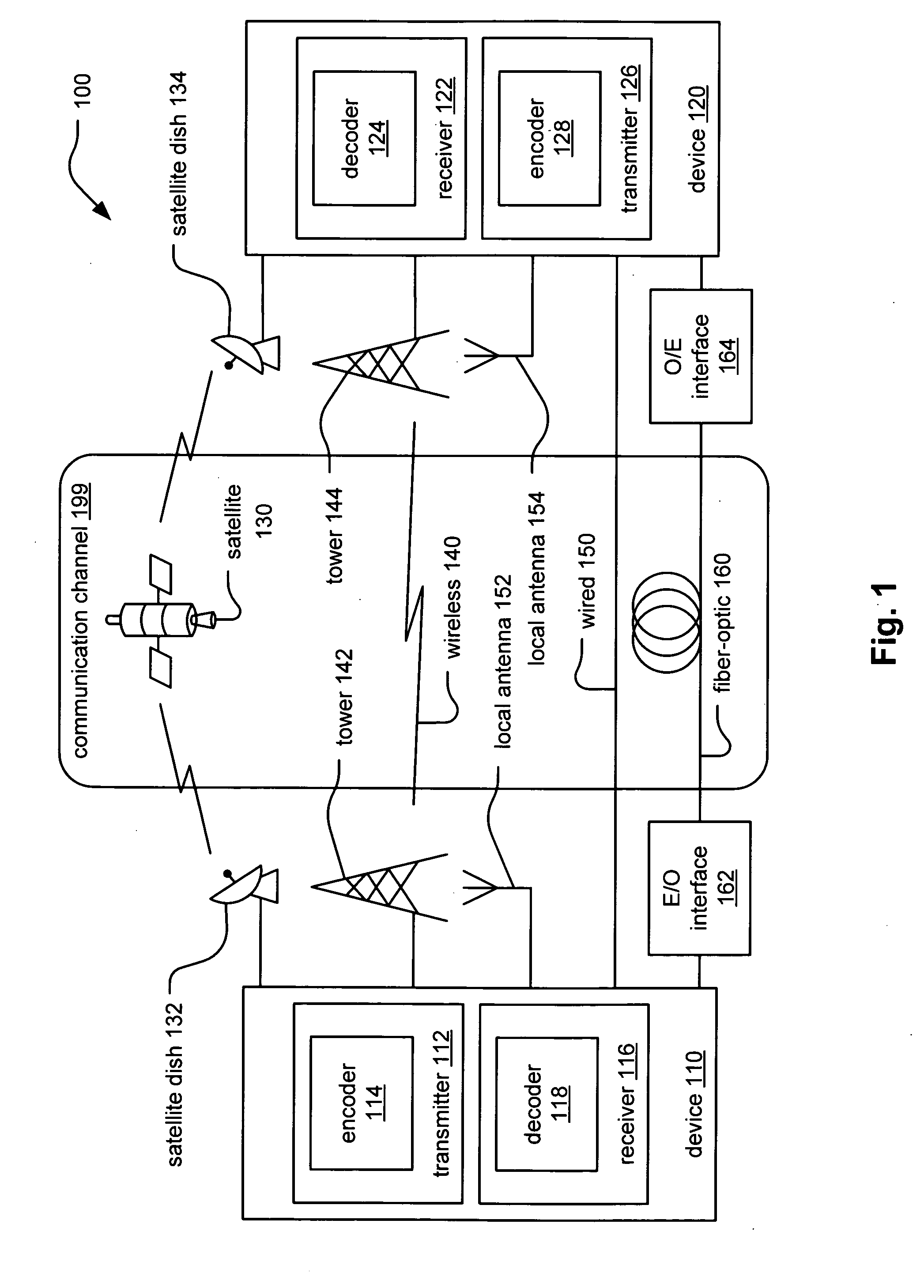

LDPC (Low Density Parity Check) coding and interleaving implemented in multiple-input-multiple-output (MIMO) communication systems. Initially, a novel approach is presented by which a wide variety of irregular LDPC codes may be generated using GRS or RS codes. These irregular LDPC codes can provide better overall performance than regular LDPC codes in terms of providing for lower BER (Bit Error Rate) as a function of SNR (Signal to Noise Ratio). A variety of communication device types are also presented that may employ the error correcting coding using a GRS-based irregular LDPC code, along with appropriately selected interleaving, to provide for even better performance. These communication devices may be implemented to in wireless communication systems including those that comply with the recommendation practices and standards being developed by the IEEE 802.11n Task Group (i.e., the Task Group that is working to develop a standard for 802.11 TGn (High Throughput)).

Owner:AVAGO TECH INT SALES PTE LTD

Transmitting apparatus and interleaving method thereof

ActiveUS20150236721A1Improve decoding performanceImprove reception performanceError correction/detection using LDPC codesError correction/detection using multiple parity bitsParity-check matrixLow density

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low density parity check (LDPC) codeword by LDPC encoding based on a parity check matrix; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Apparatus and method for transmitting and receiving data in a communication system using low density parity check code

ActiveUS20090125781A1Reduce signal distortionImprove performanceModulated-carrier systemsError correction/detection using LDPC codesCommunications systemLow-density parity-check code

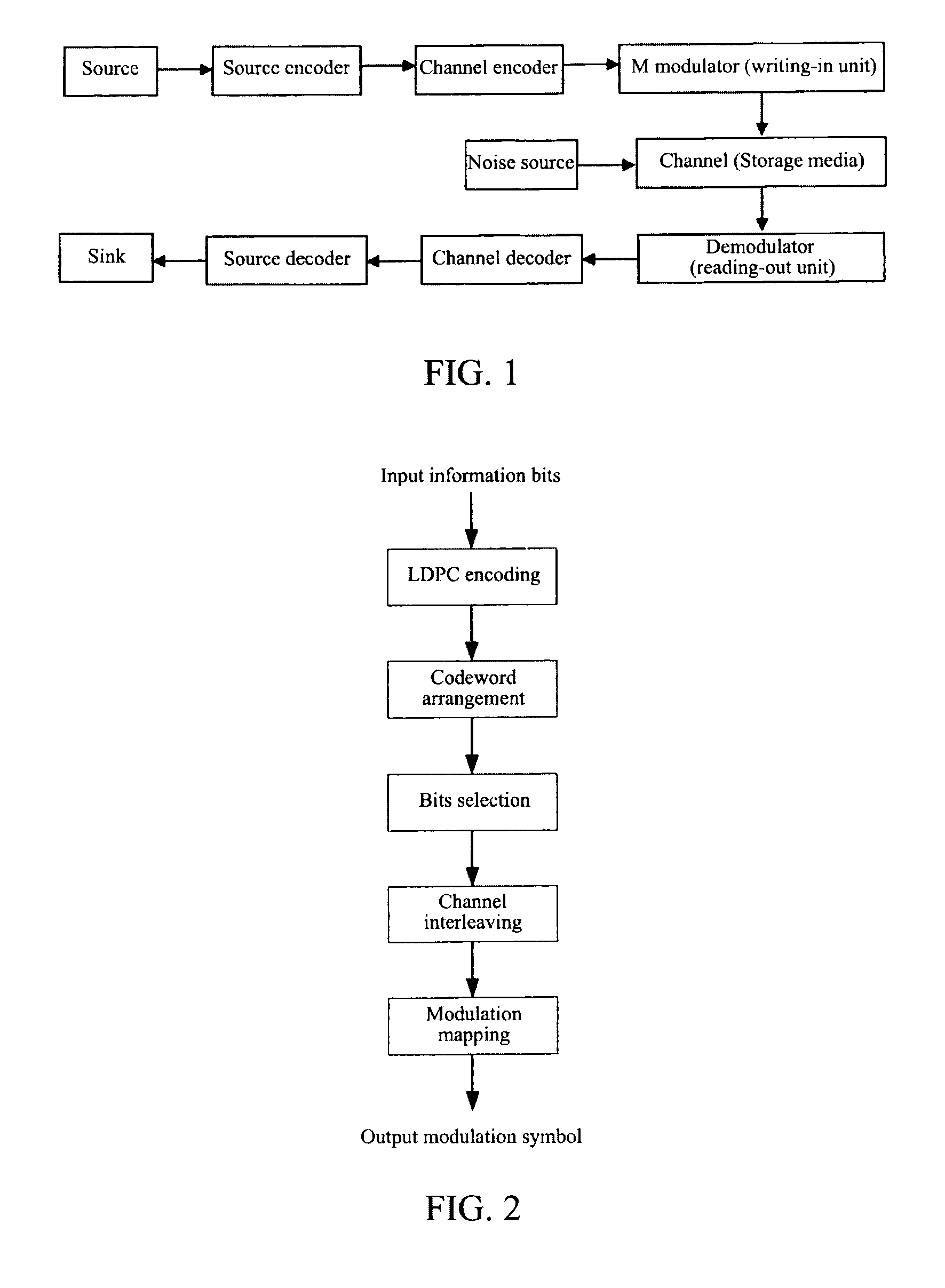

A method for transmitting data in a communication system using a Low Density Parity Check (LDPC) matrix includes generating an LDPC codeword by encoding information data bits, interleaving the LDPC codeword, mapping the interleaved LDPC codeword to a modulation signal, and generating a mapped signal by mapping the LDPC codeword bits separately to a bit corresponding to a real part and a bit corresponding to an imaginary part of said modulation signal, among bits constituting the modulation signal, generating a modulation signal by high-order-modulating the mapped signal and Radio Frequency (RF)-processing the modulation signal, and transmitting the RF-processed signal via a transmission antenna.

Owner:POSTECH ACAD IND FOUND +1

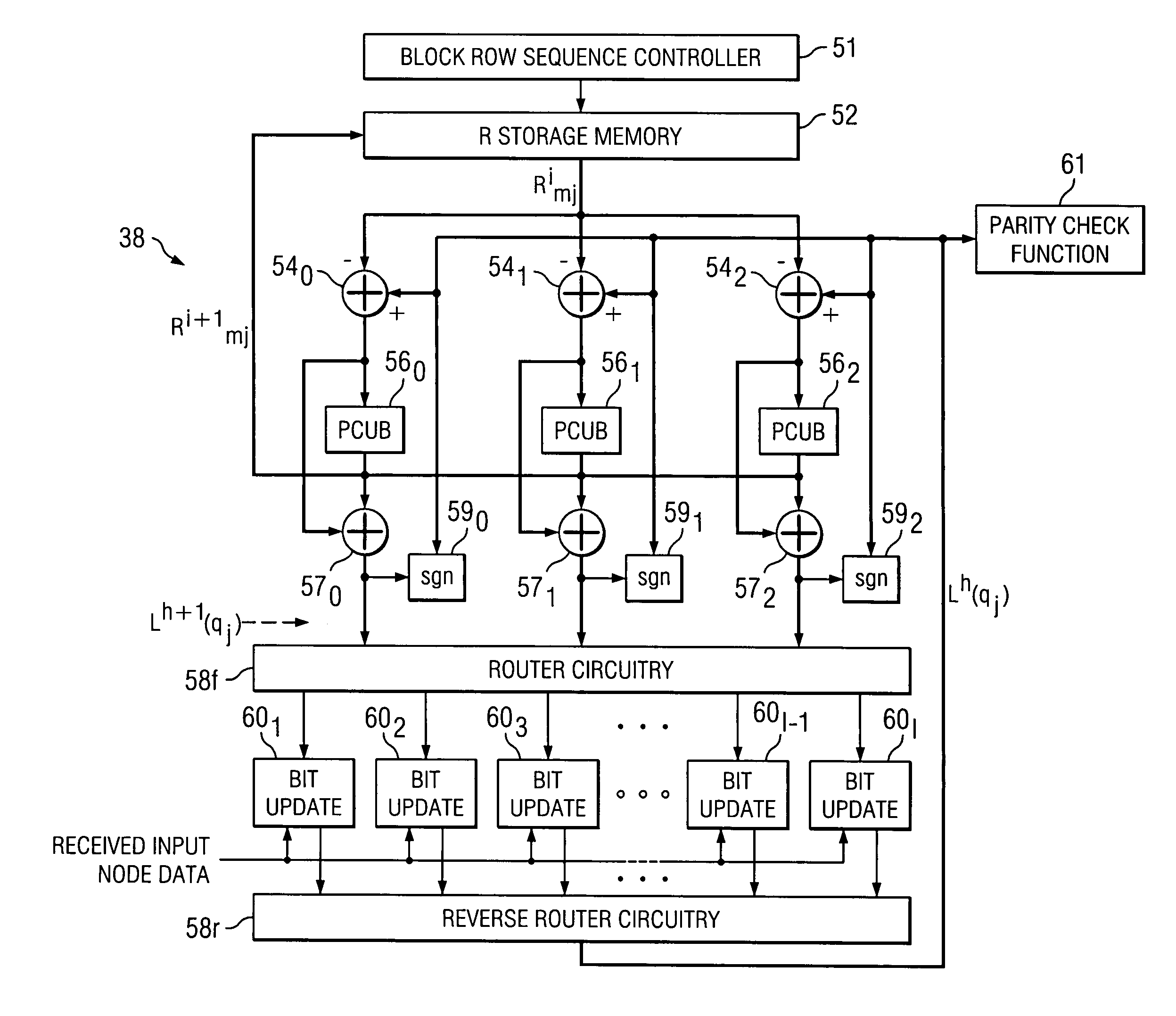

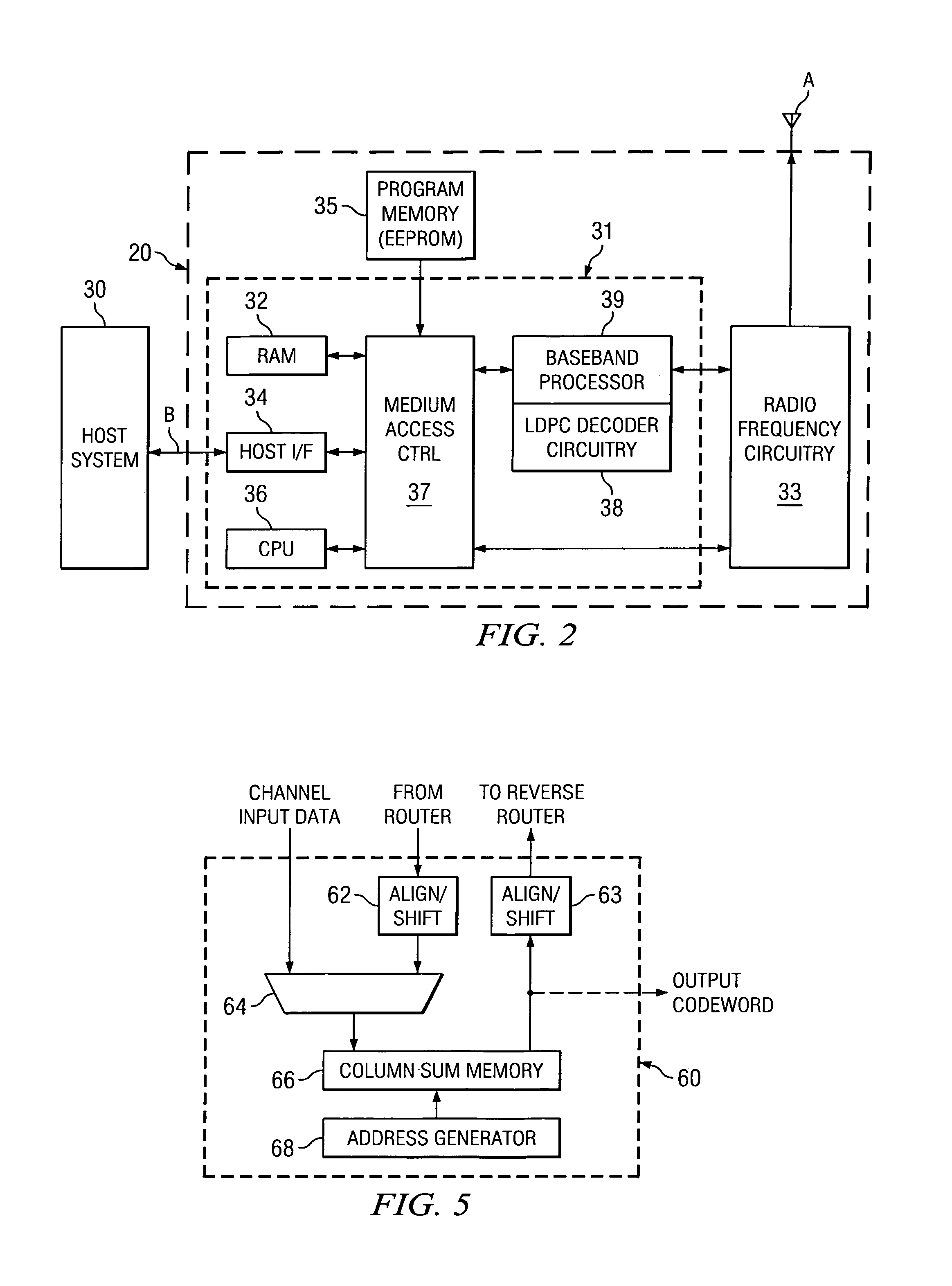

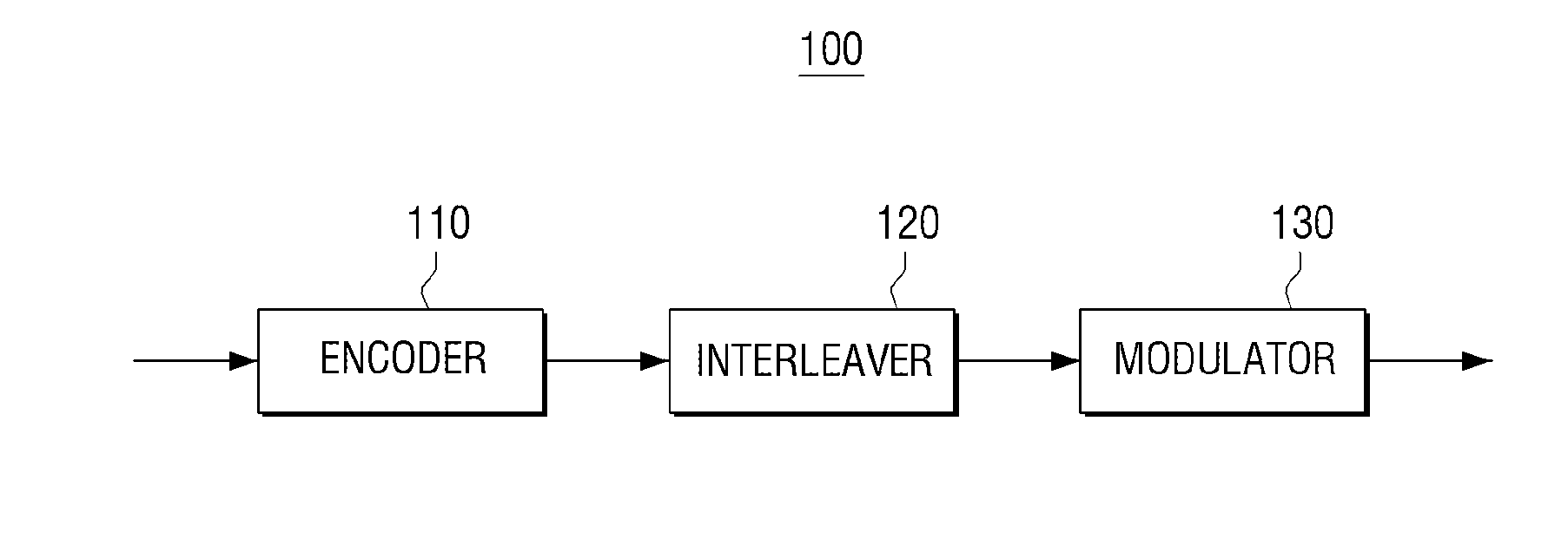

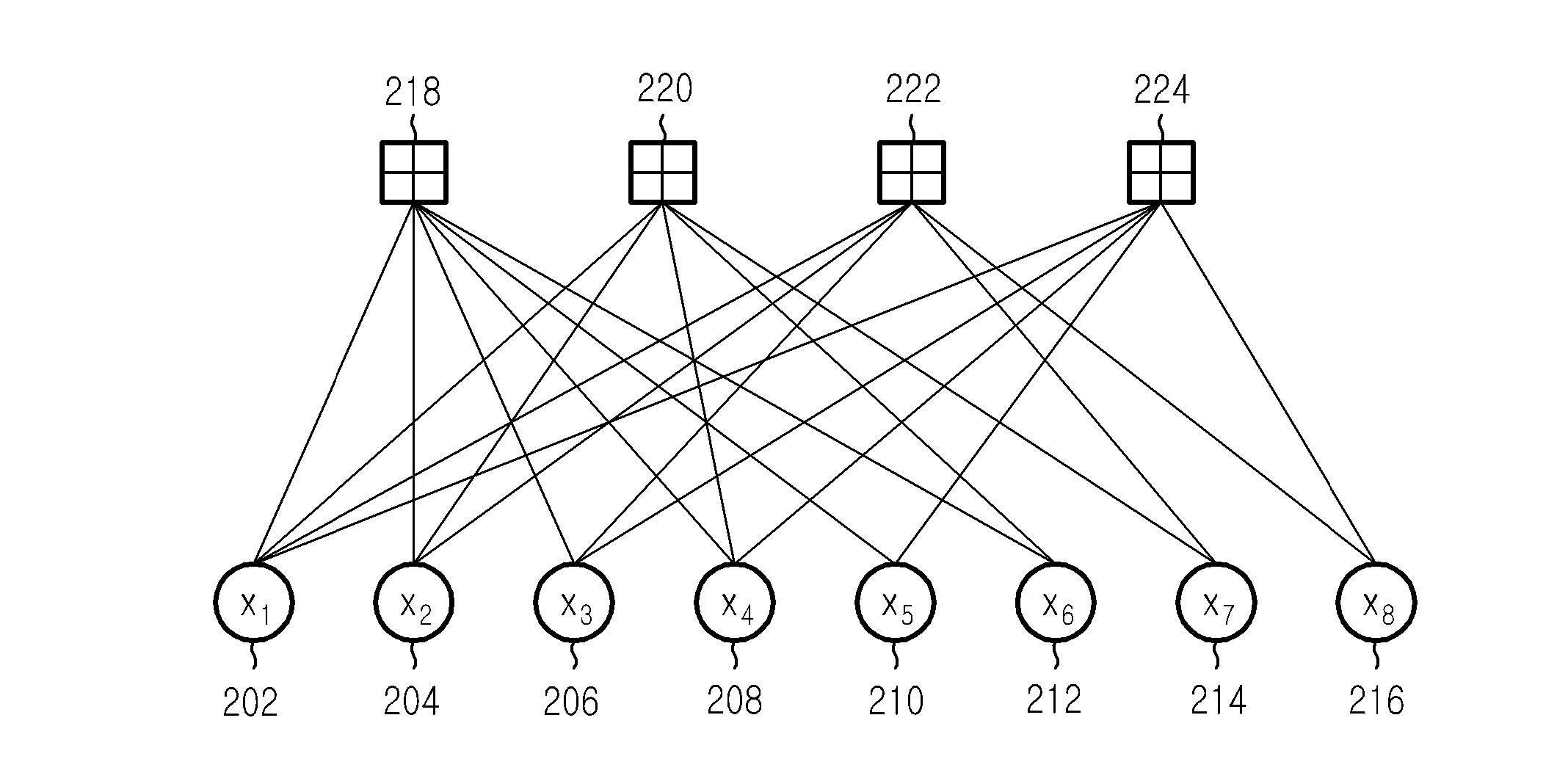

Layered low density parity check decoding for digital communications

ActiveUS7139959B2Efficient implementationMost efficientError preventionError detection/correctionParity-check matrixTheoretical computer science

A low density parity check (LDPC) code that is particularly well adapted for hardware implementation of a belief propagation decoder circuit (38) is disclosed. The LDPC code is arranged as a parity check matrix (H) whose rows and columns represent check sums and input nodes, respectively. The parity check matrix is grouped into subsets of check sum rows, in which the column weight is a maximum of one. The decoder circuitry includes a parity check value estimate memory (52). Adders (54) generate extrinsic estimates, from immediately updated input node probability estimates, and the extrinsic estimates are applied to parity check update circuitry (56) for generating new parity check sum value estimates. These parity check sum value estimates are stored back into the memory (52), and after addition with the extrinsic estimates, are stored in a column sum memory (66) of a corresponding bit update circuit (60) as updated probability values for the input nodes.

Owner:TEXAS INSTR INC

Transmitting apparatus and signal processing method thereof

ActiveUS20150095744A1Overcome disadvantagesError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow densityModulation order

A transmitting apparatus and a receiving apparatus are provided. The transmitting apparatus includes an encoder configured to generate a low density parity check (LDPC) codeword by performing LDPC encoding, an interleaver configured to interleave the LDPC codeword, and a modulator configured to modulate the interleaved LDPC codeword according to a modulation method to generate a modulation symbol. The interleaver performs interleaving by dividing the LDPC codeword into a plurality of groups, rearranging an order of the plurality of groups in group units, and dividing the plurality of rearranged groups based on a modulation order according to the modulation method.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitting apparatus and signal processing method thereof

ActiveUS20150082131A1Improve decoding performanceImprove reception performanceError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow-density parity-check codeLow density

A transmitting apparatus and a receiving apparatus are provided. The transmitting apparatus includes: an encoder configured to generate a low density parity check (LDPC) codeword by performing LDPC encoding; an interleaver configured to interleave the LDPC codeword; and a modulator configured to modulate the interleaved LDPC codeword according to a modulation method to generate a modulation symbol. The interleaver includes a block interleaver formed of a plurality of columns each comprising a plurality of rows, and the block interleaver is configured to divide the plurality of columns into at least two parts and interleave the LDPC codeword.

Owner:SAMSUNG ELECTRONICS CO LTD

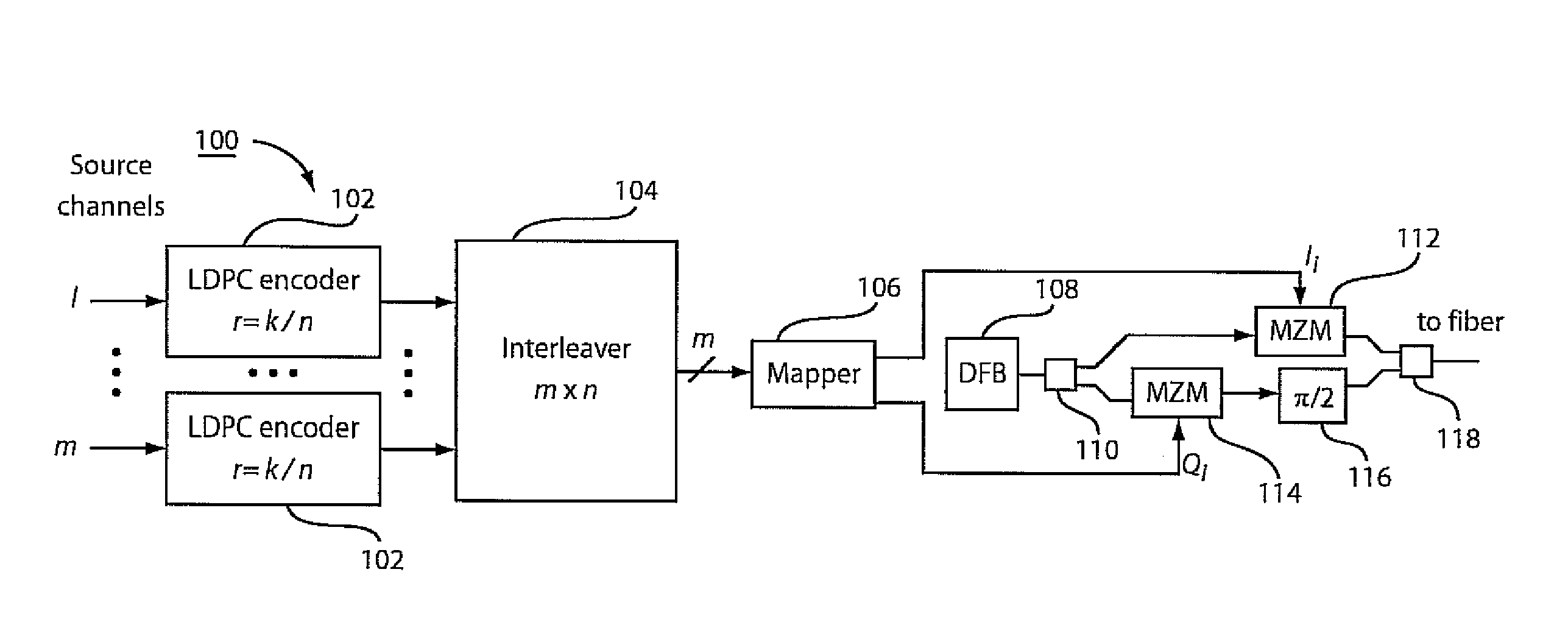

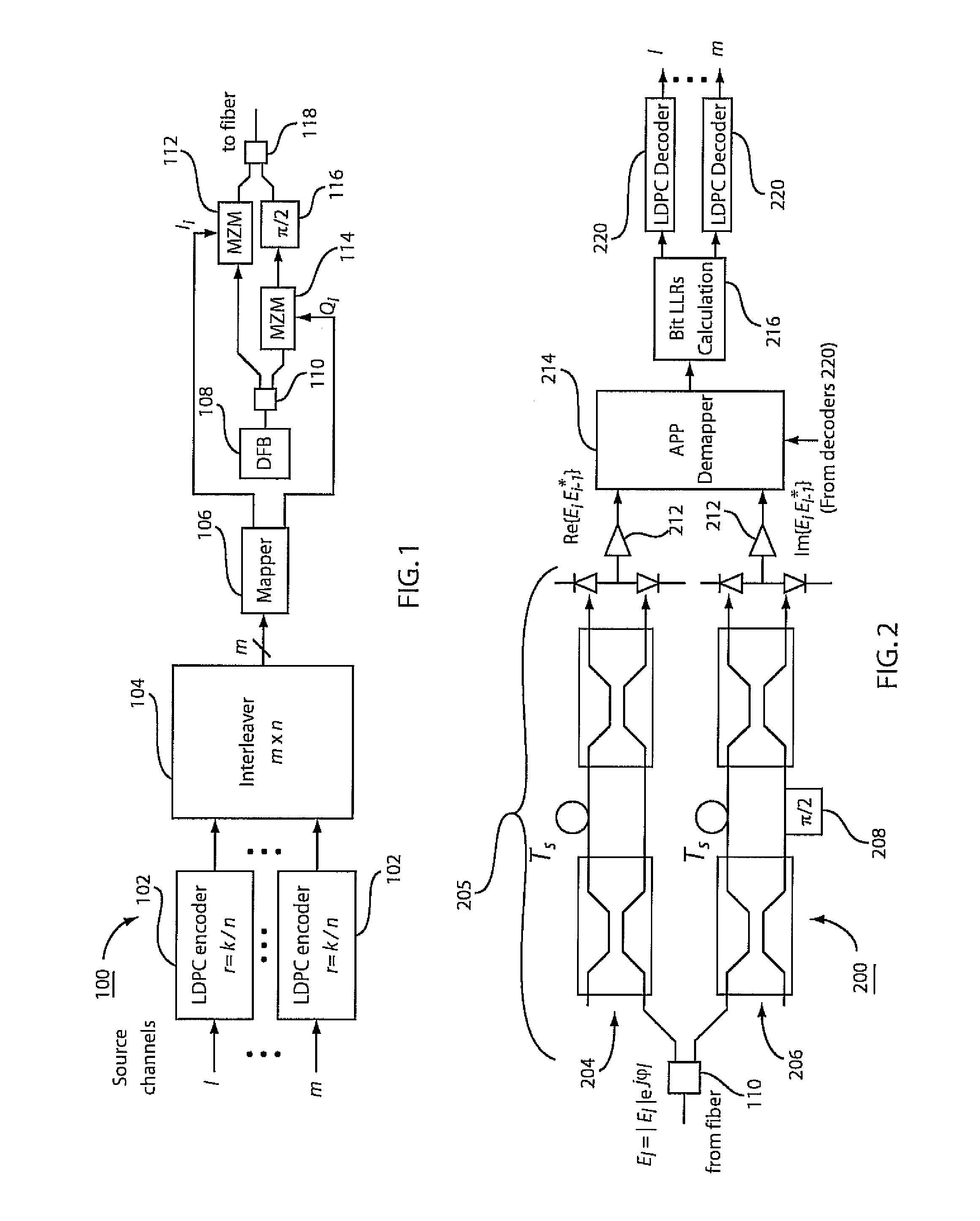

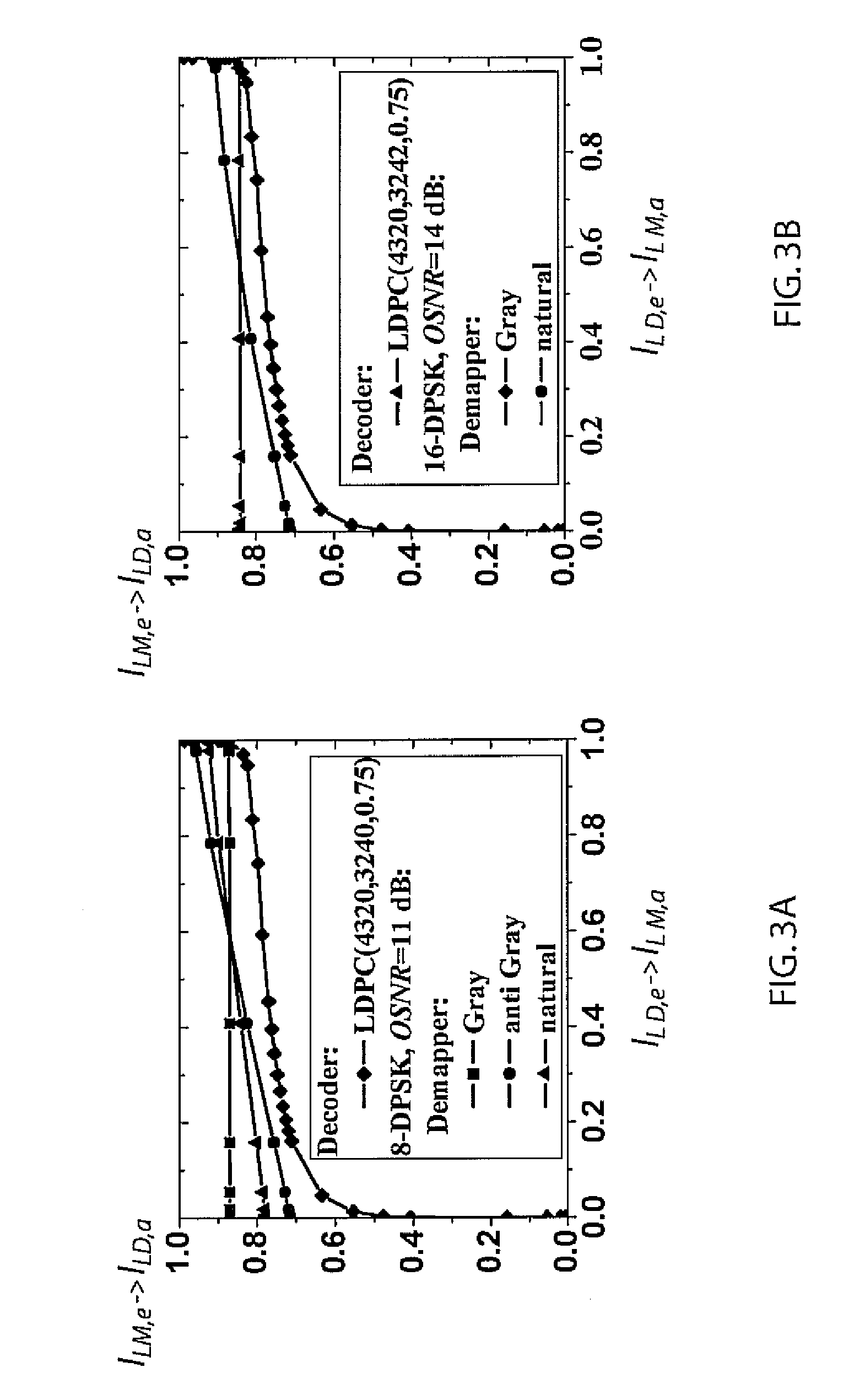

Bit-interleaved ldpc-coded modulation for high-speed optical transmission

ActiveUS20080163025A1Easy to implementImprove toleranceElectronic circuit testingError correction/detection using LDPC codesConstellationBit interleaved coded modulation

A transmitter includes a plurality of encoders configured to receive source bit streams from m information sources, each of the plurality encoders including identical (n,k) low-density parity check (LDPC) codes of code rate r=k / n, where k is a number of information bits and n is codeword length. An interleaver is configured to collect m row-wise codewords from the plurality of encoders, and a mapper is configured to receive m bits at a time column-wise from the interleaver and to determine an M-ary signal constellation point. A modulator is configured to modulate a light source in accordance with the output of the mapper at a transmission rate Rs / r (Rs—the symbol rate, r—the code rate). A receiver and transmission and receiving methods are also disclosed.

Owner:NEC CORP

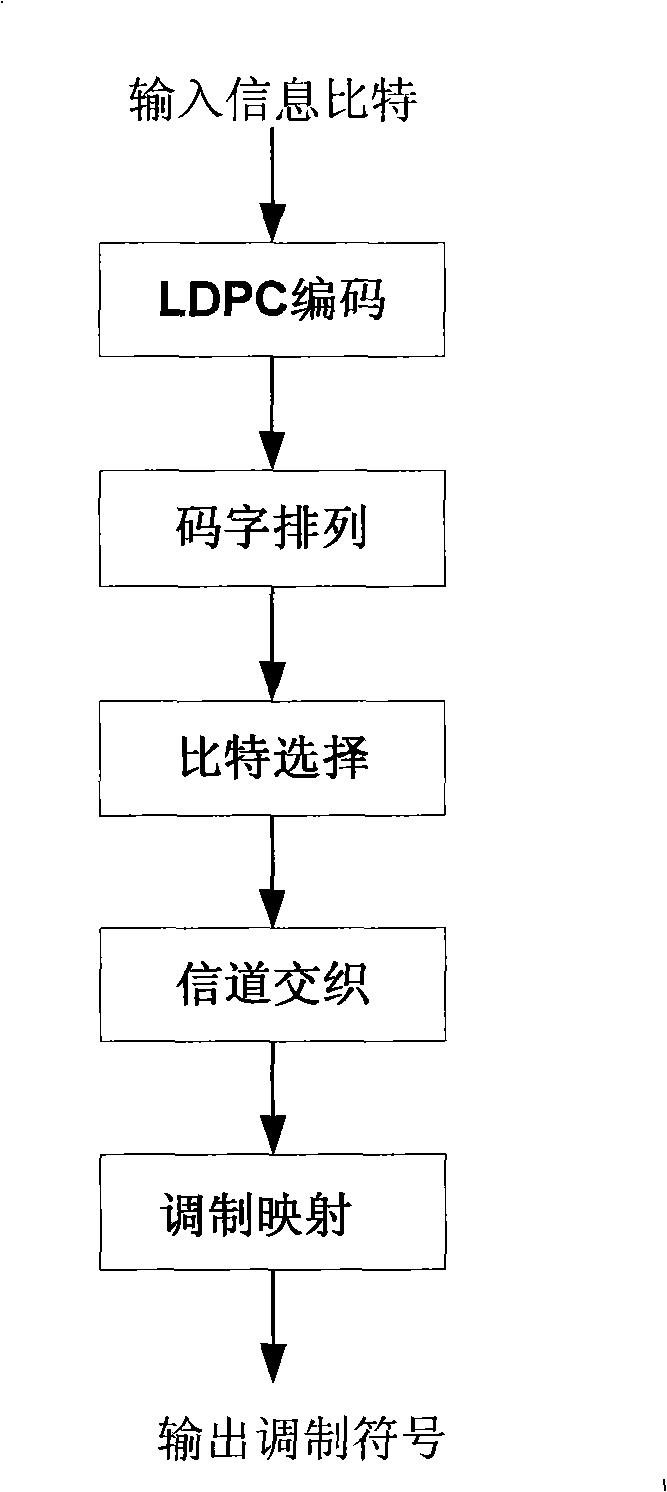

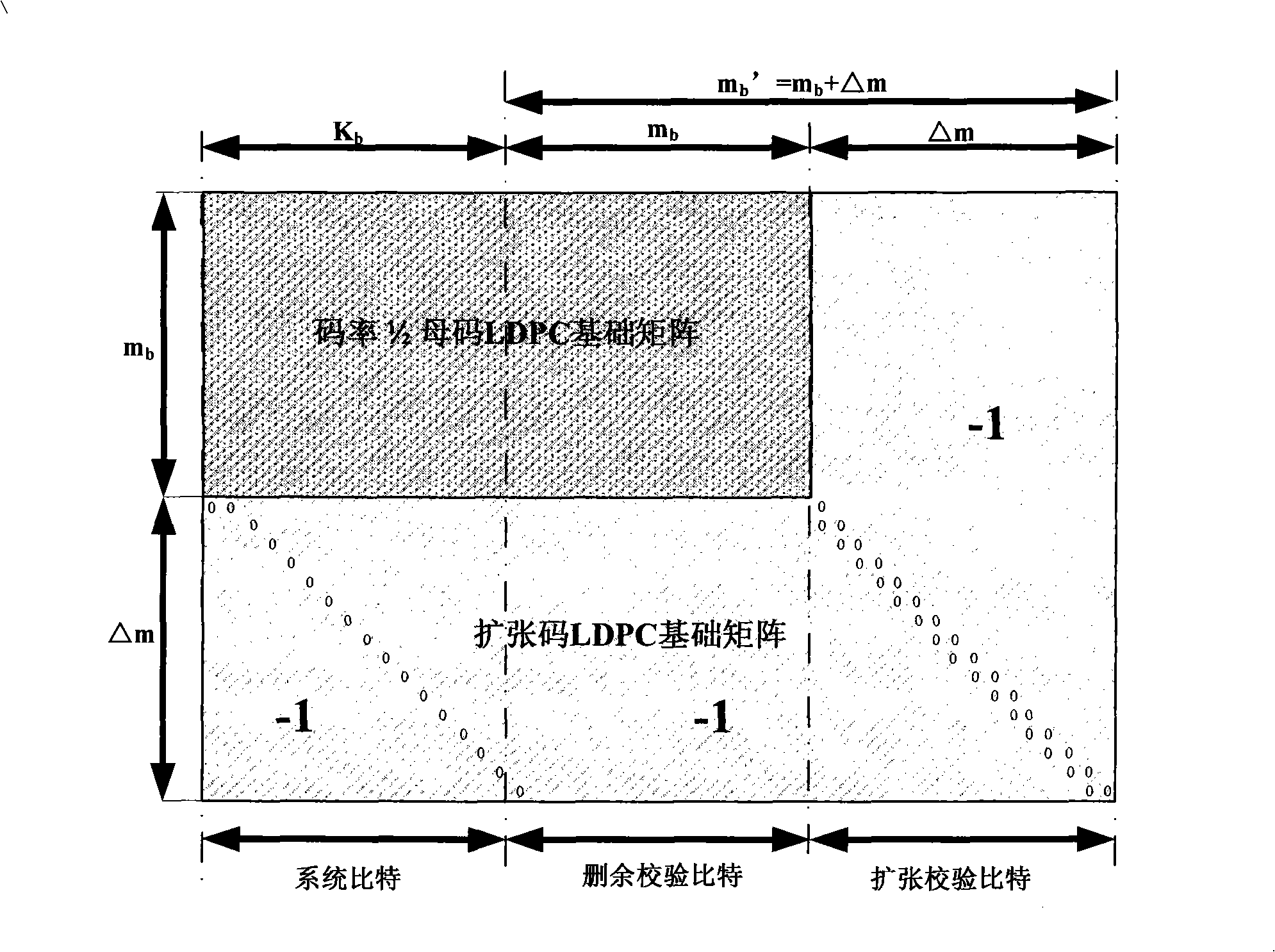

Method for encoding channel of mixed automatic request retransmission and modulation mapping of LDPC code

ActiveCN101325474AImprove protectionHigh gainError prevention/detection by using return channelError correction/detection using LDPC codesComputer hardwareCoding block

A retransmitted channel coding of mixing automatic request of a low density parity check LDPC code is disclosed, comprising: (a) performing the structurization coding on the information bit sequence with the length K of the channel coder, transmitting the generated code word to the mixing automatic request retransmission HARQ buffer; (b) rearranging the code word bit of LDPC HARQ mother code in the HARQ buffer, then selecting the code word bit sequentially, generating the binary sequence of the HARQ pack; (c) mapping the code word bit of the HARQ pack to a planisphere, which ensures that the high-order bit of the coding block of the HARQ pack is mapped onto the bit of the planisphere with high reliability. The method of the invention provides largest planisphere gain for the LDPC code word, causing the LDPC HARQ channel coding with optimum performance.

Owner:ZTE CORP

Apparatus and method for transmitting and receiving data in a communication or broadcasting system using linear block code

ActiveUS20120051460A1Reduce signal distortionImprove performanceError preventionAmplitude demodulation by homodyne/synchrodyne circuitsBlock codeLinearity

Provided is a method for transmitting data in a communication or broadcasting system using a linear block code by generating a codeword by encoding input information data bits, interleaving the codeword; outputting modulation signal-constituting bits by bit-mapping the interleaved codeword using a bit-mapping table predetermined depending on a modulation scheme and a coding rate, outputting a modulation signal by modulating the modulation signal-constituting bits and transmitting the modulation signal via a transmit antenna.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitting apparatus and interleaving method thereof

ActiveUS20150341053A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError correction/detection using LDPC codesParity-check matrixLow density

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding of input bits based on a parity check matrix including information word bits and parity bits, the LDPC codeword including a plurality of bit groups each including a plurality of bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the interleaver is further configured to interleave the LDPC codeword such that a bit included in a predetermined bit group from among the plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitting apparatus and signal processing method thereof

ActiveUS20150128005A1Overcome disadvantagesError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow-density parity-check codeLow density

A transmitting apparatus and a receiving apparatus are provided. The transmitting apparatus includes an encoder configured to generate a low density parity check (LDPC) codeword by performing LDPC encoding, an interleaver configured to interleave the LDPC codeword, and a modulator configured to modulate the interleaved LDPC codeword according to a modulation method to generate a modulation symbol. The interleaver performs interleaving by dividing the LDPC codeword into a plurality of groups, rearranging an order of the plurality of groups in group units, and dividing the plurality of rearranged groups based on a modulation order according to the modulation method.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of error floor mitigation in low-density parity-check codes

ActiveUS20120266040A1Improve performanceError correction/detection using LDPC codesCode conversionComputer hardwareMaximum magnitude

A digital communication decoding method for low-density parity-check coded messages. The decoding method decodes the low-density parity-check coded messages within a bipartite graph having check nodes and variable nodes. Messages from check nodes are partially hard limited, so that every message which would otherwise have a magnitude at or above a certain level is re-assigned to a maximum magnitude.

Owner:CALIFORNIA INST OF TECH

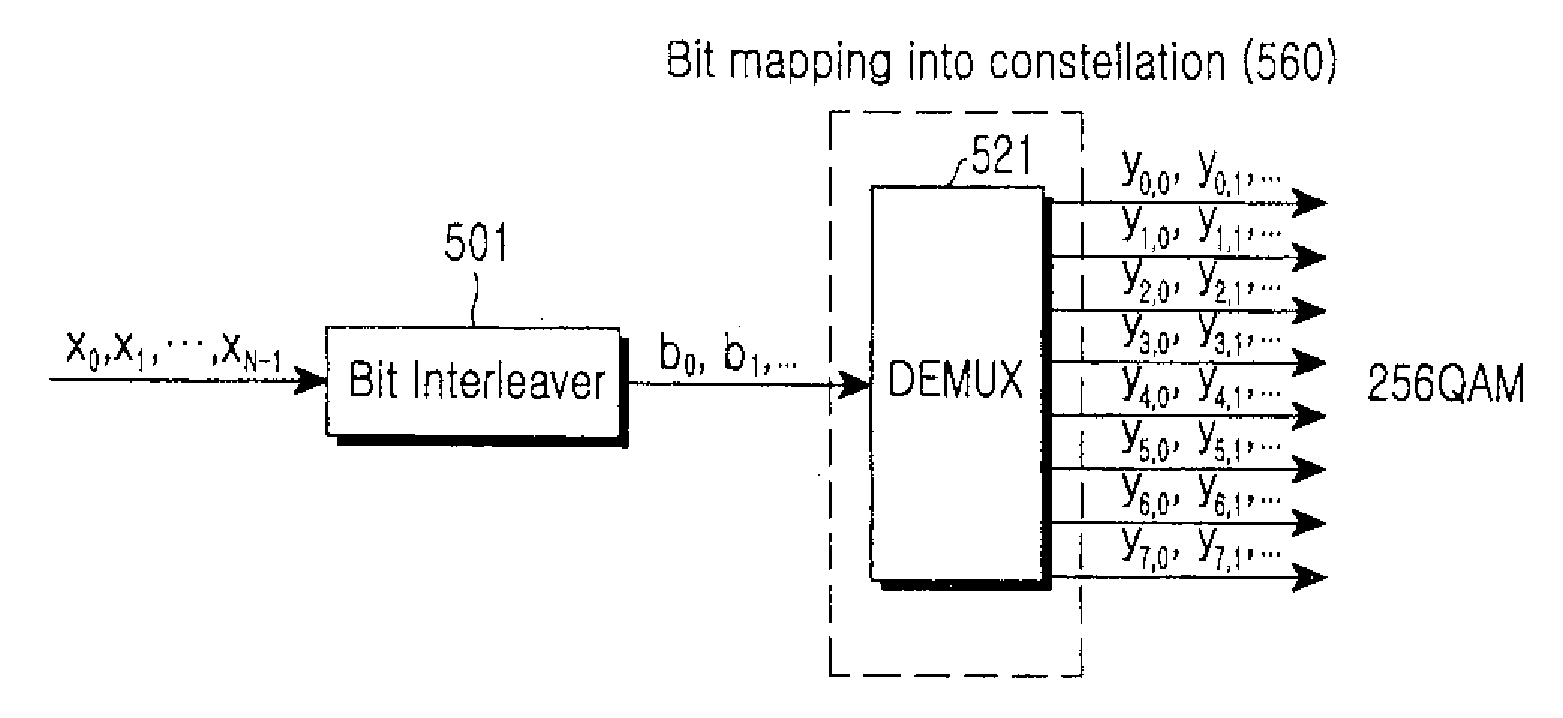

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 4/15 and 256-symbol mapping, and bit interleaving method using same

ActiveUS20150256202A1Effective distributionEfficiently distributedError correction/detection using LDPC codesBurst error correctionSymbol mappingParallel computing

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 4 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 256-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Channel coding, modulating and mapping method for hybrid automatic repeat request of low density parity check code

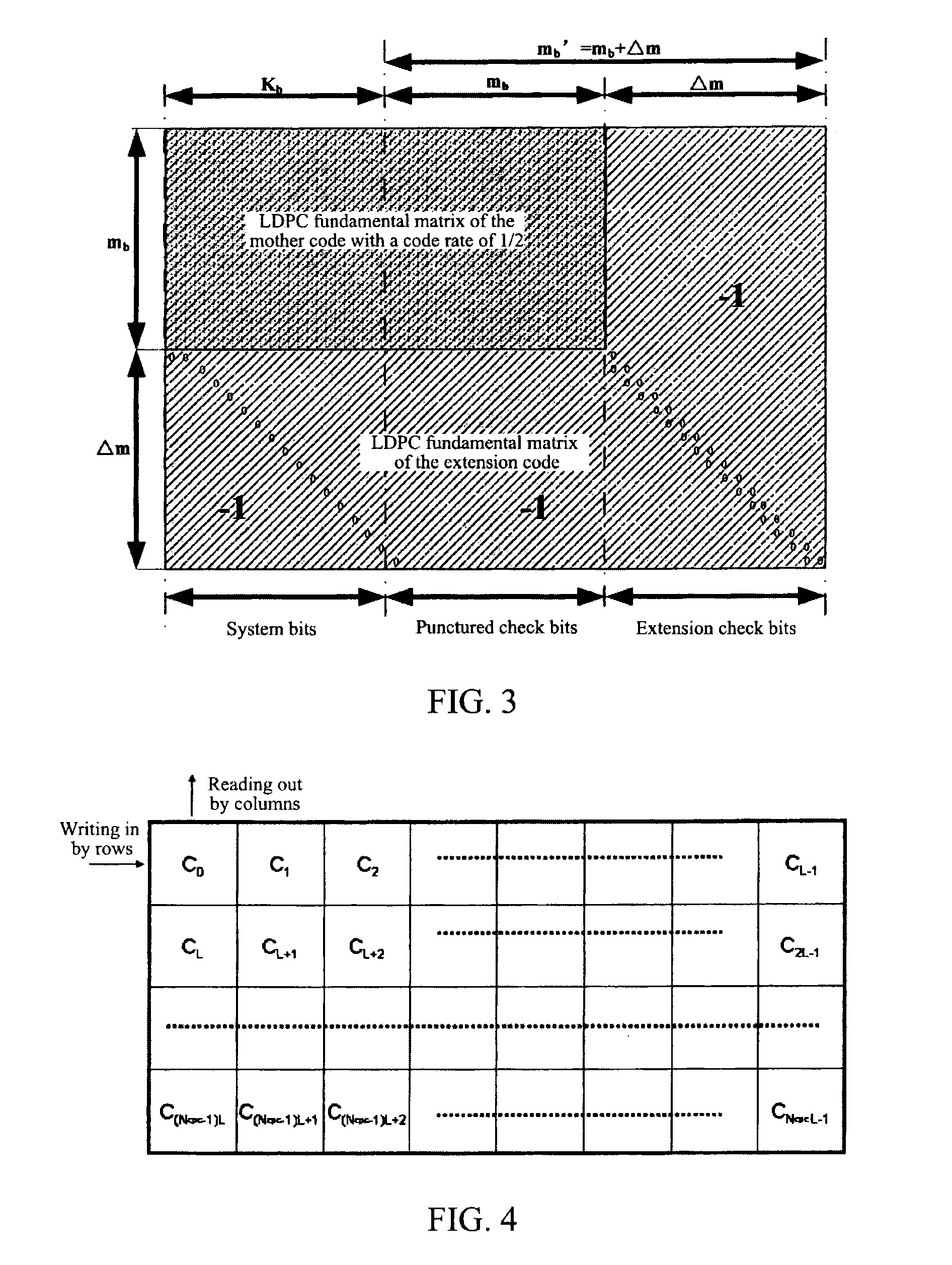

ActiveUS20110239075A1Improve protectionLow reliabilityError prevention/detection by using return channelError correction/detection using LDPC codesLow-density parity-check codeComputer science

The present invention discloses a method for channel coding and modulation mapping in HARQ of the LDPC code, comprising: performing structural LDPC encoding of an information bit sequence with a length of K input by a channel encoder, and sending a generated codeword to a HARQ buffer; rearranging codeword bits of a LDPC HARQ mother code in the HARQ buffer, and sequentially selecting codeword bits to generate a binary sequence of a HARQ packet; mapping codeword bits of the HARQ packet to a constellation, and high-order bits in encoding blocks of the HARQ packet being mapped to high reliability bits in the constellation. The present invention provides the LDPC codeword with the maximal constellation gain, so that the LDPC HARQ channel encoding has the optimal performance.

Owner:ZTE CORP

LOW DENSITY PARITY CHECK (LDPC) CODING FOR A 32k MODE INTERLEAVER IN A DIGITAL VIDEO BROADCASTING (DVB) STANDARD

ActiveUS20120189079A1Improve performanceLow Density Parity Check (LDPCTransmission path divisionError correction/detection using LDPC codesParity-check matrixCarrier signal

A data processing apparatus communicates data bits on a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processing apparatus comprises a parity interleaver operable to perform parity interleaving on Low Density Parity Check (LDPC) encoded data bits obtained by performing LDPC encoding according to a parity check matrix of an LDPC code including a parity matrix corresponding to parity bits of the LDPC code, the parity matrix having a stepwise structure, so that a parity bit of the LDPC encoded data bits is interleaved to a different parity bit position. A mapping unit maps the parity interleaved bits onto data symbols corresponding to modulation symbols of a modulation scheme of the OFDM sub-carrier signals.

Owner:SONY CORP

Popular searches

Single error correction Record information storage Error correction/detection by combining multiple code structures Error detection only Digital signal error detection/correction Substation equipment Error correction/detection using interleaving techniques Redundant data error correction Baseband systems Satellite broadcast receiving

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com