Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

109results about "Burst error correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

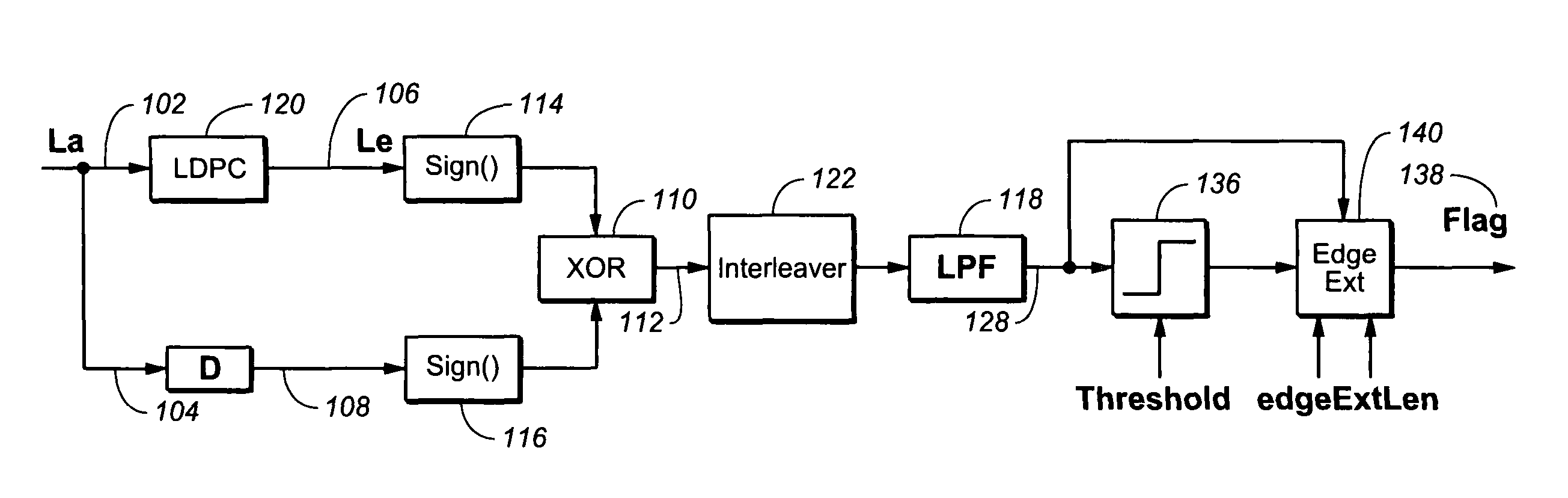

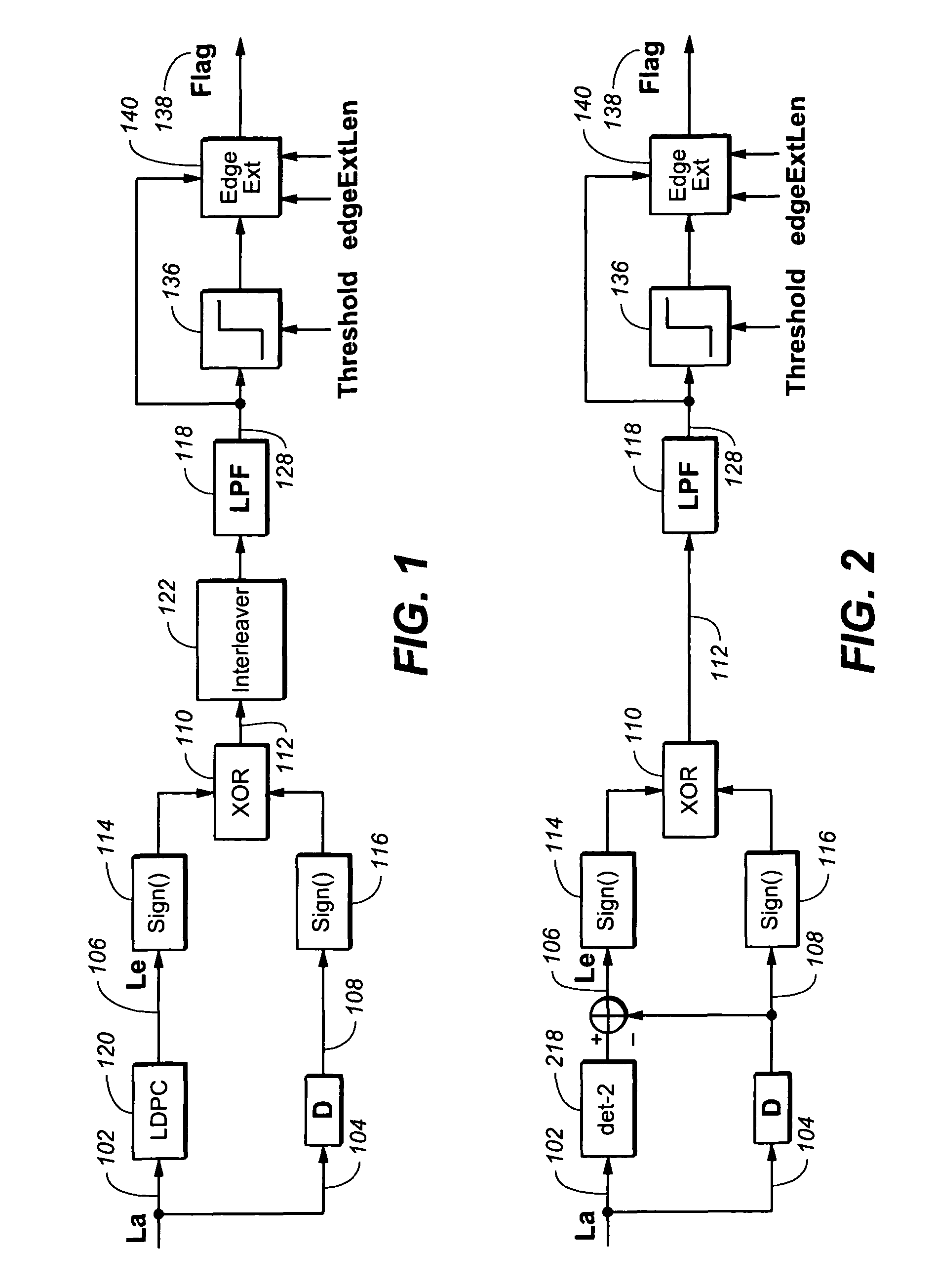

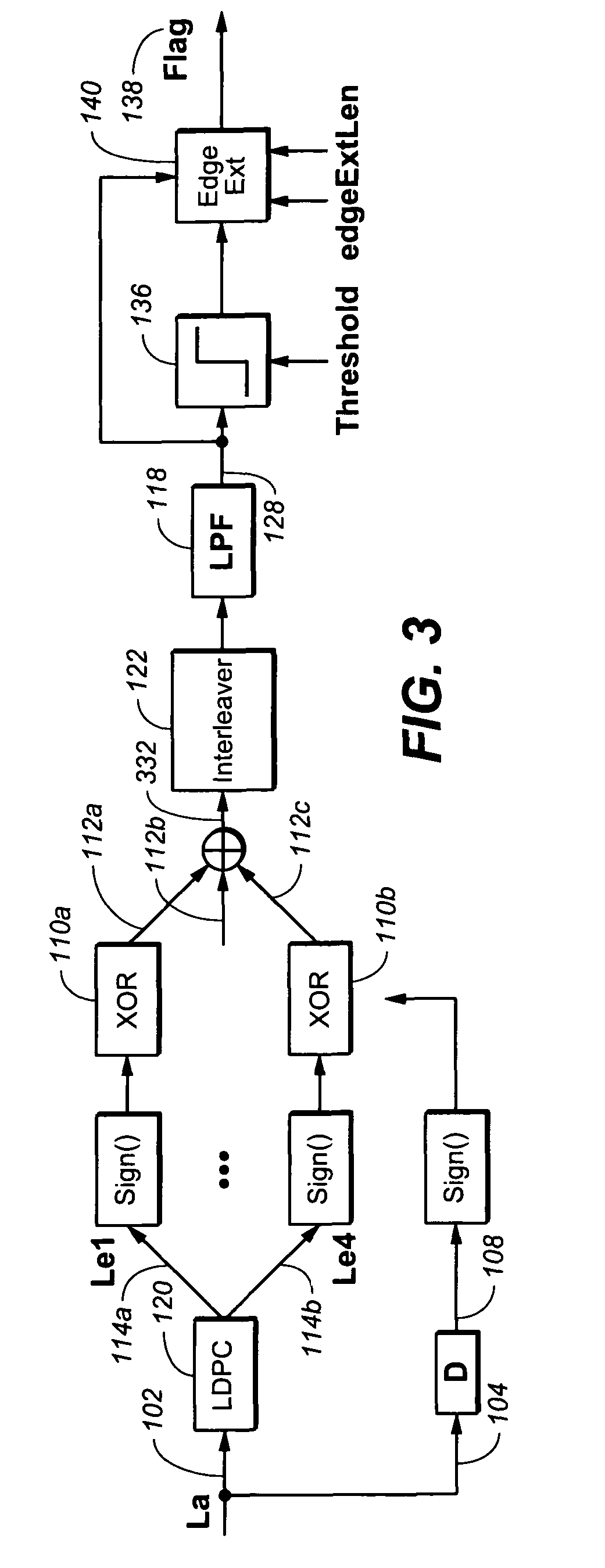

Method for detecting short burst errors in LDPC system

The present invention is a device for detecting short burst errors. The device includes a first signal input, wherein the first signal input is configured to receive a first signal. The device includes a second signal input, wherein the second signal input is configured to receive a second signal. The device includes a logic gate, wherein the logic gate is operable for receiving the first signal vial the first signal input, receiving the second signal via the second signal input, and generating a logic output gate signal based on the received first signal and the second signal. Furthermore, the device includes a filter, wherein the filter is configured for receiving the logic output gate signal from the logic gate and generates a filter output signal based upon the received logic output gate signal, wherein the filter output signal is operable for flagging errors.

Owner:AVAGO TECH INT SALES PTE LTD

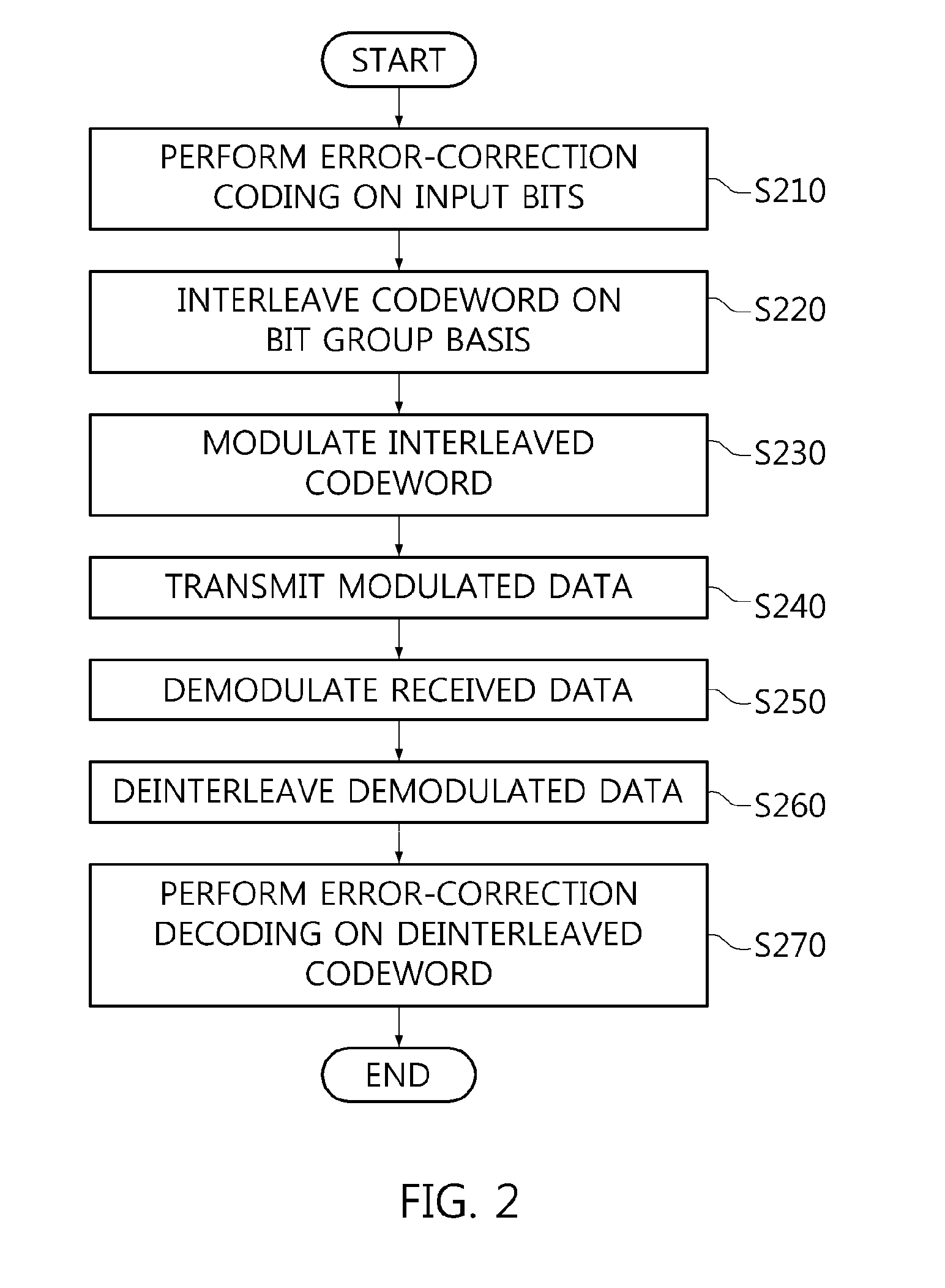

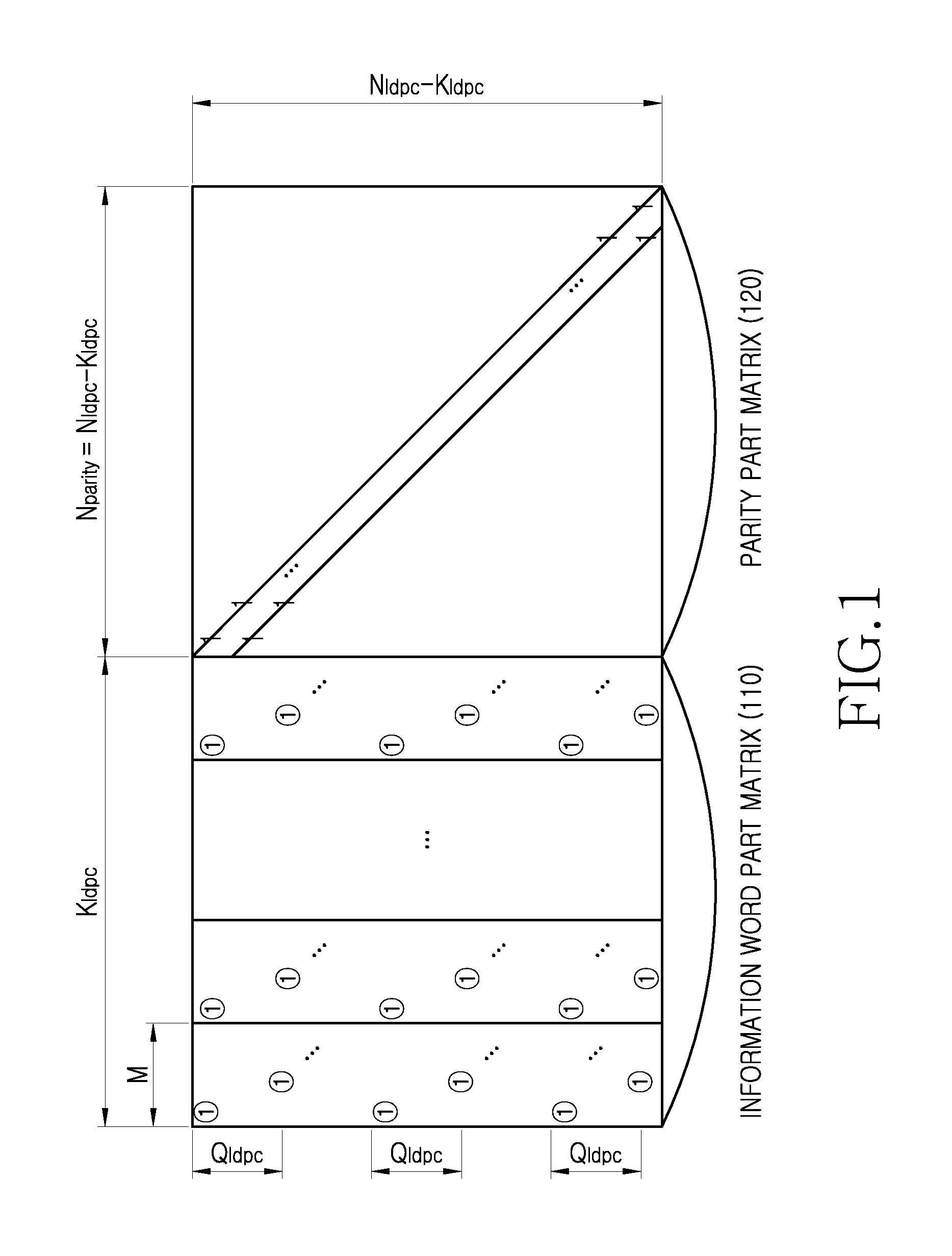

Bit interleaver for low-density parity check codeword having length of 64800 and code rate of 4/15 and 256-symbol mapping, and bit interleaving method using same

ActiveUS20150256202A1Effective distributionEfficiently distributedError correction/detection using LDPC codesBurst error correctionSymbol mappingParallel computing

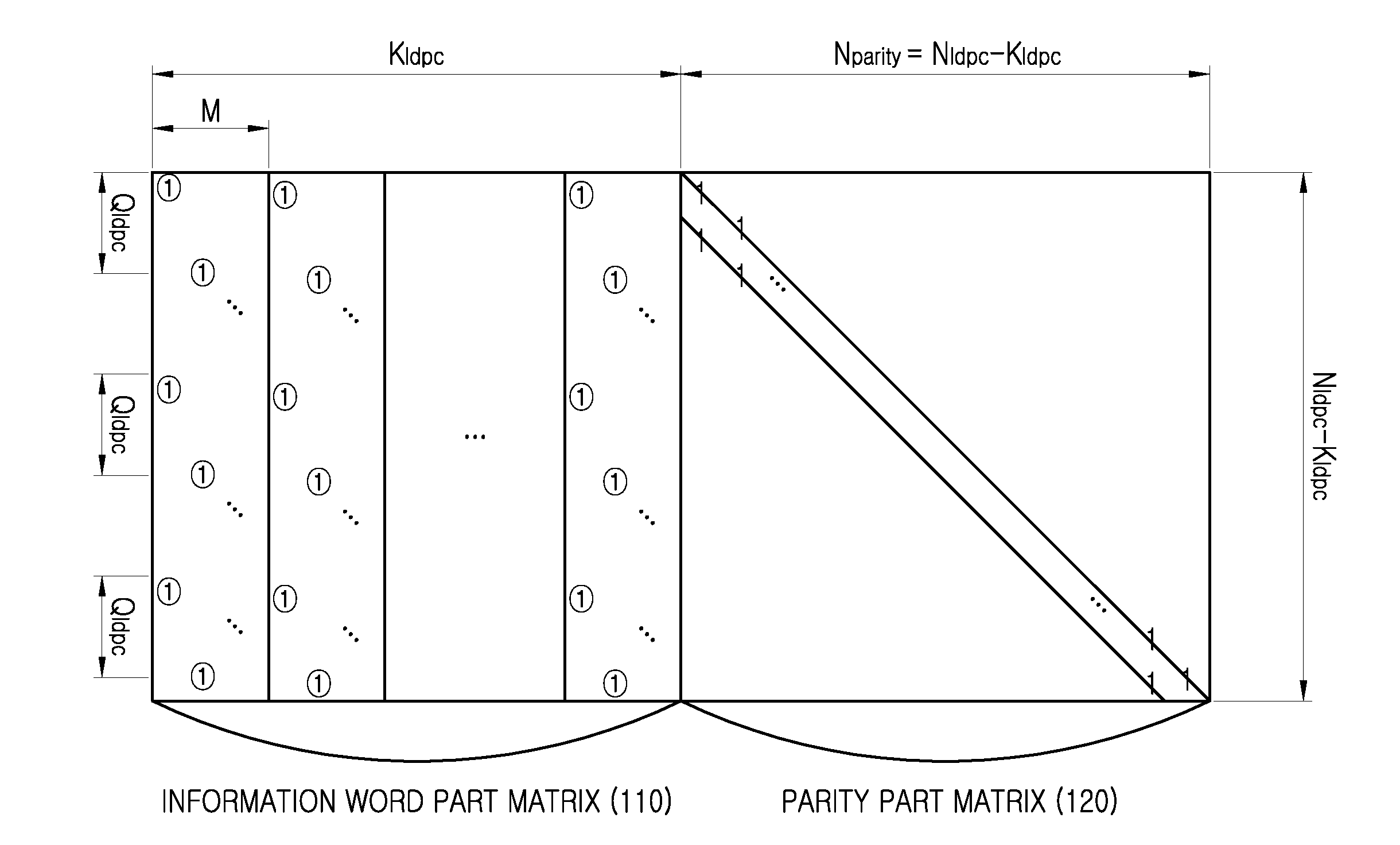

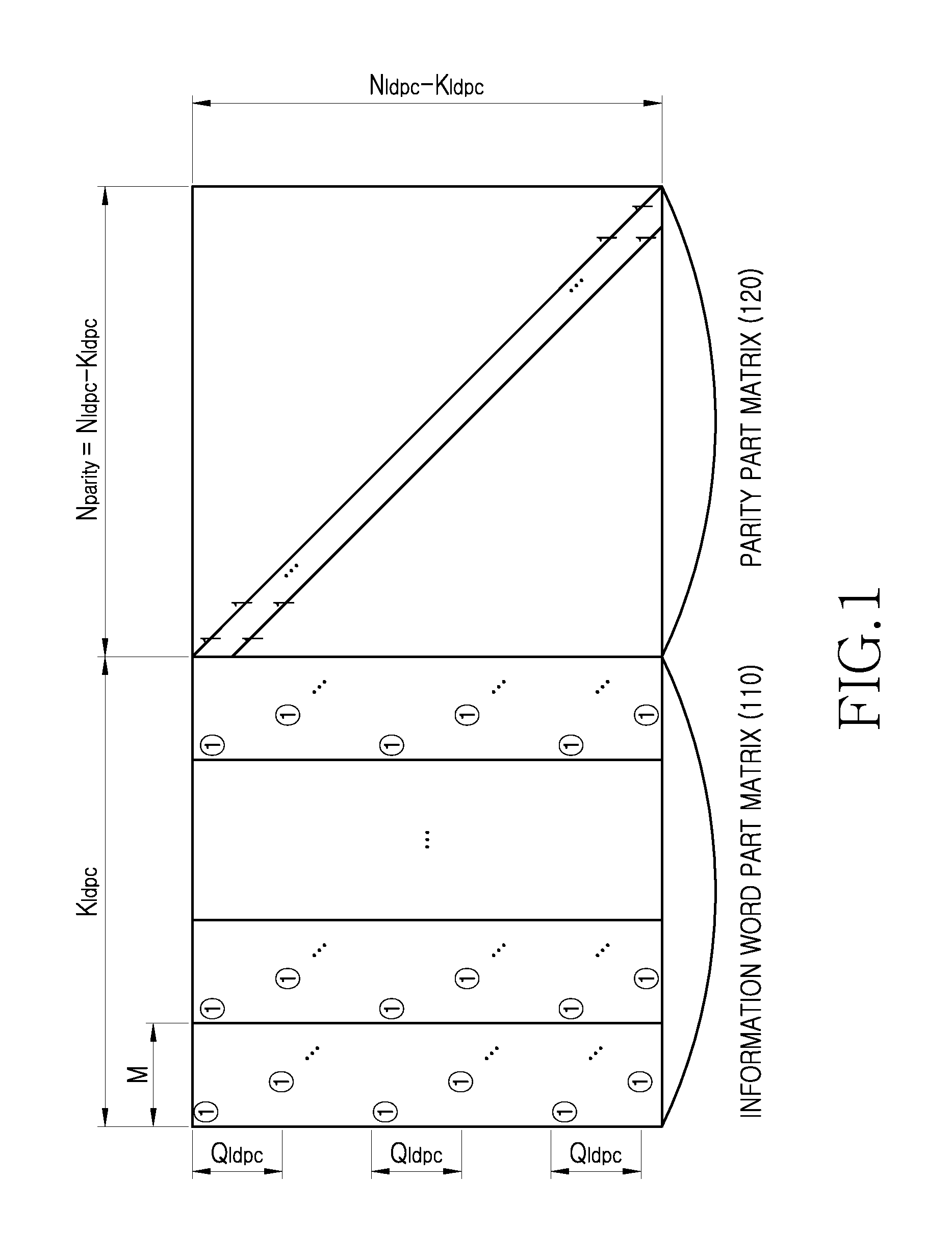

A bit interleaver, a bit-interleaved coded modulation (BICM) device and a bit interleaving method are disclosed herein. The bit interleaver includes a first memory, a processor, and a second memory. The first memory stores a low-density parity check (LDPC) codeword having a length of 64800 and a code rate of 4 / 15. The processor generates an interleaved codeword by interleaving the LDPC codeword on a bit group basis. The size of the bit group corresponds to a parallel factor of the LDPC codeword. The second memory provides the interleaved codeword to a modulator for 256-symbol mapping.

Owner:ELECTRONICS & TELECOMM RES INST

Method for creating an error correction coding scheme

InactiveUS20080244353A1Reduce data lossEasy constructionBurst error correctionCode conversionMain diagonalData set

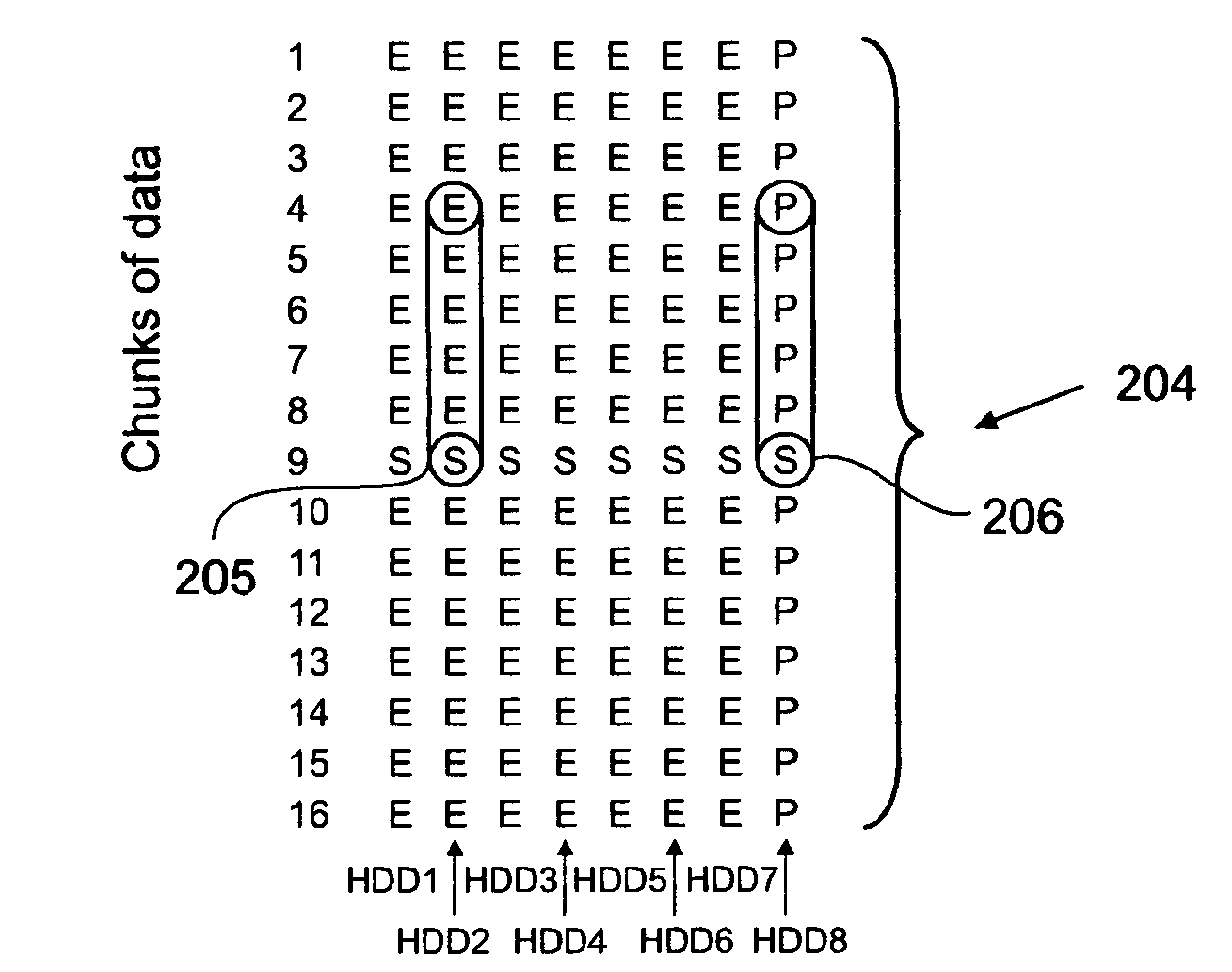

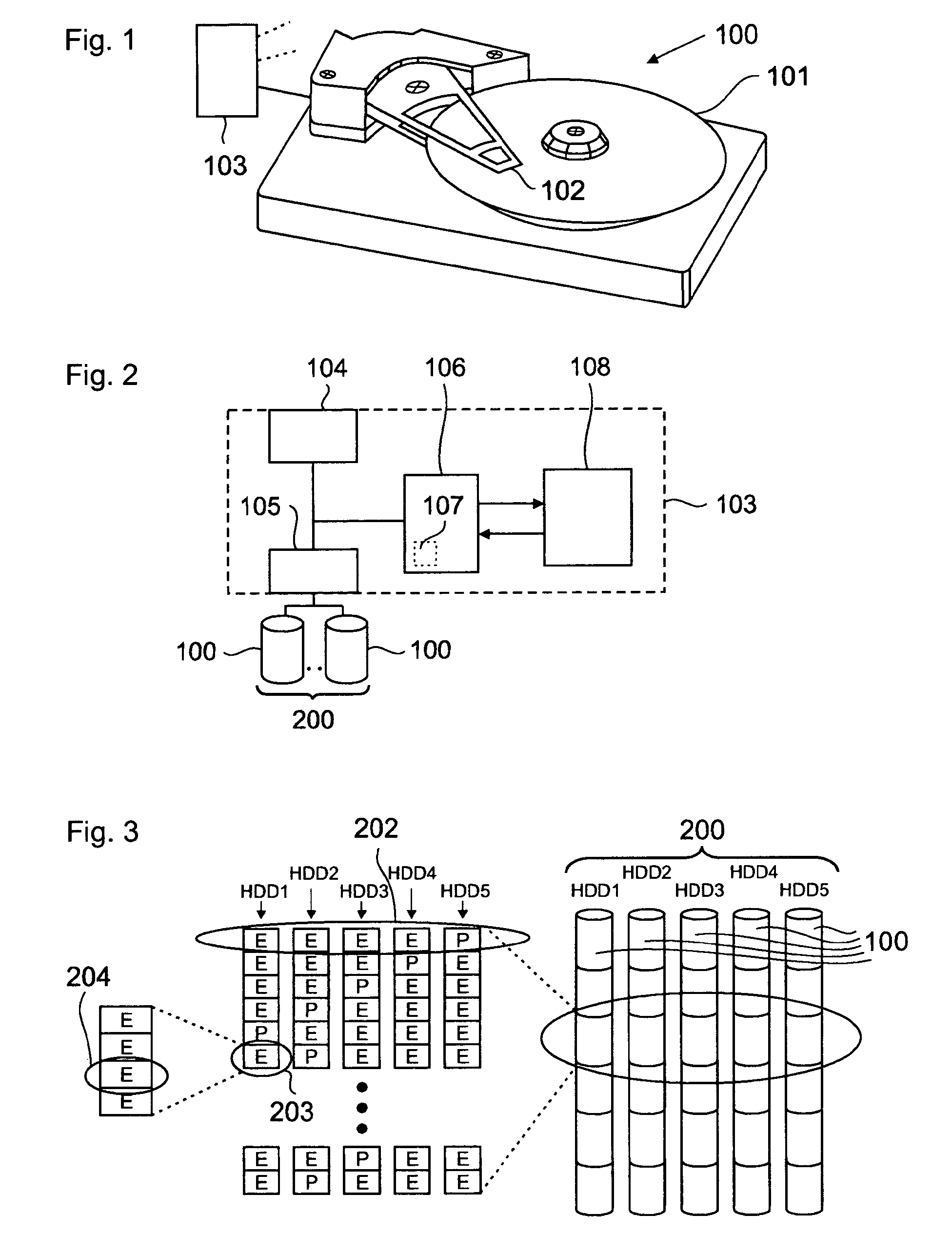

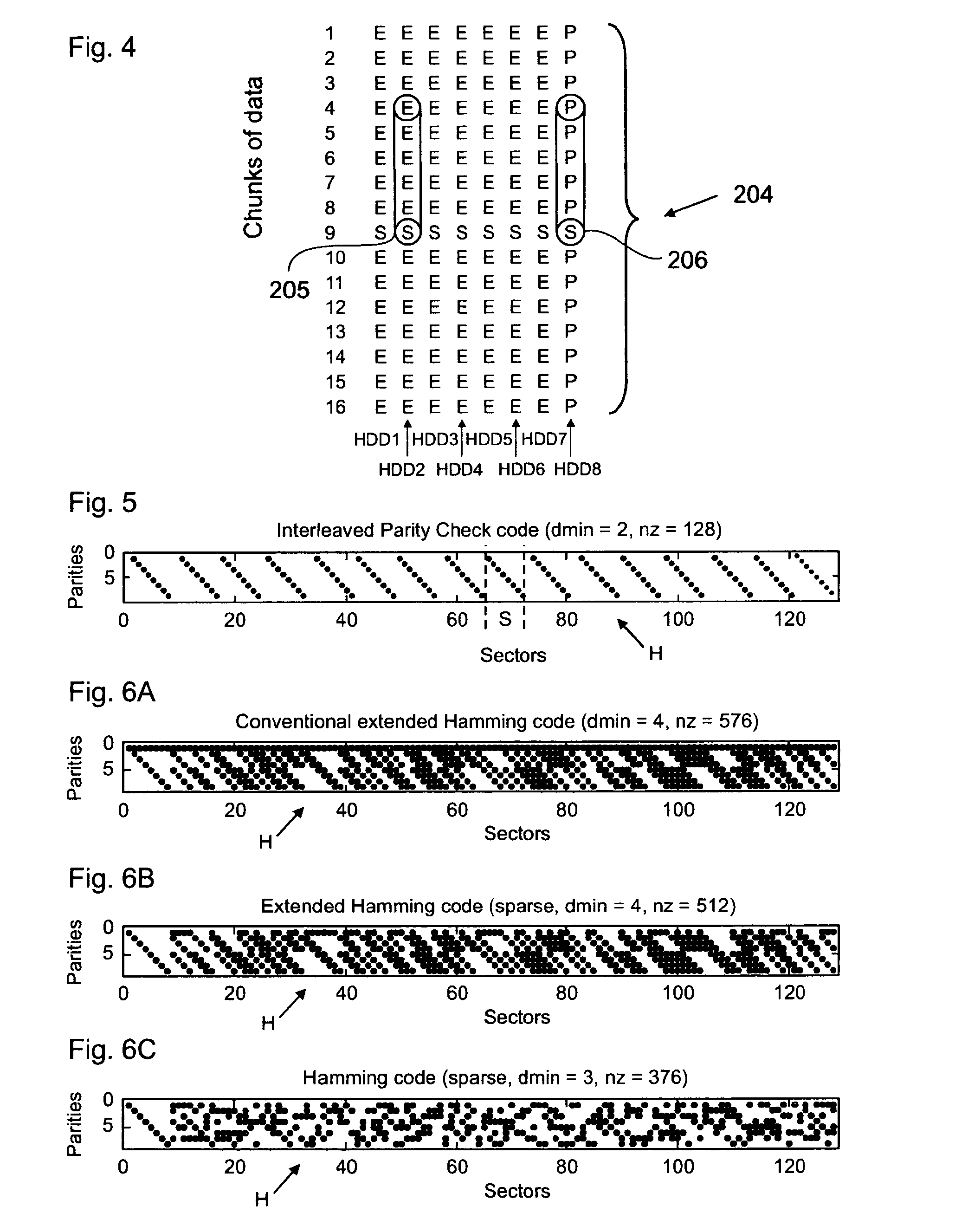

The present invention relates to a method for reducing data loss comprising a first computing step for computing an intermediate result for each redundancy information entity of a redundancy set by processing respectively associated data information entities of a given data set on at least two main diagonals of a parity check matrix representing an error correction coding scheme. The method further comprises a second computing step for computing the information content of the respective redundancy information entity dependent on the respective intermediate result.

Owner:GLOBALFOUNDRIES INC

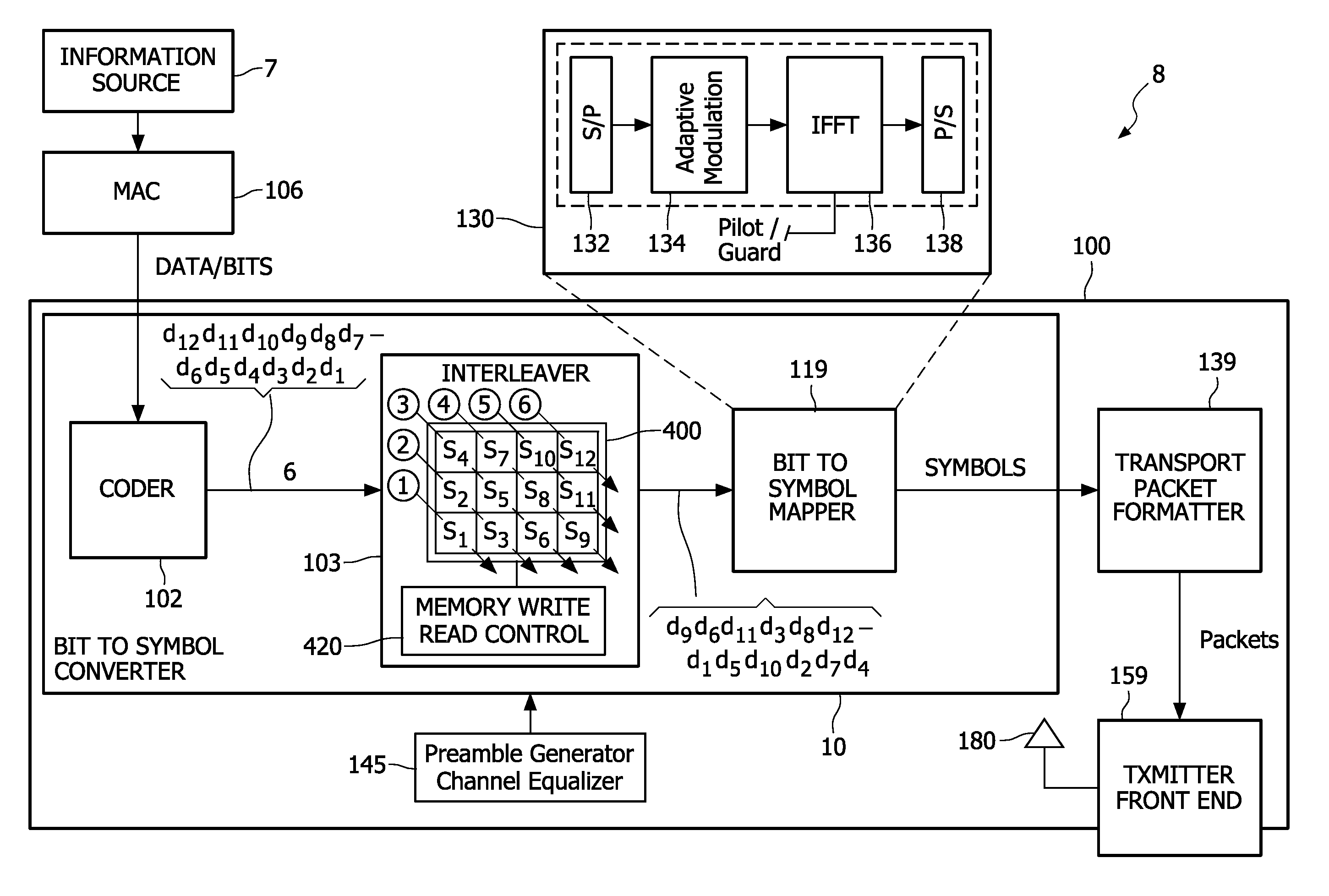

System, apparatus and method for interleaving data bits or symbols

InactiveUS20100002792A1Error correction/detection using convolutional codesTransmission path divisionSymbol mappingComputer science

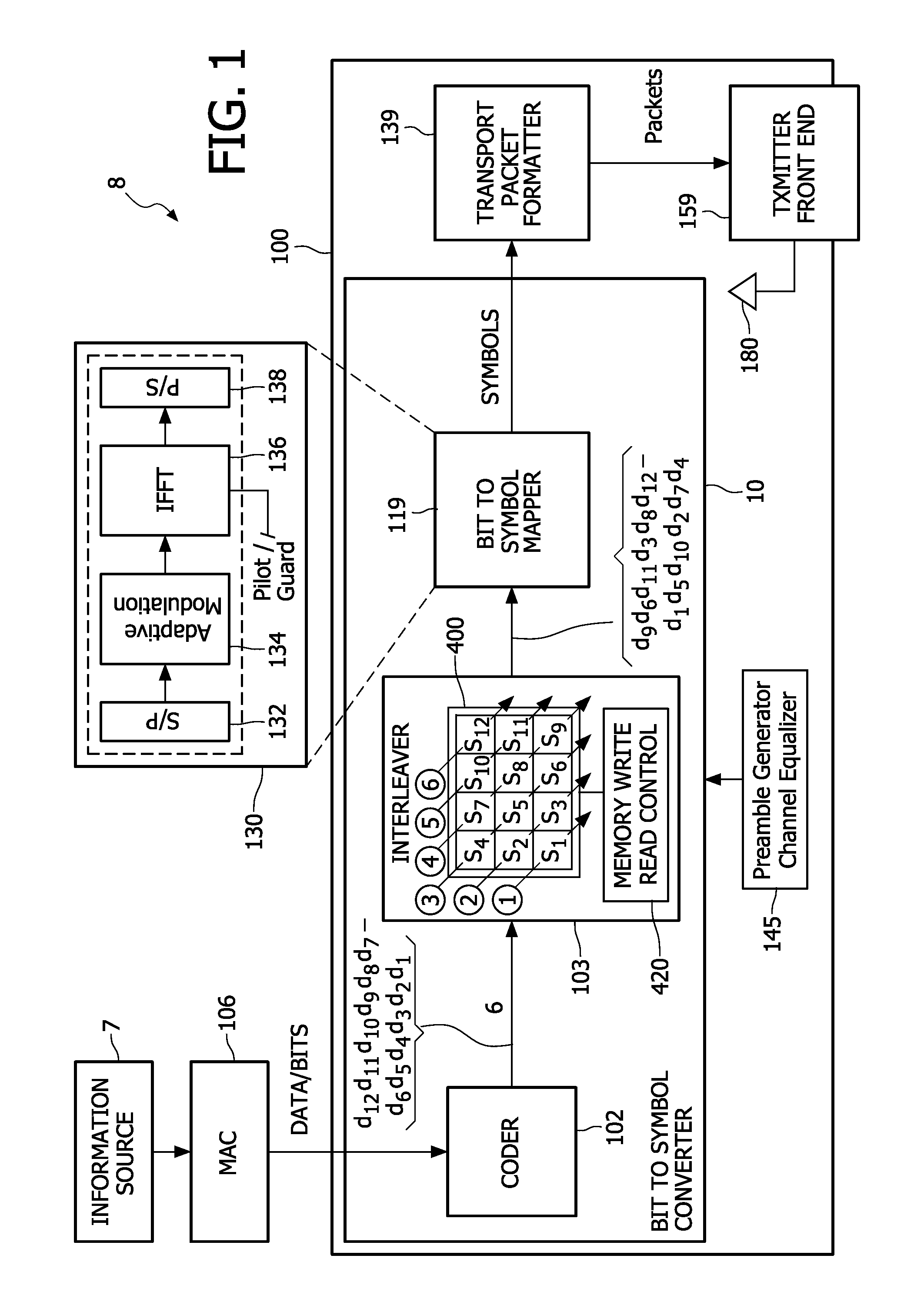

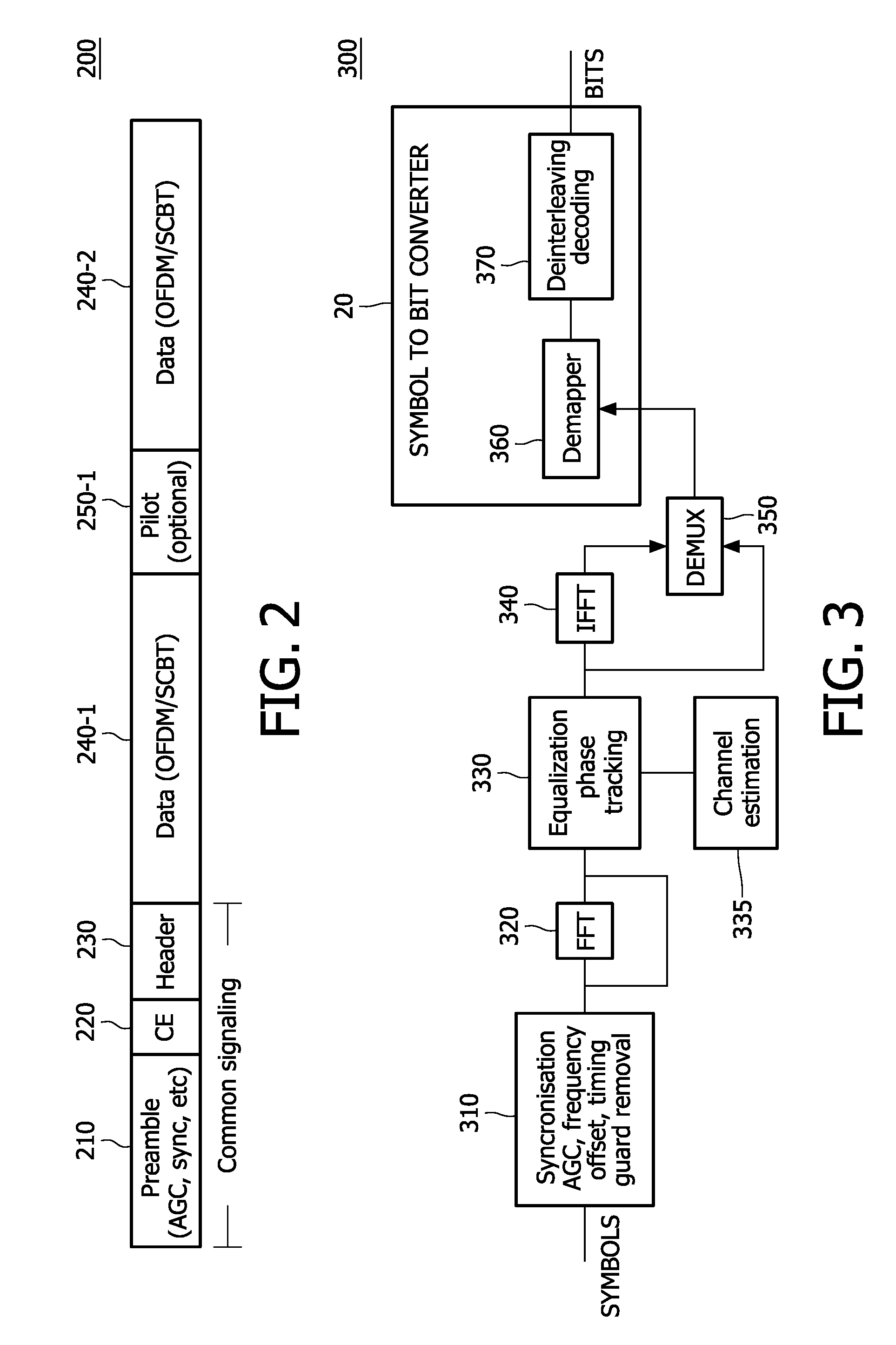

A data transmission system respectively encodes successive bits representing information to be transmitted. An interleaver receives the bits from the encoder and interleaves the bits. The interleaver includes a memory and a memory read write controller configured to write the bits to the memory in accordance with a diagonal write pattern and to read the bits from the memory in a diagonal read pattern. A symbol mapper receives the interleaved bits and maps the encoded interleaved bits into symbols using a transmission format.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

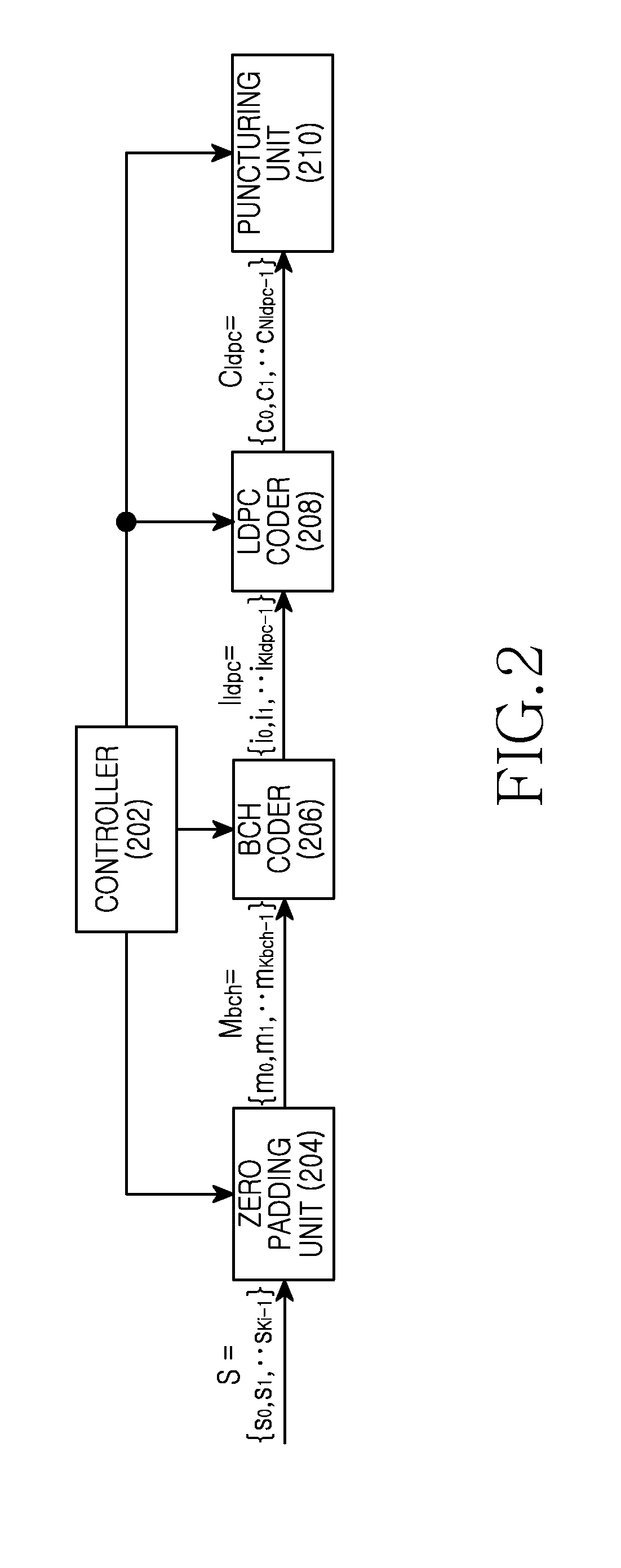

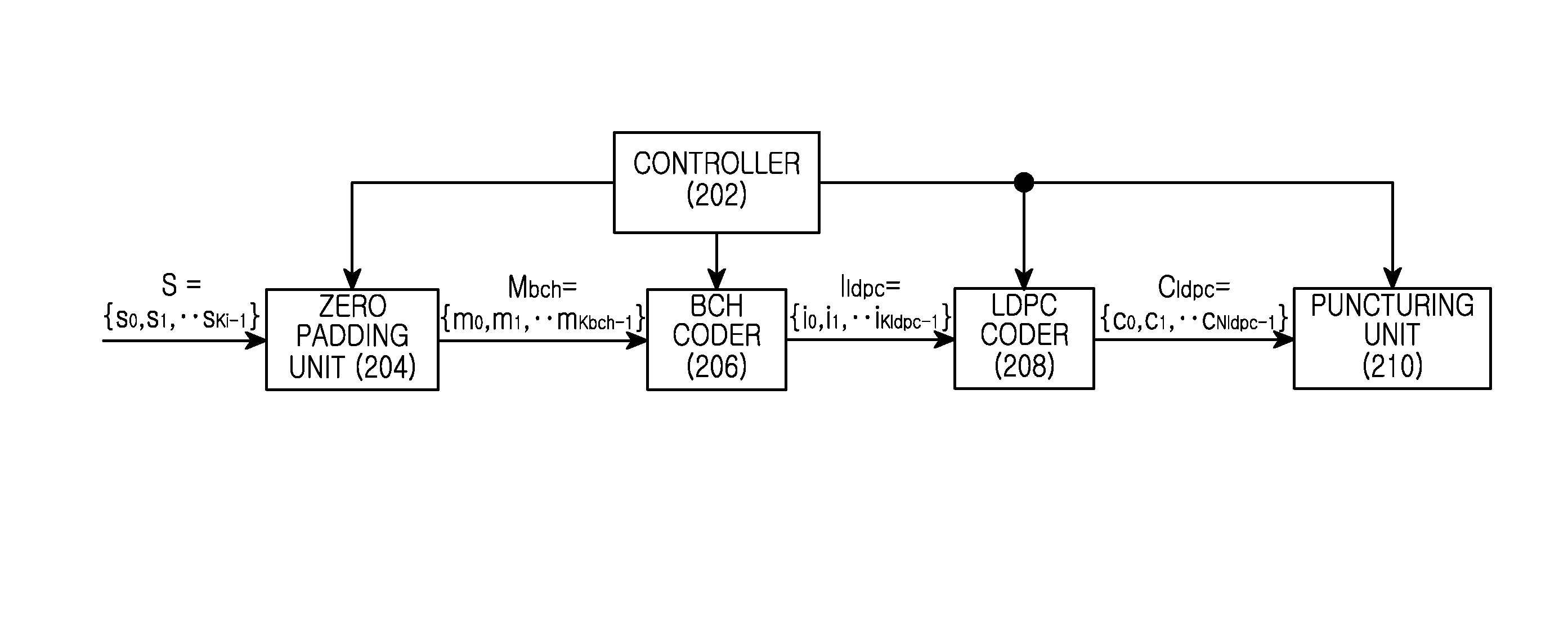

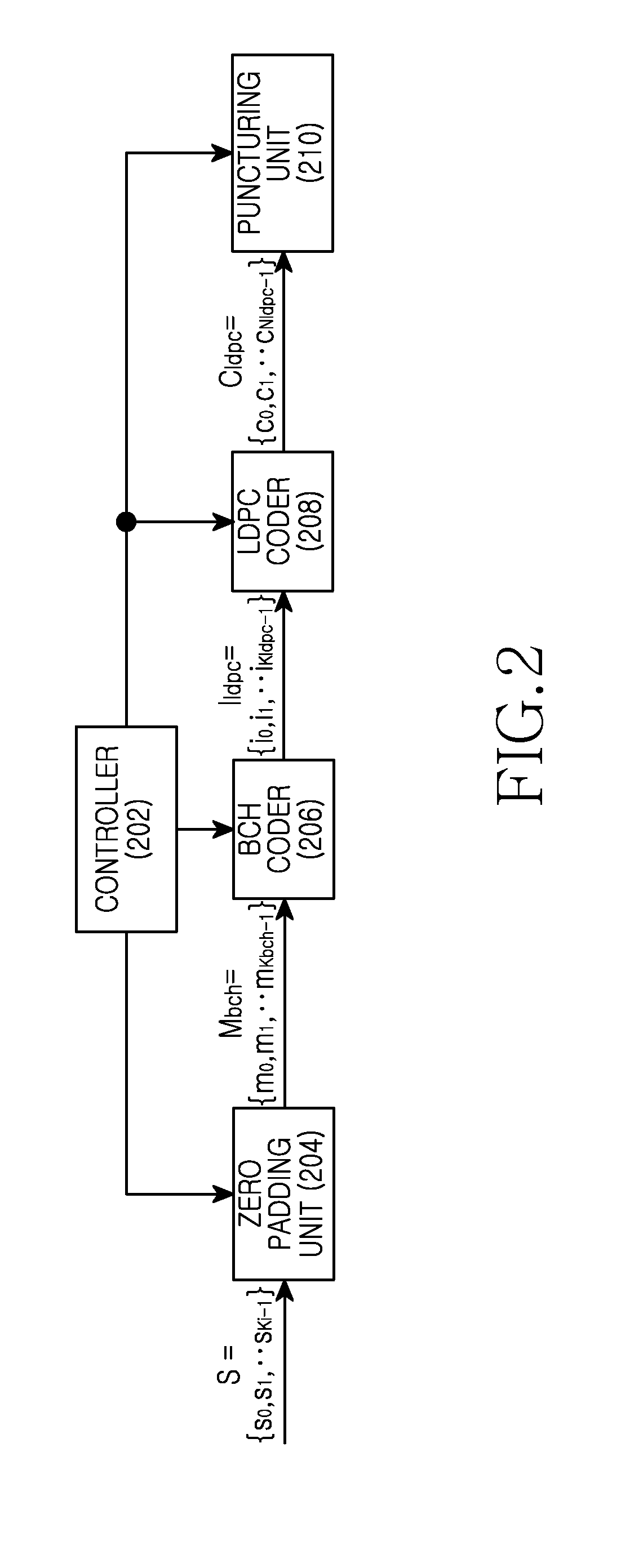

Apparatus and method for transmitting and receiving data in communication/broadcasting system

ActiveUS20120185757A1Improve performanceError correction/detection using concatenated codesError correction/detection using LDPC codesZero paddingLow density

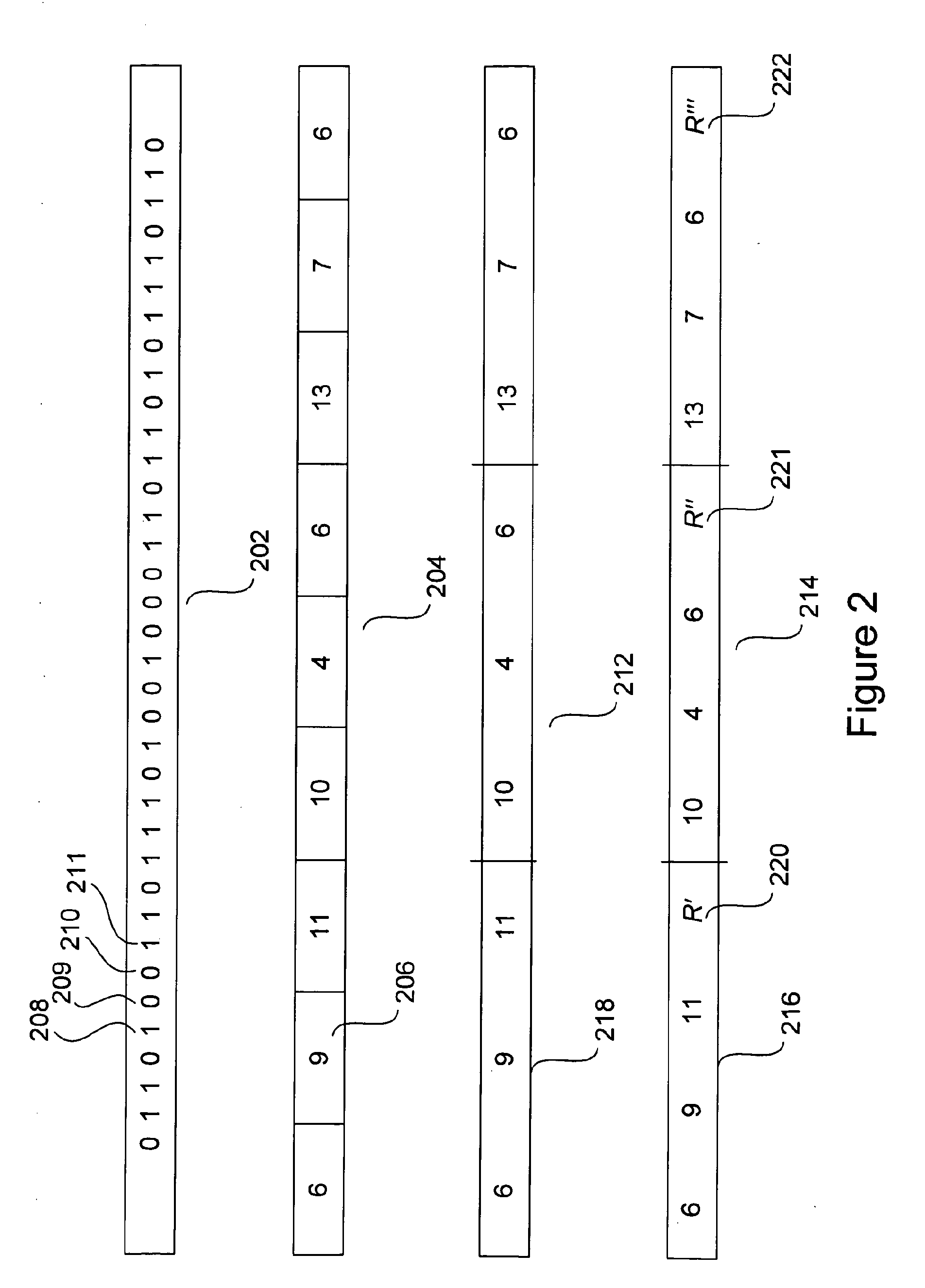

An apparatus and method for transmitting and receiving data in a wireless communication is provided. The method includes determining a number of zero-padding bits, determining a number (Npad) of bit groups in which all bits are padded with zeros, padding the all bits within 0th to (Npad−1)th bit groups indicated by a shortening pattern with zeros, mapping information bits to bit positions which are not padded in Bose Chaudhuri Hocquenghem (BCH) information bits, BCH encoding the BCH information bits to generate Low Density Parity Check (LDPC) information bits, and LDPC encoding the LDPC information bits to generate a zero-padded codeword, wherein the shortening pattern is defined as an order of bit groups defined as 6, 5, 4, 9, 3, 2, 1, 8, 0, 7, 10 and 11.

Owner:SAMSUNG ELECTRONICS CO LTD

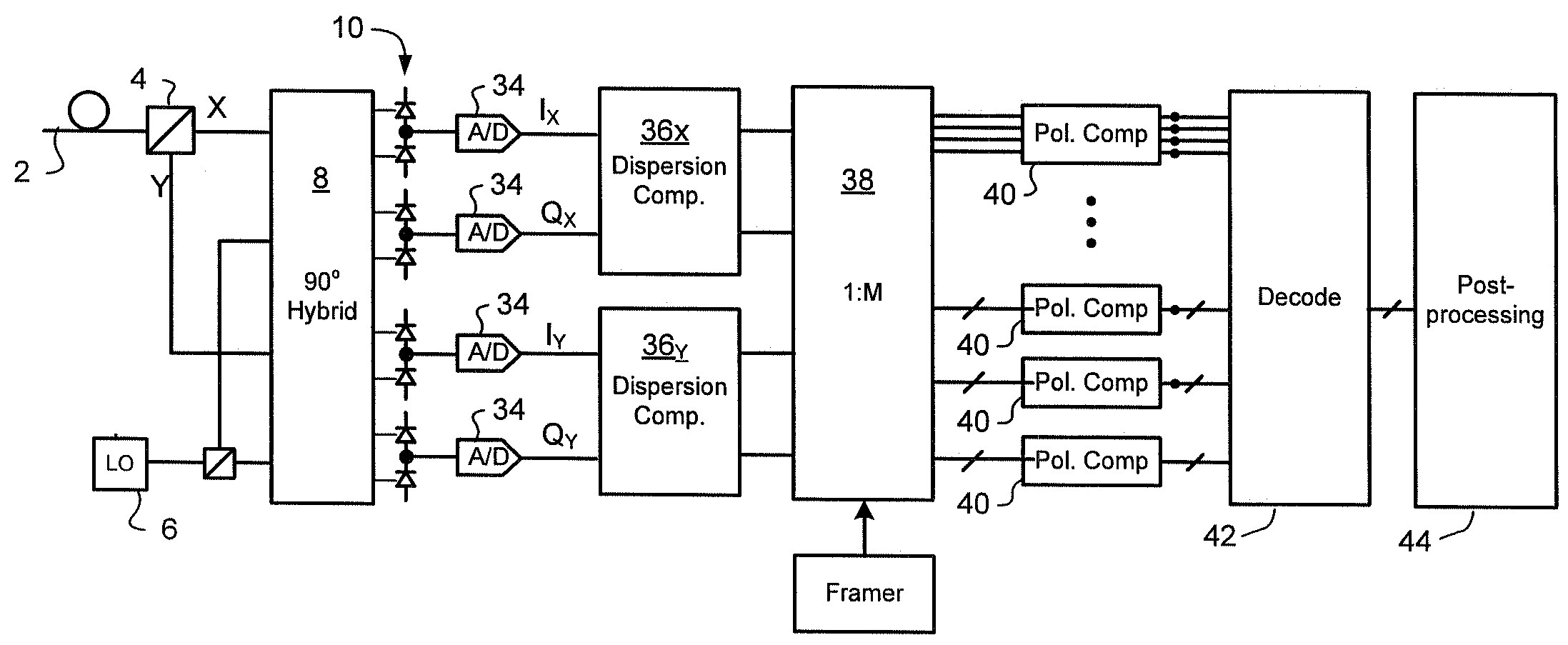

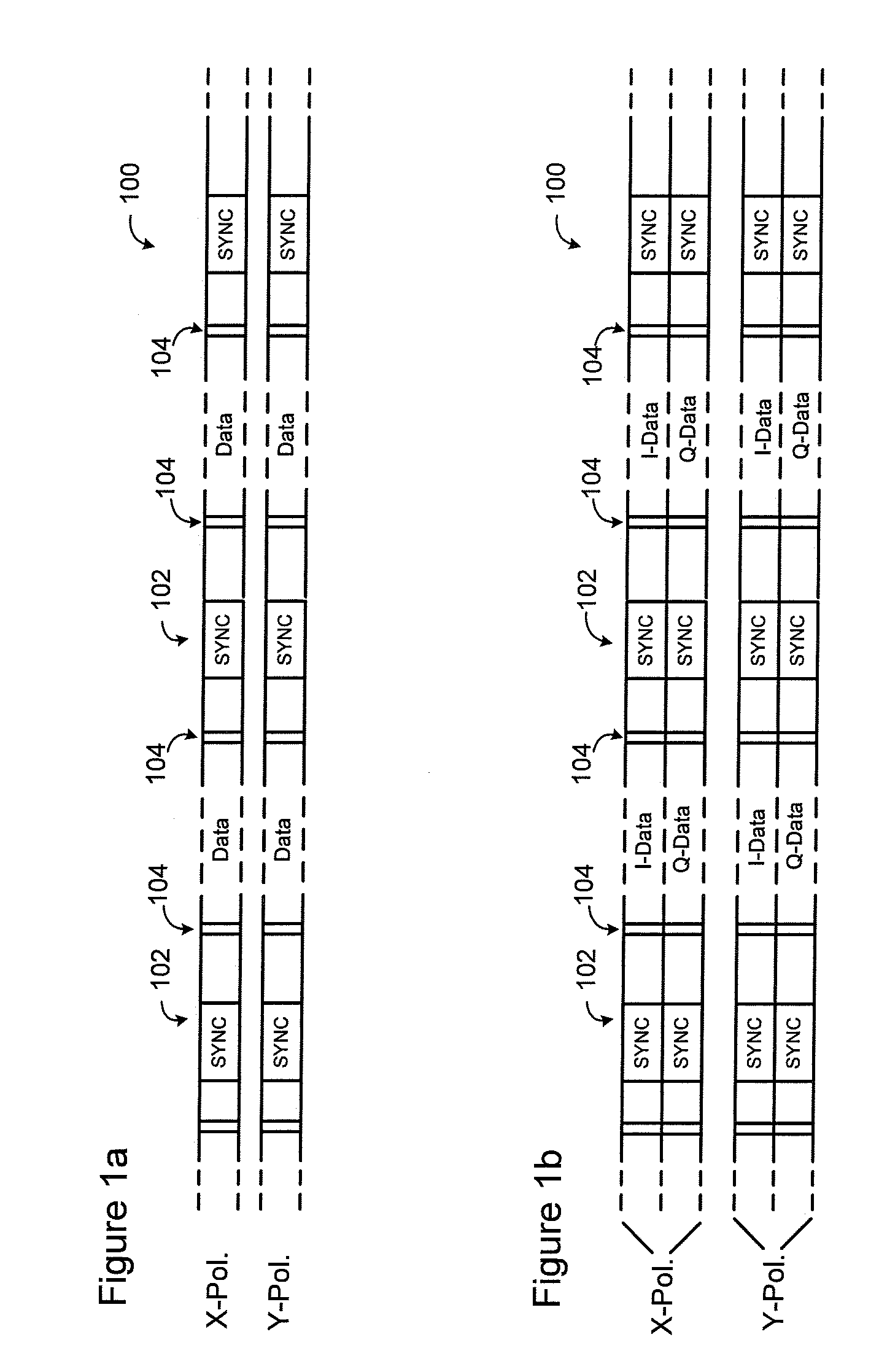

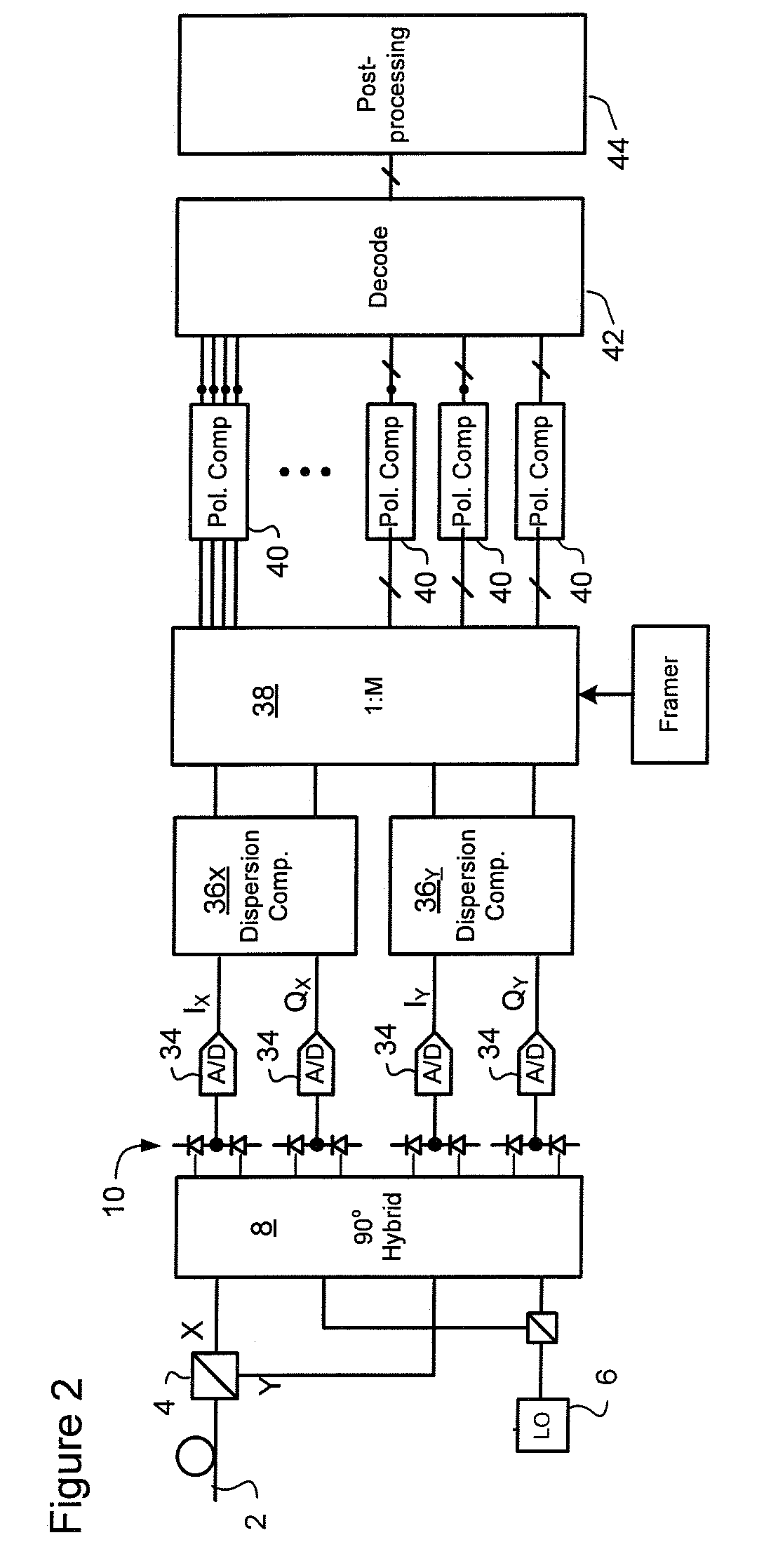

Cycle slip location and correction

Methods and techniques are disclosed for correcting the effect of cycle slips in a coherent communications system. A signal comprising SYNC bursts having a predetermined periodicity and a plurality of known symbols at predetermined locations between successive SYNC bursts is received. The received signal is partitioned into data blocks. Each data block encompasses at least data symbols and a set of check symbols corresponding to the plurality of known symbols at predetermined locations between a respective pair of successive SYNC bursts in the signal. Each data block is processed to detect a cycle slip. When a cycle slip is detected, the set of check symbols of the data block are examined to identify a first slipped check symbol, and a phase correction applied to data symbols of the data block lying between the first slipped check symbol and an end of the data block.

Owner:CIENA

Method and apparatus for using fire decoder to correct burst errors in a real-time communications system

InactiveUS6754871B1Error preventionBurst error correctionProcessor registerReal time communication systems

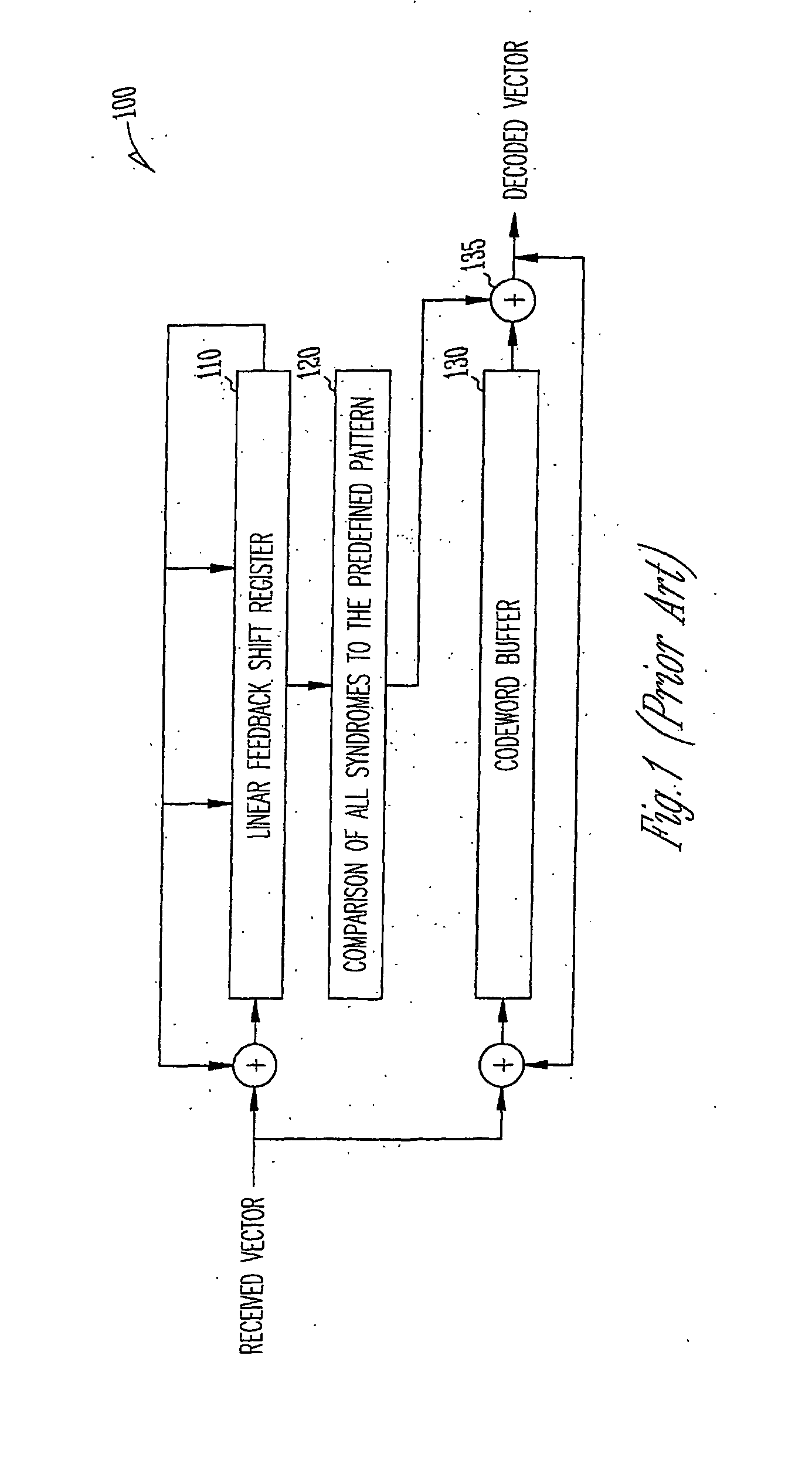

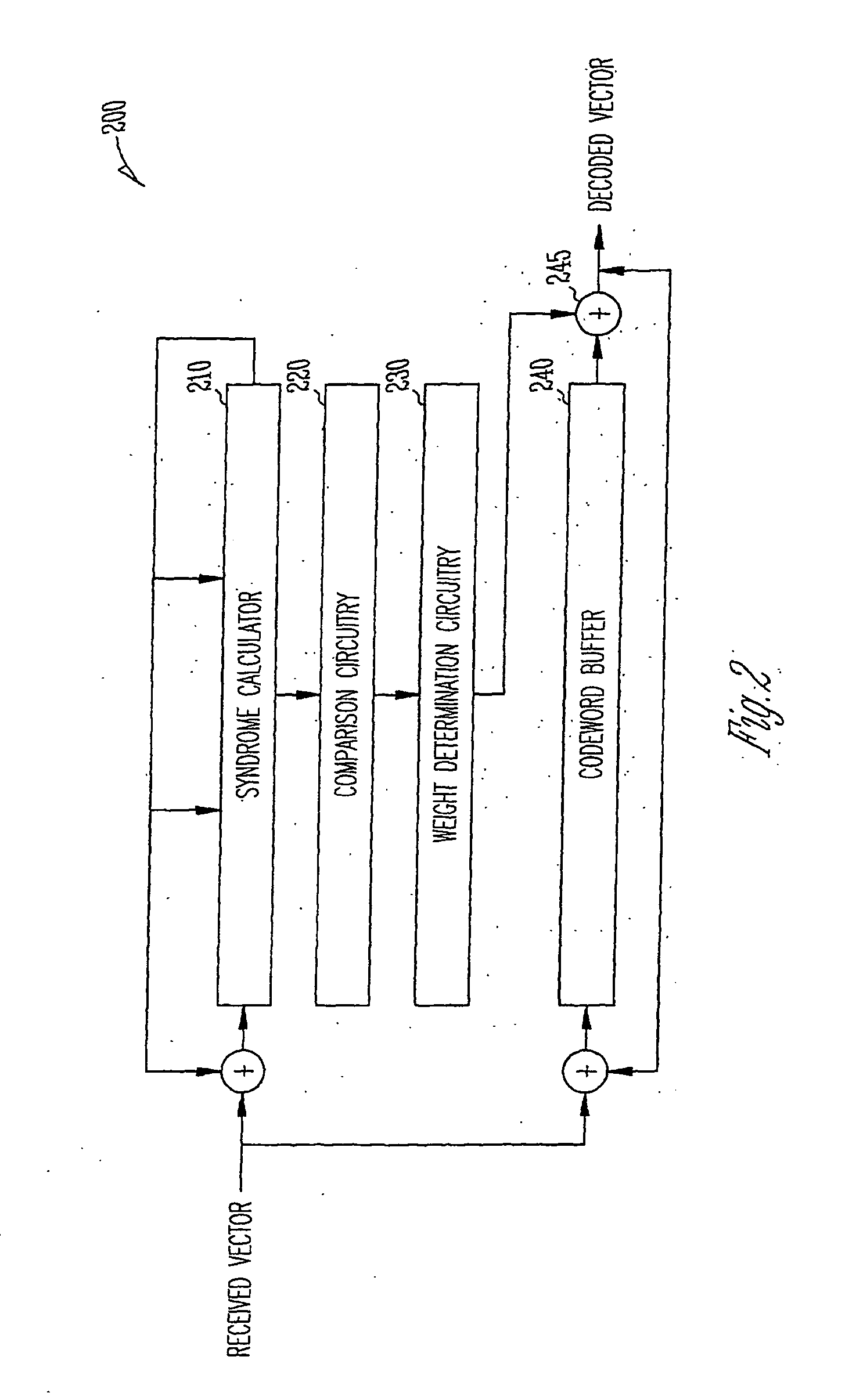

Error bursts are detected and corrected in a communication system using shortened cyclic codes, such as shortened Fire codes. Data is loaded into a first error syndrome register and a second error syndrome register. The data in the registers may be evaluated to determine if the data bits contain a correctable error. Shortened zero bits are shifted into the second error syndrome register. A number of zero bits are shifted into the first error syndrome register to trap an error burst pattern in the data. A determination is made as to the number of zero bits shifted into the second error syndrome register to trap the location of the error burst in the data. Using the number of zero bits shifted into the second error syndrome register and the error burst pattern, the error in the data is located and corrected.

Owner:CISCO TECH INC

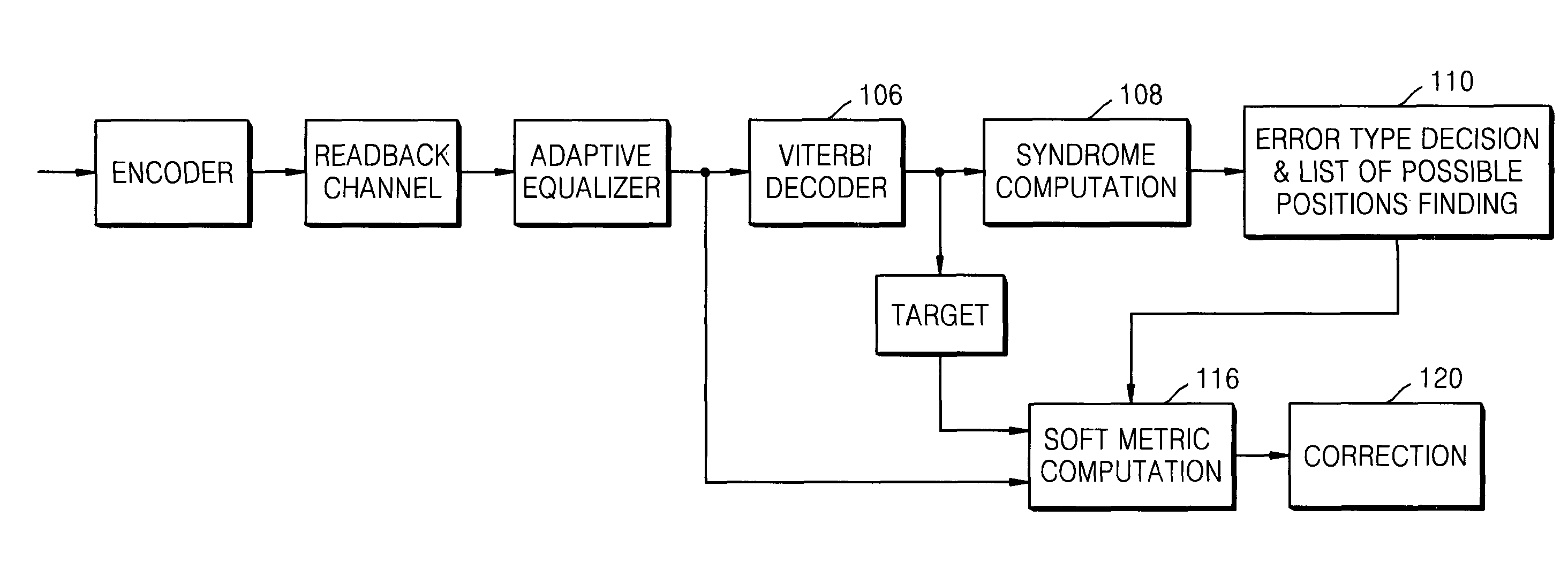

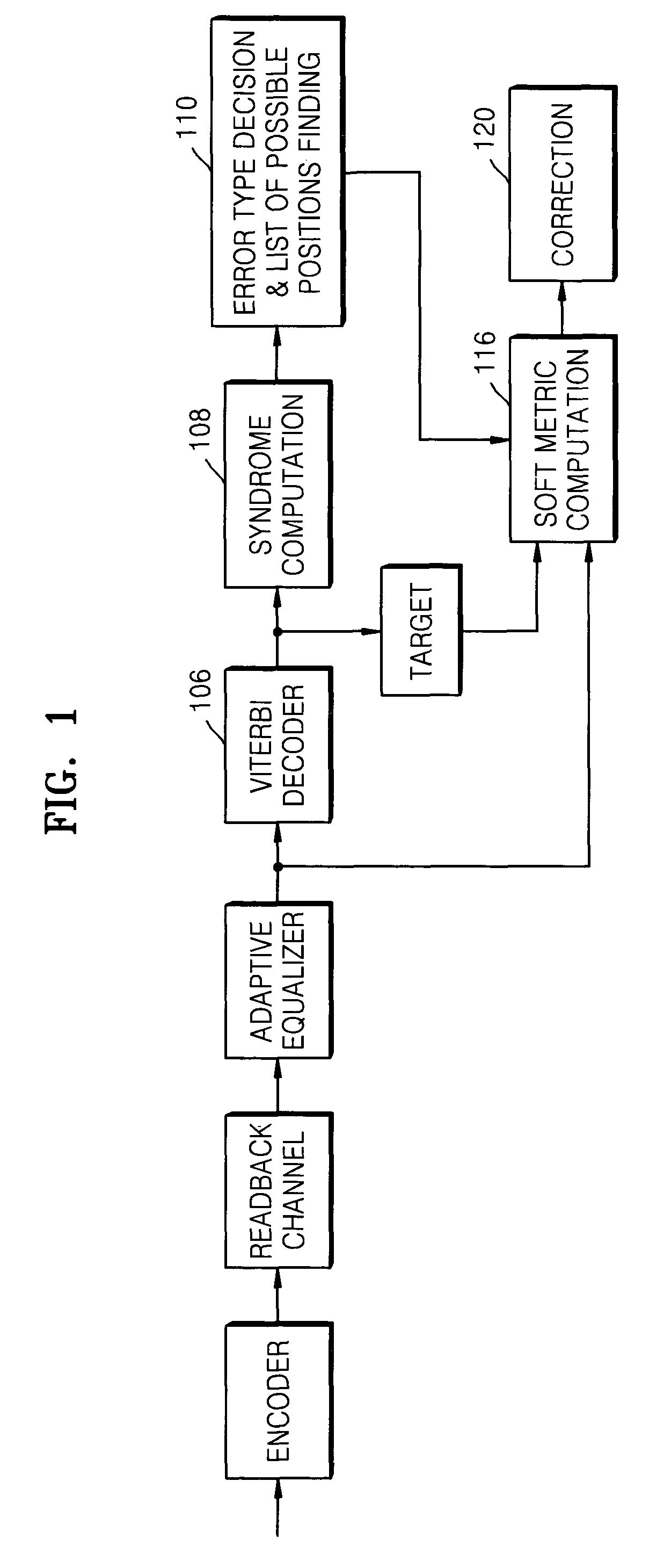

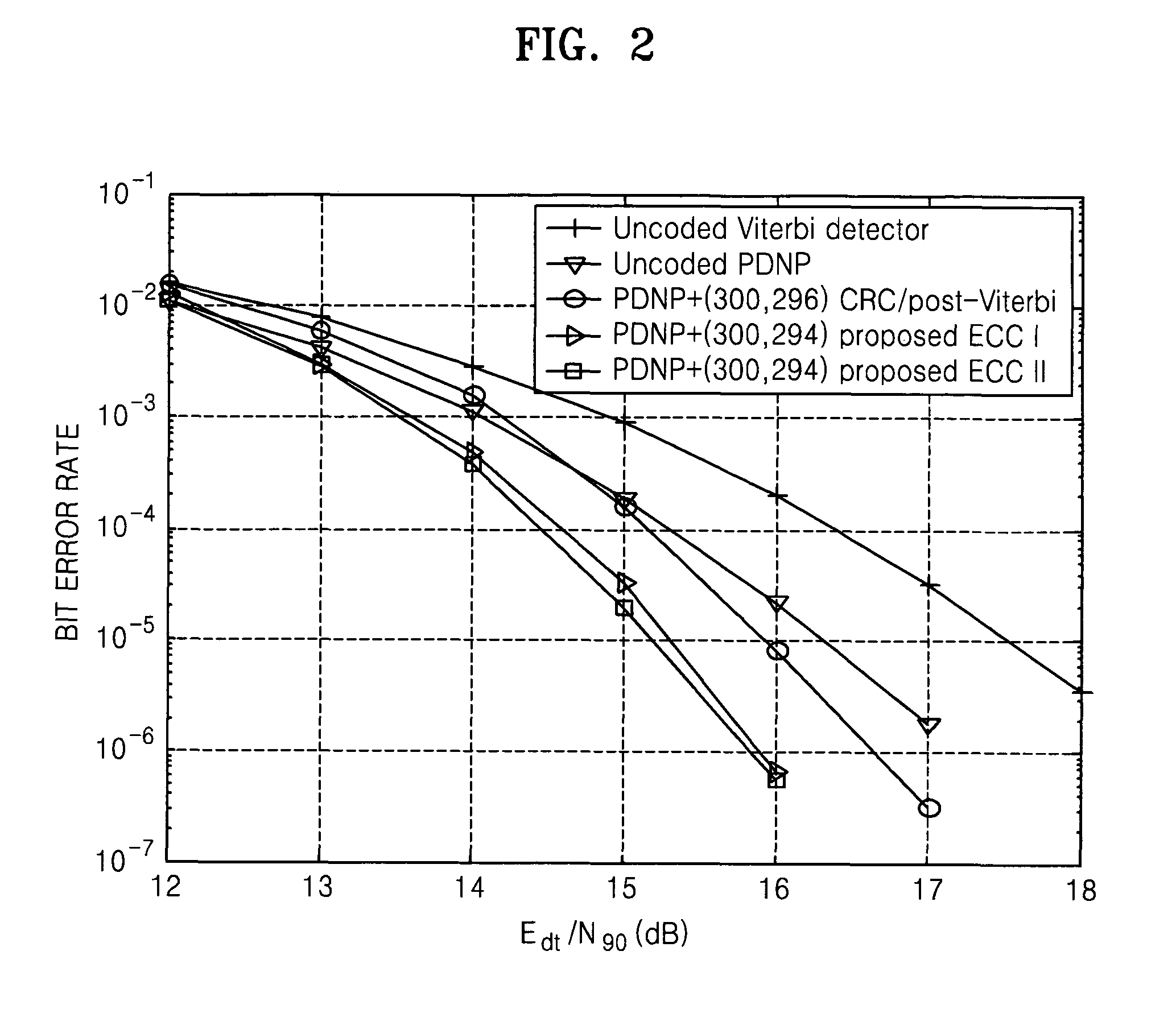

Error correction method and apparatus for predetermined error patterns

In a method of detecting an error pattern in a codeword transmitted across a noisy communication channel, a codeword is detected. A syndrome is then generated by applying a generator polynomial to the codeword. The generator polynomial is adapted to produce a distinct syndrome set for each of “L” (L>1) different error patterns potentially introduced in the codeword during transmission across the communication channel. A type of an error pattern within the codeword is detected based on the syndrome or a shifted version of the syndrome, and then a start position of the error pattern within the codeword.

Owner:RGT UNIV OF MINNESOTA +1

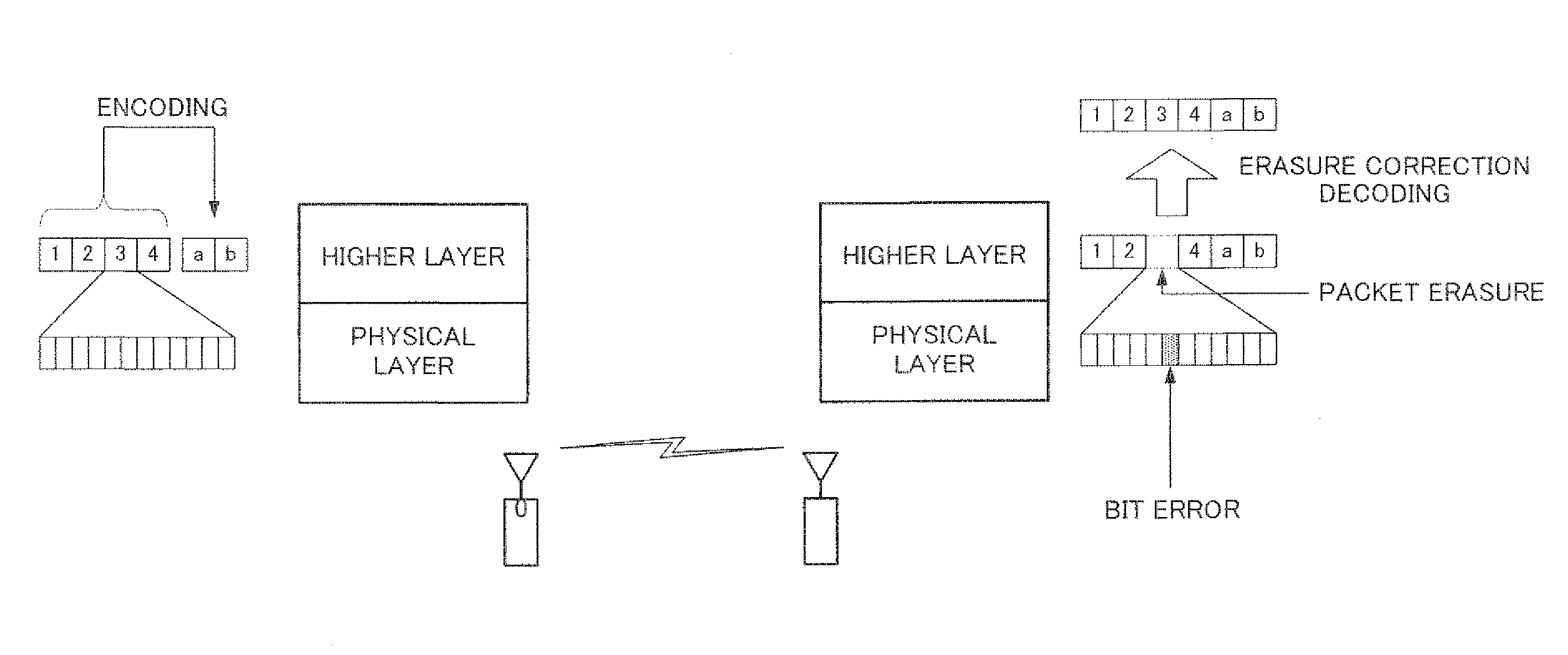

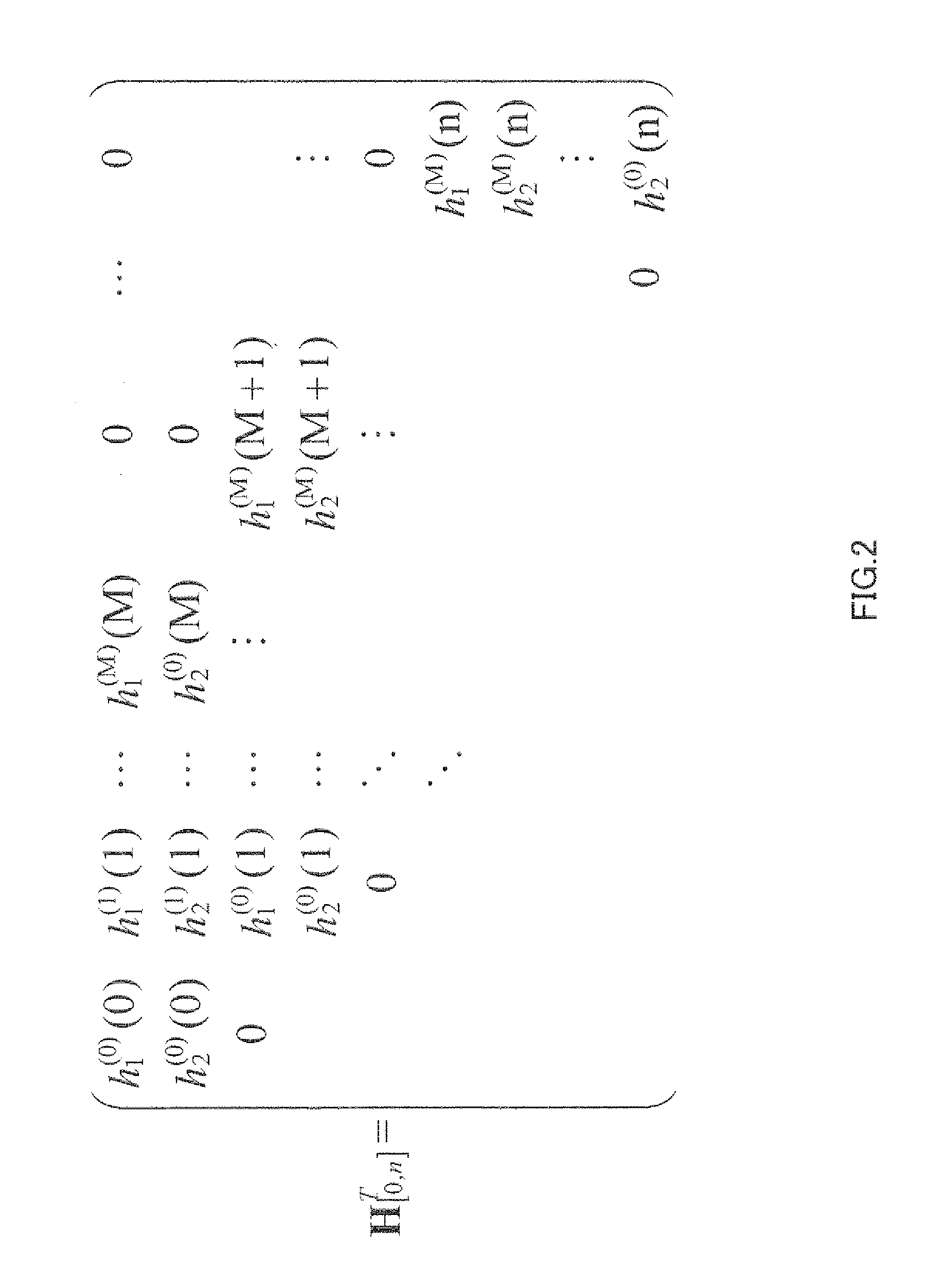

Loss correction encoding device and loss correction encoding method

ActiveUS20110087948A1Correction capabilityBurst error correctionCode conversionCheekComputer science

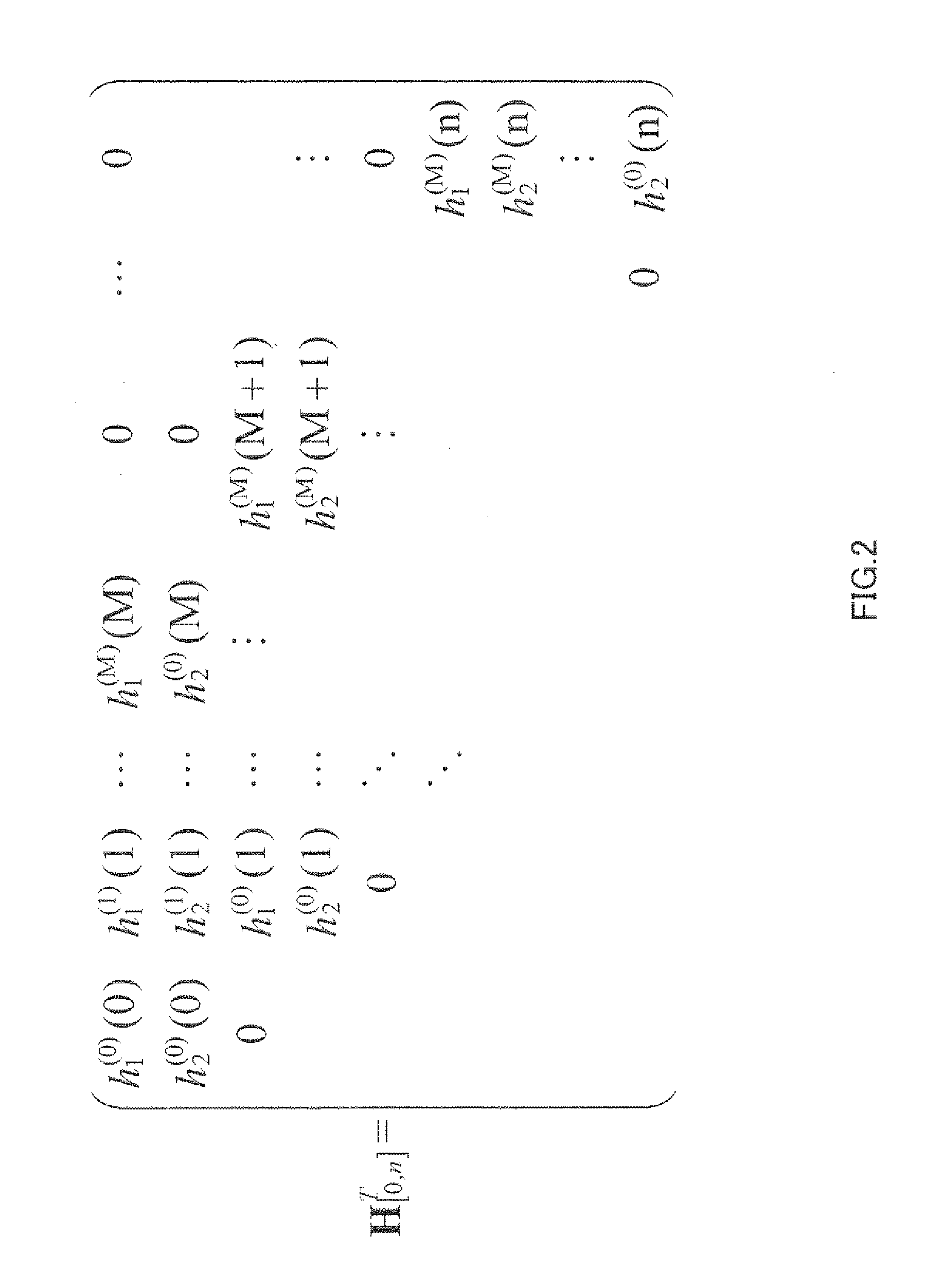

A loss correction encoding device having an improved capability of loss correction using LDPC-CC is disclosed. In the loss correction encoding device (120), a rearranging unit (122) rearranges information data contained in n information packets according to the constraint length Kmax and the encoding rate (q−1) / q of a cheek polynomial of the loss correction code used in a loss correction encoding unit (123). Specifically, the rearranging unit (122) rearranges the information data in such a way that continuous Kmax×(q−1) pieces of information data after rearrangement are contained in different information packets. The rearranging unit (122) distributes the information data to information blocks from n information packets (n satisfies formula (1)).Kmax×(q−1)≦n (1)

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

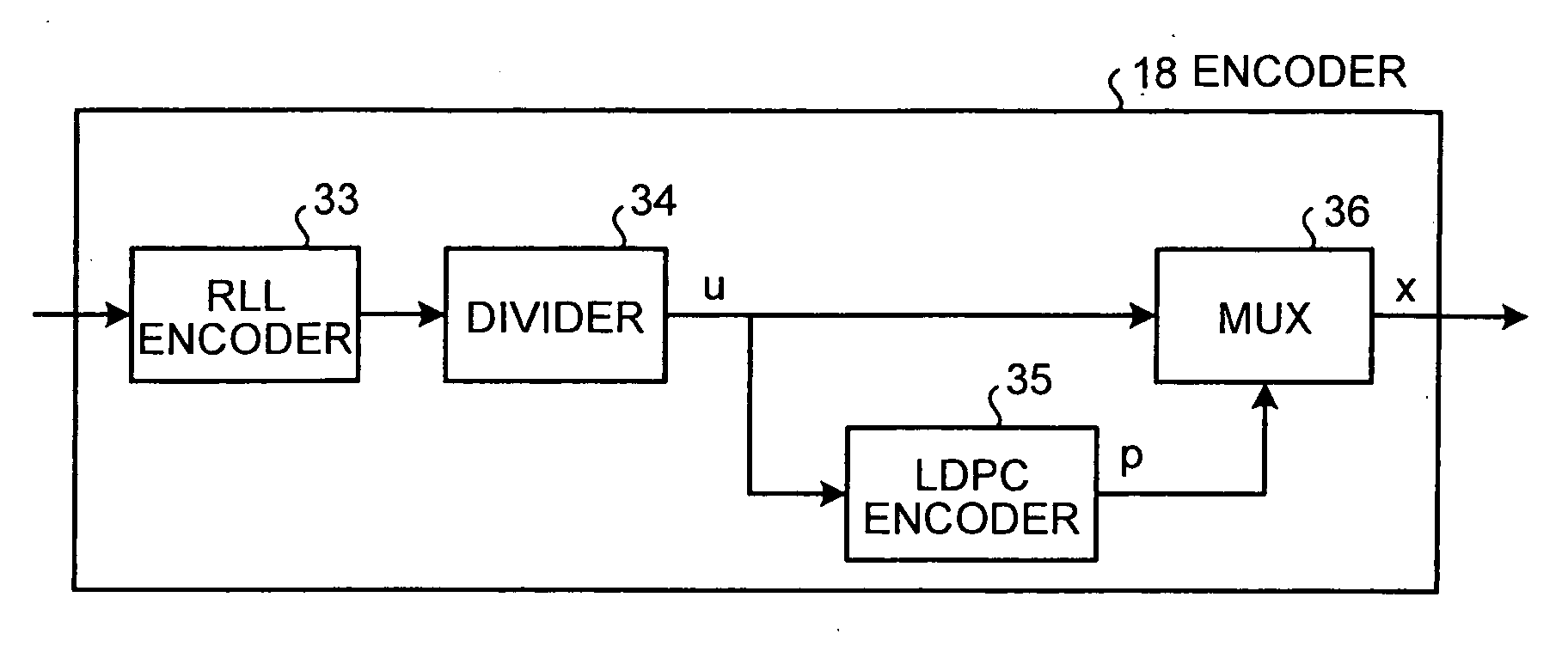

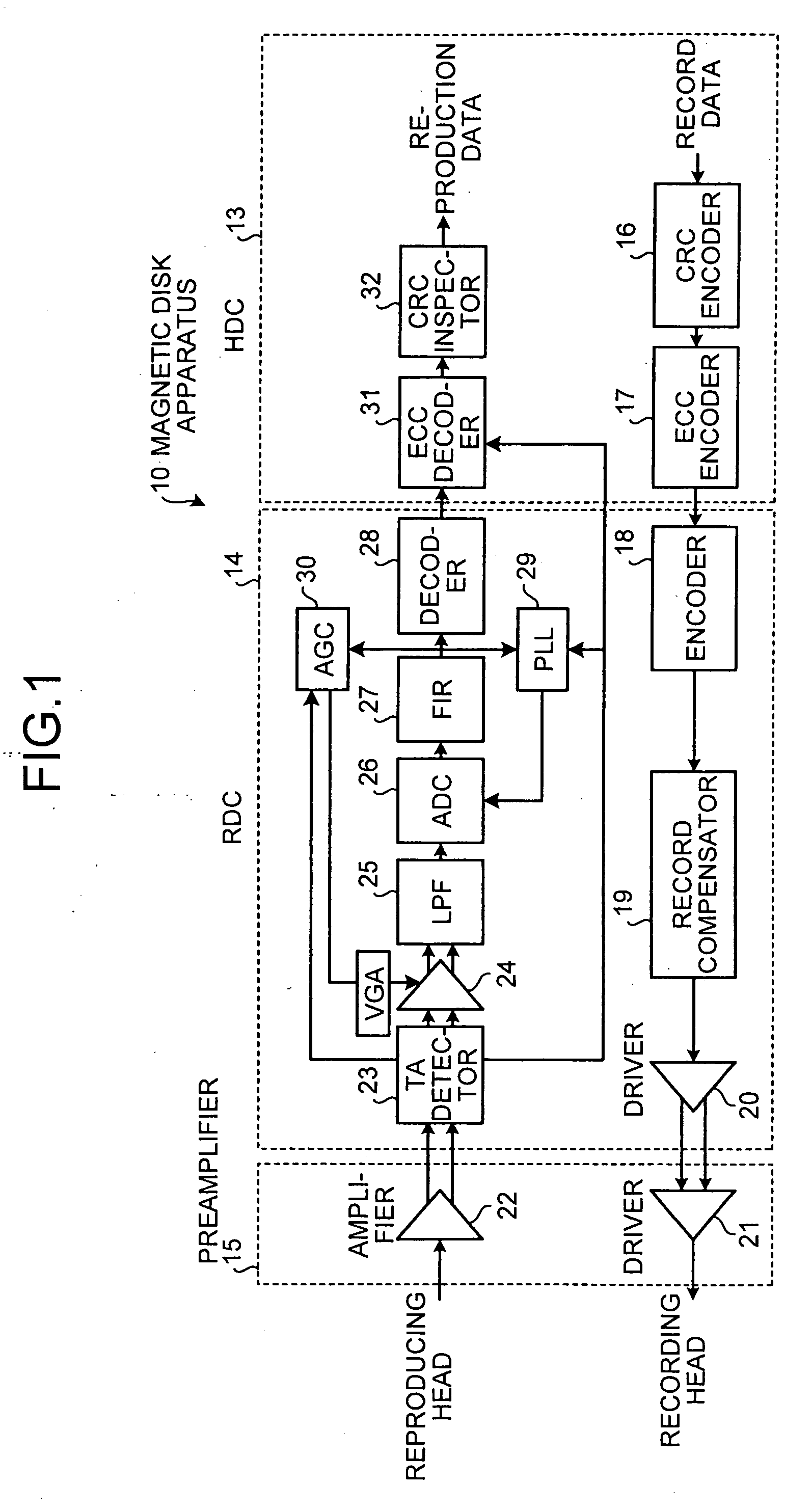

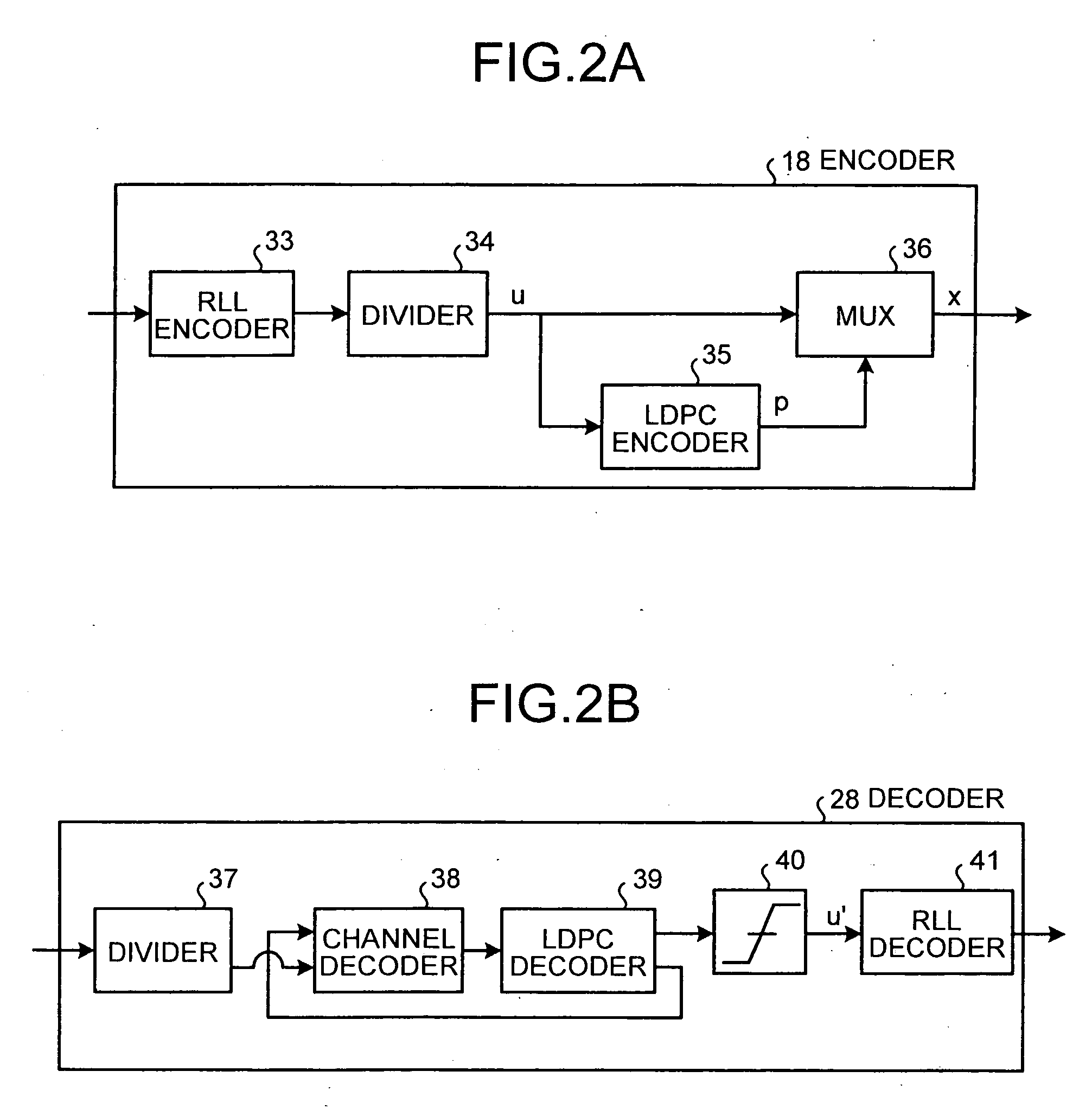

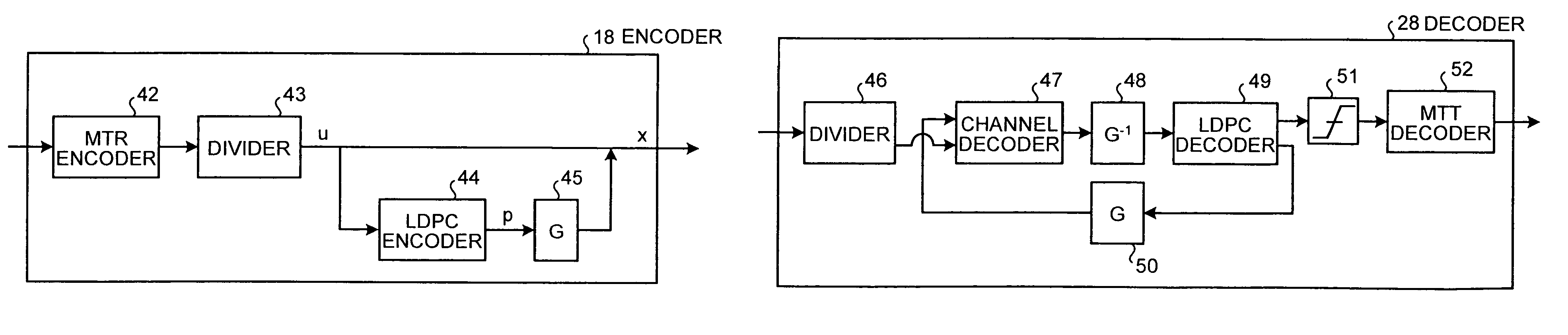

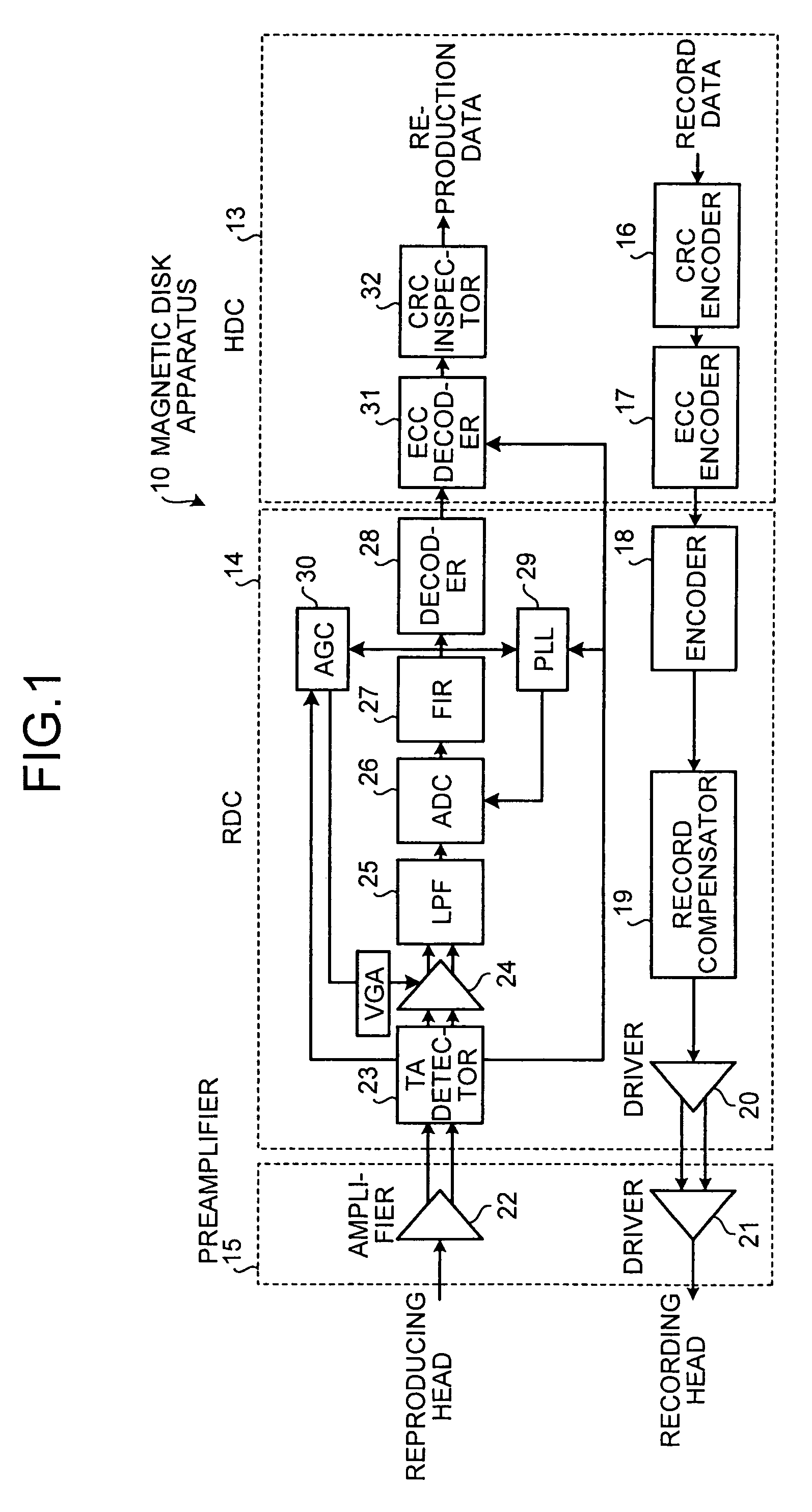

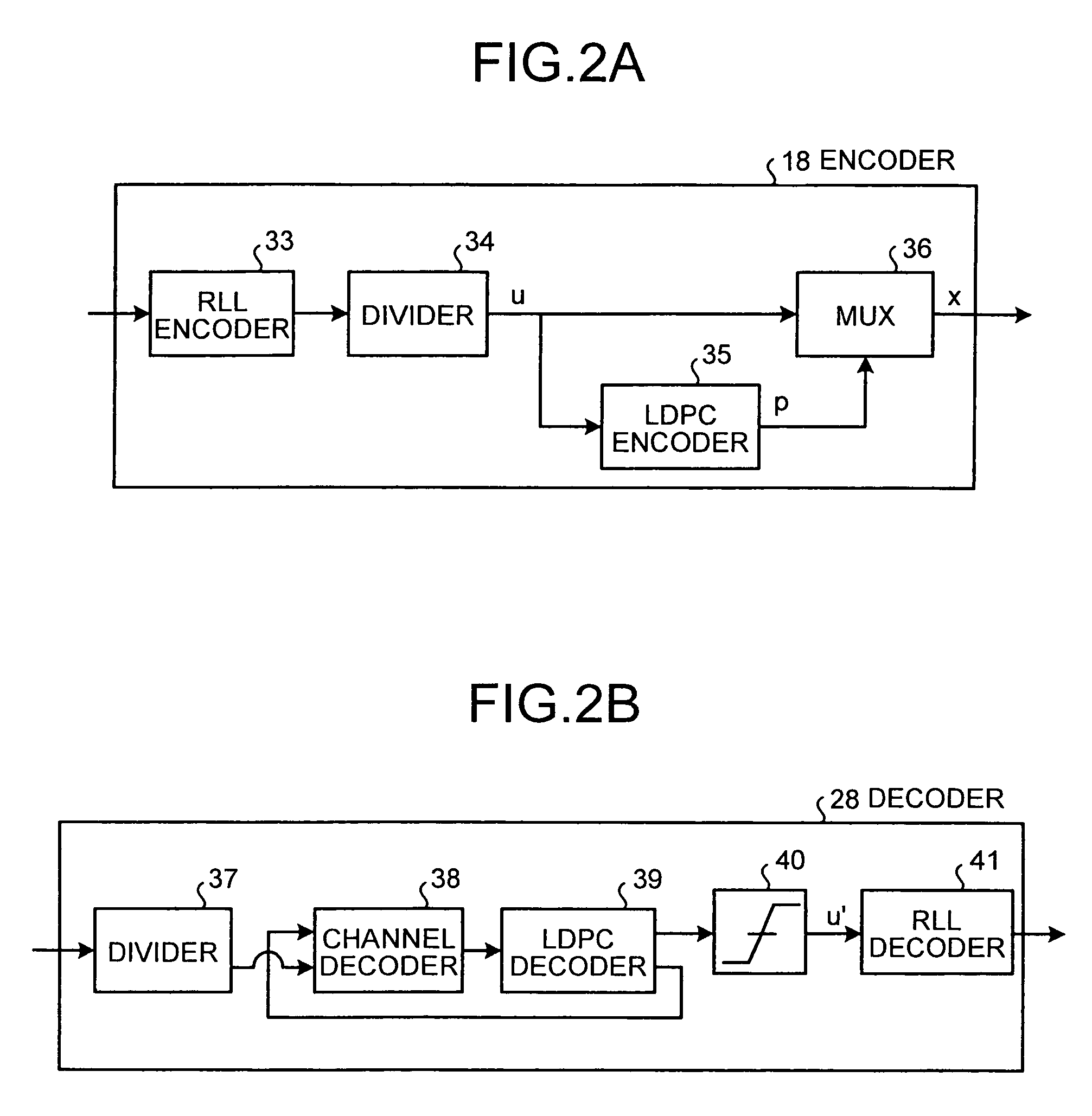

Method, apparatus, and circuit for record reproduction

InactiveUS20050066261A1Reduce circuit sizeBurst error correctionError correction/detection using multiple parity bitsComputer scienceOperating system

A record reproduction apparatus includes an encoding unit that encodes sector data to be written into a recording medium, by dividing the data into a predetermined number of blocks, and an iterative decoding unit that iteratively decodes the sector data read from the recording medium, by dividing the sector data into the predetermined number of blocks.

Owner:FUJITSU LTD

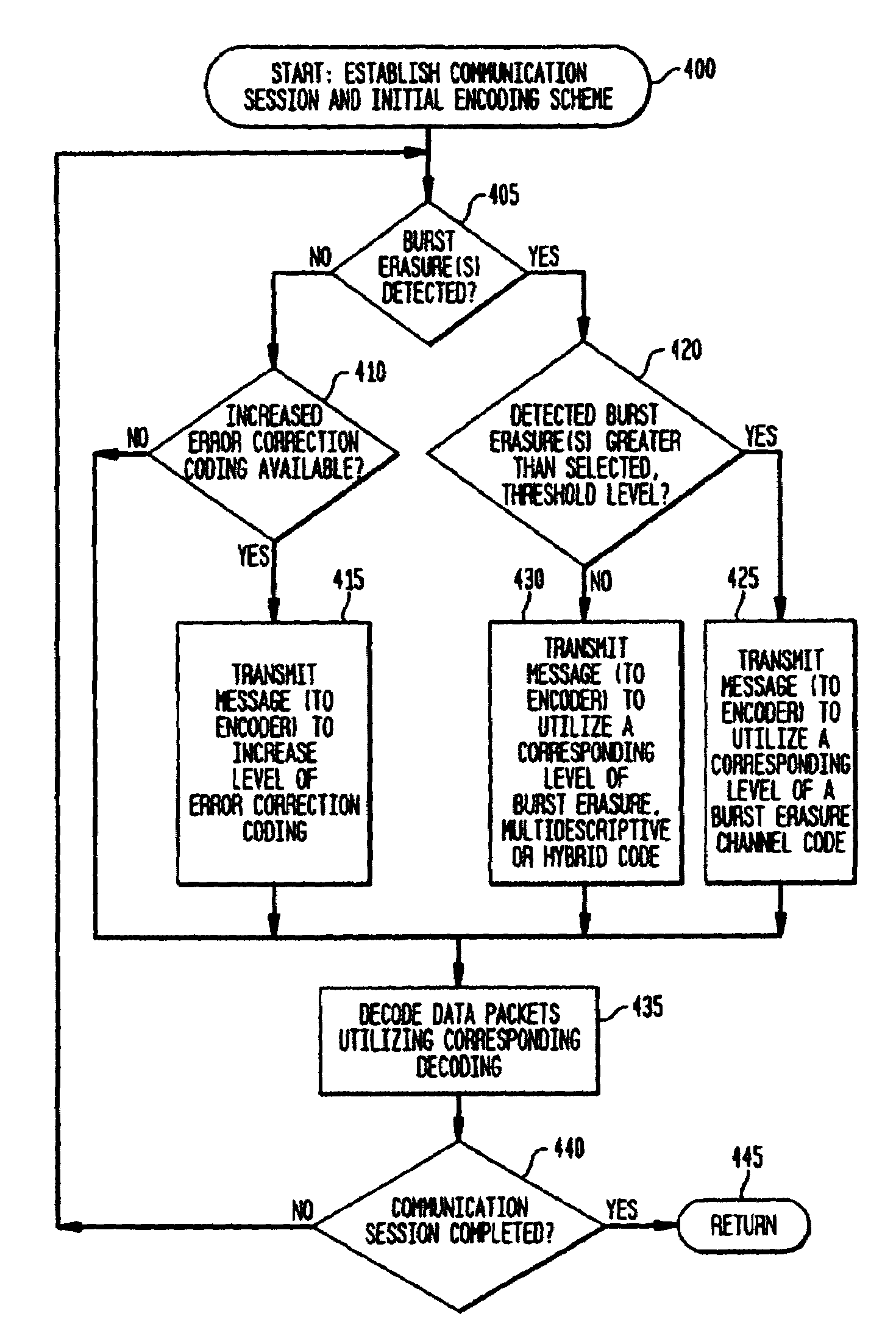

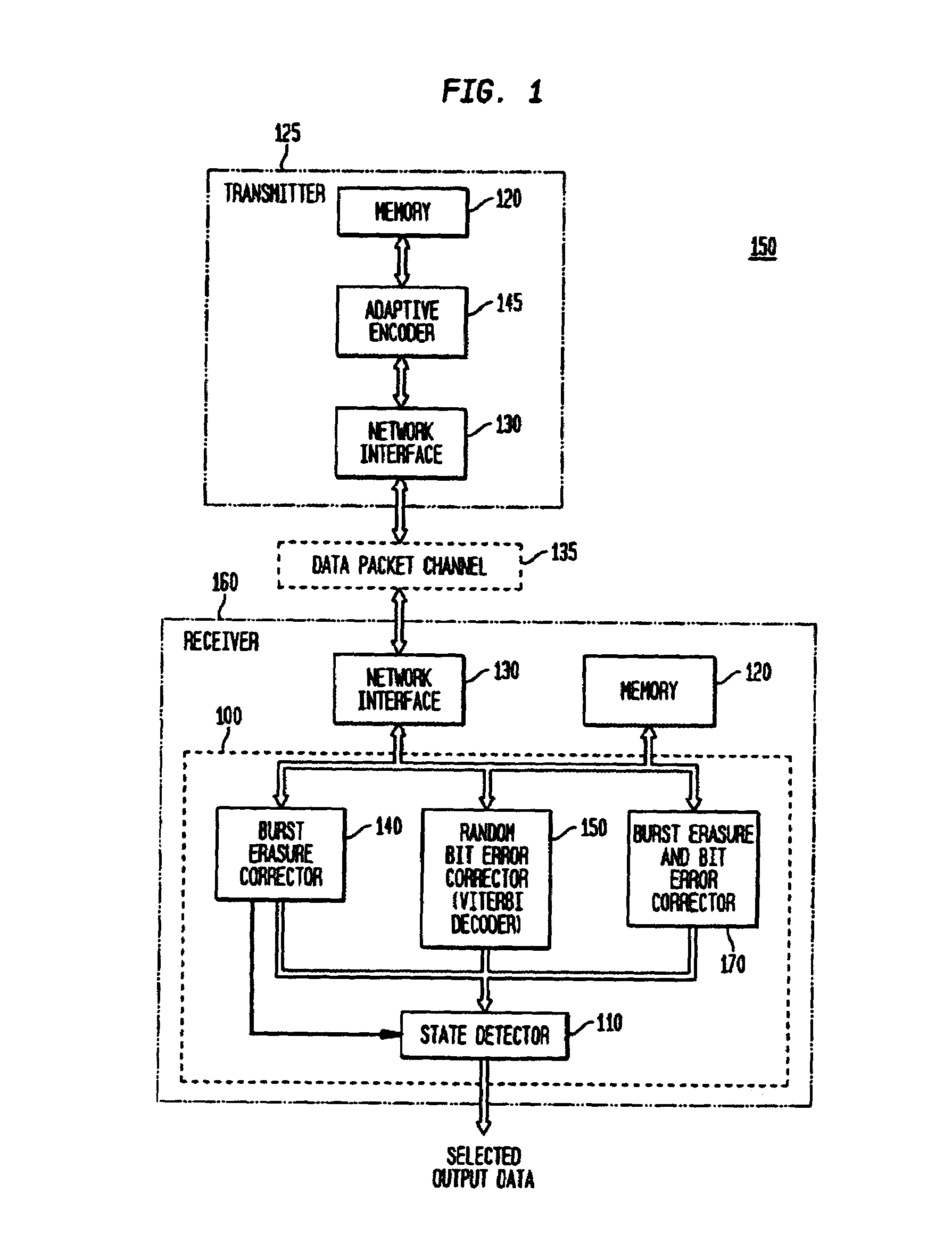

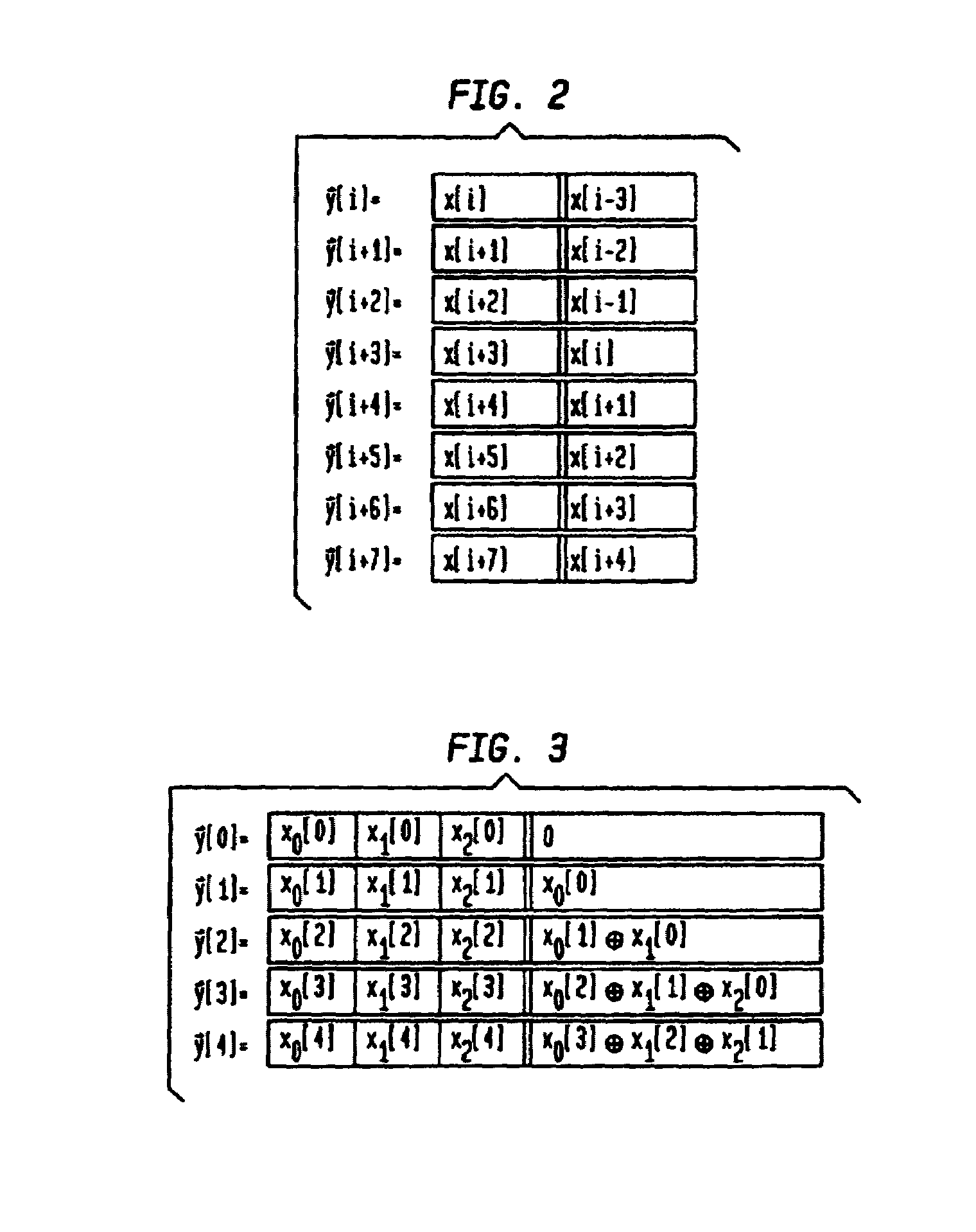

Apparatus and method for adaptive, multimode decoding

ActiveUS7003712B2Improve received signal qualityImprove errorOther decoding techniquesOther error detection/correction/protectionCommunications systemSignal quality

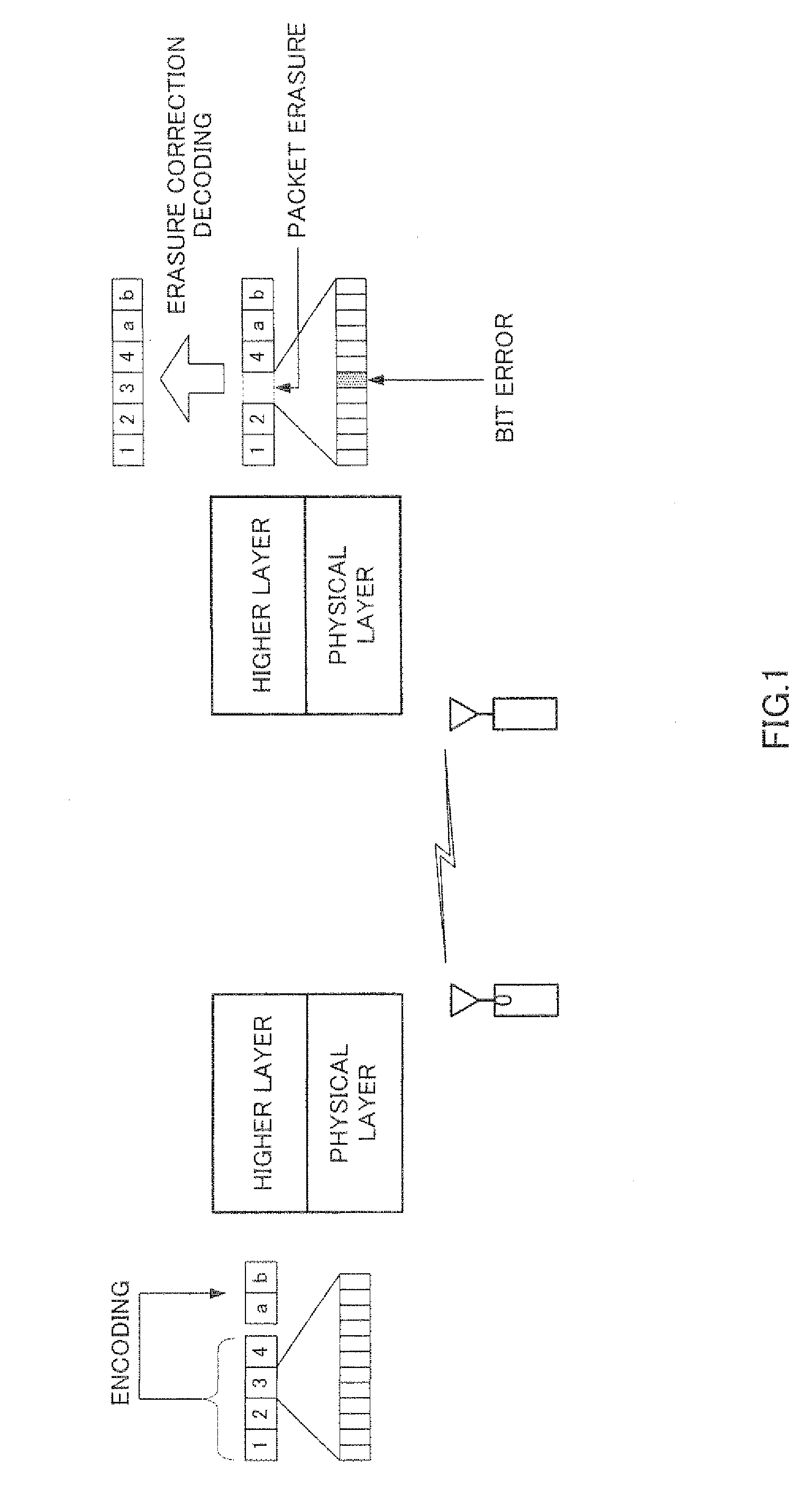

The present invention provides for adaptive and multimode decoding, in a data packet-based communication system, to provide improved received signal quality in the presence of burst erasures or random bit errors, with particular suitability for real-time, delay sensitive applications, such as voice over Internet Protocol. In the presence of burst erasures, the adaptive multimode decoder of the present invention provides burst erasure correction decoding, preferably utilizes a maximally short (MS) burst erasure correcting code, which has a comparatively short decoding delay. Depending upon the level of such burst erasures, different rate MS codes may be utilized, or other codes may be utilized, such as hybrid or multidescriptive codes. When no burst erasures are detected, the adaptive multimode decoder of the present invention provides random bit error correction decoding, in lieu of or in addition to corresponding burst erasure correction coding.

Owner:AGERE SYST GUARDIAN

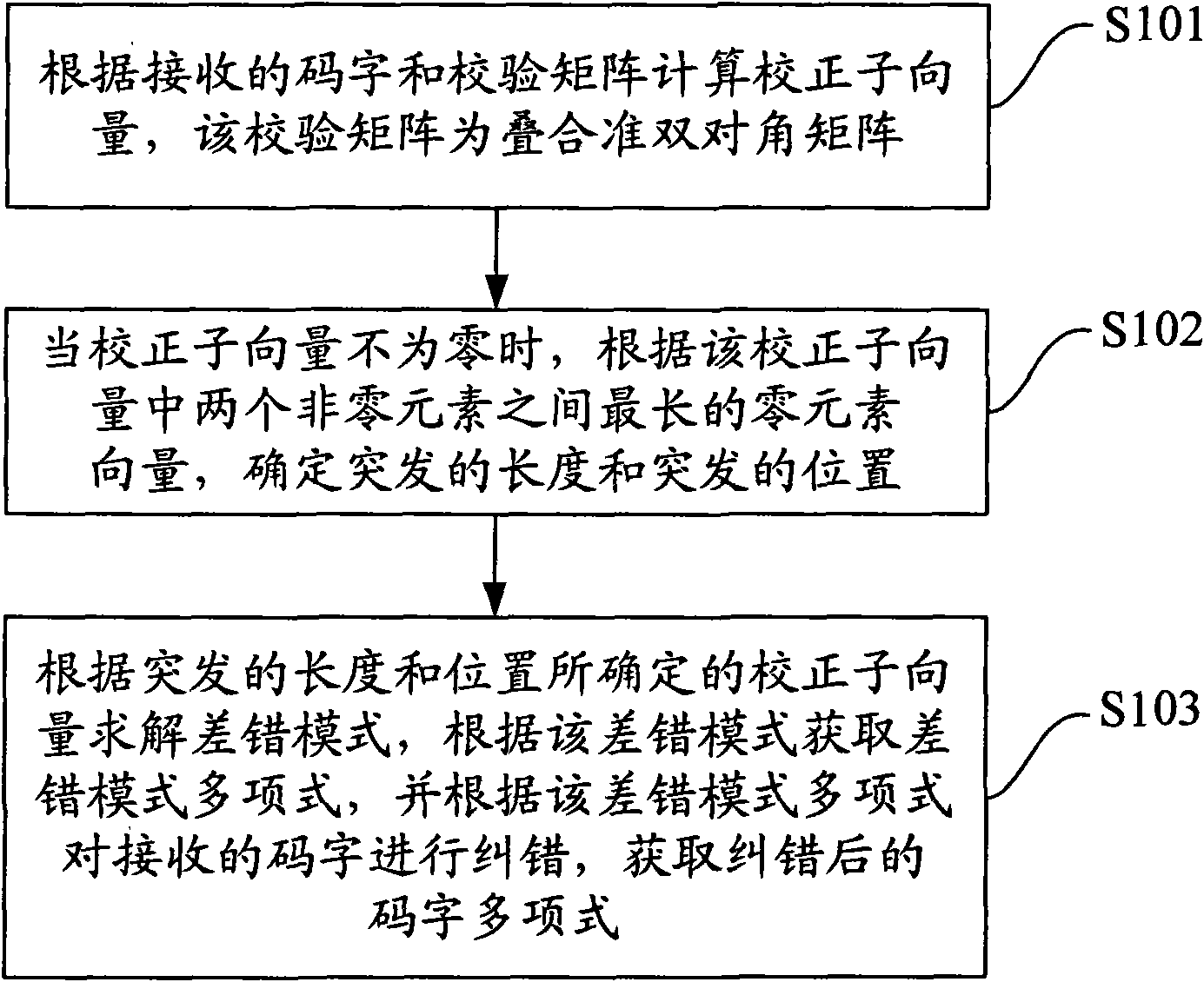

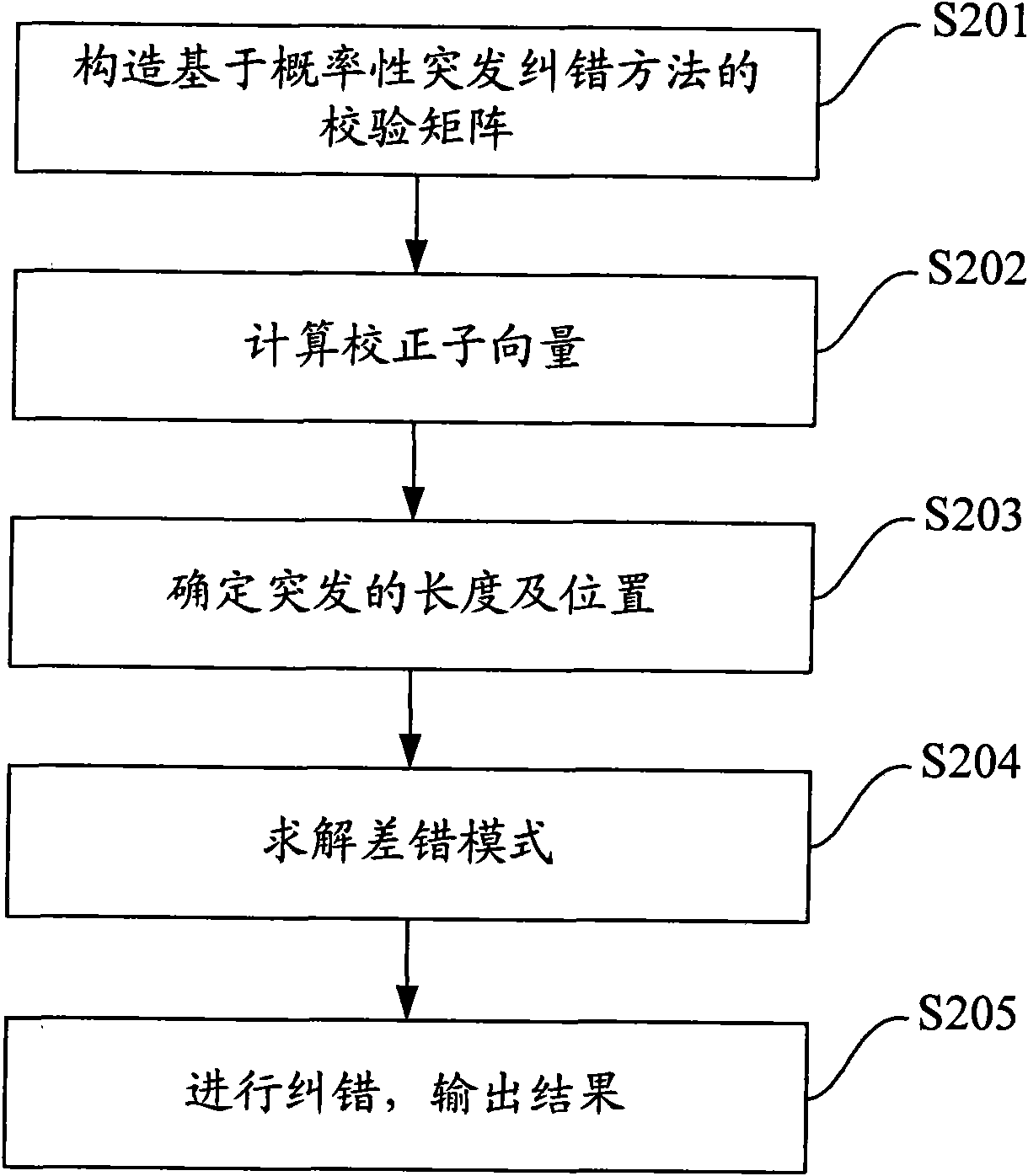

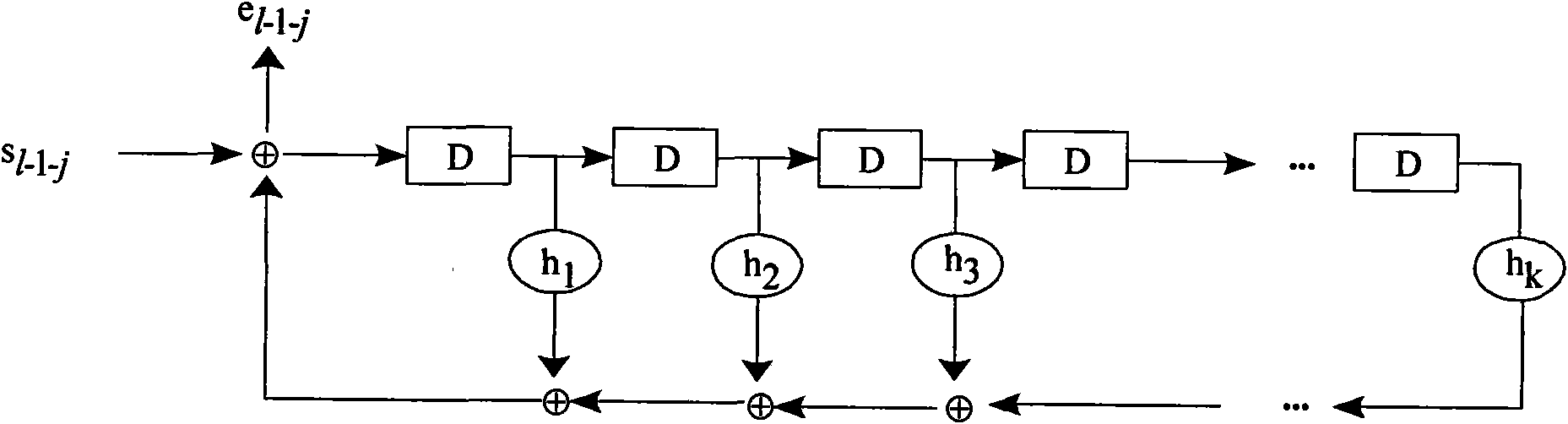

Burst correcting method, equipment and device

ActiveCN101621299AError correction burst errorError preventionBurst error correctionEuclidean vectorBurst error

The embodiment of the invention discloses a burst correcting method, equipment and a device. The burst correcting method comprises calculating a corrector subvector according to received codes and a rectifying matrix, wherein, the rectifying matrix is an overlapped quasi-bidiagonal matrix; determining the burst length and the burst position according to the longest zero element vector between thetwo non-zero element vectors in the corrector subvector when the corrector subvector is non-zero element vector; solving an error mode according to the determined corrector subvector based on the burst length and the burst position, obtaining a multinomial error mode according to the error mode, and correcting the received codes according to the multinomial error mode to obtain a corrected multinomial code. The embodiment of the invention provides a concrete implementation method which regards circulating codes, is based on probabilistic burst correction, and can correct more burst errors in comparison with regular circulating code deciphering method.

Owner:XFUSION DIGITAL TECH CO LTD

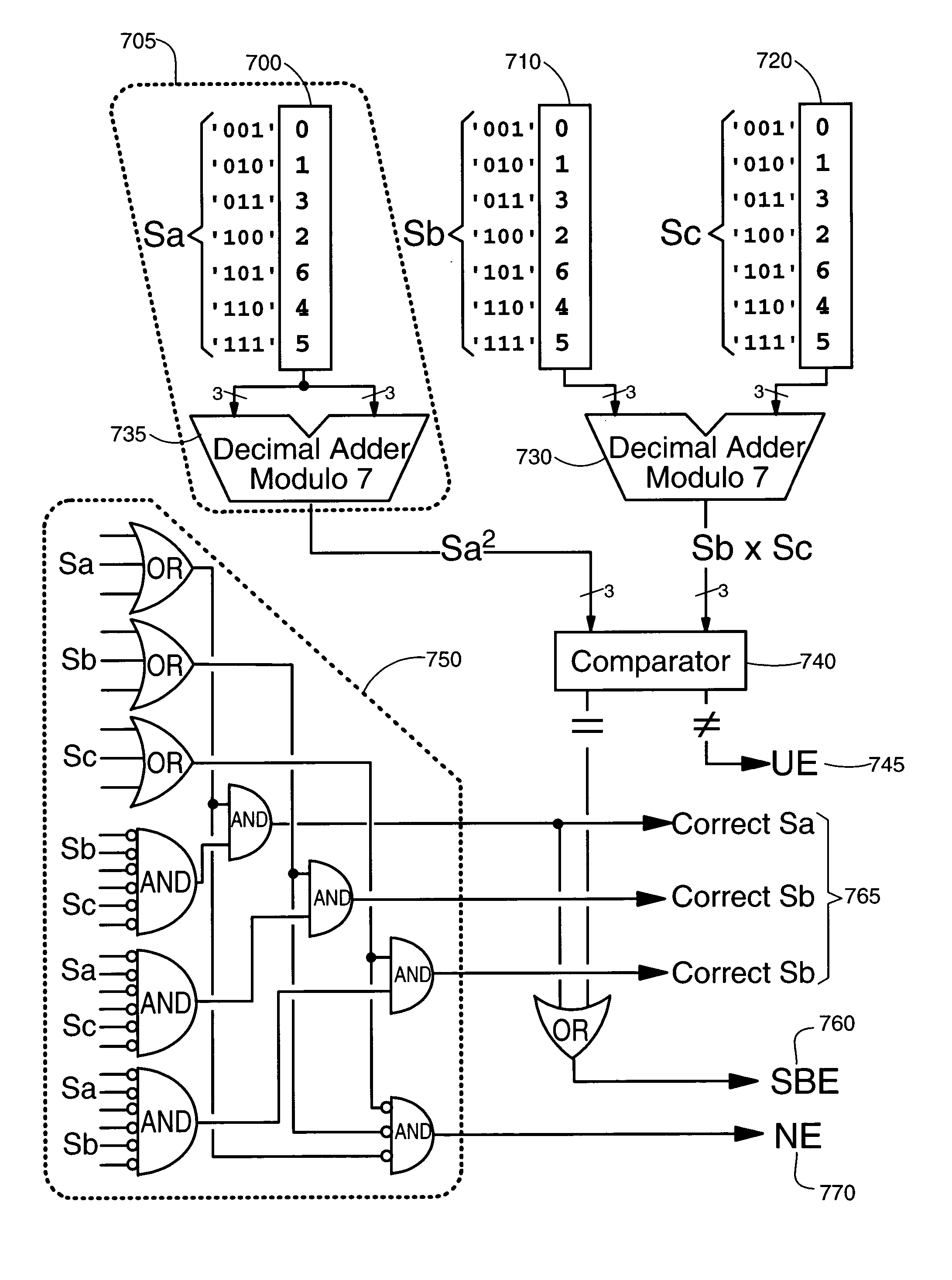

Single-burst-correction / double-burst-detection error code

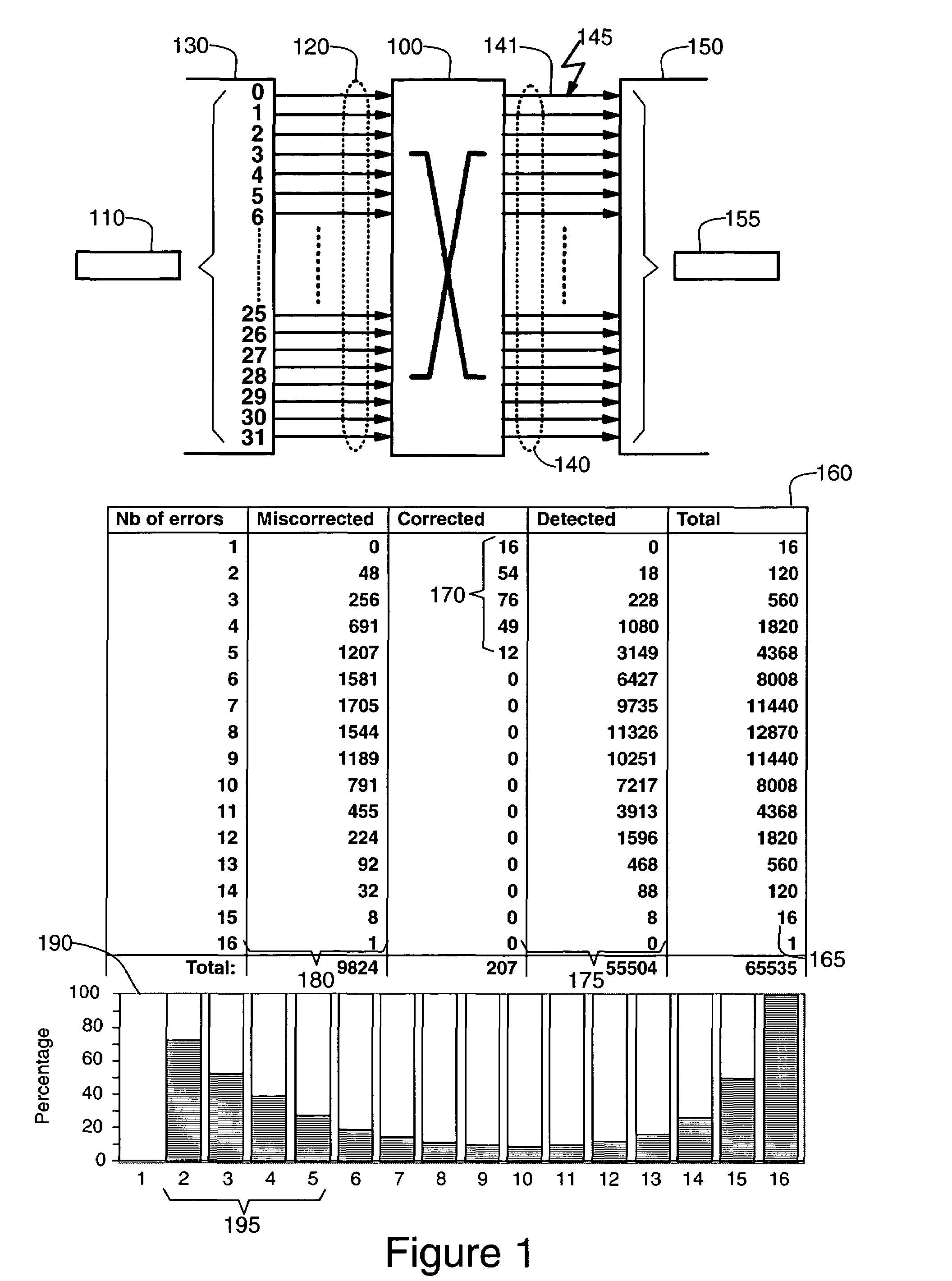

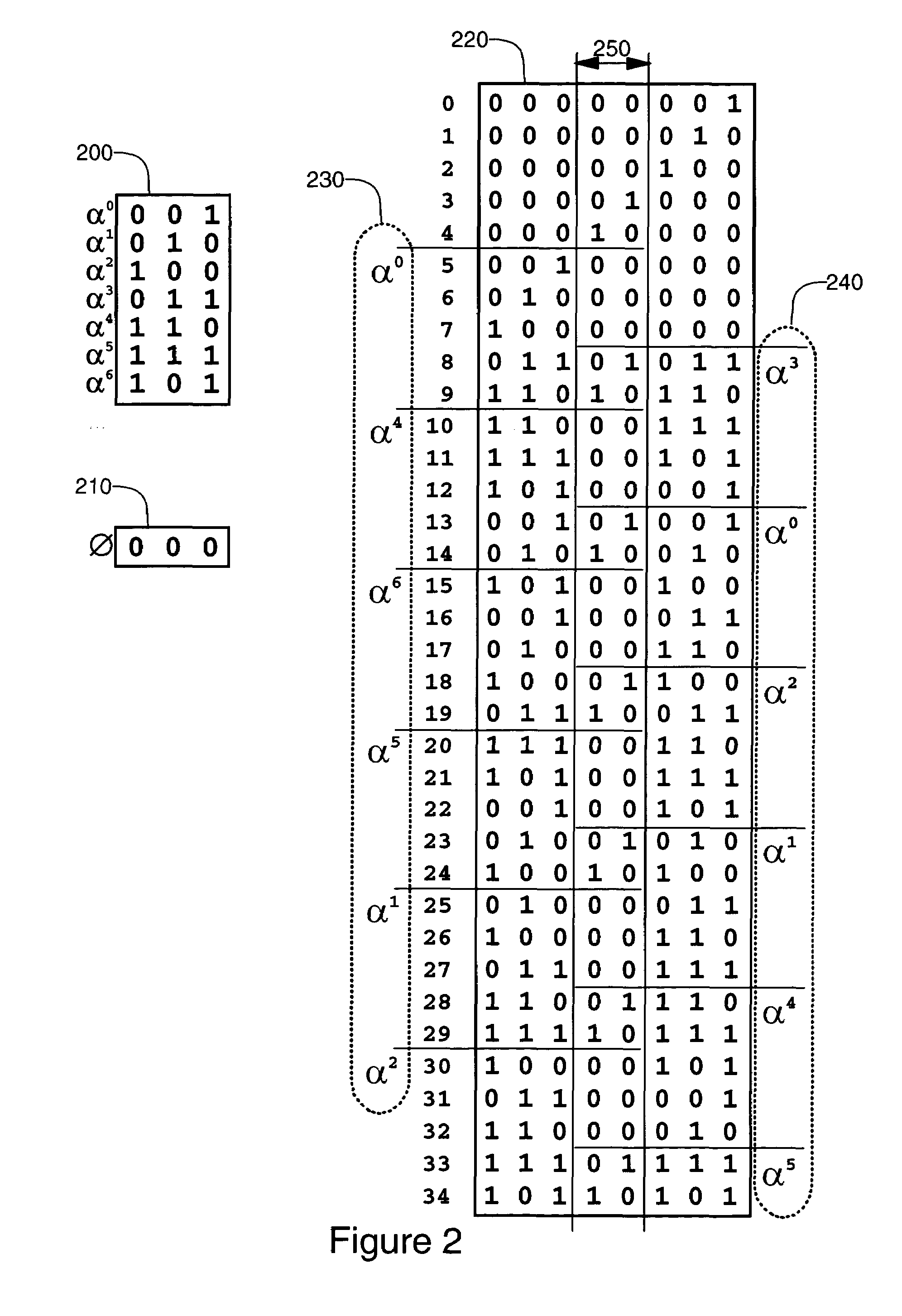

InactiveUS7249309B2Improve decoding performanceImprove performanceBurst error correctionIndividual digits conversionComputer hardwareP-matrix

A method and apparatus for performing encoding and decoding of bit chain data packets conveying errors which do not spread on more than n bits, at very high speed. In one embodiment, a matrix of the corresponding Systematic code is built using p×p matrix blocks comprising elements of a galois field, generated by an irreducible generator polynomial of degree p, p being greater or equal to n.

Owner:IBM CORP

Method, apparatus and program storage device for correcting a burst of errors together with a random error using shortened cyclic codes

A method, apparatus and program storage device for correcting a burst of errors together with a random error using cyclic or shortened cyclic codes is disclosed. The present invention solves the above-described problems by providing a received word to a syndrome register defined by a polynomial of degree n-k, said polynomial generating a cyclic or shortened cyclic code, wherein n is the length and k is the number of information bits in the codeword. The syndrome gets modified each time the received (possibly noisy) word is shifted. The contents of the syndrome register are processed to identify a random error together with an error burst of the received word. Then correction of the random error and the burst is made and a corrected codeword is generated.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

Apparatus and method for transmitting and receiving data in communication/broadcasting system

ActiveUS8782499B2Improve performanceTransmission systemsError correction/detection using concatenated codesZero paddingLow density

An apparatus and method for transmitting and receiving data in a wireless communication is provided. The method includes determining a number of zero-padding bits, determining a number (Npad) of bit groups in which all bits are padded with zeros, padding the all bits within 0th to (Npad−1)th bit groups indicated by a shortening pattern with zeros, mapping information bits to bit positions which are not padded in Bose Chaudhuri Hocquenghem (BCH) information bits, BCH encoding the BCH information bits to generate Low Density Parity Check (LDPC) information bits, and LDPC encoding the LDPC information bits to generate a zero-padded codeword, wherein the shortening pattern is defined as an order of bit groups defined as 6, 5, 4, 9, 3, 2, 1, 8, 0, 7, 10 and 11.

Owner:SAMSUNG ELECTRONICS CO LTD

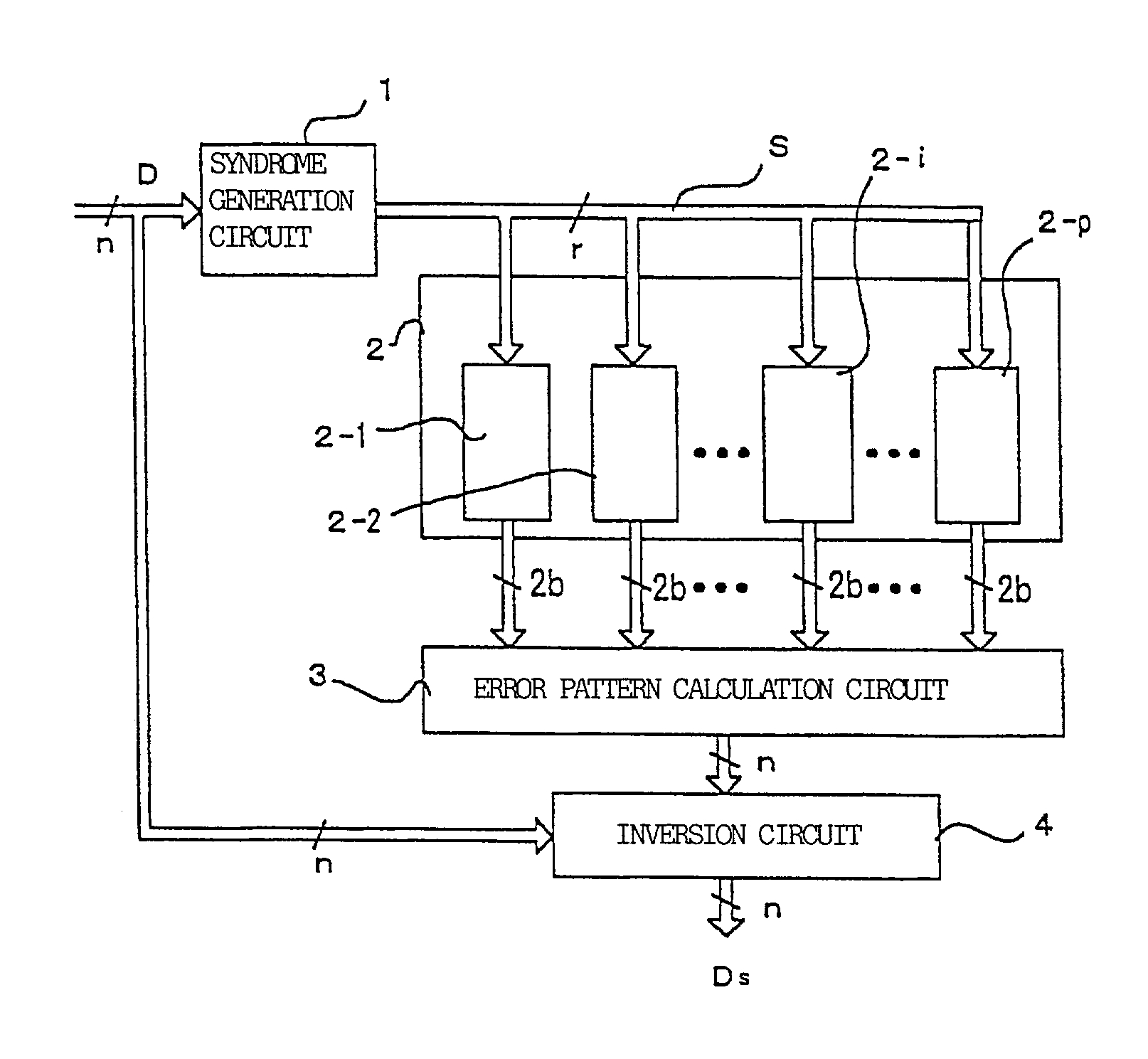

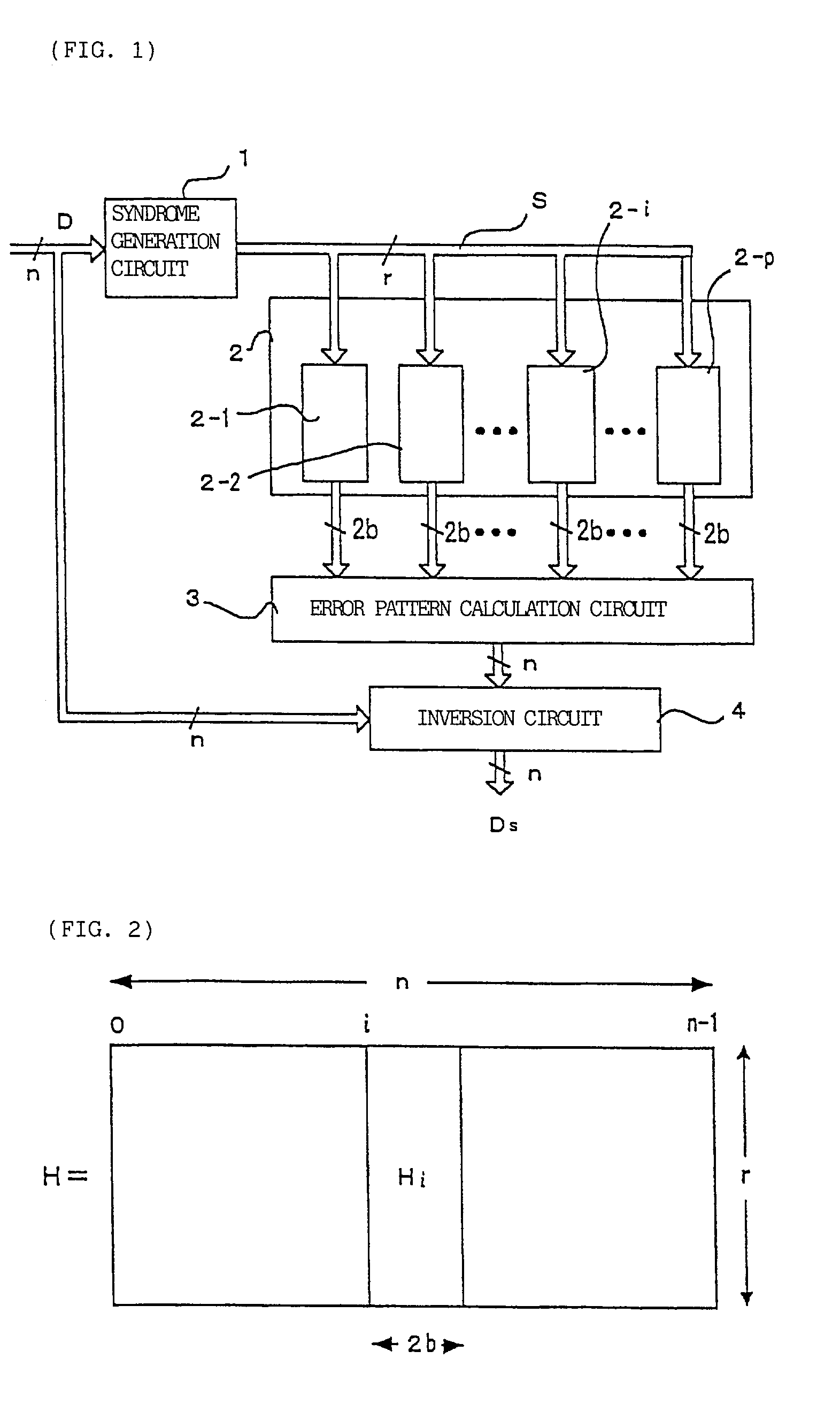

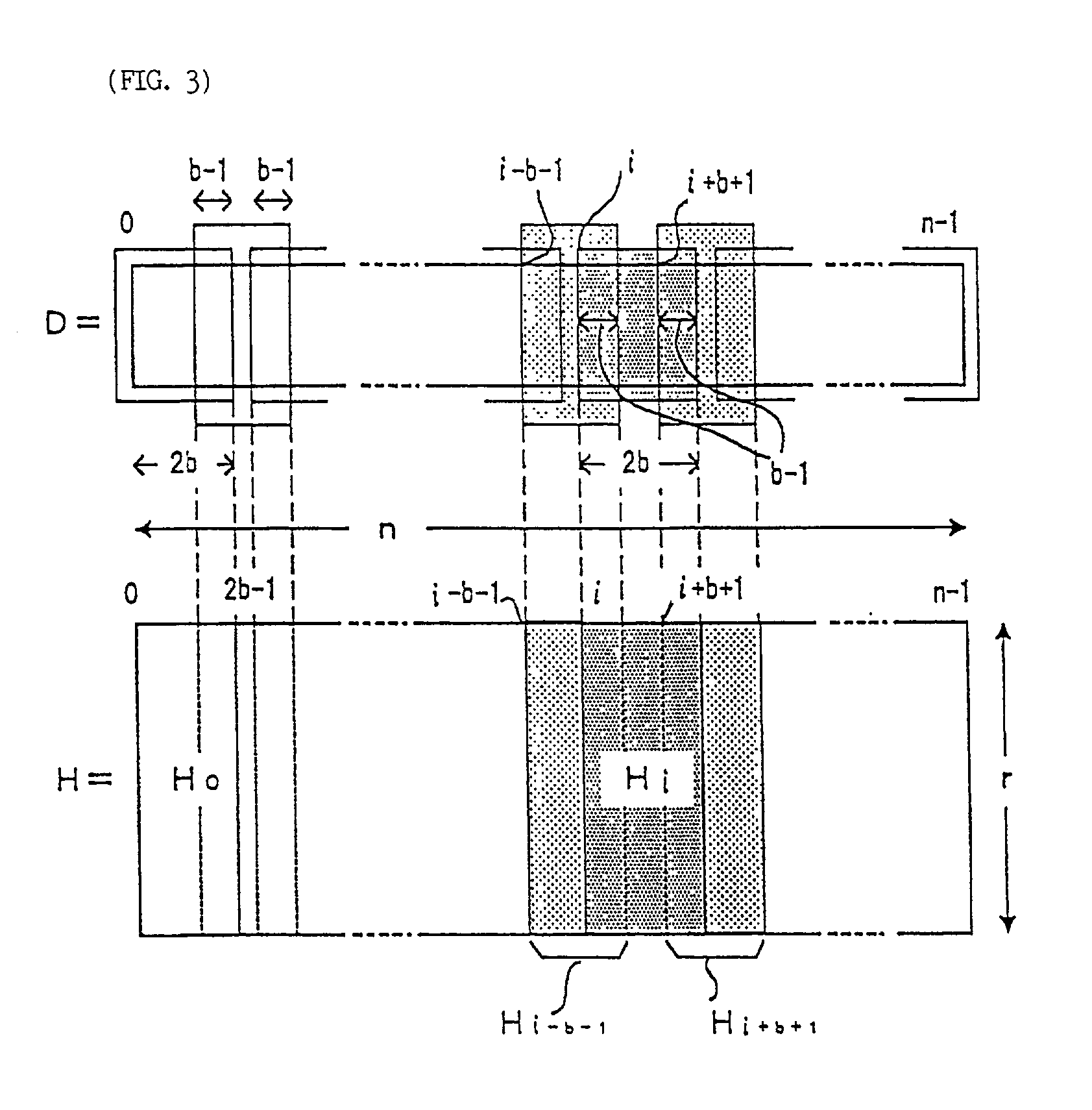

Burst error pattern generation method, and burst and byte error detection correction apparatus

A syndrome S is found from a received information D and a parity check matrix for correcting burst errors up to b bits. The syndrome S is inputted to p sets of burst error pattern generation circuits that correspond to information frames overlapping each other by (b−1) bits and each having a length of 2b bits. If a burst error is included entirely in any one of the p sets of burst error pattern generation circuits, then the burst error pattern is outputted. An error pattern calculation circuit executes OR respectively on overlapping bits output from the error pattern generation circuits. By executing exclusive OR on an output of the error pattern calculation circuit and received information D, corrected information Ds is obtained. As a result, a burst error in the received information can be detected and corrected.

Owner:FANUC LTD +1

Error burst detection for assessing reliability of a communication link

Methods, apparatus, and systems for preventing false packet acceptance in high-speed links. In accordance with one aspect, embodiments are disclosed that facilitate assessing the probability of error bursts in receivers that include decision feedback equalizers (DFEs) and that perform non-contiguous mapping of received bits to frame bits. From this probability, calculation of a mean-time to false packet acceptance (MTTFPA) may be determined, and indication that a projected link MTTFPA is too low can be used to trigger an alert or invoke some safety mechanism. Associated operations may then be performed to ensure the link is prevented from being operated in an unsafe condition under which false packet acceptance may occur.

Owner:INTEL CORP

Wireless communication device, wireless communication method, and program

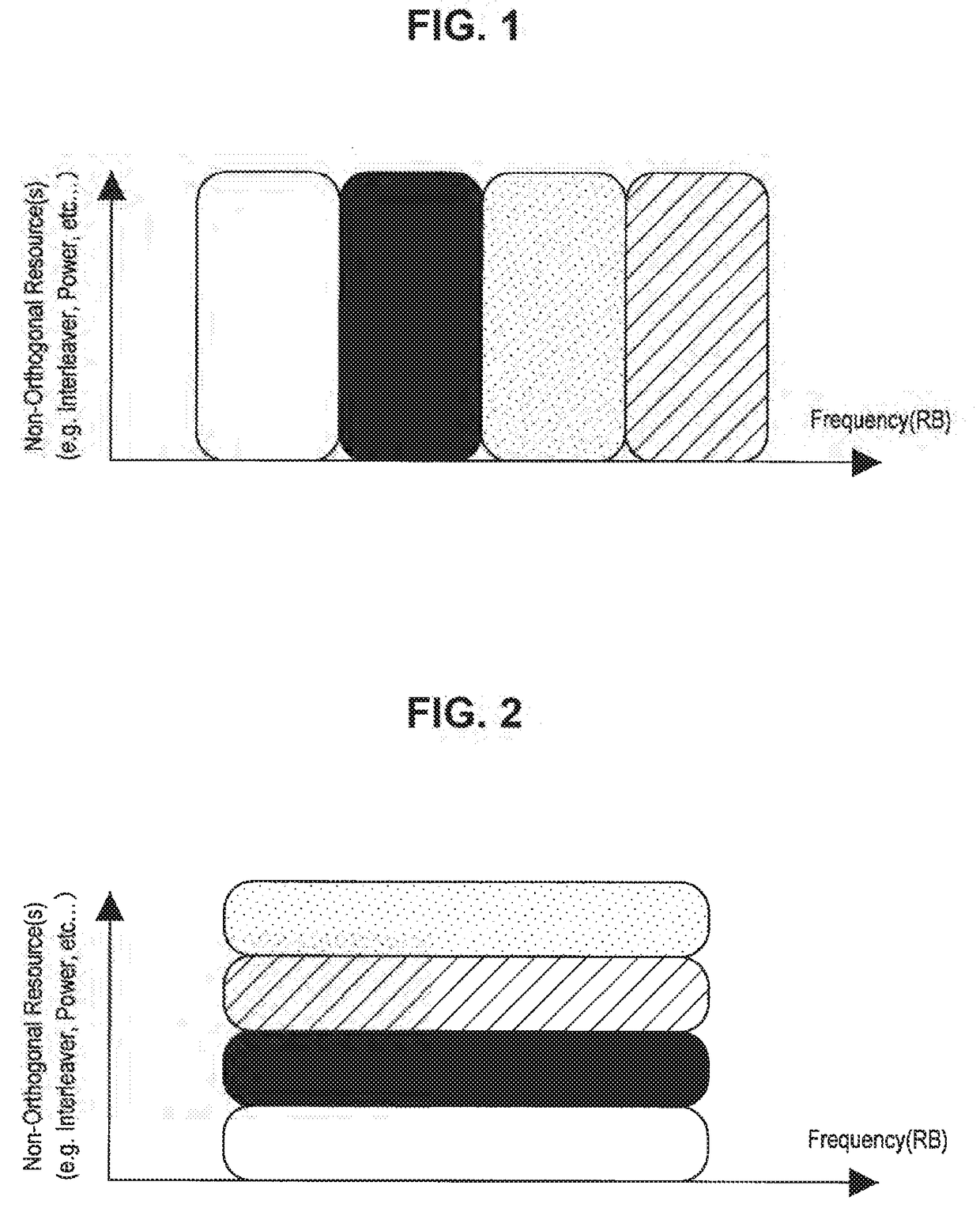

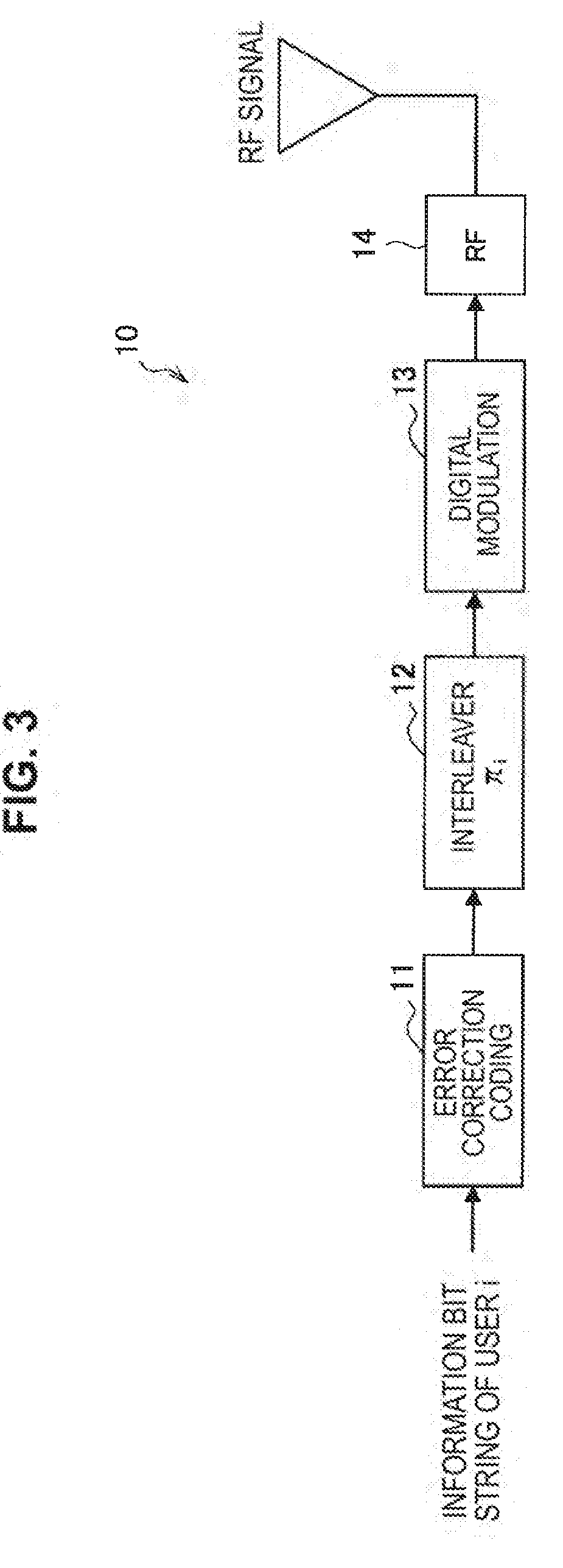

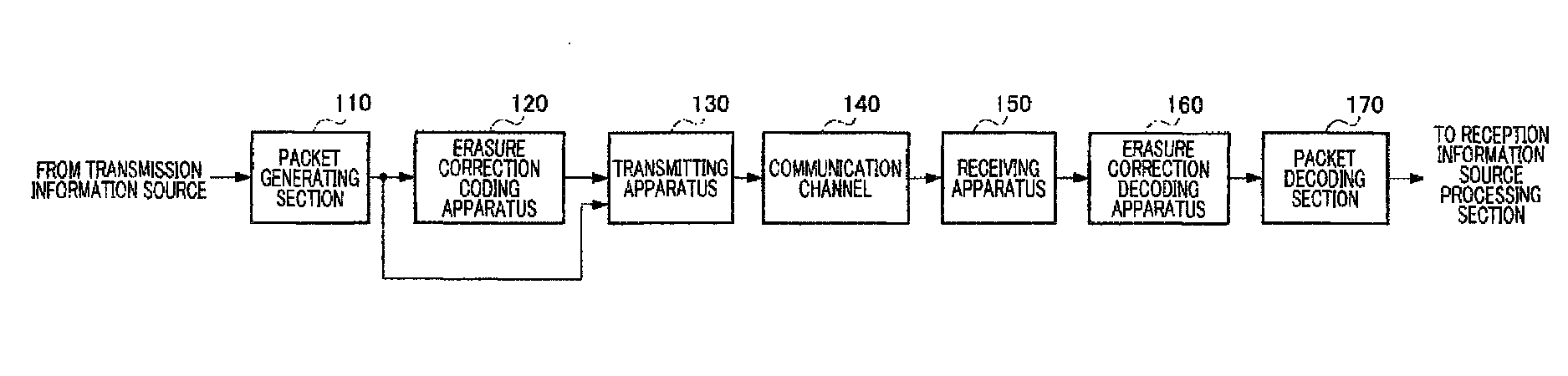

ActiveUS20170156131A1Easy to optimizeConvenient wireless communicationError prevention/detection by using return channelError correction/detection using convolutional codesCommunication unitComputer science

A wireless communication device, a wireless communication method, and a program capable of contributing to improvement of wireless communication technology related to IDMA. The wireless communication device includes: a wireless communication unit that performs wireless communication using interleave division multiple access (IDMA) with another wireless communication device; and a controller that controls an interleave length in an interleave process for IDMA by the wireless communication unit.

Owner:SONY CORP

Loss correction encoding device and loss correction encoding method

ActiveUS8522109B2Correction capabilityBurst error correctionCode conversionComputer scienceInformation data

A loss correction encoding device having an improved capability of loss correction using LDPC-CC is disclosed. In the loss correction encoding device (120), a rearranging unit (122) rearranges information data contained in n information packets according to the constraint length Kmax and the encoding rate (q−1) / q of a cheek polynomial of the loss correction code used in a loss correction encoding unit (123). Specifically, the rearranging unit (122) rearranges the information data in such a way that continuous Kmax×(q−1) pieces of information data after rearrangement are contained in different information packets. The rearranging unit (122) distributes the information data to information blocks from n information packets (n satisfies formula (1)).Kmax×(q−1)≦n (1).

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

Method and apparatus for using fire decoder to correct burst errors in a real-time communications system

InactiveUS7231579B1Delay minimizationError preventionBurst error correctionCommunications systemAlgorithm

Error bursts are detected and corrected in a communication system using shortened cyclic codes, such as shortened Fire codes. Data is loaded into a first error syndrome register and a second error syndrome register. The data in the registers may be evaluated to determine if the data bits contain a correctable error. Shortened zero bits are shifted into the second error syndrome register. A number of zero bits are shifted into the first error syndrome register to trap an error burst pattern in the data. A determination is made as to the number of zero bits shifted into the second error syndrome register to trap the location of the error burst in the data. Using the number of zero bits shifted into the second error syndrome register and the error burst pattern, the error in the data is located and corrected.

Owner:CISCO TECH INC

Techniques for detecting and correcting errors using multiple interleave erasure pointers

InactiveUS7231578B2Correction capabilityTransmission systemsBurst error correctionBlock codeError location

Techniques for detecting and correcting burst errors in data bytes formed in a two-level block code structure. A second level decoder uses block level check bytes to detect columns in a two-level block code structure that contain error bytes. The second level decoder generates erasure pointers that identify columns in the two-level block structure effected by burst errors. A first level decoder then uses codeword check bytes to correct all of the bytes in the columns identified by the erasure pointers. The first level decoder is freed to use all of the codeword check bytes only for error byte value calculations. The first level decoder does not need to use any of the codeword check bytes for error location calculations, because the erasure pointers generated by the second level decoder provide all of the necessary error locations. This techniques doubles the error correction capability of the first level decoder.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV +1

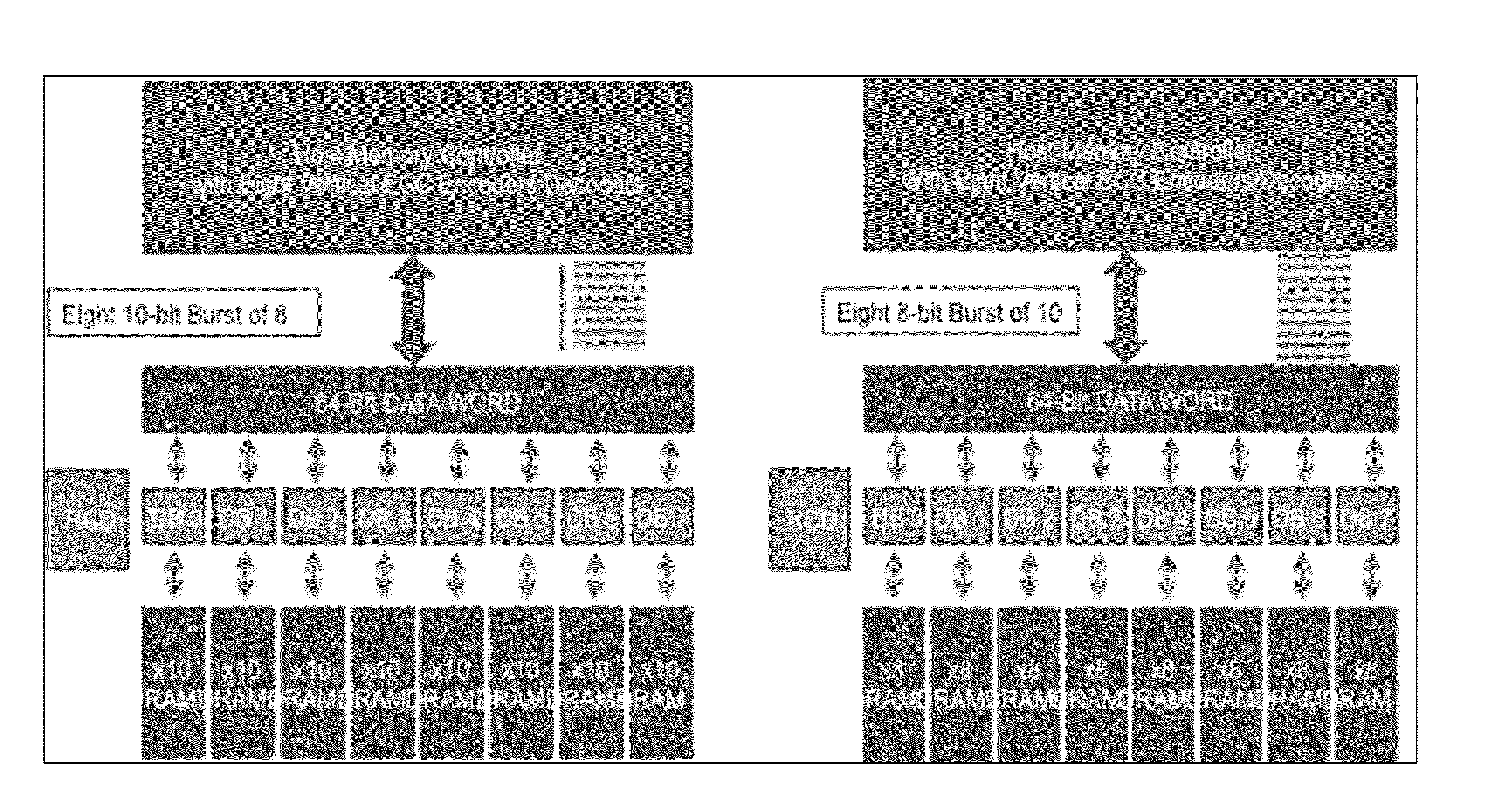

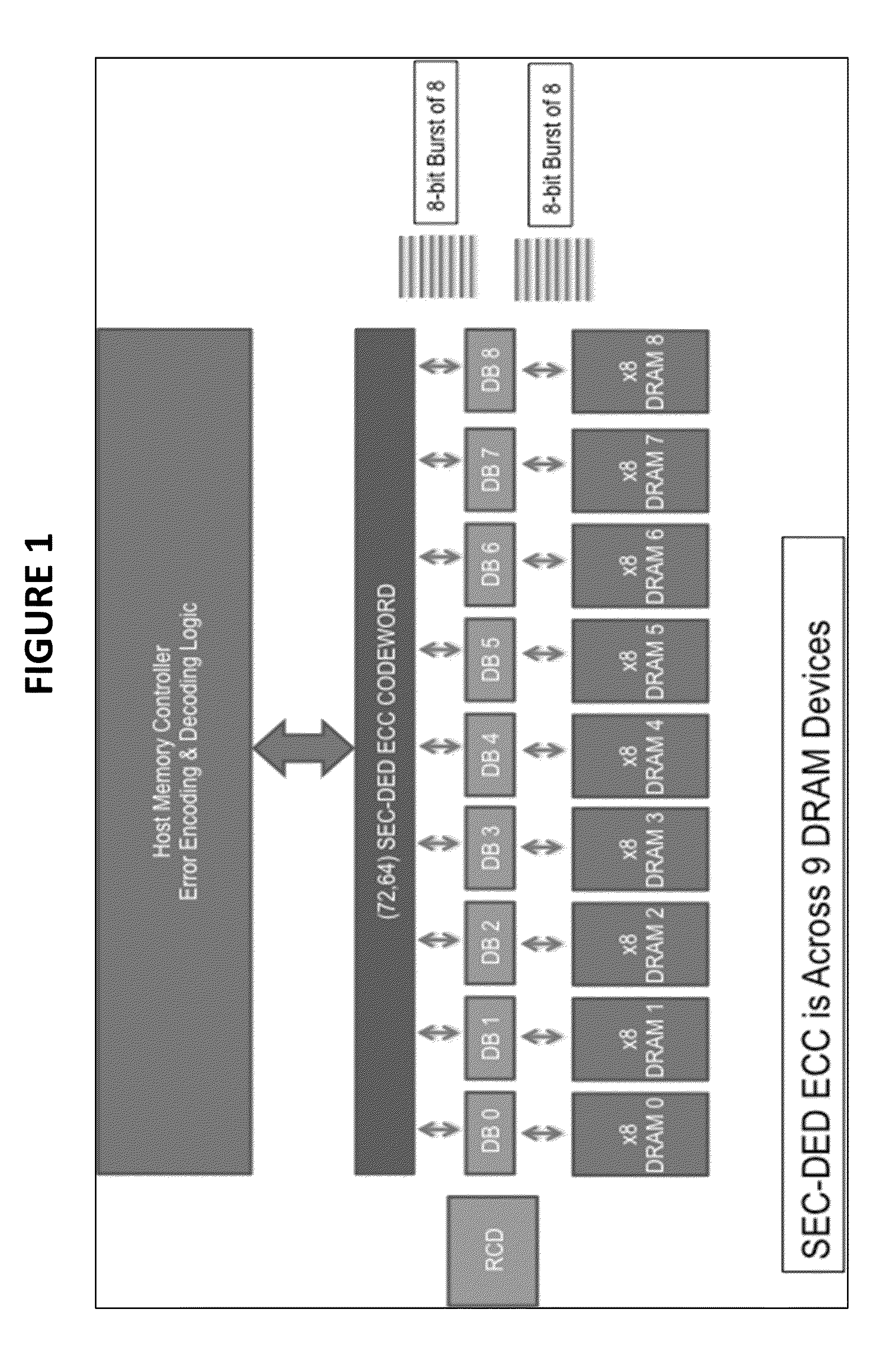

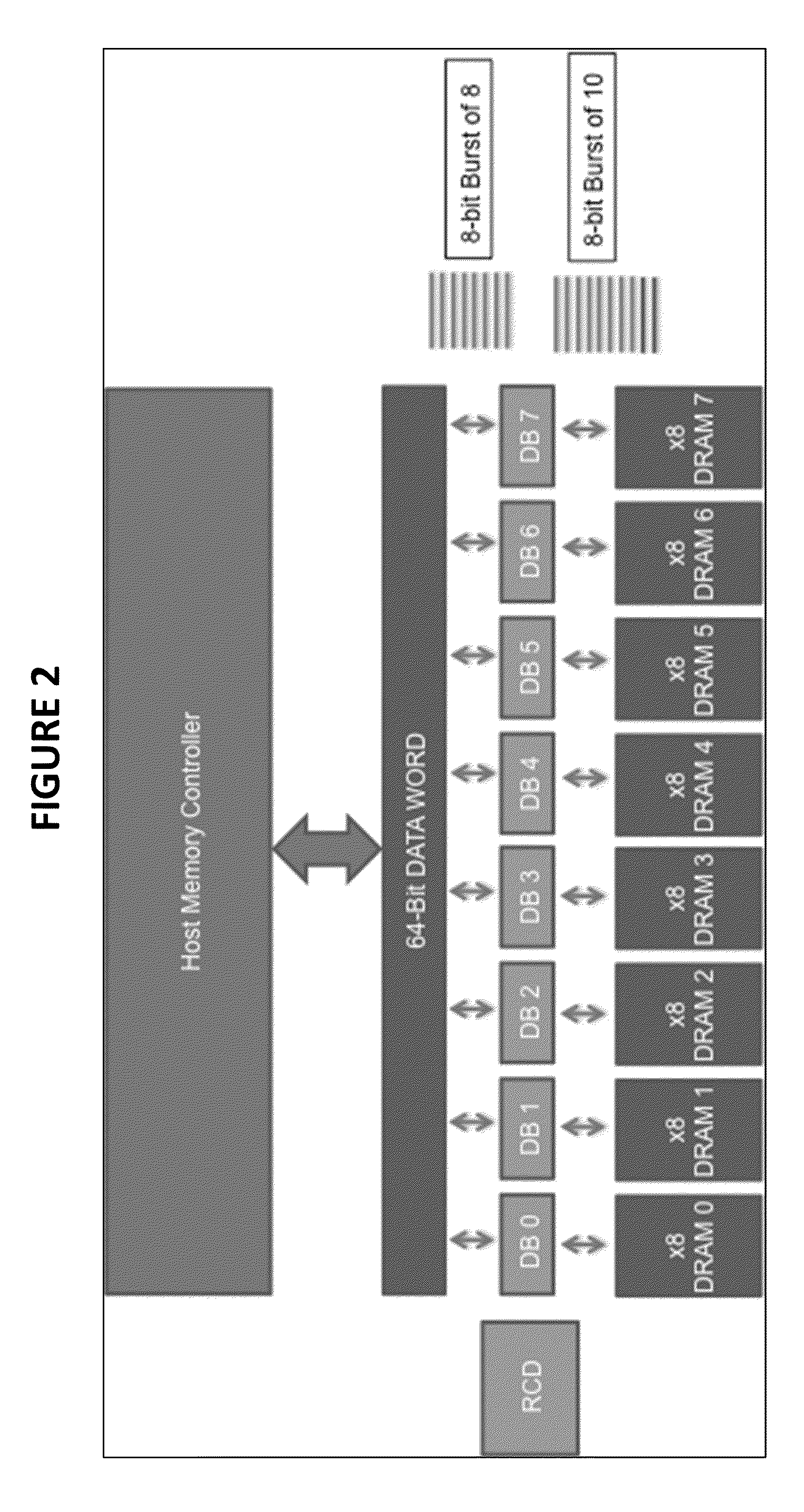

Vertical error correction code for DRAM memory

Techniques for operating a DIMM apparatus. The apparatus comprises a plurality of DRAM devices numbered from 0 through N−1, where N is an integer greater than seven (7), each of the DRAM devices is configured in a substrate module; a buffer integrated circuit device comprising a plurality of data buffers (DB) numbered from 0 through N−1, where N is an integer greater than seven (7), each of the data buffers corresponds to one of the DRAM devices; and a plurality of error correcting modules (“ECMs”) associated with the plurality of DRAM devices.

Owner:RAMBUS INC

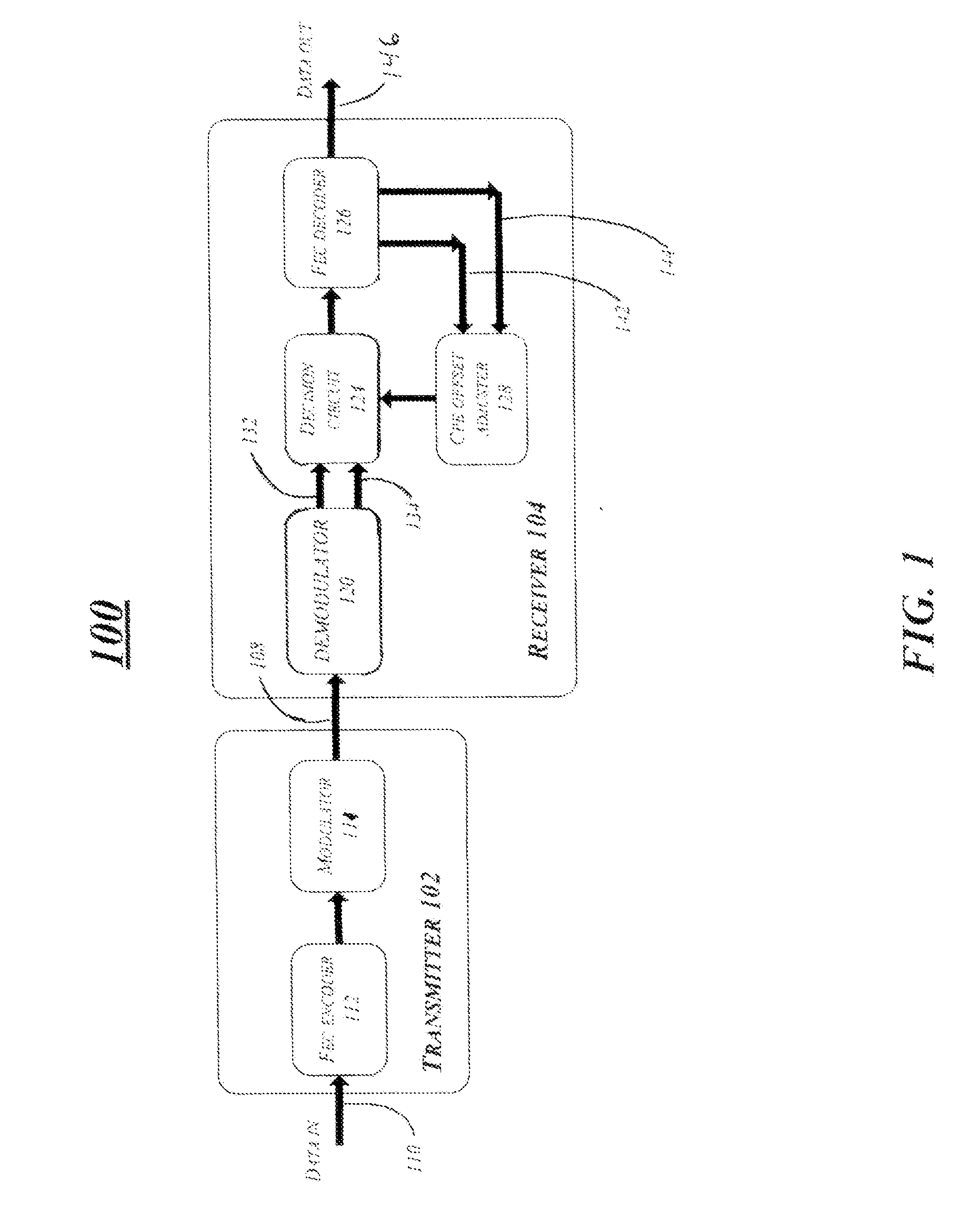

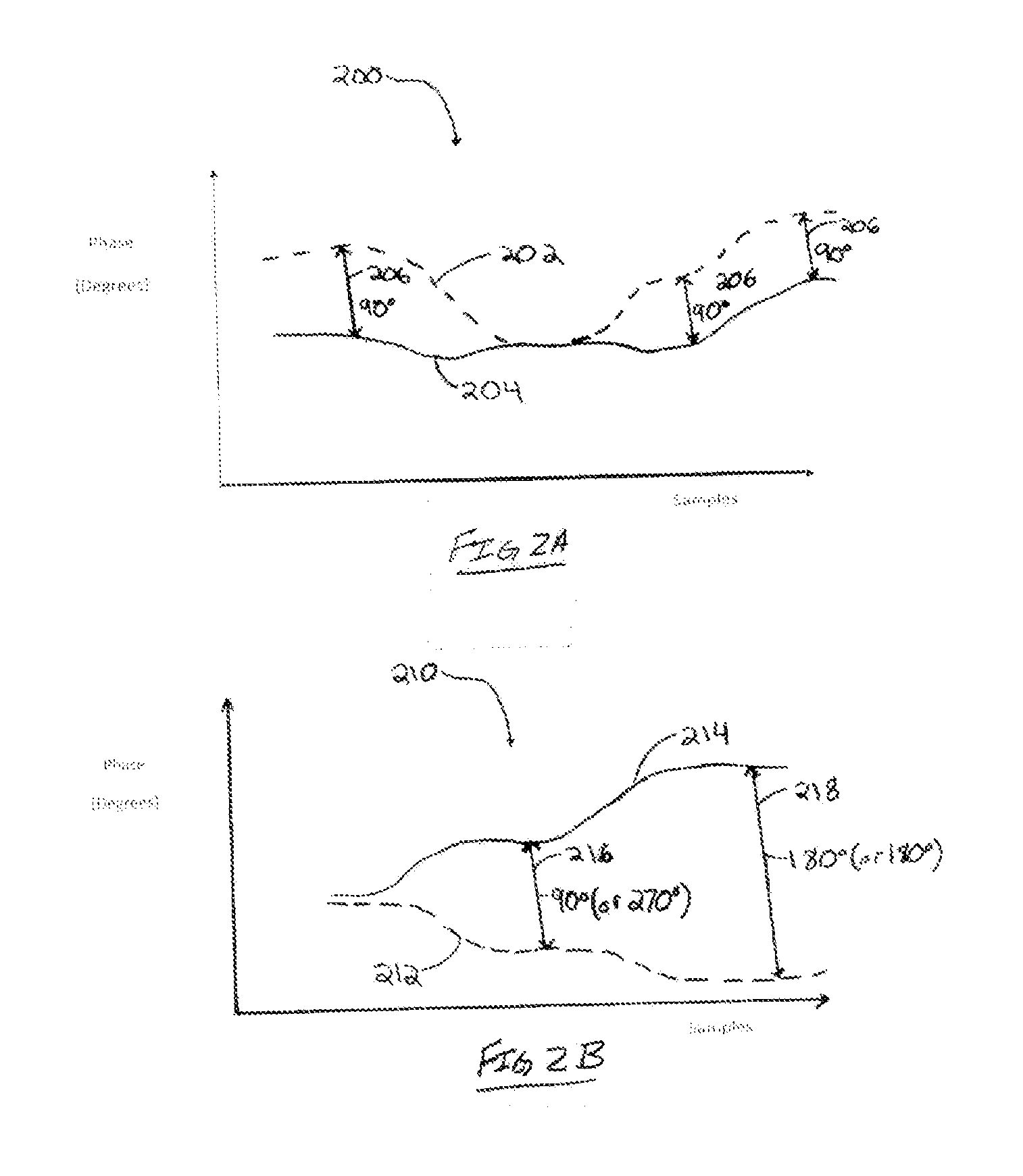

Joint carrier phase estimation and forward error correction

InactiveUS20120096327A1Error correction/detection using convolutional codesError preventionCommunications systemAmbiguity

Methods and systems for processing an optical signal in a communication system are disclosed. The disclosed methods yield benefits for estimation and tracking of carrier phase of received signals at a digital coherent receiver without the use of differential coding. Specifically, phase ambiguity is removed by calculating the slope of the CPE at a location where the CPE begins to lose track of the received carrier phase signal. As such, a CPE offset adjustment may be applied in accordance with the calculated slope to reduce the number of ones and zeros corrected by a FEC decoder. Thus, the FEC aided CPE scheme may be a feed forward scheme that requires no training.

Owner:SUBCOM LLC

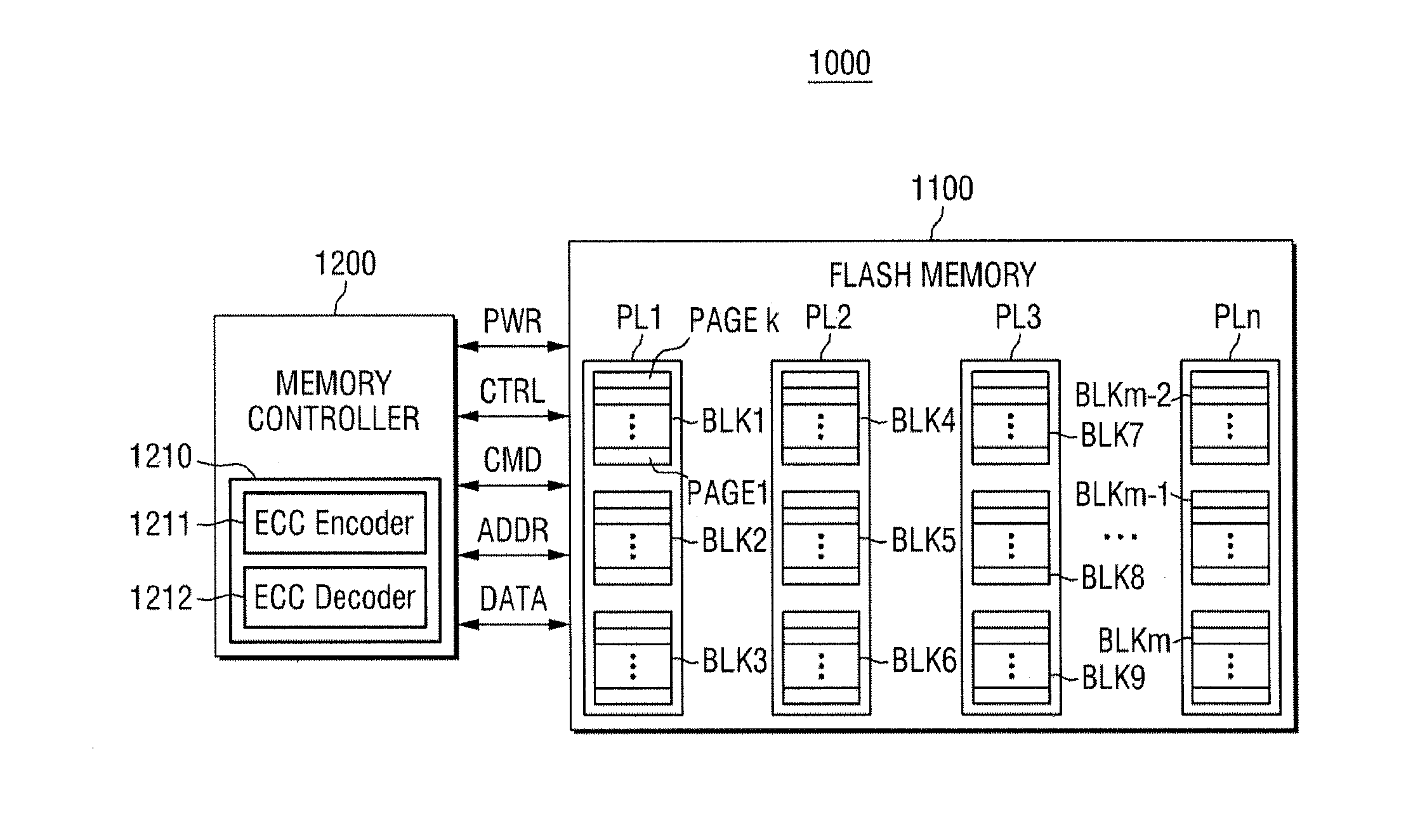

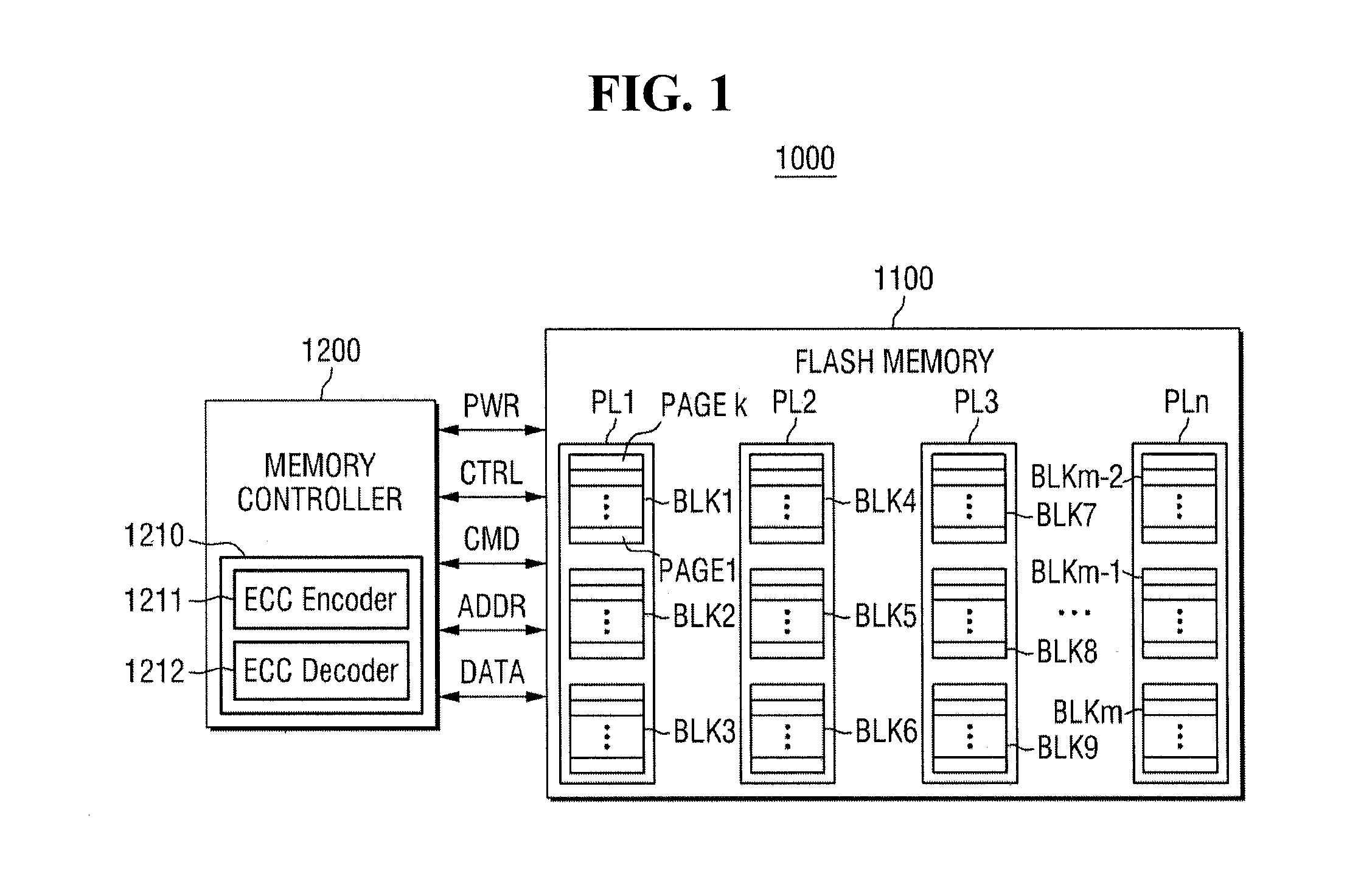

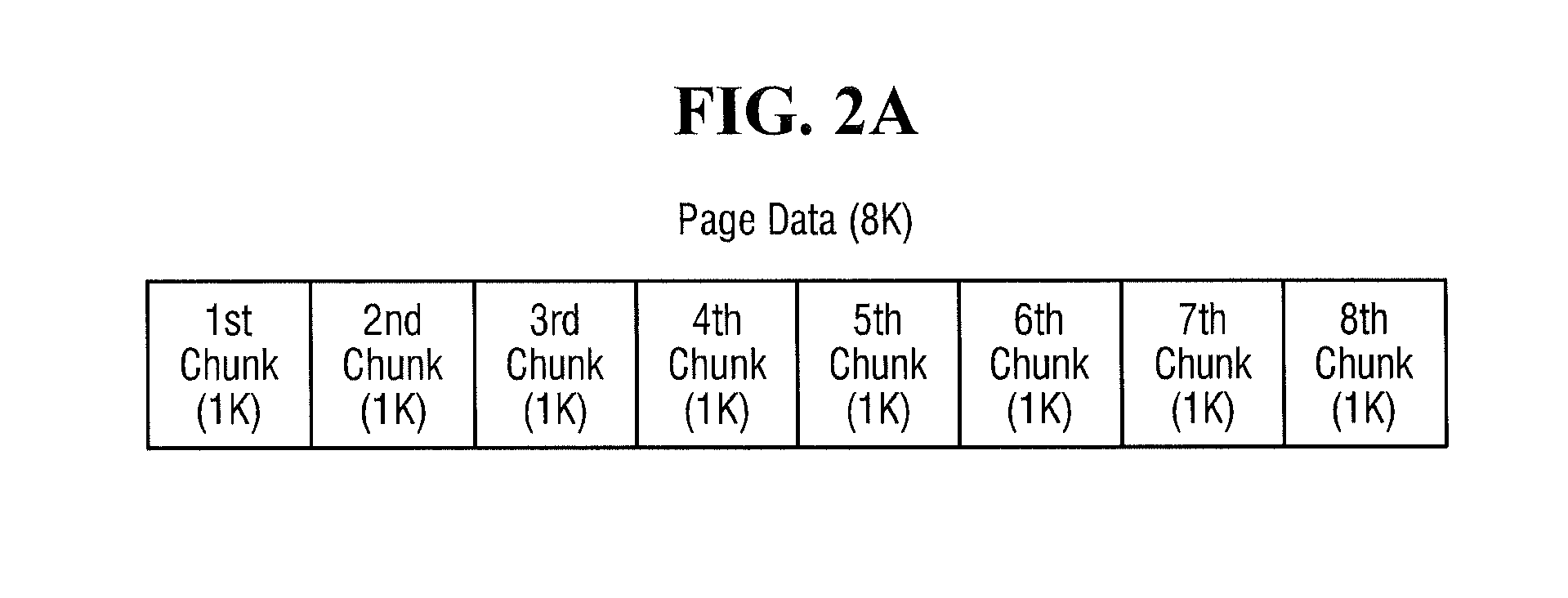

Operating method of error correction code decoder and memory controller including the error correction code decoder

ActiveUS20150046771A1Increase speedShorten the timeError correction/detection using convolutional codesError correction/detection using block single space codingMemory controllerCorrection code

Owner:SAMSUNG ELECTRONICS CO LTD

Record reproduction method, apparatus, and circuit for using error correcting code

InactiveUS7590929B2Reduce circuit sizeBurst error correctionError correction/detection using multiple parity bitsError correctingUser Error

A record reproduction apparatus includes an encoding unit that encodes sector data to be written into a recording medium, by dividing the data into a predetermined number of blocks, and an iterative decoding unit that iteratively decodes the sector data read from the recording medium, by dividing the sector data into the predetermined number of blocks.

Owner:FUJITSU LTD

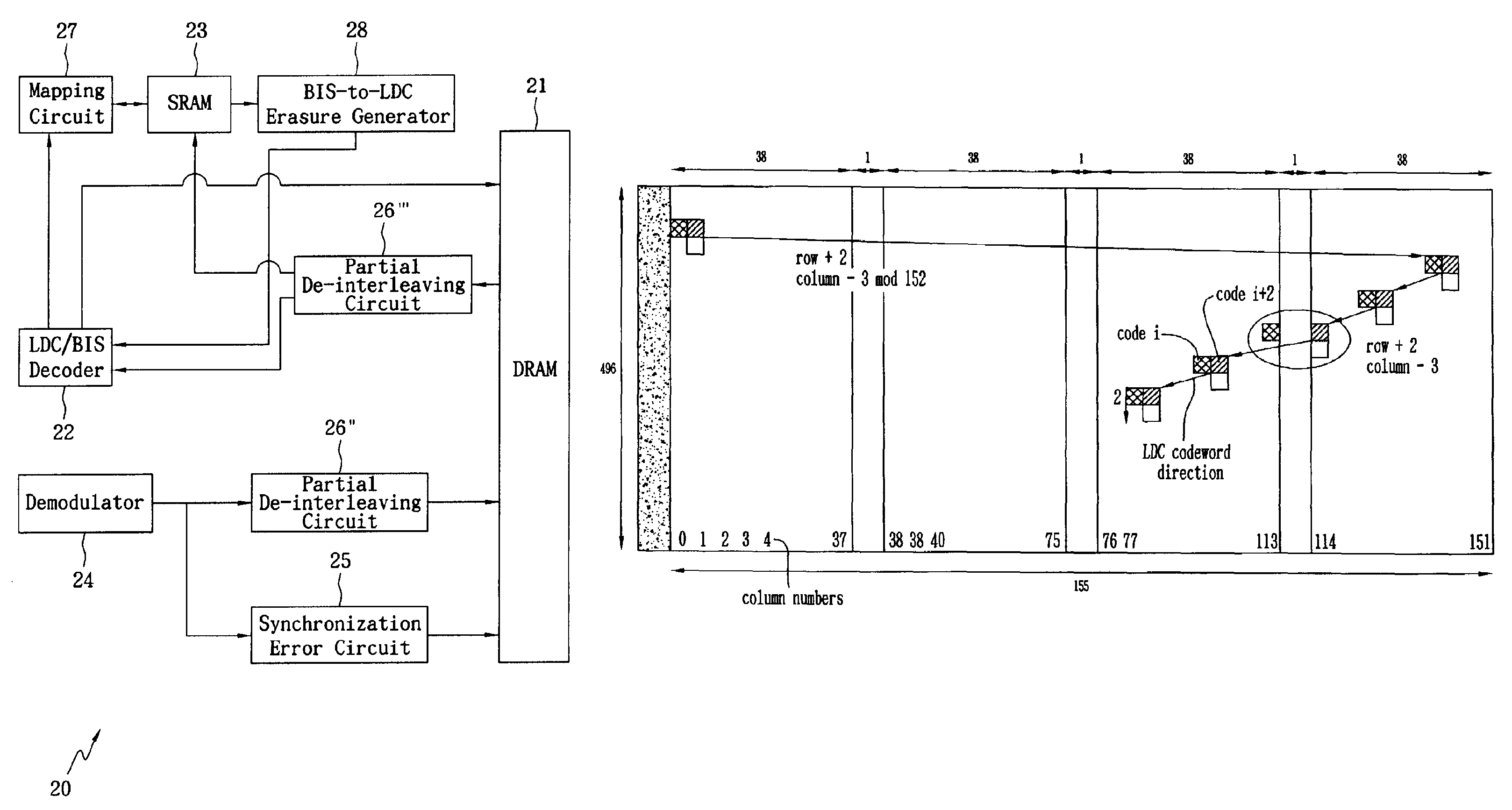

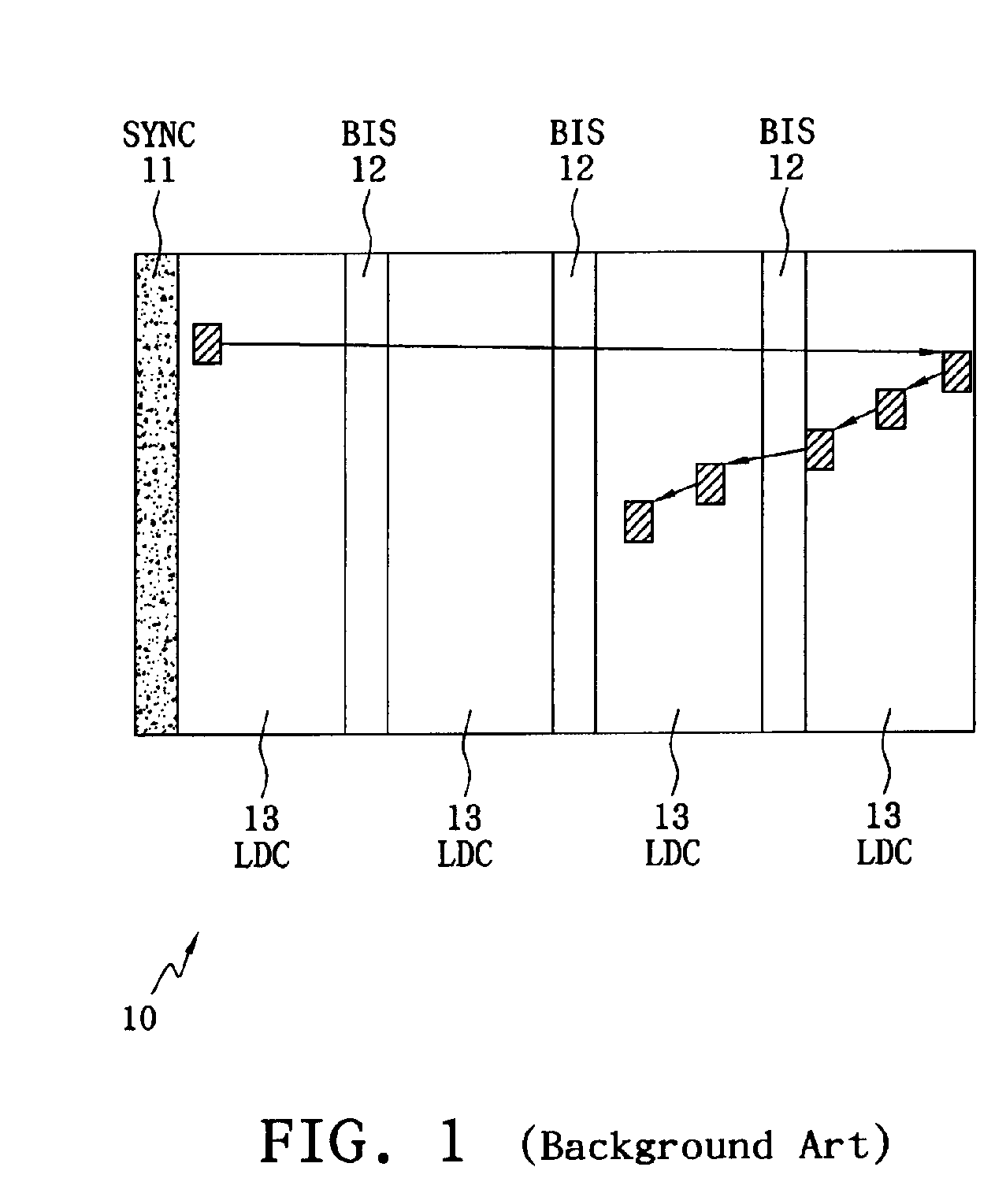

Method and apparatus for decoding multiword information

ActiveUS7281193B2Efficient decodingImprove the protective effectBurst error correctionCode conversionComputer science

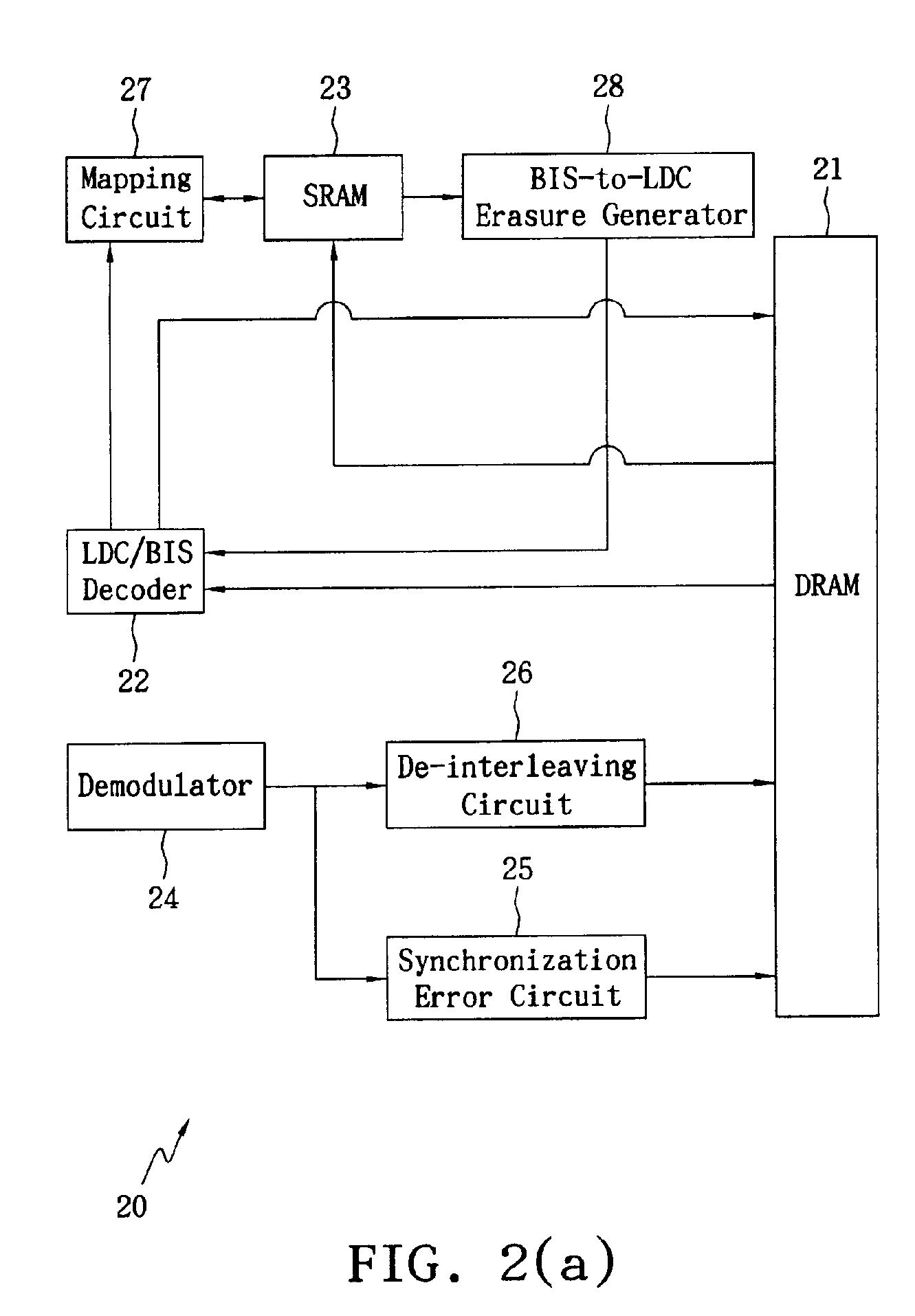

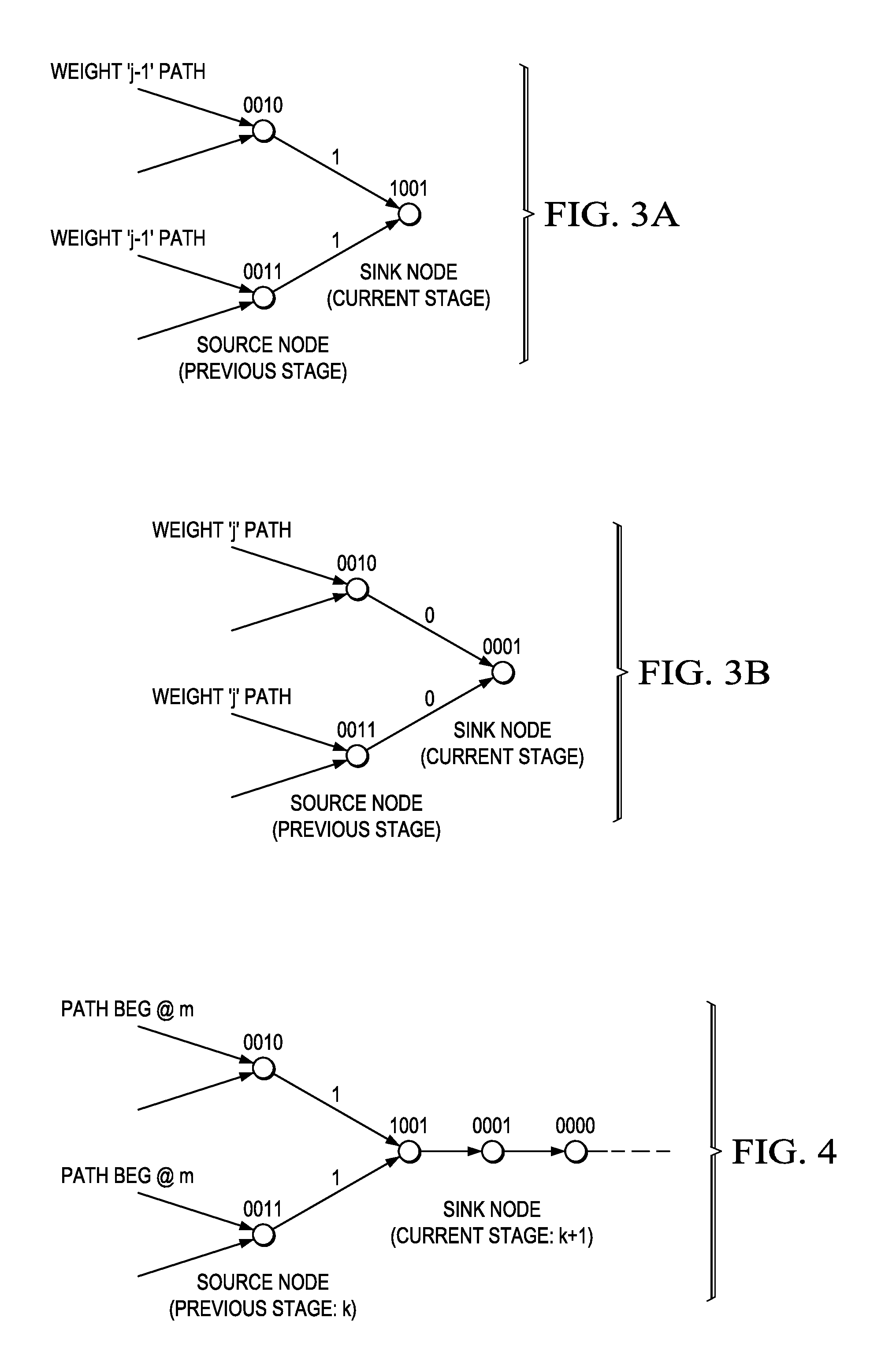

A method for decoding multiword information comprises multiple steps. In step (a), a multiword information cluster, e.g., ECC, including high protective codewords, e.g., BIS, and low protective codewords, e.g., LDC, is provided. In step (b), the high and low protective codewords are stored into a first memory, e.g., DRAM. In step (c), the high protective codewords are decoded to generate high protective word erasure indicators showing whether decoding errors occur. In step (d), the high protective word erasure indicators are stored into a second memory, e.g., SRAM. In step (e), the low protective codewords are decoded. In the meanwhile, an erasure bit for a low protective codeword is marked by finding high protective codewords close to the low protective codeword in the multiword information cluster and looking up the high protective word erasure indicators of the high protective codewords close to the low protective codeword.

Owner:MEDIATEK INC

Method for optimizing block coding parameters, a communications controller employing the method and a communications node and link employing the controller

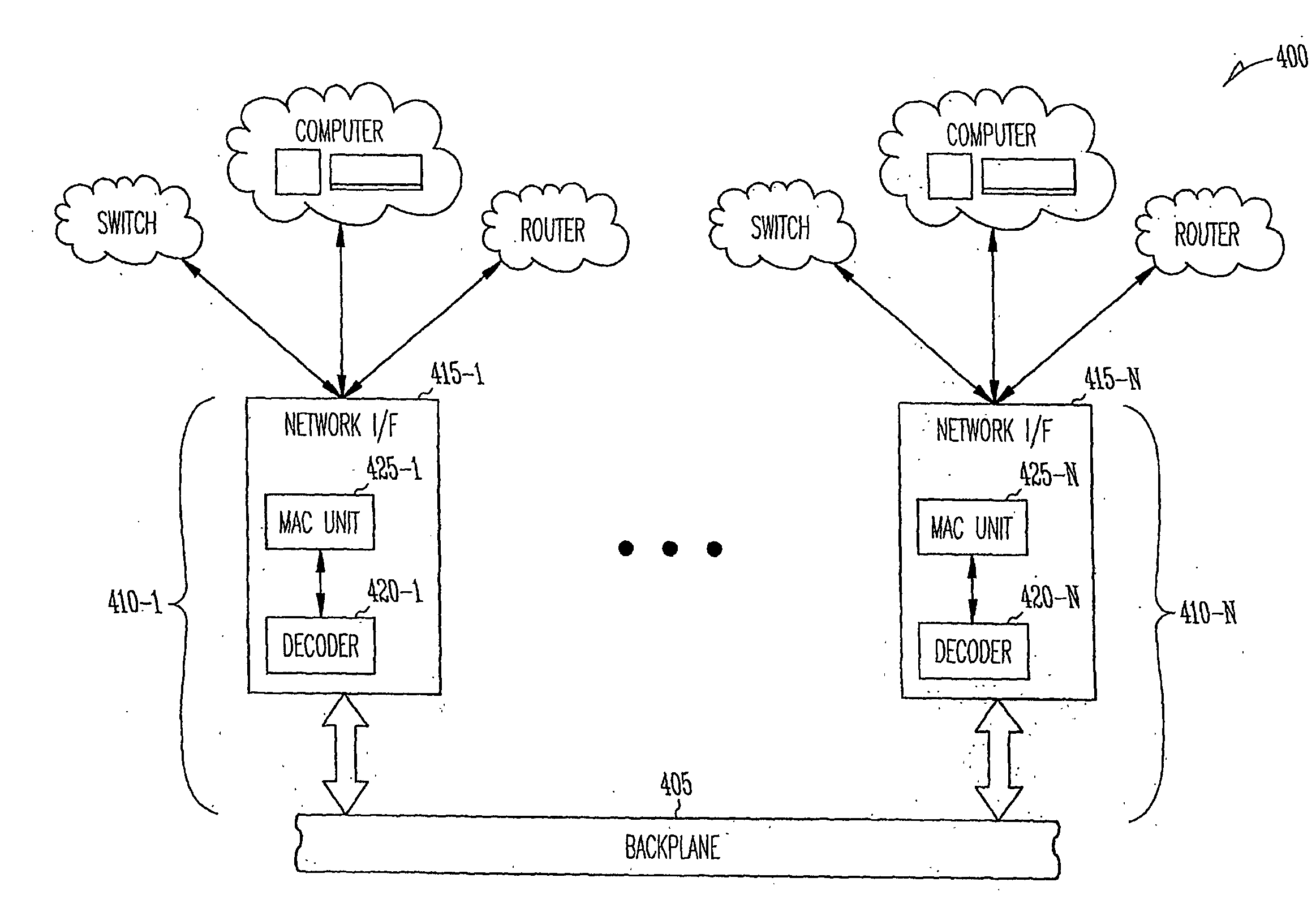

InactiveUS20090187807A1Correction capabilitySpecific performanceFault responseBurst error correctionCommunications systemTelecommunications link

A method of determining optimal FEC configuration parameters, a communications controller, a communications link and a communications node is disclosed. In one embodiment, the communications controller, includes: (1) a processor, (2) a communications system information collector configured to receive operational information from a communications system having a block encoder, a block decoder and a decision feedback equalizer, (3) a code determiner configured to employ the operational information to select, from a set of candidate codes, a random error correction code or a burst error correction code that has a least error correction capability and satisfies a target performance specification for the communications system and (4) a parameter selector configured to select configuration parameters associated with the selected random error correction code or the selected burst error correction code and send the selected configuration parameters to the block encoder and the block decoder.

Owner:TEXAS INSTR INC

Modification to meggitt decoder for burst error correction codes

InactiveUS20100031120A1Error preventionError detection/correctionComputer hardwareSelection criterion

Apparatus and methods are provided to correct burst errors from a communication channel. Embodiments may include correcting burst errors in received data using a decoder configured as a Meggitt decoder with an additional selection criterion to correct a burst error having a length larger than the code error correction capability.

Owner:INTEL CORP

Method and system for detection and correction of phased-burst errors, erasures, symbol errors, and bit errors in a received symbol string

InactiveUS20100299575A1Increase the number ofNon-binary linear block codesBurst error correctionComputer hardwareBurst error

Owner:HEWLETT PACKARD DEV CO LP

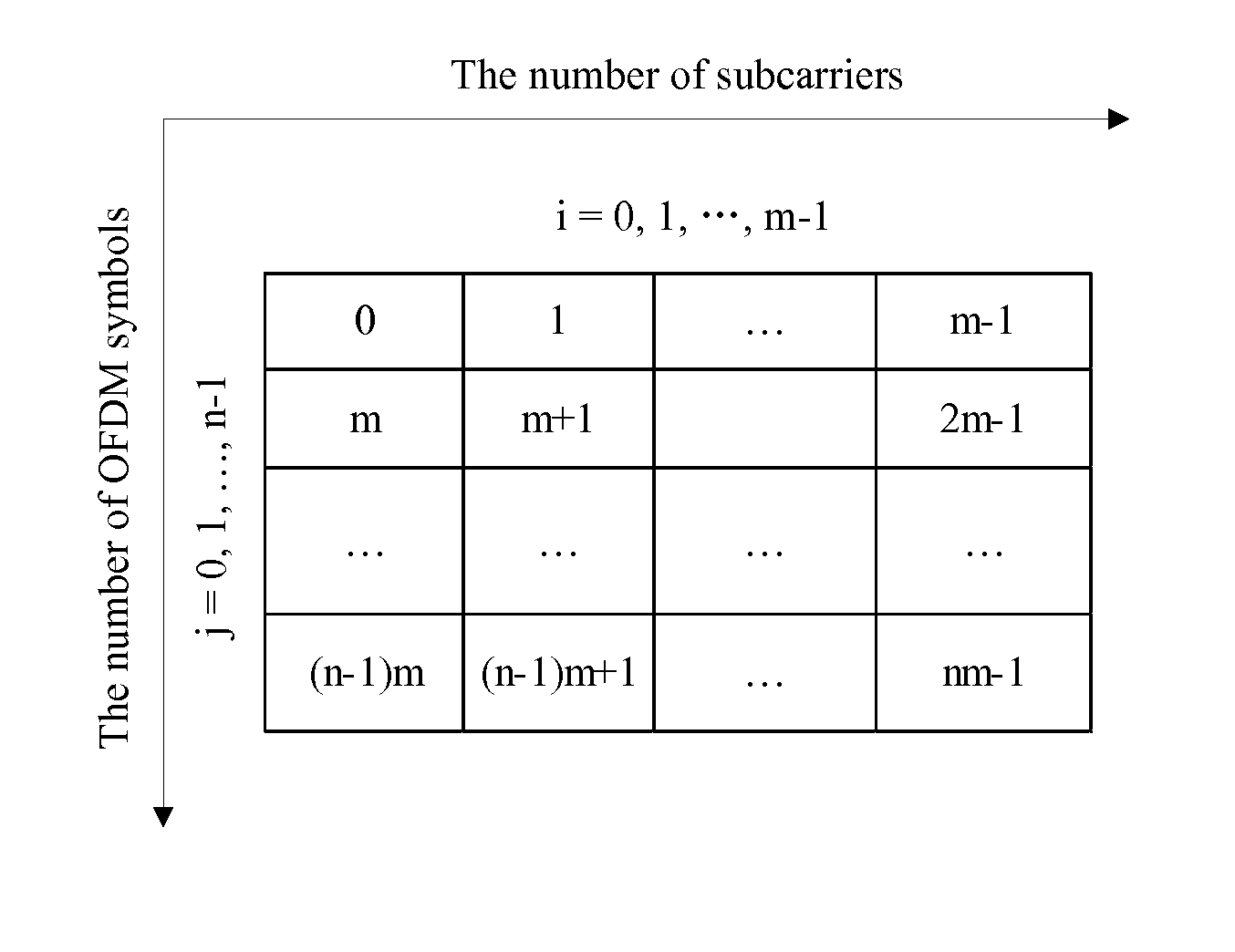

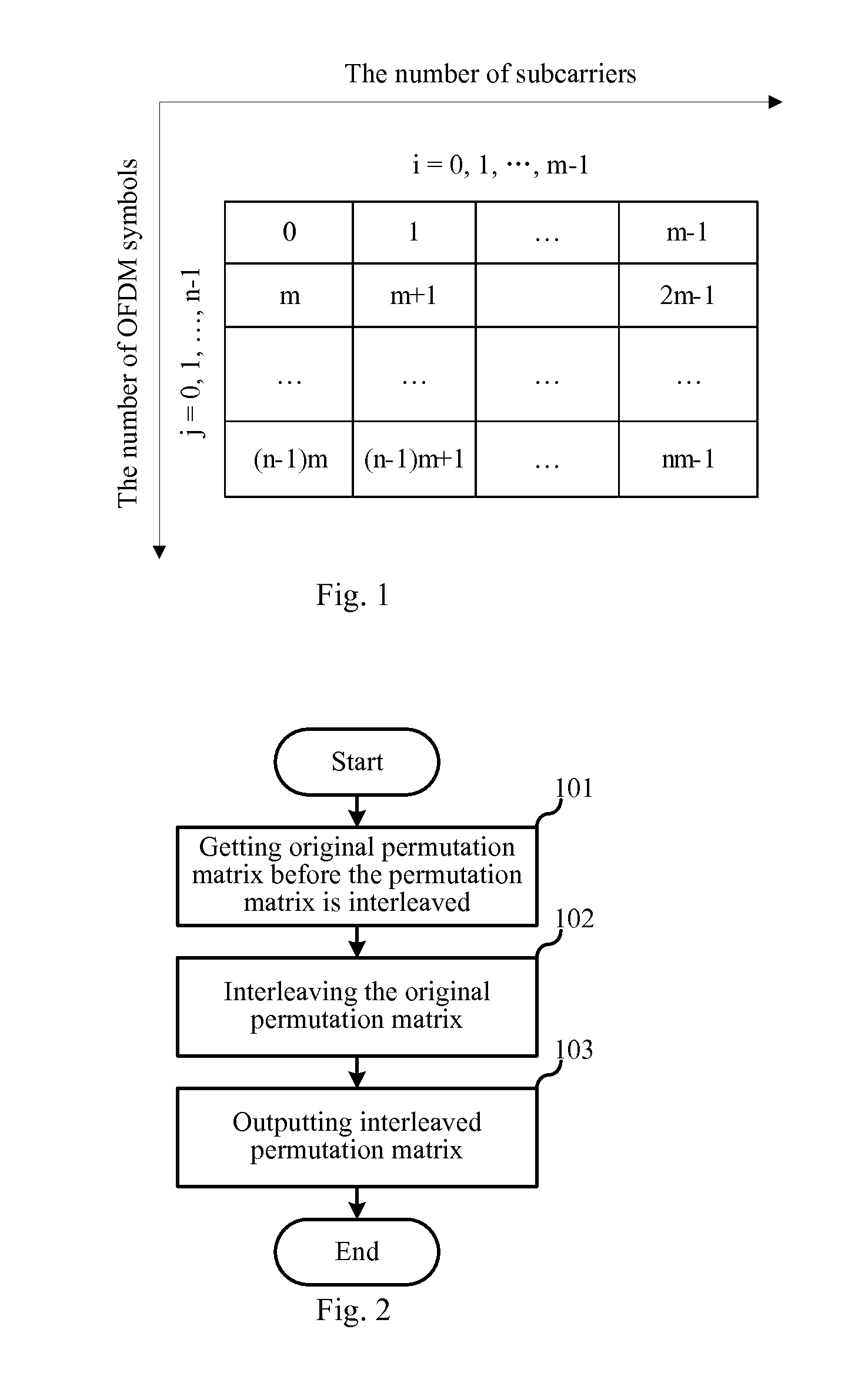

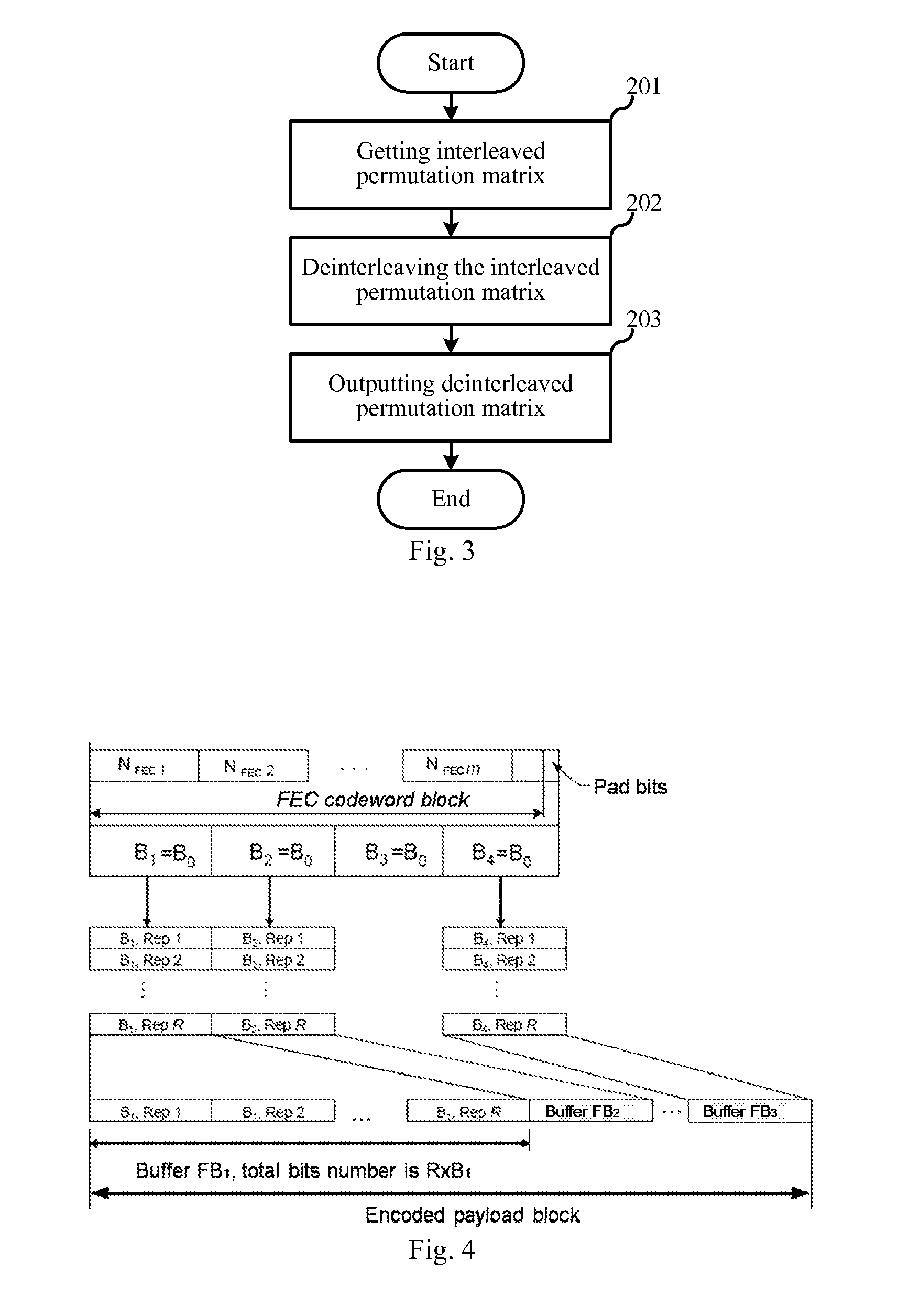

Data block interleaving and deinterleaving method and apparatus for communication equipments

ActiveUS20150263765A1Simple hardware implementationReduce hardware complexityBurst error correctionCode conversionHardware implementationsComputer science

The present invention relates to communication field, disclosing a data block interleaving and deinterleaving method and apparatus for communication equipments. In the present invention, a recursive method for calculating interleaver or deinterleaver addresses for existing power line communication standards is proposed. The complex modulo operation is simplified to a series of Add-Compare-Subtract operations. Therefore, the hardware implementation complexity is significantly reduced.

Owner:HI TREND TECH SHANGHAI

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com