Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33 results about "Bidiagonal matrix" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

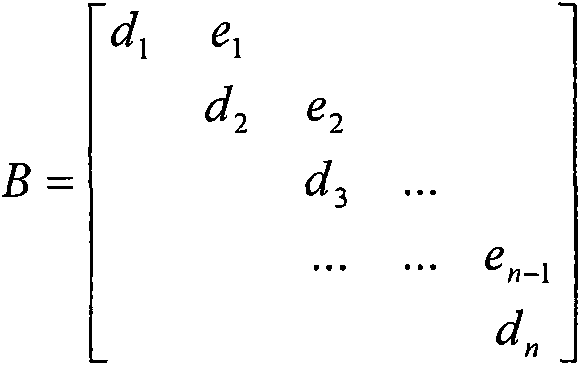

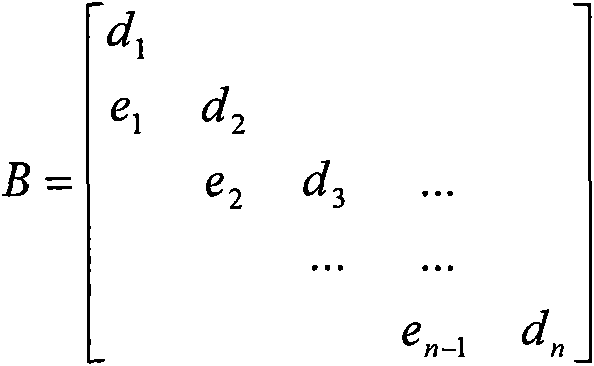

In mathematics, a bidiagonal matrix is a banded matrix with non-zero entries along the main diagonal and either the diagonal above or the diagonal below. This means there are exactly two non zero diagonals in the matrix.

Apparatus and method for encoding a low density parity check code

ActiveUS7178082B2Low Density Parity CheckEasy to calculateError detection/correctionError correction/detection using multiple parity bitsTheoretical computer scienceDiagonal matrix

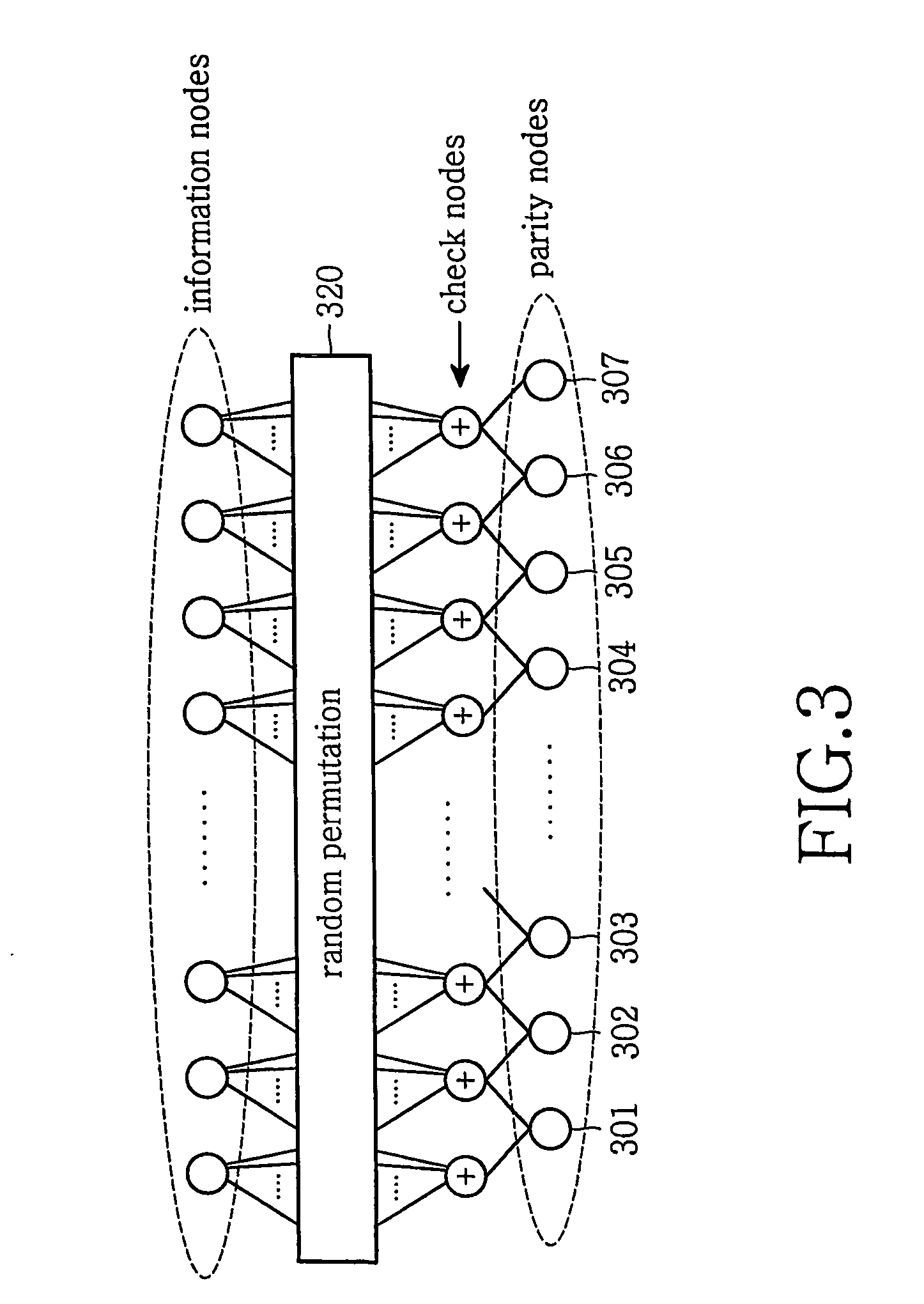

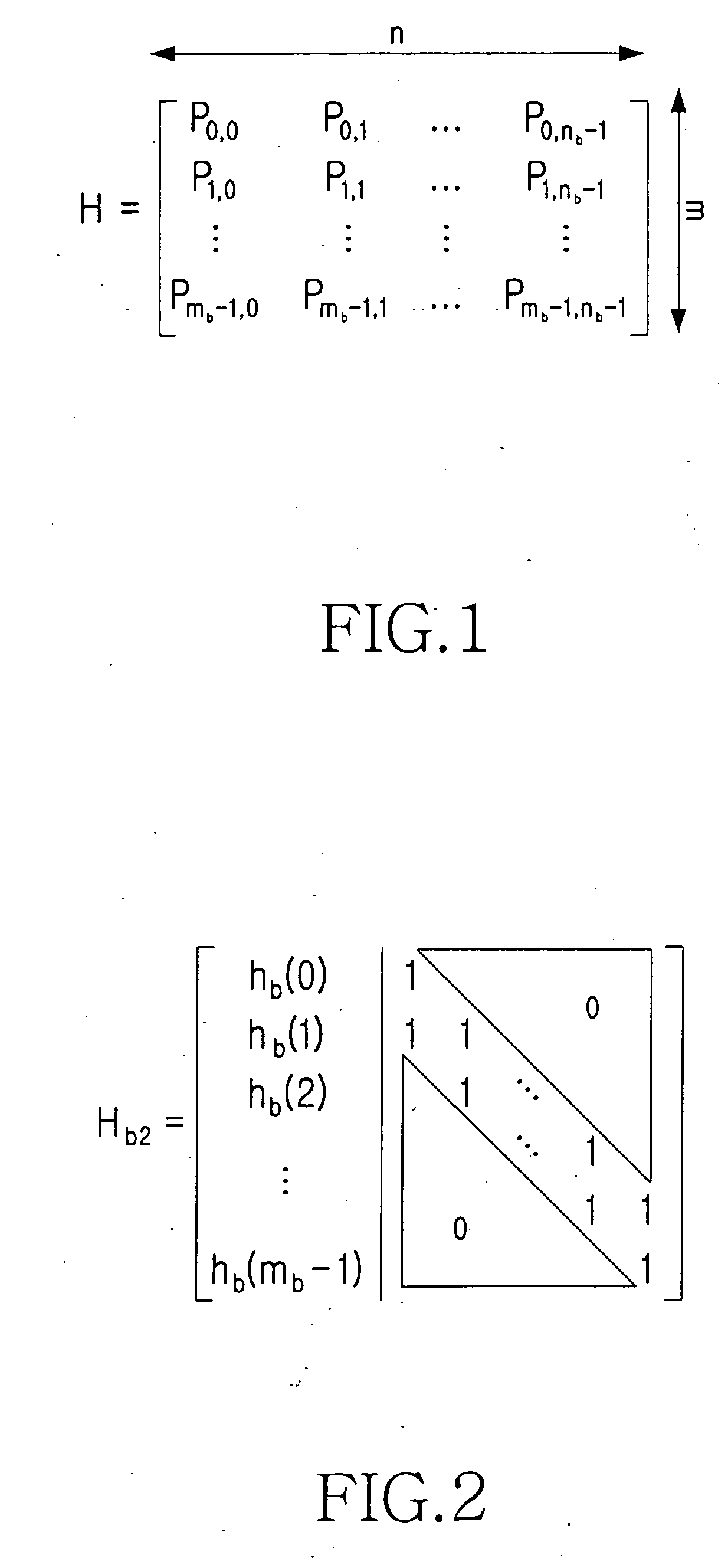

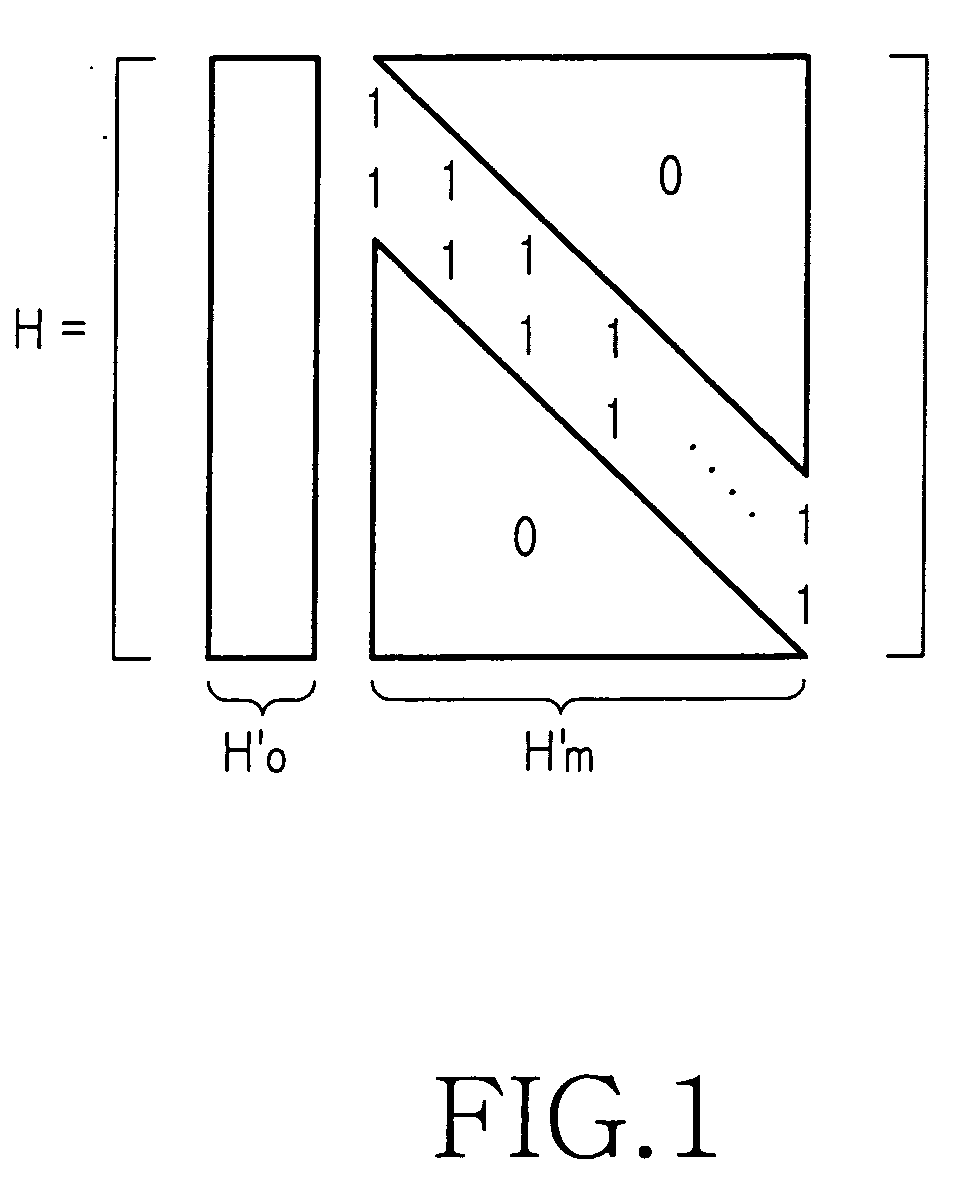

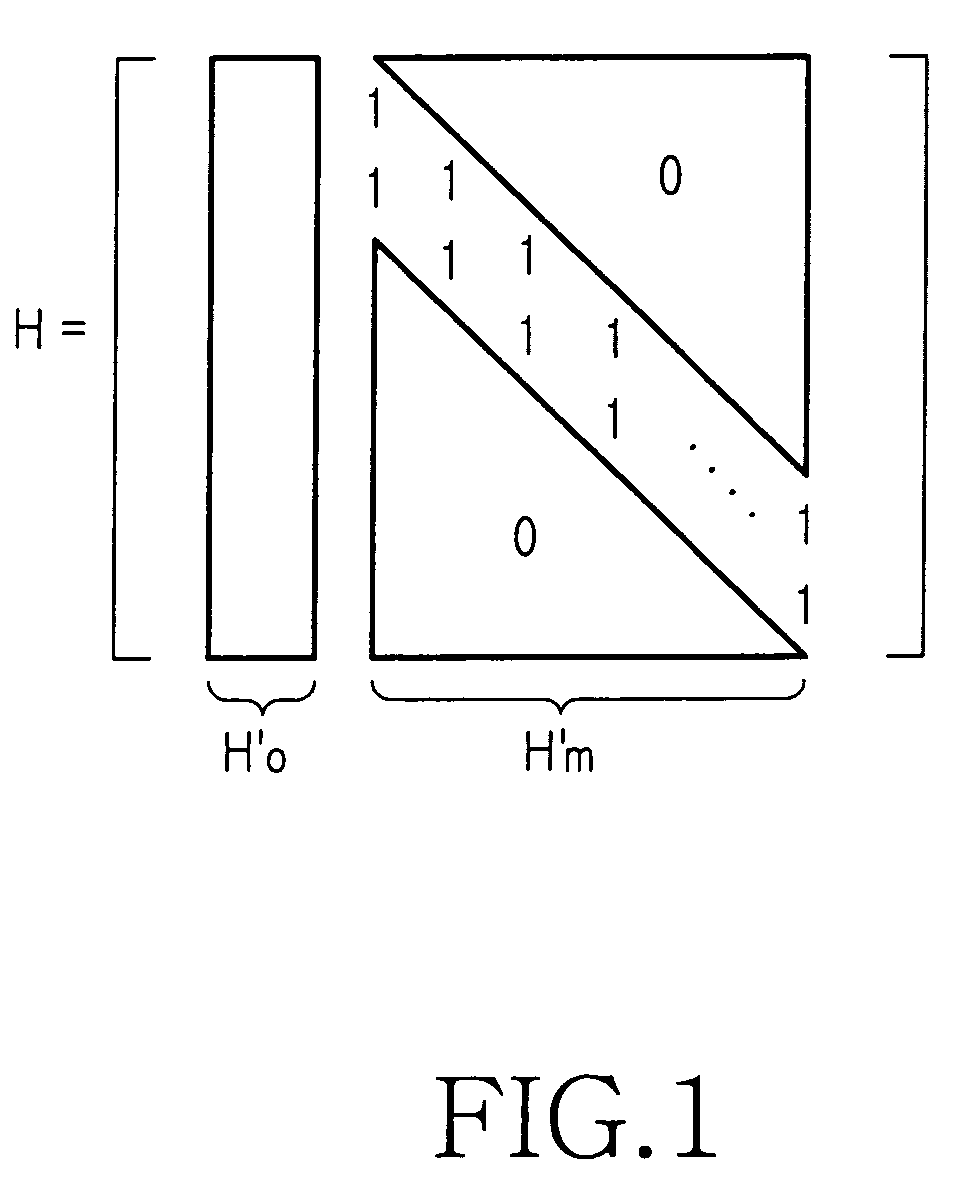

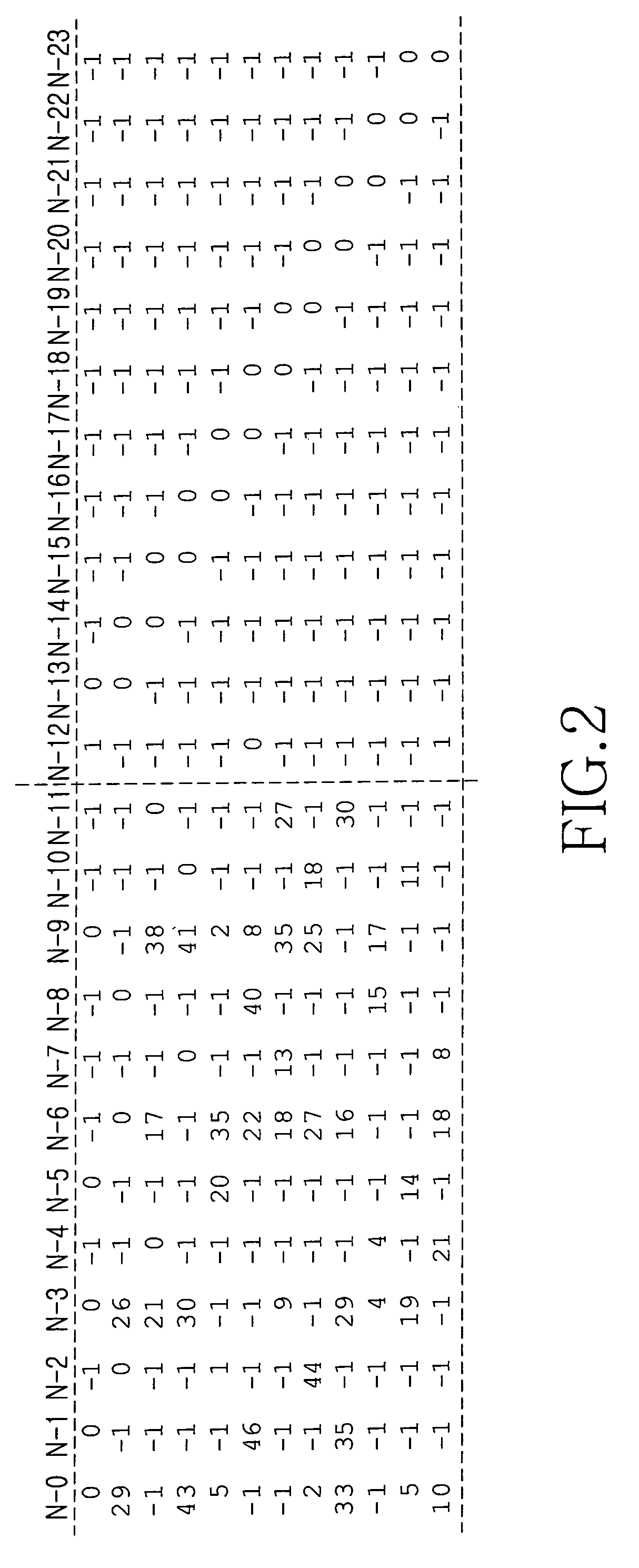

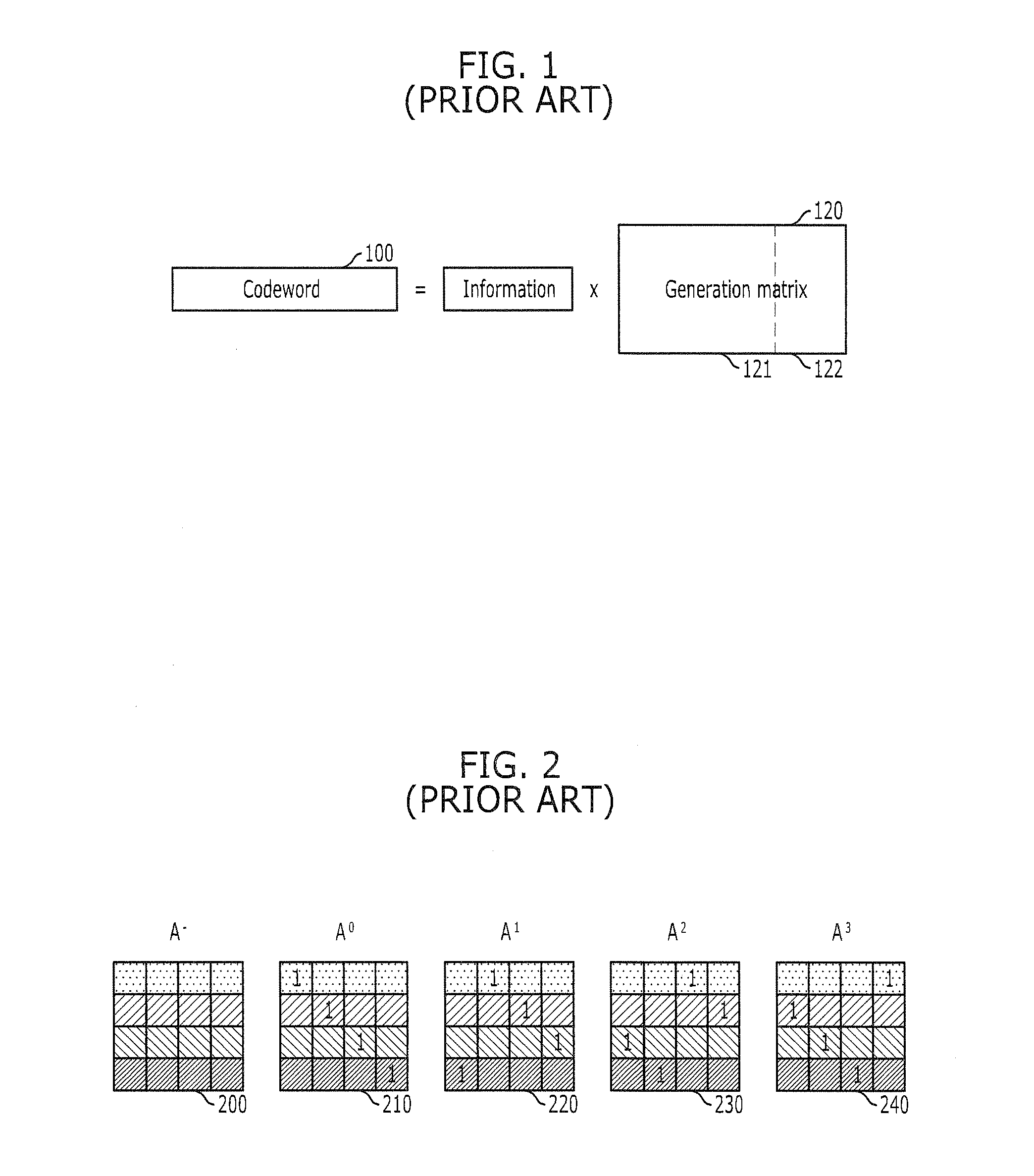

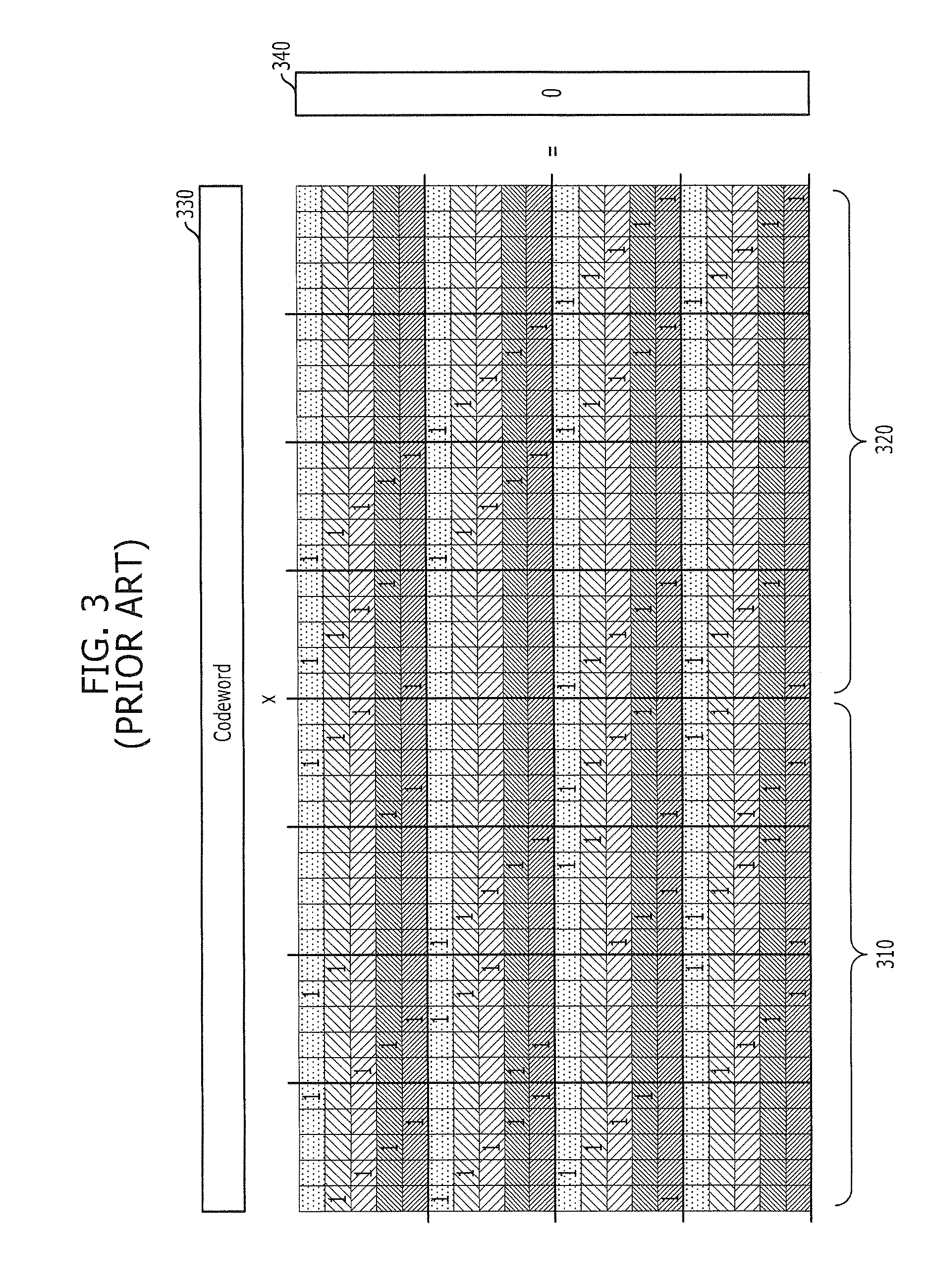

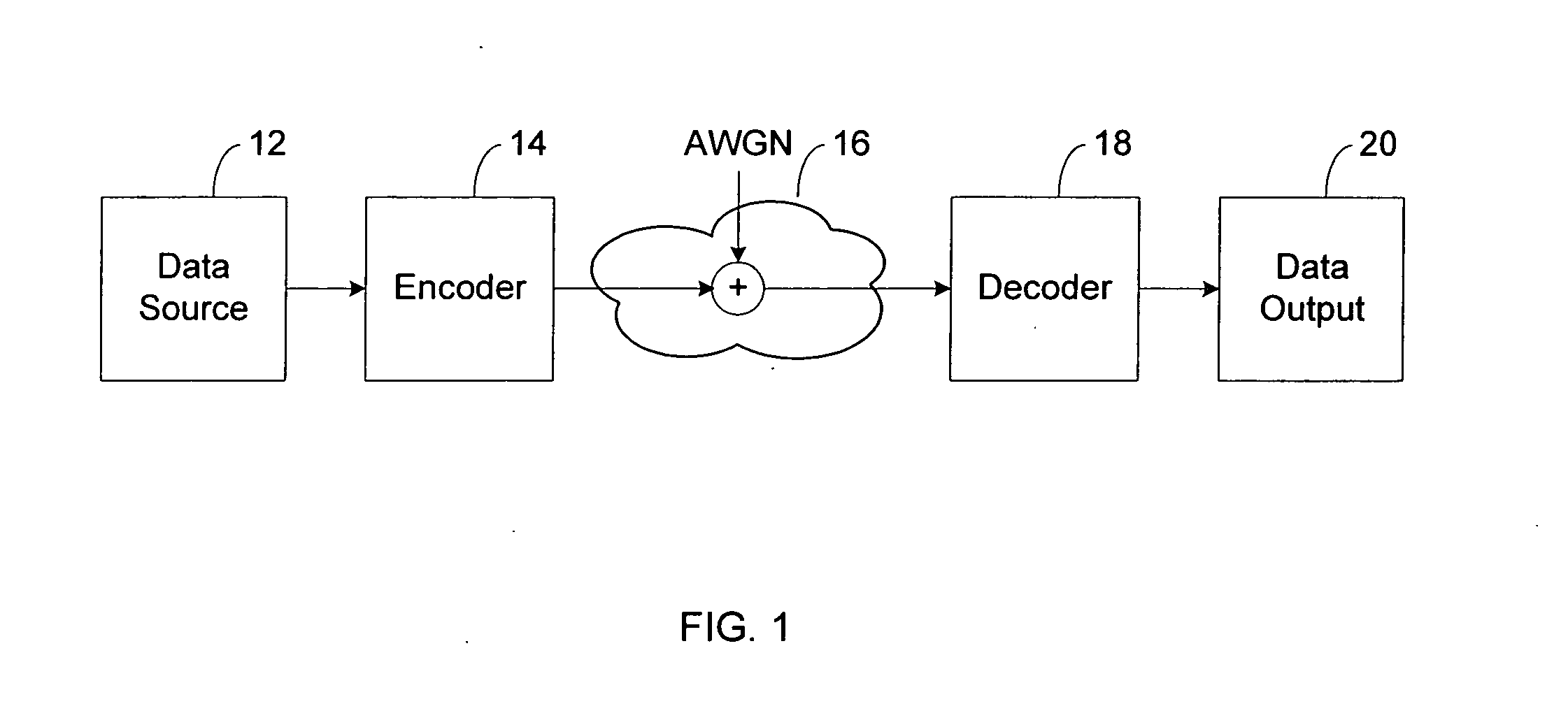

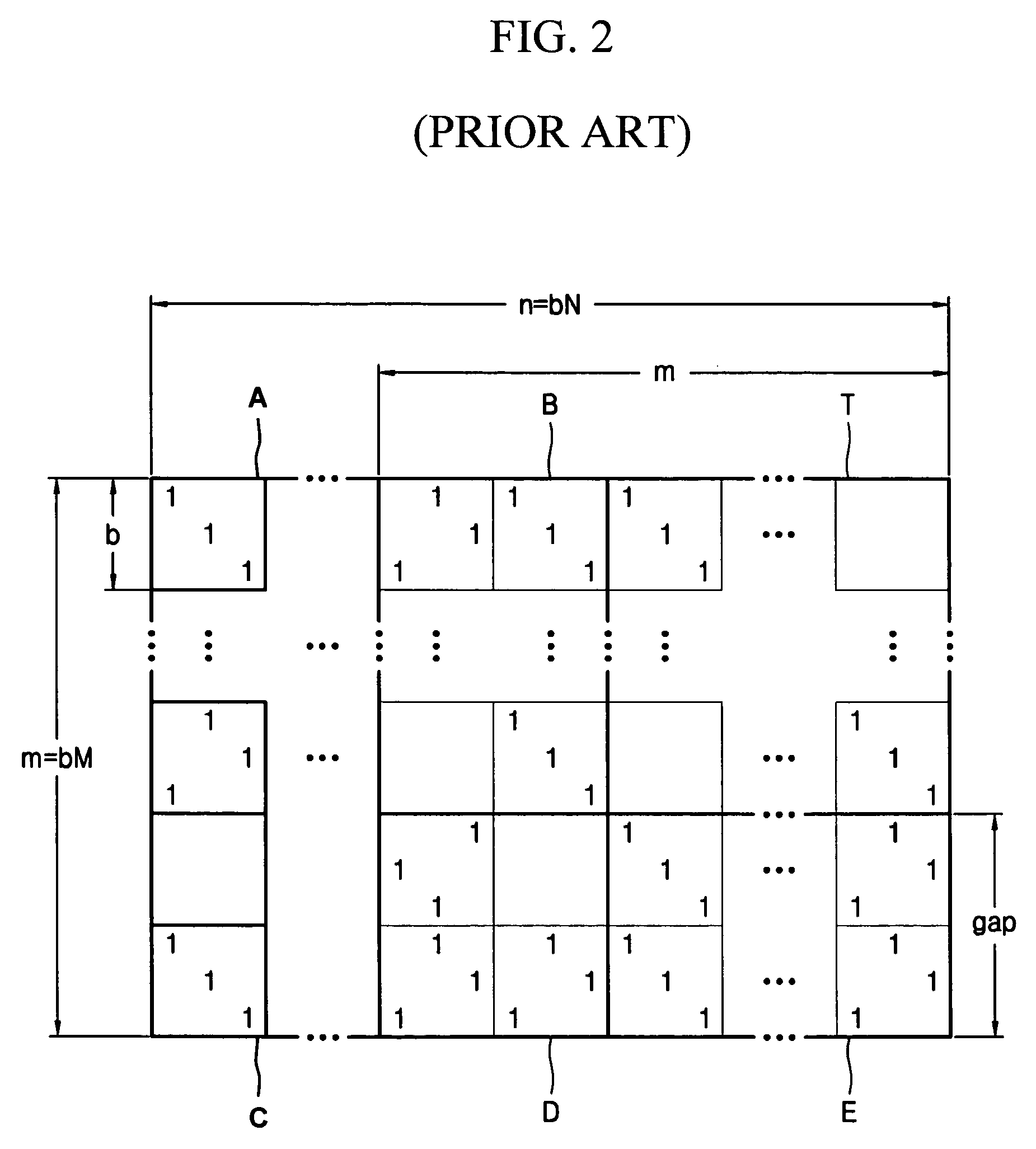

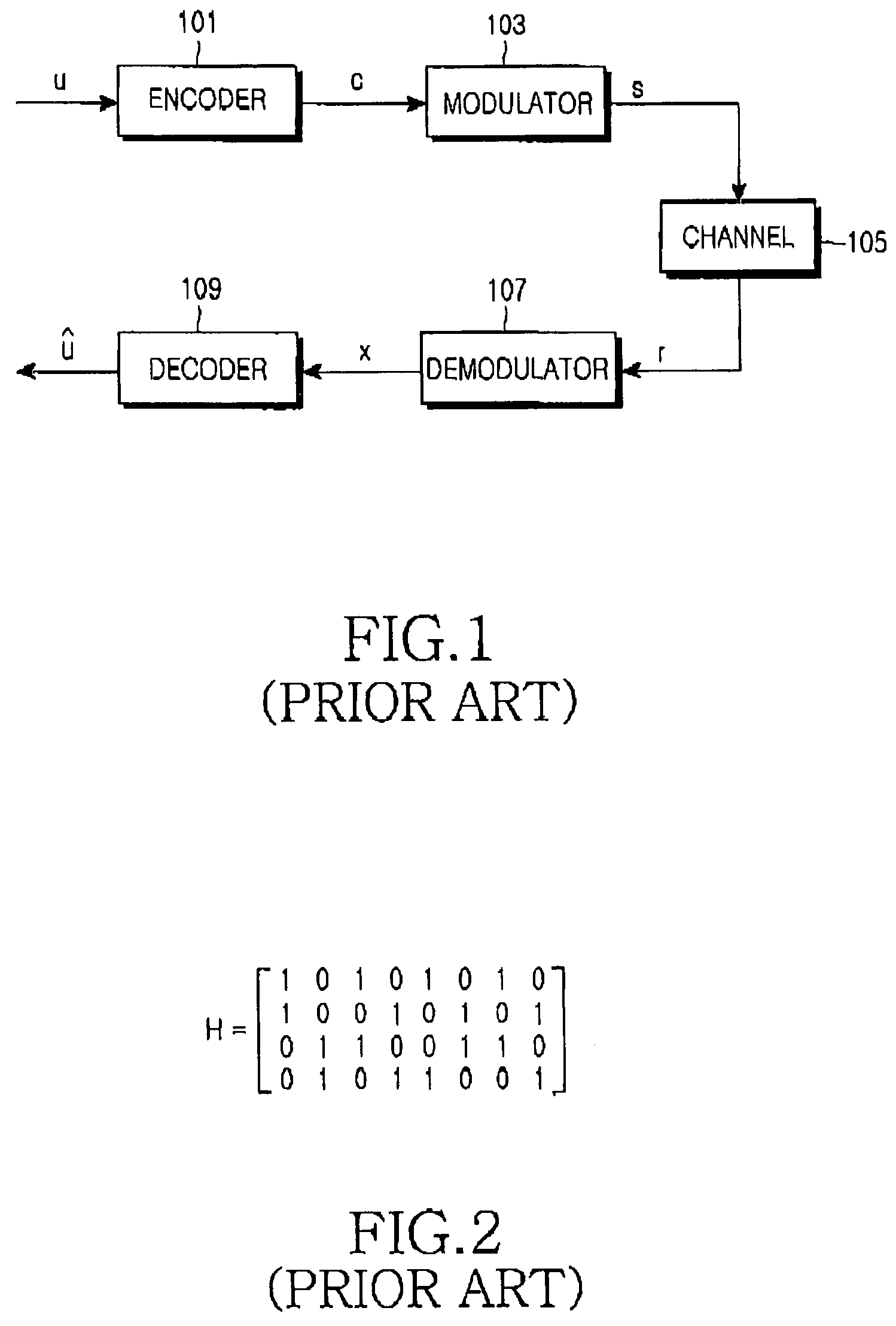

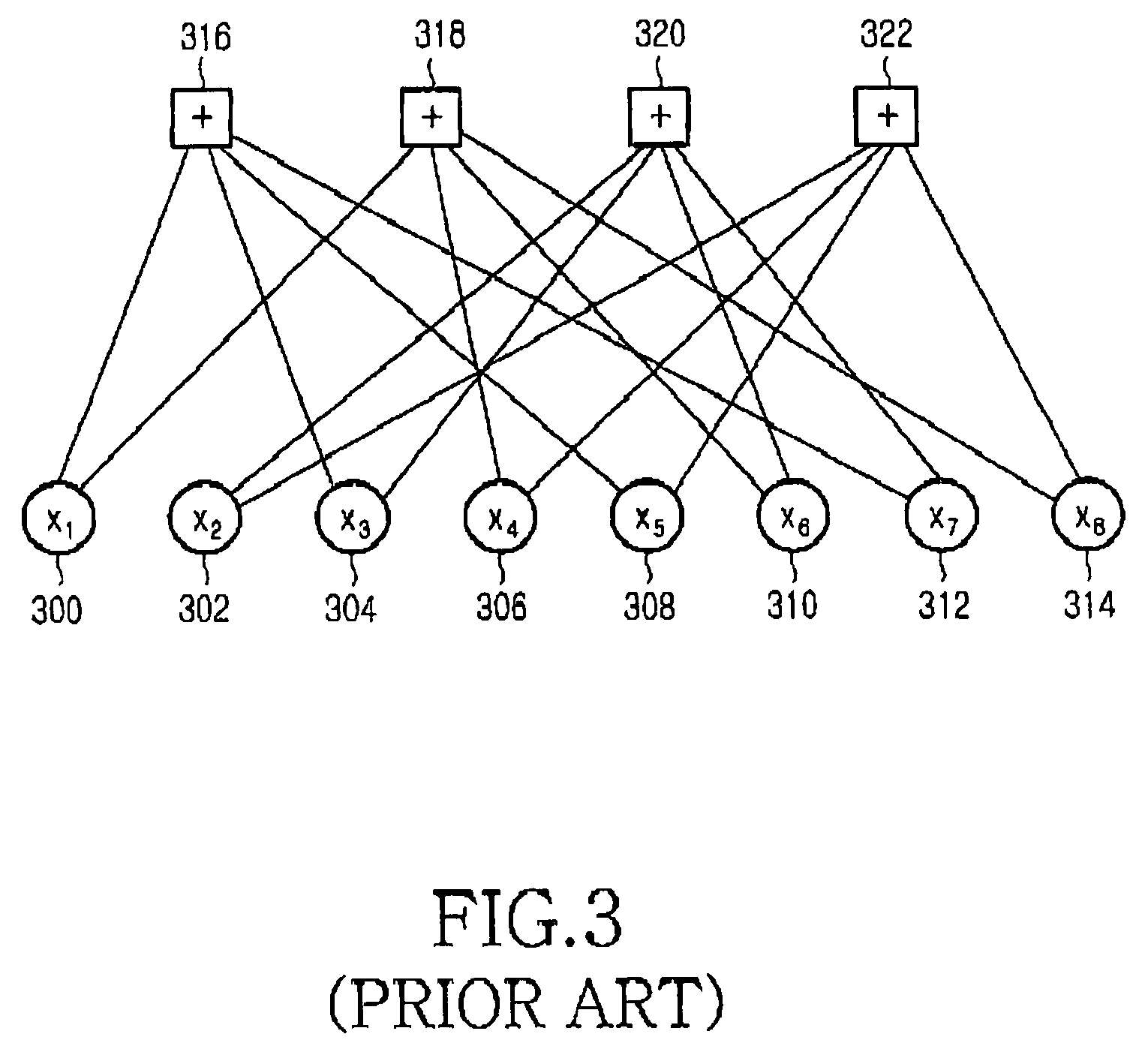

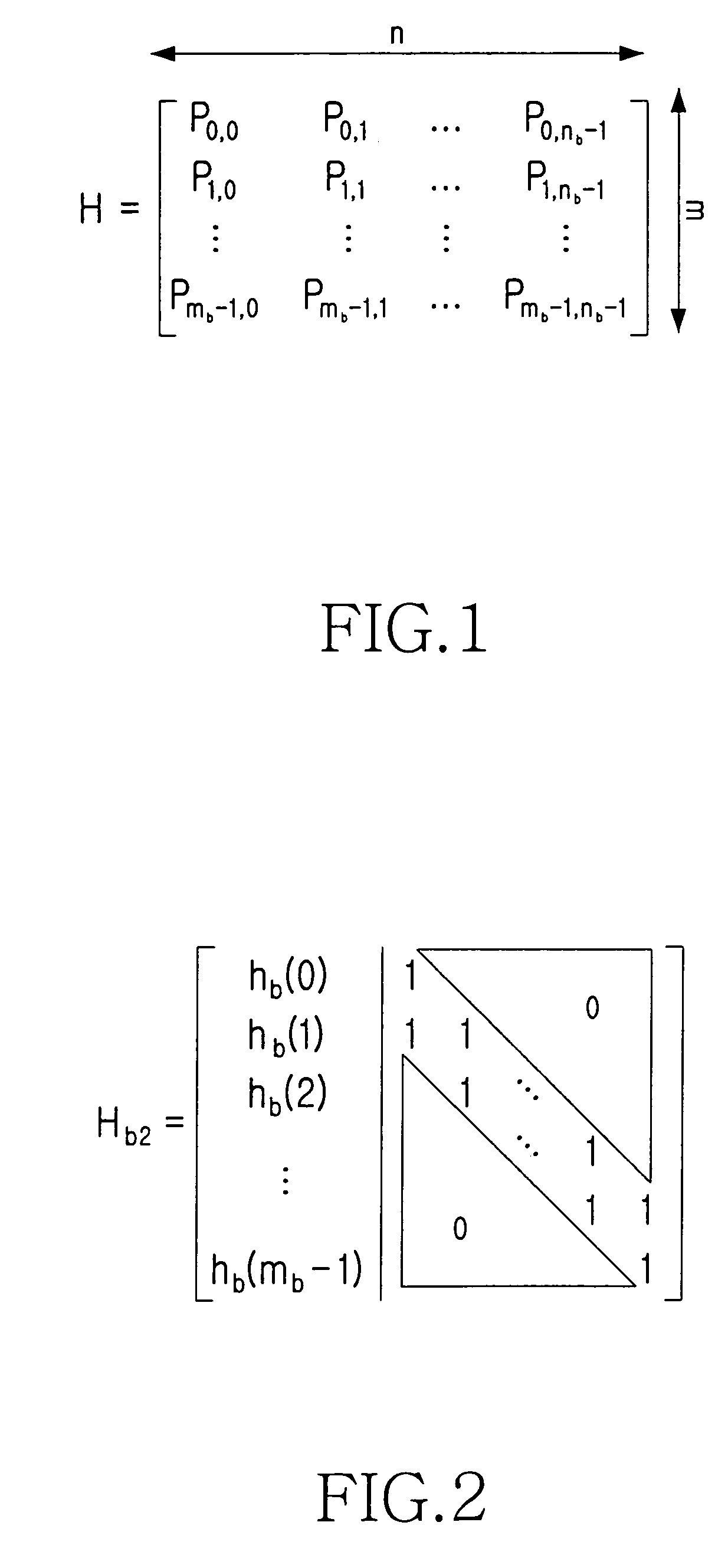

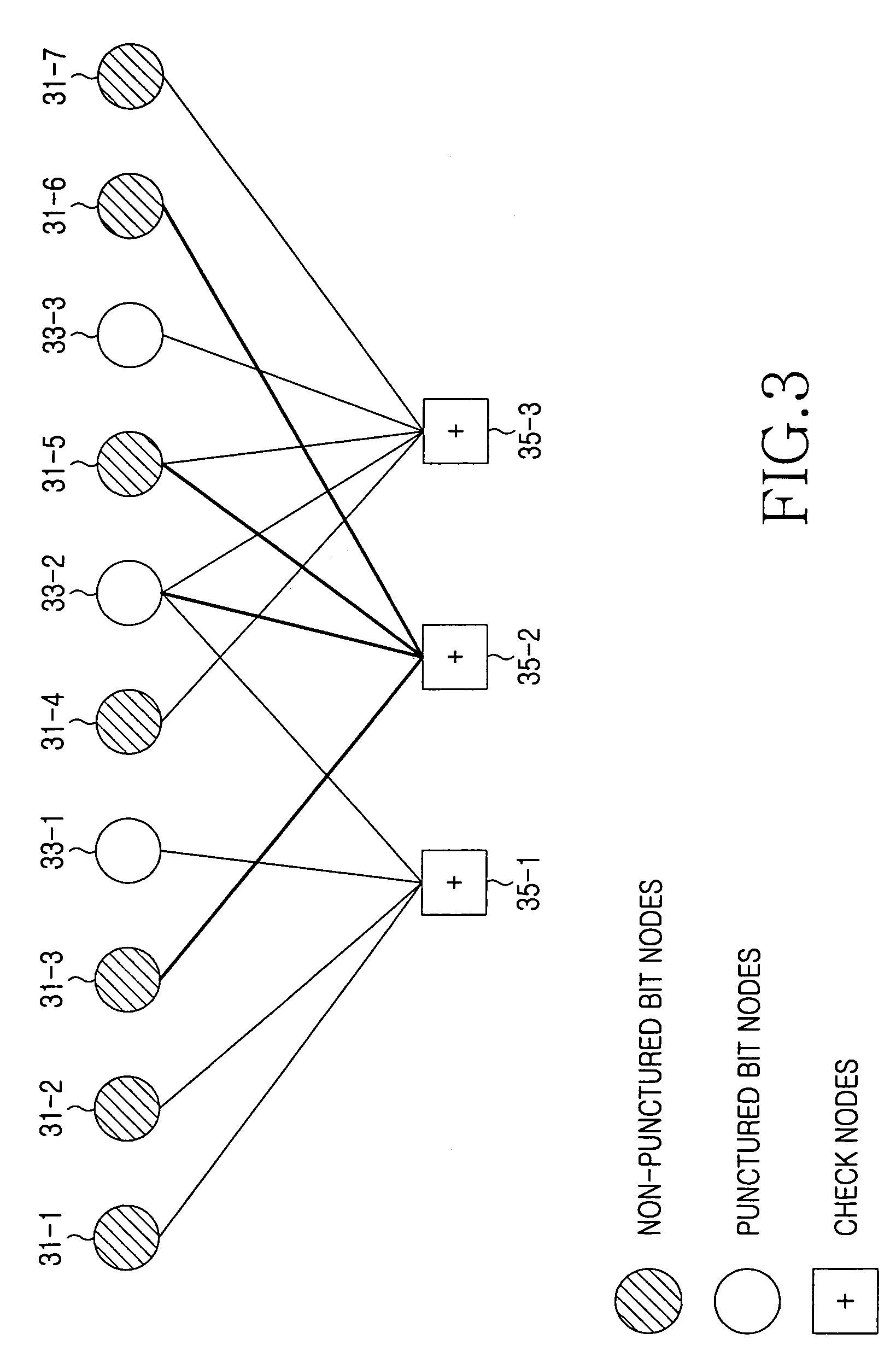

An apparatus and method for generating an encoding matrix for a low density parity check (LDPC) code having a dual-diagonal matrix as a parity check matrix are disclosed. The apparatus and method construct an information sub-matrix of the encoding matrix with a predetermined number of square matrixes according to a predetermined code rate such that each of the square matrixes has columns and rows with a weight of 1 and has a different offset value, combine the square matrixes with the dual-diagonal matrix, and perform inter-row permutation on the information sub-matrix.

Owner:SAMSUNG ELECTRONICS CO LTD

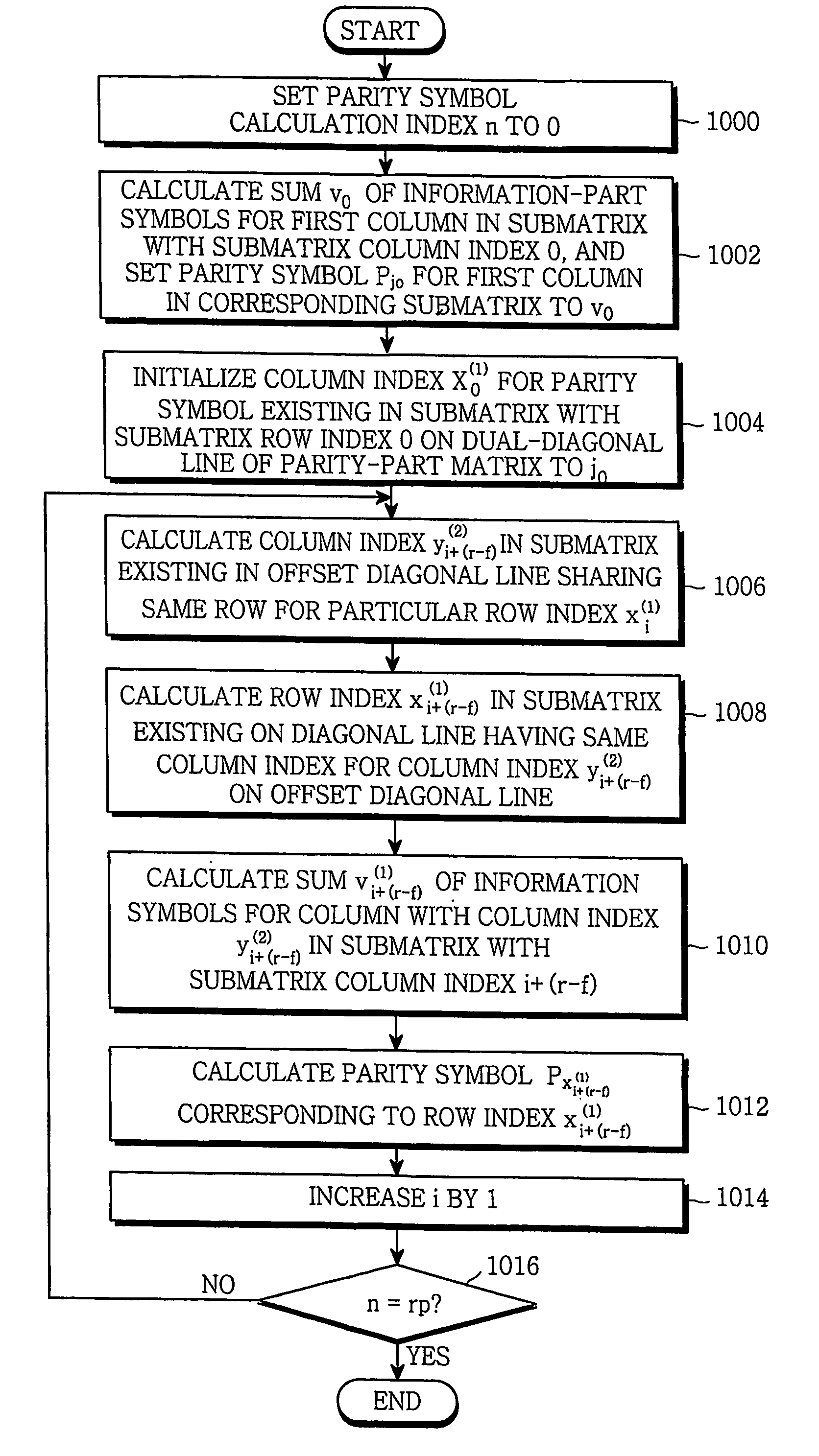

Method for encoding low-density parity check code

ActiveUS20070022354A1Simplify the coding processImprove performanceError detection/correctionError correction/detection using multiple parity bitsTheoretical computer scienceDiagonal matrix

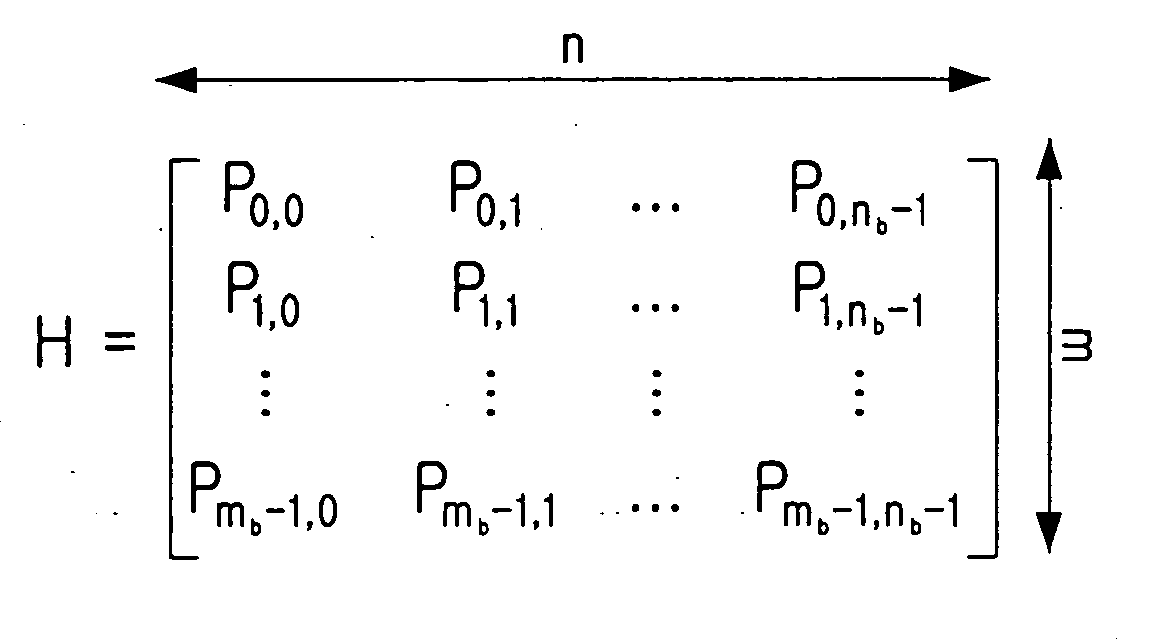

An apparatus and method for encoding low-density parity check (LDPC) codes. The method for generating a low-density parity check code formed of an information-part matrix and a parity-part matrix comprises the steps of converting the information-part matrix into an array code structure and assigning a degree sequence to each submatrix column; extending a dual-diagonal matrix corresponding to the parity-part matrix such that an offset value between diagonals has a random value; lifting the normalized dual-diagonal matrix; determining an offset value for cyclic column shift for each submatrix of the lifted normalized dual-diagonal matrix; and determining a parity symbol corresponding to a column of the parity-part matrix.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for puncturing low density parity check code

InactiveUS20060206781A1Avoid performanceError correction/detection using multiple parity bitsCode conversionTheoretical computer scienceDiagonal matrix

Owner:K2M +1

Method for padding and puncturing low density parity check code

InactiveUS20070011567A1Simple calculationReduce latencyError correction/detection using multiple parity bitsCode conversionTheoretical computer scienceDiagonal matrix

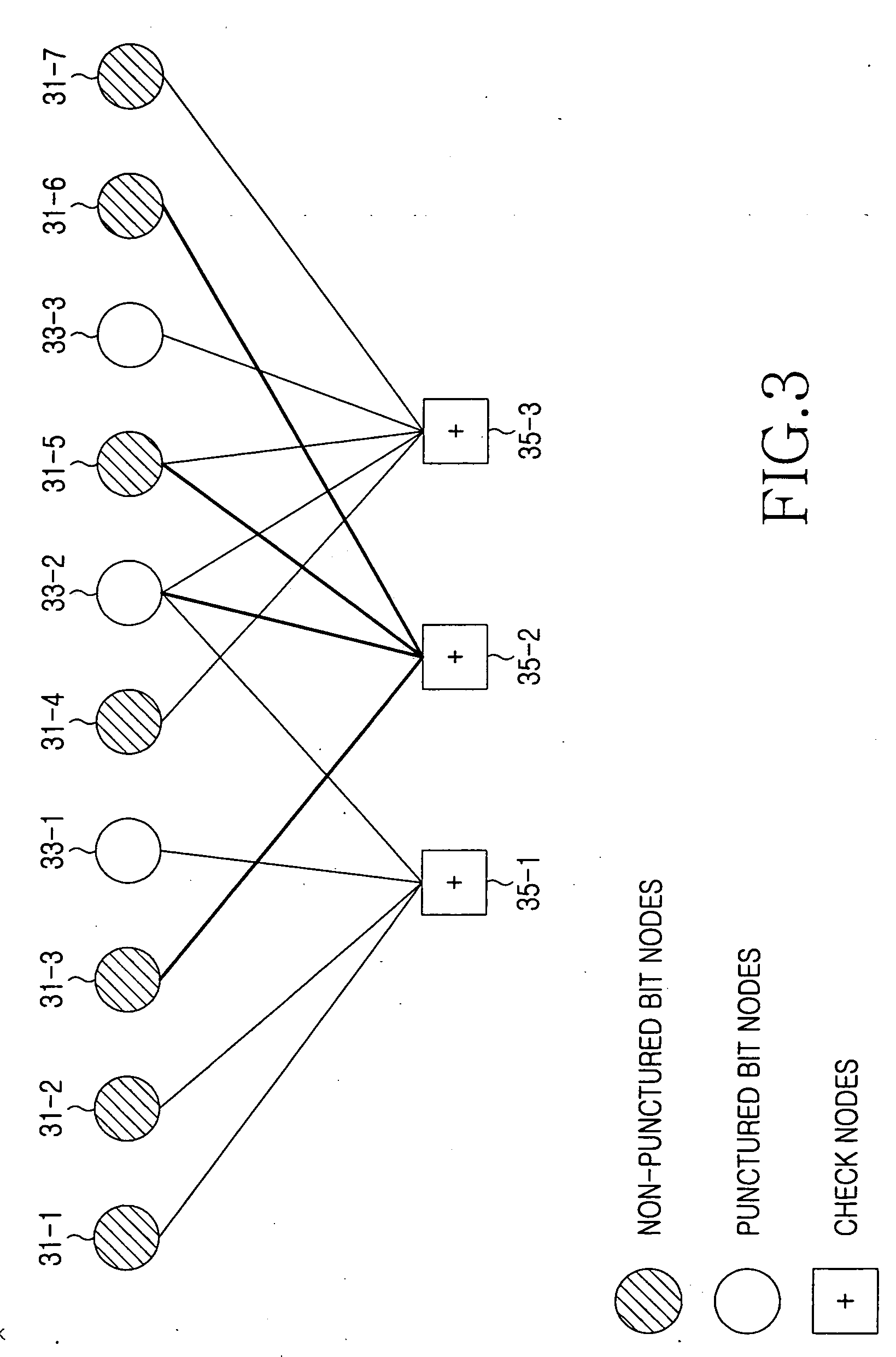

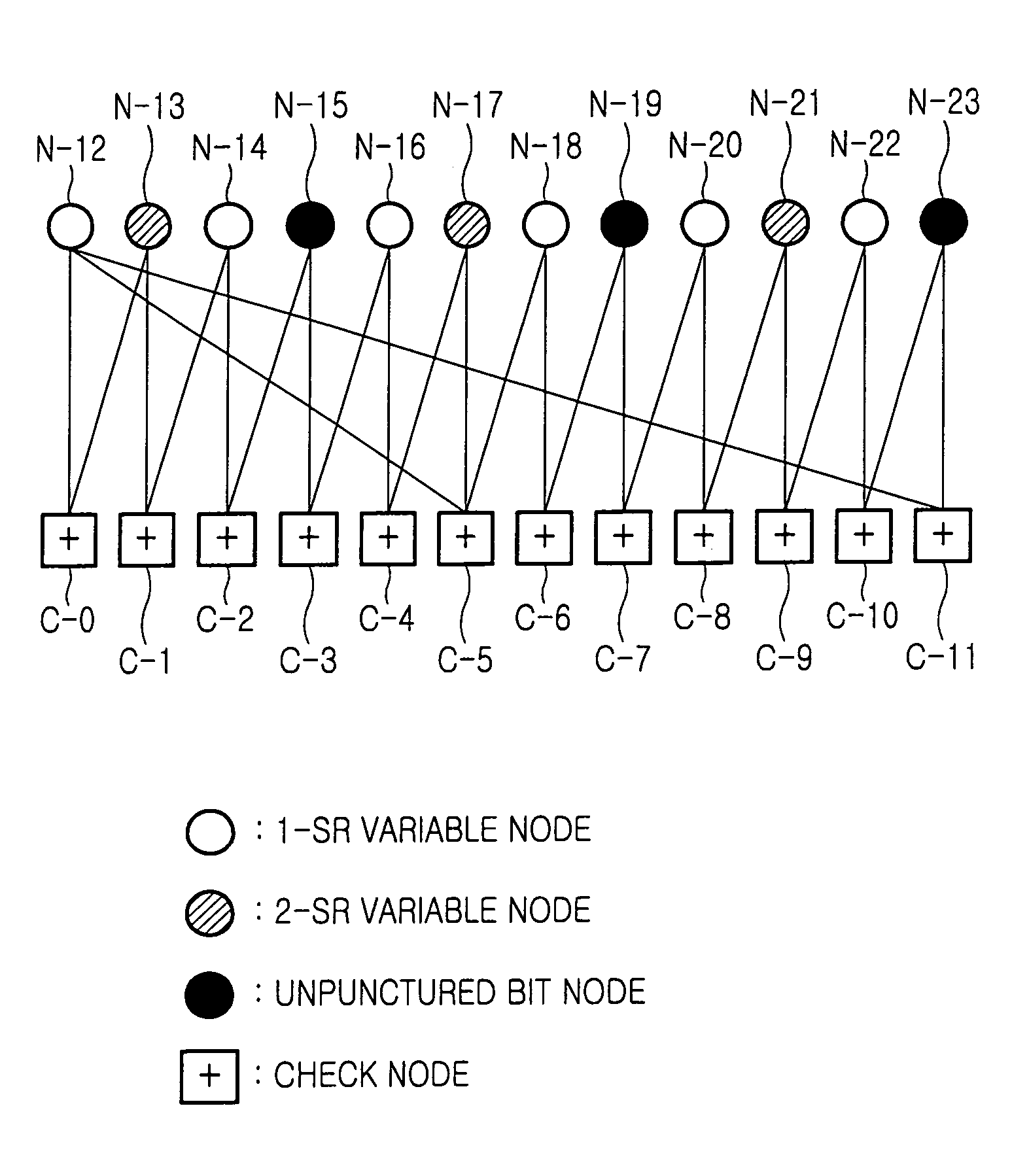

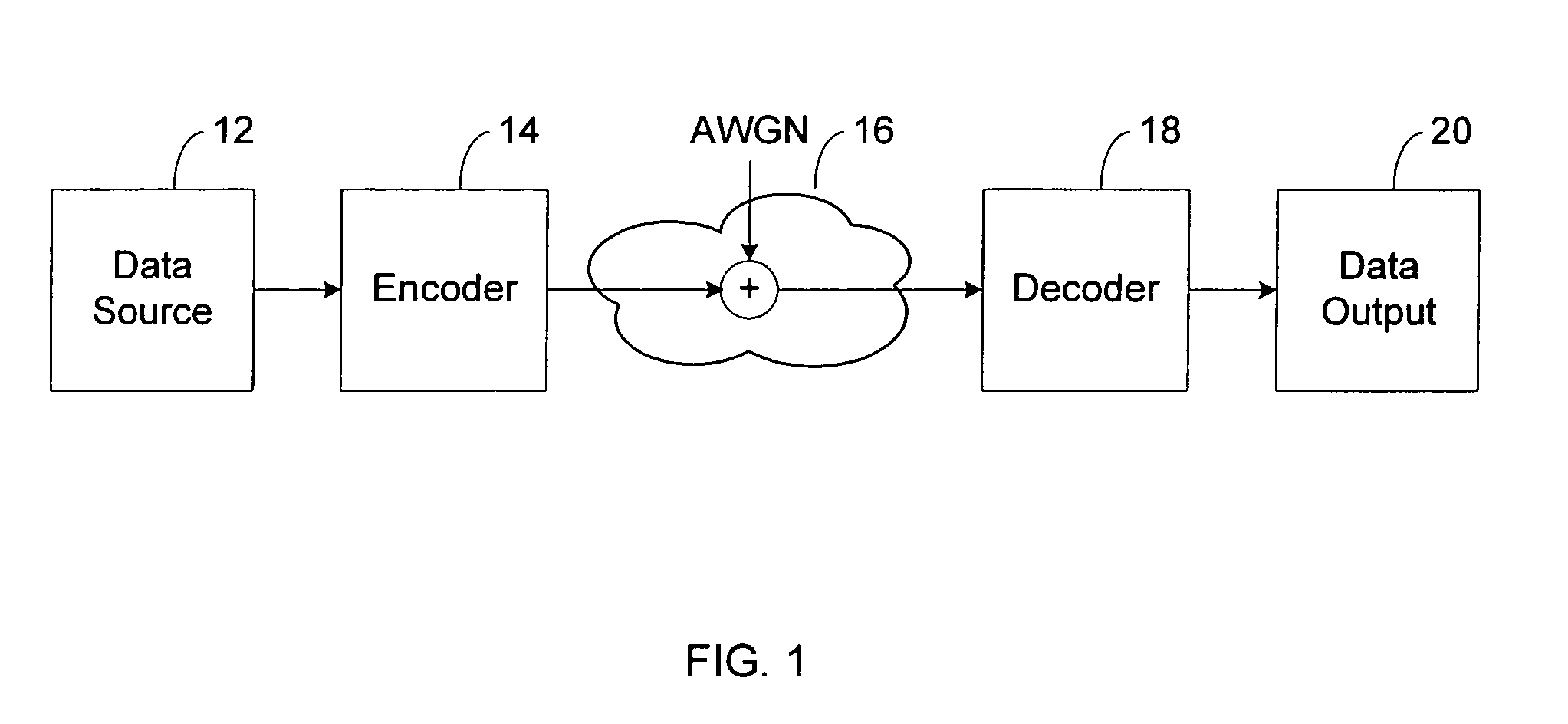

Disclosed is a method for puncturing a Low Density Parity Check (LDPC) code that is expressed by a factor graph having a check node and a variable node, connected to each other by an edge, and is decoded by a parity check matrix including a parity part having a single weight-3 column and a dual-diagonal matrix. The method includes selecting 1-step recoverable (1-SR) variable nodes with the highest quality including a variable node mapped to a weight-3 column, and setting a first puncturing priority group using the selected 1-SR variable nodes, selecting k-step recoverable (k-SR) variable nodes with the highest quality in the next step k taking into account the variable nodes selected in the current step, and setting a priority group for each individual step, puncturing an LDPC code mapped to a variable node belonging to a corresponding group according to priority of each group obtained in the preceding steps.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for padding and puncturing low density parity check code

InactiveUS8006162B2Error correction/detection using multiple parity bitsCode conversionAlgorithmParity-check matrix

Disclosed is a method for puncturing a Low Density Parity Check (LDPC) code that is expressed by a factor graph having a check node and a variable node, connected to each other by an edge, and is decoded by a parity check matrix including a parity part having a single weight-3 column and a dual-diagonal matrix. The method includes selecting 1-step recoverable (1-SR) variable nodes with the highest quality including a variable node mapped to a weight-3 column, and setting a first puncturing priority group using the selected 1-SR variable nodes, selecting k-step recoverable (k-SR) variable nodes with the highest quality in the next step k taking into account the variable nodes selected in the current step, and setting a priority group for each individual step, puncturing an LDPC code mapped to a variable node belonging to a corresponding group according to priority of each group obtained in the preceding steps.

Owner:SAMSUNG ELECTRONICS CO LTD

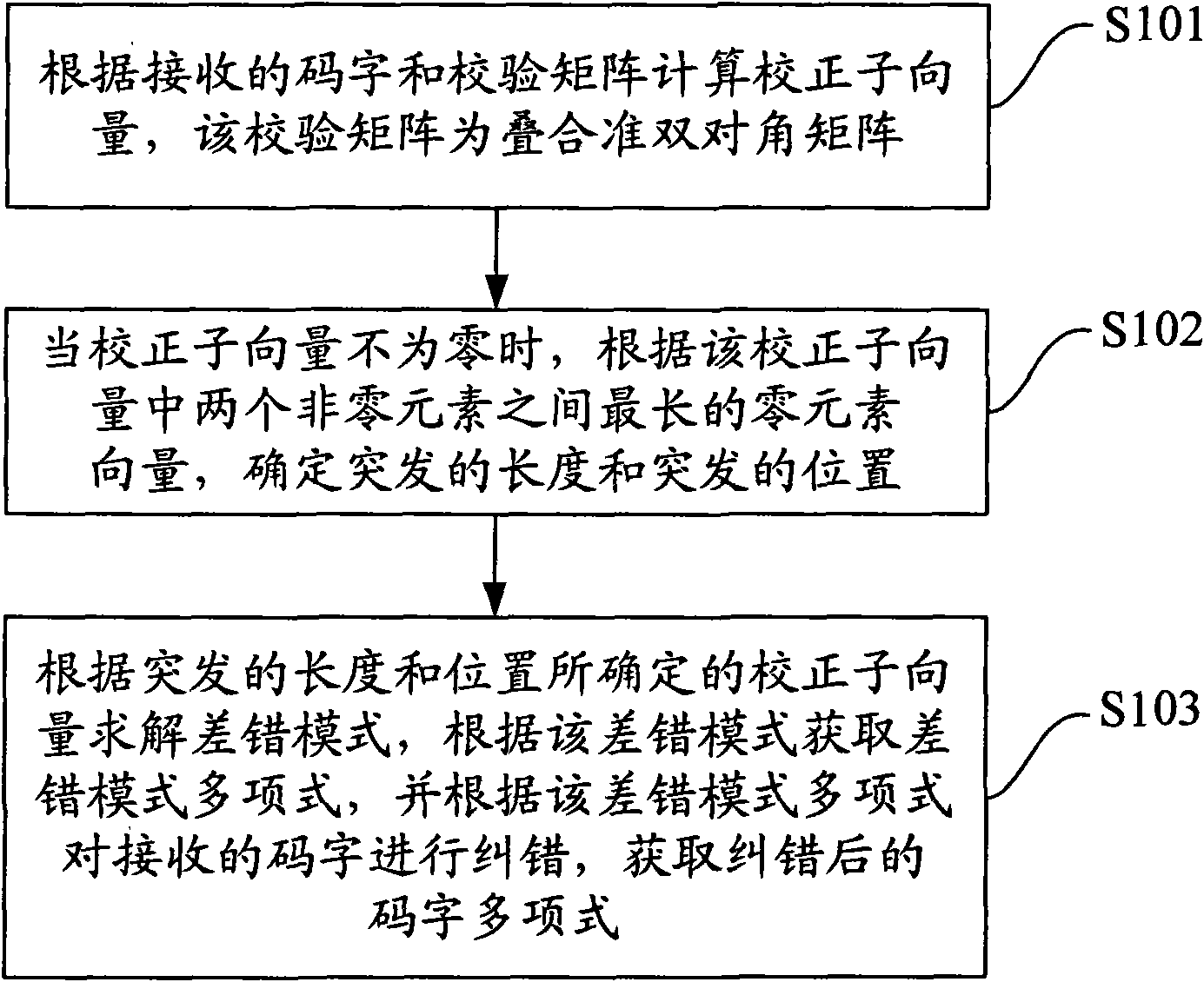

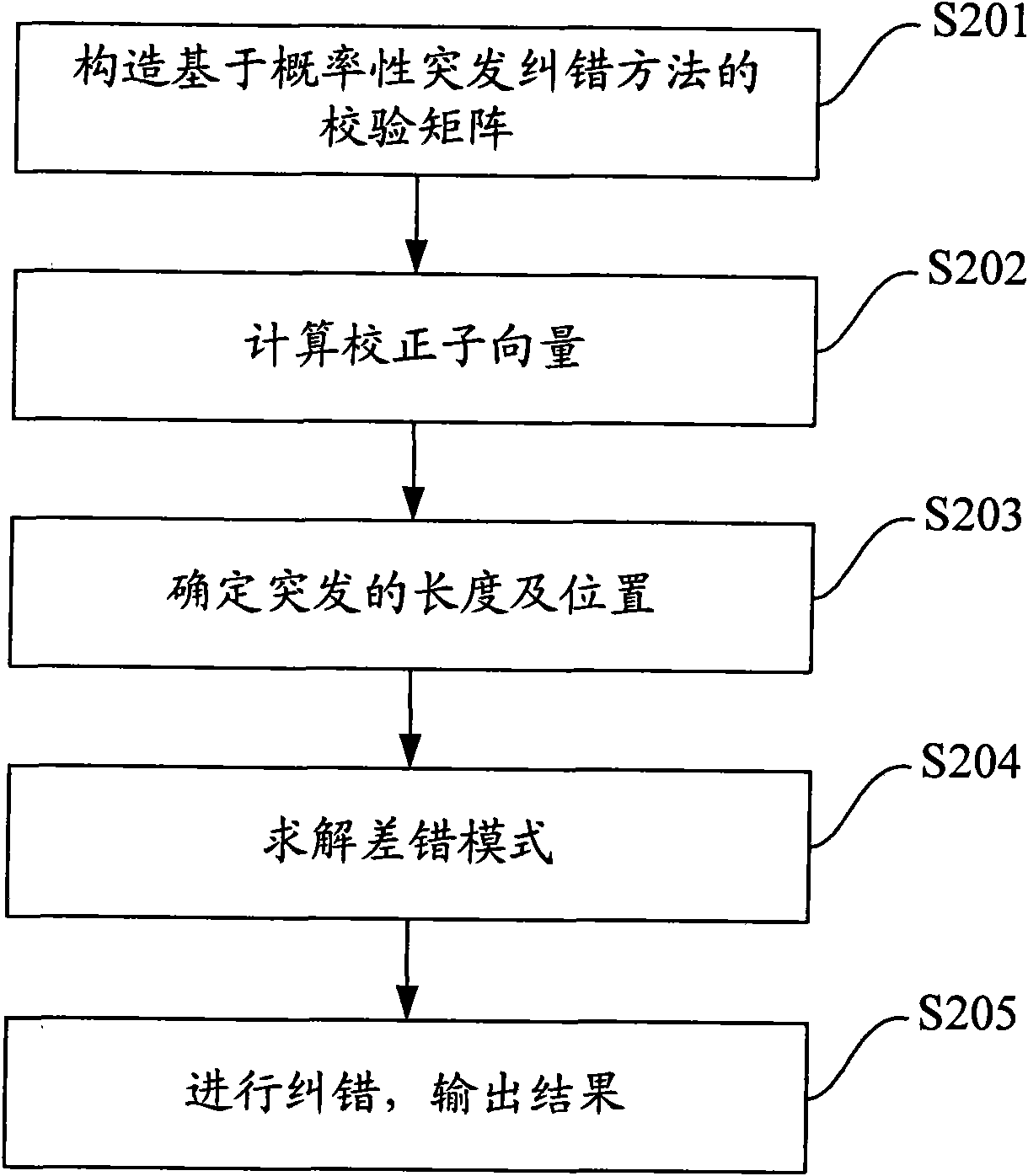

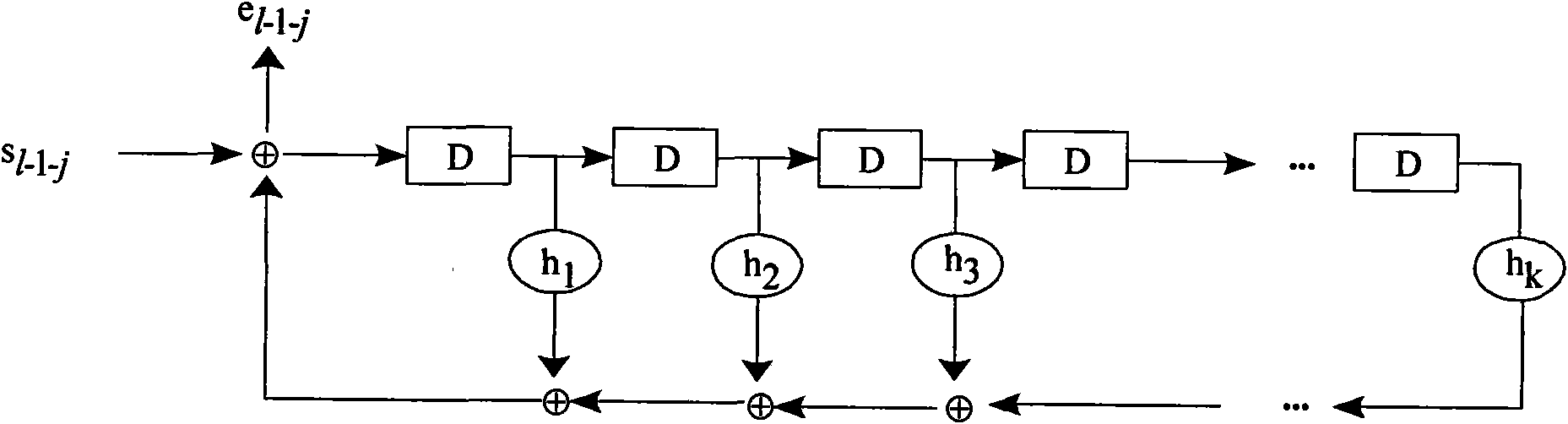

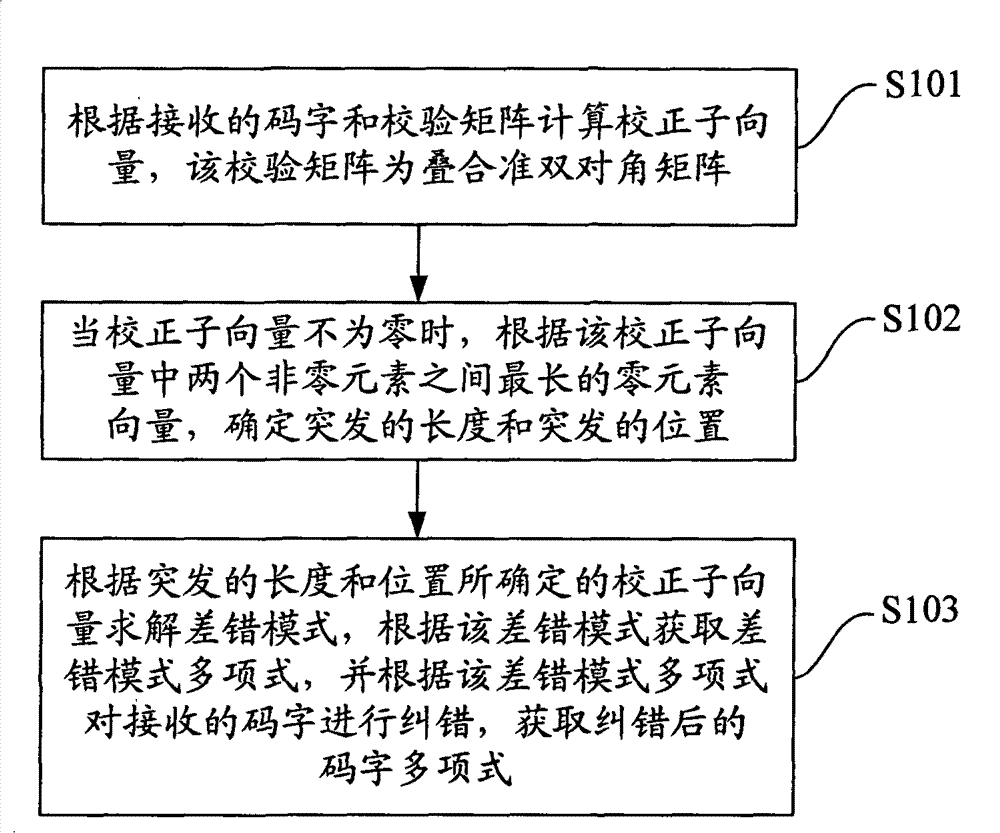

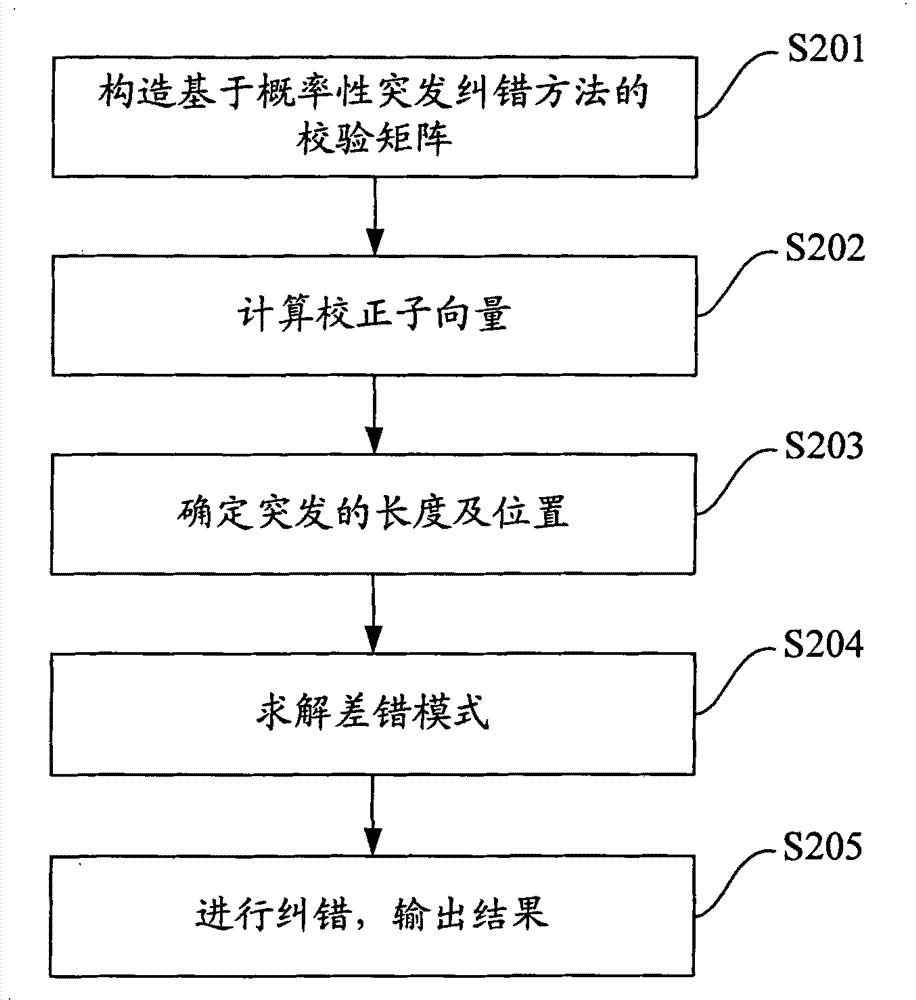

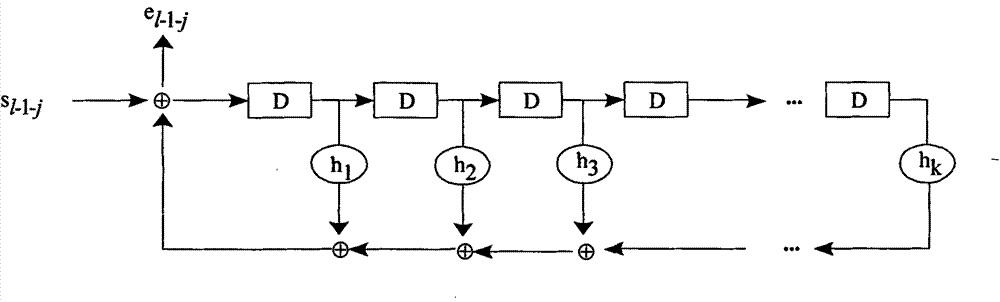

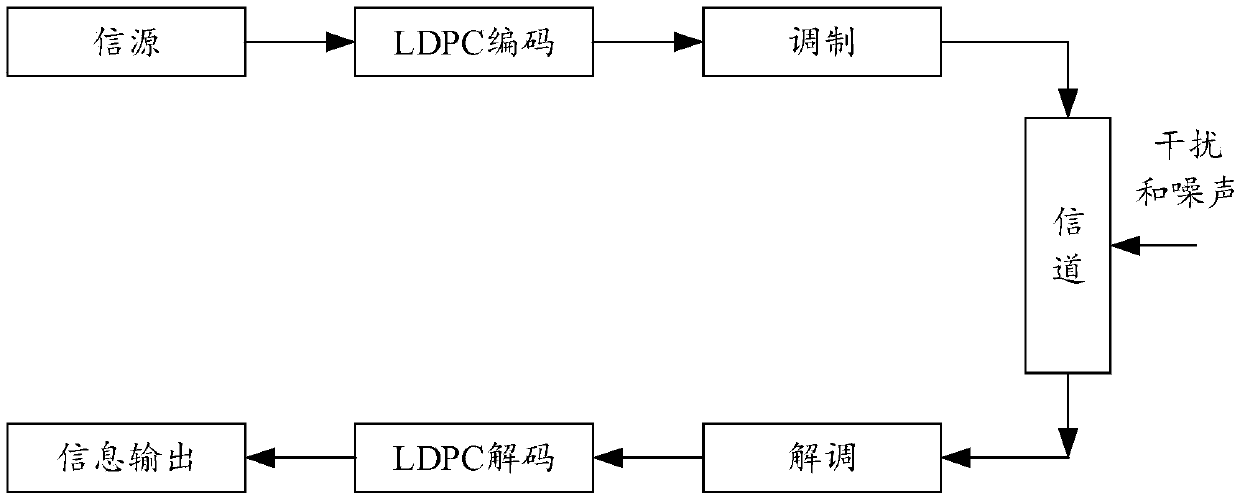

Burst correcting method, equipment and device

ActiveCN101621299AError correction burst errorError preventionBurst error correctionEuclidean vectorBurst error

The embodiment of the invention discloses a burst correcting method, equipment and a device. The burst correcting method comprises calculating a corrector subvector according to received codes and a rectifying matrix, wherein, the rectifying matrix is an overlapped quasi-bidiagonal matrix; determining the burst length and the burst position according to the longest zero element vector between thetwo non-zero element vectors in the corrector subvector when the corrector subvector is non-zero element vector; solving an error mode according to the determined corrector subvector based on the burst length and the burst position, obtaining a multinomial error mode according to the error mode, and correcting the received codes according to the multinomial error mode to obtain a corrected multinomial code. The embodiment of the invention provides a concrete implementation method which regards circulating codes, is based on probabilistic burst correction, and can correct more burst errors in comparison with regular circulating code deciphering method.

Owner:XFUSION DIGITAL TECH CO LTD

Method for encoding low-density parity check code

ActiveUS7458009B2Simplify the coding processImprove performanceError detection/correctionError correction/detection using multiple parity bitsAlgorithmDiagonal matrix

An apparatus and method for encoding low-density parity check (LDPC) codes. The method for generating a low-density parity check code formed of an information-part matrix and a parity-part matrix comprises the steps of converting the information-part matrix into an array code structure and assigning a degree sequence to each submatrix column; extending a dual-diagonal matrix corresponding to the parity-part matrix such that an offset value between diagonals has a random value; lifting the normalized dual-diagonal matrix; determining an offset value for cyclic column shift for each submatrix of the lifted normalized dual-diagonal matrix; and determining a parity symbol corresponding to a column of the parity-part matrix.

Owner:SAMSUNG ELECTRONICS CO LTD

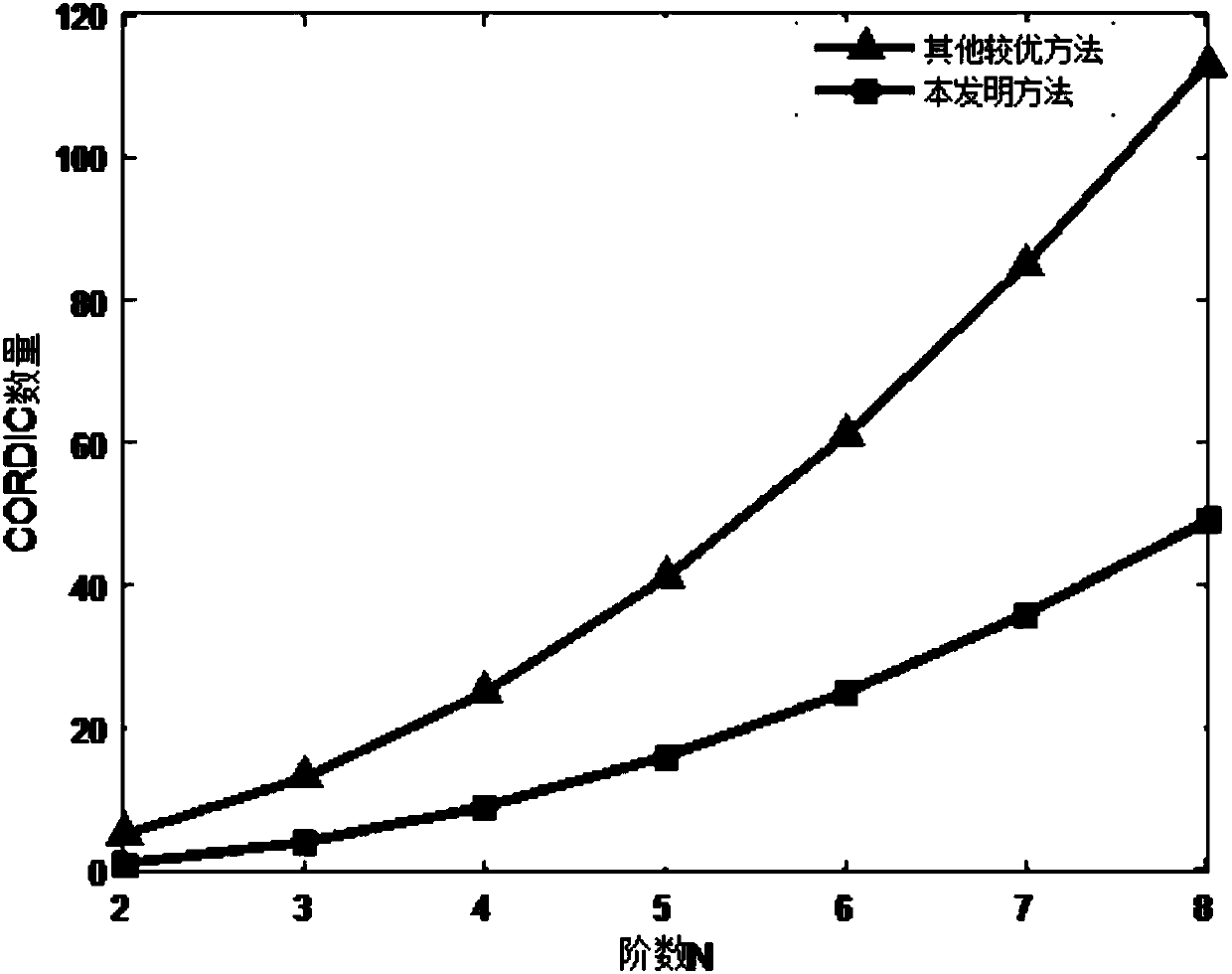

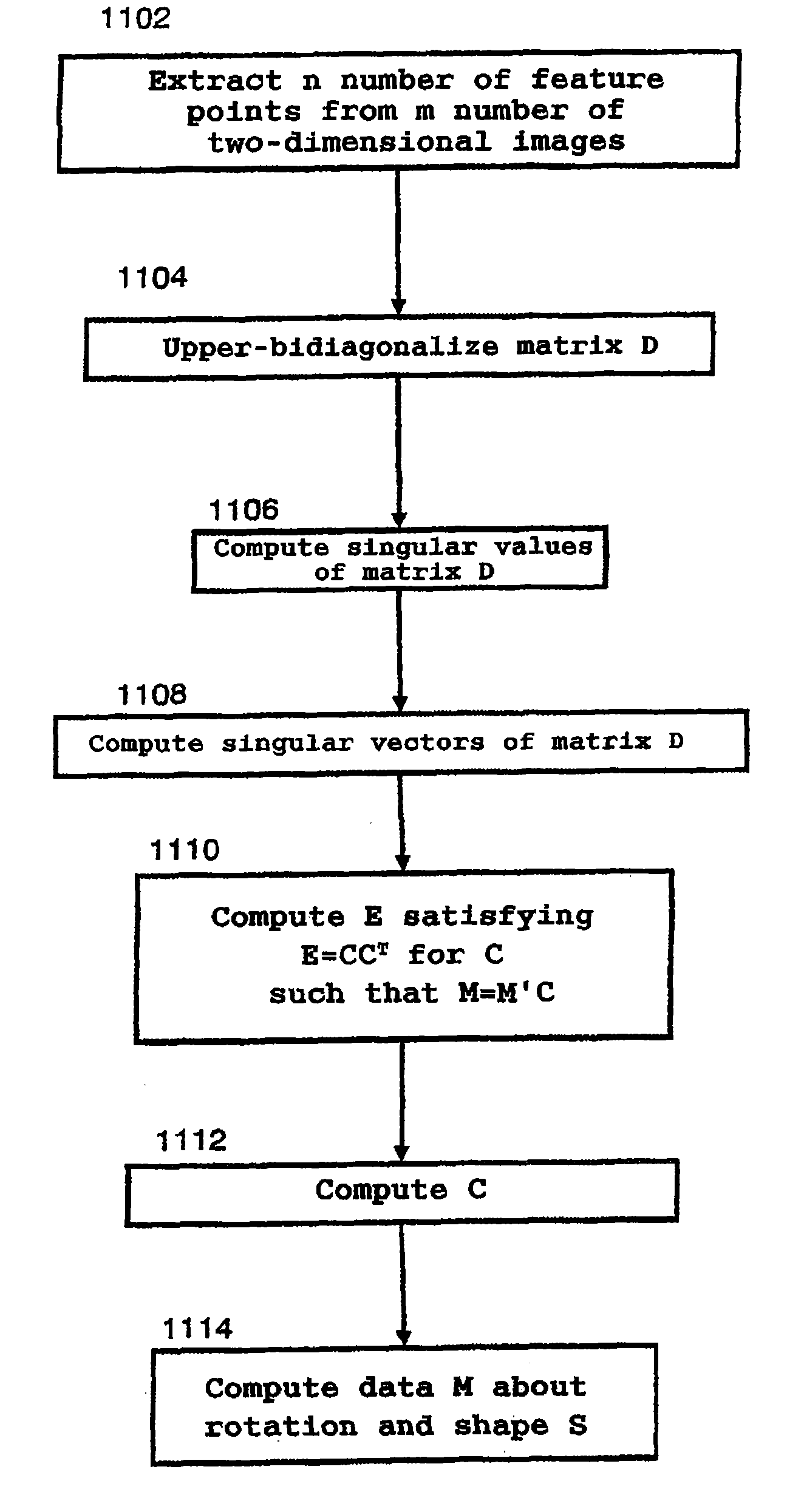

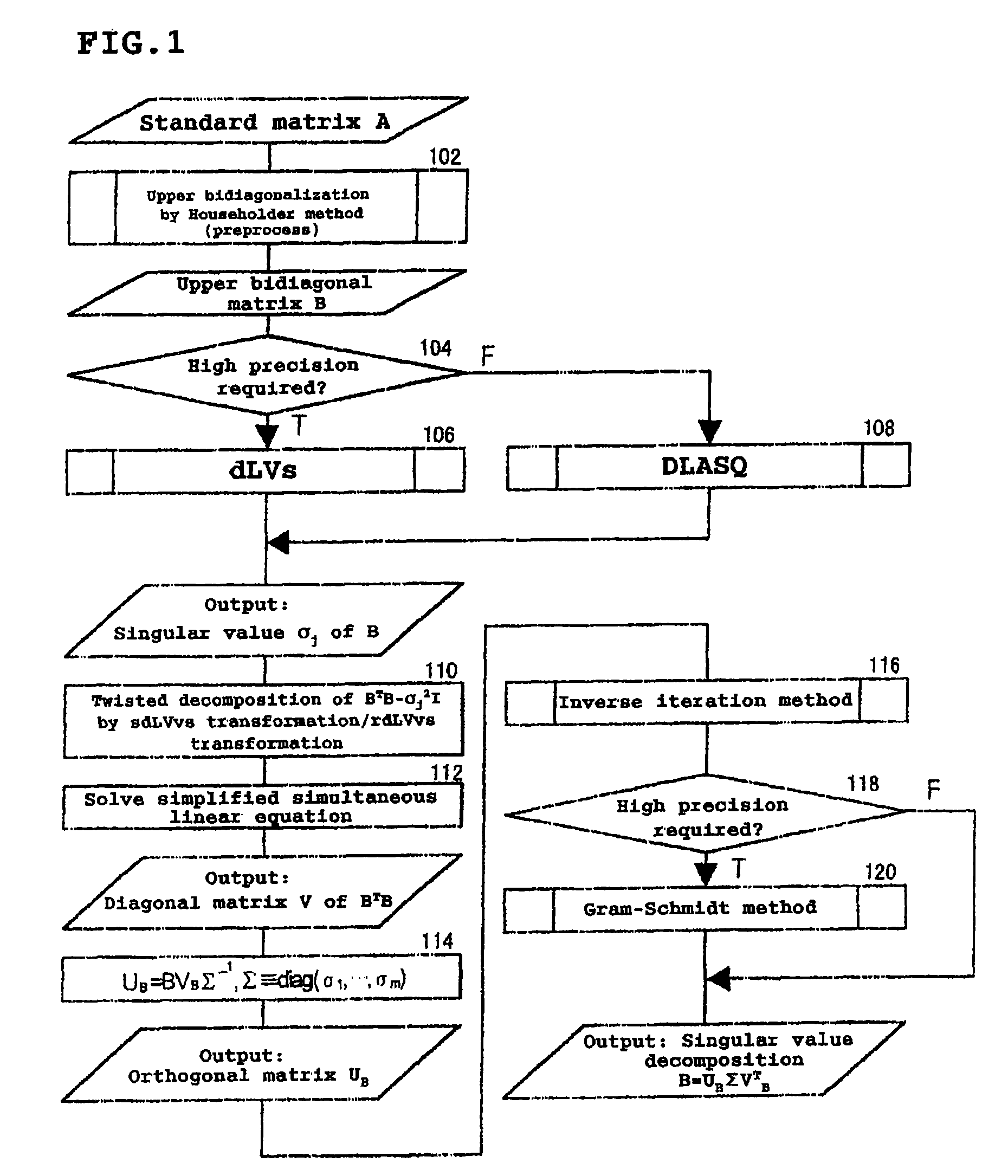

High-speed high-accuracy matrix singular value decomposition method, program, and device

ActiveUS20090028455A1Shorten the timeAmount of timeImage analysisCharacter and pattern recognitionAlgorithmDecomposition

A singular value decomposition method according to the present invention is a method for performing a singular value decomposition on an arbitrary matrix A using a computer, the method including the steps of: performing an upper bidiagonalization on the matrix A so as to obtain an upper bidiagonal matrix B of the matrix A; obtaining at least one singular value σ of the matrix B as singular values of the matrix A; and obtaining a singular vector of the matrix A for the σ. The step of obtaining a singular vector of the matrix A includes a step of performing a Twisted decomposition on a matrix BTB−σ2I (where I is a unit matrix) by using a Miura inverse transformation, an sdLVvs transformation, an rdLVvs transformation and a Miura transformation so as to diagonalize a matrix BTB.

Owner:JAPAN SCI & TECH CORP

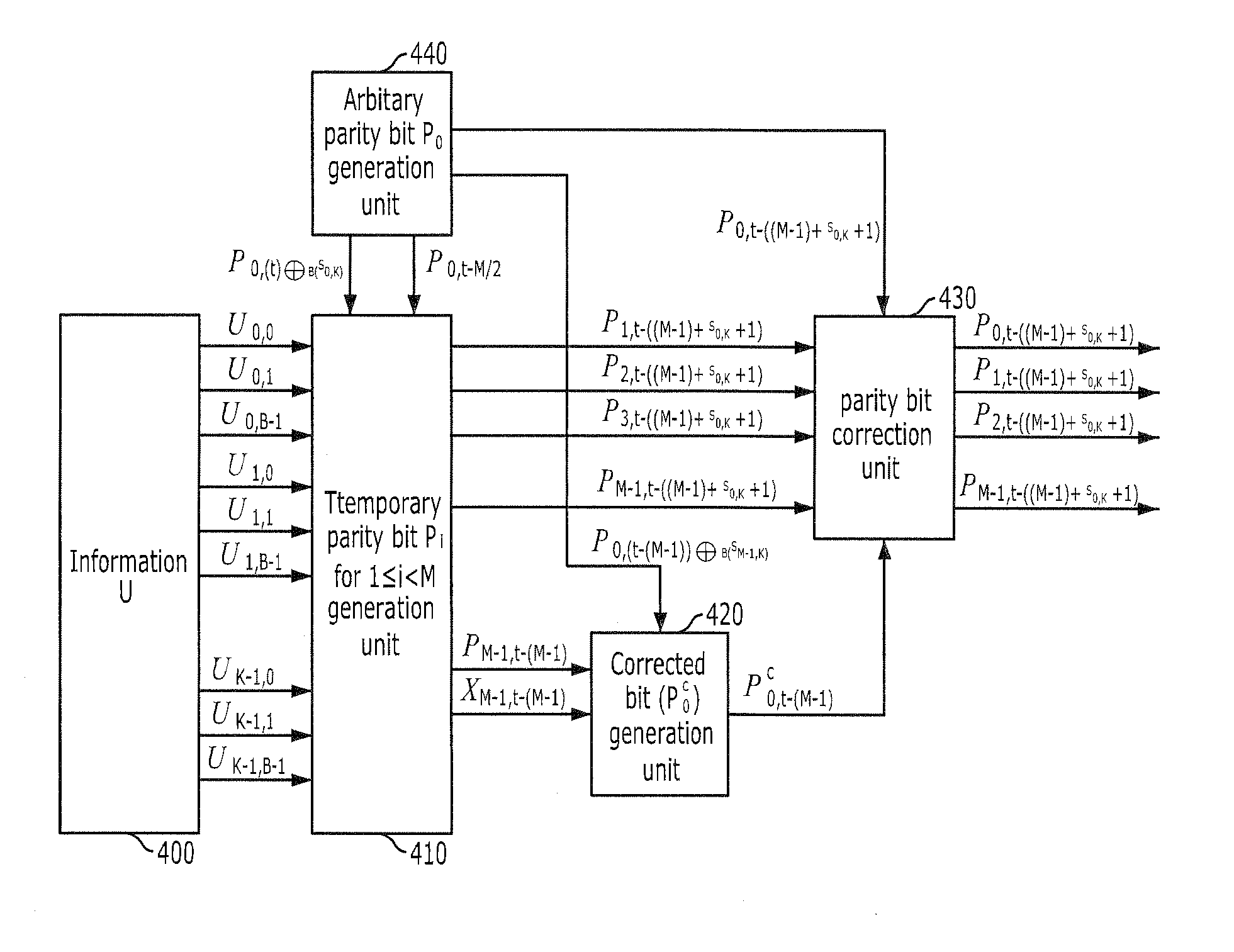

Apparatus and method for coding qc-ldpc code

InactiveUS20100162074A1Reduce complexityReduce waiting timeError preventionError correction/detection using multiple parity bitsDiagonal matrixTheoretical computer science

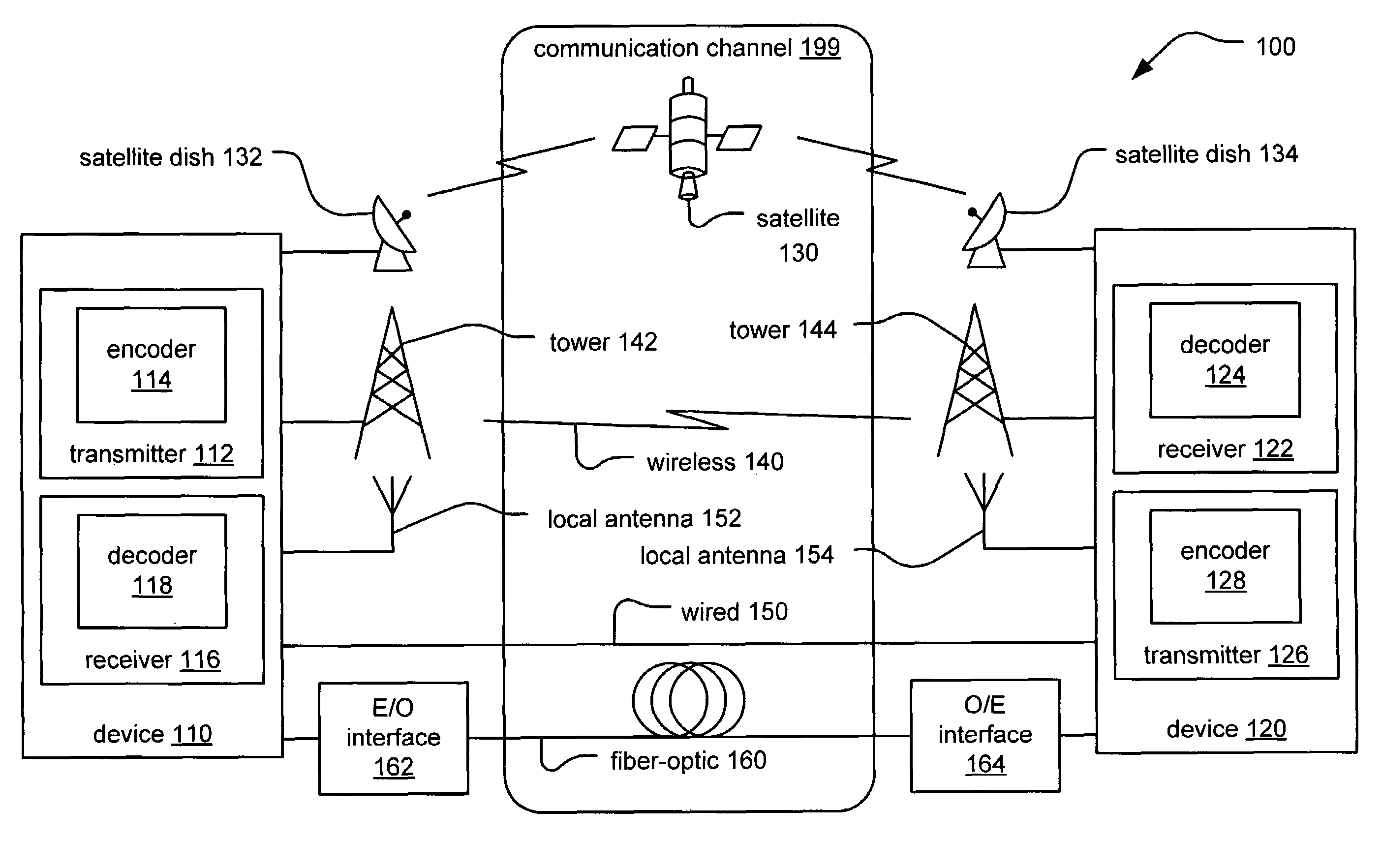

A high-speed quasi-cyclic low density parity check (QC-LDPC) coding apparatus for coding inputted information into a generator matrix having a dual diagonal matrix format includes: a parity bit generation unit configured to generate an arbitrary parity bit; a temporary parity bit generation unit configured to constitute the inputted information with circulants, and shift and combine the respective circulants at each row to generate a temporary parity bit; a corrected bit generation unit configured to generate corrected bits of parity bits by using an output of the temporary parity bit generation unit; and a parity bit correction unit configured to correct the temporary parity bit by reflecting an output of the corrected bit generation unit to the output of the temporary parity bit generation unit.

Owner:ELECTRONICS & TELECOMM RES INST

Clash-free irregular-repeat-accumulate code

ActiveUS20070011566A1Error detection/correctionError correction/detection using multiple parity bitsTheoretical computer scienceDiagonal matrix

Methods, apparatuses, and systems are presented for performing data encoding involving receiving a sequence of data bits, encoding the sequence of data bits in accordance with a parity check matrix (H-matrix) to generate a sequence of encoded bits, wherein the H-matrix is capable of being partitioned into a first matrix and a second matrix, the first matrix being a dual-diagonal matrix, the second matrix comprising one or more vertically stacked sub-matrices, each sub-matrix consisting of a plurality of columns, each column having a column weight of no more than 1, wherein the second matrix is capable of being expressed as a product of a parity check matrix, an interleaver permutation matrix, and a repeat block matrix, and the interleaver permutation matrix satisfies a clash-free interleaver constraint, and outputting the sequence of encoded bits.

Owner:TRELLIS WARE TECH

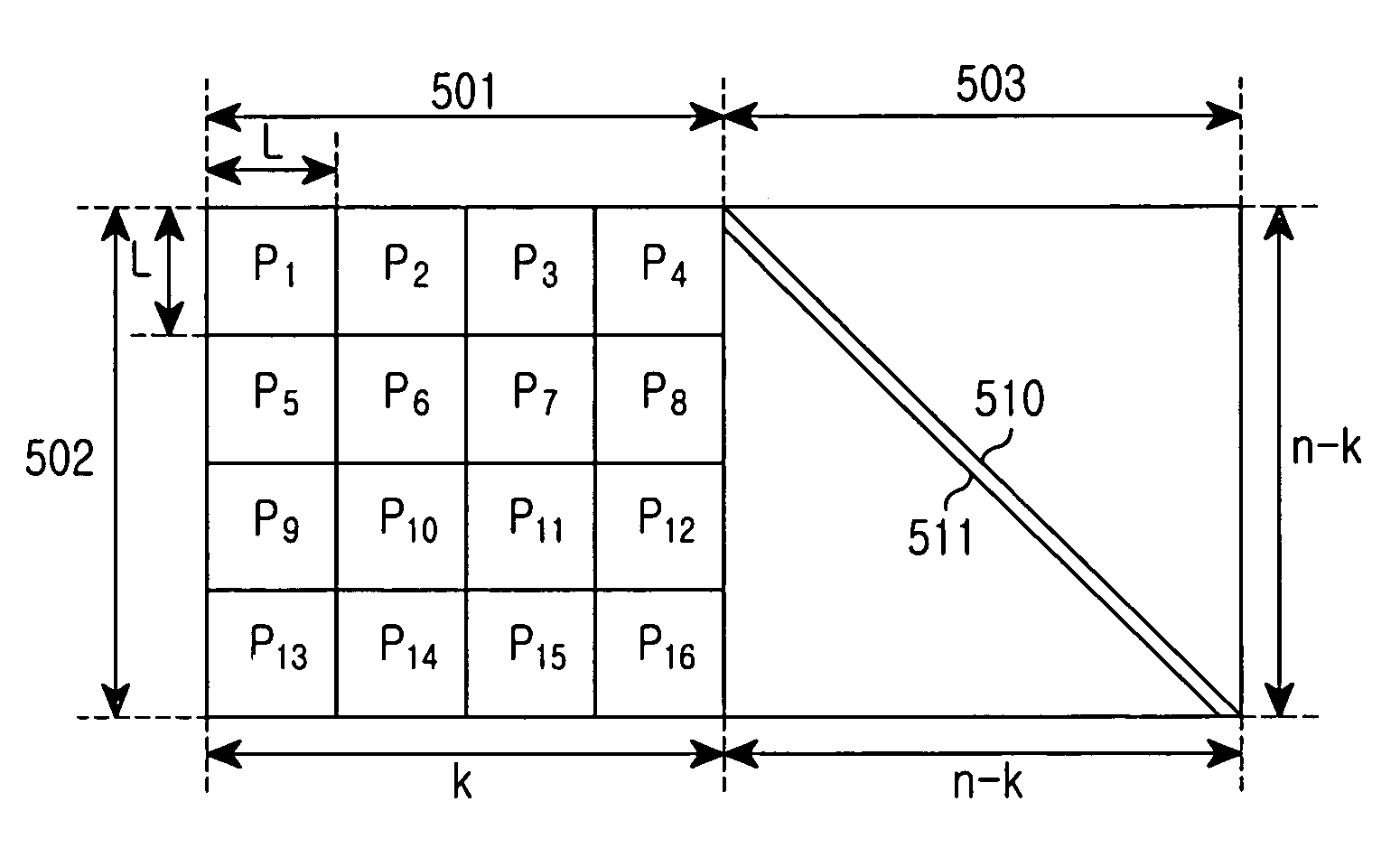

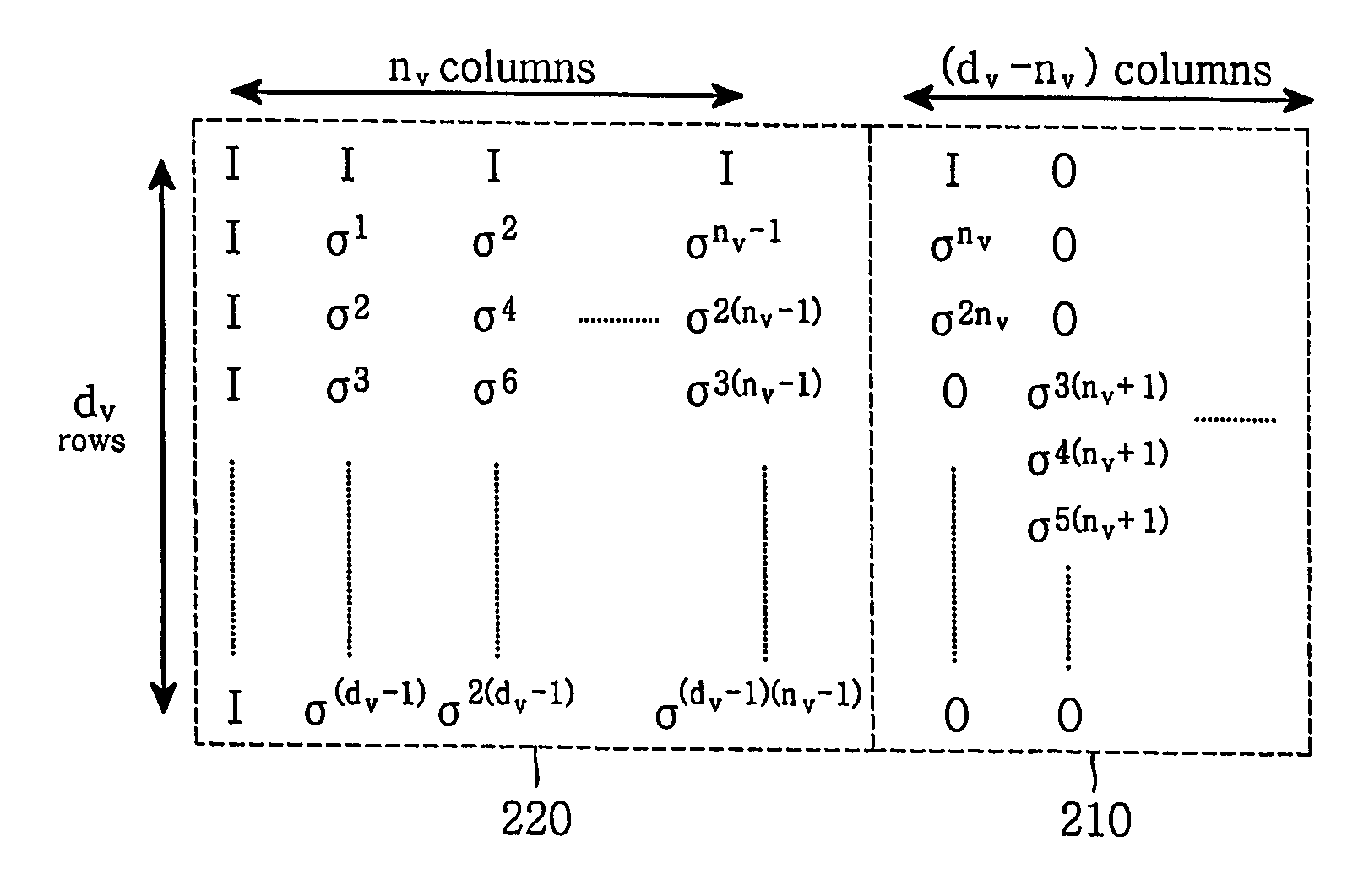

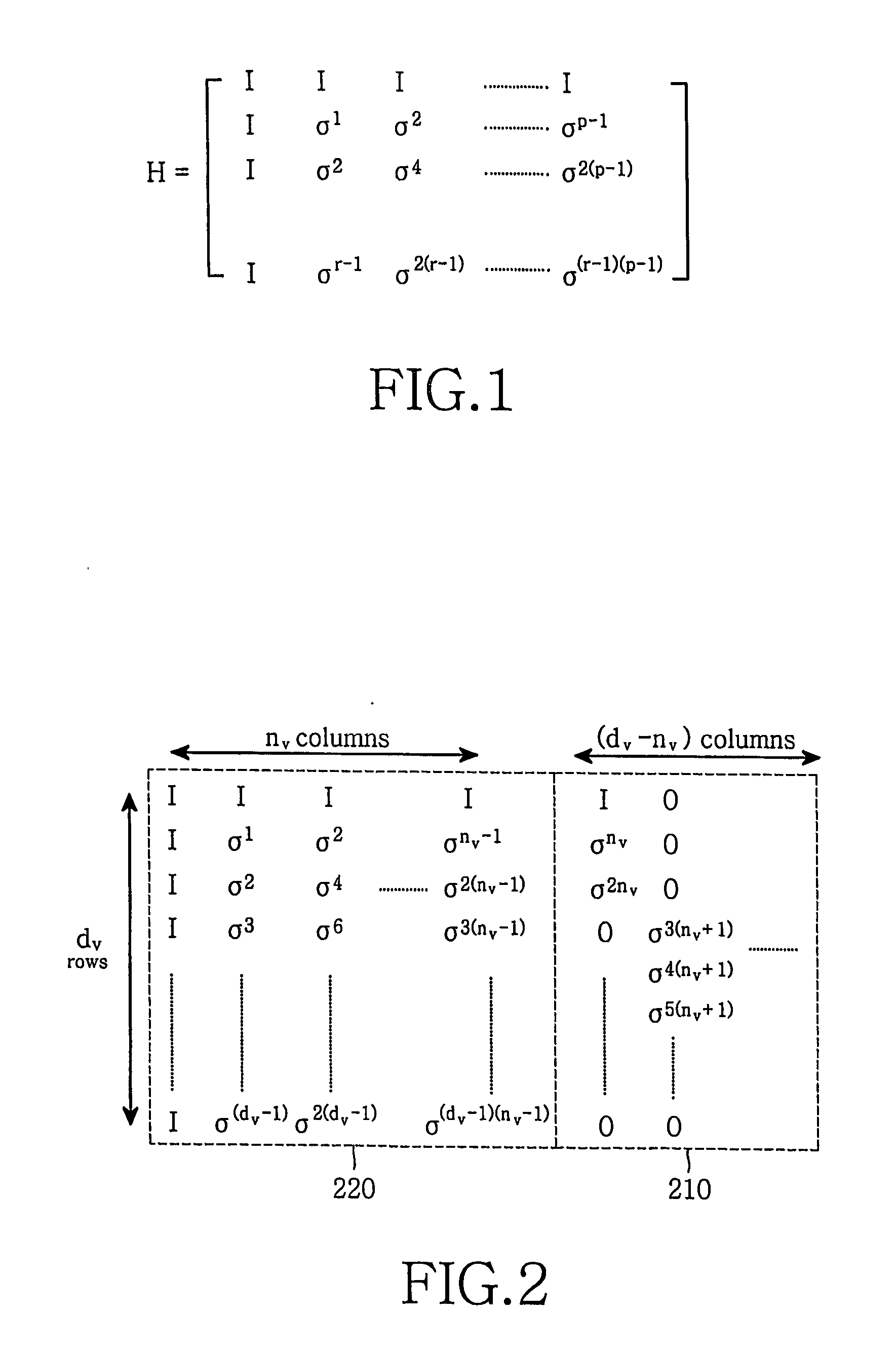

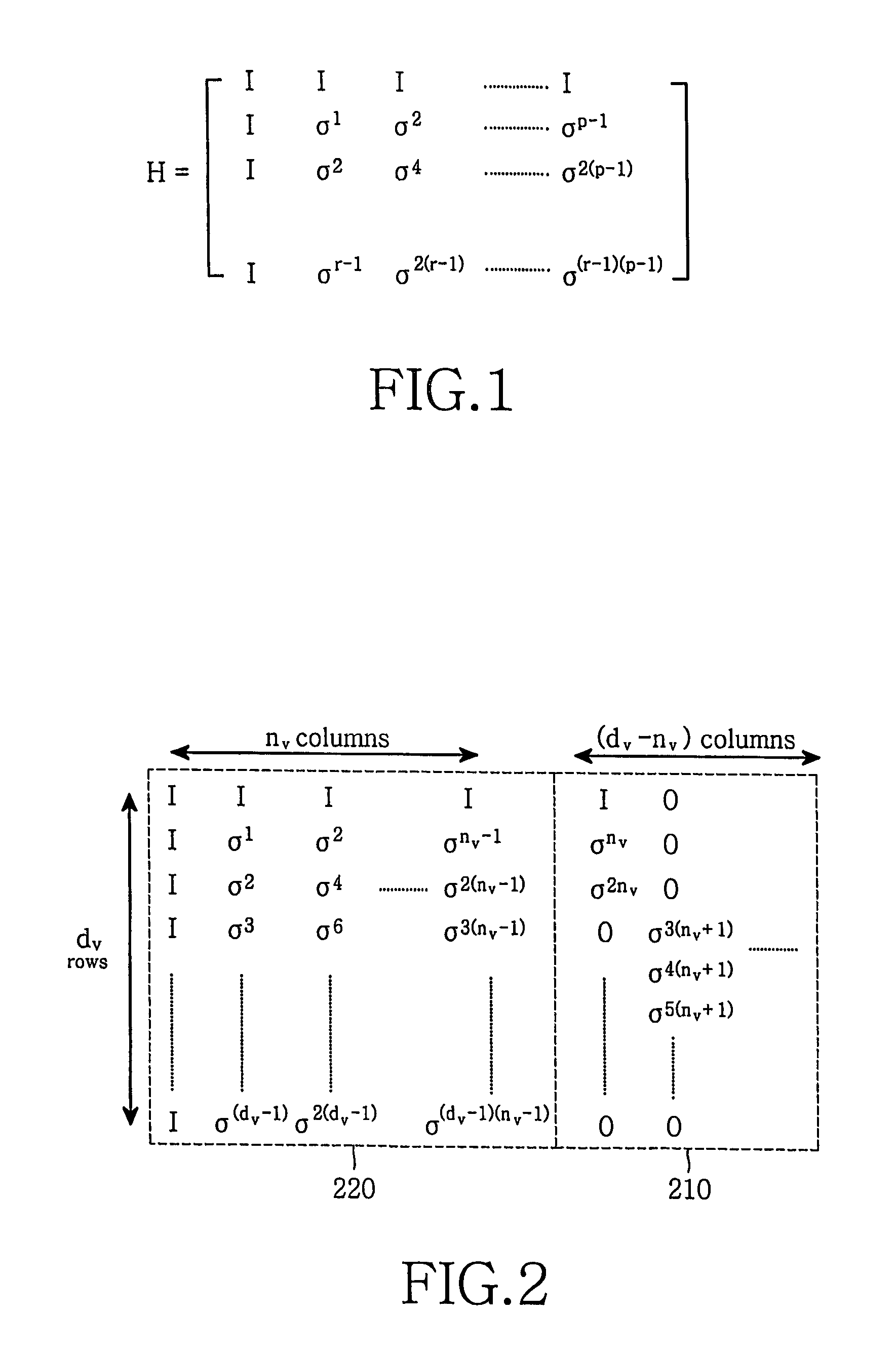

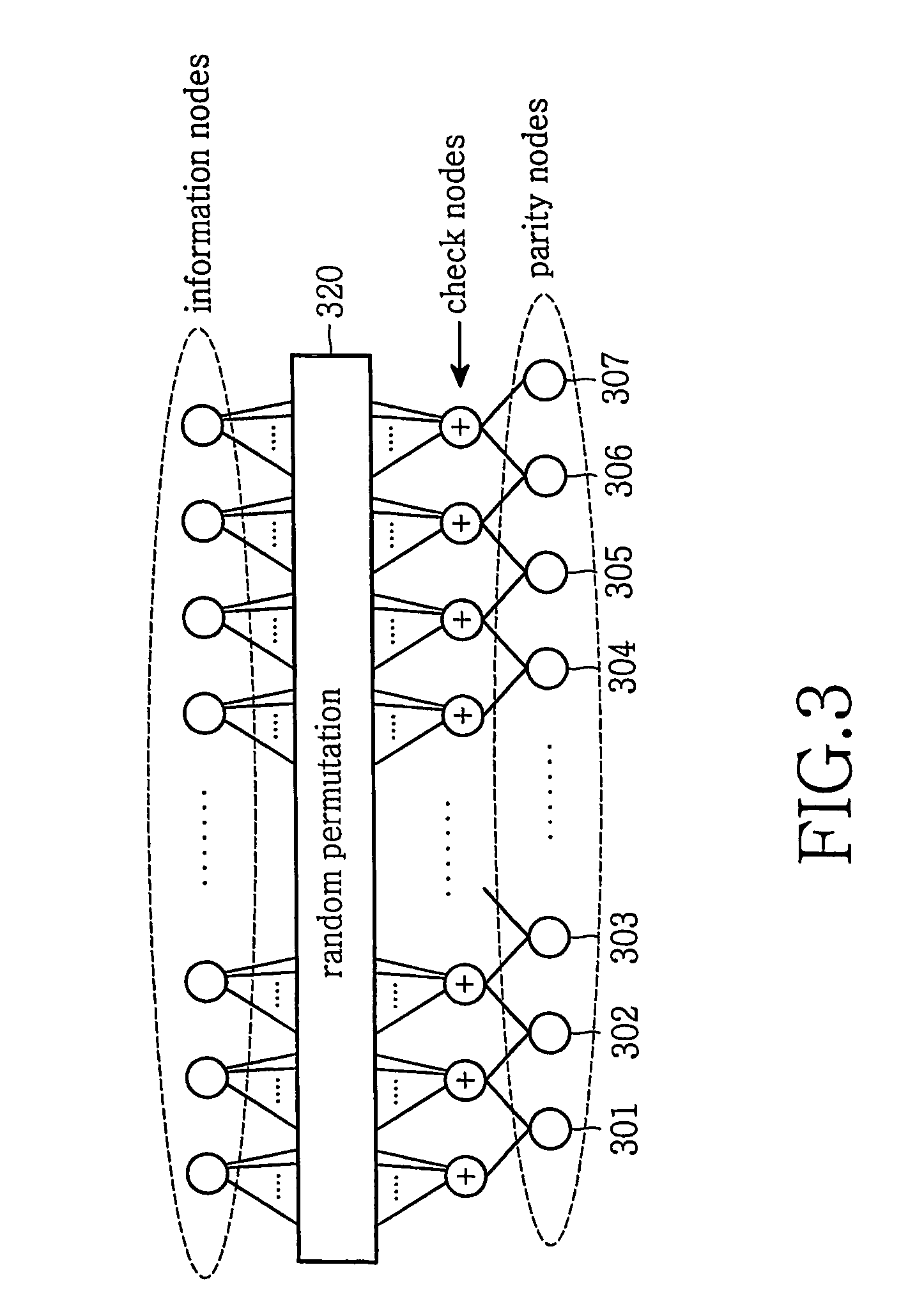

Algebraic construction of LDPC (Low Density Parity Check) codes with corresponding parity check matrix having CSI (Cyclic Shifted Identity) sub-matrices

ActiveUS7617439B2Data representation error detection/correctionError correction/detection using LDPC codesParity-check matrixTheoretical computer science

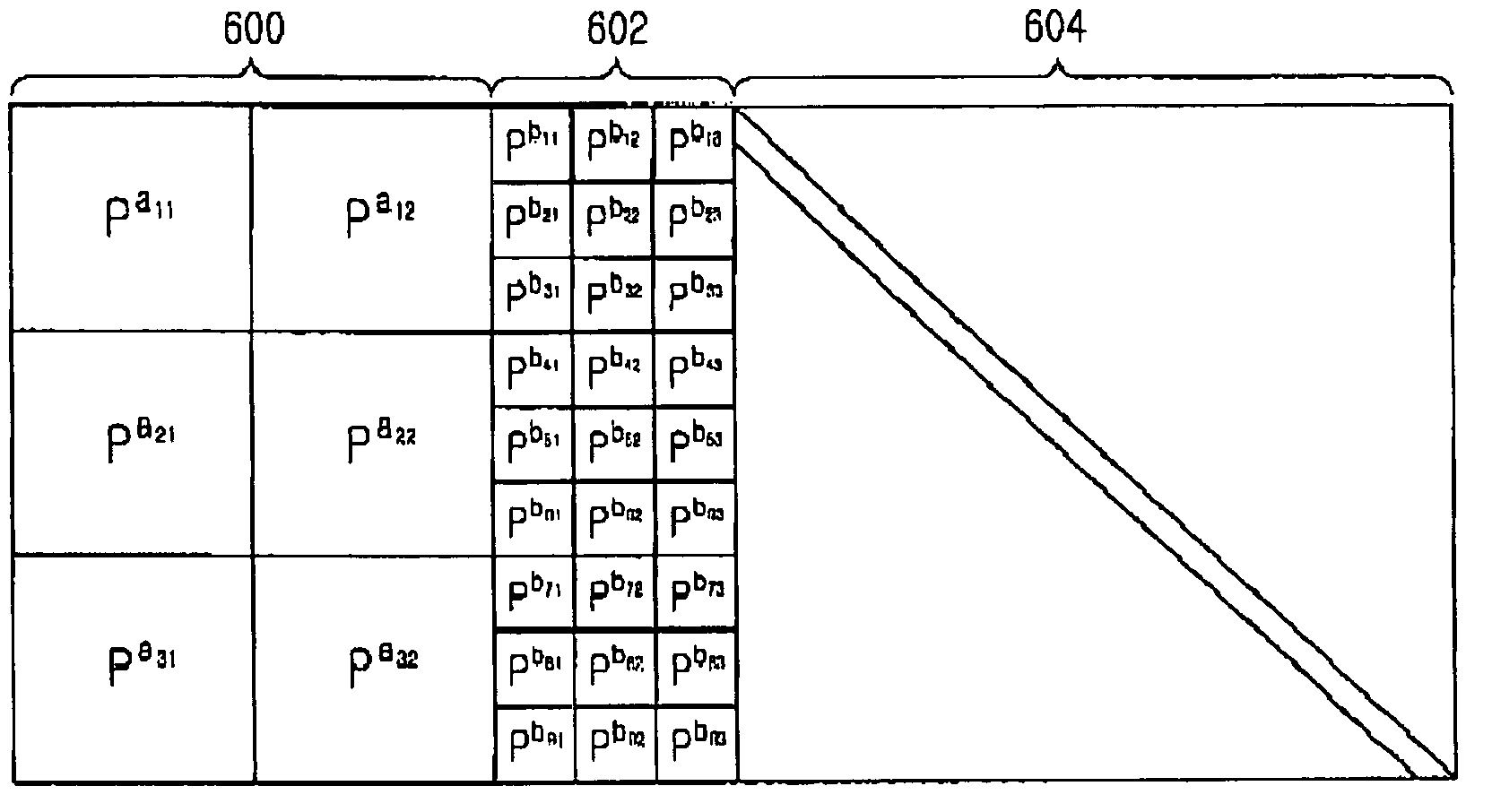

Algebraic method to construct LDPC (Low Density Parity Check) codes with parity check matrix having CSI (Cyclic Shifted Identity) sub-matrices. A novel approach is presented by which identity sub-matrices undergo cyclic shifting, thereby generating CSI sub-matrices that are arranged forming a parity check matrix of an LDPC code. The parity check matrix of the LDPC code may correspond to a regular LDPC code, or the parity check matrix of the LDPC code may undergo further modification to transform it to that of an irregular LDPC code. The parity check matrix of the LDPC code may be partitioned into 2 sub-matrices such that one of these 2 sub-matrices is transformed to be a block dual diagonal matrix; the other of these 2 sub-matrices may be modified using a variety of means, including the density evolution approach, to ensure the desired bit and check degrees of the irregular LDPC code.

Owner:AVAGO TECH INT SALES PTE LTD

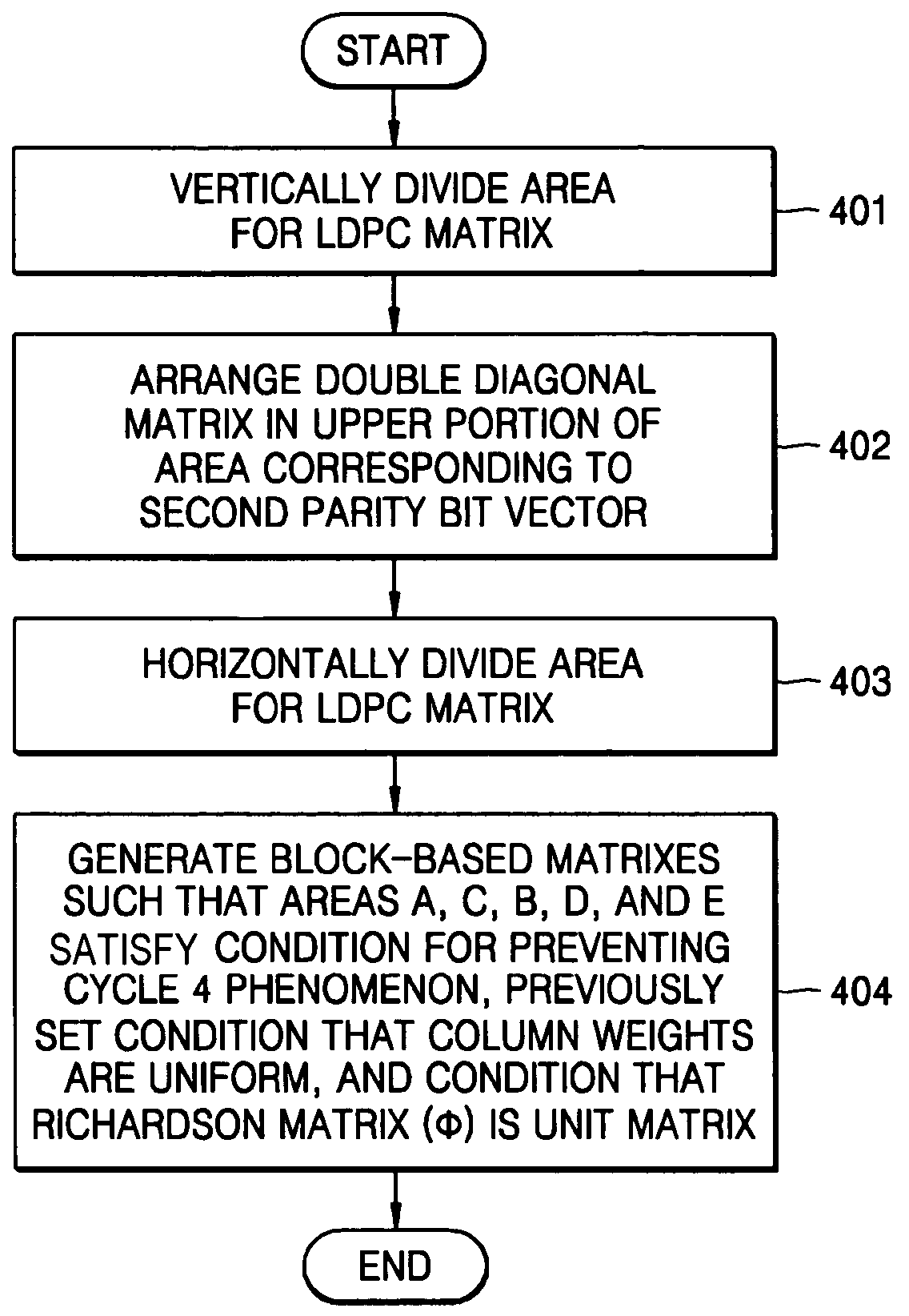

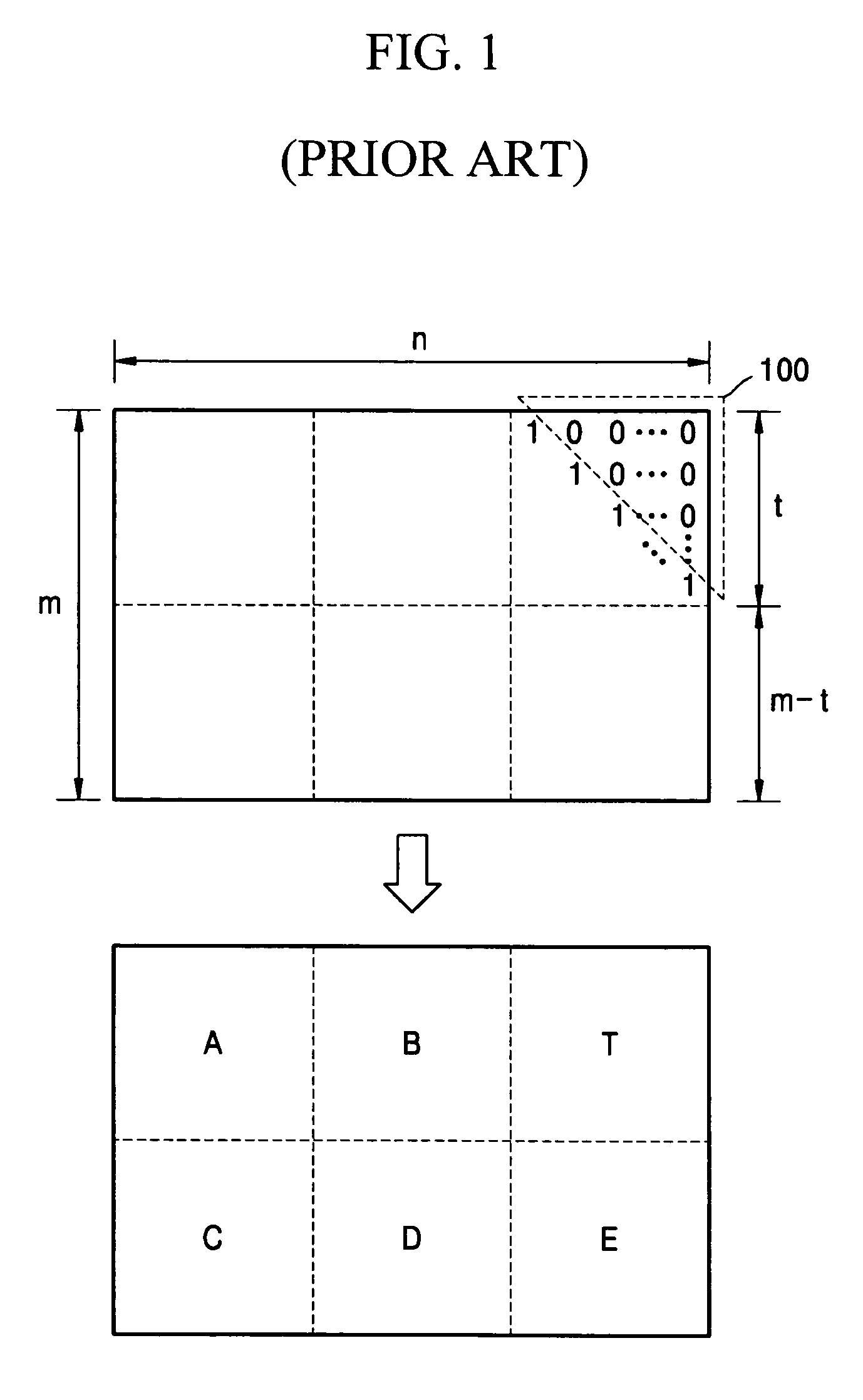

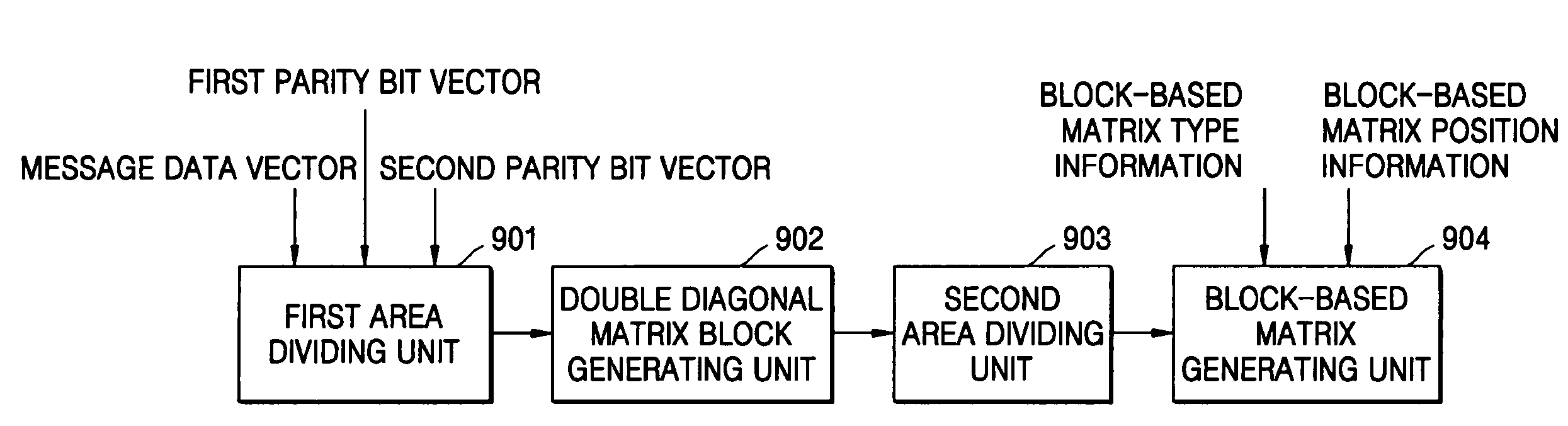

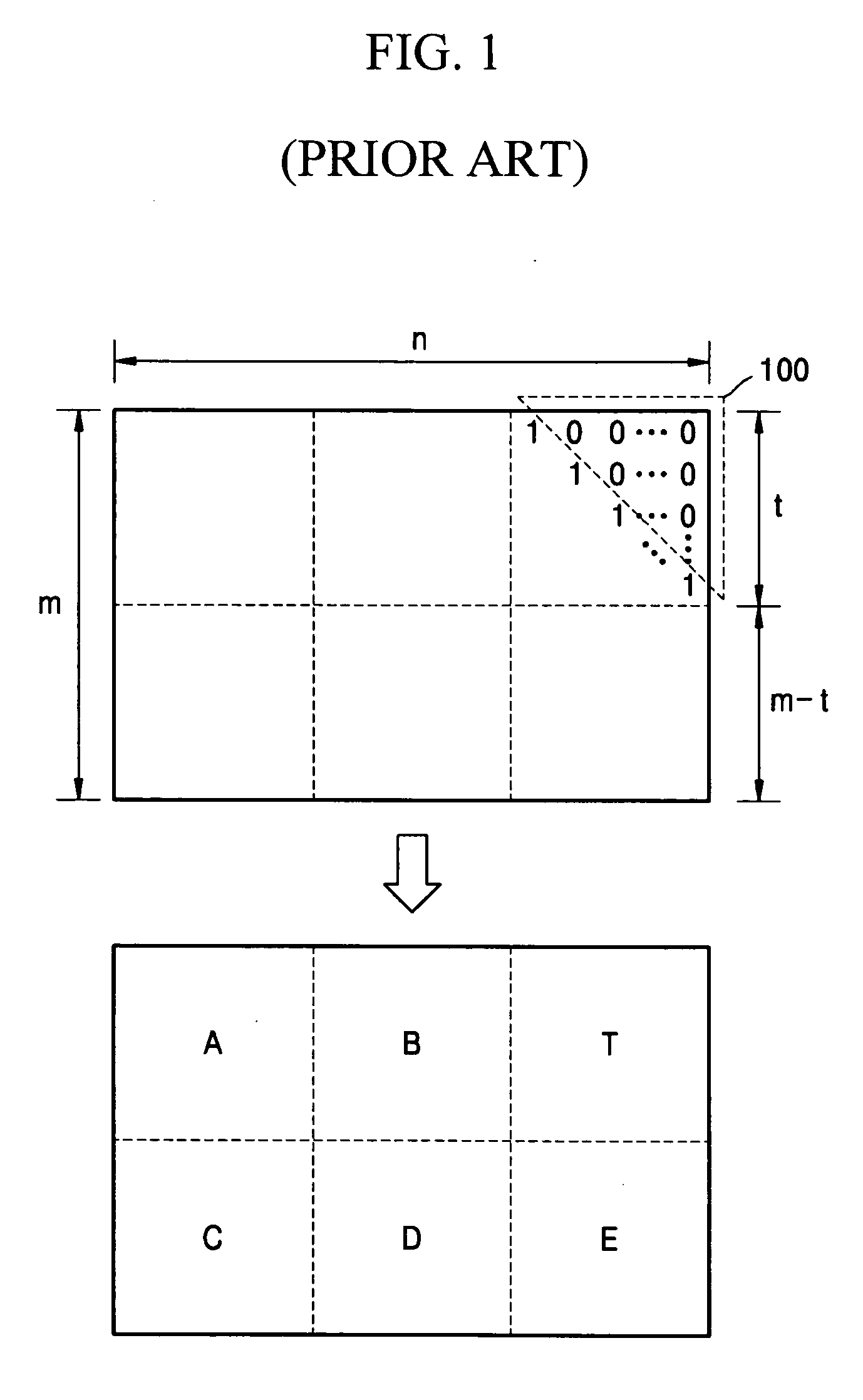

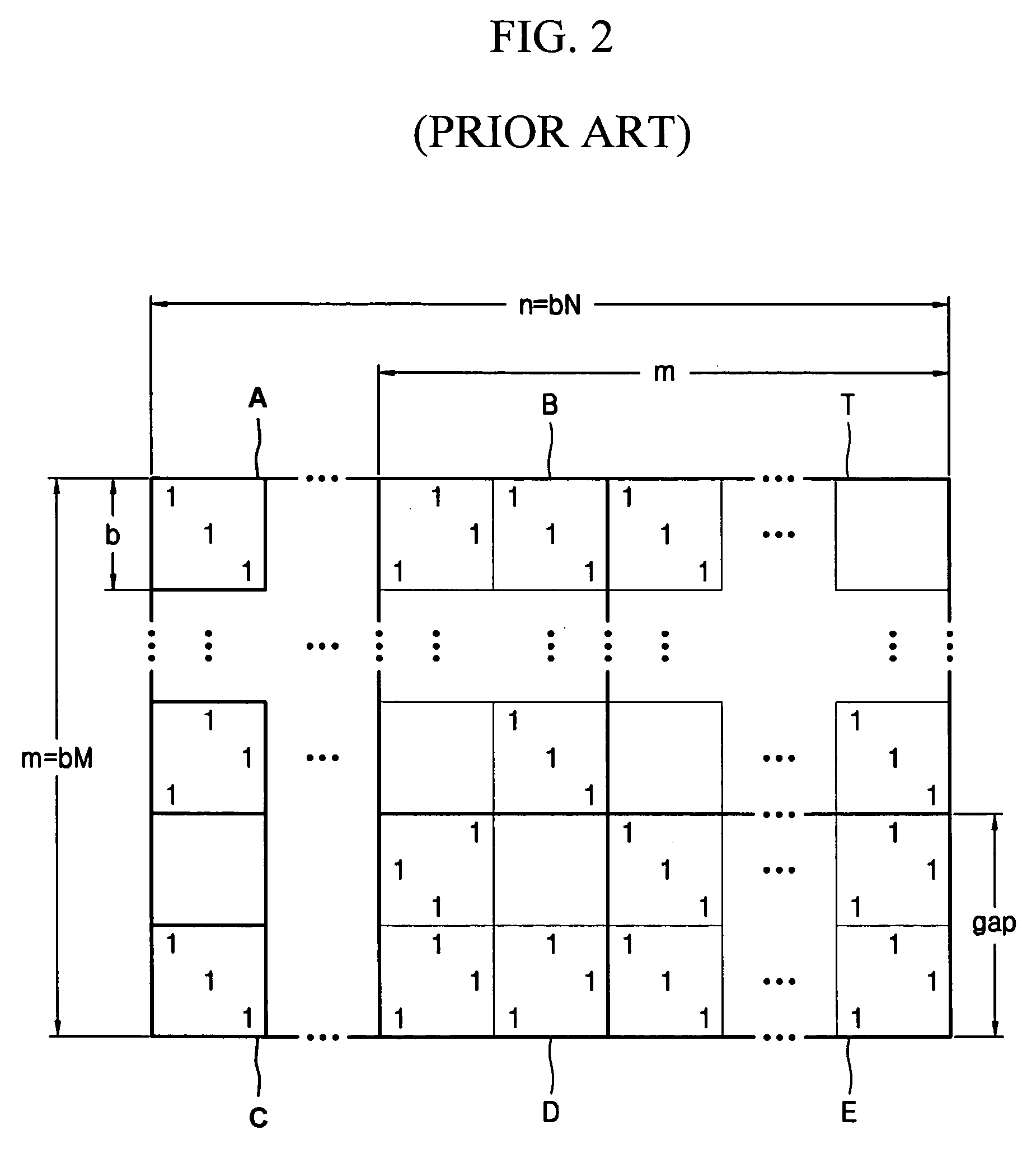

Method and apparatus for generating block-based low-density parity check matrix and recording medium having recorded thereon code for implementing the method

A method of and an apparatus for generating a block-based low density parity check (LDPC) matrix, where calculation of an inverse matrix is not necessary and back-substitution is possible over the entire matrix area, and a recording medium having recorded thereon code for implementing the method. An area of the LDPC matrix is vertically divided based on respective lengths of first and second parity bit vectors and, a block-based matrix is generated such that a double diagonal matrix is arranged in an upper portion of an area corresponding to the second parity bit vector among areas into which the LDPC matrix is vertically divided., The area of the LDPC matrix is horizontally divided based on a position of the double diagonal matrix, and block-based matrices are generated in the divided areas of the LDPC matrix, to satisfy a condition that column weights (Wc) are uniform.

Owner:SAMSUNG ELECTRONICS CO LTD

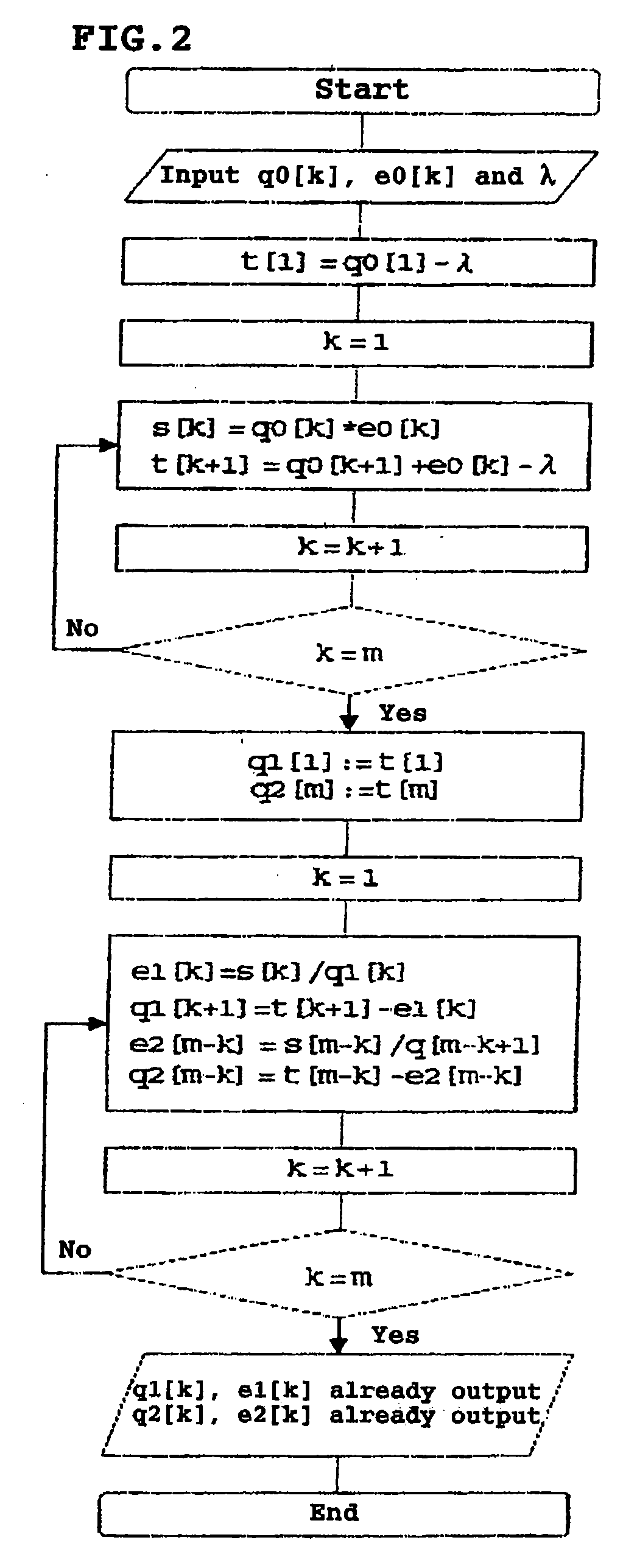

Apparatus and method for coding and decoding irregular repeat accumulate codes

ActiveUS7302629B2Minimize complexityError prevention/detection by using return channelOther decoding techniquesTheoretical computer scienceDiagonal matrix

An apparatus and method for coding an irregular Repeat Accumulate (RA) code. A repeater repeats a received information word such that the information word corresponds to weights of a first information part and a second information part of a parity check matrix in which permutation matrixes are arranged in the first information part and the second information part corresponding to the information word such that a minimum length of a cycle on a factor graph of the irregular RA code becomes a predetermined length and weights are irregular, and a dual diagonal matrix is arranged in a parity part corresponding to a parity. An interleaver interleaves a signal output from the repeater using an interleaving scheme predefined for the parity check matrix. An accumulator generates the irregular RA code by accumulating a signal output from the interleaver according to a weight of the parity part.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for puncturing low density parity check code

InactiveUS7743312B2Avoid performanceError correction/detection using multiple parity bitsCode conversionTheoretical computer scienceDiagonal matrix

A method is provided for puncturing a low density parity check (LDPC) code decoded by a parity check matrix that is expressed by a factor graph including a check node and a bit node, being connected to each other at an edge, and includes a parity part having a dual diagonal matrix with a single 3-weight column and the remaining columns being 2-weight columns. The method includes generating a puncturing pattern such that bits of the LDPC code are punctured in an order of a bit mapped to a column with a higher weight from among the columns constituting the parity part; and puncturing the LDPC code according to the generated puncturing pattern.

Owner:K2M +1

Clash-free irregular-repeat-accumulate code

ActiveUS7584400B2Error detection/correctionError correction/detection using multiple parity bitsAlgorithmParity-check matrix

Methods, apparatuses, and systems are presented for performing data encoding involving receiving a sequence of data bits, encoding the sequence of data bits in accordance with a parity check matrix (H-matrix) to generate a sequence of encoded bits, wherein the H-matrix is capable of being partitioned into a first matrix and a second matrix, the first matrix being a dual-diagonal matrix, the second matrix comprising one or more vertically stacked sub-matrices, each sub-matrix consisting of a plurality of columns, each column having a column weight of no more than 1, wherein the second matrix is capable of being expressed as a product of a parity check matrix, an interleaver permutation matrix, and a repeat block matrix, and the interleaver permutation matrix satisfies a clash-free interleaver constraint, and outputting the sequence of encoded bits.

Owner:TRELLIS WARE TECH

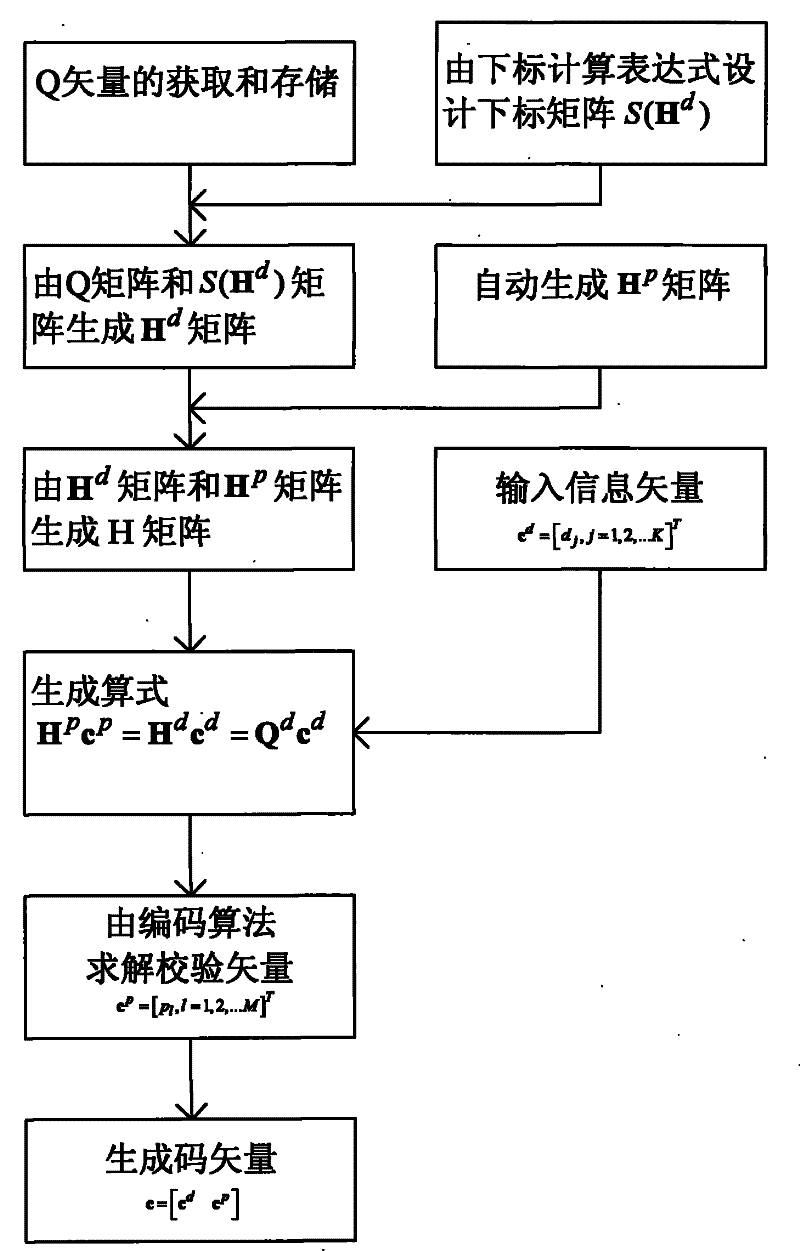

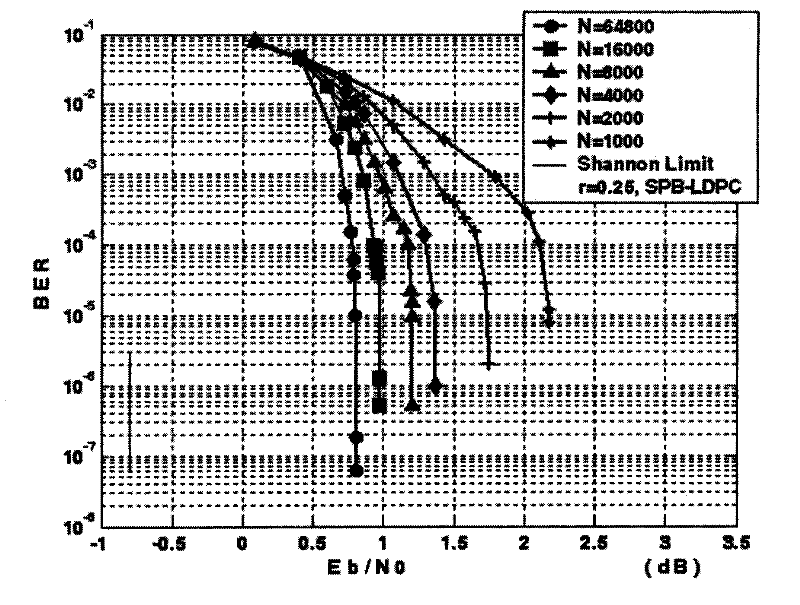

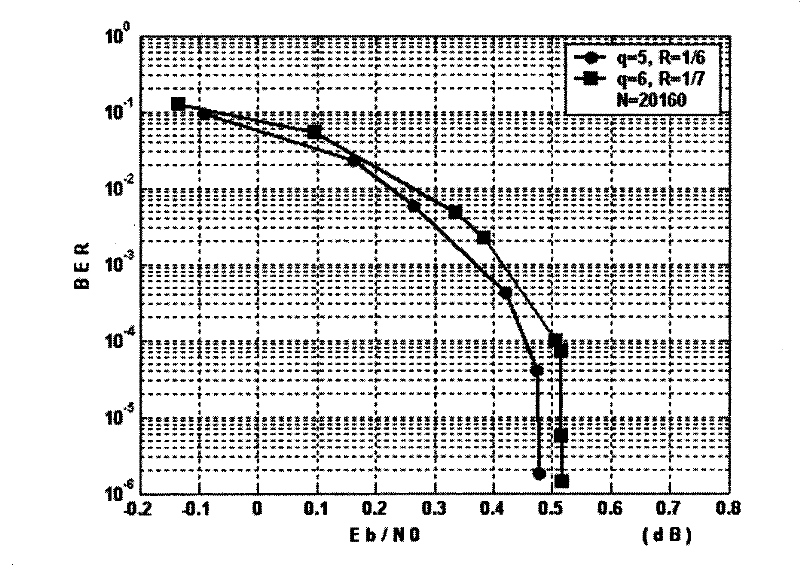

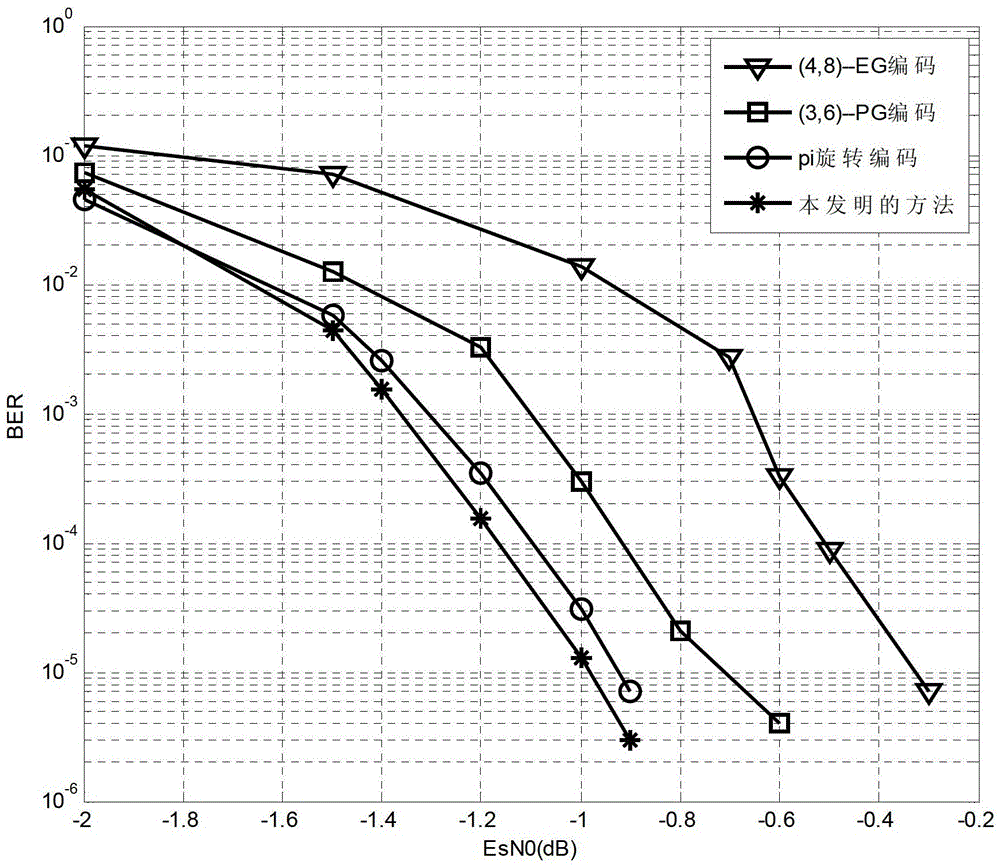

Encoding method for low code rate LDPC code

InactiveCN101488760AReduce in quantityImprove performanceError correction/detection using multiple parity bitsComputation complexitySignal-to-quantization-noise ratio

The invention discloses an encoding method of low bit-rate LDPC (Low Density Parity Check) code, including the following steps: step 1, matrixes H and H are respectively constructed, the H matrix is a diagonal matrix, H is an array matrix with q multiplied by 1 and consists of q end-around-shift permutation matrixes Q; the permutation matrix Q consists of b multiplied by b step permutation matrixes Q having row weight and line weight of 1, at most one element of 1 on each diagonal line and the rest elements of 0; step 2, an H matrix with the size of equal to bq multiplied b(q+1) is constructed; step 3, check vector c is constructed, c is equal to (p1, 1=1, 2, ..., M), p1 represents the value of any first check bit, and M is the length of check bit; step 4, according to the check vector c=(p1), the inputted information vector c is equal to (dj), and coded code word c=(cc) is obtained. In the method of the invention, an algebraic method used by end-around-shift value of Q permutation matrix leads belief propagation iterative decoding algorithm to be more easily realized in parallel; bidiagonal matrix structural characteristic of H matrix can encode low rate LDPC code in a recursion manner, and has linear time computing complexity. The simulation performance is superior to the performance of the existing low rate error correcting code, thereby being capable of reaching a signal noise ratio of 0.4 dB and having ratio compatibility.

Owner:HUAZHONG UNIV OF SCI & TECH

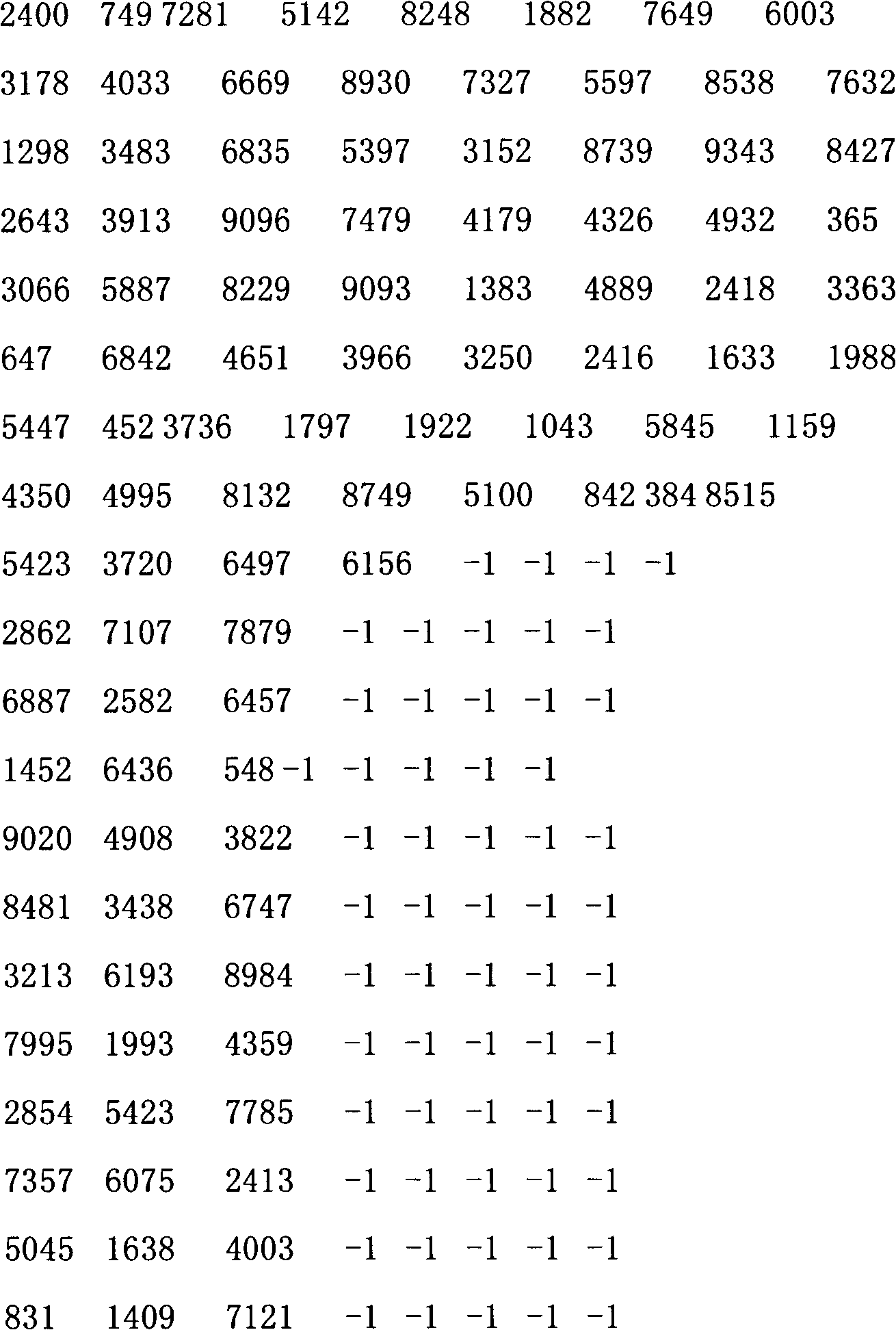

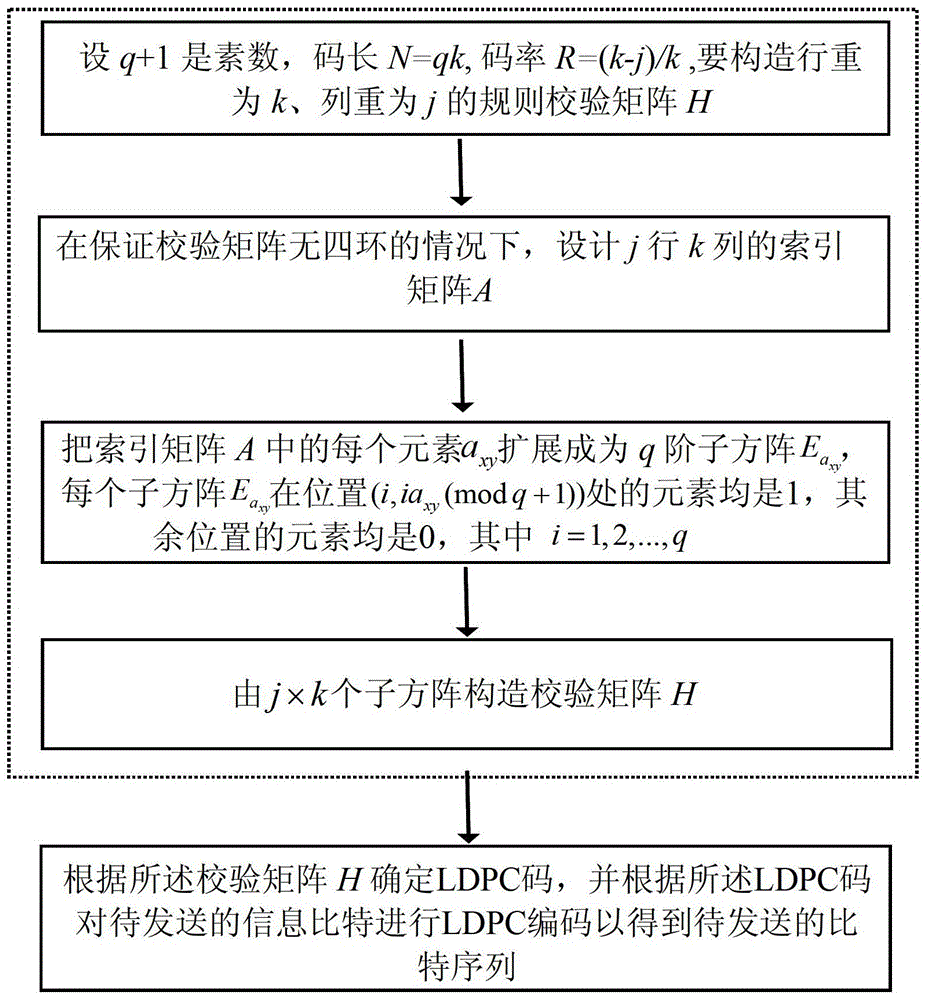

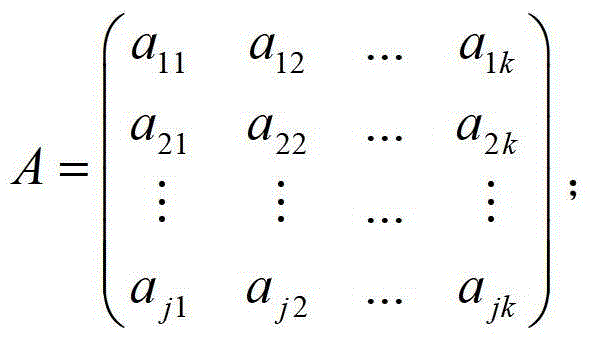

Method for generating LDPC (Low Density Parity Check) code check matrix, and LDPC code coding method

ActiveCN103236860ASave storage spaceGuaranteed performanceError correction/detection using multiple parity bitsDiagonal matrixTheoretical computer science

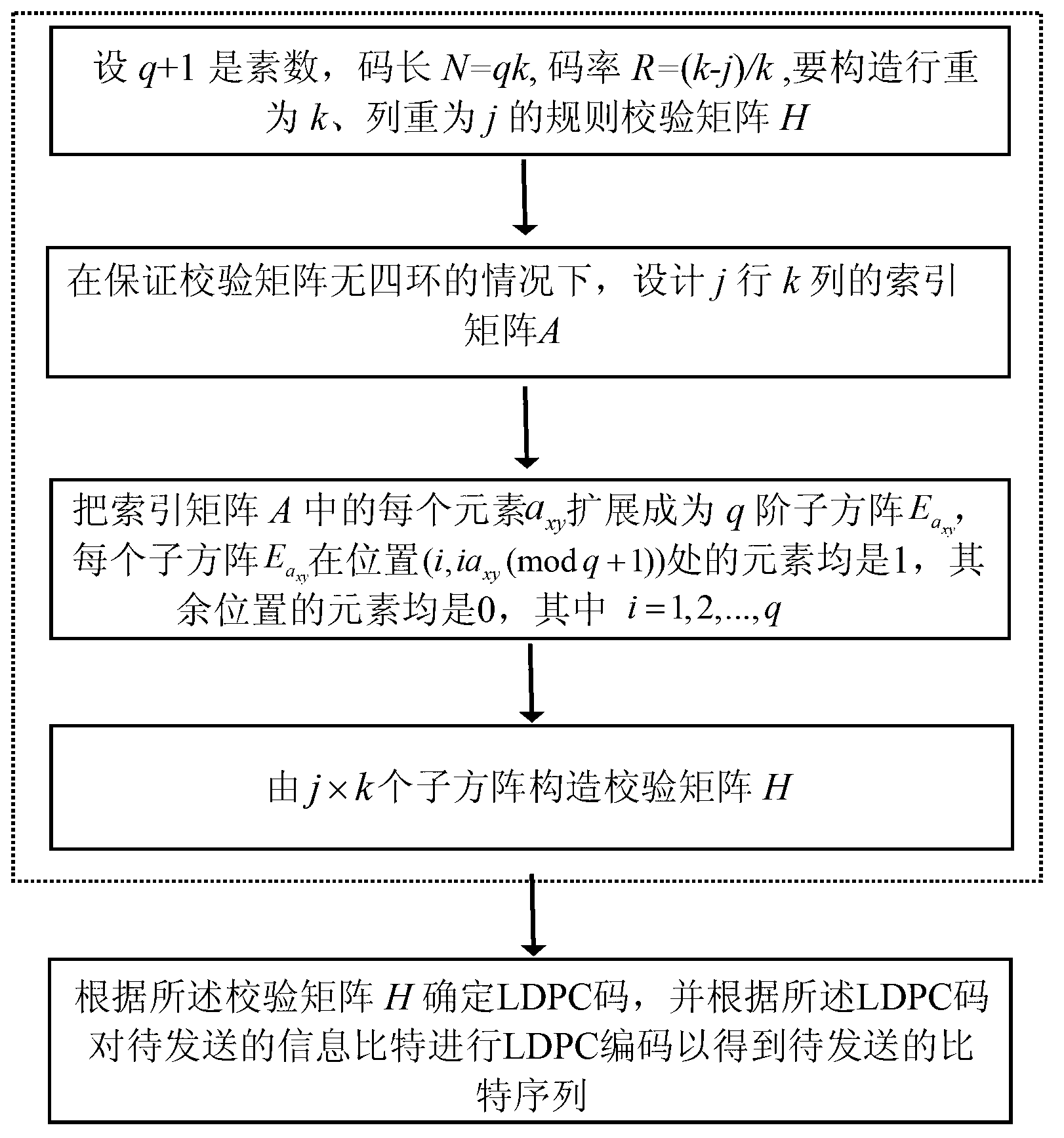

The invention discloses a method for generating an LDPC (Low Density Parity Check) code check matrix and an LDPC code coding method based on the LDPC code check matrix. The method for generating the LDPC code check matrix comprises the following steps of firstly establishing an index matrix, then establishing a check matrix by the indexing matrix, and specifically, generating the check matrix after expanding each number axy in the index matrix A into a q order (0, 1) matrix; and enabling elements in the positions (i, iaxy (modq+1)) to be 1, enabling elements in other positions to be 0, wherein i = 1, 2, 3 ellipsis q. In addition, the check matrix being a combination of a matrix which is generated by adopting the method and a double-diagonal matrix is provided. The invention also provides the LDPC code coding method by adopting the check matrix generated by any optional method. The method for generating the LDPC code check matrix and the LDPC code coding method have the advantages of easiness in design, low coding complexity, small storage space and excellent performance.

Owner:GUANGZHOU HAIGE COMM GRP INC

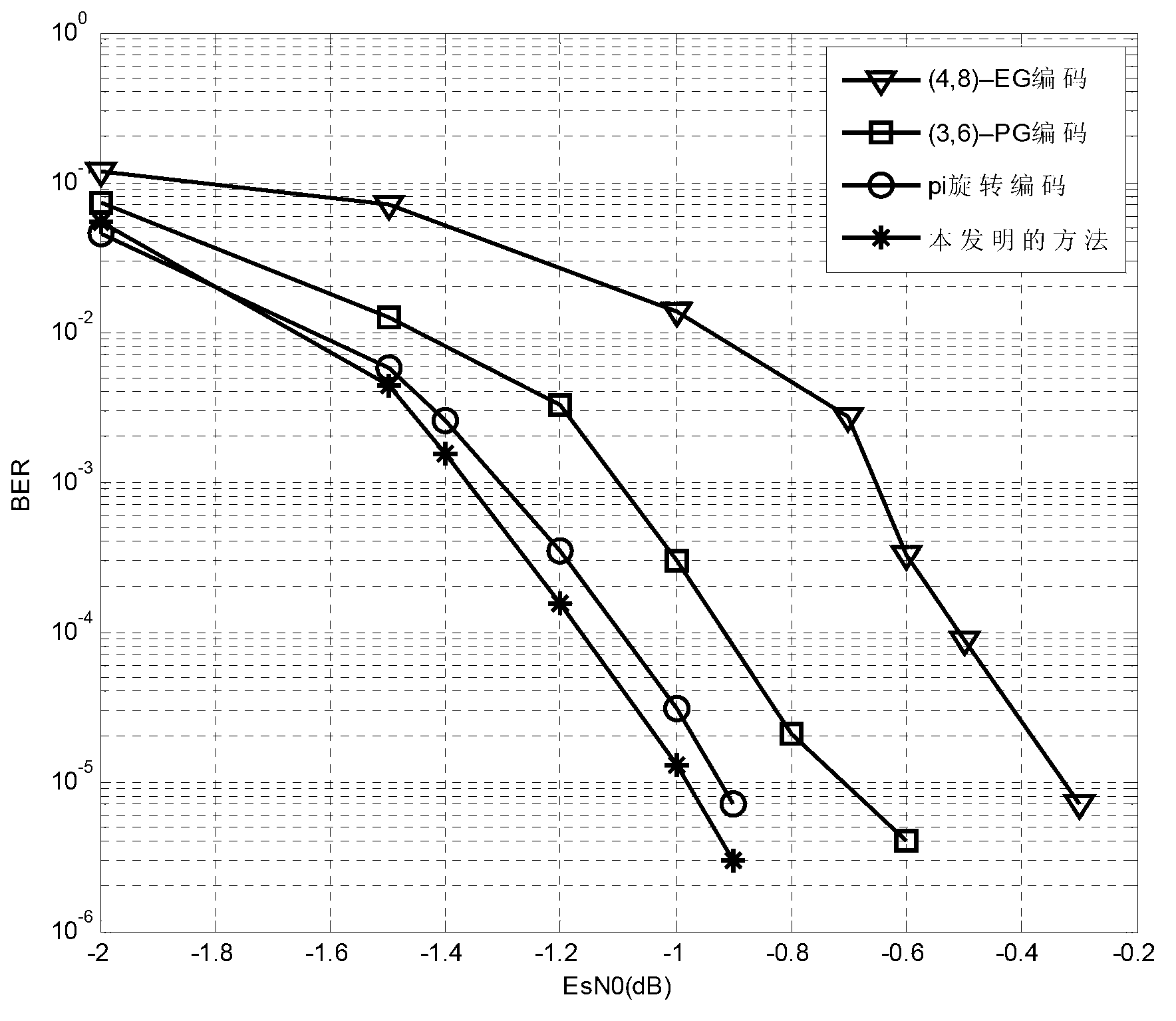

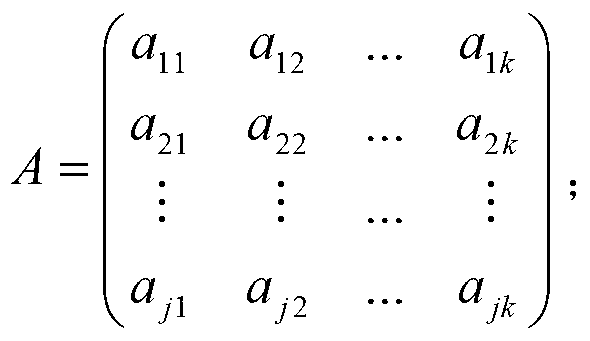

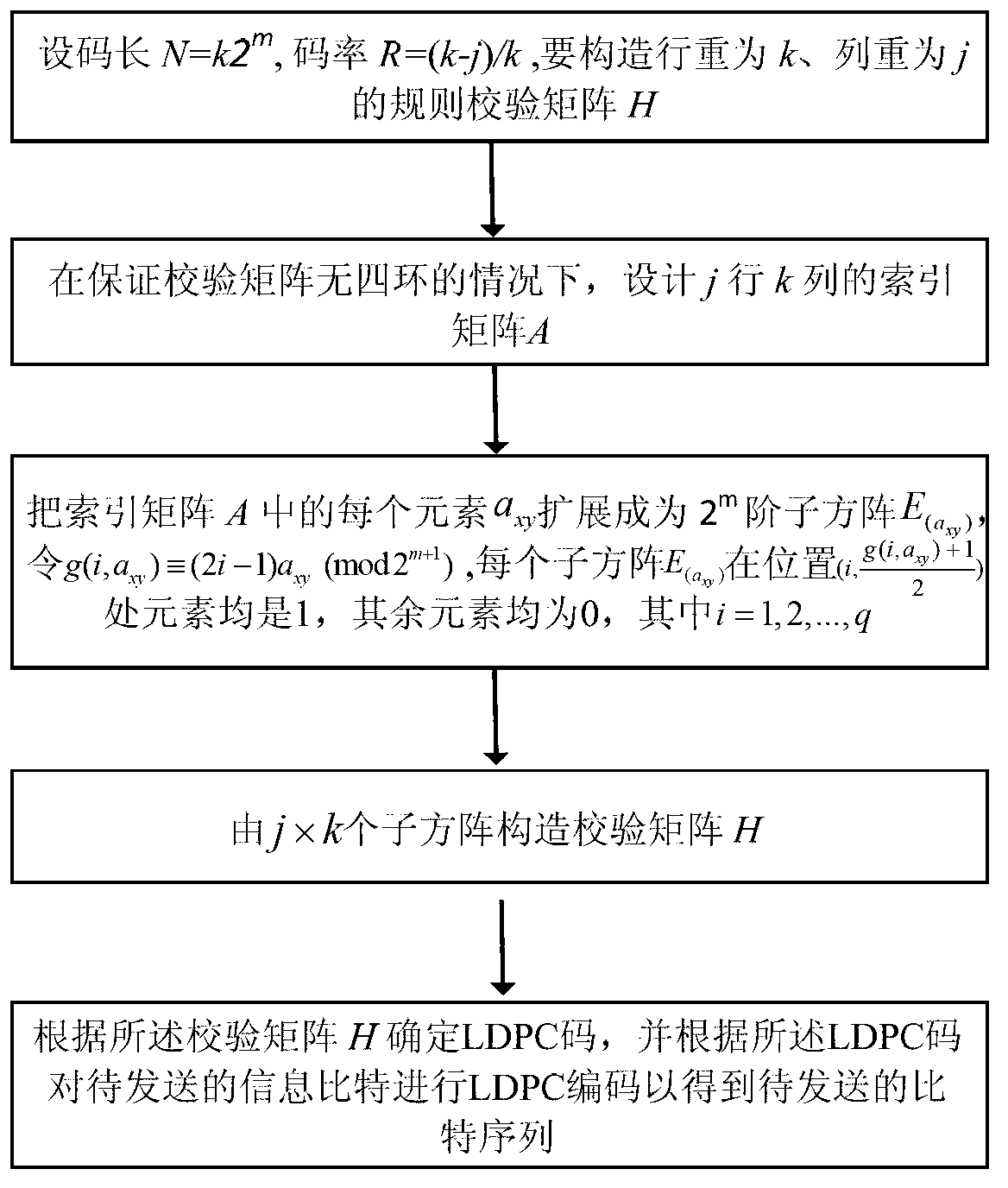

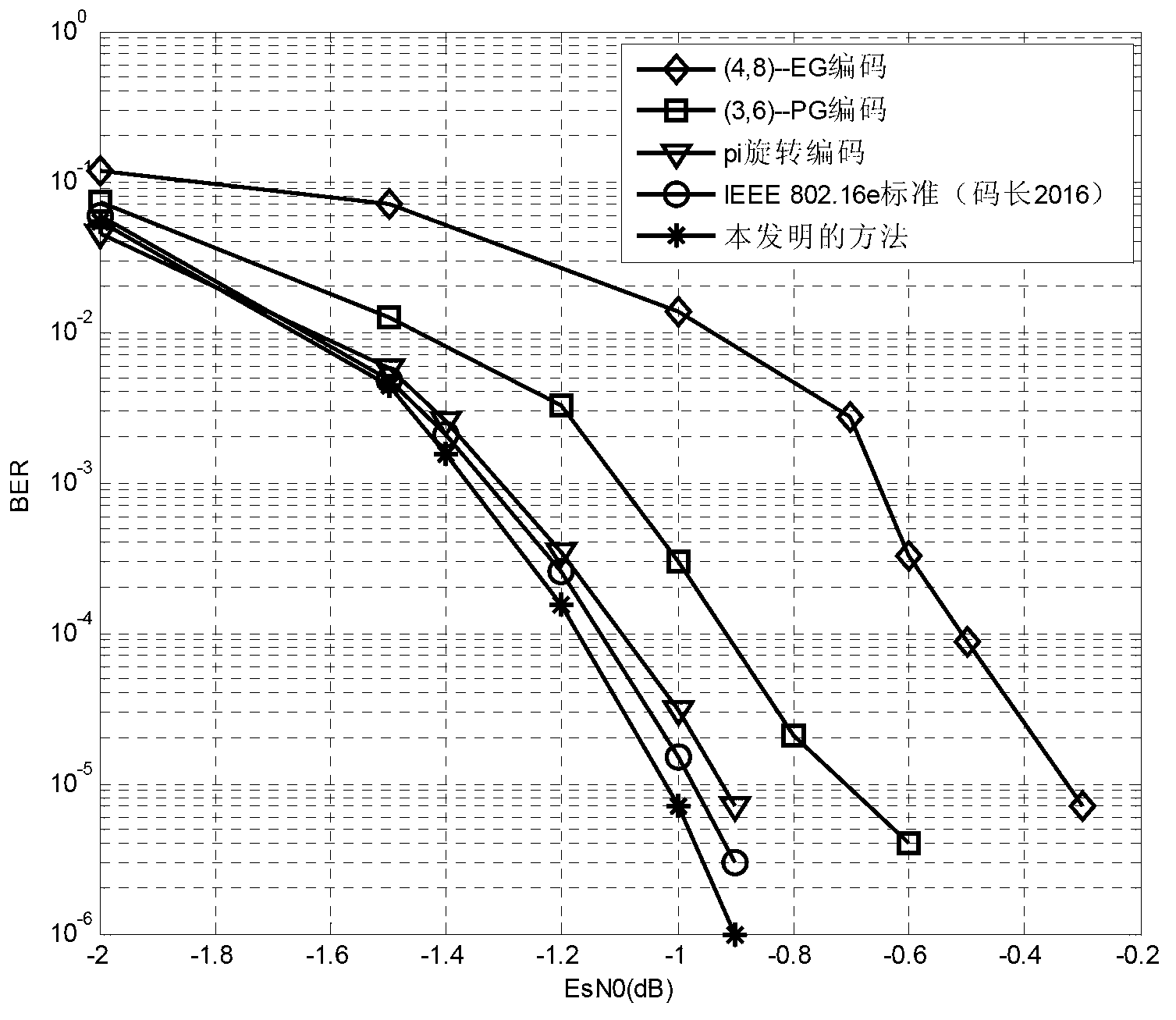

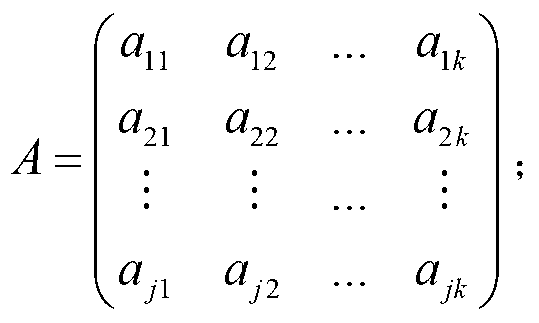

Method for generating LDPC (Low Density Parity Check) code check matrix and LDPC code coding method

ActiveCN103220005ASimple designReduce orderError correction/detection using multiple parity bitsRound complexityDiagonal matrix

The invention discloses a method for generating an LDPC (Low Density Parity Check) code check matrix and an LDPC code coding method based on the check matrix. The method for generating the LDPC code check matrix comprises the steps of firstly constructing an index matrix and then constructing the check matrix by using the index matrix and specifically comprises the steps of: extending each element axy in the index matrix into a 2<m>-order (0,1) square matrix, namely a formula shown in a drawing, and then forming the check matrix; and constructing an equation shown in a drawing, wherein the element of each square matrix in the position of a formula shown in a drawing is 1, the other elements are all 0, and i is equal to 1, 2, 3 or 2<m>. Furthermore, a combination of the check matrix generated by using the method and a dual-diagonal matrix is provided. The invention further provides the LDPC code coding method adopting the check matrix generated by adopting any of the methods. The methods have the advantages of easiness in design, low coding complexity, small storage space and excellent performance.

Owner:GUANGZHOU HAIGE COMM GRP INC

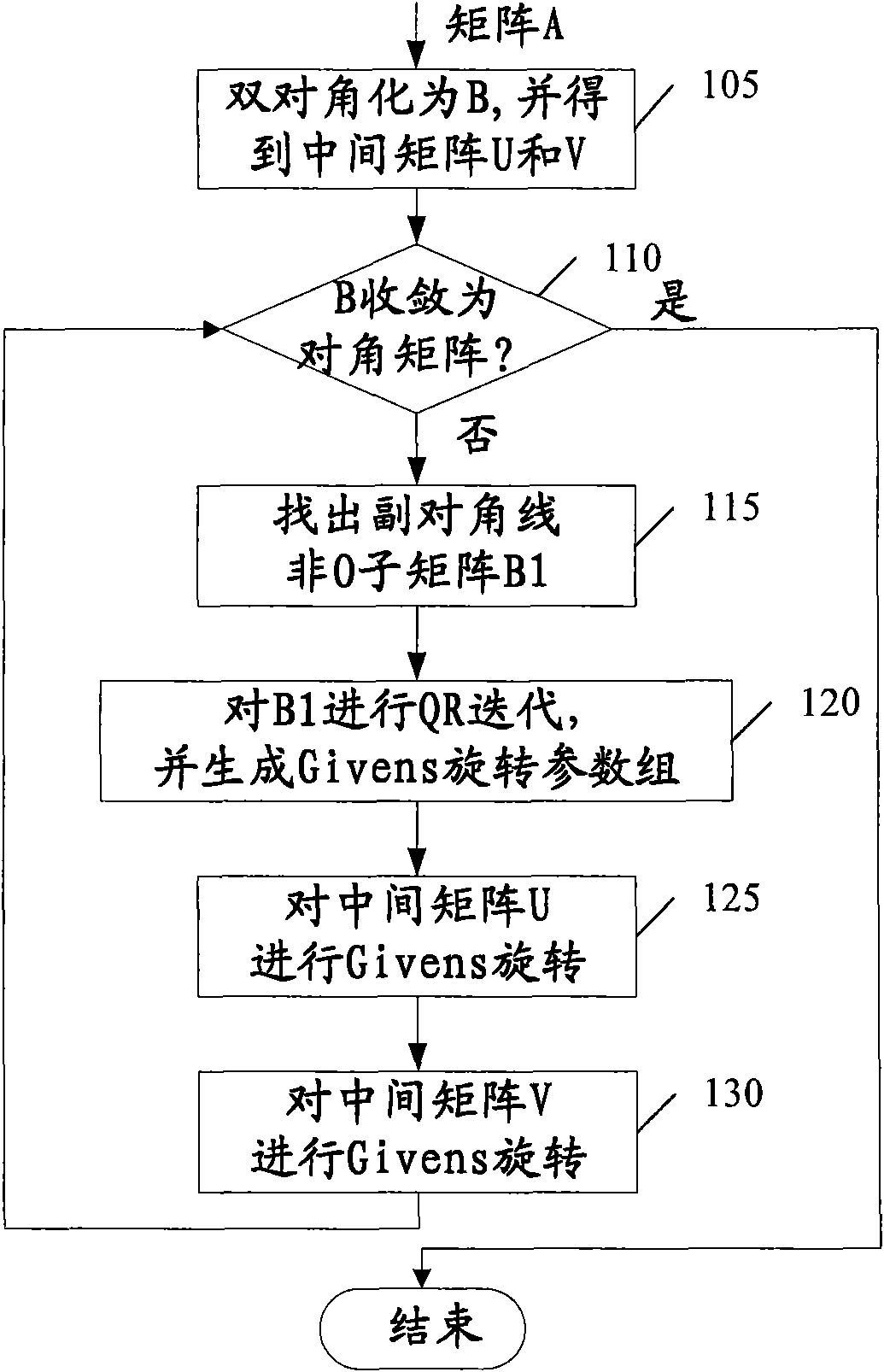

Method and device for singular value and feature value composition of matrix on processing system

The invention provides a method and a device for the singular value and feature value composition of a matrix on a processing system. The method for singular value composition includes: the matrix is converted into a bidiagonal matrix, and a sandwich matrix which needs to be converted into a singular vector matrix is obtained at the same time; submatrixes of which the elements are not zero are found out and converted in an iterative way on the vice diagonals in the bidiagonal matrix so that the bidiagonal matrix can be converged into a diagonal matrix and the sandwich matrix can be converted into the singular vector matrix; in each iterative step: Givens rotation parameter groups generated in the QR iterative processes of the submatrixes and the positions of the left boundary and the right boundary of the corresponding submatrixes which need to use the Givens rotation parameter groups in the sandwich matrix are accumulated in a memory; and when the number of the accumulated Givens rotation parameter groups reaches the preset threshold value, the Givens rotation parameter groups are utilized to carry out the Givens rotation of the sandwich matrix, wherein the threshold value is an integer which is higher than or equal to 2.

Owner:IBM CORP

Method and apparatus for generating block-based low-density parity check matrix and recording medium having recorded thereon code for implementing the method

A method of and an apparatus for generating a block-based low density parity check (LDPC) matrix, where calculation of an inverse matrix is not necessary and back-substitution is possible over the entire matrix area, and a recording medium having recorded thereon code for implementing the method. An area of the LDPC matrix is vertically divided based on respective lengths of first and second parity bit vectors and, a block-based matrix is generated such that a double diagonal matrix is arranged in an upper portion of an area corresponding to the second parity bit vector among areas into which the LDPC matrix is vertically divided., The area of the LDPC matrix is horizontally divided based on a position of the double diagonal matrix, and block-based matrices are generated in the divided areas of the LDPC matrix, to satisfy a condition that column weights (Wc) are uniform.

Owner:SAMSUNG ELECTRONICS CO LTD

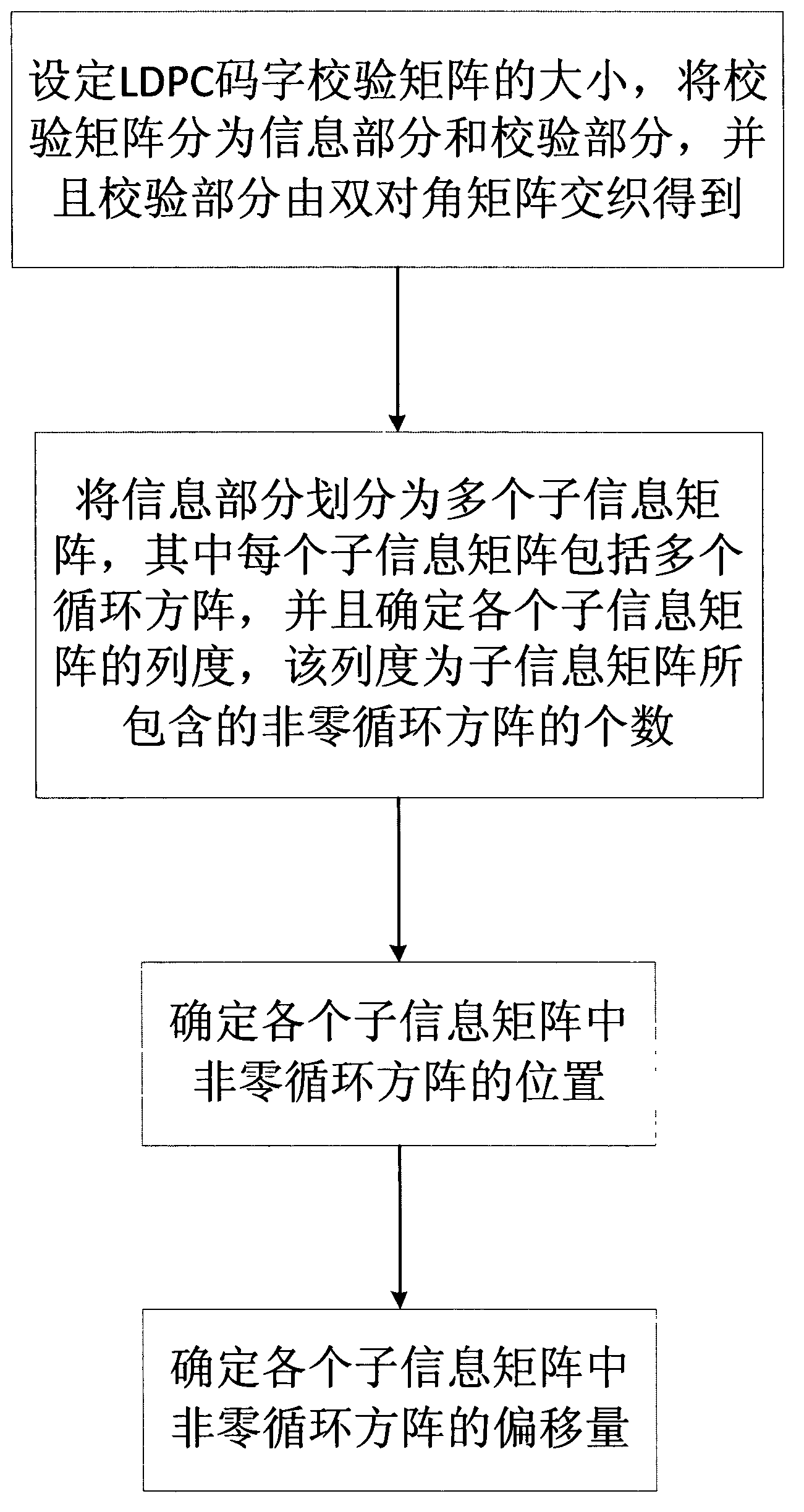

Method for constructing LDPC codes and codes

ActiveCN103427848AIncrease the minimum Hamming distanceLower error floorError correction/detection using multiple parity bitsAlgorithmDiagonal matrix

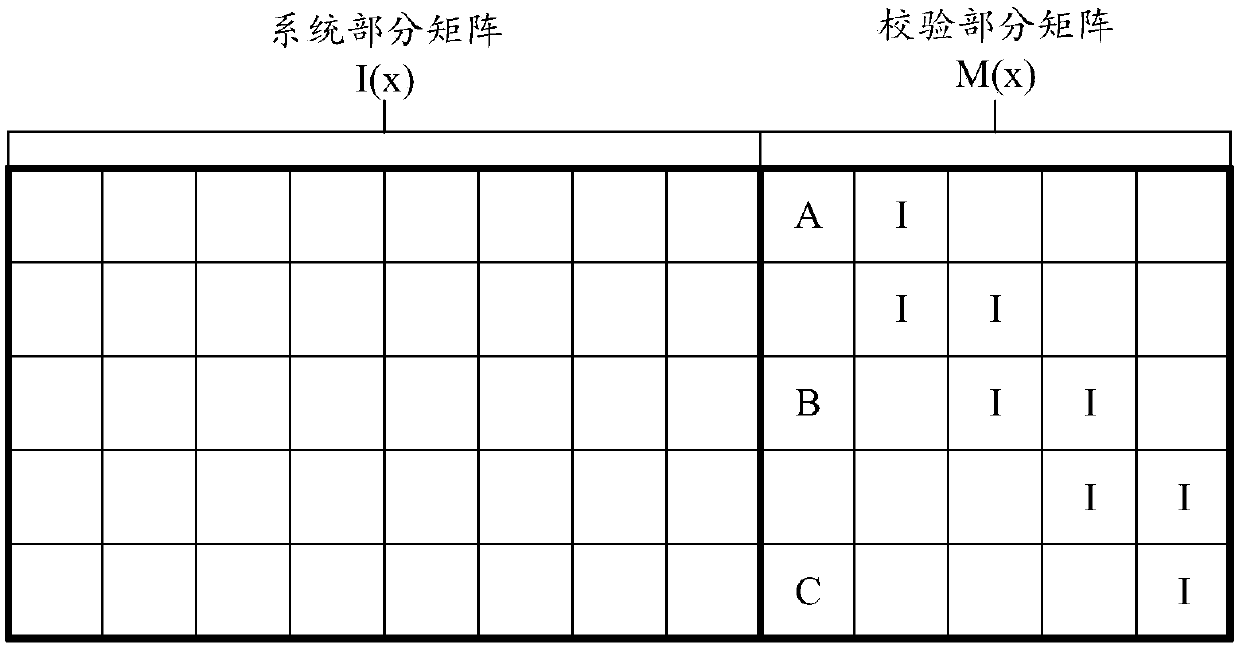

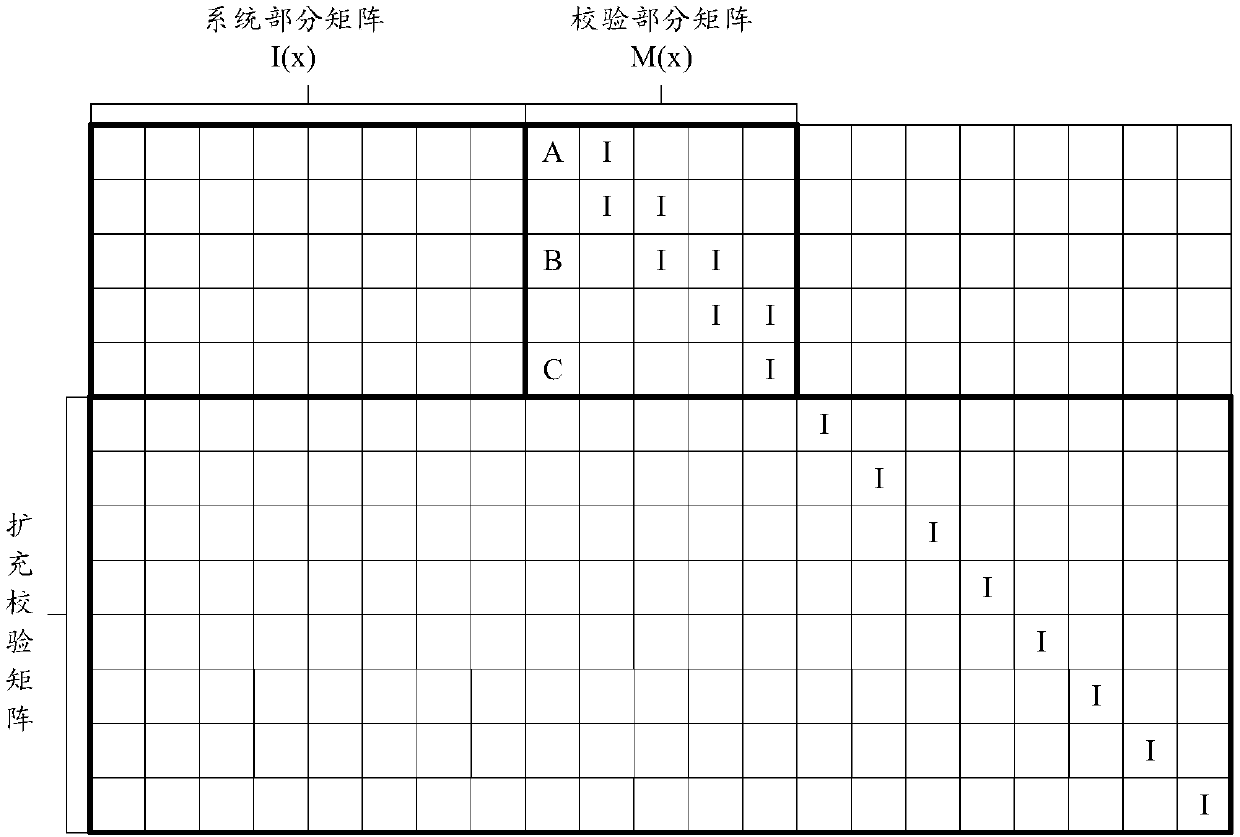

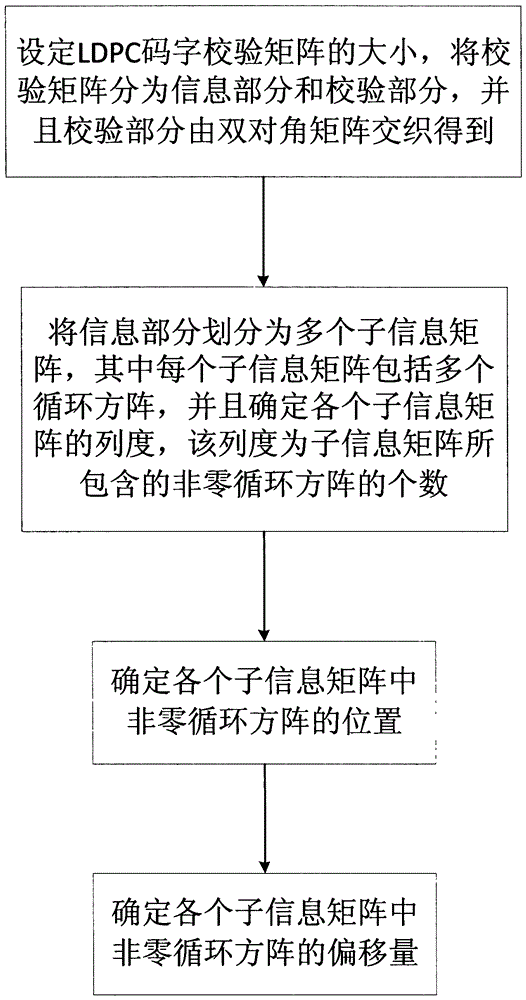

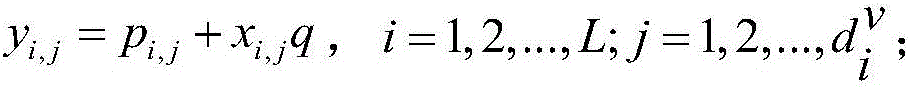

The invention discloses a method for generating LDPC codes. The method comprises the following steps that: step one, the size of a check matrix of the LDPC codes is set, wherein the check matrix is divided into an information portion and a check portion, wherein the check portion is obtained through dual diagonal matrix interweaving; step two, the information portion is divided into a plurality of sub information matrixes, wherein each sub information matrix comprise a plurality of circulatory arrays, and the column degree of each sub information matrix is determined, wherein the column degree is the number of non-zero circulatory arrays contained in the sub information matrix; step three, the positions of the non-zero circulatory arrays of each sub information matrix are determined; and step four, the offset of the non-zero circulatory arrays of each sub information matrix is determined. According to the method of the invention, on the one hand, the minimum distance of the codes is decreased through adopting an interweaving method, and on the other hand, optimal degree distribution and optimal circulatory matrix distribution can be researched by means of tools.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

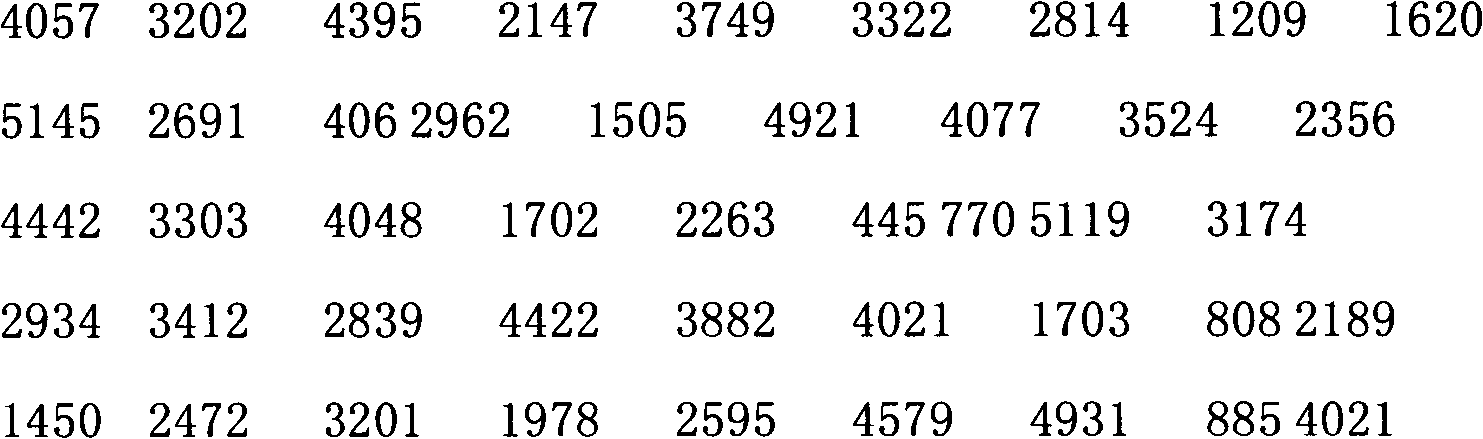

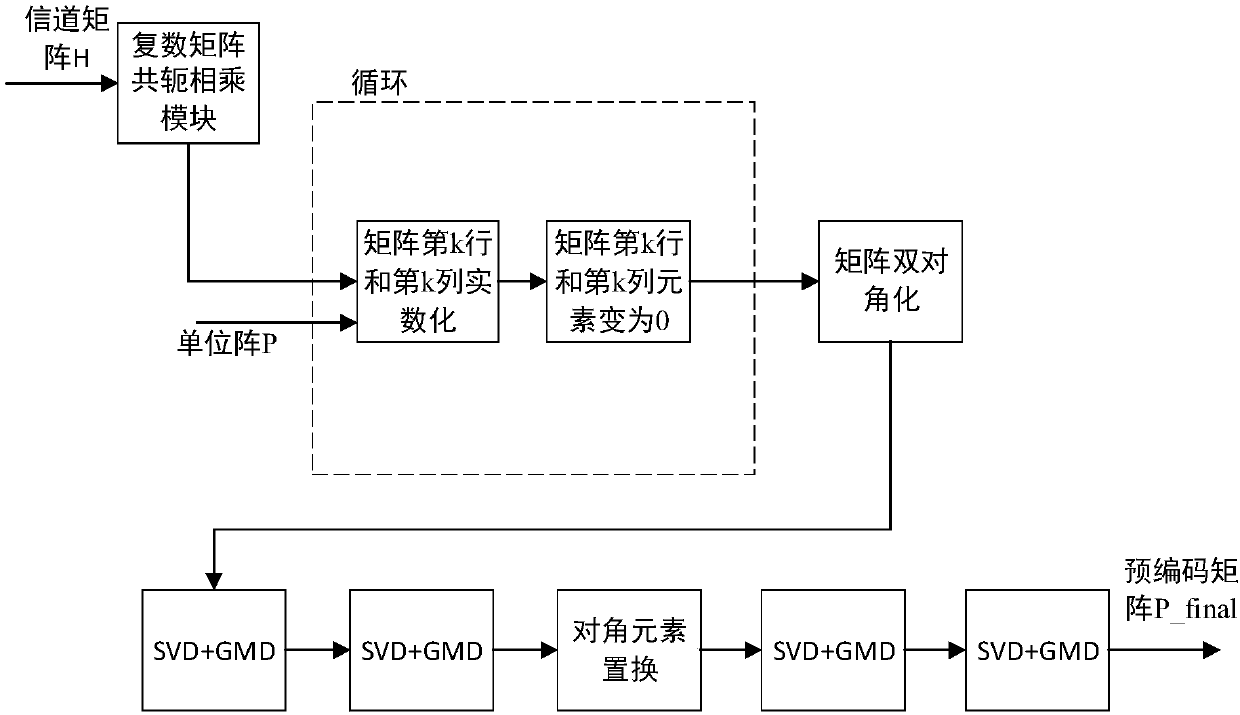

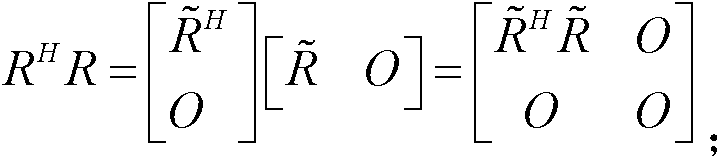

Low-complexity geometric mean value decomposition precoding implementation method based on bidiagonalization

The present invention provides a low-complexity geometric mean value decomposition precoding implementation method based on bidiagonalization. The method comprises the following steps: (1) calculatinga conjugate transpose of a channel matrix and own product; (2) based on a given Hermitian matrix bidiagonalization method, changing the channel matrix into a bidiagonal matrix through Givens rotation; (3) based on a given geometric mean value decomposition method, changing the bidiagonal matrix into an upper triangular matrix where the diagonal elements all equal to the geometric mean value of the channel matrix eigenvalues through Givens rotation; (4) constructing a precoding matrix with the geometric mean value decomposed, that is, the product of all Givens right rotation matrices. The technical scheme can determine the number of iterations, and uses the Hermitian matrix for solutions further to reduce the implementation complexity and reduce the use of the CORDIC (Coordinate Rotation Digital Computer) module. The method utilizes the properties of the Hermitian matrix to effectively reduce the implementation complexity of geometric mean value decomposition precoding based on bidiagonalization.

Owner:SOUTHEAST UNIV

High-speed high-accuracy matrix singular value decomposition method, program, and device

ActiveUS8306361B2Easy to viewValueImage analysisCharacter and pattern recognitionAlgorithmPartition of unity

A singular value decomposition method according to the present invention is a method for performing a singular value decomposition on an arbitrary matrix A using a computer, the method including the steps of: performing an upper bidiagonalization on the matrix A so as to obtain an upper bidiagonal matrix B of the matrix A; obtaining at least one singular value σ of the matrix B as singular values of the matrix A; and obtaining a singular vector of the matrix A for the σ. The step of obtaining a singular vector of the matrix A includes a step of performing a Twisted decomposition on a matrix BTB−σ2I (where I is a unit matrix) by using a Miura inverse transformation, an sdLVvs transformation, an rdLVvs transformation and a Miura transformation so as to diagonalize a matrix BTB.

Owner:JAPAN SCI & TECH CORP

Burst correcting method, equipment and device

ActiveCN101621299BError correction burst errorError preventionBurst error correctionDiagonal matrixBurst error

A method, a device, and an apparatus for correcting bursts are disclosed. The method includes: calculating a correction vector according to a received codeword and a check matrix, wherein the check matrix is an Overlapped Quasi Dual Diagonal Matrix; determining a length and position of a burst according to a longest zero element vector between two nonzero elements in the correction vector when the correction vector is nonzero; and calculating out an error mode according to the correction vector and the length of the burst, obtaining an error mode polynomial according to the error mode, correcting the received codeword according to the error mode polynomial, and obtaining a corrected codeword polynomial. The PBC-based implementation method for cyclic codes herein can correct more burst errors than the conventional cyclic code decoding method.

Owner:XFUSION DIGITAL TECH CO LTD

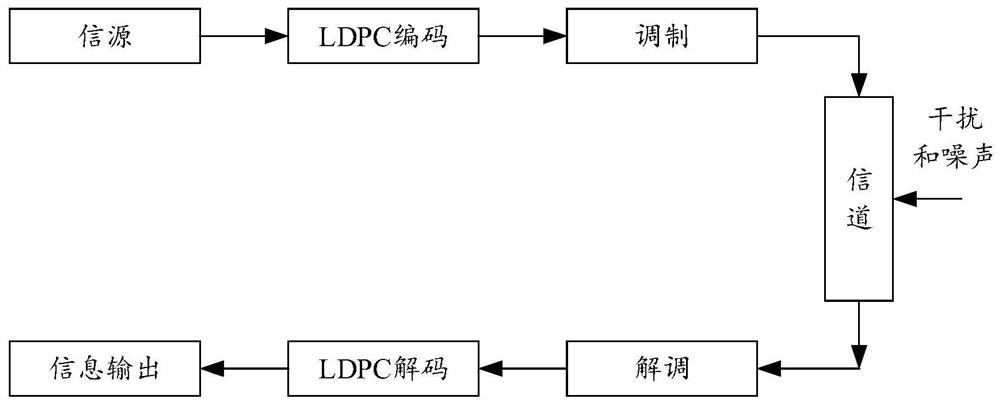

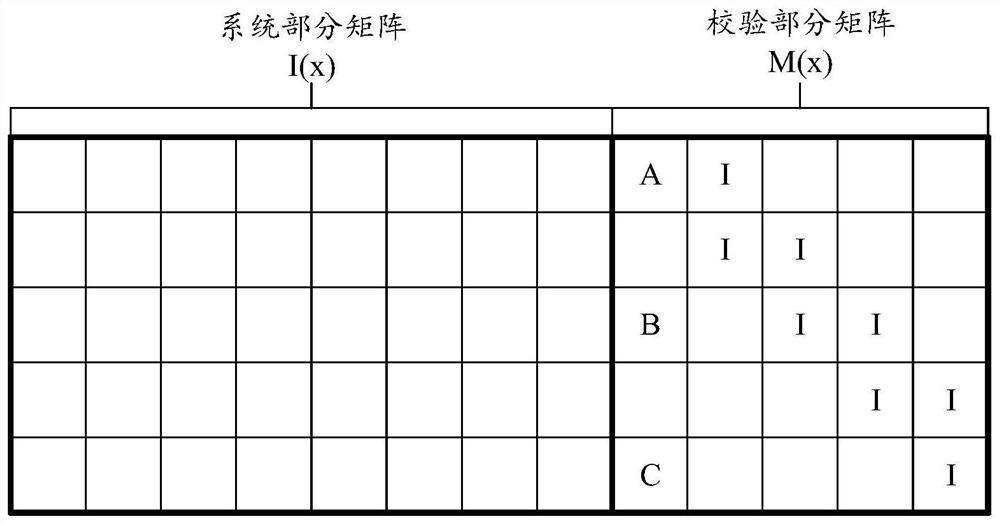

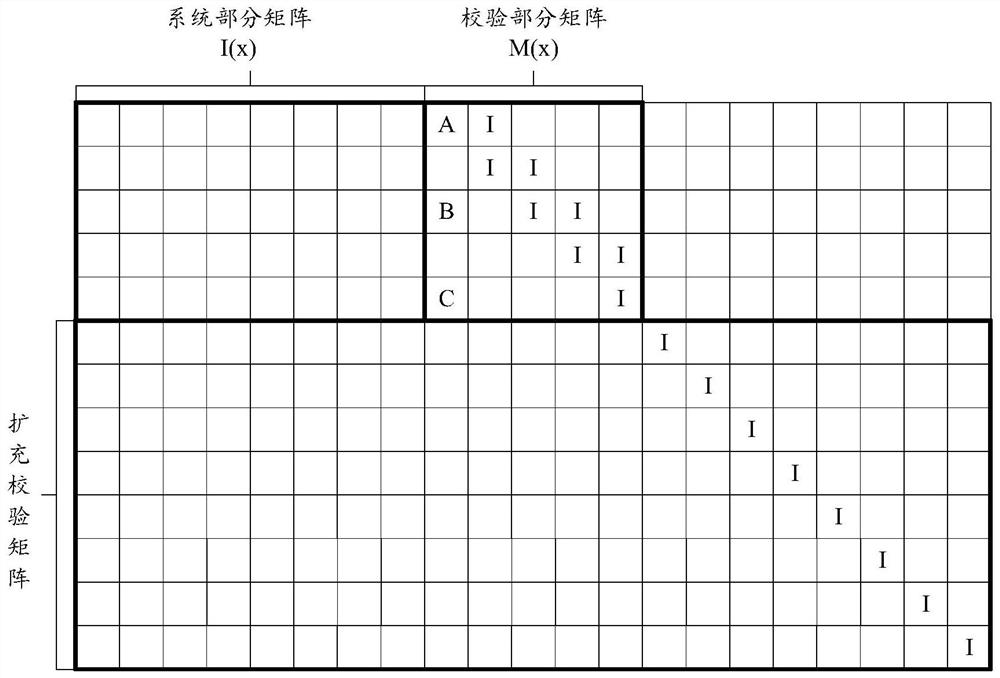

LDPC encoding method and device for communication signal

ActiveCN109951250AError preventionError correction/detection using multiple parity bitsAlgorithmColumn vector

The invention provides an LDPC encoding method and device for a communication signal, which can reduce the coding complexity. The encoding method comprises the following steps: acquiring a (N-M) * 1 information bit vector I (x) according to information bits of a communication signal to be sent; obtaining a check set vector D (x) according to the I (x) and the M * (N-M) system partial matrix N (x),the D (x) satisfying the following conditions: D (x) = {N (x) I (x)} mod2; determining an M * M check part matrix M (x), the M (x) being a bidiagonal matrix, a polynomial matrix Q (x) corresponding to a first column vector of the M (x) being expressed as Q (x) = I + xah + xbh, and Q-1 (x)=x-2 *[beta]* hQ (x), a and b are constants different from each other, and h = 2j-1, wherein [beta] is a positive integer, and j is a positive integer; determining a check bit vector C (x) corresponding to the I (x) according to the D (x) and the M (x), the C (x) satisfying the following conditions: D (x) = {M (x) C (x)} mod2; and according to the I (x) and the C (x), generating a coding code word corresponding to the to-be-sent communication signal.

Owner:HUAWEI TECH CO LTD

Code word construction method and code word of ldpc code

ActiveCN103427848BIncrease the minimum Hamming distanceLower error floorError correction/detection using multiple parity bitsDiagonal matrixComputer science

The invention discloses a method for generating LDPC codes. The method comprises the following steps that: step one, the size of a check matrix of the LDPC codes is set, wherein the check matrix is divided into an information portion and a check portion, wherein the check portion is obtained through dual diagonal matrix interweaving; step two, the information portion is divided into a plurality of sub information matrixes, wherein each sub information matrix comprise a plurality of circulatory arrays, and the column degree of each sub information matrix is determined, wherein the column degree is the number of non-zero circulatory arrays contained in the sub information matrix; step three, the positions of the non-zero circulatory arrays of each sub information matrix are determined; and step four, the offset of the non-zero circulatory arrays of each sub information matrix is determined. According to the method of the invention, on the one hand, the minimum distance of the codes is decreased through adopting an interweaving method, and on the other hand, optimal degree distribution and optimal circulatory matrix distribution can be researched by means of tools.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

Encoding method for low code rate LDPC code

InactiveCN101488760BReduce in quantityImprove performanceError correction/detection using multiple parity bitsComputation complexityBelief propagation

The invention discloses an encoding method of low bit-rate LDPC (Low Density Parity Check) code, including the following steps: (1) matrixes Hand H<d> are respectively constructed, the Hmatrix is a diagonal matrix, H<d> is an array matrix with q multiplied by 1 and is formed by q end-around-shift permutation matrixes Q; the permutation matrix Q is composed of b multiplied by b step permutation matrixes Q having row weight and line weight of 1, at most one element of 1 on each diagonal line and the rest elements of 0; (2) an H matrix with the size of equal to bq multiplied b(q+1) is constructed; (3) a check vector cis constructed, cis equal to (pl, 1=1, 2, ..., M)<T>, wherein p1 represents the value of any first check bit, and M is the length of check bit; (4) according to the check vector c=(p1), the inputted information vector c<d> is equal to (dj), and coded code word c=(c<d>c) is obtained. In the method of the invention, an algebraic method used by end-around-shift value of Q permutation matrix leads belief propagation iterative decoding algorithm to be more easily realized in parallel; bidiagonal matrix structural characteristic of Hmatrix can make the low rate LDPC code be encoded in a recursion manner, and have linear time computing complexity. The simulation performance is superior to the performance of the existing low rate error correcting code, thereby being capable of reaching a signal noise ratio of 0.4 dB and having ratio compatibility.

Owner:HUAZHONG UNIV OF SCI & TECH

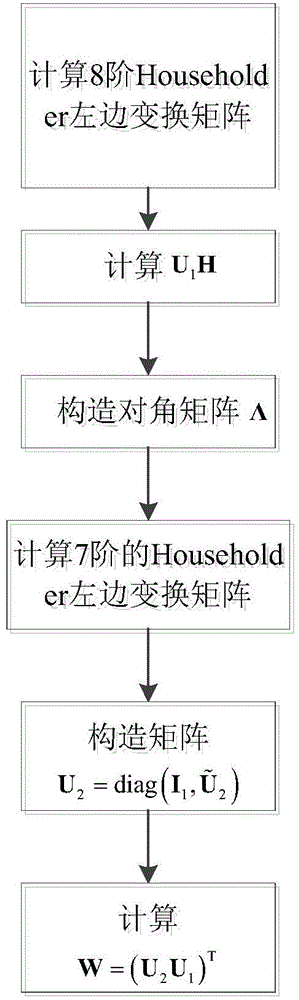

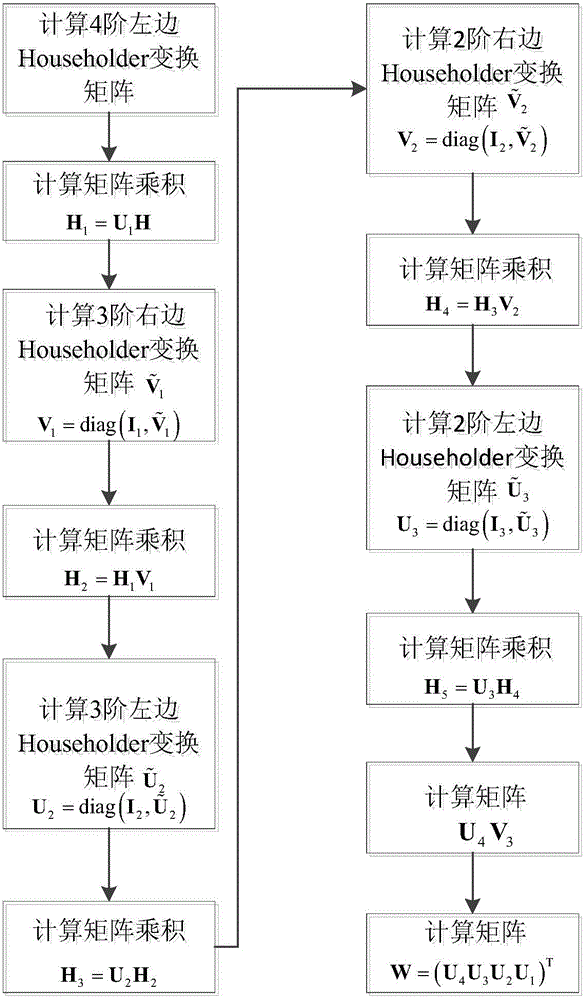

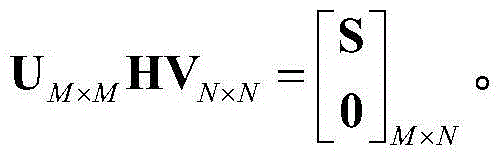

Base station transmitting antenna beam forming method based on Householder operation

The invention discloses a base station transmitting antenna beam forming method based on Householder operation. The base station transmitting antenna beam forming method is designed for solving the problem that in the prior art, an algorithm for obtaining a beam forming weighted matrix is complex. The method includes the steps that received sounding reference signals (SRSes) are used for obtaining an up channel estimation matrix H, Householder conversion is used for converting the complex matrix H into double diagonal matrixes, and a column vector of a Householder conversion device on the left side serves as the weight vector of base station transmitting antenna beam forming.

Owner:ZHONGKE JINGSHANG SUZHOU INFORMATION TECHCO

Method for generating ldpc code check matrix, and the ldpc code encoding method

ActiveCN103236860BSave storage spaceGuaranteed performanceError correction/detection using multiple parity bitsParity-check matrixTheoretical computer science

Owner:GUANGZHOU HAIGE COMM GRP INC

ldpc encoding method and device for communication signals

ActiveCN109951250BError preventionError correction/detection using multiple parity bitsSoftware engineeringMechanical engineering

The present application provides an LDPC encoding method and a device for a communication signal, for reducing encoding complexity. The encoding method comprises: acquiring an (N-M) × 1 information bit vector I(x) according to information bits of a communication signal to be sent; acquiring a check set vector D(x) according to I(x) and an M × (N-M) system partial matrix N(x), where D(x) meets the following condition: D(x) = {N(x) I(x)} mod 2; determining an M × M check partial matrix M(x), wherein M(x) is a bidiagonal matrix, a polynomial matrix Q(x) corresponding to a first column vector of M(x) is represented as Q(x) = I + x ah + x bh , Q -1 (x) = x -2×β×h Q(x), a and b are different constants, h = 2 j-1 , and β and j are positive integers; determining, according to D(x) and M(x), a check bit vector C(x) corresponding to I(x), where C(x) meets the following condition: D(x) = {M(x) C(x)} mod 2; and generating, according to I(x) and C(x), a code word corresponding to the communication signal to be sent.

Owner:HUAWEI TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com