Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2304 results about "Error correcting" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Error correction is often done by the teacher providing corrections for mistakes made by students. However, it is probably more effective for students to correct their own mistakes. In order to do this, students and the teacher should have a common shorthand for correcting mistakes. Teaching students to correct their own mistakes.

System and method for error correcting a received data stream in a concatenated system

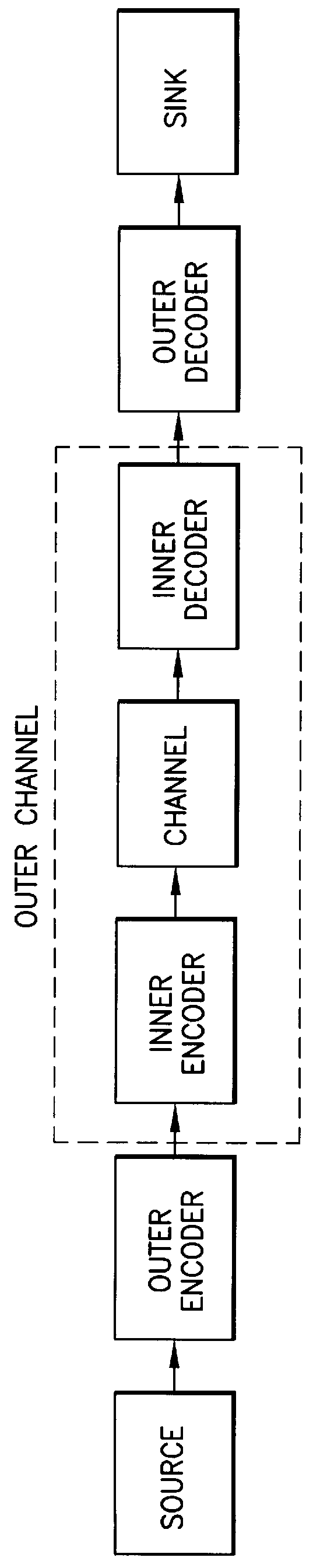

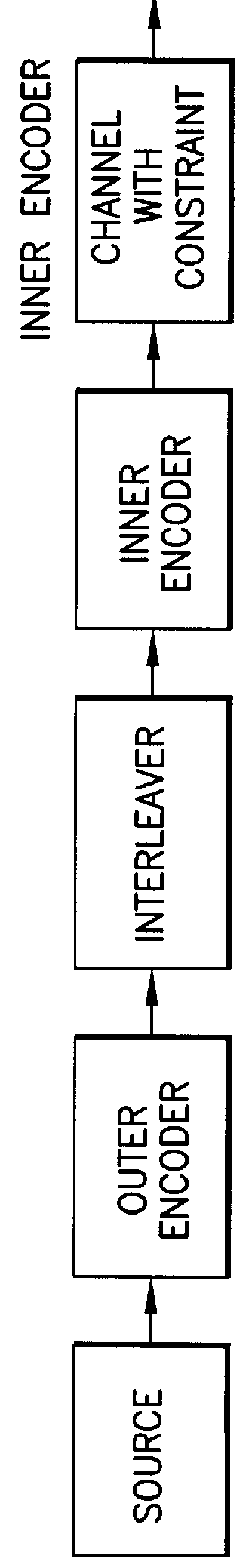

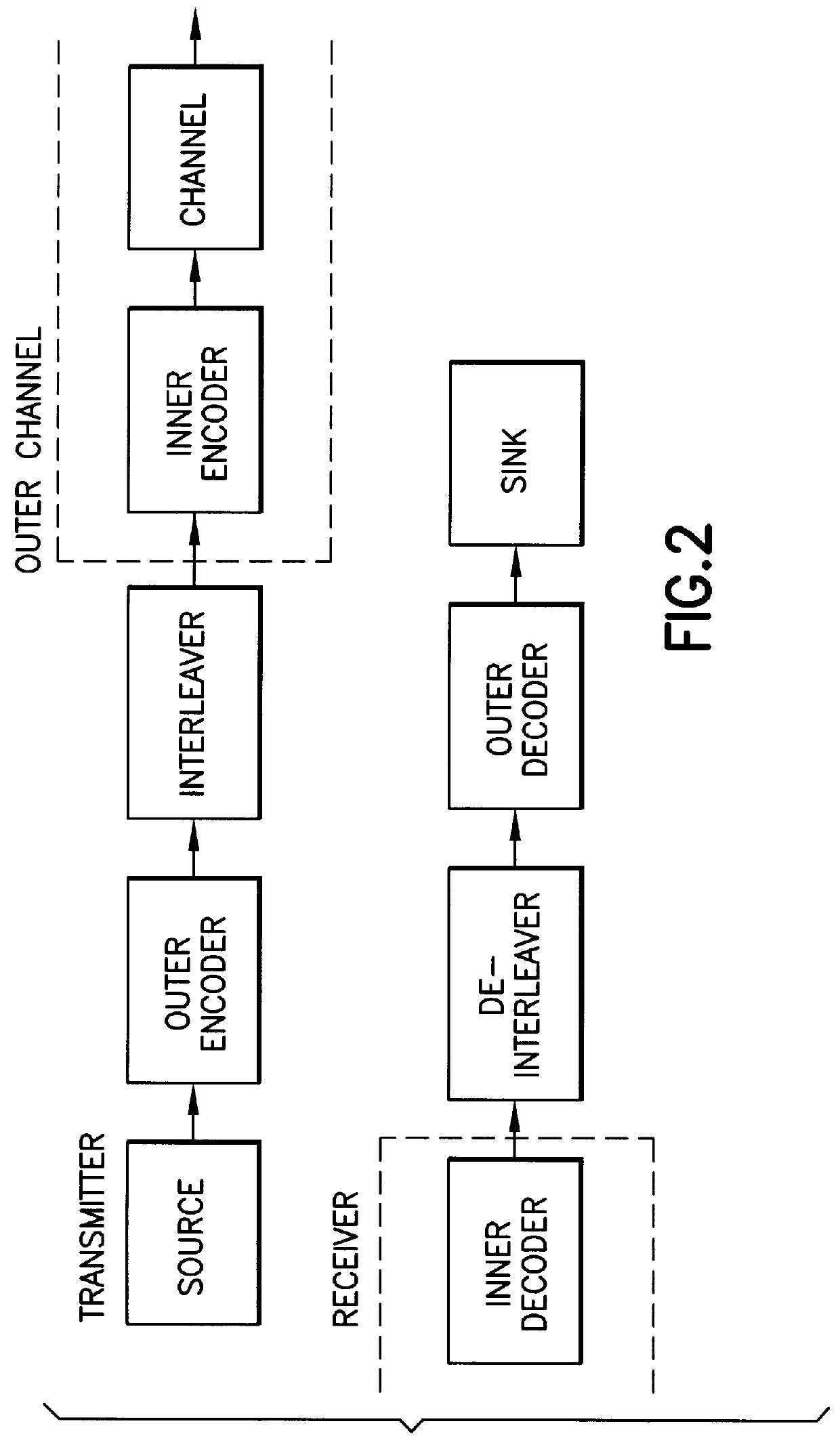

A received signal is first converted into a digital sequence that may contain "erasures" (or ambiguity symbols) as well as errors. Then iterative decoding is applied in order to eliminate or reduce the erasures. This decoding procedure works effectively with the associated transmitter that adopts a concatenation of an outer coder, a permutation and an inner coder. The principal of the invention is also applicable to a system in which the inner coder is replaced by a "digital modulator" that introduces some constraint, or a channel that introduces some memory such as partial response signaling, intersymbol interference or multipath propagation. The invention can be applied to many existing systems while maintaining "backward compatibility" in the sense that the transmitter side need not be modified.

Owner:THE TRUSTEES FOR PRINCETON UNIV

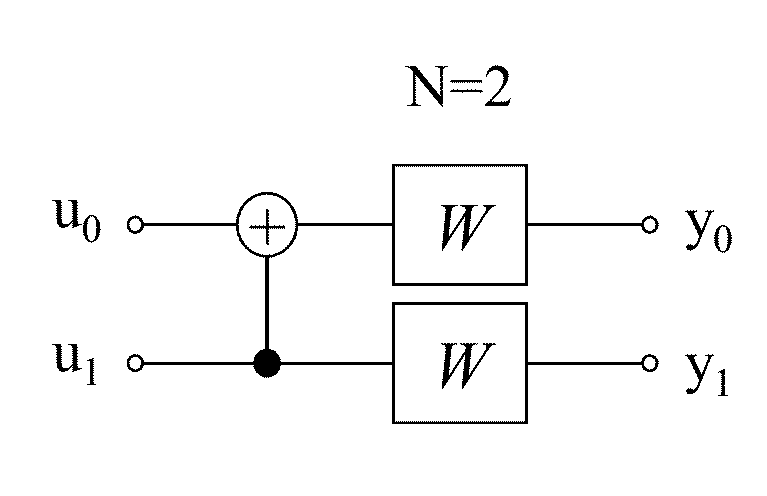

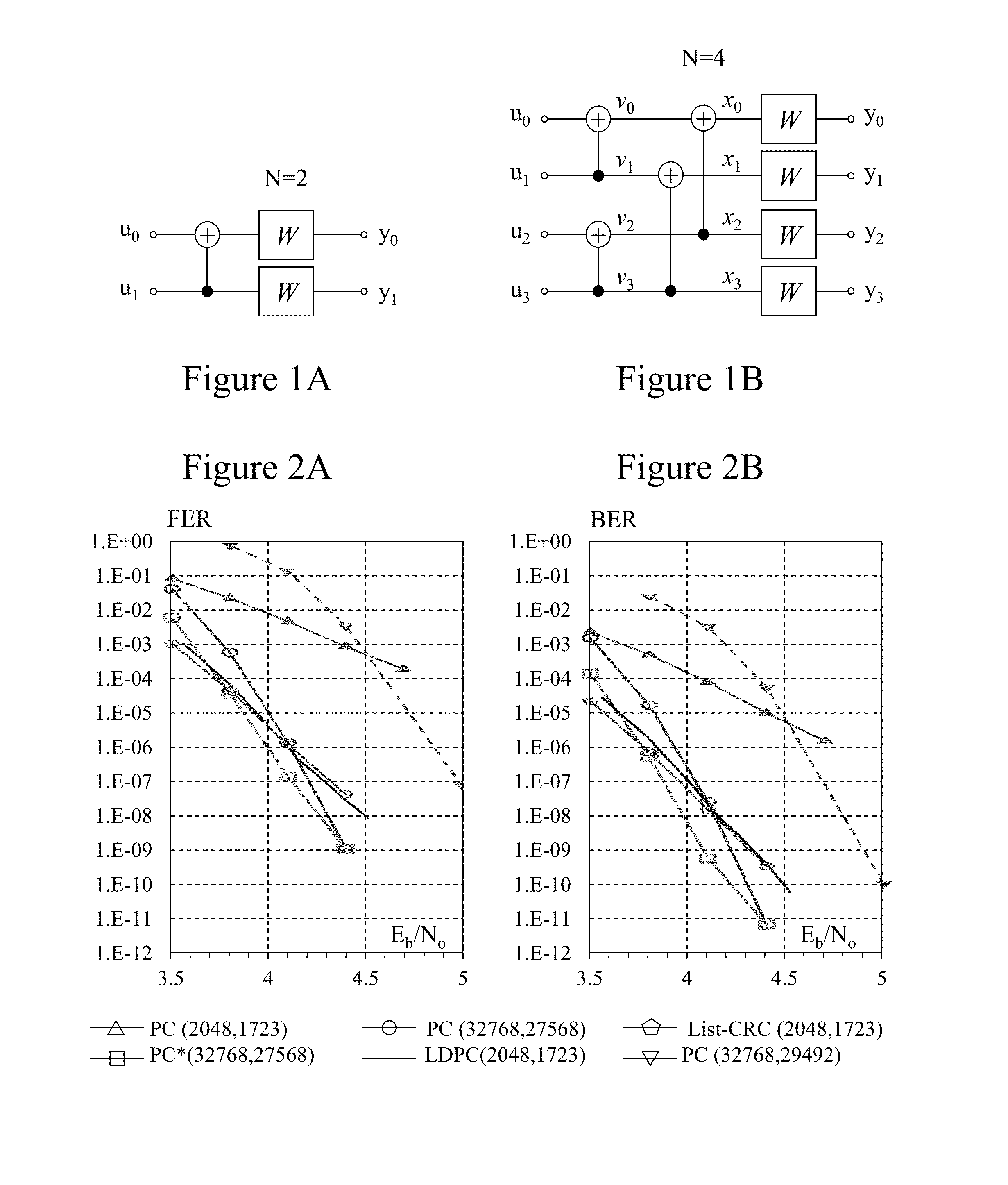

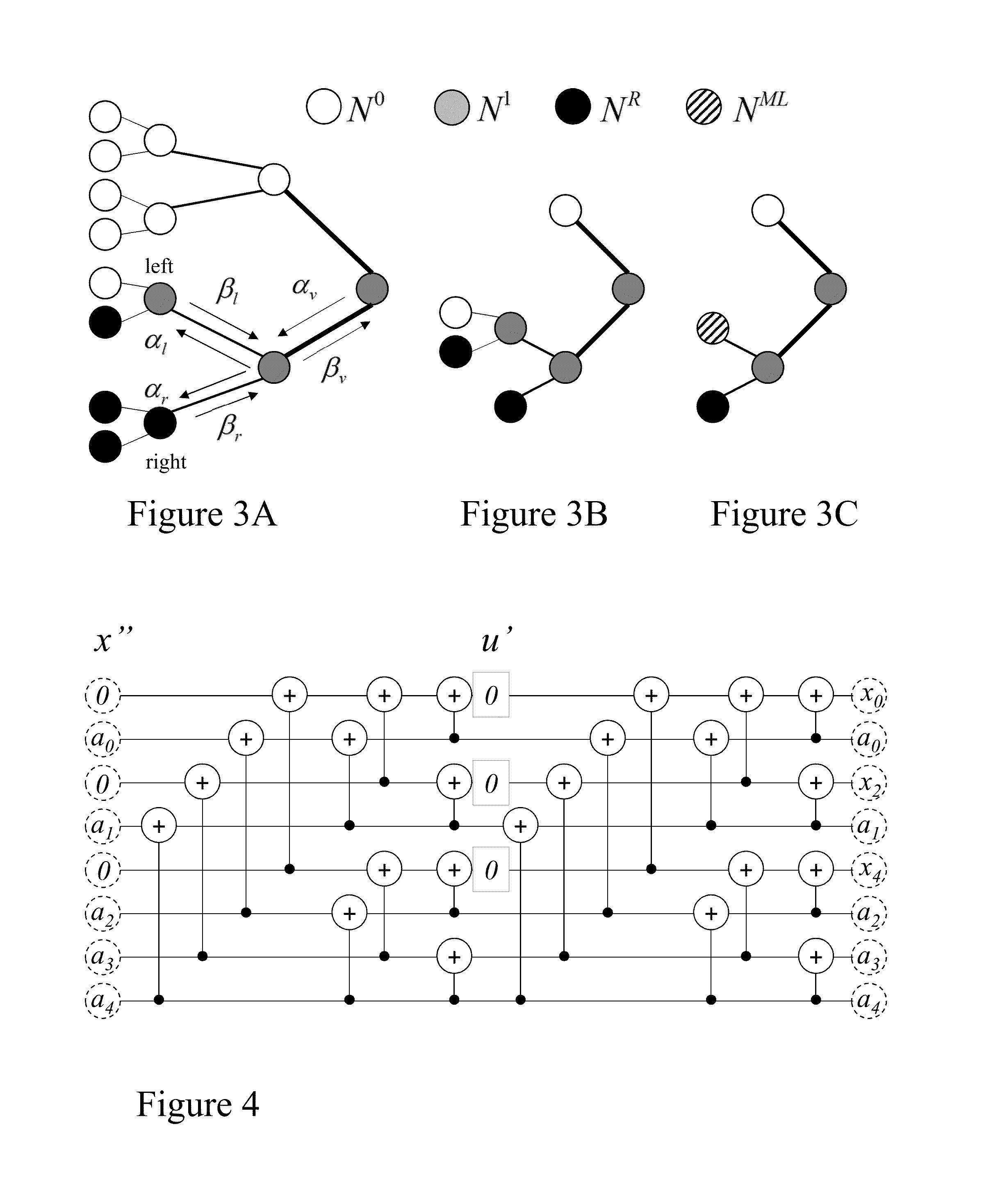

Flexible polar encoders and decoders

Modern communication systems must cope with varying channel conditions and differing throughput constraints. Polar codes despite being the first error-correcting codes with an explicit construction to achieve the symmetric capacity of memoryless channels are not currently employed against other older coding protocols such as low-density parity check (LDPC) codes as their performance at short / moderate lengths has been inferior and their decoding algorithm is serial leading to low decoding throughput. Accordingly techniques to address these issues are identified and disclosed including decoders that decode constituent codes without recursion and / or recognize classes of constituent directly decodable codes thereby increasing the decoder throughput. Flexible encoders and decoders supporting polar codes of any length up to a design maximum allow adaptive polar code systems responsive to communication link characteristics, performance, etc. whilst maximizing throughput. Further, designers are provided flexibility in implementing either hardware or software implementations.

Owner:POLAR TECH

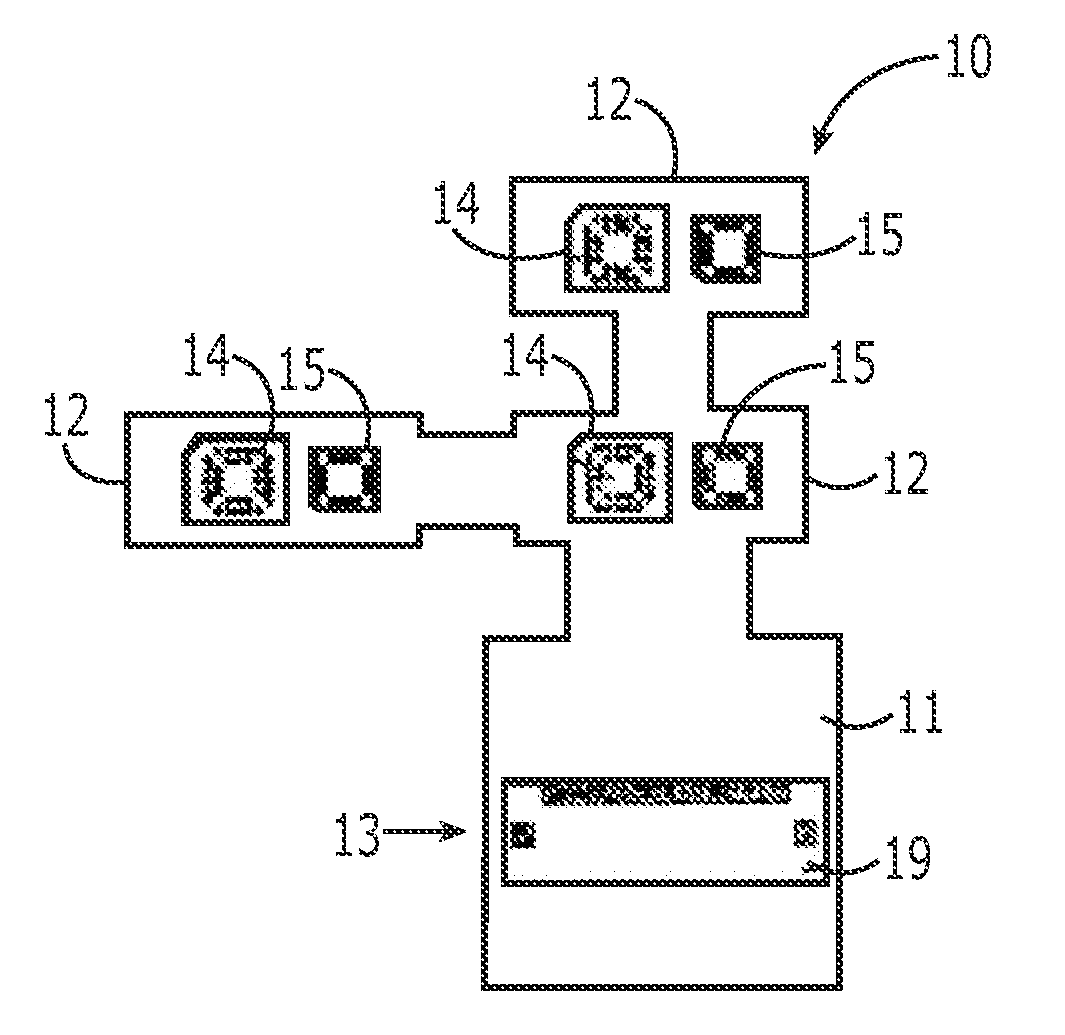

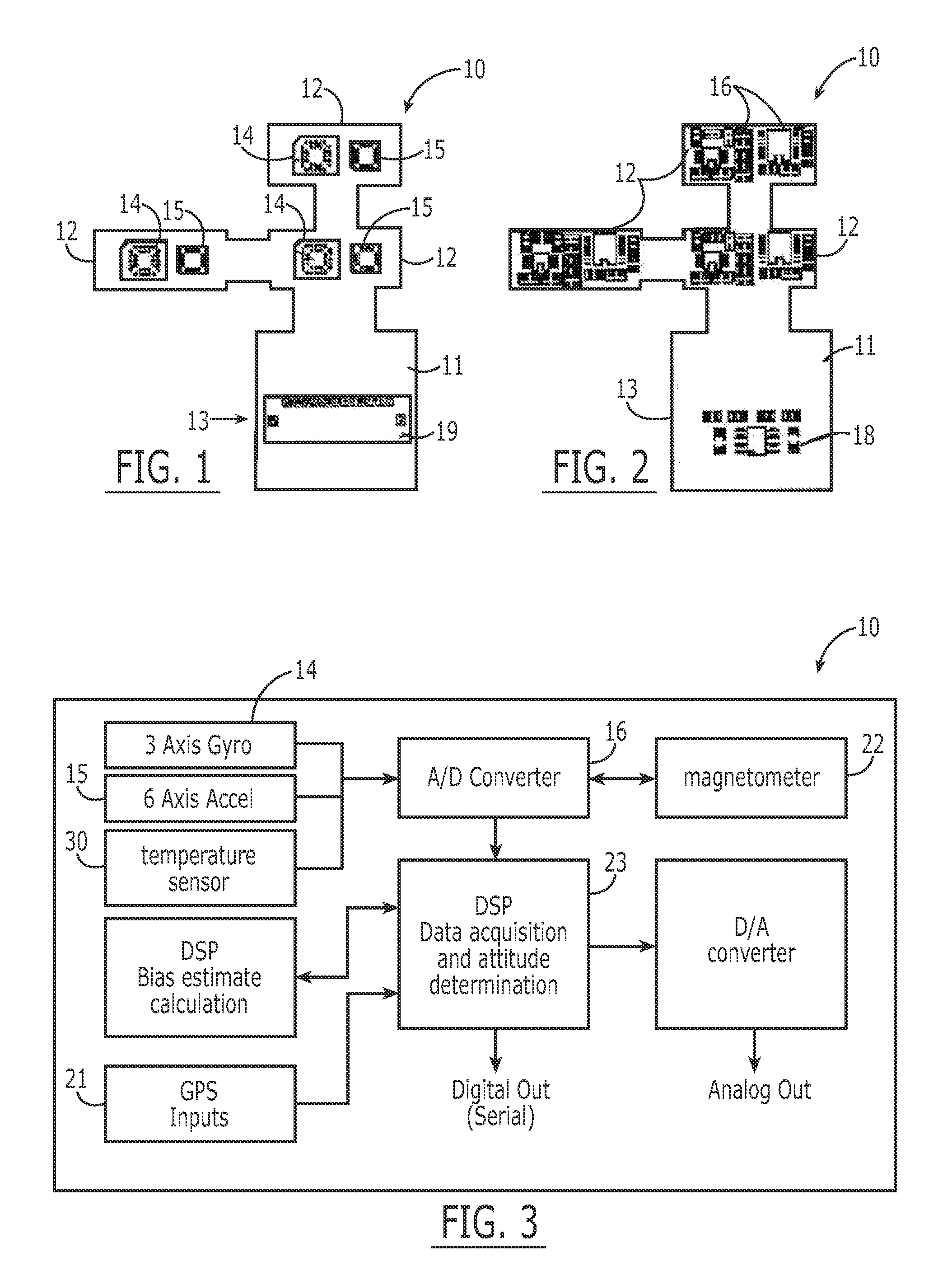

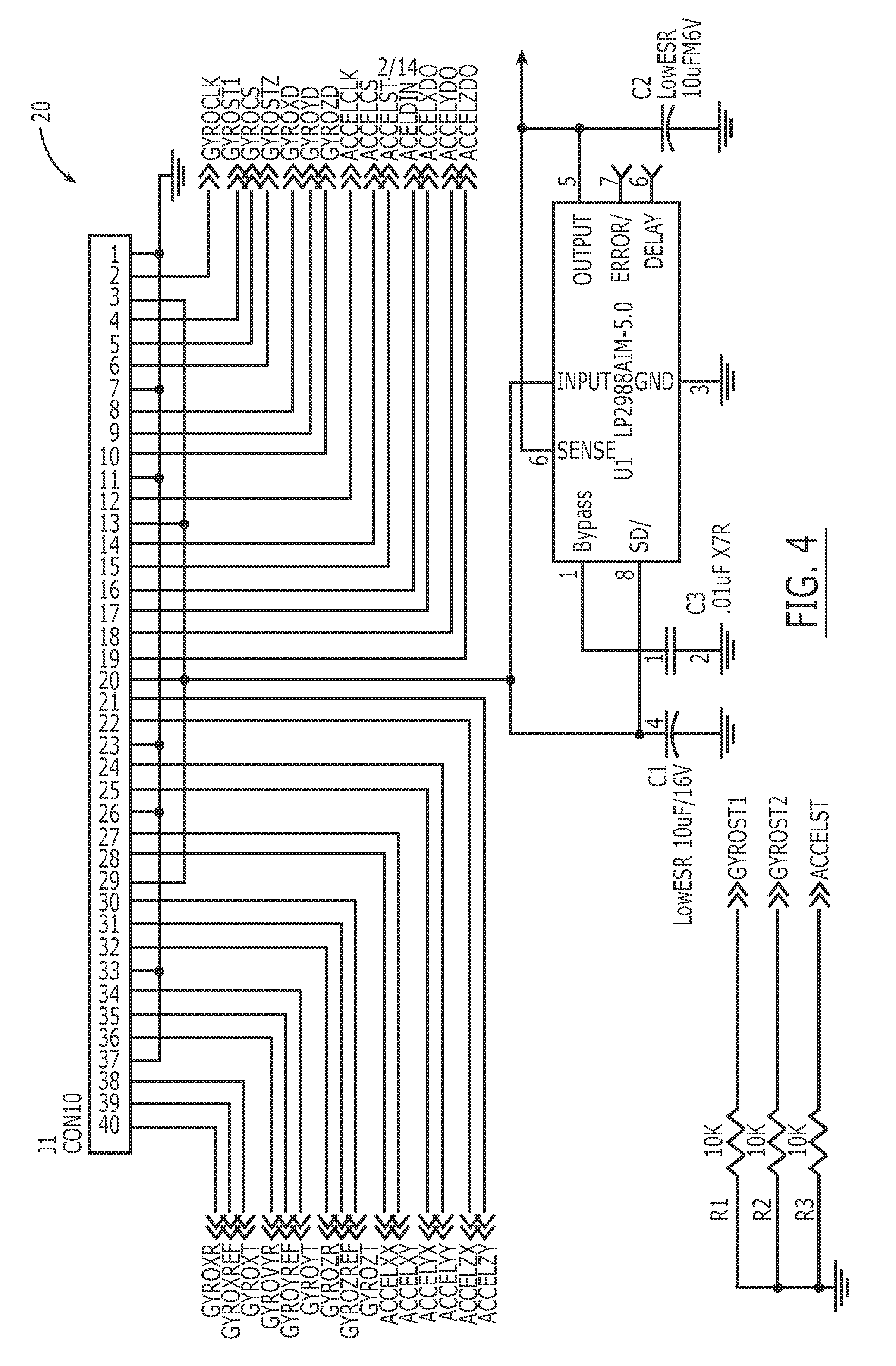

Miniaturized Inertial Measurement Unit and Associated Methods

InactiveUS20070032951A1Reduce noiseThe result is accurateNavigation by speed/acceleration measurementsDigital computer detailsDigital signal processingAccelerometer

A self-contained, integrated micro-cube-sized inertial measurement unit is provided wherein accuracy is achieved through the use of specifically oriented sensors, the orientation serving to substantially cancel noise and other first-order effects, and the use of a noise-reducing algorithm such as wavelet cascade denoising and an error correcting algorithm such as a Kalman filter embedded in a digital signal processor device. In a particular embodiment, a pair of three sets of angle rate sensors are orientable triaxially in opposite directions, wherein each set is mounted on a different sector of a base orientable normal to the other two and comprising N gyroscopes oriented at 360 / N-degree increments, where N≧2. At least one accelerometer is included to provide triaxial data. Signals are output from the angle rate sensors and accelerometer for calculating a change in attitude, position, angular rate, acceleration, and / or velocity of the unit.

Owner:JAYMART SENSORS

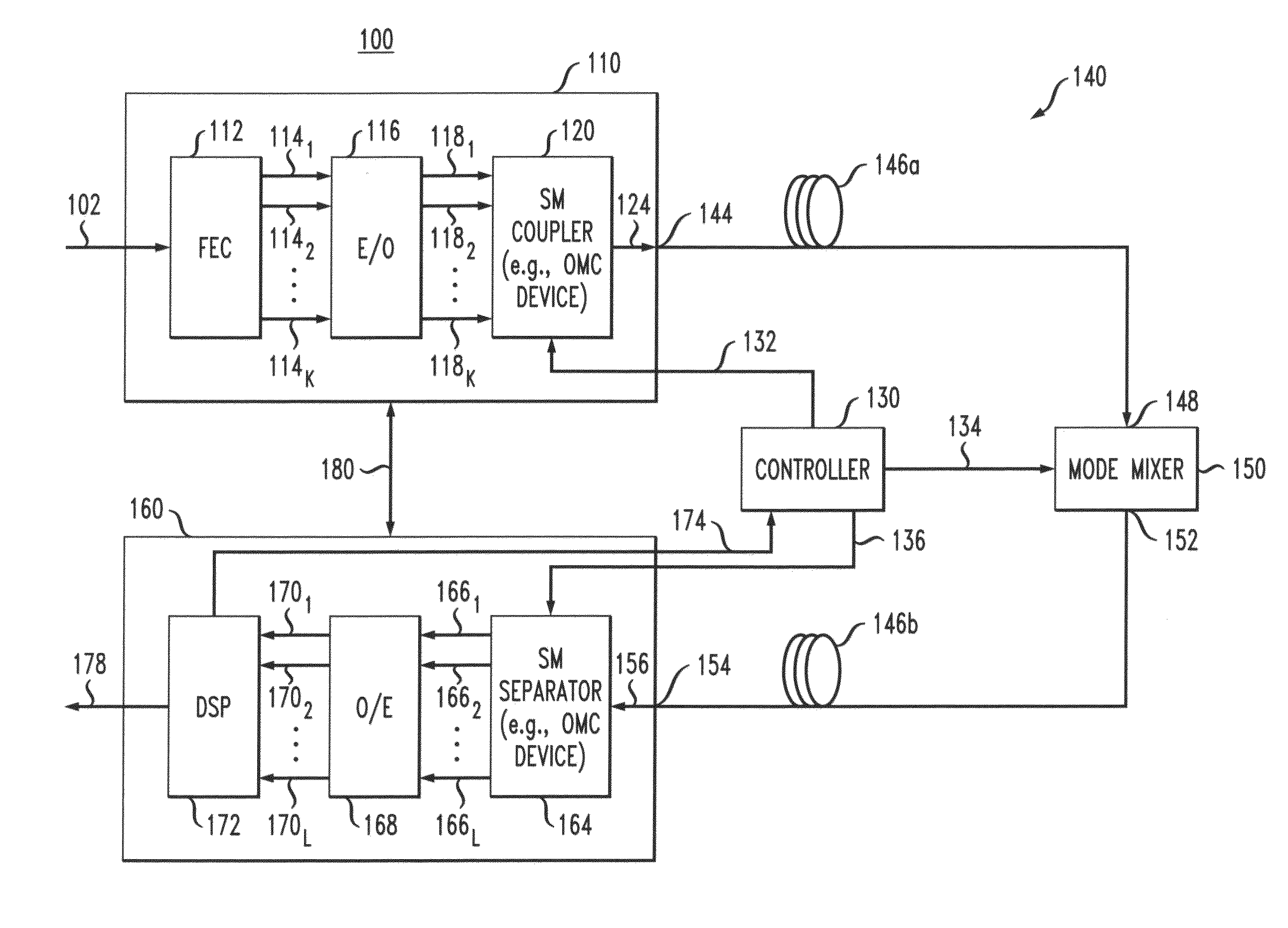

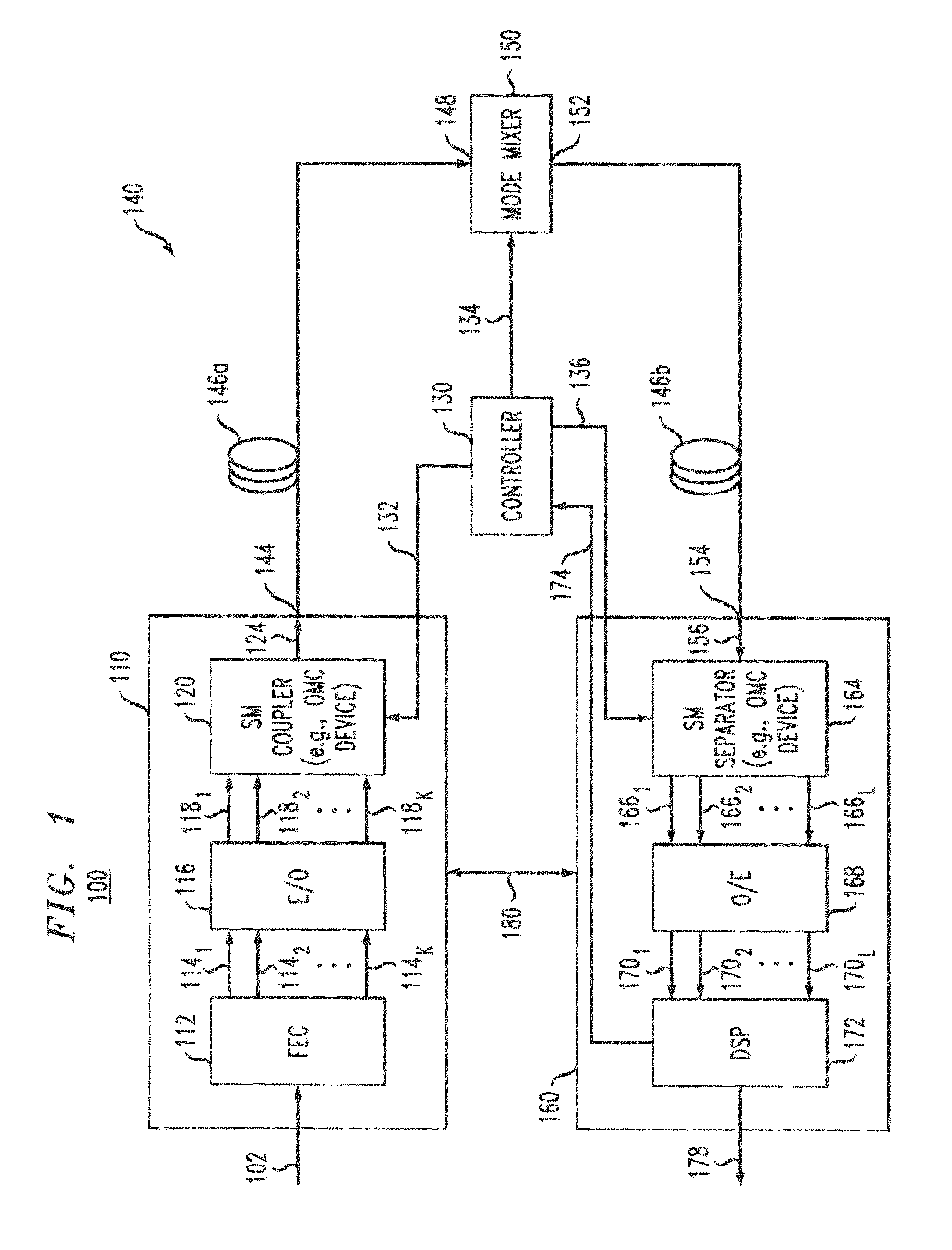

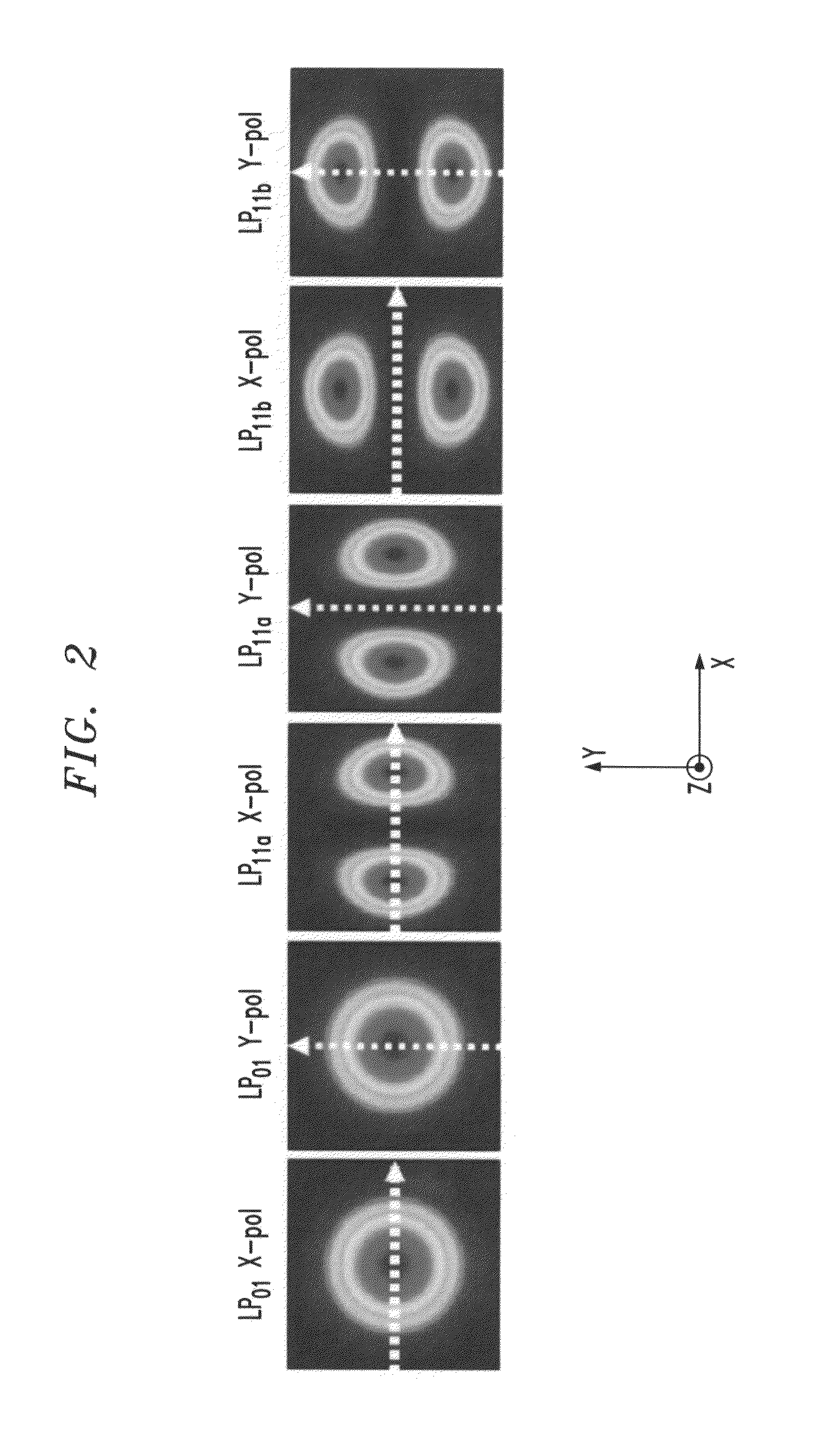

Intra-link spatial-mode mixing in an under-addressed optical MIMO system

ActiveUS20120224807A1Reduce frequencyReduce outage rateOptical mode multiplex systemsCoupling light guidesCoherence timeError correcting

The outage probability in an under-addressed optical MIMO system may be reduced by configuring an intra-link optical mode mixer to dynamically change the spatial-mode mixing characteristics of the link on a time scale that is faster than the channel coherence time. Provided that the MIMO system employs an FEC code that has a sufficient error-correcting capacity for correcting the amount of errors corresponding to an average state of the MIMO channel, this relatively fast dynamic change tends to reduce the frequency of events during which the number of errors per FEC-encoded block of data exceeds the error-correcting capacity of the FEC code.

Owner:ALCATEL LUCENT SAS

Order invariant fuzzy commitment system

ActiveUS7602904B2Error preventionPublic key for secure communicationFuzzy commitment schemeTheoretical computer science

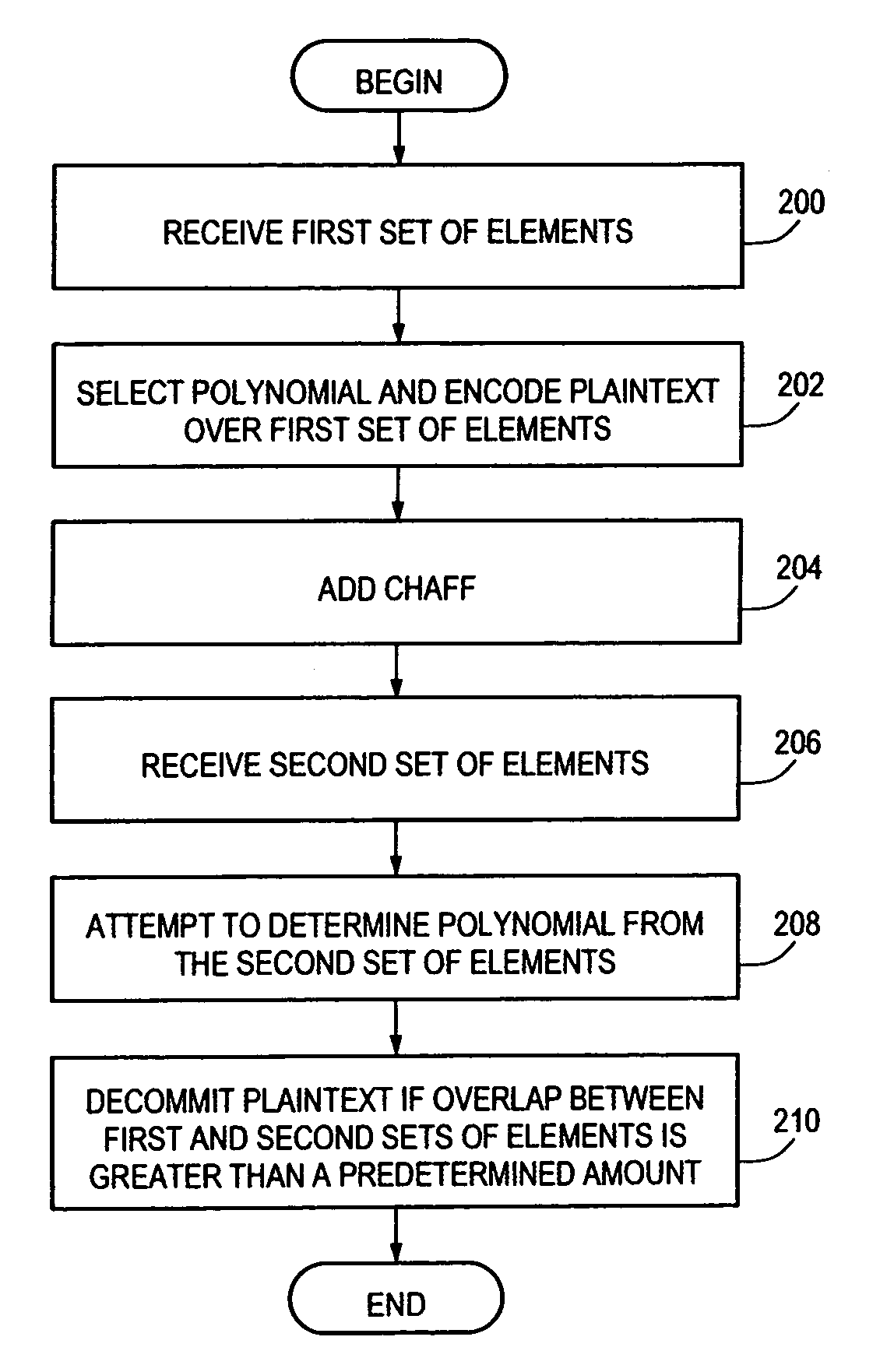

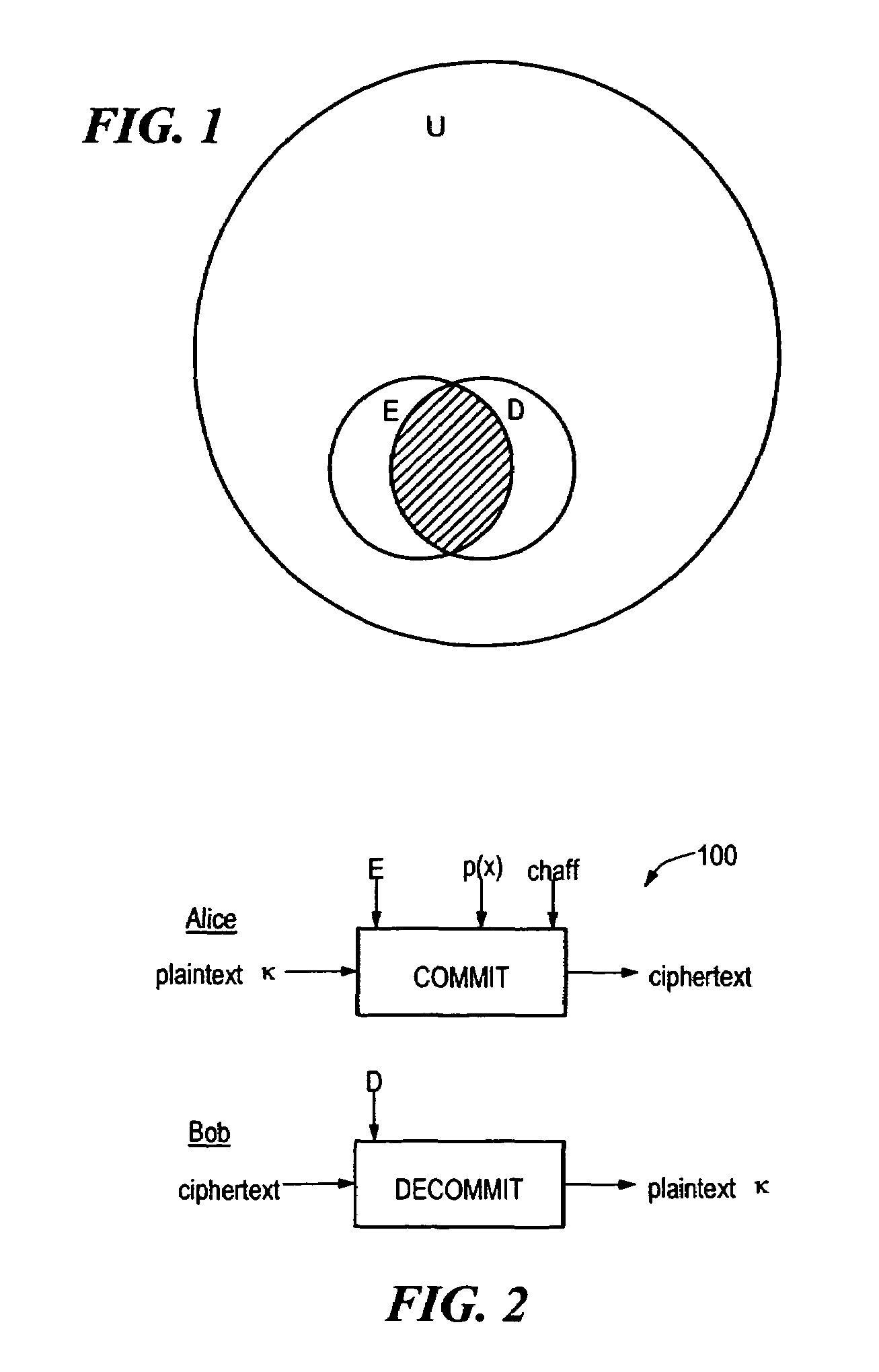

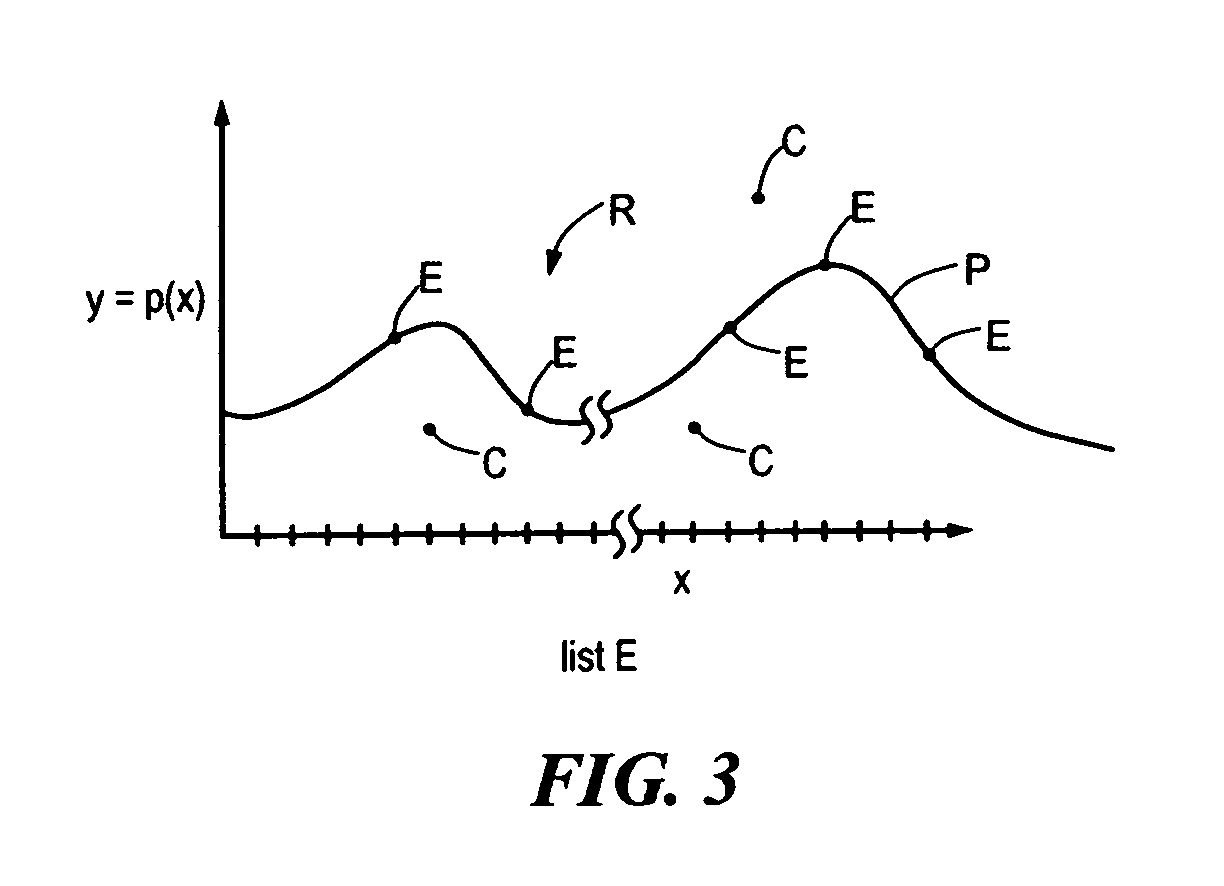

A system provides an order-invariant fuzzy commitment scheme. In an exemplary embodiment, the scheme includes receiving a first set of elements and selecting a polynomial for encoding an item under the first set of elements to generate an order-invariant fuzzy commitment of the item. The system utilizes an error-correcting code for decommitting the item if a second set of elements has a specified level of overlap with the first set of elements.

Owner:RSA

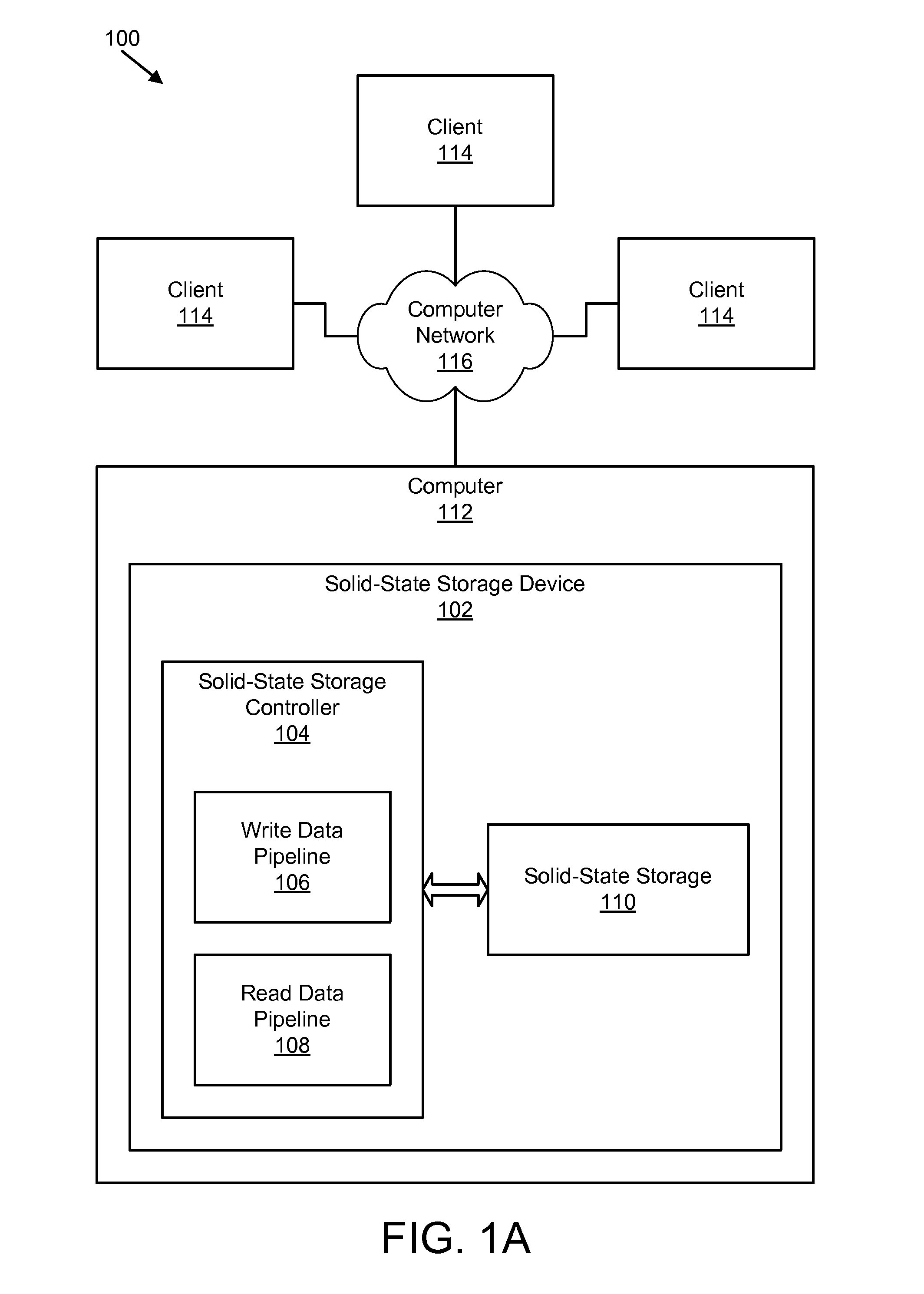

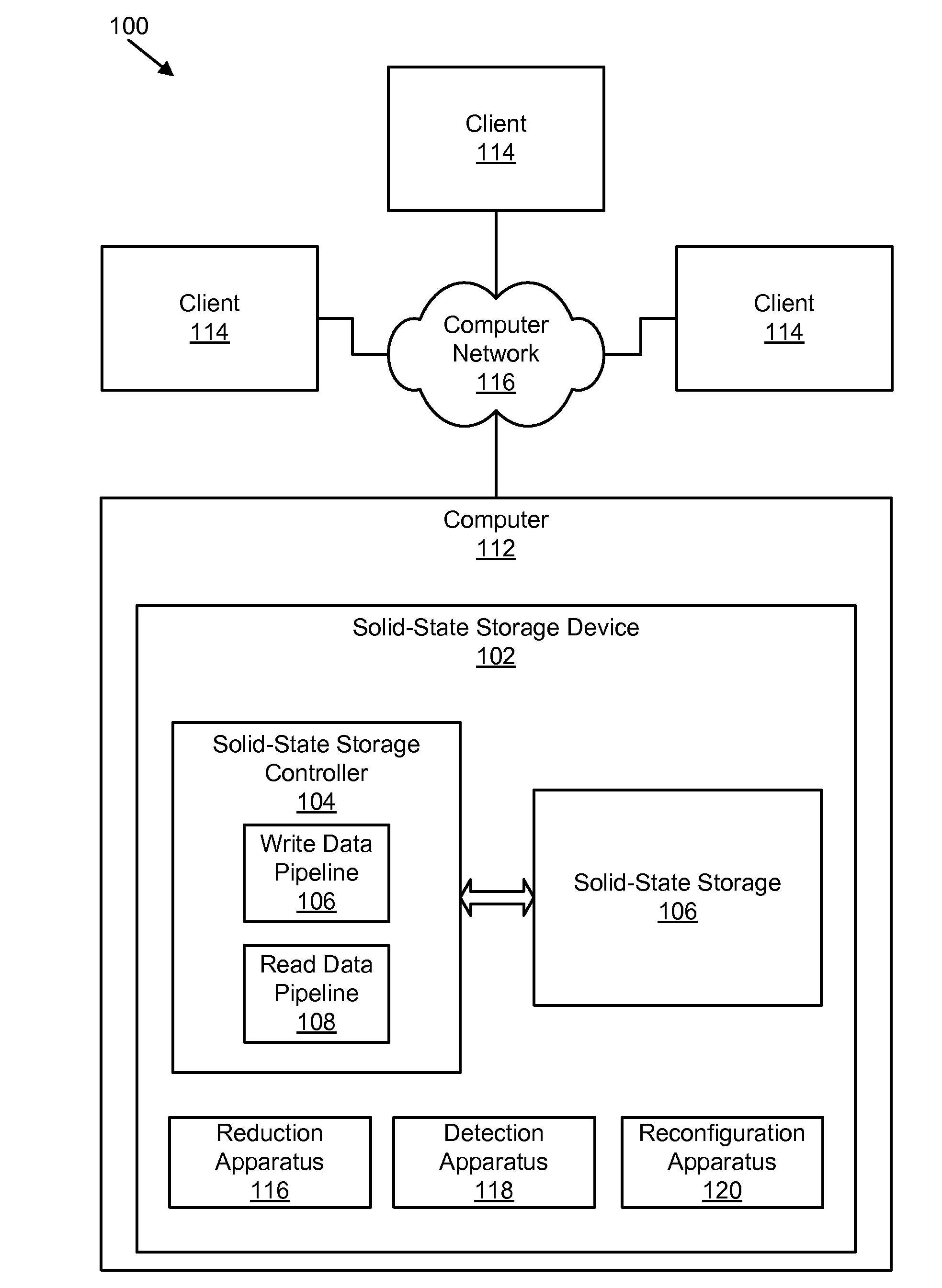

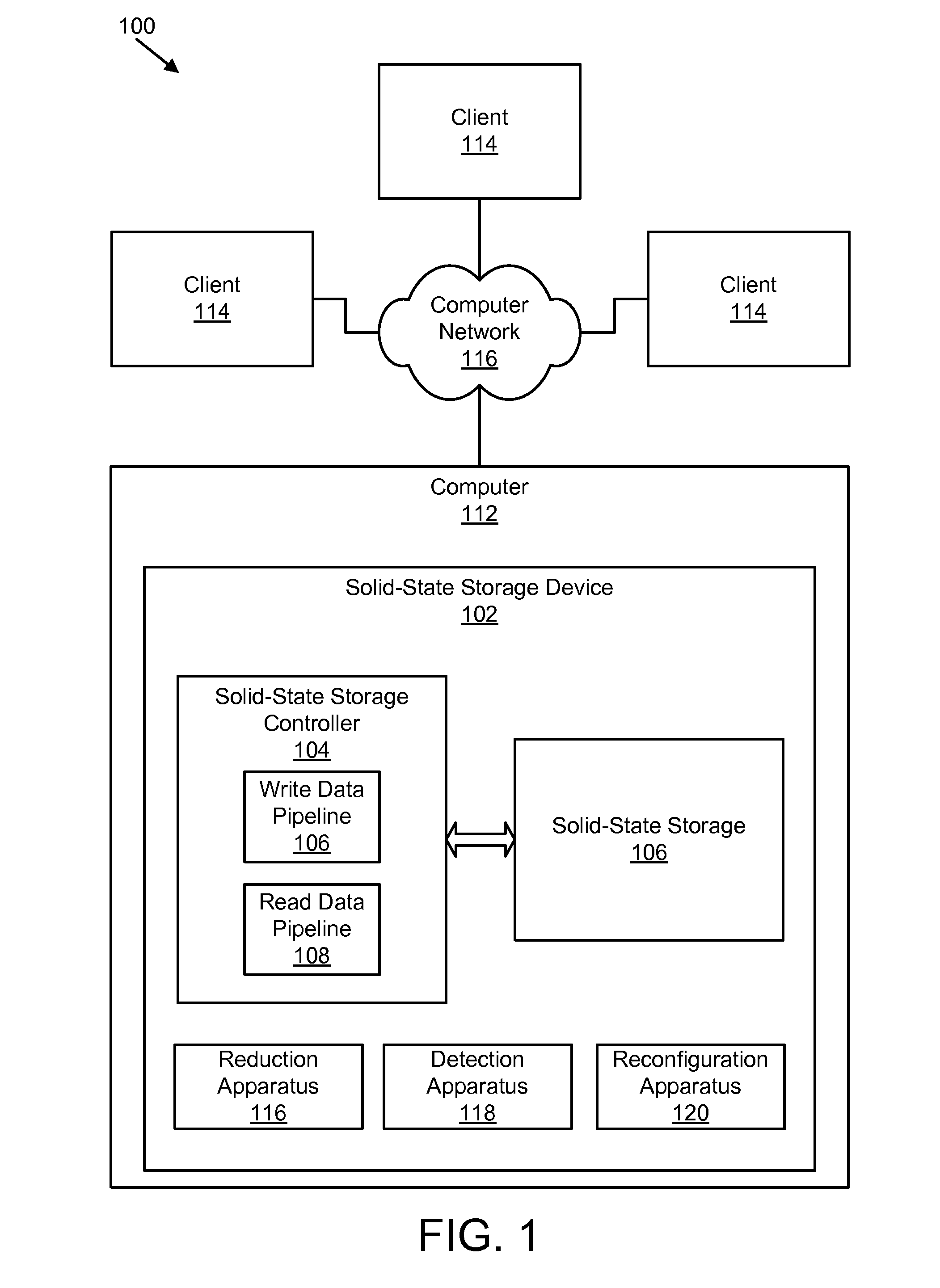

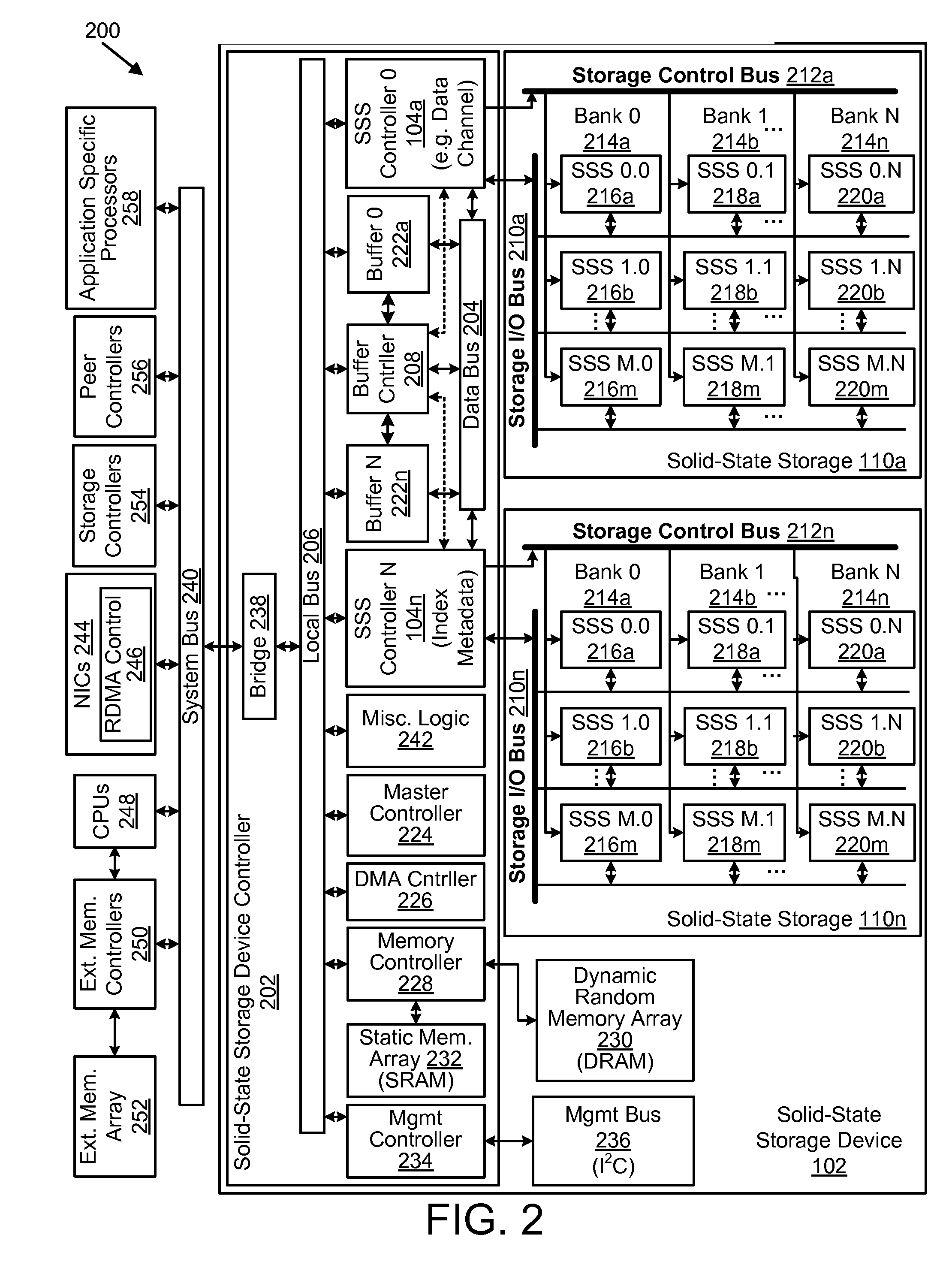

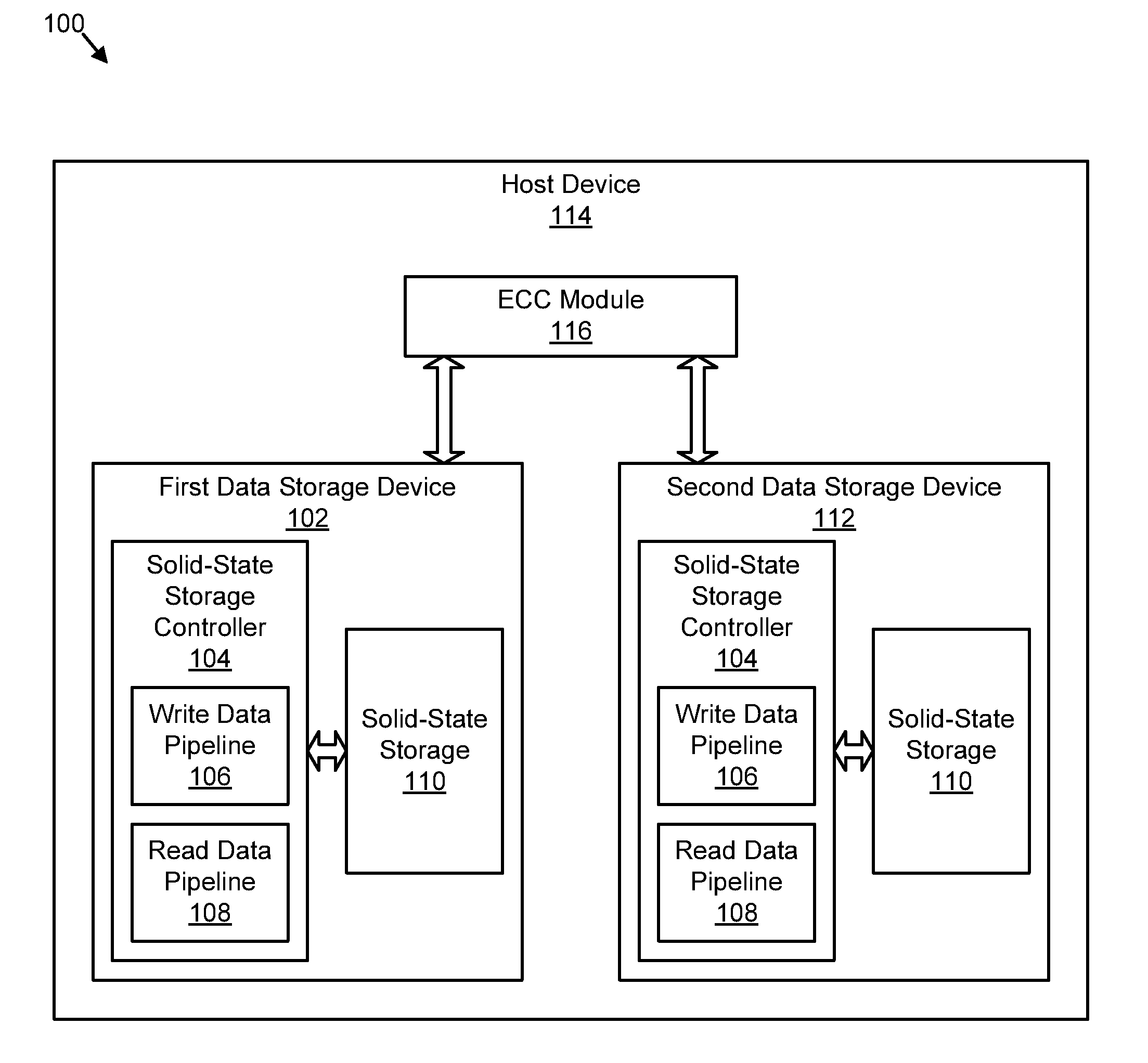

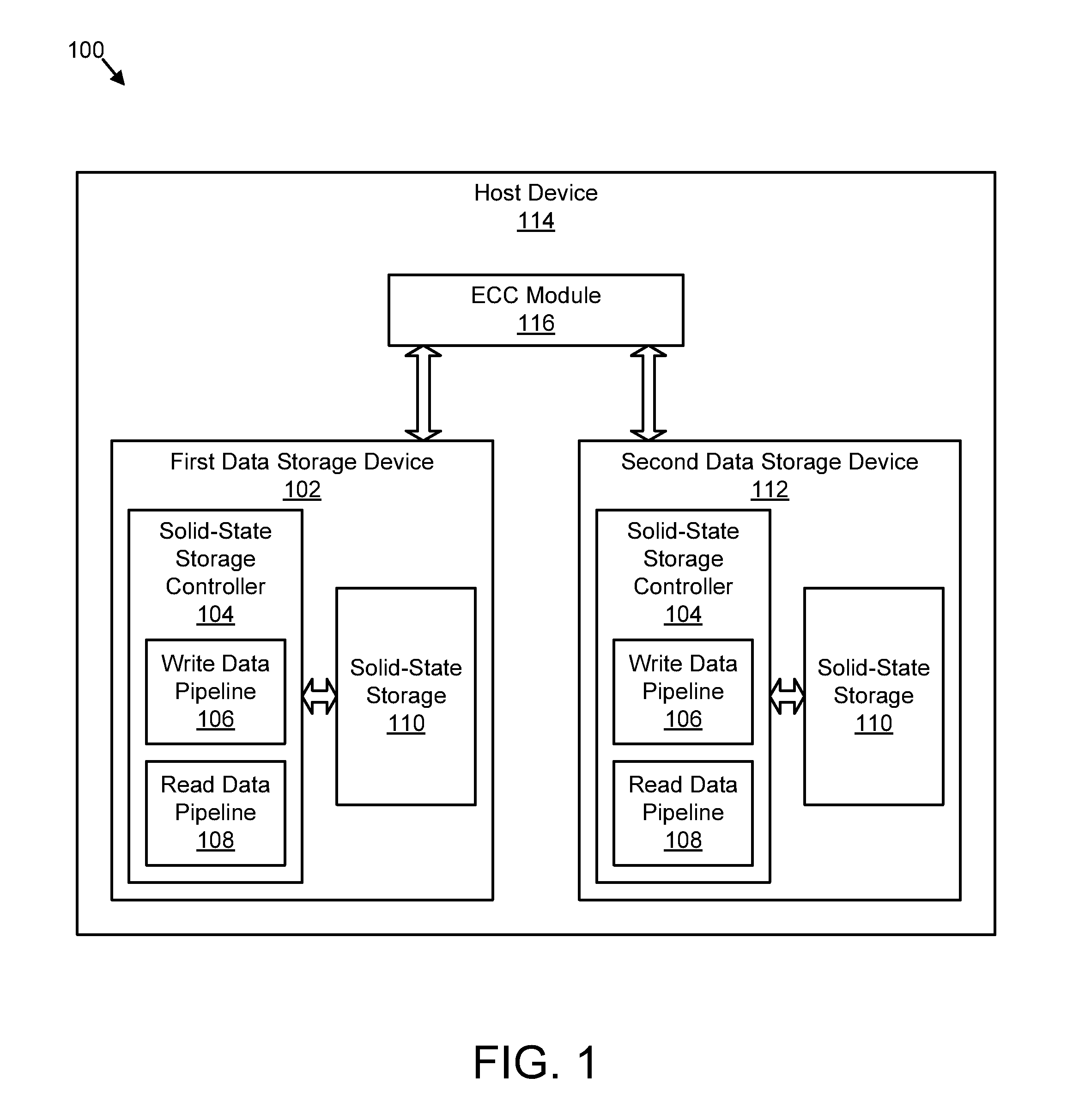

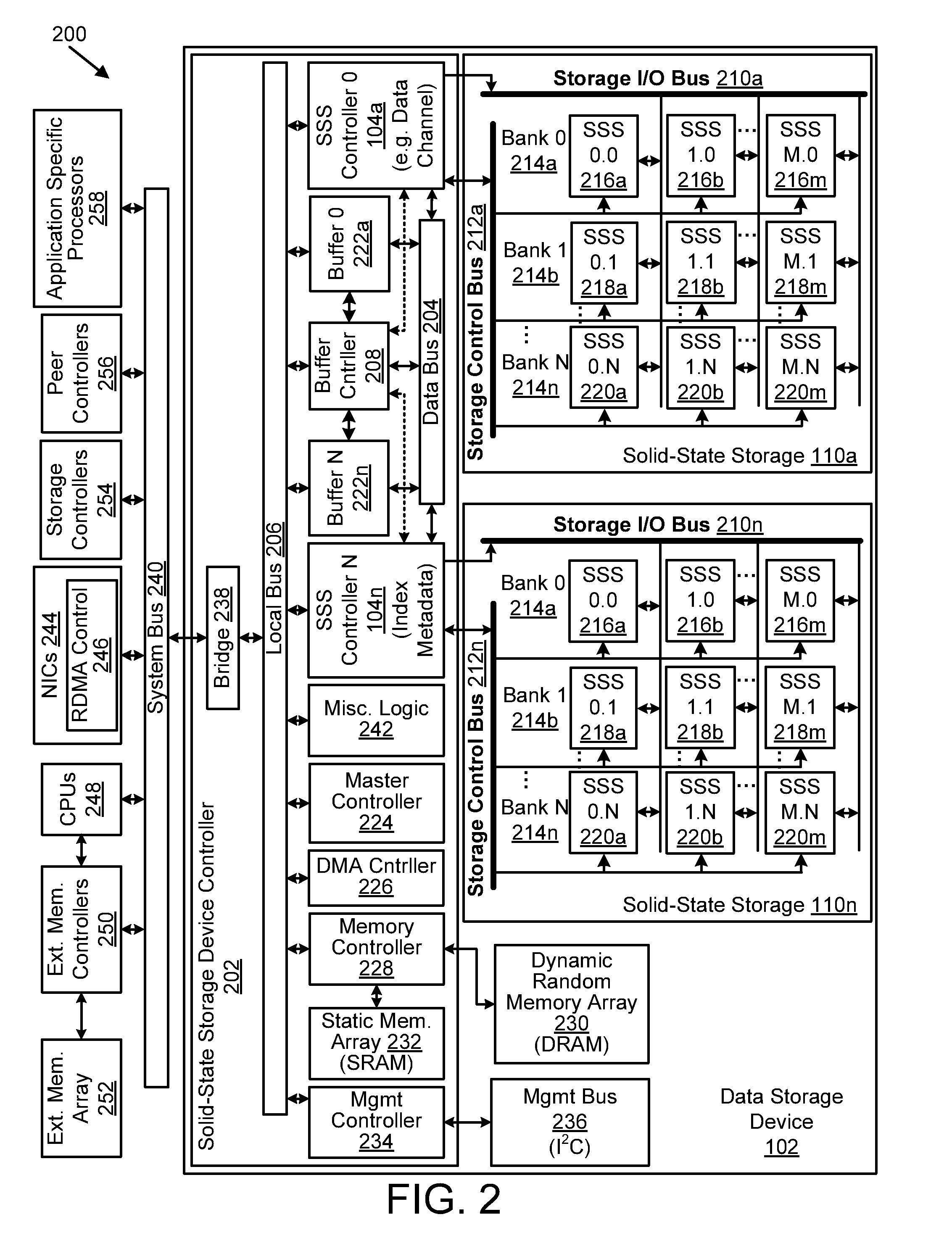

Apparatus, system, and method for managing data using a data pipeline

ActiveUS20080141043A1Energy efficient ICTInput/output to record carriersSolid-state storageData segment

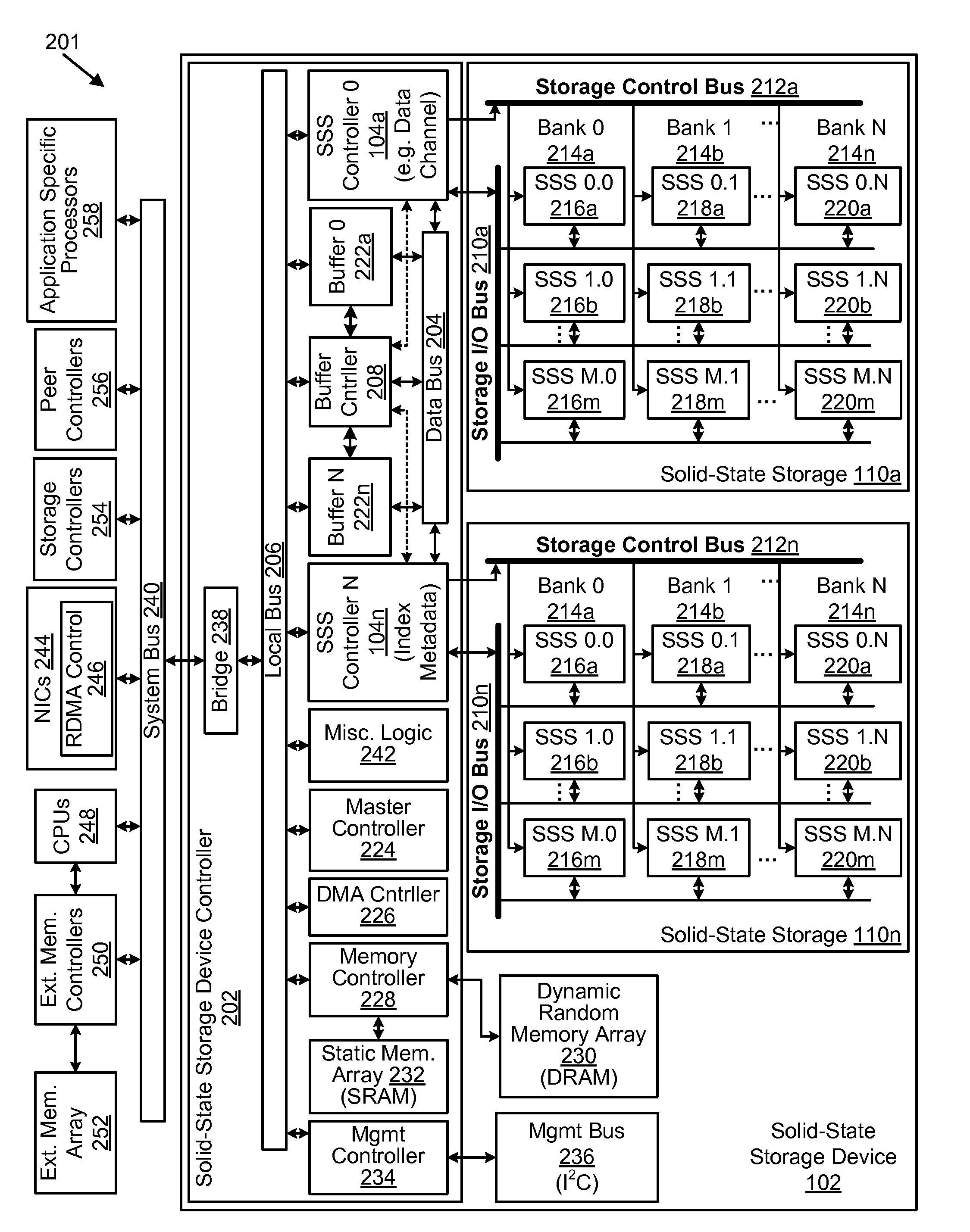

An apparatus, system, and method are disclosed for managing data in a solid-state storage device. A solid-state storage and solid-state controller are included. The solid-state storage controller includes a write data pipeline and a read data pipeline The write data pipeline includes a packetizer and an ECC generator. The packetizer receives a data segment and creates one or more data packets sized for the solid-state storage. The ECC generator generates one or more error-correcting codes (“ECC”) for the data packets received from the packetizer. The read data pipeline includes an ECC correction module, a depacketizer, and an alignment module. The ECC correction module reads a data packet from solid-state storage, determines if a data error exists using corresponding ECC and corrects errors. The depacketizer checks and removes one or more packet headers. The alignment module removes unwanted data, and re-formats the data as data segments of an object.

Owner:UNIFICATION TECH LLC

Distortion resistant double-data correcting color transition barcode and method of generating and using same

InactiveUS6070805AEliminate useDigitally marking record carriersRecord carriers used with machinesError checkingLinear growth

A color barcode symbology is disclosed that can be accurately decoded despite severe distortions, misreads or altered symbols. This disclosed barcode is a color transition barcode having linear growth properties designed to resist the single or combined effects of: scaling distortions, perspective distortions, shear distortions, and wave distortions of both the uniform and non-uniform type distributed across the barcode's vertical or horizontal axis. This color barcode symbology is also resistant to missing symbols and altered symbols while offering, high security, error checking, and double error correcting capability.

Owner:ZEBRA TECH CORP

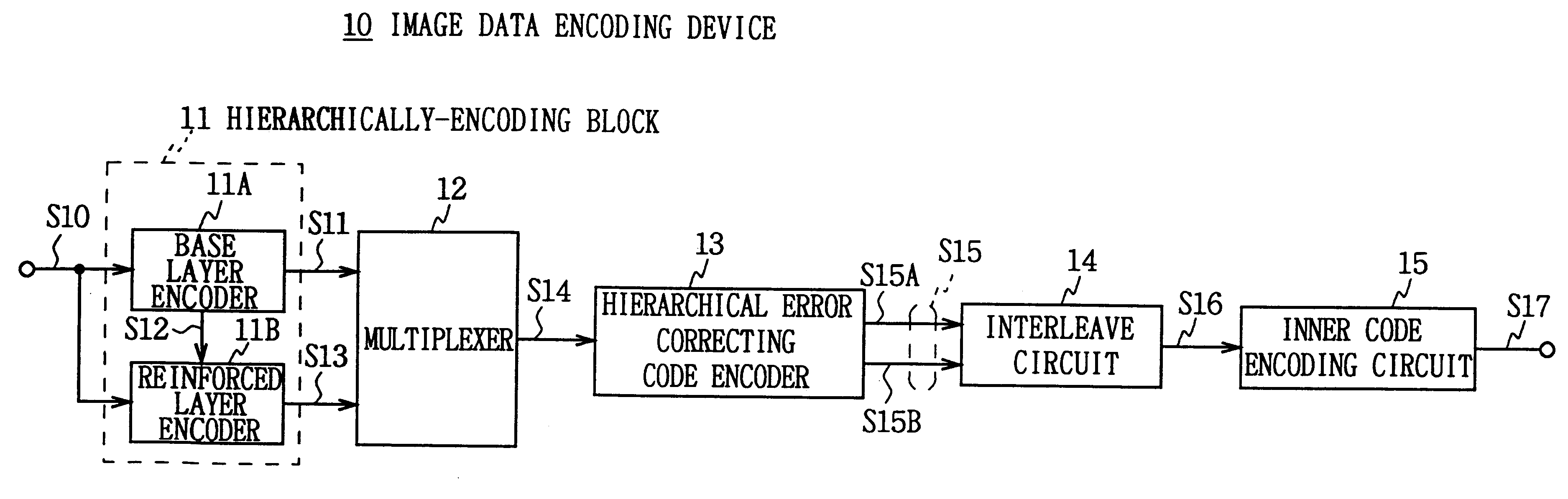

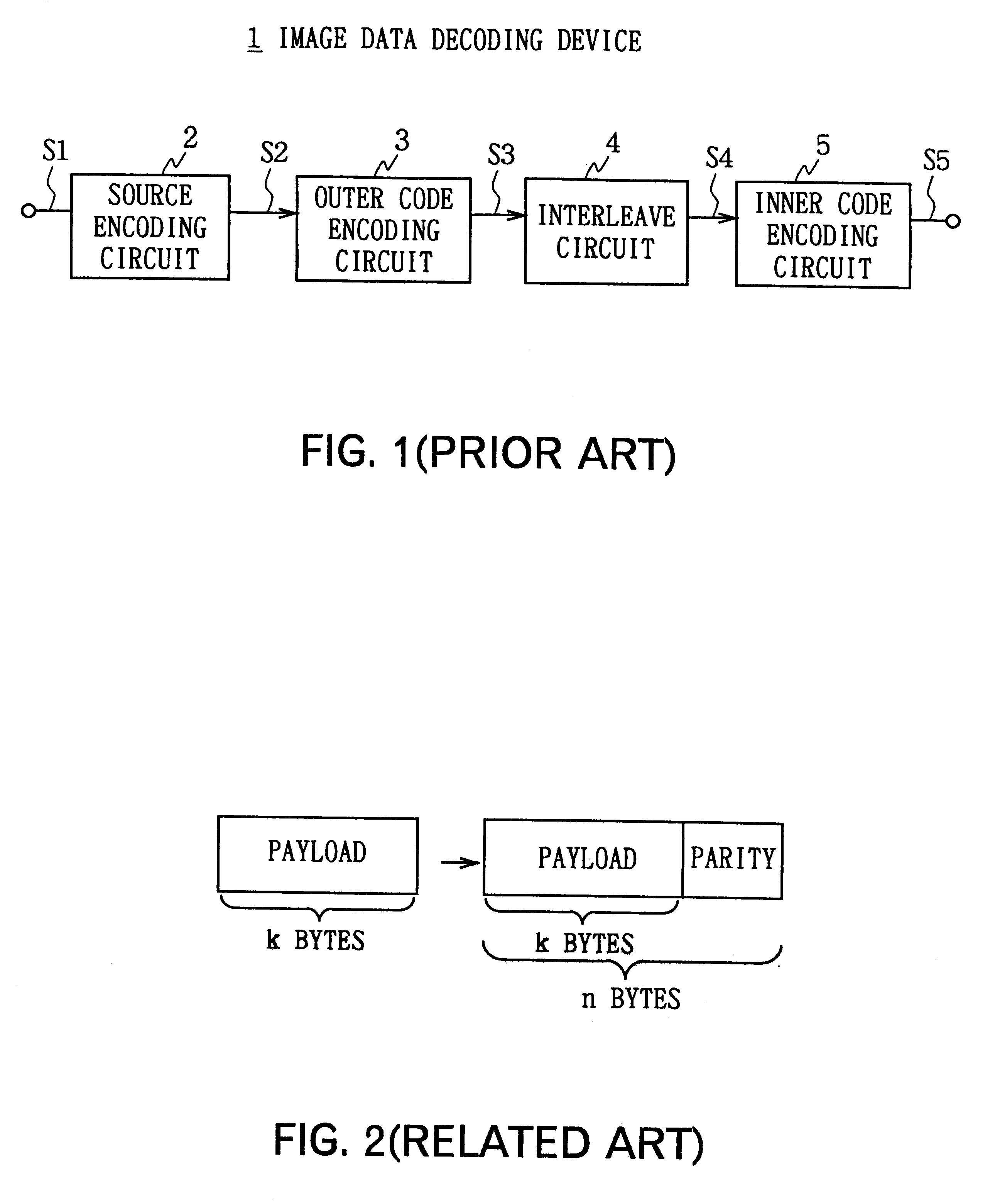

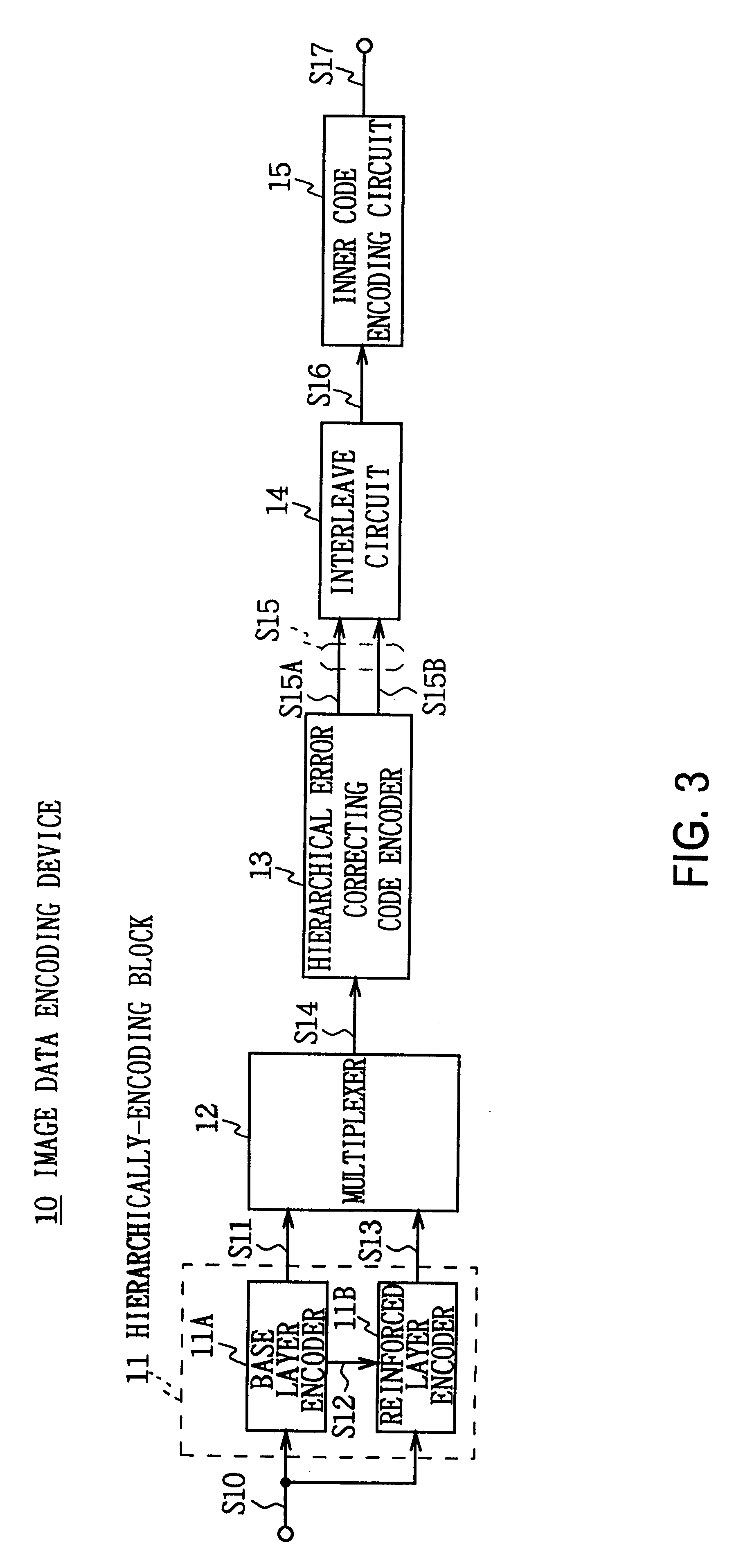

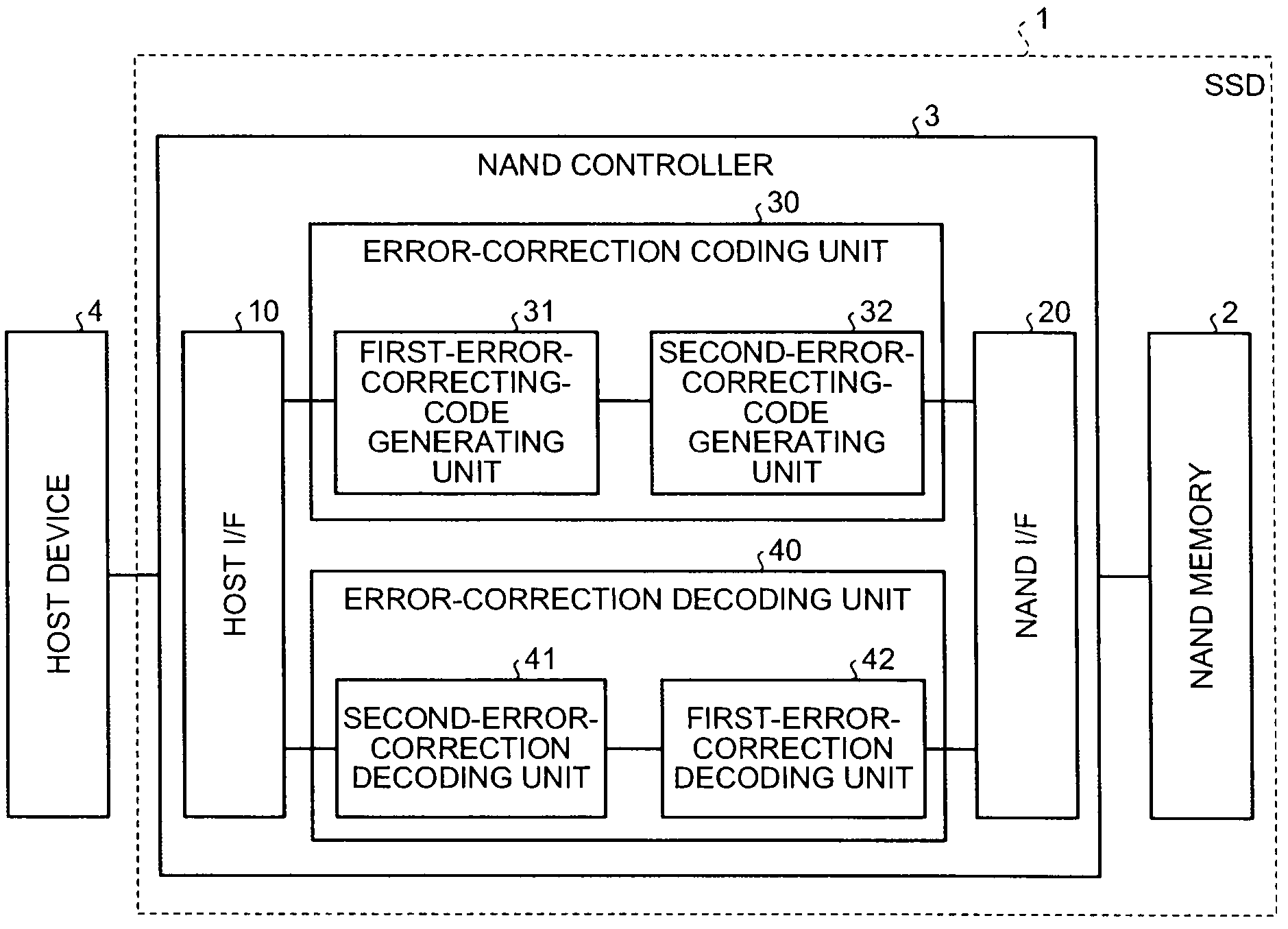

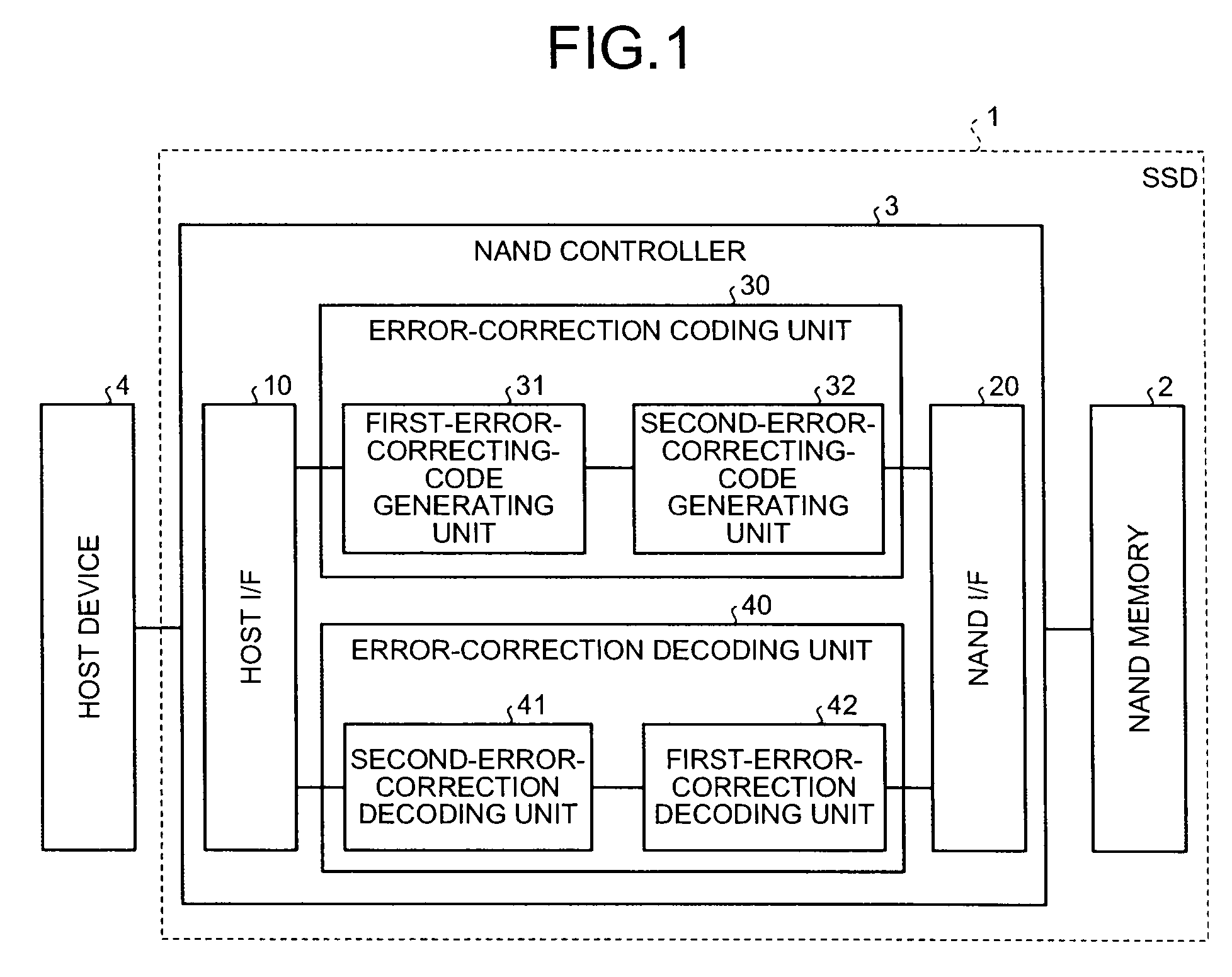

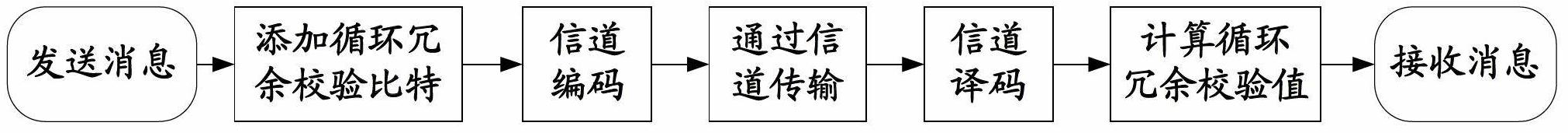

Method for adding and encoding error correcting codes and its device and method for transmitting data having error correcting codes added

A method for encoding error correcting codes to generate plural coded data having different error correction ability according to significance. An error correcting code having different code length is added to a fixed length of input data according to the significance of the input data (S14). The error correcting codes added which have different error correction ability corresponding to its code length are encoded to generate coded data having different packet length according to the code length of the error correcting code. Thus, plural coded data (S15A and S15B) which have different error correction ability according to significance can be generated. Thereby, even if a quality of transmission system deteriorates when the above coded data is transmitted, the coded data having high error correction ability can be surely decoded.

Owner:SONY CORP

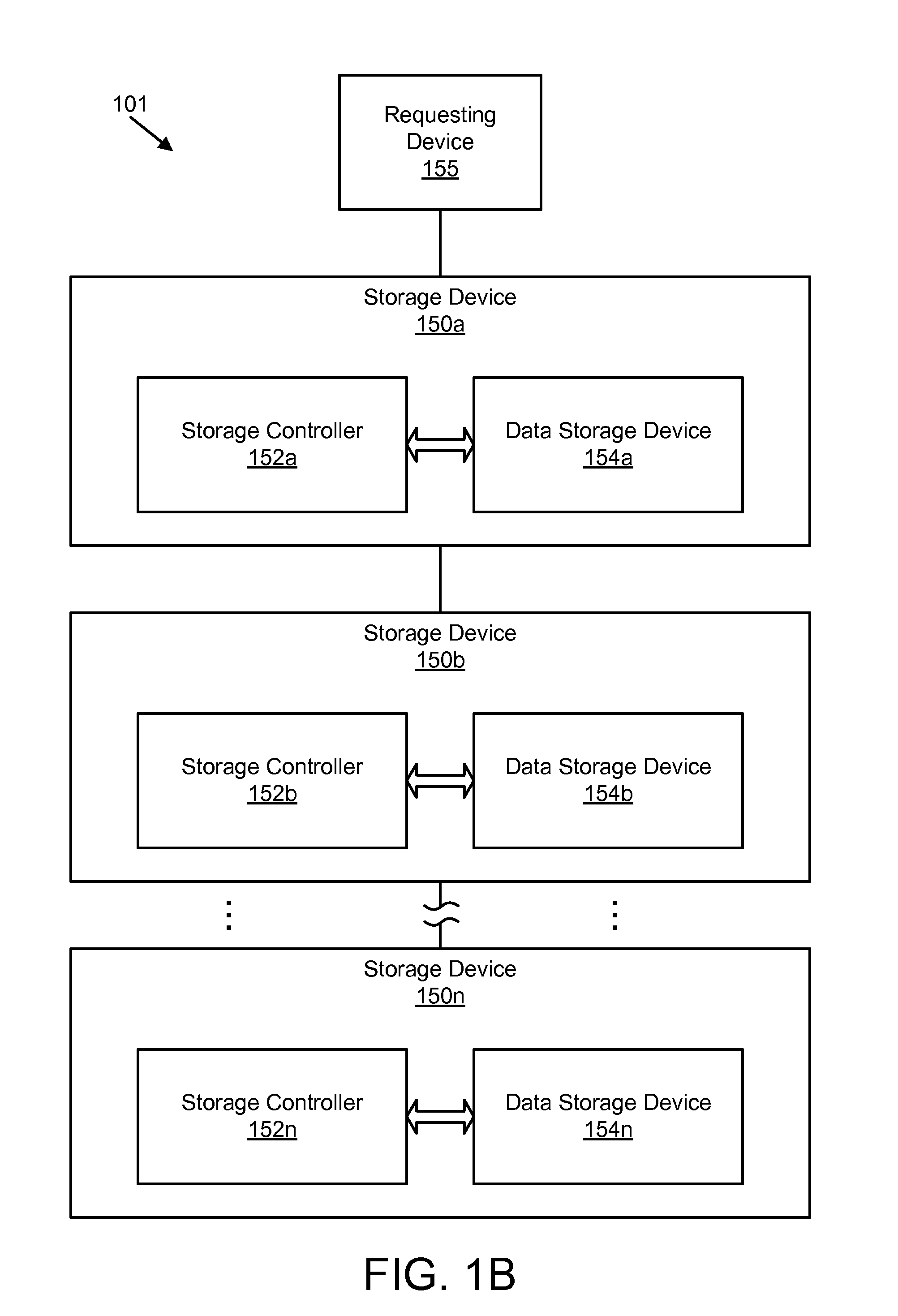

Apparatus, system, and method for detecting and replacing failed data storage

An apparatus, system, and method are disclosed for detecting and replacing failed data storage. A read module reads data from an array of memory devices. The array includes two or more memory devices and one or more extra memory devices storing parity information from the memory devices. An ECC module determines, using an error correcting code (“ECC”), if one or more errors exist in tested data and if the errors are correctable using the ECC. The tested data includes data read by the read module. An isolation module selects a memory device in response to the ECC module determining that errors exists in the data read by the read module and that the errors are uncorrectable using the ECC. The isolation module also replaces data read from the selected memory device with replacement data and available data wherein the tested data includes the available data combined with the replacement data.

Owner:SANDISK TECH LLC

Error correcting device and error correcting method

An error correcting device for correcting erroneous data included in data read out from a nonvolatile memory includes a determining unit that determines whether the data read out from the nonvolatile memory include an error beyond an error correcting capability of the error correcting device. When the determining unit has determined that an error beyond the error correcting capability exists, the error correcting device does not perform the correction of the error.

Owner:KK TOSHIBA

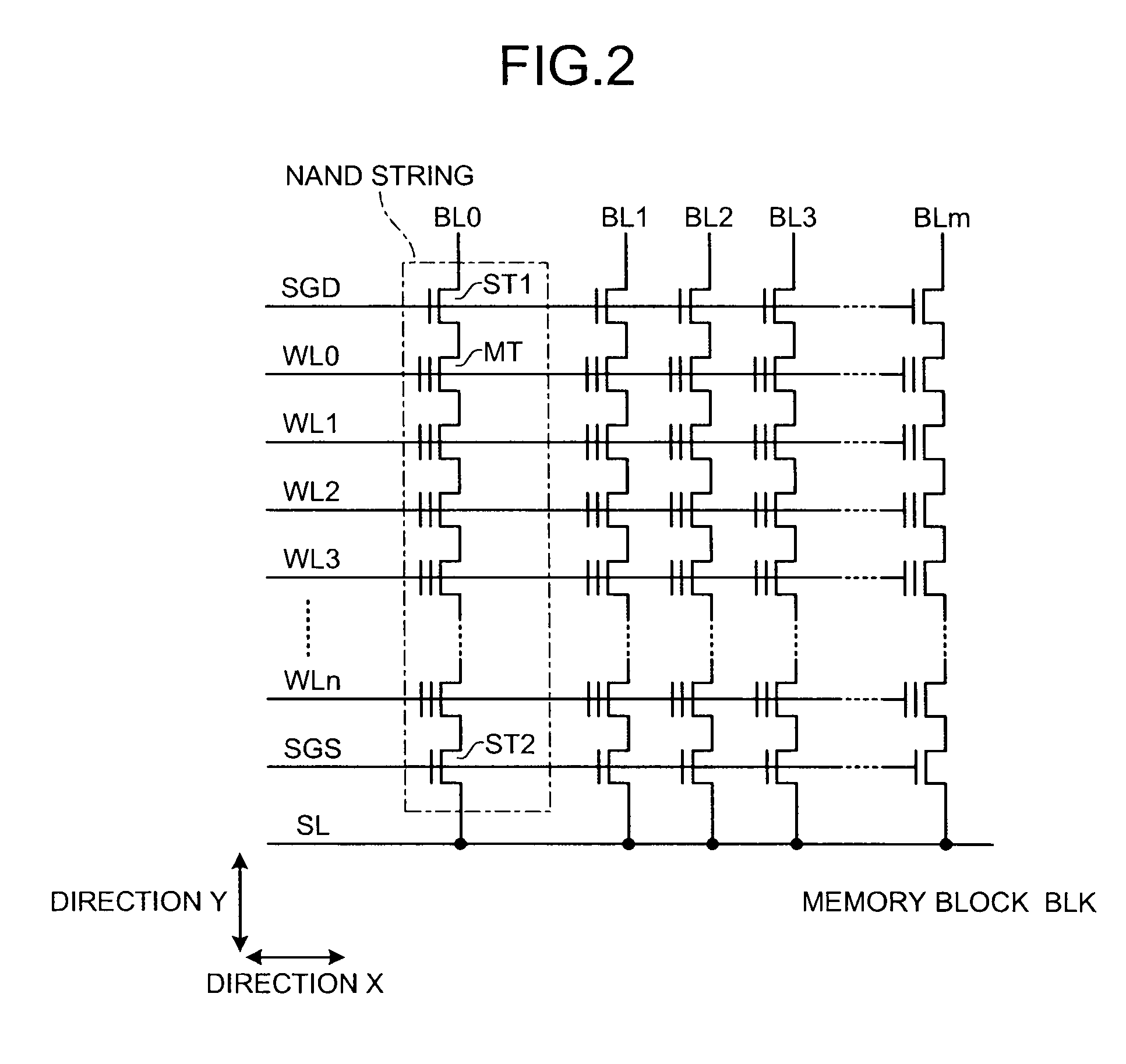

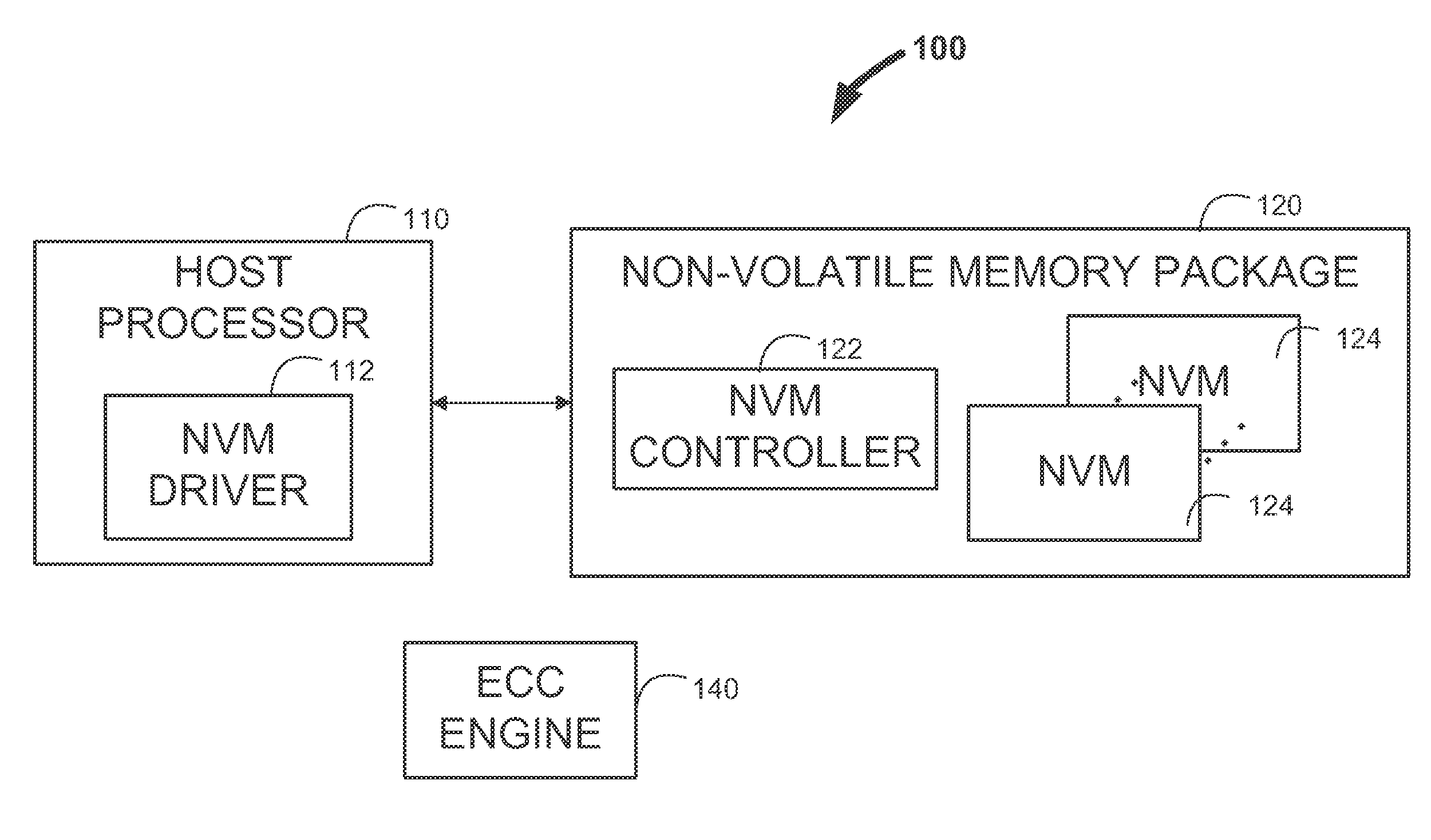

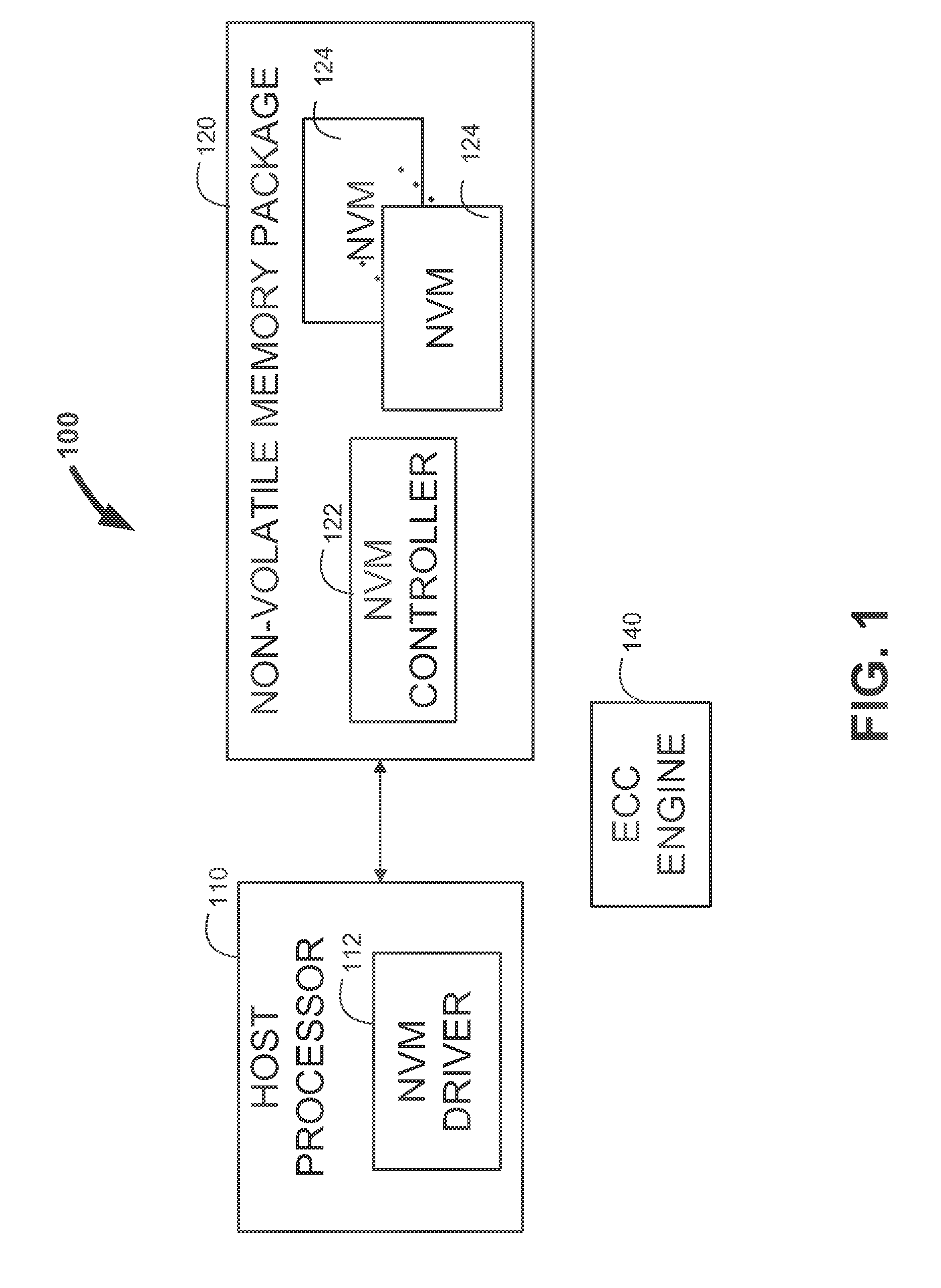

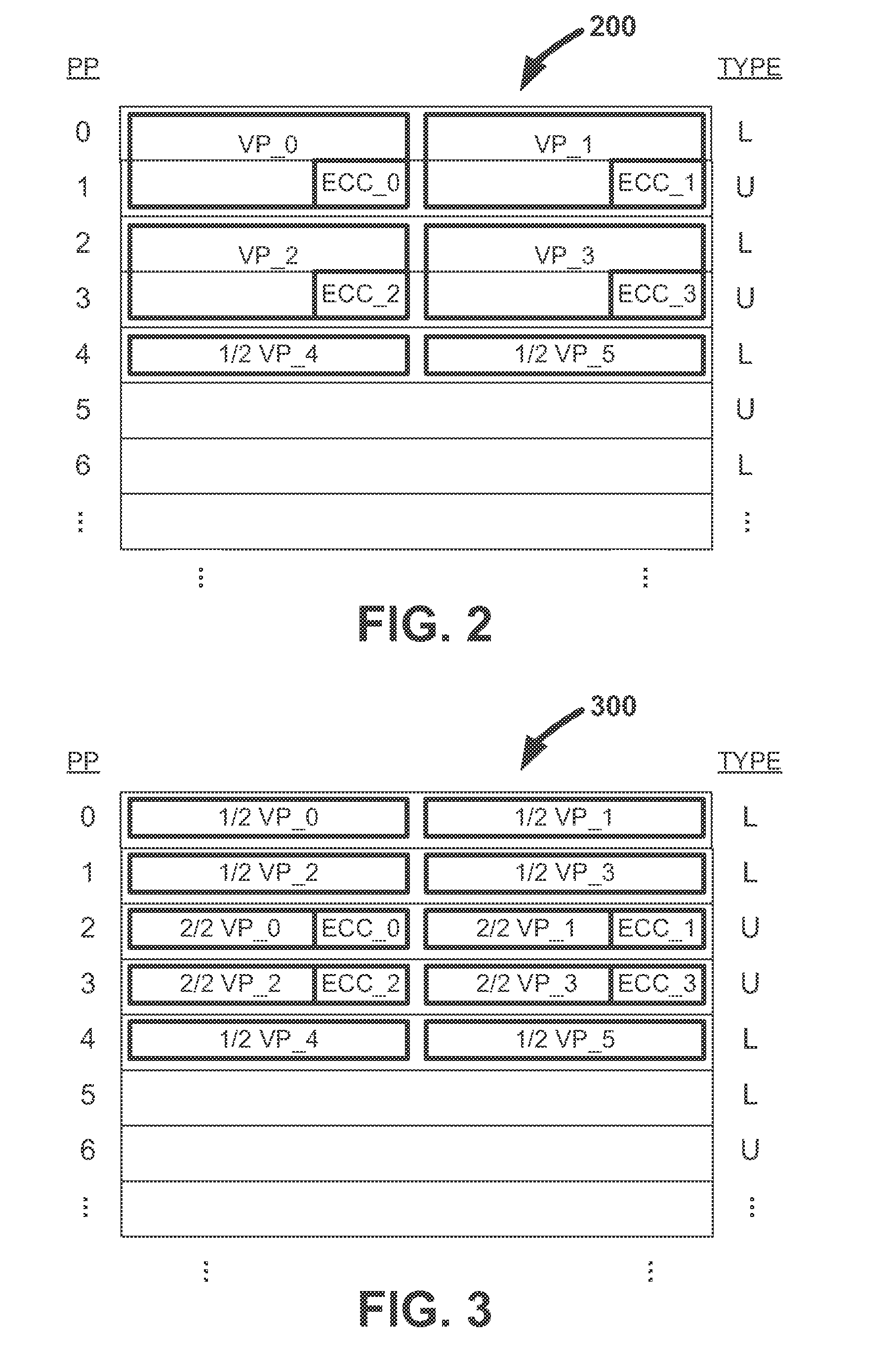

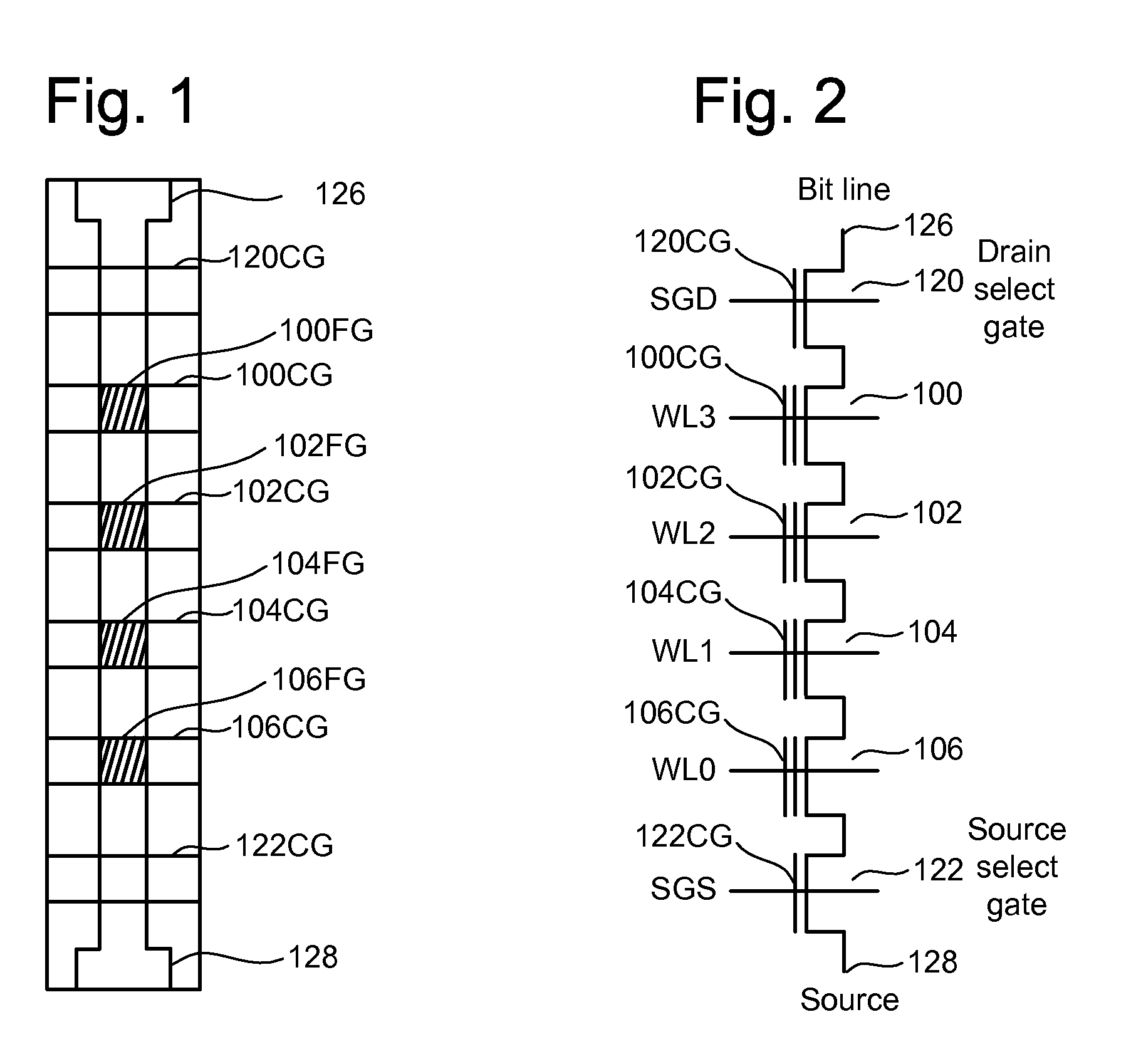

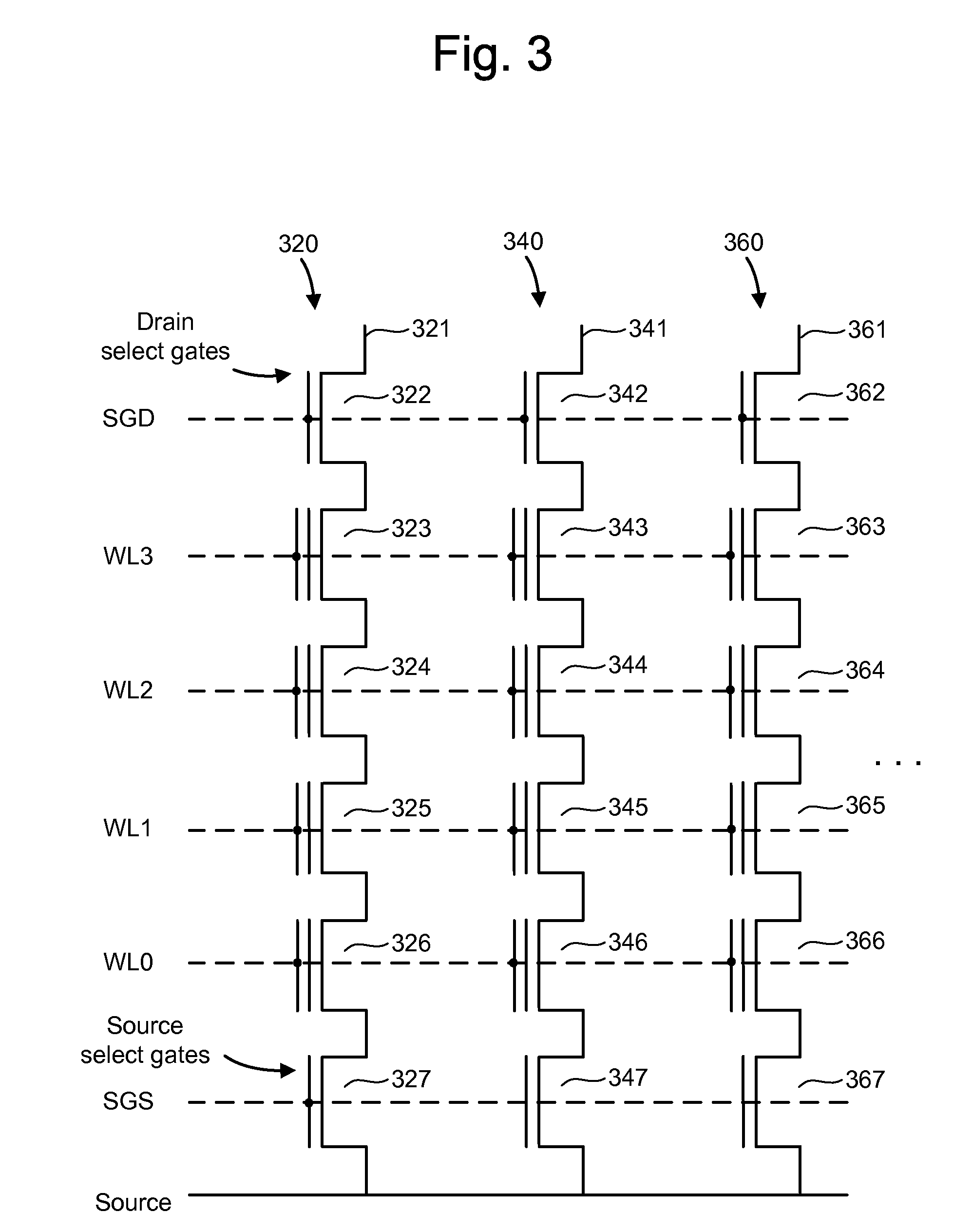

Codeword remapping schemes for non-volatile memories

ActiveUS20110209028A1Efficient and effectiveCorrection errorMemory architecture accessing/allocationMemory adressing/allocation/relocationError correctingVolatile memory

Systems and methods are disclosed for remapping codewords for storage in a non-volatile memory, such as flash memory. In some embodiments, a controller that manages the non-volatile memory may prepare codeword using a suitable error correcting code. The controller can store a first portion of the codeword in a lower page of the non-volatile memory may store a second portion of the codeword in an upper page of the non-volatile memory. Because upper and lower pages may have different resiliencies to error-causing phenomena, remapping codewords in this manner may even out the bit error rates of the codewords (which would otherwise have a more bimodal distribution).

Owner:APPLE INC

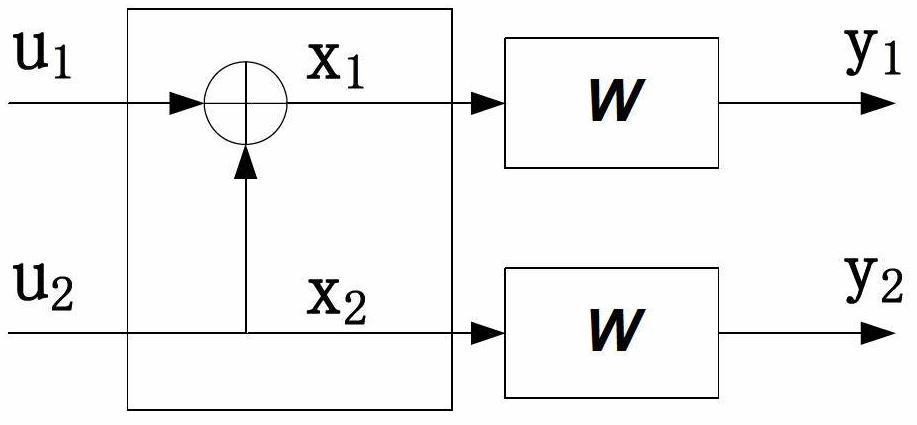

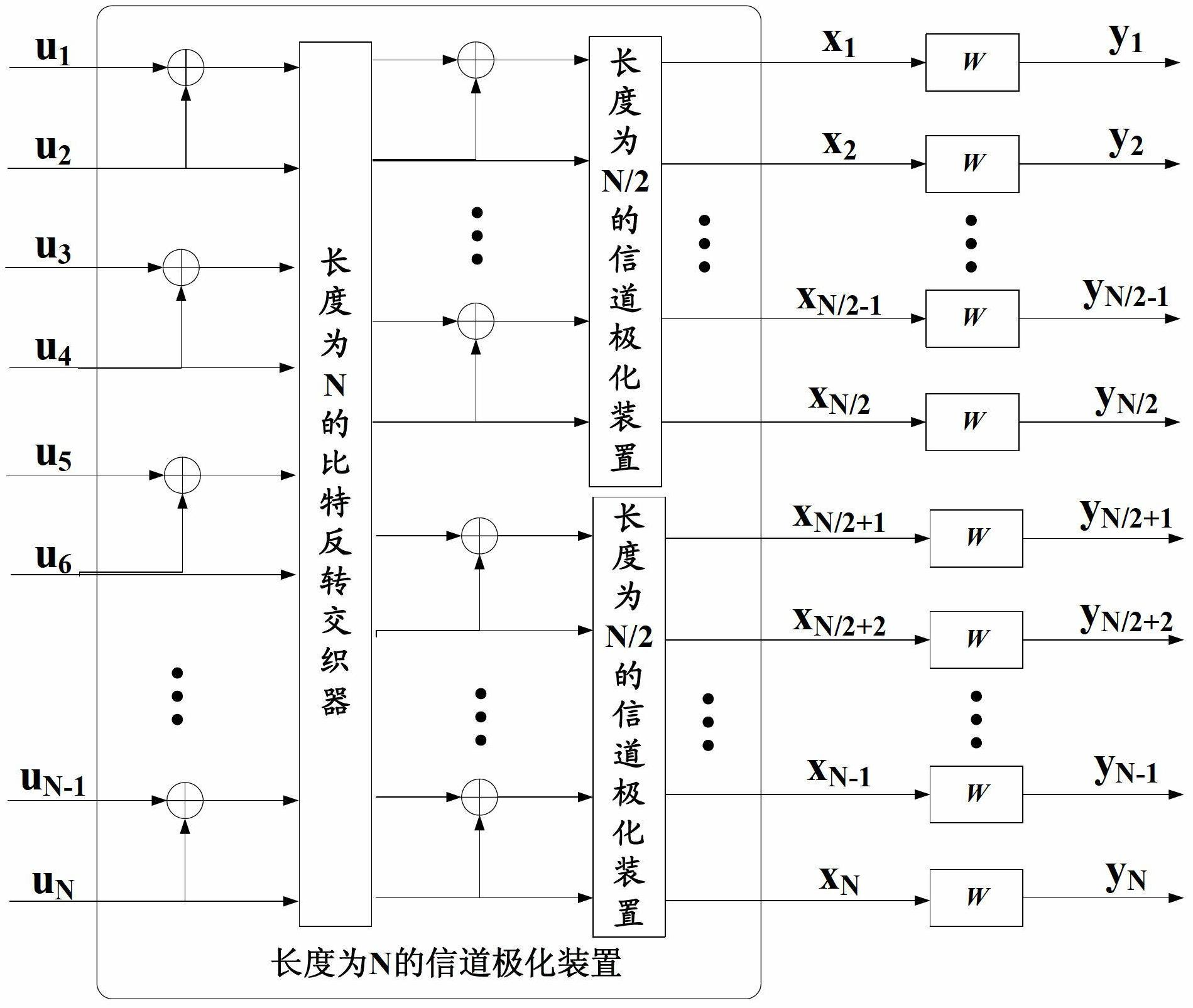

Polarization code decoding method for cyclic redundancy check assistance

InactiveCN102694625AStrong error correction abilityReduce operational complexityError preventionError correction/detection using linear codesCommunications systemCode division multiple access

The invention relates to a polarization code decoding method for cyclic redundancy check assistance. When a polarization code is decoded, in all the routes with cyclic redundancy check values of corresponding bit estimation sequences of being zero from a root node to leaf nodes on a code tree corresponding to the polarization code, one route with maximum reliability metric value is searched by taking a list or stack as assistance for route search, and the bit estimation sequence corresponding to the route is output as a decoding result. The method comprises the following operation steps of: determining parameters according to a search assistance method, constructing an auxiliary structure of the decoding method, searching a candidate bit estimation sequence and executing cyclic redundancy check. By adopting the method disclosed by the invention, error correcting capability of a communication system which adopts the polarization code as channel coding is greatly improved, operation steps are simpler, and operation complexity is equivalent to or even lower than that of a Turbo code coding and decoding method used in a WCDMA (wideband code division multiple access) system, thus the method disclosed by the invention has a good practical prospect.

Owner:BEIJING UNIV OF POSTS & TELECOMM

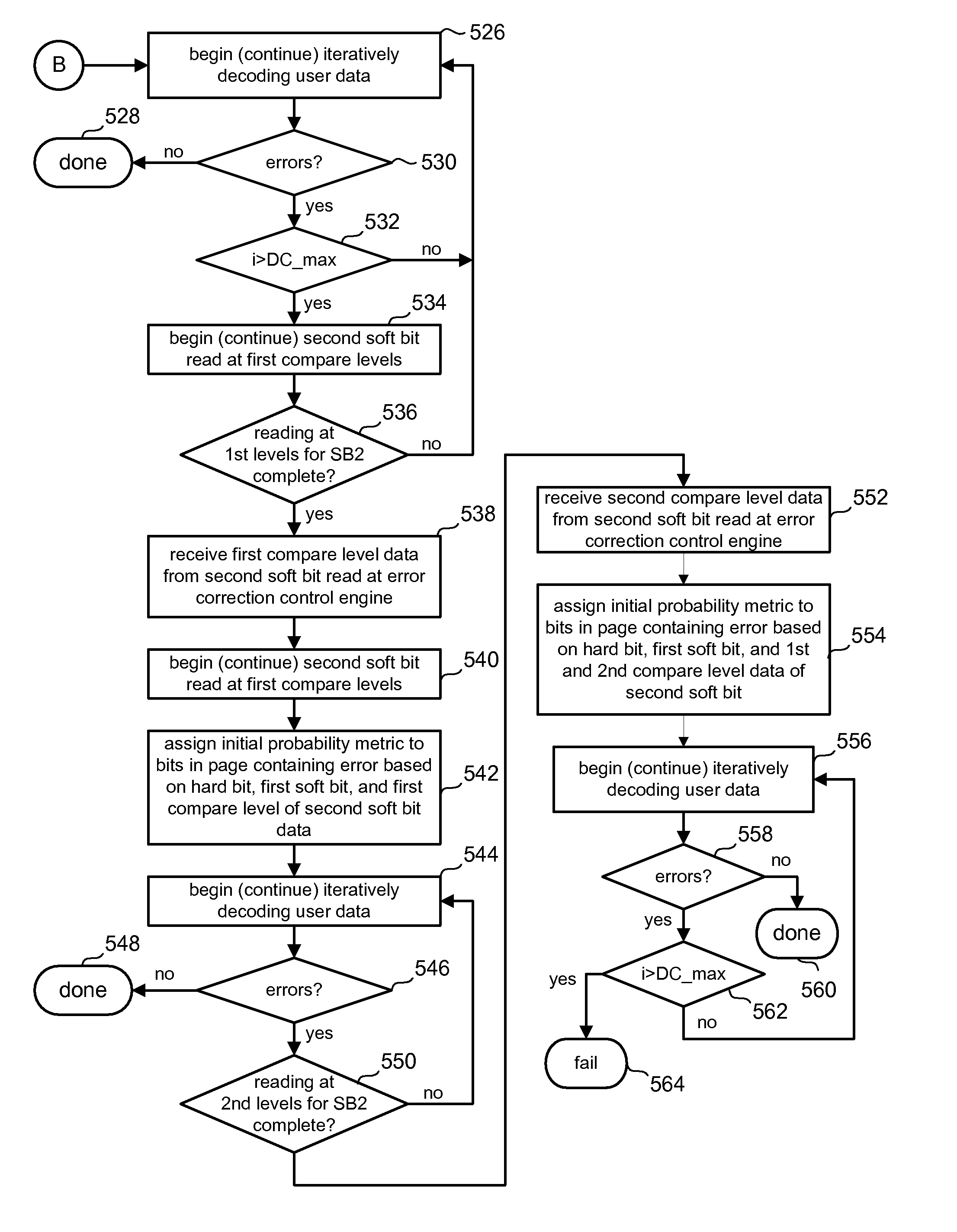

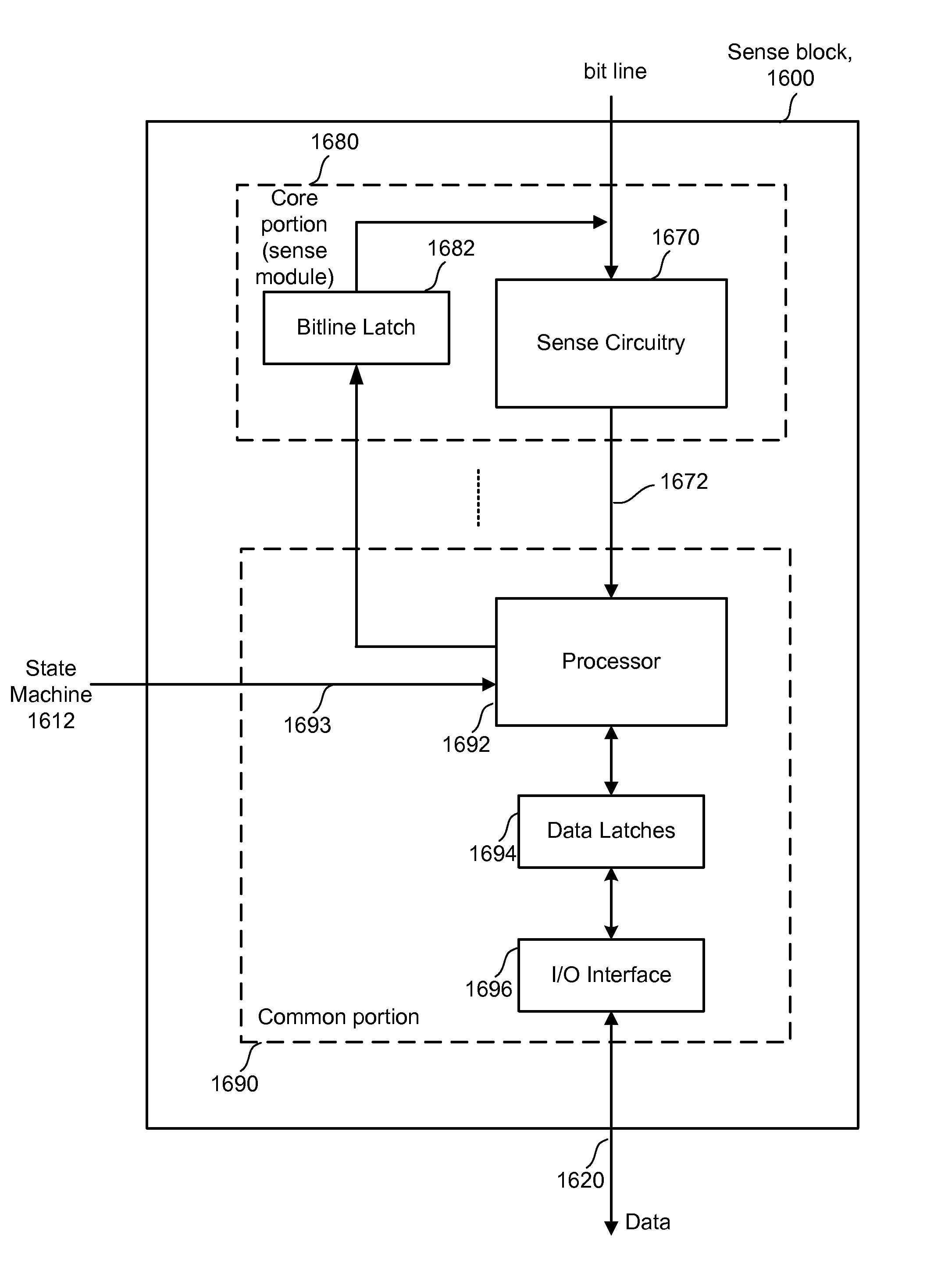

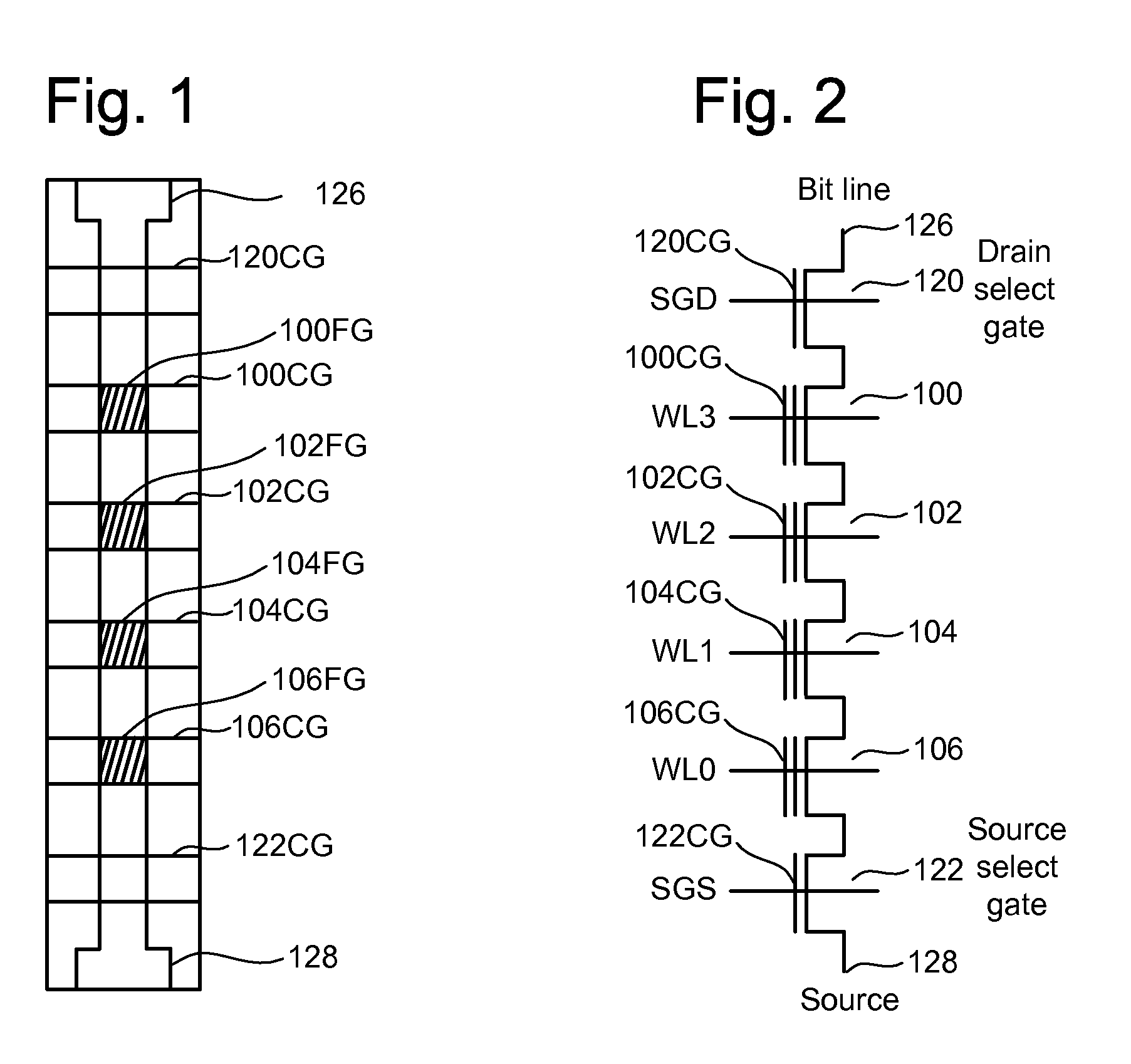

Soft bit data transmission for error correction control in non-volatile memory

ActiveUS20080244338A1High resolutionError detection/correctionCode conversionLow-density parity-check codeSoft data

Data stored in non-volatile storage is decoded using iterative probabilistic decoding. An error correcting code such as a low density parity check code may be used. In one approach, initial reliability metrics, such as logarithmic likelihood ratios, are used in decoding sensed states of a set of non-volatile storage element. The decoding attempts to converge by adjusting the reliability metrics for bits in code words which represent the sensed state. Soft data bits are read from the memory if the decoding fails to converge. Initial reliability metric values are provided after receiving the hard read results and at each phase of the soft bit operation(s). In one embodiment, a second soft bit is read from the memory using multiple subsets of soft bit compare levels. While reading at the second subset of compare levels, decoding can be performed based on the first subset data.

Owner:SANDISK TECH LLC

Codes For Limited Magnitude Asymetric Errors In Flash Memories

ActiveUS20080168320A1Increase speedReach levelError preventionTransmission systemsReduced sizeErrors and residuals

Error correction is tailored for the use of an ECC for correcting asymmetric errors with low magnitude in a data device, with minimal modifications to the conventional data device architecture. The technique permits error correction and data recovery to be performed with reduced-size error correcting code alphabets. For particular cases, the technique can reduce the problem of constructing codes for correcting limited magnitude asymmetric errors to the problem of constructing codes for symmetric errors over small alphabets. Also described are speed up techniques for reaching target data levels more quickly, using more aggressive memory programming operations.

Owner:CALIFORNIA INST OF TECH

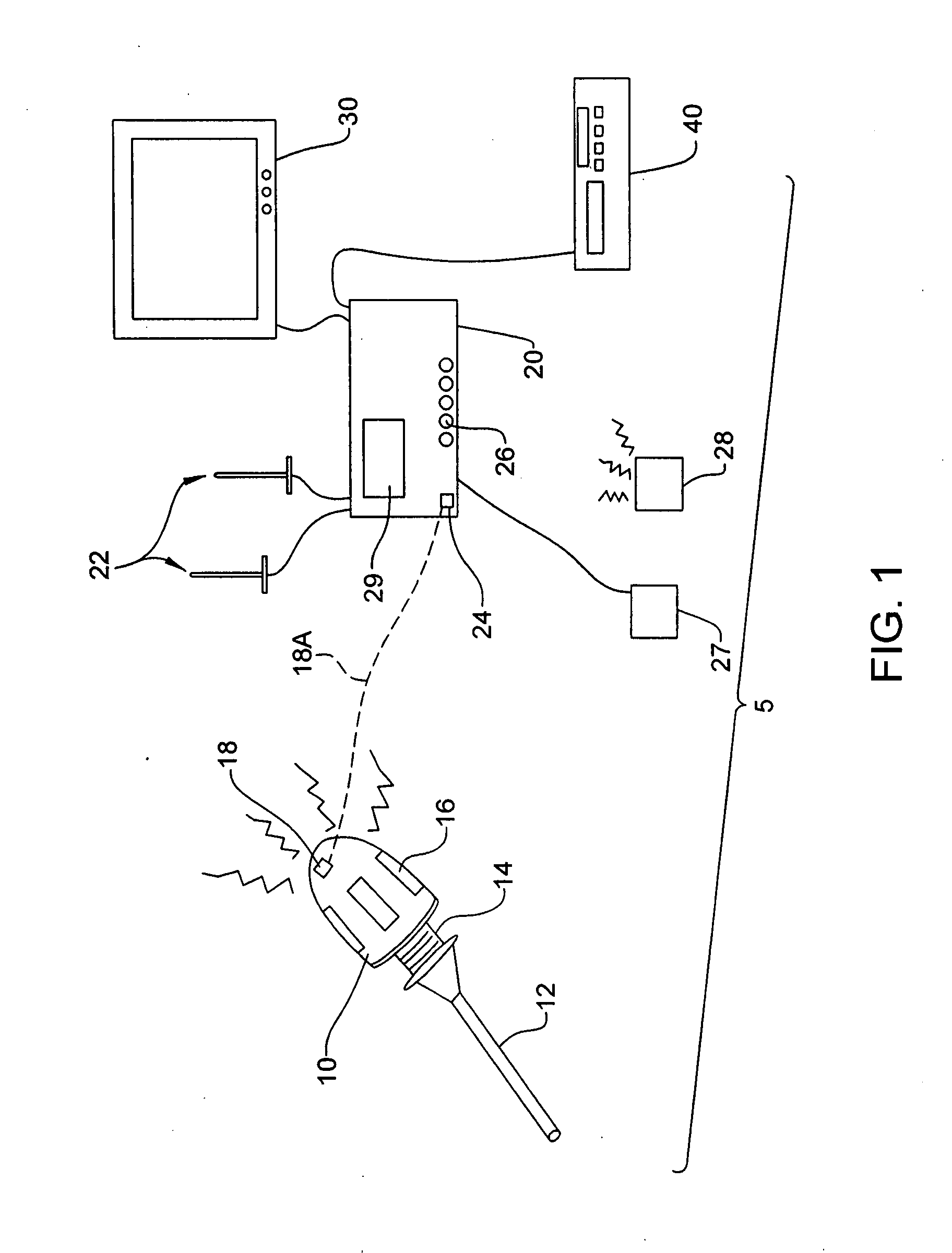

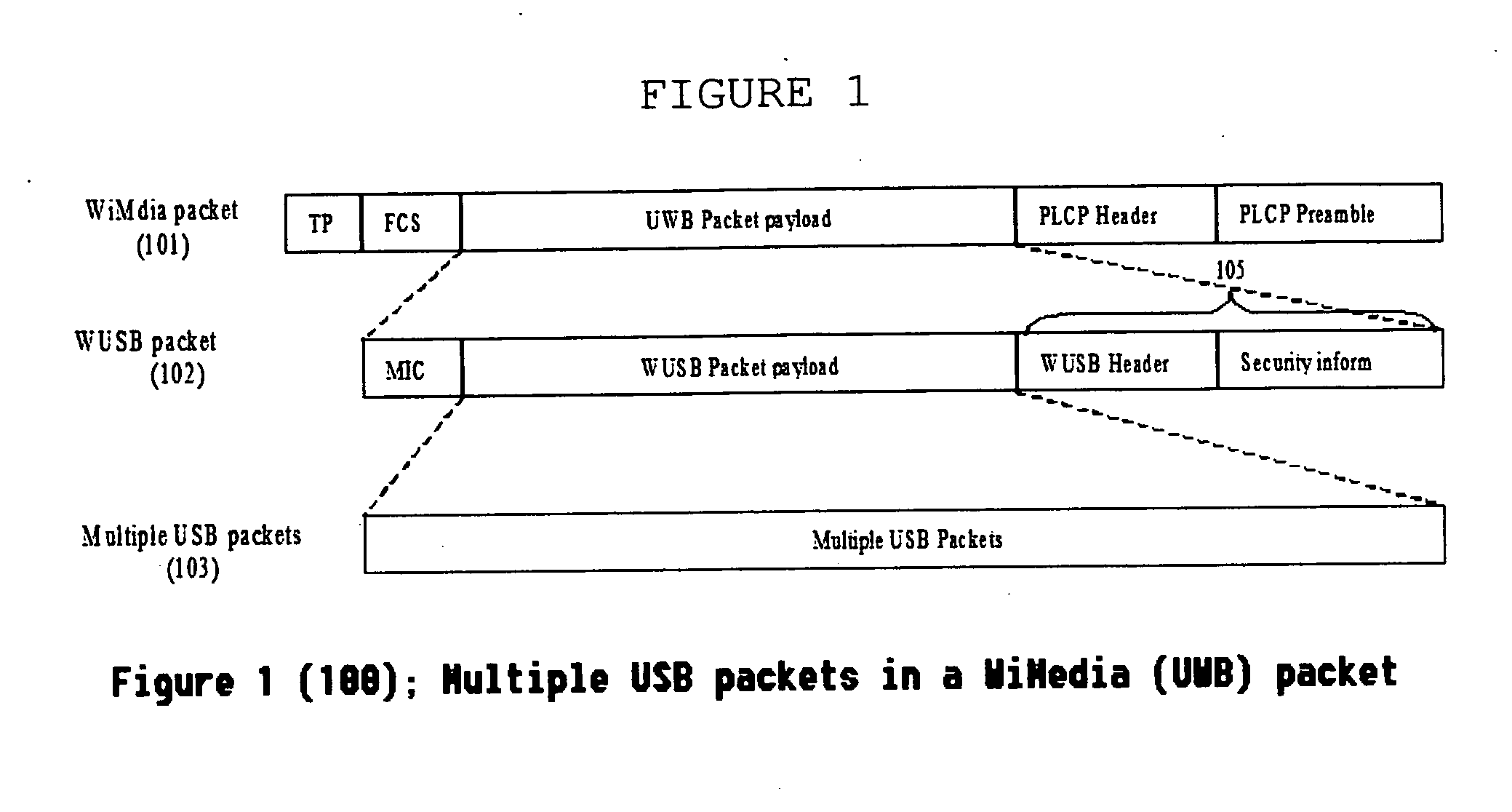

Wireless endoscopic camera

ActiveUS20080139881A1Reliable but high-performance wireless transmissionImprove fidelityEnergy efficient ICTTelevision system detailsData streamEndoscopic camera

A system and method for wirelessly transmitting a video image signal from an endoscopic camera to a receiver or control unit for storage and / or display on a video monitor. Use of a frame-specific, variable compression algorithm capable of progressively encoding a data stream provides for a better performing and higher quality wireless endoscopic camera system capable of generating images at varying resolutions. Use of a short-range, high-performance wireless technology, such as Ultrawideband (UWB), improves the performance capabilities of the system, while minimizing power consumption and extending battery life. Implementations of error correcting codes, as well as the use of multiple transmitting and receiving antennas, further improve the fidelity of the wireless communication.

Owner:STRYKER CORP

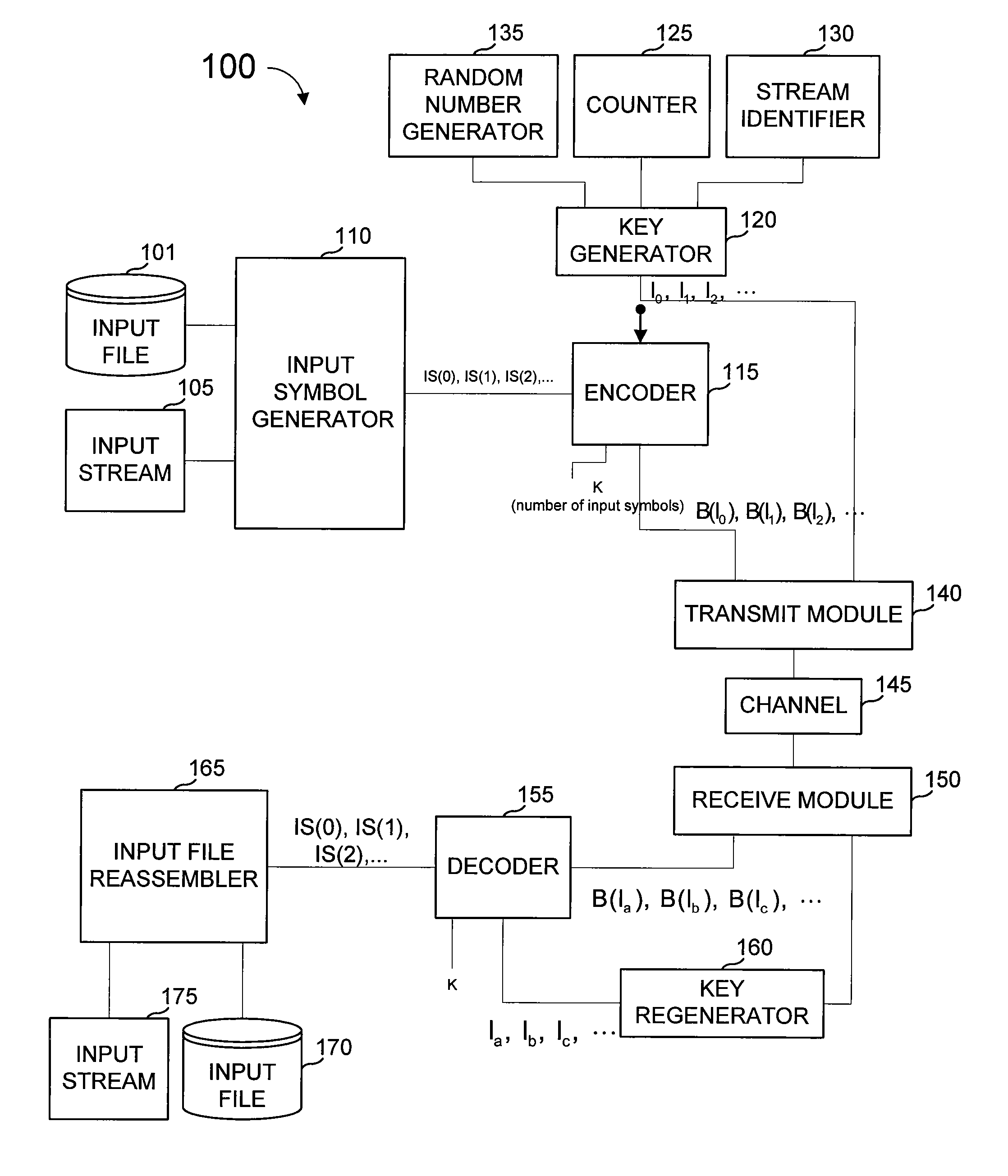

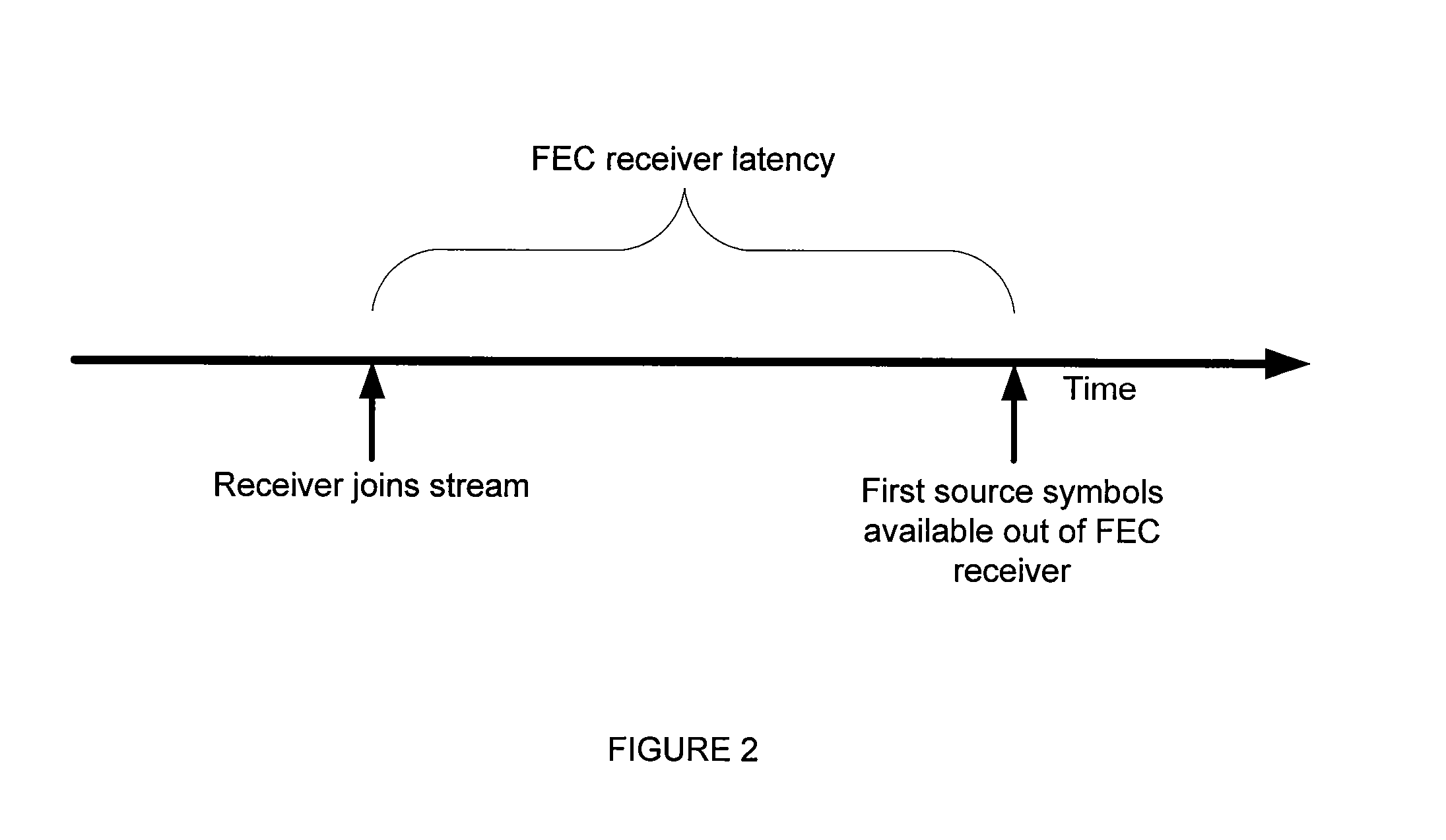

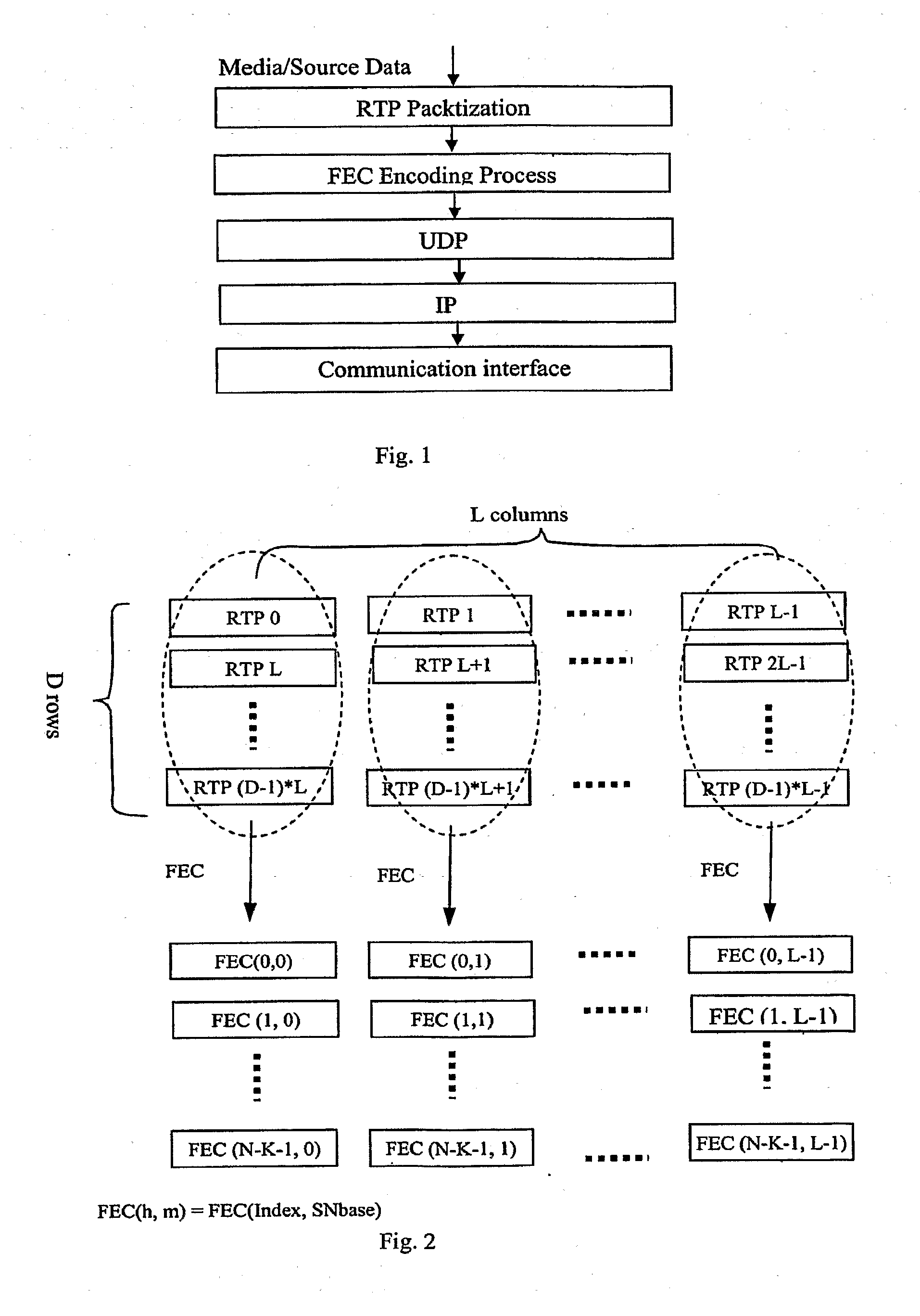

Forward error-correcting (FEC) coding and streaming

InactiveUS20060279437A1Simple logic requirementDelay minimizationError preventionCode conversionForward error correctionComputer science

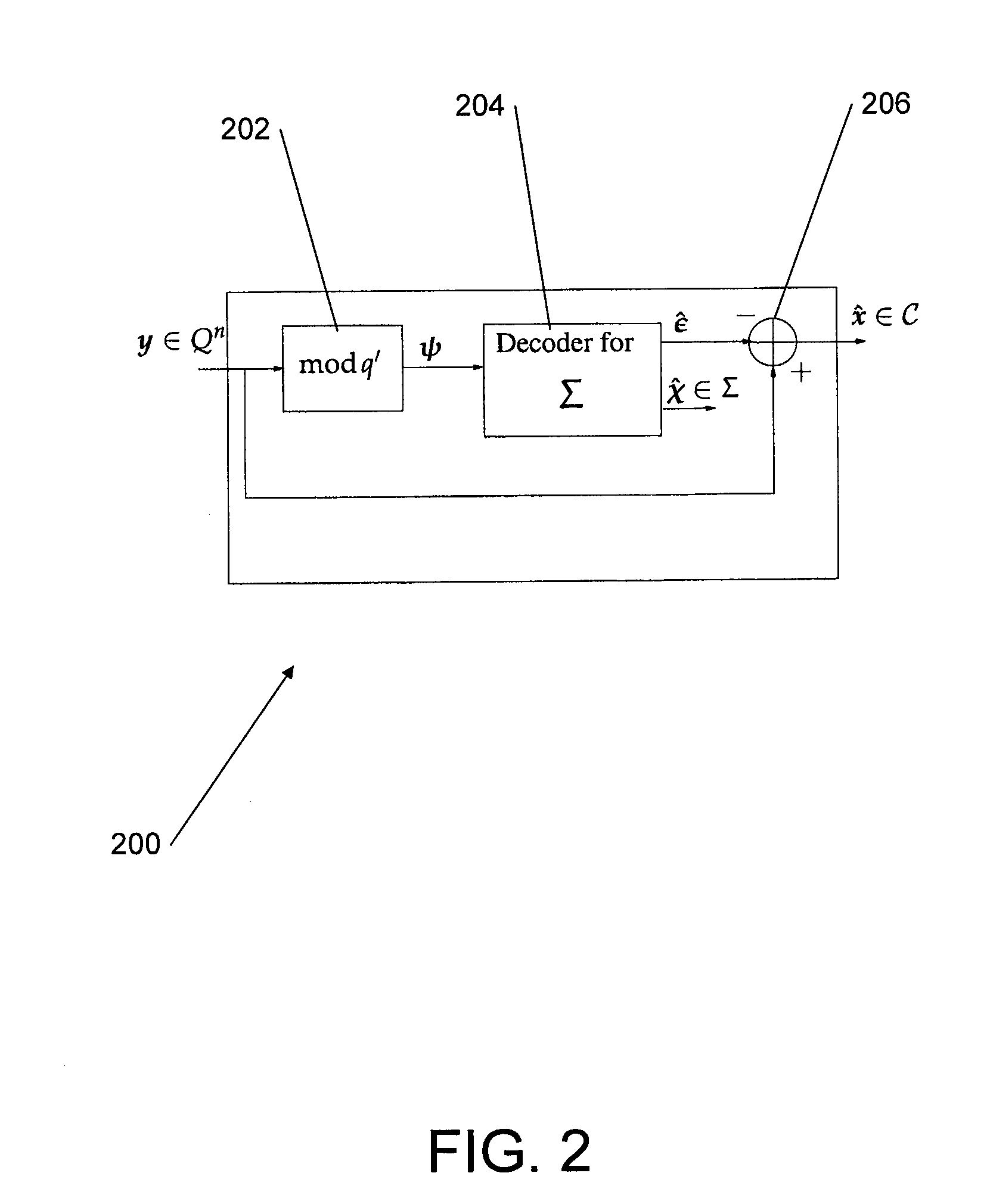

In a data decoder for decoding data from received symbols received over a channel from an encoder, wherein the received data can include erasures and include source symbols and repair symbols and wherein the decoder uses in decoding a generator matrix, any square submatrix of which is invertible, such that the decoder can perform decoding operations concurrently with the arrival of the source symbols and repair symbols, a method of decoding comprising representing in decoder memory a system of equations derived, at least in part, from the generator matrix, substituting received source symbols into the system of equations as the source symbols are received before receiving all source symbols, identifying, using decoder logic, repair equations to be used for solving the system of equations as repair symbols arrive, calculating, using decoder logic, vector values for equations as source symbols arrive, and converting the system of equations into an upper triangular form as repair symbols arrive at the decoder. Novel methods can be used for interleaving and specifying encoding structure for a large class of FEC codes, scheduling the sending of packets and the like.

Owner:QUALCOMM INC

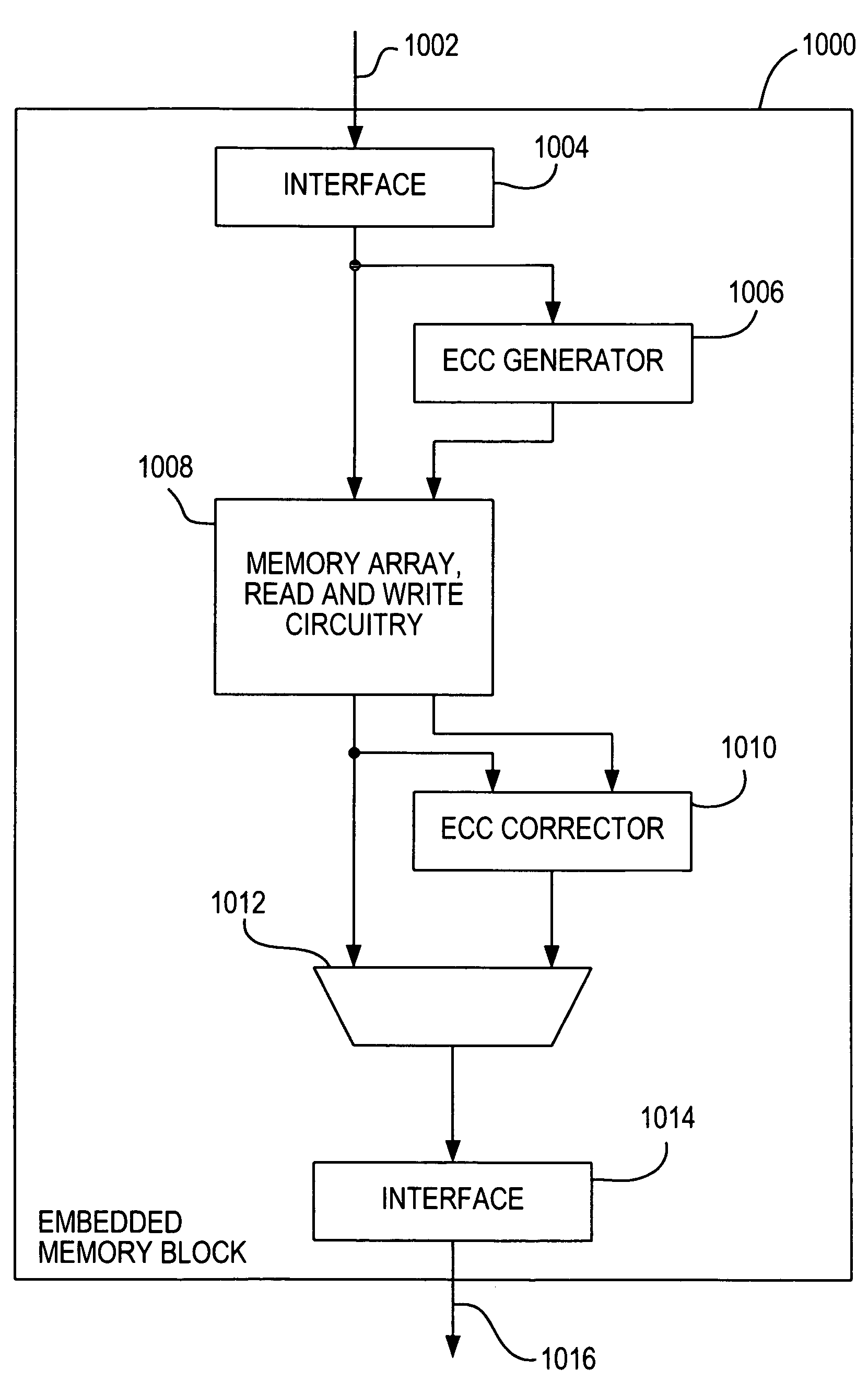

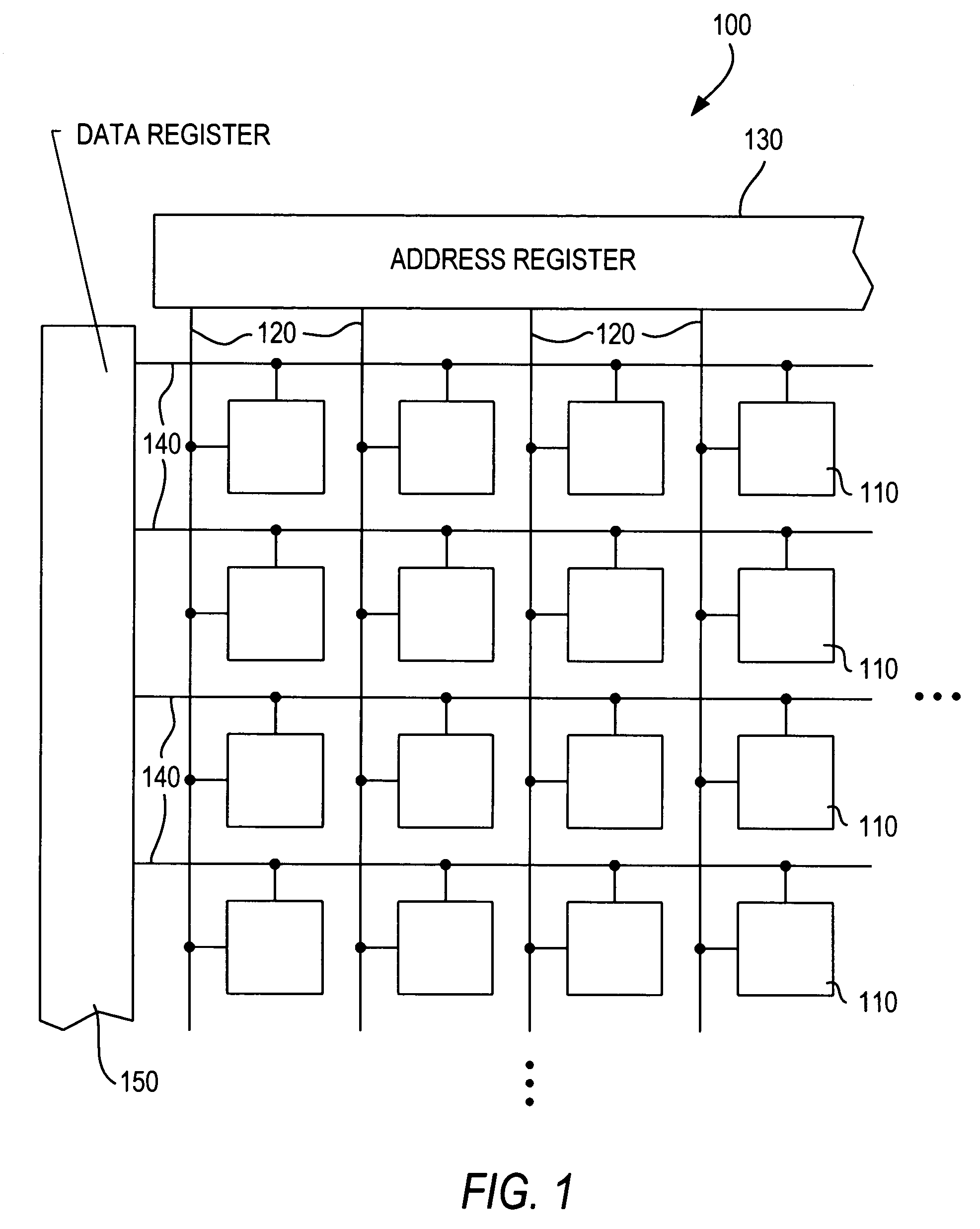

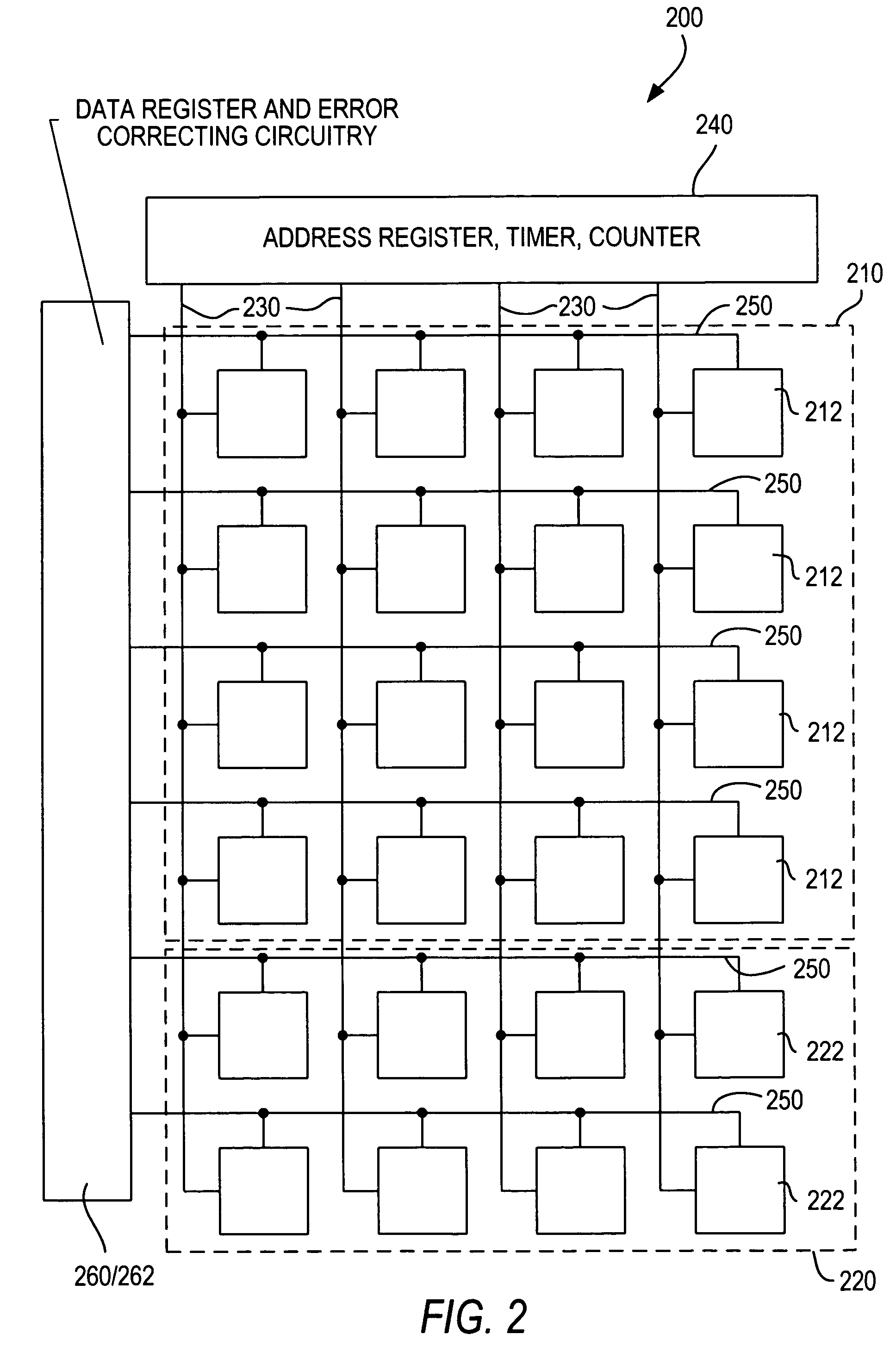

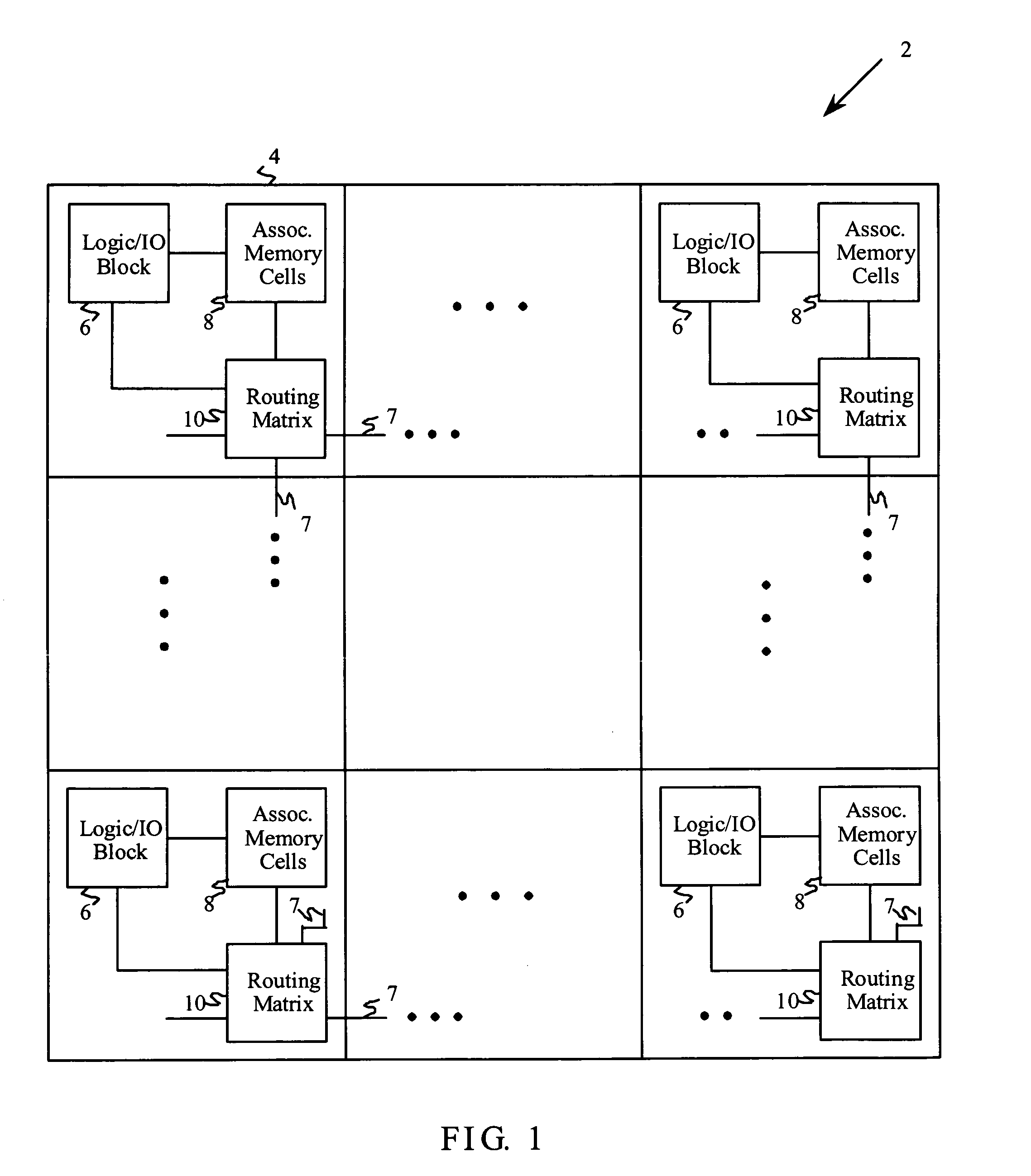

Error correction for programmable logic integrated circuits

InactiveUS7328377B1Increase delayReduces static hazardsError detection/correctionProgrammable logic controllerProgrammable logic device

Systems and methods for detecting and correcting errors in programmable logic ICs are provided. In one embodiment, a scrubber periodically reads the memory cells in a programmable logic IC, detects and corrects any errors, and writes the corrected contents back into the memory cell. In another embodiment, regions of memory cells in a programmable logic IC each have associated error correcting circuitry which operates to continuously detect and correct errors as they occur. Error correcting circuitry can further be designed to reduce static hazards. It may be more desirable to design programmable logic IC routing architectures that reduce the number of memory cells needed to implement a given function. Error correcting circuitry can be provided for configuration memory or for an embedded memory block on a programmable logic IC.

Owner:ALTERA CORP

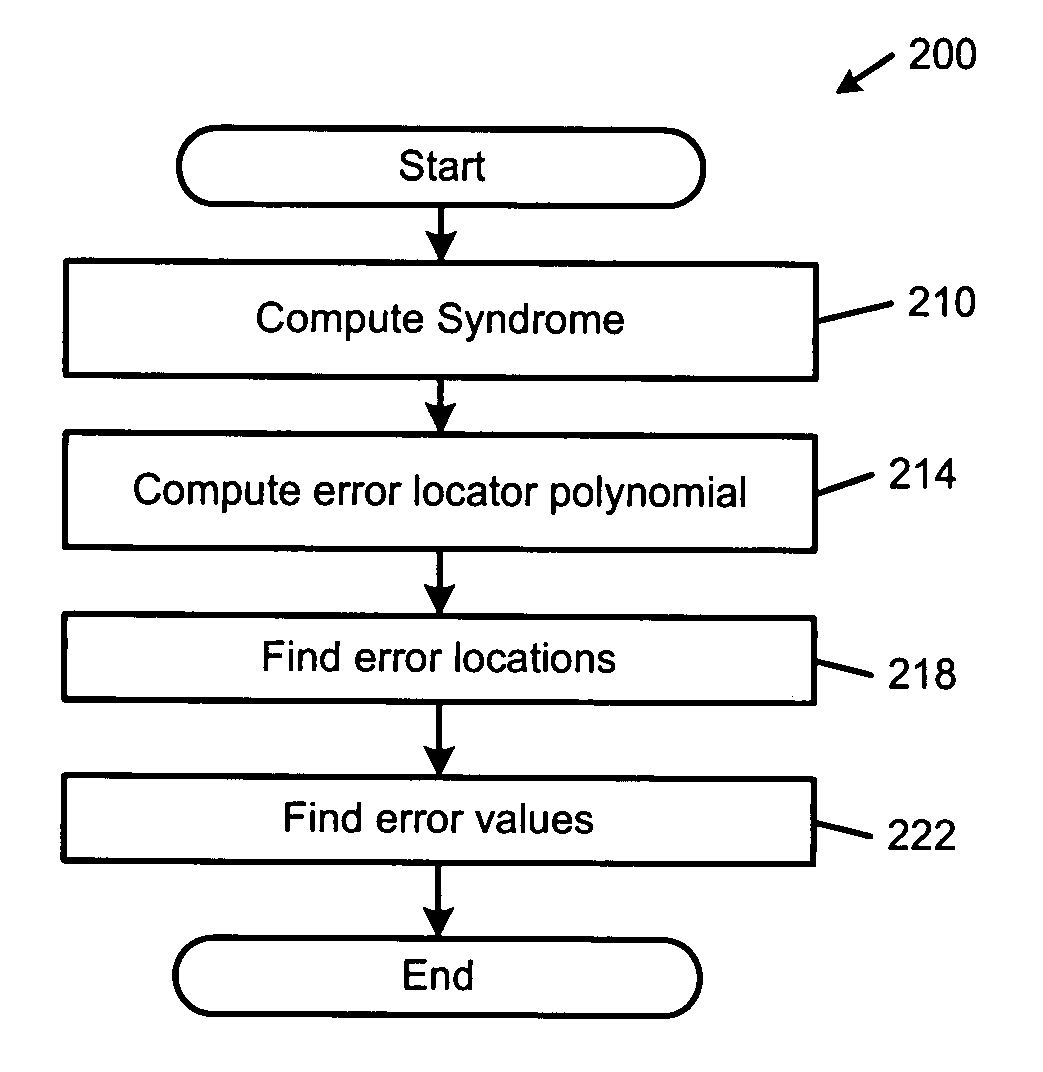

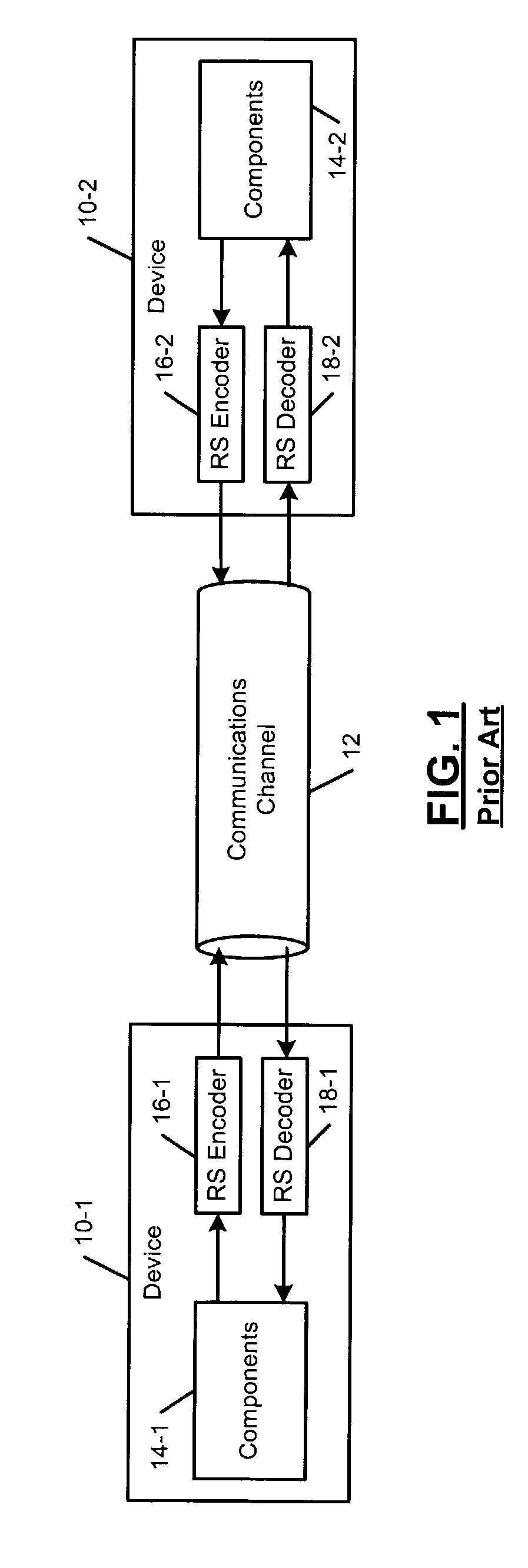

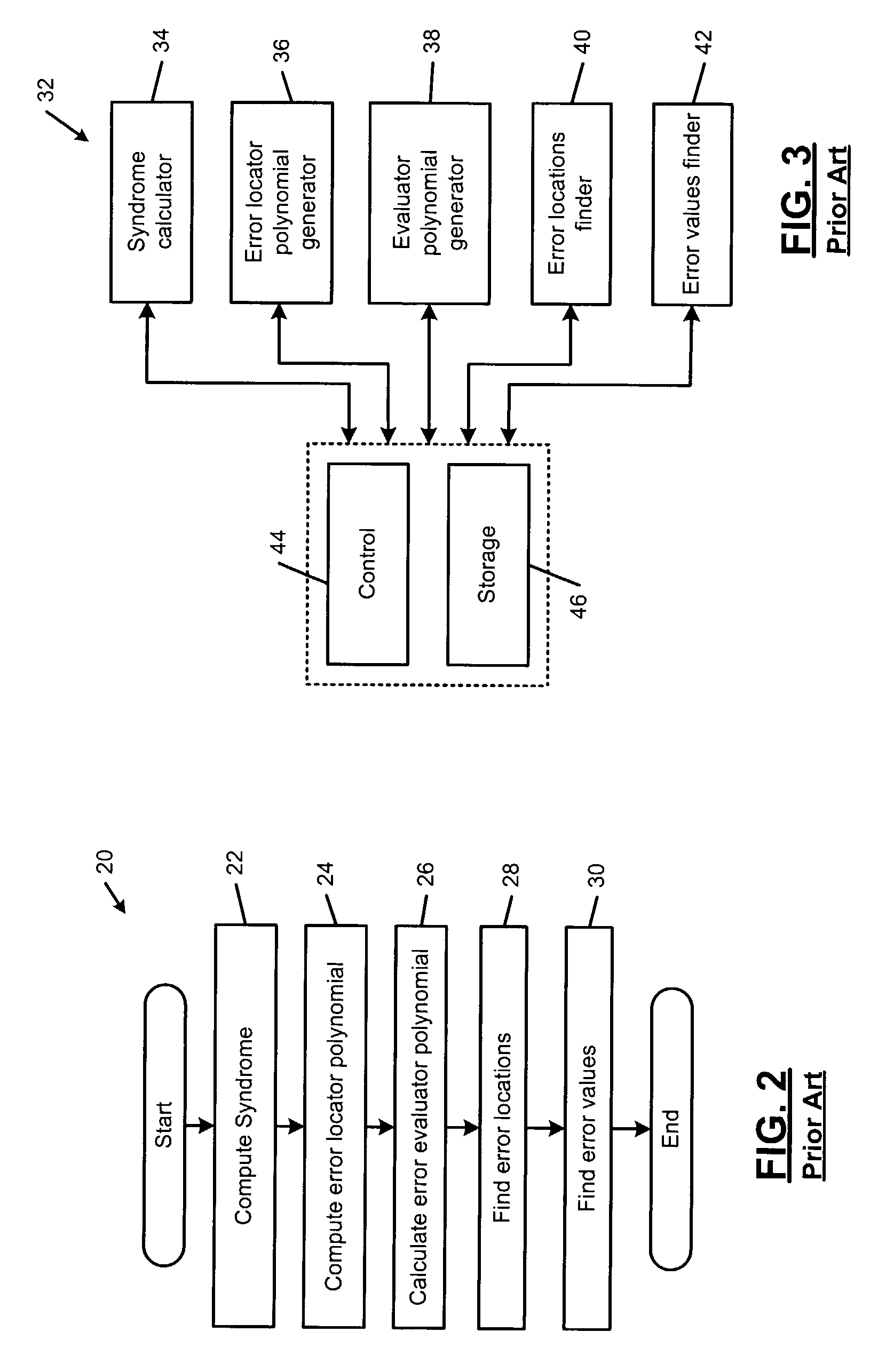

Error evaluator for inversionless Berlekamp-Massey algorithm in Reed-Solomon decoders

ActiveUS7010739B1Data representation error detection/correctionCode conversionError locationReed solomon decoder

An error correcting Reed-Solomon decoder includes a syndrome calculator that calculates syndrome values. An error locator polynomial generator communicates with the syndrome calculator and generates an error locator polynomial. An error location finder communicates with at least one of the syndrome calculator and the error locator polynomial generator and generates error locations. An error values finder communicates with at least one of the syndrome calculator, the error location finder and the error locator polynomial generator and generates error values using an error value relationship that is not based on the traditional error evaluator polynomial. The error locator polynomial generator is an inversionless Berlekamp-Massey algorithm (iBMA), which calculates an error locator polynomial and a scratch polynomial. The error value relationship is based on the error locator polynomial and the scratch polynomial.

Owner:MARVELL ASIA PTE LTD

Apparatus, system, and method for providing error correction

An apparatus, system, and method are disclosed for providing error correction for a data storage device. A determination module determines a set of error-correcting code (“ECC”) characteristics for a data storage device. The set of ECC characteristics includes at least one attribute selected from a plurality of supported attributes. A decoder configuration module configures an ECC decoder to operate in compliance with the set of ECC characteristics. An ECC module validates requested data read from the data storage device using the ECC decoder.

Owner:SANDISK TECH LLC

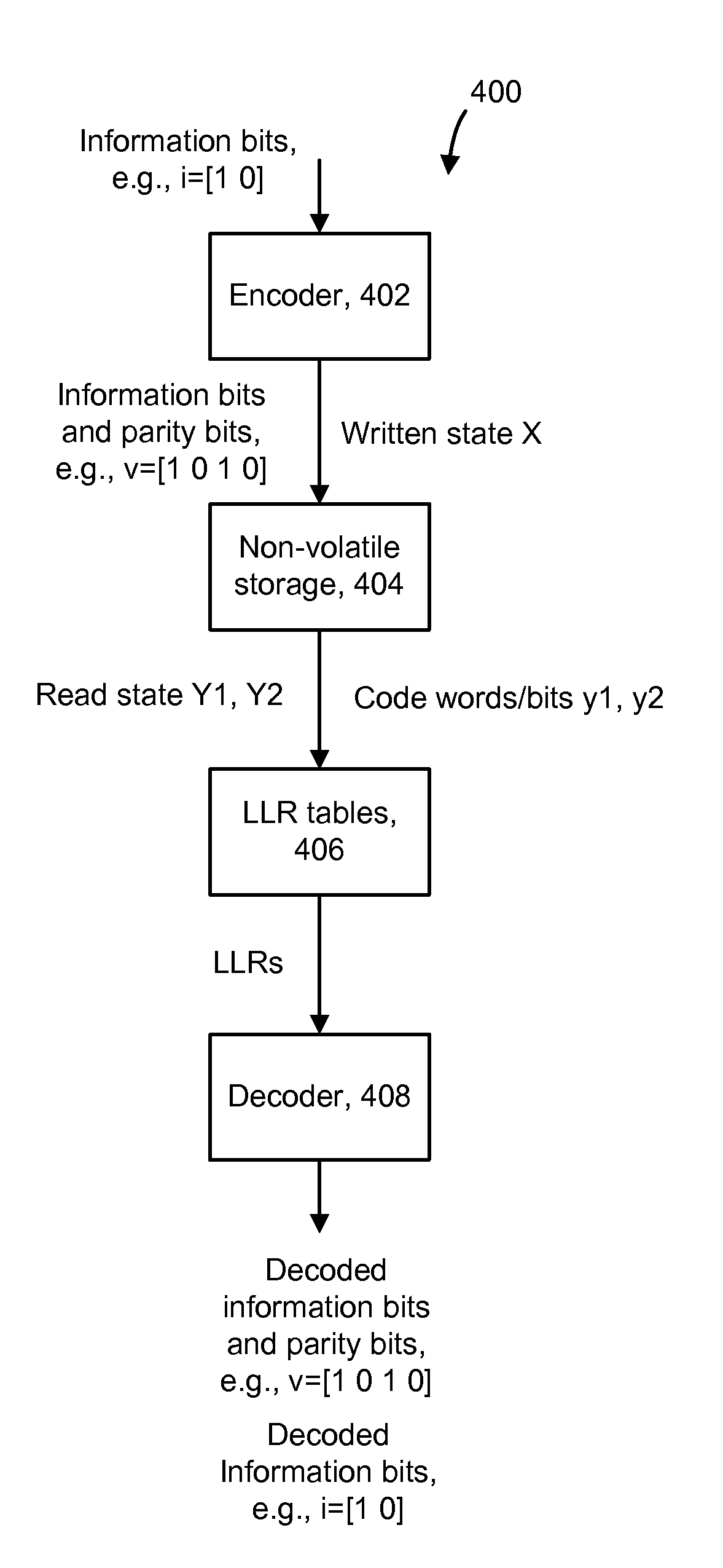

Method for decoding data in non-volatile storage using reliability metrics based on multiple reads

ActiveUS20080250300A1Other decoding techniquesError correction/detection using multiple parity bitsLow-density parity-check codeDependability

Data stored in non-volatile storage is decoded using iterative probabilistic decoding and multiple read operations to achieve greater reliability. An error correcting code such as a low density parity check code may be used. In one approach, initial reliability metrics, such as logarithmic likelihood ratios, are used in decoding read data of a set of non-volatile storage element. The decoding attempts to converge by adjusting the reliability metrics for bits in code words which represent the sensed state. If convergence does not occur, e.g., within a set time period, the state of the non-volatile storage element is sensed again, current values of the reliability metrics in the decoder are adjusted, and the decoding again attempts to converge. In another approach, the initial reliability metrics are based on multiple reads. Tables which store the reliability metrics and adjustments based on the sensed states can be prepared before decoding occurs.

Owner:SANDISK TECH LLC

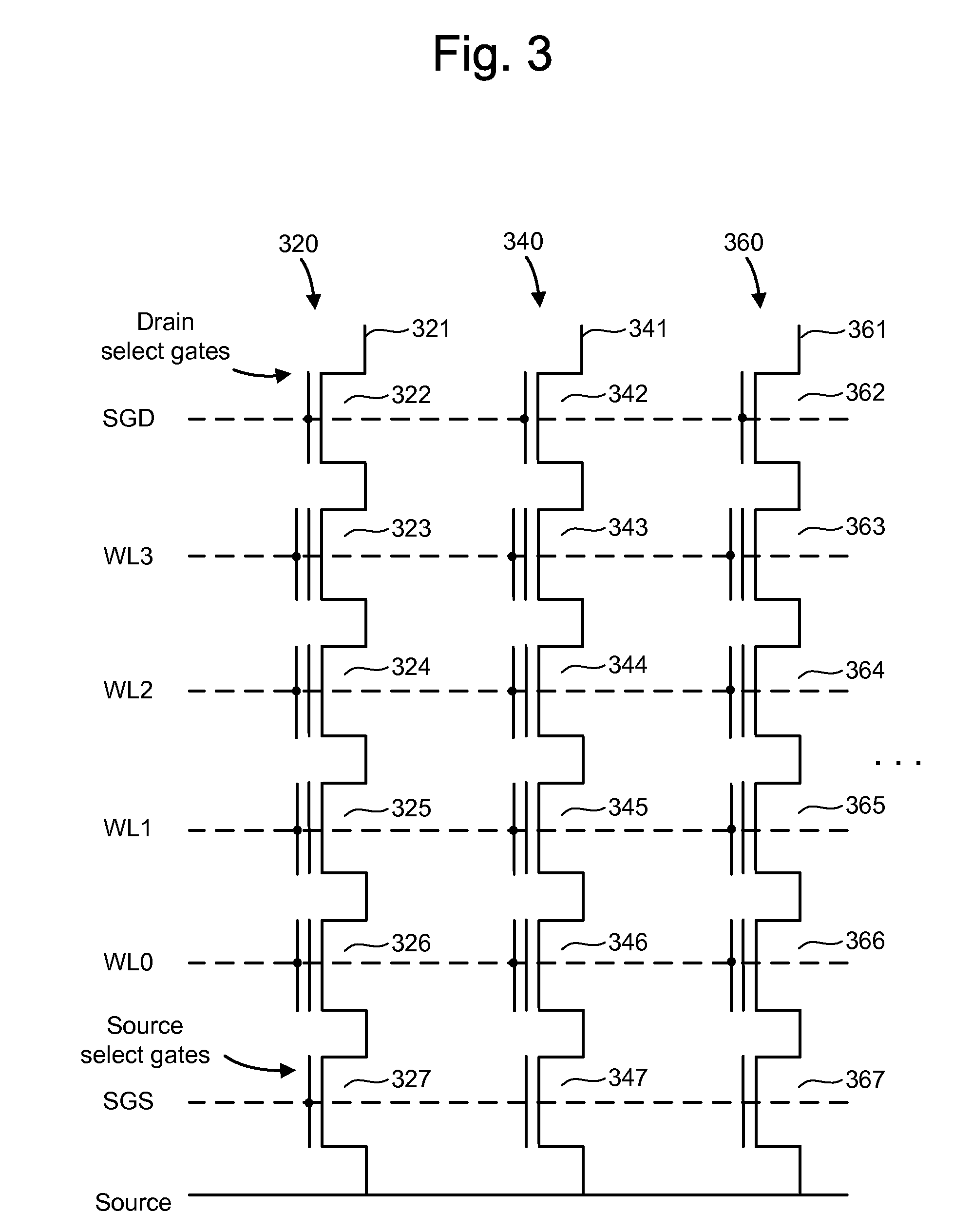

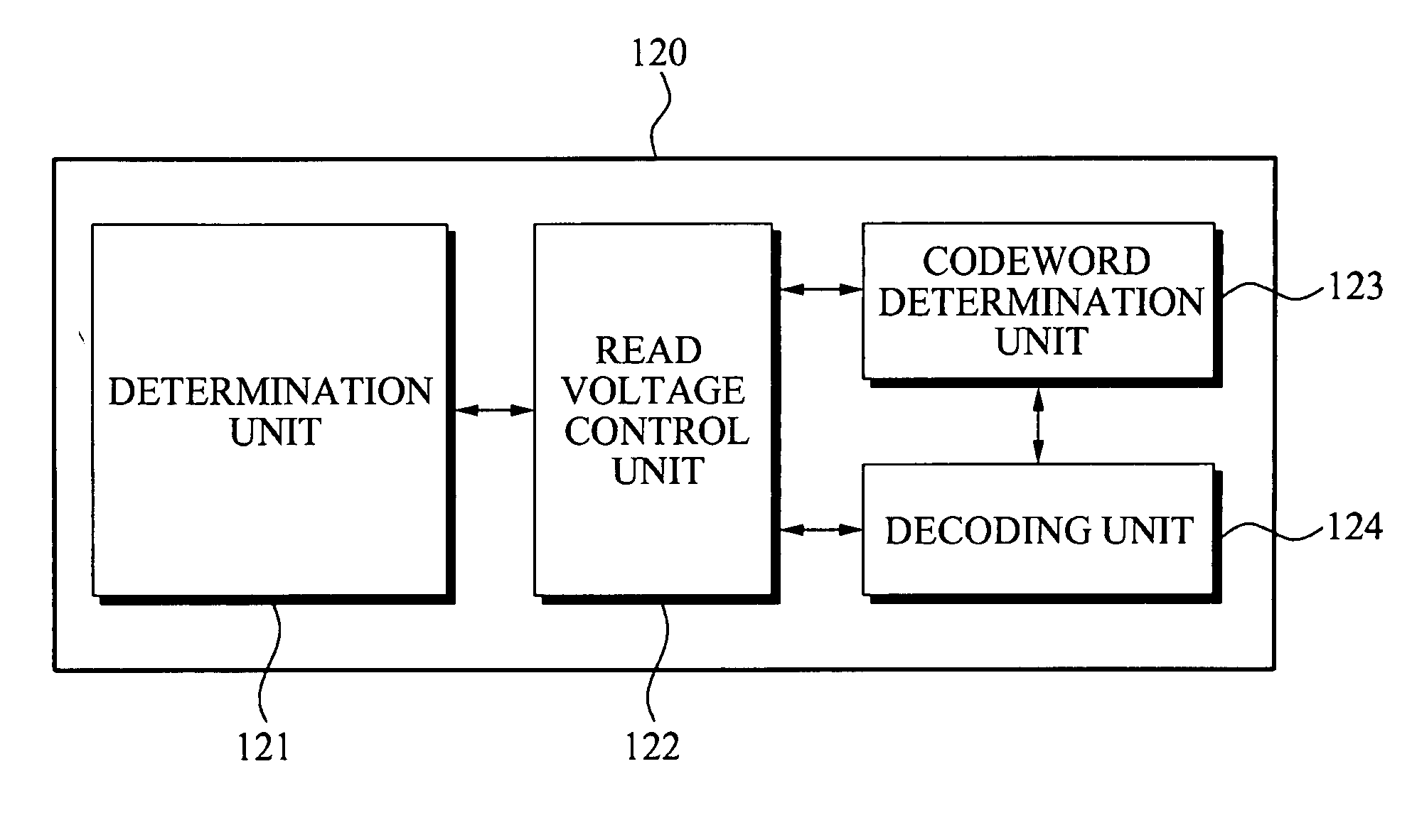

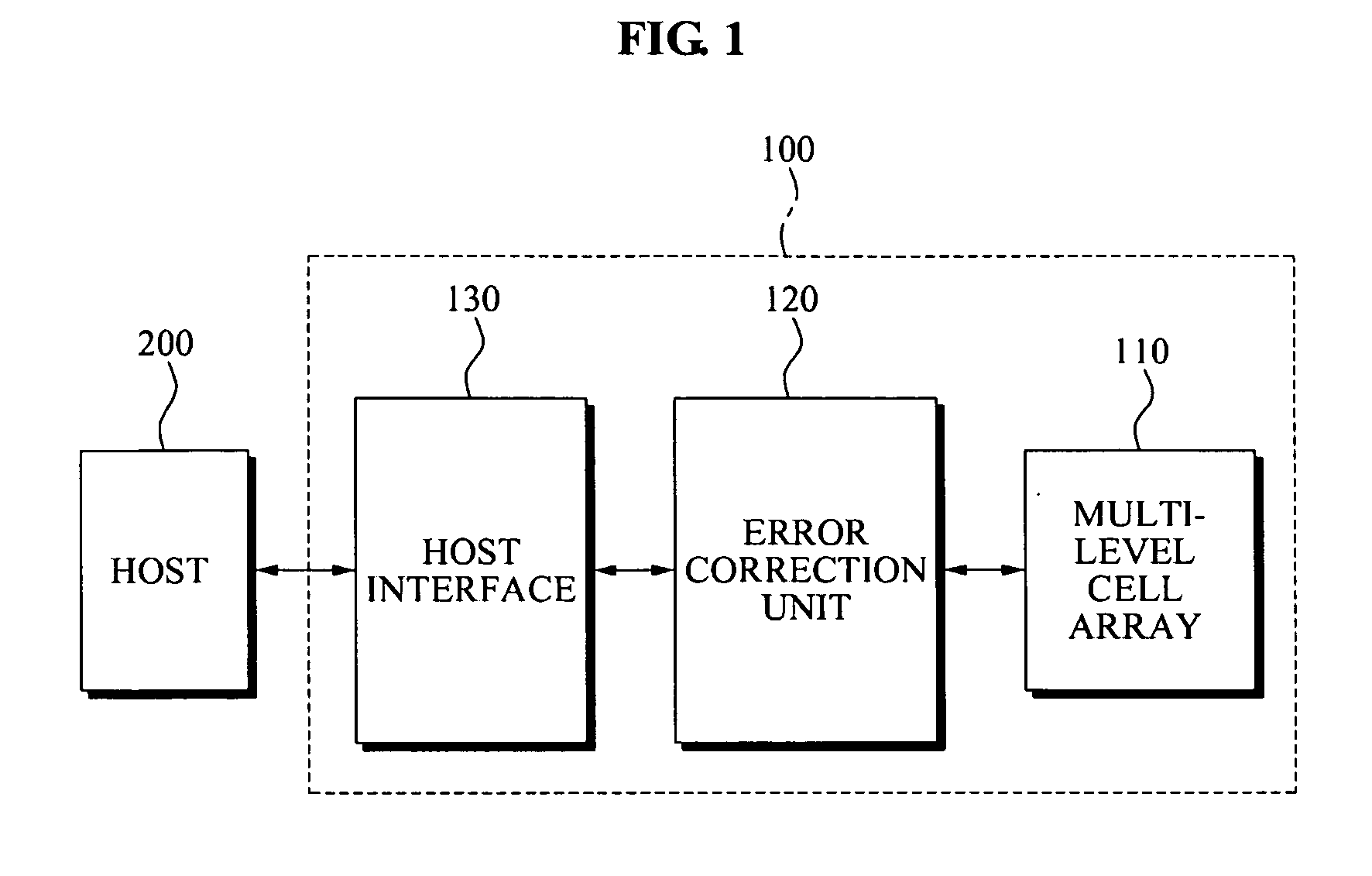

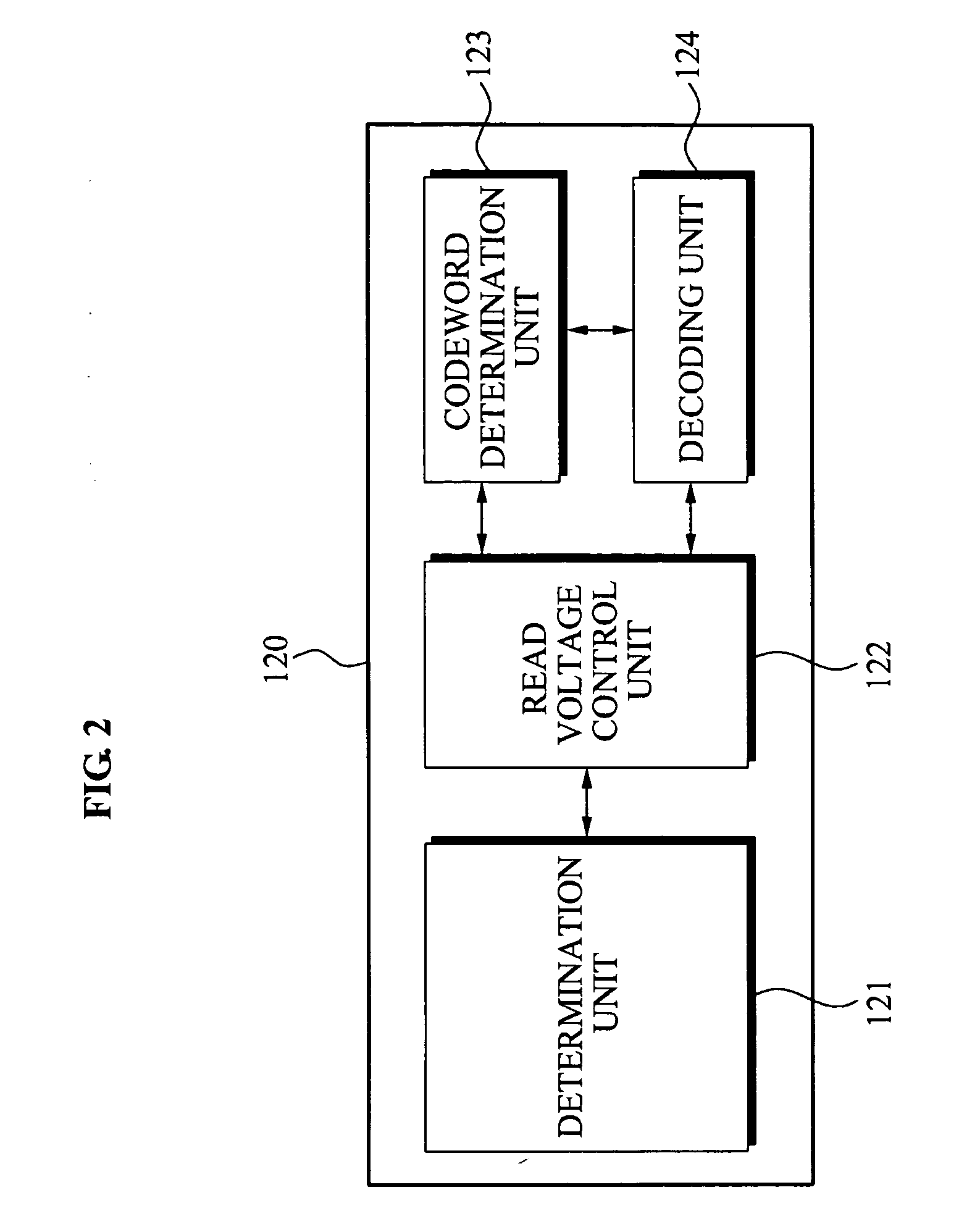

Error correction apparatus, method thereof and memory device comprising the apparatus

InactiveUS20090292972A1Effective correctionIncrease probabilityRead-only memoriesCode conversionComputer hardwareError correcting

An error correction apparatus, a method thereof, and a memory device including the apparatus are provided. The error correction apparatus may include: a determination unit configured to determine whether a number of errors in a read word being read and extracted from a multi-level cell (MLC) exists in an error correcting capability range; a read voltage control unit configured to either increase or decrease a read voltage applied to the MLC when the number of errors in the read word is outside the error correcting capability range; and a codeword determination unit configured to analyze a bit error based on the increase or decrease of the read voltage, and to select a codeword corresponding to the analyzed bit error based on a selected read error pattern. Through this, it may be possible to efficiently correct a read error that occurs when the data of the memory device is maintained for a long time.

Owner:SAMSUNG ELECTRONICS CO LTD

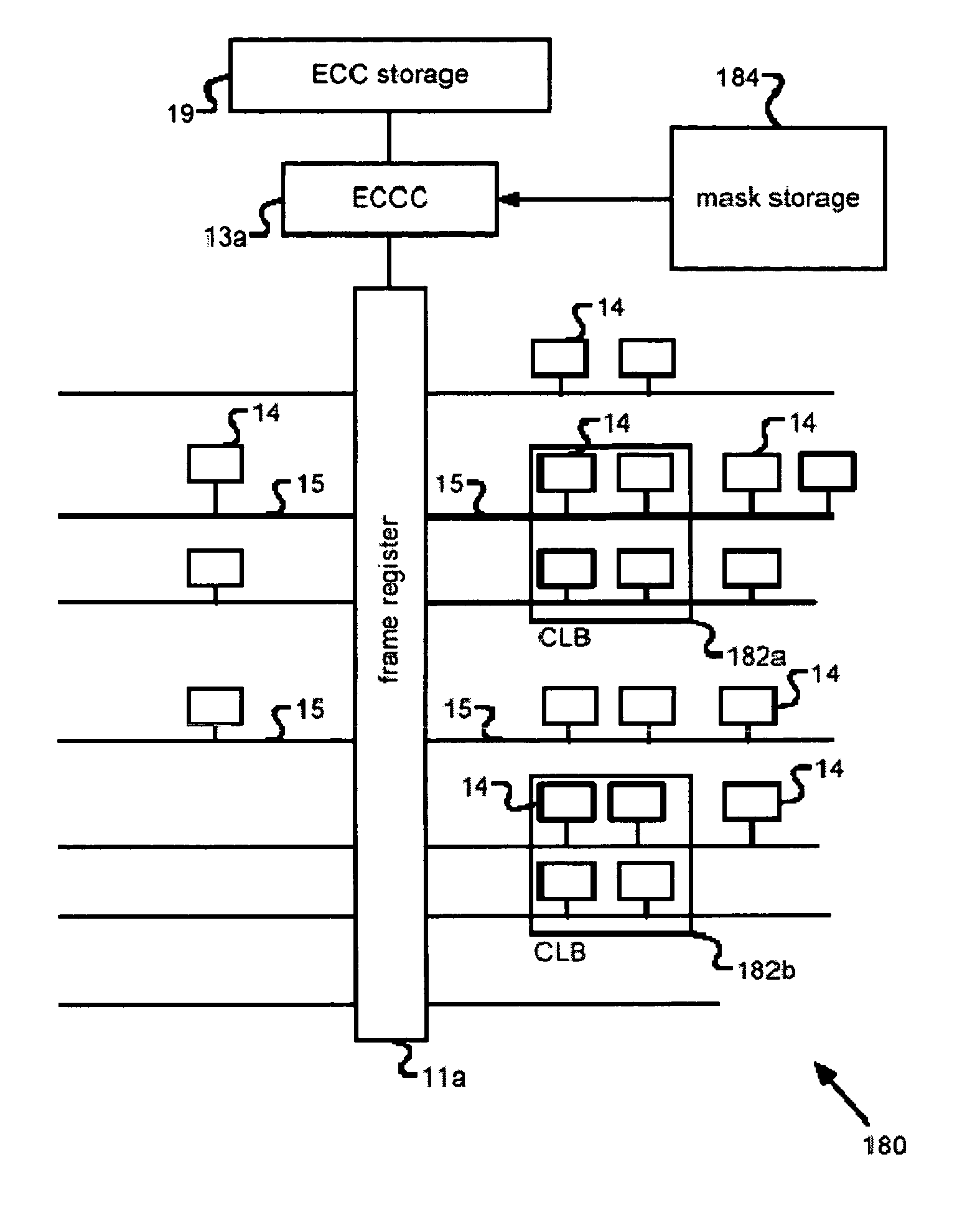

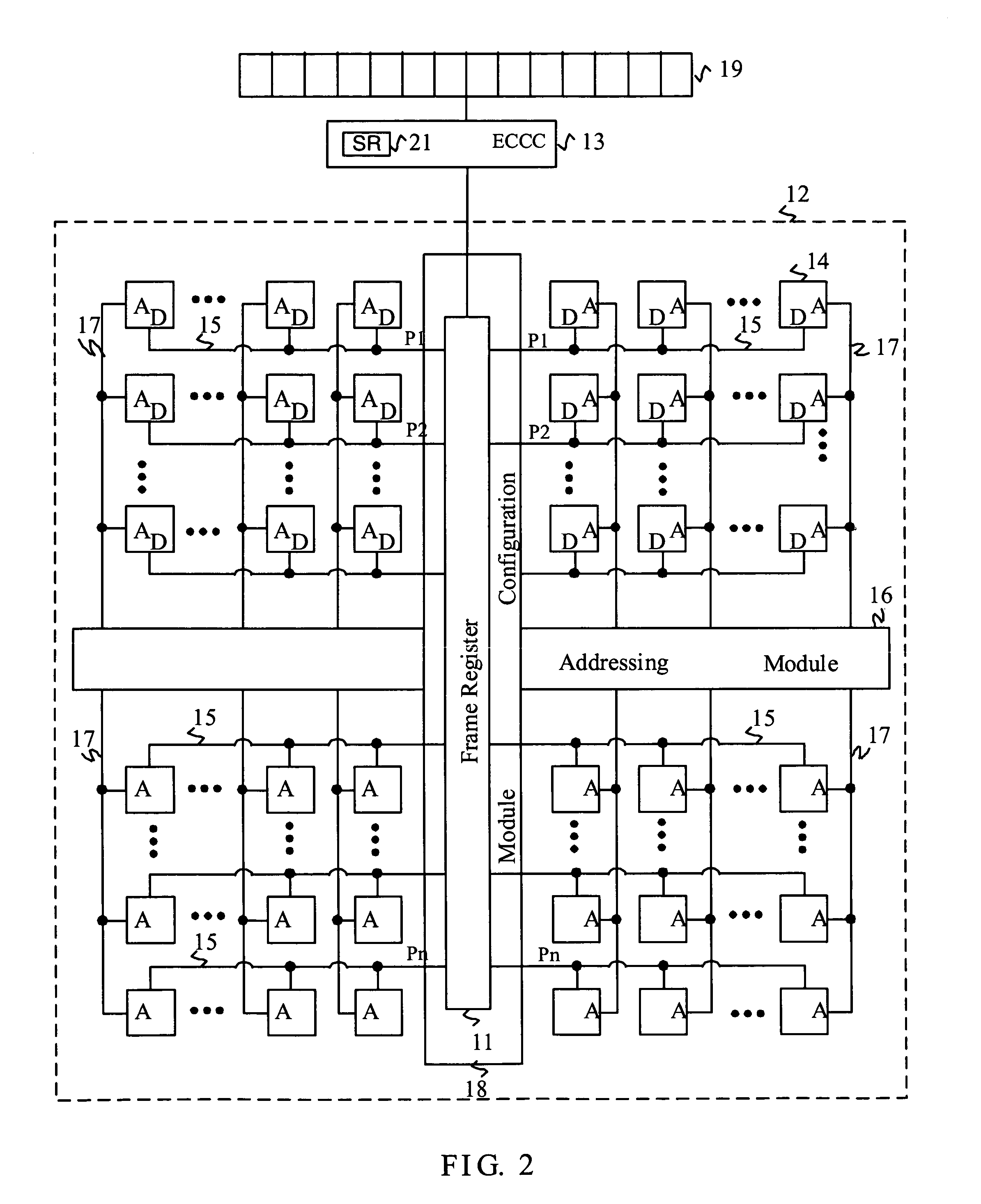

FPGA configuration memory with built-in error correction mechanism

A system and method are disclosed for error correction in a programmable logic device (PLD). A frame circuit retrieves data from each column of configuration memory of the PLD, and a check memory stores of a plurality of check words. A buffer circuit is coupled to the check memory and to the frame circuit. The buffer circuit assembles blocks of data from data retrieved by the frame circuit and from corresponding check words in the check memory. A plurality of storage elements are provided for storage of status information. A check circuit is coupled to the storage elements and to the buffer circuit. Each block is checked by the check circuit using an error correcting code, and data indicating detected errors is stored in the storage elements.

Owner:XILINX INC

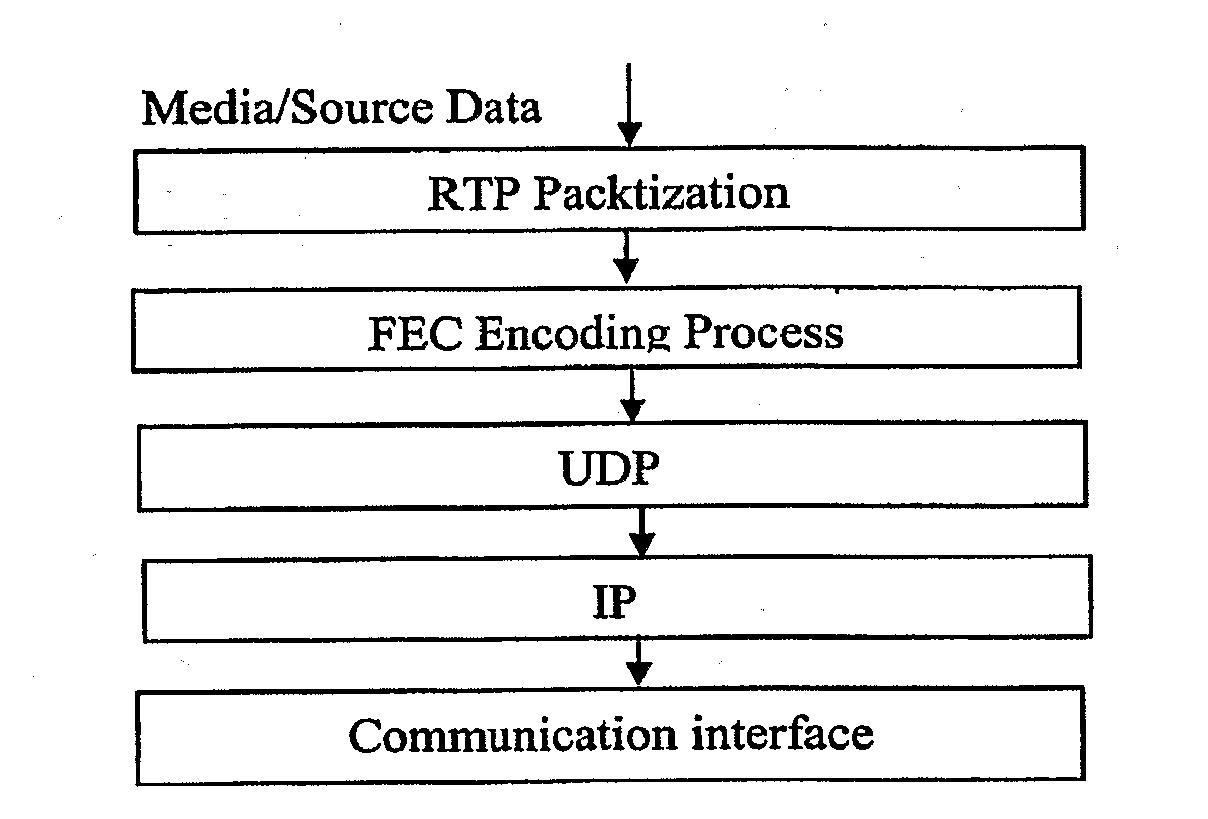

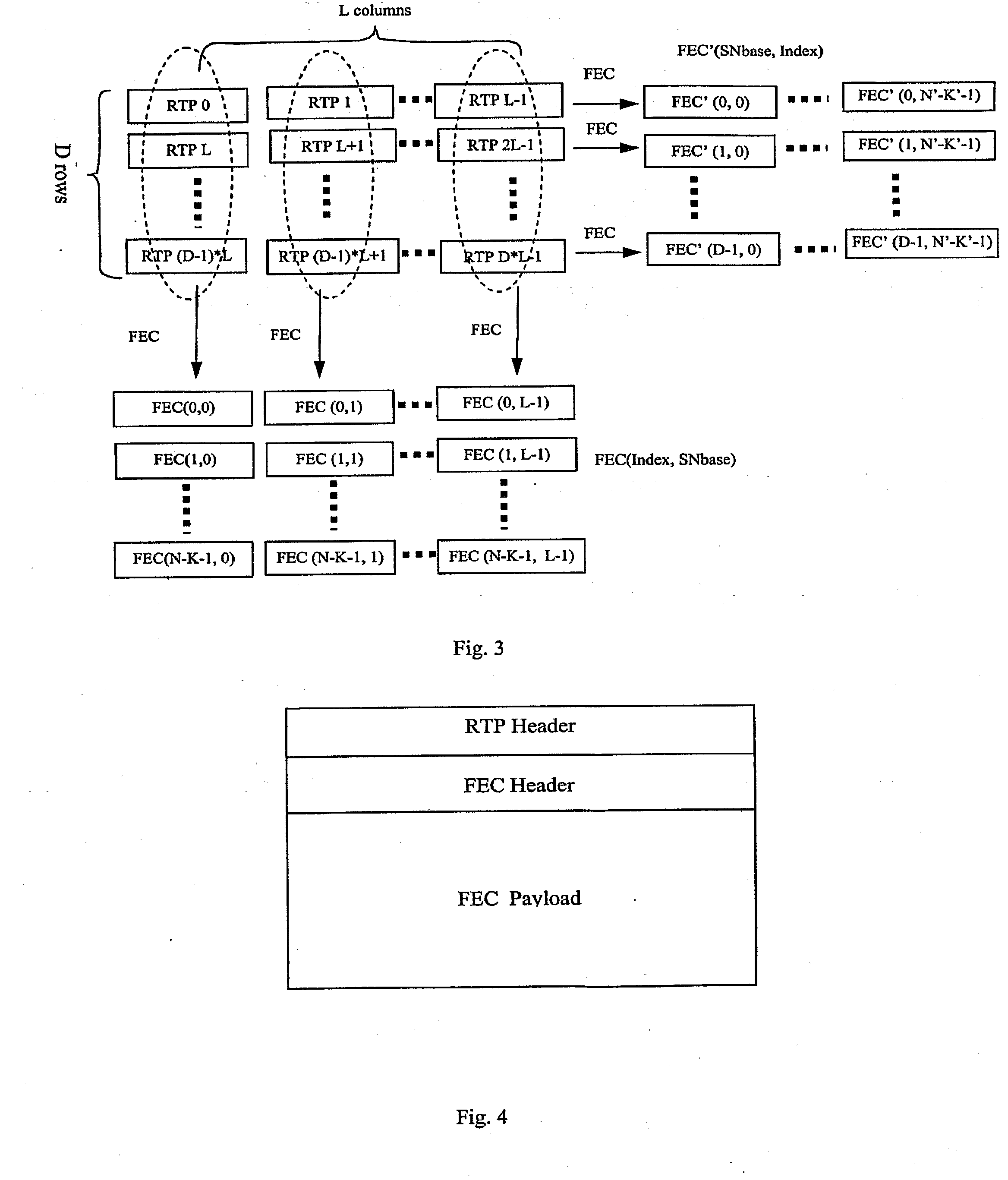

Method to support forward error correction for real-time audio and video data over internet protocol networks

A method and apparatus are described for protecting real time media including receiving media packets, generating media bit strings from the media packets, applying a forward error correcting code across the generated media bit strings to generate at least one forward error correcting bit string and generating at least one forward error correcting packet from the at least one forward error correcting bit string. Also described are a method and apparatus for recovering from losses of real time media packets including forming media bit strings from received media packets, forming forward error correcting bit strings from received forward error correcting packets, decoding the formed media bit strings and forward error correcting bit strings to obtain recovered media bit strings and recover lost media packets from the recovered media bit strings. Further described is a data structure for a forward error correcting header on computer readable media.

Owner:THOMSON LICENSING SA

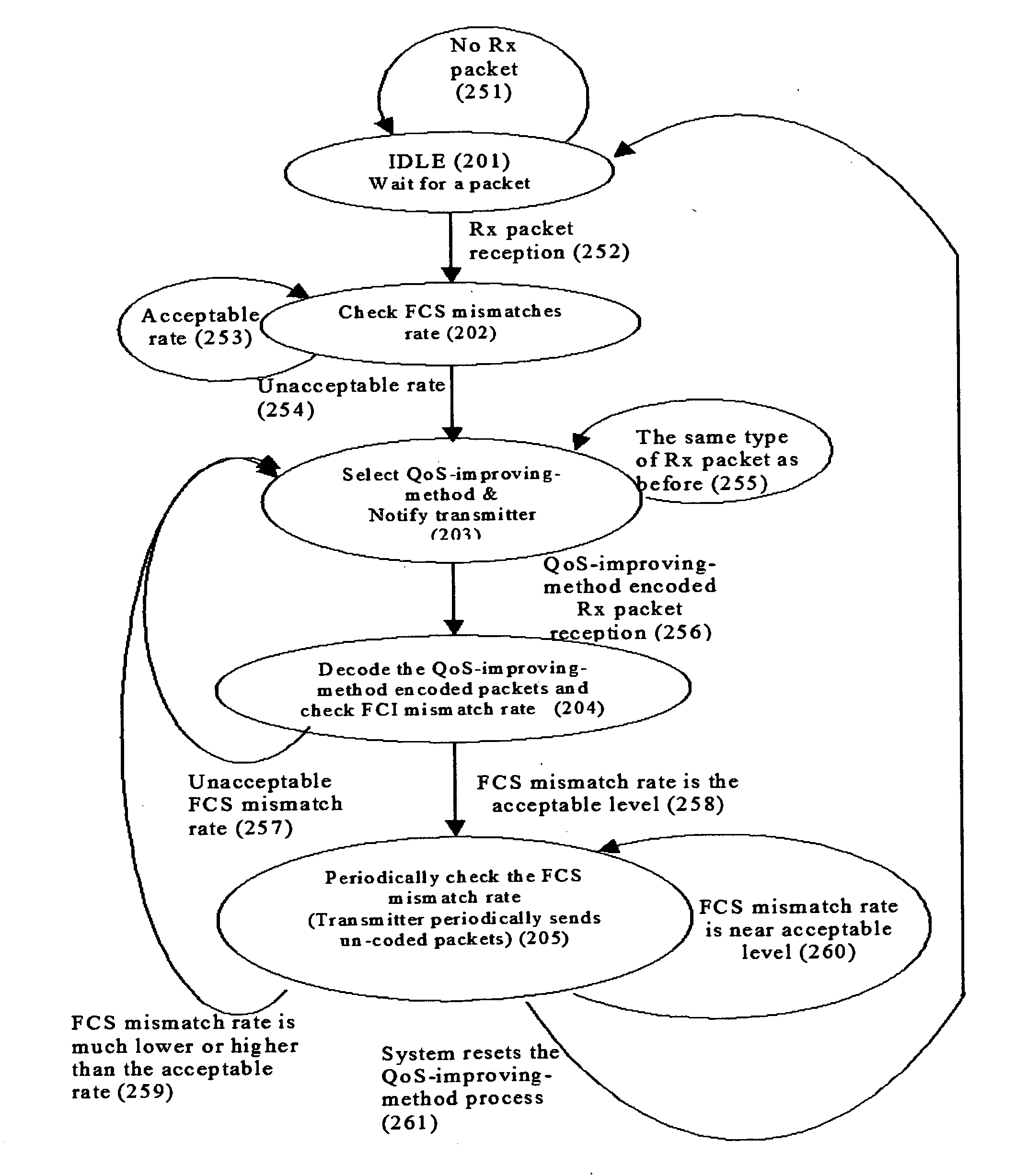

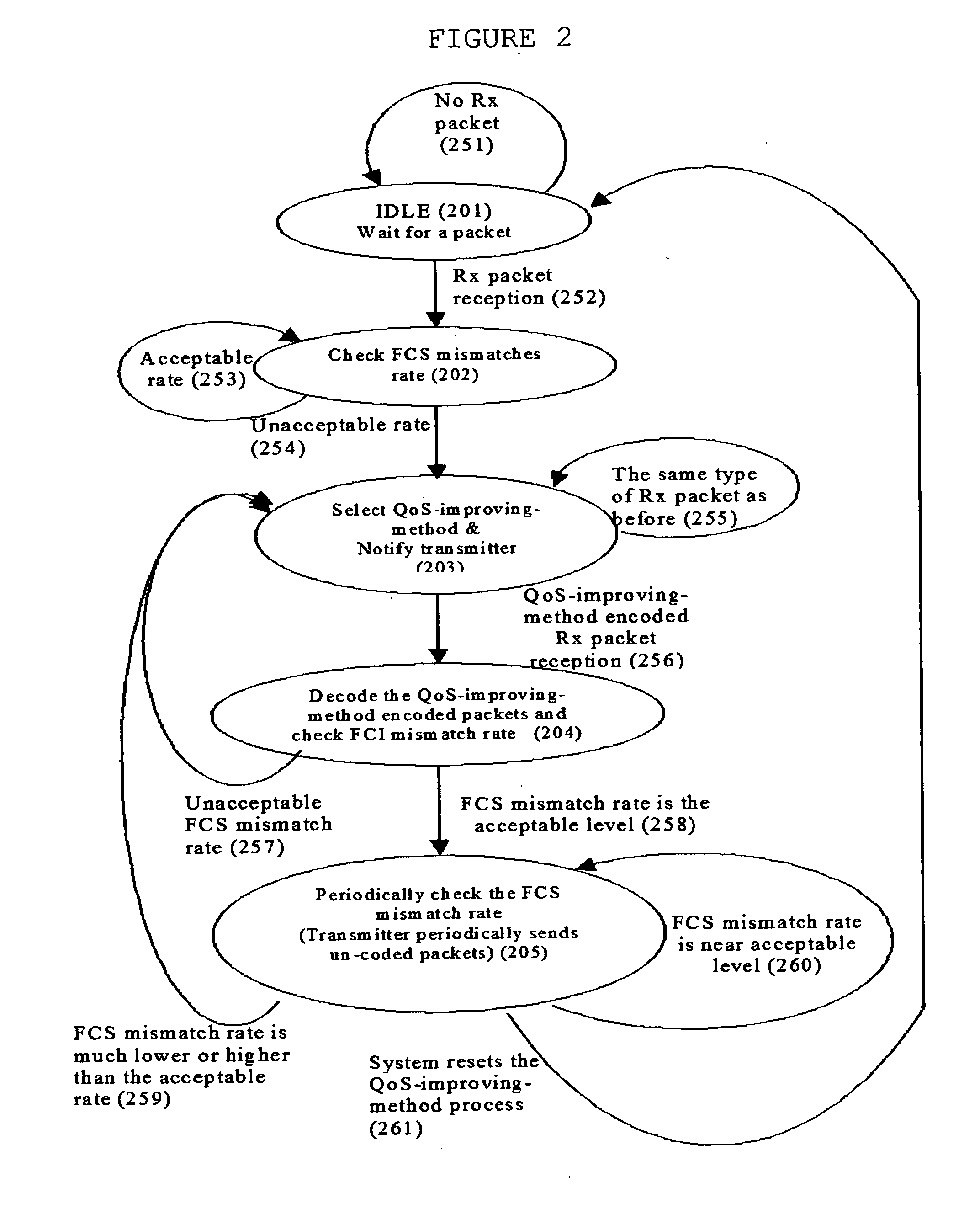

Method of improving wireless communication QoS by means of automatic packet sizing and forward error correcting based on the dynamic error rate forecast

InactiveUS20070097985A1Network traffic/resource managementData switching by path configurationForward error correctionError correcting

A method to meet the adequate QoS of wireless network by automatically sizing the packet length and / or by adding appropriate FEC (Forward Error Correction) based on the error rate forecast that is derived from the past behavior of the wireless communication channel.

Owner:LEE HYUN

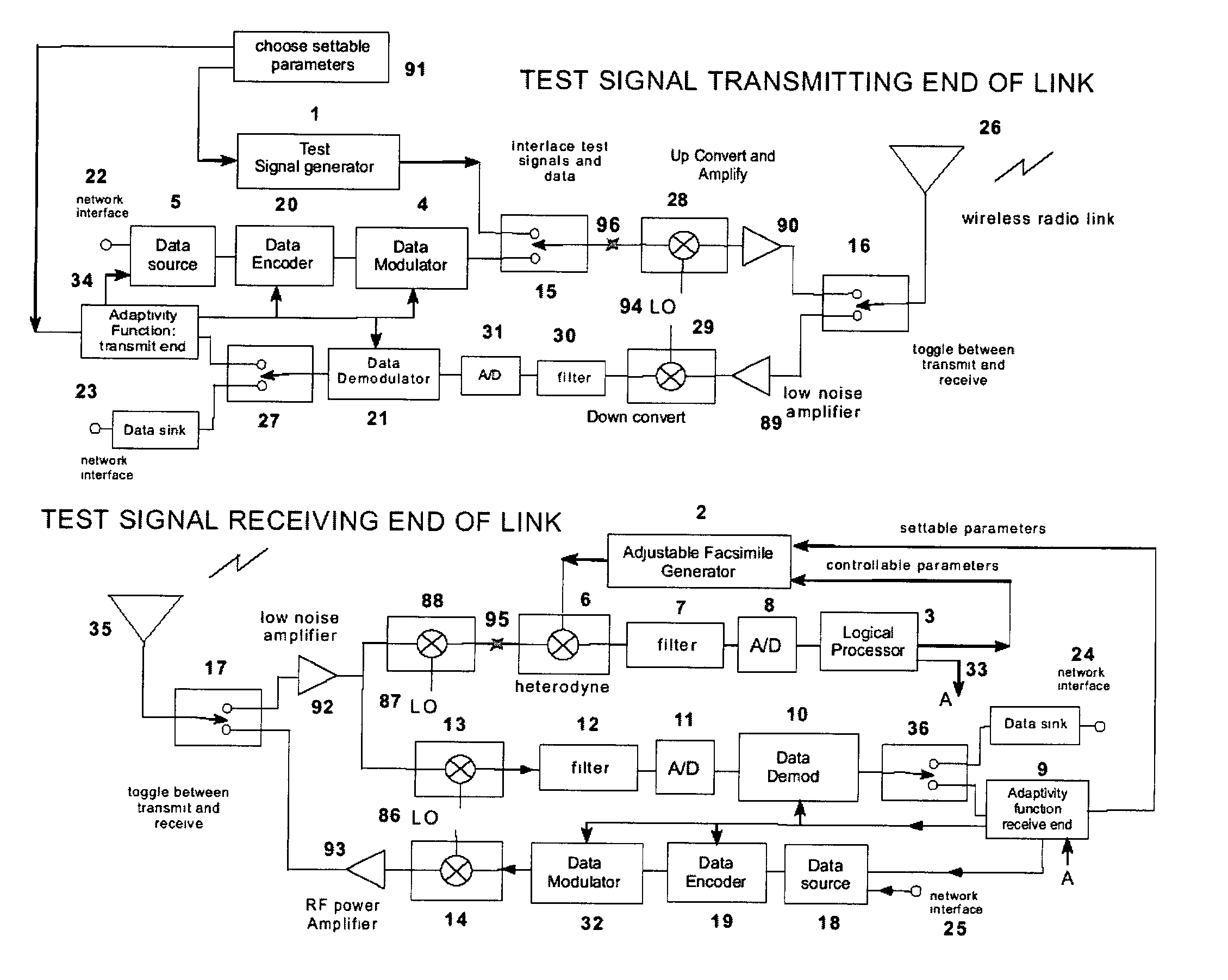

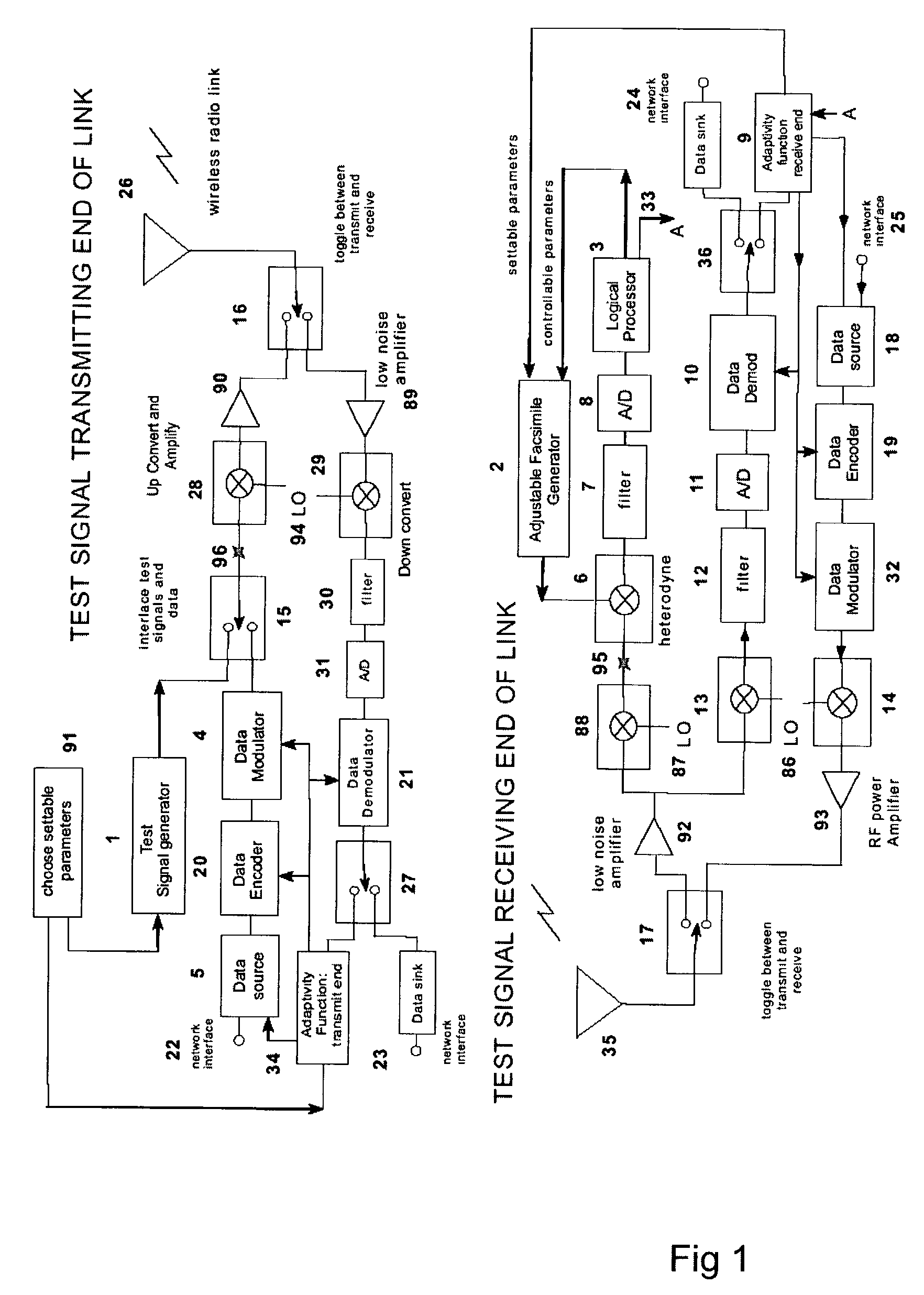

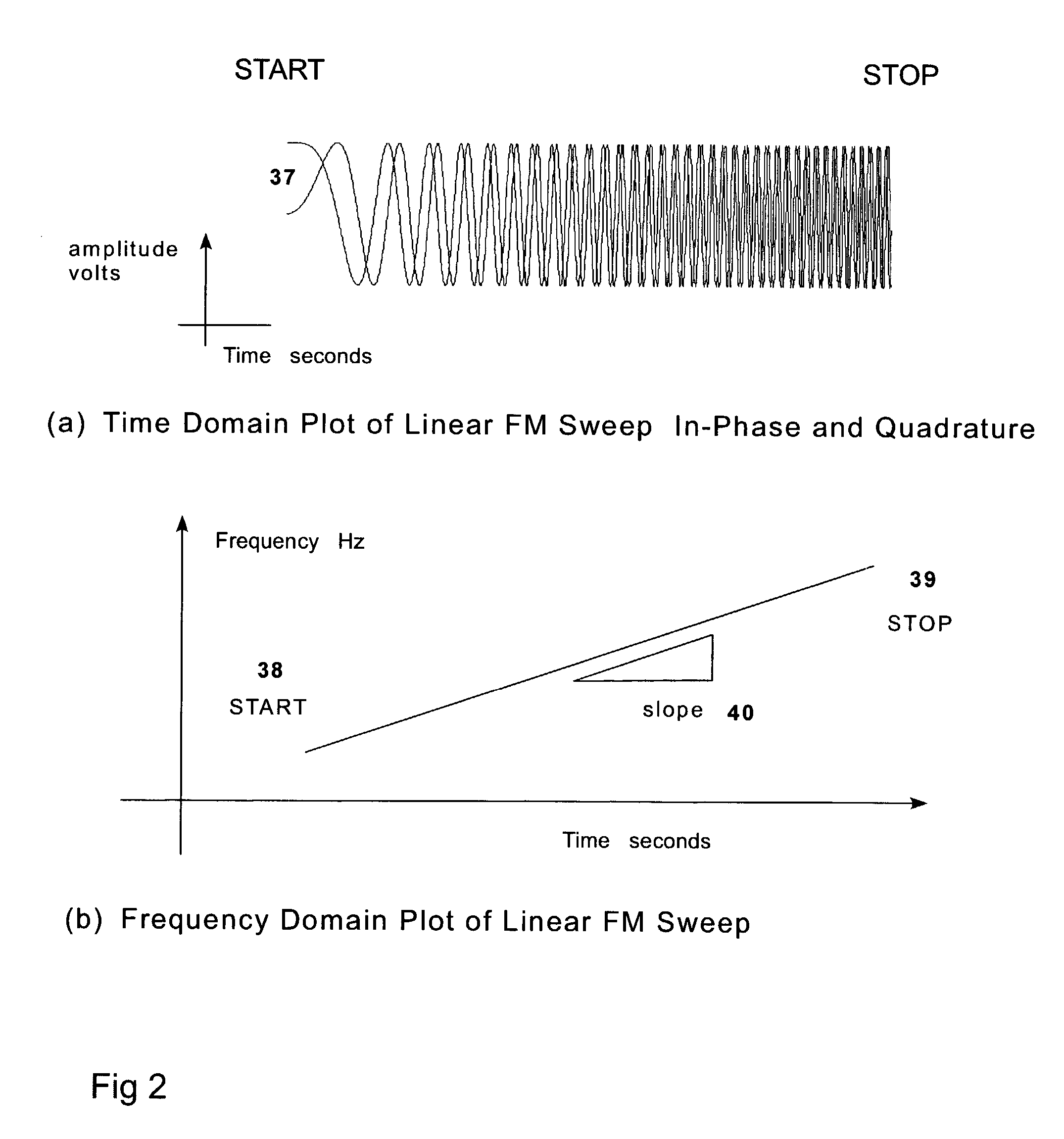

Vector network analyzer applique for adaptive communications in wireless networks

A test signal generator at a transmitter station and a facsimile generator at a receiver station go through an acquisition and tracking process which aligns the two signals so that a logical processor can compute the frequency transfer function of the entire propagation path for use in an adaptive, concurrently sent communication signal. The frequency transfer function is conveyed back to the transmit end via a control channel permitting an adaptivity function at the transmit end to influence subsequent selection of communication parameters, among which are typically transmitted data rate, selection of modulation, selection of forward error correcting coding, and selection of frequency band for transmission. The same measurement is conveyed to an adaptivity function at the receive end for use in the communications receiver to select demodulator variables such as gain control, and equalization of amplitude and phase, versus frequency. The adaptivity function also permits interspersing of reverse-direction communications over the same frequency bands in a time-share mode between forward-direction and reverse-direction communication with the measurement signals having to be transmitted in only one direction. An alternate embodiment invention of this type is described which is additionally useful for mobile communications channels. Another variation embodiment is described for pure propagation measurements only, absent conveyance of end-user information.

Owner:SARABAND WIRELESS

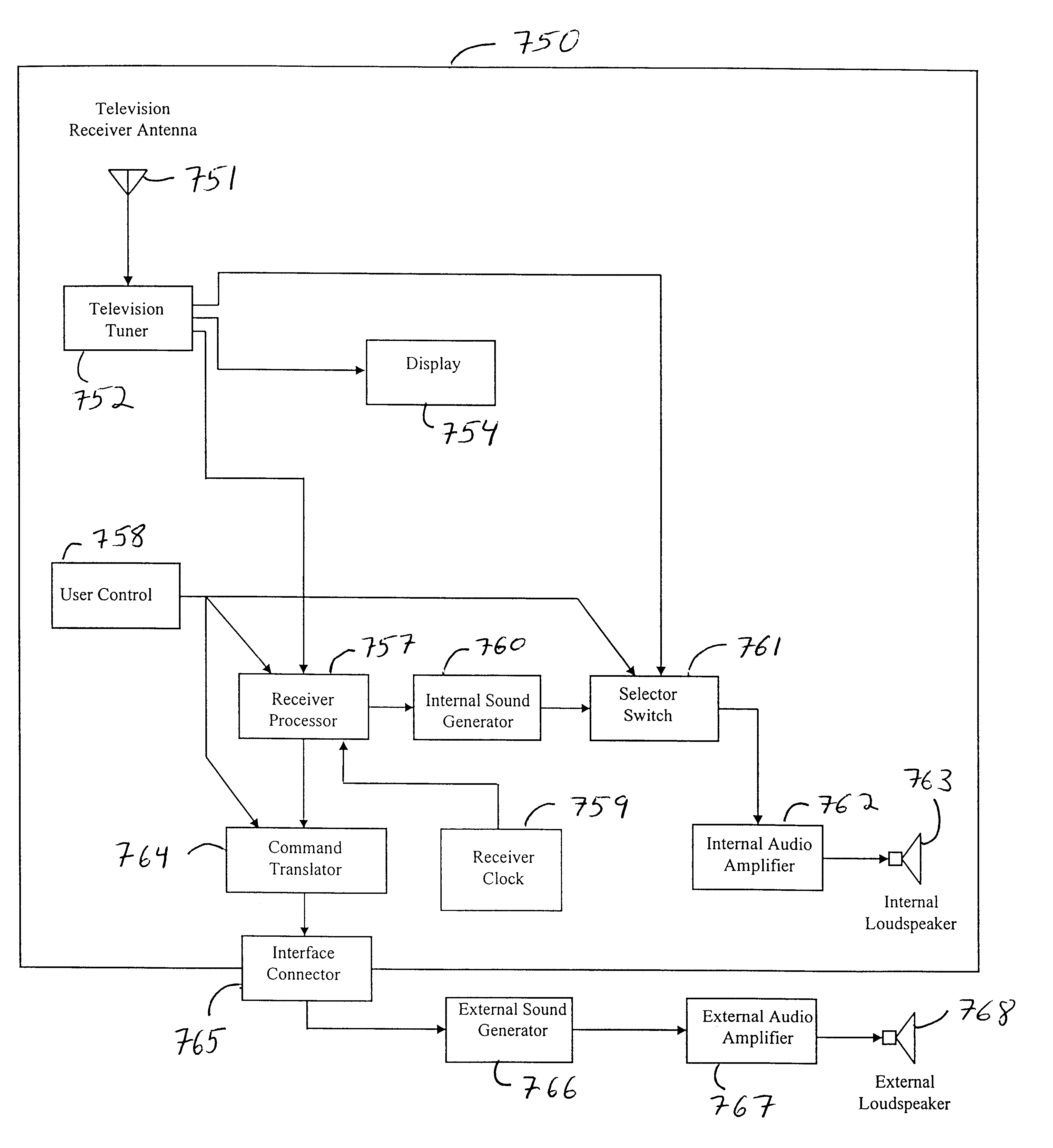

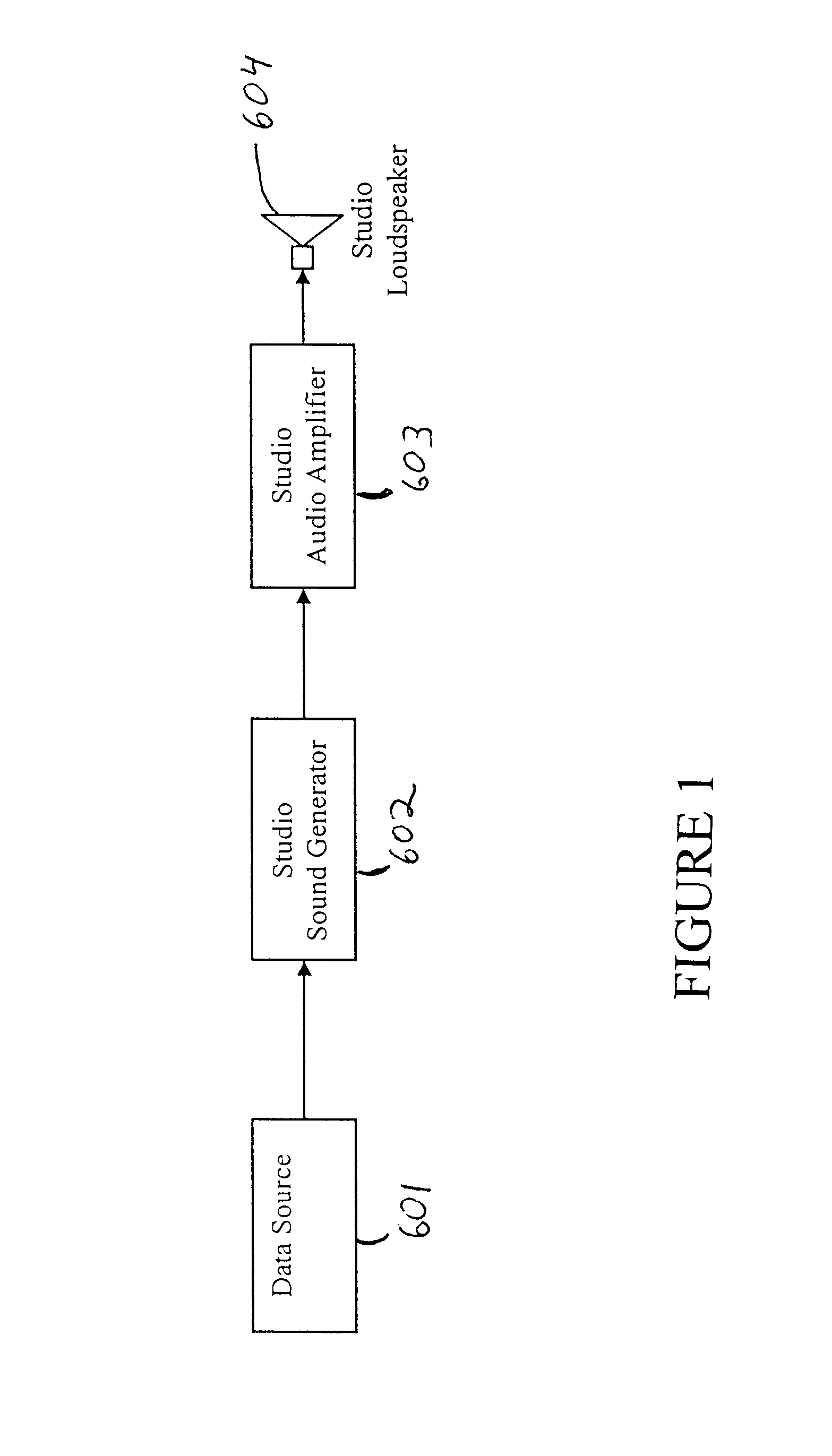

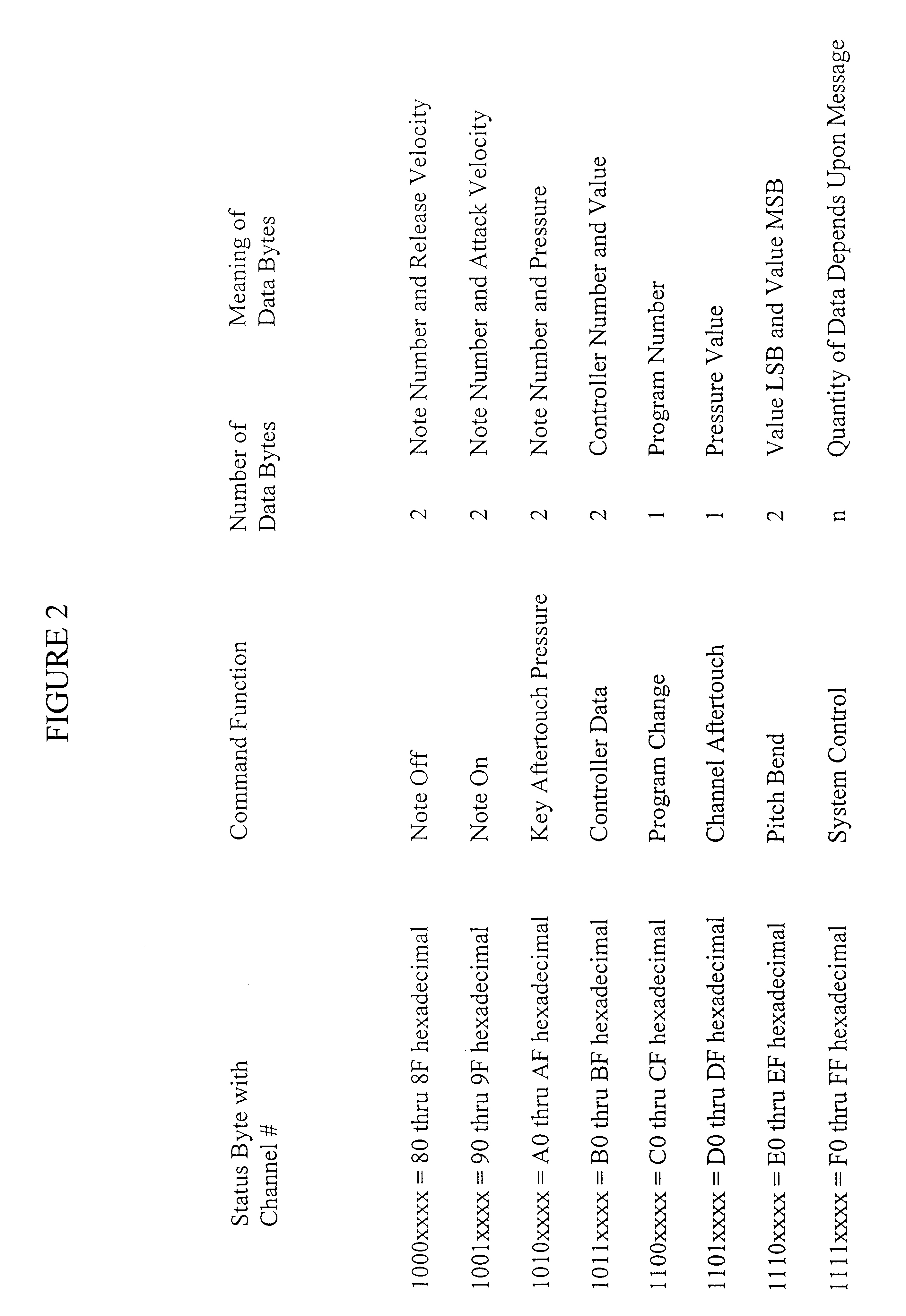

Method and apparatus for audio broadcast of enhanced musical instrument digital interface (MIDI) data formats for control of a sound generator to create music, lyrics, and speech

InactiveUS6462264B1Inhibit outputImprove speech clarityElectrophonic musical instrumentsCode conversionCarrier signalData format

A method and apparatus for the transmission and reception of broadcasted instrumental music, vocal music, and speech using digital techniques. The data is structured in a manner similar to the current standards for MIDI data. Transmitters broadcast the data to receivers which contain internal sound generators or an interface to external sound generators that create sounds in response to the data. The invention includes transmission of multiple audio data signals for several languages on a conventional radio and television carrier through the use of low bandwidth data. Error detection and correction data is included within the transmitted data. The receiver has various error compensating mechanisms to overcome errors in data that cannot be corrected using the error correcting data that the transmitter sent. The data encodes for elemental vocal sounds and music.

Owner:ELAM CARL

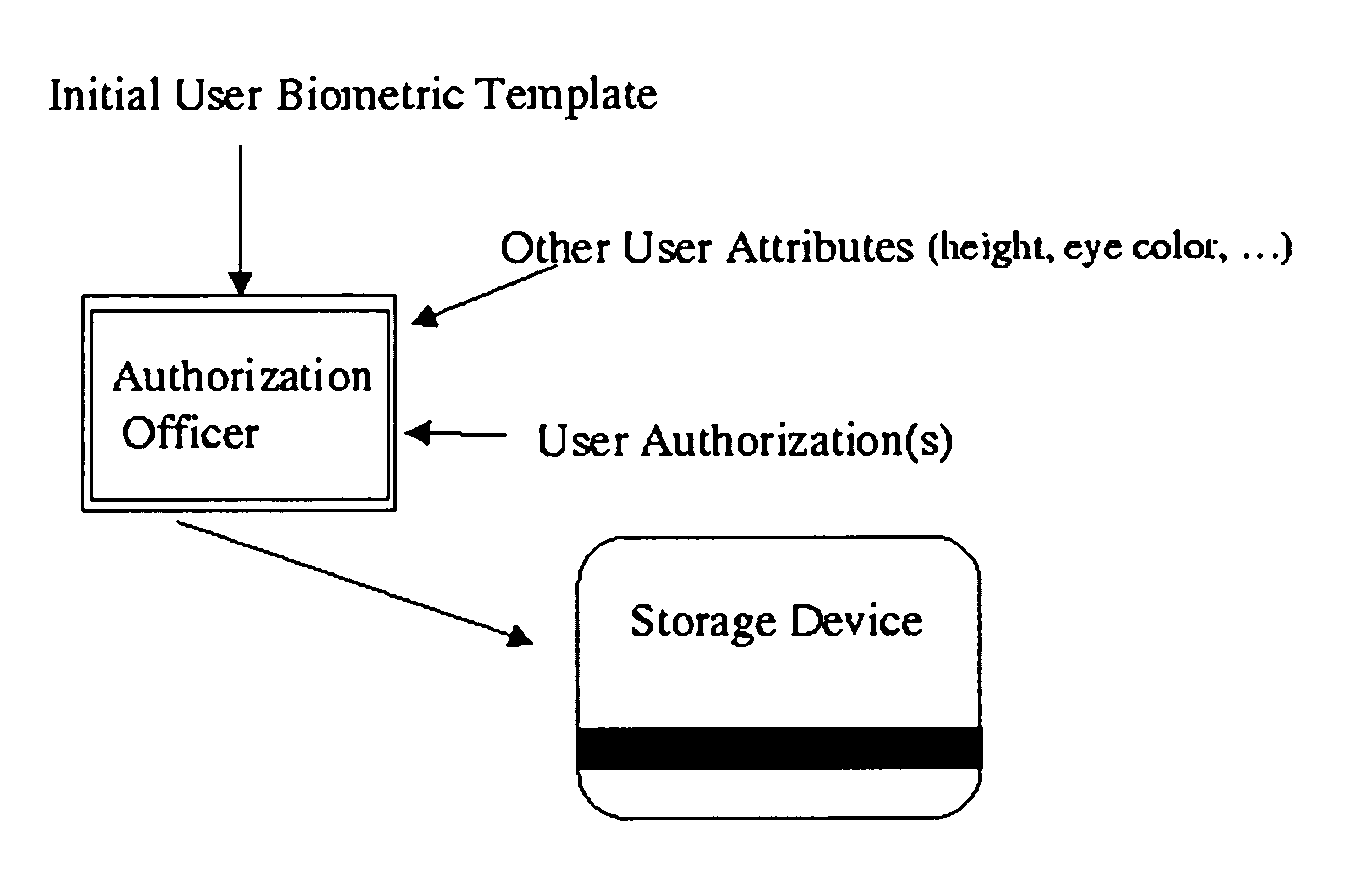

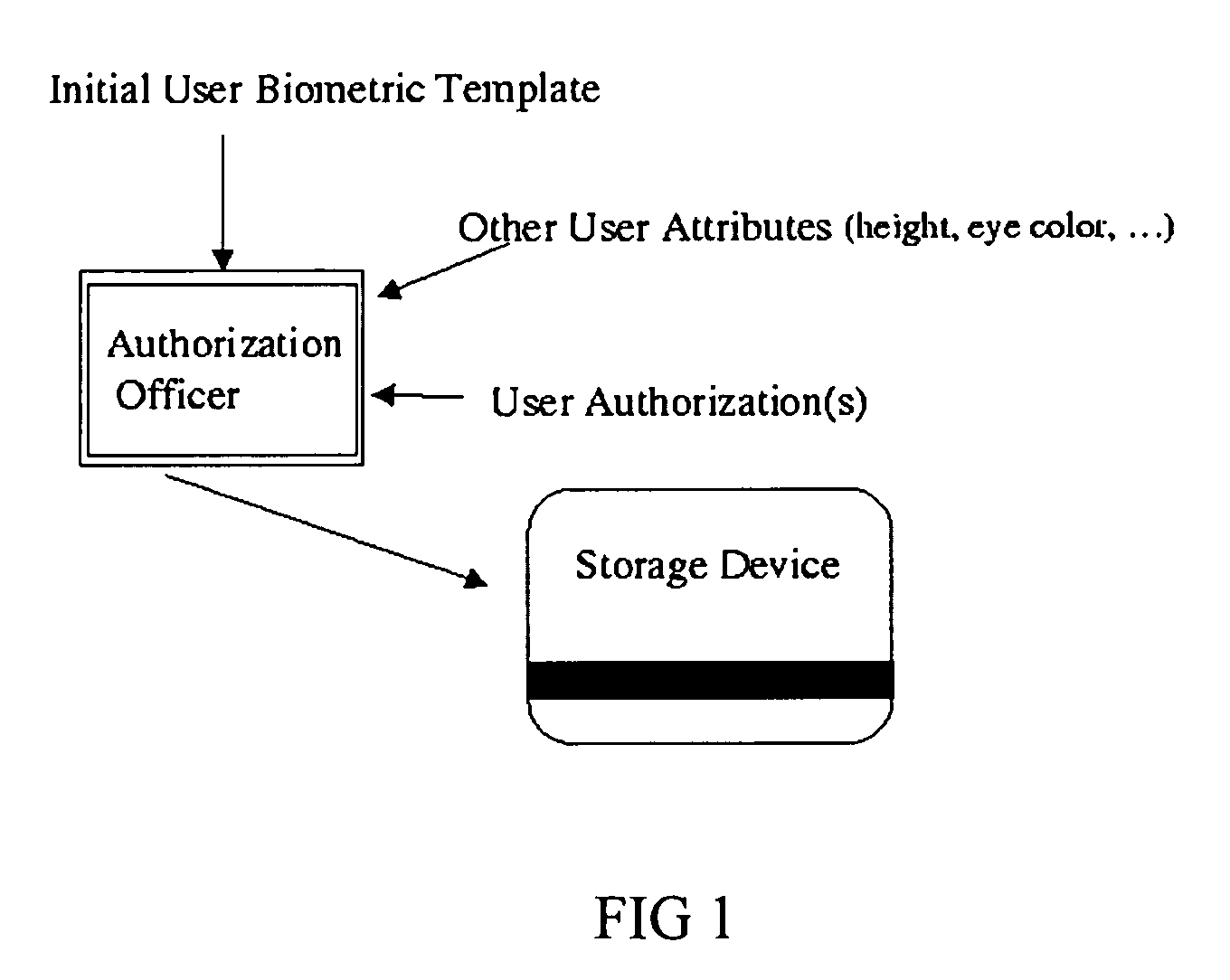

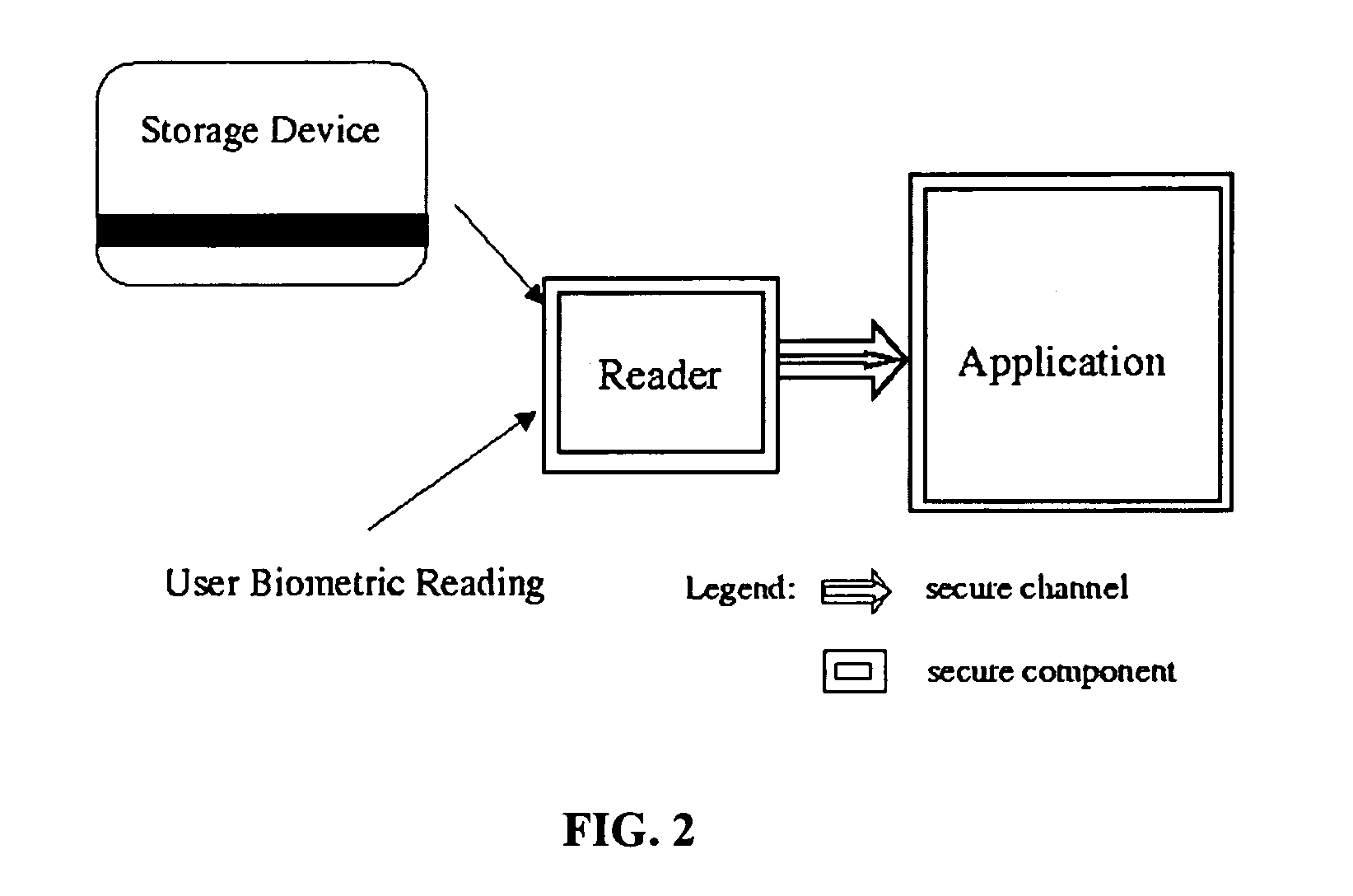

System and method for authenticated and privacy preserving biometric identification systems

InactiveUS7711152B1Opportunities decreaseElectric signal transmission systemsImage analysisOnline modelControl system

A system and method for the identification of users and objects using biometric techniques is disclosed. This invention describes a biometric based identification and authorization systems which do not require the incorporation of an on-line database of stored complete biometrics for the security infrastructure. In order to remove the connectivity requirements, an off-line biometric system is achieved by incorporating an identity verification template (IVT) on a storage device / token (e.g., magnetic strip or smart-card) during the user's registration which provides for a reliable storage medium; however, there are no security requirements required of the token even to protect the privacy of the stored biometric. The IVT does not contain complete information of the user's biometric but allows for the verification of the user when that user later provides a biometric reading. To deal with errors that may be introduced into later scans of the biometric (for example at the time of verification) error correcting techniques, well known in the art of communication and error control systems, are incorporated into the system. The system is also usable in the online model. Moreover, it may also be used to enable cryptographic operations by being used to partially compose or encrypt private keys for cryptographic operation.

Owner:GIDIPO LLC

Method for decoding data in non-volatile storage using reliability metrics based on multiple reads

ActiveUS7904793B2Other decoding techniquesRead-only memoriesLow-density parity-check codeDependability

Data stored in non-volatile storage is decoded using iterative probabilistic decoding and multiple read operations to achieve greater reliability. An error correcting code such as a low density parity check code may be used. In one approach, initial reliability metrics, such as logarithmic likelihood ratios, are used in decoding read data of a set of non-volatile storage element. The decoding attempts to converge by adjusting the reliability metrics for bits in code words which represent the sensed state. If convergence does not occur, e.g., within a set time period, the state of the non-volatile storage element is sensed again, current values of the reliability metrics in the decoder are adjusted, and the decoding again attempts to converge. In another approach, the initial reliability metrics are based on multiple reads. Tables which store the reliability metrics and adjustments based on the sensed states can be prepared before decoding occurs.

Owner:SANDISK TECH LLC

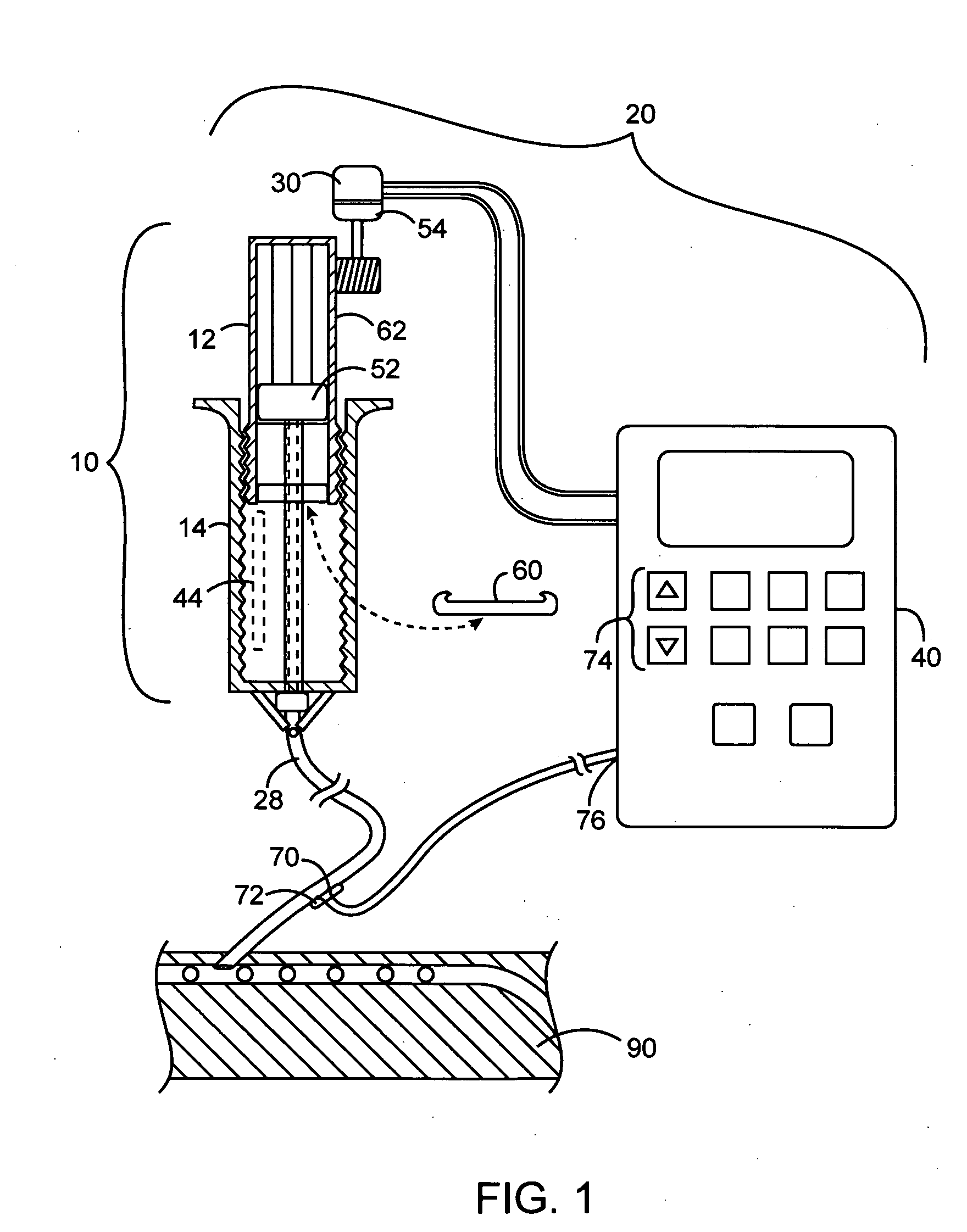

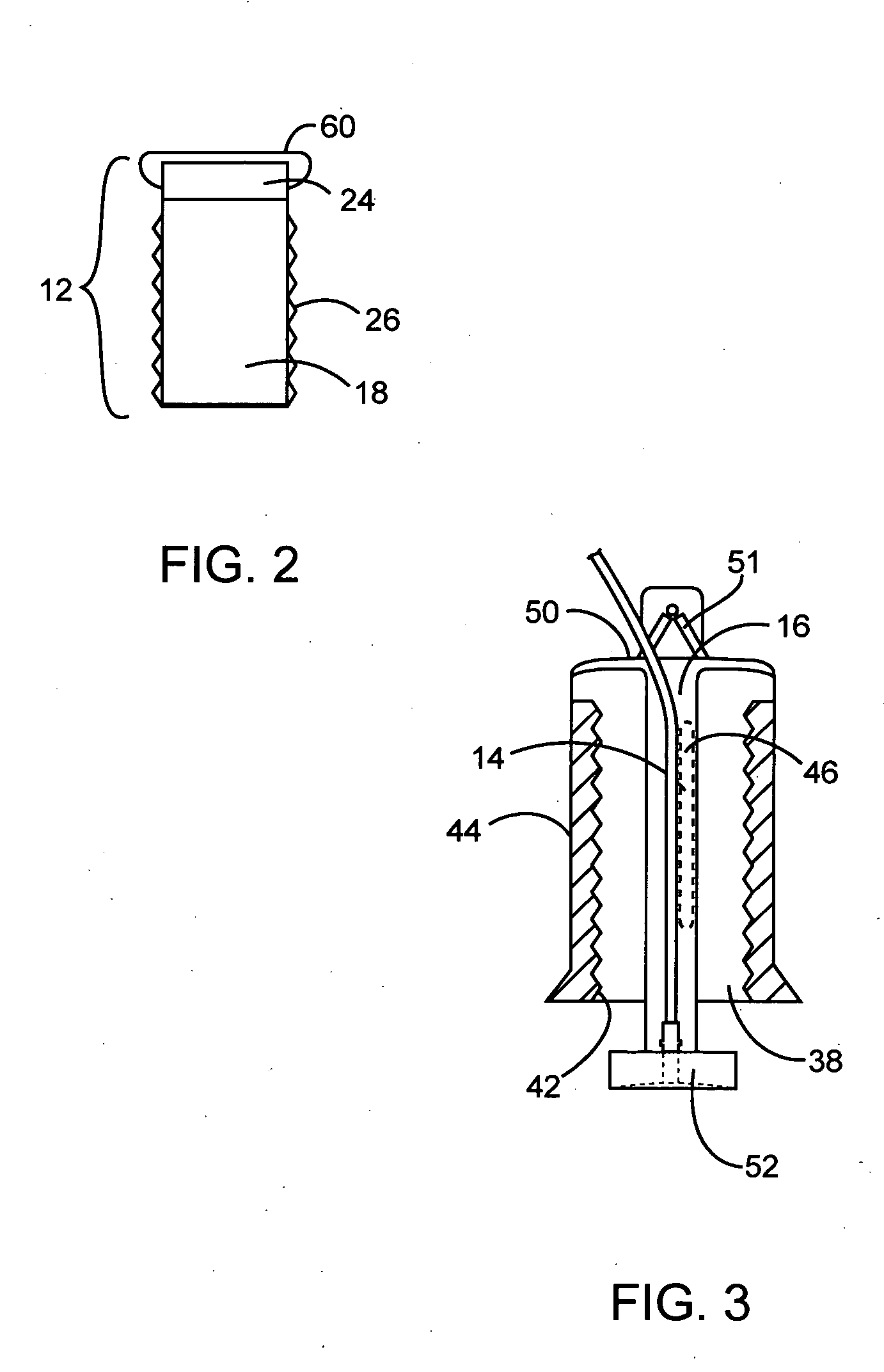

Quantitative chronological medical infusion device

InactiveUS20060079831A1Reduce riskReduced glucose levelMedical devicesIntravenous devicesLine sensorHigh rate

The present invention is a medical infusion and aspiration system delivering precisely timed and accurately calculated, adjusted pulsated delivery in high rates of flow delivering an effective profile of pulses tailored to provide momentary spikes of levels of freely available medicines based upon the uptake of the medicine and optimally on real time measurements of the medicine or response of the patient, termed Quantitative Chronological Delivery. The system comprises any pumping mechanism, and optimally a pumping mechanism, and a cassette or cartridge having a reservoir area where the plunger rotates as it advances in reference to the cartridge to provide additional accuracy and overcome the forces of inertia and slip-stick as well as eliminate backlash. Optimally, the systems incorporates an encoded area and an opening for connection to an infusion tube with an in-line sensor area where sampling probes are located. The infusion is adjusted in both amount and duration between pulses to provide quantitatively controlled, chronologically optimized infusion. A motor causes bi-directional pumping to allow for samples to be presented to the sensor area. The system accuracy allows for more concentrated medicines, as a sealed container can eliminate the need for diluting or withdrawing medicine to load a reservoir, and achieves extraordinary accuracy without error correcting software or expensive volumetric measurement and control systems.

Owner:BIONICA INT

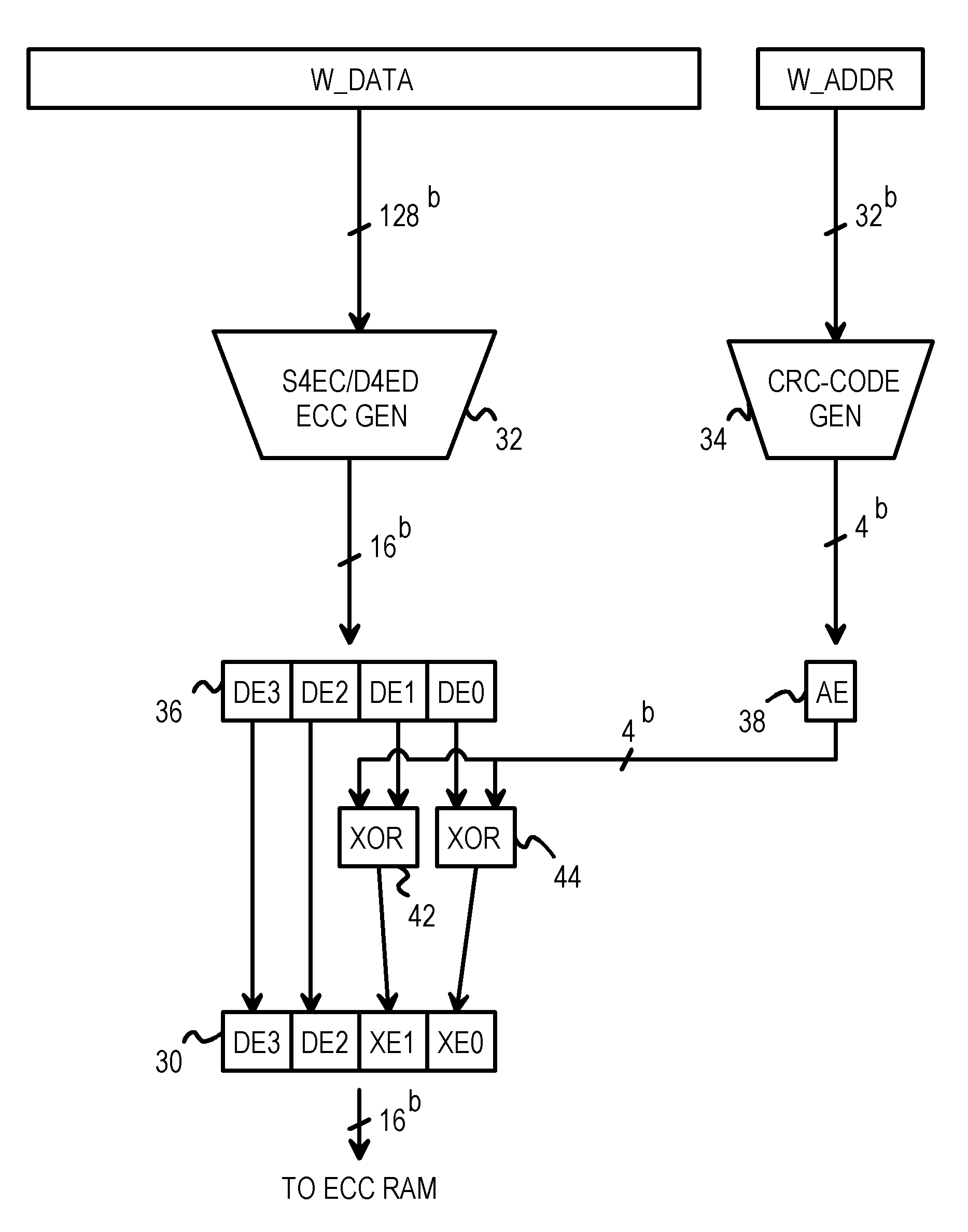

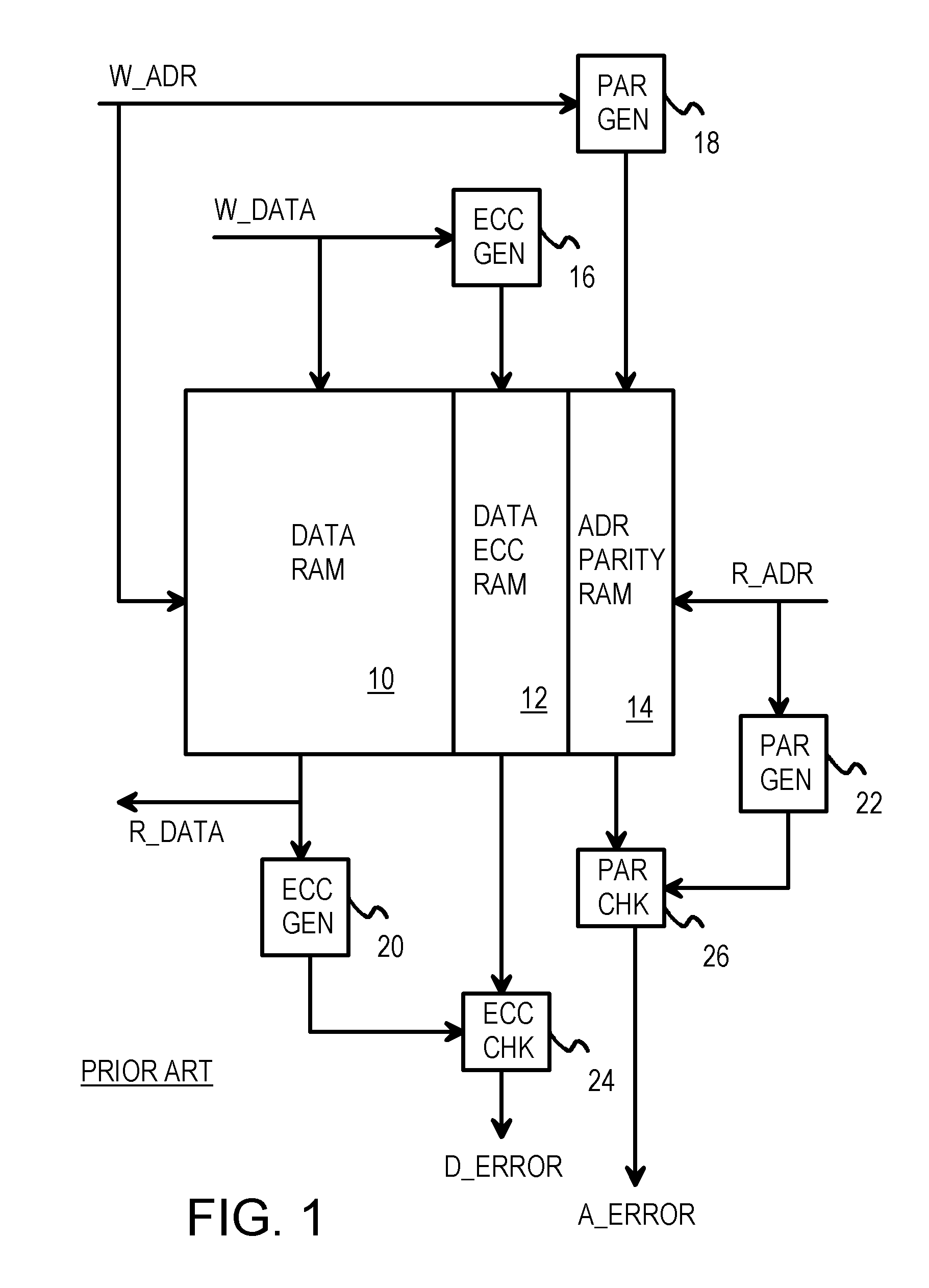

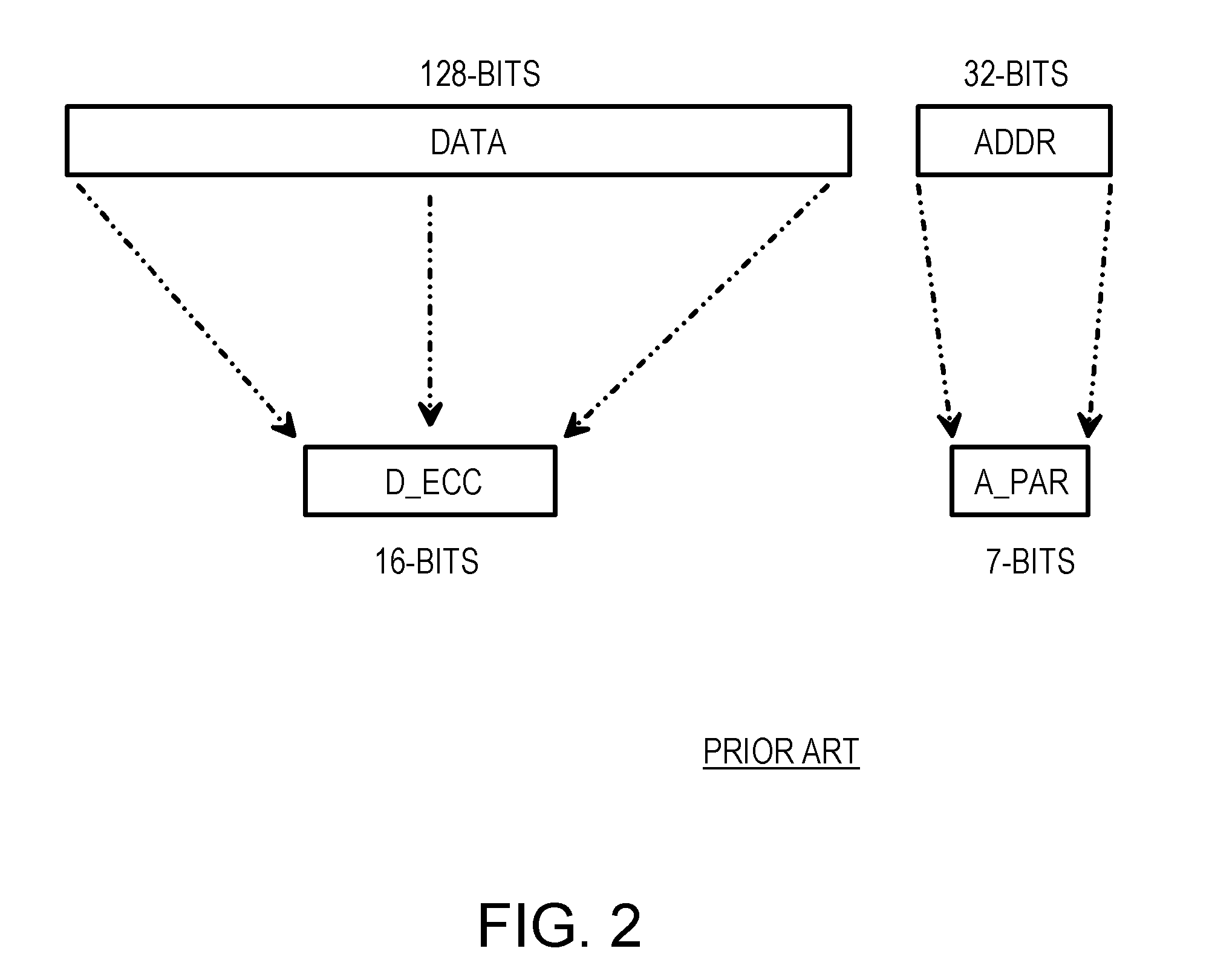

Address error detection by merging a polynomial-based CRC code of address bits with two nibbles of data or data ECC bits

A memory system provides data error detection and correction and address error detection. A Single-byte Error-Correcting / Double-byte Error-Detecting (SbEC / DbED) code with the byte being a 4-bit nibble is used to detect up to 8-bit errors and correct data errors of 4 bits or less. Rather than generating address parity, which is poor at detecting even numbers of errors, a cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to just 4 address check bits using the CRC code. The 4 address check bits are merged (XOR'ed) with two 4-bit nibbles of the data SbEC / DbED code to generate a merged ECC codeword that is stored in memory. An address error causes a 2-nibble mis-match due to the redundant merging of the 4 address check bits with 2 nibbles of data correction code. The CRC code is ideal for detecting even numbers of errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com