Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

70 results about "Decoding throughput" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Flexible polar encoders and decoders

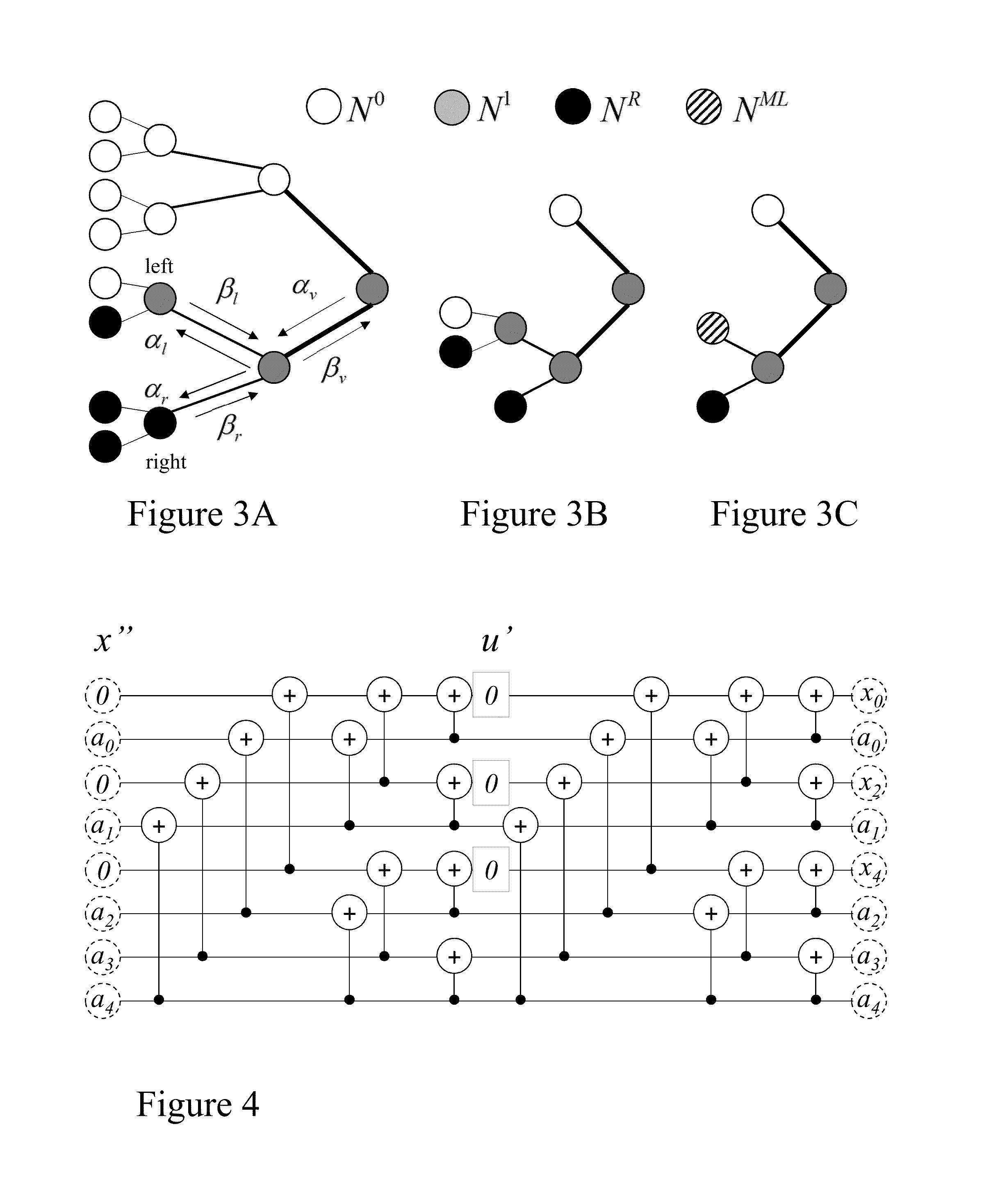

Modern communication systems must cope with varying channel conditions and differing throughput constraints. Polar codes despite being the first error-correcting codes with an explicit construction to achieve the symmetric capacity of memoryless channels are not currently employed against other older coding protocols such as low-density parity check (LDPC) codes as their performance at short / moderate lengths has been inferior and their decoding algorithm is serial leading to low decoding throughput. Accordingly techniques to address these issues are identified and disclosed including decoders that decode constituent codes without recursion and / or recognize classes of constituent directly decodable codes thereby increasing the decoder throughput. Flexible encoders and decoders supporting polar codes of any length up to a design maximum allow adaptive polar code systems responsive to communication link characteristics, performance, etc. whilst maximizing throughput. Further, designers are provided flexibility in implementing either hardware or software implementations.

Owner:POLAR TECH

Polar code decoding method and decoding device

ActiveCN104124979AImprove decoding throughputReduce Decoding LatencyError preventionError correction/detection using linear codesDecoding methodsComputer science

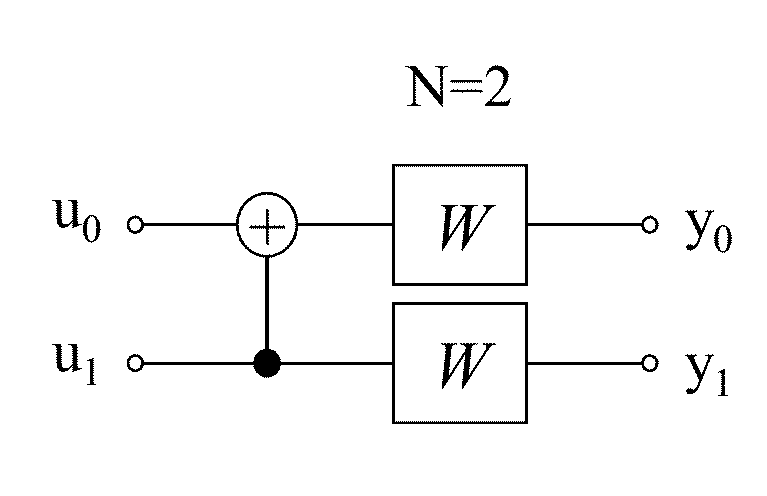

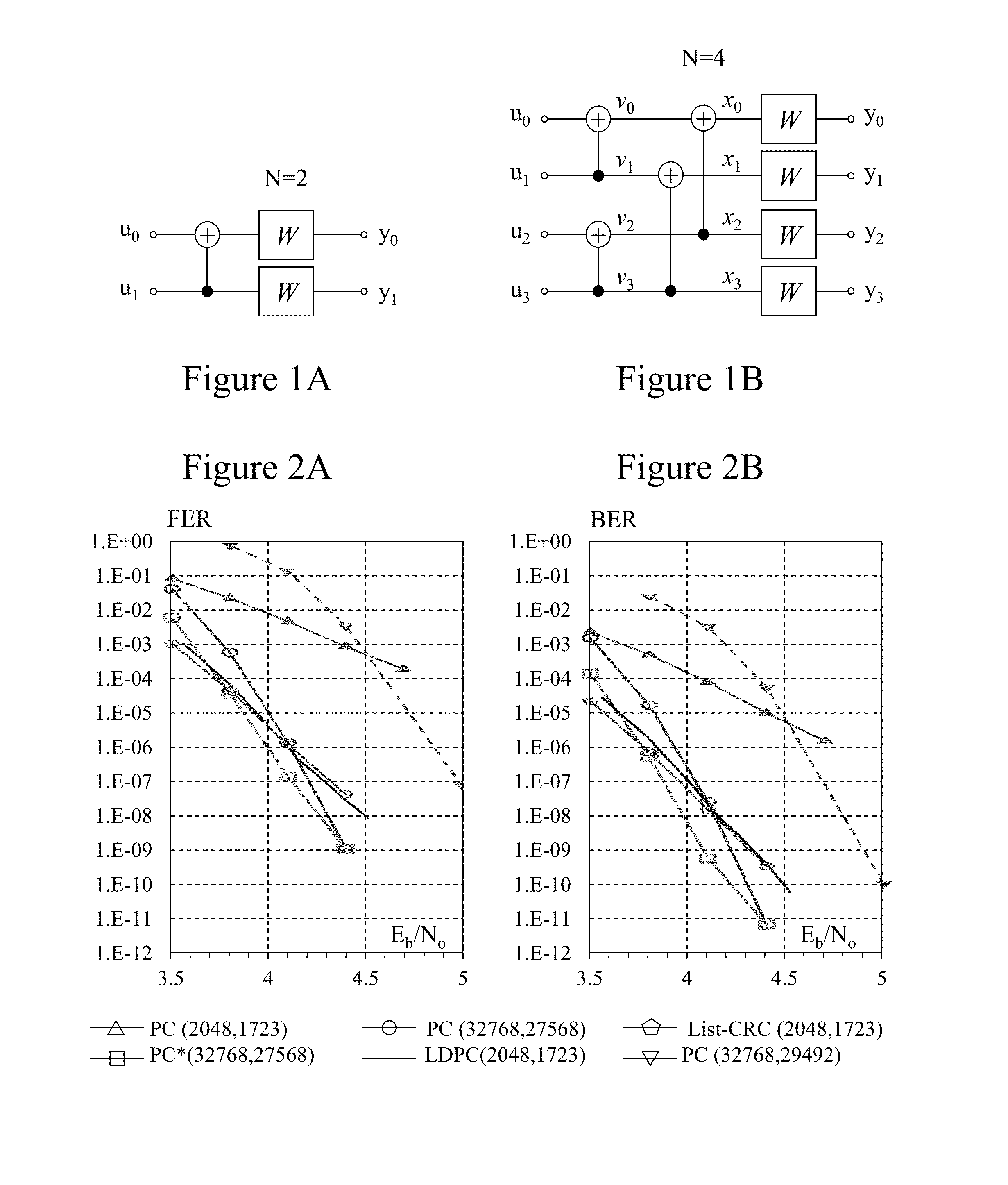

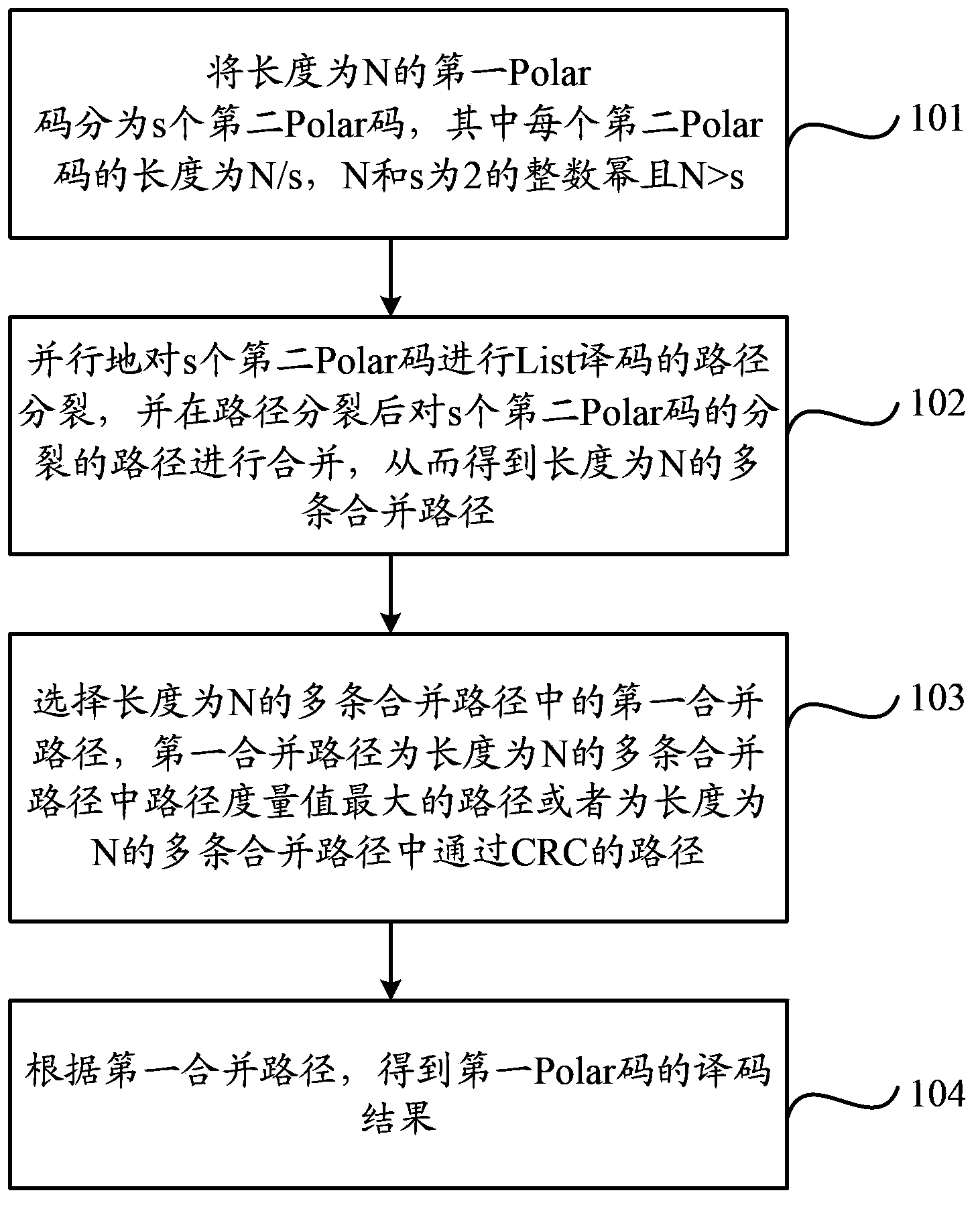

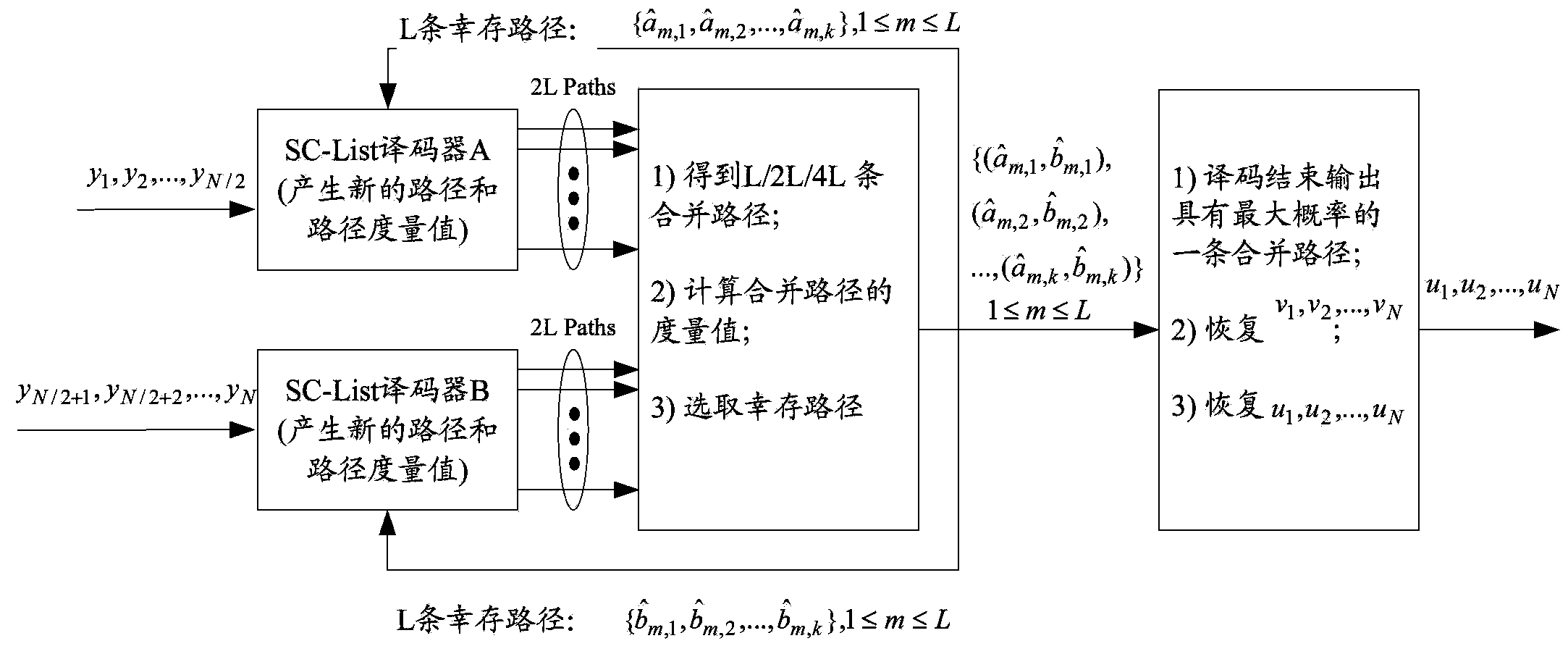

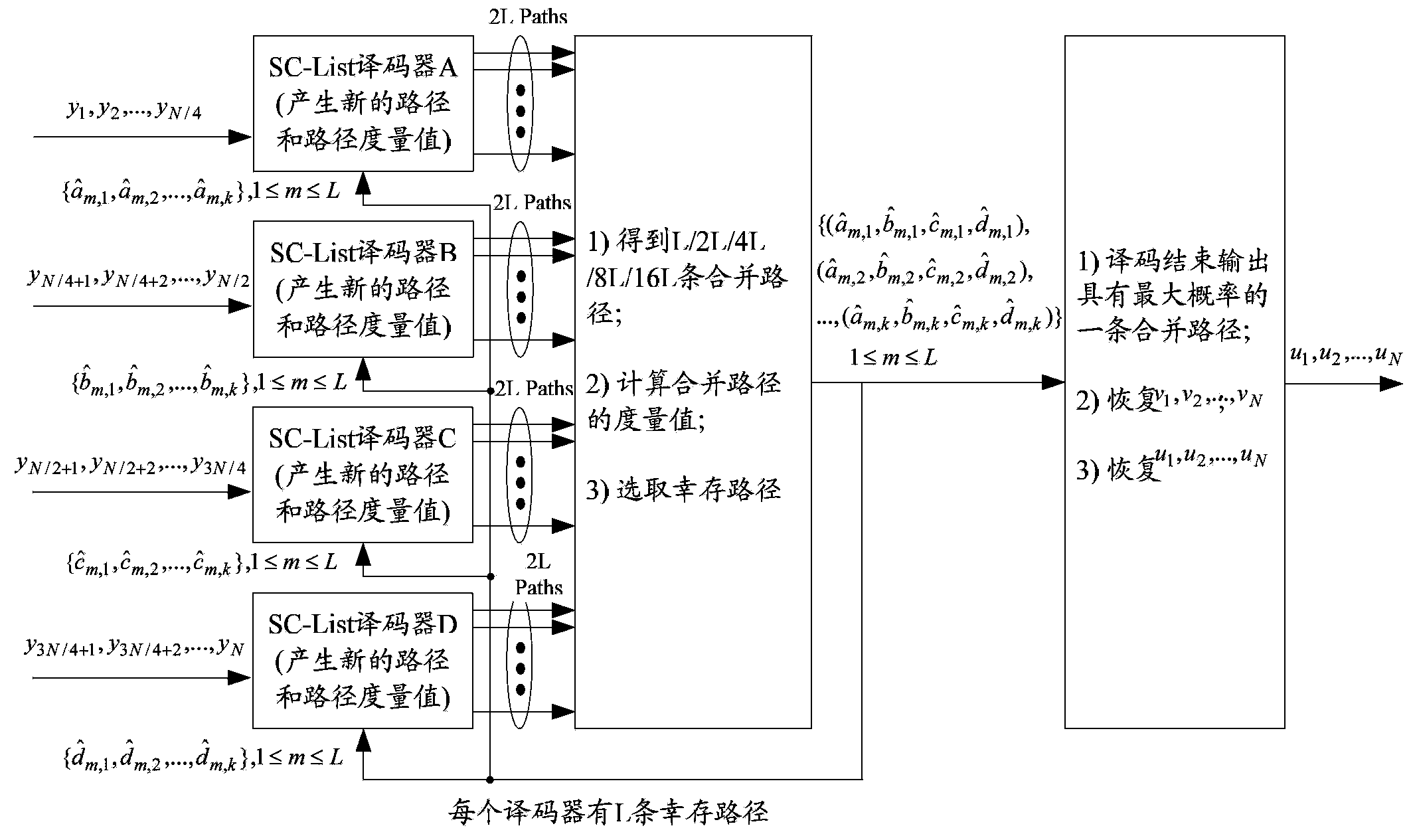

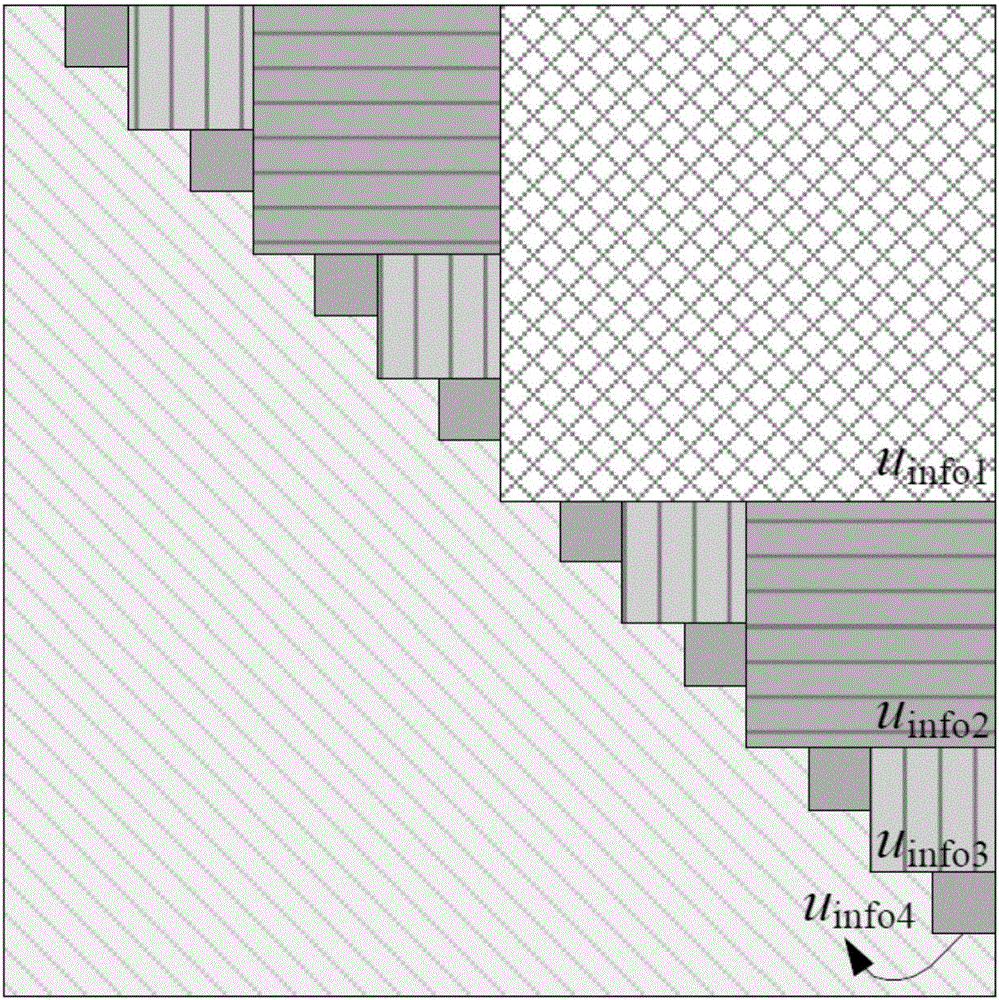

Embodiments of the present invention provide a decoding method and a decoding apparatus for a polar code. The method comprises: grouping a first polar code having a length of N into s second polar codes, a length of each second polar code being N / s, N and s being integer powers of 2, and N>s; performing path splitting of list decoding on s second polar codes concurrently, and combining split paths of s second polar codes after path splitting, so as to obtain multiple combined paths having a length of N; choosing a first combined path from multiple combined paths having a length of N bits, the first combined path being a path having the greatest path metric value among the multiple combined paths having a length of N bits, or a path passing cyclic redundancy check (CRC) among the multiple combined paths having a length of N bits; and obtaining a decoding result of the first polar code according to the first combined path. In this case, a decoding throughput of the polar code can be improved, and a decoding delay can be decreased.

Owner:HUAWEI TECH CO LTD

System and method for efficient horizontal maximum distance separable raid

InactiveUS8522125B1Improve decoding performanceFast decodingError detection/correctionCode conversionRAIDErasure code

In recent years, researchers have found that some XOR erasure codes lead to higher performance and better throughput in fault-tolerant distributed data storage applications. However, little consideration has been given to the advantages of parallel processing or hardware implementations taking advantage of the emergence of multi-core processors. An efficient horizontal MDS-like (Maximum Distance Separable) RAID-6 scheme, called EEO, is provided which significantly improves the performance of the decoding procedure in parallel implementations with little storage overhead. EEO is the fastest and most efficient double disk failure recovering algorithm in RAID-6, at the cost of only two more parity symbols. In practice, it is very useful for application where high decoding throughput is desired.

Owner:JOLLY SEVEN SERIES 70 OF ALLIED SECURITY TRUST I

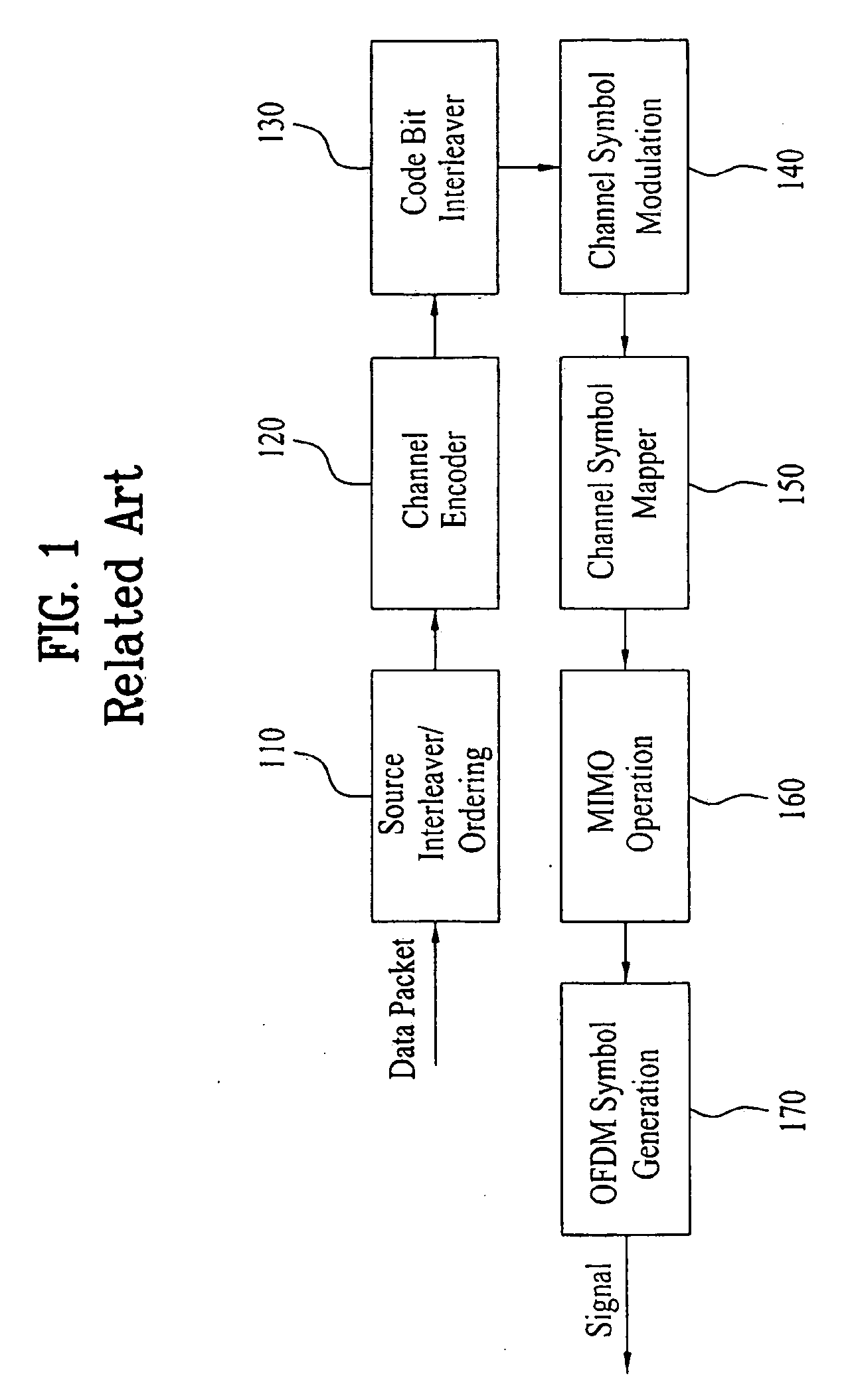

Edge-based decoders for low-density parity-check codes

ActiveUS8429483B1Improve decoding throughputError detection/correctionCode conversionData retrievalParity-check matrix

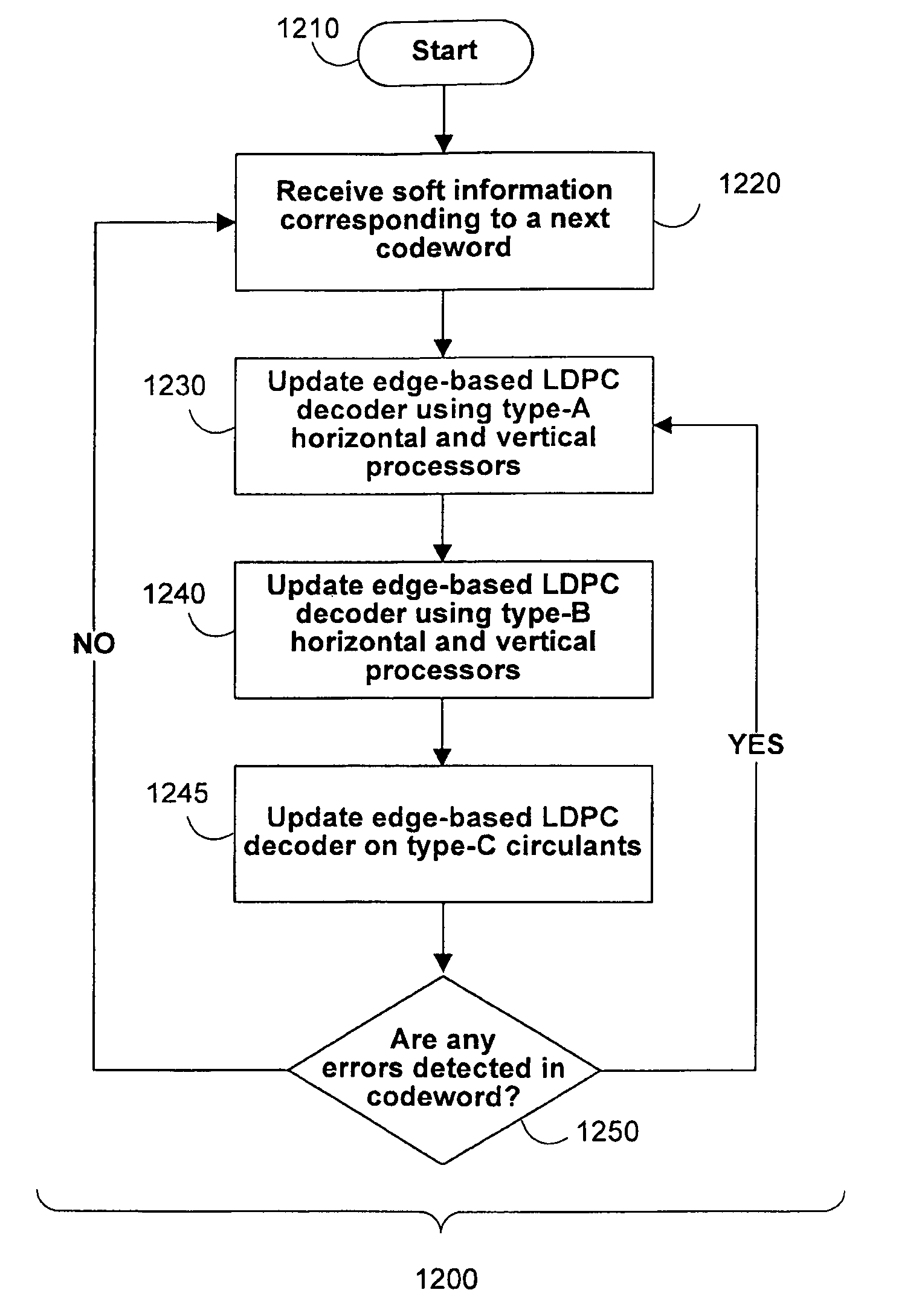

Systems, methods, and apparatus are provided for increasing decoding throughput in an LDPC decoder, such as in a wireless communications receiver or in a data retrieval unit. A checker-board parity check matrix and edge-based LDPC decoder structure are provided in which both vertical and horizontal processors are used simultaneously. Horizontal processors may be grouped into type-A and type-B horizontal processors, and similarly, vertical processors may be grouped into type-A and type-B vertical processors. Type-A processors may be used in different clock cycles than type-B processors to update memory locations in a decoding matrix without causing memory access conflicts.

Owner:MARVELL ASIA PTE LTD

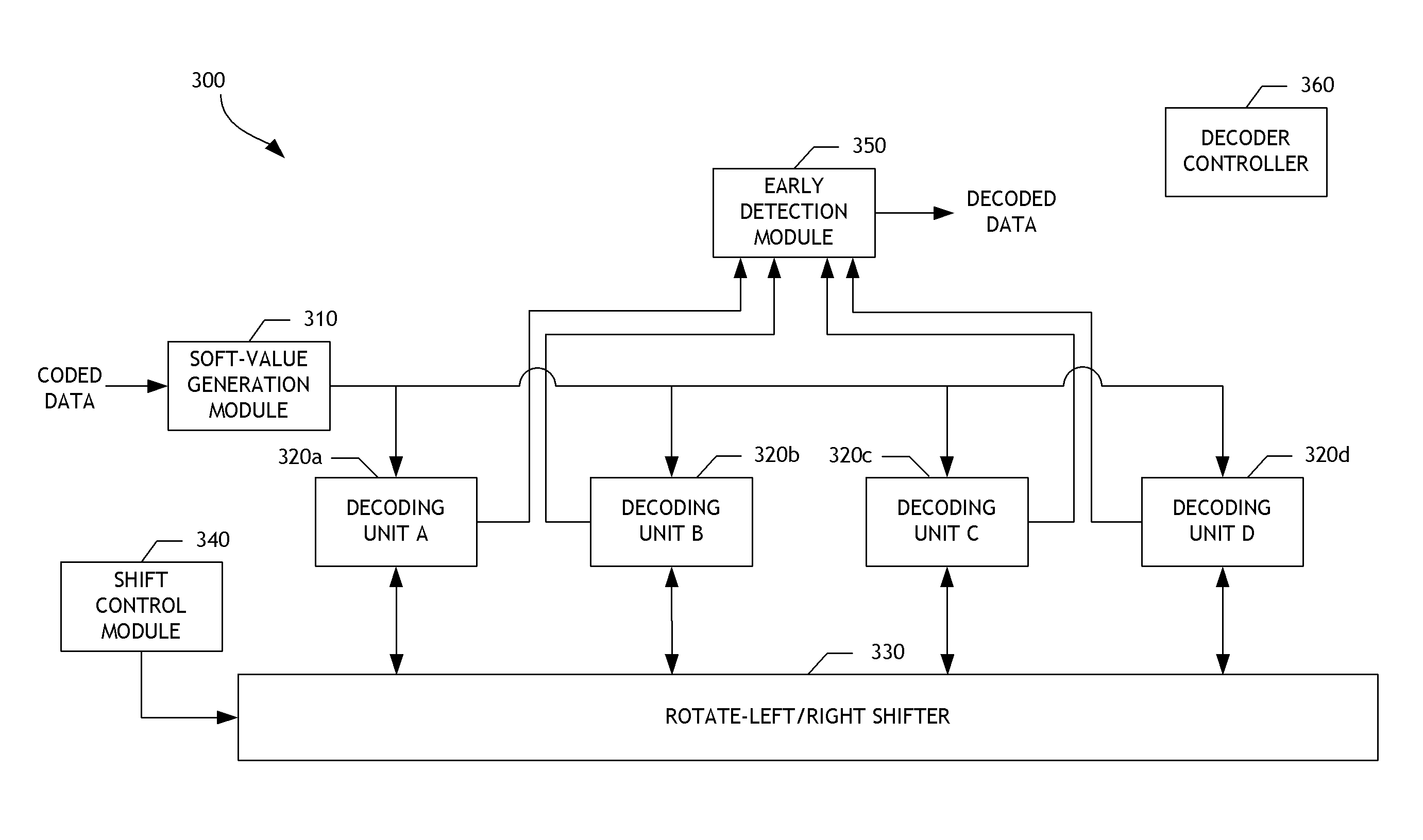

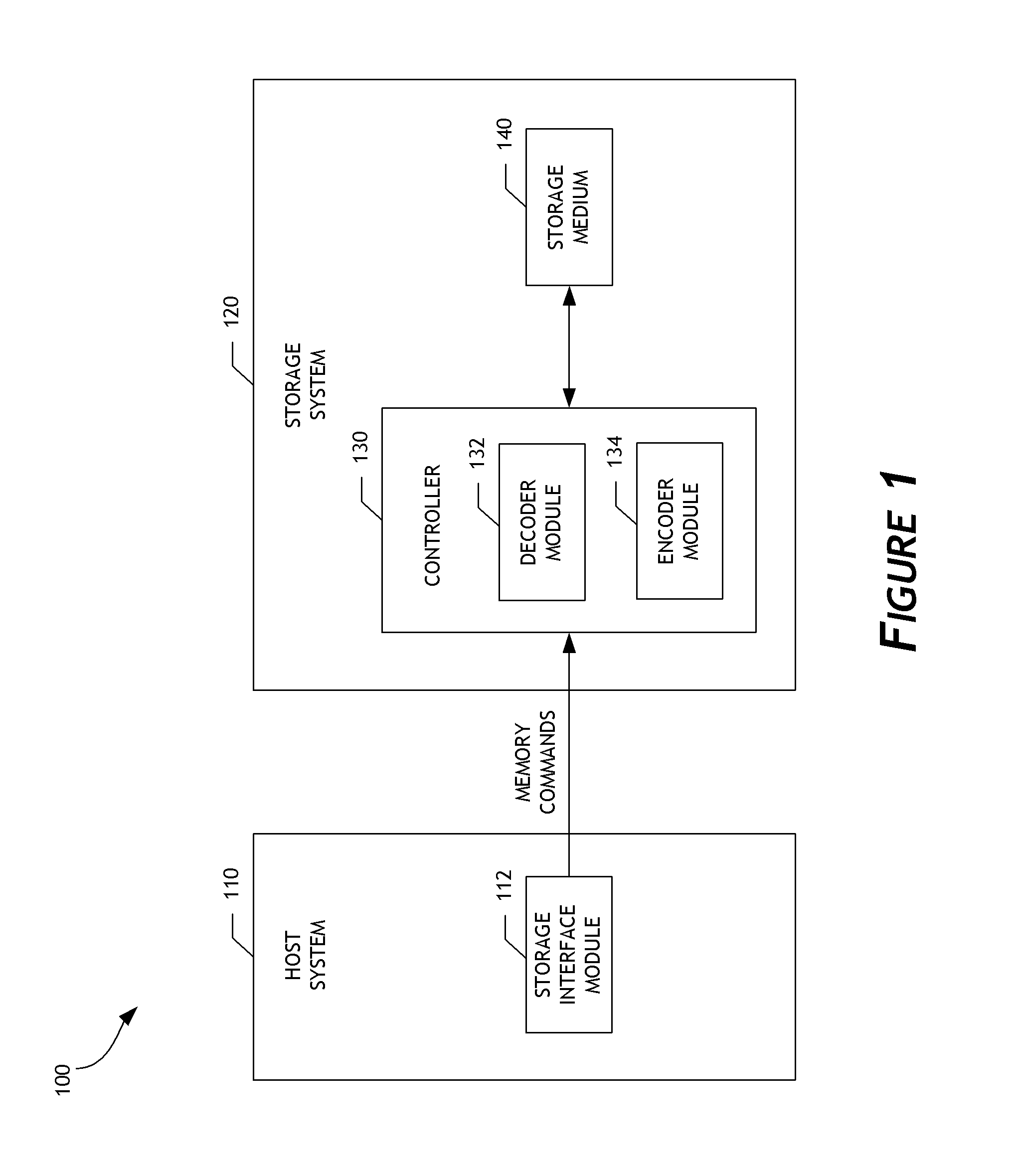

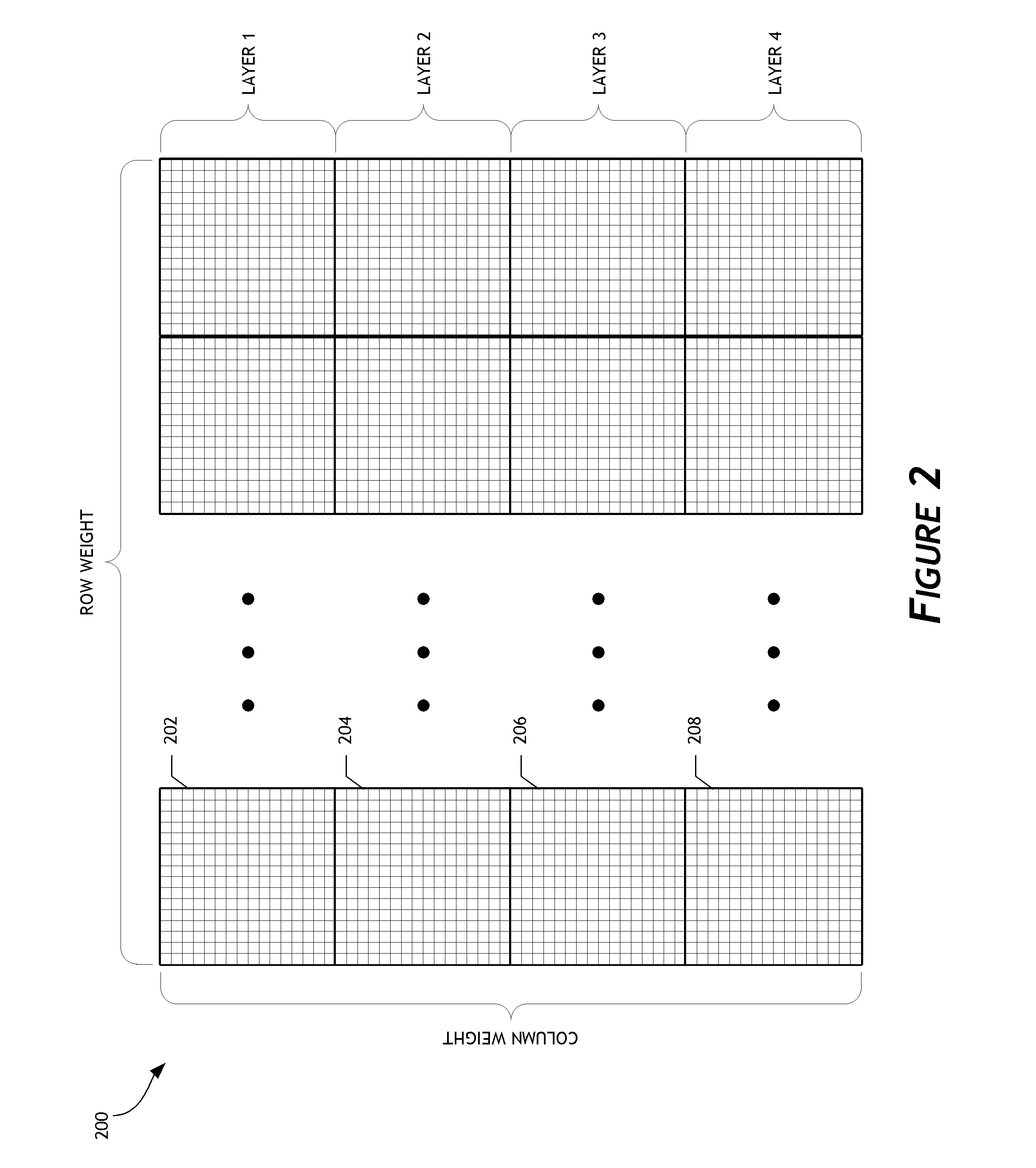

Decoder supporting multiple code rates and code lengths for data storage systems

ActiveUS8966339B1Reduce memory spaceHigh bit rateCode conversionError correction/detection using linear codesParallel computingCode rate

Embodiments of decoders supporting multiple code rates and code lengths for data storage systems are disclosed. The decoders can provide for flexible and scalable decoding, particularly when quasi-cyclic low-density parity-check code (QC-LDPC) decoding is used. The decoder can be scaled in size based on, for example, the desired decoding throughput and / or computational cycle duration. In one embodiment, a rotate-left / right shifter is configured to support data having processing units of one of multiple matrix sizes and independently shift portions of the data. In another embodiment, one or more decoding modules are configured to share with one or more other decoding modules an output value from a layer decoding operation. This sharing can facilitate parallel decoding of data by the decoding modules. As a result, decoding speed, efficiency, and system performance can be improved.

Owner:WESTERN DIGITAL TECH INC

Parallel hierarchical decoder for low density parity code (LDPC) in mobile digital multimedia broadcasting system

InactiveCN101931416AReduce the number of iterationsImprove bit error performanceError correction/detection using multiple parity bitsSignal-to-noise ratio (imaging)Parallel computing

The invention discloses a parallel hierarchical decoder for a low density parity code (LDPC) in a mobile digital multimedia broadcasting system. The parallel hierarchical decoder adopts a partially parallel structure and is characterized in that: 1) each line of a check matrix is taken as a layer, check nodes of each layer are updated sequentially for each variable node, the variable node is updated after the check nodes of each layer are updated and a value obtained after updating is used in the updating of the check nodes of a next layer until an iteration is finished; and 2) the check nodes of a plurality of lines are selected for parallel computation under the condition that 1) is met, so that a partially parallel decoding structure can be realized. Compared with the conventional LDPC decoder, the parallel hierarchical decoder has the advantages of reducing average iteration times needed when a decoding convergence condition [bit error rate (BER) is less than or equal to 10 to 6] is met under the condition of the same signal to noise ratio and the same maximum iteration time, achieving higher error code performance, greatly increasing decoding throughput rate or effectively reducing power consumption and improving the error code performance of a system.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

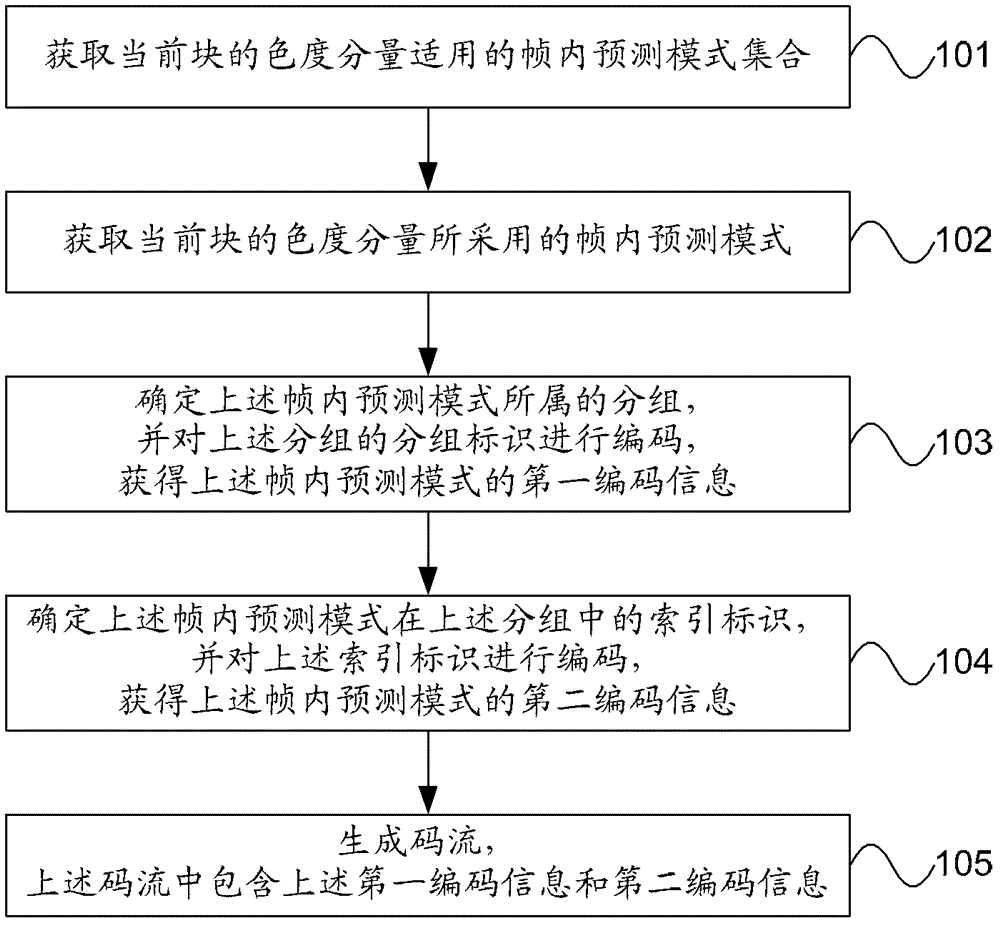

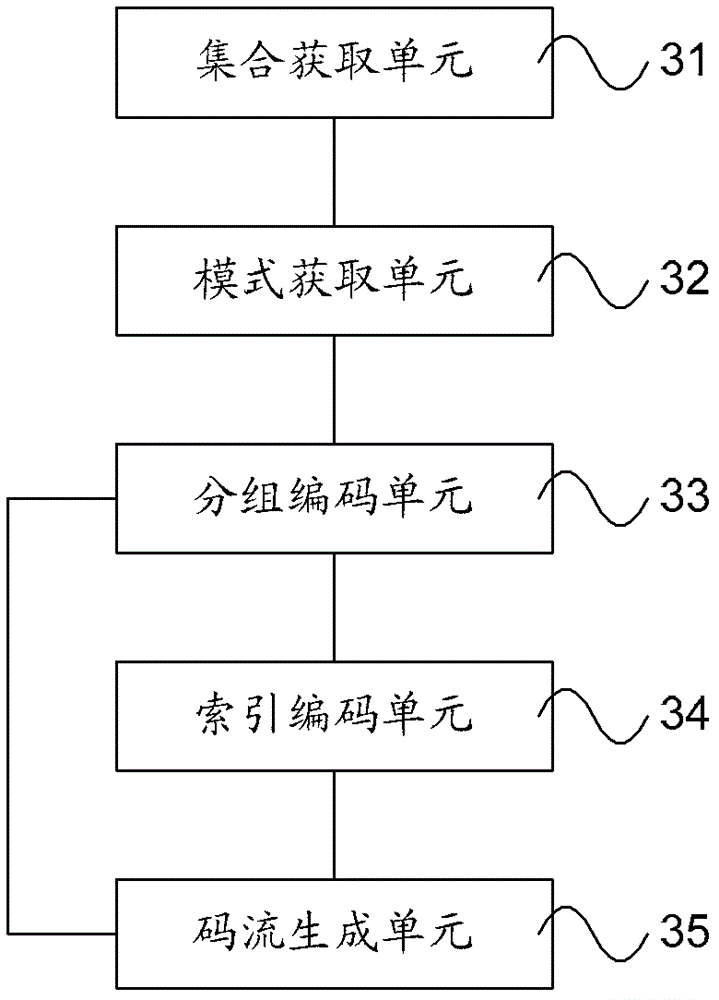

Coding and decoding methods, equipment and system of intra-frame chroma prediction modes

The invention provides coding and decoding methods, equipment and a system of intra-frame chroma prediction modes. According to the invention, intra-frame prediction modes of an intra-frame prediction mode set which is suitable for the chroma of a current block are divided into a first subgroup and a second subgroup, the amount of the intra-frame predication modes in correspondence with the first subgroup is at least two, and the amount of the intra-frame predication modes in correspondence with the second subgroup is 2<N>, wherein N is a positive integer. Due to the fact that the most required coded bit number is lower than that in the prior art, decoding throughput can be improved.

Owner:HUAWEI TECH CO LTD

Symbol mapping method for repetition channel coding

ActiveUS20090175373A1DistanceMaximize distanceError prevention/detection by using return channelElectric signal transmission systemsComputer architectureResource block

A symbol mapping method for repetition coding is disclosed. The symbol mapping method comprises performing repetition coding on codeword to output repeated codeword symbols, and mapping the repeated codeword symbols with subcarriers located in different localized resource blocks. According to the embodiments of the present invention, it is possible to obtain maximum reliability in a receiving side by mapping codeword bits with subcarriers to reduce the number of bits having low reliability when a transmitting side uses repetition coding. Also, it is possible to improve decoding throughput and obtain channel diversity.

Owner:OPTIS CELLULAR TECH LLC

Multi-mode viterbi decoding apparatus and decoding method thereof

ActiveCN103427850ASimple designImprove decoding throughputOther decoding techniquesDecoding methodsComputer science

The invention provides a multi-mode viterbi decoding apparatus and a decoding method thereof. The decoding apparatus comprises an input data storage module, a branch path metric module, a mode selection module, a parallel add-compare-select module, a residual path storage module, a backtracking module and a sequential control module, wherein the parallel add-compare-select module is used for performing accumulative calculation on the metric values and branch path metric values of corresponding states according to a state transfer graph for obtaining accumulative values, and sending residual path selection results to the residual path storage module by taking the greatest accumulative value as the new metric value of a next state until data to be decoded ends; and the backtracking module is used for selecting different backtracking modes according to different encoding modes, and begins backtracking from any a state or the state corresponding to the greatest accumulative value so as to obtain decoding results according to the residual path selection results stored by the residual path storage module. By using the multi-mode viterbi decoding apparatus and the decoding method thereof, enormous resources can be shared, design can be optimized, and the decoding throughput can be improved.

Owner:SANECHIPS TECH CO LTD

Continuous elimination list decoding method of software polarization code

ActiveCN106253911AReduce in quantityThe acceleration effect is obviousError correction/detection using linear codesDecoding methodsComputer science

The invention discloses a continuous elimination list decoding method of a software polarization code. Through establishment of a reference matrix and combination with the position of a current decoding bit, an upper bound and a lower bound of a phase needing to be copied are positioned; and the upper bound and the lower bound are mapped to a memory, only values between the two bounds are copied, and thus the quantity of copy operation is reduced. Compared to a conventional decoding technology, the method has the following advantages: under the condition that the decoding performance is not affected, the same data is prevented from being copied when a path is updated, the path updating time delay is substantially reduced, and the decoding throughput is improved; after the current bit is decoded, the reference matrix is updated; and the decoding method provided by the invention has universality and can be applied to different polarization code lengths, code rates and path numbers.

Owner:SOUTHEAST UNIV

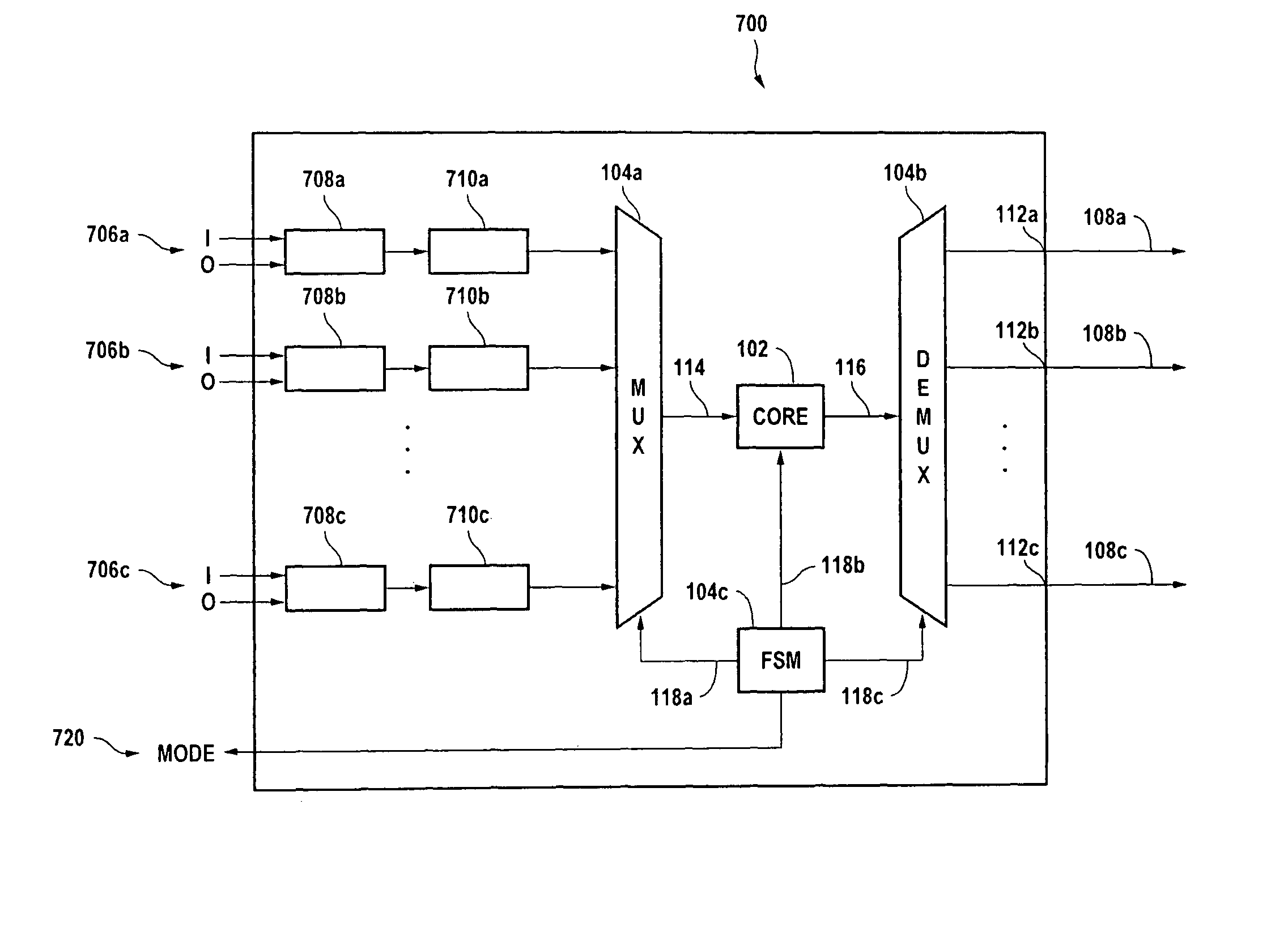

Flexible polar encoders and decoders

Modern communication systems must cope with varying channel conditions and differing throughput constraints. Polar codes despite being the first error-correcting codes with an explicit construction to achieve the symmetric capacity of memoryless channels are not currently employed against other older coding protocols such as low-density parity check (LDPC) codes as their performance at short / moderate lengths has been inferior and their decoding algorithm is serial leading to low decoding throughput. Accordingly techniques to address these issues are identified and disclosed including decoders that decode constituent codes without recursion and / or recognize classes of constituent directly decodable codes thereby increasing the decoder throughput. Flexible encoders and decoders supporting polar codes of any length up to a design maximum allow adaptive polar code systems responsive to communication link characteristics, performance, etc. while maximizing throughput. Further, designers are provided flexibility in implementing either hardware or software implementations.

Owner:POLAR TECH

High speed bit flat surface decoding method and circuit suitable for Jpeg2000 standard

InactiveCN101192303AImprove decoding efficiencyImage codingTelevision systemsCoding blockDigital image

The invention discloses a method and an electric circuit structure for bit plane quick decoding of EBCOT coefficient in coding and decoding standard of ISO / IEC JPEG2000 image compressing so as to improve JPEG2000 EBCOT decoding efficiency. The position plane decoding electric circuit of the invention can make the original coding block expansion analog pixel to form a new coding block being divided into three bank storage coefficients and coefficient state information, so the invitation capacity of a storage can be reduced, the coefficient can be scanned by using 6x4 window to accelerate the decoding process, simultaneously, a parallel technology is used to further improve the total EBCOT decoding throughput. The invention can improve JPEG2000 image decoding efficiency and can be widely used in digital image product series.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

Symbol mapping method for repetition channel coding

ActiveUS8391405B2Maximum reliabilityReduce in quantityError prevention/detection by using return channelElectric signal transmission systemsComputer architectureSymbol mapping

A symbol mapping method for repetition coding is disclosed. The symbol mapping method comprises performing repetition coding on codeword to output repeated codeword symbols, and mapping the repeated codeword symbols with subcarriers located in different localized resource blocks. According to the embodiments of the present invention, it is possible to obtain maximum reliability in a receiving side by mapping codeword bits with subcarriers to reduce the number of bits having low reliability when a transmitting side uses repetition coding. Also, it is possible to improve decoding throughput and obtain channel diversity.

Owner:OPTIS CELLULAR TECH LLC

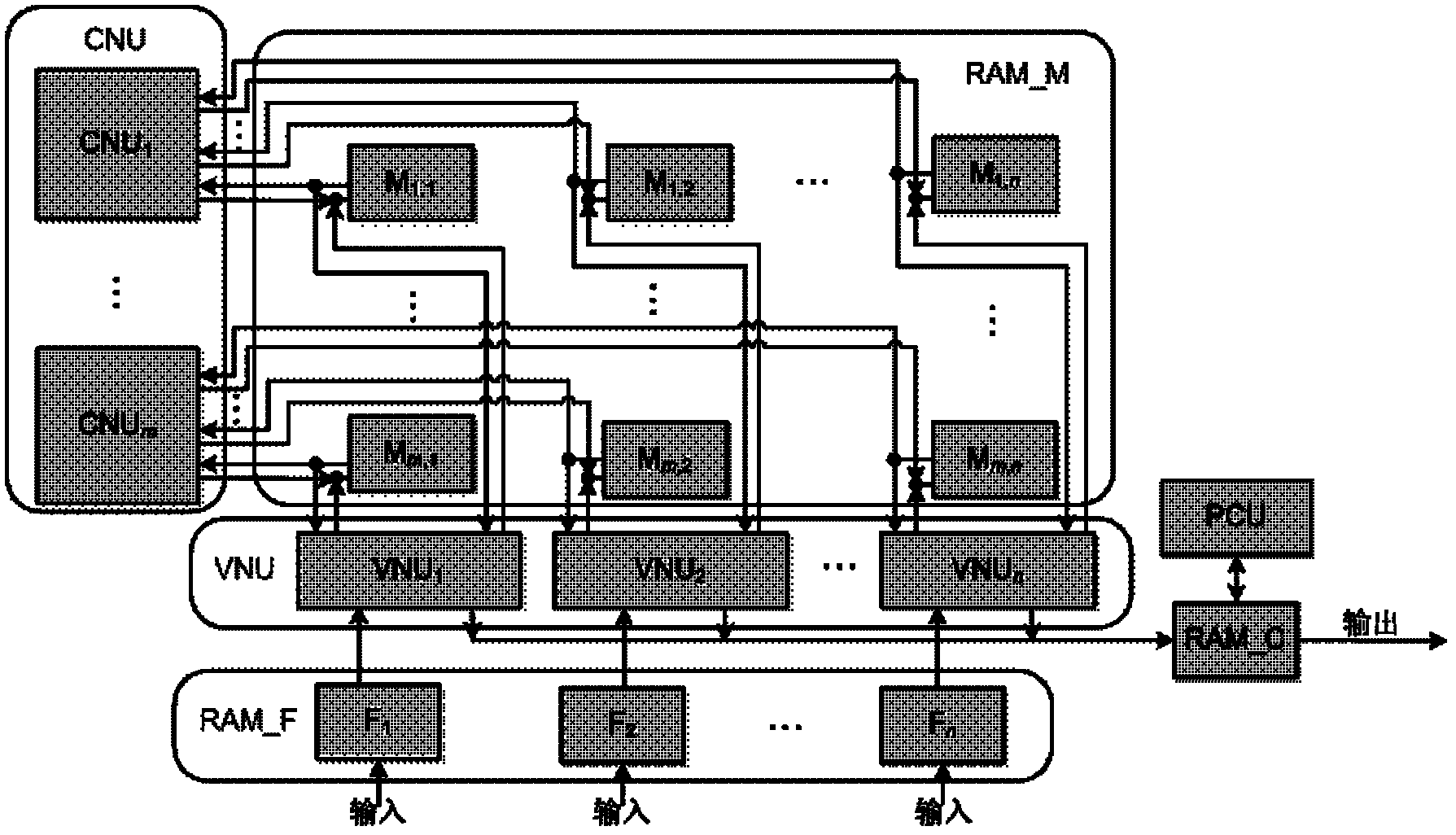

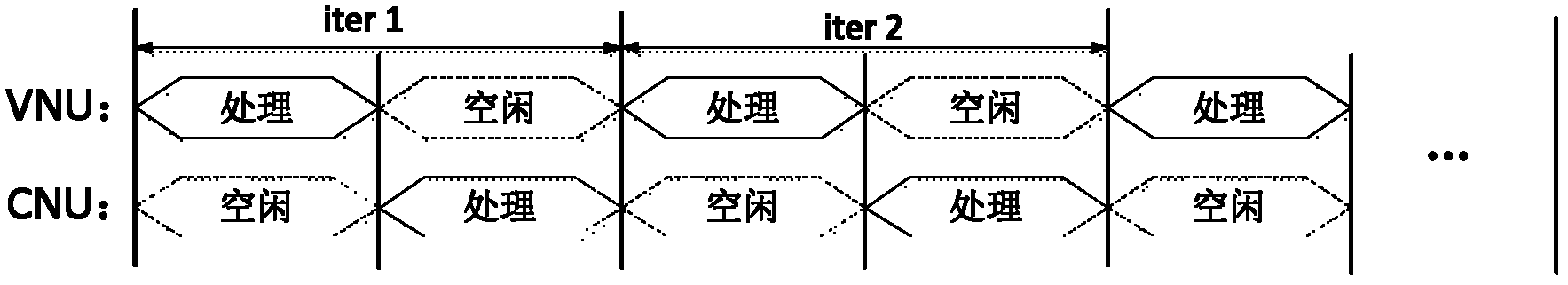

Quasi-cyclic low-density parity check code decoder based on FPGA (field-programmable gate array) and decoding method

InactiveCN102594369AImprove decoding throughputImprove resource utilizationError correction/detection using multiple parity bitsCyclic codesInformation accessField-programmable gate array

The invention discloses a low-storage capacity high-speed QC-LDPC (quasi-cyclic low-density parity check) code decoder based on an FPGA (field-programmable gate array) and a decoding method, which are mainly used for solving the problem of low utilization efficiency of memory resources of a node update processing unit and an RAM (random access memory) of the decoder in the prior art. The decoder can simultaneously process two frames of decoding data, the decoder is used for setting an external information value of the first frame of data as all-zero and setting the second frame of data as a channel for receiving likelihood ratio information in the data initialization phase, so that a variable node processing unit and a check node processing unit can completely alternately process the two data frames in parallel in the whole decoding process, effectively shorten the work clock cycle required for processing the two frames of data and enable the decoding throughput to be about two times as that of a traditional design method. According to the decoder disclosed by the invention, a dynamic address access management method is adopted in external information access, and the parallel access of the two frames of decoding data can be realized in the single RAM; and compared with the existing decoder, the utilization efficiency of BRAM (broadcast recognition access method) resources is doubled in comparison with the existing decoders, and the decoder can be used for error correction in information transmission of a physical layer based on LDPC codes.

Owner:XIDIAN UNIV

Parallel multicode-rate convolutional code decoding method and realization device thereof

InactiveCN101764622AMeet the requirements of high-speed information transmission communication systemImprove decoding throughputError correction/detection using convolutional codesControl signalAmbiguity

The invention discloses a parallel multicode-rate convolutional code decoding method and a realization device thereof. The parallel multicode-rate convolutional code decoding method comprises the following steps of: S1. receiving Nin paths of parallel input signals, and shifting the input signals under the effect of a shifting control signal and outputting the input signals, wherein output signals are also Nin paths of parallel signals, and the Nin is positive integers; S2. partially eliminating the phase ambiguity of the output signals; S3. taking the signals processed in the S2 as effectivedata, adding guard intervals for the effective data to assemble into a data frame, and taking the data frame as the input of a parallel convolutional code; S4. carrying out the convolutional decodingon the assembled data frame after being processed in the step S3; and S5. merging multipath outputs of the parallel convolutional decoding into one path and outputting in parallel. The invention provides the parallel multicode-rate convolutional code decoding method aiming at the defect that the throughput rate of the traditional convolutional decoding can not satisfy high-speed communication, improves the decoding throughput rate and the effective payload velocity by adopting a parallel partitioning processing technology, and can satisfy requirements of high-velocity information transmissioncommunication systems, such as satellite communication, and the like.

Owner:TSINGHUA UNIV

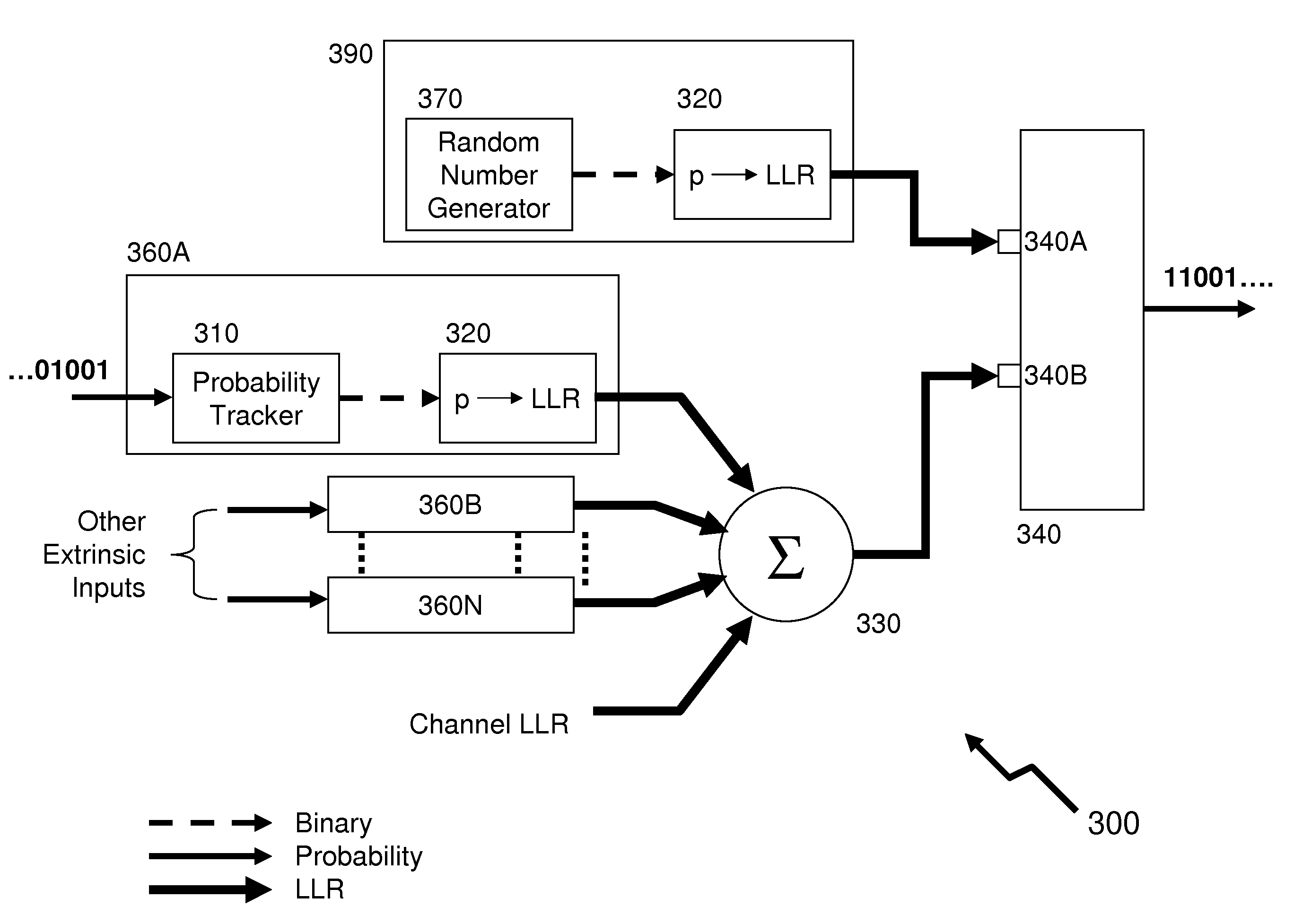

Method and system for decoding

ActiveUS8898537B2Error correction/detection using LDPC codesError correction/detection using multiple parity bitsAlgorithmReturn channel

Low-Density Parity-Check (LDPC) codes offer error correction at rates approaching the link channel capacity and reliable and efficient information transfer over bandwidth or return-channel constrained links with data-corrupting noise present. LDPC codes also offer error correction performance approaching channel capacity exponentially fast in terms of the code length, linear processing complexity, and parallelism that scales with the code length. They also offer challenges relating to the decoding complexity of the binary error-correction codes themselves and error floors limiting achievable bit-error rates. A new Relaxed Half-Stochastic (RHS) decoding algorithm is presented that reduces decoding complexity for high decoding throughput applications. The RHS algorithm uses an approach based on stochastic decoding algorithms but differs significantly from the conventional approaches of LDPC decoder implementation. The RHS algorithm also leads to a randomized decoding technique called redecoding that addresses the error floor limitation.

Owner:POLAR TECH

Multi-element LDPC code high-speed parallel decoder based on GPU, and decoding method thereof

InactiveCN108462495AReduce synchronization overheadReduce startup overheadResource allocationError correction/detection using multiple parity bitsDecoding methodsThree stage

The invention discloses a multi-element LDPC code high-speed parallel decoder based on a GPU, and a decoding method thereof, and belongs to the technical field of the communication. The decoding method is divided into three stages: an initialization stage, a decoding stage and a judgment stage; once iterative decoding of the decoder is accomplished by only using a kernel function, the synchronization expenditure between the thread blocks and the starting expenditure of the kernel function are greatly reduced, and the access mount of the whole memory is lowered; the use rate of a hardware resource is maximized by designing different parallelism degrees under different systems, thereby improving the decoding throughput to 100M level. Through a memory-access way provided by the invention, theshared memory on a GPU chip is sufficiently utilized, the access to the whole memory is greatly reduced, and the memory-access efficiency and the memory-access bandwidth are improved.

Owner:BEIHANG UNIV

Multi-channel LDPC decoder architecture

Owner:ENTROPIC COMM INC

High-throughput-rate LDPC decoding algorithm and architecture for 5G terminal

PendingCN111211790AReduce implementation complexityReduce lossesError preventionError correction/detection using multiple parity bitsShift registerParallel computing

The invention relates to a high-throughput-rate LDPC decoding algorithm and architecture for a 5G terminal, and belongs to the technical field of wireless communication. According to the scheme, the requirement of high throughput rate of data in 5G communication can be met. The architecture mainly comprises a VCN module, a control logic module and a message RAM module. The algorithm comprises thesteps: layering a check matrix according to a base graph and an expansion factor of a 5G QC-LDPC code, forming a layer block structure on each layer, enabling a computing unit of a VCN module to adopta minimum sum decoding algorithm to update nodes, and updating all check nodes in the layer block structures in parallel, thereby increasing the decoding throughput rate; storing the updated posterior information in an interlayer shift register and transmitting the updated posterior information to the next layer to assist subsequent node updating, wherein the symbol information and amplitude information of the node update message are separately processed and stored, so the complexity is reduced. The scheme is suitable for a 5G communication standard, has the characteristics of low complexityand high throughput rate, and is suitable for the field of channel decoding of a wireless communication technology.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Deeply-pipelined high-throughput LDPC decoder architecture

ActiveUS20180123734A1Facilitate communicationError preventionCode conversionComputer architectureLow density

Certain aspects of the present disclosure generally relate to methods and apparatus for decoding low density parity check (LDPC) codes, and more particularly to a deeply-pipelined layered LDPC decoder architecture for high decoding throughputs.

Owner:QUALCOMM INC

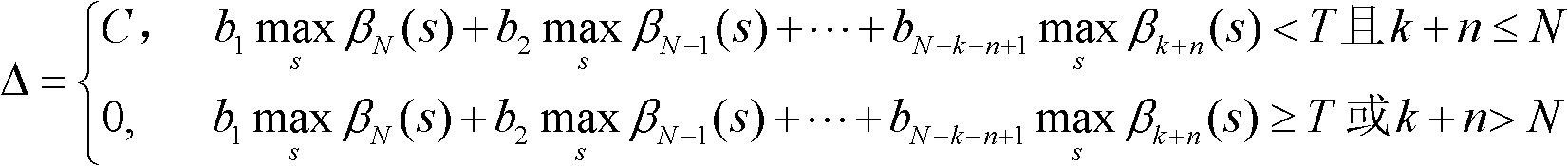

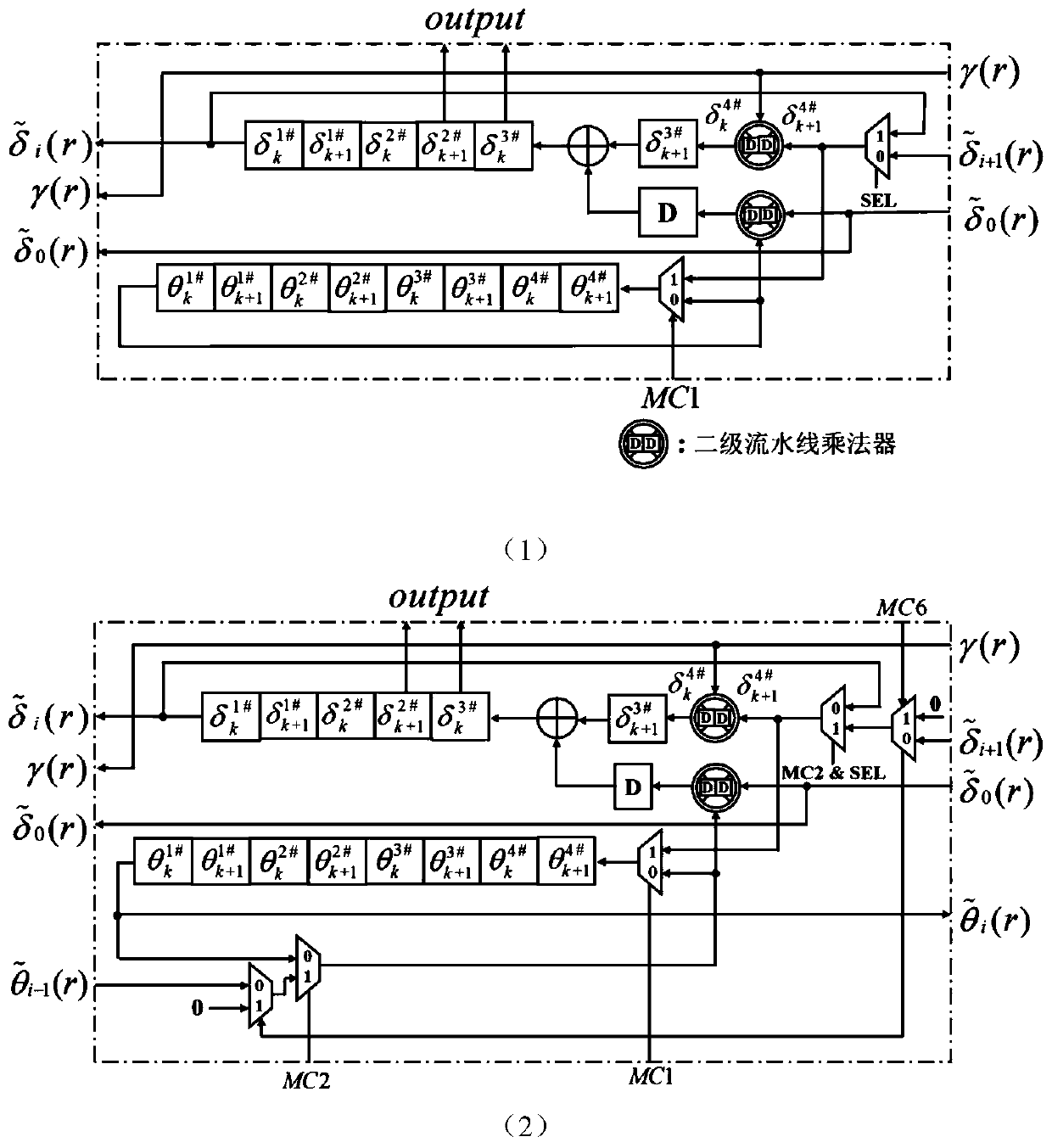

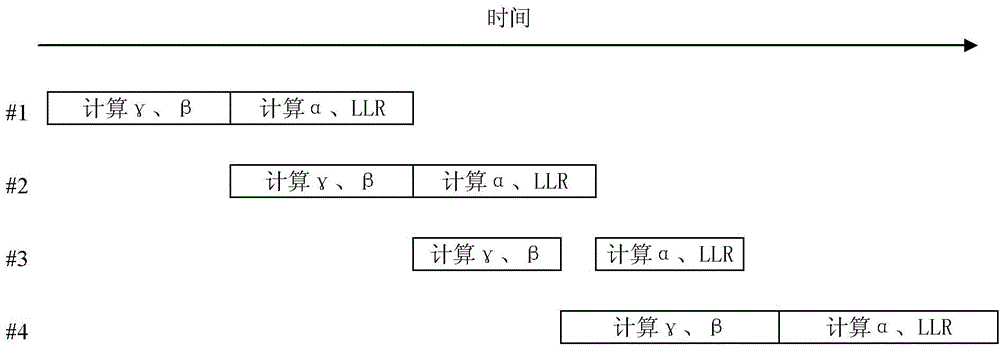

A Control Method of State Metric Overflow in Turbo Code Decoder

InactiveCN102270994AReduce computationFast operationError correction/detection by combining multiple code structuresTurbo codedDecoding throughput

The invention relates to an overflow control method for a state metric of a Turbo code decoder. A correction value delta of a branch metric of a current beat is determined according to logarithm metric sizes of all states before n times that are obtained by recursions from a current time k; a branch metric of the current time k is calculated and is corrected; and finally, a state metric of the current time k is calculated according to the corrected branch metric and amplitude limiting is carried out; when the calculated result is larger than a maximum max, the value of the state metric is max; when the calculated result is less than a minimum min, the value of the state metric is min; and the state metric that has been processed by the amplitude limiting is used for a next recursion. According to the invention, it can be ensured that state metrics of forward and backward recursions during a MAP decoding algorithm process of a Turbo code will not overflow; determination operations can be completed in advance; it is allowed to realize anti-overflow control by a pipelining method. Therefore, an influence of an anti-overflow operation on a recursion speed of a state metric can be reduced, so that a recursion speed during hardware realization can be improved and a decoding throughput capacity can be enhanced.

Owner:TSINGHUA UNIV

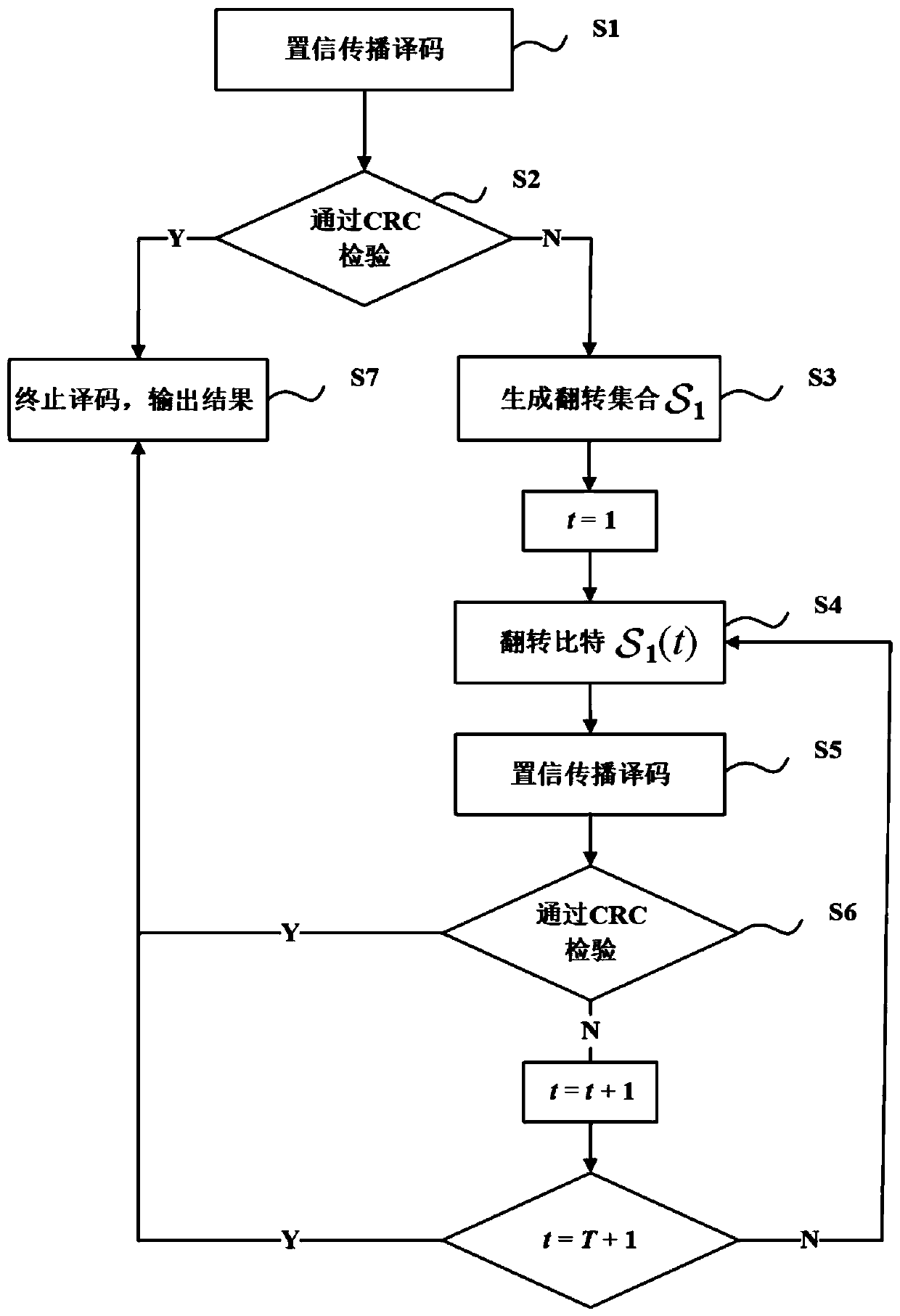

Polarization code belief propagation decoding method and device and storage medium

ActiveCN111416624AAchieve throughputAchieve error correction performance indicatorsError correction/detection using multiple parity bitsCode conversionParallel computingEngineering

The invention discloses a polarization code belief propagation decoding method and device, and a storage medium. The method comprises the following steps: carrying out belief propagation decoding on information received by a decoder; judging whether a decoding result of the belief propagation decoding meets a judgment condition or not, if so, stopping executing the belief propagation decoding, andotherwise, generating an overturning set based on the decoding result; performing flip-based decoding according to the flip set. According to the method disclosed in the invention, the error correction performance of the list decoding method and equipment can be continuously eliminated while the high decoding throughput rate is achieved, and soft information can be iteratively output; thus co-architecture design of joint detection decoding, LDPC and polarization codes becomes possible.

Owner:PURPLE MOUNTAIN LAB

Forward error correction decoding decoder based on burst error detection

PendingCN110971244AReduce decoding timeImprove throughputCode conversionCyclic codesAlgorithmError location

The invention belongs to the field of error control coding in channel coding, and aims to shorten the delay of a critical path of a decoder on the premise of ensuring the decoding performance so as toimprove the decoding throughput rate. Therefore, the technical scheme adopted by the invention is as follows. The invention discloses a forward error correction decoding decoder based on burst errordetection which comprises a syndrome calculation SC module, a key equation solving KES module and a money search and error estimation CSEE module. A syndrome calculated by the SC module is output to the KES module, and an error position polynomial lambda (X) and an error estimation polynomial omega (X) calculated by the KES module are output to the CSEE module. The decoder is mainly applied to decoder design and manufacturing occasions.

Owner:TIANJIN UNIV

LDPC-BCH decoding method based on graphics processor

ActiveCN109586733AImprove decoding performanceEliminate Bit Error PlatformsError correction/detection using multiple parity bitsCode conversionMillisecondDecoding throughput

The invention relates to an LDPC-BCH decoding method based on a graphics processor and belongs to the communication technology field. The method is characterized by converting check matrixes with different code lengths and code rates into a quasi-cyclic structure; carrying out compression, inter-row interweaving, and inline interweaving on the check matrix of the quasi-cyclic structure; and in iterative decoding, using whether BCH code decoding is correct as an iterative termination condition to eliminate an error code platform and improve the error correction performance of a decoder, whereinthe above step especially includes: carrying out matrix interweaving on the check portion of the outside information of an input codeword variable node; operating resource distribution; updating theposterior logarithmic likelihood value of a variable node and a logarithmic likelihood values transmitted by the check node to the variable node; carrying out hard decision; and when the BCH code decoding is correct or reaches the maximum number of iterations, terminating the iterative decoding, and outputting an information bit and a decoding success identifier. Decoder delay is in the order of milliseconds, and a decoding throughput is in the order of hundreds of megabytes. Error correction performance is comparable to the error correction performance recommended by a second generation digital satellite broadcasting standard.

Owner:TSINGHUA UNIV

BCH (Bose, Ray-Chaudhuri, Hocquenghem) decoding system with pipeline structures

ActiveCN107688506AReduce overheadImprove decoding efficiency and throughputCode conversionCyclic codesComputer moduleComputer memory

The invention discloses a BCH (Bose, Ray-Chaudhuri, Hocquenghem) decoding system with pipeline structures, and belongs to the technical field of computer memory error correction. The BCH decoding system comprises a parallel correction factor computing module, a key equation solving-parallel Chien search module, an FIFO (first in, first out) memory module and a BCH decoding controller module. The parallel correction factor computing module is used for carrying out parallel computing according to received data to obtain correction factors; the key equation solving-parallel Chien search module isused for acquiring key equations by means of computing according to the correction factors and finding out solution of the key equations; the FIFO memory module is used for aching data read from NAND(not and) Flash chips, and data in the FIFO memory module can be outputted step by step when the solution of the key equations is computed; the BCH decoding controller module is used for implementingparallel execution on BCH decoding two-stage pipelines. The BCH decoding system has the advantages that hardware resources in different modules in BCH decoders are reused, BCH decoding can be carriedout by the aid of the parallel pipeline structures, accordingly, BCH decoding throughput can be effectively improved, and the hardware expense can be reduced.

Owner:HUAZHONG UNIV OF SCI & TECH

Sliding window classification method and device in Turbo decoding

ActiveCN104796161AReduce decoding delayImprove throughputError correction/detection using interleaving techniquesSlide windowClassification methods

The embodiment of the invention discloses a sliding window classification method and device in Turbo decoding. The method includes the steps of firstly, determining the sizes of Turbo decoding blocks; secondly, determining the size of sliding windows of the first classification according to the sizes of the Turbo decoding blocks; thirdly, determining the sizes and the corresponding numbers of the sliding windows of the first classification, sliding windows of the second classification and sliding windows of the third classification according to the size of the sliding windows of the first classification and allowable deviation between lengths of the sliding windows. The sizes and the numbers of the sliding windows can be set according to the lengths of the decoding blocks and the allowable deviation between the lengths of the sliding windows, and the aims of saving hardware resources, shortening decoding time delay and increasing the decoding throughput rate are achieved.

Owner:BEIJING SMART LOGIC TECH CO LTD

VSS LDPC decoder with improved throughput for hard decoding

ActiveUS10122382B2Other decoding techniquesError correction/detection using multiple parity bitsComputer hardwareChecksum

Memory systems may include a memory storage, a pre-processing checksum unit suitable for, during a first decoding iteration, receiving hard read data including channel input (Lch) sign values, and computing a checksum of the Lch sign values as a checksum_pre value, and a low-density parity-check (LDPC) decoder including an Lch memory and a checksum update unit, the LDPC decoder suitable for, during the first decoding iteration, storing the Lch sign values in the Lch memory of the LDPC decoder, receiving, with the checksum update unit, the checksum_pre value, and decoding a codeword in at least a second decoding iteration based at least in part on the checksum_pre value computed and received being a parity check on the hard read performed in the first decoding iteration.

Owner:SK HYNIX INC

Encoding and decoding method, device and system for intra prediction mode of chroma component

ActiveCN103369315BImprove throughputDigital video signal modificationTheoretical computer scienceIntra-frame

The invention provides coding and decoding methods, equipment and a system of intra-frame chroma prediction modes. According to the invention, intra-frame prediction modes of an intra-frame prediction mode set which is suitable for the chroma of a current block are divided into a first subgroup and a second subgroup, the amount of the intra-frame predication modes in correspondence with the first subgroup is at least two, and the amount of the intra-frame predication modes in correspondence with the second subgroup is 2<N>, wherein N is a positive integer. Due to the fact that the most required coded bit number is lower than that in the prior art, decoding throughput can be improved.

Owner:HUAWEI TECH CO LTD

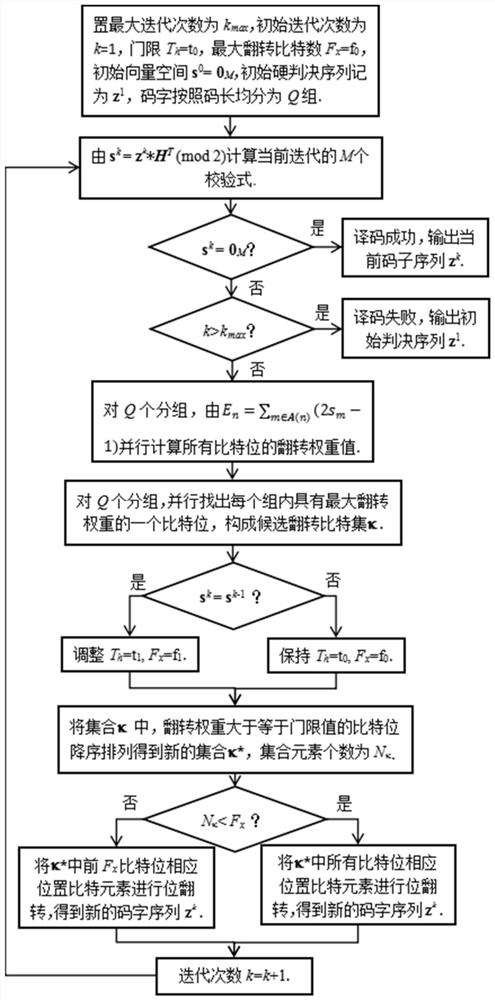

LDPC (Low Density Parity Check) code dynamic flipping decoding method based on grouping parallel processing

ActiveCN111900998AImprove decoding performanceReduce Decoding LatencyError correction/detection using multiple parity bitsDecoding methodsEngineering

The invention discloses an LDPC (Low Density Parity Check) code dynamic flipping decoding method based on grouping parallel processing. The method detects whether flip sequences of two adjacent iterations in an iterative flip decoding process cause decoding to be in a state loop or not, and after the state loop is detected, a packet bit flip threshold and a flip bit number are dynamically changed,so that the invalid iteration of bit flip decoding is effectively avoided and system performance is improved. Whether a state cycle condition exists in grouped bit flipping decoding or not is judgedthrough simple check formula calculation, that is, when two adjacent check formula sequences are the same, a judgment is made that iterative decoding falls into an error cycle, and bits cannot be flipped effectively. After the cyclic state is judged, the state cycle is effectively broken by adopting a method of dynamically changing the packet bit flipping threshold and the flipping bit number, andperformance improvement is obtained. The improved method is established on the basis of hard decision flipping decoding, and is fast in iterative convergence, high in decoding throughput rate and lowin implementation complexity.

Owner:SOUTHEAST UNIV

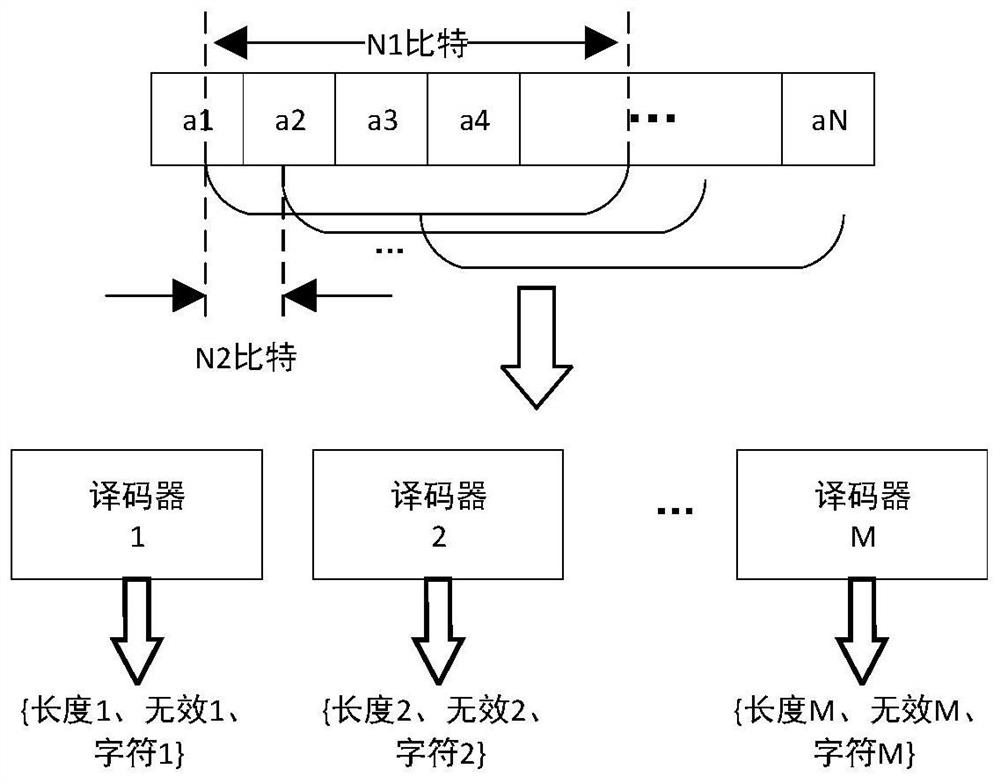

Decoding method, decoder, equipment and medium

The invention discloses a decoding method, a decoder, equipment and a medium, and the method comprises the steps: grouping an input bit stream, and obtaining input bit groups; inputting the input bitgroups into different Huffman decoders respectively, so that the Huffman decoders decode the input bit groups in parallel to obtain preliminary decoding results corresponding to the input bit groups,wherein the preliminary decoding results comprise code word lengths, invalid flags and decoding characters; determining a length vector based on the codeword lengths and the invalid flags, and determining a target position vector based on the length vector; and determining a target decoding result corresponding to the input bit stream based on the target position vector and the character vector. Therefore, the bit streams subjected to Huffman coding can be decoded in parallel, the decoding time is saved, the decoding efficiency is improved, the decoding throughput rate is also improved, and the equipment performance is improved.

Owner:山东云海国创云计算装备产业创新中心有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com