Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

488 results about "Fifo memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A FIFO memory is a storage device that allows data to be read from its array in the same order it is written. The SN54ABT7819 is a high-speed, low-power BiCMOS bidirectional clocked FIFO memory.

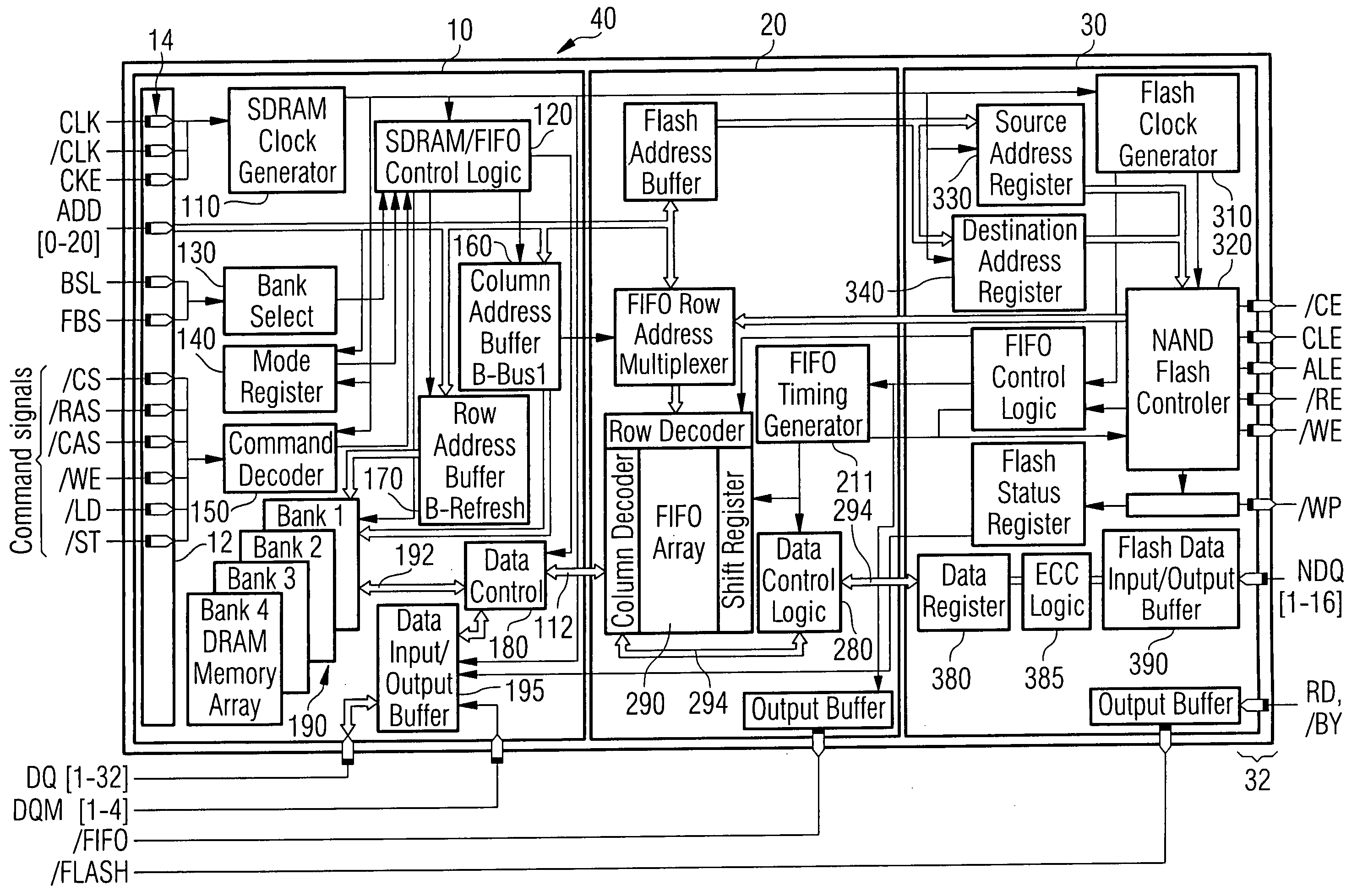

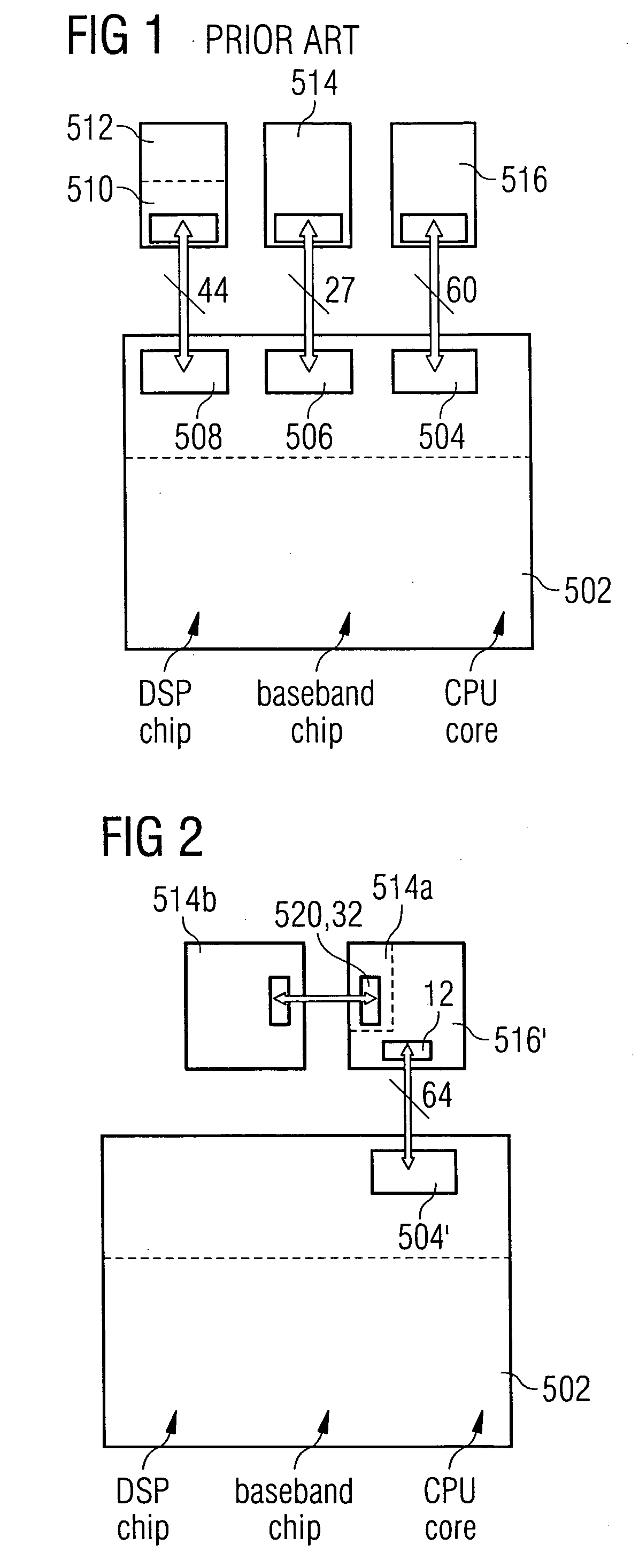

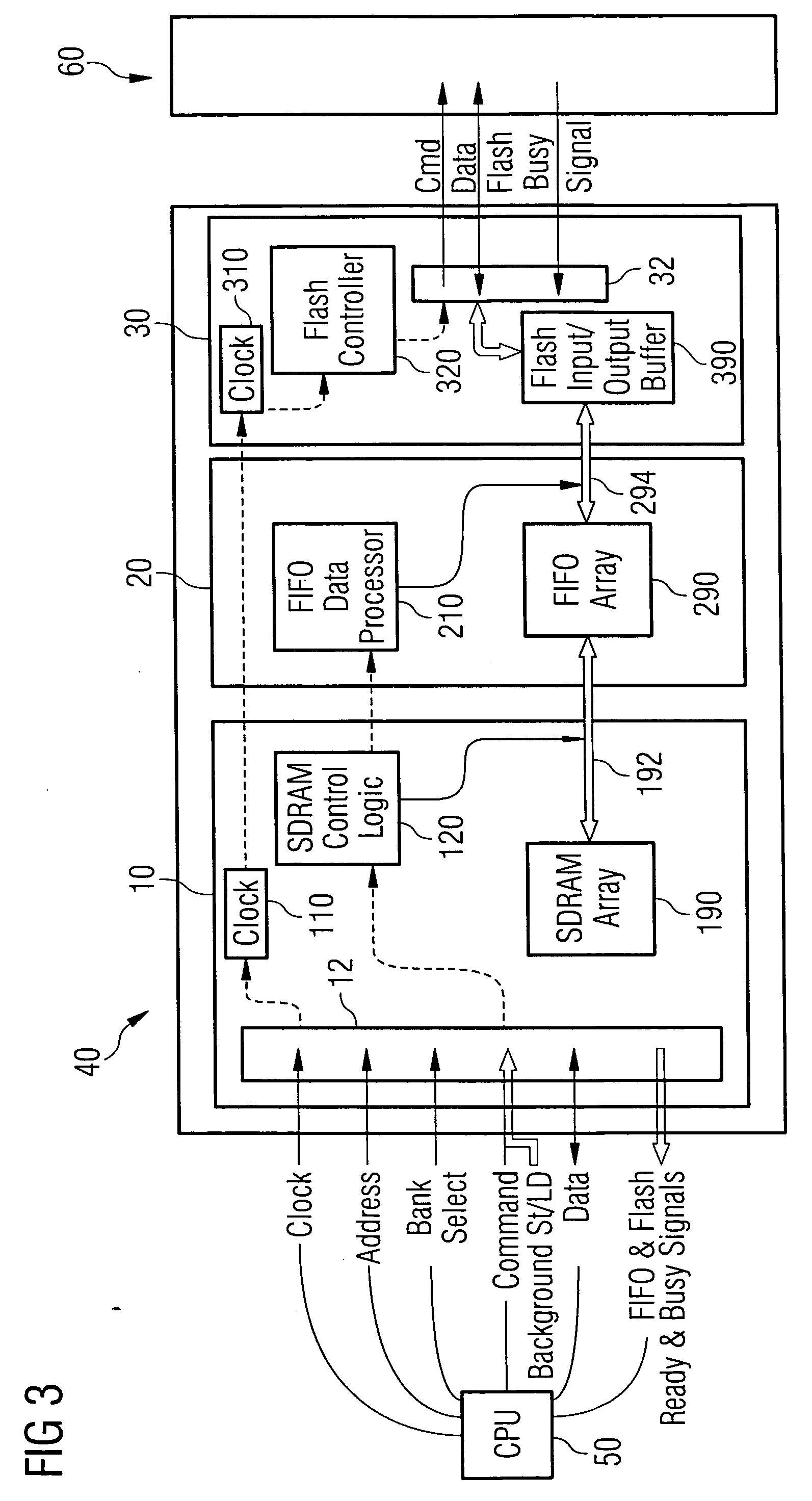

DRAM chip device well-communicated with flash memory chip and multi-chip package comprising such a device

An SDRAM memory chip device comprises a non-volatile memory controller for operating a non-volatile memory, e.g., a NAND-flash, and a FIFO memory buffer. The FIFO memory buffer serves to operate background store and load operations between a FIFO buffer array and the non-volatile memory, while a host system such as a CPU exchanges data with the SDRAM work memory. The SDRAM memory chip device, therefore, has at least two additional pins as compared with conventional SDRAM standard for generating a set of additional commands. These commands are employed by the FIFO memory buffer to manage the data transfer between the FIFO buffer and each of the non-volatile memory and the volatile SDRAM memory. Two further pins reflecting the flash memory status provide appropriate issuance of load or store signals by the host system.

Owner:INFINEON TECH AG

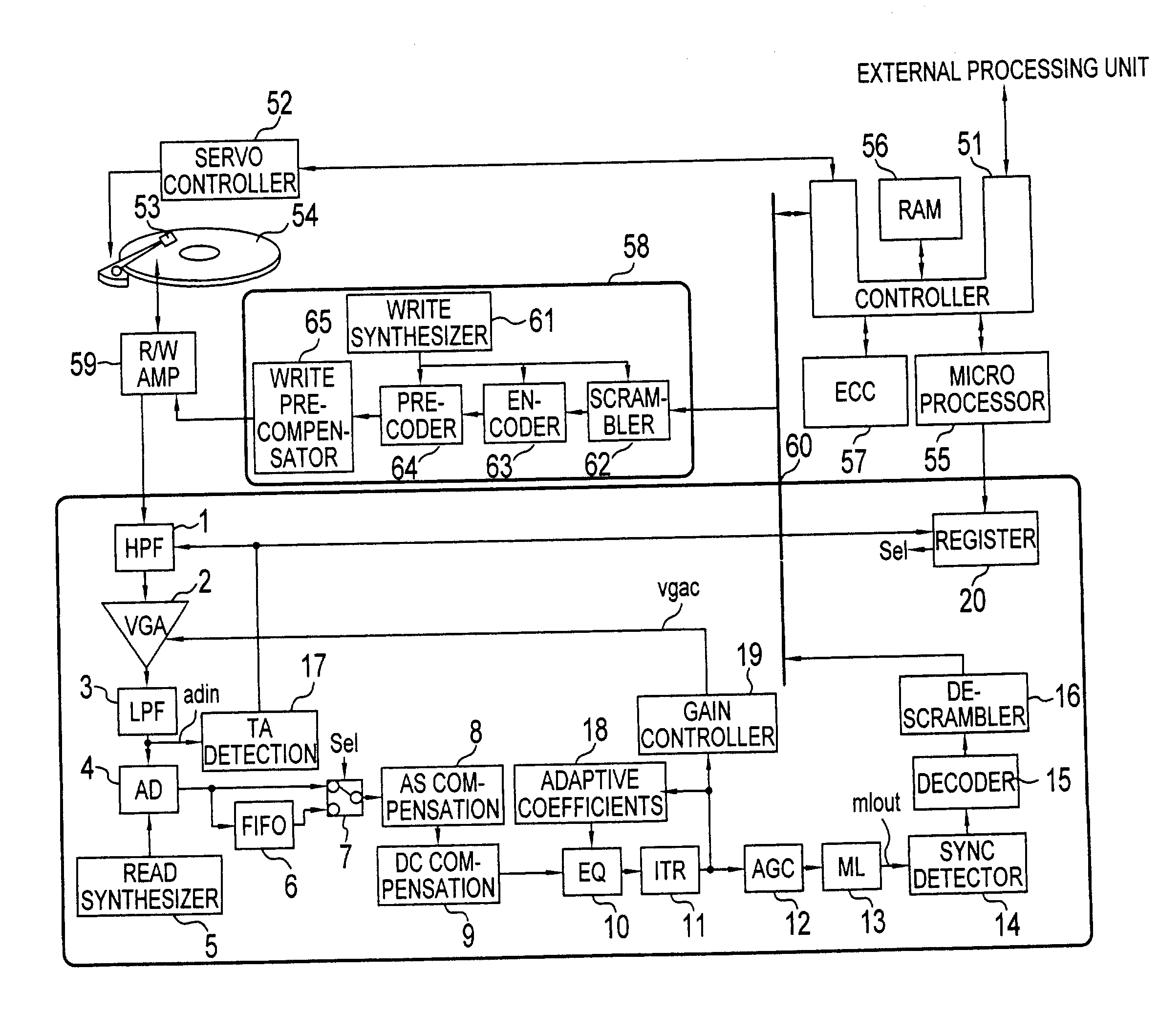

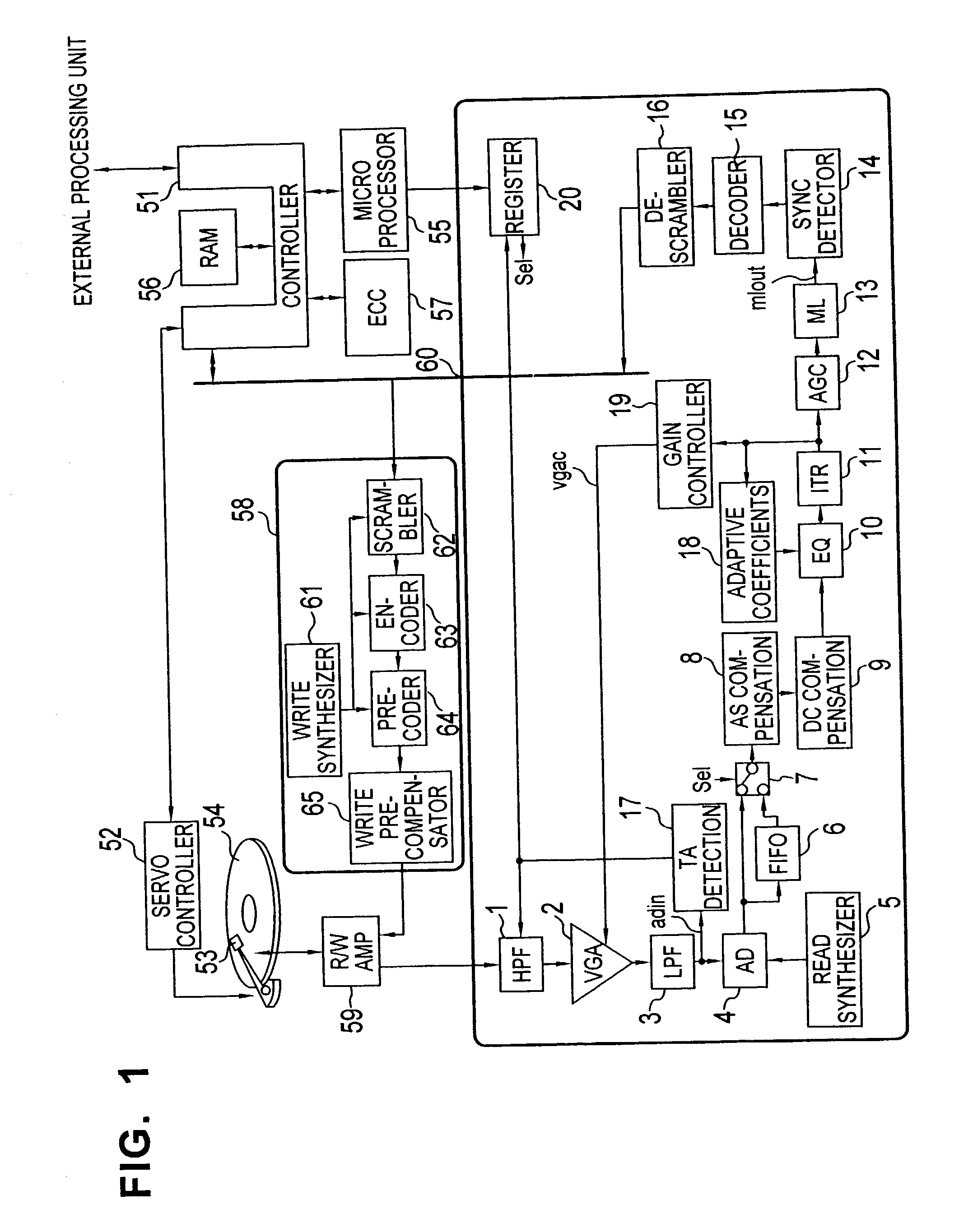

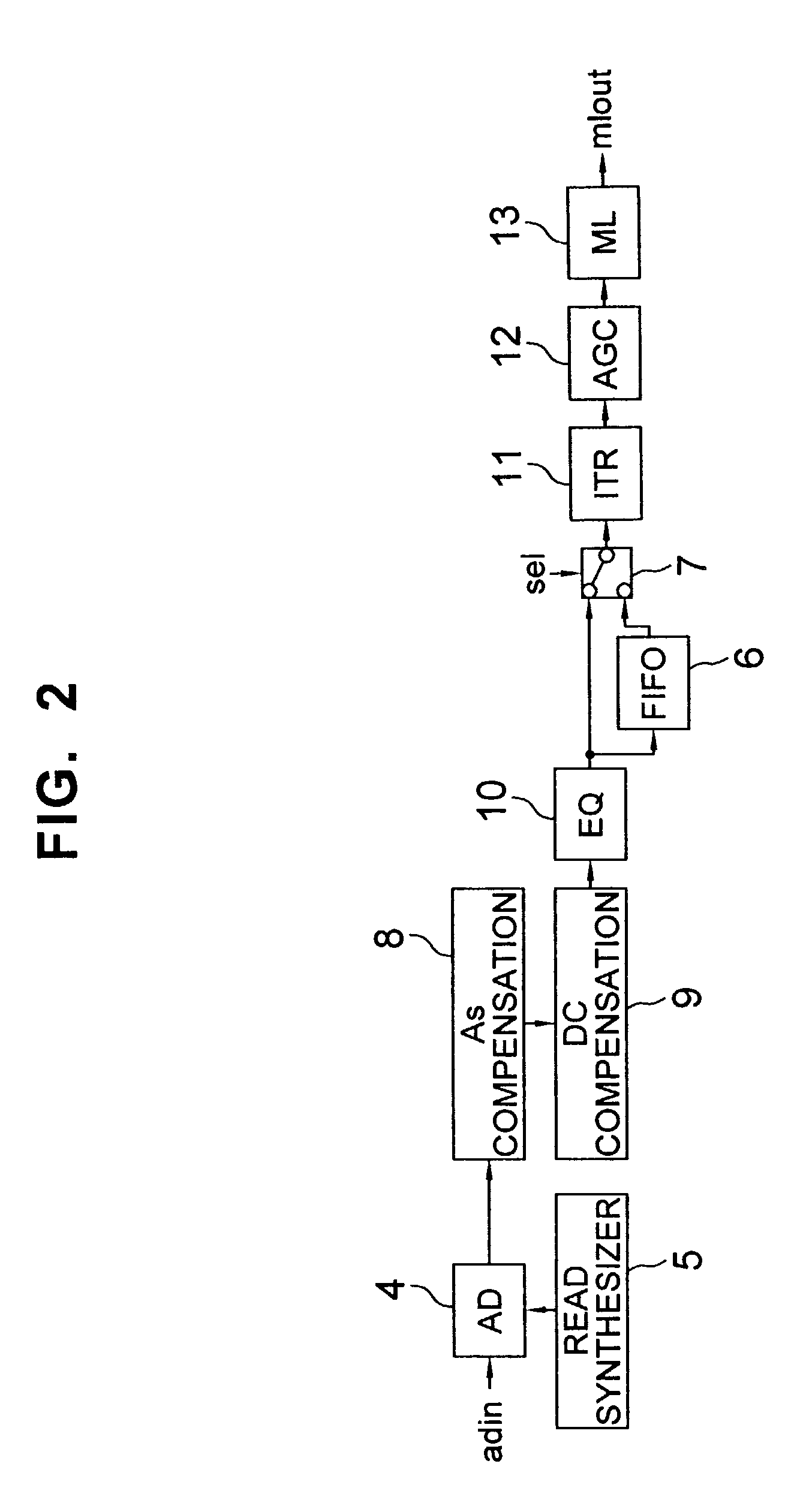

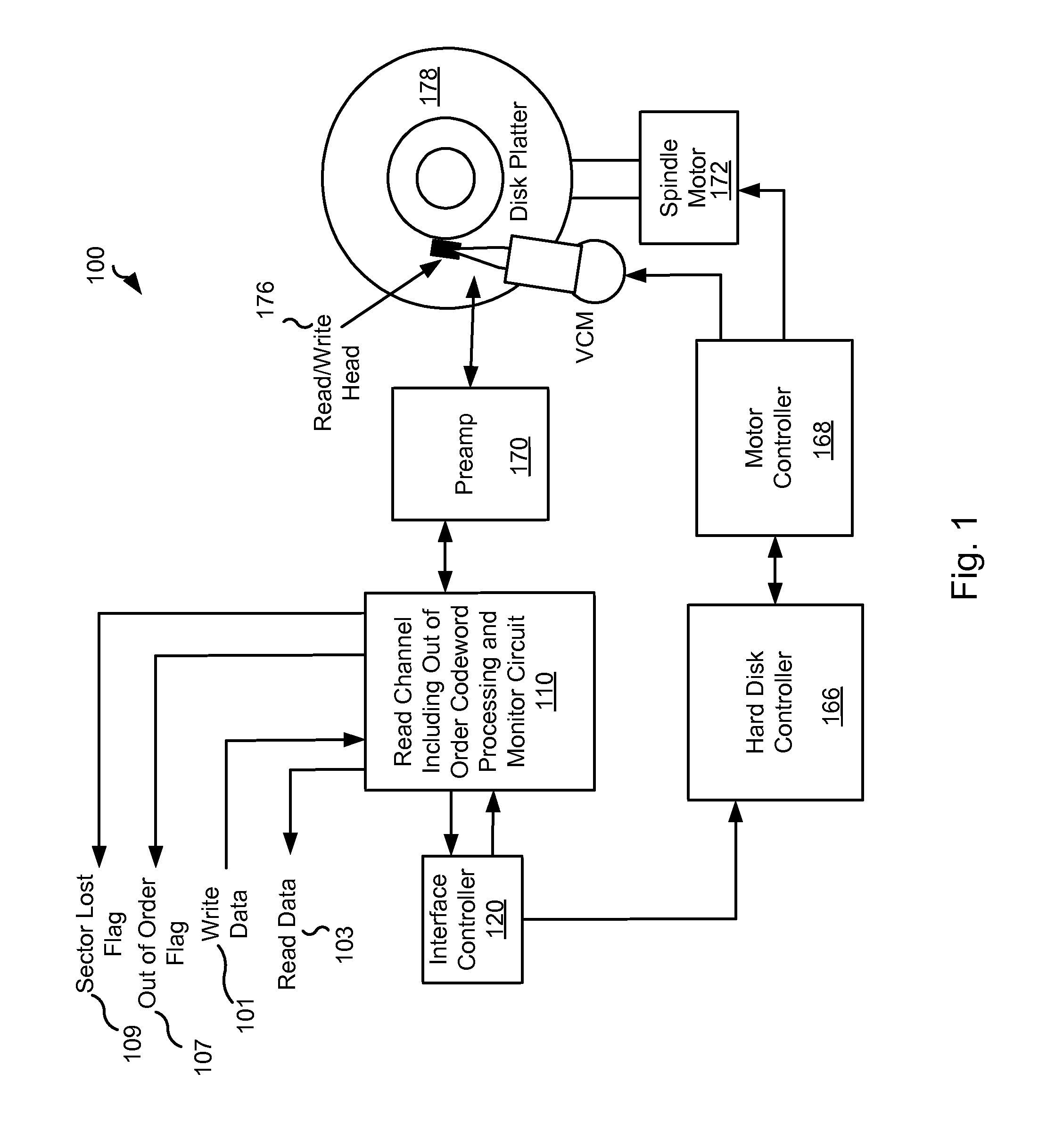

Signal processing apparatus and a data recording and reproducing apparatus including local memory processor

InactiveUS6519715B1Modification of read/write signalsError detection/correctionSignal processing circuitsAuxiliary memory

In a data recovery processing, the conventional overhead, primarily, latency due to a rotational recording media is removed. Secondary, in a signal processing or in a recording and reproducing apparatus, reliability of data reproduction is improved by repeatedly processing data. These processing are achieved that input signal, i.e., raw analog signal read from the recording media is digitized to be stored in a secondary storage such as a memory or a FIFO memory. The apparatus includes a signal processing circuit to repeatedly process the stored digital signal in the secondary storage. When detecting data, operation of the circuit is efficiently controlled by a change over detector parameters, in which characteristics for the detecting performance. Resultantly, data recovery processing speed is increased and reliability of data reproduced is improved.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD +1

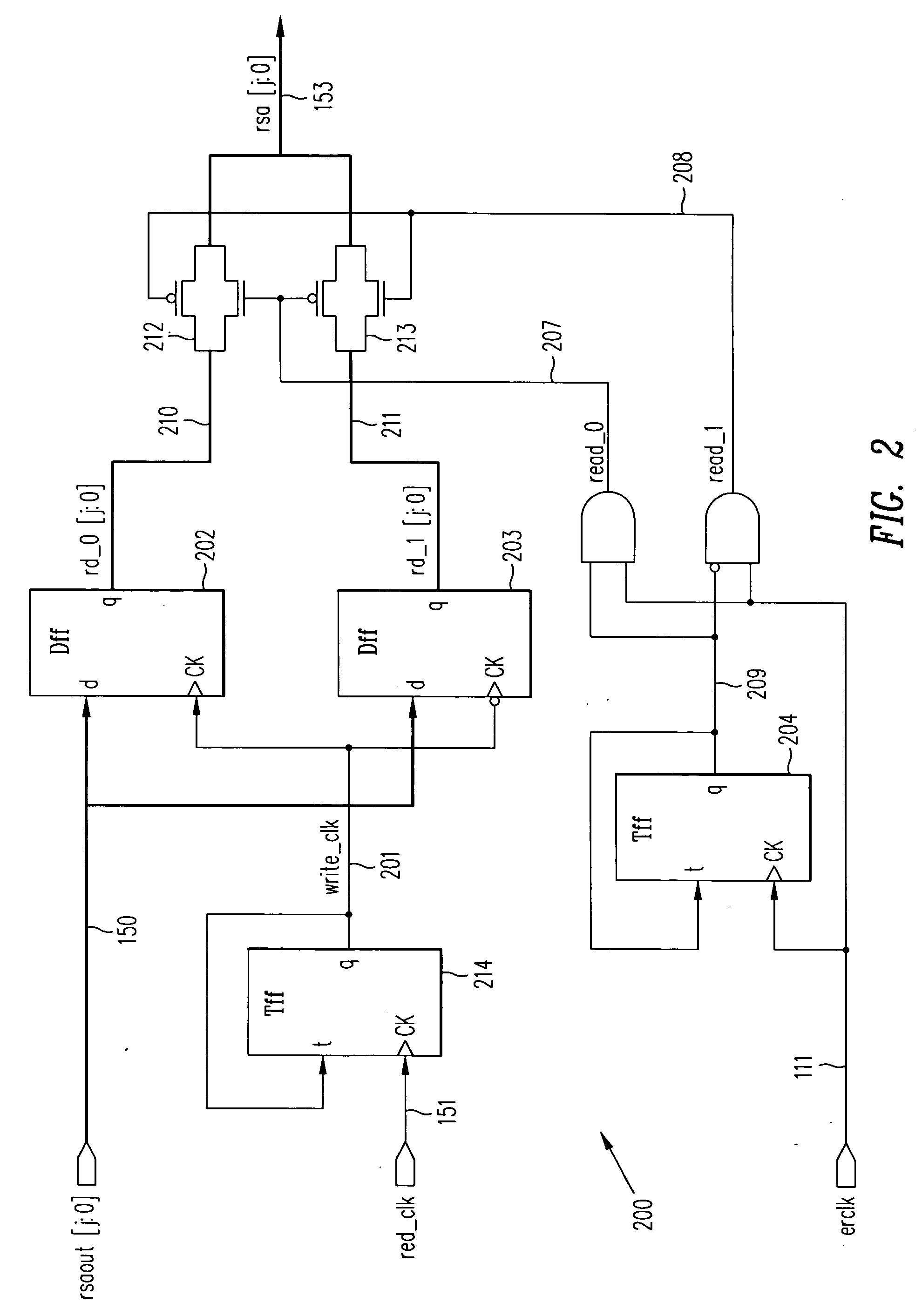

Method and apparatus for asynchronous read control

A method and apparatus for operating a memory is presented. Information is stored in the memory based on a first time domain and information is read from the memory based on a second time domain. A cooperative relationship is maintained between a write pointer which points to memory locations, where data will be stored and a read pointer which points to memory locations, from which data will be read. A FIFO memory is presented which has memory locations and a register array is presented which stores a bit array that has bit locations. Each bit location in the bit array corresponds to a memory location in the memory. As the write pointer points to a memory location and data is stored in the memory location, a bit (e.g. flag) is set in the bit array. The Flag designates whether the data stored in the memory location is available for reading. Prior to reading information from the memory location, a test is made of the bit location that corresponds to the memory location. The bit value denotes whether the data stored in the memory location is valid data and available for reading.

Owner:AVAGO TECH INT SALES PTE LTD

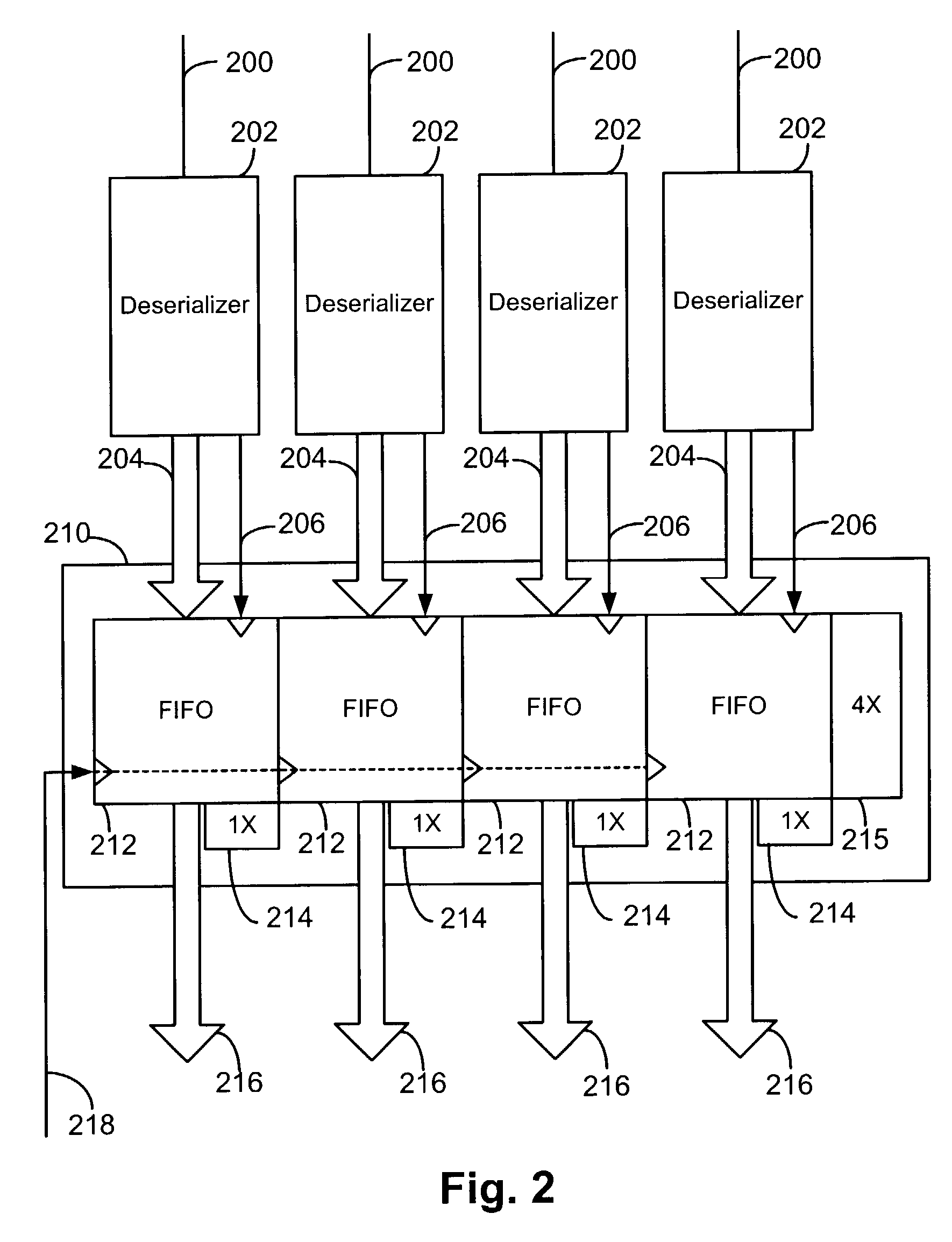

Architectures, circuits, systems and methods for reducing latency in data communications

ActiveUS20050034009A1Reduce in quantityReduce needPulse transformerError detection/correctionData streamTransceiver

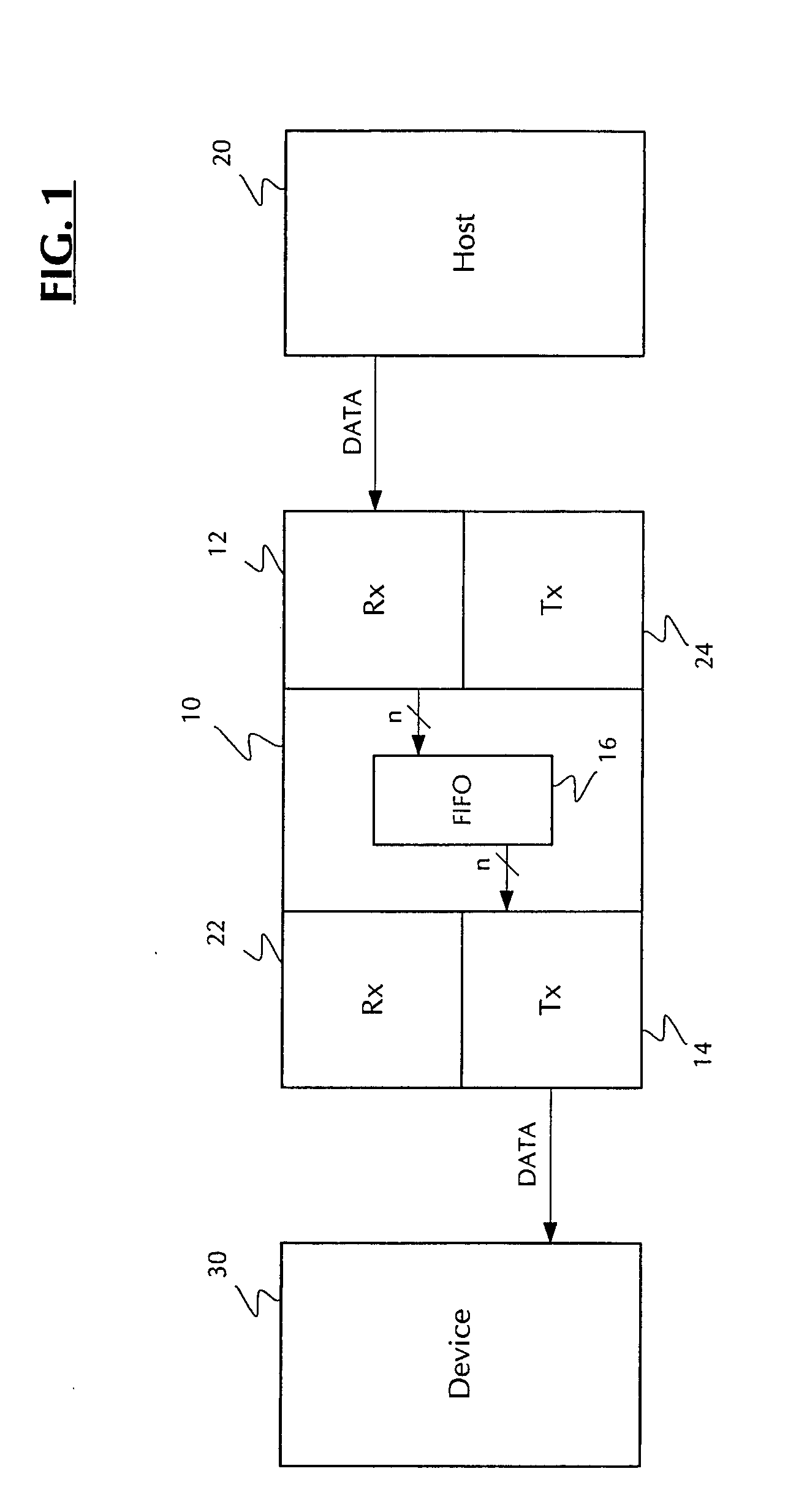

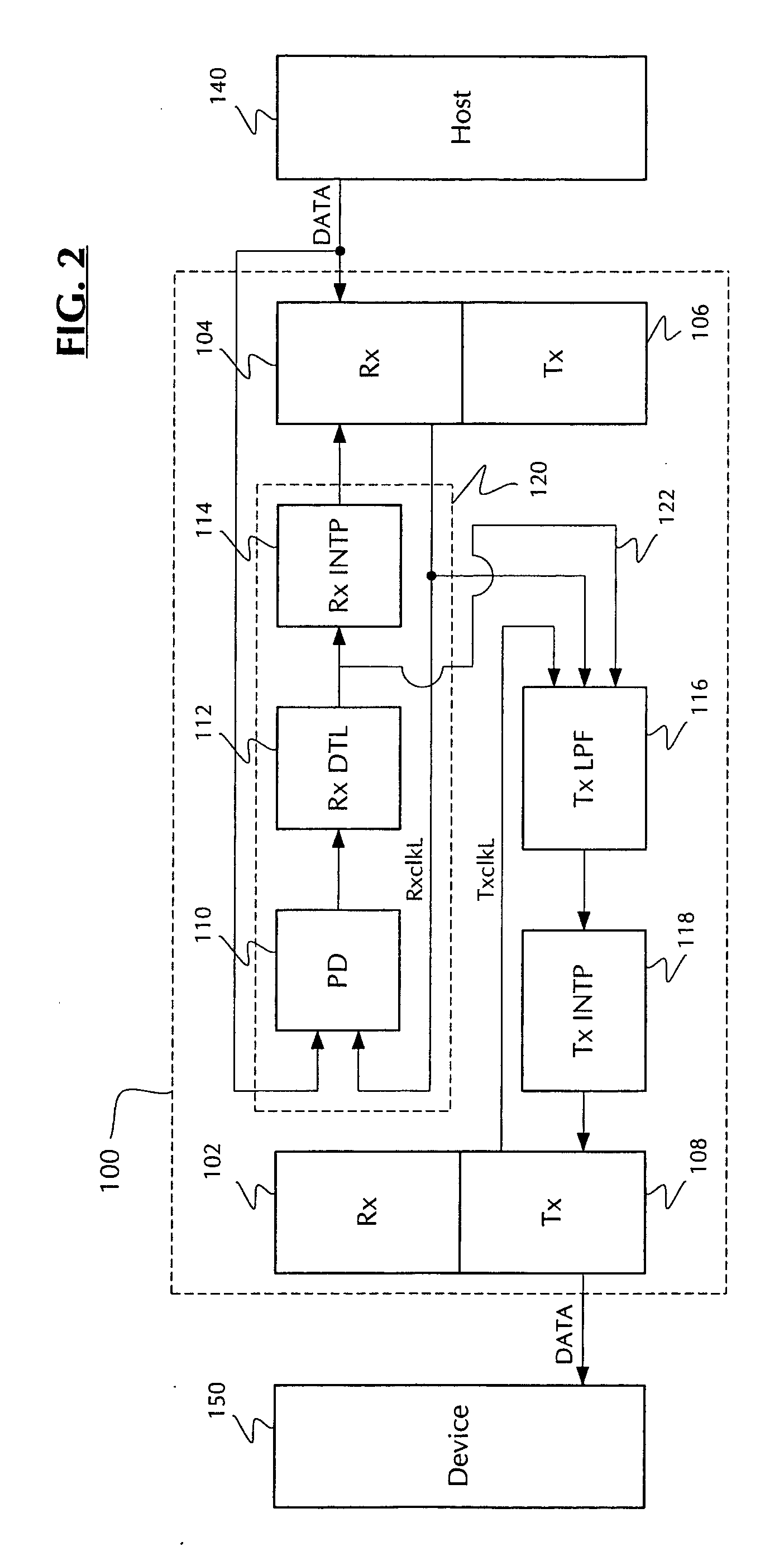

Circuits, architectures, systems and methods for facilitating data communications and / or reducing latency in data communications. The architecture includes a clock recovery loop receiving data from a host device and providing a recovered clock signal, a filter circuit receiving recovered clock signal information and providing a control signal that adjusts the transmitter clock in response to recovered clock signal information and the two clock signals, and a transmitter receiving the control signal and transmitting data to a destination device in accordance with the transmitter clock. The circuitry generally includes a clock alignment block receiving first and second periodic signals and providing a control signal in response thereto, a filter for first periodic signal information, and a logic circuit configured to combine the control signal and the filtered information, thereby providing an adjustment signal for the second periodic signal. The systems generally relate to those that include the present architecture and / or circuit. The method generally includes determining a phase difference between first and second periodic signals, one of the periodic signals being recovered from a data stream; adjusting the other periodic signal in response to the phase difference and filtered information from the recovered periodic signal; and transmitting the data stream in accordance with said adjusted periodic signal. The present invention advantageously eliminates a FIFO memory in the data path, thereby reducing transceiver latency and improving system performance.

Owner:MARVELL ASIA PTE LTD

Method and apparatus for sampling digital data at a virtually constant rate, and transferring that data into a non-constant sampling rate device

InactiveUS6865241B1Faster data rateImprove data throughputElectric digital data processingSynchronising arrangementDigital dataConstant frequency

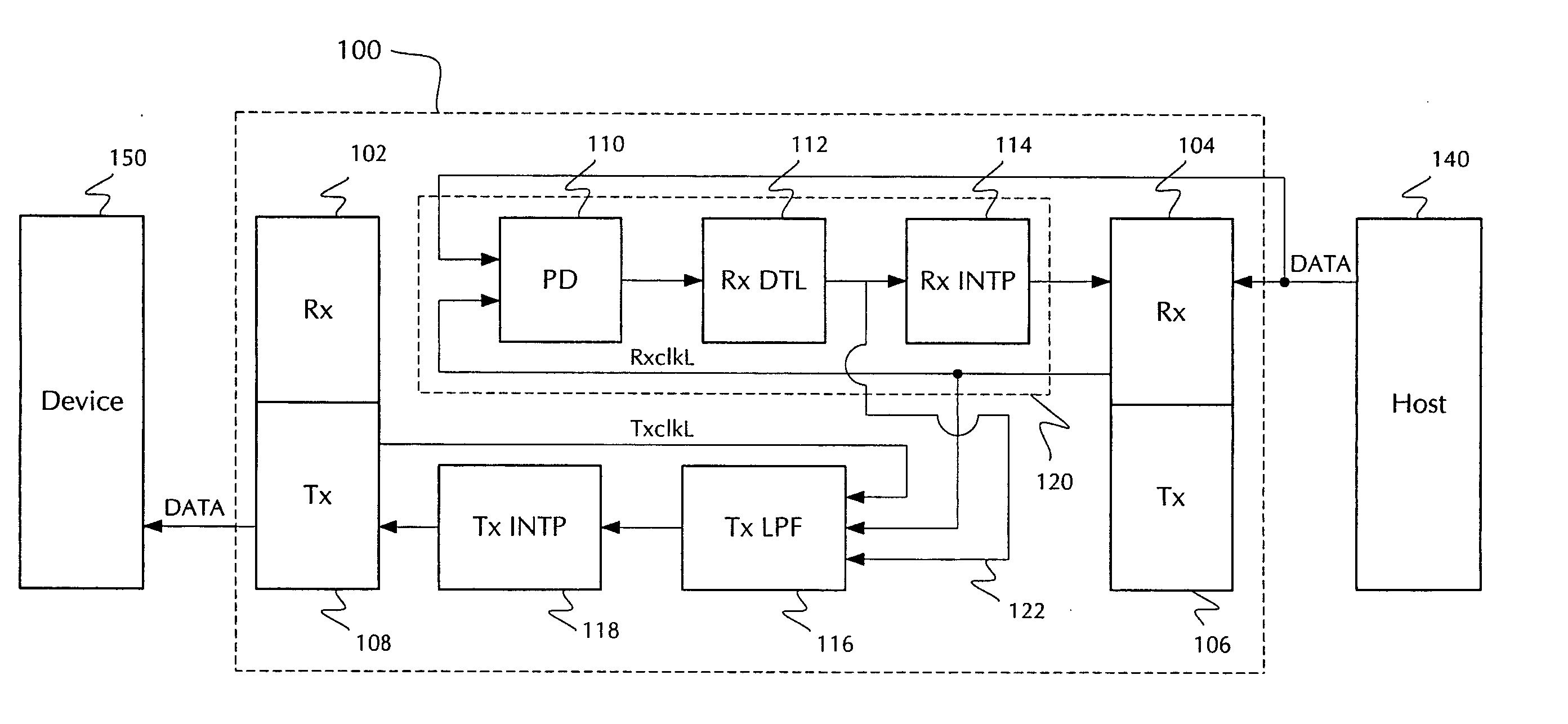

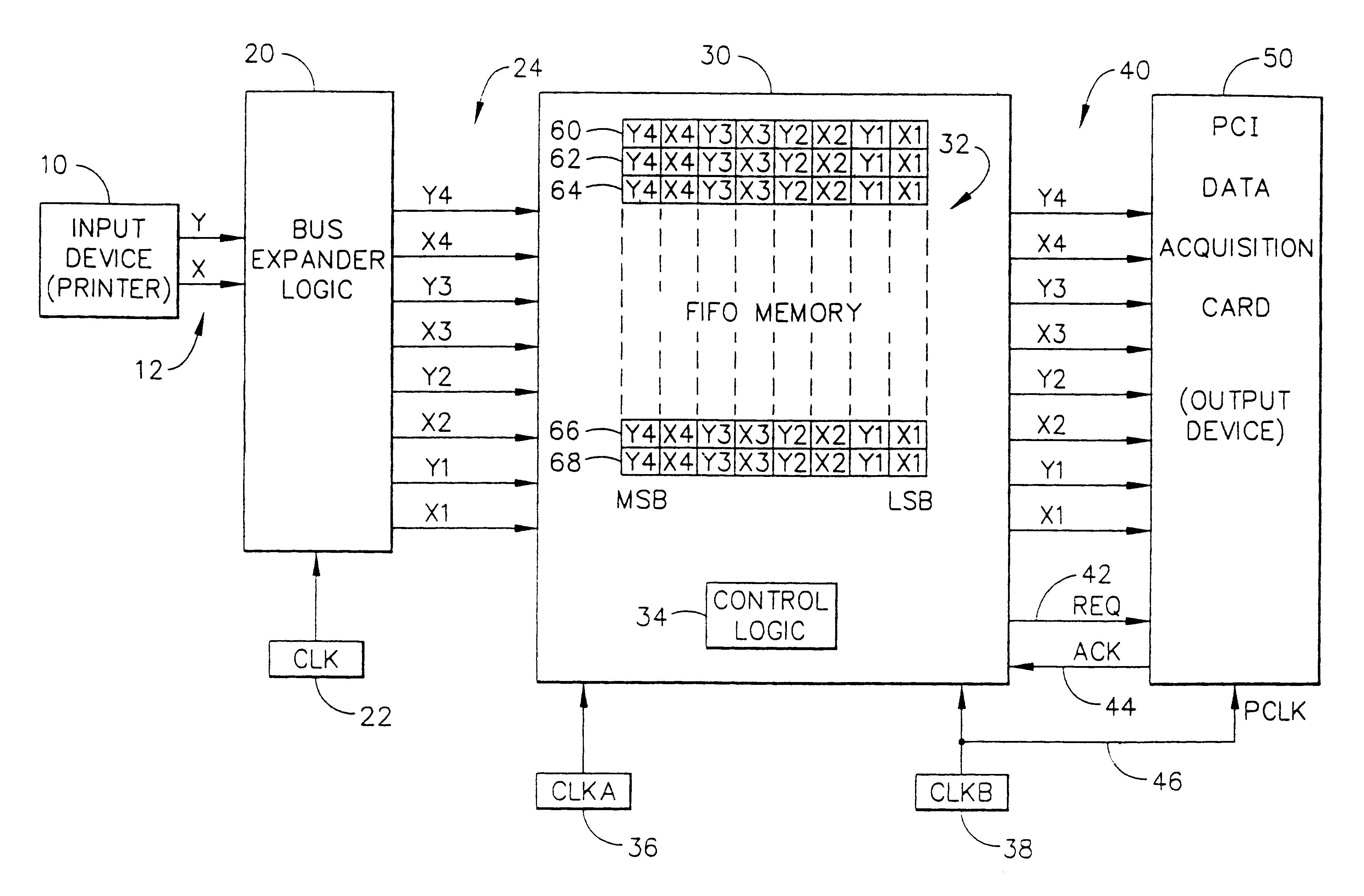

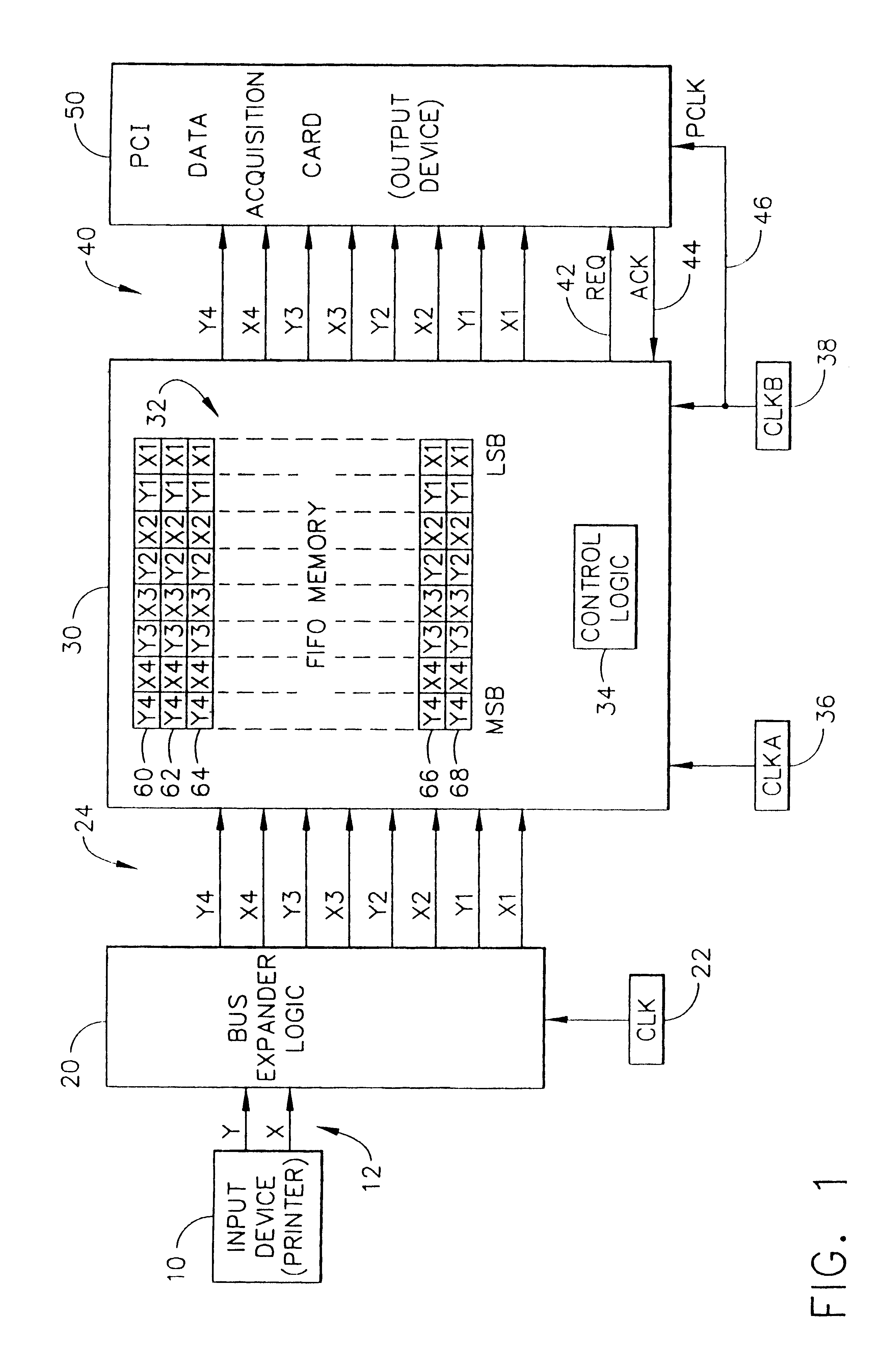

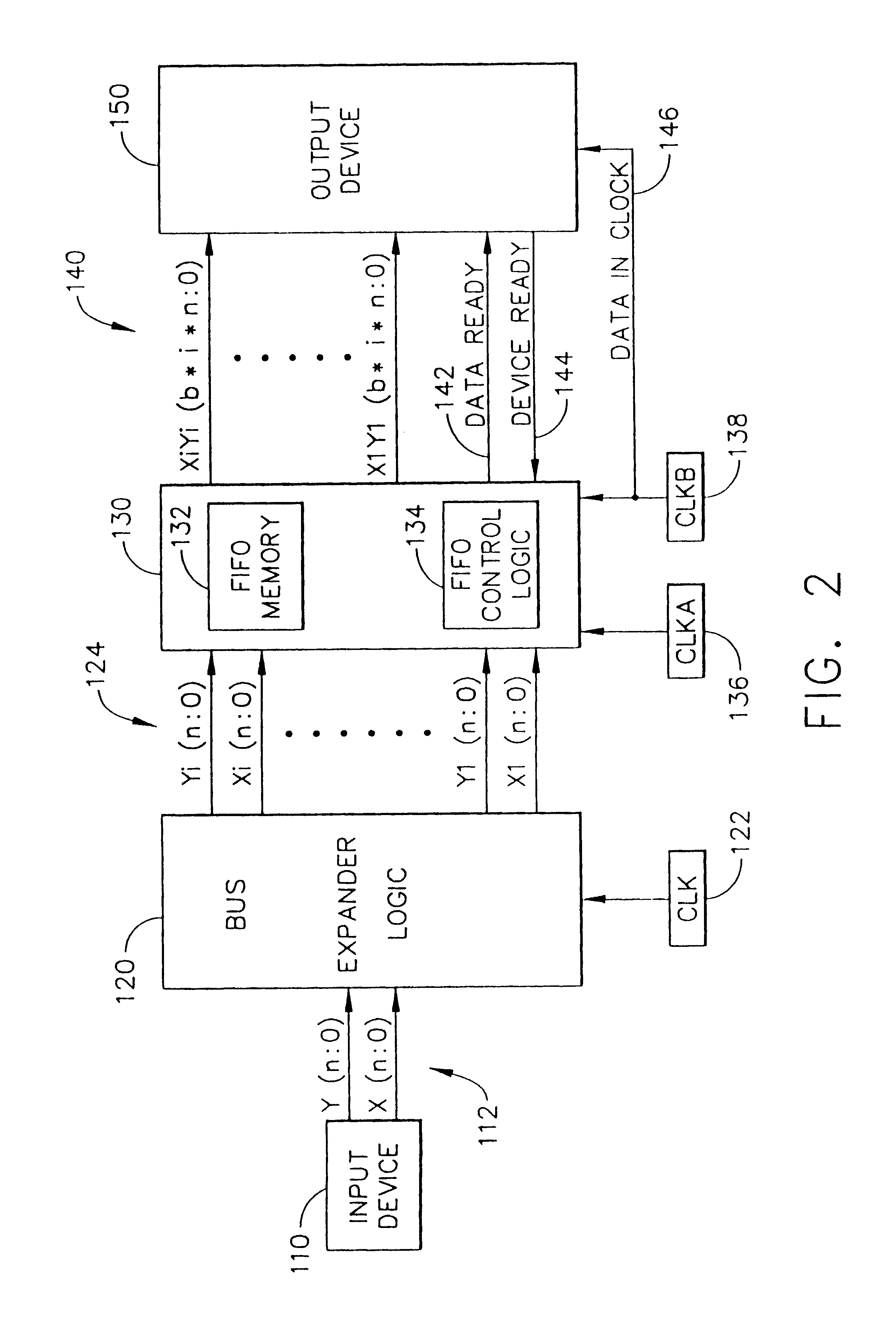

An improved data acquisition system interface provides virtually constant sampling of input signals and provides those signals in a digitized format to a data acquisition unit that may not be able to sample at a constant rate without missing or “losing” some of the samples. The present invention acts as a front end interface that temporarily latches the sampled data, expands the data into multiple parallel signals, then stores the multiple parallel signals in a dual-port FIFO memory unit. Finally, the multiple parallel signals are transferred into the data acquisition unit at a lower frequency, and the transfer operations take place only when the data acquisition unit is ready to accept data. Since the front end misses no sampling intervals (i.e., it always takes a sample according to an extremely constant frequency crystal clock), then the data acquisition unit will be provided with all of these samples without losing any data. The only requirement is that the data throughput of the multiple parallel signals into the data acquisition unit be greater than or equal to the data sampling rate of the original signal at the front end. The present invention can be used with pure digital signals to capture their precise times of logic state transitions, or with serial data signals in which the precise moments of transition can be used to decipher the serial data. Moreover, the interface can be used with analog signals that are digitized using an analog-to-digital converter.

Owner:LEXMARK INT INC

Queuing system using dual receive FIFO

InactiveUS6944688B1Improve data throughputImprove efficiencySecuring communicationInput/output processes for data processingData treatmentFifo memory

A queuing system utilizing dual first-in, first-out (FIFO) memories is provided. The present queuing system is configured to use a first FIFO memory to receive and transfer a plurality of frames to a second FIFO memory wherein the frames include encrypted frame contents. The first FIFO memory is configured to transfer an interrupt to an associated processor in response to completion of the receipt of a valid frame. Next, the processor is configured to reinitialize the first FIFO memory for receipt of a subsequent frame.Additionally, the second FIFO memory is suitably adapted to concurrently store a plurality of frames transferred from the first FIFO memory. Finally, the present system is configured to transfer one of the stored frames out of the second FIFO memory in response to the completion of a data processing operation (e.g. initialization of a decryption algorithm).

Owner:CISCO TECH INC

Asynchronous sample rate converter and method

ActiveUS7262716B2Exact matchReduce usageDigital technique networkCode conversionFifo memoryTime signal

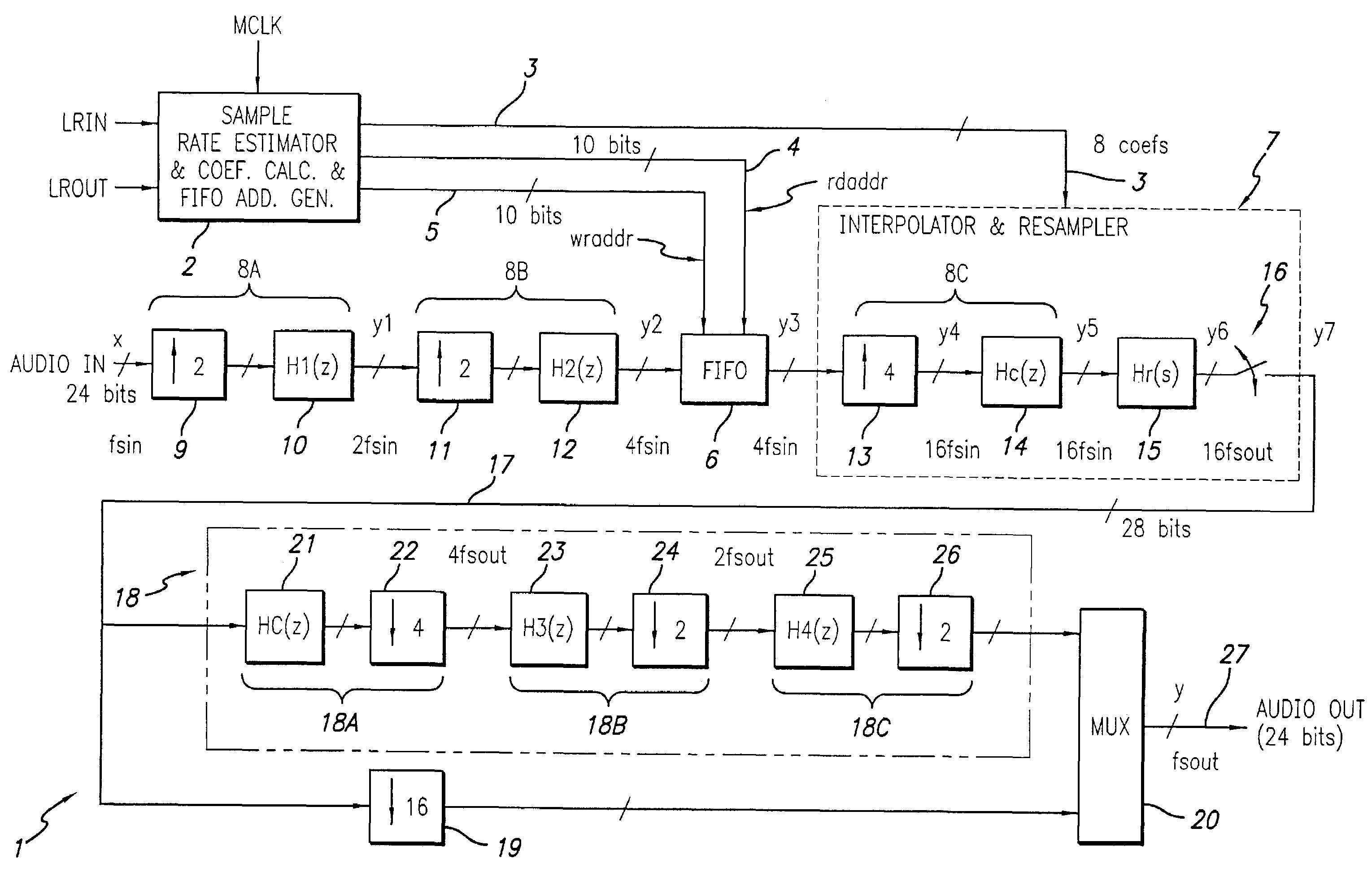

An asynchronous sample rate converter interpolates and filters a digital audio input signal to produce a filtered, up-sampled first signal. A FIFO memory receives the first signal and stores samples thereof at locations determined by a write address and presents stored samples from locations determined by a read address. The presented samples are passed through an interpolation and resampling circuit to produce a continuous-time signal which is re-sampled to produce a signal that is up-sampled relative to a desired output. That signal then is filtered and down-sampled to produce the output signal. Sample rate estimating circuitry computes a difference signal representative of a time at which a data sample of the audio input signal is received and a time at which a corresponding audio output sample is required, and address generation circuitry generates the read and write addresses. A coefficient calculation circuit calculates filter coefficients for the interpolation and resampling circuit in response to the difference signal.

Owner:TEXAS INSTR INC

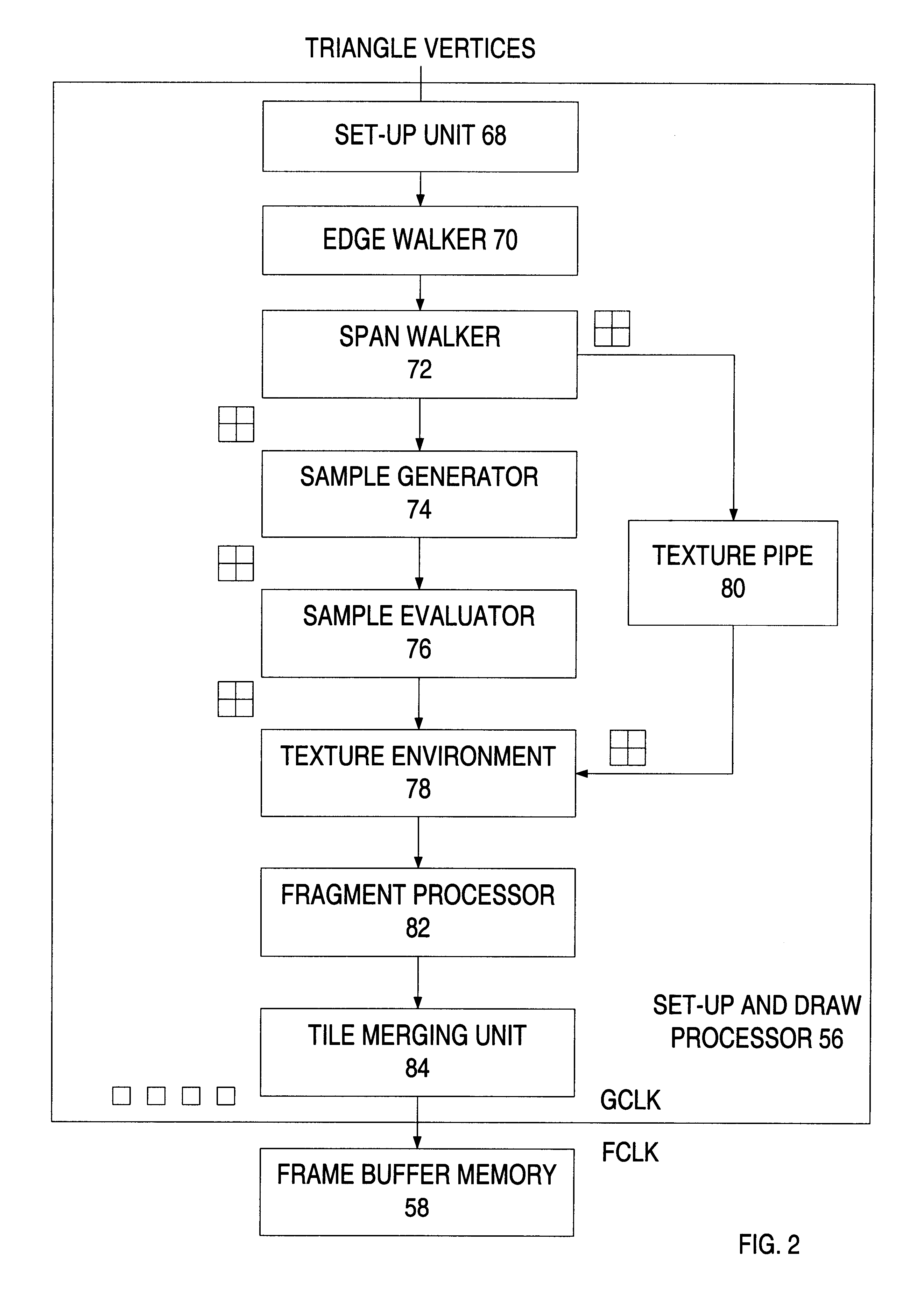

Rasterization using two-dimensional tiles and alternating bins for improved rendering utilization

InactiveUS20020171658A1Cathode-ray tube indicatorsProcessor architectures/configurationGraphicsMemory bank

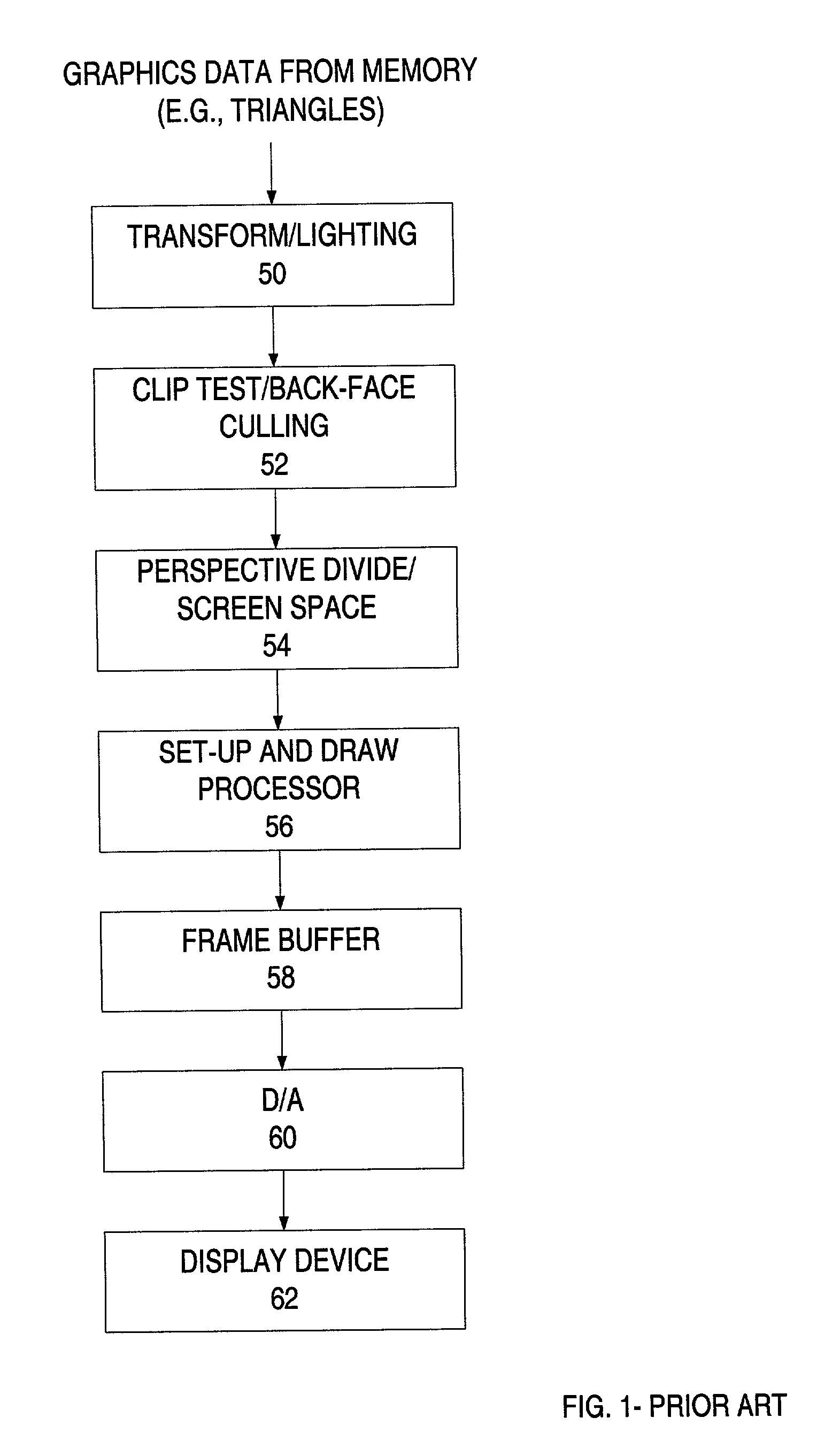

A system and method for rasterizing and rendering graphics data is disclosed. Vertices may be grouped to form primitives such as triangles, which are rasterized using two-dimensional arrays of samples bins. Individual samples may be selected from the bins according to different criteria such as memory bank allocation to improve utilization of the system's rendering pipeline. Since the arrays may have more bins than the number of evaluation units in the rendering pipeline, the samples from the bins may be stored to FIFO memories to allow invalid or empty samples (those outside the primitive being rendered) to be removed. The samples may then be filtered to form pixels that are displayable to form an image on a display device.

Owner:ORACLE INT CORP

Rasterization using two-dimensional tiles and alternating bins for improved rendering utilization

InactiveUS6803916B2Cathode-ray tube indicatorsProcessor architectures/configurationGraphicsMemory bank

A system and method for rasterizing and rendering graphics data is disclosed. Vertices may be grouped to form primitives such as triangles, which are rasterized using two-dimensional arrays of samples bins. Individual samples may be selected from the bins according to different criteria such as memory bank allocation to improve utilization of the system's rendering pipeline. Since the arrays may have more bins than the number of evaluation units in the rendering pipeline, the samples from the bins may be stored to FIFO memories to allow invalid or empty samples (those outside the primitive being rendered) to be removed. The samples may then be filtered to form pixels that are displayable to form an image on a display device.

Owner:ORACLE INT CORP

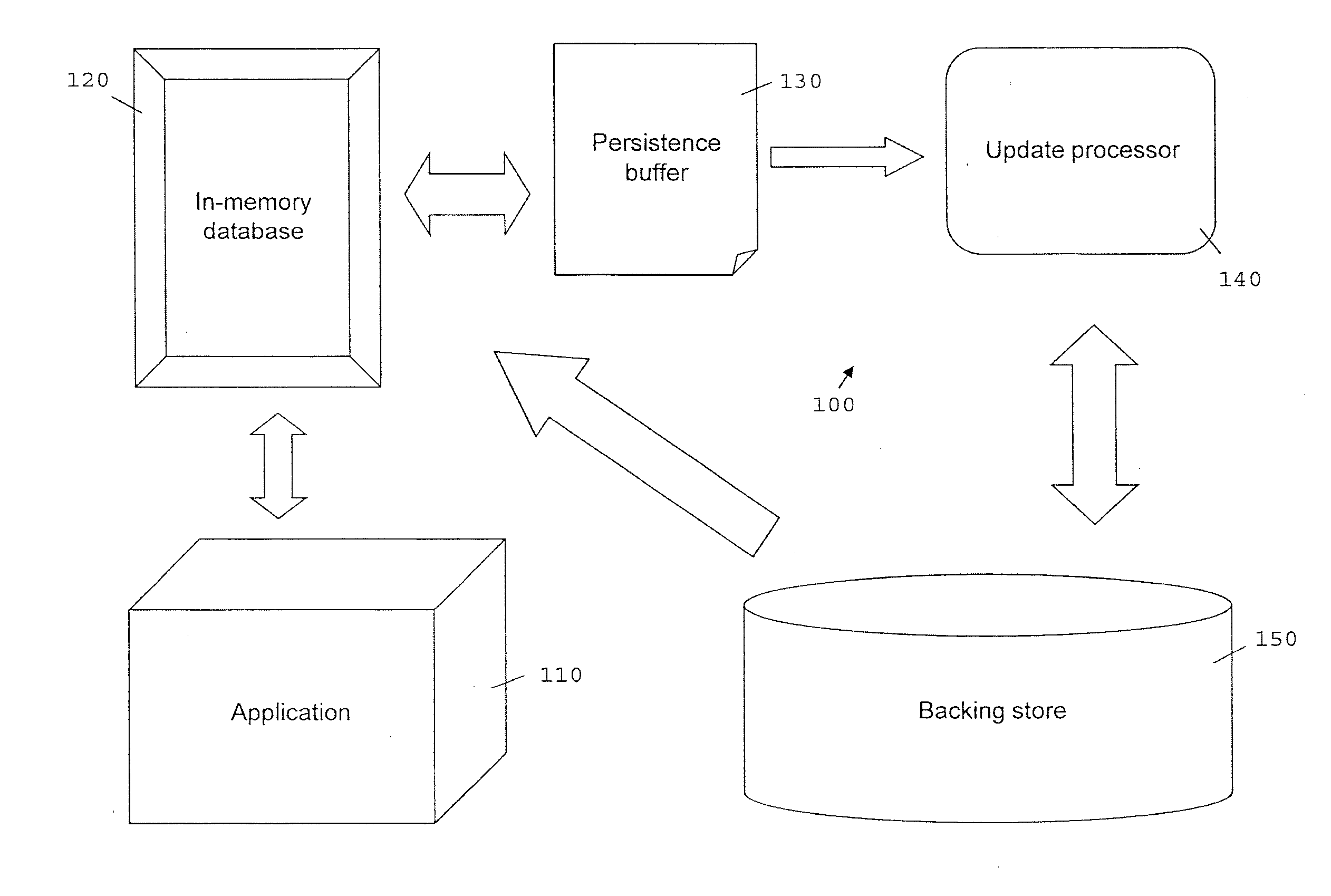

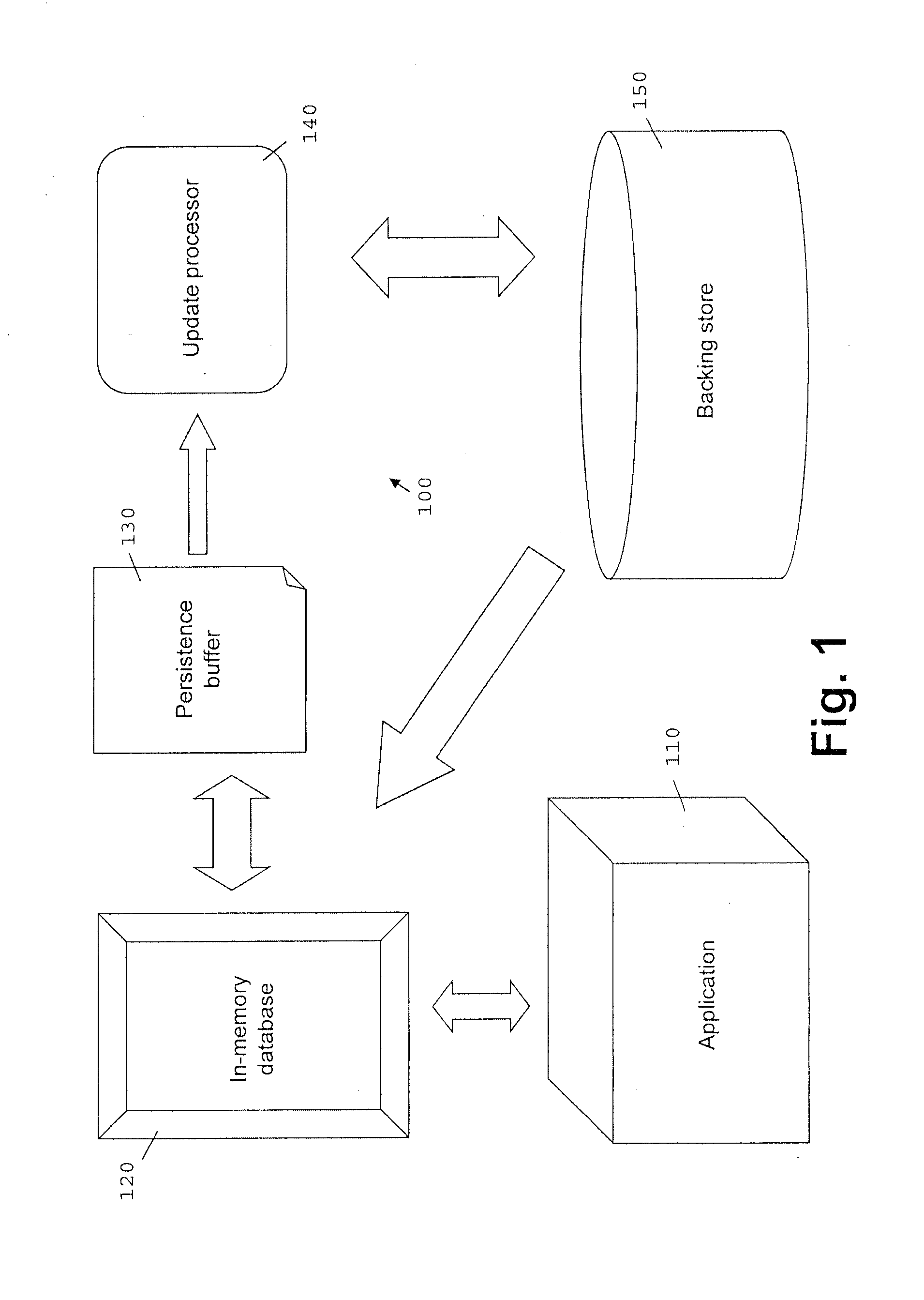

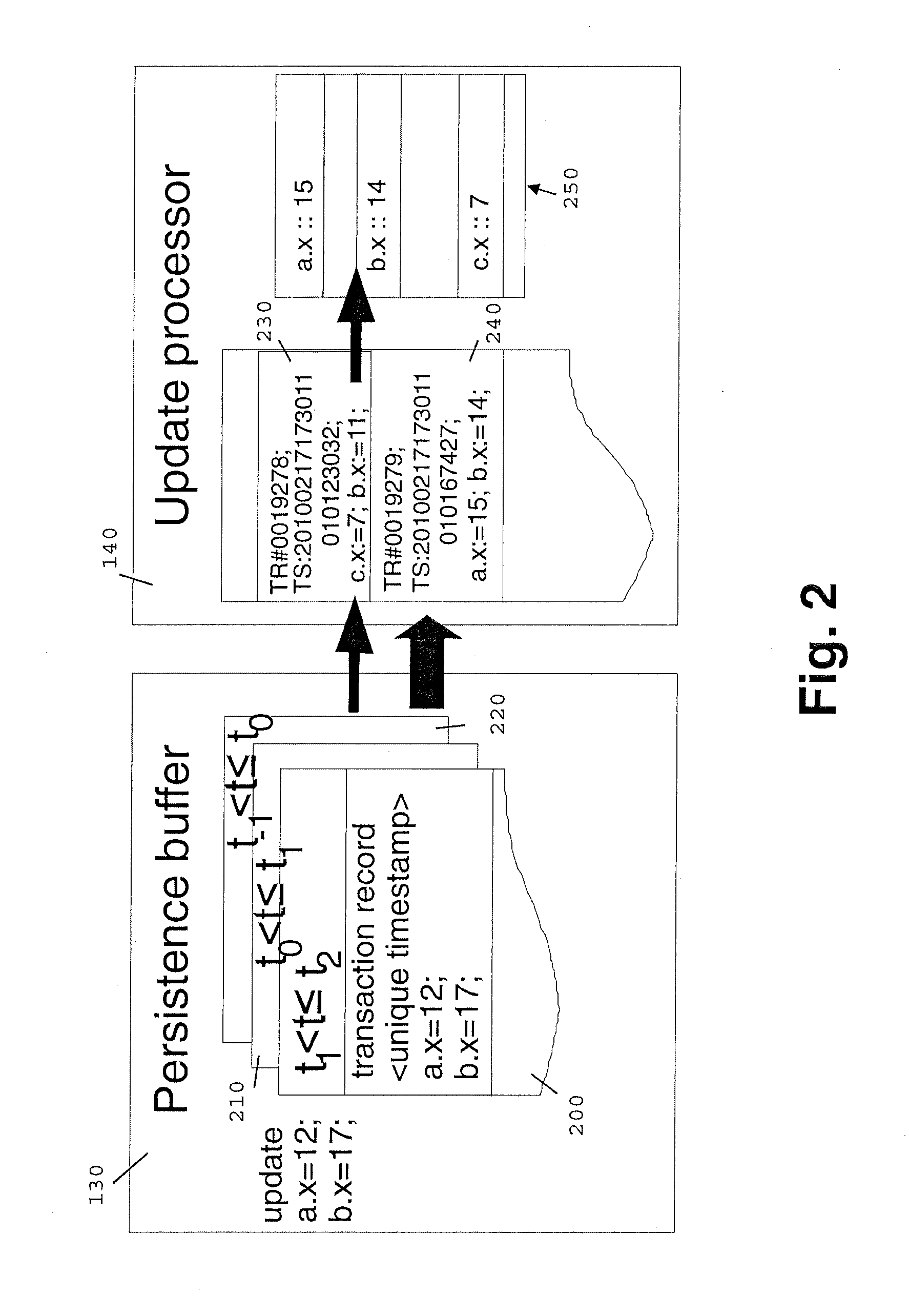

Persisting of a low latency in-memory database

ActiveUS20120265743A1Digital data information retrievalDigital data processing detailsIn-memory databaseTransaction data

Processing is provided for operating an in-memory database, wherein transaction data is stored by a persistence buffer in an FIFO queue, and update processor subsequently: waits for a trigger; extracts the last transactional data associated with a single transaction of the in-memory database from the FIFO memory queue; determines if the transaction data includes updates to data fields in the in-memory database which were already processed; and if not, then stores the extracted transaction data to a store queue, remembering the fields updated in the in-memory database, or otherwise updates the store queue with the extracted transaction data. The process continues until the extracting is complete, and the content of the store queue is periodically written into a persistent storage device.

Owner:IBM CORP

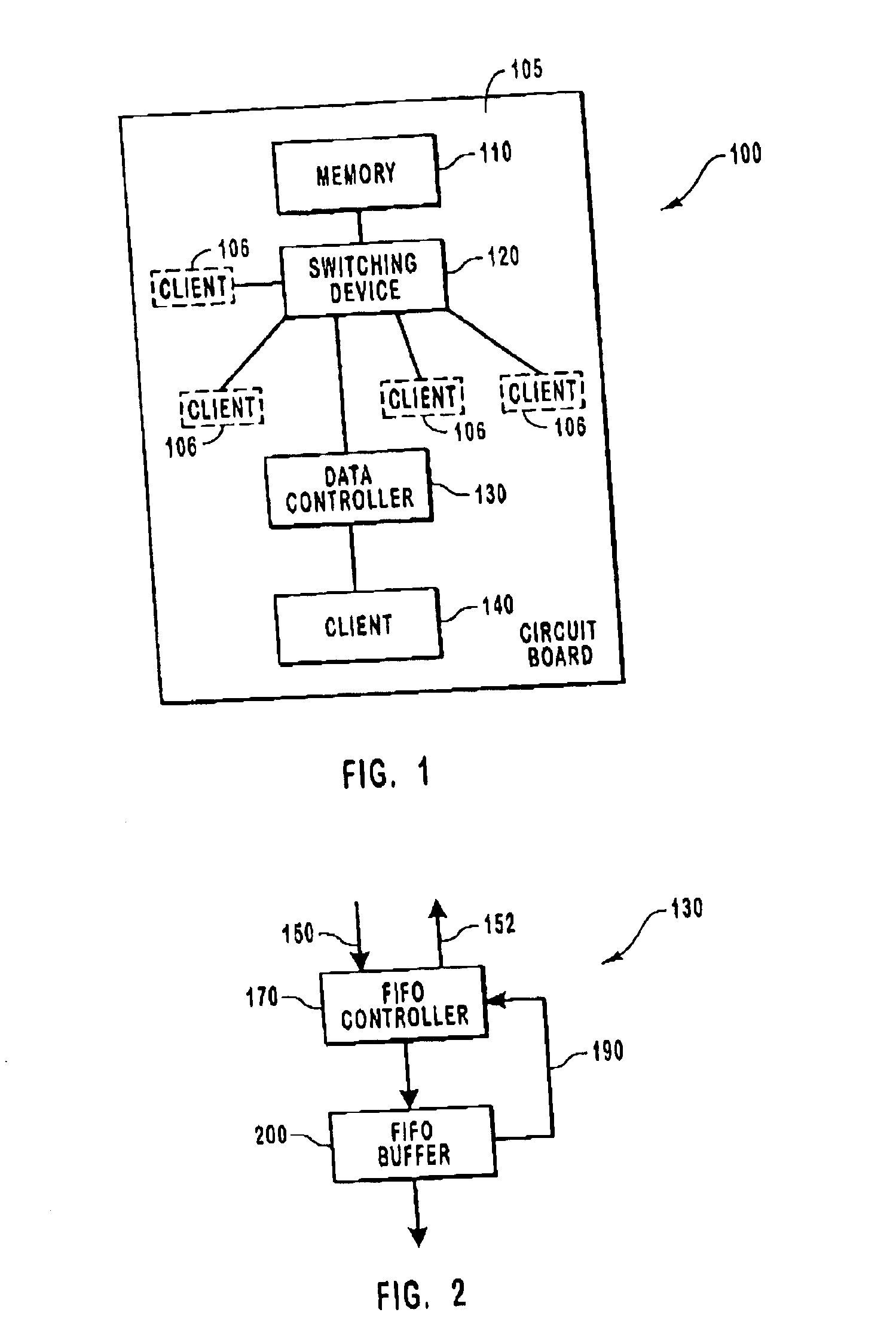

Integrated FIFO memory management control system using a credit value

InactiveUS6877049B1Improve predictabilityRelatively large bandwidthInput/output processes for data processingData conversionData controlControl system

An integrated data controller that utilizes a first-in first-out (FIFO) management system that compensates for the unpredictable nature of latency associated with requesting data from memory and enables the timing of data requests to be determined based on the number of pending requests and the amount of data currently residing in the buffer. The FIFO management system includes a FIFO controller and a FIFO buffer that monitor a credit value and a trigger value to determine when to make data request bursts upon a memory unit. The trigger value is an indication of whether there is a sufficient amount of free space for it to be beneficial to make a data request burst and the credit value is a number that indicates the number of a data blocks that should be requested in the data request burst.

Owner:VIAVI SOLUTIONS INC

Signal processing apparatus and a data recording and reproducing apparatus including local memory processor

InactiveUS20030028820A1Modification of read/write signalsError detection/correctionSignal processing circuitsAuxiliary memory

In a data recovery processing, the conventional overhead, primarily, latency due to a rotational recording media is removed. Secondary, in a signal processing or in a recording and reproducing apparatus, reliability of data reproduction is improved by repeatedly processing data. These processing are achieved that input signal, i.e., raw analog signal read from the recording media is digitized to be stored in a secondary storage such as a memory or a FIFO memory. The apparatus includes a signal processing circuit to repeatedly process the stored digital signal in the secondary storage. When detecting data, operation of the circuit is efficiently controlled by a change over detector parameters, in which characteristics for the detecting performance. Resultantly, data recovery processing speed is increased and reliability of data reproduced is improved.

Owner:WESTERN DIGITAL TECH INC +1

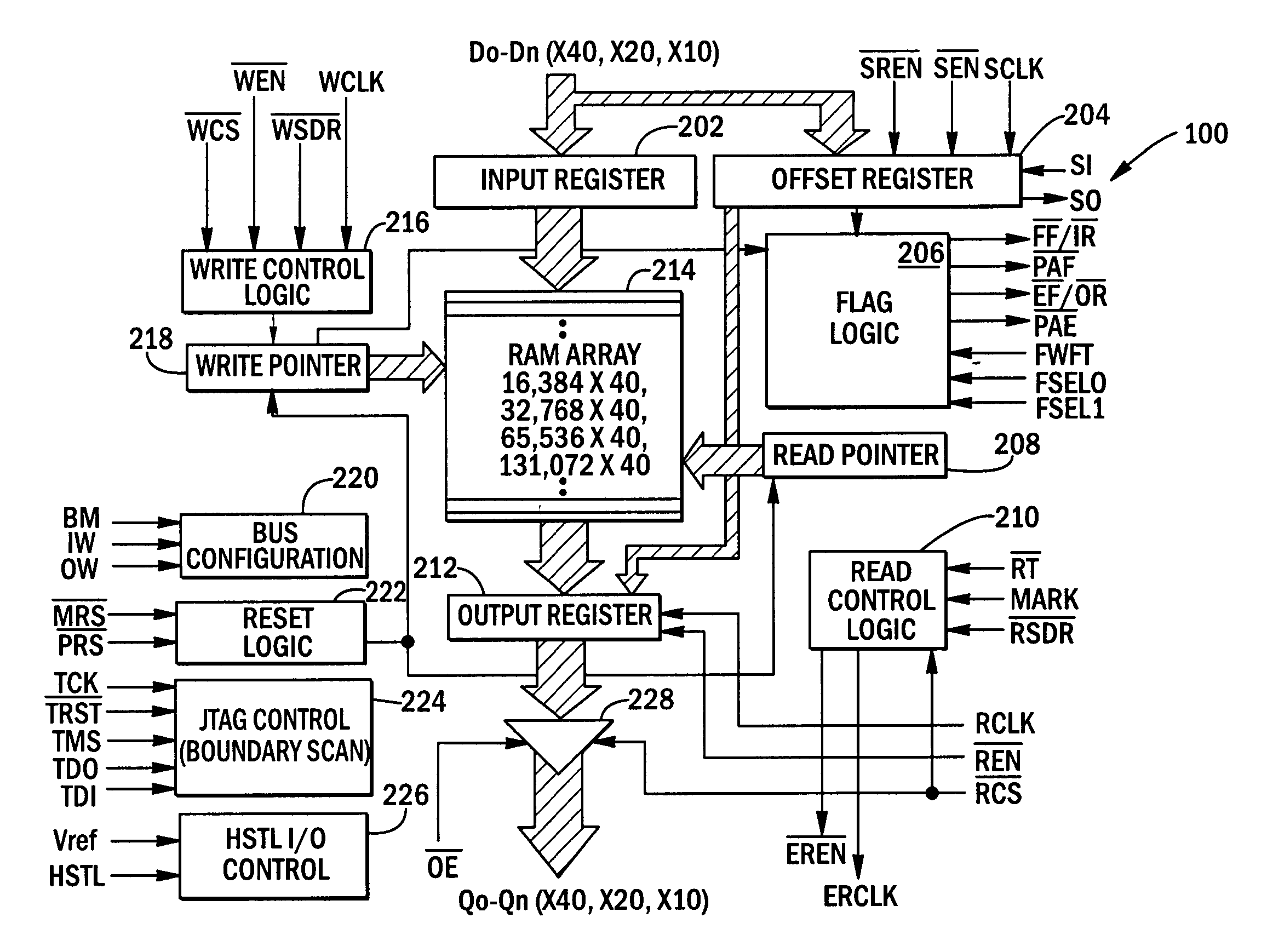

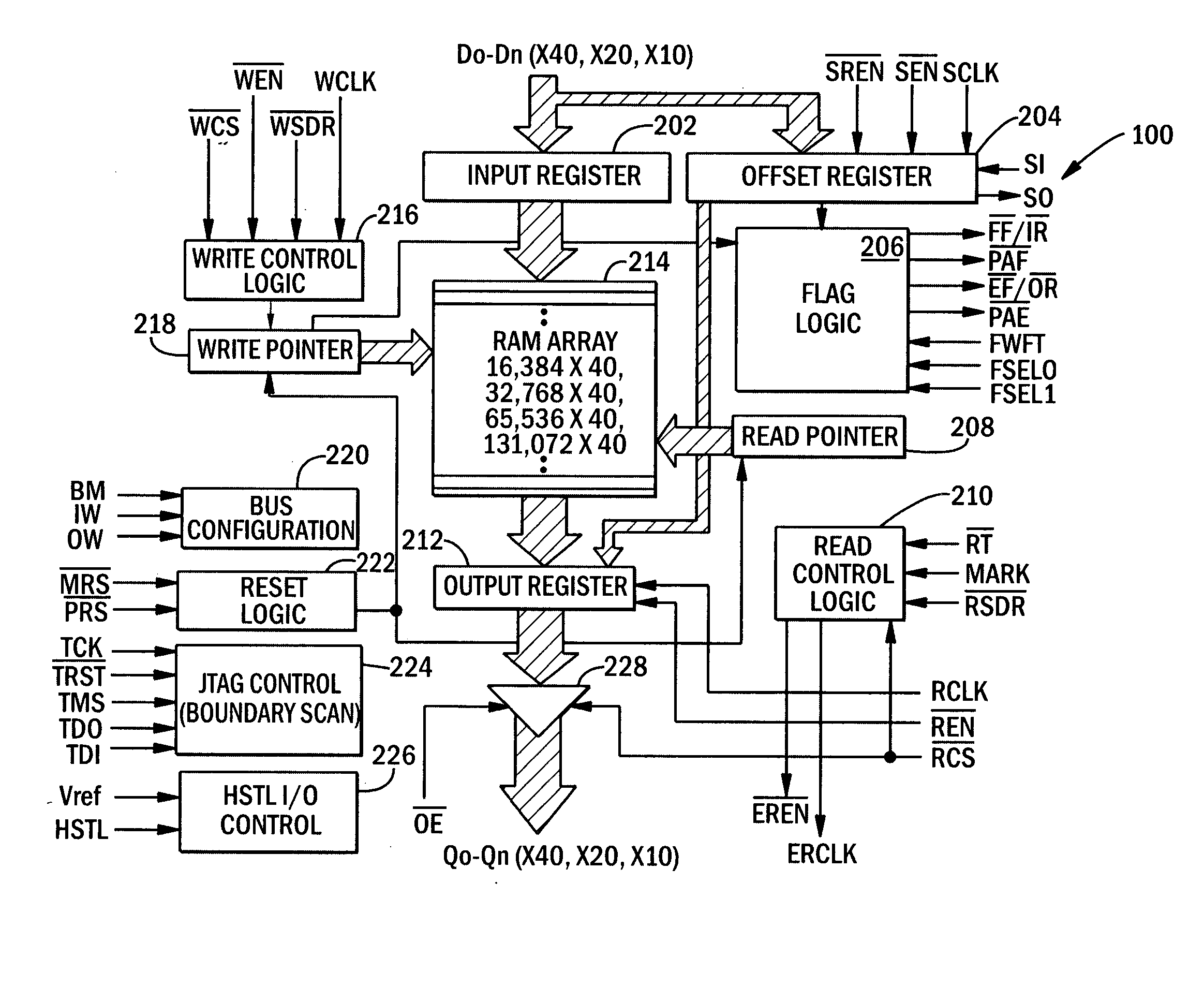

FIFO memory devices having write and read control circuits that support x4N, x2N and xN data widths during DDR and SDR modes of operation

InactiveUS20050041450A1High data rateExtending of speed of deviceMemory loss protectionDigital storageFifo memoryOperating system

First-in first-out (FIFO) memory devices are configured to support all four of the following FIFO memory modes: (1) DDR write with DDR read, (2) DDR write with SDR read, (3) SDR write with DDR read and (4) SDR write with SDR read. These FIFO memory devices provide flexible x4N, x2N and xN bus matching on both read and write ports and enable data to be written and read on both rising and falling edges of the write and read clock signals. Custom flag generation and retransmit circuitry is also provided that can efficiently handle any width DDR write mode with any width SDR read mode or any width SDR write mode with any width DDR read mode.

Owner:INTEGRATED DEVICE TECH INC

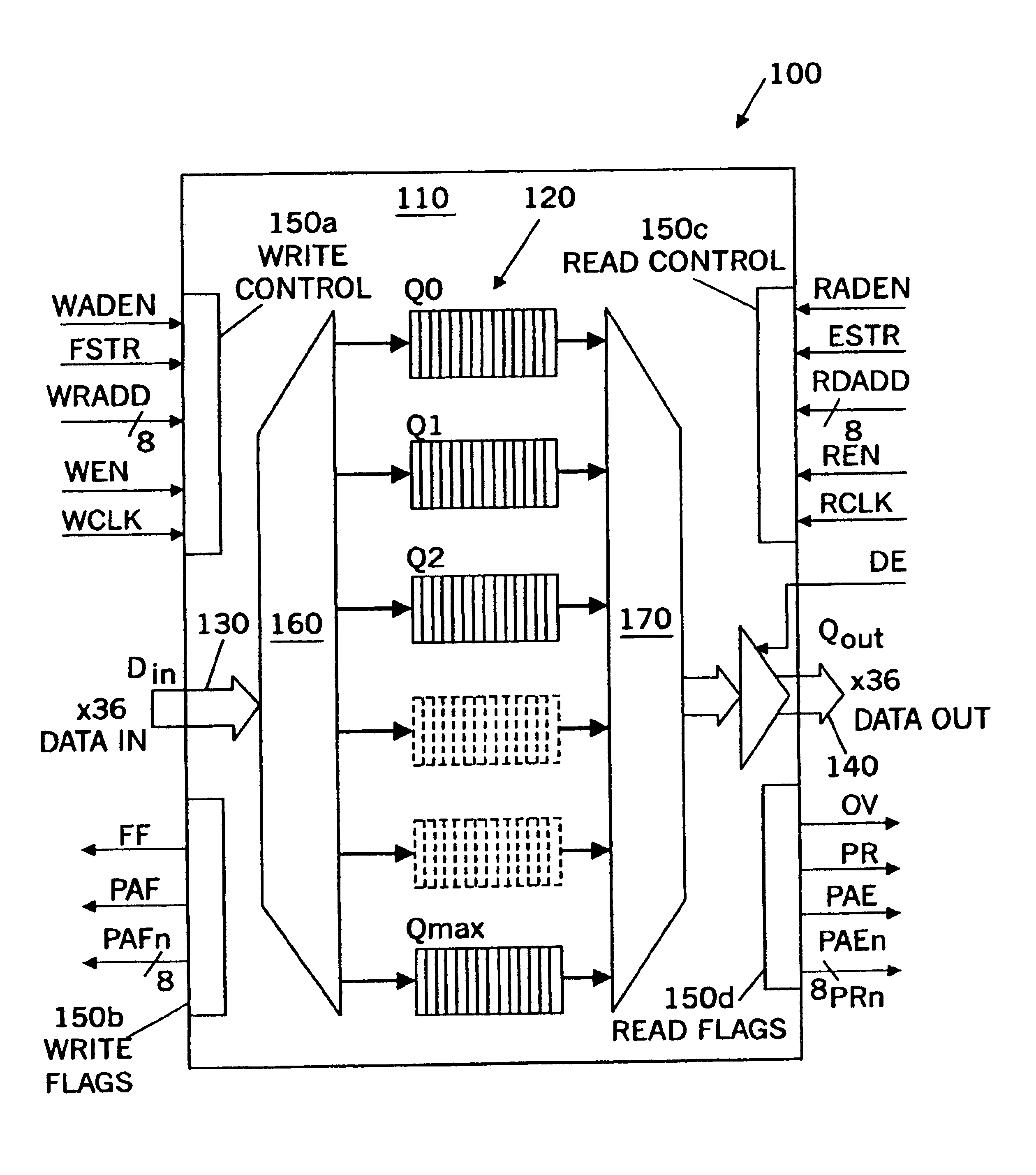

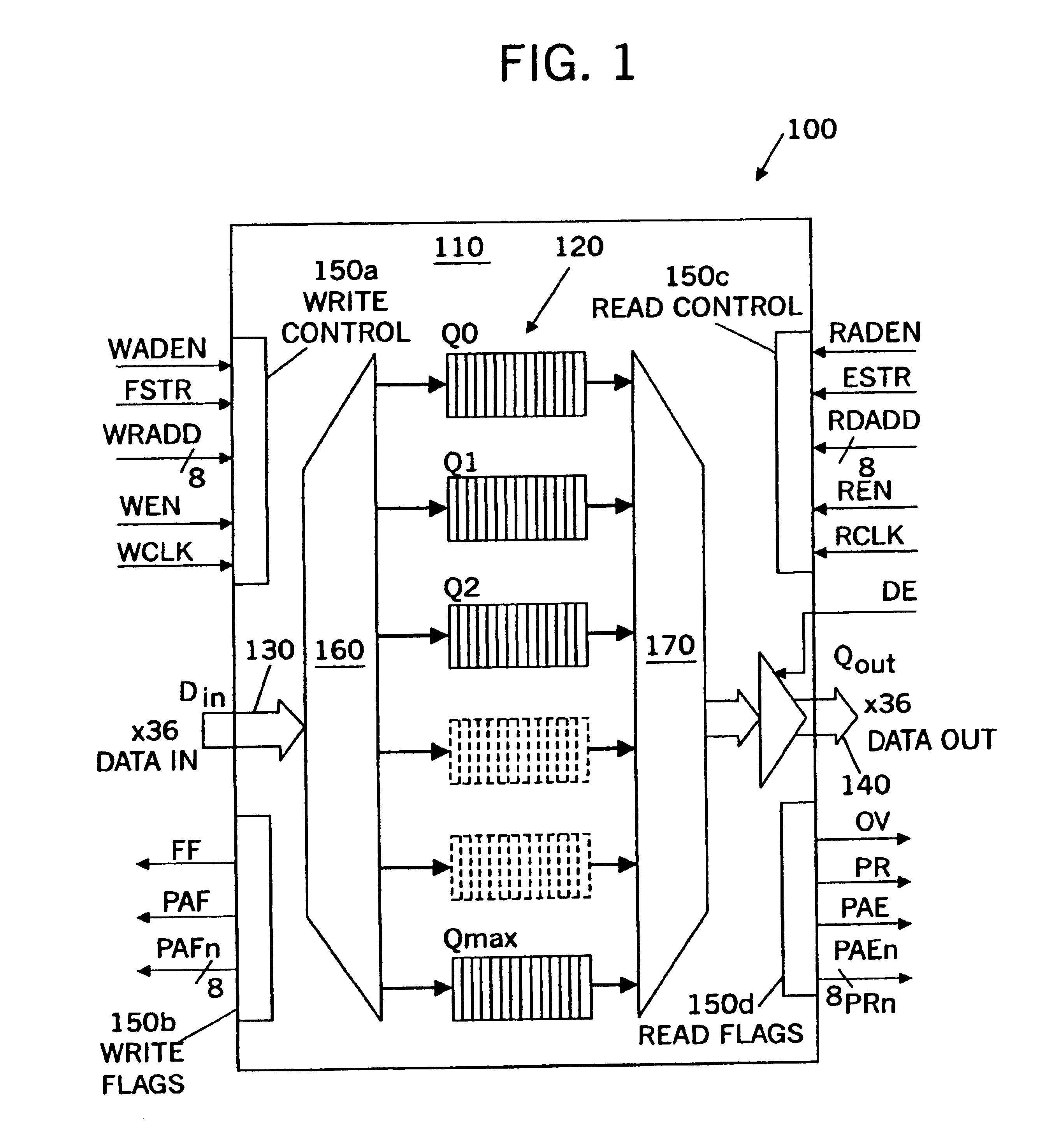

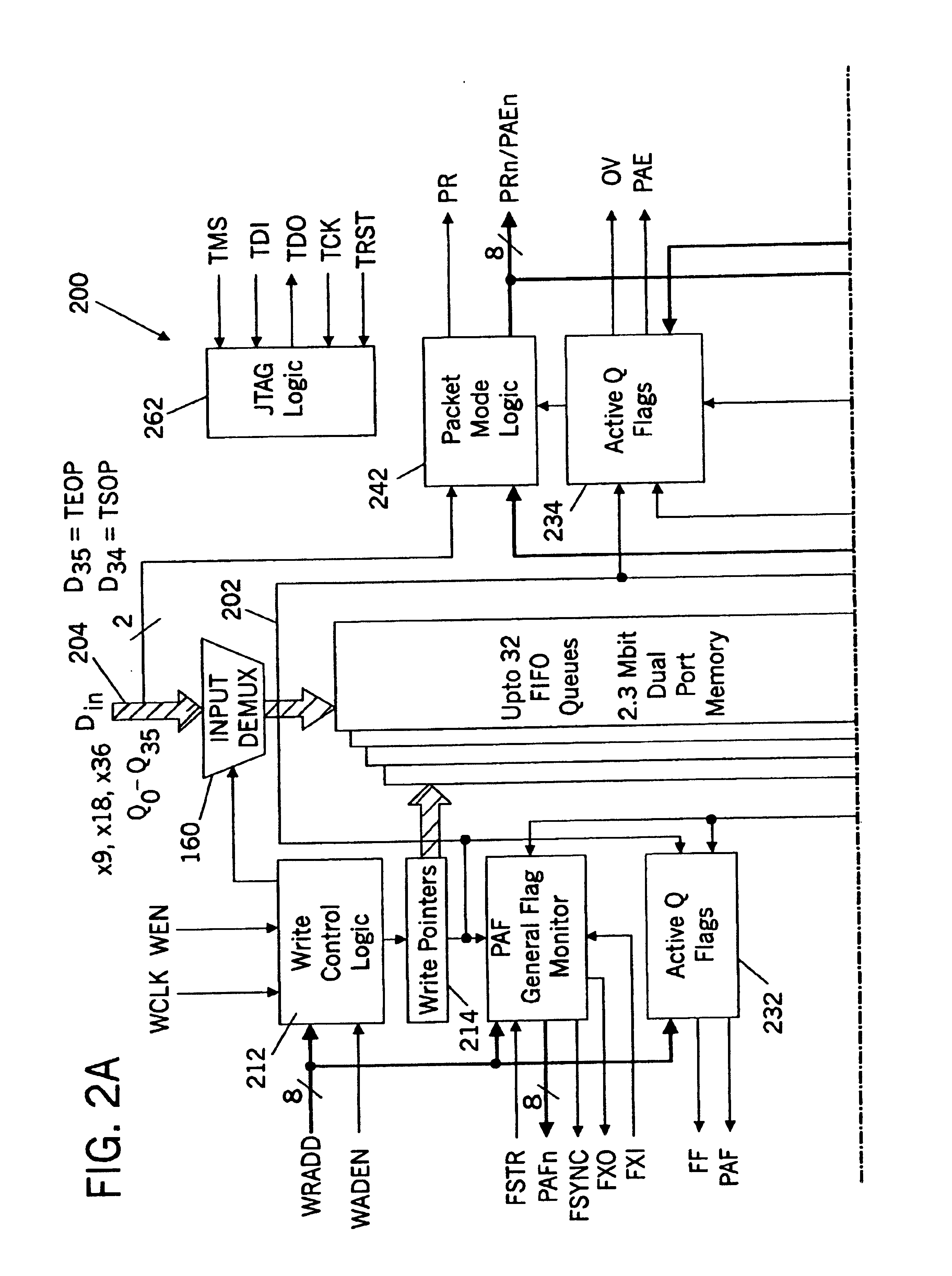

Integrated circuit FIFO memory devices that are divisible into independent FIFO queues, and systems and methods for controlling same

InactiveUS6907479B2Improve scalabilityEfficient storageMemory systemsInput/output processes for data processingProcessor registerFifo queue

Integrated circuit FIFO memory devices may be controlled using a register file, an indexer and a controller. The FIFO memory device includes a FIFO memory that is divisible into up to a predetermined number of independent FIFO queues. The register file includes the predetermined number of words. A respective word is configured to store one or more parameters for a respective one of the FIFO queues. The indexer is configured to index into the register file, to access a respective word that corresponds to a respective FIFO queue that is accessed. The controller is responsive to the respective word that is accessed, and is configured to control access to the respective FIFO queue based upon at least one of the one or more parameters that is stored in the respective word. Thus, as the number of FIFO queues expands, the number of words in the register file may need to expand, but the controller and / or indexer need not change substantially. The register file may include multiple register subfiles, and the controller may include multiple controller subblocks.

Owner:INTEGRATED DEVICE TECH INC

Systems and Methods for Monitoring Out of Order Data Decoding

Various embodiments of the present invention provide systems and methods for monitoring out of order data decoding. For example, a method for monitoring out of order data processing is provided that includes receiving a plurality of data sets that is associated with a plurality of identifiers with each of the plurality of identifiers indicates a respective one of the plurality of data sets; storing each of the plurality of identifiers in a FIFO memory in an order that the corresponding data sets of the plurality of data sets was received; processing the plurality of data sets such that at least one of the plurality of data sets is provided as an output data set; accessing the next available identifier from the FIFO memory; and asserting an out of order signal when the next available identifier is not the same as the identifier associated with the output data set.

Owner:AVAGO TECH INT SALES PTE LTD

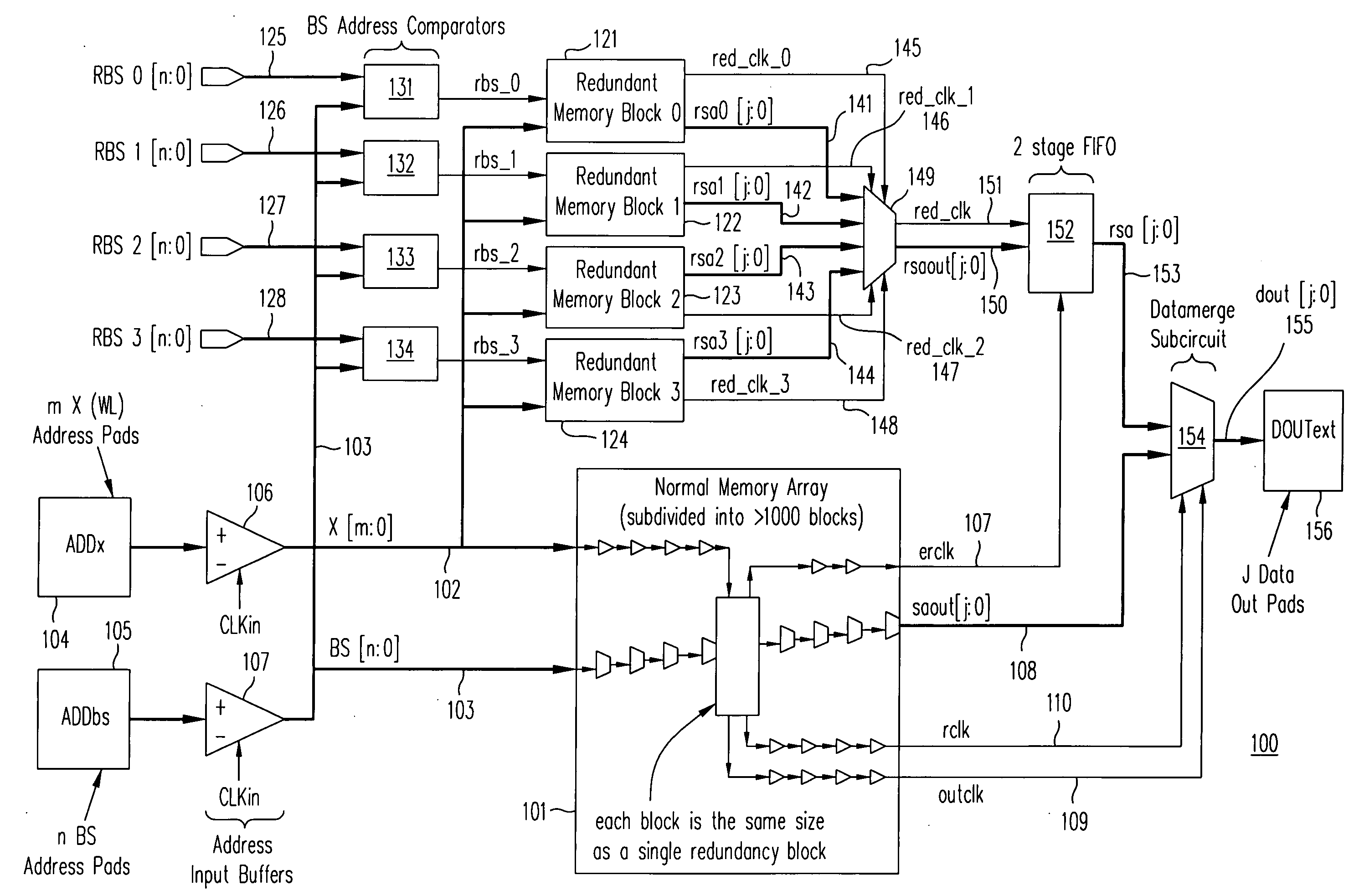

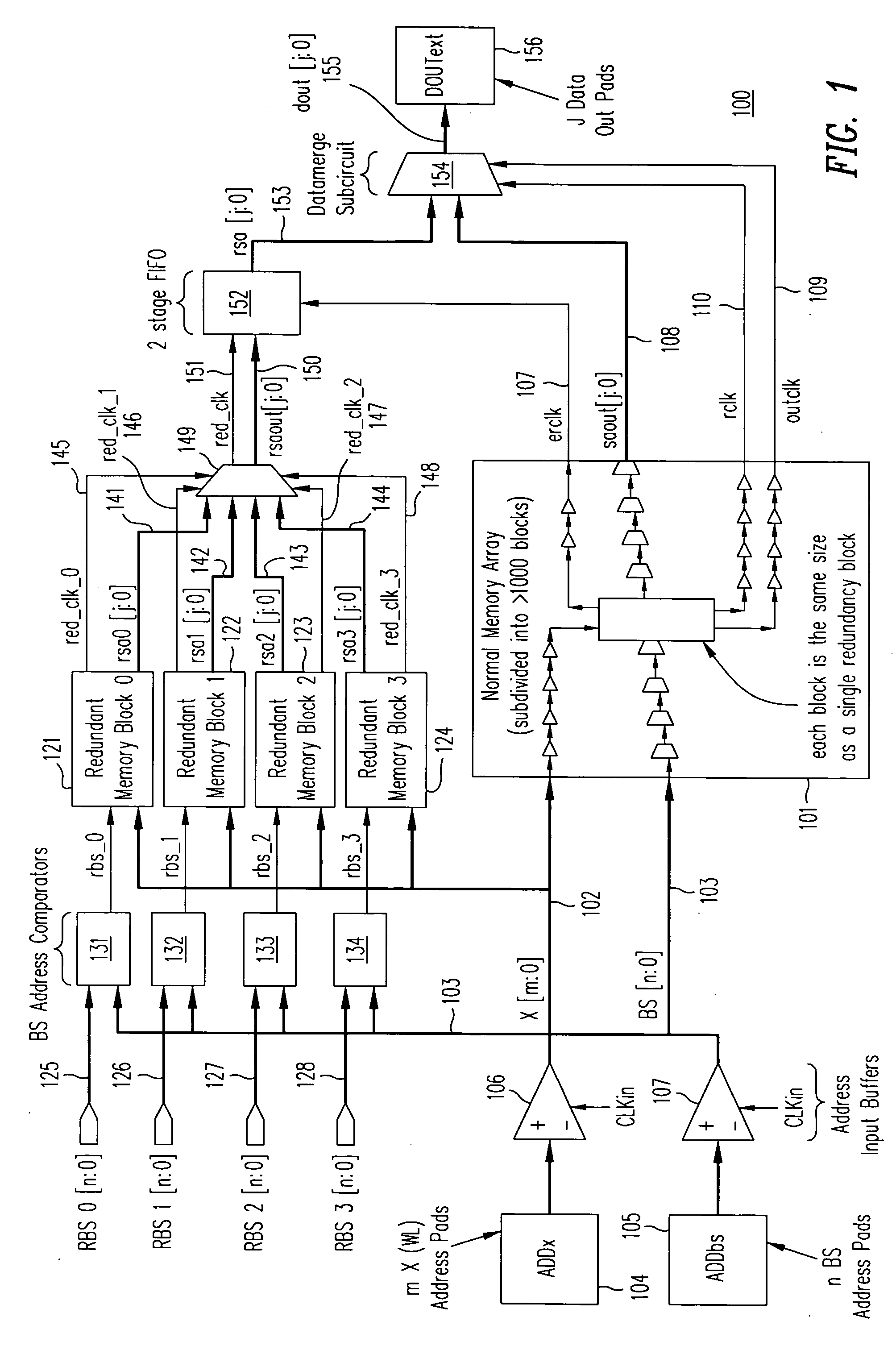

System and method for providing a redundant memory array in a semiconductor memory integrated circuit

A memory device that has an internal memory array provides timing signals to control the output timing of one or more redundant memory blocks that substitute for defective memory blocks in the internal memory array. In one embodiment, the internal memory array includes a pipelined output stage, and the timing signals ensure that the data is output from the memory devices in the order memory access requests are issued, even when the latency of the redundant memory blocks is less than the latency of the main memory array by up to two clock periods. In one embodiment, a FIFO memory queues the output data of the redundant memory blocks waiting to be output.

Owner:MOSAIC SYST

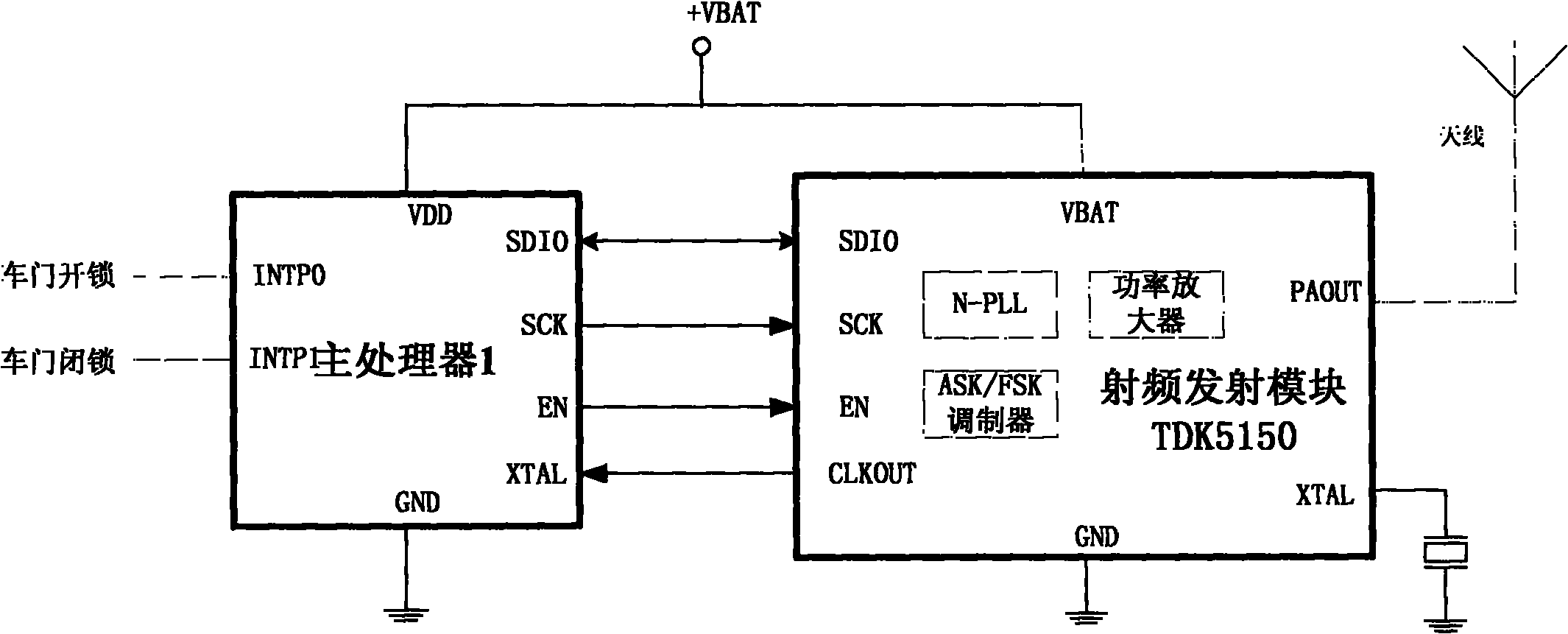

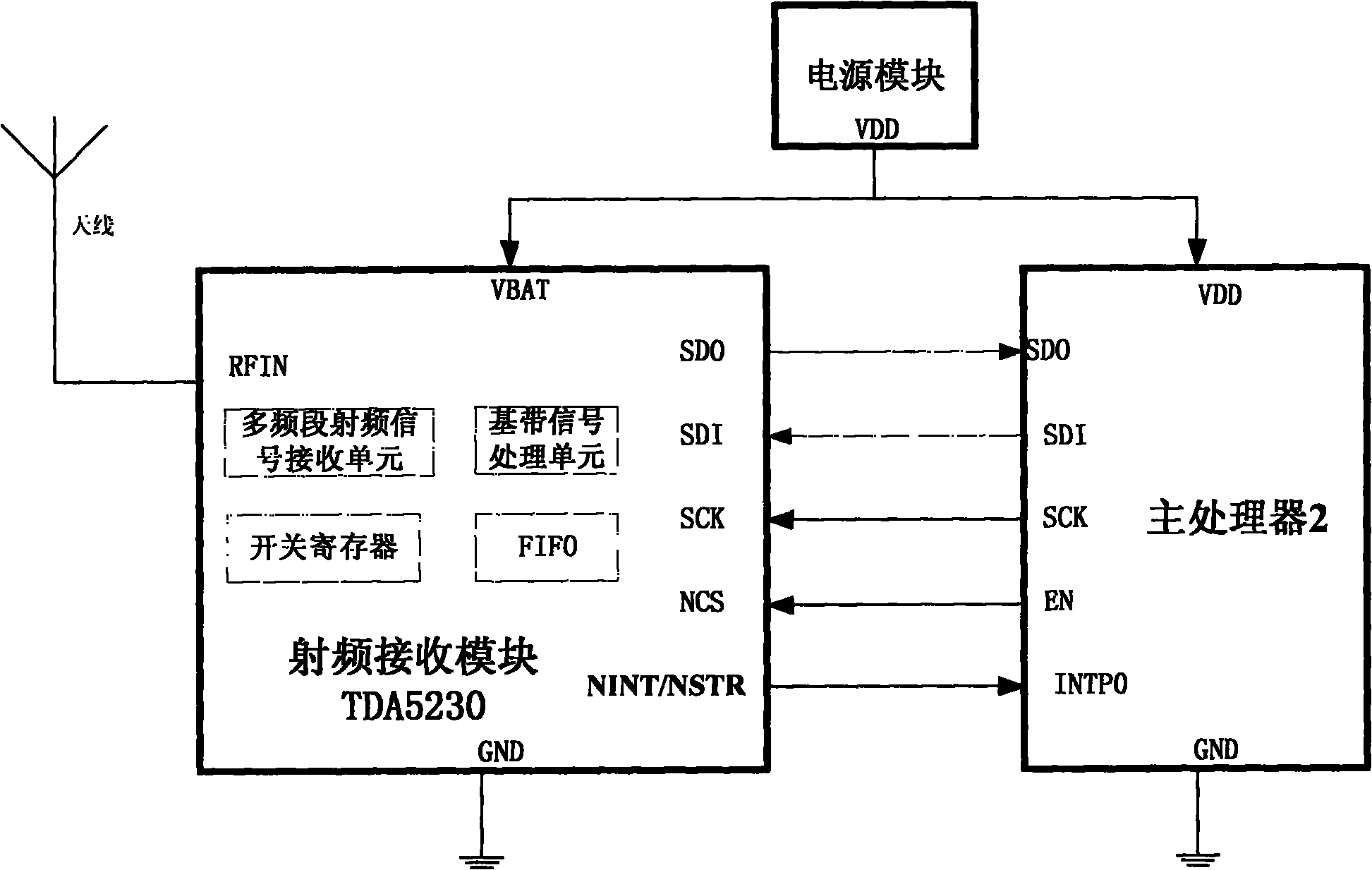

Intelligent remote control key entry method and device of automobile

ActiveCN101840625ASolve signal interferenceAvoid interferenceTransmission systemsEncryption apparatus with shift registers/memoriesTransmitted powerEngineering

The invention discloses an intelligent remote control key entry method and a device of an automobile. The device comprises an automobile key transmitting part and an automobile key receiving part, the automobile key transmitting part combines the a transmitting frequency band, transmitting power and transmission coding data into radio-frequency signals numbering N of different frequency bands, and a power amplifier and a radio-frequency antenna are used for transmitting the radio-frequency signals; the receiving part receives data transmitted by the automobile key transmitting part; after receiving frequency is determined, whether the receiving frequency is effective data is judged, interference information data is filtered, and information data conforming to requirements is stored in an FIFO memory; and data is decryption and matching operation are carried out on the data, then an automobile door is opened / closed according to the information code content. The invention adopts microprocessor control, digital phase-locked frequency selection and a multiband communication technology, solves the problem of signal interference caused by communication at single frequency band in the common PKE system by utilizing multiband radio-frequency signal reorganization and a data frame structure format so as to avoid the interference phenomena among multiple keys of the same automobile type. The invention has the characteristics of simple structure, small volume, low power consumption, high sensitivity and the like.

Owner:QIMING INFORMATION TECH

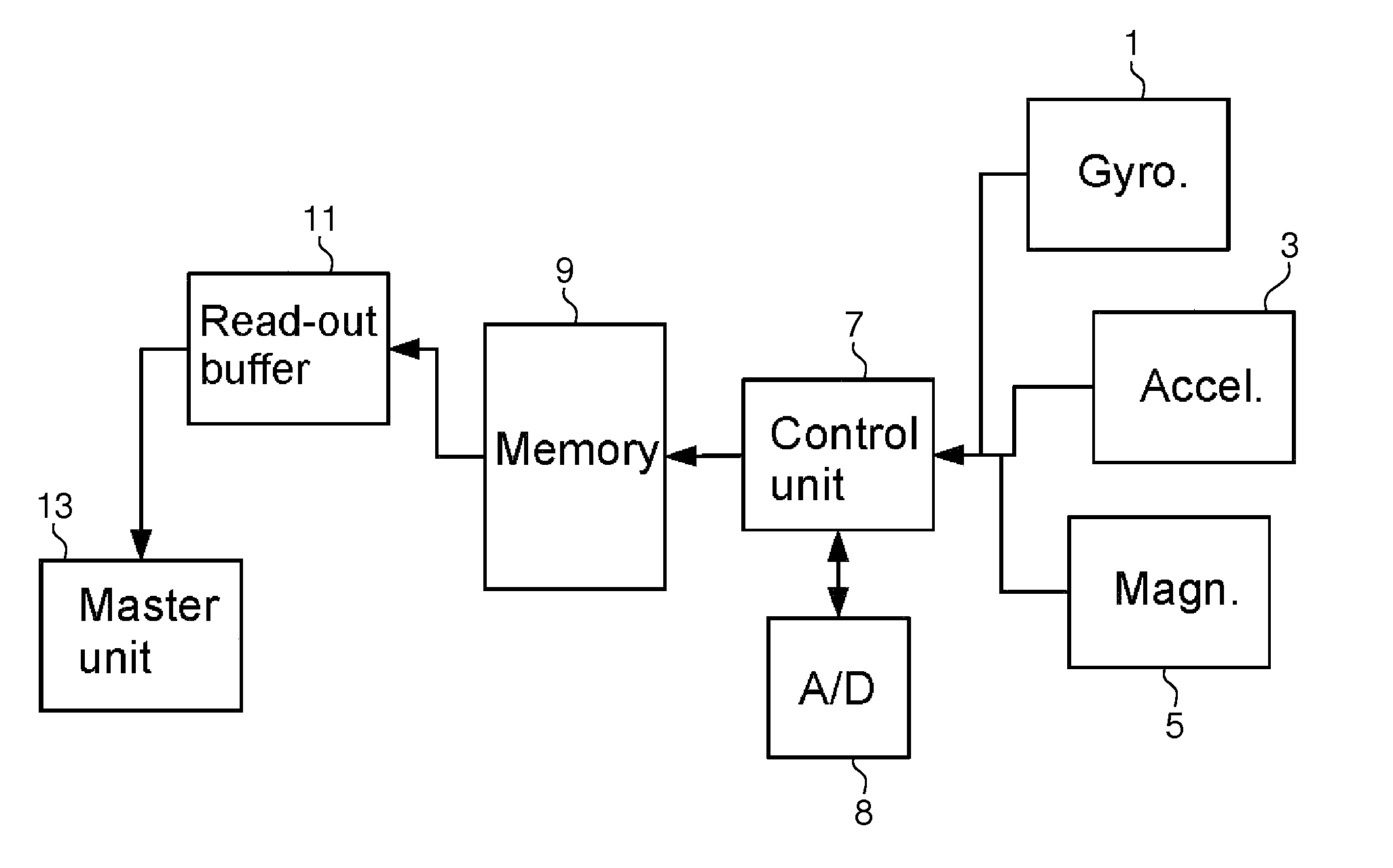

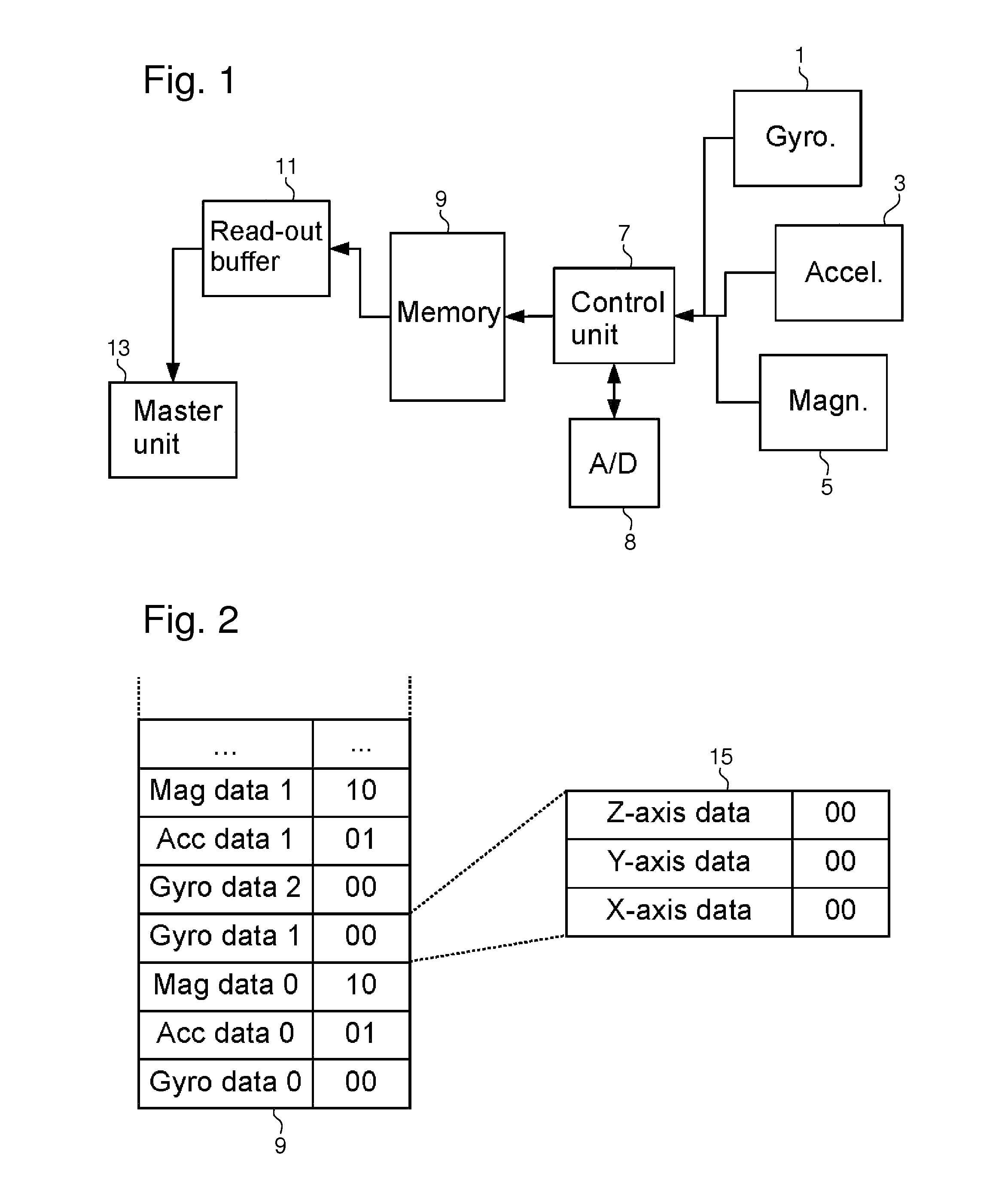

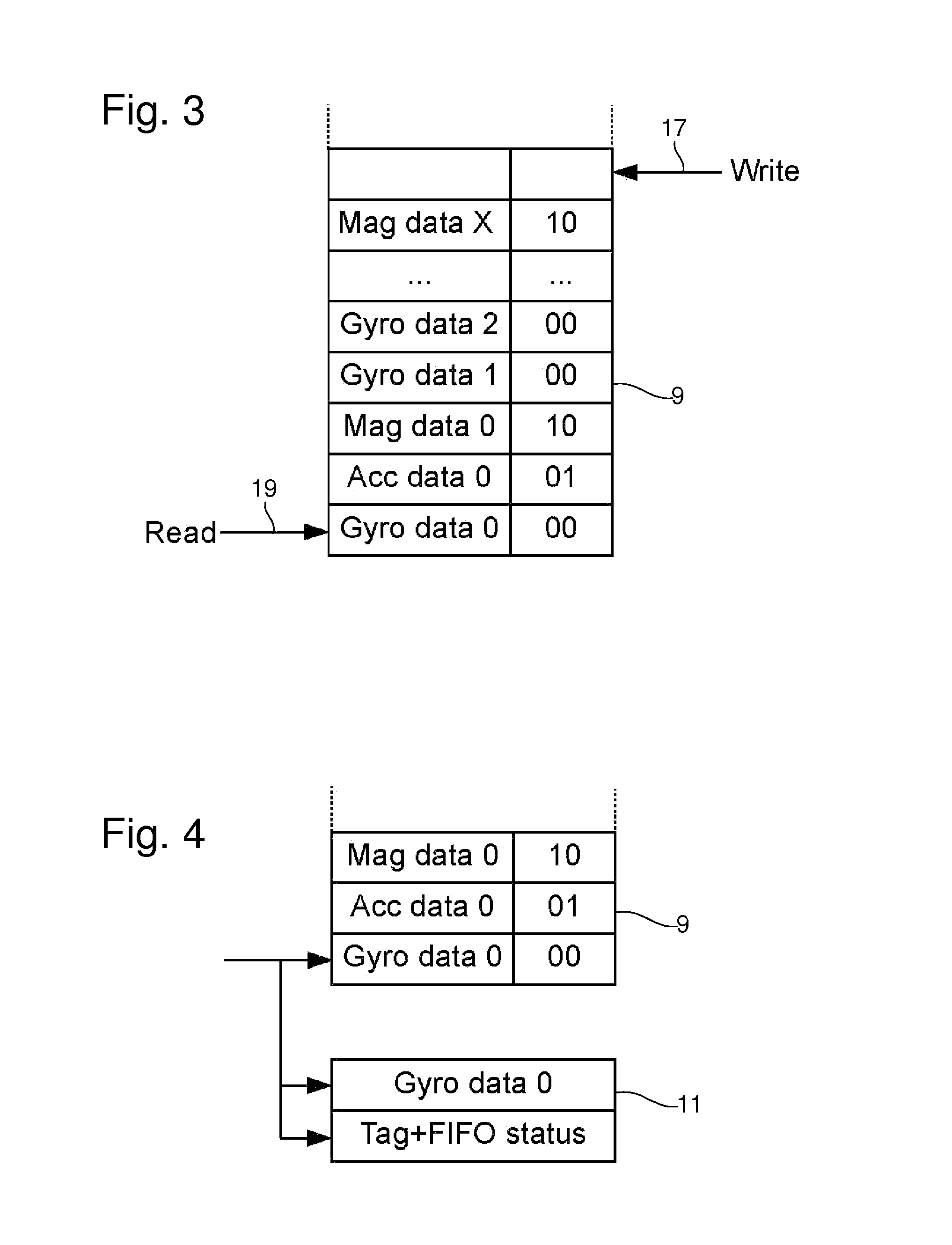

Operating a FIFO memory

ActiveUS20150331805A1Memory space can be efficientlyMinimize power consumptionMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer hardwareSample Measure

Owner:EM MICROELECTRONIC-MARIN

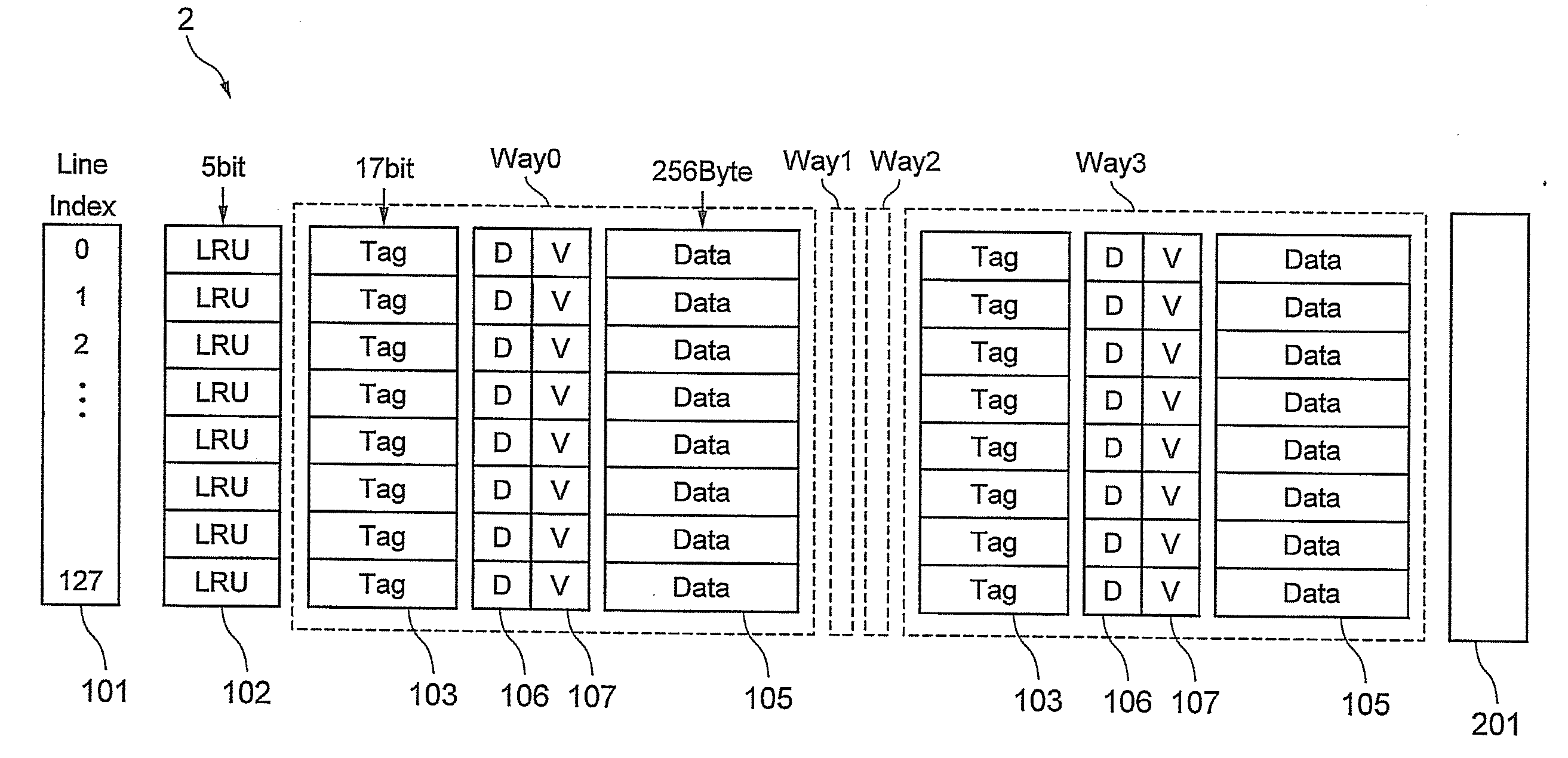

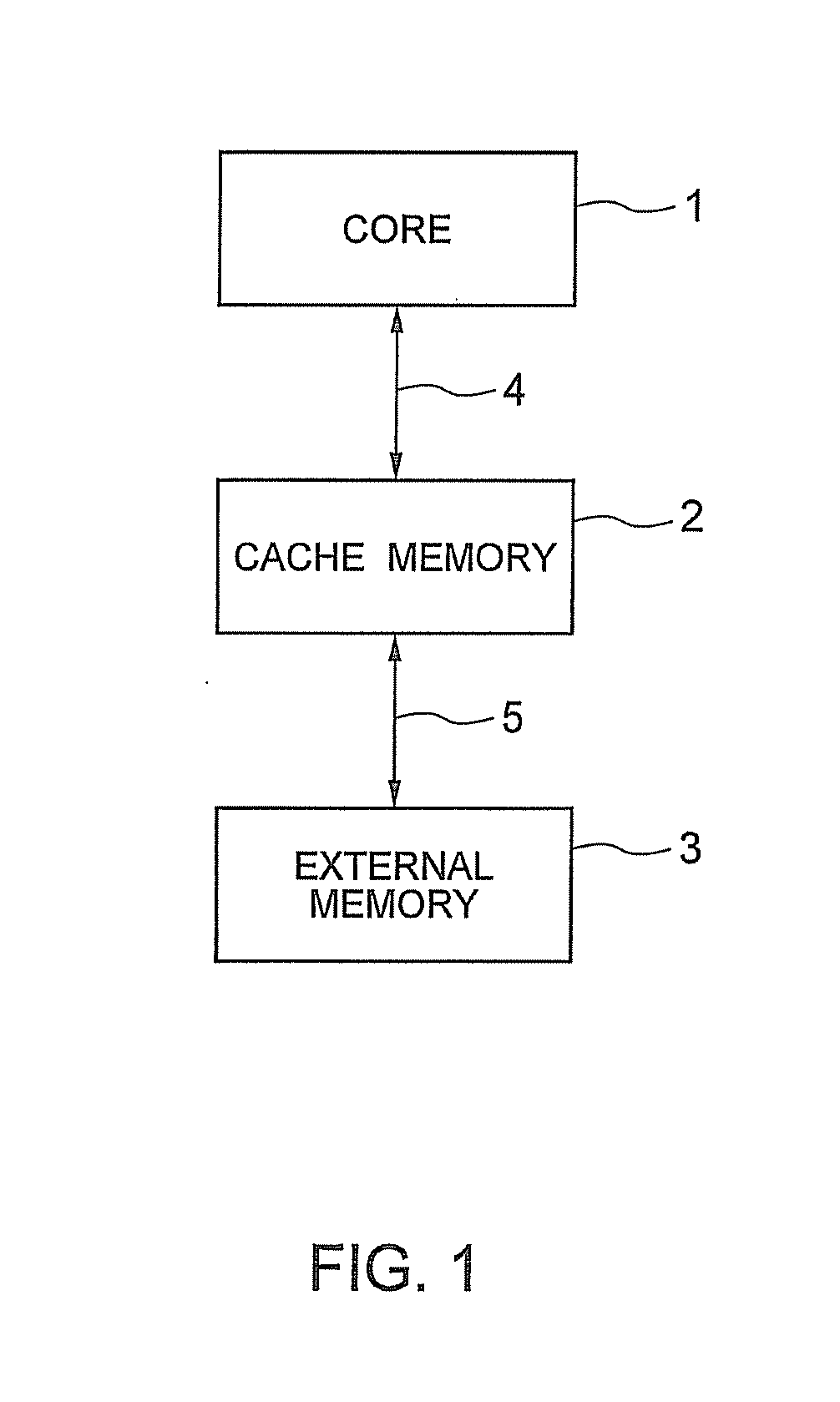

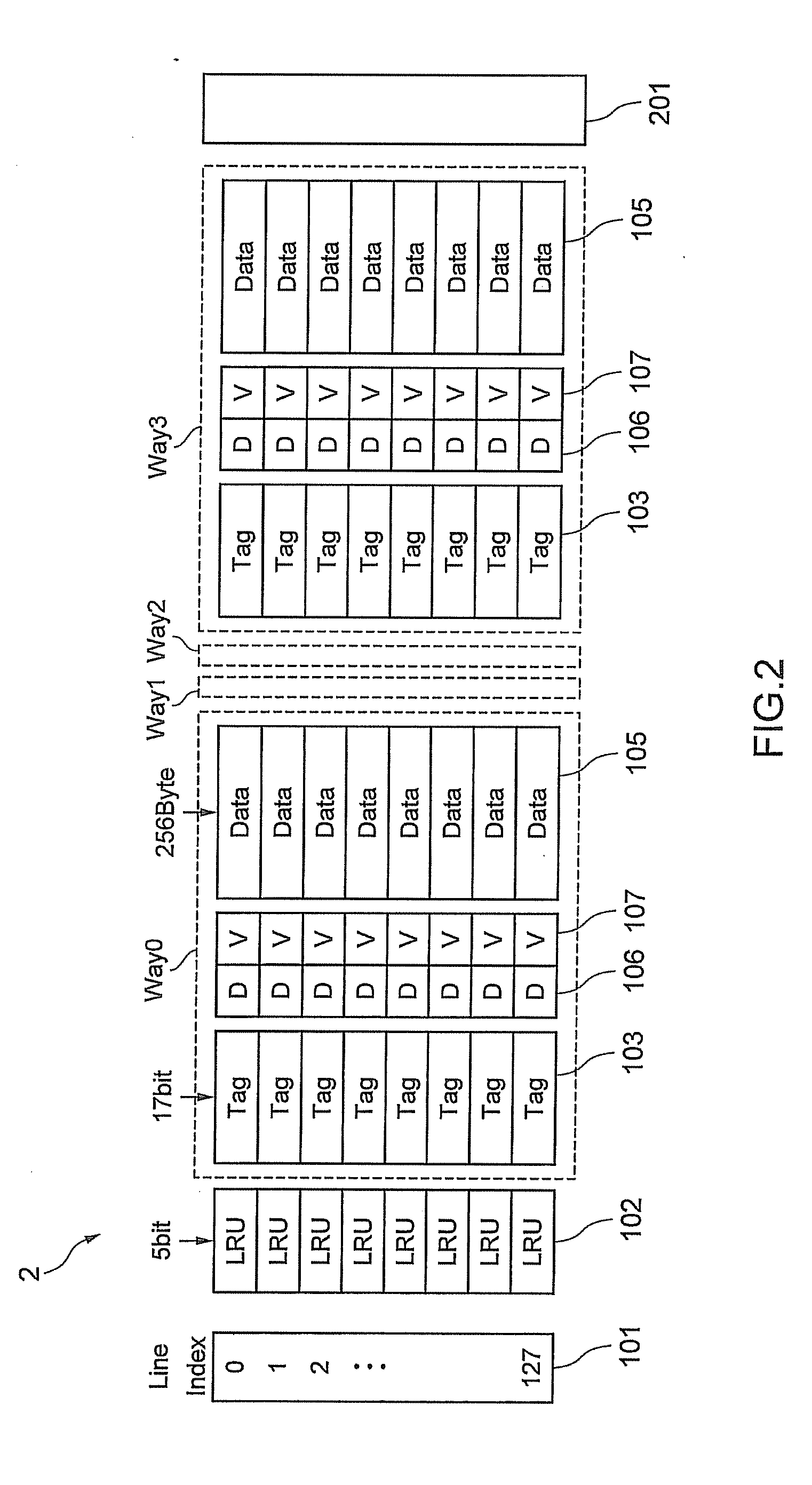

Cache memory and cache system

A cache memory has one or a plurality of ways having a plurality of cache lines including a tag memory which stores a tag address, a first dirty bit memory which stores a first dirty bit, a valid bit memory which stores a valid bit, and a data memory which stores data. The cache memory has a line index memory which stores a line index for identifying the cache line. The cache memory has a DBLB management unit having a plurality of lines including a row memory which stores first bit data identifying the way and second bit data identifying the line index, a second dirty bit memory which stores a second dirty bit of bit unit corresponding to writing of a predetermined unit into the data memory, and a FIFO memory which stores FIFO information prescribing a registered order. Data in a cache line of a corresponding way is written back on the basis of the second dirty bit.

Owner:KK TOSHIBA

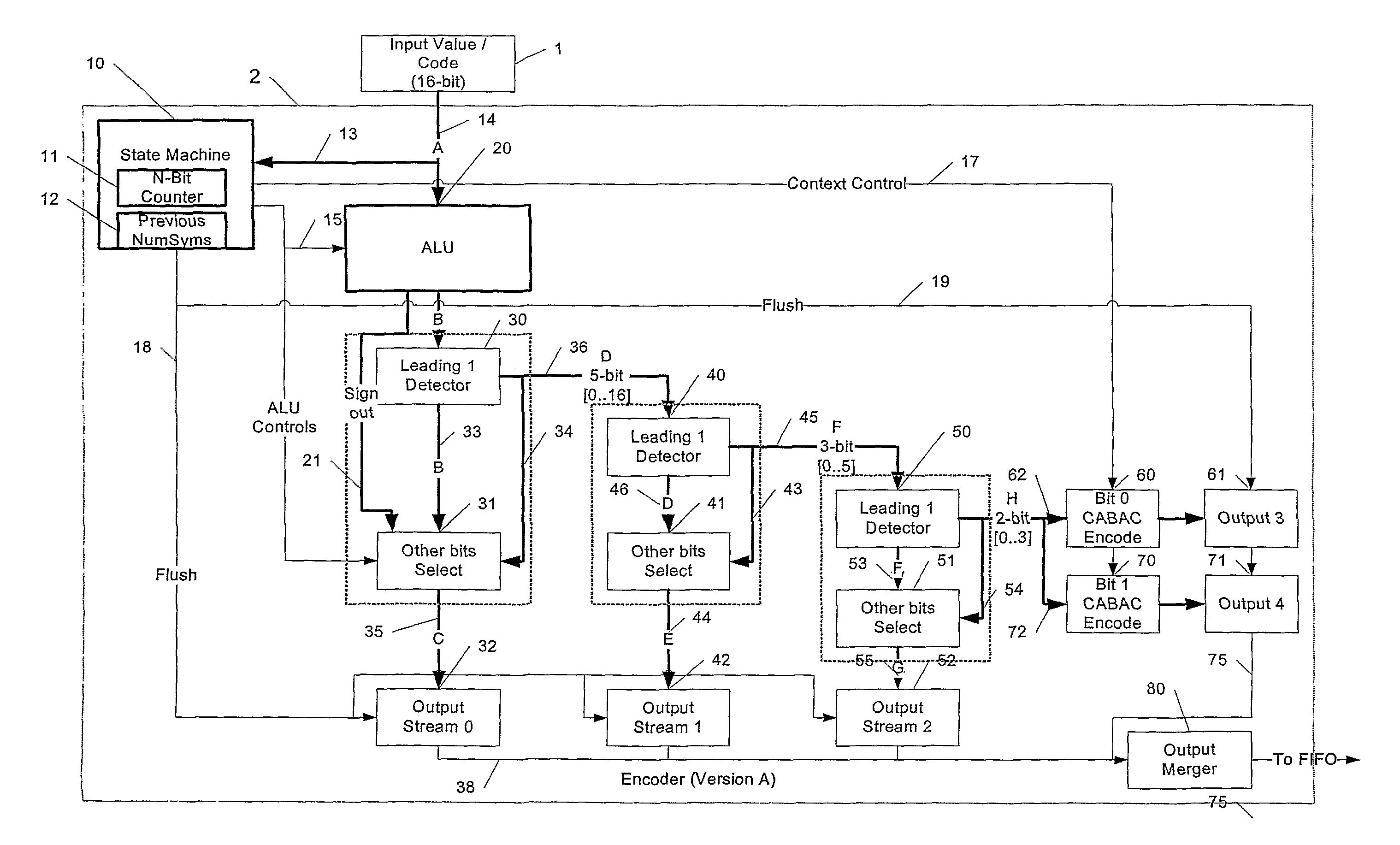

Method of decoding data and apparatus therefor

ActiveUS7796065B2Low costImproving pipeliningCode conversionCharacter and pattern recognitionComputer hardwareParallel encoding

Incoming decoded data (1), for example from an H264 decoder, is fed to an encoder unit (2) that entropy encodes the decoded data using a parallel encoding scheme that includes context-based arithmetic encoding. The syntax is chosen so that the context does not depend on the immediately previously encoded symbol. The output of the encoder (2) is fed to a FIFO memory whose output is fed to a complimentary decoder (4) whose output produces a delayed copy of the incoming decoded data (1).

Owner:IMAGINATION TECH LTD

Circuitry and methods for efficient FIFO memory

ActiveUS7149139B1Efficient processSimilar and good performanceDigital storageData conversionMemory bankParallel computing

Circuitry and methods for an efficient FIFO memory are provided. This efficient FIFO memory has two smaller standard single-port memory banks instead of one large dual-port memory bank, as in typical FIFO memories. Whereas the dual-port memory based FIFO memory can read and write data at the same time, a typical single-port memory based FIFO cannot. The operation of the two single-port memory banks are coordinated in order to provide similar or better performance than a dual-port memory based FIFO.

Owner:MARVELL ISRAEL MISL

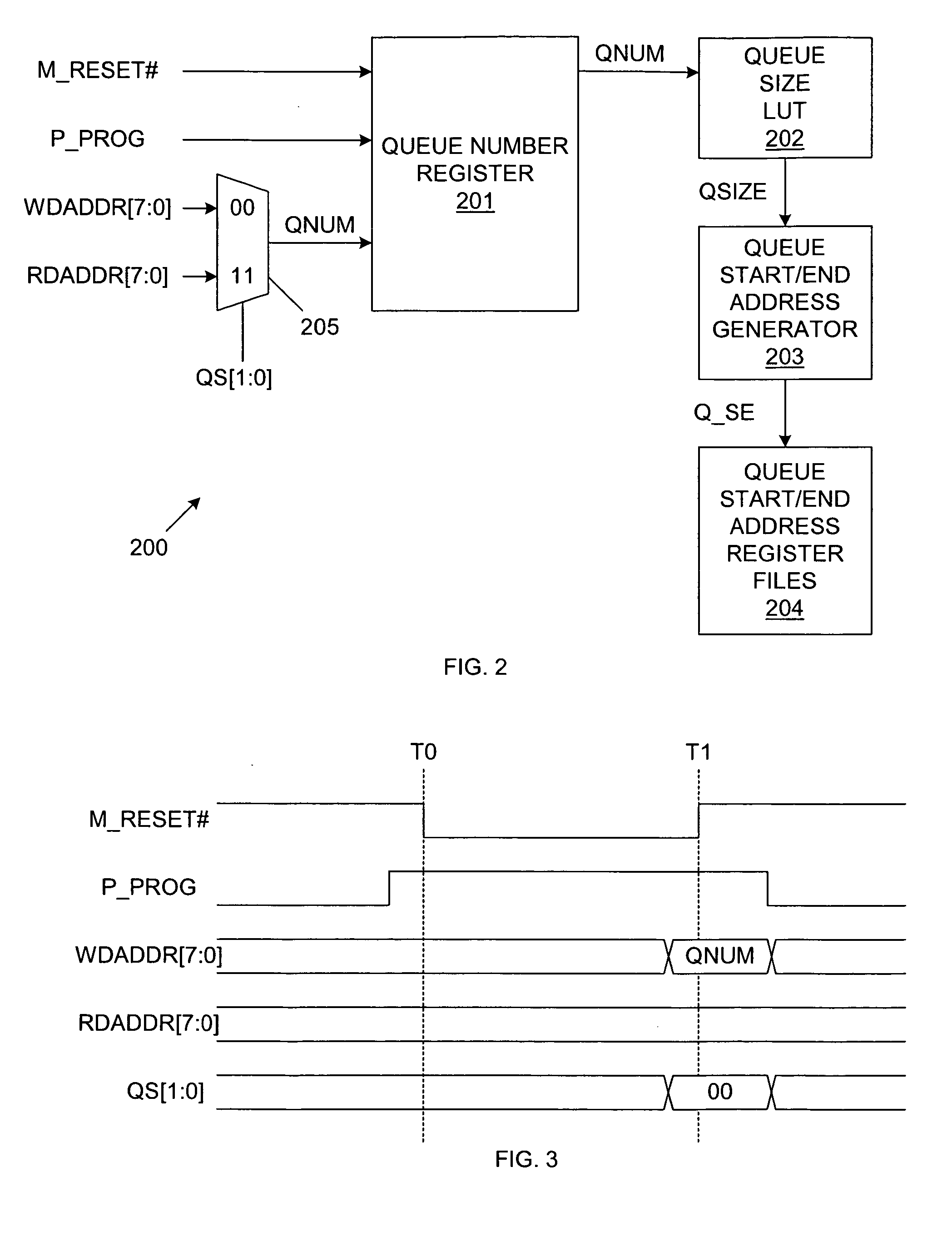

Multi-queue address generator for start and end addresses in a multi-queue first-in first-out memory system

ActiveUS20060020743A1Proper operationMemory adressing/allocation/relocationMicro-instruction address formationQueue numberAddress generator

A multi-queue FIFO memory device that uses existing pins of the device to load a desired number of queues (N) into a queue number register is provided. The queue number register is coupled to a queue size look-up table (LUT), which provides a queue size value in response to the contents of the queue number register. The queue size value indicates the amount of memory (e.g., the number of memory blocks) to be included in each of the N queues. The queue size value is provided to a queue start / end address generator, which automatically generates the start and end address associated with each queue in response to the queue size value. These start and end addresses are stored in queue address register files, which enable proper memory read / write and flag counter operations.

Owner:INTEGRATED DEVICE TECH INC

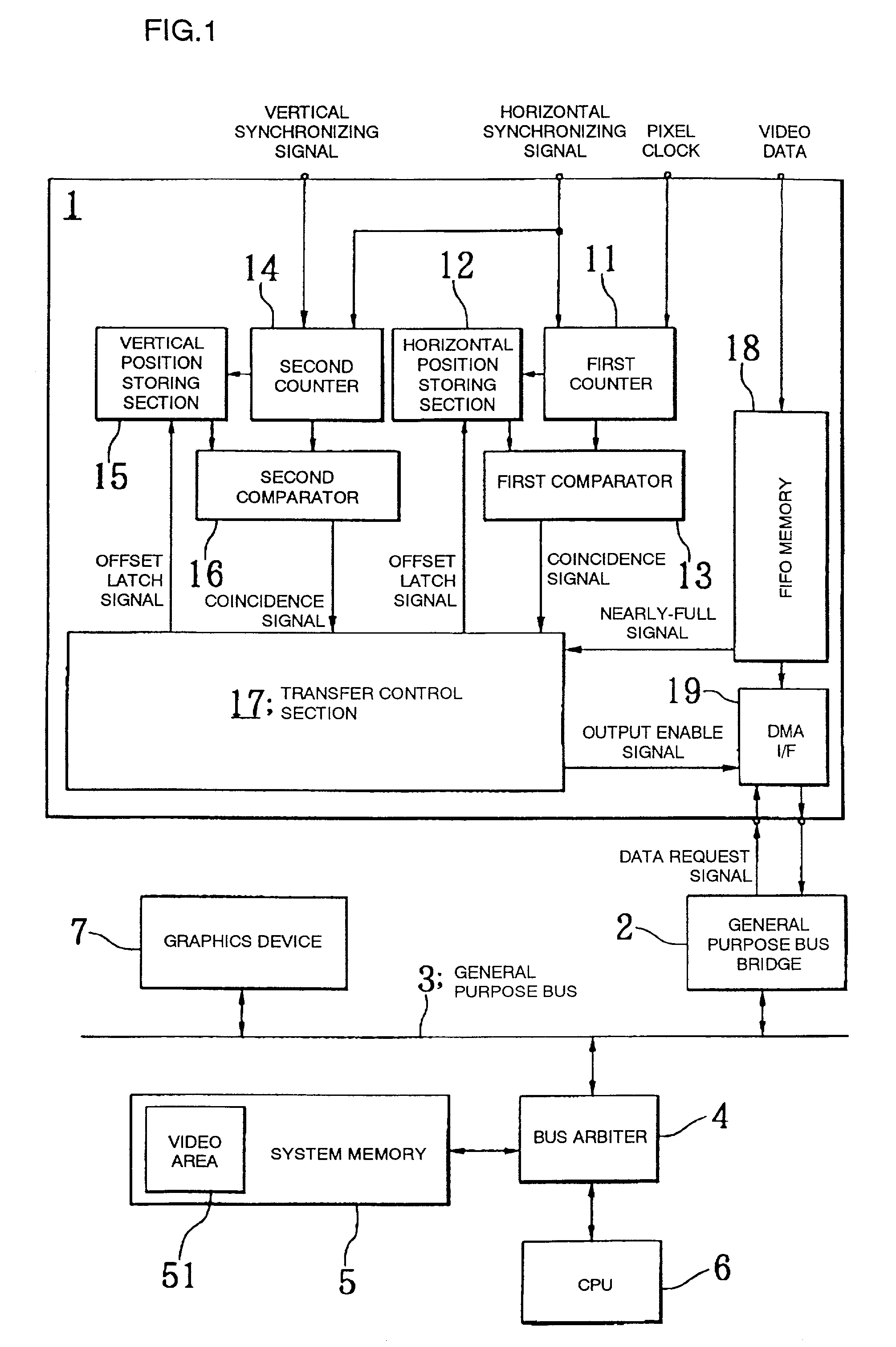

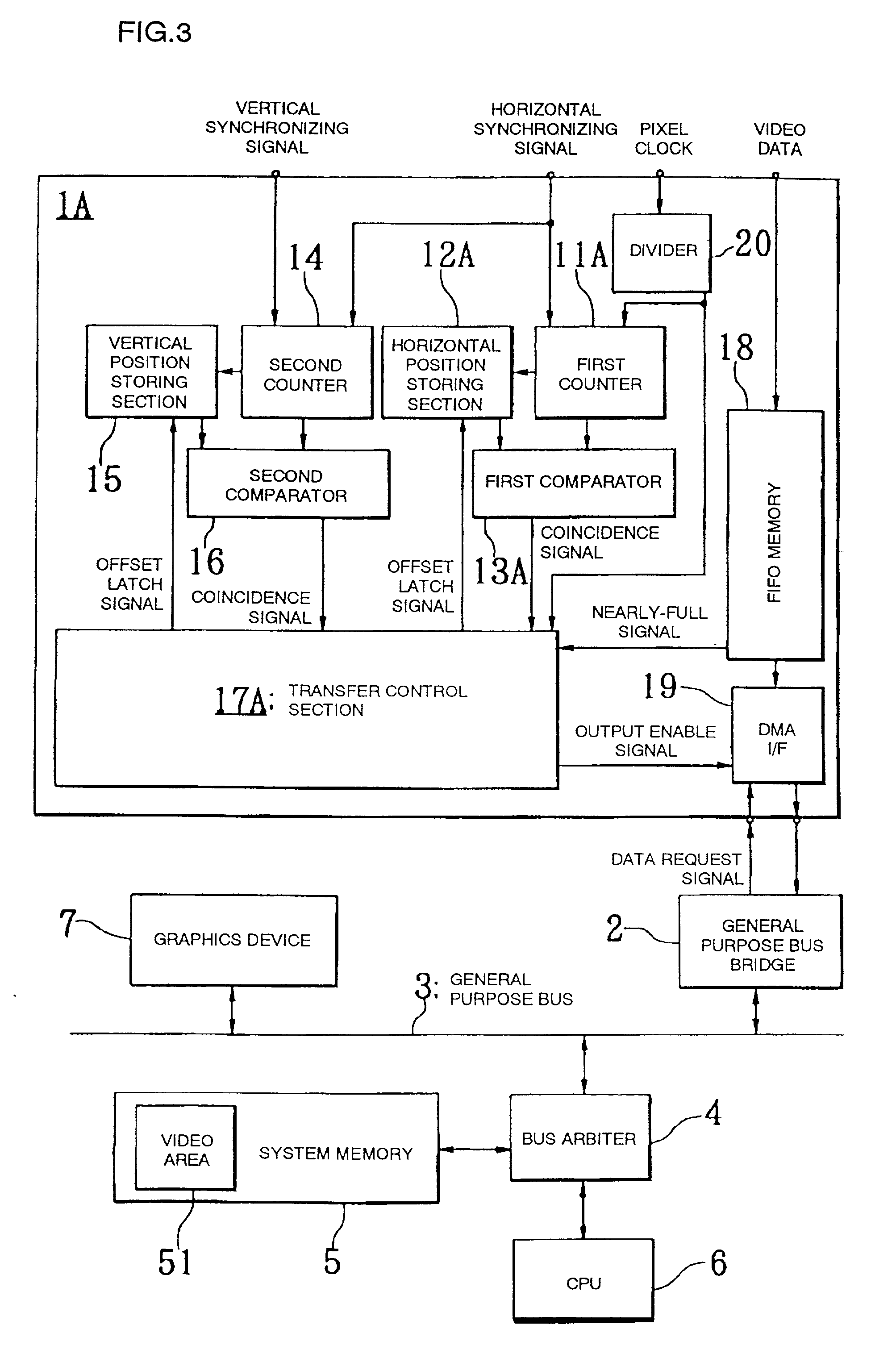

Apparatus and method for transferring video data

InactiveUS20010020951A1Image memory managementCathode-ray tube indicatorsComputer hardwareGeneral purpose

Overlay display can be performed correctly even in a heavy load state regarding video data amount on a general purpose bus. The video data transfer apparatus of the present invention comprises an FIFO memory for video data and outputting a nearly-full signal when held data become close to full and a transfer control section stopping an output enable signal so as to stop output from the FIFO memory at the time of output of the nearly-full signal and restoring the output enable signal so as to perform control in which the video data on and after an output stop position are outputted from the FIFO memory when the same position as the output stop position appears in a frame on and after the frame of the output stop time when the nearly-full signal disappears.

Owner:NEC CORP

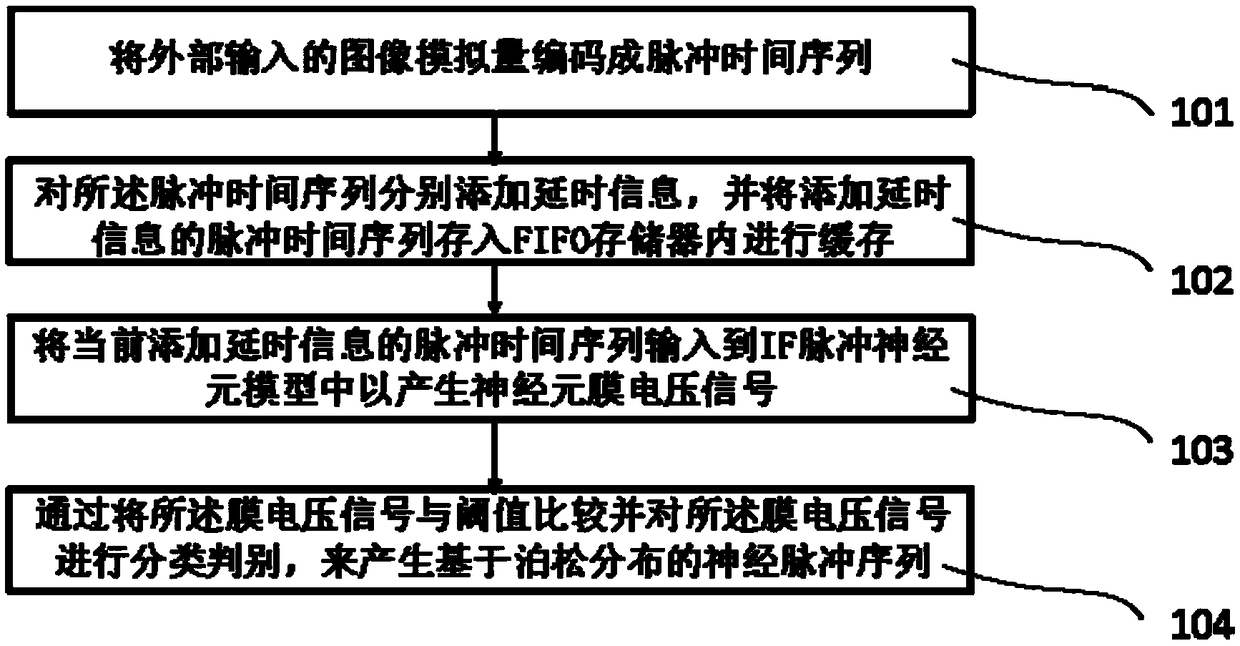

Image classification method and device based on pulse neural network

InactiveCN108846408AStrong computing powerReduce complexityCharacter and pattern recognitionNeural architecturesNeuronal modelsClassification methods

The invention discloses an image classification method based on a pulse neural network. The method comprises a step of encoding an externally input image analog quantity into a pulse time series, a step of adding time delay information to the pulse time series and storing the pulse time sequence with the added time delay information into an FIFO memory for buffering, a step of inputting the pulsetime sequence with the currently added time delay information into an IF pulse neuron model to generate a neuron membrane voltage signal, wherein a pipeline architecture is adopted by the IF pulse neuron model and a neuron model calculation method is optimized, and a step of generating a neural pulse sequence based on a Poisson distribution by comparing the membrane voltage signal and a thresholdand carrying out classification and judgment on the membrane voltage signal. According to the image classification method, the pulse neural network has powerful computing power and can simulate various neuron signals and arbitrary continuous functions, the operation efficiency is high, and so the pulse neural network has a hardware realization value.

Owner:ACADEMY OF MILITARY MEDICAL SCI

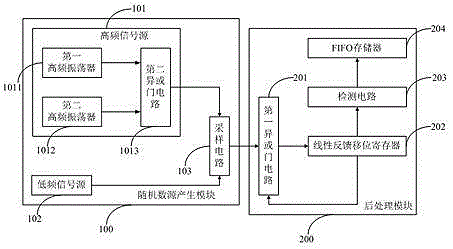

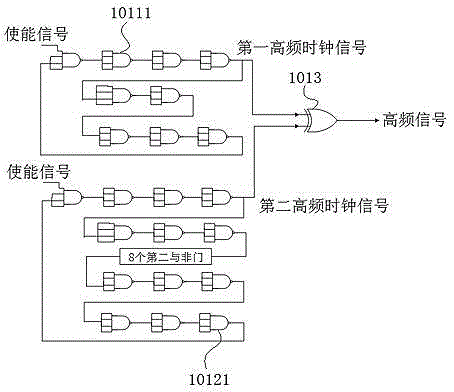

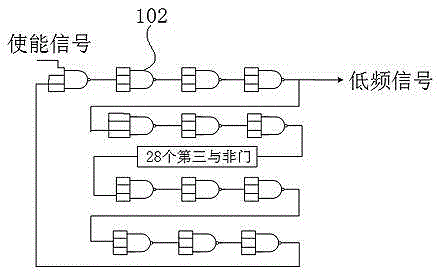

True random number generator based on digital circuit

ActiveCN105426159AIncrease unpredictabilityQuality improvementRandom number generatorsExclusive orComputer module

The invention discloses a true random number generator based on a digital circuit. The true random number generator comprises a random number source generating module used for generating digital signals with random character, and a postprocessing module used for conducting algorithm processing on the digital signals with random character, conducting detection and then generating true random number signals, wherein the postprocessing module comprises a first exclusive-OR gate circuit, a linear feedback shift register, a detection circuit and an FIFO memory which are sequentially connected, the input signals of the first exclusive-OR gate circuit are the digital signals with random character, the input signals of the linear feedback shift register are signals generated after the digital signals with random character and feedback signals of the linear feedback shift register are subjected to exclusive-OR by the first exclusive-OR gate circuit, and the detection circuit detects the digital signals with random character with a predetermined detection algorithm so as to generate true random number data and stores the true random number data in the FIFO memory. The true random number generator is simple in circuit structure, low in cost and high in adaptability.

Owner:SHANGHAI AISINOCHIP ELECTRONICS TECH

Integrated DDR/SDR flow control managers that support multiple queues and mux, demux and broadcast operating modes

InactiveUS20050018514A1High data rateExtending of speed of deviceDigital storageData conversionMultiplexingMultiplexer

An integrated circuit chip includes a plurality of independent FIFO memory devices that are each configured to support all four combinations of DDR and SDR write modes and DDR and SDR read modes and collectively configured to support all four multiplexer, demultiplexer, broadcast and multi-Q operating modes.

Owner:INTEGRATED DEVICE TECH INC

Sequential flow-control and FIFO memory devices that are depth expandable in standard mode operation

ActiveUS20050005082A1Eliminate needMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer hardwareOperation mode

FIFO memory devices are configured to support a pair of hybrid operating modes that enable the FIFO memory device to be depth-expandable with other FIFO memory devices in a collective standard mode of operation. The pair of hybrid operating modes including a first hybrid mode that supports a write interface configured in standard mode and a read interface configured in first-word fall-through (FWFT) mode and a second hybrid mode that supports a write interface configured in FWFT mode and a read interface configured in standard mode.

Owner:INTEGRATED DEVICE TECH INC

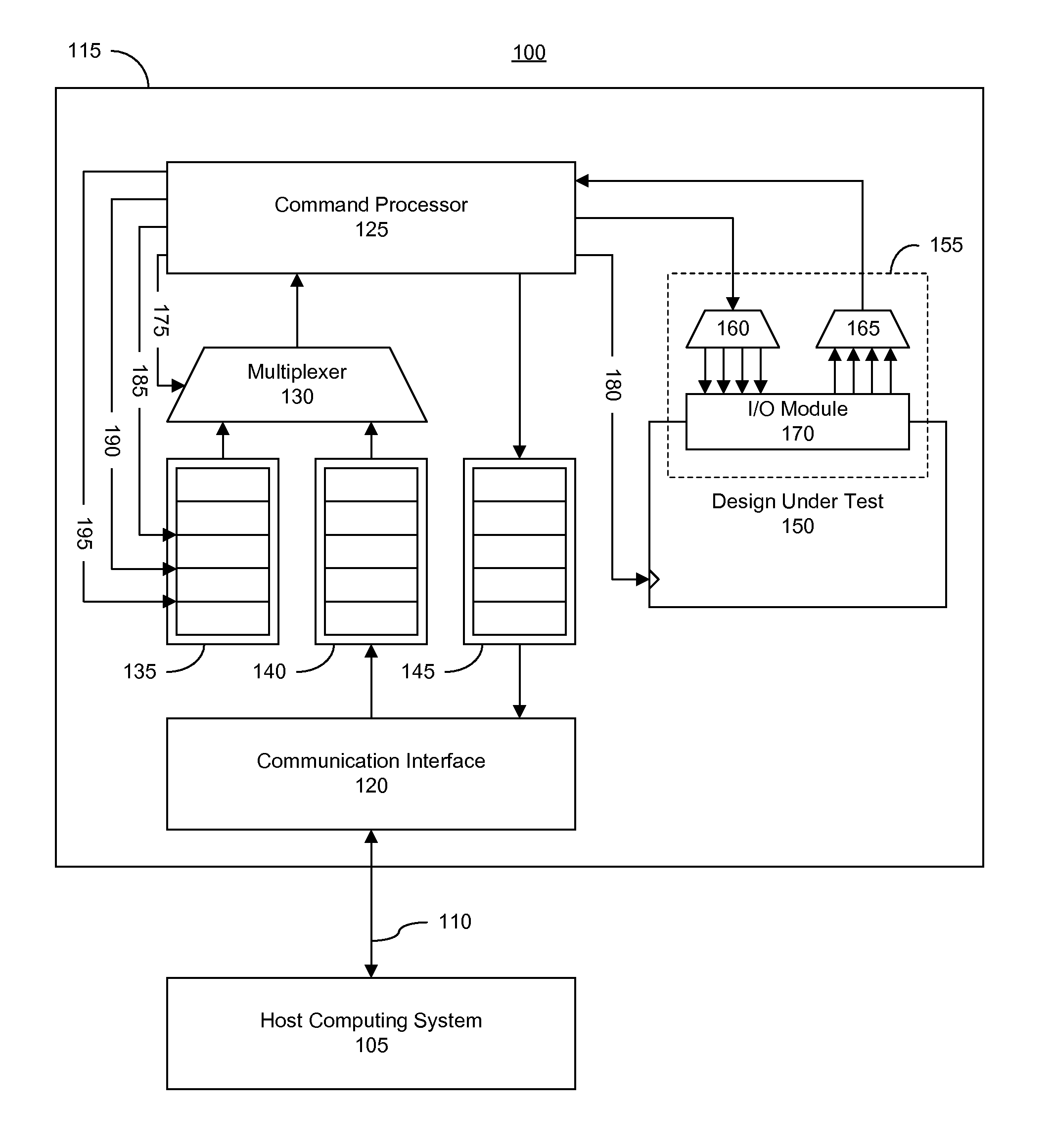

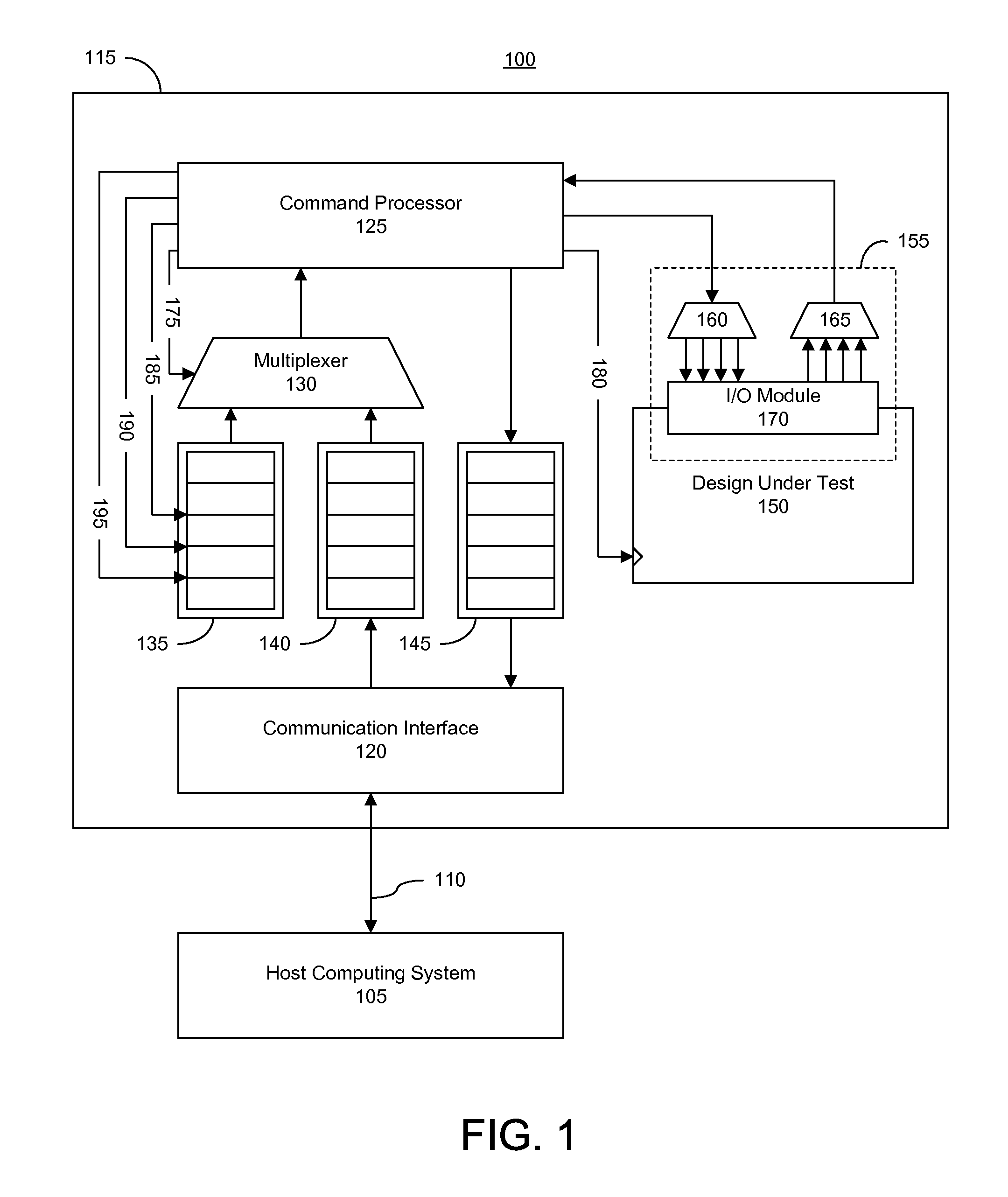

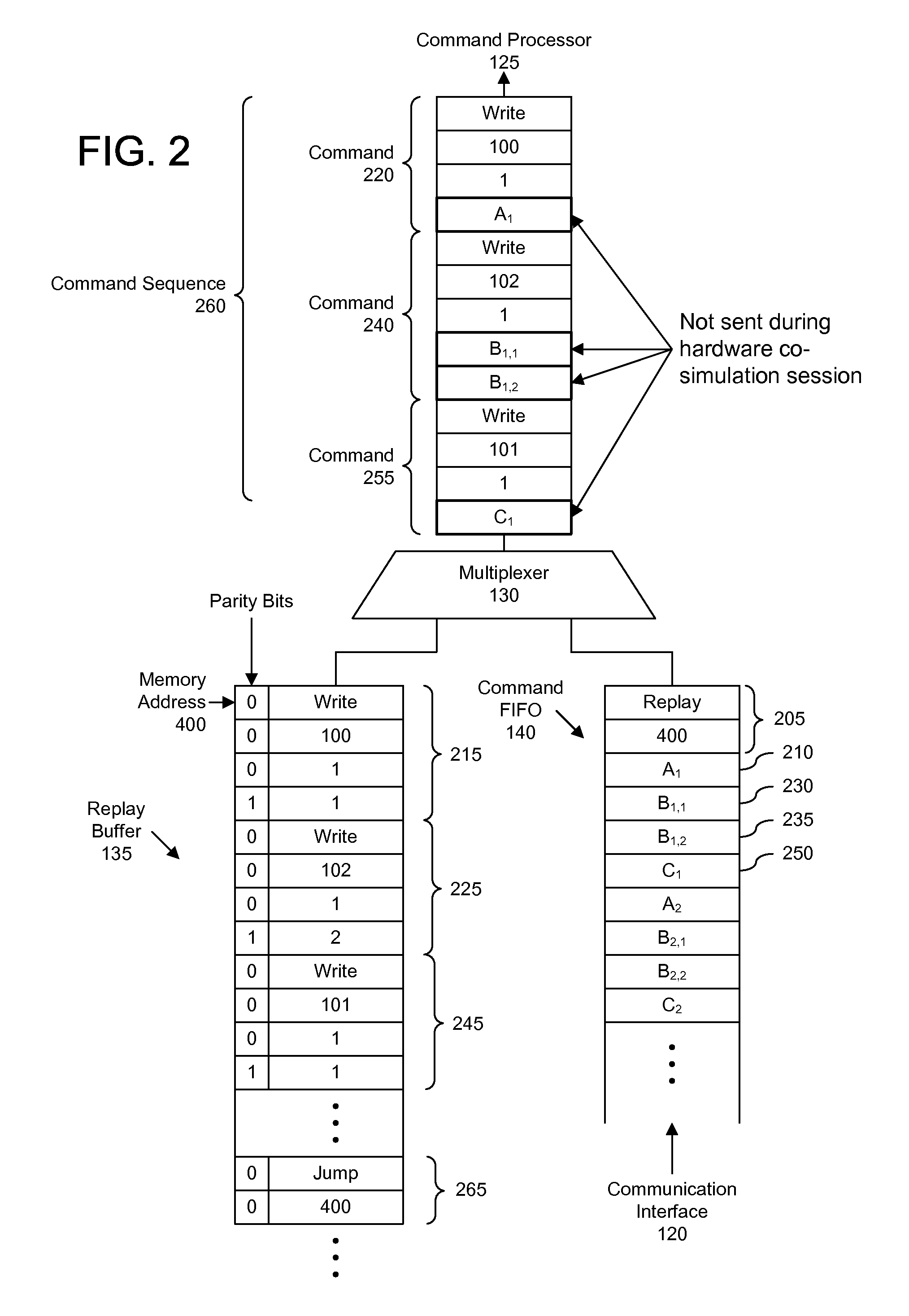

Accelerating hardware co-simulation using dynamic replay on first-in-first-out-driven command processor

An integrated circuit configured for hardware co-simulation can include a command processor, a replay buffer storing a command template, wherein the command template specifies an incomplete command, and a command first-in-first out (FIFO) memory storing complementary data for completion of the command template. The integrated circuit further can include a multiplexer coupled to the command processor, the replay buffer, and the command FIFO. The multiplexer, under control of the command processor, can selectively provide data from the replay buffer or the command FIFO to the command processor. The command processor, responsive to a replay command read during a hardware co-simulation session, can enter a replay mode, obtain the command template from the replay buffer, obtain the complementary data from the FIFO memory according to a symbol read from the command template, and form a complete command by joining the command template with the complementary data.

Owner:XILINX INC

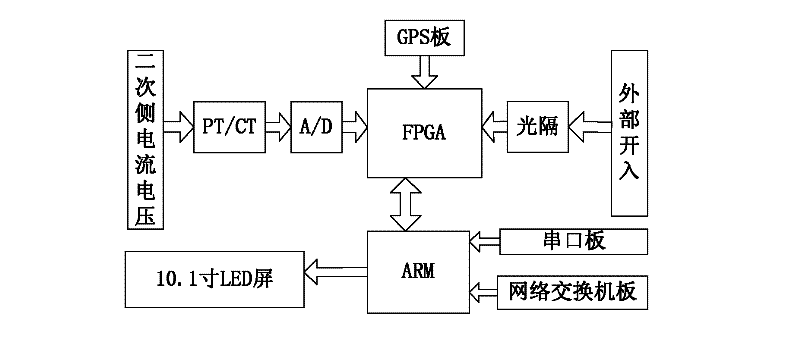

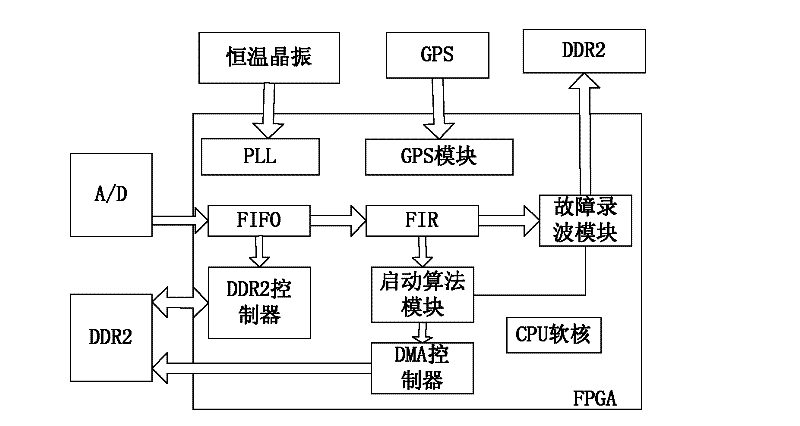

Failure message integrated device based on FPGA and ARM hardware platform

ActiveCN102401871ASave screen cabinet resourcesHighly integratedFault locationLow-pass filterElectric power system

The invention discloses a failure message integrated device based on FPGA and ARM hardware platform, which comprises a PT / CT board, an ARM board, a network switch board, a serial port board, a GPS board and a high speed acquisition board composed of an A / D sampling chip and an FPGA; the FPGA has a DDR2 controller, an DMA controller, an FIFO memory and an FIR low-pass filter; and the FPGA is also provided with a starting algorithm module and a fault recorder module. The device organically combines the functions of the fault recorder, a travelling wave distance measuring device and a failure message management sub-station by using parallel processing capability of the high speed AD chip and the FPGA, for realizing accurate localization of fault points when a power transmission line in an electric power system has a fault, and obtaining a complete fault report, thereby complying with intelligentization and miniaturization needs of secondary device of power grid.

Owner:ANHUI NANRUI JIYUAN POWER GRID TECH CO LTD +1

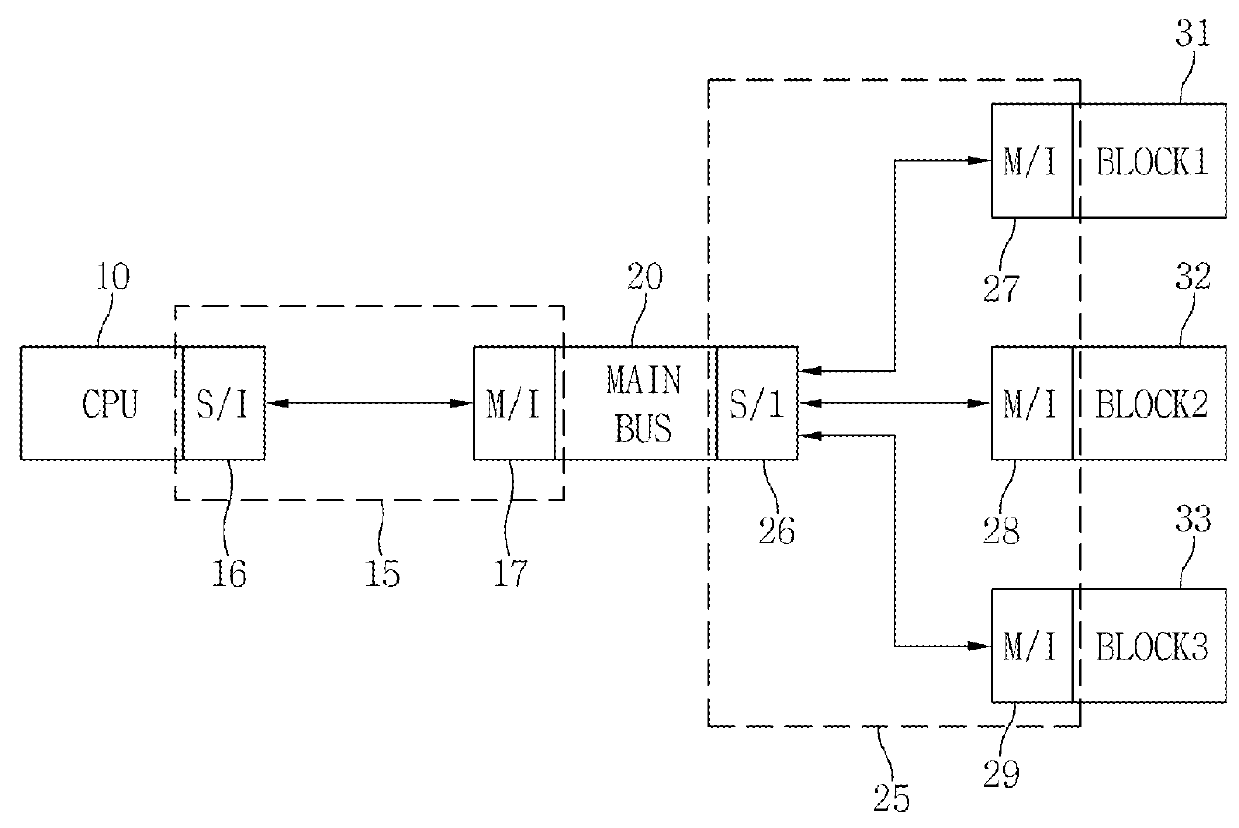

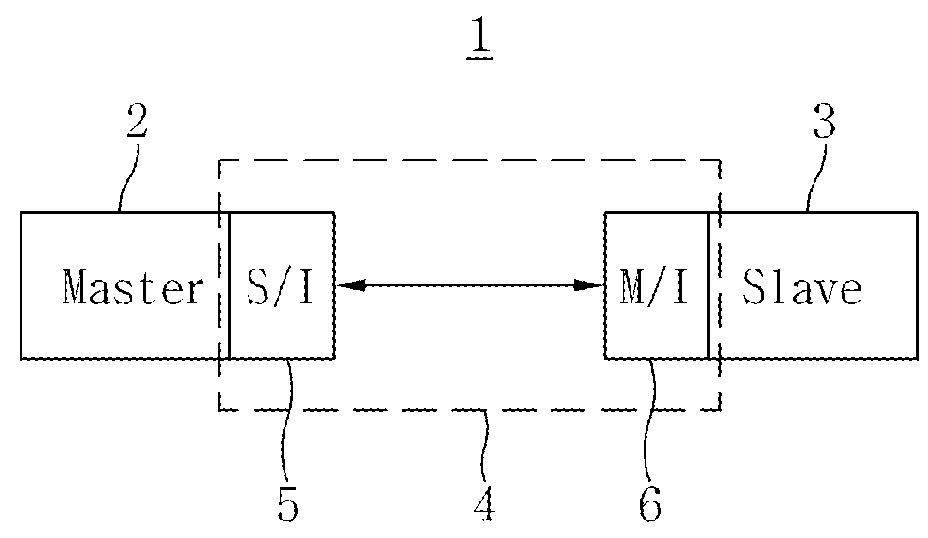

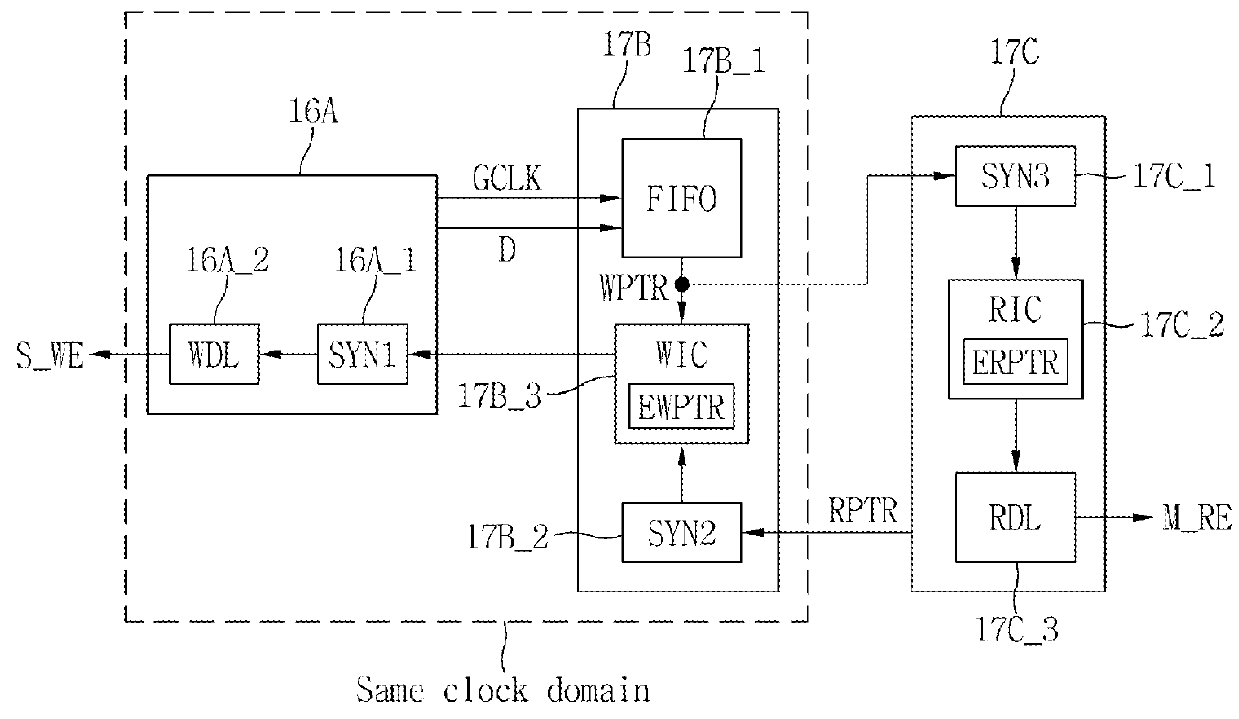

System-on-chip and driving method thereof

A system-on-chip (SoC) may include a master, a slave, and an asynchronous interface having a first first-in first-out (FIFO) memory connected to the master and the slave. A write operation of the FIFO memory is controlled based upon a comparison of a write pointer and an expected write pointer of the FIFO memory, and a read operation of the FIFO memory is controlled based upon a comparison of a read pointer and an expected read pointer of the FIFO.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com