Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1103results about How to "Improve data throughput" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

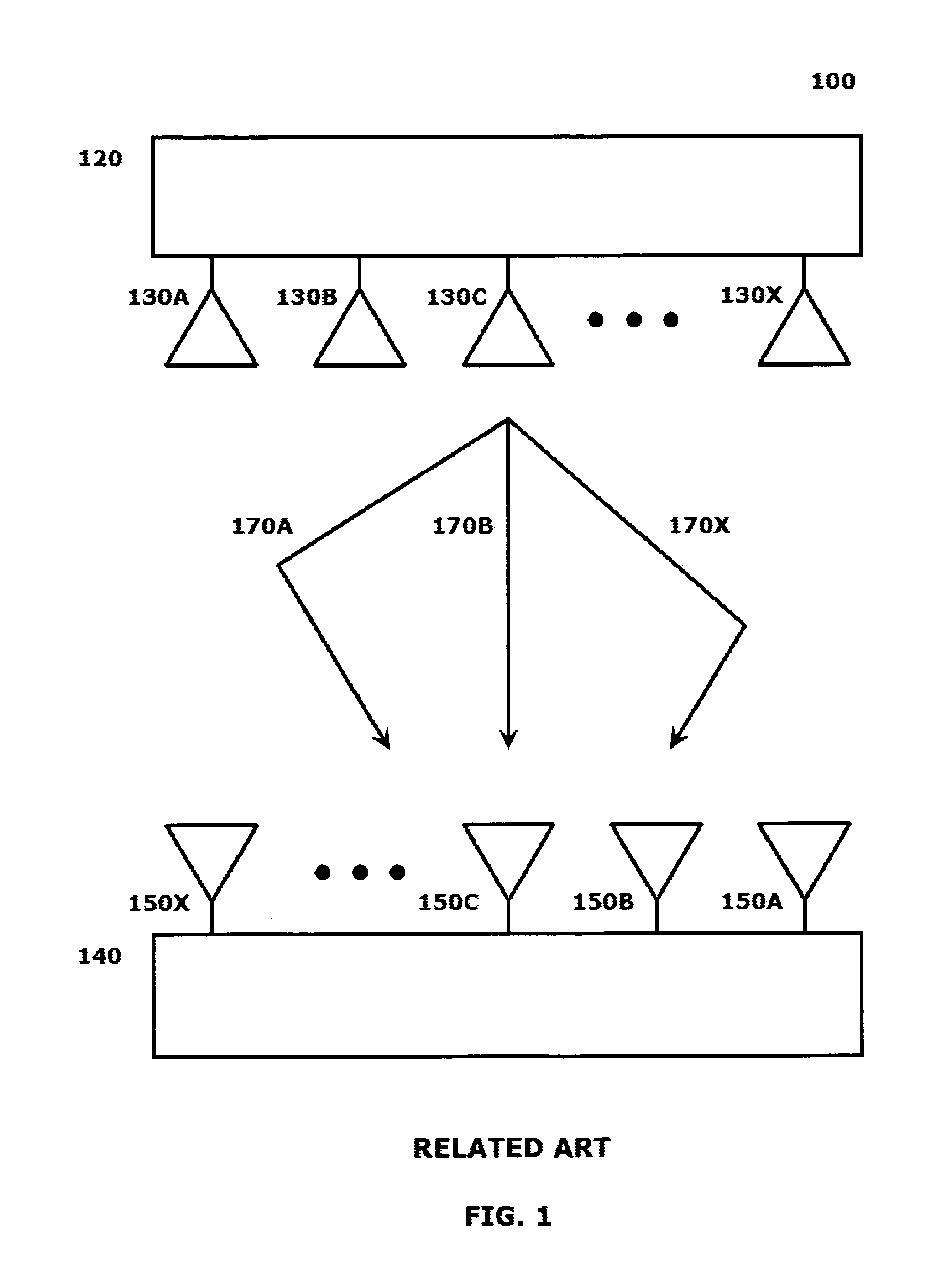

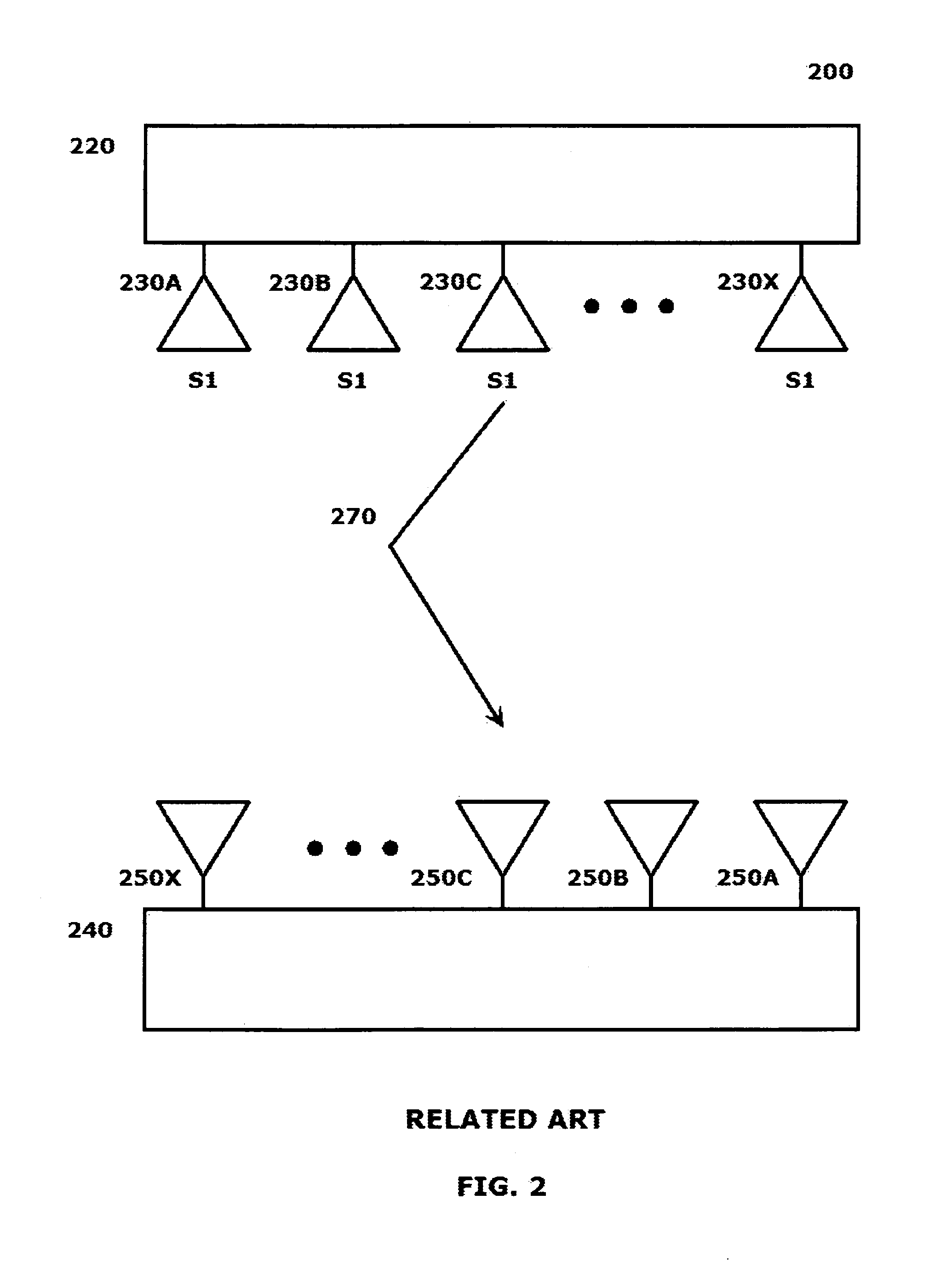

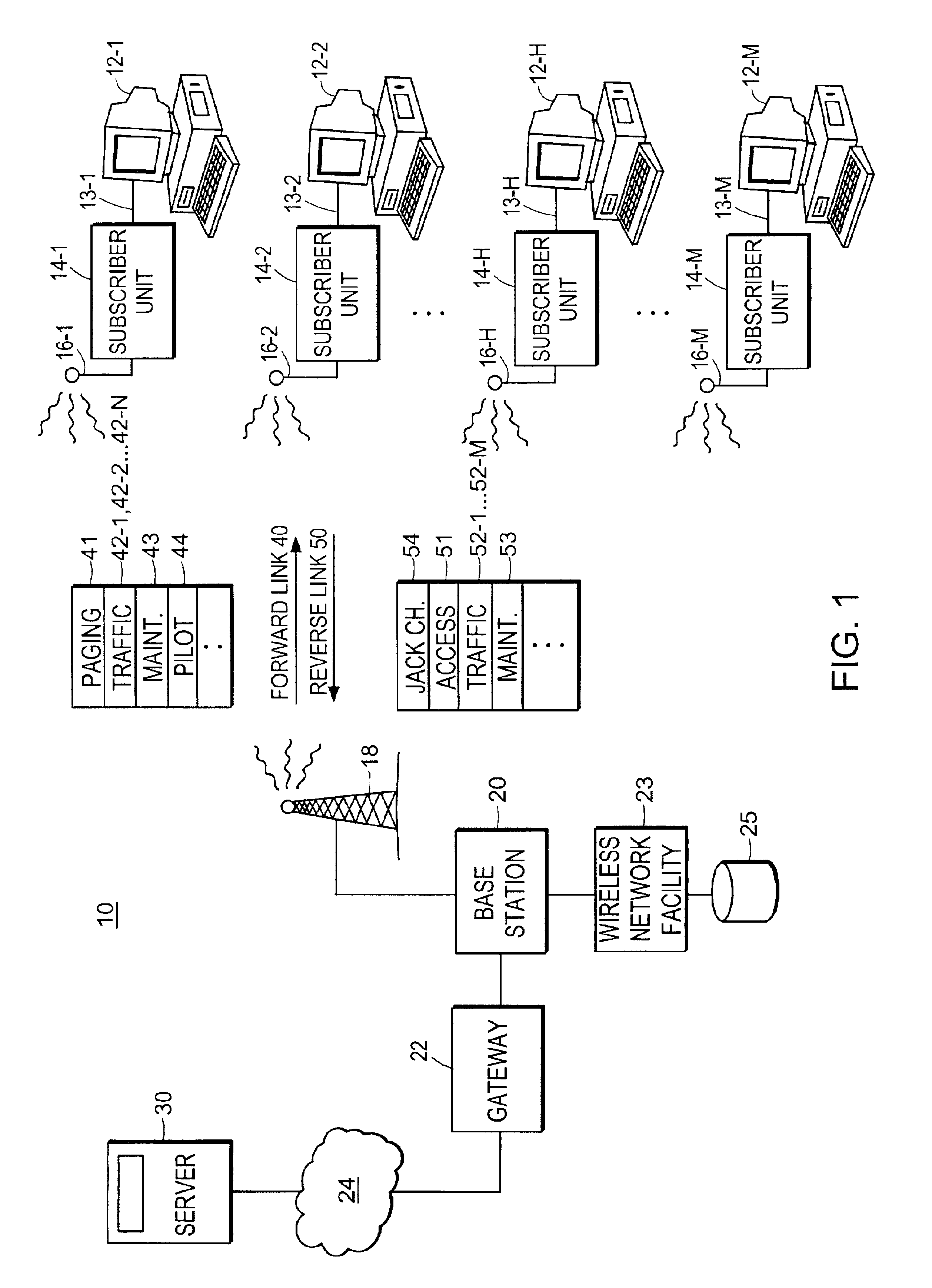

Systems and method for providing in-flight broadband mobile communication services

InactiveUS20110182230A1Efficient use ofImproving average and peak data throughputFrequency-division multiplex detailsNetwork topologiesTransceiverSpatial division multiple access

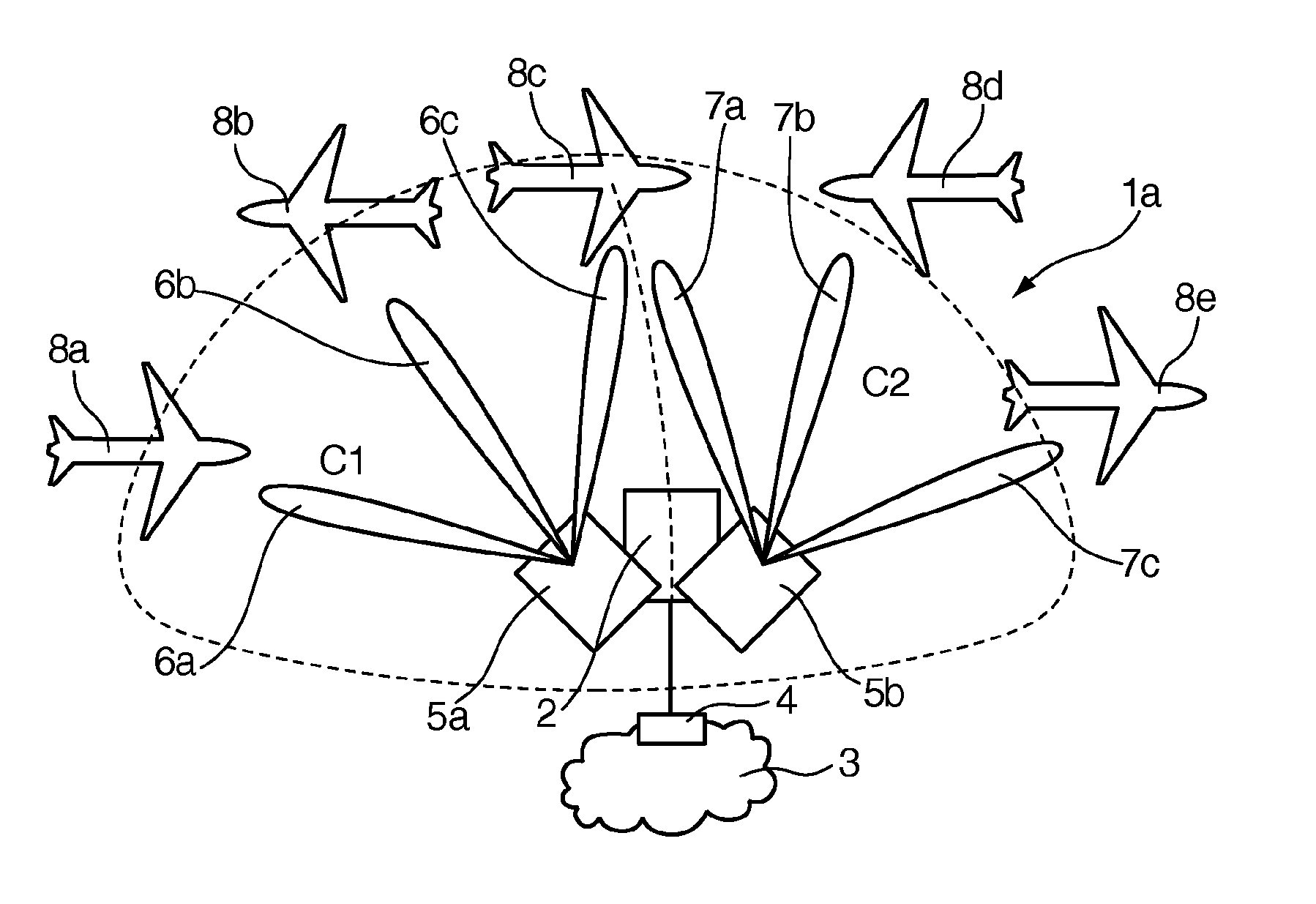

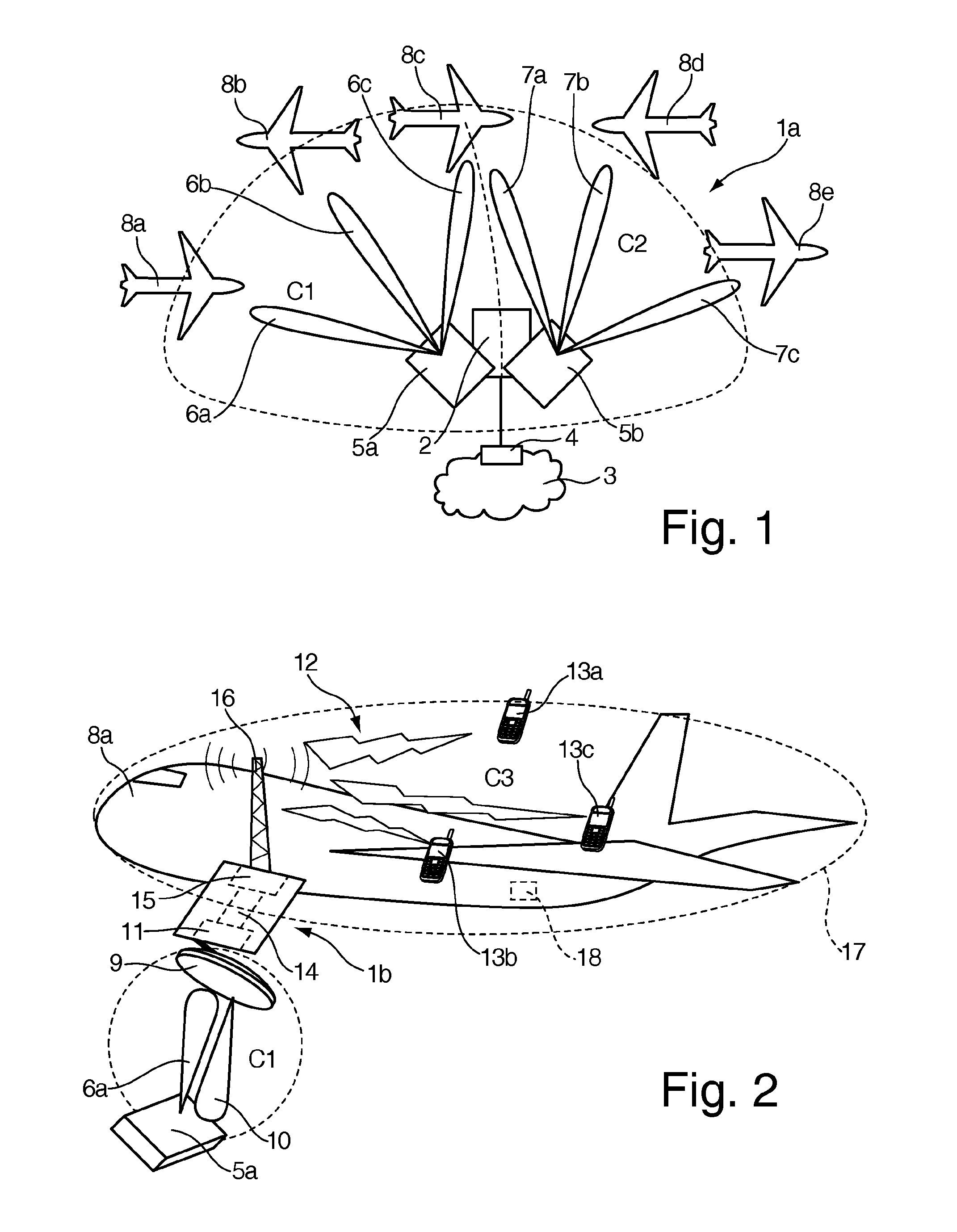

The invention relates to a ground-based wireless cellular communication system (1a) for providing in-flight broadband mobile communication services, comprising: at least one ground-based base station (2) adapted for generating at least one cell (C1, C2) defining a solid angle of the space surrounding the base station (2), the ground- based base station (2) further comprising at least one antenna array (5a, 5a) using two-dimensional-beamforming for generating at least one beam (6a-c, 7a-c) for serving at least one airplane (8a-c, 8c-e) in the space covered by the at least one cell (C1, C2) using spatial-division multiple access, SDMA. The invention also relates to an airplane equipment for providing in-flight broadband mobile communication services, comprising: at least one antenna for exchange of user data with the ground-based wireless cellular communication system (1a), a transceiver unit connected to the at least one antenna for handling the air-to-ground and ground-to-air communication with the ground-based wireless cellular communication system (1a), and an inside-airplane communication system for distributing the user data to and from terminals within the airplane.

Owner:RPX CORP

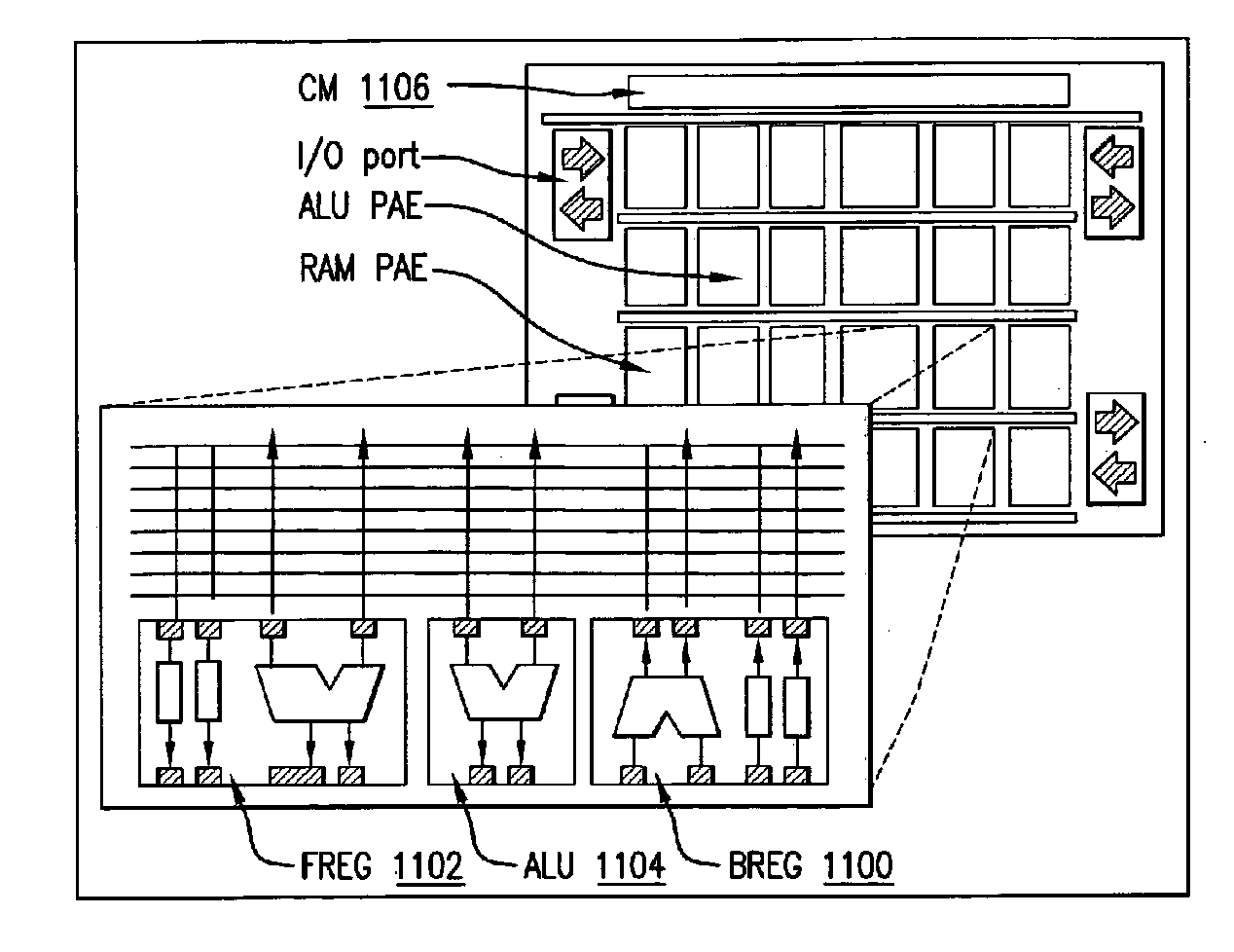

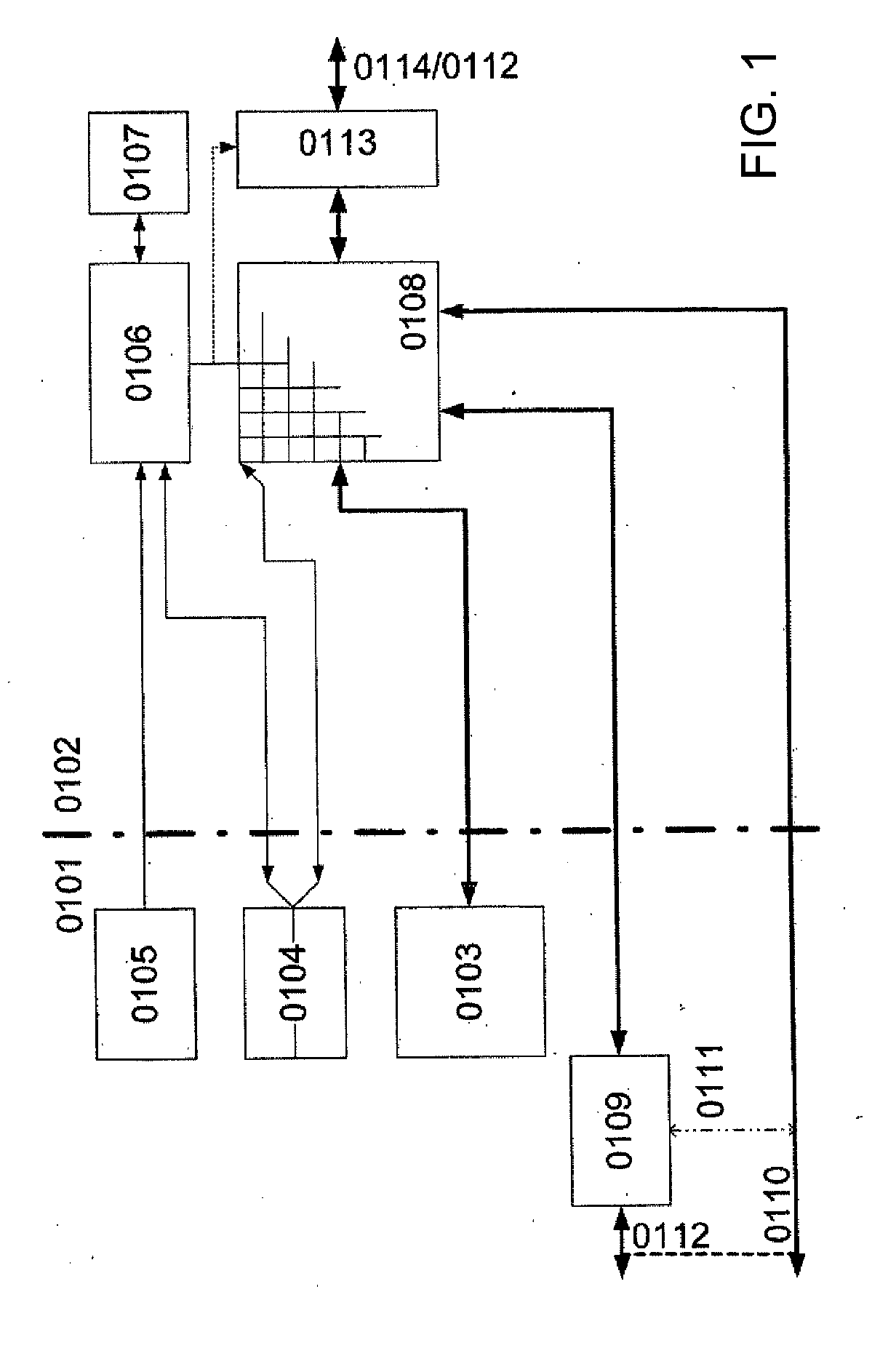

Data processing method and device

ActiveUS20070050603A1Improve data throughputDelay problemMemory adressing/allocation/relocationConcurrent instruction executionParallel computingData processing

In a data-processing method, first result data may be obtained using a plurality of configurable coarse-granular elements, the first result data may be written into a memory that includes spatially separate first and second memory areas and that is connected via a bus to the plurality of configurable coarse-granular elements, the first result data may be subsequently read out from the memory, and the first result data may be subsequently processed using the plurality of configurable coarse-granular elements. In a first configuration, the first memory area may be configured as a write memory, and the second memory area may be configured as a read memory. Subsequent to writing to and reading from the memory in accordance with the first configuration, the first memory area may be configured as a read memory, and the second memory area may be configured as a write memory.

Owner:SCIENTIA SOL MENTIS AG

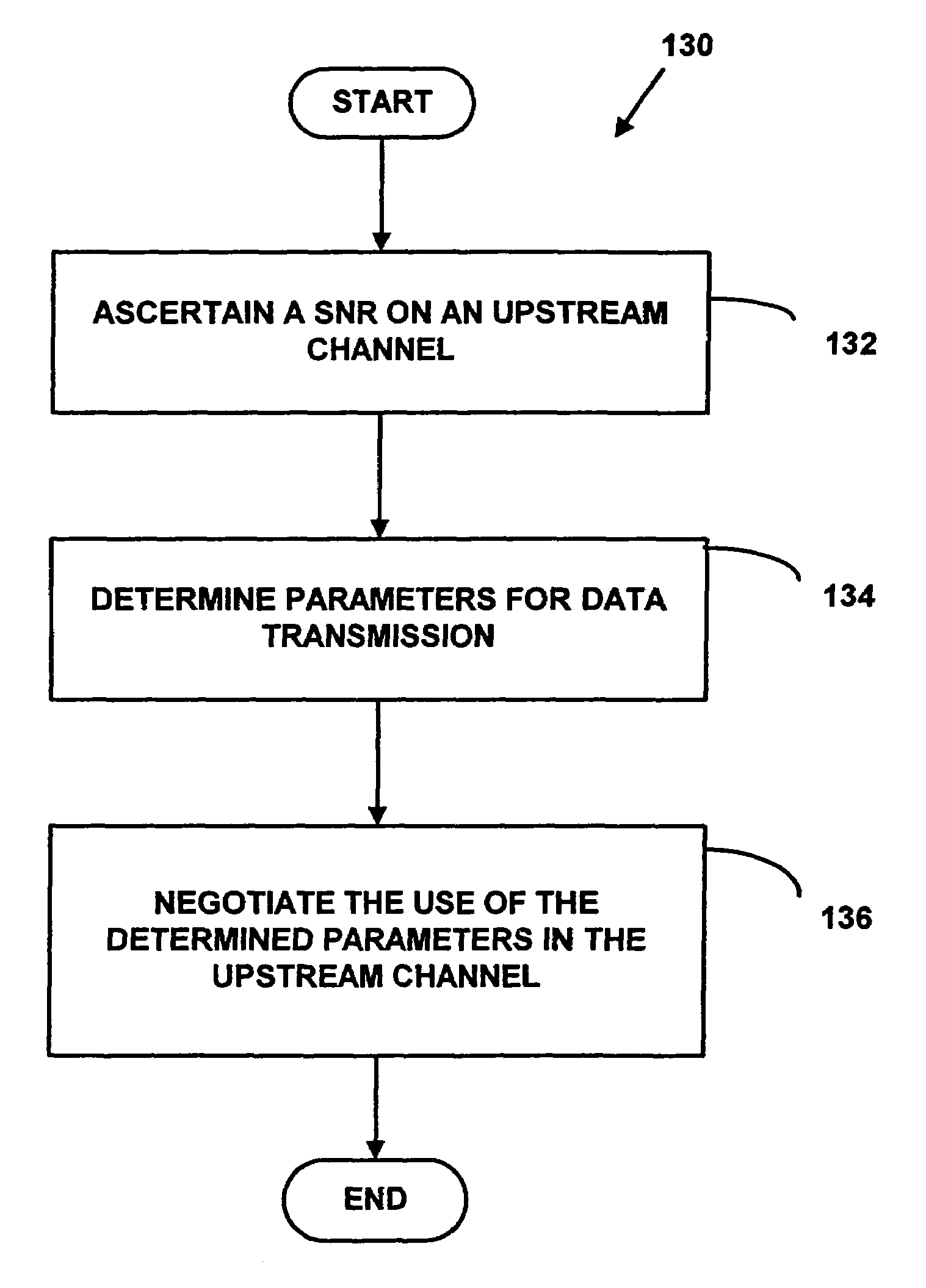

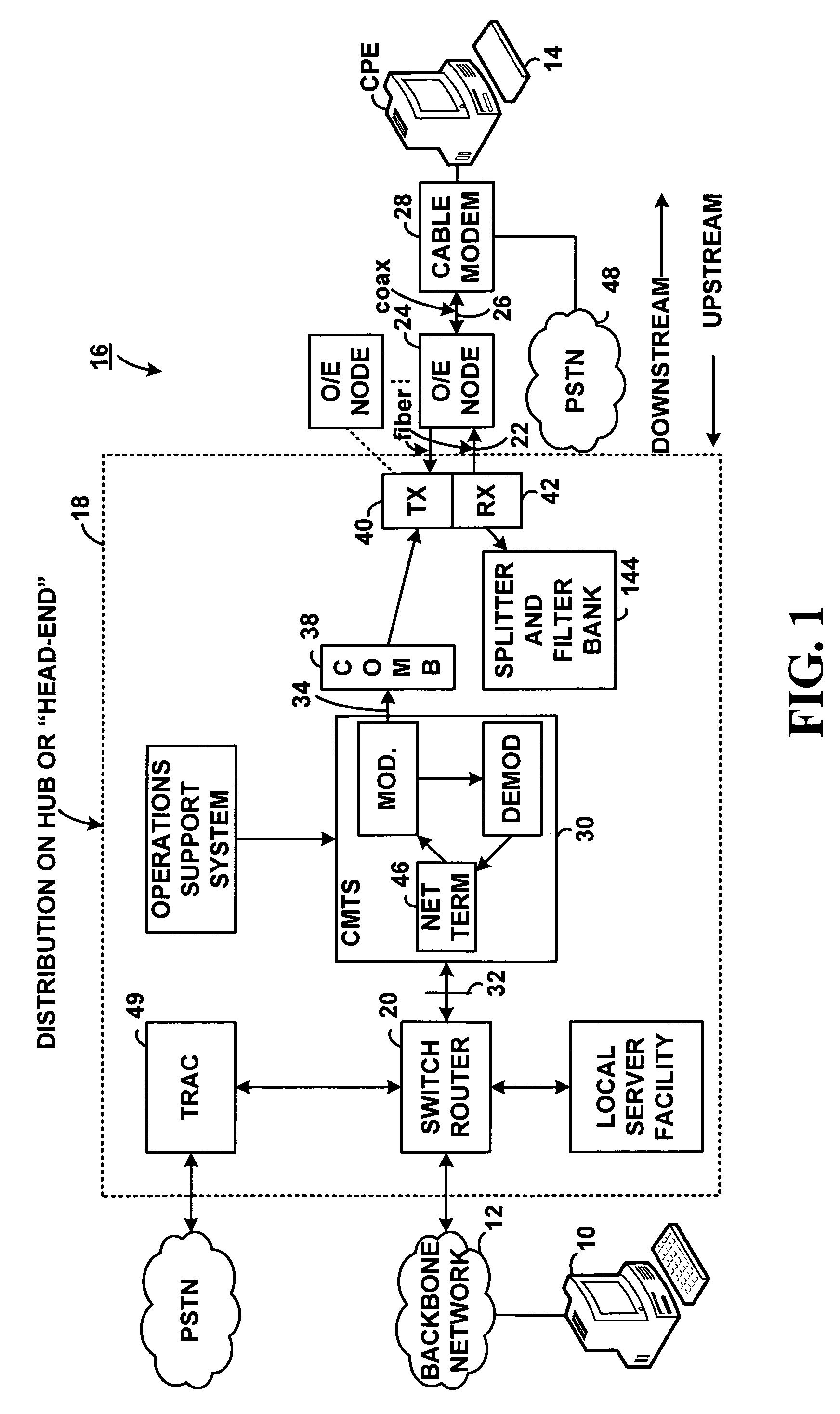

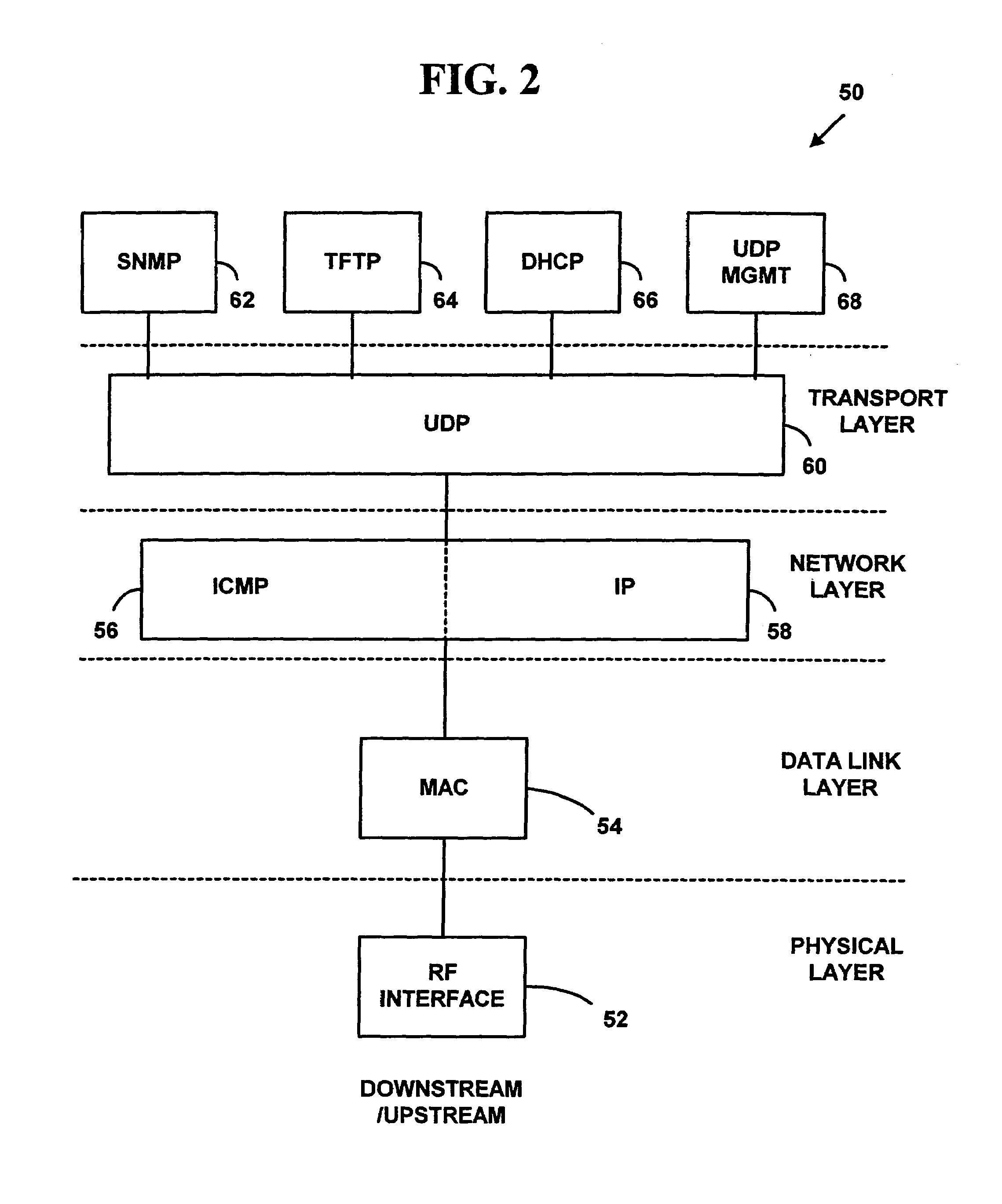

Method for dynamic performance optimization in a data-over-cable system

InactiveUS6985437B1Improve performanceOvercome problemsFrequency-division multiplex detailsTransmission systemsModem deviceData system

A method and system for optimizing performance in a data-over-cable system. The method includes determining parameters for data transmission on an upstream channel of the data-over-cable system, and negotiating use of the parameters. A measurement is made of a signal-to-noise ratio (“SNR”) on the upstream channel. Associated with the SNR and a target packet-error-ratio (“PER”) are parameters that provide optimal data throughput. The parameters, such as symbol rate, type of modulation, or amount of error correction, are used to construct a message that is sent to the cable modems. The message instructs the cable modems to reconfigure themselves to transmit according to the parameters. The reconfiguration helps ensure optimal performance.

Owner:HEWLETT PACKARD DEV CO LP

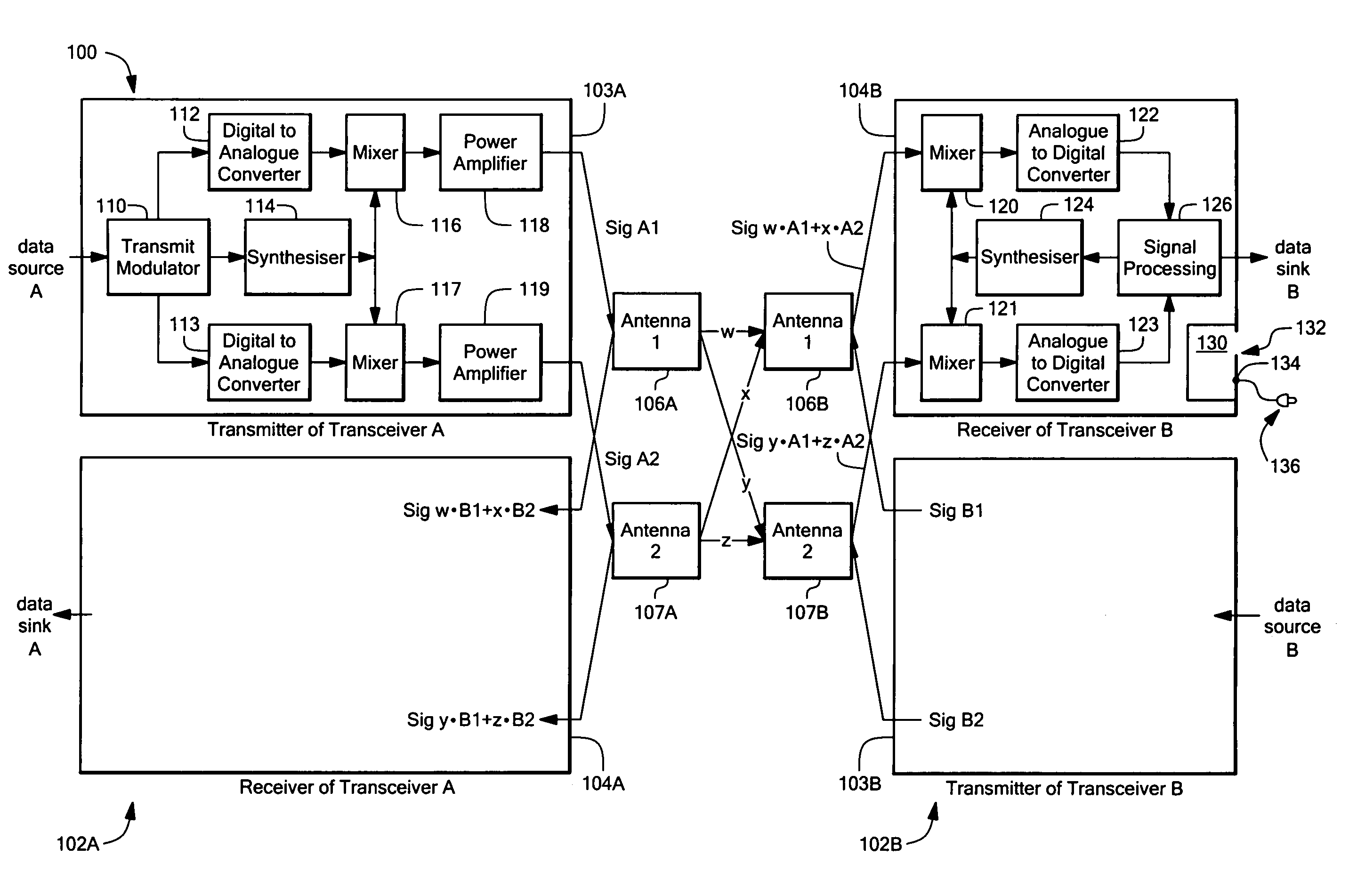

Implementing MIMO in mmWave wireless communication systems

ActiveUS9537546B2Improve wireless communication performanceHigh data rateSpatial transmit diversityConnection managementTelecommunications linkCommunications system

Owner:INTEL CORP

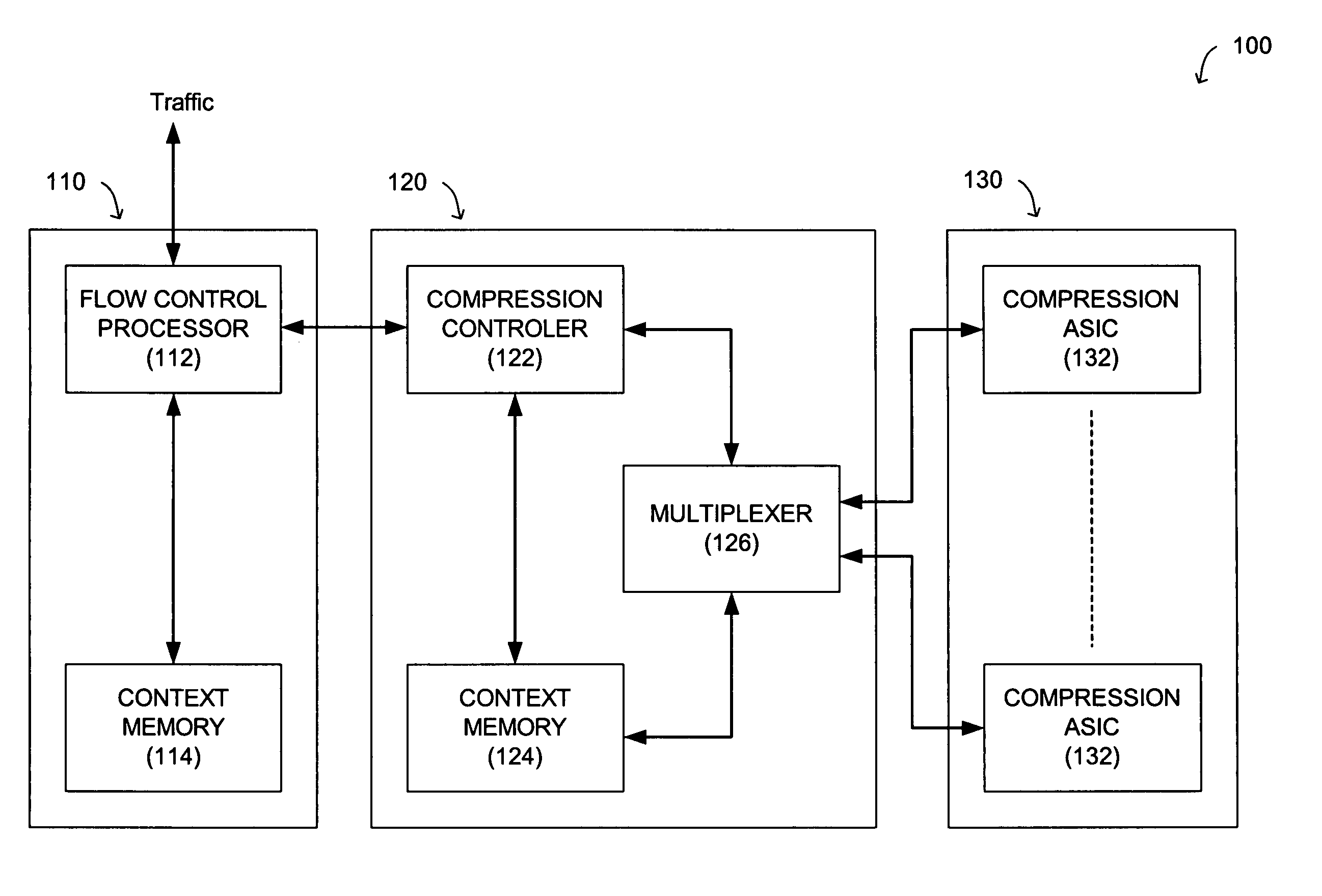

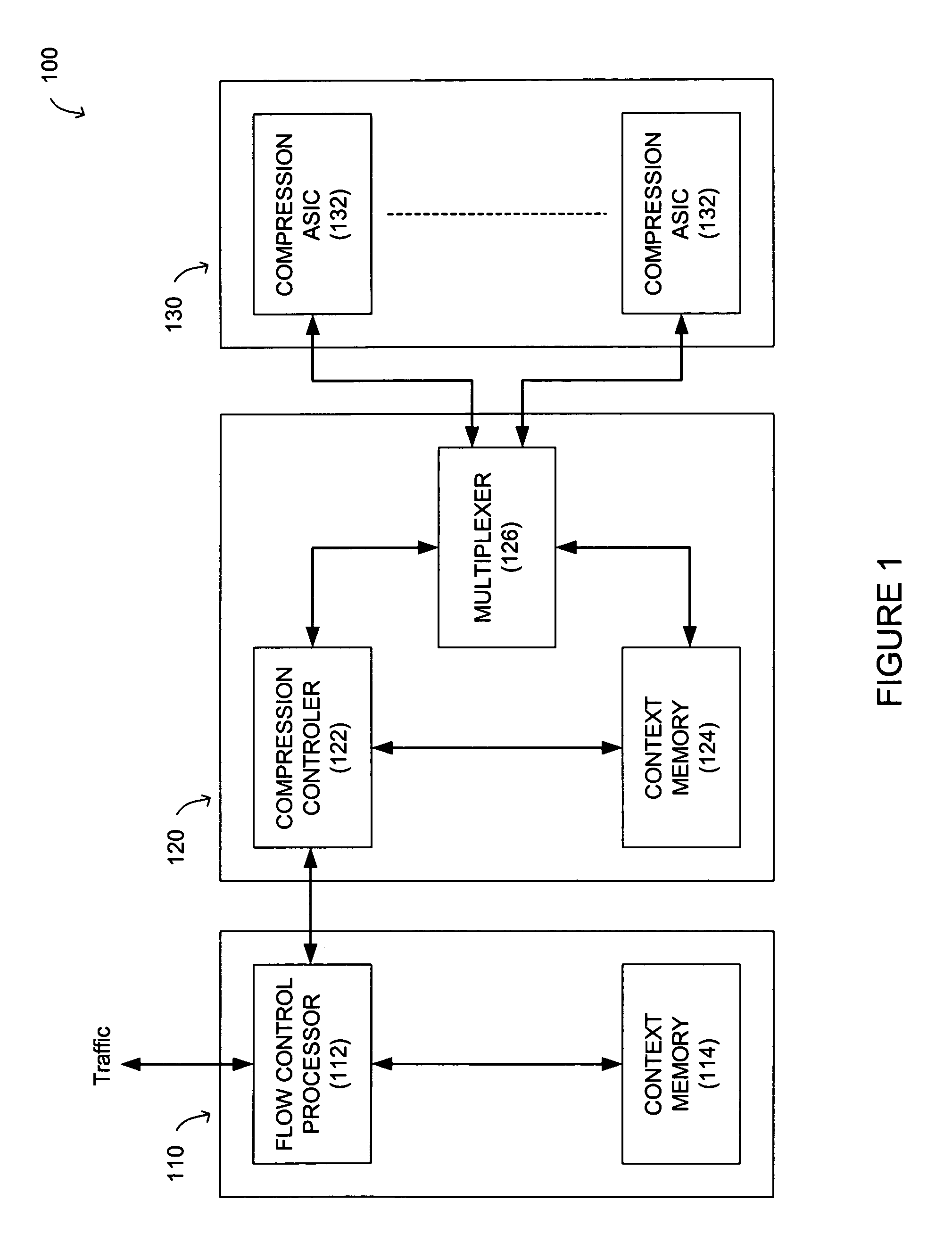

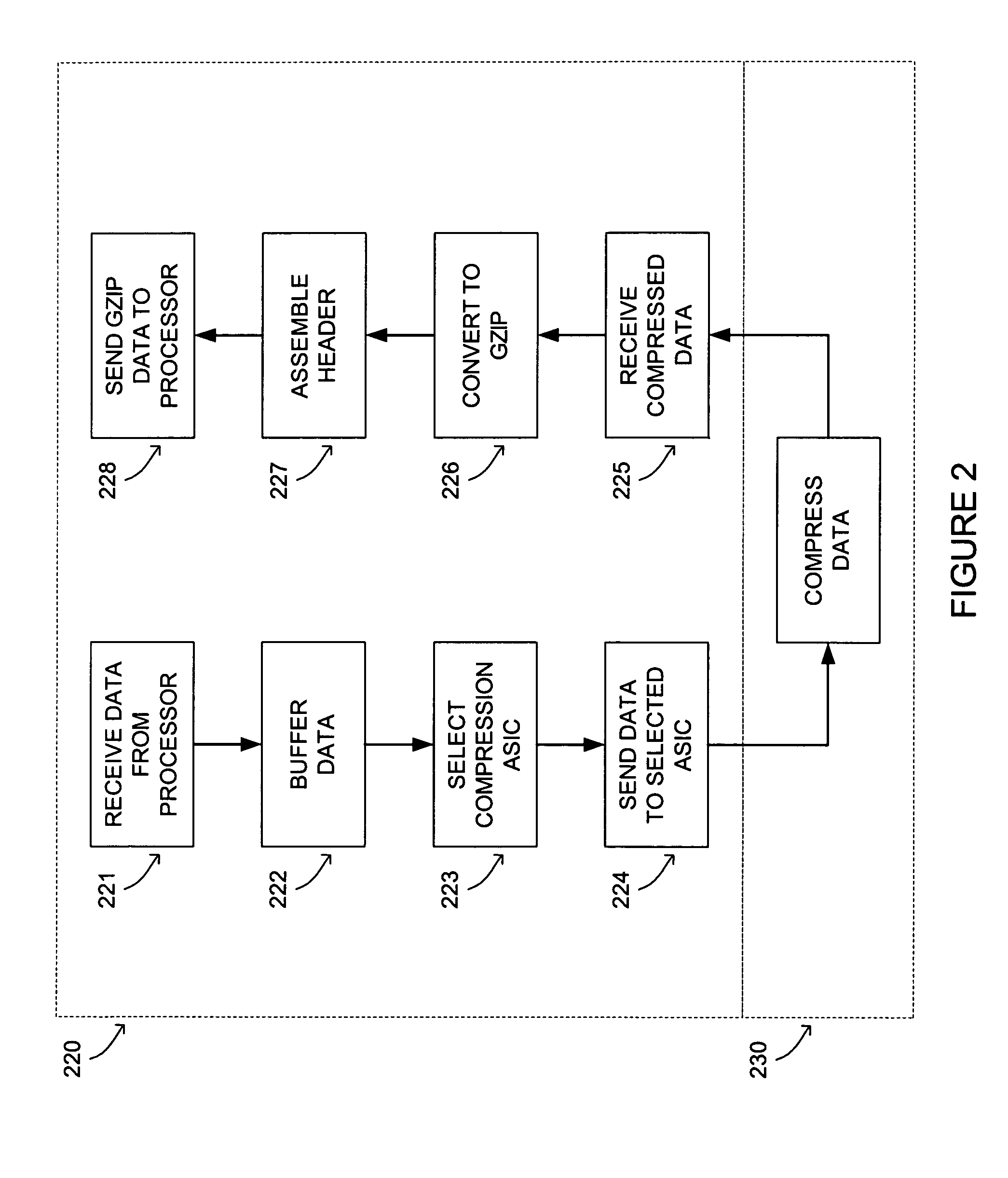

Hardware accelerated compression

ActiveUS7051126B1Improve compression speedImprove data throughputCode conversionMultiple digital computer combinationsData streamHardware acceleration

A compression system is arranged to use software and / or hardware accelerated compression techniques to increase compression speeds and enhance overall data throughput. A logic circuit is arranged to: receive a data stream from a flow control processor, buffer the data stream, select a hardware compressor (e.g., an ASIC), and forward the data to the selected hardware compressor. Each hardware compressor performs compression on the data (e.g., LZ77), and sends the compressed data back to the logic circuit. The logic circuit receives the compressed data, converts the data to another compressed format (e.g., GZIP), and forwards the converted and compressed data back to the flow control processor. History associated with the data stream can be stored in memory by the flow control processor, or in the logic circuit.

Owner:F5 NETWORKS INC

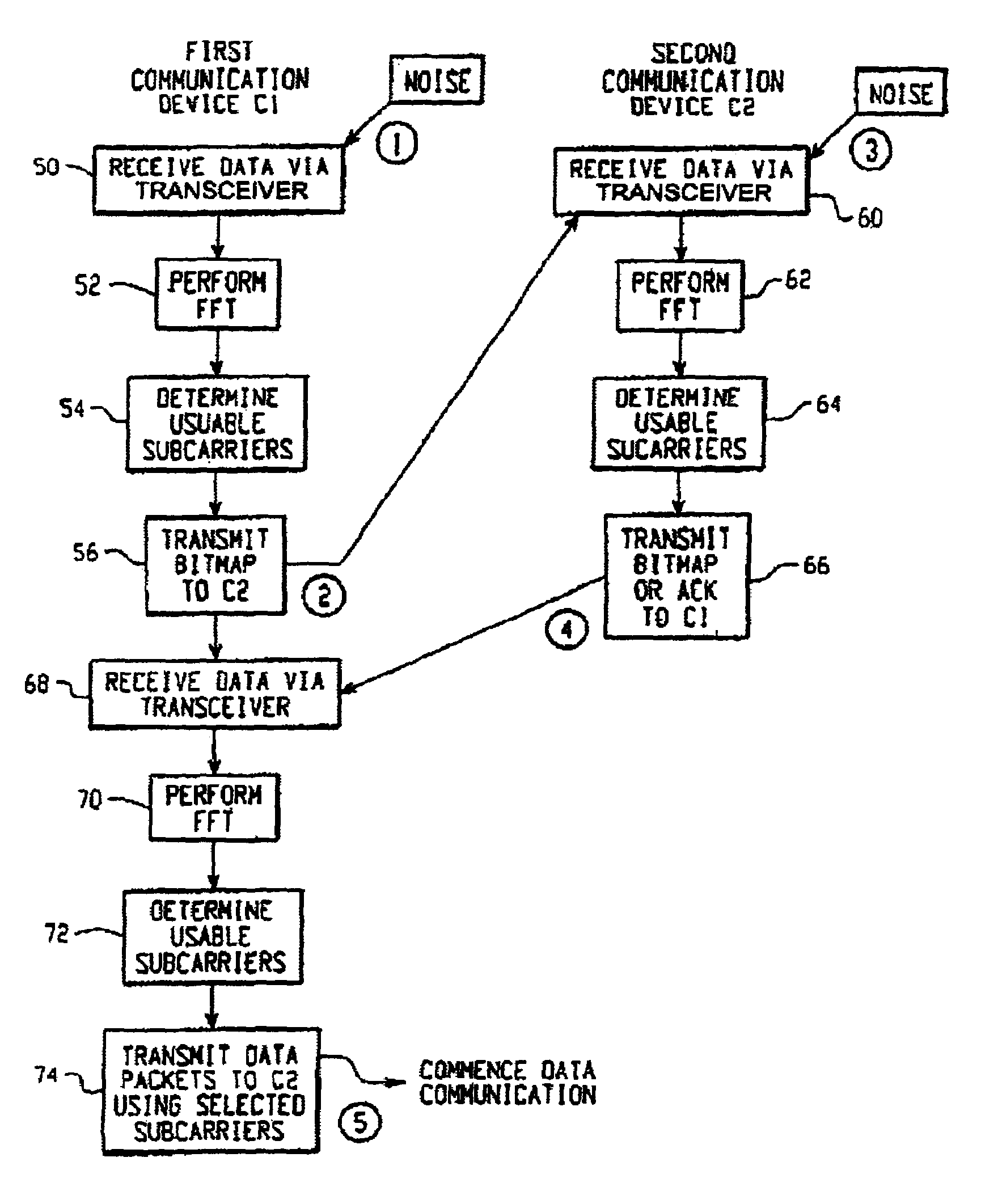

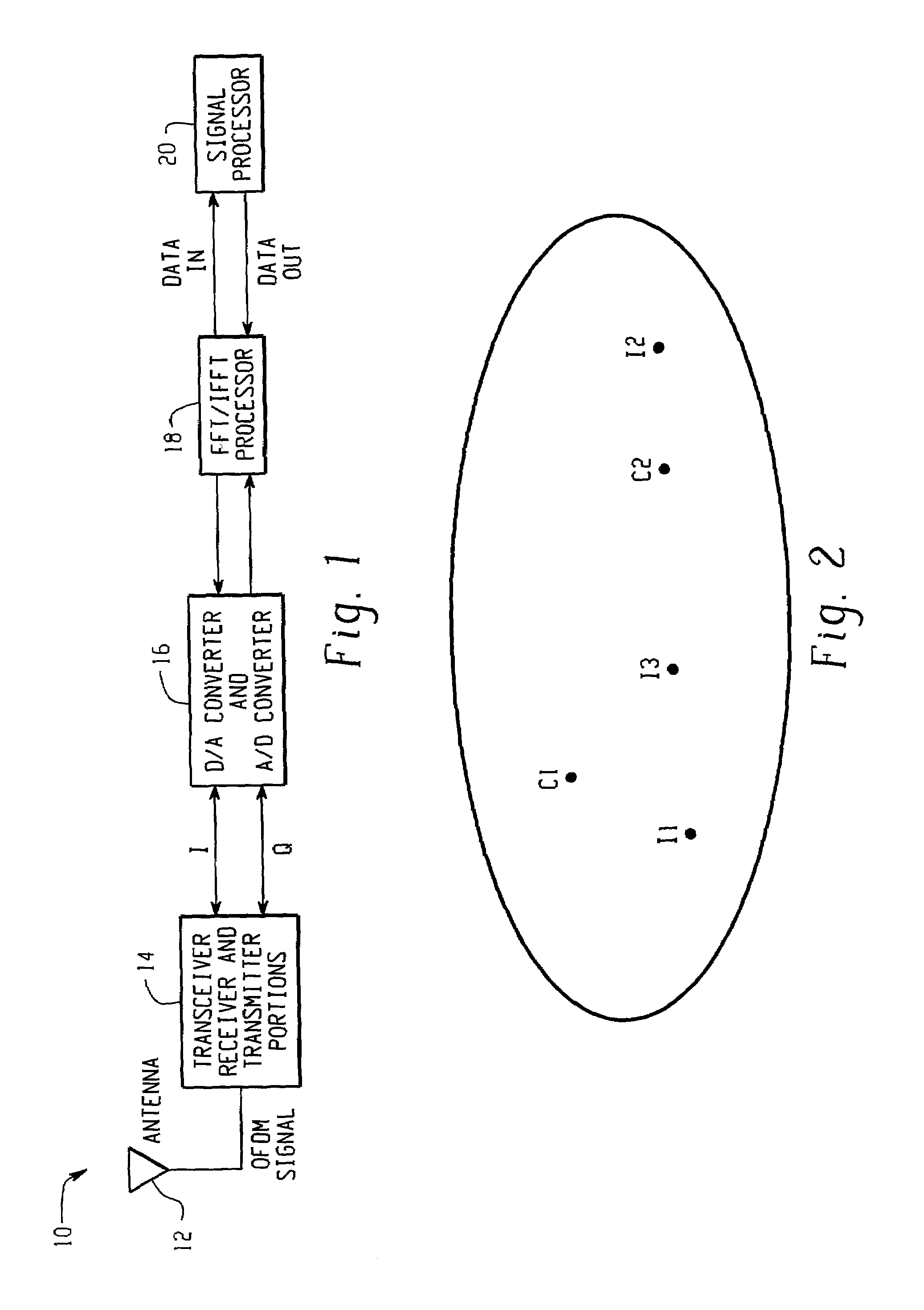

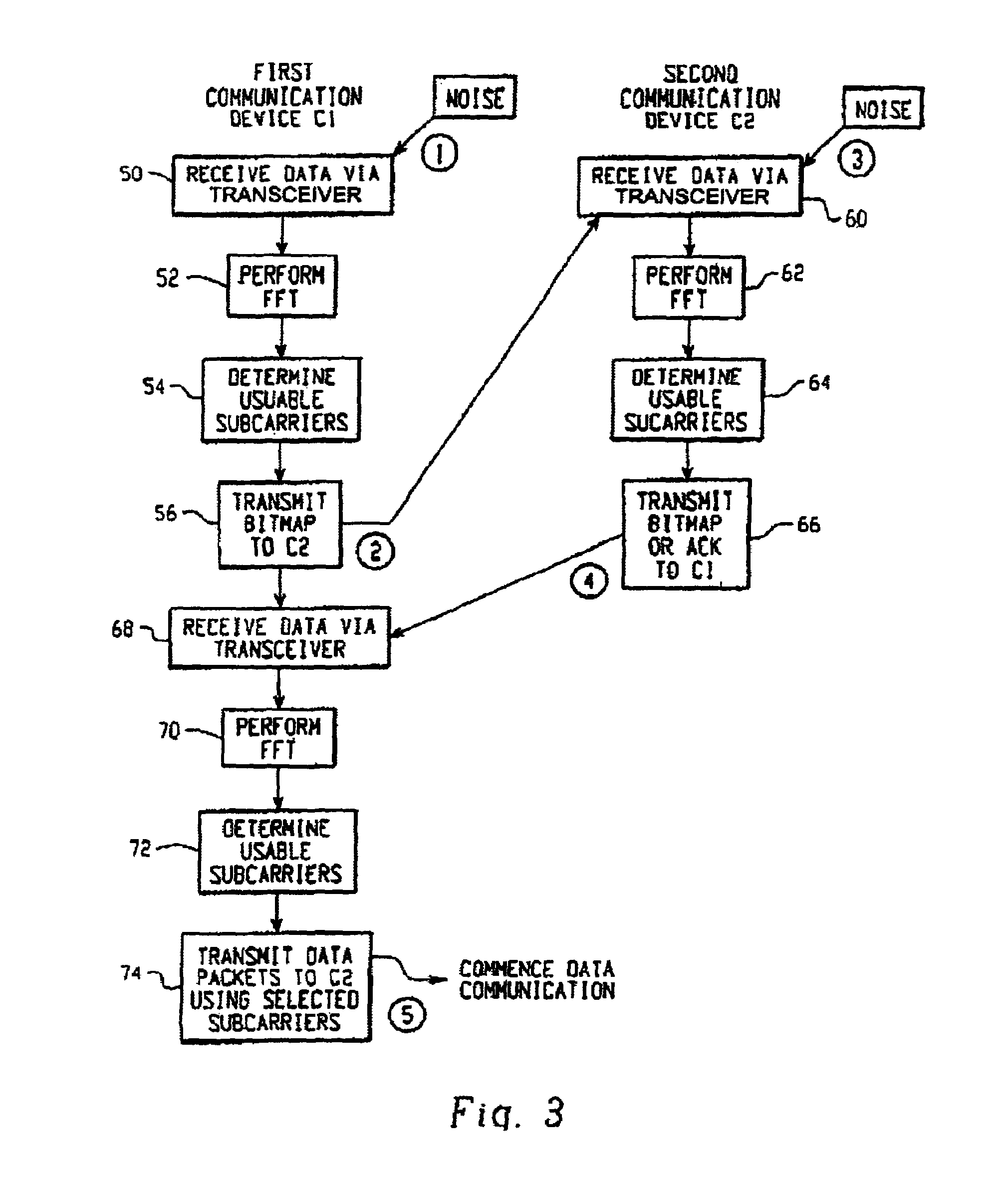

Adaptive control system for interference rejections in a wireless communications system

InactiveUS6934340B1Improved interference rejectionImprove robustnessSecret communicationMulti-frequency code systemsCommunications systemControl system

An adaptive control system for controlling the effects of narrow to medium bandwidth interferers in a wireless communications system (e.g., wireless LAN devices) by identifying which sub-carriers in a multi-carrier system are located on frequencies that are subject to interfering signals, and using only those sub-carriers that are not subject to interference for communications between wireless communications devices.

Owner:CISCO TECH INC

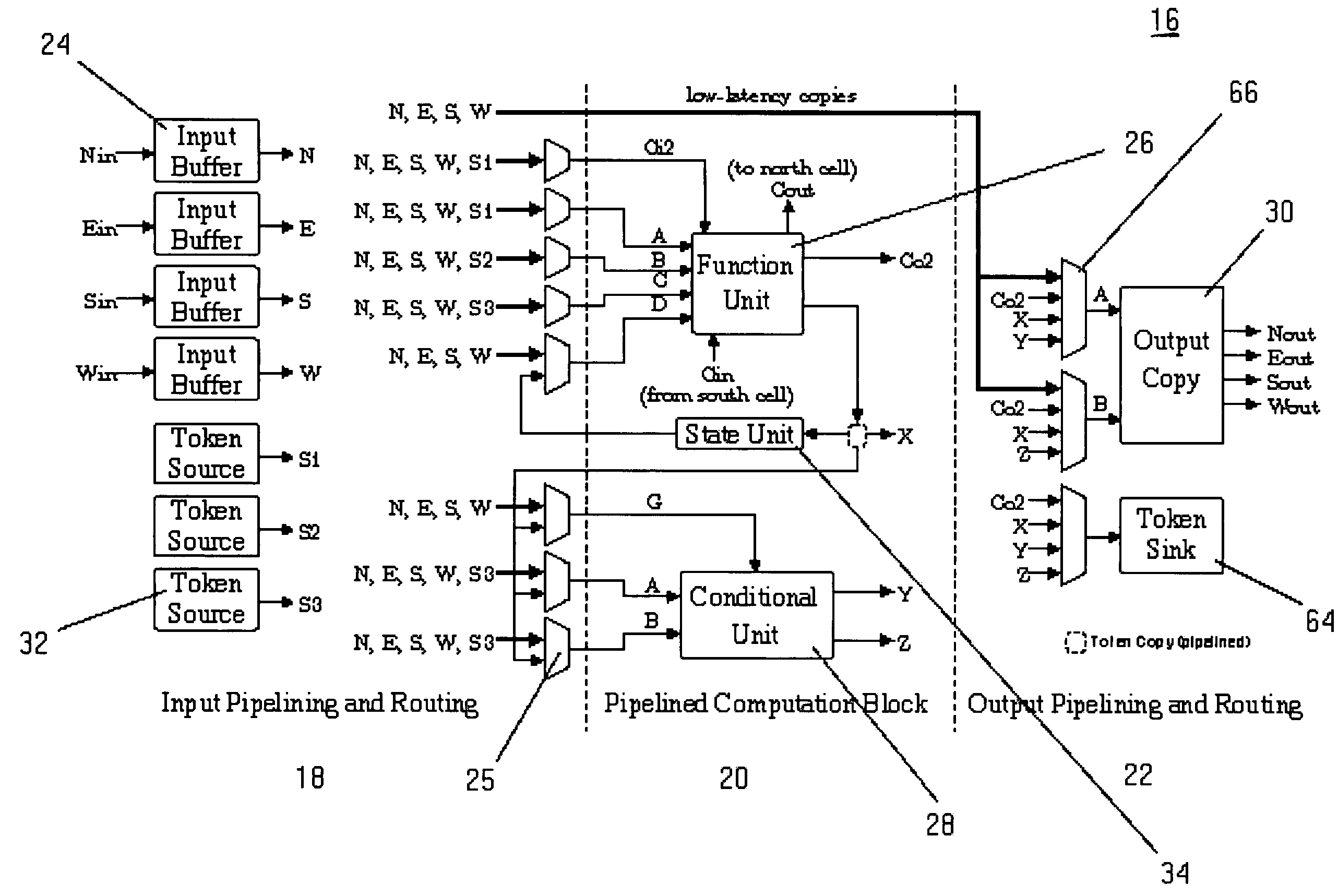

Data Processing System Having Integrated Pipelined Array Data Processor

InactiveUS20150106596A1Improve executionImprove performanceMemory architecture accessing/allocationInstruction analysisData processing systemParallel computing

A data processing system having a data processing core and integrated pipelined array data processor and a buffer for storing list of algorithms for processing by the pipelined array data processor.

Owner:SCIENTIA SOL MENTIS AG

TCP host

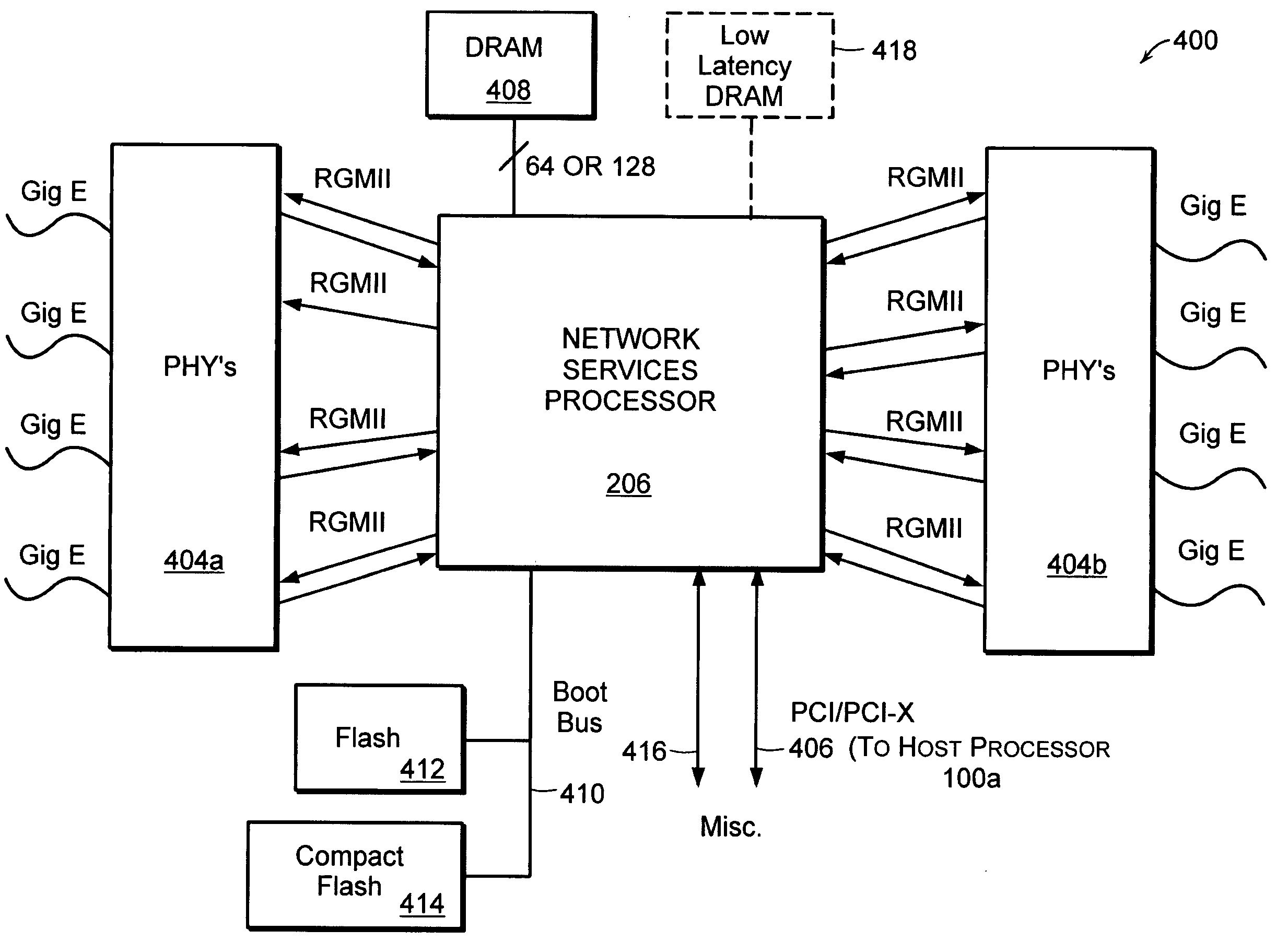

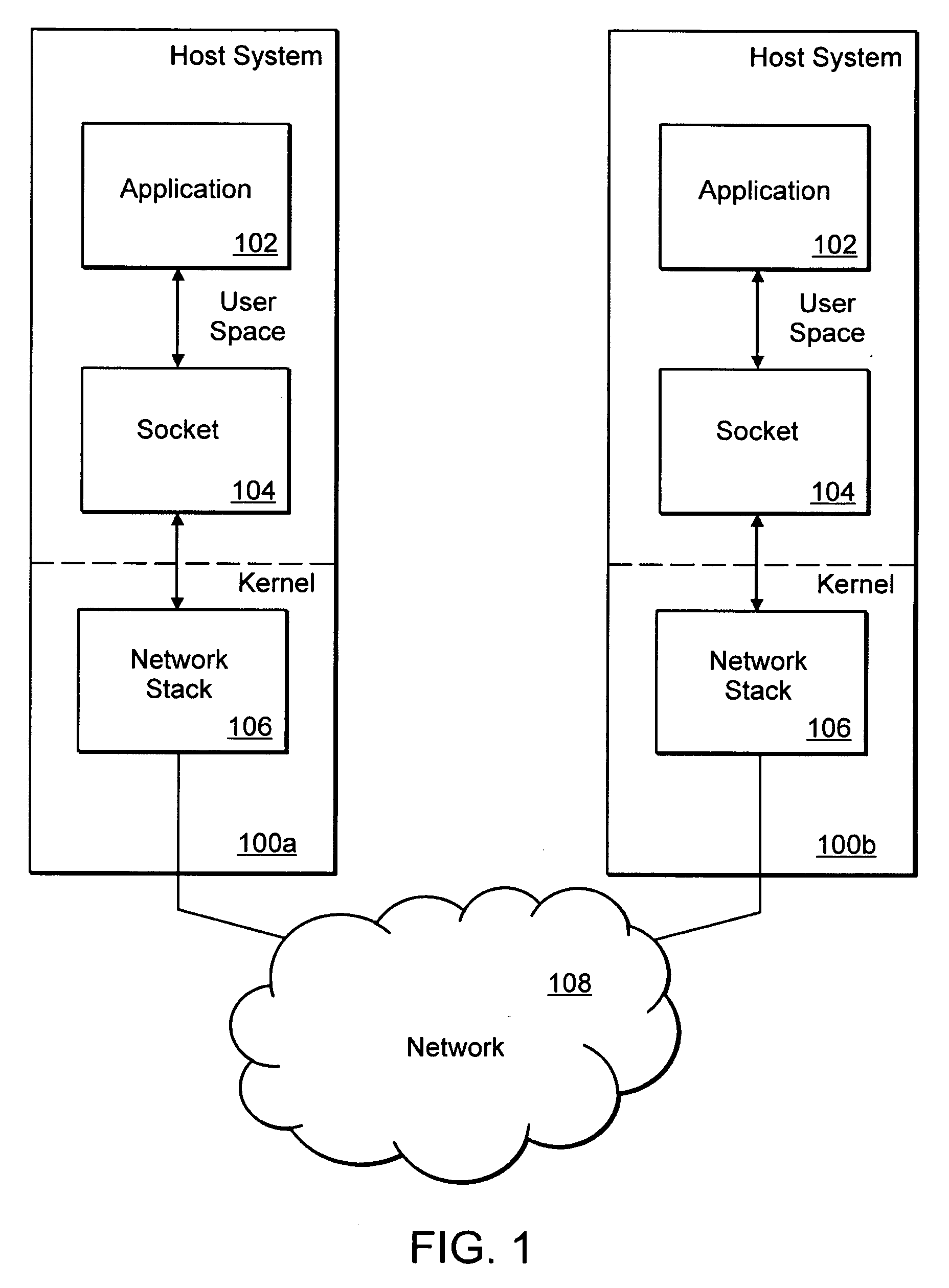

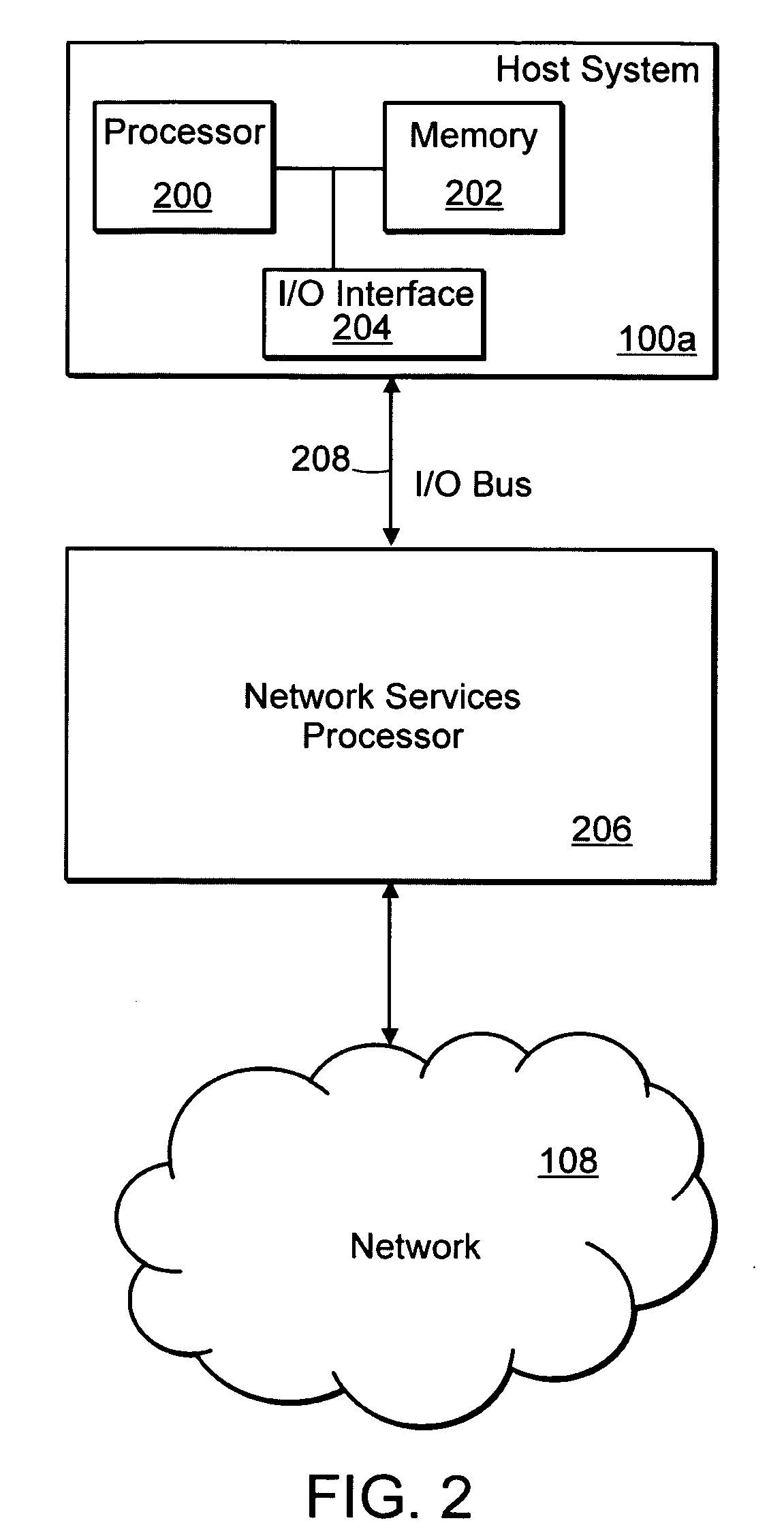

ActiveUS20060075119A1Eliminate needImproves host performanceMultiple digital computer combinationsTransmissionApplication softwareHost memory

A network application executing on a host system provides a list of application buffers in host memory stored in a queue to a network services processor coupled to the host system. The application buffers are used for storing data transferred on a socket established between the network application and a remote network application executing in a remote host system. Using the application buffers, data received by the network services processor over the network is transferred between the network services processor and the application buffers. After the transfer, a completion notification is written to one of the two control queues in the host system. The completion notification includes the size of the data transferred and an identifier associated with the socket. The identifier identifies a thread associated with the transferred data and the location of the data in the host system.

Owner:MARVELL ASIA PTE LTD

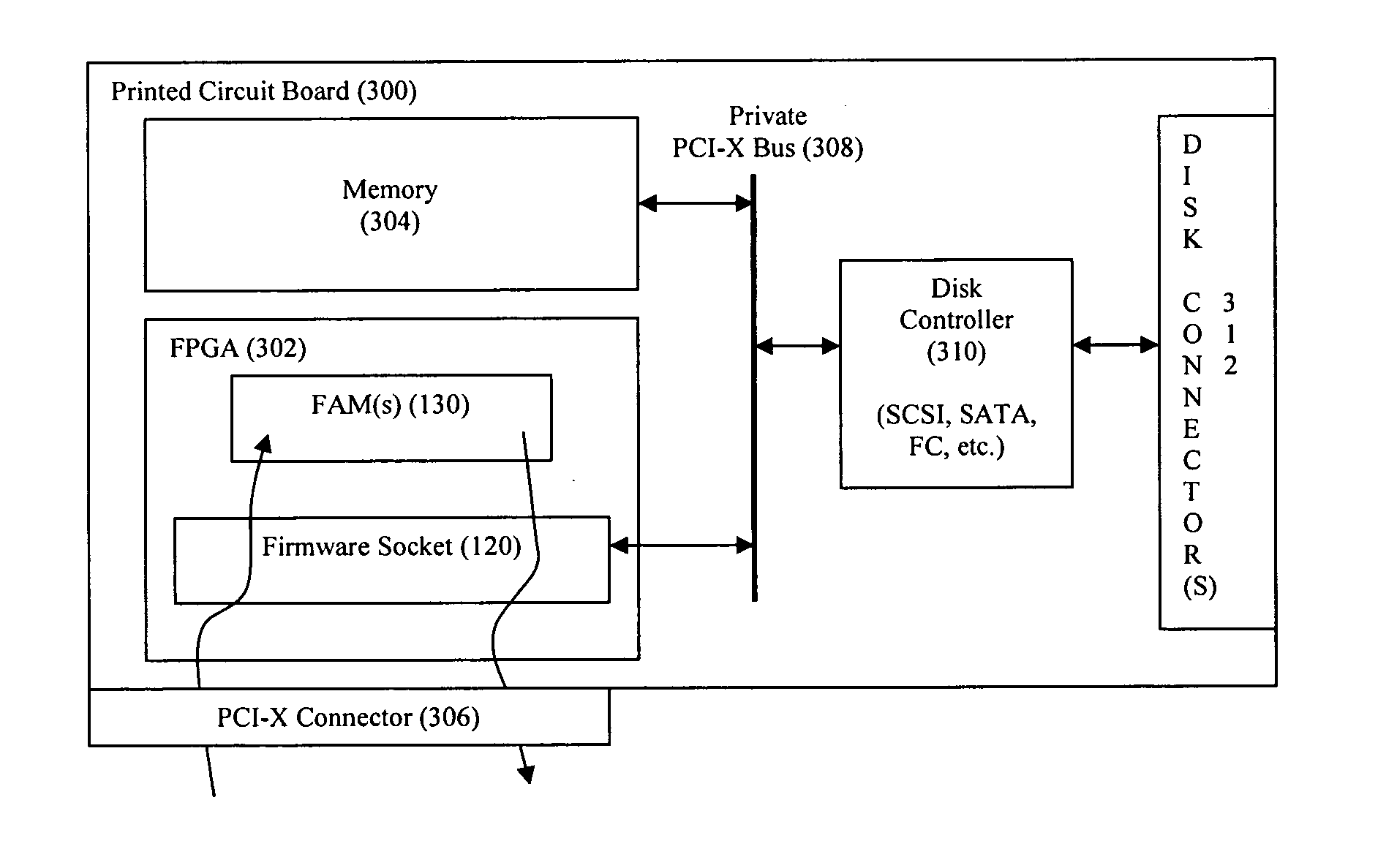

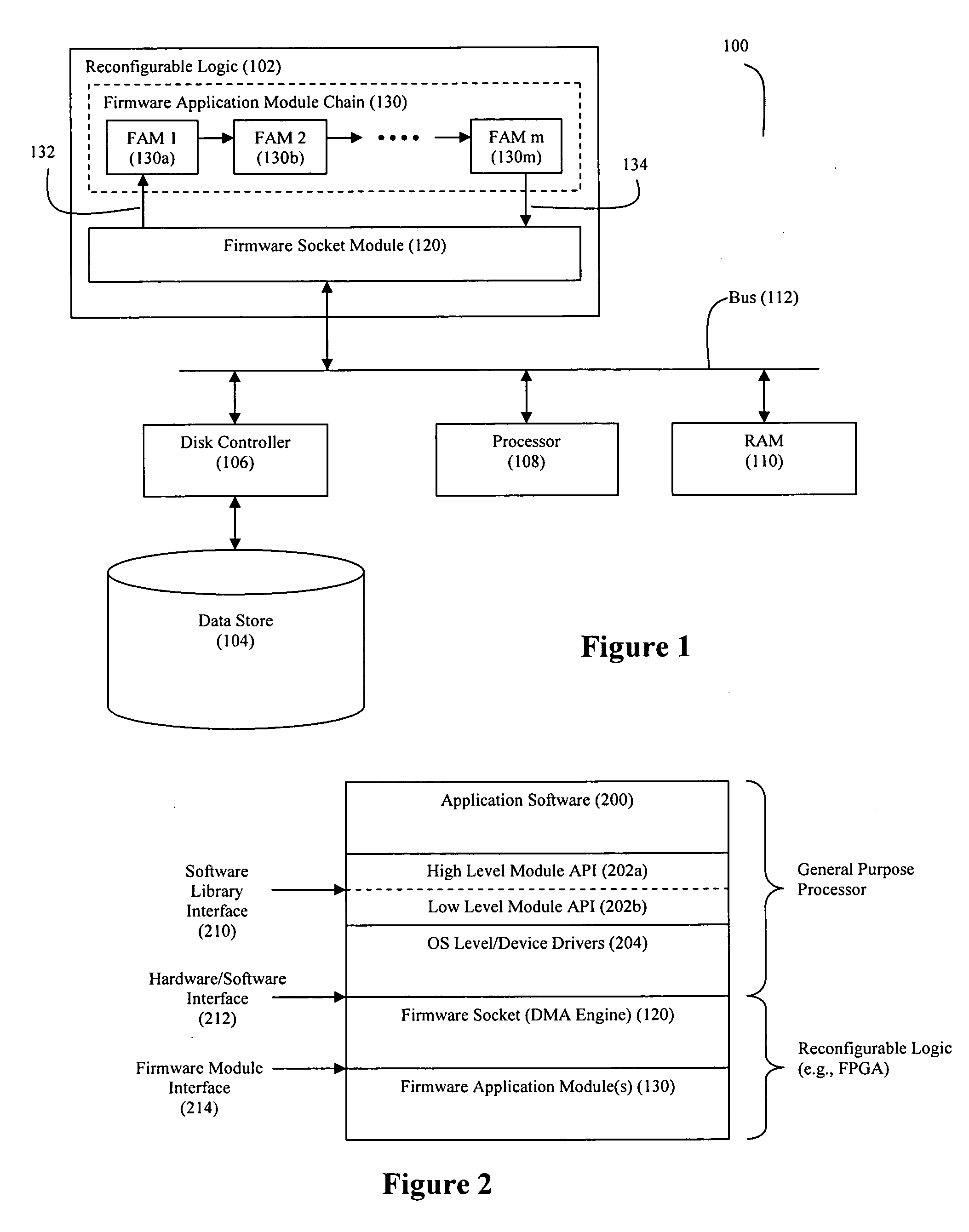

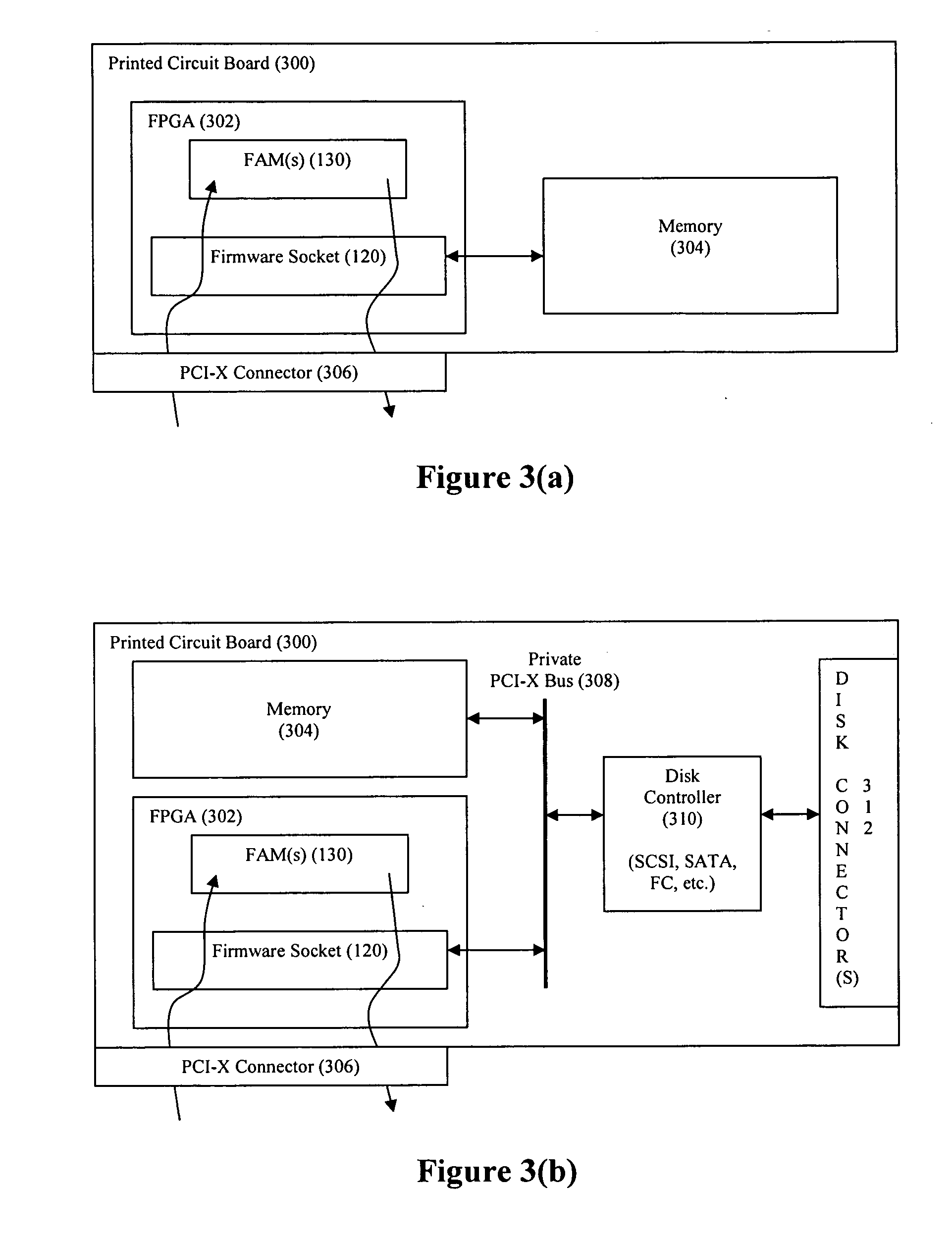

Firmware socket module for FPGA-based pipeline processing

ActiveUS20070174841A1Improve throughputFacilitate easeDigital computer detailsMultiprogramming arrangementsData processingSoftware

A firmware socket module is deployed on a reconfigurable logic device, wherein the firmware socket module has a communication path between itself and an entry point into a data processing pipeline, wherein the firmware socket module is configured to provide both commands and target data to the entry point in the data processing pipeline via the same communication path, wherein each command defines a data processing operation that is to be performed by the data processing pipeline, and wherein the target data corresponds to the data upon which the data processing pipeline performs its commanded data processing operation. Preferably, the firmware socket module is configured to provide the commands and target data in a predetermined order that is maintained throughout the data processing pipeline. Also, the firmware socket module may be configured to (1) access an external input descriptor pool buffer that defines the order in which commands and target data are to be provided to the data processing pipeline, and (2) transfer the commands and target data from an external memory to the data processing pipeline in accordance with the identified defined order. Results of the processing by the data processing pipeline are also returned to external memory by the firmware socket module, whereupon those results can be subsequently used by software executing on a computer system.

Owner:IP RESERVOIR

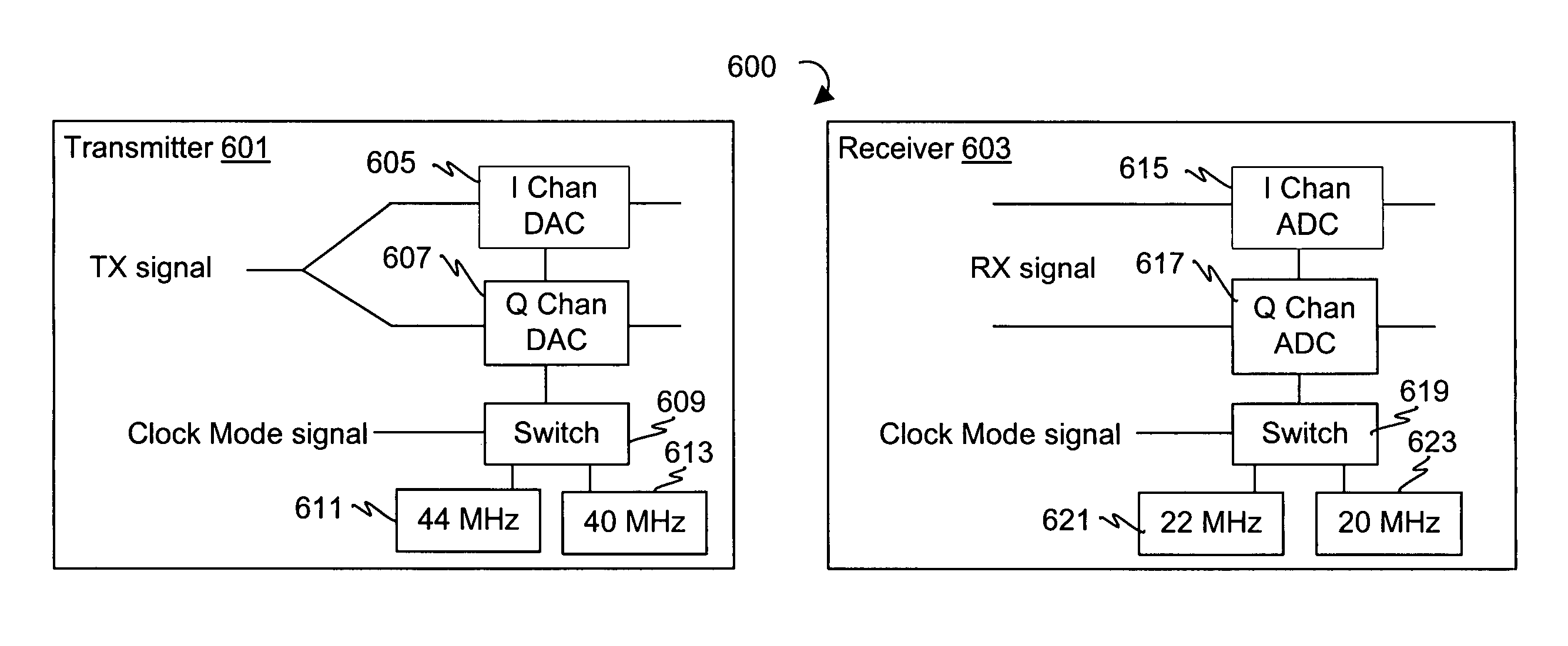

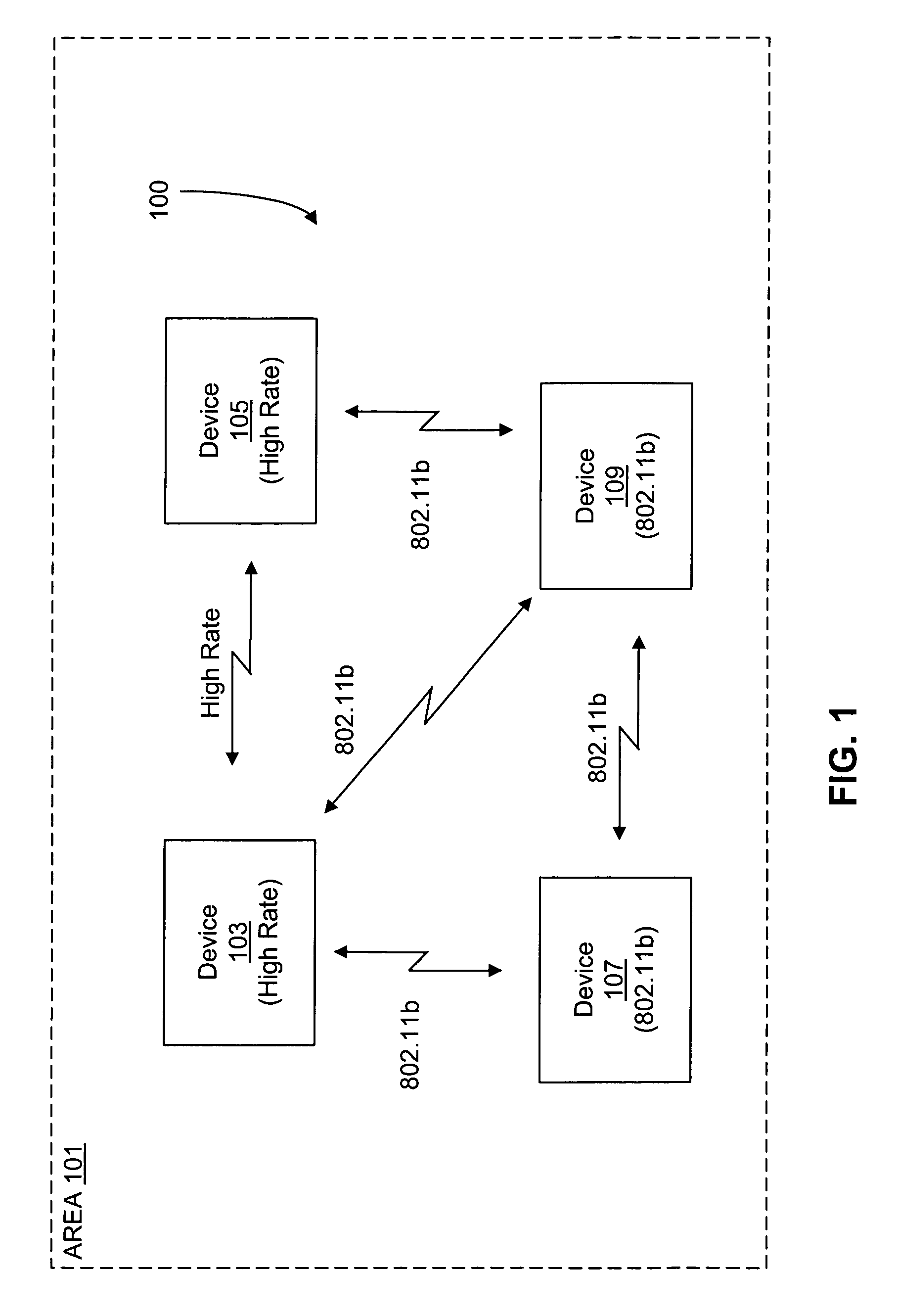

Dual packet configuration for wireless communications

InactiveUS7274652B1Facilitate communicationEasy to understandMultiple modulation transmitter/receiver arrangementsNetwork topologiesCarrier signalSubcarrier

A dual packet configuration for wireless communications including a first portion that is modulated according to a serial modulation and a second portion that is modulated according to a parallel modulation. The serial modulation may be DSSS whereas the parallel modulation may be OFDM. The first portion may include a header, which may further include an OFDM mode bit and a length field indicating the duration the second portion. The first portion may be in accordance with 802.11b to enable dual mode devices to coexist and communicate in the same area as standard 802.11b devices. The dual mode devices can communicate at different or higher data rates without interruption from the 802.11b devices. The packet configuration may include an OFDM signal symbol which further includes a data rate section and a data count section. In this manner, data rates the same as or similar to the 802.11a data rates may be specified between dual mode devices. The first and second portions may be based on the same or different clock fundamentals. For OFDM, the number of subcarriers, pilot tones and guard interval samples may be modified independently or in combination to achieve various embodiments. Also, data subcarriers may be discarded and replaced with pilot tones for transmission. The receiver regenerates the discarded data based on received data, such as using ECC techniques.

Owner:CISCO TECH INC

Increased throughput across data network interface by dropping redundant packets

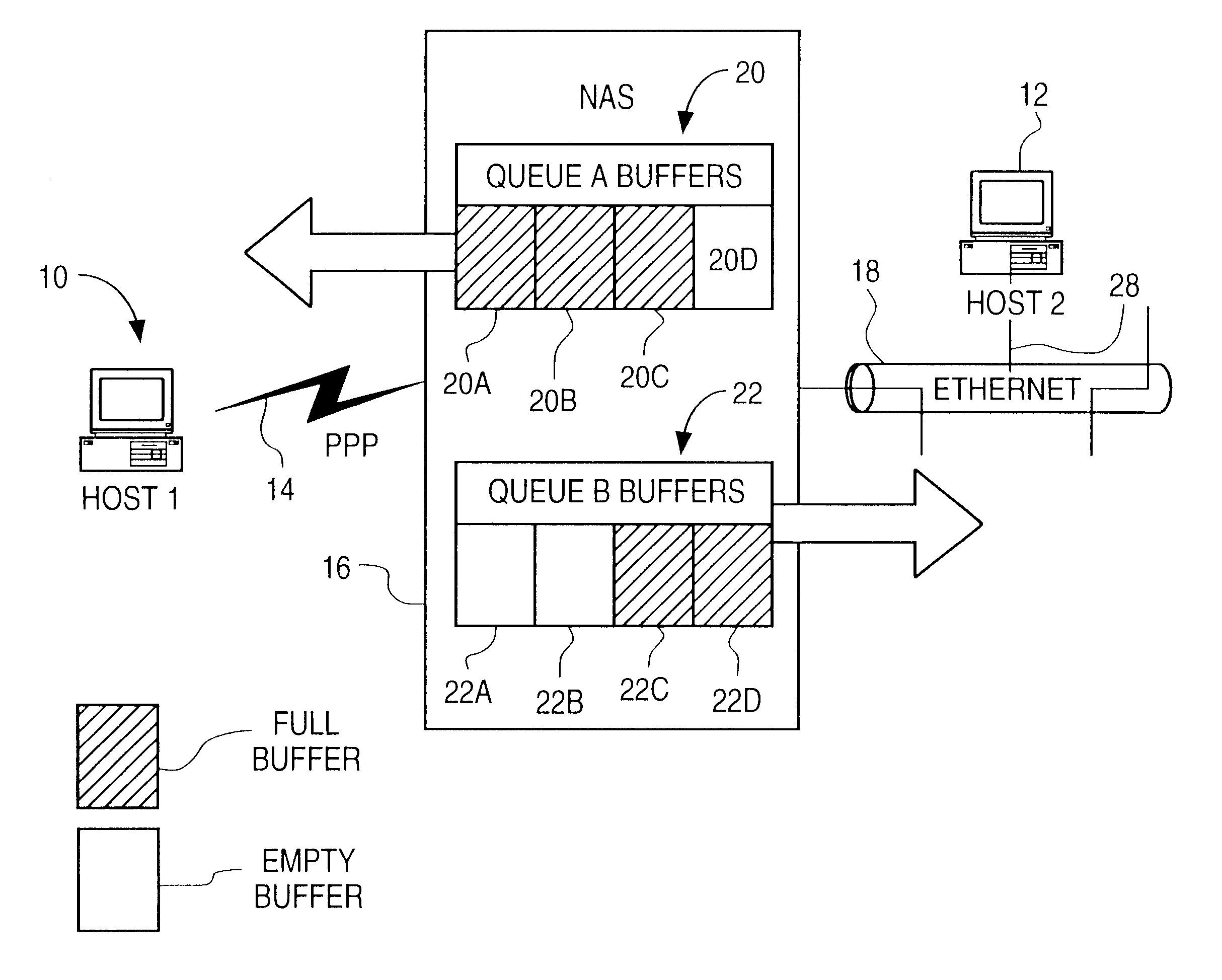

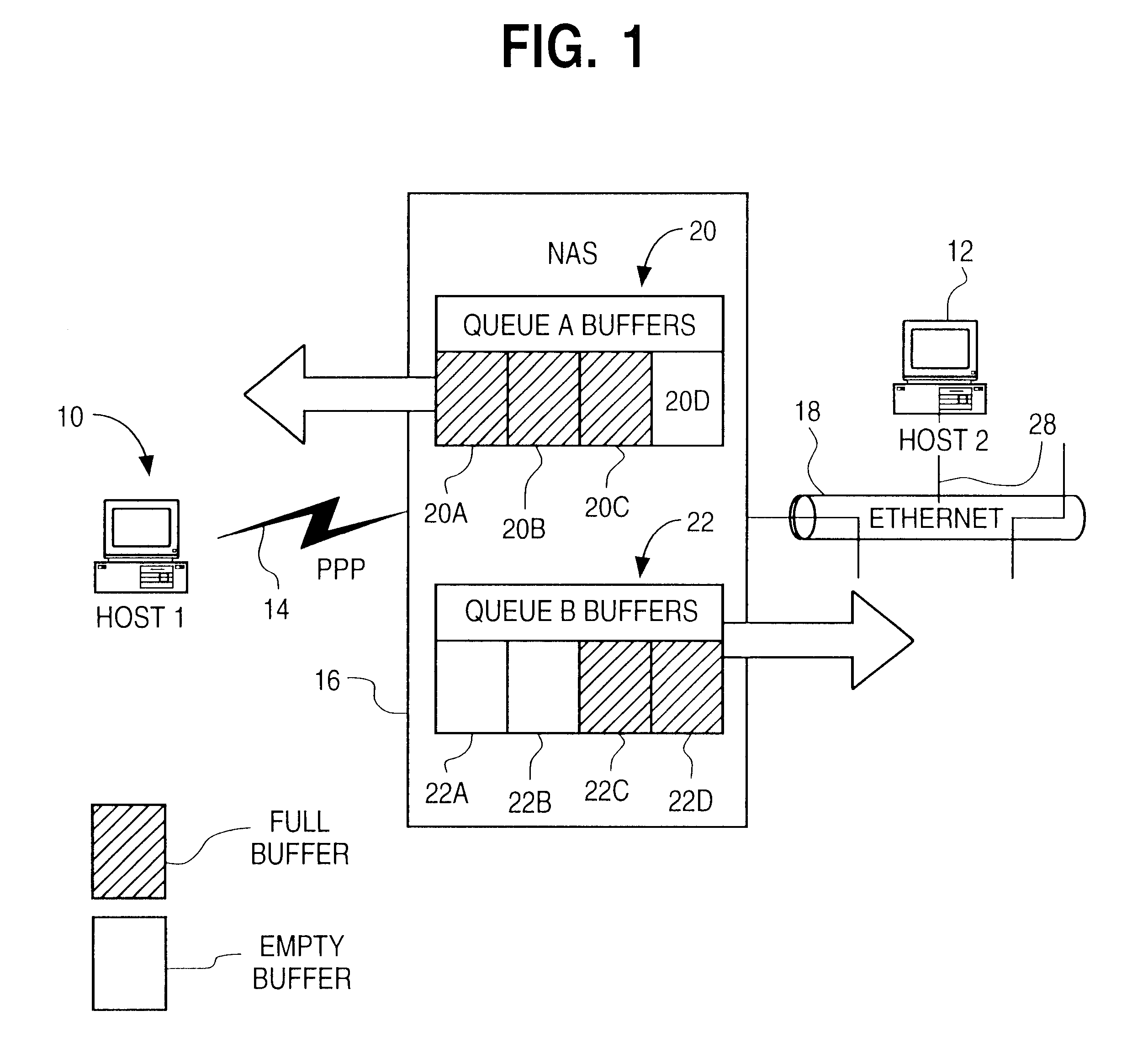

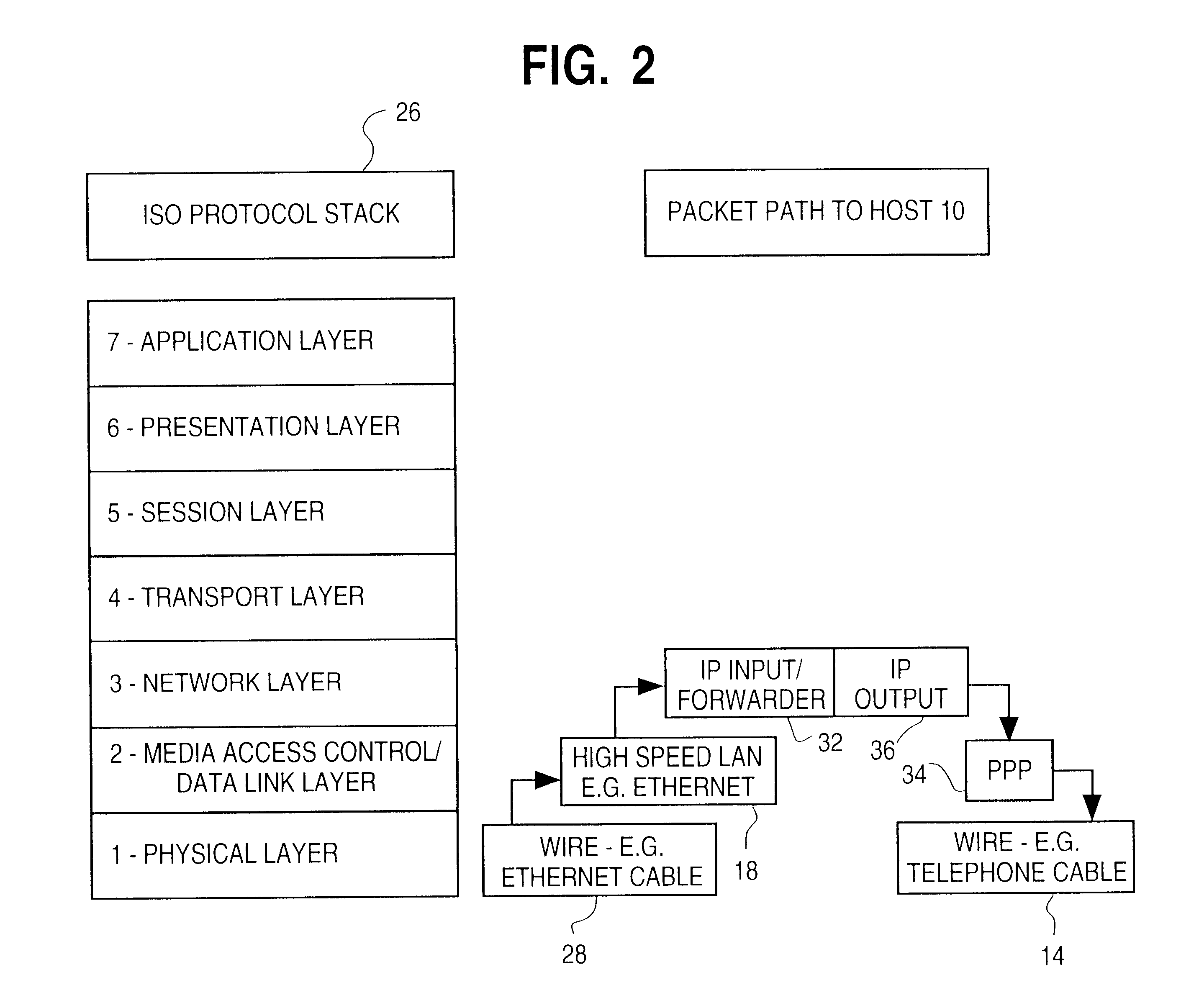

InactiveUS6700871B1Improve data throughputImprove throughputError prevention/detection by using return channelTransmission systemsNetwork access serverLow speed

In a typical remote access application, such as access from the home to a packet-switched high speed network such as the Internet, the low-speed dial up connection to a network access is the main bottleneck in terms of the bandwidth and efficiency of transfer of data across the network access server. The present invention increases throughput through the network access server by identifying and dropping redundant, e.g., retransmitted, packets en route from the LAN or WAN to the remote terminal, thereby preserving precious bandwidth.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

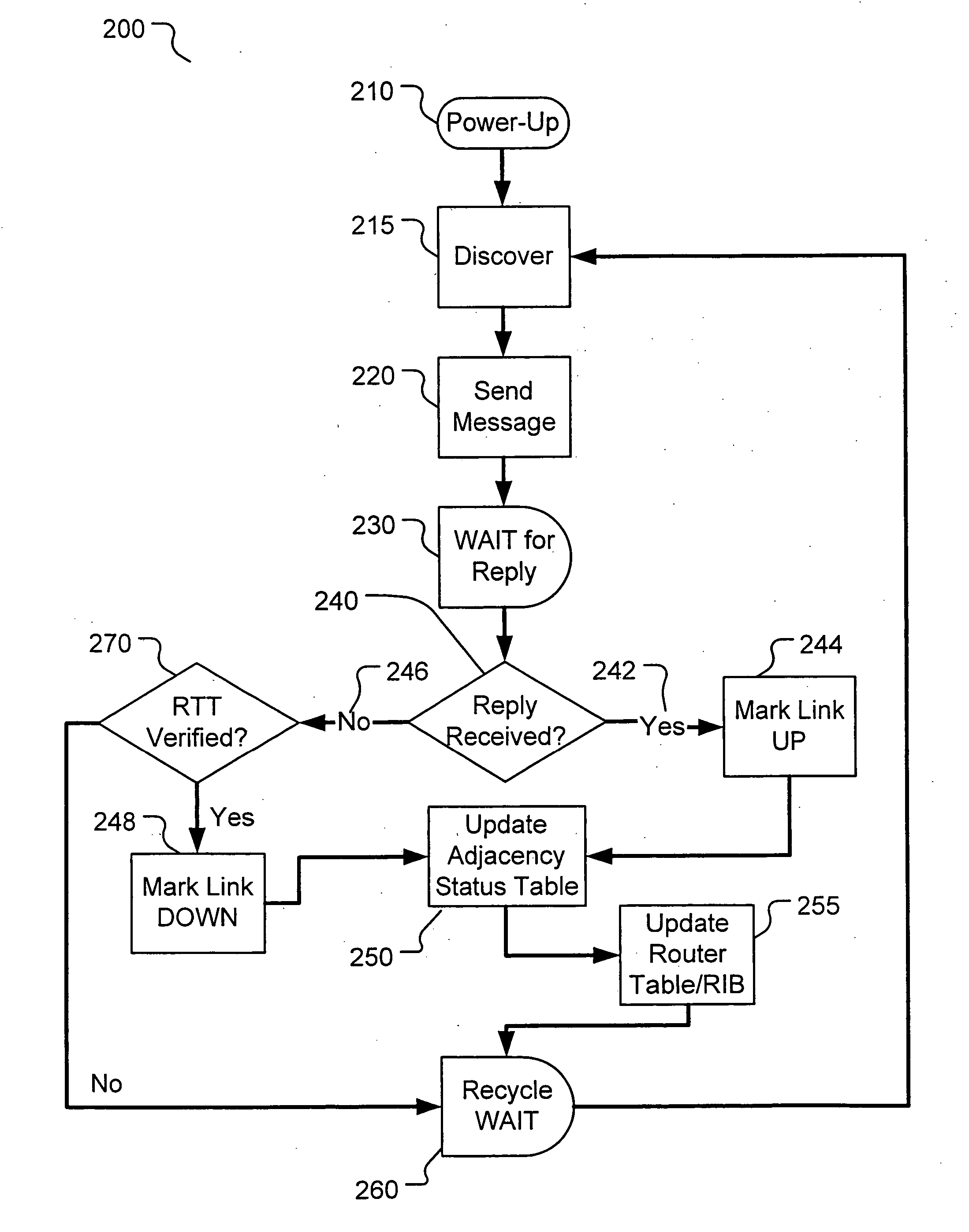

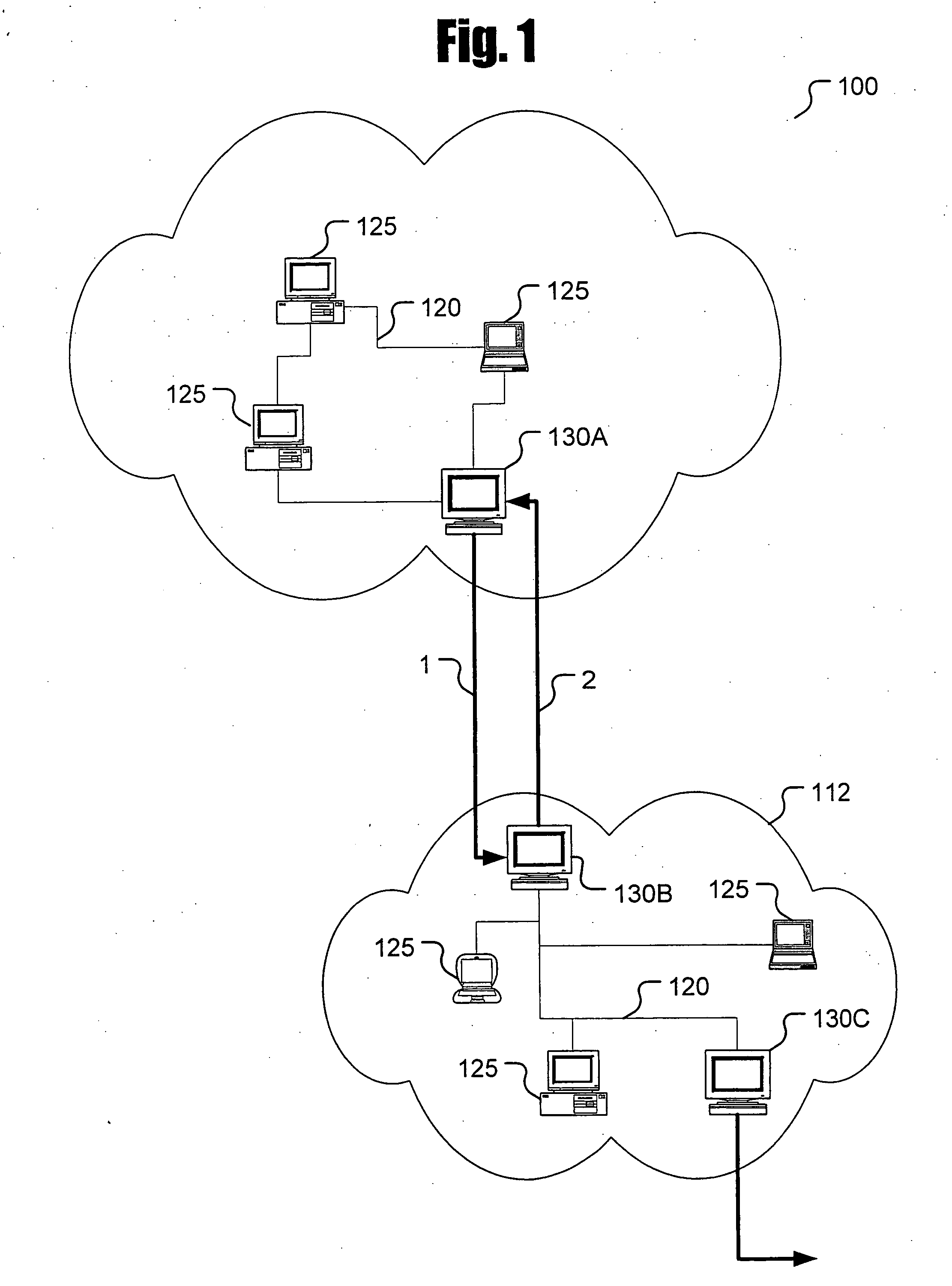

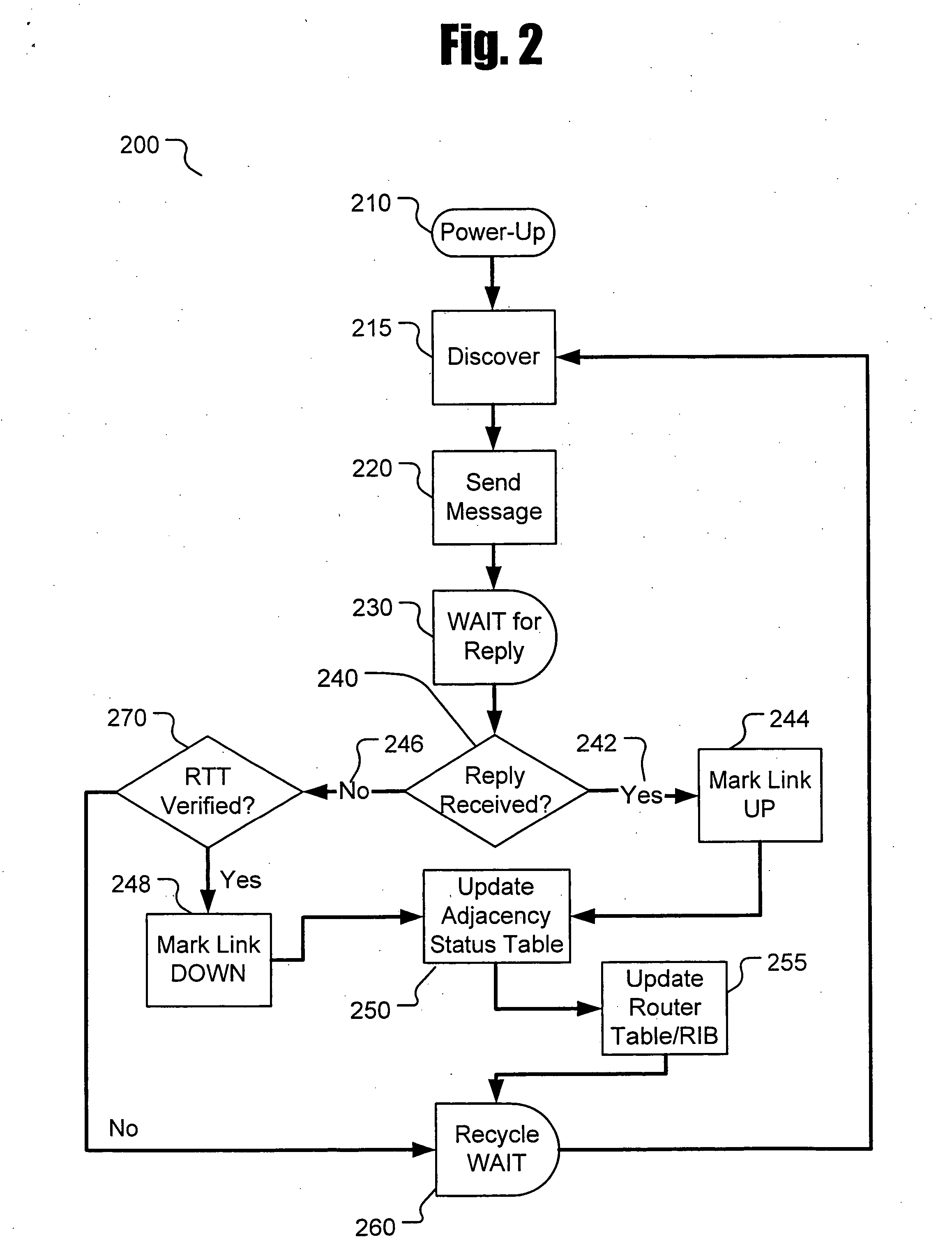

Ethernet network availability

ActiveUS20050018612A1Reduce amountQuicker amortizationError preventionTransmission systemsLogical link controlReal-time computing

Disclosed is a method and apparatus for improving LAN availability and robustness employing adjacency status self-discovery on segment-to-segment communications paths. In some embodiments, the method and system may employ Logical Link Control Type 1 test frame messages between segment nodes to determine status. Adjacent node status may be determined by waiting a period of time for an acknowledgment message and marking the tested link as “down” if no response is received. Also disclosed is a method for compacting data transmitted over a network to reduce overhead.

Owner:GENBAND US LLC

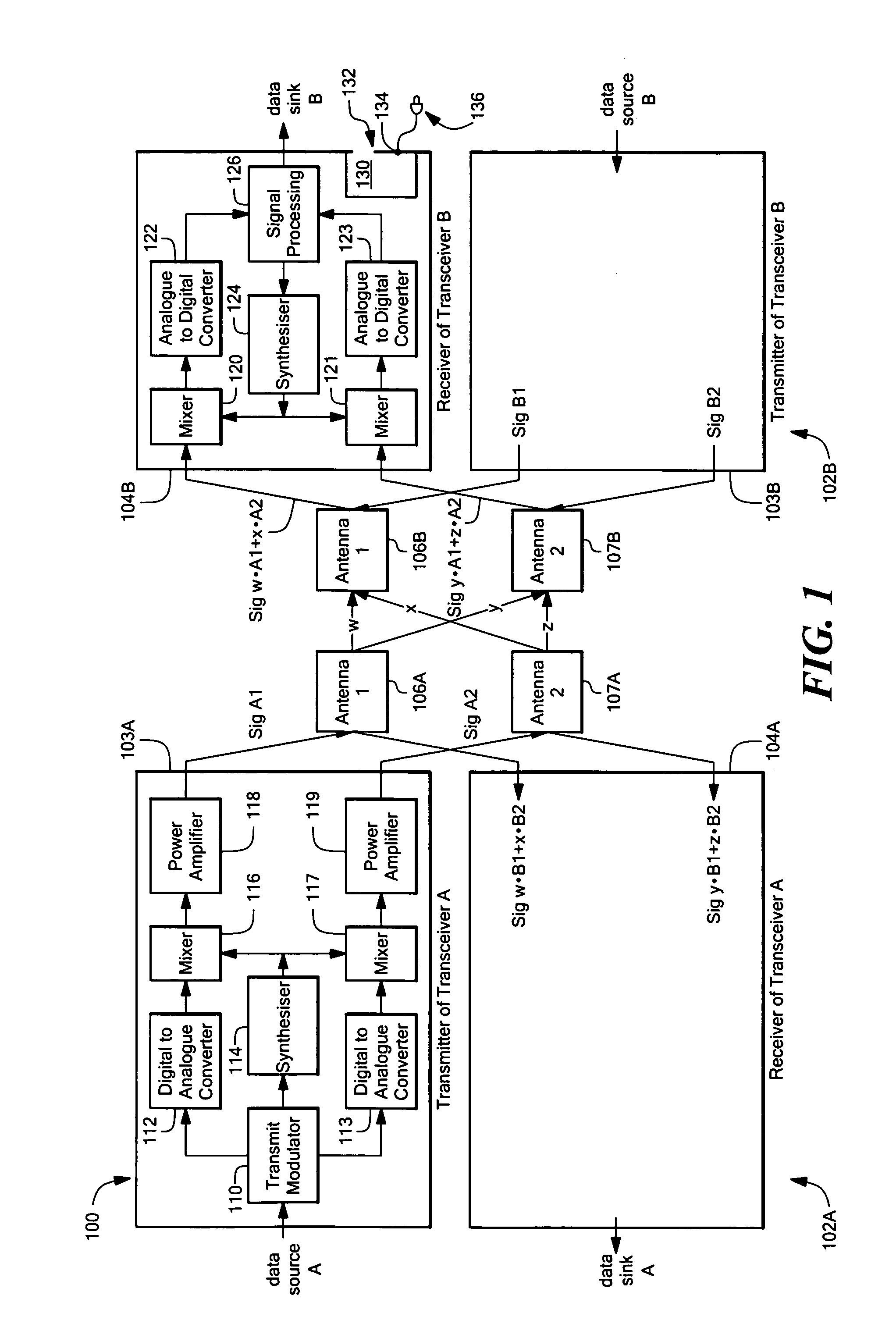

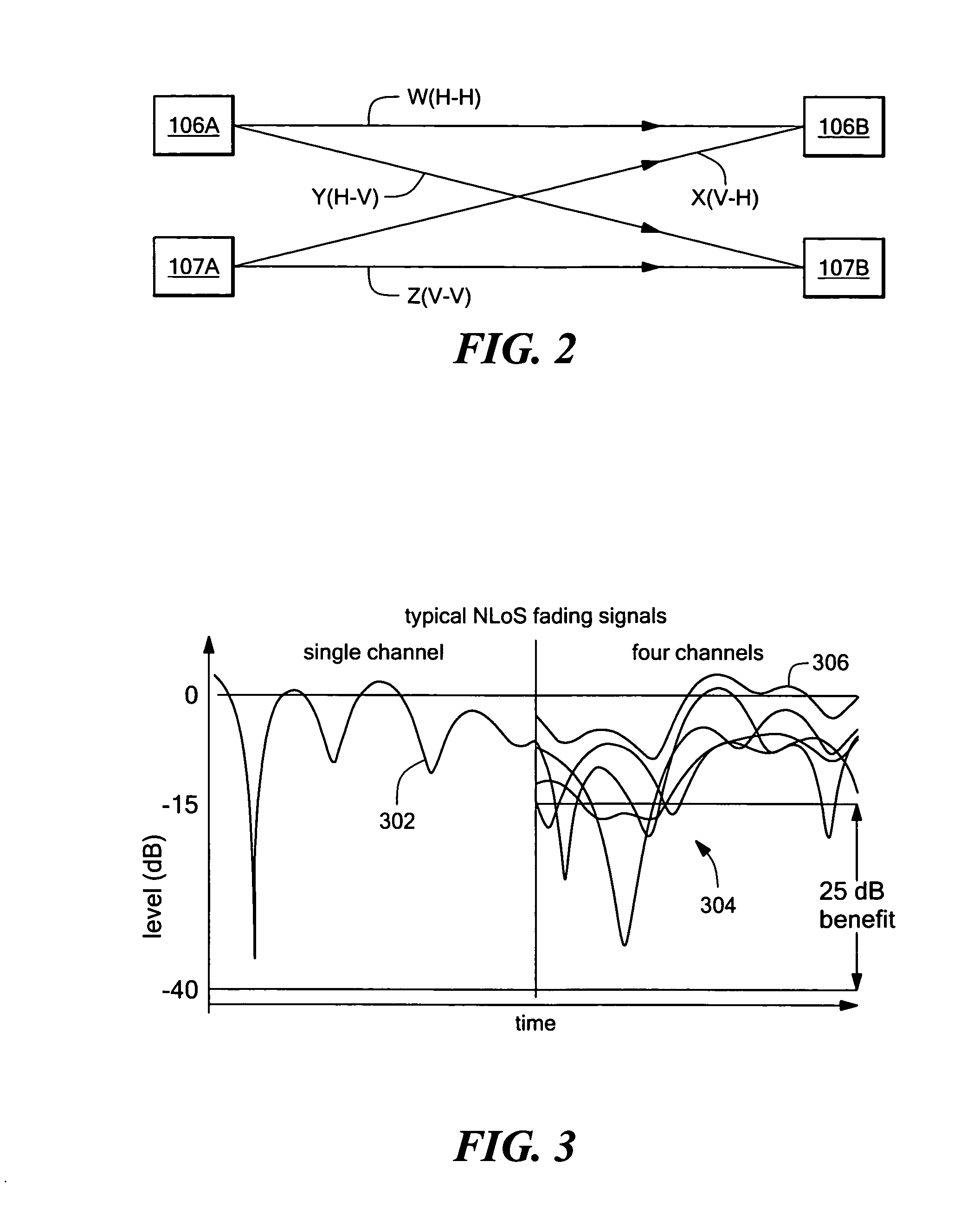

Multiple input multiple output (MIMO) wireless communications system

ActiveUS7333455B1Minimize waterMinimize ground bounce nullPower managementModulated-carrier systemsPolarization diversityFrequency spectrum

A wireless broadband communications system that can transmit signals over communications links with multiple modes of diversity, thereby allowing signals having very low correlation to propagate over the link along multiple orthogonal paths. The system can be implemented as a non-line-of-sight (NLOS) system or a line-of-sight (LOS) system. The NLOS system employs orthogonal frequency division modulation (OFDM) waveforms to reduce multi-path interference and frequency selective fading, adaptive modulation to assure high data rates in the presence of channel variability, and spectrum management to achieve increased data throughput and link availability. The LOS system employs space-time coding and spatial and polarization diversity to minimize ground bounce nulls. The system achieves levels of link availability, data throughput, and system performance that have heretofore been unattainable in wireless broadband communications systems.

Owner:MOTOROLA SOLUTIONS INC

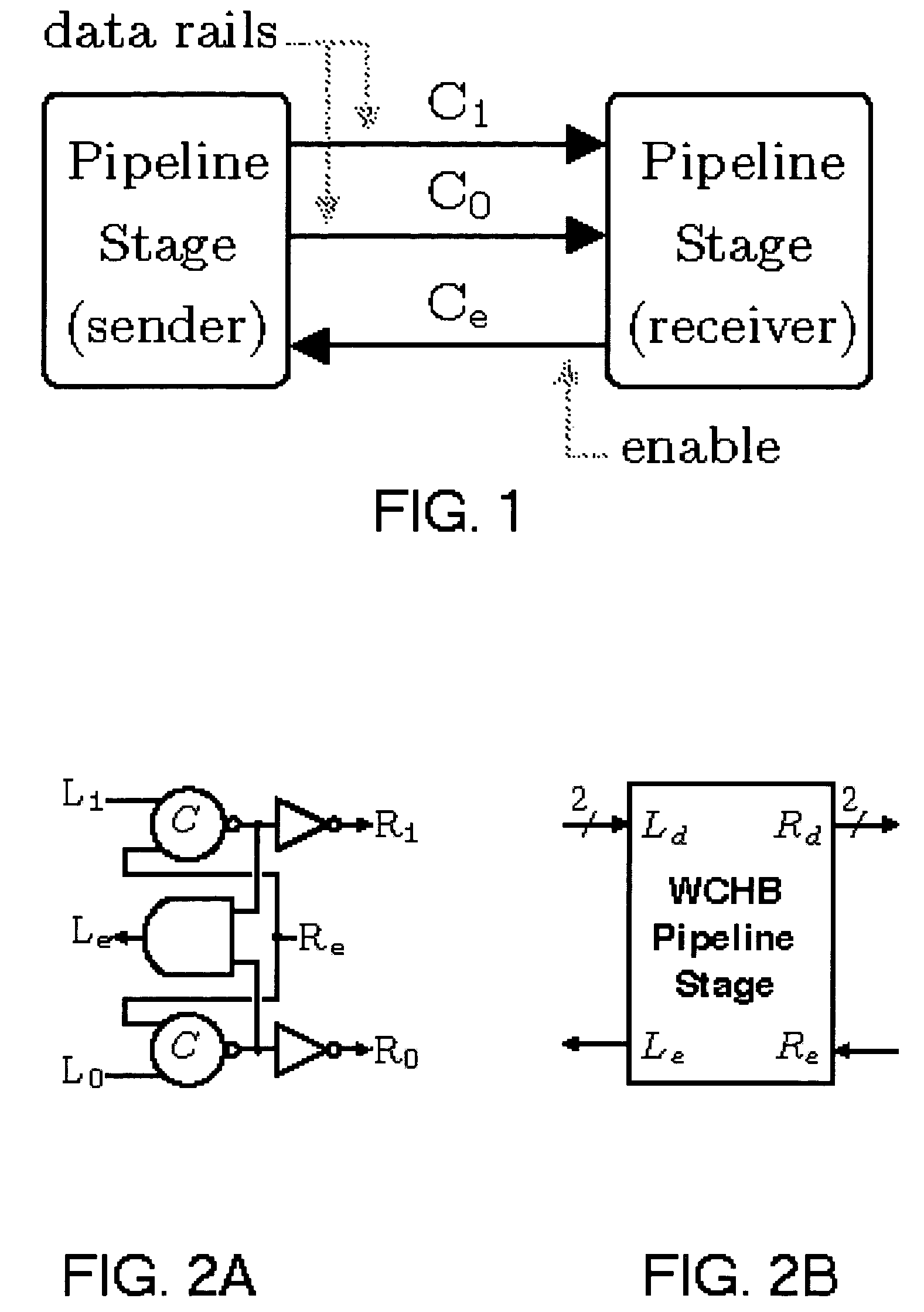

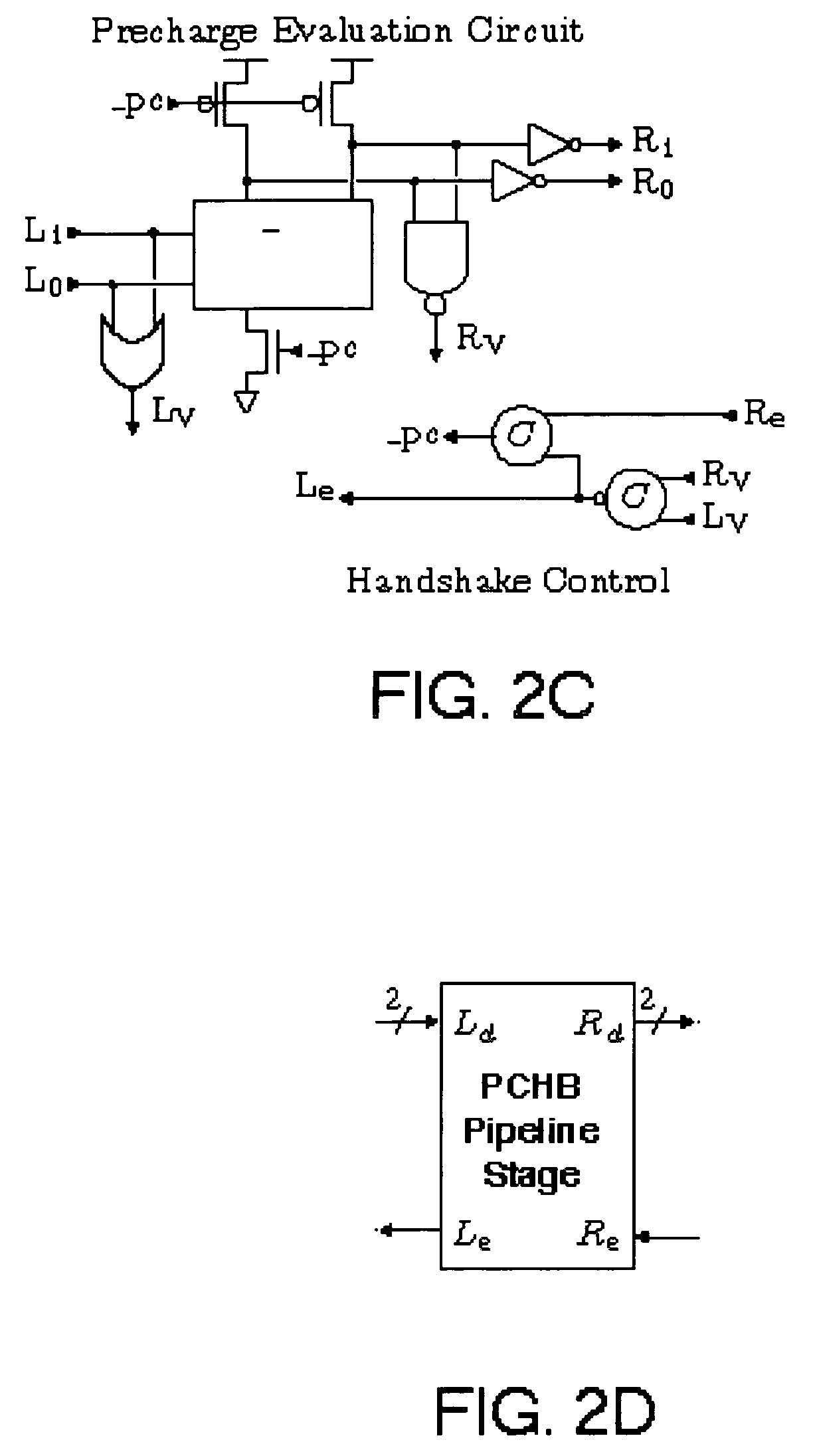

Programmable asynchronous pipeline arrays

ActiveUS7157934B2Improve data throughputEfficient implementationSolid-state devicesLogic circuits using elementary logic circuit componentsComputer scienceInterconnect architecture

Owner:CORNELL RES FOUNDATION INC +1

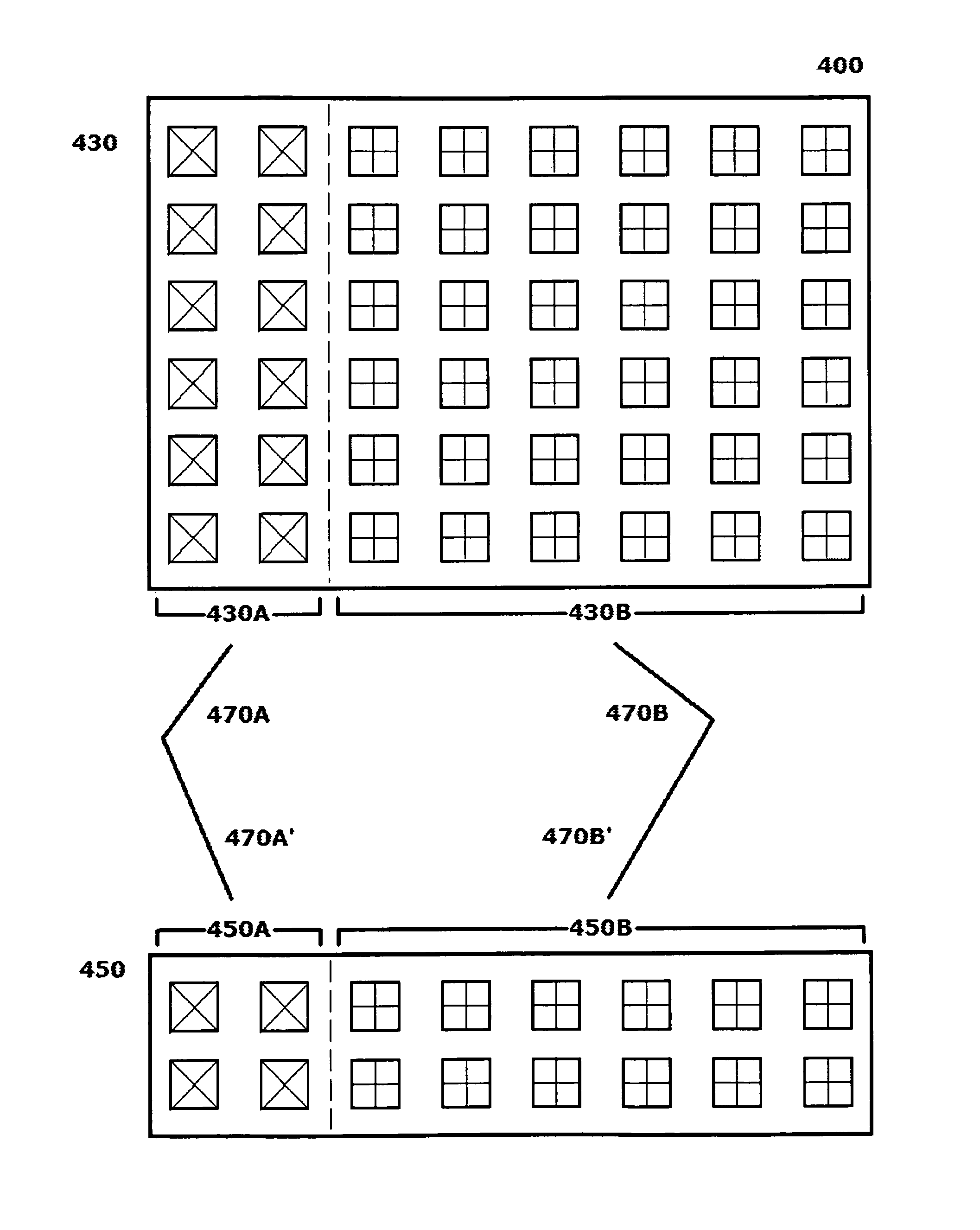

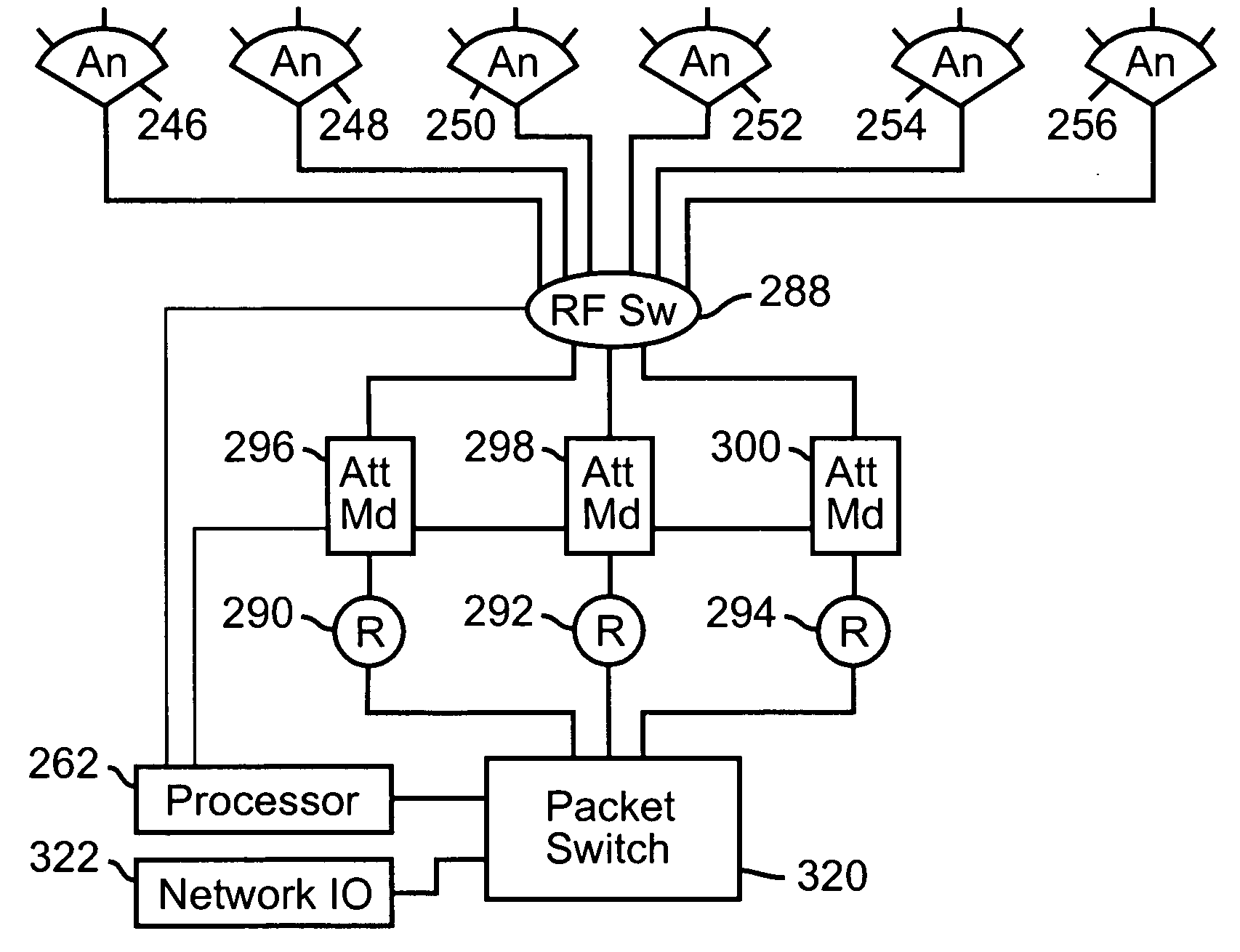

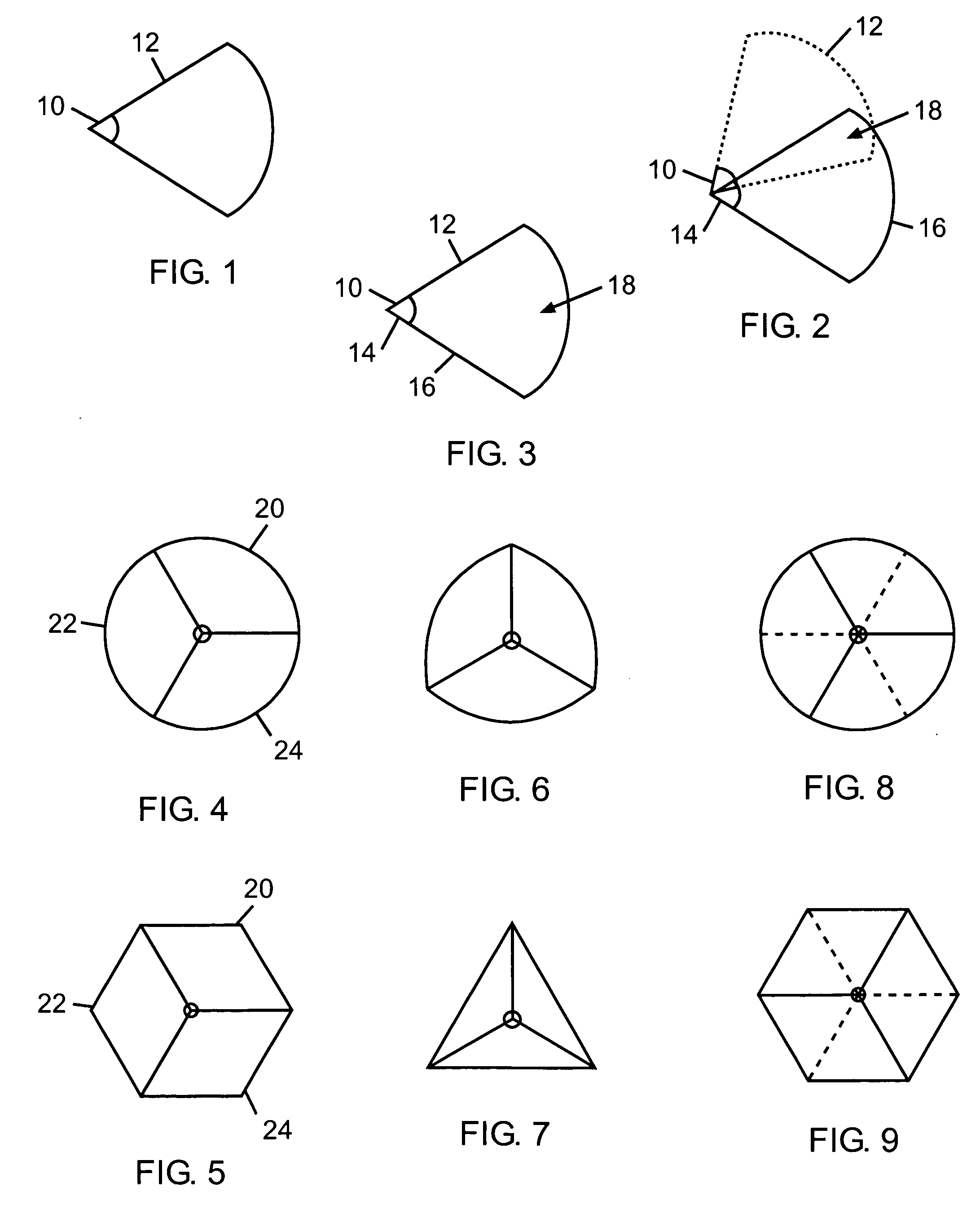

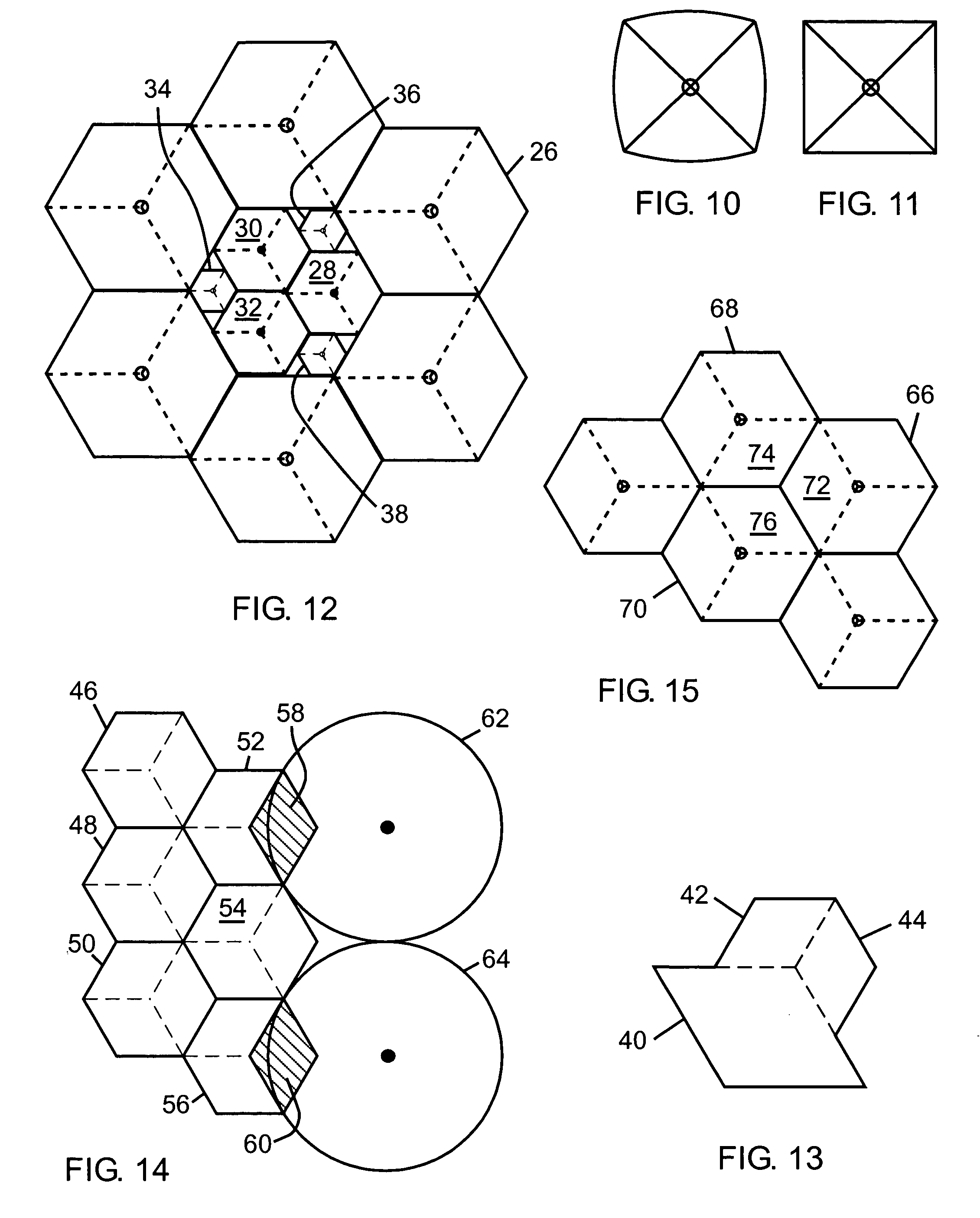

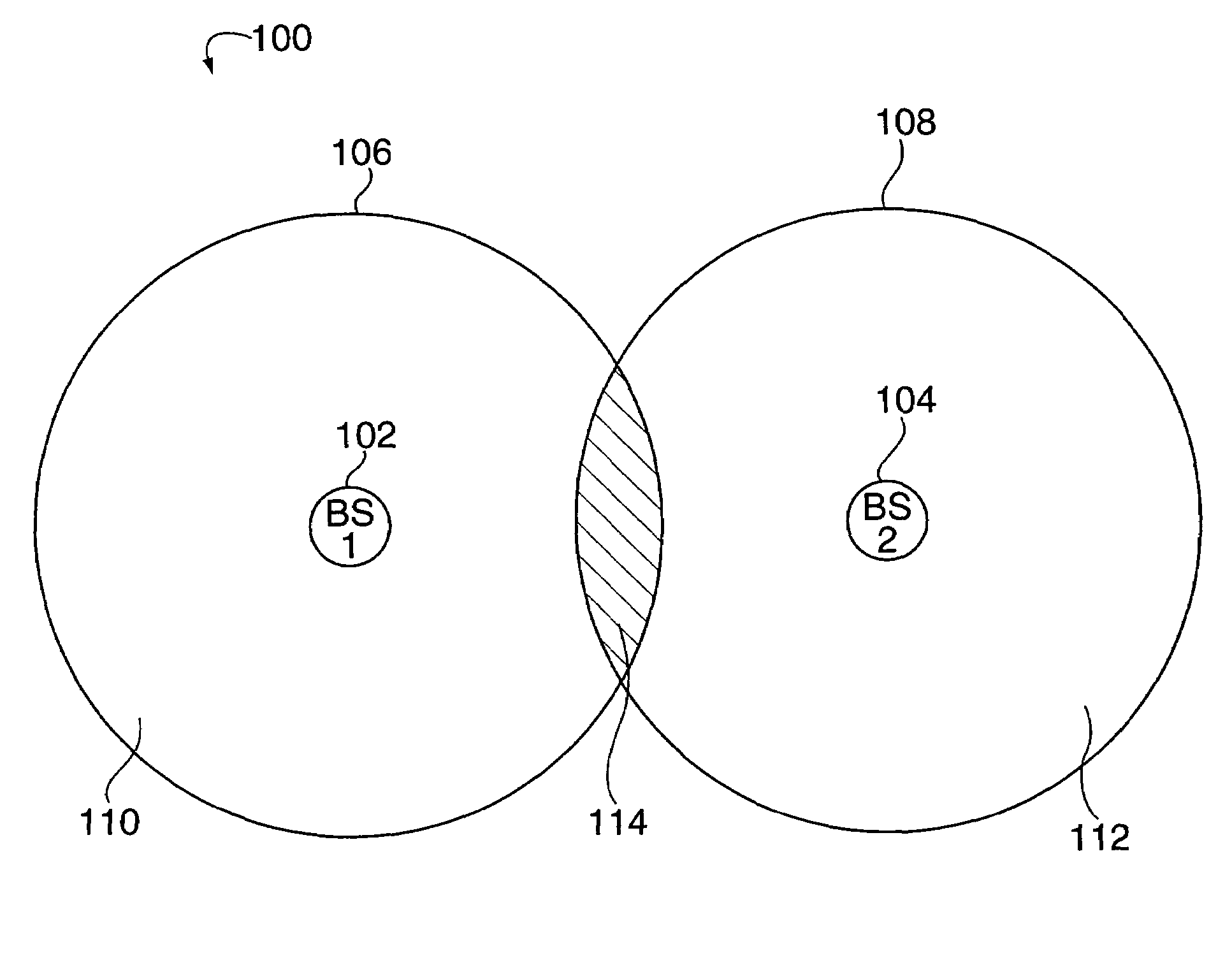

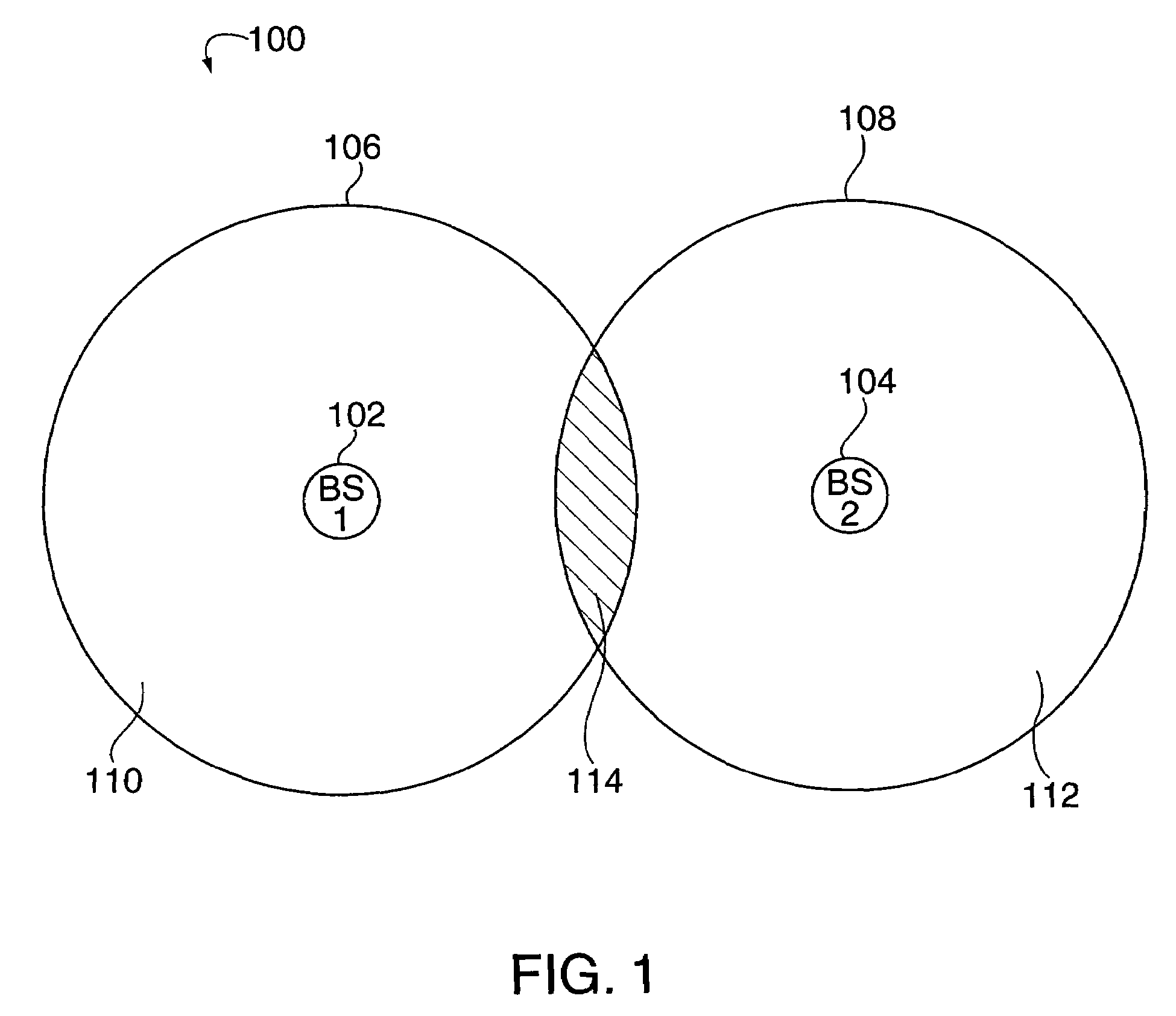

Methods and apparatus for high throughput multiple radio wireless cells and networks

InactiveUS20050003763A1Minimize interferenceImprove data throughputSite diversitySpatial transmit diversityUltrasound attenuationWireless

Methods and apparatus for high throughput wireless cells and networks are described. The wireless cells may be equipped with multiple radios. Antennas may be arranged into overlapping and non-overlapping patterns. Channels may be assigned to foster servicing clients, and inter-cell communication. Attenuation may be used to decrease interference. Networks may be formed using a variety of methods and apparatus.

Owner:ROTANI

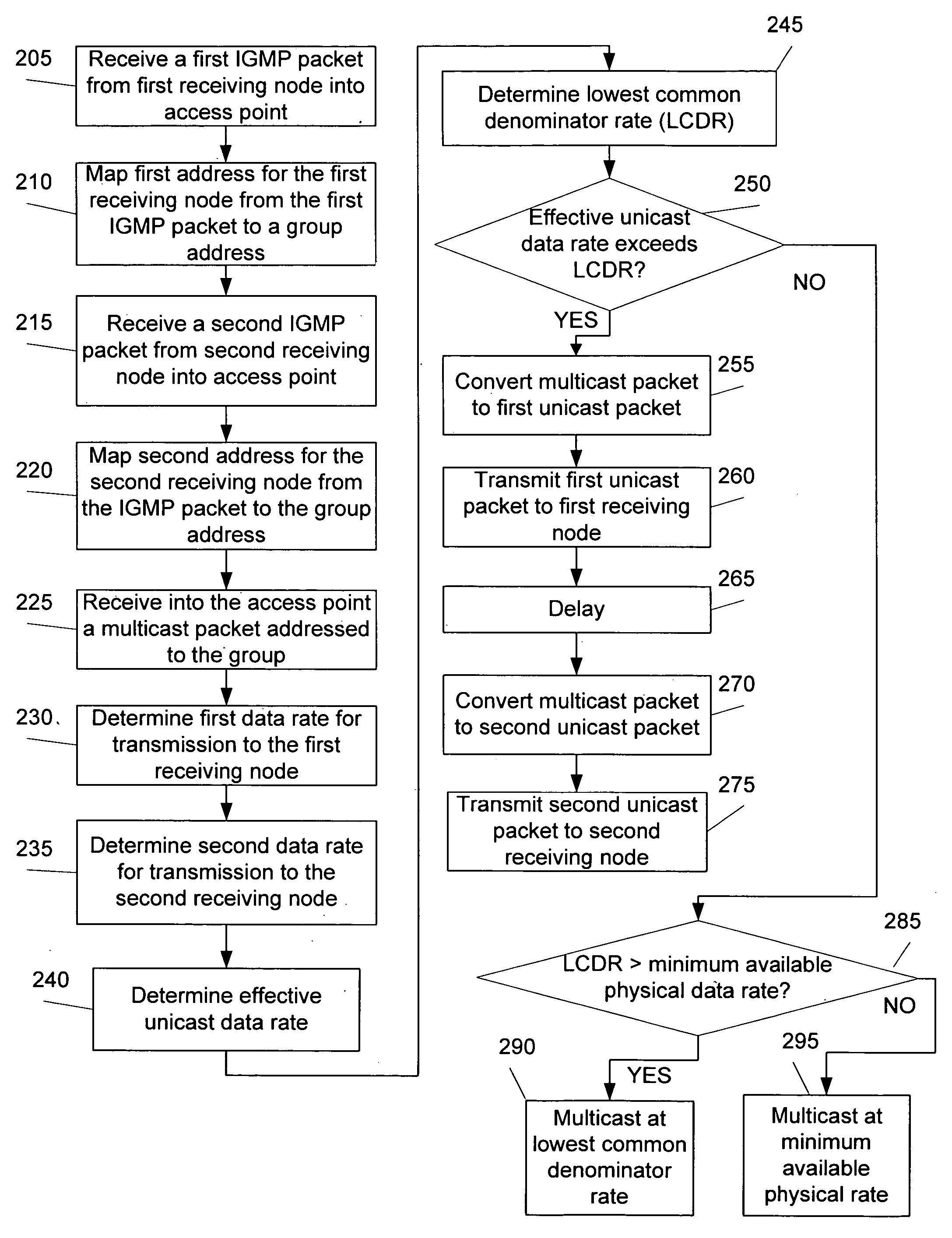

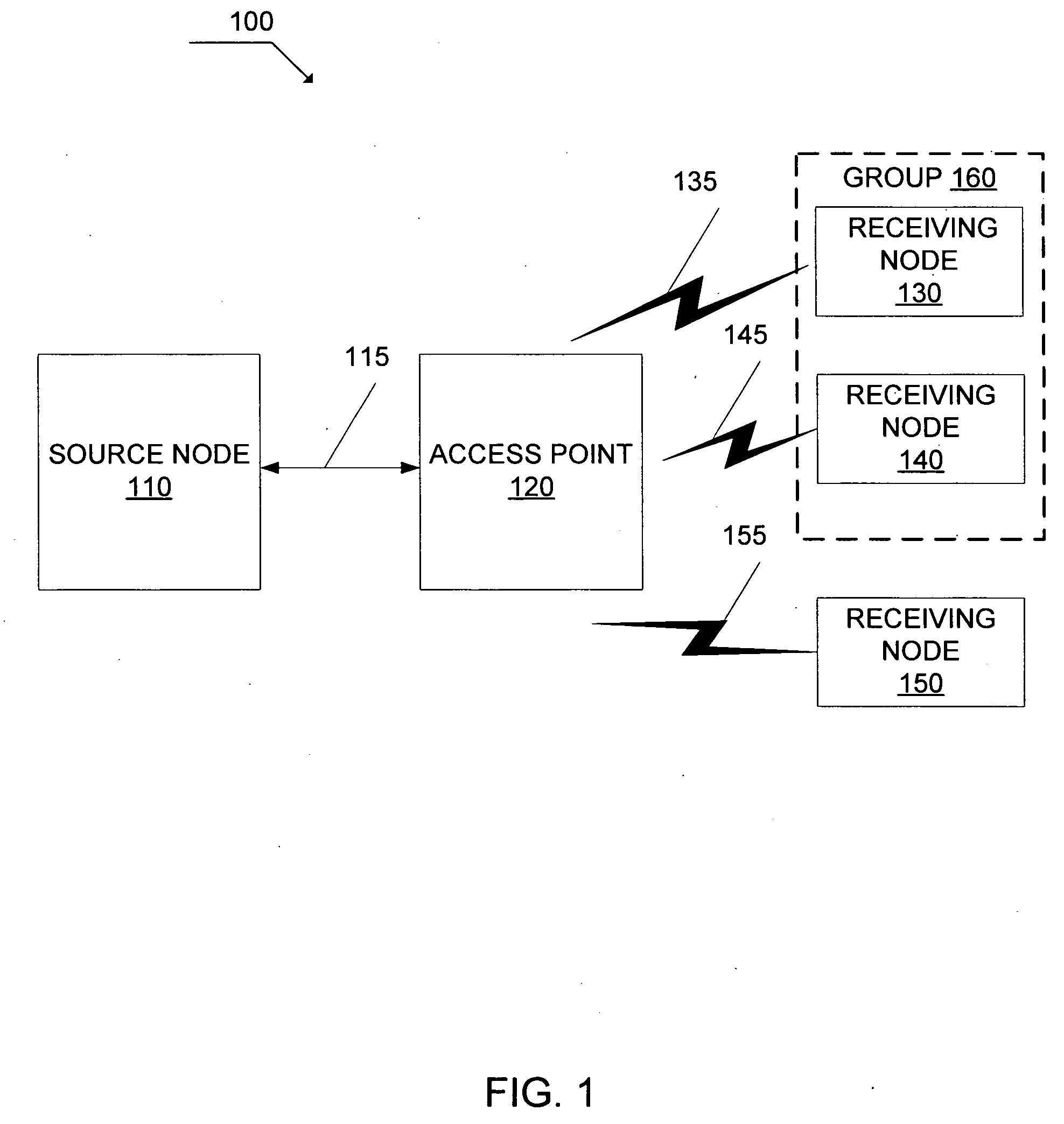

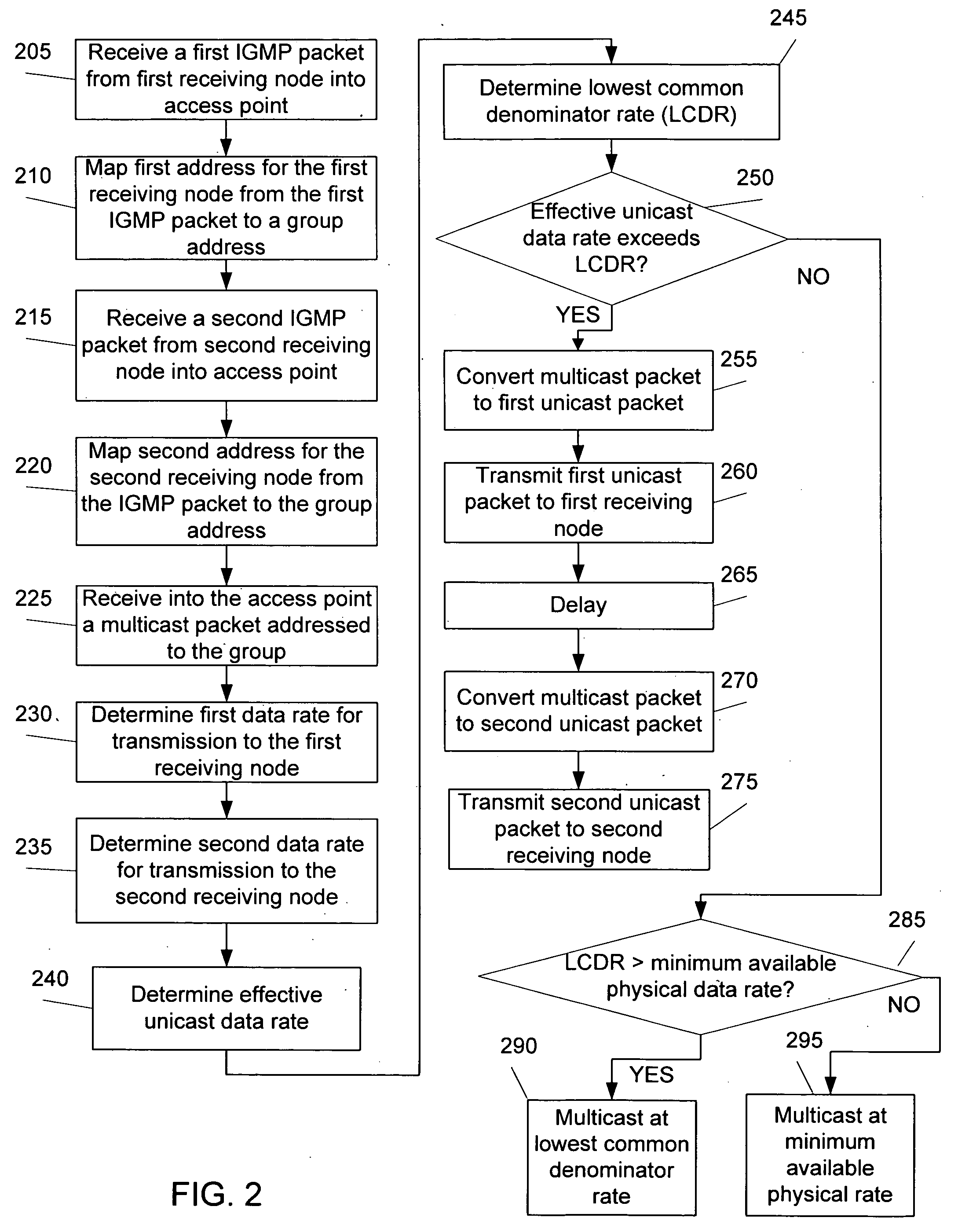

Systems and methods for improved data throughput in communications networks

ActiveUS20060098613A1Improve data throughputIncrease data rateNetwork traffic/resource managementSpecial service for subscribersBroadcast packetTelecommunications

An access point of a communications network is disclosed configured to receive a multicast or broadcast packet from a source. The access point converts the multicast or broadcast packet into a unicast packet addressed to a station associated with the access point. The access point then transmits the unicast packet over the communications network from the access point to the station. The access point further may determine a minimum data rate by which the access point may transmit the multicast or broadcast packet to the station and determines an effective unicast rate for transmitting the unicast packet to the station. If the effective unicast rate does not exceed the minimum data rate, the access point does not transmit the unicast packet to the station and transmits the multicast or broadcast packet.

Owner:ARRIS ENTERPRISES LLC

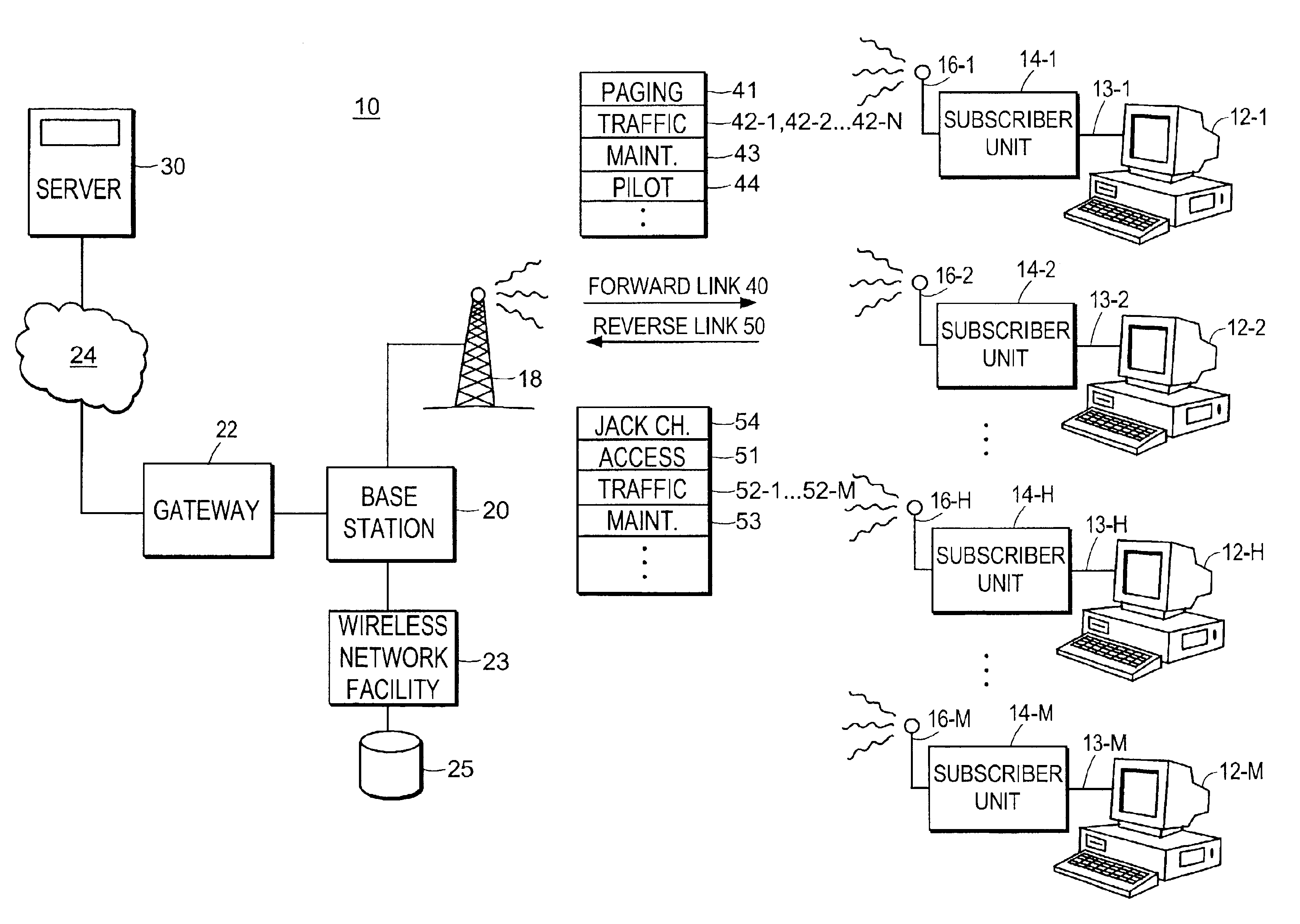

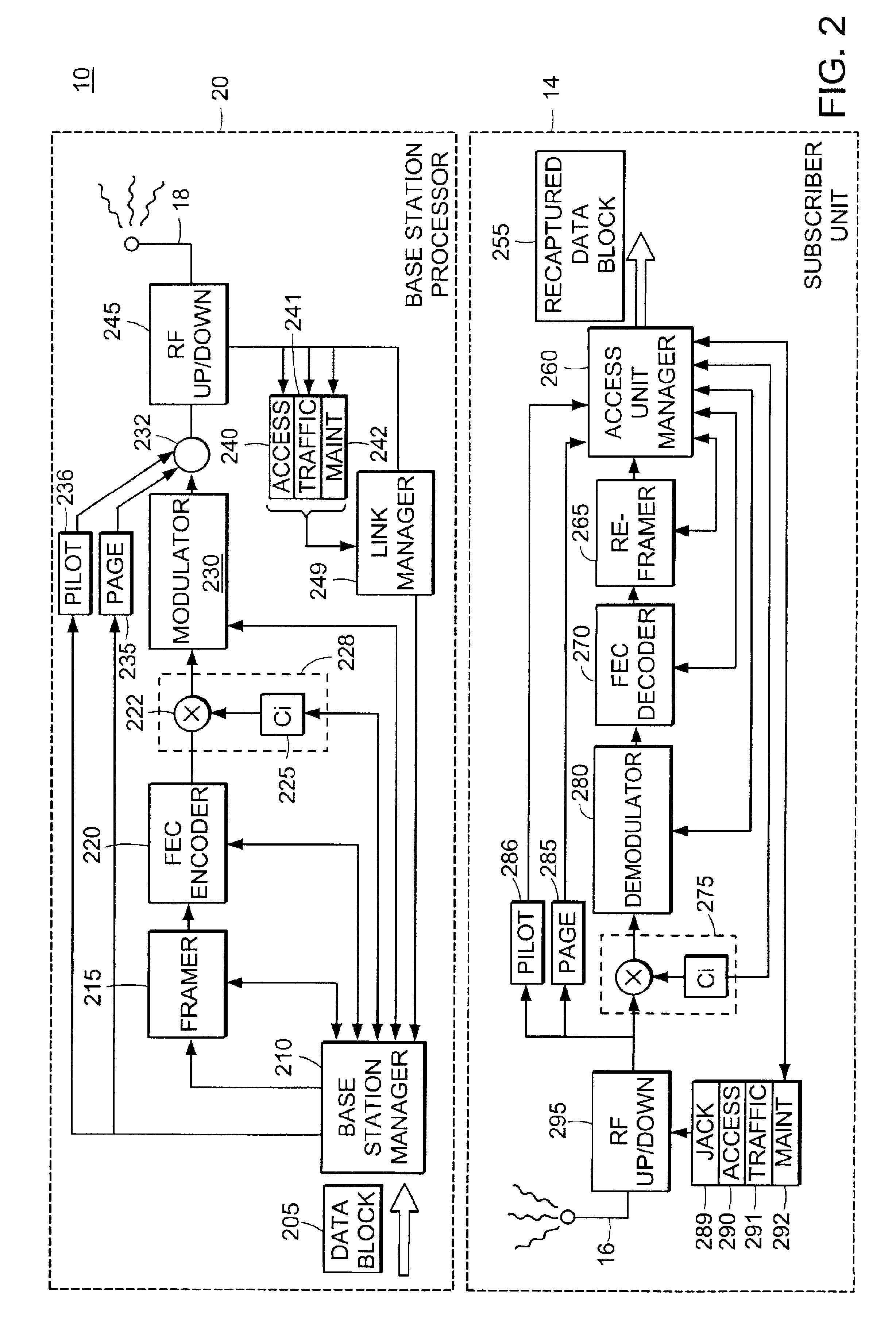

Alternate channel for carrying selected message types

InactiveUS6954448B2Increase profitLess bitError prevention/detection by using return channelNetwork traffic/resource managementMessage typeTraffic channel

In an illustrative embodiment of the present invention, a channel is allocated to carry messages from each of multiple subscriber units to a base station. Selected messages generated by a subscriber unit that would otherwise be transmitted over an assigned reverse link traffic channel are instead encoded and transmitted to the base station over a shared reverse link channel. Preferably, the shared reverse link channel is time-slotted and each subscriber unit transmits information to the base station in an assigned time slot so that the base station receiving the messages can identify from which subscriber unit a message is sent. Certain bits in a time slot of the shared channel as set by a subscriber unit can be used to communicate a particular message to the base station. For instance, a single bit that is transmitted in a time slot can be encoded to transmit a substitute message from one of the multiple subscriber units to a base station, where the setting of the bit itself indicates a message type.

Owner:APPLE INC

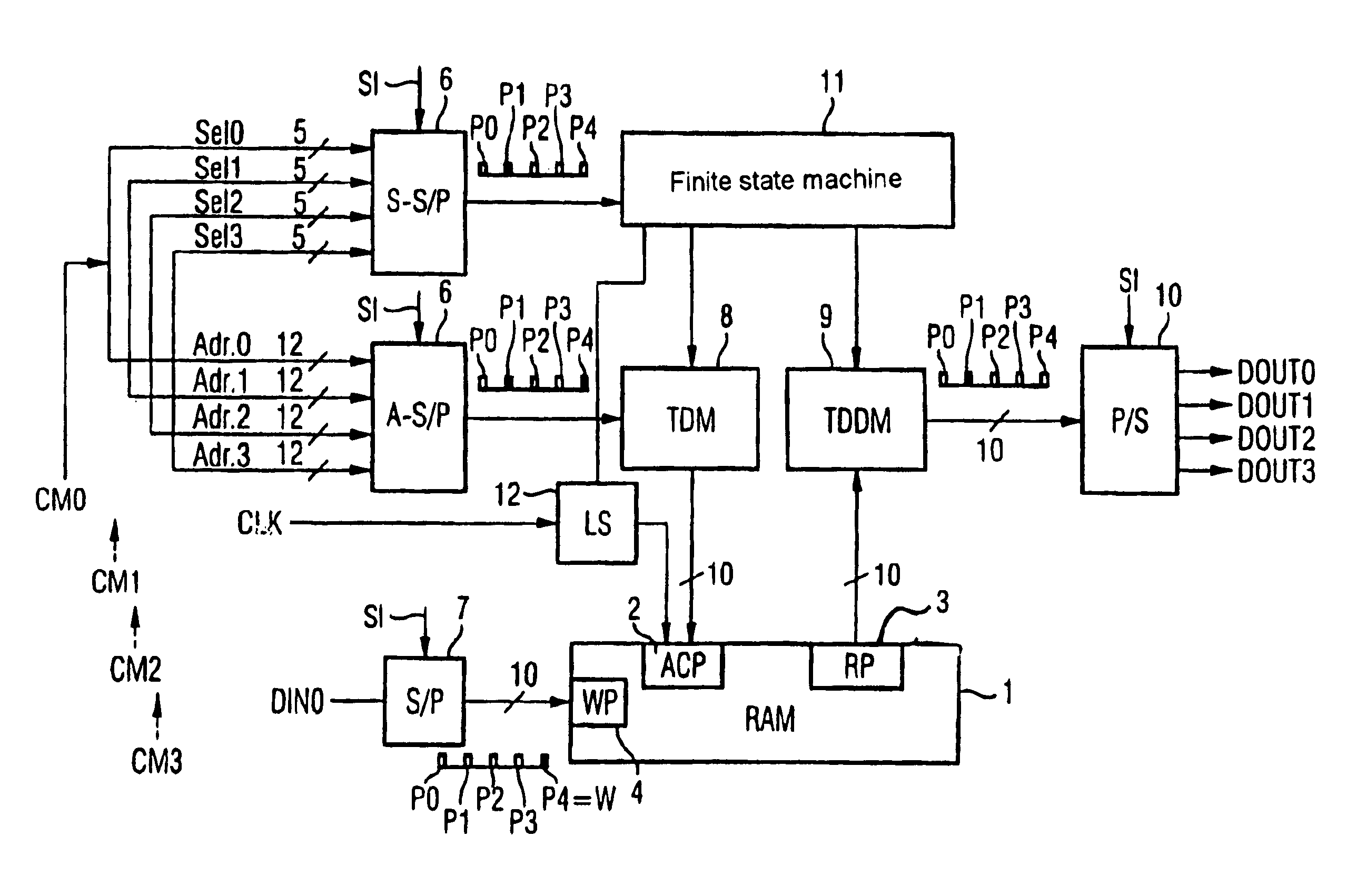

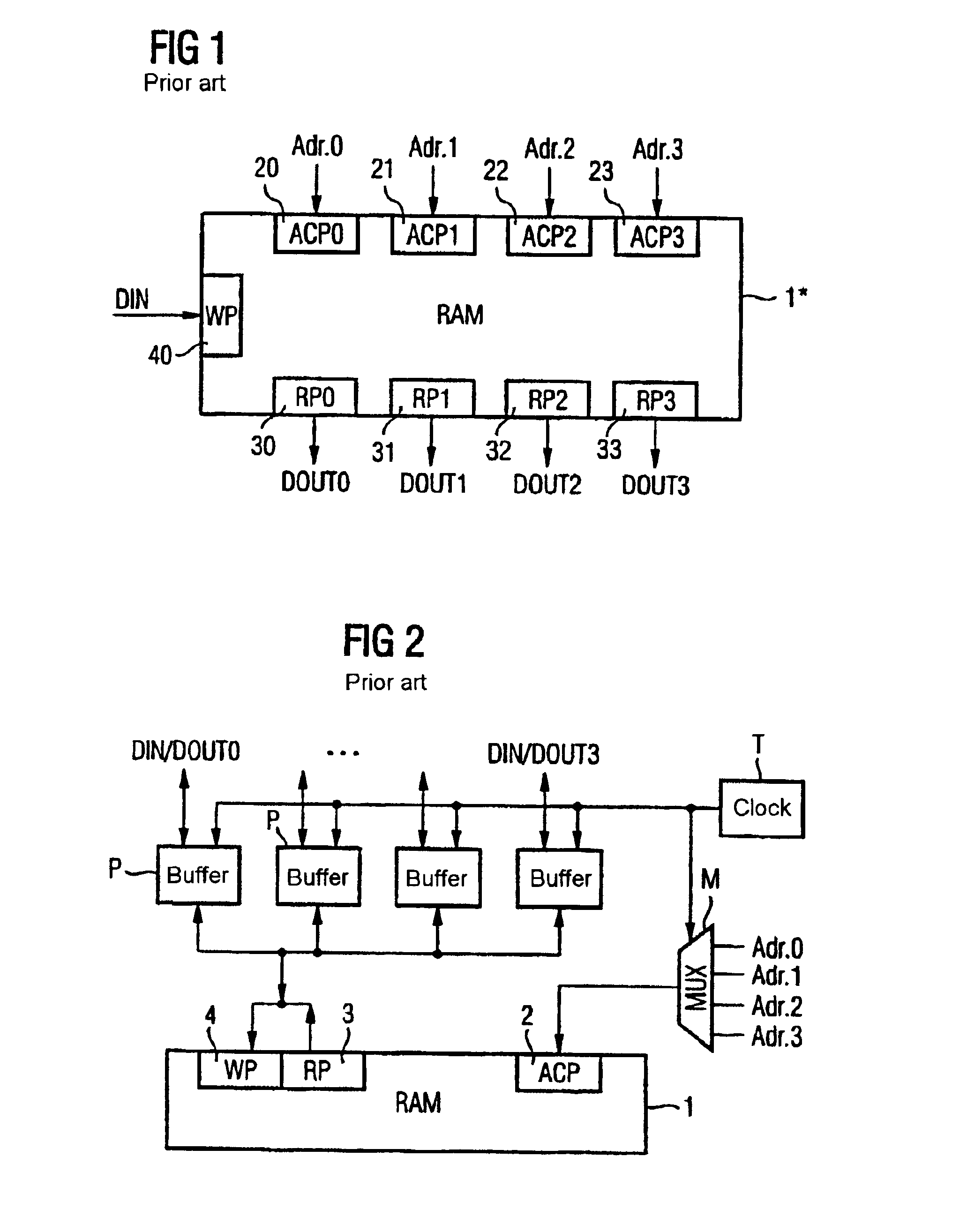

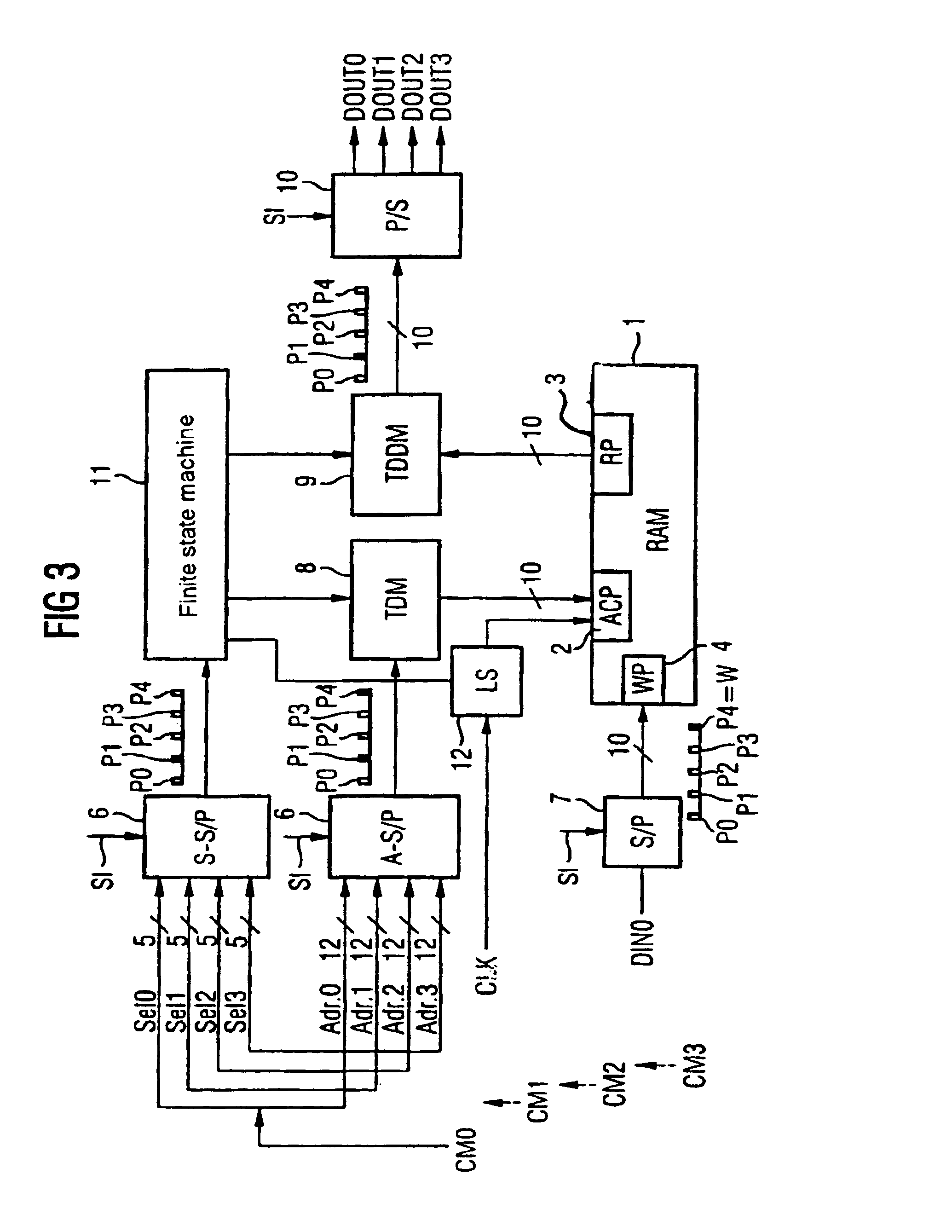

Multiport-RAM memory device

InactiveUS6842436B2Reduce power consumptionLow power lossEnergy efficient ICTTime-division multiplexEmbedded systemPower control

The invention relates to a multiport-RAM memory device, comprising a RAM memory unit (1), a number of serial / parallel converters (5, 6, 7) and a parallel / serial converter (10), for converting serial signals into parallel signals. Said multiport-RAM memory device further comprises a control unit (11) and two timeslot allocation devices (8, 9), whereby an emulation of a number of connections by using the simple RAM memory unit (1) may be achieved. Furthermore, a power controller (12) can significantly reduce the power demand.

Owner:NOKIA SOLUTIONS & NETWORKS GMBH & CO KG

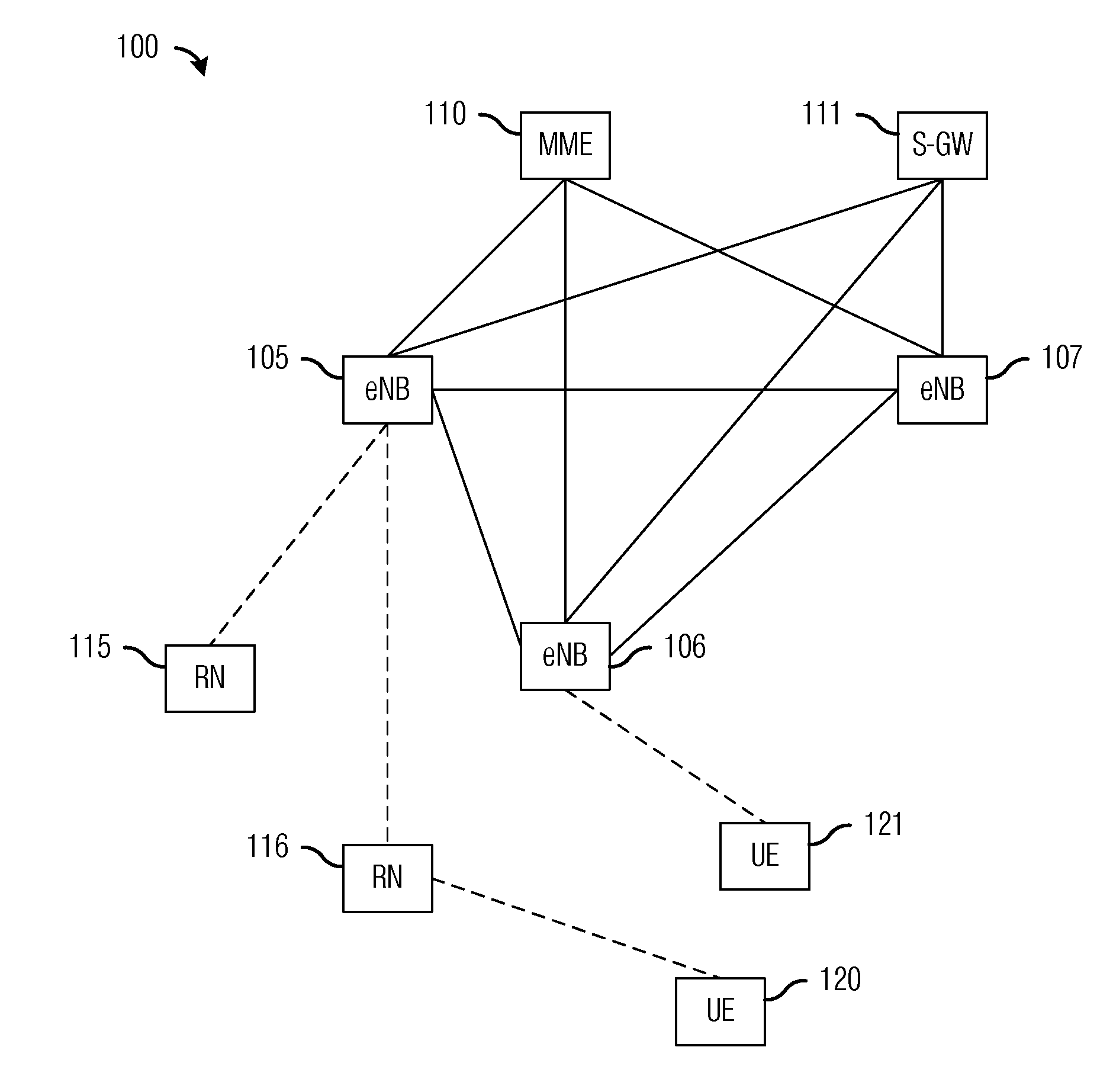

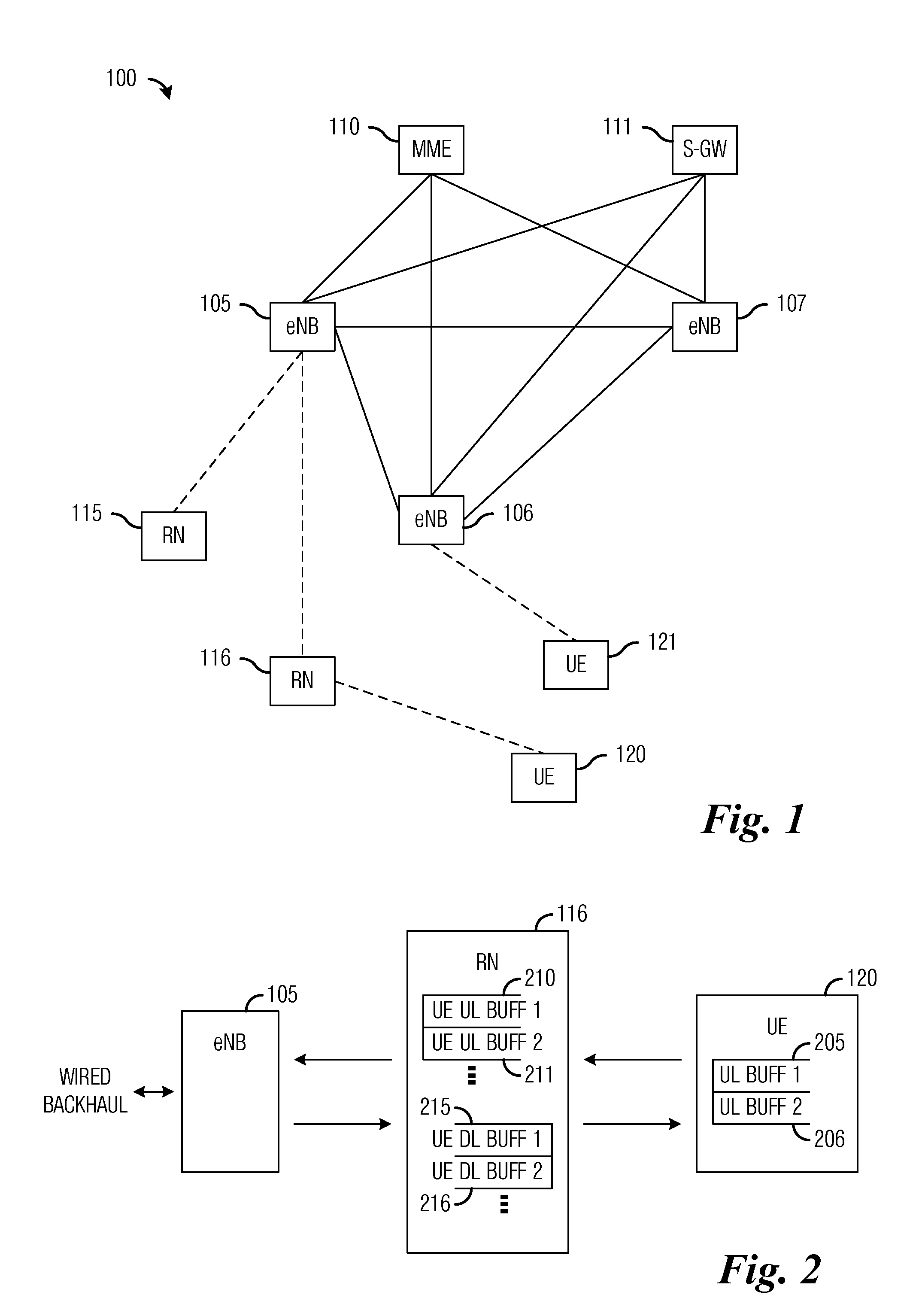

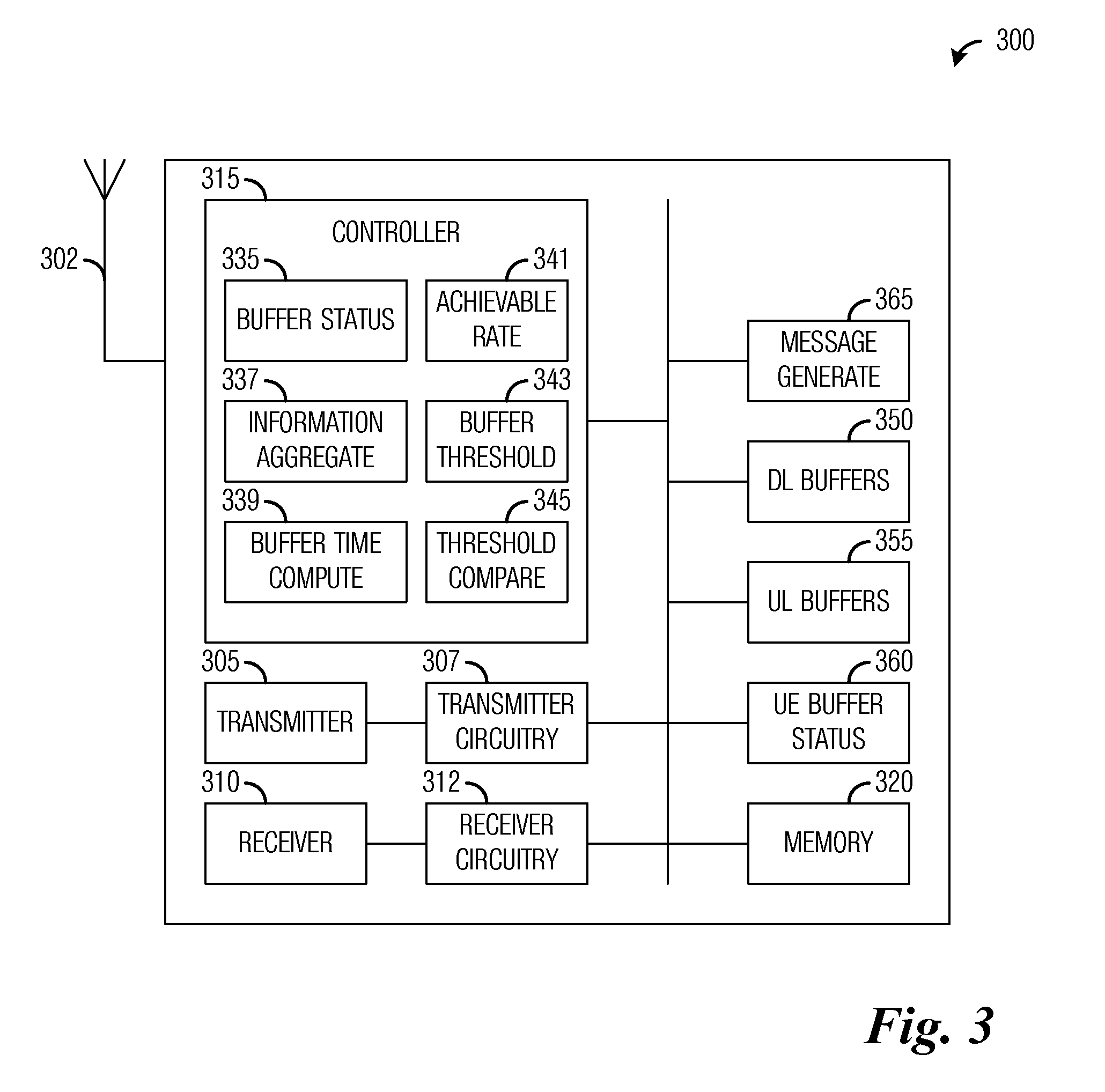

System and Method for Relay Node Flow Control in a Wireless Communications System

ActiveUS20100302946A1Improve data throughputError preventionFrequency-division multiplex detailsCommunications systemCommunication control

A system and method for relay node flow control and / or congestion control in a wireless communications system are provided. A method for relay operation includes determining a buffer status of a buffer for data to be transmitted on a communications channel allocated from network resources controlled by a communications controller, computing buffer status information based on the buffer status, and transmitting the buffer status information to the communications controller.

Owner:FUTUREWEI TECH INC

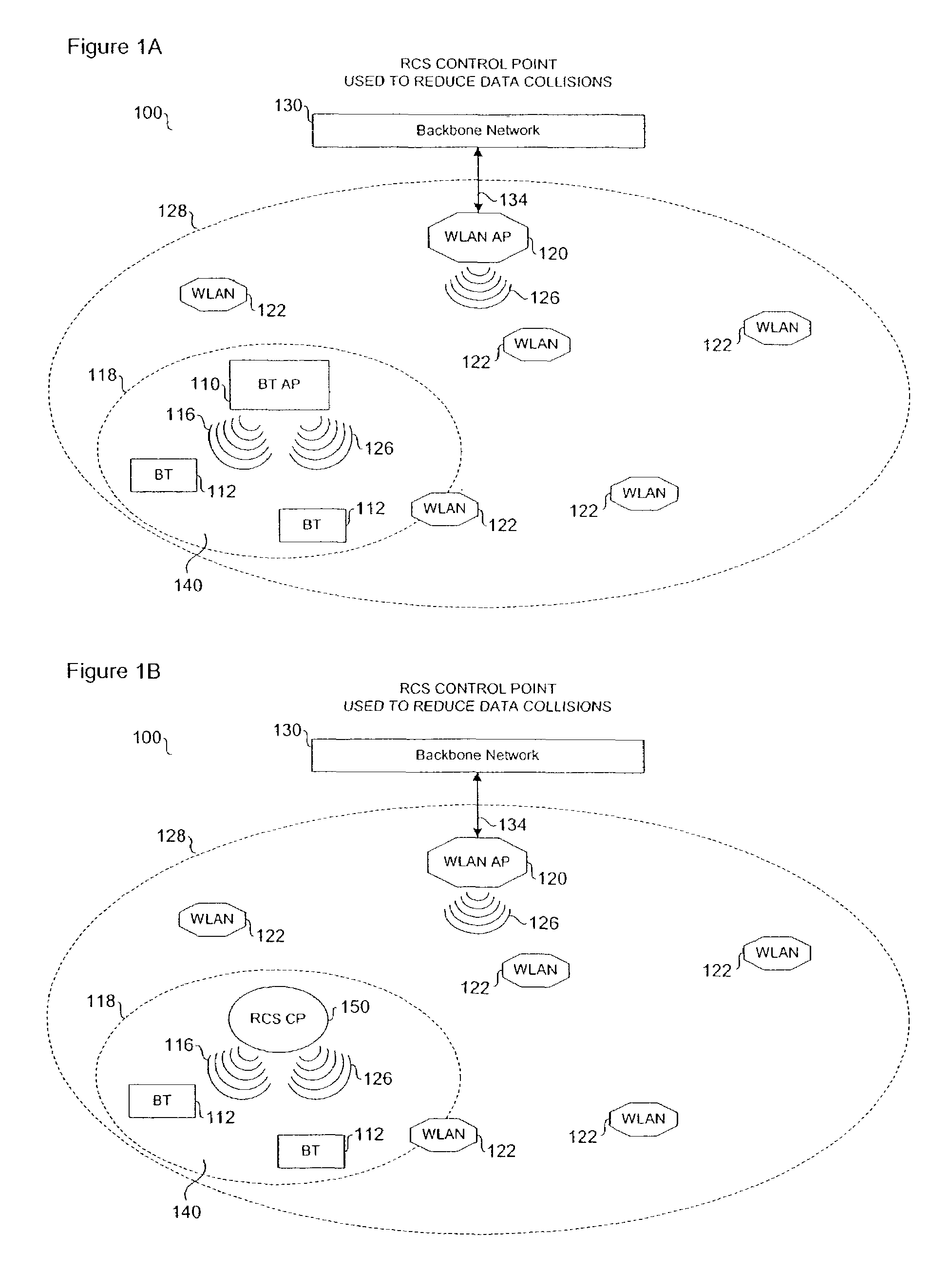

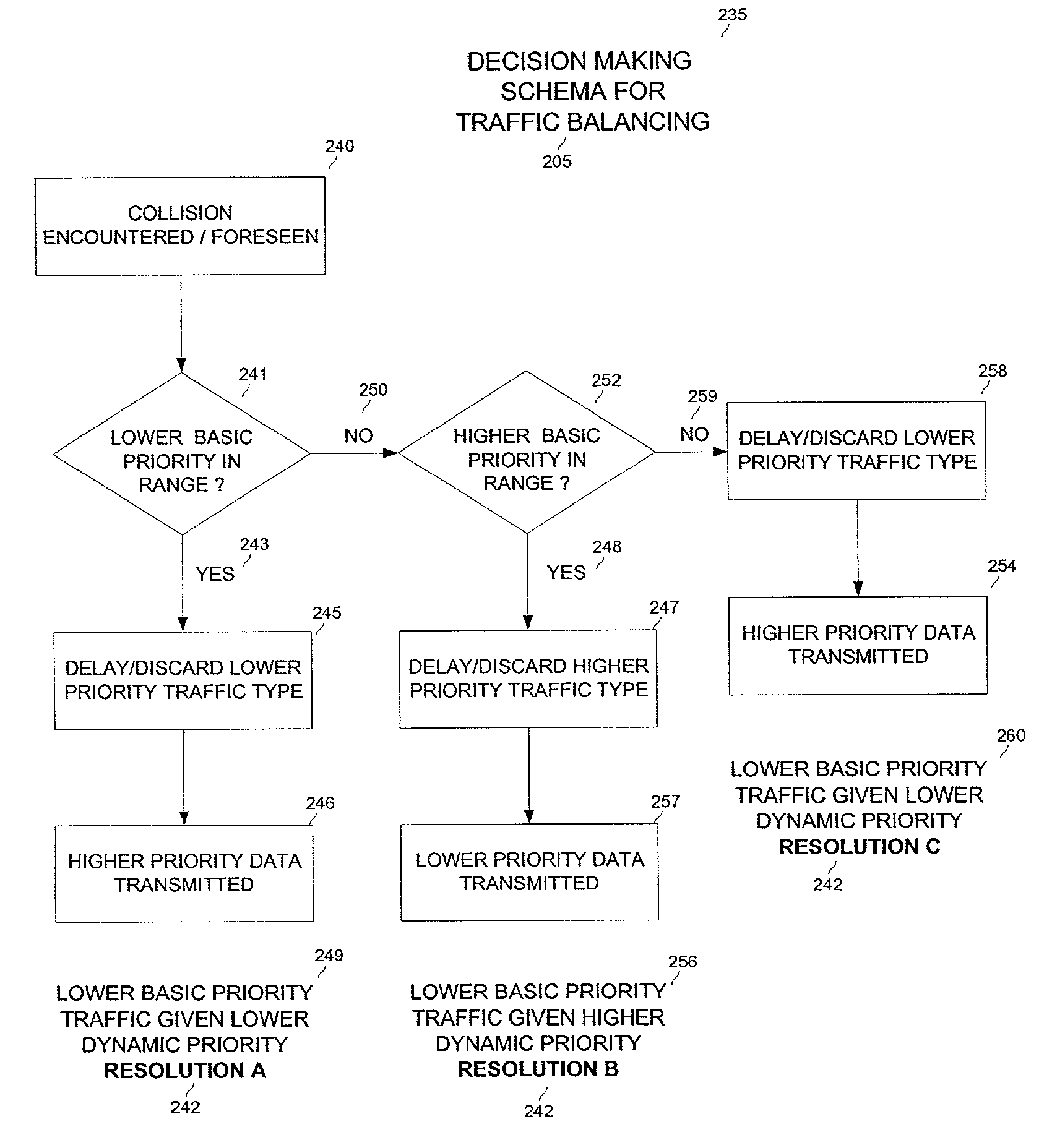

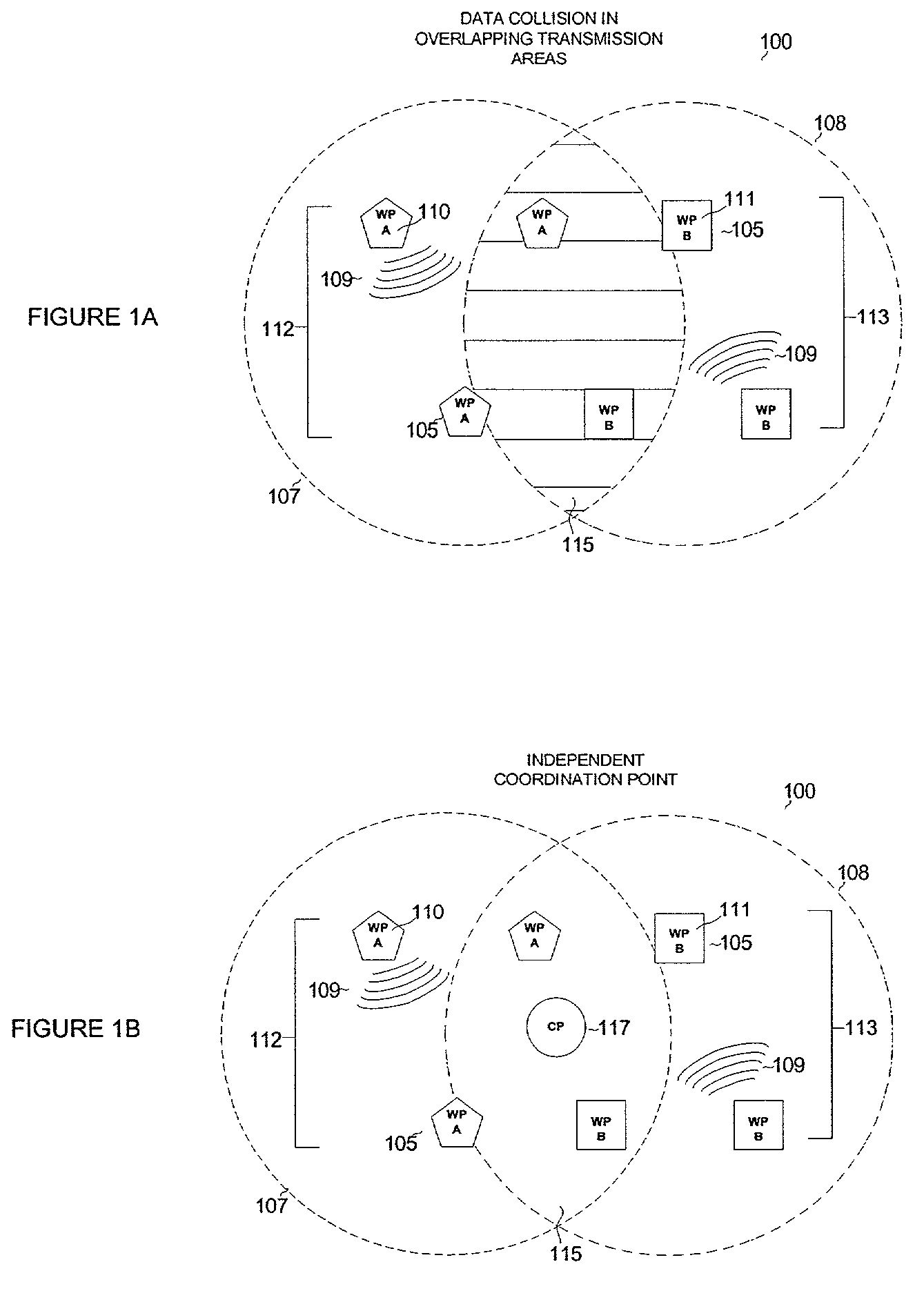

Remotely-cooperative scheduling solution for moderating wireless protocols

ActiveUS7215659B1Reduce frequency-overlapping collisionAvoid collisionTime-division multiplexRadio/inductive link selection arrangementsWireless transmissionWireless mesh network

Wireless communication networks utilize various communication protocols to exchange data between wireless network devices. Overlapping communication frequencies between data exchange protocols present a collision problem when data transmissions interfere with one another during wireless transit. A device for moderating transmission traffic in a wireless network where overlapping communication frequencies coexist is described to reduce or avoid interference caused by signal collisions.

Owner:AVAGO TECH INT SALES PTE LTD

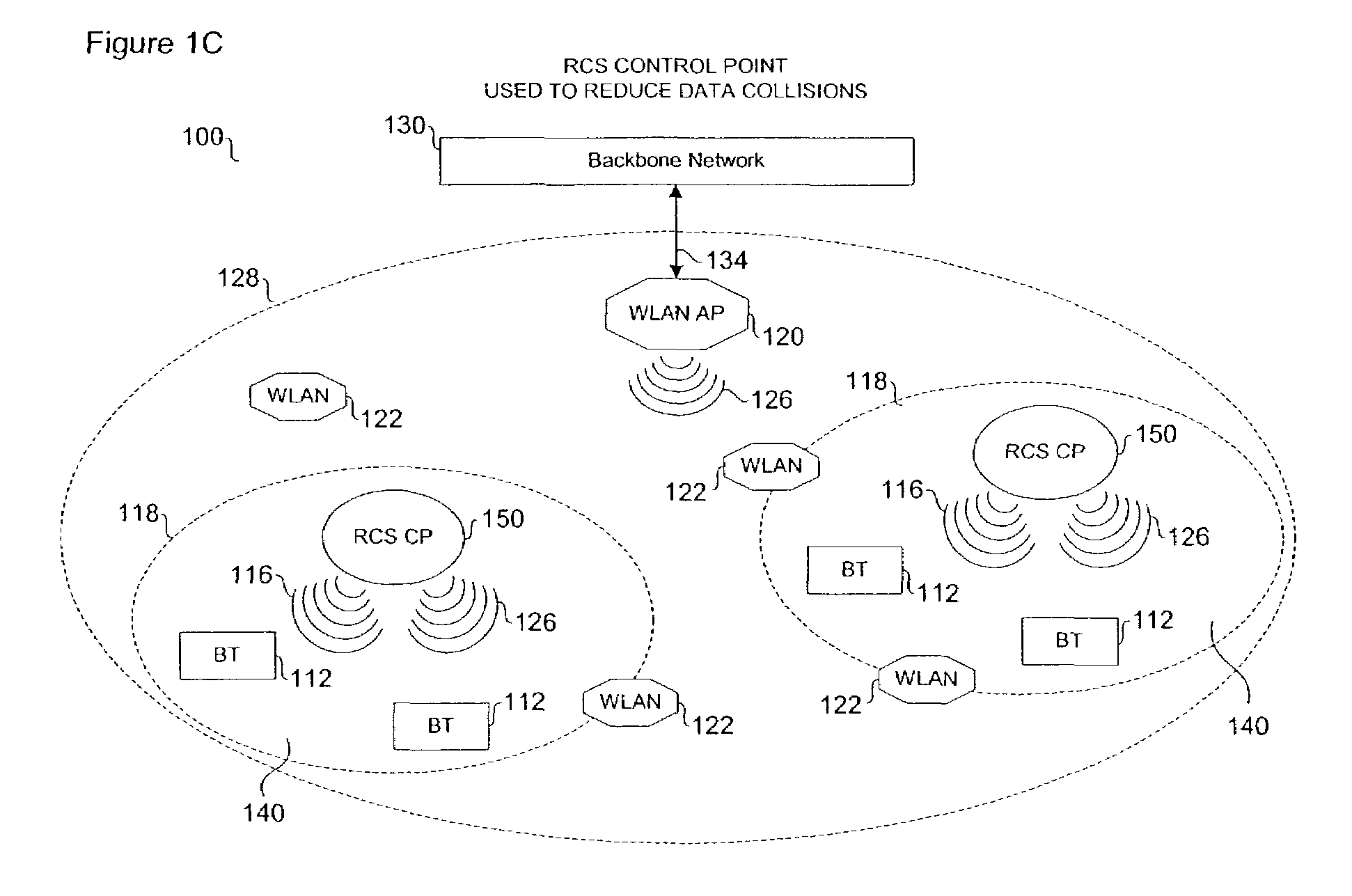

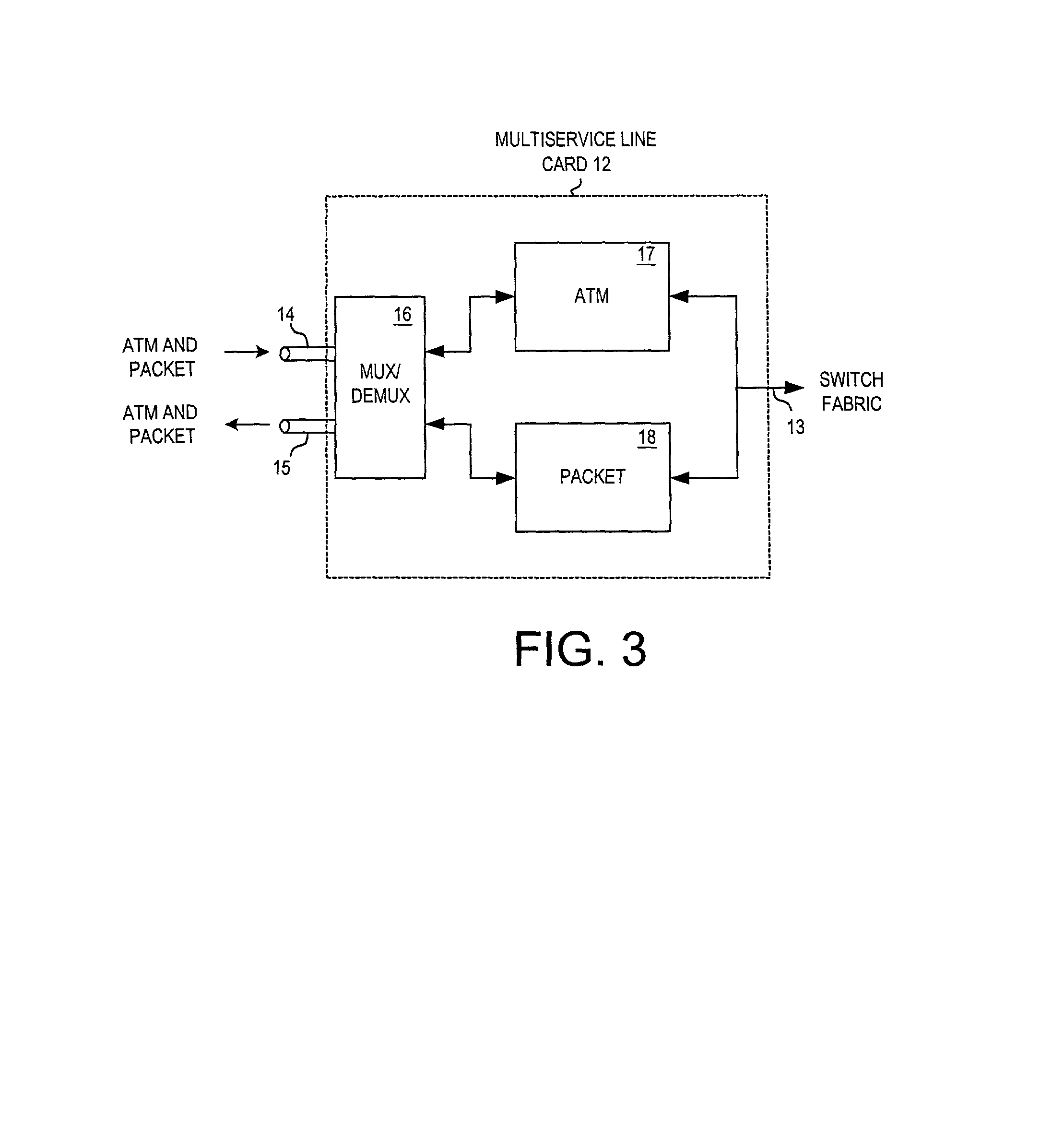

Using an embedded indication of egress application type to determine which type of egress processing to perform

ActiveUS7139271B1Reduce numberReduce amount of memoryTime-division multiplexData switching by path configurationCell basedPoint of entry

A multi-service segmentation and reassembly (MS-SAR) integrated circuit is disposed on a line card in a router or switch. The MS-SAR can operate in an ingress mode so that it receives packet and / or cell format data and forwards that data to either a packet-based or a cell-based switch fabric. The MS-SAR can also operate in an egress mode so that it receives data from either a packet-based or a cell-based switch fabric and outputs that data in packet and / or cell format. The MS-SAR has a data path through which many flows of different traffic types are processed simultaneously. Each flow is processed by functional blocks along the data path in accordance with one of several application types, the application type for a flow being predetermined by the host processor of the router or switch. Segmentation, reassembly and partitioning techniques are disclosed that reduce costs and facilitate high-speed operation.

Owner:MARVELL ASIA PTE LTD

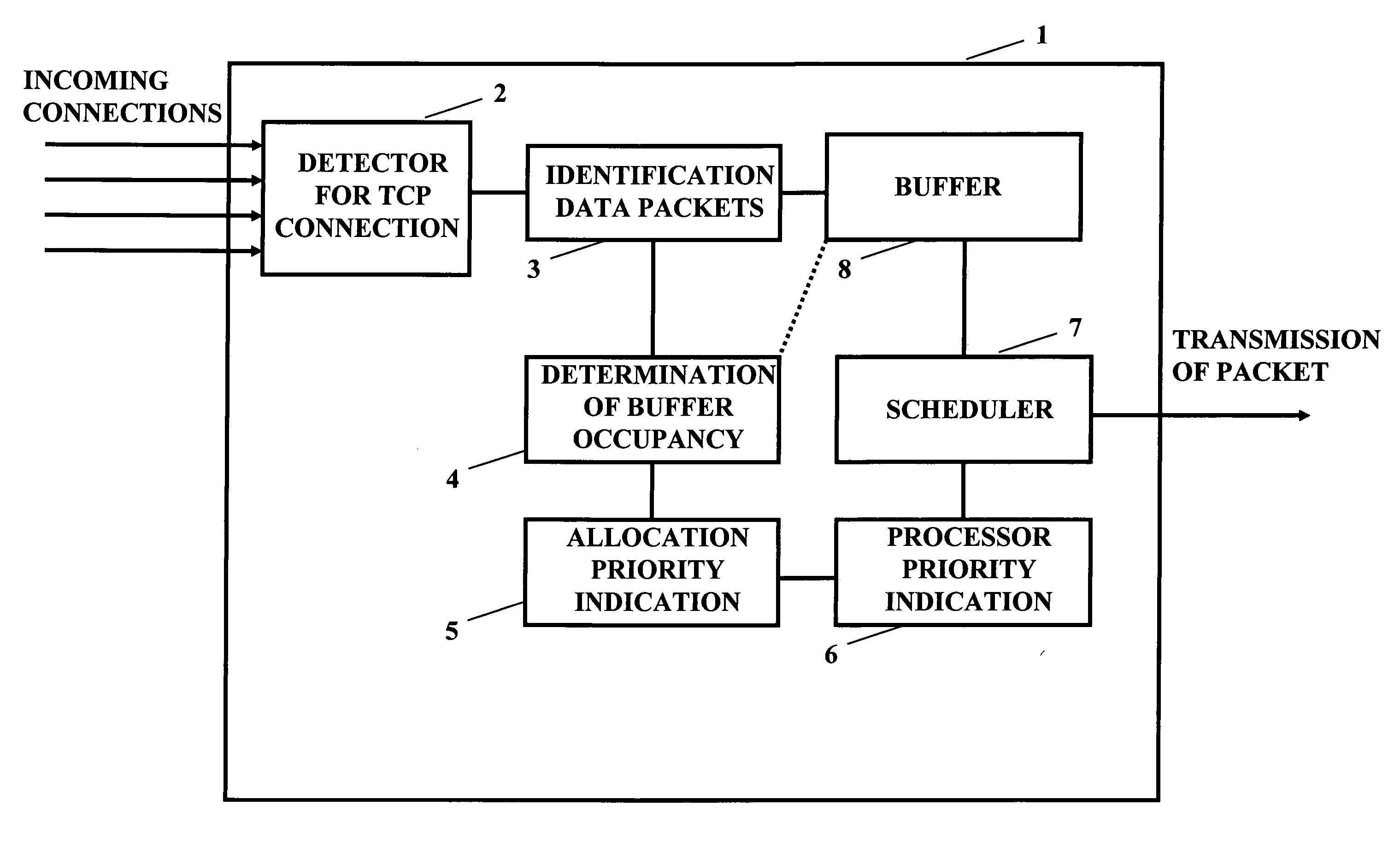

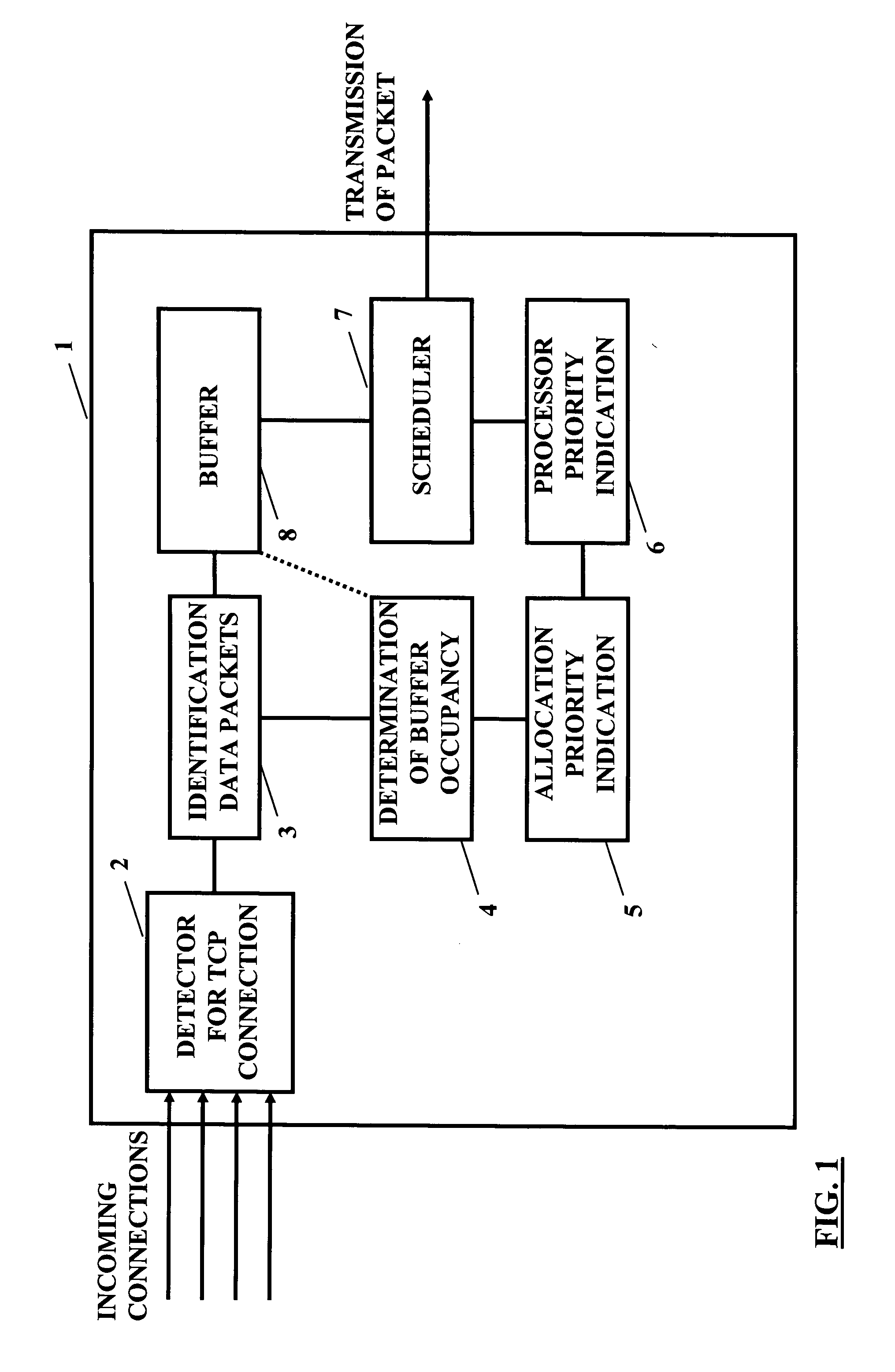

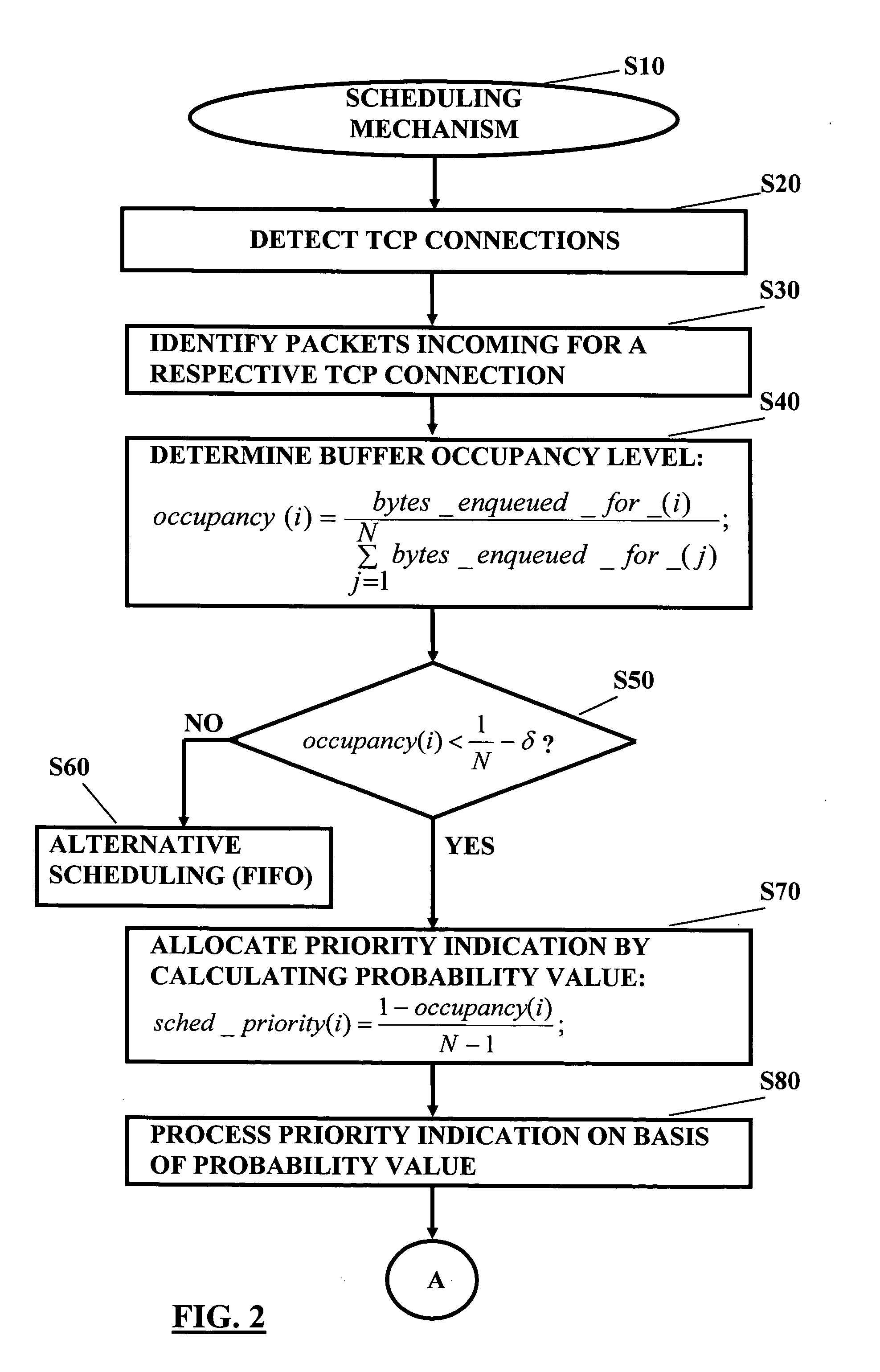

Expedited data transmission in packet based network

ActiveUS20050220097A1Blocking in networkImprove data throughputData switching by path configurationData transmissionDistributed computing

An improved scheduling mechanism usable for a data transmission in a packet based network is provided. A plurality of connections is detected, and for each of the connections, a buffer occupancy level is determined. Then, the connections having a smaller buffer occupancy level are prioritized in comparison to the other connections, and packets of the plurality of connections are scheduled on the basis of the result of the prioritizing. The scheduling mechanism is implemented in a network element of the packet based network or in a sender and receiver.

Owner:NOKIA TECHNOLOGLES OY

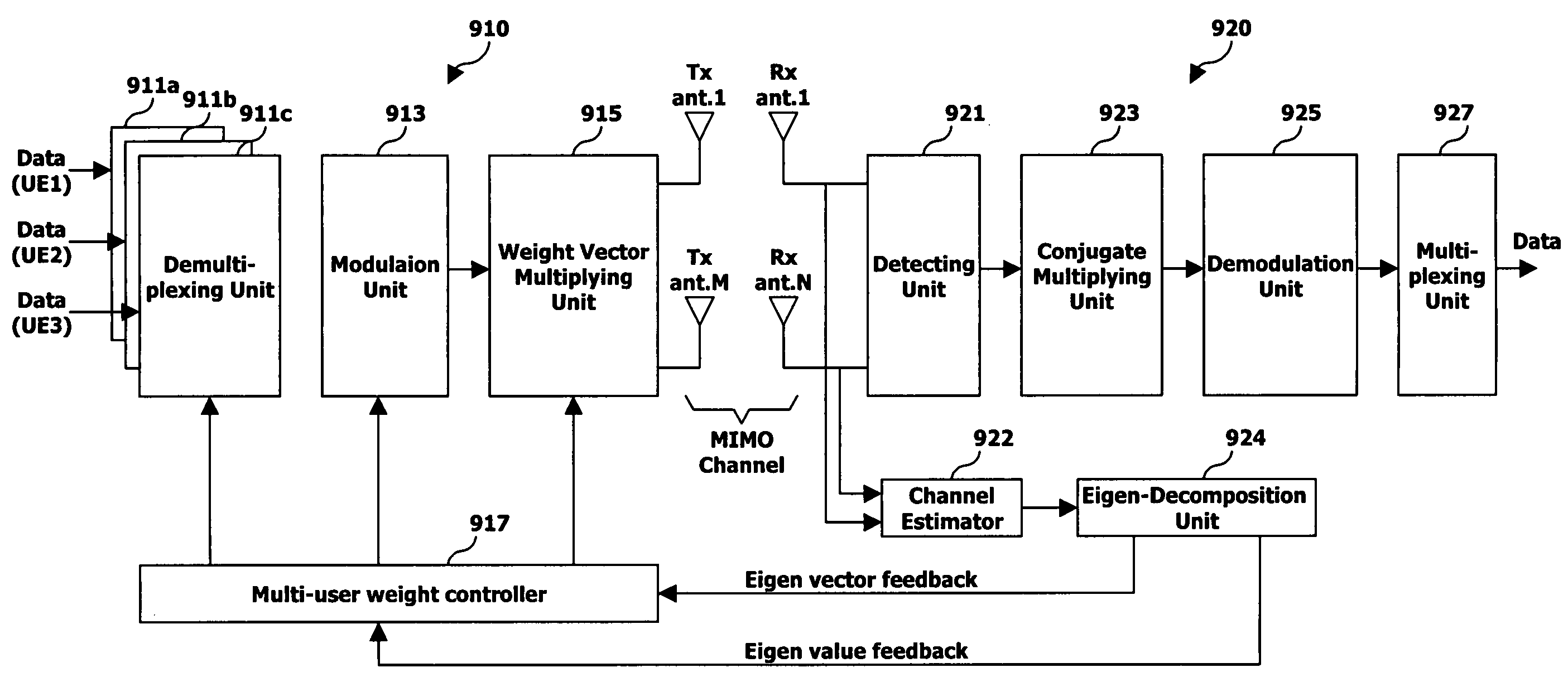

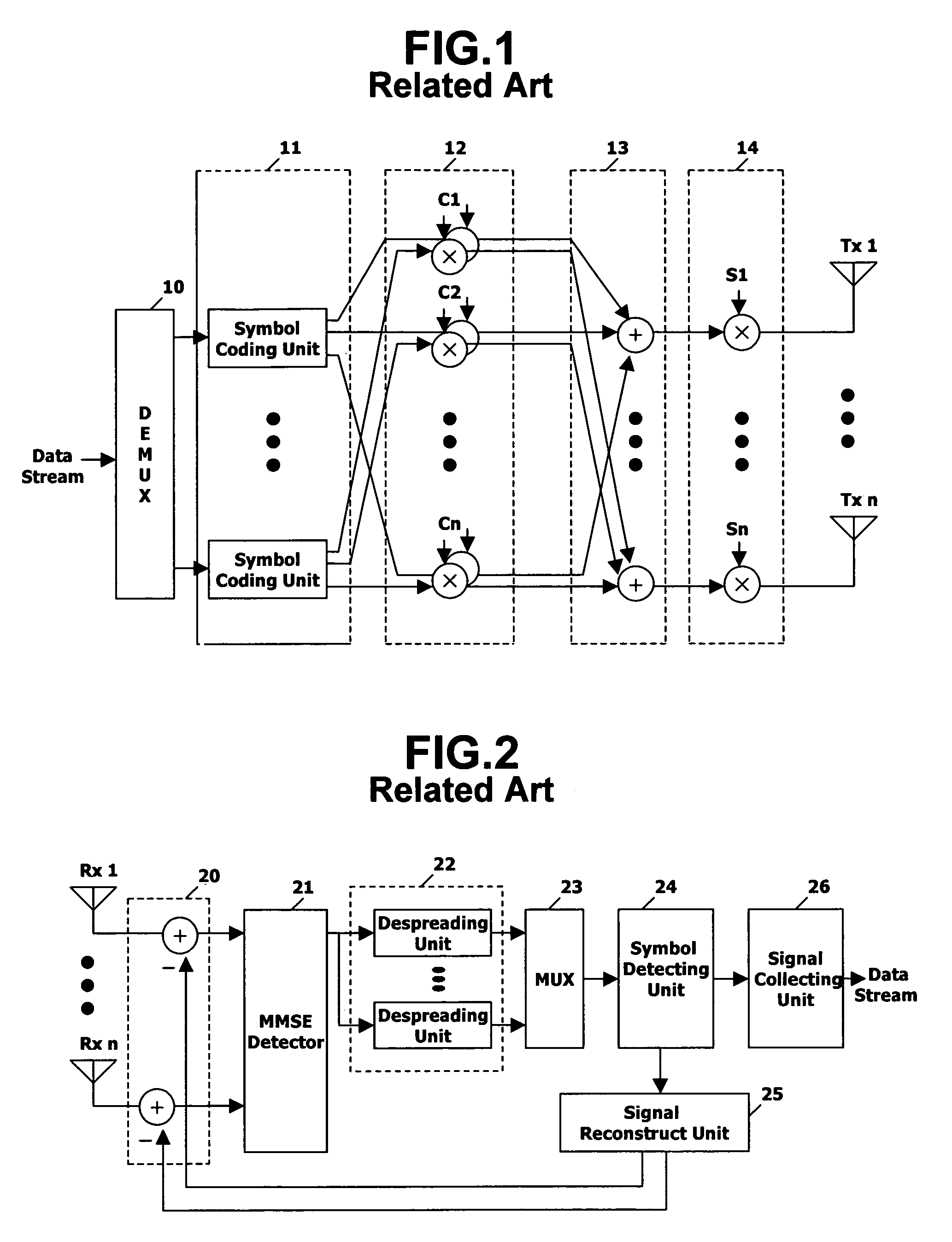

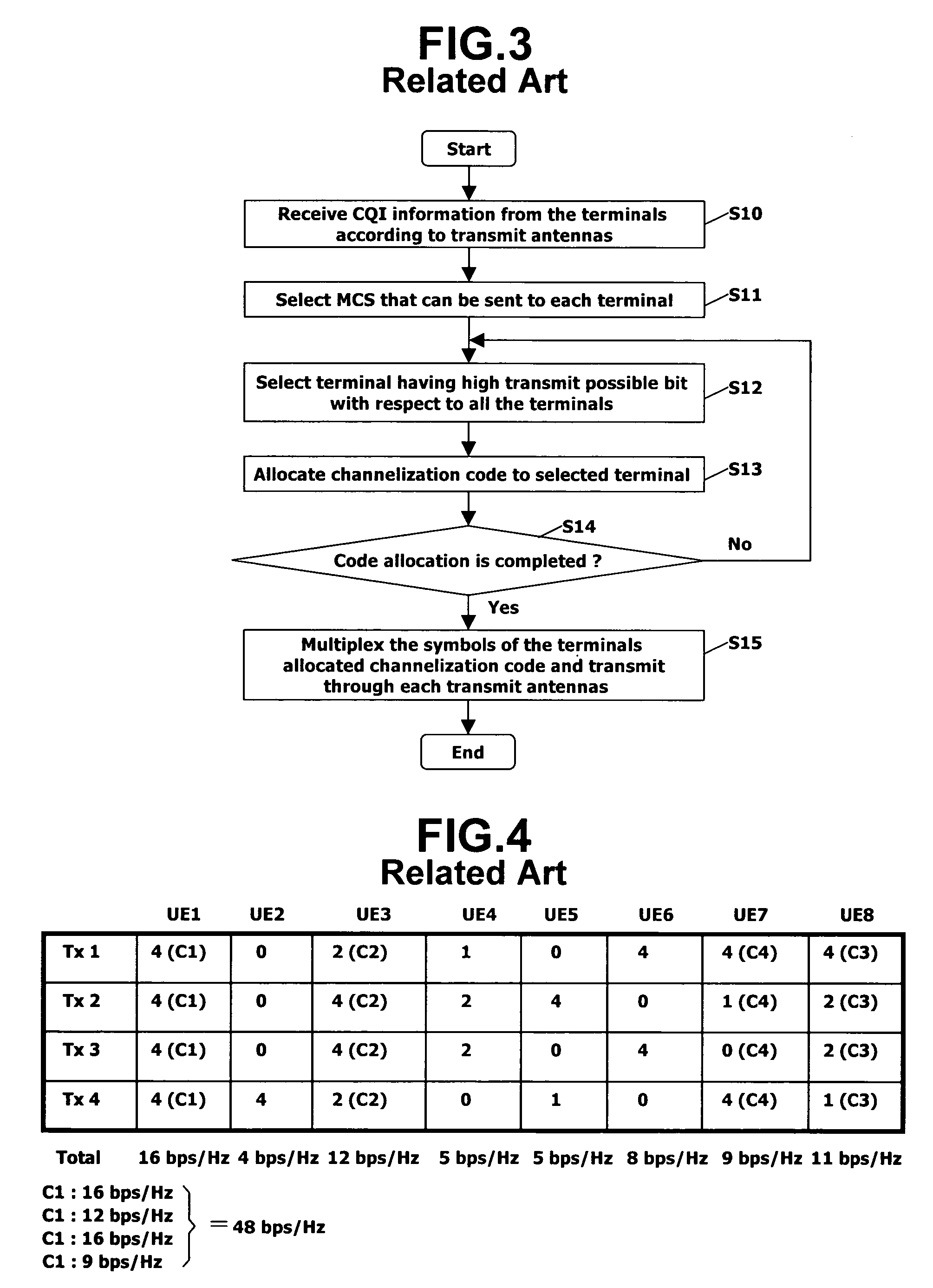

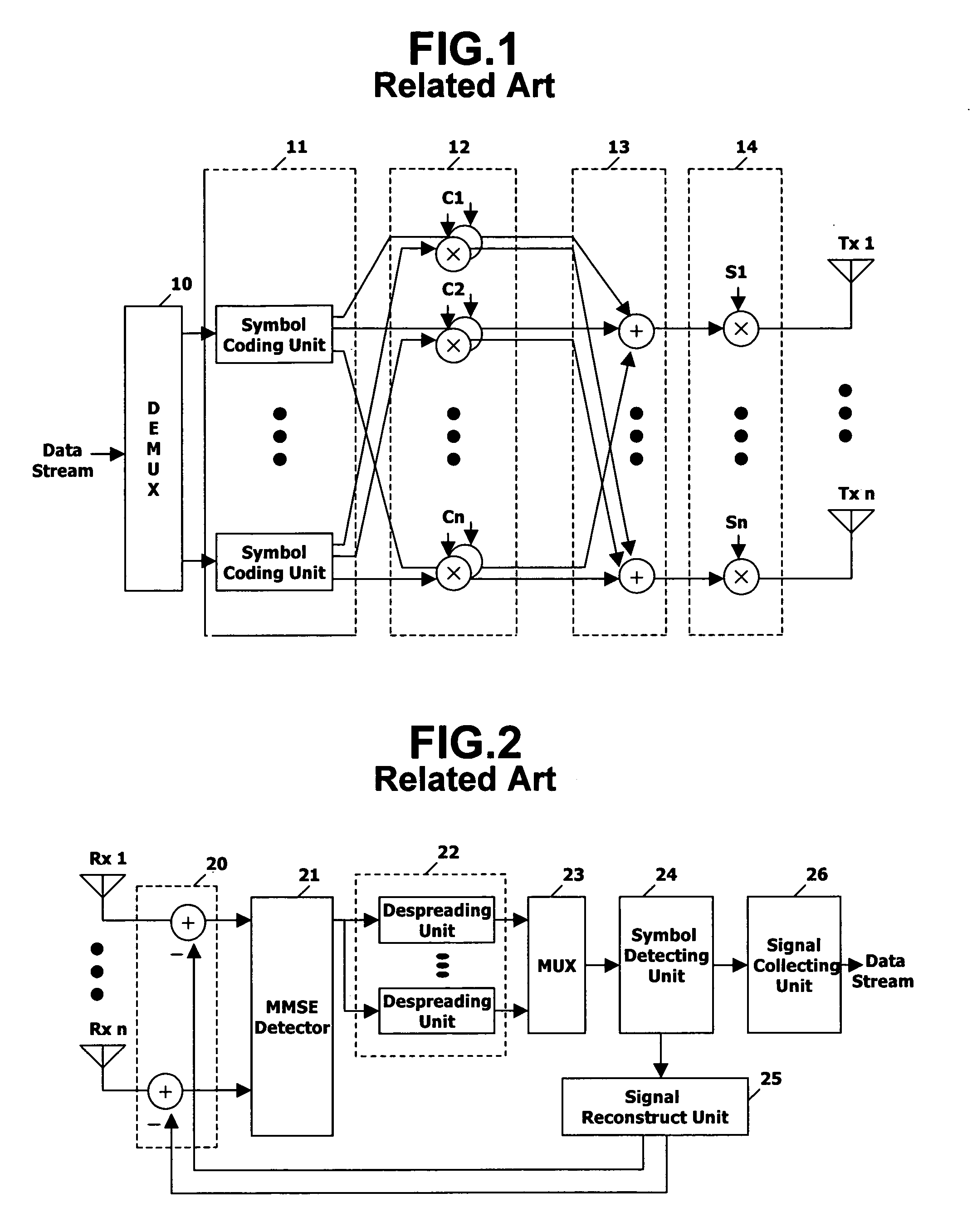

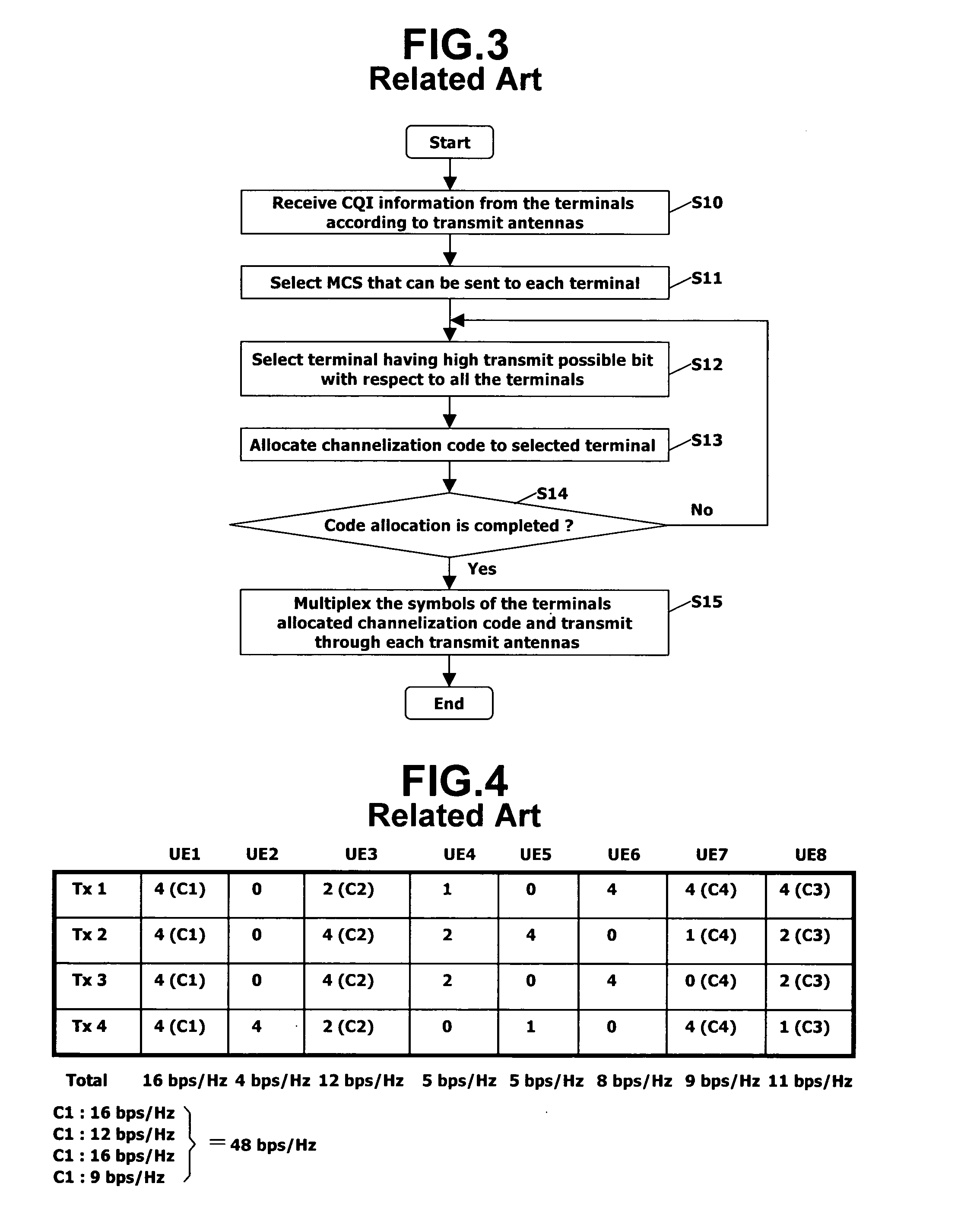

Method and apparatus for allocating channelization codes for wireless communications

InactiveUS7372912B2Easy to detectImprove limited useSpatial transmit diversityMultiplex communicationCode sharingEngineering

Owner:LG ELECTRONICS INC

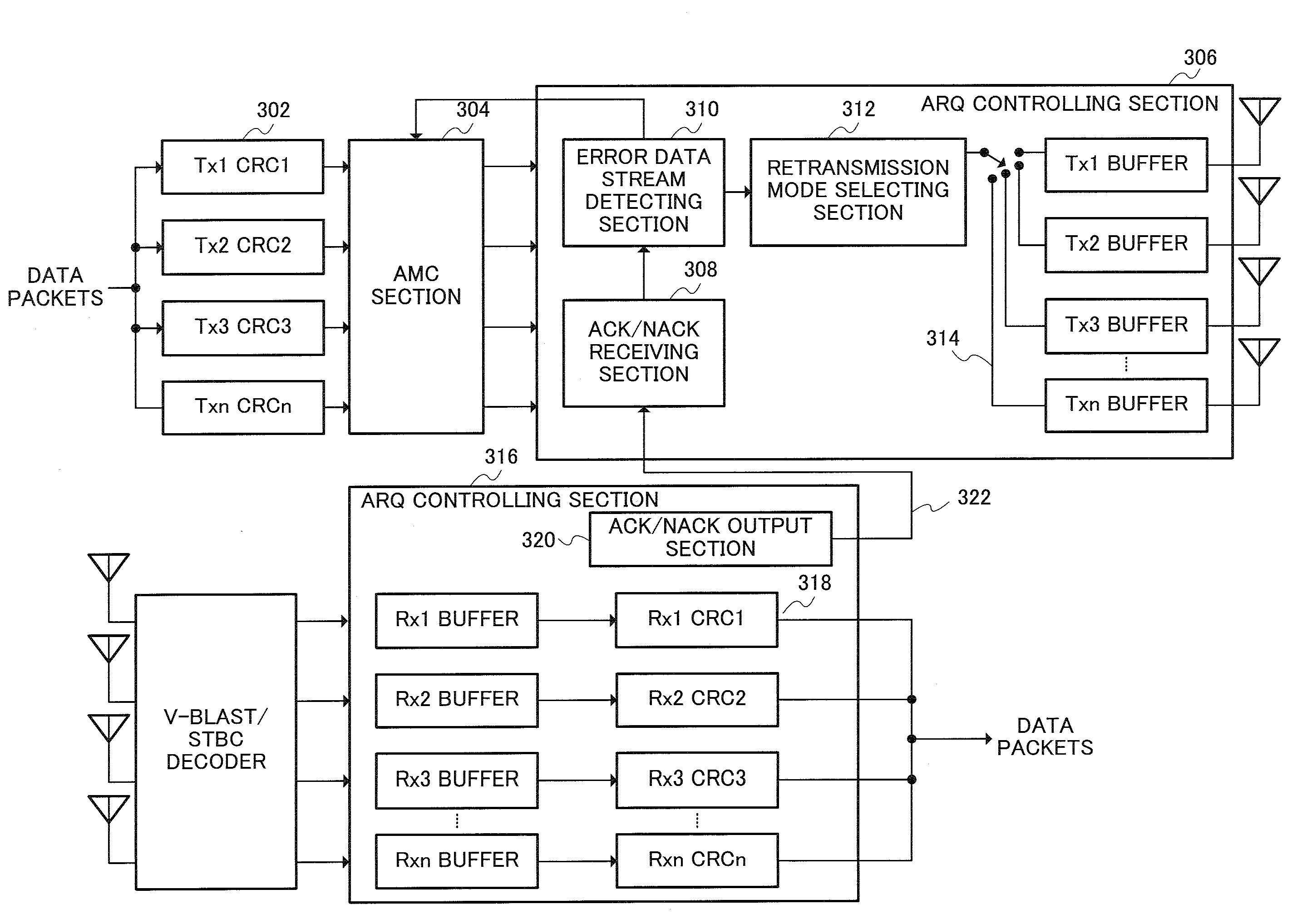

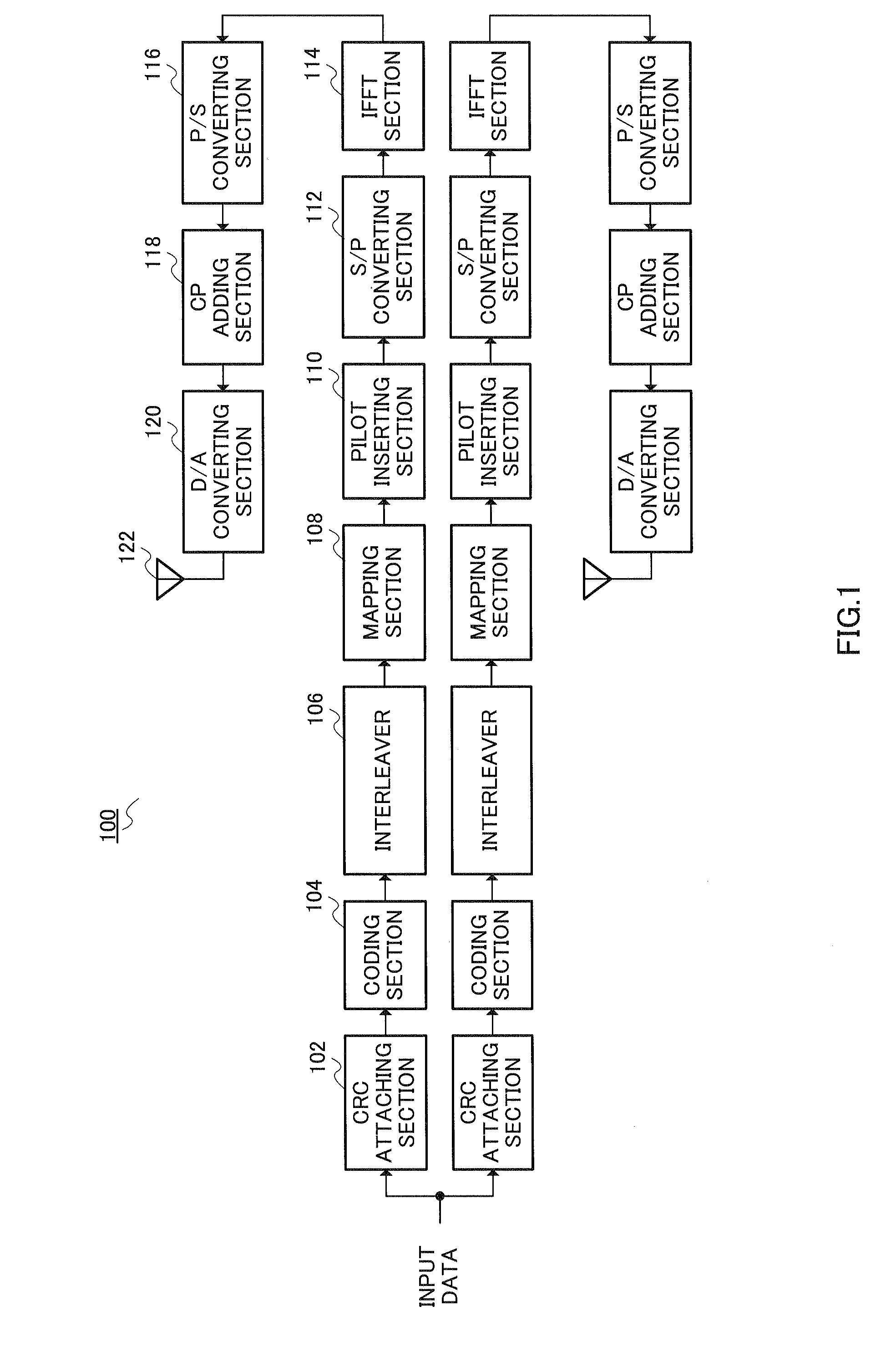

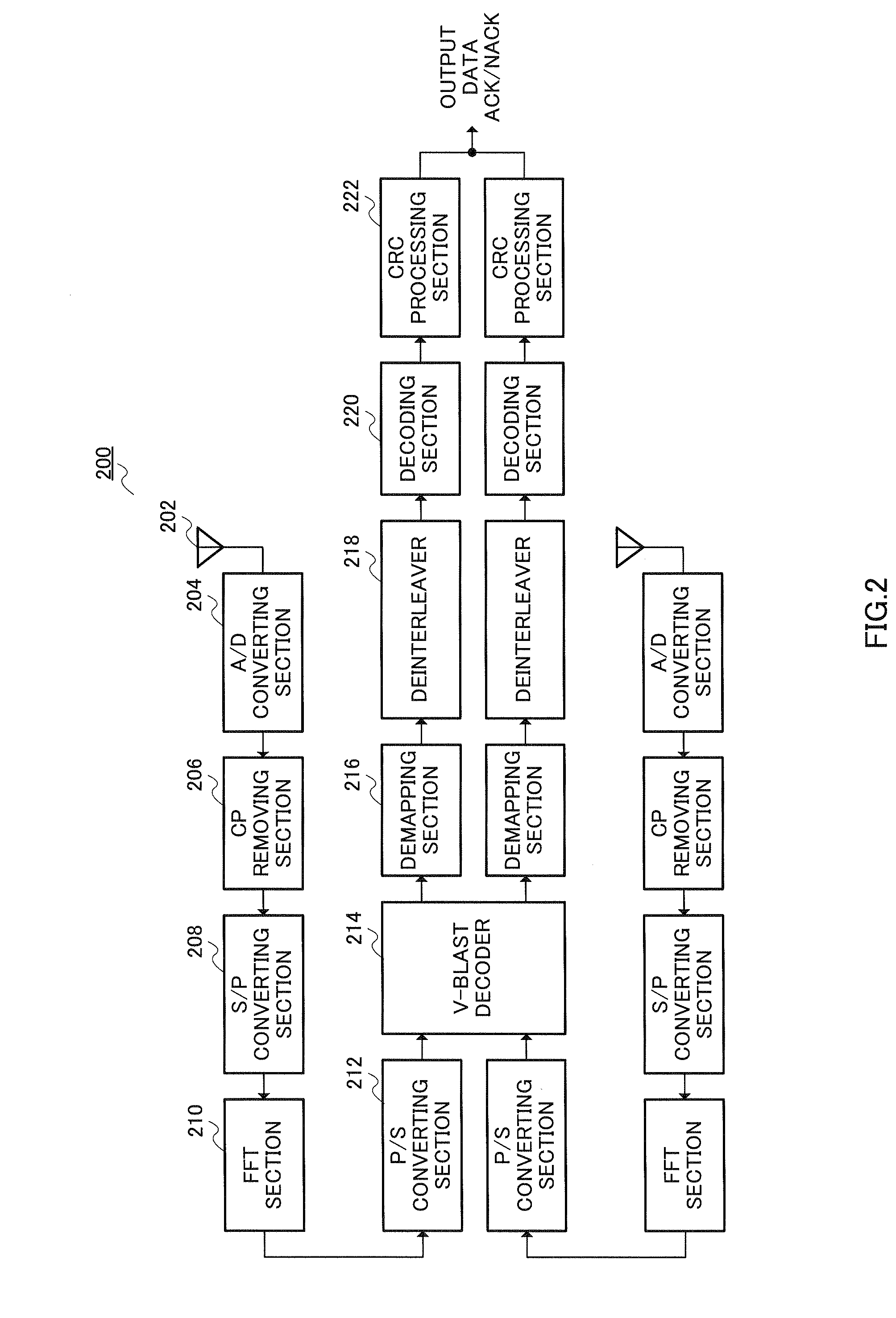

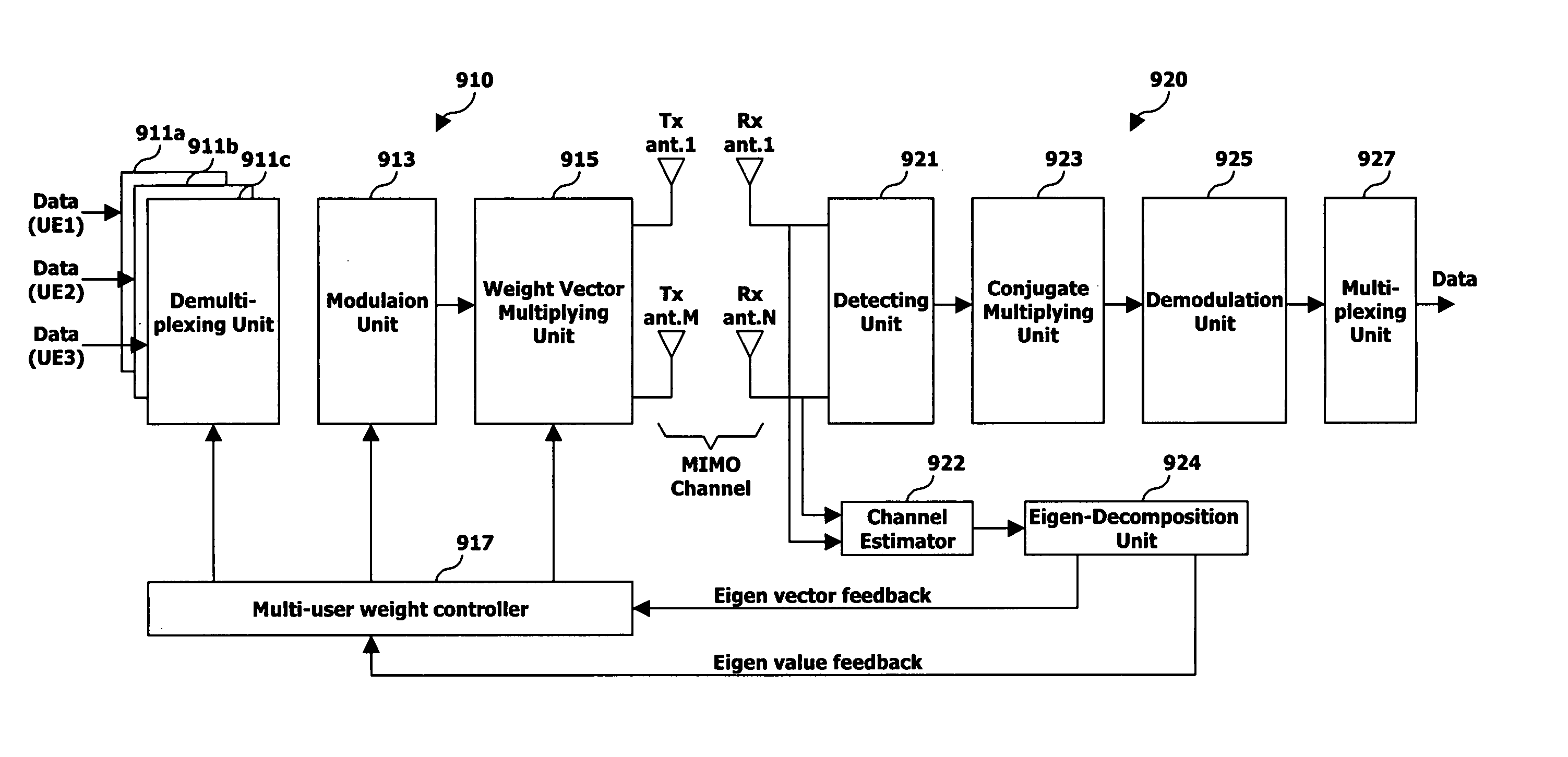

Automatic Retransmission Request Control System and Retransmission Method in Memo-Ofdm System

ActiveUS20070255993A1Improvement of data throughput performanceReduce in quantityError prevention/detection by using return channelError correction/detection using convolutional codesData streamAutomatic repeat request

An automatic retransmission request control system in OFDM-MIMO communication system. In this system, an ACK / NACK output part (320) of a receiver transmits, to a transmitter, a feedback information of positive or negative response based on the result of a cyclic redundancy check. An error data stream decision part (310) of the transmitter determines, based on the feedback information, a data stream that need be retransmitted, and a retransmission mode selection part (312) selects a retransmission mode from among (a) a mode in which to transmit the data, which are to be retransmitted, via the same antenna as in the previous transmission, while transmitting, at the same time, new data by use of an antenna via which no data retransmission is requested; (b) a mode in which to transmit the data, which are to be retransmitted, via an antenna via which no retransmission is requested, while transmitting new data via another antenna at the same time; (c) a mode in which to use STBC to retransmit the data via an antenna via which no retransmission is requested; and (d) a mode in which to use STBC to retransmit the data via all the available antennas.

Owner:INVT SPE LLC

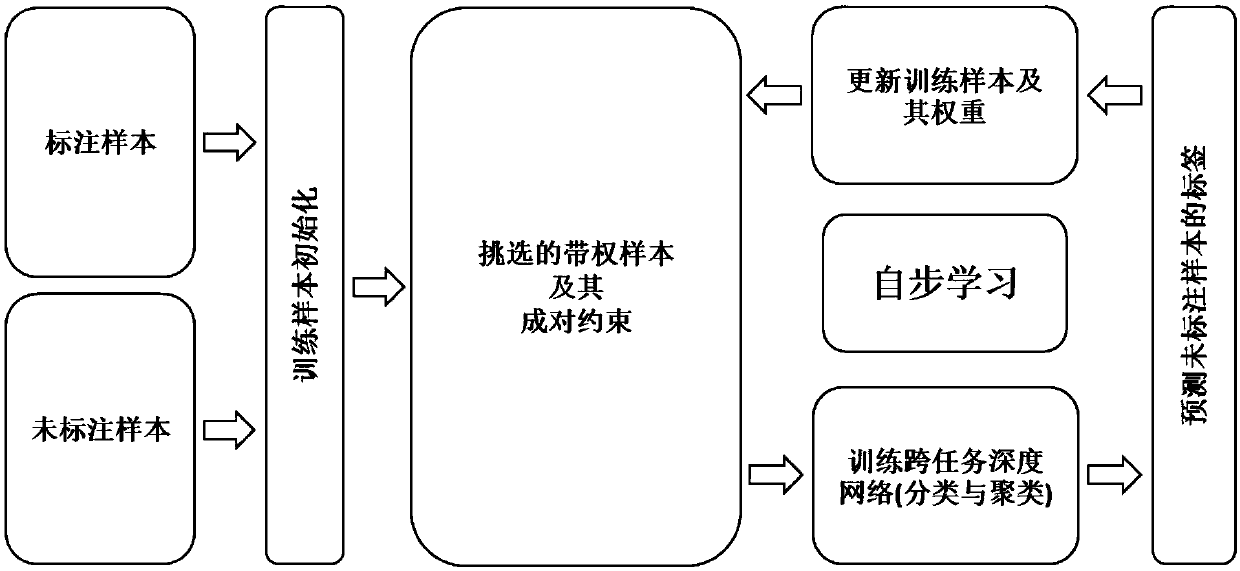

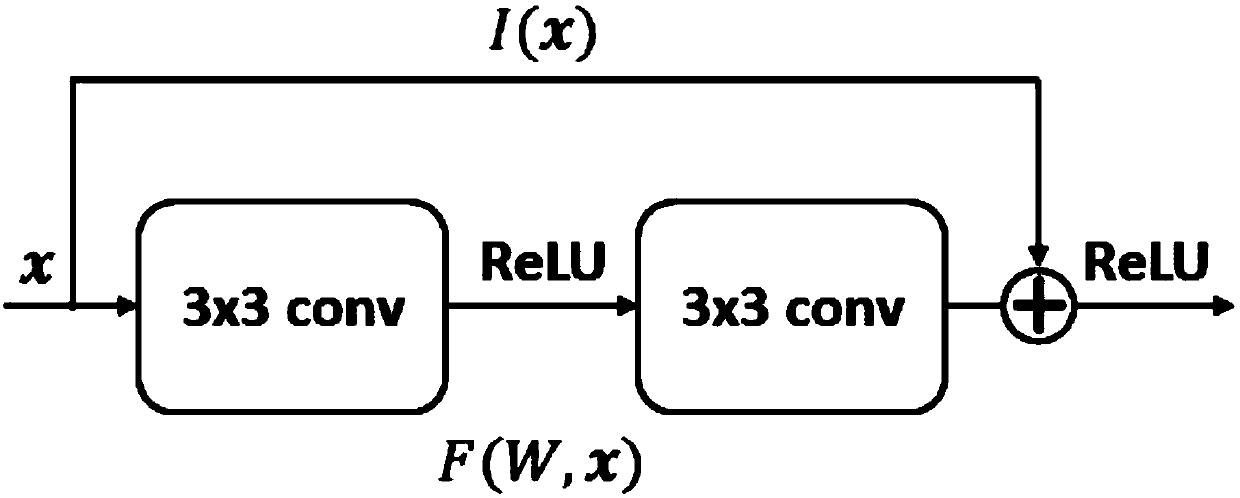

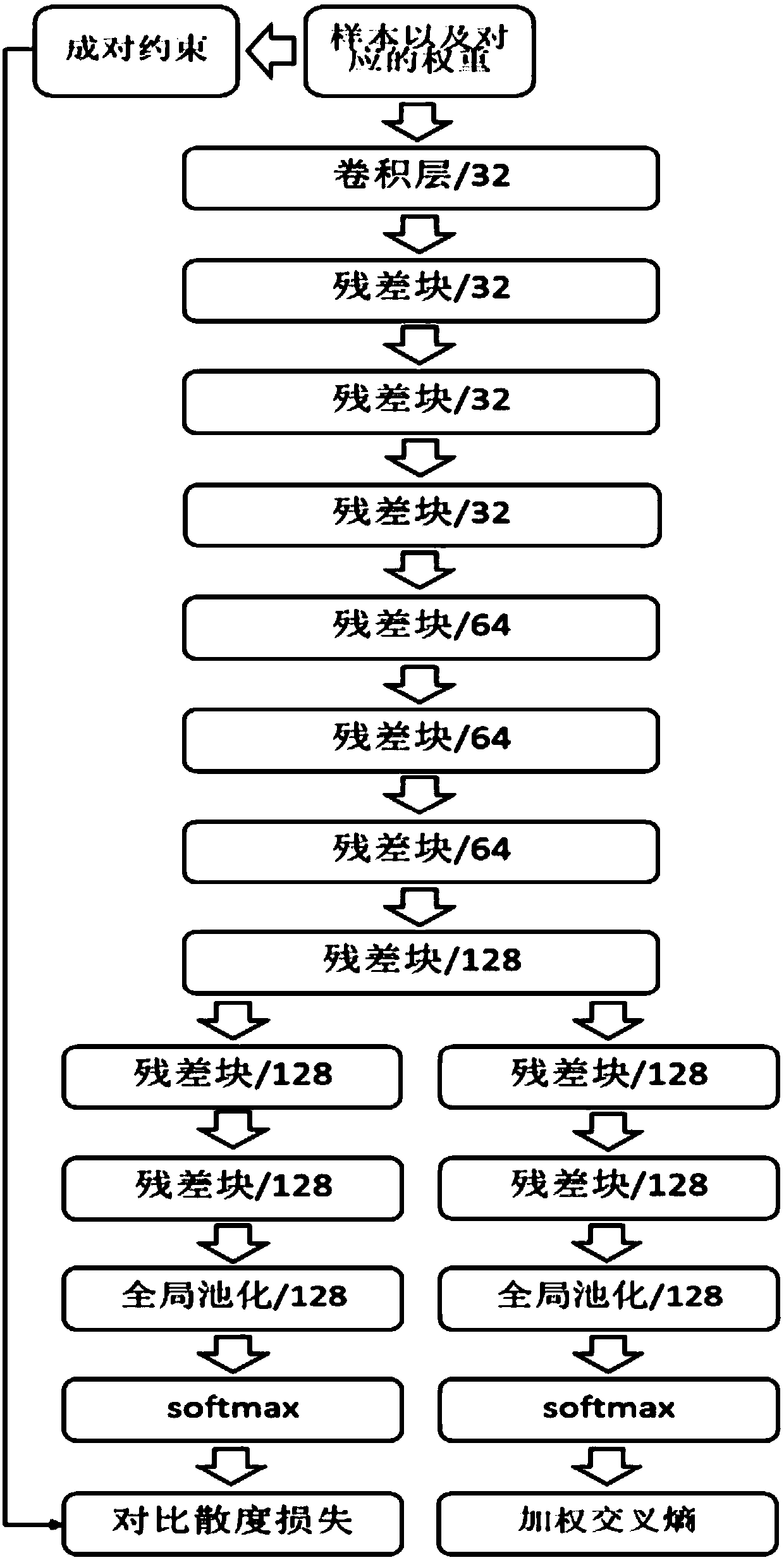

Image classification method based on semi-supervised self-paced learning cross-task deep network

InactiveCN108764281AImprove classification abilityEasy to classifyCharacter and pattern recognitionNeural architecturesNetwork performanceData set

The invention discloses an image classification method based on a semi-supervised self-paced learning cross-task deep network. The method includes the steps of randomly selecting a small amount of labeling samples from the whole image data set, reserving the labels, and remaining all the samples as unlabelled samples having the real labels to be unknown in the whole process, wherein the weight ofthe labeled samples is constant to be one in the training process, the weight of the unlabelled samples is initialized to be zero, and only the labeled samples are used as a training set in the initial process; S2, training a cross-task deep network by the training set; S3, according to the trained cross-task deep network, predicting the pseudo labels of all the unlabelled samples, and giving a corresponding weight of each unlabelled sample; S4, according to a self-paced learning normal form, selecting an unlabelled sample with a high confidence degree, and adding to the training set; and S5,repeating the steps S2-S4 until the cross-task deep network performance is saturated or reaches a preset cycle number. According to the method, the human design feature is not needed to be input, andthe classification can be realized by directly inputting the original image.

Owner:SOUTH CHINA UNIV OF TECH

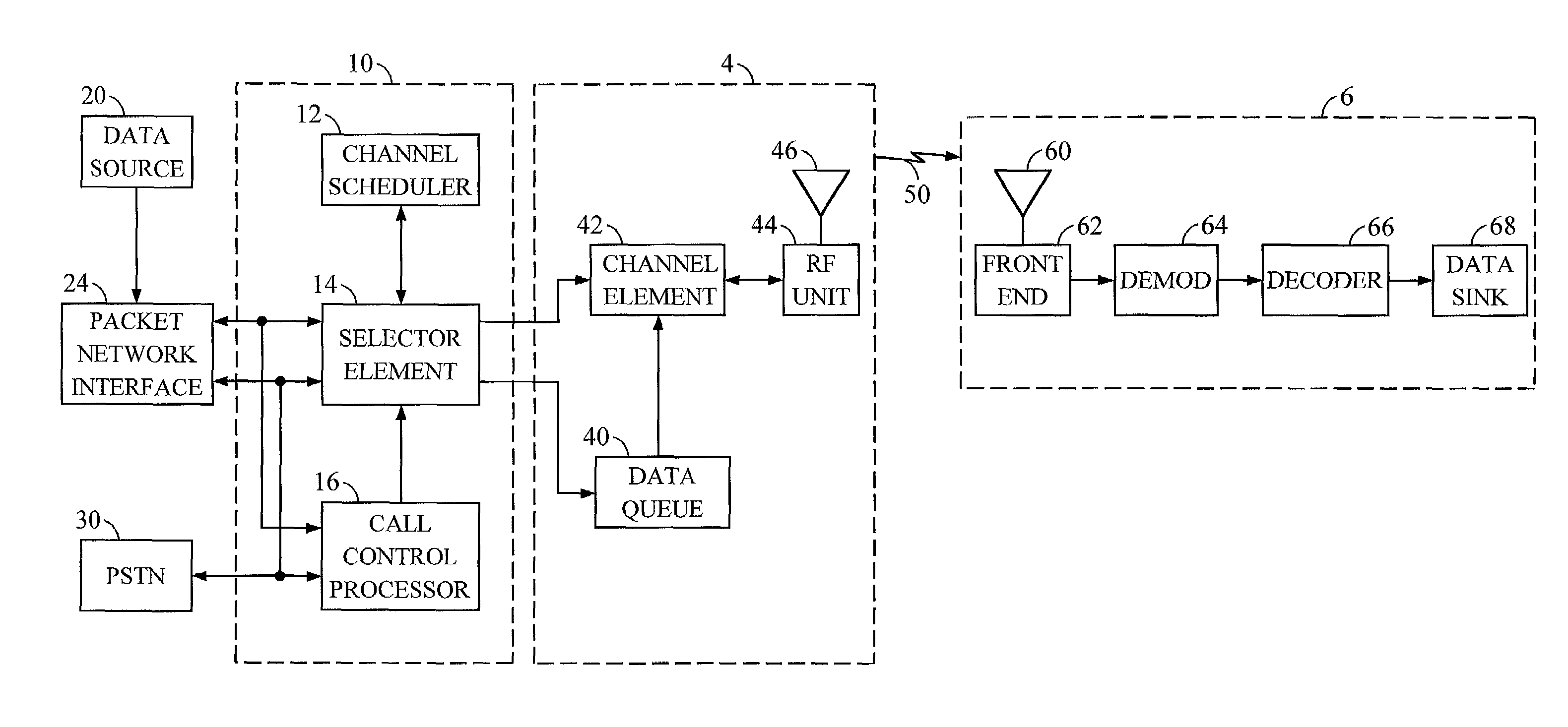

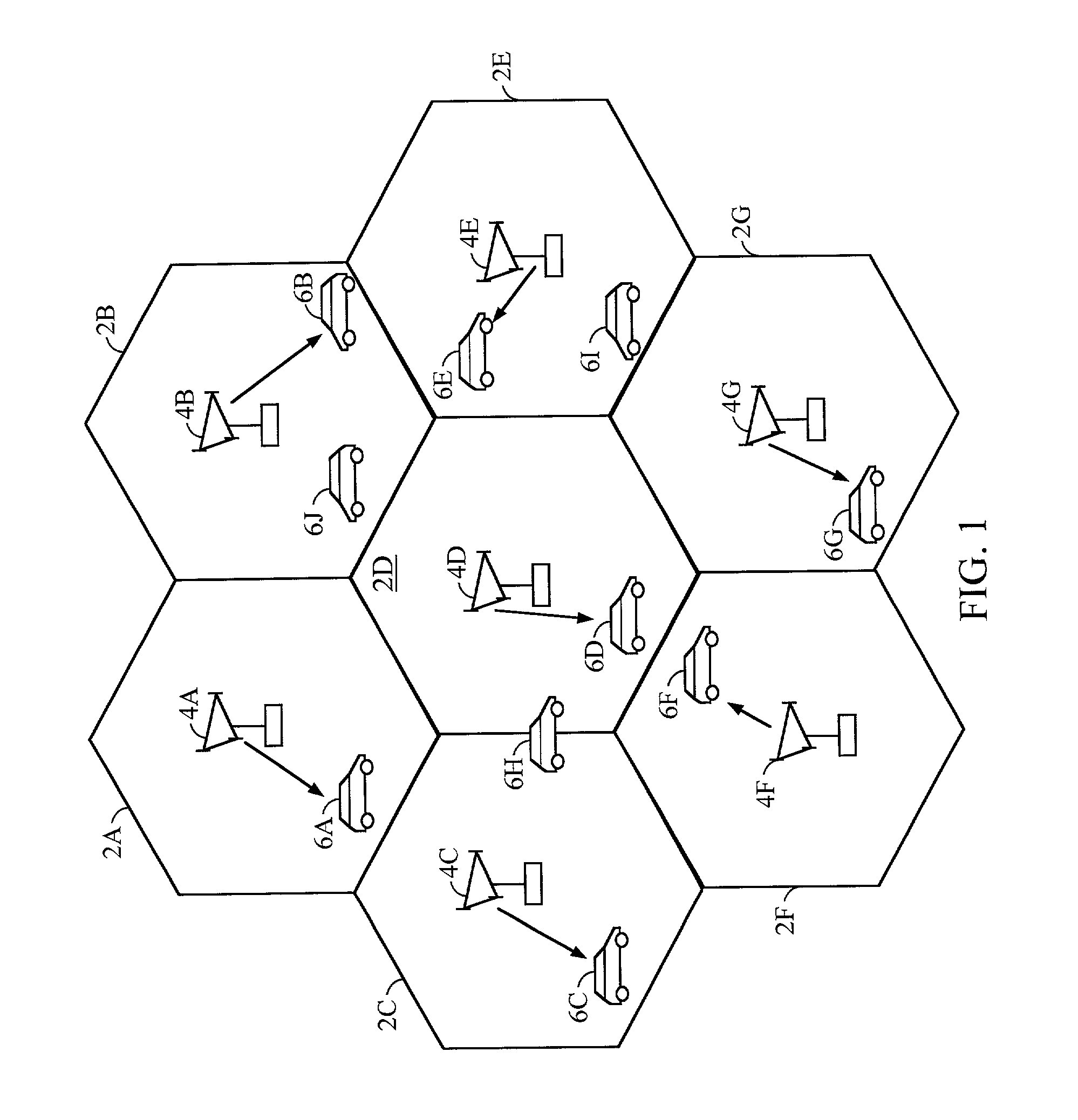

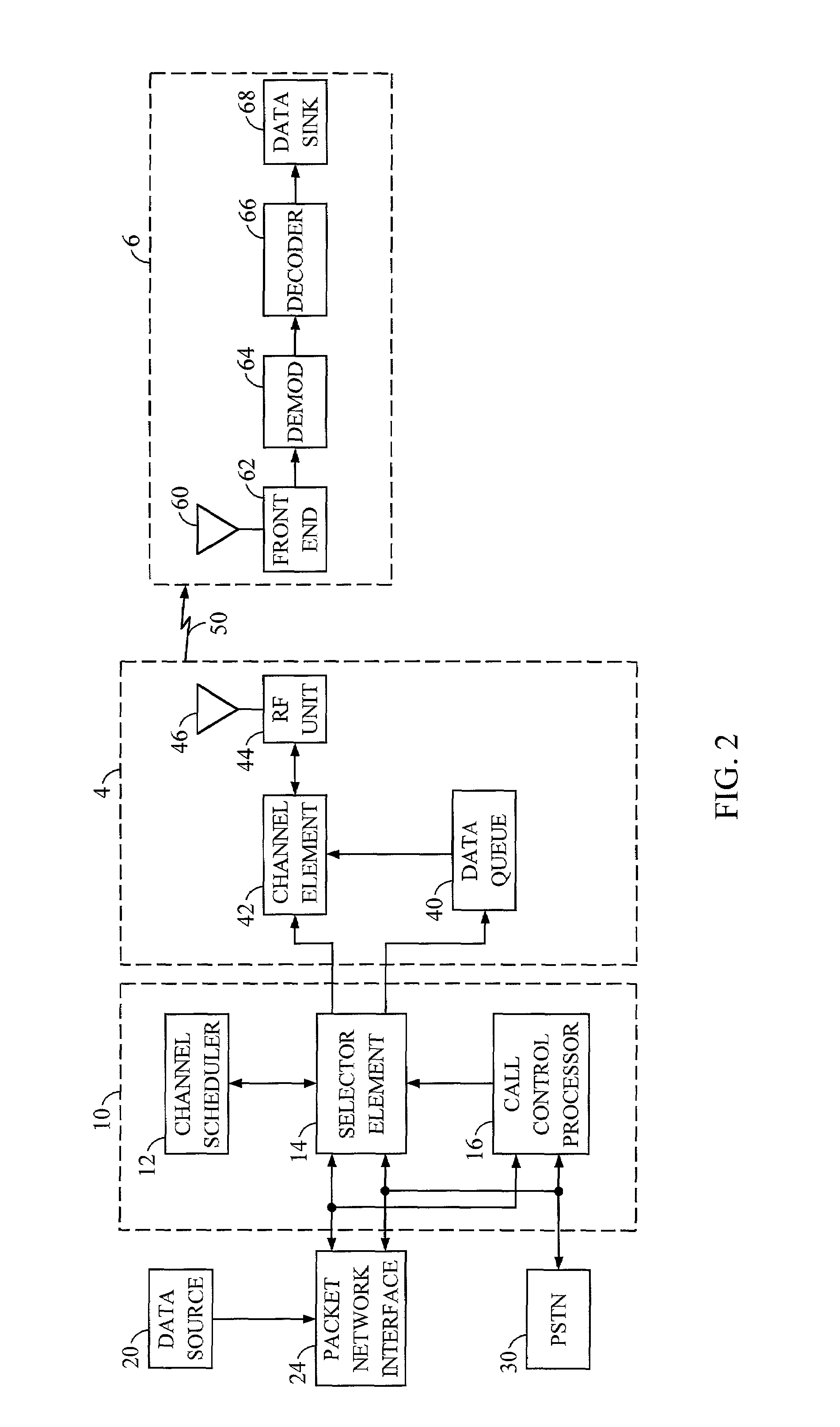

System for allocating resources in a communication system

InactiveUS7016318B2Facilitate transmissionOptimizationError preventionFrequency-division multiplex detailsCommunications systemResource allocation

A communication network having a plurality of subscriber units receive a finite resource from a common node is disclosed. Individual subscriber units may seize the finite resource of the common node to the exclusion of all other subscriber units in the network. A scheduler allocates the finite resource to the individual subscriber units based upon a weight associated with the individual subscriber units. The scheduler determines the weight for each of the subscriber units based upon an instantaneous rate of consuming the finite resource.

Owner:QUALCOMM INC

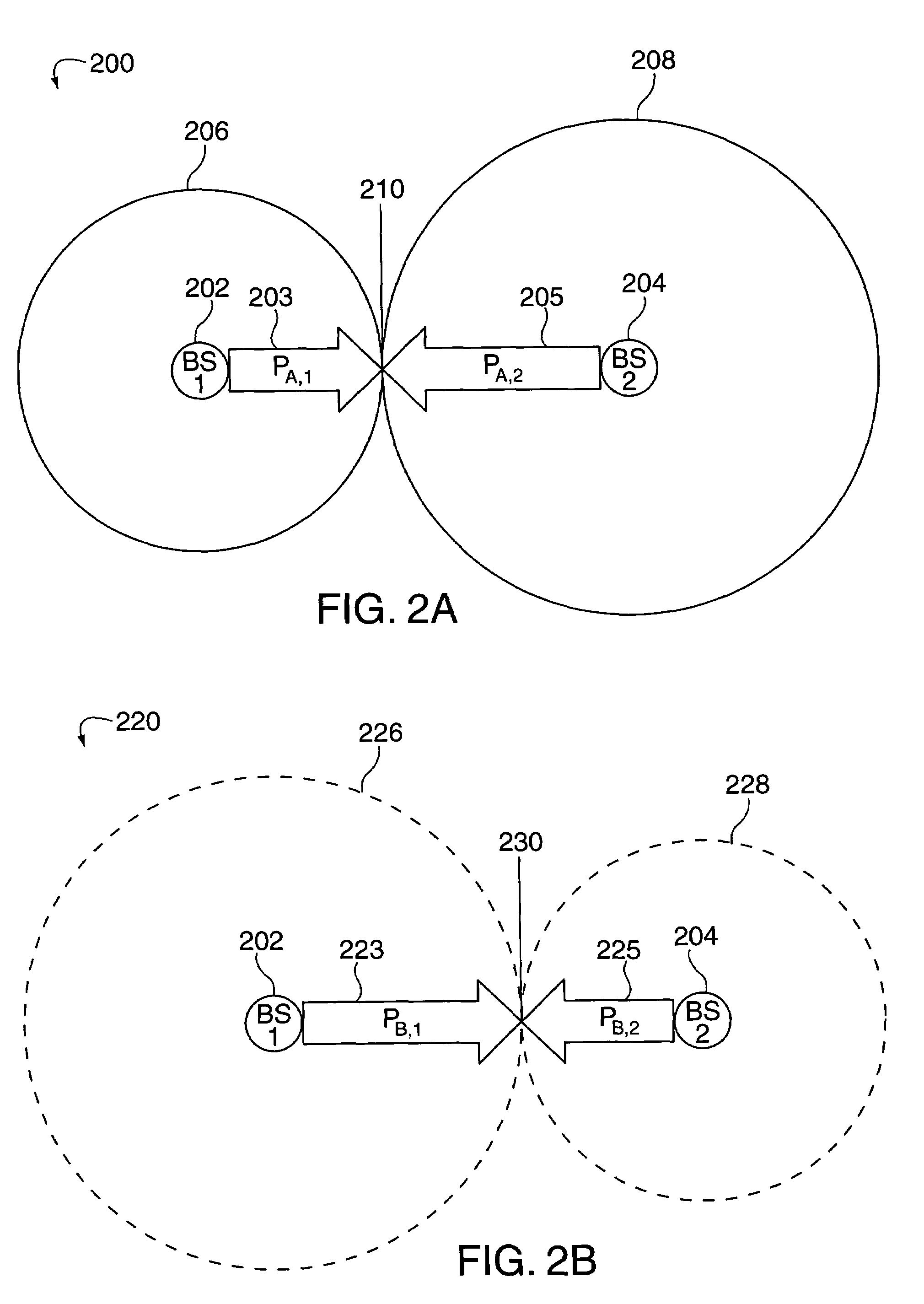

Method of creating and utilizing diversity in multiple carrier communication system

InactiveUS7363039B2Low reliabilityReduce quality problemsEnergy efficient ICTPower managementFrequency spectrumCommunications system

In many cellular systems, reusing spectrum bandwidth, creates problems in boundary regions between the cells and sectors where the signal strength received from adjacent base stations or adjacent sector transmissions of a single base station may be nearly equivalent. The invention creates a new type of diversity, referred to as multiple carrier diversity by utilizing multiple carriers, assigning different power levels to each carrier frequency at each base station, and / or offsetting sector antennas. The cell and / or sector coverage areas can be set so as to minimize or eliminate overlap between cell and / or sector boundary regions of different carrier frequencies. Mobile nodes traveling throughout the system can exploit multiple carrier diversity by detecting carriers and selecting to use a non-boundary carrier based on other system criteria in order to improve performance. Boundary carriers may, but need not be, identified and excluded from consideration for use by a wireless terminal.

Owner:QUALCOMM INC

Method and apparatus for allocating channelization codes for wireless communications

InactiveUS20050002467A1Easy to detectImprove limited useSpatial transmit diversityMultiplex communicationCode sharingEngineering

A data transmission method for a MIMO (Multiple-input Multiple-Output) system allowing multiple terminals to share channelization codes according to the channel states, by receiving channel information from terminals, allocating channelization codes for each transmit antenna based upon the received channel information, and transmitting data via each transmit antenna according to the allocated channelization codes. When there are many user terminals and if the number of channelization codes are limited, namely, when the total number of channel codes used to distinguish the terminals is less than the total number of terminals, channelization code sharing per transmit antenna among multiple terminals is performed, such that the throughput of data that can be sent by using each channelization code is increased.

Owner:LG ELECTRONICS INC

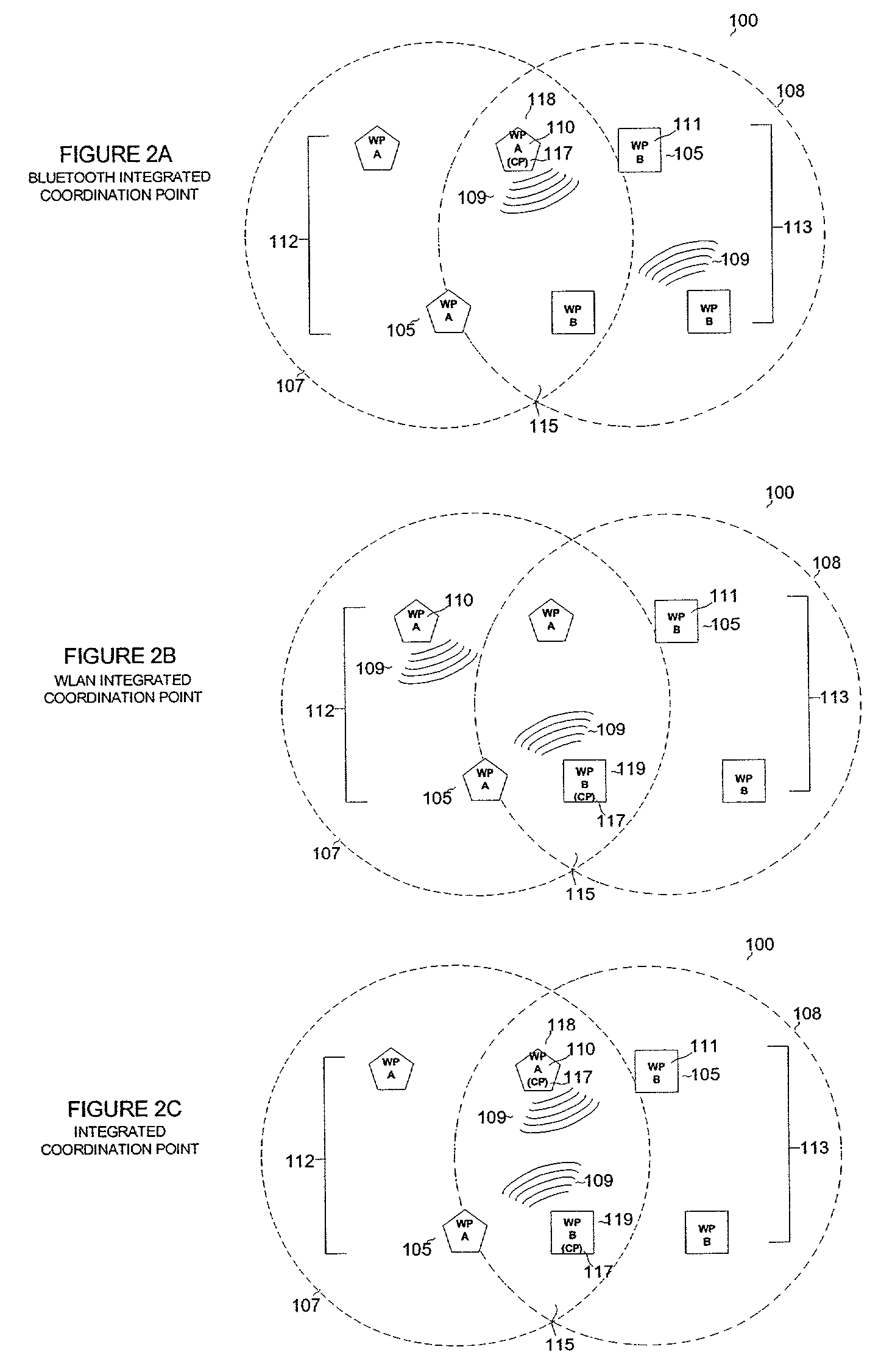

Coordination architecture for wireless communication devices using multiple protocols

ActiveUS7233602B2Reduce collisionImprove current qualityError prevention/detection by using return channelNetwork traffic/resource managementQuality of servicePointing device

A system and methods for coordinating transmissions in a wireless network wherein a plurality of frequency-overlapping protocols are used to exchange information between devices. In this system, a coordination point device integrates a monitoring functionality to identify impending data collisions between the frequency-overlapping protocols. The coordination point device further identifies quality of service parameters to determine if the protocols are operating within desirable ranges. Moderation one or more of the protocols is then performed to avoid data collisions arising from overlapping transmissions between the protocols while maintaining data throughput within acceptable ranges.

Owner:AVAGO TECH INT SALES PTE LTD

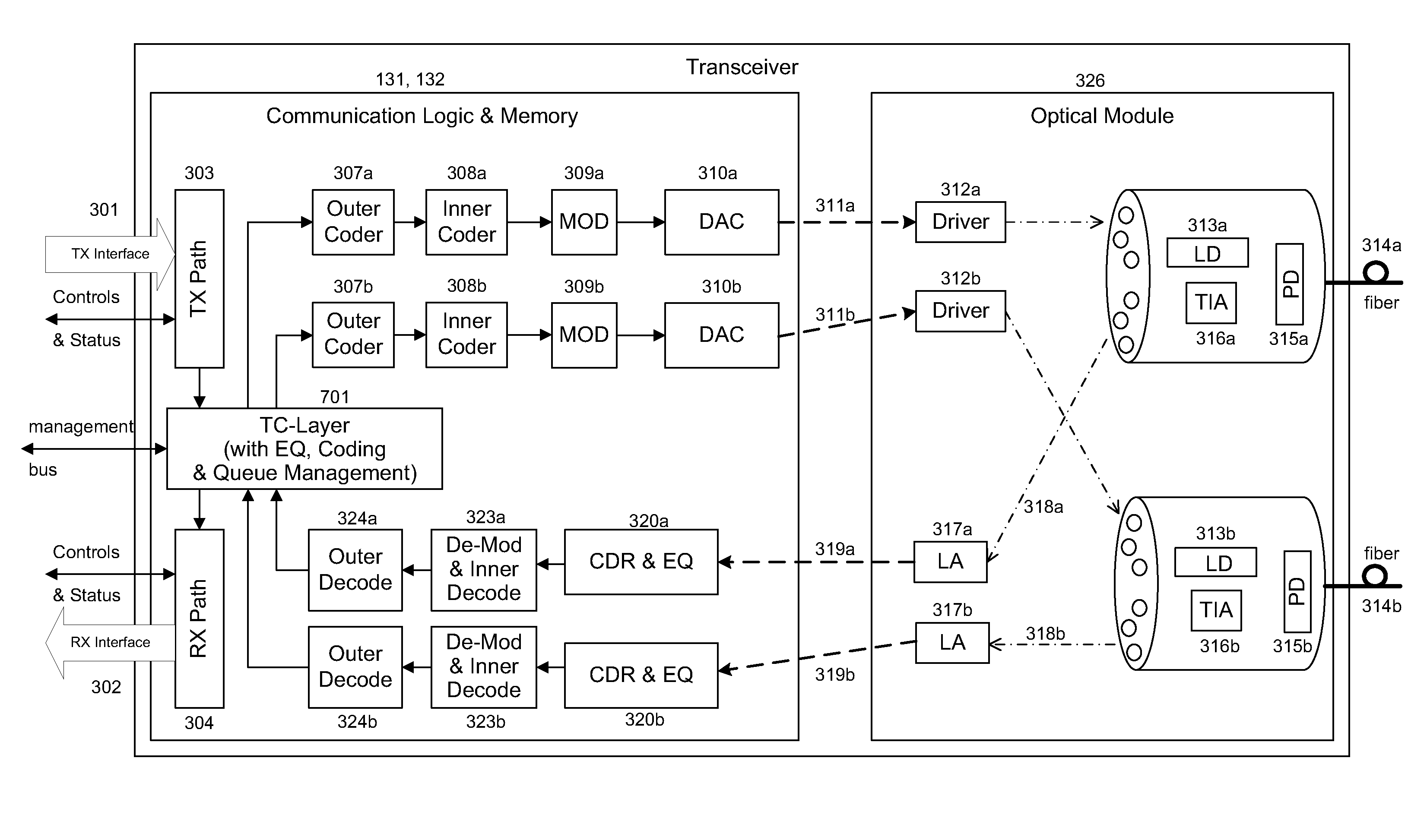

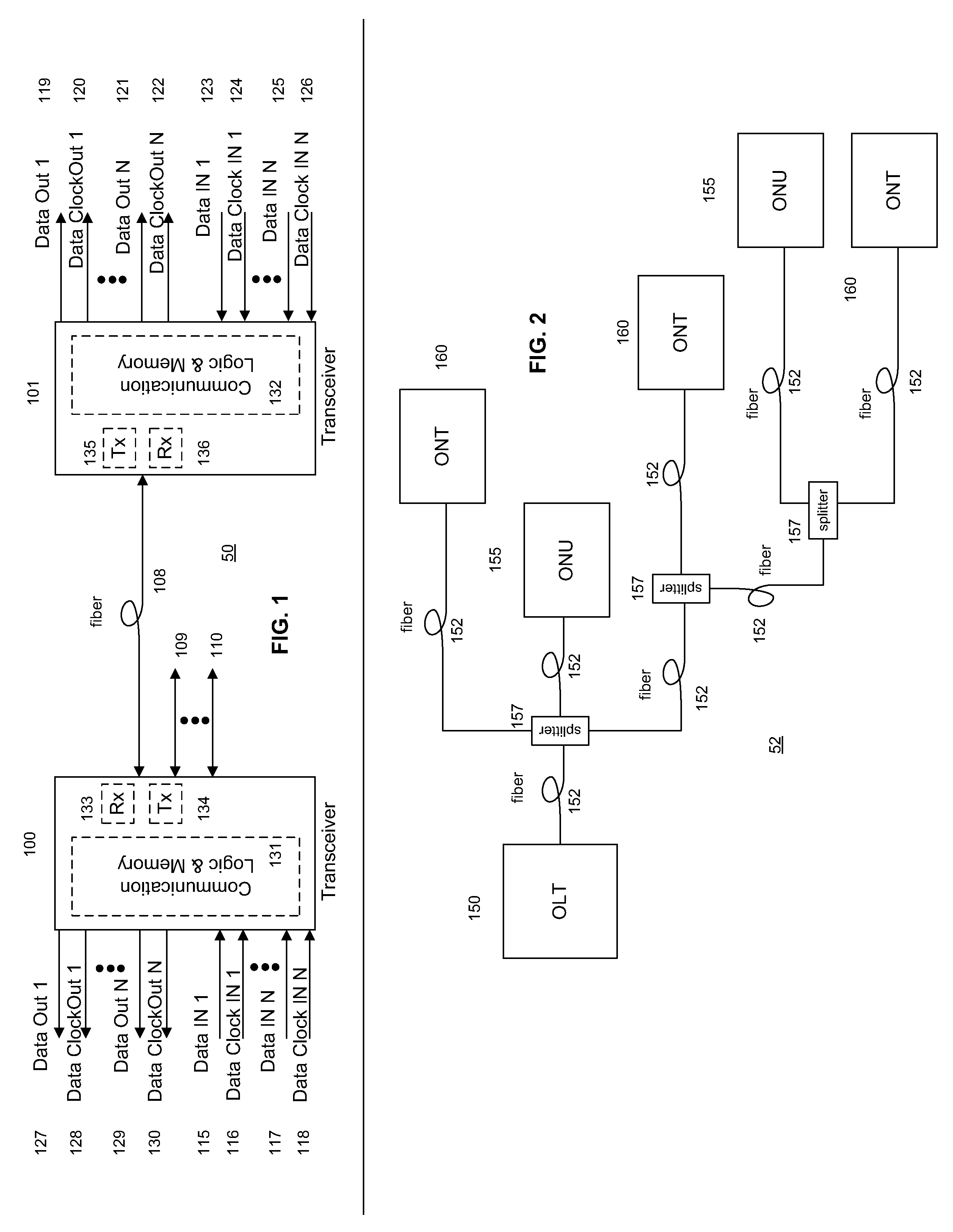

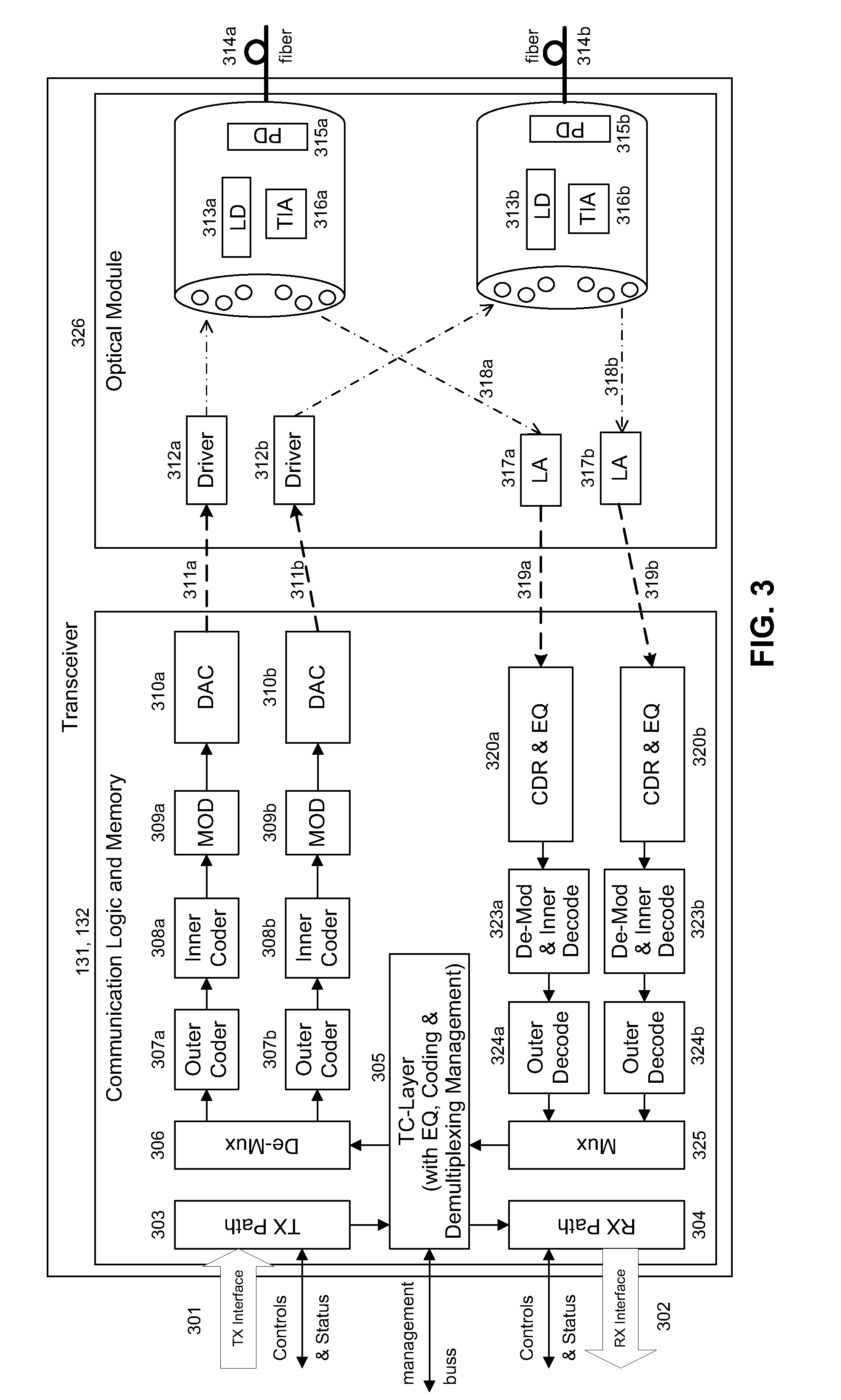

System and method for performing high-speed communications over fiber optical networks

ActiveUS20100158530A1Low line rateIncrease data throughputWavelength-division multiplex systemsDistortion/dispersion eliminationFiberWaiting period

Processing a received optical signal in an optical communication network includes equalizing a received optical signal to provide an equalized signal, demodulating the equalized signal according to an m-ary modulation format to provide a demodulated signal, decoding the demodulated signal according to an inner code to provide an inner-decoded signal, and decoding the inner-decoded signal according to an outer code. Other aspects include other features such as equalizing an optical channel including storing channel characteristics for the optical channel associated with a client, loading the stored channel characteristics during a waiting period between bursts on the channel, and equalizing a received burst from the client using the loaded channel characteristics.

Owner:SOTO ALEXANDER I +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com