Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

75 results about "Ground bounce" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

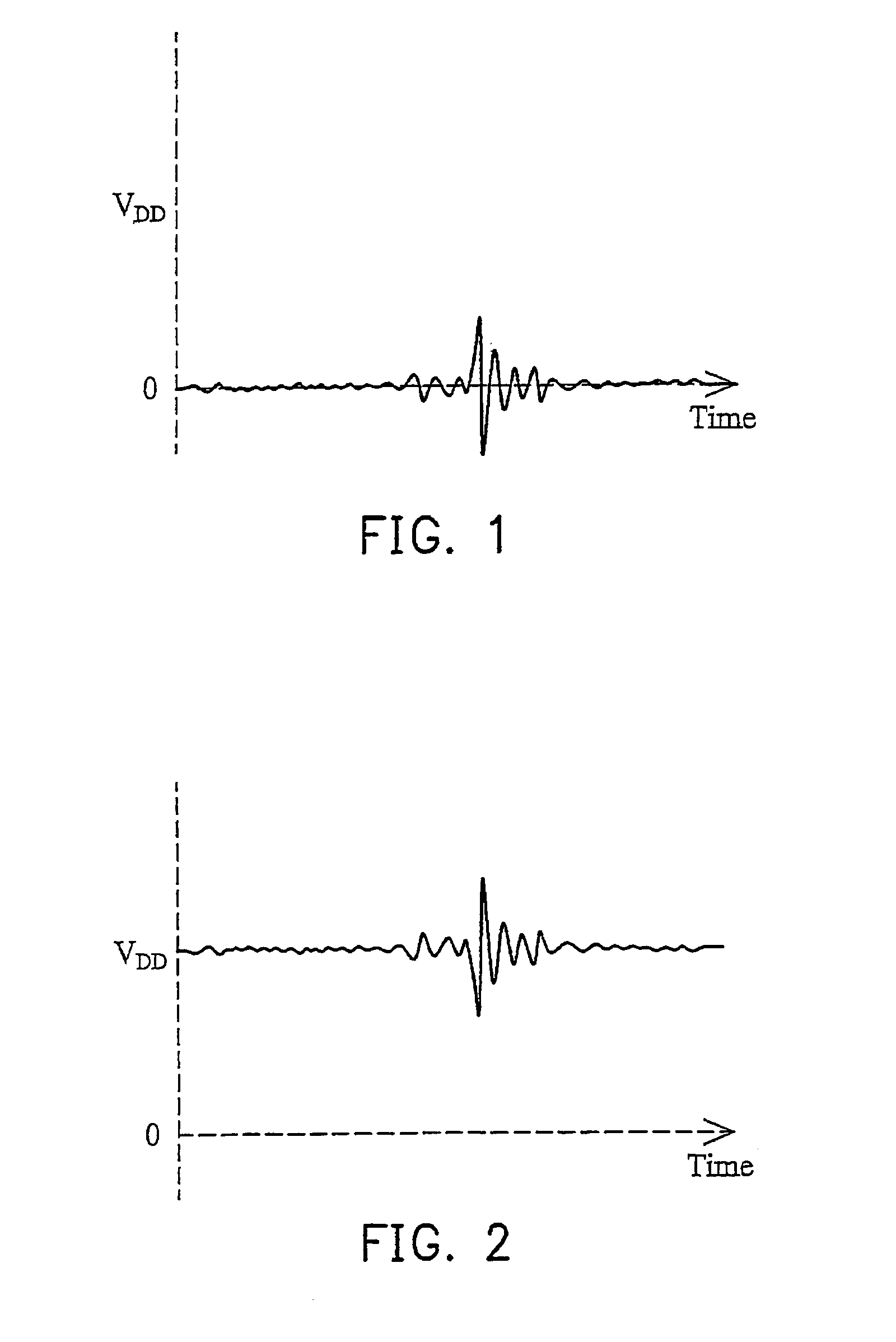

In electronic engineering, ground bounce is a phenomenon associated with transistor switching where the gate voltage can appear to be less than the local ground potential, causing the unstable operation of a logic gate.

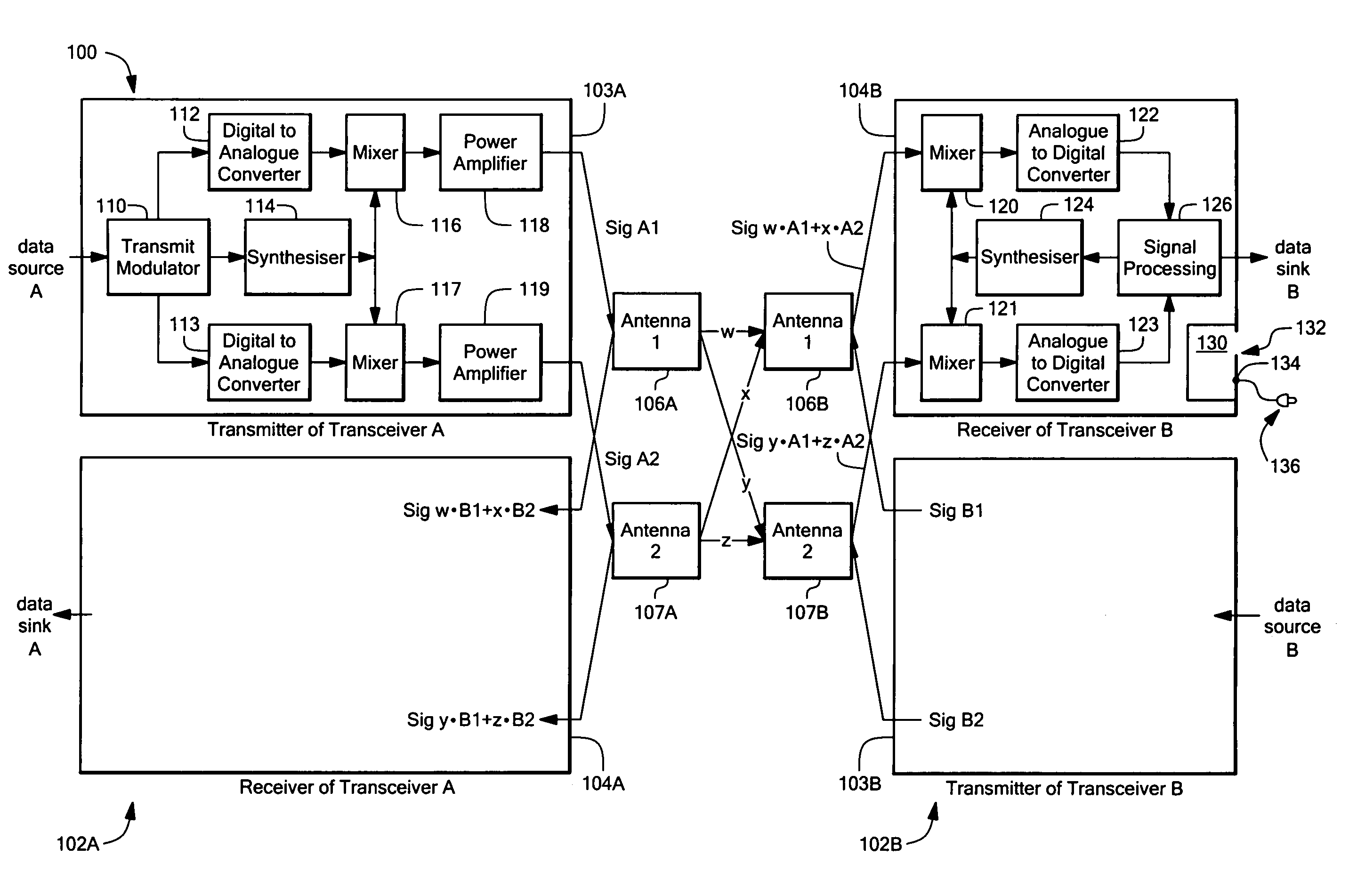

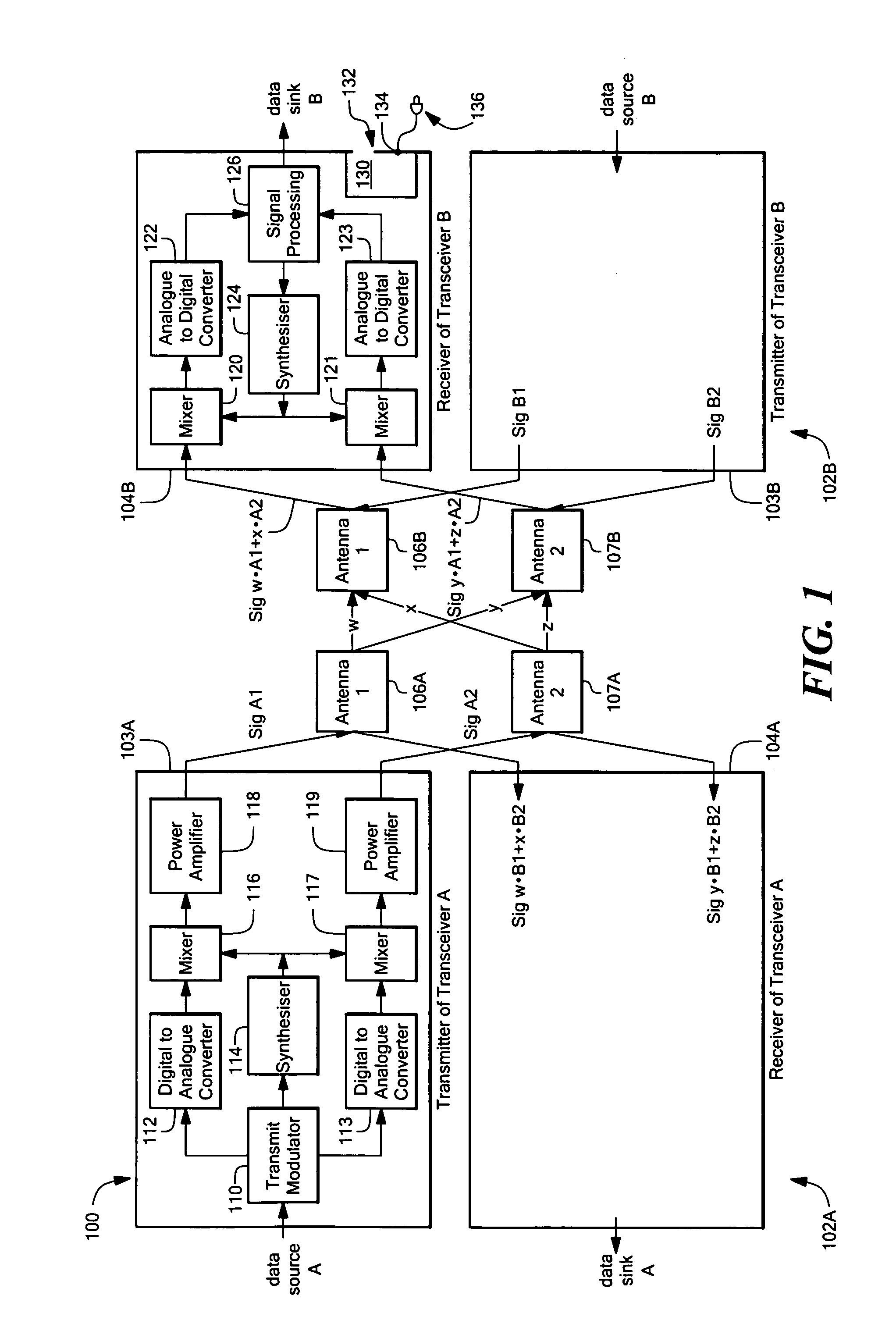

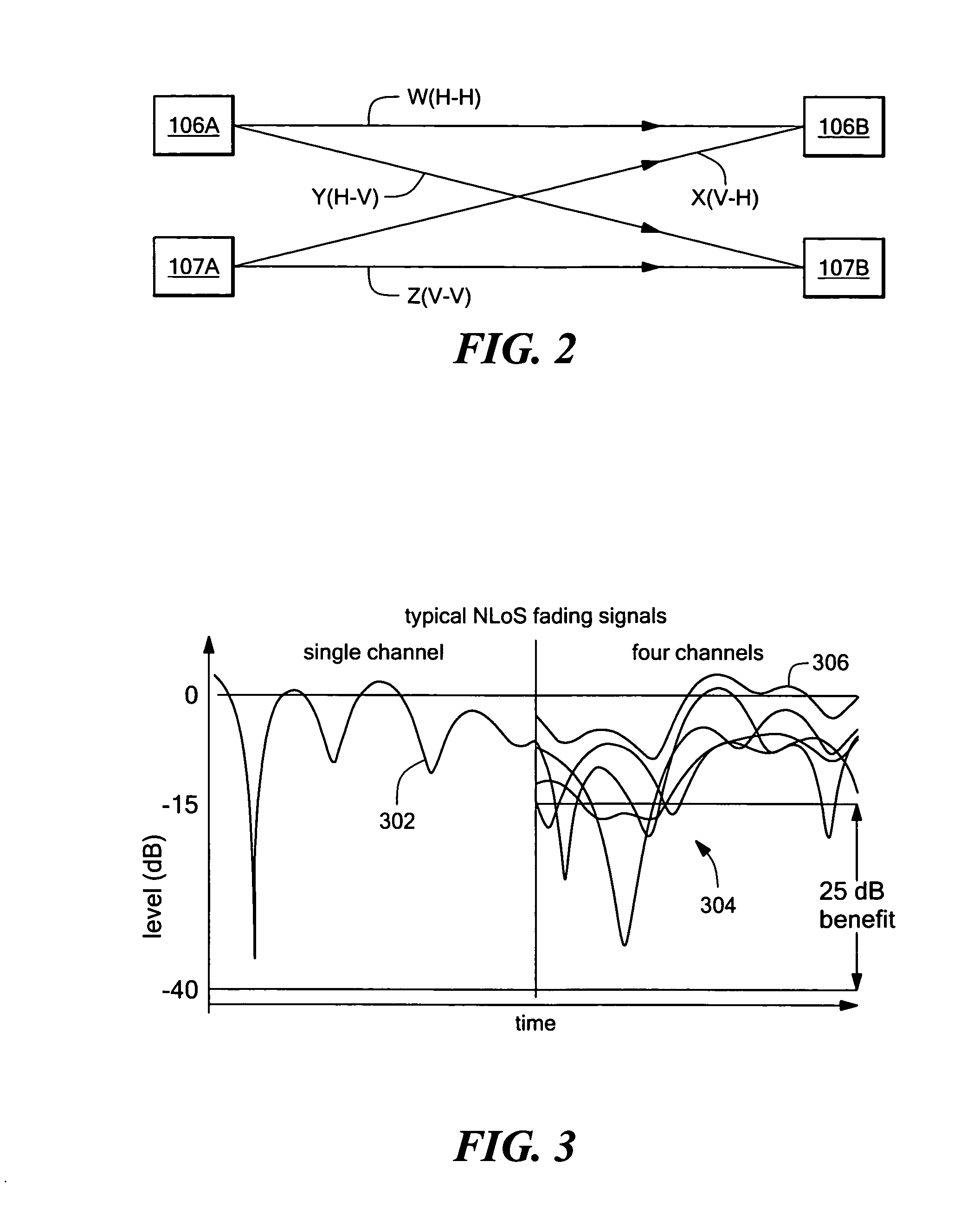

Multiple input multiple output (MIMO) wireless communications system

ActiveUS7333455B1Minimize waterMinimize ground bounce nullPower managementModulated-carrier systemsPolarization diversityFrequency spectrum

A wireless broadband communications system that can transmit signals over communications links with multiple modes of diversity, thereby allowing signals having very low correlation to propagate over the link along multiple orthogonal paths. The system can be implemented as a non-line-of-sight (NLOS) system or a line-of-sight (LOS) system. The NLOS system employs orthogonal frequency division modulation (OFDM) waveforms to reduce multi-path interference and frequency selective fading, adaptive modulation to assure high data rates in the presence of channel variability, and spectrum management to achieve increased data throughput and link availability. The LOS system employs space-time coding and spatial and polarization diversity to minimize ground bounce nulls. The system achieves levels of link availability, data throughput, and system performance that have heretofore been unattainable in wireless broadband communications systems.

Owner:MOTOROLA SOLUTIONS INC

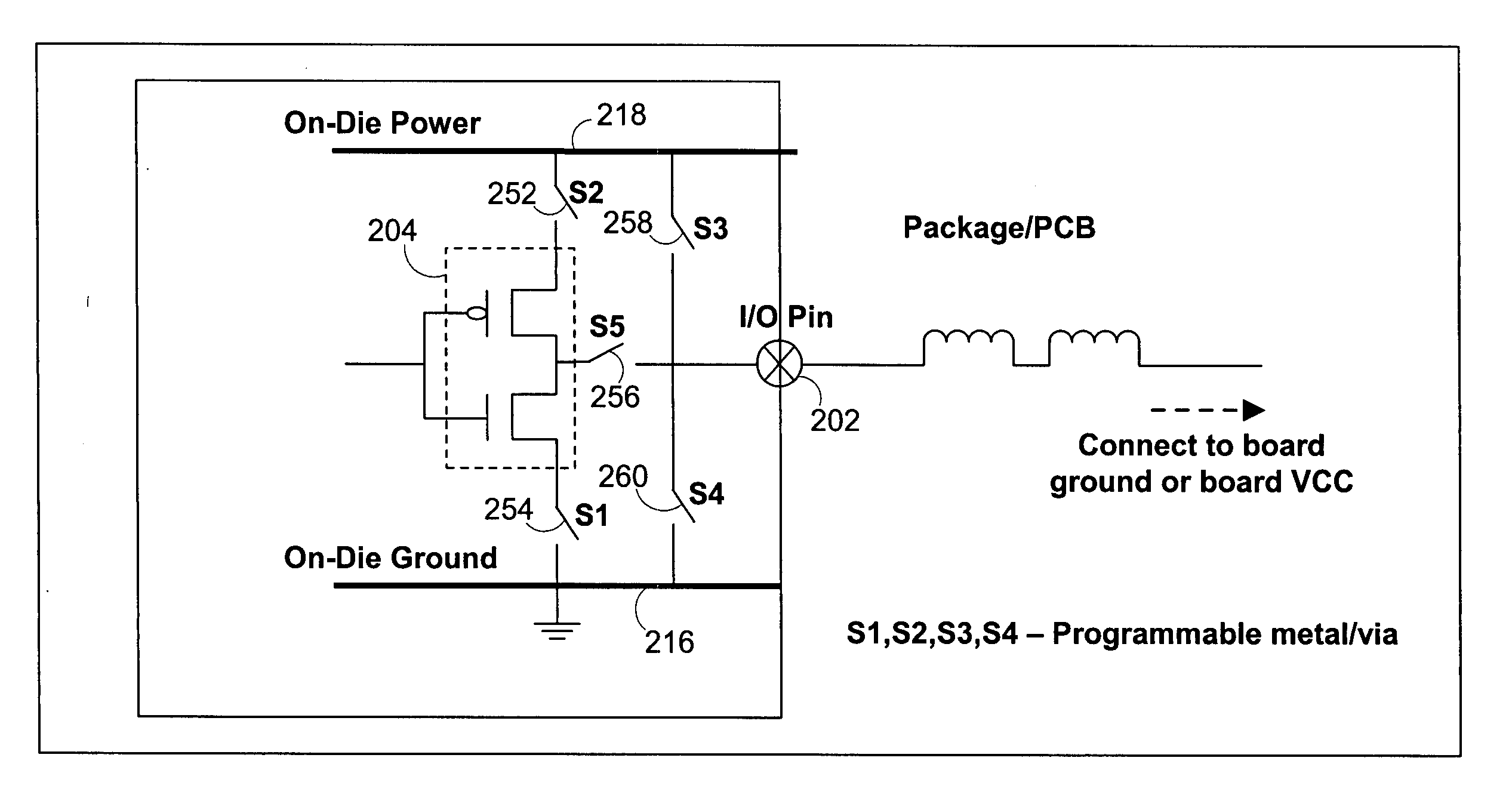

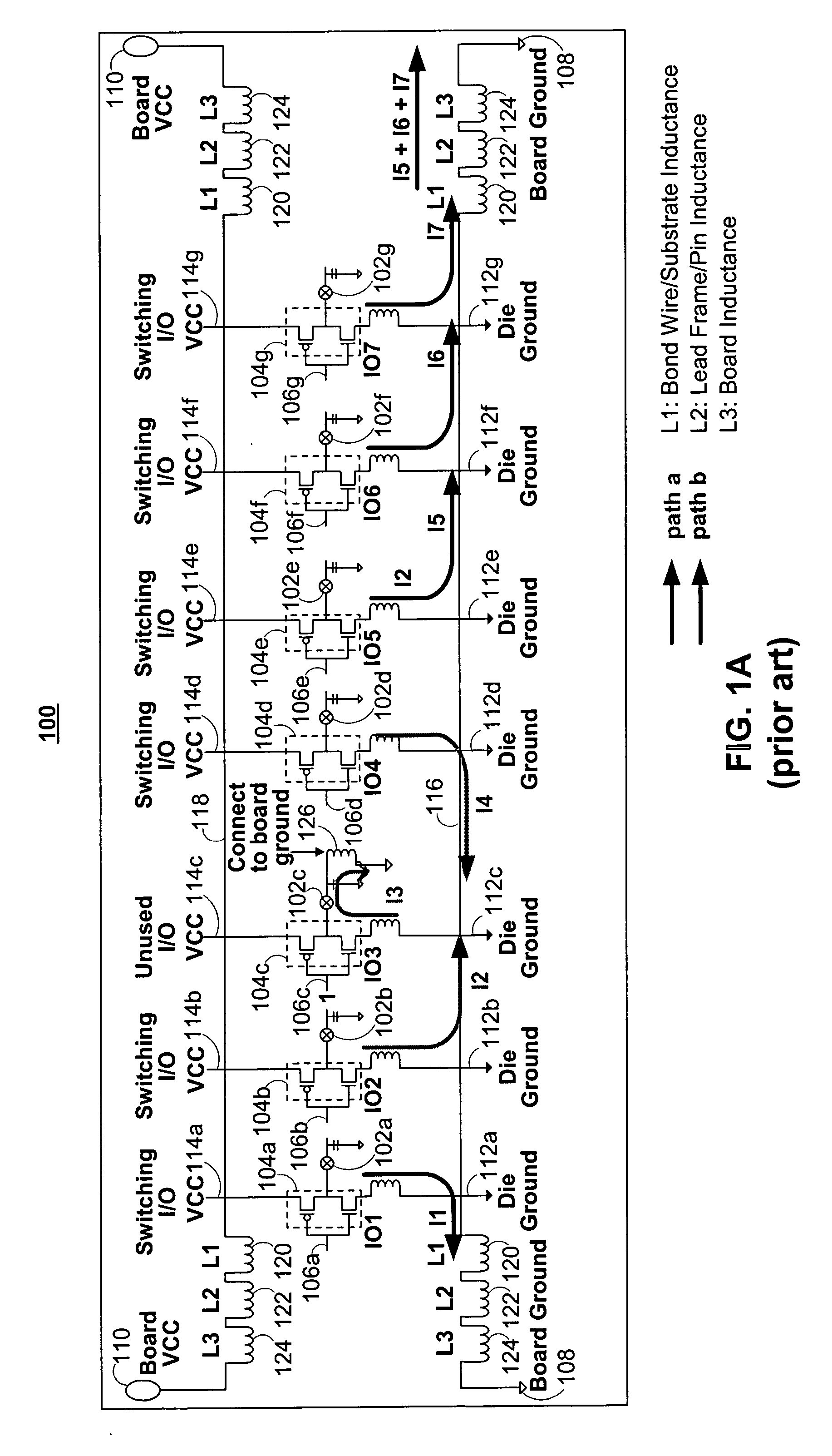

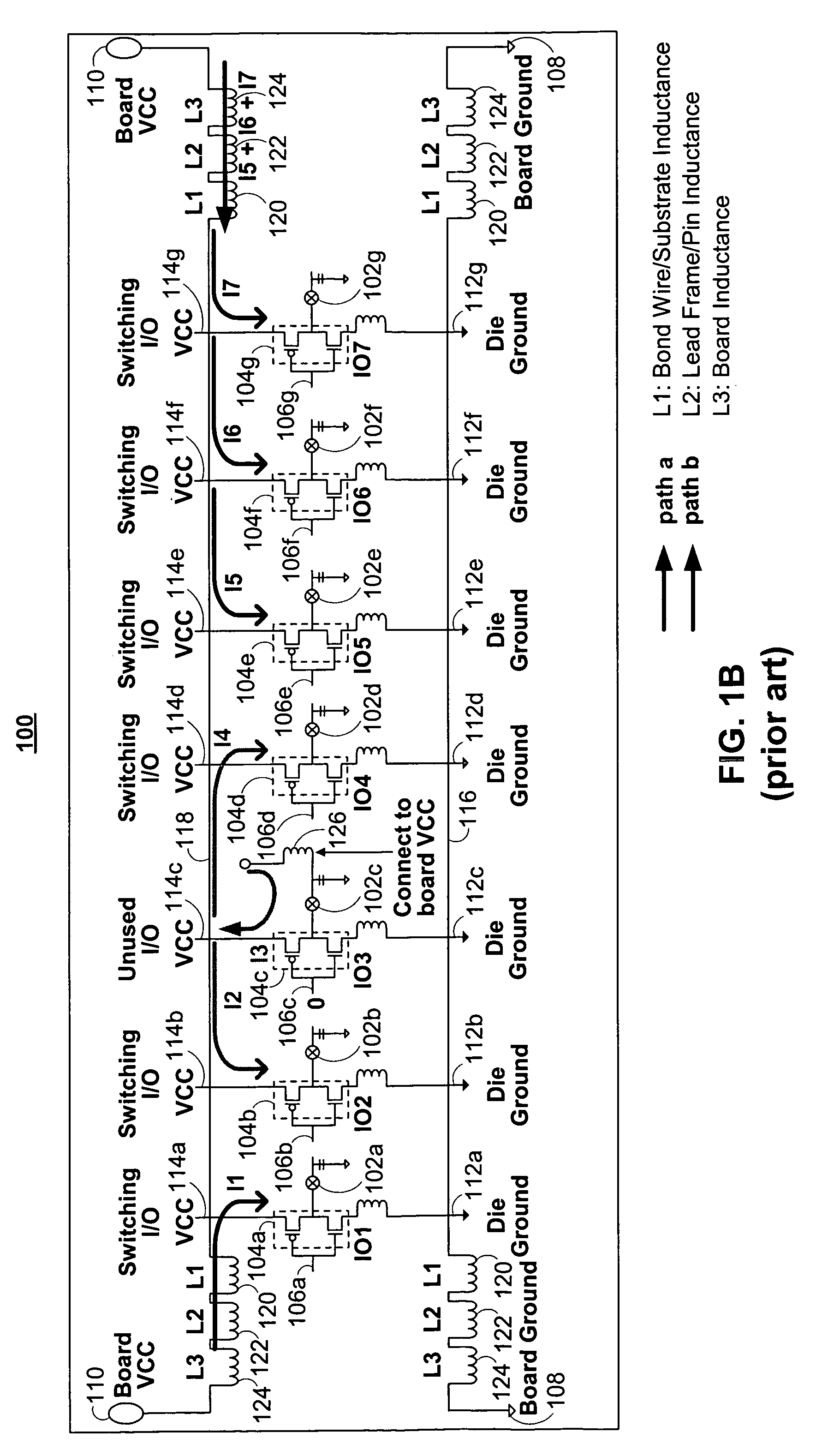

I/O circuitry for reducing ground bounce and VCC sag in integrated circuit devices

InactiveUS20070007991A1Reducing ground bounceReduce ground bounceElectronic switchingHeating/cooling contact switchesGround bounceEngineering

Methods and circuitry for reducing ground bounce and VCC sag effects in integrated circuit (“IC”) devices is provided. In particular, a via-programmable design for I / O circuitry in IC devices is provided. The via-programmable I / O circuitry is used to disconnect I / O pin driver circuitry from and create a substantially direct connection between unused I / O pins and the ground and / or VCC signals of an IC device to reduce ground bounce and VCC sag, respectively.

Owner:ALTERA CORP

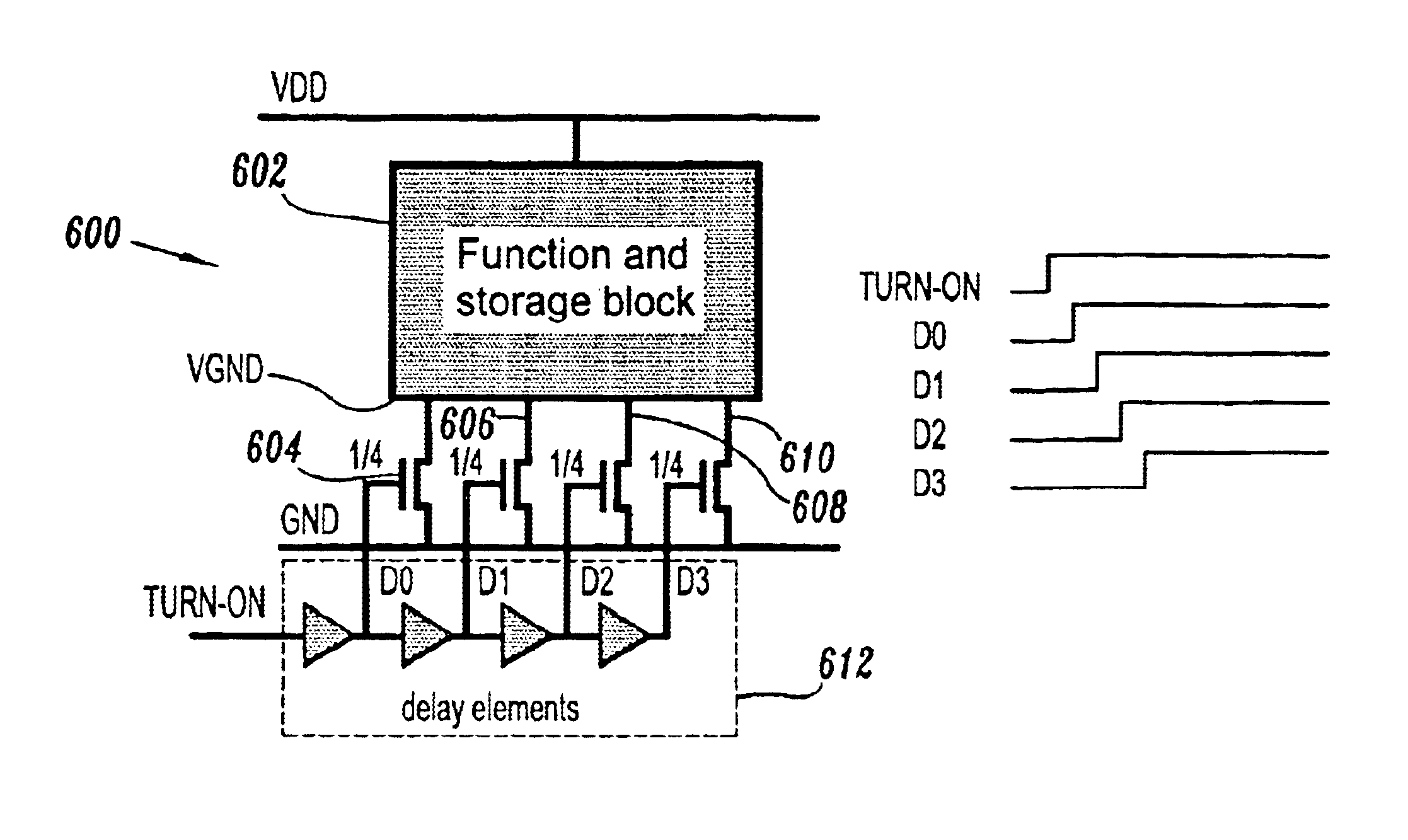

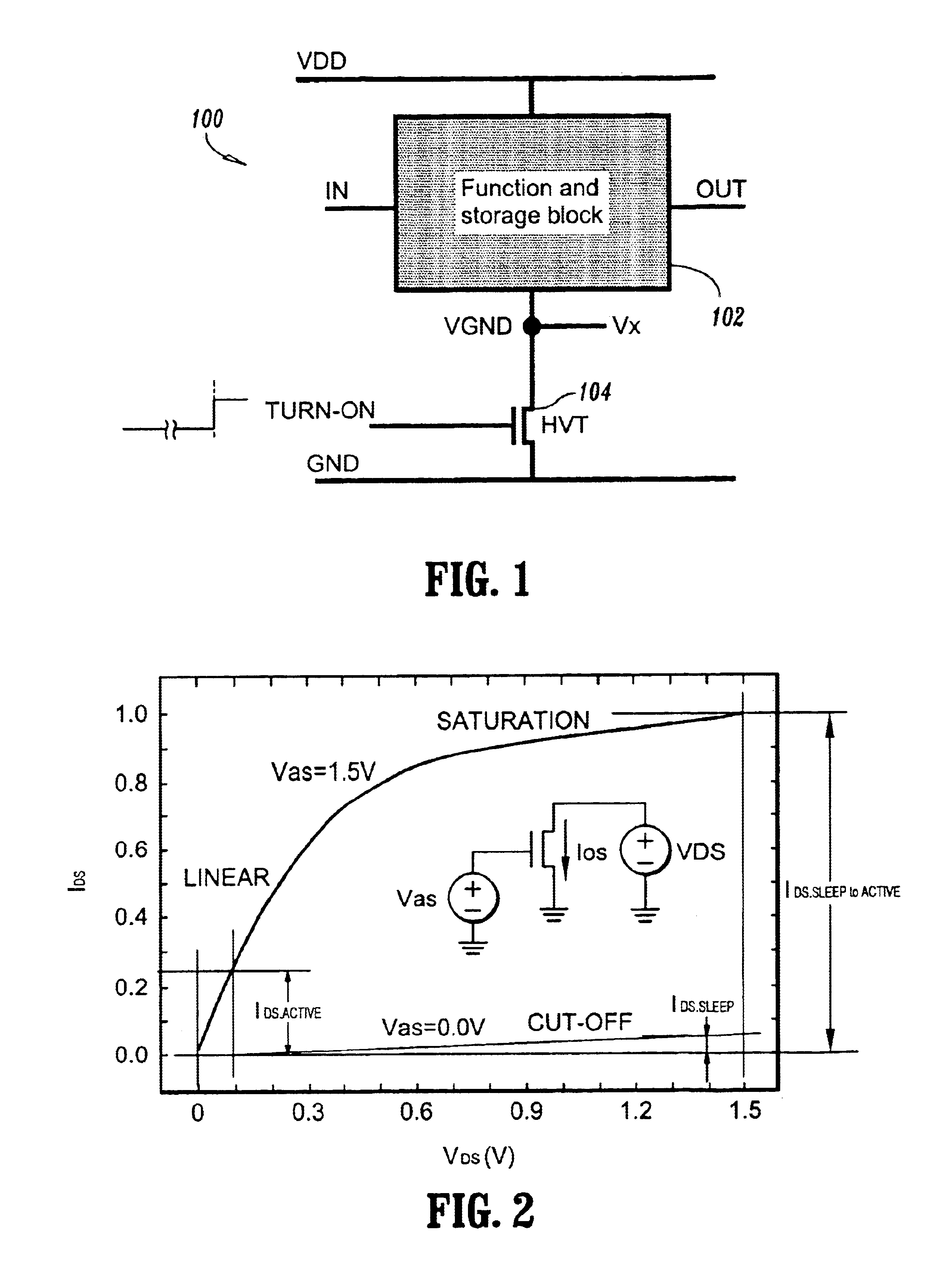

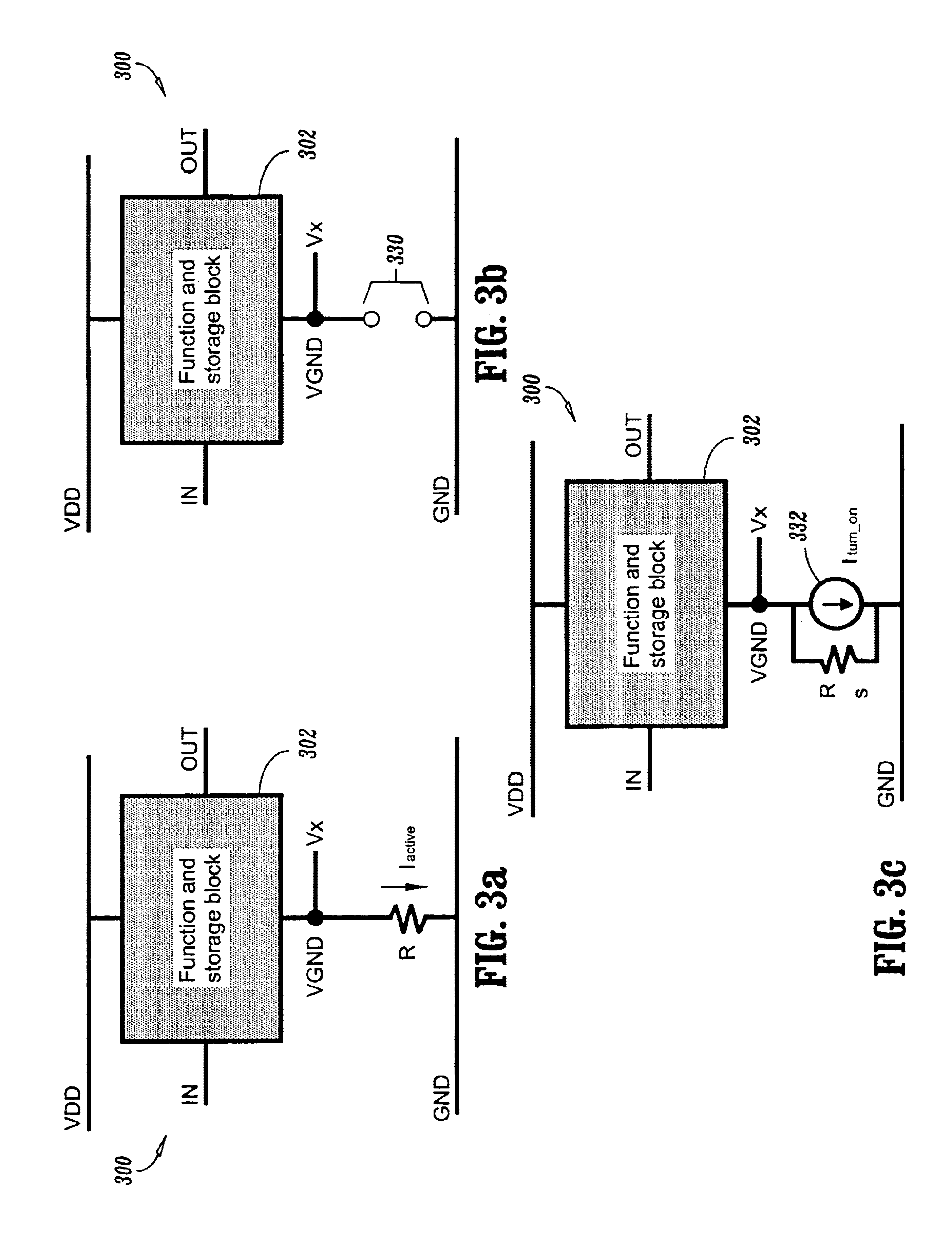

Non-abrupt switching of sleep transistor of power gate structure

InactiveUS6876252B2Reduce ground bounceWeakening rangeElectronic switchingStatic storageMinimum timeGround bounce

A semiconductor integrated circuit including a non-abrupt switching mechanism for a sleep transistor of a power gate structure to reduce ground bounce is provided. The semiconductor integrated circuit comprises a supply voltage line; a ground voltage line; a virtual ground voltage line; a logic circuit coupled to the supply voltage line and the virtual ground voltage line; at least one sleep transistor for controlling current flow to the logic circuit, the sleep transistor being coupled to the virtual ground voltage line and the ground voltage line; and a non-abrupt switching circuit for sequentially controlling the sleep transistor. The switching mechanism reduces the magnitude of voltage glitches on the power and ground rails as well as the minimum time required to stabilize power and ground.

Owner:MEDIATEK INC

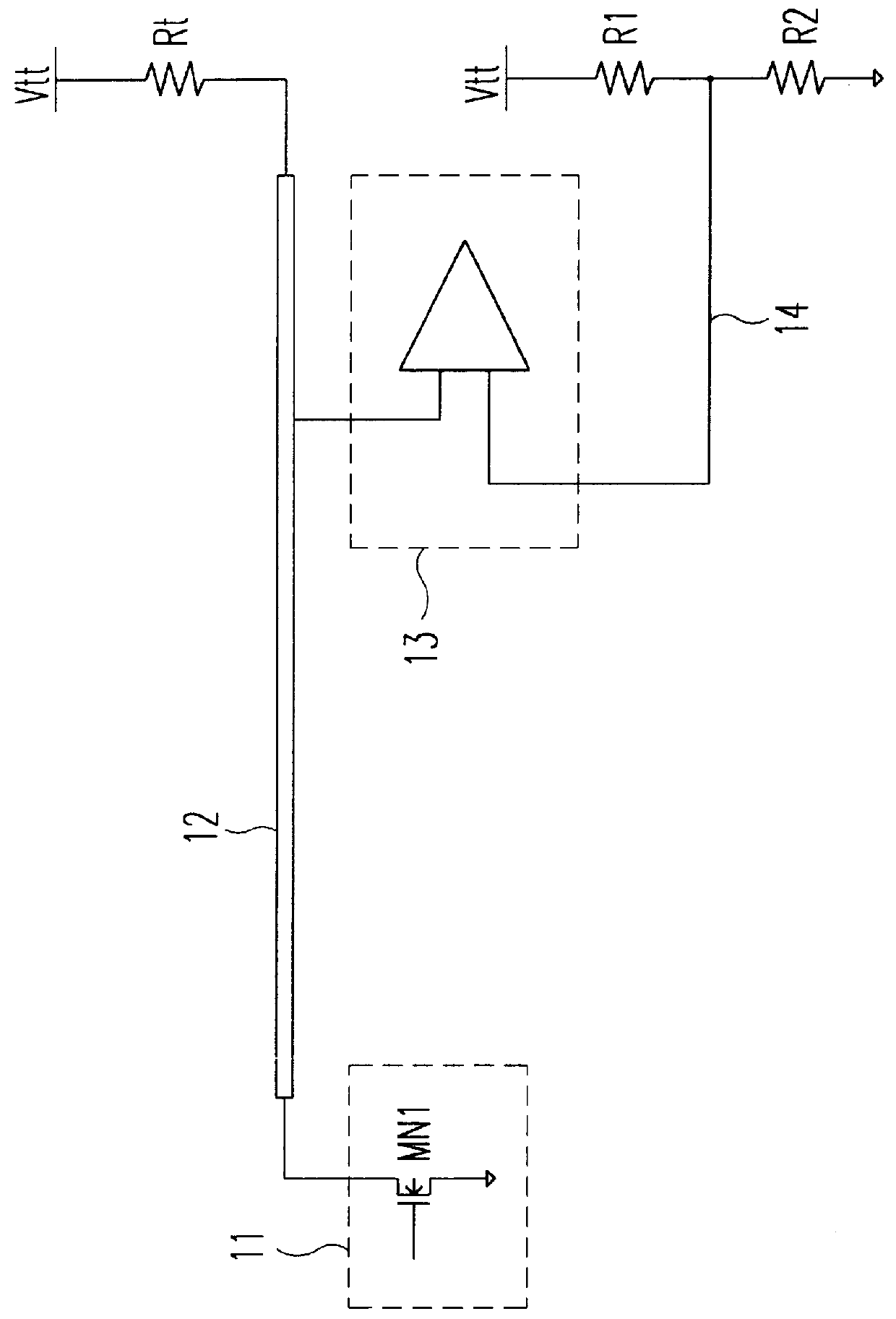

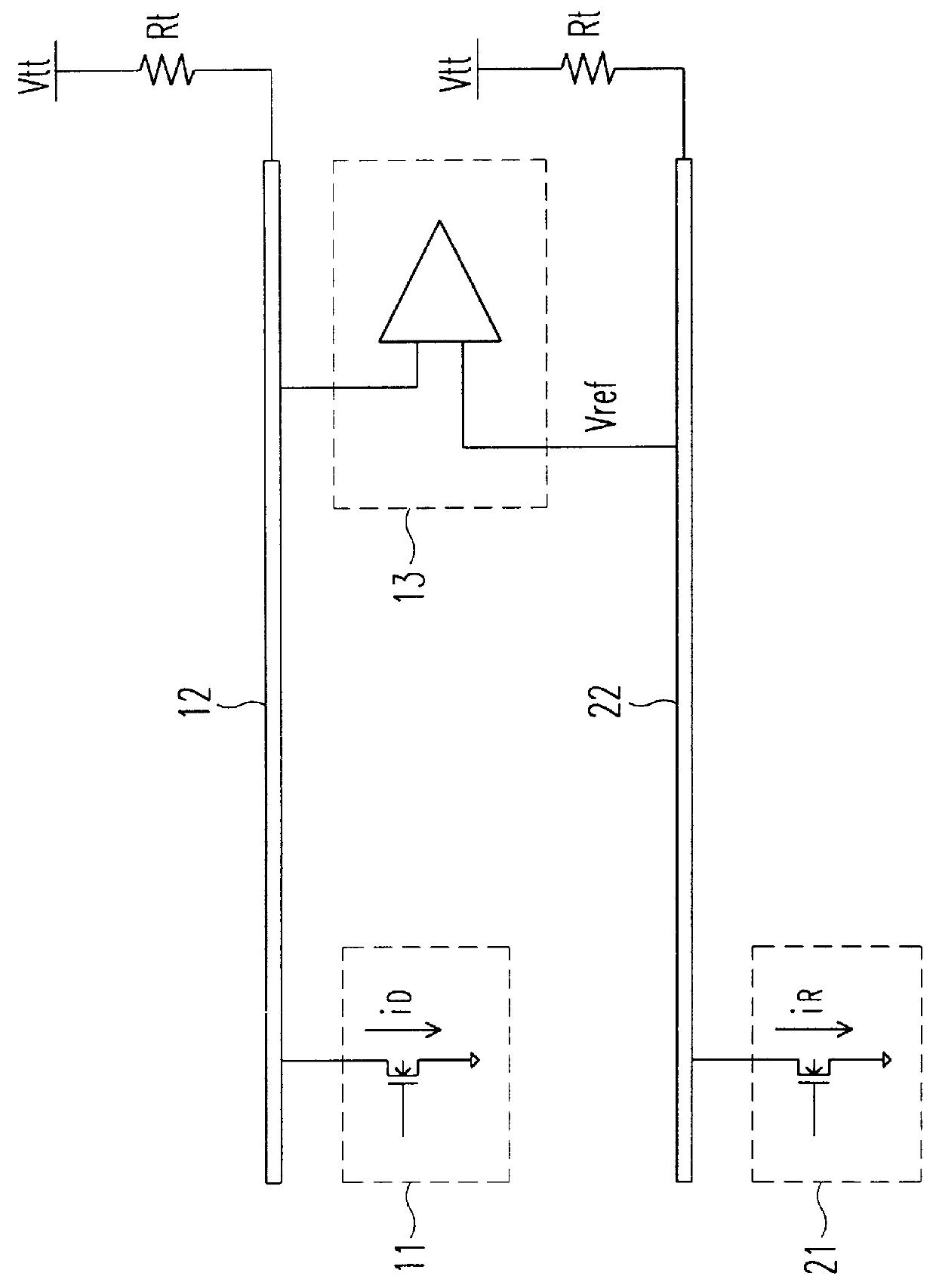

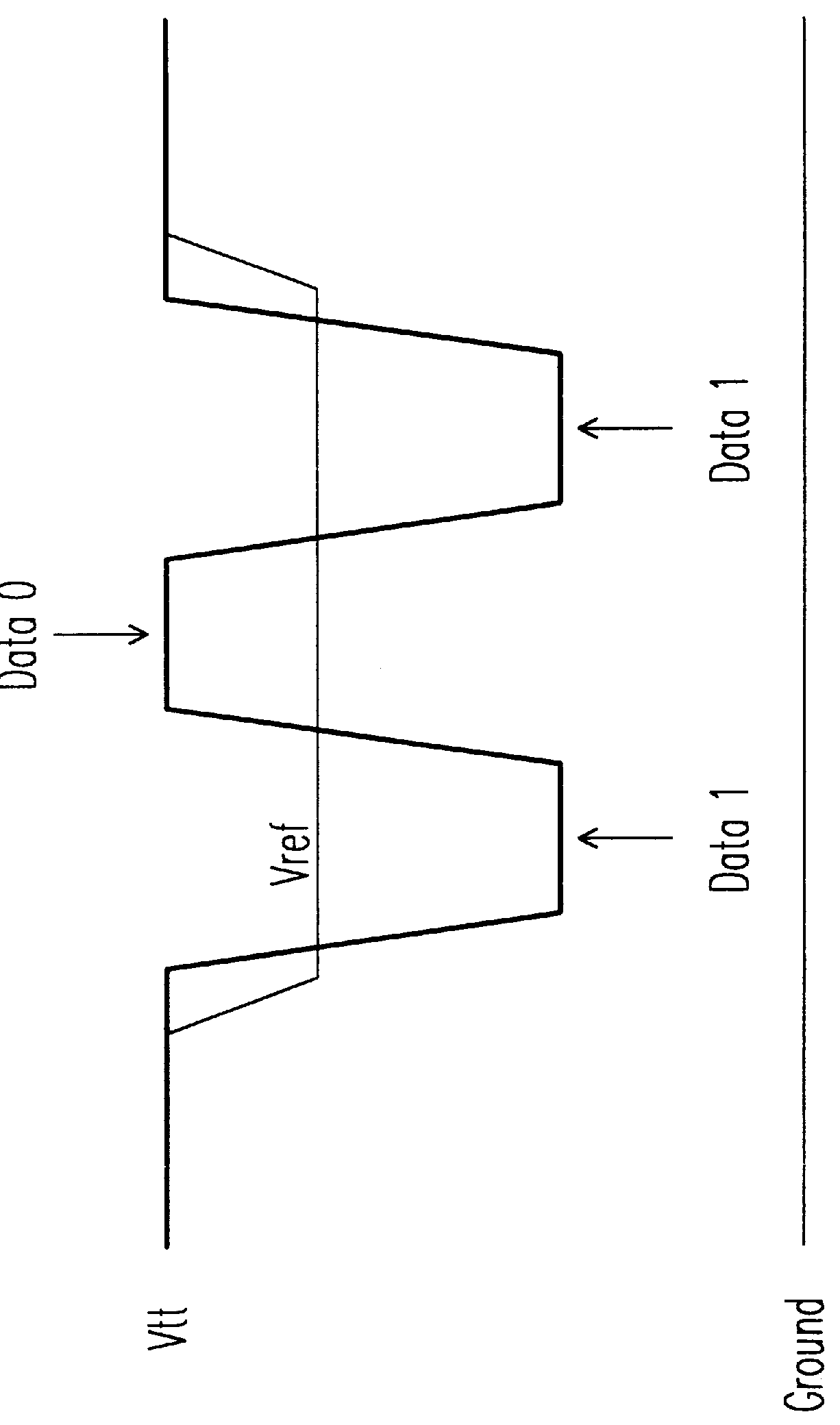

Bus interface circuit in a semiconductor memory device

InactiveUS6078978AReliability increasing modificationsElectronic switchingMemory interfaceGround bounce

This invention relates to a bus interface circuit in a semiconductor memory device. This invention comprises a data driver to transmit a data signal through a first transmission line of which one end is terminated; a reference voltage driver to transmit a reference voltage signal through a second transmission line of which one end is terminated; and a receiver to determine a logic state by comparing the data signal transmitted by the first transmission line with the reference voltage signal transmitted by the second transmission line. Accordingly, a high-speed bus interface circuit of the present invention can decrease a common mode noise, influence of ground bounce, an output voltage swing and a power consumption by simultaneously driving a data driver and a reference voltage driver in a memory interface using a transmission line being either single or parallel terminated to transmit to a receiver.

Owner:HYUNDAI ELECTRONICS IND CO LTD

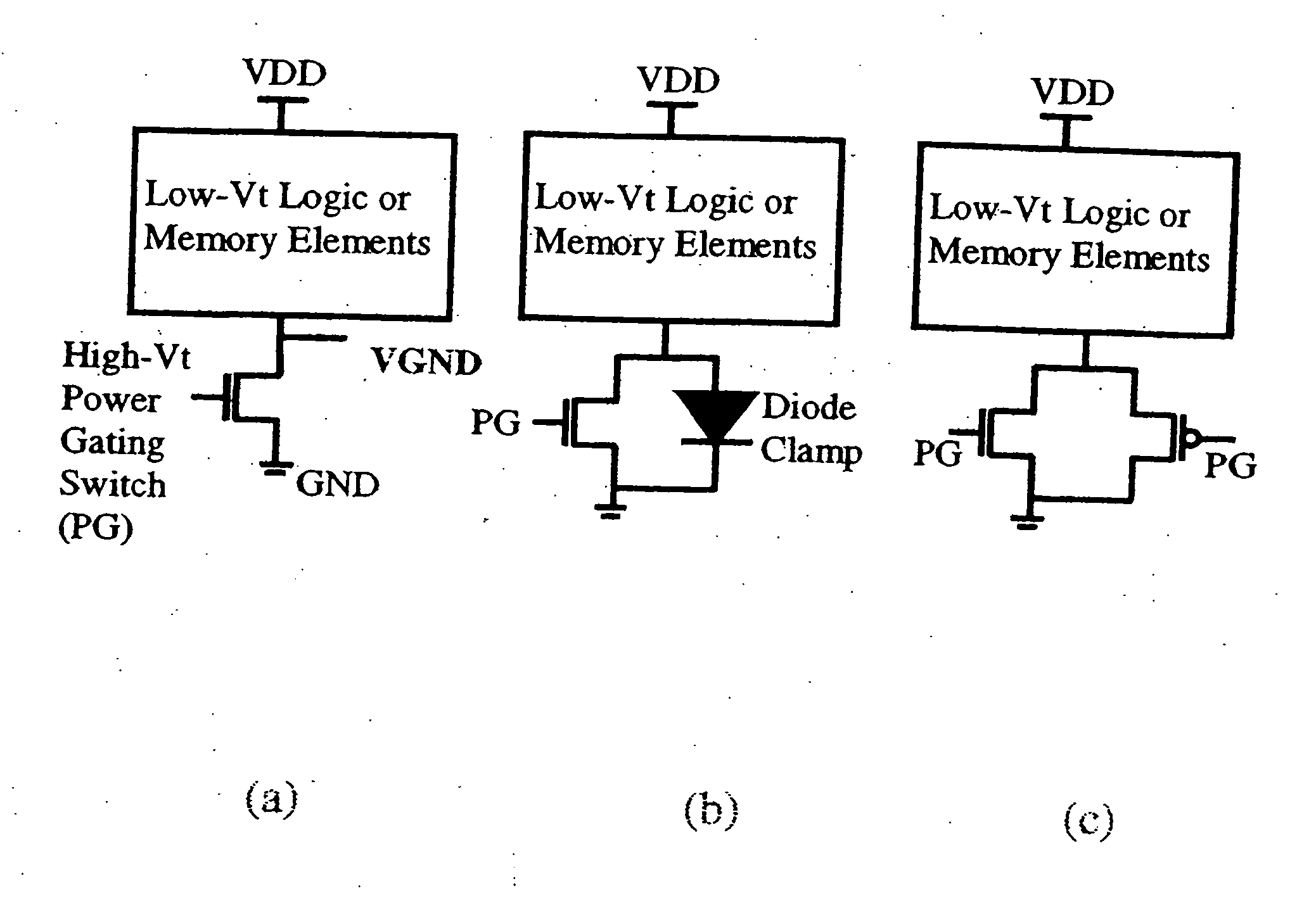

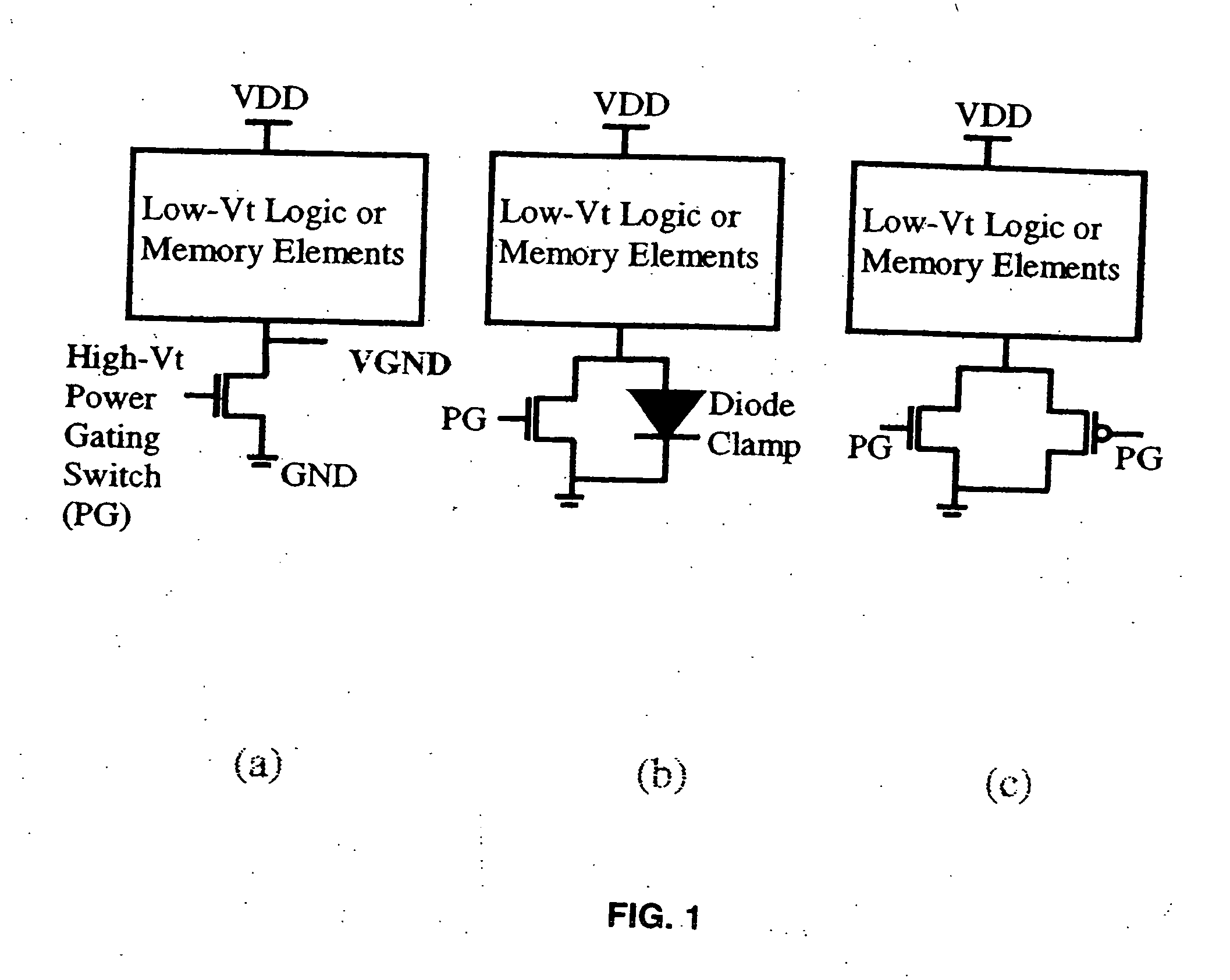

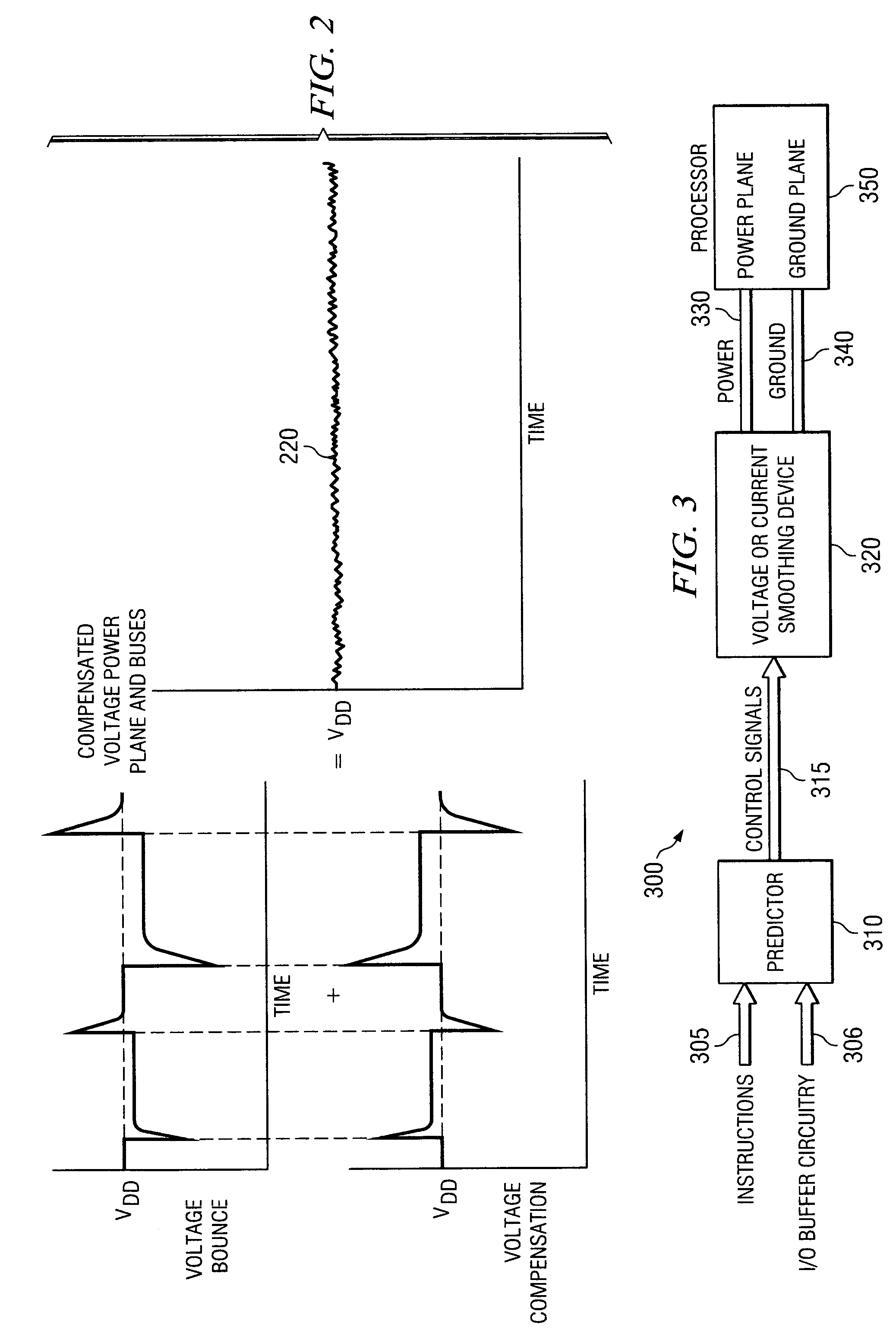

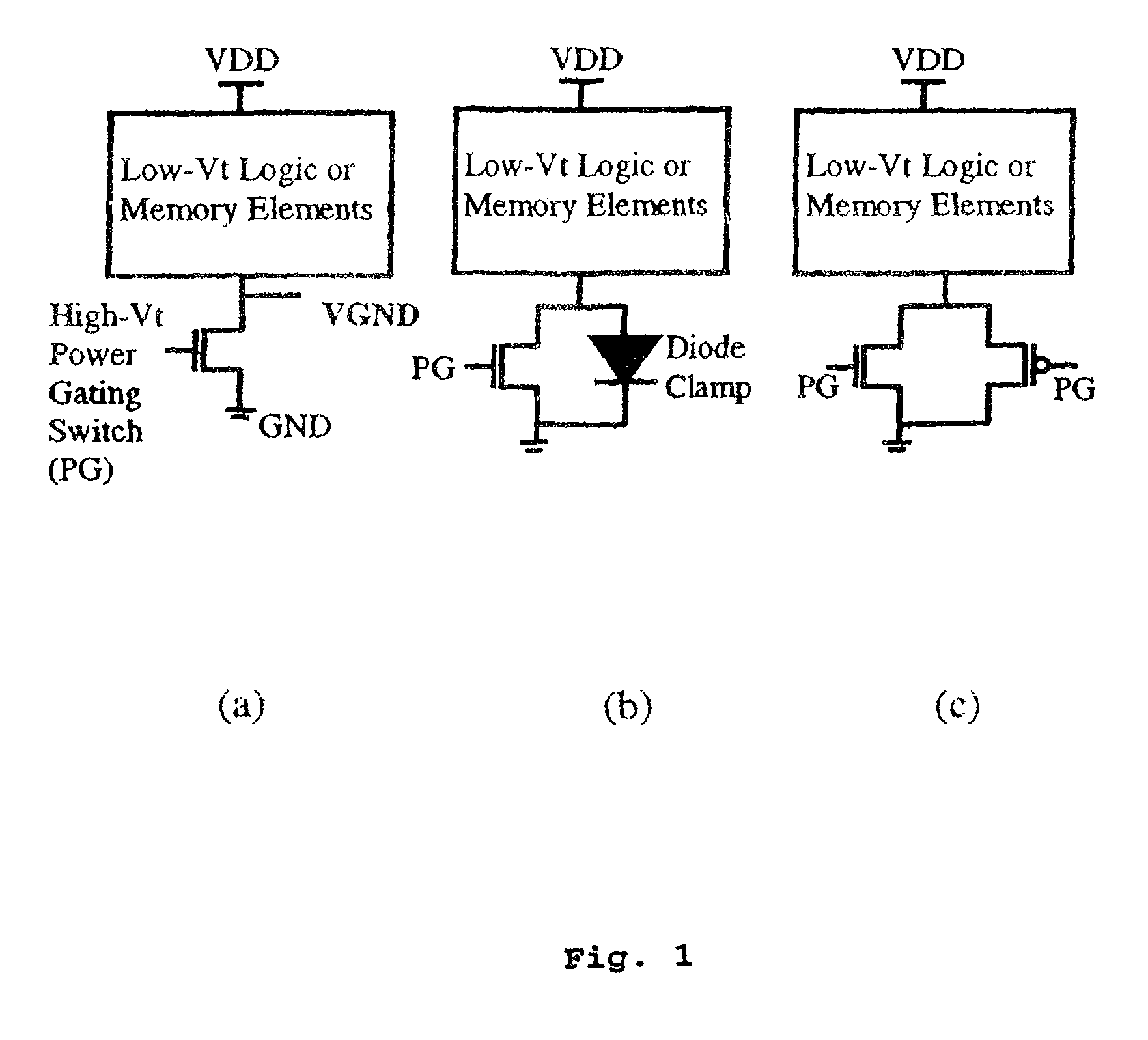

High-density low-power data retention power gating with double-gate devices

A new power gating structure with robust data retention capability using only one single double-gate device to provide both power gating switch and virtual supply / ground diode clamp functions. The scheme reduces the transistor count, area, and capacitance of the power gating structure, thus improving circuit performance, power, and leakage. The scheme is compared with the conventional power gating structure via mixed-mode physics-based two-dimensional numerical simulations. Analysis of virtual supply / ground bounce for the proposed scheme is also presented.

Owner:GLOBALFOUNDRIES US INC

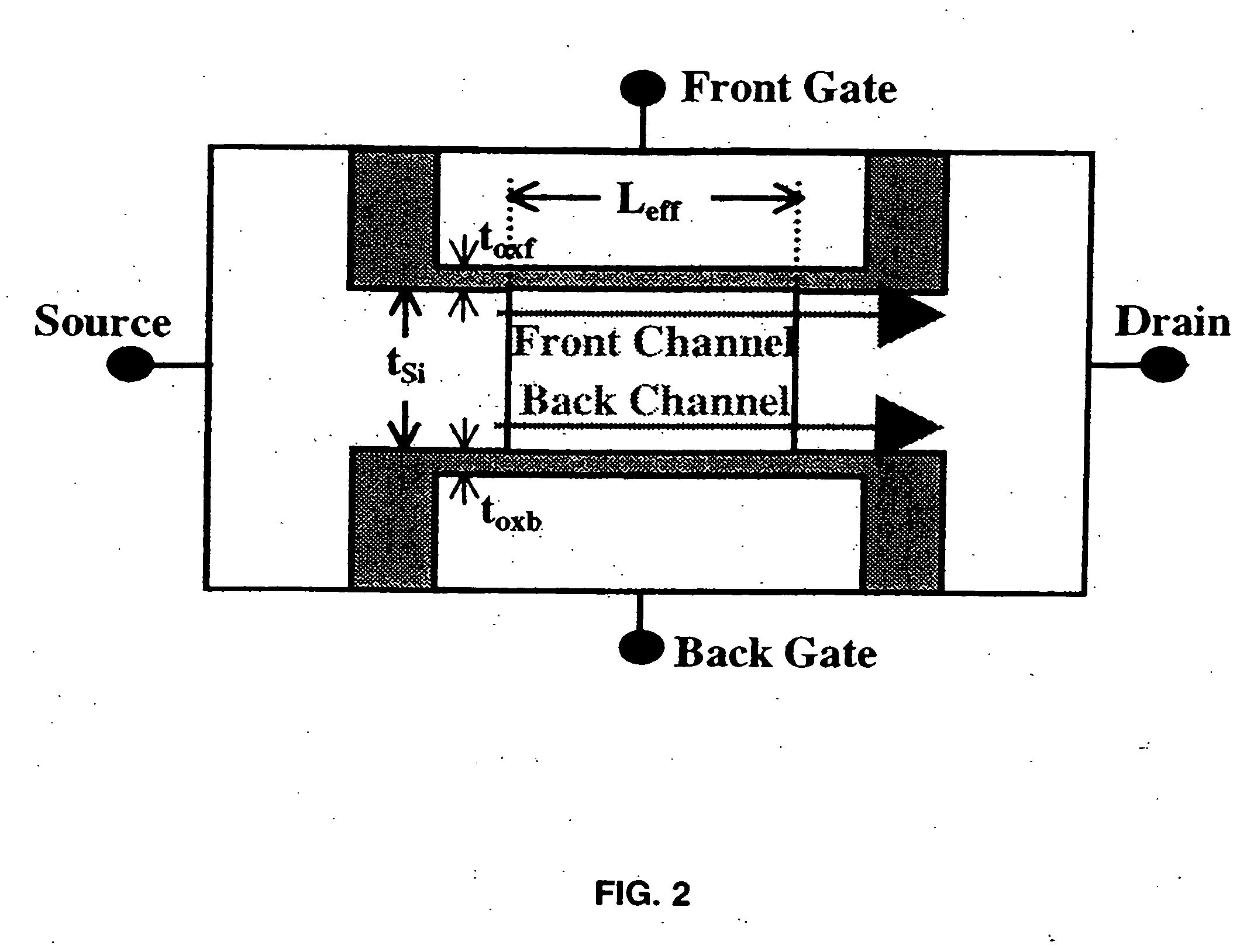

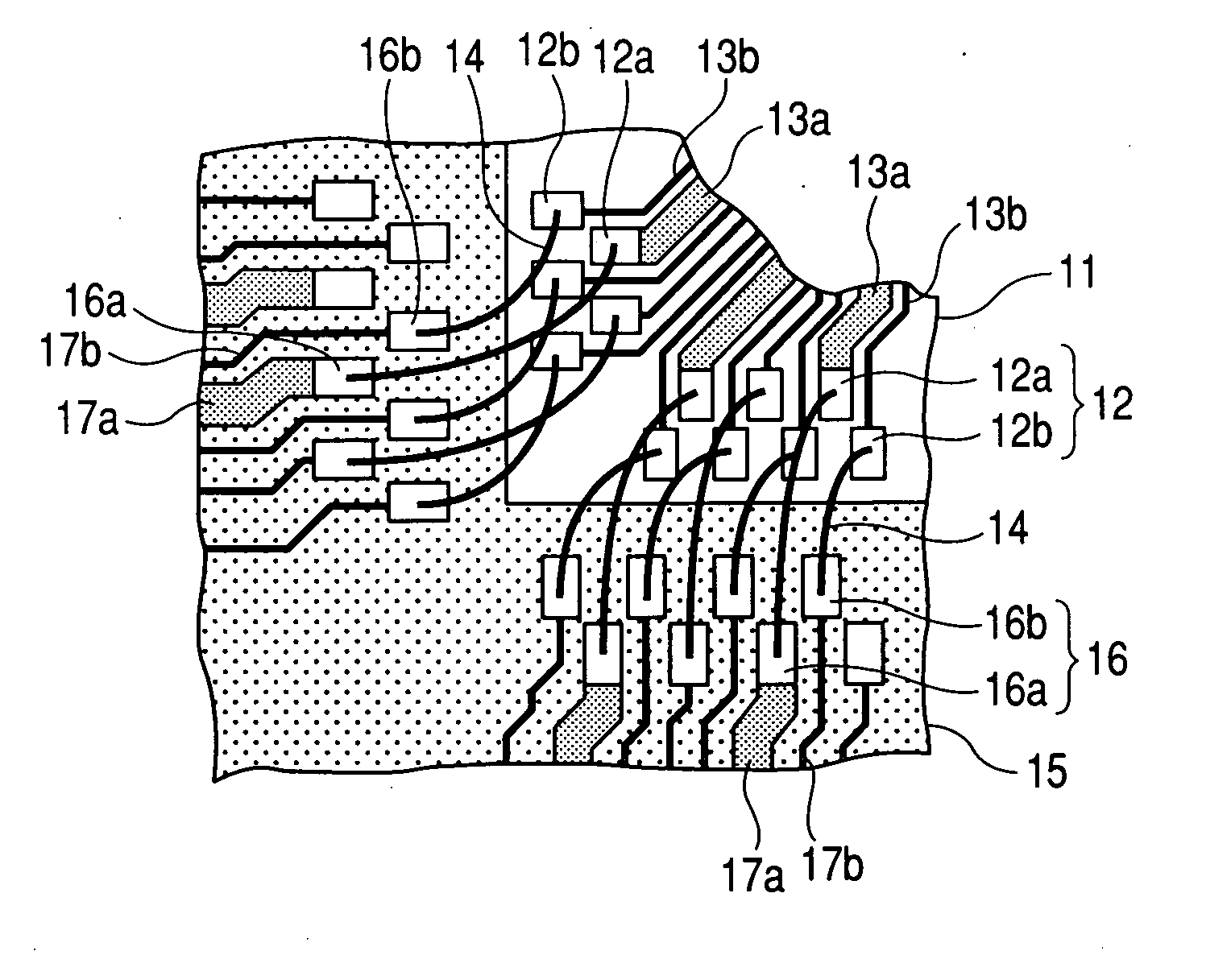

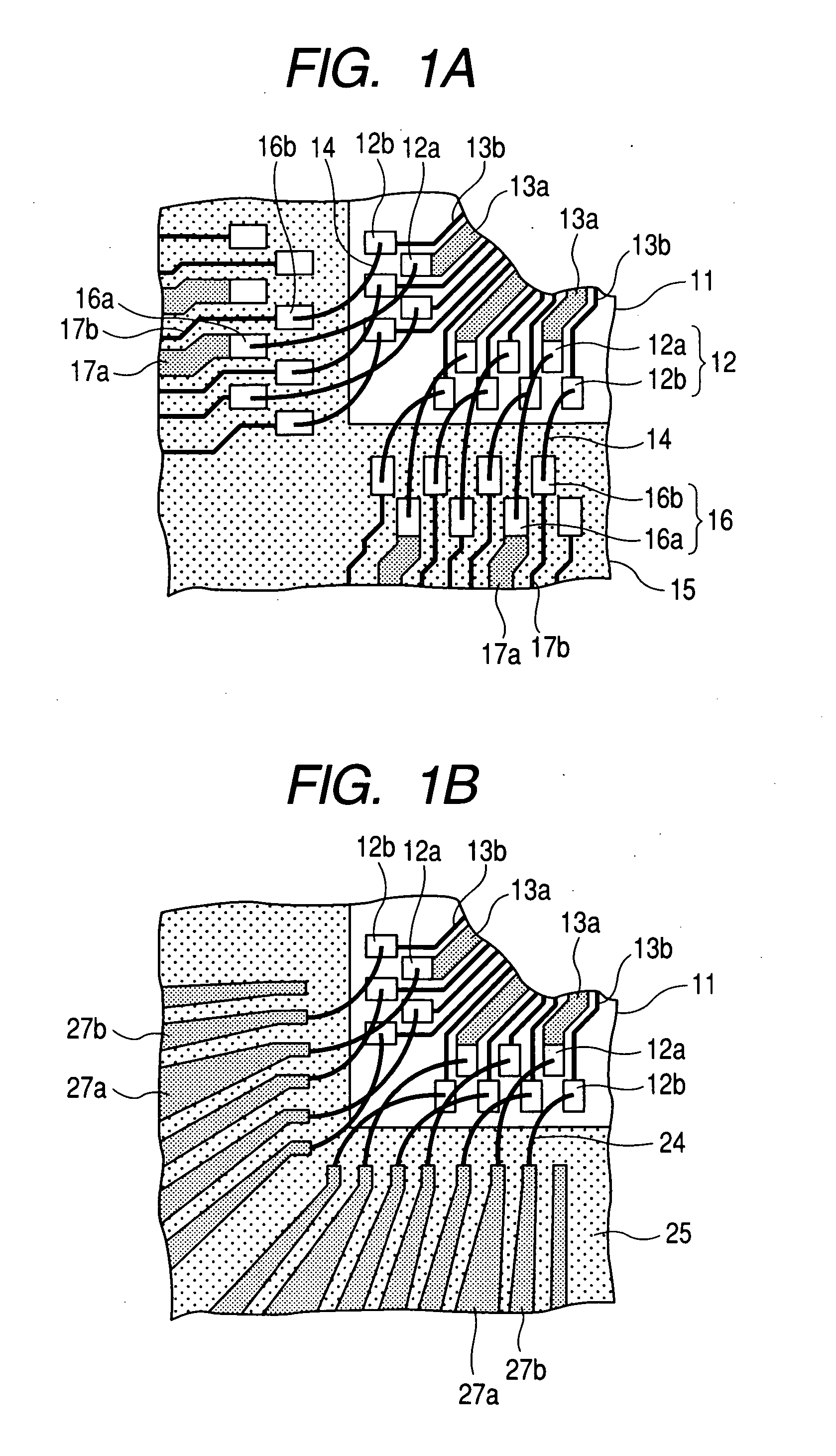

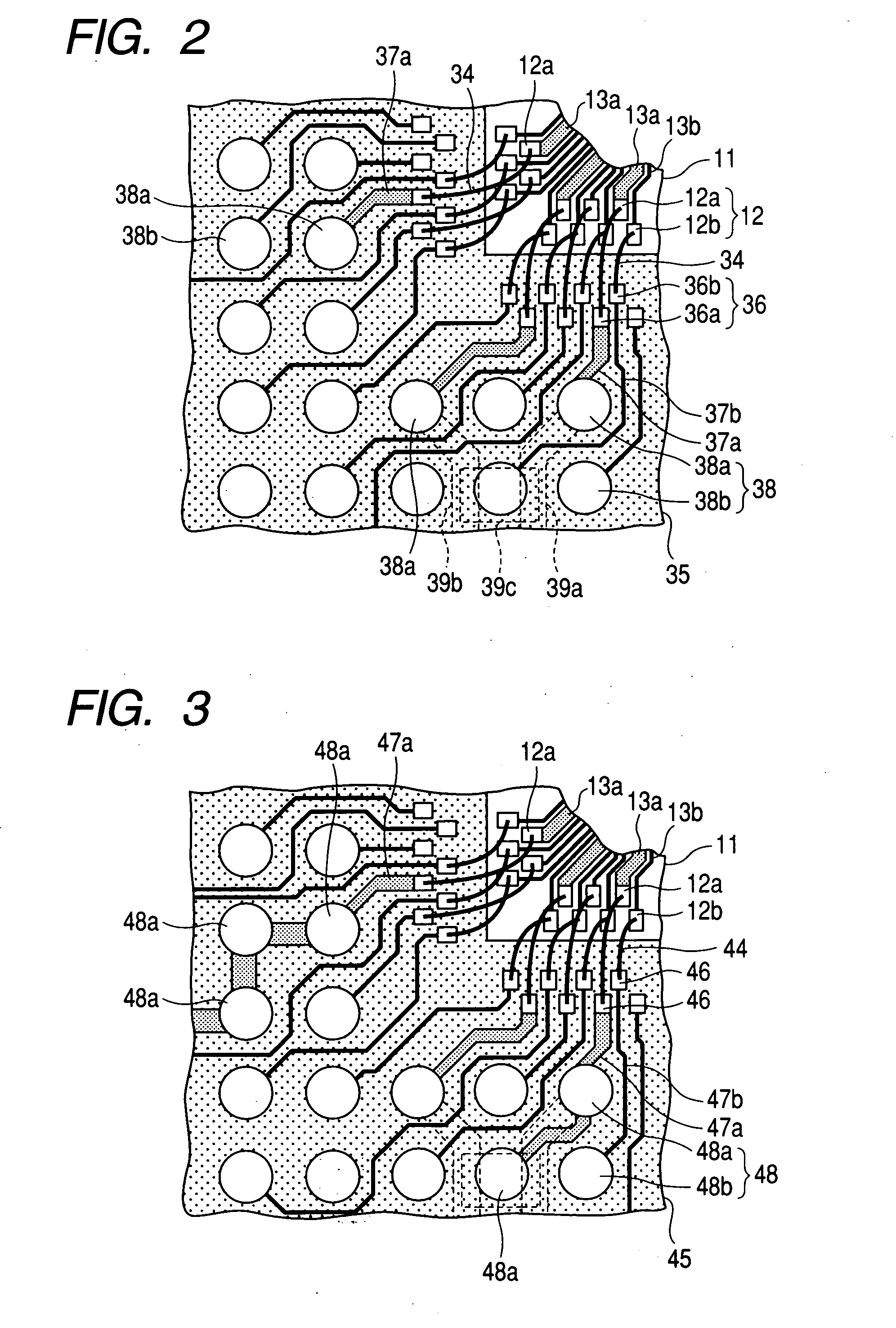

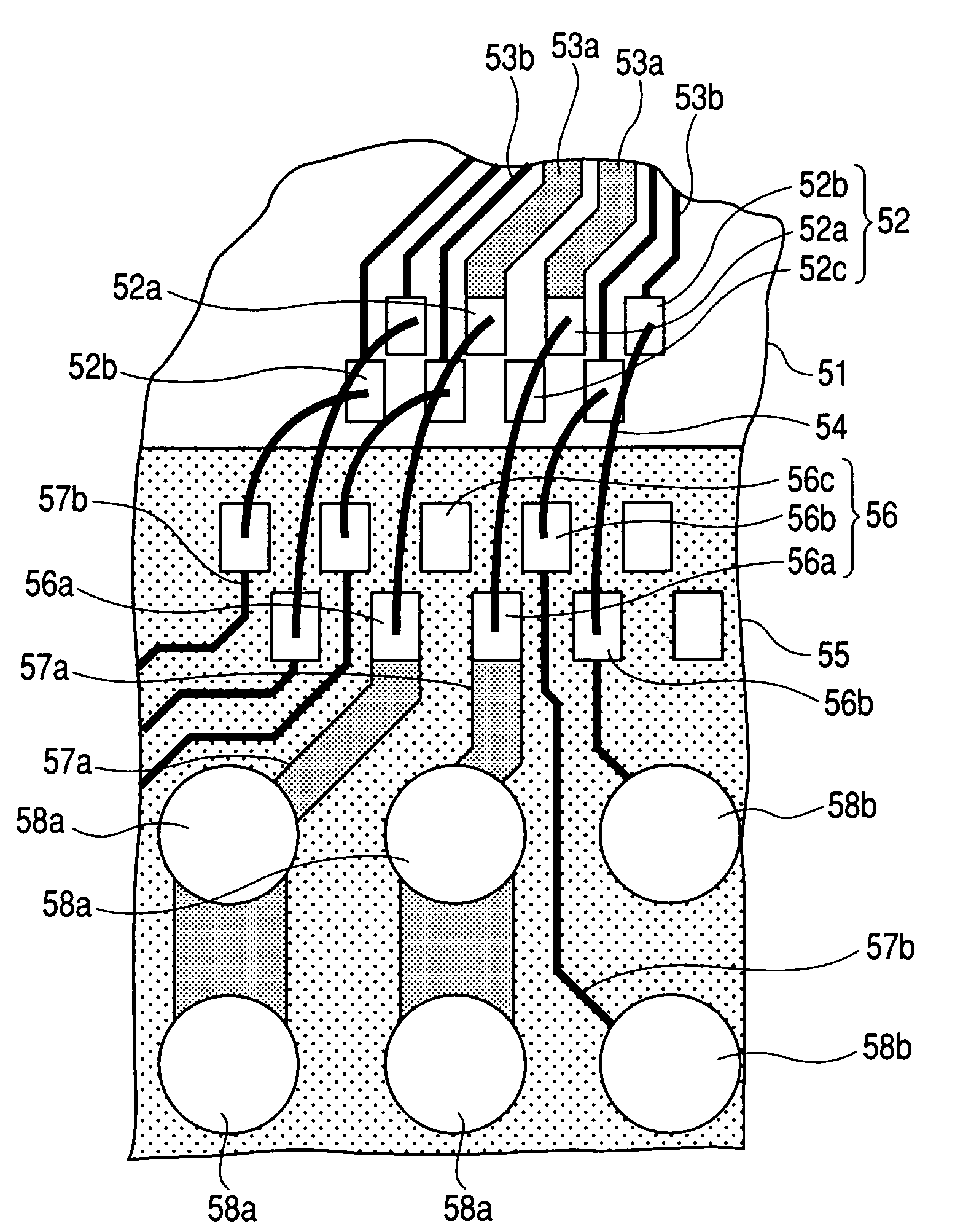

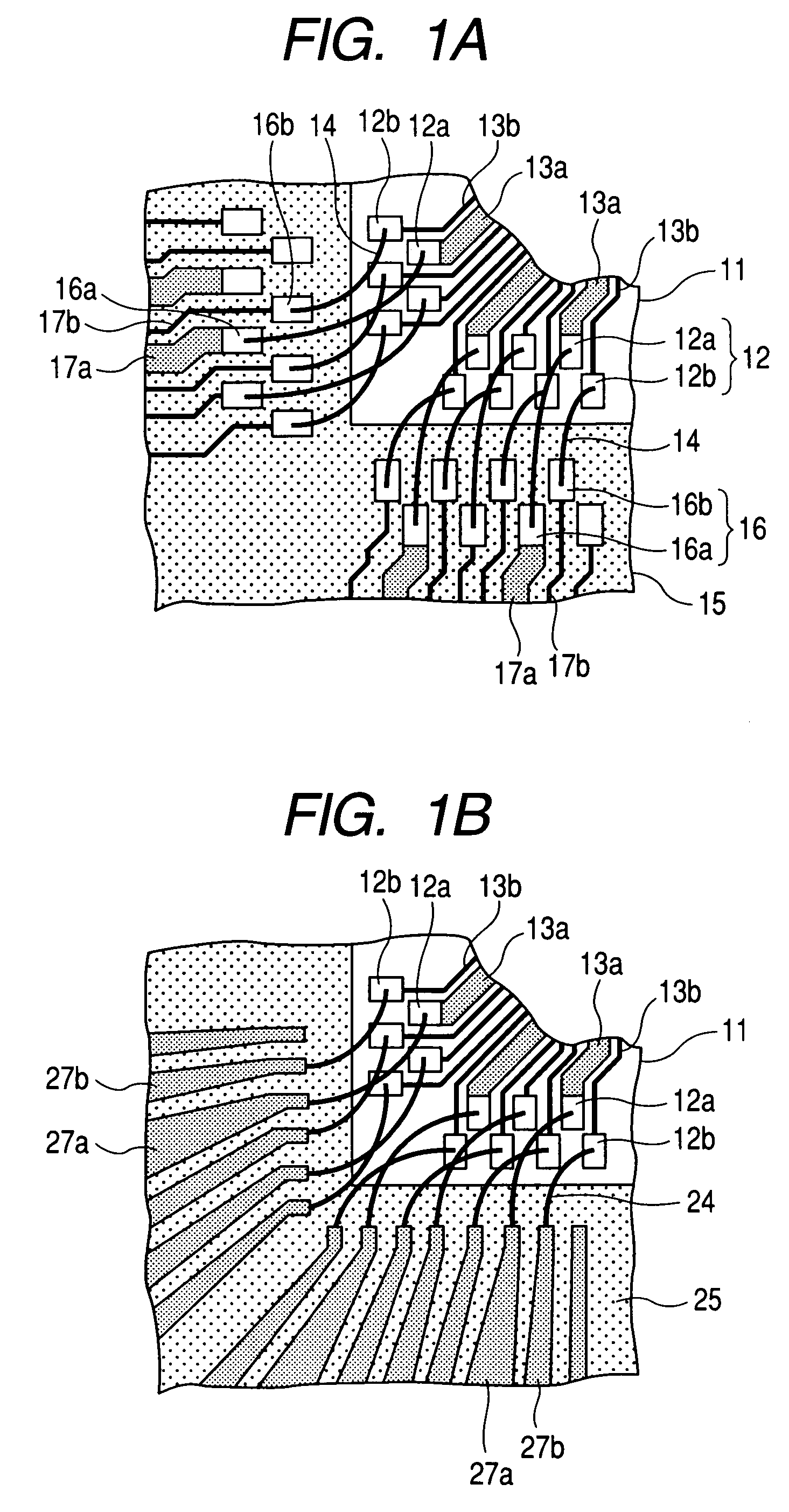

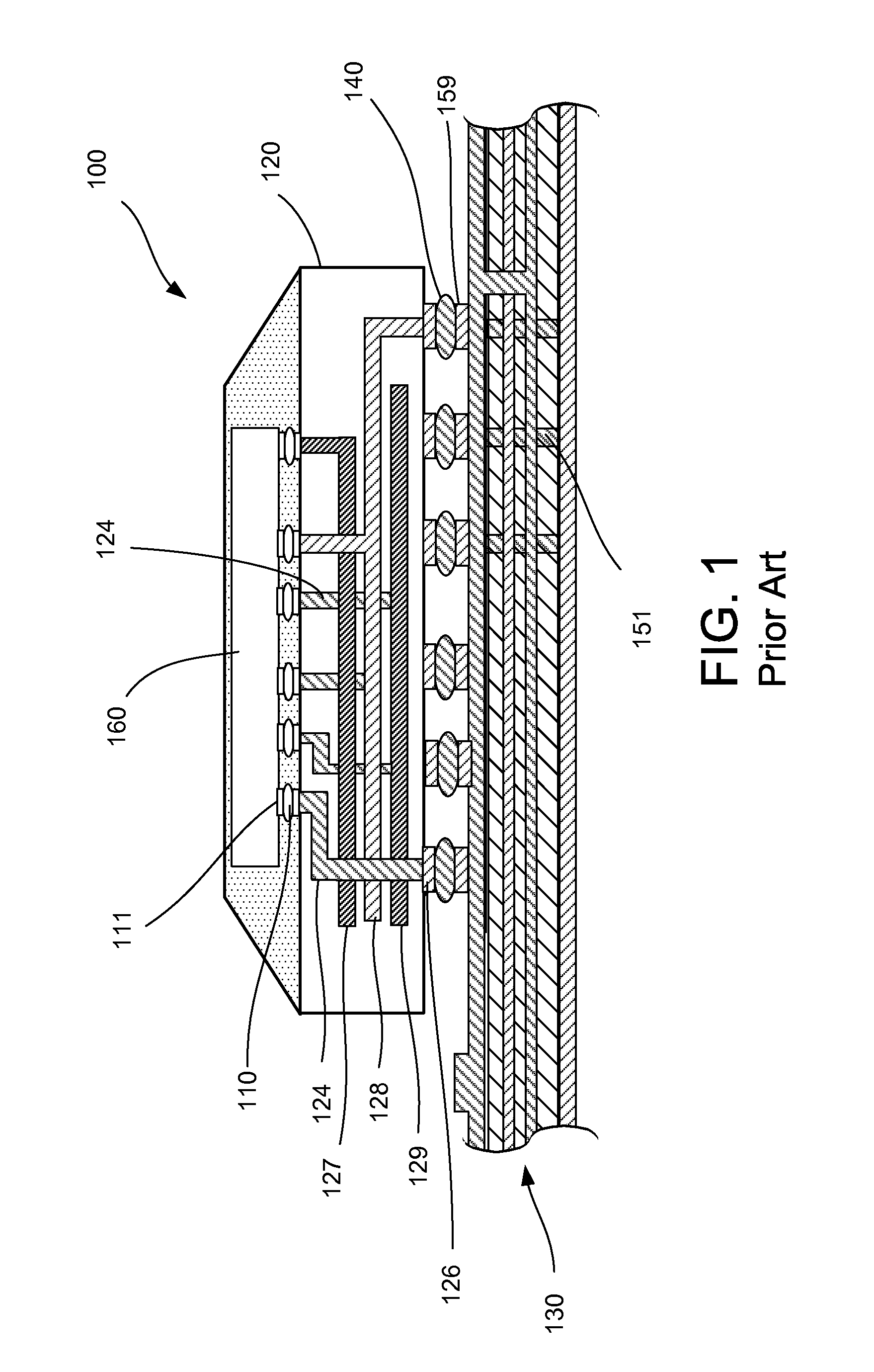

Semiconductor integrated circuit device

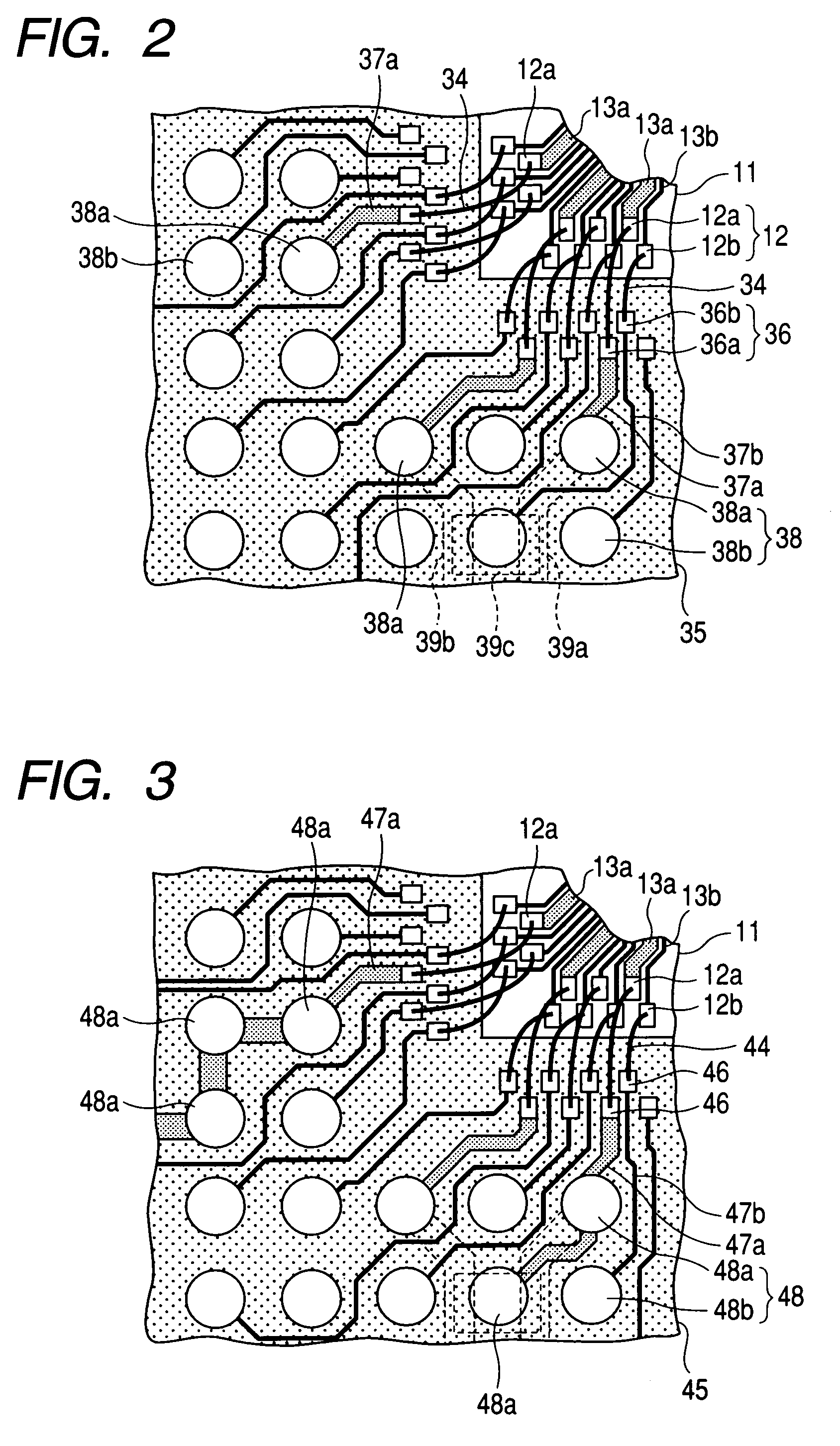

InactiveUS20050184403A1Lower impedanceReduce package sizeSemiconductor/solid-state device detailsSolid-state devicesLine widthLead bonding

A semiconductor integrated circuit device is provided which comprises a semiconductor chip having wire bonding pads and a package encapsulating the semiconductor chip and connected via bonding wires to the wire bonding pads, wherein wire bonding pads on the semiconductor chip are arranged in two rows in a staggered manner along a periphery of the semiconductor chip, and of the wire bonding pads, power supply pads are arranged in a rear row located close to a semiconductor integrated circuit unit as an active area on the semiconductor chip and in a front row, only signal pads are arranged. Because the power supply pads are provided in the rear row, the line width of a power supply line led out from each power supply pad can be made equal to the width of the pad, thus reducing the impedance of the connection circuit between the semiconductor chip and the package, and suppressing generation of radiation noise, ground bounce and so on.

Owner:CANON KK

Semiconductor integrated circuit device

InactiveUS7259467B2Lower impedanceReduce package sizeSemiconductor/solid-state device detailsSolid-state devicesLine widthLead bonding

Owner:CANON KK

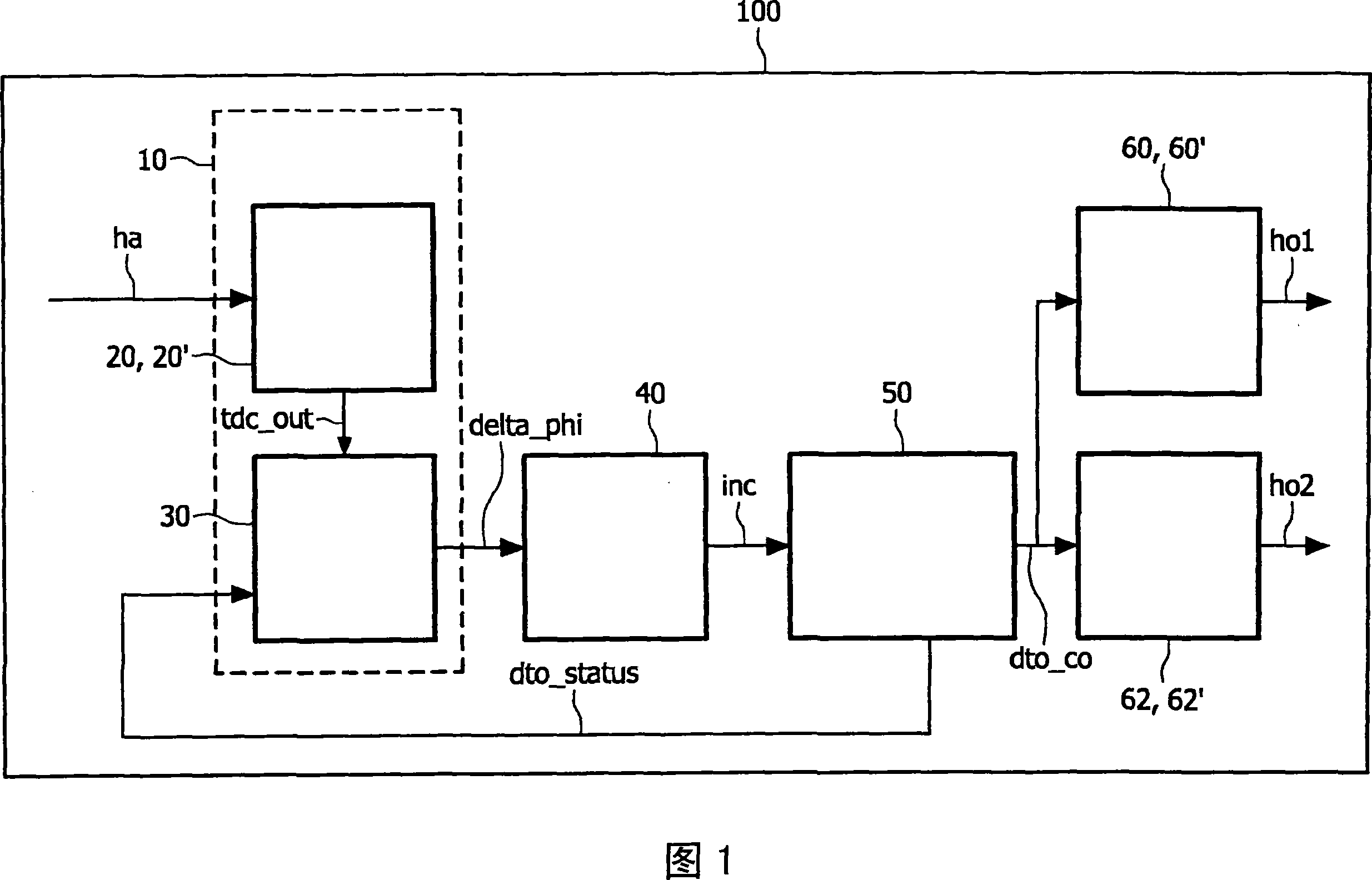

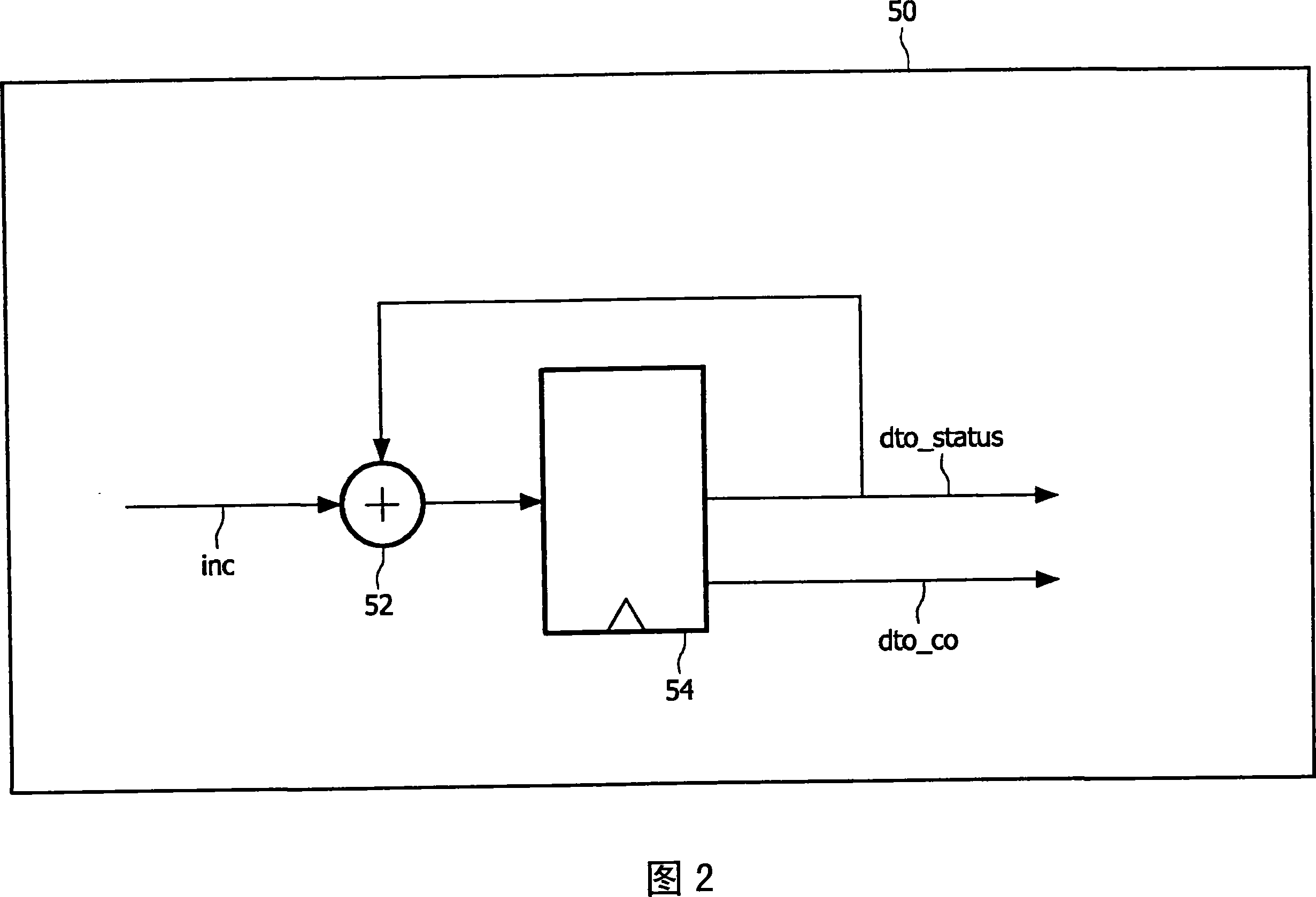

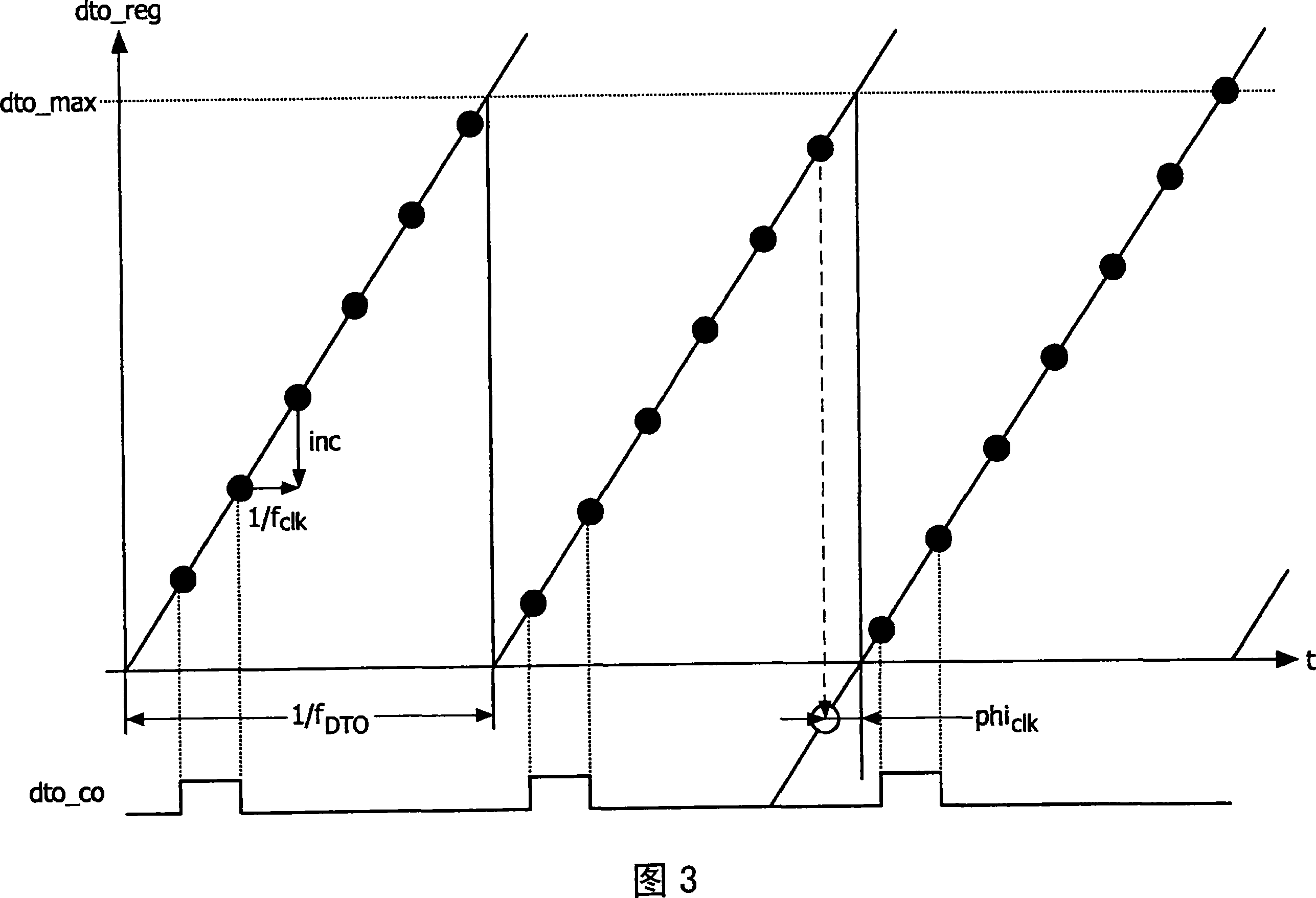

Circuit arrangement, in particular phase-locked loop, as well as corresponding method

In order to further develop a circuit arrangement (100), in particular to a phase-locked loop for sub-clock or sub-pixel accurate phase-measurement and phase-generation, as well as a corresponding method in such way that no clock multiplier phase-locked loop is to be provided behind the time-to-digital converter and that neither an analog delay line nor a signal divider unit is to be provided between the digital ramp oscillator or discrete time oscillator and the digital-to-time converter, wherein less analog circuitry is susceptible for noise and for ground bounce in the digital environment, it is proposed to provide at least one phase measurement unit (10); - at least one loop filter unit (40; 40') being provided with at least one output signal (delta-phi) of at least one phase detector unit (30); at least one digital ramp oscillator unit or discrete time oscillator unit (50; 50') being provided with at least one output signal, in particular with at least one increment (inc), of the loop filter unit (40; 40'), the status signal (dto-status) of at least one register unit (54; 54') of the digital ramp oscillator unit or discrete time oscillator unit (50; 50') being fed back as input signal to the phase detector unit (30); and at least one digital-to-time converter unit (60, 62; 60', 62') being provided with at least one output signal (dto-co) of the digital ramp oscillator unit or discrete time oscillator unit (50; 50') and generating at least one output signal (hoi, ho2).

Owner:NXP BV

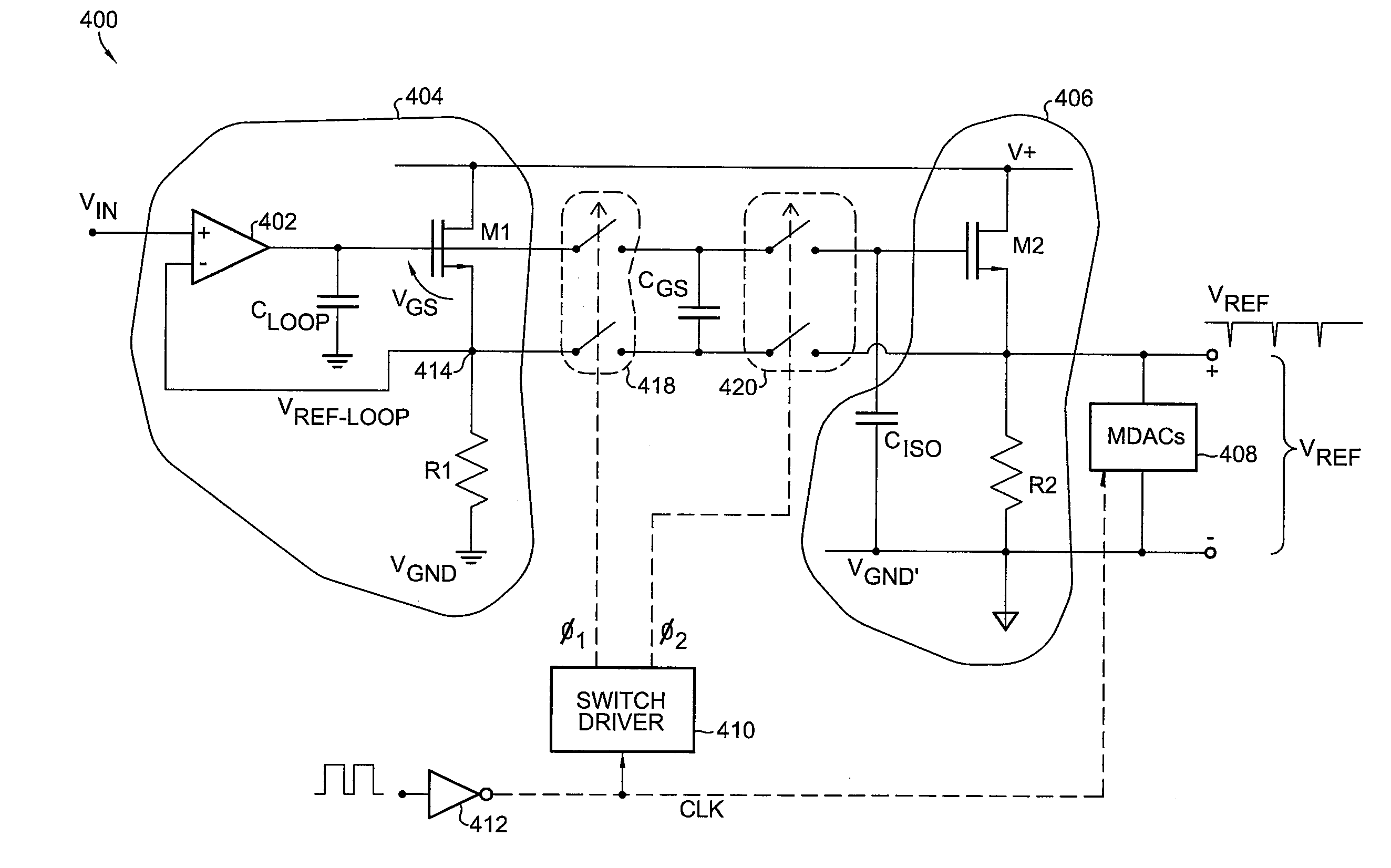

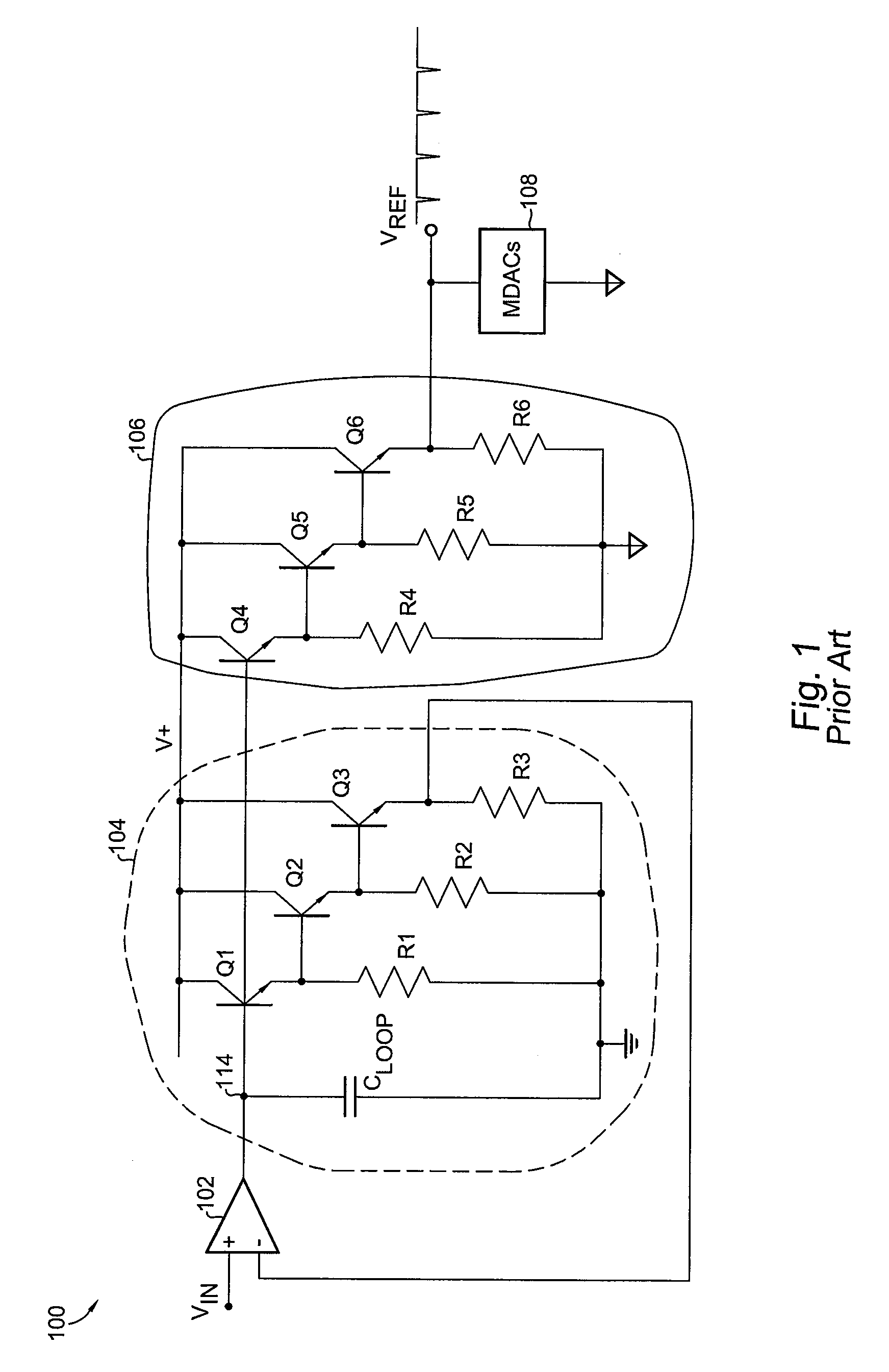

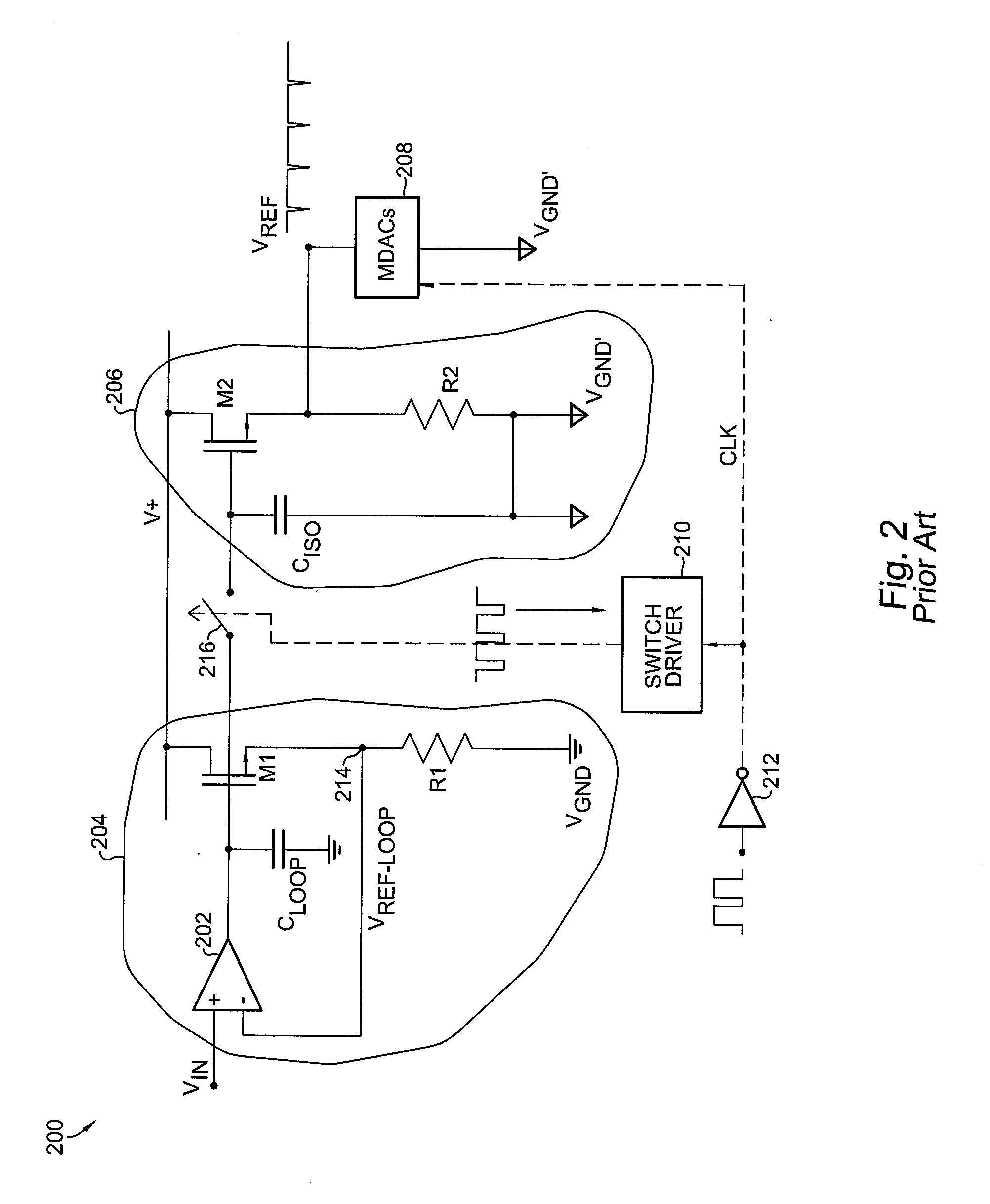

Radiation tolerant circuit for minimizing the dependence of a precision voltage reference from ground bounce and signal glitch

A radiation-hardened reference circuit includes a precision voltage reference circuit for generating a current-controlling voltage at first and second terminals, a driver circuit for receiving the current-controlling voltage at first and second terminals and for generating an output reference voltage, and a differential sampling circuit having first and second input terminals coupled to the first and second terminals of the voltage reference circuit, and first and second output terminals coupled to the first and second terminals of the driver circuit.

Owner:CAES COLORADO SPRINGS LLC

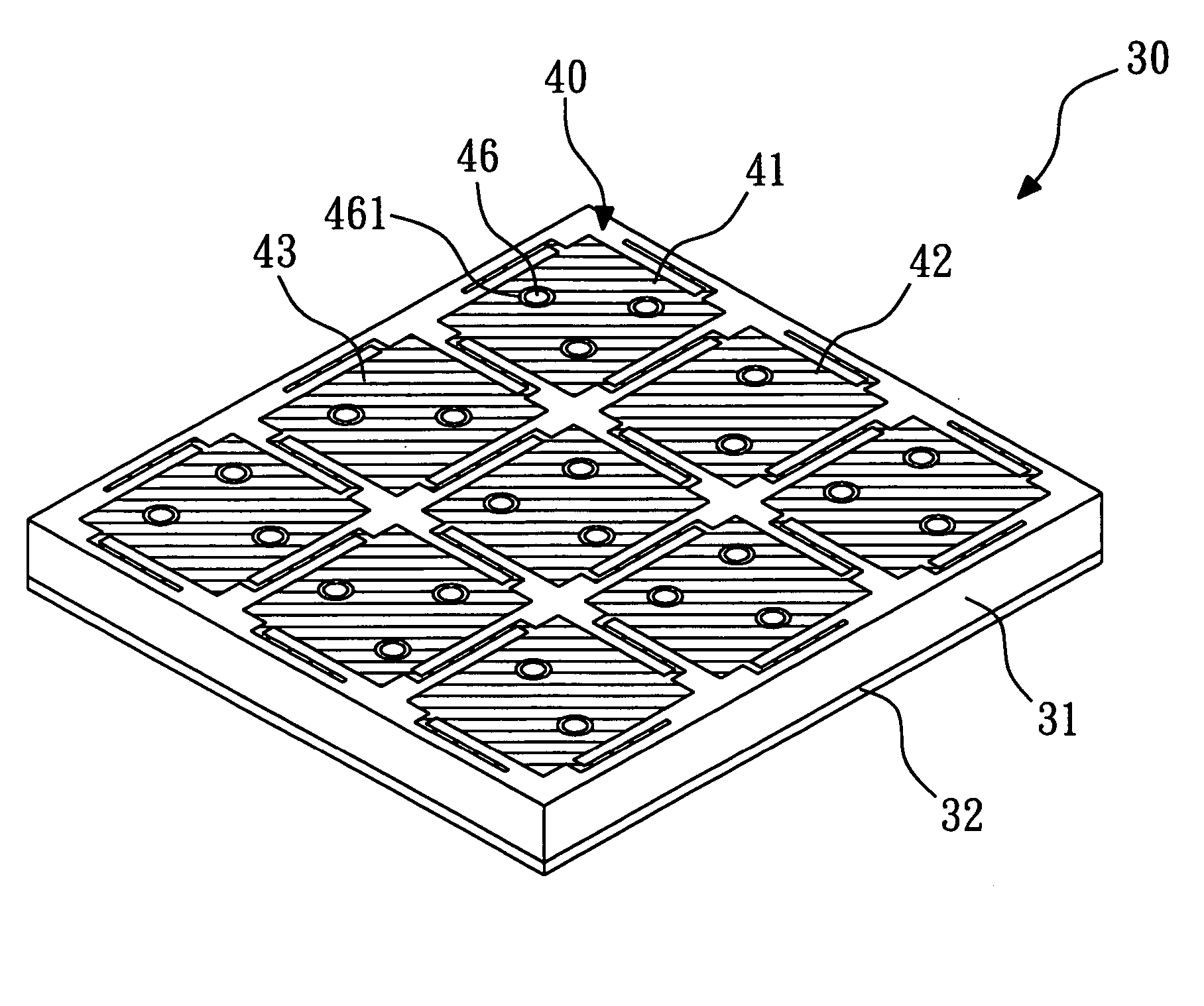

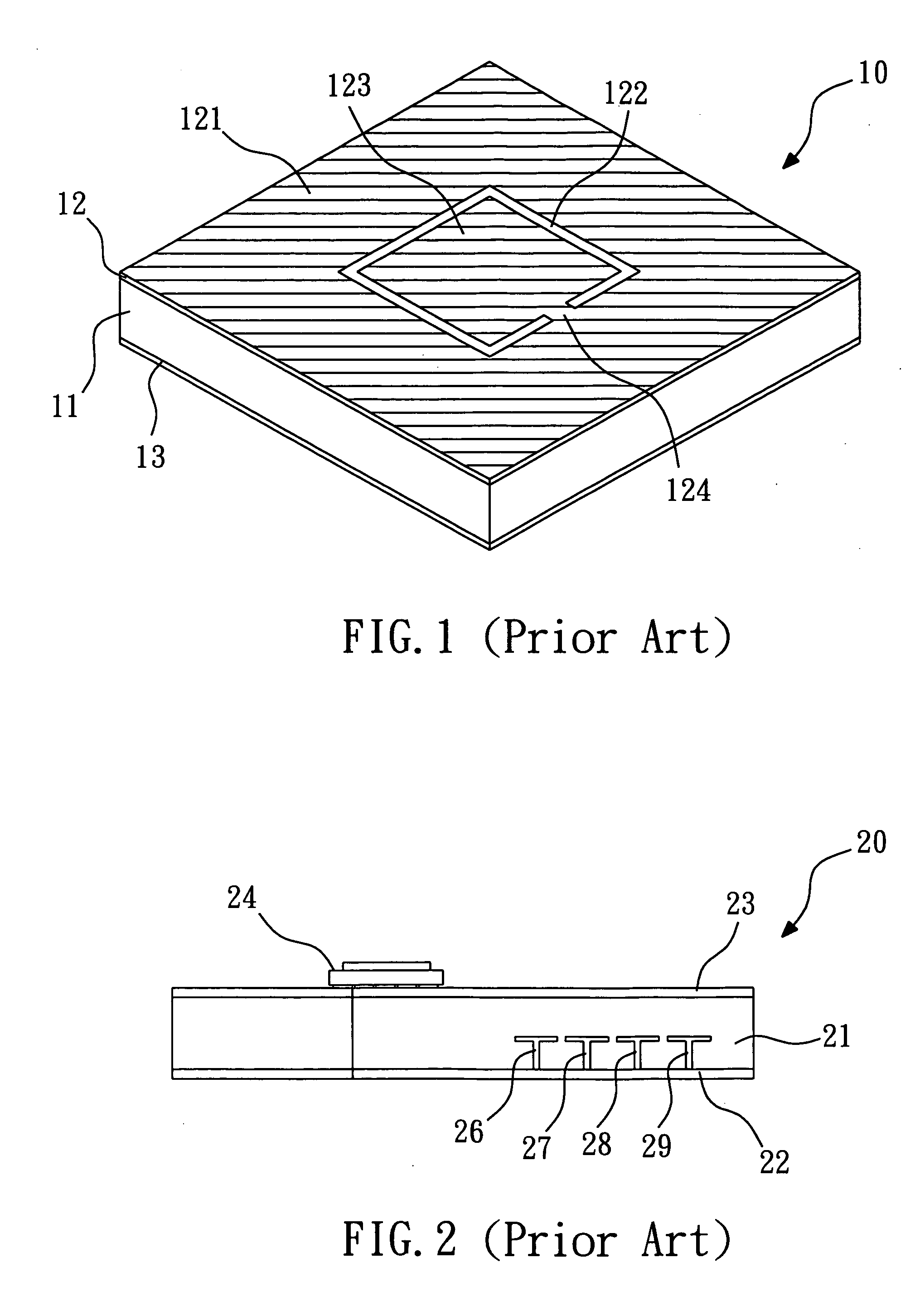

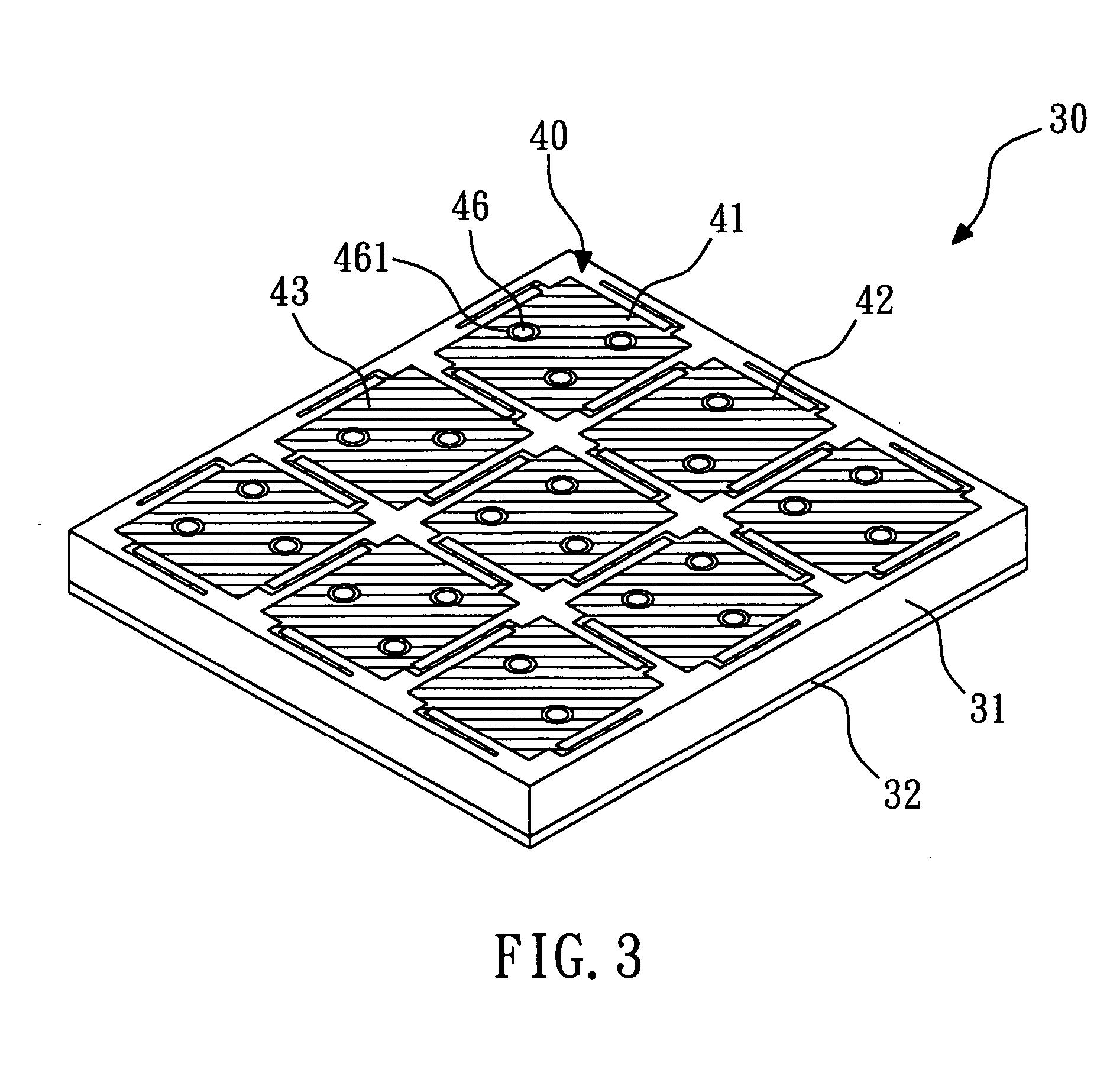

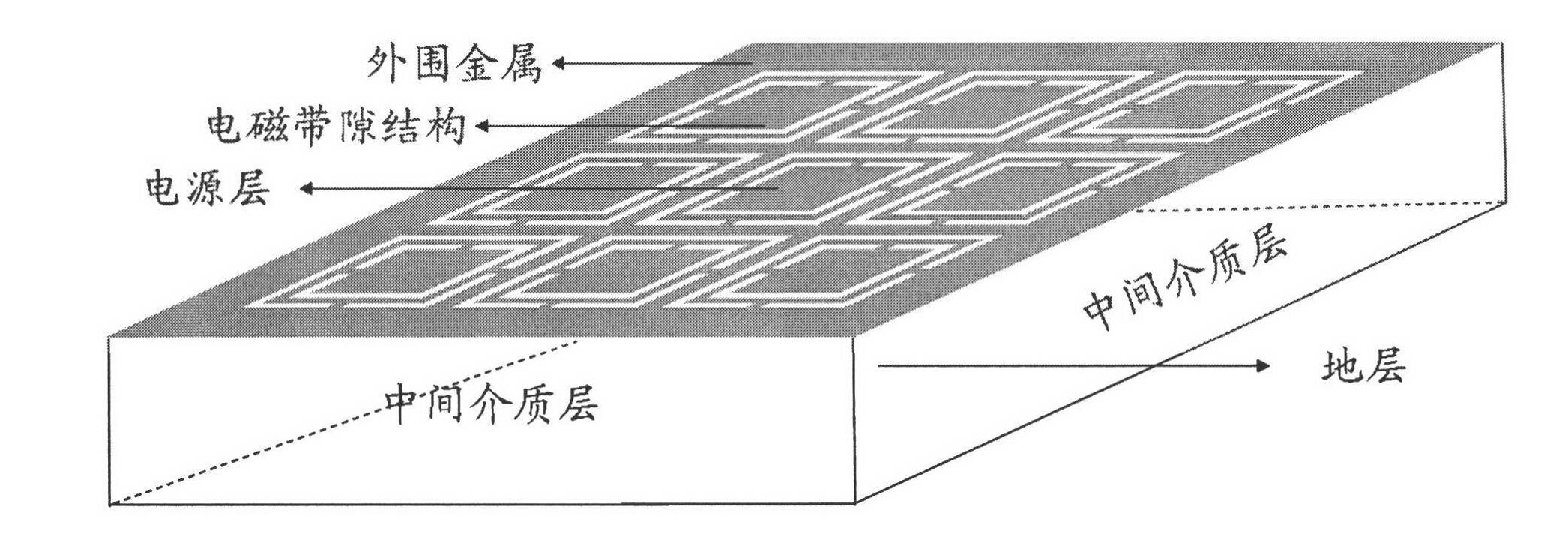

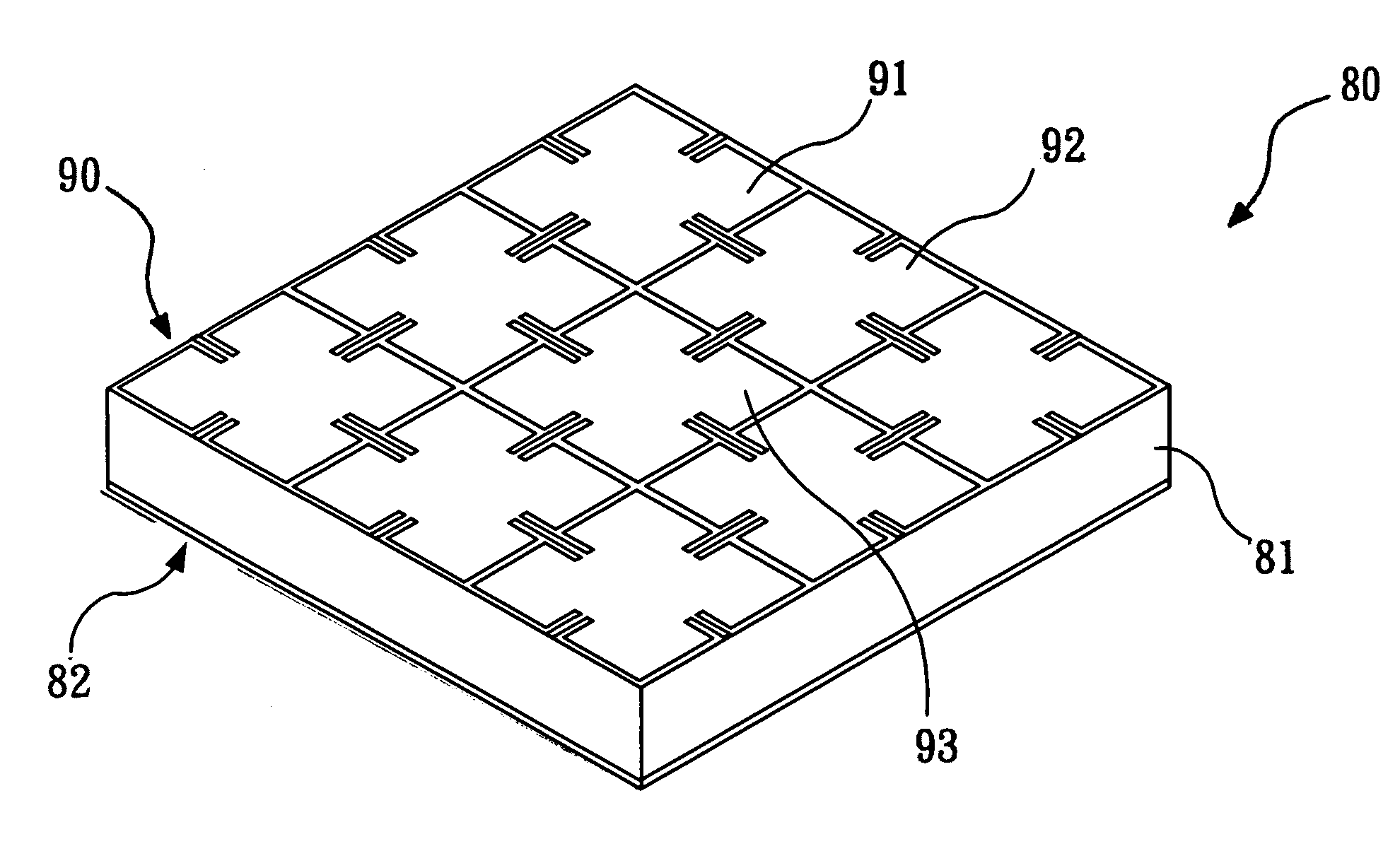

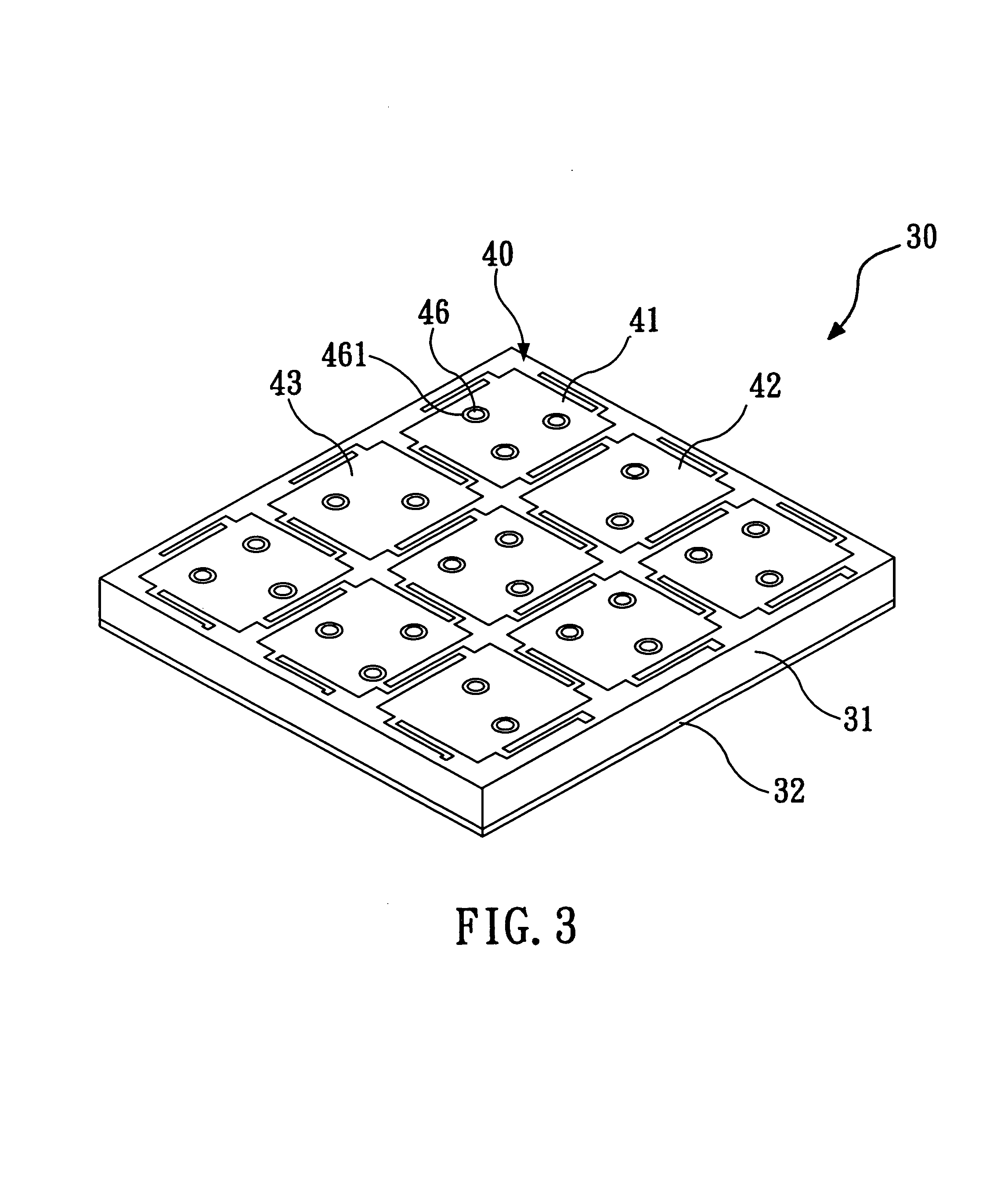

Power plane system of high-speed digital circuit for suppressing ground bounce noise

ActiveUS20050168238A1Broaden stop-band bandwidthElectromagnetic radiation can be suppressed efficientlyReliability increasing modificationsCross-talk/noise/interference reductionGround bounceElectromagnetic radiation

The invention relates to a power plane system for suppressing ground bounce noise. The power plane system of the invention comprises a substrate, a power layer and a ground layer. The power layer comprises a plurality of metal units. There is a distance between two adjacent metal units. A plurality of bridges is used for connecting the metal units. The ground layer has a grounding metal plate. According to the invention, when the ground bounce noise occurs, the metal units can broaden the stop-band bandwidth. Therefore, the signals in the stop-band hardly are transmitted so as to suppress the ground bounce noise, and the high frequency ground bounce noise and the electromagnetic radiation can be suppressed efficiently.

Owner:NAT SUN YAT SEN UNIV

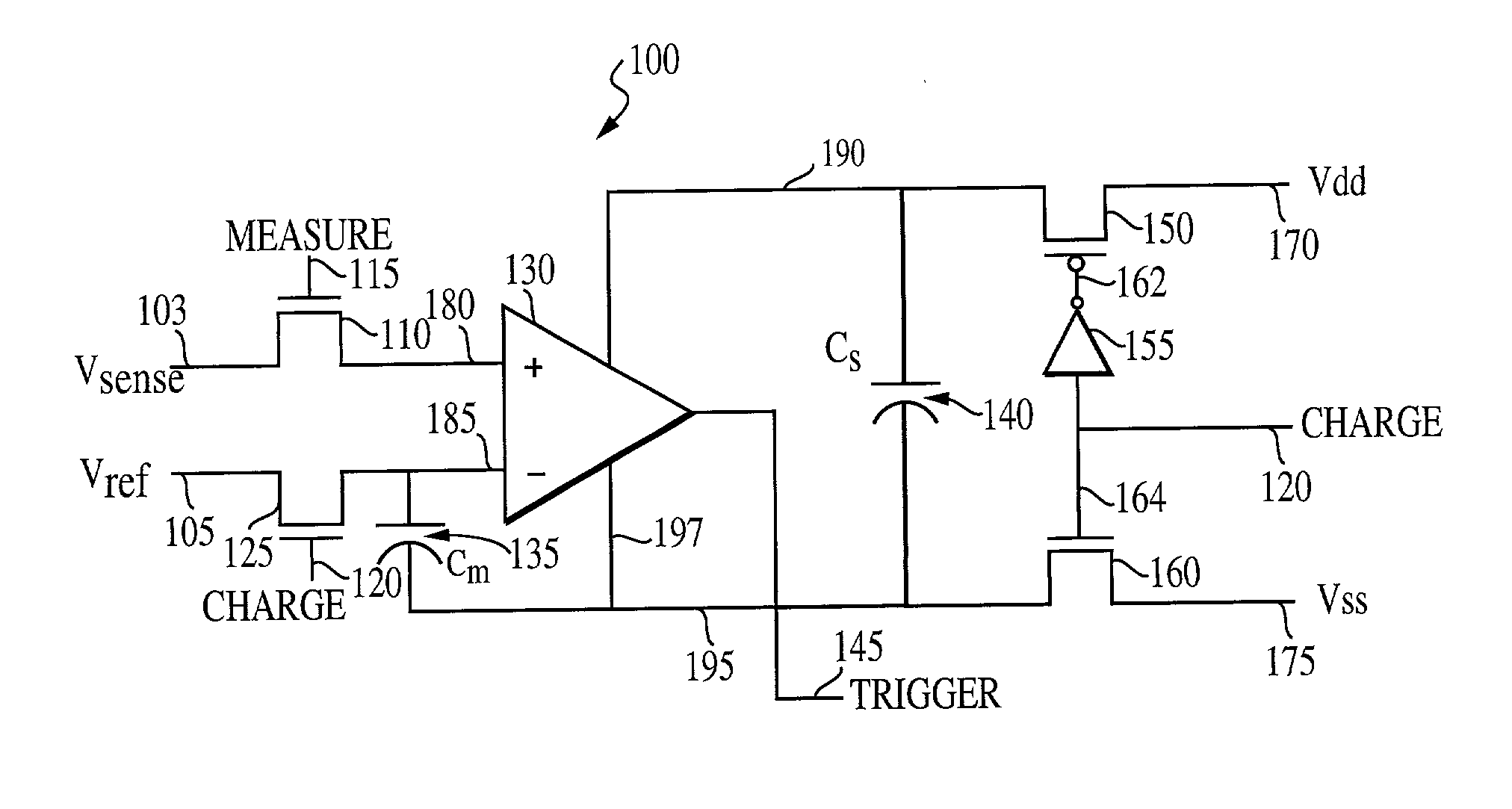

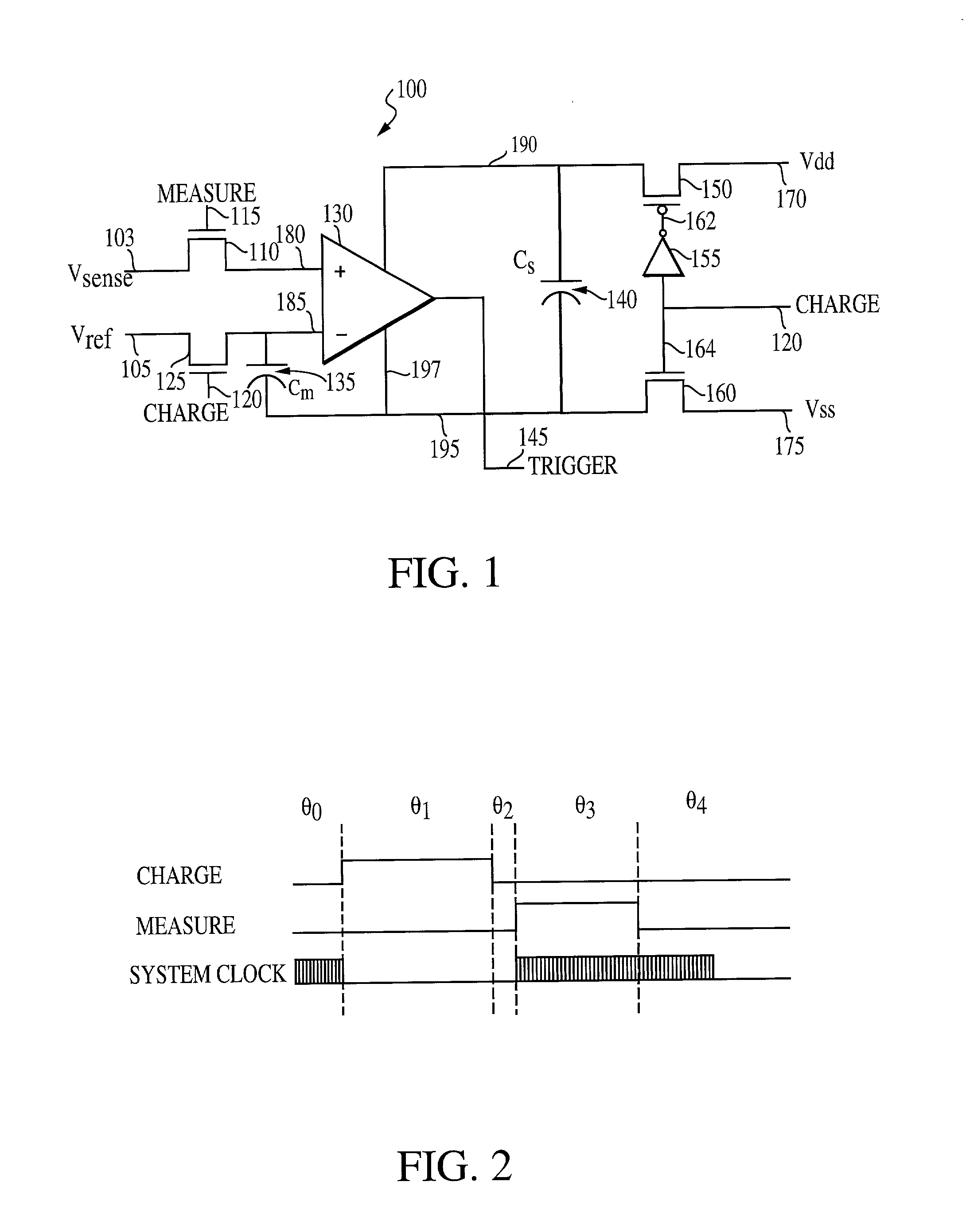

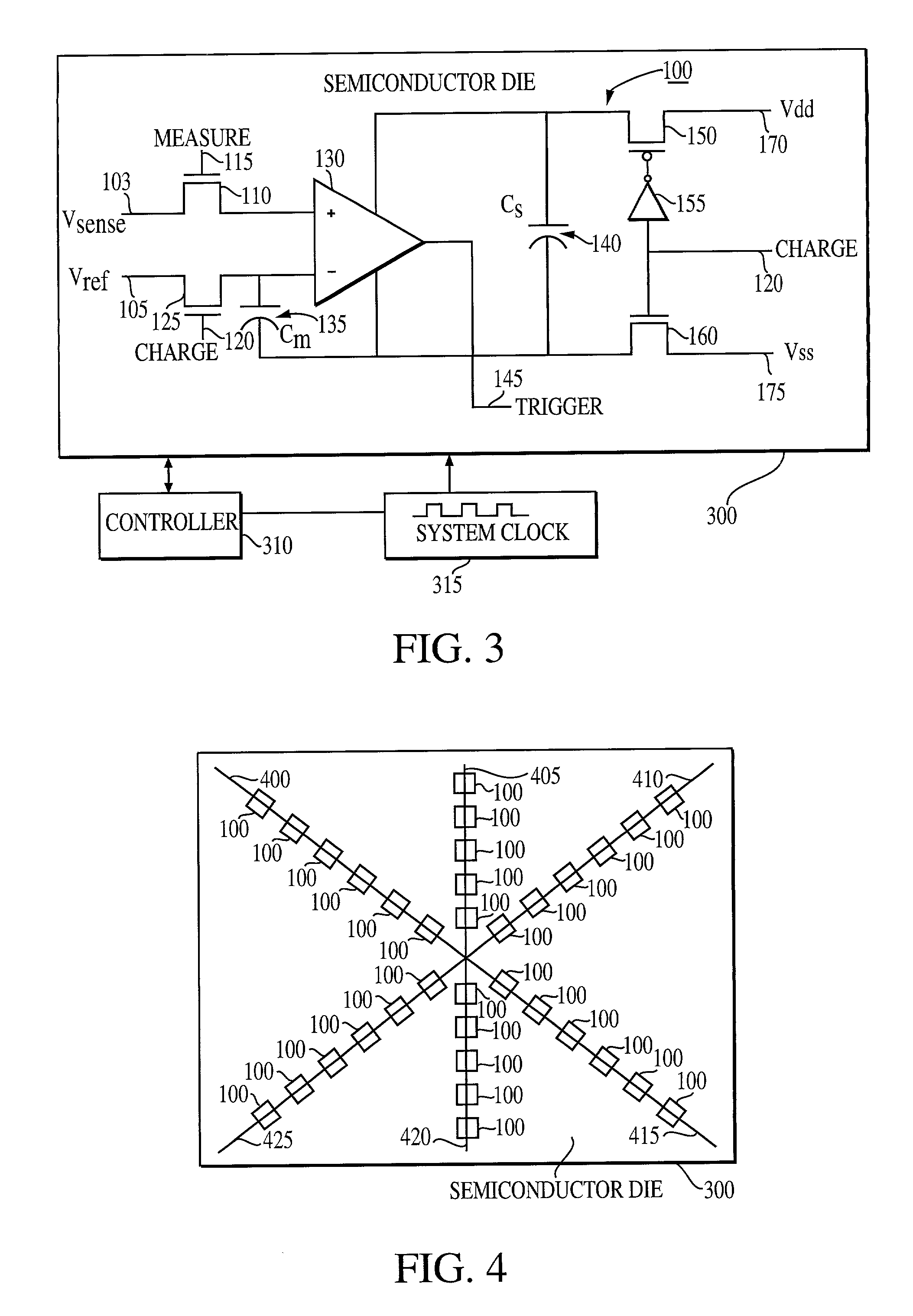

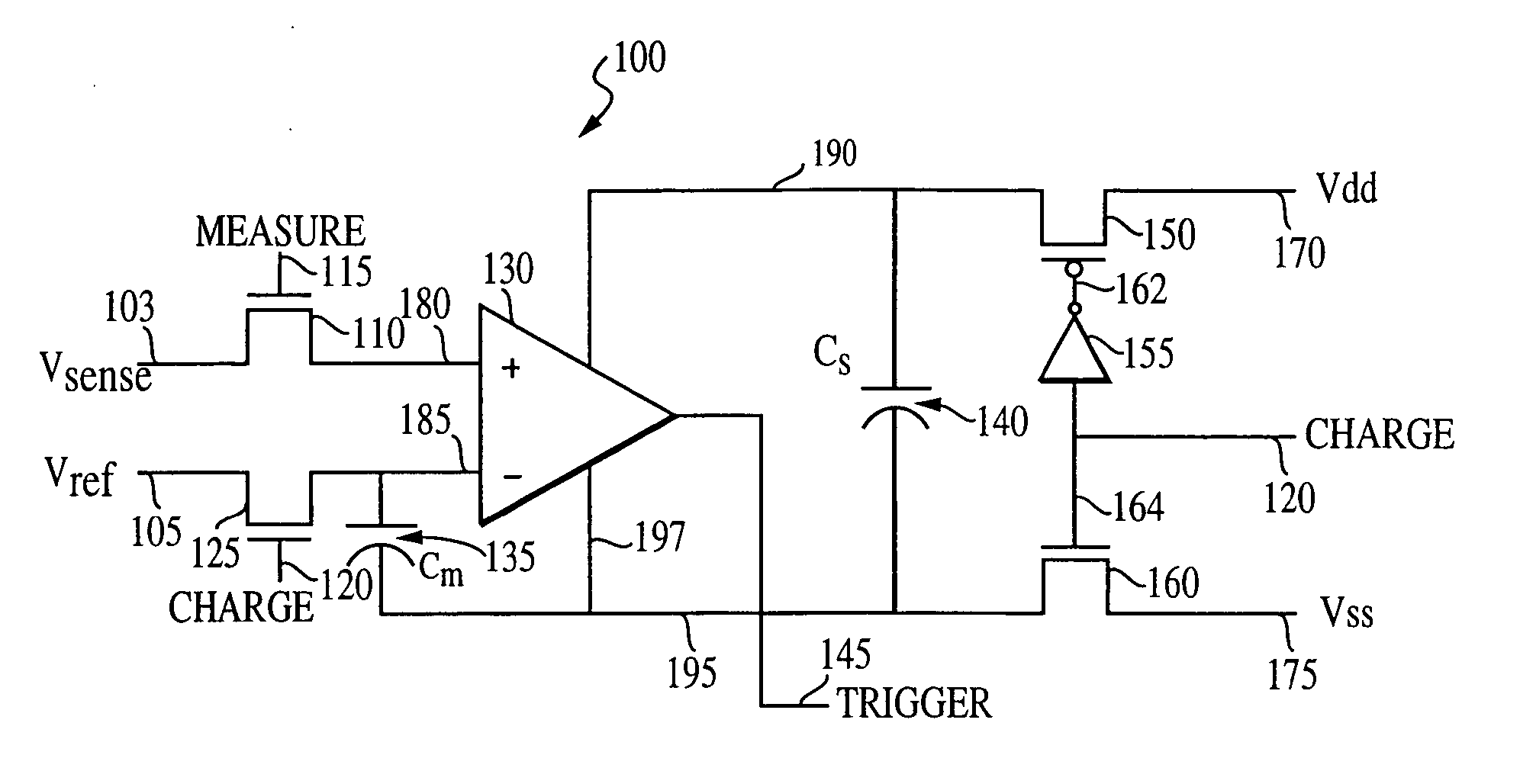

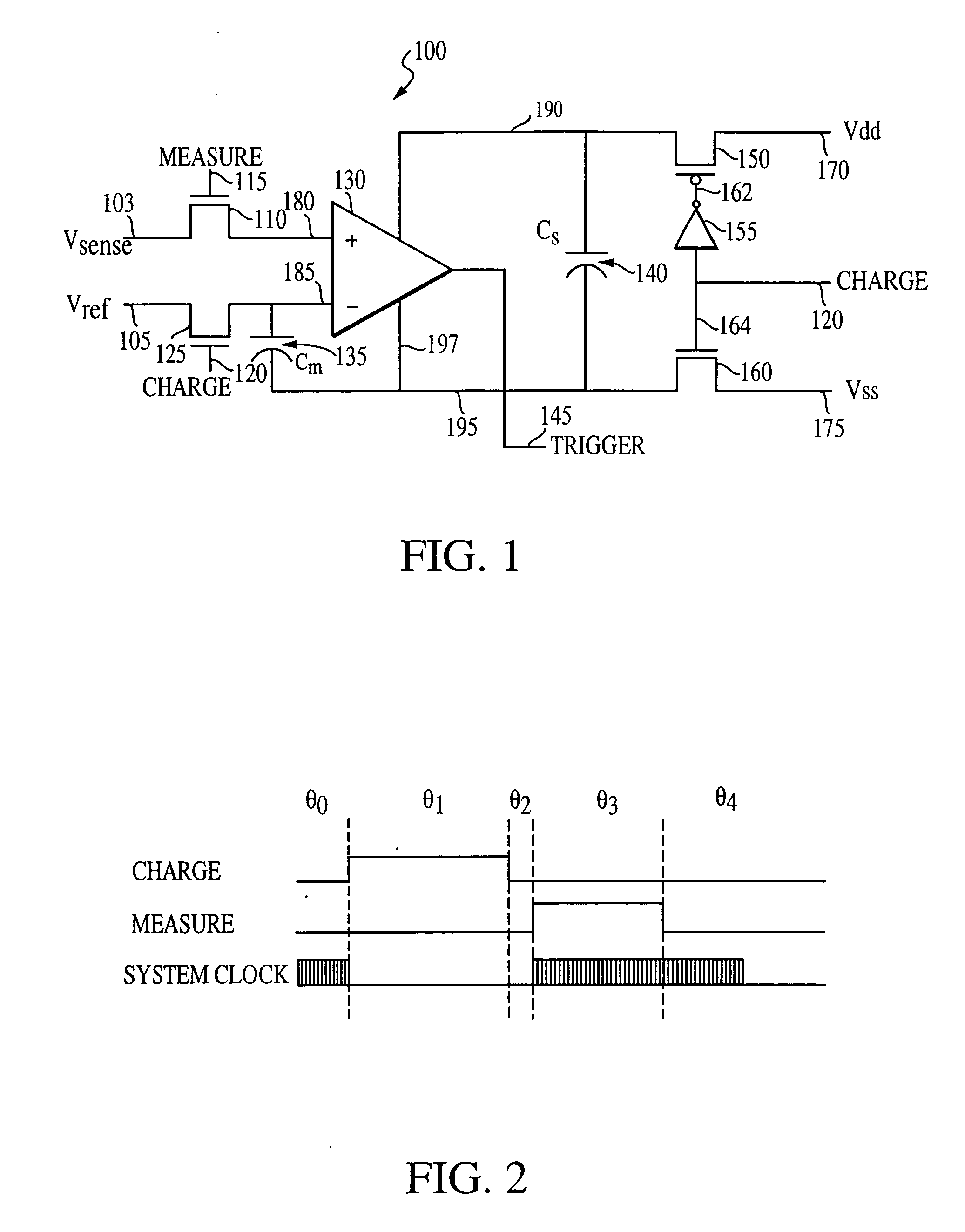

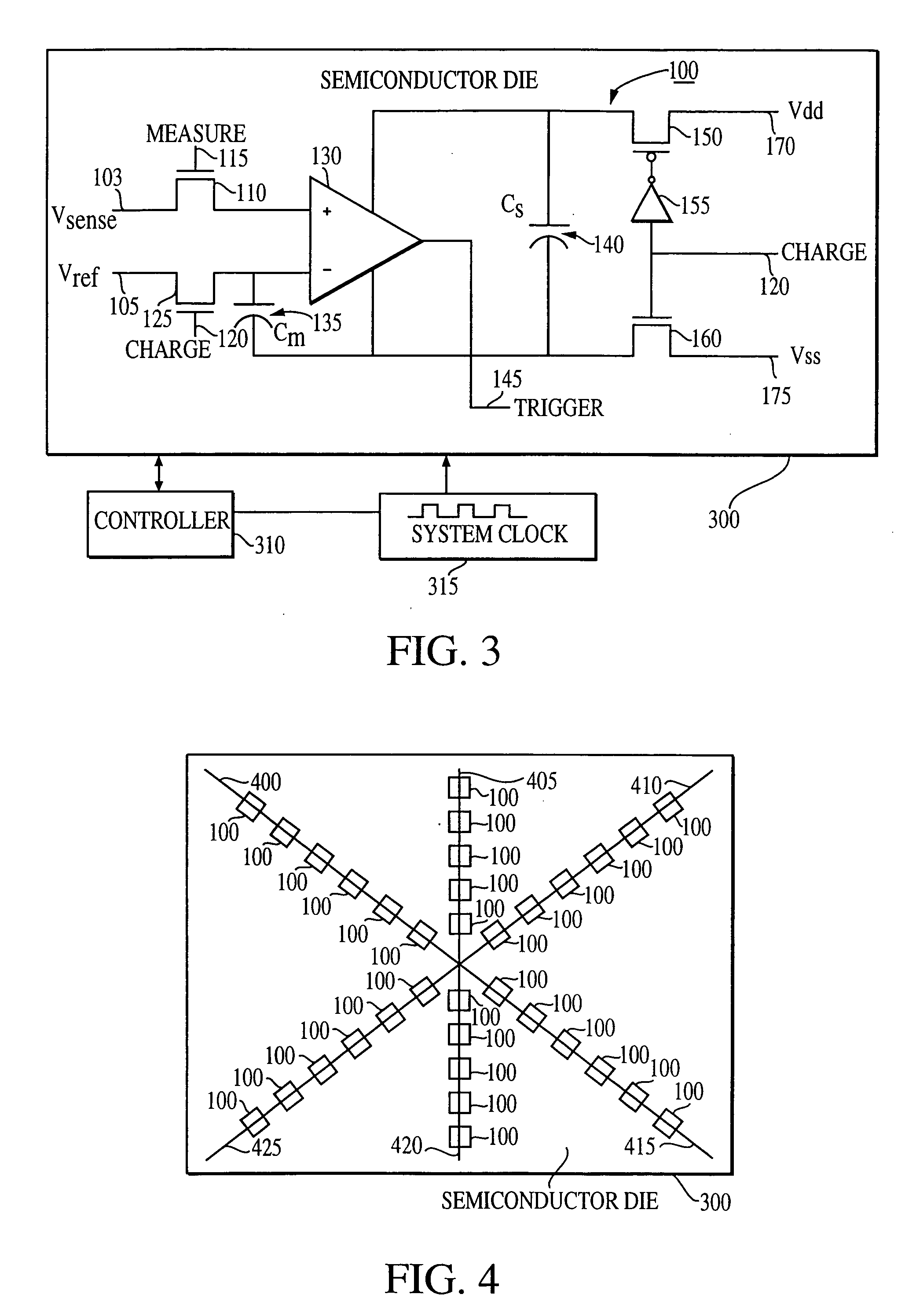

Circuit for measuring on-chip power supply integrity

A test circuit and method for measuring power supply integrity is provided. The circuit may be incorporated on-chip and is small enough to be integrated many times across the surface of the die for measuring integrity parameters at several locations on the chip. The circuit instantaneously measures, e.g., the rail voltage of a power supply, which may be fluctuating at the time of measurement. In addition, the circuit isolates itself from all chip power rails for the duration of the measurement, thereby eliminating any influence of external noise on the measurement. A storage capacitor is charged up to full power rail voltage for powering up a comparator. Then, the comparator is isolated from the power rails and the measurements are taken. Based upon the measurements, certain power supply integrity parameters are quantified including ground bounce and power droop.

Owner:MICRON TECH INC

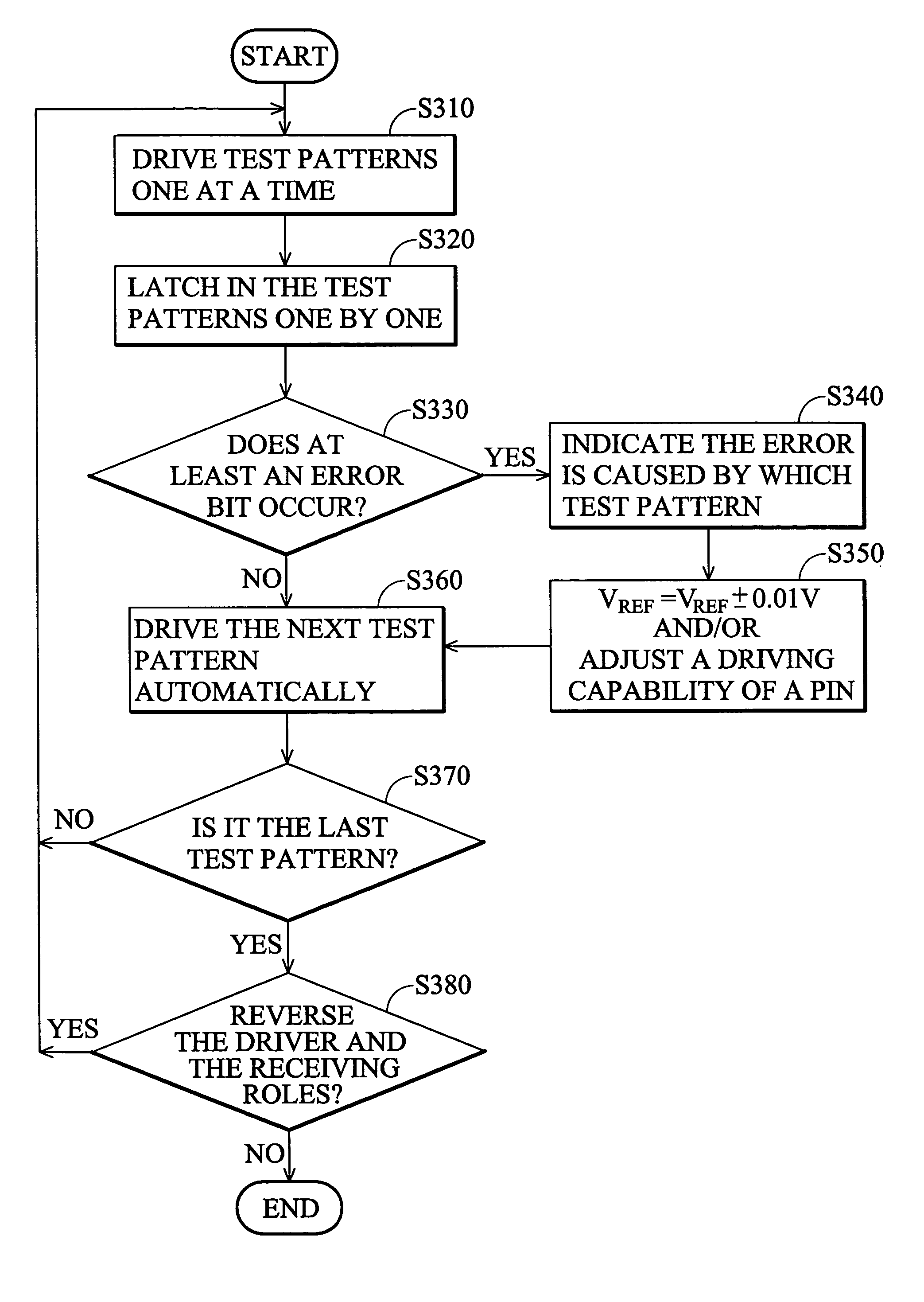

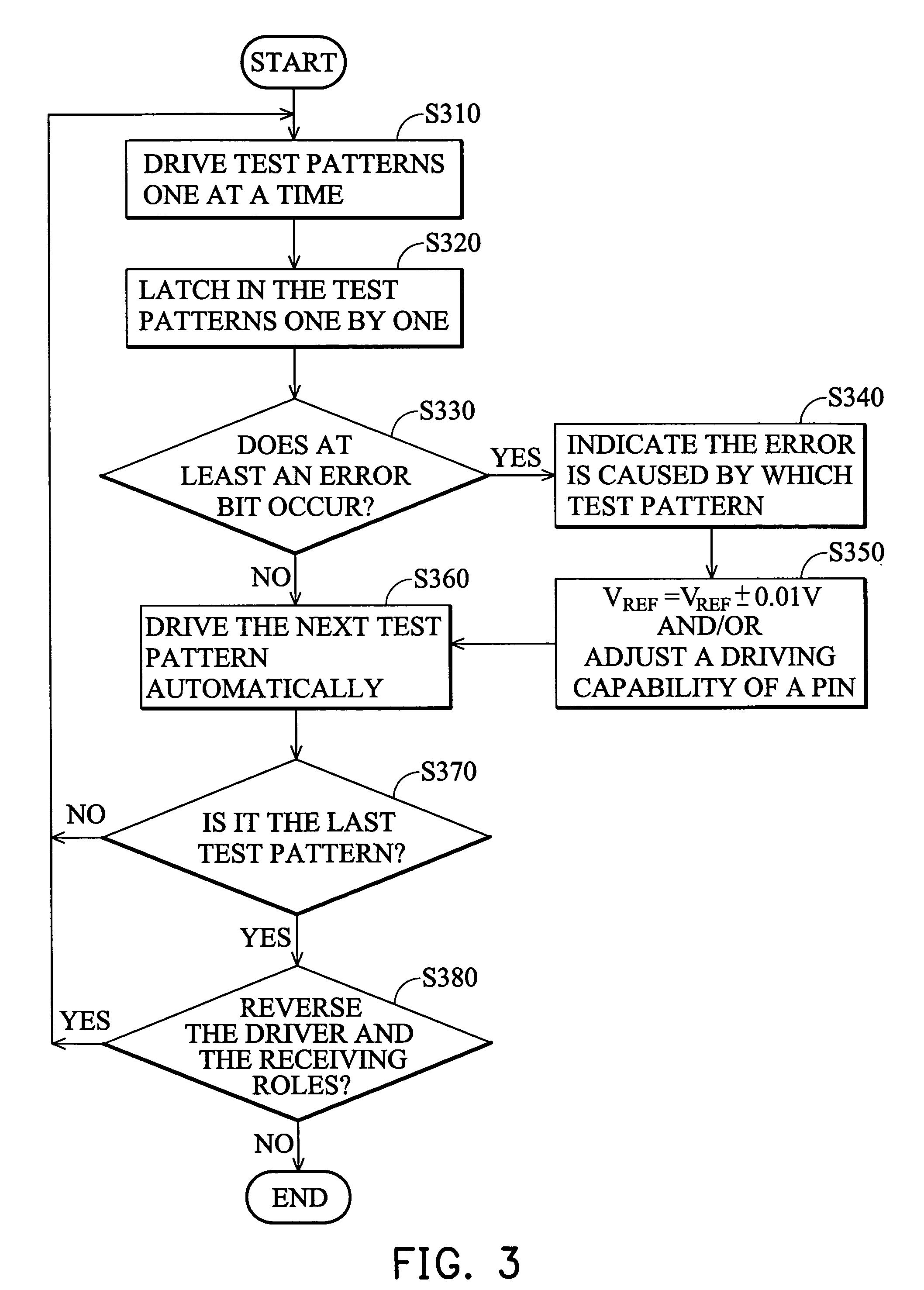

Signal testing of integrated circuit chips

ActiveUS7287205B2Easily and autonomously detect ground bounceDigital circuit testingError detection/correctionGround bounceEngineering

A method for testing signals of integrated circuits (ICs). According to the invention, a first IC chip successively drives a number of test patterns one at a time. At the receiving end, a second IC chip latches in the test patterns one by one. Meanwhile, the second IC chip determines whether a currently latched test pattern is correct or not. If it is incorrect and at least an error bit occurs, depending on the type of the test patterns, the second IC chip indicates that there exists ground bounce or power bounce in a signal trace corresponding to the error bit.

Owner:VIA TECH INC

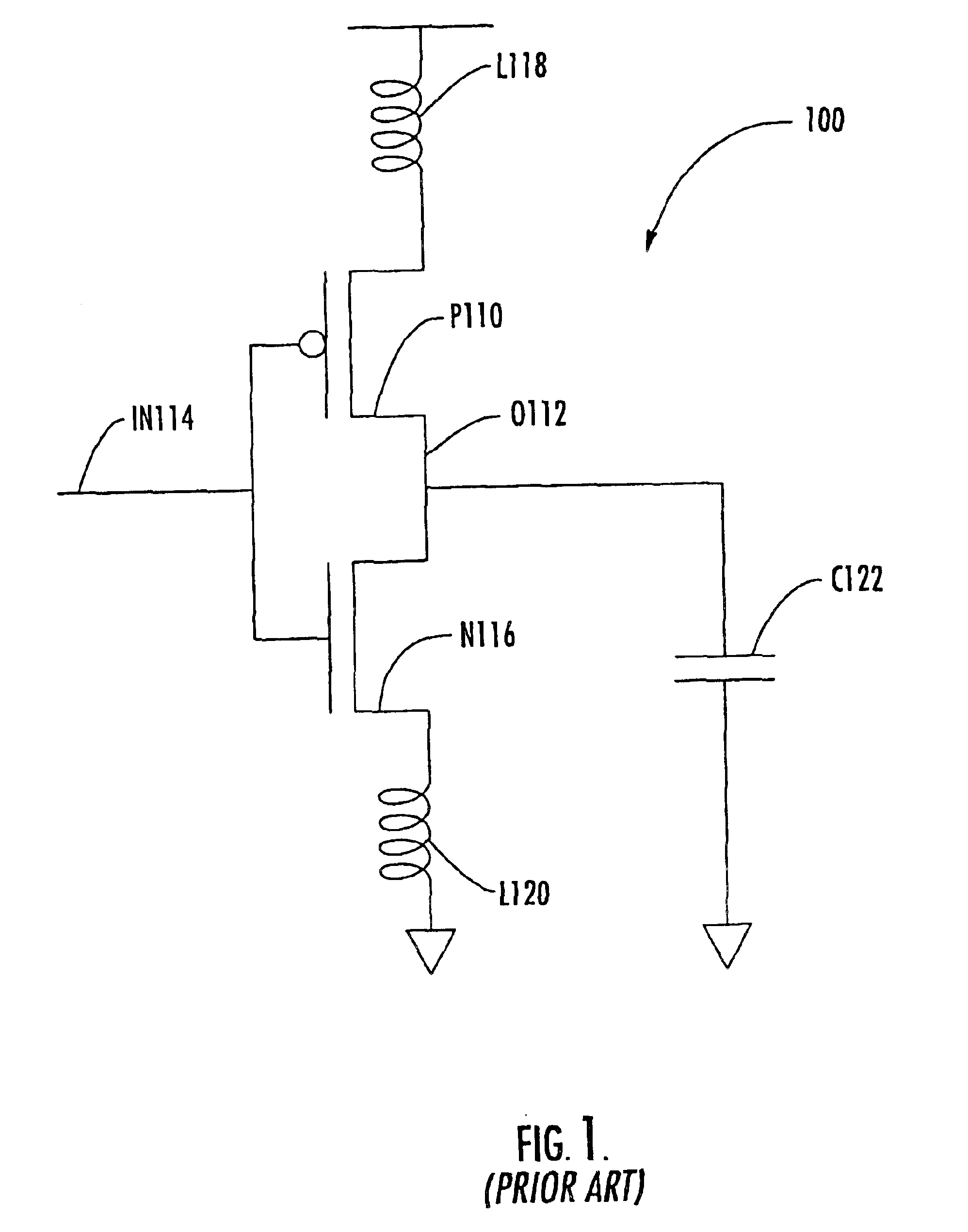

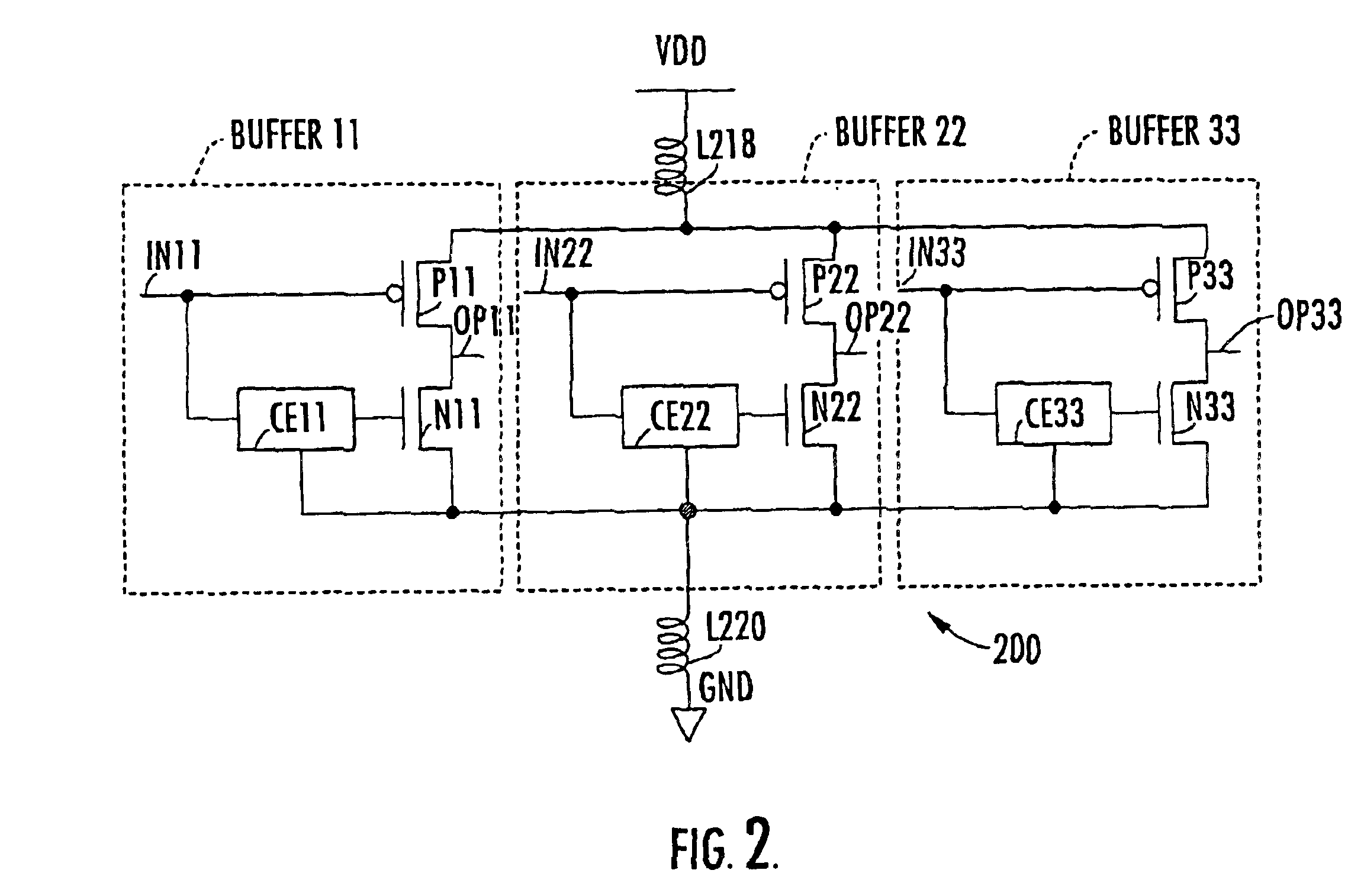

I/O buffer with variable conductivity

InactiveUS6838906B2Easy to optimizeImprove conductivityLogic circuits characterised by logic functionElectronic switchingDelayed timeGround bounce

A driver structure for an I / O buffer circuit is disclosed. The driver structure includes a pre-push-pull driver and a post-push-pull driver. A delay circuit along is connected in series between the input signals of the pre-push-pull driver and the post-push-pull driver. After a delay time following a transition of the input signal, the circuit operation of the post-push-pull driver is turned off before the amplitude of the output signal reaches its maximum overshooting. This changes the output conductivity to inhibit the overshooting in the output signal, preventing power bounce and ground bounce at the receiving end.

Owner:VIA TECH INC

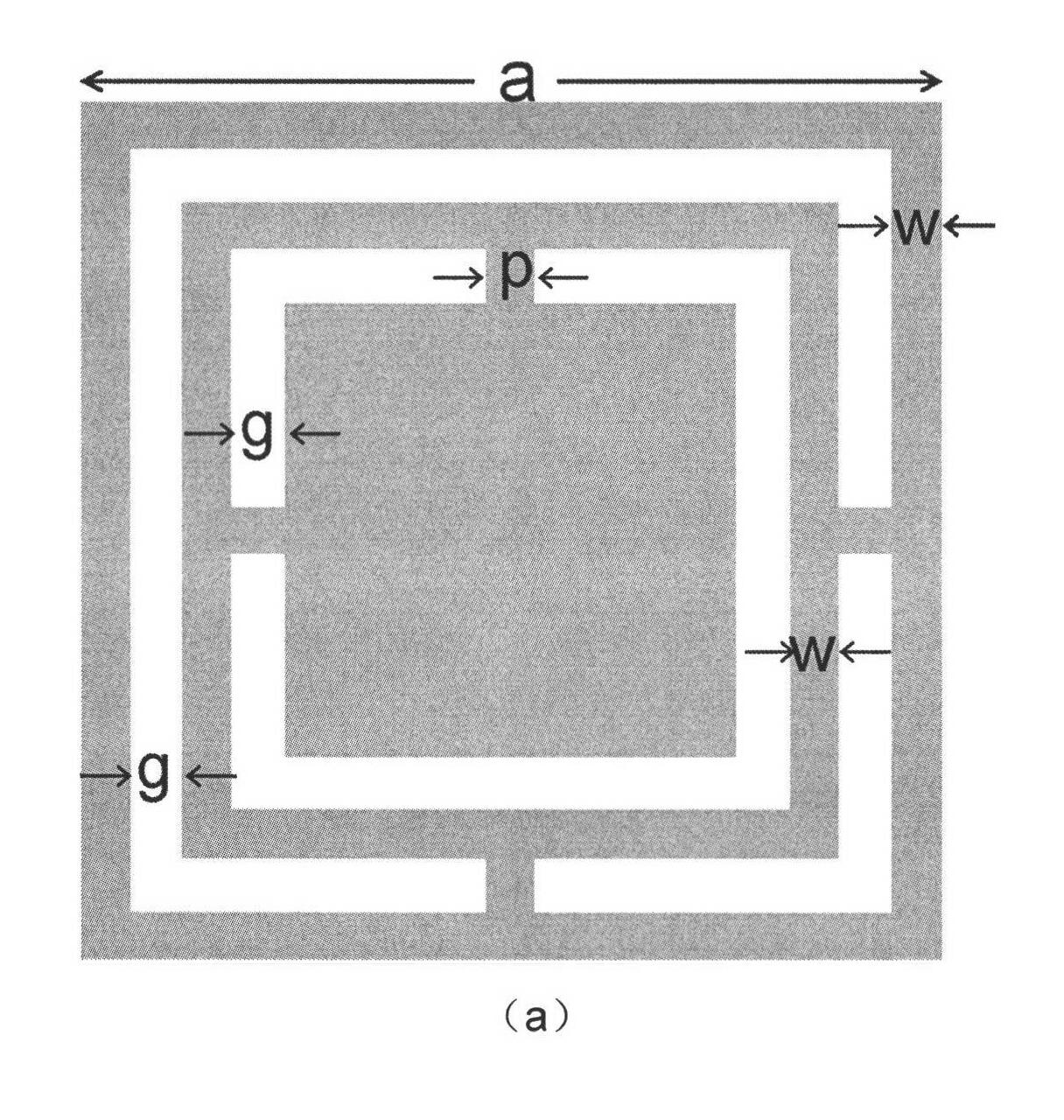

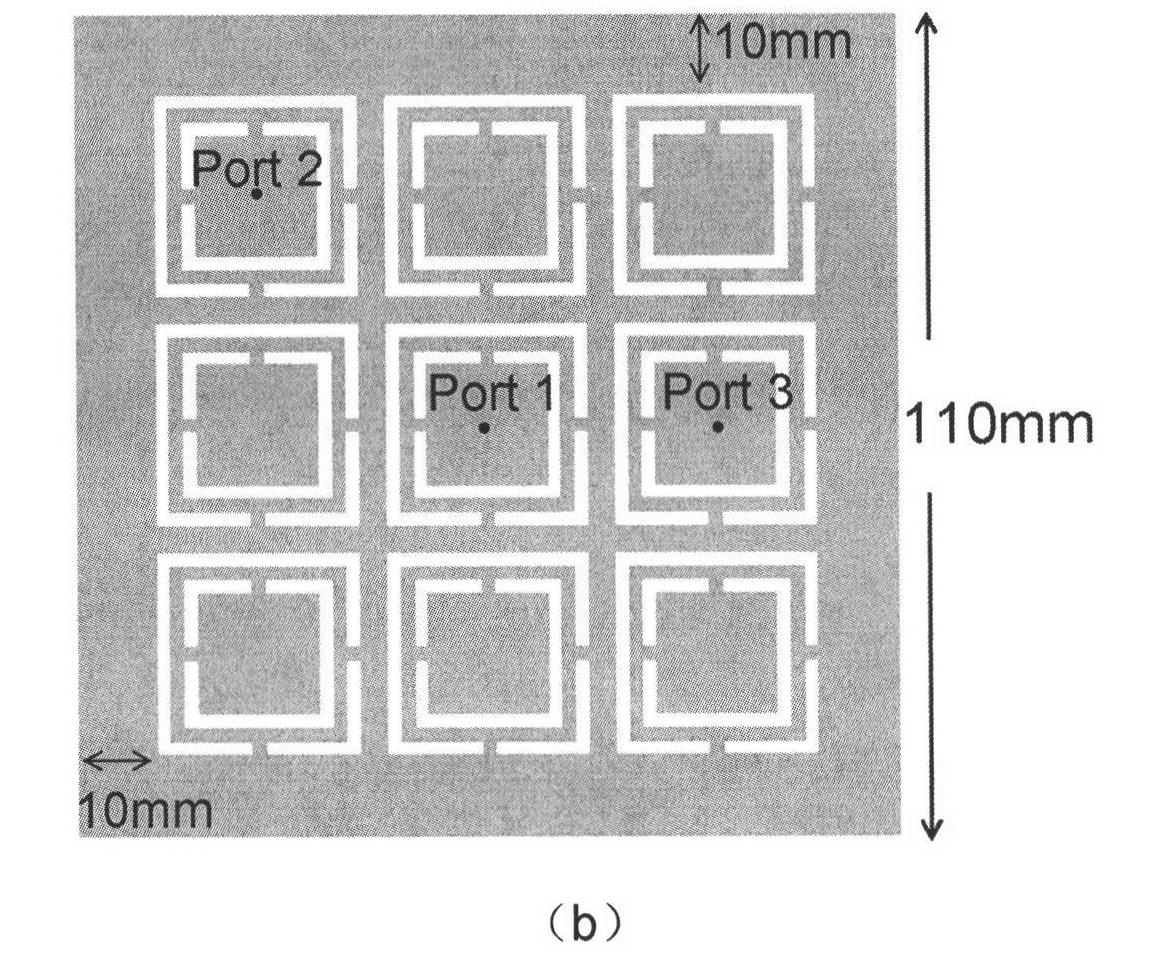

Ultra wide band electromagnetic band gap structure for suppressing ground bounce noise of high speed circuit/microwave circuit

InactiveCN102131343AImprove integritySuppresses ground bounce noisePrinted circuit detailsWaveguide type devicesMicrowaveGround bounce

The invention provides a novel ultra wide band electromagnetic band gap structure which belongs to the technical field of information. The structure is mainly used for replacing a power layer of the traditional high speed circuit / microwave circuit so as to suppress ground bounce noise in the structures and realize better power integrity. The structure has a typical three-layer circuit board structure comprising a dielectric layer in the middle and two metal layers up and down, wherein the electromagnetic band gap structure is arranged on the upper layer. In the invention, a typical example is verified, i.e. a sample prepared in an experiment is tested through a network analyzer, which confirms that the structure provided by the invention can realize noise suppression superior to -30dB to any two ports in a frequency range from 500MHz to 5.5GHz.

Owner:NANJING UNIV

Power plane system of high-speed digital circuit for suppressing ground bounce noise

ActiveUS7148425B2Broaden stop-band bandwidthEffective radiationReliability increasing modificationsSemiconductor/solid-state device detailsGround bounceEngineering

The invention relates to a power plane system for suppressing ground bounce noise. The power plane system of the invention comprises a substrate, a power layer and a ground layer. The power layer comprises a plurality of metal units. There is a distance between two adjacent metal units. A plurality of bridges is used for connecting the metal units. The ground layer has a grounding metal plate. According to the invention, when the ground bounce noise occurs, the metal units can broaden the stop-band bandwidth. Therefore, the signals in the stop-band hardly are transmitted so as to suppress the ground bounce noise, and the high frequency ground bounce noise and the electromagnetic radiation can be suppressed efficiently.

Owner:NAT SUN YAT SEN UNIV

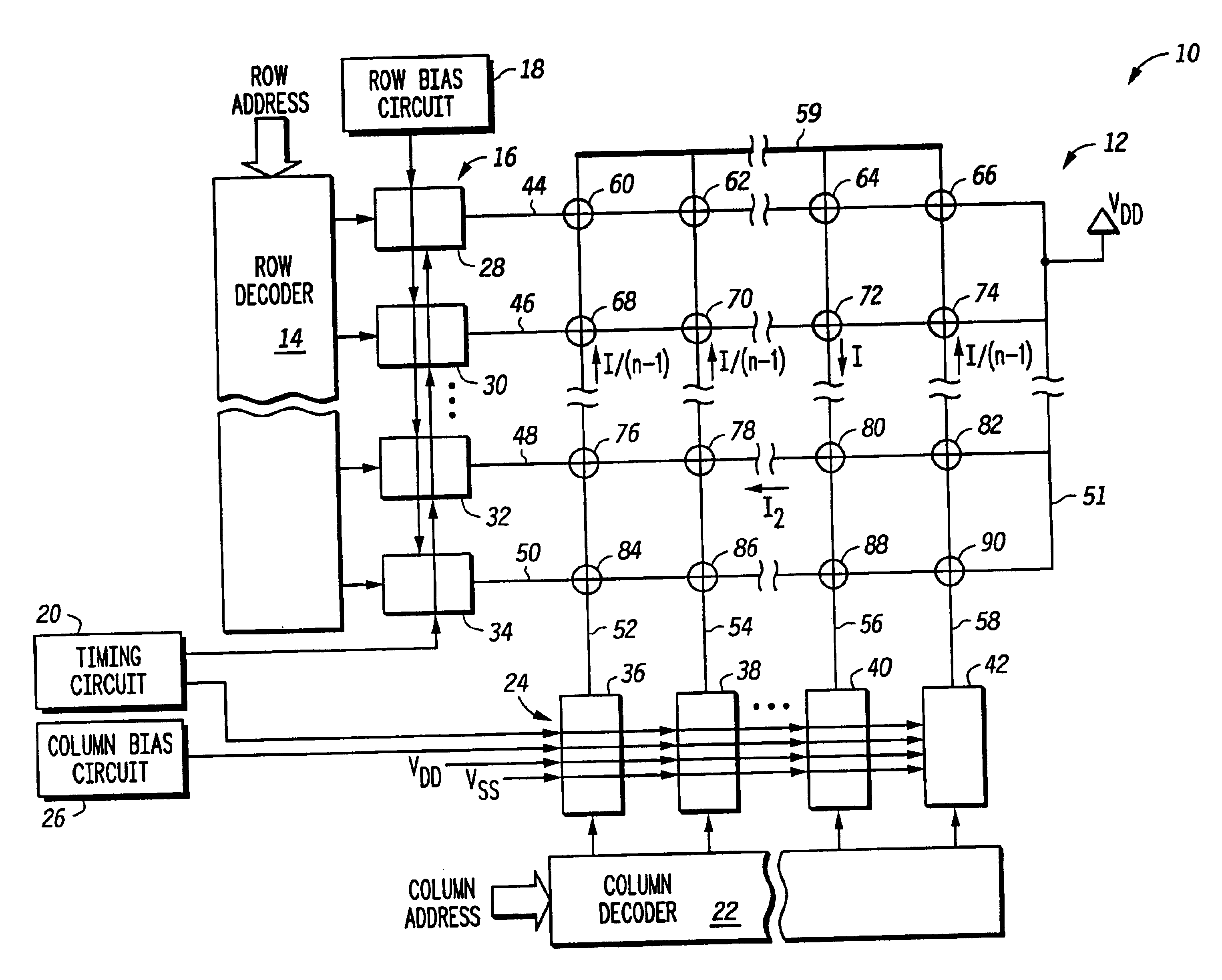

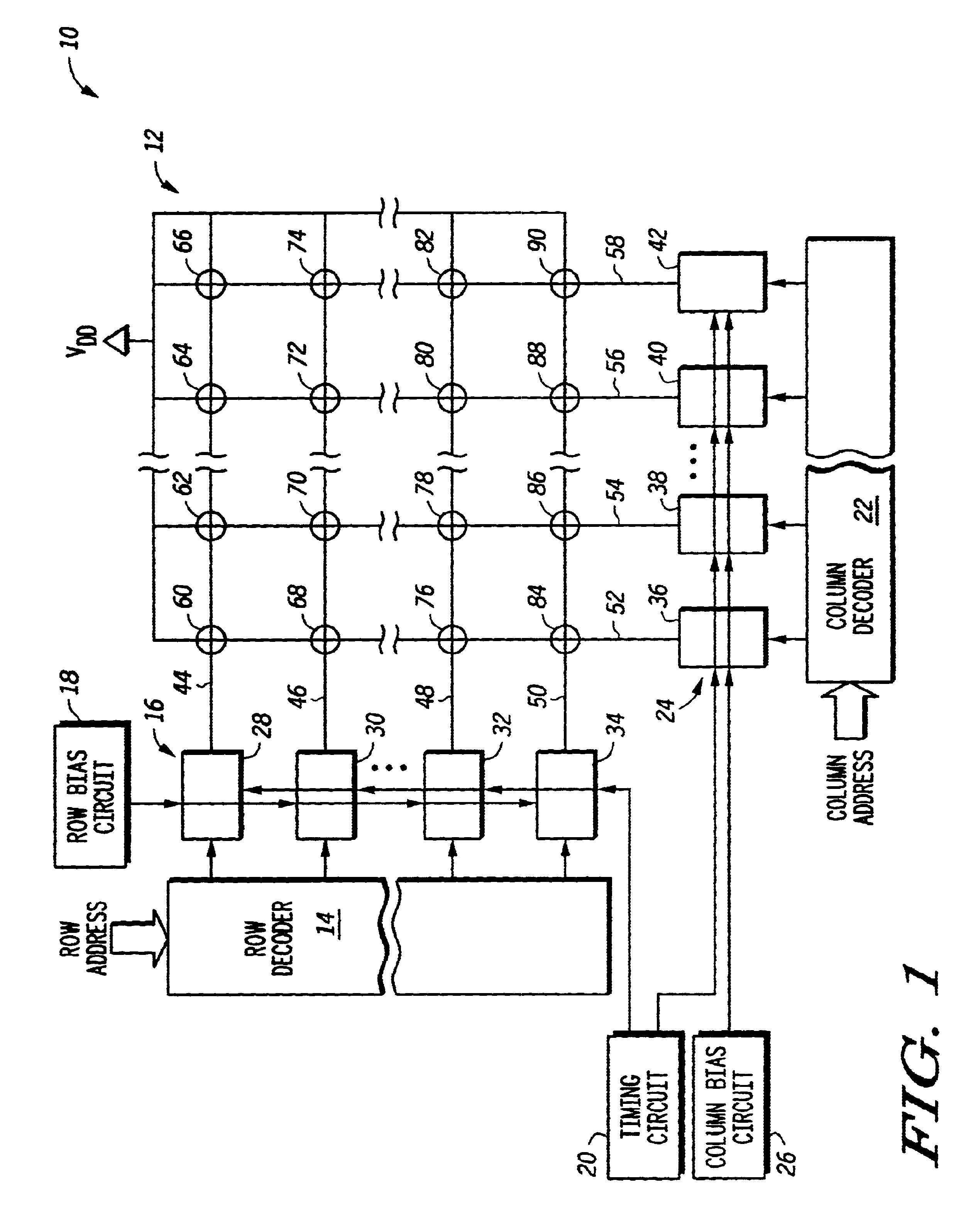

Write driver for a magnetoresistive memory

A write driver uses a reference current that is reflected to a driver circuit by a voltage. The driver circuit is sized in relation to the device that provides the voltage so that the current through the driver is a predetermined multiple of the reference current. This voltage is coupled to the driver circuit through a switch. The switch is controlled so that the driver circuit only receives the voltage when the write line is to have write current through it as determined by a decoder responsive to an address. The driver is affirmatively disabled when the write line is intended to not have current passing through it. As an enhancement to overcome ground bounce due to high currents, the input to the driver can be capacitively coupled to the ground terminal that experiences such bounce. Additional enhancements provide benefits in amplitude and edge rate control.

Owner:EVERSPIN TECHNOLOGIES

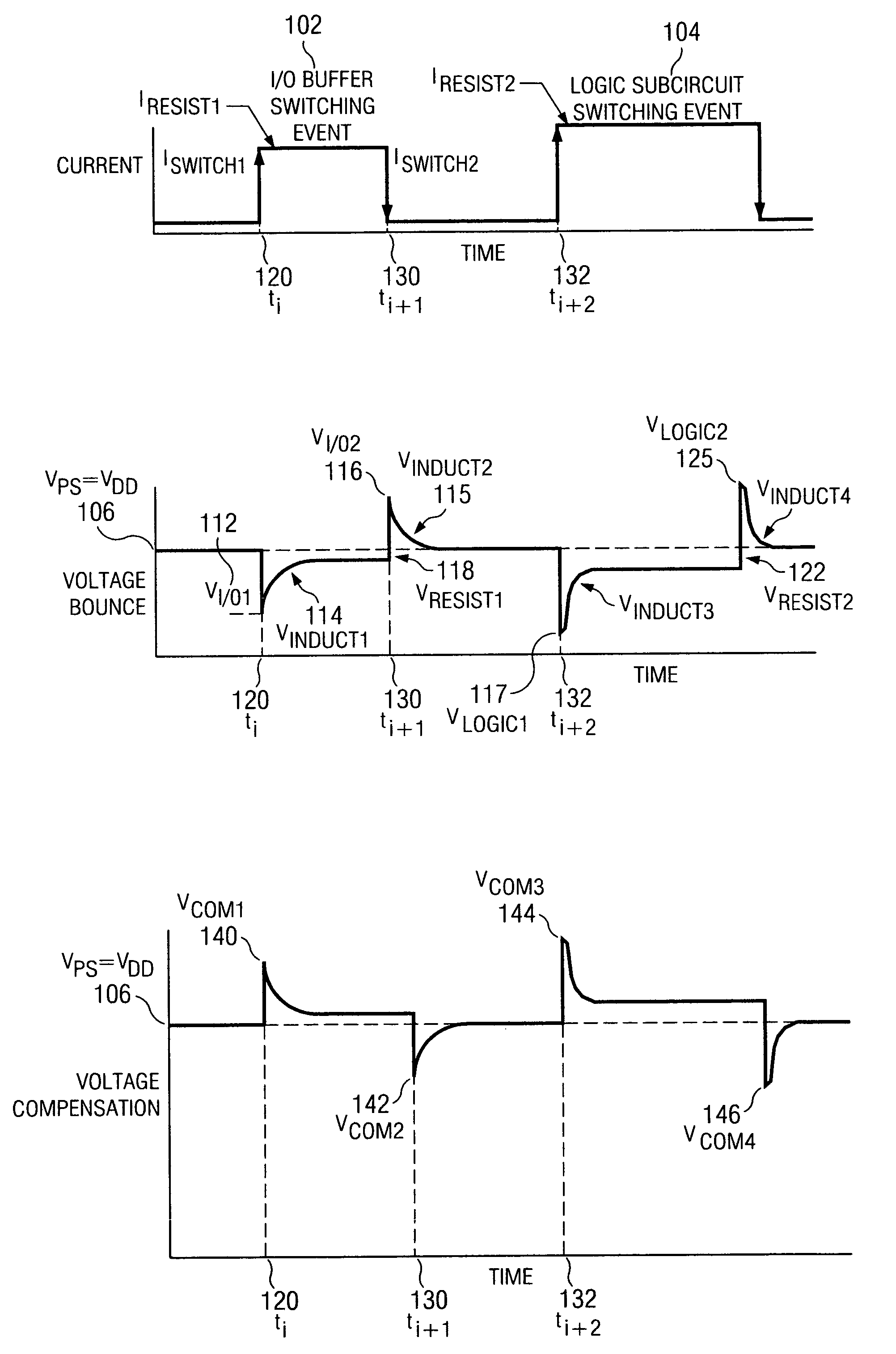

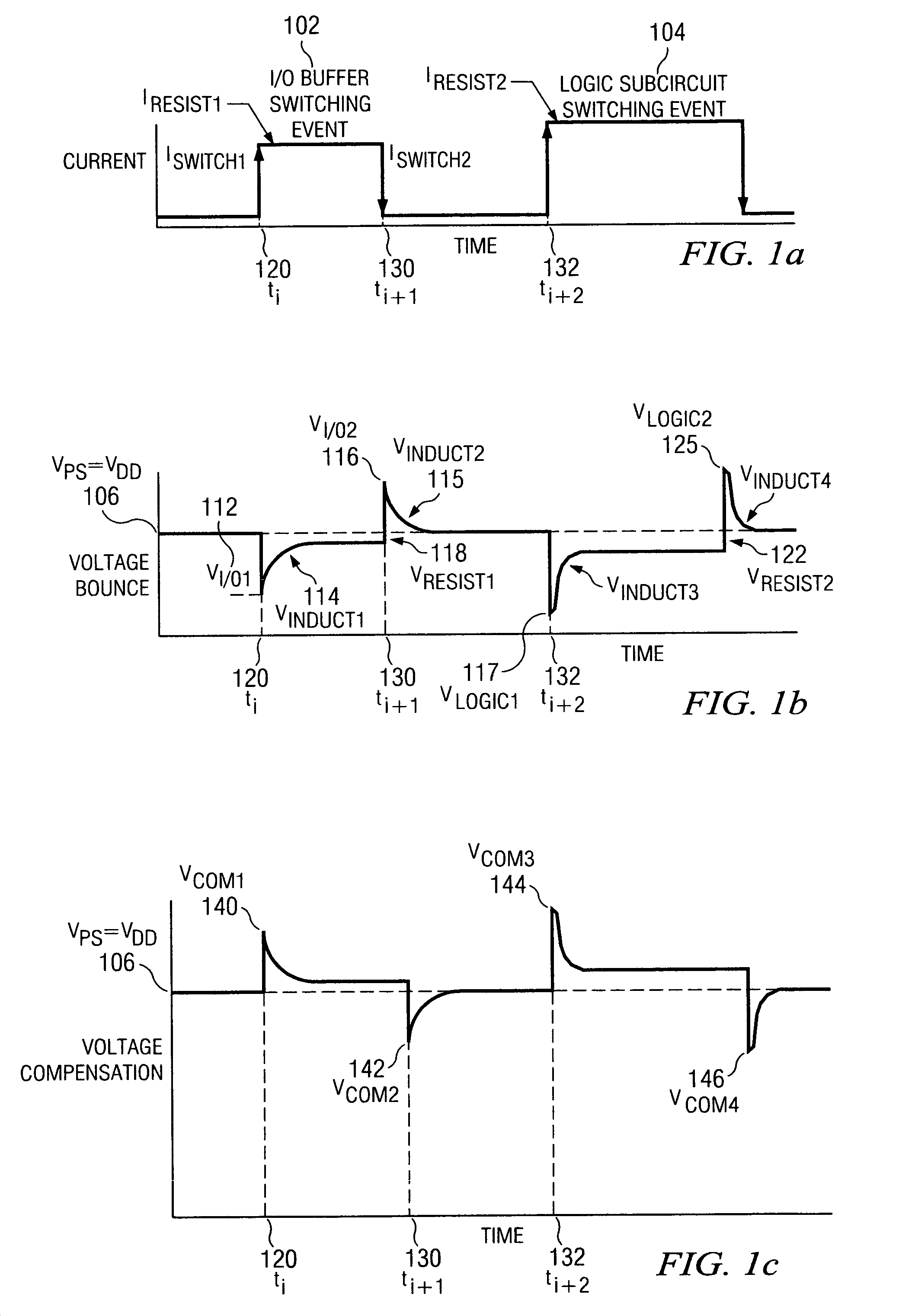

Method and apparatus to minimize power and ground bounce in a logic device

ActiveUS7296168B2Reduce the required powerMinimize power and ground bounceVolume/mass flow measurementLoad balancing in dc networkGround bounceEngineering

Owner:TEXAS INSTR INC

High-density low-power data retention power gating with double-gate devices

A new power gating structure with robust data retention capability using only one single double-gate device to provide both power gating switch and virtual supply / ground diode clamp functions. The scheme reduces the transistor count, area, and capacitance of the power gating structure, thus improving circuit performance, power, and leakage. The scheme is compared with the conventional power gating structure via mixed-mode physics-based two-dimensional numerical simulations. Analysis of virtual supply / ground bounce for the proposed scheme is also presented.

Owner:GLOBALFOUNDRIES US INC

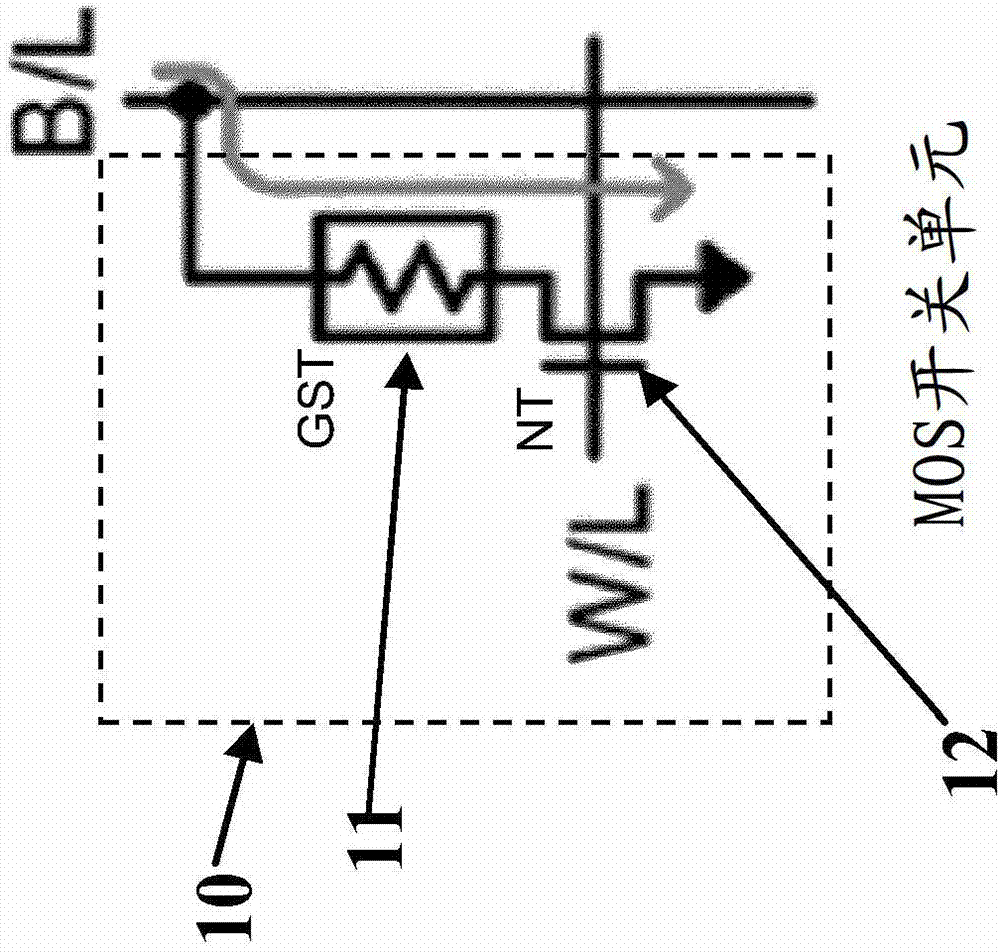

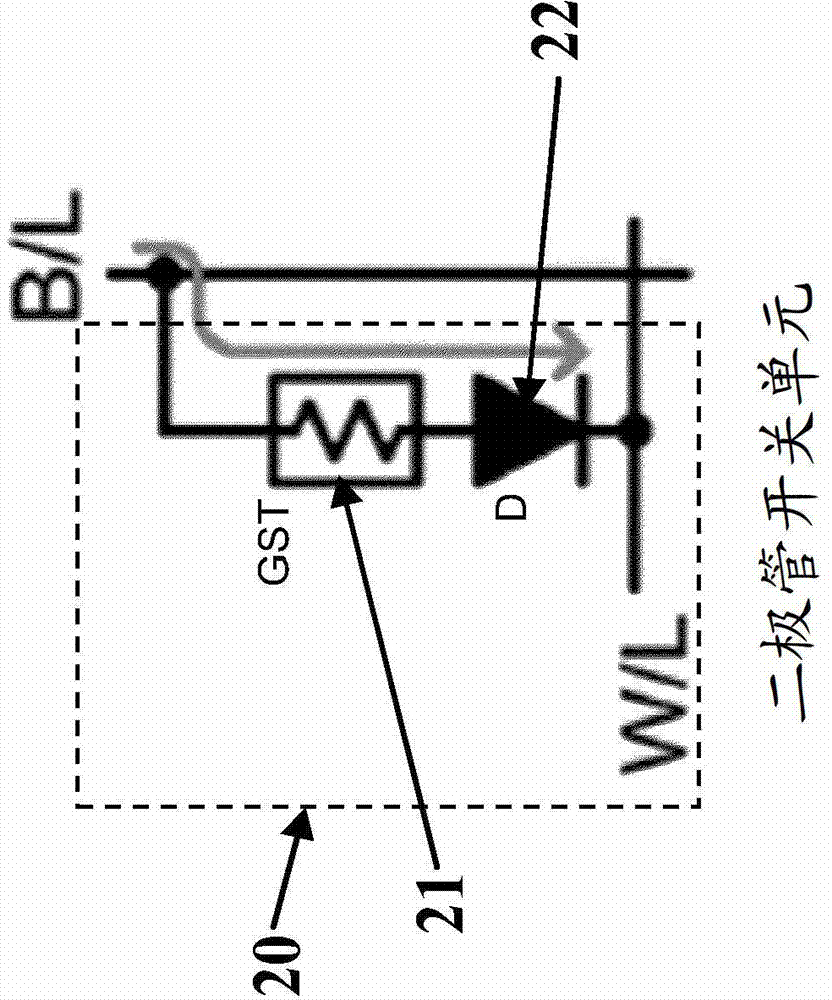

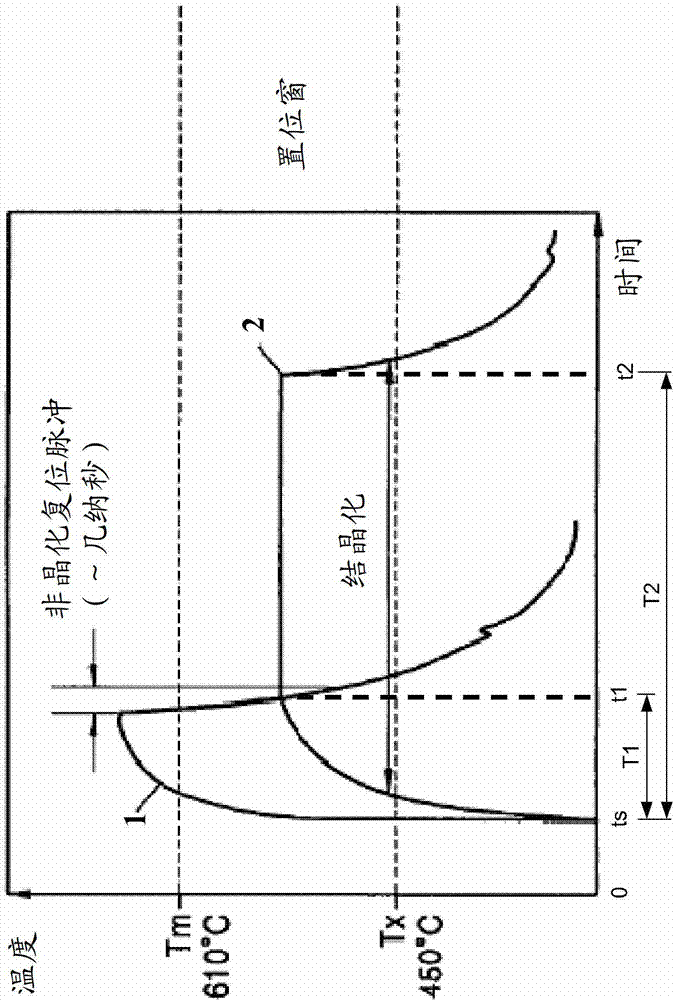

Phase change memory array blocks with alternate selection

A phase change memory is disclosed. The phase change memory has a plurality of block units. The block units are alternately selected. The alternate block unit selection suppresses peak current ground bouncing on sub-wordline and connected ground line through sub-wordline driver transistor. An alternate bitline selection avoids adjacent cell heating interference in the selected block unit.

Owner:CONVERSANT INTPROP MANAGEMENT INC

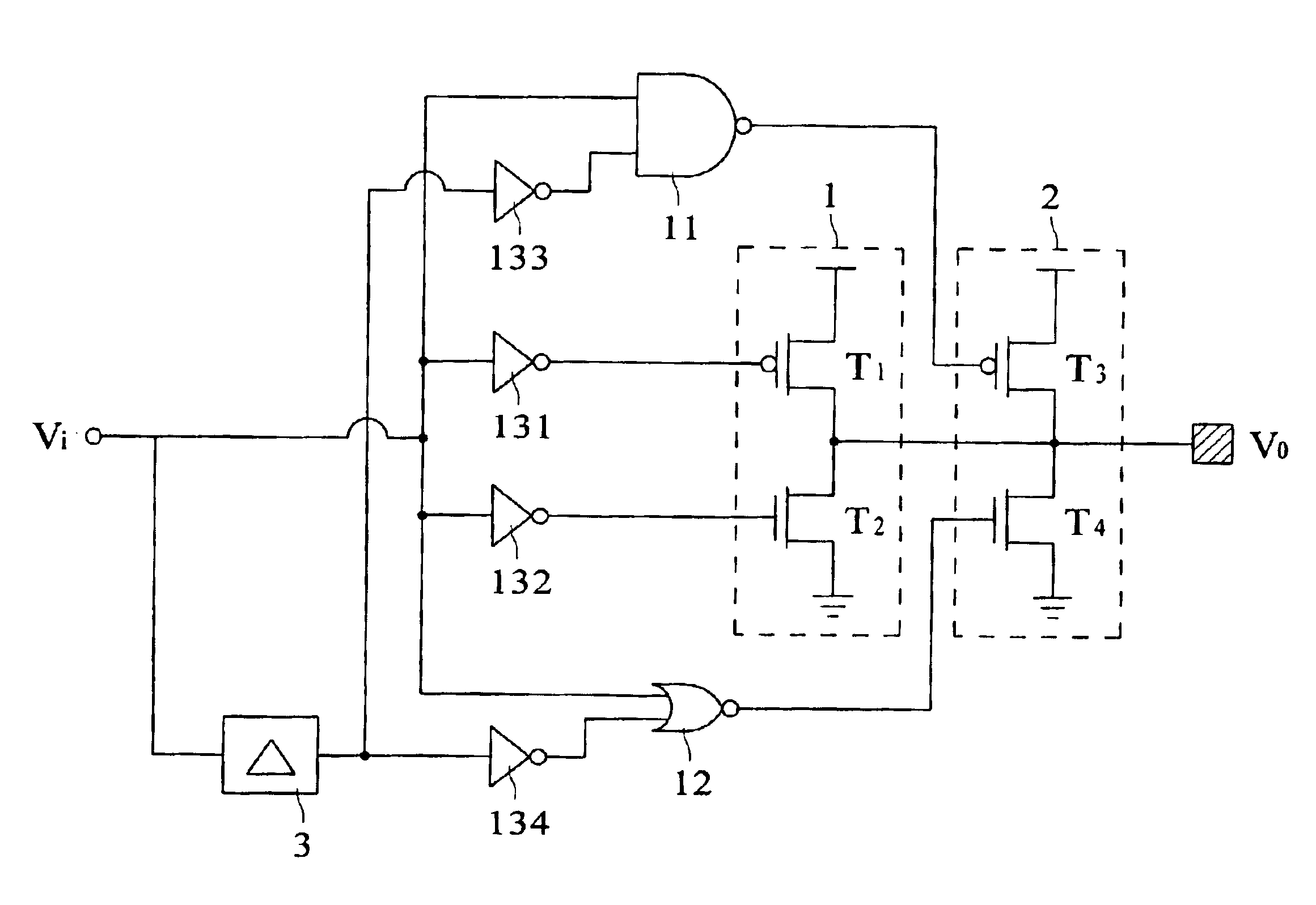

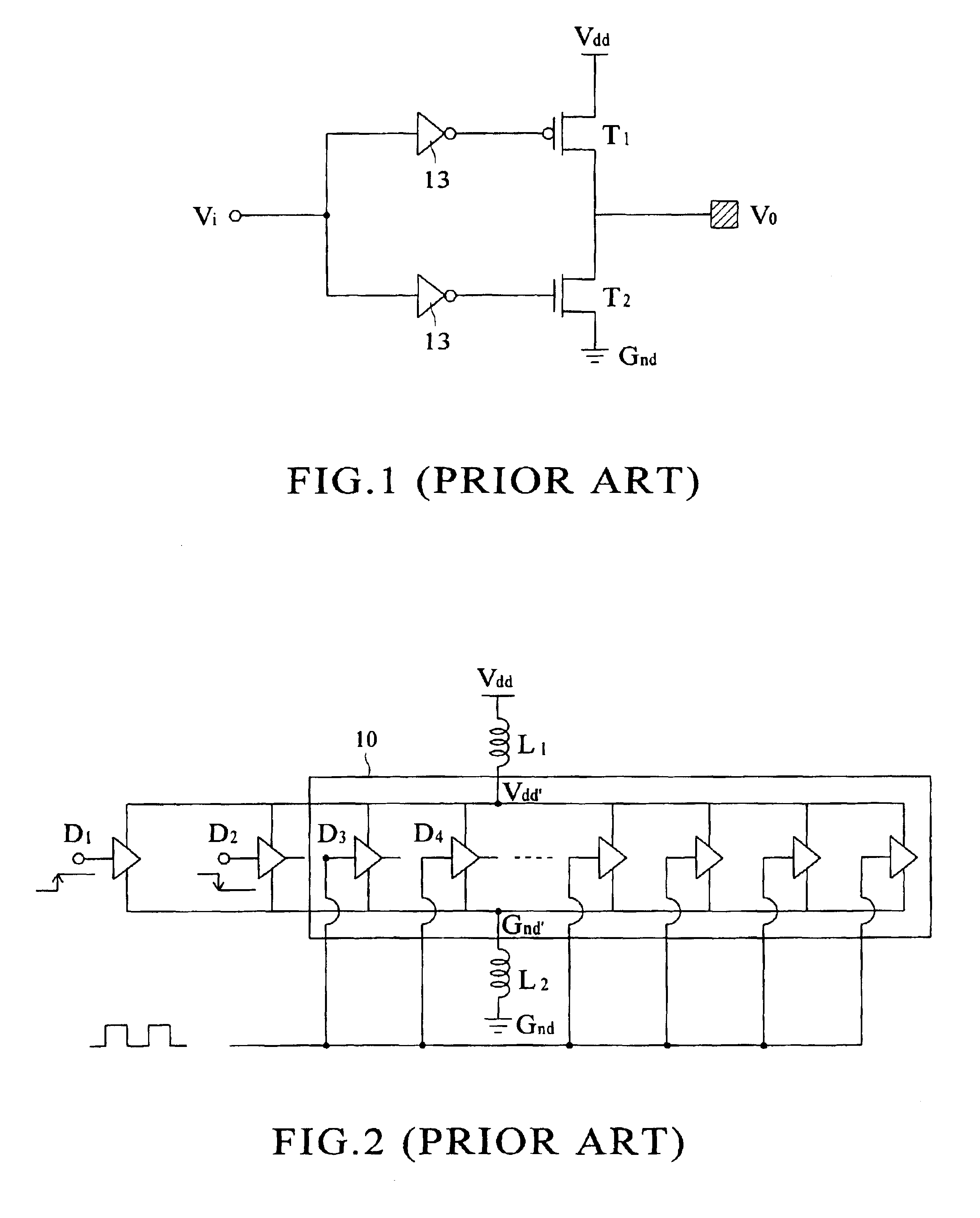

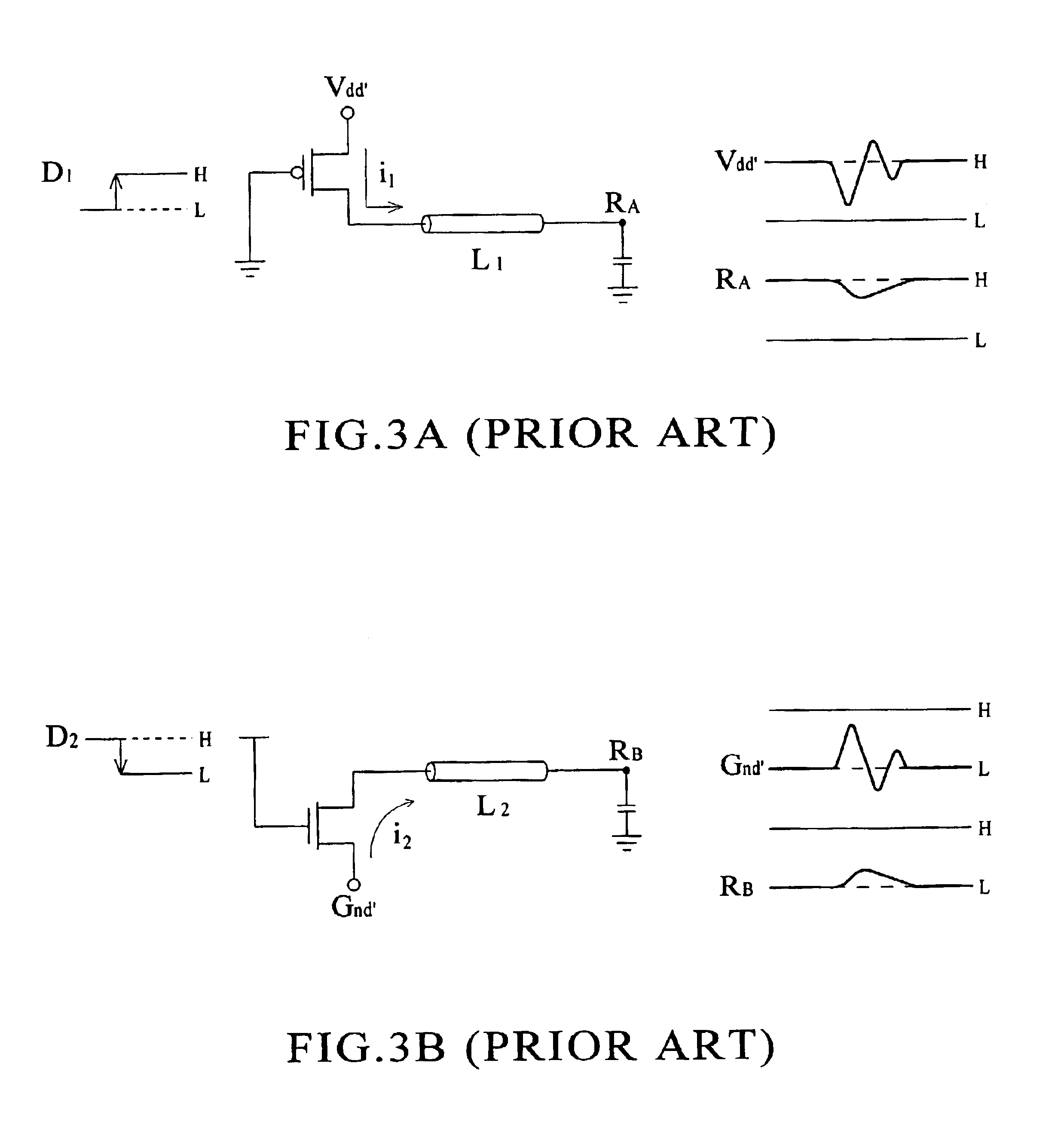

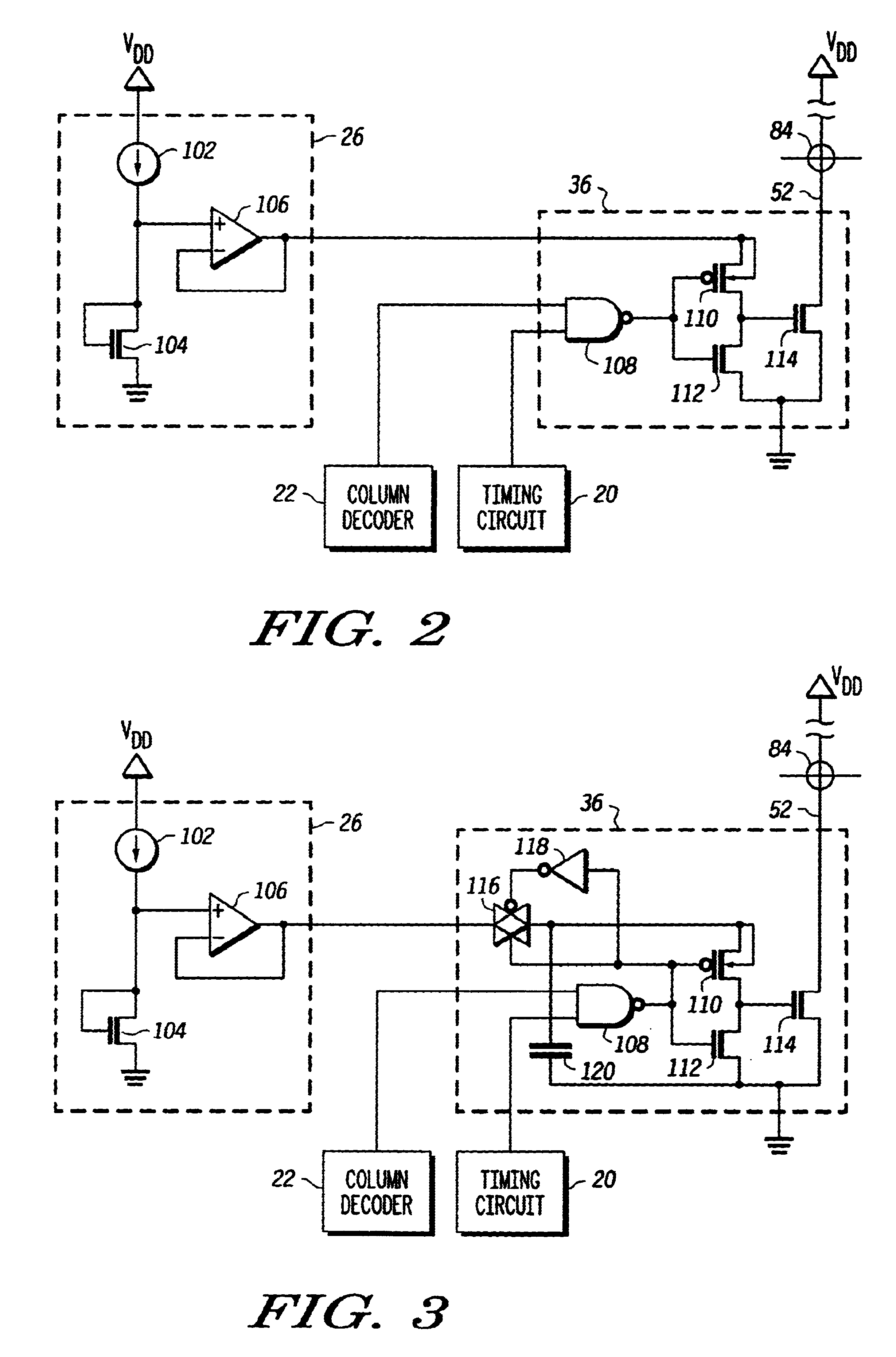

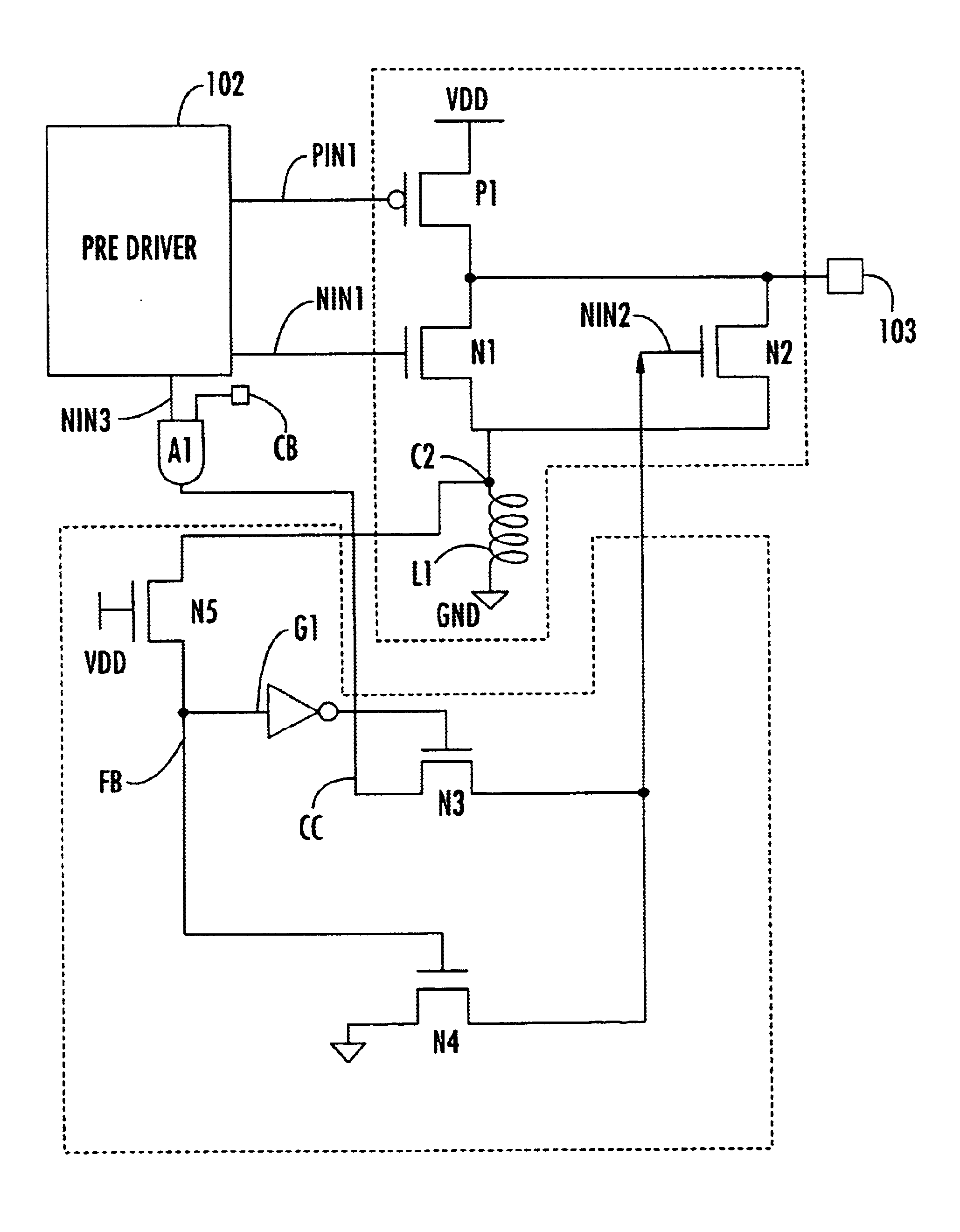

CMOS buffer with reduced ground bounce

InactiveUS6856179B2Reduced ground bounceReliability increasing modificationsElectronic switchingCMOSGround bounce

A CMOS output buffer uses feedback from a ground node to reduce ground bounce by utilizing a tolerable ground bounce limit, making it less sensitive to operating conditions and processing parameters. An input to the NMOS device of the output buffer is provided by the output of a control element which receives a first input from a pre-driver and a second input (i.e., the feedback) from the ground node.

Owner:STMICROELECTRONICS PVT LTD

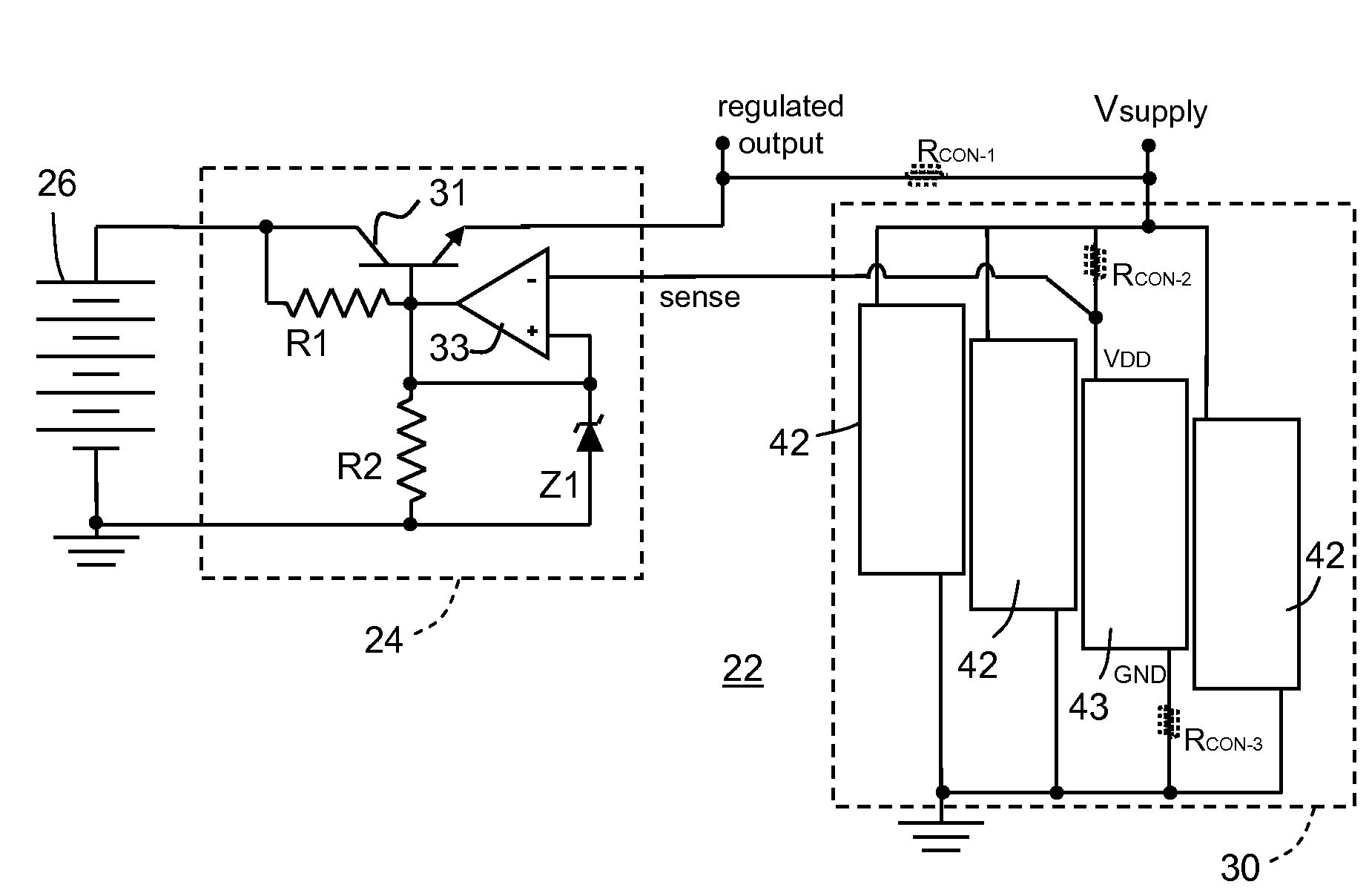

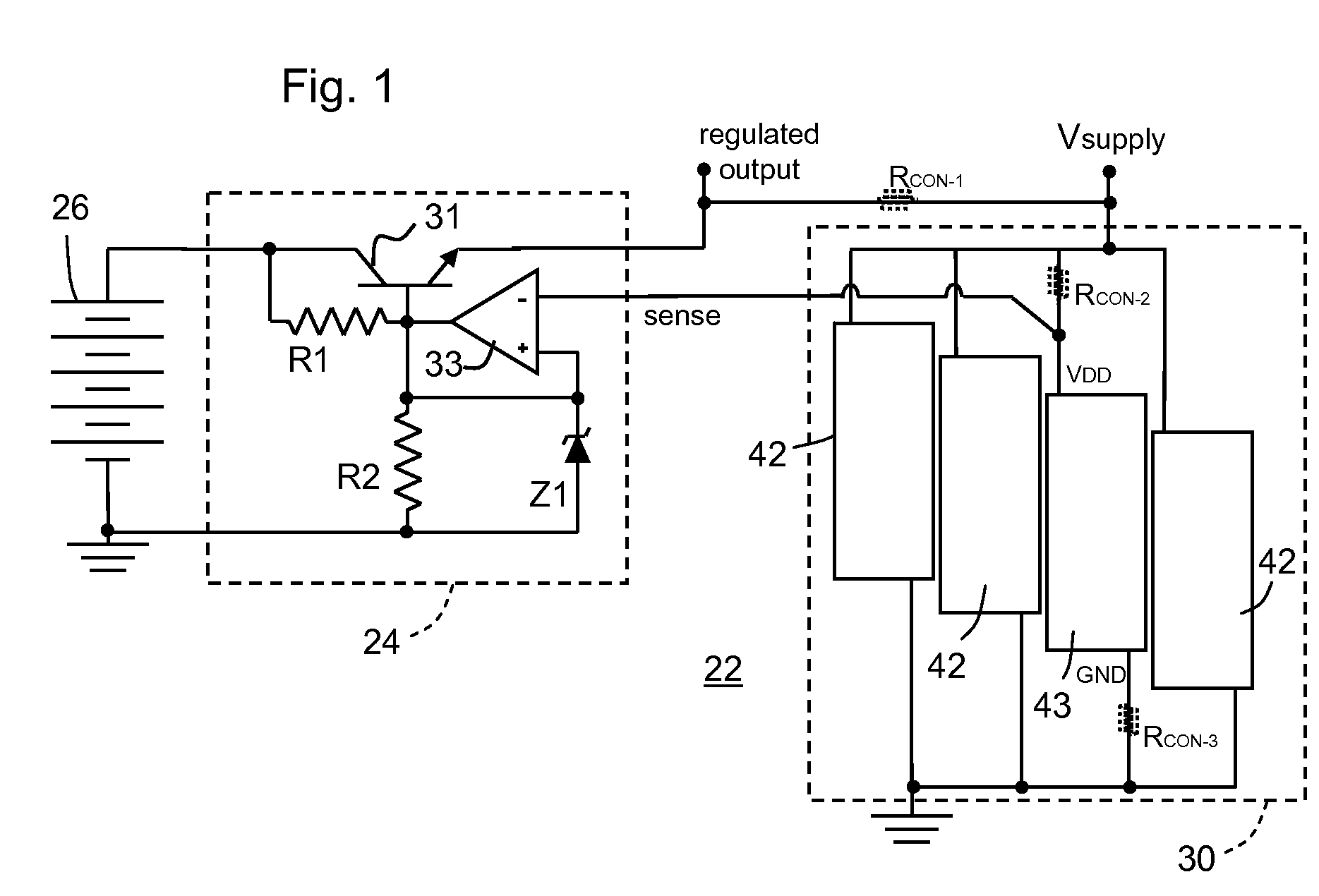

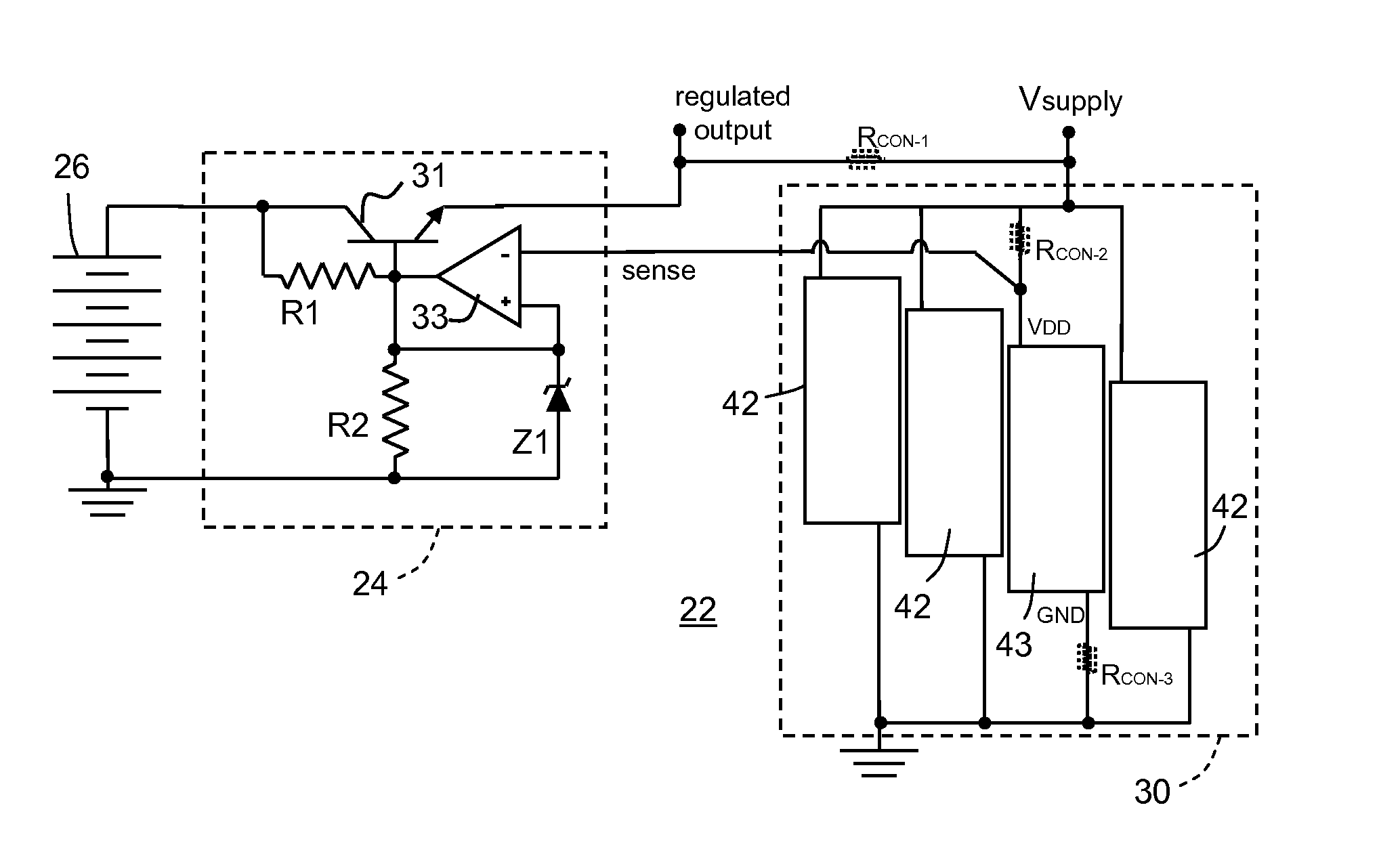

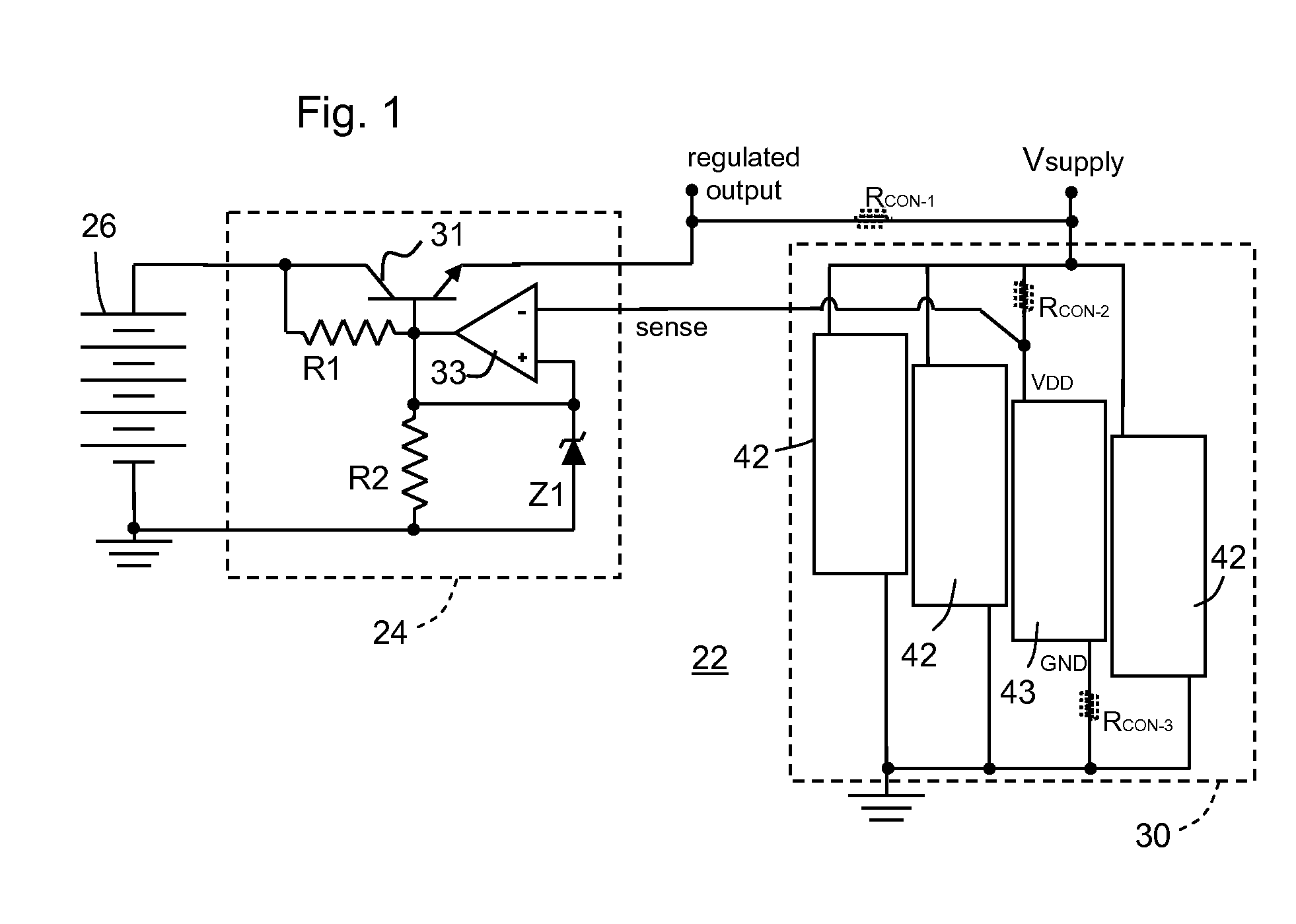

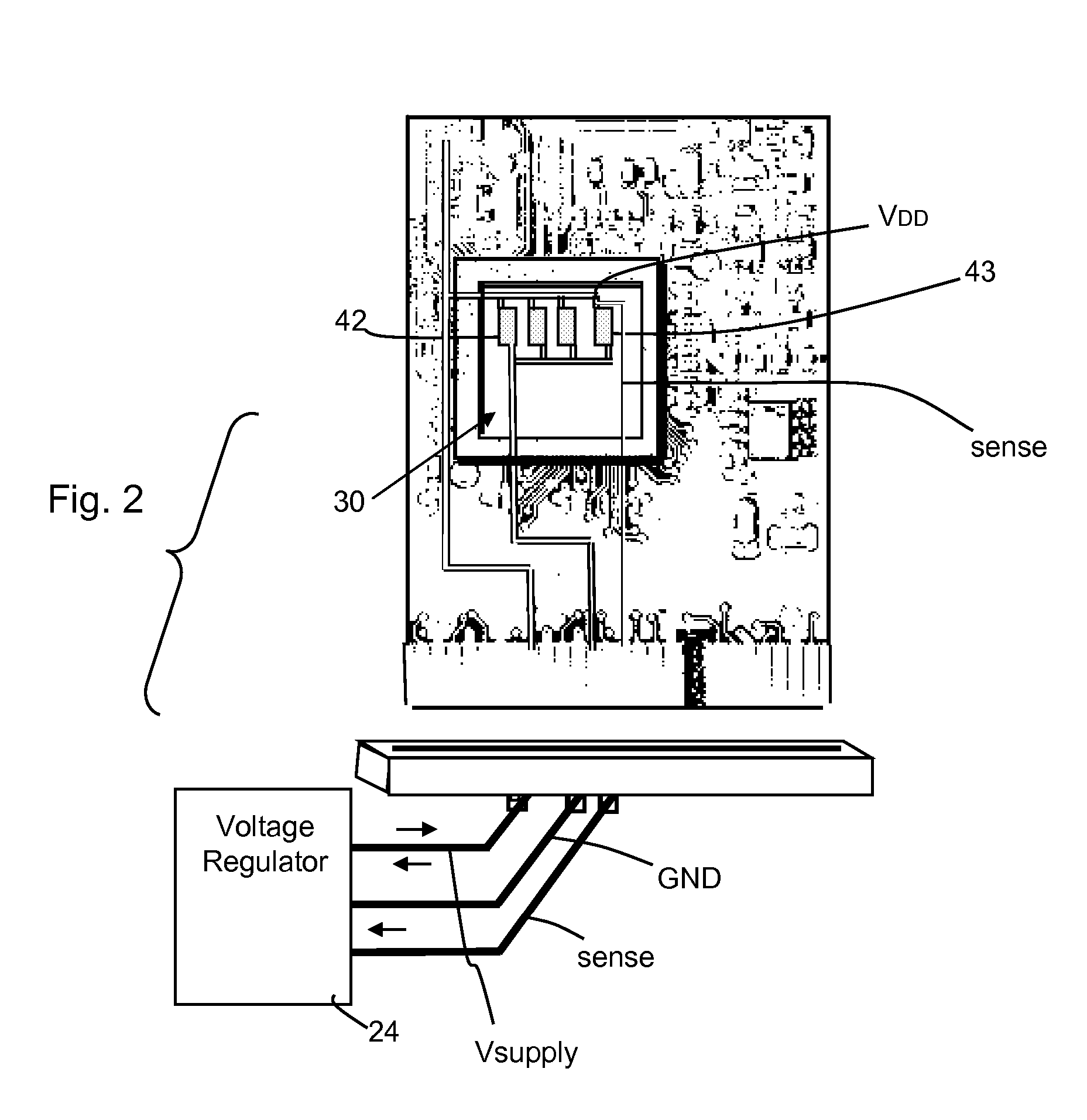

Power supply regulation using kelvin tap for voltage sense feedback from point within integrated circuit load

ActiveUS7339357B2Dc-dc conversionElectric variable regulationVery large scale integrated circuitsOn board

A remote sensing power supply regulator uses high impedance sensing inputs coupled internally to at least one circuit element within an integrated circuit, so as to regulate the voltages produced by the power supply to a level that maintains nominal voltage levels at the internal circuit element within the very large scale integrated circuit. The sense point can be chosen to serve one or a group of on-board load elements that are operationally sensitive to voltage droop and / or ground bounce.

Owner:AVAGO TECH INT SALES PTE LTD

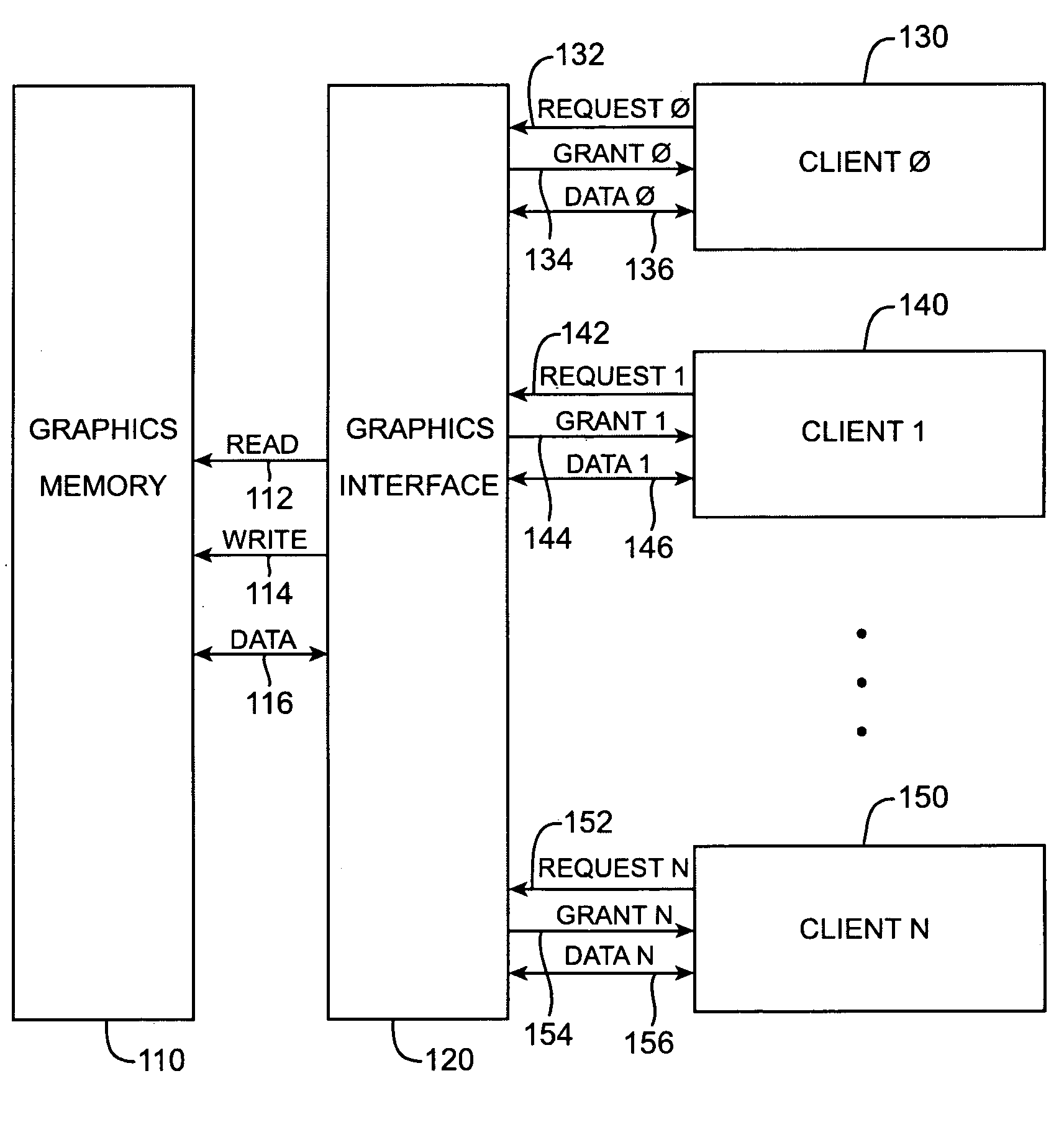

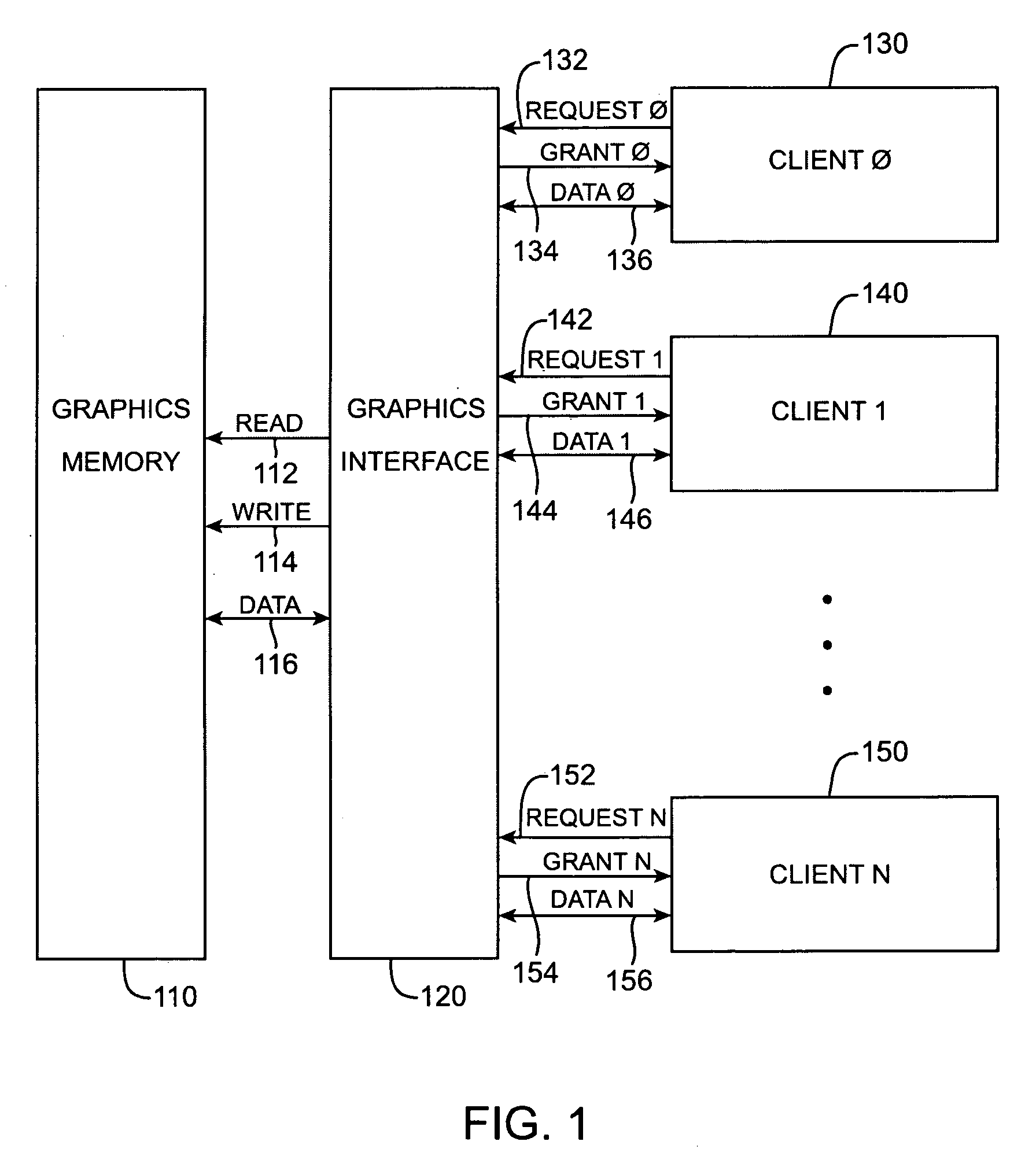

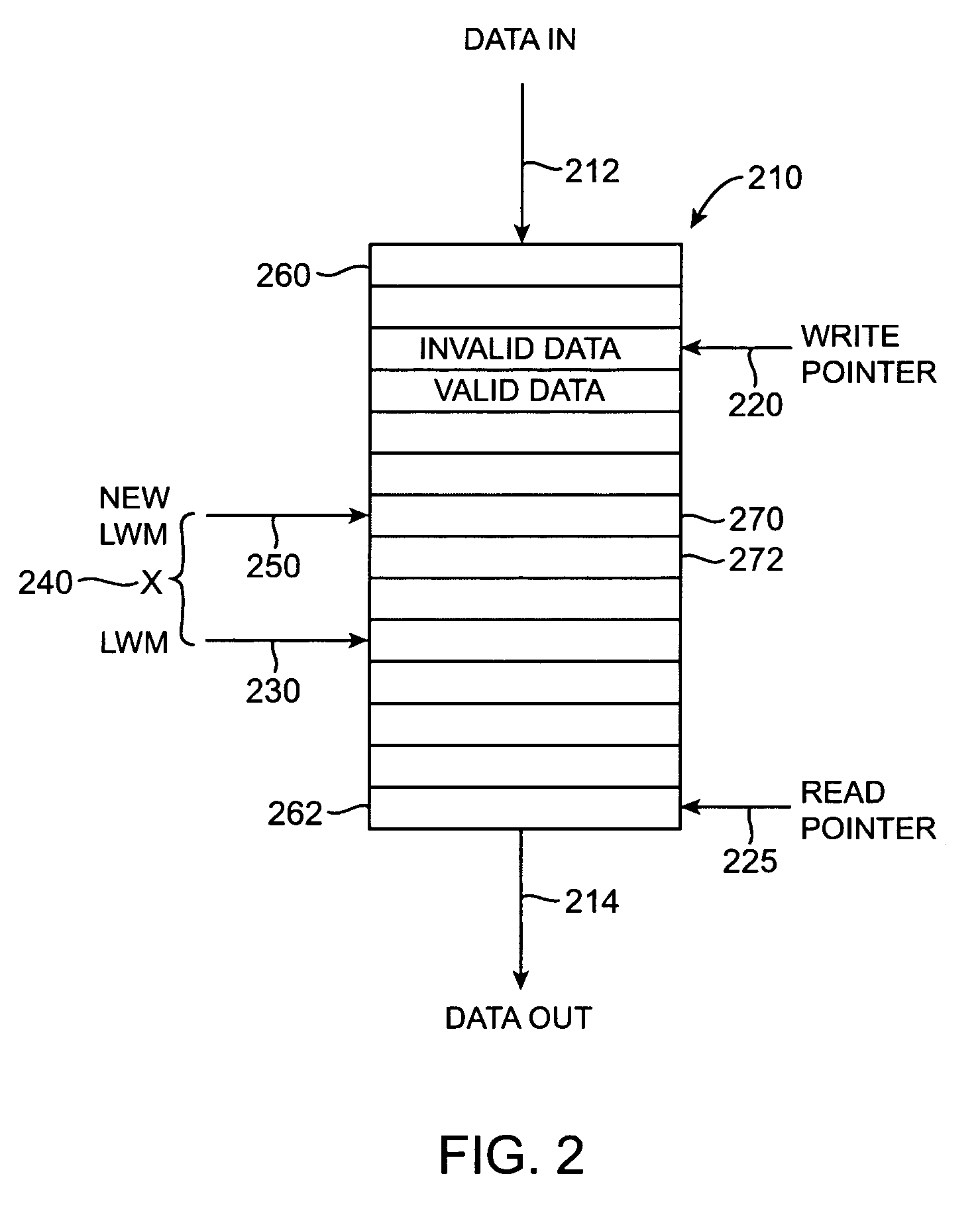

Memory request timing randomizer

InactiveUS7081896B1Artifact is reduced and eliminatedEasy accessCathode-ray tube indicatorsElectric digital data processingGraphicsGraphic system

Methods and apparatus for changing the timing of memory requests in a graphics system. Reading data from memory in a graphics system causes ground bounce and other electrical noise. The resulting ground bounce may be undesirably synchronized with a video retrace signal sent to a display, and may therefore cause visible artifacts. Embodiments of the present invention shift requests made by one or more clients by a duration or durations that vary with time, thereby changing the timing of the data reads from memory. The requests may be shifted by a different duration for each memory request, for each frame, or multiples of requests or frames. The durations may be random, pseudo-random, or determined by another algorithm, and they may advance or delay the requests. By making the ground bounce and other noise asynchronous with the video retrace signal, these artifacts are reduced or eliminated.

Owner:NVIDIA CORP

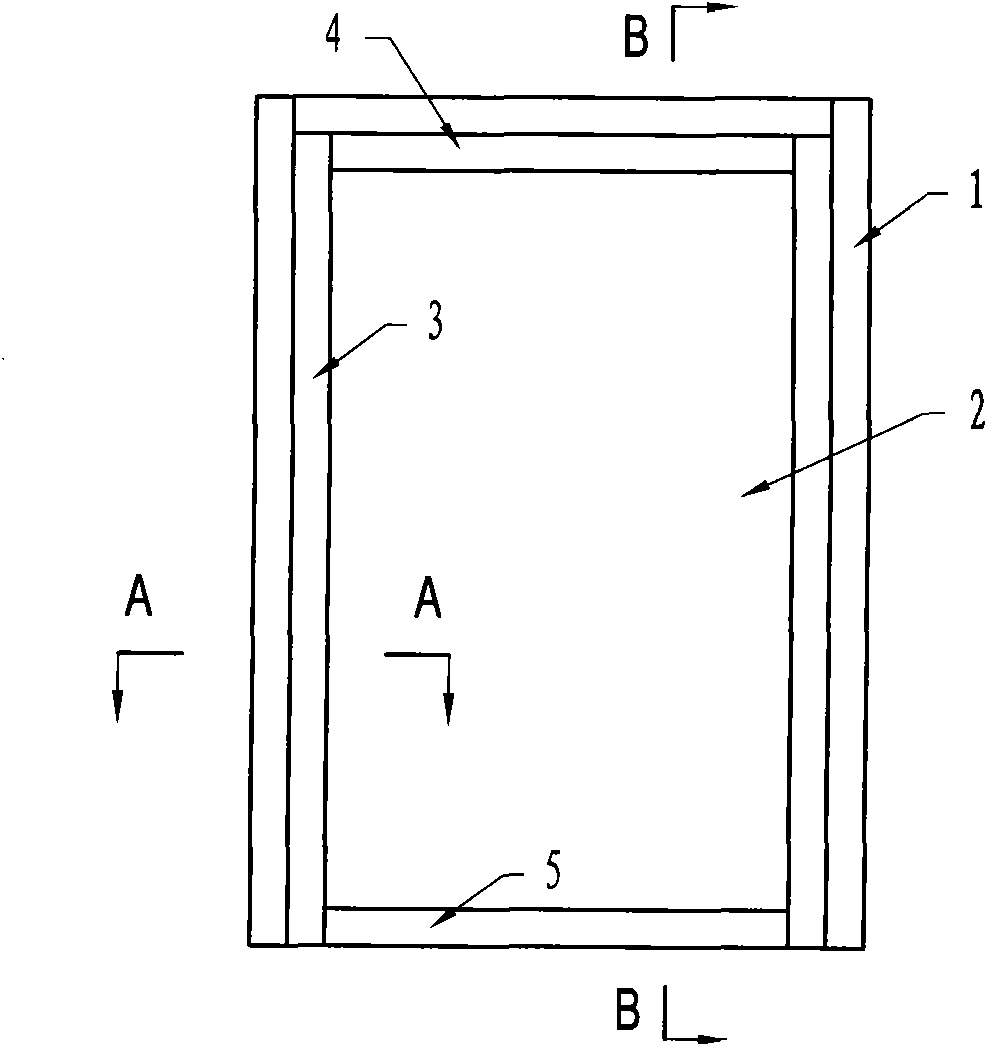

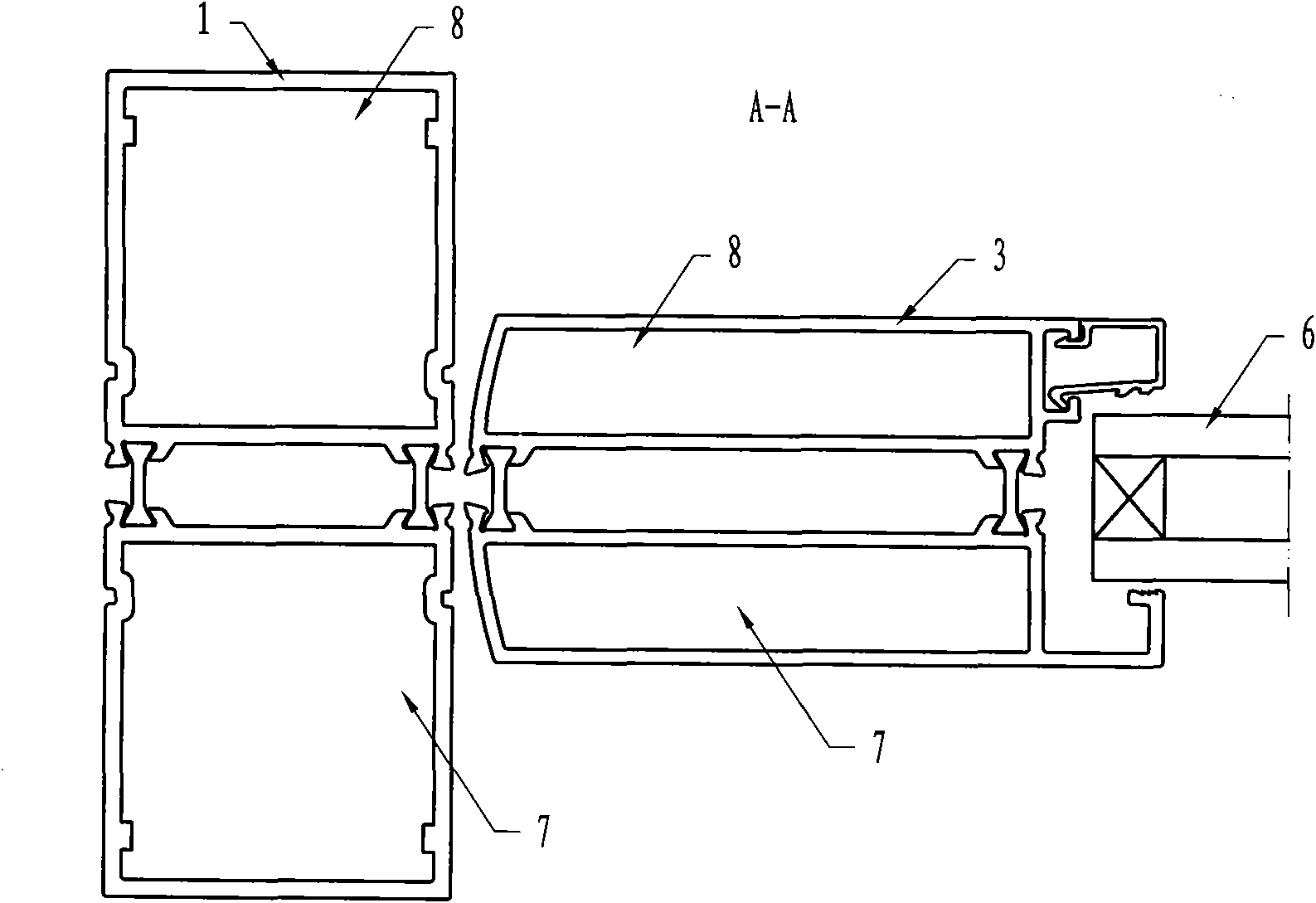

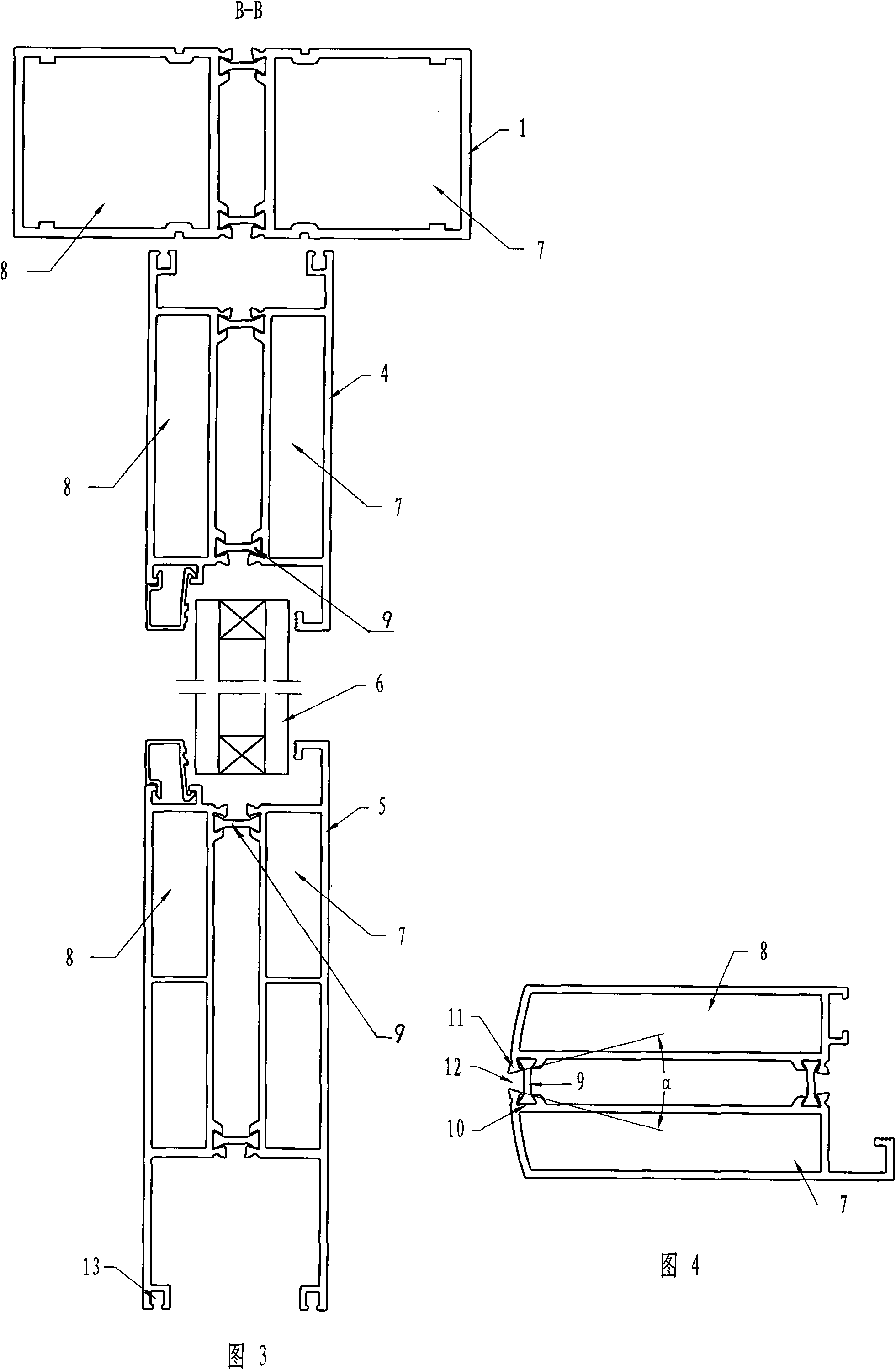

Heat-insulation aluminium alloy ground bounce door

InactiveCN101852051ASimple designGuaranteed sealing performanceSealing arrangementsThermal insulationGround bounce

The invention discloses a heat-insulation aluminium alloy ground bounce door, which comprises a door frame and a door leaf, wherein the door leaf comprises a door pile, a top, a bottom and hollow glass; the door frame, the door pile, the top and the bottom respectively comprise an outdoor frame, an indoor frame and heat insulation strips; the outdoor frame and the indoor frame are connected by the heat insulation strips; the outer side walls of the notches of the heat-insulation strips on the door pile are strung and form seal element notches together with the heat-insulation strips. The invention has the characteristics of reasonable structure, heat insulation, obvious sound insulation effect, good sealing performance and the like.

Owner:余定泉

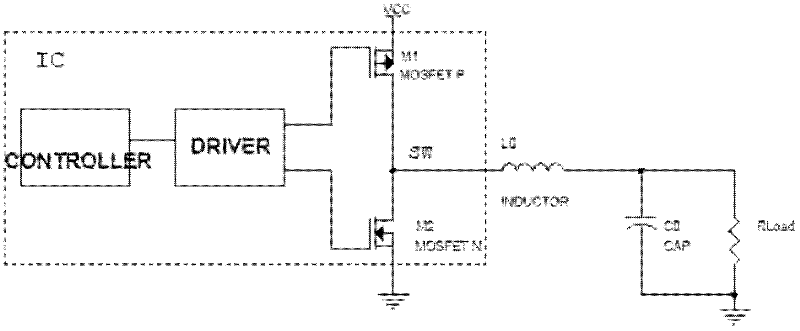

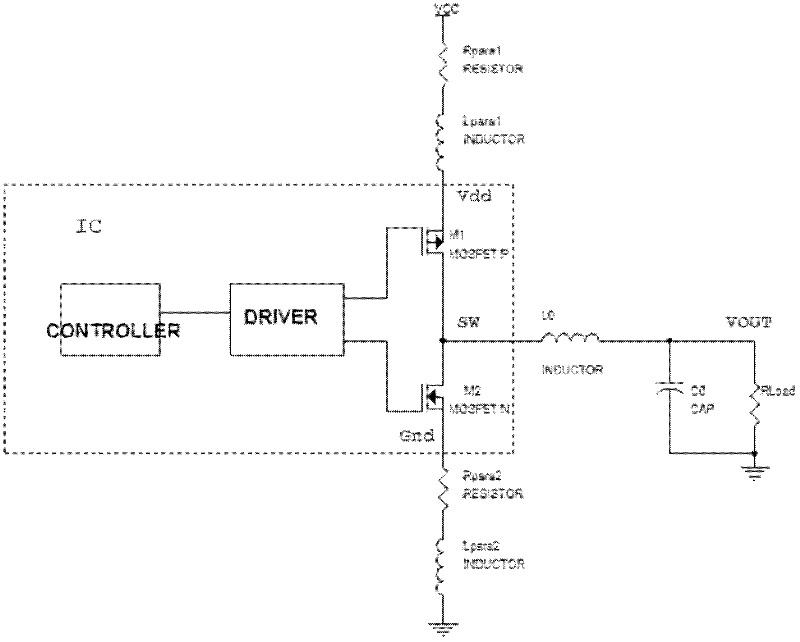

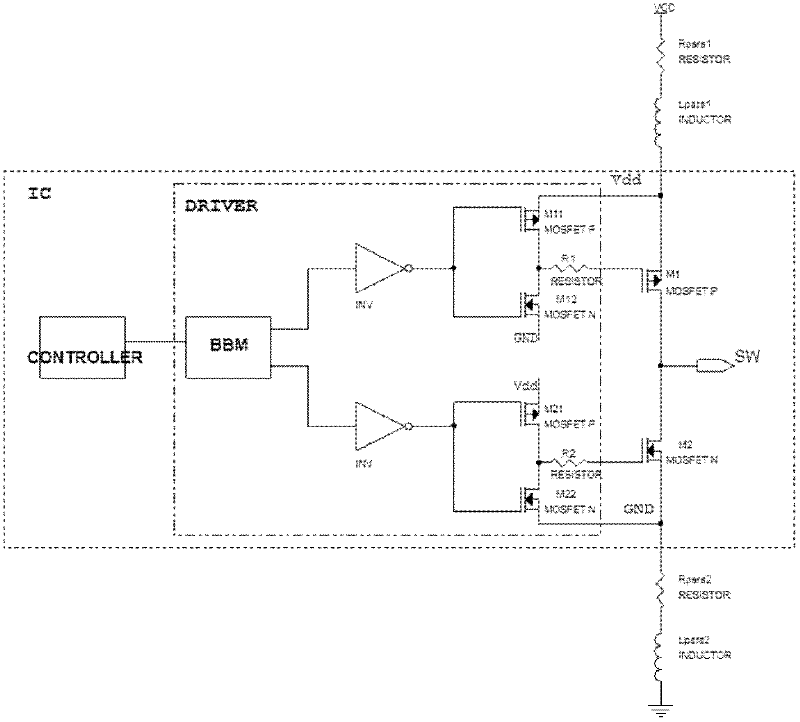

Power switch driver, IC chip, and DC-DC converter

ActiveCN102545560ALower ground bounceLower impedanceDc-dc conversionElectric variable regulationDc dc converterCoupling

The invention discloses a power switch driver, an IC chip and a DC-DC converter, for lowering ground bounce of a switch power source and for lowering impedance from the gate of a power switch to the power source or the ground when the power switch is switched off while ensuring a low opening speed of the power switch so as to prevent instant-on of the power switch through coupling of a parasitic capacitor. The power switch driver provided by the invention comprises an N-channel metal oxide semiconductor field effect transistor NMOS for controlling a P-type power switch, and a P-channel metal oxide semiconductor field effect transistor PMOS for controlling an N-type power switch, and also includes a first resistor connected with source of the NMOS, and a second resistor connected with source of the PMOS.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

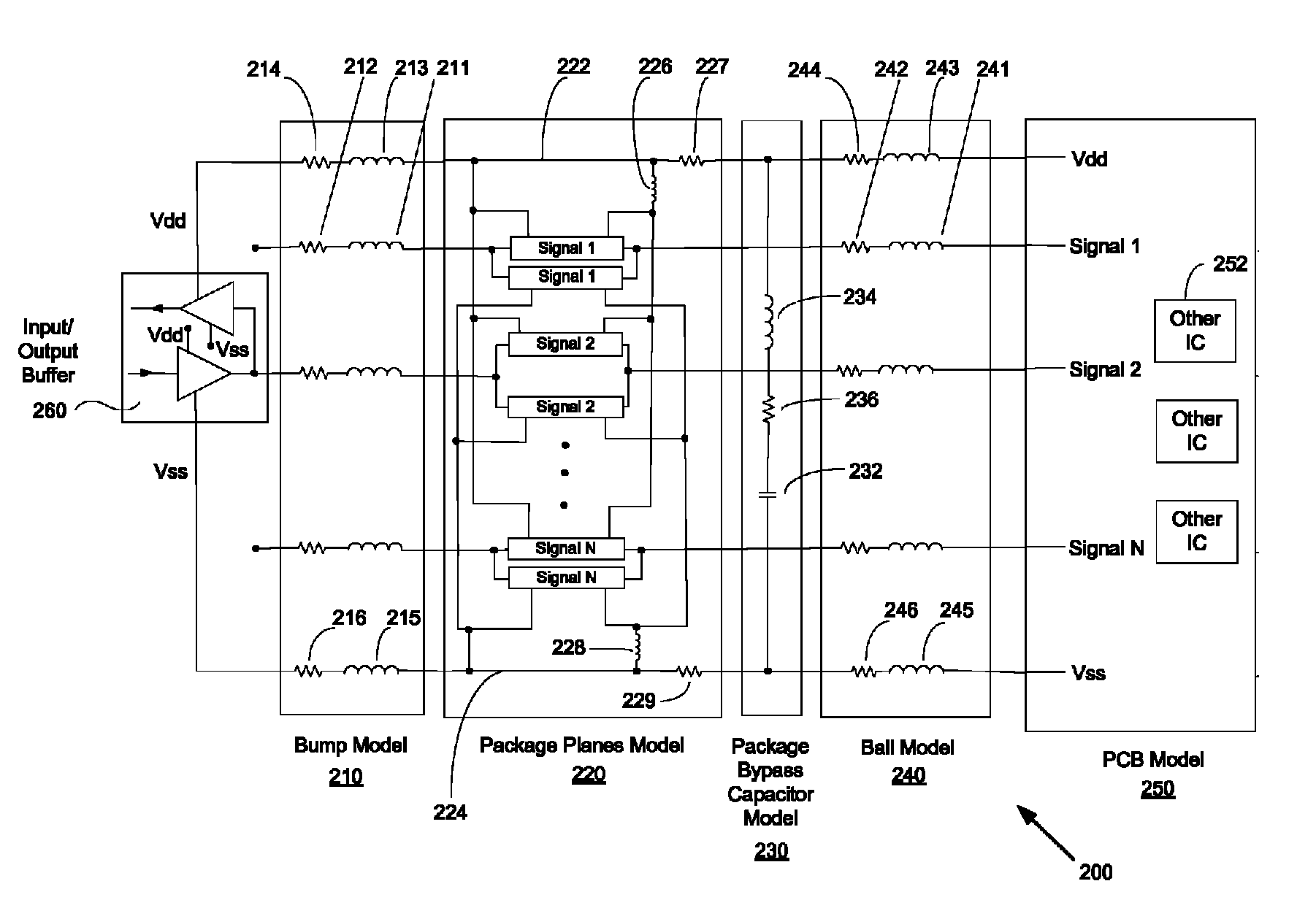

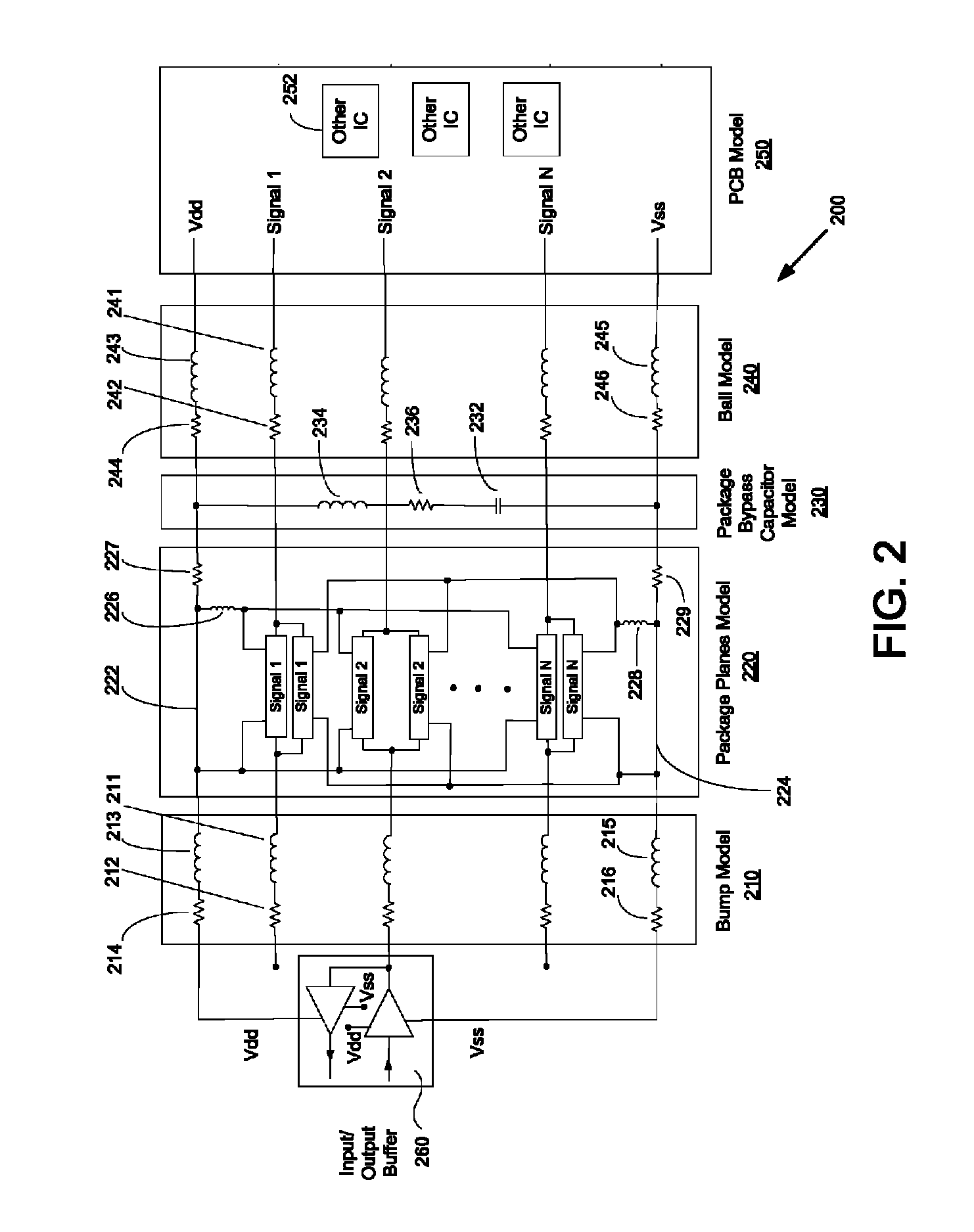

Integrated circuit package component and ball grid array simulation model

InactiveUS8386229B1Efficient designAnalogue computers for electric apparatusComputer aided designElectrical conductorGround bounce

A simulation model is provided for flip-chip BGAs to help engineers determine the effects of IC package components. The simulation model includes a bump model, a package planes model, a package bypass capacitor model, a ball model and a PCB model. The simulation model in particular includes resistors, inductors, capacitors and transmission lines to simulate the electrical interaction between signal conductors, power / ground planes, vias and balls that exist in a flip-chip ball grid array (BGA) package. The simulation model helps engineers understand actual physical effects of flip-chip and IC package interactions, as well as the impact of the effects of power supply droop, ground bounce and crosstalk between adjacent signals, not only on the IC package level, but at the computer system level.

Owner:XILINX INC

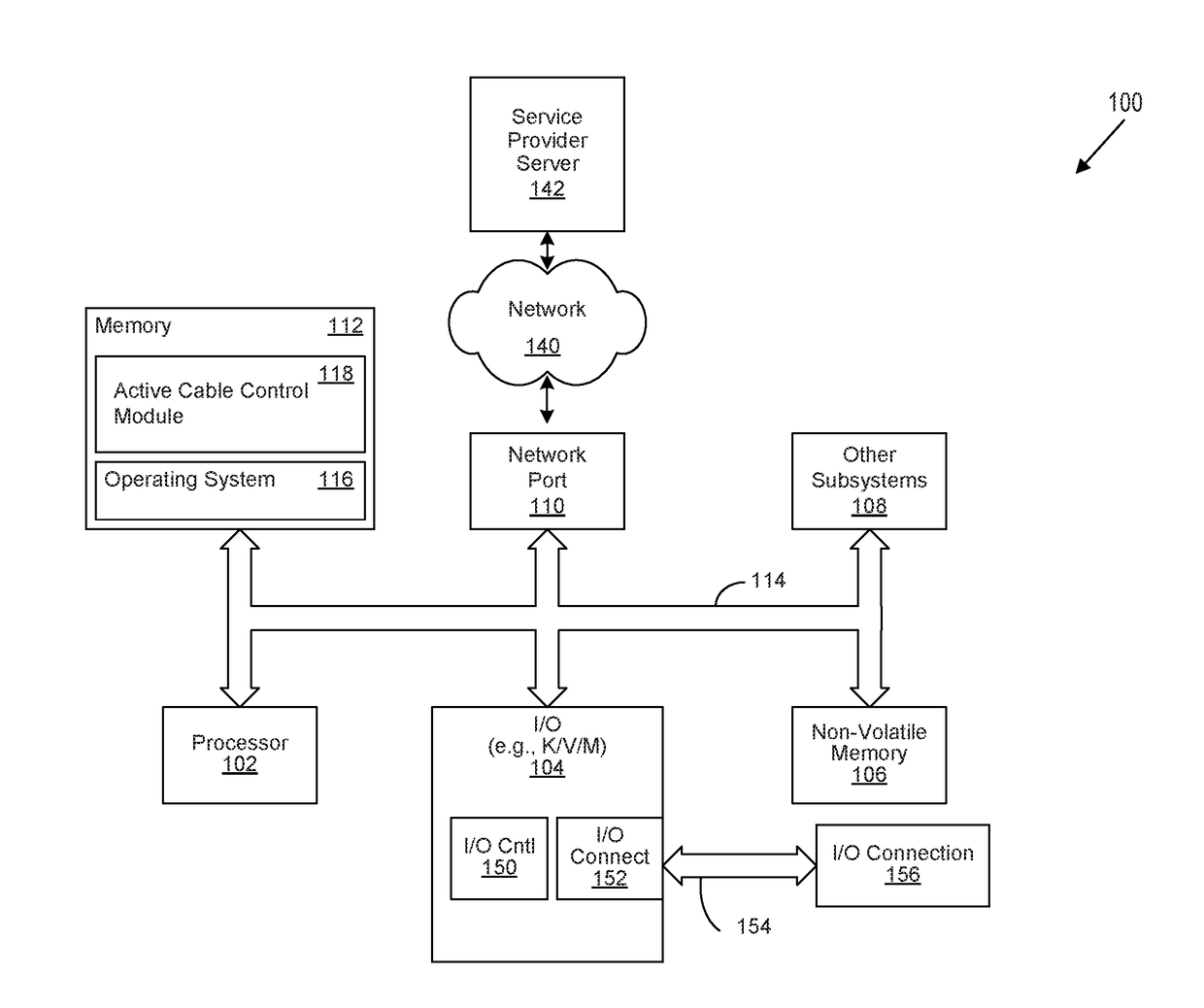

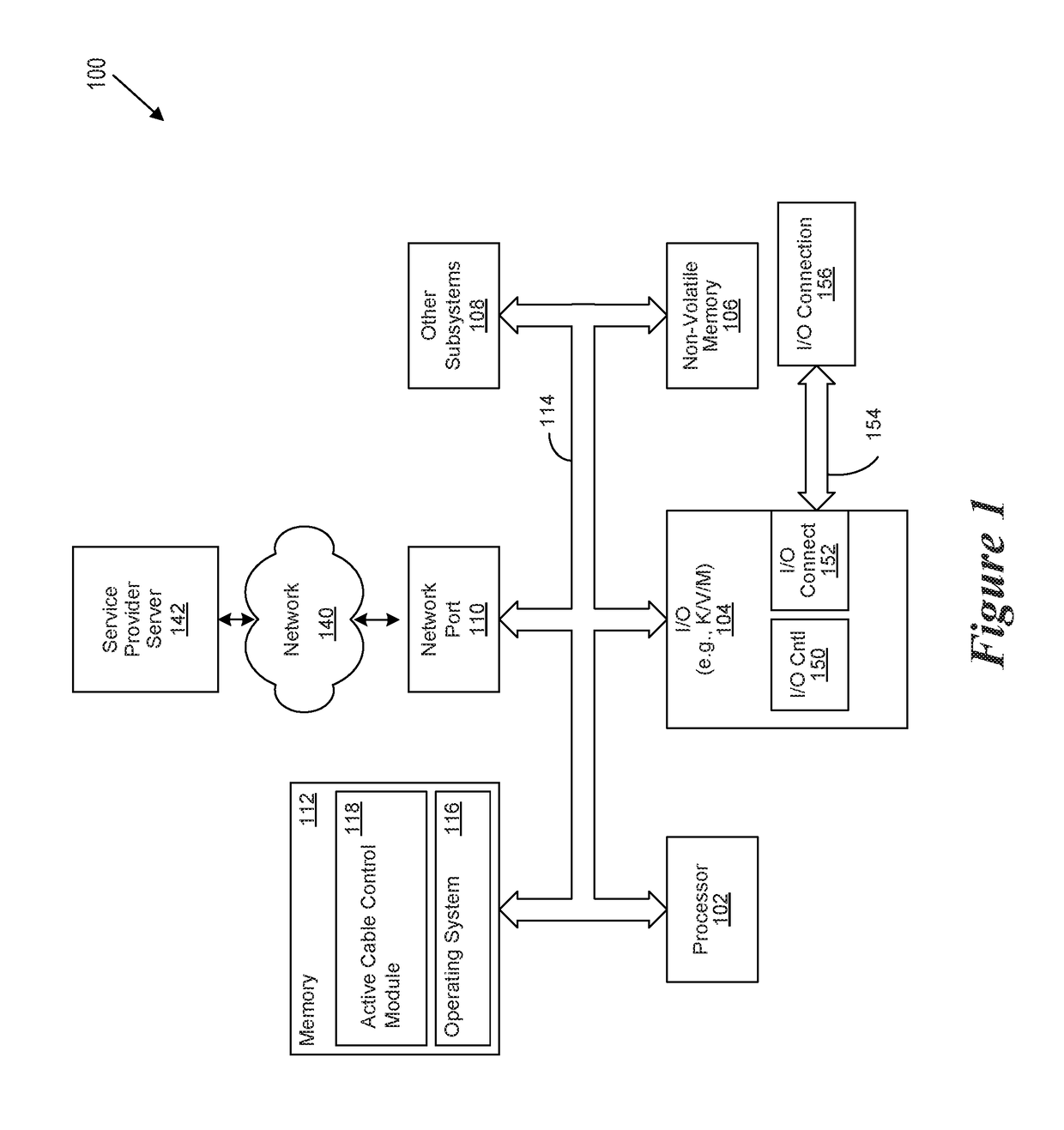

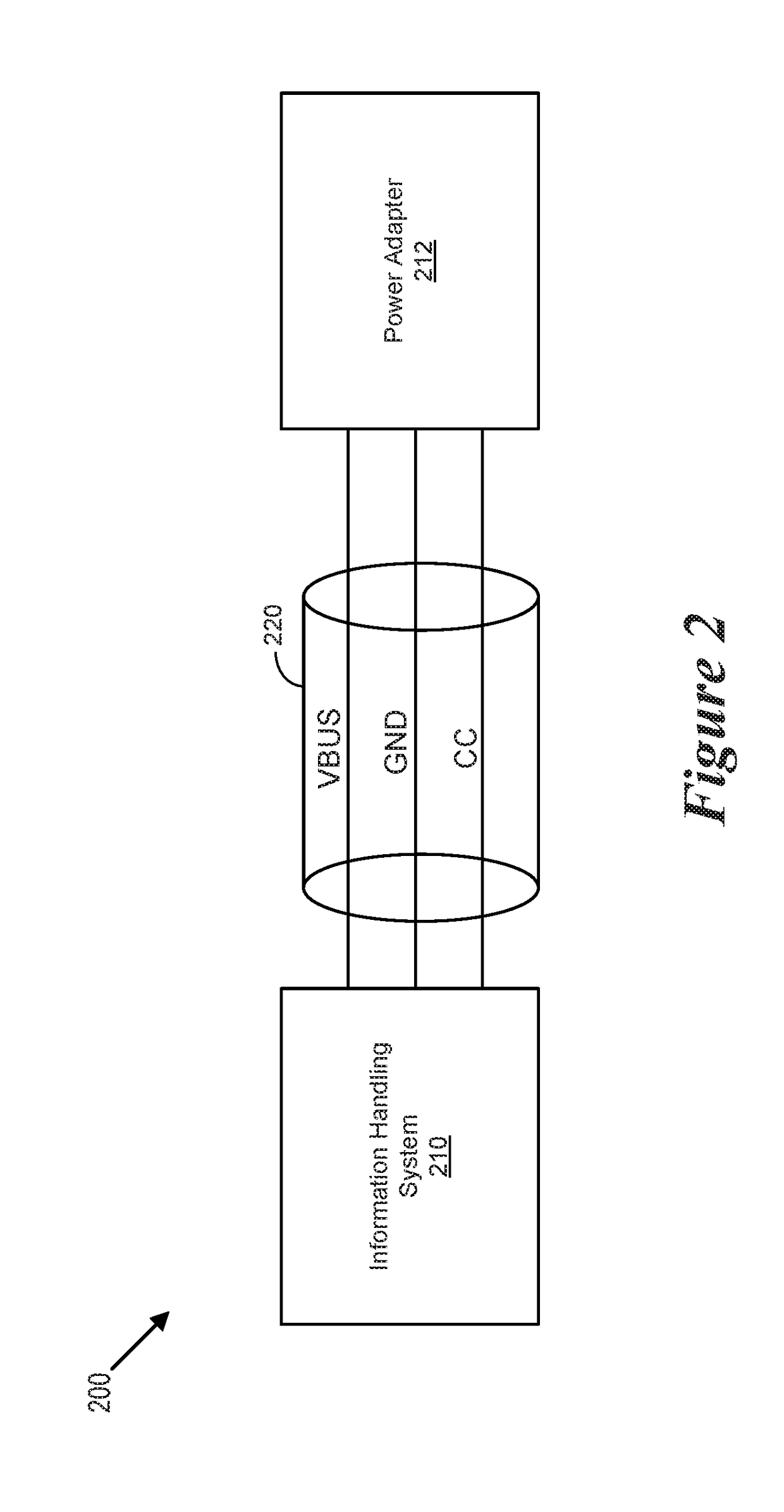

Enhanced Ground Bounce Immunity on USB Type-C Power Delivery Communication

ActiveUS20170242814A1Less-flexibleDiameter minimizationPower supply for data processingSpecific program execution arrangementsVoltage dropGround bounce

A system and method for enhancing ground bounce immunity of cables such as USB type-C cables. More specifically, in certain embodiments, ground bounce immunity is enhanced by making use of alternate modes of operation of cables conforming to the USB 3.1 specification to achieve a higher power over a cable that conforms to the USB 3.1 voltage drop specification requirements on the ground signal paths when the cable is operating at normal power levels (i.e., at a power level supported by the USB 3.1 specification). In certain embodiments, ground bounce immunity is enhanced by making use of alternate modes of operation of USB 3.1 type cables and standard use USB3.1 power delivery negotiation protocol to allow a host and end device to negotiate higher power than what would normally conform to the USB 3.1 specification.

Owner:DELL PROD LP

Circuit for measuring on-chip power supply integrity

InactiveUS20050007126A1Exclude influenceError preventionCurrent/voltage measurementGround bounceEngineering

A test circuit and method for measuring power supply integrity is provided. The circuit may be incorporated on-chip and is small enough to be integrated many times across the surface of the die for measuring integrity parameters at several locations on the chip. The circuit instantaneously measures, e.g., the rail voltage of a power supply, which may be fluctuating at the time of measurement. In addition, the circuit isolates itself from all chip power rails for the duration of the measurement, thereby eliminating any influence of external noise on the measurement. A storage capacitor is charged up to full power rail voltage for powering up a comparator. Then, the comparator is isolated from the power rails and the measurements are taken. Based upon the measurements, certain power supply integrity parameters are quantified including ground bounce and power droop.

Owner:MICRON TECH INC

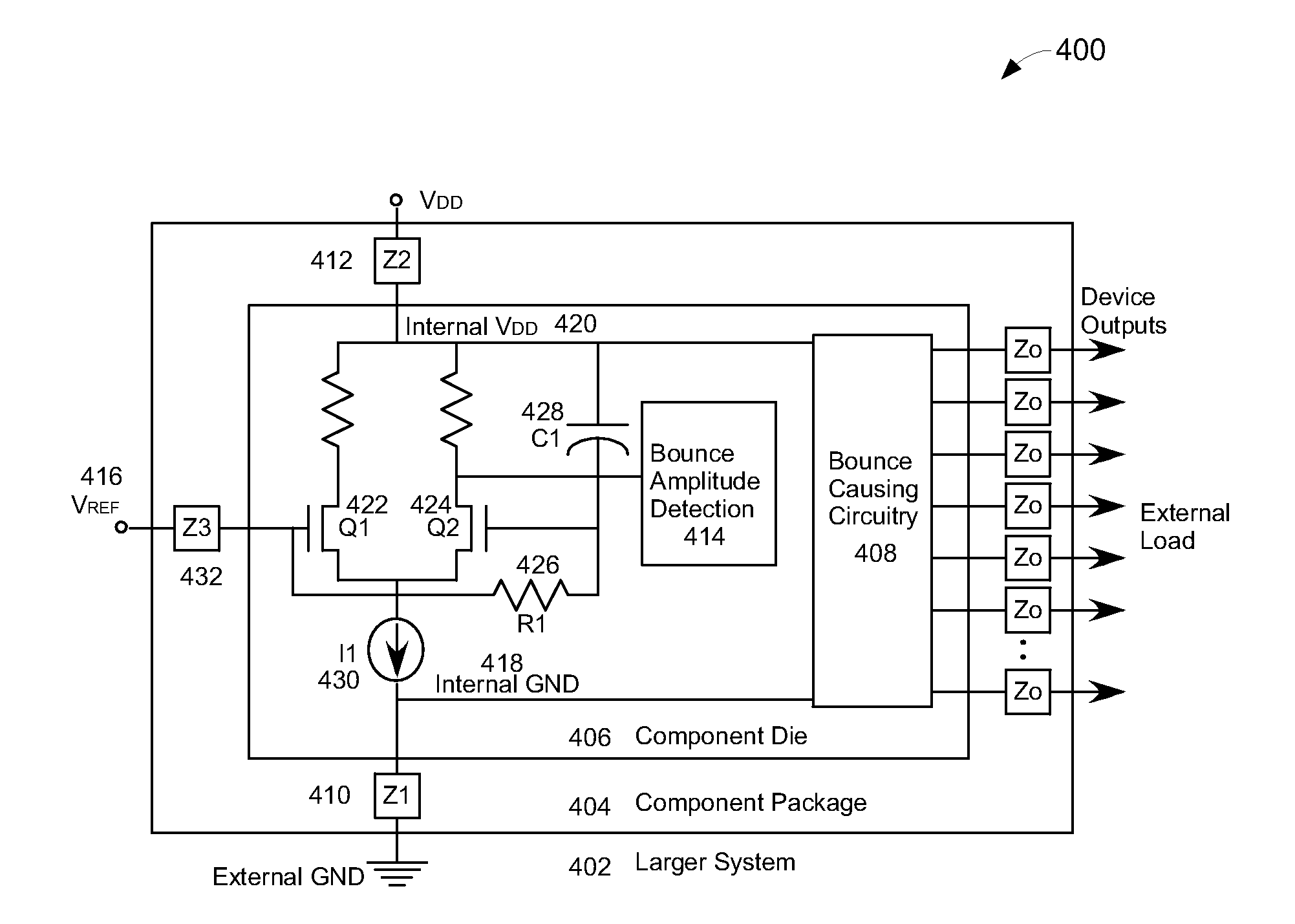

Method and apparatus for ground bounce and power supply bounce detection

A method and apparatus for ground bounce and power supply bounce detection in devices have been disclosed. In one case one input to a differential amplifier is coupled to a reference voltage and another input to the differential amplifier is coupled to a measurement point and the output of the differential amplifier is coupled through a diode to a sample and hold circuit which is coupled to an analog to digital converter.

Owner:INTEGRATED DEVICE TECH INC

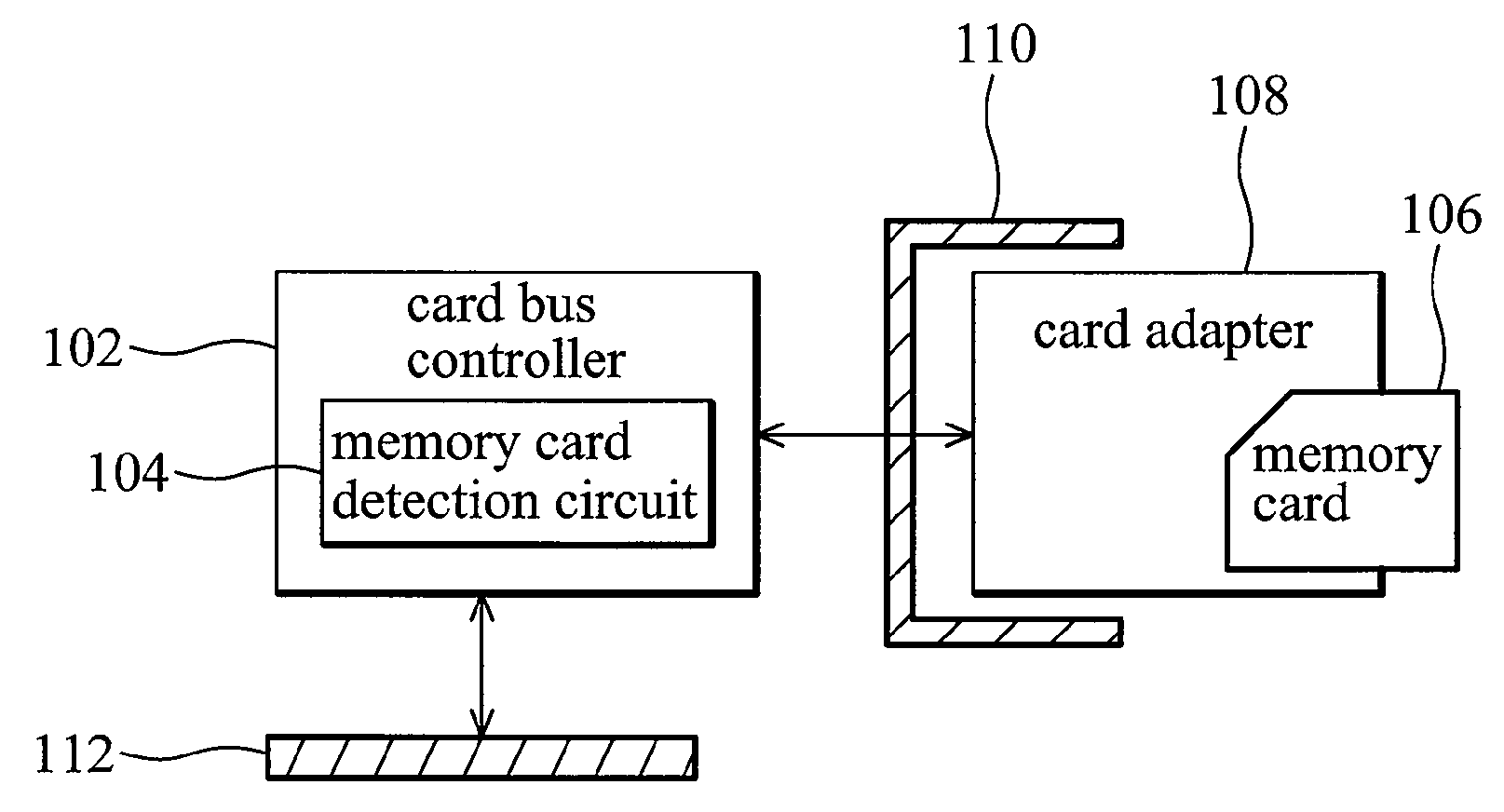

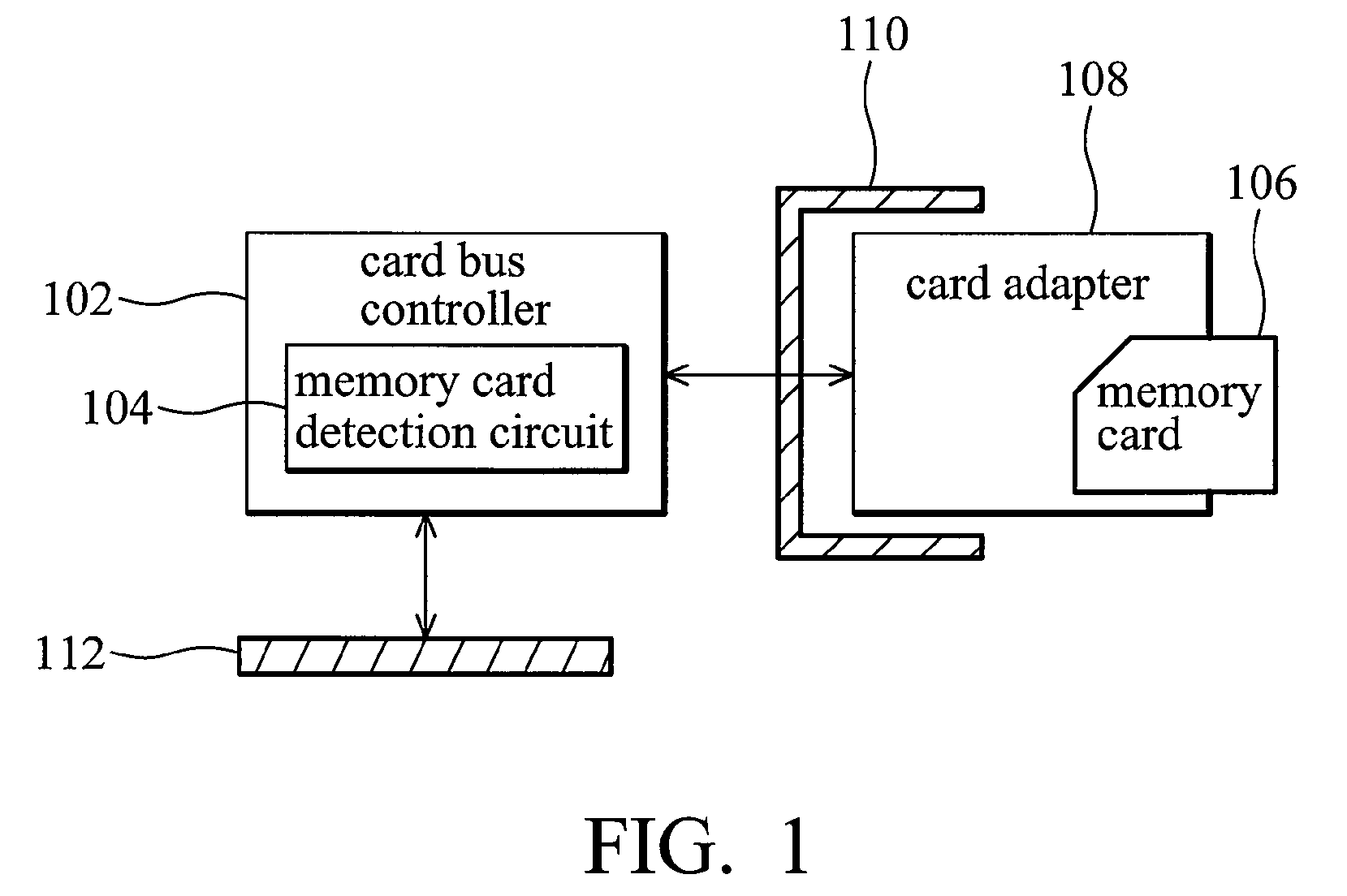

Memory card detection circuit and method thereof

ActiveUS20080016082A1Sensing record carriersSpecial data processing applicationsGround bounceMemory cards

The invention provides a memory card detection circuit of a computer. The memory card detection circuit comprises a plurality of query pins through which a memory card is coupled to the computer and a plurality of latch circuits respectively coupled to each of the query pins. The latch circuits generates query signals indicating whether ground bounce occurs in the voltage of the query pins due to a voltage difference between two ends of the query pins shortly after the memory card is coupled to the computer through the query pins. The query signals identify the type of the memory card without waiting until ground bounce is resolved.

Owner:VIA TECH INC

Power supply regulation using kelvin tap for voltage sense feedback from point within integrated circuit load

ActiveUS20070247127A1Dc-dc conversionElectric variable regulationVery large scale integrated circuitsPower conditioner

A remote sensing power supply regulator uses high impedance sensing inputs coupled internally to at least one circuit element within an integrated circuit, so as to regulate the voltages produced by the power supply to a level that maintains nominal voltage levels at the internal circuit element within the very large scale integrated circuit. The sense point can be chosen to serve one or a group of on-board load elements that are operationally sensitive to voltage droop and / or ground bounce.

Owner:AVAGO TECH INT SALES PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com