Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

99 results about "Power integrity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Power integrity or PI is an analysis to check whether the desired voltage and current are met from source to destination. Today, power integrity plays a major role in the success and failure of new electronic products. There are several coupled aspects of PI: on the chip, in the chip package, on the circuit board, and in the system. Four main issues must be resolved to ensure power integrity at the printed circuit board level...

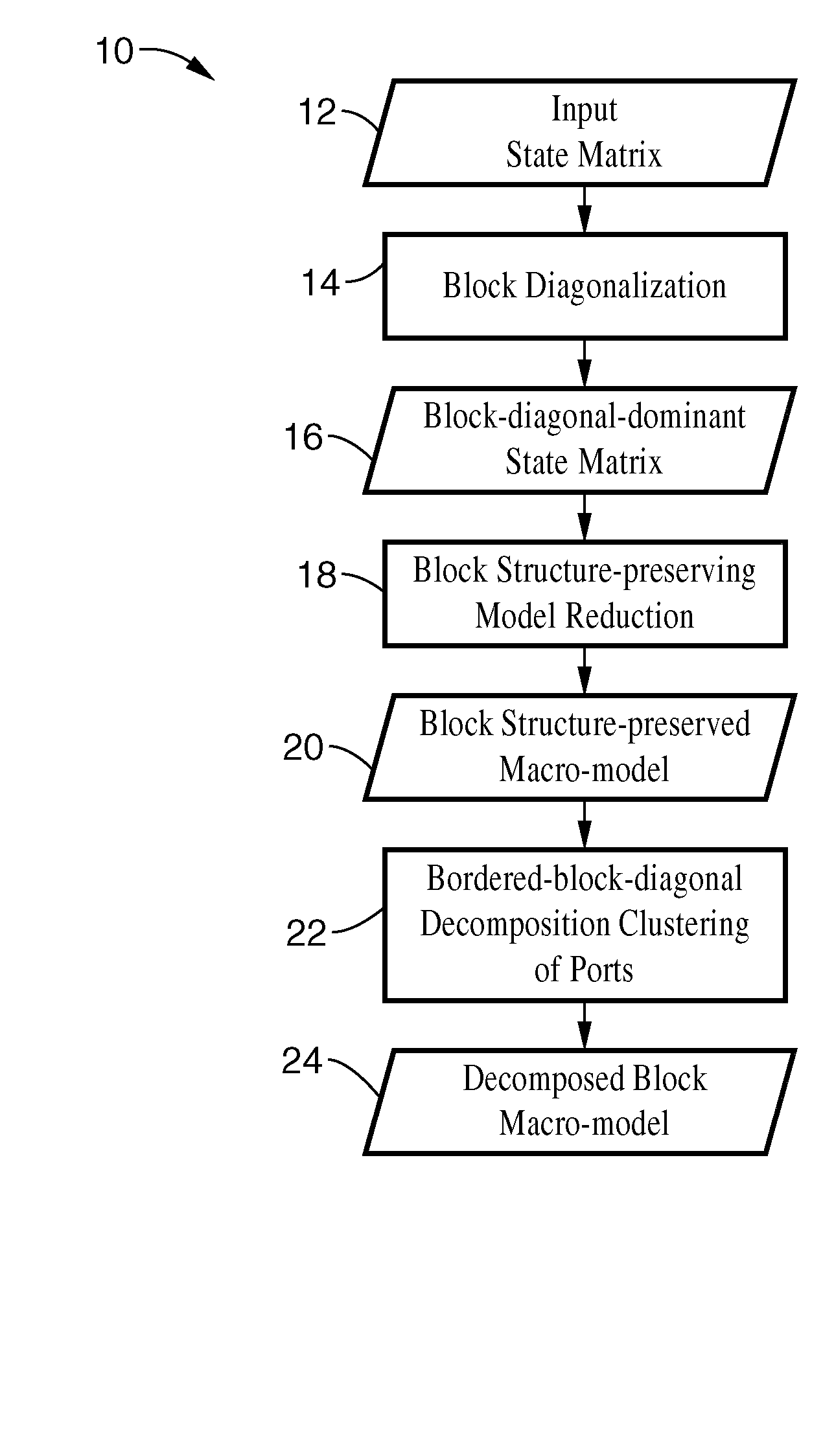

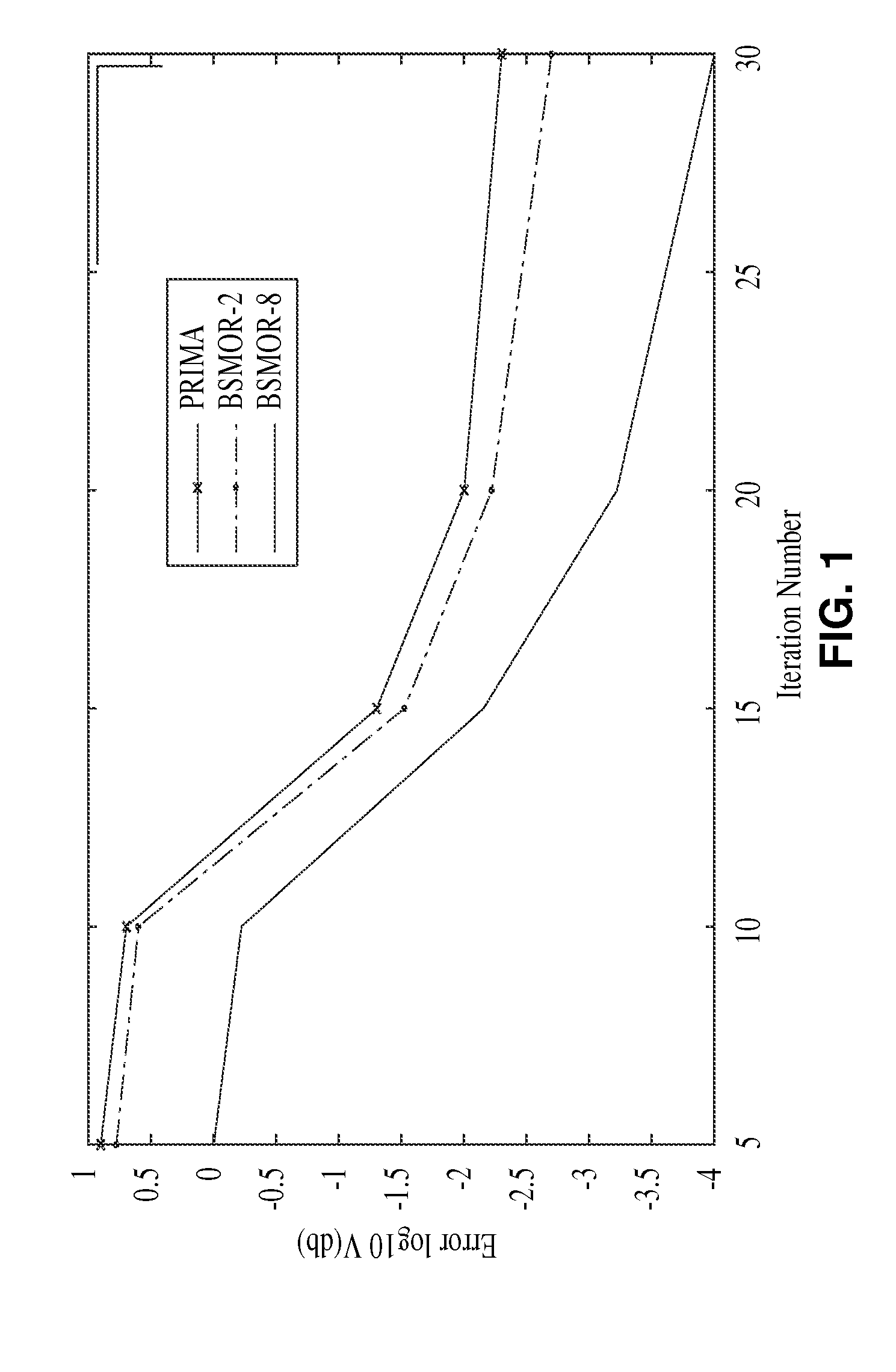

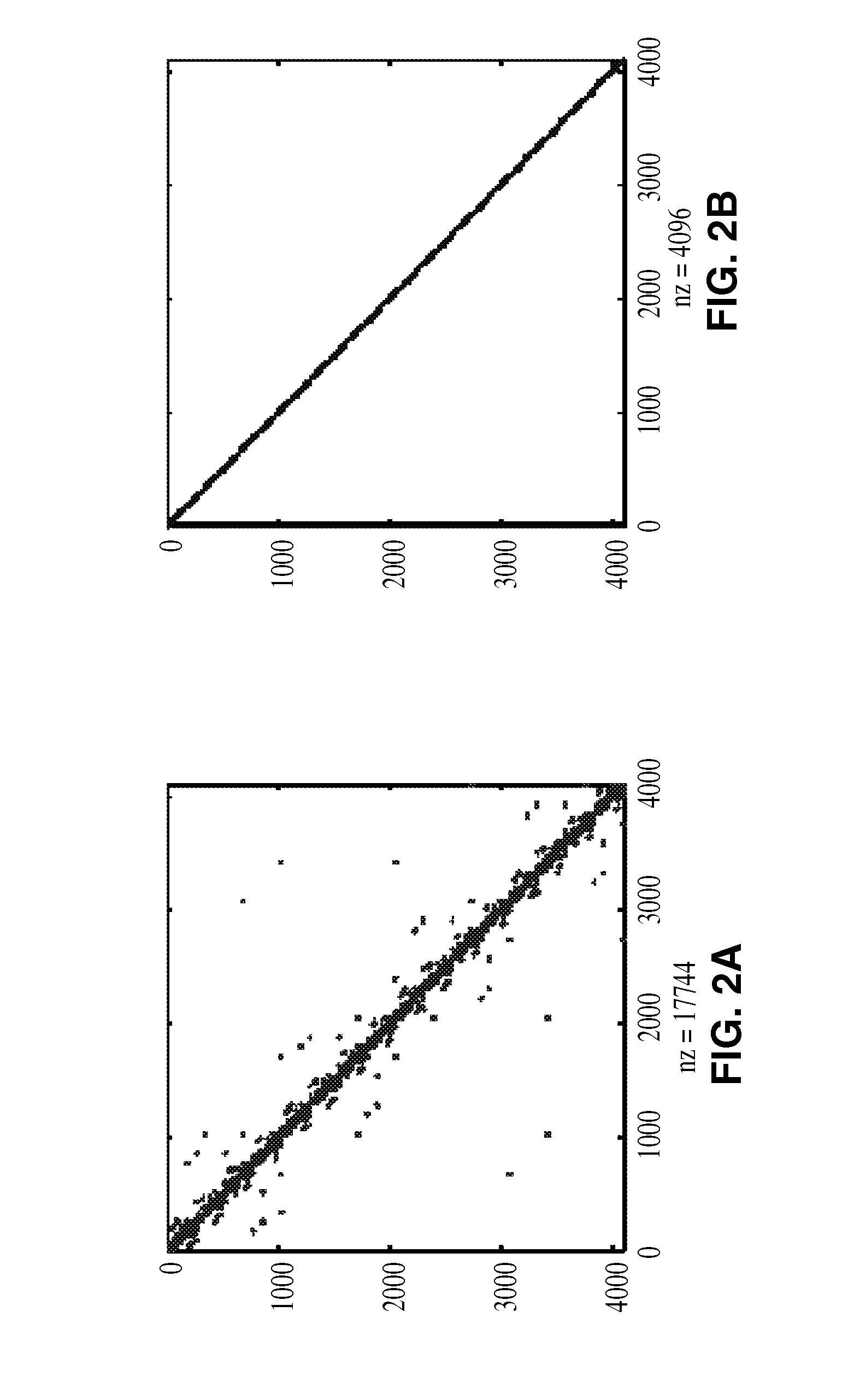

Structured and parameterized model order reduction

InactiveUS20080072182A1Reduce redundancyNon-uniformity is constantDetecting faulty computer hardwareComputation using non-denominational number representationStructured modelOrder reduction

Model-order reduction techniques are described for RLC circuits modeling the VLSI layouts. A structured model order reduction is developed to preserve the block-level sparsity, hierarchy and latency. In addition, a structured and parameterized model order reduction is developed to generate macromodels for design optimizations of VLSI layouts. The applications are thermal via allocation under the dynamic thermal integrity and via stapling to simultaneously optimize thermal and power integrity.

Owner:RGT UNIV OF CALIFORNIA

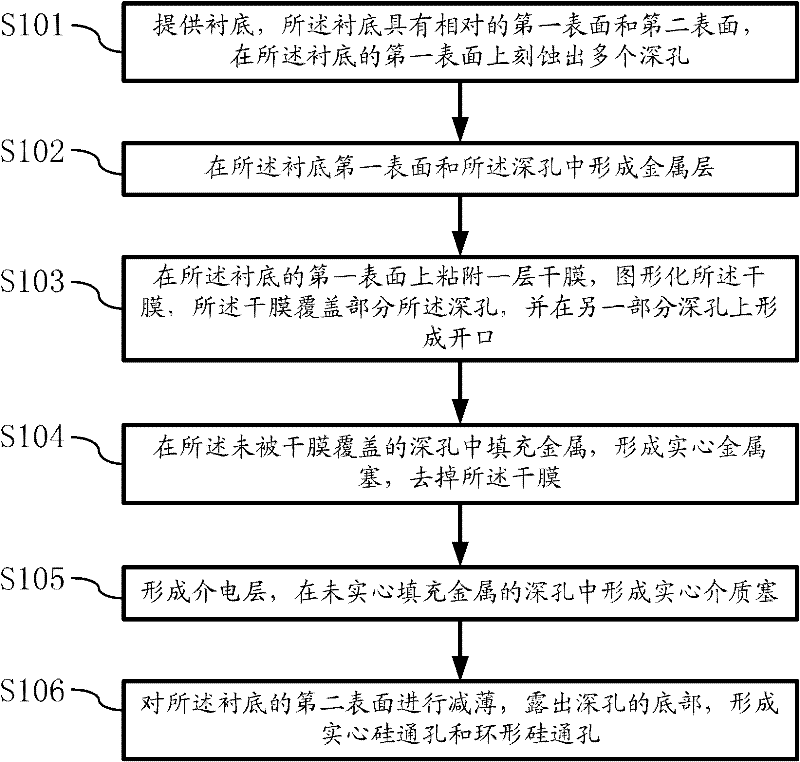

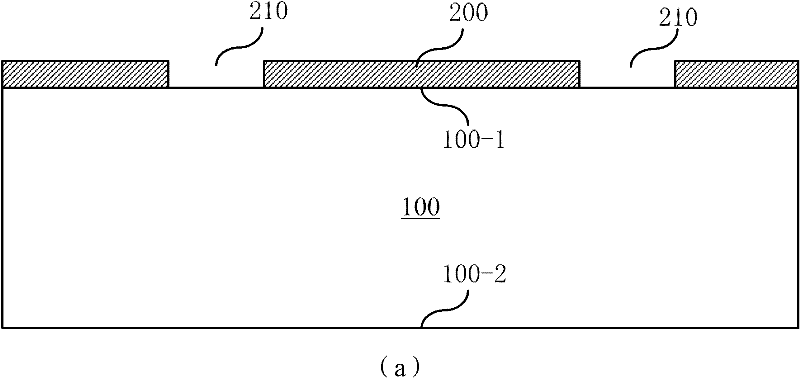

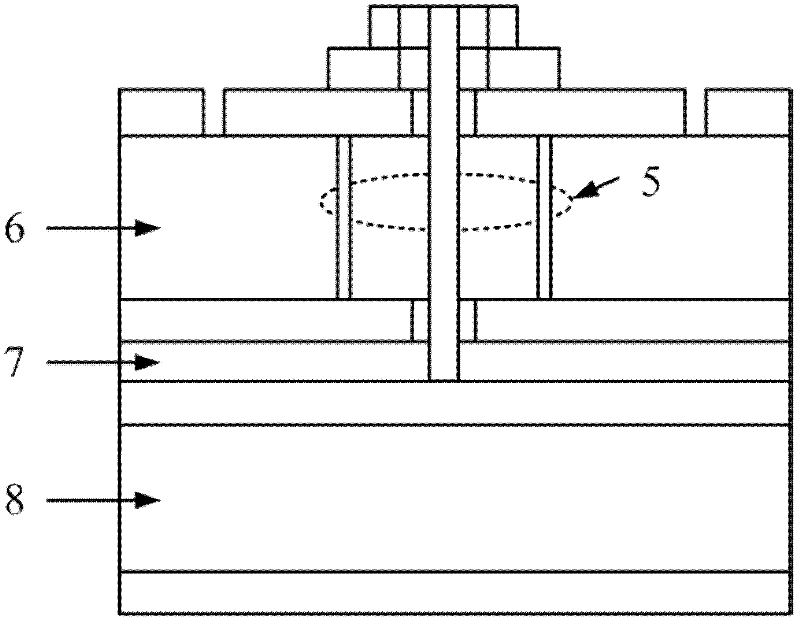

Semiconductor structure with through holes and manufacturing method thereof

InactiveCN102214624AImprove integrityIncrease stressSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor structure

The invention discloses a semiconductor structure with through holes and a manufacturing method thereof. The semiconductor structure comprises a substrate, a plurality of annular through holes and a plurality of solid through holes; the annular through holes and the solid through holes are embedded in the substrate; the solid through holes are through holes filled by metal; and the annular through holes are through holes filled by solid dielectric plugs and metal rings surrounding the solid dielectric plugs. The manufacturing method comprises the steps of: (1) etching a plurality of deep holes on a first surface of the substrate; (2) forming a metal layer; (3) attaching a dry film on the first surface of the substrate and patterning the dry film such that the dry film generates openings on one part of deep holes; (4) filling metal in the deep holes with the openings on the dry film, and removing the dry film; (5) filling dielectric in the remaining deep holes to form the solid dielectric plugs; and (6) thinning a second surface of the substrate. The solid through holes of the semiconductor structure disclosed by the invention can be used for the heat radiation of laminated chips to improve the completeness of a power supply; and the annular through holes can be used for solving the problems, such as stress, warping deformation and the like of the through hole structures.

Owner:PEKING UNIV

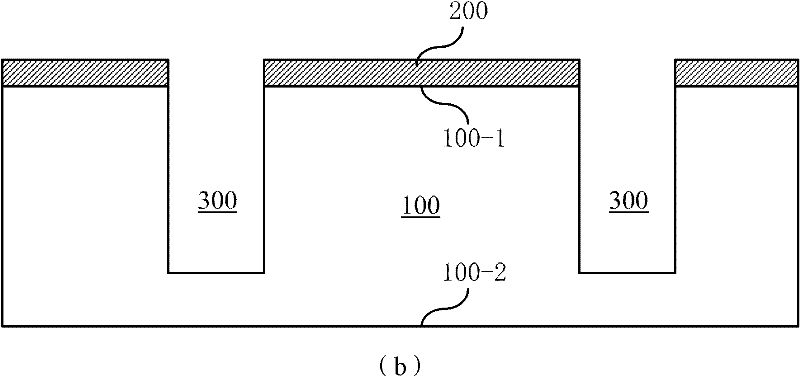

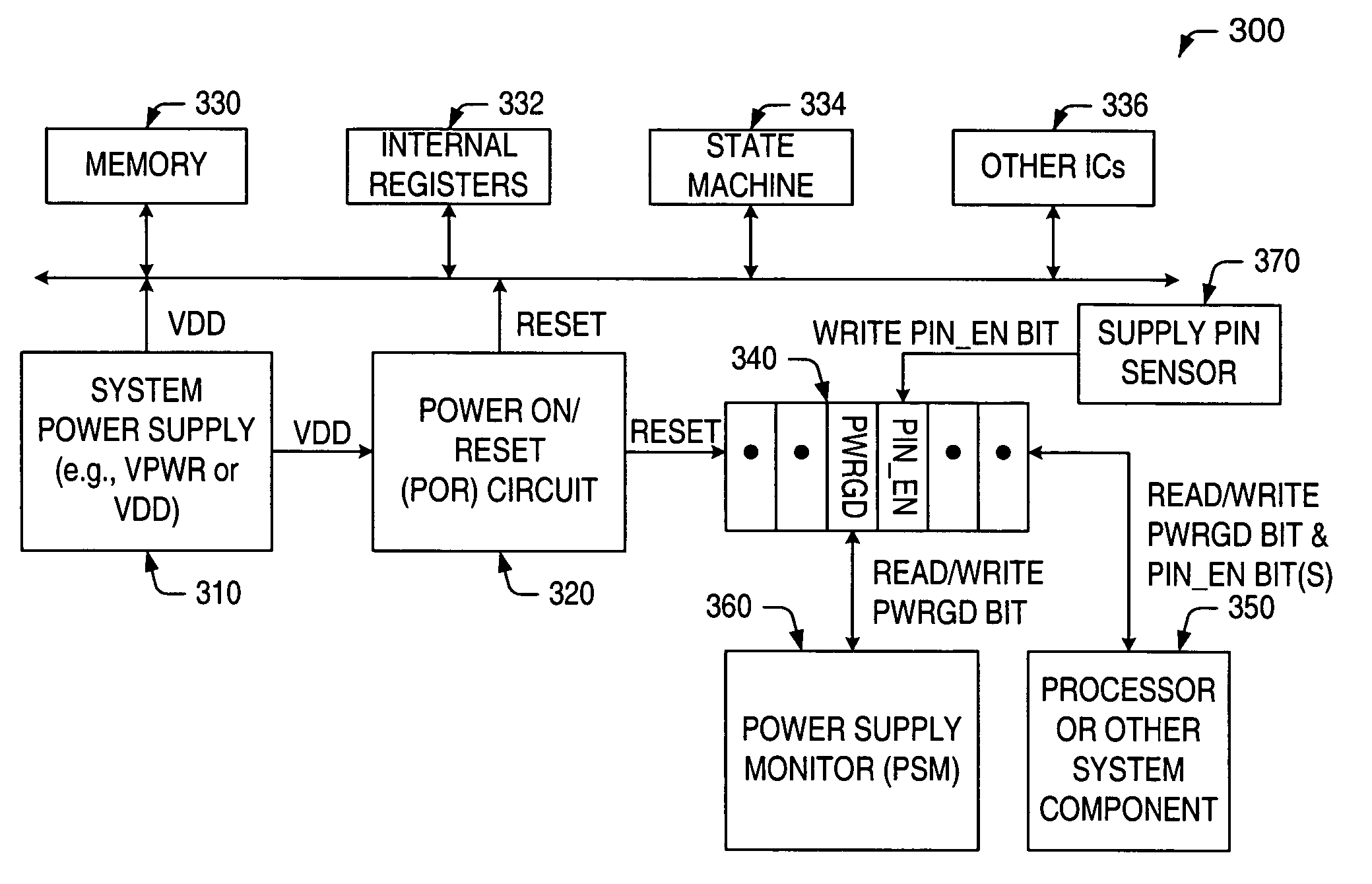

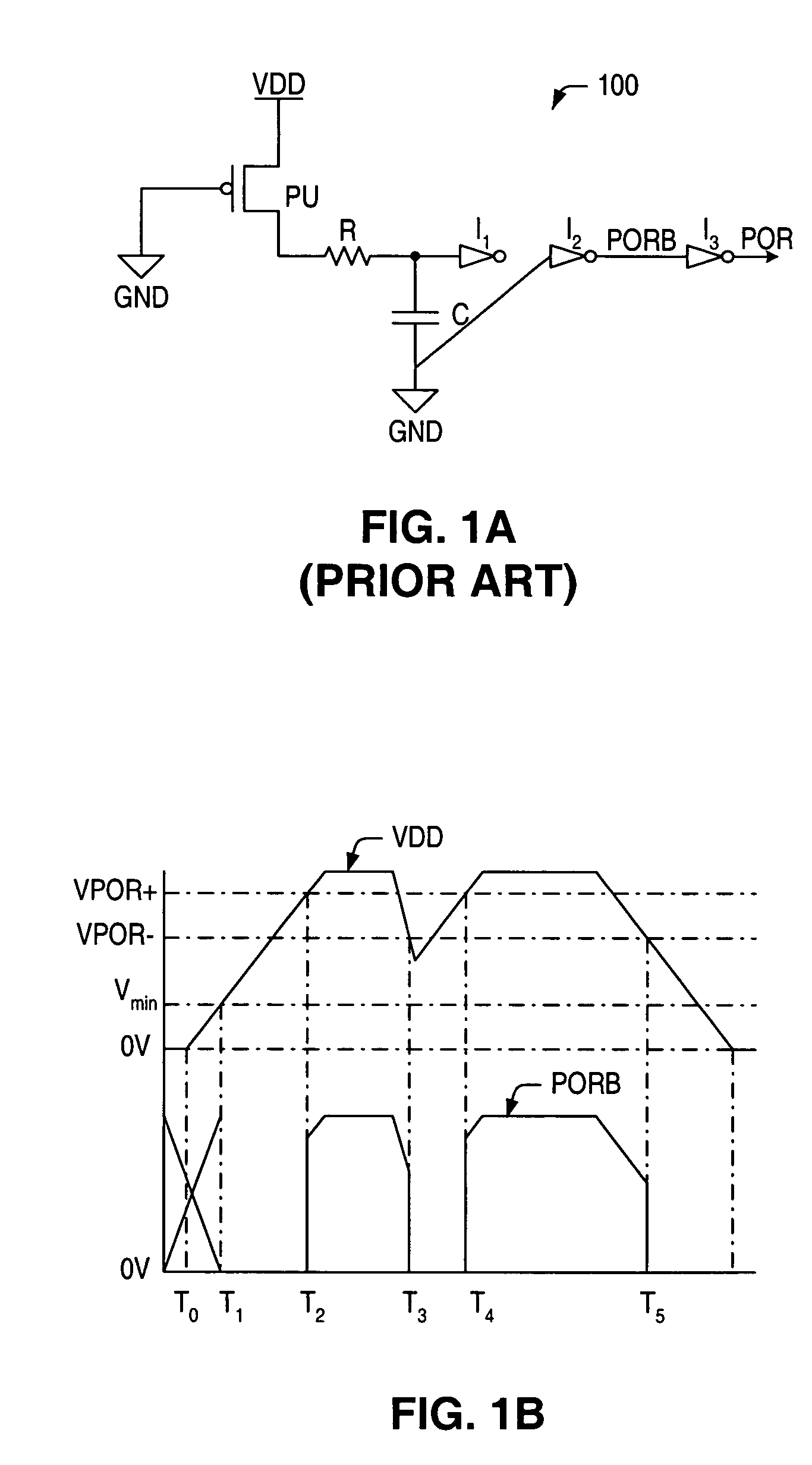

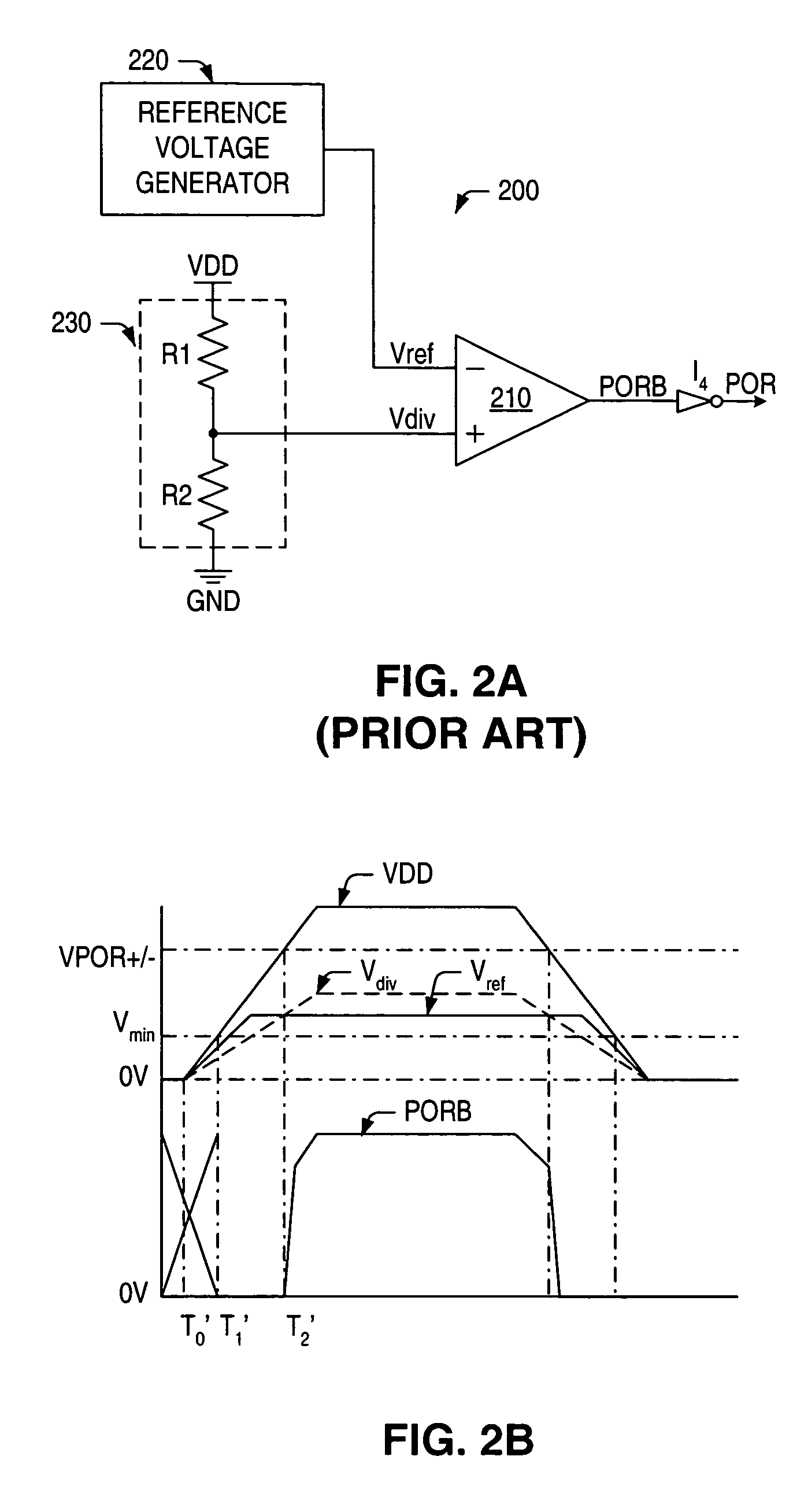

Circuit and method for monitoring the integrity of a power supply

ActiveUS20060284655A1Pulse automatic controlCurrent/voltage measurementElectricityElectrical connection

Circuits and methods are provided herein for monitoring the integrity of a power supply, the circuits and methods providing additional resources / information for diagnosing a cause behind a reset signal, and in some cases, a reason behind a power failure. A first method described herein provides exemplary steps for monitoring a level of a power supply voltage supplied to one or more system components. A second method describes exemplary steps for monitoring an electrical connection between the power supply (or ground supply) and one or more supply pins. Each of the methods involves monitoring a state of one or more bits stored, e.g., within a status register. The methods may be used separately, or in conjunction with one another, for detecting the occurrence of a power abnormality.

Owner:CYPRESS SEMICON CORP

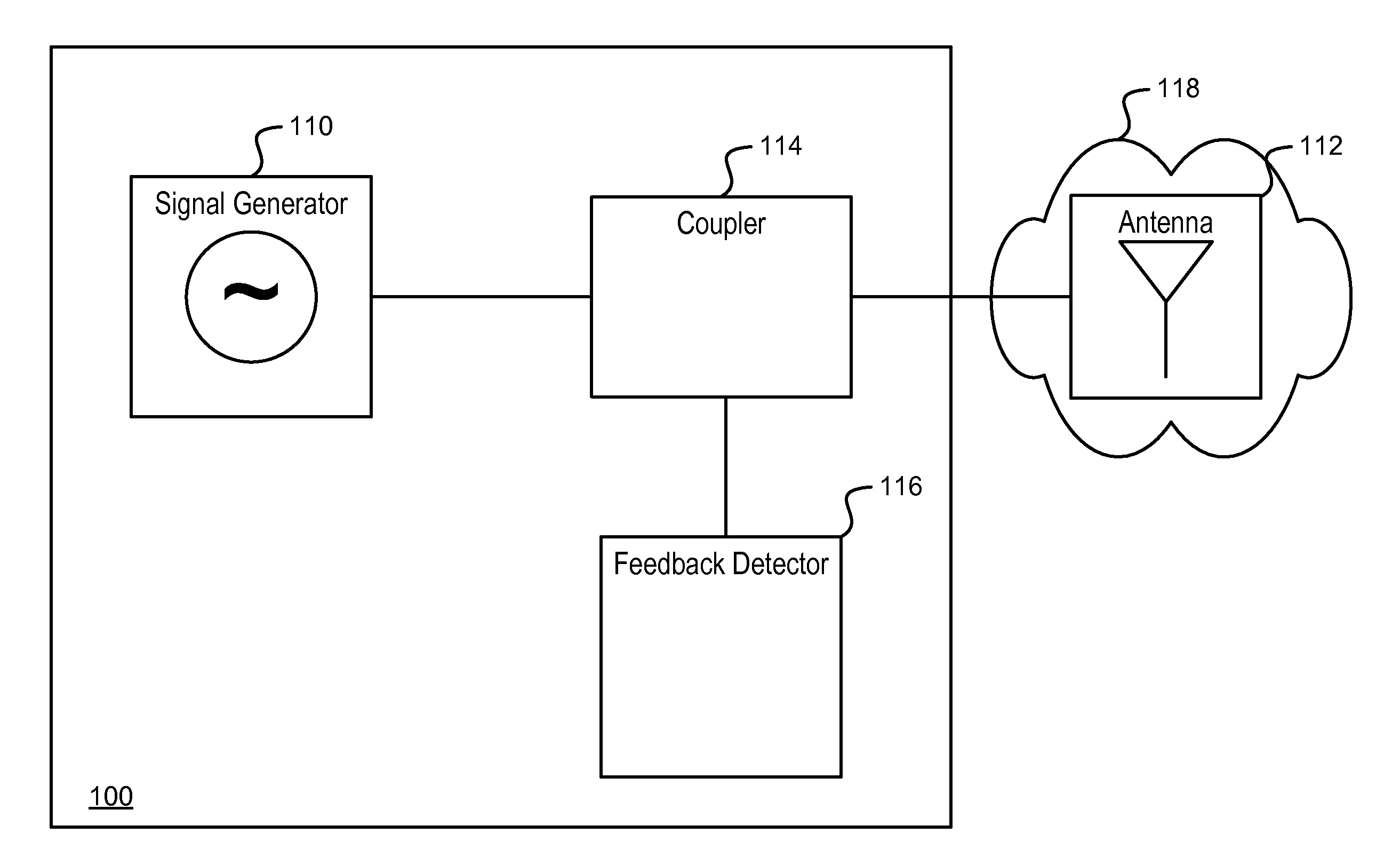

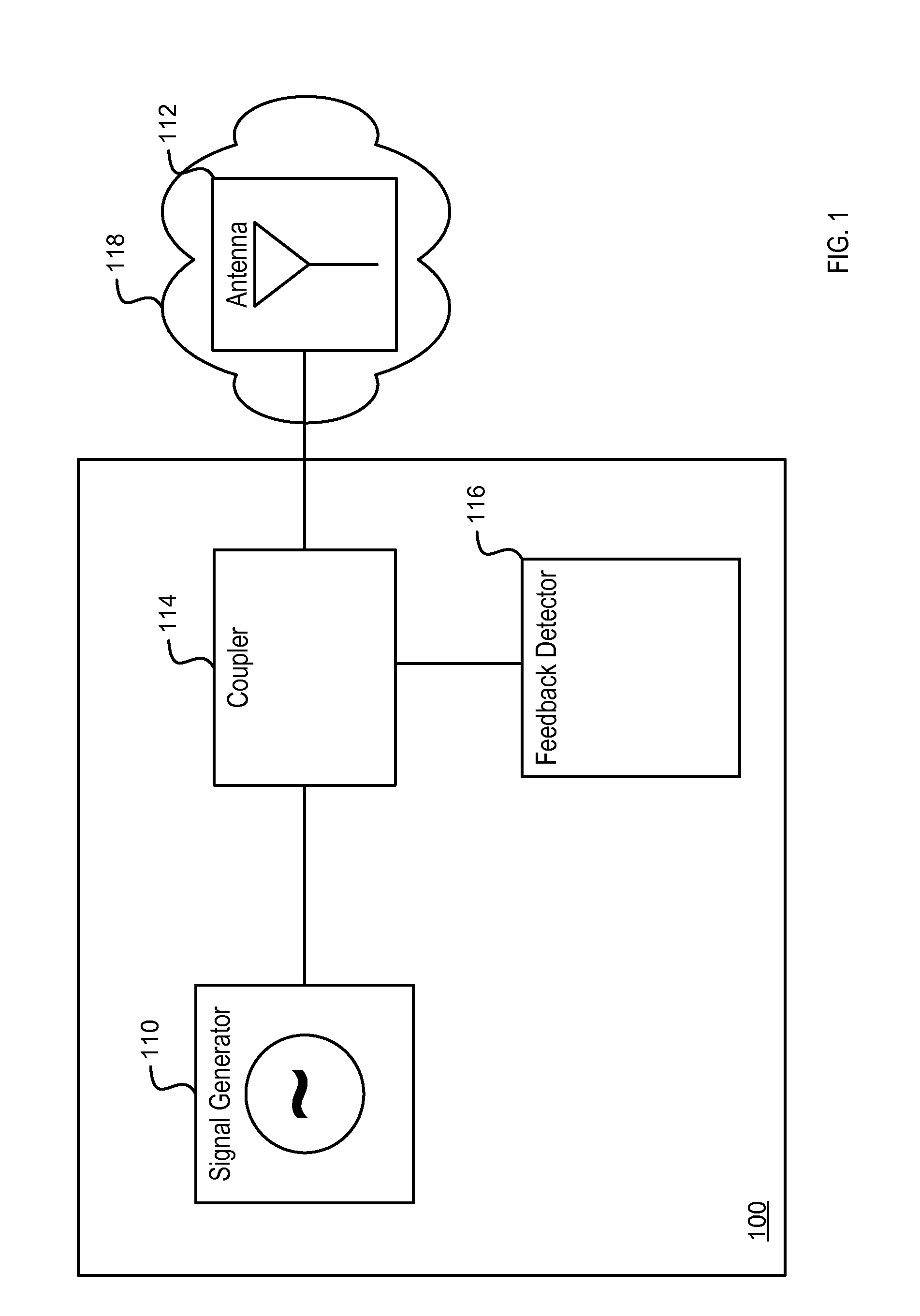

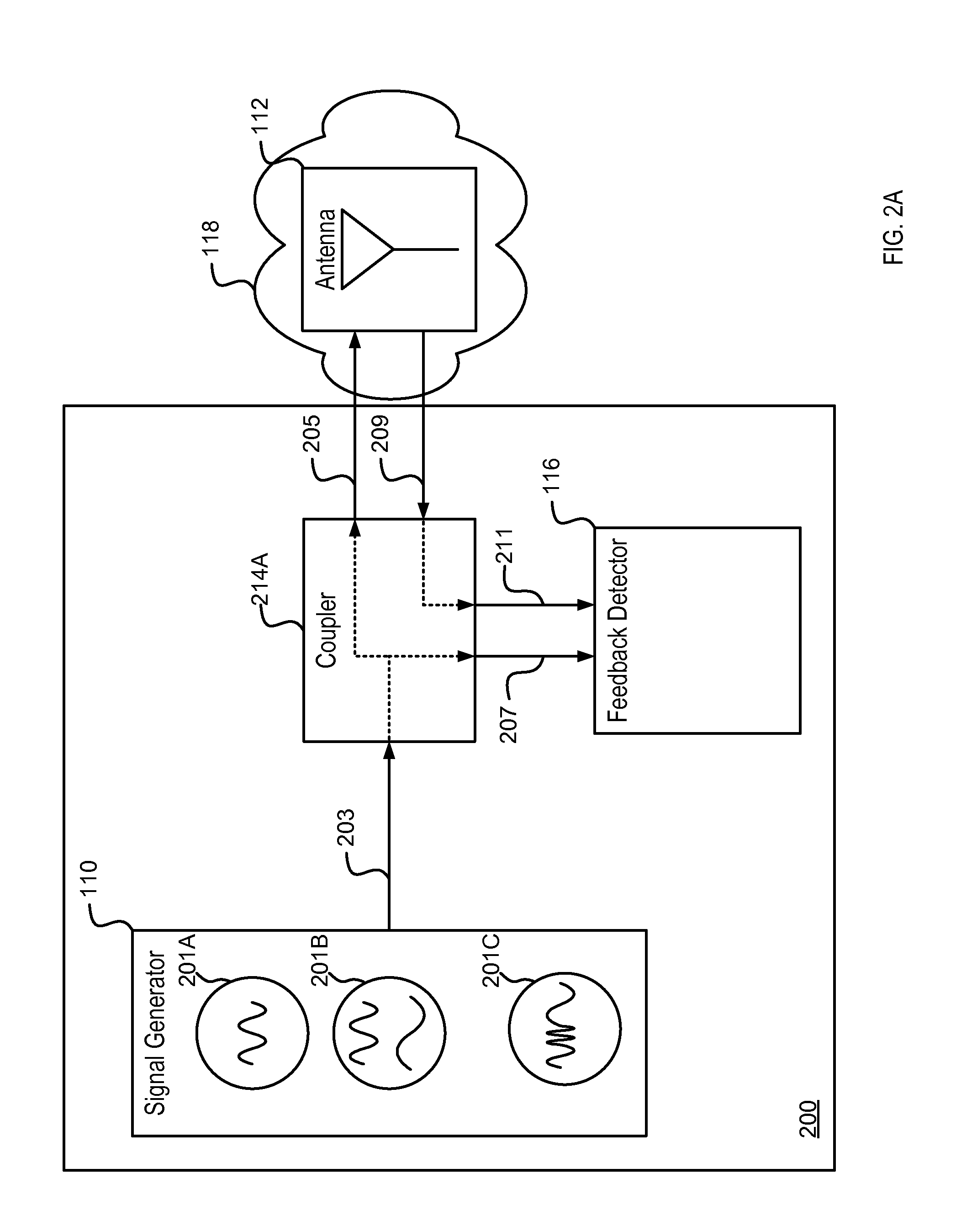

Antenna Environment Sensing Device

Embodiments relate to a sensing device configured to sense the environment of an antenna in a wireless communications or wireless power transfer device without impacting data signal or transferred power integrity. By incorporating a sensing device in the wireless device that operates outside the data signal operating and operational power transfer frequency(s) of the antenna, send / receive data signal integrity may be retained while sensing the environment of the antenna. The sensing device may further use properties of the sensed environment to adjust the configuration of a tunable antenna to decrease signal degradation due to the environment and increase battery life or power transfer efficiency of the wireless device.

Owner:COMMSENSE

System and method for adapting electrical integrity analysis to parametrically integrated environment

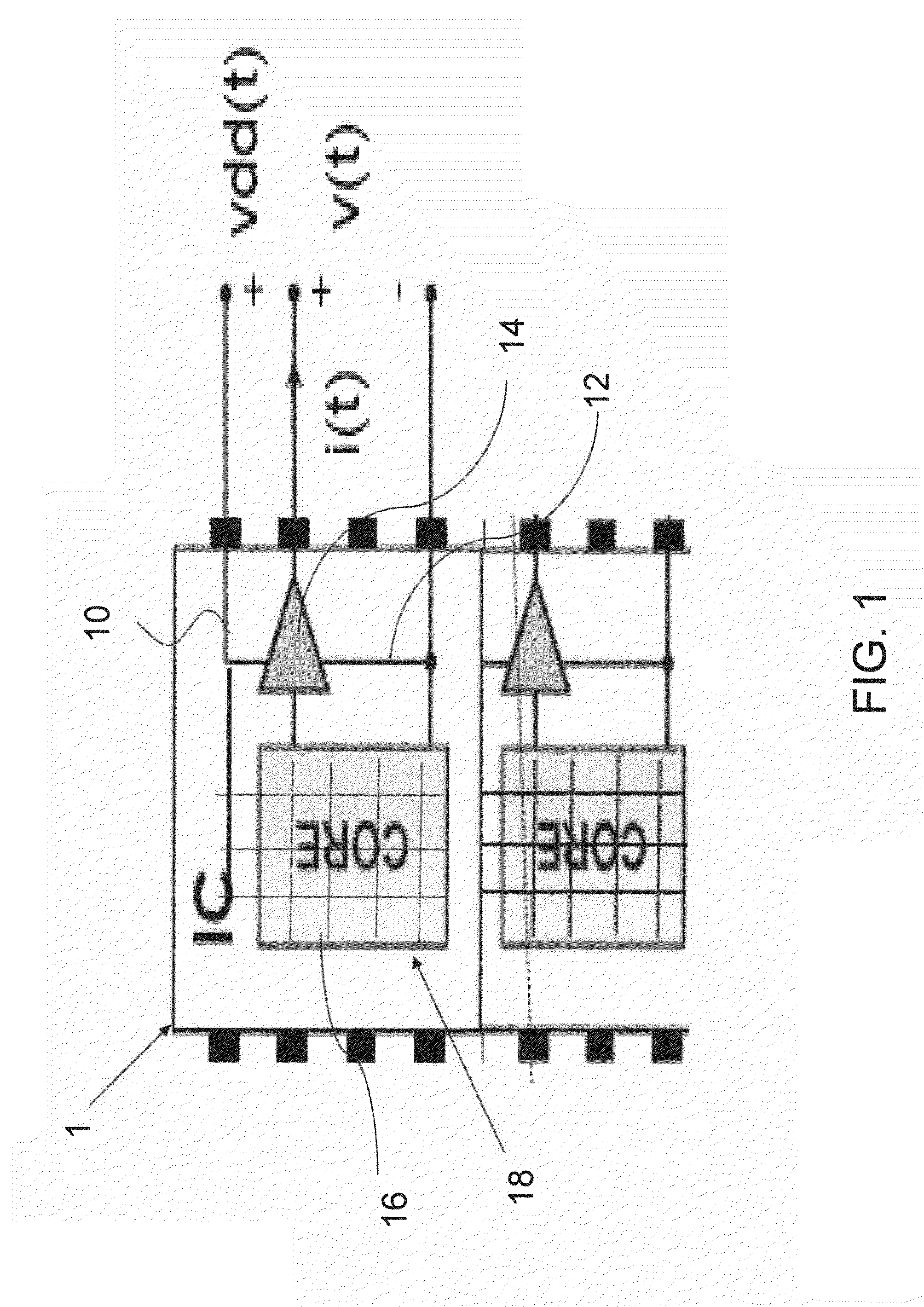

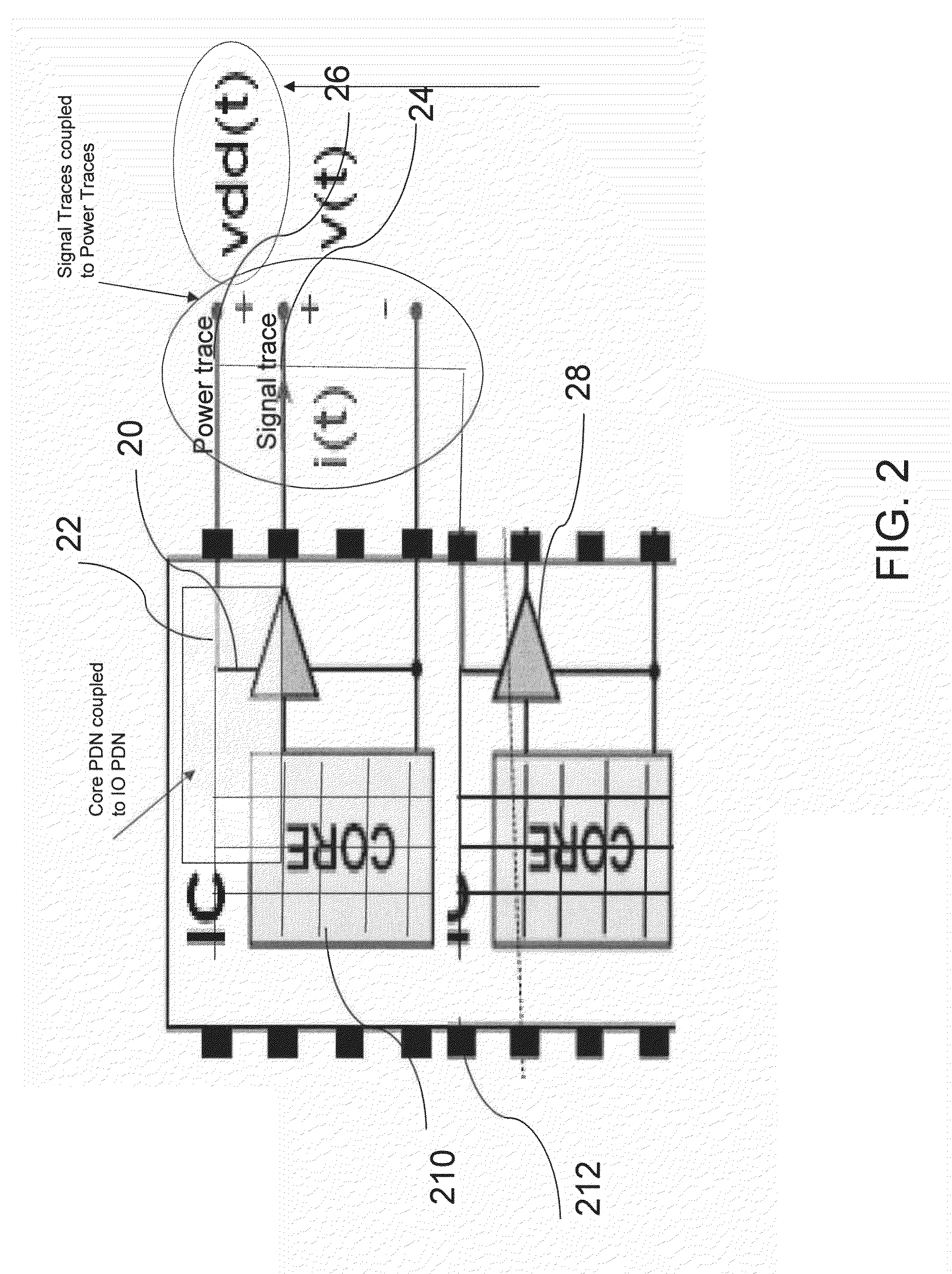

ActiveUS8286110B1Detecting faulty computer hardwareComputer aided designVoltage regulator moduleElectronic systems

A system and method is provided for generating a programmably implemented model which emulates a power delivery network serving an integrated circuit (IC) core in an electronic system. The system and method generally comprise measures for establishing a power integrity (PI) topology including models for a voltage regulator module that generates at least one predetermined supply voltage level, and for a conductive power rail portion of the power delivery network (PDN). The system and method further comprise measures for interconnecting to the conductive power rail portion model a first behavioral model indicative of the current consumption characteristics of the IC core, and a second behavioral model indicative of the current consumption of an IO interface buffer driving an output signal of the electronic system.

Owner:CADENCE DESIGN SYST INC

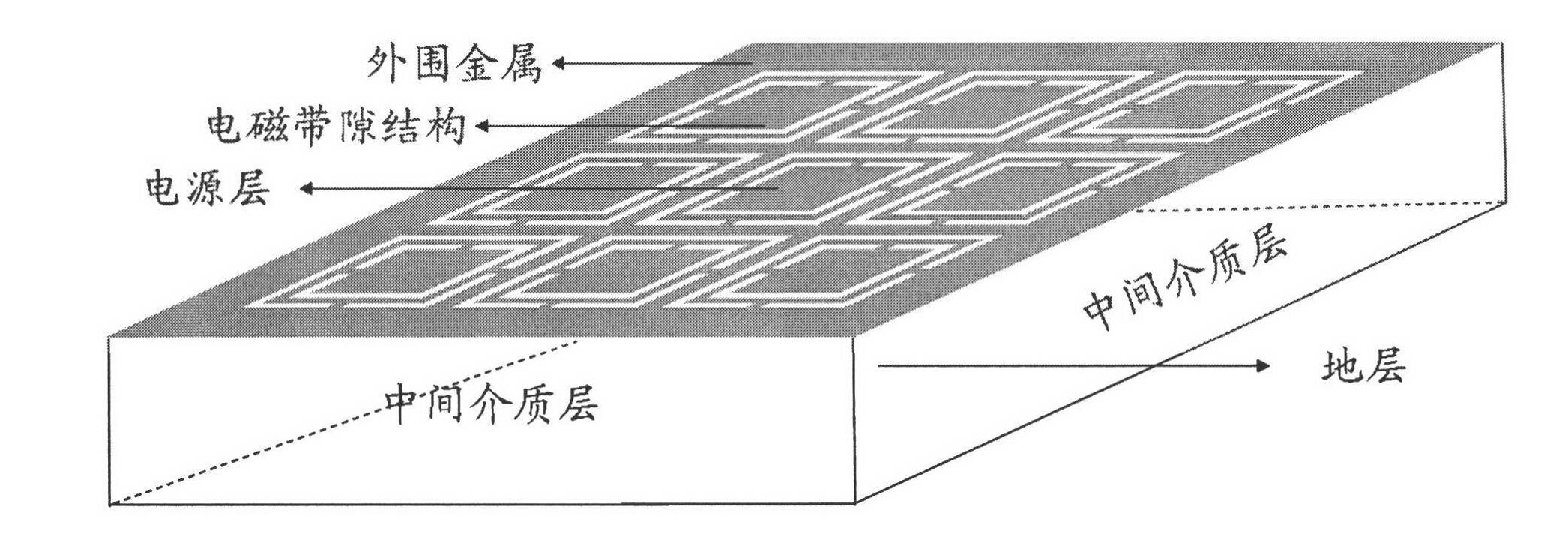

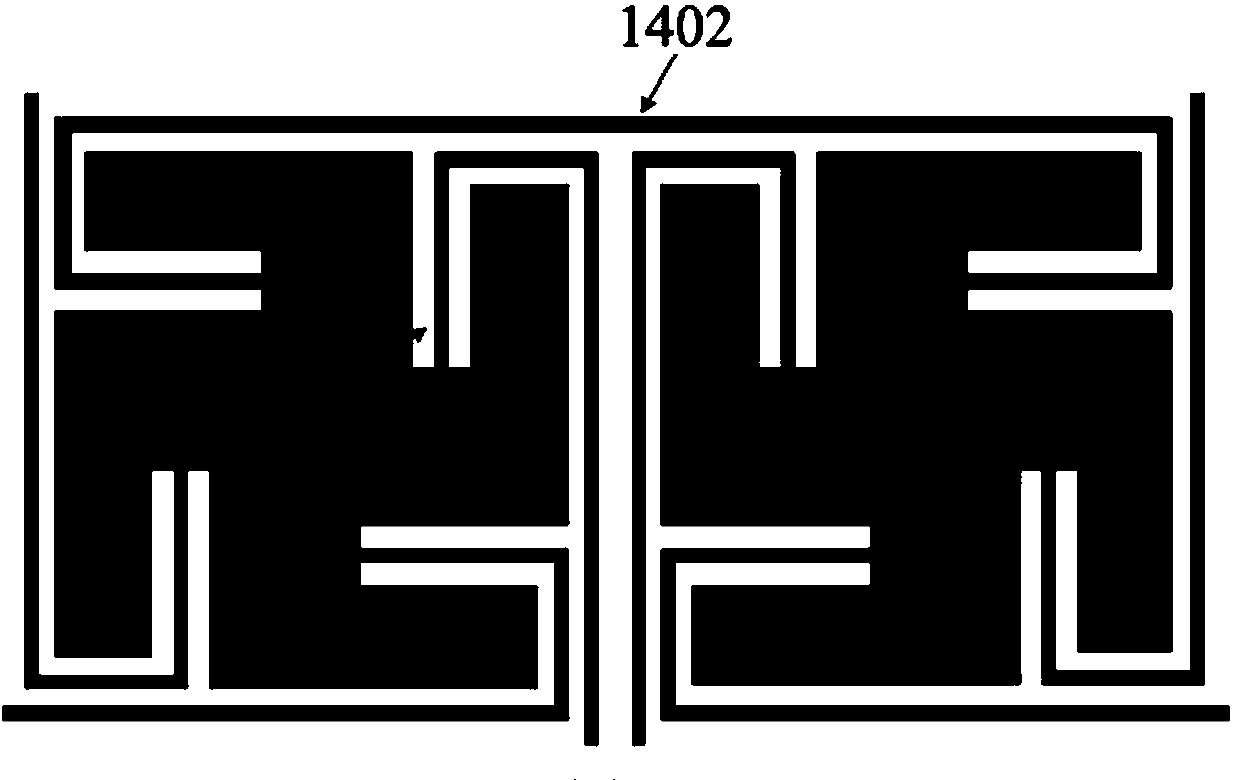

Power supply distribution network based on local electromagnetic band gap structure

InactiveCN102957310AImprove signal integrityReduce distractionsPower conversion systemsElectromagnetic interferenceEngineering

The invention discloses a power supply distribution network based on a local electromagnetic band gap structure. The electromagnetic band gap structure is locally etched on a power supply plane, and a ground plane is kept intact. Basic units of the electromagnetic band gap structure are formed by complementary split ring resonators, and the adjacent basic units of the electromagnetic band gap structure are connected by a Z-shaped bridge. The problems that the inhibiting degree of synchronous switching on and off noise in a hybrid circuit system is not high enough and the inhibiting frequency band is not wide enough are effectively solved, and the problem that the destructiveness of the traditional global electromagnetic band gap structure to the power supply plane is large can be solved. The power supply distribution network disclosed by the invention has excellent power supply integrity, and the influence of electromagnetic interference can be lowered.

Owner:SHANGHAI JIAO TONG UNIV

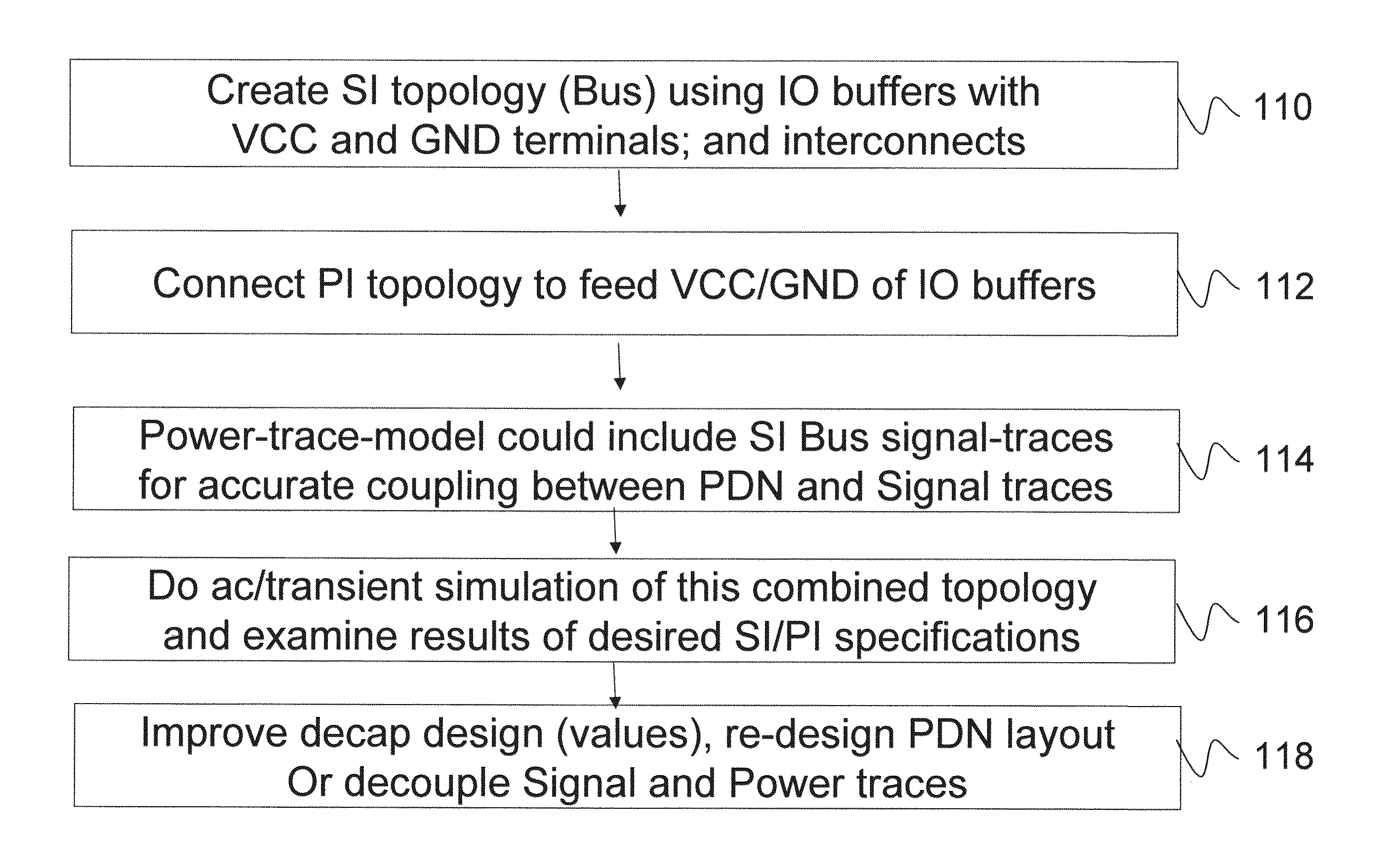

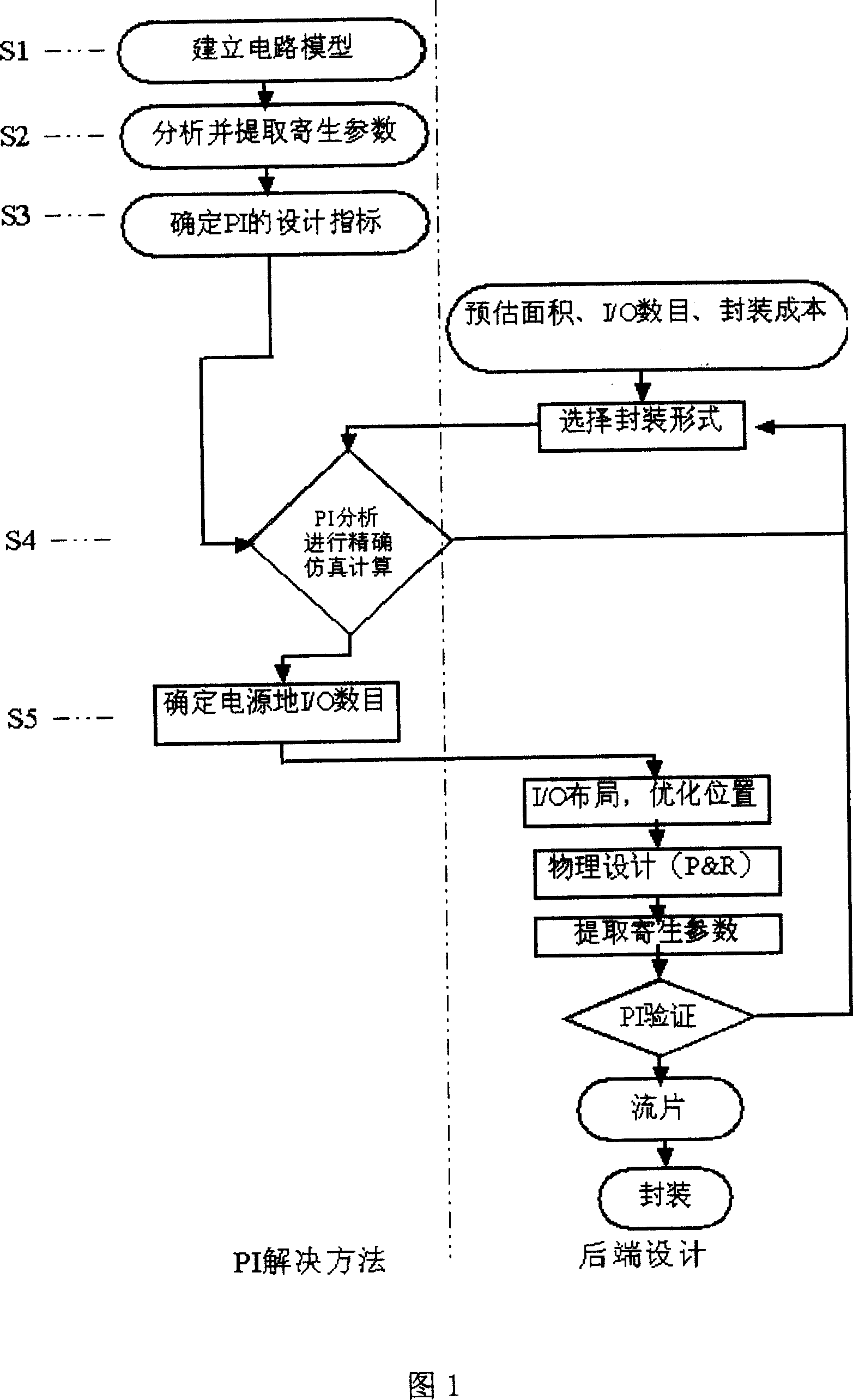

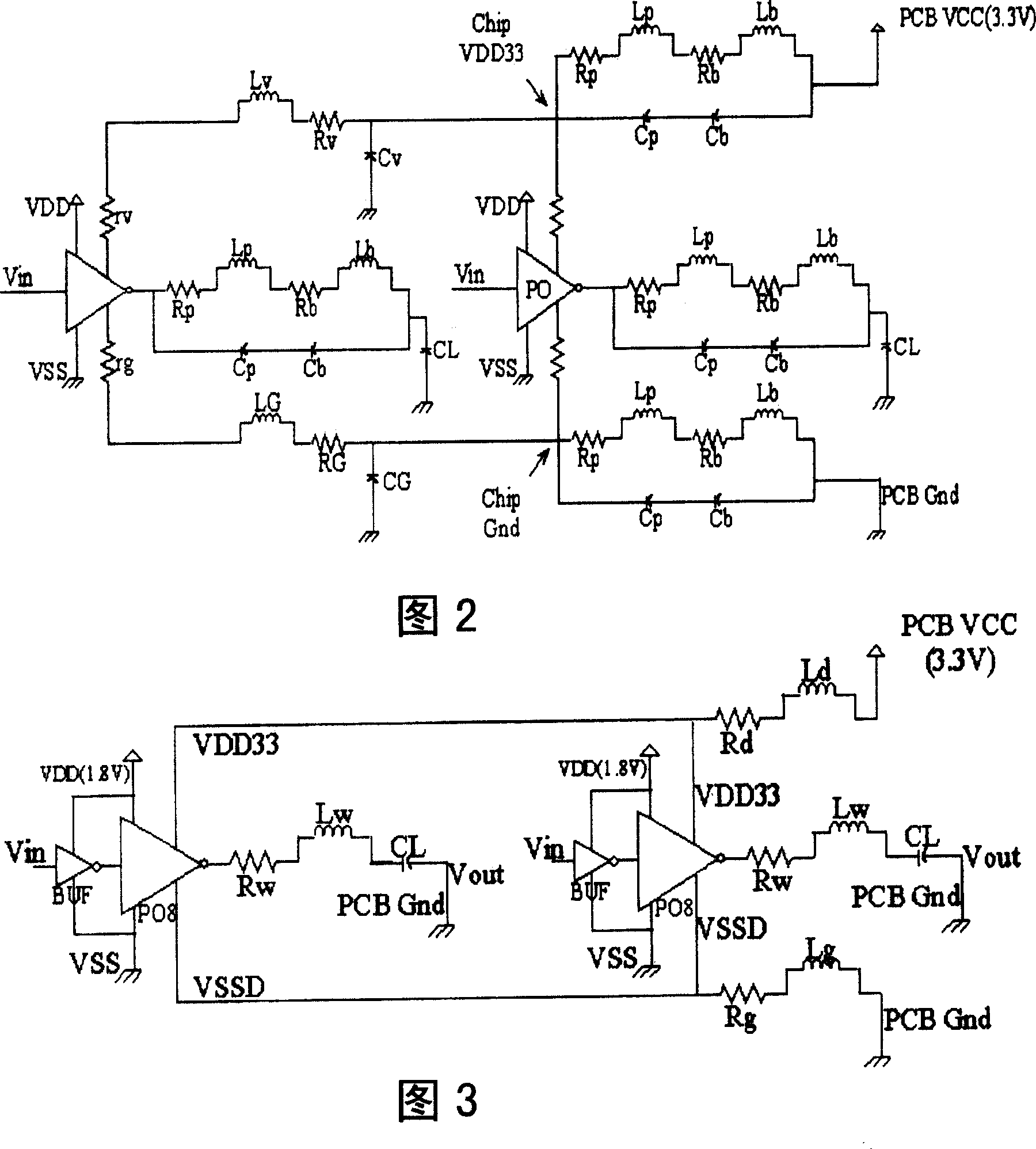

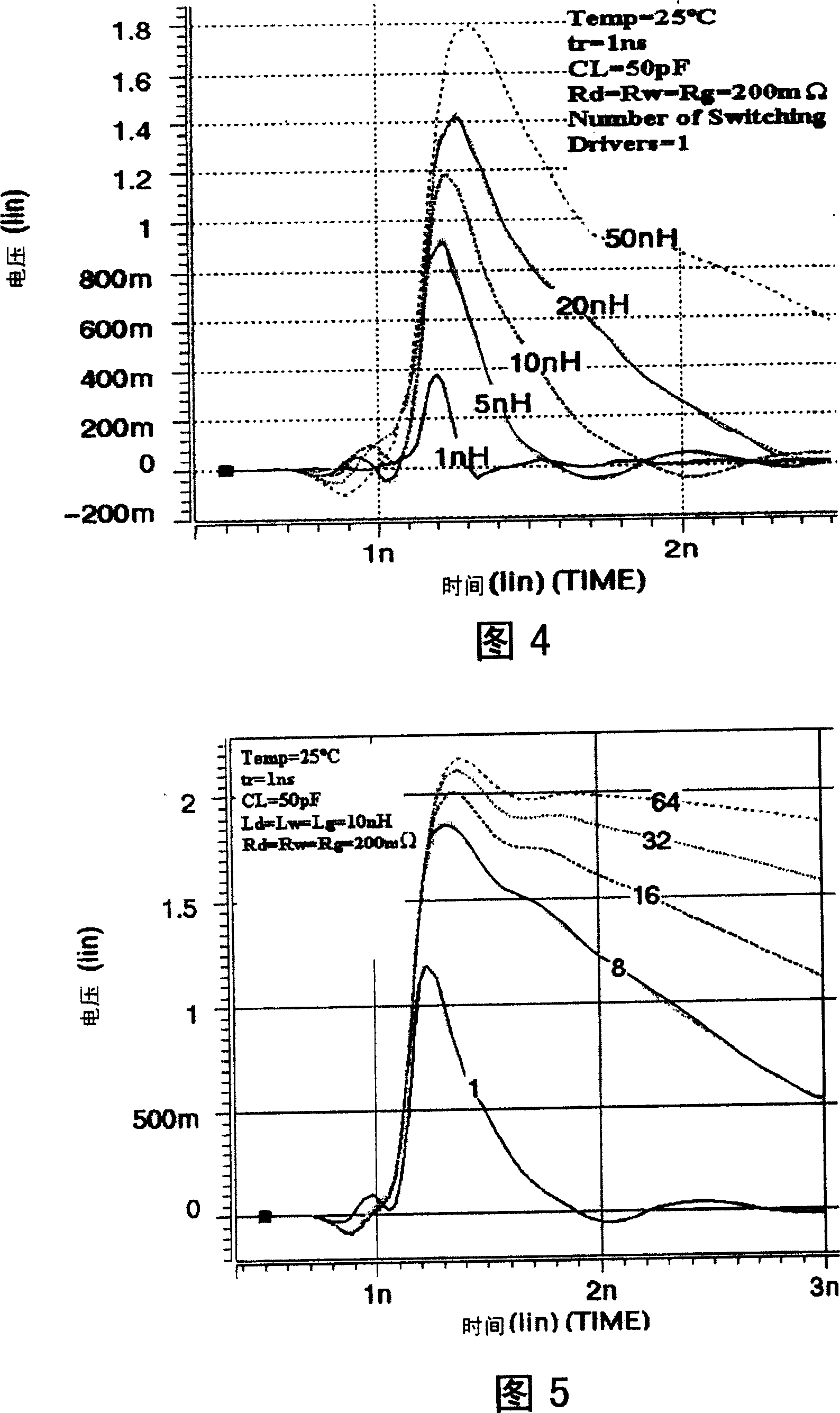

PI solution method based on IC package PCB co-design

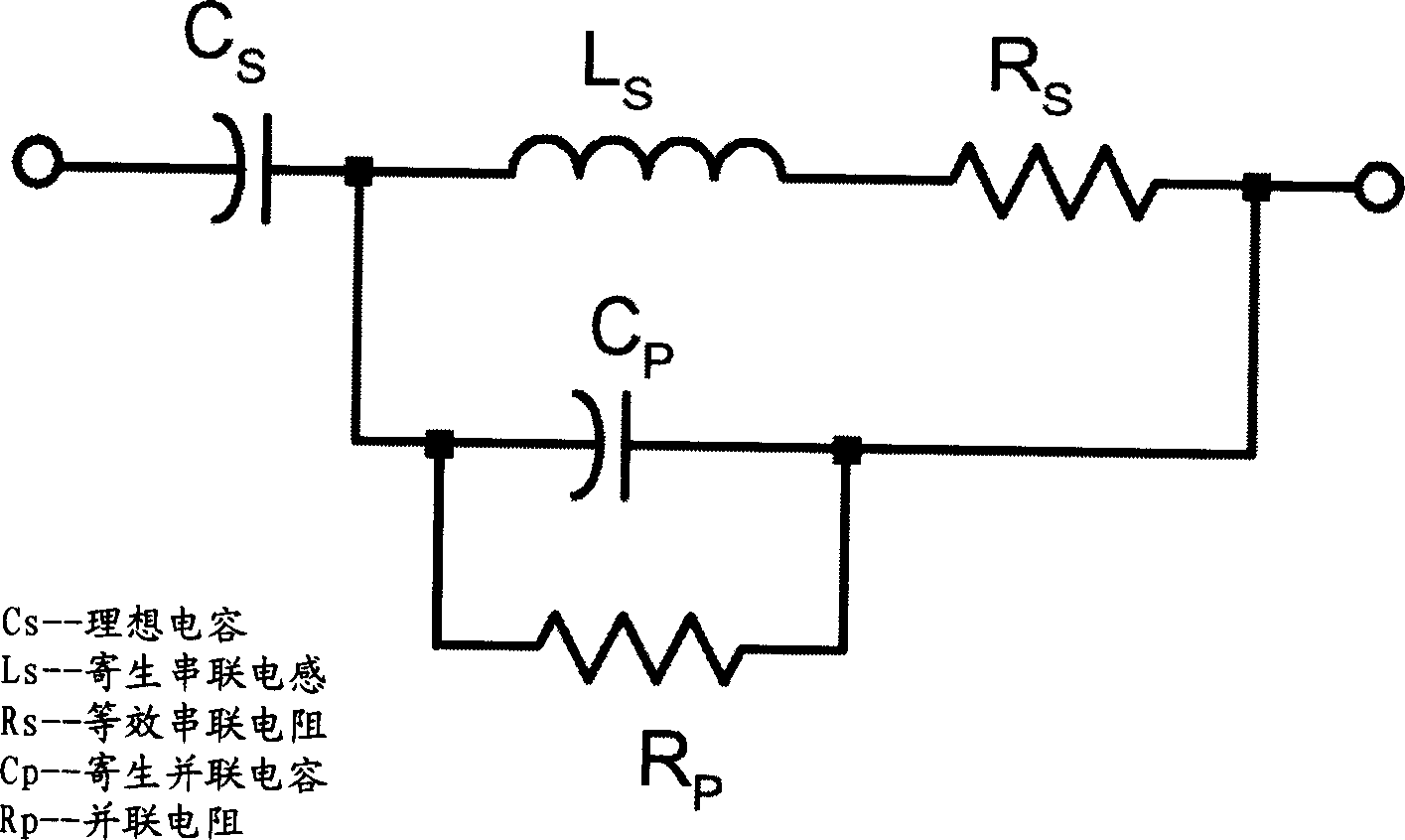

ActiveCN101071449AFit for integrity issuesResolve integritySpecial data processing applicationsPower integrityCircuit models

The invention relates to the field of very large scale integrated (VLSI) circuit technique, especially a PI solving method for IC-package-PCB cooperative design for solving power supply integrity problem in back-end design, comprising: 1) building a circuit model suitable for VLSI PI analysis; 2) analyzing and extracting parasitical parameters corresponding to the circuit mode; 3) determining design indexes in the PI design; 4) utilizing EDA tool and owned algorithm model to make accurate simulation and calculation; 5) on the premise of considering power supply integrity, according to the PI design indexes and simulated results, quickly determining a proper number of I / Os of power supply.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

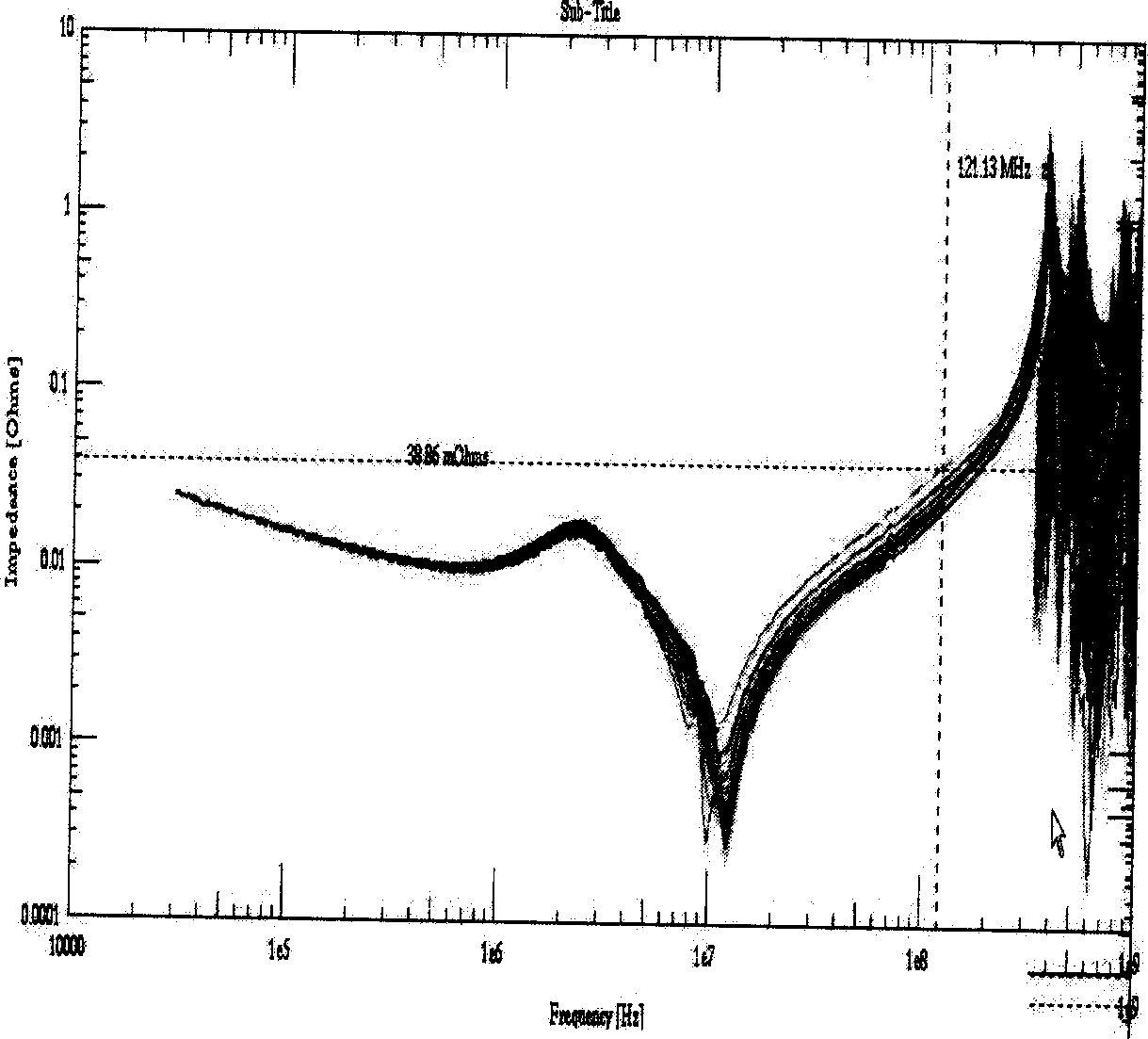

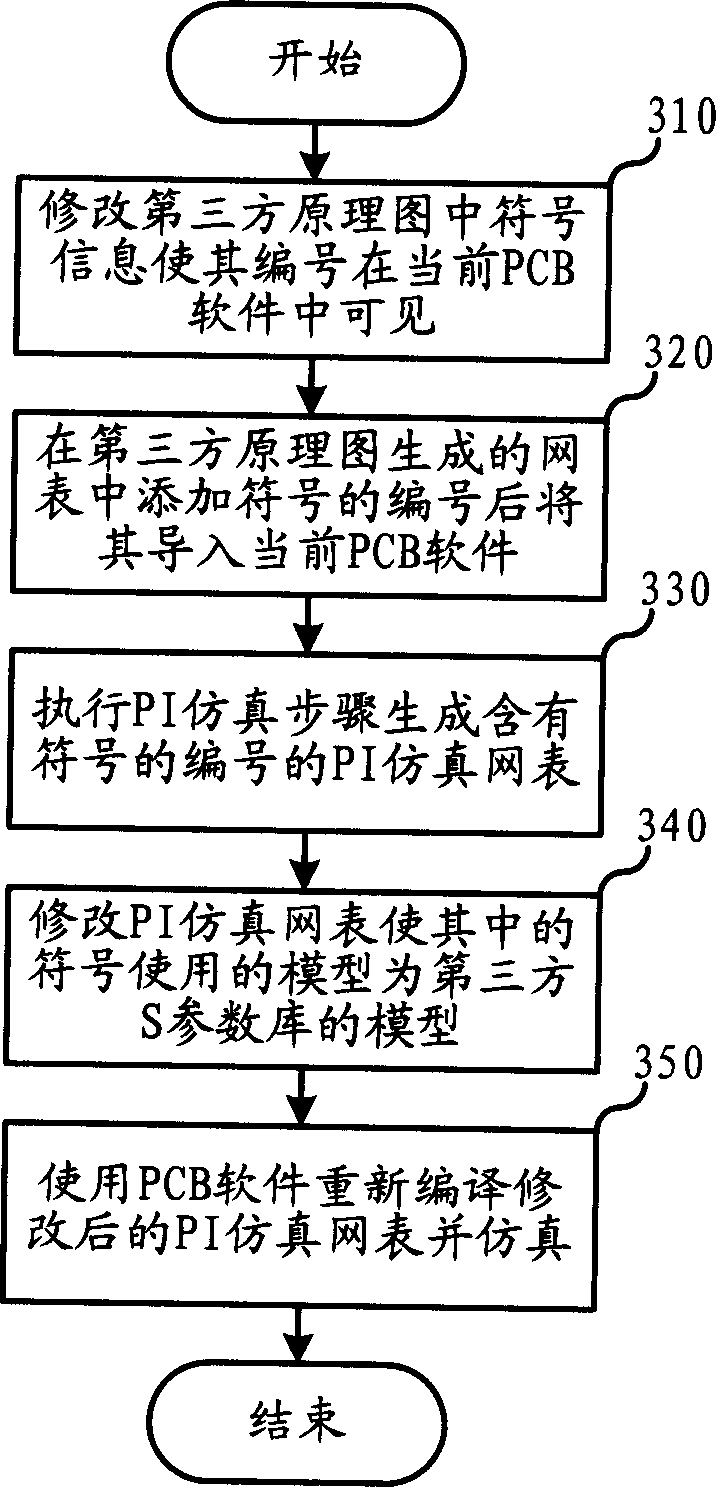

Method for printed circuit board power completeness simulation

InactiveCN1858751API simulation is accurateGuaranteed accuracySpecial data processing applicationsThird partyPower integrity

This invention discloses a method for emulating the integrated power supply of a PCB, in which, accurate PI emulation to a PCB is carried out by a device attribute provided by a third party theoretical plot and related power integrality emulation software and the first attribute related to the device models and parameters in the third theoretical plot is added to the second attribute of the same plot symbol, only the second attribute of the theoretical plot symbol is preserved in the net list generated in the theoretical plot, after an emulation tool is called into the list, related models and parameters are presented to related devices based on the first attribute included in the second attribute, then a net list is generated in related supply integrality emulation software, finally, the net list is modified to be replaced to models and parameters assigned in the third party theoretical plot for further compiling and emulation and the parameters assigned in the third party theoretical plot can be the parameter S library.

Owner:HUAWEI TECH CO LTD

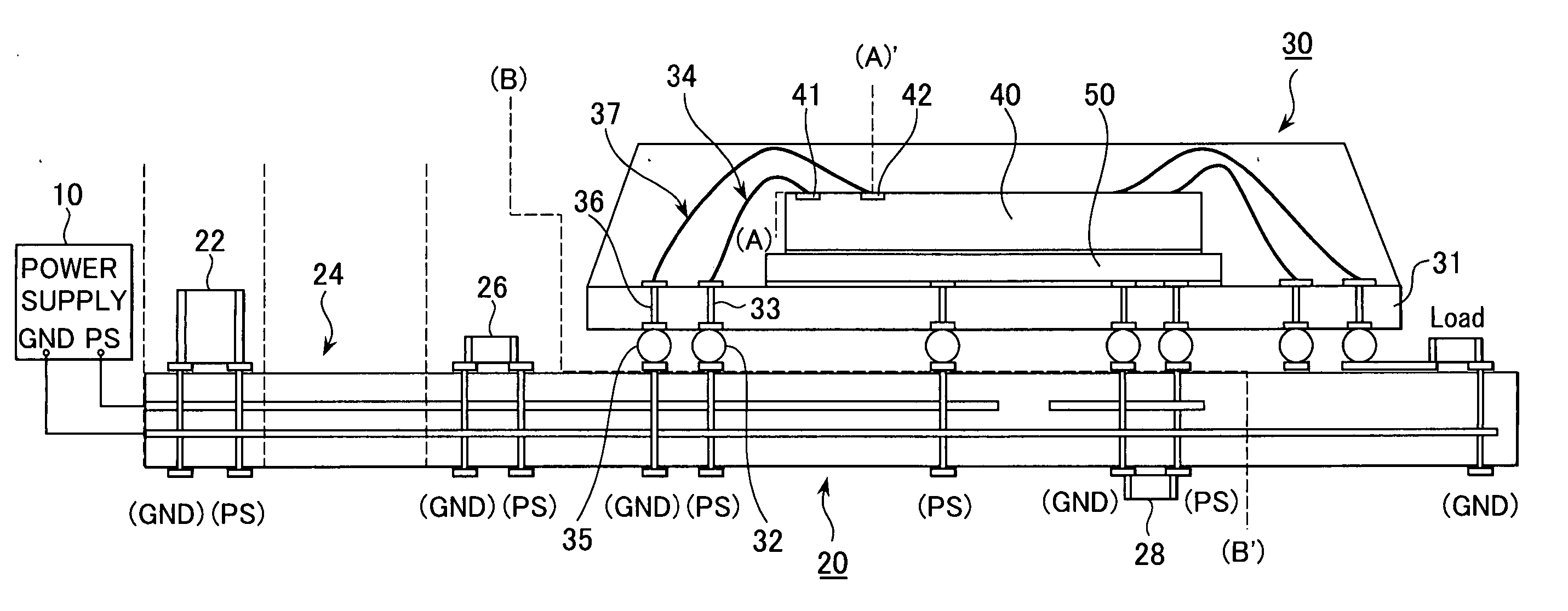

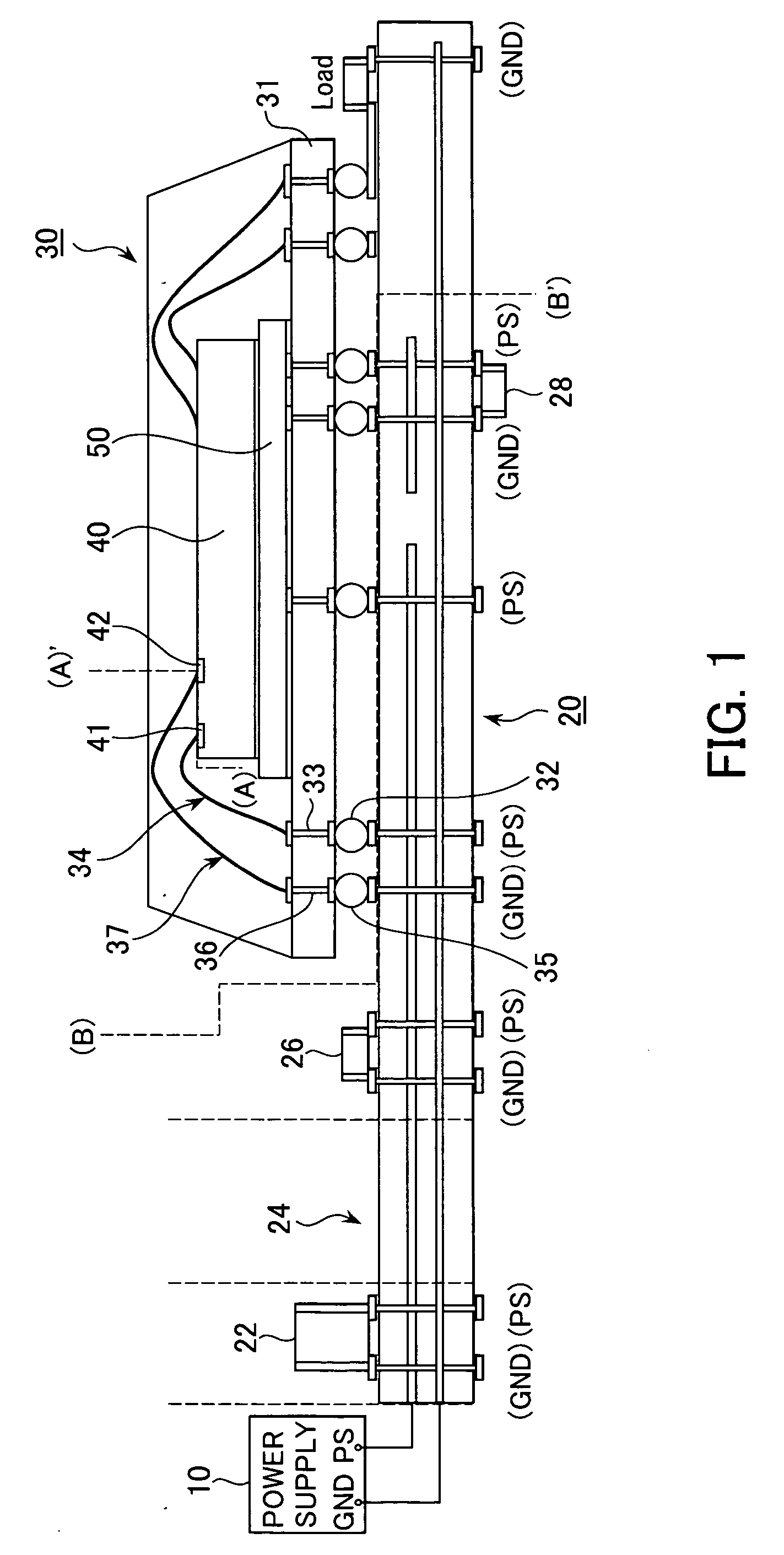

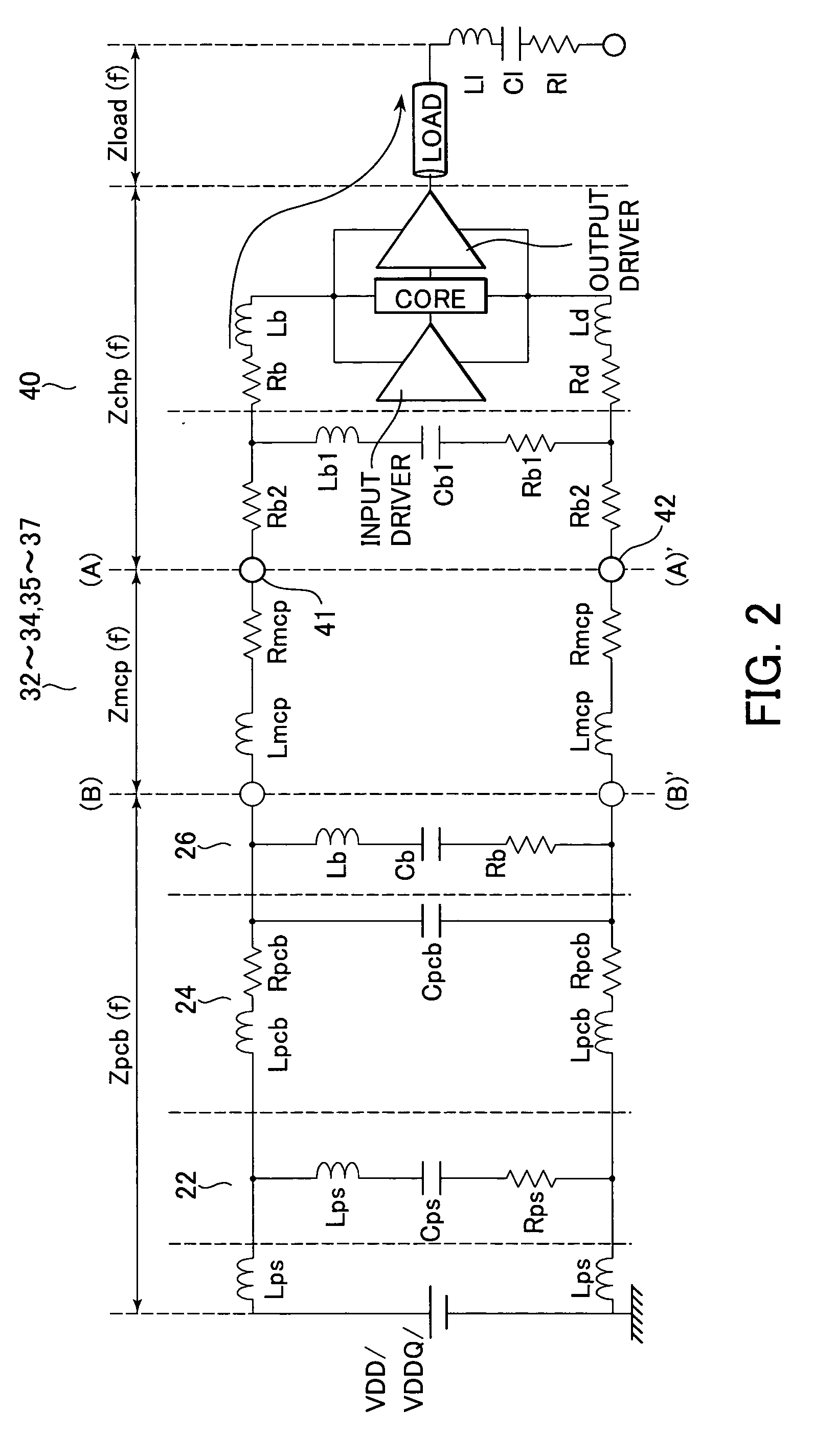

Method for designing semiconductor apparatus, system for aiding to design semiconductor apparatus, computer program product therefor and semiconductor package

InactiveUS20070057380A1Shorten the design cycleCross-talk/noise/interference reductionSemiconductor/solid-state device detailsSemiconductor packageSemiconductor chip

A method for designing a semiconductor apparatus comprising a semiconductor package in consideration of power integrity for a semiconductor chip included in the semiconductor package is disclosed. A target variable for an adjustment target is calculated on the basis of target information about the adjustment target, wherein the target variable is represented in frequency domain, and the adjustment target includes a part of the semiconductor package. The target variable is compared with a predetermined constraint, which is represented in frequency domain, to identify a problematic section, wherein the problematic section corresponds to a frequency region at which the target variable exceeds the predetermined constraint. Design guidelines are decided to solve the identified problematic section.

Owner:LONGITUDE SEMICON S A R L

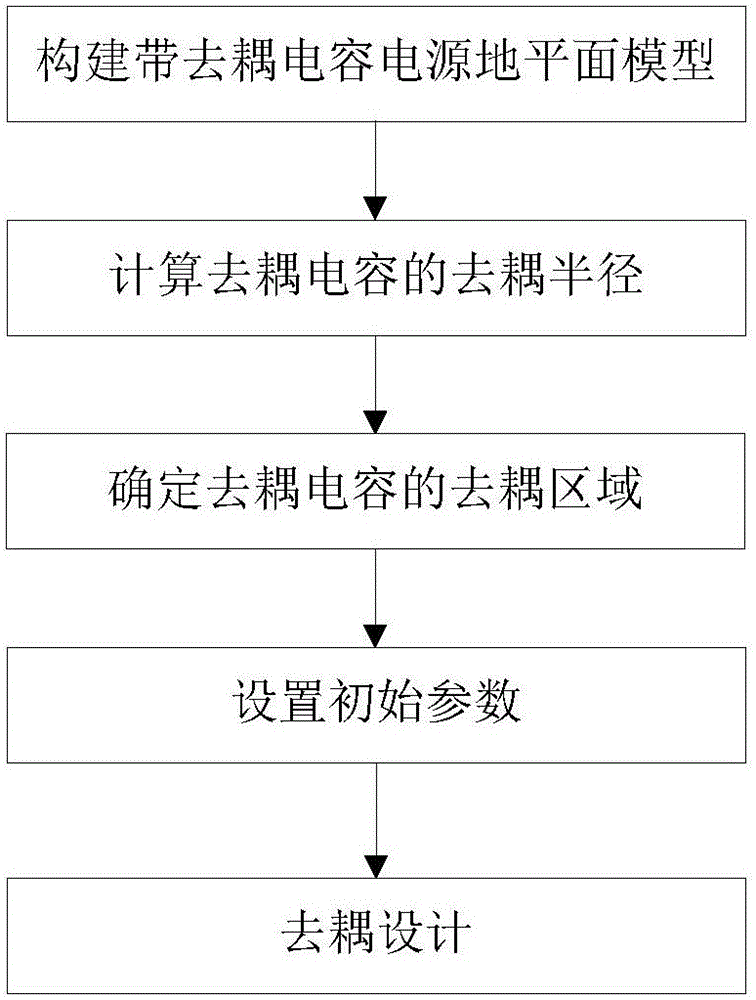

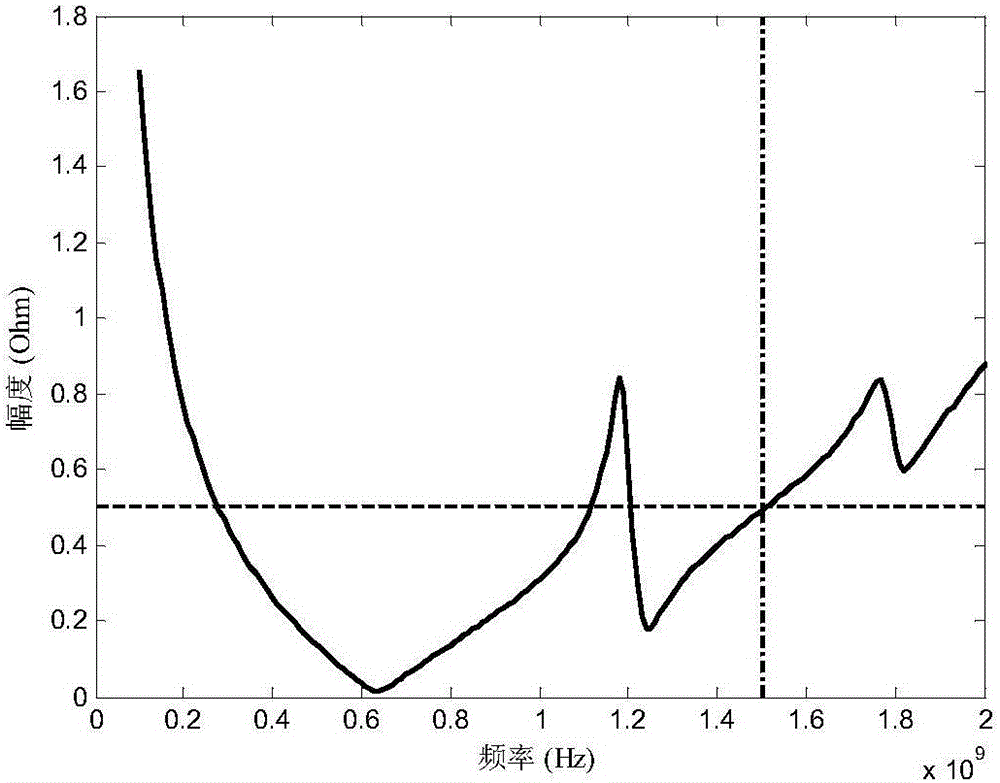

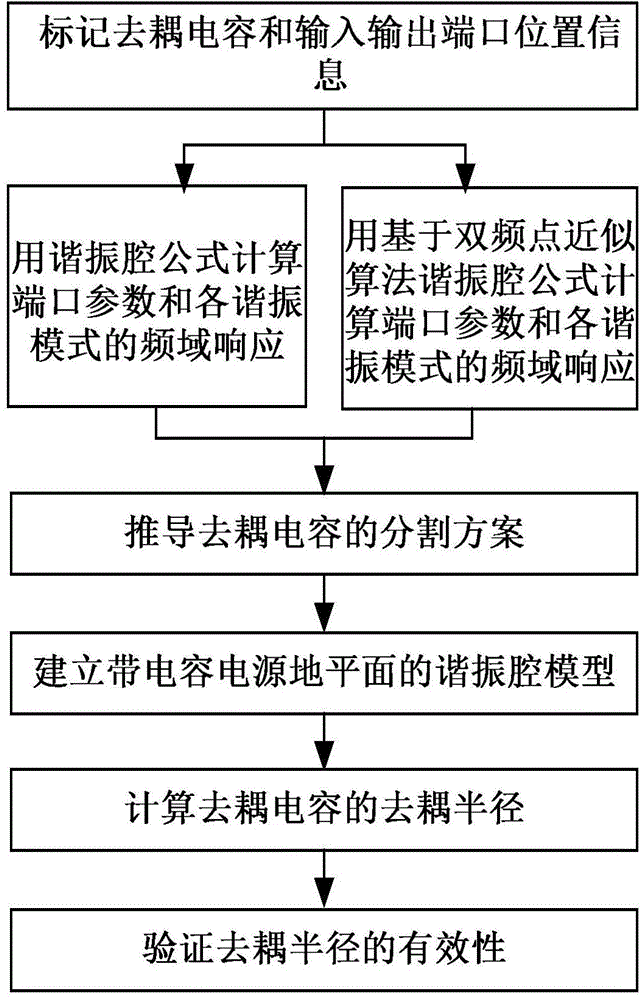

Power distribution network design method based on decoupling region of decoupling capacitor

ActiveCN105956289AShorten the development cycleReduce design costCAD circuit designSpecial data processing applicationsResonant cavityCapacitance

The invention discloses a power distribution network design method based on a decoupling region of a decoupling capacitor. The power distribution network design method comprises the steps of: firstly, based on a resonant cavity model, modeling a power ground plane with decoupling capacitors; based on the modeling method, calculating out transverse and longitudinal decoupling radii of the decoupling capacitors; according to a frequency point corresponding to the maximum amplitude of an impedance of an input output port, selecting the required decoupling capacitor, and according to the transverse and longitudinal decoupling radii of the decoupling capacitor, selecting an installation position of the decoupling capacitor; and finally, drawing an impedance curve of a power distribution network. According to the invention, the problem that in the power distribution network design, the installation position of the decoupling capacitor cannot be obtained is solved; a rapid, simple and convenient method is provided for selection and placement of the decoupling capacitor in the power distribution network, and reliable guidance is provided for power integrity design in the practical engineering.

Owner:XIDIAN UNIV

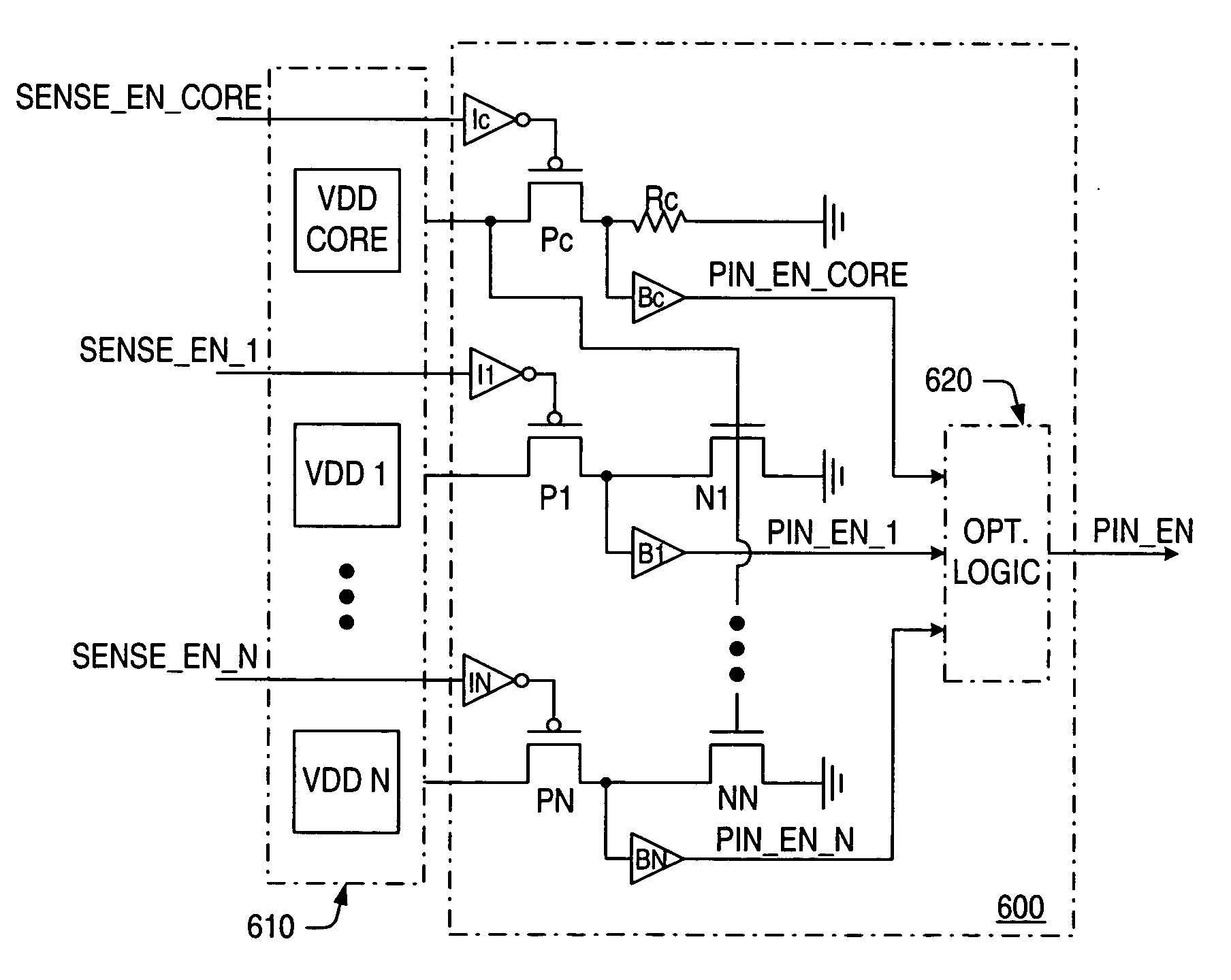

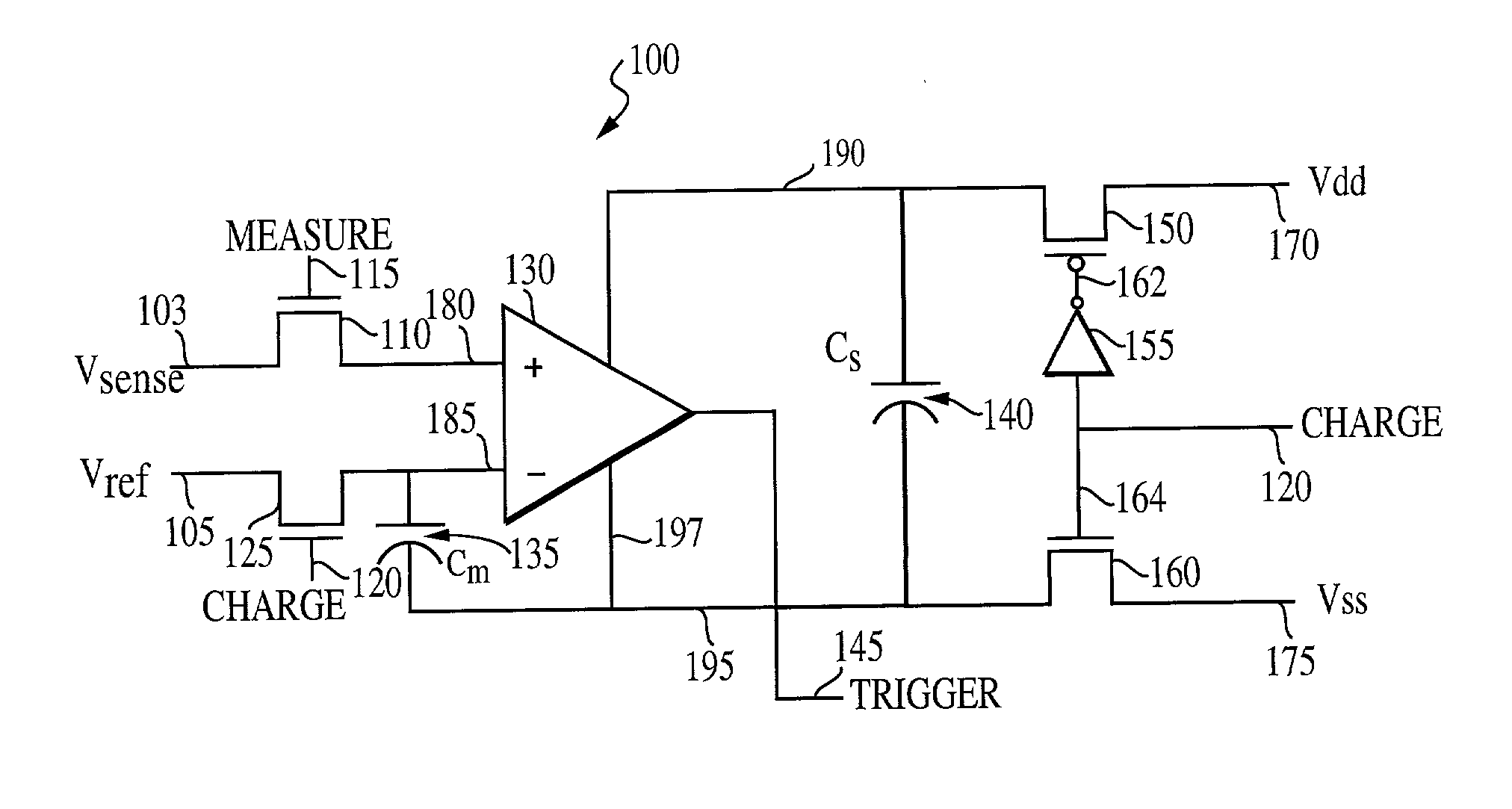

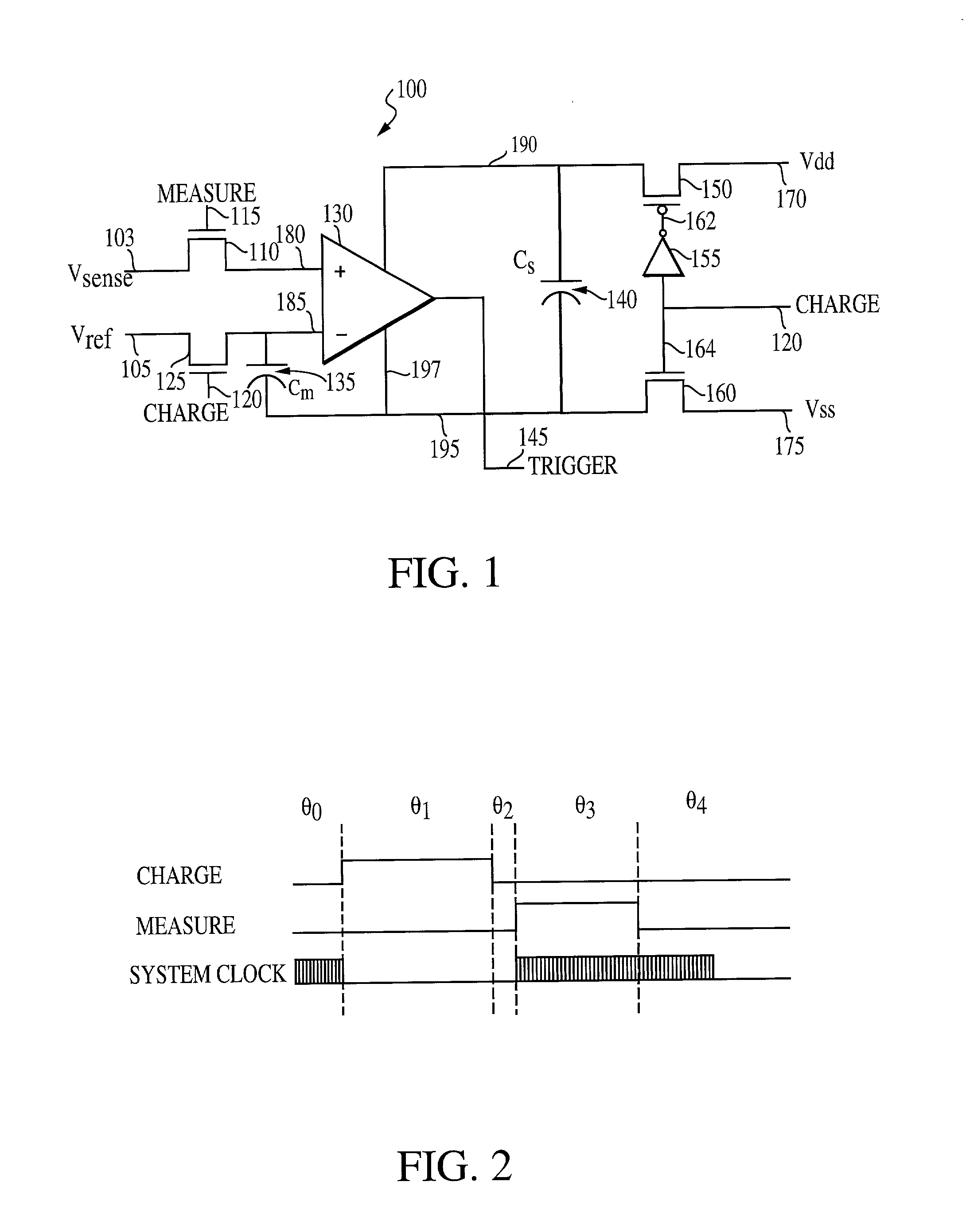

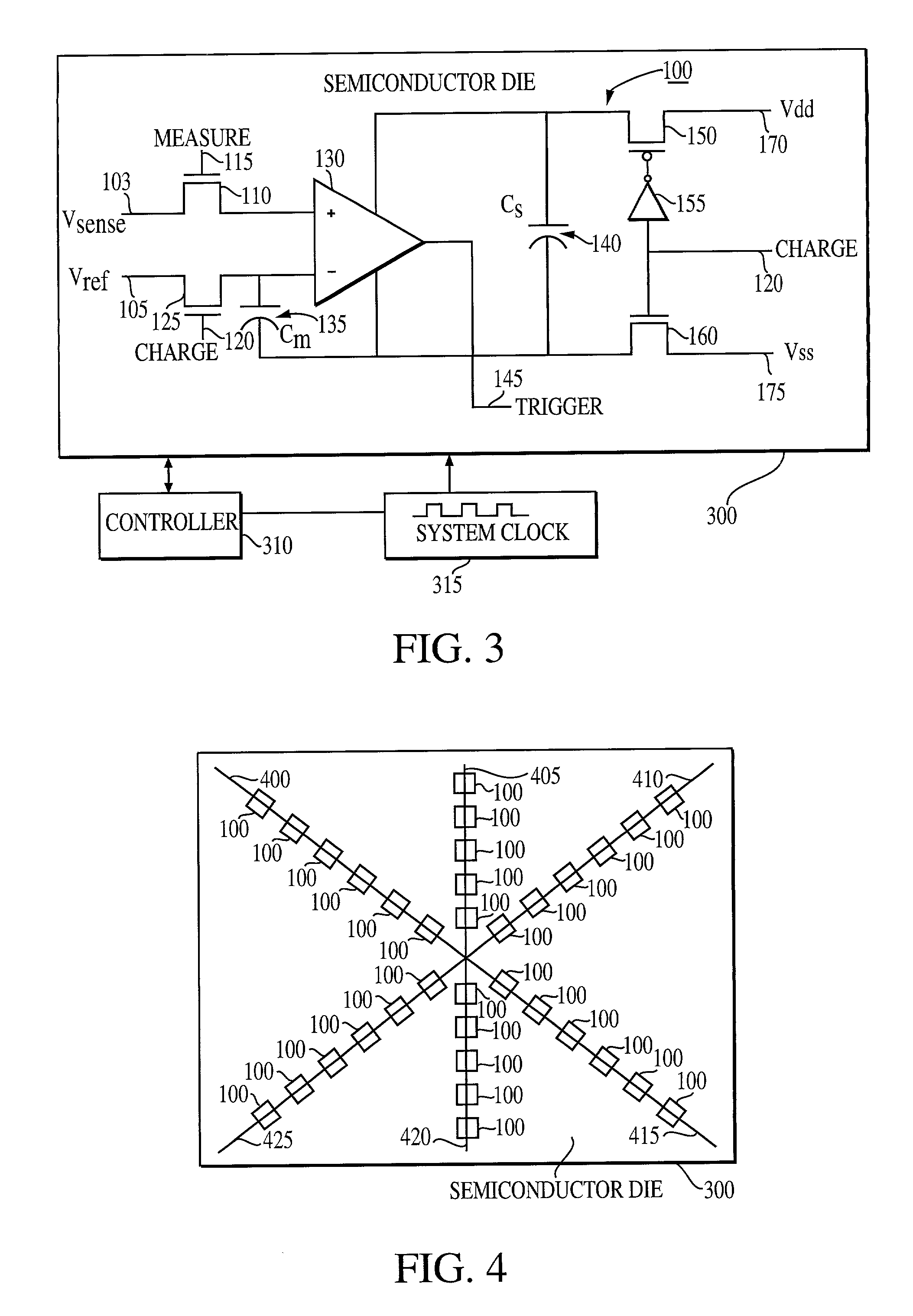

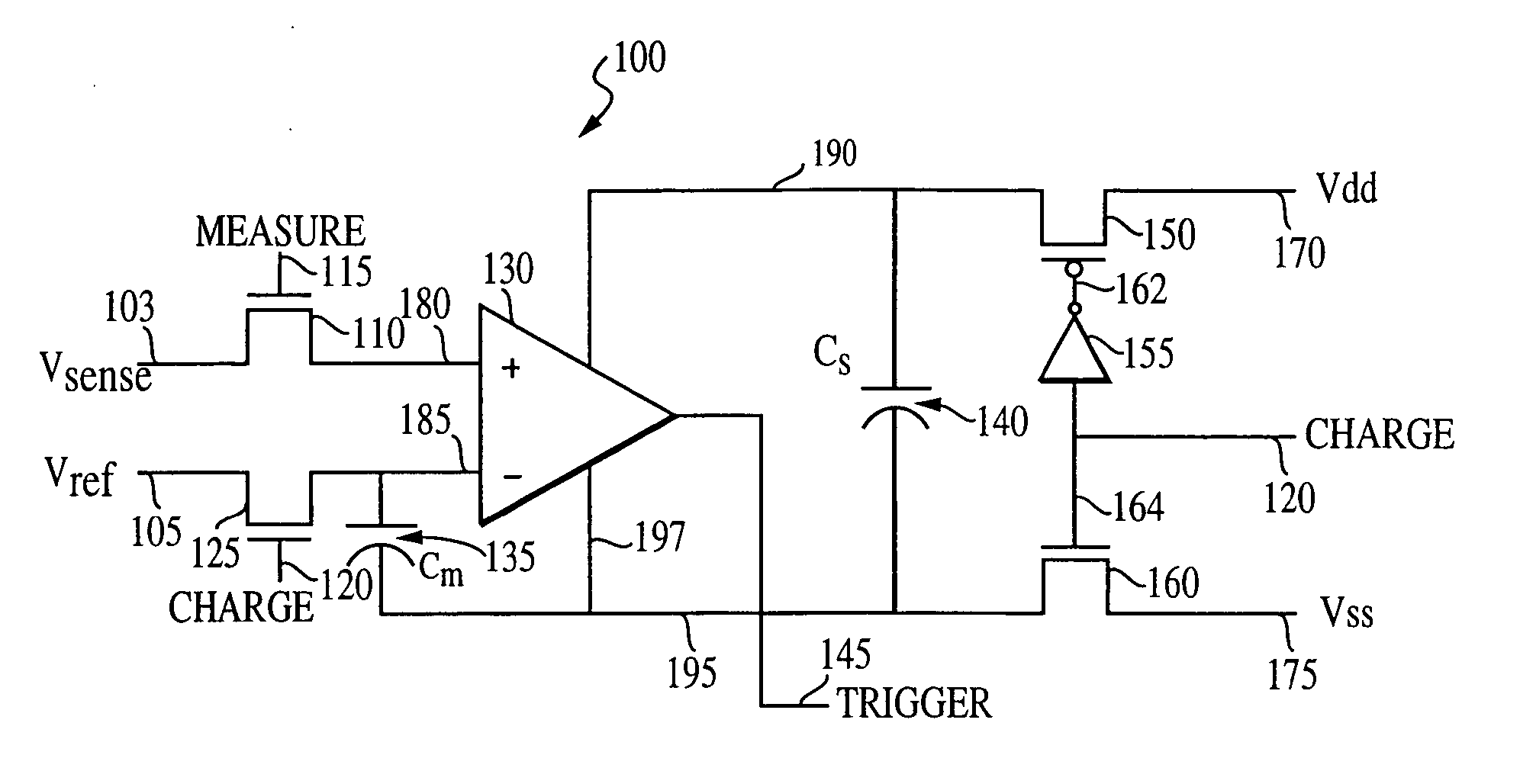

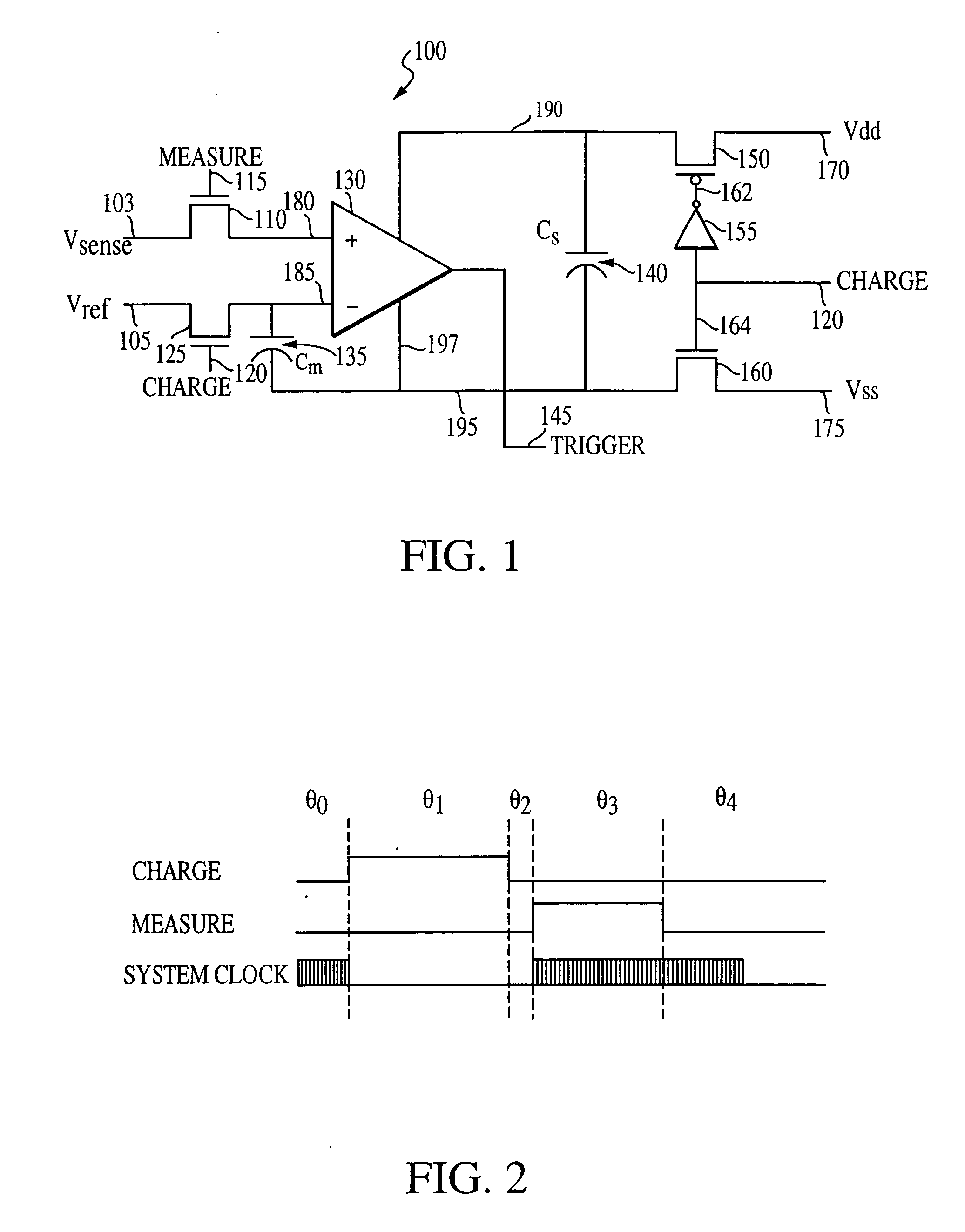

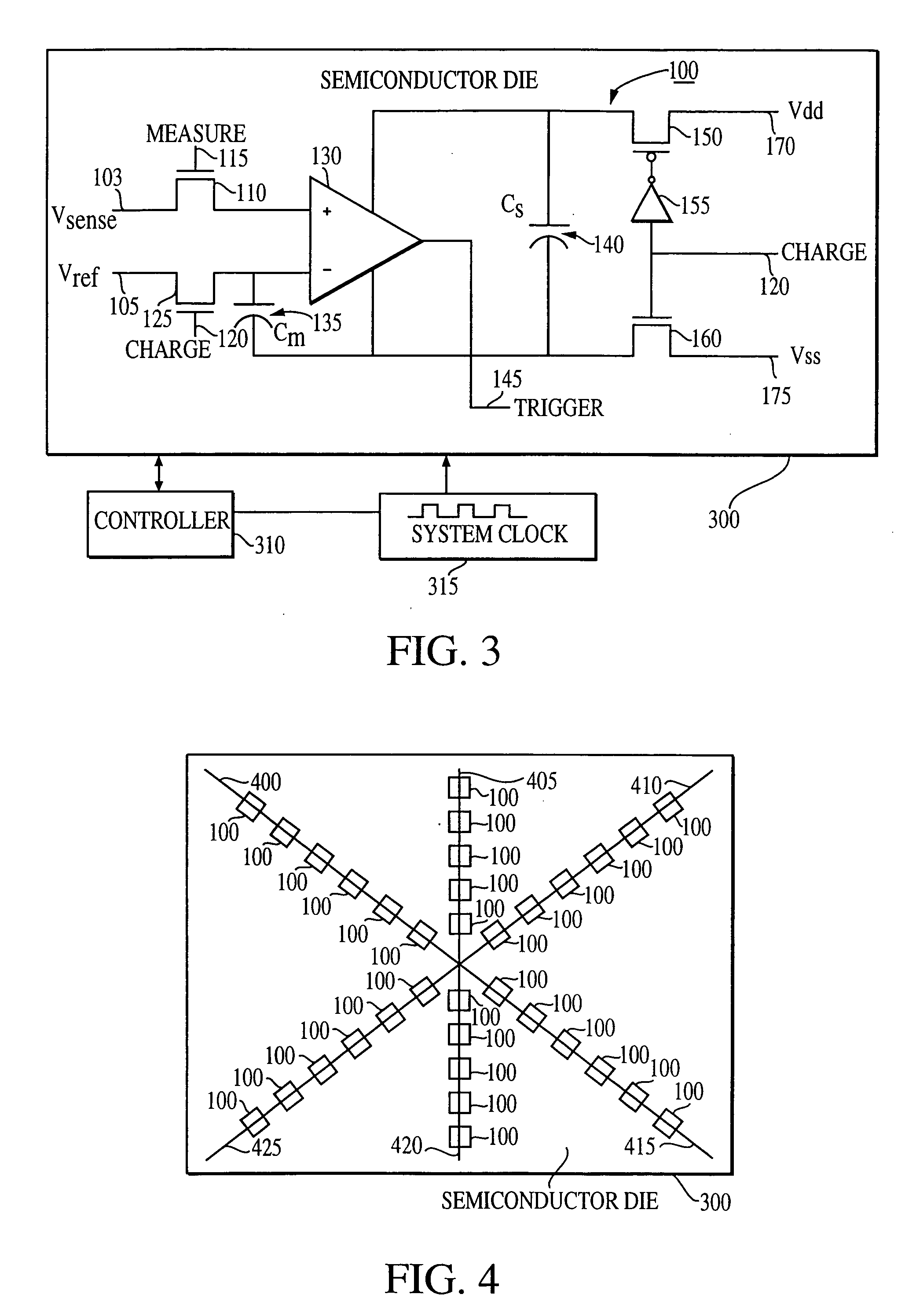

Circuit for measuring on-chip power supply integrity

A test circuit and method for measuring power supply integrity is provided. The circuit may be incorporated on-chip and is small enough to be integrated many times across the surface of the die for measuring integrity parameters at several locations on the chip. The circuit instantaneously measures, e.g., the rail voltage of a power supply, which may be fluctuating at the time of measurement. In addition, the circuit isolates itself from all chip power rails for the duration of the measurement, thereby eliminating any influence of external noise on the measurement. A storage capacitor is charged up to full power rail voltage for powering up a comparator. Then, the comparator is isolated from the power rails and the measurements are taken. Based upon the measurements, certain power supply integrity parameters are quantified including ground bounce and power droop.

Owner:MICRON TECH INC

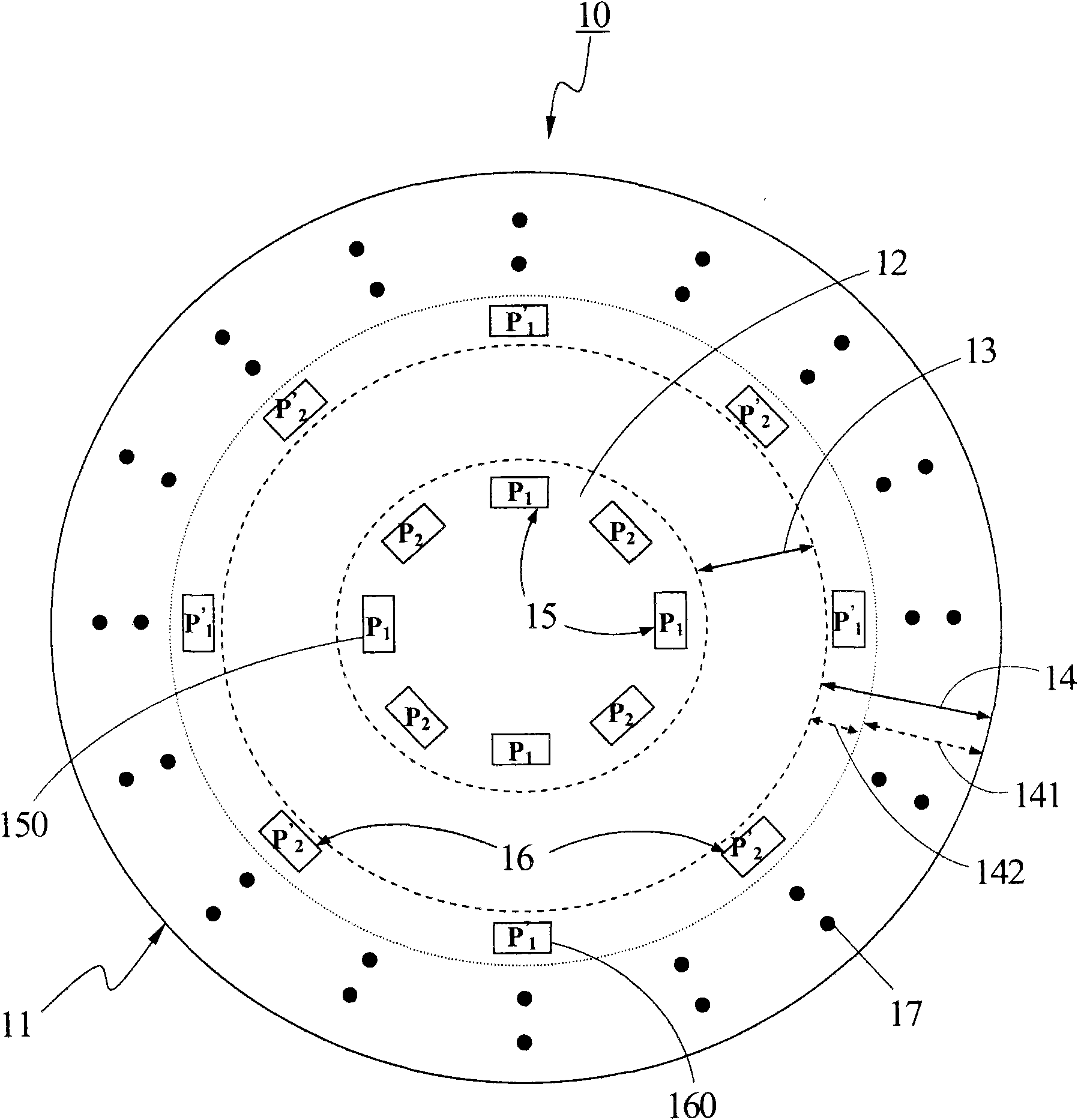

Hybrid mesh partition method with design of integrity of system-level packaging power supply

InactiveCN101976287AReduce the number of nodesMeet modeling needsSpecial data processing applicationsEngineeringGrid partition

The invention relates to a hybrid mesh partition method in the field of electronic technologies, in particular to the hybrid mesh partition method with the design of integrity of a system-level packaging power supply. The hybrid mesh partition method comprises the following steps: (1) decomposing an irregular power supply / ground plane into a series of convex polygons by utilizing convex partition treatment; (2) obtaining an optimal rectangular mesh based on the recursive partitioning technology of the rectangular mesh, setting auxiliary ports on sides of the rectangular mesh, and establishing the transfer impedance relationship among the ports; (3) adopting a triangular mesh to fill the remaining structure, and carrying out modeling of an equivalent circuit for the triangular mesh; (4) establishing the electrical relationship among the ports at an interface of the rectangular mesh and the triangular mesh; and (5) solving simultaneous overall equations. The hybrid mesh partition method has the advantages of a wide range of applications, few internal nodes, high analysis precision and efficiency and the like.

Owner:SHANGHAI JIAO TONG UNIV

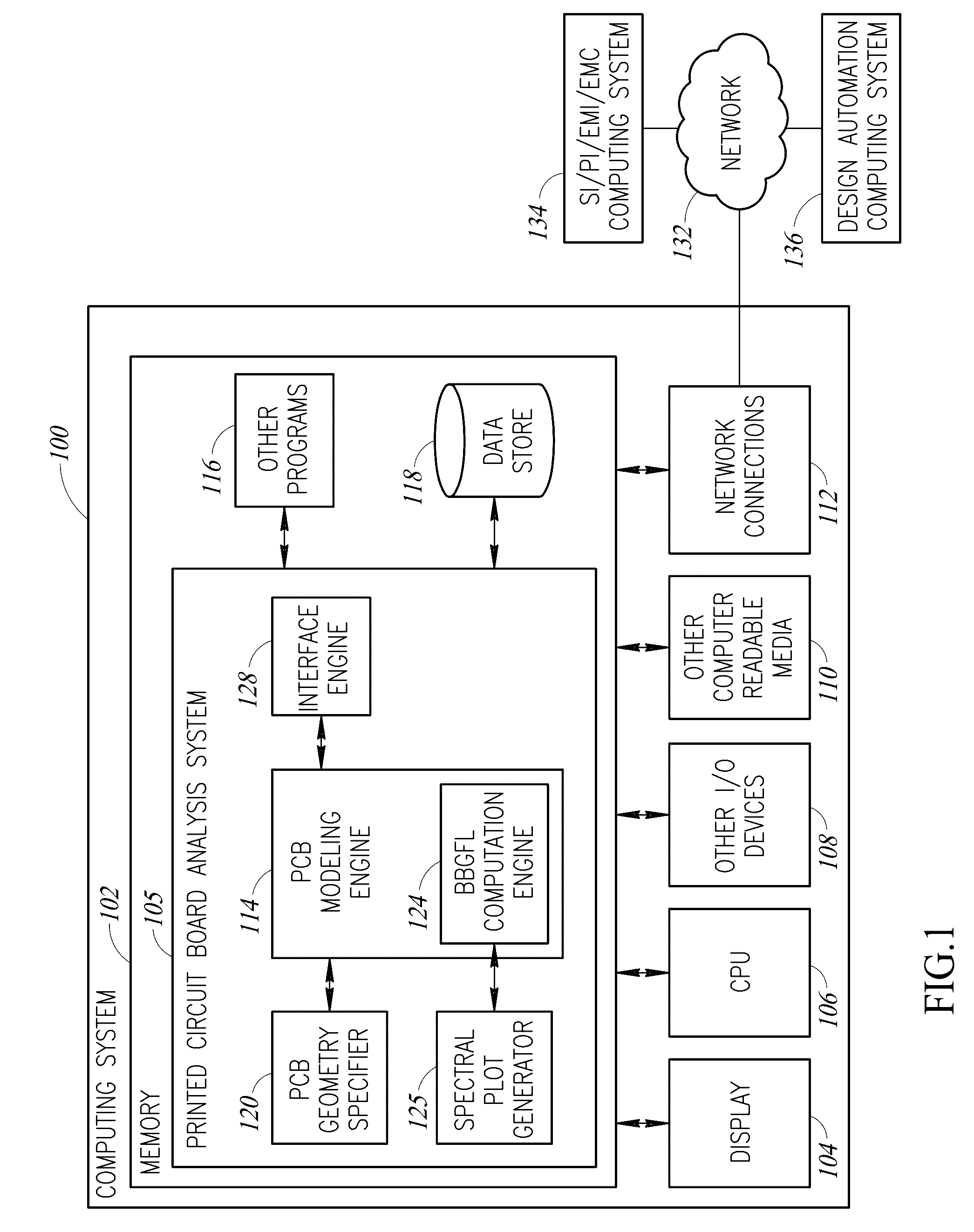

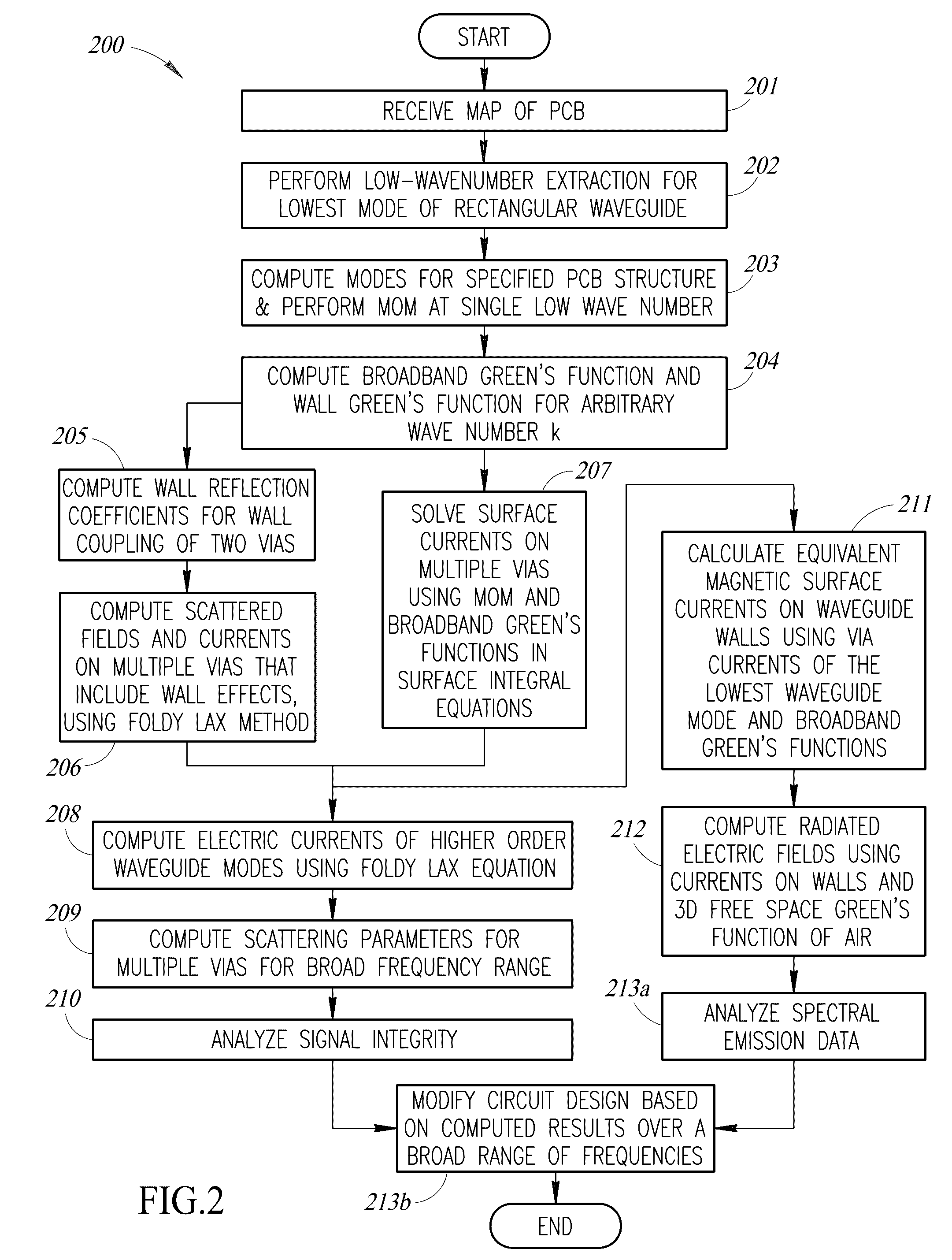

Full wave modeling and simulations of the waveguide behavior of printed circuit boards using a broadband green's function technique

ActiveUS20160314231A1Fast simulationReduce extractionCAD circuit designSpecial data processing applicationsPresent methodFull wave

A broadband Green's function computation technique that employs low wavenumber extraction on a modal summation is used to model the waveguide behavior of electronic components, systems, and interconnects on a printed circuit board. Use of the broadband technique permits discretizing the surface of the printed circuit board across a wide range of frequencies all at once. The broadband Green's function is also extended to via waveguides on circuit boards and power / ground plane waveguides of arbitrary shape. Such a method can analyze a given circuit board geometry over a broad frequency range several hundred times faster than is otherwise possible with existing commercial analysis tools. The present method is useful in electronic design automation for analyzing signal integrity and power integrity, reducing electromagnetic interference and ensuring electromagnetic compatibility.

Owner:TSANG LEUNG W +1

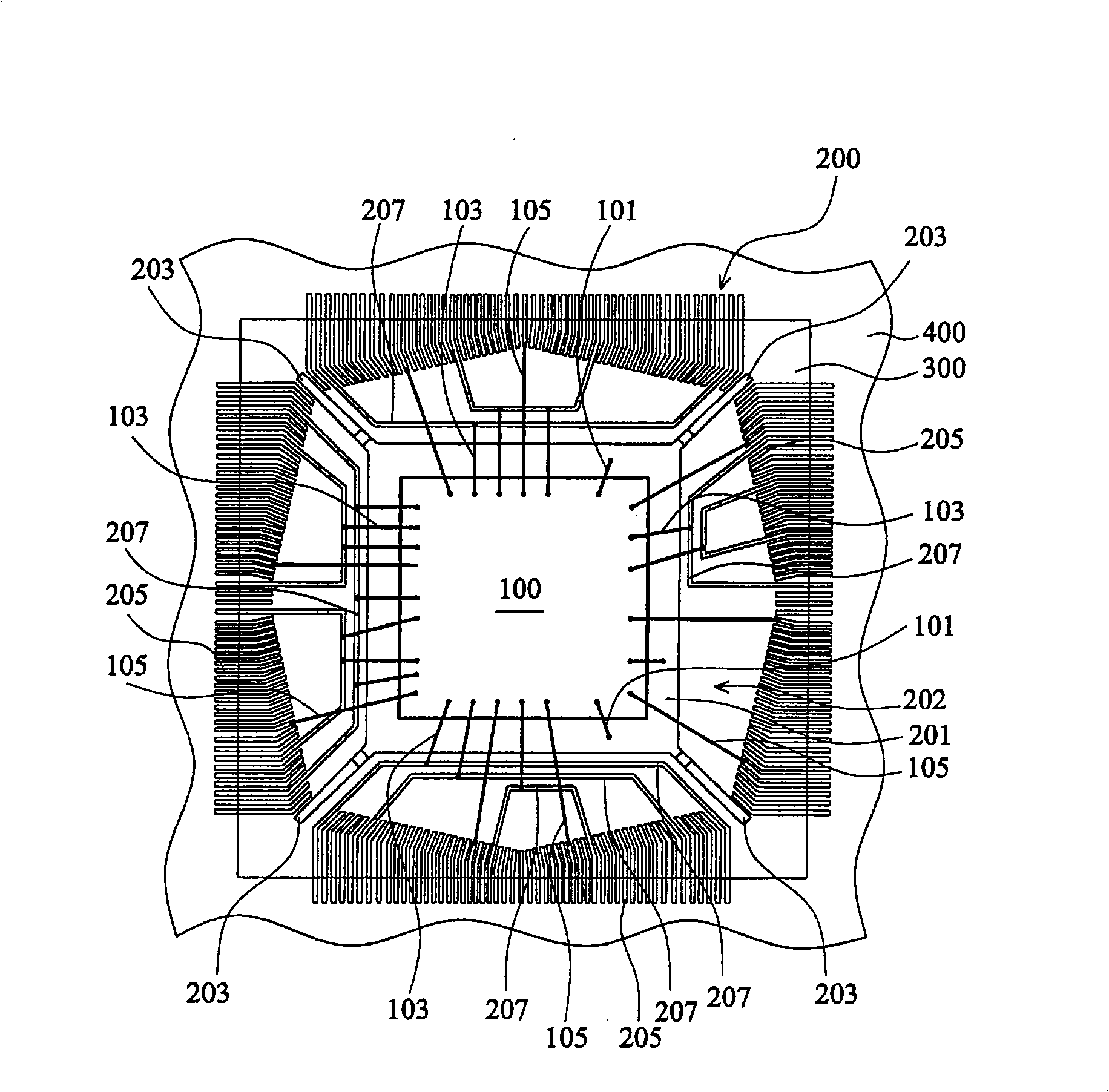

Electronic package an electronic device

ActiveCN101350318AReduce inductanceLower the resistance valueSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceElectric power system

The invention discloses an electronic package and an electronic device. The electronic package comprises a die pad, a die, a plurality of leads, a common electrode bar layer, and a molding compound. The die is attached onto the pad. The plurality of leads surrounds the die pad and spaced therefrom to define a ring gap therebetween. The common electrode bar layer is in the ring gap and substantially coplanar to the die pad, in which at least one of the plurality of leads extends to the common electrode bar layer. The molding compound partially encapsulates the die pad and the common electrode bar layer, such that the bottom surfaces of the die pad and the common electrode bar layerare exposed. The invention is capable of reducing inductance and resistance of the circuit, obtaining greater integrity of electric power, improving IR drop problem of the core electric power, and is helpful to high-speed operation and device performance improvement.

Owner:MEDIATEK INC

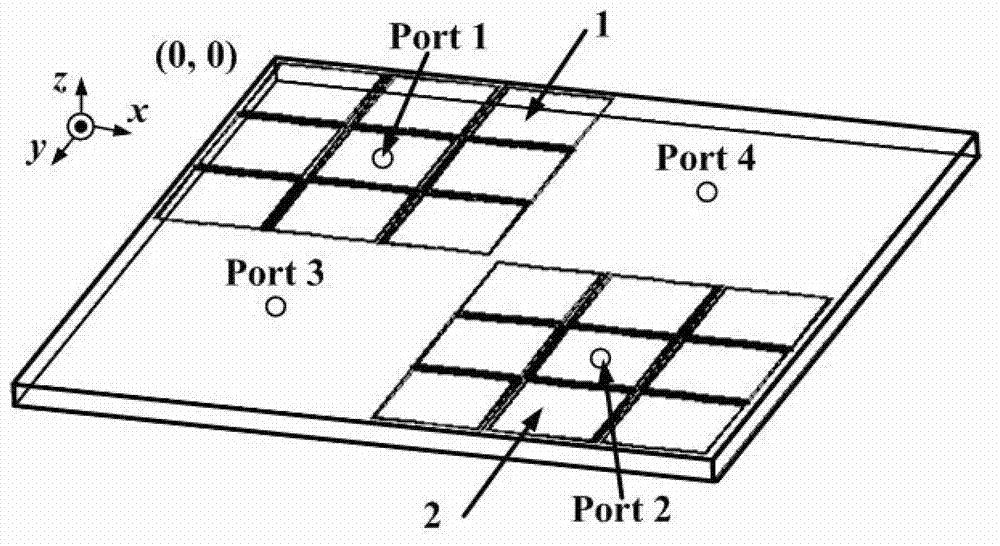

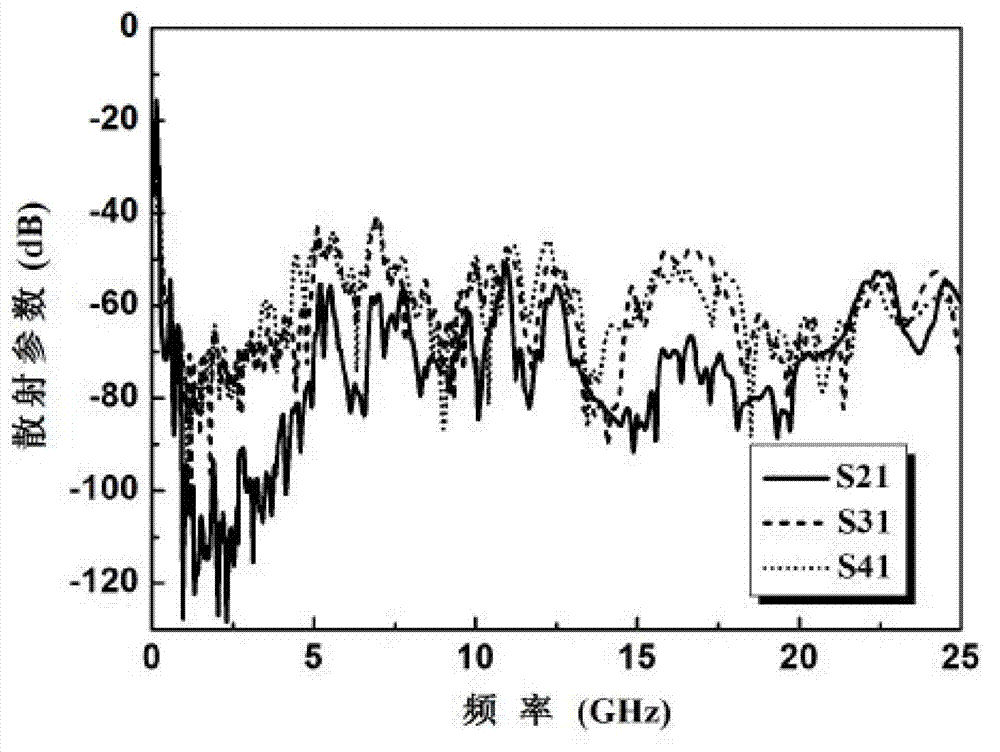

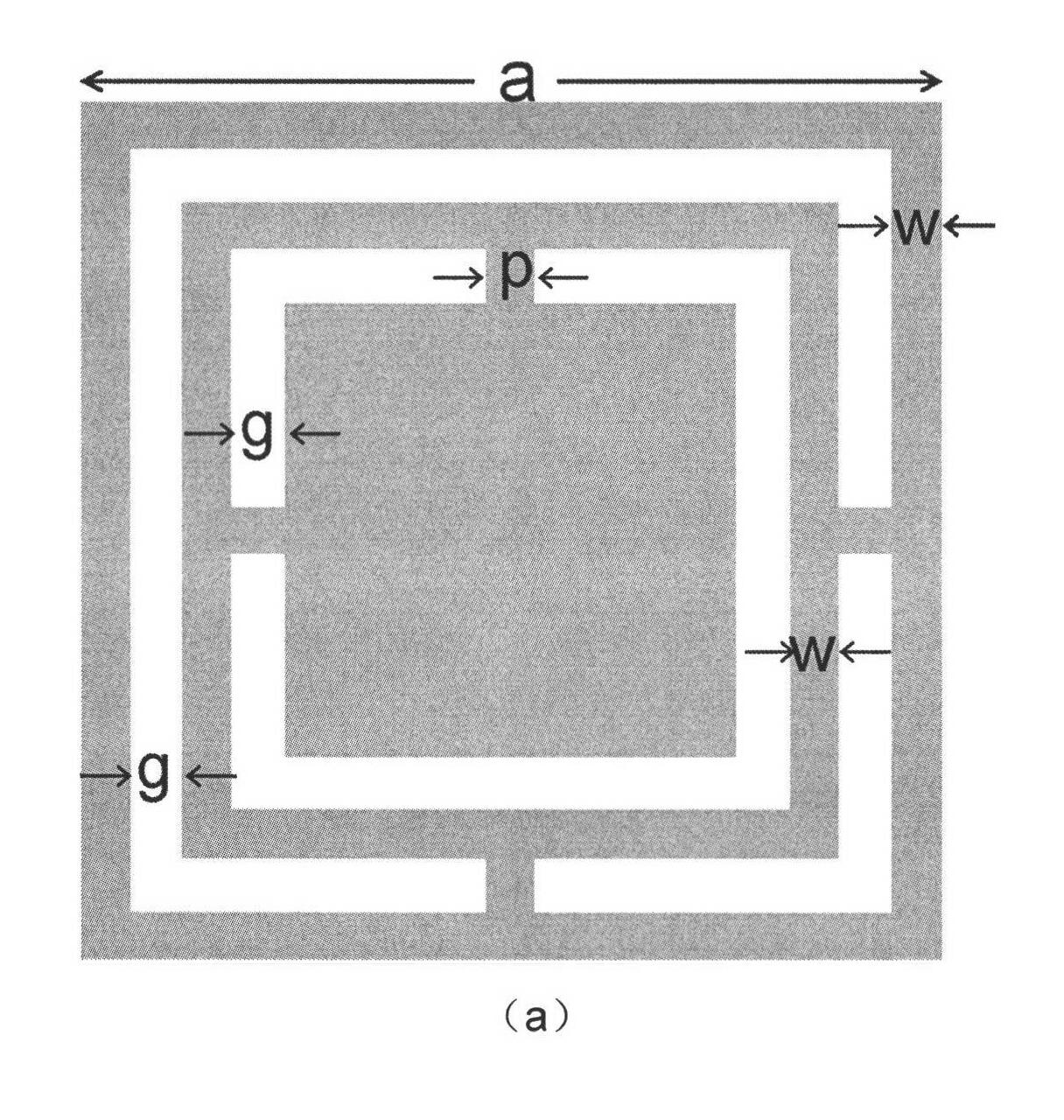

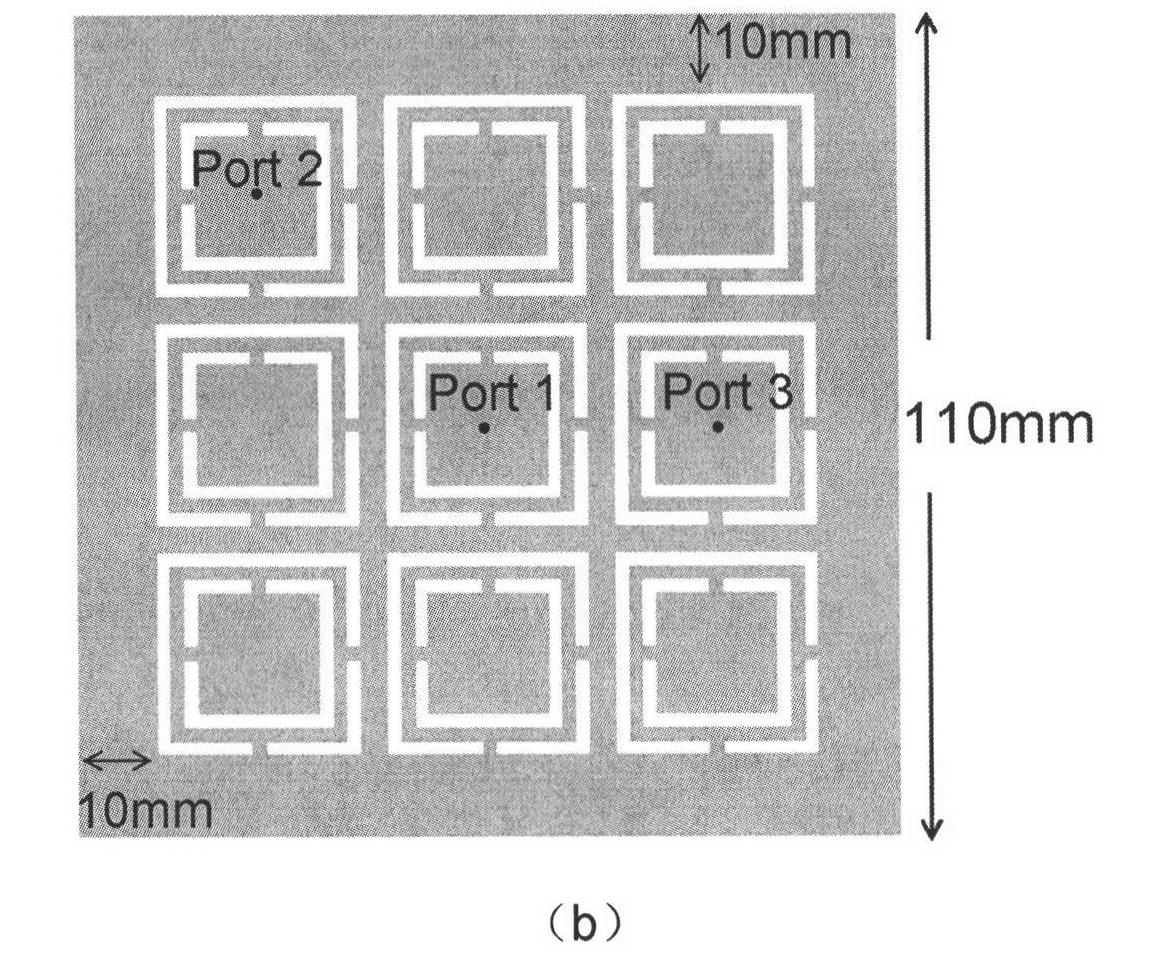

Ultra wide band electromagnetic band gap structure for suppressing ground bounce noise of high speed circuit/microwave circuit

InactiveCN102131343AImprove integritySuppresses ground bounce noisePrinted circuit detailsWaveguide type devicesMicrowaveGround bounce

The invention provides a novel ultra wide band electromagnetic band gap structure which belongs to the technical field of information. The structure is mainly used for replacing a power layer of the traditional high speed circuit / microwave circuit so as to suppress ground bounce noise in the structures and realize better power integrity. The structure has a typical three-layer circuit board structure comprising a dielectric layer in the middle and two metal layers up and down, wherein the electromagnetic band gap structure is arranged on the upper layer. In the invention, a typical example is verified, i.e. a sample prepared in an experiment is tested through a network analyzer, which confirms that the structure provided by the invention can realize noise suppression superior to -30dB to any two ports in a frequency range from 500MHz to 5.5GHz.

Owner:NANJING UNIV

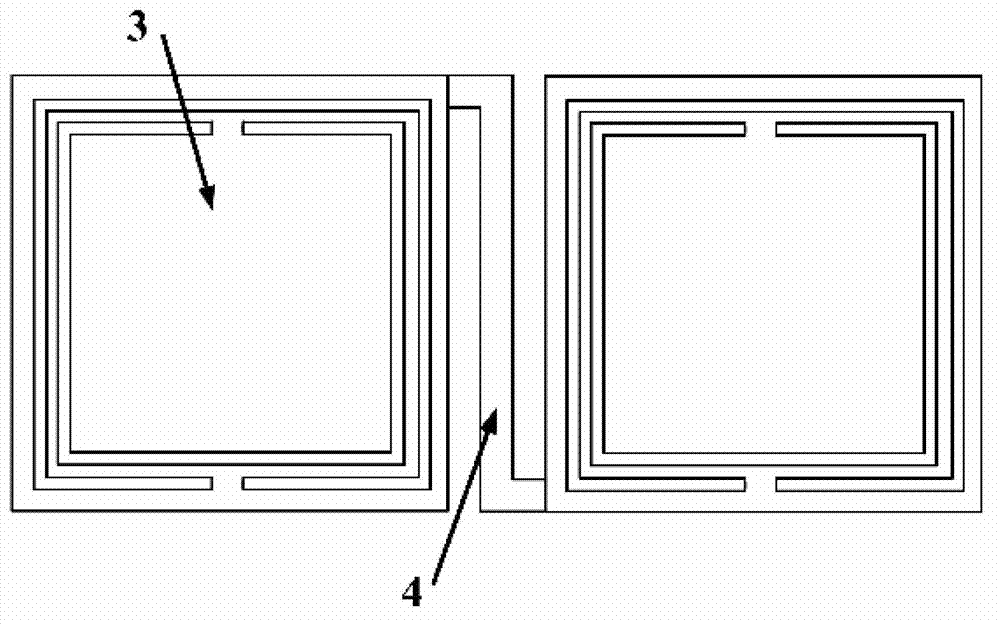

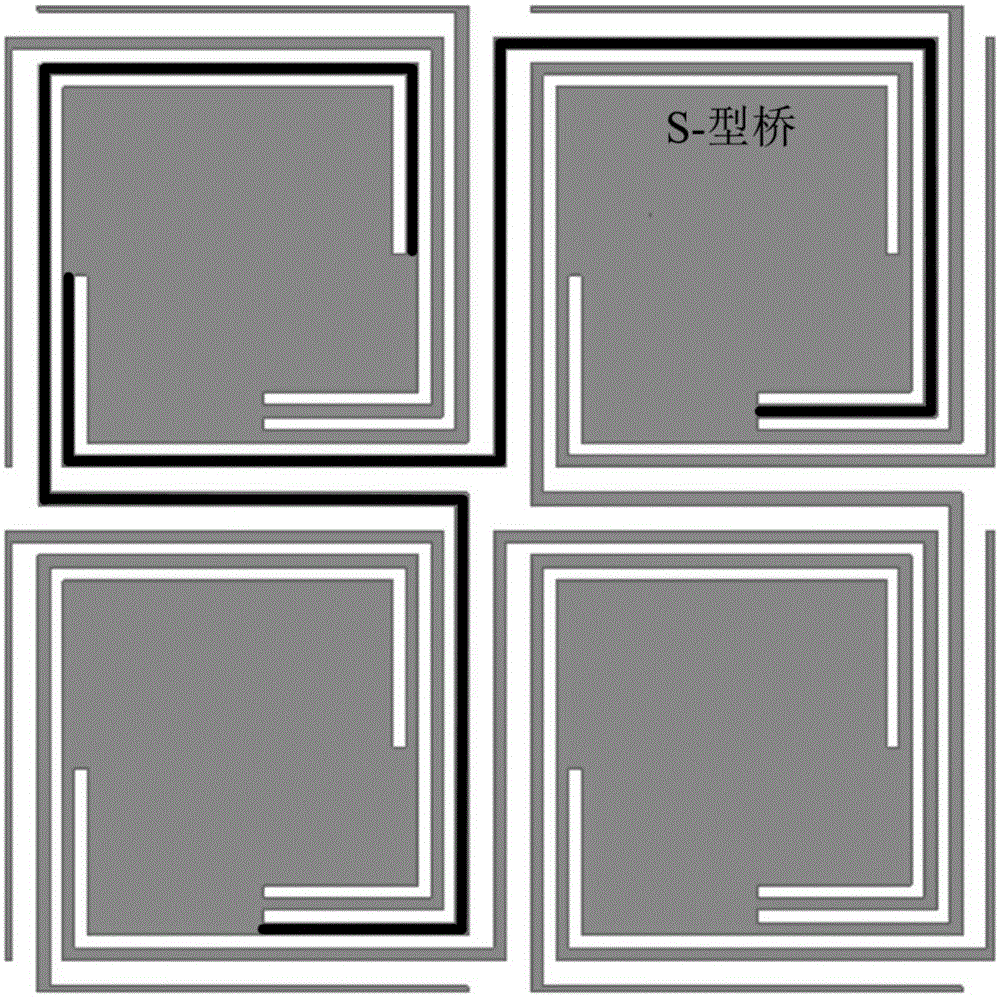

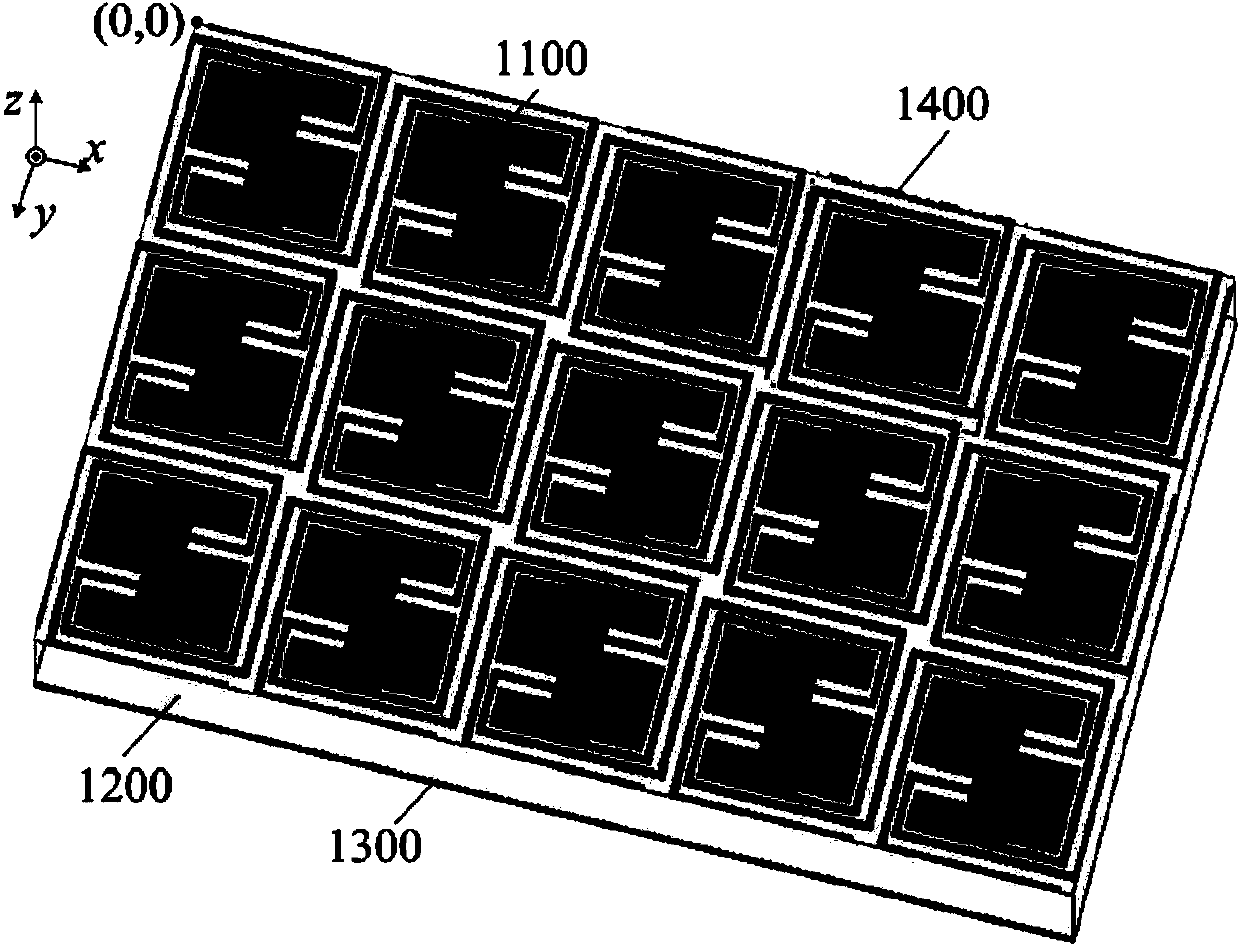

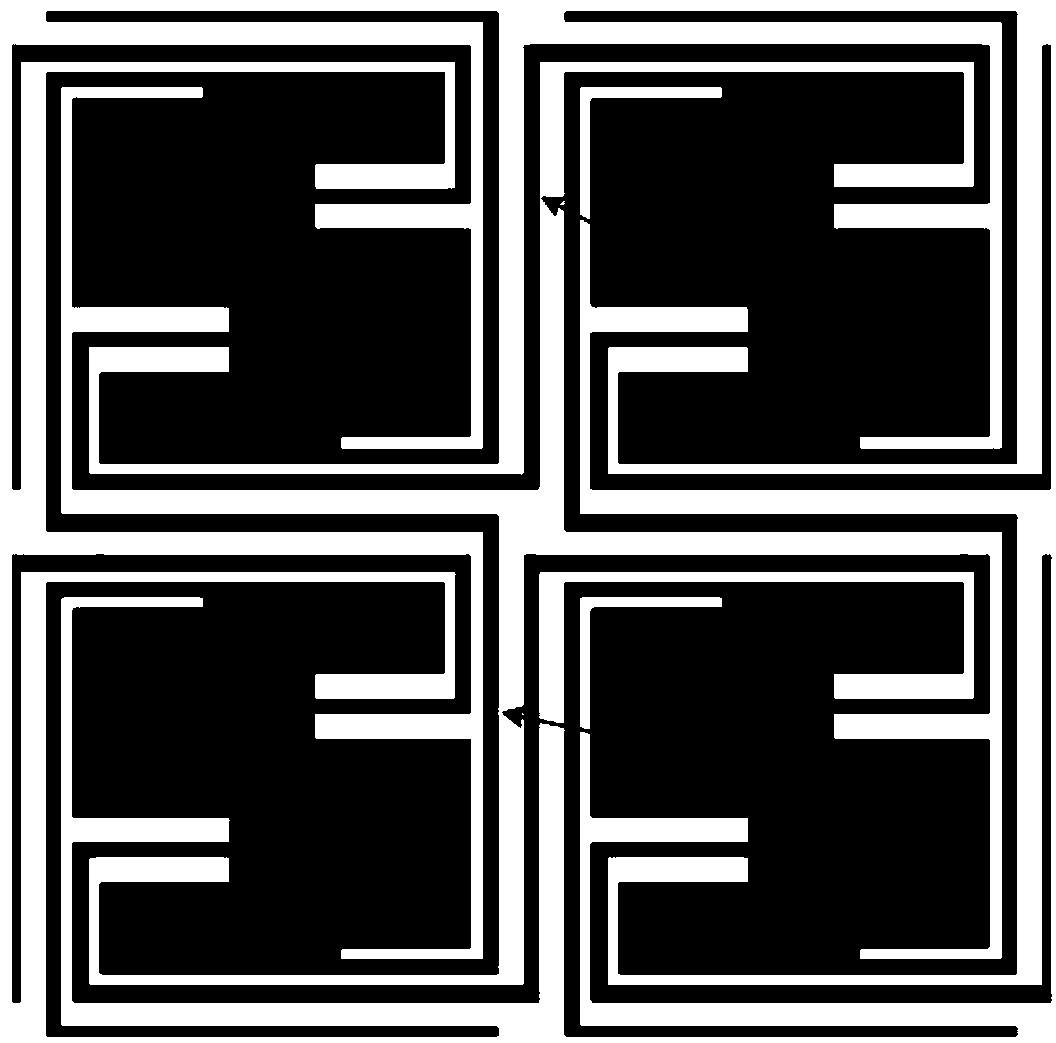

Power supply allocation network based on plane S-type bridge electromagnetic band-gap structures

ActiveCN105207467AStrong noise suppression abilityImprove integrityPower conversion systemsDielectric substrateEngineering

The invention provides a power supply allocation network based on plane S-type bridge electromagnetic band-gap structures. The power supply allocation network comprises a power supply plane, a dielectric substrate and a ground plane. The dielectric substrate covers the ground plane. The power supply plane is arranged on the dielectric substrate. Plane S-type bridge electromagnetic band-gap structure units periodically extend on a two-dimensional plane on which the power supply plane is positioned so that a matrix is formed. Each plane S-type bridge electromagnetic band-gap structure unit comprises a patch and four half S-type bridges. The connecting parts of the patch and the half S-type bridges are provided with slots so that slits are formed. The four half S-type bridges are respectively provided with four lead-out ends which are arranged at the upper, lower, left and right parts of the whole structure unit. The four lead-out ends of one plane S-type bridge electromagnetic band-gap structure unit are respectively connected with one of the lead-out ends of the upper, lower, left and right adjacent plane S-type bridge electromagnetic band-gap structure units so that a plane S-type bridge is formed. The power supply allocation network based on the plane S-type bridge electromagnetic band-gap structures has great simultaneous switching noise suppression capacity within wide frequency range and has great power supply integrity.

Owner:ZHEJIANG UNIV OF TECH

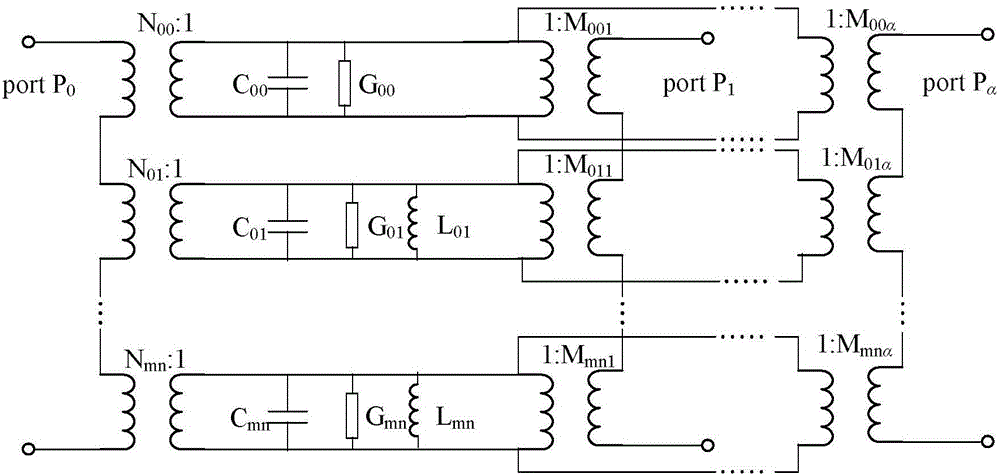

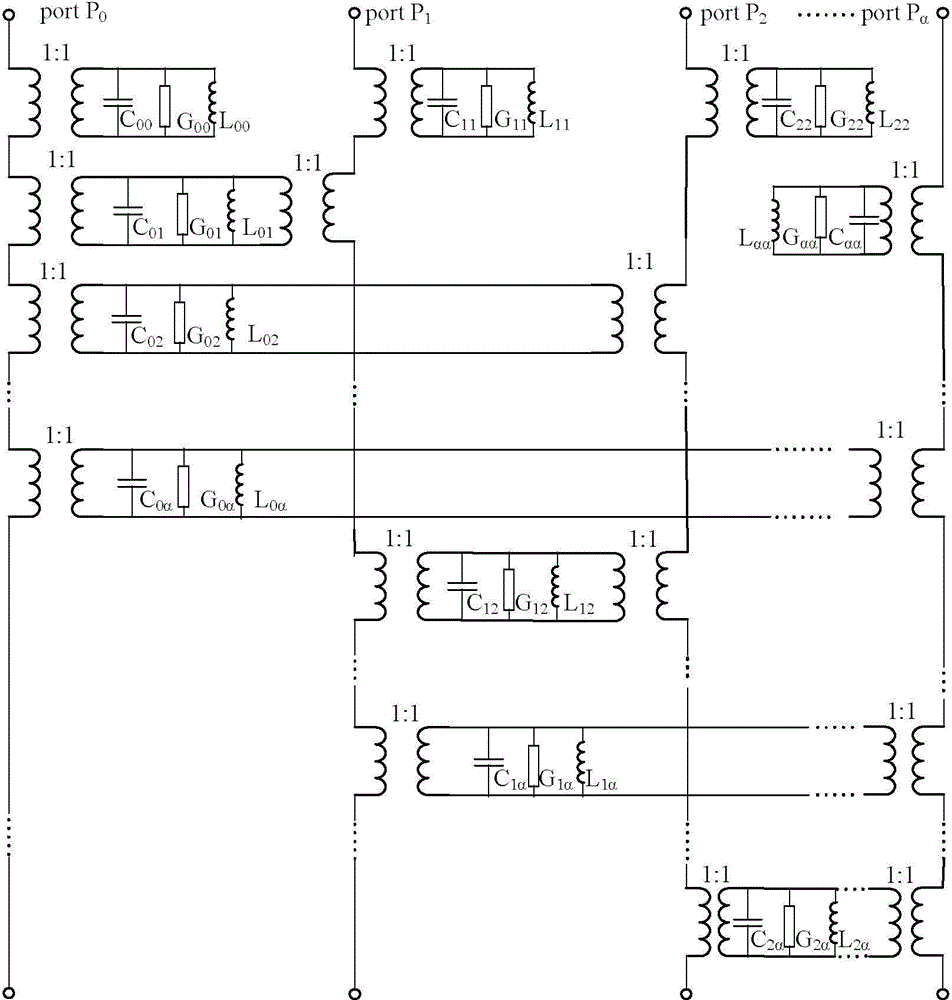

Capacitor-carried power supply ground plane modeling and capacitor decoupling radius simulating method

ActiveCN104933270AReliable guidanceCalculation method is fastSpecial data processing applicationsCapacitanceEngineering

The invention discloses a capacitor-carried power supply ground plane modeling and capacitor decoupling radius simulating method. The method includes the steps of recording coordinates of an input / output port and a decoupling capacitor port, calculating port coefficients and frequency domain responses of all resonance modes according to a resonant cavity formula or based on a double-frequency-point approximation algorithm resonant cavity formula, obtaining all capacitor division schemes according to the port coefficients, the frequency domain responses of all the resonance modes, the number of the modes, the capacitor frequency domain responses and the number of capacitors, converting the divided capacitors into a power supply ground plane resonant cavity model to obtain a capacitor-carried power supply ground plane resonant cavity formula, calculating power supply ground plane actual frequency domain impedance distribution through the resonant cavity formula, and extracting the capacitor decoupling radius on the basis of the impedance distribution. By means of the method, the problem that capacitor-carried power supply ground plane modeling can not be conducted through a resonant cavity algorithm is solved, a rapid, easy and convenient method is provided for load-carried power supply ground plane modeling, and reliable guidance is provided for selection and placement of the decoupling capacitors in power supply integrity design through the decoupling radius.

Owner:XIDIAN UNIV

Circuit and method for monitoring the integrity of a power supply

Circuits and methods are provided herein for monitoring the integrity of a power supply, the circuits and methods providing additional resources / information for diagnosing a cause behind a reset signal, and in some cases, a reason behind a power failure. A first method described herein provides exemplary steps for monitoring a level of a power supply voltage supplied to one or more system components. A second method describes exemplary steps for monitoring an electrical connection between the power supply (or ground supply) and one or more supply pins. Each of the methods involves monitoring a state of one or more bits stored, e.g., within a status register. The methods may be used separately, or in conjunction with one another, for detecting the occurrence of a power abnormality.

Owner:CYPRESS SEMICON CORP

Circuit for measuring on-chip power supply integrity

InactiveUS20050007126A1Exclude influenceError preventionCurrent/voltage measurementGround bounceEngineering

A test circuit and method for measuring power supply integrity is provided. The circuit may be incorporated on-chip and is small enough to be integrated many times across the surface of the die for measuring integrity parameters at several locations on the chip. The circuit instantaneously measures, e.g., the rail voltage of a power supply, which may be fluctuating at the time of measurement. In addition, the circuit isolates itself from all chip power rails for the duration of the measurement, thereby eliminating any influence of external noise on the measurement. A storage capacitor is charged up to full power rail voltage for powering up a comparator. Then, the comparator is isolated from the power rails and the measurements are taken. Based upon the measurements, certain power supply integrity parameters are quantified including ground bounce and power droop.

Owner:MICRON TECH INC

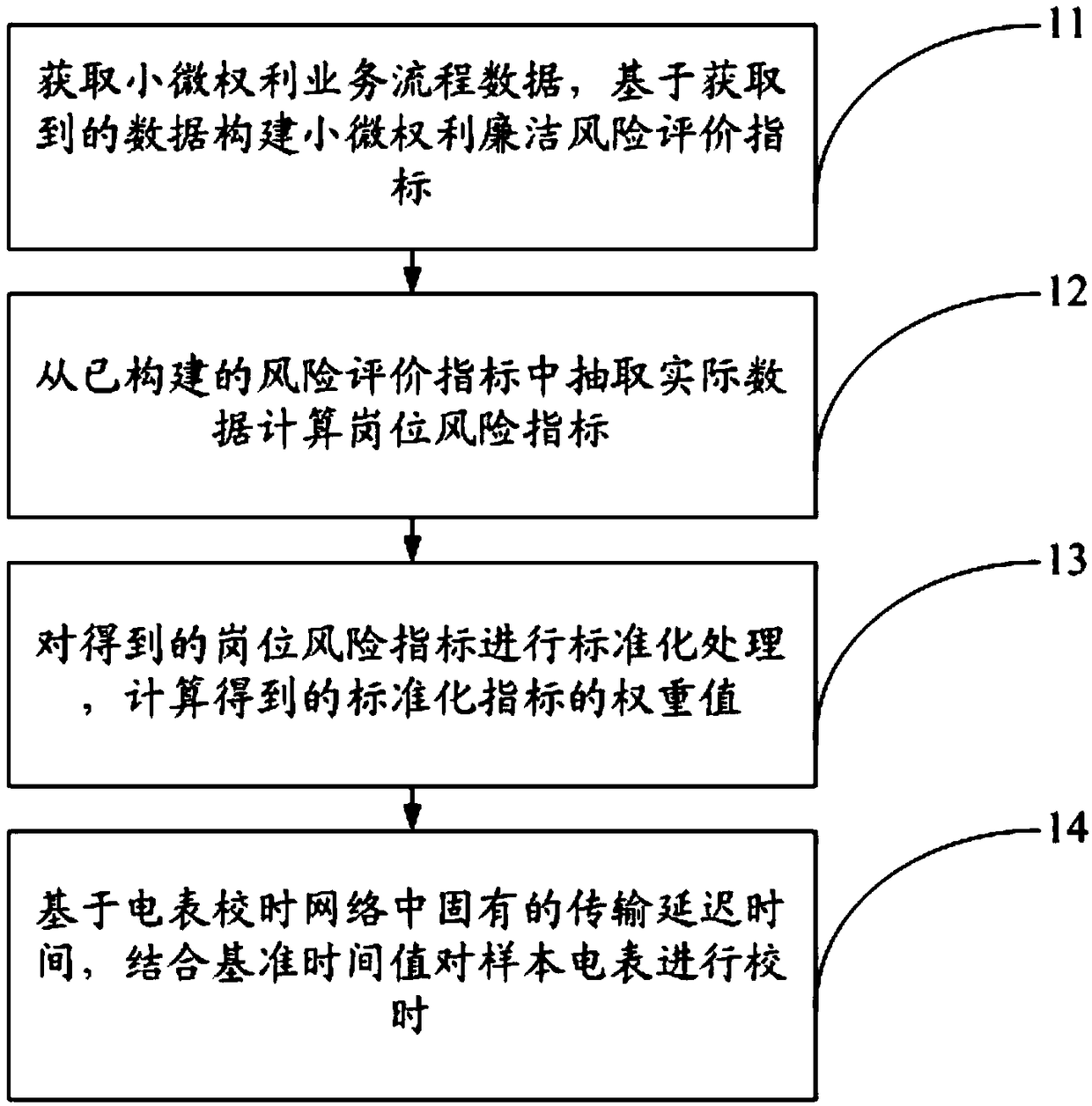

Method for constructing a small power integrity risk index of a power supply station based on big data

InactiveCN109190907AImprove risk prevention and control capabilitiesResourcesLogisticsData centerEngineering

The invention provides a method for constructing a small power integrity risk index of a power supply station based on big data, belonging to the data processing field. The method includes: building asmall and micro power integrity risk evaluation data center based on business information system, building small and micro power integrity risk evaluation index, based on the actual data, evaluatingthe small micro-power integrity risk indicators, extracting the actual data to evaluate and screen the indicators, determining the index weight, calculating the small micro-power integrity risk index,carrying out the small micro-power integrity risk rating, and carrying out the trend analysis and early warning of the small micro-power integrity risk index based on the actual data. By using the rich business data accumulated in existing business information systems, current data is rated by constructing an evaluation system, so corresponding measures are taken according to the rating results to improve the small power risk management and information level of power supply substation, effectively identify the small power integrity risk and enhance the risk prevention and control capacity.

Owner:STATE GRID ZHEJIANG LINAN POWER SUPPLY +1

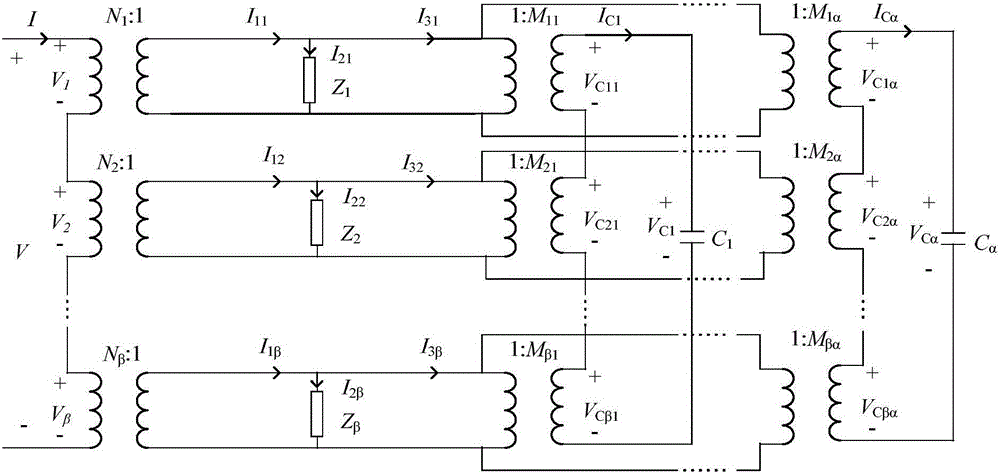

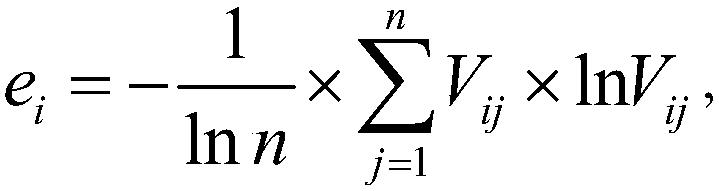

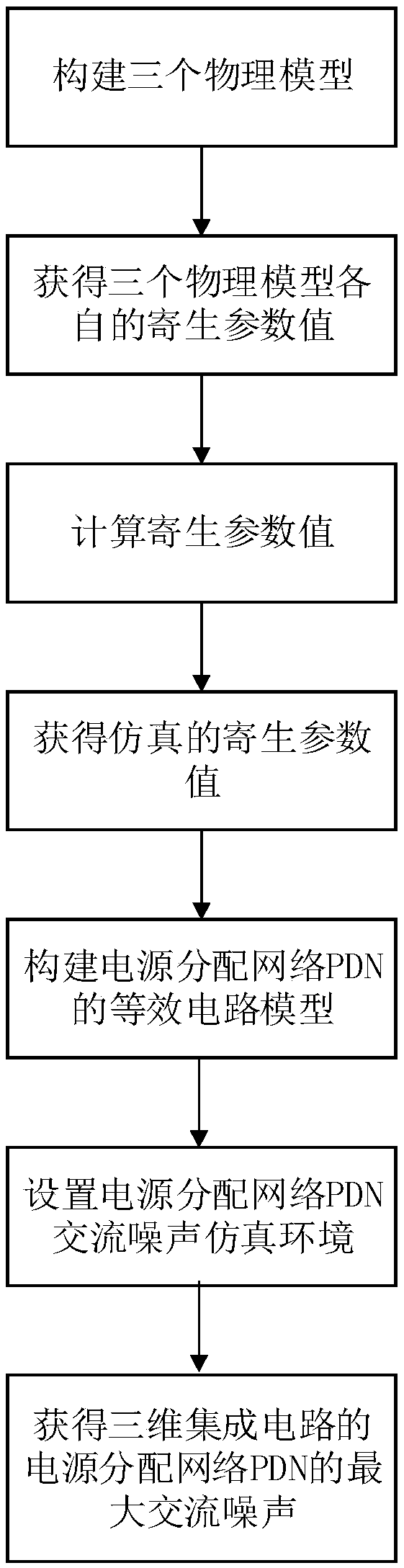

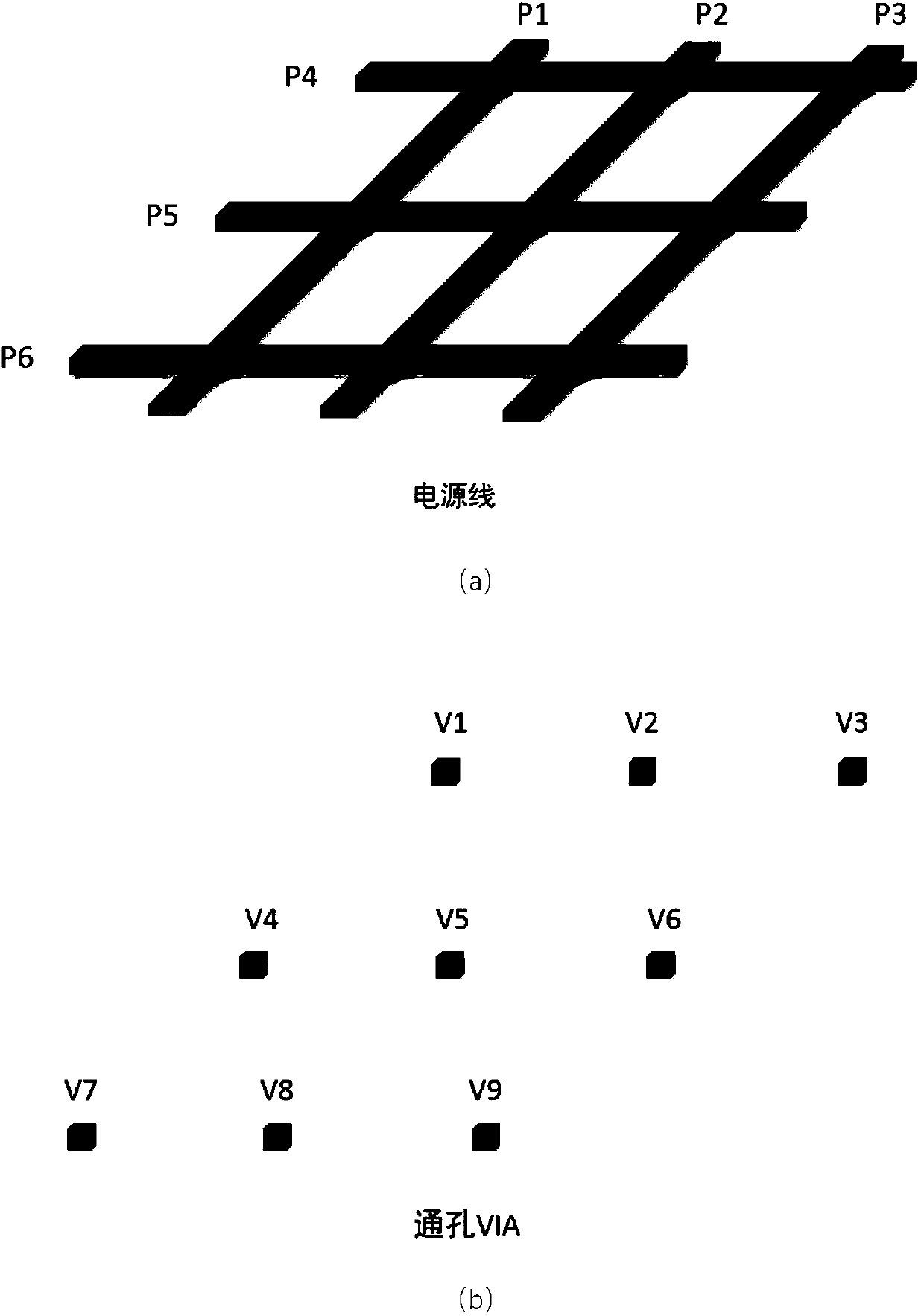

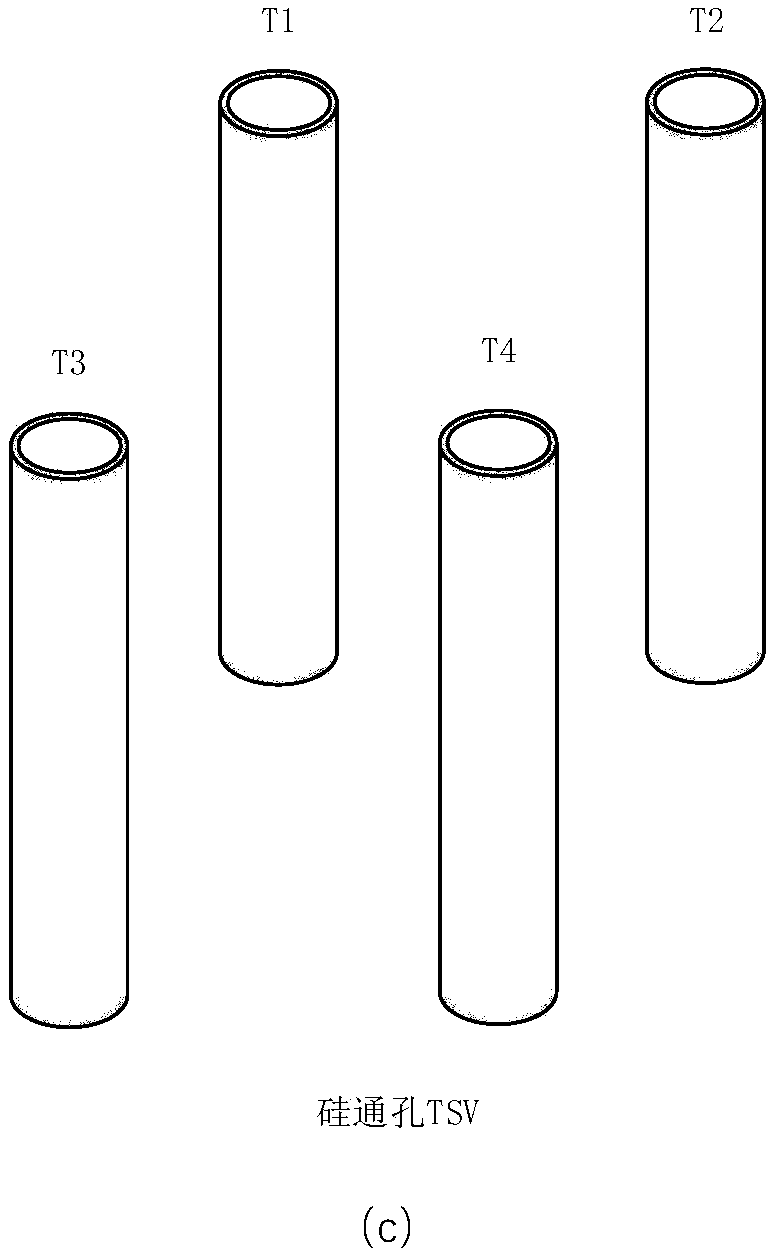

PDN alternating current noise analysis method for a three-dimensional integrated circuit

ActiveCN109522653AOvercome the disadvantage of slow analysis speedFast analysisSpecial data processing applicationsPhysical modelEngineering

The invention discloses a PDN alternating current noise analysis method of a three-dimensional integrated circuit, which is used for analyzing the magnitude of PDN alternating current noise of the three-dimensional integrated circuit. The method comprises the following implementation steps: (1) constructing three physical models; (2) obtaining respective parasitic parameter values of the three physical models; (3) calculating parasitic parameter values; (4) obtaining simulated parasitic parameter values; (5) constructing an equivalent circuit model of the power distribution network PDN; (6) setting a power distribution network PDN alternating current noise simulation environment; And (7) obtaining the maximum alternating current noise of the power distribution network PDN of the three-dimensional integrated circuit. The method can quickly and accurately analyze and obtain the magnitude of the alternating current noise of the PDN of the three-dimensional integrated circuit, and can be used for providing a basis for design analysis of the integrity of the power supply in the power distribution network of the high-speed three-dimensional integrated circuit and evaluation of the packaging reliability.

Owner:XIDIAN UNIV

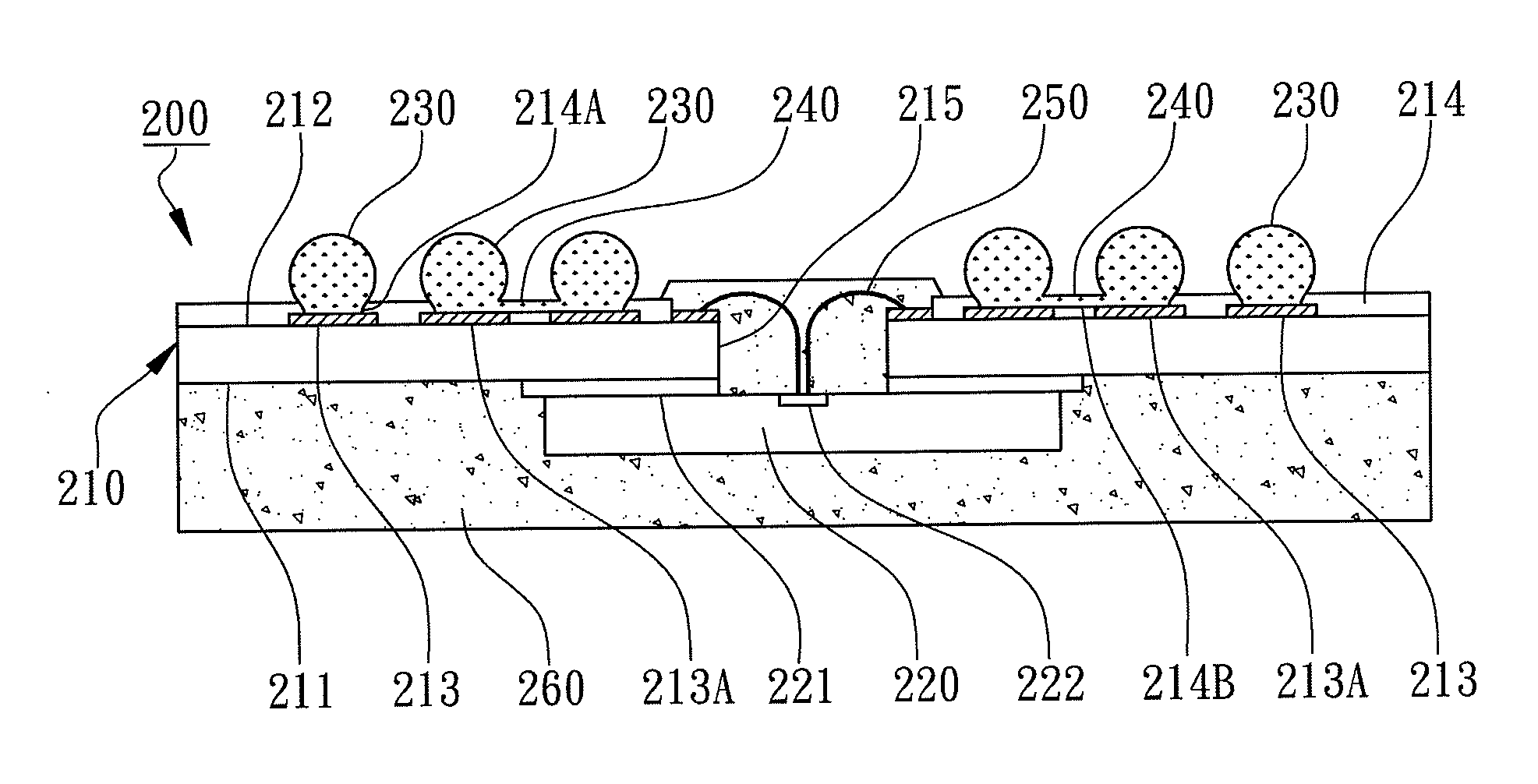

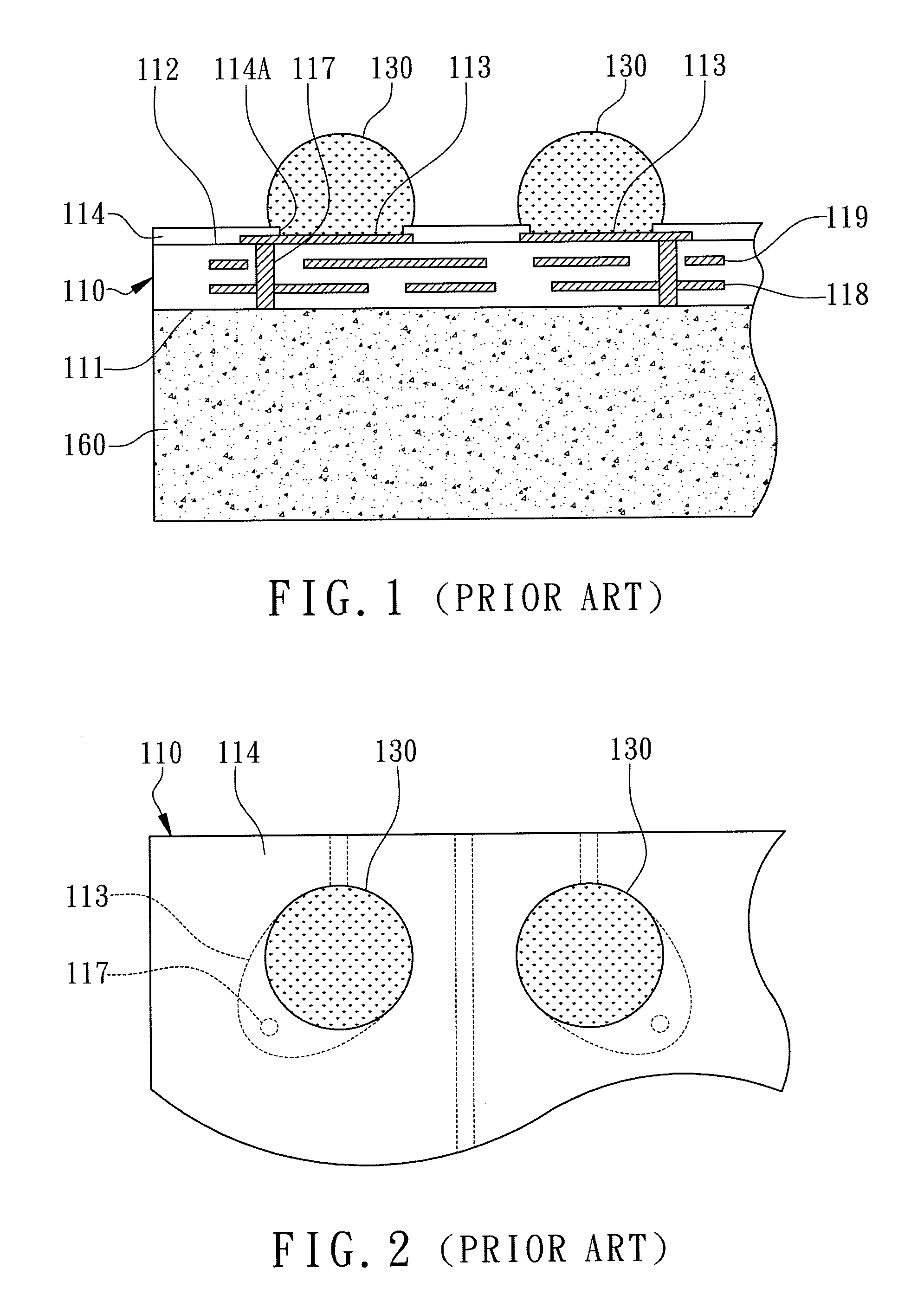

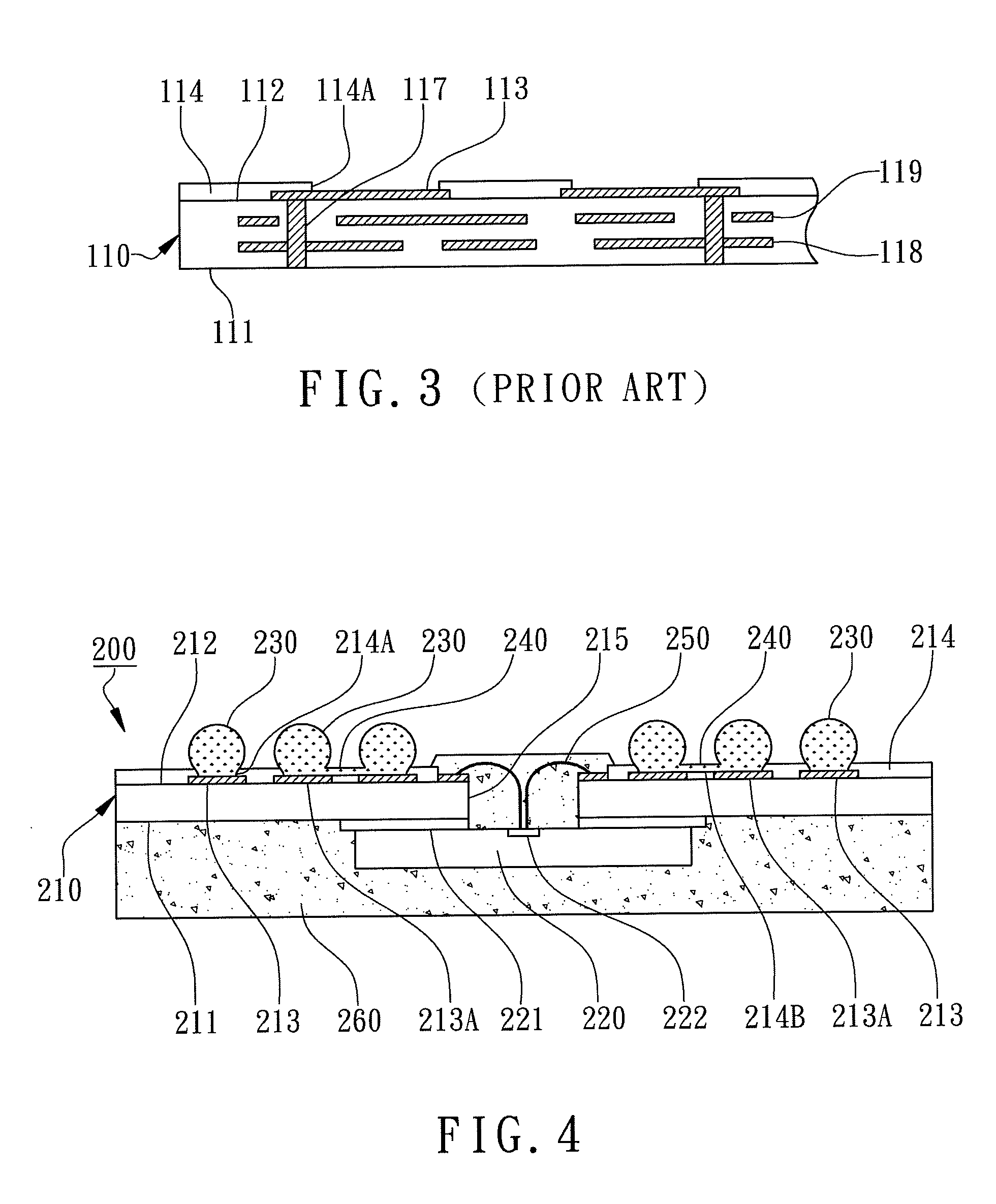

Ball grid array package

InactiveUS20120049359A1Reduce disposalThinnerSemiconductor/solid-state device detailsSolid-state devicesSolder maskSolder ball

A BGA package comprises a substrate, a chip disposed on the substrate, and a plurality of solder balls disposed under the substrate. The substrate further has a plurality of ball pads and a solder mask having a plurality of openings to expose the ball pads where the ball pads include two or more non-signal pads. Solder mask further has a trench connecting the ones of the openings on the non-signal pads where the trench is filled with solder paste so that the solder balls bonded to the non-signal pads are electrically connected together to achieve power integrity and to reduce numbers of power / ground layers to make the package thinner and the substrate cost lower.

Owner:POWERTECH TECHNOLOGY

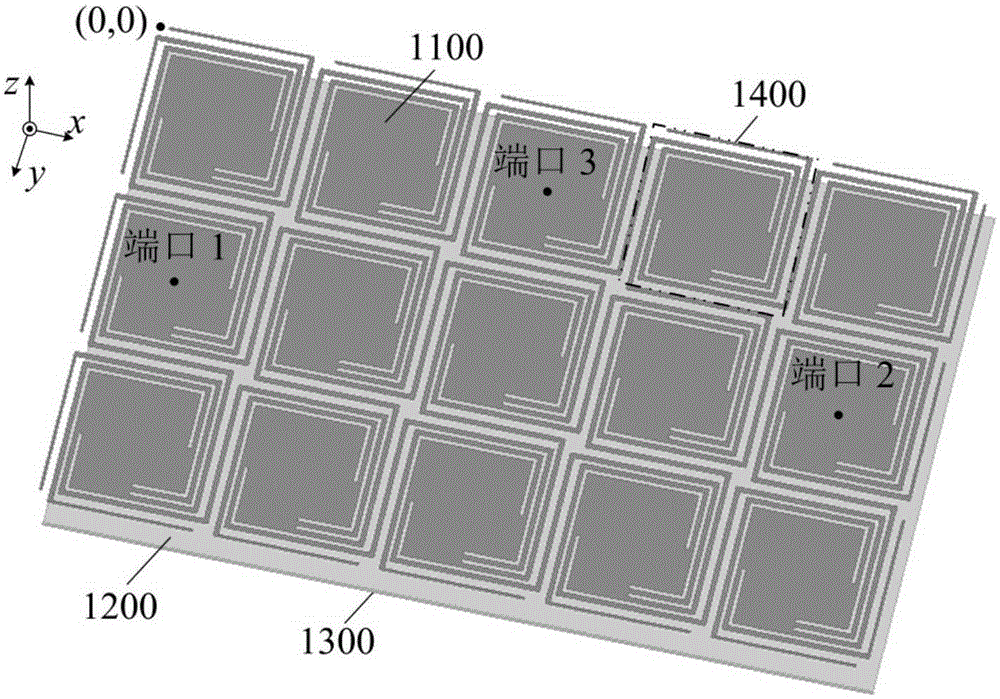

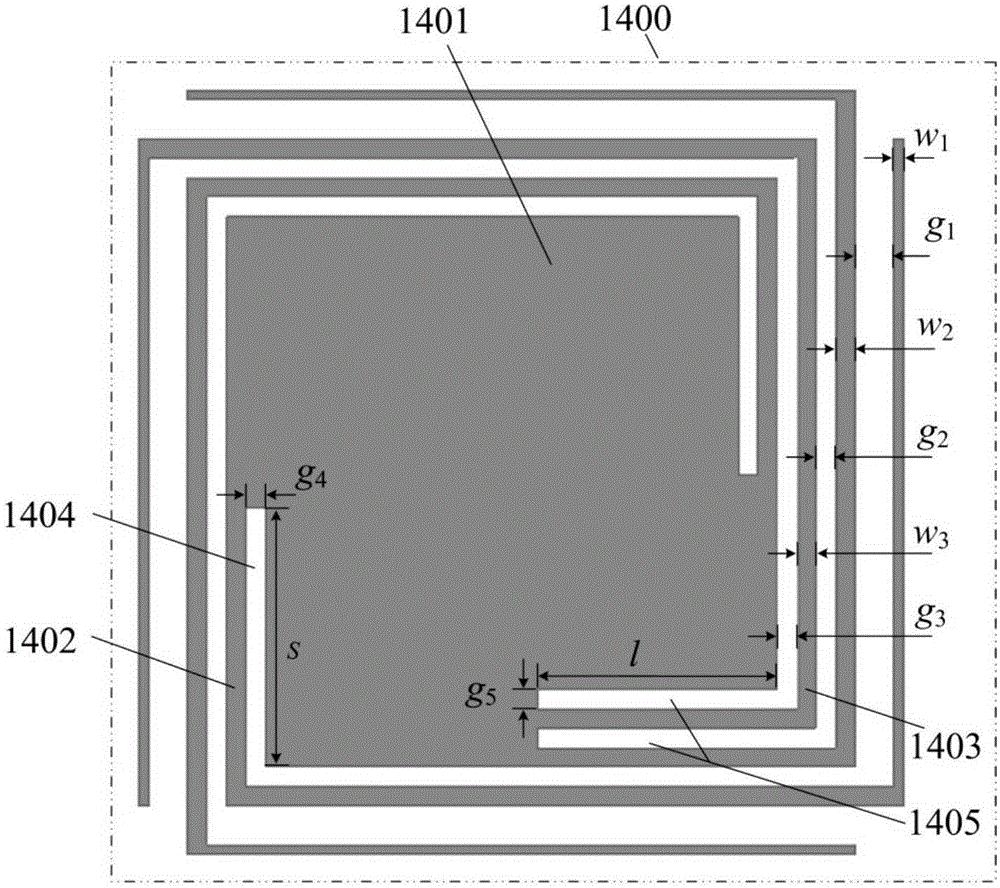

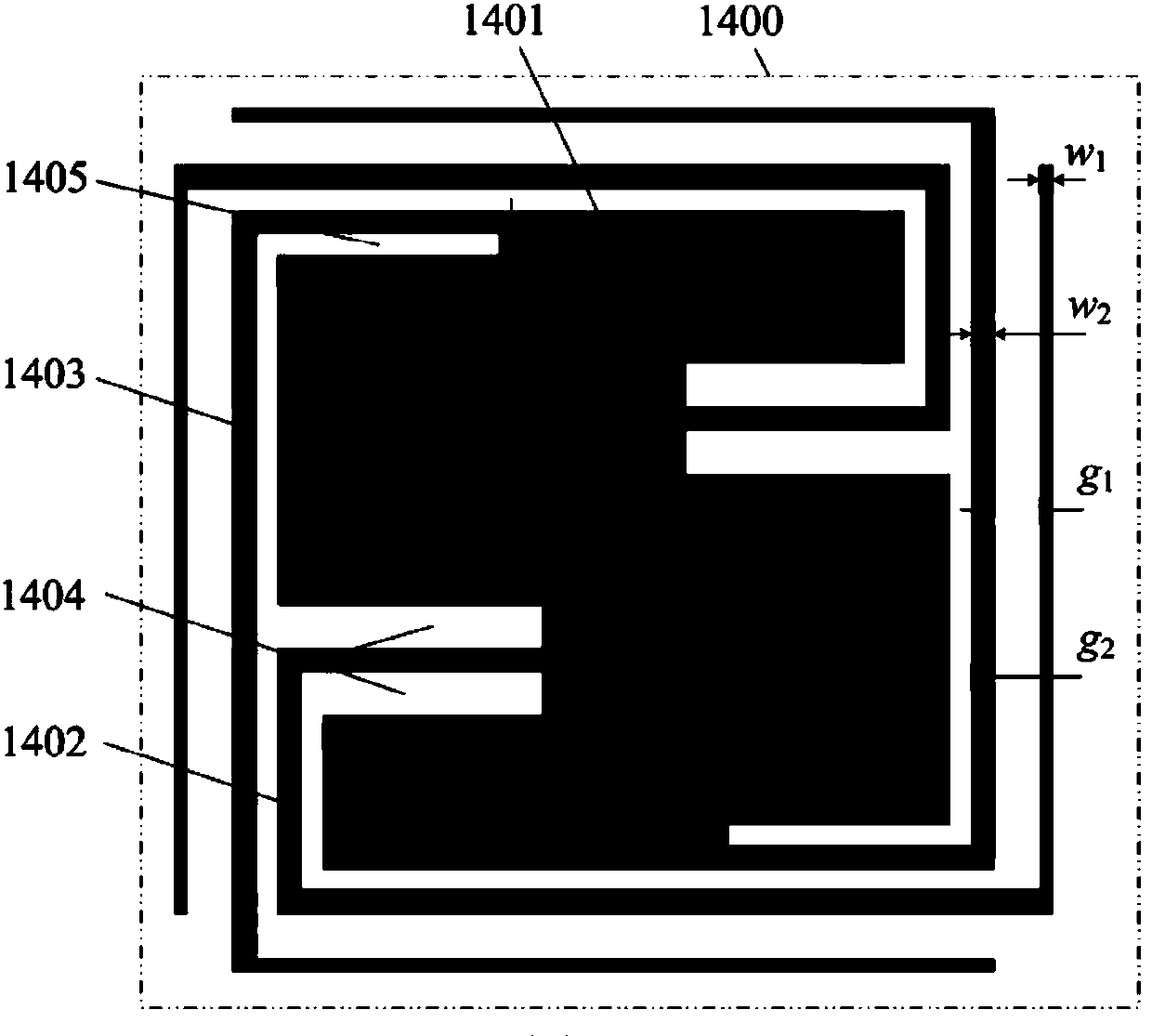

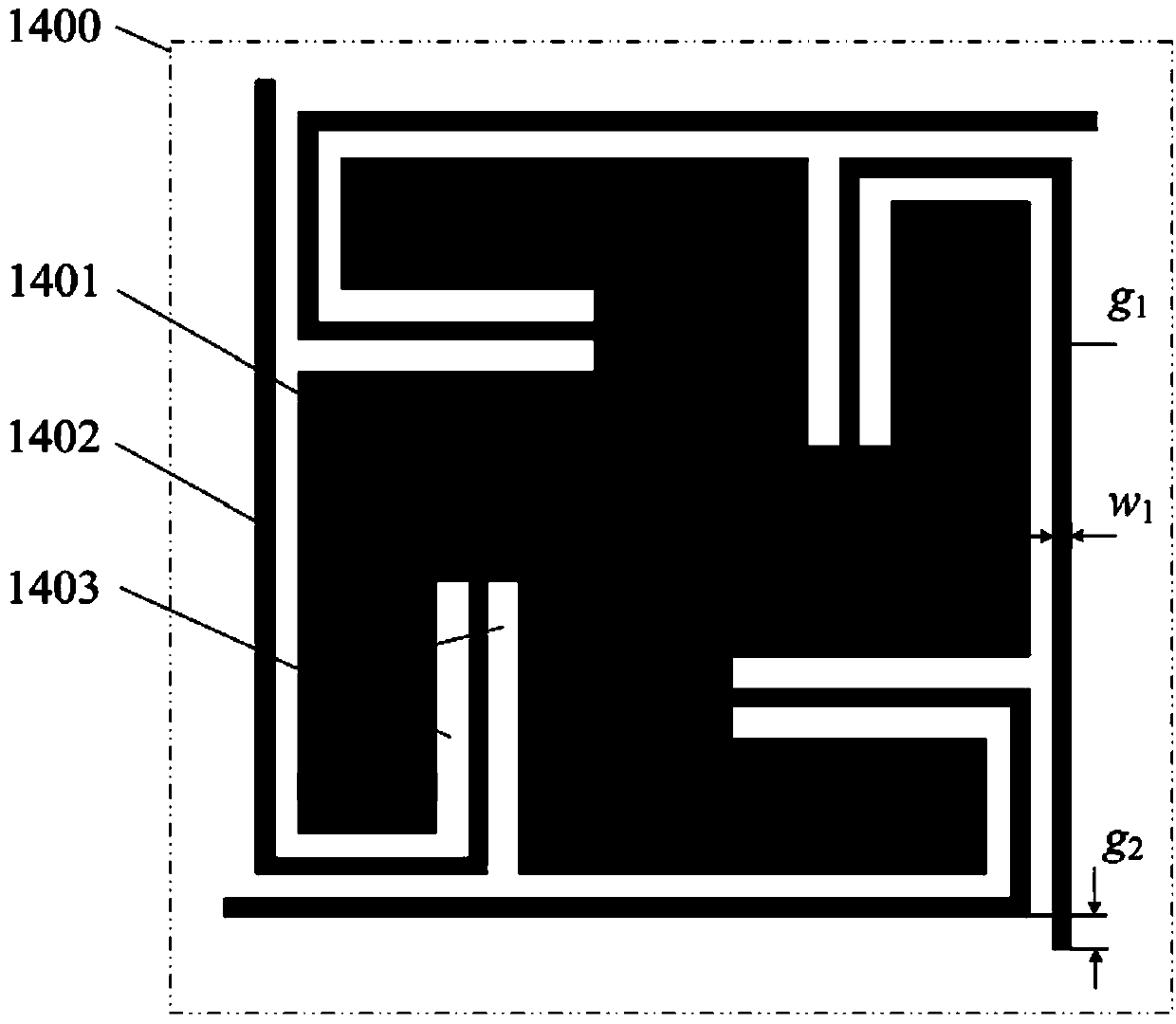

Power distribution network based on plane hybrid-bridge electromagnetic band gap structure

The invention discloses a power distribution network based on a plane hybrid-bridge electromagnetic band gap structure. The power distribution network comprises a power plane, a dielectric substrate and a ground plane, wherein the power plane, the dielectric substrate and the ground plane are sequentially arranged. The power plane comprises an electromagnetic band gap structure unit matrix. Each plane hybrid-bridge electromagnetic band gap structure unit is provided with four S-type bridges, two of the four S-type bridges are S1-type bridges connected with two longitudinally-adjacent pasters, and the other two of the four S-type bridges are S2-type bridges connected with two transversely-adjacent pasters. According to the power distribution network, the plane hybrid-bridge electromagnetic band gap structure units are periodically carved in the power plane of the power distribution network, simultaneous switching noise between the power plane and the ground plane in the power distribution network can be suppressed within a wide frequency range, and the good power integrity of a system can be obtained.

Owner:ZHEJIANG UNIV OF TECH

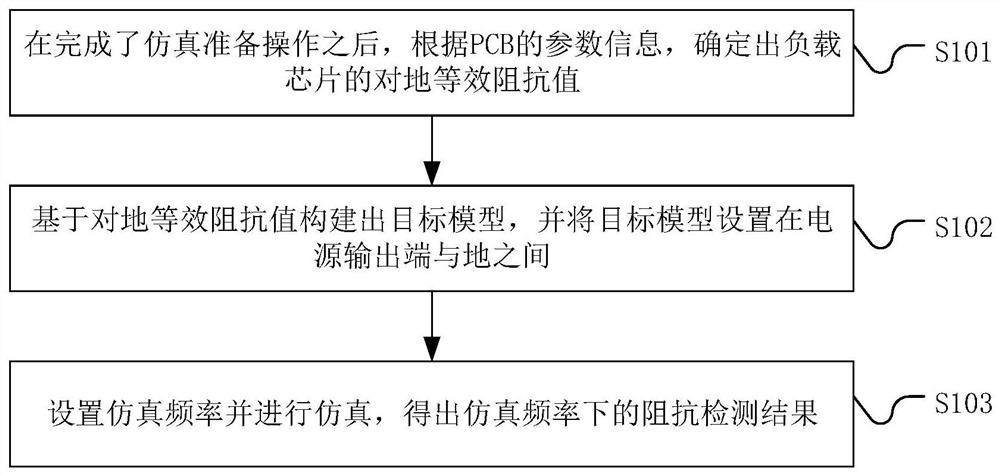

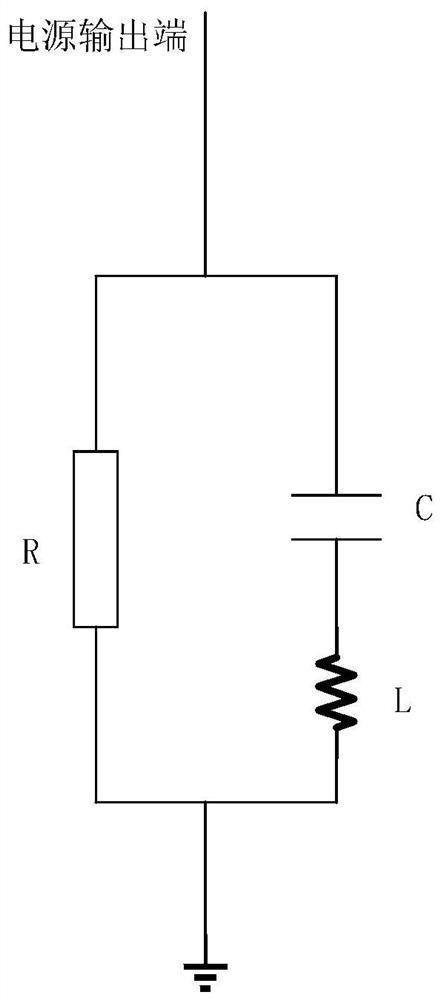

Impedance detection method, system and device for PCB power supply and storage medium

PendingCN112069755AImprove integrityAccurate Design FlawsCAD circuit designSpecial data processing applicationsControl theoryPower integrity

The invention discloses an impedance detection method for a PCB power supply. The method comprises the steps of determining a ground equivalent impedance value of a load chip according to the parameter information of a PCB after simulation preparation operation is completed; constructing a target model based on the equivalent impedance value to the ground, and setting the target model between thepower supply output end and the ground; and setting a simulation frequency and carrying out simulation to obtain an impedance detection result under the simulation frequency. By applying the scheme provided by the invention, a more accurate impedance detection result can be obtained, the design defect of the PCB power supply can be determined more accurately, the risk design is avoided, and the power supply integrity is improved. The invention further provides an impedance detection system and device for the PCB power supply and a storage medium, which have corresponding technical effects.

Owner:INSPUR BUSINESS MACHINE CO LTD

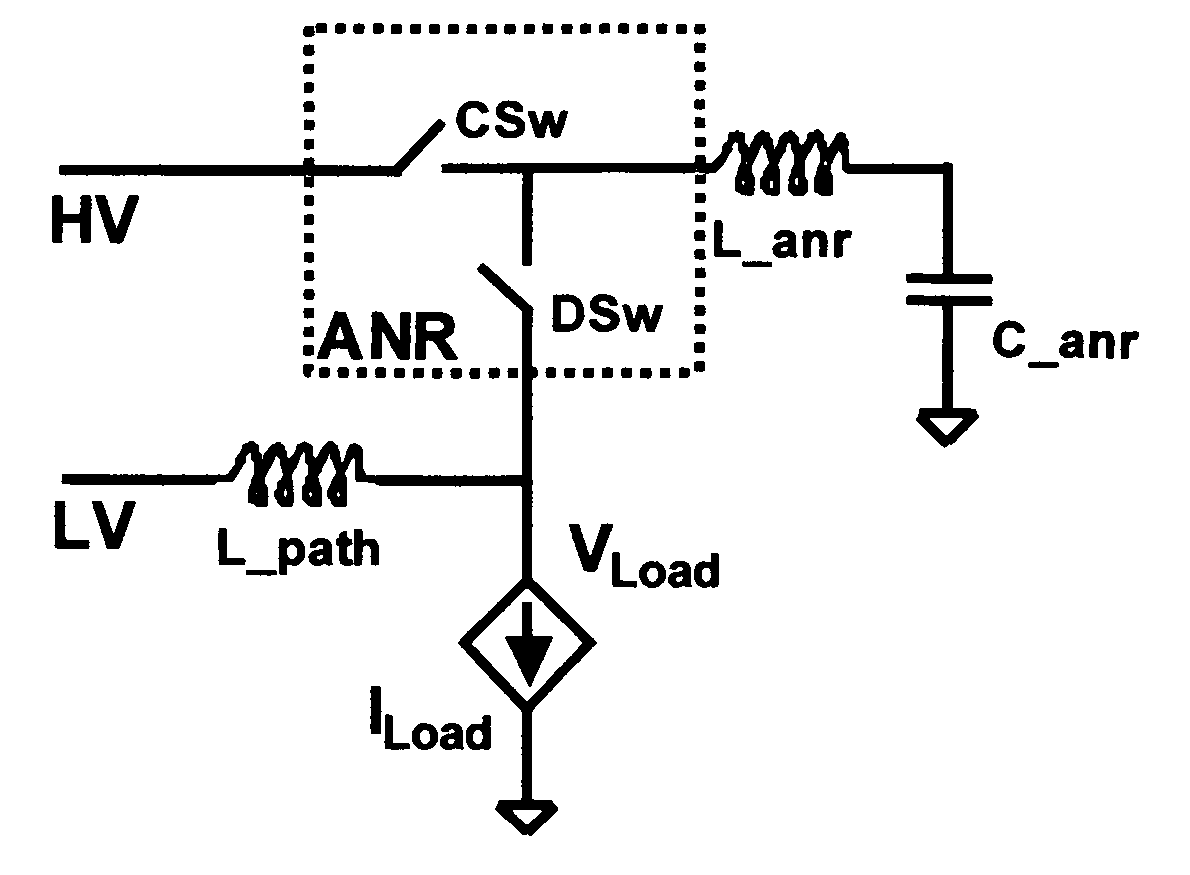

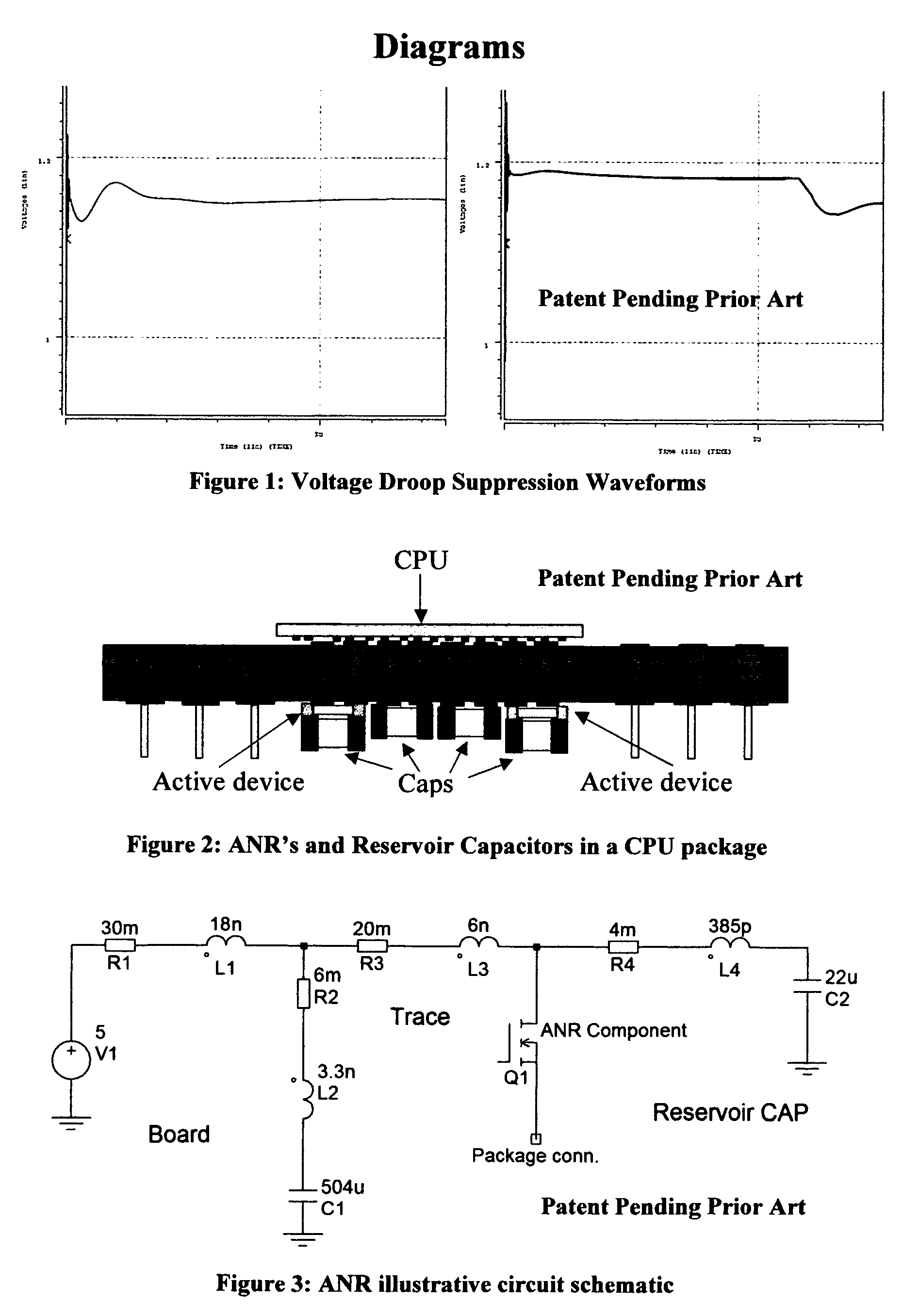

Active noise regulator

InactiveUS20060186937A1Minimizes noise powerNoise minimizationElectronic switchingElectric pulse generatorPower gridAbsorbed power

The invention proposes noise suppression circuits mounted on the package of a high power, high frequency ULSI component. In this architecture, termed an active noise regulator (ANR), charge is stored on dedicated reservoir capacitors at a voltage substantially higher than the operating voltage of the ULSI device. These reservoir capacitors are mounted upon active circuits packaged to match the size and form factor of the capacitors and this assembly is then attached to the package substrate. Charge is conveyed from the reservoir capacitors to the ULSI power grid when there is a sudden load current demand in the ULSI device. The capacitors are depleted by the flow of charge through inductances in the discharge pathway. The capacitors are then recharged either by the overshoot that results from a sudden release of the ULSI load current demand or by a gated charging pathway connected to a high voltage supply. The use of the depleted reservoir capacitor to absorb power grid voltage overshoots assists in maintaining power integrity for the ULSI device while conserving energy in the power pathways. The circuits within the active device may be any combination of semiconductor switches and / or voltage regulators, and may also contain voltage and current sensing circuitry.

Owner:NAIR RAJENDRAN

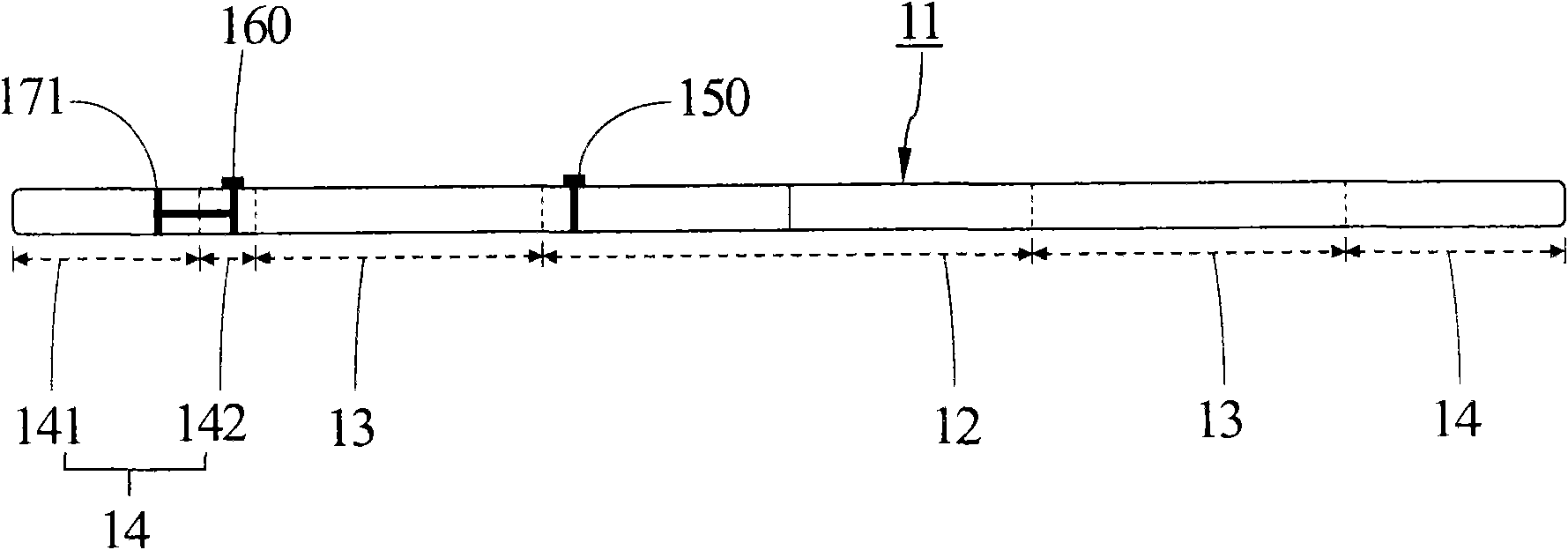

Probe card and printed circuit board used for same

ActiveCN102156205AAvoid attenuationImprove integrityElectrical measurement instrument detailsElectrical testingProbe cardEngineering

The invention provides a probe card and a printed circuit board used for the same, which are used for promoting the power integrity during testing. The printed circuit board provided by the invention is defined as a welding spot area, a routing area and an input area, wherein the welding spot area comprises a plurality of first power welding pad groups; the input area comprises a plurality of second welding pad groups corresponding to the first power welding pad groups; and each first power welding pad group is insulated from each second welding pad group. The probe card provided by the invention adopts the printed circuit board and is combined with an external wire or an external power plane to obtain the better power integrity.

Owner:MICROELECTRONICS TECH INC

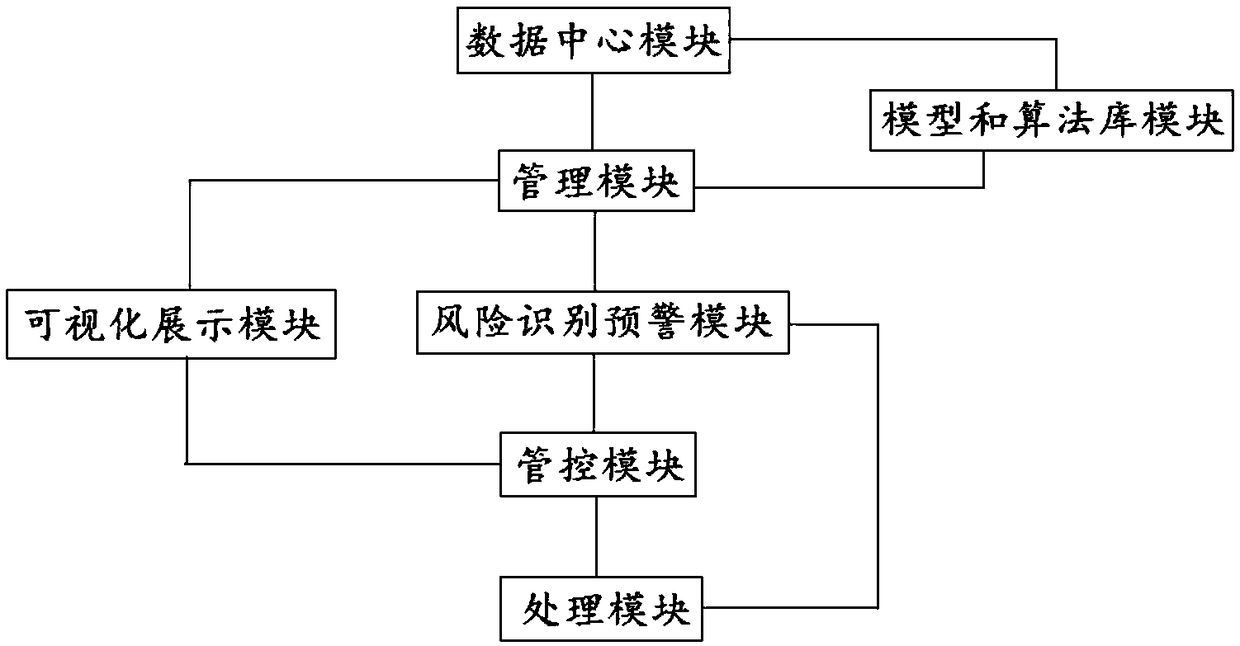

Power Supply Station Small Power Integrity Risk Supervision and Control System Based on Enterprise Cloud Platform

The invention relates to the application field of big data, in particular to a power supply station small power clean and honest risk supervision and control system based on an enterprise cloud platform. The system comprises a data center module, a model and algorithm library module, a management module, a risk identification and early warning module, a management control module and a processing module. The data center module is connected with an enterprise cloud platform; The model and algorithm library module are connected with a data center module and a management module; The management module is connected with a data center module; The risk identification and early warning module is connected with the management module; The management and control module is connected with a risk identification and early warning module; The processing module is connected with a risk identification and early warning module and a management and control module. The invention has the beneficial effects of realizing the supervision and control of the small power incorruptibility risk of the power supply substation.

Owner:STATE GRID ZHEJIANG LINAN POWER SUPPLY +2

Power distribution network based on plane C-type bridge electromagnetic band gap structure

The invention discloses a power distribution network based on a plane C-type bridge electromagnetic band gap structure. The power distribution network comprises a power plane, a dielectric substrate and a ground plane, wherein the power plane, the dielectric substrate and the ground plane are sequentially arranged. The power plane comprises an electromagnetic band gap structure unit matrix. Each electromagnetic band gap structure unit is of a central symmetry structure and provided with four C-type bridges in a led mode, the four C-type bridges are connected with four adjacent electromagnetic band gap structure units respectively, and the two ends of any C-type bridge are connected to the opposite sides of two adjacent electromagnetic band gap structure units respectively. According to the power distribution network, the plane C-type bridge electromagnetic band gap structure units are periodically carved in the power plane of the power distribution network, simultaneous switching noise between the power plane and the ground plane in the power distribution network can be suppressed within a wide frequency range, and the good power integrity of a system can be obtained.

Owner:ZHEJIANG UNIV OF TECH

Power distribution network in high-speed circuit system

InactiveCN102522962AReduce radiation lossBreak continuityDigital technique networkCapacitanceReturn current

The invention discloses a power distribution network in a high-speed circuit system. The metal surface at one side of a buried capacitor is locally etched with a complementary split ring resonator, and the metal surface at the other side of the buried capacitor keeps complete; and simultaneously, the upper side and the lower side of the buried capacitor are respectively added with a layer of FR-4 medium, and SMA (shape memory alloy) coaxial joints are used for connecting a circuit board to a vector network analyzer to test a noise suppression transmission coefficient among ports. According to the power distribution network, the problems that the noise suppression band of a synchronous switch in the high-speed circuit system is not wide and the suppression degree is not deep are effectively solved, and simultaneously the damage for a return current path of a circuit is less. The mixed high-speed circuit system based on the power distribution network has good power integrity, and is convenient for standard technical processing of printed circuit boards.

Owner:SHANGHAI JIAO TONG UNIV

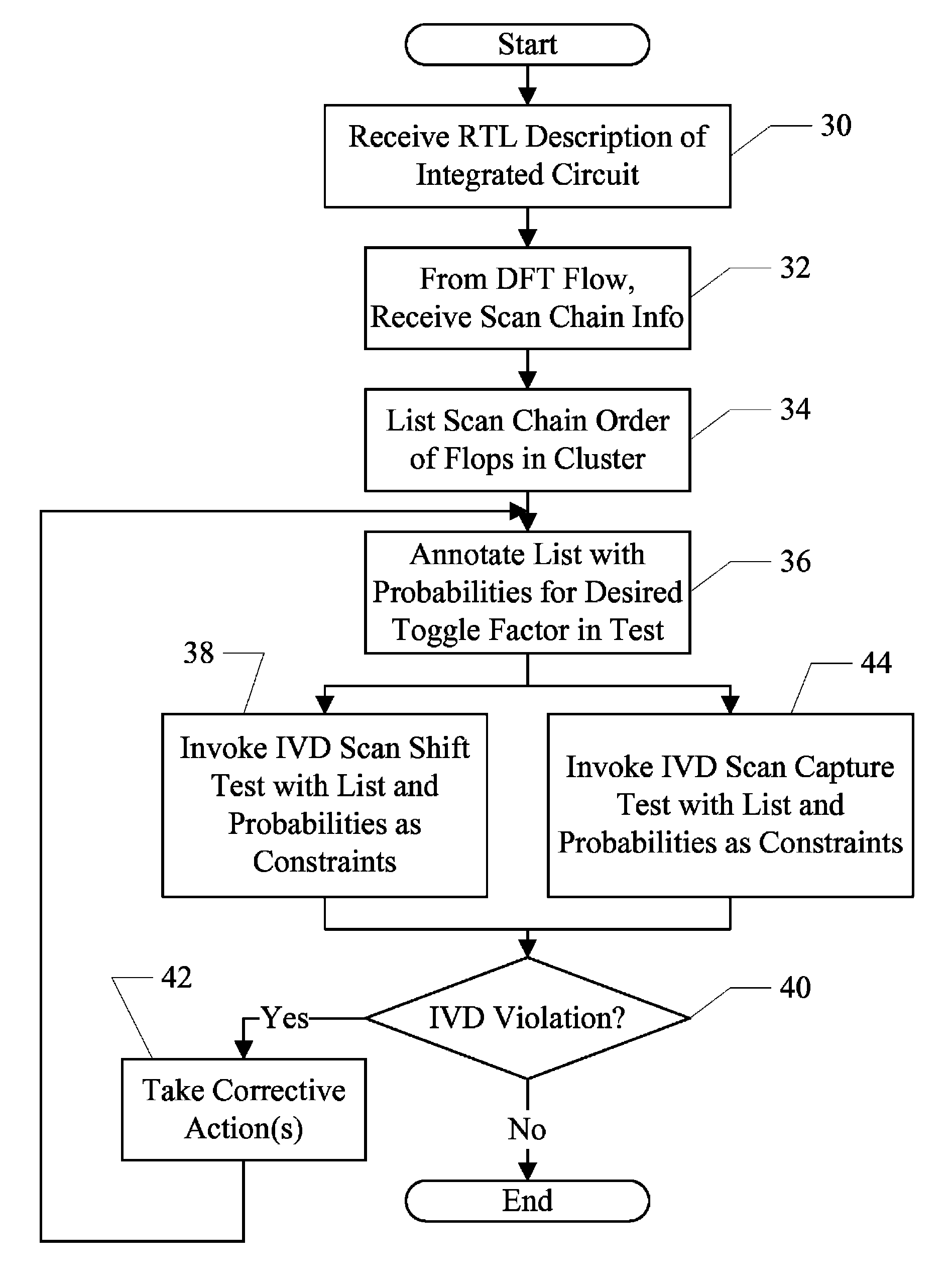

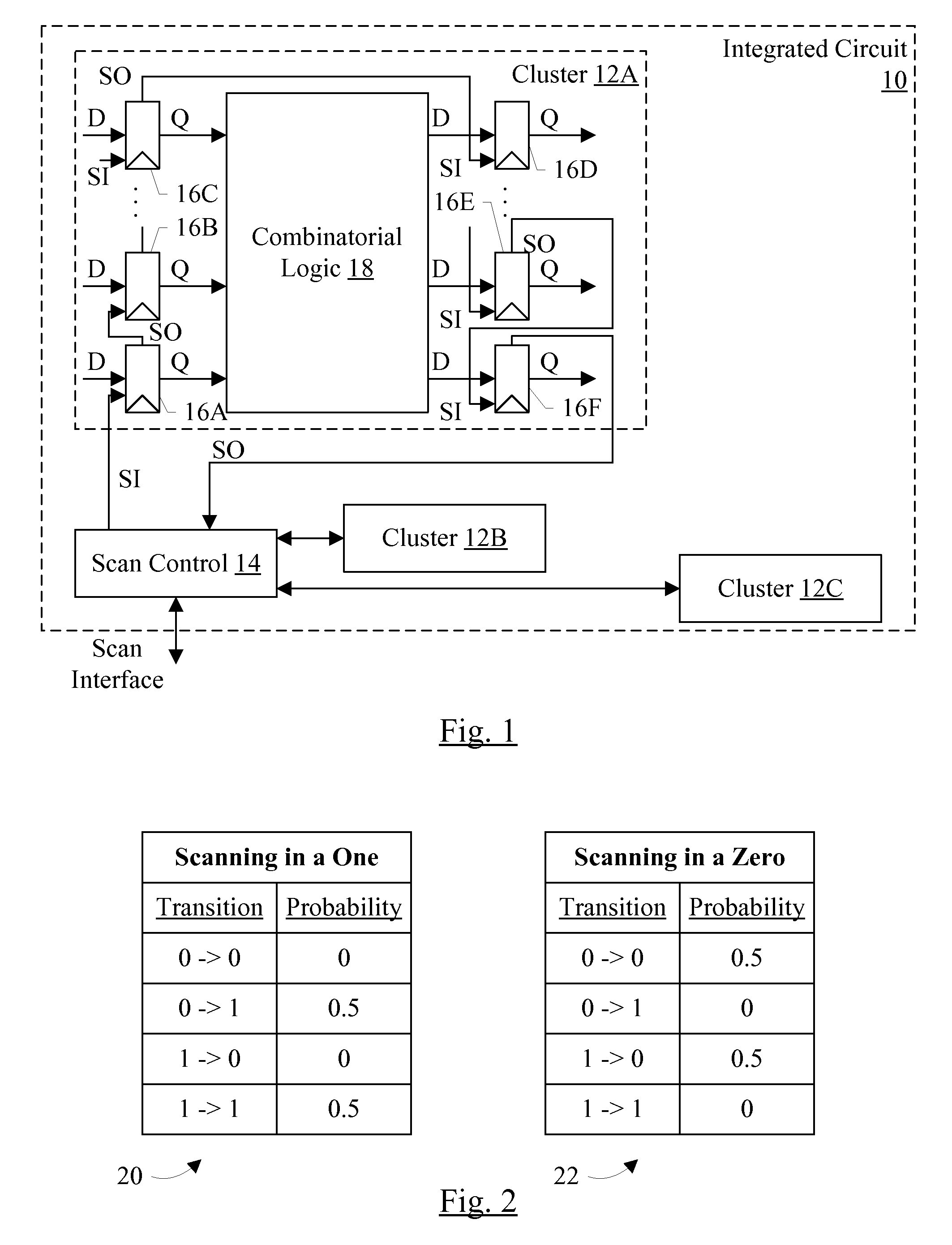

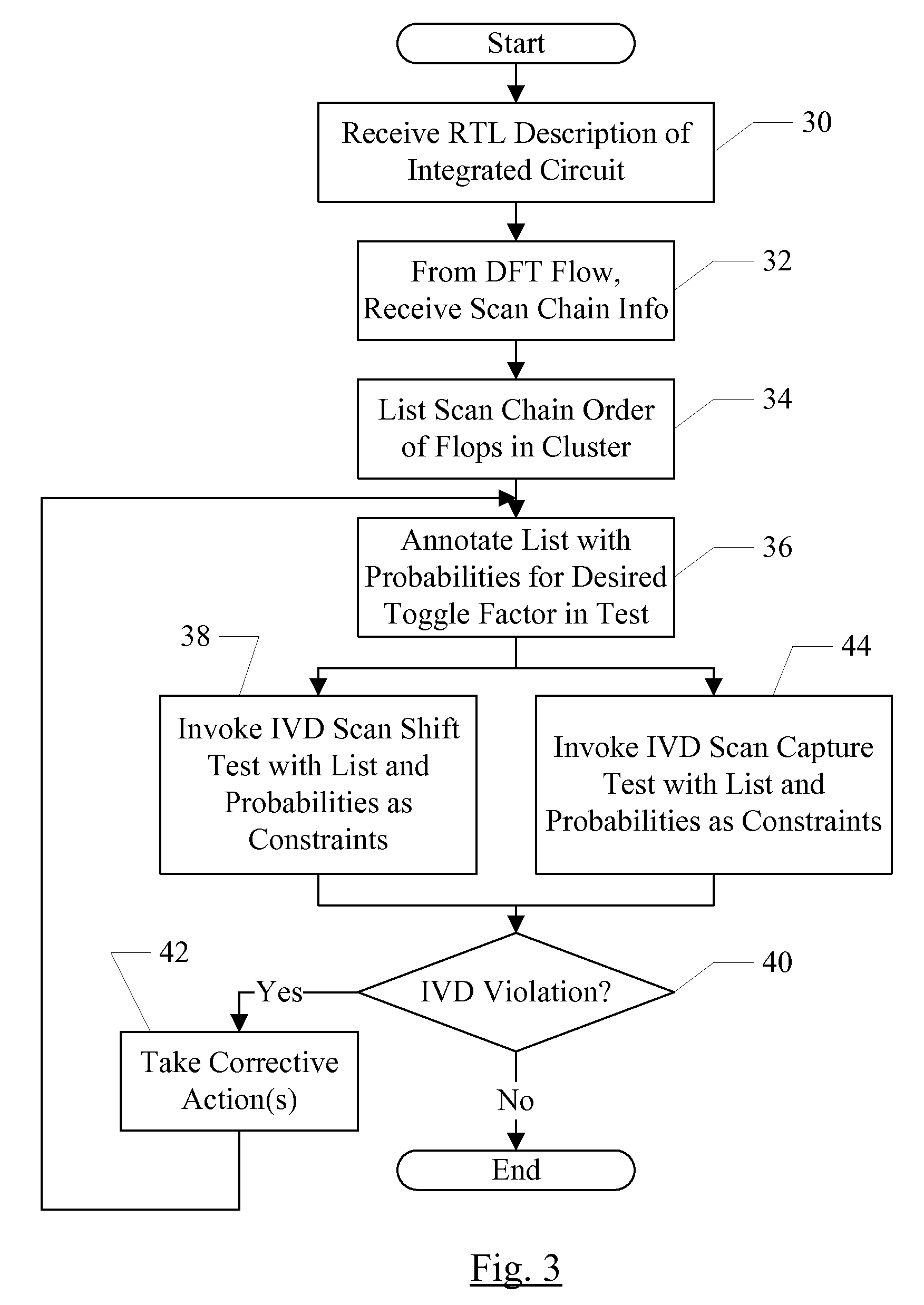

Vectorless IVD analysis prior to tapeout to prevent scan test failure due to voltage drop

InactiveUS8413102B2Improve testabilityLengthy delaysDetecting faulty computer hardwareElectrical testingDesign cycleVoltage drop

In one embodiment, a vectorless IVD methodology may be used to estimate IVD issues for an integrated circuit earlier in the design cycle of the integrated circuit, e.g. when corrective actions may still be taken to correct IVD failures. In the methodology, scan chains for various clusters in the integrated circuit may be identified, even though the scan chains may still be subject to change as the design evolves. A power integrity tool may analyze the scan chains based on a probability of transitions in the devices within the scan chain (e.g. flops) for a theoretical worst-case test vector. If the result of analysis identifies IVD failures in the clusters, corrective action may be taken such as modifying the design. Alternatively, the corrective action may include identifying one or more flops that experience failure as devices to be excluded from the test vector generation process for scan testing.

Owner:APPLE INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com