Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

85 results about "Model order reduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Model order reduction (MOR) is a technique for reducing the computational complexity of mathematical models in numerical simulations. As such it is closely related to the concept of metamodeling with applications in all areas of mathematical modelling.

Structured and parameterized model order reduction

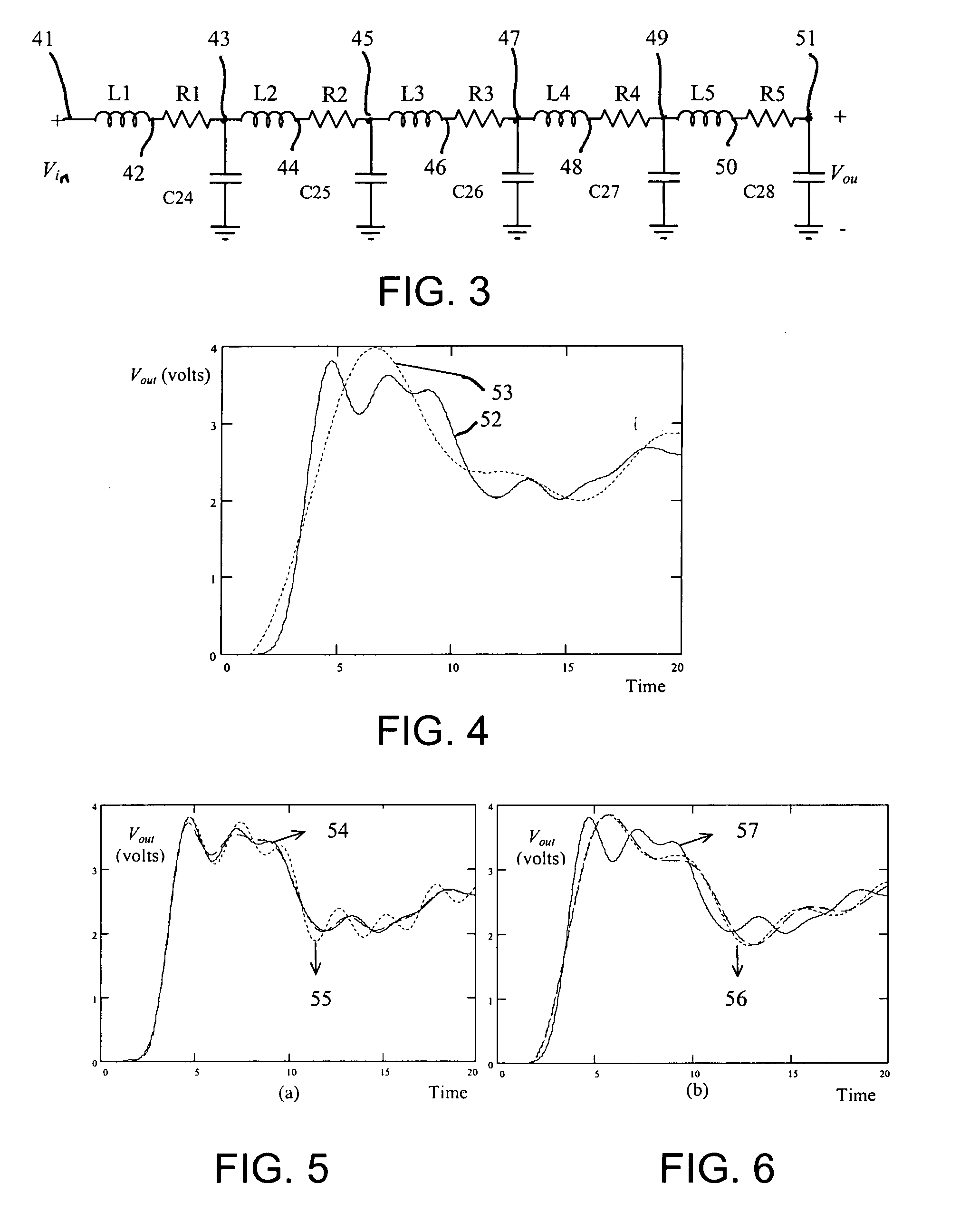

InactiveUS20080072182A1Reduce redundancyNon-uniformity is constantDetecting faulty computer hardwareComputation using non-denominational number representationStructured modelOrder reduction

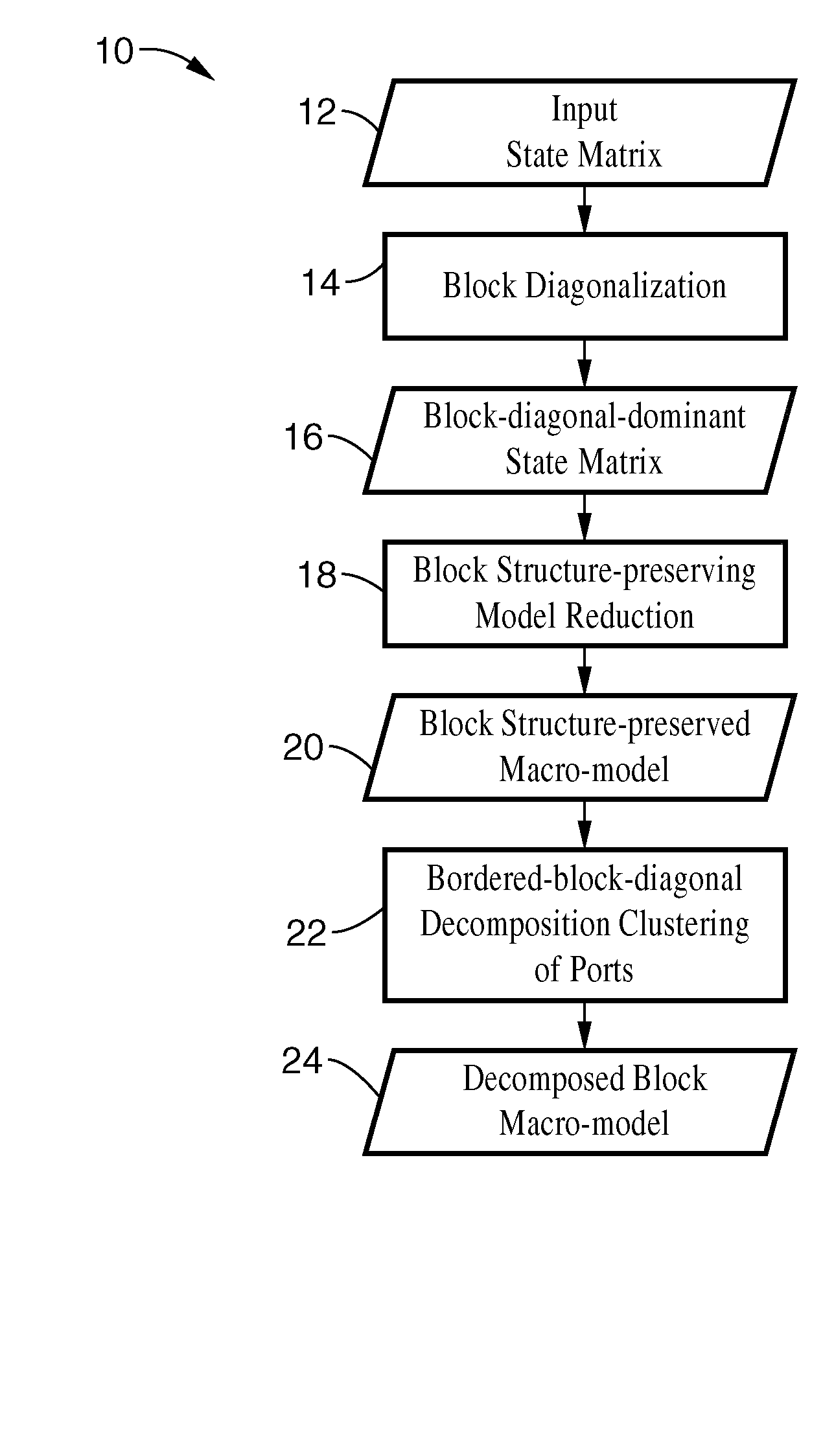

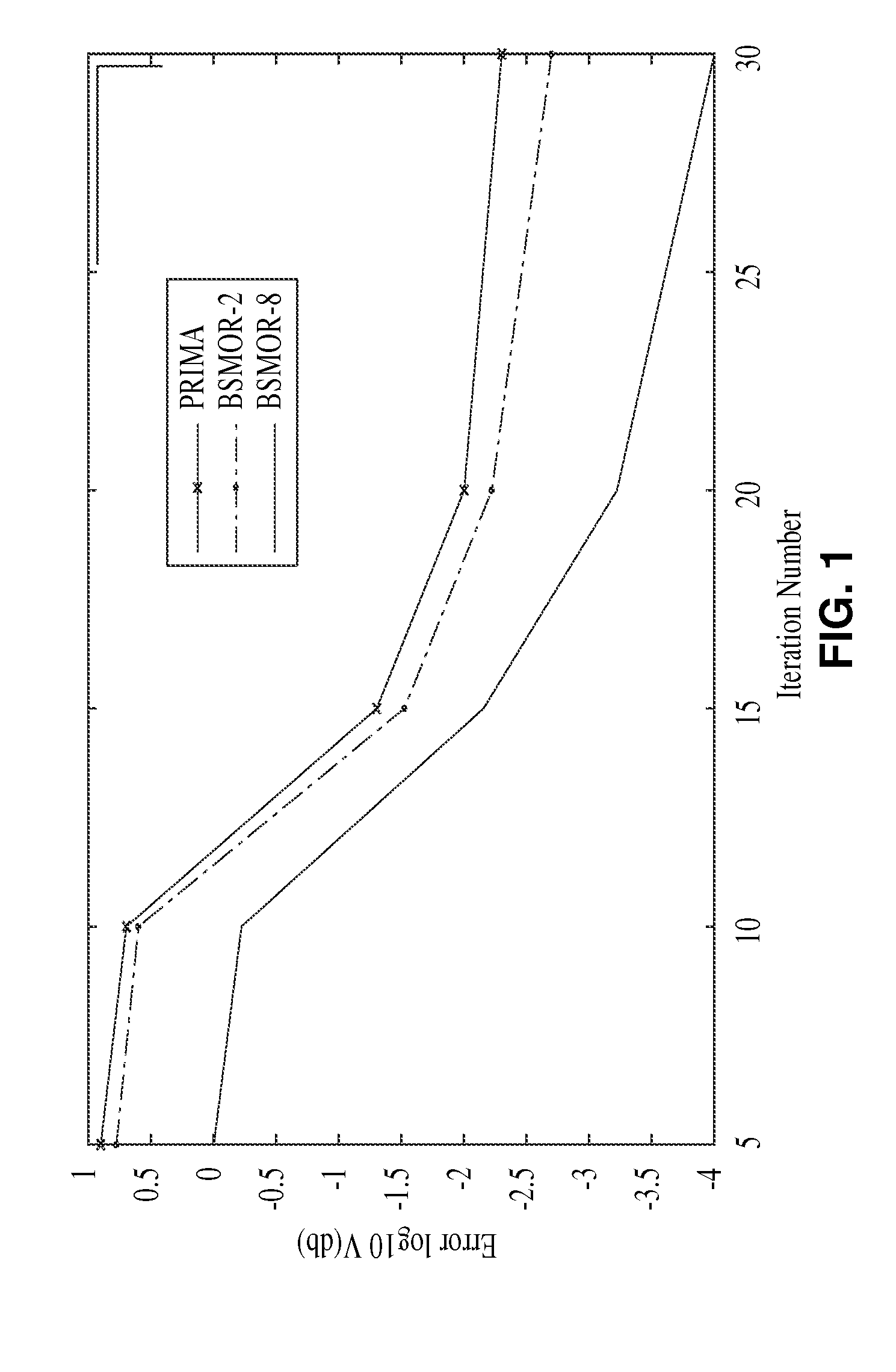

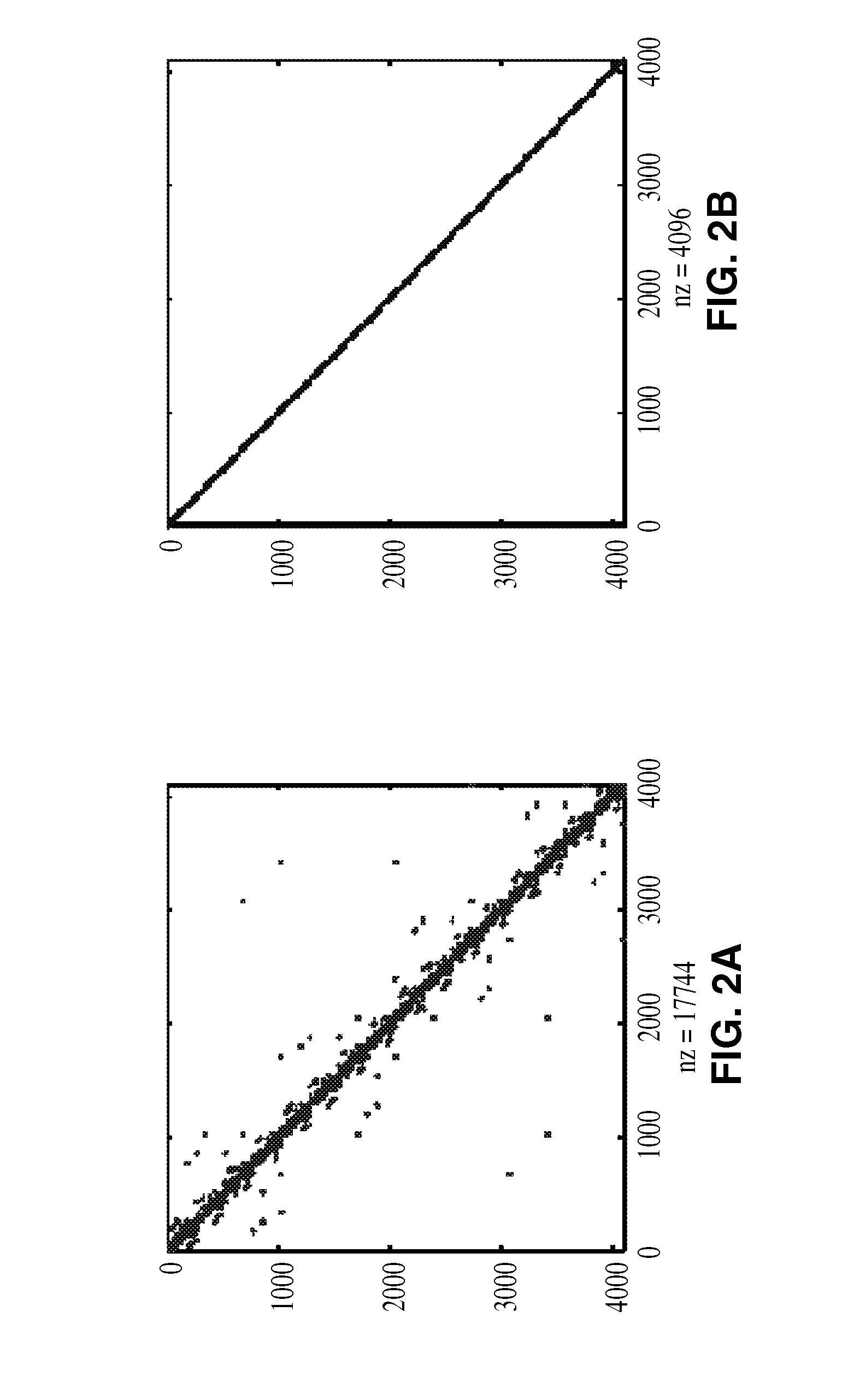

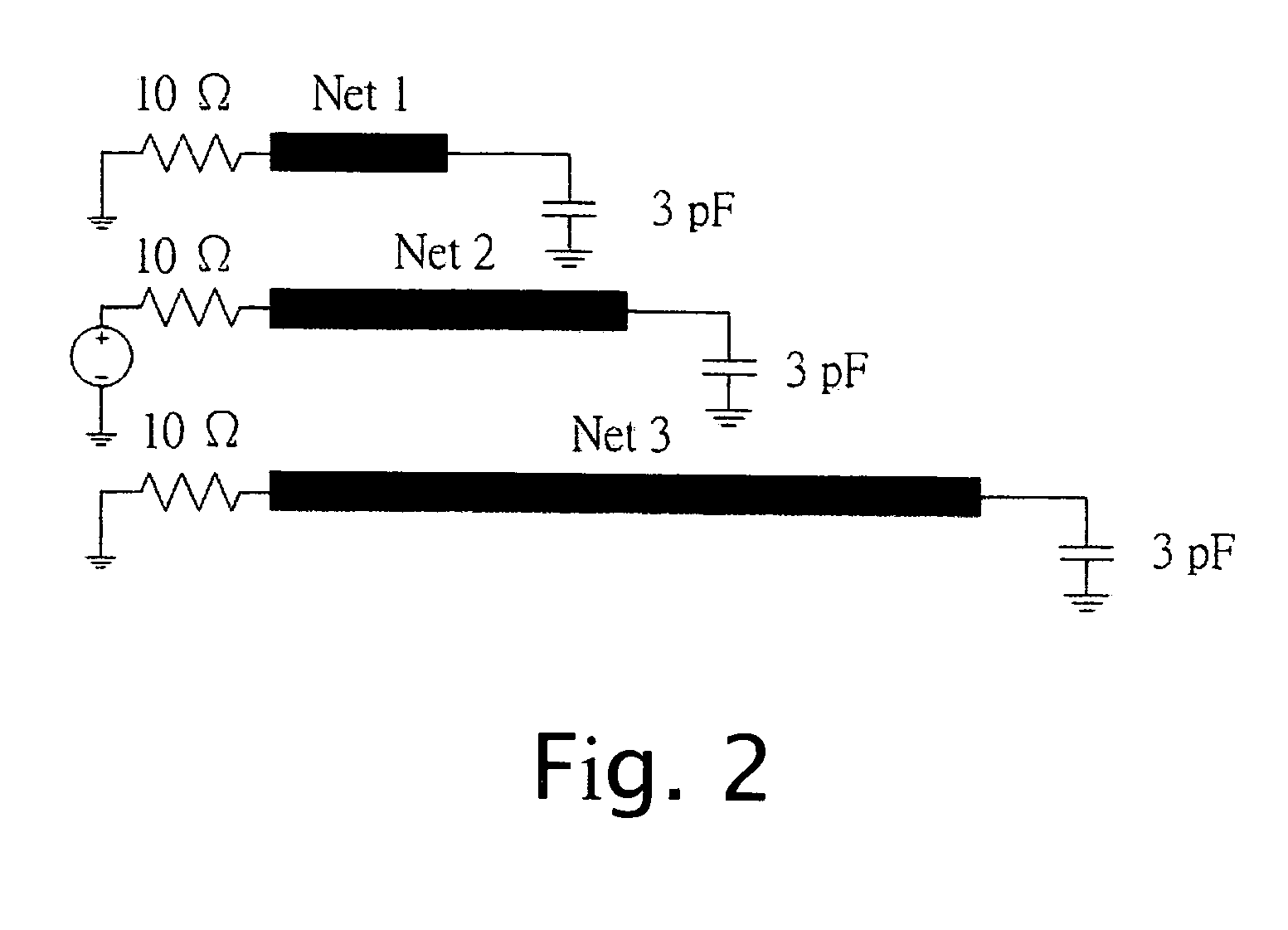

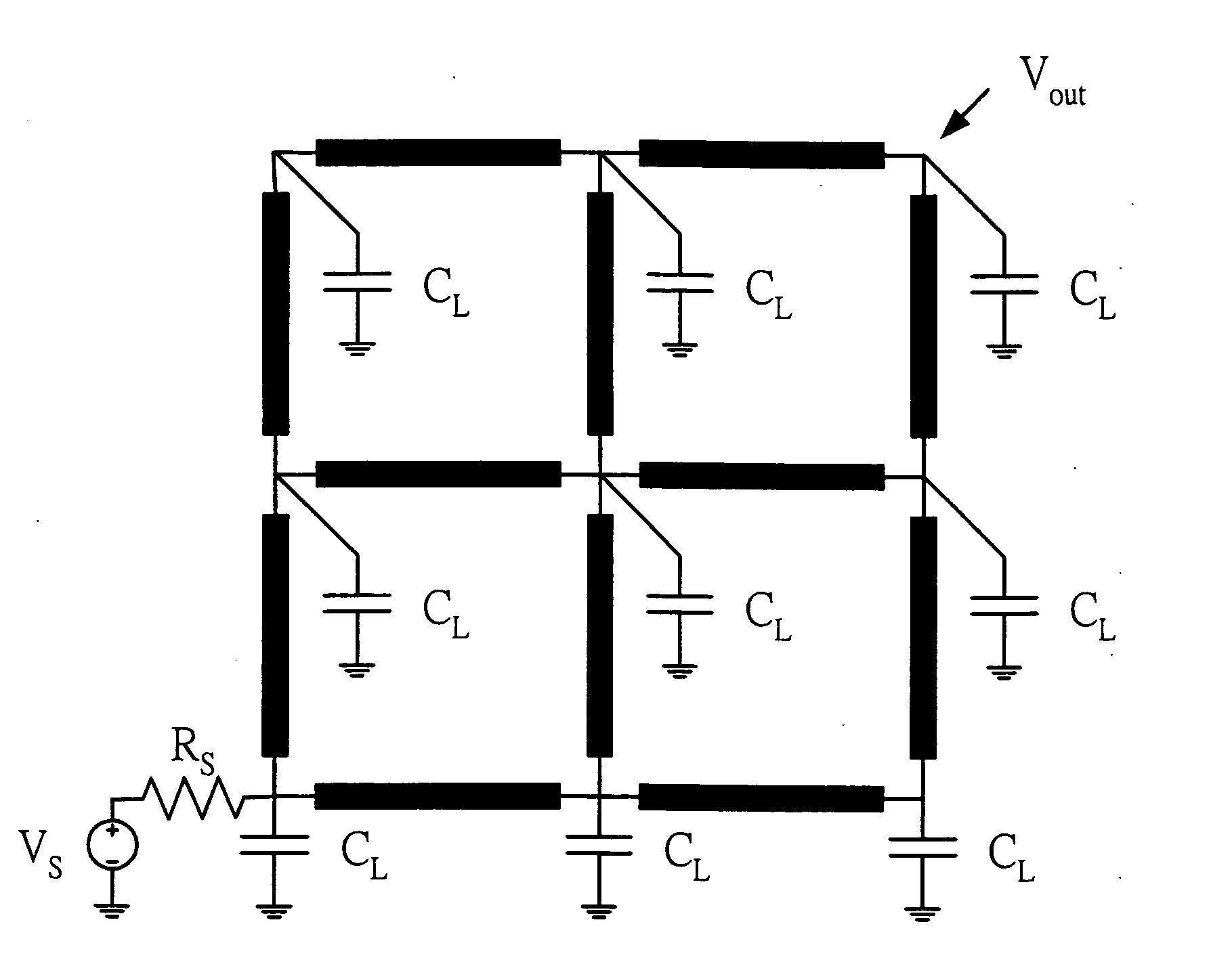

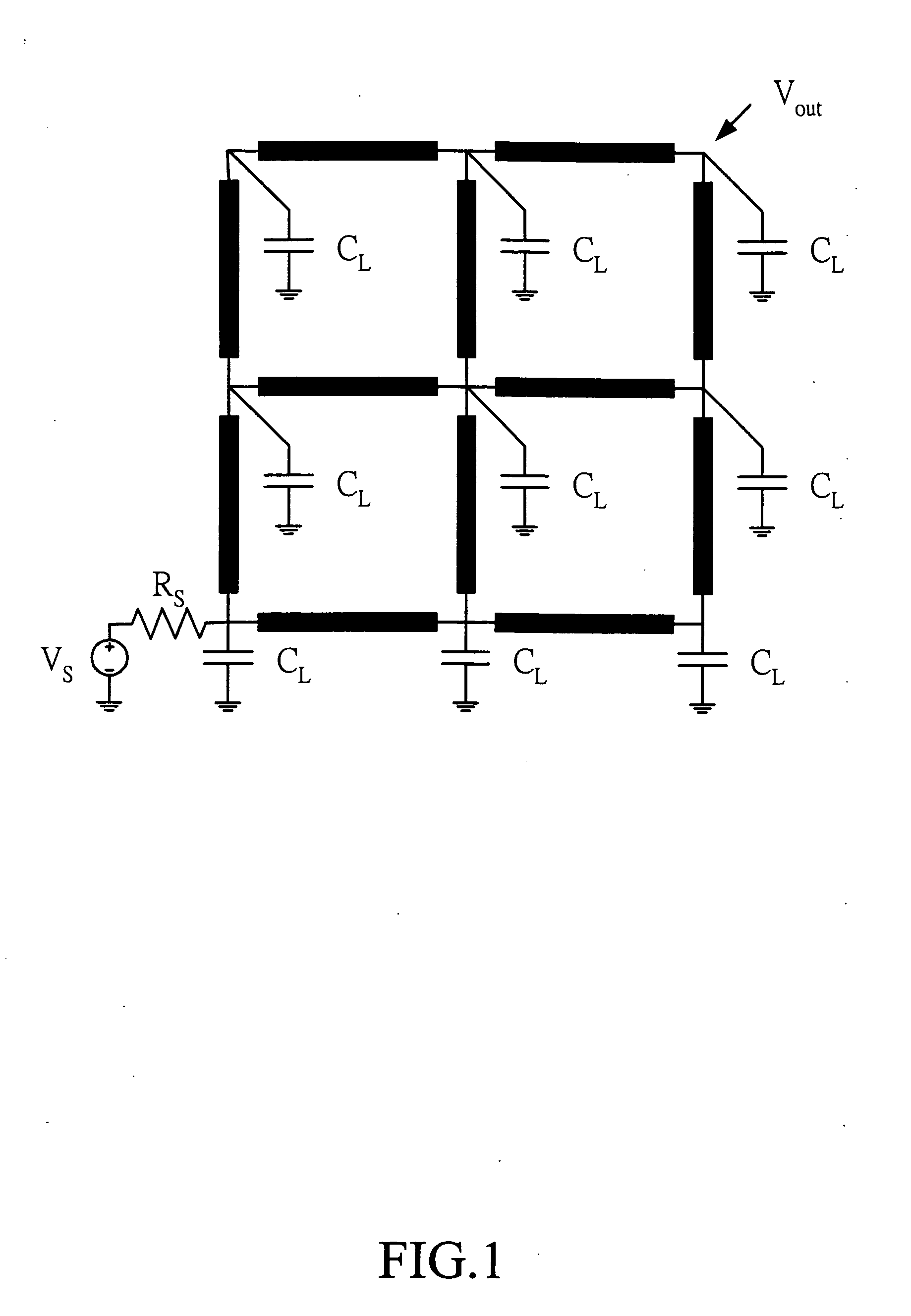

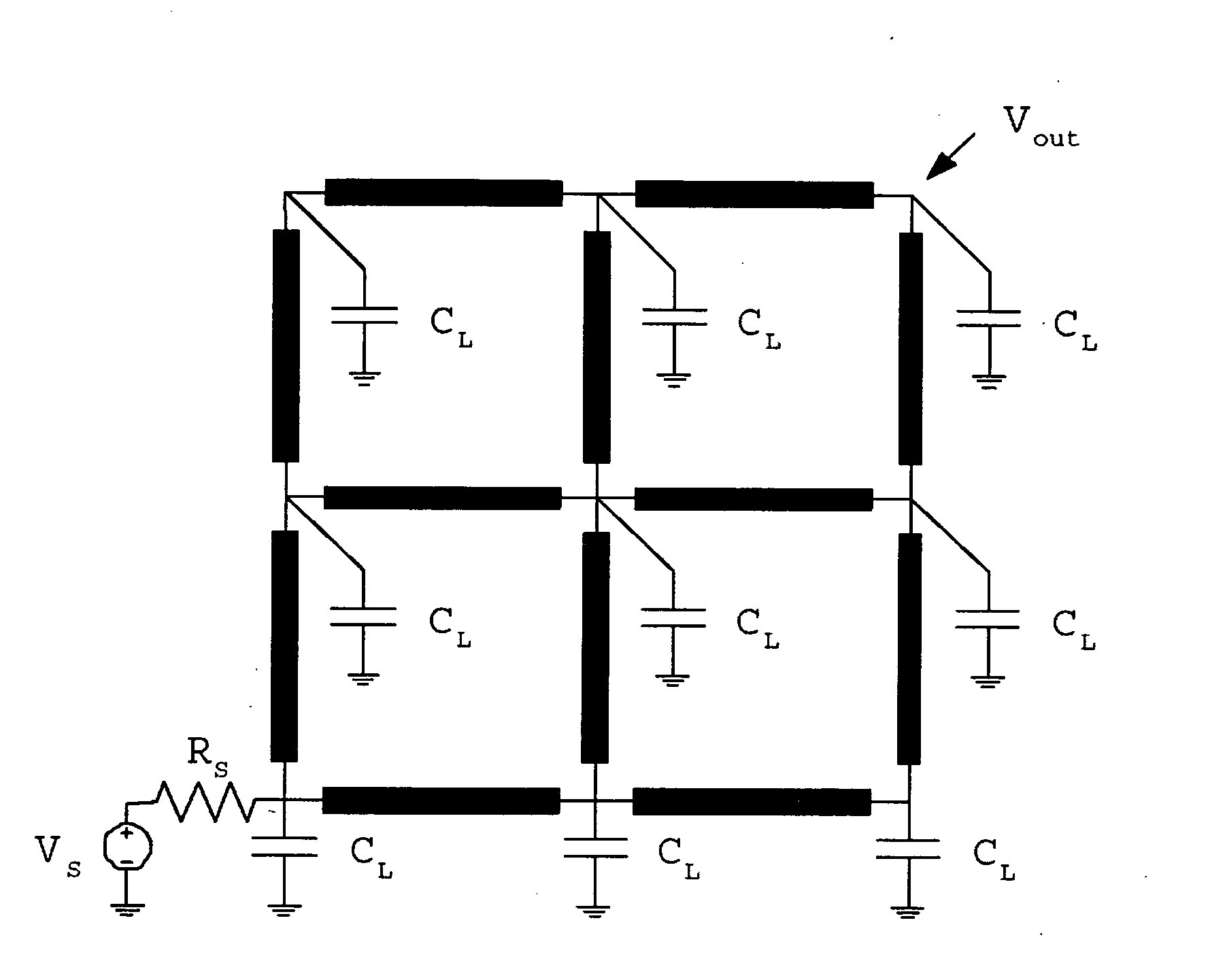

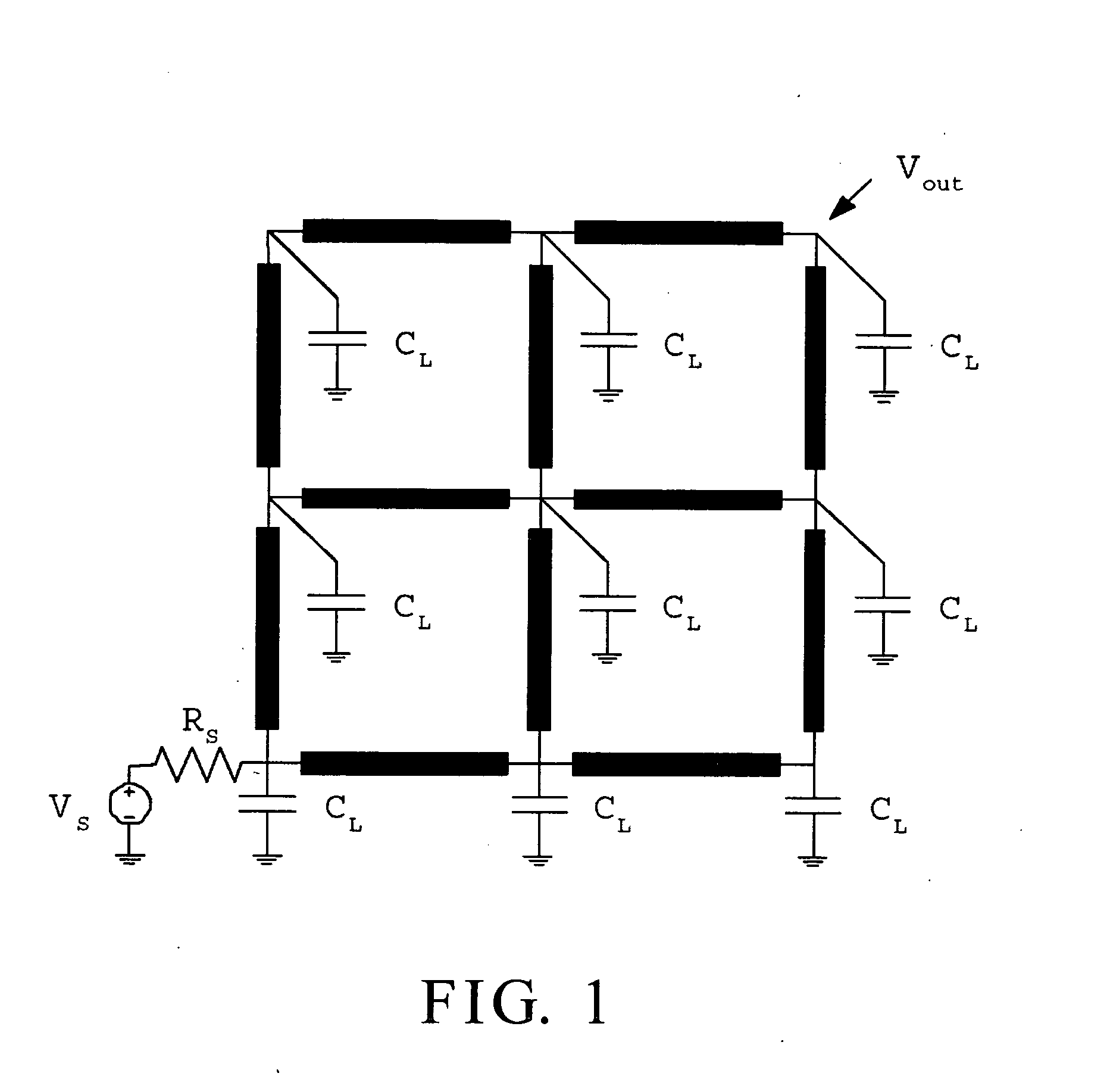

Model-order reduction techniques are described for RLC circuits modeling the VLSI layouts. A structured model order reduction is developed to preserve the block-level sparsity, hierarchy and latency. In addition, a structured and parameterized model order reduction is developed to generate macromodels for design optimizations of VLSI layouts. The applications are thermal via allocation under the dynamic thermal integrity and via stapling to simultaneously optimize thermal and power integrity.

Owner:RGT UNIV OF CALIFORNIA

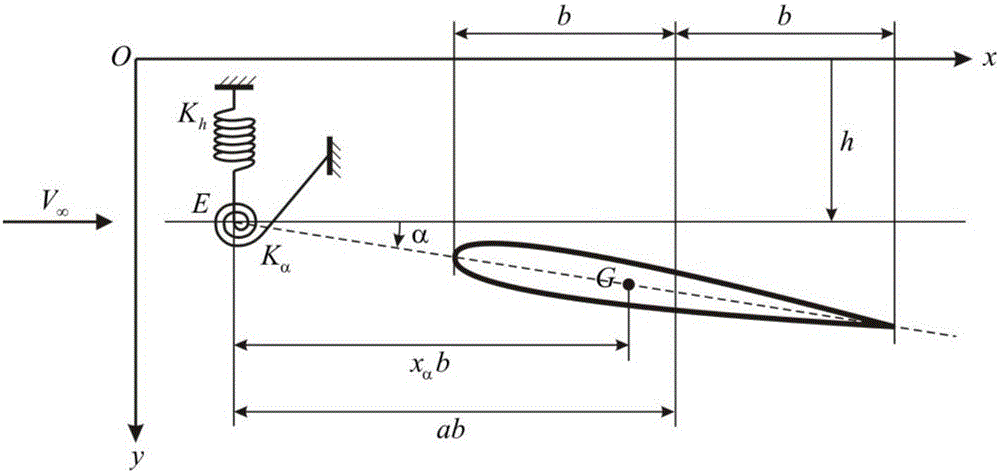

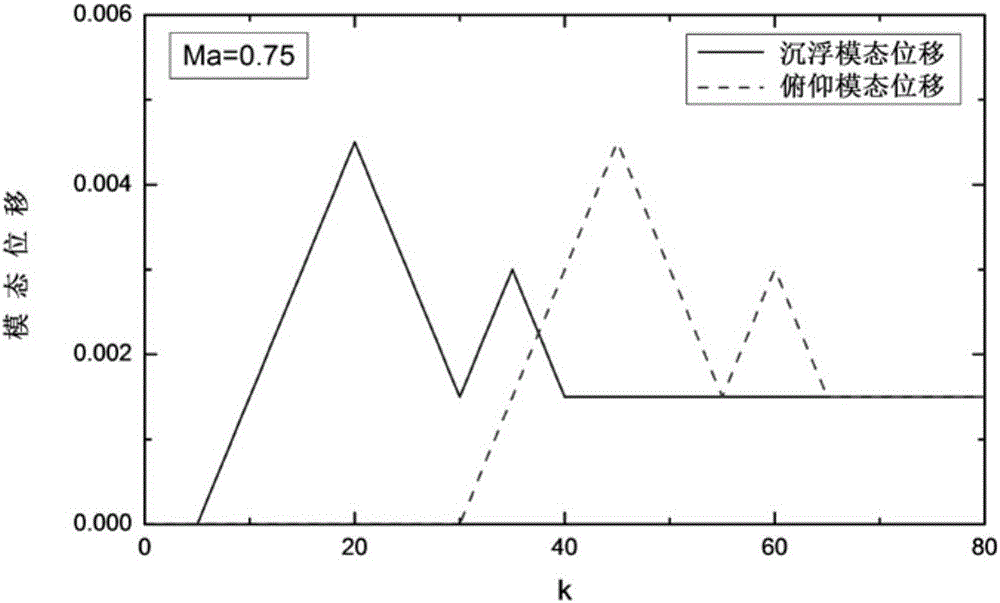

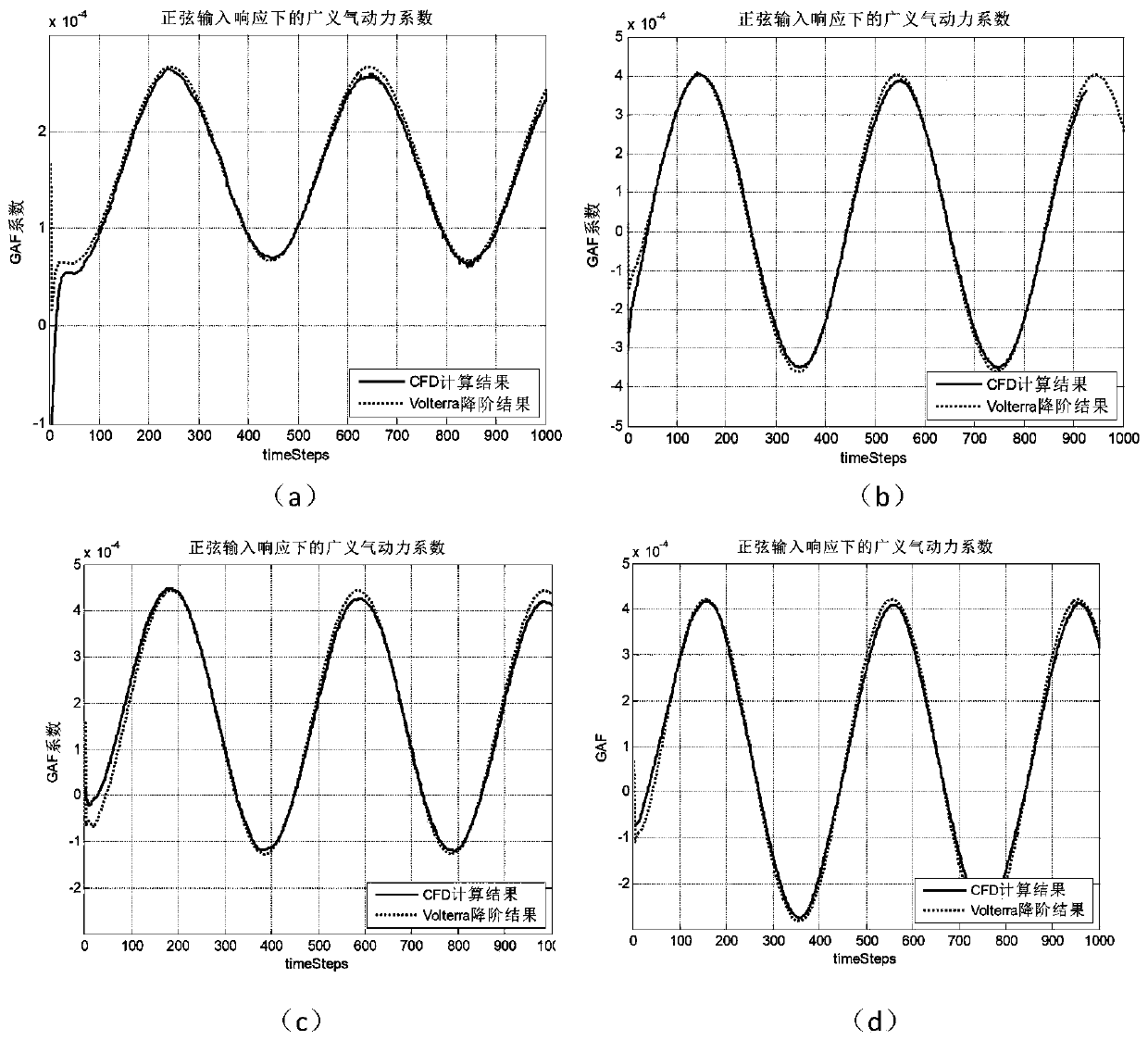

Method for analyzing wing structure aero-elasticity stability based on aerodynamic force uncertain order reduction

ActiveCN105843073ATaking into account the accuracyRobustnessSimulator controlOrder reductionMathematical model

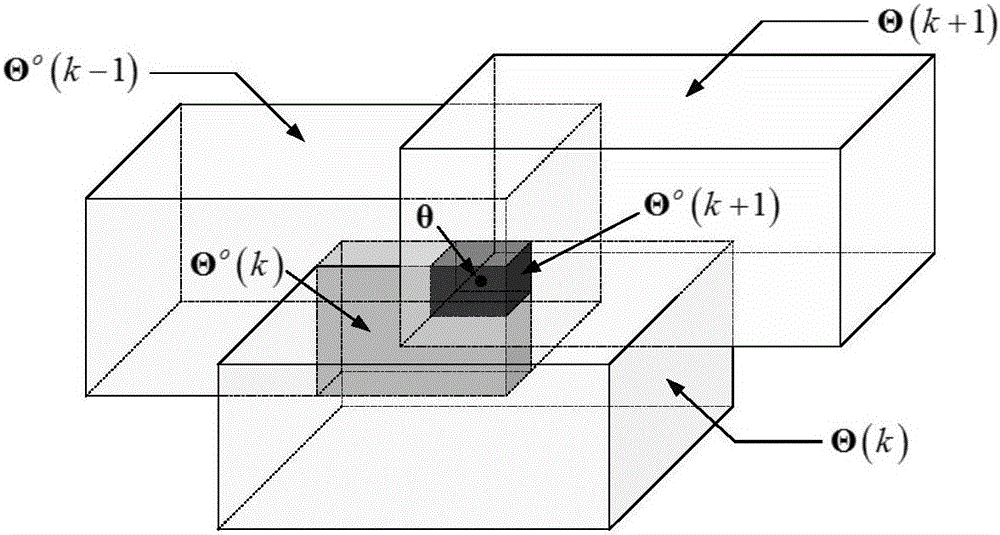

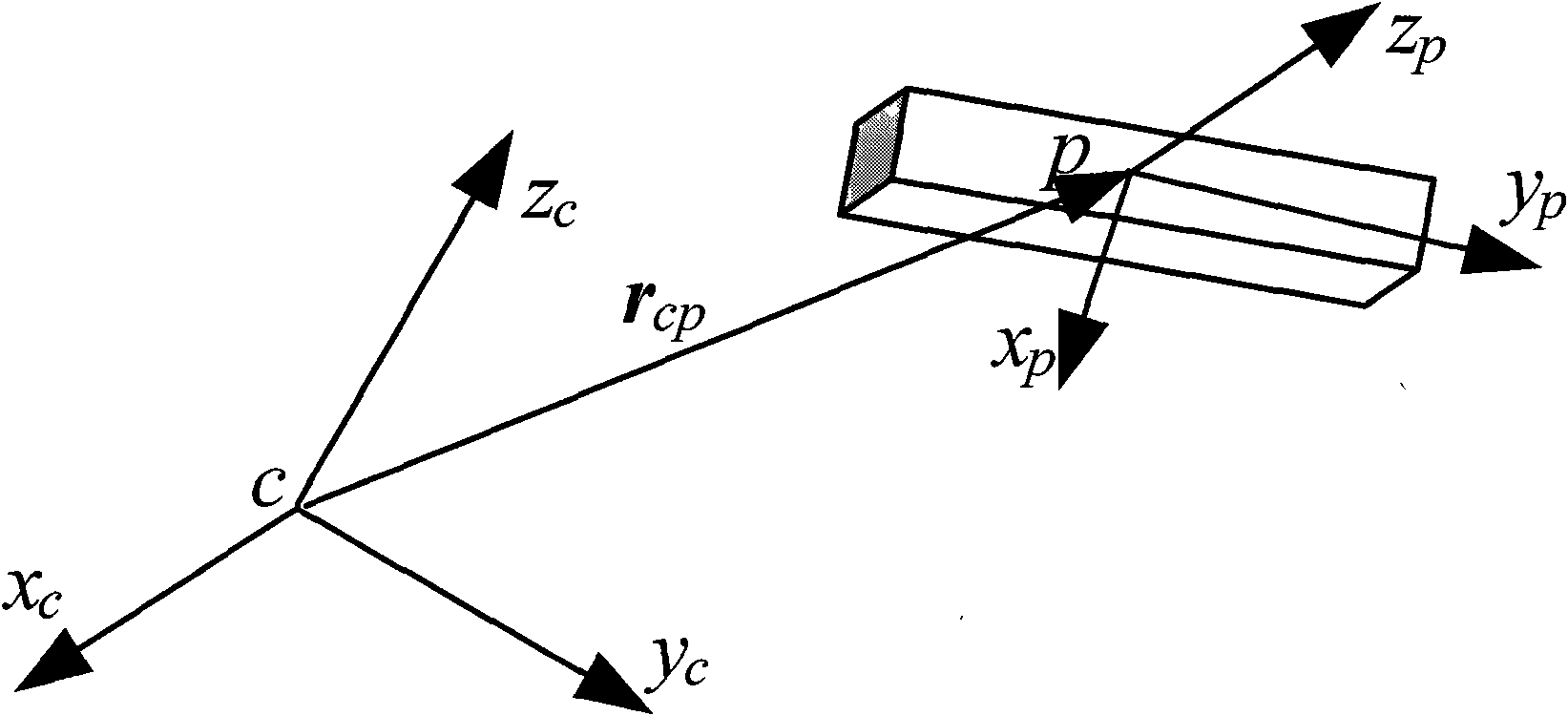

The invention discloses a method for analyzing wing structure aero-elasticity stability based on aerodynamic force uncertain order reduction. The method is based on unsteady aerodynamic force model order reduction method based on CFD technology; uncertainty of numerical calculation and aerodynamic parameters during aerodynamic force identification process is taken into comprehensive consideration and is uniformly quantified as an uncertain bounded interval noise sequence in an identification model; uncertain order reduction of the aerodynamic force model is realized by means of interval set membership identification algorithm; unsteady aerodynamic uncertain order reduction model based on CFD technology is established; mathematical model of uncertain aero-elasticity system of state space form is established coupled with structural motion equation; an effective method for predicting system robustness stability boundary from the prospective of section state matrix characteristic values. The aero-elasticity system uncertainty modeling thinking and stability boundary prediction technology provided by the invention gives consideration to calculation efficiency, analysis precise and system robustness.

Owner:BEIHANG UNIV

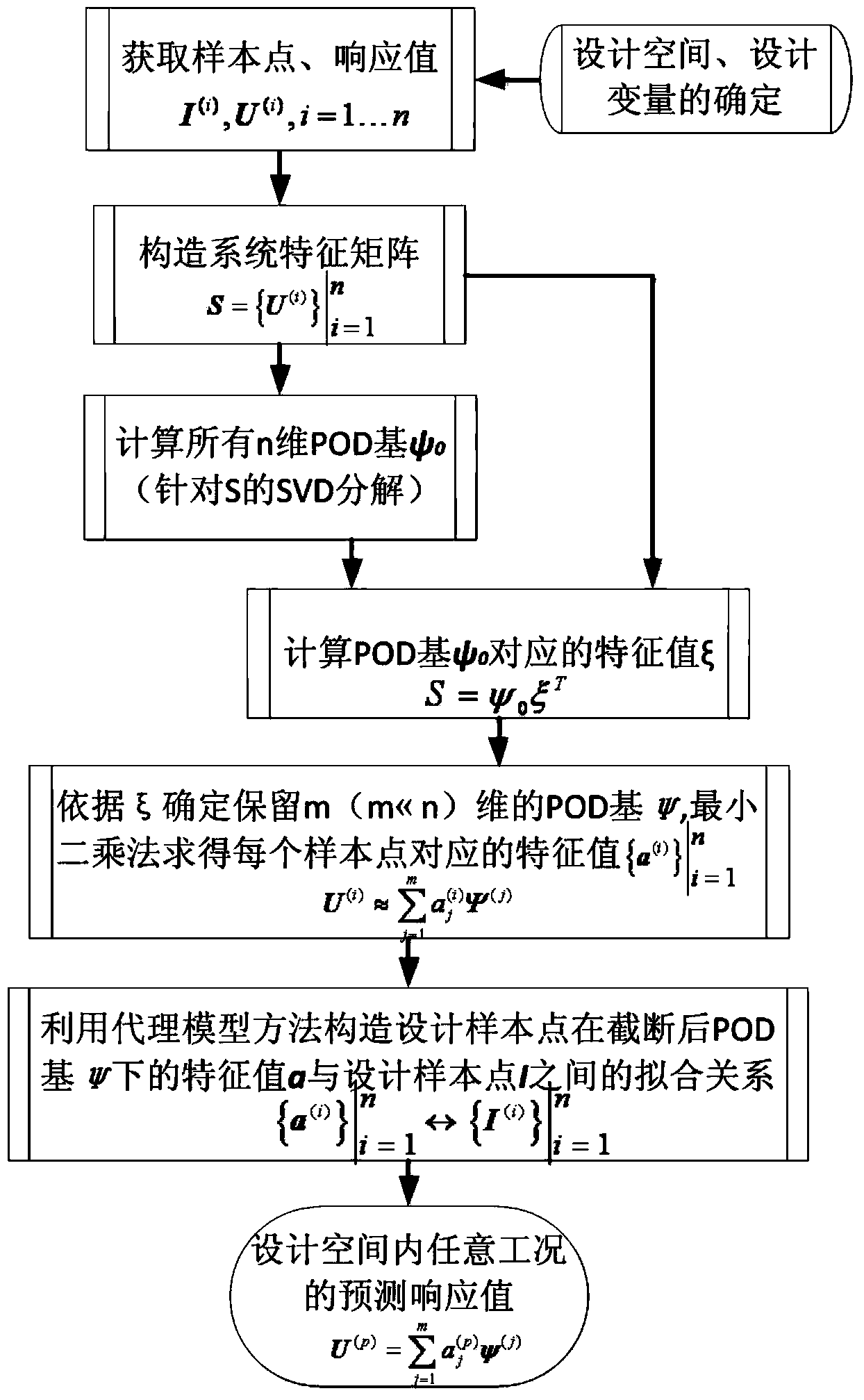

Efficient model order reduction via multi-point moment matching

InactiveUS20050096888A1Efficient methodImprove efficiencyComputation using non-denominational number representationComputer aided designState variableEngineering

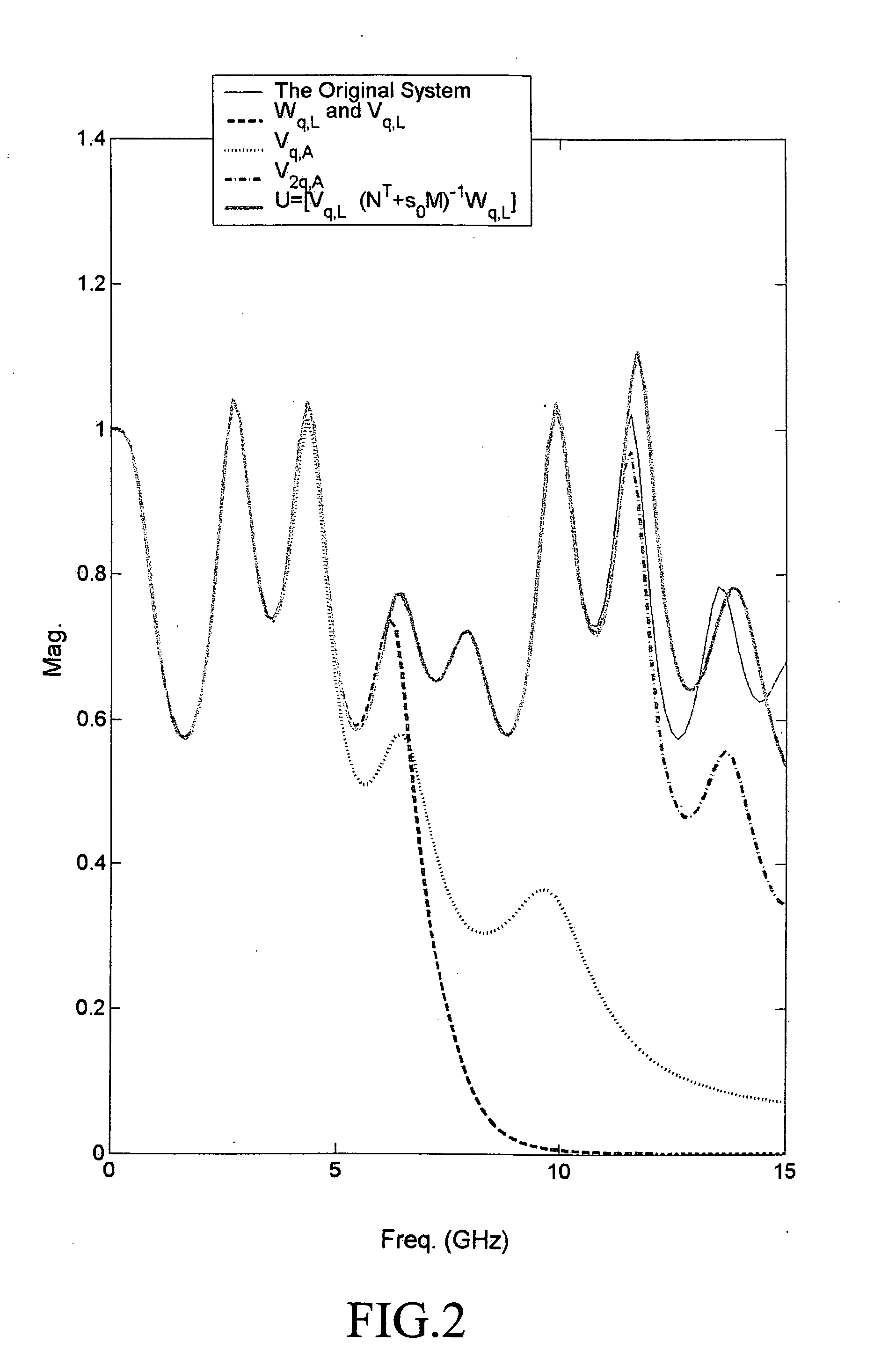

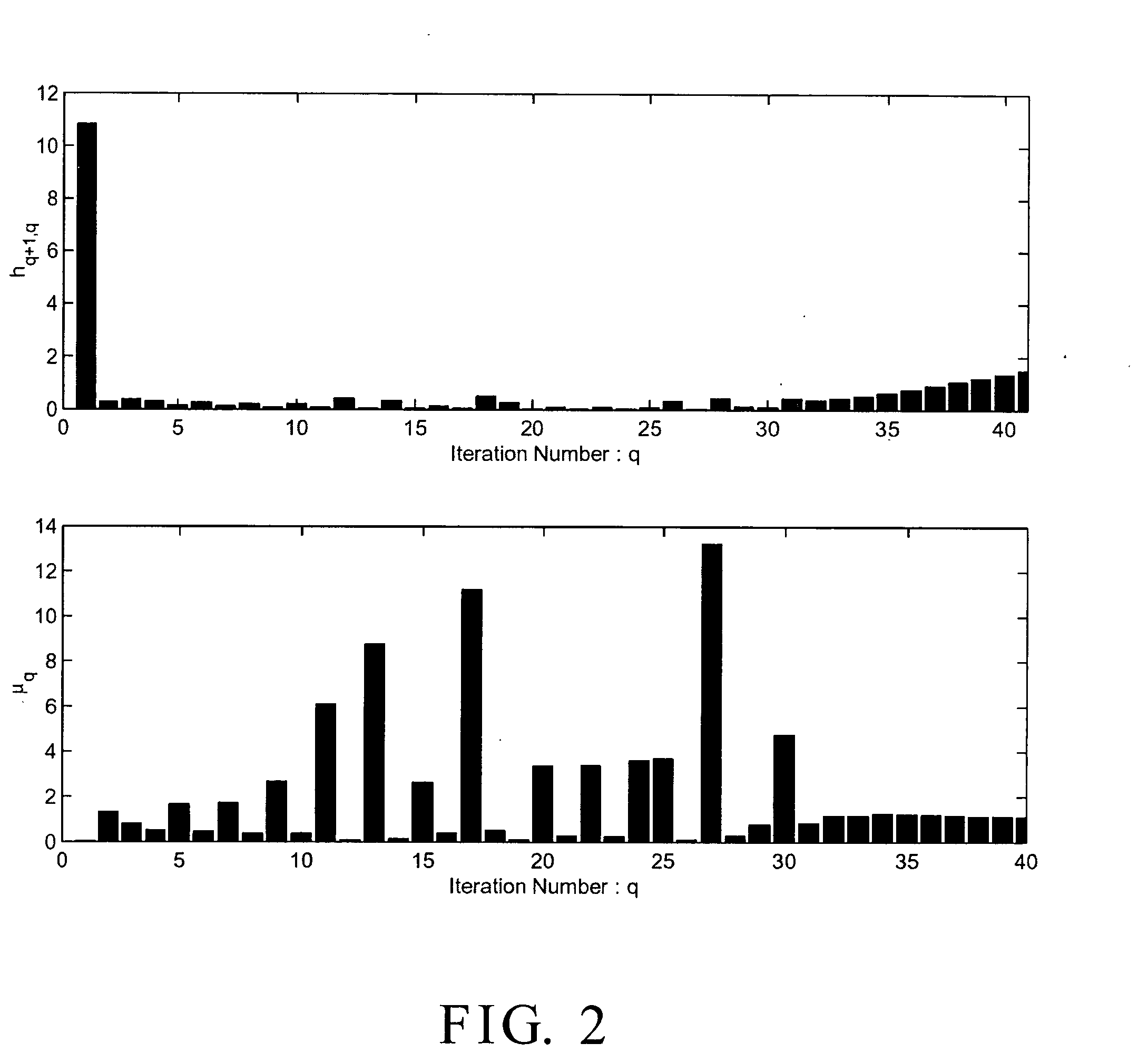

A method for mapping moments in a reduced order system of approximation order q for use in simulating a circuit or system having n state variables at n nodes, the circuit or system having I inputs. The method includes calculating only q+I moments, where q is the approximation order and I is the number of inputs of the circuit or system being simulated, sorting the state variables at the n nodes, selecting q nodes of the n nodes, and calculating the dominate poles and zeros using a multi-point moment matching algorithm to simultaneously match q+I moments at the selected q nodes of the circuit or system. In one embodiment, the method includes using extra dummy inputs such that the total number of inputs equals I, such that K*I>q where K is a constant having a value in the range of about 4 to 8.

Owner:ISMAIL YEHEA I

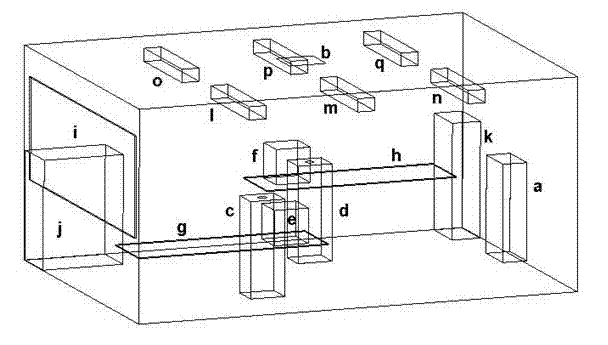

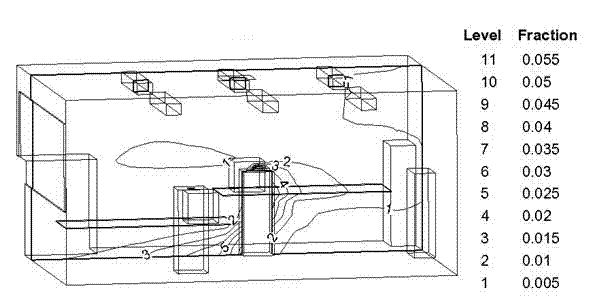

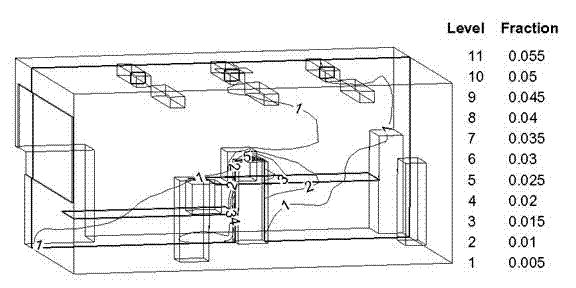

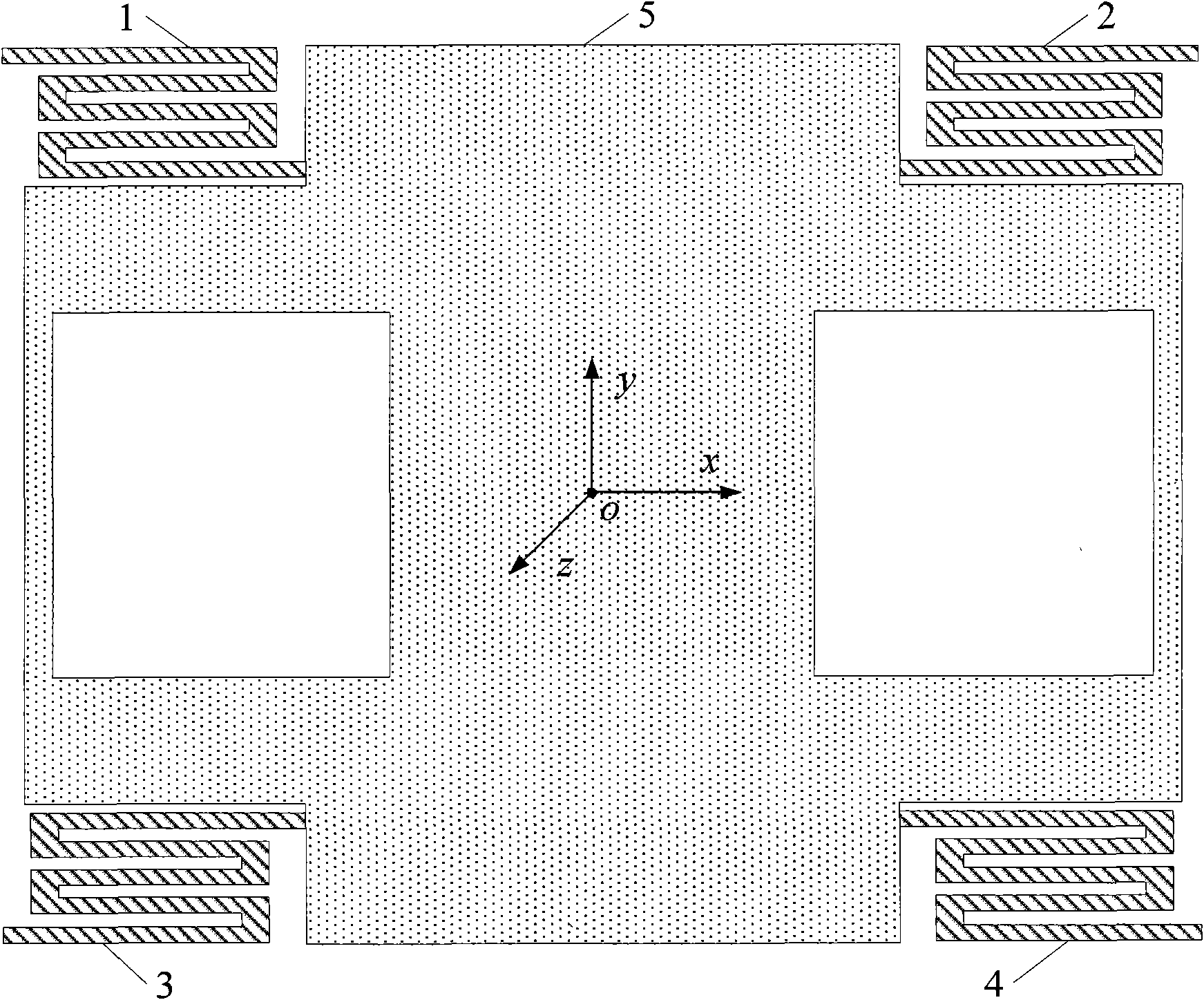

Indoor thermal environment control method based on model reduction and multi-model prediction control

InactiveCN103995548AHigh precisionPrecise temperature control effectTemperature control using electric meansModel order reductionSoftware

The invention discloses an indoor thermal environment control method based on model reduction and multi-model prediction control. The method includes the three main steps that firstly, a temperature variation section of an indoor user region is segmented, modeling is conducted on the equilibrium state position of each segment through computional fluid dynamics (CFD) software and the proper orthogonal decomposition (POD) technology, and a low-order linear building thermal environment in a multi-model type is reconstructed; secondly, multi-model switching time is reasonably selected through an optimization algorithm; thirdly, accurate control over the user region temperature is conducted on each sub model through a prediction control method. Low-order models of the building indoor thermal environment are constructed through the POD technology and the multi-model method, the influence of space distribution on the temperature variation can be fully taken into consideration in a temperature regulation strategy, and accuracy of indoor temperature control is improved. Compared with an existing temperature control strategy adopted in large space, the indoor thermal environment control method has the advantages that accuracy is high, and energy saving of a building is facilitated.

Owner:JIANGSU UNIV

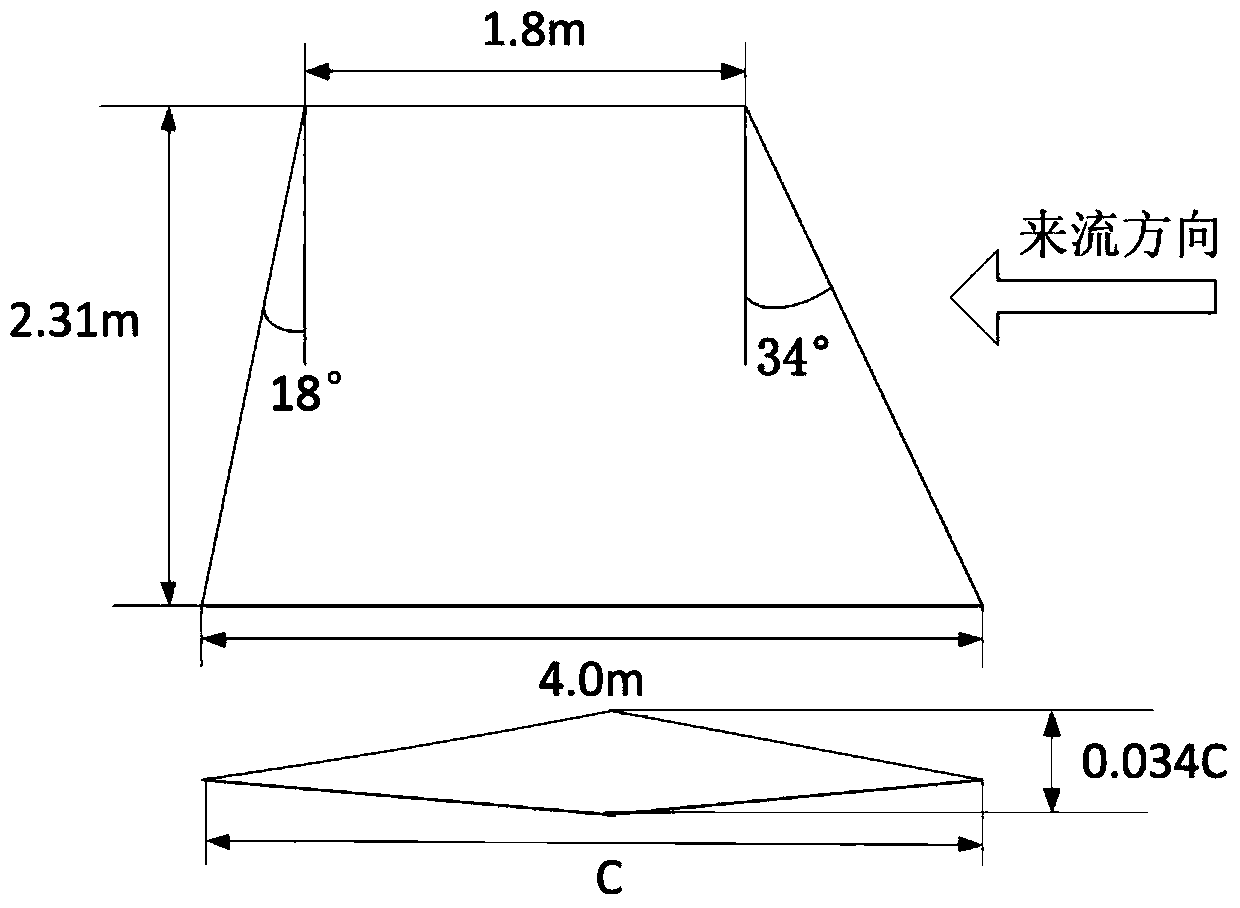

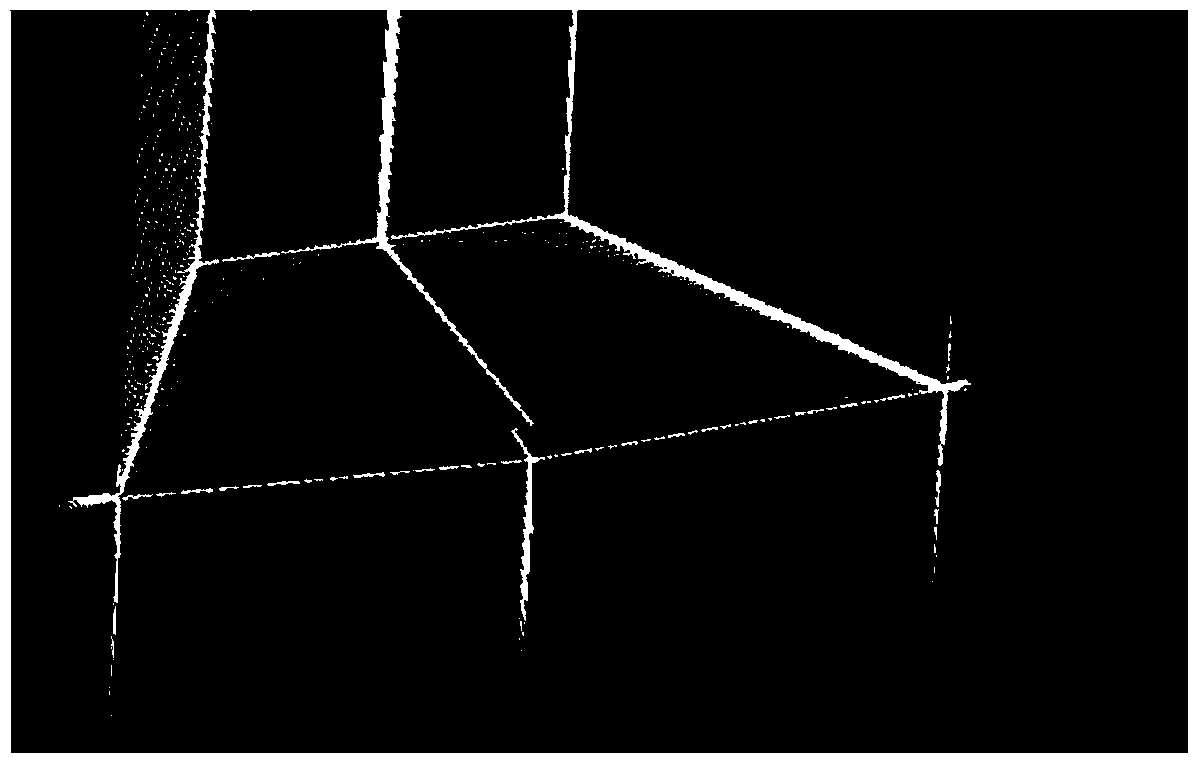

POD (proper orthogonal decomposition) and surrogate model based order reduction method for hypersonic aerodynamic thermal models

InactiveCN103902782AHigh precisionImprove efficiencySustainable transportationSpecial data processing applicationsAviationEngineering

The invention relates to a POD (proper orthogonal decomposition) and surrogate model based order reduction method for hypersonic aerodynamic thermal models and belongs to the technical field of aerospace. A hypersonic aircraft aerodynamic thermal environment is predicted and obtained by the aid of a POD and surrogate model method, nonlinear characteristics of real gas effect, turbulence viscosity and the like of high-precision numerical calculation are reserved, the hypersonic aircraft aerodynamic thermal environment can be provided for design of the hypersonic aerocraft by the aid of model order reduction method which is high in precision and efficiency, related thermal boundary conditions are provided for aerodynamic thermal elastic design, the thermal environment is provided for thermal protection design of the hypersonic aerocraft, design efficiency can be greatly improved, design circle is shortened, and design cost is reduced.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Building indoor environment optimization method based on model order reduction technology

InactiveCN103049612AQuick solveHigh precisionSpecial data processing applicationsGenetic algorithmComputer science

The invention discloses a building indoor environment optimization method based on the model order reduction technology. The method mainly includes the three steps: (1) using CFD (computational fluid dynamics) software for steady-state simulation of the indoor environment, and constructing variation spaces of various environmental parameters; 2) reconstructing low-order parameter variation subspaces by the aid of the POD (proper orthogonal decomposition) technology; and 3) searching the optimal air conditioner air supply temperature and the optimal air conditioner air supply speed by operating the genetic algorithm. The variation subspaces of the indoor environmental parameters are constructed by the aid of the POD technology, so that influences of spatial distribution on the environmental parameters are considered fully in an optimizing strategy, and optimization accuracy is improved. The POD model order reduction method maps a control equation in an original space into one orthogonal subspace, and accordingly mapping error can be guaranteed to minimum in the energy sense. Besides, compared with a present environment optimization strategy, the building indoor environment optimization method based on the model order reduction technology has the advantages of high optimization precision, high speed and the like.

Owner:JIANGSU UNIV

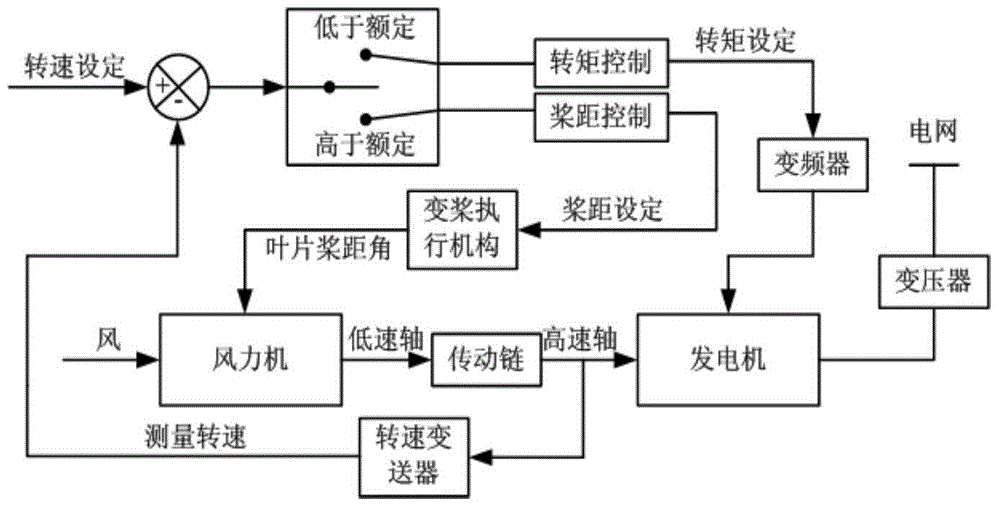

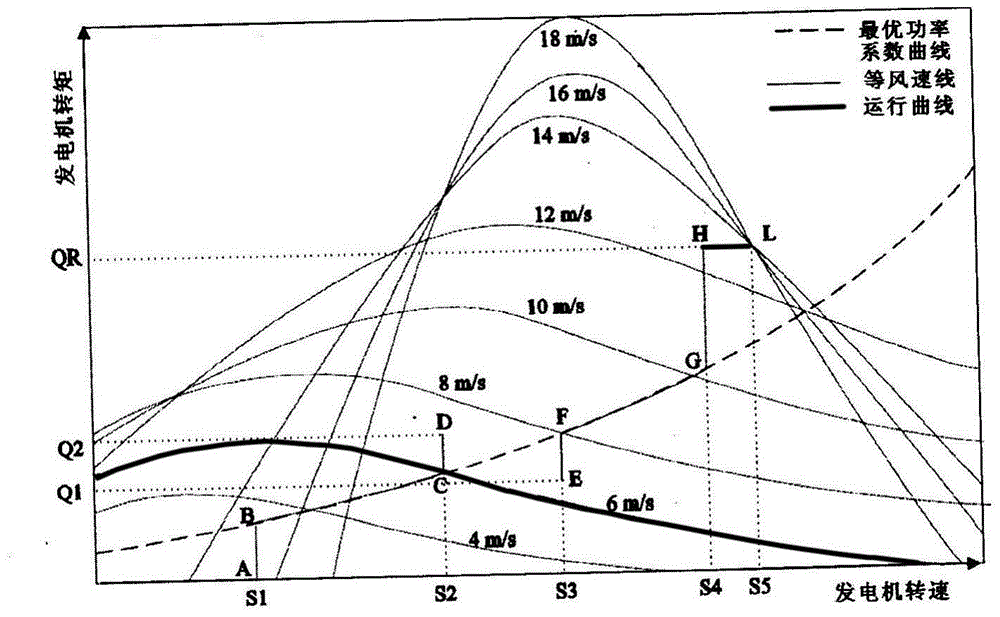

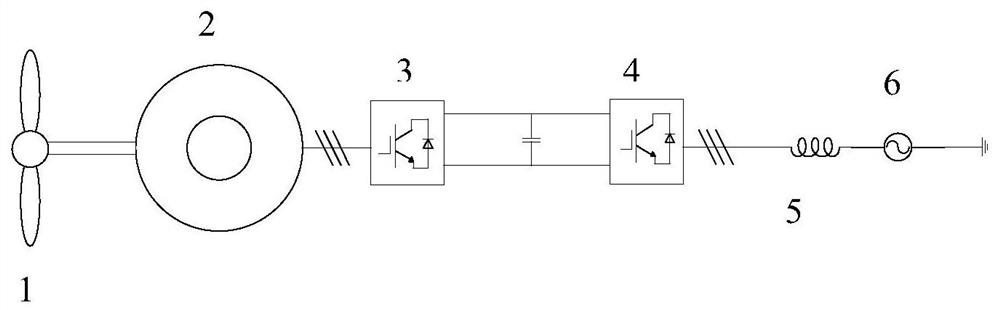

Method for identifying and setting parameters of wind generating set controller

InactiveCN104533714APracticalStrong reference valueWind motor controlEngine fuctionsEngineeringBlade pitch

The invention discloses a method for identifying and setting parameters of a wind generating set controller, and belongs to the technical field of control over a wind generating set. The method comprises the steps that a Bladed software model is utilized for being linearly combined with a model order reduction algorithm to build a unit linear model suitable for setting the parameters; and then, according to the wind speed distribution probability of a wind field, optimal setting and comprehensive calculation of PI parameters of the controller are carried out, and on the basis of a parameter identifying result of Bladed software, an optimum rotary speed-torque control gain coefficient and a gain factor in self-adaptation variable pitch control are calculated. Identifying of related parameters such as a largest wind energy utilization coefficient, an optimum tip-speed ratio and an optimal propeller pitch angle is carried out according to a Bladed simulation model built according to unit equipment parameters, and the important prerequisite condition is provided for control over maximal wind energy capture of the unit is provided; the self-adaptation variable pitch control is achieved, and the robustness of a common PI variable pitch controller is improved; and the guidance is provided for design and optimization of the controller, and the method has the higher practical and reference value.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

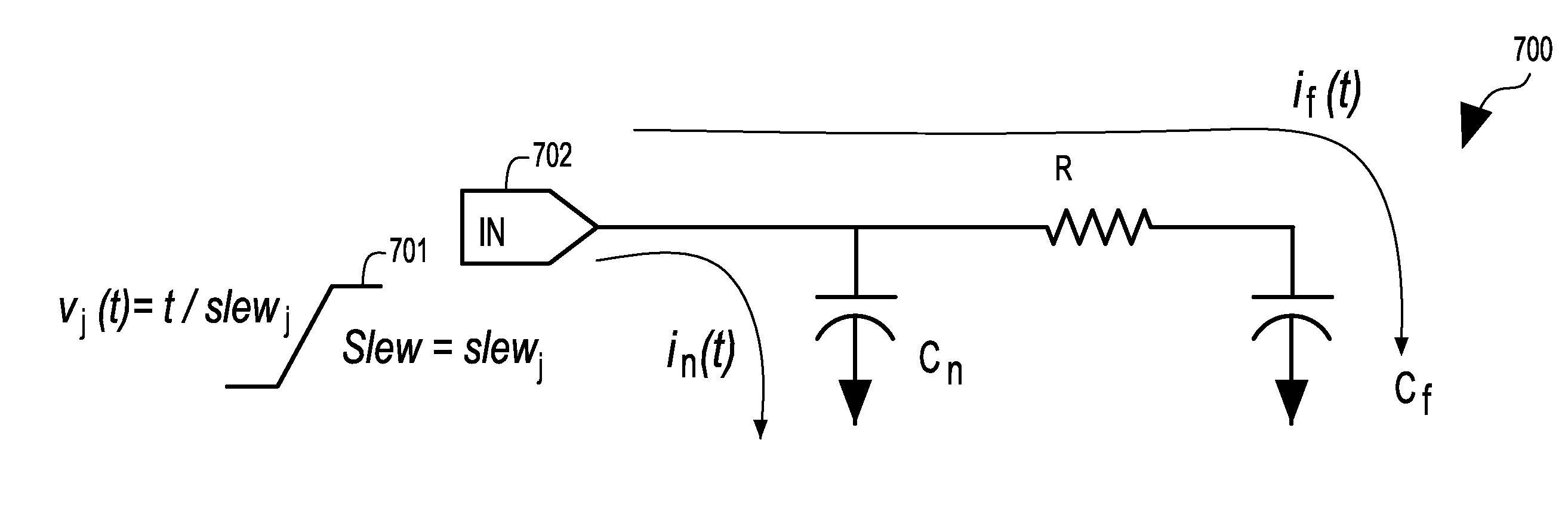

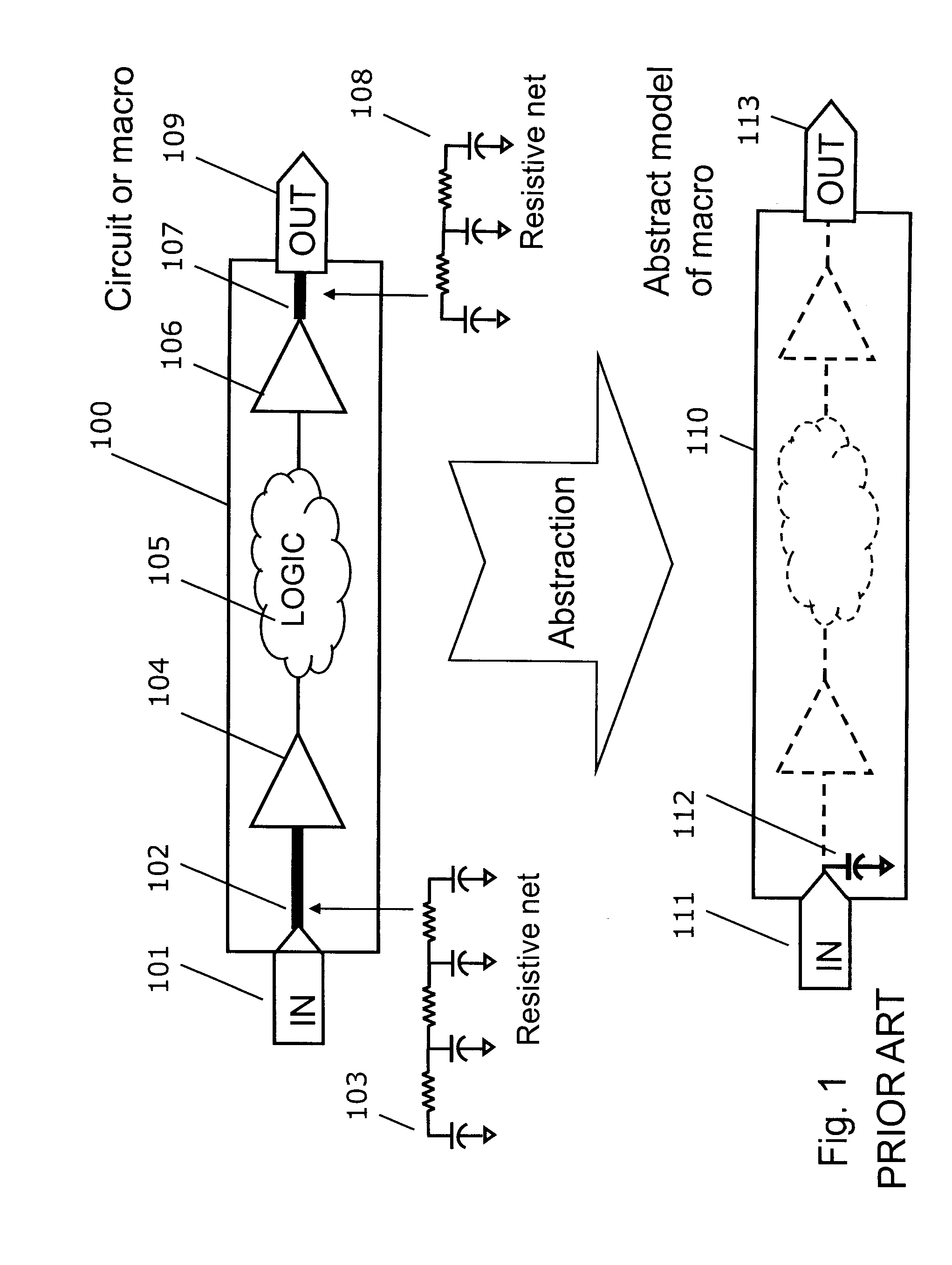

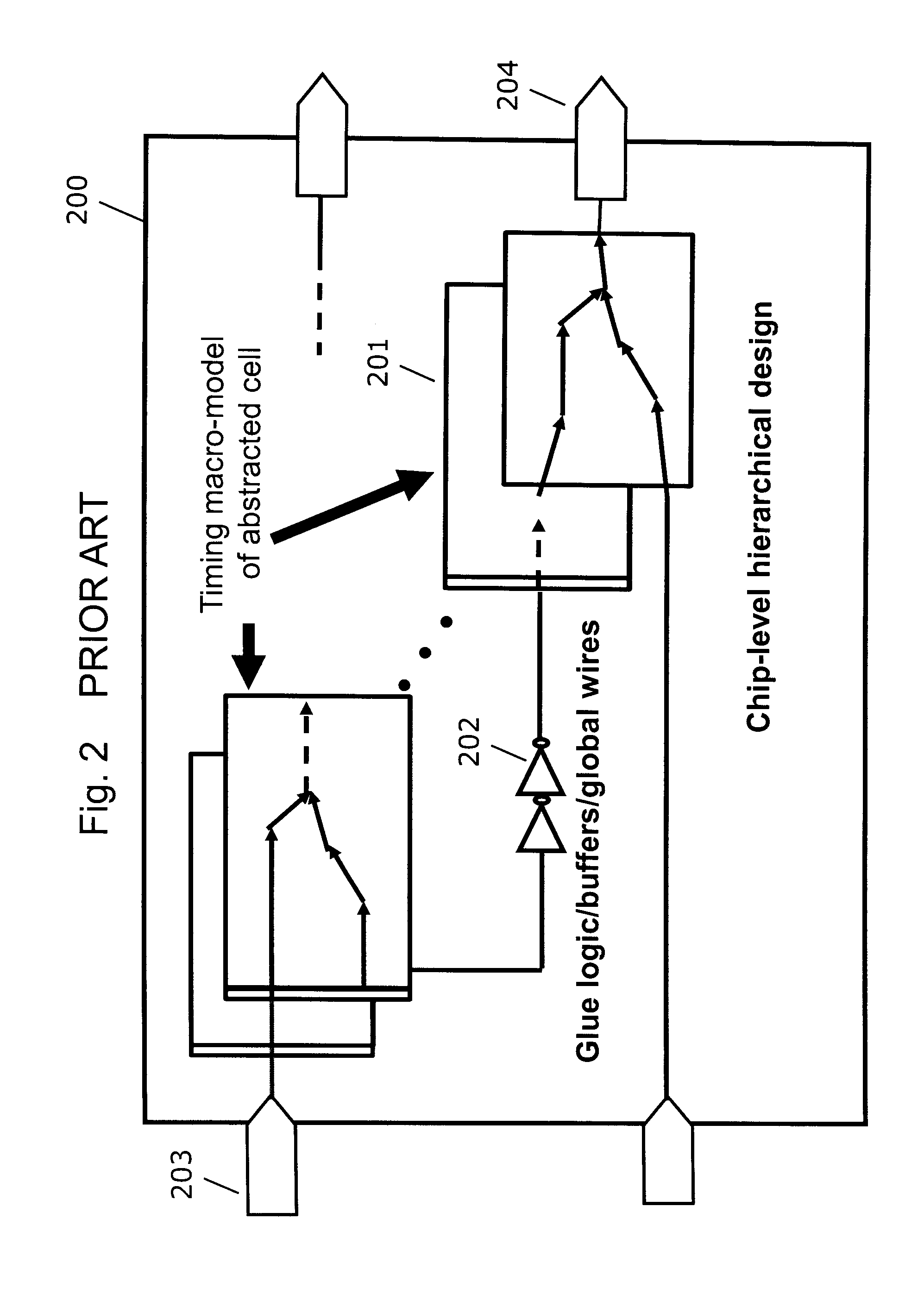

Method of Employing Slew Dependent Pin Capacitances to Capture Interconnect Parasitics During Timing Abstraction of VLSI Circuits

ActiveUS20100269083A1Process can be speededAccurate timing analysisComputer aided designSpecial data processing applicationsStatic timing analysisEngineering

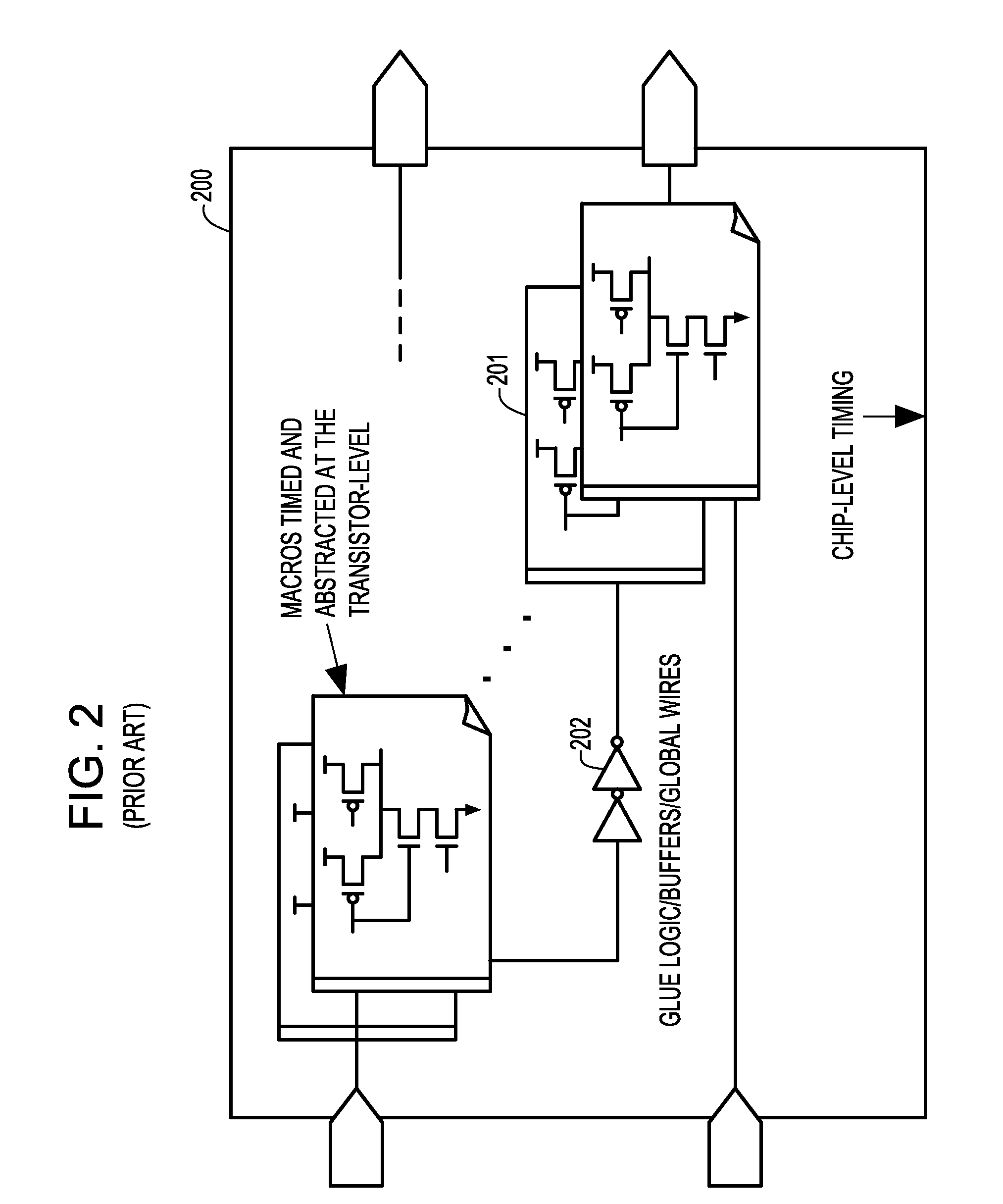

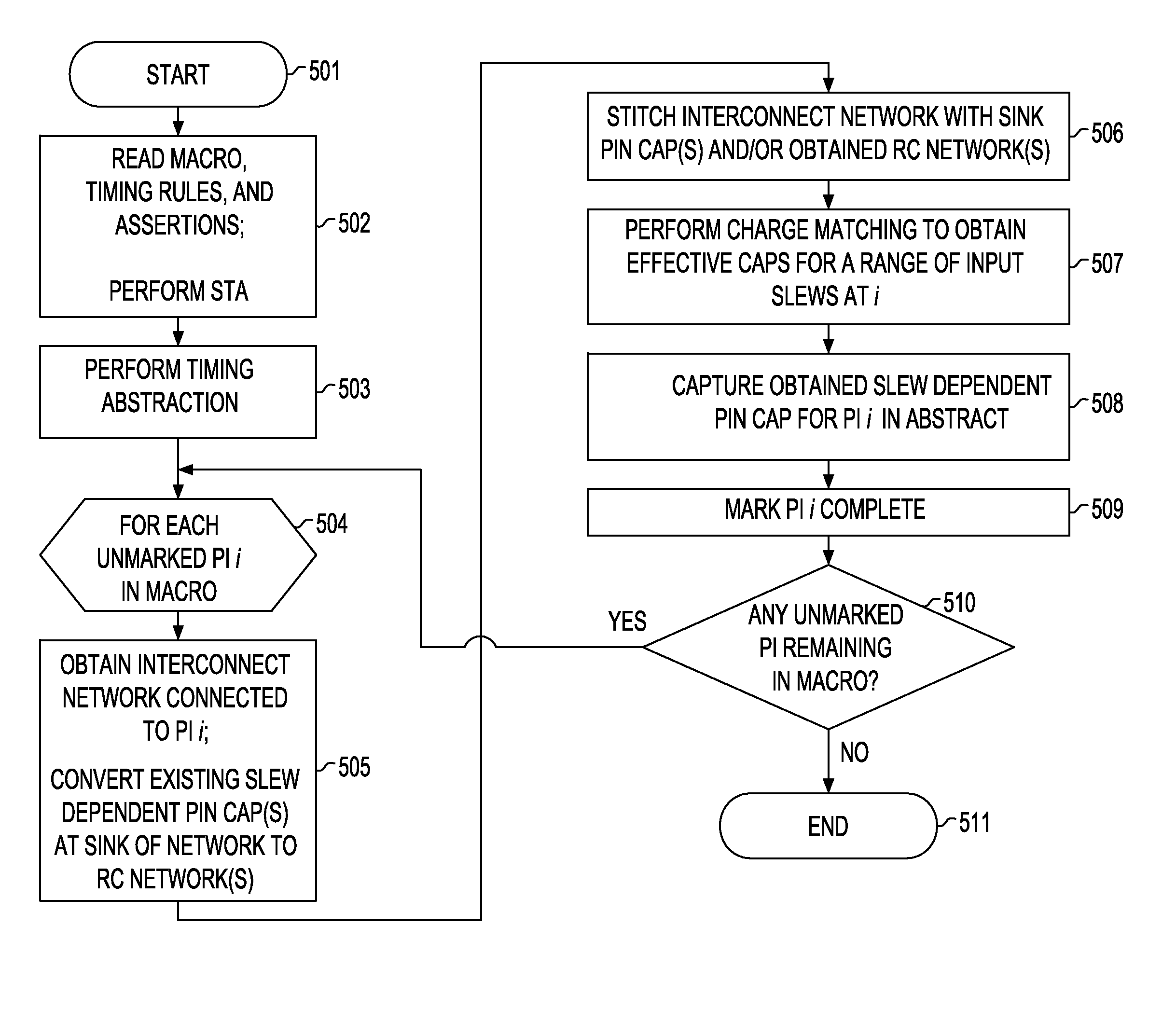

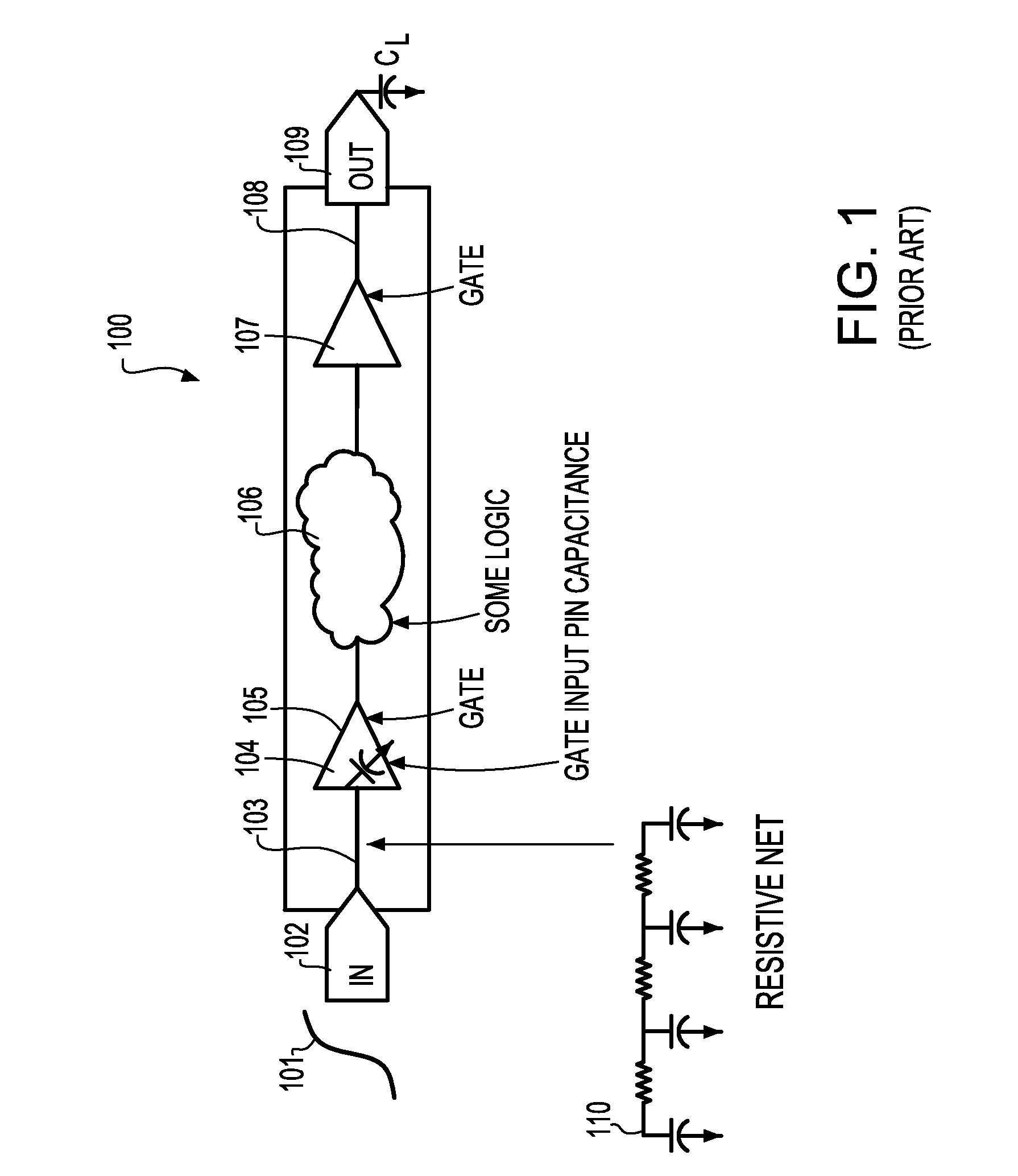

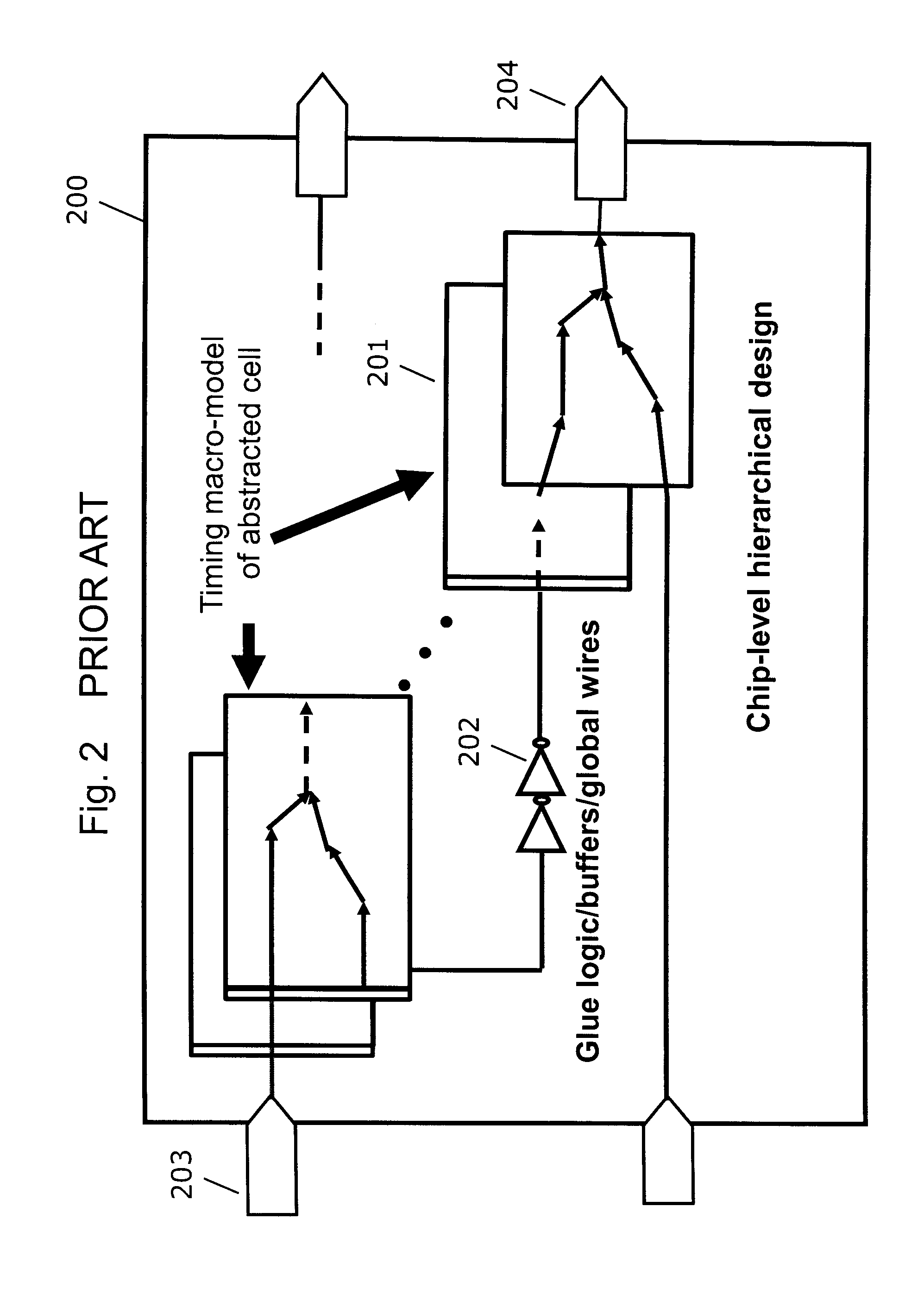

A method for converting interconnect parasitics of an interconnect network into slew dependent pin capacitances utilizes charge matching between predetermined voltage thresholds. During timing abstraction of a macro, parasitics of interconnects connected to the primary inputs are represented as slew dependent pin capacitances in an abstract model being created. Interconnect model order reduction is employed to speed the process. The generated abstract is subsequently used in place of each occurrence of the macro during chip level hierarchical static timing analysis, leading to an enhanced accuracy of the timing analysis of the logic components driving the abstracts.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

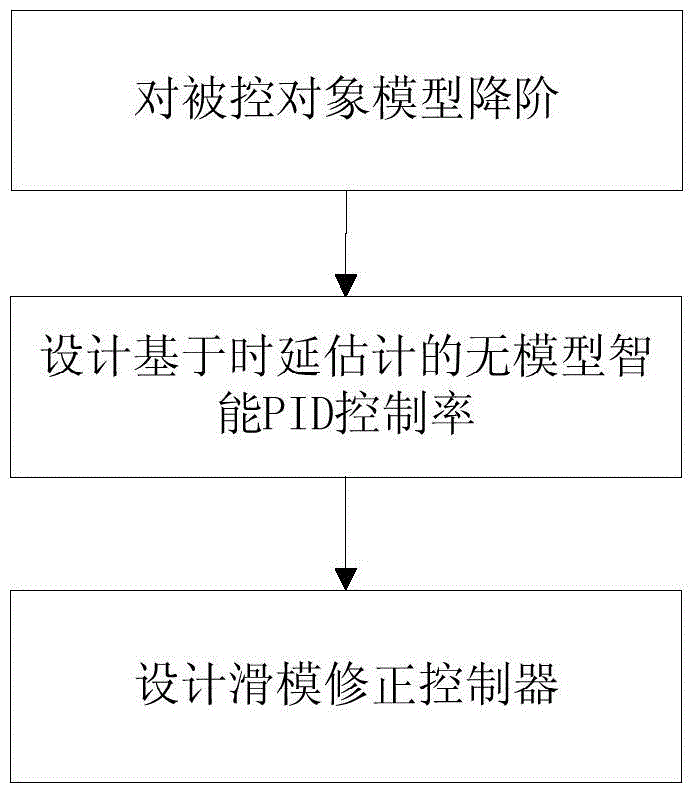

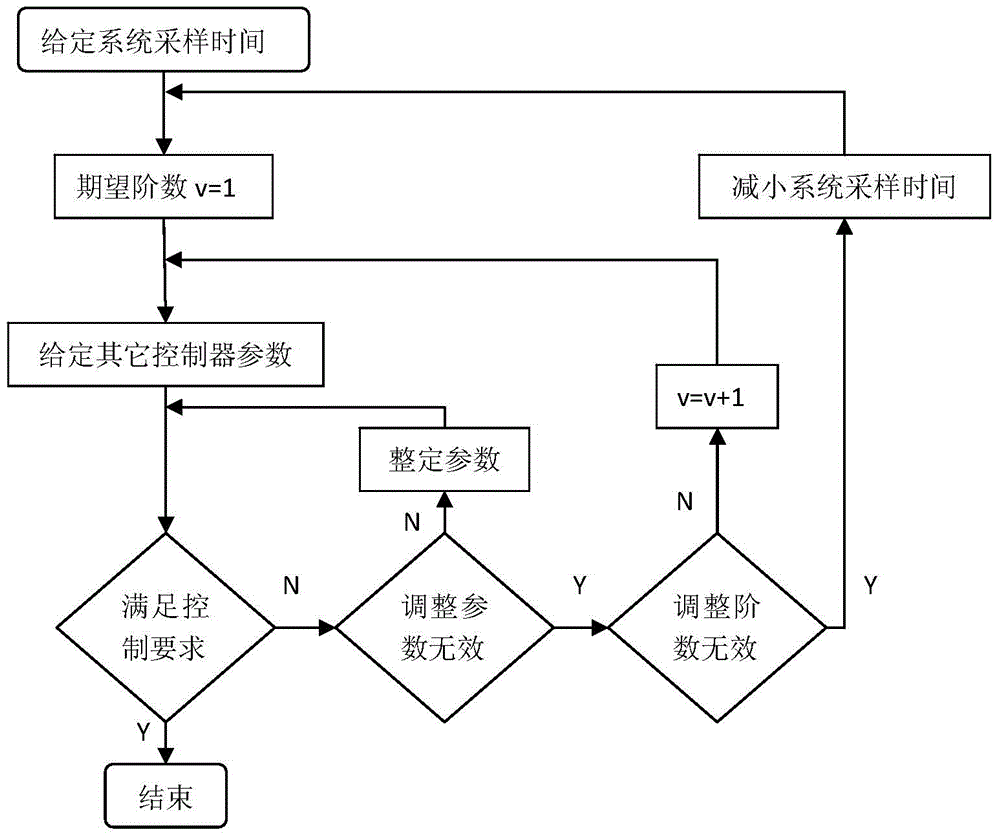

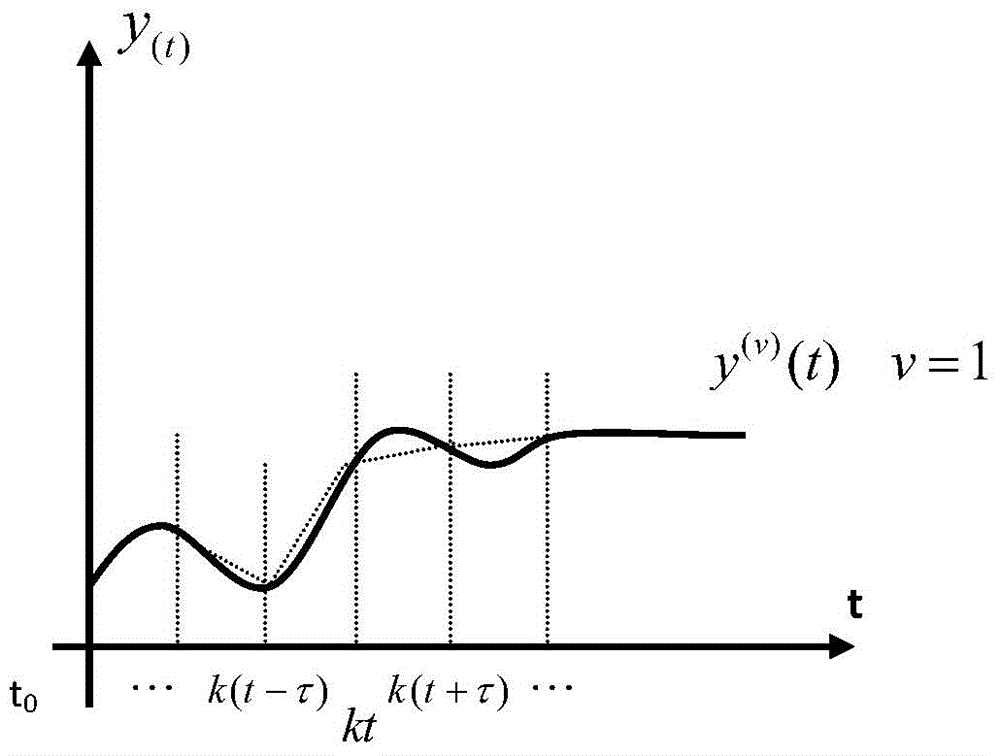

Model-free control method in intelligent control

The invention discloses a model-free control method in intelligent control. The model-free control method comprises the steps of: carrying out model order reduction on a controlled object; and designing a model-free sliding-mode controller, which is composed of a model-free intelligent PID control rate based on time delay estimation and a sliding-mode correction sub-controller. The model-free control method combines the advantages of model order reduction and modern intelligent control, utilizes a computer sampling mechanism and adopts a time delay estimation technology to for reducing the order of a high-order system, and performing online estimation on real-time local dynamic characteristics; in addition, a circulative iteration controller is designed for correcting errors caused by time delay estimation, thereby further improving following control precision; and the model-free control method can effectively overcome influence of a series of uncertain factors such as unmodeled dynamics of the complex controlled object and external interference, and has the advantages of being simple in controller design structure, few in calculation workload, independent of mathematical model and parameters of a controlled system, good control performance and effect and the like.

Owner:NANJING UNIV OF SCI & TECH

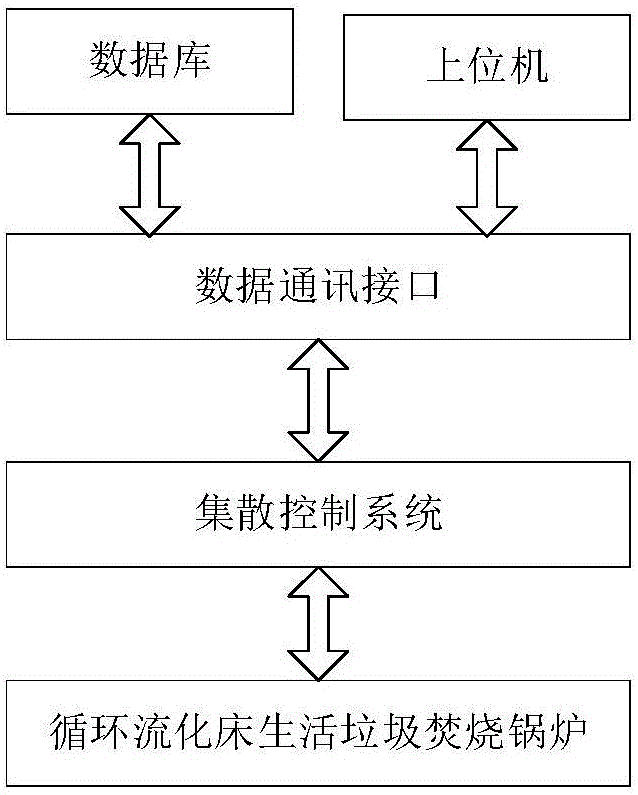

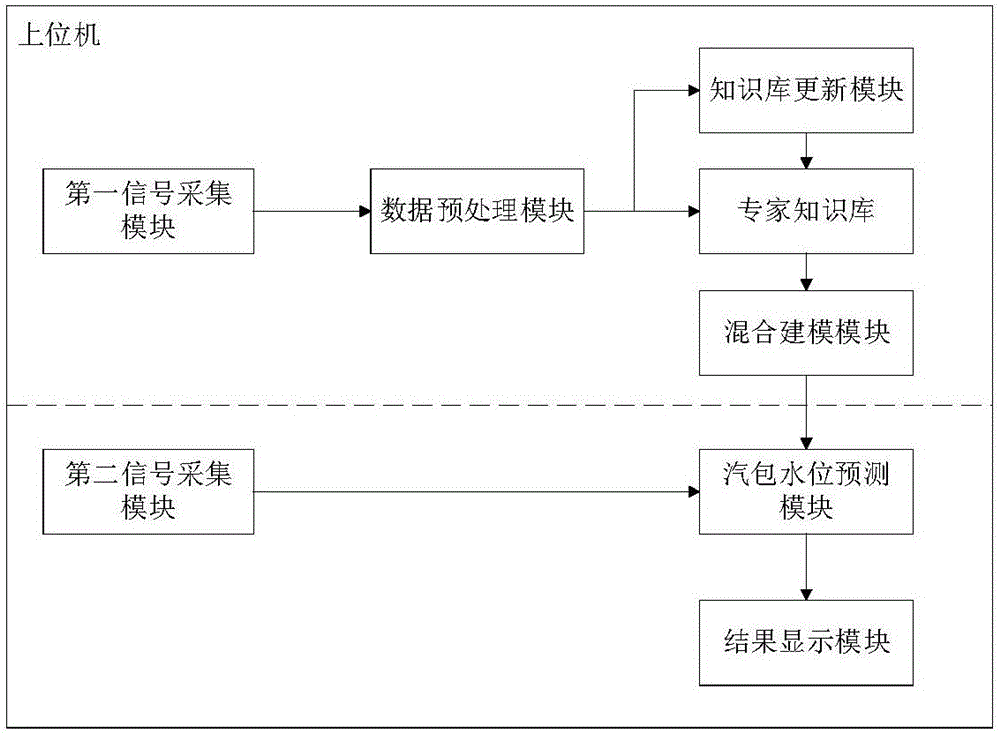

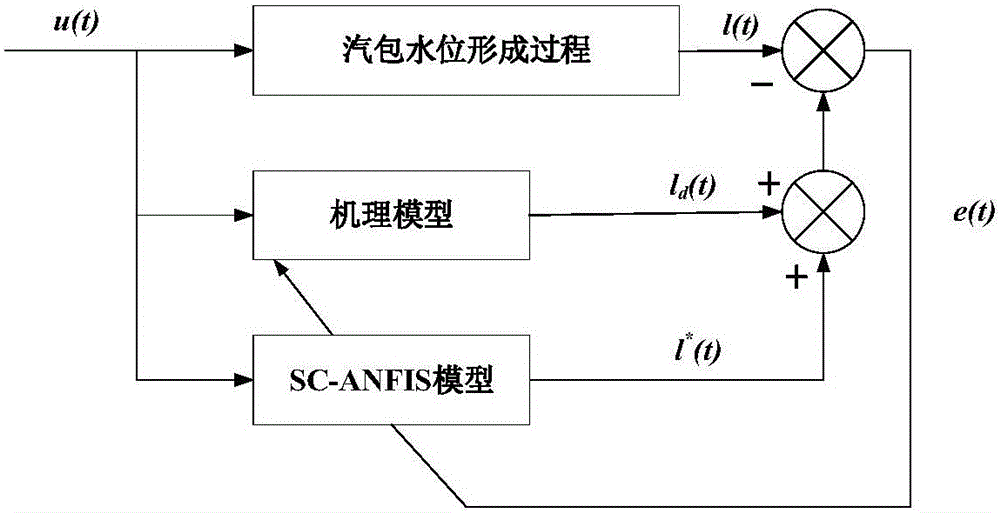

System and method for predicting drum water level of circulating fluidized bed domestic garbage incineration boiler

ActiveCN106055520AImprove forecast accuracyGeometric CADComplex mathematical operationsTacit knowledgeFluidized bed

The invention discloses a system and a method for predicting the drum water level of a circulating fluidized bed (CFB) domestic garbage incineration boiler. A moderately complex drum water level dynamic characteristic mechanism model based on a differential equation form is established first from the mechanism of drum water level change characteristic based on reasonable simplifying assumption according to a mass conservation equation, an energy conservation equation and some basic equations in combination with the unique heat absorption distribution law of the wall-cooled wall of the CFB domestic garbage incineration boiler. Then, tacit knowledge in running historical data is dug using ANFIS (Adaptive Neuro-Fuzzy Inference System) modeling to compensate errors caused by model simplifying assumption, model reduction or linear processing, incomplete cognition on the mechanism of a thing change process, different object characteristics and internal and external disturbance in the mechanism modeling process of the drum water level. The advantages of mechanism modeling and ANFIS modeling are sufficiently exerted, and the prediction precision of the drum water level is prompted.

Owner:ZHEJIANG UNIV

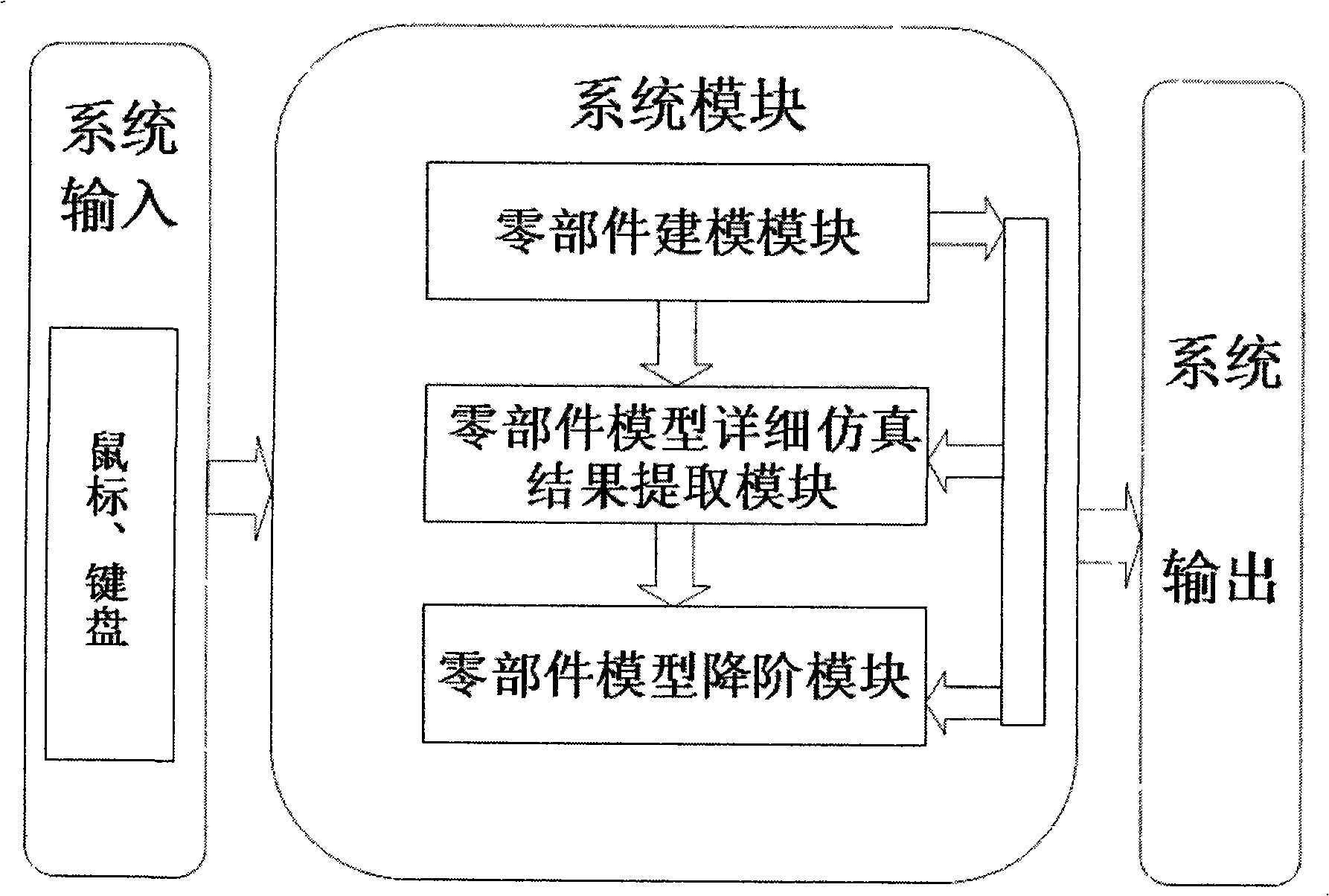

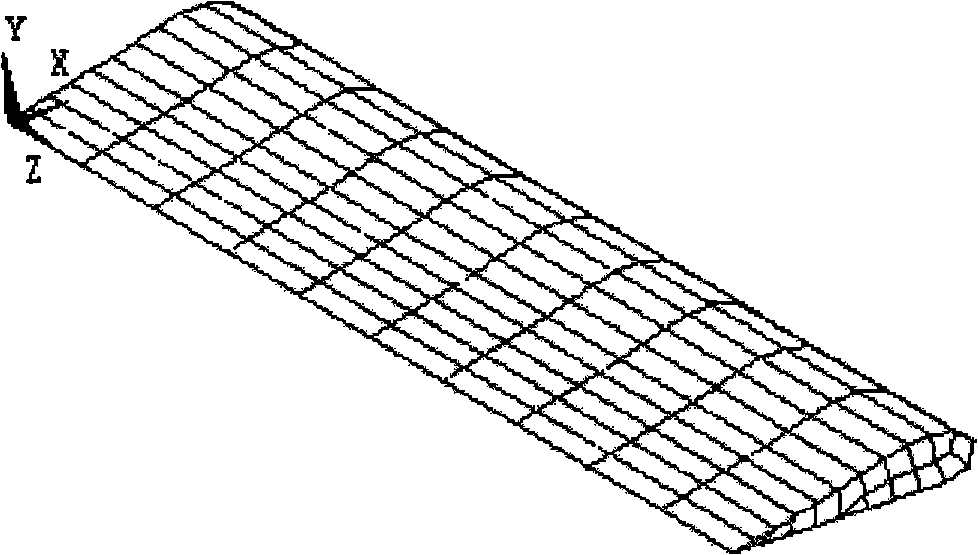

Component model order reduction method facing products grade simulated components

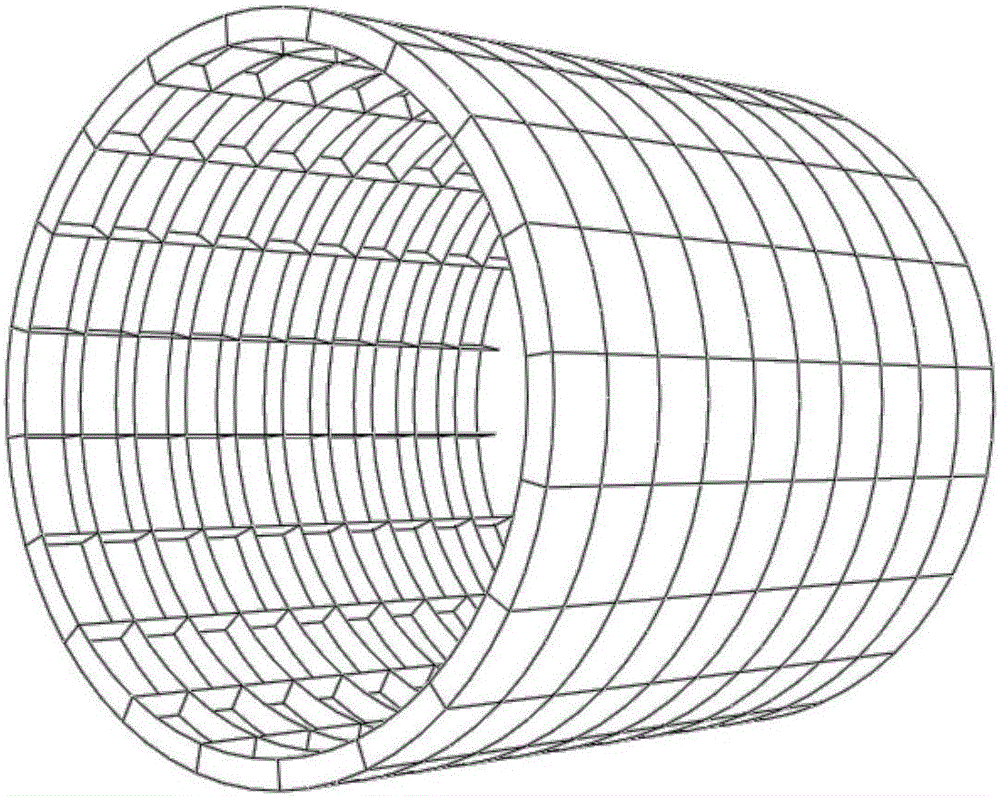

InactiveCN101266632AAccelerate Product-Level Simulation SpeedShorten the development cycleSpecial data processing applications3D modellingElement analysisOrder reduction

The invention relates to a component model order reduction method facing to product level simulation, and belongs to the CAD computer aided cooperative product simulation technology field, which is characterized in comprising following steps: using ANSYS software to establish a three-dimensional mesh module of the component and calculate modal, and extracting mass matrix and stiffness matrix of the component model; then using Mathematica software and combining an order-reduction algorithm in a finite element analysis to reduce the component model provided with n-dimensional vector into the component model consisted of m modals according to the gained the stiffness matrix and mass matrix, and a state of the structure in a maximum deformation in a setting typical load and a state in system balance. The invention improves product level simulation speed of complex products, improves a reuse degree of simulation data, and is simply operated, and easy to realize.

Owner:TSINGHUA UNIV

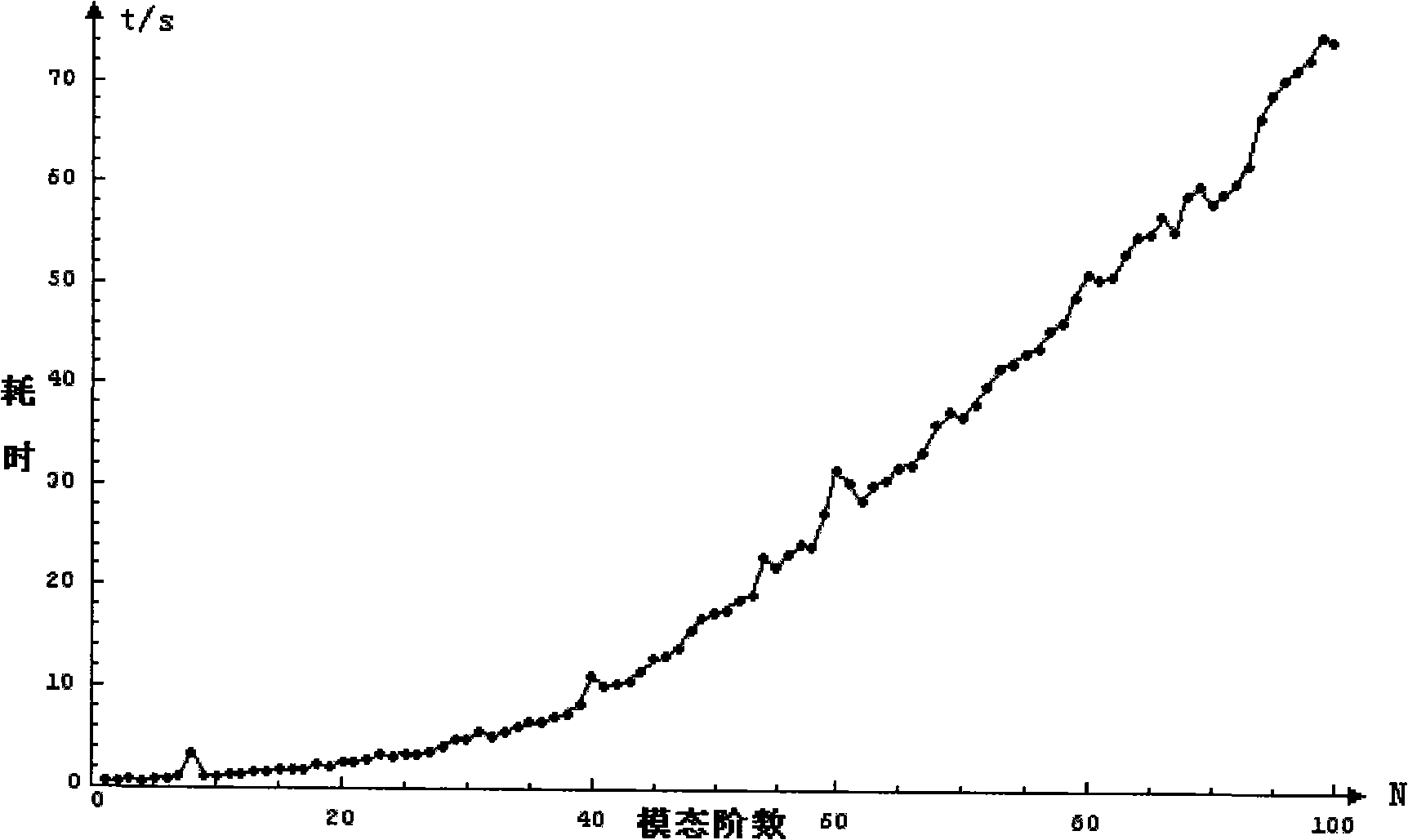

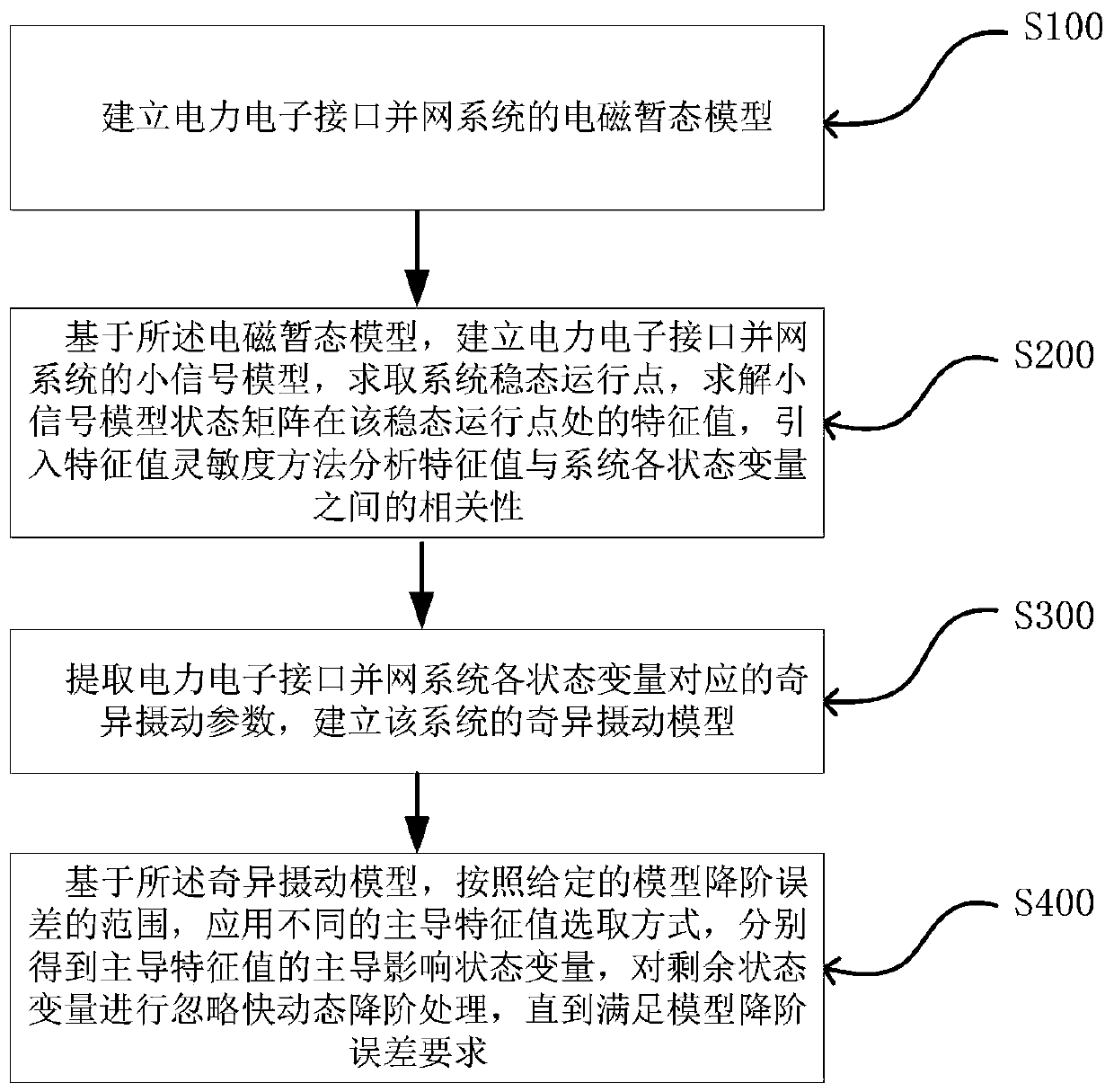

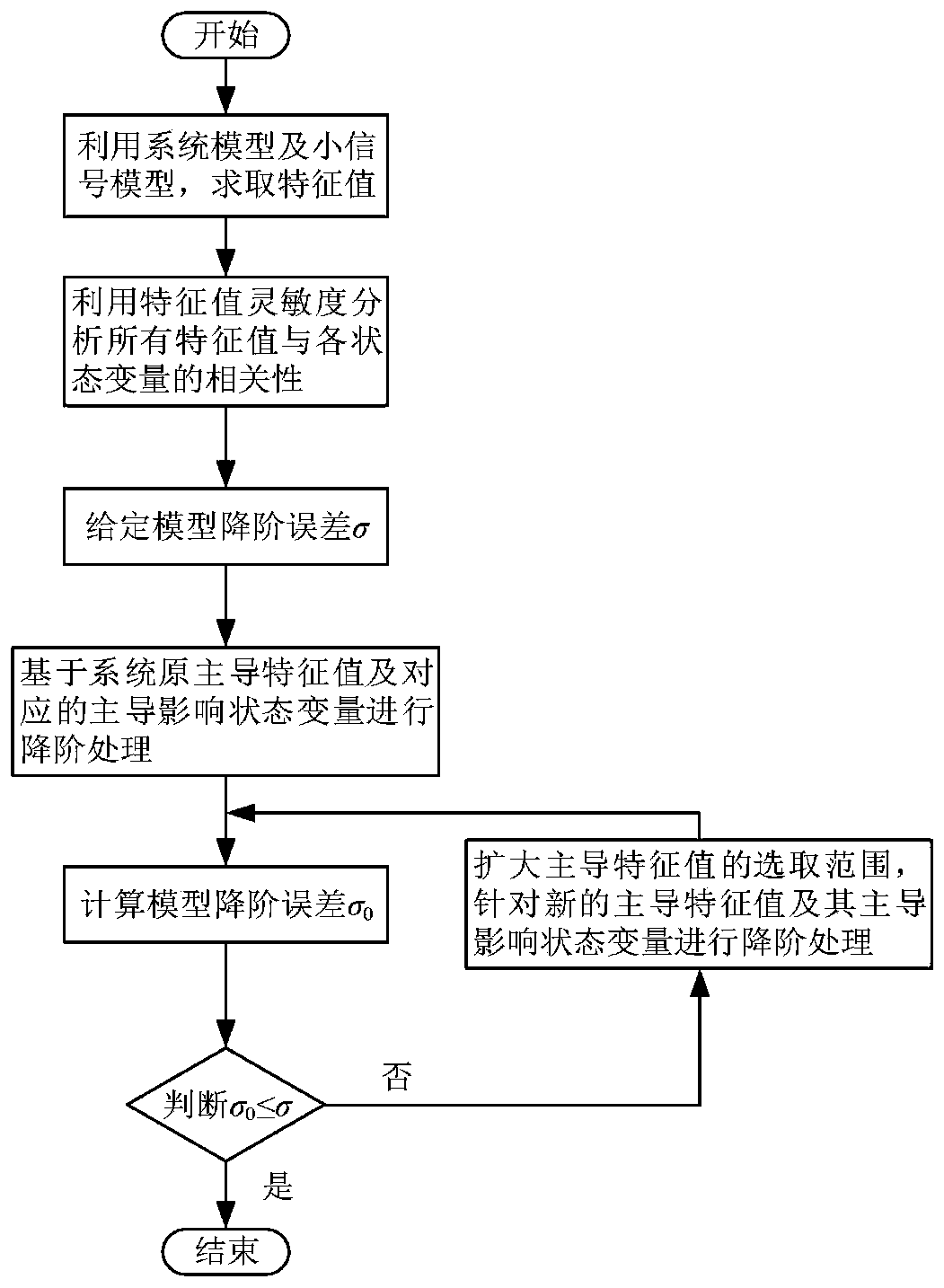

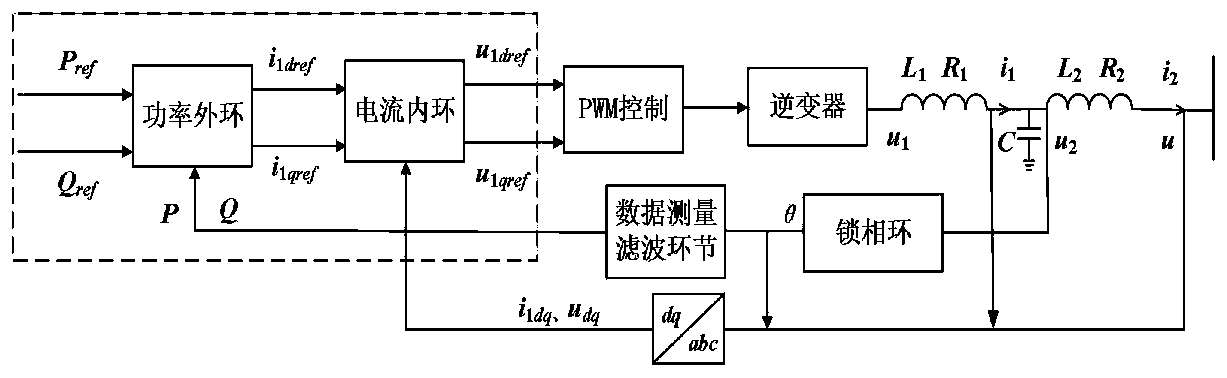

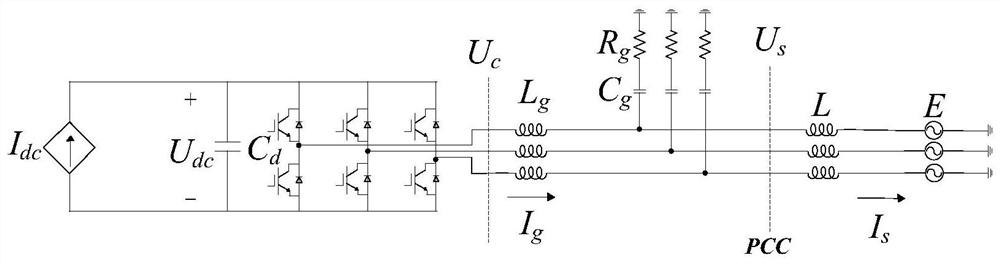

Method for selecting reduced-order variable of power electronic interface grid-connected system model reduced order

ActiveCN110262236AThe order reduction error requirement meets theAdaptive controlEngineeringReduced order

The invention relates to a method for selecting a reduced-order variable of a power electronic interface grid-connected system model reduced order, which can improve the adverse effect that the current application does not consider the reduced-order processing of different state variables aiming at different model reduced order errors. The method comprises the following steps of: 1, establishing an electromagnetic transient model of a power electronic interface grid-connected system; 2, solving a characteristic value of the system at a steady-state operation point, and introducing a characteristic value sensitivity method to analyze the correlation between the characteristic value and each state variable of the system; 3, extracting singular perturbation parameters corresponding to each state variable of the system, and establishing a singular perturbation model of the system; and 4, according to a given model order reduction error range, applying different dominant characteristic value selection modes to obtain the dominant influence state variable of the dominant characteristic value, and the remaining state variables are subjected to order reduction processing. According to the method, different state variables can be selected for order reduction processing according to the requirement of the model order reduction error, and the practicability and the effectiveness of the order reduction variable selection method are fully considered.

Owner:HEFEI UNIV OF TECH

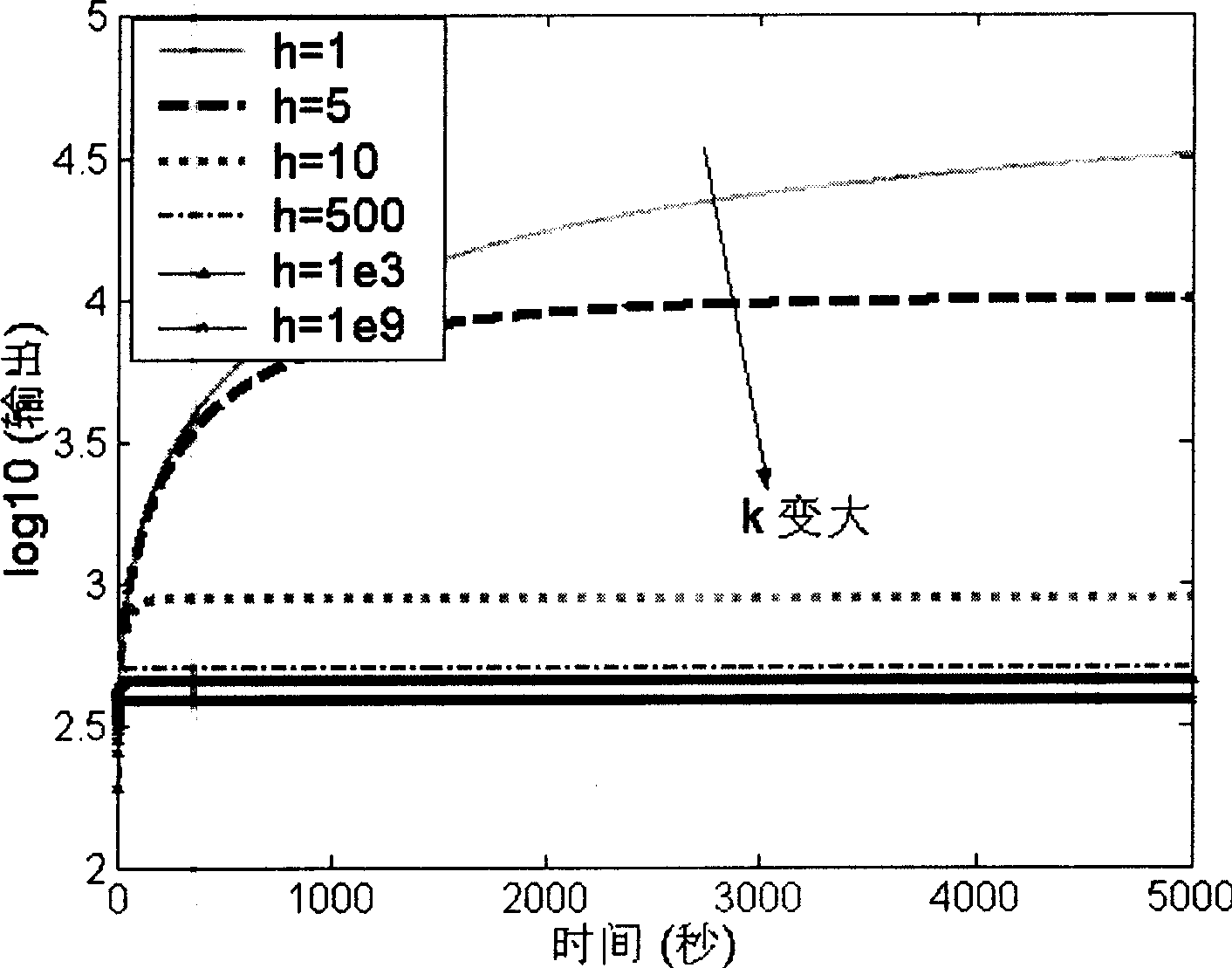

Model order reducing method for a parameter system

InactiveCN1707467AHigh order reduction accuracyHigh precisionSpecial data processing applicationsHat matrixEngineering

The present invention belongs to the field of microelectromechanical MEMS and electronic technology, and is especially one kind of order reducing method for system model with parameters. The model order reducing technology can raise simulating and verifying speed of system model effectively and improve the design scheme of circuit and device timely. The present invention establishes model order reducing method to parameter system. Transfer function of parameter system is multiple series developed to constitute son projection matrix, and the son projection matrix is orthogonalized to constitute projection matrix. The projection matrix is used in reducing order of the original parameter system and the obtained reduced-order system is independent on some special values of the system parameters and can maintain order reducing precision on different values. The present invention has greatly raised order reducing precision and efficiency.

Owner:FUDAN UNIV

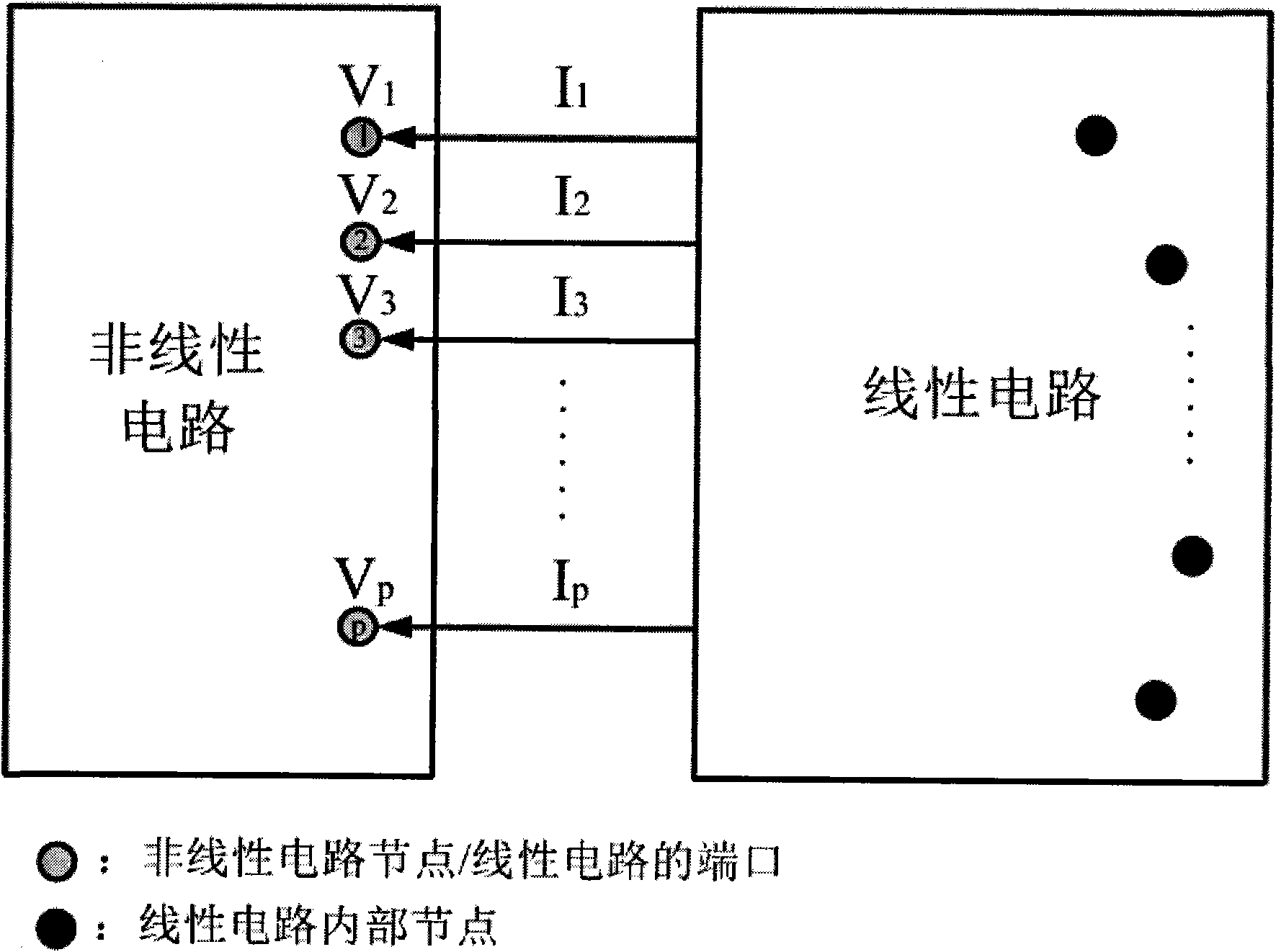

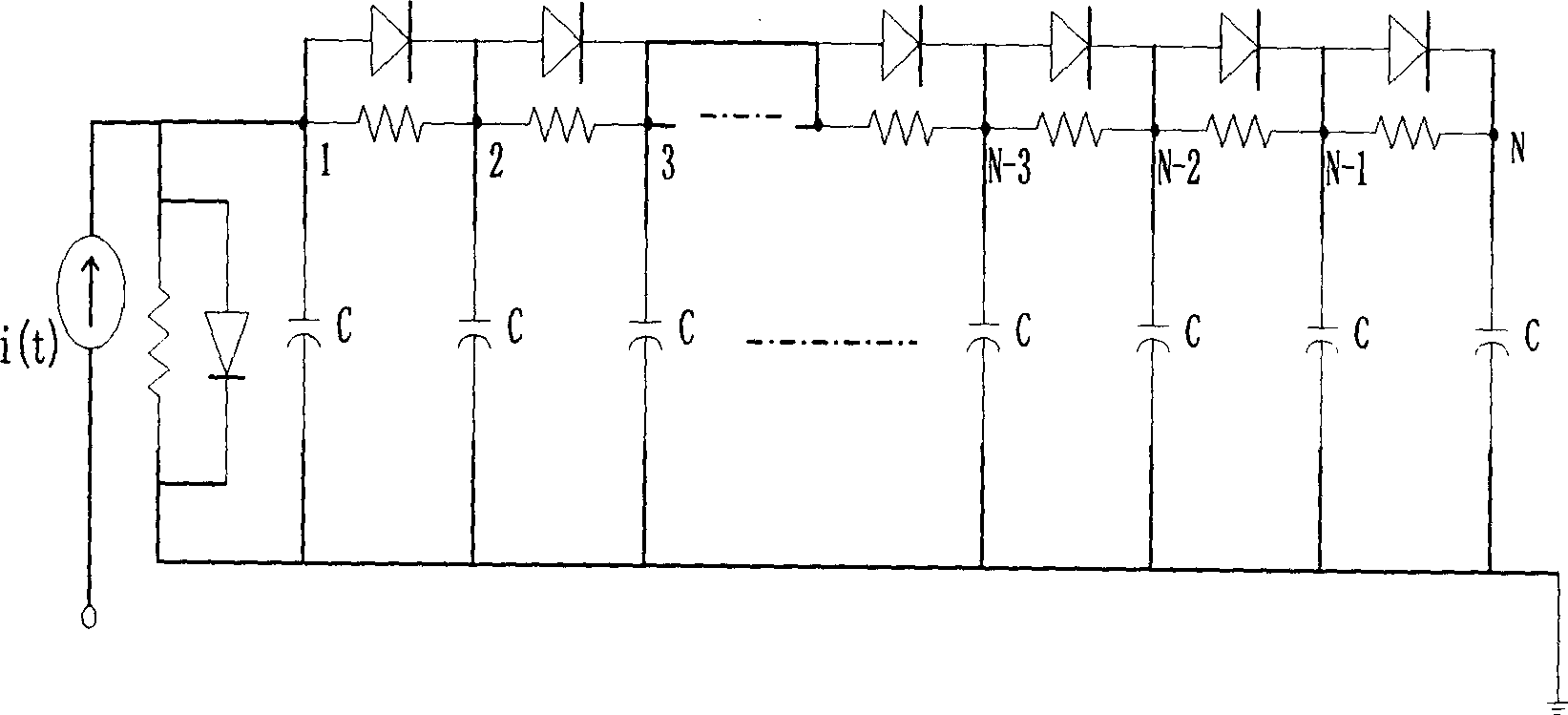

Nonlinear circuit time domain model reduction method and device

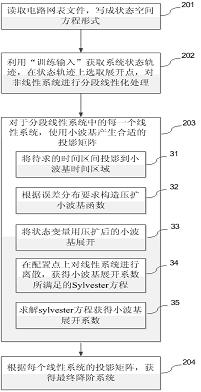

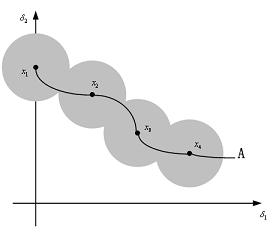

ActiveCN102467593AHigh precisionEasy to controlSpecial data processing applicationsTerm memoryLinear circuit

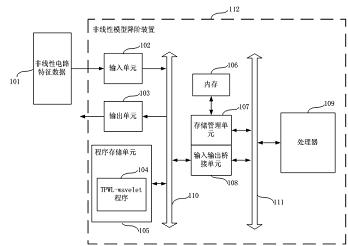

The invention belongs to the field of design of an integrated circuit and relates to a nonlinear circuit time domain model reduction method and a nonlinear circuit time domain model reduction device. The method comprises the following steps of: forming a track in a state space through a 'training signal', and selecting an expansion point on the track to approach a nonlinear circuit through a segmented linear method; and obtaining a final reduction model through a time domain model reduction method based on wavelet collocation. The device comprises an input unit, an output unit, a program storage unit, an external bus, a memory, a storage management unit, an input / output bridging unit, a system bus and a processor. A nonlinear system is directly subjected to model reduction in a time domain, the time domain reduction accuracy of the nonlinear system can be guaranteed, and a time domain error can be controlled; therefore, an accurate and compact reduction model can be acquired, and the simulation accuracy and efficiency are improved.

Owner:FUDAN UNIV

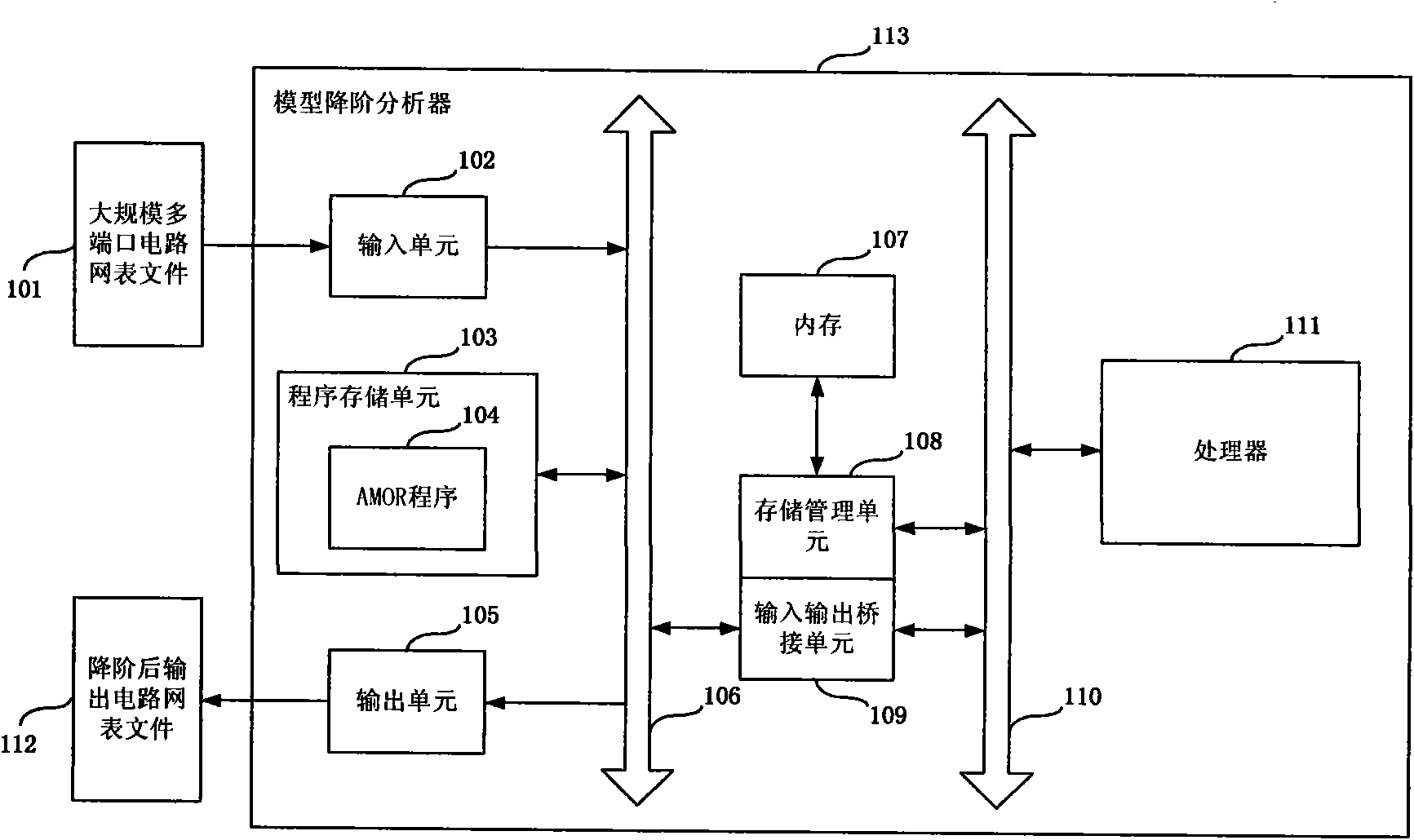

Method and device for reducing interconnection line model of great quantity of ports

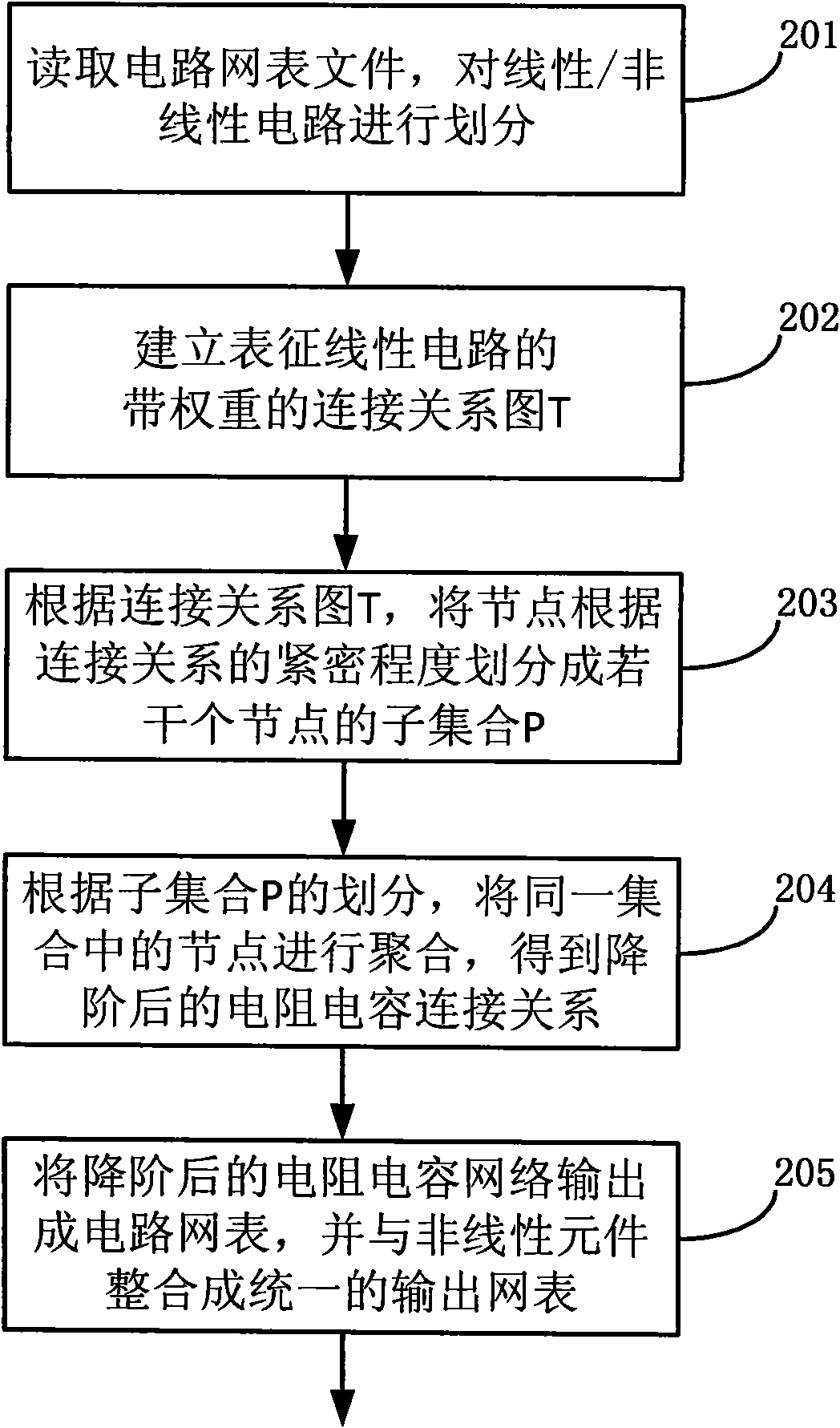

ActiveCN102339335AShort simulation timeImprove efficiencySpecial data processing applicationsReduced modelCapacitance

The invention belongs to the field of integrated circuits, and relates to a method and device for reducing an interconnection line model of a great quantity of ports. The method comprises the following steps of: constructing an undirected graph according to connection relationship of resistors and capacitors of an interconnection line circuit of a great quantity of ports, partitioning the undirected graph by utilizing a spectrum partitioning method, and finally carrying out coarse graining on nodes in a same partition set, thus obtaining a reduced circuit. The device comprises an input unit, an output unit, a program storage unit, an external bus, a memory, a storage management unit, an input and output bridging unit, a system bus and a processor; and an AMOR program of the reduction method can be realized through storage of the program storage unit. According to the invention, model reduction is carried out on the interconnection line of a great quantity of the ports without introduction of nonzero components, and the reduced model is ensured to be shorter in simulation time and higher in efficiency, and simultaneously the resistance value and capacitance of the obtained reduced circuit are positive values, thus having physical realizability and ensuring the passiveness of the reduced circuit.

Owner:FUDAN UNIV

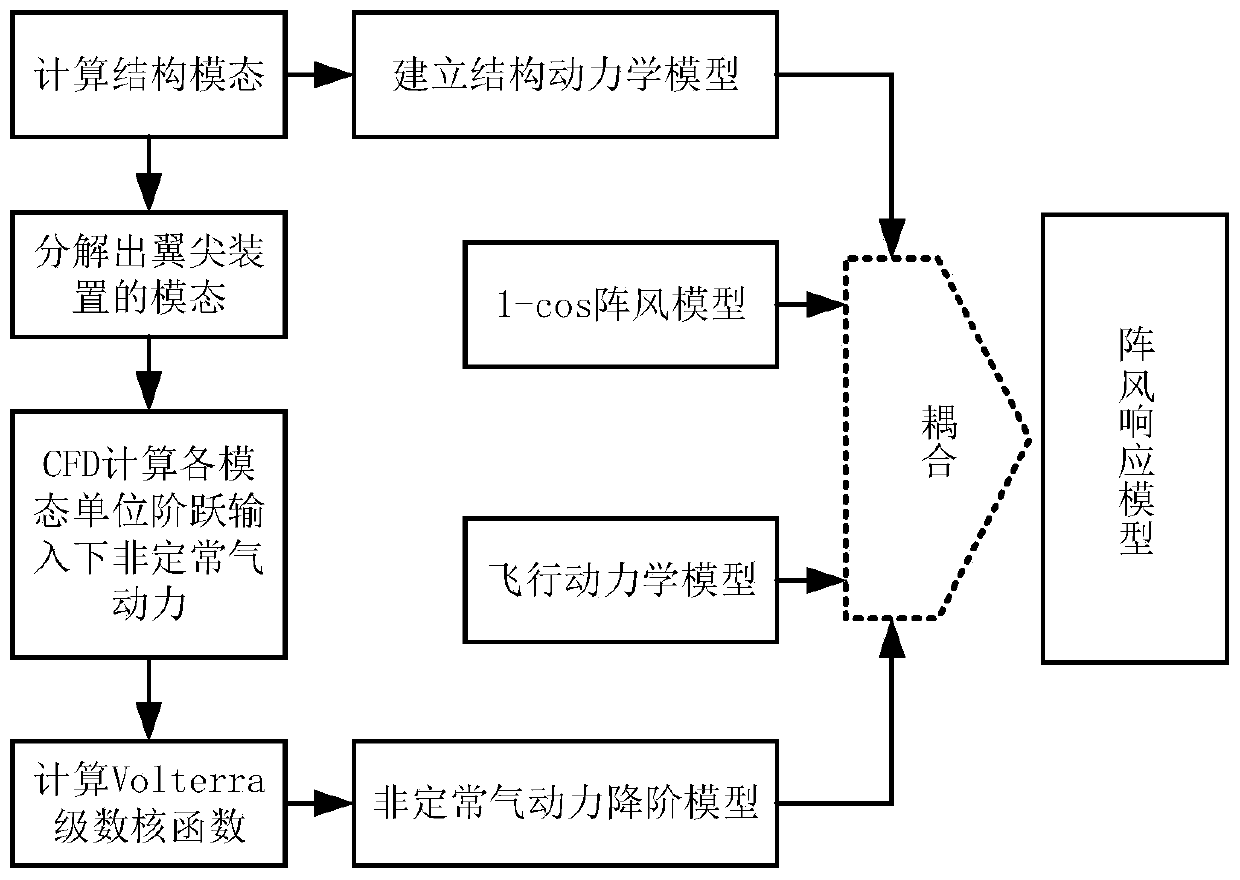

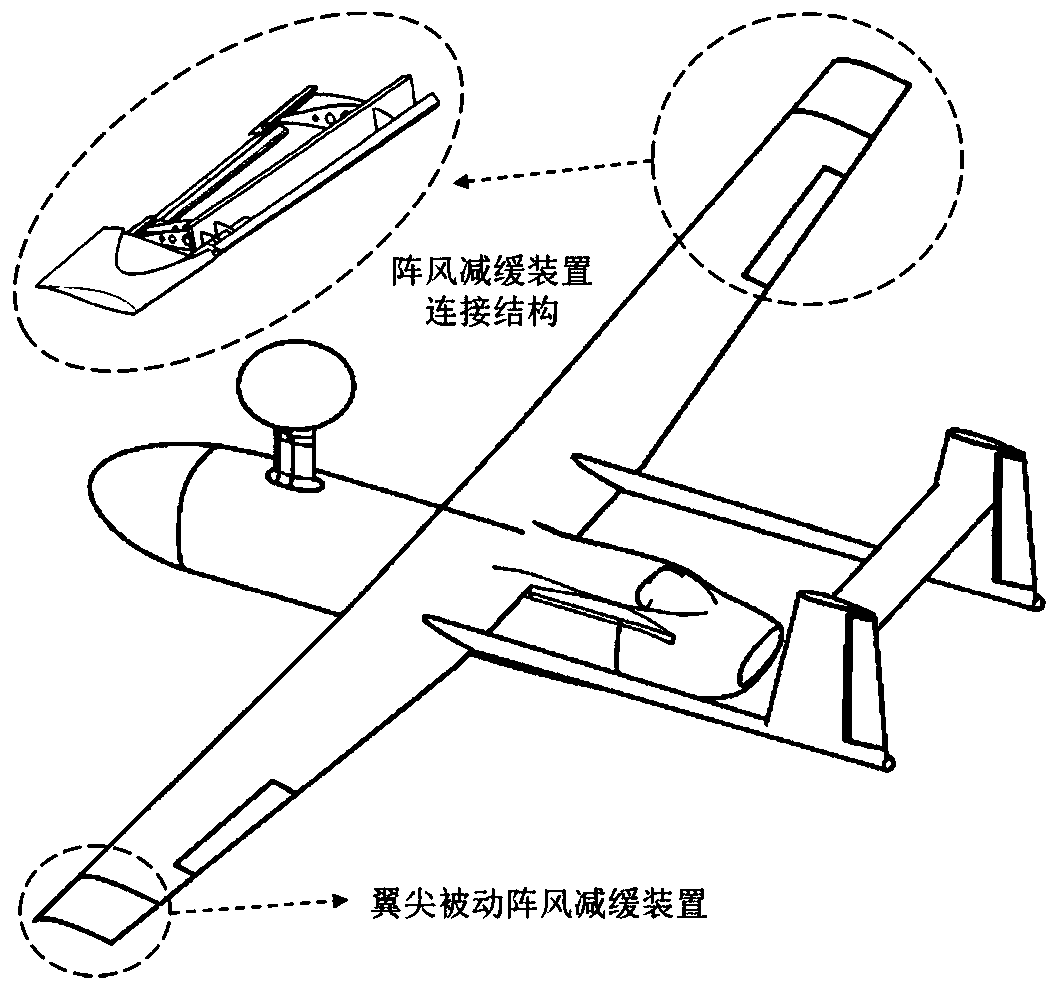

A modeling analysis method for gust response of a fixed-wing aircraft

ActiveCN109840349AReduce orderHigh precisionSustainable transportationComplex mathematical operationsAtmospheric modelModelling analysis

The invention discloses a modeling analysis method for gust response of a fixed-wing aircraft, which reduces the order of a model by reducing the order of an aerodynamic model, has higher precision and small calculated amount compared with the traditional method, and is suitable for engineering analysis. After the model is coupled with an aircraft structure model, an atmosphere model, a steering engine model and the like, a gust response model with low order is obtained, and gust response analysis and gust slowing control design are facilitated.

Owner:XIAN AISHENG TECH GRP +1

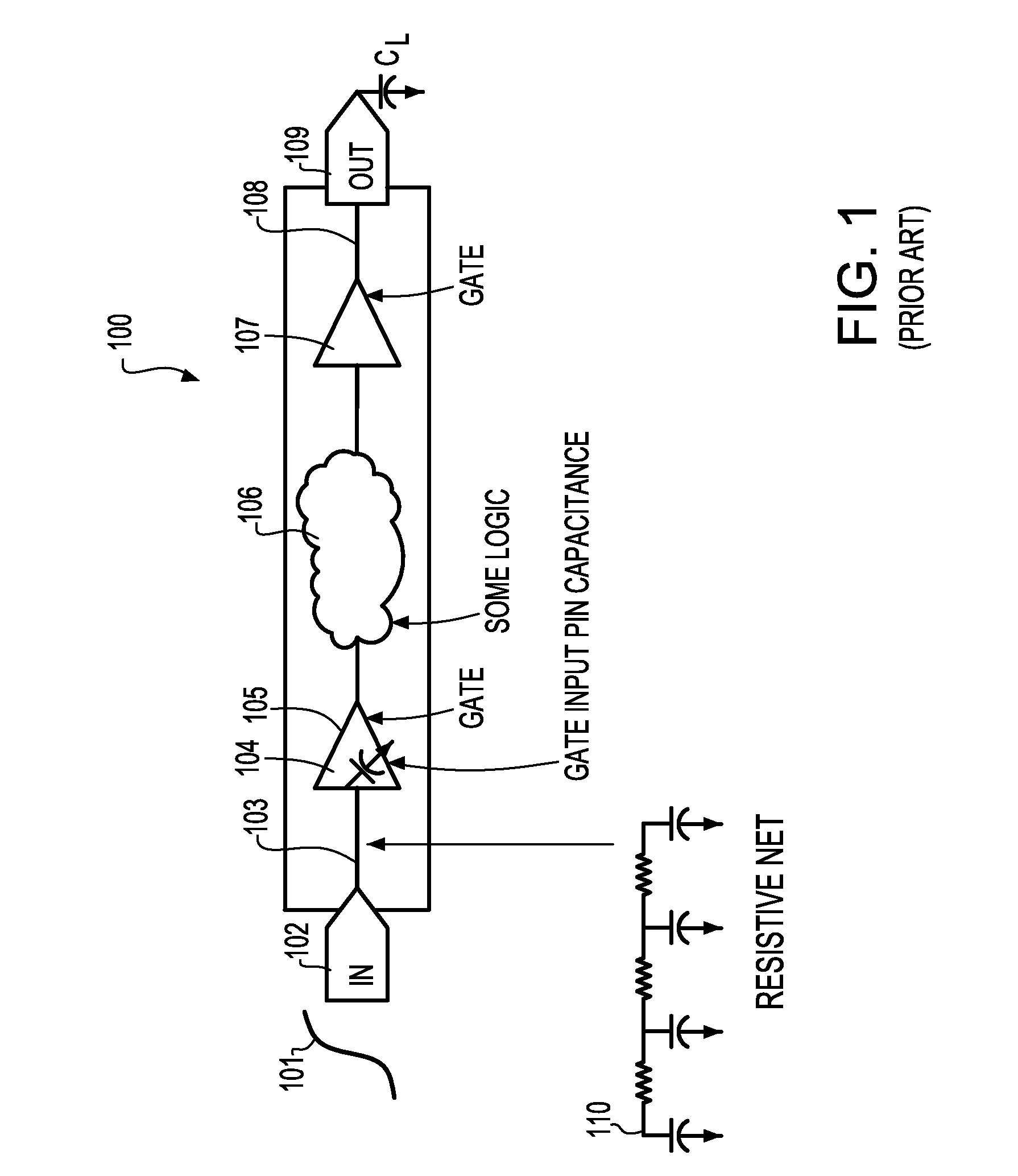

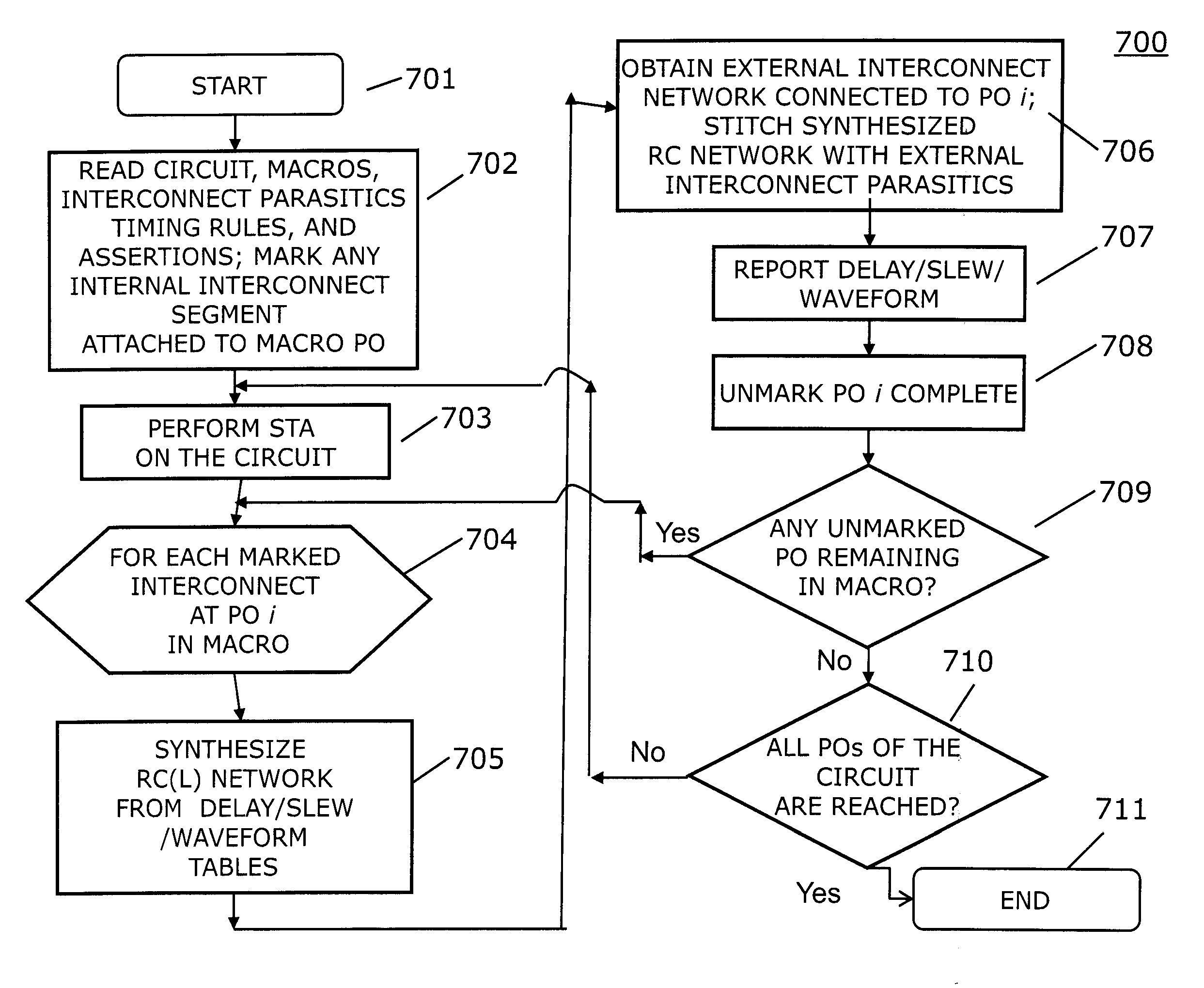

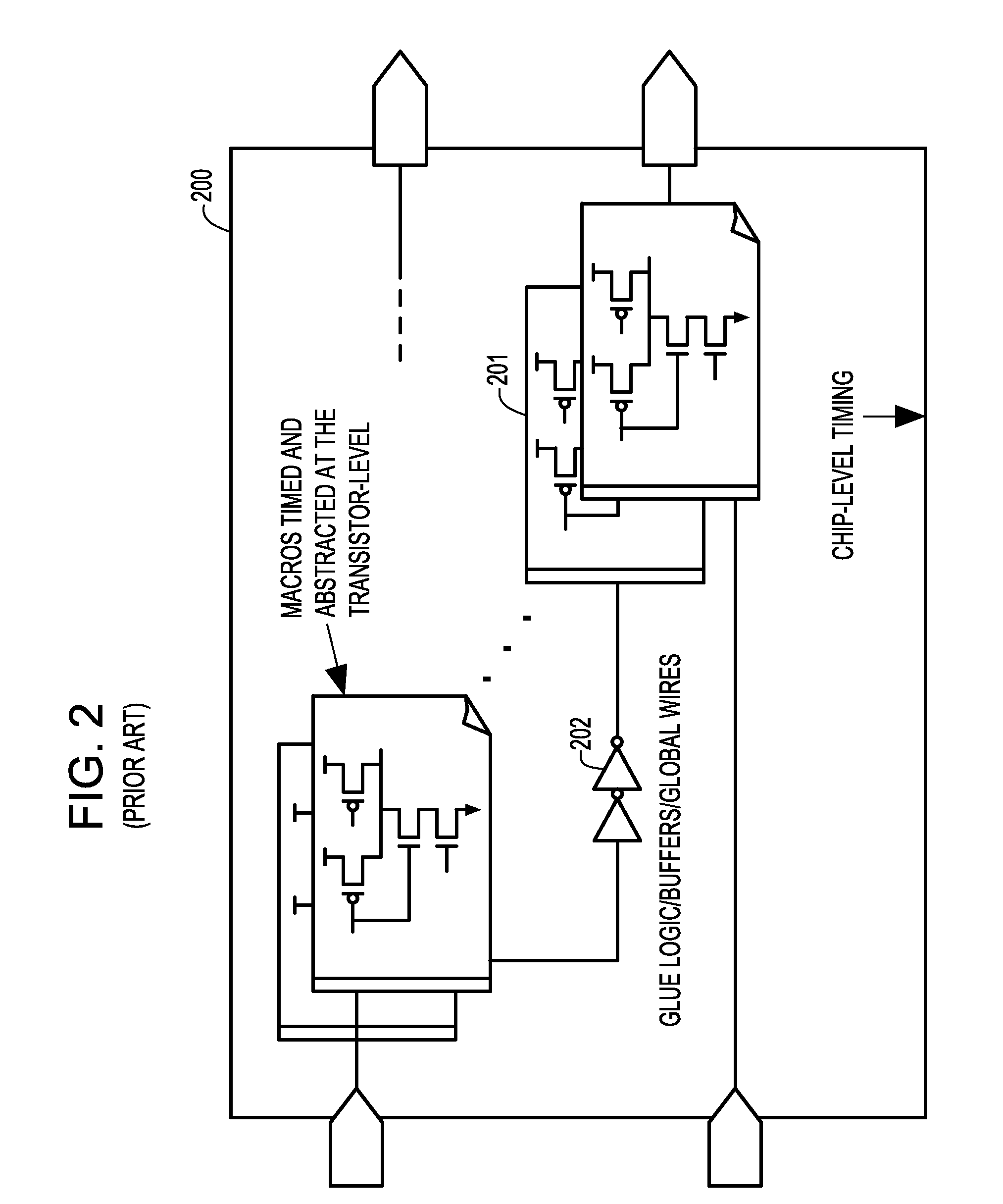

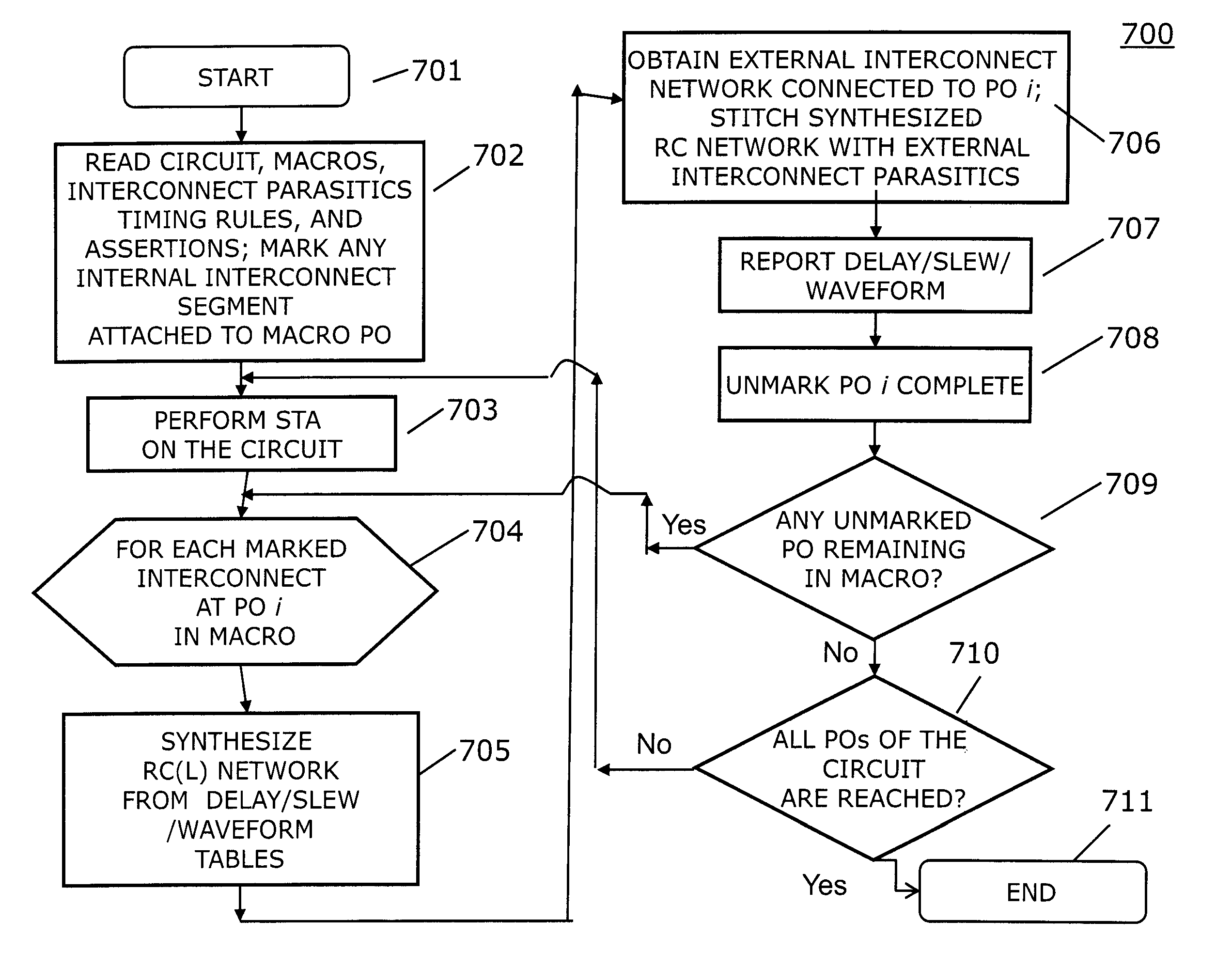

Method of Performing Static Timing Analysis Considering Abstracted Cell's Interconnect Parasitics

InactiveUS20110016442A1Accurate analysisDetecting faulty computer hardwareComputer aided designStatic timing analysisEngineering

An abstraction model supporting multiple hierarchical levels is inputted into a generalized static timing analysis of a hierarchical IC chip design to analyze and optimize the design of circuits integral to the chip containing a plurality of macro abstracts. An electrical network, synthesized for an internal abstract interconnect segment, is performed only once per macro and is applied to multiple instances of the macro abstract model in the IC chip design. The synthesized electrical network is a resistive capacitive or a resistive inductive capacitive network or a combination thereof. The synthesized electrical network is then used to match impulse response transfer functions of the network and the abstract interconnect segment's timing model. This network is stitched with the electrical parasitics of external interconnect segments connected to macro primary outputs. Various model order reductions are then performed on the electrical parasitics of external interconnects prior to network stitching. A static timing analysis is performed on the final network.

Owner:GLOBALFOUNDRIES INC

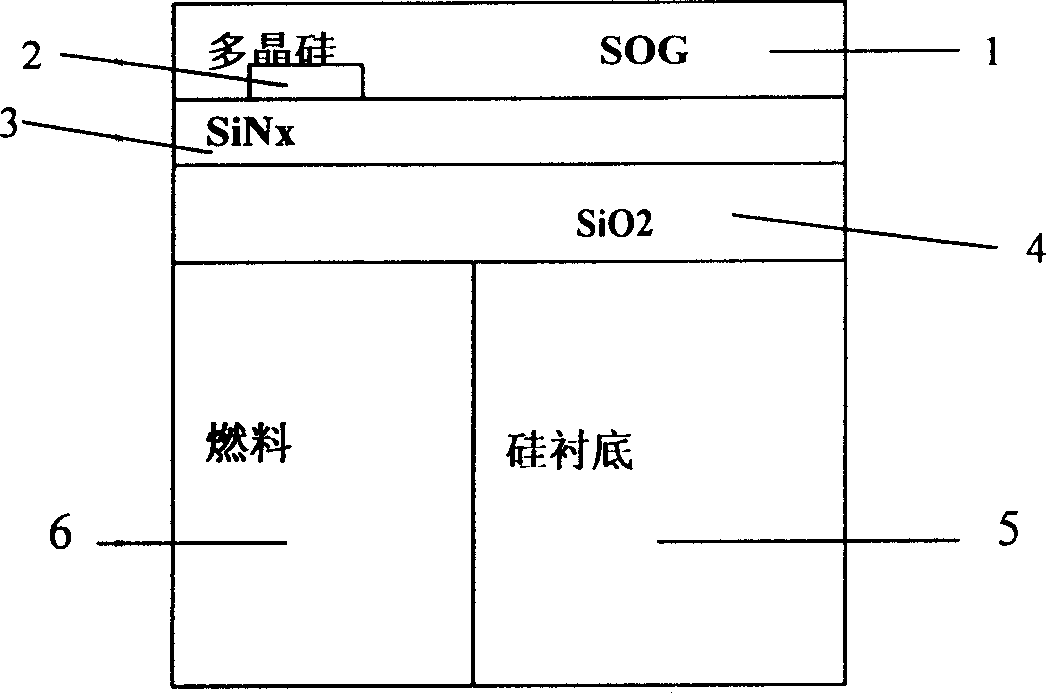

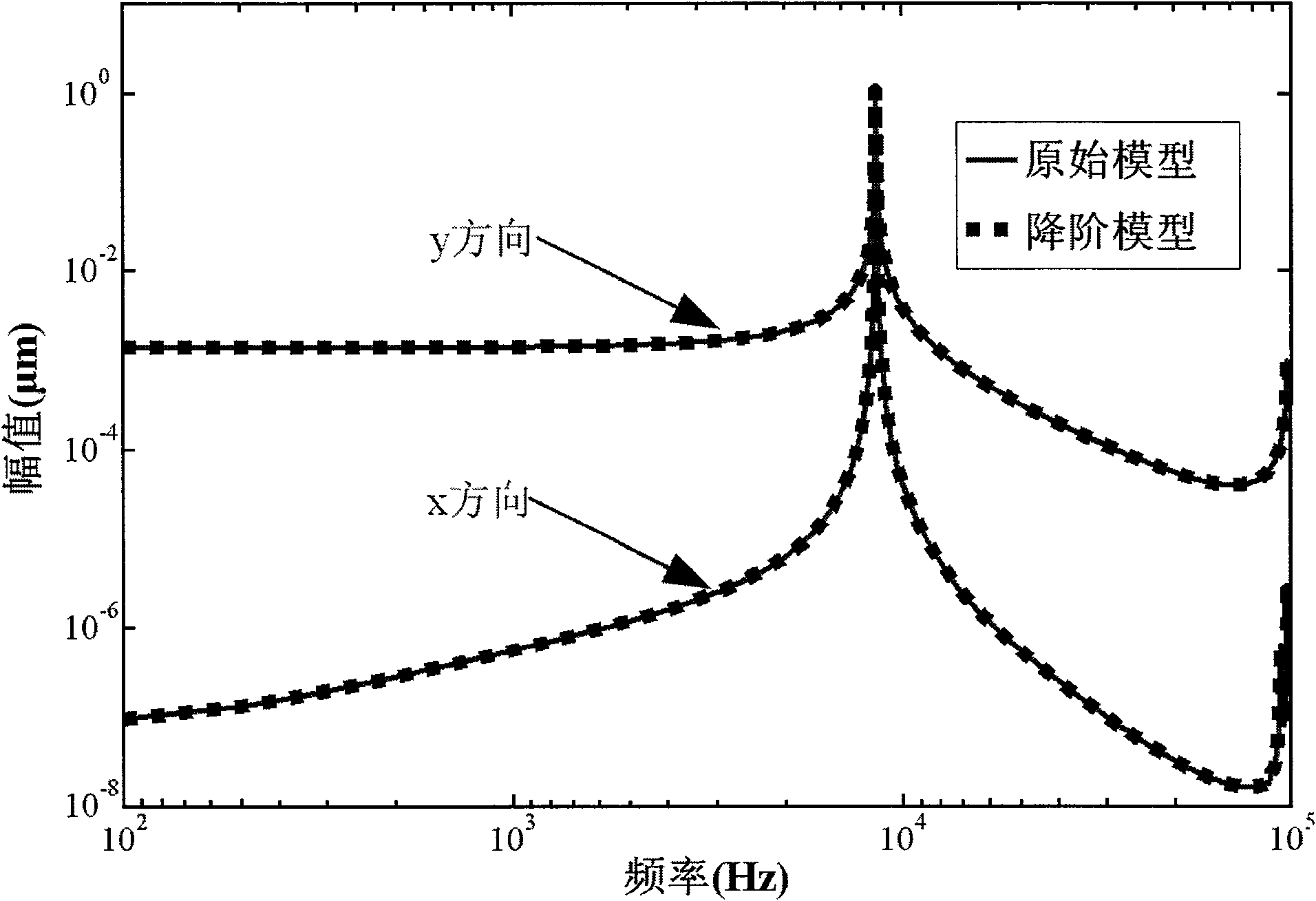

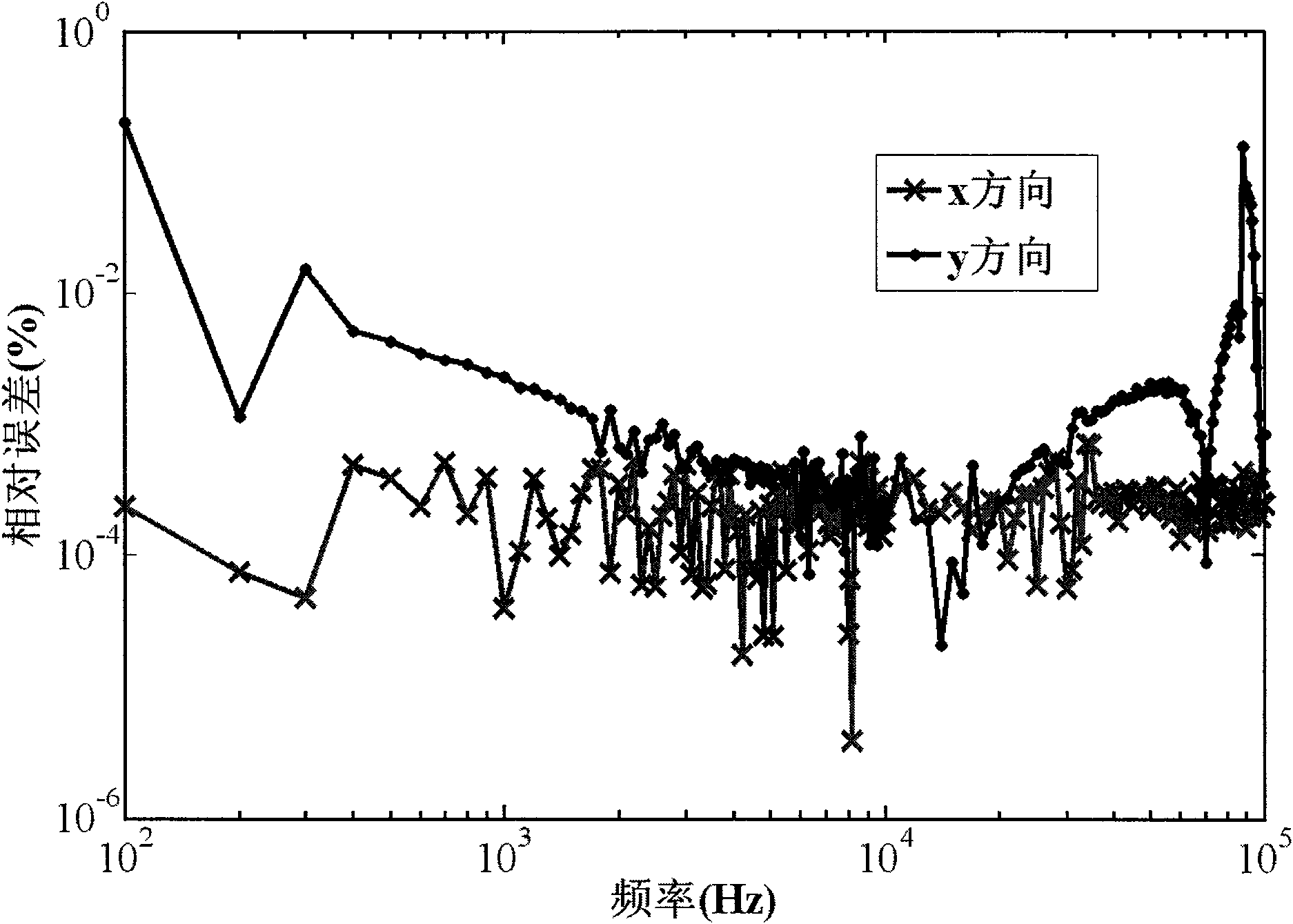

Temperature parameterized reduced-order modeling method for micro-electromechanical system

InactiveCN101567018AImprove computing efficiencyImprove calculation accuracySemi-permeable membranesPiezoelectric/electrostrictive/magnetostrictive devicesTemperature stressHat matrix

The invention discloses a temperature parameterized reduced-order modeling method for a micro-electromechanical system, and belongs to the field of micro-electromechanical system design and model order reduction. The method comprises the following steps: extracting quality, rigidity and temperature stress rigidity matrixes, and establishing a two-order dynamical equation related to temperature; constructing an orthogonal mapping matrix V; and projecting the primary two-order dynamical equation to a subspace in which the orthogonal mapping matrix V is positioned so as to acquire a temperature parameterized low-order model. The reduced-order method can greatly reduce the freedom scale of the primary model through an order reduction algorithm so as to improve the system-level modeling and simulating speed based on the reduced-order model. Simultaneously, by adopting the matrix matching principle, transfer functions of the reduced-order model and the primary model can be approximate better so as to have higher precision. During order reduction, a projection matrix irrelative with parameters can be generated, and finally, a temperature parameter in the primary system is reserved in the low-order model.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Order reducing method for non-linear circuit model based on direct progection and variation analysis

InactiveCN1527228AHigh order reduction accuracyHigh precisionElectronic circuit testingAnalogue computers for electric apparatusHat matrixEngineering

The model order reducing technology is one very useful technology for raising circuit simulating and verifying speed in improving circuit design scheme. The present invention establishes one kind of directly projecting method of reducing order of non-linear circuit model, and features the combination of direct projection and variation analysis in control theory. The sub-system obtained through variation analysis is used in constituting son projection matrix V1, V2, ..., Vn; and the relation between the original system and the son system is then used in constituting united projection matrix V. The projection matrix V is finally used in realizing direct projection of one approximate non-linear system on the original non-linear system. Compared with the order reducing the sub-system method, the present invention has greatly raised order reducing precision and efficiency.

Owner:FUDAN UNIV

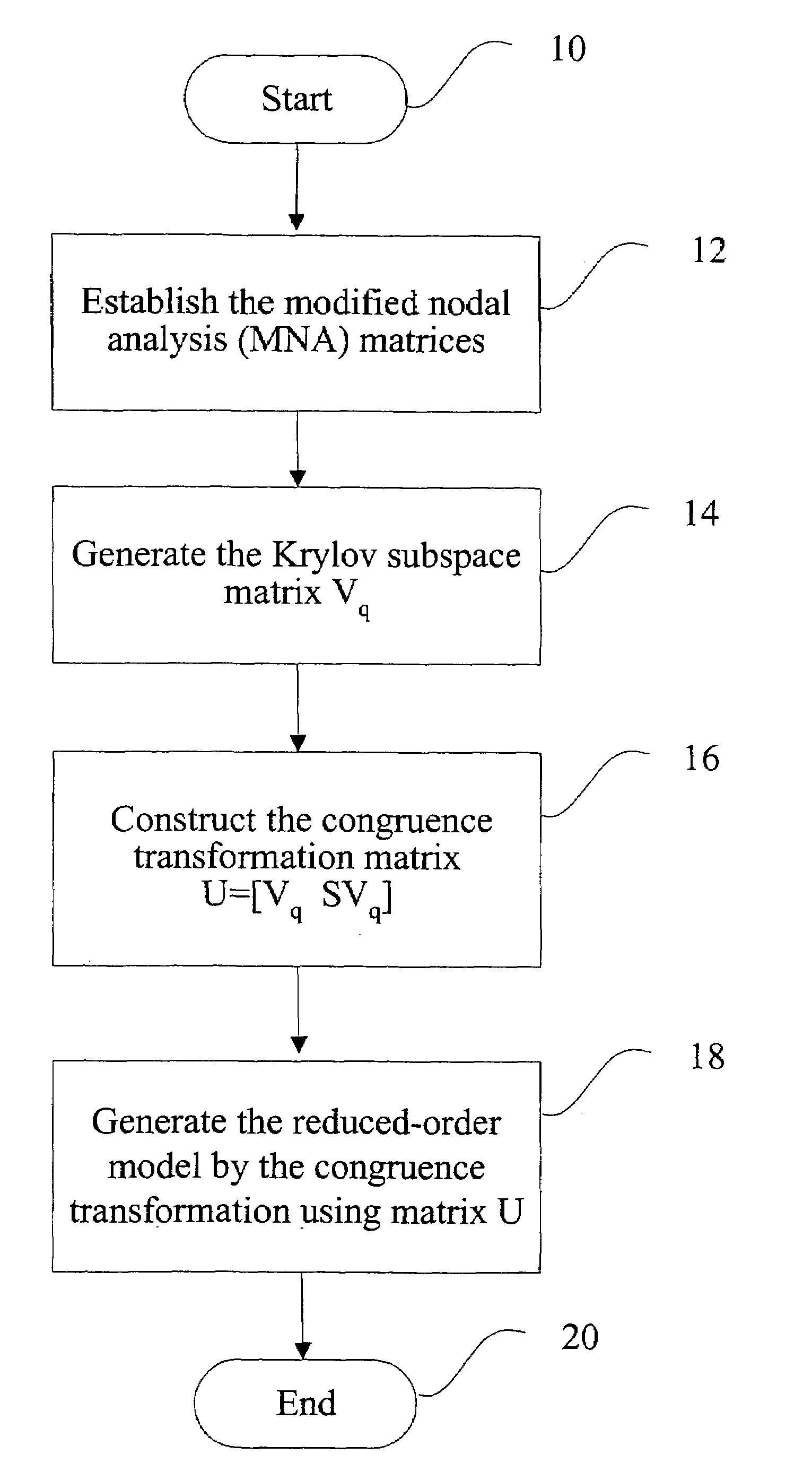

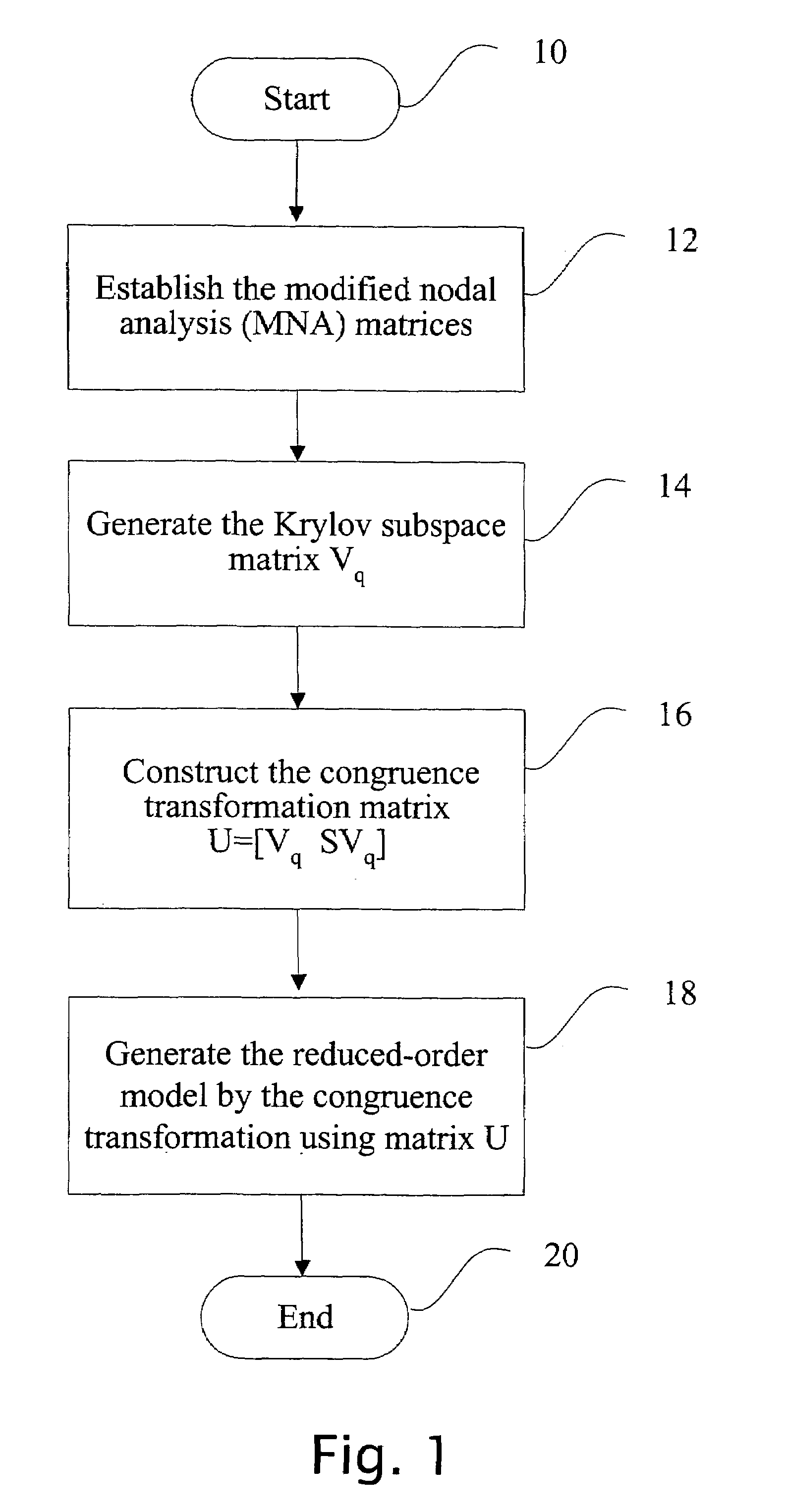

Method and apparatus for model-order reduction and sensitivity analysis

InactiveUS7216309B2Reduce computing costLow costDetecting faulty computer hardwareComputation using non-denominational number representationVlsi interconnectAlgorithm

Computer time for modeling VLSI interconnection circuits is reduced by using symmetric properties of modified nodal analysis formulation. The modeling uses modified nodal analysis matrices then applies a Krylov subspace matrix to construct a congruence transformation matrix to generate the reduced order model of the VLSI.

Owner:CHANG GUNG UNIVERSITY

Reduced order model-based free vibration analysis method for beam structure

ActiveCN106294975AReduce adverse effectsImprove computing efficiencyDesign optimisation/simulationSpecial data processing applicationsReduced modelFine structure

The invention belongs to the field of aerospace complex beam structure component calculation, and provides a reduced order model-based free vibration analysis method for a beam structure. The method comprises the following steps: 1) obtaining a mass matrix and a stiffness matrix of a fine structure by using finite element software; 2) using a polynomial interpolation function to construct a reduced base vector, so as to realize order reduction of an original complex beam structure; and 3) solving a kinetic equation of the reduced order model, and obtaining the overall frequency and part of low-order frequencies of the structure. According to the method disclosed by the present invention, the polynomial interpolation function is used to construct the reduced base vector, nodes in a finite element model of the complex structure are condensed to the section centroid in the form of displacement interpolation so as to realize the order reduction of the original structure, and the calculation precision of the reduced order model can be controlled by polynomial orders. The method disclosed by the present invention has the advantages that: without depending on the experience of the user, the adverse influence of the difference of selection of the master and slave freedom degrees on the calculation precision is reduced; a large amount of matrix operation is not needed, so that the calculation efficiency of order reduction of the model is improved; and the obtained reduced order model has a wide application range.

Owner:DALIAN UNIV OF TECH

Method of employing slew dependent pin capacitances to capture interconnect parasitics during timing abstraction of VLSI circuits

ActiveUS8103997B2Accurate timing analysisProcess can be speededComputer aided designSpecial data processing applicationsStatic timing analysisModel order reduction

A method for converting interconnect parasitics of an interconnect network into slew dependent pin capacitances utilizes charge matching between predetermined voltage thresholds. During timing abstraction of a macro, parasitics of interconnects connected to the primary inputs are represented as slew dependent pin capacitances in an abstract model being created. Interconnect model order reduction is employed to speed the process. The generated abstract is subsequently used in place of each occurrence of the macro during chip level hierarchical static timing analysis, leading to an enhanced accuracy of the timing analysis of the logic components driving the abstracts.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

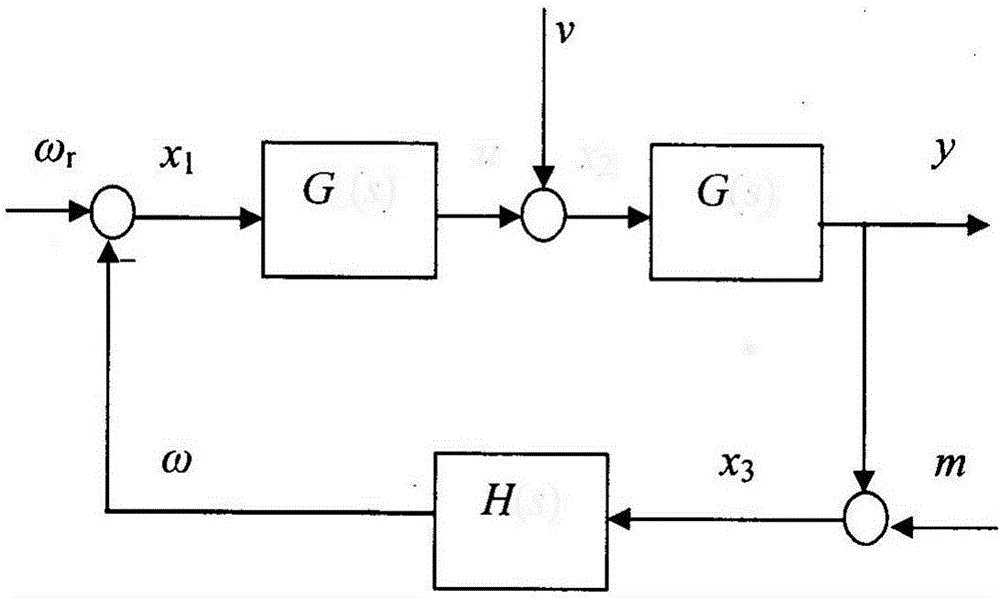

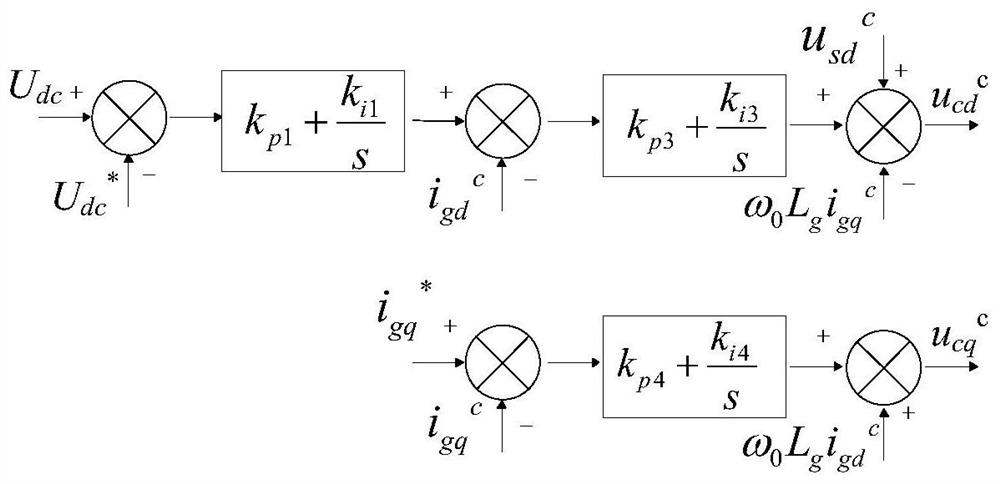

Model order reduction feedback control method for direct-drive fan subsynchronous oscillation suppression

ActiveCN112018783AGood subsynchronous oscillation suppression effectSimple designSingle network parallel feeding arrangementsPower oscillations reduction/preventionSmall-signal modelOrder reduction

The invention relates to a model order reduction feedback control method for direct-driven fan subsynchronous oscillation suppression. The method comprises the following steps: 1, linearizing mathematical models of a direct-driven fan and a controller of the direct-driven fan, and establishing a direct-driven fan small signal model containing all state variables; 2, performing order reduction on the small signal model according to the characteristic value of the complete small signal model, the observability of the state variable and the influence degree on oscillation, and establishing an order reduction model of the direct-driven fan; and 3, designing a feedback controller by utilizing the reduced-order small-signal model of the direct-driven fan. According to the invention, through linearization of mathematical models of the direct-drive fan and the controller thereof, a small signal model of the direct-drive fan containing all state variables is obtained for analysis and calculation. Order reduction is carried out on the small signal model to obtain an order reduction model of the direct drive fan, and convenience is provided for design of a feedback controller. A feedback controller is designed by using a reduced-order direct-drive fan small-signal model, and a good direct-drive fan subsynchronous oscillation suppression effect is achieved.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

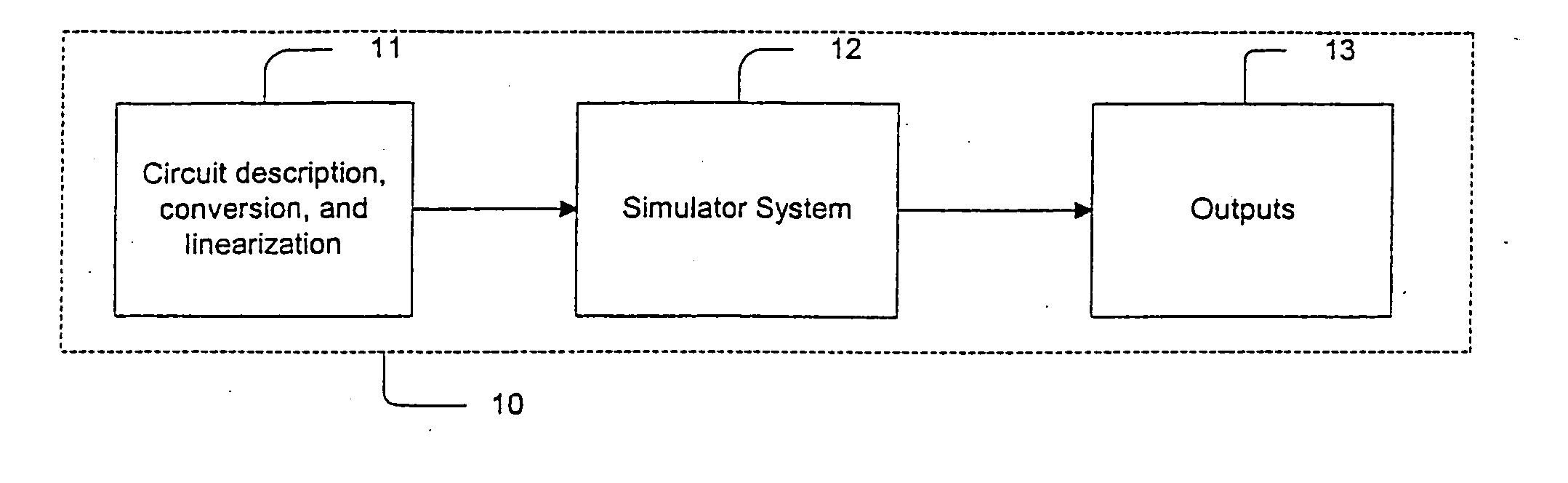

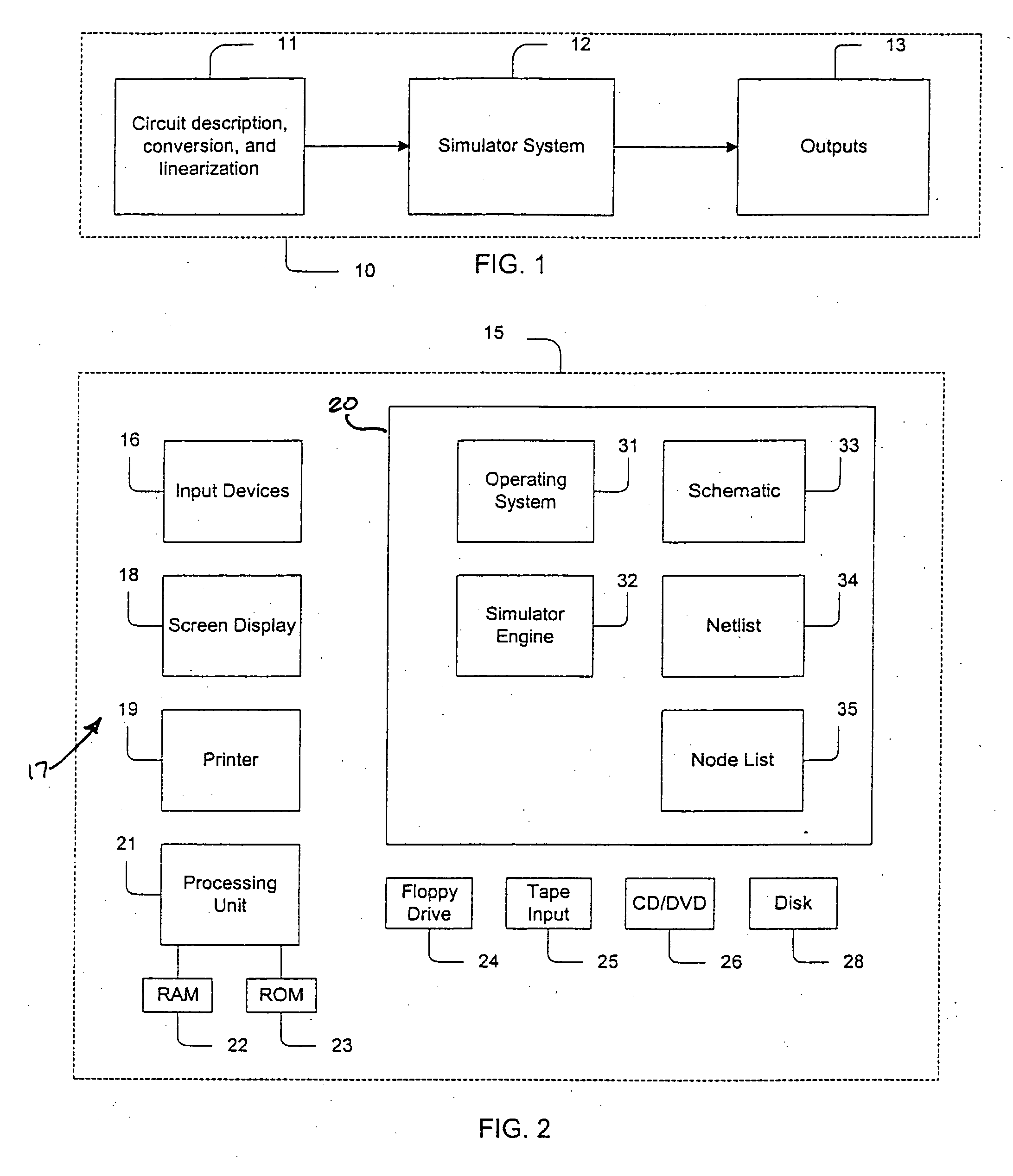

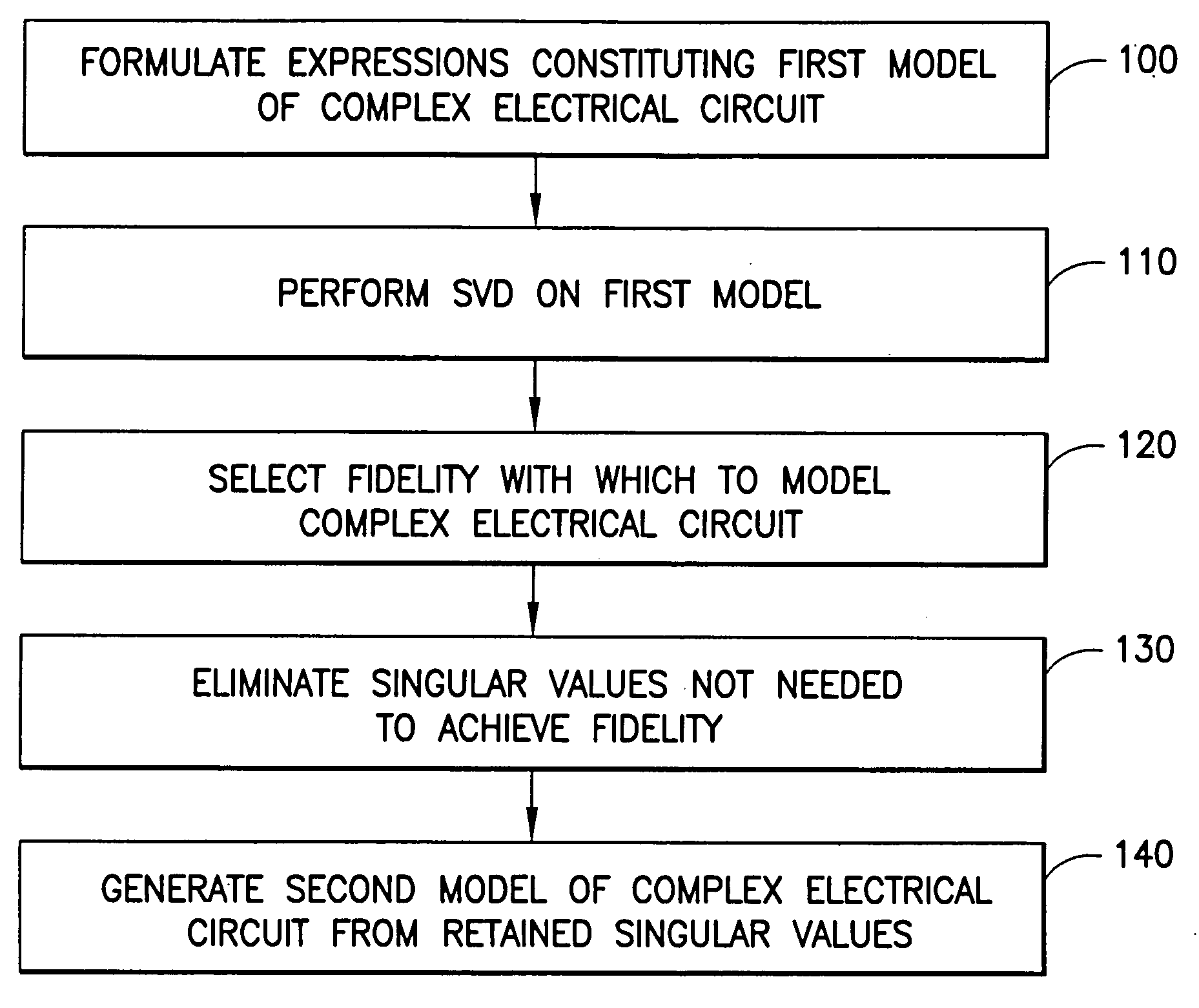

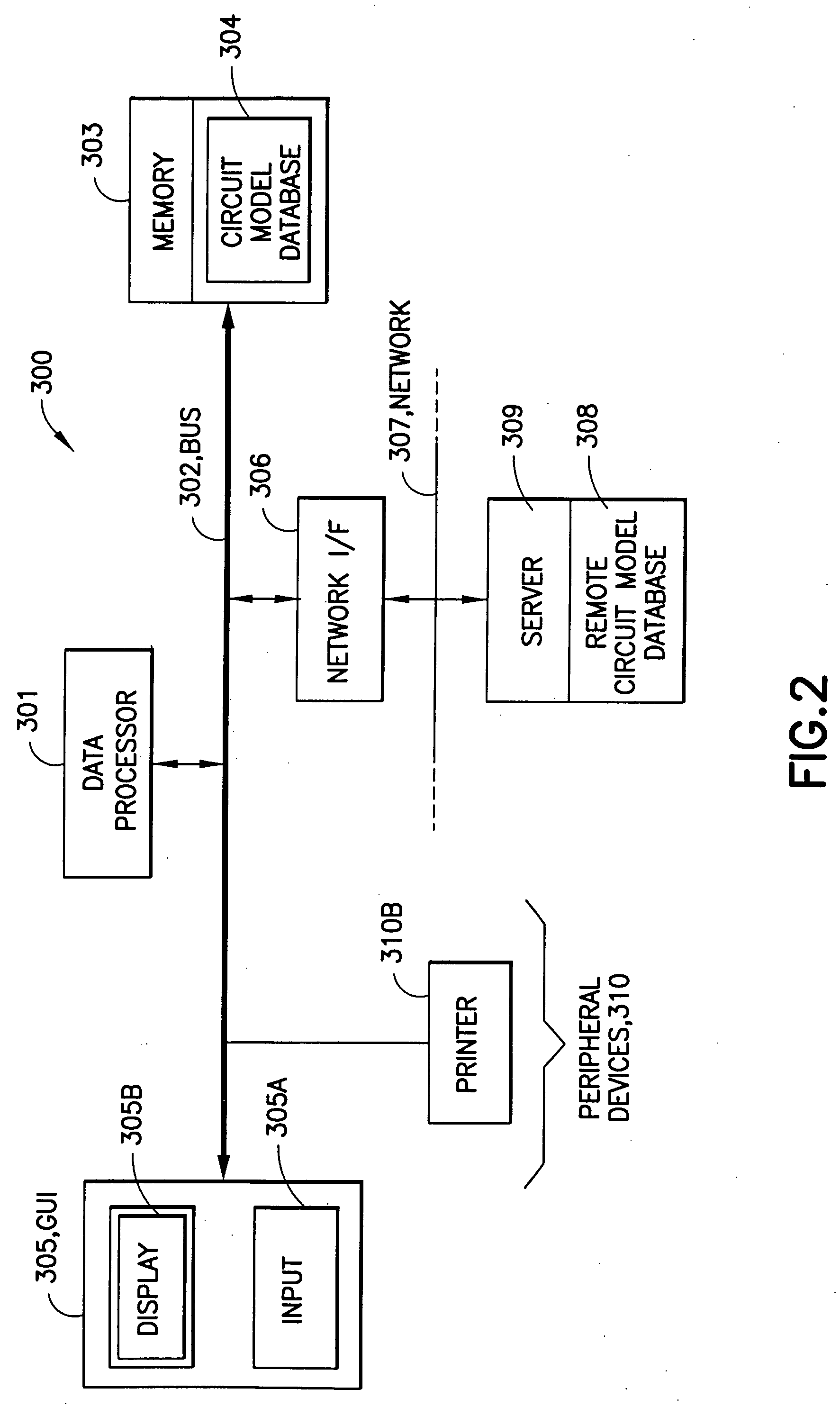

System and method for efficient model order reduction in electric and electronic circuit design

InactiveUS20060080068A1Computation using non-denominational number representationComputer aided designOrder formEngineering

The present invention comprises a system and method for reducing the order of models used to simulate complex electric circuits and linear systems. In particular, the method of the present invention comprises formulating expressions relating the input and output terminals of a complex electric circuit, wherein the expressions comprise a first model of the electric circuit; performing mathematical operations on the first model to reveal correlations between at least two input terminals or between at least two output terminals; and substituting a reduced order second model for the original first model, whereby the reduced order second model eliminates some or all aspects of correlations between input terminals or between output terminals. The system of the present invention comprises a computer system for performing model order reduction.

Owner:IBM CORP

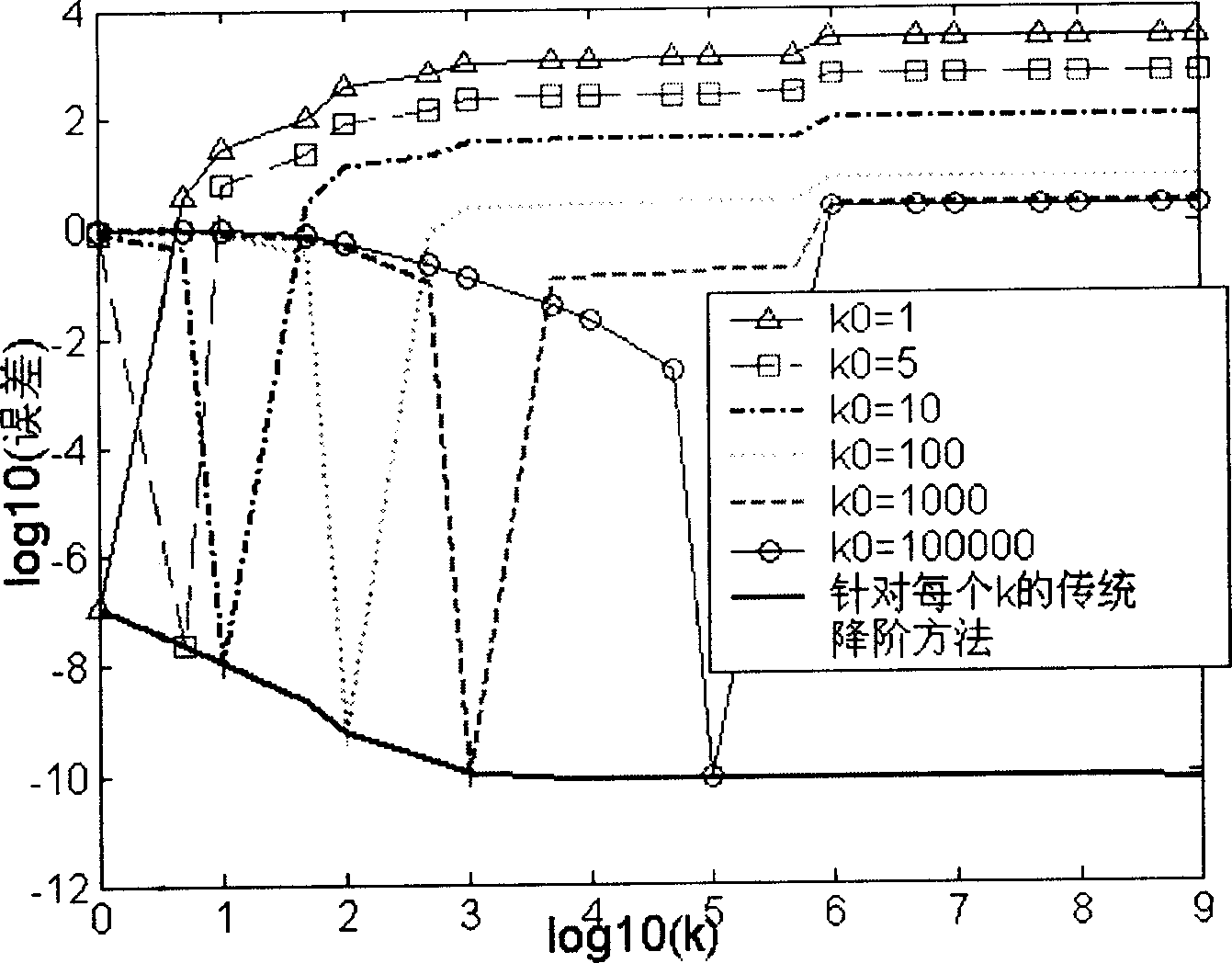

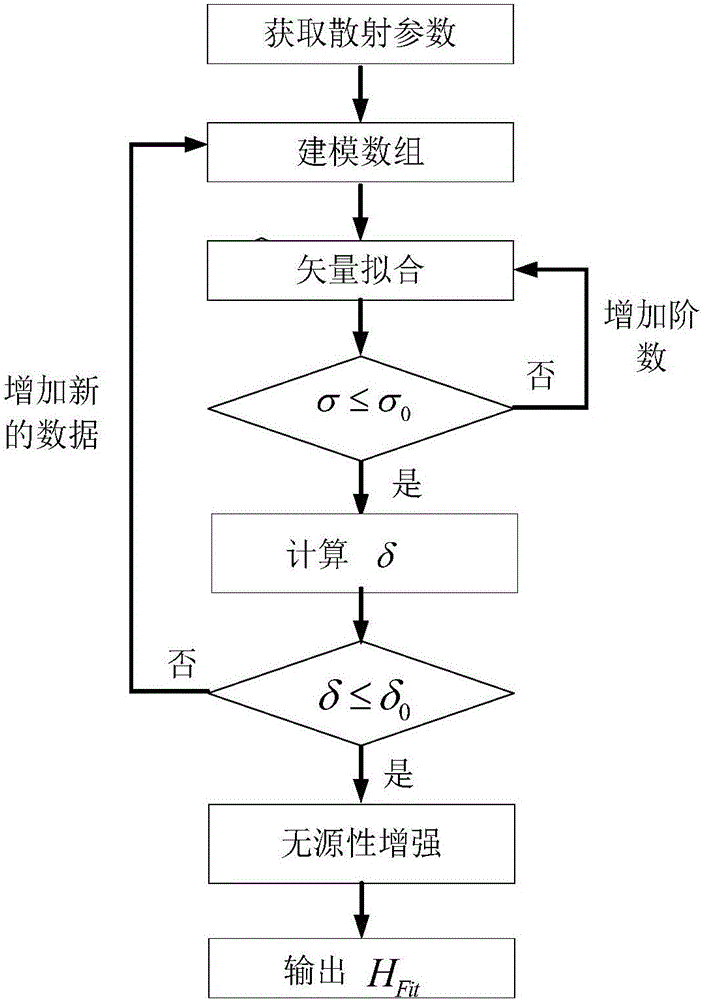

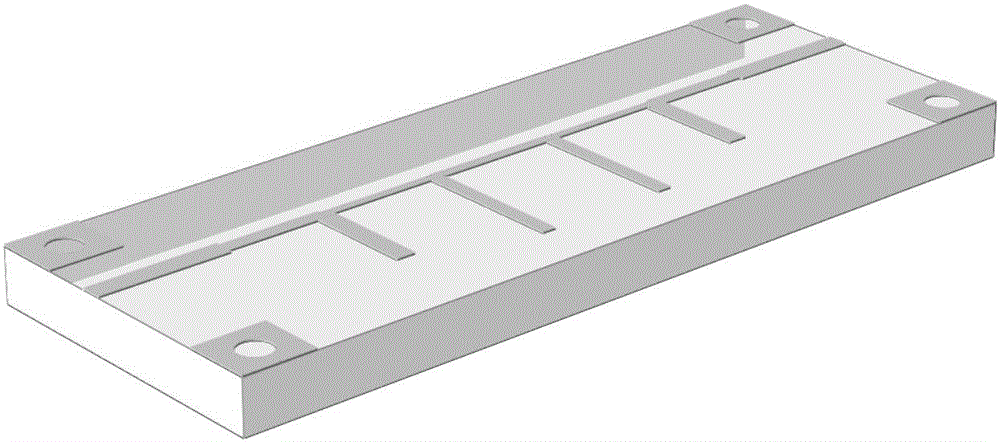

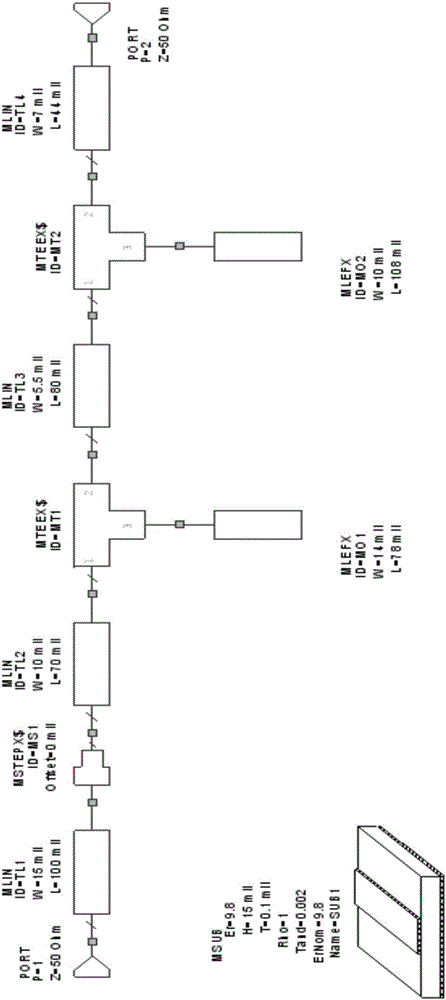

Vector fitting model order reduction method based on error control in linear system

ActiveCN106372348AImprove Simulation EfficiencyImprove accuracyDesign optimisation/simulationSpecial data processing applicationsAlgorithmState space

The invention discloses a vector fitting model order reduction method based on error control in a linear system. Specific to the conventional vector fitting, the order of a constructed pole-residue model is always very high under a wide frequency band, particularly in a highly-dynamic linear system with a resonance point. An error control function is introduced, data including important features of the linear system are selected in a continuous iteration way, and certain slightly-varied data representing details are neglected, so that the order of the constructed model is effectively reduced under the condition of sacrificing certain modeling accuracy. A low-order pole-residue macro model is obtained under the condition that the modeling accuracy requirement is met. The pole-residue macro model is further transformed into a state space model, passive processing is performed, and the constructed pole-residue macro model is output lastly. By adopting the vector fitting model order reduction method, the balance between model accuracy and complexity is realized, and the simulation efficiency of electromagnetically-compatible electromagnetic emission is increased.

Owner:BEIHANG UNIV

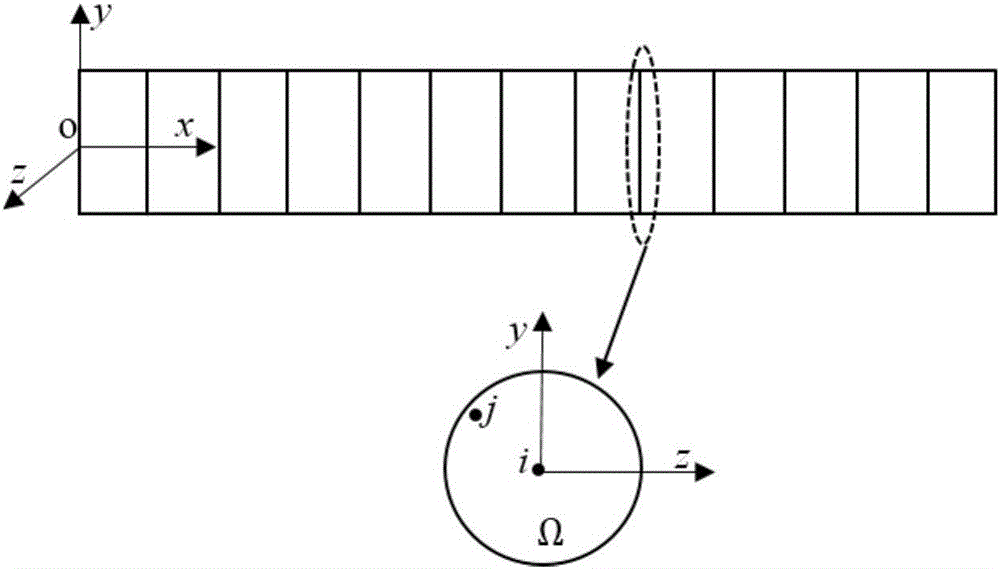

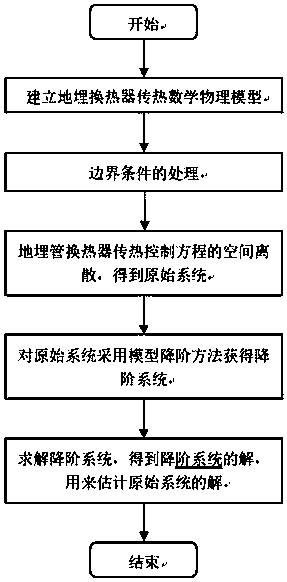

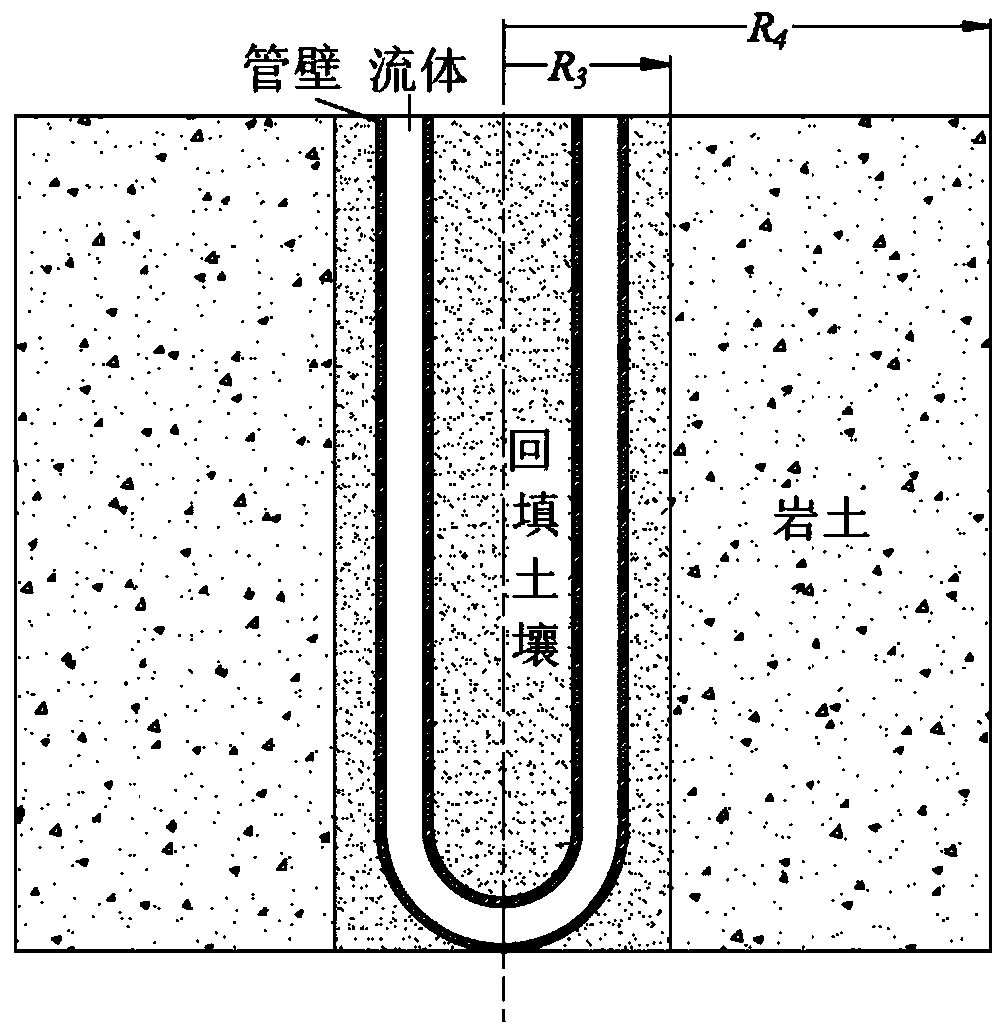

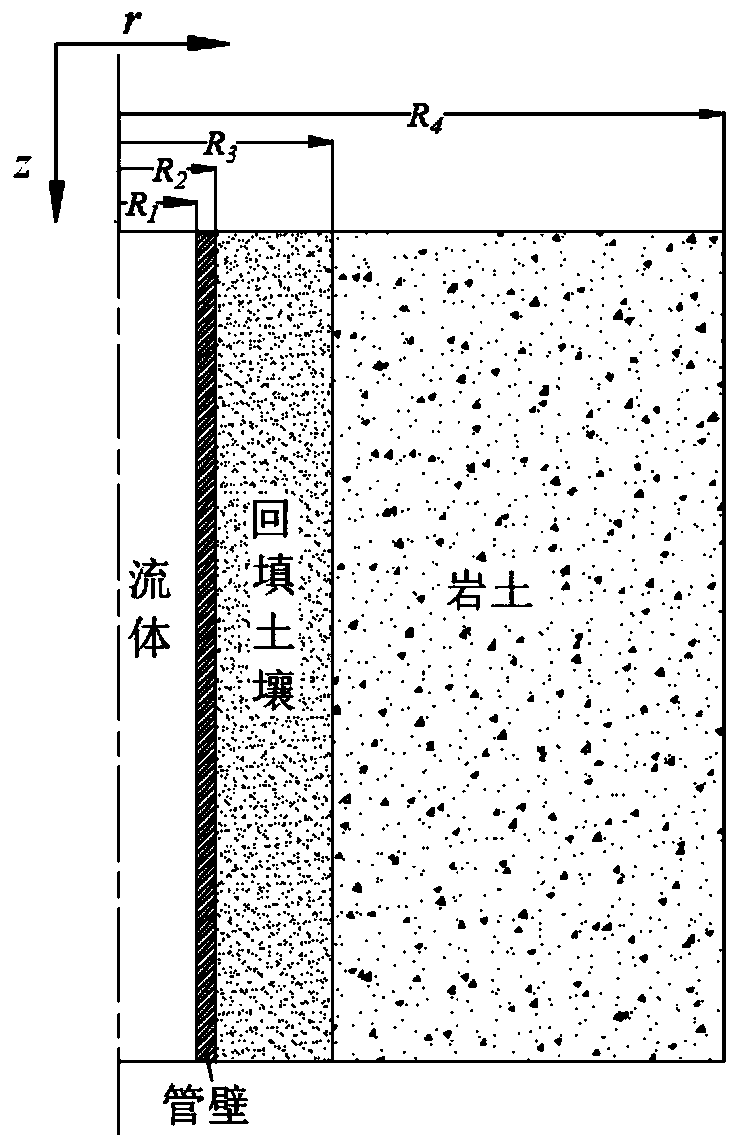

Heat transfer coupling simulation order reduction method for buried pipe heat exchanger

ActiveCN110968967AShort timeSave costsGeothermal energy generationDesign optimisation/simulationMathematical modelEngineering

The invention discloses a heat transfer coupling simulation order reduction method for a buried pipe heat exchanger. The method comprises the following steps: step 1, establishing a control equation;step 2, boundary determination; 3, obtaining an original system in a state space form of the mathematical model of the heat transfer problem of the buried pipe heat exchanger; 4, performing order reduction on the original system obtained in the step 3 by adopting a model order reduction method to obtain a price reduction system formula; 5, performing numerical solution on the reduced-order systemformula to obtain a solution of the reduced-order system; and step 6, through the reduced-order system coefficient matrix obtained in the step 4 and the reduced-order system state variable obtained inthe step 5, performing calculating to obtain an output variable, i.e., an approximate solution of an original system output variable, i.e., a numerical solution of an output variable of a control equation under a corresponding boundary condition. The scale of the order reduction system is far smaller than that of an original system, only one small-scale system needs to be solved, and therefore computing resources are saved, and the running time of a computing program is greatly shortened.

Owner:XI AN JIAOTONG UNIV

Method of performing static timing analysis considering abstracted cell's interconnect parasitics

InactiveUS8122411B2Detecting faulty computer hardwareComputer aided designStatic timing analysisEngineering

Owner:GLOBALFOUNDRIES INC

Generalizations of adjoint networks techniques for RLC interconnects model-order reductions

InactiveUS20060100831A1Reduce complexityAccuracy efficiencyAnalogue computers for electric apparatusComputation using non-denominational number representationComputation complexityRound complexity

The adjoint network reduction technique has been shown to reduce 50% of the computational complexity of constructing the congruence transformation matrix. The method was suitable for analyzing the special multi-port driving-point impedance of RLC interconnect circuits. This paper extends this technique for the general circumstances of RLC interconnects. Comparative studies among the conventional methods and the proposed methods are also investigated. Experimental results will demonstrate the accuracy and the efficiency of the proposal method.

Owner:CHANG GUNG UNIVERSITY

Interconnect model-order reduction method

InactiveUS20070033549A1The process is fast and accurateEfficiently provideDetecting faulty computer hardwareComputer aided designSubspace modelReduced order

An interconnect model-order reduction method for reduction of a nano-level semiconductor interconnect network as an original interconnect network by using iteration-based Arnoldi algorithms disclosed. The method is performed based on a projection method and has become a necessity for efficient interconnect modeling and simulations. To select order of the reduced-order model that can efficiently reflect essential dynamics of the original interconnect network, a residual error between transfer functions of the original interconnect network and the reduced interconnect model may be considered as a reference in determining if the iteration process should end, analytical expressions of the residual error being derived herein. Furthermore, the approximate transfer function of the reduced interconnect model may also be expressed as an addition of the original interconnect model and some additive perturbations. A perturbation matrix is only related with resultant vectors at a previous step of the Arnoldi algorithm. Therefore, the residual error information may be taken as a reference for the order selection scheme used in Krylov subspace model-order algorithm.

Owner:CHANG GUNG UNIVERSITY

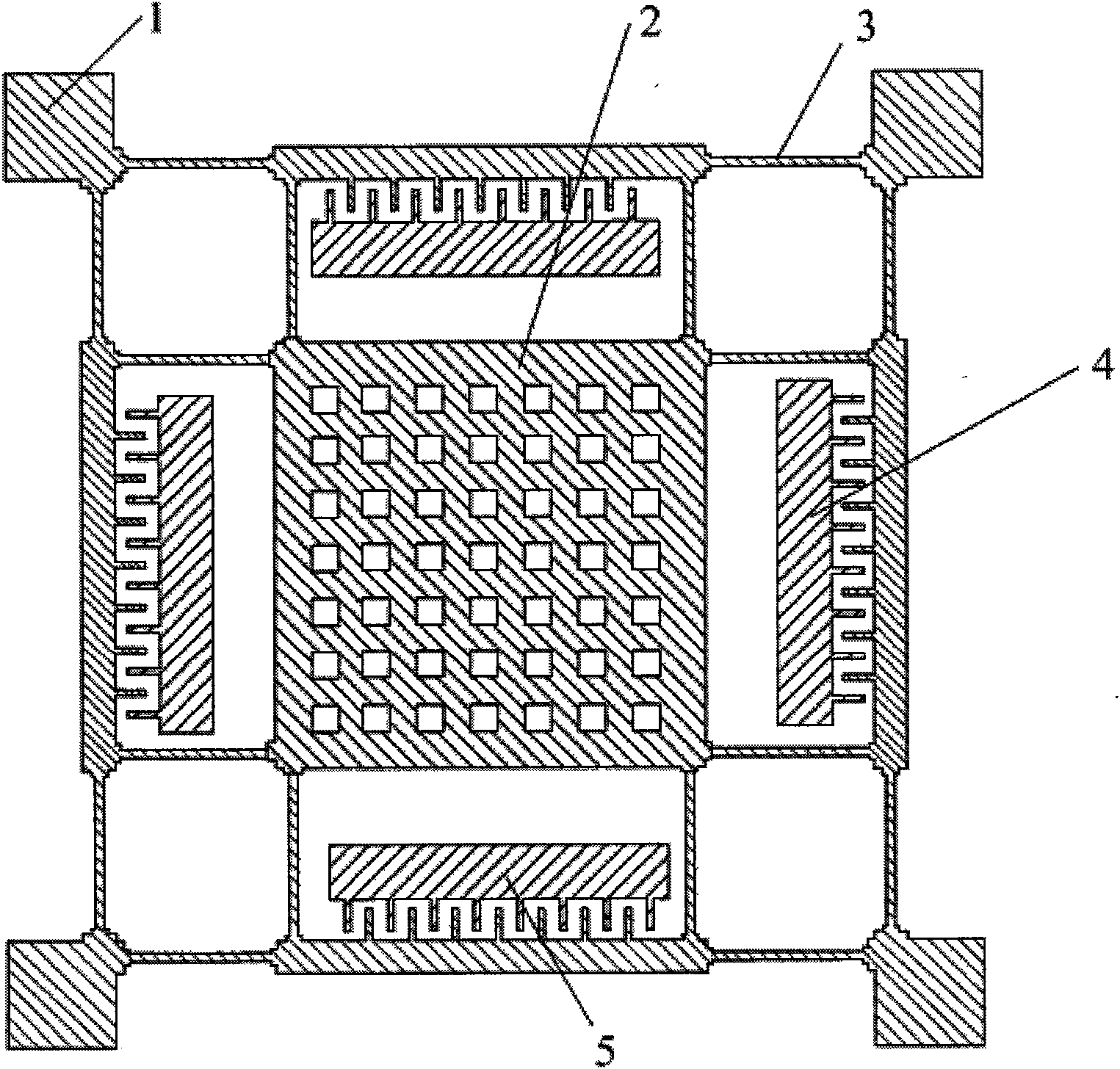

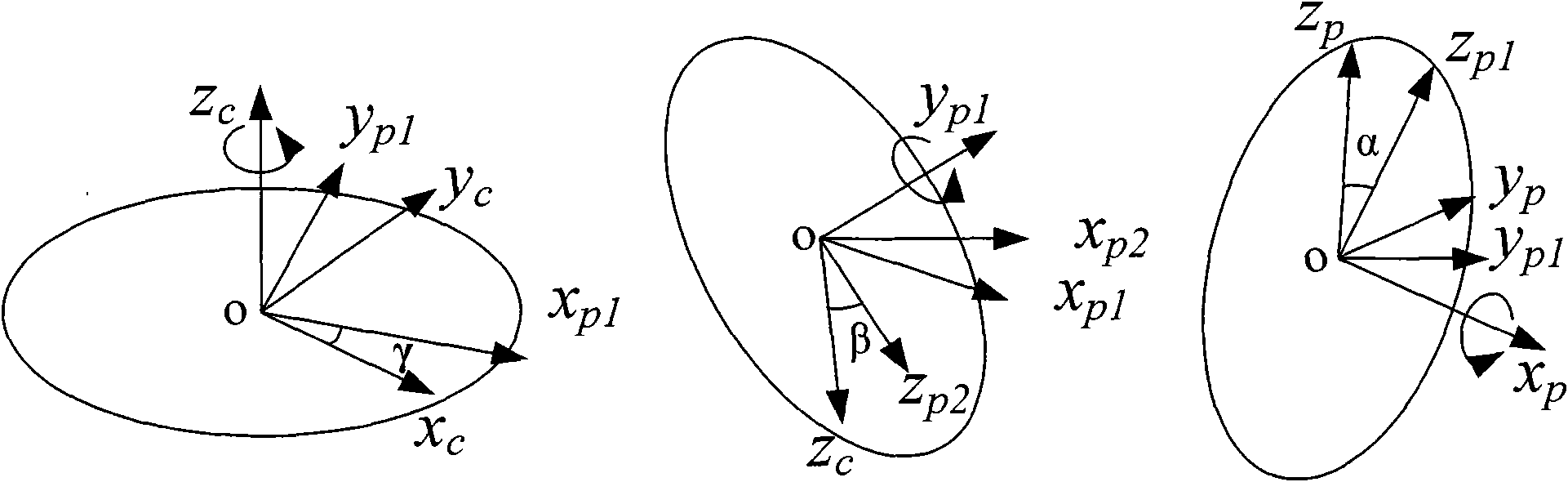

Angle parametrized macro modelling method of micro-electro-mechanism system

InactiveCN101551835AImprove design efficiencySemi-permeable membranesPiezoelectric/electrostrictive/magnetostrictive devicesSystems designOrder reduction

The invention discloses an angle parametrized macro modelling method of micro-electro-mechanism system, belonging to a field of micro-electro-mechanism system design and model order reduction. The method comprises: firstly, randomly selecting one from microstructure with same geometric shape as a reference microstructure, extracting macro model thereof by the numerical value order reduction method; then establishing conversion equations between force and displacement of other orientation microstructures relative to reference microstructure by employing a matrix coordinate transform method, and finally, substituting the conversion equations between force and displacement into a behavior equation of the macro model, and implementing angle parametrized macro modeling of MEMS. The method of the invention implements angle parametrized macro modeling by the matrix coordinate transform method, and by setting relative angle parameters, avoids identity of structure and repeat macro modeling process of MEMS microstructure of different initial orientations, thereby increasing speed of MEMS grade modeling and emulation based on the macro model, and further raising design efficiency of entire MEMS.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com