Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

132 results about "Resistive capacitive" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Capacitive Touchscreens. Unlike resistive touchscreens, capacitive panels are made of glass coated with a transparent conductor, like indium tin oxide. When one touches the screen, it causes the local electrostatic field to distort.

Adaptive Capacitive Sensing

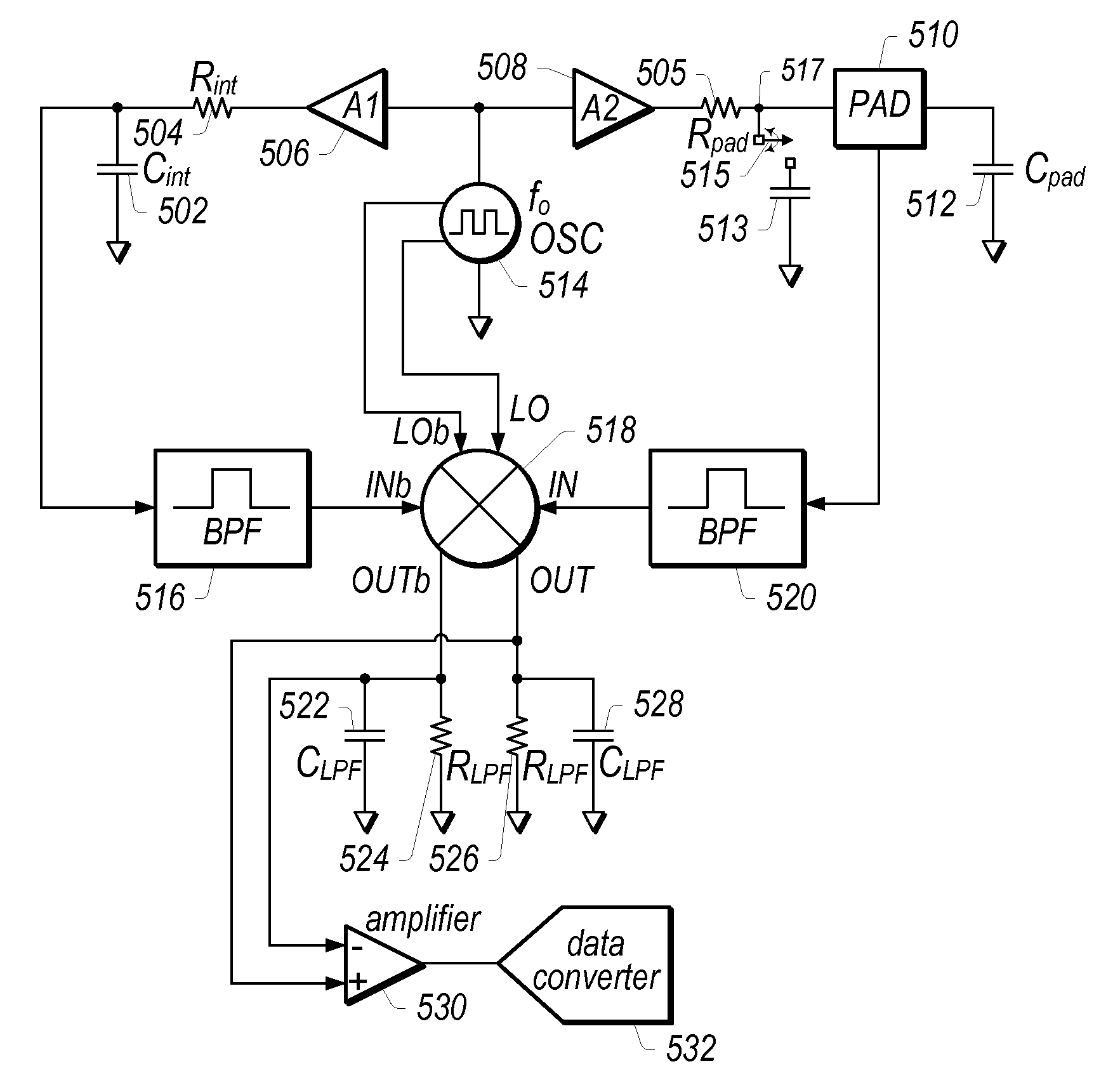

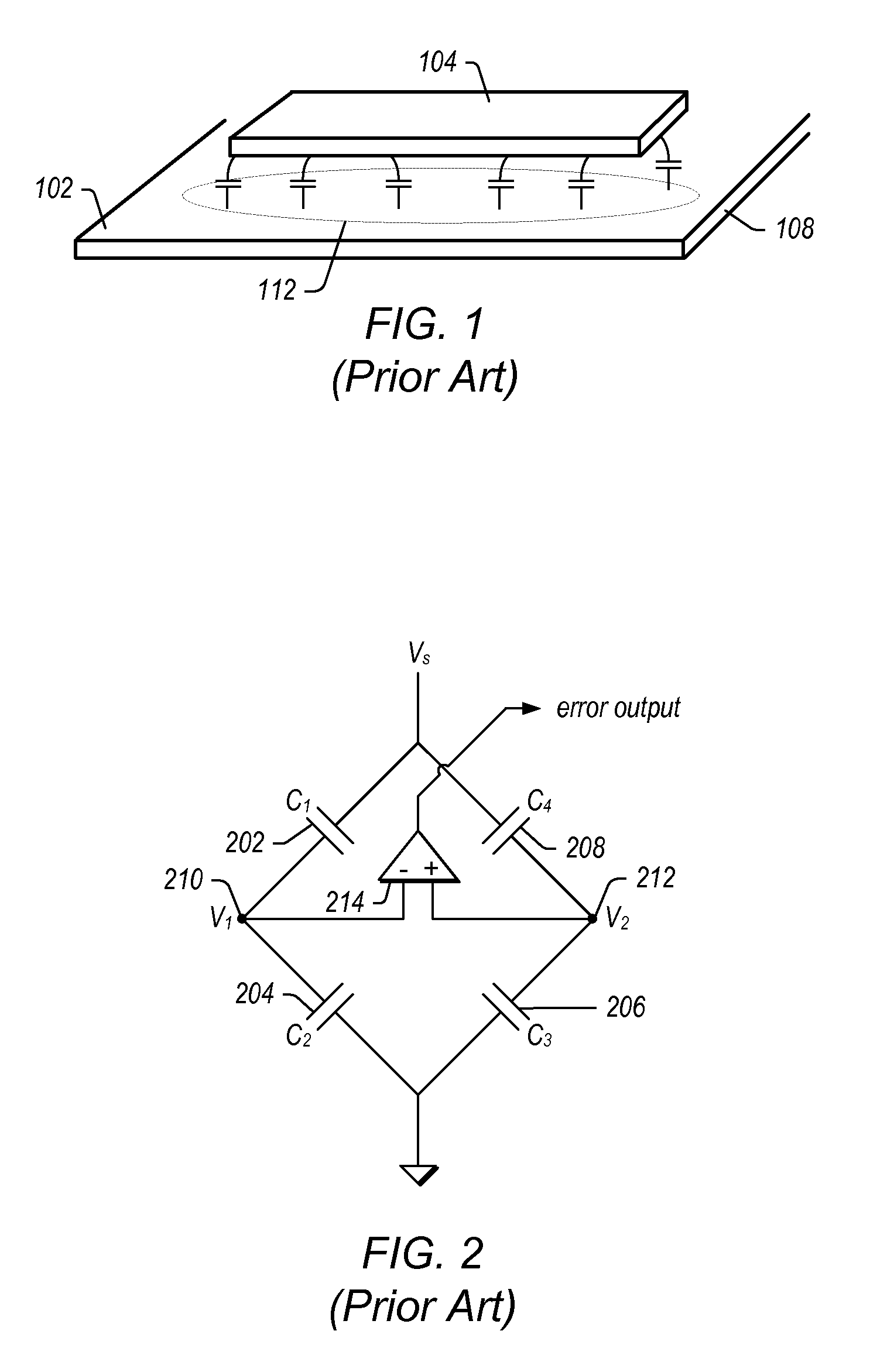

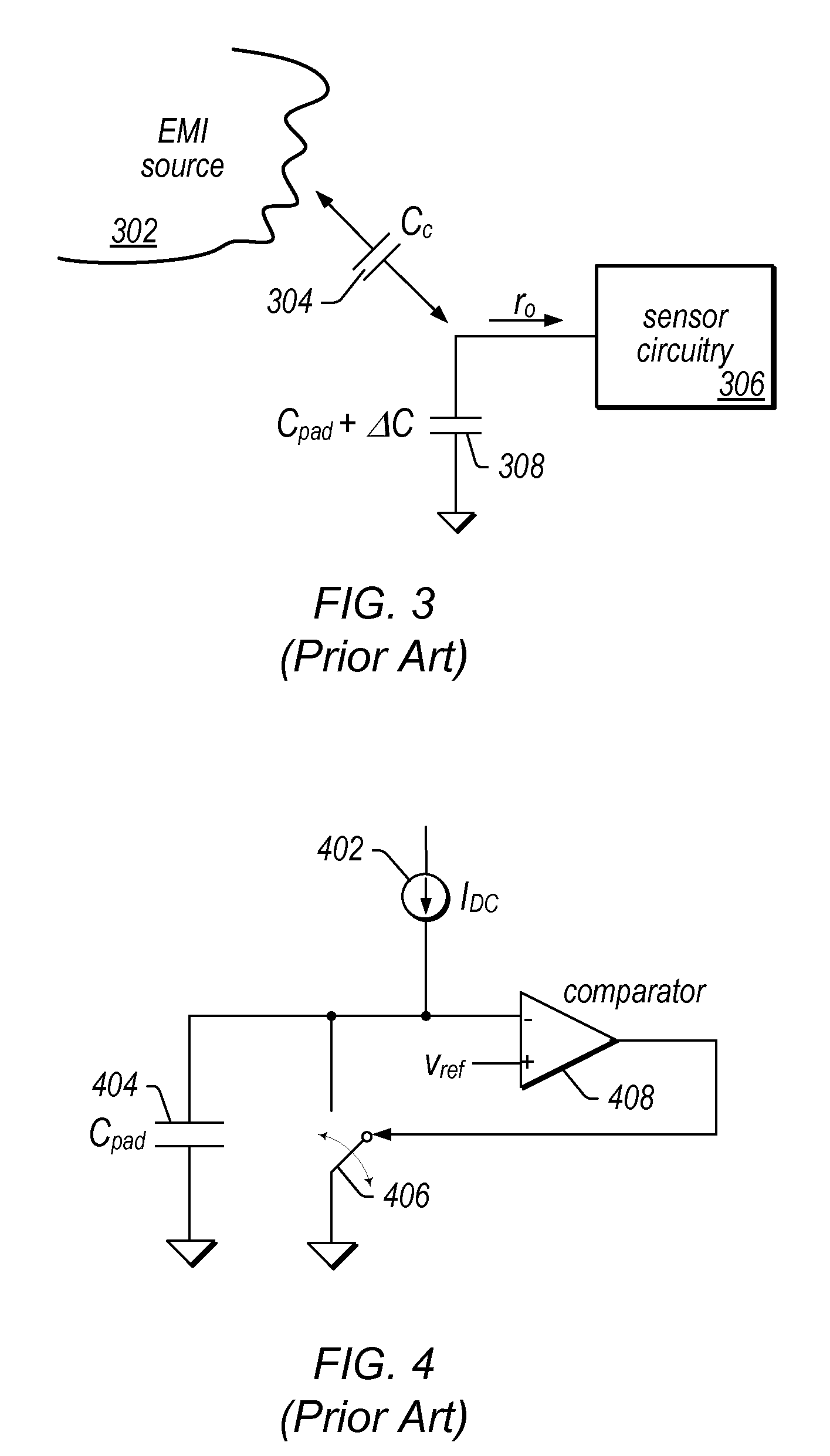

InactiveUS20090322351A1Minimize susceptibilityInterference minimizationAmplifier modifications to reduce noise influenceResistance/reactance/impedenceCapacitanceFrequency mixer

A capacitive sensing circuit may comprise an RC (resistive-capacitive) bridge circuit, with a switching signal simultaneously applied to a reference path, and a signal path comprising the capacitance to be detected. Small perturbations in the capacitance may be detected by mixing / correlating a difference signal representative of the difference between the reference path signal and the signal path signal, to the switching signal. The output of the mixer may be filtered to virtually eliminate all EMI signals. A narrowband approach may also allow filtering of unwanted signals, enabling operation in systems susceptible to high levels of noise. Frequency stepping of the switching signal may minimize inband signal interference, and allow operation in the presence of many signals that would otherwise result in failure of the sensing circuit. Pad calibration may be implemented to free the user from a need to characterize each button channel capacitance and tailor the operation for each channel.

Owner:STANDRD MICROSYSTEMS CORPORATION

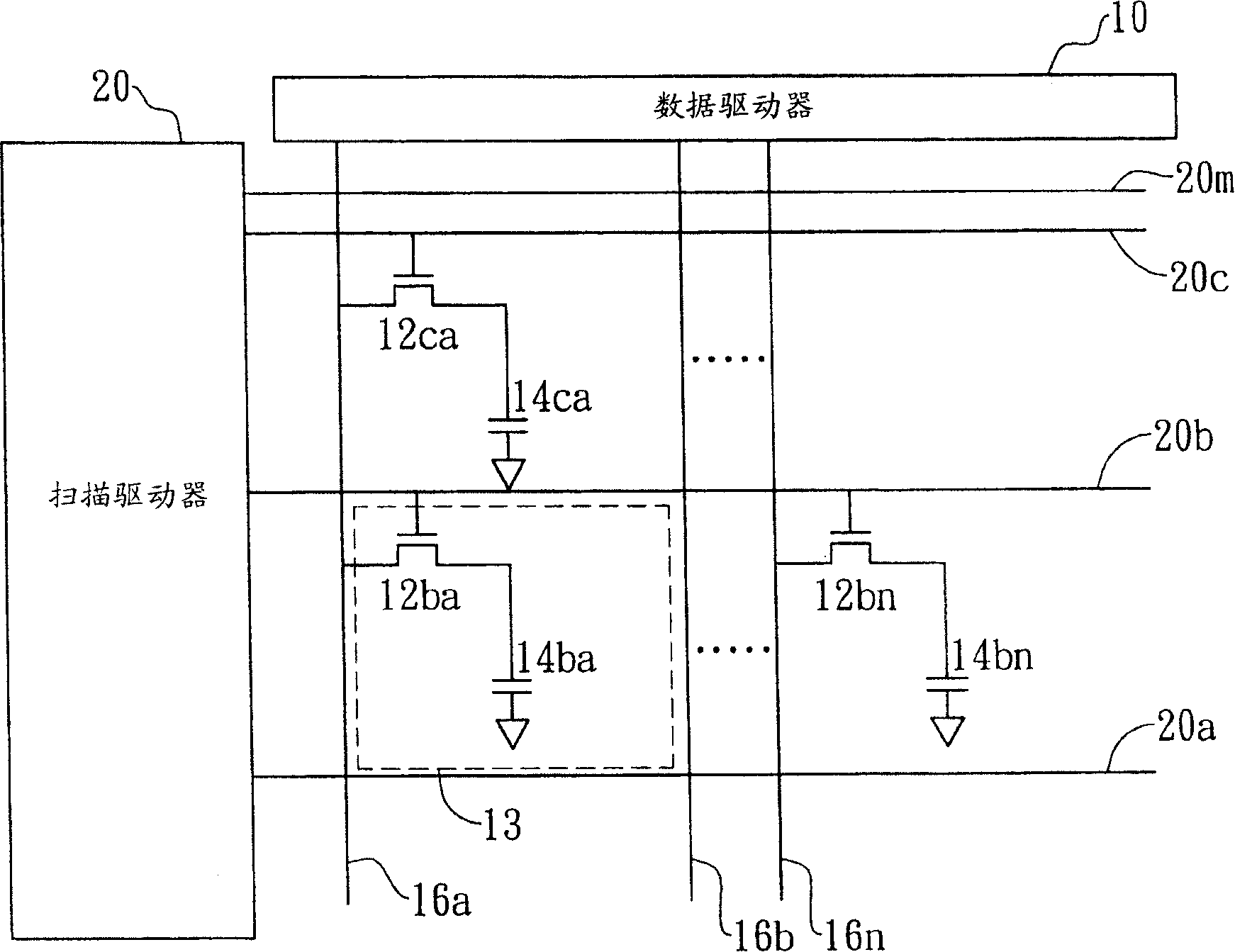

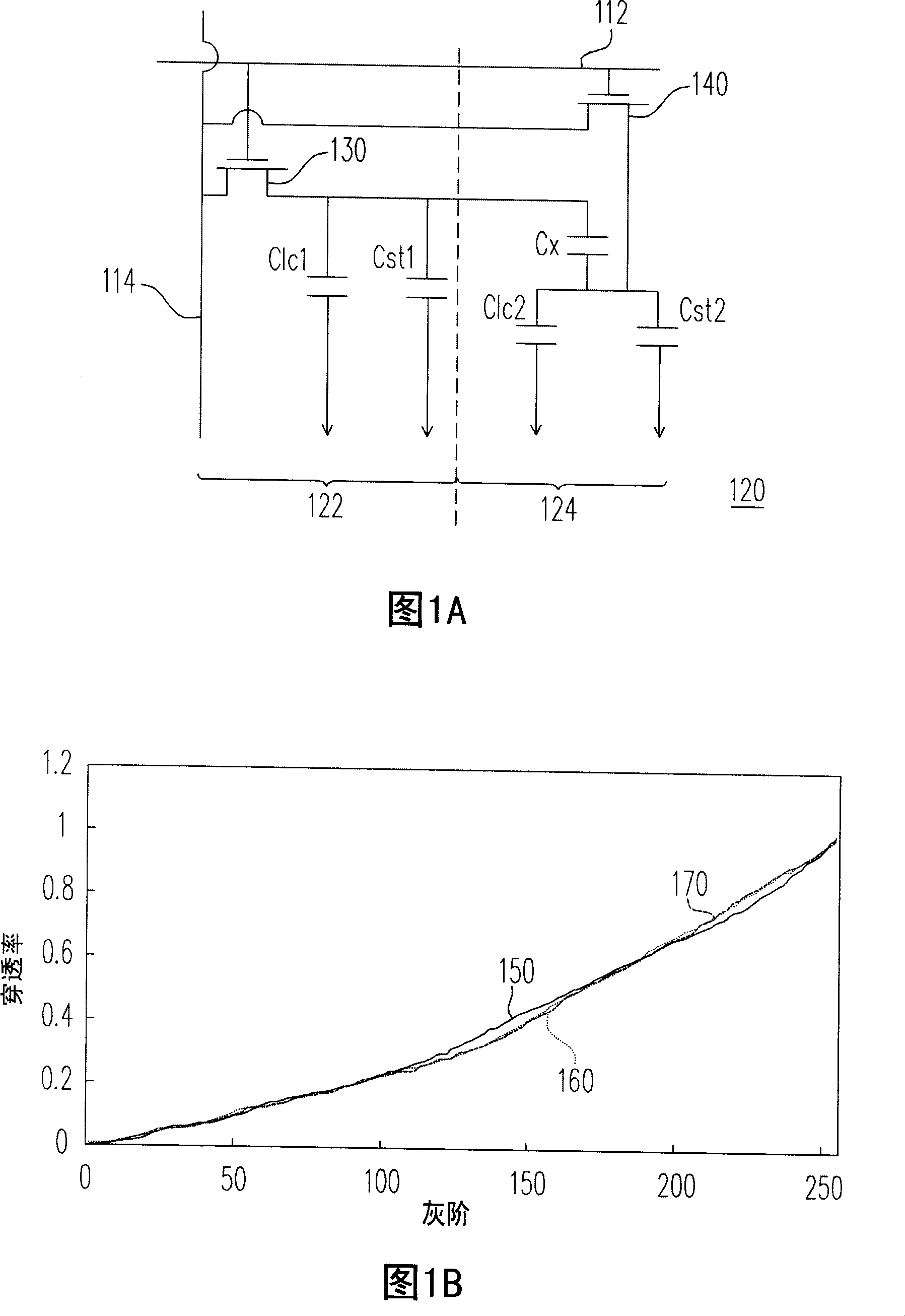

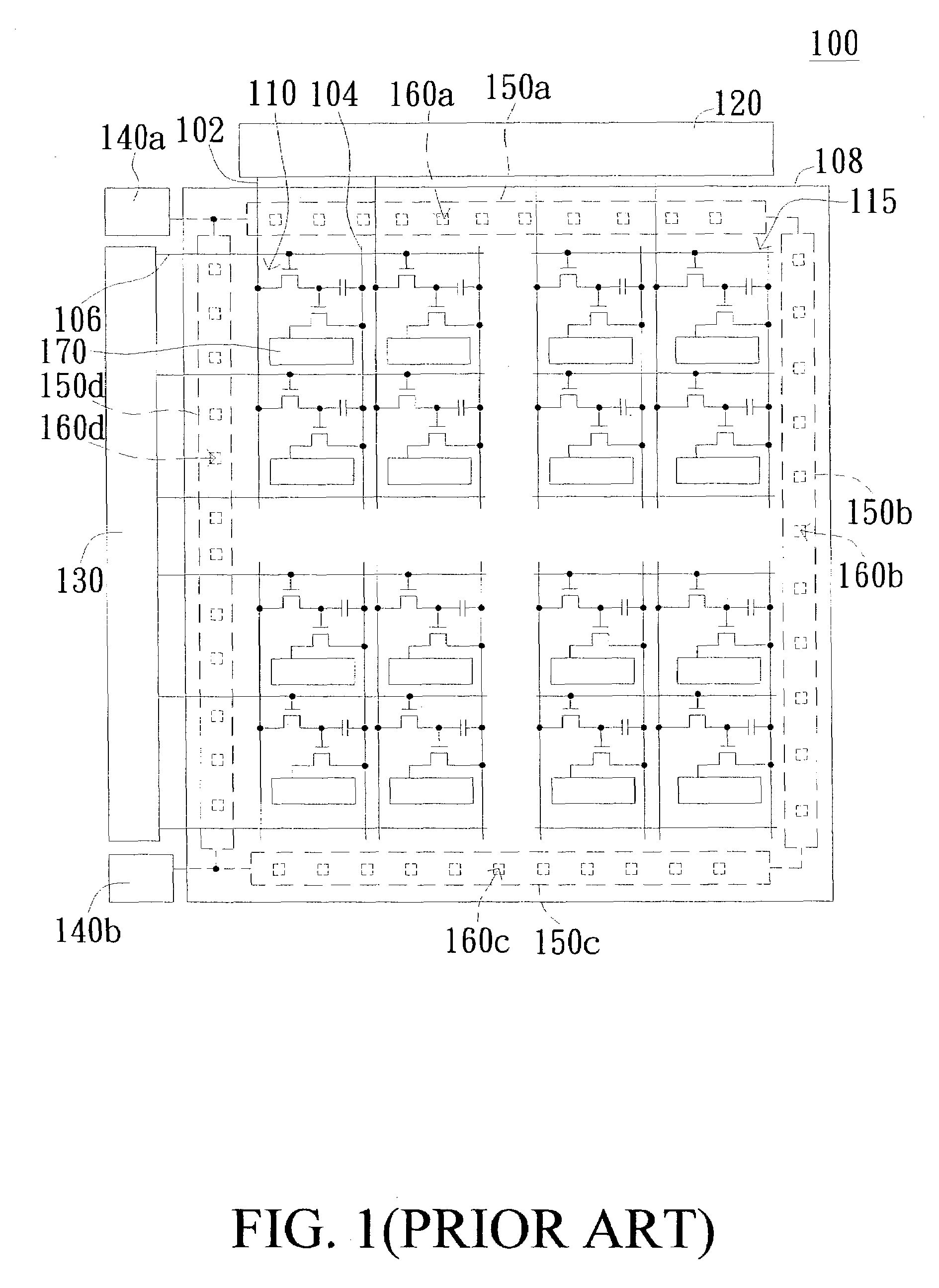

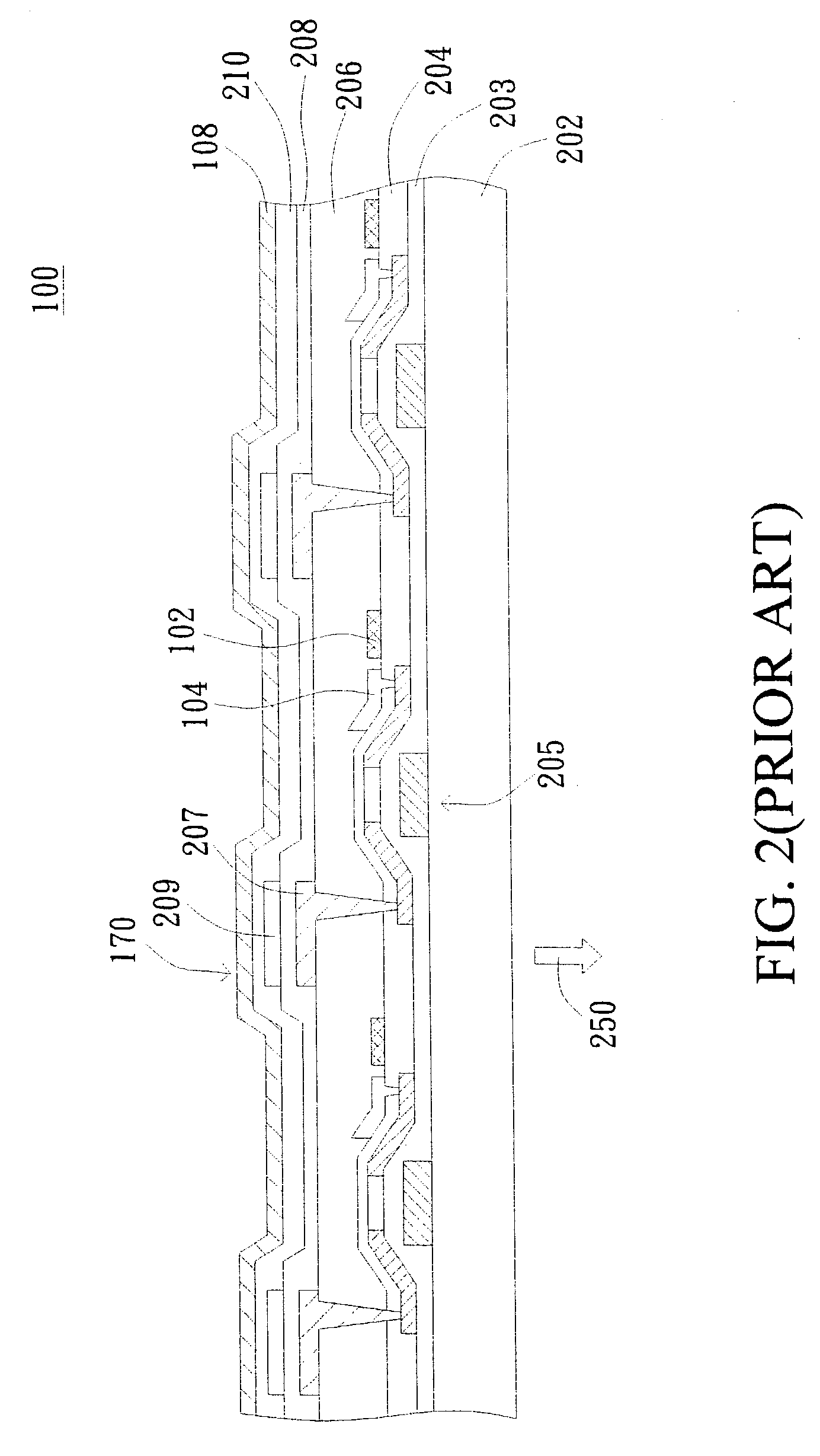

Driving method for liquid crystal panel, display driving circuit and liquid crystal display device

InactiveCN102568430AUniform display brightnessImprove uniformityStatic indicating devicesNon-linear opticsCapacitanceLiquid-crystal display

The invention discloses a driving method for a liquid crystal panel, a display driving circuit and a liquid crystal display device. The driving method for the liquid crystal panel comprises the following steps: A, acquiring a coordinate position of a pixel to be displayed of a current frame of the liquid crystal panel and an ideal voltage value required by a gray level for corresponding displaying the pixel; and B, according to the coordinate position of the current pixel on the liquid crystal panel, determining an offset voltage for promoting the uniformity of the liquid crystal panel and then loading the offset voltage onto a corresponding data line. According to the invention, the difference of charging time in each region, which is generated due to charging caused by resistance-capacitance waveform delay variation (resistance-capacitance delay (RC delay)), of the liquid crystal panel is effectively improved; the display uniformity of the liquid crystal panel, particularly a large-scale liquid crystal panel, is promoted; and the taste performance of the liquid crystal panel is improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

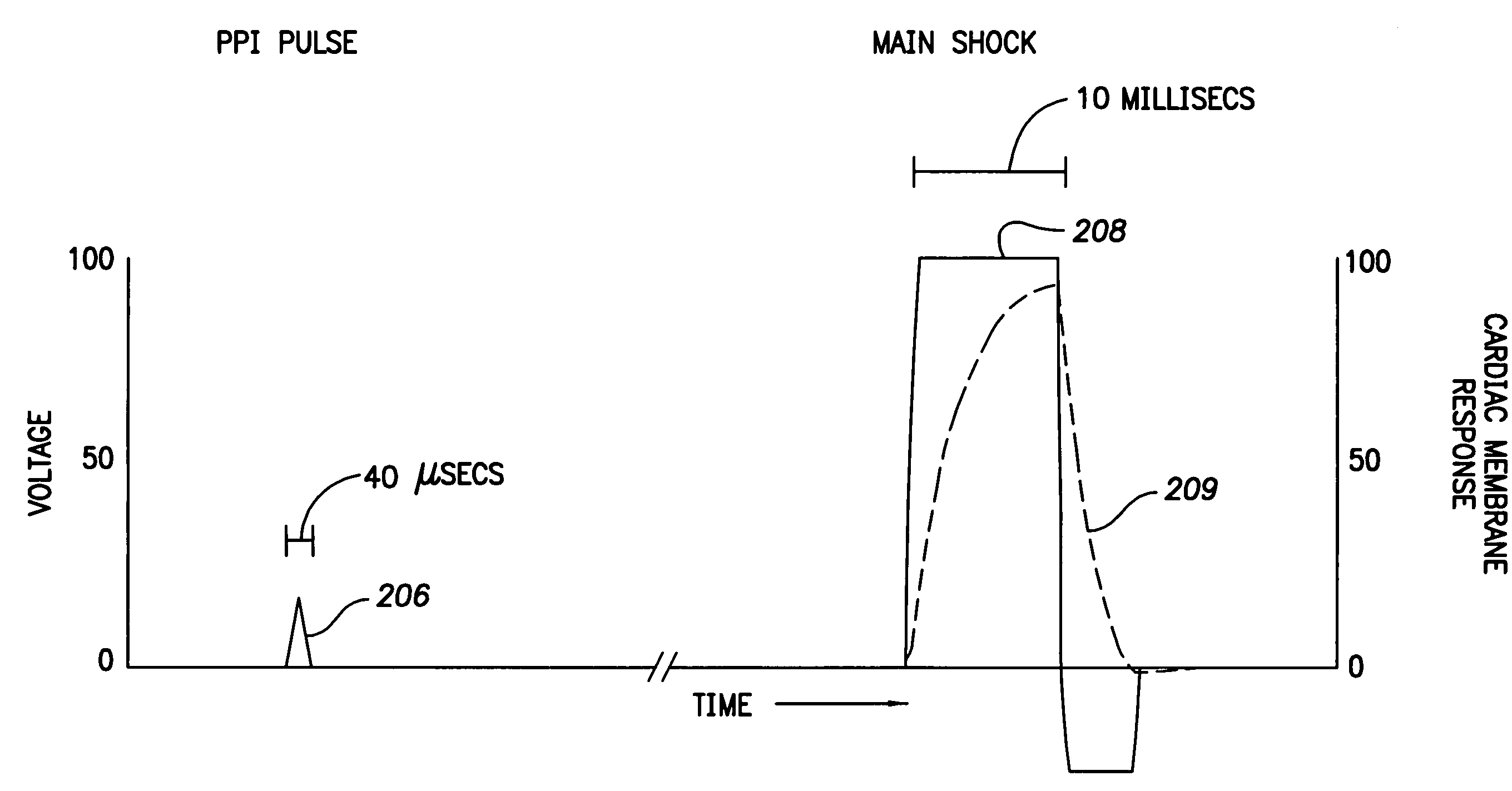

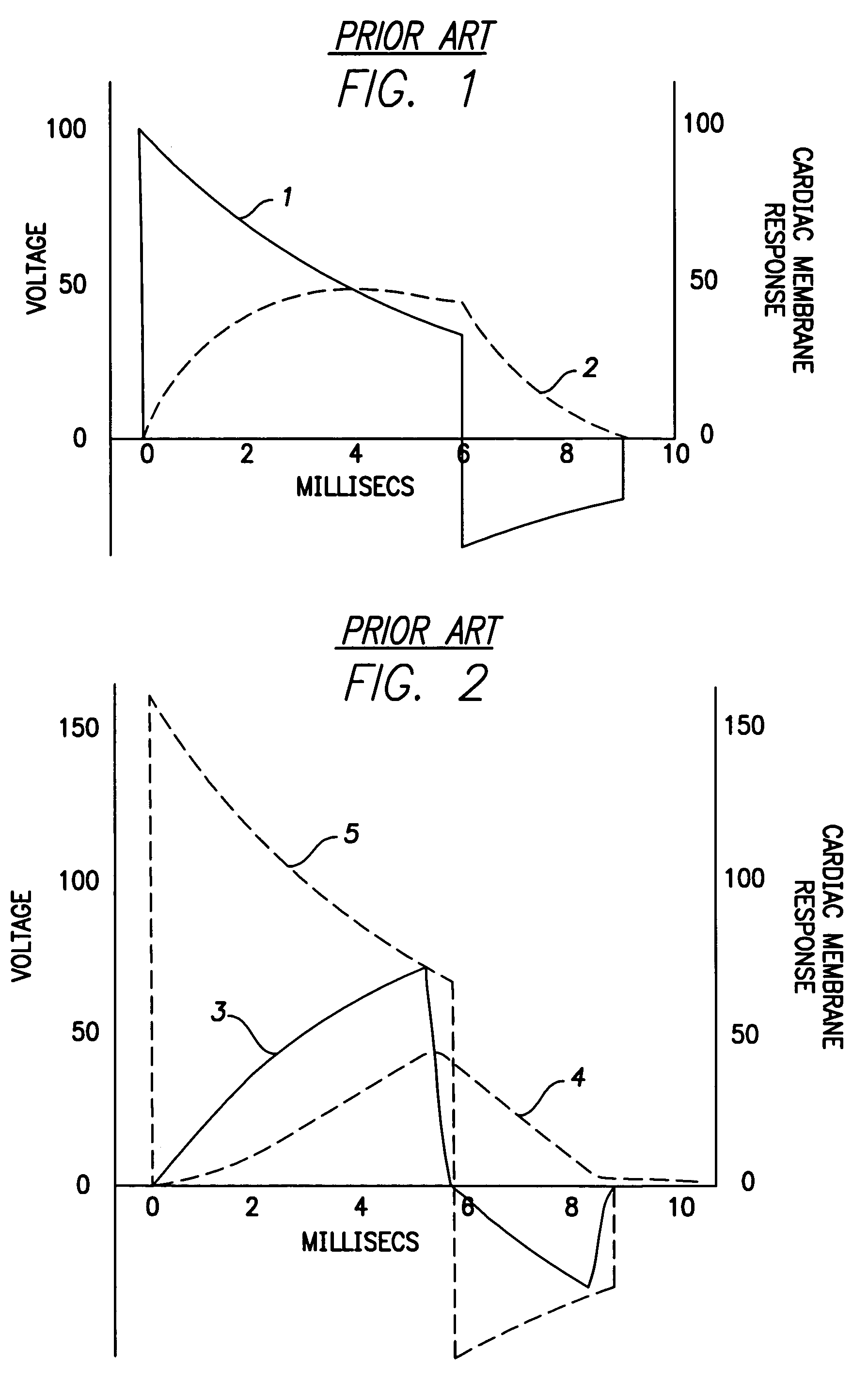

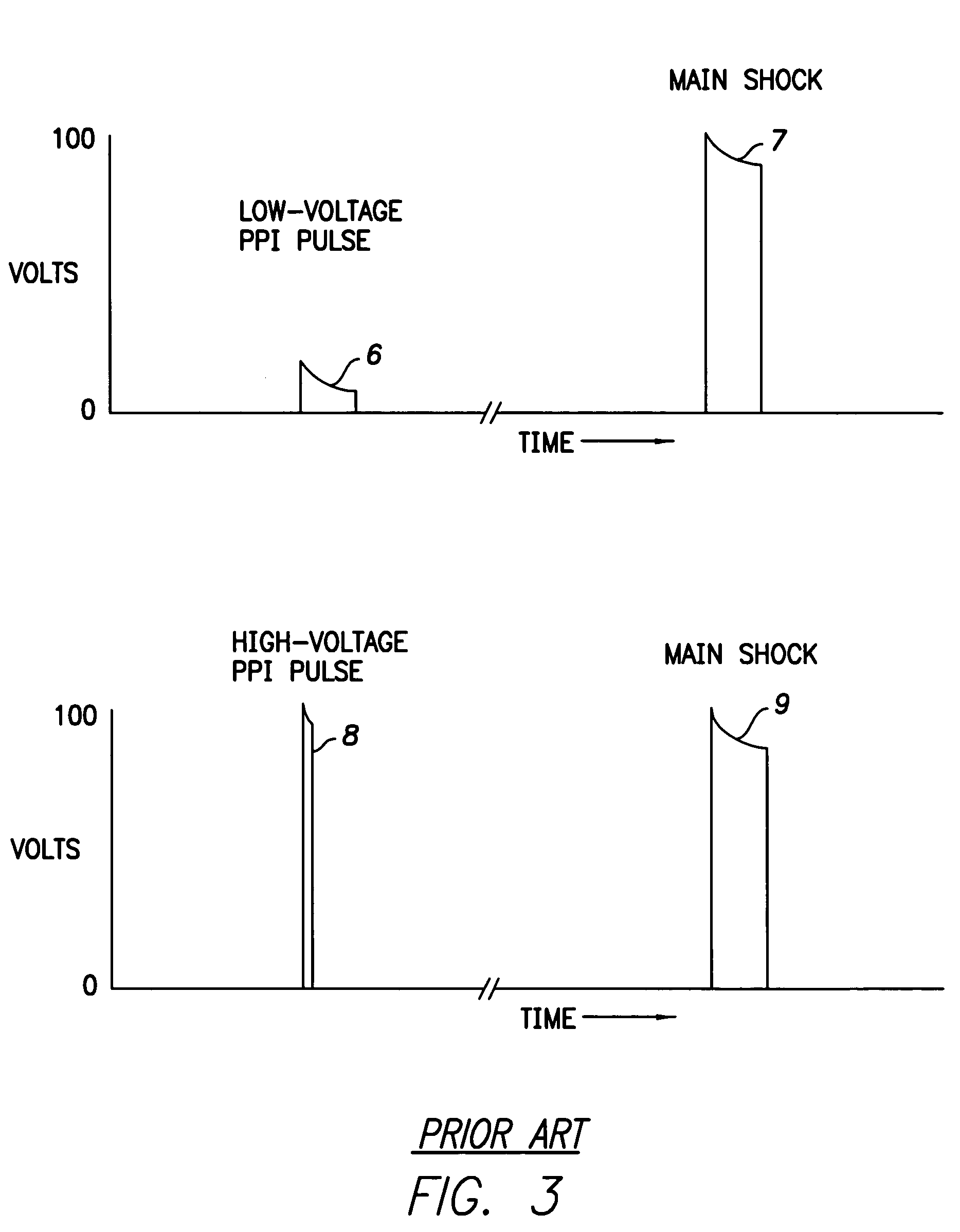

System and method for reducing pain associated with cardioversion shocks generated by implantable cardiac stimulation devices

Techniques are provided for generating pre-pulse pain inhibition (PPI) pulses and subsequent main cardioversion shocks. The PPI pulses are relatively low-voltage pulses each having a chevron-shaped waveform. The main shocks are relatively high-voltage shocks each having a plateau-shaped waveform. By employing plateau-shaped waveforms for the main shocks, a greater cardiac membrane response can be achieved at an equivalent peak voltage as compared to conventional shock waveforms. Peak voltage is a significant contributor to pain caused by cardioversion shocks. Hence, by using the plateau-shaped waveform, pain reduction can be achieved without loss of shock effectiveness. Moreover, by employing chevron-shaped PPI pulses in combination with plateau-shaped main shocks, a relatively simple shocking circuit having a single high-voltage shocking capacitor may be used, thus eliminating the need for both low-voltage PPI capacitors and higher voltage main shock capacitors. The shocking circuit includes a low-pass resistive-capacitive filter.

Owner:PACESETTER INC

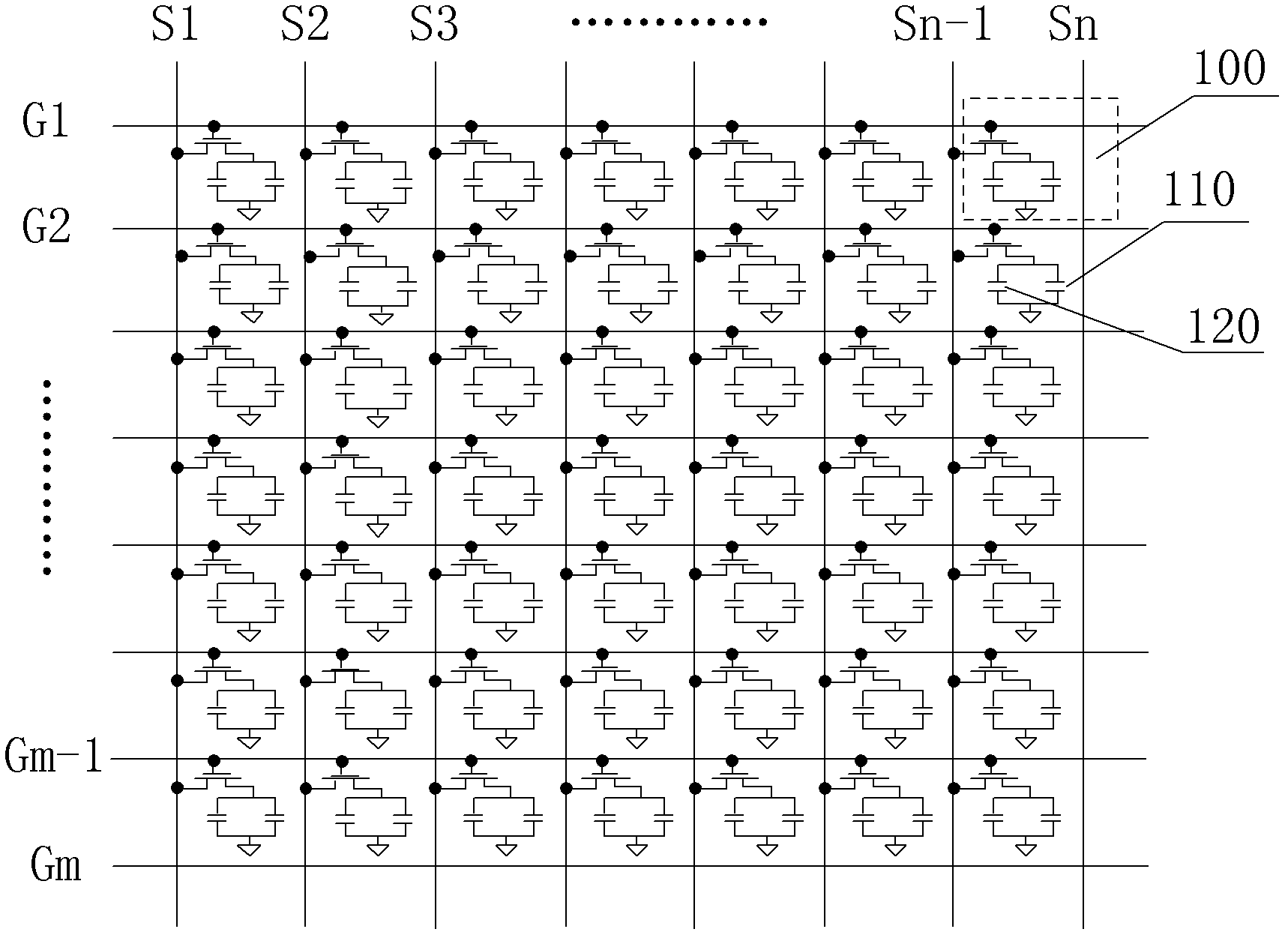

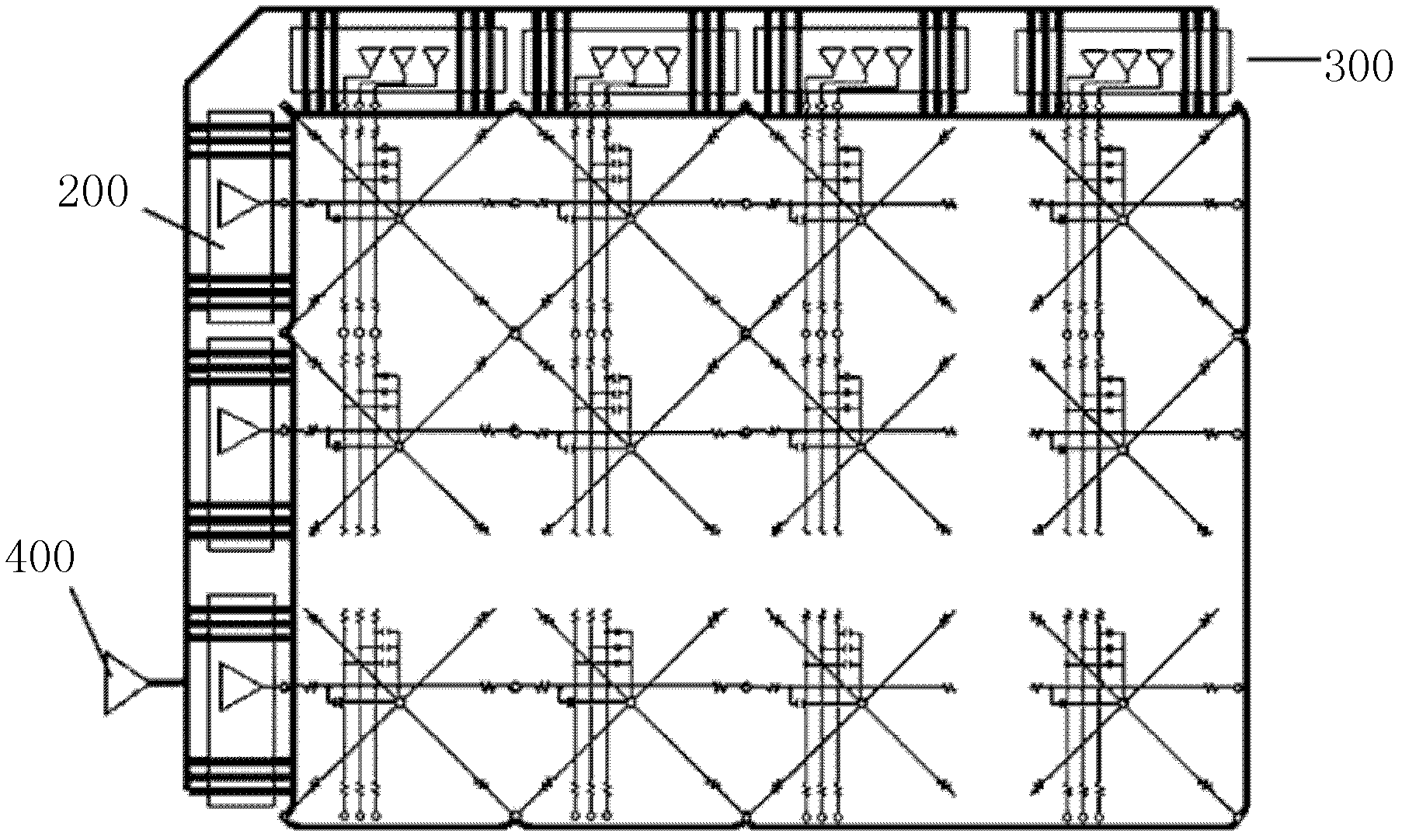

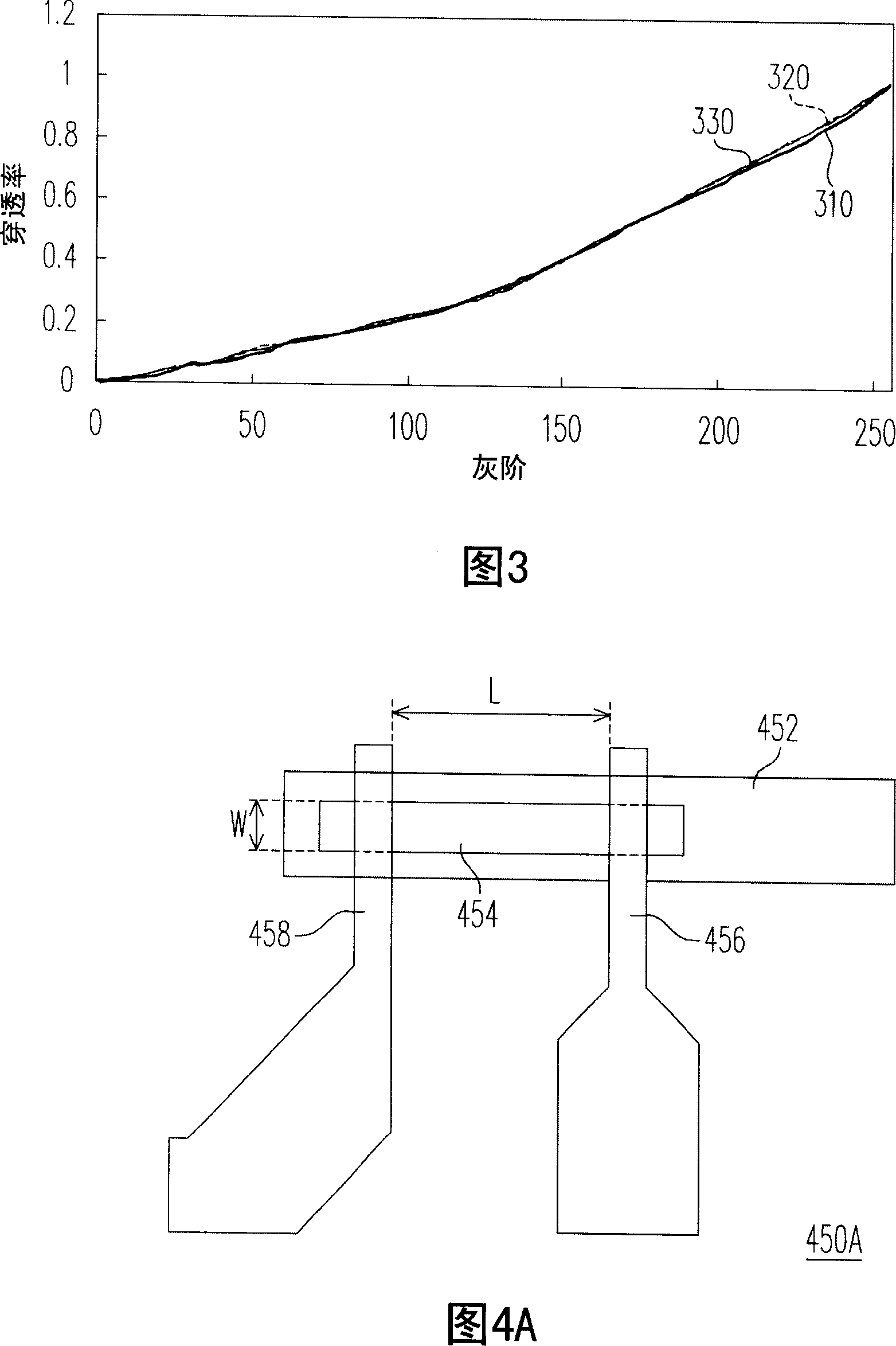

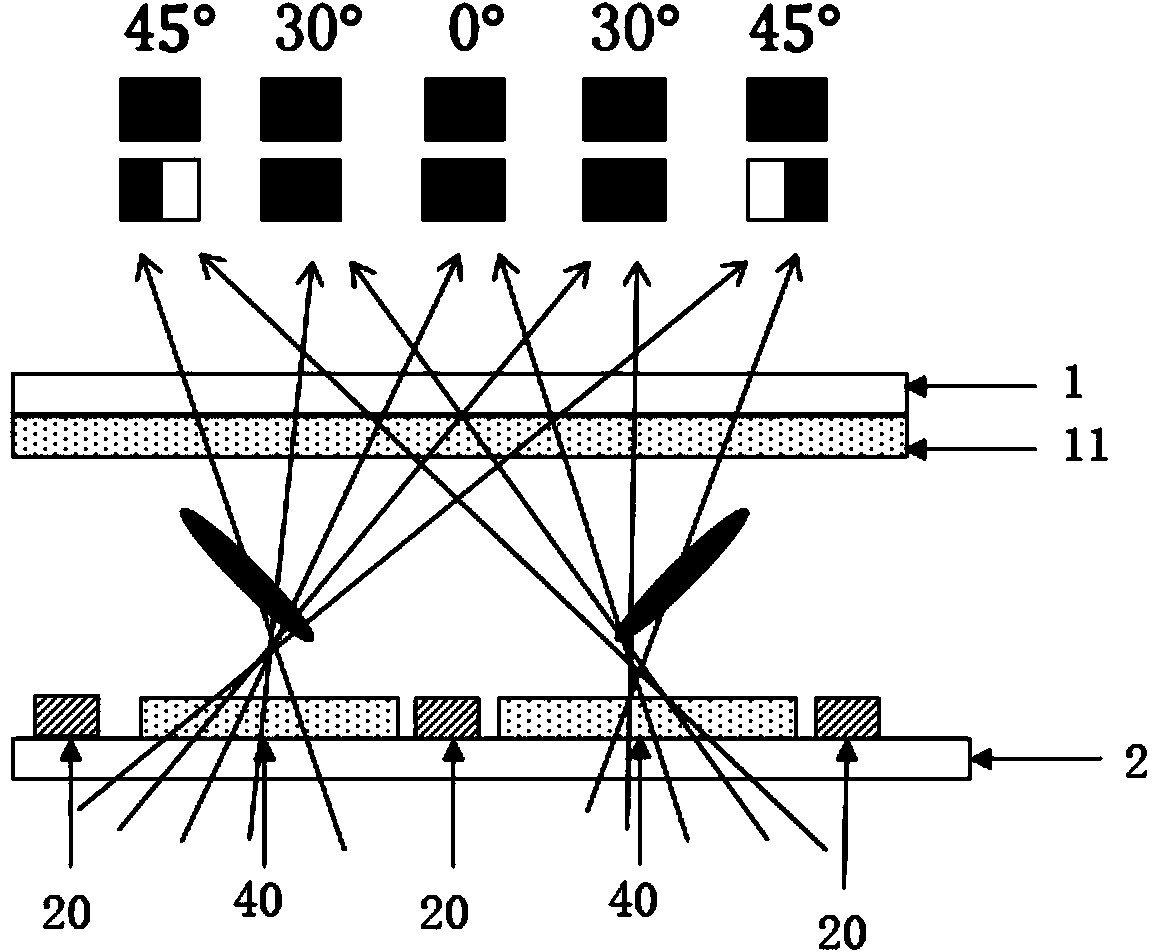

Unit pixel structure for liquid crystal displays

ActiveCN103901681ADoes not increase the loadImprove light transmission efficiencyNon-linear opticsCapacitanceElectrical resistance and conductance

The invention provides a unit pixel structure for liquid crystal displays. A liquid crystal display comprises an array substrate, a color film substrate, and liquid crystal; the array substrate and the color film substrate face each other; the liquid crystal is arranged between the array substrate and the color film substrate; the liquid crystal is in a UV vertical alignment mode; the array substrate comprises scan lines, data lines and pixel electrodes; the scan lines and the data lines intersect crisscross; the pixel electrodes are limited by the scan lines and the data lines intersecting; black lines occur to a pixel electrode area due to UV vertical alignment; the edge of the pixel electrodes is partially provided with a radial slit pattern protruding out. The unit pixel structure has the advantages that the edge black lines expand out of the pixel electrodes, force of the ITO fringe field upon liquid crystal molecules moves out, the dark lines are moved out of an aperture area, a Fine Slit structure enables the black lines to move out to be eliminated, load of resistance and capacitance of an array panel is not increased much, aperture ratio is not lowered, and light transmitting efficiency of UV vertical alignment displays is increased.

Owner:NANJING CEC PANDA LCD TECH

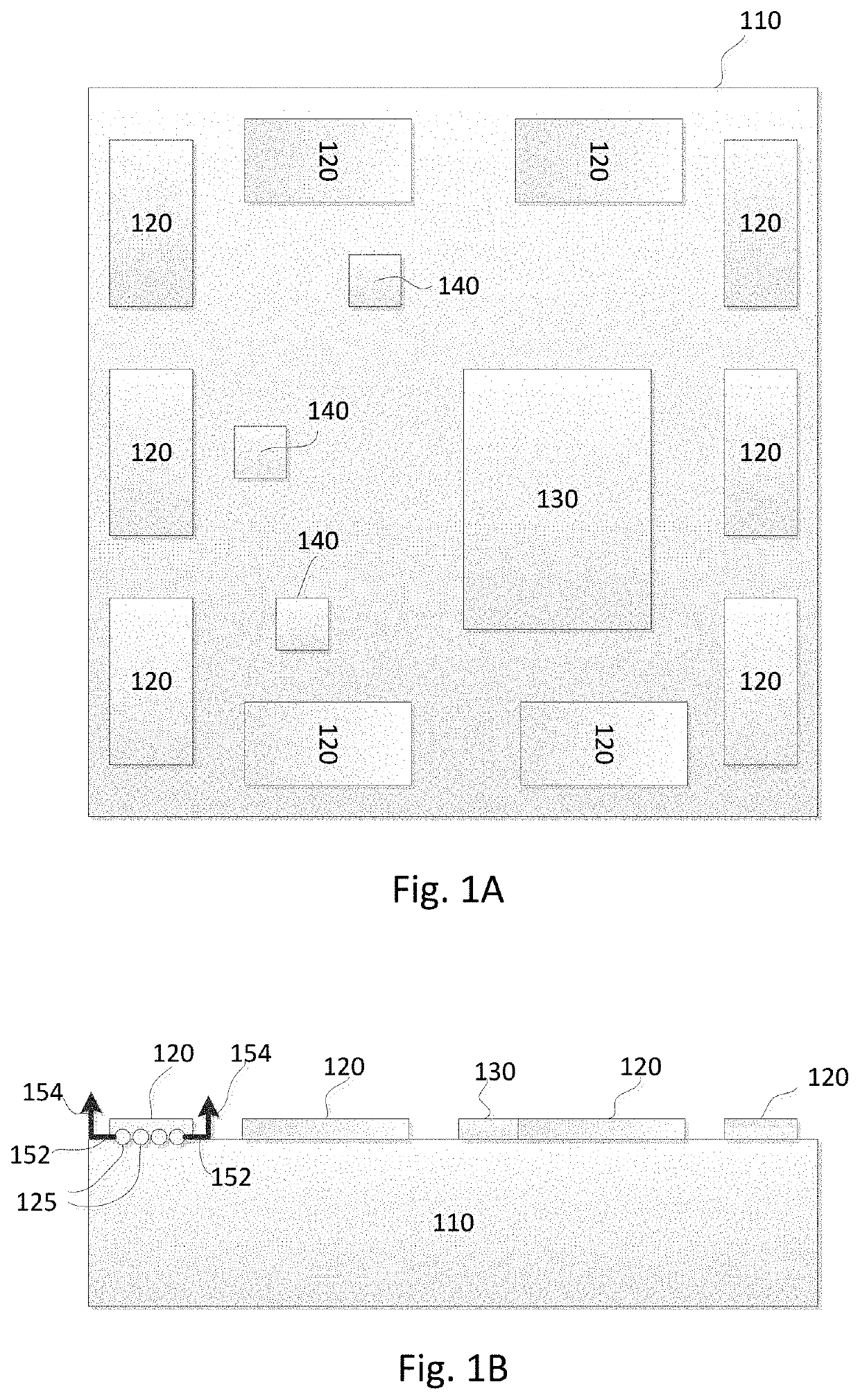

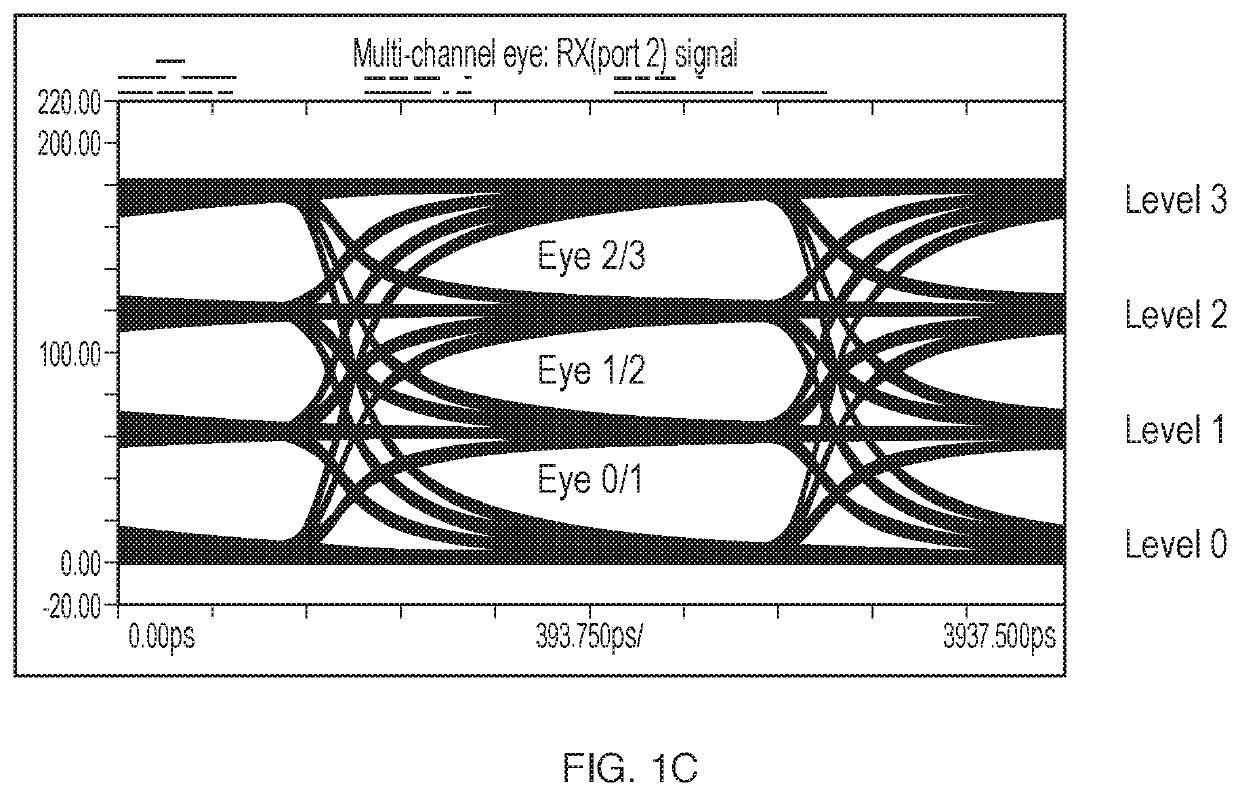

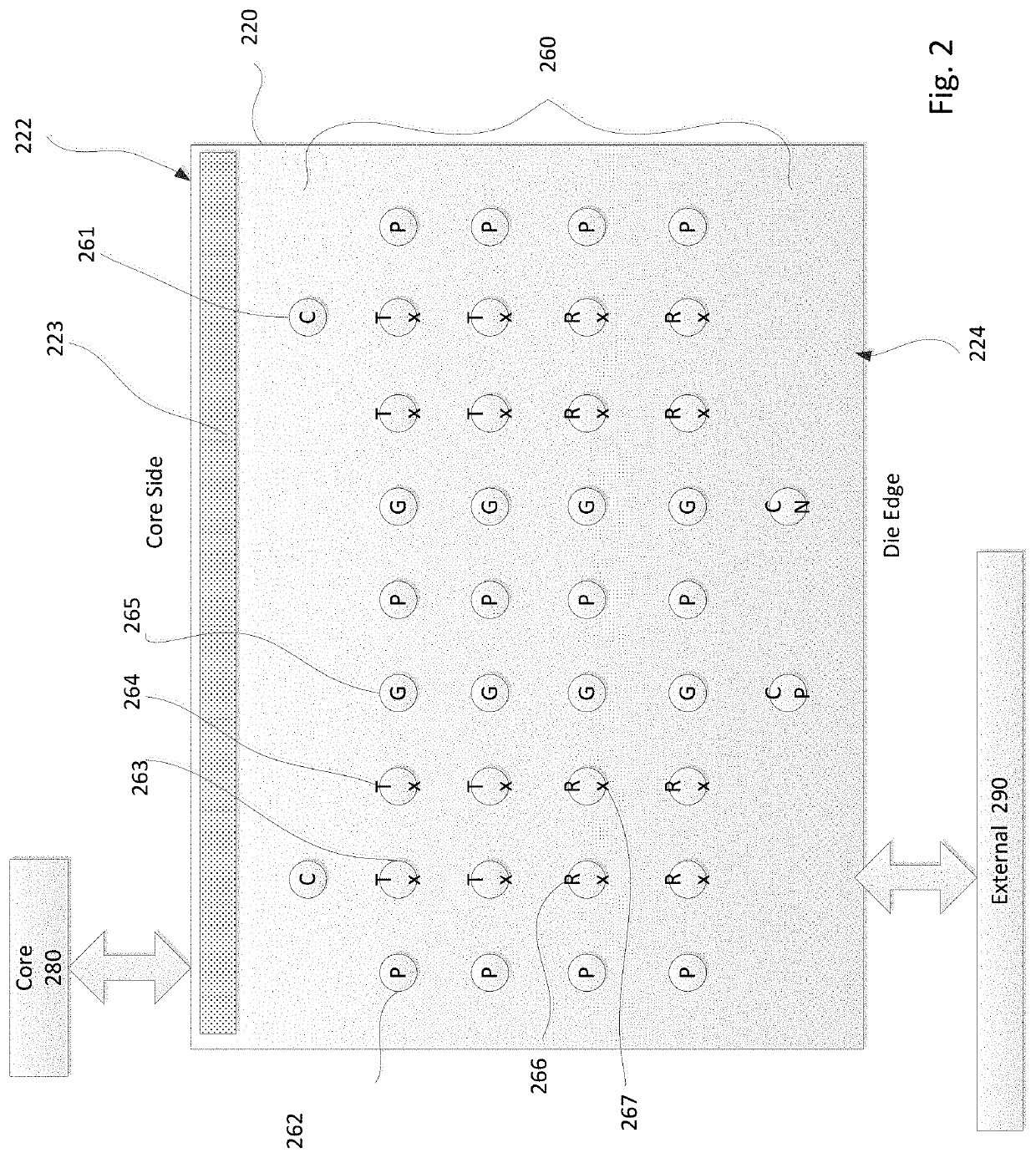

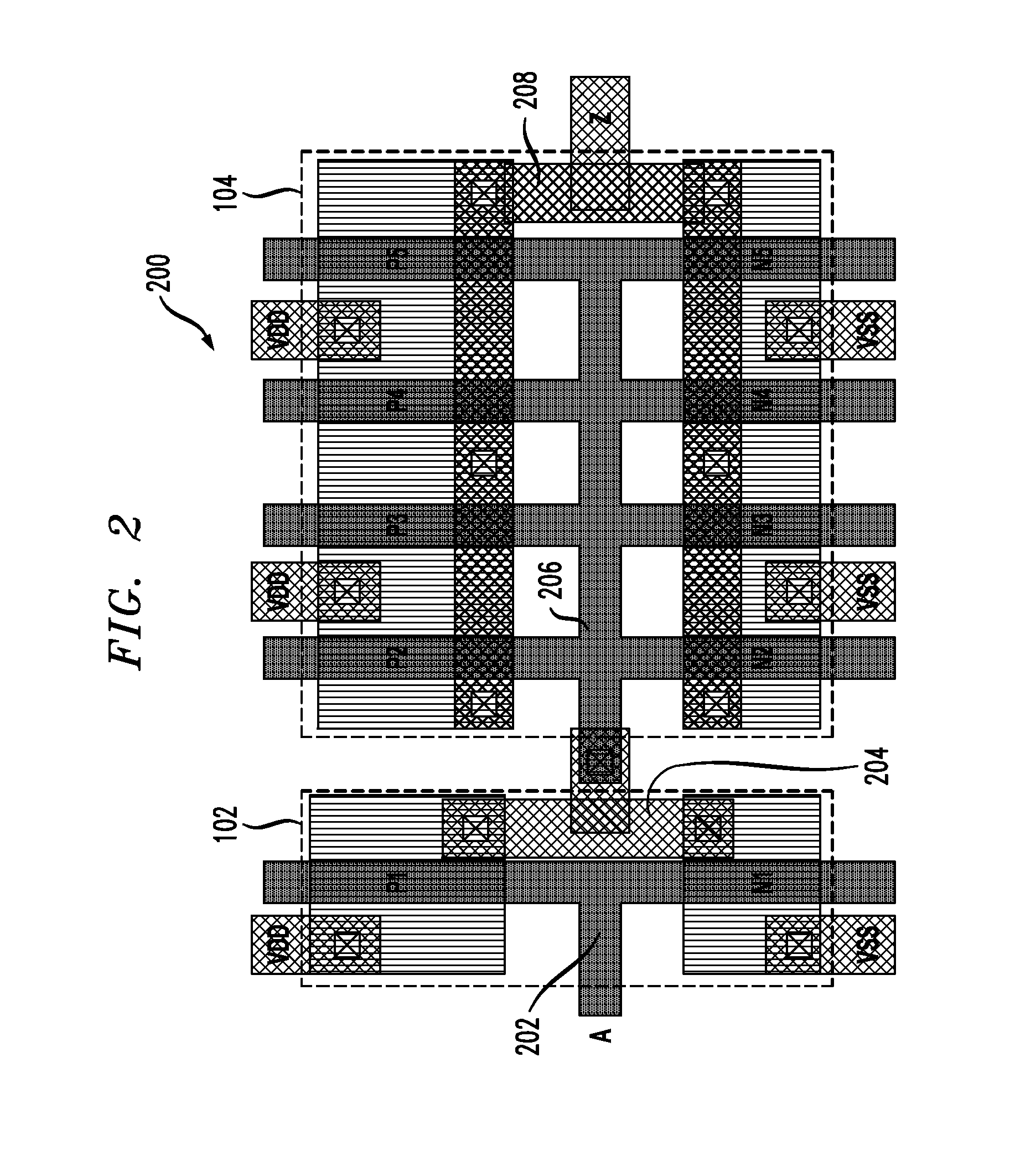

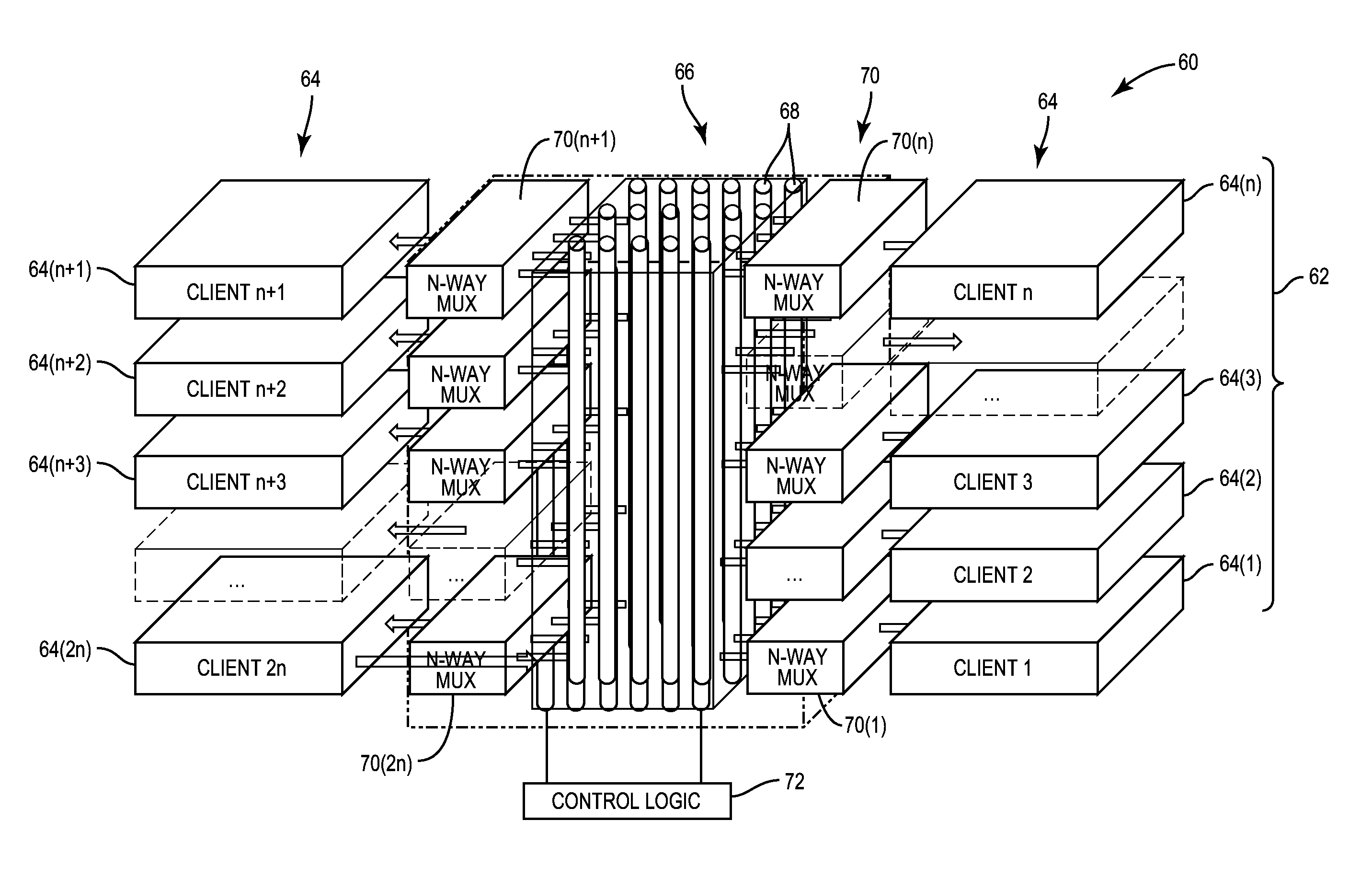

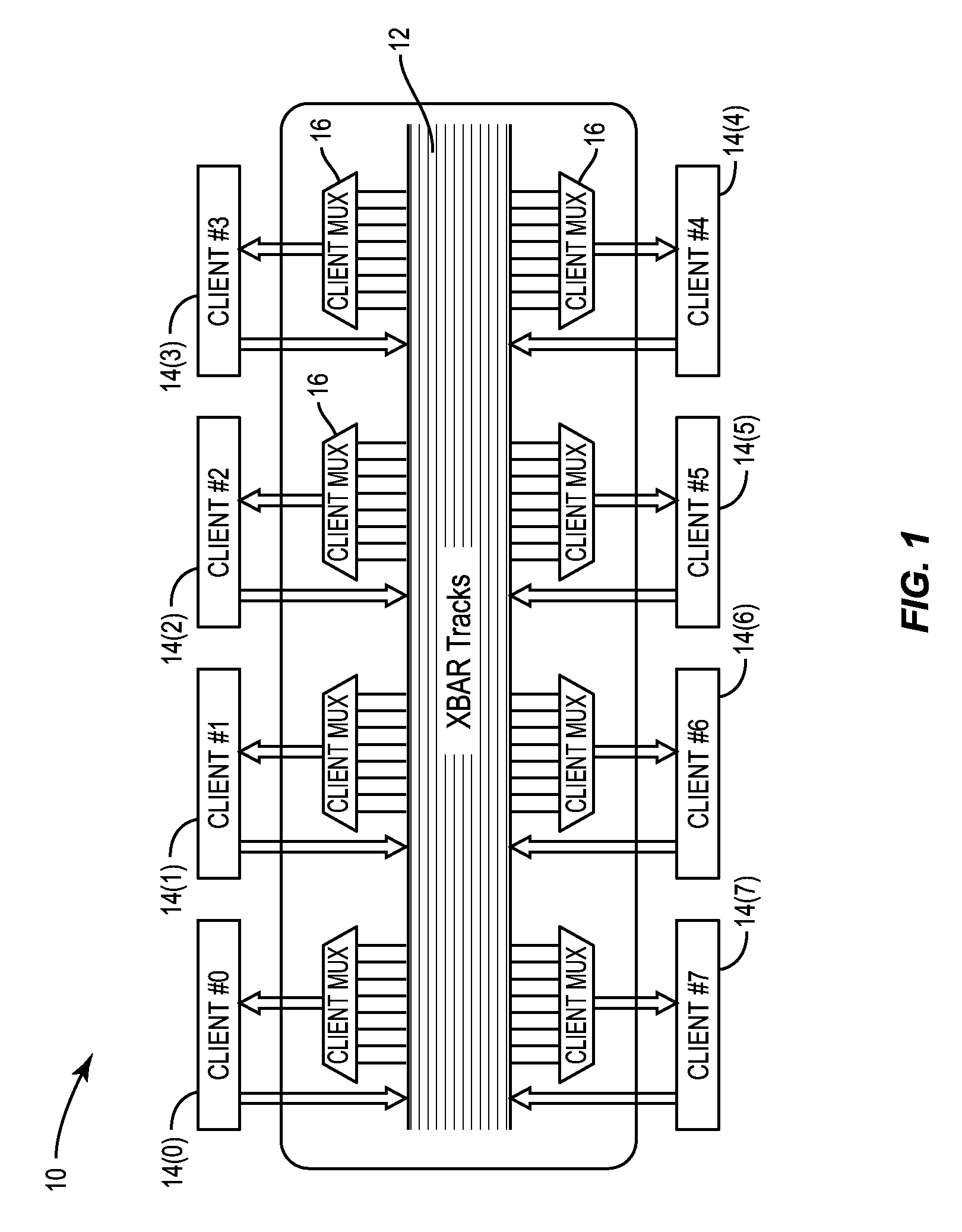

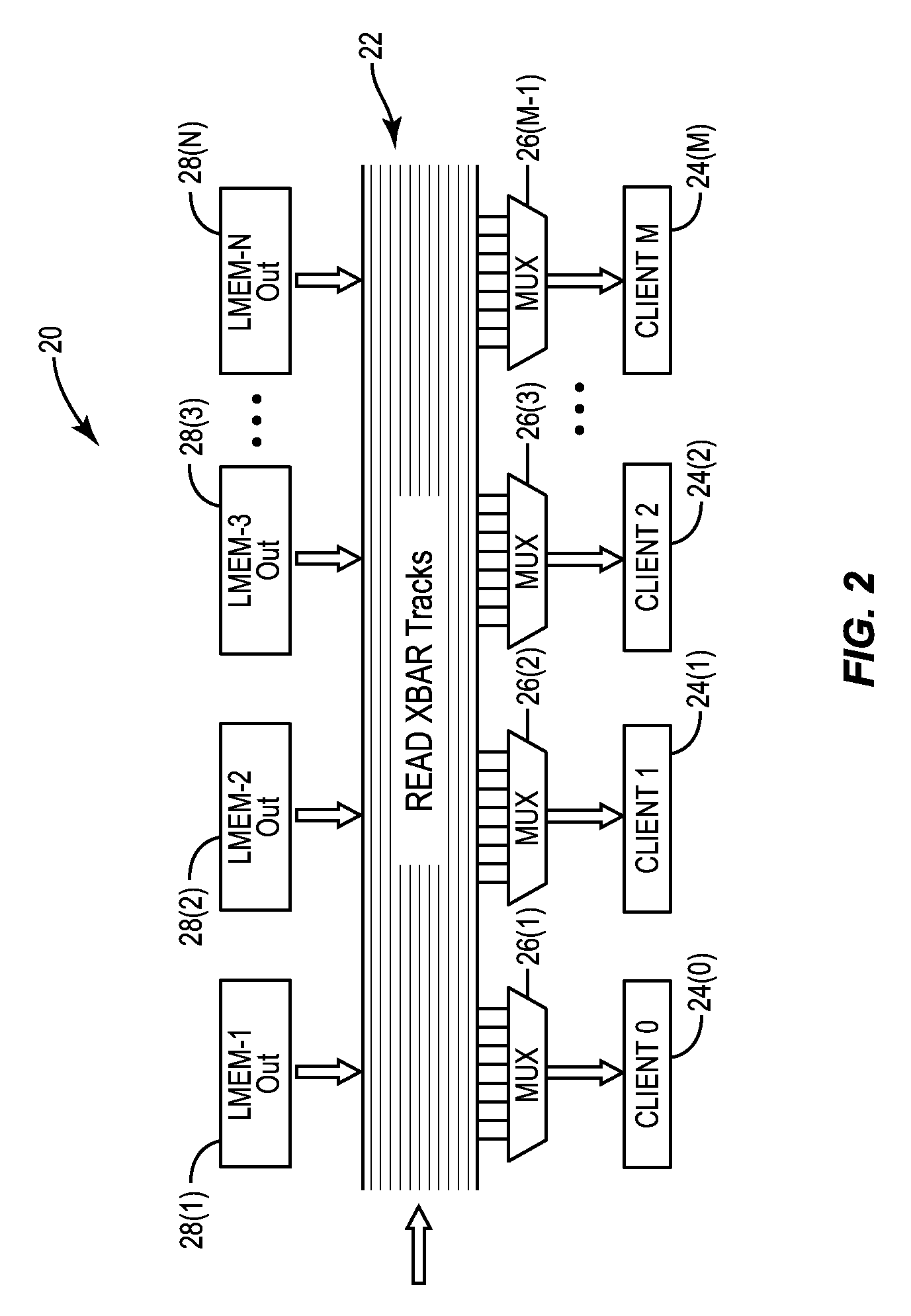

Hard IP blocks with physically bidirectional passageways

ActiveUS10923413B2Not to adversely impact transmitted signalSemiconductor/solid-state device detailsSolid-state devicesCapacitanceComputer architecture

Hard IP blocks, such as SerDes chips, are designed with keepout zones beneath the surface interconnects, the keepout zones being spaces within the chip where there is no circuitry. Connections can be formed between surface interconnects on an under surface of the SerDes chip that faces the host die, and surface interconnects on an upper surface of the SerDes chip that interfaces without external devices. Accordingly, redistribution layers routing around an outer periphery of the SerDes chip are no longer needed, and the resistive capacitive load remains low so as not to adversely impact transmitted signals.

Owner:XCELSIS CORP

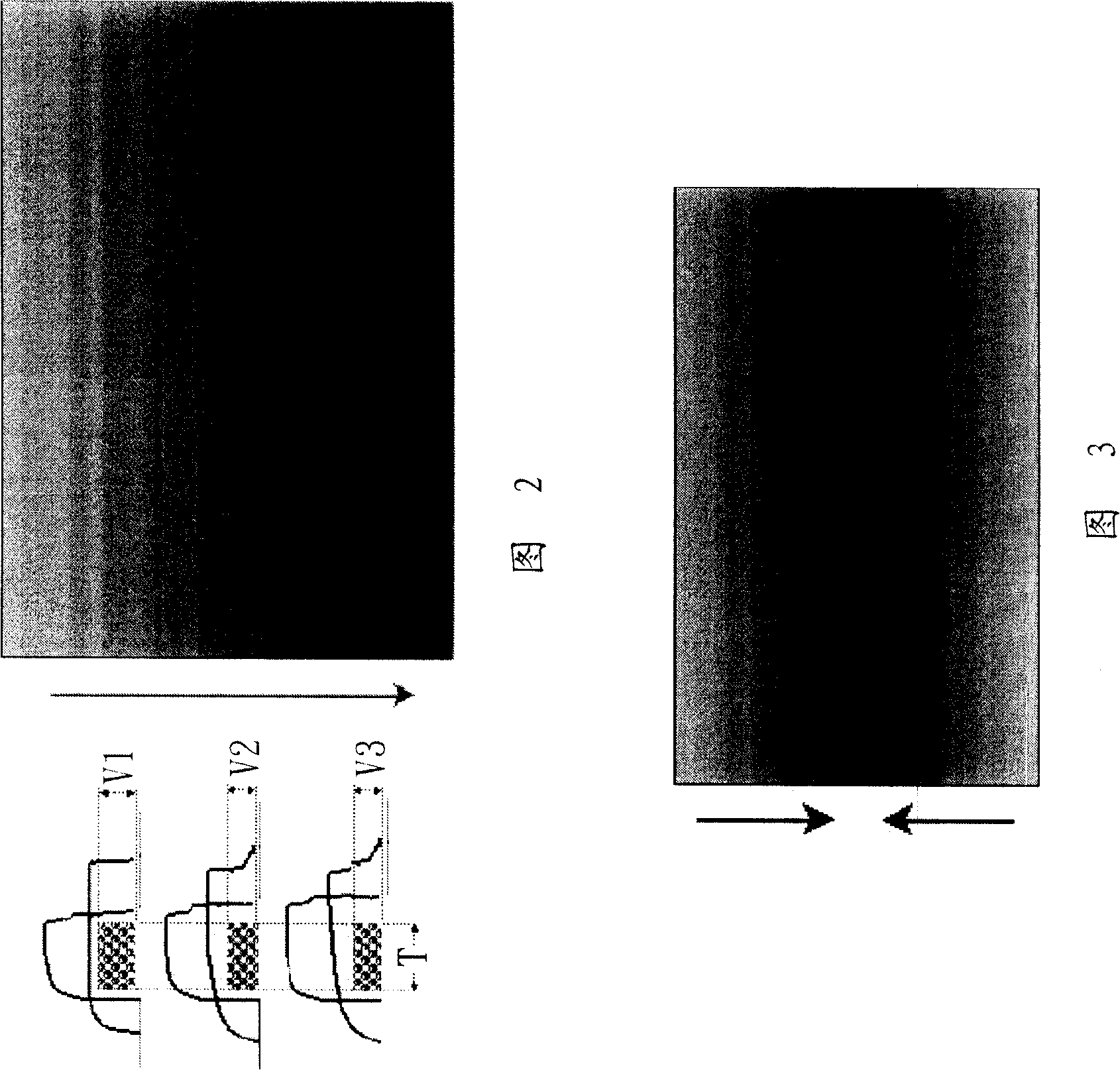

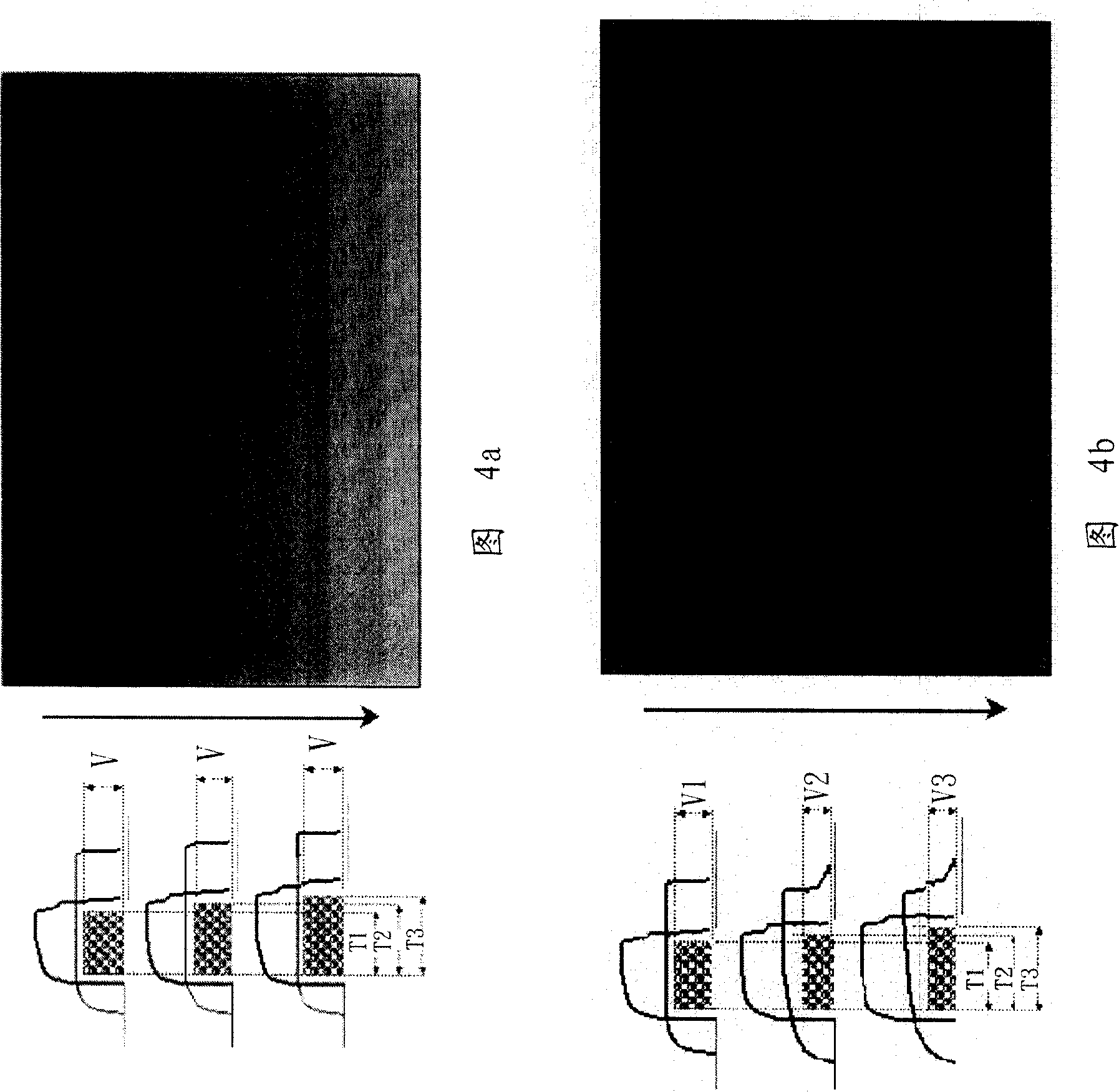

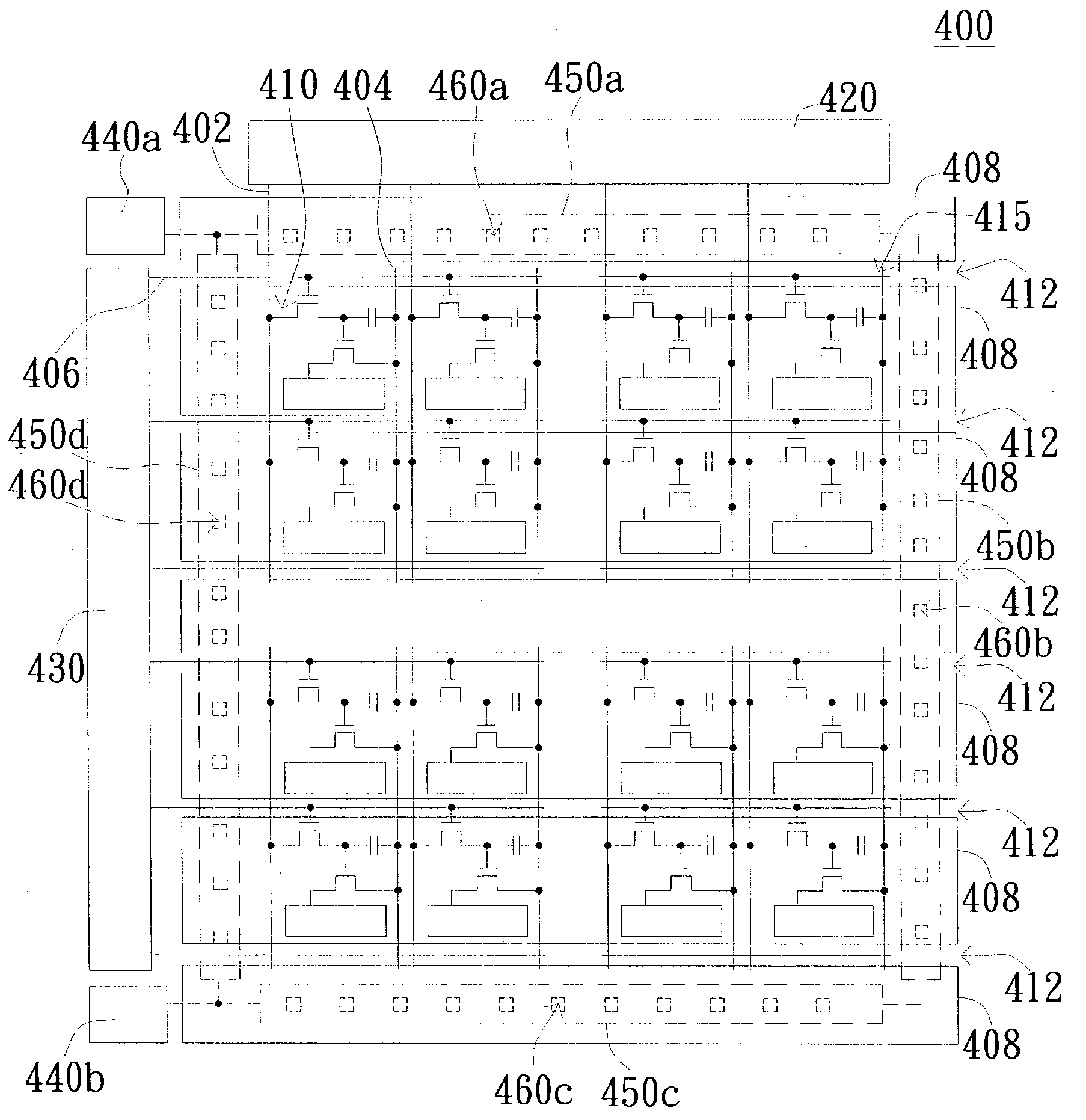

Liquid crystal display panel data signal distortion compensating process and circuit

ActiveCN101191924AImprove the phenomenon of uneven brightnessStatic indicating devicesLine resistanceCapacitance

The present invention relates to a data signal distortion compensation method and circuit for liquid crystal display panels, which is a method and a circuit that utilize adjusting the linear increase of the opening time width of scanning signals. As the total electric charge amount of the capacitance supplied to one row of display units can be the same, the reflected brightness can be the same as well. Therefore, the present invention can obviously improve the uneven brightness phenomenon caused by the on-line resistance-capacitance effect of data, so as to improve the phenomenon that liquid crystal display panels are uneven in brightness.

Owner:INNOLUX CORP

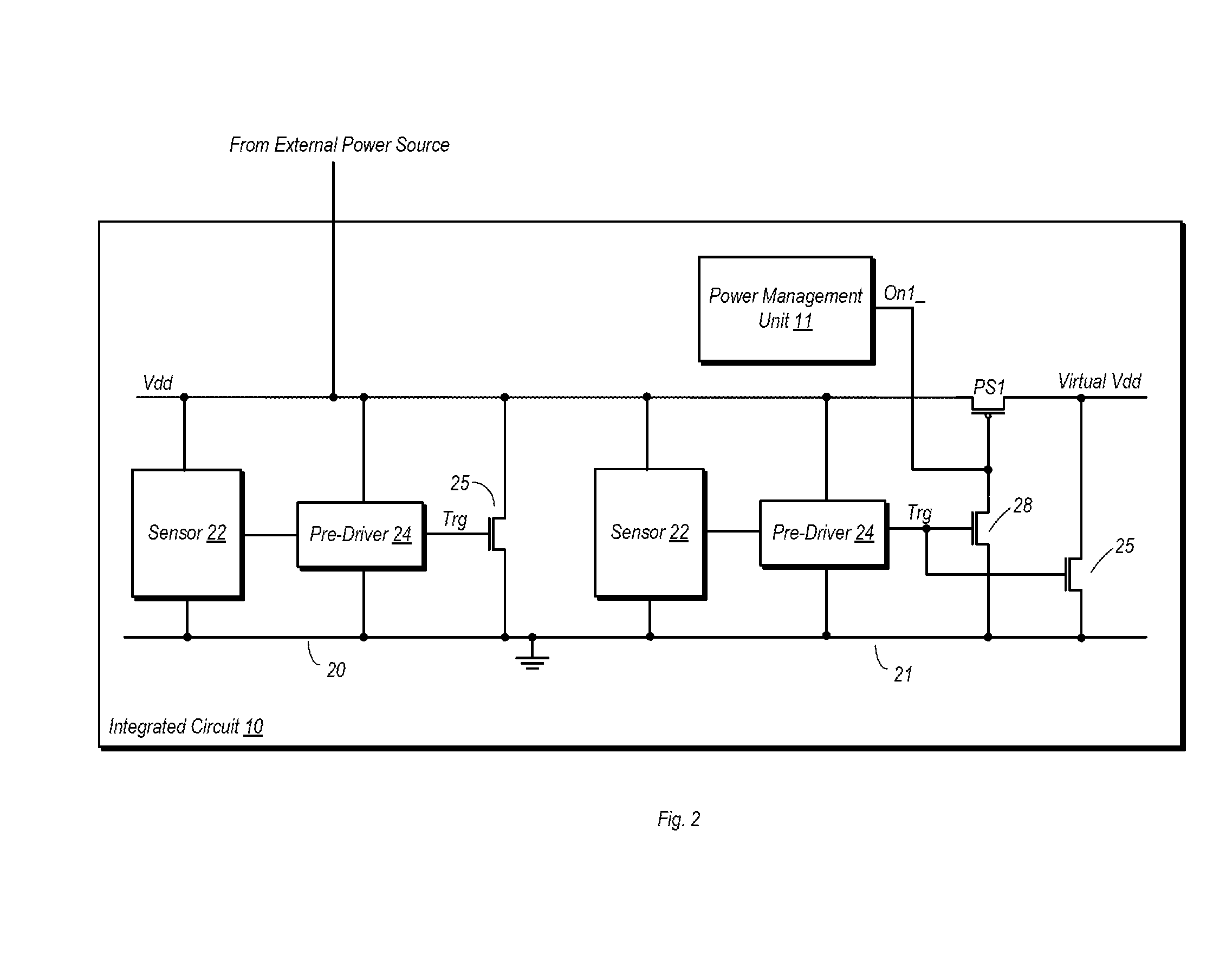

Optimized ESD Clamp Circuitry

ActiveUS20150270258A1Save extra spaceOptimize quantityTransistorSolid-state devicesRC time constantEngineering

ESD protection circuitry is disclosed. In one embodiment, an integrated circuit includes first and second sensor circuits. The first sensor circuit has a first resistive-capacitive (RC) time constant, while the second sensor circuit has a second RC time constant. The RC time constant of the first sensor circuit is at least one order of magnitude greater than that of the second sensor circuit. A first clamp transistor is coupled to and configured to be activated by the first sensor circuit responsive to the latter detecting an ESD event. A second clamp transistor is coupled to and configured to be activated by the second sensor circuit responsive to the latter detecting the ESD event.

Owner:APPLE INC

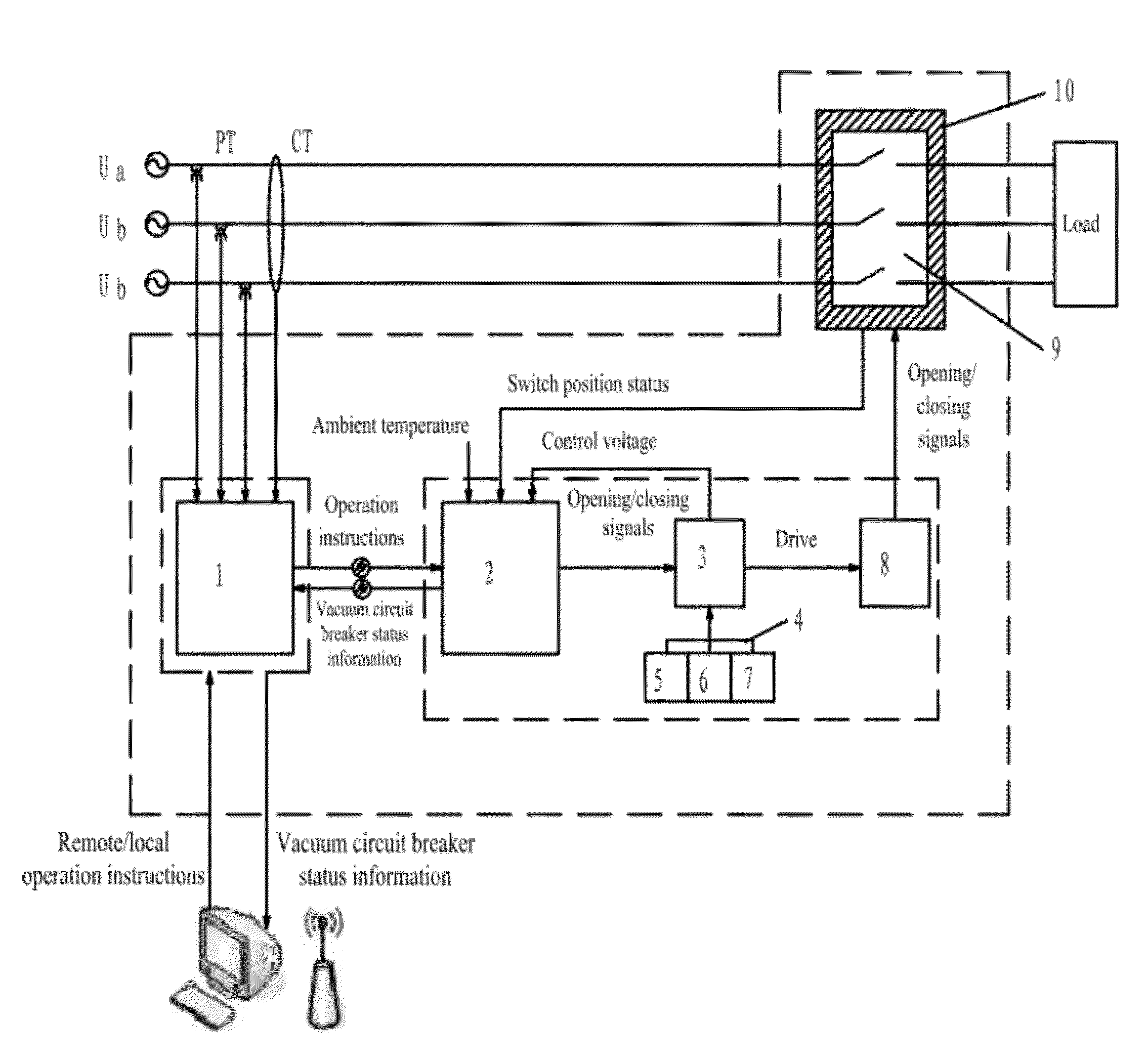

High-voltage, super-voltage and heavy current breaker

InactiveUS20120187089A1Increase the rated working voltageIncrease capacityHigh-tension/heavy-dress switchesAir-break switchesCapacitanceUltra high pressure

A high-voltage, super-voltage and heavy current breaker is formed by combining intelligent optical vacuum breaker modules (21) with phase selection function in series and / or parallel connection. Each vacuum breaker module (21) is connected each other in series after being connected in parallel with a resistance capacitance device or with a resistance capacitance device and a zinc oxide arrester valve plate (22). Tight coupling reactors are connected with several serial branches of the vacuum breaker module (21) simultaneously to achieve parallel connection of several serial branches of the vacuum breaker module (21). The breaker distributes the high-voltage and heavy current into the low voltage and low current serial and parallel vacuum breaker modules (21) to share.

Owner:CHEN XUANSHU +7

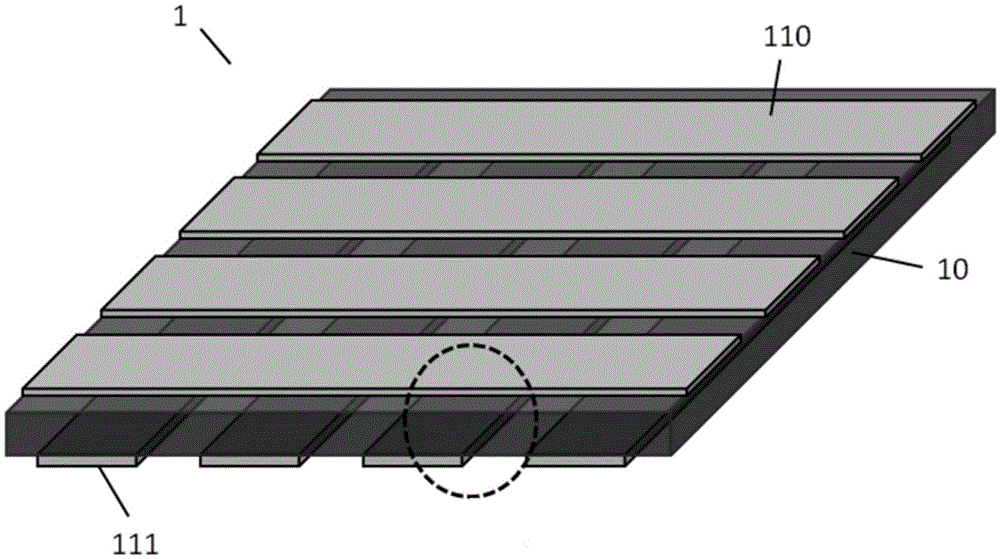

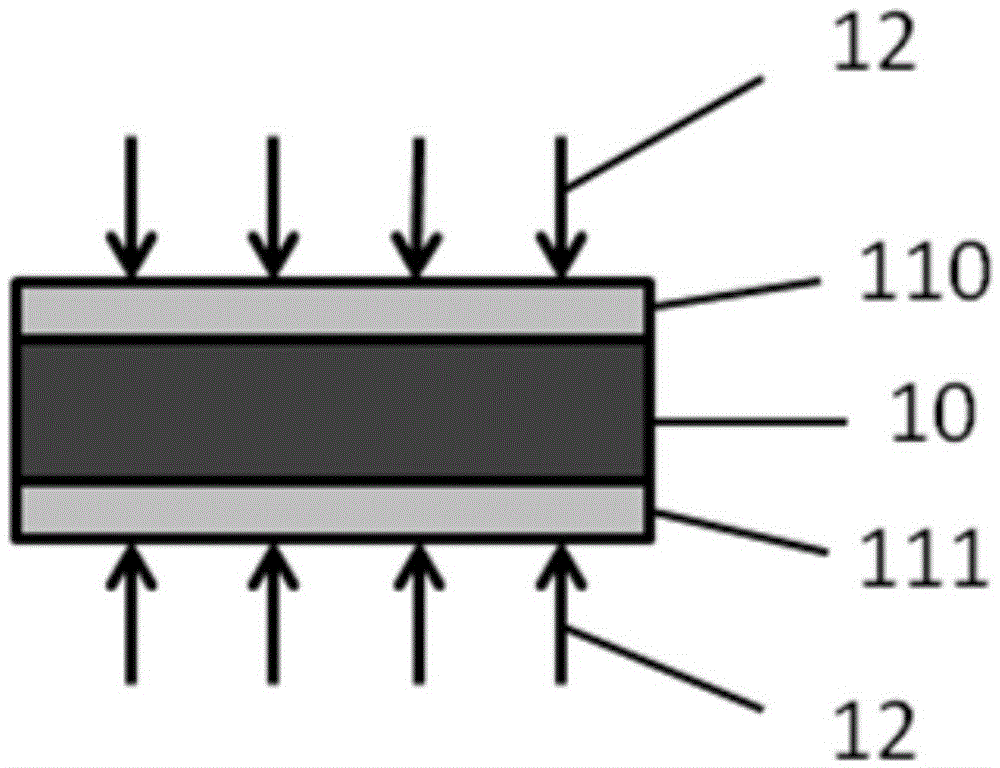

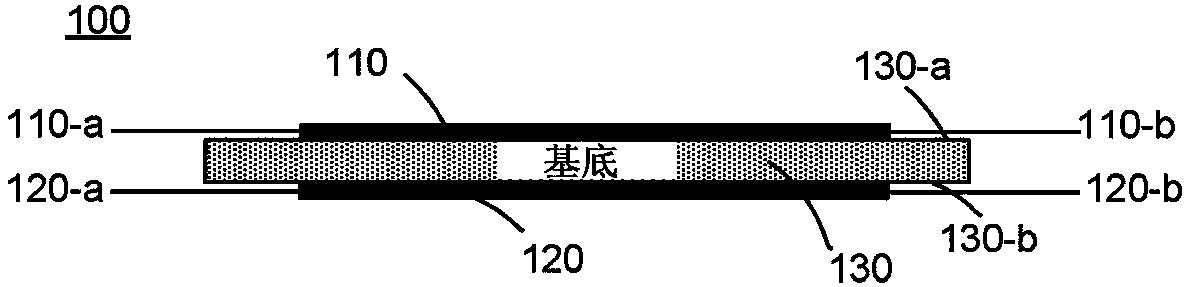

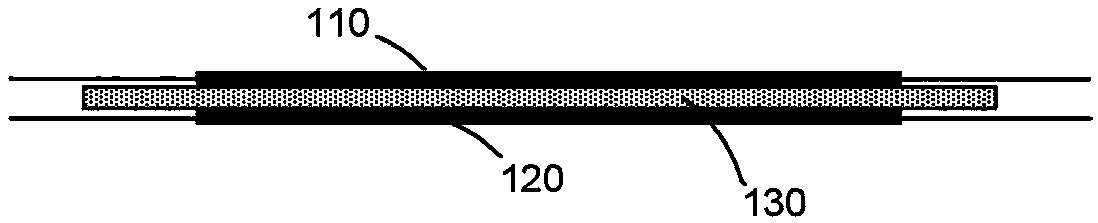

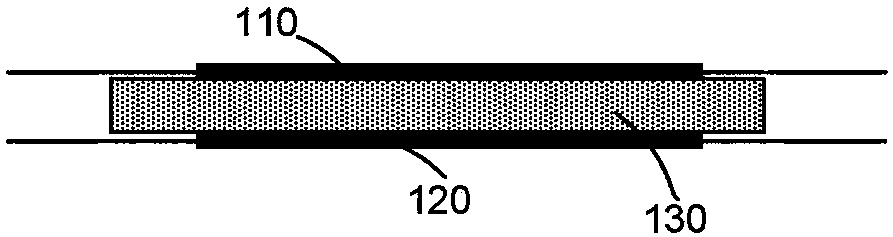

Resistance-capacitance hybrid pressure sensor and use method thereof

InactiveCN105607790ASimple structureMature structureInput/output processes for data processingCapacitanceElectrical resistance and conductance

The invention discloses a resistance-capacitance hybrid pressure sensor and a use method thereof. The resistance-capacitance hybrid pressure sensor comprises a piezoresistive material layer, a conductive electrode layer and substrate layers, wherein the piezoresistive material layer is made of a resistance pressure sensitive material; the conductive electrode layer is divided into an upper layer and a lower layer which are respectively located on the upper surface and lower surface of the piezoresistive material layer; the substrate layers are respectively arranged on the upper surface and lower surface of the conductive electrode layer. The pressure sensor is prepared into an array applied to electronic equipment, such as, a touch screen, and the like and is used for respectively measuring capacitance and resistance under different application environments, so that the pressure sensor has the advantages of high sensitivity, strong durability, mature technique, and the like of a capacitive touch screen as well as the advantages of capability of detecting pressure, strong water resistance, and the like, of a resistance-type touch screen. The resistance-capacitance hybrid pressure sensor has a sensor structure with two functions, is simple in structure and principle, is capable of utilizing the technique and equipment of the present capacitive touch screen, is low in cost and is fit for wide popularization.

Owner:SHANGHAI JIAO TONG UNIV +1

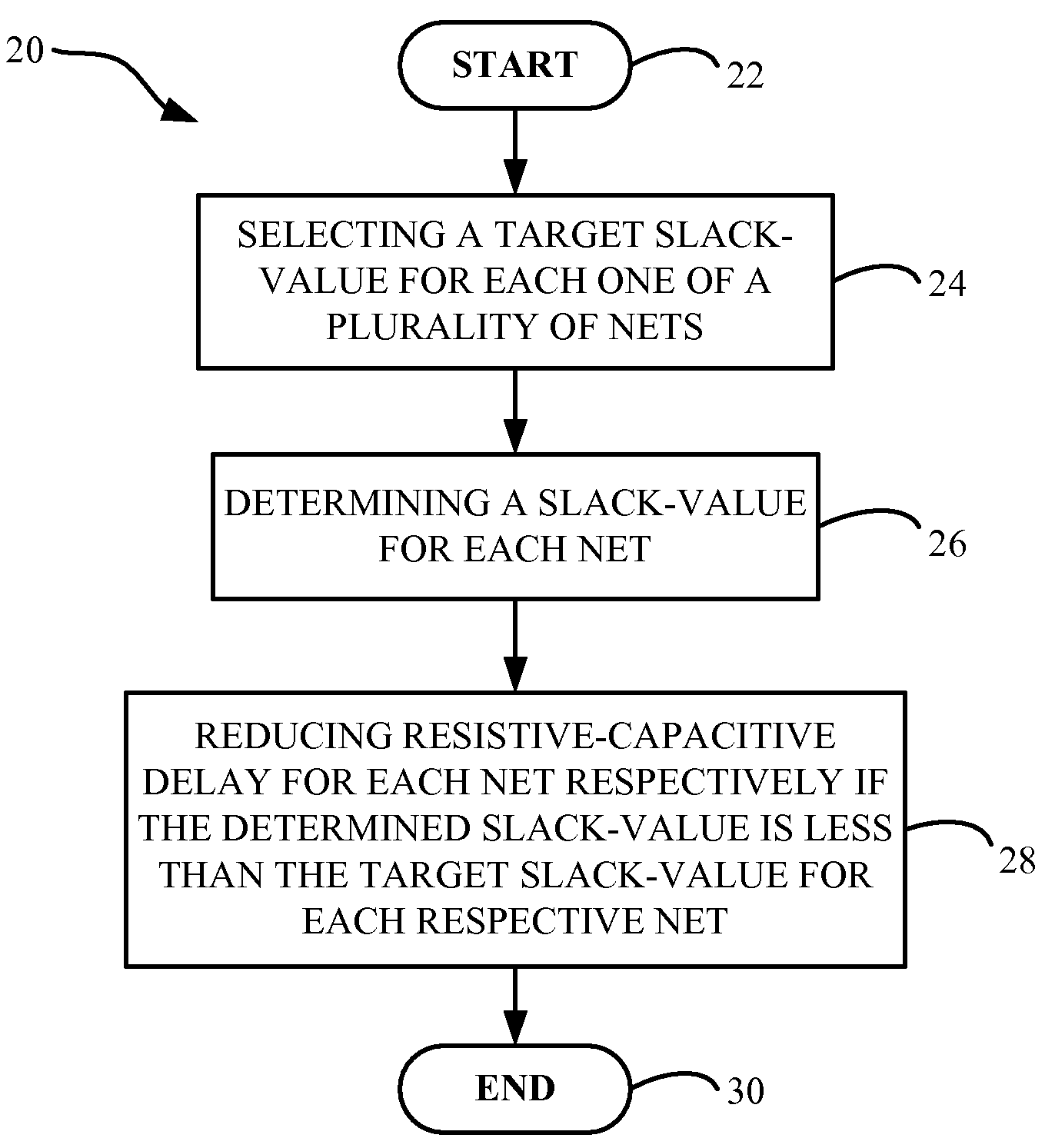

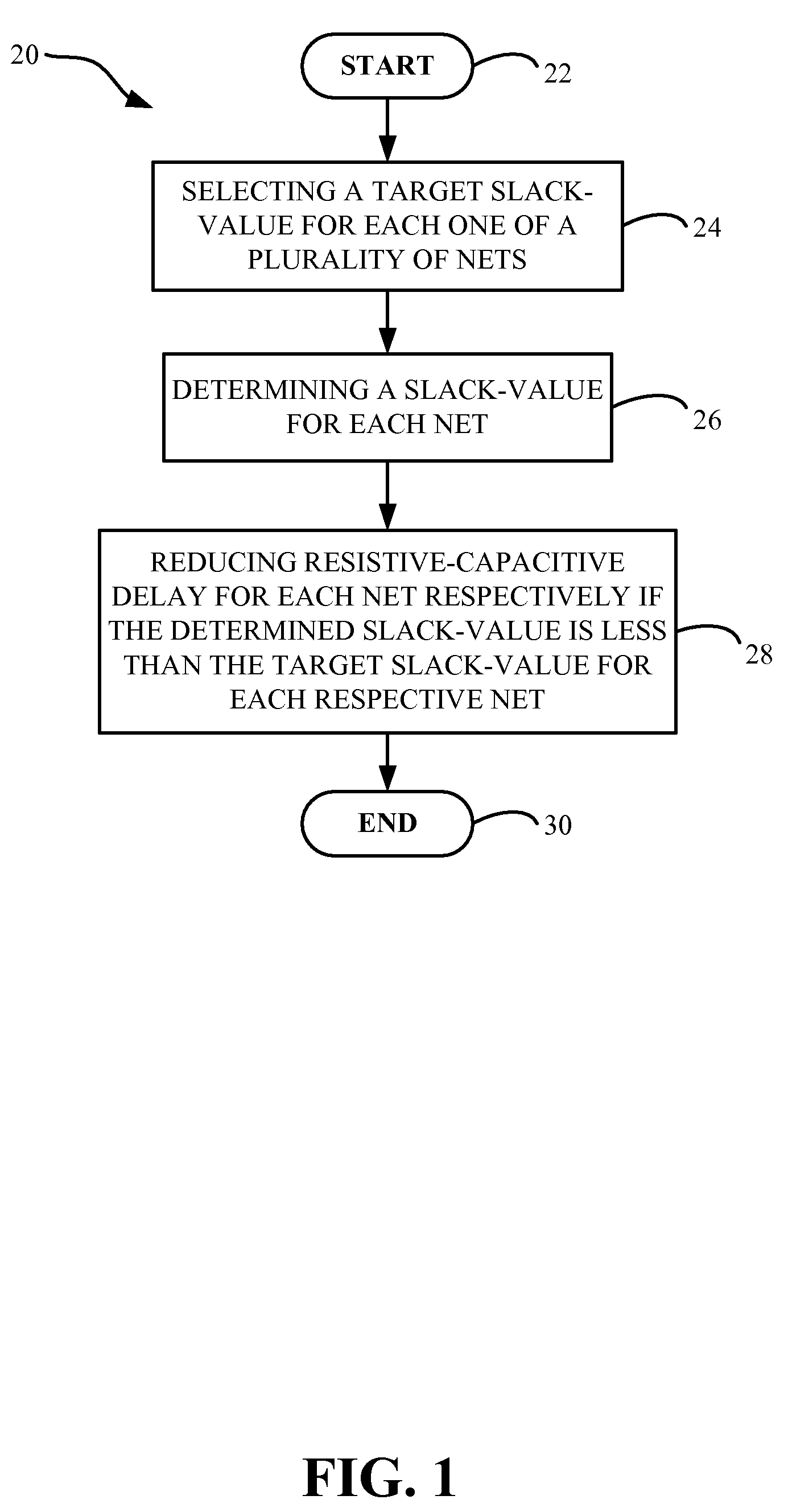

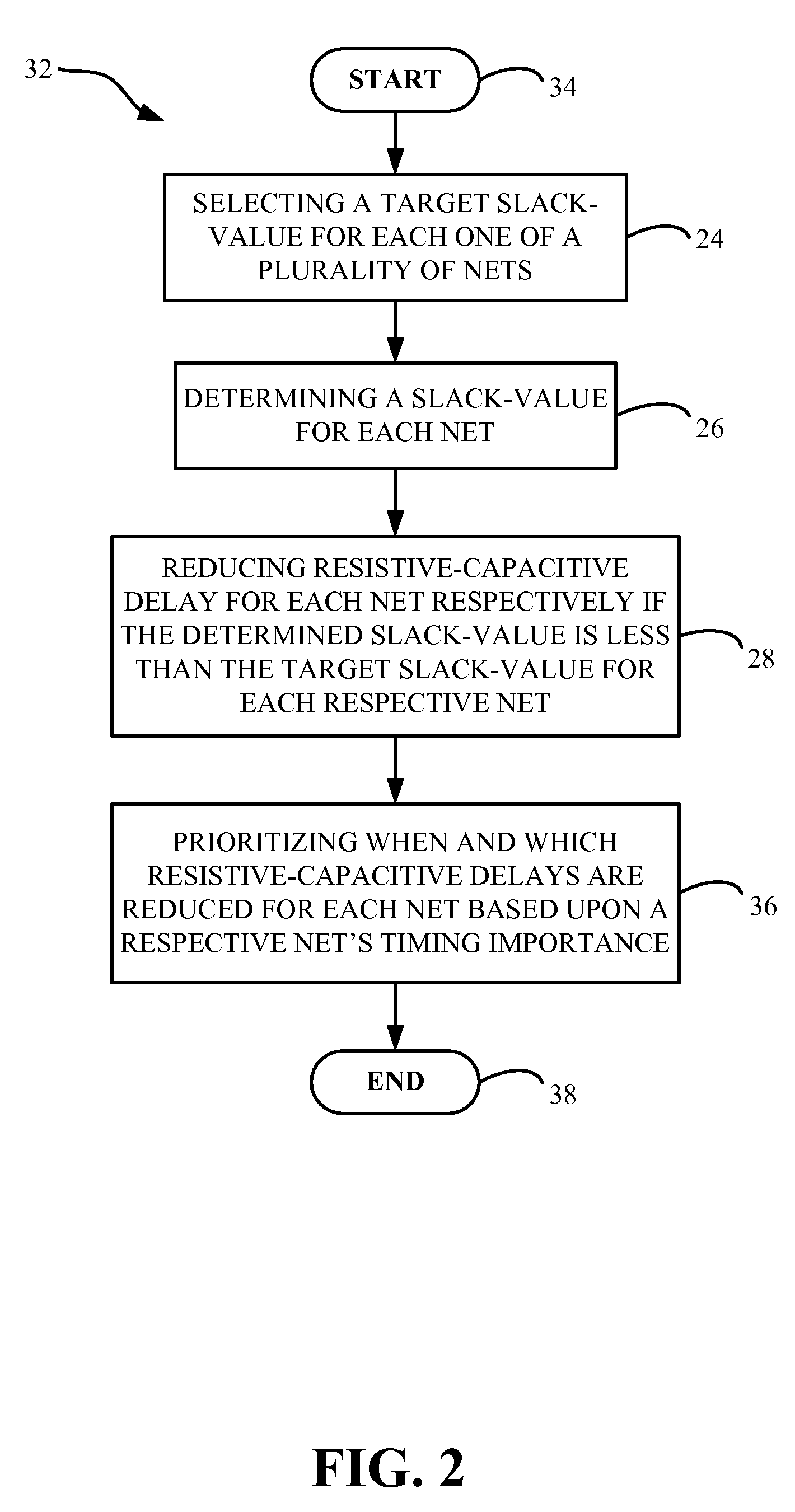

System for Improving a Logic Circuit and Associated Methods

InactiveUS20090106709A1Increase heightReduce RC delayComputer aided designSoftware simulation/interpretation/emulationElectrical resistance and conductanceCapacitance

A system for improving a logic circuit may include a processor, and a logic circuit analyzer in communication with the processor to model a plurality of nets. The system may also include an interface in communication with the logic circuit analyzer to select a target slack-value for each one of the plurality of nets. The logic circuit analyzer may determine a slack-value for each net. In addition, the logic circuit analyzer may selectively reduce resistive-capacitive delay for each net respectively if the determined slack-value is less than the target slack-value for each respective net.

Owner:GLOBALFOUNDRIES INC

Barium titanate based electric resistor non-linear to voltage and its preparing process

InactiveCN1397959ALarge capacityLower sintering temperatureVaristor coresNonlinear resistorSilver electrode

This invention provides a Ba titanate base voltage nonlinear resistor composed of ceramic material of Ba titanate as the main component added with sintered silver electrodes. A preparation method of the said resistor contains 1) Main components of the synthesis are (Bal-xSrx)m TiO2, in which x=0-0.2, m=0.96-100; 2) The main component is added with proportional weighted additives to be mixed with water to become pulp after balmill 3) The pulp is added with PVA solution to be dried to granulation 4) The granulation powders are processed to blank pieces after dry press 5) The blank pieces are sinerted to semiconductive ceramic plates in a reducbility atmosphere 6) To be heat treated in 900-1100 deg.c 7) Electrode is mounted.

Owner:SOUTH CHINA UNIV OF TECH

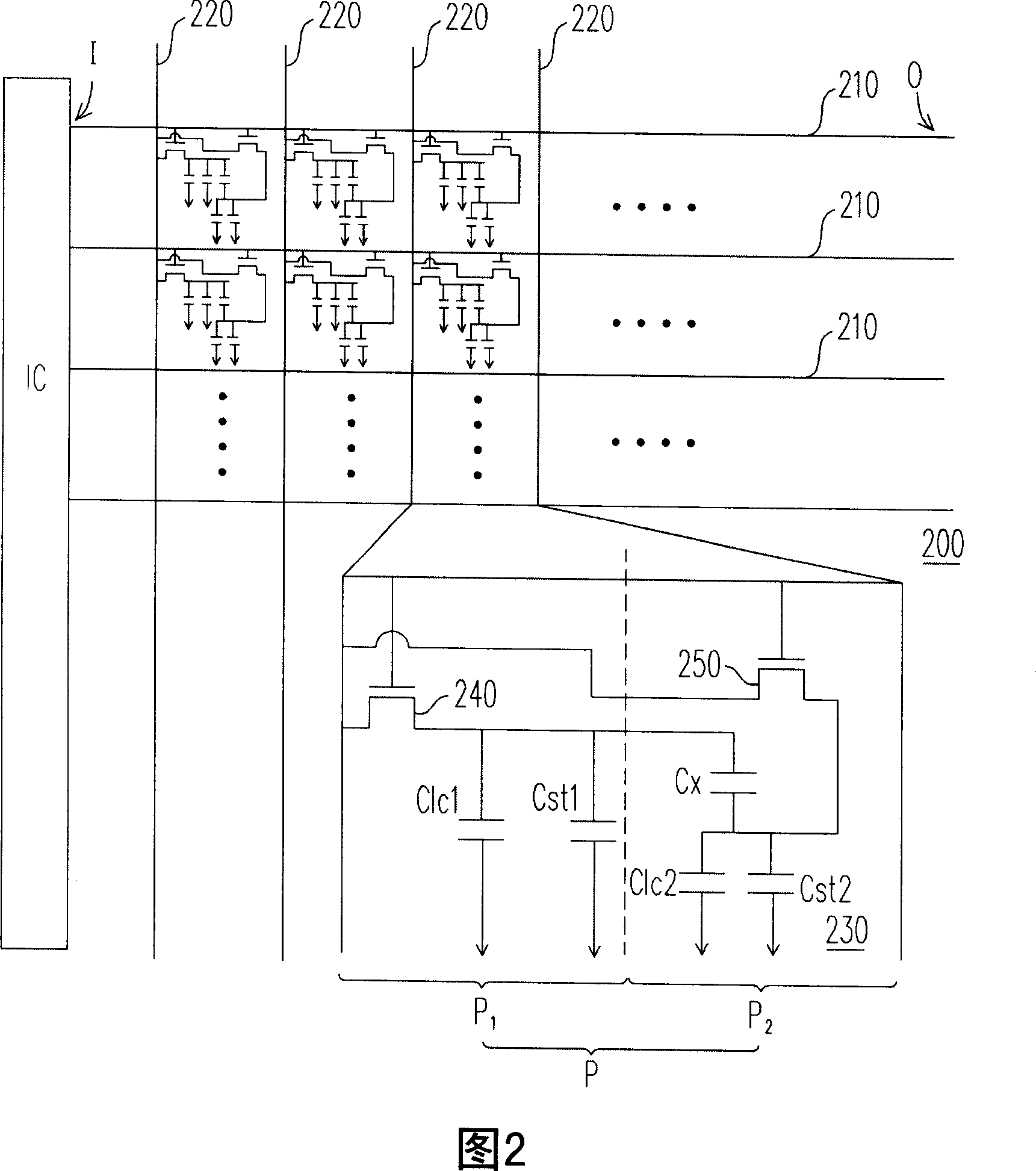

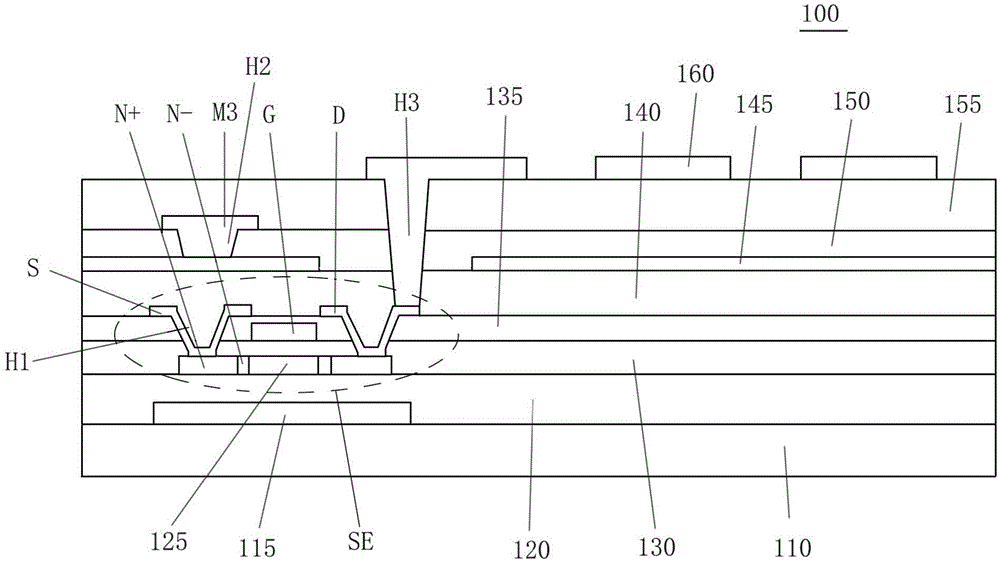

Thin film transistor array base and its pixel structure

ActiveCN101005084AImprove the phenomenon of resistor capacitor hysteresisNo added lossTransistorSolid-state devicesCapacitanceElectrical resistance and conductance

The base plate of thin film transistor (TFT) array includes a substrate, multiple pieces of scanning wiring collocated on the substrate, multiple pieces of data wiring collocated on the substrate, and multiple pixel structures. Possessing inputting ends and tail ends of drive signal, the multiple pieces of scanning wiring and data wiring divide the substrate into multiple pixel areas. Each pixel area includes the pixel area for the first time (PAF) and the pixel area for the second time (PFS). Being collocated in pixel areas, pixel structure is driven by scanning wiring and data wiring. In a pixel area affiliated with, pixel structure includes first TFT corresponding to PAF, and second TFT corresponding to PAS. On the same scanning wiring, ratio between width and length of channel of the second TFT is crescent from inputting end of the drive signal to tail end in order to solve issues of delay of resistance capacitance, color deflection, and deficient color saturation.

Owner:AU OPTRONICS CORP

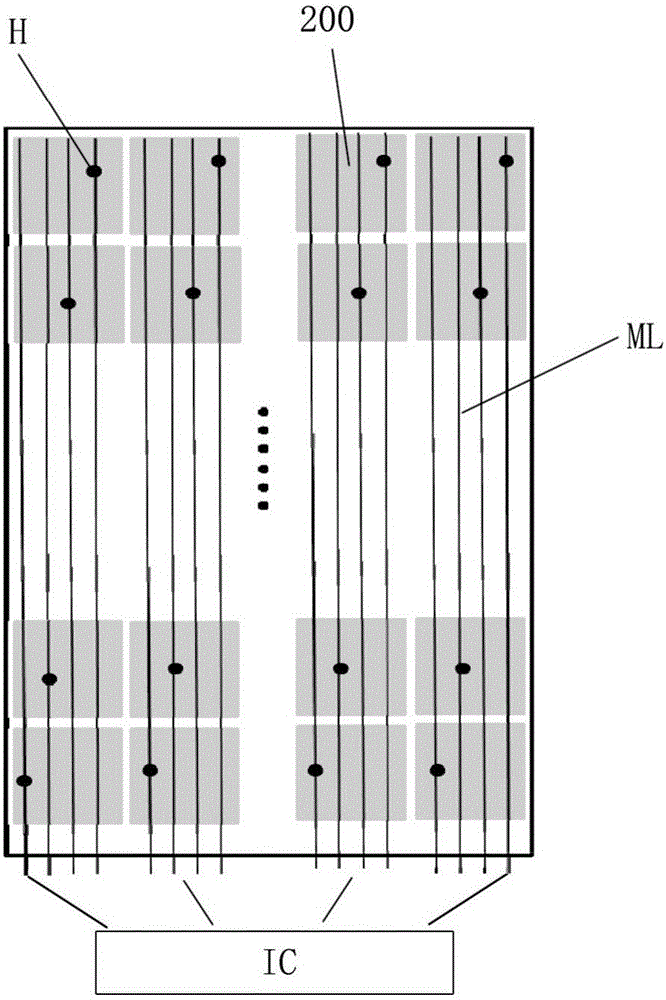

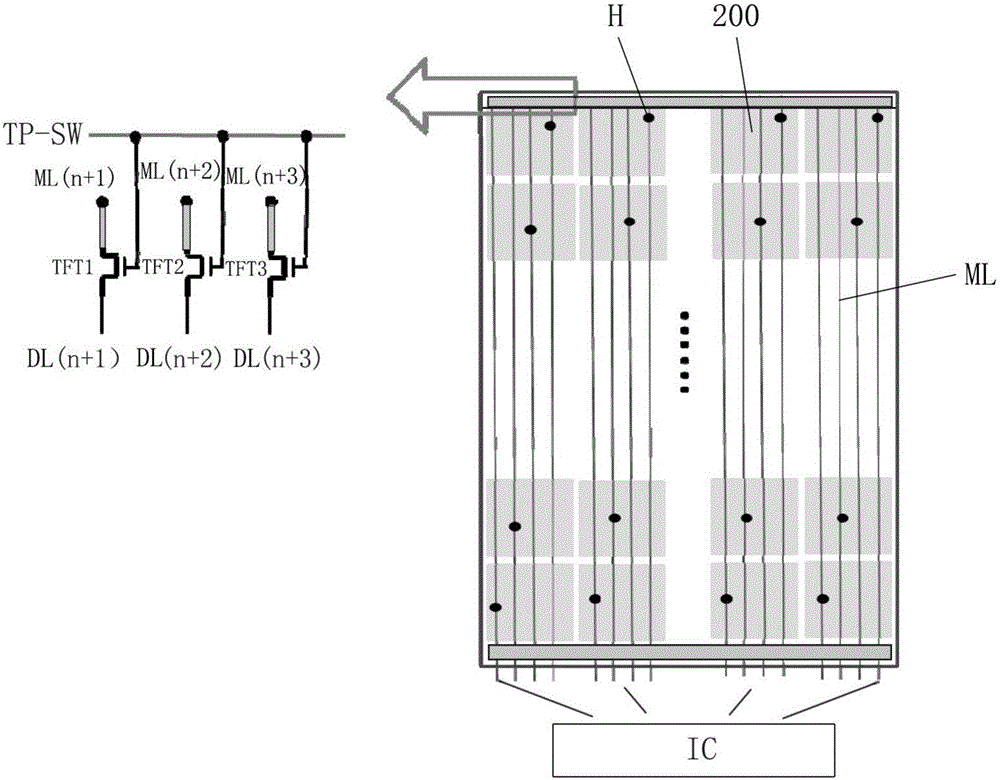

Embedded touch panel and array substrate thereof

ActiveCN106445251ALower the resistance valueReduce capacitanceNon-linear opticsInput/output processes for data processingCapacitanceElectrical resistance and conductance

The invention provides an array substrate of an embedded touch panel. The array substrate comprises touch electrodes, touch sensing chips and metal connecting lines, wherein the touch electrodes are arranged in an active region of the touch panel in an array manner; the touch sensing chips are arranged outside the active region of the touch panel; the metal connecting lines and the touch electrodes are arranged on different layers, and the metal connecting lines are connected to the touch electrodes through via holes; the metal connecting lines and data lines of the touch panel are stacked mutually in an insulating manner; the touch electrodes are connected to the touch sensing chips through the metal connecting lines; a switching circuit is arranged between the metal connecting lines and the data lines; and the switching circuit is used for conducting the metal connecting lines and the data lines at a touch phase, and disconnecting the metal connecting lines and the data lines at a display phase. The resistance and capacitance load of cabling in the active region of the touch panel is reduced, so that the working precision of the touch panel is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Organic light emitting diodes display

ActiveUS7079093B2Resistance time delayAvoid signal delayControl electrodesDischarge tube luminescnet screensResistance capacitanceTime delays

An organic light emitting diodes display device includes a number of data lines, scan lines, and cathode electrodes. These scan lines are perpendicular to the data lines to form a number of pixels, each of which possess a pixel area respectively. All the pixels areas form a pixel area array. These cathode electrodes are parallel to the scan lines or data lines and partially cover the pixel area array. Spaces between each two cathode electrodes are above the scan lines or data lines to avoid the parasitic capacitance between the cathode electrodes and scan lines or data lines. And thus the resistance capacitance time delay is prevented.

Owner:AU OPTRONICS CORP

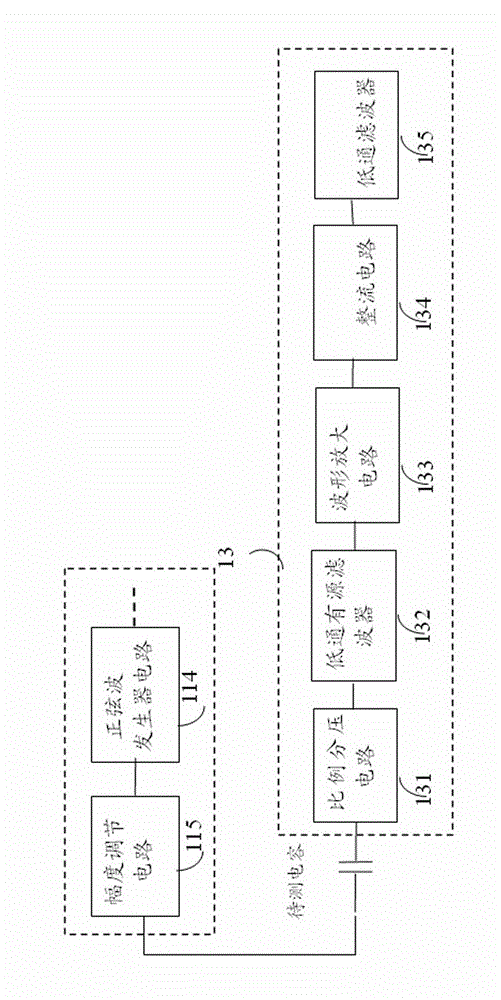

Resistor-capacitor measurement module applied to flying probe tests

InactiveCN103063922AMeet the process requirementsFast testResistance/reactance/impedenceElectrical testingCapacitanceElectrical resistance and conductance

The invention belongs to the technical field of flying probe tests, and particularly discloses a resistor-capacitor measurement module applied to the flying probe tests. The resistor-capacitor measurement module comprises a resistor test module, a capacitor test module and a control processing module. The resistor test module is used for testing a resistor value between same networks on a test substrate, and the capacitor test module is used for testing a capacitor value between different electric networks to the earth on the test substrate. The control processing module is respectively connected with the resistor test module and the capacitor test module, and is used for generating sine waves. The frequency and amplitude of the sine waves both are controllable, and the control processing module is used for controlling switching and electing between functions of the resistor test and the capacitor test, testing gear selection and probe assembly selection, receiving test data of the resistor test module and the capacitor test module for processing, and outputting test result data. The resistor-capacitor measurement module can be imbedded in a flying probe test device main system, realizes automatic probe selection test through software control, is quick in gear selection, accurate in test, and has the advantages of being high in test speed, and short in response time. The test accuracy can meet the technological requirements of the flying probe test.

Owner:THE 45TH RES INST OF CETC

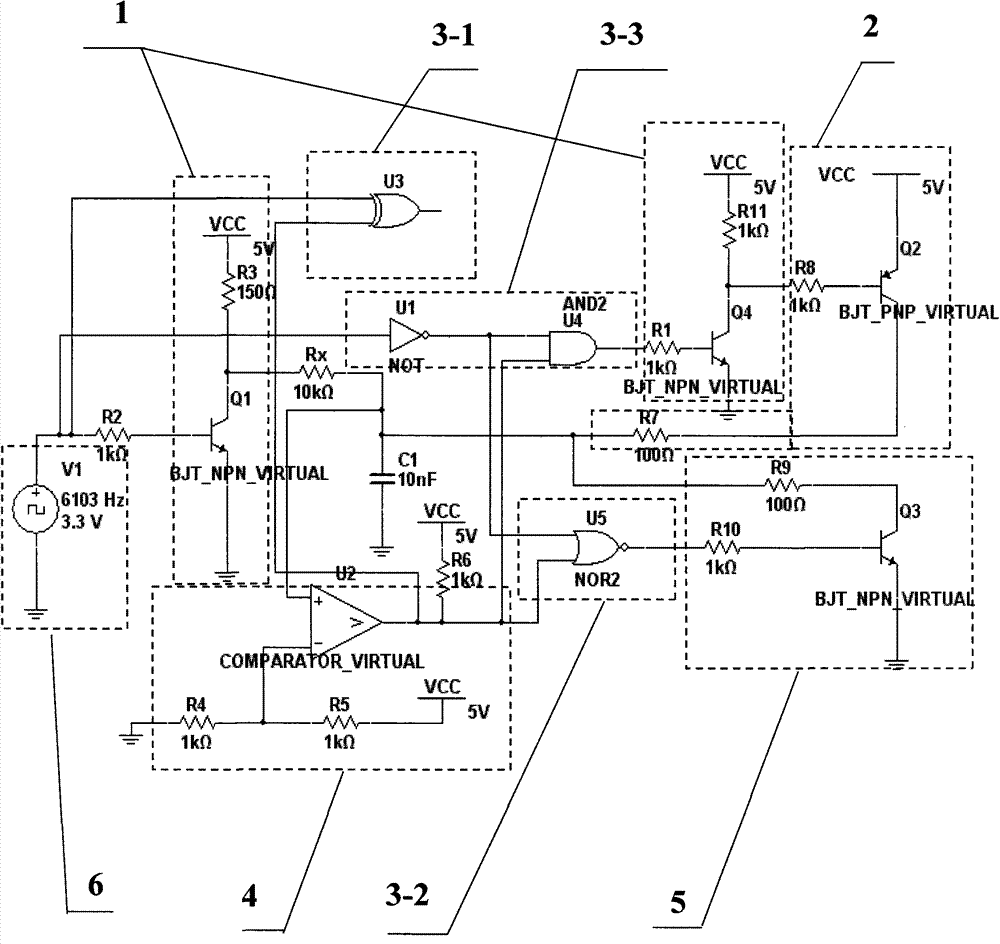

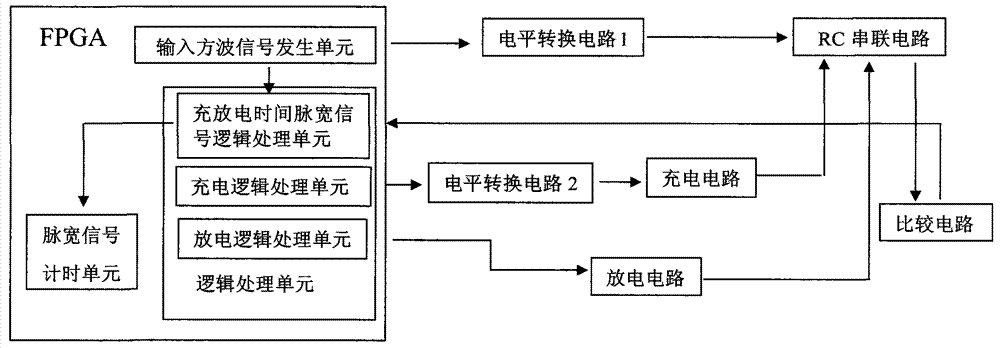

System and circuit for high-precision measuring of resistor and capacitor

InactiveCN103499743AIncrease ascent speedIncrease the speed of descentResistance/reactance/impedenceCapacitanceEngineering

The invention relates to a system for high-precision measuring of a resistor and a capacitor. The system comprises an input square wave signal generating unit, a level conversion circuit unit, a secondary charging circuit unit, a secondary discharging circuit unit, a logic processing unit, a comparison circuit unit, and a pulse width signal timing unit. The system has the advantages that the RC (resistor and capacitor) charging and discharging time is measured, the purpose of measuring the resistors and the capacitors is realized, and the secondary charging circuit, the secondary discharging unit and the logic processing are additionally arranged on the basis of the RC charging circuit and the RC discharging circuit, so the ascending and descending speed of the output signal is improved, and the single measuring speed is improved; the clock frequency of pulse counting is high, the ns-level measurement of time resolution is realized, the clock frequency is doubled to 200M by an FPGA (field programmable gate array), and the time resolution is 5ns; when the resistor is measured, the larger capacitor is selected to improve the ratio coefficient of pulse counting value to the resistor R is improved, or when the capacitor is measured, the larger resistor is selected to improve the ratio coefficient of pulse counting value to the capacitor C, so the measuring precision and the resolution are improved.

Owner:HUBEI UNIV OF TECH

Color film substrate for liquid crystal displays

InactiveCN103901663AEliminate the effects ofDoes not increase the loadNon-linear opticsCapacitanceVertical alignment

A color film substrate for liquid crystal displays is characterized in that the dark line part of the edge of a pixel area is provided with a laminated structure which comprises at least two structure layers, the width of the part, close to a glass substrate, of the laminated structure is larger than the width of the part, far away from the glass structure, of the laminated structure, and each structure layer of the laminated structure and the adjacent layer are arranged in a segmental differential manner. Liquid crystal molecules on the surface of the laminated structure can be controlled to arrange in a slope form along segmental differential lamination, so that the influence of ITO fringe electric field upon the liquid crystal molecules is eliminated and dark lines are eliminated or decreased. Meanwhile, the laminated structure enables the black lines to move out to be eliminated, load of resistance and capacitance of an array panel is not increased much, aperture ratio is not lowered, and light transmitting efficiency of UV vertical alignment displays is increased.

Owner:NANJING CEC PANDA LCD TECH

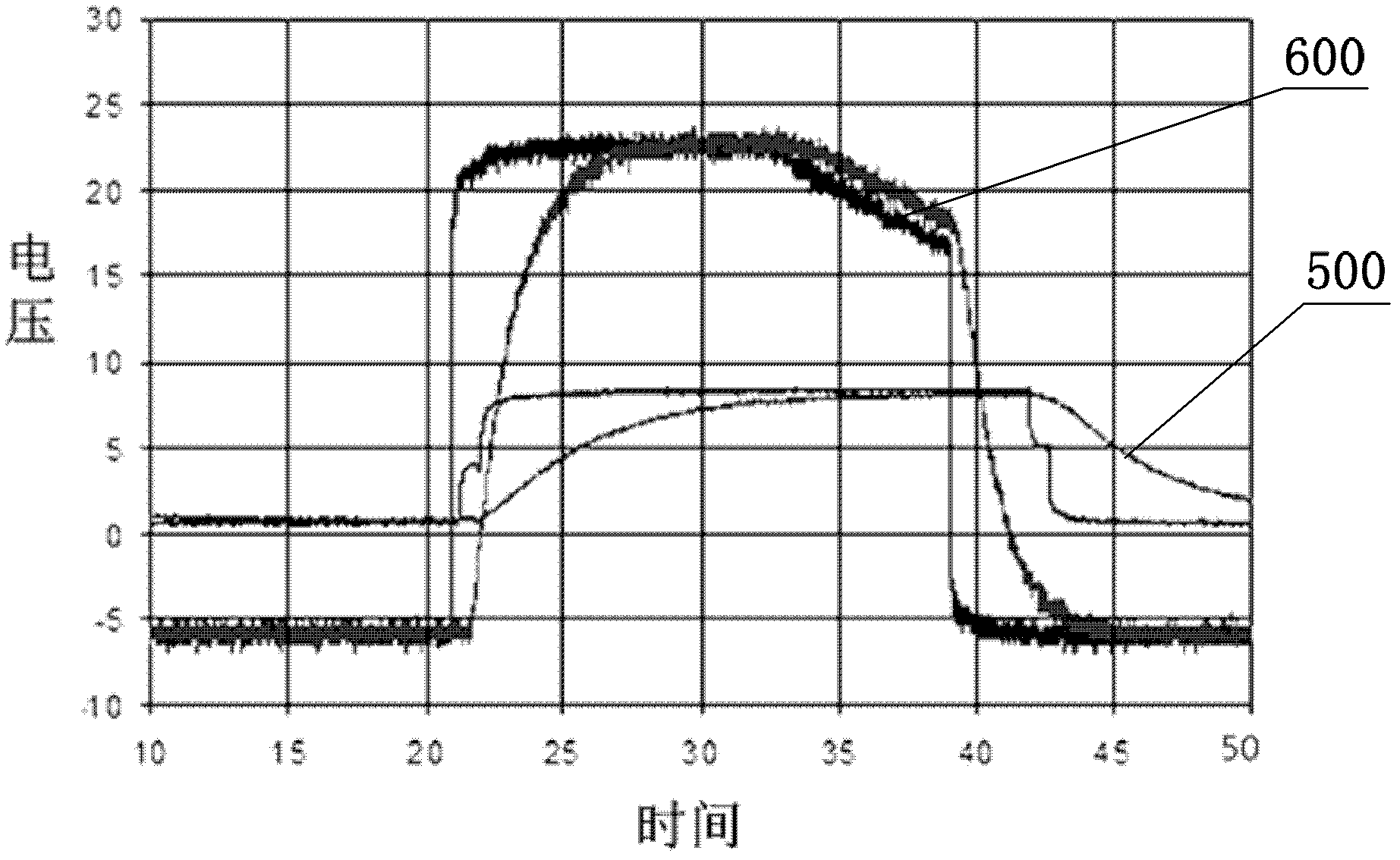

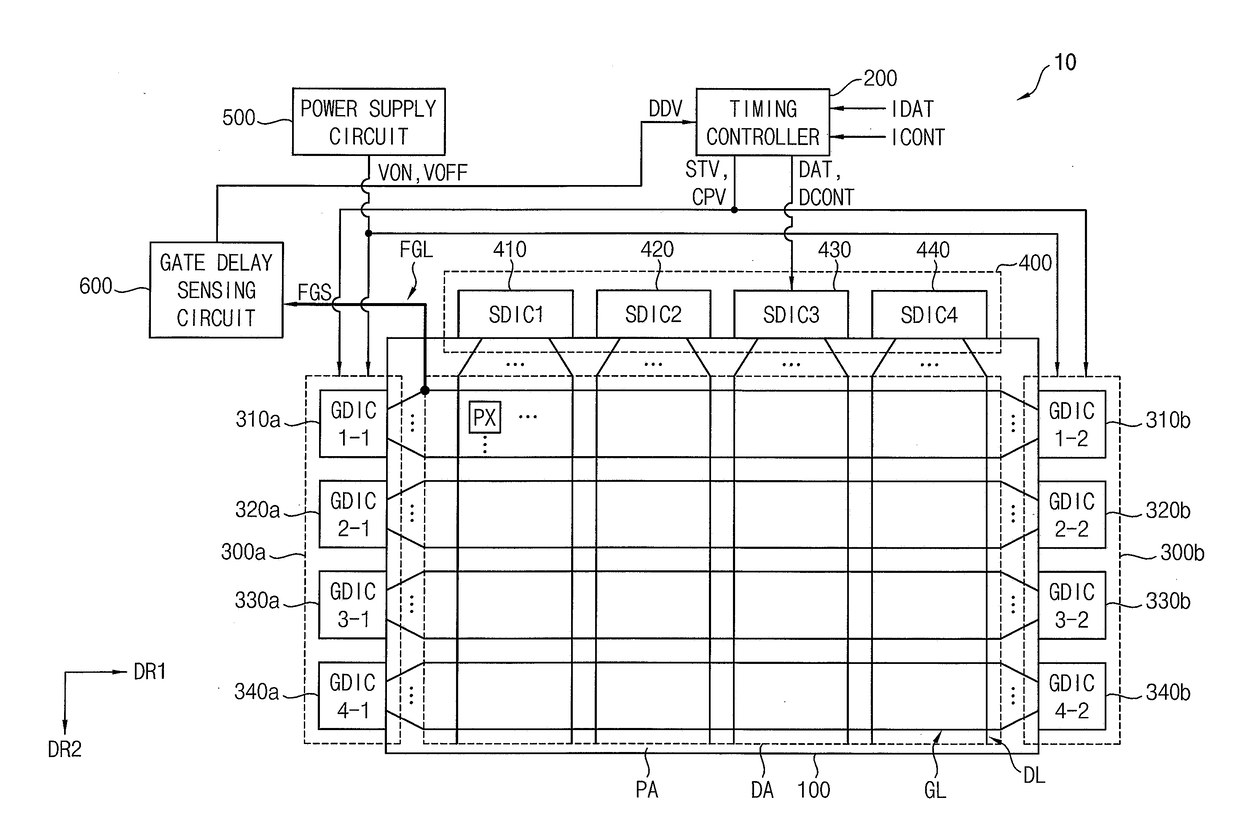

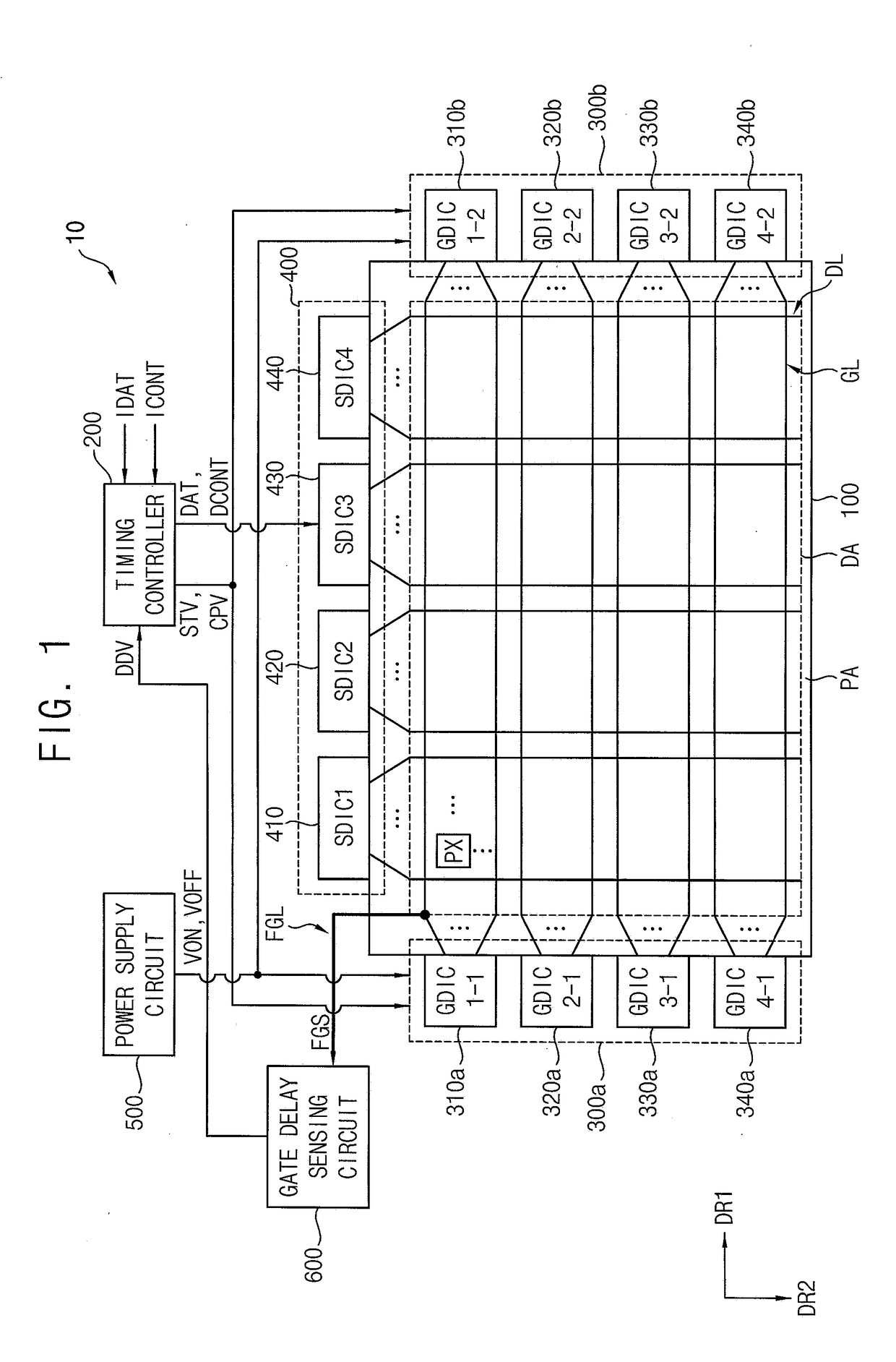

Display apparatus

ActiveUS20180315369A1Efficient detectionRate of pixel be improvedStatic indicating devicesDigital down converterEngineering

A display apparatus includes a display panel including a plurality of first gate lines, a first gate driver connected to first ends of the plurality of first gate lines, a second gate driver connected to second ends of the plurality of first gate lines, a feedback line connected adjacent to the first end of one of the plurality of first gate lines, and a gate delay sensing circuit connected to the feedback line. The gate delay sensing circuit includes a time-to-digital converter and a digital comparator. The time-to-digital converter converts an activation time of a feedback gate signal into a digital activation value. The feedback gate signal is retrieved from the feedback line. The digital comparator generates a digital delay value based on the digital activation value. The digital delay value indicates resistive-capacitive (“RC”) delay of the one of the plurality of first gate lines connected to the feedback line.

Owner:SAMSUNG DISPLAY CO LTD

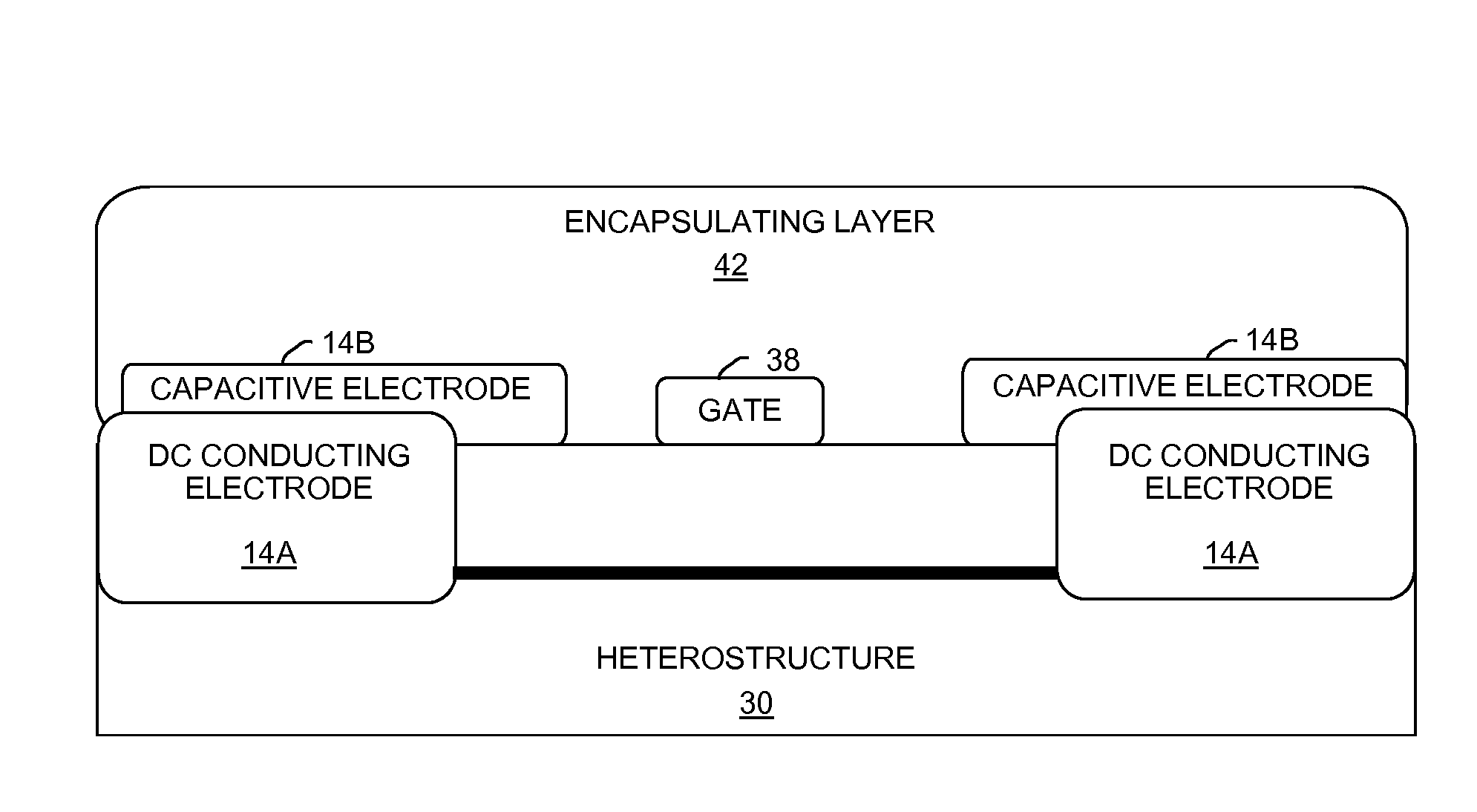

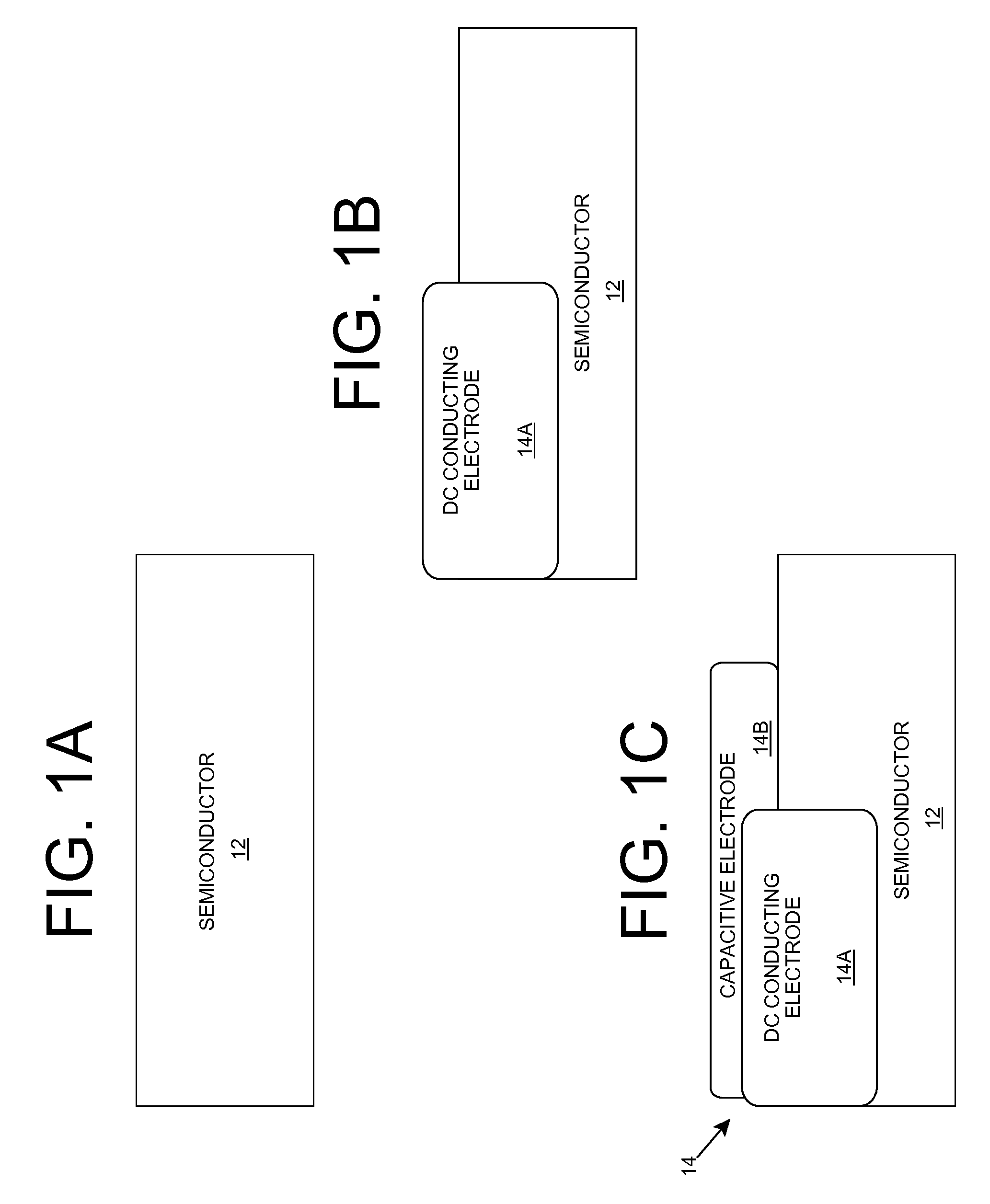

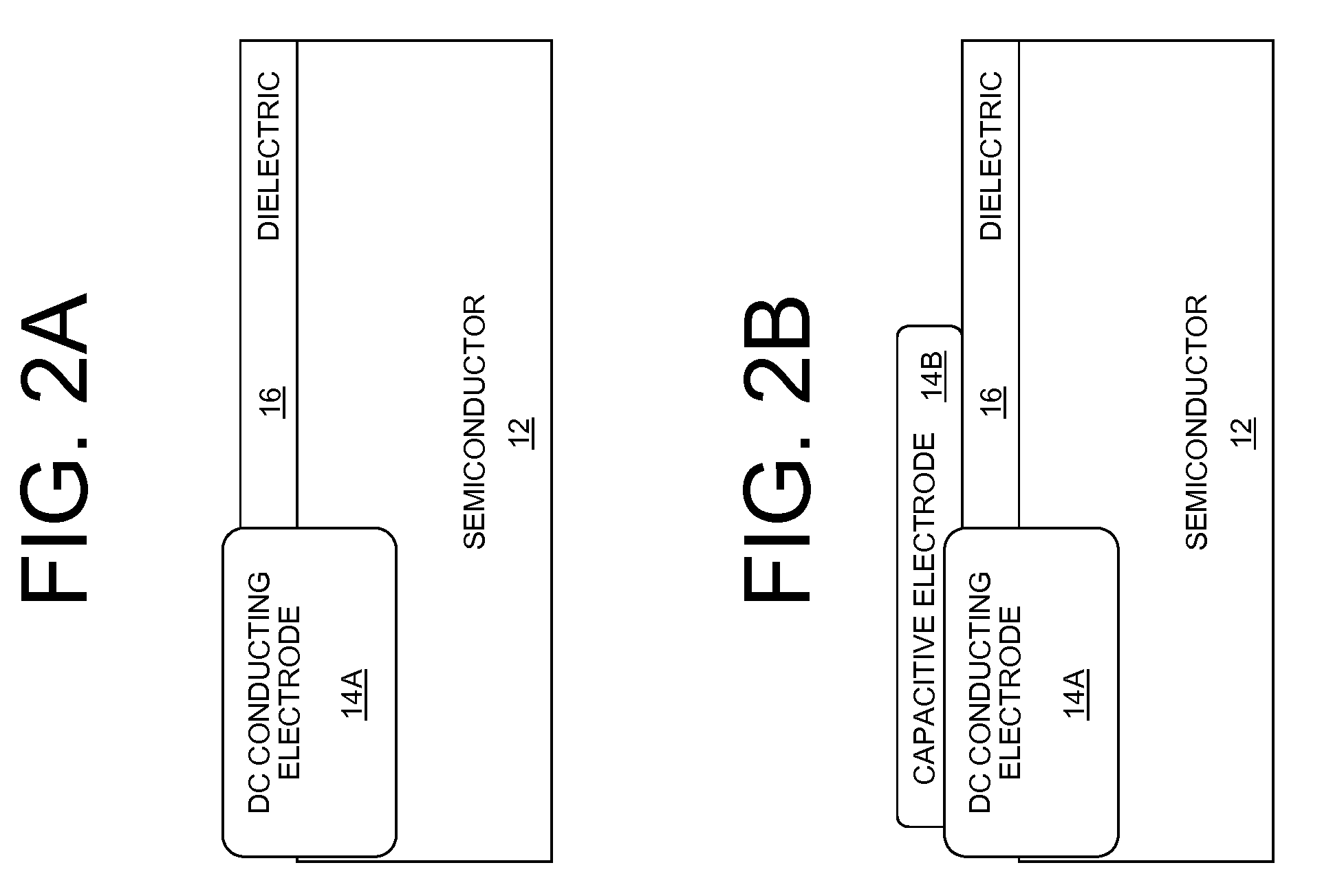

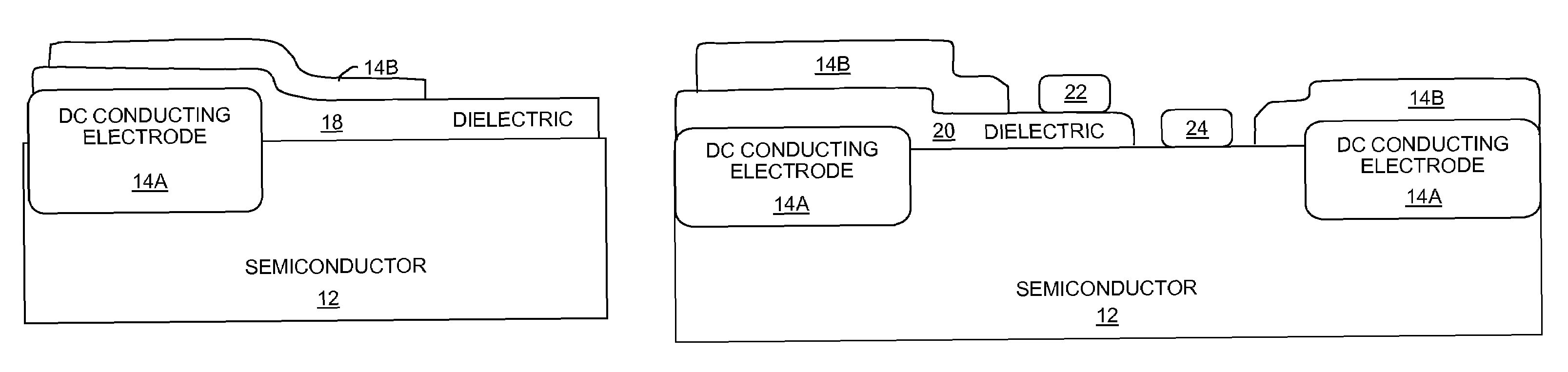

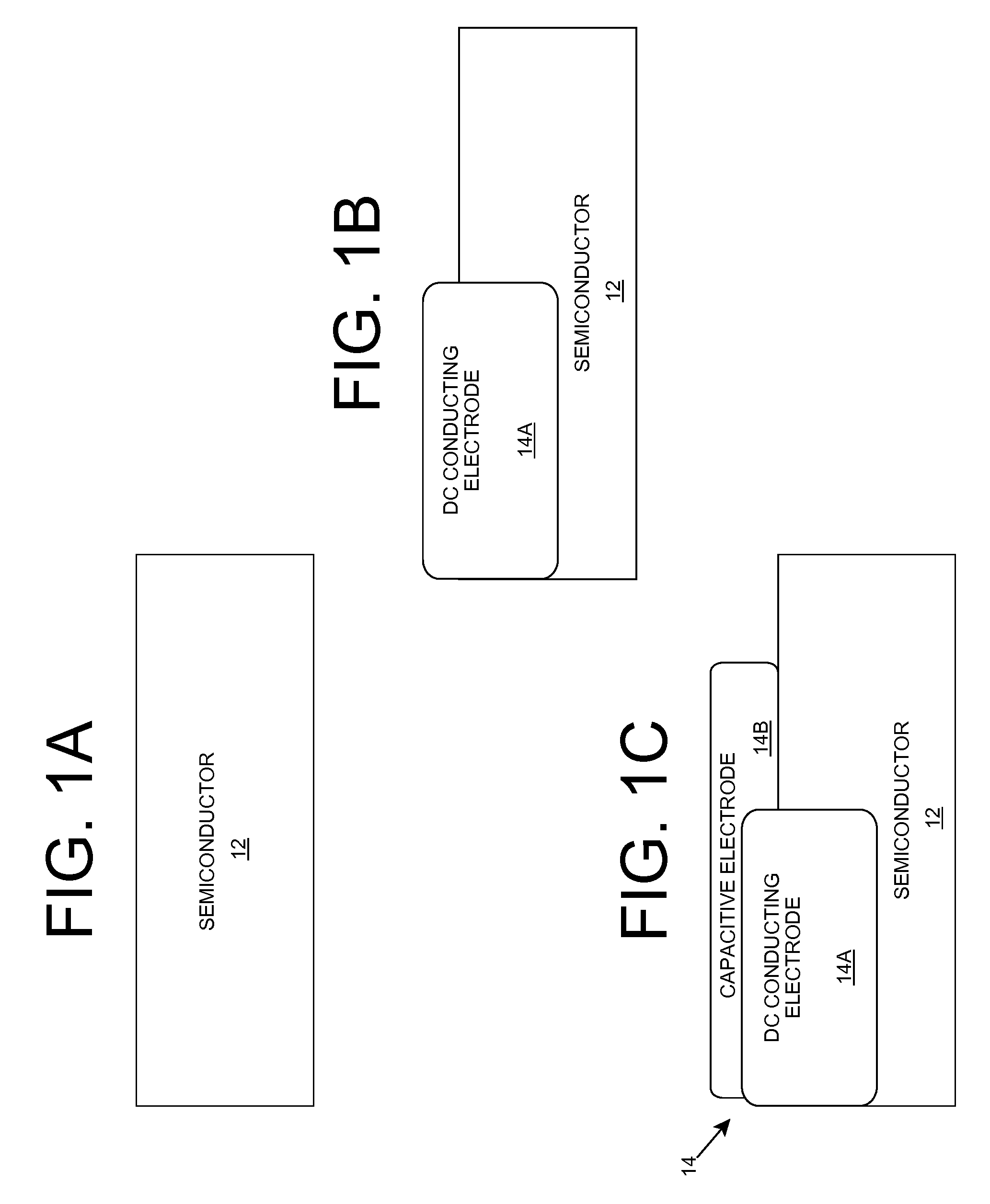

Fabrication of semiconductor device having composite contact

ActiveUS20080206974A1Contact impedance is reducedLower impedanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceContact impedance

A method of fabricating a semiconductor device with a composite contact is provided. The fabrication includes forming the composite contact to a semiconductor layer in a semiconductor structure. The composite contact is formed by forming a DC conducting electrode attached to a semiconductor layer in a semiconductor structure and forming a capacitive electrode that is partially over the DC conducting electrode and extends beyond the DC conducting electrode. The composite contact provides a combined resistive-capacitive coupling to the semiconductor layer. As a result, a contact impedance is reduced when the corresponding semiconductor device is operated at high frequencies.

Owner:SENSOR ELECTRONICS TECH

Fabrication of semiconductor device having composite contact

ActiveUS7674666B2Lower impedanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceContact impedance

A method of fabricating a semiconductor device with a composite contact is provided. The fabrication includes forming the composite contact to a semiconductor layer in a semiconductor structure. The composite contact is formed by forming a DC conducting electrode attached to a semiconductor layer in a semiconductor structure and forming a capacitive electrode that is partially over the DC conducting electrode and extends beyond the DC conducting electrode. The composite contact provides a combined resistive-capacitive coupling to the semiconductor layer. As a result, a contact impedance is reduced when the corresponding semiconductor device is operated at high frequencies.

Owner:SENSOR ELECTRONICS TECH

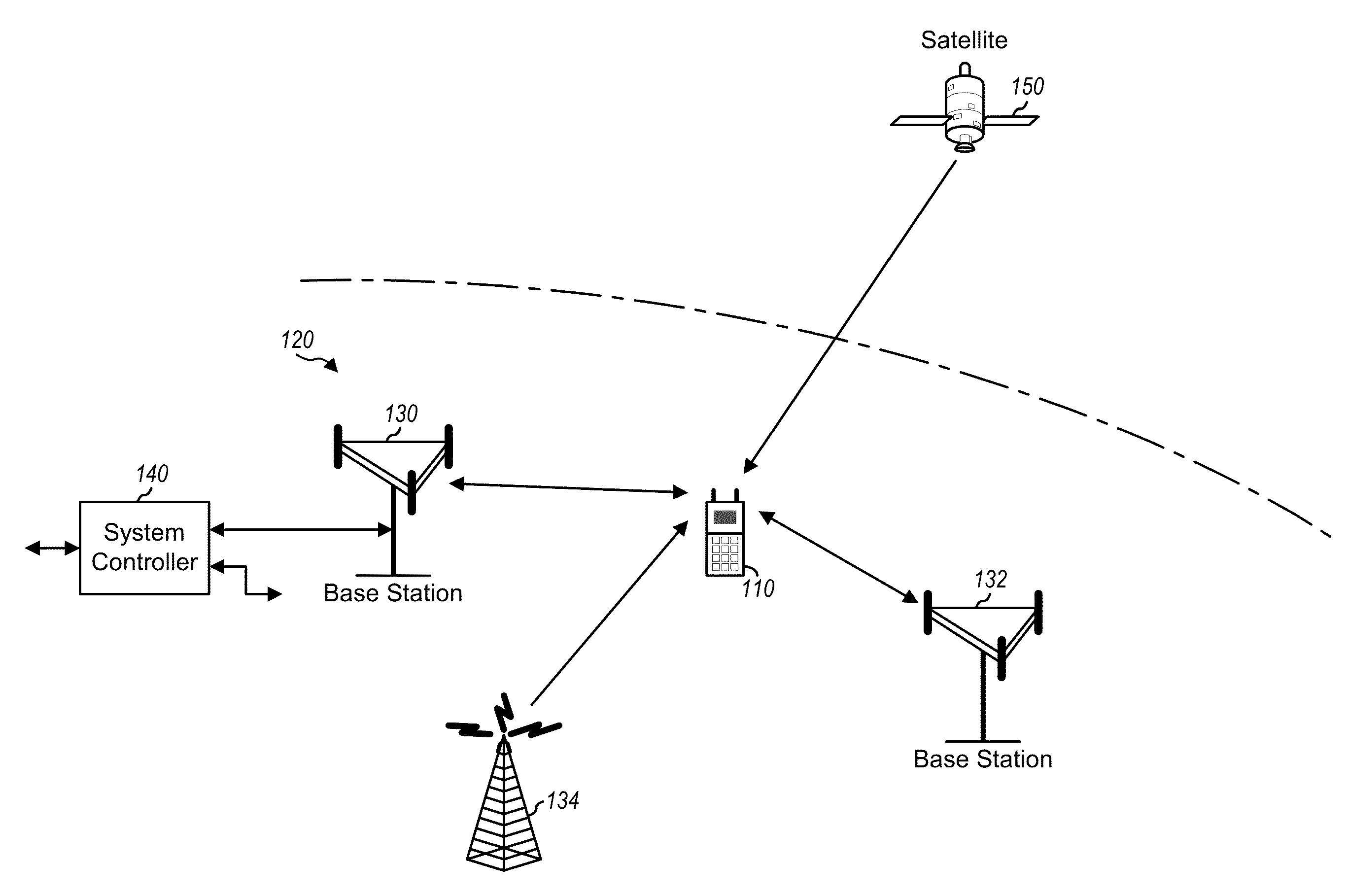

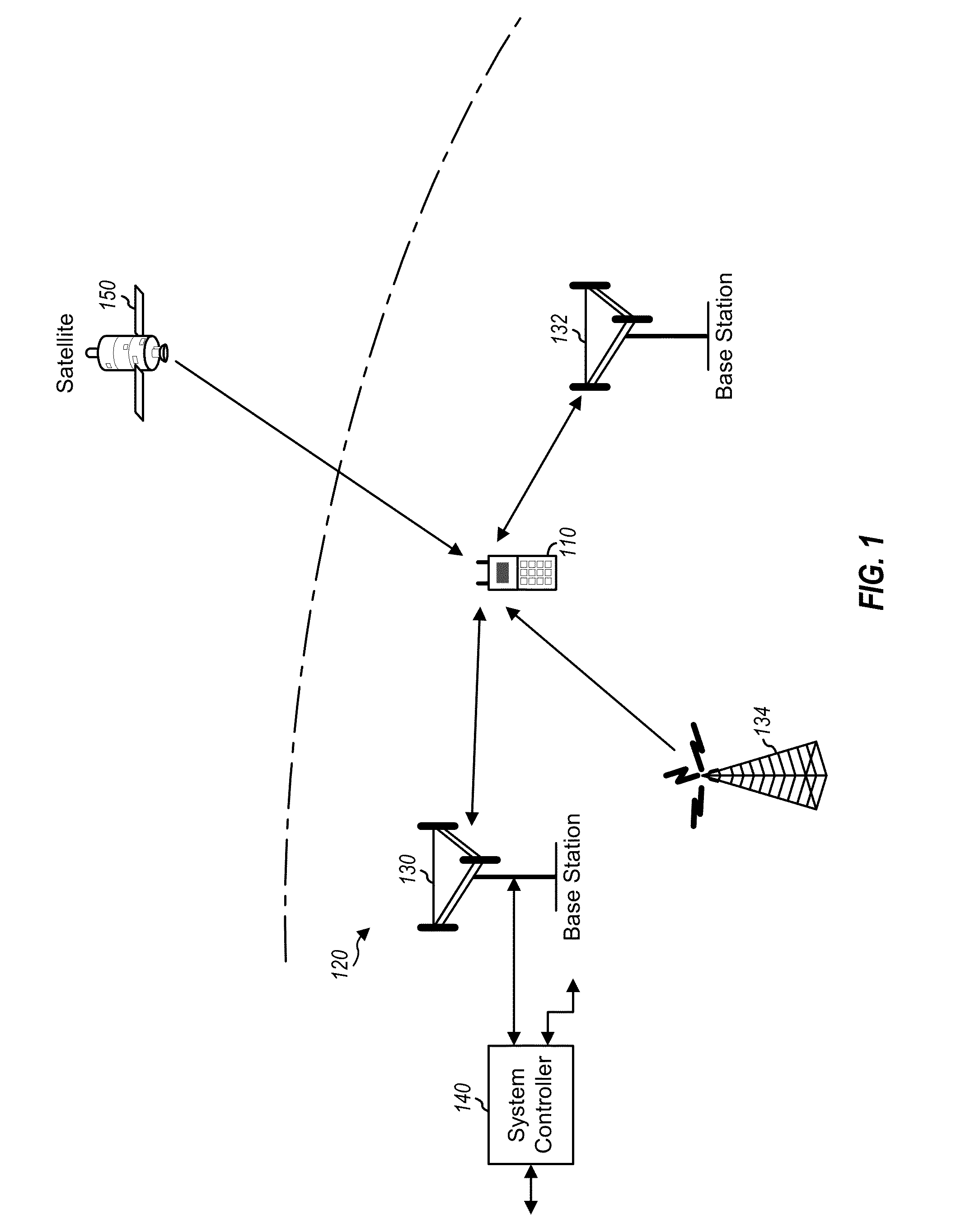

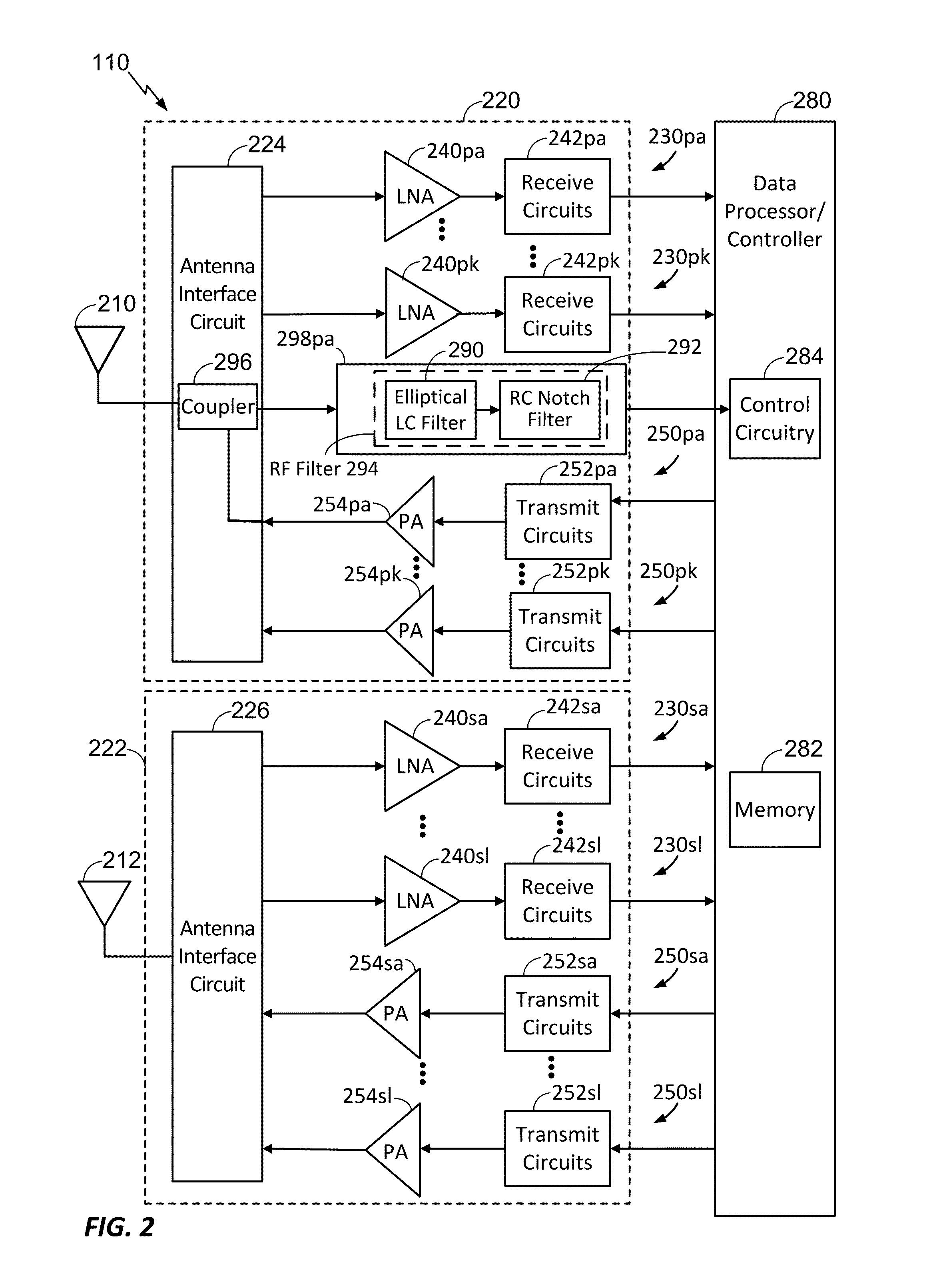

Feedback receive path with RF filter

An apparatus includes an elliptical inductance-capacitance (LC) filter and a resistive-capacitive (RC) notch filter serially coupled to the elliptical LC filter. The elliptical LC filter and the RC notch filter are configured to filter a radio-frequency (RF) signal received by a feedback receive path.

Owner:QUALCOMM INC

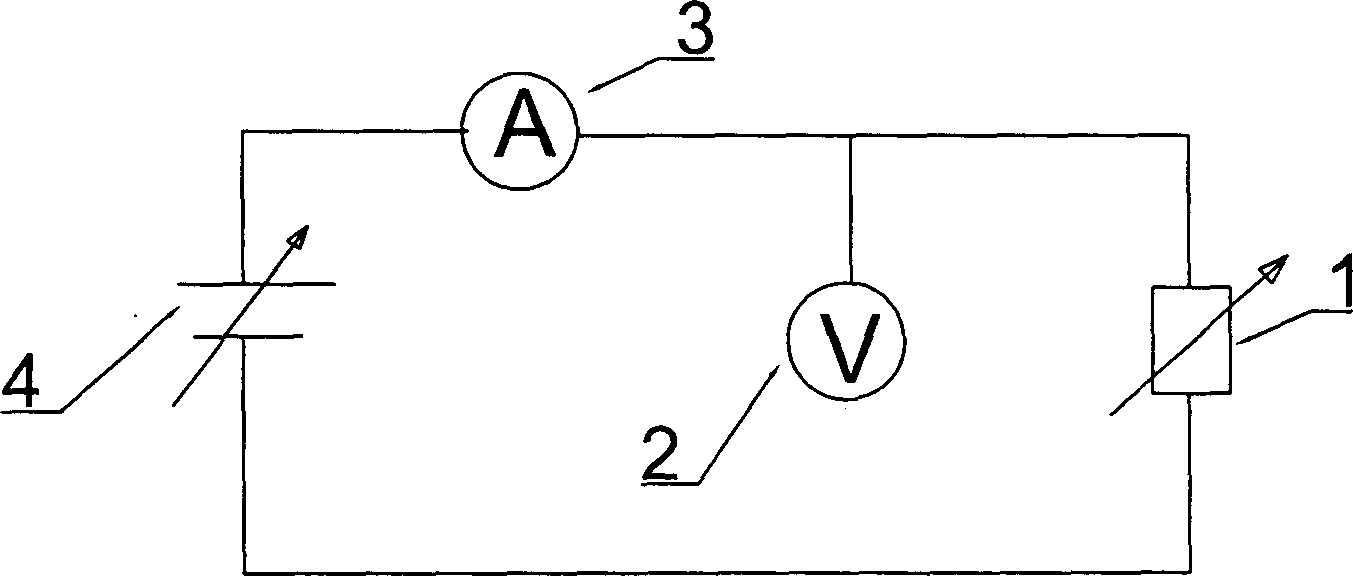

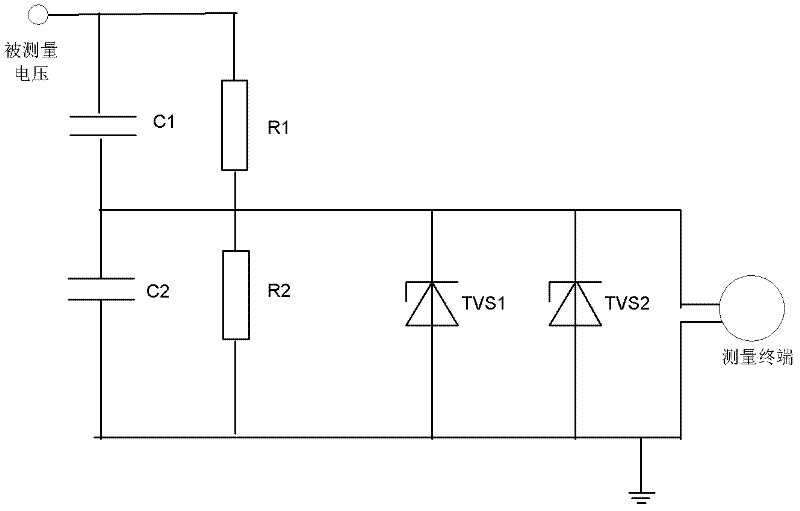

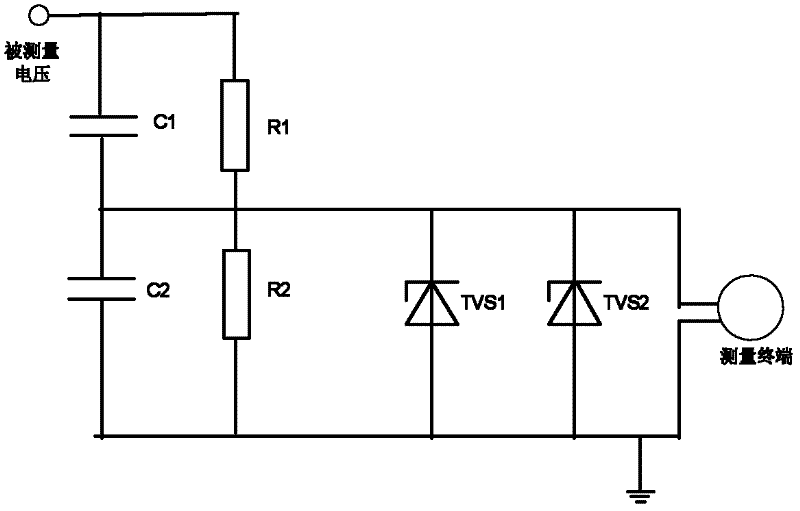

Device for measuring arc voltage of direct current circuit breaker

InactiveCN102435814AImprove reliabilitySimple structureOverload protection arrangementsCurrent/voltage measurementDc circuit breakerEngineering

The invention provides a device for measuring the arc voltage of a direct current circuit breaker. The device comprises a to-be-measured arc voltage input terminal, a measurement terminal, a resistive-capacitive voltage divider module in serial connection with the to-be-measured arc voltage input terminal, and an over-voltage protection module in serial connection with the measurement terminal, wherein the to-be-measured arc voltage input terminal, the resistive-capacitive voltage divider module, the over-voltage protection module and the measurement terminal are connected successively in series. The device for measuring the arc voltage of the direct current circuit breaker disclosed by the invention can accurately measure the arc voltage between fractures of the direct current circuit breaker, and has the characteristic of simple structure and is easy to realize.

Owner:CHINA ELECTRIC POWER RES INST +1

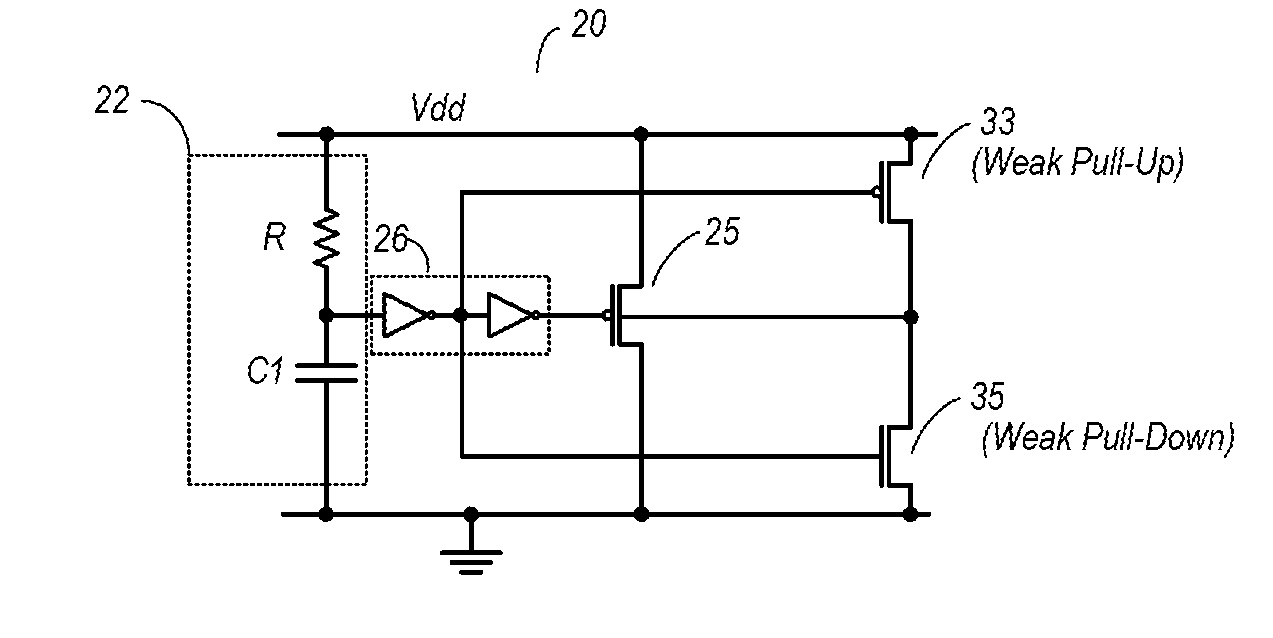

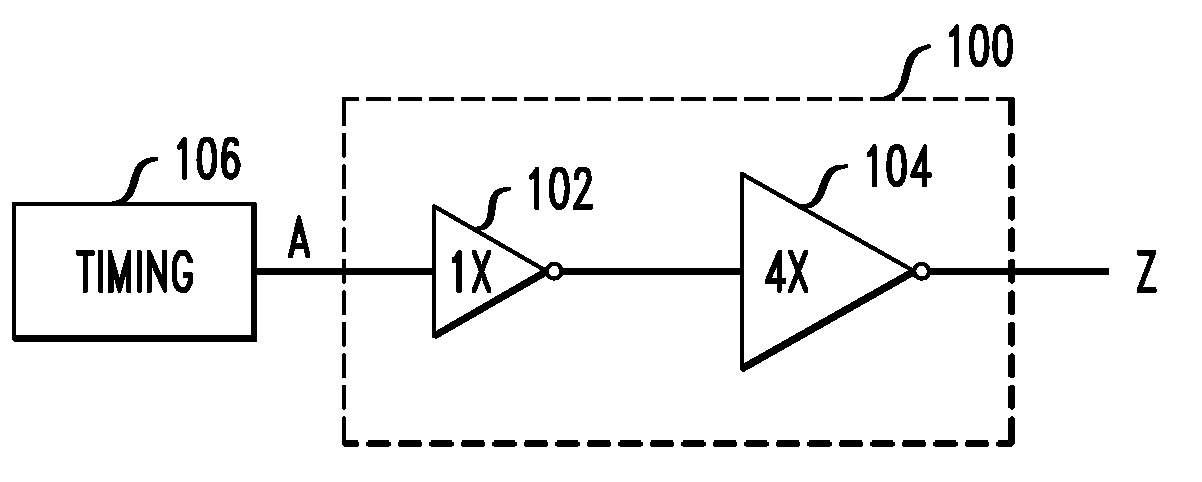

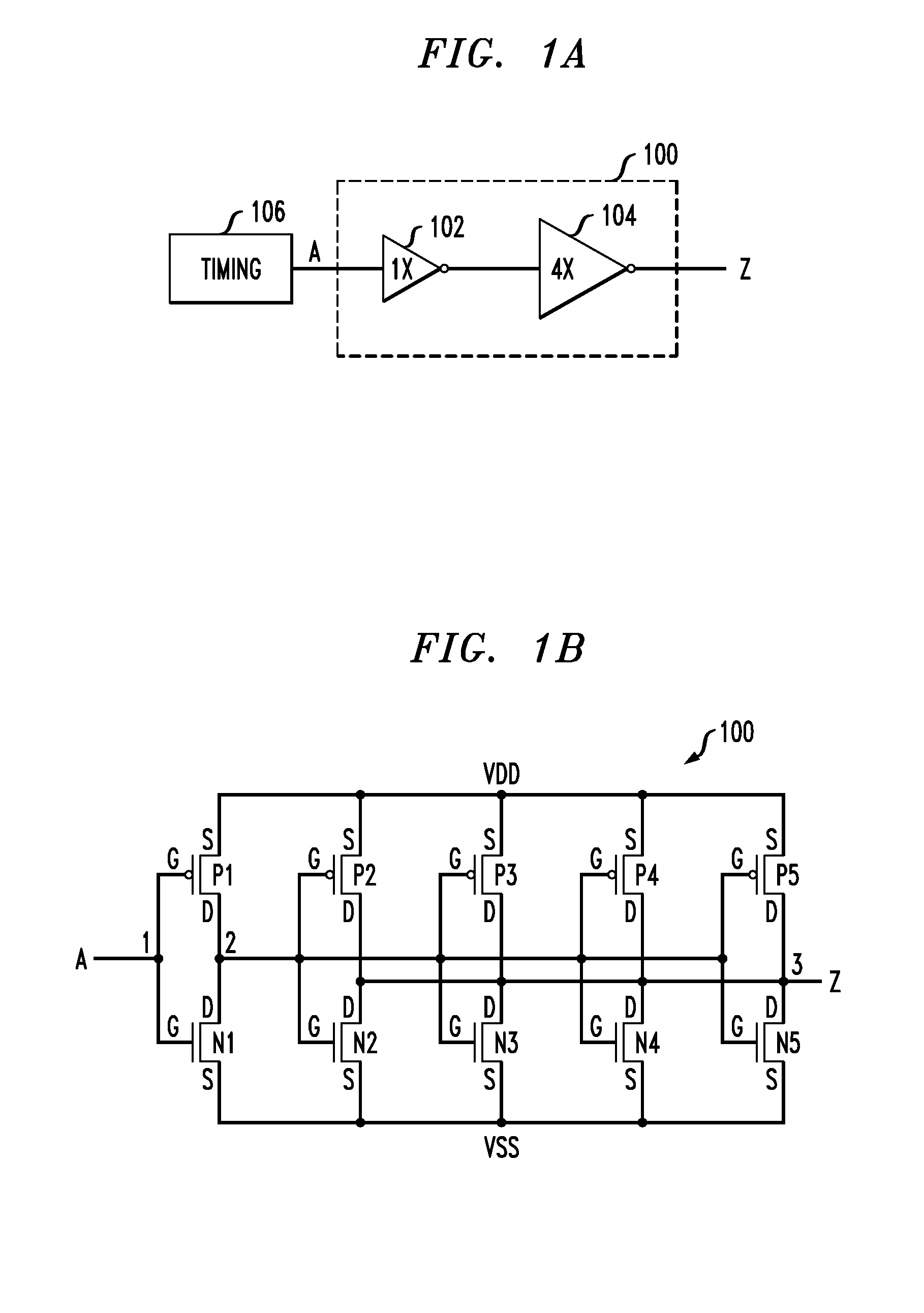

Fine-grained Clock Skew Tuning in an Integrated Circuit

An apparatus for controlling clock skew in an integrated circuit (IC) includes timing circuitry operative to generate a clock signal for distribution in the IC and at least one buffer circuit operative to receive the clock signal, or a signal indicative of the clock signal, and to generate a delayed version of the clock signal as an output thereof. The buffer circuit includes at least first and second inverter stages and a resistive-capacitive (RC) loading structure. An output of the first inverter stage is connected to an input of the second inverter stage via the RC loading structure. The buffer circuit has a delay associated therewith that is selectively varied as a function of one or more adjustable characteristics of the RC loading structure. Clock skew in the IC is controlled as a function of the delay of the buffer circuit.

Owner:AVAGO TECH INT SALES PTE LTD

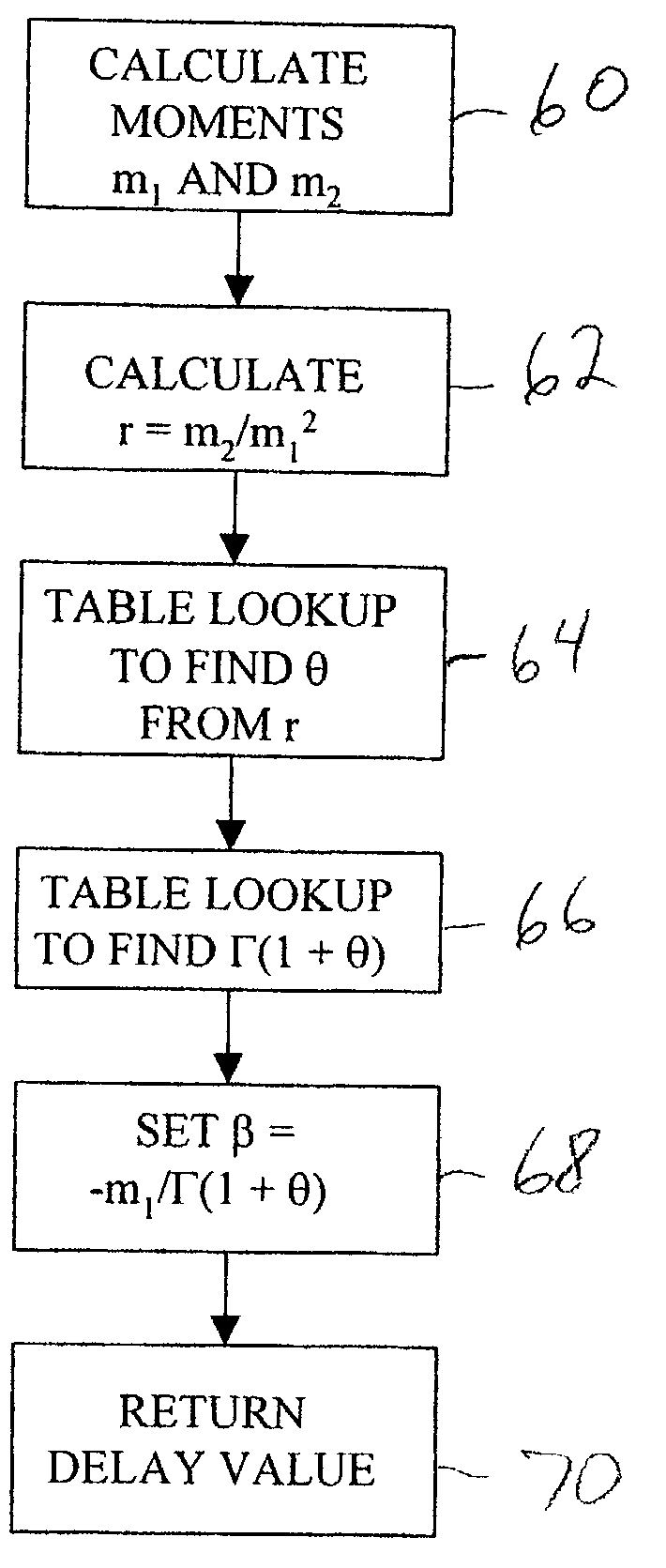

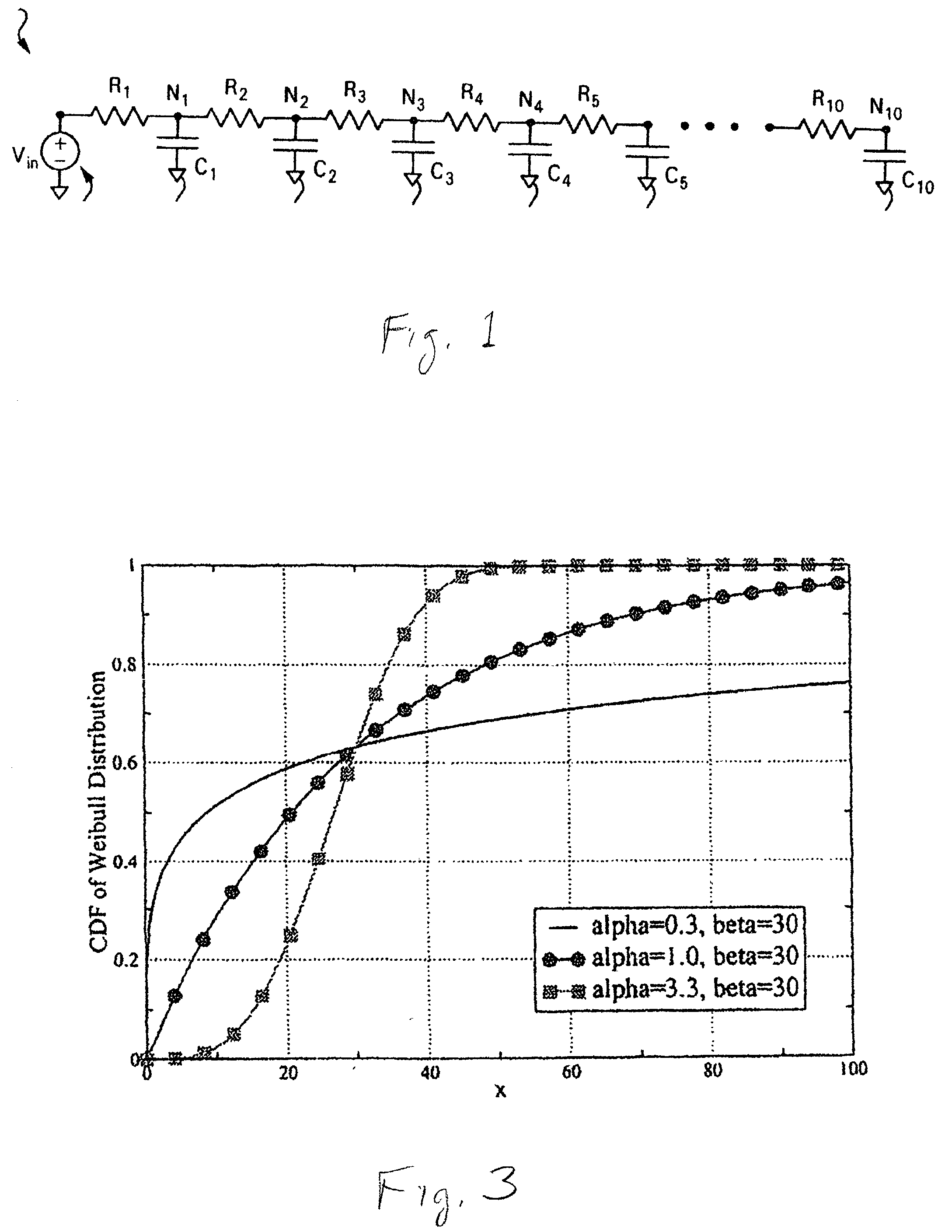

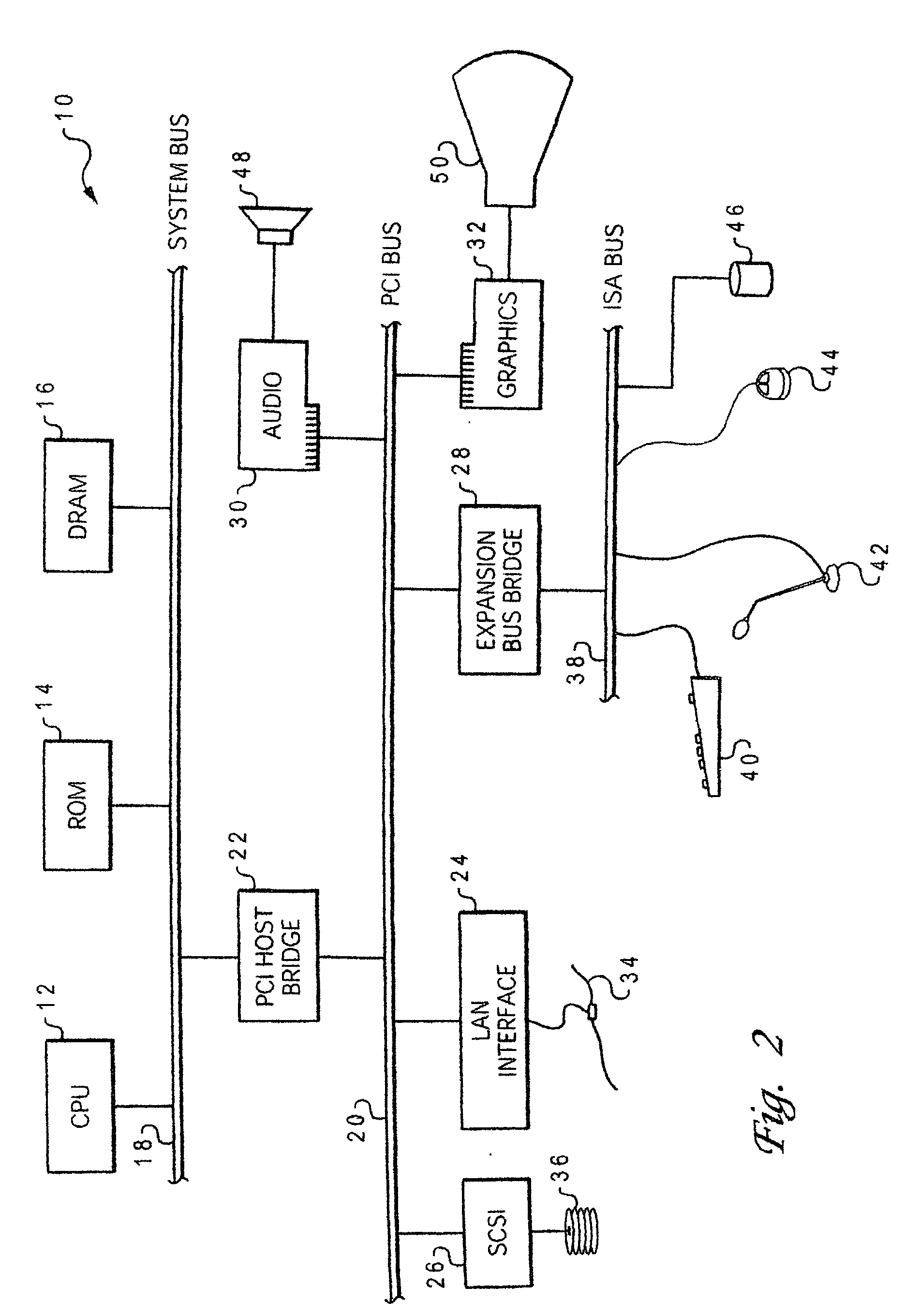

Robust delay metric for RC circuits

InactiveUS20040064798A1Easy to useComputer aided designSoftware simulation/interpretation/emulationElectrical resistance and conductanceImpulse response

Physical design optimizations for integrated circuits, such as placement, buffer insertion, floorplanning and routing, require fast and accurate analysis of resistive-capacitive (RC) delays in the network. A method is disclosed for estimating delays at nodes in an RC circuit by calculating a first and second impulse response moments of the RC circuit, and matching the impulse response moments to a Weibull distribution. Based on the match, a signal delay value is computed. The invention may thus be used to determine whether the RC circuit meets a desired optimization condition, based on the signal delay value. In the exemplary implementation, the signal delay value at a delay point is calculated by finding a percentile of the Weibull distribution corresponding to the delay point. This implementation is accurate and very efficient as it uses only two very small look-up tables.

Owner:GLOBALFOUNDRIES INC

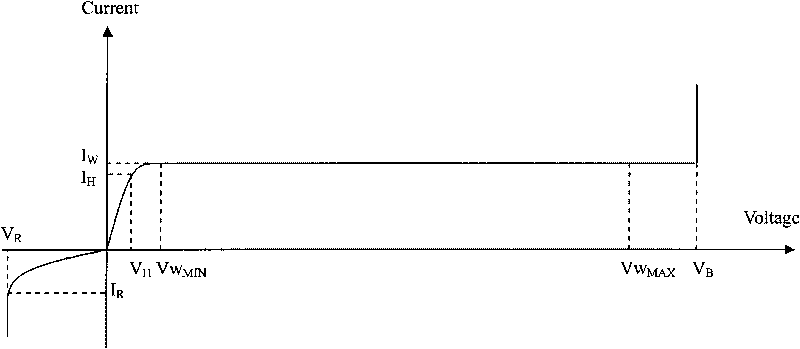

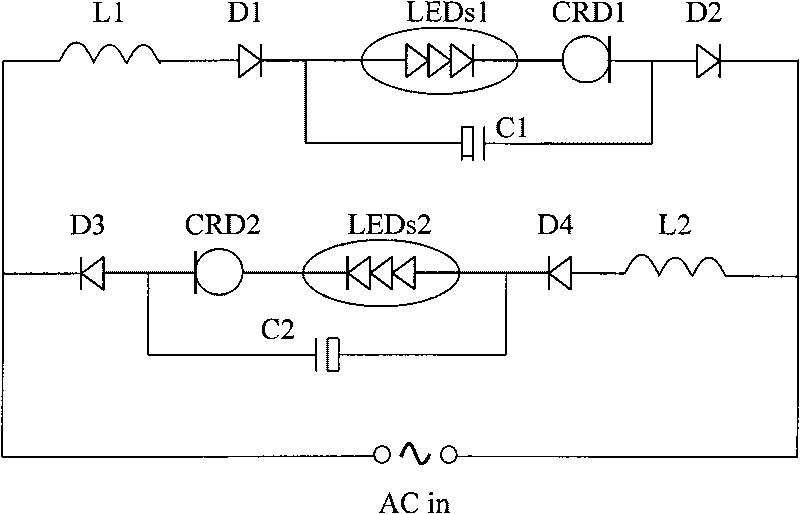

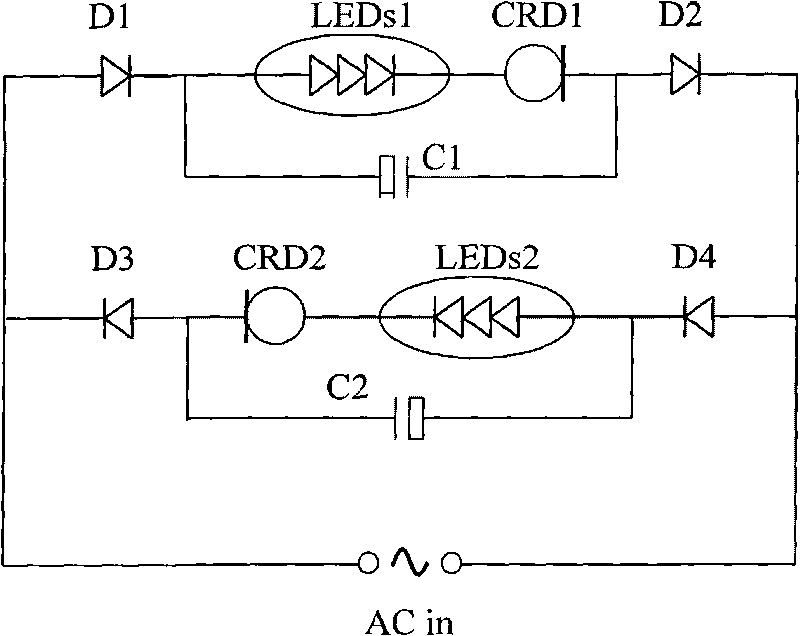

Municipal power constant current LED lamp circuit

InactiveCN101754514AReasonable topology designSimple preparation processPoint-like light sourceElectric circuit arrangementsPower factorEffect light

The invention discloses an LED lighting lamp circuit directly used for the power supply of a municipal electric network. A low-cost resistive-capacitive and voltage-reducing driving circuit has simple structure and low cost, but has poor performance and low efficiency, and can damage an LED light source device to a certain degree; a series voltage regulating circuit has large volume, heavy weight, more heating, low efficiency, high cost and no energy saving; a PWM voltage regulating or constant current switch has relatively good power supply performance and higher efficiency, but has relatively higher cost, low MTBF index and low reliability, and can also introduce EMI electromagnetic interference. The invention has the advantages of good constant current effect, low cost, high efficiency, long life and no EMI. The key to realize the advantages is that two ways of series LED light source circuits reversely connected in parallel are adopted, and each way is connected with a CRD device to realize constant current; and L and C are adopted to realize PFC and suppress voltage fluctuation, and the power factor and lighting effect are improved under the premise of keeping the structure of the circuit simple and the cost low.

Owner:深圳市明连兴光电科技有限公司

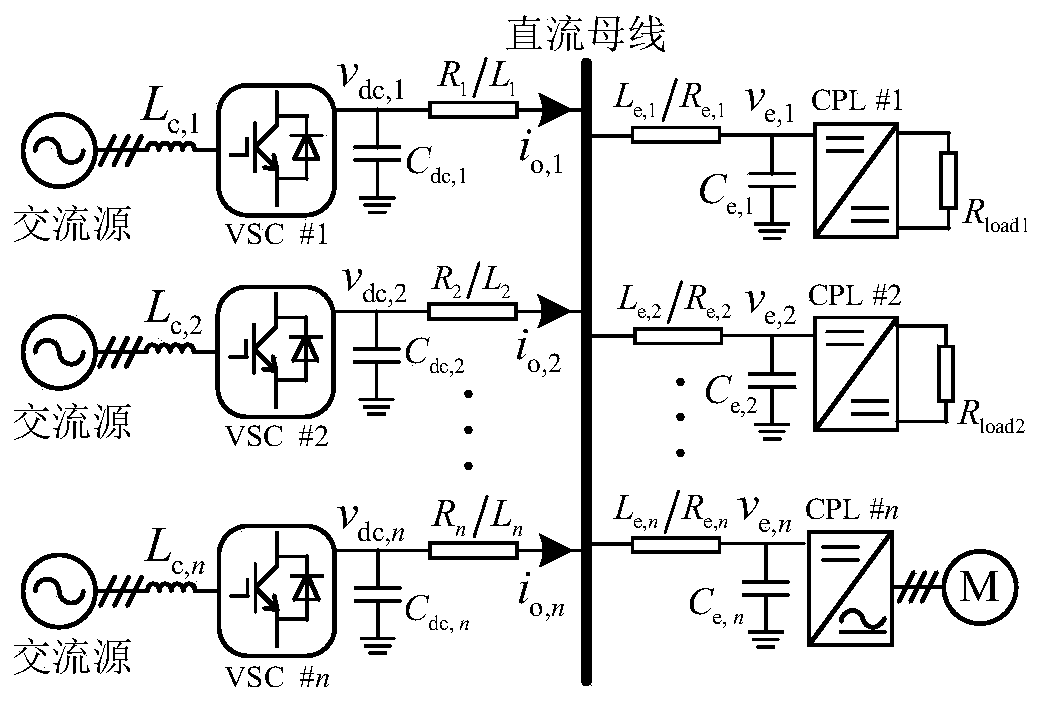

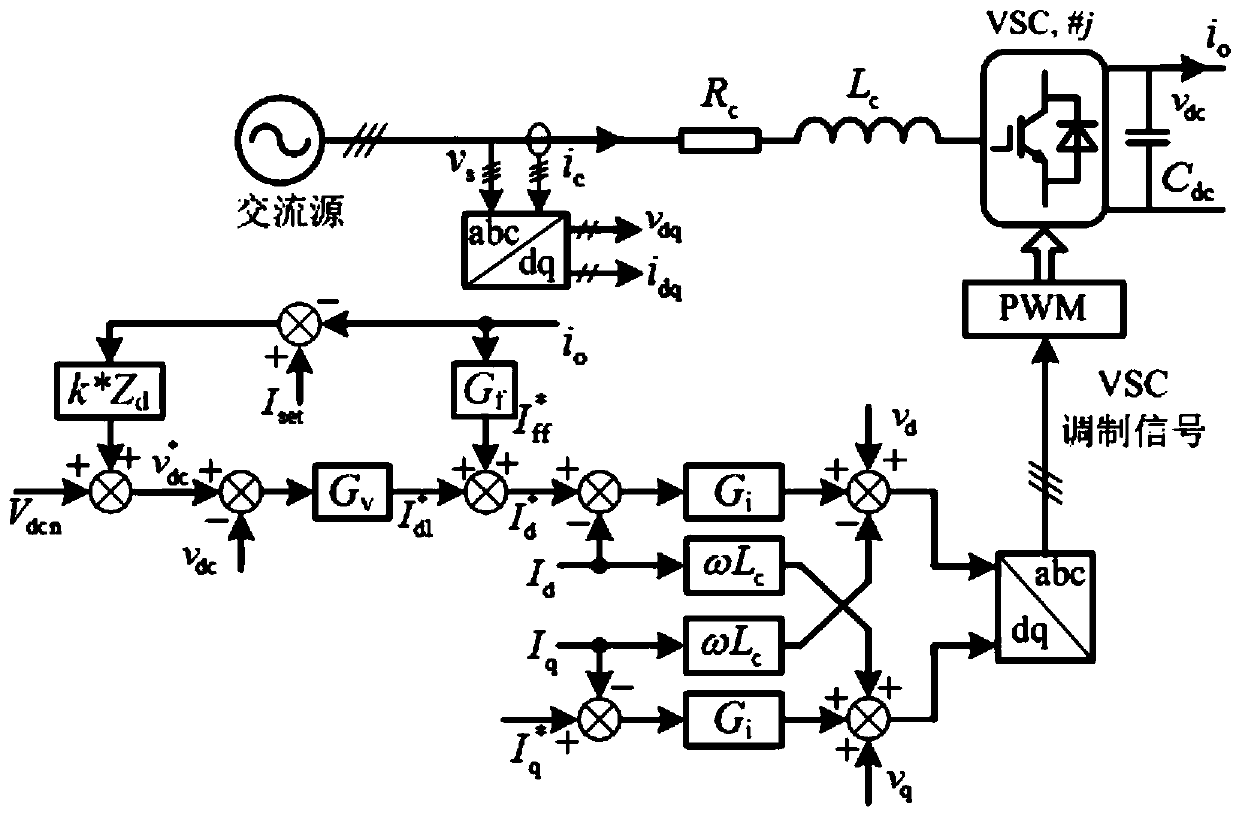

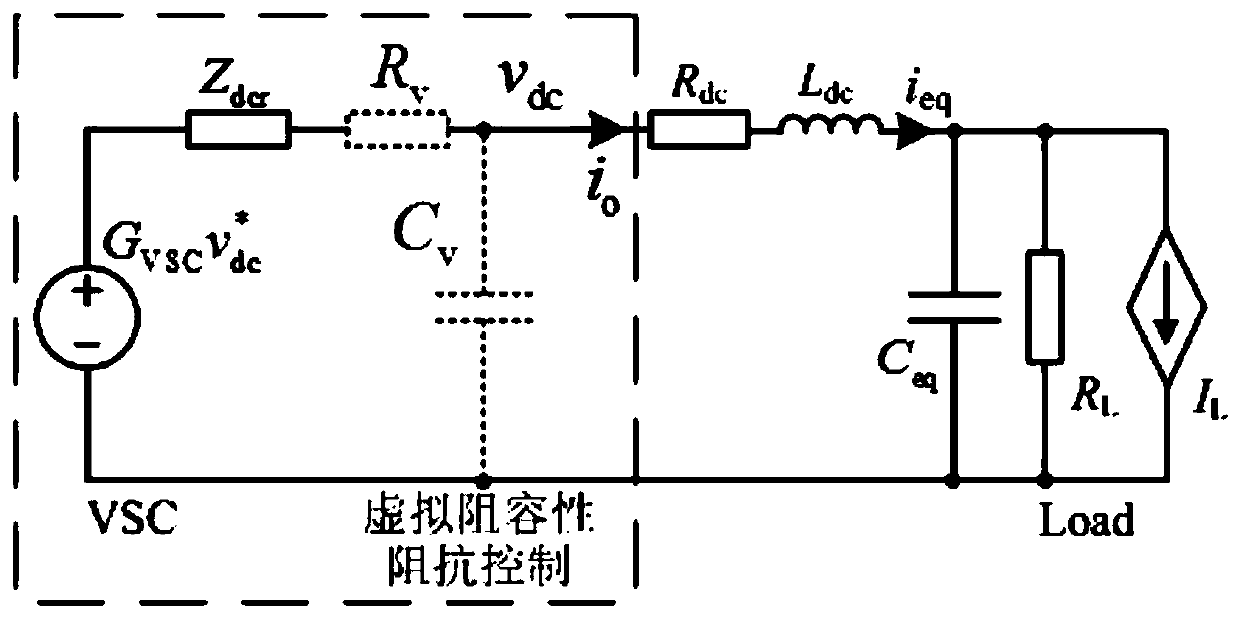

Voltage stability control method for connecting multi-voltage-source converter to medium-voltage DC system

ActiveCN110601221ATaisho dampingOscillation suppressionElectric power transfer ac networkPower oscillations reduction/preventionVoltage sourceVoltage control

The invention discloses a voltage stability control method for connecting a multi-voltage-source converter to a medium-voltage DC system. The method mainly comprises four parts composed of virtual resistive-capacitive impedance reconstruction, DC-side current feedforward, VSC DC port voltage control, and AC port current control. When the VSC uses DC voltage droop control to adjust the DC output voltage, the output impedance of the VSC exhibits negative resistance outside a voltage control bandwidth. Through the virtual resistive-capacitive impedance, the output impedance characteristics of multiple VSC DC ports are reconstructed, such that the VSC output impedance maintains large positive resistance outside the voltage control bandwidth so as to compensate the negative damping of the system outside the voltage control bandwidth and suppress the voltage oscillation of the medium-voltage DC System. Based on the virtual resistive-capacitive impedance, the DC output current feedforward isintroduced. The VSC DC port voltage control uses proportional integral control. The AC port current control is decoupling control in a synchronous rotation coordinate system. The method can enhance the inertia of the DC system while suppressing the oscillation of the DC system so as to realize the stable control of the bus voltage.

Owner:HUNAN UNIV +2

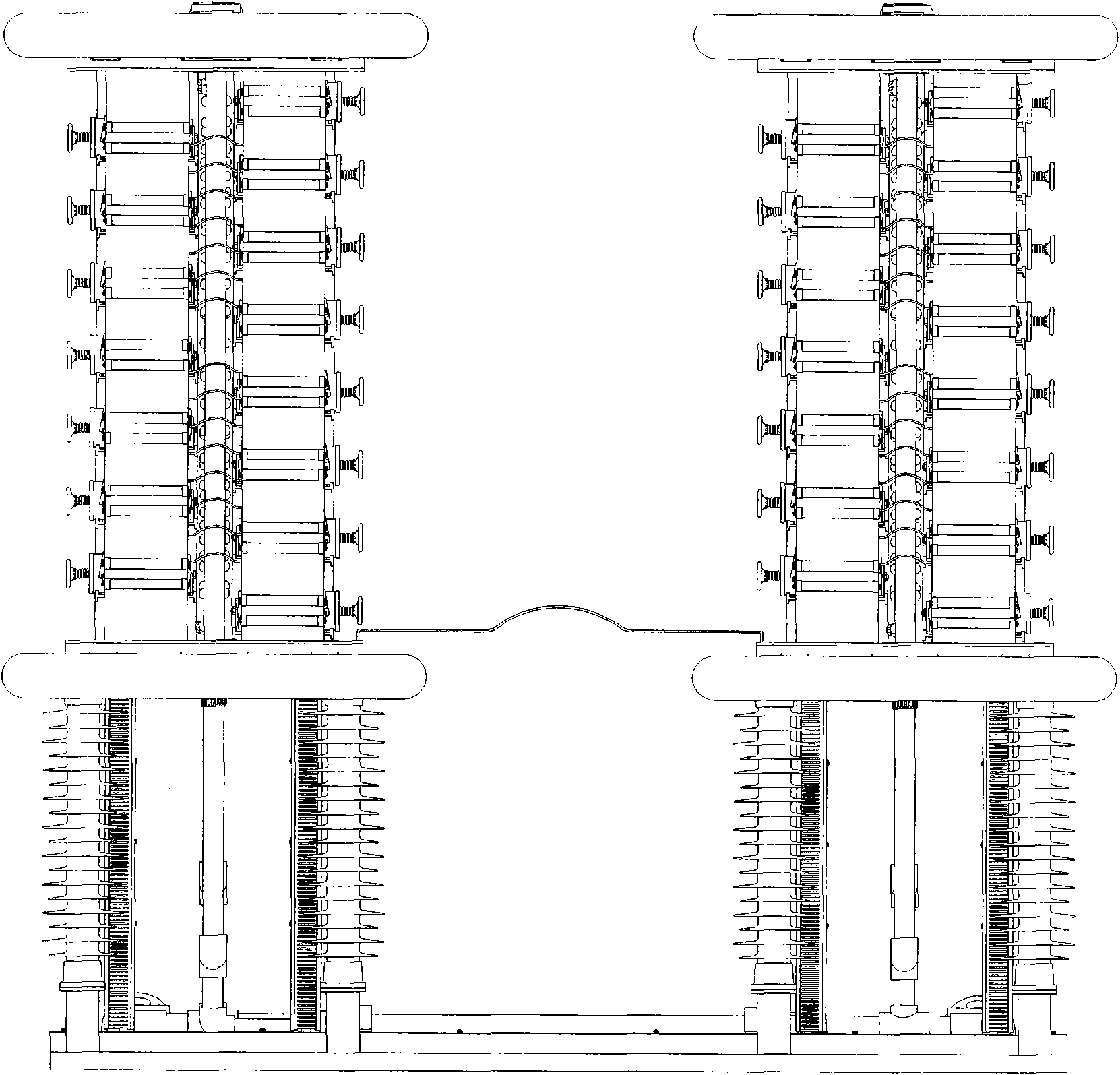

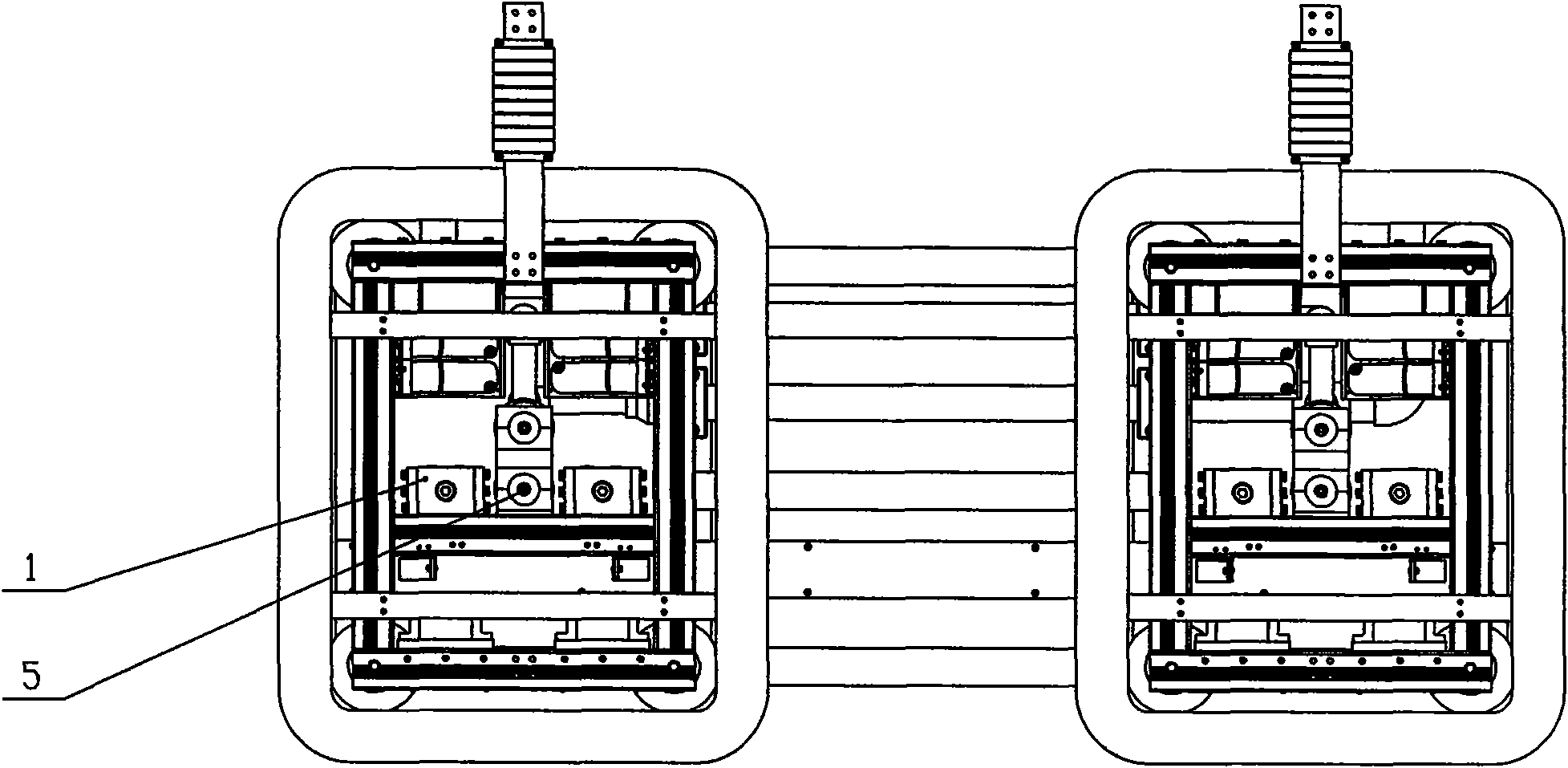

66kv optically-controlled water-cooling thyristor valve box

ActiveCN101651135AReasonable layoutSimple and exquisite appearanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceModular design

The invention relates to an optically-controlled water-cooling radiating thyristor valve box which is characterized in that the valve box is in a dual body vertical structure; a left valve unit and aright valve unit are connected in series to form a uniphase valve box; the left valve unit and the right valve unit are connected by a copper foil soft contactor; a water pipe unit of each valve unitis mounted in the middle of the valve unit, and a thyristors unit needing water cooling and a water-cooling resistance of a resistive-capacitive protective unit are mounted at two sides of the water pipe unit; other elements of the resistive-capacitive protective unit without needing of water cooling except the water-cooling resistance, a cabling channel unit, an equalizing ring unit are mounted at the periphery of the valve box. The water-cooling resistance and a damping capacitance are mounted on a resistive-capacitive bracket side by side in a concentrated layout manner. The resistive-capacitive protective unit uses modular design, and can assemble two eudipleural resistive-capacitive protective units by arranging the same water-cooling resistance and the damping capacitance on the resistive-capacitive bracket. The invention has the advantages of high reliability, small occupied area, separately arrangement of circuit and waterway and pure water cooling.

Owner:辽宁荣信兴业智能电气有限公司

Resistive-capacitive deformation sensor

InactiveCN107949779AForce measurementElectrical/magnetic solid deformation measurementElastic substrateEngineering

A deformation sensing apparatus comprises an elastic substrate, a first strain-gauge element formed on a first surface of the elastic substrate, and configured to output a first signal in response toa strain applied in a first direction, and a second strain-gauge element formed on a second surface of the elastic substrate opposite to the first surface, and configured to output a second signal inresponse to a strain applied in the same first direction.

Owner:META PLATFORMS TECH LLC

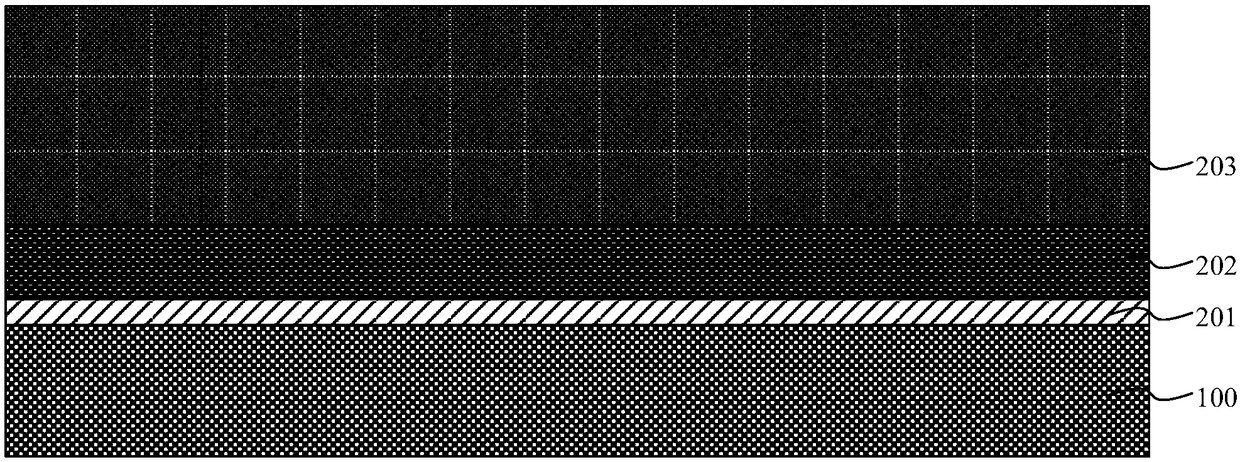

Semiconductor transistor structure and preparation method thereof

PendingCN109390402AReduce the value of parasitic capacitanceLow switching energySemiconductor/solid-state device manufacturingSemiconductor devicesResistance capacitanceIsolation layer

The present invention provides a semiconductor transistor structure and a preparation method thereof. The structure comprises: a semiconductor substrate; a grid module located on the semiconductor substrate, wherein the grid module comprises a grid dielectric layer and a grid conductive layer located on the grid dielectric layer; a side wall isolation structure located at the side wall of the gridmodule, wherein the side wall of the grid module comprises a first isolation layer, an air insulation layer and a second isolation layer arranged in order from inside to outside; and bolt conductivelayers located at two sides of the grid module, wherein the side wall isolation structure is configured to separate the bolt conductive layers from the grid module. The semiconductor transistor structure and the preparation method thereof can effectively reduce the stray capacitance value so as to improve the resistance-capacitance delay increasing speed and reduce the switching energy.

Owner:CHANGXIN MEMORY TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com