Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

589results about How to "Save extra space" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

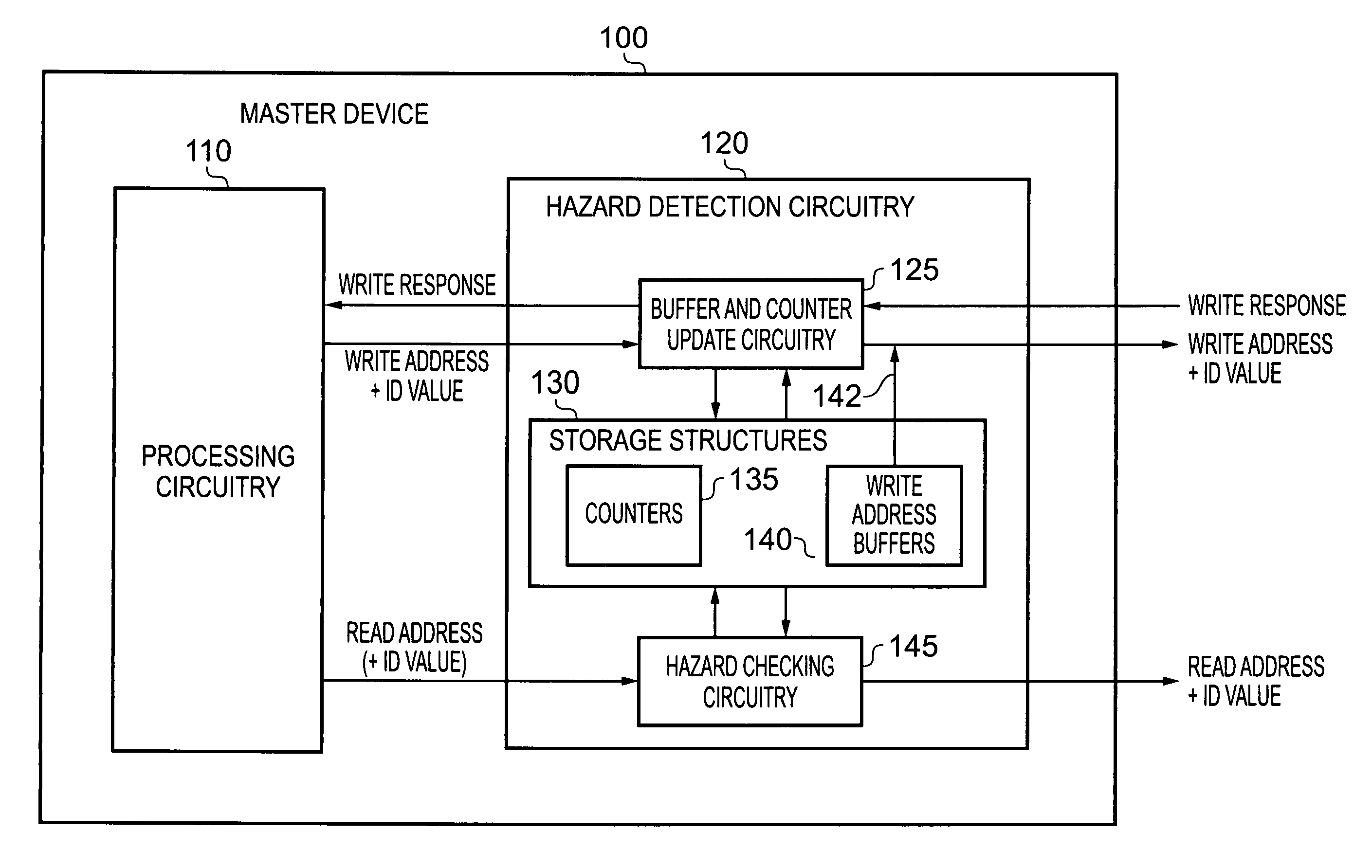

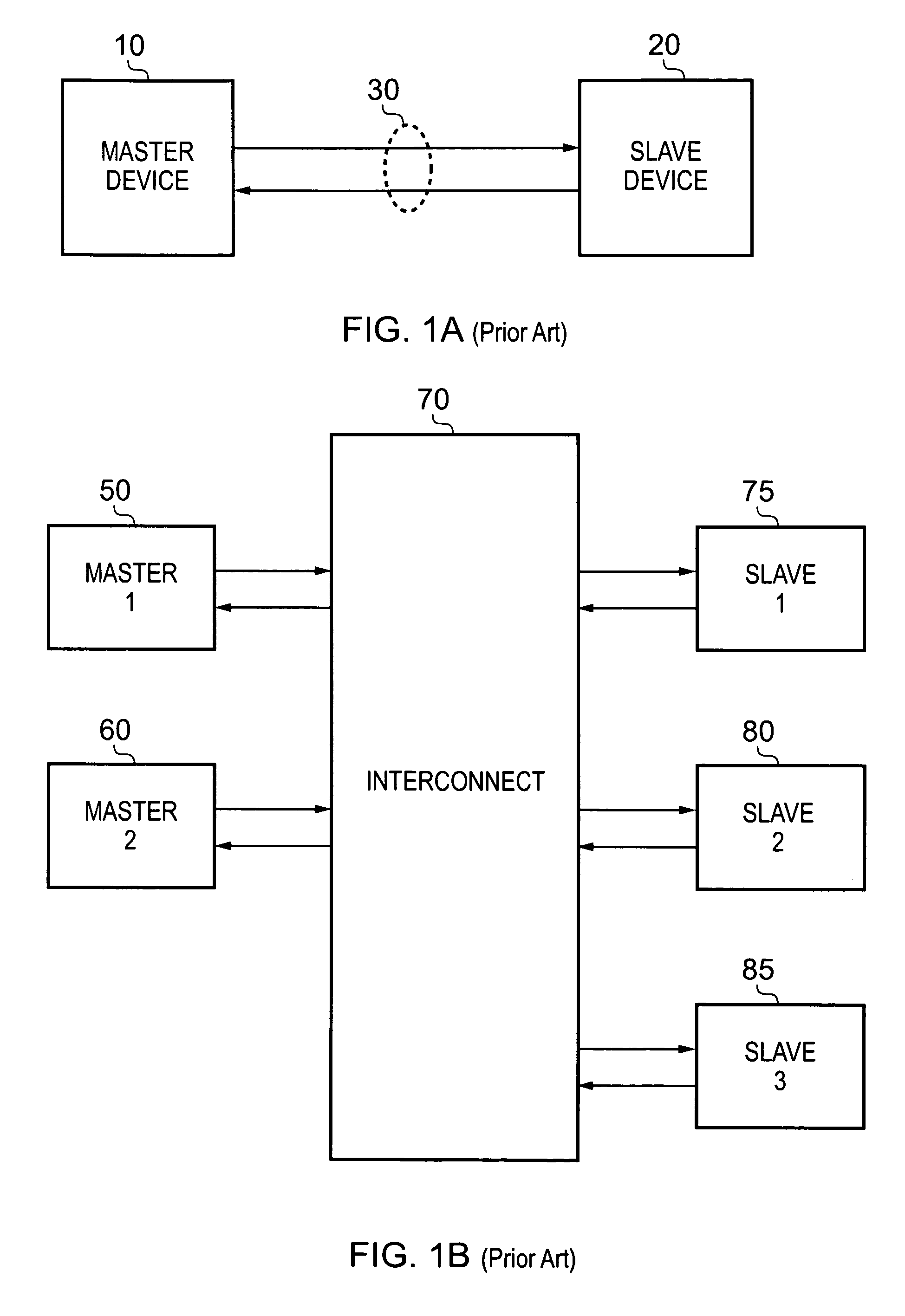

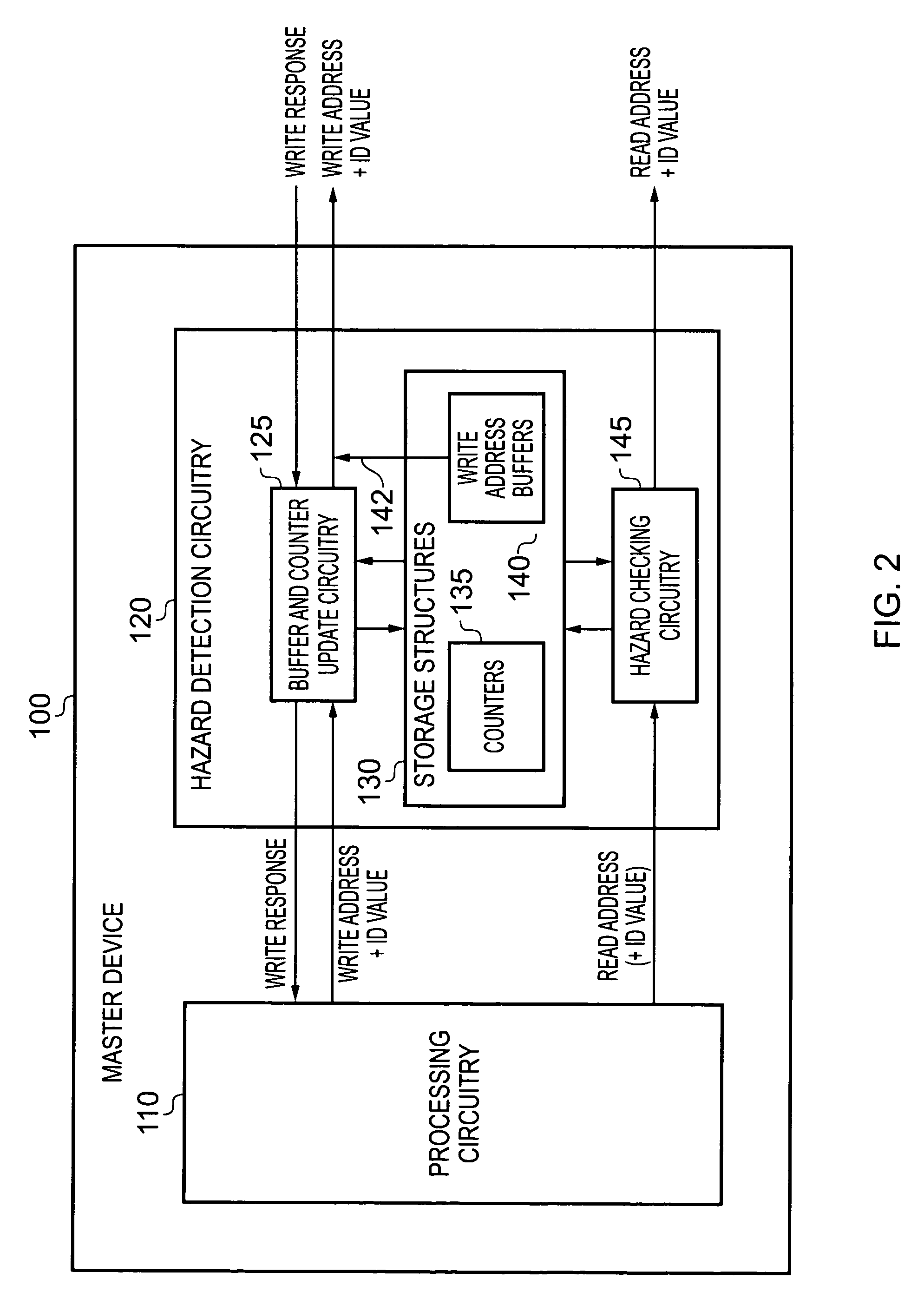

Data processing apparatus and method for performing hazard detection

ActiveUS20100250802A1Avoid possibilityAvoiding WAW hazardMemory systemsInput/output processes for data processingAccess historyData buffer

A data processing apparatus and method are provided for performing hazard detection in respect of a series of access requests issued by processing circuitry for handling by one or more slave devices. The series of access requests include one or more write access requests, each write access request specifying a write operation to be performed by an addressed slave device, and each issued write access request being a pending write access request until the write operation has been completed by the addressed slave device. Hazard detection circuitry comprises a pending write access history storage having at least one buffer and at least one counter for keeping a record of each pending write access request. Update circuitry is responsive to receipt of a write access request to be issued by the processing circuitry, to perform an update process to identify that write access request as a pending write access request in one of the buffers, and if the identity of another pending write access request is overwritten by that update process, to increment a count value in one of the counters. On completion of each write access request by the addressed slave device, the update circuitry performs a further update process to remove the record of that completed write access request from the pending write access history storage. Hazard checking circuitry is then responsive to at least a subset of the access requests to be issued by the processing circuitry, to reference the pending write access history storage in order to determine whether a hazard condition occurs. The manner in which the update circuitry uses a combination of buffers and counters to keep a record of each pending write access request provides improved performance with respect to known prior art techniques, without the hardware cost that would be associated with increasing the number of buffers.

Owner:ARM LTD

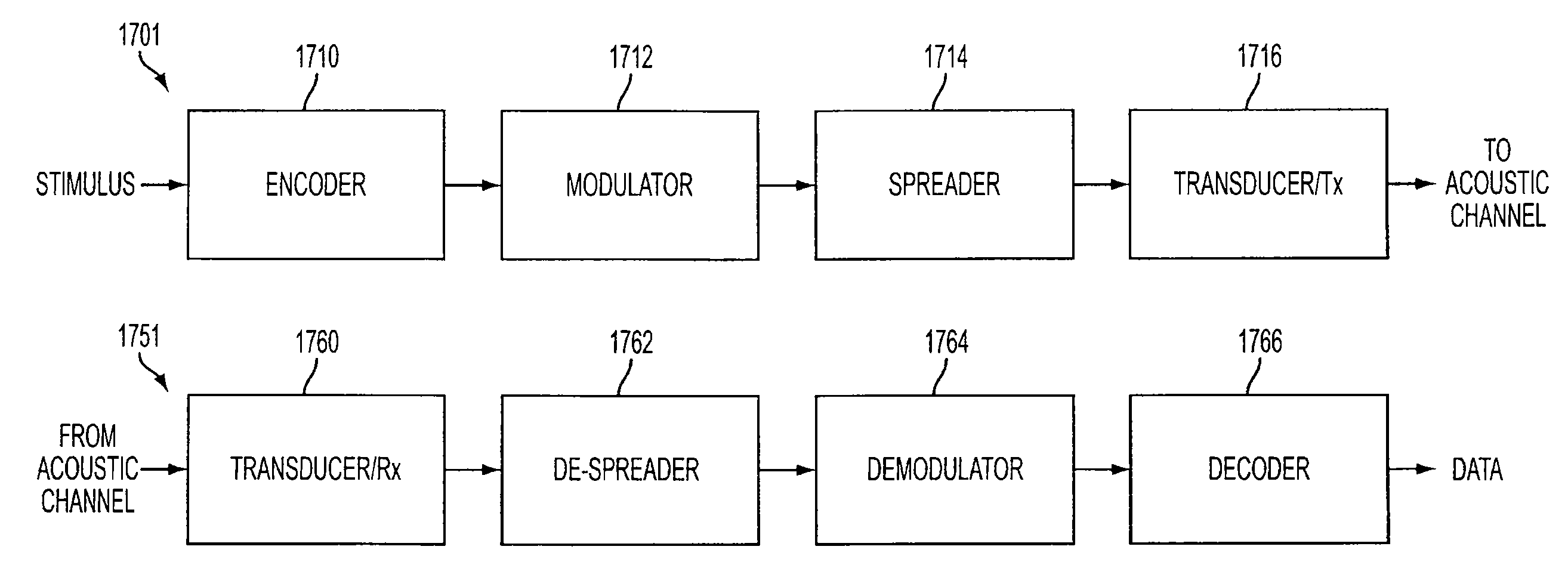

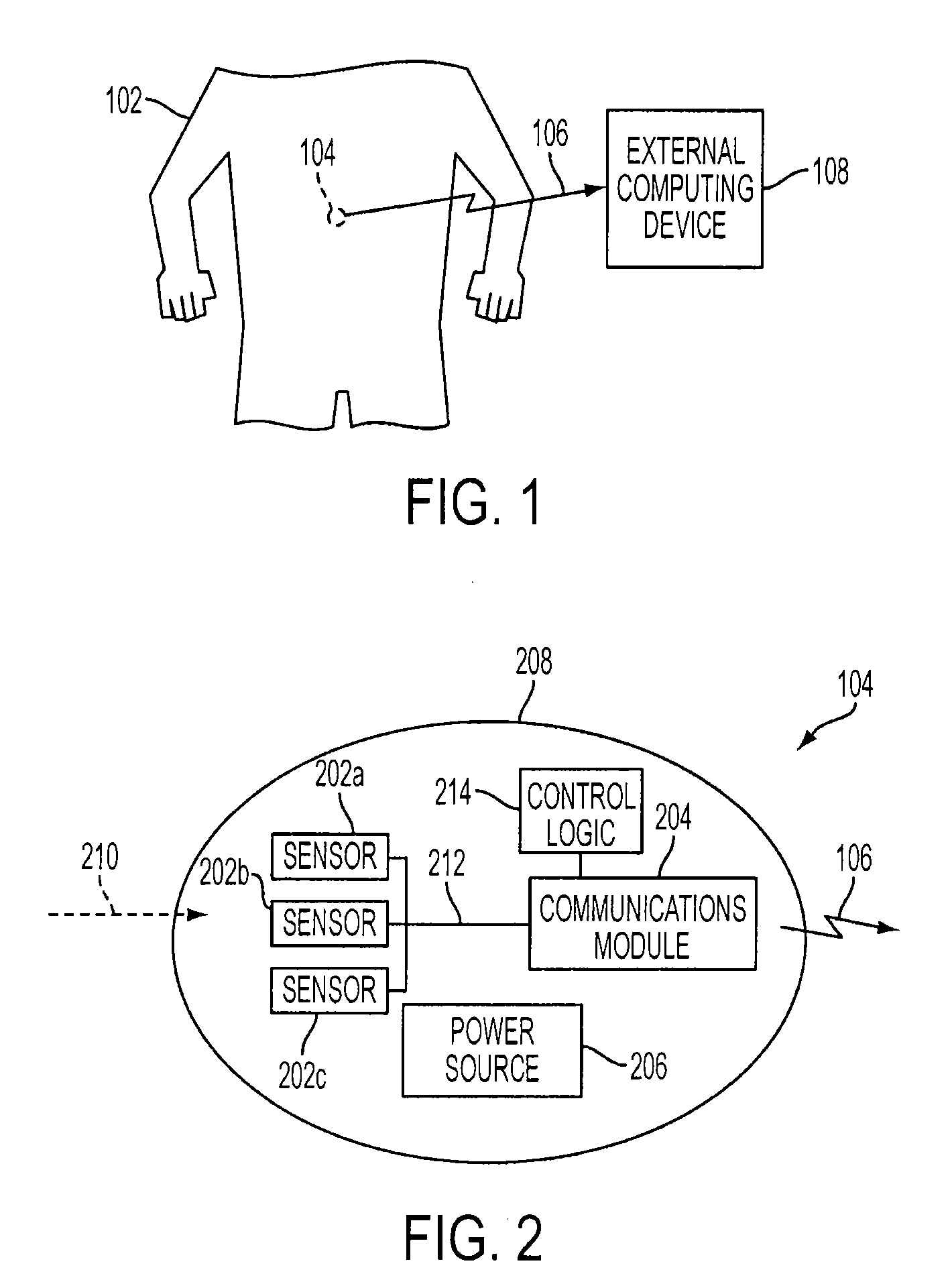

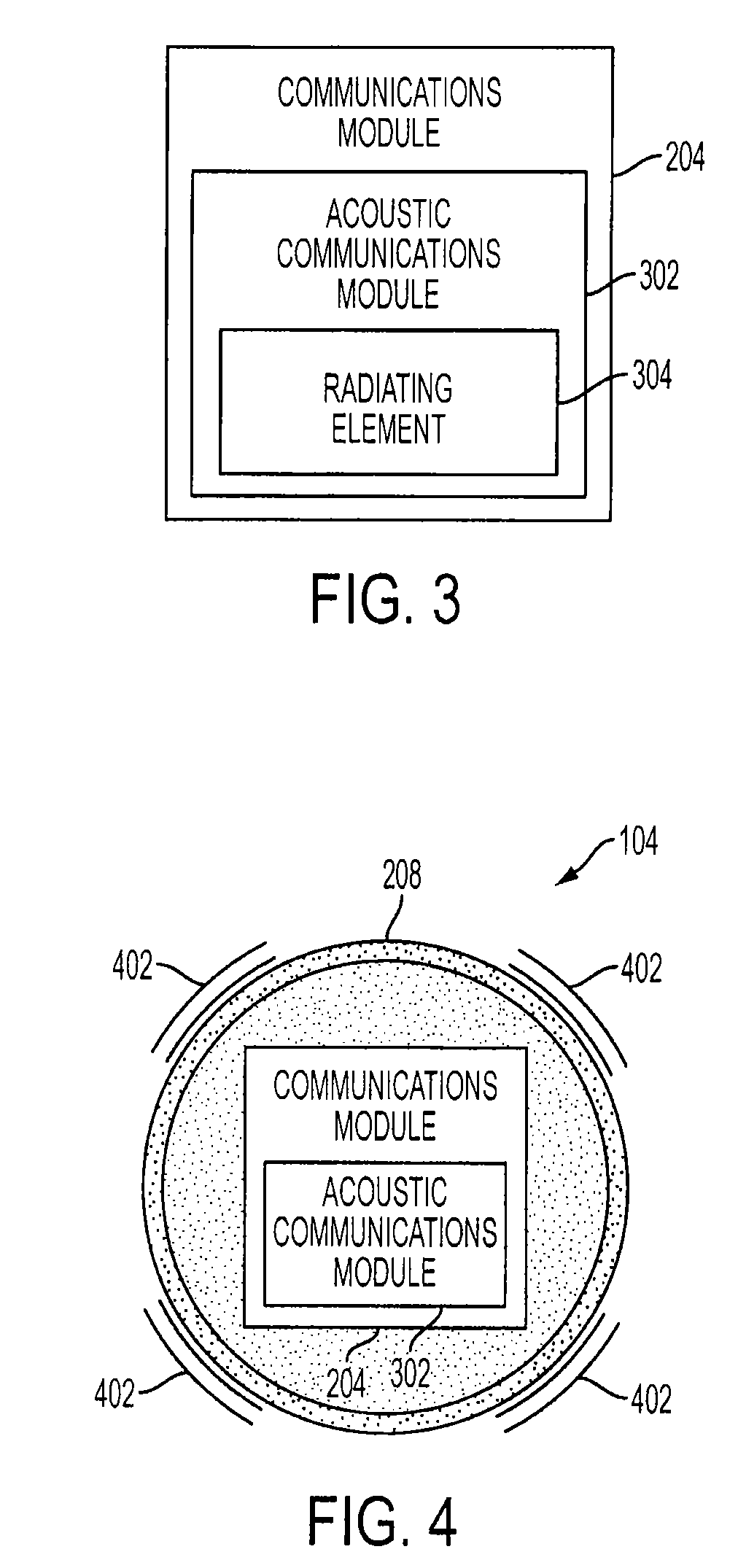

System and Method for Acoustic Data Transmission

InactiveUS20080112885A1Reduce Intersymbol InterferenceImprove system performanceSonic/ultrasonic/infrasonic transmissionEndoscopesSignal-to-noise ratio (imaging)Transducer

Embodiments of the present invention are directed to acoustic data transmission using a spreading code. A system for acoustic data transmission includes an ingestible capsule and an acoustic receiver. The ingestible capsule includes a modulator, a spreader, and an acoustic transmitter. The modulator modulates data according to a modulation scheme. The spreader spreads the modulated data according to a spreading code. The acoustic transmitter acoustically transmits the modulated and spread data through a body of an animal. The acoustic receiver includes an acoustic transducer a de-spreader and a demodulator. The acoustic transducer receives the acoustically transmitted signal and forms an electrical signal therefrom. The de-spreader de-spreads the received signal in accordance with the spreading code. The demodulator demodulates the received and de-spread signal in accordance with the modulation scheme, wherein a phase of the spreading code is synchronized with the received signal whereby a signal-to-noise ratio of the received signal is increased.

Owner:INNURVATION

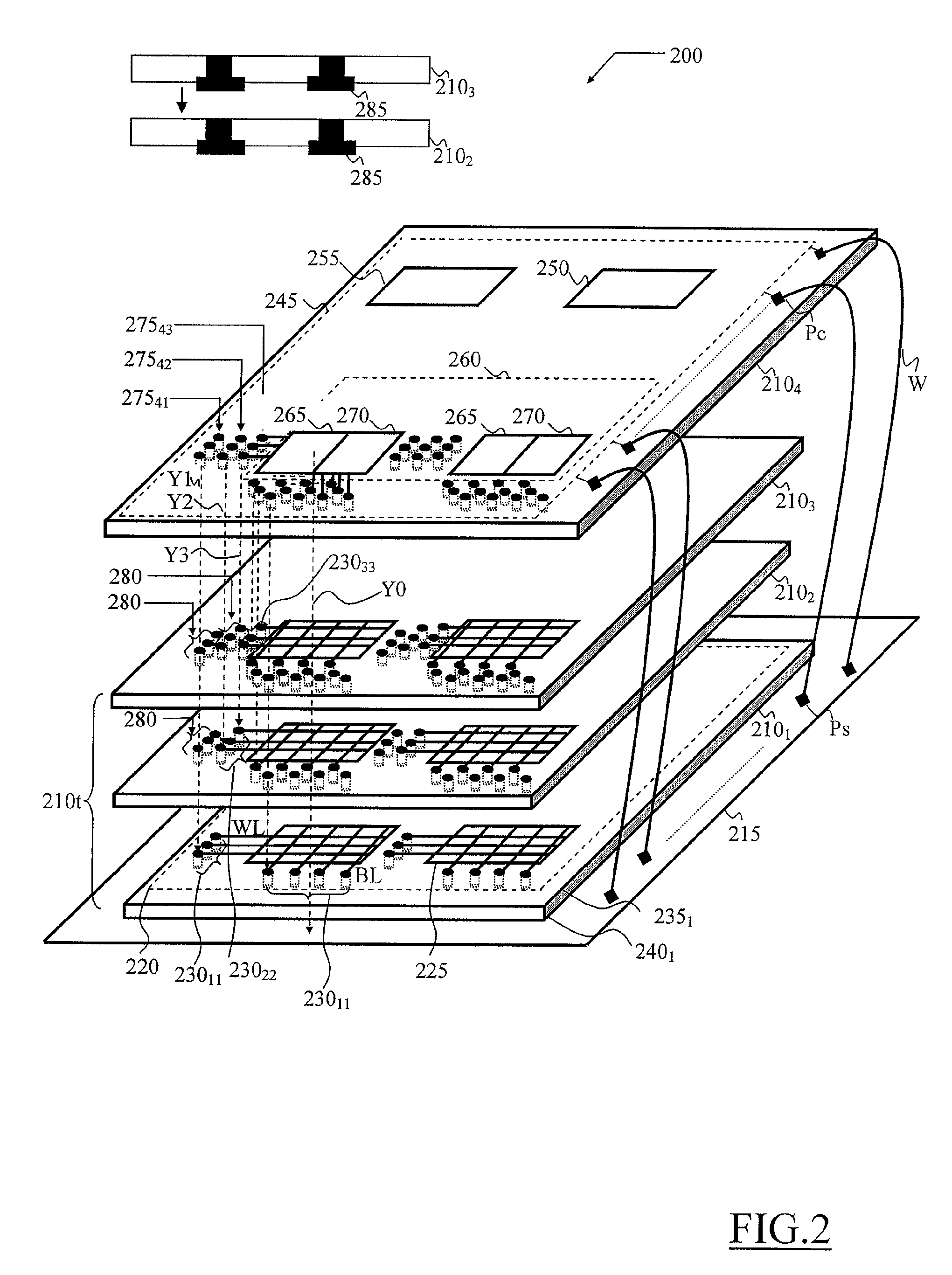

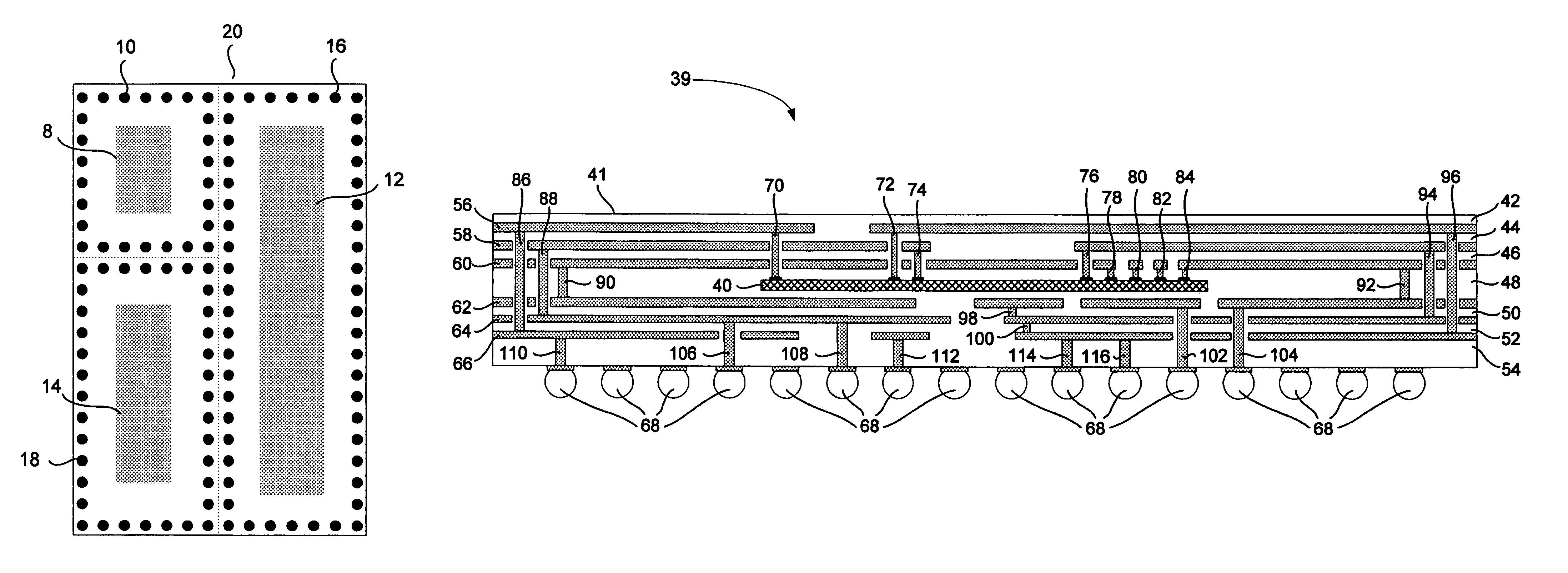

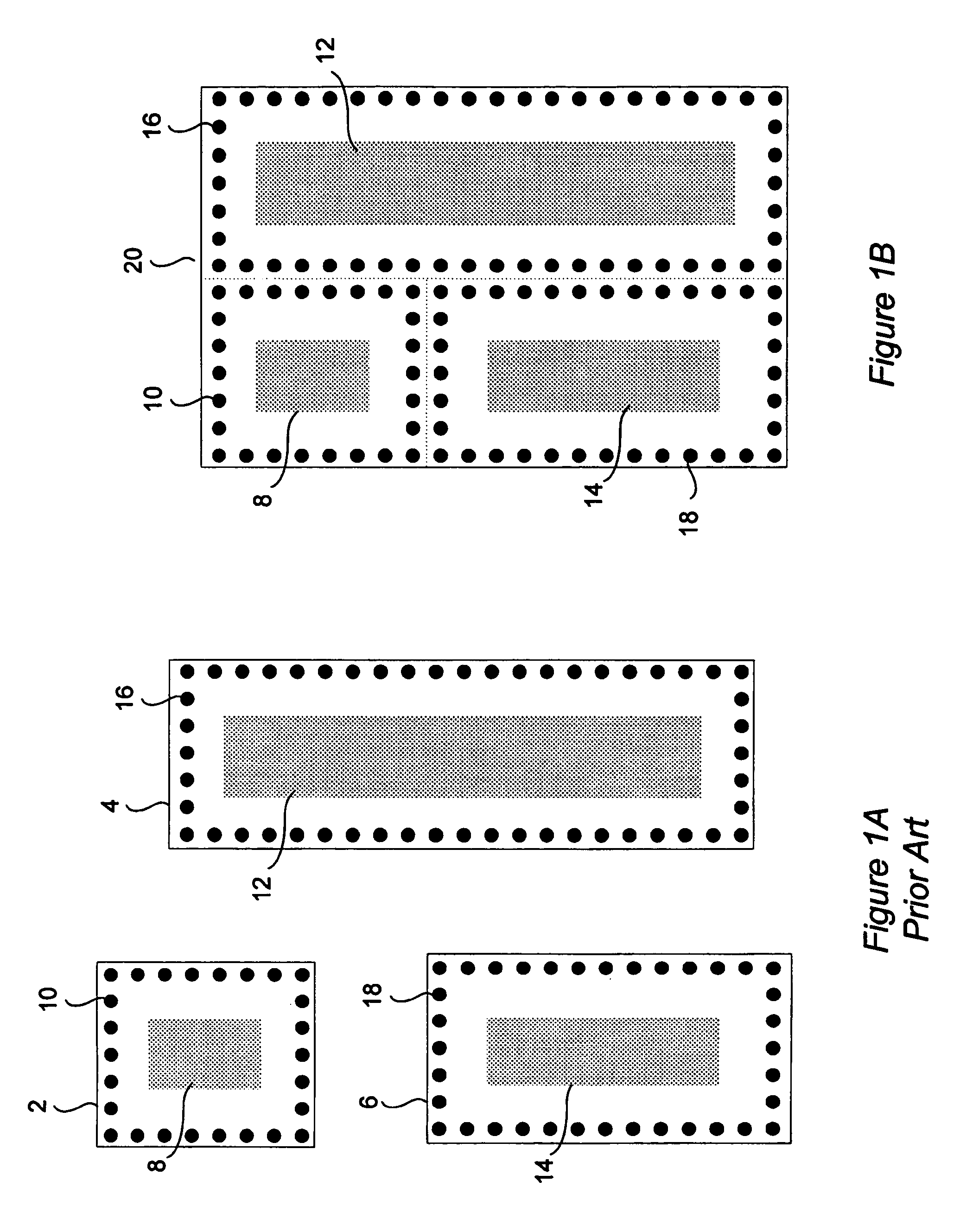

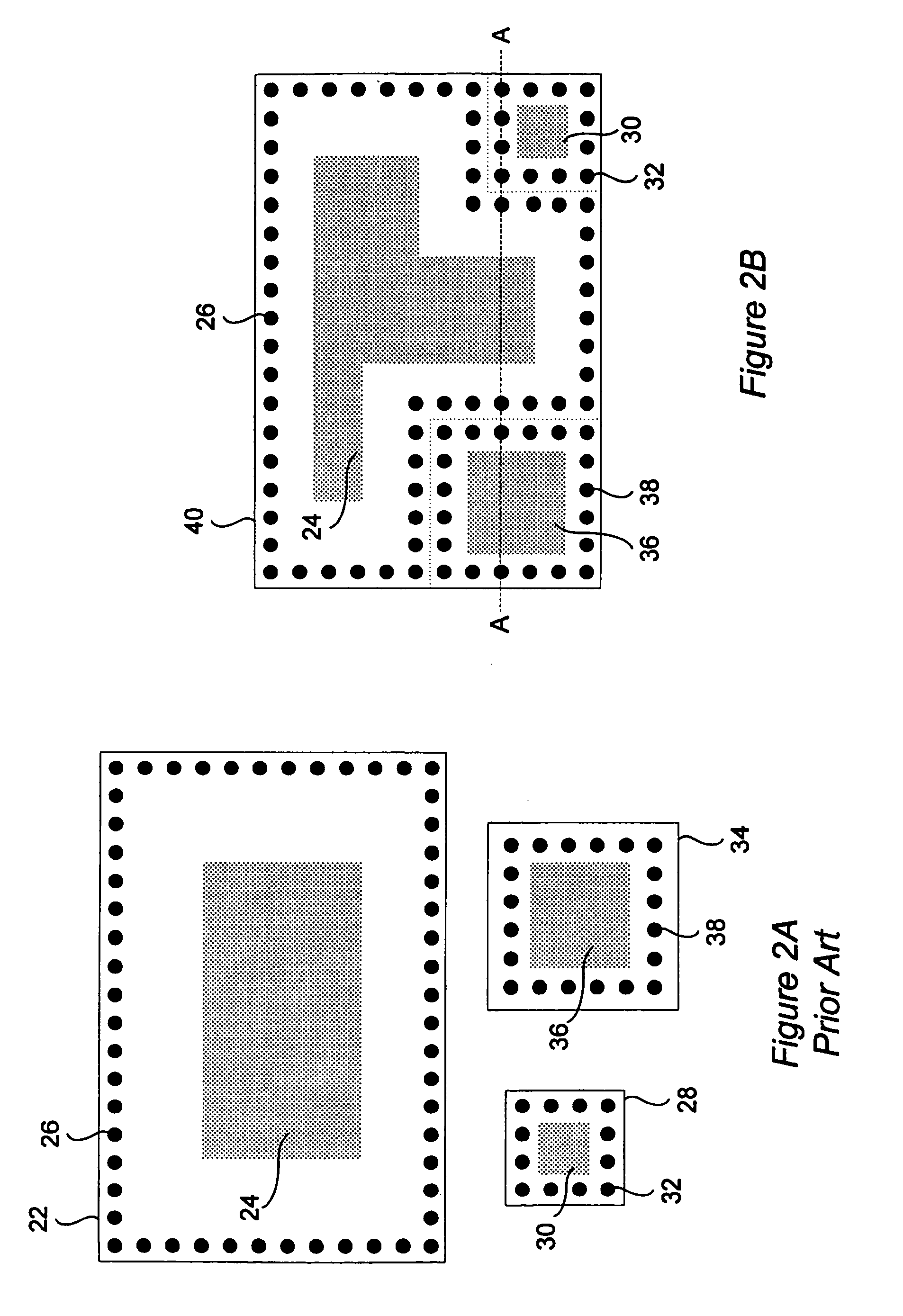

Multi chip electronic system

ActiveUS8228684B2Save extra spaceAmortization of costSubstation/switching arrangement detailsSemiconductor/solid-state device detailsElectricityElectronic systems

An electronic system adapted to perform a corresponding function and including at least a first subsystem and a second subsystem, the first subsystem and the second subsystem being operatively couplable to each other through a plurality of electric connections to perform the function of the system, in which the first subsystem and the second subsystem are respectively integrated on a first material chip and on a second material chip, the plurality of electric connections including a plurality of conductive through holes formed in at least one of the first and second chips and adapted to form a corresponding plurality of inter-chip electric connections when the first and the second chips are superimposed.

Owner:STMICROELECTRONICS SRL

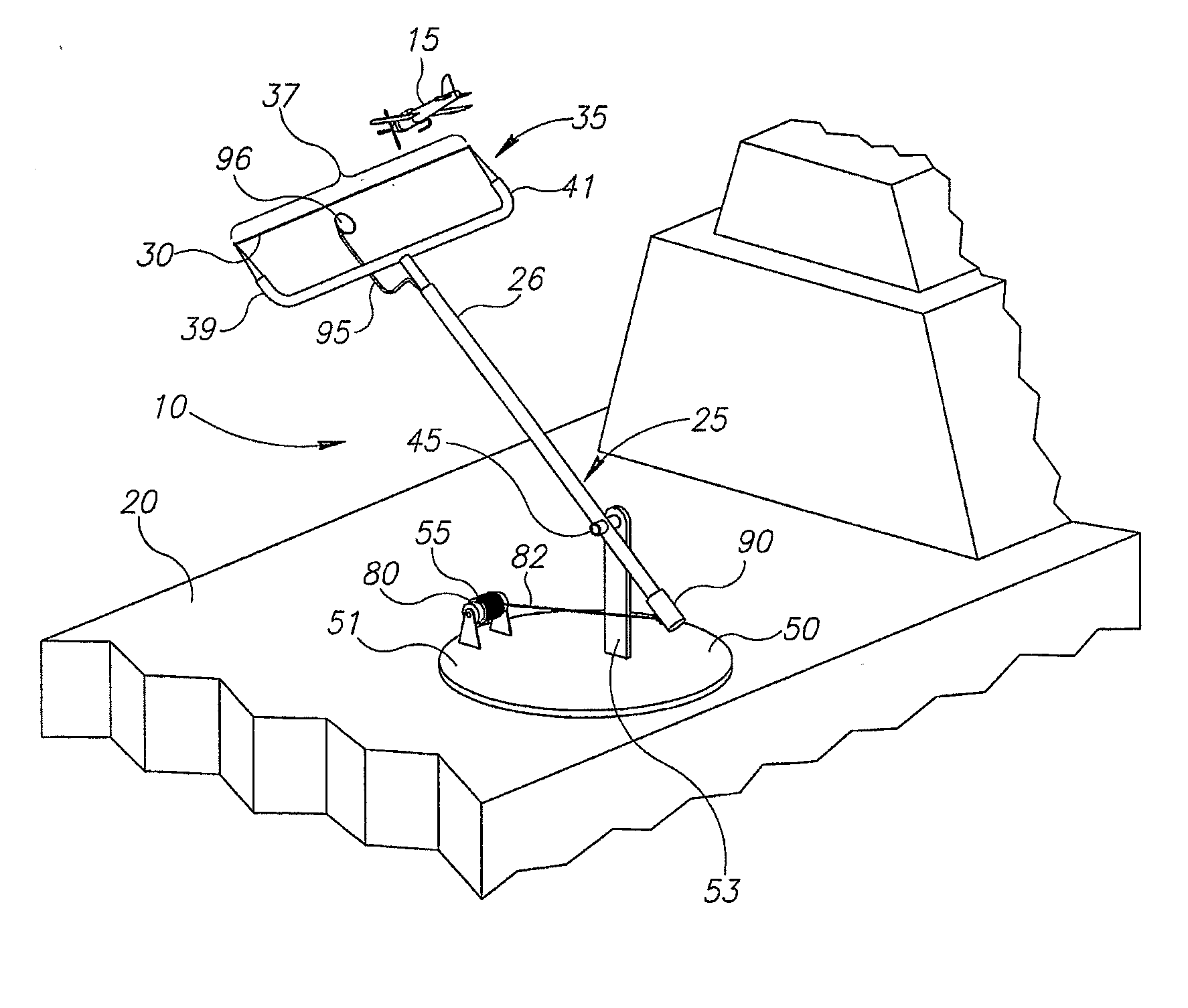

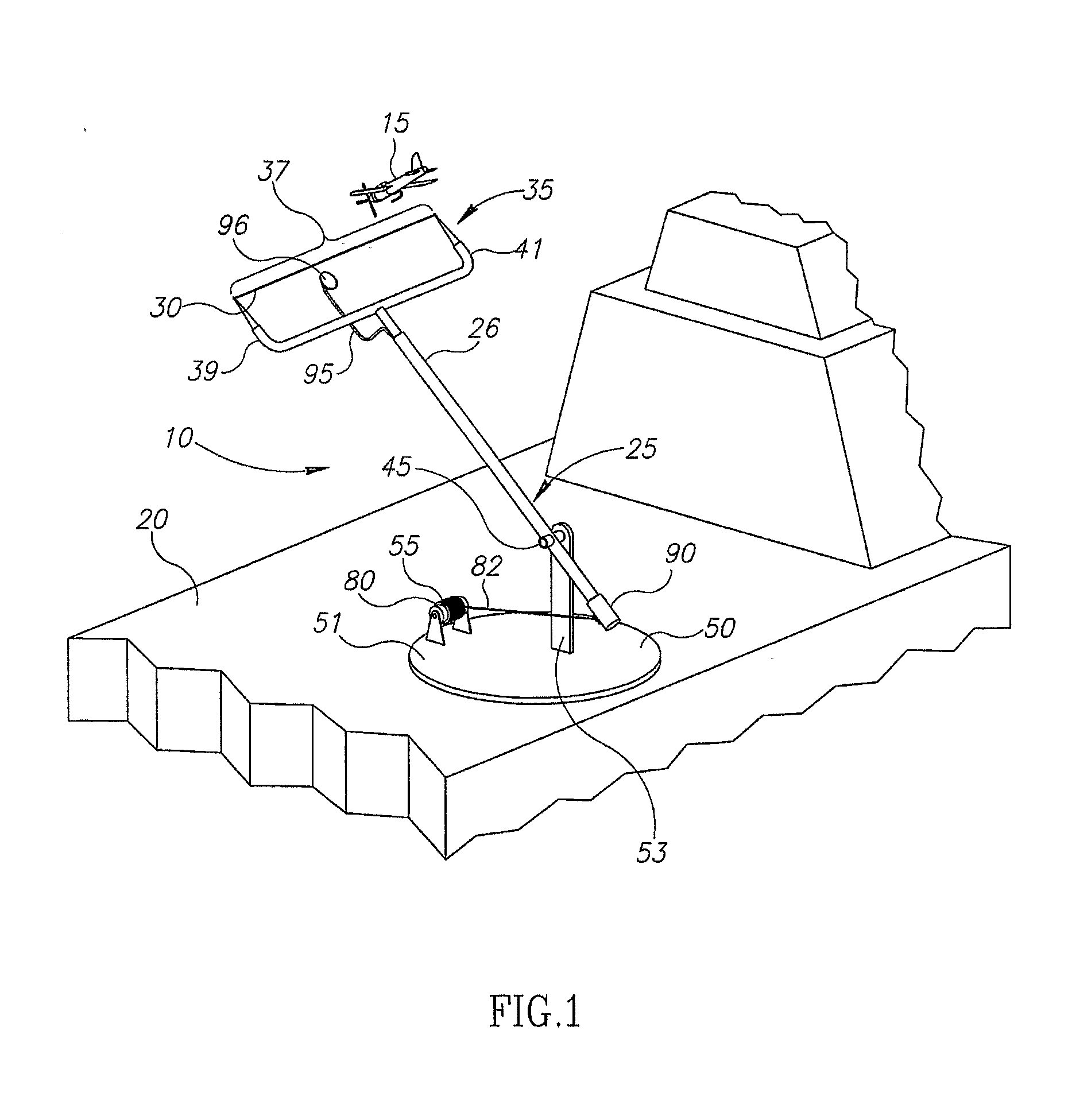

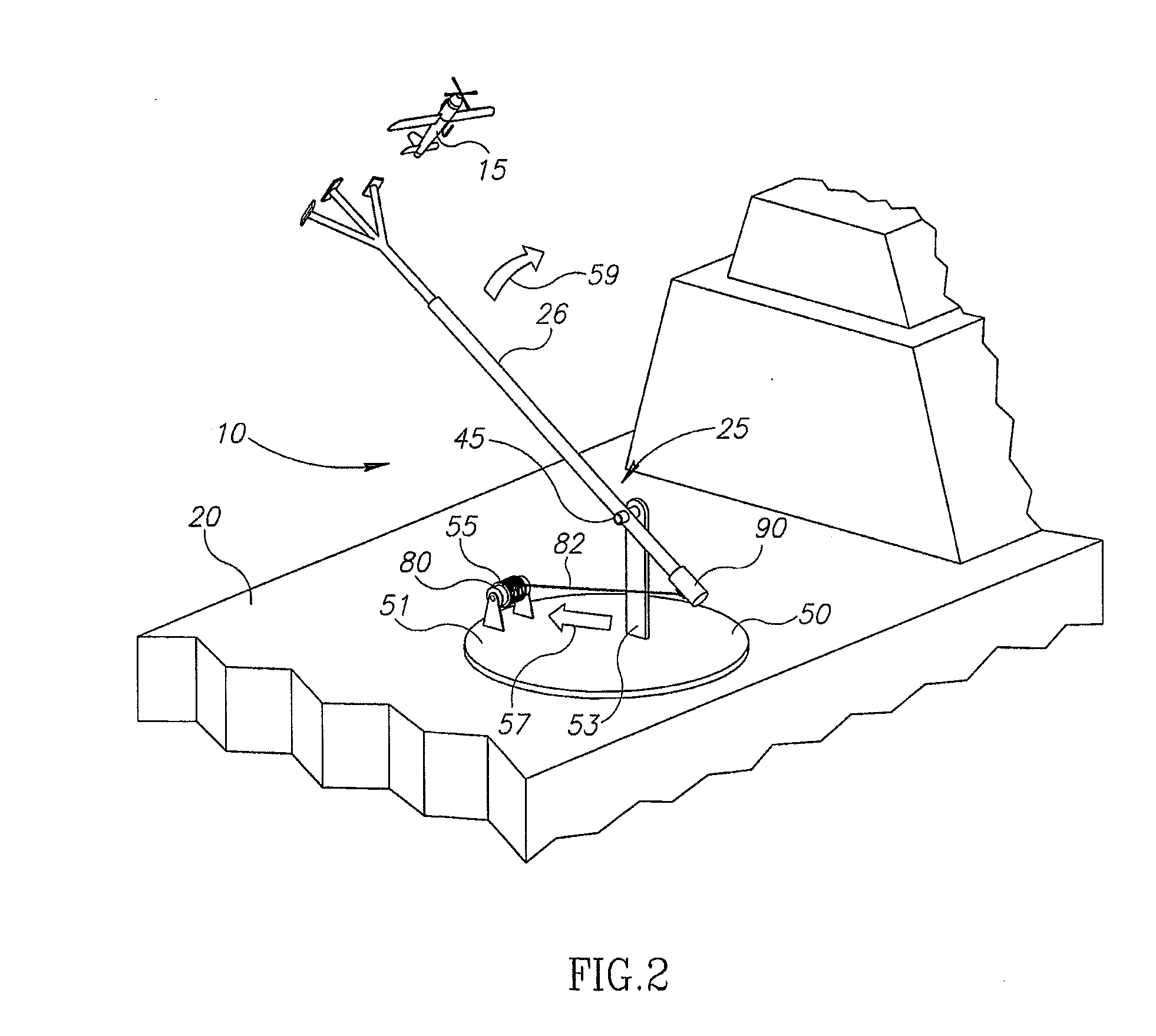

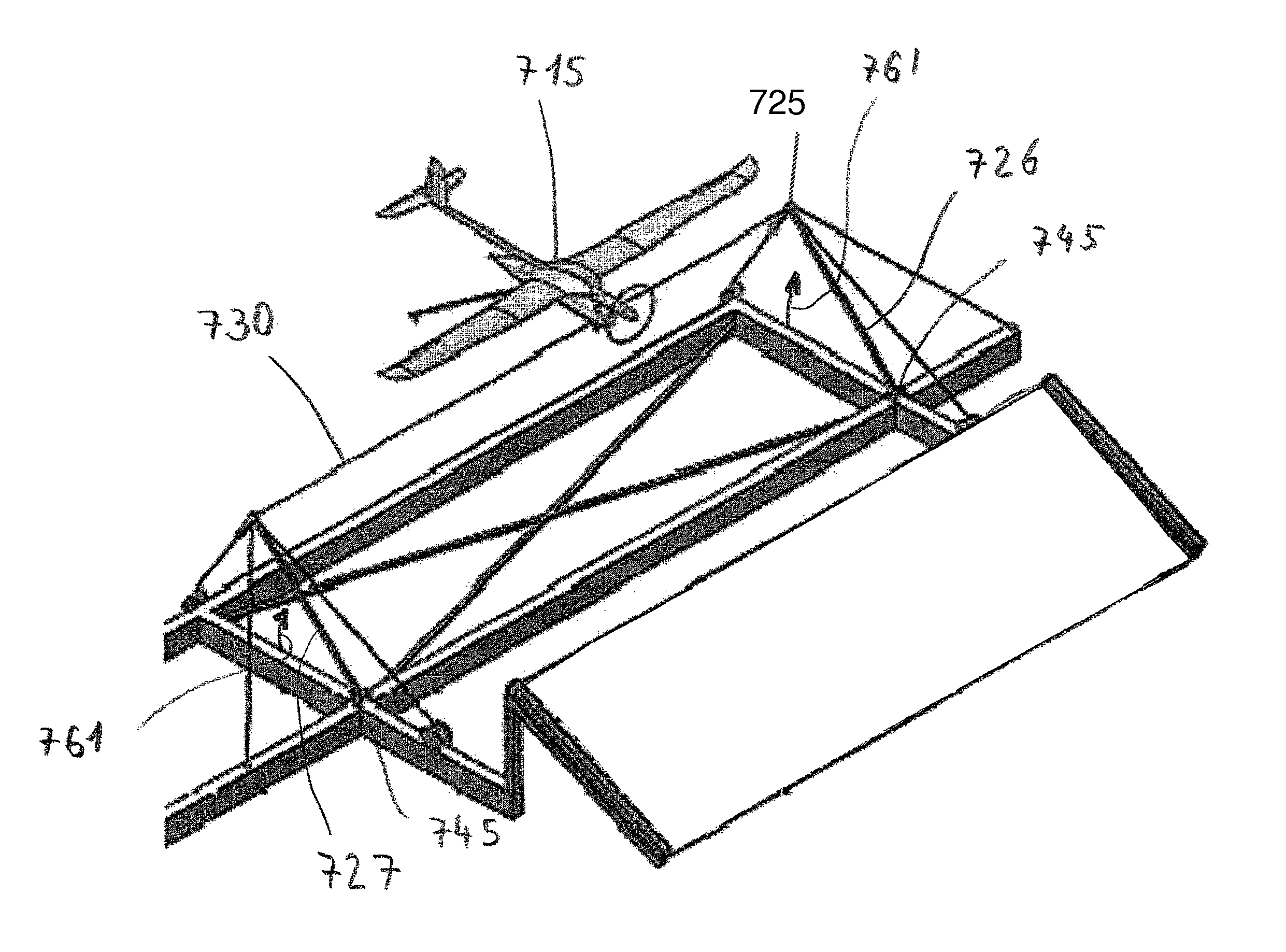

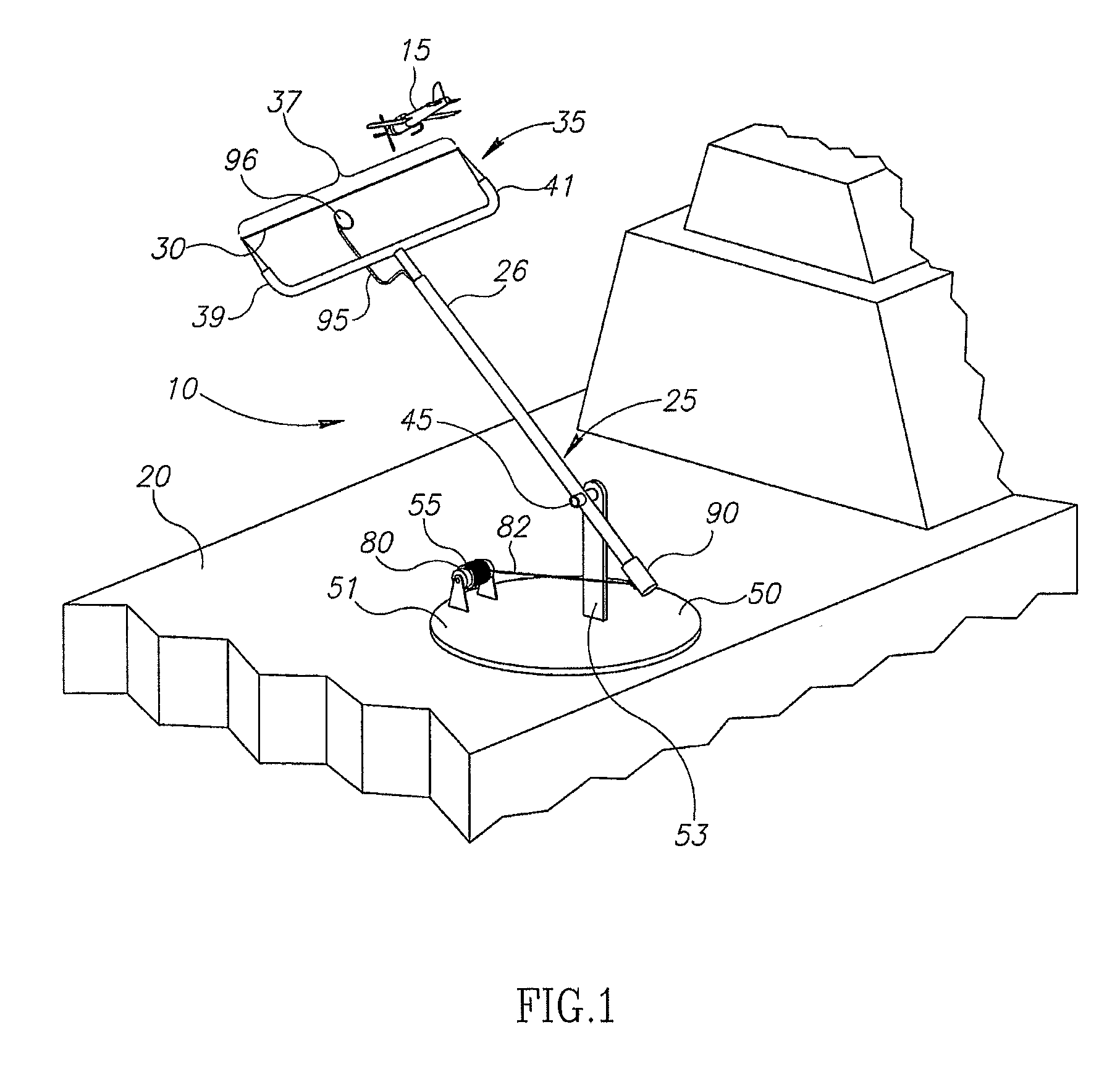

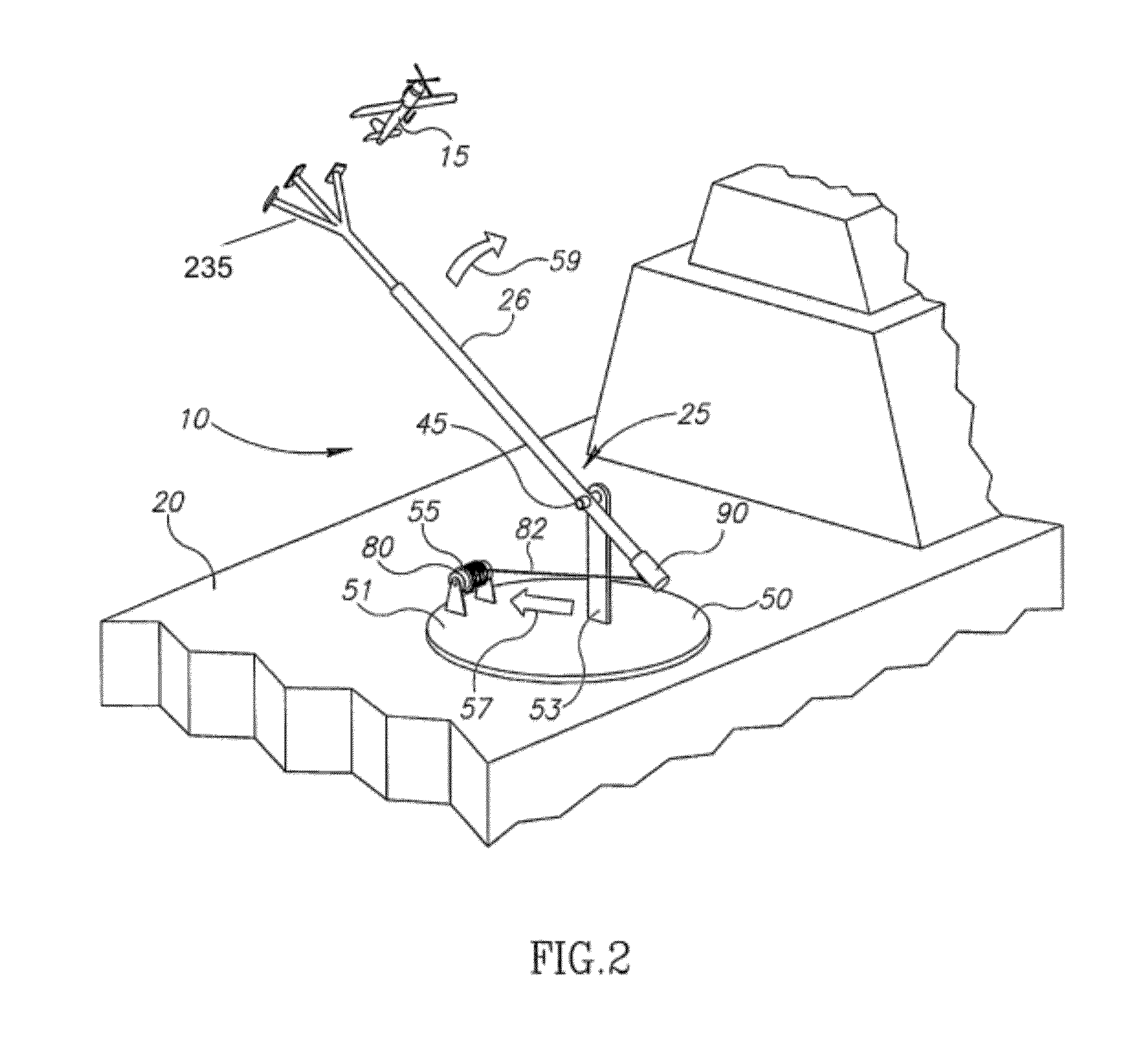

Unmanned aerial vehicle launching and landing system

ActiveUS20090224097A1Easy maintenanceEasy to operateArresting gearLaunching/towing gearUncrewed vehicleArresting gear

The present invention relates to a system for landing UAV's. The system comprises a slingshot structure that includes arm based structure and an axis means installed along the arm of the structure and wherein it enables the arm to move around it in addition, the system comprises base means connecting the axis means to a platform at which the system is installable. The system also include a controlled pulling and braking means that connects between the arm of the structure and the platform upon which the system is installable and a stretchable elastic means installed in a stretched manner at a gap formed between two arms and set to connect with a landing UAV. At the landing phase, the controlled pulling and braking means of the system, essentially breaks the motion of the arm based structure that is propelled to revolve around the system's axis means, from a time that the UAV forms contact with the elastic means and with it propels the structure to move around the axis means.

Owner:ELBIT SYST LTD

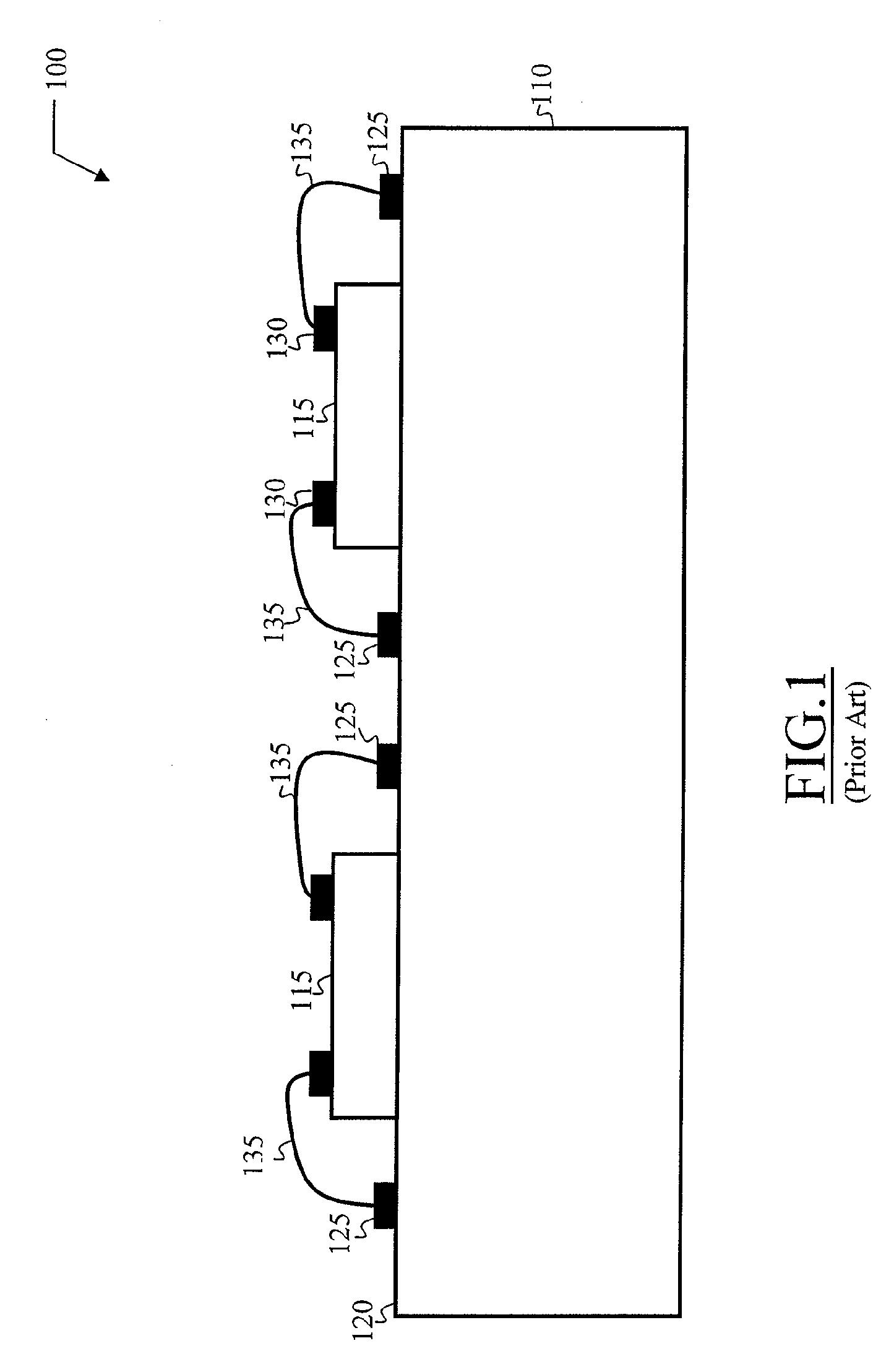

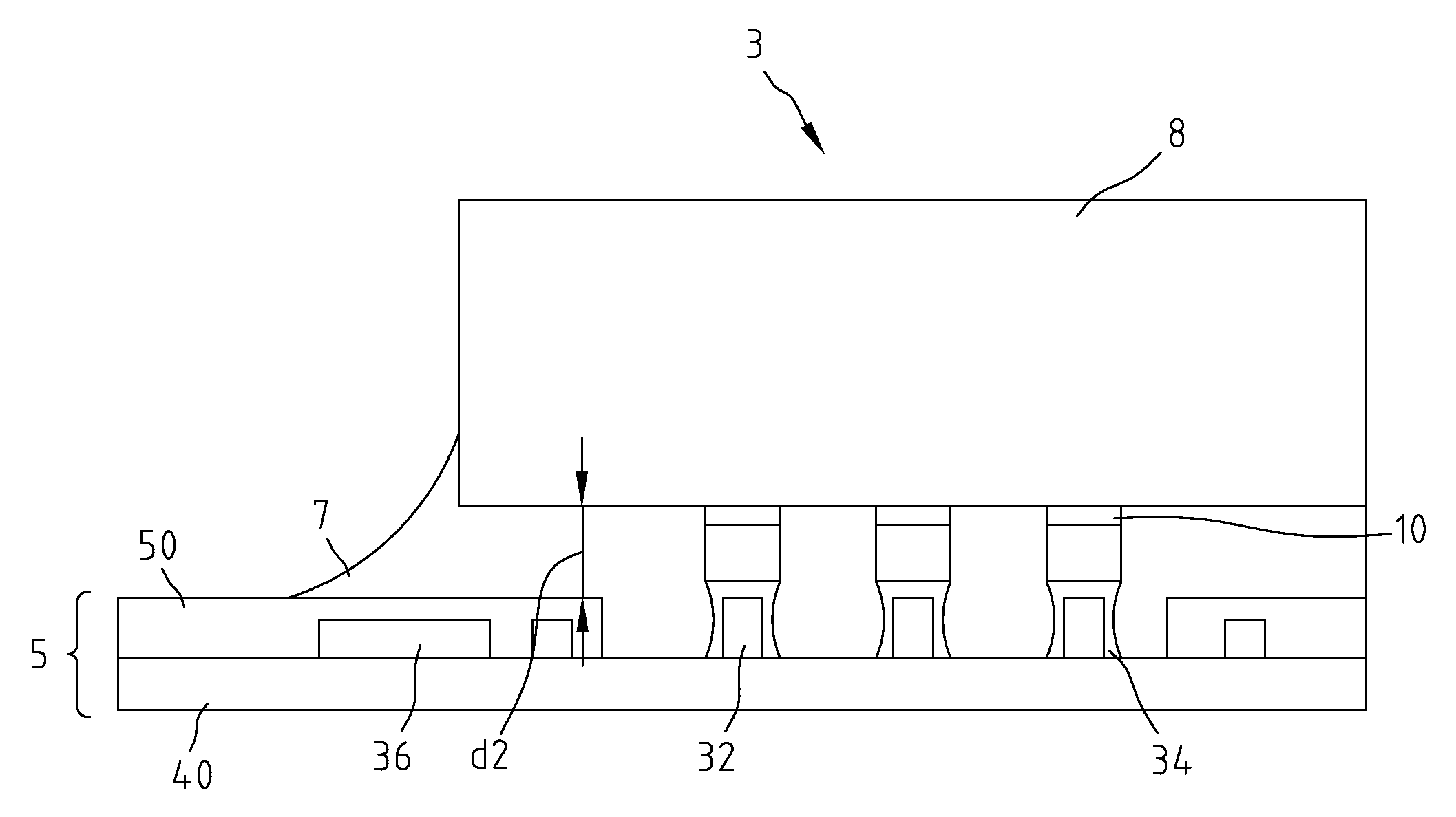

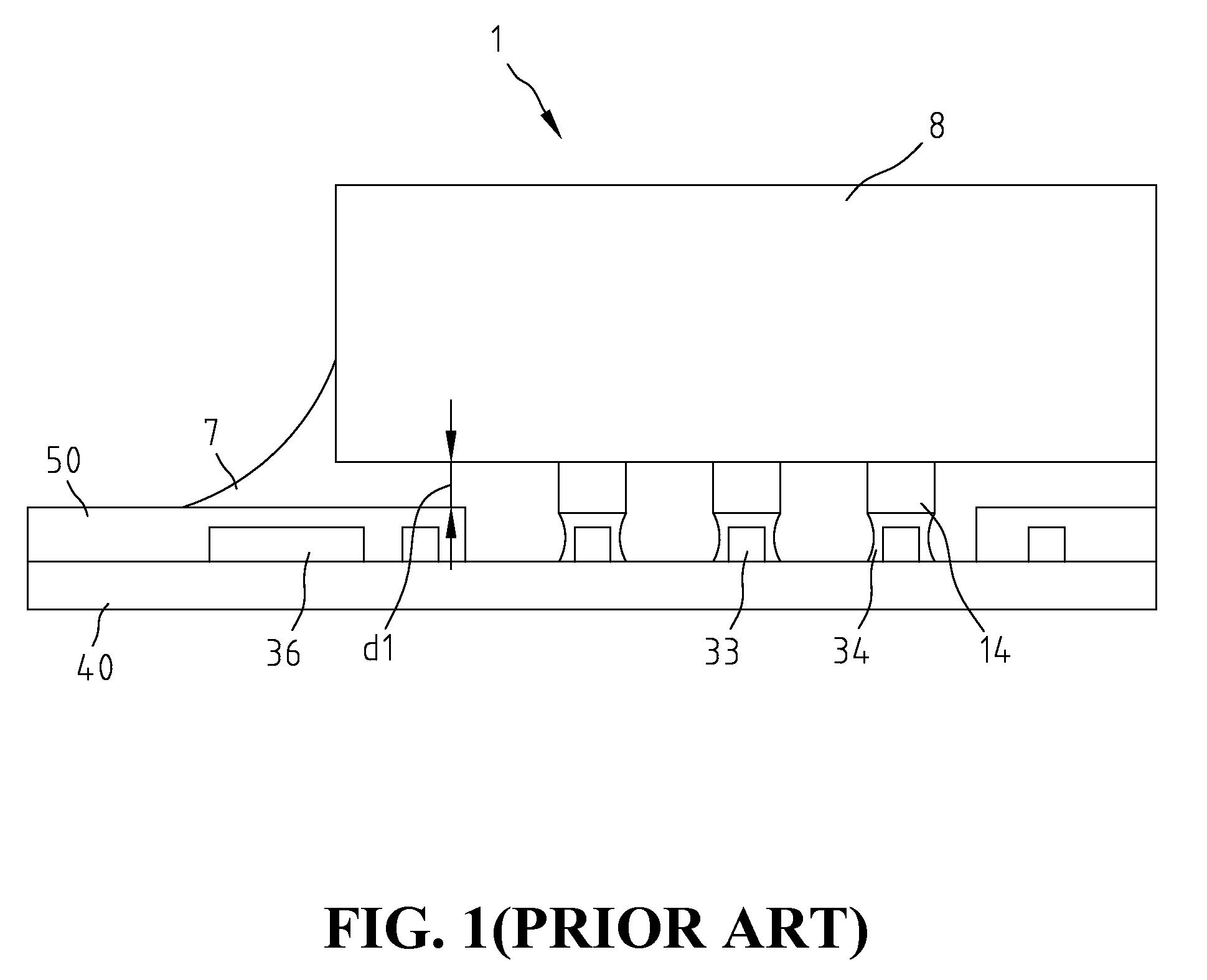

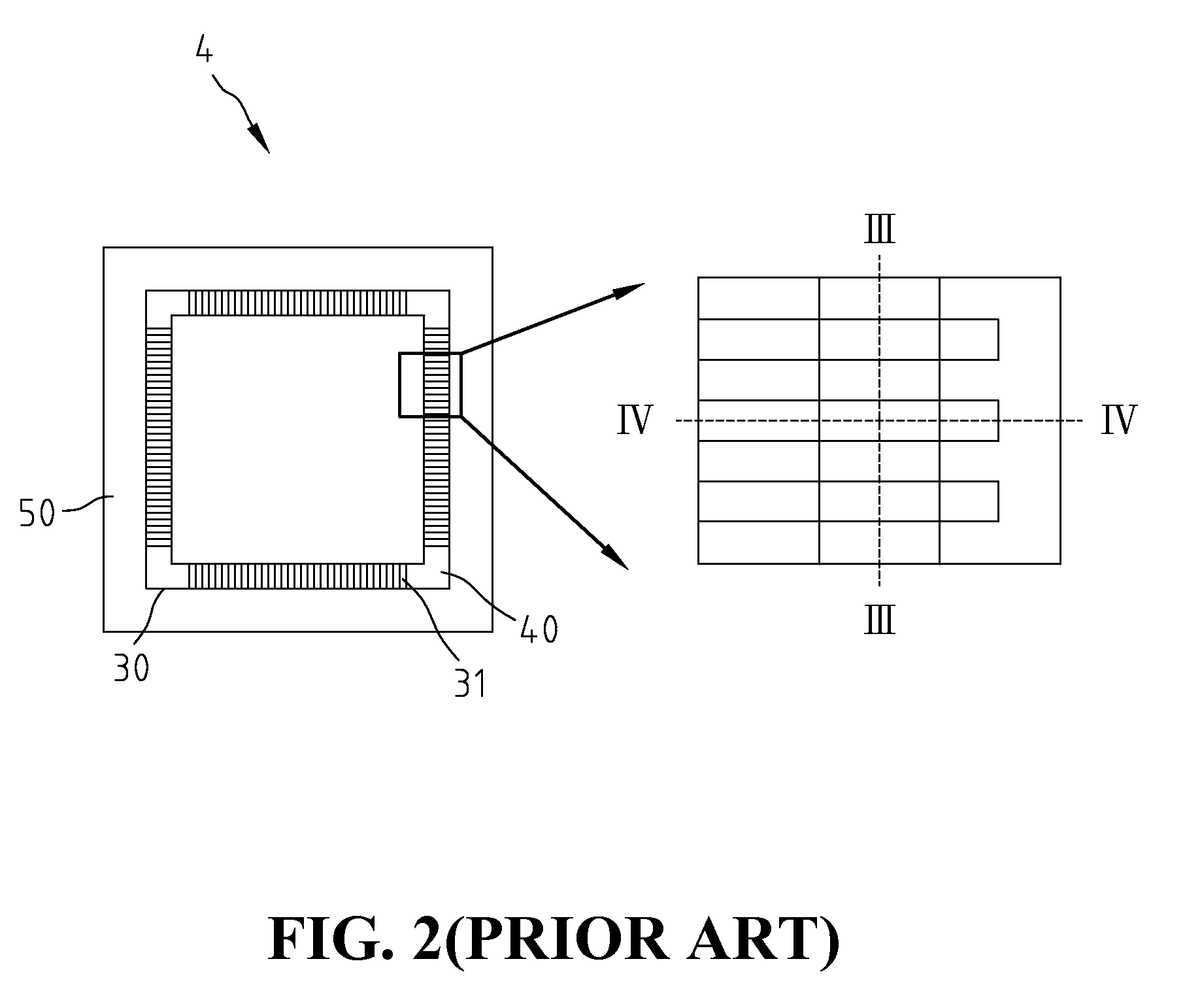

Flip-Chip Package Structure

InactiveUS20110049703A1Save substrate areaMade smallSemiconductor/solid-state device detailsSolid-state devicesSolder maskLead bonding

A flip-chip (FC) package structure is provided. The FC package structure includes a substrate, a chip, a plurality of copper platforms, a plurality of copper bumps, a plating layer, a circuit layer and a solder mask layer. The copper bumps are disposed on the substrate. The copper platforms are stacked on the copper bumps. The plating layer covers the copper bumps and the copper platforms, for contacting with chip foot pads configured at a bottom of the chip. The FC package structure does not need to reserve a space for wire bonding, thus saving the area of the substrate. The copper platforms are stacked on the copper bumps, and are higher than the circuit pattern layer. Therefore, the chip is blocked up, and the gap between the chip and the substrate is enlarged, thus preventing the risk of configuring voids when filling the cladding material and improving the packaging yield.

Owner:KINSUS INTERCONNECT TECH

Unmanned aerial vehicle launching and landing system

The invention relates to a system for landing UAV's. The system comprises a slingshot structure that includes arm based structure and an axis installed along the arm of the structure and enabling the arm to move around it. The system comprises a base connecting the axis to a platform at which the system is installable. The system also includes a controlled pulling and braking means that connects the arm of the structure and the platform upon which the system is installable and stretchable elastic installed in a stretched manner at a gap formed between two arms and set to connect with a landing UAV. At the landing phase, the controlled pulling and braking of the system essentially breaks the motion of the arm based structure that is propelled to revolve around the system's axis, and propels the structure to move around the axis.

Owner:ELBIT SYST LTD

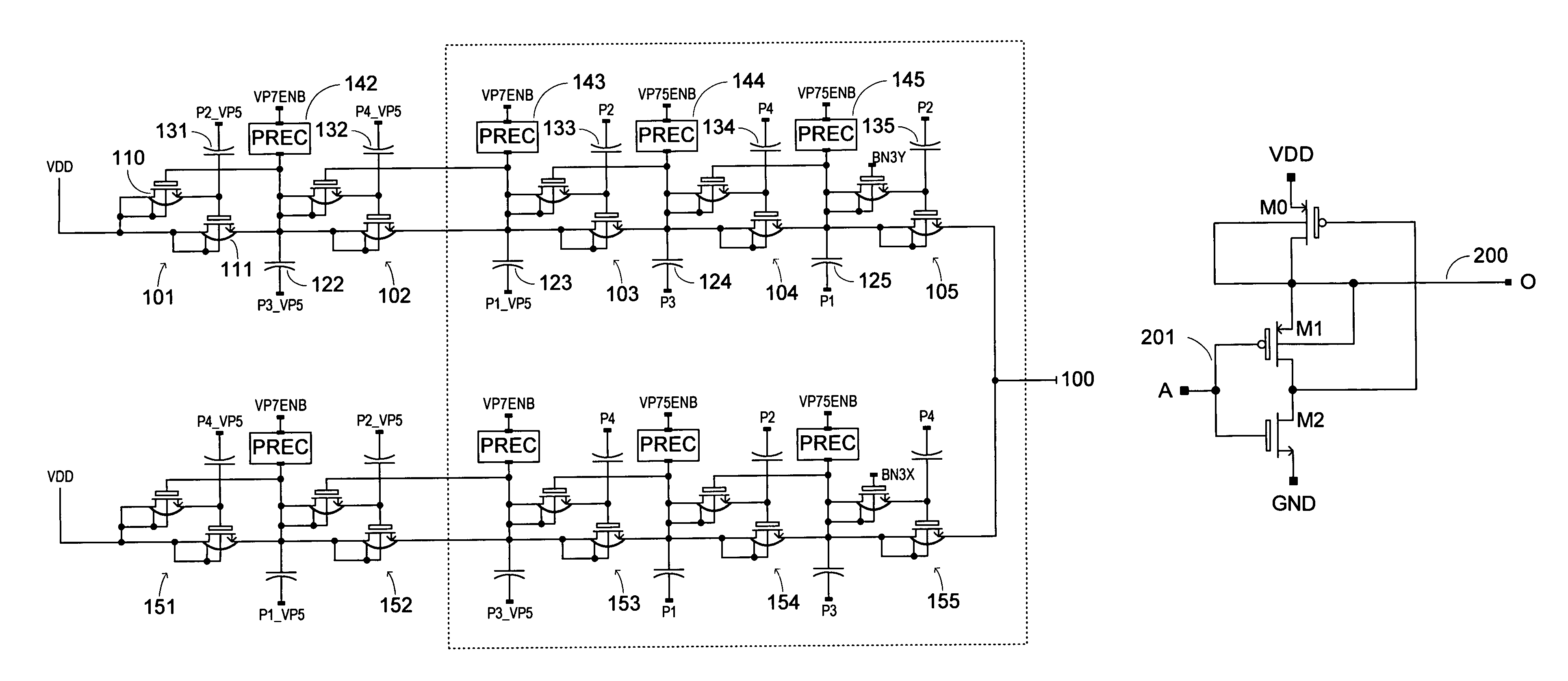

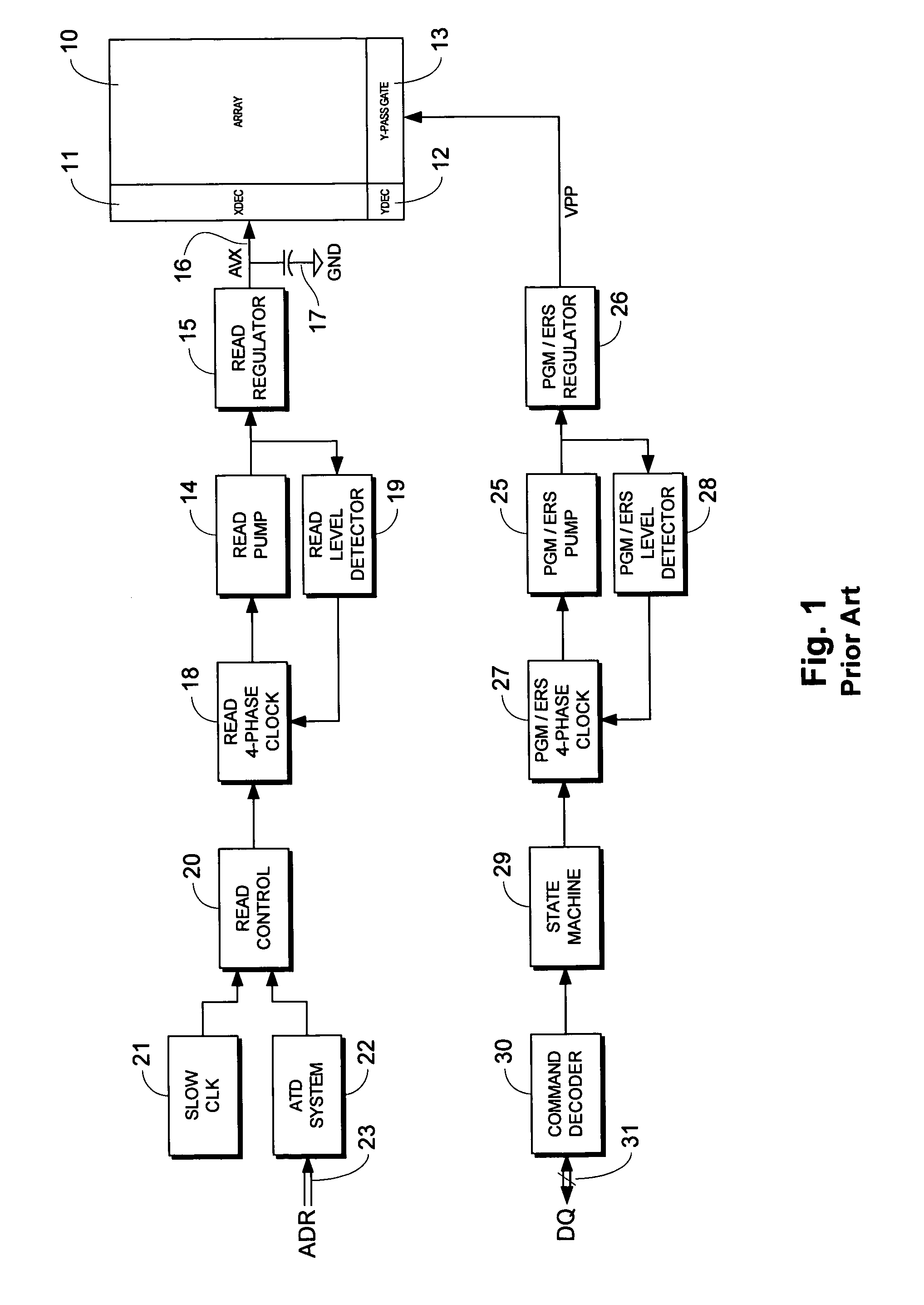

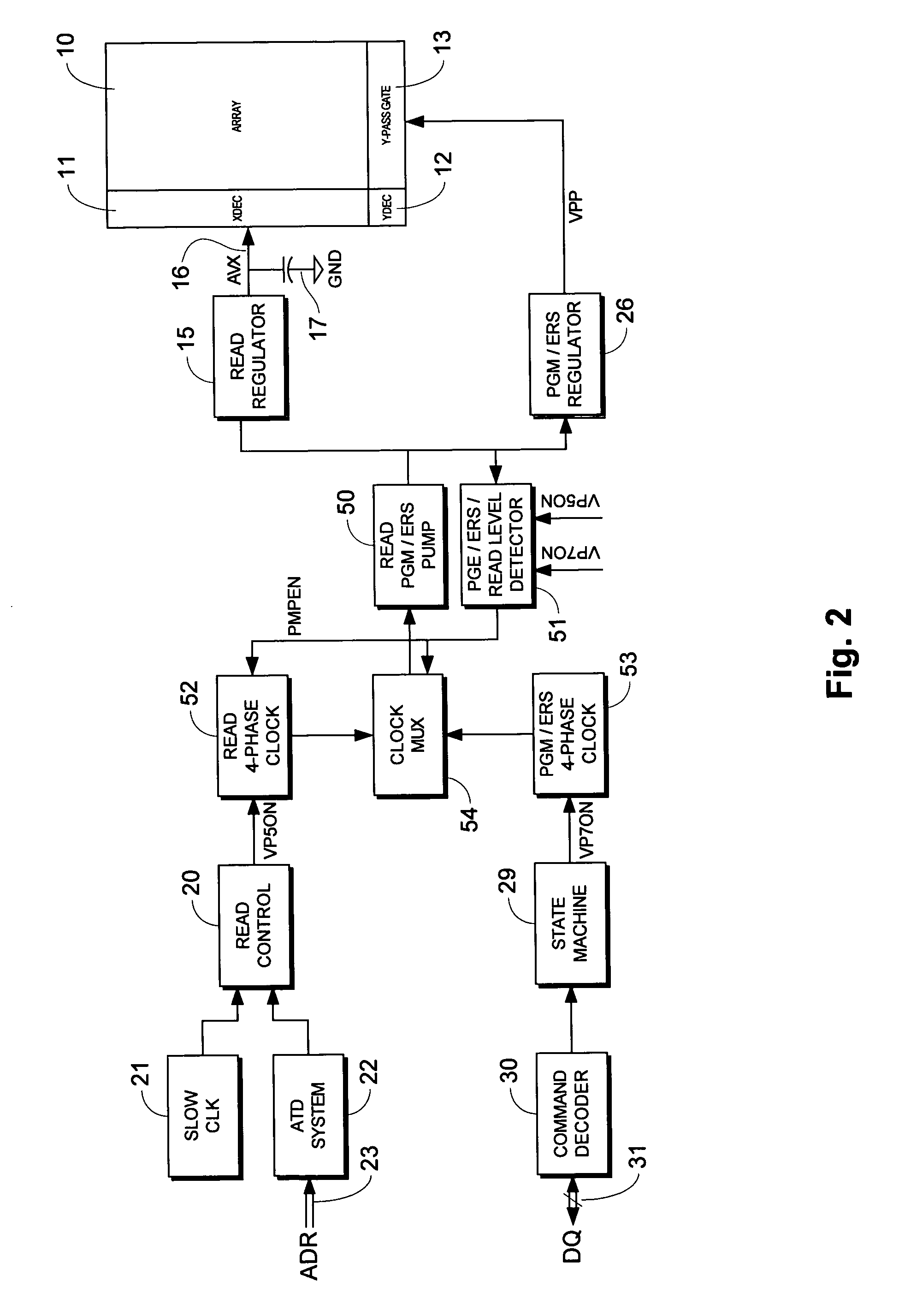

Multi-stage charge pump without threshold drop with frequency modulation between embedded mode operations

ActiveUS7595682B2Operating environmentReduce in quantityAc-dc conversionApparatus without intermediate ac conversionLow voltageEngineering

A multimode charge pump circuit has a single charge pump that is responsive to a set of clock signals. The set of clock signals is provided in a first mode with a variable frequency according to a first function of the supply potential and temperature, and in a second mode with a variable frequency according to a second function of the supply potential and temperature. Circuitry configures all of the plurality of stages in series during the first mode in order to produce a higher voltage output, and configures a subset of the plurality of stages in series, while disabling the other stages, during the second mode in order to produce a lower voltage output. A precharge circuit is provided that operates as a supply node in the second mode, and as a precharge / clamp in the first mode.

Owner:MACRONIX INT CO LTD

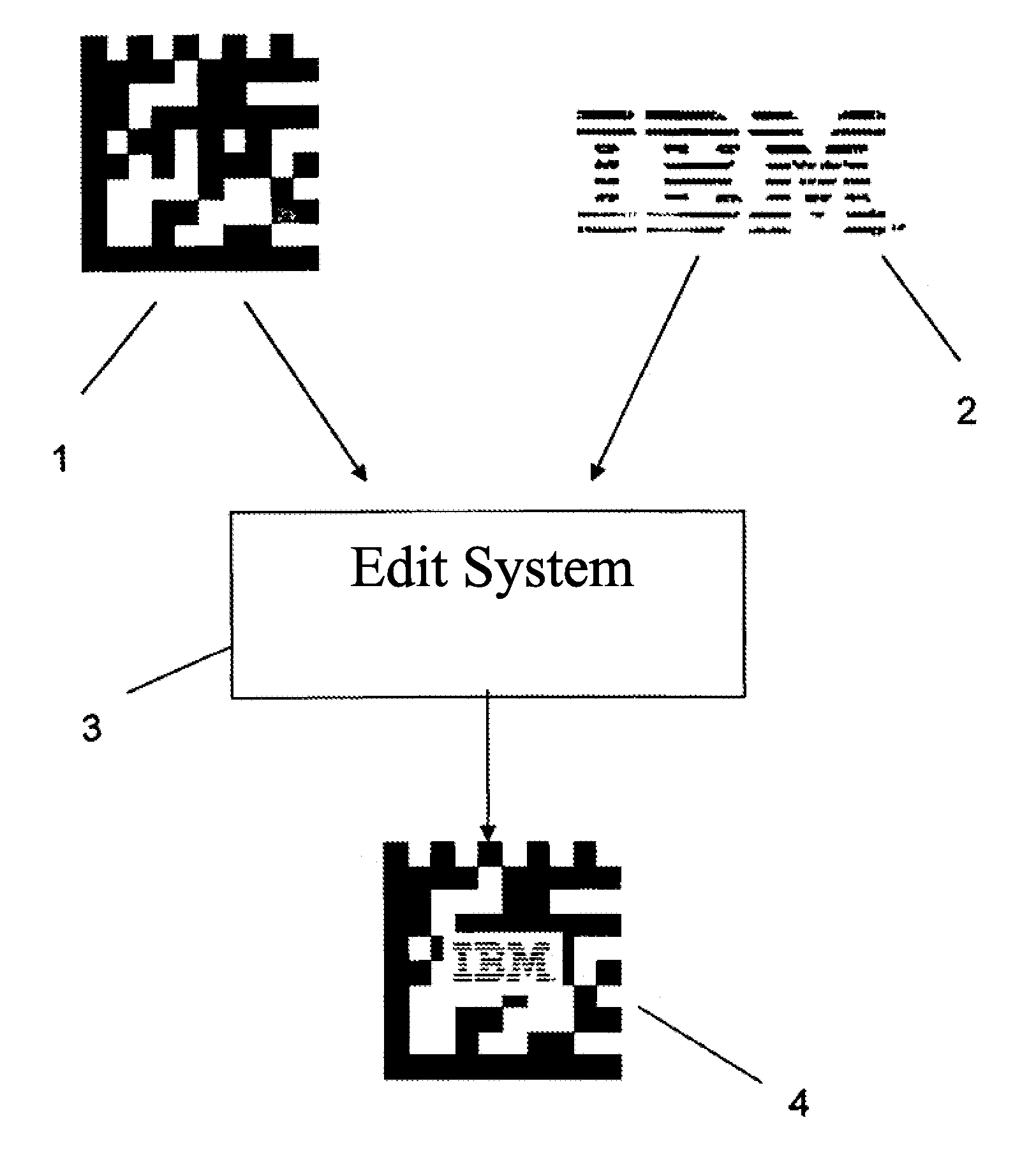

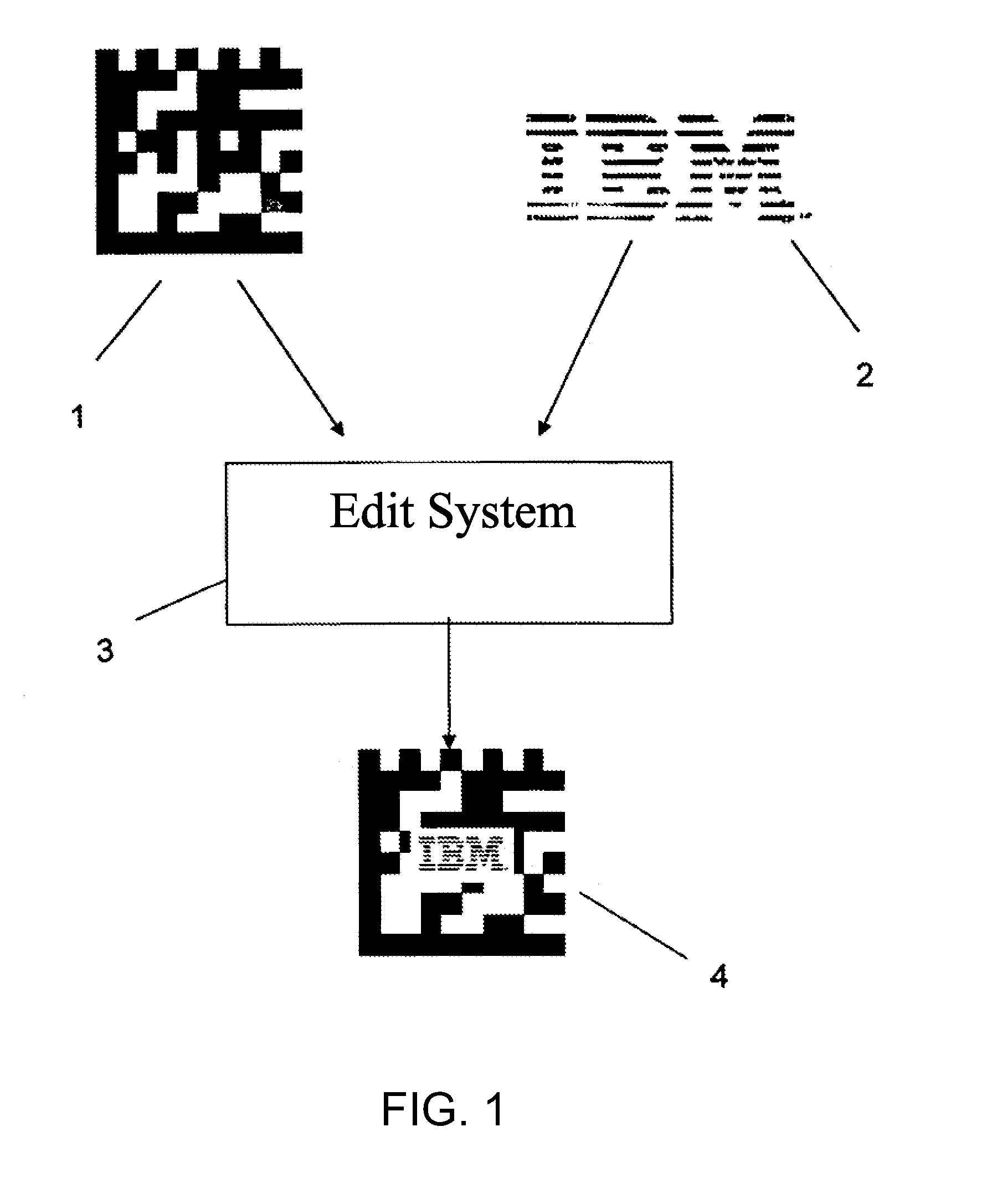

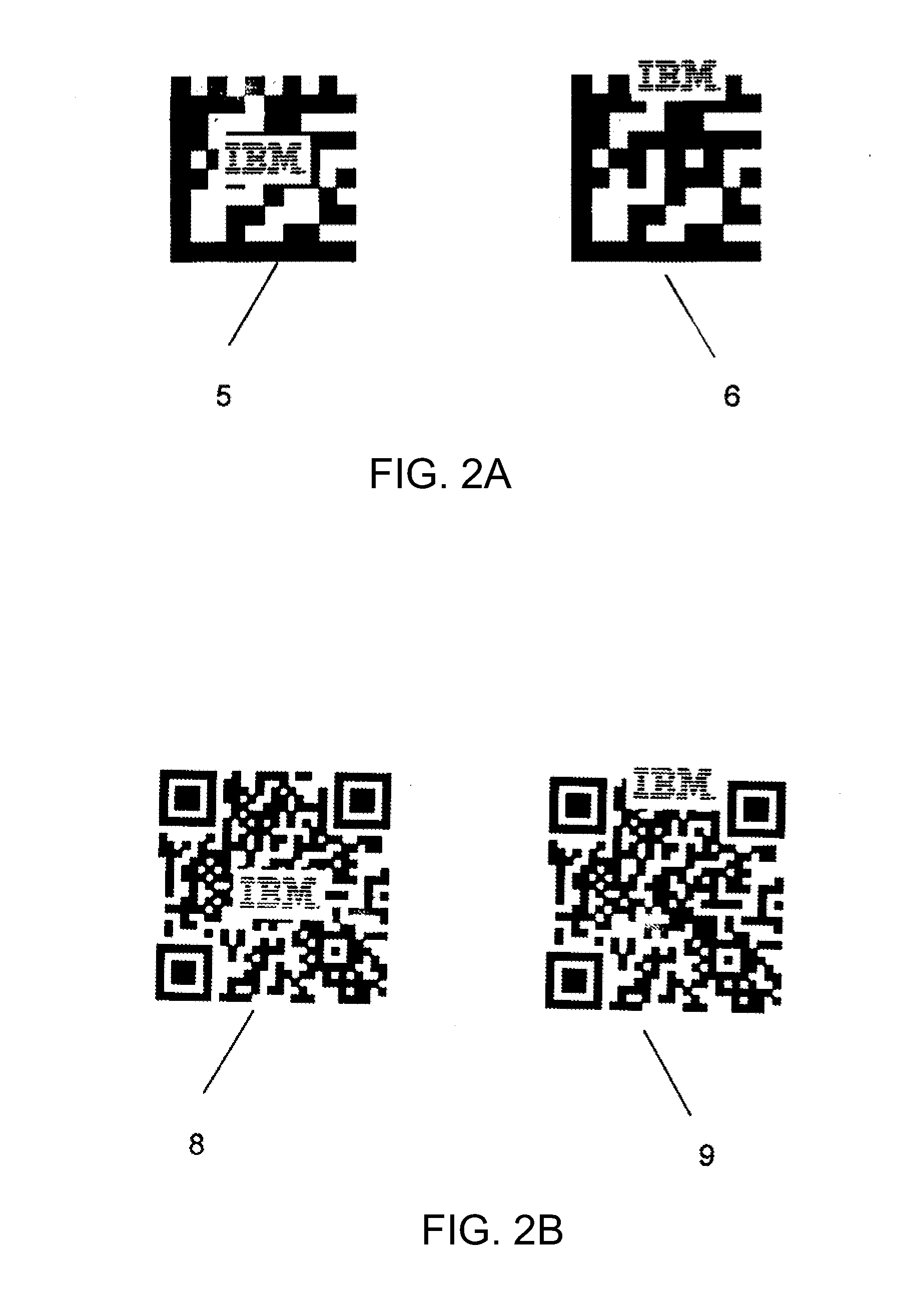

System for Synthesizing a Two Dimensional Code and a Logo and the Method Thereof

InactiveUS20090255992A1Good effectSave extra spaceCharacter and pattern recognitionRecord carriers used with machinesTheoretical computer scienceIdentification device

Briefly, a system for synthesizing a two dimensional code and a logo and the method thereof are presented. The system for generating a synthesized two dimensional code comprises synthesizing means, for synthesizing an original two dimensional code and a visually readable logo to form the synthesized two dimensional code, with at least a part of the visually readable logo being overlapped with the original two dimensional code; identifying means, for reading and identifying the synthesized two dimensional code; and adjusting means, if the synthesized two dimensional code being identified by the identifying means has a code error rate of the synthesized two dimensional code larger than an error correction rate, the adjusting means adjusting the size of the visually readable logo and / or the location of the visually readable logo with respect to the original two dimensional code. The present invention may integrate enterprise logo(s), brand logo(s) and product logo(s) with a two dimensional code as a whole, which may save areas and achieve better effect for brand and product promotion.

Owner:GMEDIA CORP

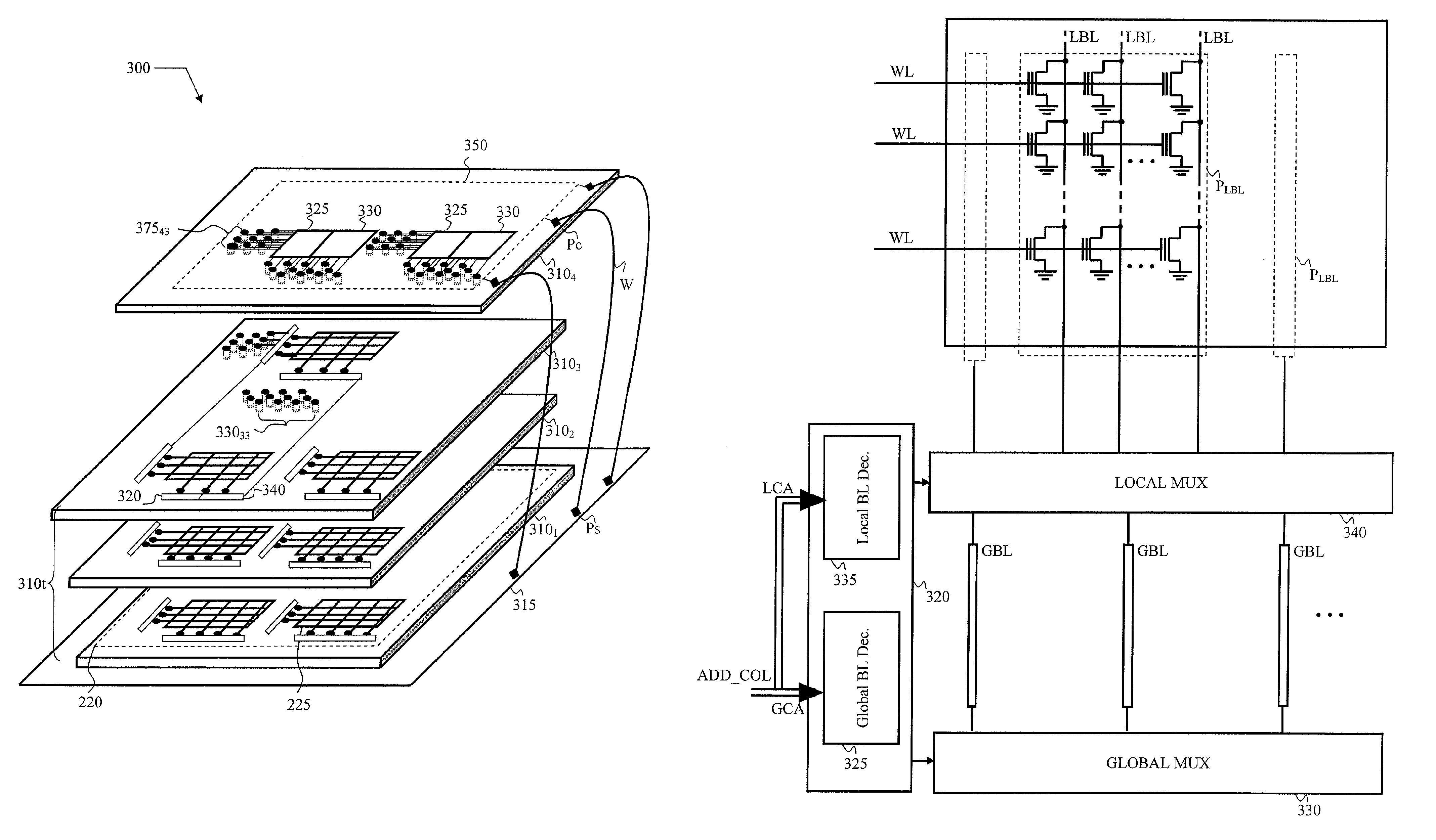

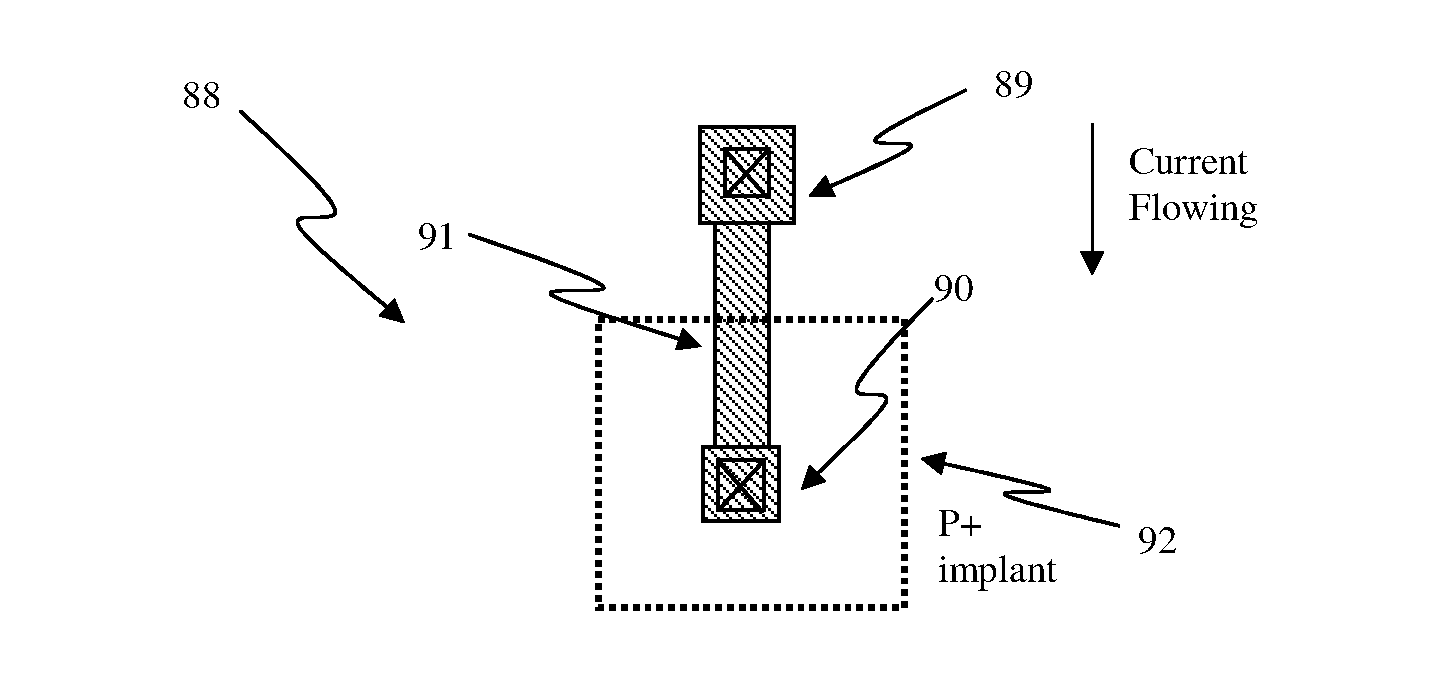

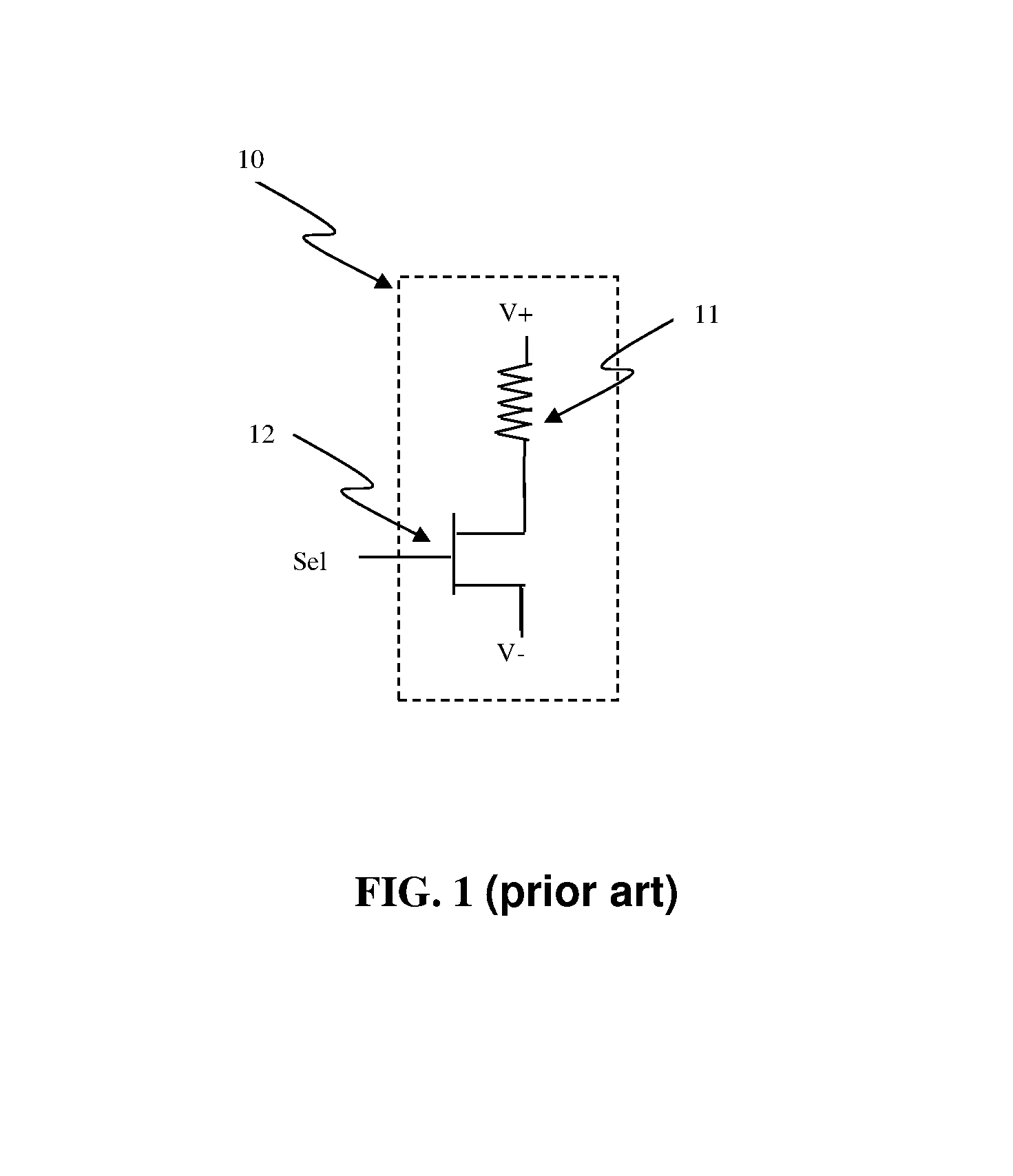

Circuit and system of using polysilicon diode as program selector for one-time programmable devices

ActiveUS20120044737A1Avoid shortingSave extra spaceSolid-state devicesRead-only memoriesLow voltageHemt circuits

Polysilicon diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has an OTP element coupled to a diode in a memory cell. The diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. By applying a high voltage to an OTP element coupled to the P-terminal of a diode and switching the N-terminal of a diode to a low voltage for suitable duration of time, a current flows through the OTP element may change the resistance state. On the polysilicon diode, the spacing and doping level of a gap between the P- and N-implants can be controlled for different breakdown voltages and leakage currents. The Silicide Block Layer (SBL) can be used to block silicide formation on the top of polysilicon to prevent shorting. If the OTP element is a polysilicon electrical fuse, the fuse element can be merged with the polysilicon diode in one piece to save area.

Owner:ATTOPSEMI TECH CO LTD

Pfet-based ESD protection strategy for improved external latch-up robustness

InactiveUS20050045952A1Avoid latch-upLatch-up robustness be improveTransistorSemiconductor/solid-state device detailsElectrostatic dischargeIntegrated circuit

A method and apparatus for protection against electrostatic discharge (ESD) with improved latch-up robustness featuring a silicide blocked p-type field effect transistor is disclosed. The transistor has a snapback voltage that is less than the breakdown voltage of its gate oxide. The transistor is part of an integrated circuit and coupled to an I / O pad having no n-diffusions connected directly to it. A given integrated circuit may employ one or more the transistors configured in accordance with the invention that are associated with one or more I / O pads within the integrated circuit.

Owner:IBM CORP

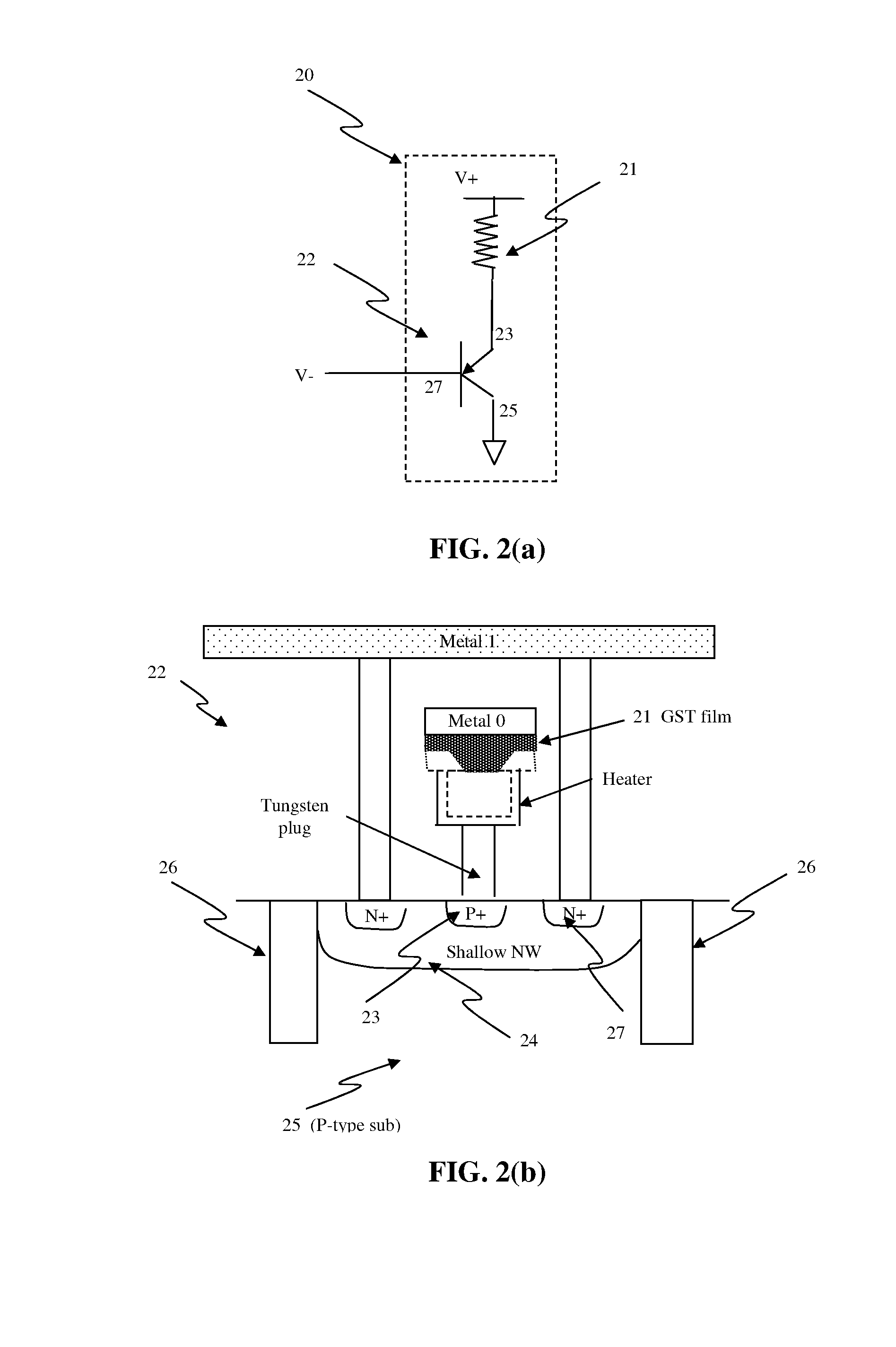

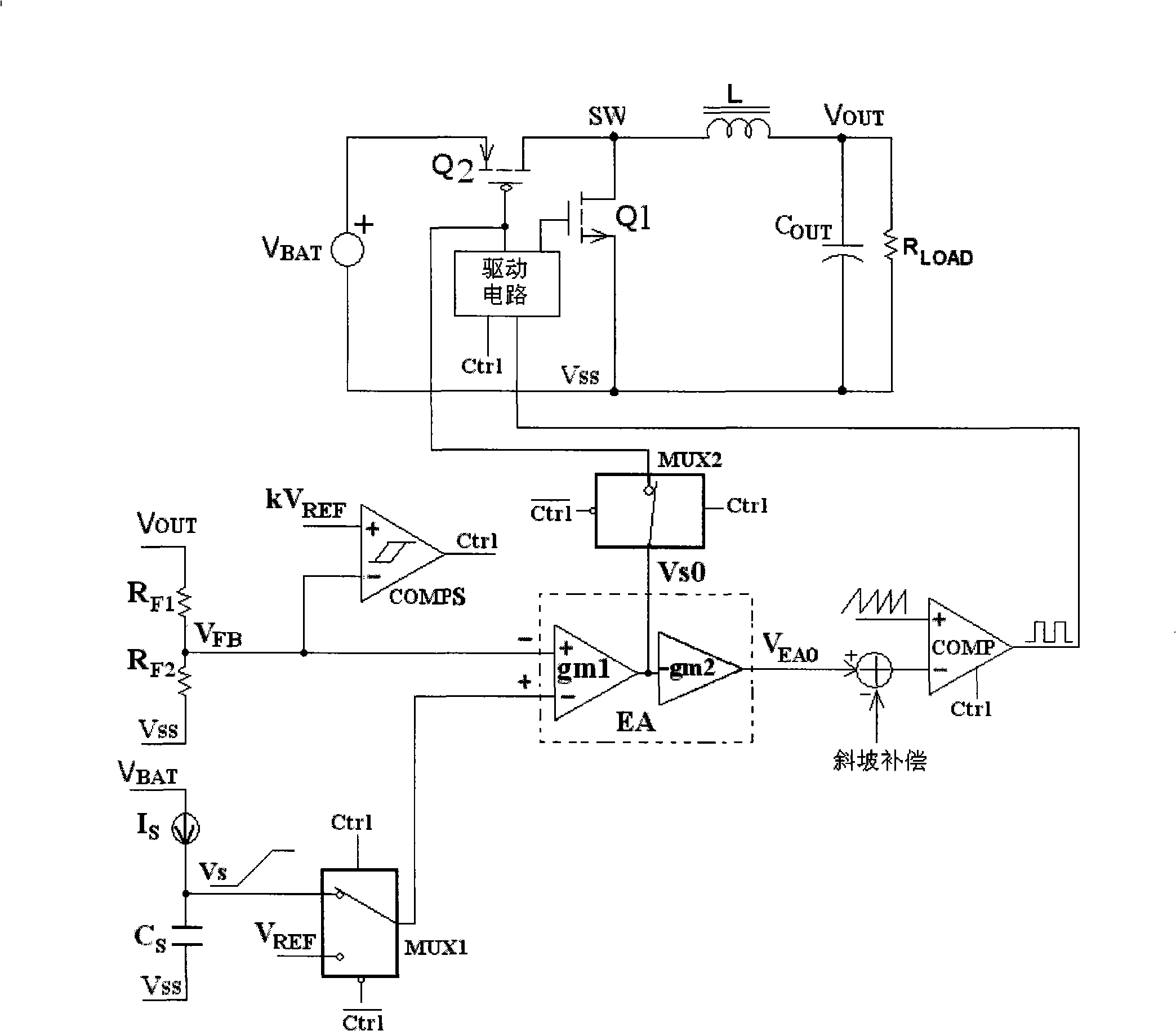

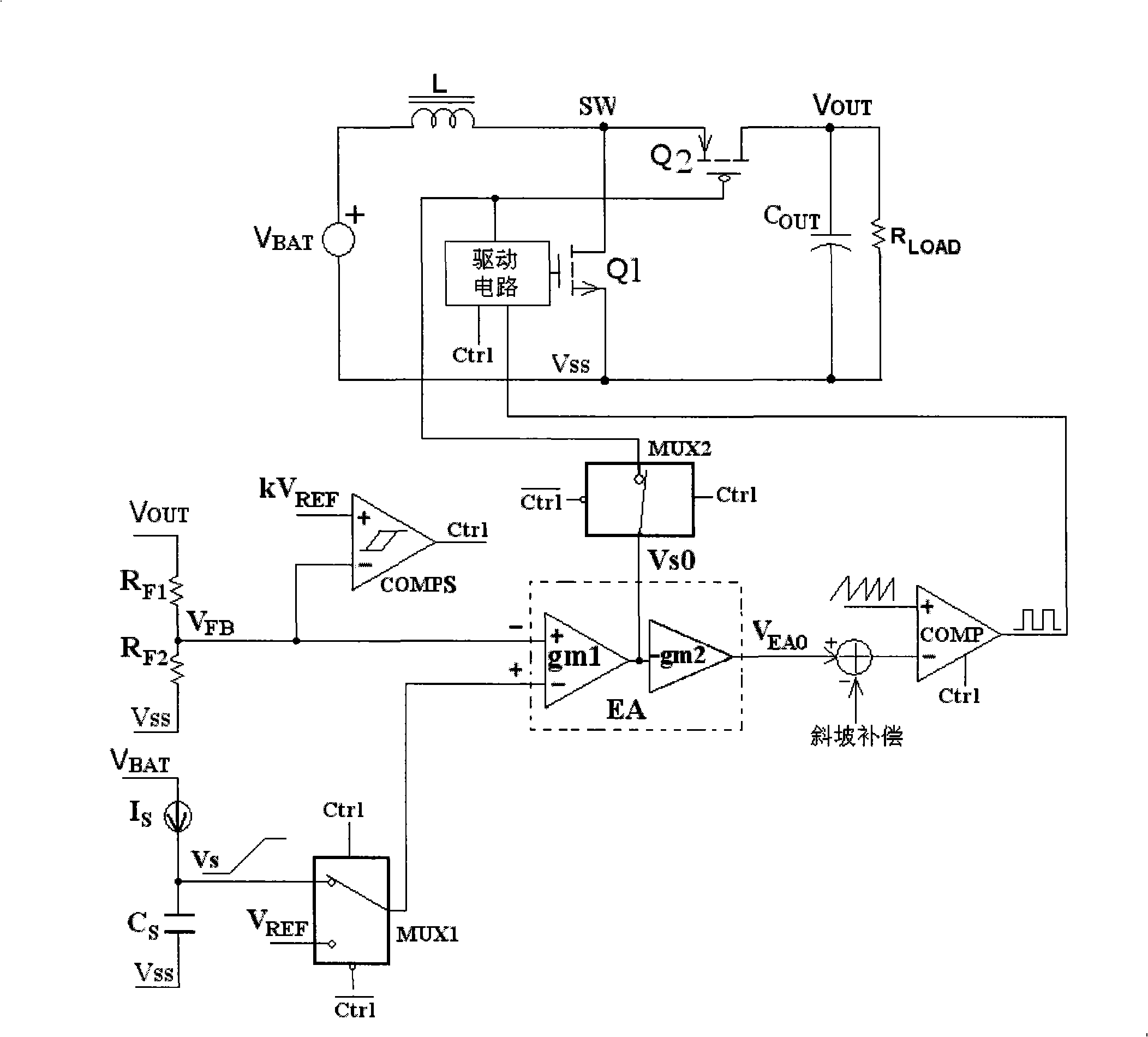

Soft starting device capable of implementing linear control

InactiveCN101295922ASave extra spaceSave powerDc-dc conversionElectric variable regulationCapacitanceVoltage generator

The invention discloses a soft start device that can realize linear control, which comprises a working circuit, a soft start circuit and a start control circuit; the working circuit comprises a DC power source, a load capacitance, a power tube and a feedback circuit which are connected between the DC power source and the load capacitance and also a soft start circuit and a start control circuit, and the power tube is provided with a control end; the soft start circuit comprises a voltage generator, the output voltage of which is increased gradually after start, and an error amplifier, the input end of which is connected with the output end of the voltage generator; the input end of the error amplifier is connected between the output end of the power tube and the ground, while the output end of the error amplifier is connected to the control end of the power tube; when the start control circuit detects that the start begins, the soft start circuit is set to be in normal working state and a feedback circuit is set to be in off working state. The adoption of the device of the invention can avoid surge current at the moment when the power source charges the load capacitance at the instance when the circuit is electrified, can repeatedly use the existing error amplifier in the original circuit structure and save the areas and energy consumption of chips.

Owner:VIMICRO CORP

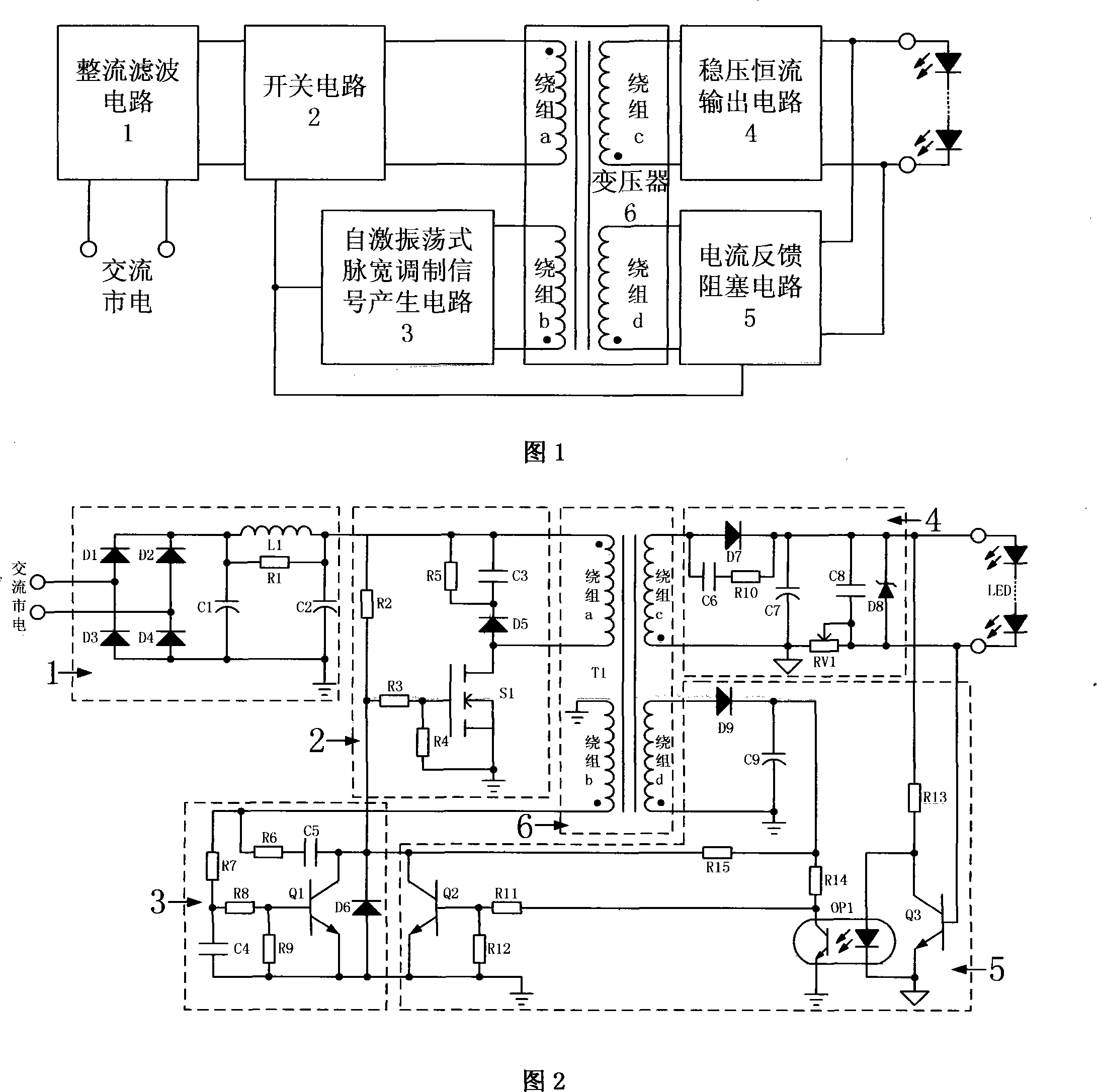

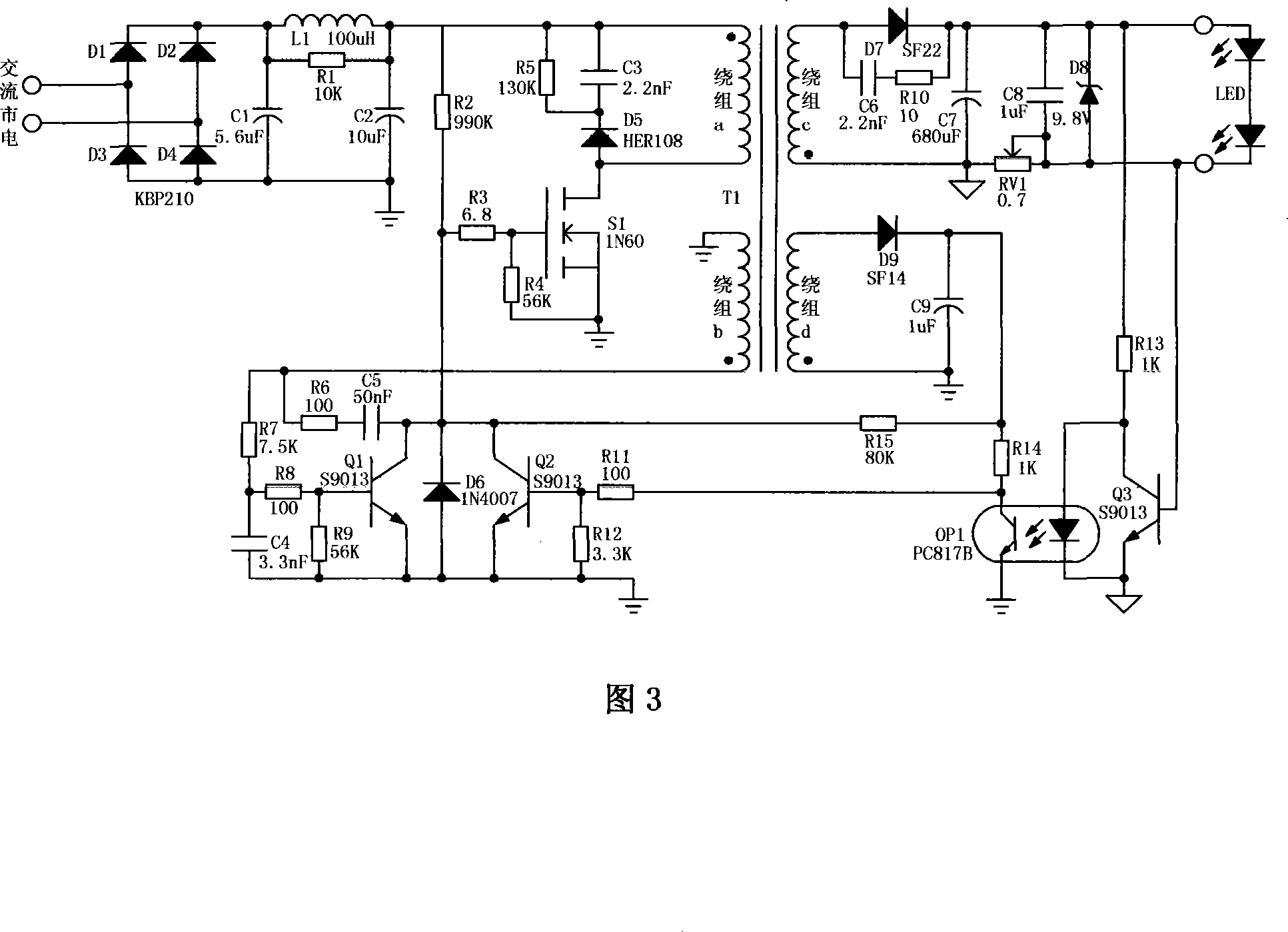

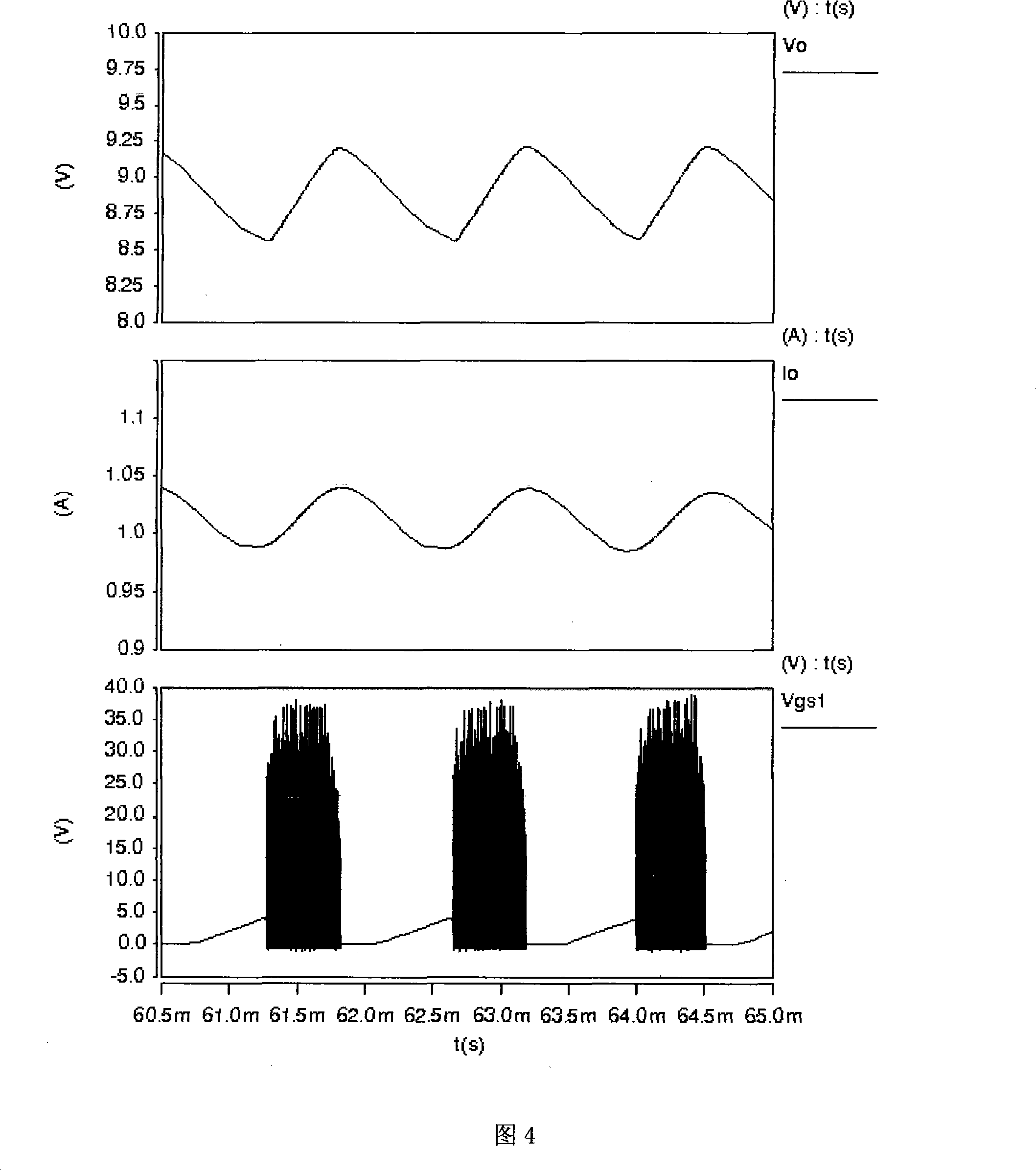

Self-excited oscillation type high power LED constant-current driving circuit

InactiveCN101227778ALow costImprove reliabilityElectric light circuit arrangementElectric variable regulationTransformerSelf-oscillation

The invention provides a self-oscillation type high power LED constant-current drive circuit with low cost, high reliability and stability and high drive efficiency, the circuit comprises a rectifier and filter circuit, a switching circuit, a steady voltage constant current output circuit, a transformer, a self-oscillation type pulse width modulation signals generating circuit and a current feedback obstruction circuit, wherein the rectifier and filter circuit accesses commercial power into rectification, changes the commercial power into direct current, and then outputs commercial power to the switching circuit to switch in a self-oscillation type with high frequency, then high frequency voltage of the steady voltage constant current output circuit is transformed into direct voltage through the transformer to drive the LED, simultaneously sampling current signals produces jam signals through the current feedback obstruction circuit to control the switching circuit to work, the circuit does not adopt any driving chips and only uses fewer common individual devices to form a self-oscillation type structure to drive the switching circuit and to combine current feedbacks, which realizes constant current driving of the high power LED.

Owner:NANTONG LIWANG MACHINE TOOL +1

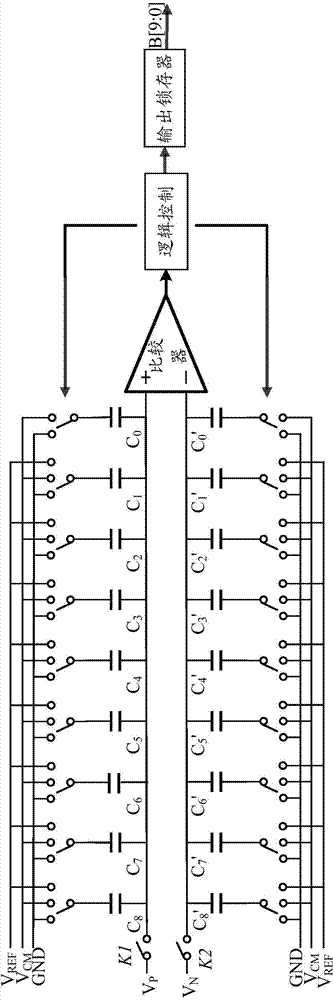

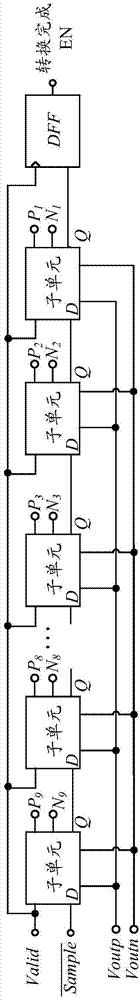

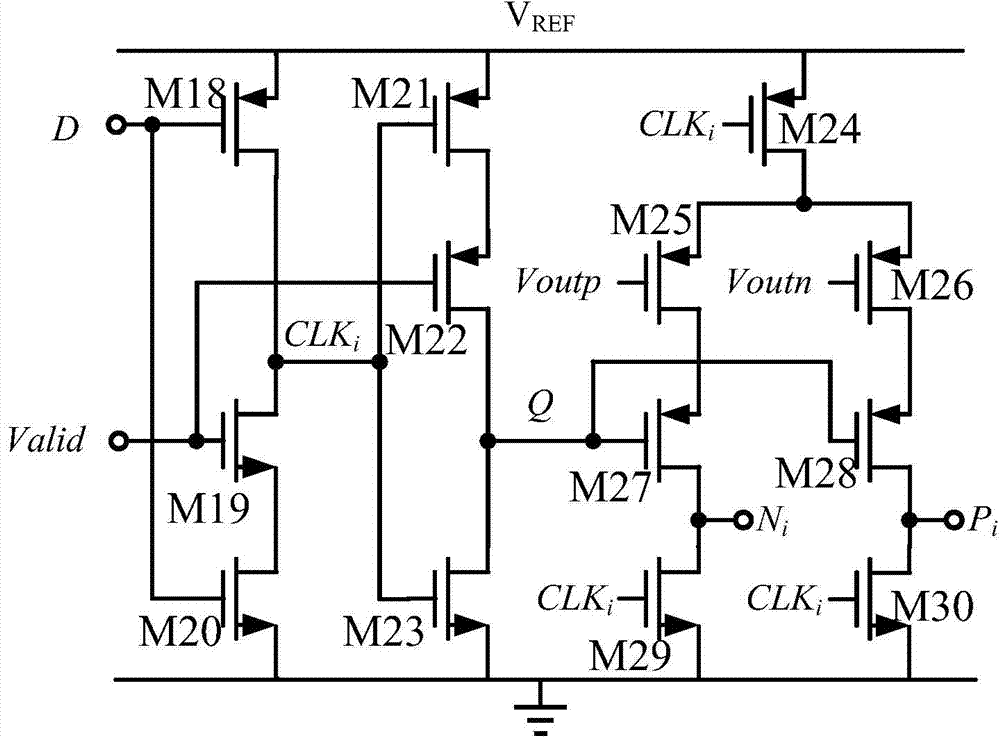

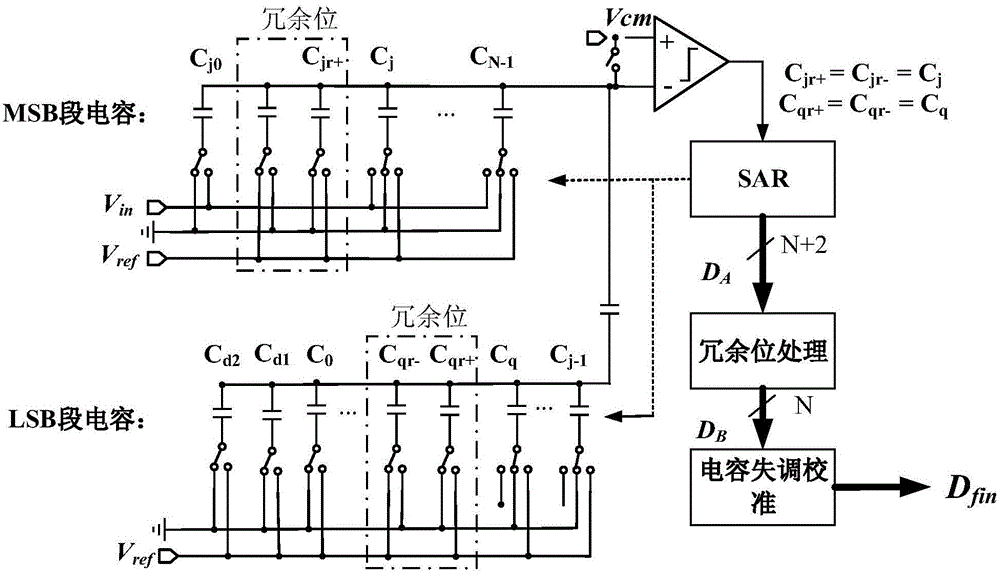

10-bit ultra-low-power successive approximation register analog-to-digital converter based on charge redistribution

ActiveCN104124972AReduce areaSave extra spaceAnalogue/digital conversionElectric signal transmission systemsComparators circuitsUltra low power

The invention provides a 10-bit ultra-low-power successive approximation register analog-to-digital converter based on charge redistribution. The analog-to-digital converter comprises a sampling network, a differential capacitor array, a comparator and a successive approximation control logic device; the differential capacitor array is connected with the sampling network, the comparator is connected with the differential capacitor array, and the successive approximation control logic device is connected with the comparator. The differential capacitor array includes a first capacitor array connected with a non-inverting input end of a comparator circuit and a second capacitor array connected with an inverting input end of the comparator circuit. Each of the first capacitor array and the second capacitor array consists of nine groups of capacitors which are of binary structures; bottom plates of all redundant capacitors are selectively connected with common-mode voltage or ground and the rest eight groups of capacitors are selectively connected with the common-mode voltage, power voltage or ground. An output end of the successive approximation control logic device controls switching of capacitor switches of the differential capacitor array to be connected with the voltage selectively. The first capacitor array and the second capacitor array sample input signals and input samples to the comparator, and a comparison result of the comparator is input to the successive approximation control logic device.

Owner:XIDIAN UNIV

Semiconductor package

InactiveUS7327006B2Shorten the timeIncrease the areaSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package includes a combination die embedded in a base. The combination die includes a plurality of functional blocks, where the functional blocks are insulated from one another on the combination die. Each functional block has plural die connectors. The base includes insulating layers conductive layers and vias. Each conductive layer has parts removed to form a pattern. The base is provided with a plurality of external connectors. A conductive path, made from a part of at least one of the conductive layers and at least one of the vias, connects one of the die connectors to a respective one of the external connectors.

Owner:NOKIA CORP

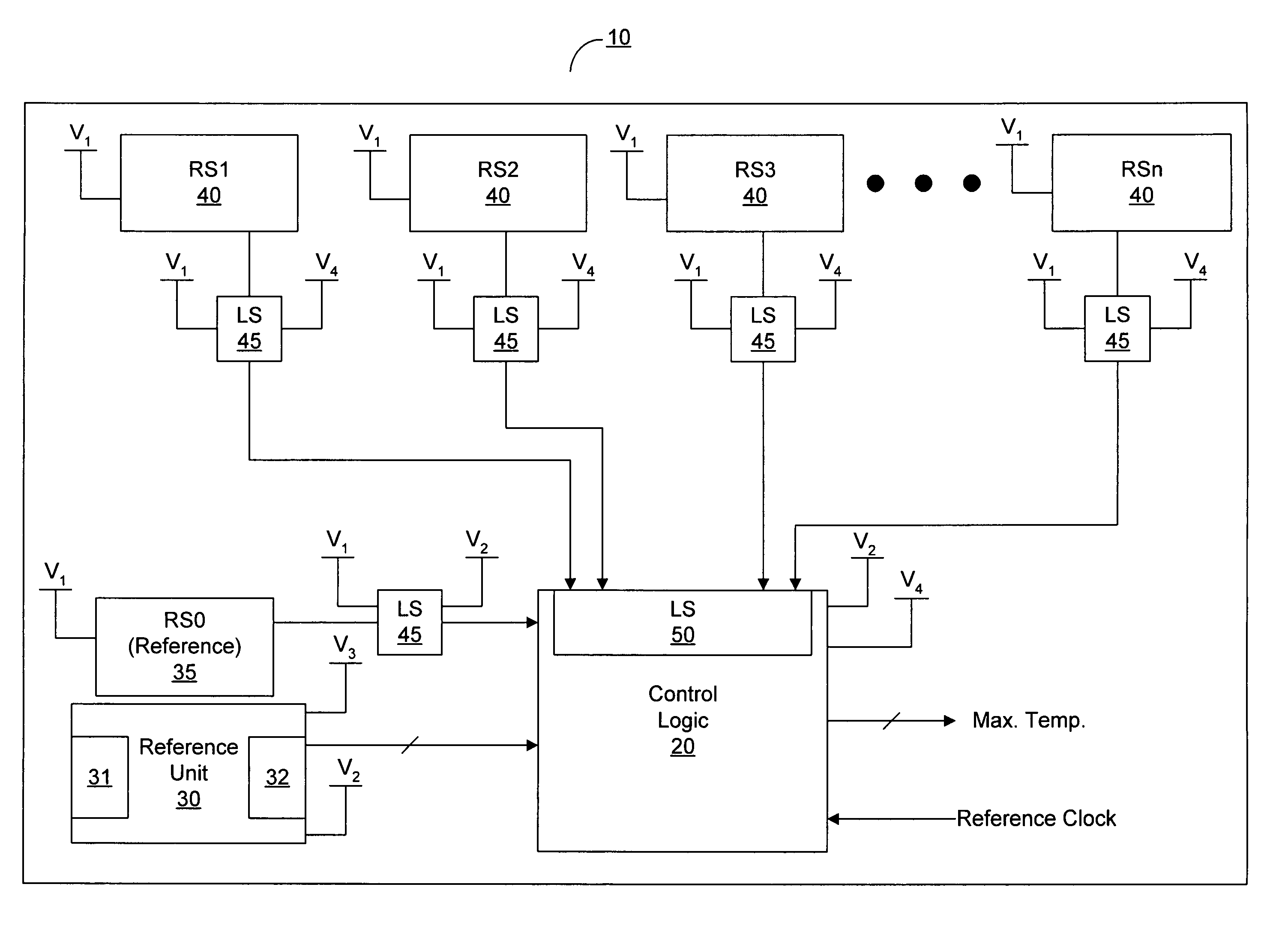

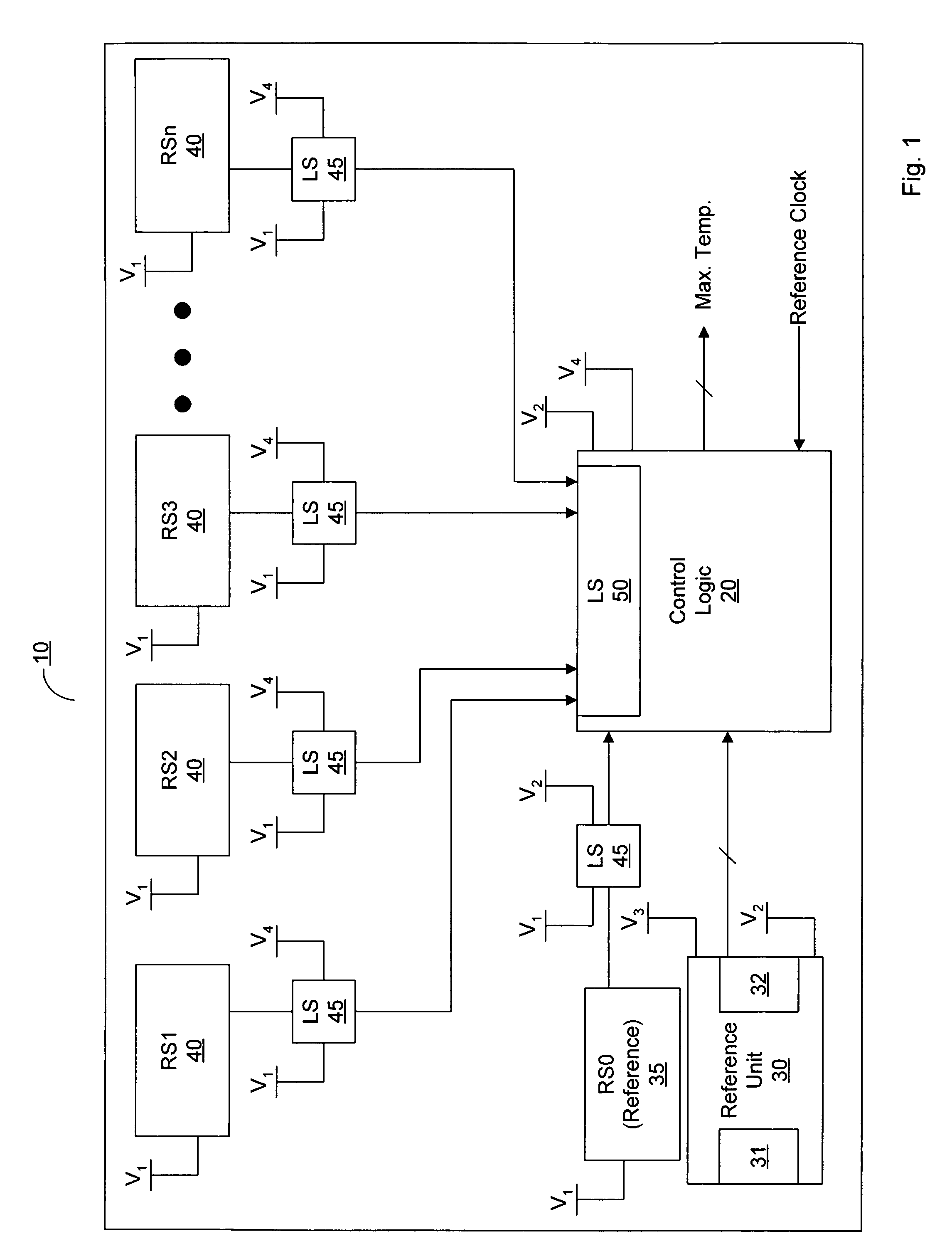

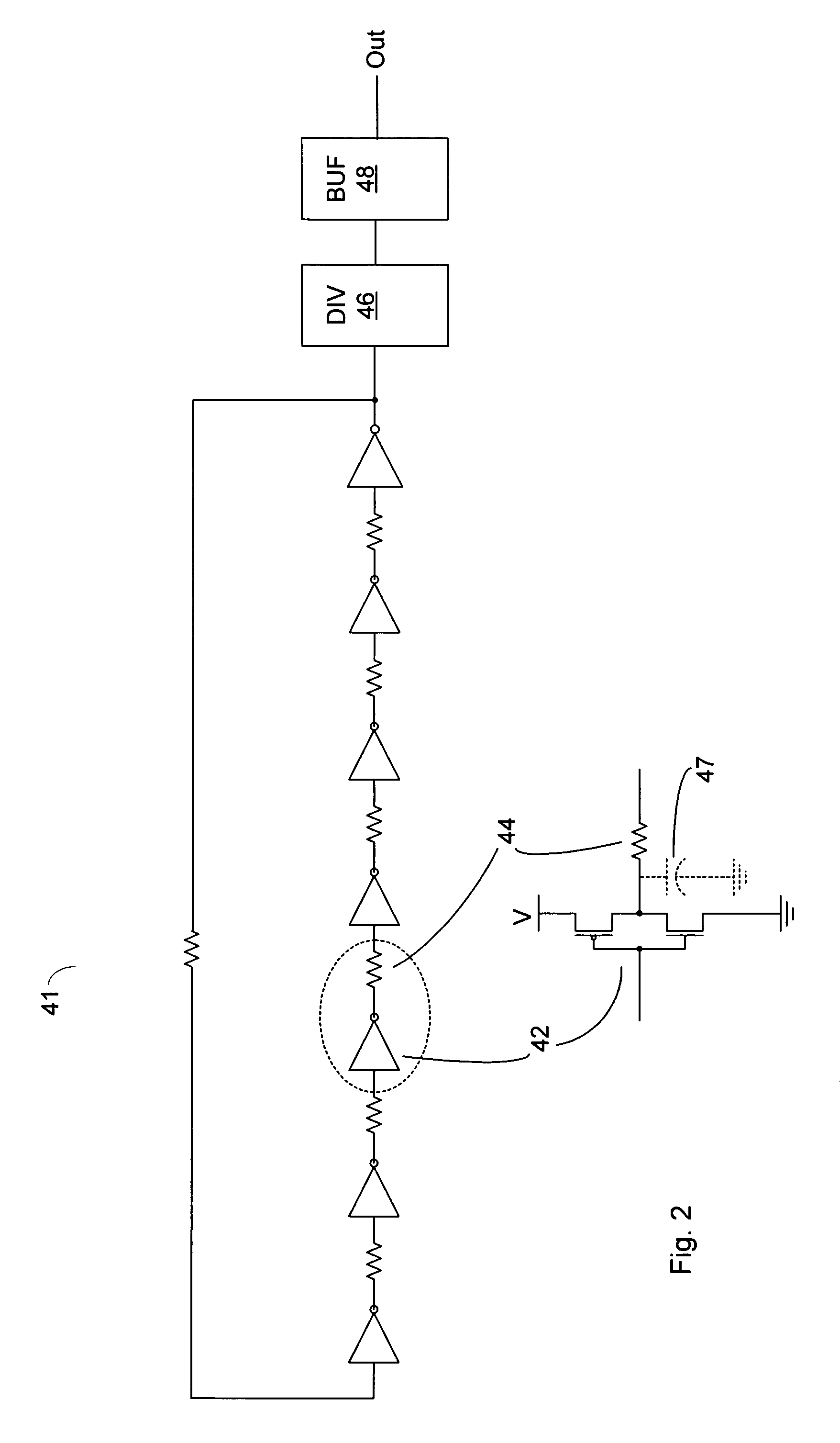

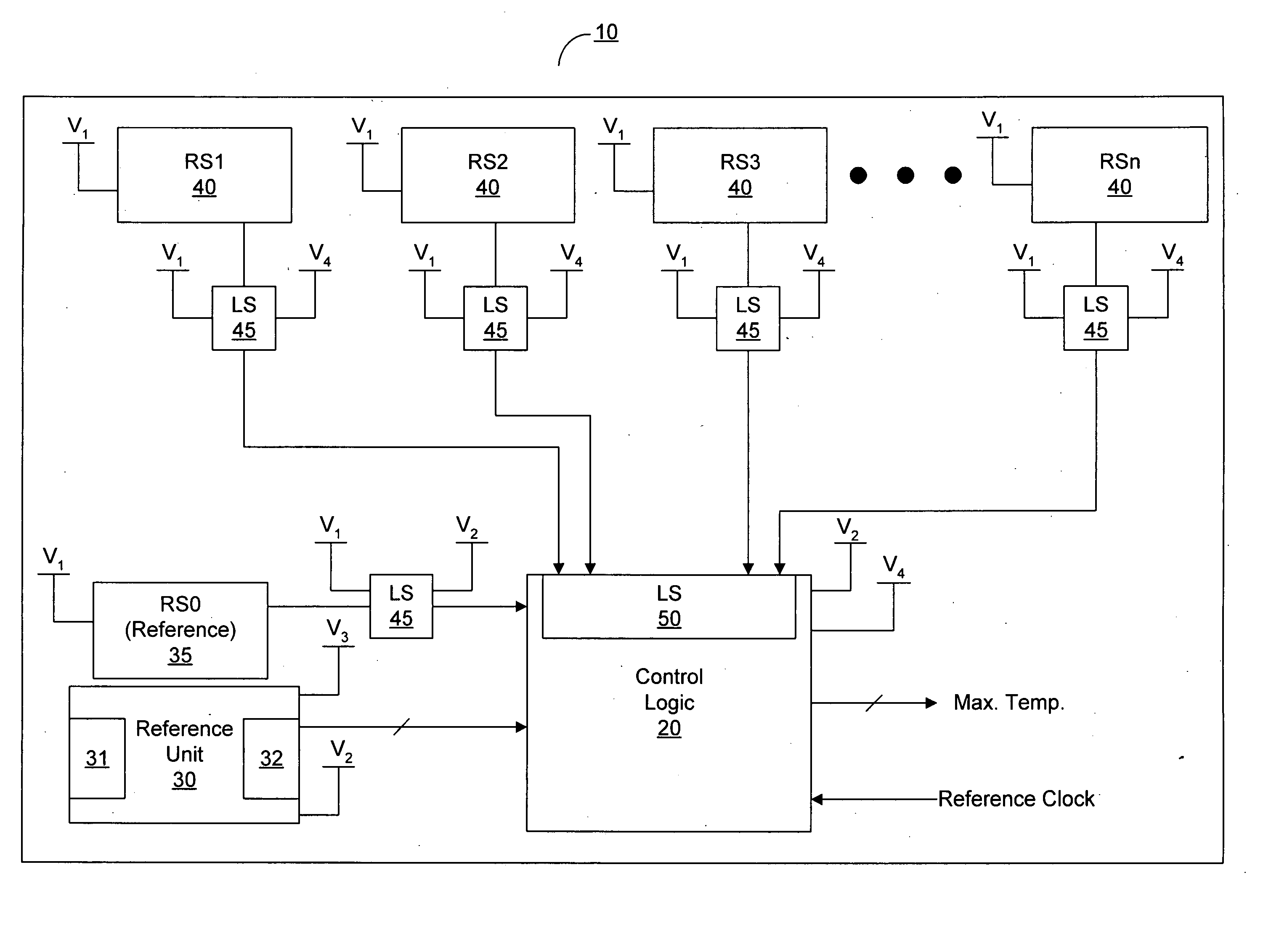

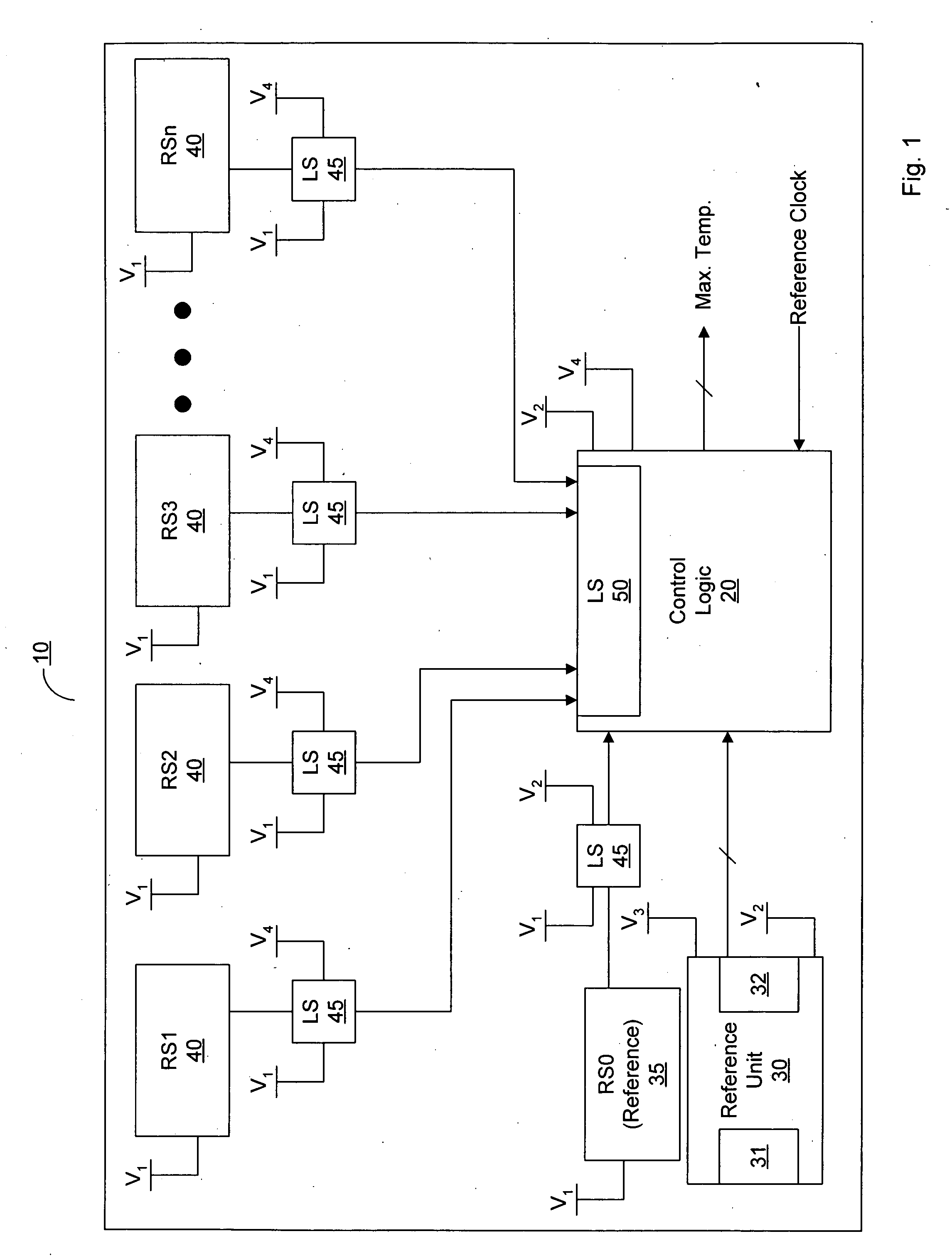

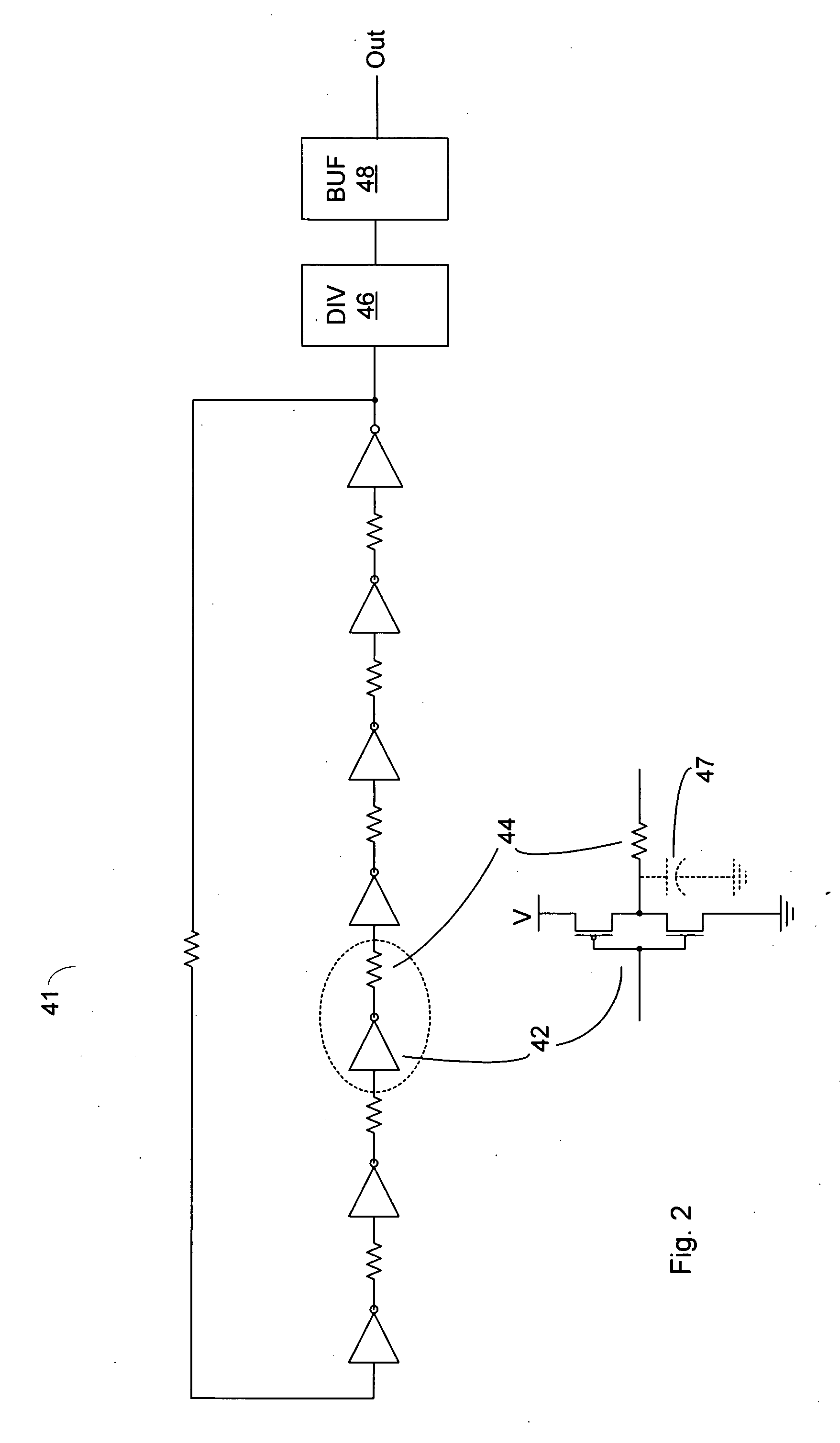

Method and apparatus for temperature sensing in integrated circuits

InactiveUS7455450B2Easy wiringSave extra spaceThermometer detailsThermometers using material expansion/contactionEngineeringMaximum temperature

A method and apparatus for temperature sensing in an IC. The IC includes a plurality of remote temperature sensors each coupled to a control logic unit. The plurality of remote temperature sensors may be distributed throughout the integrated circuit. The integrated circuit includes a reference unit coupled to provide a reference temperature to the control logic unit and a reference sensor coupled to provide a signal having a reference frequency to the control logic unit. The reference unit and the reference sensor are located near each other. The control logic unit is configured to correlate the reference frequency received from the reference sensor with the reference temperature received from the reference unit. The control logic unit is further configured to determine the temperature of each of the remote temperature sensors based on this correlation, and also configured to determine the maximum temperature of all of the temperature sensors.

Owner:ADVANCED MICRO DEVICES INC

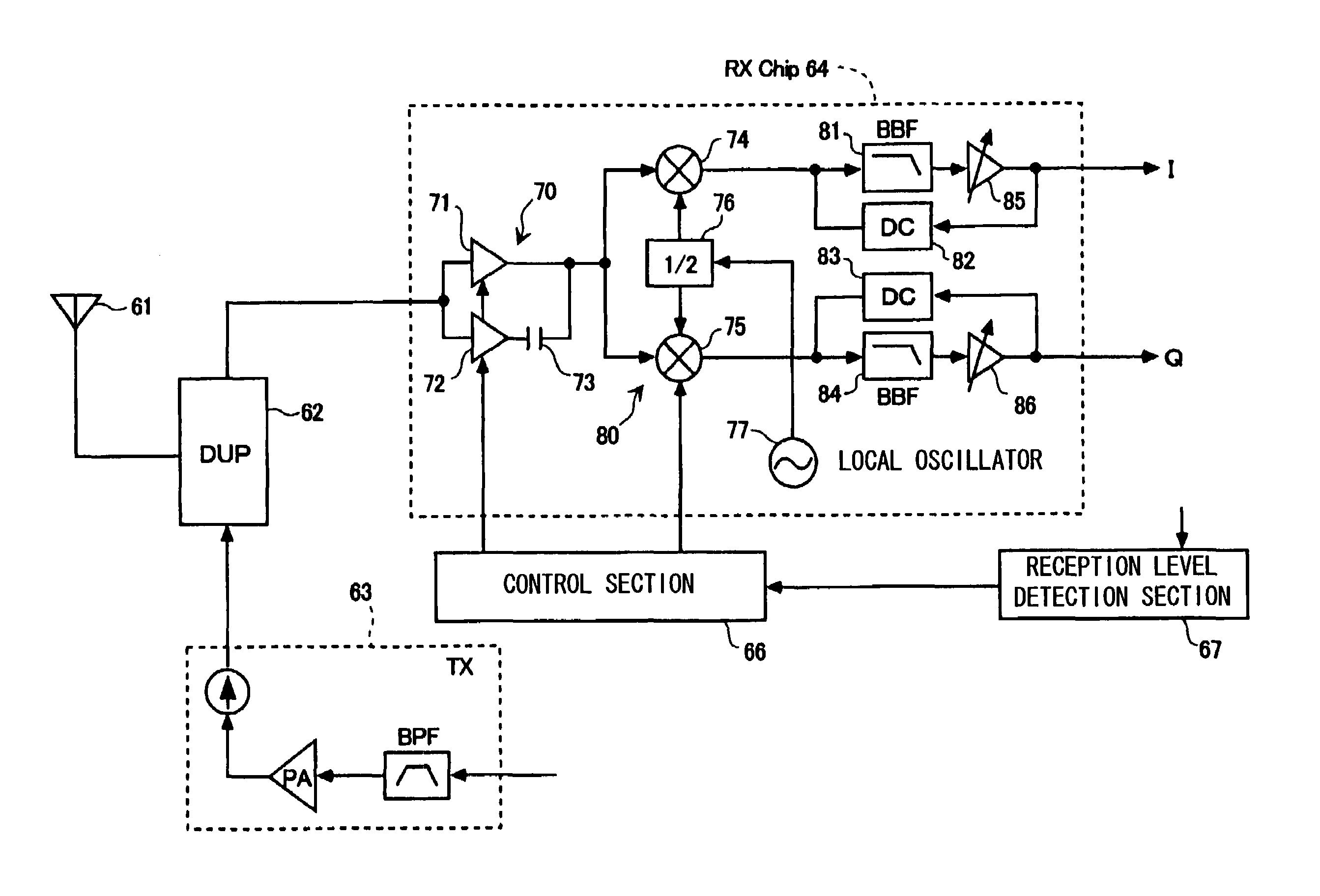

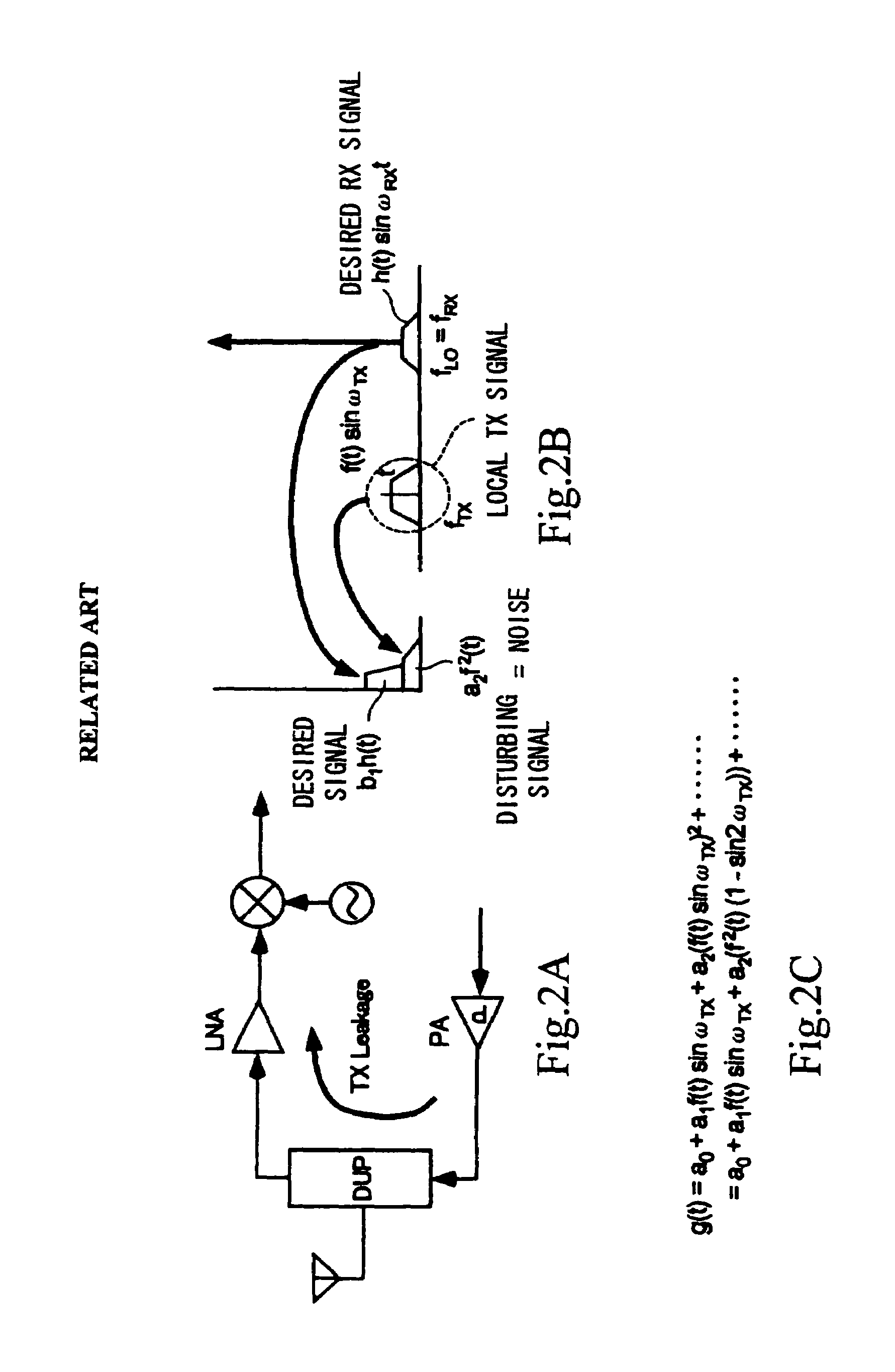

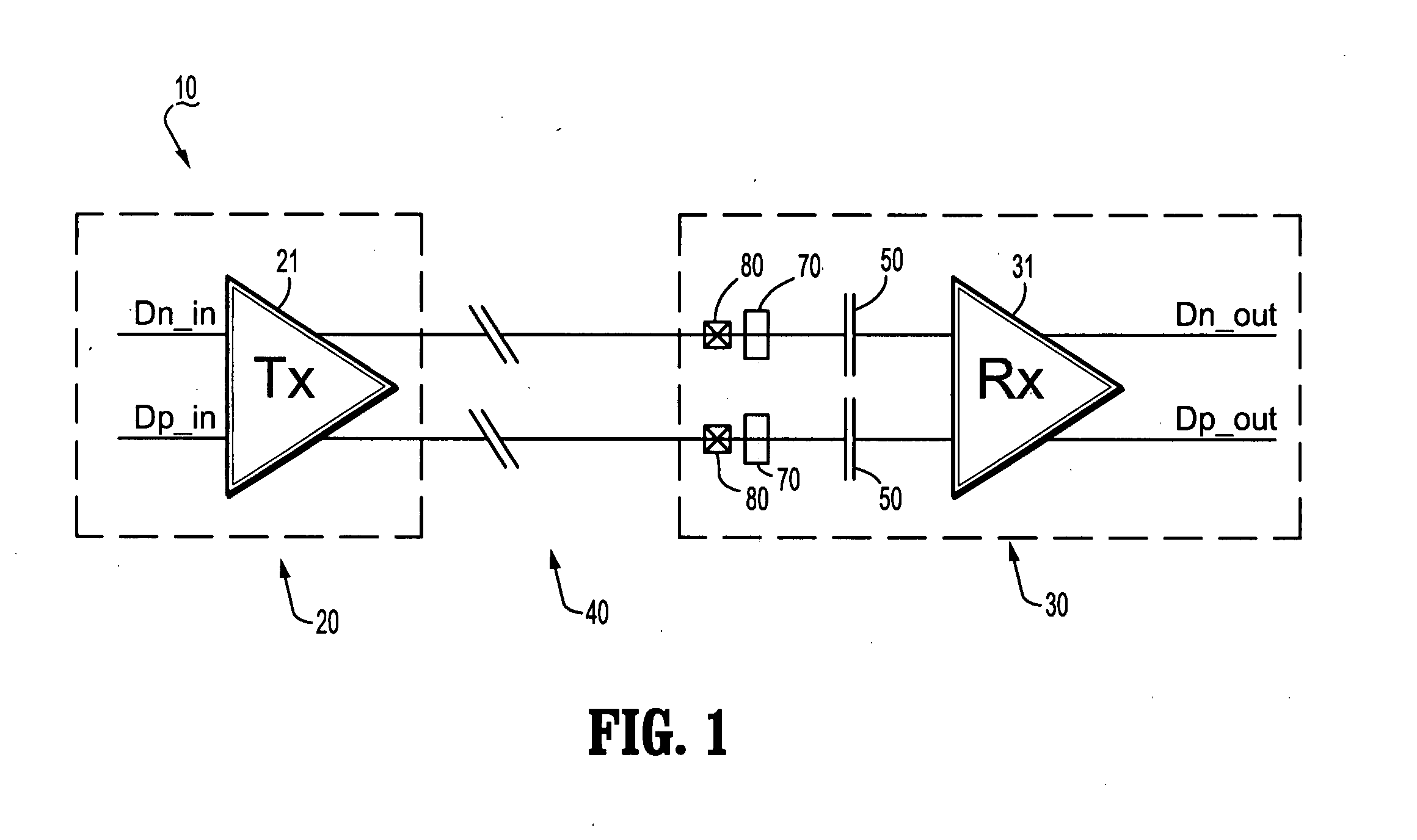

Receiver circuit and radio communication terminal apparatus

ActiveUS7221919B2Reduce power consumptionReduce areaGain controlDc level restoring means or bias distort correctionCapacitanceAudio power amplifier

There are provided, as a low noise amplifier (70) a low noise amplifier (71) with a low gain and a low noise amplifier (72) with a high gain, selectively operable under control of a bias current, and an output from the low noise amplifier (72) and a quadrature demodulator (80) are connected with a serial capacitance (73) and also an output from the low noise amplifier (71) and the quadrature demodulator (80) are serially connected. A control section (66) controls a reception circuit so that the low noise amplifier (71) operates when a reception signal level is high and the low noise amplifier (72) operates when the reception signal level is low. When the low noise amplifier (72) operates, a DC bias current thereof is made flow separately from a DC bias current of the quadrature demodulator (80), and, when the low noise amplifier (71) operates, a DC bias current thereof is shared with the quadrature demodulator.

Owner:SNAPTRACK

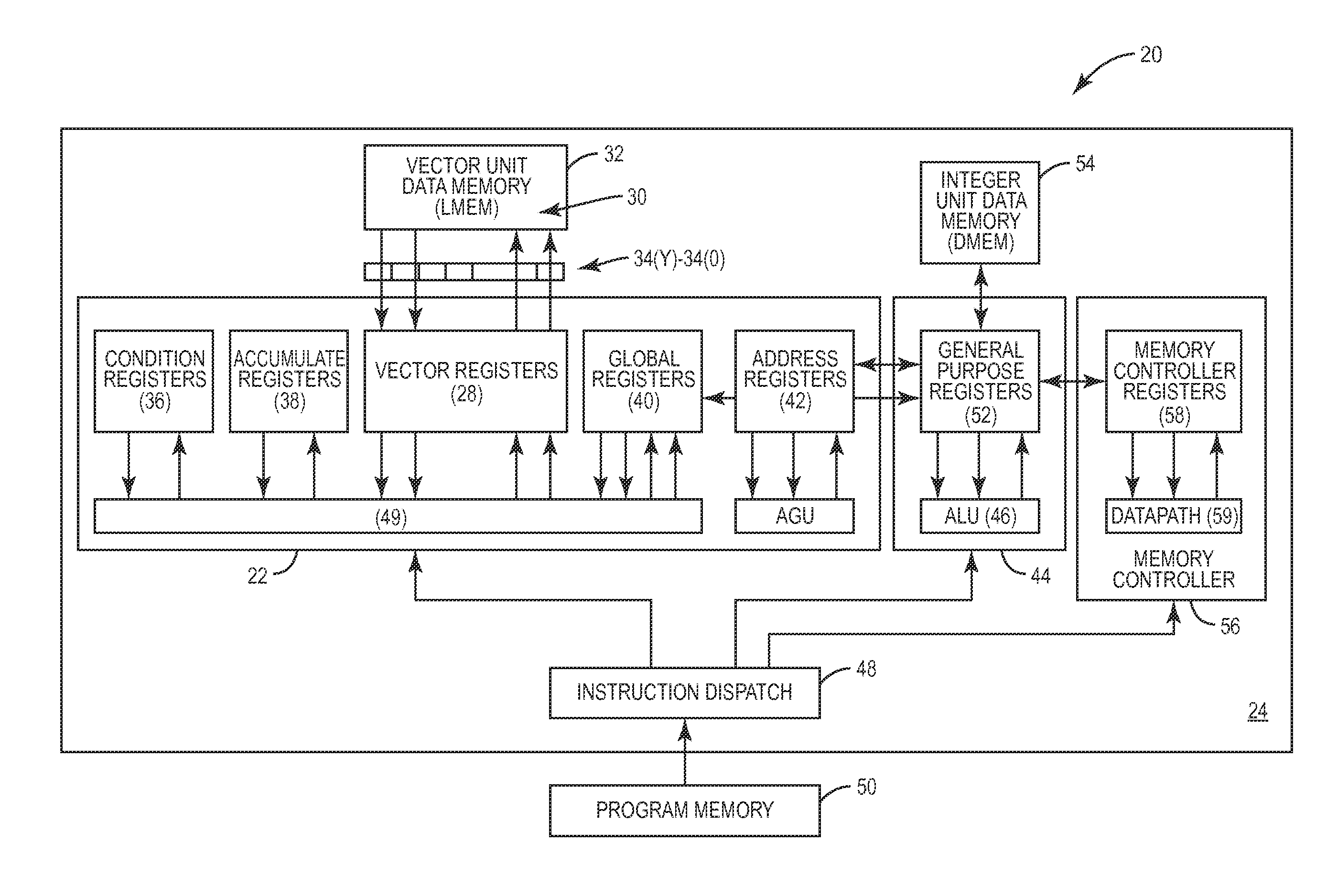

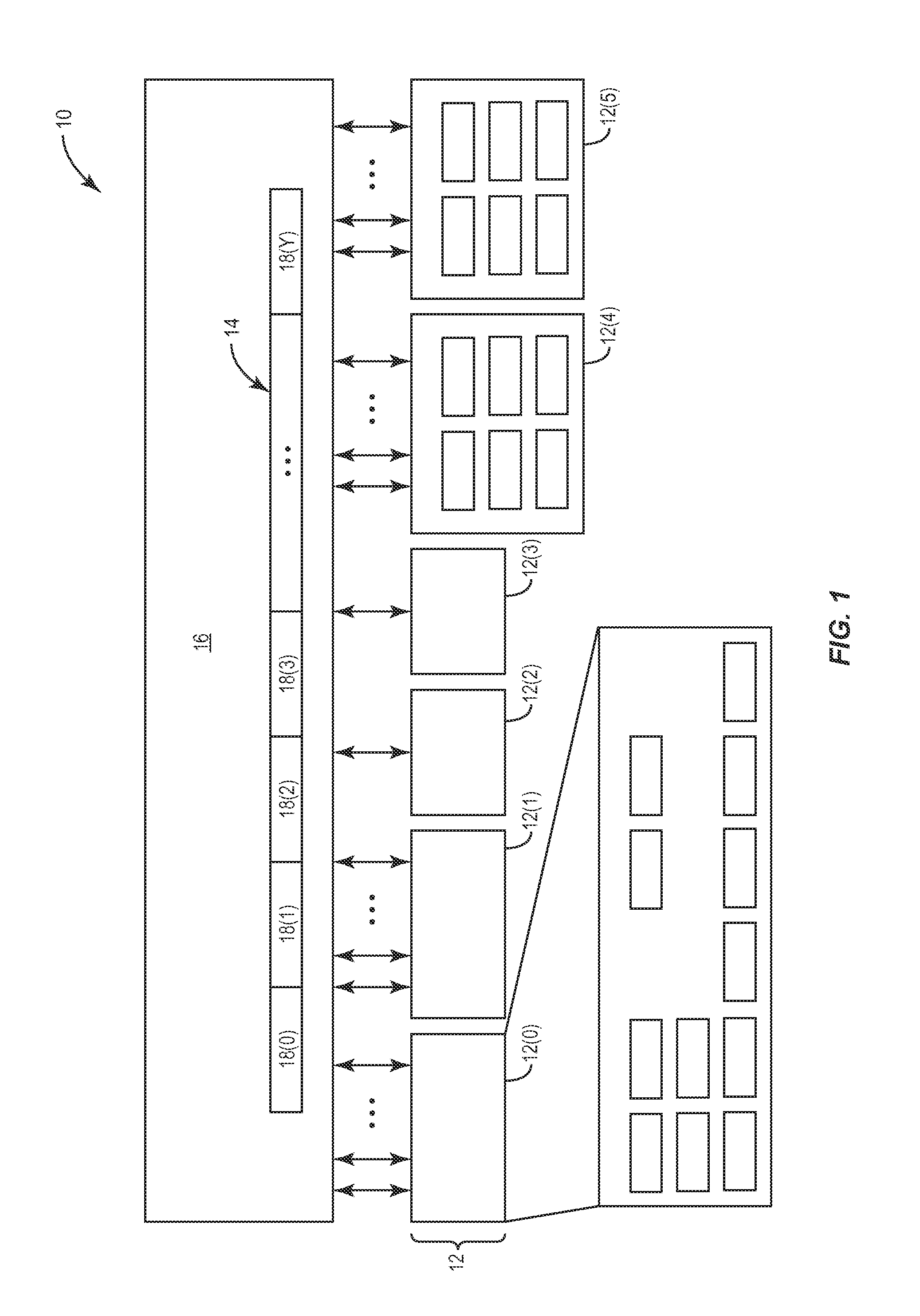

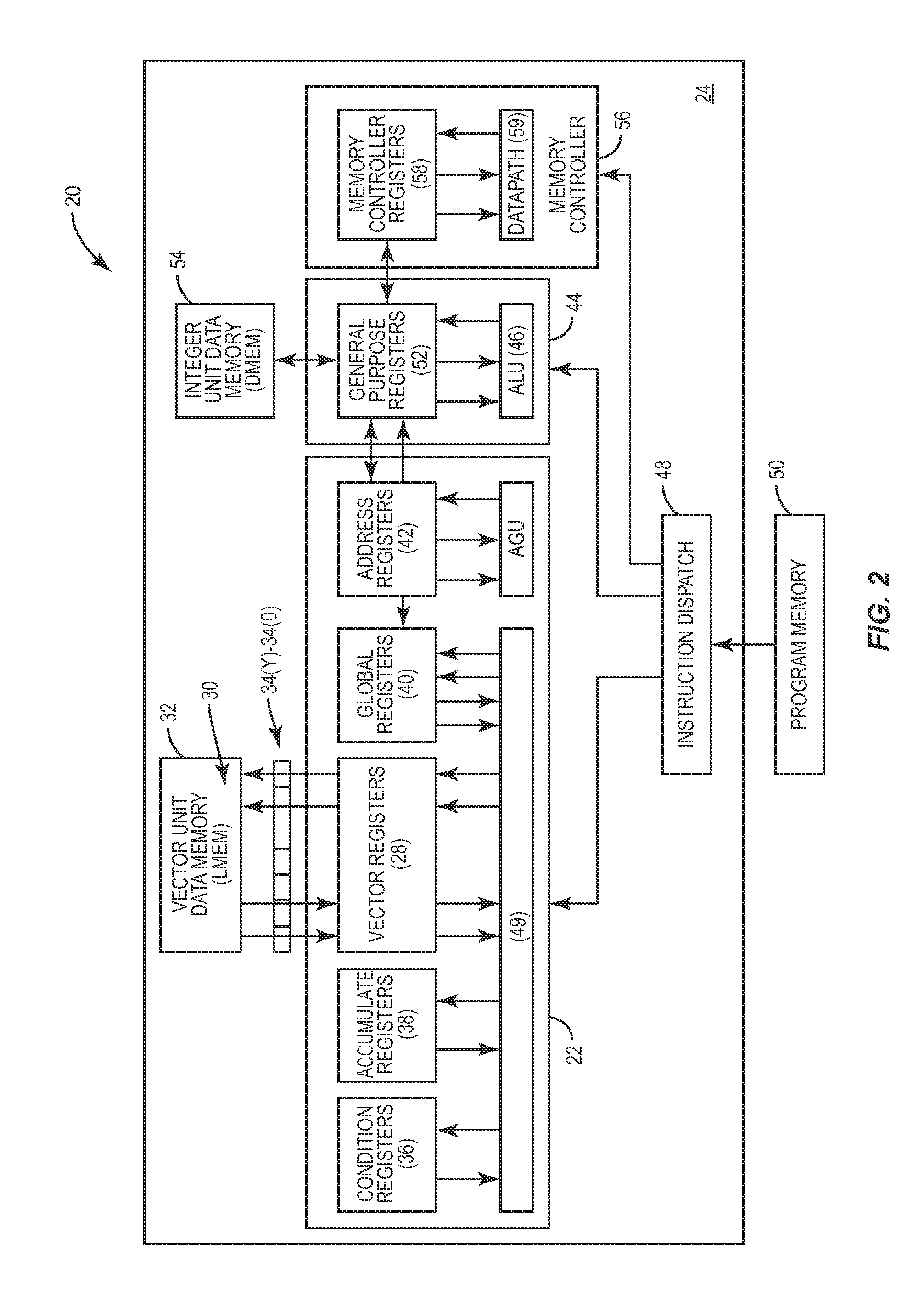

Vector processing engines having programmable data path configurations for providing multi-mode radix-2x butterfly vector processing circuits, and related vector processors, systems, and methods

ActiveUS20140280420A1Save extra spaceFast processing efficiencyDigital data processing detailsDigital computer detailsFourier transform on finite groupsDatapath

Vector processing engines (VPEs) having programmable data path configurations for providing multi-mode Radix-2X butterfly vector processing circuits. Related vector processors, systems, and methods are also disclosed. The VPEs disclosed herein include a plurality of vector processing stages each having vector processing blocks that have programmable data path configurations for performing Radix-2X butterfly vector operations to perform Fast Fourier Transform (FFT) vector processing operations efficiently. The data path configurations of the vector processing blocks can be programmed to provide different types of Radix-2X butterfly vector operations as well as other arithmetic logic vector operations. As a result, fewer VPEs can provide desired Radix-2X butterfly vector operations and other types arithmetic logic vector operations in a vector processor, thus saving area in the vector processor while still retaining vector processing advantages of fewer register writes and faster vector instruction execution times over scalar processing engines.

Owner:QUALCOMM INC

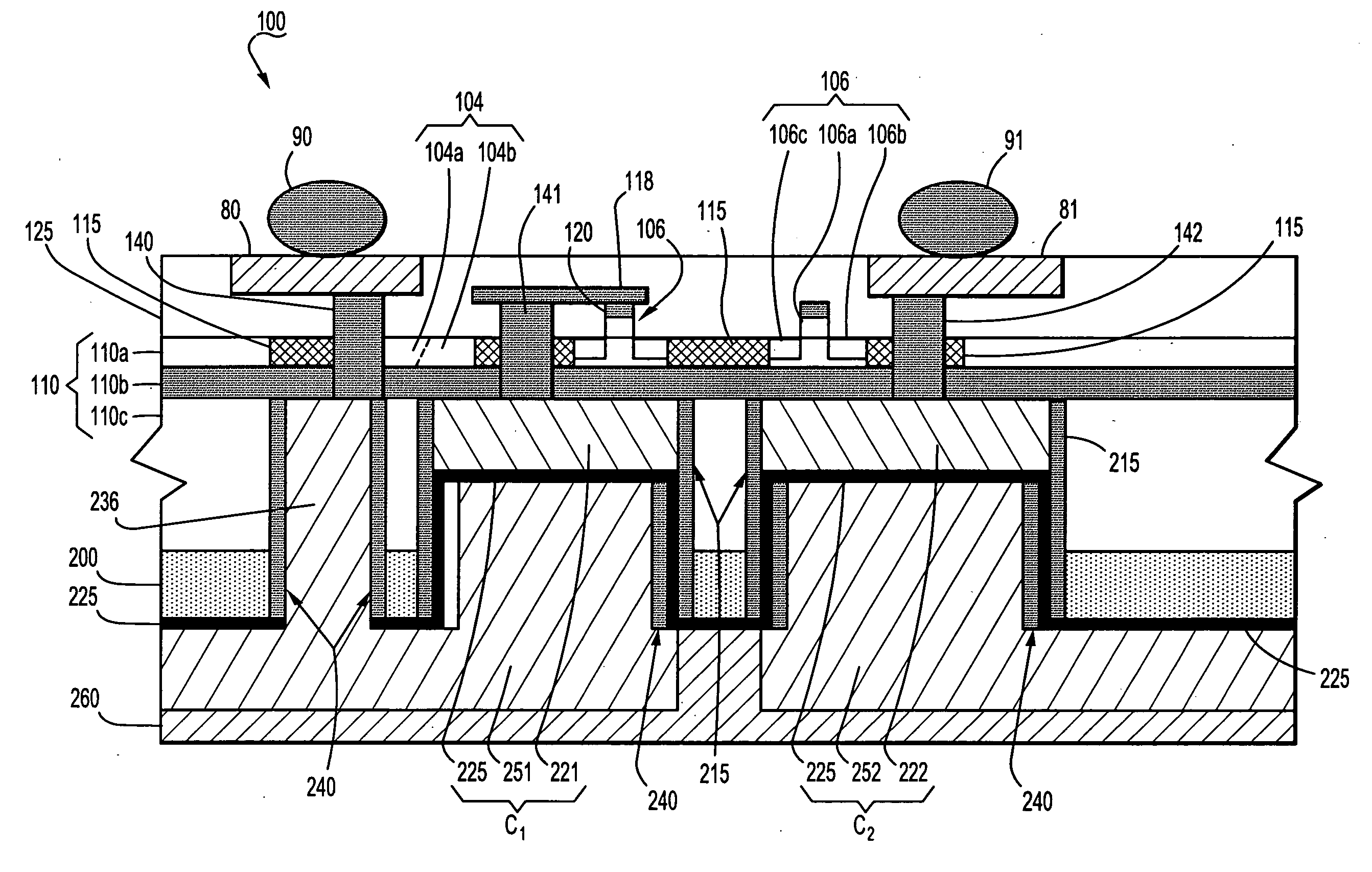

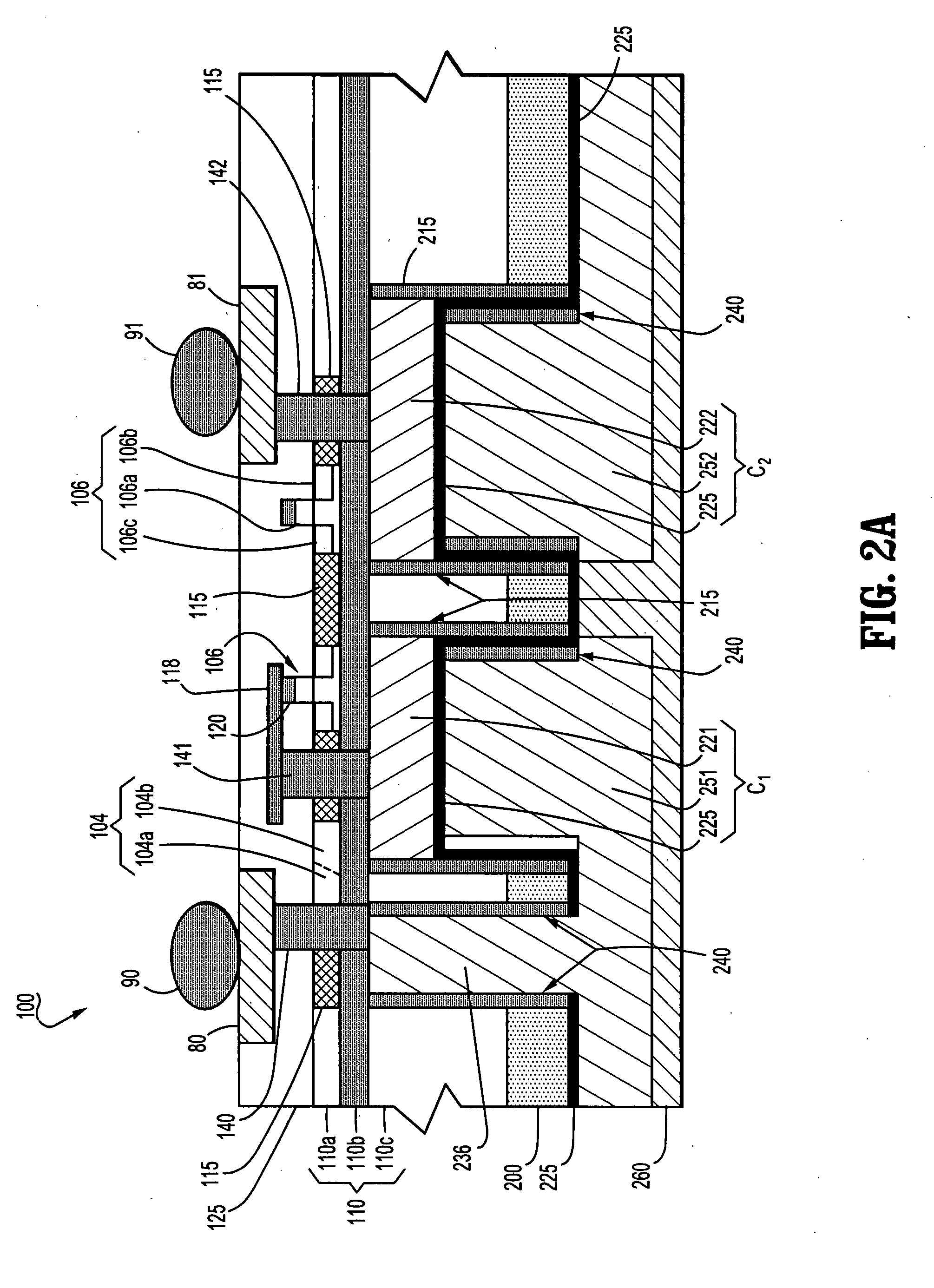

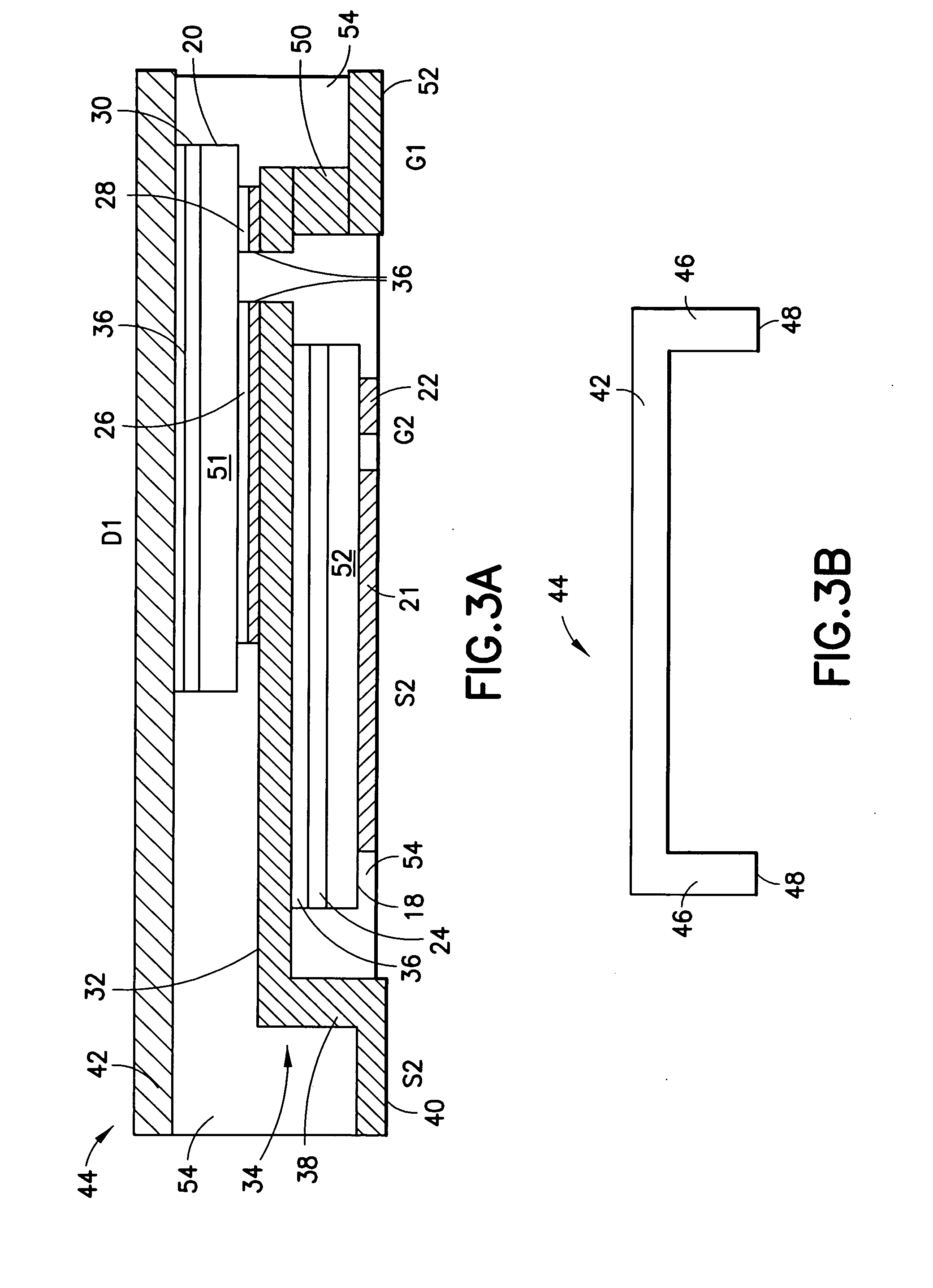

Semiconductor integrated circuit devices having high-Q wafer back-side capacitors

ActiveUS20070278619A1Series resistance is minimizedSave extra spaceSemiconductor/solid-state device detailsSolid-state devicesInterconnectionSemiconductor

Methods are provided for fabricating semiconductor IC (integrated circuit) chips having high-Q on-chip capacitors formed on the chip back-side and connected to integrated circuits on the chip front-side using through-wafer interconnects. In one aspect, a semiconductor device includes a semiconductor substrate having a front side, a back side, and a buried insulating layer interposed between the front and back sides of the substrate. An integrated circuit is formed on the front side of the semiconductor substrate, an integrated capacitor is formed on the back side of the semiconductor substrate, and an interconnection structure is formed through the buried insulating layer to connect the integrated capacitor to the integrated circuit.

Owner:GLOBALFOUNDRIES US INC

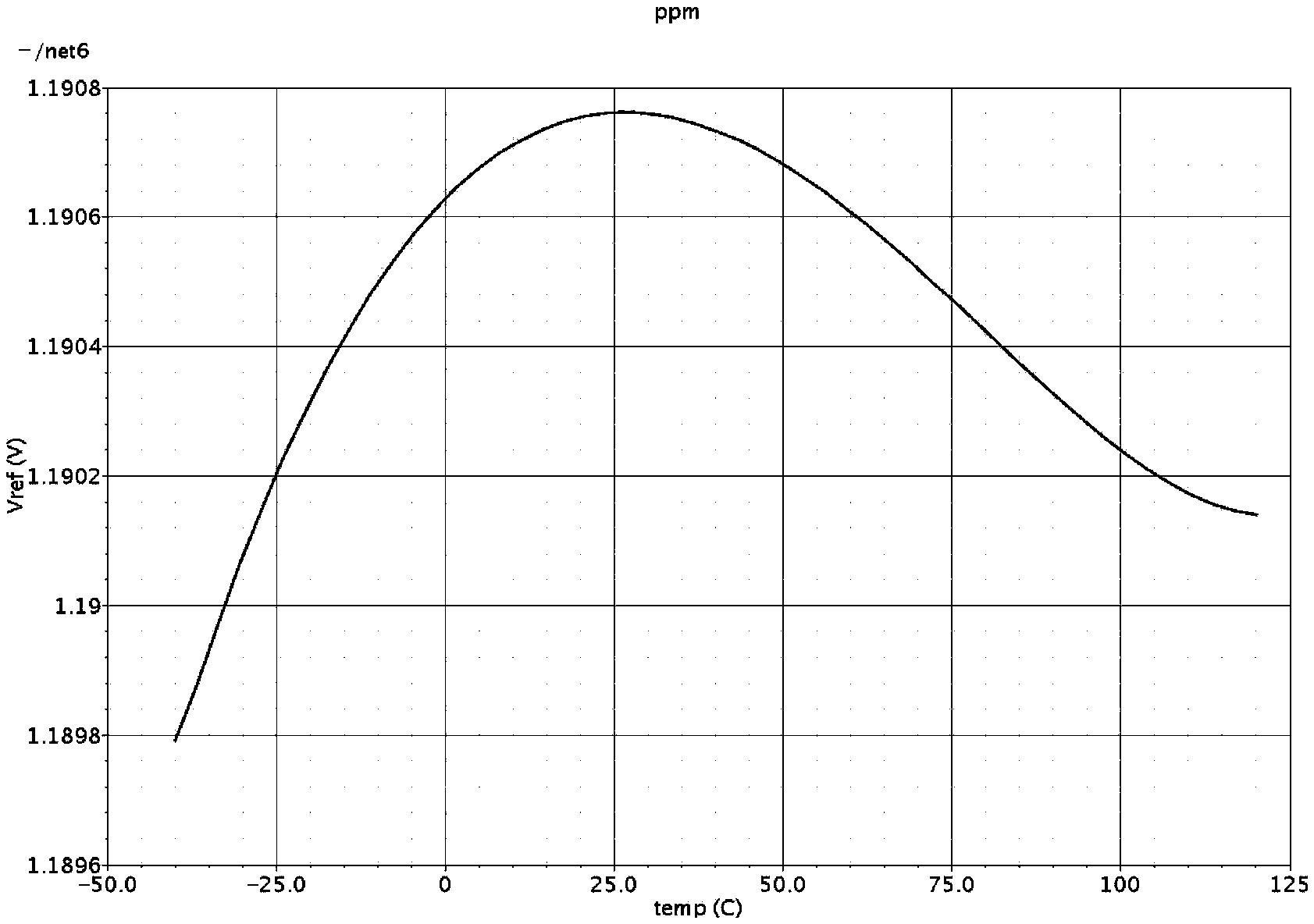

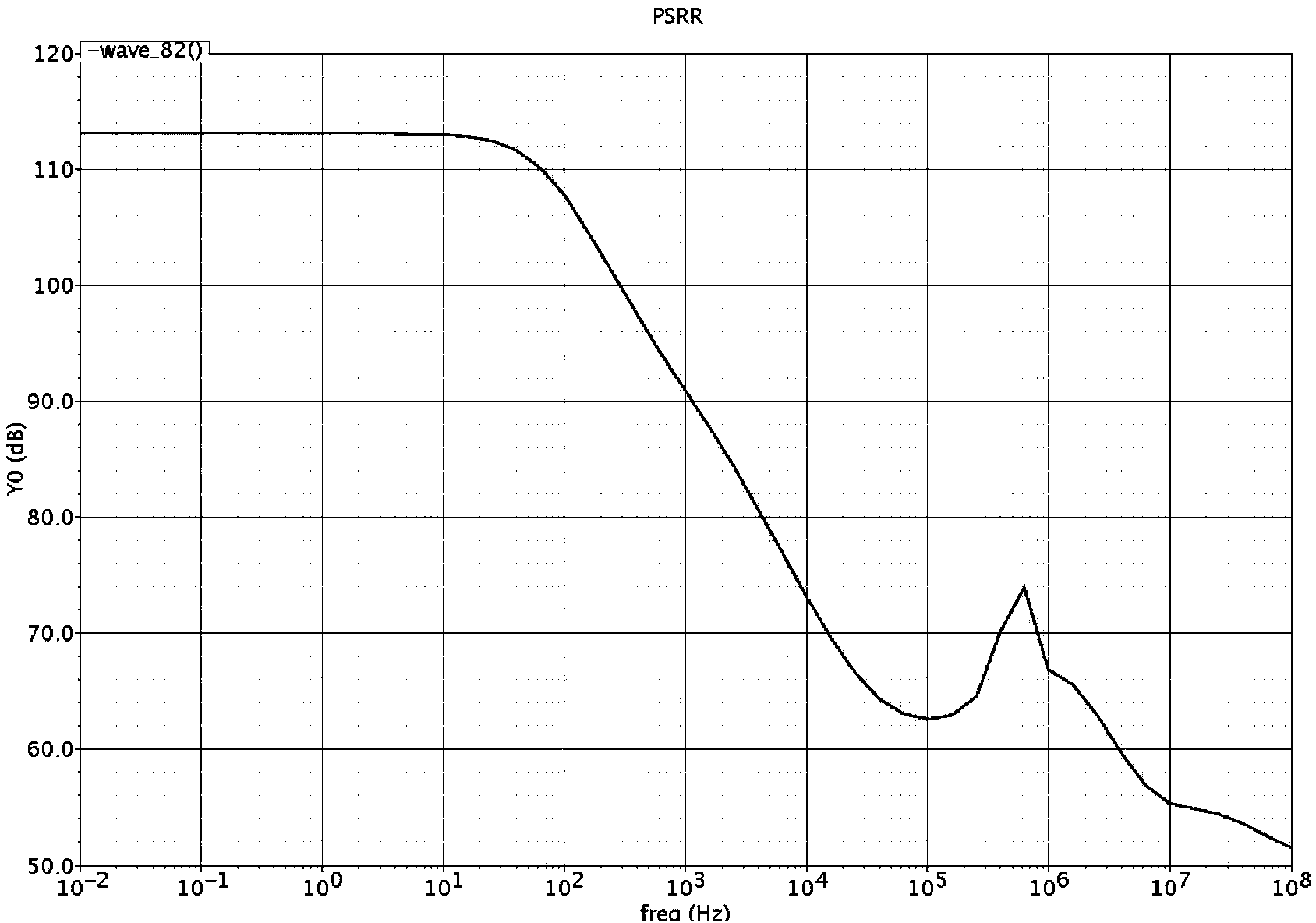

Band-gap reference circuit

ActiveCN104122918AImprove power supply rejection ratioSave area and powerElectric variable regulationPower supply rejection ratioEngineering

The invention relates to a band-gap reference circuit. The band-gap reference circuit comprises a reference voltage source VREF, a band-gap core circuit, a negative feedback circuit and a starting circuit, wherein gate voltage V_REG is stretched by the reference voltage source VREF so that internal voltage pre-stabilization can be achieved, an internal voltage pre-stabilizing circuit is formed, the band-gap core circuit is provided with an automatic biasing cascode amplifying circuit used for increasing a power supply rejection ratio, the negative feedback circuit provides the supply voltage VDD, processed through voltage stabilization, for the band-gap core circuit, and the starting circuit stretches the reference voltage source VREF when work begins so that the automatic biasing cascode amplifying circuit can work normally. According to the band-gap reference circuit, due to the facts that the supply voltage VDD processed through voltage stabilization is provided for the band-gap core circuit through the negative feedback circuit, and the automatic biasing cascode amplifying circuit is adopted inside for increasing the power supply rejection ratio, area and power consumption are saved.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

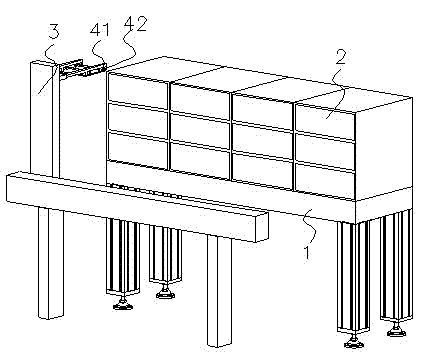

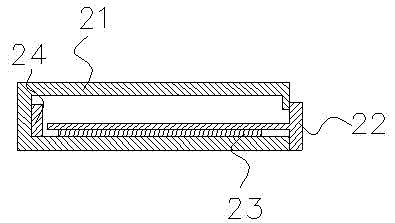

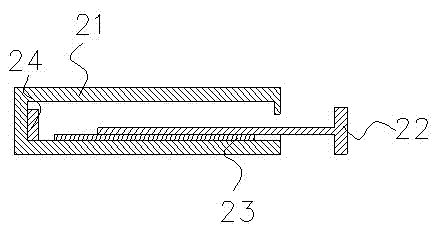

Circuit board testing system

ActiveCN102830343AIntensifyFully automatedElectronic circuit testingControl systemProgrammable logic controller

The invention discloses a circuit board testing system, which comprises a test tank, a material taking and putting mechanism and a control system, wherein the control system comprises a PC (personal computer) processor and a PLC (Programmable Logic Controller) control system. A box-type test machine comprises a box body, a drawer-type fixture, a fixture driving component and a test device, wherein one side of the box body is opened; the drawer-type fixture is arranged in the box body in an insertion mode from the opened side of the box body; the fixture driving component is connected with the drawer-type fixture and is used for driving the drawer-type fixture to pop out or retract back to the opened side of the box body; and the test device is arranged in the box body and is communicated with a circuit board to be tested. According to the circuit board testing system, the automation of the circuit board testing system can be realized.

Owner:SUZHOU SIFO SMART AUTOMATION INC CO

An electrically programmable fuse for silicon-on-insulator (SOI) technology

ActiveUS20060108662A1Minimizes outdiffusionProgram have been very successfulSemiconductor/solid-state device detailsSolid-state devicesDielectricEngineering

A fuse structure and method of forming the same is described, wherein the body of the fuse is formed from a crystalline semiconductor body on an insulator, preferably of a silicon-on-insulator wafer, surrounded by a fill-in dielectric. The fill-in dielectric is preferably a material that minimizes stresses on the crystalline body, such as an oxide. The body may be doped, and may also include a silicide layer on the upper surface. This fuse structure may be successfully programmed over a wide range of programming voltages and time.

Owner:GLOBALFOUNDRIES US INC

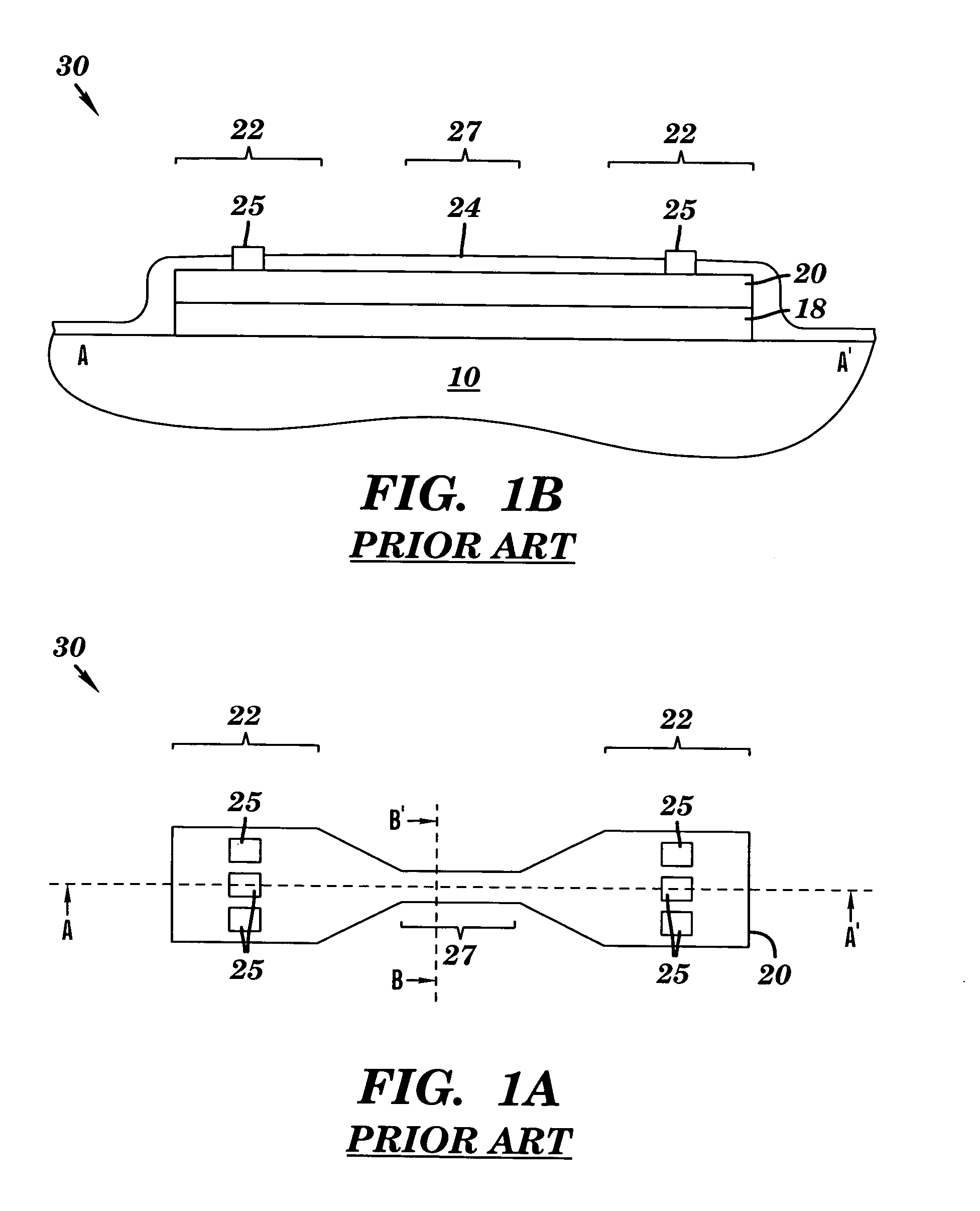

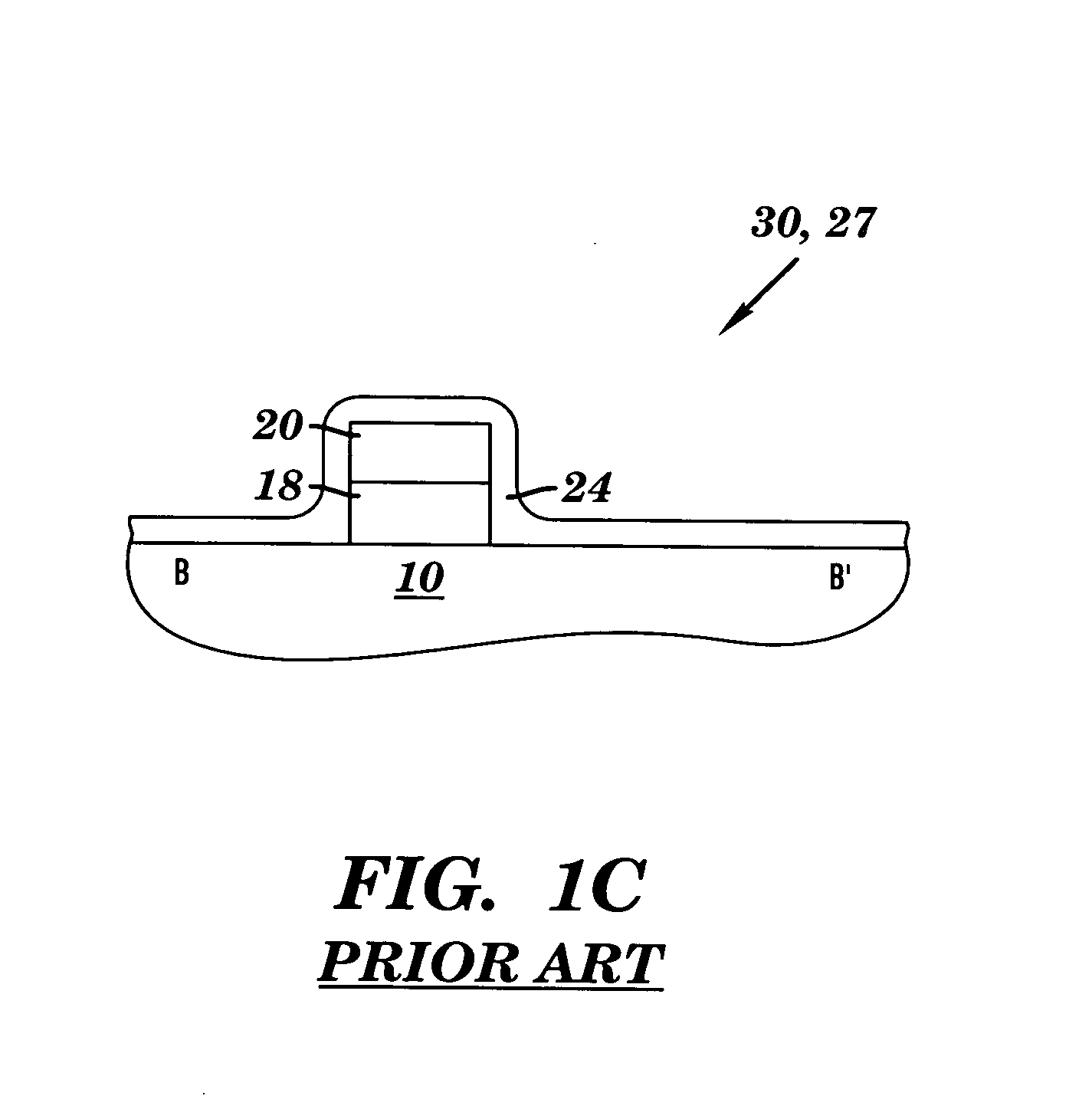

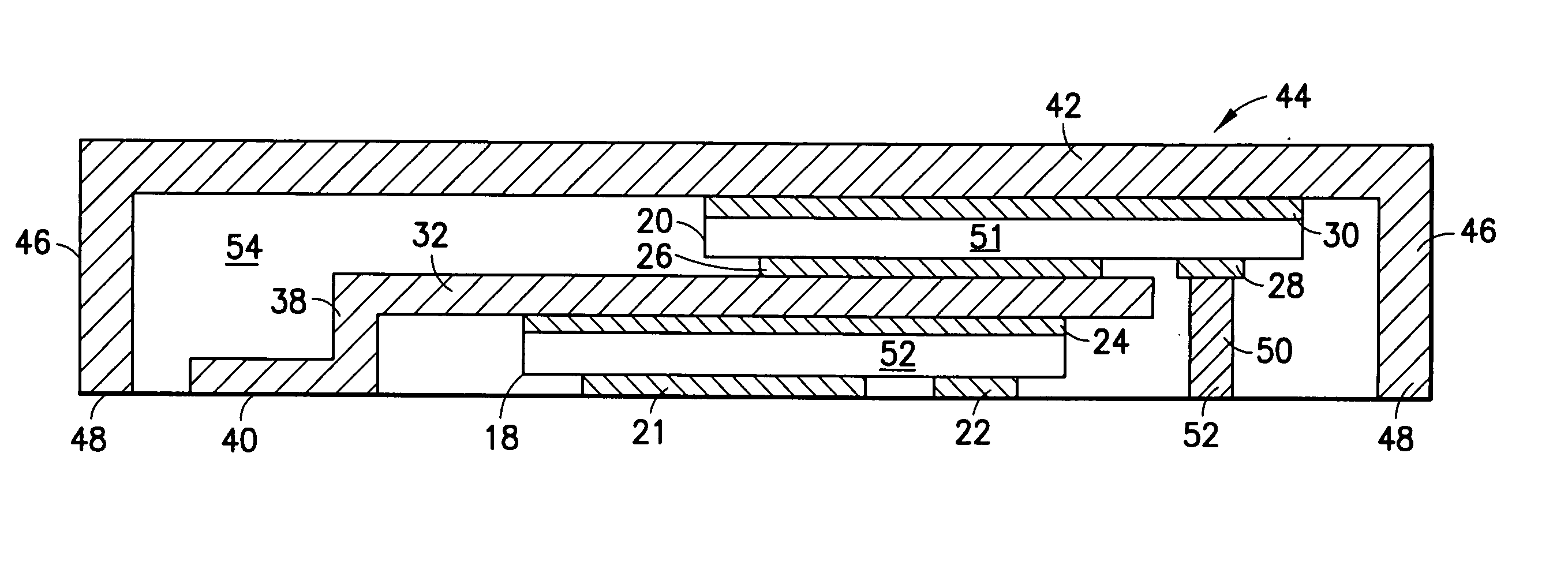

Semiconductor package that includes stacked semiconductor die

InactiveUS20070108575A1Save extra spaceReducing the consequent parasiticsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package that includes at least two semiconductor devices that are coupled to one another through a conductive clip.

Owner:INFINEON TECH AMERICAS CORP

Method and apparatus for temperature sensing in integrated circuits

InactiveUS20070081575A1Easy wiringSave extra spaceThermometer detailsThermometers using material expansion/contactionEngineeringControl logic

A method and apparatus for temperature sensing in an IC. The IC includes a plurality of remote temperature sensors each coupled to a control logic unit. The plurality of remote temperature sensors may be distributed throughout the integrated circuit. The integrated circuit includes a reference unit coupled to provide a reference temperature to the control logic unit and a reference sensor coupled to provide a signal having a reference frequency to the control logic unit. The reference unit and the reference sensor are located near each other. The control logic unit is configured to correlate the reference frequency received from the reference sensor with the reference temperature received from the reference unit. The control logic unit is further configured to determine the temperature of each of the remote temperature sensors based on this correlation, and also configured to determine the maximum temperature of all of the temperature sensors.

Owner:ADVANCED MICRO DEVICES INC

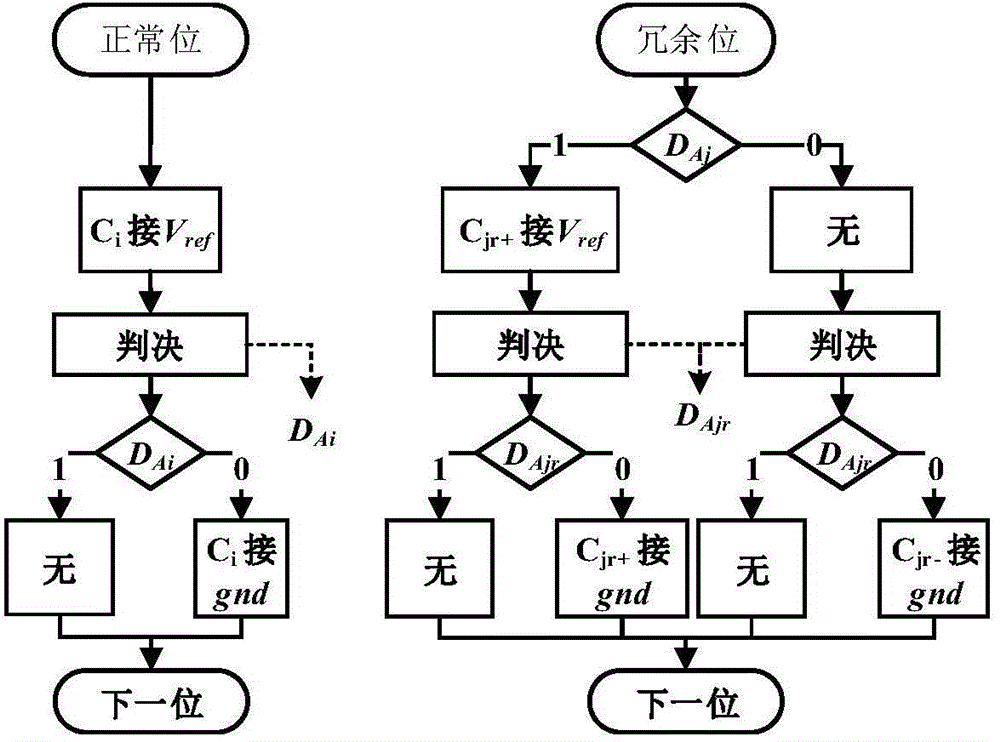

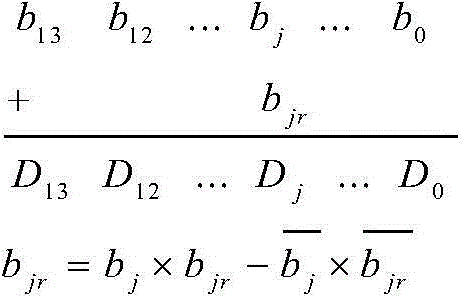

Capacitance mismatch calibrating circuit and calibrating method applied to single-end SAR ADC

ActiveCN104917527ASave area and powerEasy to implementElectric signal transmission systemsAnalogue/digital conversion calibration/testingCapacitanceDigital-to-analog converter

The invention discloses a capacitance mismatch calibrating circuit and calibrating method applied to a single-end SAR ADC (Successive Approximation Analog-to-Digital Converter). By using the method, error caused by capacitance mismatch of the SAR ADC can be calibrated. According to the method, only two pairs of redundant capacitance need to be inserted in an analog domain for compensation of capacitance mismatch in a digital domain. A binary capacitance DAC (Digital-to-Analog Converter) containing two pairs of redundant dot capacitance includes a segmentation binary capacitance DAC and redundant capacitance Cjr+, Cjr- inserted to the lowest bit of aN MSB segment of a segmentation capacitance, and redundant capacitance Cqr+, Cqr- inserted to an LSB segment. A redundant bit calculation module adds the inserted redundant bits to other normal bits and obtains N-bit valid output. A capacitance mismatch calibrating module performs compensation to capacitance mismatch on the output result. Compared with the traditional SAR ADC structure, only two pairs of redundant capacitance are added. The calculation of mismatch compensation is performed in the digital domain, so that the layout size and analog circuit complexity is reduced.

Owner:SOUTHEAST UNIV

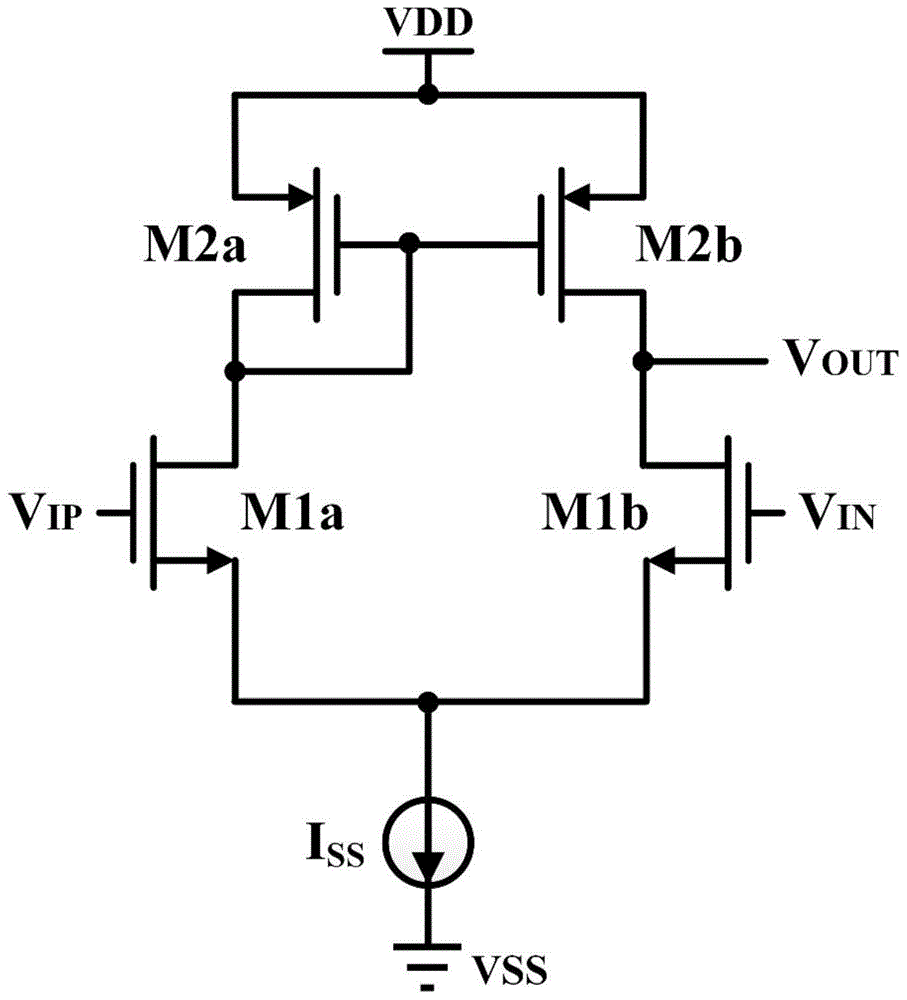

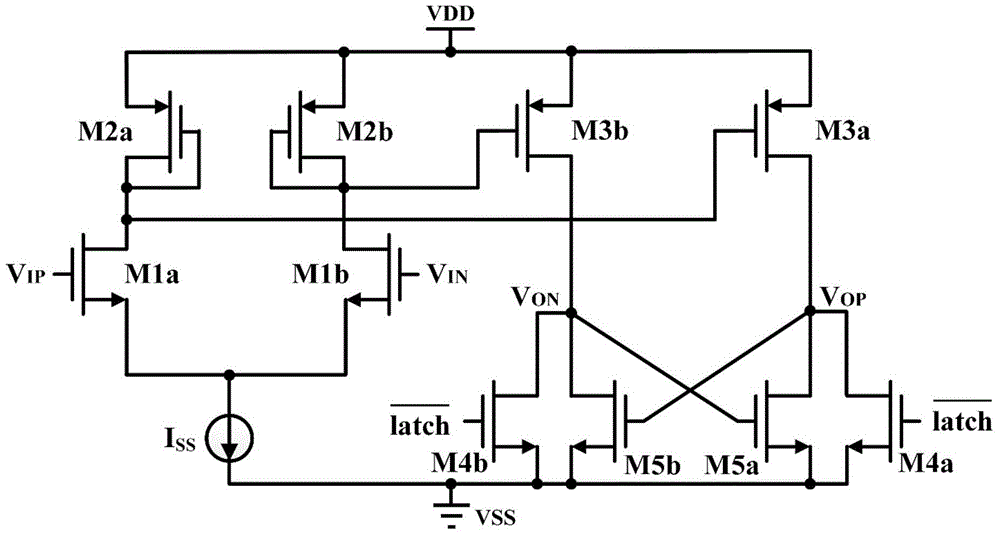

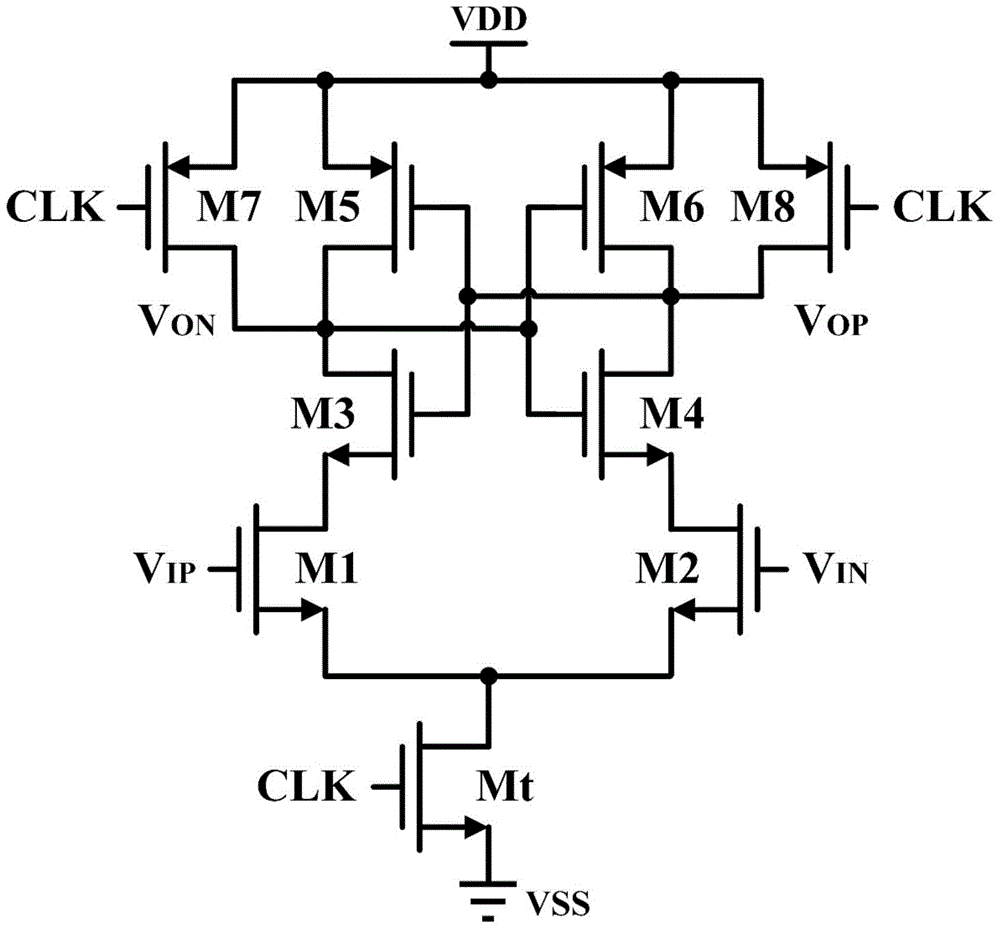

High-speed low-power-consumption dynamic comparator

ActiveCN105680834ATiming is simpleImprove energy efficiencyMultiple input and output pulse circuitsDifferential signalingEngineering

The invention discloses a high-speed low-power-consumption dynamic comparator, comprising a pre-amplification circuit and a regeneration latch circuit; the pre-amplification circuit comprises a clock output end, a first differential signal input end, a second differential signal input end, an output node FN and an output node FP; the pre-amplification circuit is connected with a direct current power, the output node FN synthesizes the output voltage VDD of the direct current power and a first differential input signal to output the first differential input signal, and the output node FP synthesizes the output voltage VDD of the direct current power and a second differential input signal to output the second differential input signal; the regeneration latch circuit is connected with the output node FN and the output node FP of the pre-amplification circuit, and can be used for latching the first differential input signal and the second differential input signal and outputting a first output signal and a second output signal. The dynamic comparator provided by the invention can quickly achieve low power consumption dynamic latching function under the high speed application.

Owner:INST OF ADVANCED TECH UNIV OF SCI & TECH OF CHINA

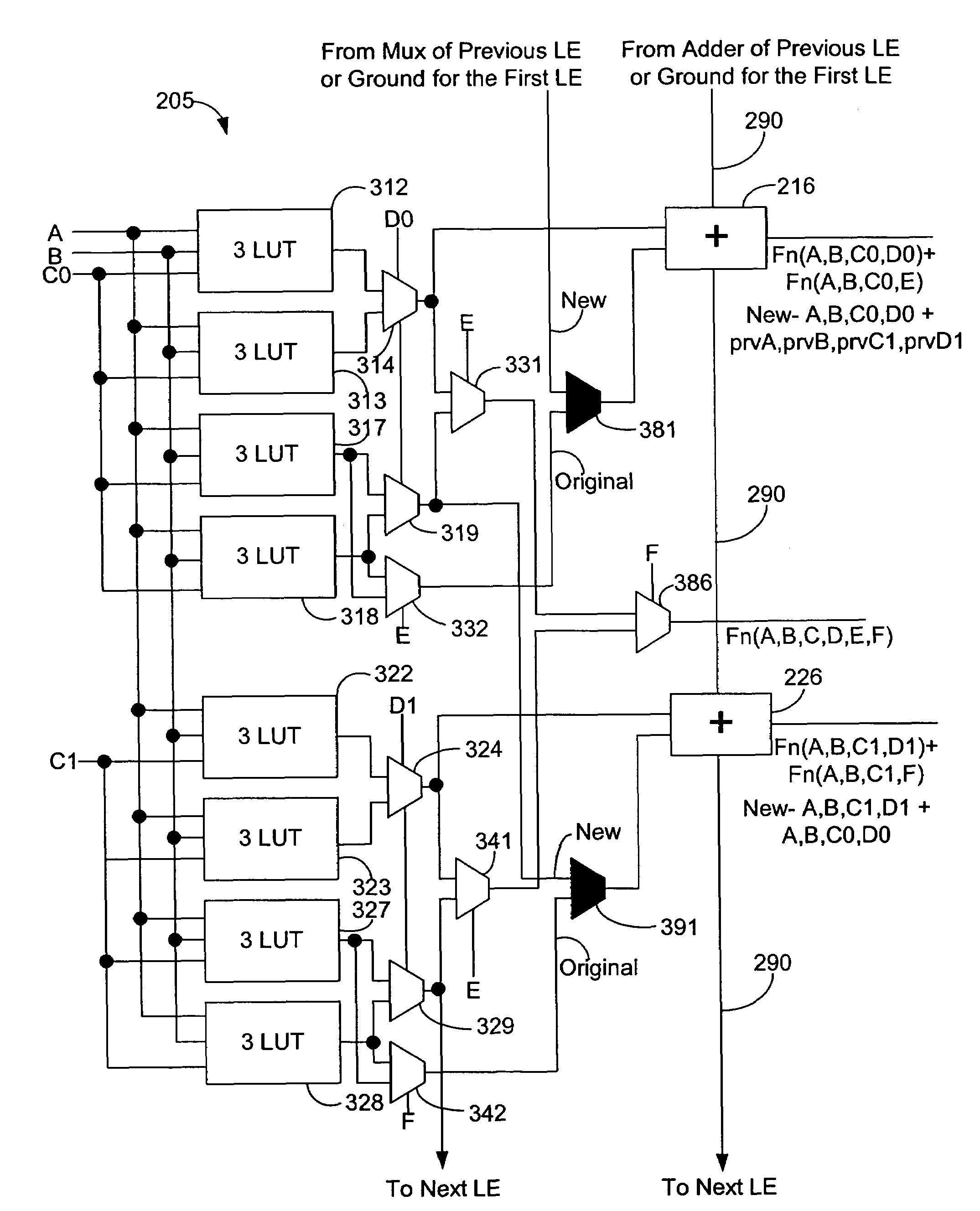

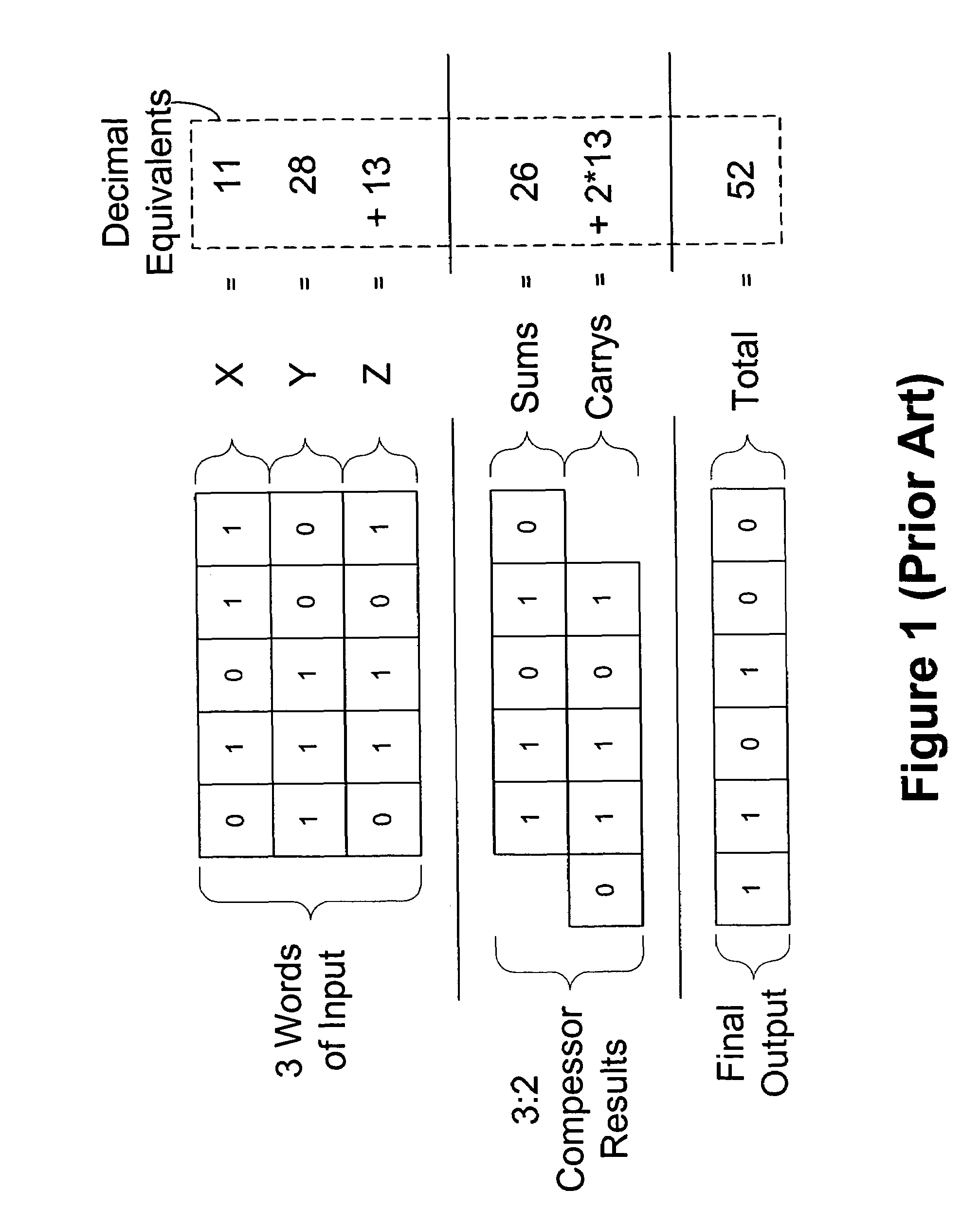

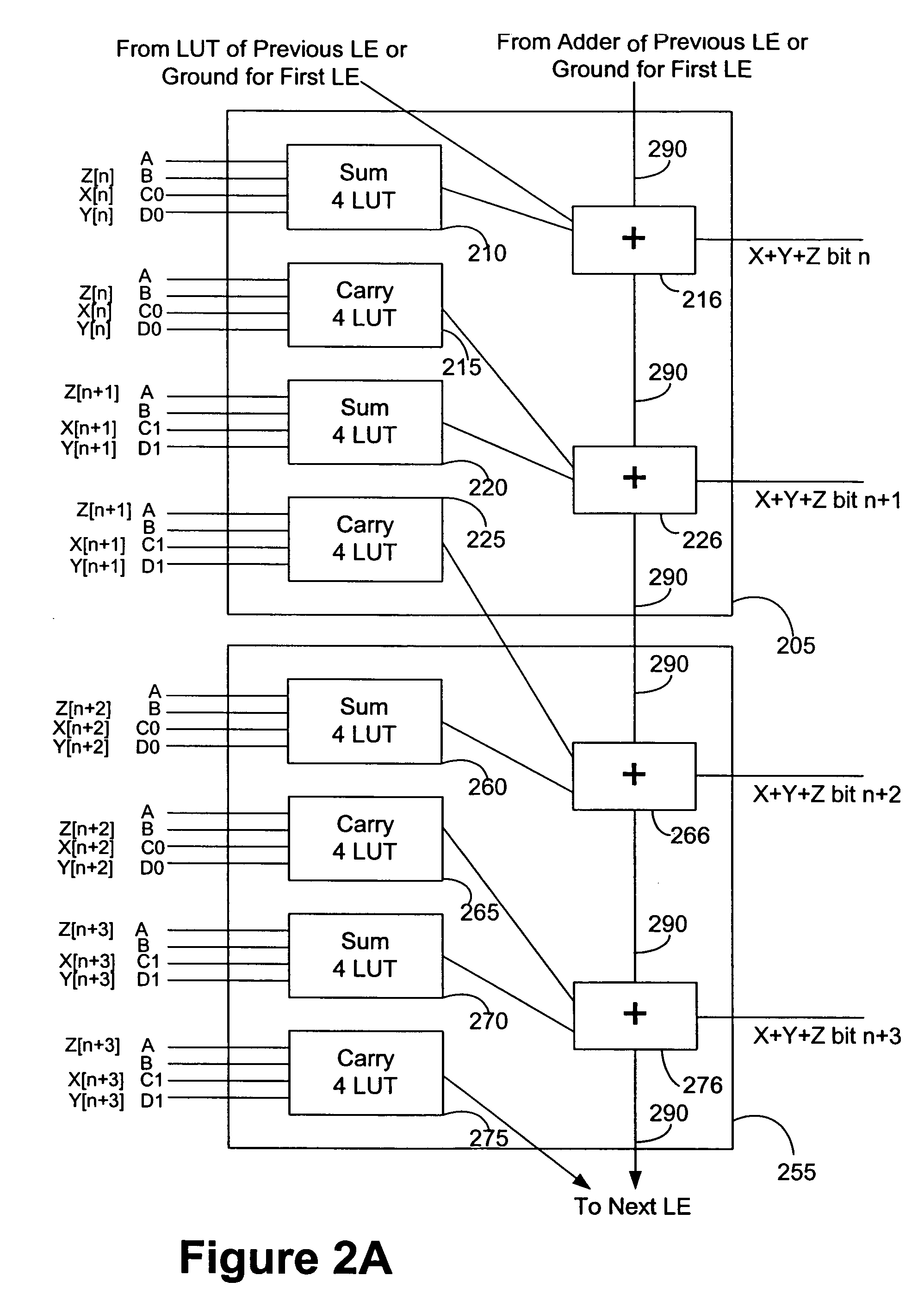

Logic cell supporting addition of three binary words

InactiveUS7565388B1Increase circuit speedShorten the counting processComputation using non-contact making devicesLogic circuitsLogic cellTheoretical computer science

Logic circuits that support the addition of three binary numbers using hardwired adders are described. In one embodiment, this is accomplished by using a 3:2 compressor (i.e., a Carry Save Adder method), using hardwired adders to add the sums and carrys produced by the 3:2 compression, and sharing carrys data calculated in one logic element (“LE”) with the following LE. In such an embodiment, with the exception of the first and last LEs in a logic array block (“LAB”), each LE in effect lends one look-up table (“LUT”) to the LE below (i.e., the following LE) and borrows one LUT from the LE above (i.e., the previous LE). The LUT being lent or borrowed is one that implements the carry function in the 3:2 compressor model. In another aspect, an embodiment of the present invention provides LEs that include selectors to select signals corresponding to the addition of three binary numbers mode.

Owner:ALTERA CORP

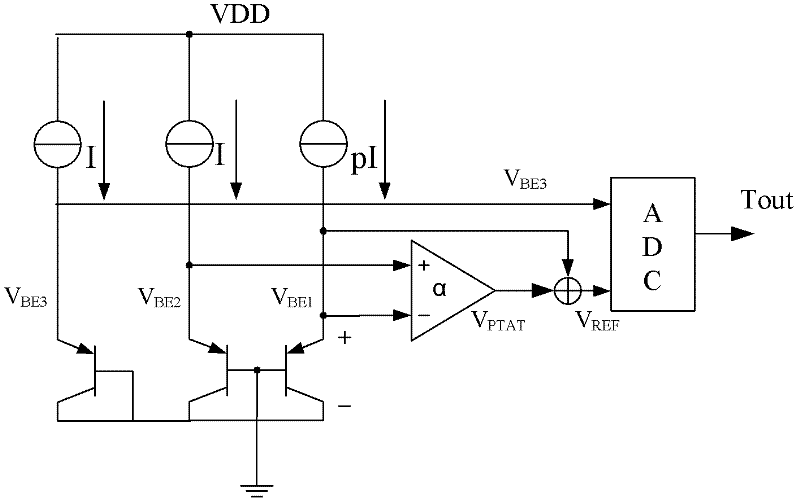

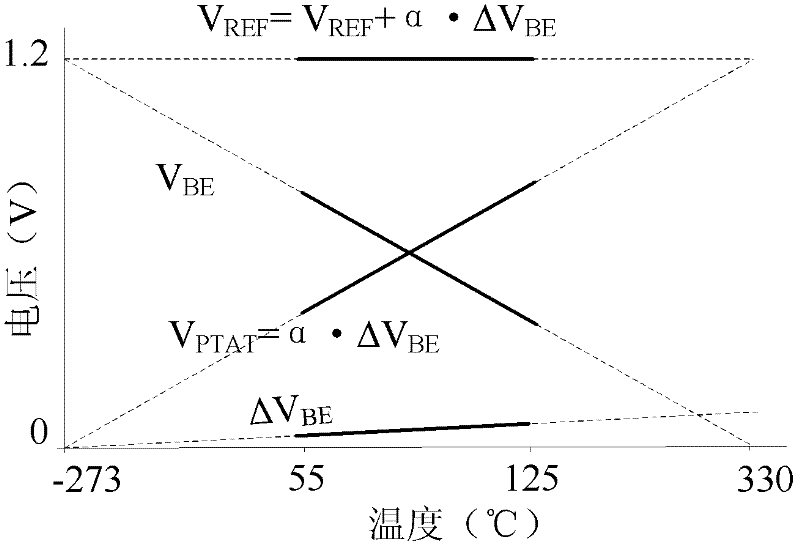

Temperature sensor

ActiveCN102589734AHigh precisionEliminate the effects ofThermometers using electric/magnetic elementsUsing electrical meansAudio power amplifierVoltage reference

The invention relates to a temperature sensor, which comprises a reference generation circuit, a signal amplification circuit and an analog-to-digital conversion circuit, wherein the reference generation circuit is used for generating BE node temperature sensing voltage for sensing temperature and reference voltage; the signal amplification circuit comprises a first amplifier, a second amplifier,a third amplifier and a first summator which are used for amplifying and adding the BE node temperature sensing voltage and the reference voltage and outputting a sum signal containing the BE node temperature sensing voltage and the reference voltage and an amplification signal of the reference voltage; and the analog-to-digital conversion circuit is used for performing analog-to-digital conversion and generating a digital signal representing the ratio of the two signals. Compared with the prior art, the temperature sensor detects the temperature by sharing the reference voltage generated by the reference generation circuit and the BE node voltage of a bipolar transistor so as to eliminate the influence of mismatch of the redundant current mirrors on the BE node voltage, improve the precision of the temperature sensor, save power consumption and area and reduce the influence of the process tolerance of the bipolar transistor on the precision of the sensor.

Owner:HI TREND TECH SHANGHAI

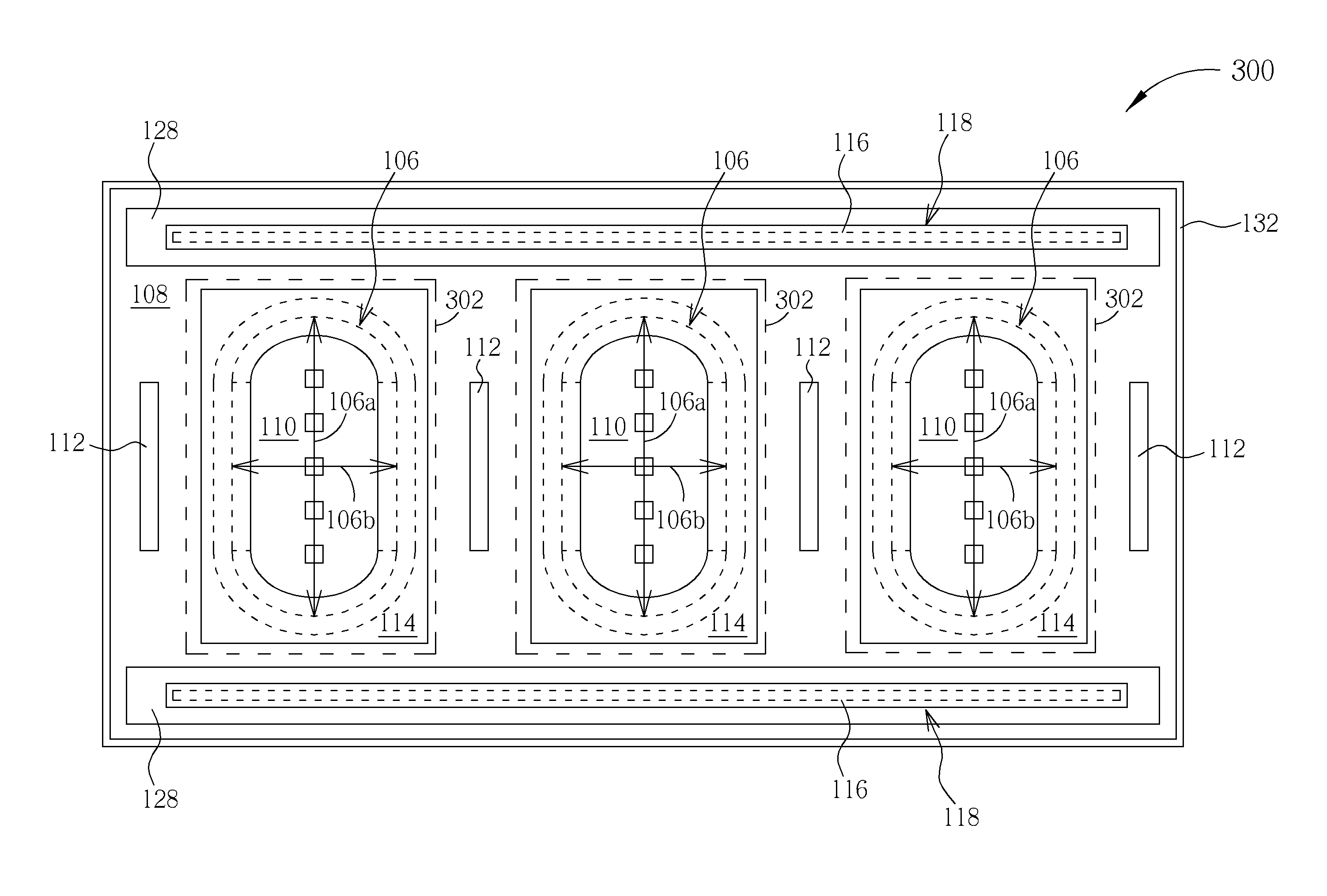

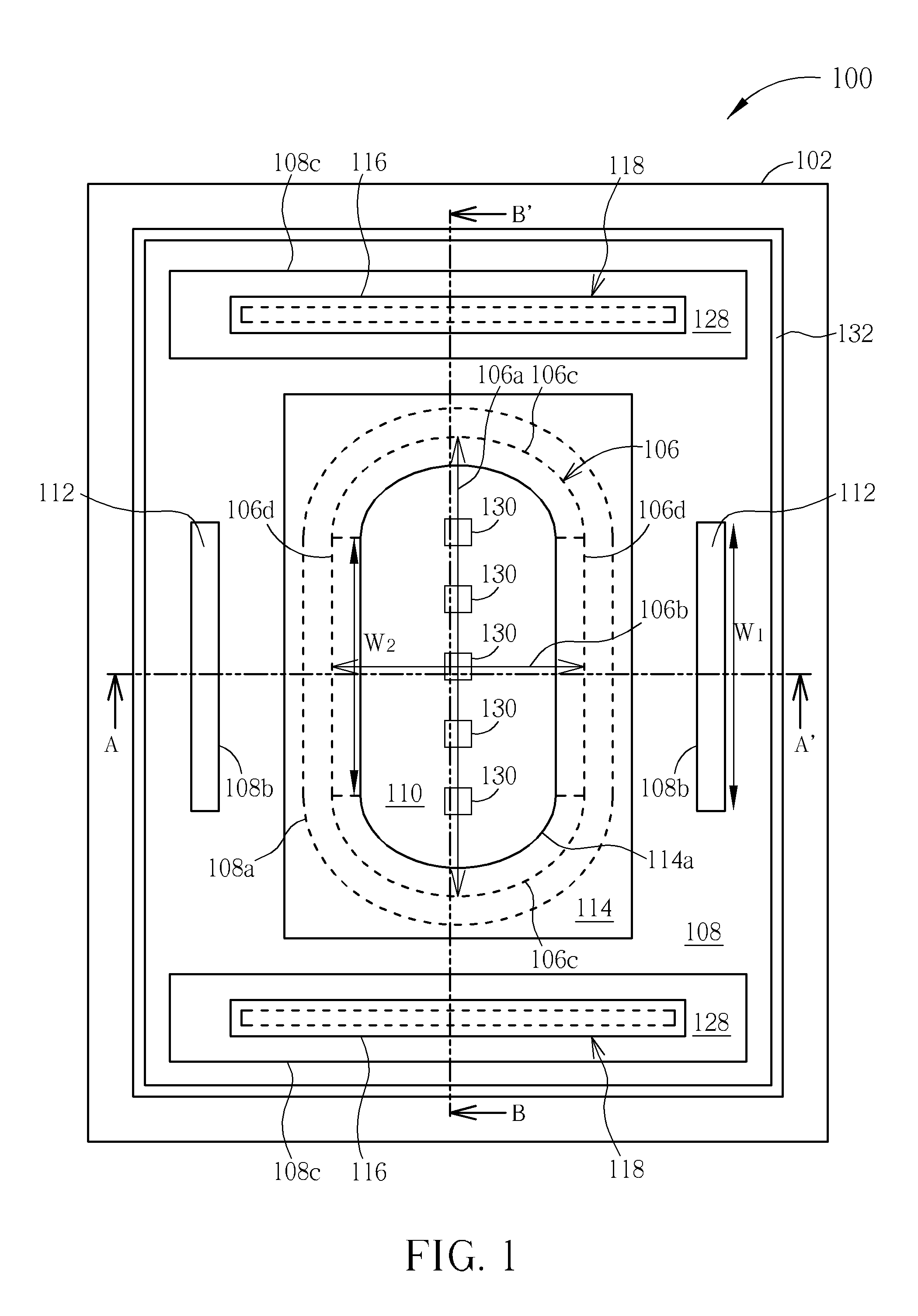

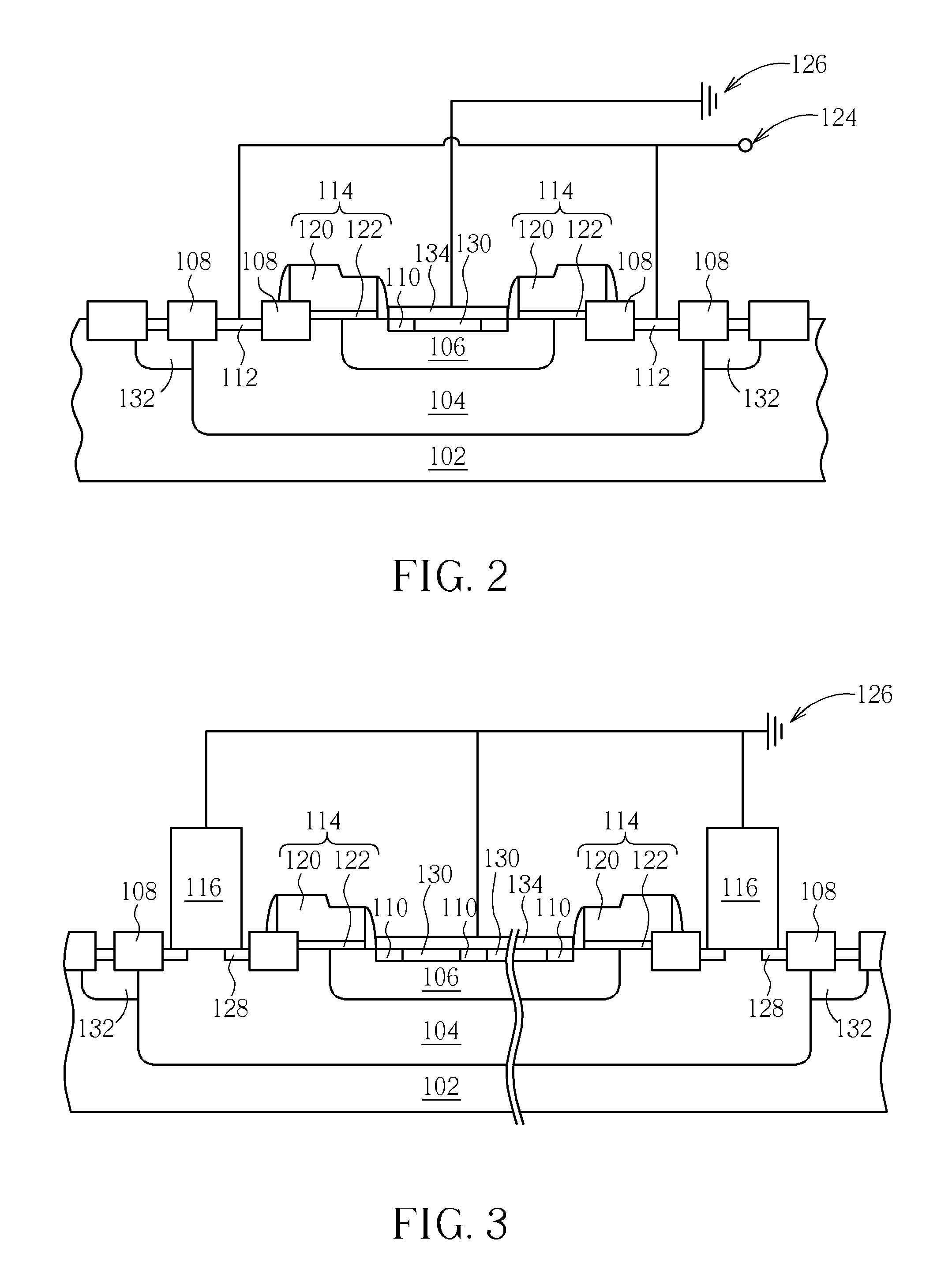

Lateral Diffused Metal-Oxide-Semiconductor Device

The present invention provides a lateral diffused metal-oxide-semiconductor device including a first doped region, a second doped region, a third doped region, a gate structure, and a contact metal. The first doped region and the third doped region have a first conductive type, and the second doped region has a second conductive type. The second doped region, which has a racetrack-shaped layout, is disposed in the first doped region, and has a long axis. The third doped region is disposed in the second doped region. The gate structure is disposed on the first doped region and the second doped region at a side of the third doped region. The contact metal is disposed on the first doped region at a side of the second doped region extending out along the long axis, and is in contact with the first doped region.

Owner:MARLIN SEMICON LTD

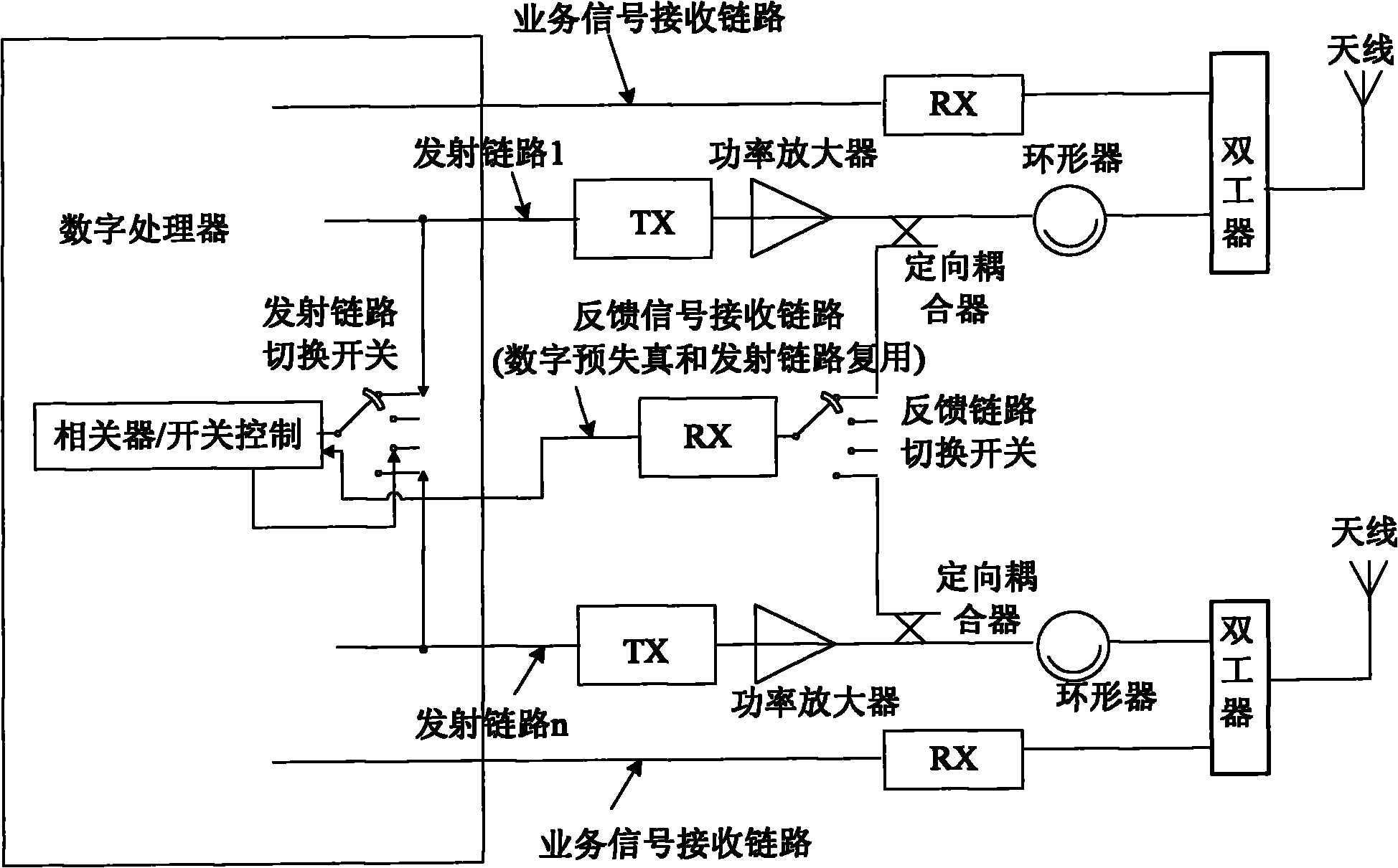

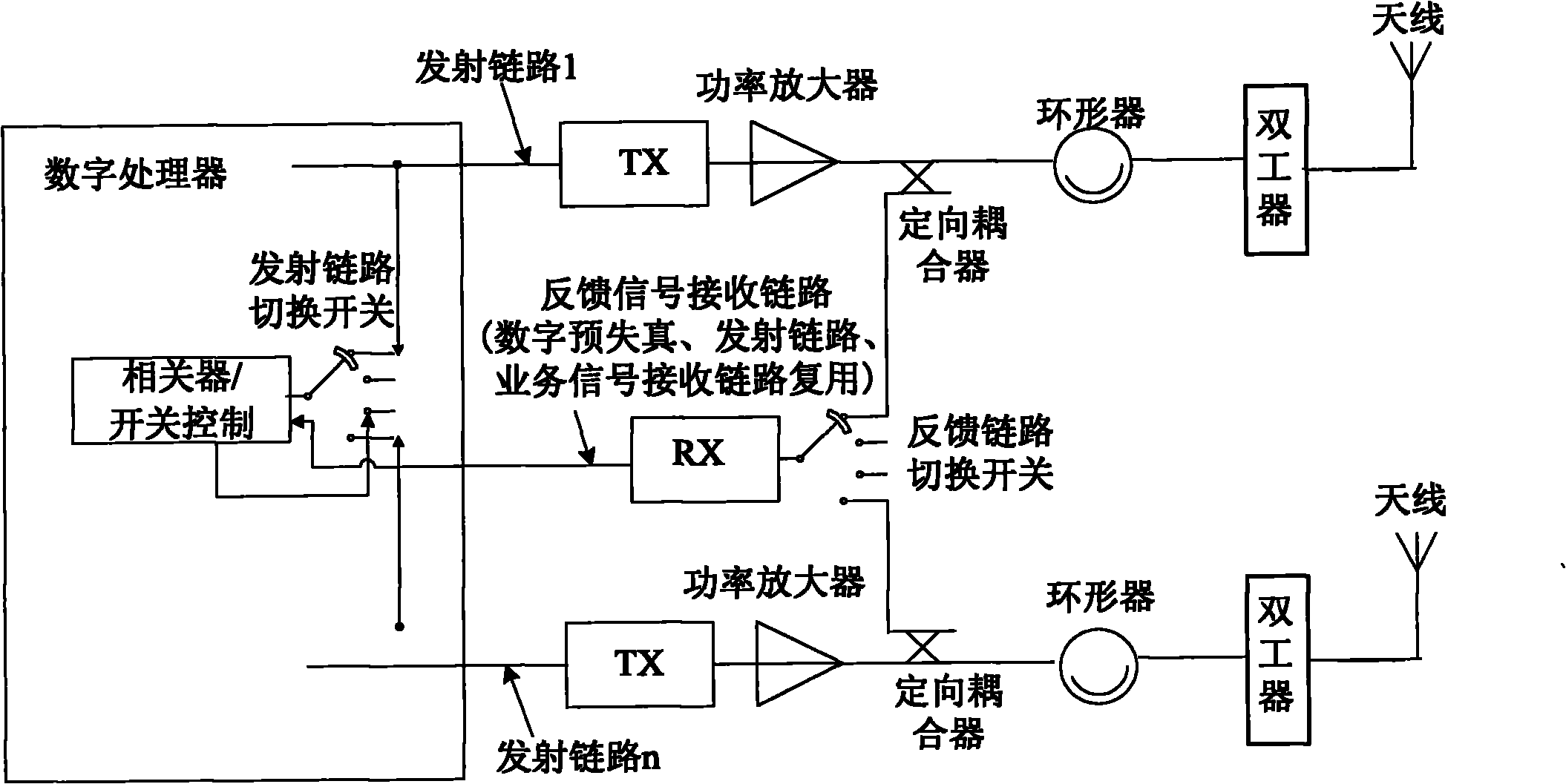

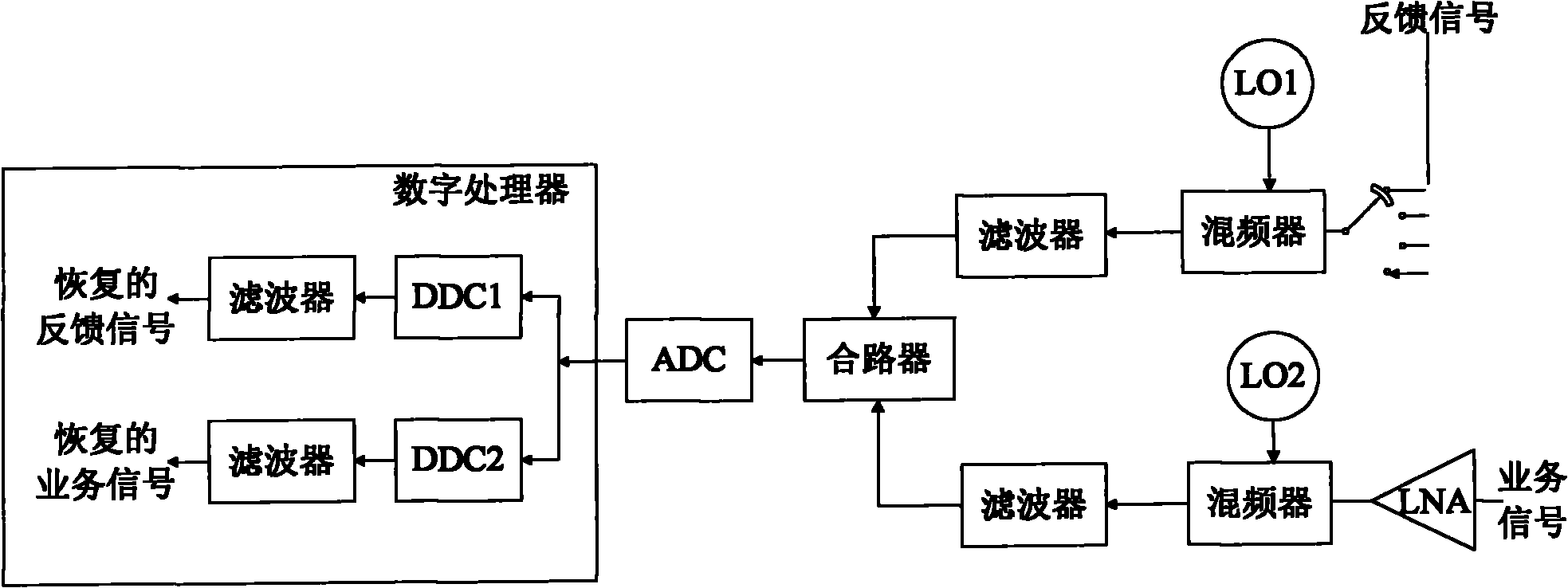

Multi-antenna system and method for multiplexing feedback signal receiving link thereof

ActiveCN102158265ASave extra spaceSpatial transmit diversitySynchronous/start-stop systemsEngineeringPredistortion

The invention provides a multi-antenna system and a method for multiplexing a feedback signal receiving link thereof. The multi-antenna system comprises a plurality of transmitting links, the feedback signal receiving link and a digital processing unit. When the digital processing unit and a feedback link changeover switch select to connect the same transmitting link, the feedback signal receiving link is used for receiving a feedback signal from the connected transmitting link through a directional coupler of the connected transmitting link and transmitting the feedback signal to the digital processing unit; the digital processing unit is used for figuring out a digital predistortion coefficient according to the received feedback signal and performing digital predistortion treatment on the transmitting link; and simultaneously, the digital processing unit is used for getting calibration parameters of the plurality of transmitting links according to the received feedback signals of the plurality of transmitting links, and taking one transmitting link as a reference link to calibrate other one or plural transmitting links. The system and the method can save the area and the cost of a board through multiplexing a predistortion treatment circuit and the feedback signal receiving link.

Owner:HUAWEI TECH CO LTD

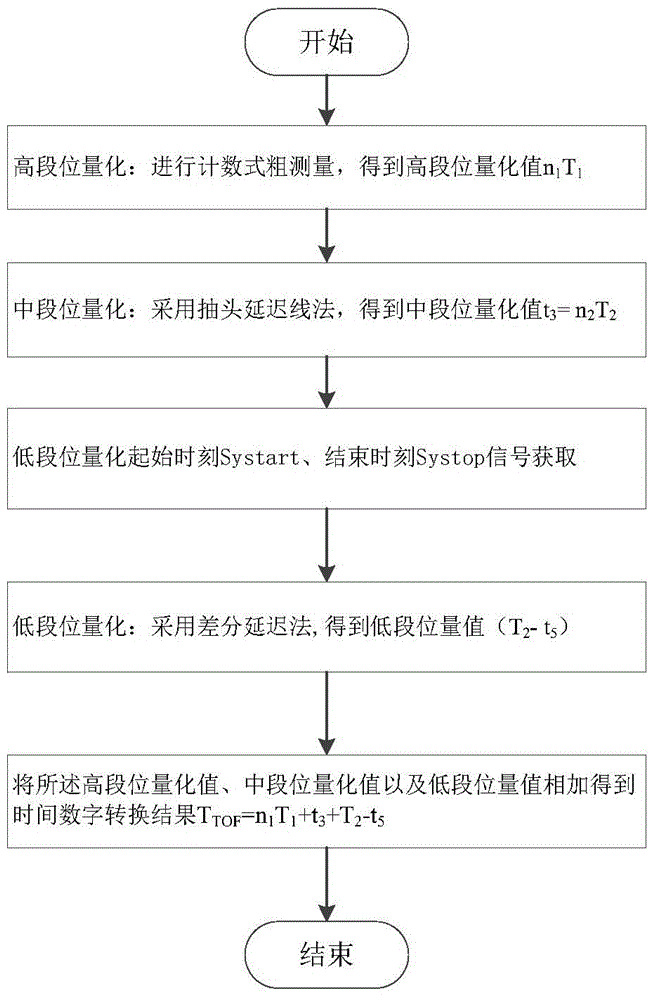

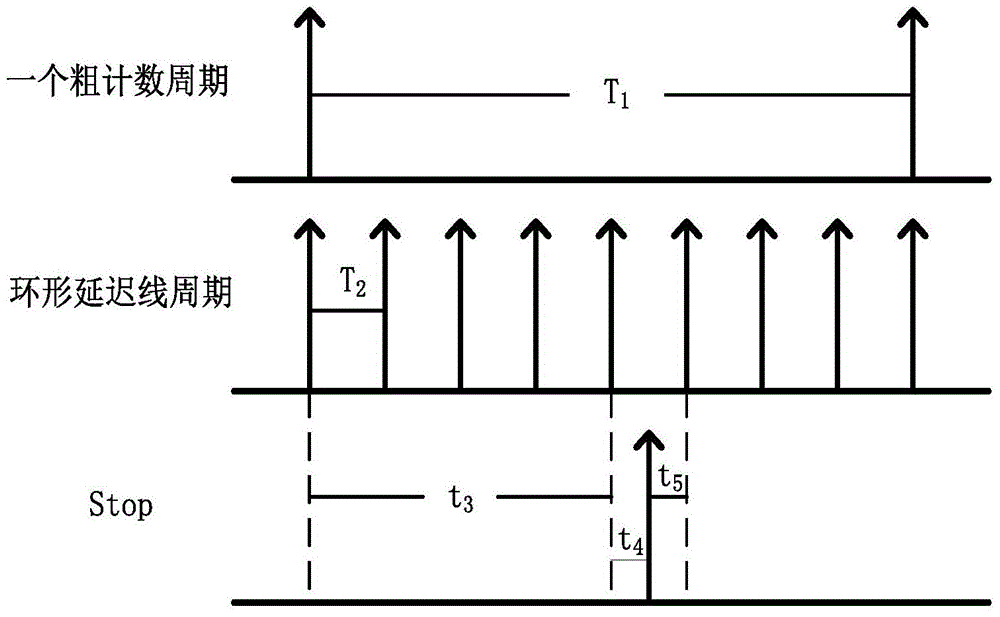

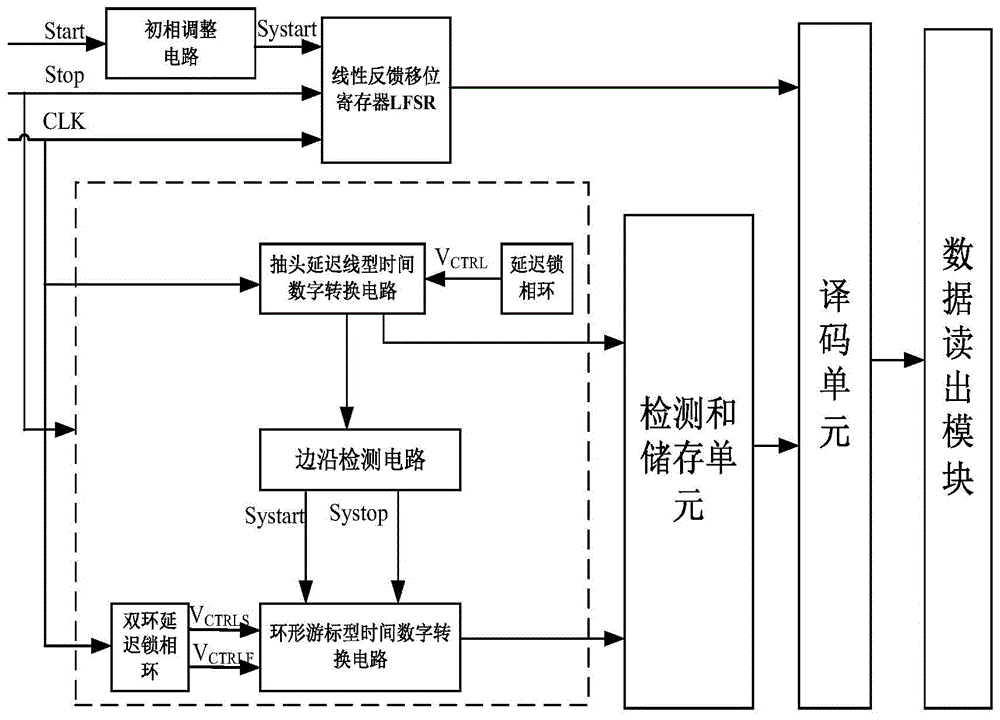

Dual-loop DLL-based three-segment type high-precision time-to-digital conversion method and circuit

InactiveCN104320130AHigh precision measurementImprove detection accuracyAnalogue/digital conversionElectric signal transmission systemsEngineeringVoltage control

The invention discloses a dual-loop DLL-based three-segment type high-precision time-to-digital conversion method and circuit. According to a measured time segment, a high-middle-low combined segmental type quantization method is adopted. A high-segment bit counting type quantizer in three-segment type TDC (time-to-digital conversion) is driven by a high-frequency stabilizing clock which is inputted from the outside, so that a wide-range stable distance measuring range can be realized; a middle-segment bit TDC is formed by a first DLL voltage controlled delay chain; high-segment bit subdivision can be realized through an asynchronous sampling mode, and repeatable uniform phase distinguishing can be accomplished in a stable clock period; a phase position at a termination time point is decoded, so that a middle-segment quantization function can be accomplished; and according to quantization errors generated by time-to-digital conversion in a middle-segment bit, error time is extracted, a low-segment bit accomplishes further quantization processing, and therefore, higher measurement precision can be realized.

Owner:SOUTHEAST UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com