High-speed low-power-consumption dynamic comparator

A dynamic comparator, low-power technology, applied in multiple input and output pulse circuits, etc., can solve problems such as troubles, and achieve the effects of simplifying timing, saving area and power consumption, and high energy efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

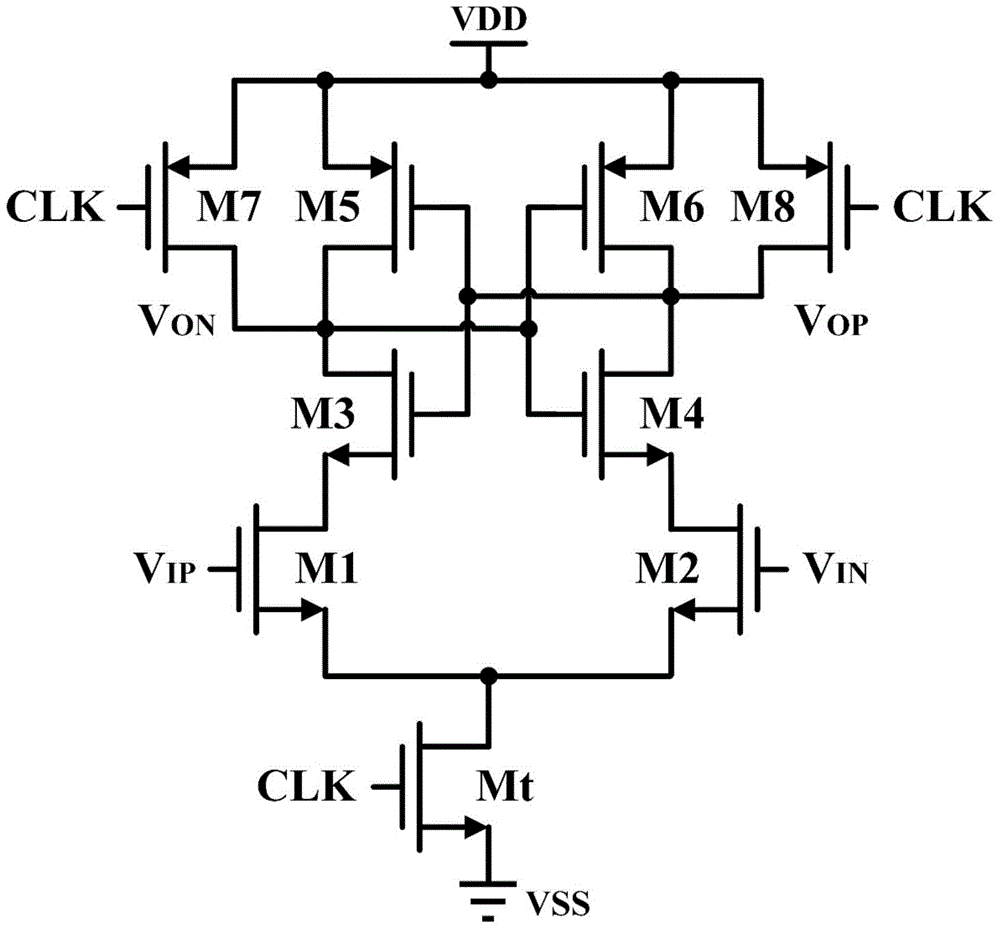

[0036] refer to Figure 5 , a high-speed and low-power dynamic comparator proposed by the present invention includes a preamplifier circuit A and a regenerative latch circuit B.

[0037] refer to Figure 6 , the preamplifier circuit A includes: a clock output terminal, a first differential signal input terminal, a second differential signal input terminal, an output node FN, an output node FP, an input module, a clock reset module, a cross-coupling module and a tail current module. The clock output terminal is used to output the clock signal CLK, and the first differential signal input terminal and the second differential signal input terminal are respectively used to access the first differential input signal V IP and the second differential input signal V IN . The input module includes a MOS transistor M1 and a MOS transistor M2, the cross-coupling module includes a MOS transistor M3 as a first on-off element and a MOS transistor M4 as a second on-off element, and the clo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com