Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

9531 results about "Low power dissipation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

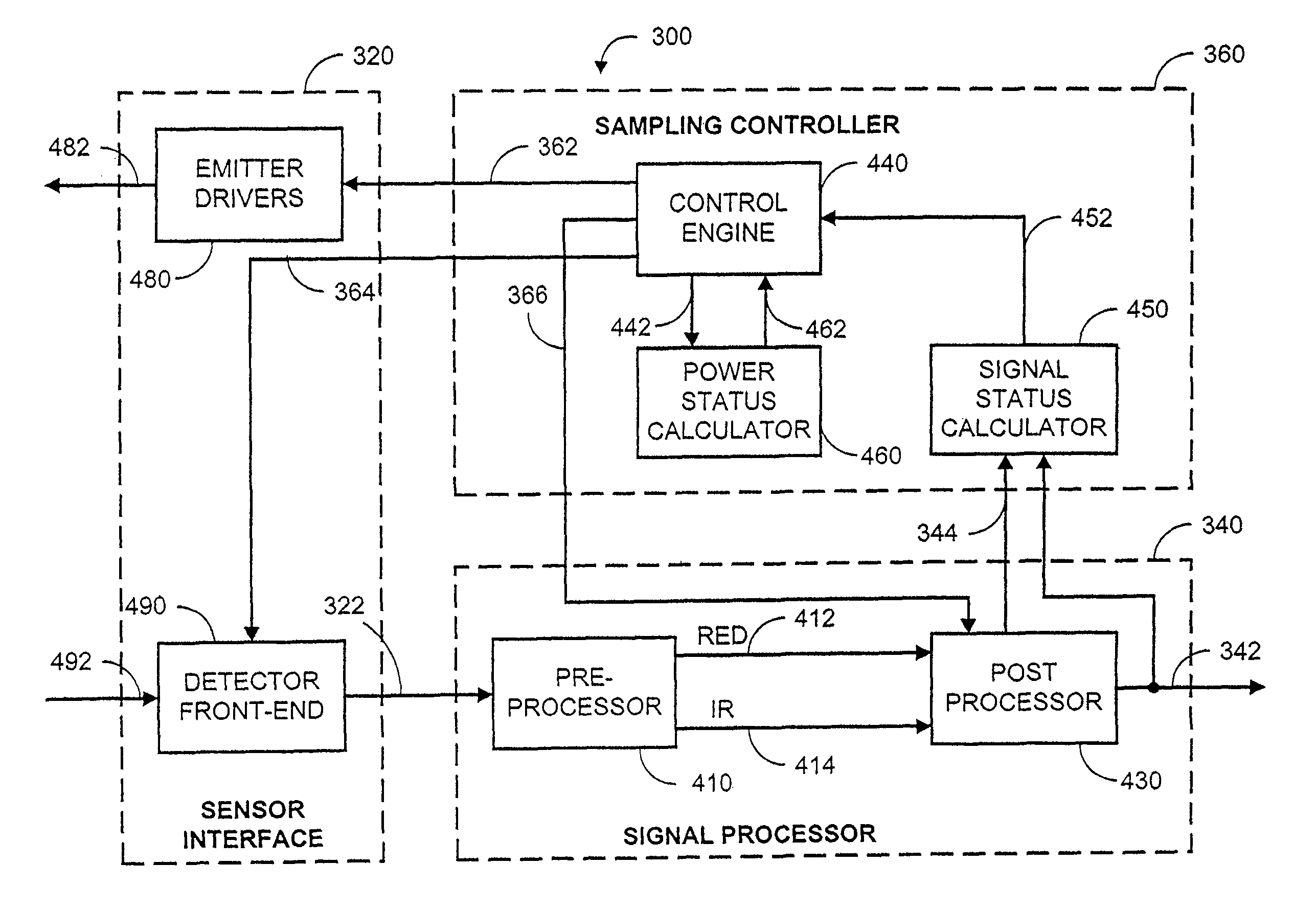

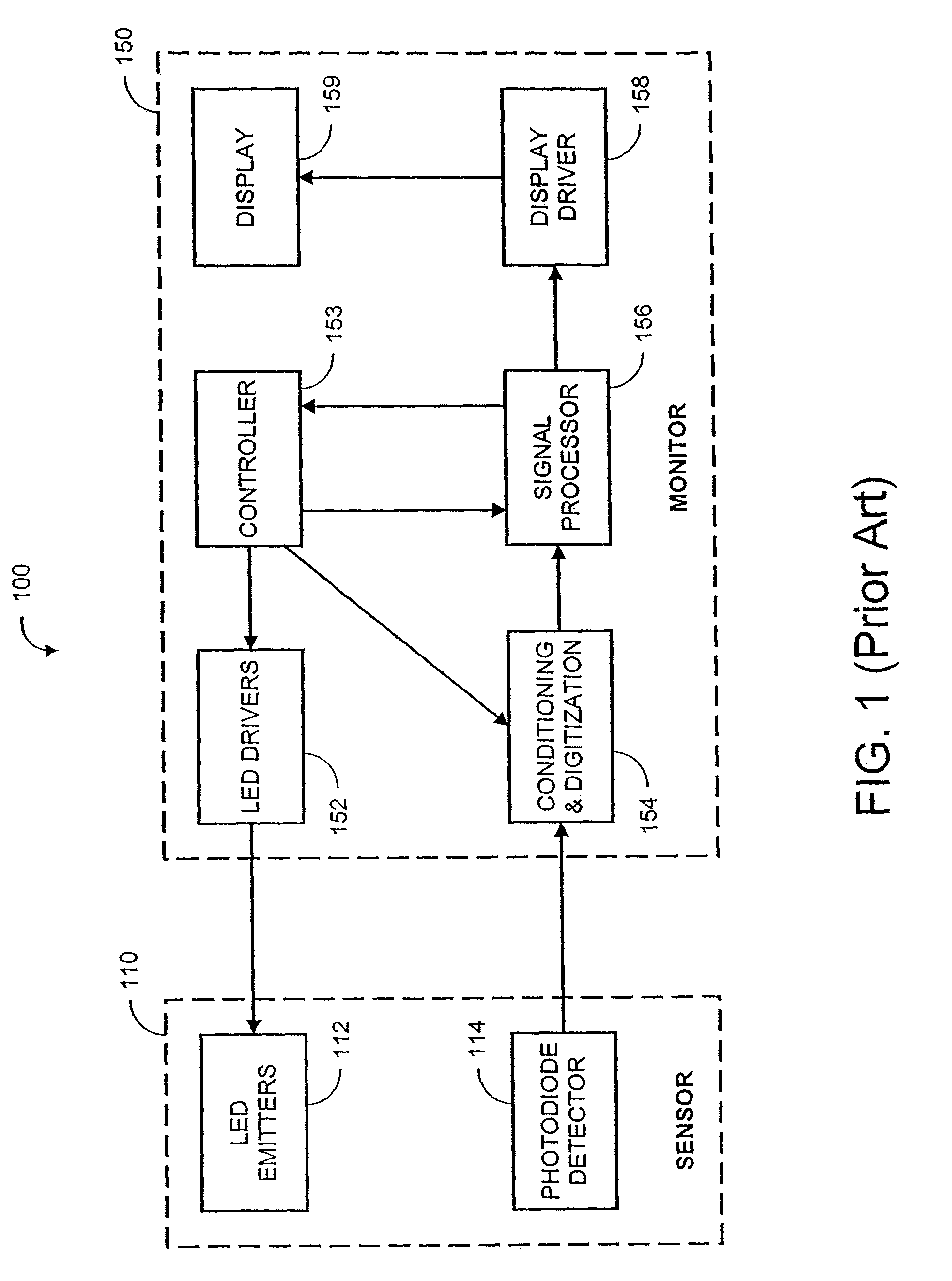

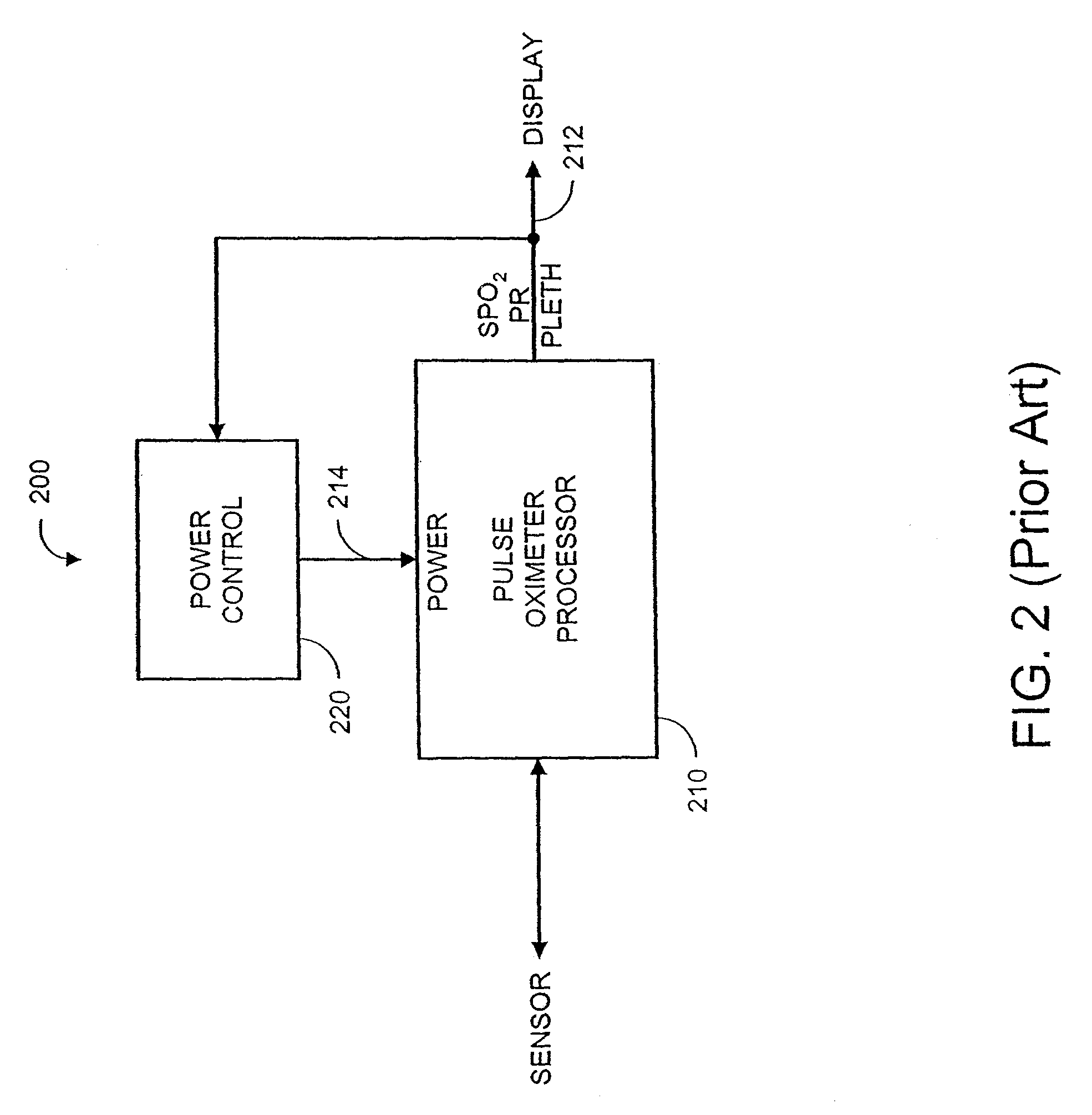

Low power pulse oximeter

ActiveUS8457703B2Reduce power consumptionIncrease demandDiagnostic recording/measuringSensorsPulse oximetersEngineering

A pulse oximeter may reduce power consumption in the absence of overriding conditions. Various sampling mechanisms may be used individually or in combination. Various parameters may be monitored to trigger or override a reduced power consumption state. In this manner, a pulse oximeter can lower power consumption without sacrificing performance during, for example, high noise conditions or oxygen desaturations.

Owner:JPMORGAN CHASE BANK NA

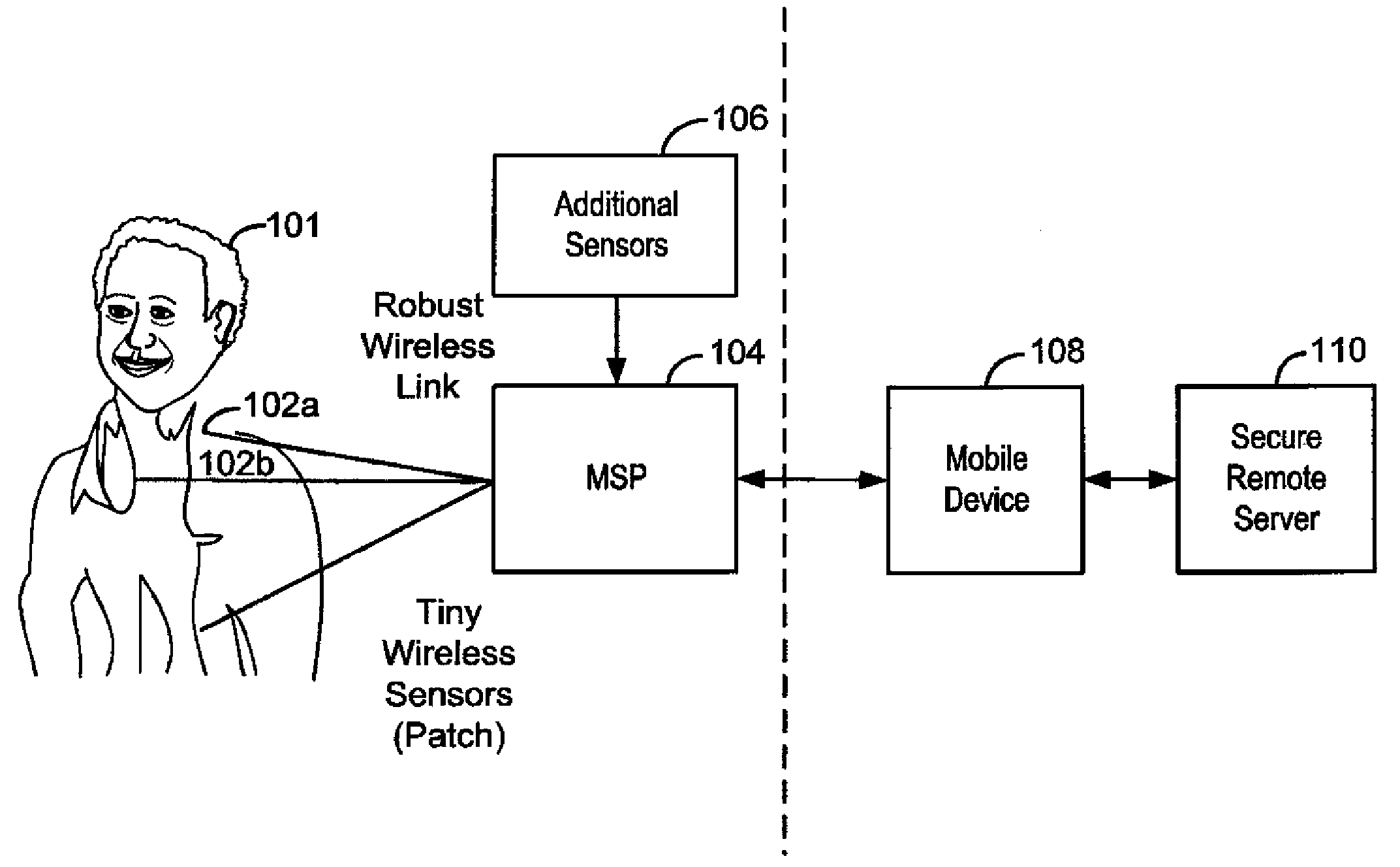

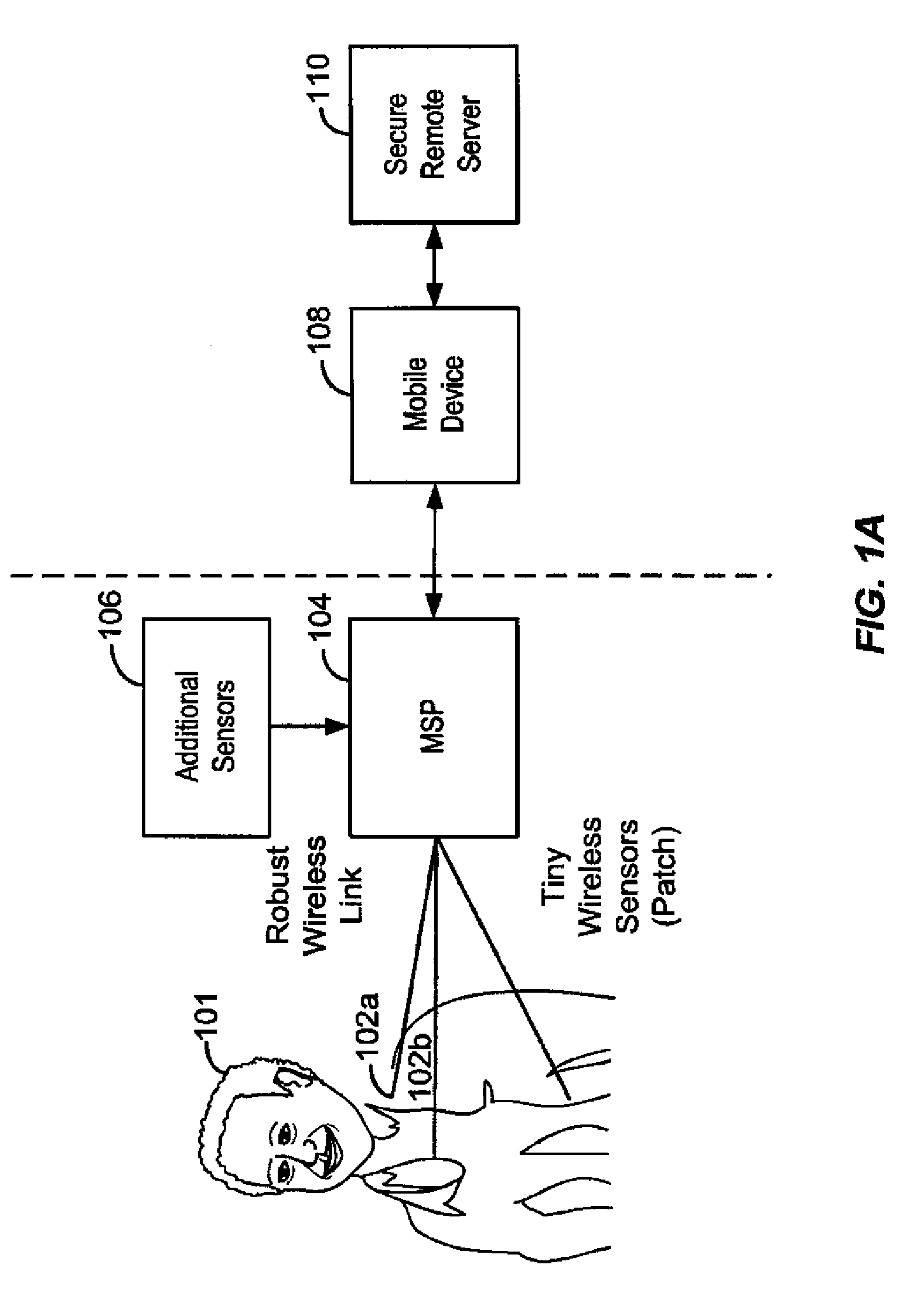

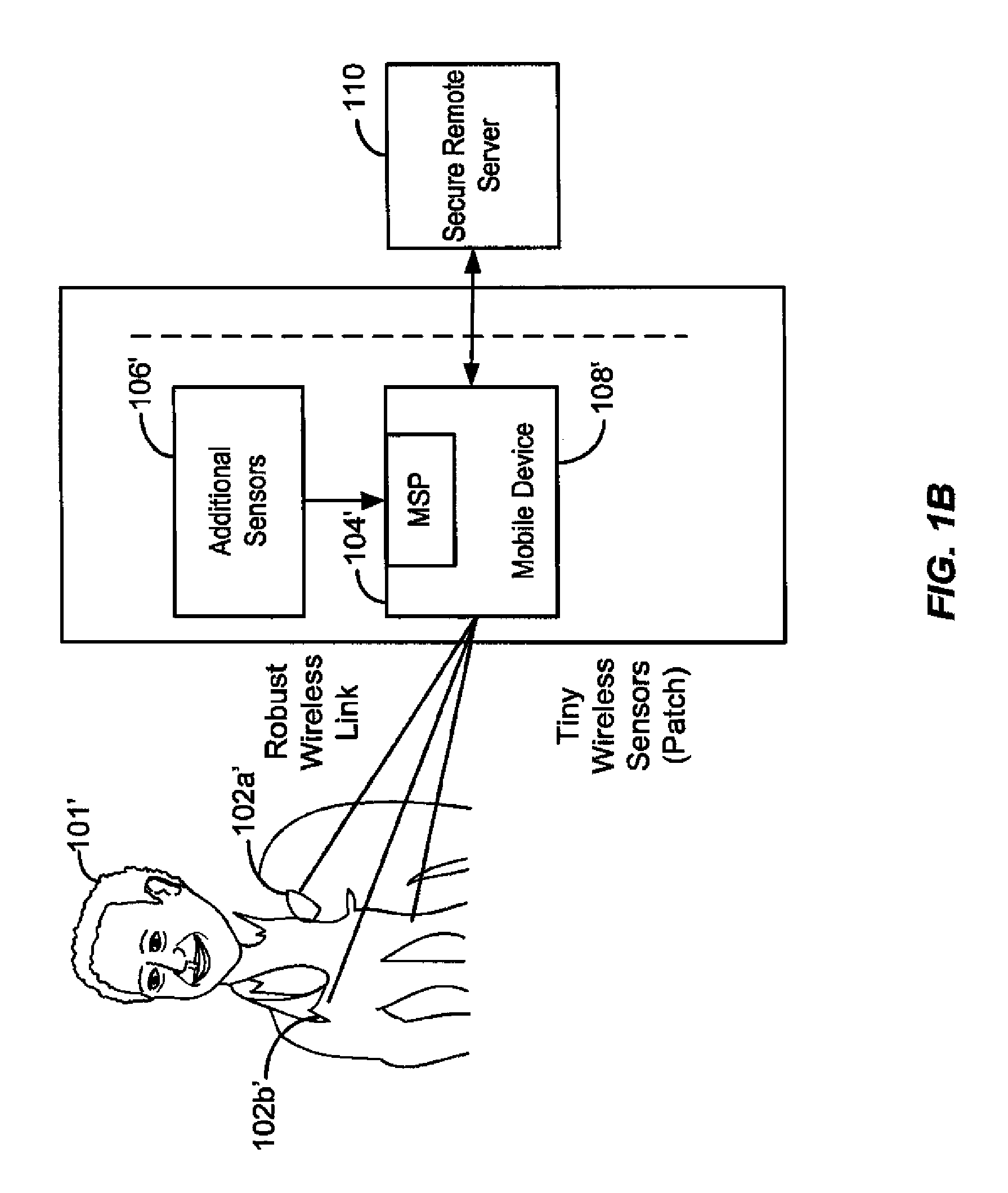

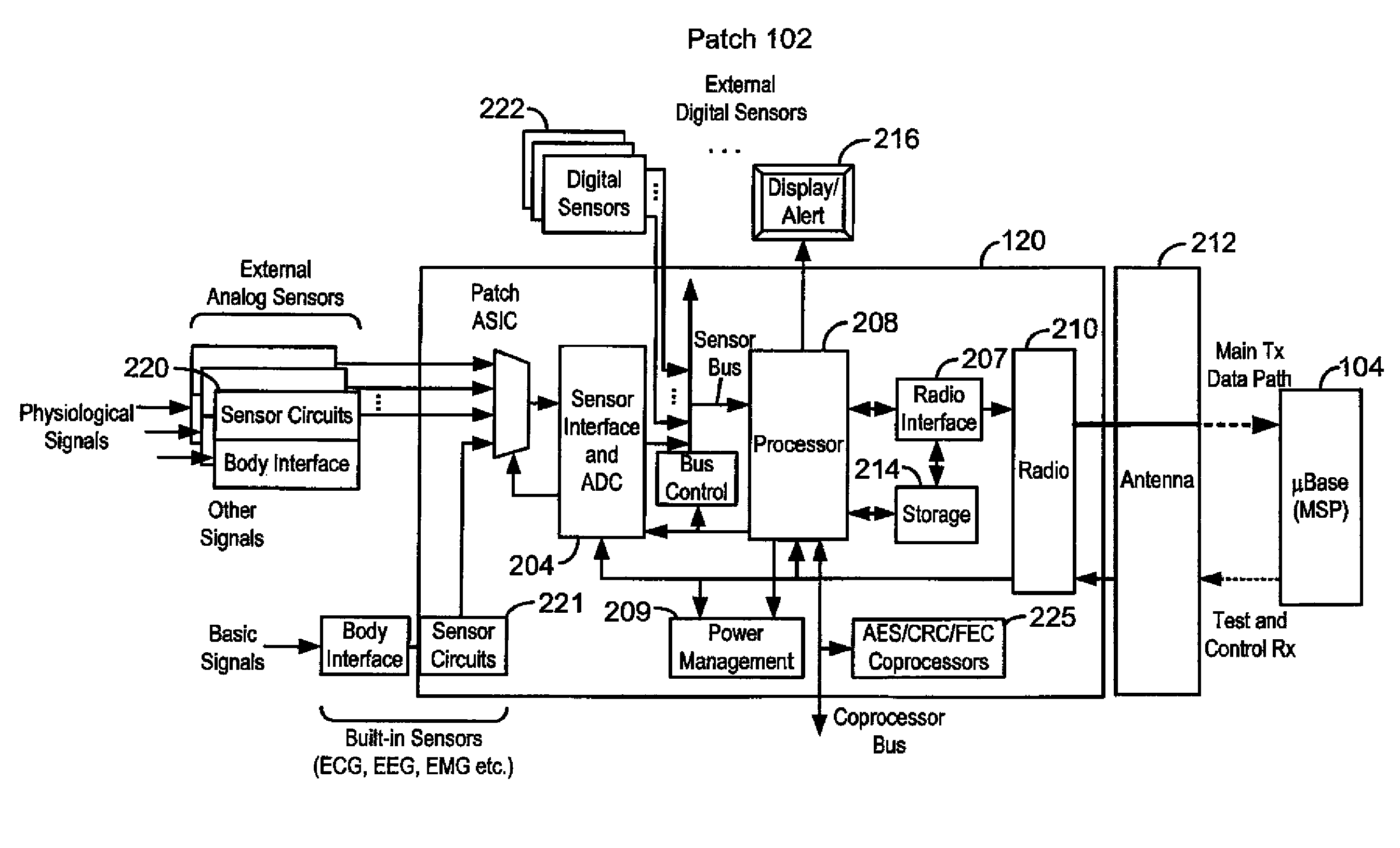

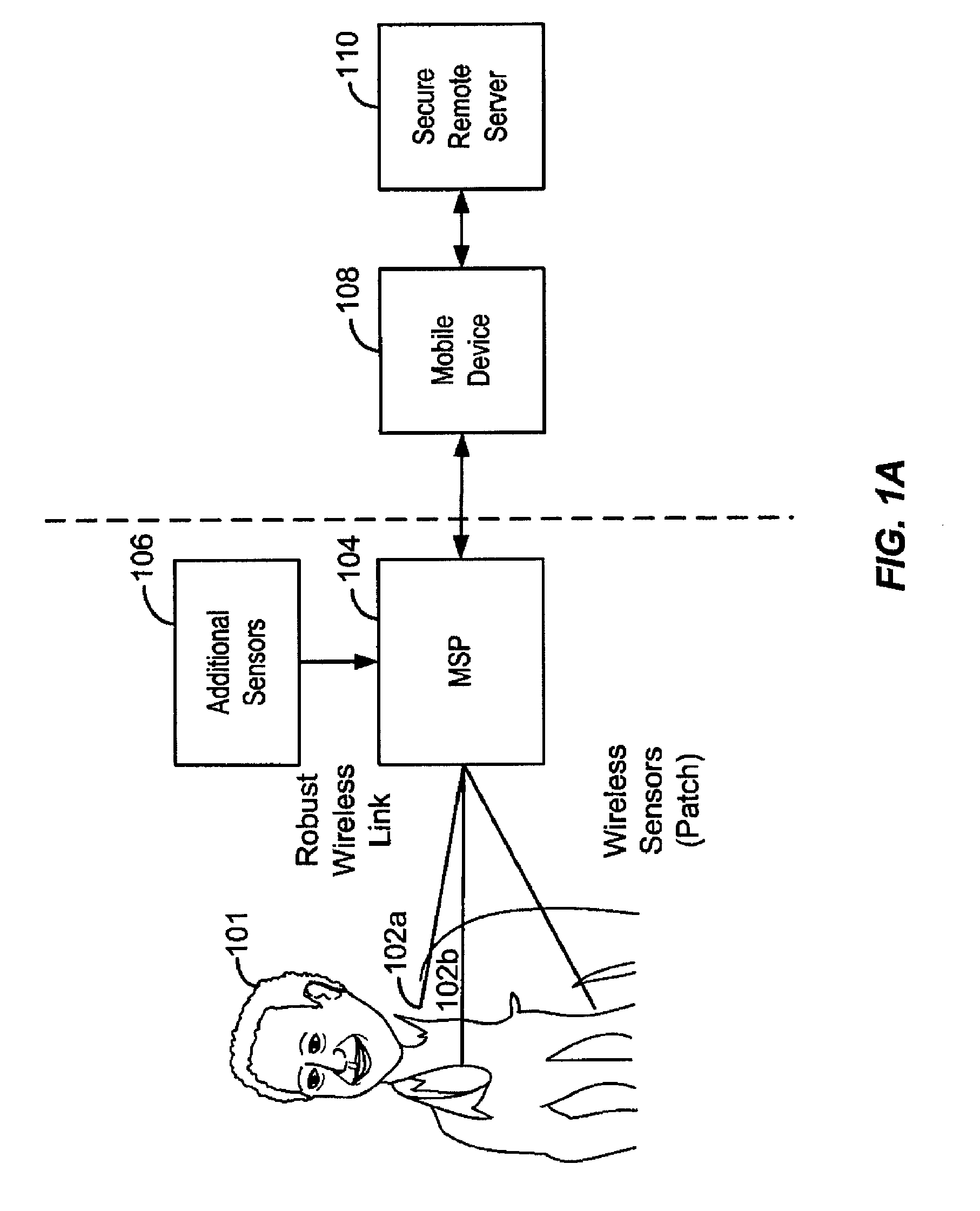

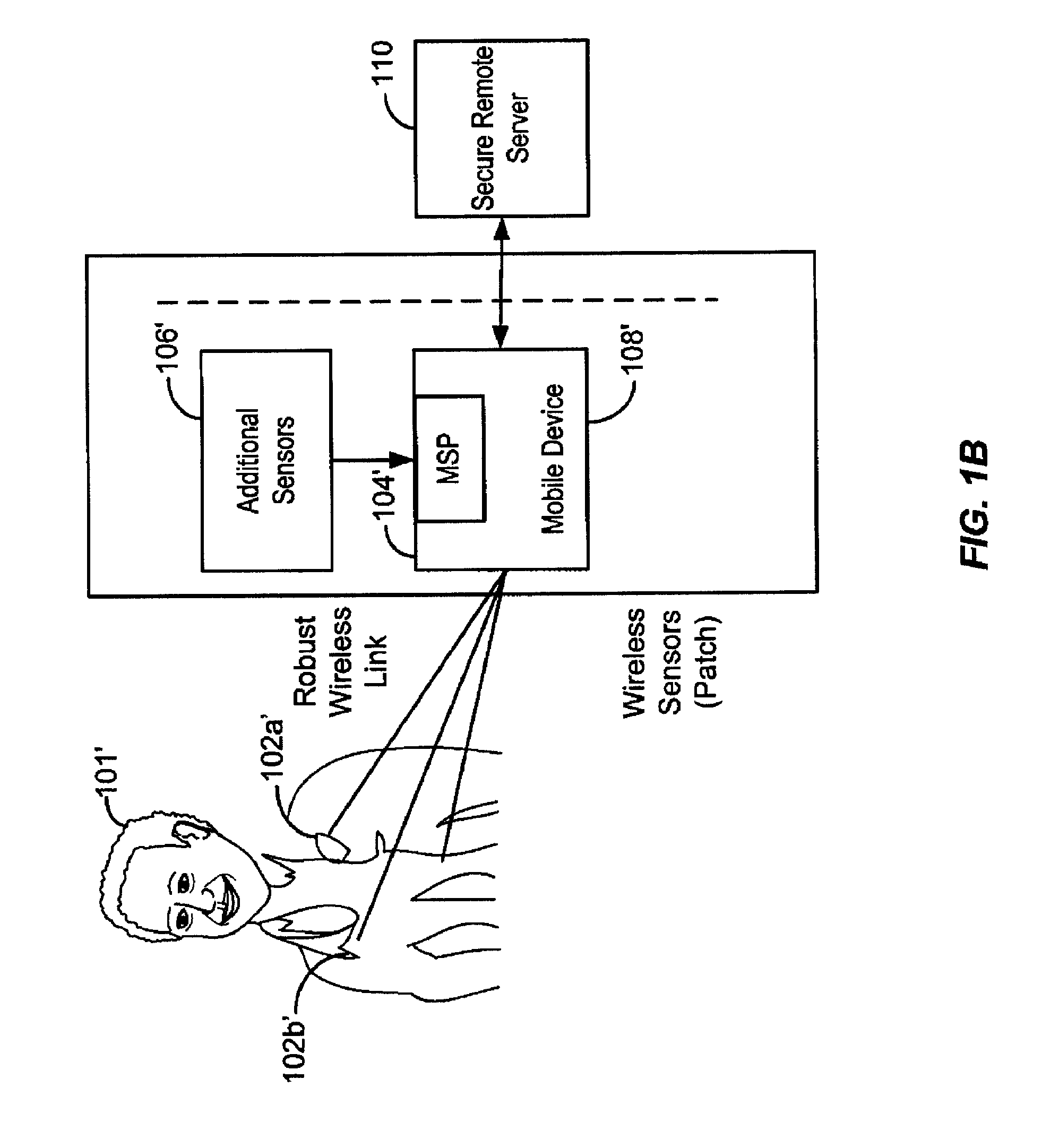

Wireless physiological sensor patches and systems

ActiveUS20090054737A1Raise and low transmit powerImprove communication qualityInertial sensorsMeasuring/recording heart/pulse rateEngineeringLow power dissipation

The present invention provides methods, devices, and systems for wireless physiological sensor patches and systems which incorporate these patches. The systems and methods utilize a structure where the processing is distributed asymmetrically on the two or more types of ASIC chips that are designed to work together. The invention also relates to systems comprising two or more ASIC chips designed for use in physiological sensing wherein the ASIC chips are designed to work together to achieve high wireless link reliability / security, low power dissipation, compactness, low cost and support a variety of sensors for sensing various physiological parameters.

Owner:HMICRO

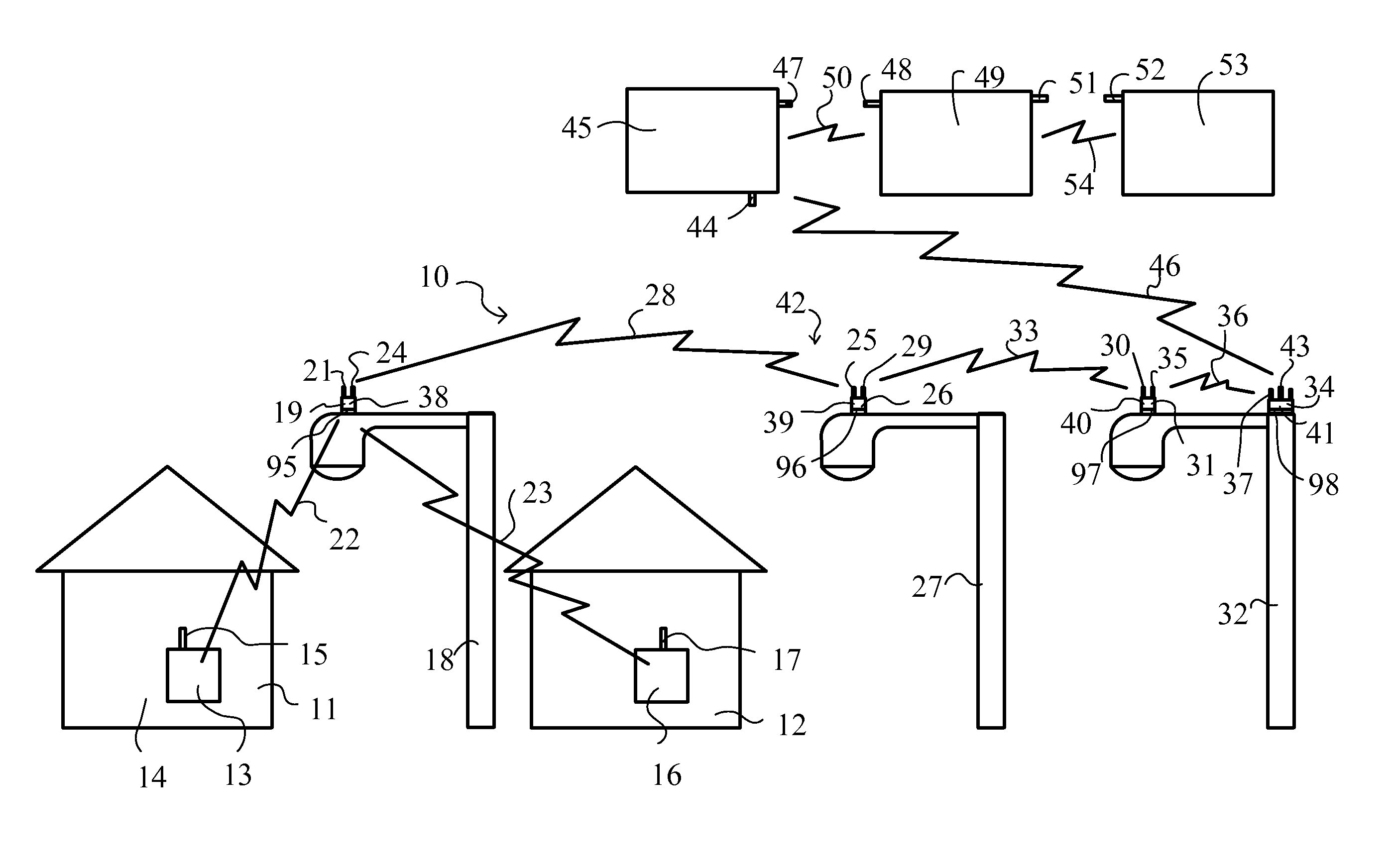

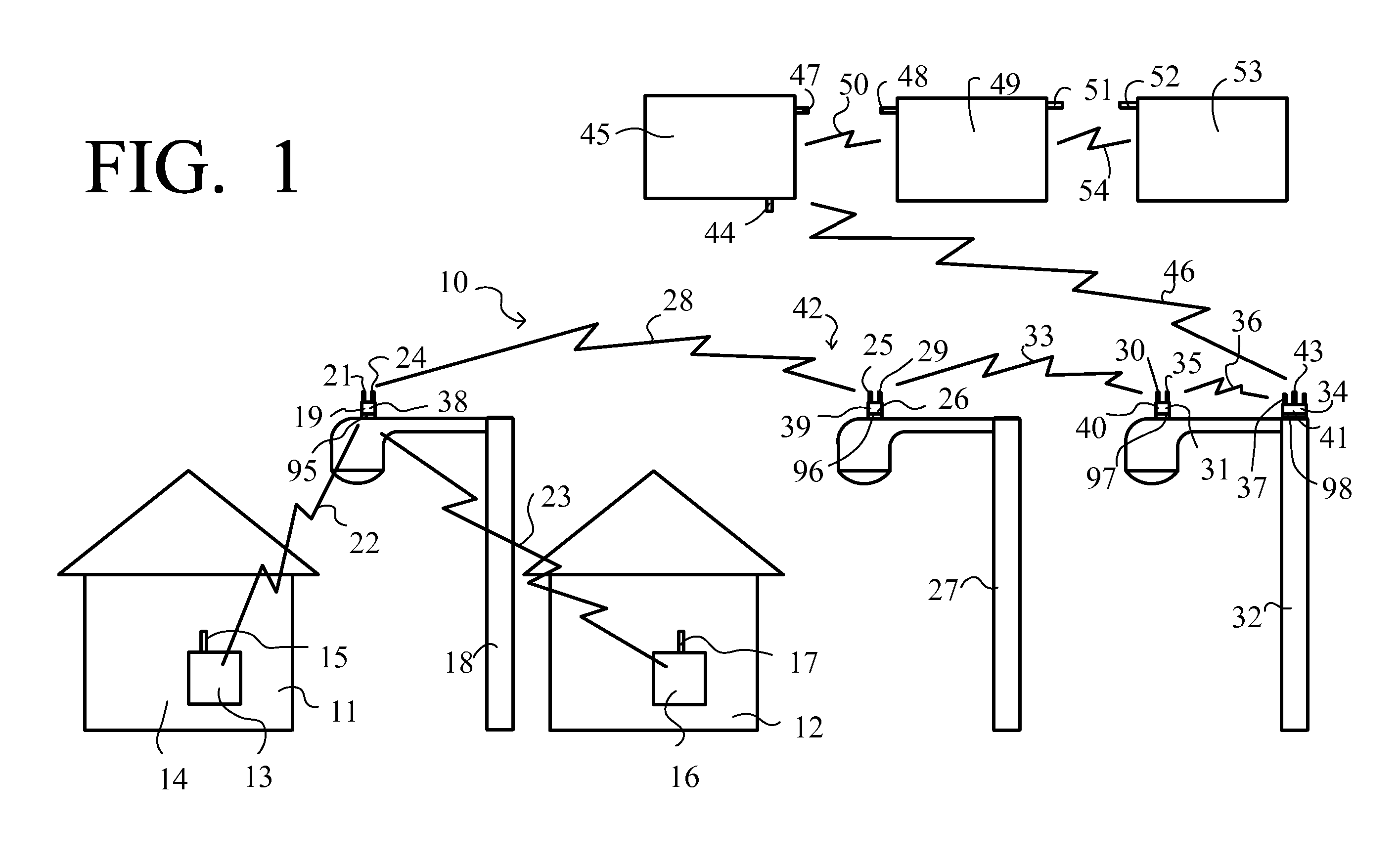

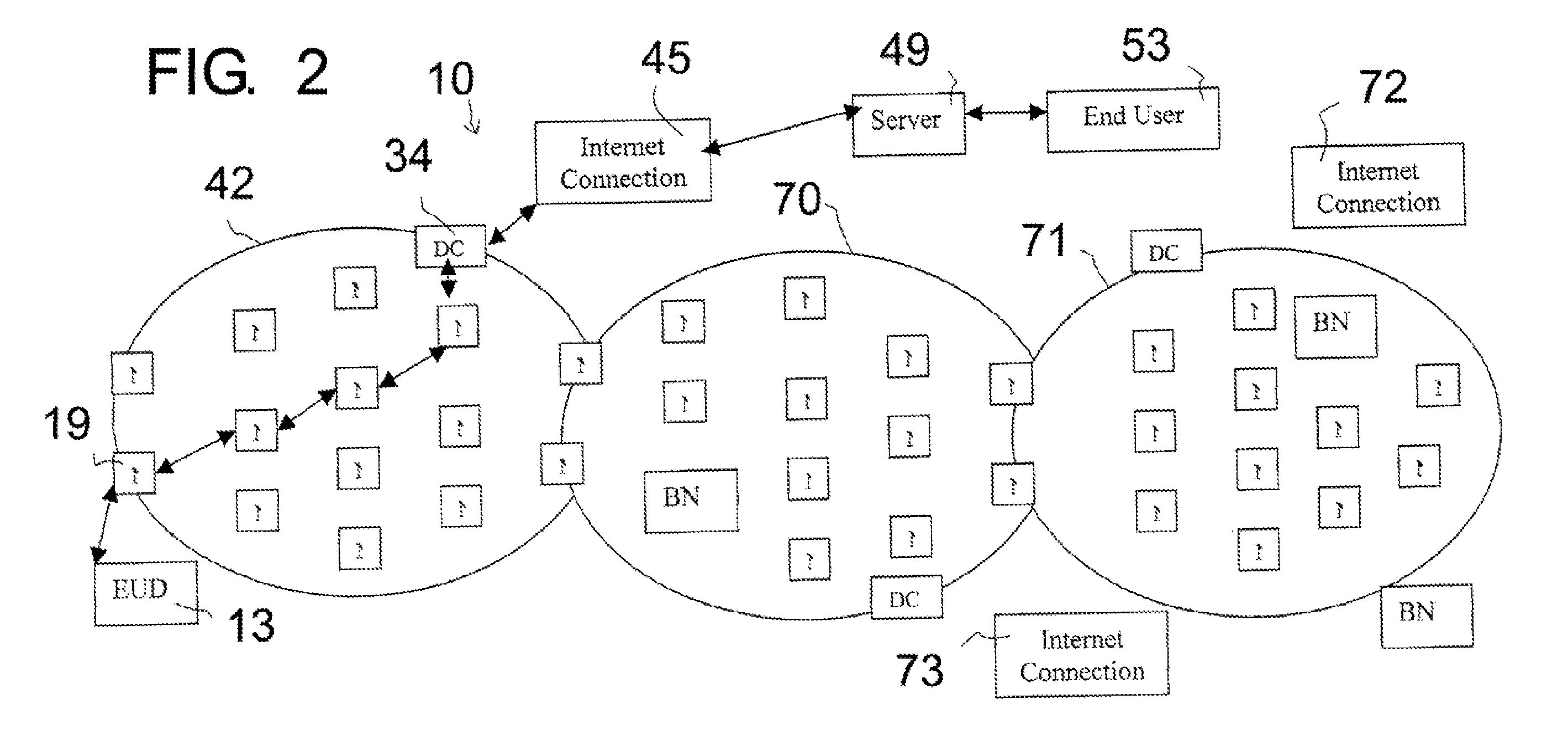

Remote monitoring and control system

ActiveUS7825793B1Substation equipmentTransmissionCommunications systemNetwork Communication Protocols

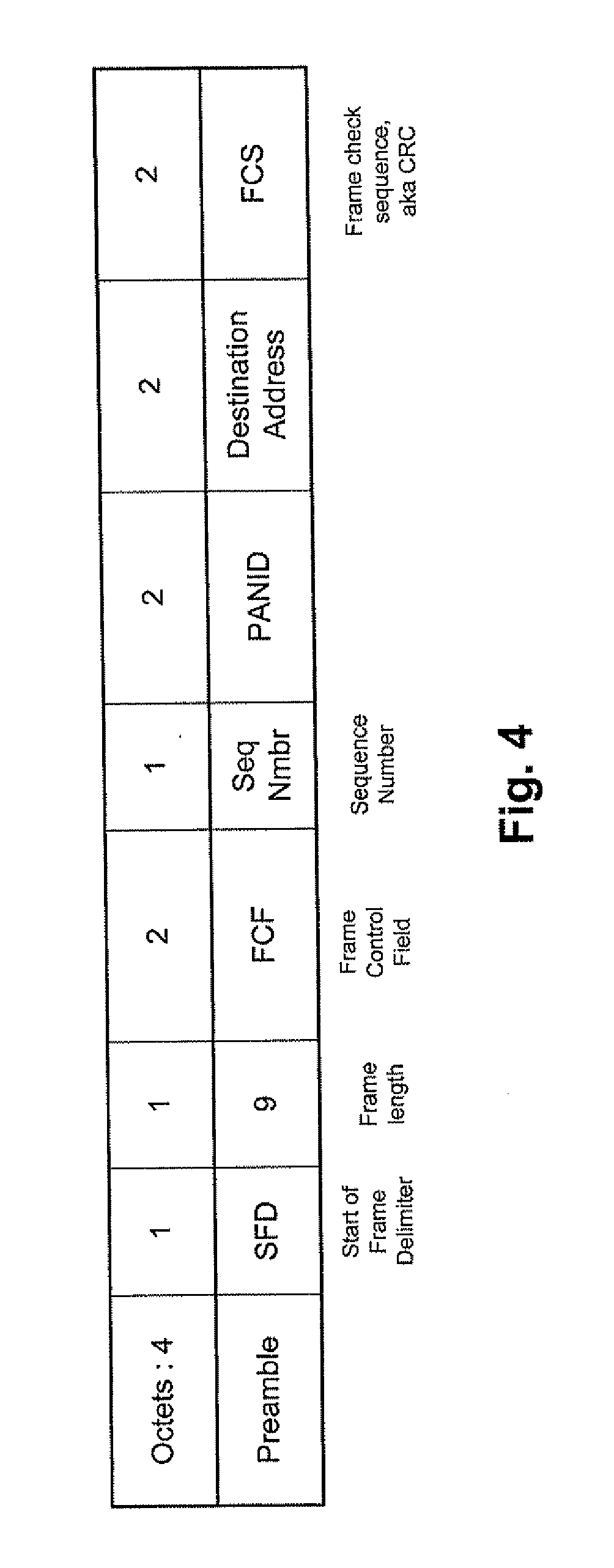

A communication system that provides communication of information between an end user device and a remote end user. The system includes a communication node mounted on the upper part of a utility pole, and drawing its power from the utility pole through a standard NEMA Locking 3 Pole Receptacle, and adapted to communicate with a nearby user device using the low-power communication protocol, such as the ZigBee protocol (ANSI IEEE 802.15.4) or Radio Frequency Identification Device (RFID) technology, and also adapted to communicate with a neighborhood mesh network of nodes mounted on utility poles. The neighborhood mesh network is capable of communicating, through a regional computer network, with the remote end user.

Owner:SUNRISE TECH

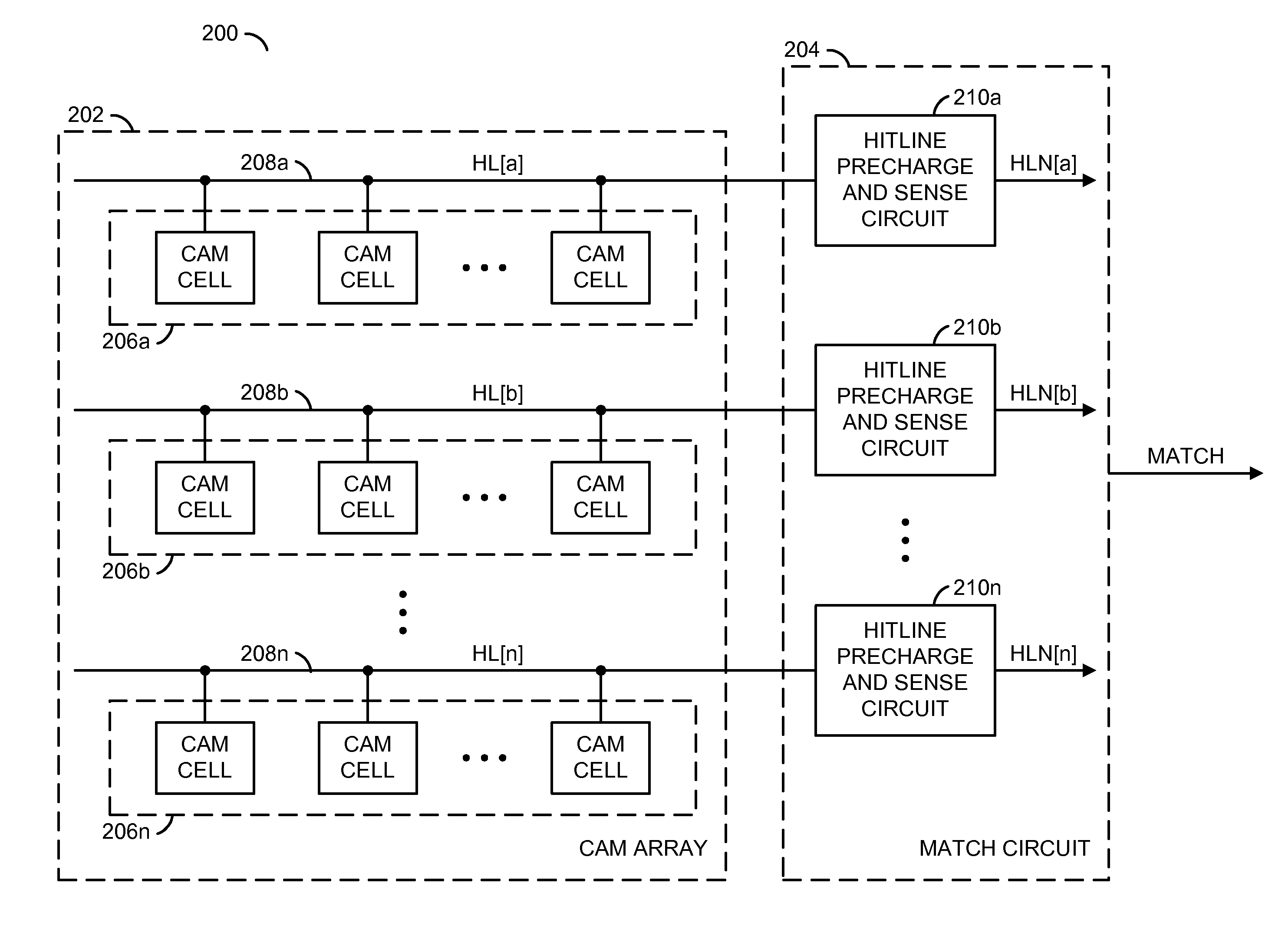

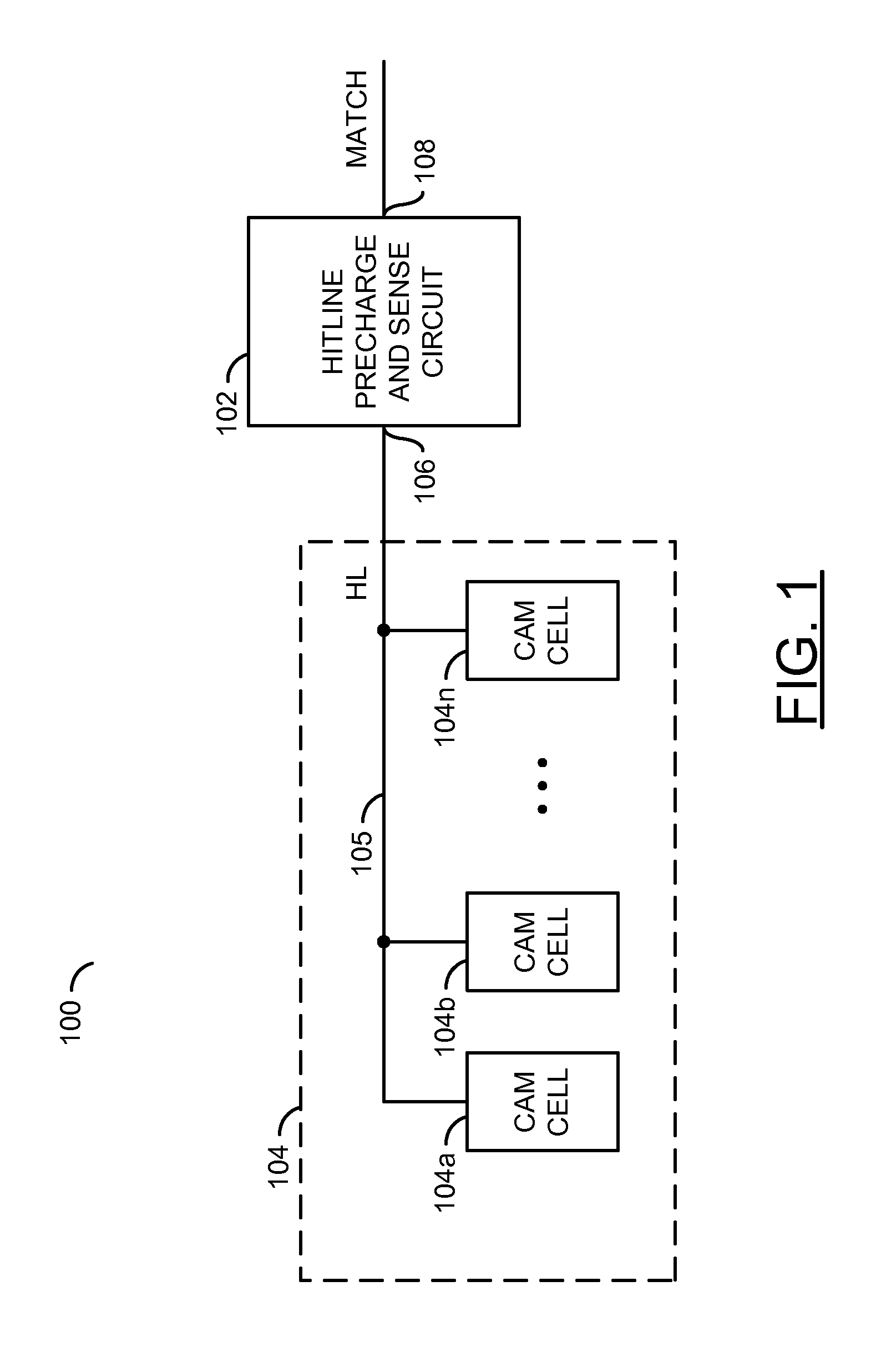

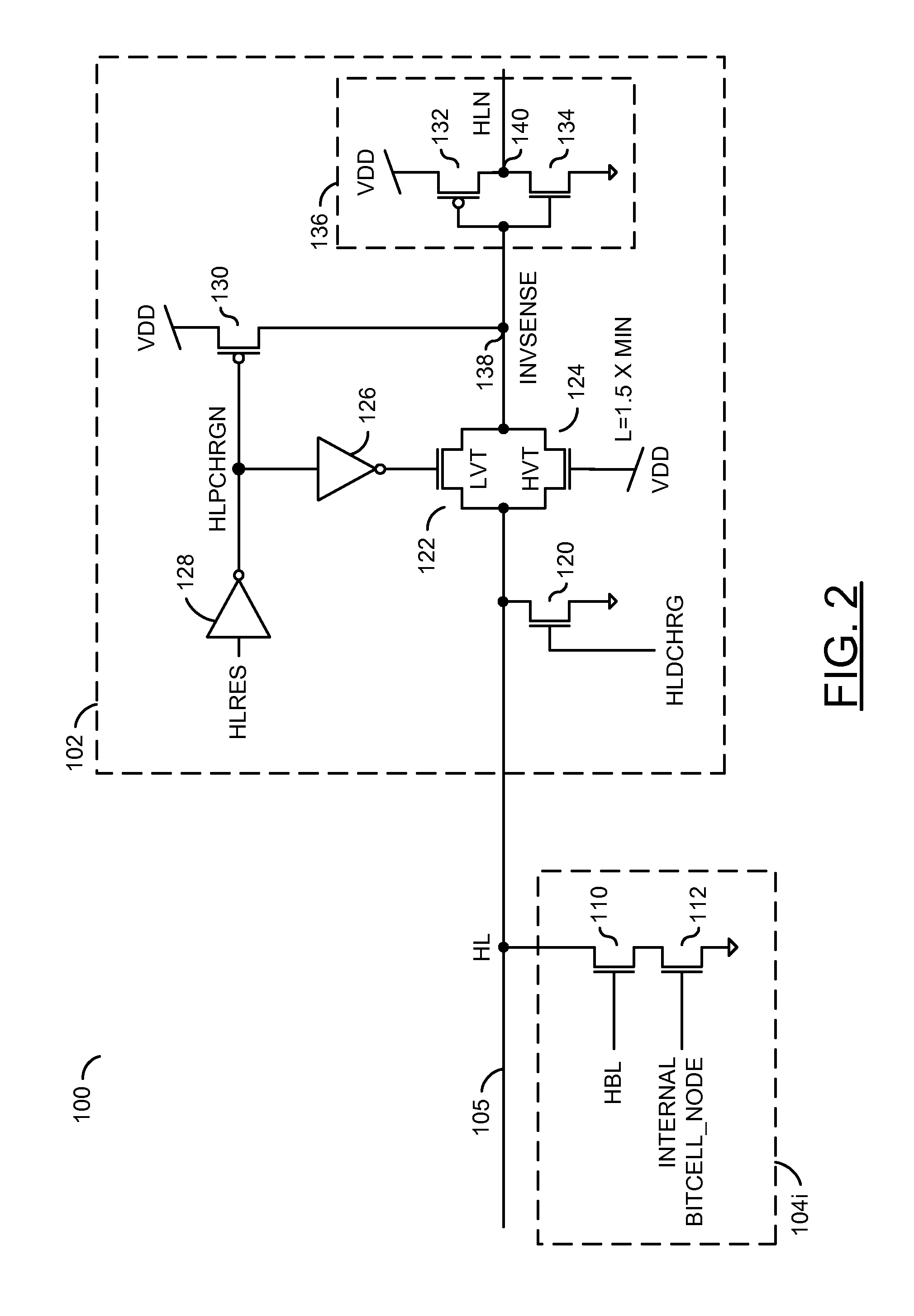

Low power content addressable memory hitline precharge and sensing circuit

An apparatus and a method of operating the apparatus. The apparatus includes a driver circuit and a memory circuit. The driver circuit may be configured to precharge a hitline in response to a predetermined voltage level and a control signal and sense a result of a compare operation based upon a hitline signal on the hitline. The driver circuit generally precharges the hitline to a voltage level lower than the predetermined voltage level and senses the result of the compare operation using the full predetermined voltage level. The memory circuit may be configured to perform the compare operation using the hitline.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

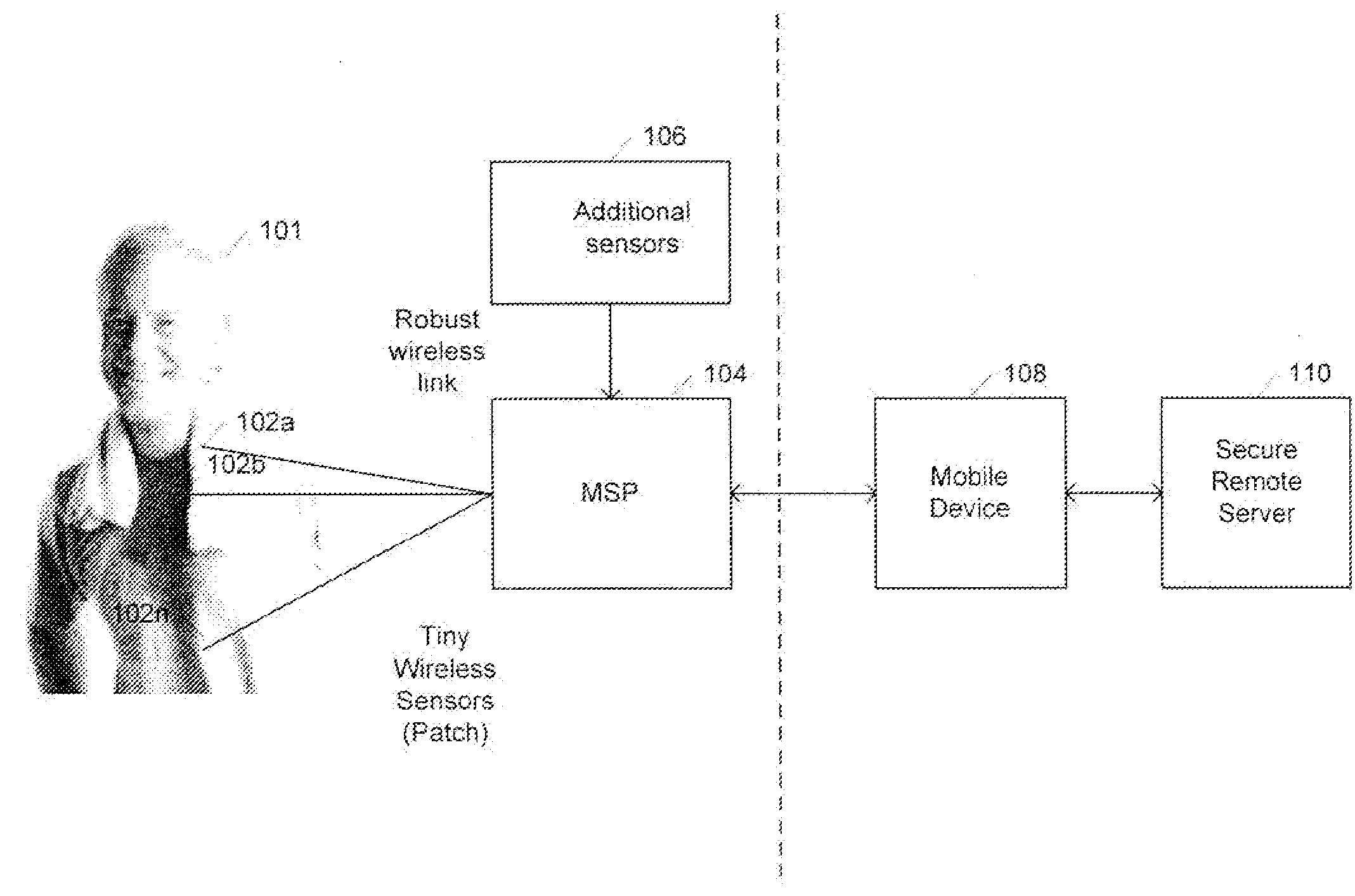

Medical signal processing system with distributed wireless sensors

InactiveUS20100049006A1High wireless link reliability/securityReduce power consumptionElectrocardiographyInertial sensorsDiseaseLine sensor

A wireless medical signal processing system for health monitoring is disclosed which achieves high wireless link reliability / security, low power dissipation, compactness, low cost and supports a variety of sensors for various physiological parameters. The system includes a medical signal processor which communicates with a wireless distributed sensor system as its peripheral for detecting physiological parameters of the person and for providing signals indicative thereof. The medical signal processor wirelessly receives the signals from the distributed wireless sensor system in a multiplexed fashion and processes the signals to provide an indication of the health of the person. The indication of health could relate to a disease state, general health or fitness level of a person. The system also includes a mobile device for receiving the indication of the health of the person to allow for a diagnosis or treatment of the person.

Owner:HMICRO

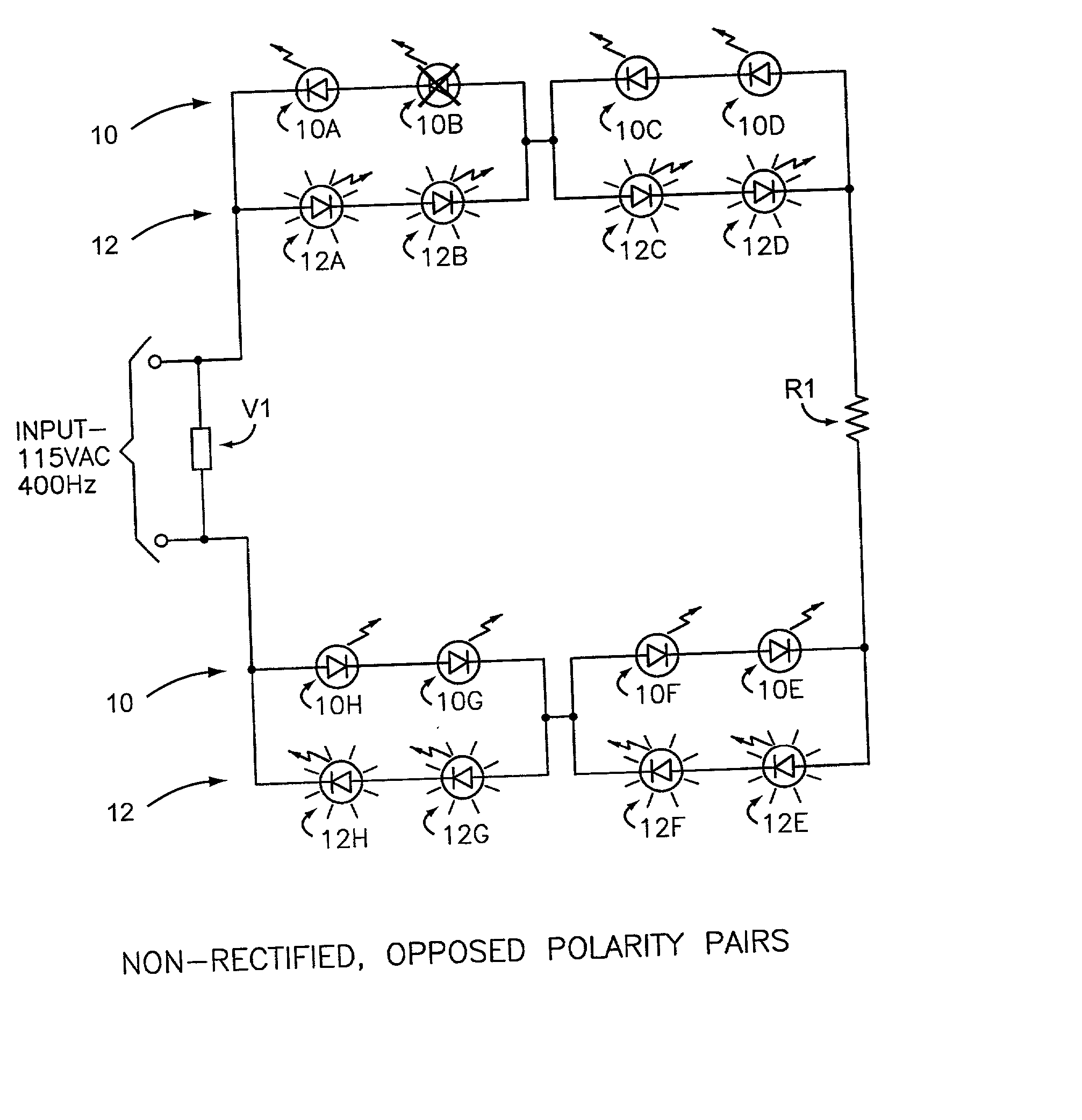

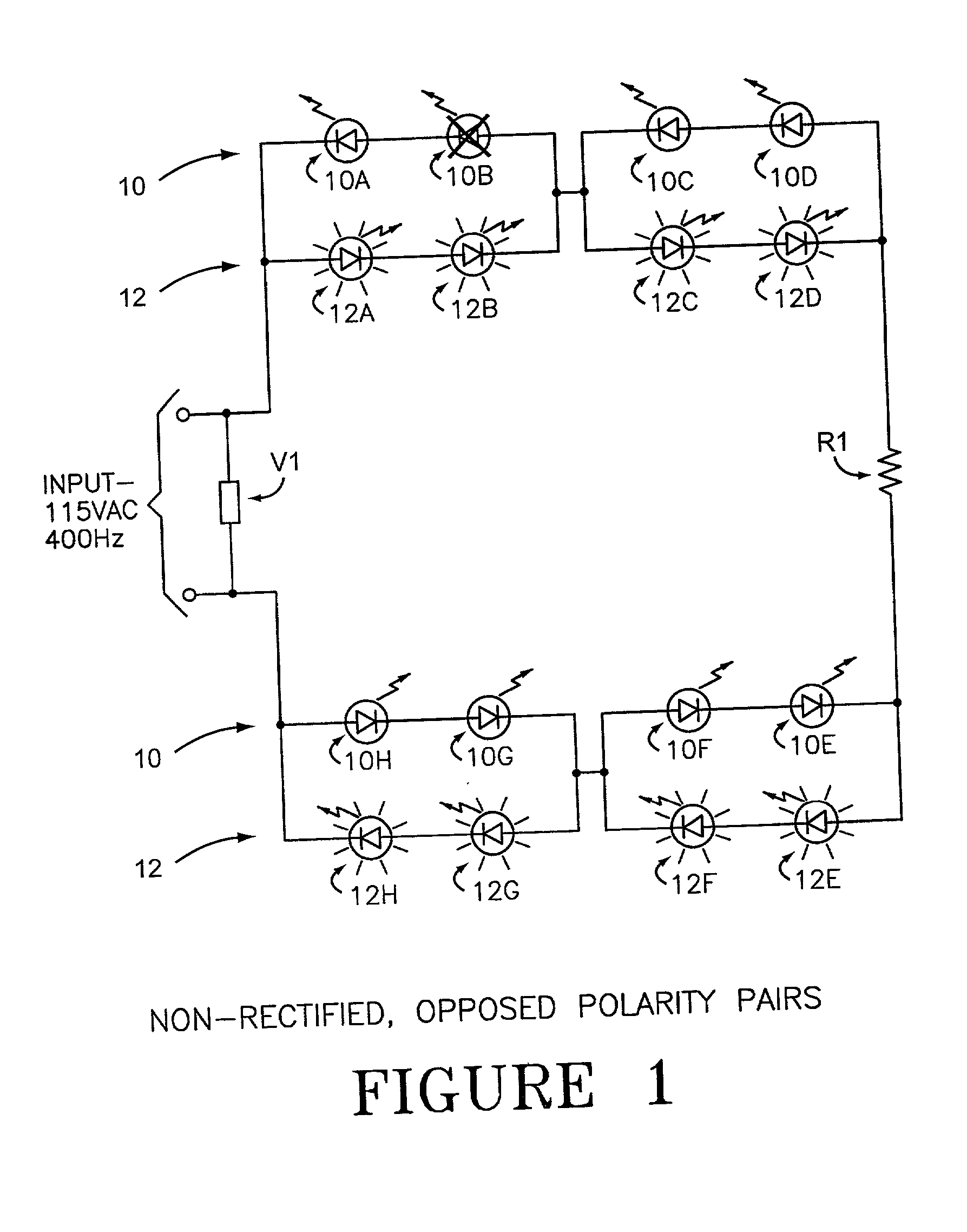

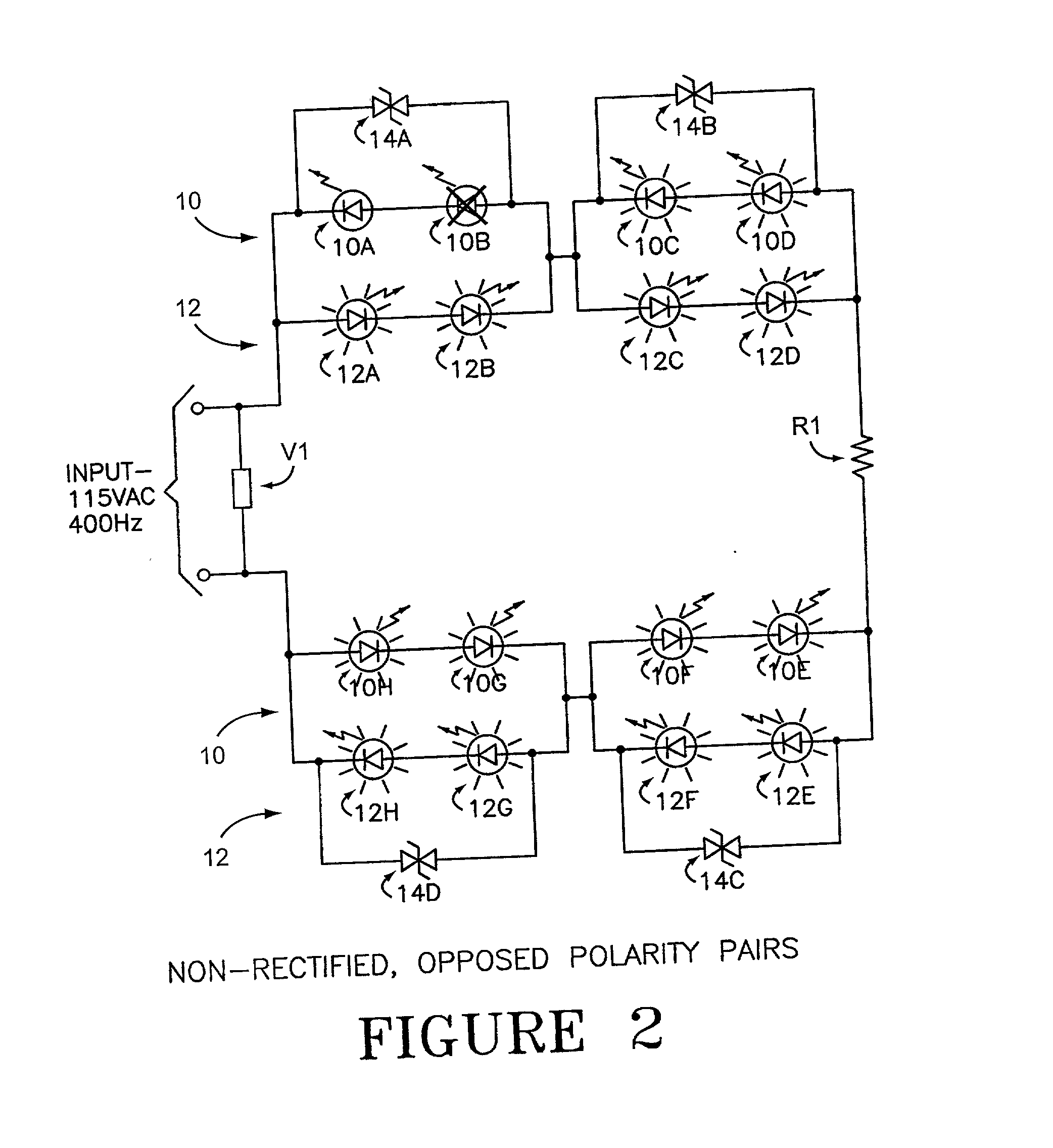

LED array primary display light sources employing dynamically switchable bypass circuitry

InactiveUS20020043943A1Reduce heat outputEasy burn-out element replacementElectrical apparatusElectroluminescent light sourcesBlack outEffect light

The invention comprises use of Dynamically Switchable Bypass (DSB) elements in association with one or more Light Emitting Diodes (LEDs) in arrays for illumination circuits to provide rugged, reliable lighting. The DSBs are selected from Transient Voltage Suppressors, including Silicon, Metal Oxide Varistors, and Multi Layer Varistors as well as Zener Diodes. The DSBs are not used as circuit protecting devices, but rather as alternative paths for electric current to bypass failed LEDs. Bi-directional TVSs are used as alternative electric paths for circuits using Alternating Current (AC) and parallel LED arrays that light on both phases of AC. Zener Diodes are used in parallel to, but in the opposite polarity orientation to, one or more LEDs in DC or rectified AC circuits. The inventive paired DSB / LED elements overcomes the black-out problems of prior series LED illumination systems, making possible the use of robust LEDs in illumination systems where reliability, long life, low power consumption, low heat output, resistance to shock, vibration, and humidity, and self-diagnosis are important. The DSB elements have breakdown voltages slightly higher than the LED(s) they support, so that when an LED fails, the conduction through the DSB begins. Because the conduction voltage of the DSB so nearly matches the conduction voltage of the LED(s), the remainder of the circuit continues to function as normal. The system is self-diagnostic in that any LED failure presents itself as a dark LED rather than as a whole string of dark LEDs. DSBs may be used with incandescent bulbs.

Owner:IDD AEROSPACE

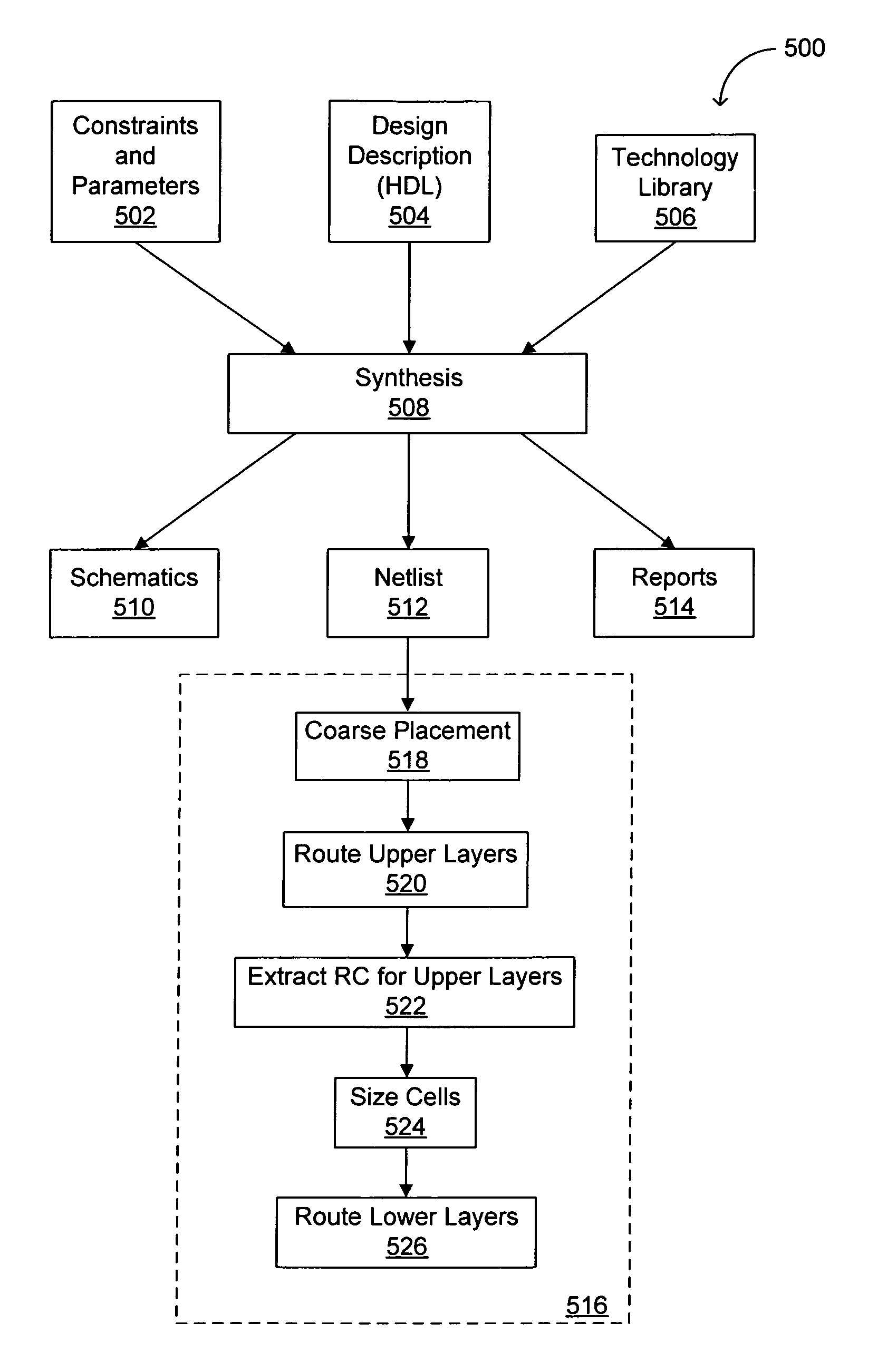

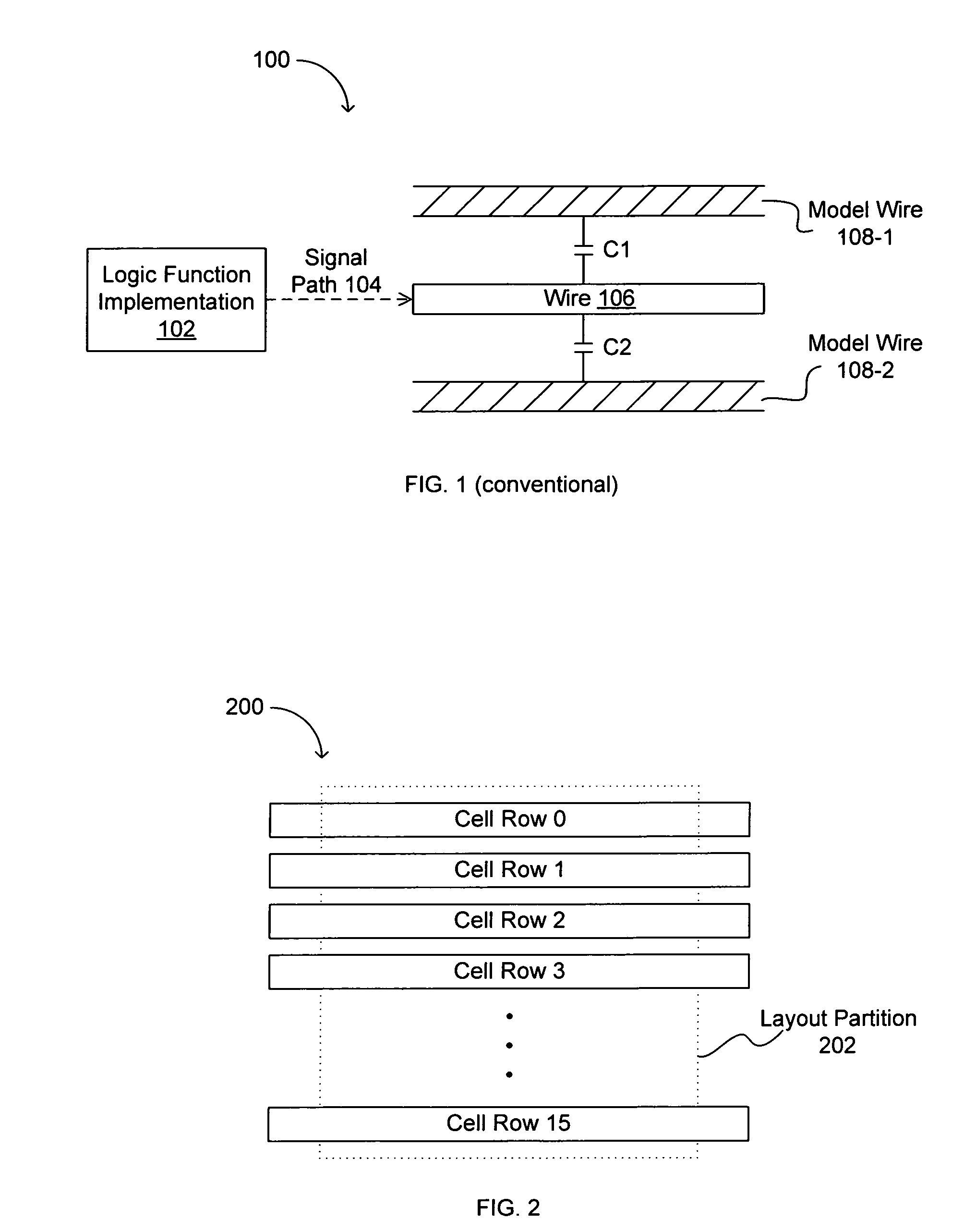

Method of placing and routing for power optimization and timing closure

InactiveUS7992122B1Reduce power consumptionImprove timing closureComputer aided designSoftware simulation/interpretation/emulationStandard cellIntegrated circuit

A method, algorithm, software, architecture and / or system for placing circuit blocks and routing signal paths or connections between the circuit blocks in a circuit design is disclosed. In one embodiment, a method of placing and routing can include: (i) routing signal paths in one or more upper metal layers for connecting circuit blocks; (ii) adjusting the circuit blocks based on electrical characteristics of the signal paths; and (iii) routing in one or more lower metal layers connections between the circuit blocks and the upper layers. The circuit blocks can include standard cells, blocks, or gates configured to implement a logic or timing function, other components, and / or integrated circuits, for example. Embodiments of the present invention can advantageously reduce power consumption and improve timing closure in an automated place-and-route flow.

Owner:GOLDEN GATE TECH

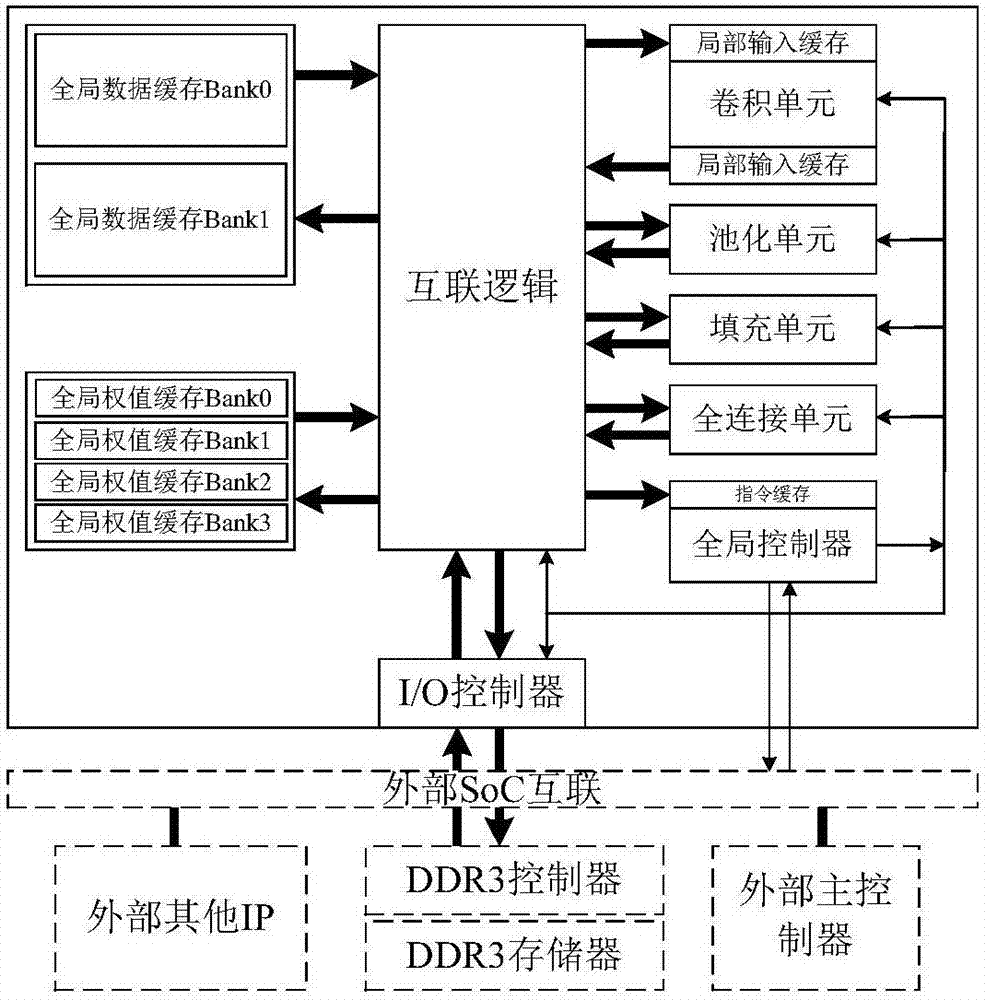

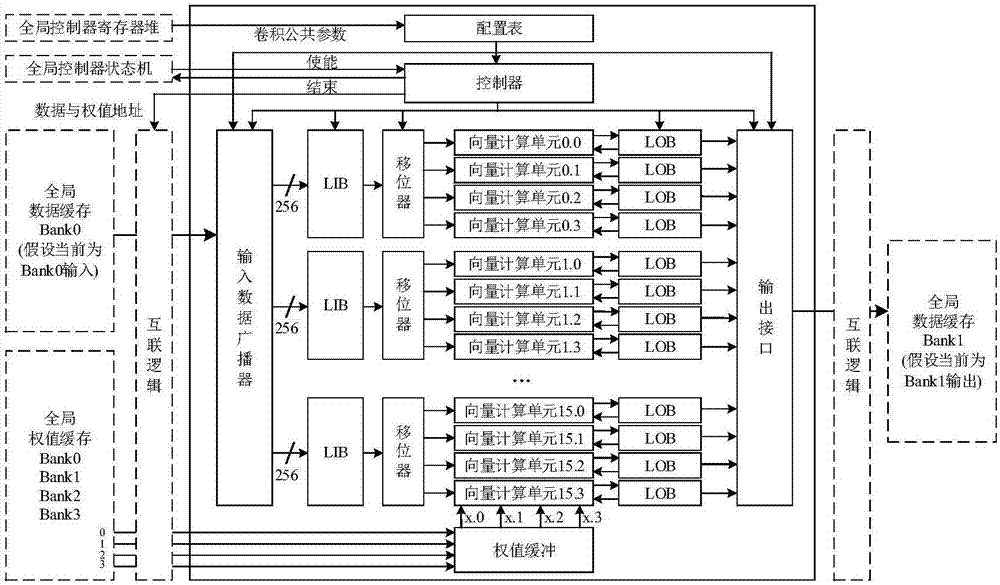

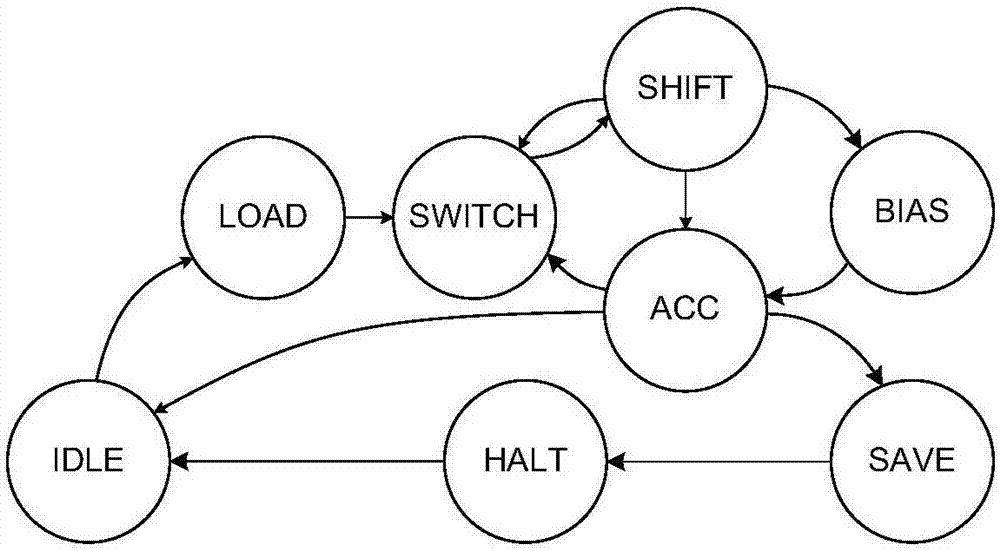

Co-processor IP core of programmable convolutional neural network

ActiveCN106940815AReduce frequencyReduce bandwidth pressureNeural architecturesPhysical realisationHardware structureInstruction set design

The present invention discloses a co-processor IP core of a programmable convolutional neural network. The invention aims to realize the arithmetic acceleration of the convolutional neural network on a digital chip (FPGA or ASIC). The co-processor IP core specifically comprises a global controller, an I / O controller, a multi-level cache system, a convolution unit, a pooling unit, a filling unit, a full-connection unit, an internal interconnection logical unit, and an instruction set designed for the co-processor IP. The proposed hardware structure supports the complete flows of convolutional neural networks diversified in scale. The hardware-level parallelism is fully utilized and the multi-level cache system is designed. As a result, the characteristics of high performance, low power consumption and the like are realized. The operation flow is controlled through instructions, so that the programmability and the configurability are realized. The co-processor IP core can be easily applied to different application scenes.

Owner:XI AN JIAOTONG UNIV

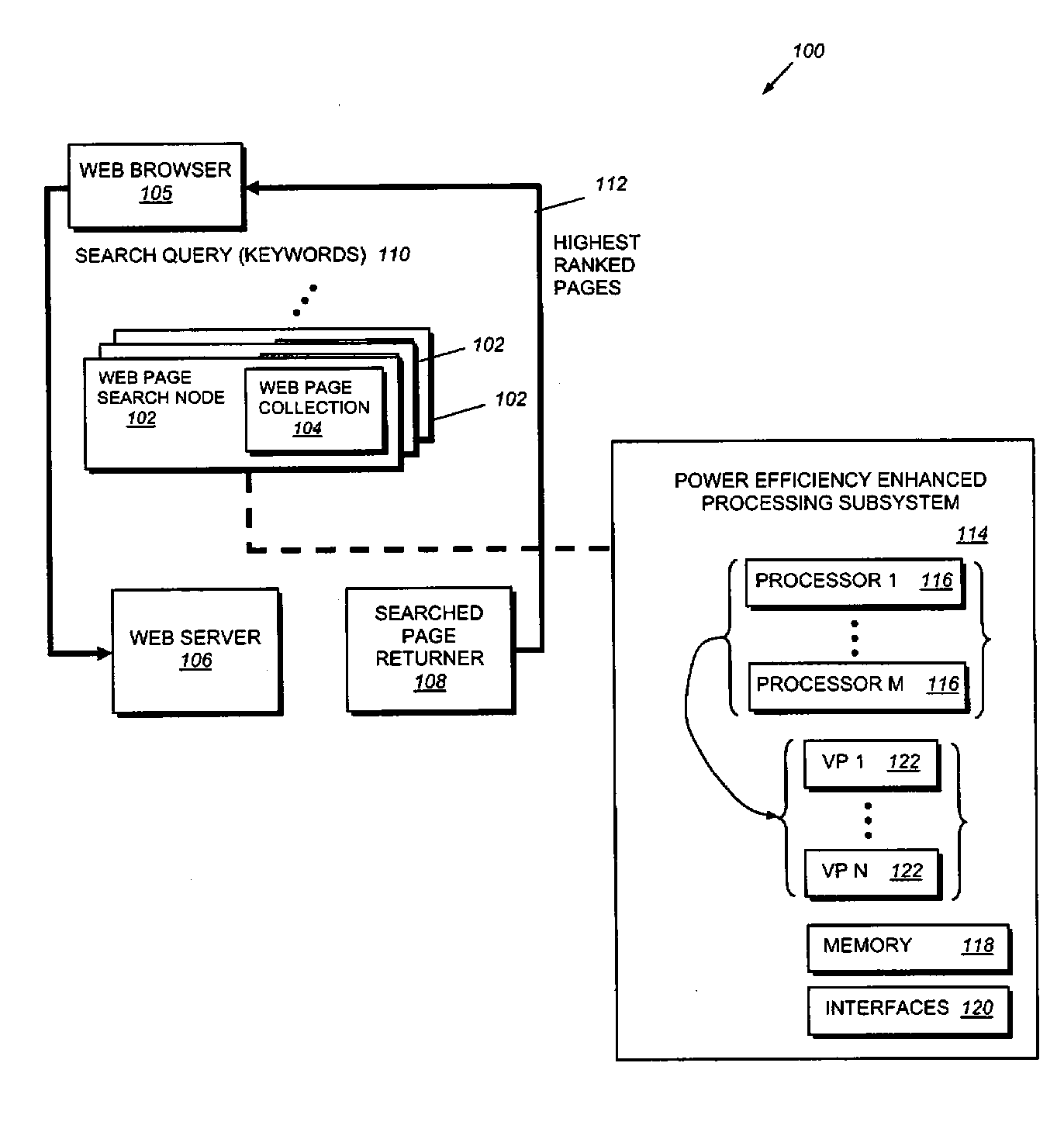

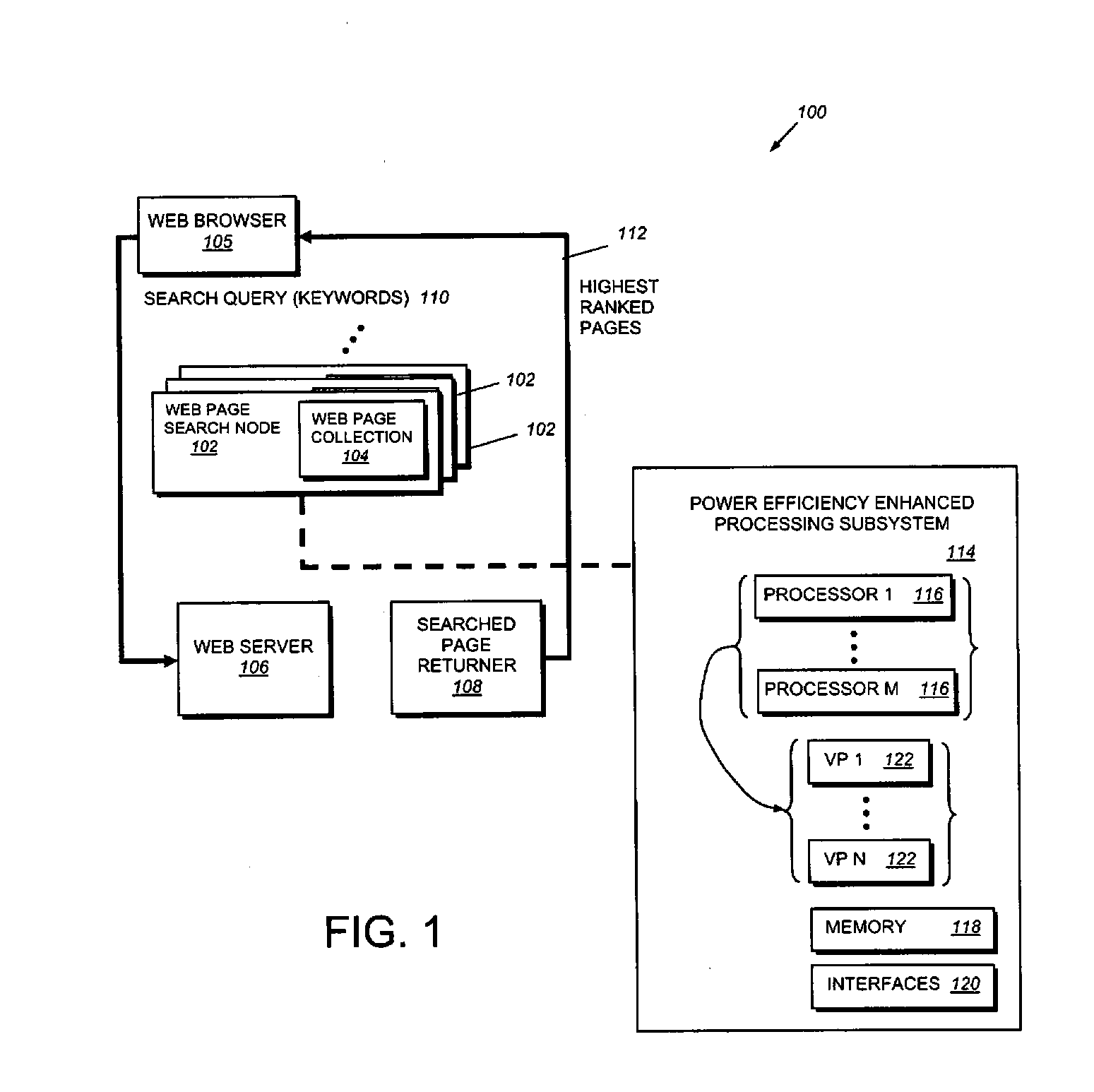

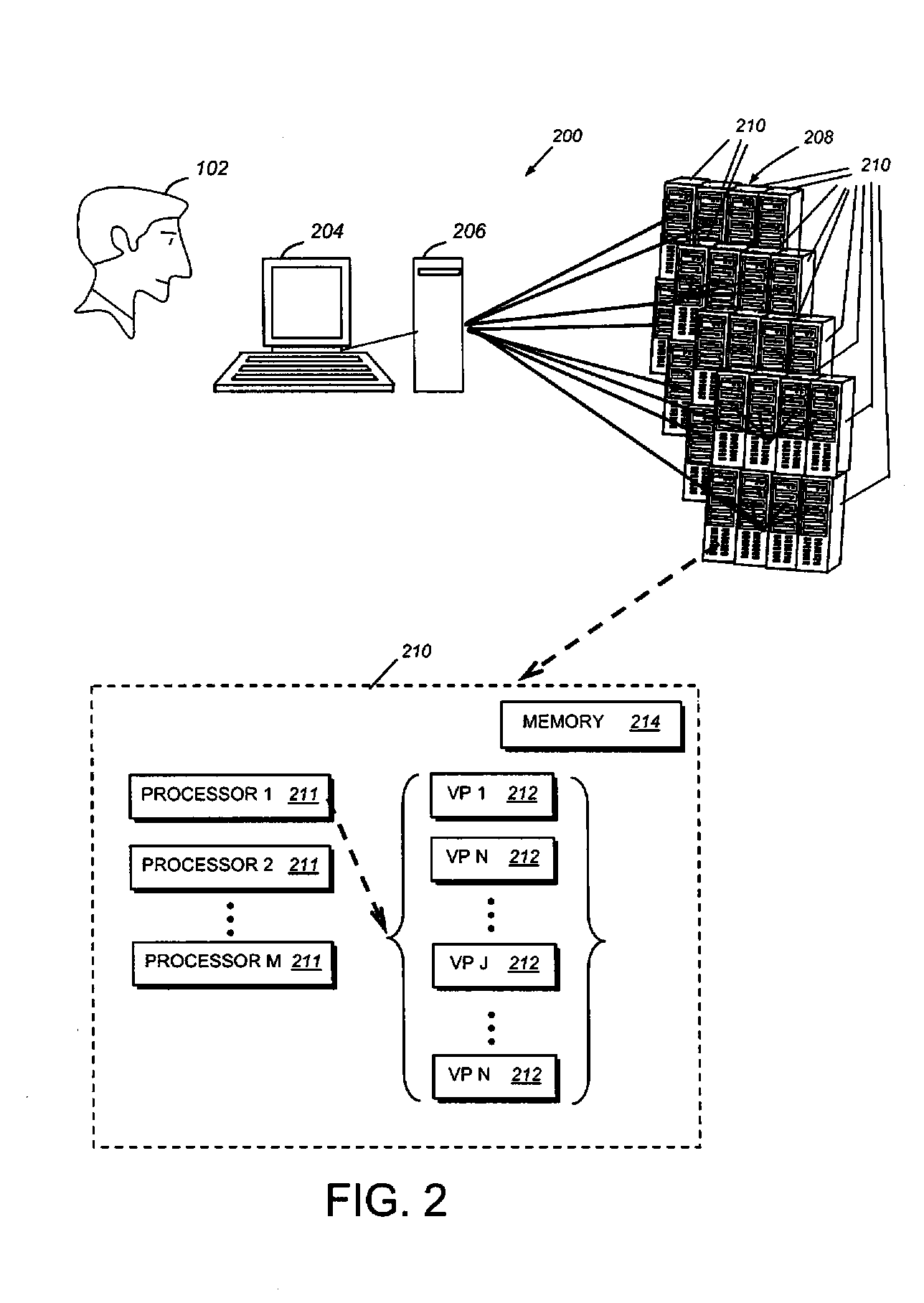

Parallel processing computer systems with reduced power consumption and methods for providing the same

ActiveUS20090083263A1Reduce power consumptionEnergy efficient ICTWeb data indexingWeb browserWeb service

This invention provides a computer system architecture and method for providing the same which can include a web page search node including a web page collection. The system and method can also include a web server configured to receive, from a given user via a web browser, a search query including keywords. The node is caused to search pages in its own collection that best match the search query. A search page returner may be provided which is configured to return, to the user, high ranked pages. The node may include a power-efficiency-enhanced processing subsystem, which includes M processors. The M processors are configured to emulate N virtual processors, and they are configured to limit a virtual processor memory access rate at which each of the N virtual processors accesses memory. The memory accessed by each of the N virtual processors may be RAM. In select embodiments, the memory accessed by each of the N virtual processors includes DRAM having a high capacity yet lower power consumption then SRAM.

Owner:GRANGER RICHARD

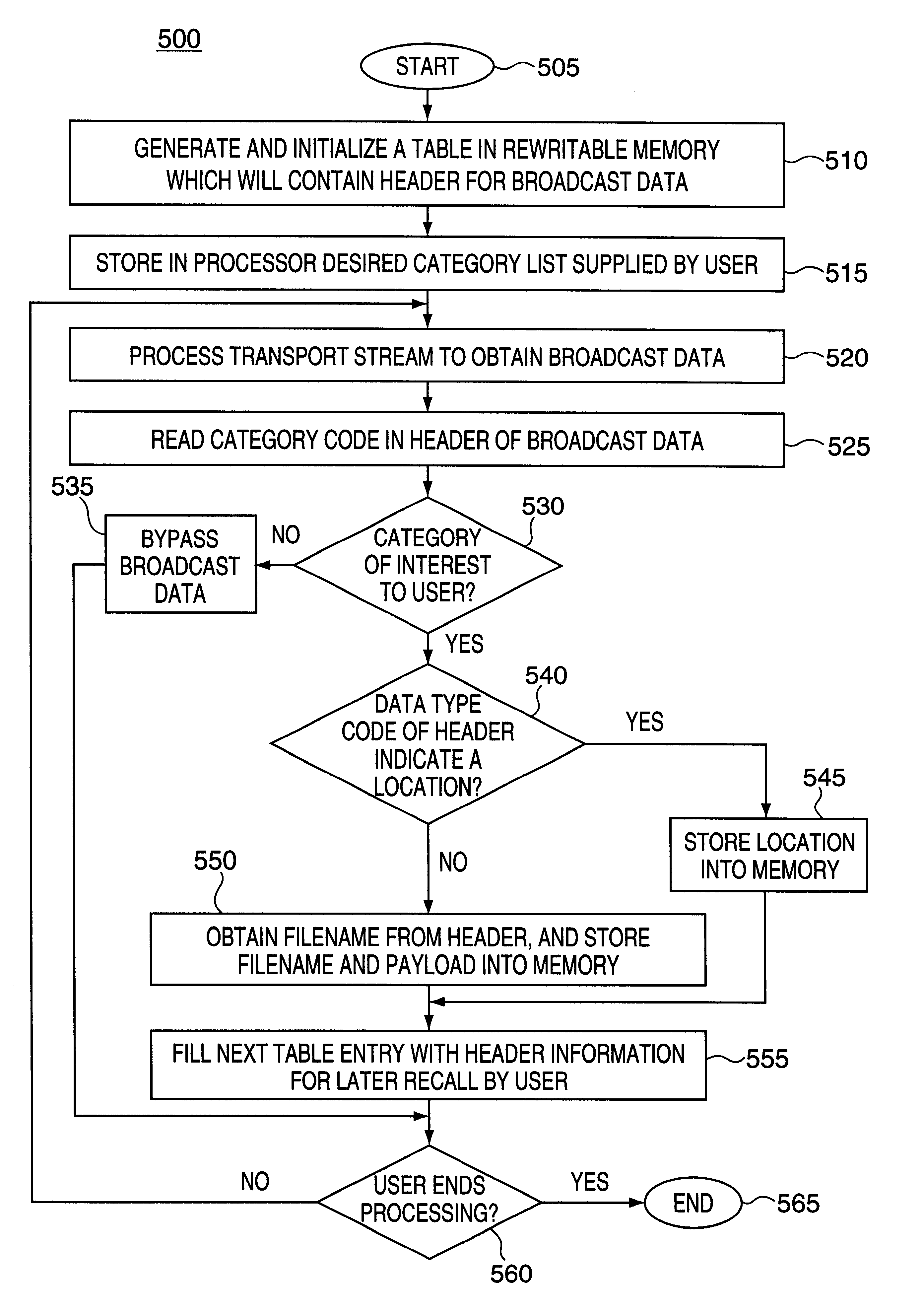

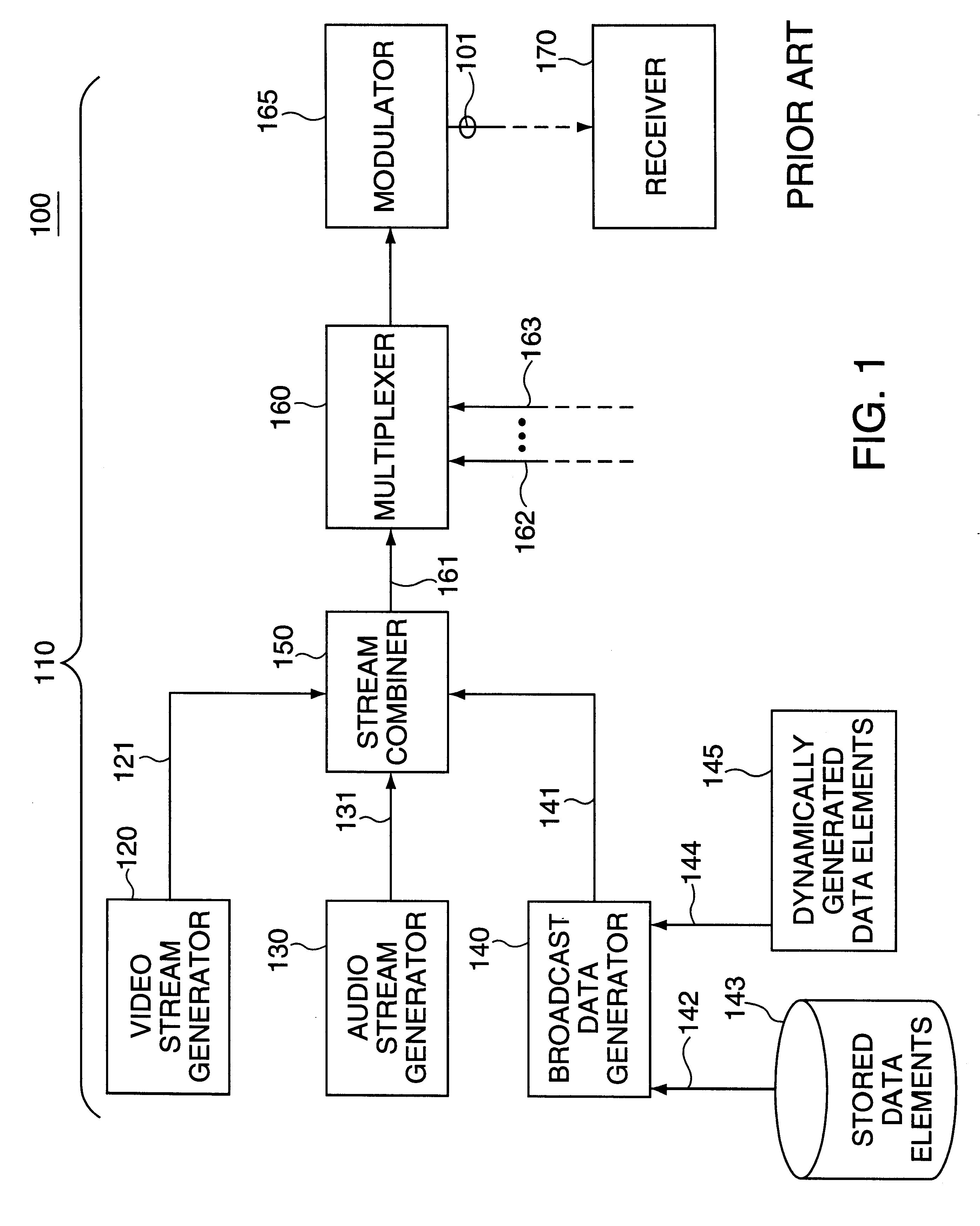

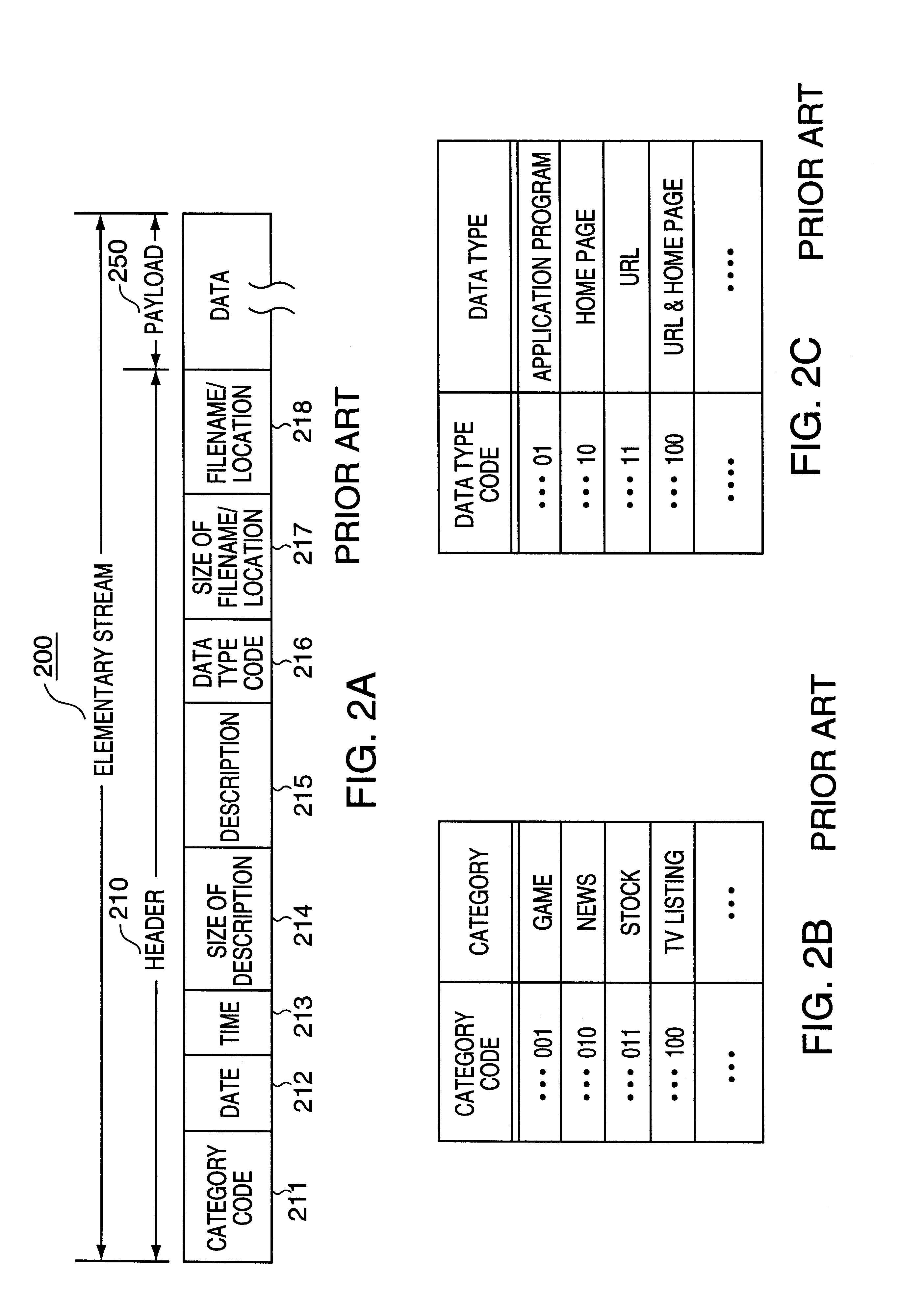

Methods and apparatus for recording video files and for generating a table listing the recorded files and links to additional information

InactiveUS6256071B1Television system detailsPulse modulation television signal transmissionElementary streamPower consumption

A receiver arranged to receive and store broadcast data transported by elementary stream of a multiplexed and modulated digital television signal in a rewritable memory during a low power consumption mode for later recall by a user of the receiver. For recall, the receiver is fully energized, and the receiver is further arranged to transfer the broadcast data stored in the rewritable memory to a receiver storage device for further processing of the data under control of the user.

Owner:HITACHI AMERICA

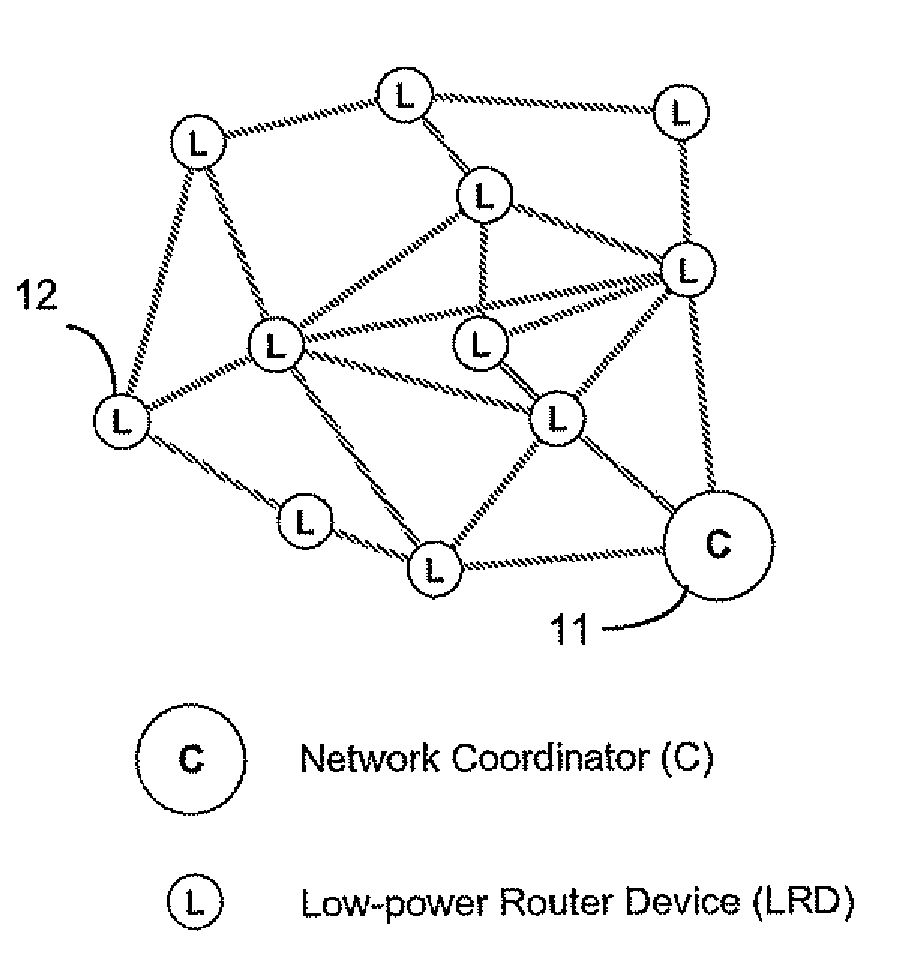

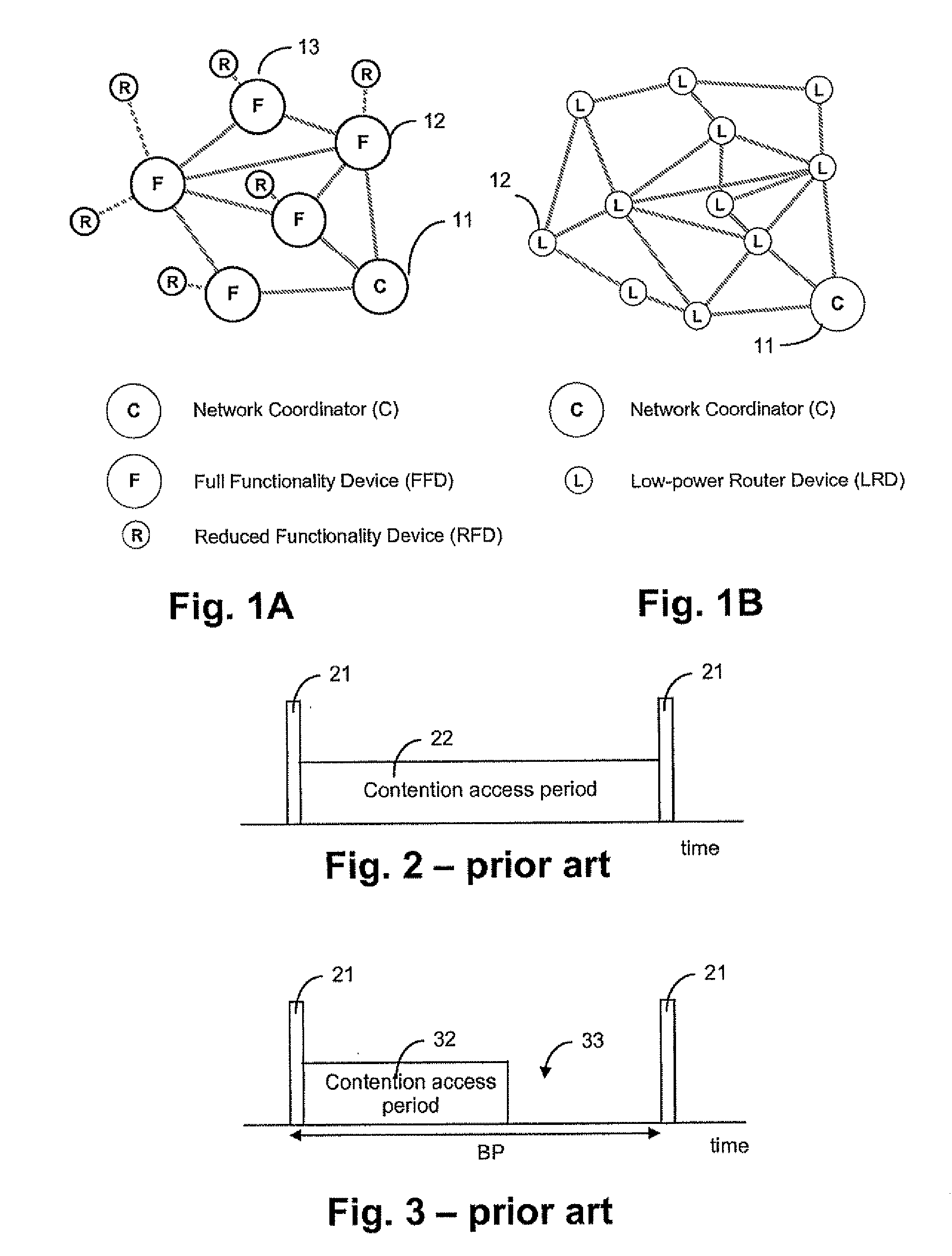

Low-power wireless multi-hop networks

A method of communication or transmission of data between a first and a second node in a wireless multi-hop network comprises bringing the first node and the second node in a fully operative mode for communication with each other and subsequently bringing the first node and the second node in a reduced operative mode where no communication with any other node is possible and, before bringing the second node in the fully operative mode, bringing the second node in a listening mode during a token listening period to check for presence of a wake-up token from the first node, and thereafter bringing the second node into the reduced operative mode if no wake-up token is received, and bringing the second node into the fully operative mode for reception of data from the first node if a wake-up token is received. This wake-up scheme is a kind of scheduled rendezvous scheme with collision avoidance, and may be called an induced wake-up scheme. It is advantageous because of its low power consumption (no des only wake up completely when a message is present for them to receive) and because of the low latency in data transfer. The wake-up tokens used enable random access to other nodes, nevertheless having a system which is low-power in operation.

Owner:GREENPEAK TECHNOLOGIES

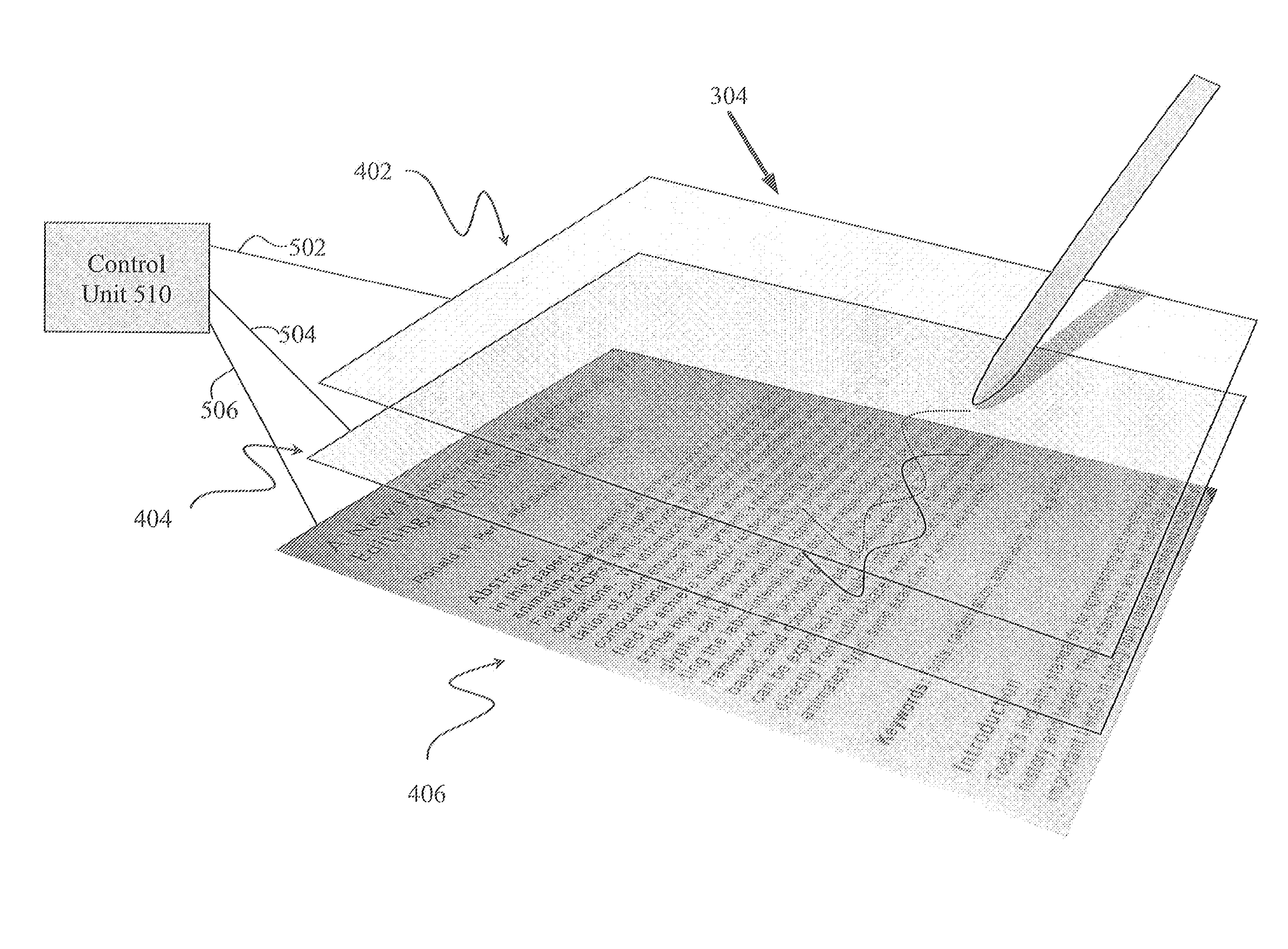

Thin multiple layer input/output device

A multilayer input / output device with a low power and a high resolution display suitable for use in paper-like computing includes a first display layer, a second display layer, an input layer and control logic. The first display layer is a low power display. The second display layer is a fast, transparent display positioned on top of the first layer. The input layer is a layer for detecting input movements or gestures by the user. The control logic is coupled to the first display layer, the second display layer and the input layer for controlling their operation according the method of the present invention. The method of the present invention selectively operates the second display layer to present movement detected by the input layer. At a predetermined time, the information presented on the second display is transferred to and presented on the first display.

Owner:E INK CORPORATION

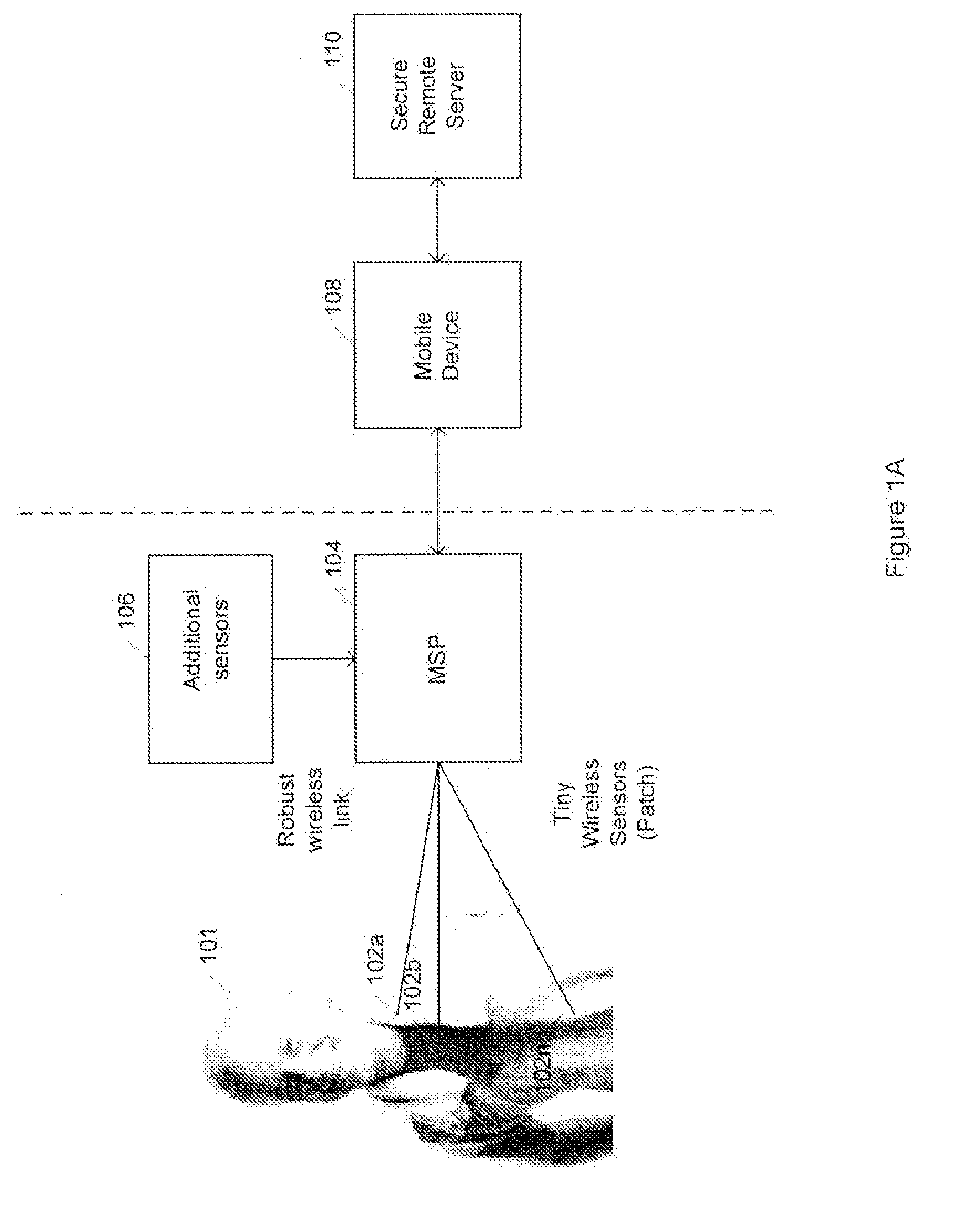

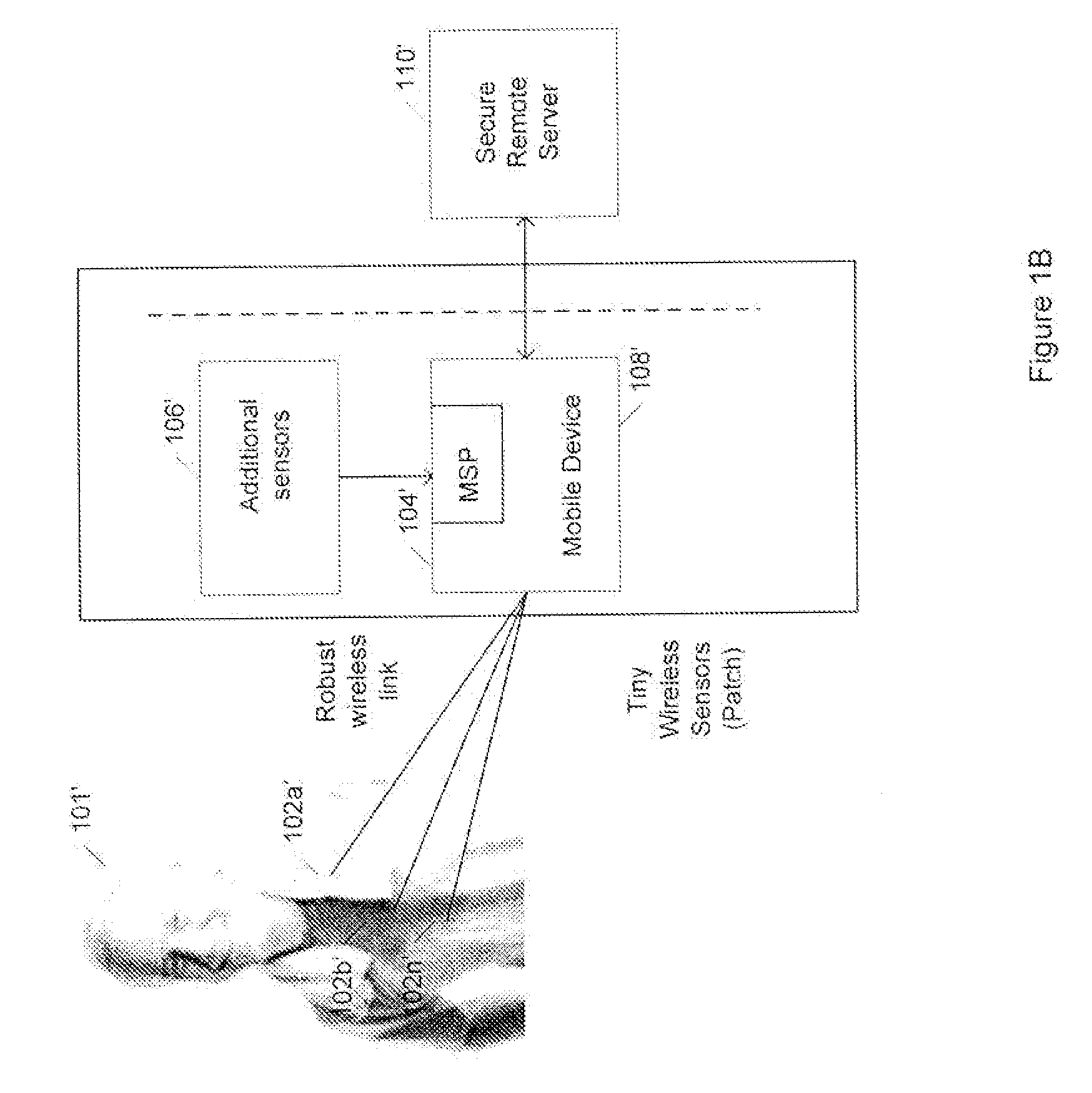

Wireless physiological sensor patches and systems

ActiveUS8926509B2Avoid and minimize interferenceBioelectric signal measurementInertial sensorsEngineeringLow power dissipation

The present invention provides methods, devices, and systems for wireless physiological sensor patches and systems which incorporate these patches. The systems and methods utilize a structure where the processing is distributed asymmetrically on the two or more types of ASIC chips that are designed to work together. The invention also relates to systems comprising two or more ASIC chips designed for use in physiological sensing wherein the ASIC chips are designed to work together to achieve high wireless link reliability / security, low power dissipation, compactness, low cost and support a variety of sensors for sensing various physiological parameters.

Owner:HMICRO

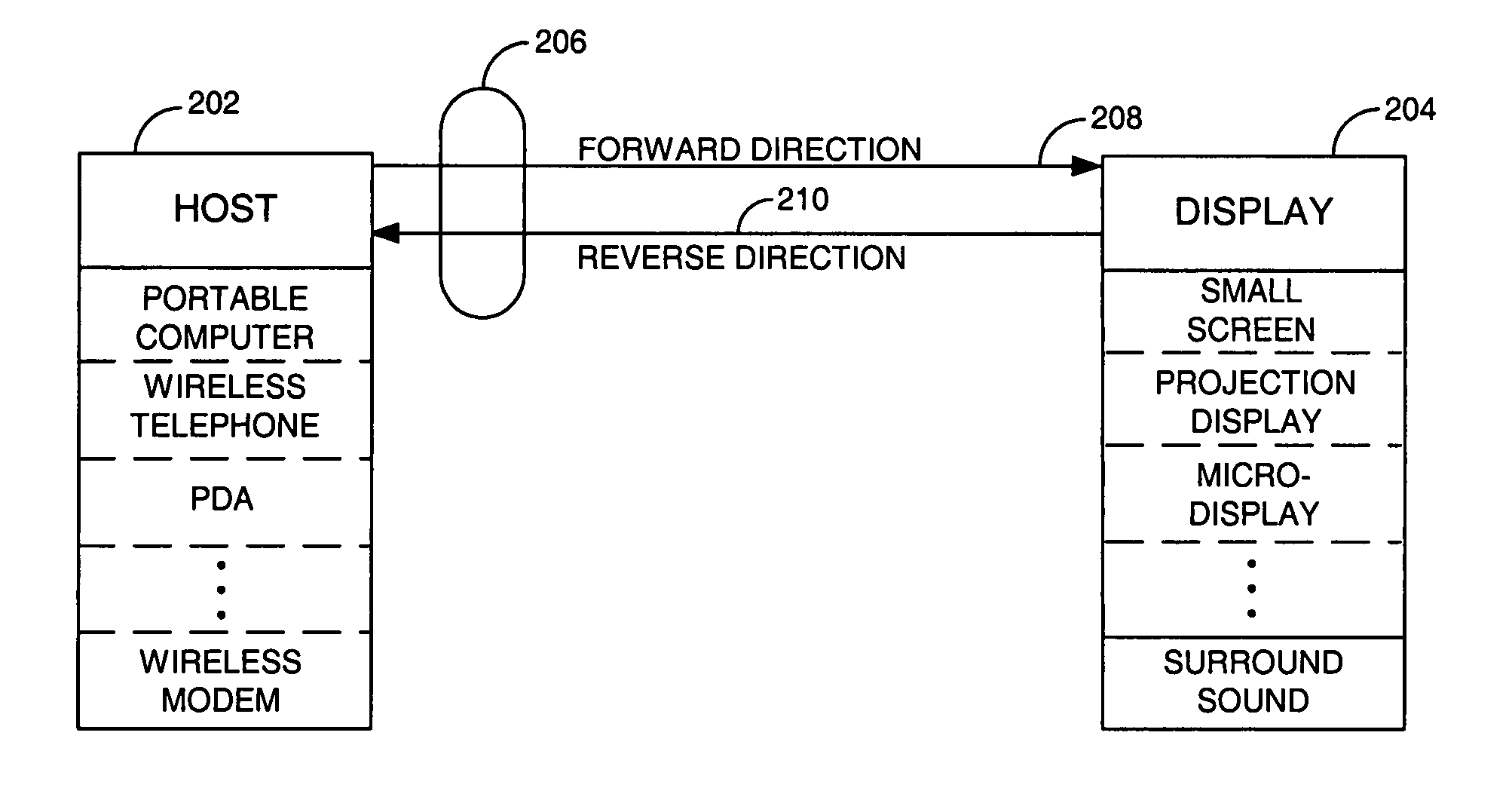

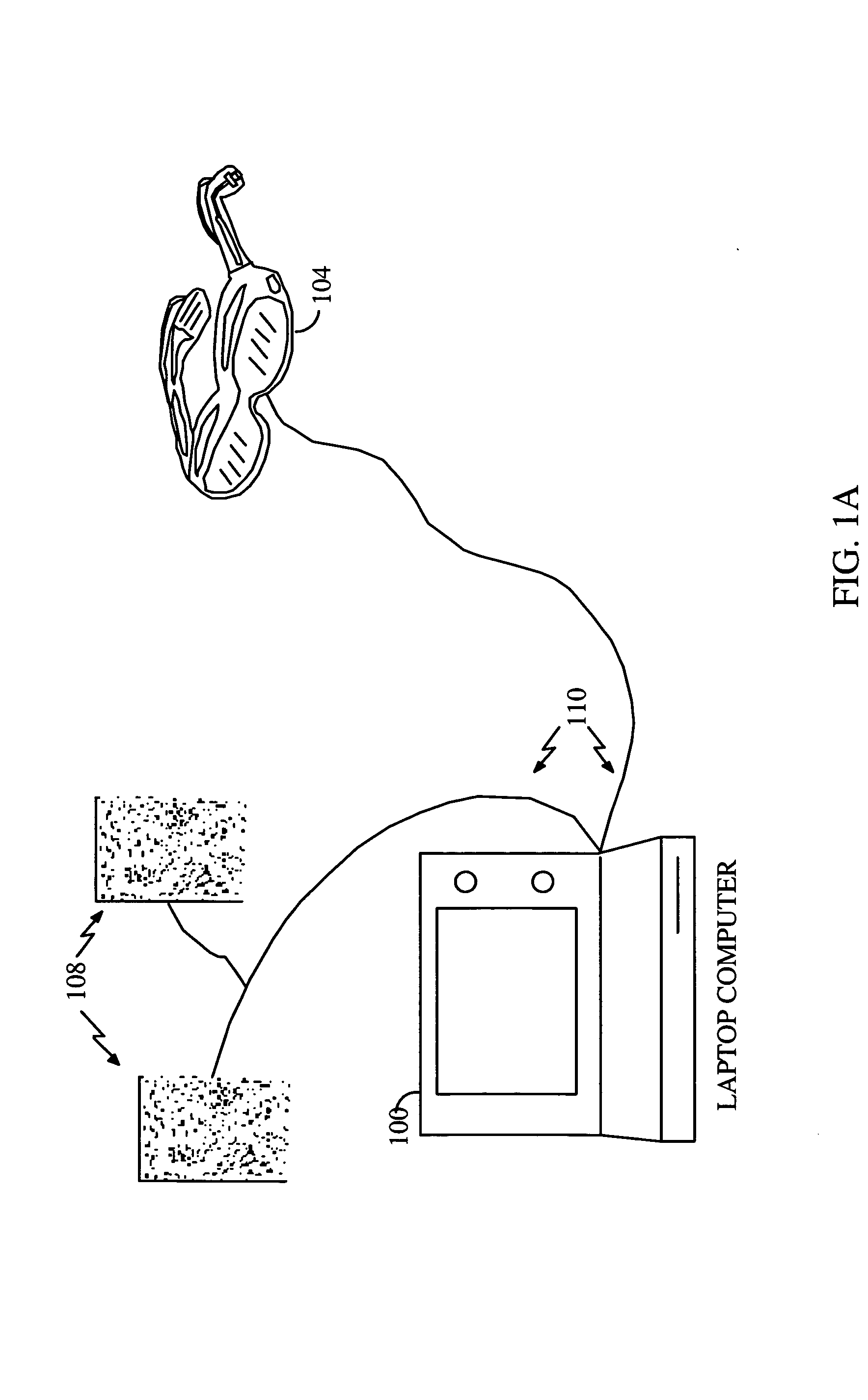

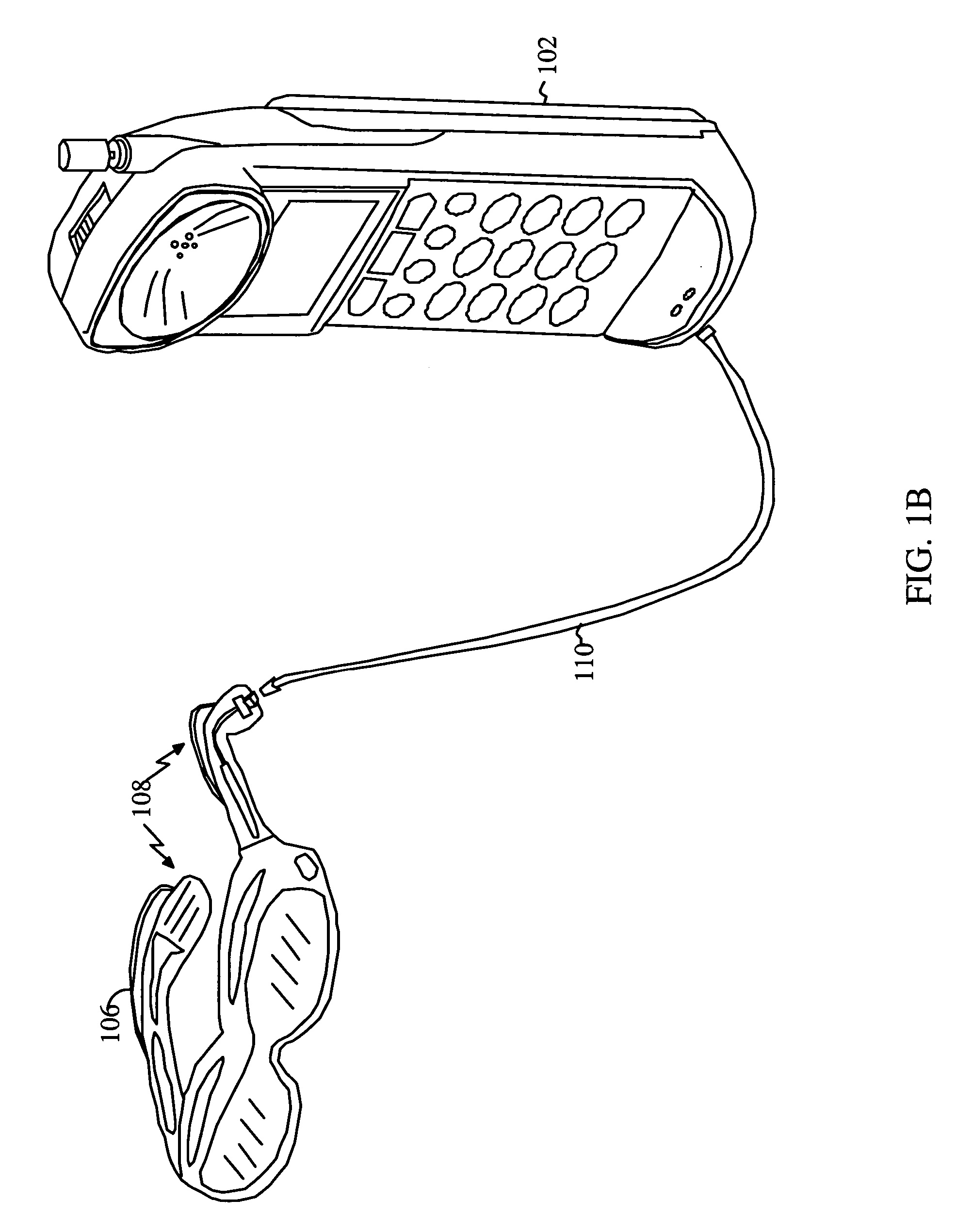

Generating and implementing a signal protocol and interface for higher data rates

ActiveUS20050021885A1Increase data rateEnergy efficient ICTPulse modulation television signal transmissionDigital dataDisplay device

A data Interface for transferring digital data between a host and a client over a communication path using packet structures linked together to form a communication protocol for communicating a pre-selected set of digital control and presentation data. The signal protocol is used by link controllers configured to generate, transmit, and receive packets forming the communications protocol, and to form digital data into one or more types of data packets, with at least one residing in the host device and being coupled to the client through the communications path. The interface provides a cost-effective, low power, bi-directional, high-speed data transfer mechanism over a short-range “serial” type data link, which lends itself to implementation with miniature connectors and thin flexible cables which are especially useful in connecting display elements such as wearable micro-displays to portable computers and wireless communication devices.

Owner:QUALCOMM INC

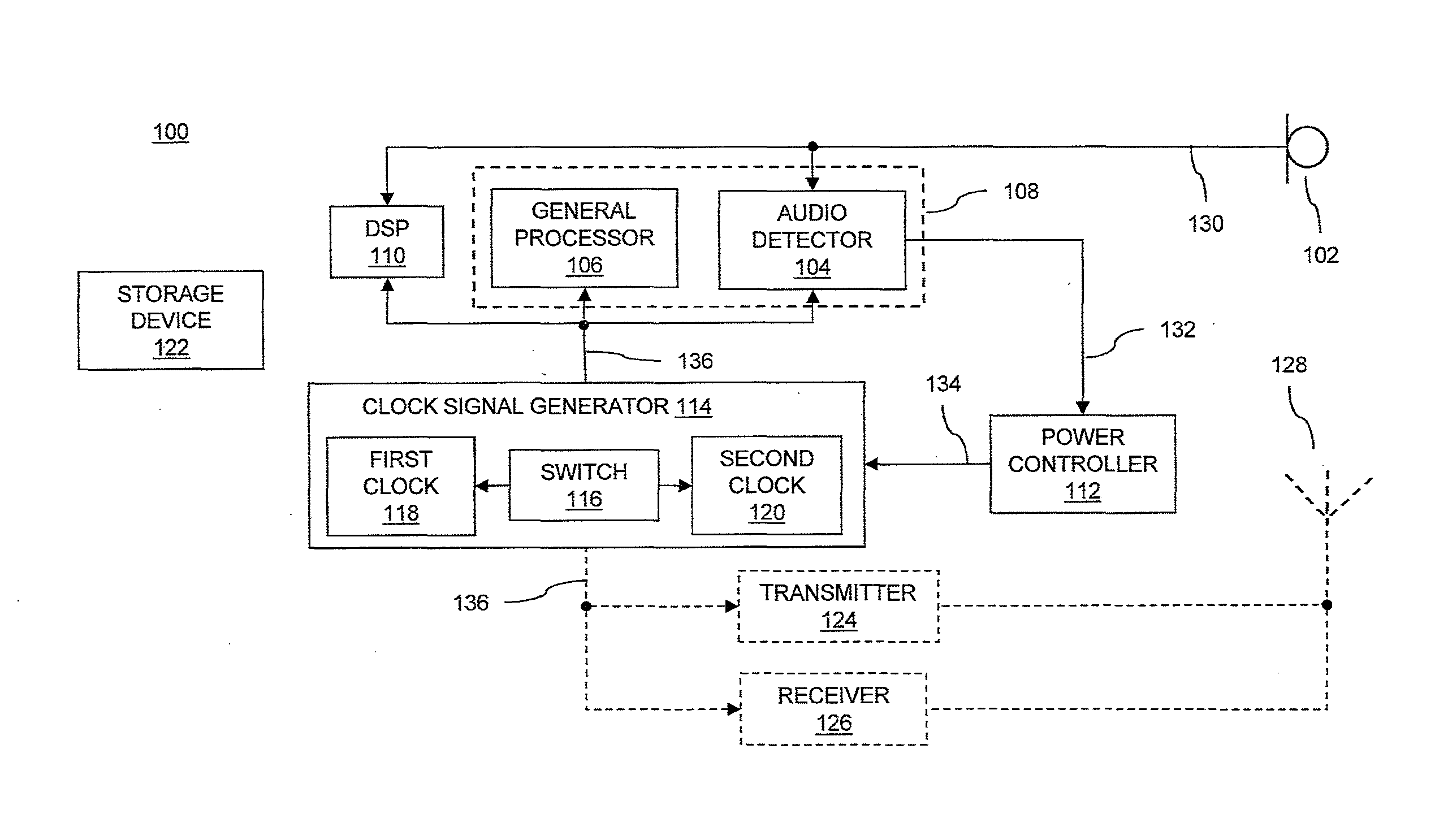

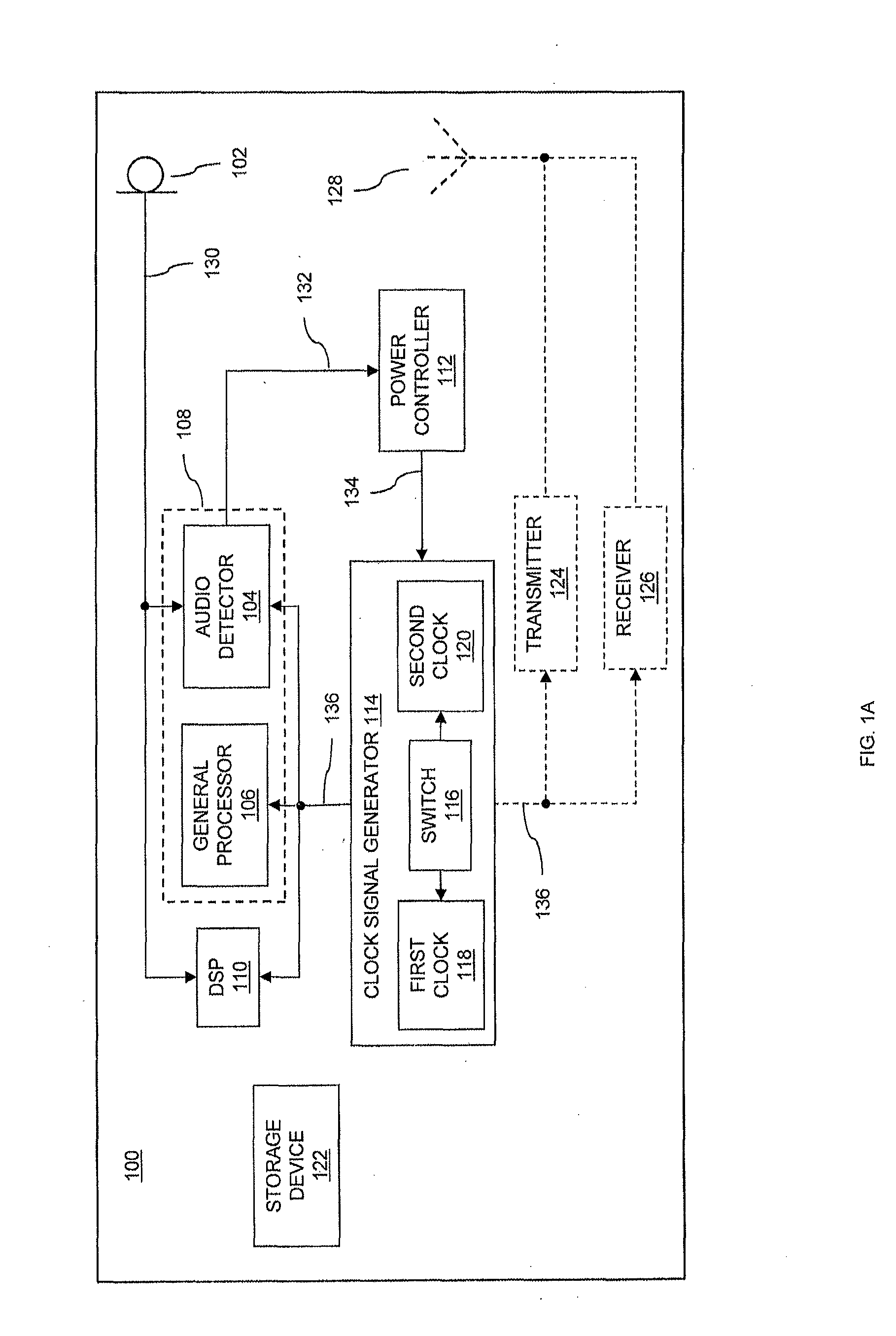

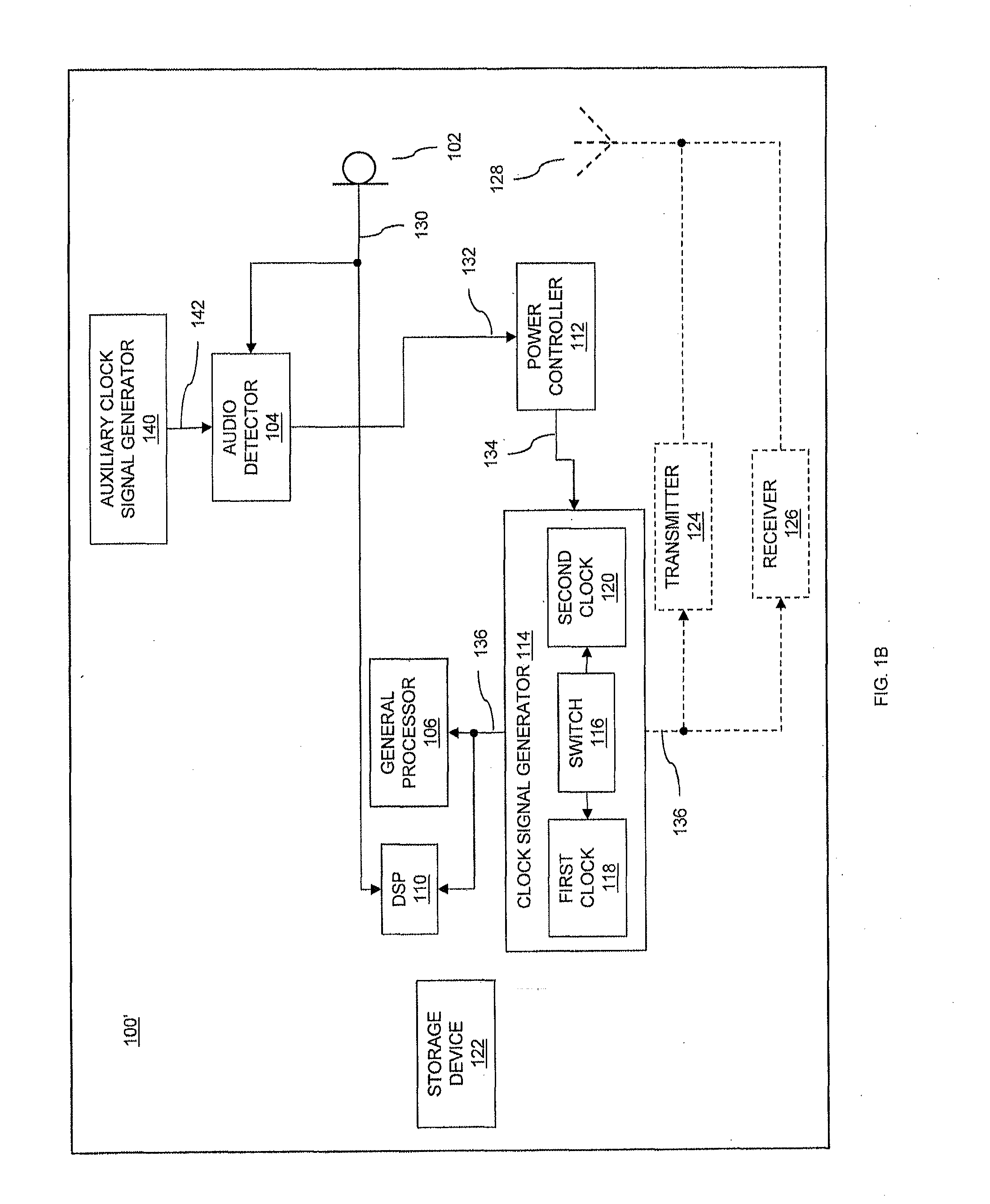

Low power audio detection

InactiveUS20130223635A1Reduce power consumptionIncrease power consumptionPower managementHearing device energy consumption reductionAudio signal flowLow power dissipation

Devices and methods of detecting a predetermined audio signal in audio signals are provided. A device includes a processor coupled to a clock signal generator, a power controller and an audio detector. The power controller controls a clock rate provided to the processor by the clock signal generator, to control the device to operate in a low power mode having a relatively low power consumption or in a normal power mode having a relatively high power consumption. The audio detector receives audio signals and detects, in the low power mode, probable presence of a predetermined audio signal in the audio signals. The power controller controls the device to switch from the low power mode to the normal power mode responsive to the detected presence of the predetermined audio signal by the audio detector.

Owner:QUALCOMM TECH INT

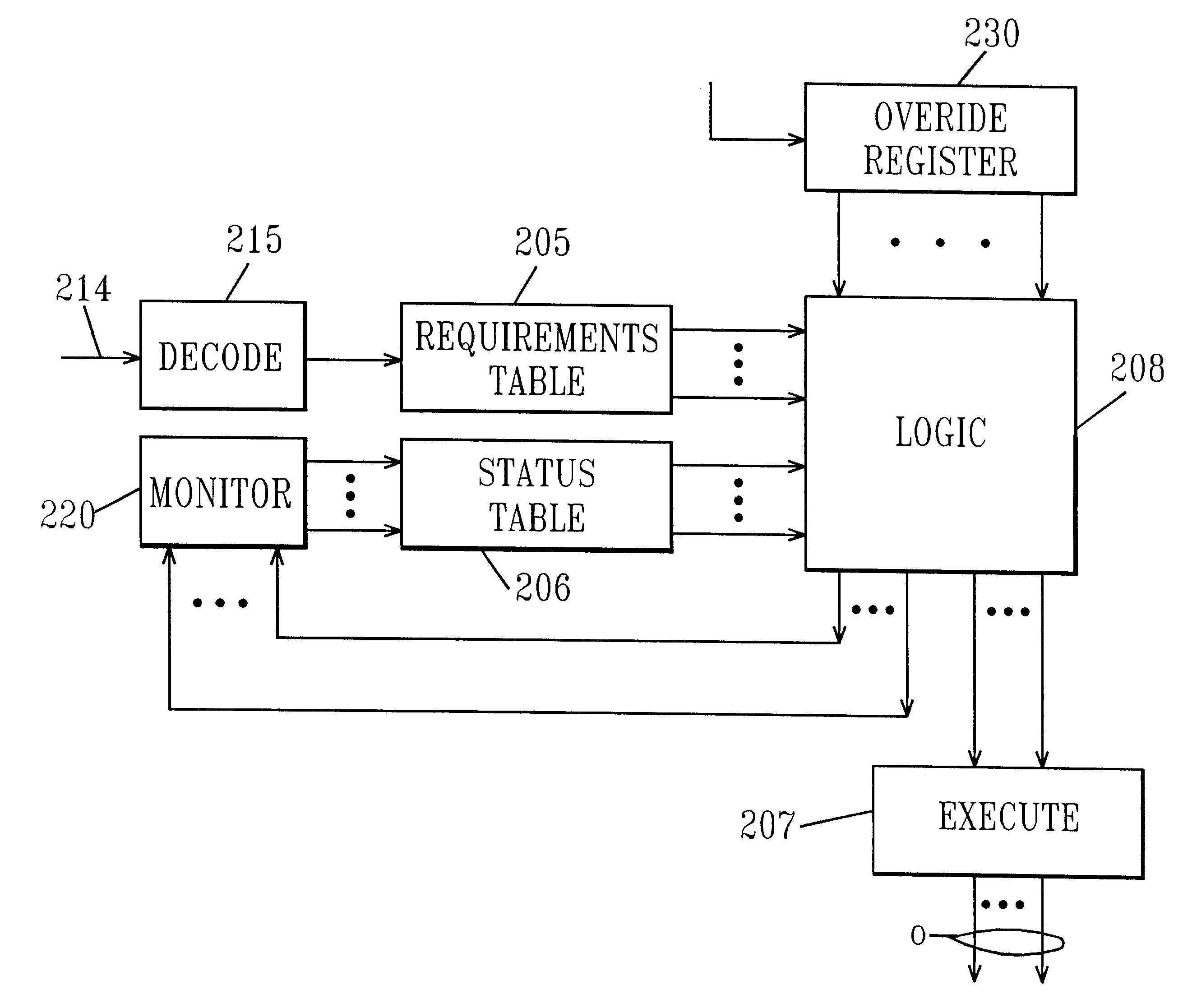

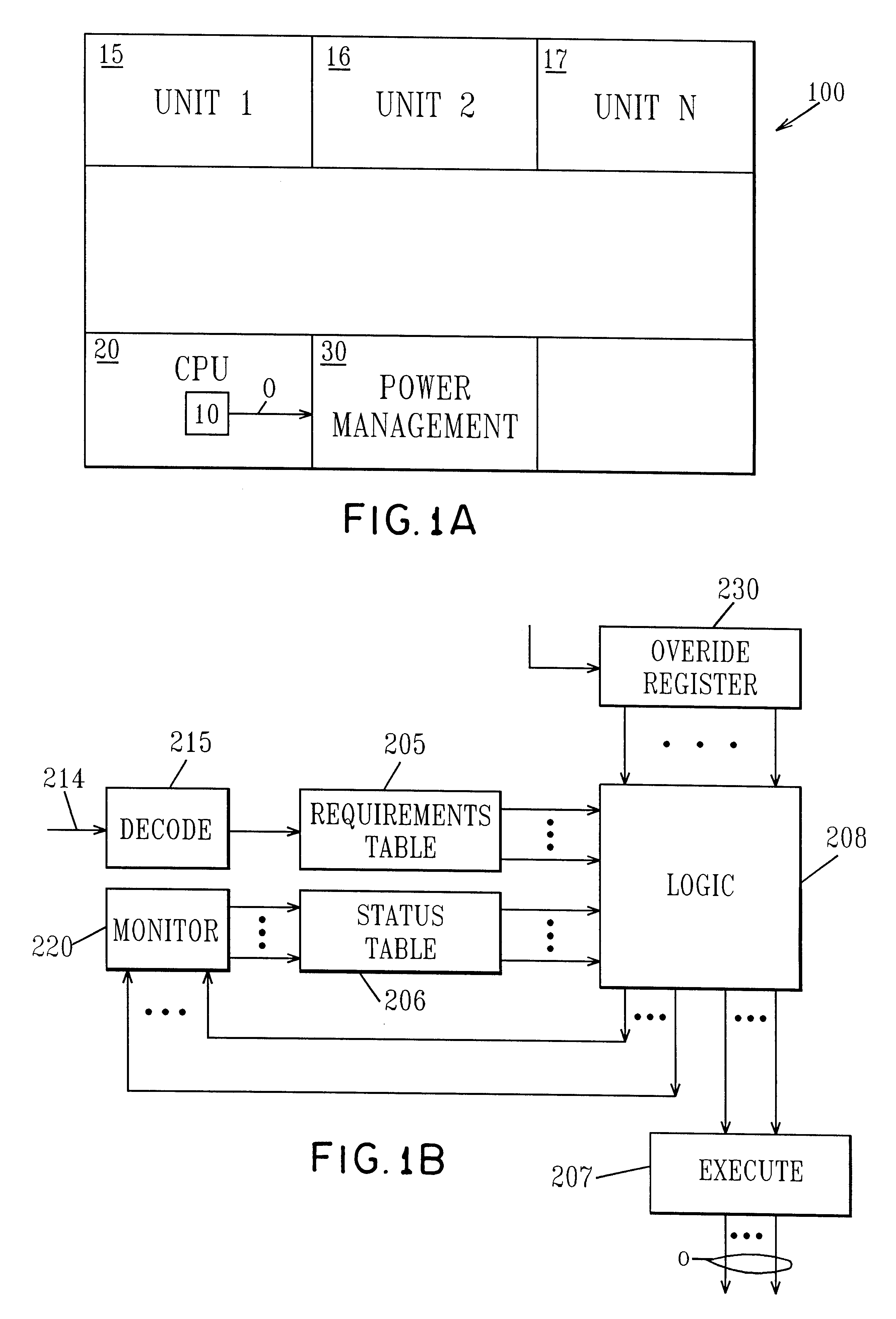

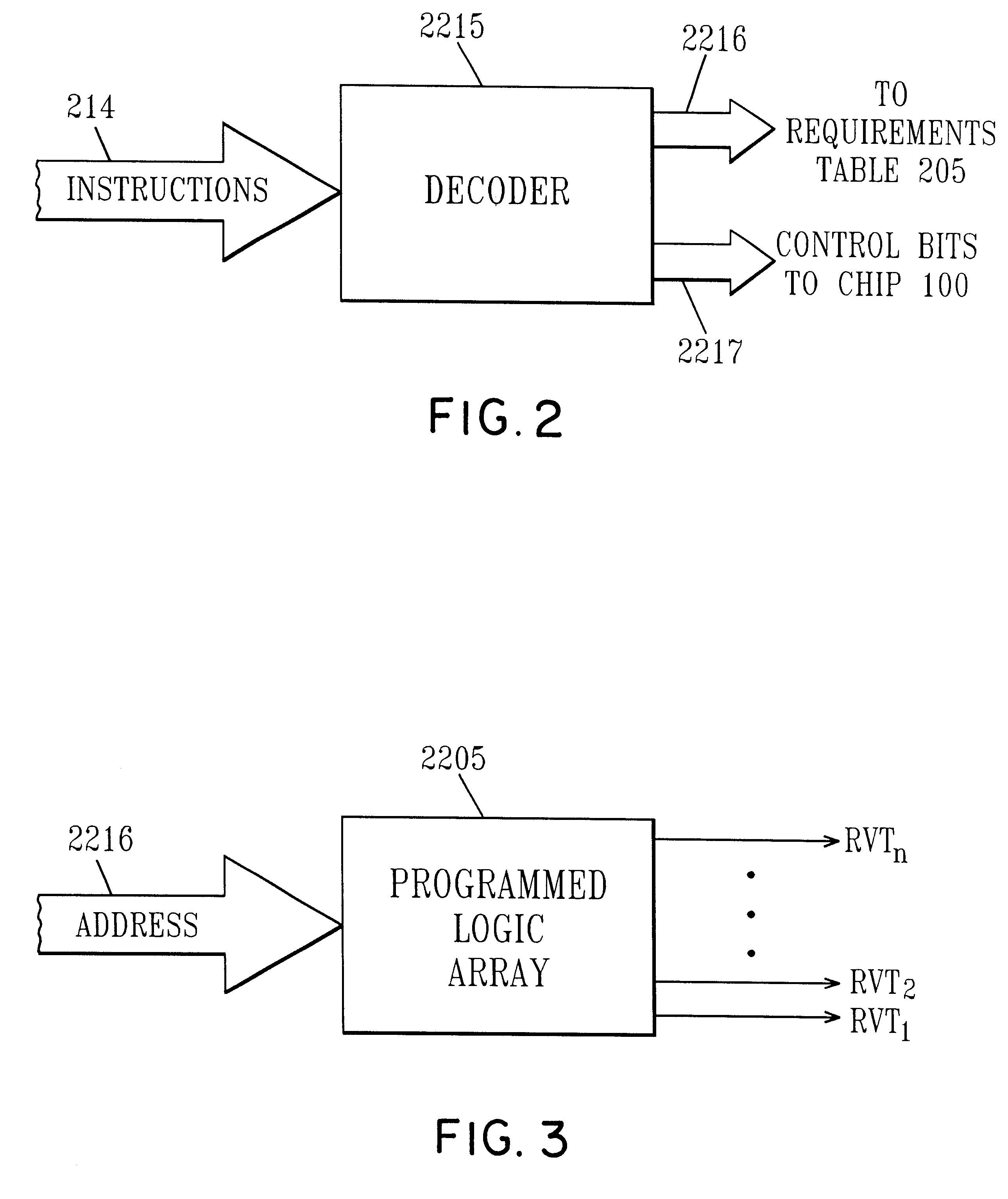

Managing Vt for reduced power using a status table

InactiveUS6345362B1Improve performanceReduce power consumptionEnergy efficient ICTVolume/mass flow measurementHemt circuitsLow power dissipation

An integrated circuit includes a CPU, a power management unit and plural functional units each dedicated to executing different functions. The power management unit controls the threshold voltage of the different functional units to optimize power / performance operation of the circuit and intelligent power management control responds to the instruction stream and decodes each instruction in turn. This information identifies which of the functional units are required for the particular instruction and by comparing that information to power status, the intelligent power control determines whether the functional units required to execute the command are at the optimum power level. If they are, the command is allowed to proceed, otherwise the intelligent power control either stalls the instruction sequence or modifies process speed.

Owner:GLOBALFOUNDRIES INC

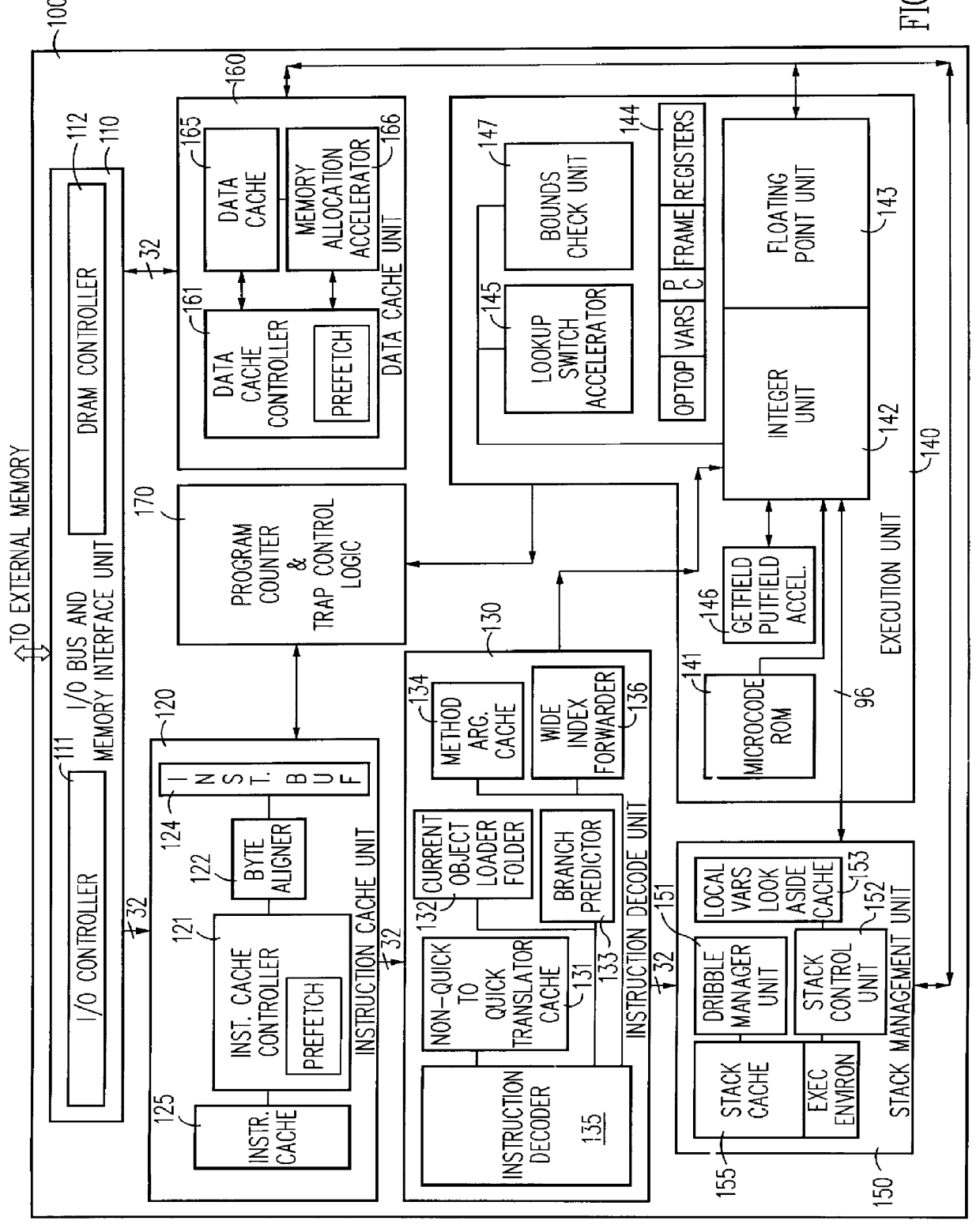

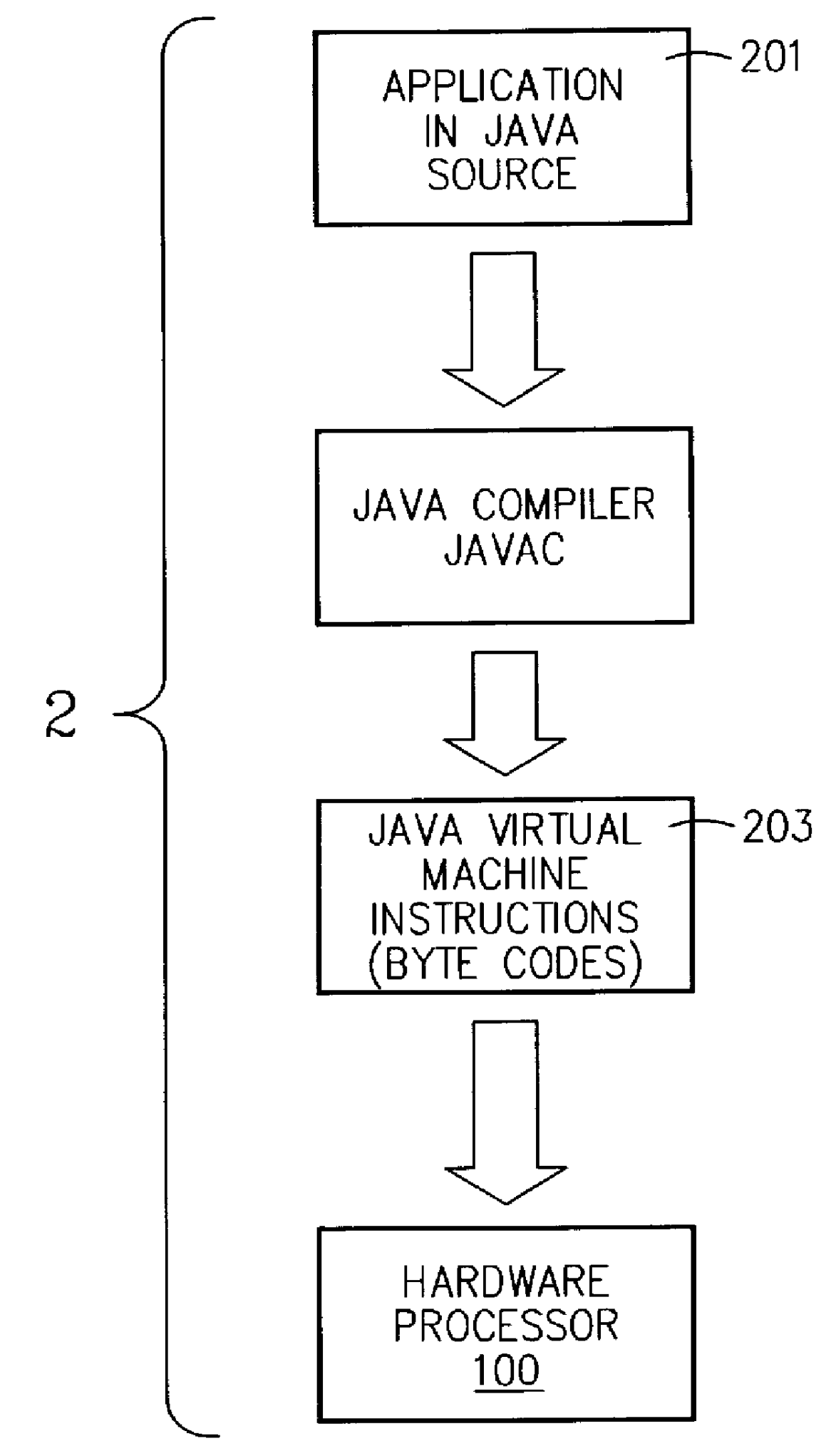

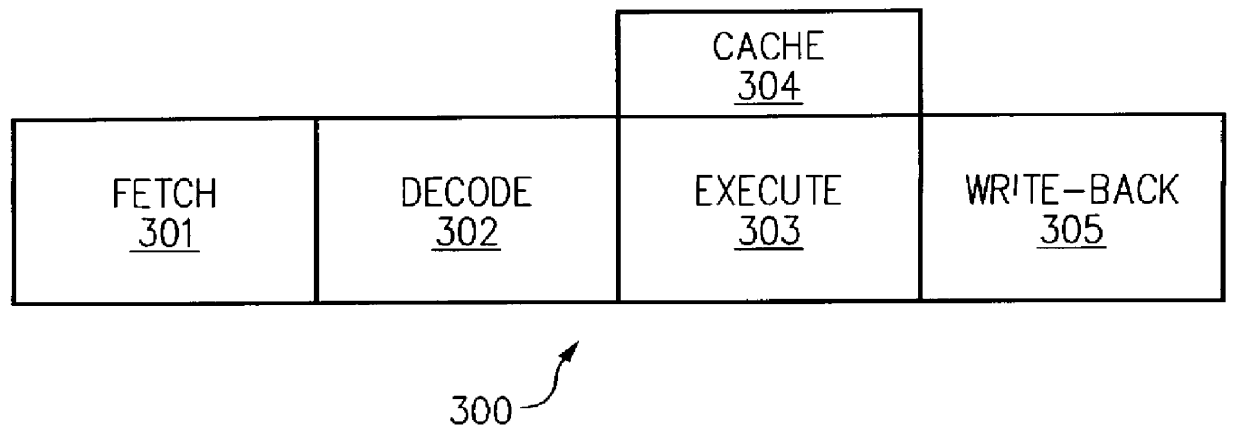

Hardware virtual machine instruction processor

InactiveUS6021469AProhibitive expenseLow costMemory architecture accessing/allocationEnergy efficient ICTThe InternetCellular telephone

A hardware virtual machine instruction processor directly executes virtual machine instructions that are processor architecture independent. The hardware processor has high performance; is low cost; and exhibits low power consumption. The hardware processor is well suited for portable applications. These applications include, for example, an Internet chip for network appliances, a cellular telephone processor, other telecommunications integrated circuits, or other low-power, low-cost applications such as embedded processors, and portable devices.

Owner:ORACLE INT CORP

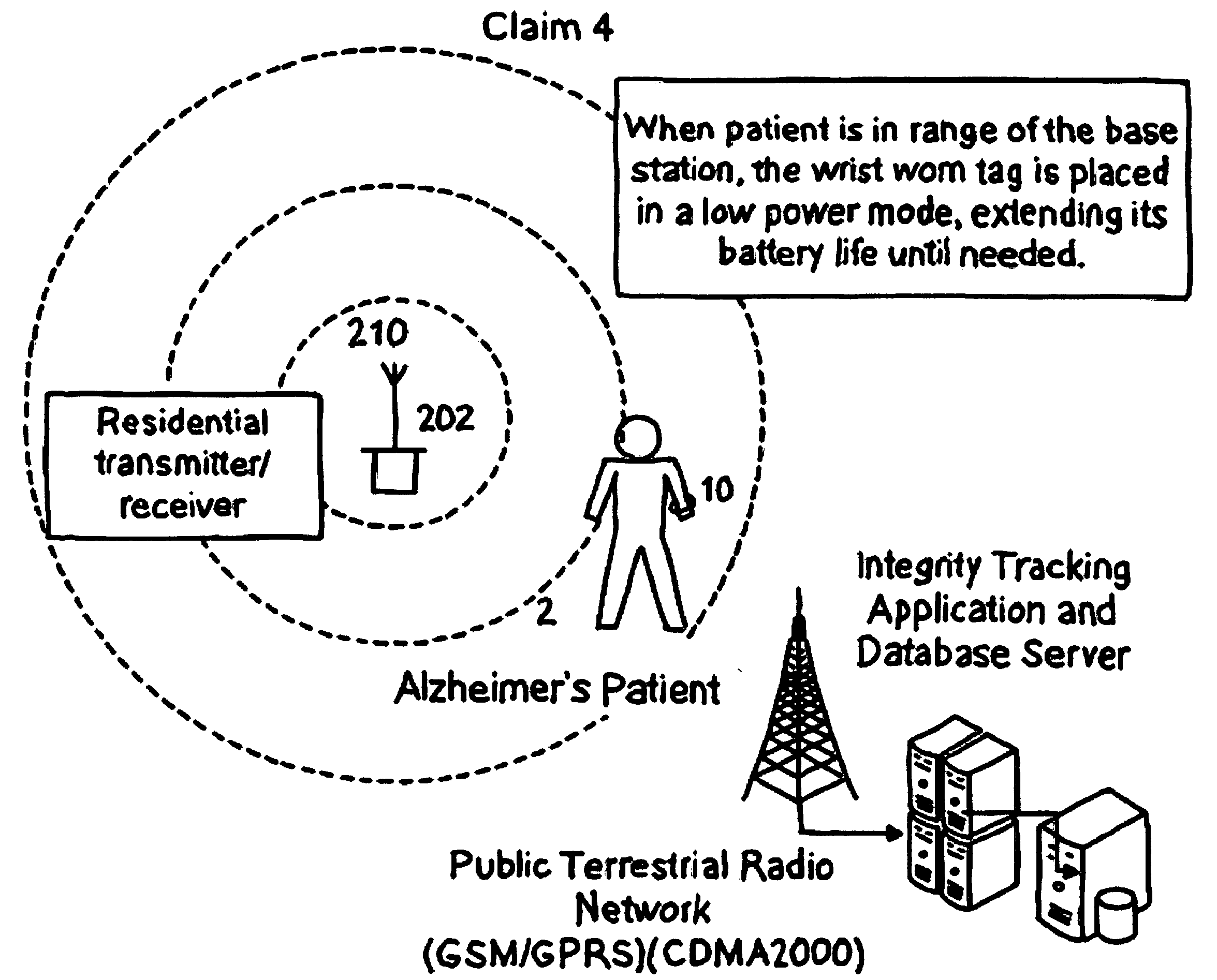

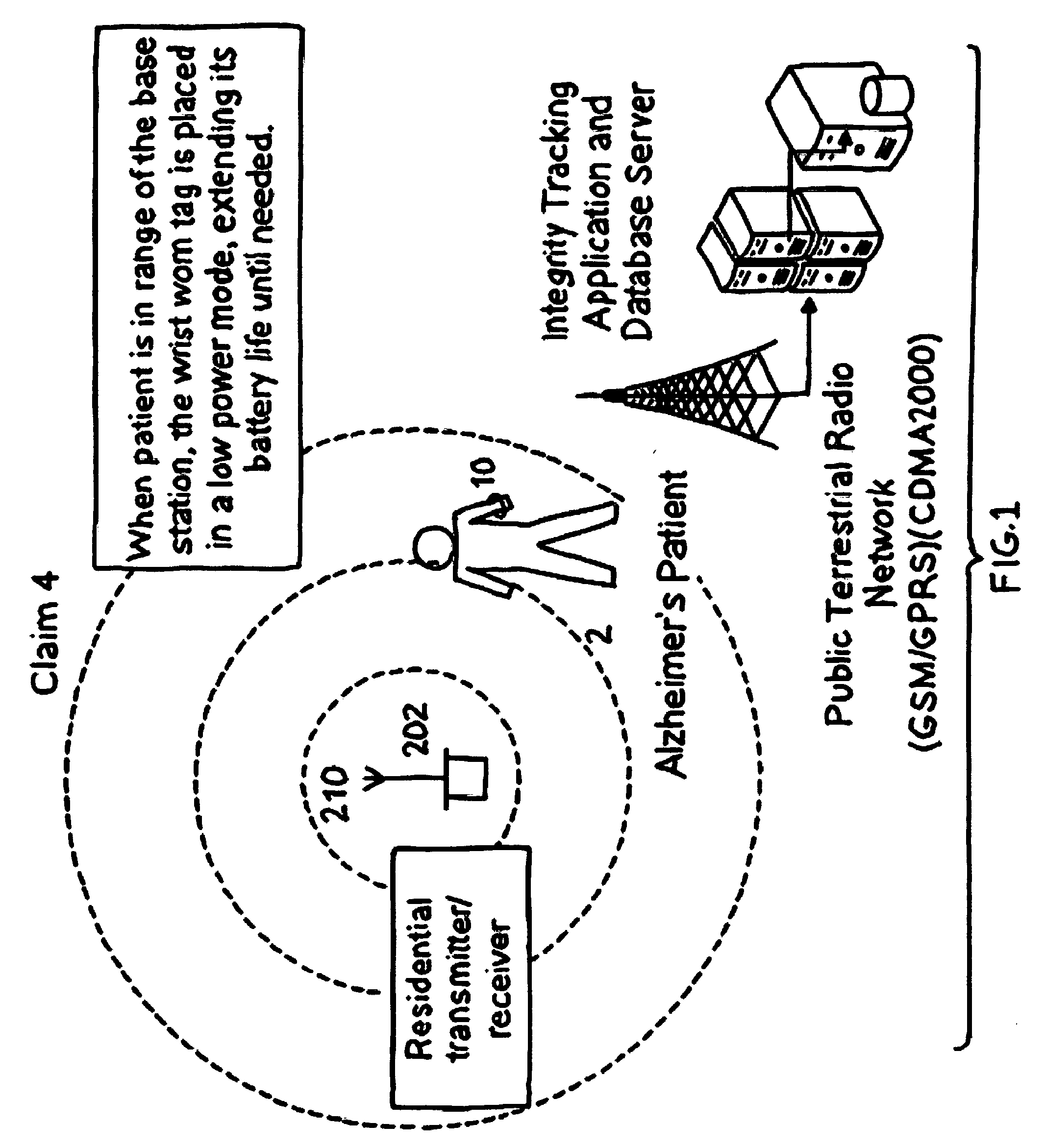

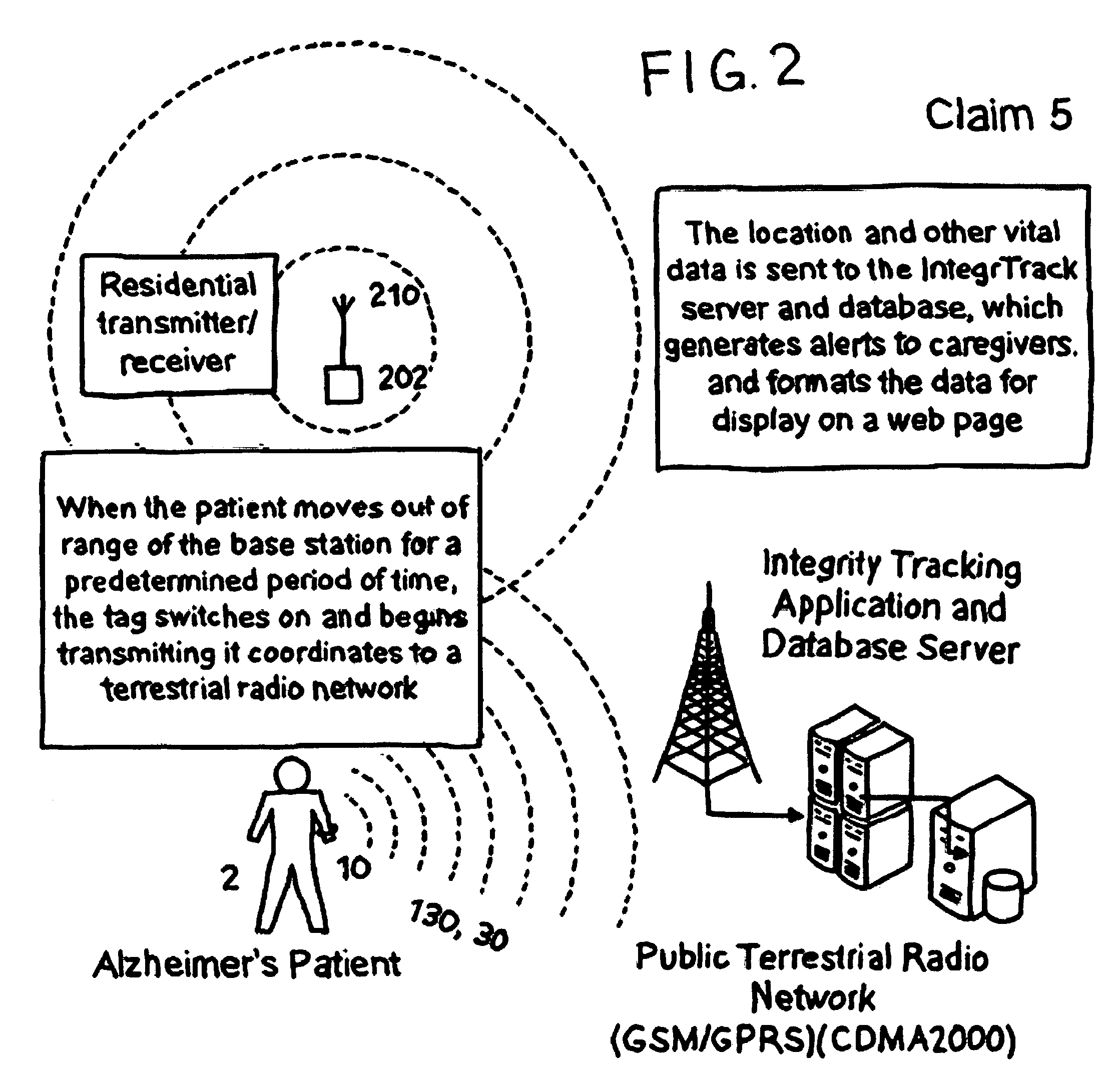

Alzheimer's patient tracking system

ActiveUS20090040041A1Reduce power consumptionLow costPower managementRoad vehicles traffic controlCaregiver personElectronic tagging

The computerized system provides a method to track Alzheimer's patients and other diseases that affect the patient's ability to contact and communicate their location or vital information to their caregivers. The system applies an electronic tag to each patient of a multiplicity of patients or only to non-confined patients and employs a computer to maintain information about their location and well being. Use is made of a global positioning system to locate a lost patient as well as to track movements of the patient. A history of the movement of the patient may also be plotted on a map. Additional components of the tag gather and relay information about the patient's condition and other environmental data. In addition, the use of a an additional external transmitter keeps the wearable tag in a low power “sleep” mode when it is in range, preserving the internal battery and only consuming power when the tag moves out of range of the external transmitter.

Owner:MOBILEHELP LLC

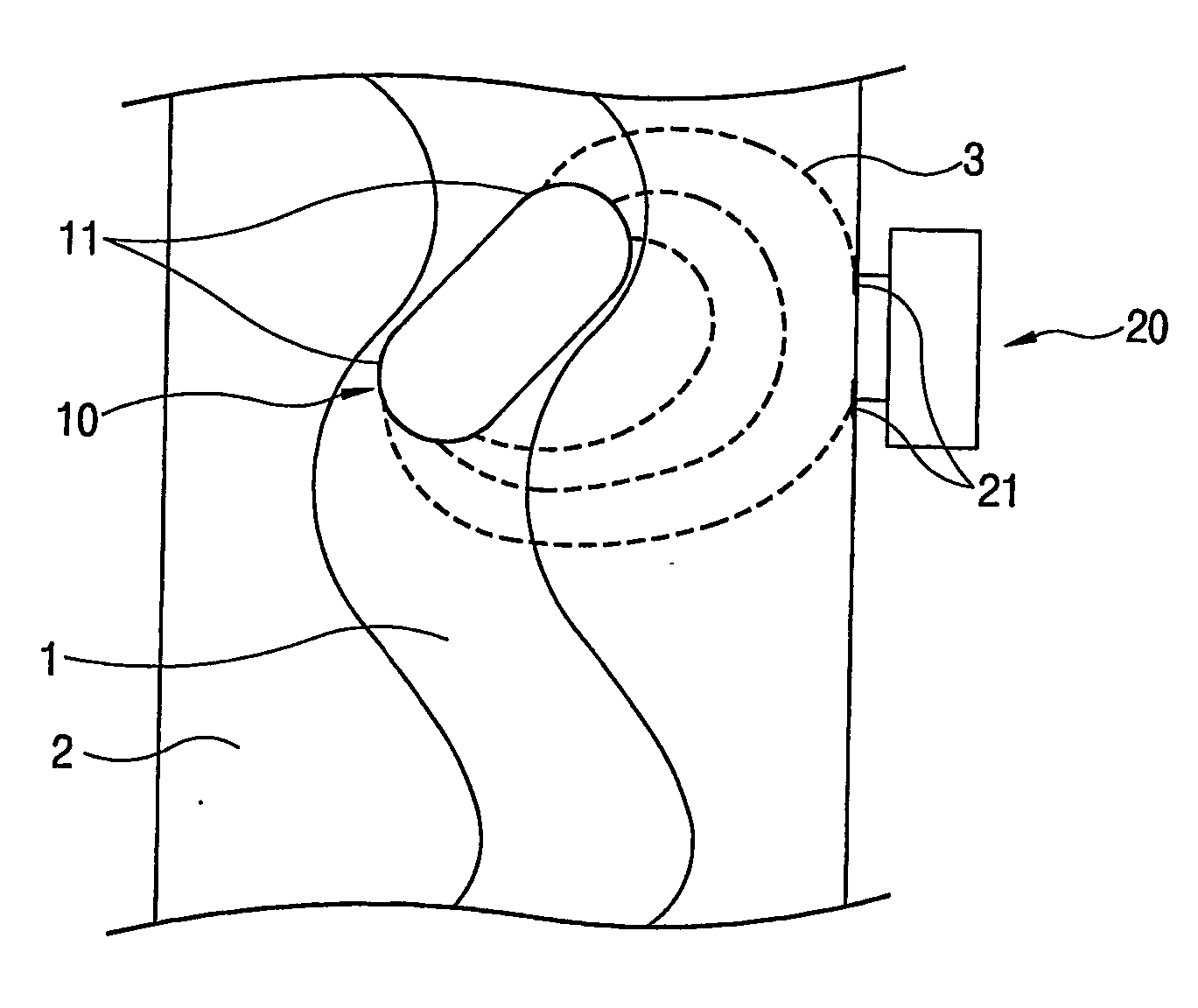

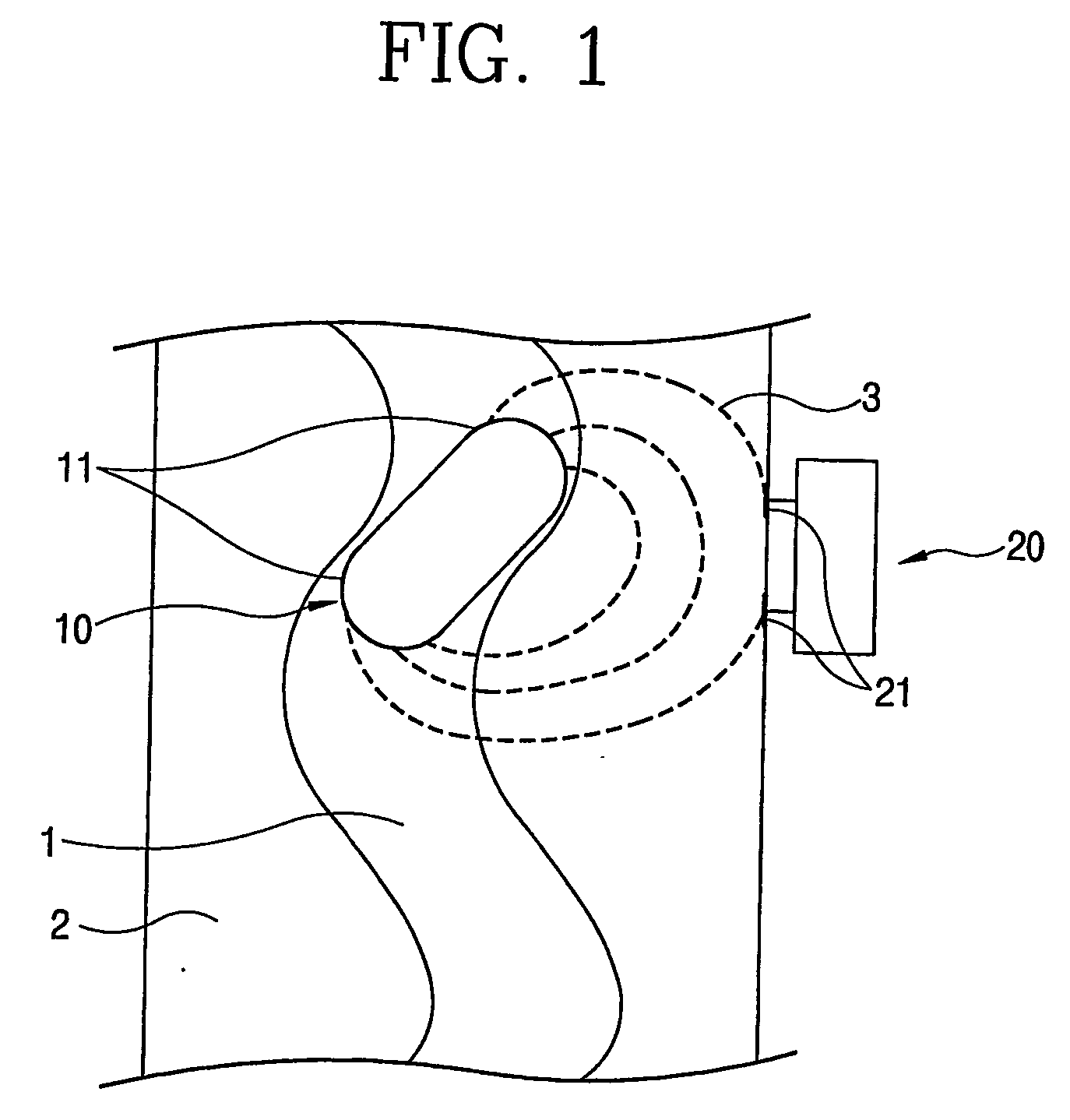

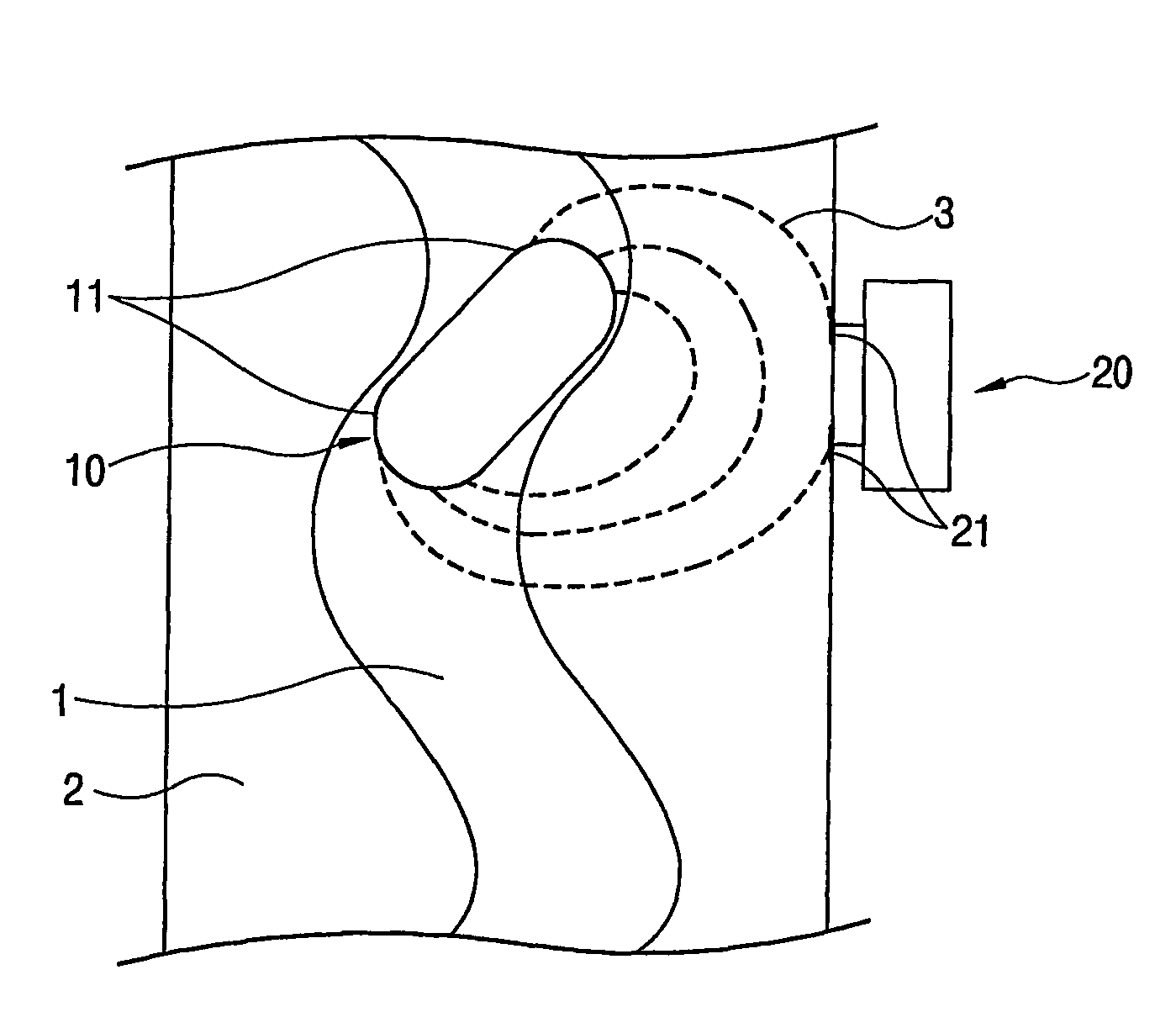

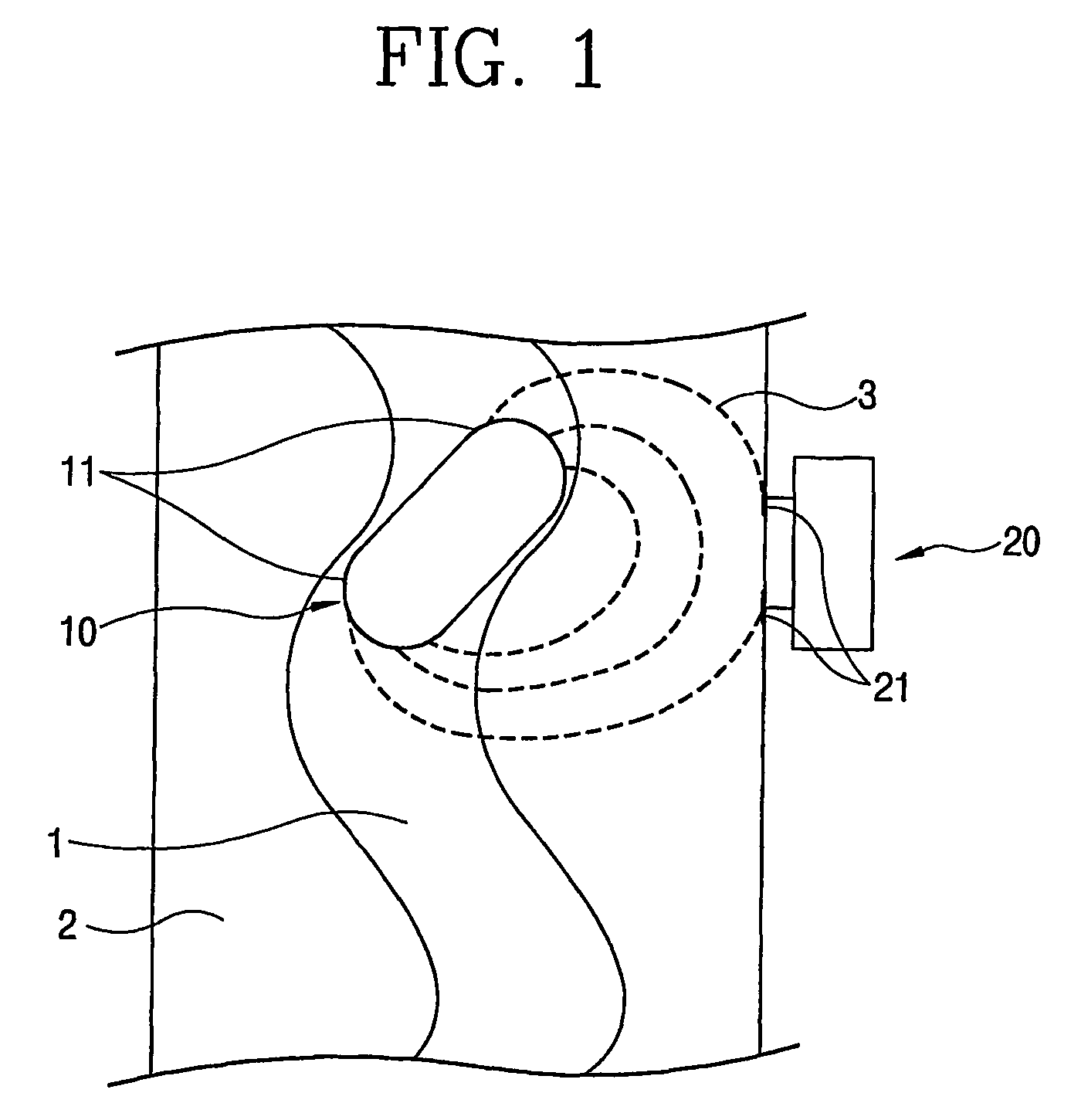

Method and system for data communication in human body and sensor therefor

The present invention provides method and system for data communication in the human body and a sensor therefor. The method and system transmit information through the human body to a receiver located outside the human body using low current and voltage polarity, so that they cause no damage to the human body and achieve low power consumption and better receiving sensitivity. In addition, the sensor contains a CMOS image sensor on which all circuits are integrated without radio transmitter and antenna, so that it achieves a low-priced and small-sized capsule type endoscope.

Owner:KOREA INST OF SCI & TECH

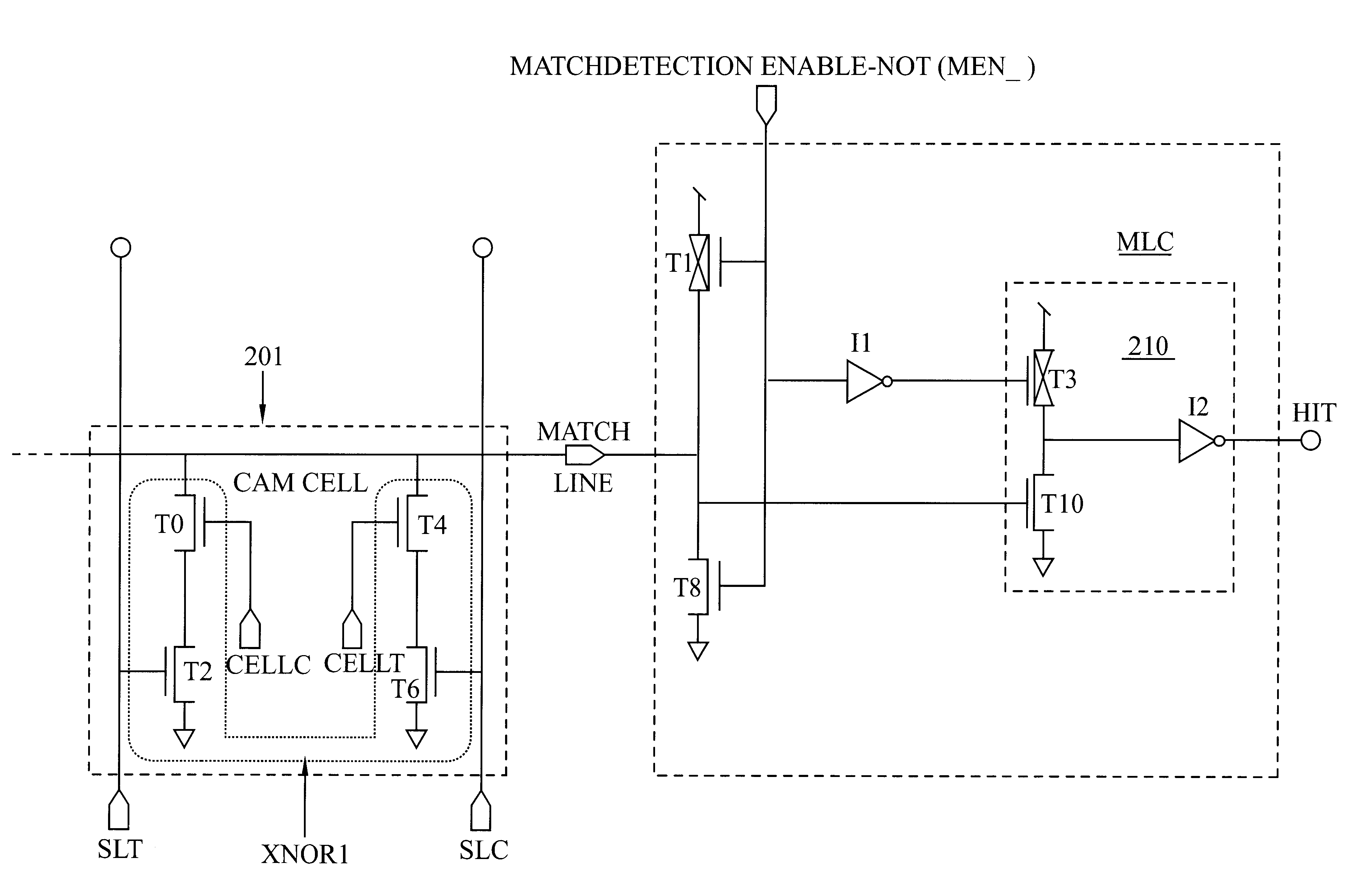

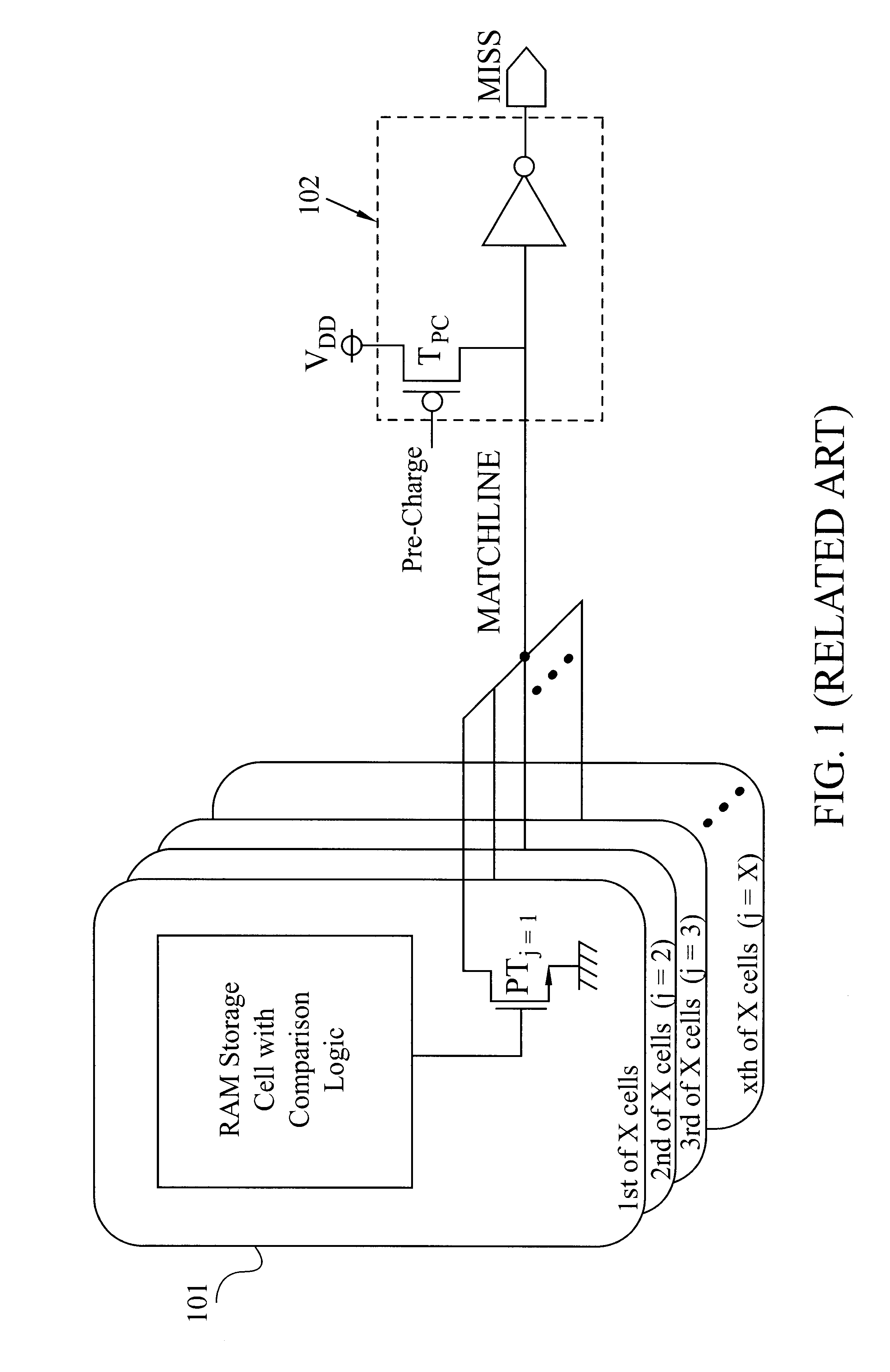

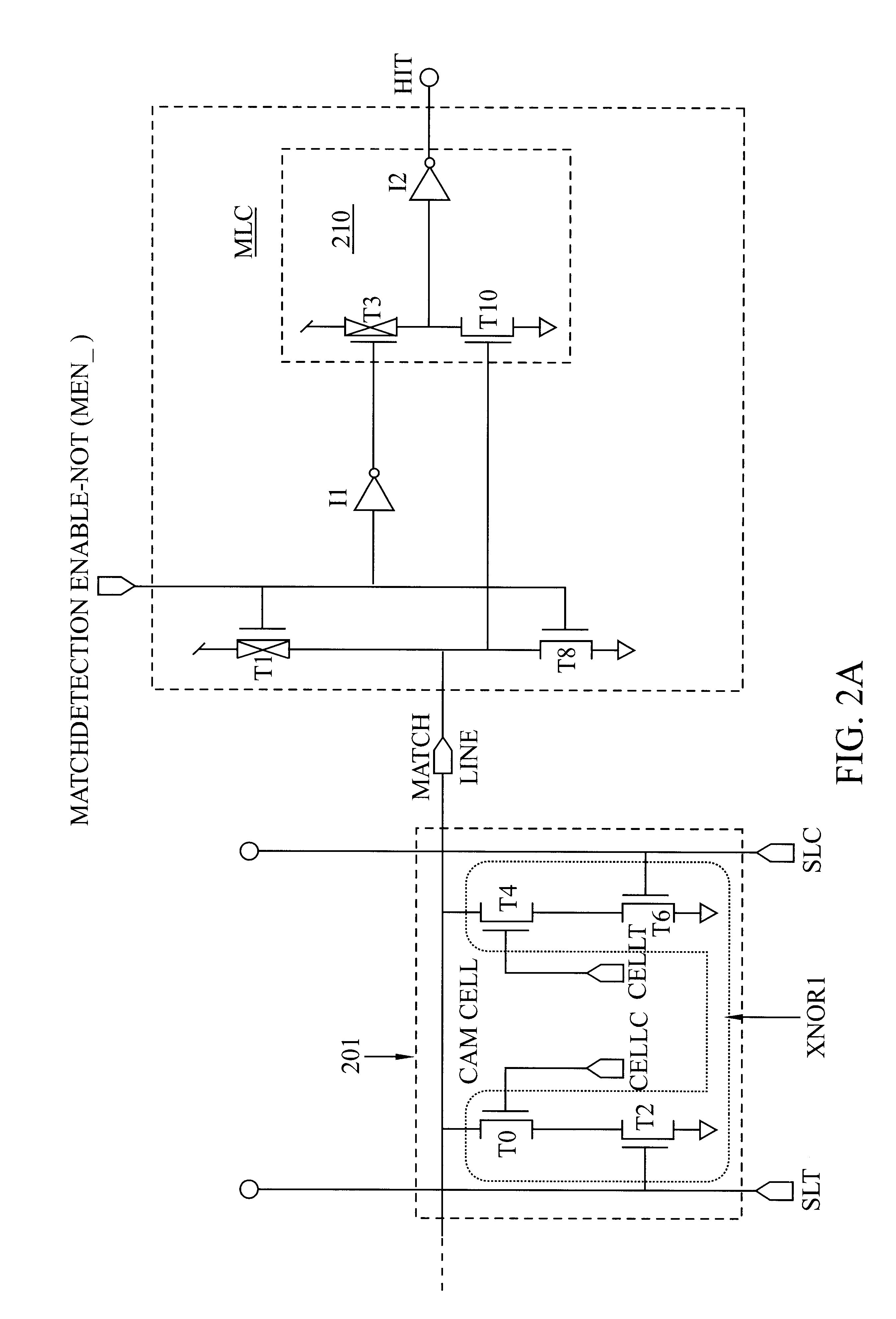

Low power CAM match line circuit

A Match-Detection Circuit and Match-Detection method, for low-power-consuming searches in a Content Addressable Memory. A HIT is output when the Match Line rises from a Low voltage level to a higher Match Detection Voltage. The Match Detection Voltage is approximately the conducting threshold voltage of an N-channel Field Effect Transistor (FET), and is normally less than One Half of the Power Supply Voltage. Circuits and methods to turn of the through-current in each MISS-ing entry by a carefully timed control signal at the end of a brief Match Detection Period, are disclosed.

Owner:IBM CORP

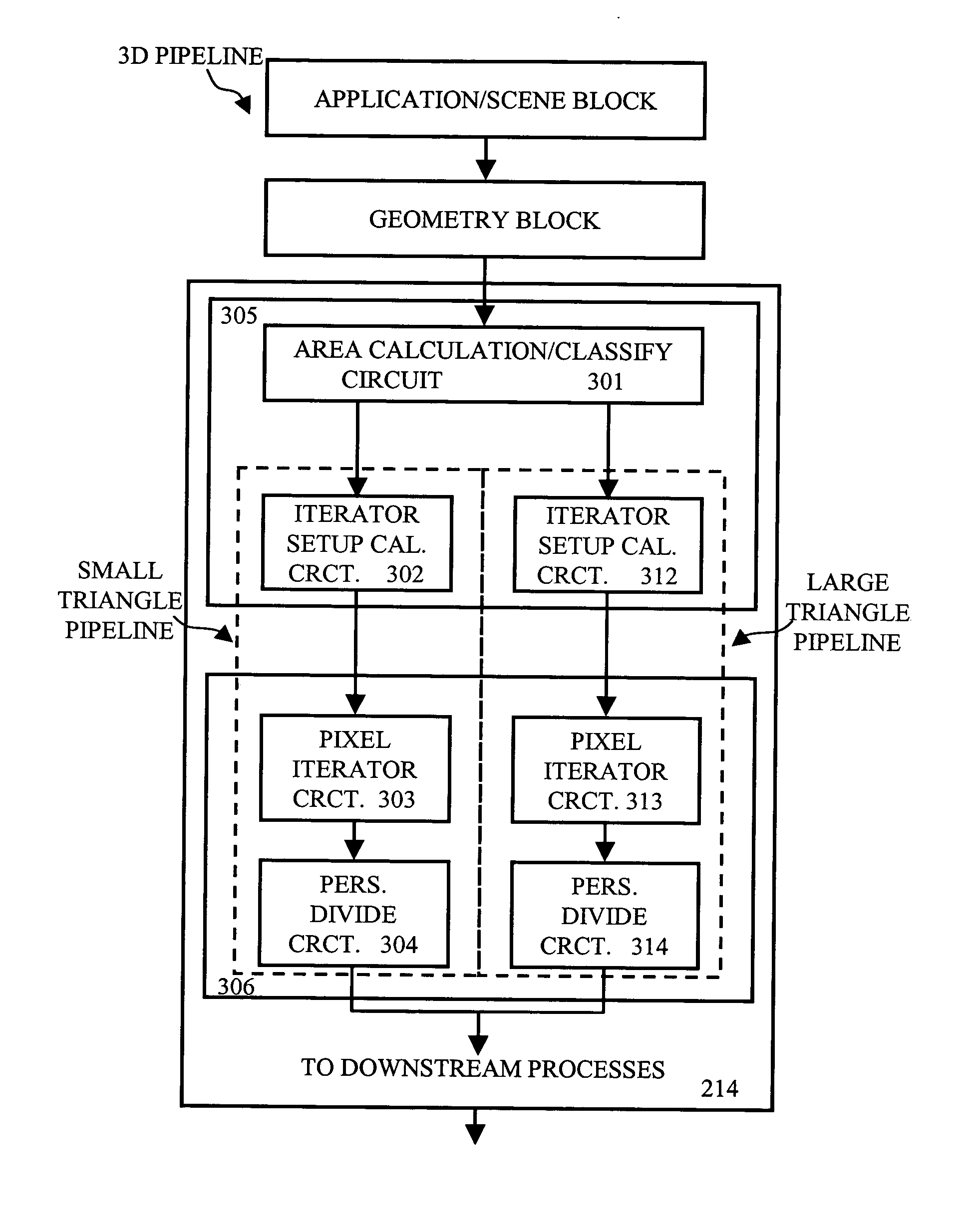

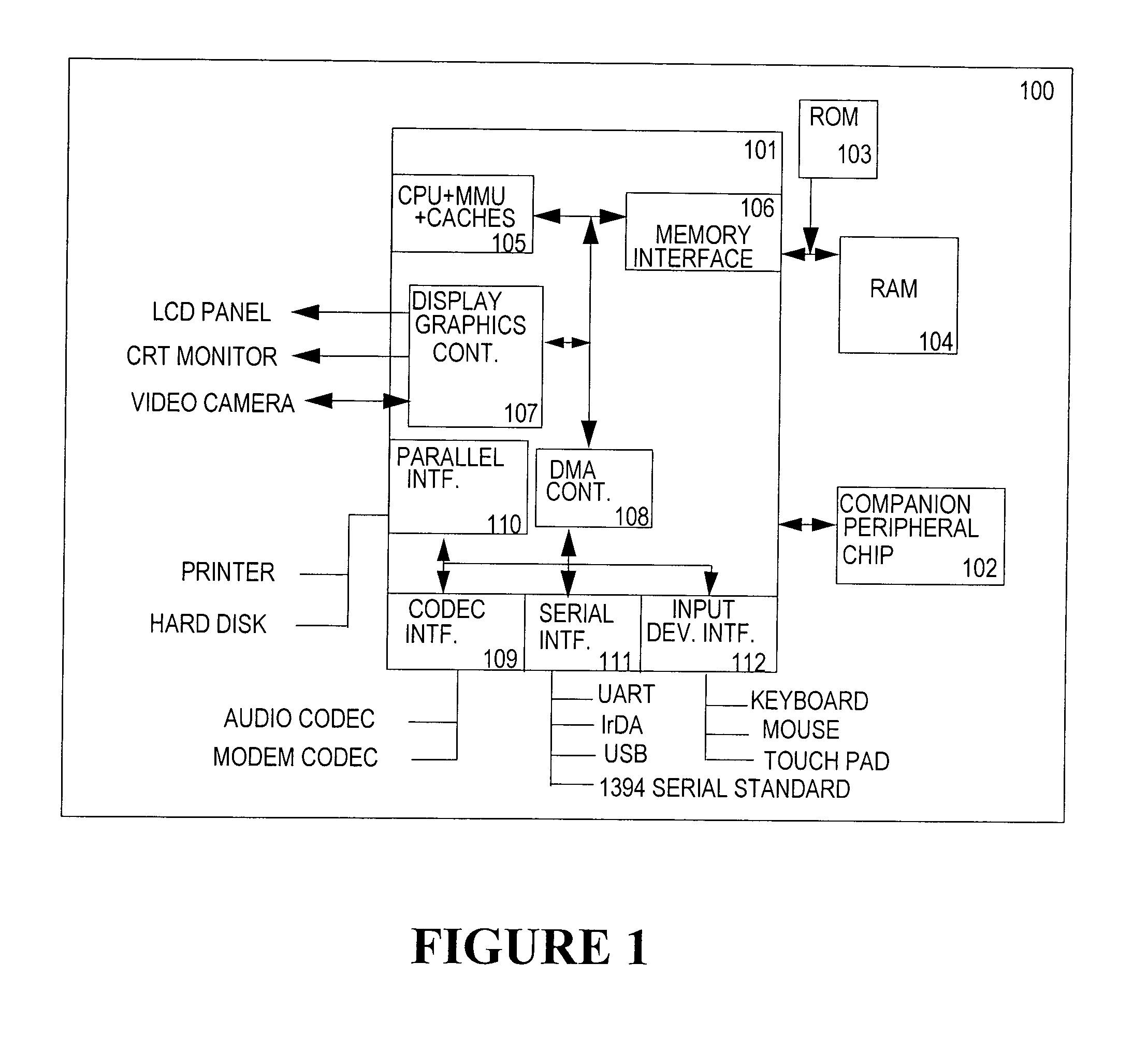

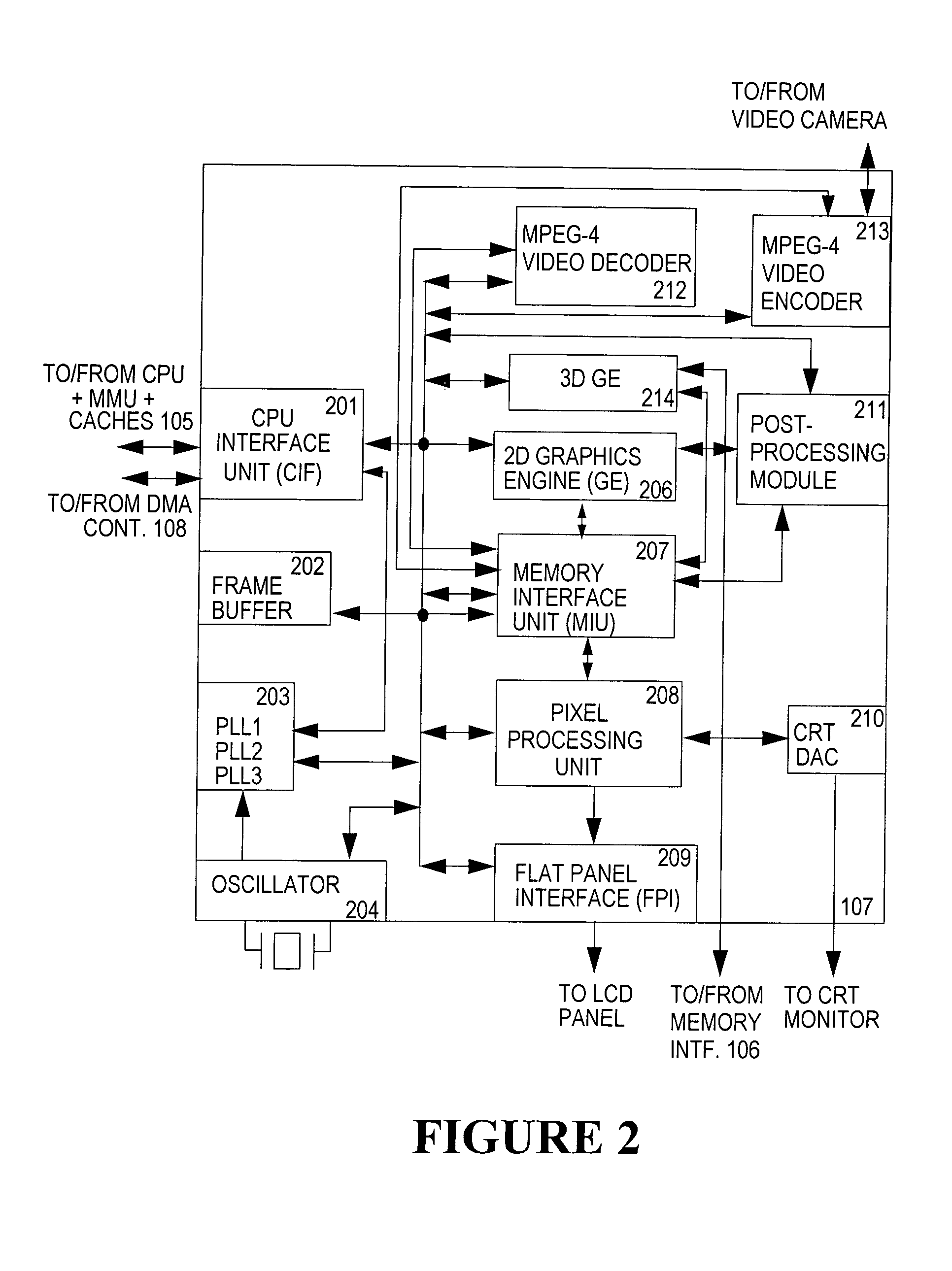

High quality and high performance three-dimensional graphics architecture for portable handheld devices

ActiveUS20050066205A1Quality improvementImprove performanceEnergy efficient ICTVolume/mass flow measurementComputational sciencePower efficient

A high quality and performance 3D graphics architecture suitable for portable handheld devices is provided. The 3D graphics architecture incorporates a module to classify polygons by size and other characteristics. In general, small and well-behaved triangles can be processed using “lower-precision” units with power efficient circuitry without any quality and performance sacrifice (e.g., realism, resolution, etc.). By classifying the primitives and selecting the more power-efficient processing unit to process the primitive, power consumption can be reduced without quality and performance sacrifice.

Owner:NVIDIA CORP

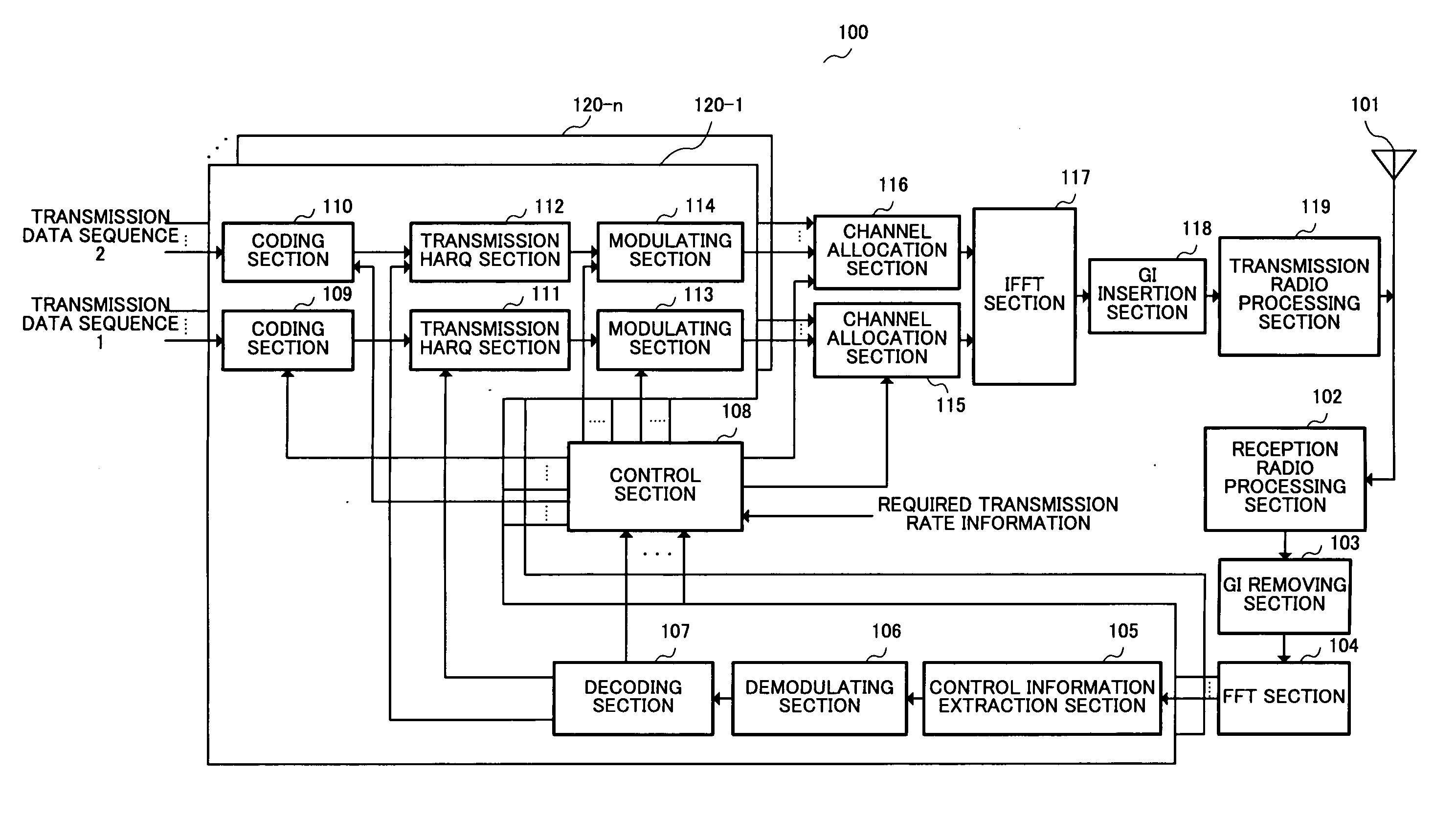

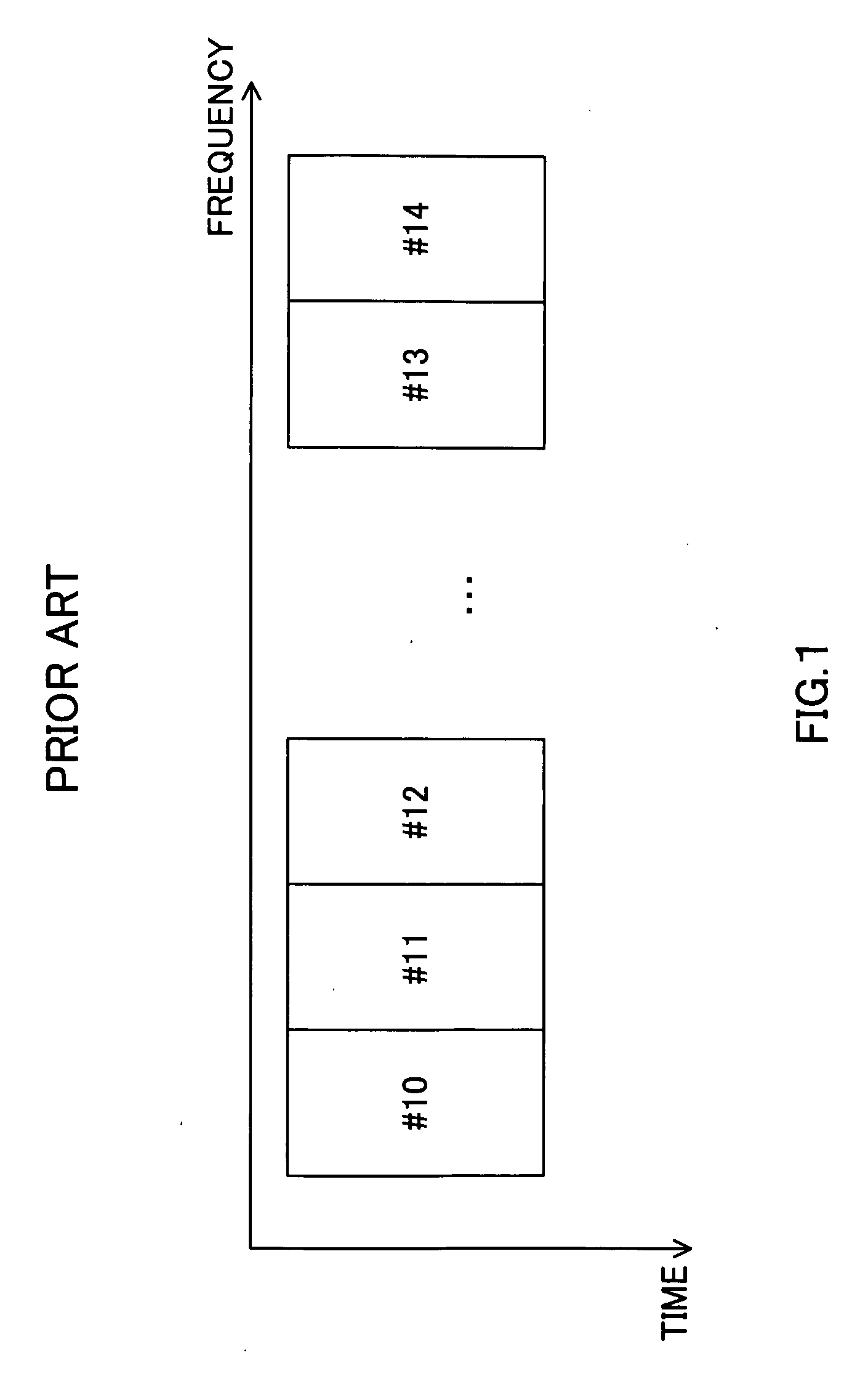

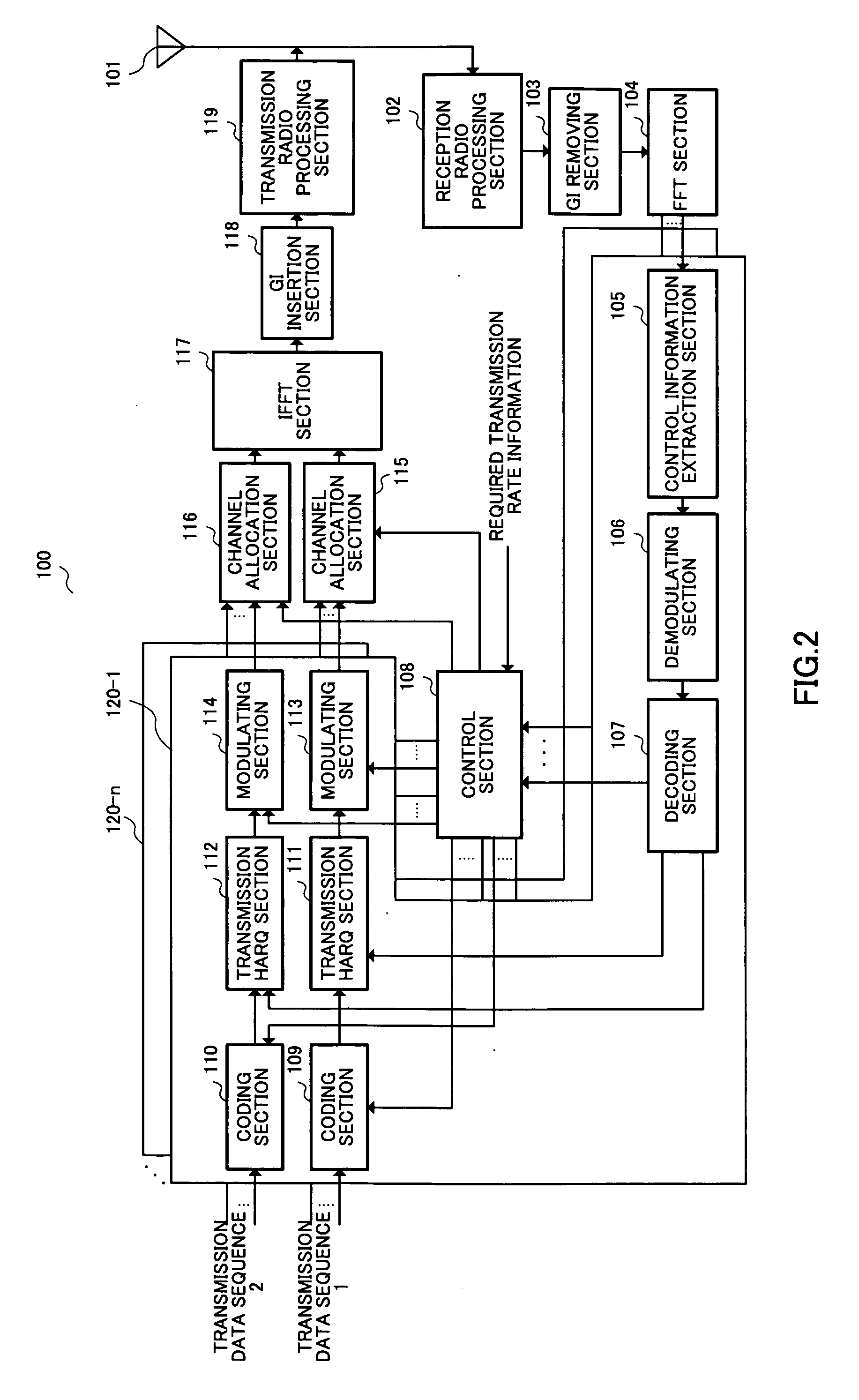

Radio communication apparatus and subcarrier assignment method

ActiveUS20060209669A1Improve transmission efficiencyReduce power consumptionEnergy efficient ICTTransmission path divisionSubcarrierTransmission rate

Wireless communication apparatus capable of increasing transmission efficiency by selecting data for scheduling according to data type, and capable of achieving low power consumption and high-speed signal processing is disclosed. With this apparatus, a control section (108) allocates transmission data sequence 1 to subcarriers of superior quality by carrying out scheduling for the transmission data sequence 1 based on CQI sent from communication terminal apparatus and required transmission rate information for each communication terminal apparatus, and allocates transmission data sequence 2 to preassigned subcarriers. Channel allocation section (115) allocates data for transmission data sequence 1 to subcarriers designated by control section (108). Channel allocation section (116) allocates data for transmission data sequence 2 to subcarriers designated by control section (108).

Owner:GK BRIDGE 1

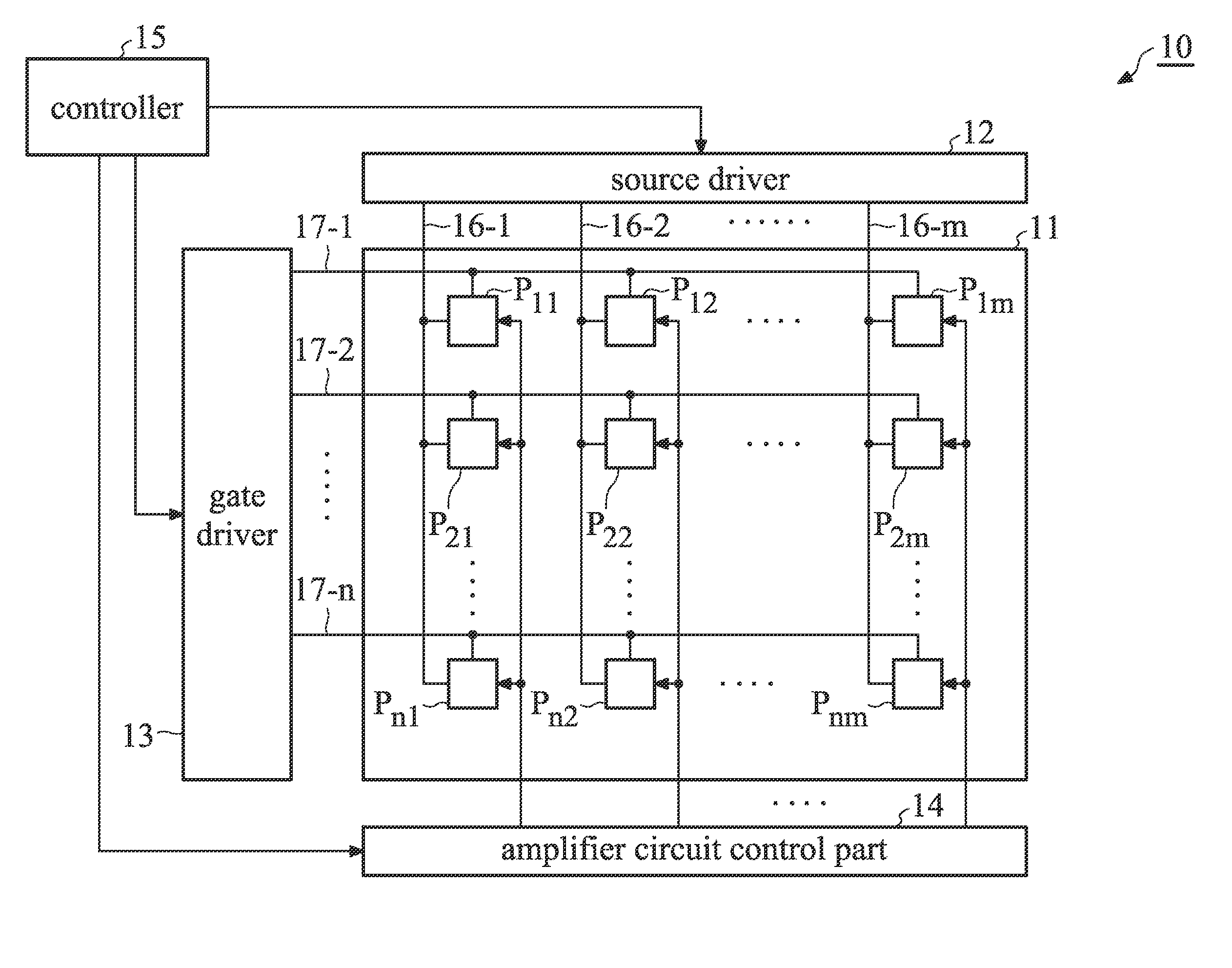

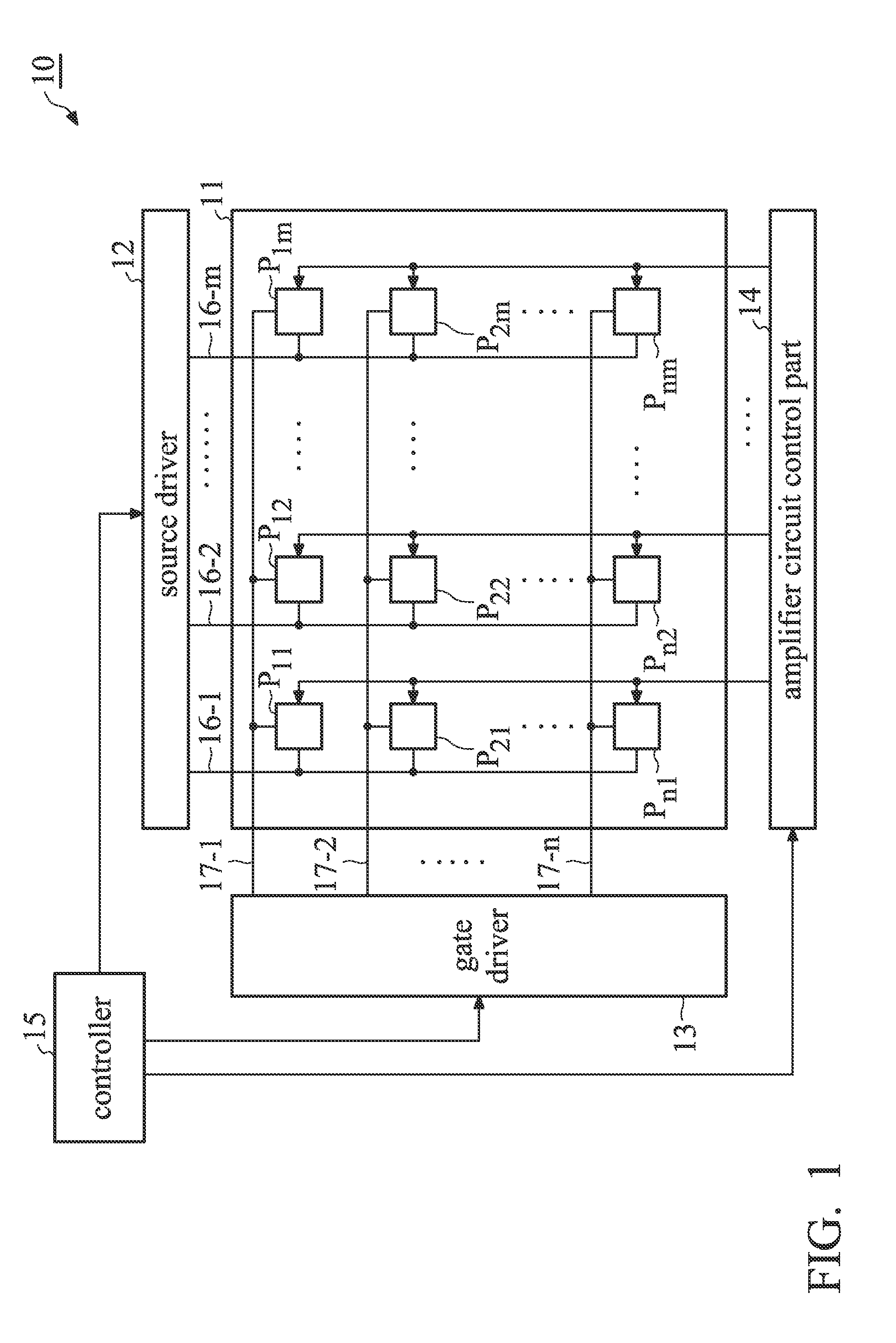

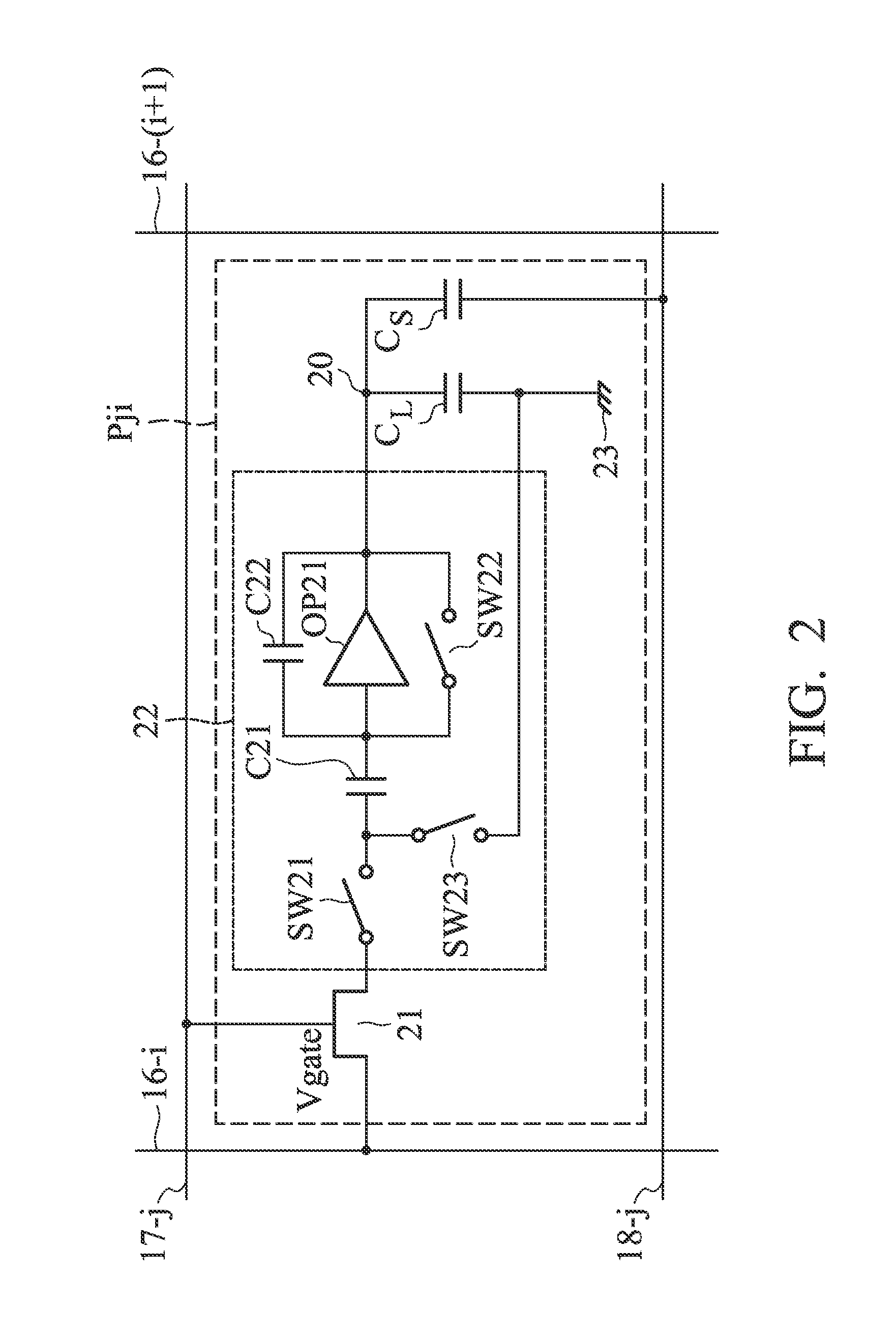

Display device and electronic device using the same

InactiveUS20120056558A1Reduce power consumptionElectrical apparatusStatic indicating devicesDisplay deviceEngineering

The invention provides a low-power consumption display device. The display device 10 is provided with a plurality of pixels P11˜Pnm arranged in a matrix formed by columns and rows, and a plurality of signal lines 16-1˜16-m arranged corresponding to every pixel rows or pixel columns. The display device further comprises a signal voltage generating part 12 electrically connected to the plurality of pixels P11˜Pnm via the plurality of signal lines 16-1˜16-m and generating signal voltages which are applied to the plurality of signal lines 16-1˜16-m, and a signal voltage amplifying part 14 amplifying the signal voltage generated by the signal voltage generating part 12 to a necessary drive voltage for each of the plurality of pixels P11˜Pnm.

Owner:INNOLUX CORP

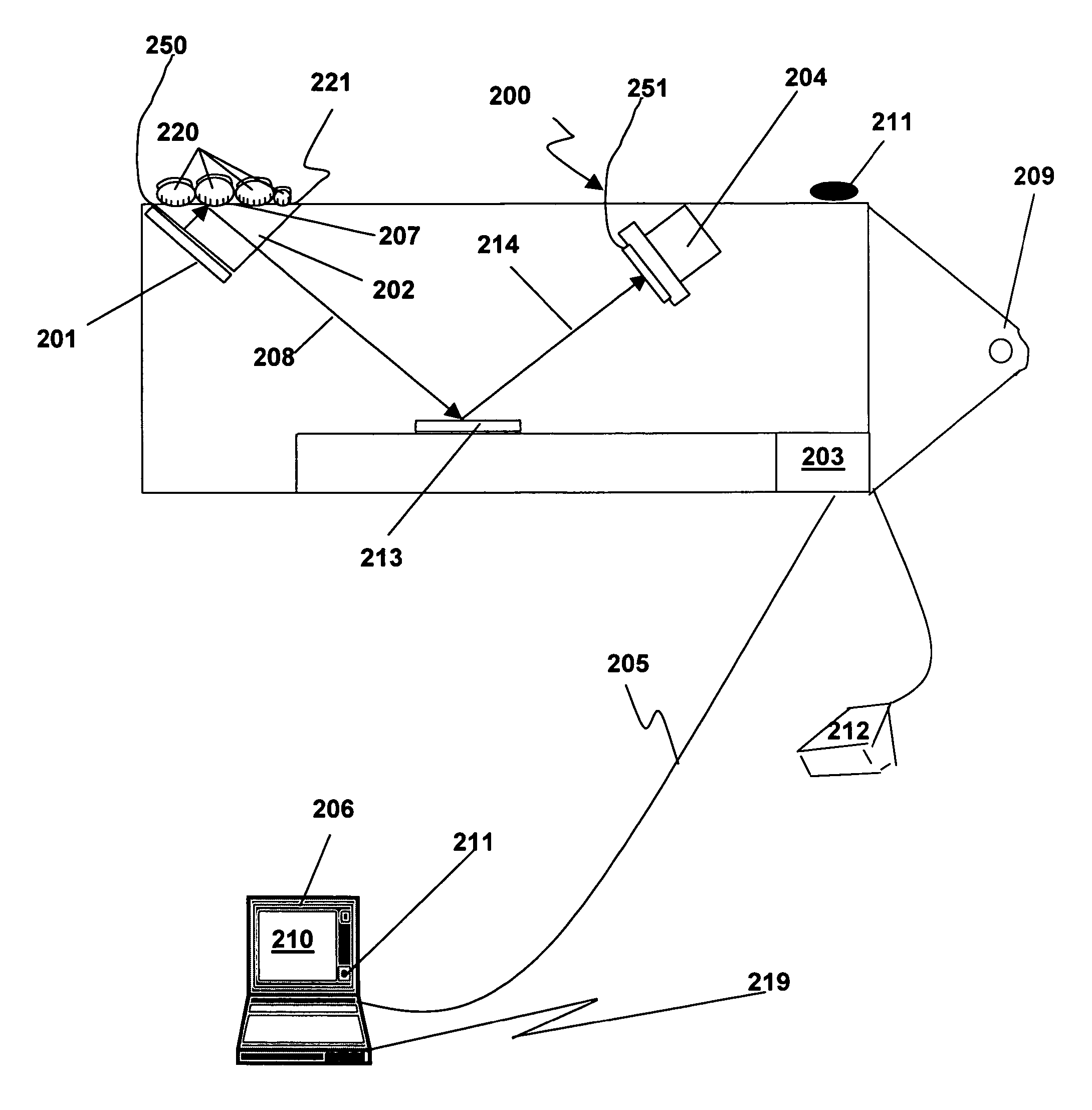

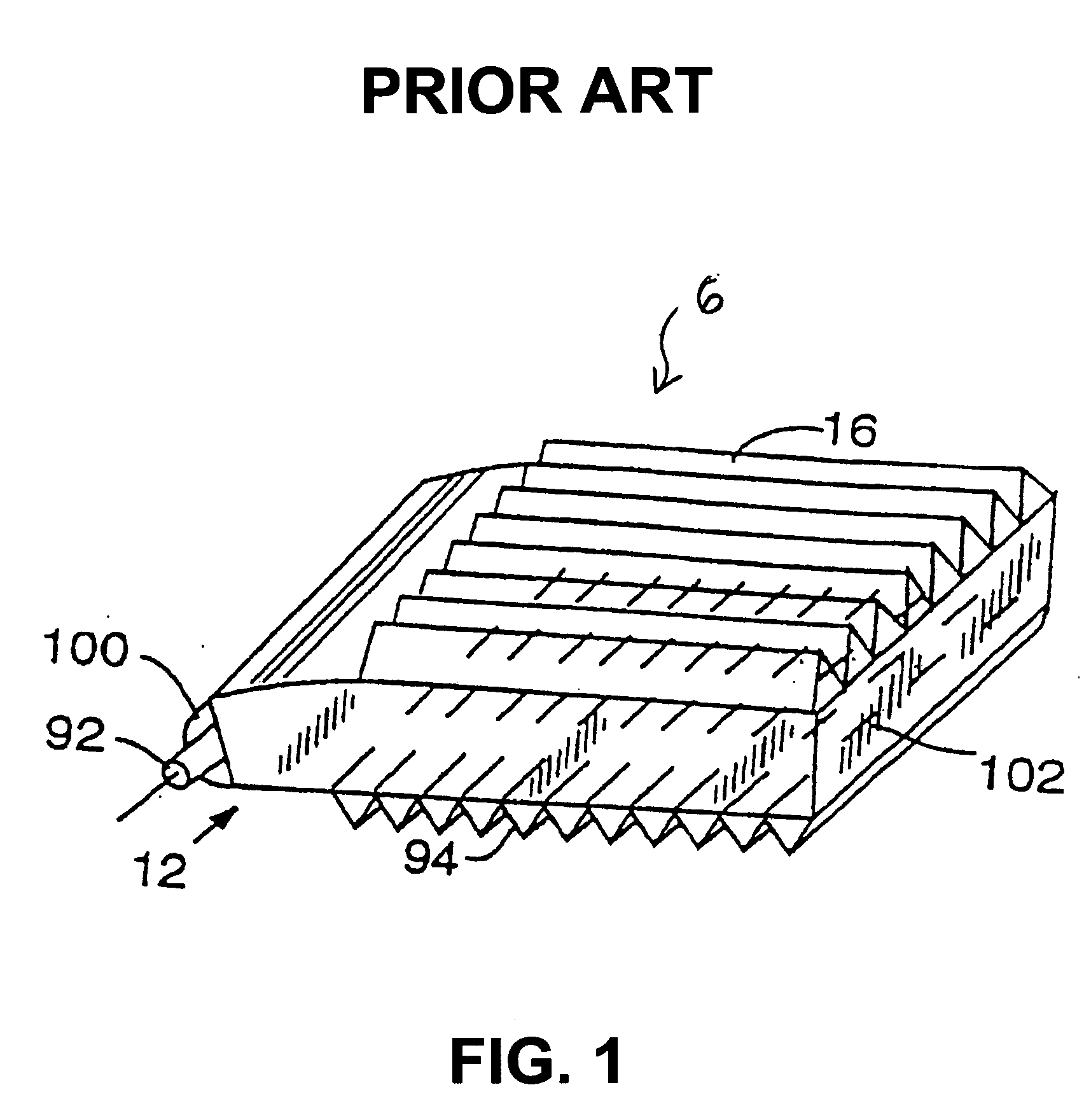

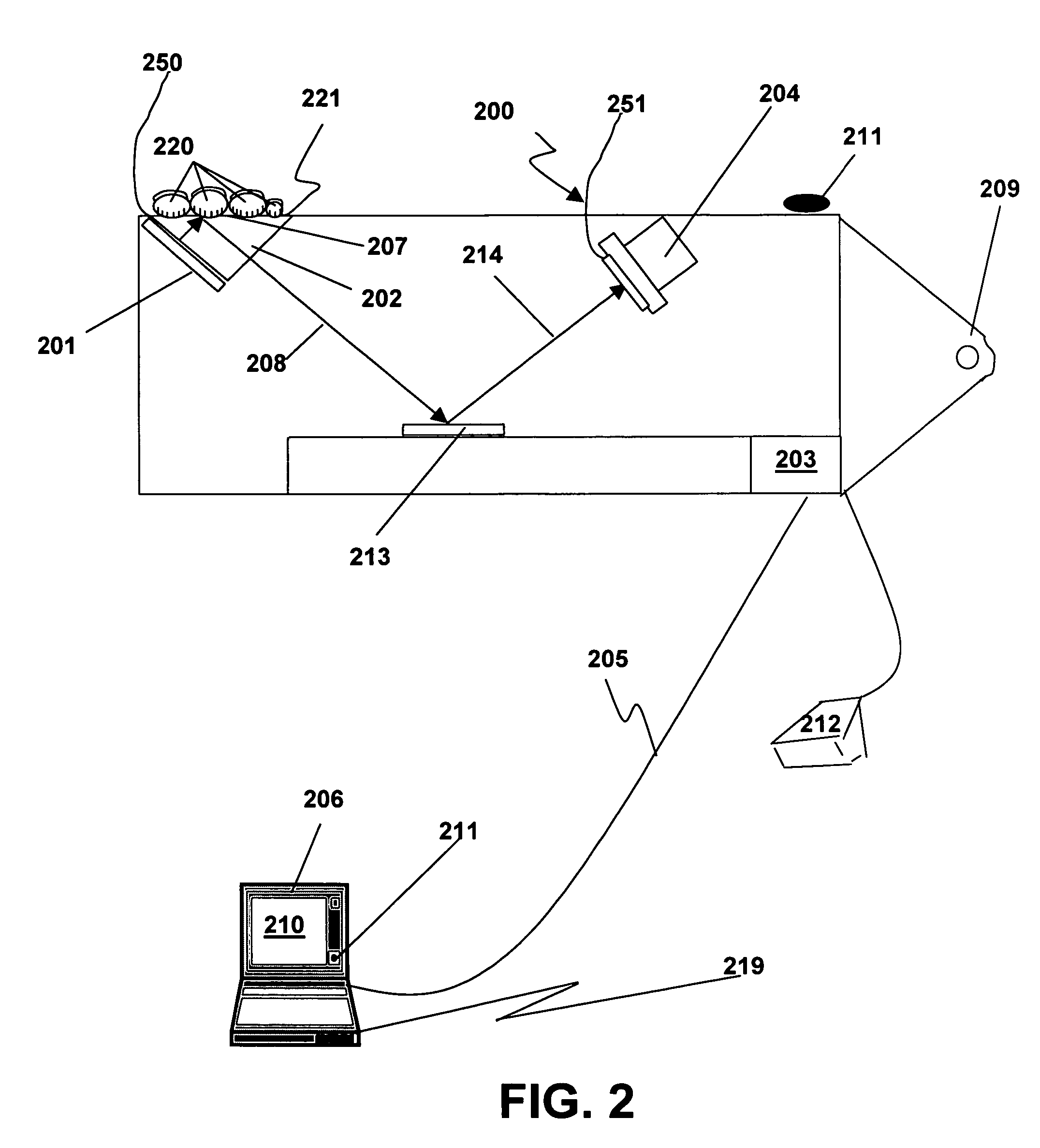

Low power fingerprint capture system, apparatus, and method

ActiveUS20050169506A1Shorter focal distanceImprove aberrationCharacter and pattern recognitionGratingBarcode reader

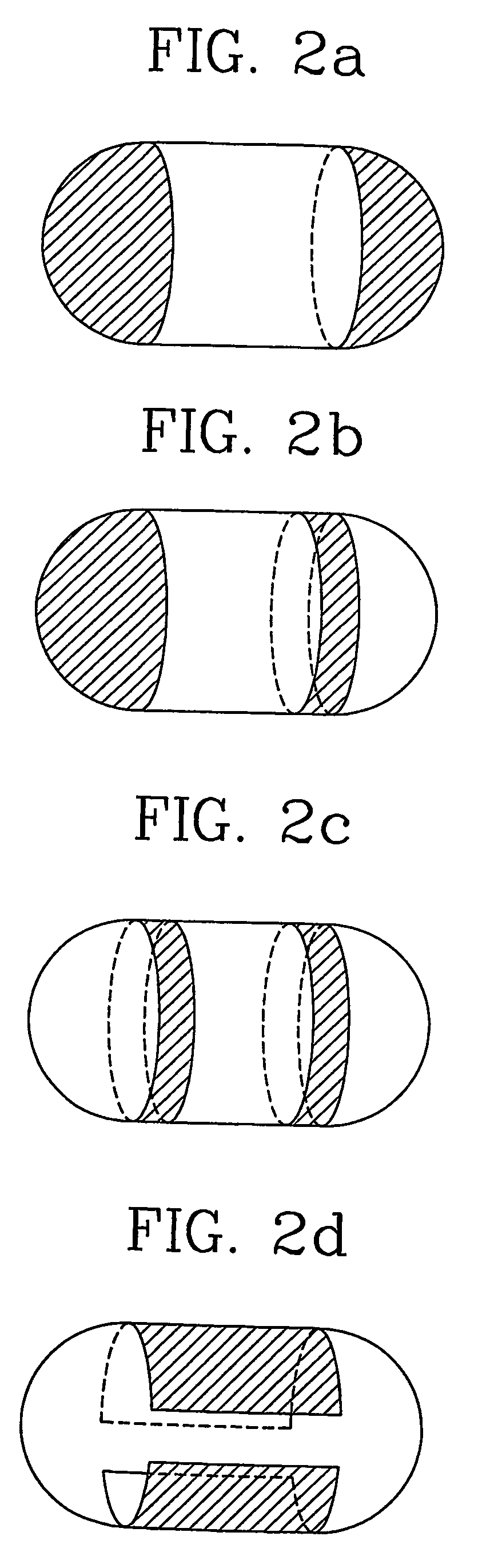

The present invention provides a large format fingerprint capture apparatus, system and method that is low power, compact, and lightweight and has a platen area greater than 3.0 square inches. The present system is typically powered, controlled, and exchanges data over a single data / control / power connection to a host PC, e.g., a desk top computer, PDA, or laptop computer although the system can also be used in a wireless fashion with a power subsystem so no physical connections are required. In a preferred embodiment the large format fingerprint device is directly connected to a completely disconnected portable PC, such as a laptop having only a battery power source. The primary system components of the present invention combine to minimize power, size and weight and, thus, enhance portability and battery life. The system typically includes a light source, a prism, a camera (including the lens), and a case. Optional elements comprise holographic elements such as gratings and holographic optical elements (HOEs), a battery subsystem, magnetic stripe reader, barcode reader, platen heater, platen blower, and mirrors to divert the image beam.

Owner:IDENTIFICATION INT

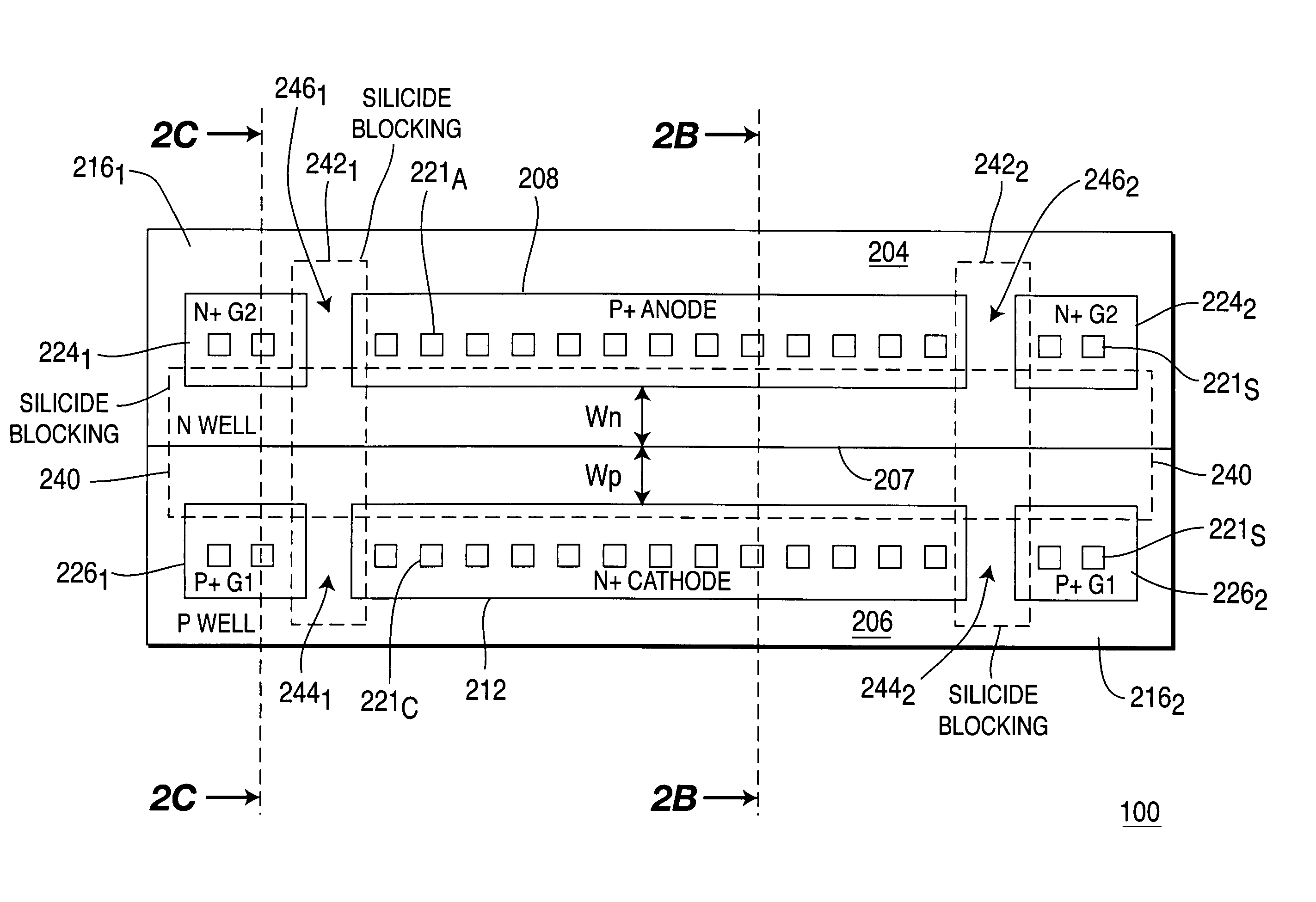

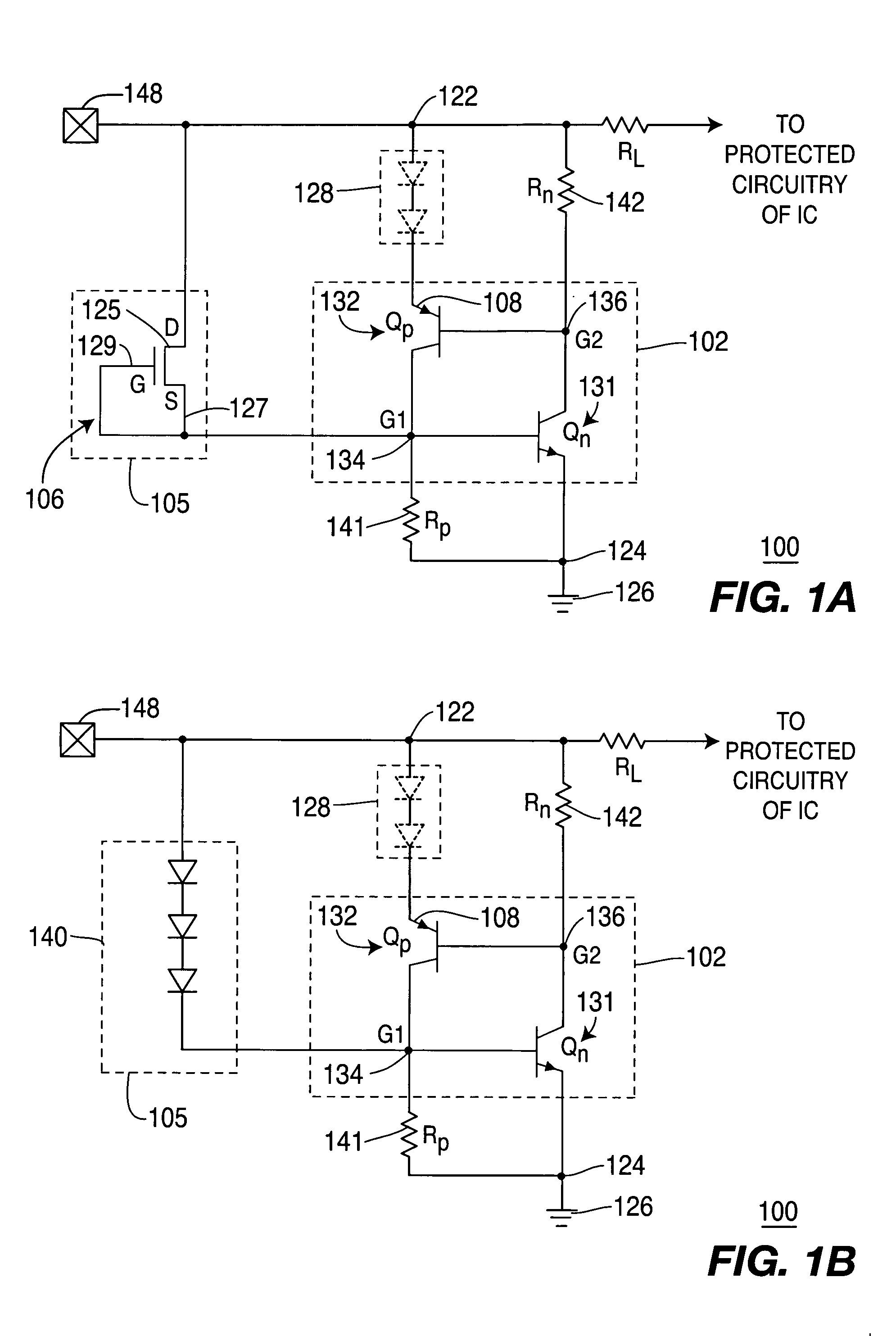

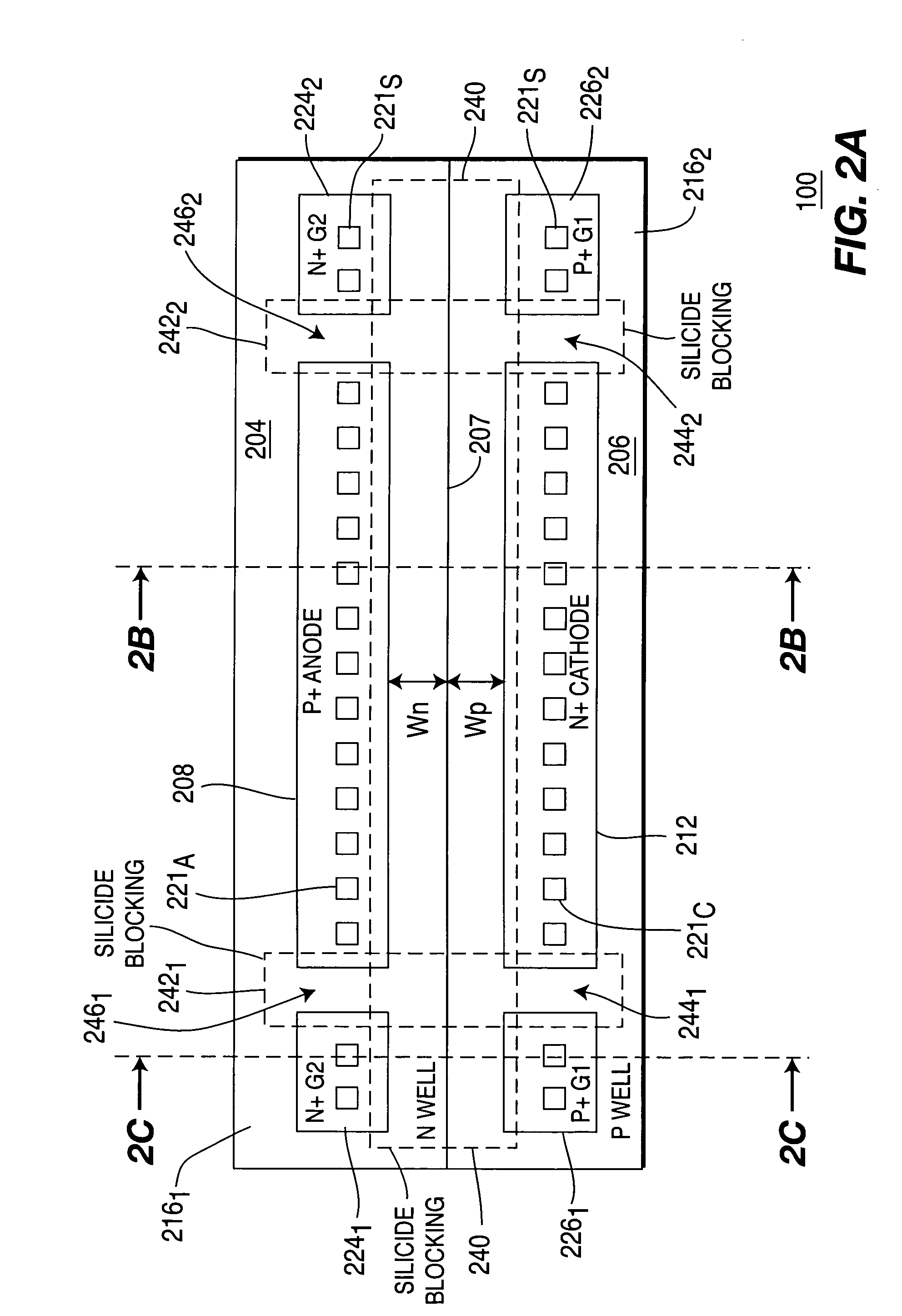

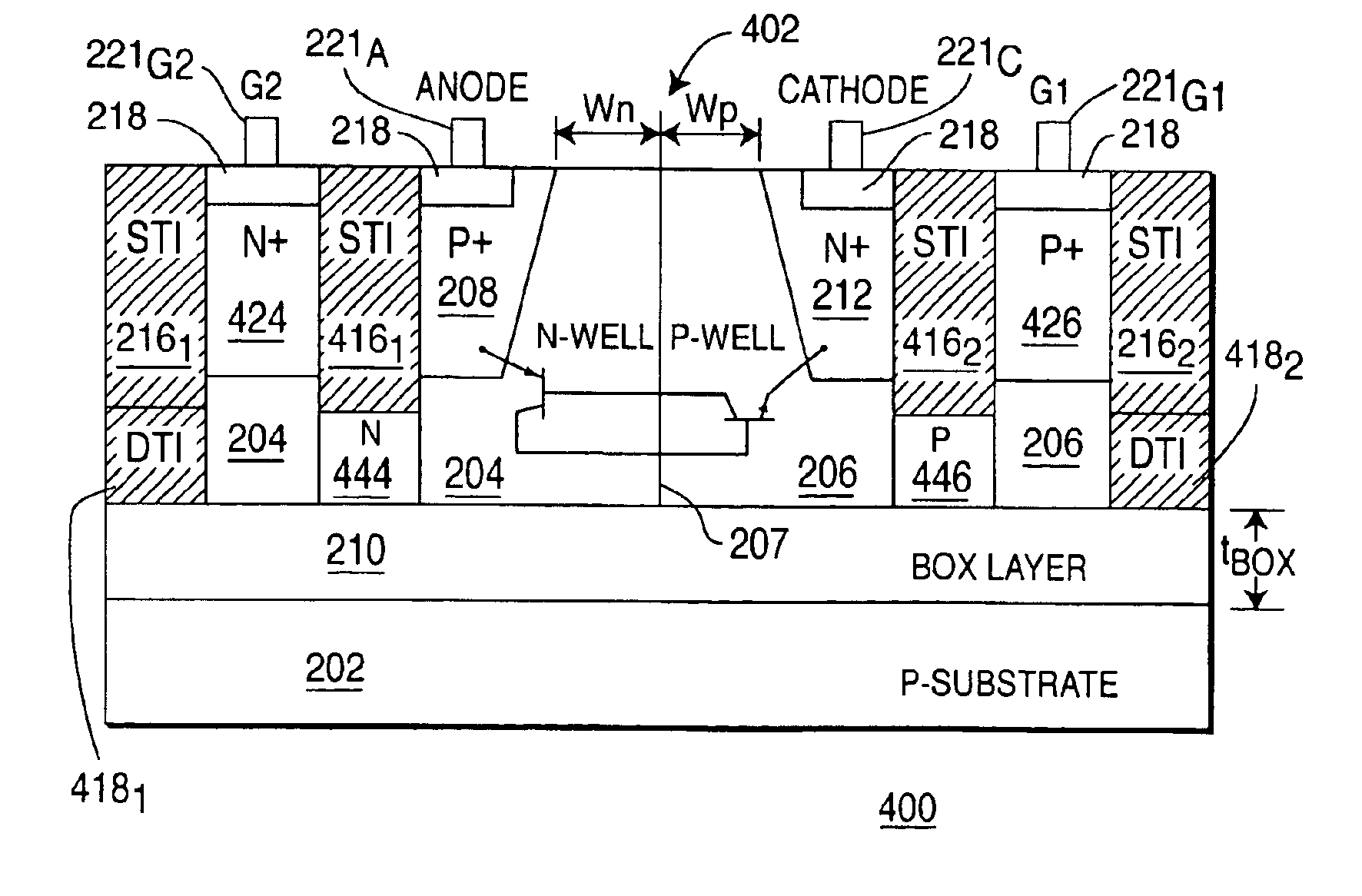

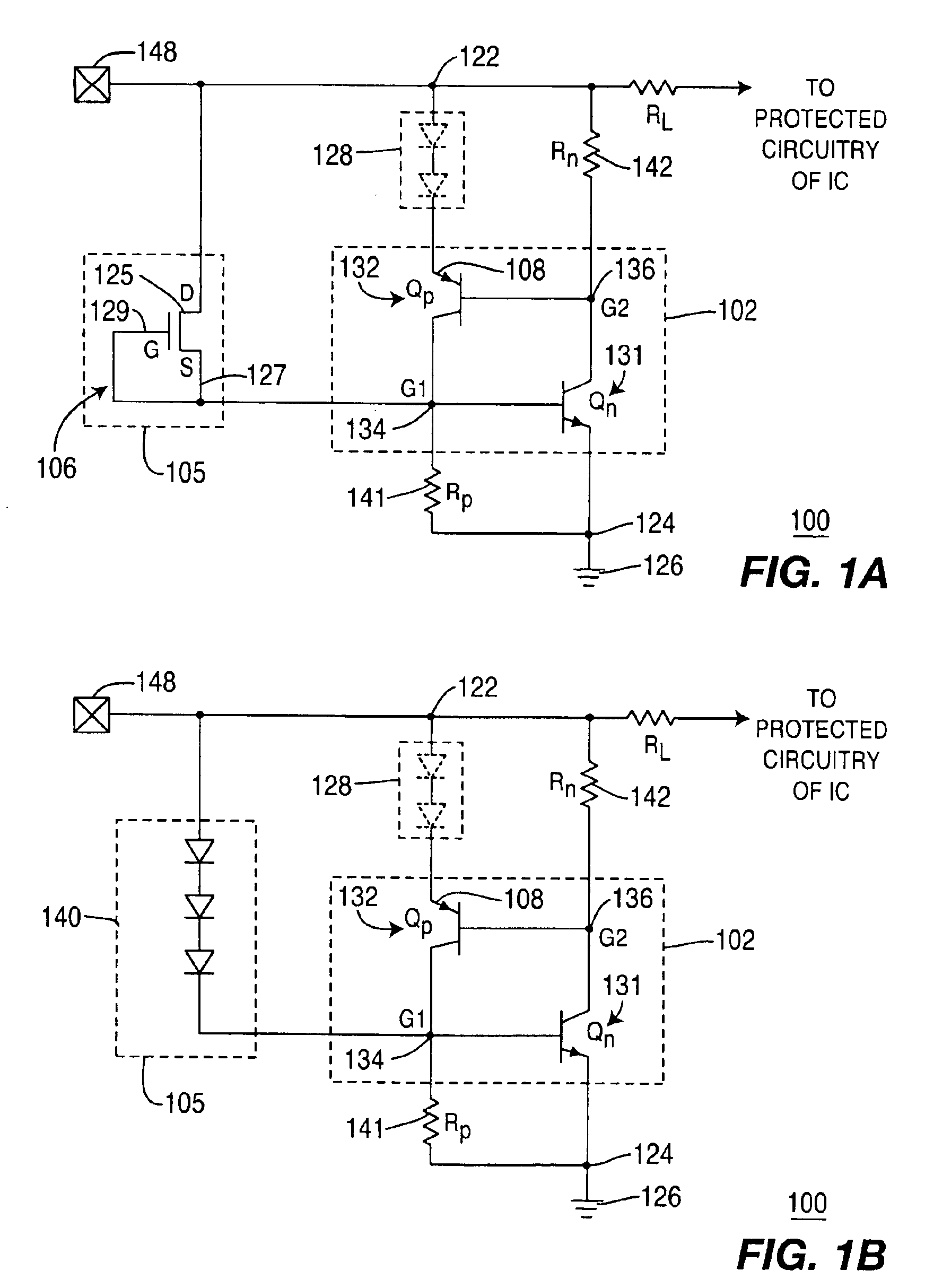

Low voltage silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection of silicon-on-insulator technologies

InactiveUS20050212051A1Low triggeringLow holding voltageTransistorThyristorSilicon-controlled rectifierLow voltage

Owner:SOFICS BVBA

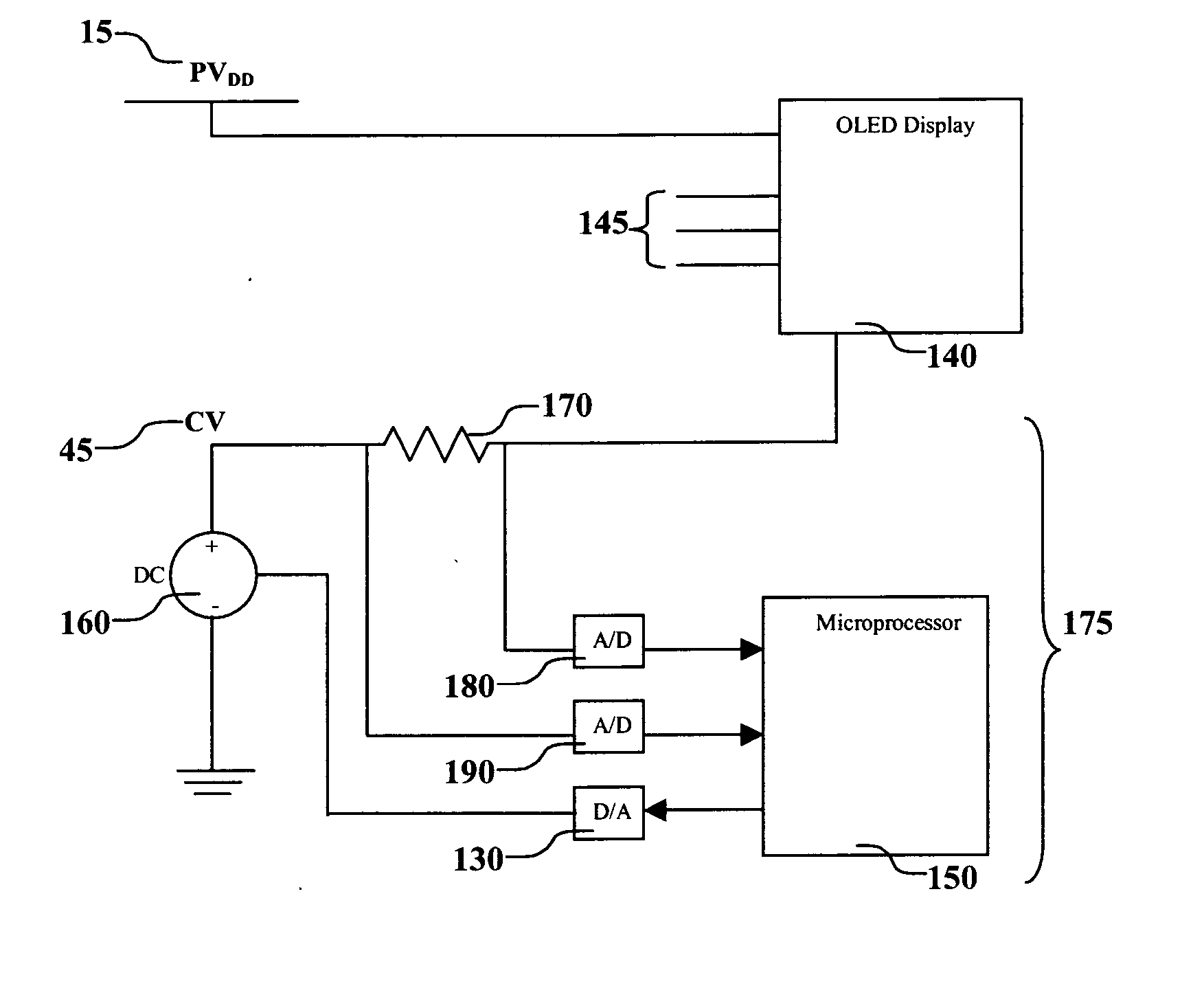

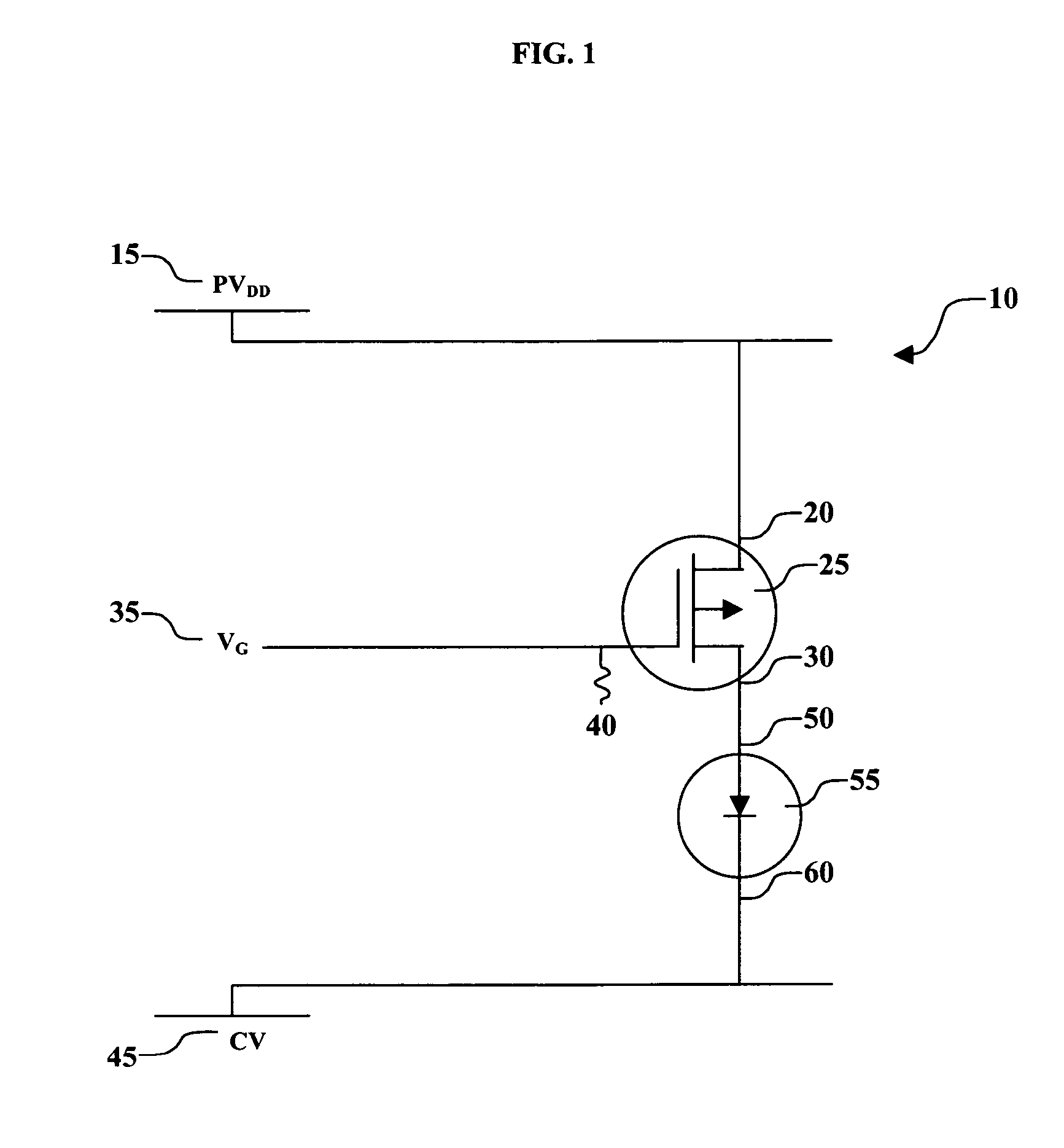

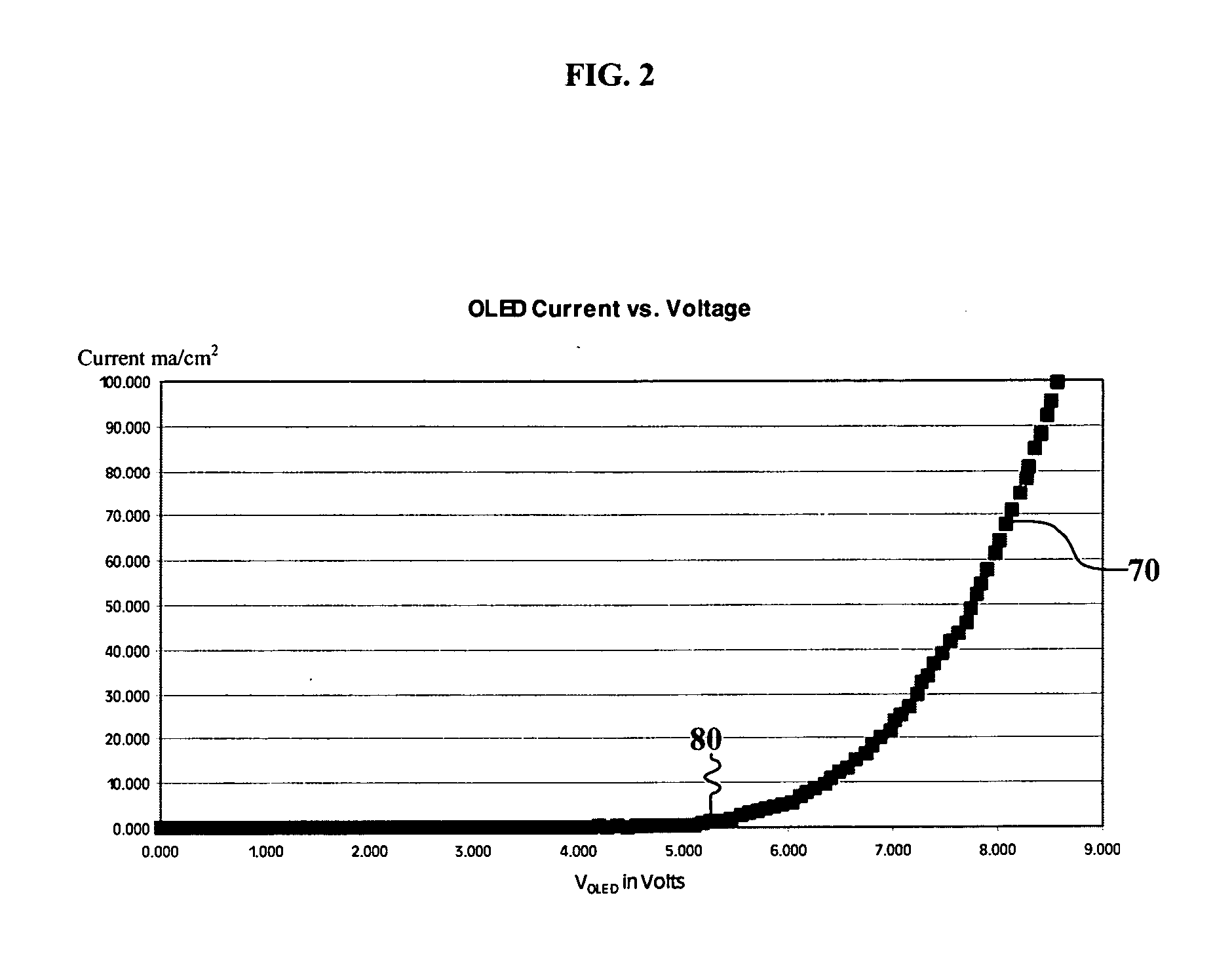

Selecting adjustment for OLED drive voltage

InactiveUS20060044227A1Reduce power consumptionExtended service lifeStatic indicating devicesDisplay deviceEngineering

A method for selecting an adjustment for at least one drive voltage used to drive an OLED display to reduce power consumption including operating the display to produce a calibration curve which depicts the drive voltage versus current or luminance, and selecting the adjustment for the drive voltage based upon the calibration curve so as to reduce the power consumed by the OLED display while maintaining desired luminance throughout the lifetime of the OLED display.

Owner:EASTMAN KODAK CO

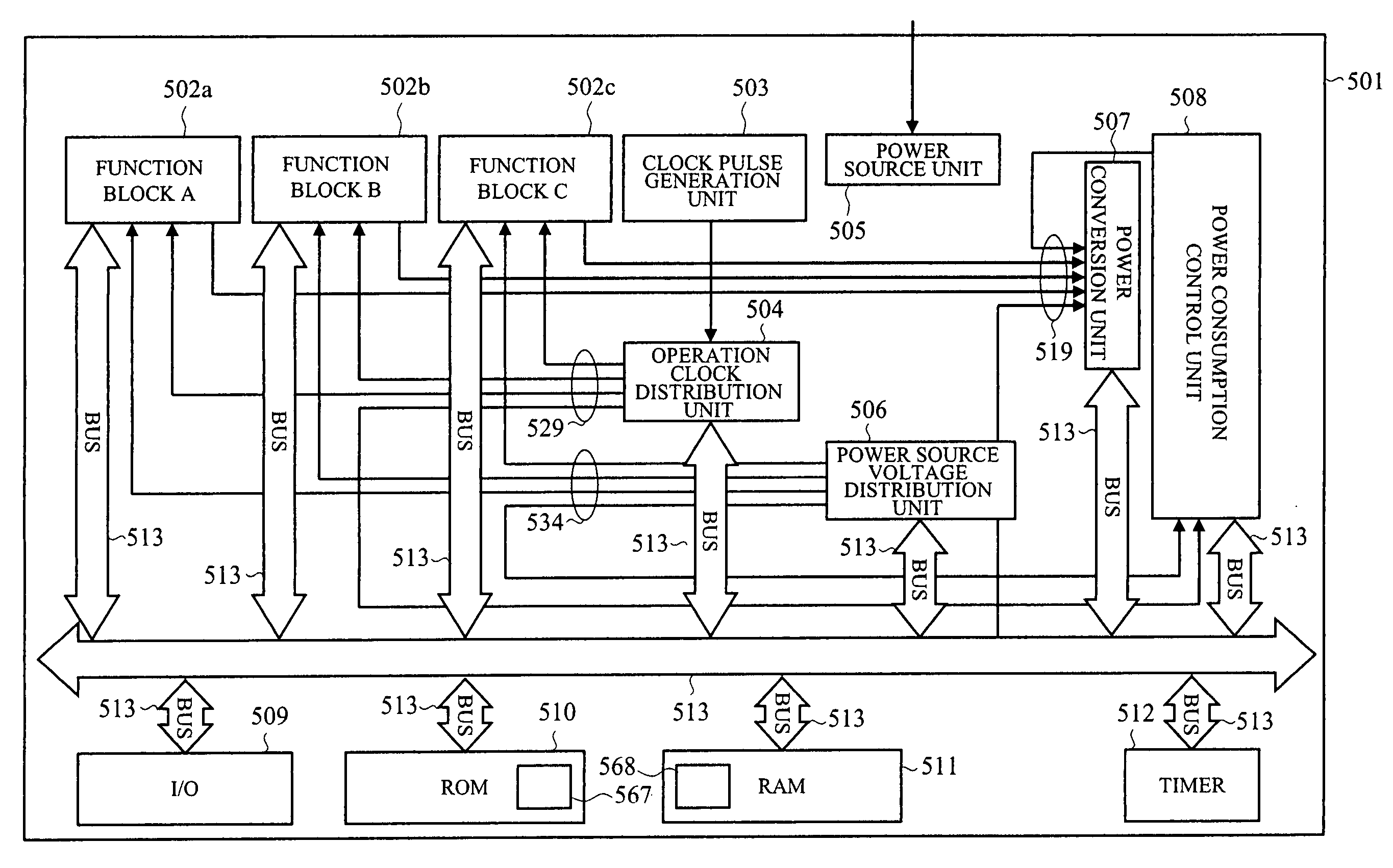

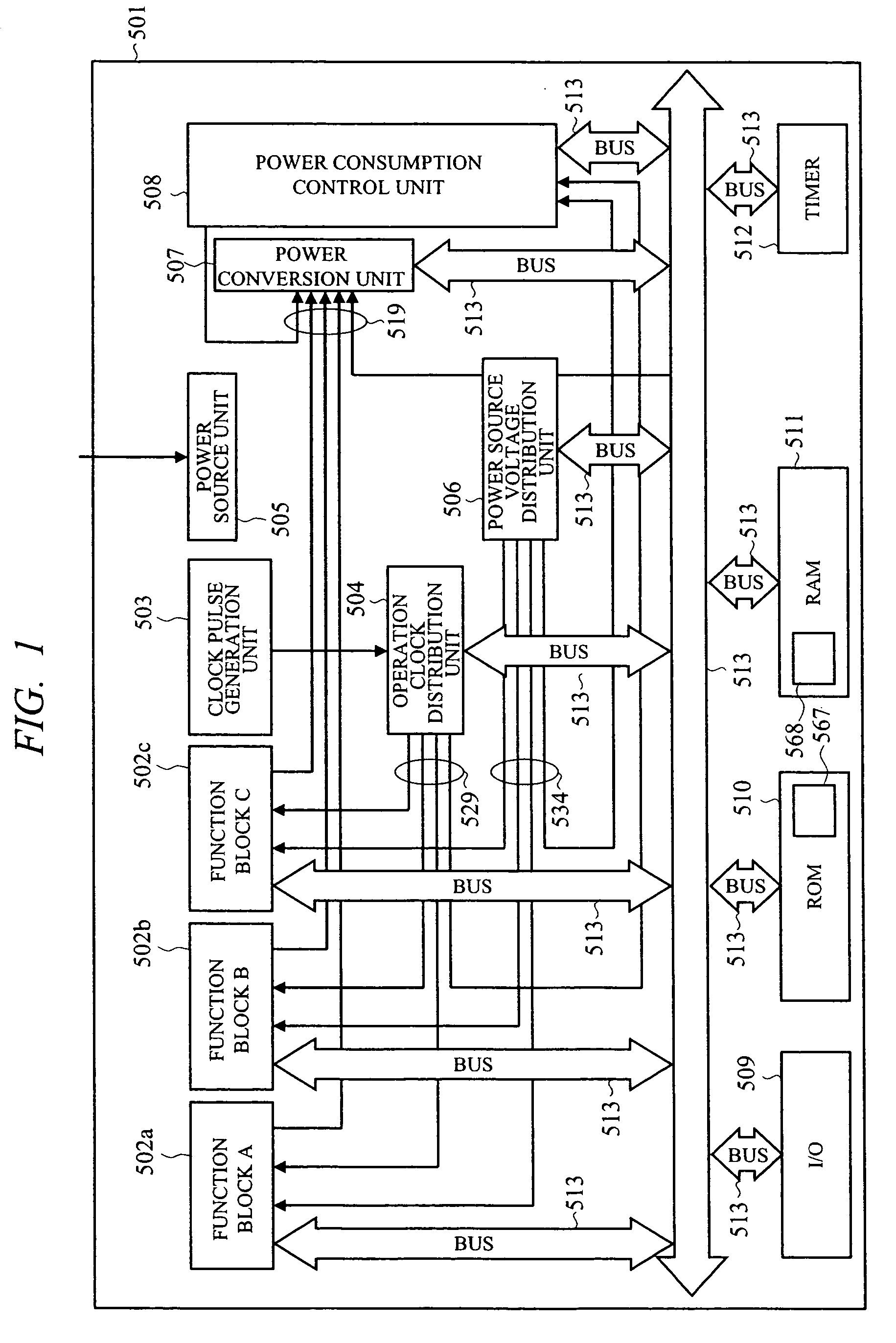

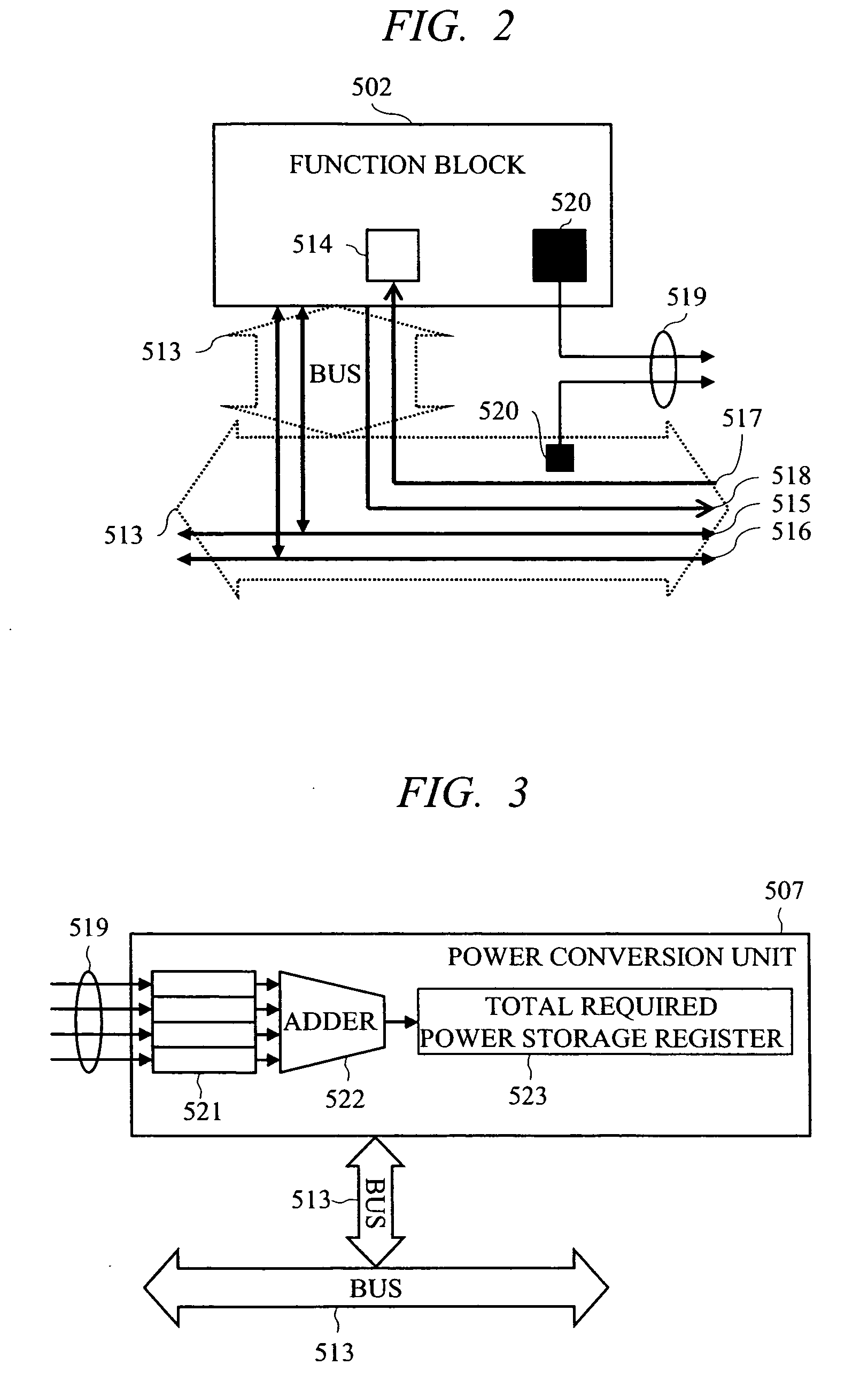

Semiconductor integrated circuit device and power consumption control device

ActiveUS20070083779A1Guaranteed uptimeReduce power consumptionEnergy efficient ICTDigital data processing detailsPower modePower budget

To perform execution scheduling of function blocks so as to control the total required power of the function blocks within a supplyable power budget value, and thereby realize stable operations at low power consumption. Function block identifiers are allotted to all the function blocks, and to a RAM area that a power consumption control device can read and write, a list to store identifiers and task priority, power mode value showing power states, and power mode time showing the holding time of power states can be linked. A single or plural link lists for controlling the schedules of tasks operating on the function blocks, a link list for controlling the function block in execution currently in high power mode, a link list for controlling the function block in stop currently in stop mode, and a link list for controlling the function block in execution currently in low power mode are allotted, and thereby the power source and the operation clock are controlled by the power consumption control device.

Owner:RENESAS ELECTRONICS CORP

Method and system for data communication in human body and sensor therefor

The present invention provides method and system for data communication in the human body and a sensor therefor. The method and system transmit information through the human body to a receiver located outside the human body using low current and voltage polarity, so that they cause no damage to the human body and achieve low power consumption and better receiving sensitivity. In addition, the sensor contains a CMOS image sensor on which all circuits are integrated without radio transmitter and antenna, so that it achieves a low-priced and small-sized capsule type endoscope.

Owner:KOREA INST OF SCI & TECH

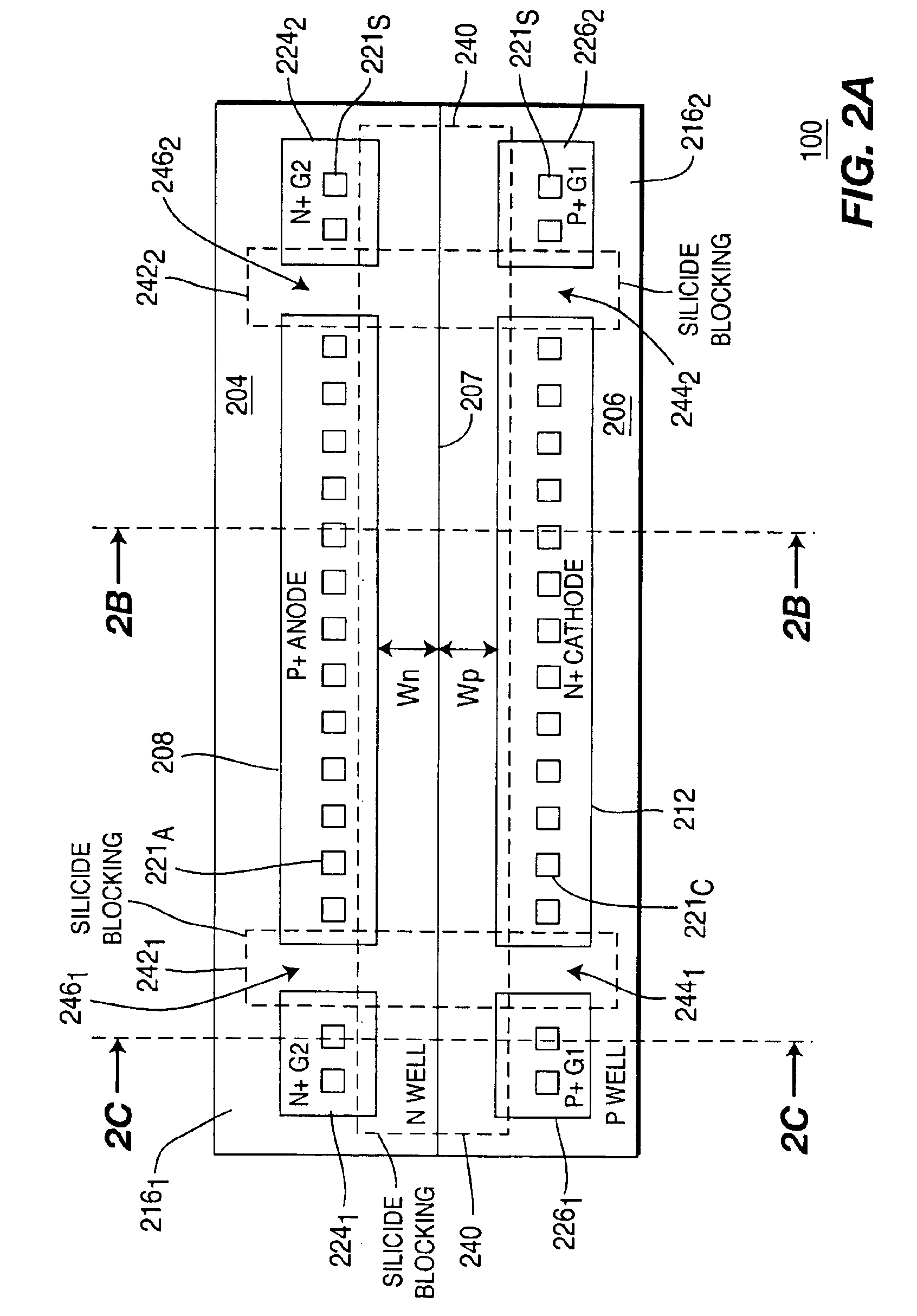

Low voltage silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection of silicon-on-insulator technologies

ActiveUS6909149B2Low triggeringLow holding voltageTransistorThyristorSilicon-controlled rectifierLow voltage

A silicon-on-insulator (SOI) electrostatic discharge (ESD) protection device that can protect very sensitive thin gate oxides by limiting the power dissipation during the ESD event, which is best achieved by reducing the voltage drop across the active (protection) device during an ESD event. In one embodiment, the invention provides very low triggering and holding voltages. Furthermore, the SOI protection device of the present invention has low impedance and low power dissipation characteristics that reduce voltage build-up, and accordingly, enable designers to fabricate more area efficient protection device

Owner:SOFICS BVBA

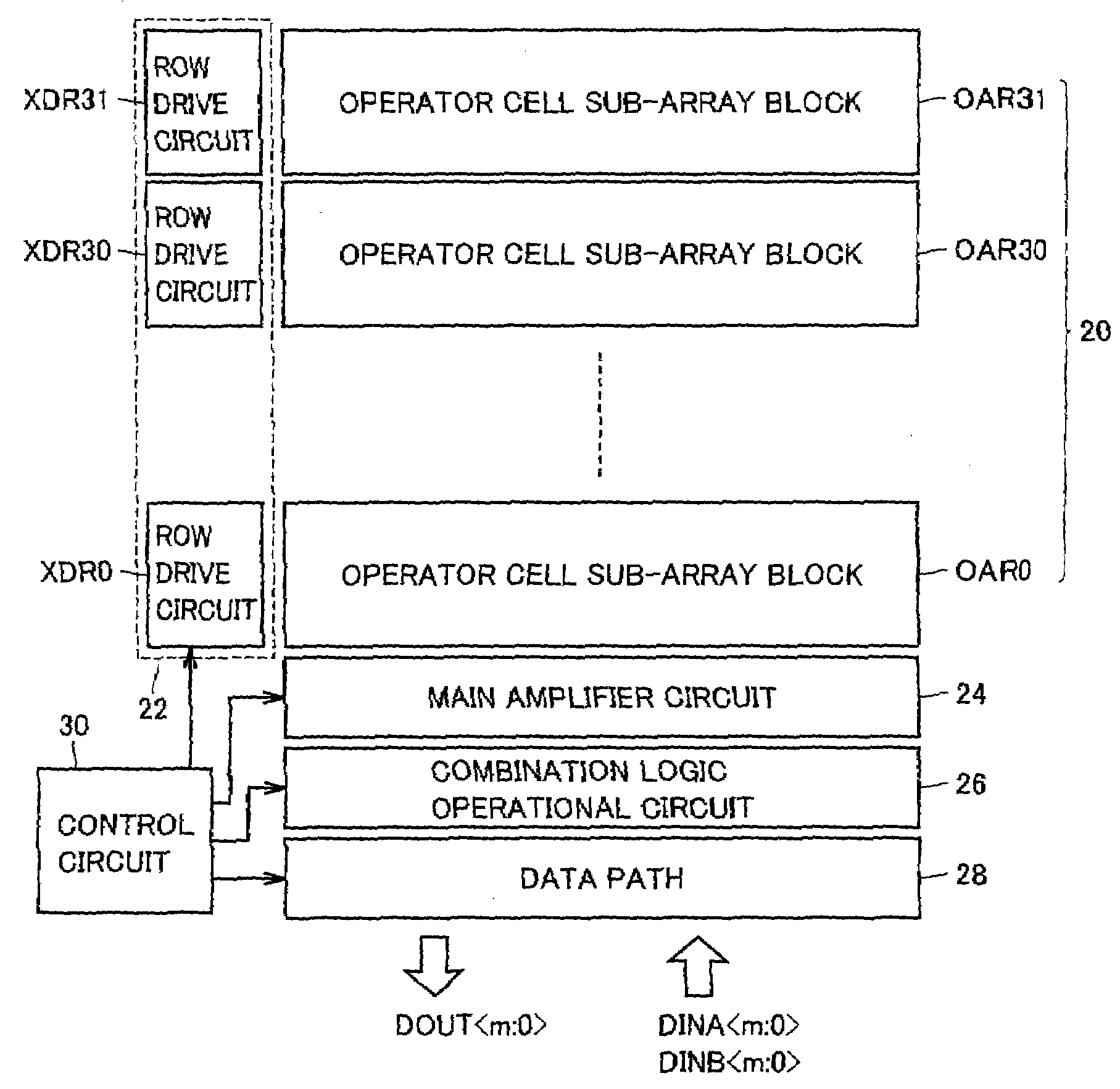

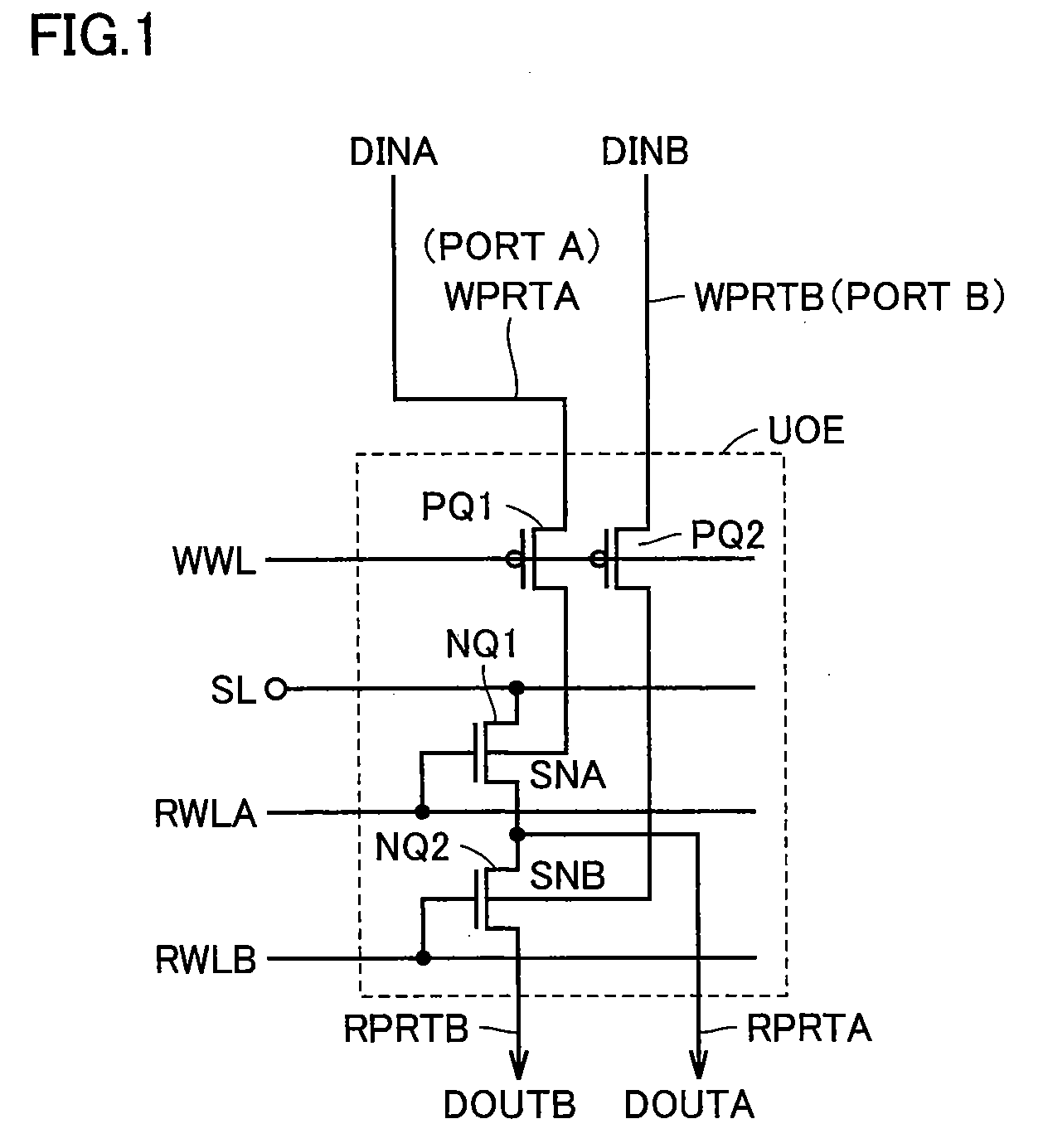

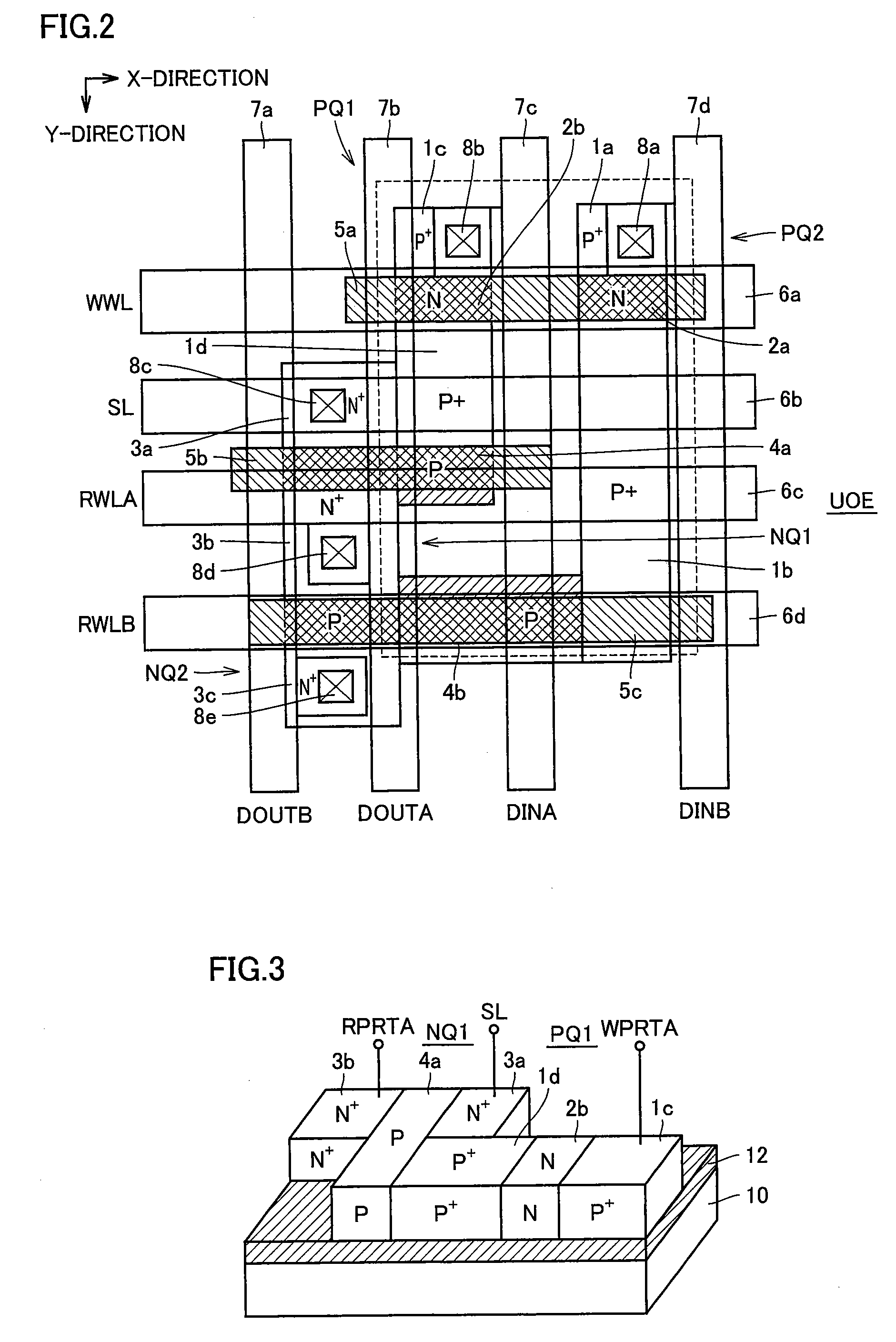

Semiconductor signal processing device

InactiveUS20090207642A1Small footprintIncrease speedSolid-state devicesDigital storageSoftware engineeringData storing

A unit operator cell includes a plurality of SOI (Silicon on Insulator) transistors, write data is stored in a body region of at least two SOI transistors, and the storage SOI transistors are connected in series with each other to a read port or each of the storage SOI transistors is singly connected to the read port. Therefore, an AND operation result or a NOT operation result of data stored in the unit operator cells can be obtained, and operation processing can be performed only by writing and reading data. A semiconductor signal processing device that can perform logic operation processing and arithmetic operation processing at high speed is implemented with low power consumption and a small occupation area.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com