Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1689 results about "Hardware structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

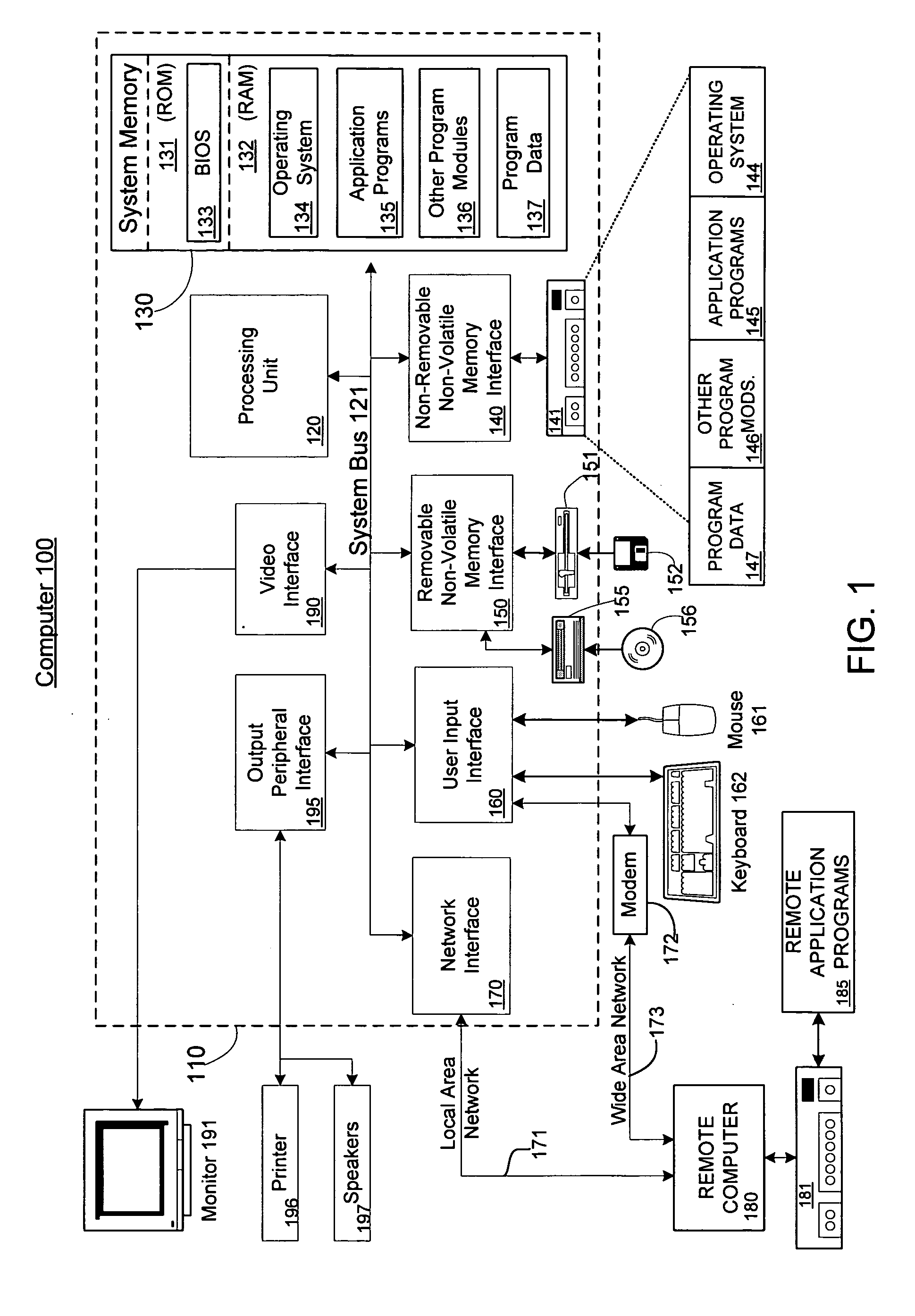

Hardware is any part of your computer that has a physical structure, such as the keyboard or mouse. It also includes all of the computer's internal parts, which you can see in the image below. Software is any set of instructions that tells the hardware what to do and how to do it.

Co-processor IP core of programmable convolutional neural network

ActiveCN106940815AReduce frequencyReduce bandwidth pressureNeural architecturesPhysical realisationHardware structureInstruction set design

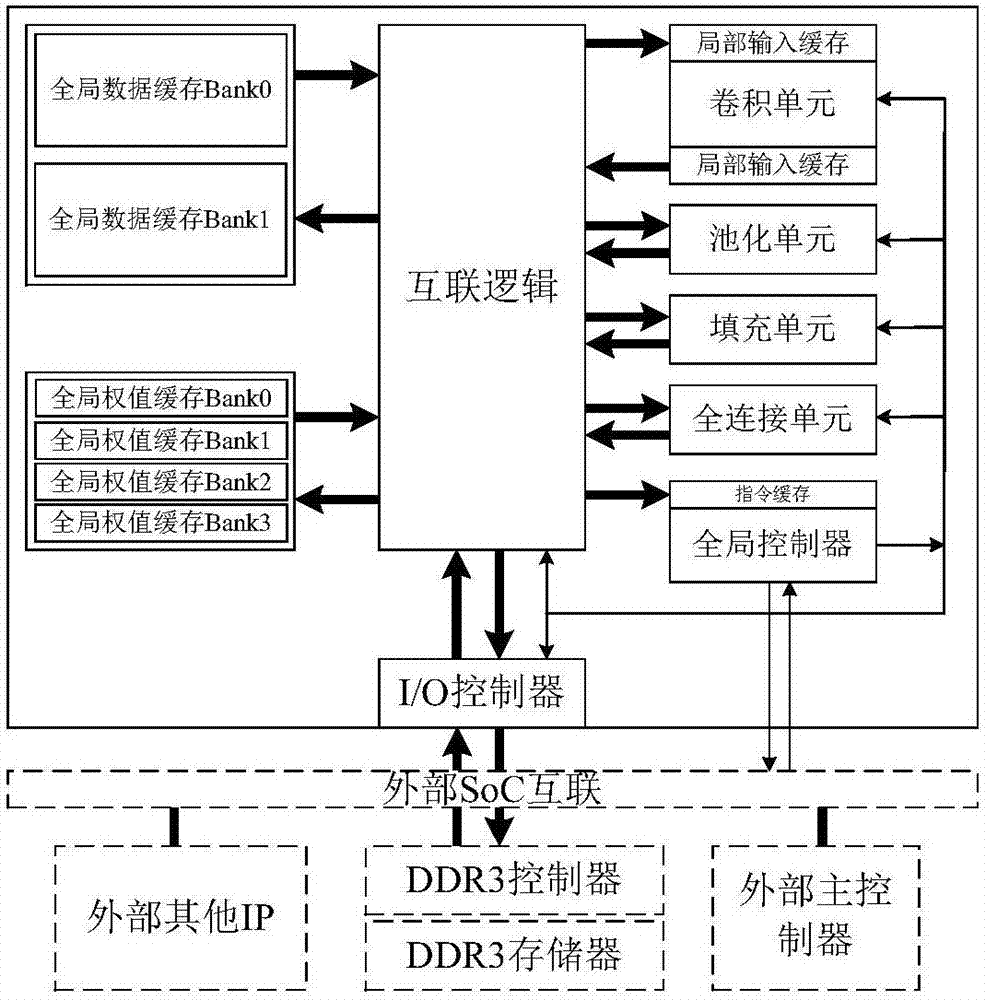

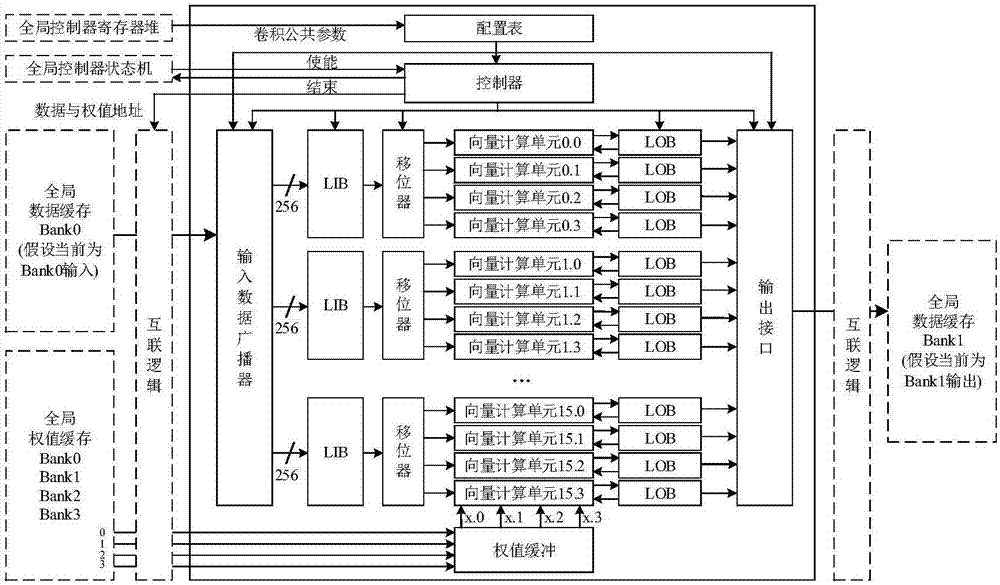

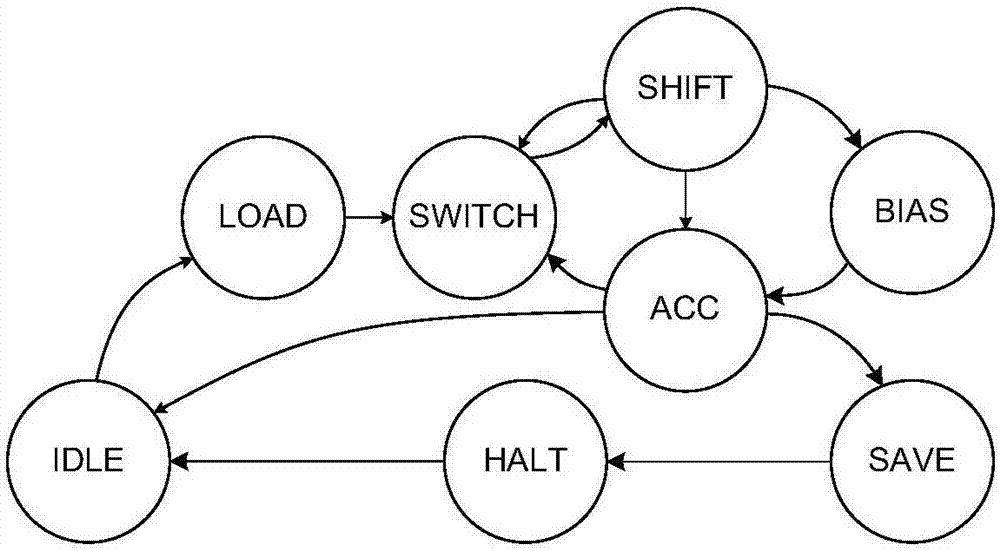

The present invention discloses a co-processor IP core of a programmable convolutional neural network. The invention aims to realize the arithmetic acceleration of the convolutional neural network on a digital chip (FPGA or ASIC). The co-processor IP core specifically comprises a global controller, an I / O controller, a multi-level cache system, a convolution unit, a pooling unit, a filling unit, a full-connection unit, an internal interconnection logical unit, and an instruction set designed for the co-processor IP. The proposed hardware structure supports the complete flows of convolutional neural networks diversified in scale. The hardware-level parallelism is fully utilized and the multi-level cache system is designed. As a result, the characteristics of high performance, low power consumption and the like are realized. The operation flow is controlled through instructions, so that the programmability and the configurability are realized. The co-processor IP core can be easily applied to different application scenes.

Owner:XI AN JIAOTONG UNIV

Display panel, display device and manufacturing method

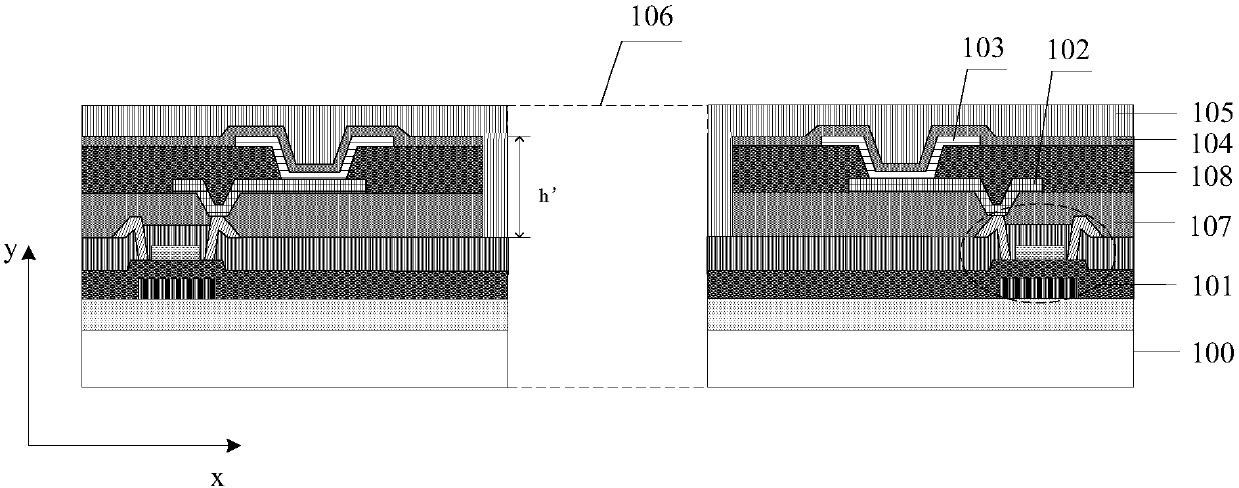

PendingCN107658332AIncrease the effective areaAchieve preparationFinal product manufactureSolid-state devicesHardware structureDisplay device

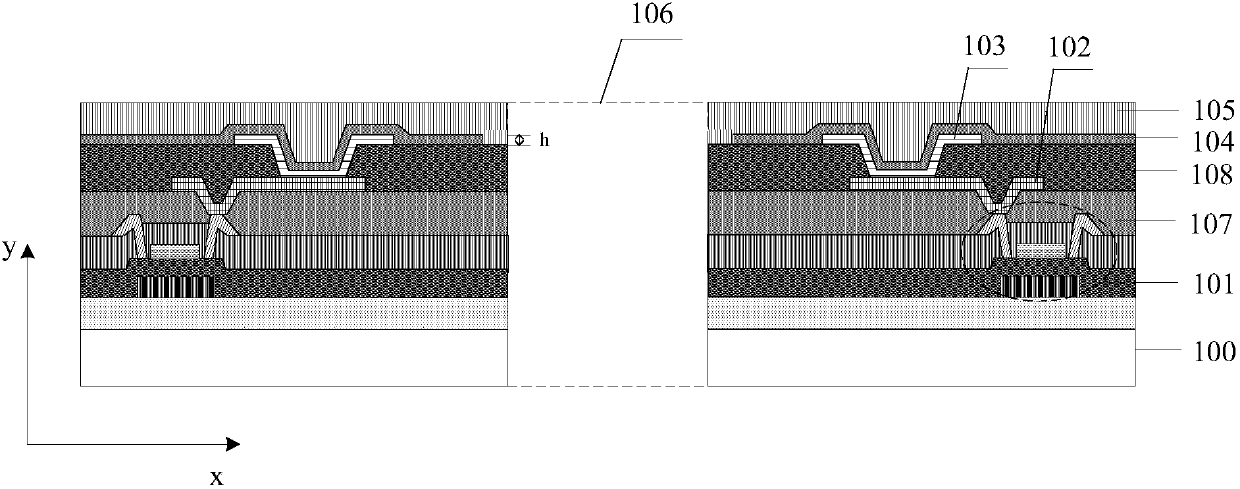

The invention relates to a display panel, a display device and a manufacturing method. The display panel, the display device and the manufacturing method are used for setting problems of area restriction of an effective displaying area and incapability of preparing a full screen caused by a manner of arranging a mounting hole in a non-displaying area of a display panel. The display panel comprisesa substrate, a TFT structure, an anode layer, a light emitting layer, a cathode layer and a packaging layer, wherein the TFT structure, the anode layer, the light emitting layer, the cathode layer and the packaging layer are successively arranged on the substrate. The displaying area is provided with the mounting hole for mounting a hardware structure. The mounting hole penetrates the structure and each film layer on the display panel. The edge of the mounting hole is provided with a packaging layer material with a preset thickness. The packaging layer material with the preset thickness at least covers the light emitting layer and the cathode layer which is adjacent with the edge of the mounting hole. The mounting hole is arranged in the displaying area, thereby realizing manufacturing ofthe full screen. Furthermore the packaging layer material with the preset thickness can perform a protecting function on the light emitting layer and the cathode layer, thereby preventing oxidation by external water and oxygen, and improving reliability at the position of the mounting hole.

Owner:BOE TECH GRP CO LTD

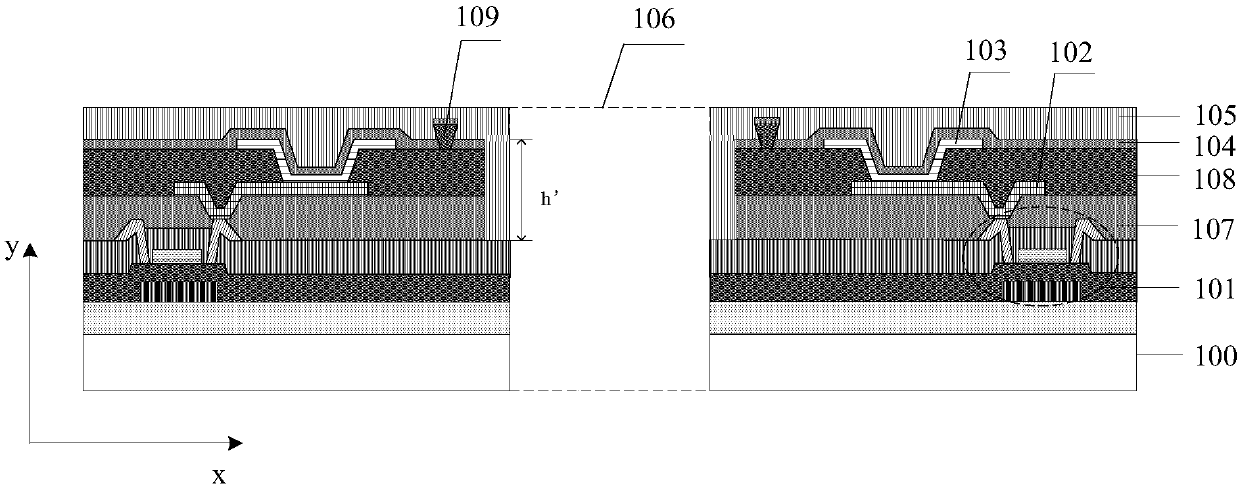

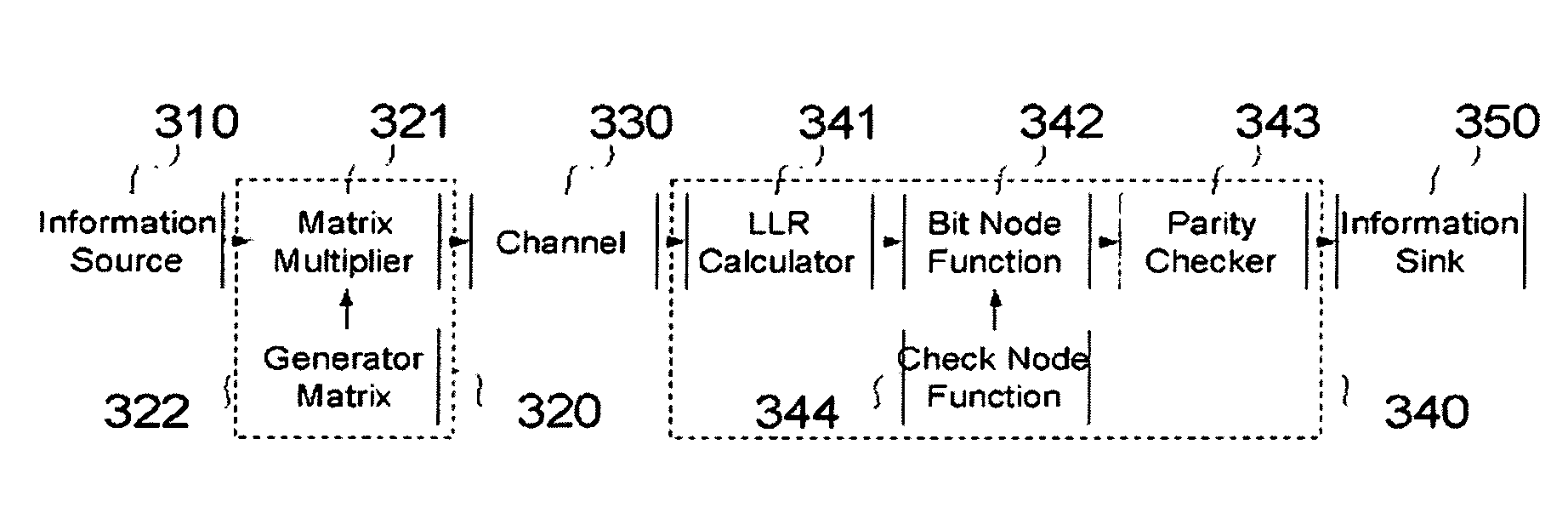

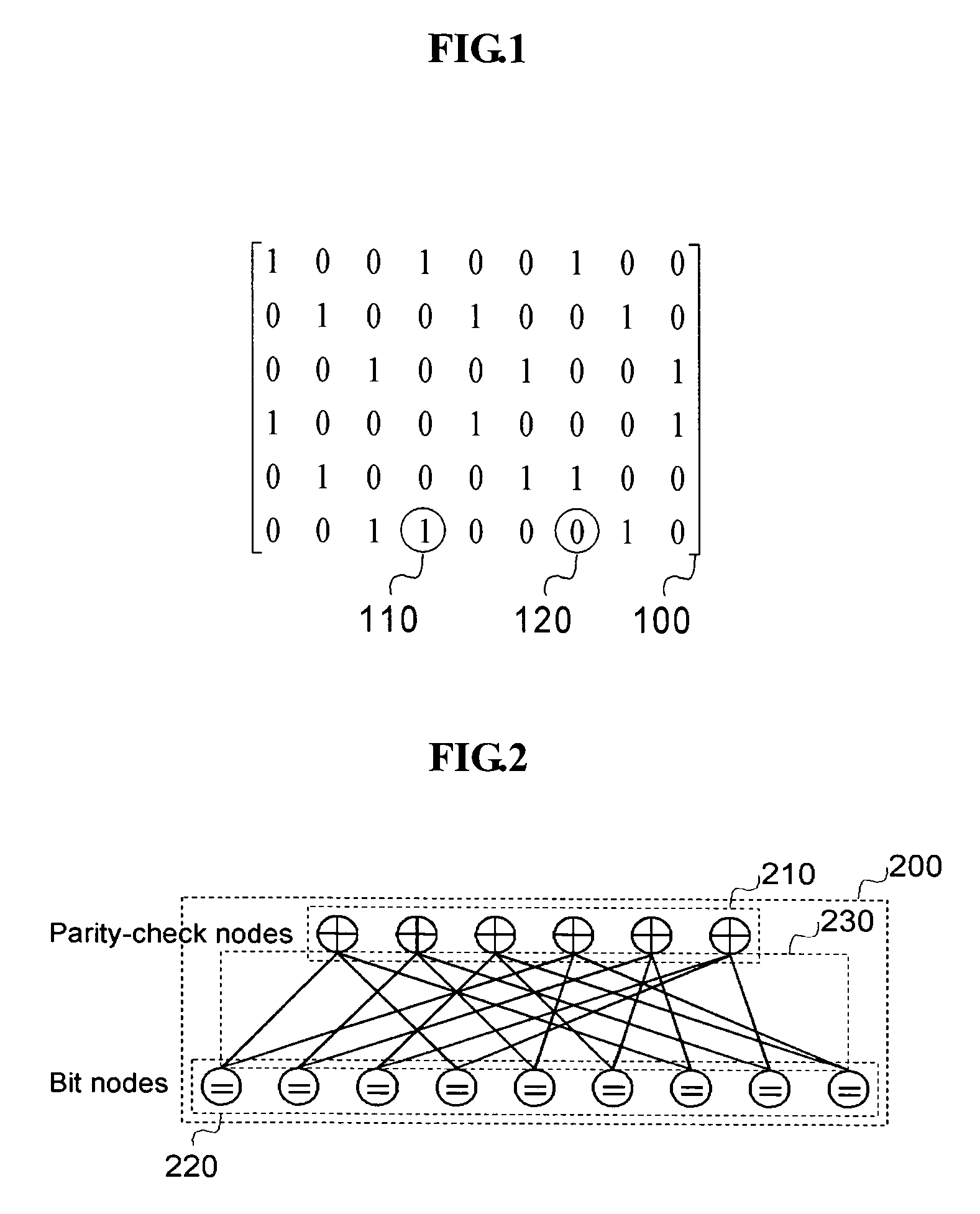

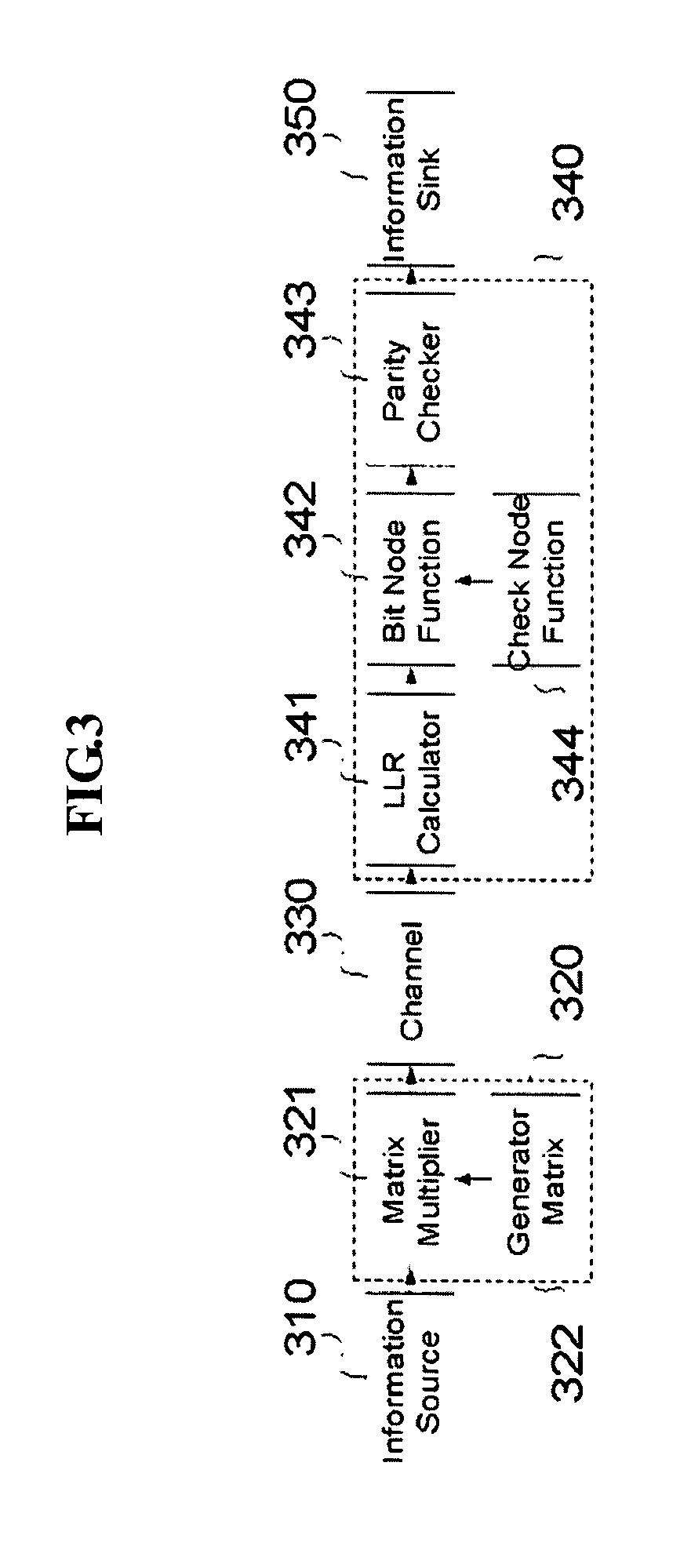

Simplified message-passing decoder for low-density parity-check codes

InactiveUS7178081B2Reduce approximation errorReduce errorsError preventionError detection/correctionHardware structureComputer hardware

Disclosed is an implementation method for simplifying a complicated message-passing function in a decoder for decoding block codes encoded with low-density parity-check (LDPC) codes and only using a summator and a shifter to simplify the hardware structure of the decoder, in which method the input interval of the message-passing function for binary representation of a message input is divided and the respective divided intervals are linearized to allow the calculation of the output of the message-passing function without using a memory. Based on the fact that the message-passing function is similar in structure to an exponential function, the linearized intervals are set to make the maximum value expressible in each digit of the binary representation as the boundary of the intervals.

Owner:ELECTRONICS & TELECOMM RES INST

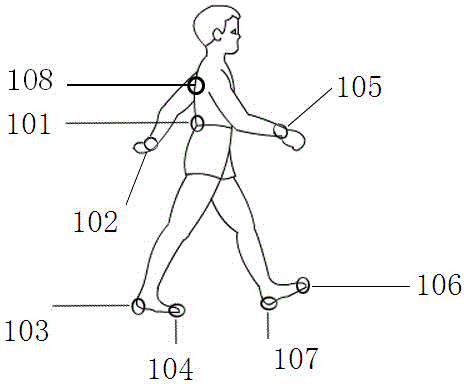

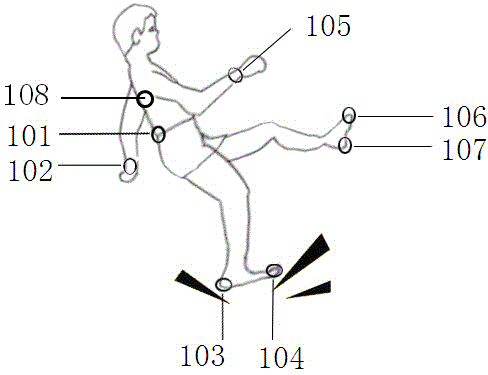

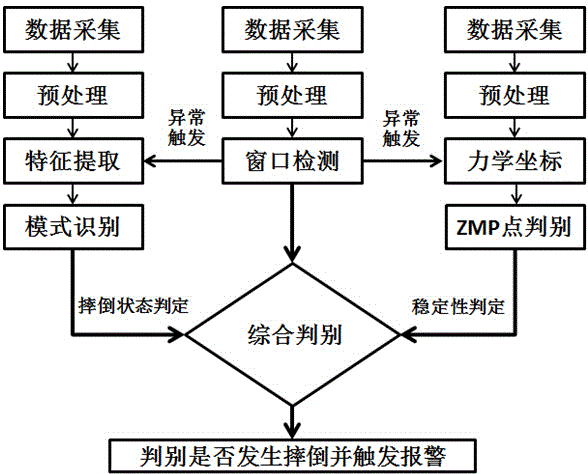

Wearing type dynamic real-time fall detection method and device

ActiveCN103976739AAchieve protectionHigh precisionCharacter and pattern recognitionDiagnostic recording/measuringHuman bodyHardware structure

The invention discloses a wearing type dynamic real-time fall detection method and device. The wearing type detection device comprises a specific hardware structure consisting of a foot part, a waist part, a wrist part and a back part. According to the dynamic real-time fall detection method, real-time judgment of the fall of human body in any state can be finished. The core algorithm of the detection device comprises a threshold opening logic structure caused by sudden change of gait acceleration, a human body posture dynamic stability judgment algorithm based on zero moment point (ZMP), and a fall mode identification algorithm based on a human body motion database. A complete dynamic real-time detection system is constructed, and the aims of wide application field, low dependence on the application environment and real-time detection are fulfilled. Moreover, the detection method and the detection device are high in accuracy, and have the advantages of low system cost, small system size and good convenience in wearing.

Owner:BEWIS TECH

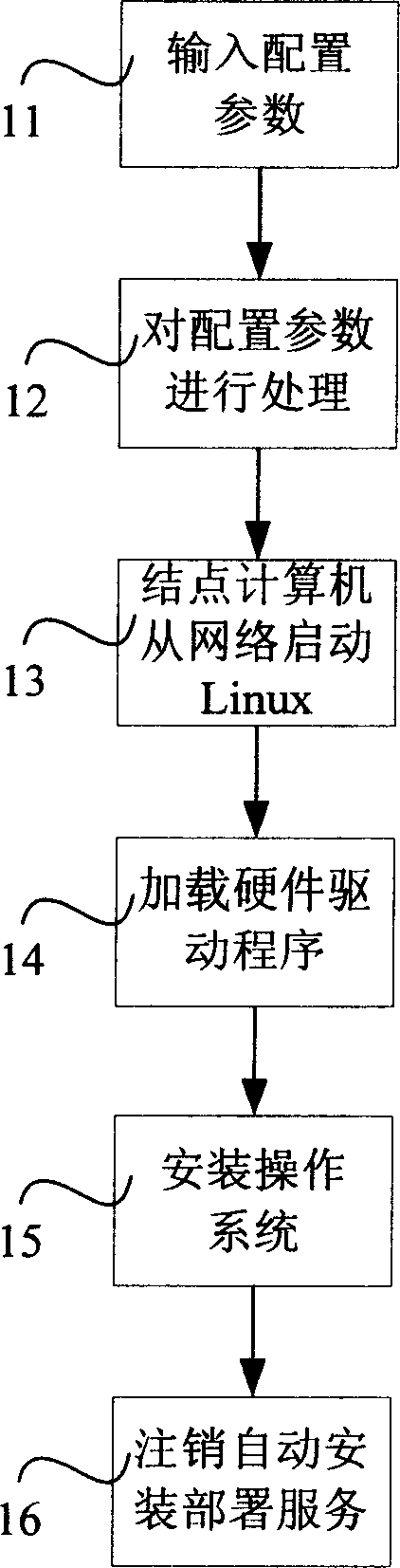

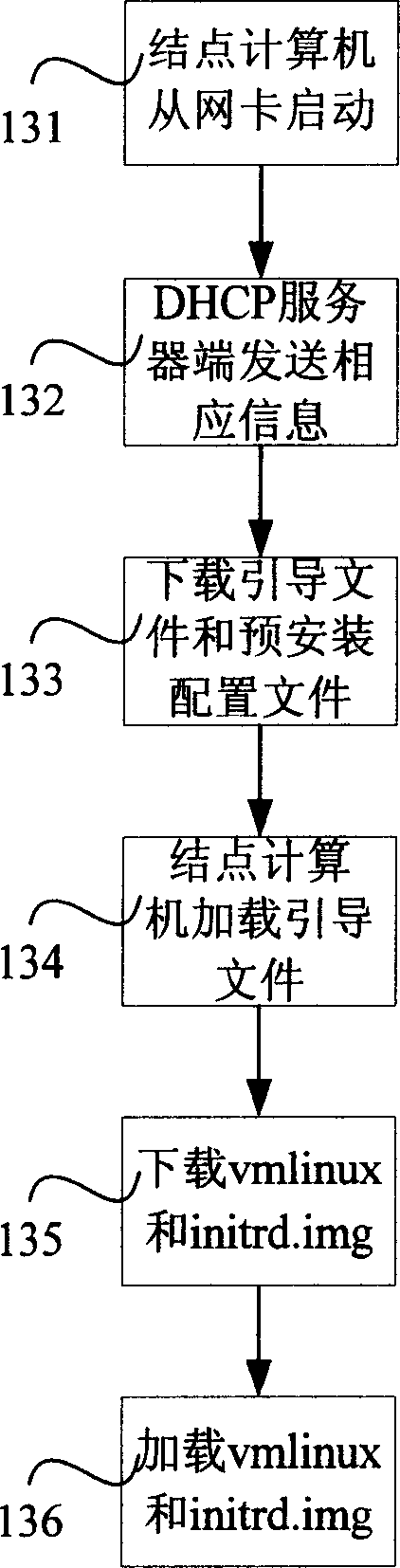

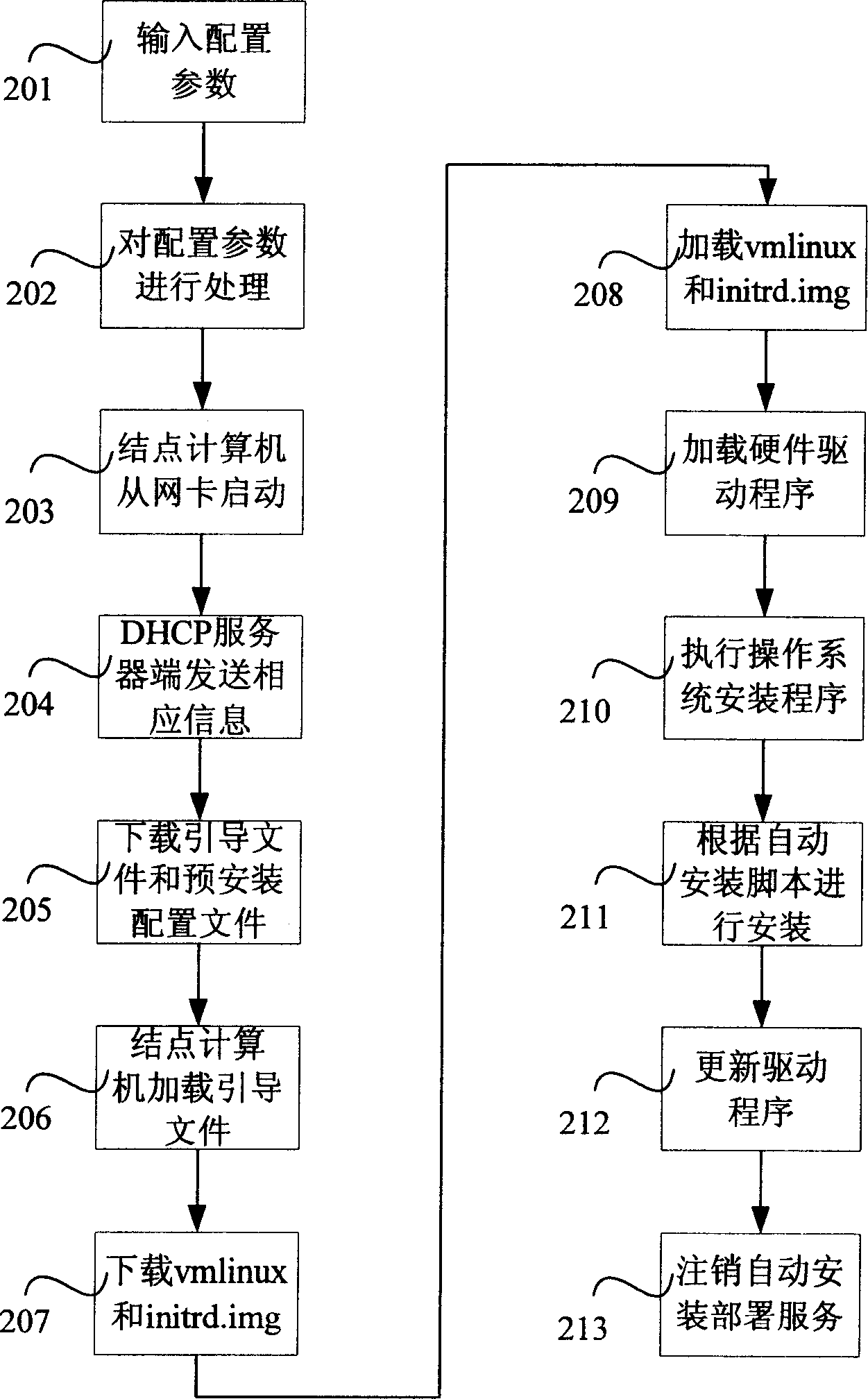

Method for automatic deploying operate system

ActiveCN1916846AQuick installationEasy and fast initializationProgram loading/initiatingHardware structureOperational system

A method for automatically arranging operation system includes using arrangement service end of server to process parameters of operation system and erection to be erected on node computer, downloading lead program and preerection file from network card by node computer and starting up preerection environmental program from network by said lead program, using said environmental program to load driving program of hardware, erecting operation system and erection driving program on node computer by said environmental program, finalizing erection of operation system and canceling automatic erection service.

Owner:LENOVO (BEIJING) LTD

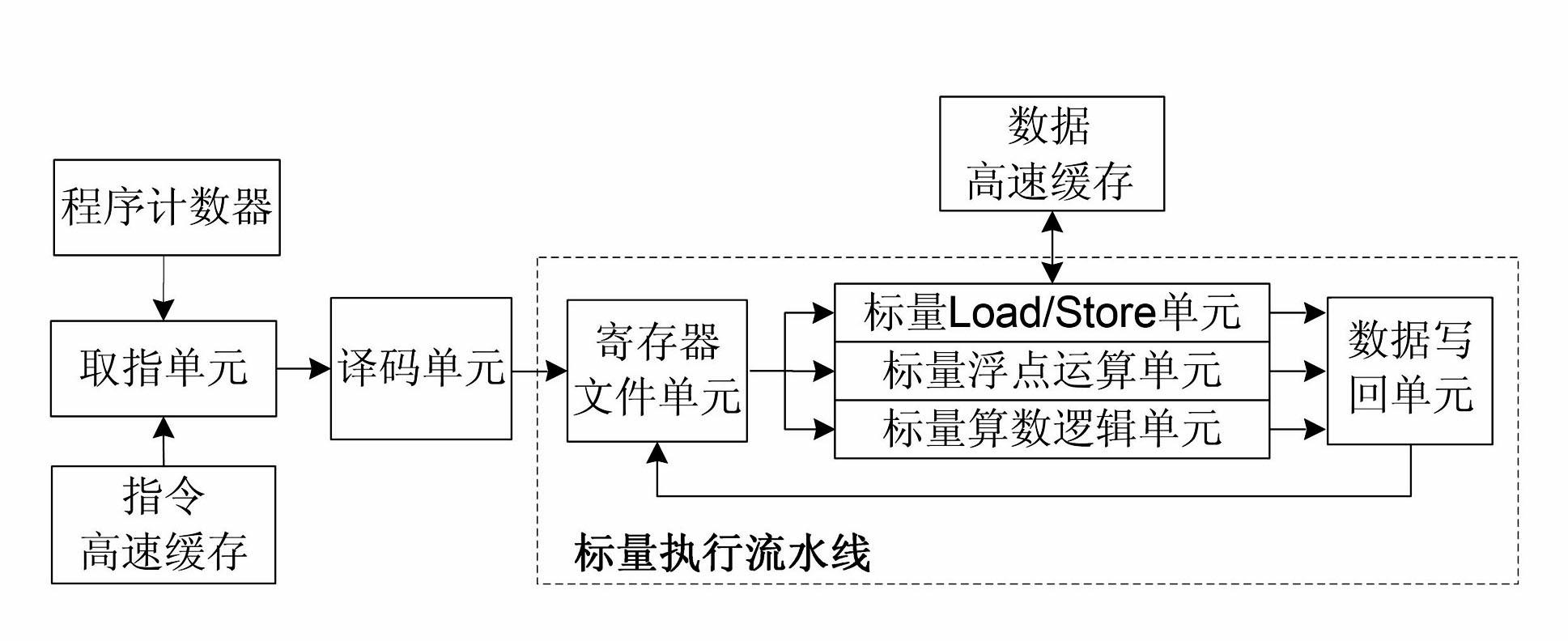

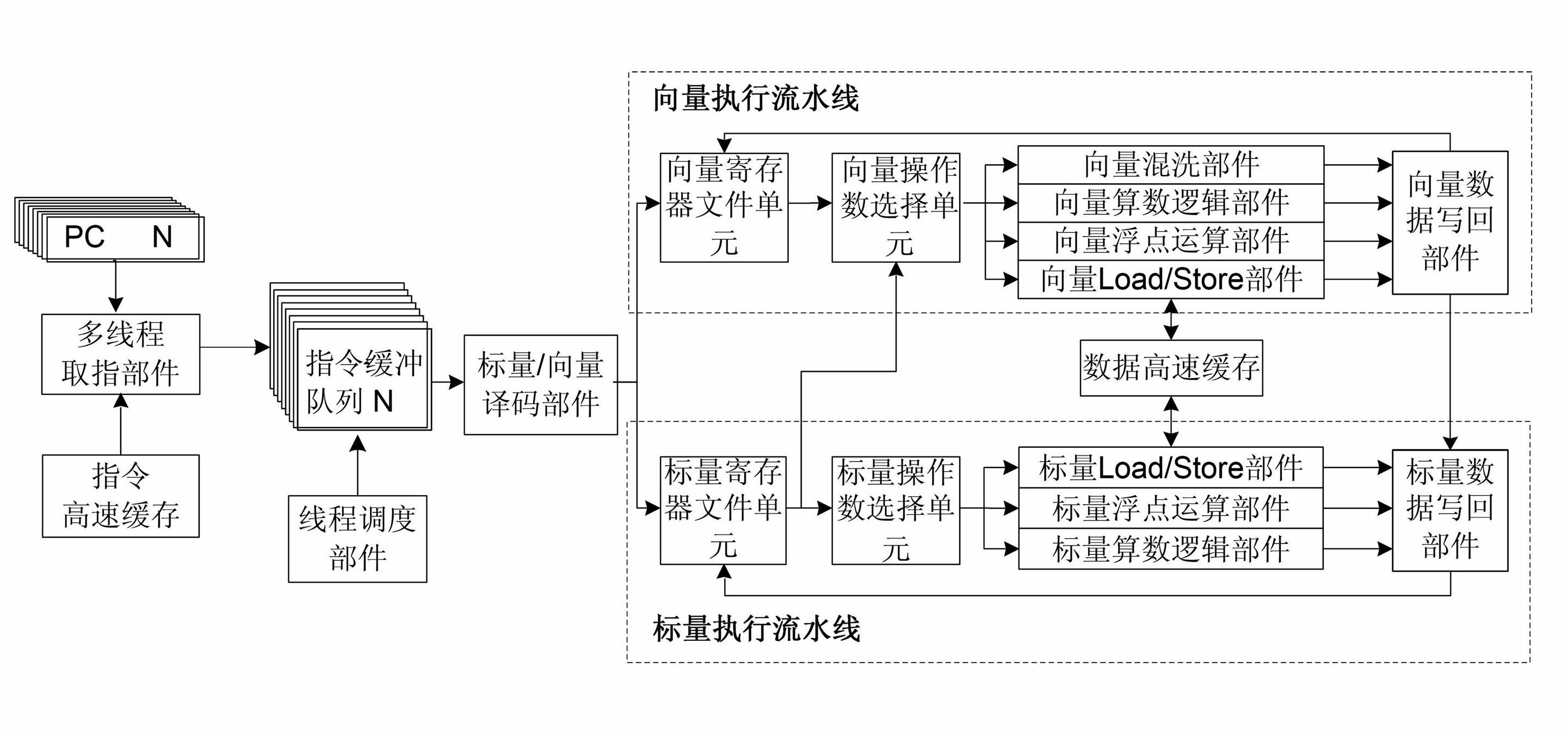

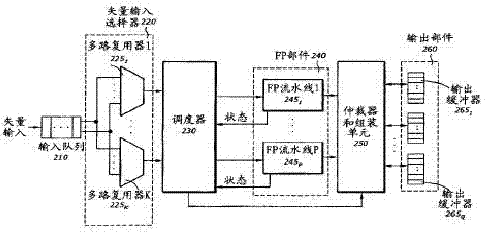

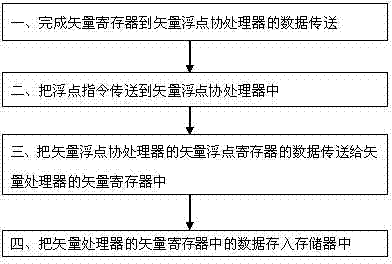

Vector crossing multithread processing method and vector crossing multithread microprocessor

InactiveCN102156637AImprove peak performanceGive full play to computing powerMultiprogramming arrangementsConcurrent instruction executionHardware structureThread scheduling

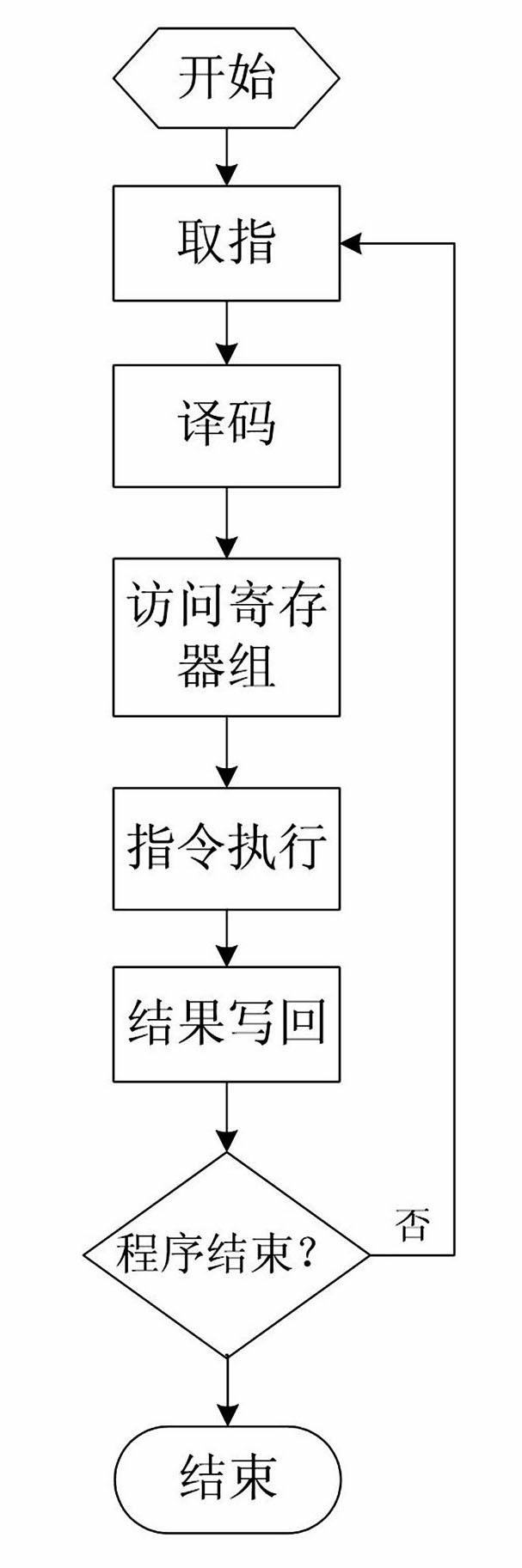

The invention discloses a vector crossing multithread processing method and a vector crossing multithread microprocessor. The processing method comprises the following steps: using a multithread instruction-acquiring part to choose a vector thread from N vector threads for reading an instruction and storing the read instruction to a corresponding instruction buffer array of the vector thread; using a thread scheduling part to choose an instruction buffer array from N instruction buffer arrays and taking out an instruction from the instruction buffer array for the purpose of decoding; and sending a decoded instruction to a vector executing streamline or scalar executing streamline so as to execute. The method can be realized by using hardware structure by the vector crossing multithread microprocessor. The method and the microprocessor provided by the invention have the advantages that the vector processing technique and multithread technique are combined, the hardware structure is simple, the operation capability is strong, the compatibility and expansibility are excellent, and the like.

Owner:NAT UNIV OF DEFENSE TECH

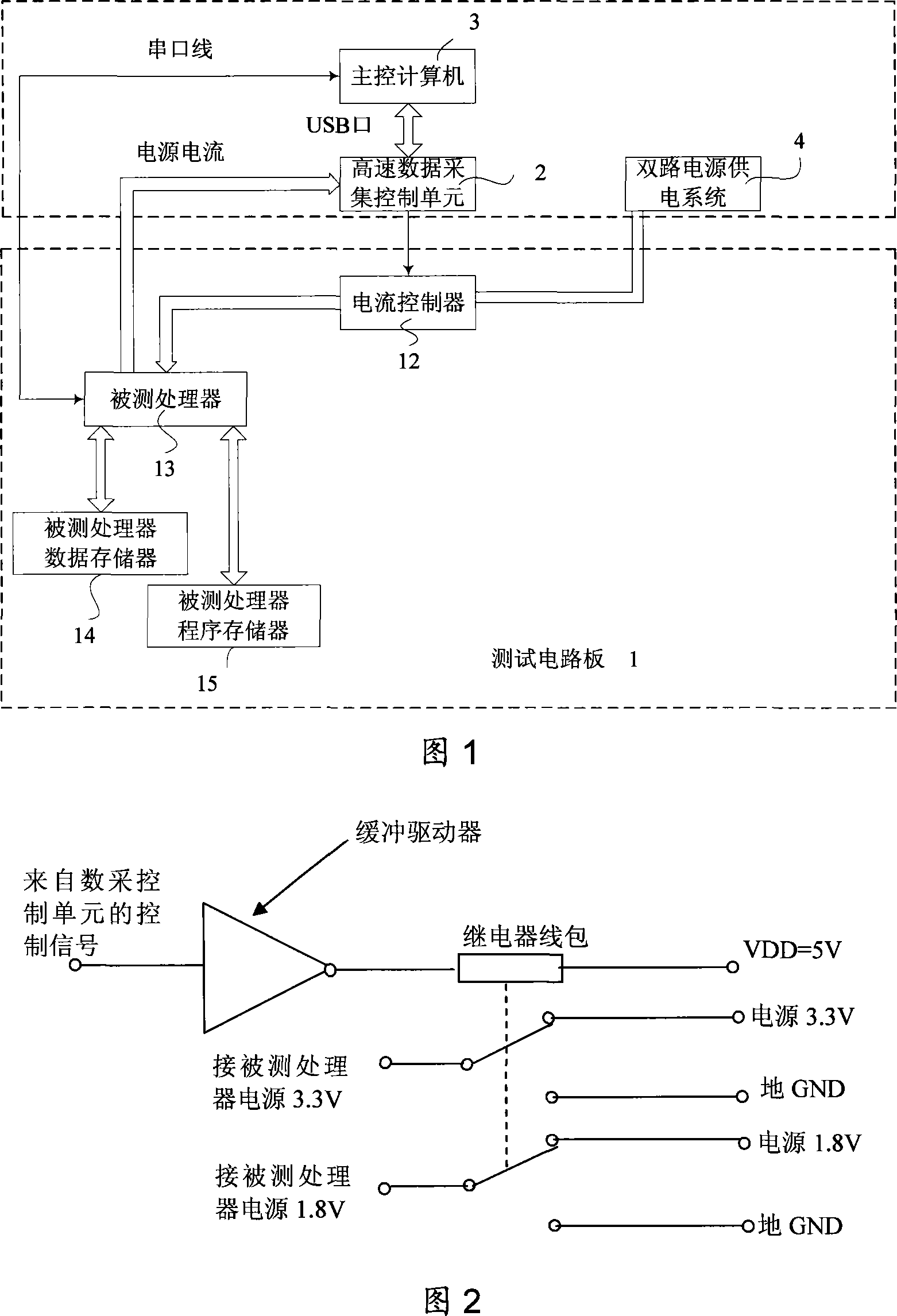

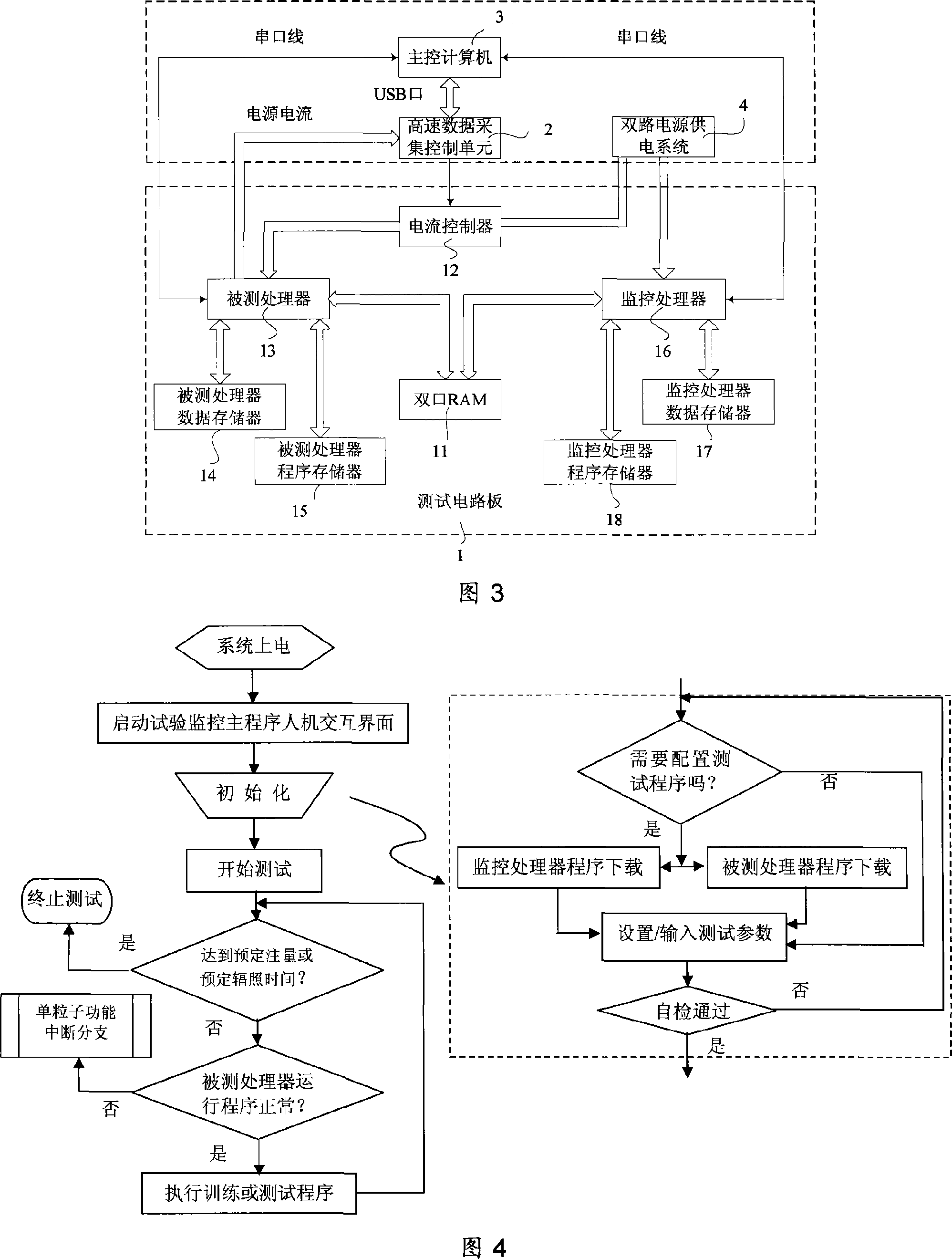

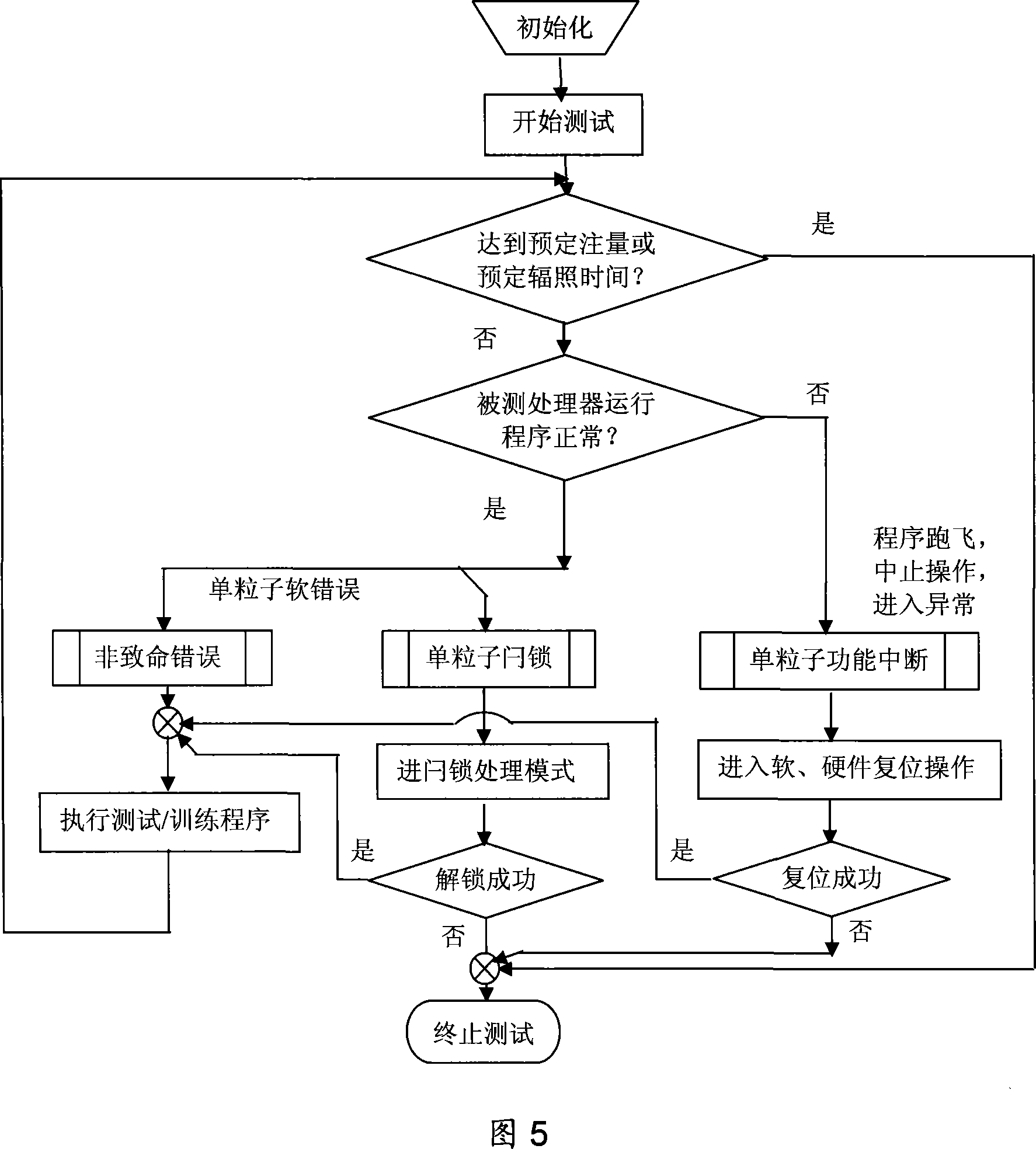

SPARC processor single particle effect detection device and method

InactiveCN101145118AAdaptableRealize Simultaneous MonitoringDigital circuit testingError detection/correctionHardware structureComputer science

The invention relates to a detecting device and a detecting method for the single event effect of a SPARC processor; the detecting device comprises a testing circuit board, a high-speed data collect and control unit, a main control computer and a dual-way power-supply system; through dual-thread control, the testing circuit board and the main control computer can realize simultaneous monitoring for single event latch and other single event effects; the testing circuit can be flexibly provided with a tested processor and a monitoring processor to carry out self-test and dual-processor supporting test; the hardware structure of the device can suit to all kinds of the single event effects of the SPARC processor; the device can realize the different testing for all kinds of the single event effects, and can solve the problem of measuring the single event effects of the SPARC processor in the environment of ground simulative radiation.

Owner:BEIJING MXTRONICS CORP +1

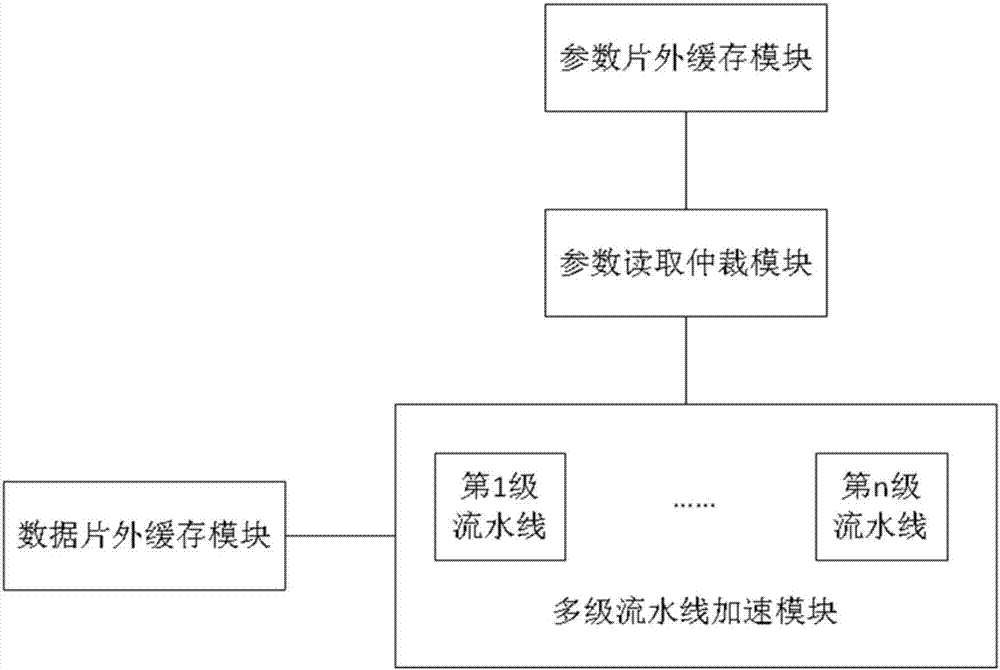

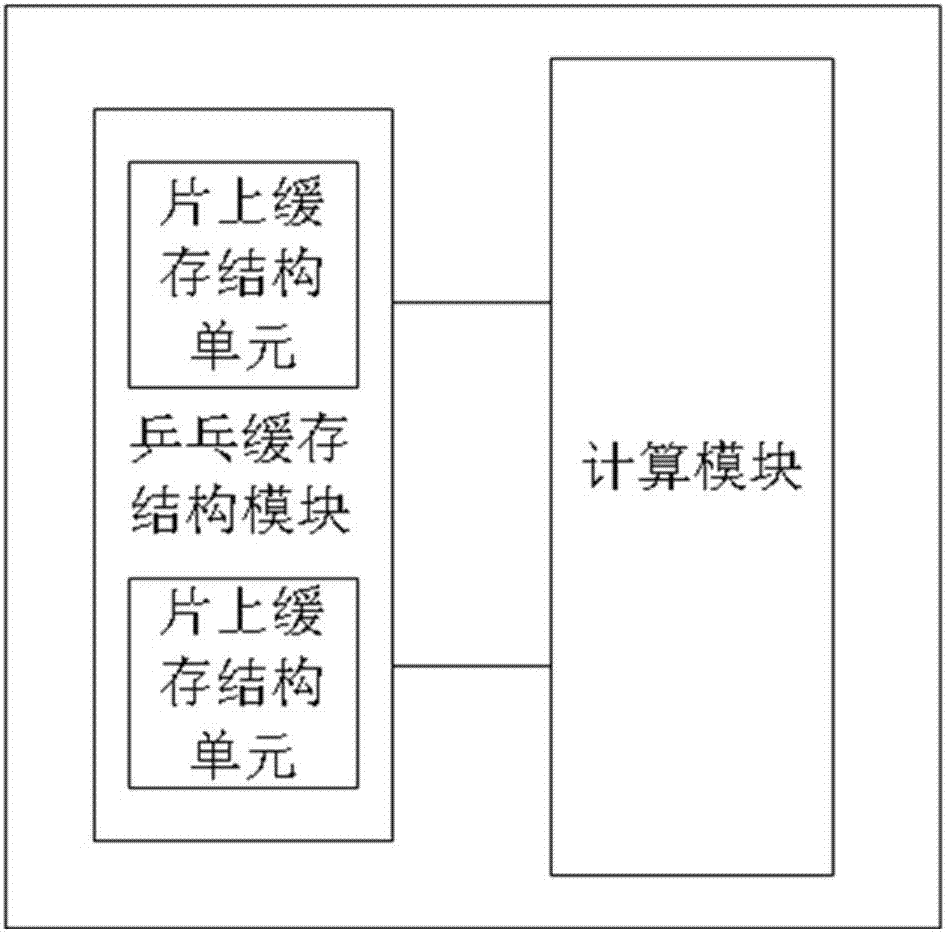

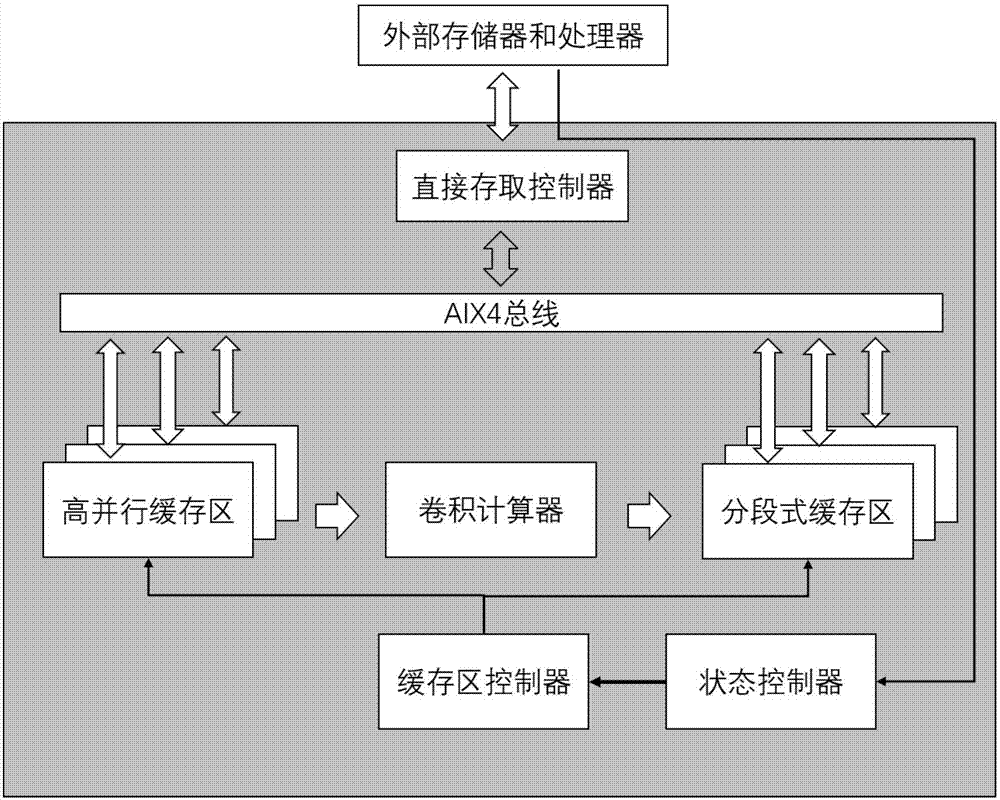

Hardware structure for realizing forward calculation of convolutional neural network

InactiveCN107066239AReduce cache requirementsImprove parallelismConcurrent instruction executionPhysical realisationHardware structureHardware architecture

The present application discloses a hardware structure for realizing forward calculation of a convolutional neural network. The hardware structure comprises: a data off-chip caching module, used for caching parameter data in each to-be-processed picture that is input externally into the module, wherein the parameter data waits for being read by a multi-level pipeline acceleration module; the multi-level pipeline acceleration module, connected to the data off-chip caching module and used for reading a parameter from the data off-chip caching module, so as to realize core calculation of a convolutional neural network; a parameter reading arbitration module, connected to the multi-level pipeline acceleration module and used for processing multiple parameter reading requests in the multi-level pipeline acceleration module, so as for the multi-level pipeline acceleration module to obtain a required parameter; and a parameter off-chip caching module, connected to the parameter reading arbitration module and used for storing a parameter required for forward calculation of the convolutional neural network. The present application realizes algorithms by adopting a hardware architecture in a parallel pipeline manner, so that higher resource utilization and higher performance are achieved.

Owner:智擎信息系统(上海)有限公司

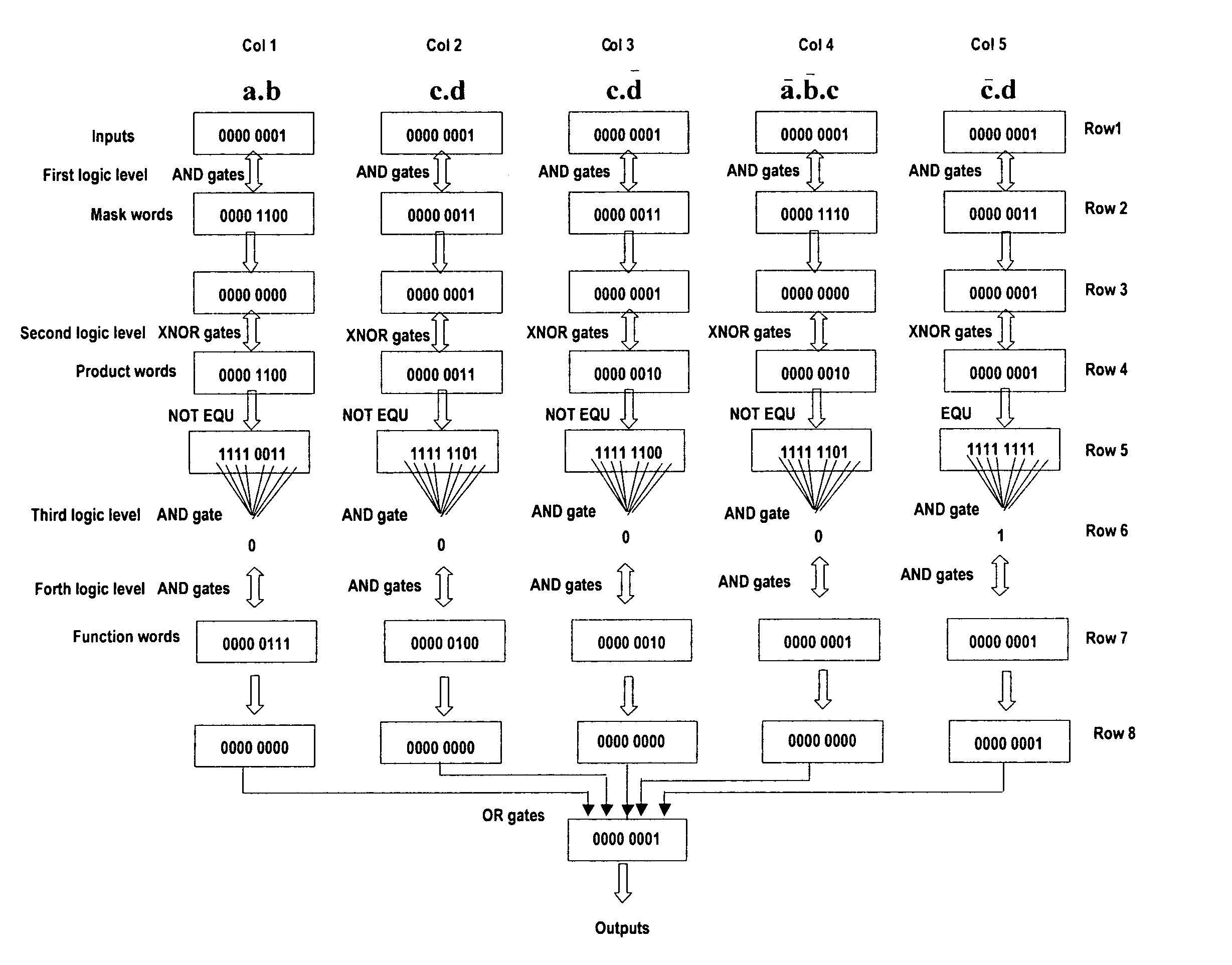

Method and VLSI circuits allowing to change dynamically the logical behavior

InactiveUS7047166B2Improve accuracyReduce manufacturing costSolid-state devicesAnalogue computers for electric apparatusFunction wordHardware structure

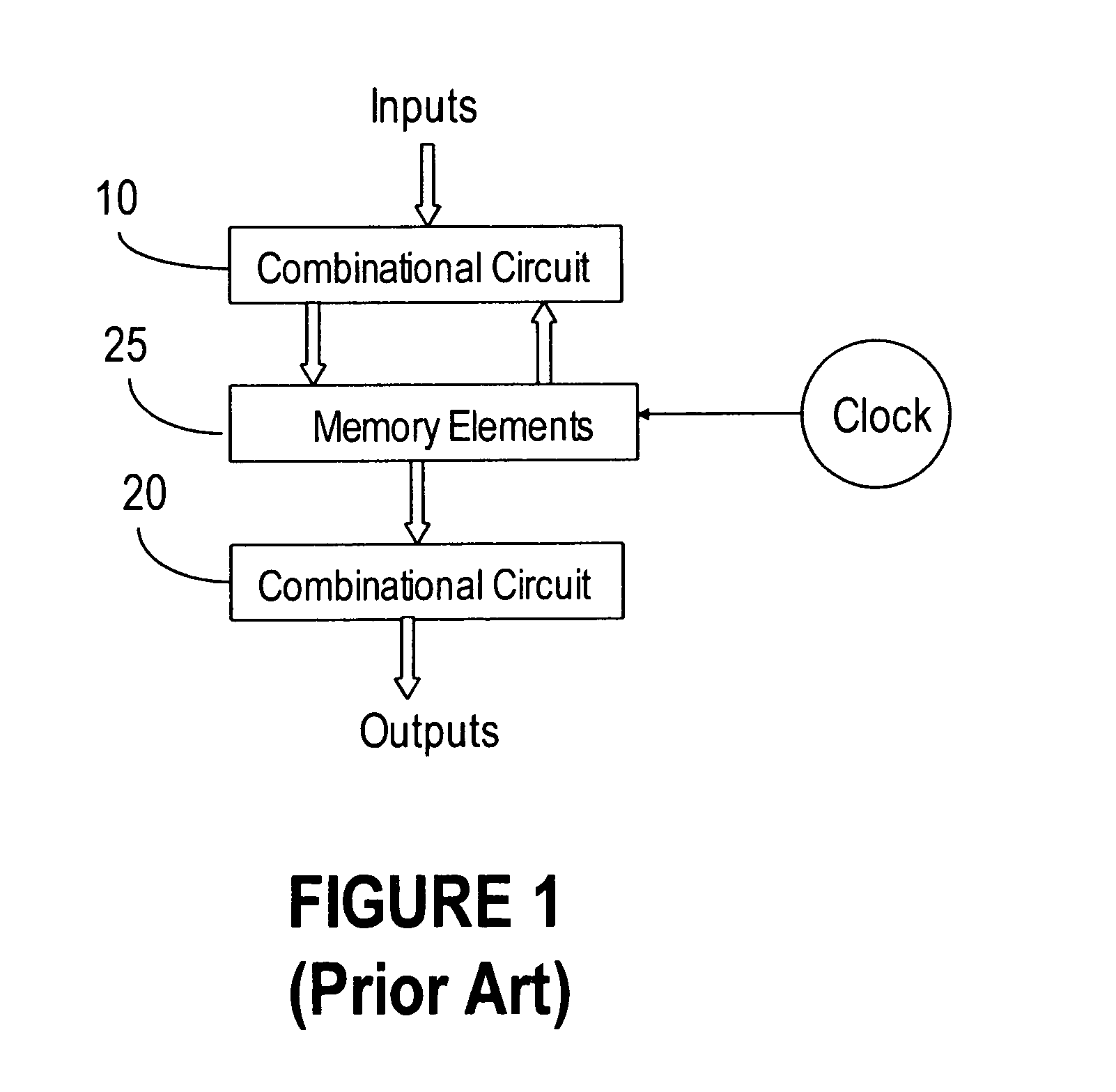

A method, named the product terms method that allows to implement and / or to change dynamically the logical behavior of any combinational or synchronous sequential circuits has been presented. The method uses for every product term of logical equations, expressed as a sum-of-product, three memory words: mask word, product word and function word. The words of all product terms are ranged in a table, which characterize the logical behavior of the circuit.The invention provides the hardware structure of several new types of VSLI circuits, having re-configurable logic behaviors. A first embodiment implements any type of multiple output combinational circuit, a second embodiment implements any synchronous sequential circuit with only clock input and, a third embodiment implements any synchronous sequential circuit s with data inputs and clock input.An expert system capable to generate the tables used for the product terms method by interpreting and analysing the logical equations either supplied by the user or found in a database is also provided.

Owner:IOAN DANCEA

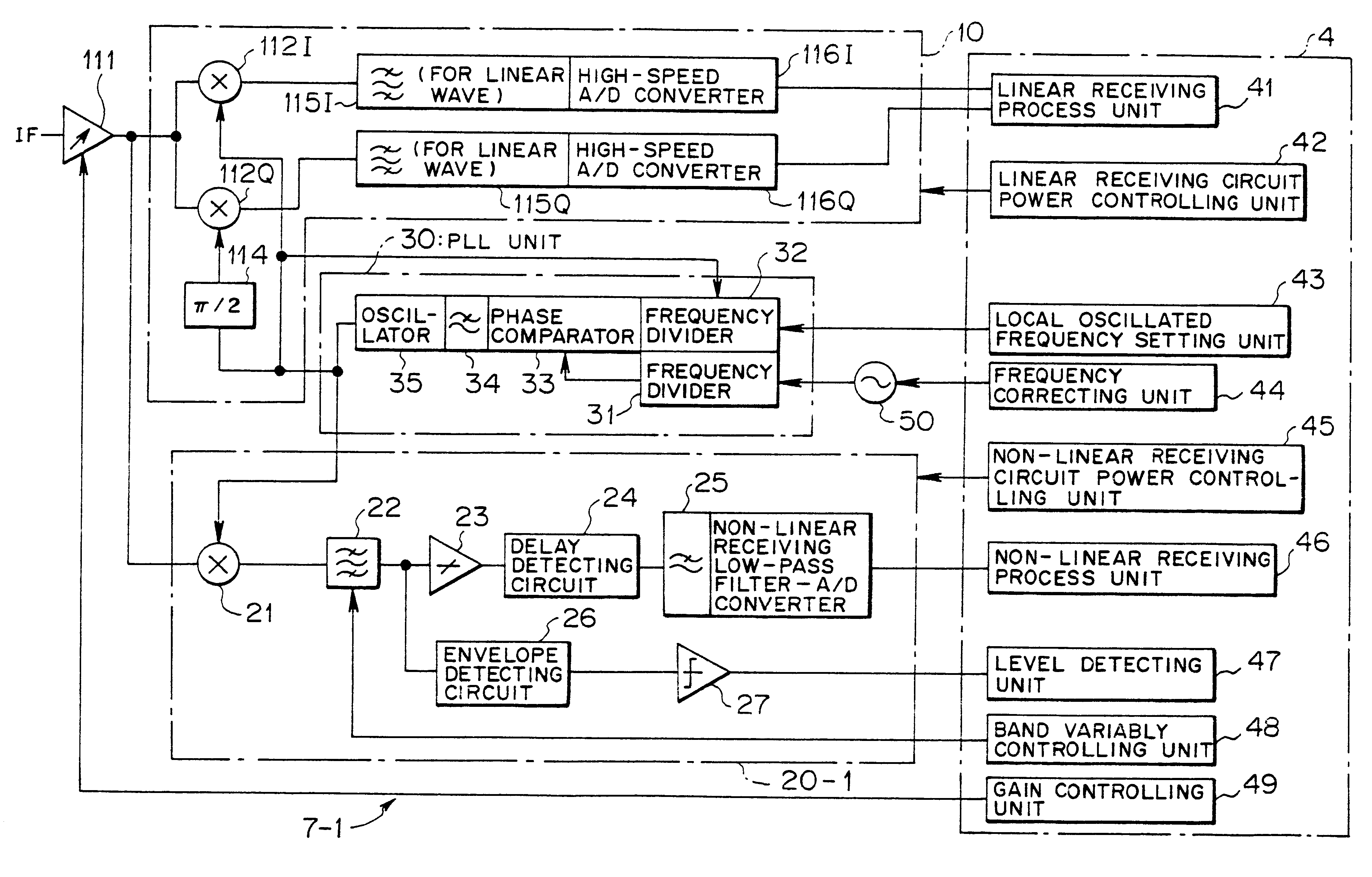

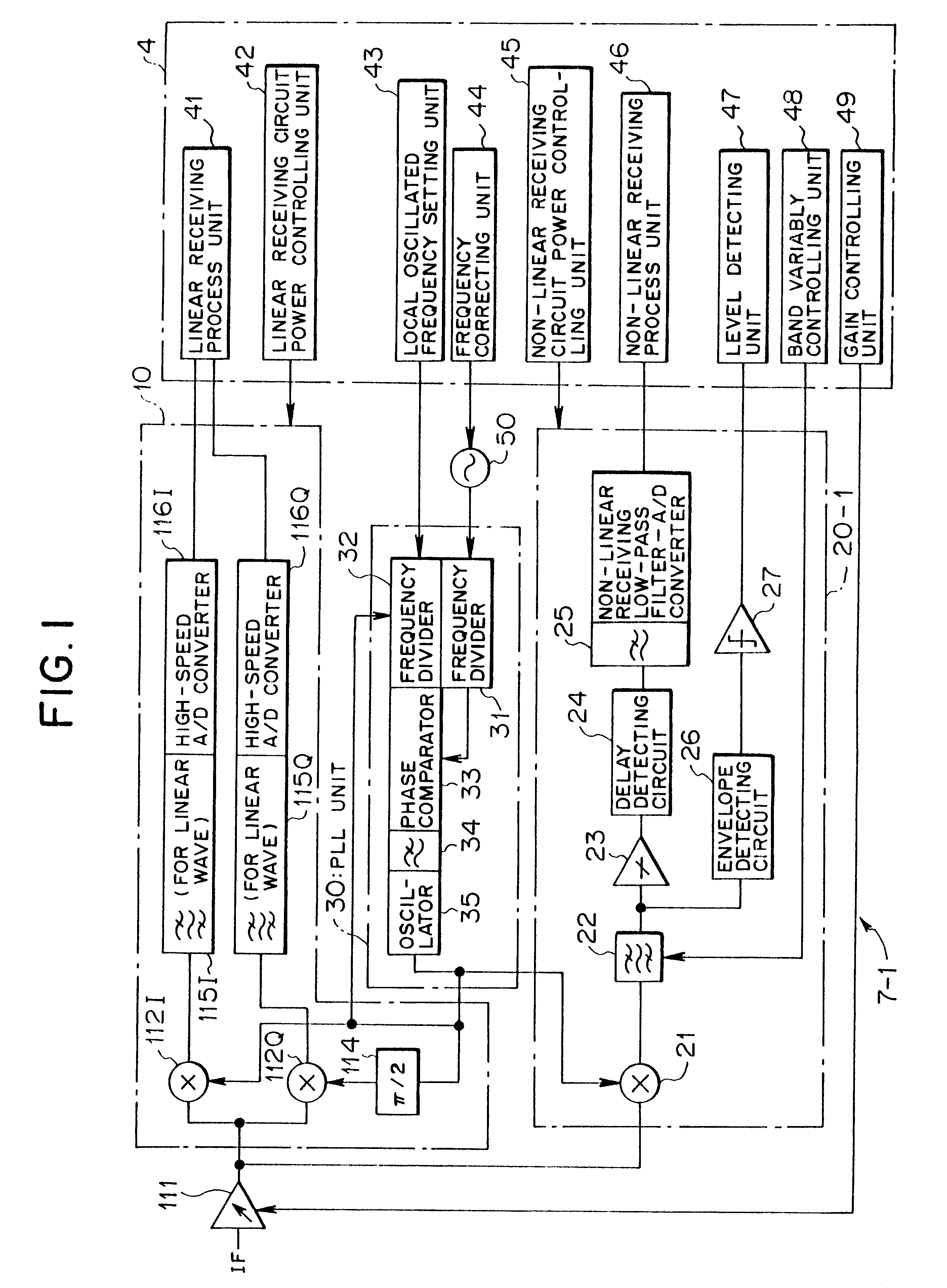

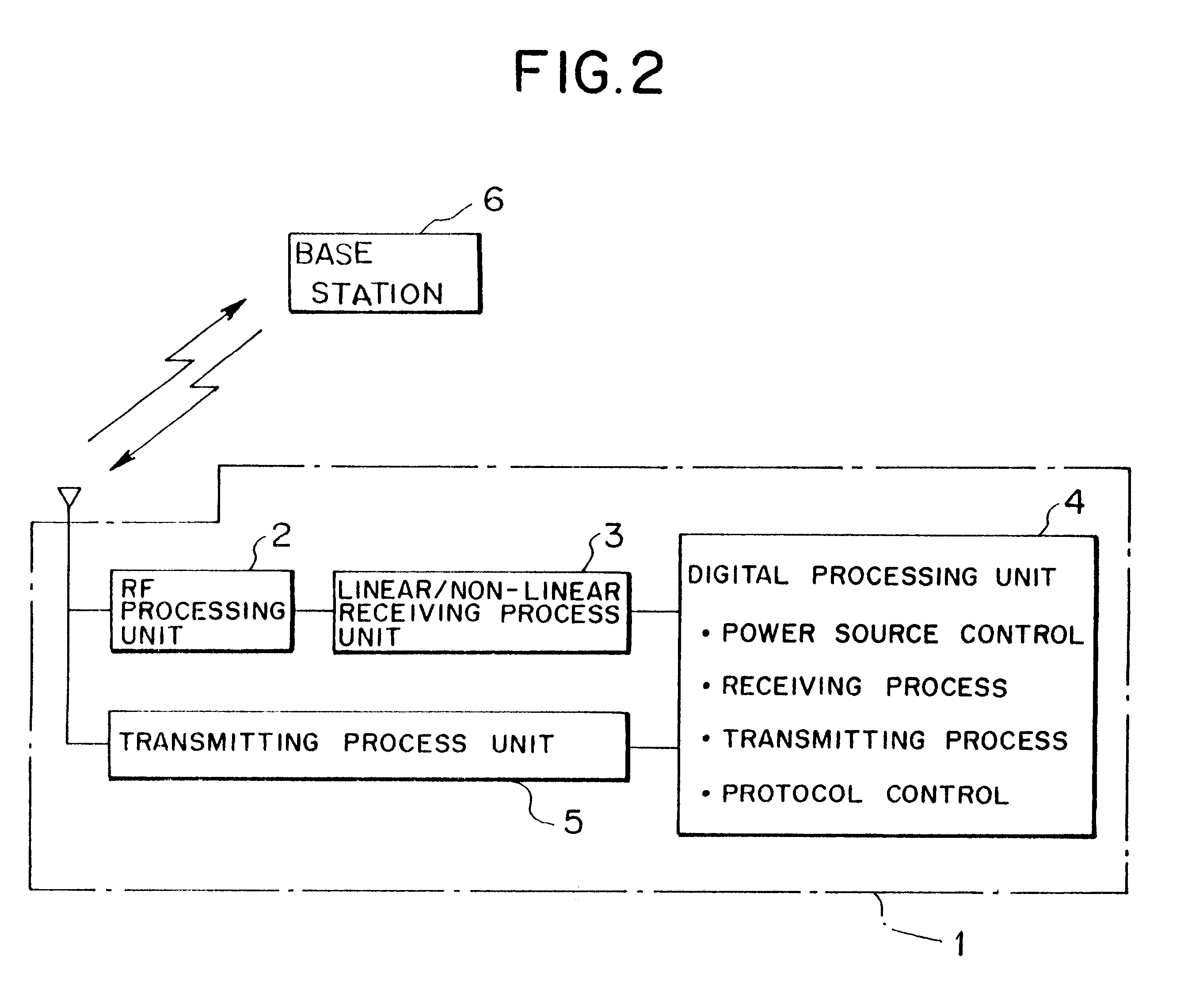

Two-mode demodulating apparatus

InactiveUS6195400B1Amplitude-modulated carrier systemsTransmission monitoringHardware structureNonlinear modulation

A two-mode demodulating apparatus for use in a radio terminal in a mobile communication system has a linear reception demodulating circuit and a non-linear reception demodulating circuit which can be selectively operated by selecting a mode. The non-linear reception demodulating circuit has a second frequency converting unit for frequency-converting a received signal into a low-frequency signal, a variable-band filtering unit for allowing a signal in a desired band contained in an output of the second frequency converting unit to pass therethrough, and a non-linear reception demodulating process unit for performing a non-linear reception demodulating process on an output from the filtering unit, thereby receiving and demodulating a linear modulated wave and a non-linear modulated wave while suppressing increases of the circuit scale and the power consumption, and generalizing a hardware structure for an applied non-linear modulating system.

Owner:FUJITSU LTD

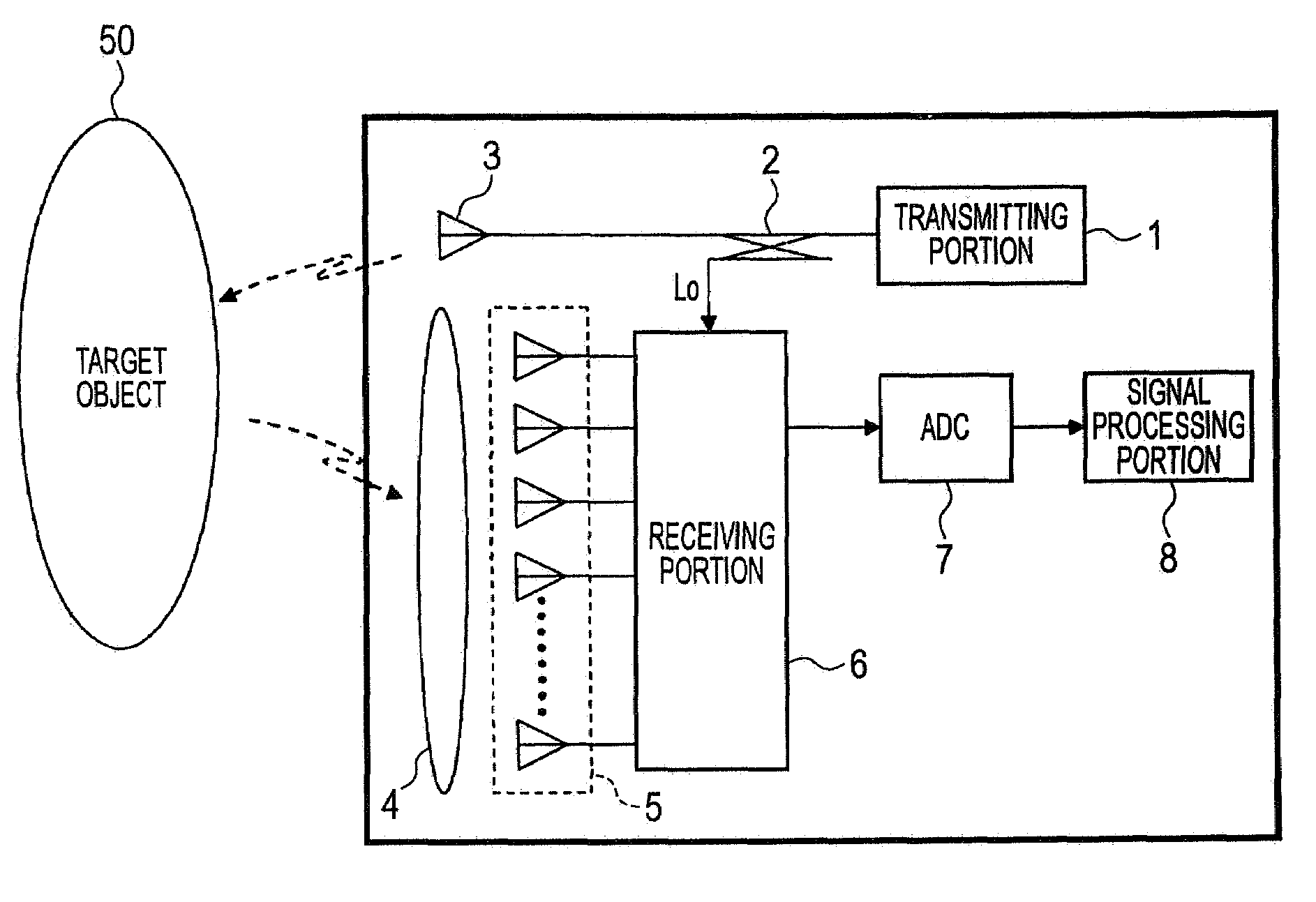

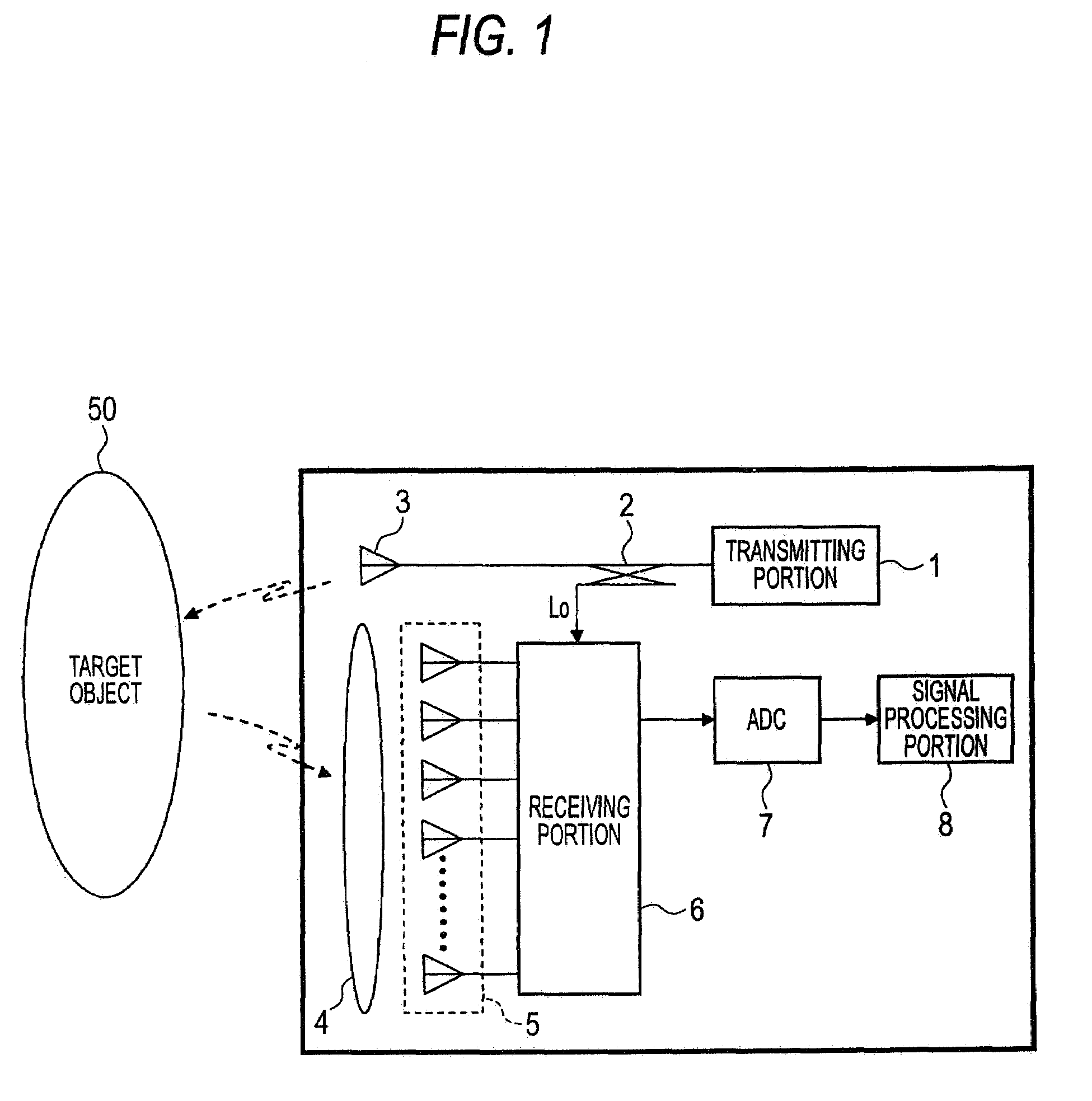

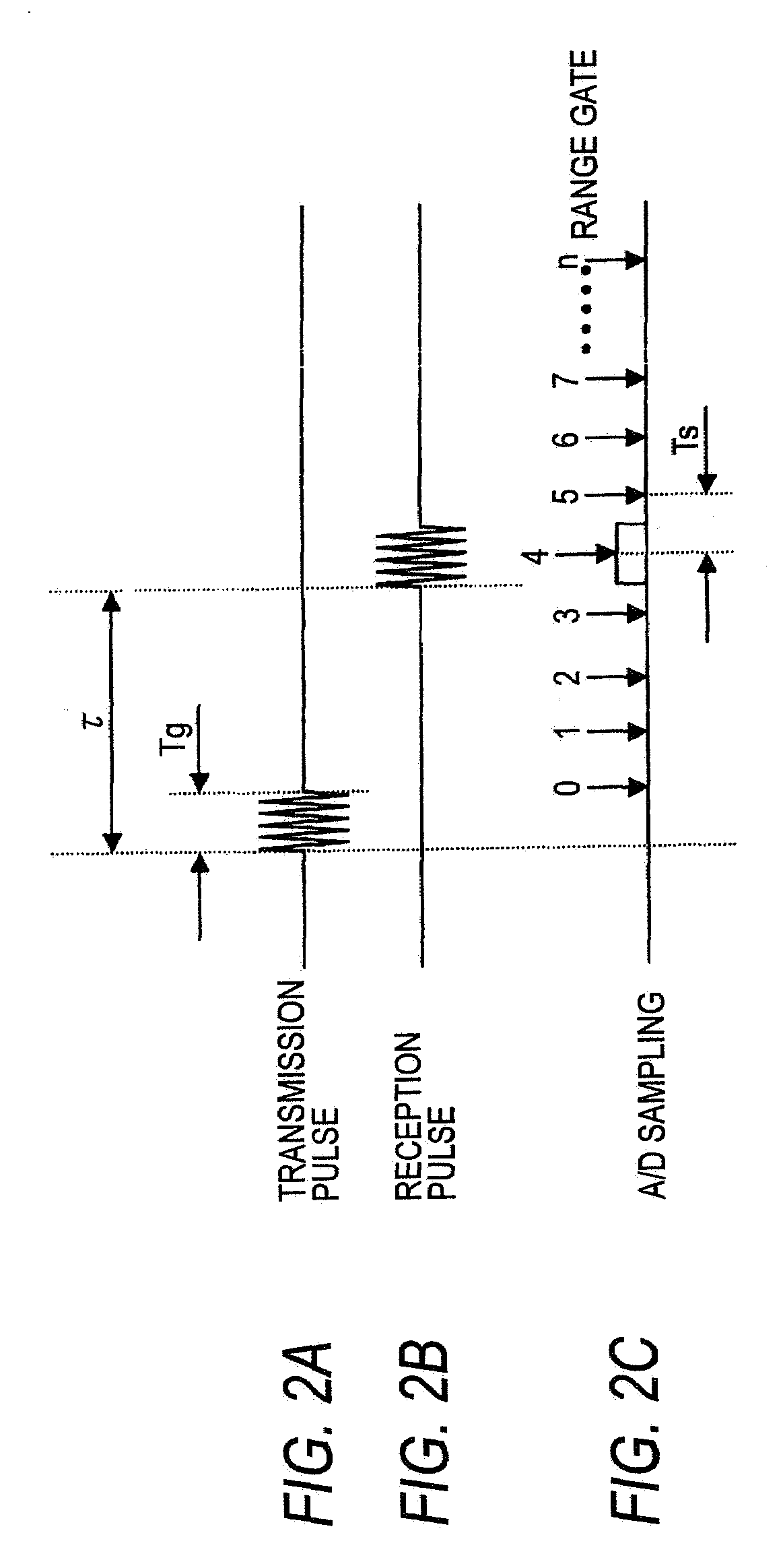

Radar device

InactiveUS20080266169A1Pedestrian/occupant safety arrangementRadio wave reradiation/reflectionHardware structureControl system

A radar device capable of detecting a target object by itself only in a range required by a vehicle control system by changing the detection angle depending on the distance without changing the hardware structure is provided. The radar device includes transmitting means for transmitting an electromagnetic wave as a transmission signal, receiving means for receiving the electromagnetic wave reflected from the target object as a reception signal, and signal processing means for detecting a target object existing around the vehicle from the transmission signal and the reception signal, and calculating the relative position and the relative speed between the object and the vehicle. The detection angle is changed depending on the distance for measurement, so that the target object is detected only in a region necessary in operating the vehicle control system.

Owner:MITSUBISHI ELECTRIC CORP

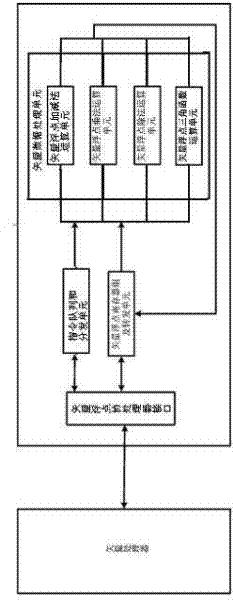

Vector floating-point computing device and method based on vector computing

InactiveCN102262525ADigital data processing detailsConcurrent instruction executionHardware structureCoprocessor

The invention discloses a vector-operation-based floating point operational device, which is a novel hardware structure, and comprises a vector processor, a storage device, a vector floating point coprocessor and a vector floating point coprocessor storage device, wherein a bus interface between the vector processor and the vector floating point coprocessor can adopt a general coprocessor bus structure. By adopting the coprocessor, on the basis of ensuring all operations of floating points, the operational speed of the floating points is improved and the design complexity is reduced.

Owner:孙瑞玮

Mobile phone input system with multi-point touch screen hardware structure

InactiveCN101458591AGuaranteed accuracyEasy to useTelephone set constructionsInput/output processes for data processingHardware structureTouchscreen

The invention provides a mobile phone input system with multi-point touch screen hardware which includes a hardware of the multi-point touch screen mobile phone and corresponding software. The system has characteristic that multiple touch points are identified simultaneously using multi-point touch screen for comparing a track database pre-set in the mobile phone with a touched track calculated by software, and obtaining a database track nearest the calculated touch track, executing an input instruction.

Owner:SAMSUNG ELECTRONICS CHINA R&D CENT +1

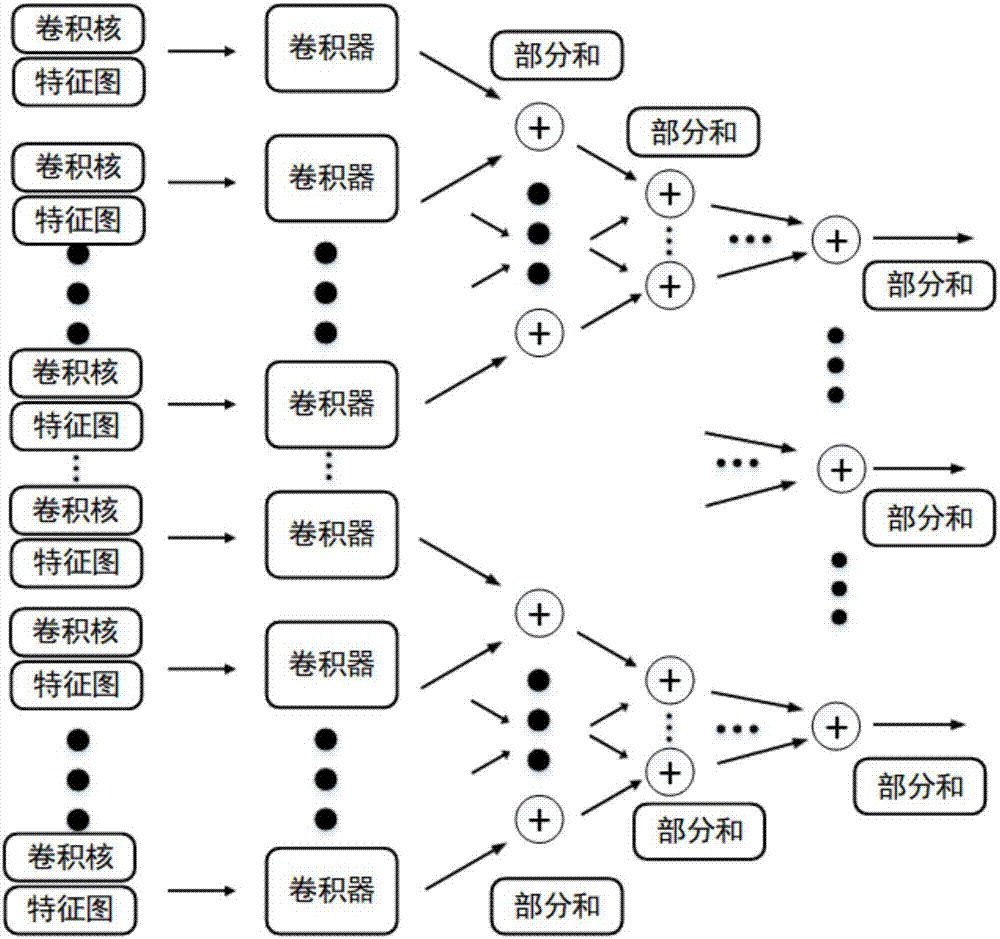

FPGA (field programmable gate array)-based universal fixed-point-number neural network convolution accelerator hardware structure

InactiveCN107392309AImprove versatilityIncrease computing speedPhysical realisationData conversionFace detectionHardware structure

The invention discloses an FPGA (field programmable gate array)-based universal fixed-point-number neural network convolution accelerator hardware structure which comprises a universal AXI4 high-speed bus interface, a universal GPIO (general purpose input / output) interface, a universal convolver, a universal read-write control unit, a universal state controller and a universal convolution result buffer. Universal memory hardware is provided, and high-parallel read-write operations are supported; the universal convolver can be used for accurate configuration of fixed point numbers, configuration of convolution operation levels and high-parallel convolution operation in coordination with high-parallel read-write operations after data storage; the universal read-write control unit includes ram, rom and Fifo read-write control logics and address generating logics; the universal state controller makes corresponding unit operating reactions aiming at a convolution layer and read-write and calculation processes to control an integral calculation process; the universal convolution result buffer is used for high-speed parallel caching and sending of a processing result to a bus according to a convolution result sectional accumulation method. By verification in application to Yolo algorithm based human face detection and CNN (convolutional neural network) based human face recognition, high operating speed and high data precision are embodied.

Owner:SOUTHEAST UNIV WUXI INST OF TECH INTEGRATED CIRCUITS +1

Antenna beam tracking device and method of moving communication satellite communication system

InactiveCN101916915ASimple designEasy wiringAntenna adaptation in movable bodiesRadio transmissionHardware structureGeolocation

The invention discloses antenna beam tracking device and method of a moving communication satellite communication system. The antenna beam tracking device comprises a geographical position detection device, a carrier gesture detection unit, a signal intensity detection unit, a signal conditioning circuit and a master control computer, wherein the master control computer controls a servo driver; and the servo driver controls an azimuth and pitching motor. The antenna beam tracking method comprises the following steps of: 1, initially capturing a target satellite; 2, tracking: setting initial parameters, storing and updating the initial parameters in real time, generating simultaneous disturbance random vectors, driving disturbance, measuring the intensity of received signals, estimating gradient, determining tracking error signals, regulating antenna beam pointing directions, and judging the received signals; and 3, recapturing. The invention has the advantages of simple design, low cost, system implementation without changing the hardware structure of an original tracking system, easy operation, high tracking accuracy and fast tracking speed and overcomes the defects of inconvenient operation, complex tracking step, lower tracking accuracy and tracking speed, and the like of the traditional method.

Owner:PLA SECOND ARTILLERY ENGINEERING UNIVERSITY

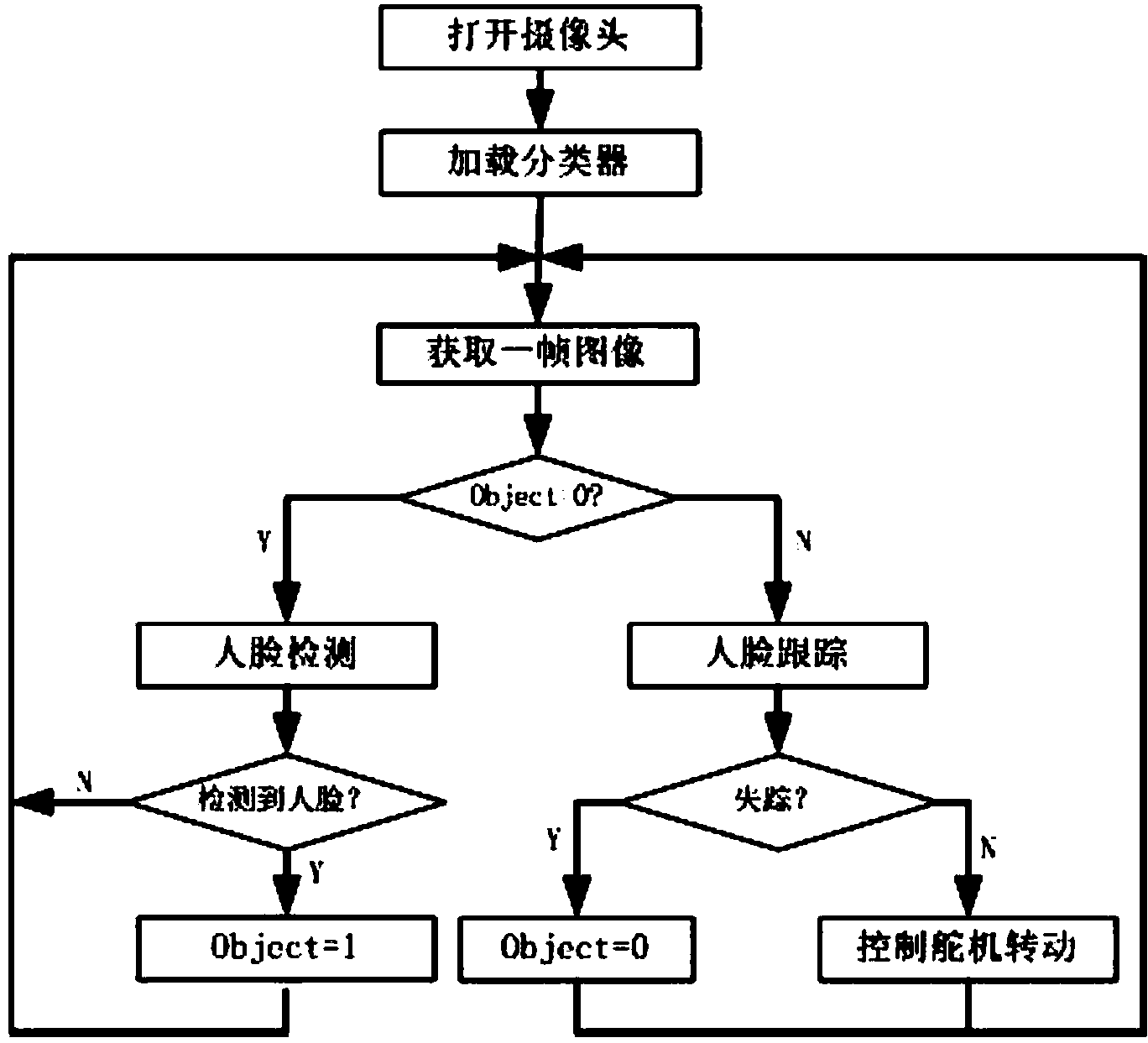

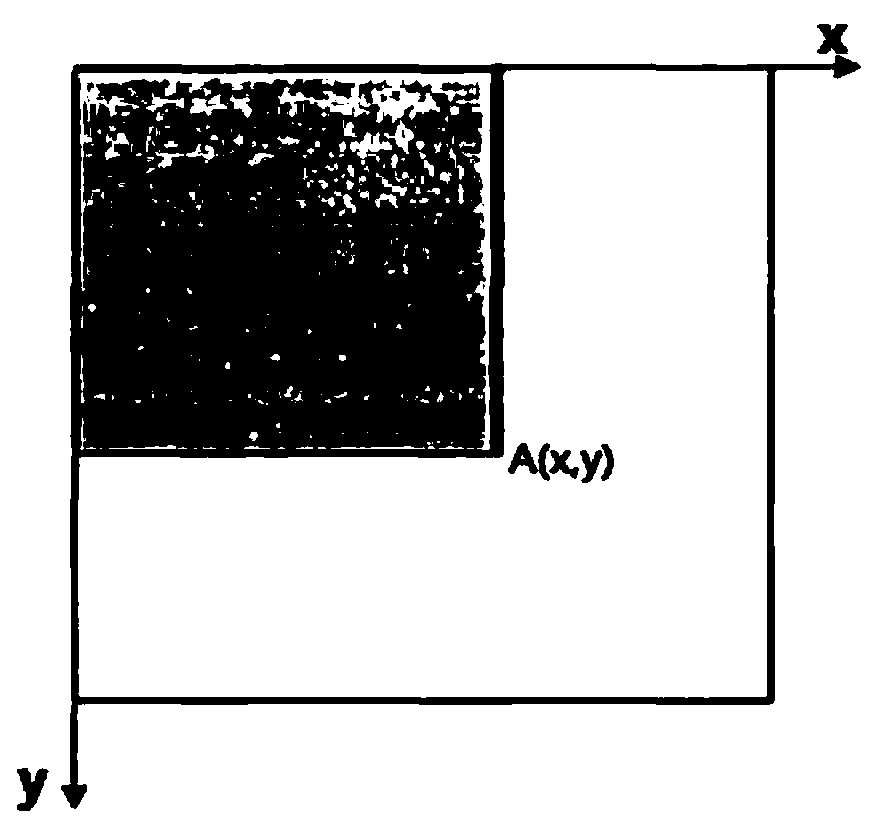

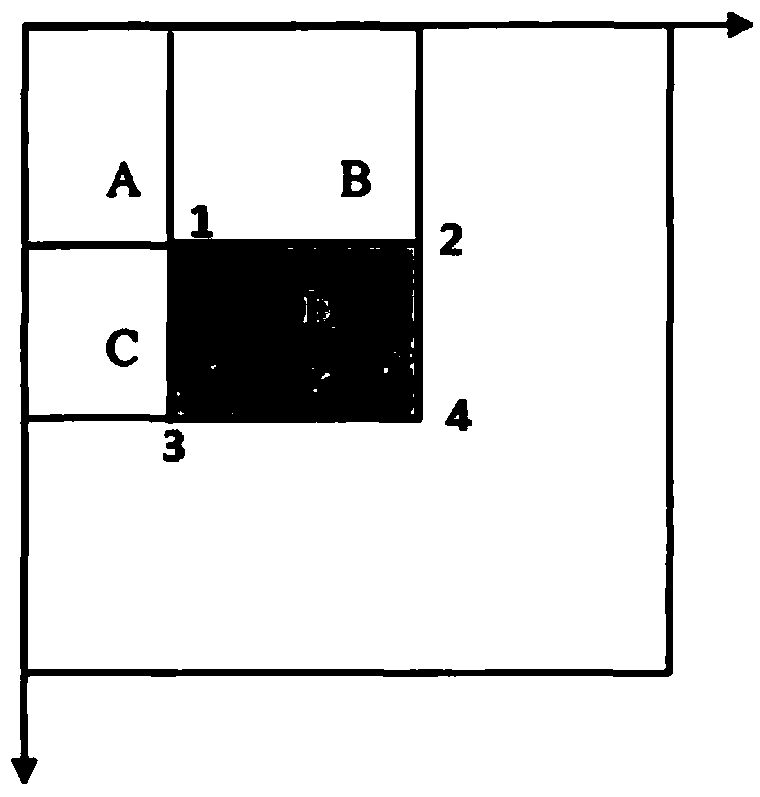

Method and system for conducting real-time tracking on faces by monocular camera

InactiveCN103905733AEasy to trackSmall amount of calculationTelevision system detailsCharacter and pattern recognitionHardware structureImaging processing

The invention discloses a method for conducting real-time tracking on faces by a monocular camera. The method comprises the steps that firstly, the camera is opened so as to search for whether the faces exist around the camera or not, images collected by the camera are transmitted to an image processor, the image processor calls an image processing program to conduct image compression, three AdaBoost cascade connection strong classifiers based on Haar characteristics are loaded on the image processing program, skin color detection is carried out on all the compressed images, a detected window is used for detecting the faces with multiple angles through the three AdaBoost cascade connection strong classifiers, after the faces are detected, real-time tracking is carried out on face targets, the difference between the central point coordinates of a face target area and the central point coordinates of the whole images is compared, the camera is adjusted to enable the central point coordinates of the face images to be approximately aligned with central point coordinates of the images, and real-time tracking on the faces is achieved. The method has the advantages that the tracking method is simple, the calculated amount is small in the tracking process, the hardware structure is simple, and real-time tracking of the face targets can be well achieved.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

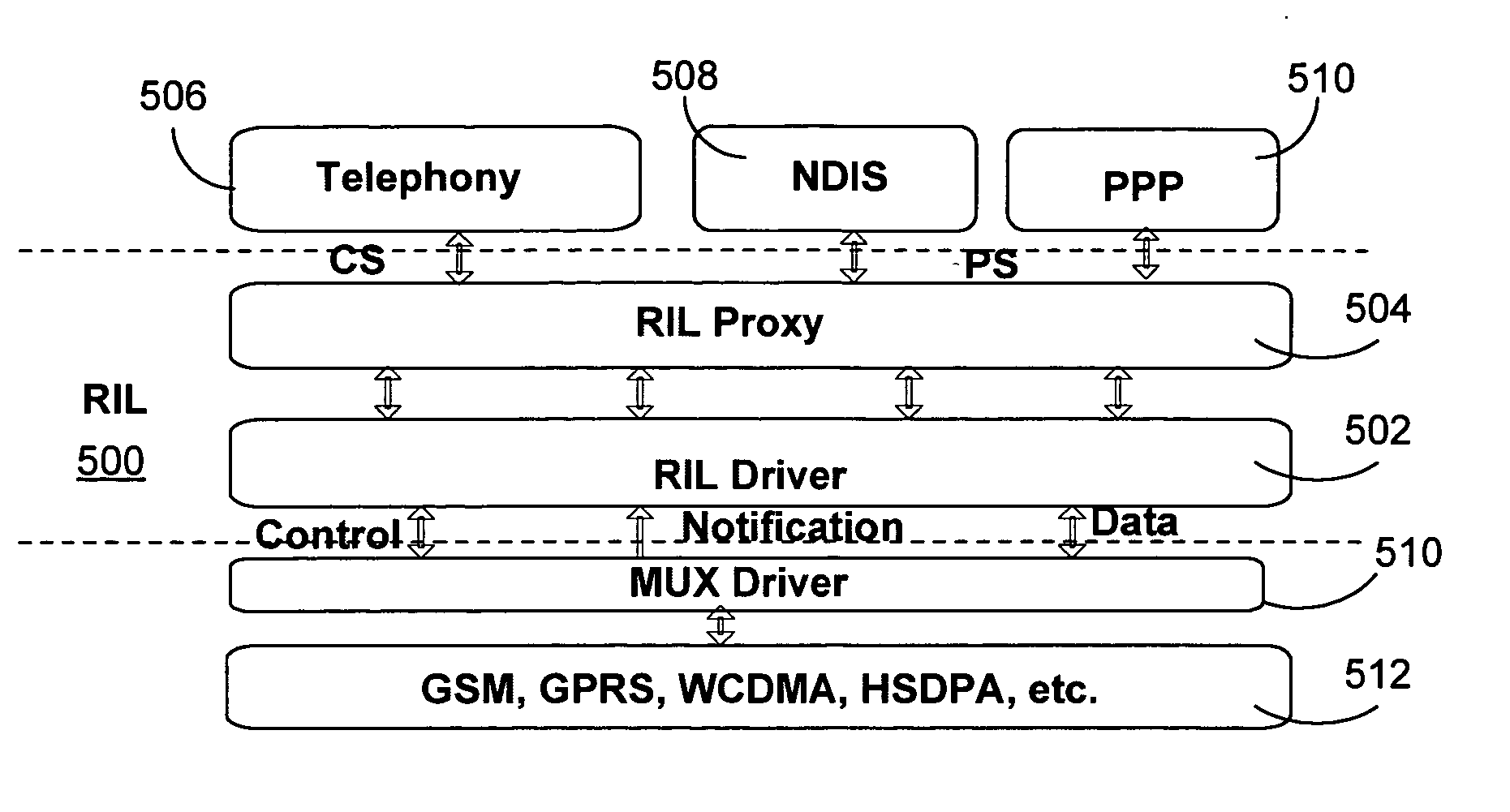

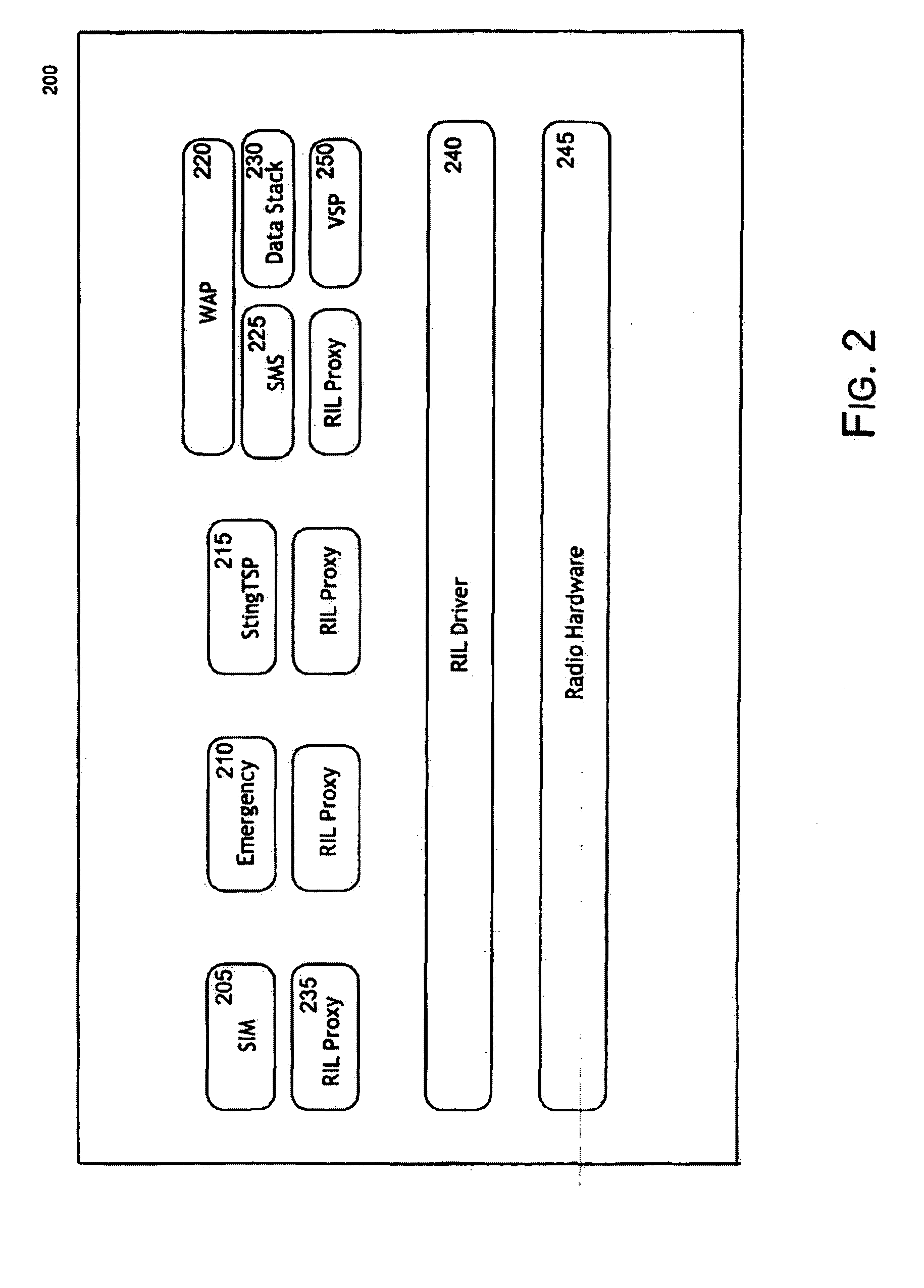

UMTS RIL extension

InactiveUS20060222009A1Time-division multiplexRadio/inductive link selection arrangementsCellular radioHardware structure

Owner:MICROSOFT TECH LICENSING LLC

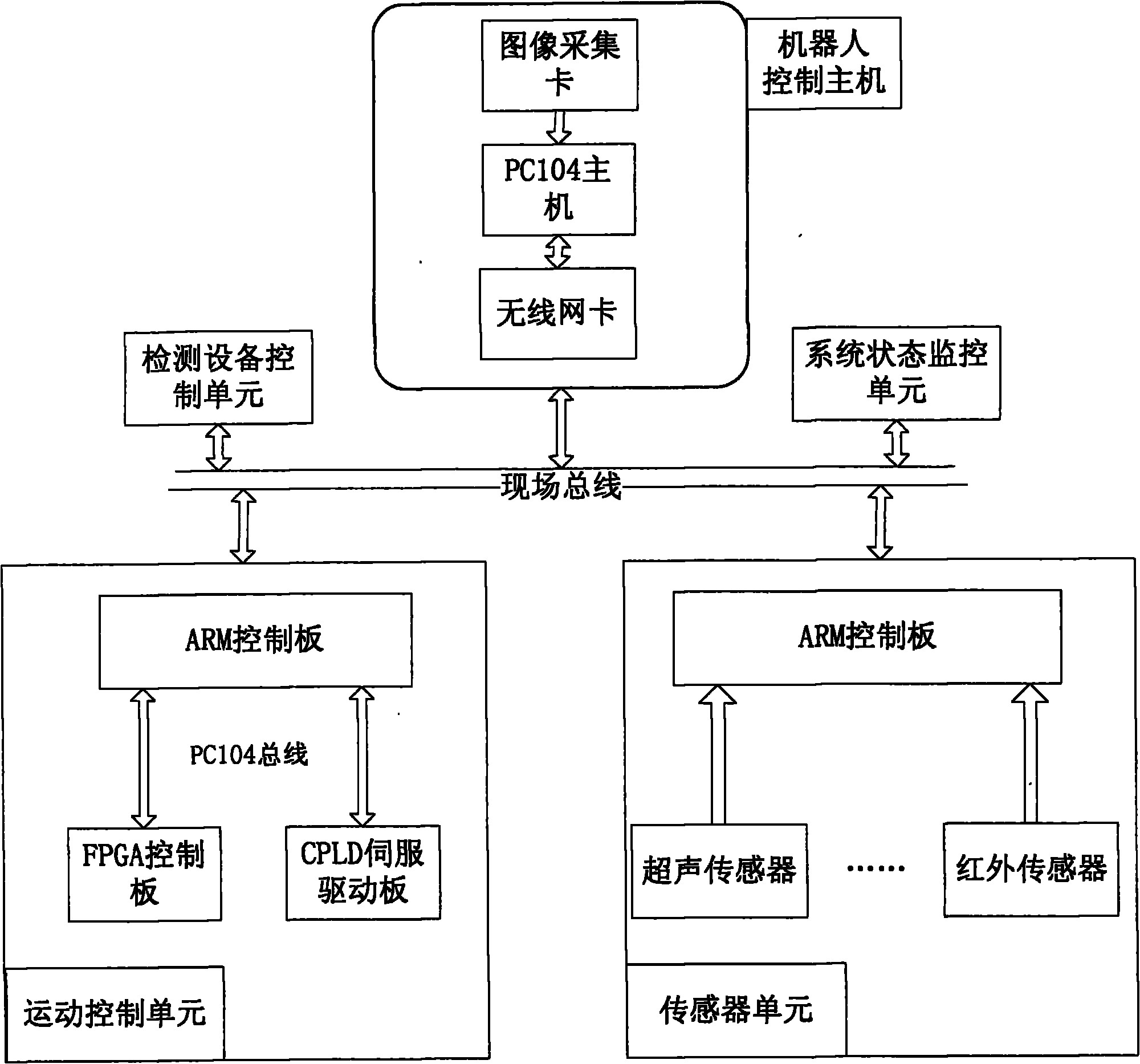

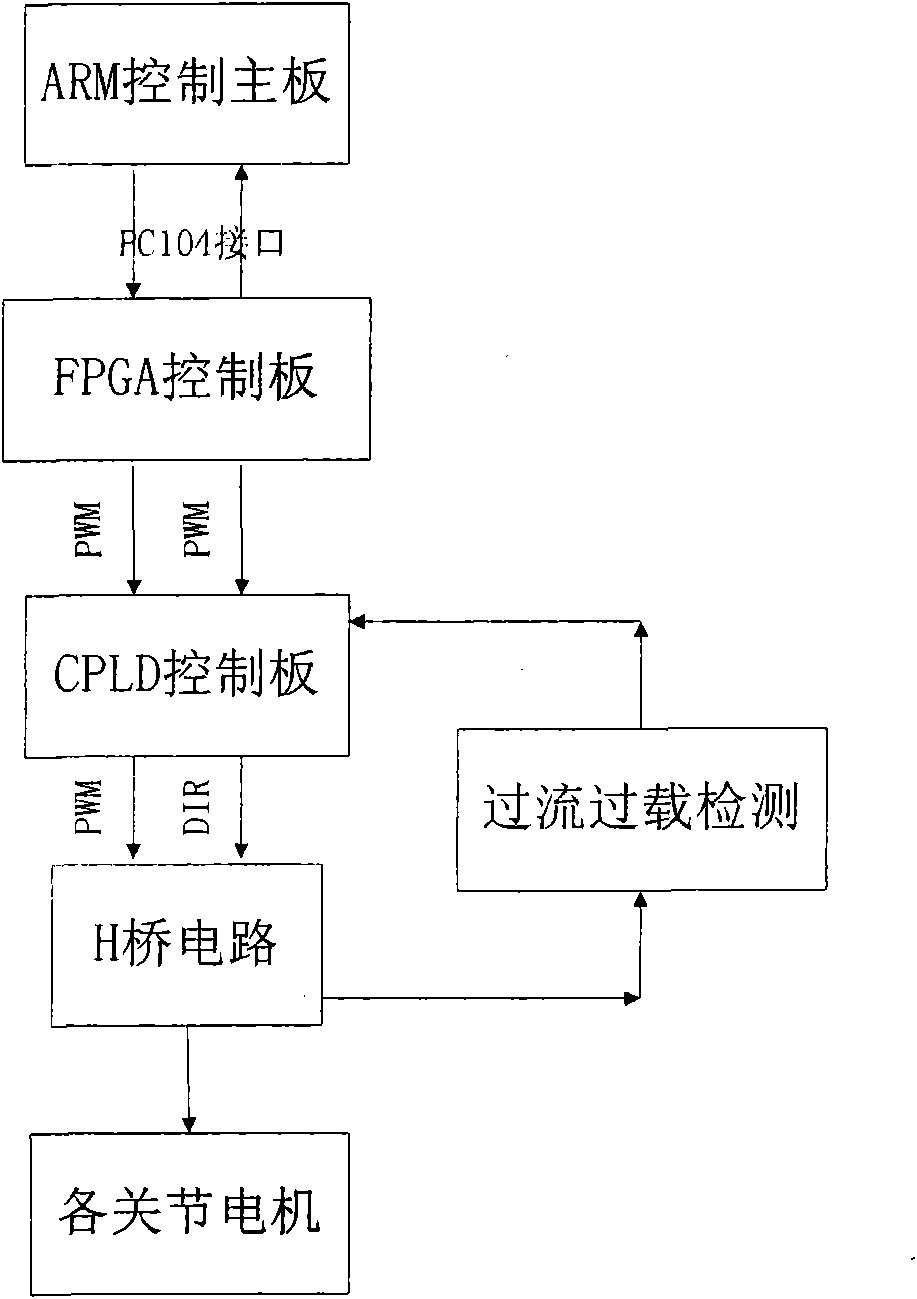

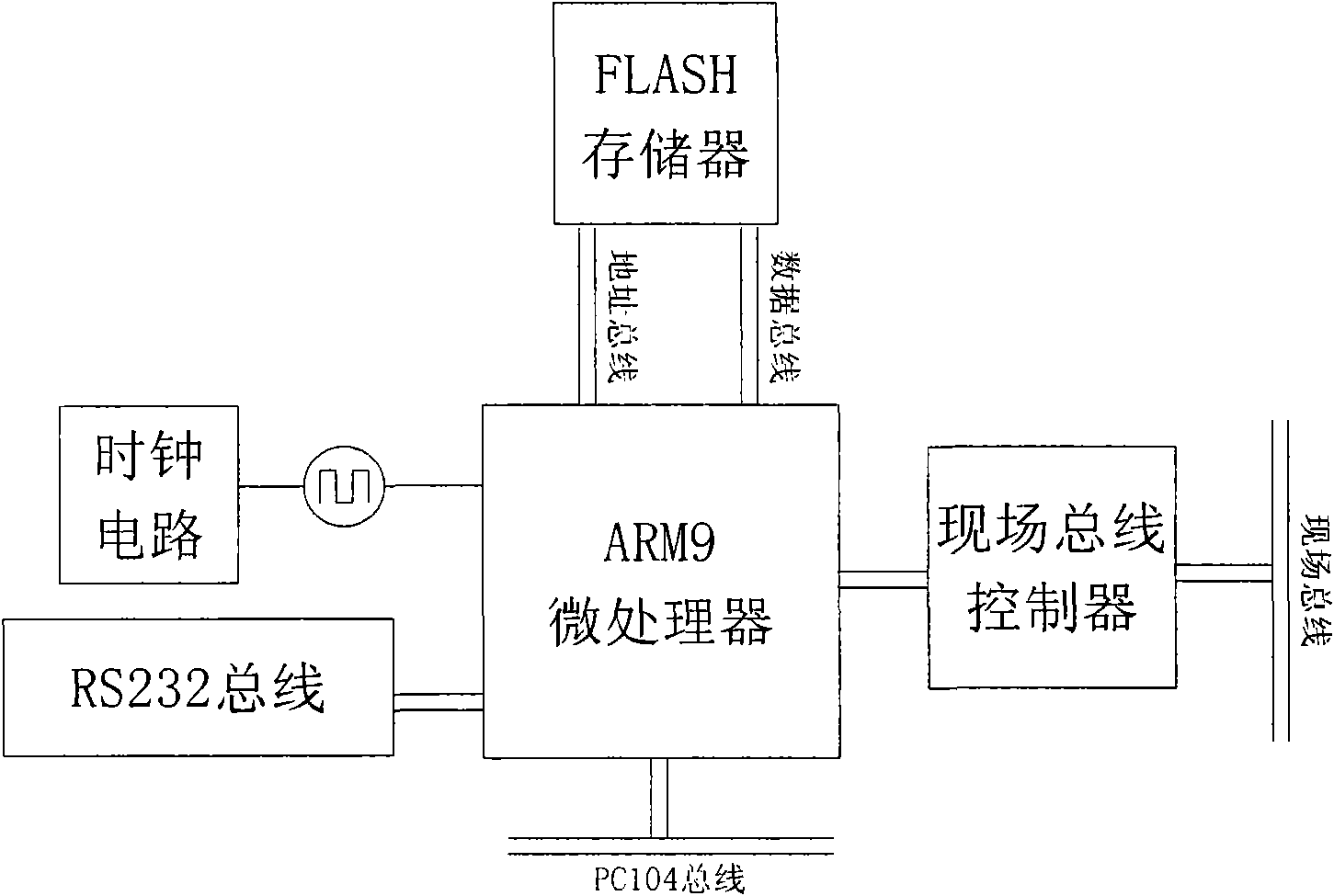

Two-arm inspection robot control system based on field bus

InactiveCN101770221AWalk accuratelyAutonomous walkingNumerical controlPosition/course control in two dimensionsHardware structureManufacturing technology

The invention discloses a two-arm inspection robot control system based on a field bus, which relates to the robot manufacture technology and is an automatic control system of an inspection system, and used for operations on a high-voltage power transmission line. The two-arm inspection robot control system comprises a robot control host machine, a motion control unit, a sensor unit, a system state monitoring unit, a detection equipment control unit and a ground base station. The robot control host machine plans actions according to information collected by the sensor unit, the motion control unit controls each joint, monitors the running state of the whole control system and each detection equipment in real time and contacts with the ground base station through a wireless network, and each unit communicates with the robot control host machine in real time through the field bus. The two-arm inspection robot control system based on the field bus adopts a distributed hardware structure, is suitable for a series of operations of routing inspection, deicing and the like on the high-voltage power transmission line, and is beneficial to ensuring the safe and reliable operation of the national power system.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

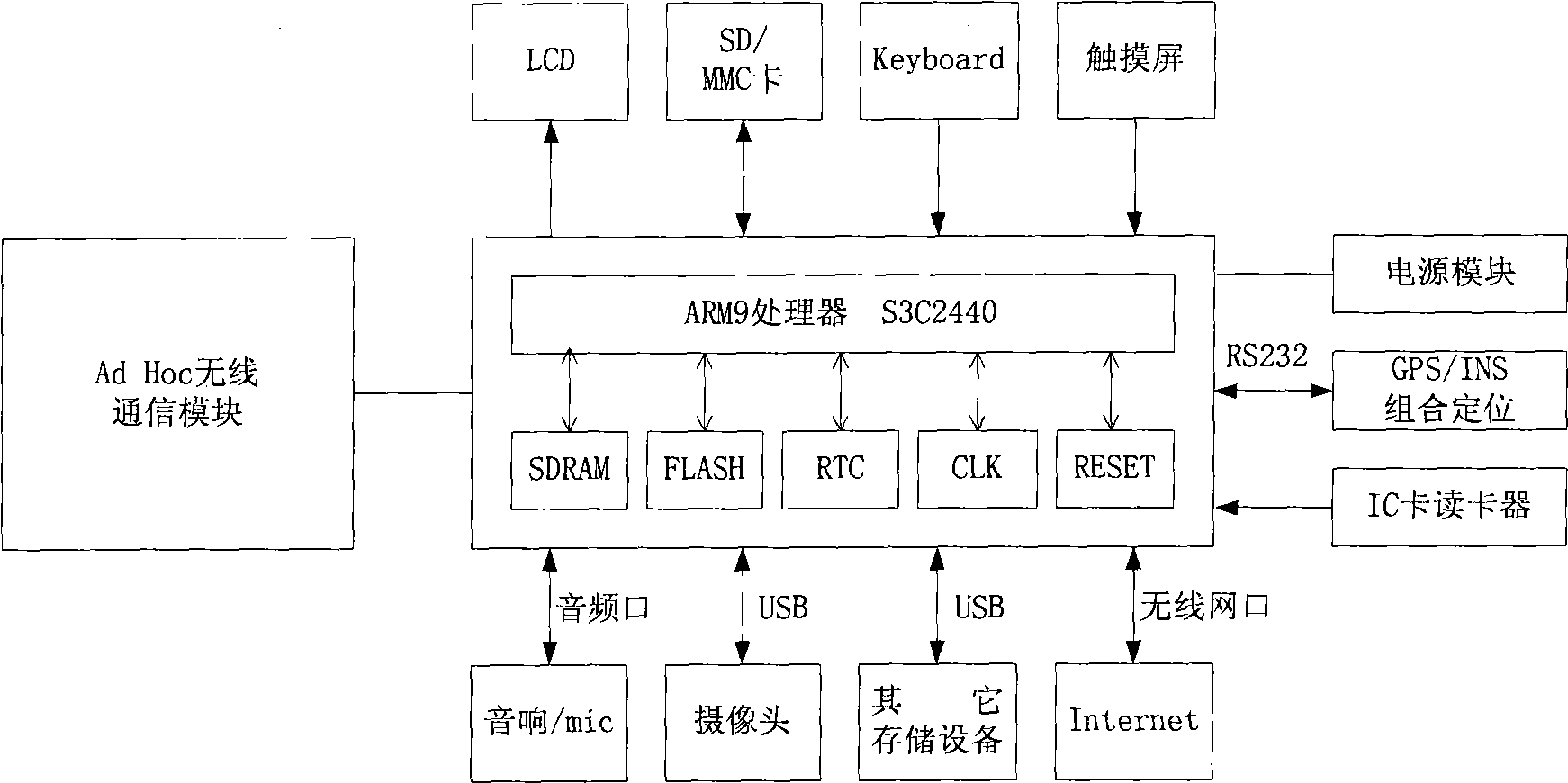

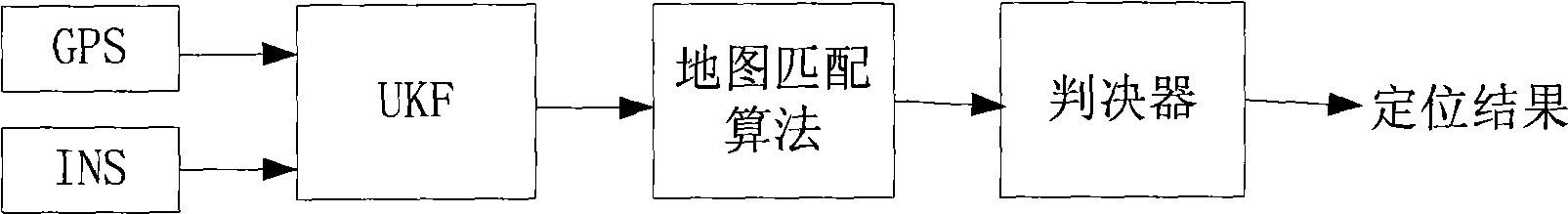

Intelligent vehicle-mounted system

InactiveCN101489196AIntelligentLow priceNetwork topologiesMessaging/mailboxes/announcementsHardware structureNetwork Communication Protocols

The present invention provides an intelligent vehicle-mounted system, wherein the hardware structure comprises a central processing controller, a wireless communication module, a power module, a GPS positioning module, a storing module, an audio / video broadcasting module and a human-machine interaction module, wherein the wireless communication module, the power module, the GPS positioning module, the storing module and the audio / video broadcasting module are connected with the central processing controller. The vehicle-mounted system software mainly comprises a main interface program, GPS positioning navigation software and multimedia broadcasting software. The vehicle-mounted system and other vehicle-mounted terminal form an Ad Hoc network through the wireless communication module. The communication protocol of vehicle-mounted system adopts an Ad Hoc routing protocol based on GPS and electronic map and an MAC protocol with adjustable power. The vehicle-mounted system supports the functions of enciphering and authenticating. The vehicle-mounted system can aim at different user grades for allocating authority and executing related authentication to the user. The independent and distributed intelligent vehicle-mounted terminal system of the invention can be applied to various vehicles for realizing the interconnection, intercommunication and information sharing of Ad Hoc mode between intelligent vehicle-mounted systems and for realizing the multi-hop communication between the vehicle and the stationary platform. The intelligent vehicle-mounted system of the invention has the advantages of intelligentization, low cost, convenient use, etc.

Owner:JINAN UNIVERSITY

Locking control method and system of large-stroke nanometer displacement positioning macro-movement bench

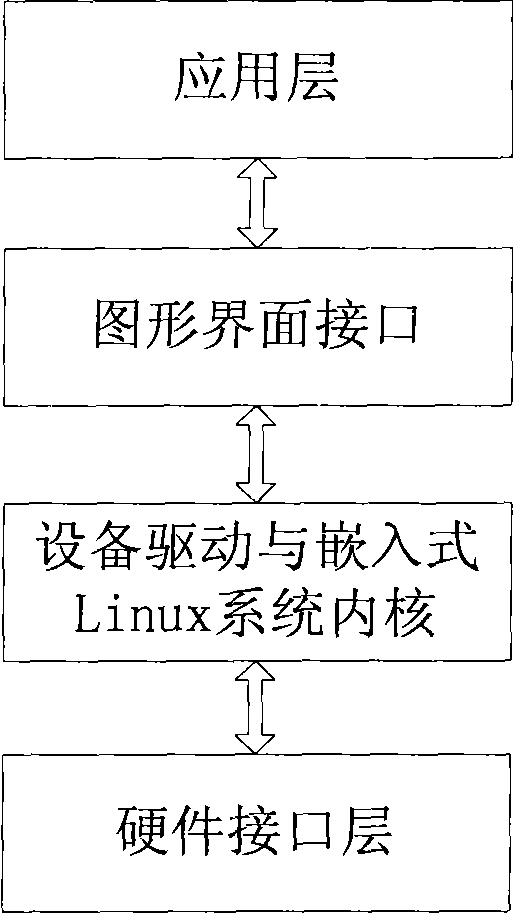

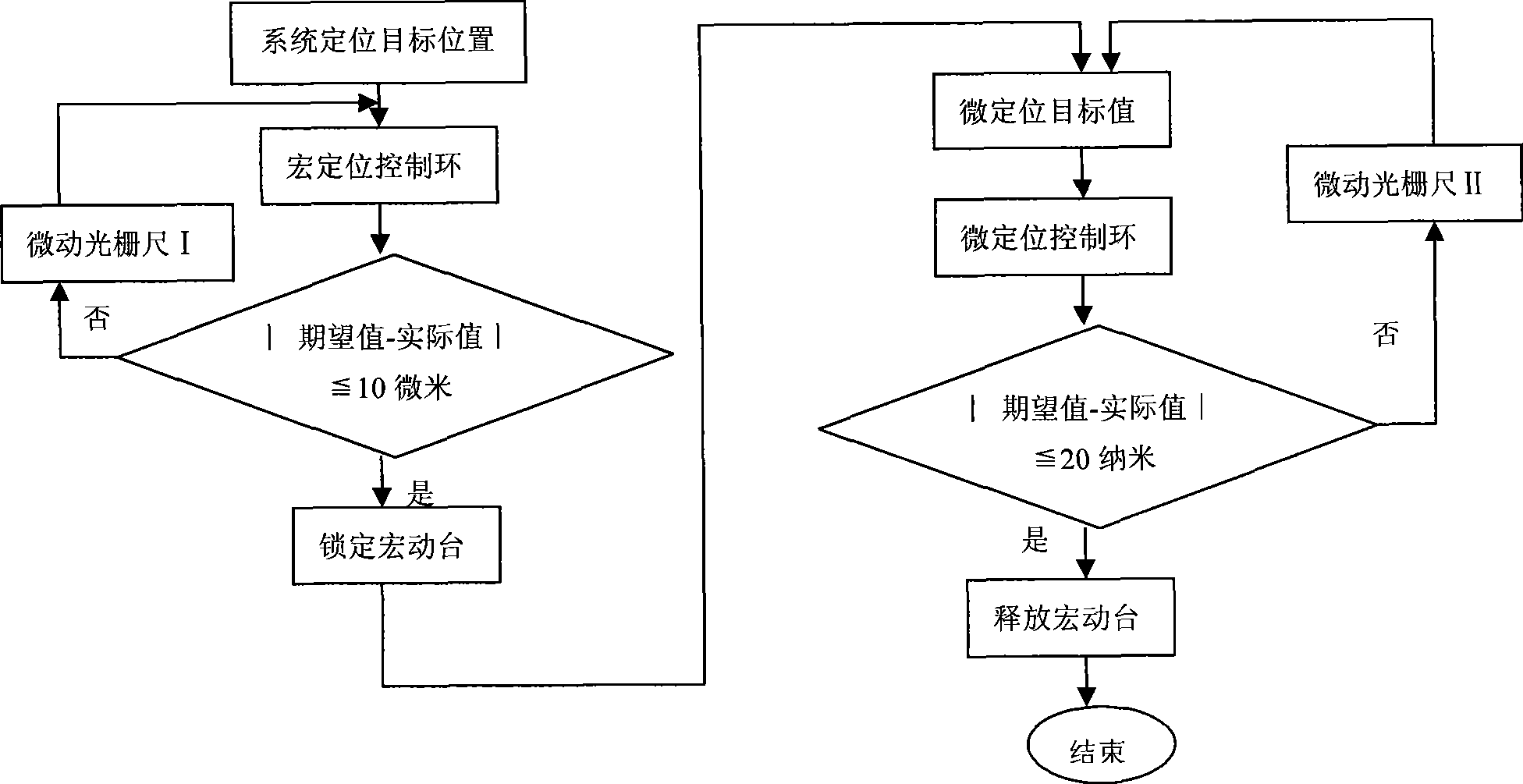

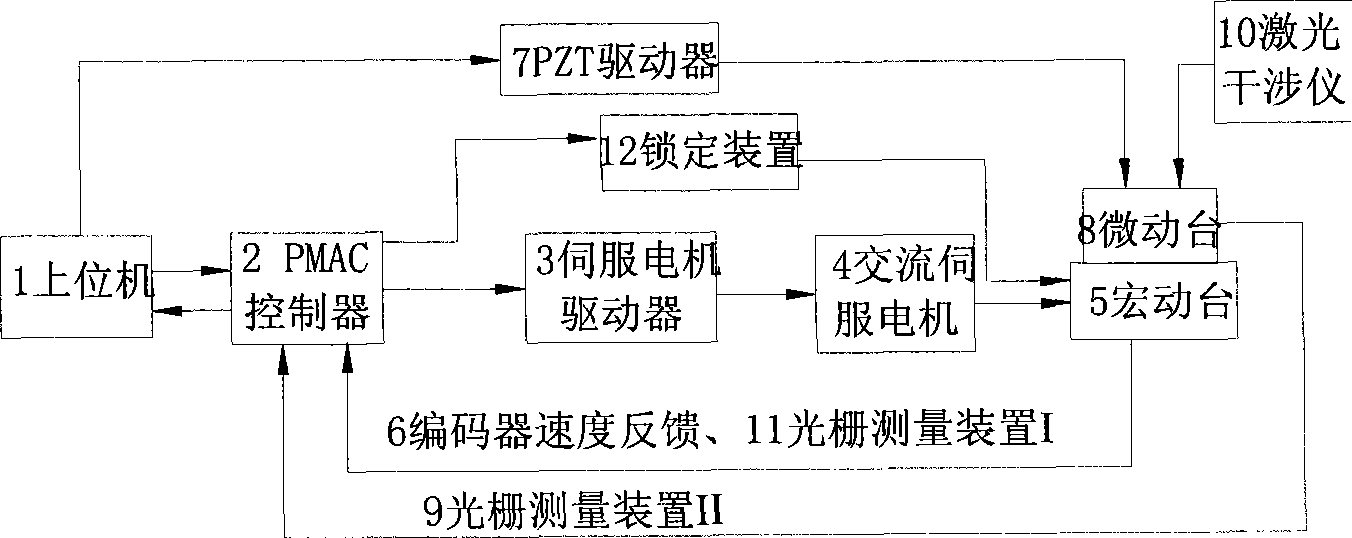

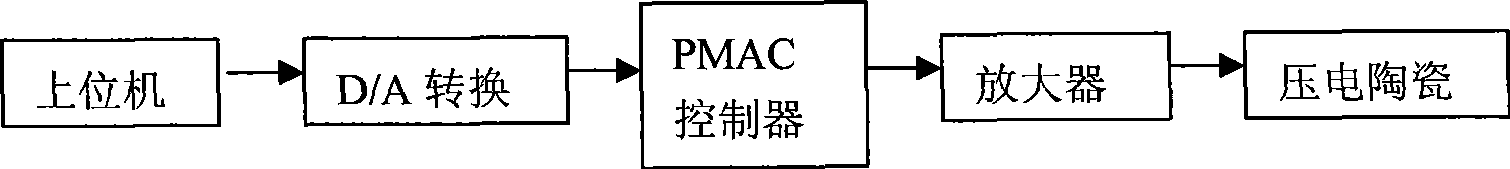

InactiveCN101369155AReduce vibrationReduce positioning errorsControl using feedbackTotal factory controlHardware structureGrating

The invention relates to a locking control method of a large-travel nano-displacement and positioning macro-motion table as well as a system thereof. The method comprises the operating steps: (1) a communication interface of a computer (upper computer ) sends an instruction for controlling, firstly, a macro-positioning system is started up to drive the macro-motion table and a micro-motion worktable to move together, and the macro-positioning is finished when the detected positioning error is smaller than the switching threshold value; (2) the computer controls and locks the macro-motion worktable, and is switched to a micro-positioning system dynamically in the meanwhile; and (3) the micro-positioning system controls the micro-motion worktable to further reach the target location required by the system and complete the positioning. The system mainly comprises: the macro-motion table and the micro-motion worktable as well as corresponding driving systems; a grating feedback system; a PMAC controller; a laser interferometer calibration system; a computer system; and a vibration isolation and noise elimination device (an air floatation vibration isolation platform) and the like. The hardware structure of the existing system is configured (a piezoelectric ceramic driving device) by adopting the method as required, when the macro-motion table meets the positioning requirements and stops the movement, piezoelectric ceramics lock the table, thereby improving the positioning accuracy of the system.

Owner:SHANGHAI UNIV

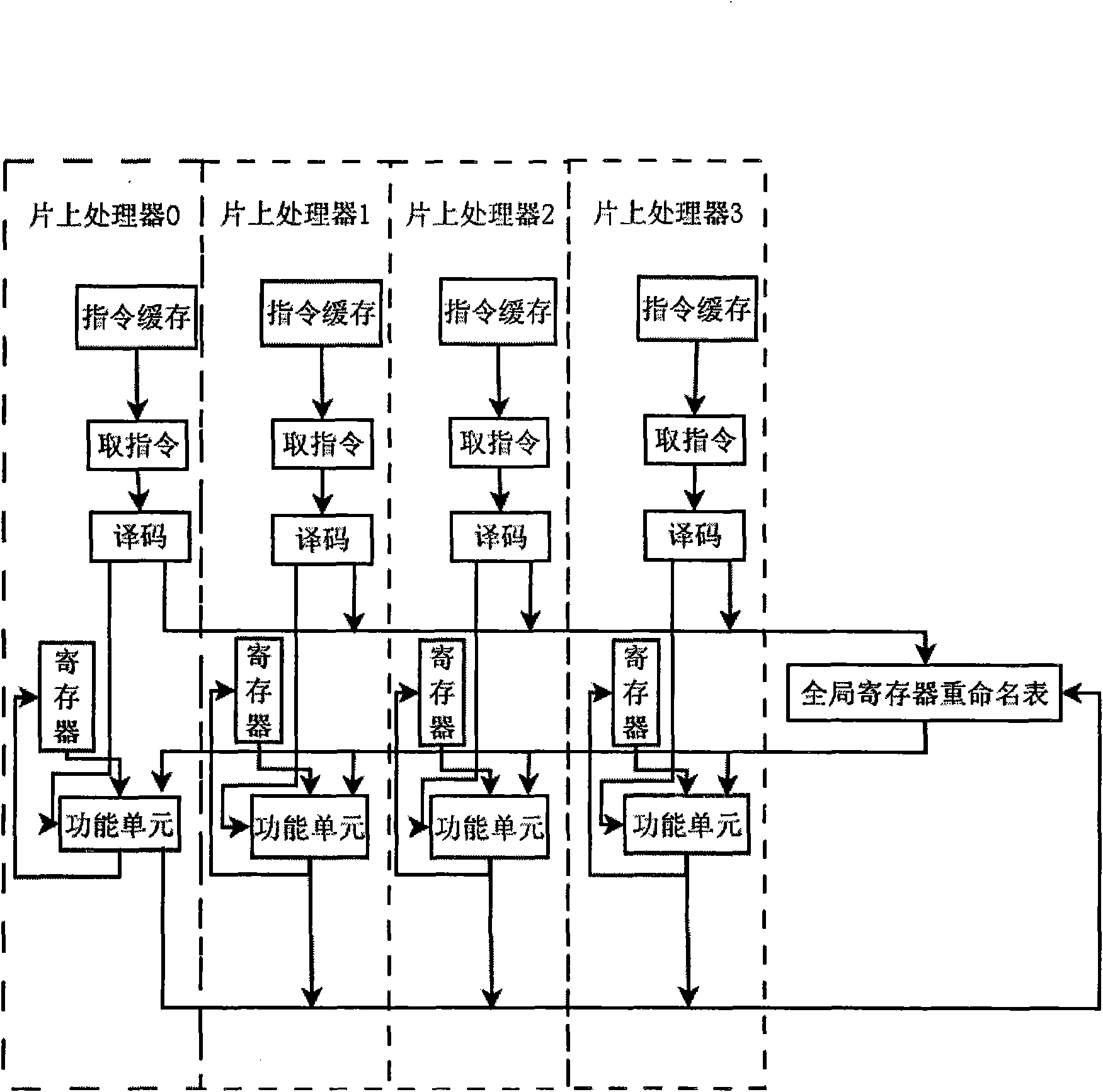

Implementation method of rename table of global register under on-chip multi-processor system framework

InactiveCN101582025AResolve dependenciesReduce trafficConcurrent instruction executionHardware structureProcessing Instruction

The invention relates to the technical field of on-chip multi-processor system structure, aiming at providing an implementation method of a rename table of a global register under on-chip multi-processor system framework. The method comprises the steps: designing the rename table of the global register; processing the dependency relationship 'writing-after-writing' of command; processing the dependency relationship 'writing-after-reading' of command; acquiring operand; writing back results; and submitting the command. As the rename table of the global register is used by the method, the dependency relationship of the commands of different processors can be recorded, and the dependency of 'writing-after-reading' and 'writing-after-writing' can be solved; the operand of the commands of the different processors can be maintained and transmitted through the rename table of the global register, so that the internuclear communication volume can be reduced; as hardware configuration used by the rename table of the global register is a logical table, the structure is simple, the complexity of hardware is low, the area of the rename table of the global register is only 1% of that of one on-chip processor, and tiny area cost is caused.

Owner:ZHEJIANG UNIV

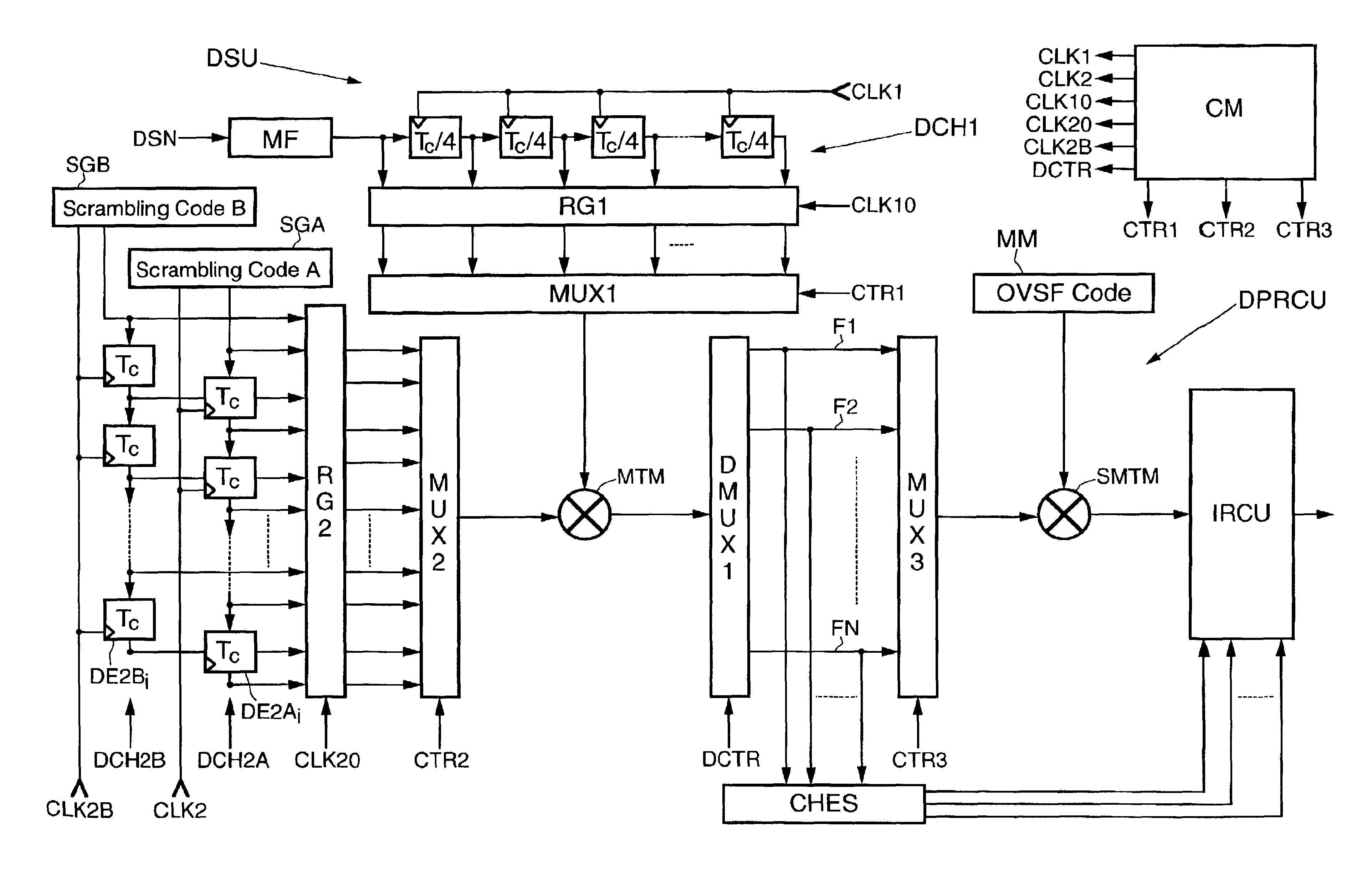

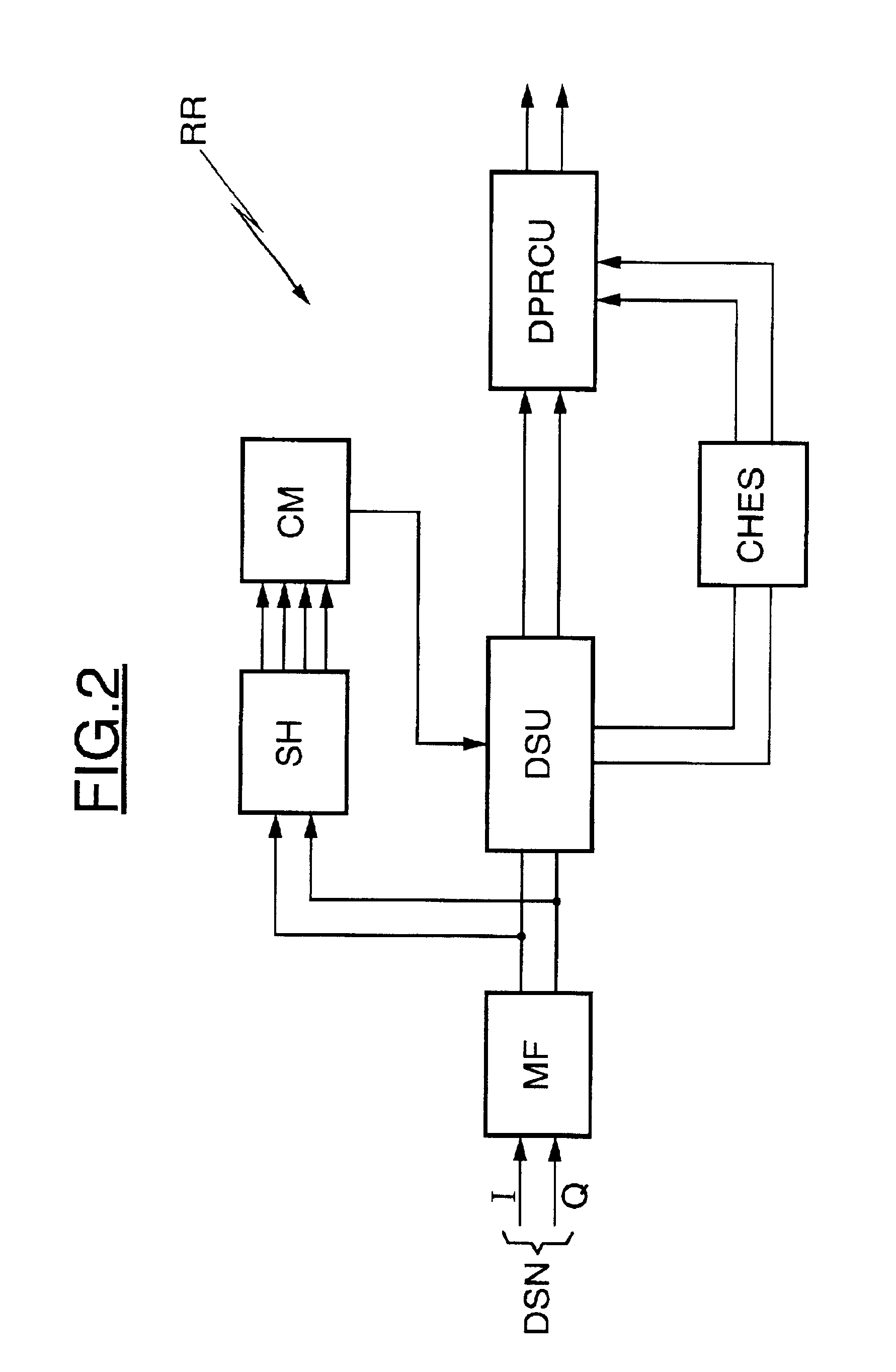

Rake receiver for a CDMA system, in particular incorporated in a cellular mobile phone

A rake receiver uses a delayed version of the received sequence and a delayed version of a scrambling code. The flexible hardware structure of the time-aligning and descrambling unit includes at least two delay chains and one multiplier. By controlling two multiplexers, the delayed versions of the received sequence can be multiplied with an arbitrary scrambling code having an arbitrary phase. During one chip period, one multiplication is performed for each path to be processed.

Owner:STMICROELECTRONICS SRL

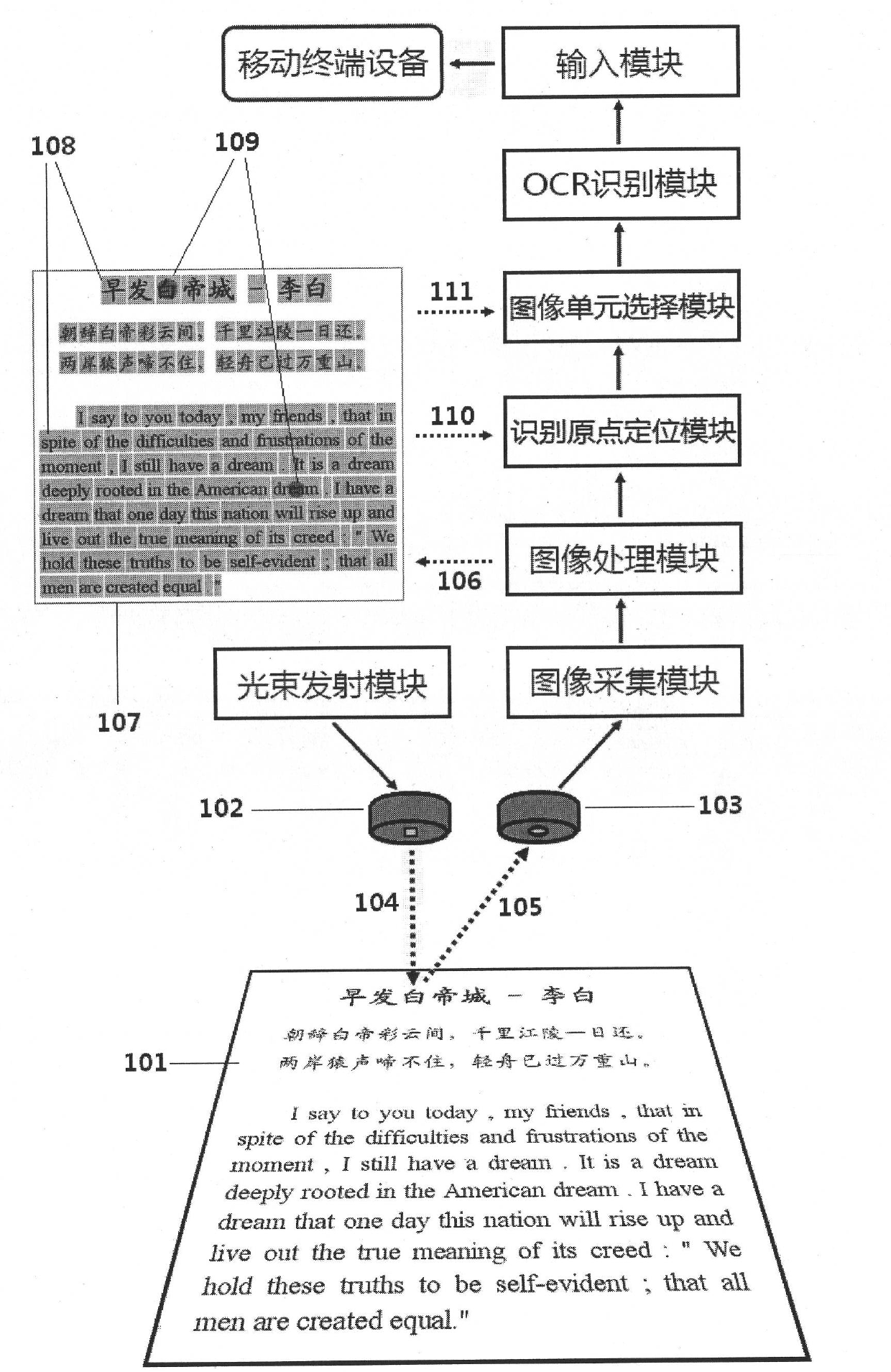

Character recognition input system using optical localization and method thereof

InactiveCN102169541AAccurate identificationEasy to operateCharacter and pattern recognitionHardware structureImaging processing

The invention provides a character recognition input system using optical localization and a method thereof. The system is provided with two optical operation devices on a hardware structure, namely a light beam emitting device and a photographic device like a camera. The construction and work method of the system are as follows: 1, the light beam emitting module starts a light beam emitting device to form a light spot on the surface of a text; 2, an image acquiring module starts the photographic device to obtain a text image; 3; an image processing module divides the text image by using a word, an individual character and a symbol as an elementary unit to form an image unit arrangement; 4, a recognition original point locating module defines the position of a light spot in the text image as a recognition original point; 5, an image unit selecting module selects single or a plurality of image units in the image unit arrangement by using the recognition original point as a start point; 6, an OCR (optical character recognition) module recognizes the selected image unit as the character and symbol; and 7, an input module inputs the character and symbol in relative software in a mobile terminal apparatus. The character recognition input system using optical localization and the method thereof are suitable for various mobile terminal apparatuses.

Owner:郝震龙

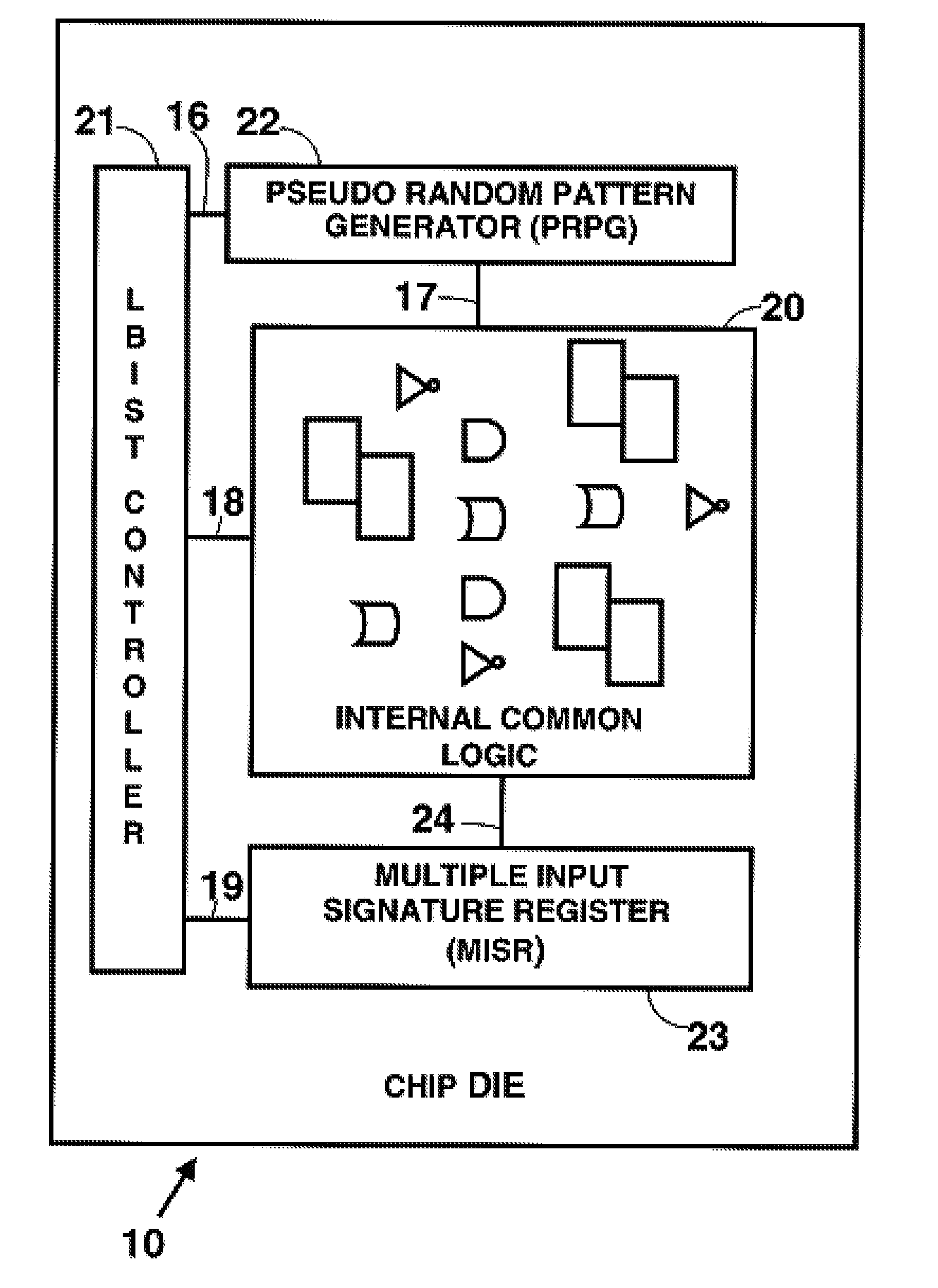

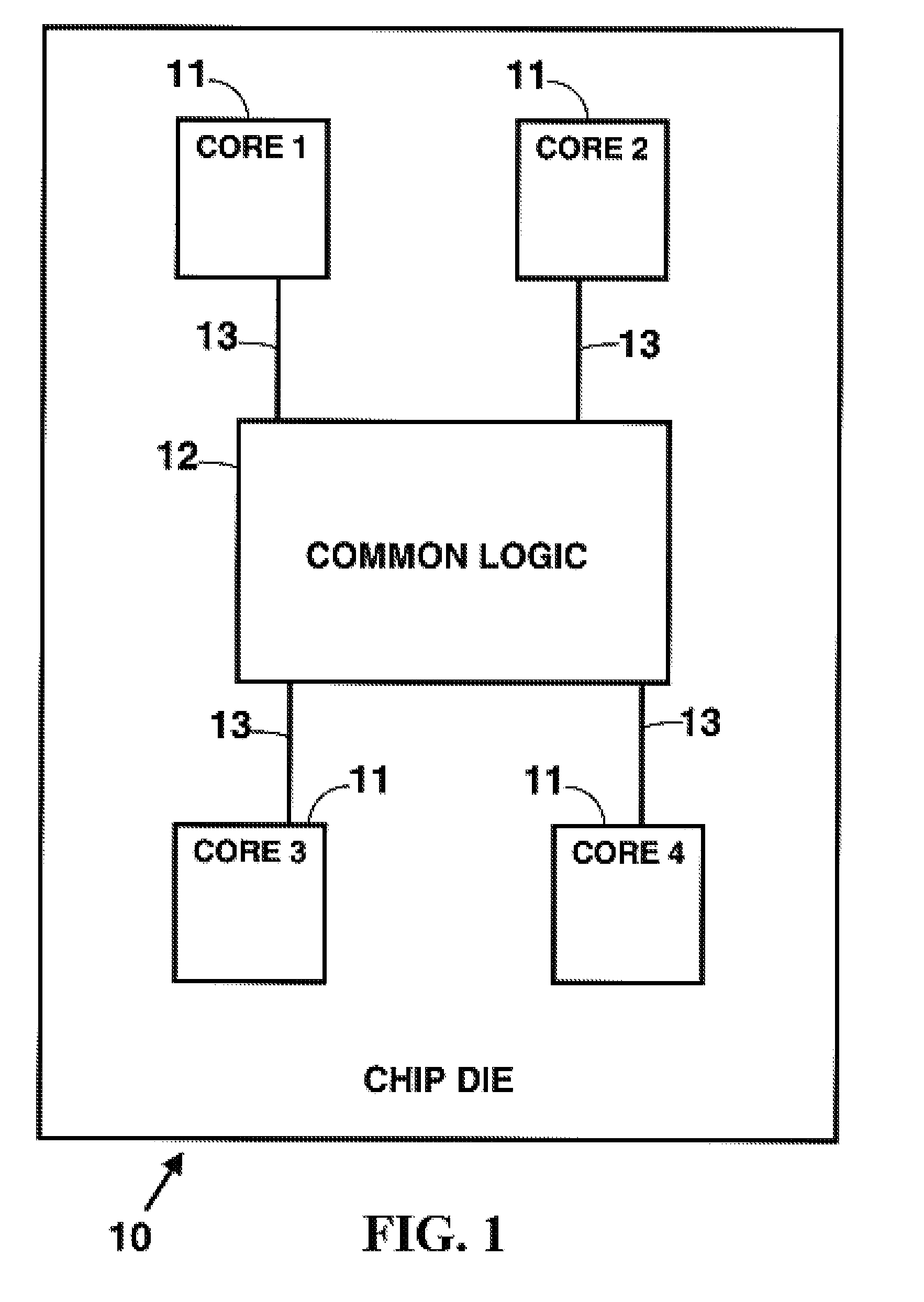

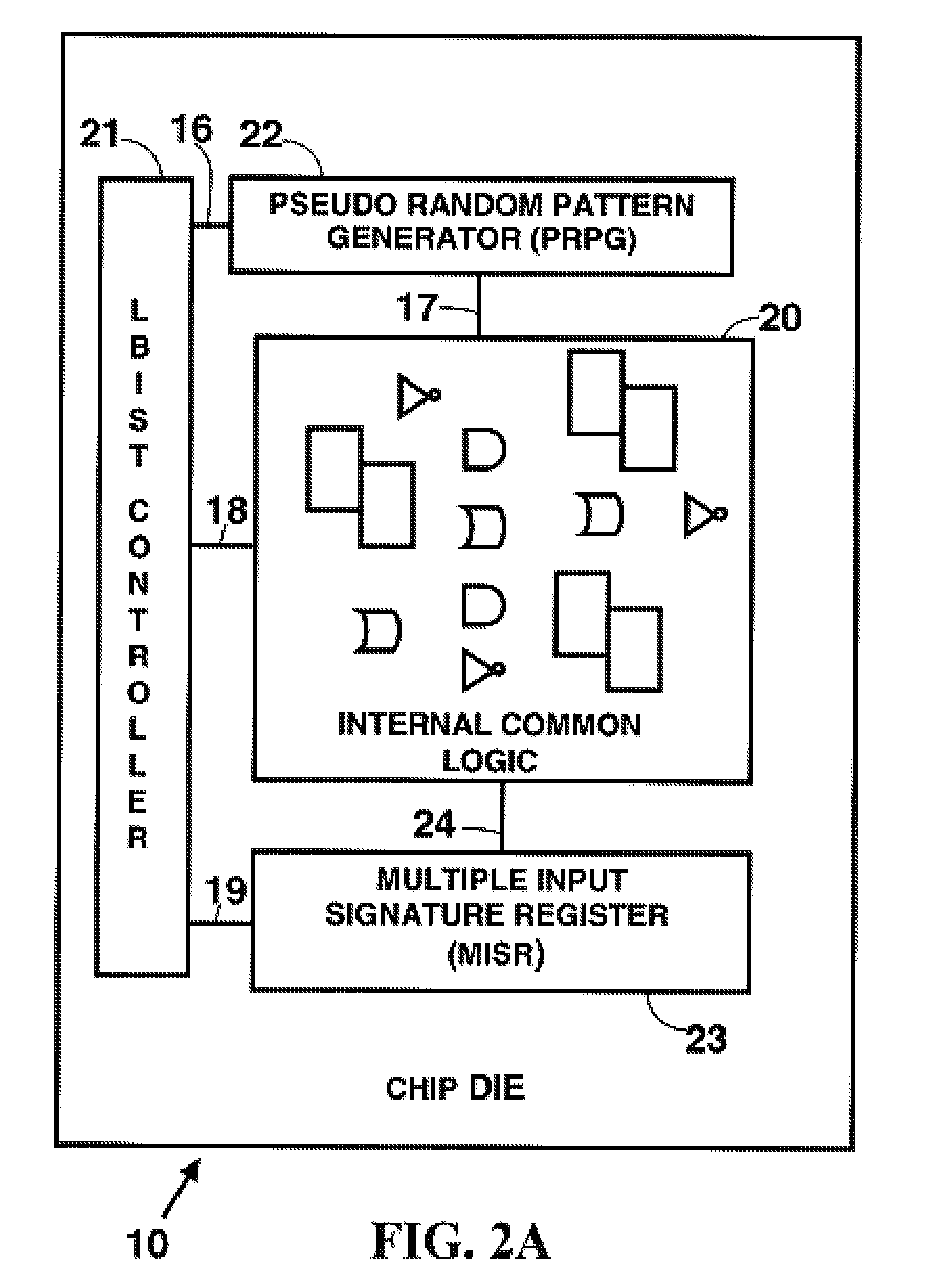

Method and System for Formal Verification of Partial Good Self Test Fencing Structures

ActiveUS20080276144A1Reduces chip test coverageElectronic circuit testingHardware structureCommon logic

The concept of applying fencing logic to Built-In Self Test (BIST) hardware structures for the purpose of segregating defective circuitry and utilizing the remaining good circuitry is a well known practice in the chip design industry. Described herein is a method for verifying that any particular implementation of partial fencing logic actually provides the desired behavior of blocking down-stream impact of all signals from fenced interfaces, and also ensuring that the partial fencing does not inadvertently preclude any common logic from being fully tested.

Owner:TWITTER INC

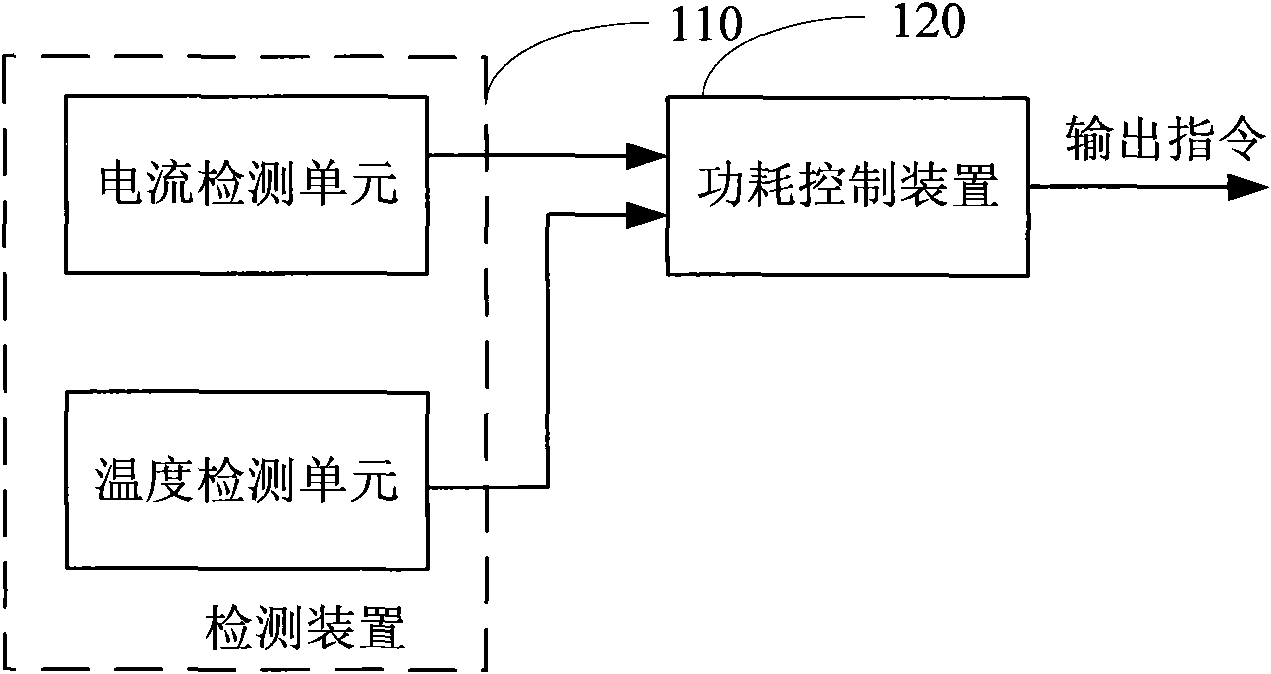

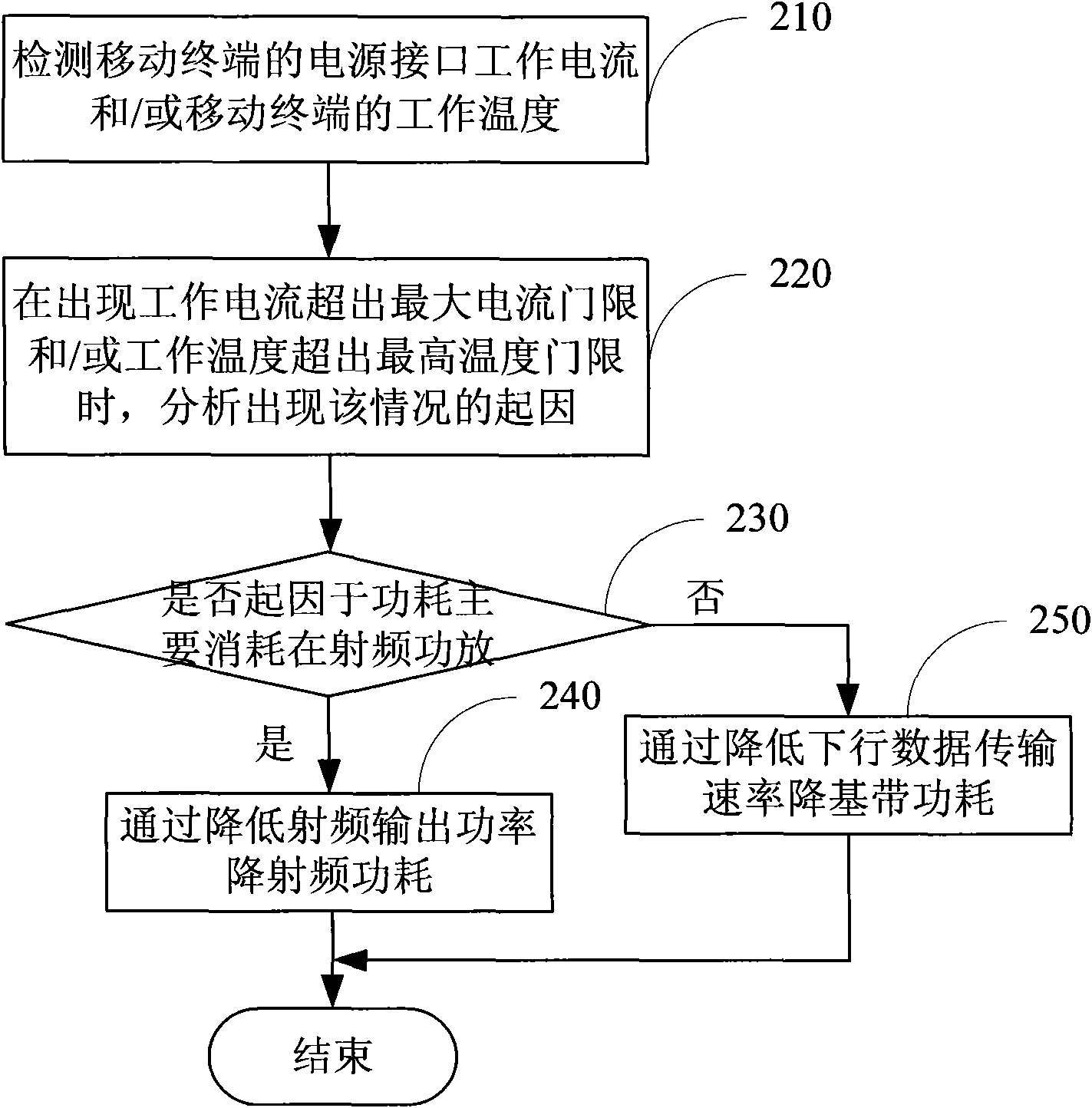

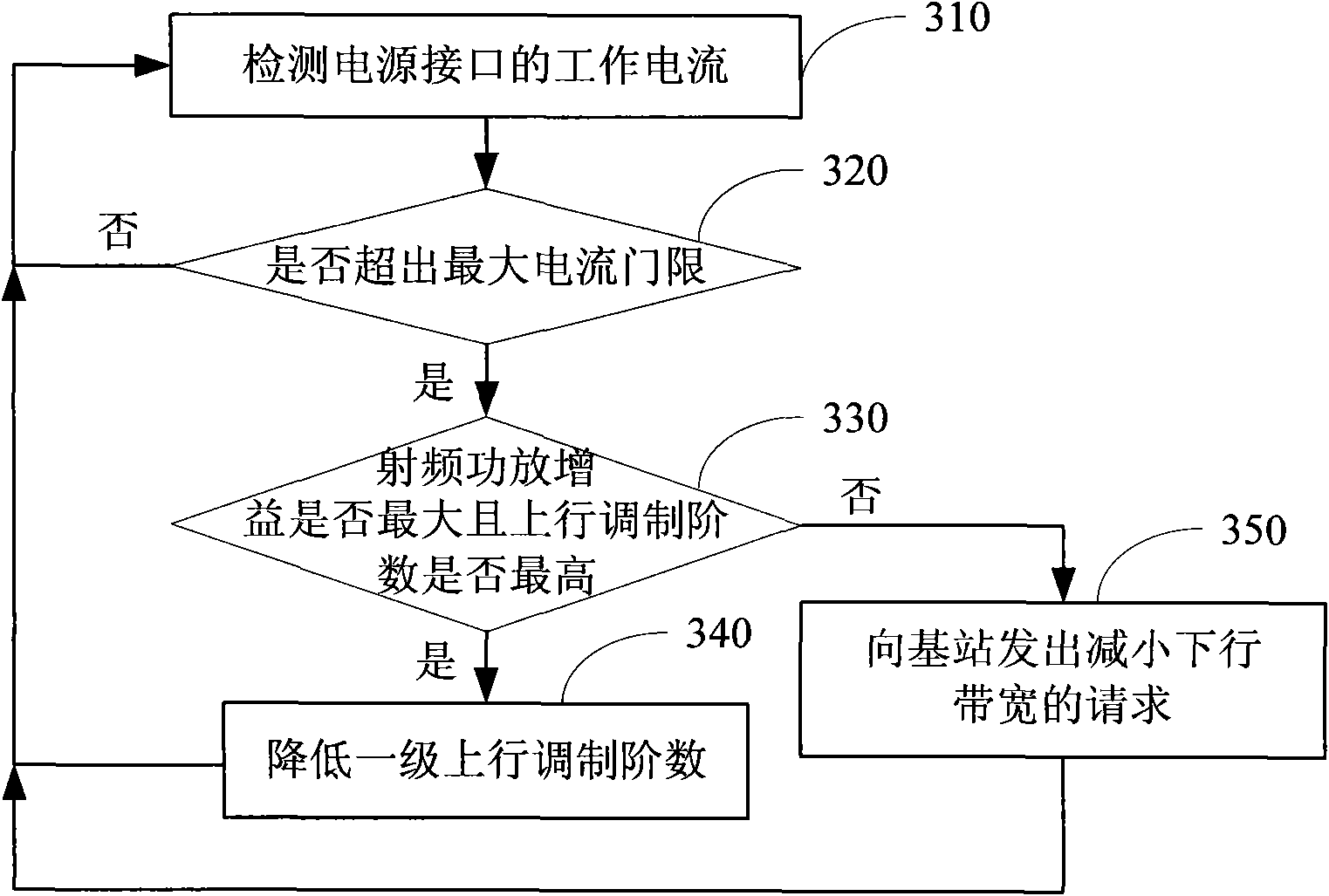

System and method for controlling power consumption of mobile terminal

ActiveCN101938819AExtended working hoursSolve the problem that power consumption cannot be effectively controlledEnergy efficient ICTPower managementHardware structureWorking temperature

The invention discloses a system and a method for controlling the power consumption of a mobile terminal. The method comprises the following steps of: detecting working temperature and / or the working current of a power interface, and judging whether the working temperature exceeds the maximum temperature threshold or not and / or whether the working current exceeds the maximum current threshold or not; and if detecting that the working temperature exceeds the maximum temperature threshold and / or the working current exceeds the maximum current threshold, reducing the power consumption of a radio-frequency power amplifier or reducing the power consumption of a base-band part. The system and the method solve the problem that the power consumption of a broad-band mobile communication terminal cannot be effectively controlled on various application occasions, and adjust the power consumption of the terminal in real time by detecting the working current and the working temperature without adding the hardware structure of the terminal or increasing the software algorithm complexity so as to meet the requirements of the limit on the maximum current of various interface protocols and the limit on the shell temperature of various terminal structures.

Owner:ZTE CORP

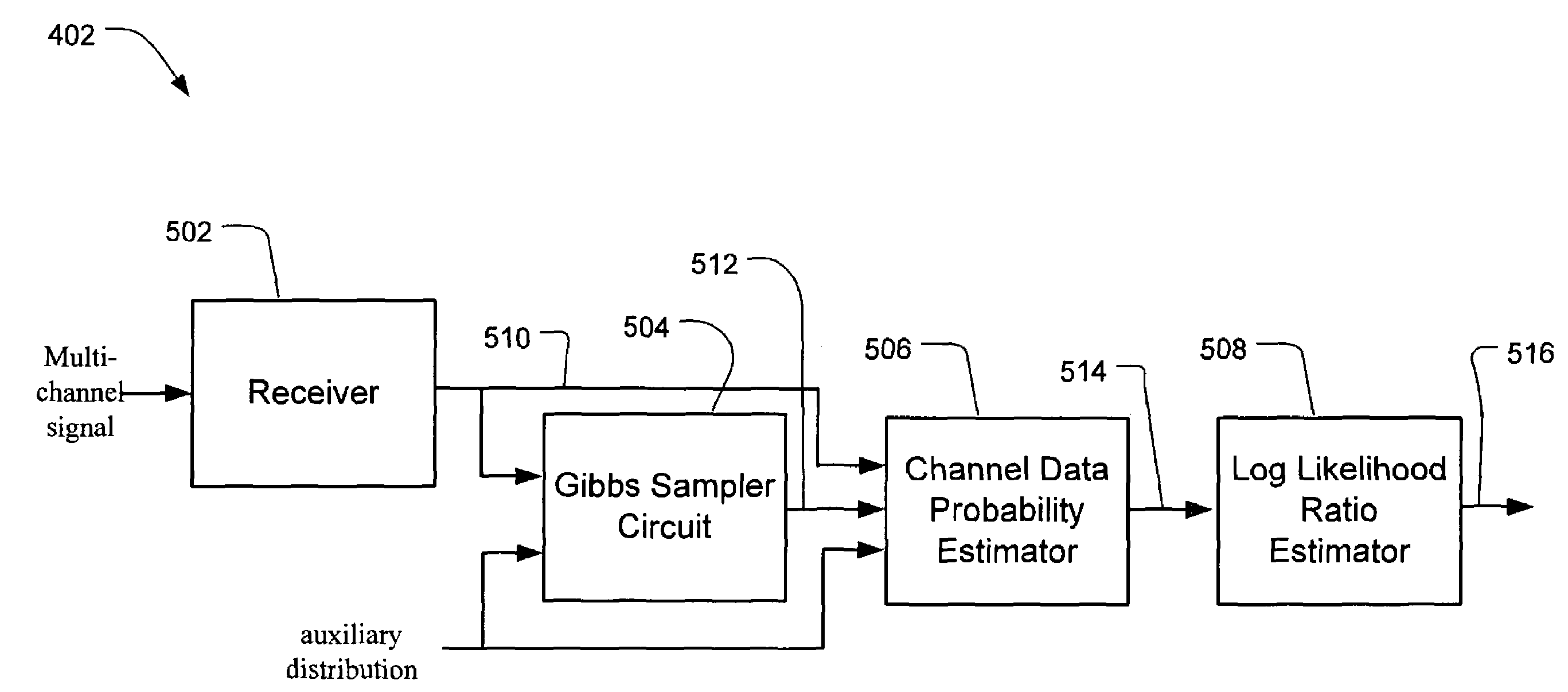

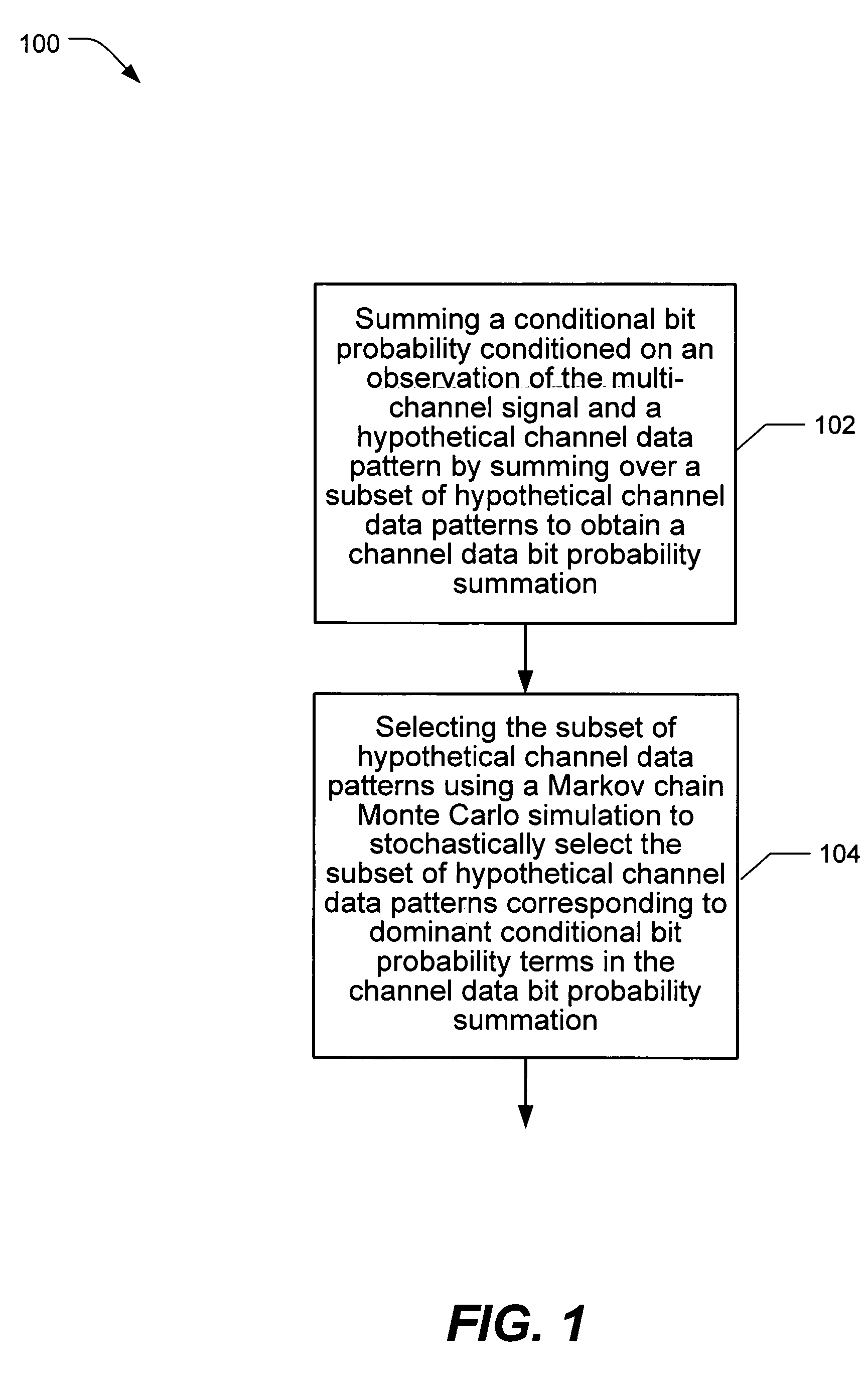

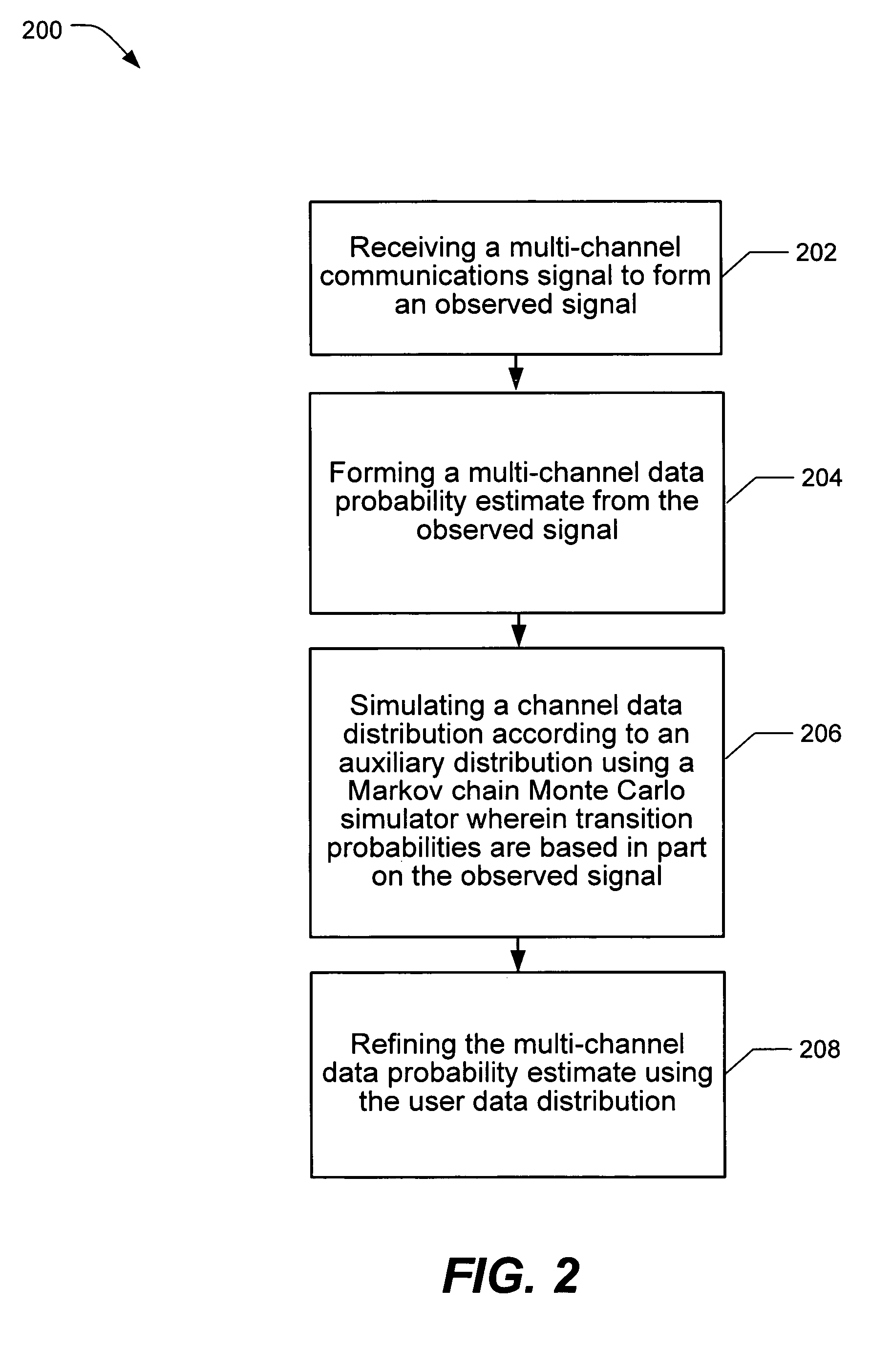

Detector and method for estimating data probability in a multi-channel receiver

InactiveUS7457367B2Improve performanceTransmission systemsFrequency-division multiplex detailsPattern recognitionChannel data

A detector and method for estimating channel data probability in a multi-user or multiple-input multiple-output communication system includes summing conditional bit probabilities conditioned on hypothetical channel data patterns over stochastically selected hypothetical channel data patterns. Various detailed hardware structures and circuits are also described.

Owner:THE UNIV OF UTAH +1

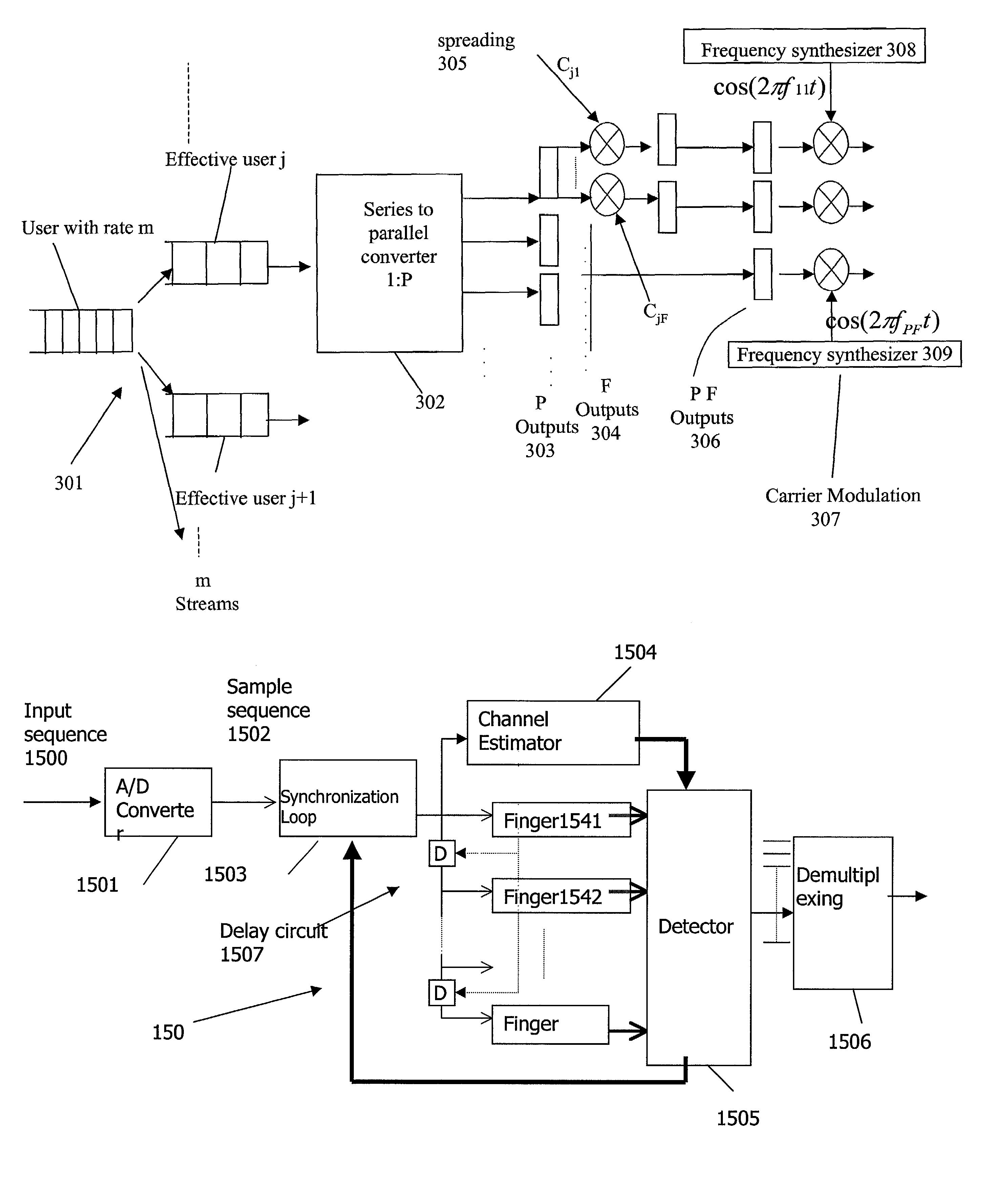

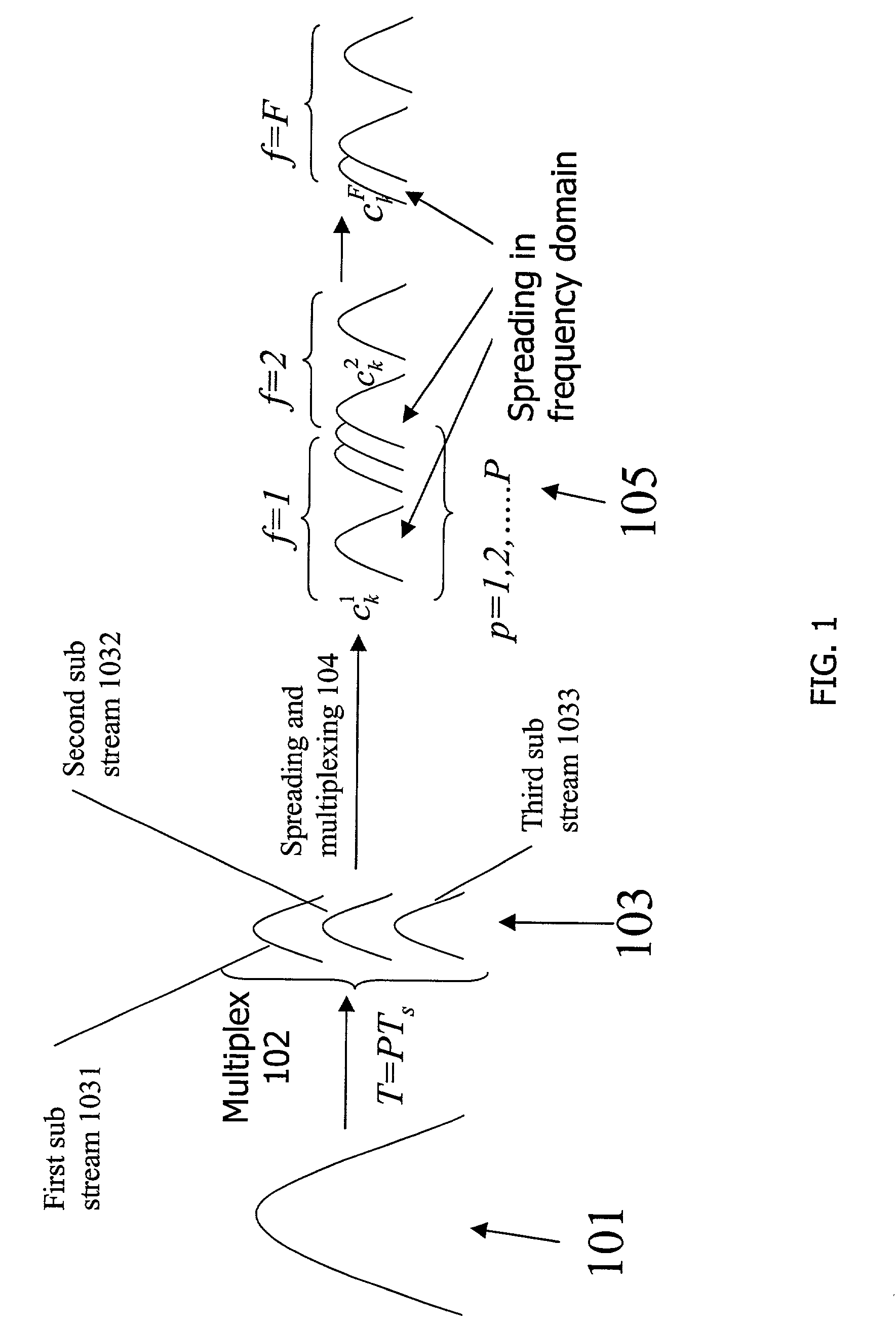

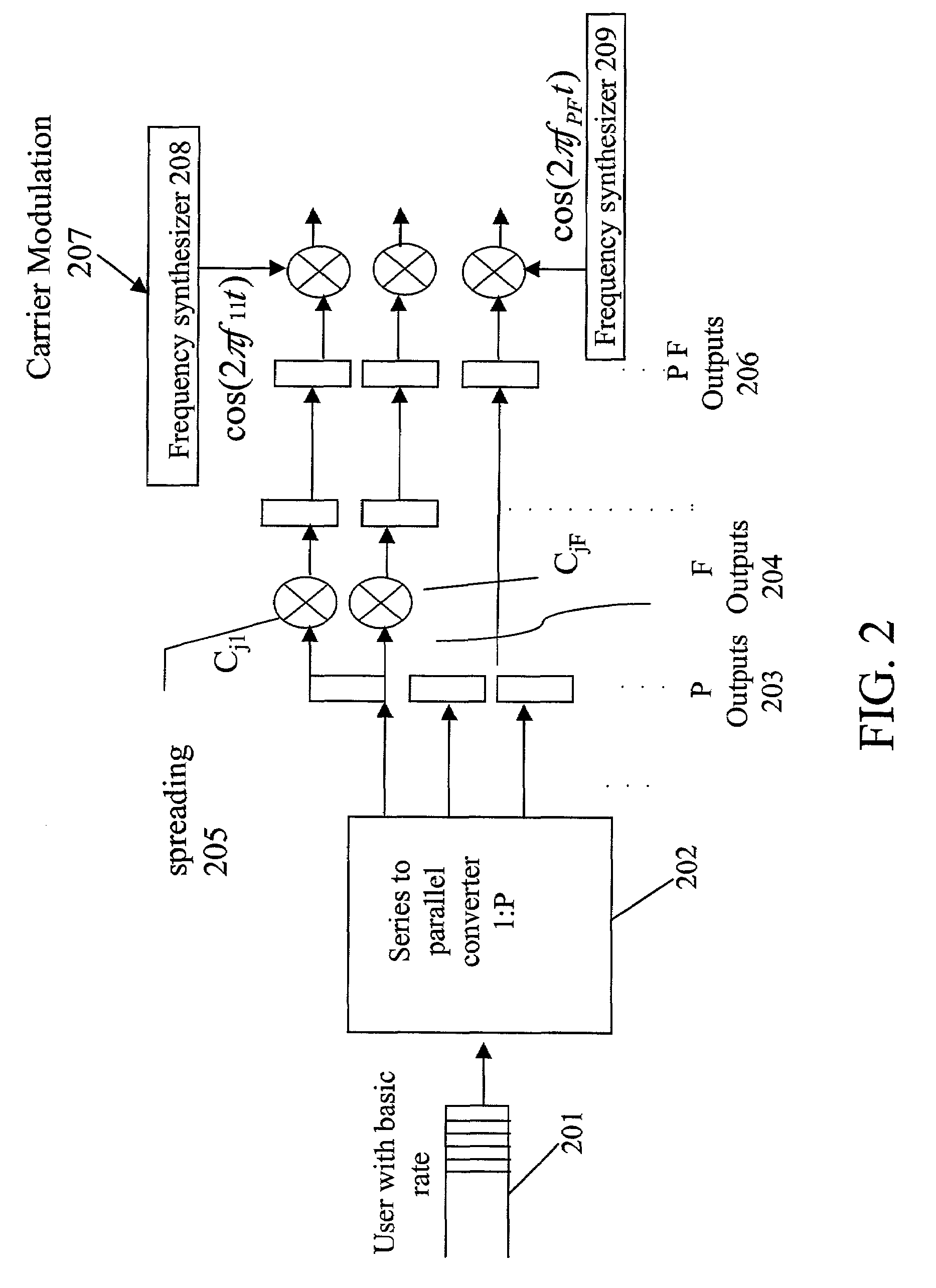

Programmable transceiver structure of multi-rate OFDM-CDMA for wireless multimedia communications

ActiveUS7035201B2Realize transmissionRadio transmissionOrthogonal multiplexHardware structureComputer hardware

Two multi-rate transmission schemes, multi-code (MC) and variable-spreading-length (VSL) code, for realizing multimedia communications on three types of OFDM-CDMA systems are proposed. These systems can be integrated into a programmable structure such that the operation can be controlled and adjusted by system parameters and thus the transceiver can be used in different systems without changing the fundamental hardware and software architecture, which serves the trend of software-radio for future application. A transceiver architecture of multi-rate OFDM-CDMA systems is illustrated and showed its programmability such that the general system can operate under different scenarios with a common hardware structure and reconfigure by software implementation.

Owner:MEDIATEK INC

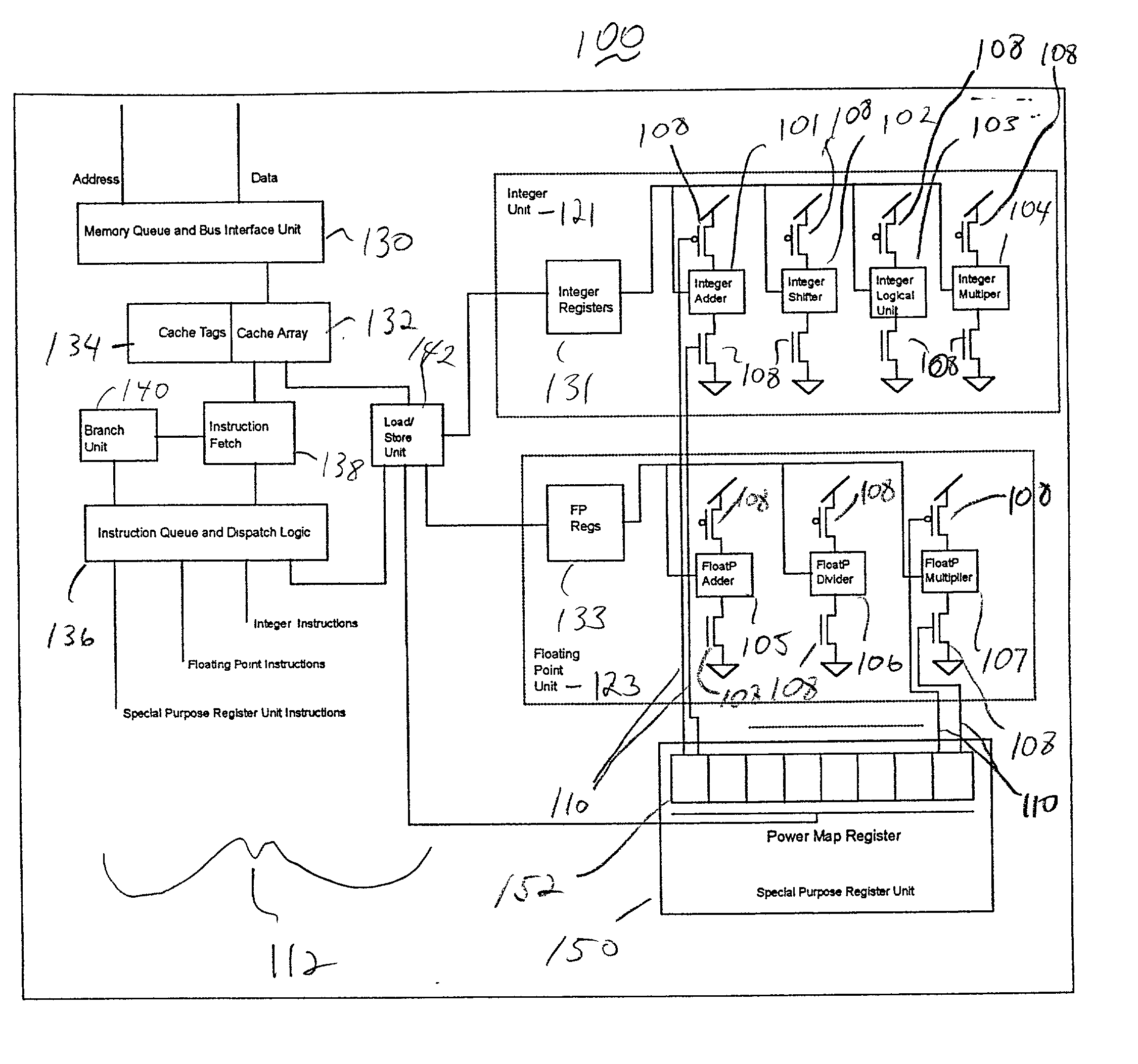

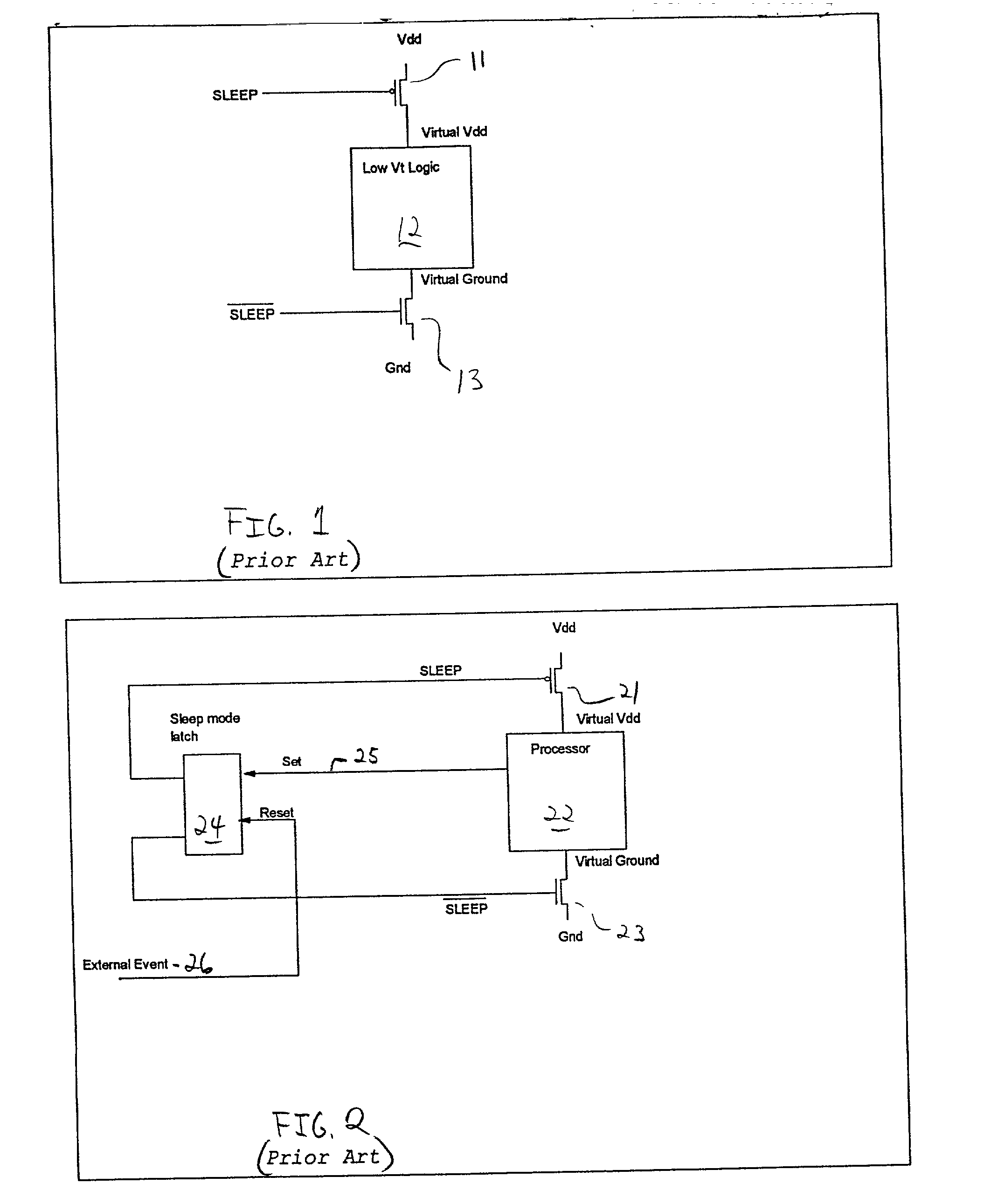

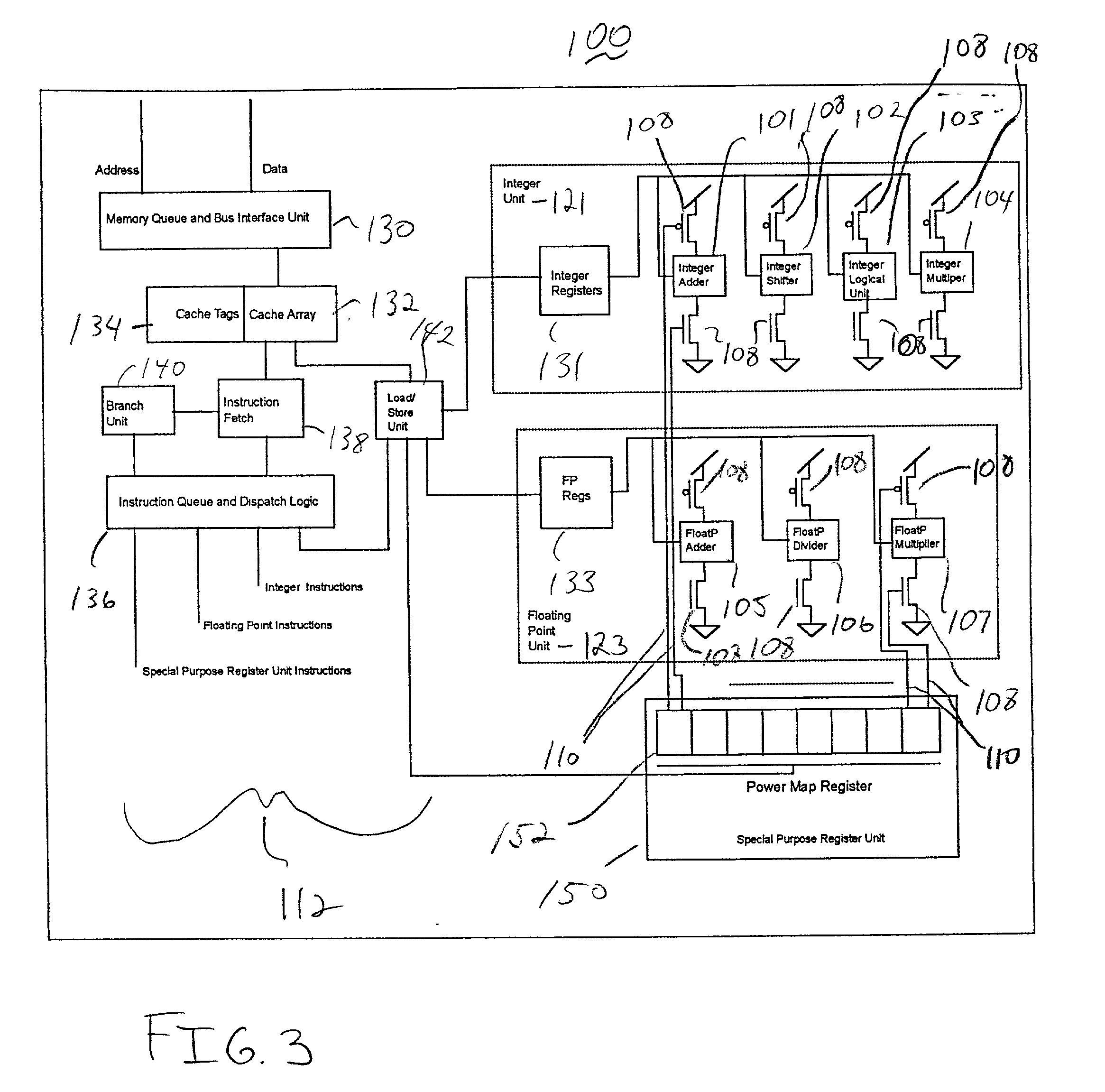

Power control of a processor using hardware structures controlled by a compiler with an accumulated instruction profile

InactiveUS20020112193A1Energy efficient ICTVolume/mass flow measurementHardware structureProgram instruction

A microprocessor includes a logic circuit. A selection device is coupled to the logic circuit, and the selection device provides switching of on / off states of the logic circuit based on a stored logical value. A program instruction is included which sets the stored logical value to control the on / off states of the logic circuit based on anticipated usage of the logical circuit in accordance with an instruction sequence of the microprocessor.

Owner:IBM CORP

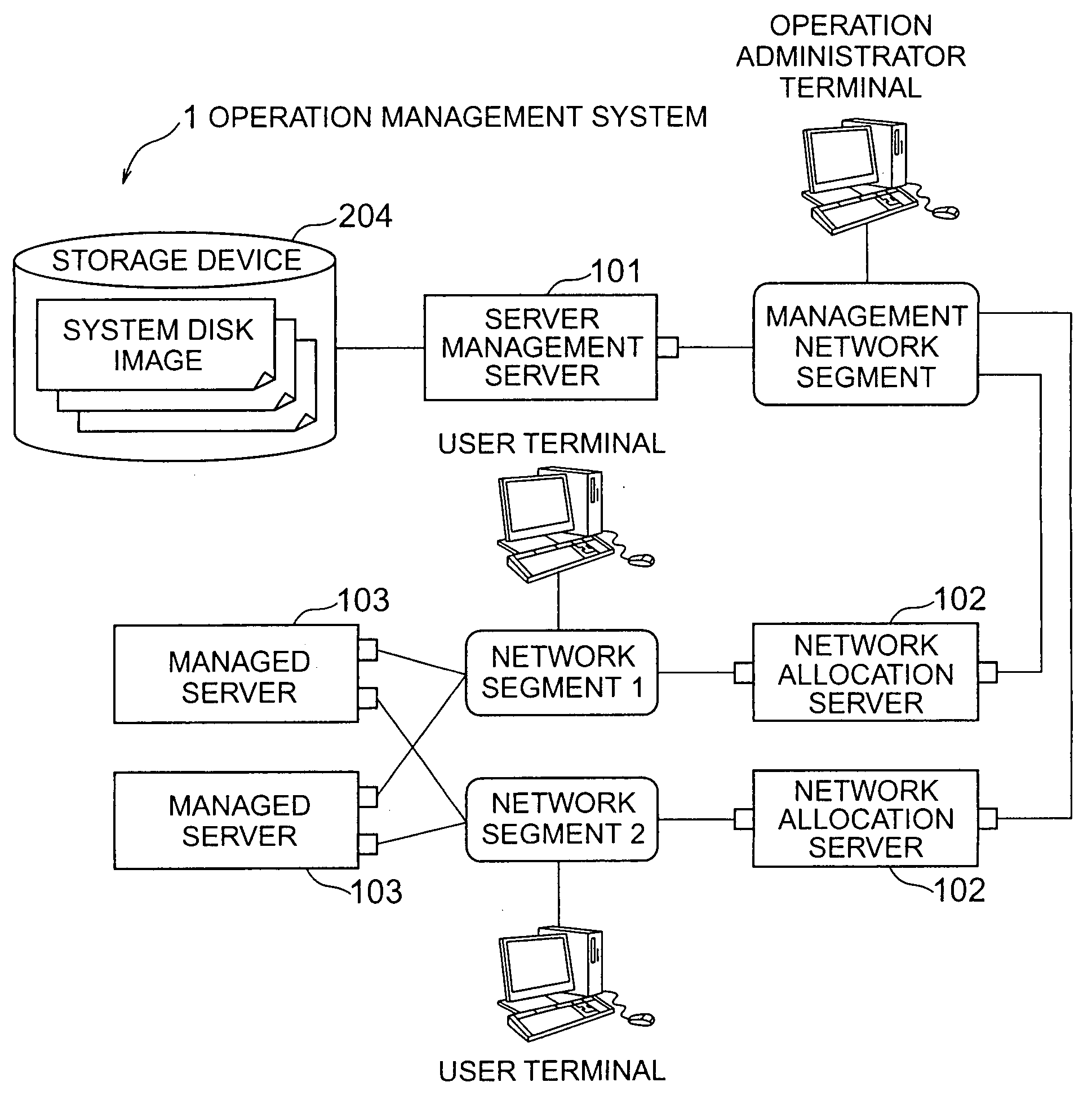

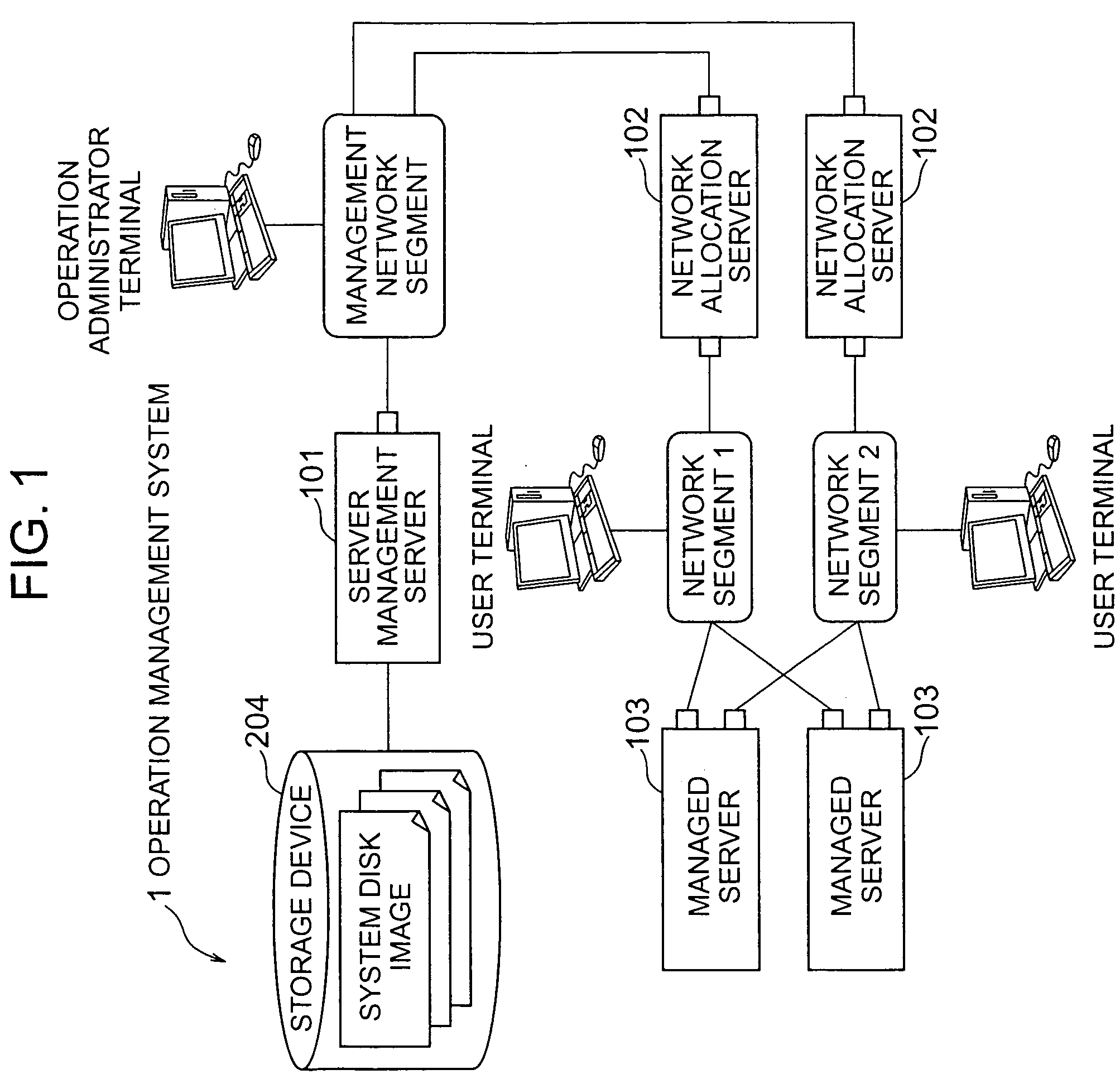

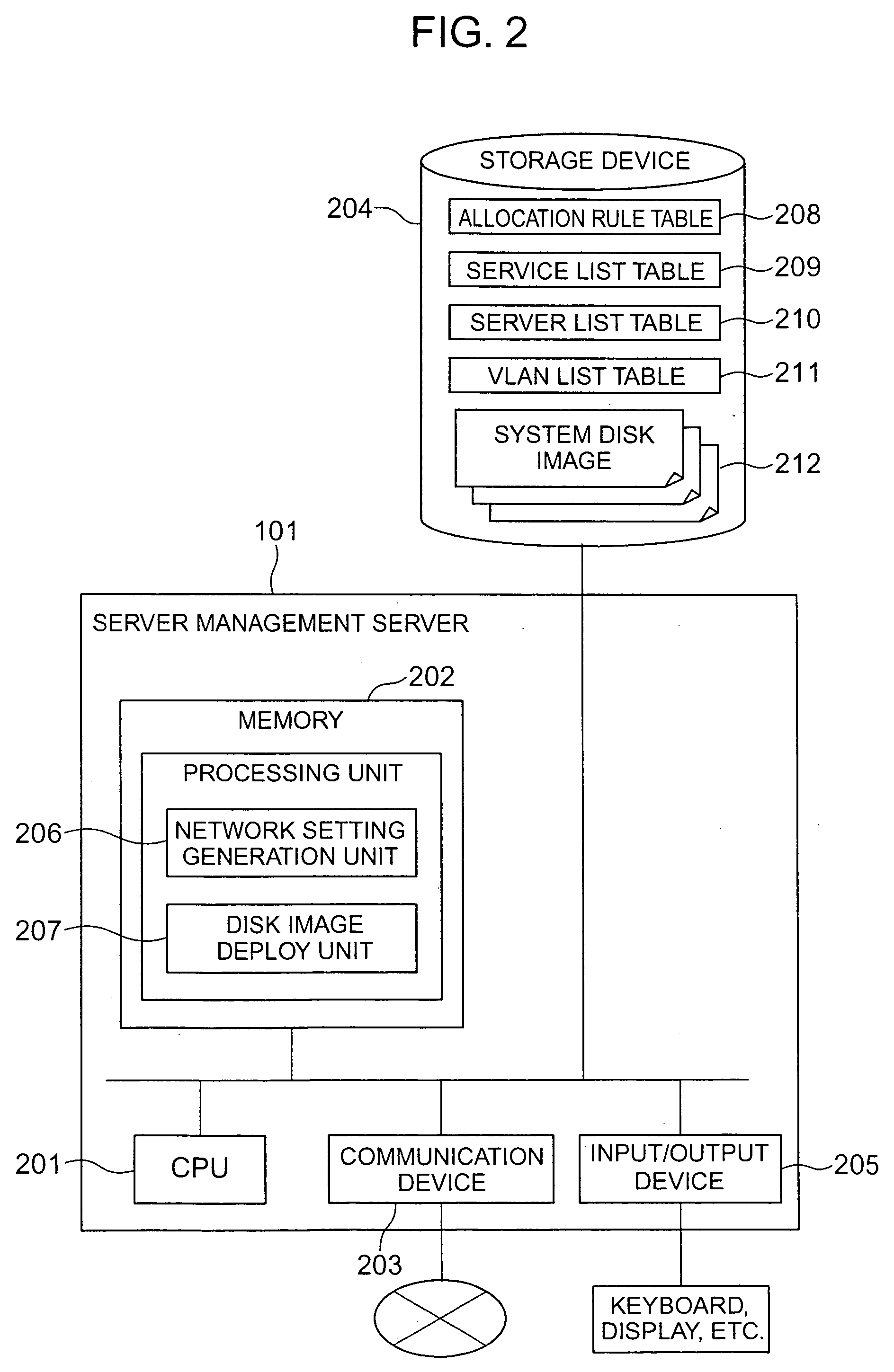

Operation management method, operation management program, operation management system and operation management apparatus

InactiveUS20080034077A1Reduce workloadSuppress system setting missDigital computer detailsResourcesHardware structureService provision

An operation management method wherein a storage device stores a plurality of pieces of first allocation information representative of a correspondence among at least business or service, network segments and logical addresses of networks, and when an instruction of setup for at least business or service provided by each managed computer is received from an external, an operation management apparatus generates a correspondence between the plurality of pieces of first allocation information and a plurality of pieces of second allocation information representative of a correspondence between the managed computers and a physical address of each of network connections. When a system configuration is changed, an operation object can be designated by using information such as business without depending upon a hardware structure.

Owner:HITACHI LTD

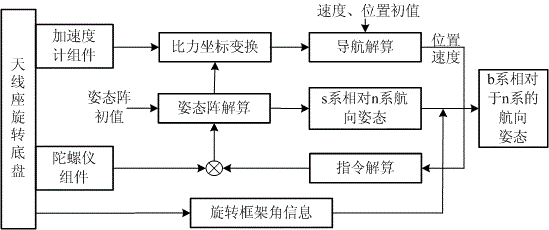

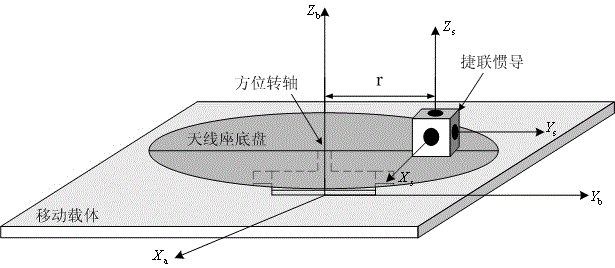

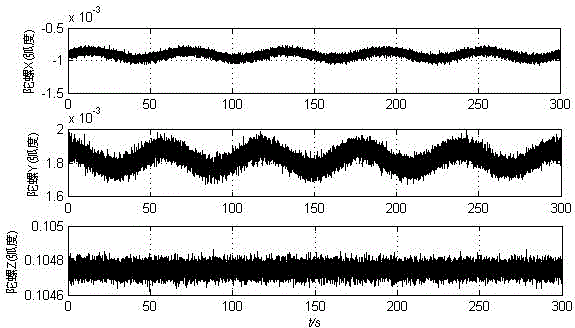

Strapdown inertial navigation initial alignment method for antenna tracking and stabilizing platform

InactiveCN103557876AAchieve conversionImprove ObservabilityNavigational calculation instrumentsNavigation by speed/acceleration measurementsHardware structureState variable

The invention belongs to the technical field of inertial navigation and also provides a strapdown inertial navigation initial alignment method for an antenna tracking and stabilizing platform, which aims to further improve the precision and the speed of initial alignment of a strapdown inertial navigation system. A kalman filter state equation with a speed error as a state variable and an observation equation with a speed error as an observation value are established, and a carrier misalignment angle is estimated by a kalman filter technology and is fed back into the system for implementing initial alignment of the system. The strapdown inertial navigation initial alignment method has the main advantages that under a condition that a conventional hardware structure of the system is not changed, the initial alignment of a rotating base is implemented by fully utilizing the structural characteristic of the antenna tracking and stabilizing platform, so that the observability of the strapdown inertial navigation system is improved, and furthermore, the precision of the initial alignment of the strapdown inertial navigation system is effectively improved.

Owner:SHANDONG UNIV OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com