Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

8552results about "Data conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

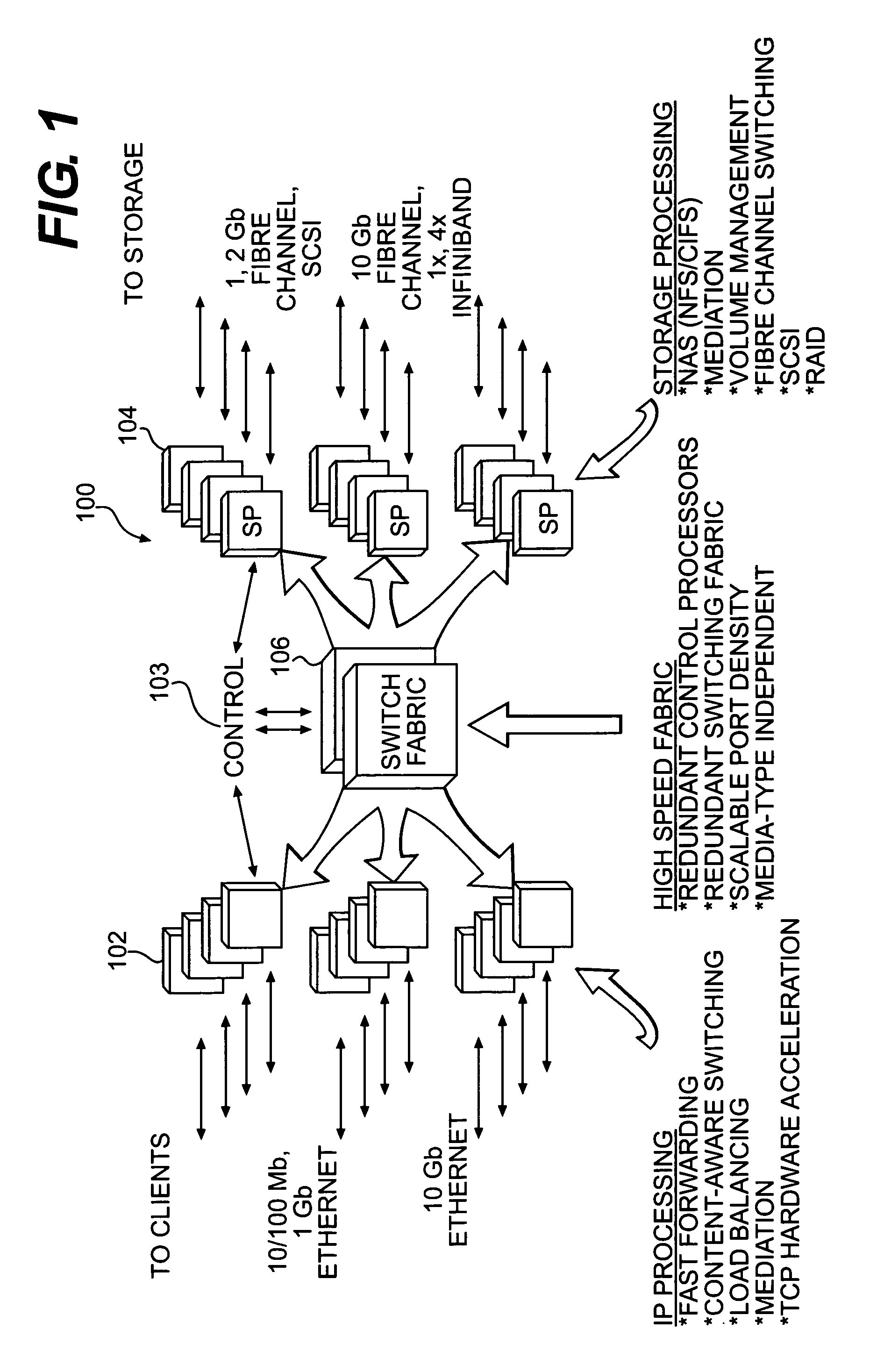

Virtual ports for data transferring of a data storage system

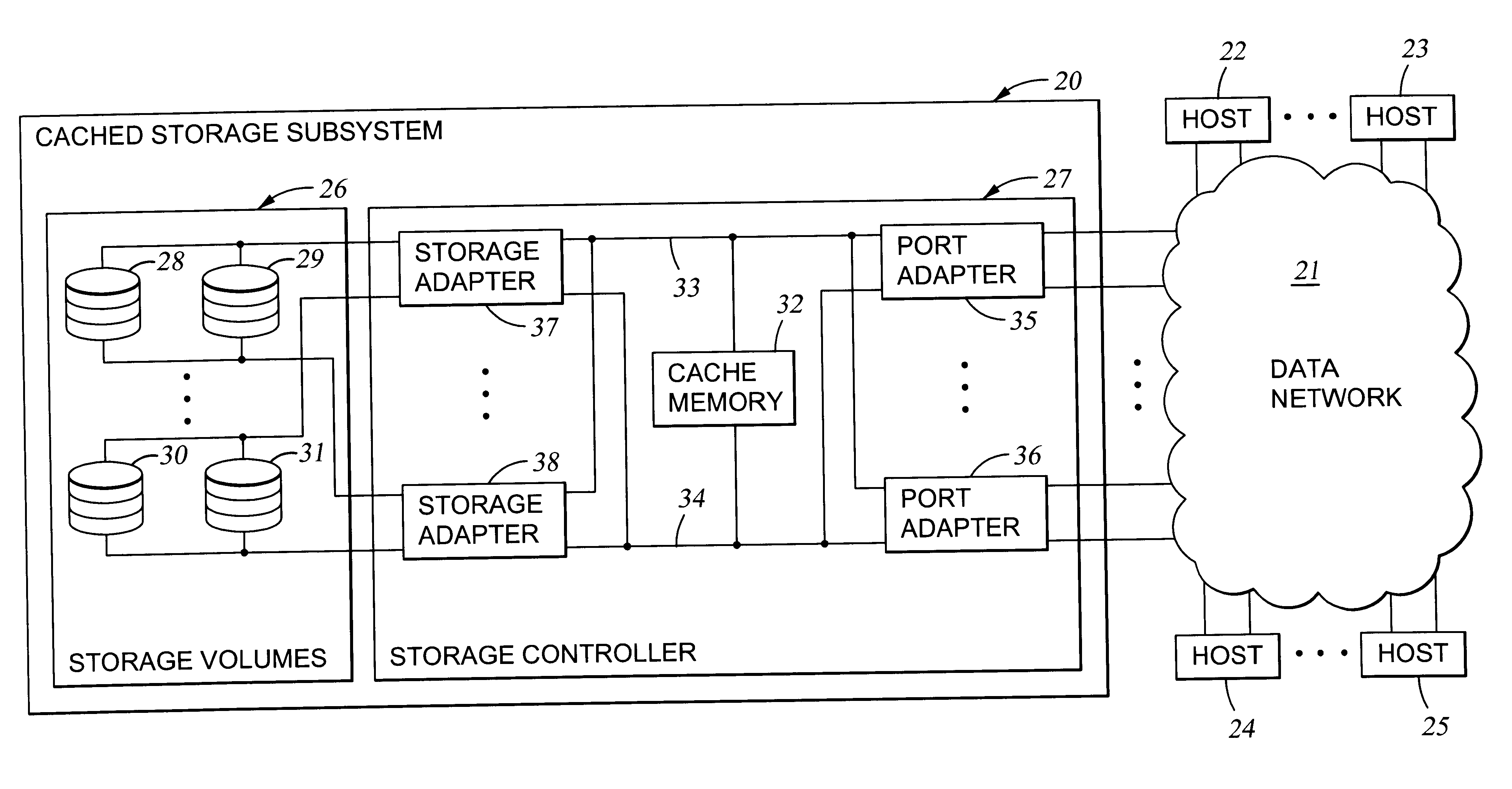

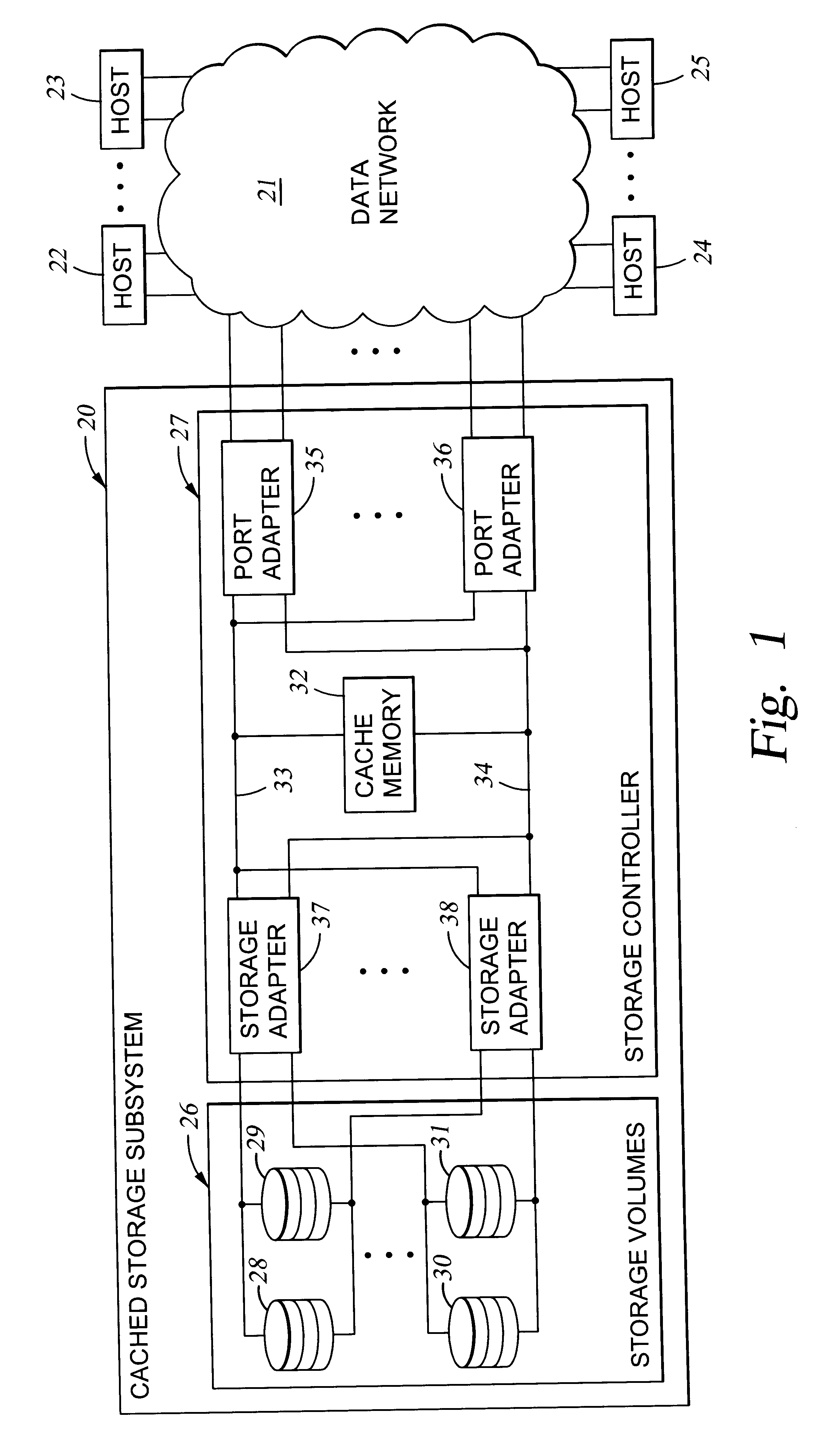

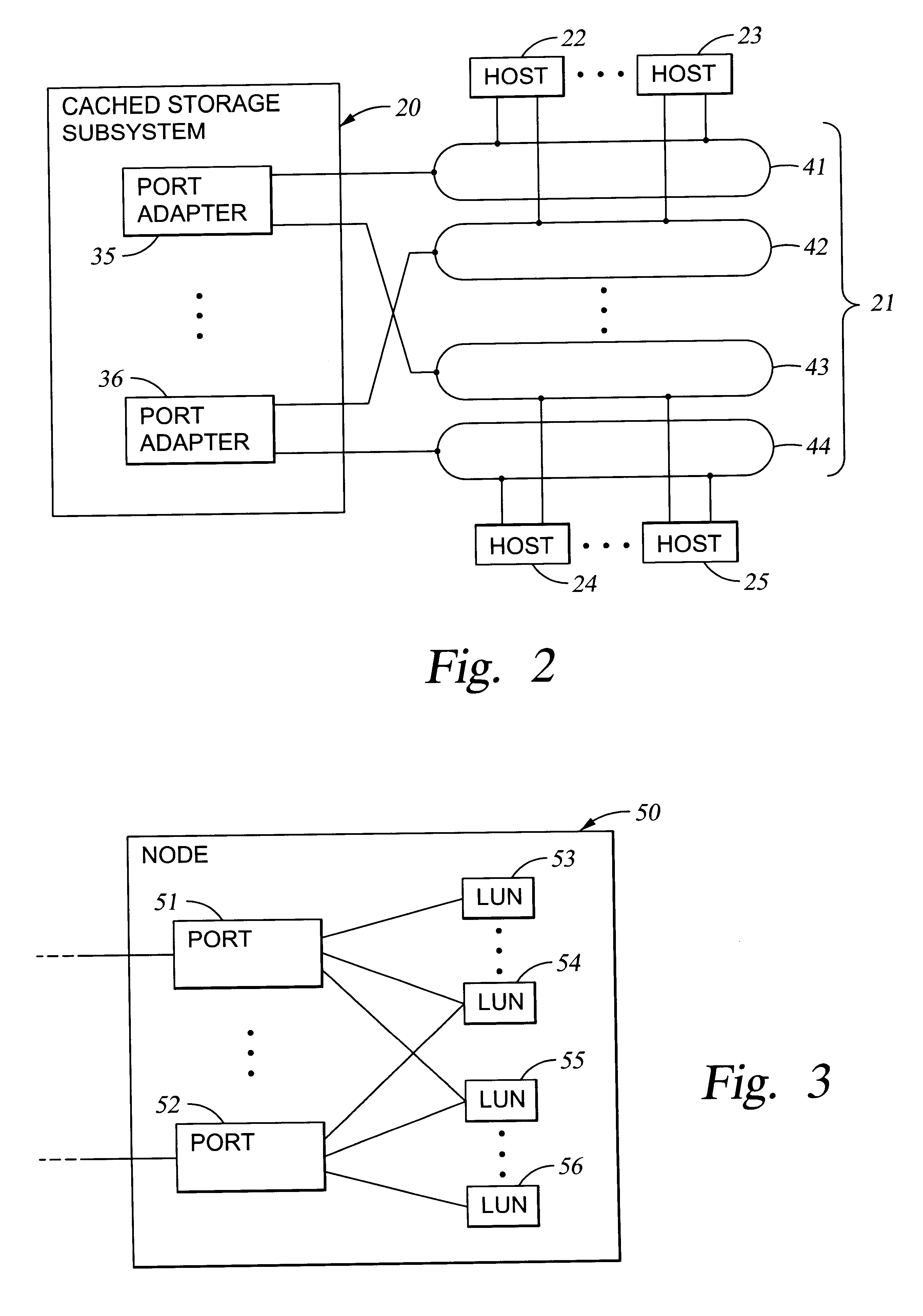

A storage controller has at least one physical data port for a data network including host processors. The storage controller is programmed to provide a plurality of virtual ports for access to storage, and a virtual switch for routing storage access requests from the physical port to the virtual ports. The virtual ports and the virtual switch are defined by software. The virtual ports appear to the hosts as physical ports in the data network. For example, in a Fiber-Channel network, the virtual ports have World Wide Names (WWNs) and are assigned temporary addresses (S_Ds), and the virtual switch provides a name server identifying the WWNs and S_IDs of the virtual ports. For convenient partitioning of storage among host processors, one or more virtual ports are assigned to each host, and a set of storage volumes are made accessible from each virtual port. A host can access storage at a virtual port only if the virtual port has been assigned to the host. Preferably, storage can be accessed through each virtual port by no more than one assigned host, although a shared volume may be accessible from more than one virtual port. The storage controller may provide a service for reporting to a host the virtual ports through which the host can access storage, and the storage volumes that are accessible to the host through each of the virtual ports.

Owner:EMC IP HLDG CO LLC

Switching system method for discovering and accessing SCSI devices in response to query

InactiveUS7089293B2Simple processRobust systemSpecial service provision for substationMultiplex system selection arrangementsStorage managementComputer engineering

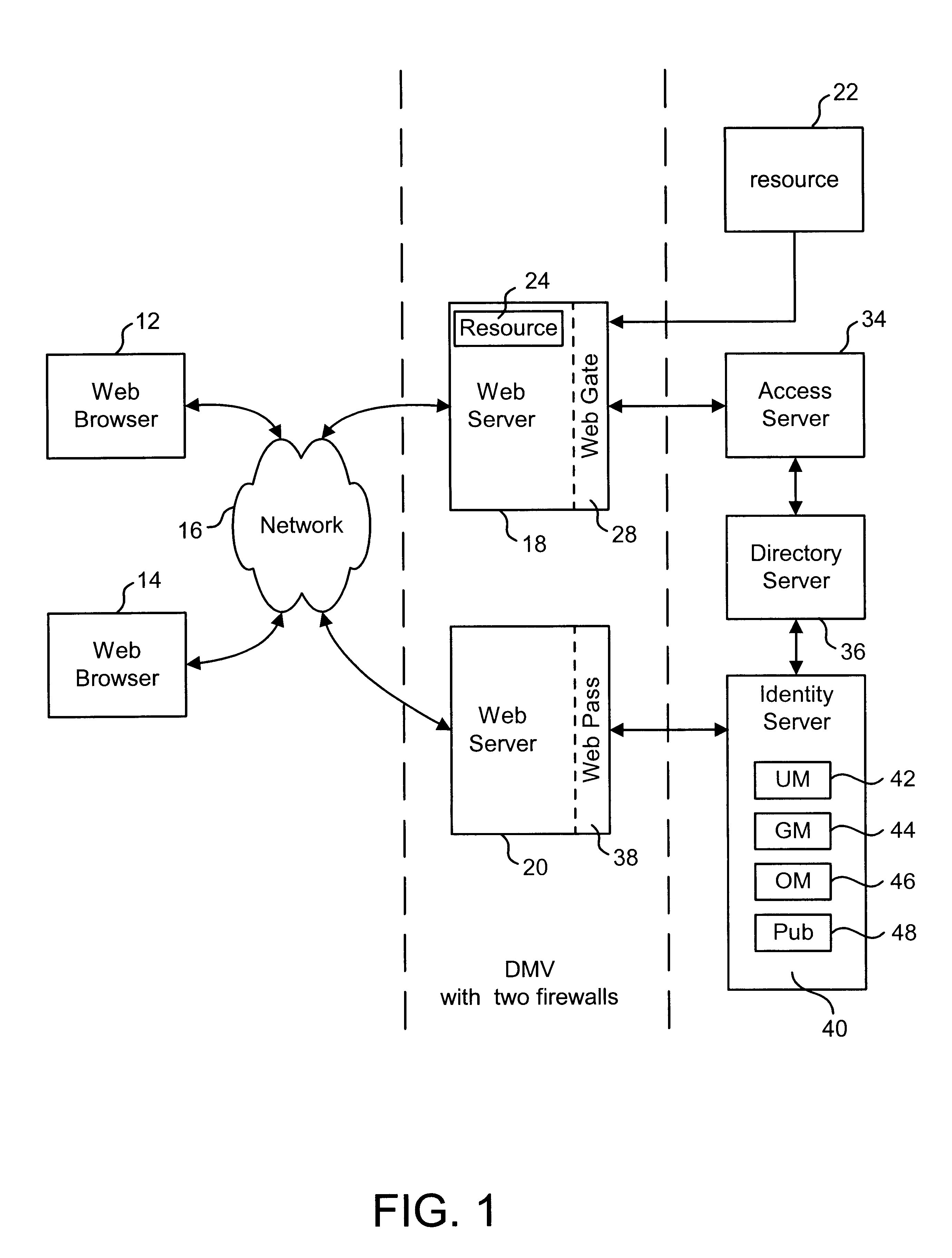

Owner:ORACLE INT CORP

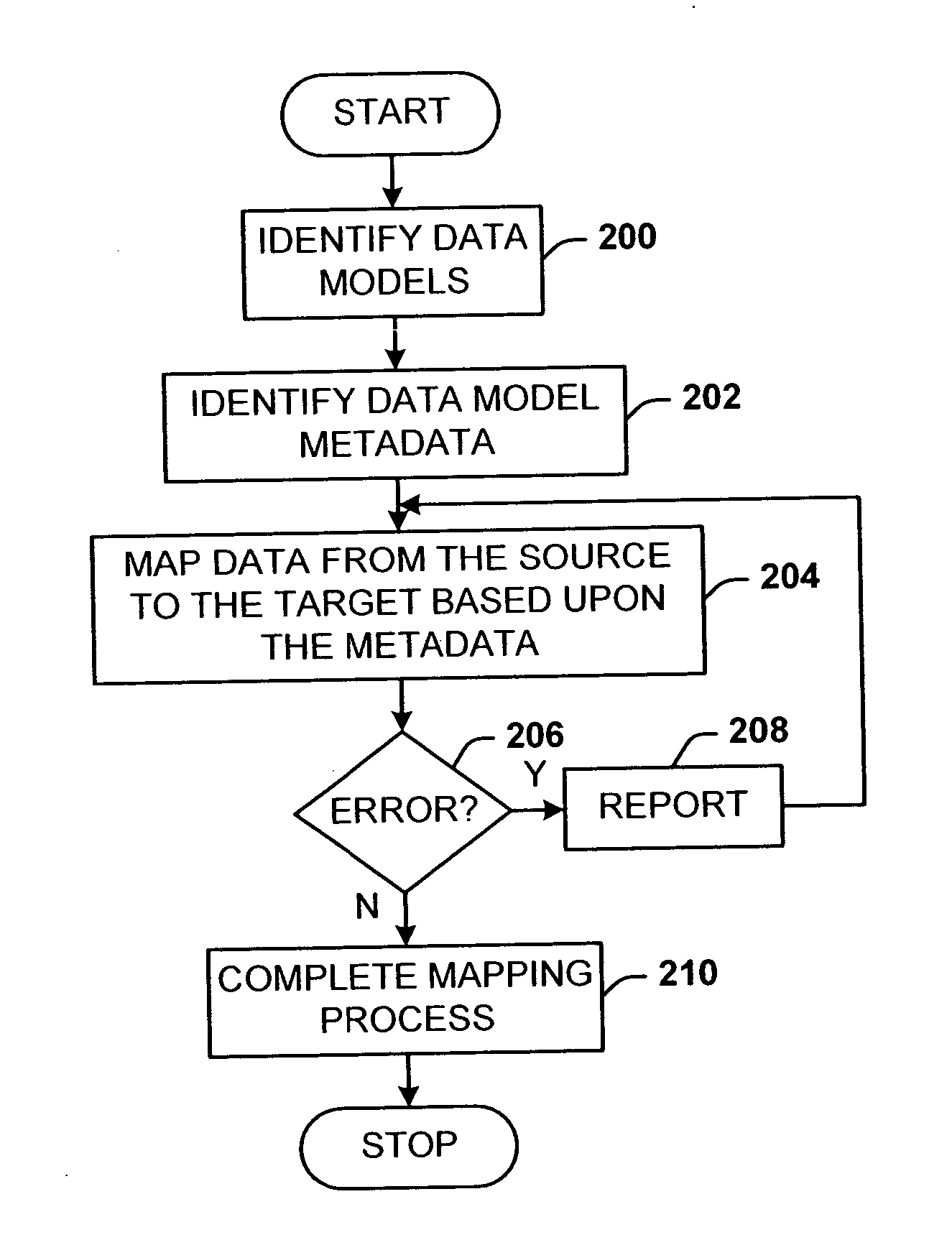

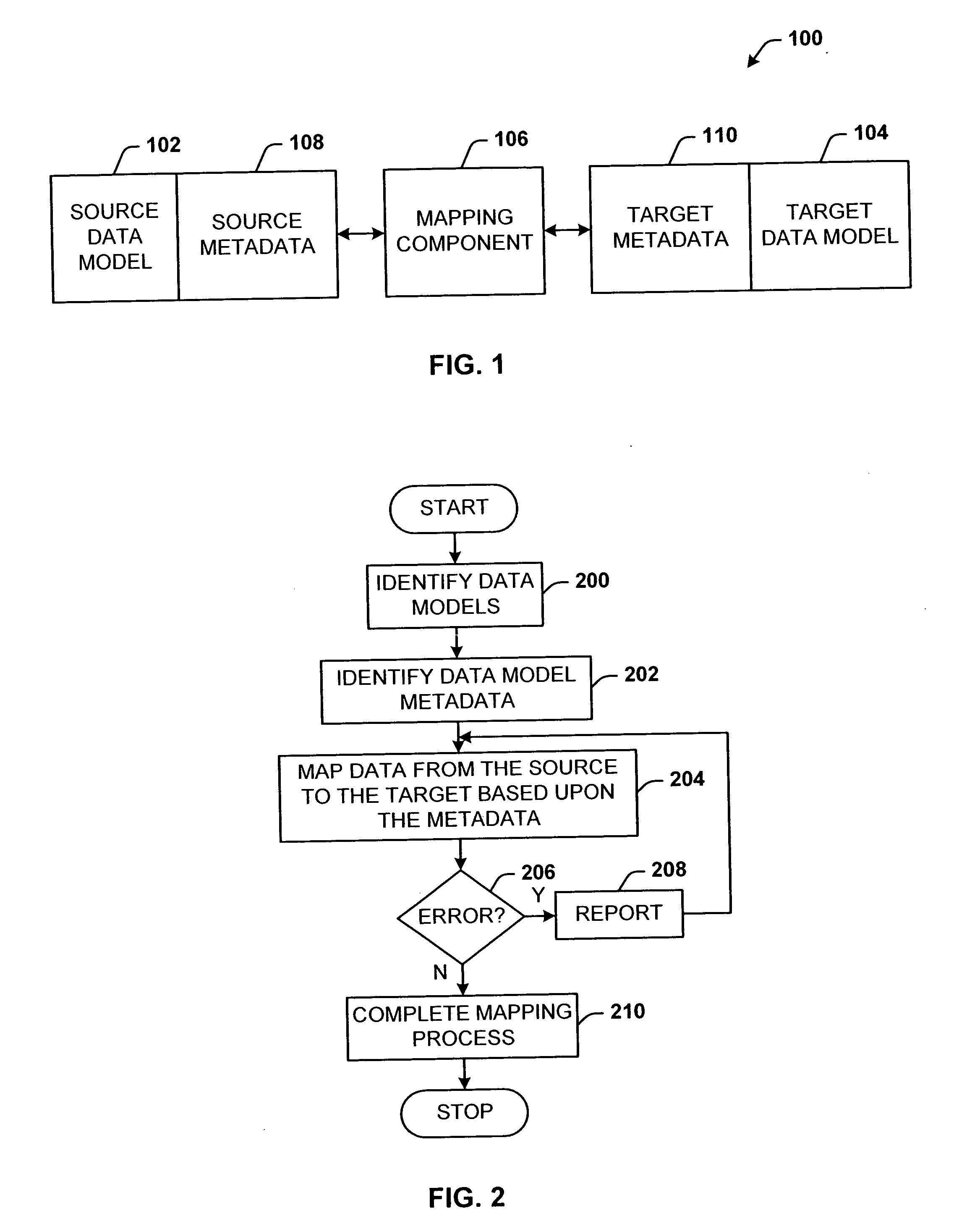

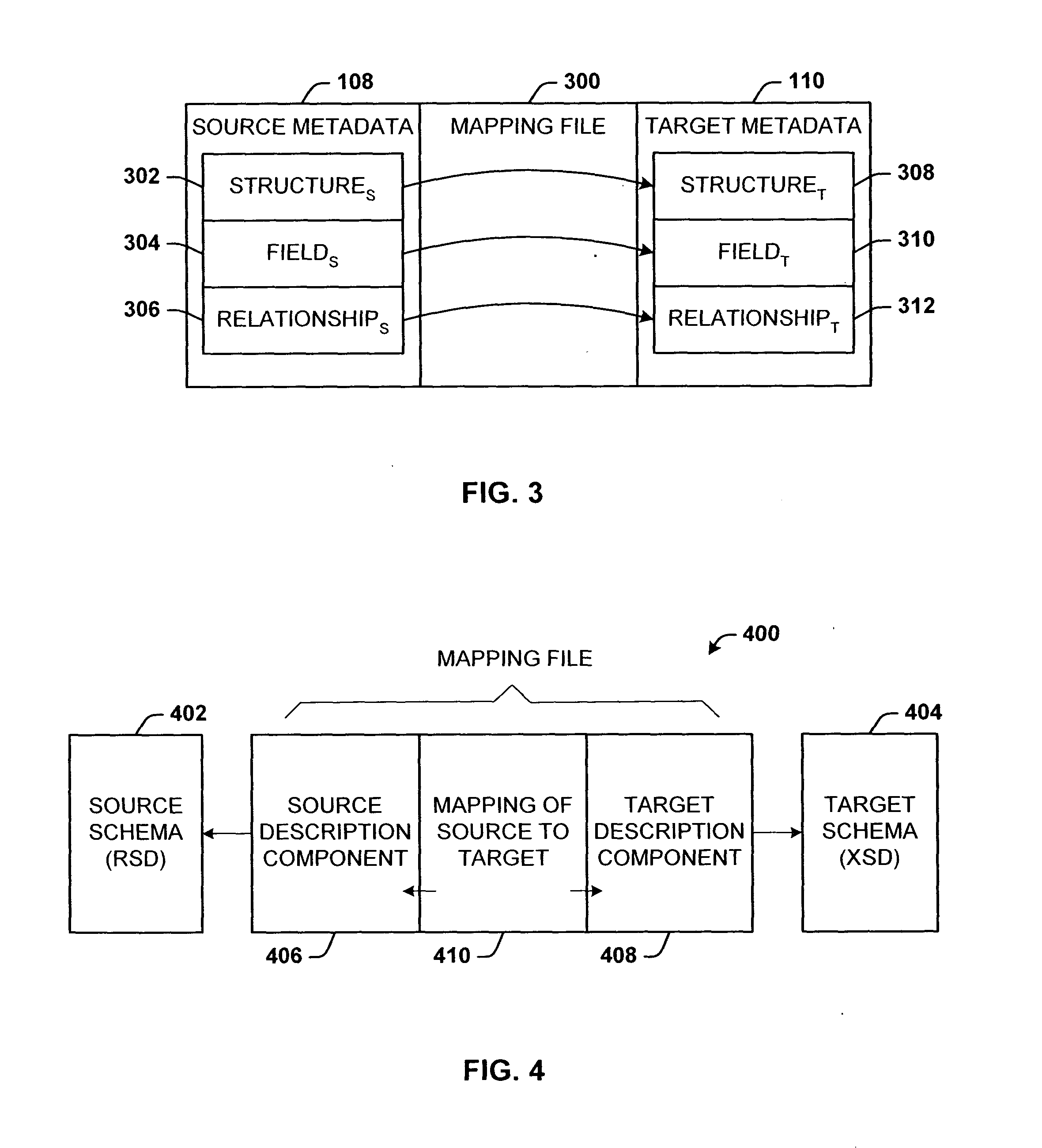

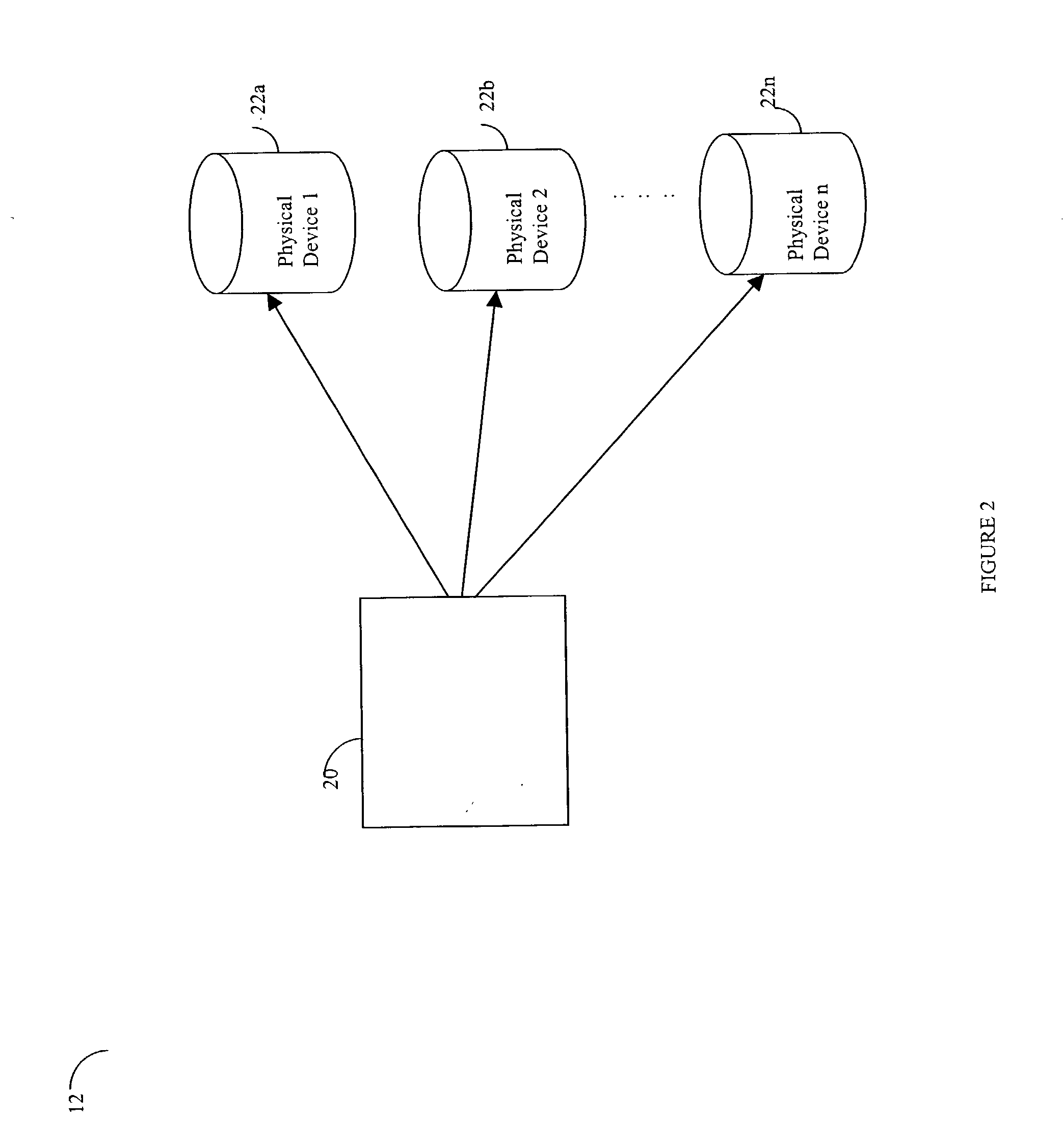

Mapping architecture for arbitrary data models

A data mapping architecture for mapping between two or more data sources without modifying the metadata or structure of the data sources themselves. Data mapping also supports updates. The architecture also supports at least the case where data sources that are being mapped, are given, their schemas predefined, and cannot be changed. The architecture includes a mapping component that receives respective metadata from at least two arbitrary data models, and maps expressions between the data models.

Owner:MICROSOFT TECH LICENSING LLC

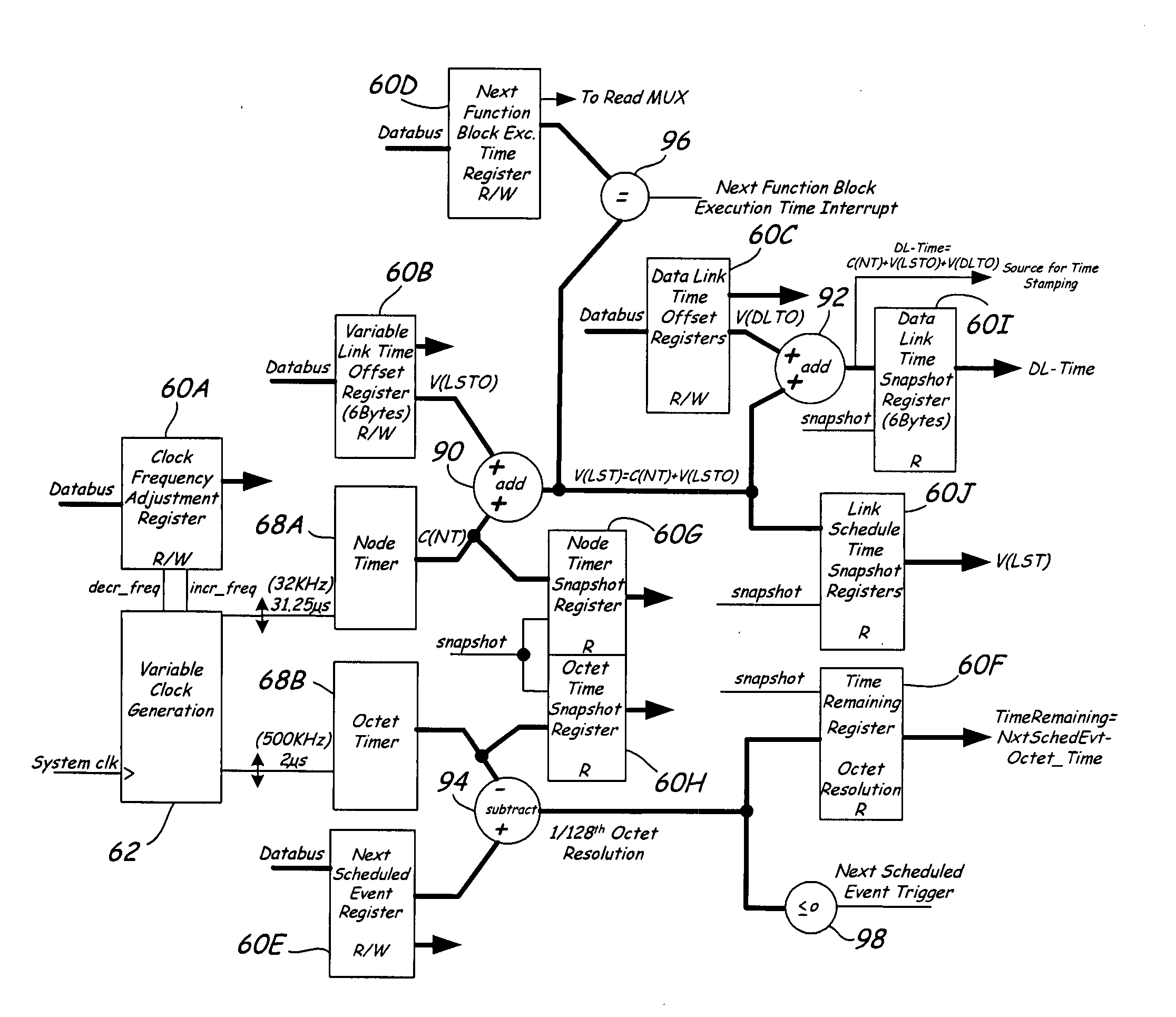

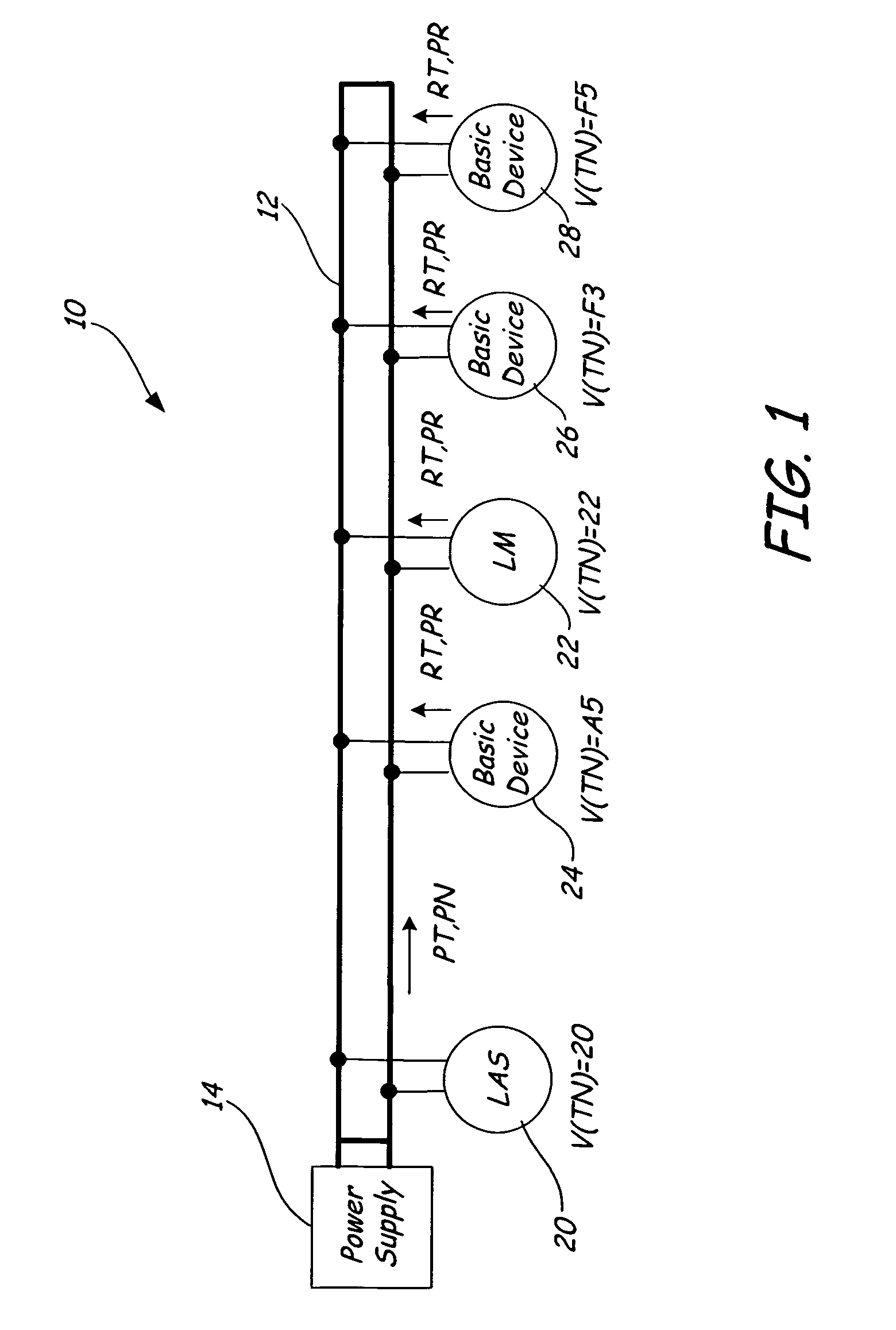

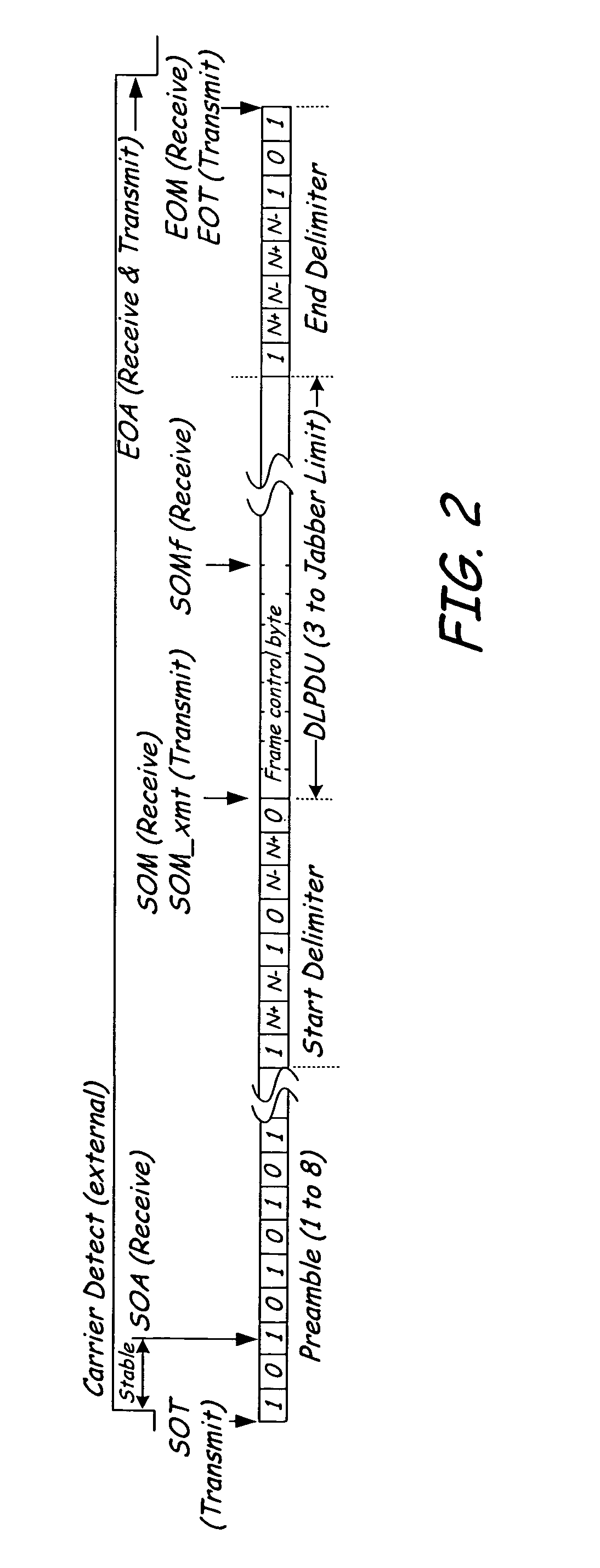

Communication controller with automatic time stamping

ActiveUS20060026314A1Programme controlInput/output to record carriersControl systemCommunication control

Devices in a process control system communicate by data messages over a communication medium segment. Each device includes a communication controller that automatically time stamps events associated with received and transmitted messages.

Owner:FISHER-ROSEMOUNT SYST INC

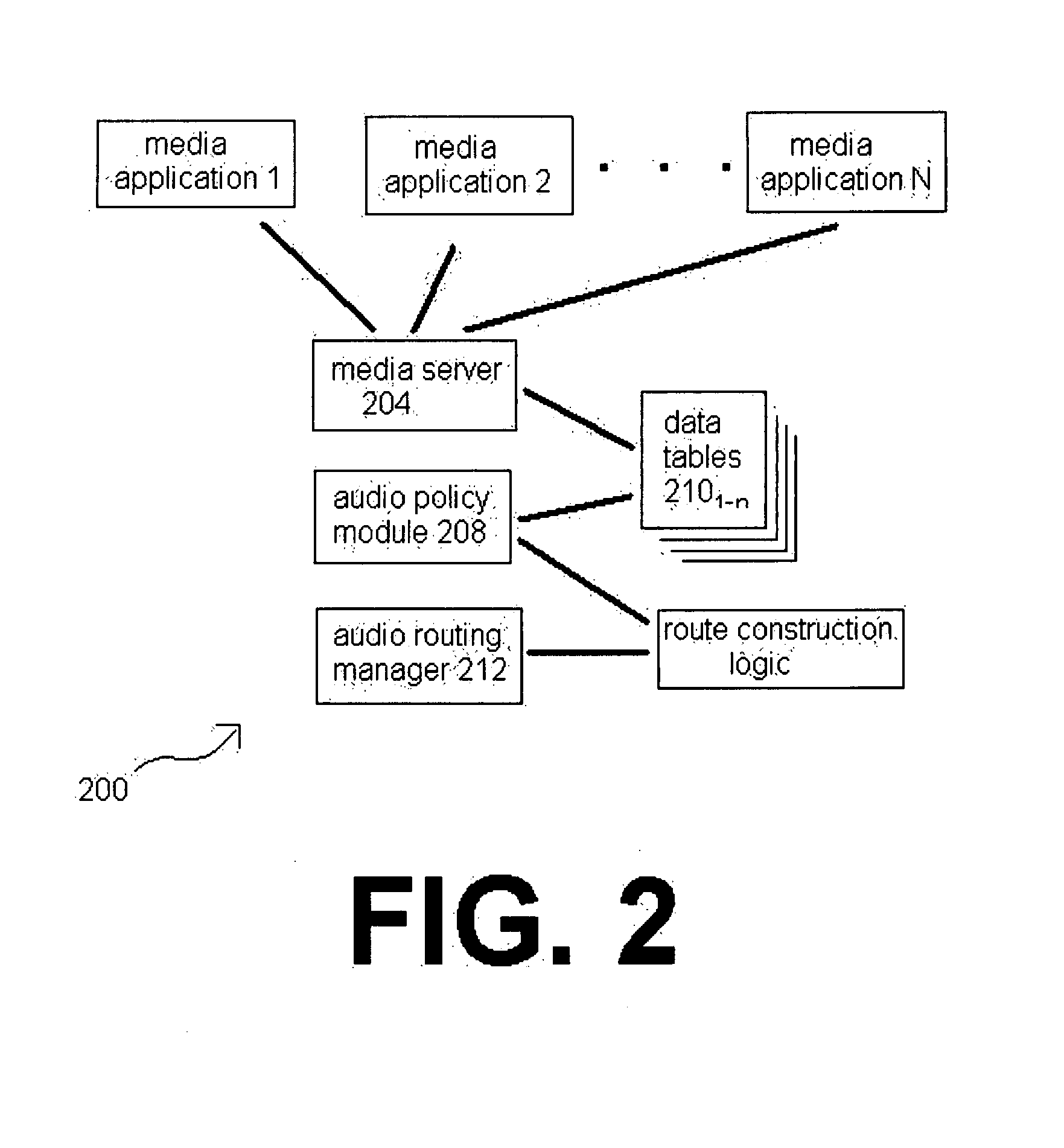

Data-driven media management within an electronic device

Owner:APPLE INC

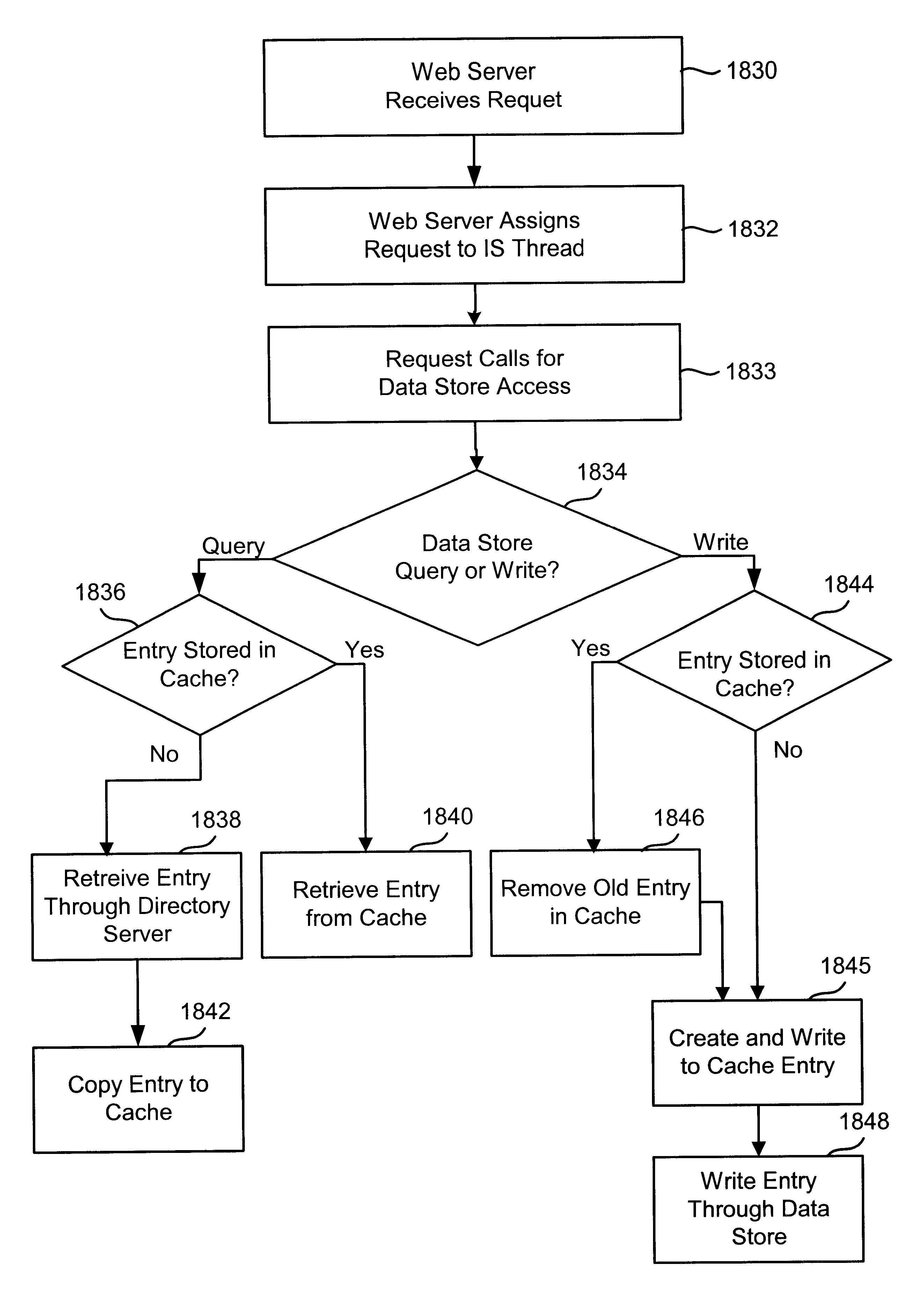

Request based caching of data store data

InactiveUS6675261B2Database management systemsMultiprogramming arrangementsData storingDocumentation

Owner:ORACLE INT CORP

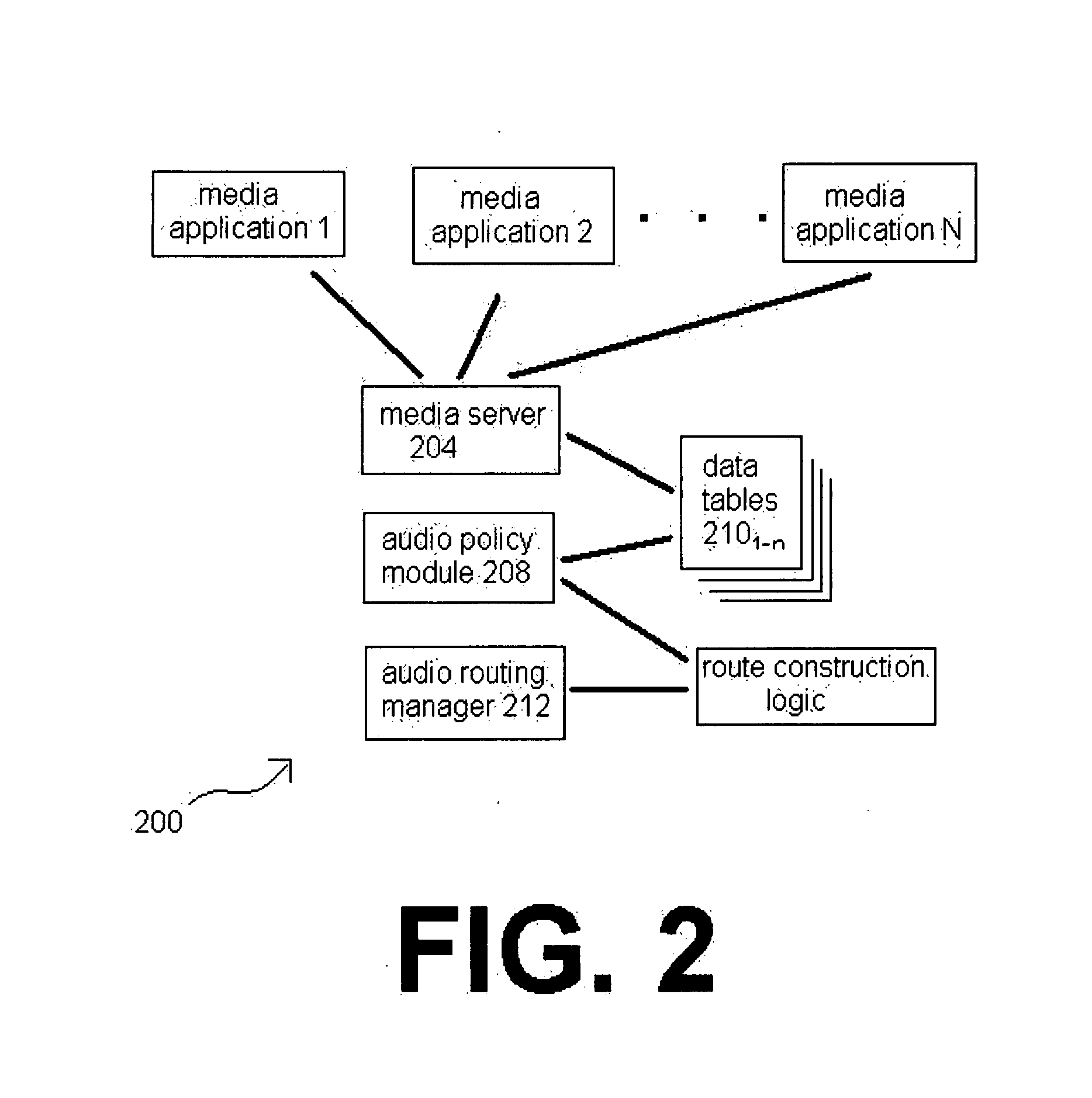

Media management and routing within an electronic device

ActiveUS20090006671A1Substation equipmentSpecial data processing applicationsComputer hardwareAudio signal

Owner:APPLE INC

Microprocessors

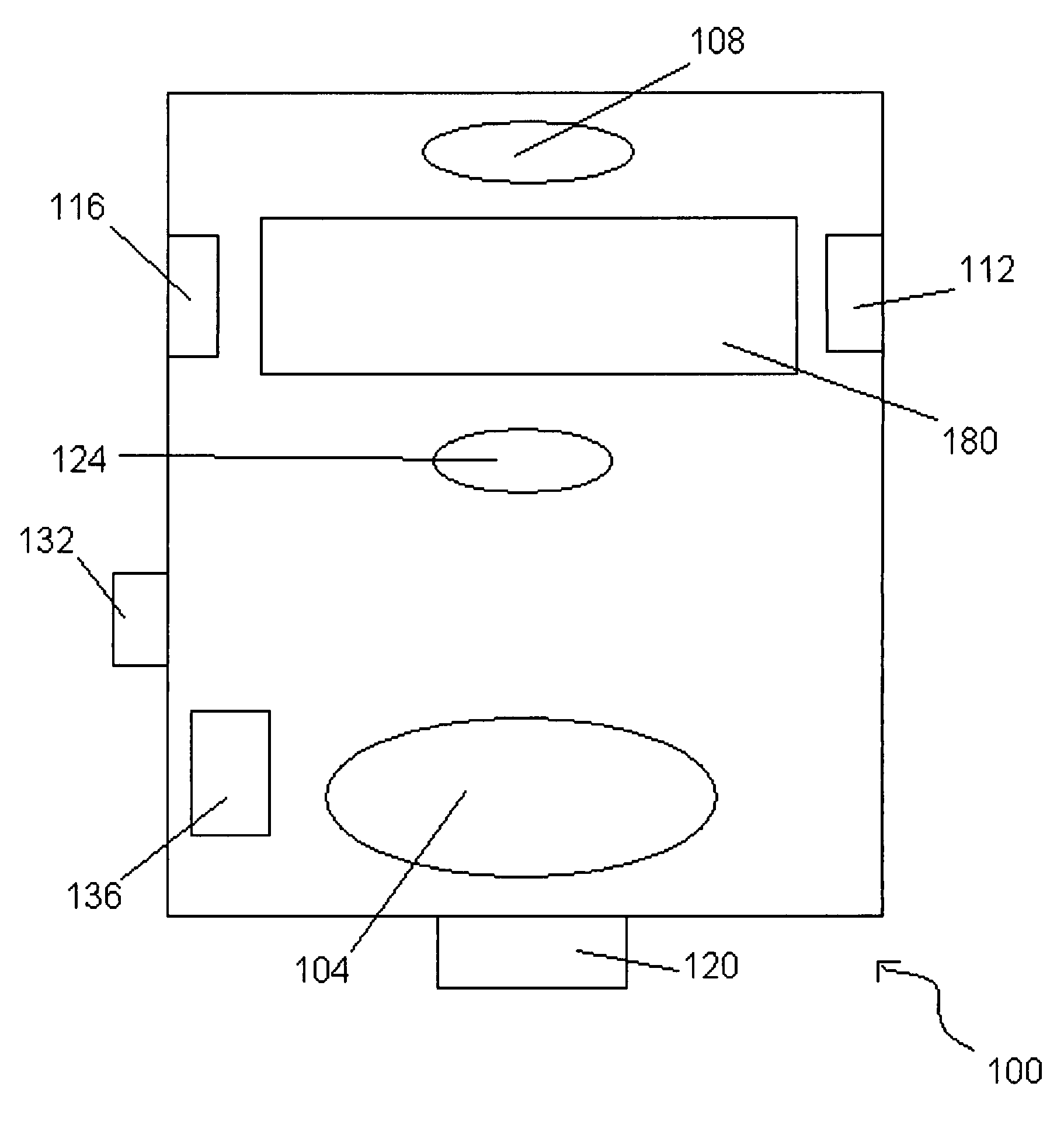

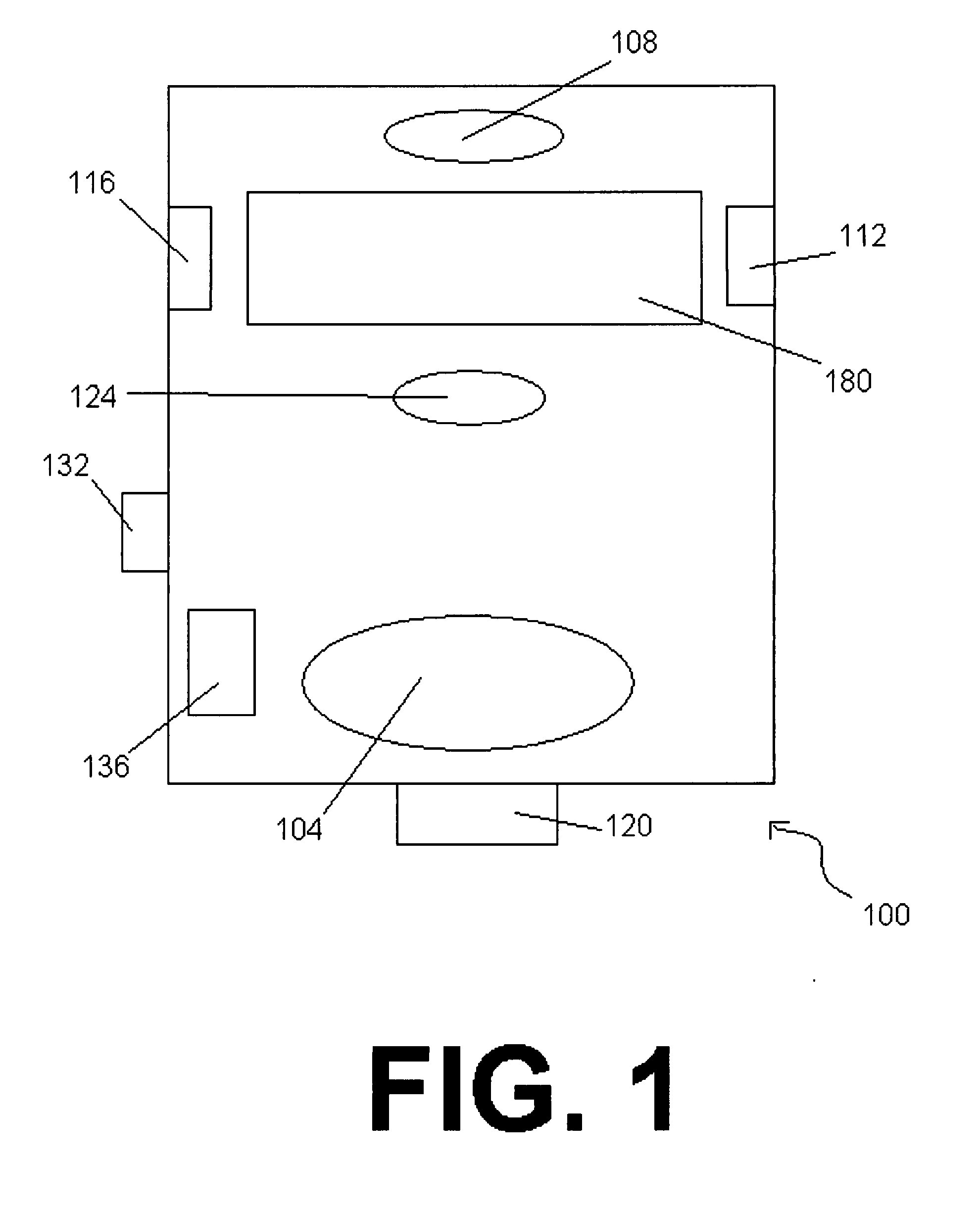

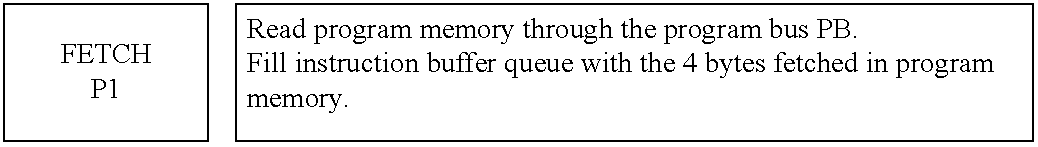

A processor (100) is provided that is a programmable fixed point digital signal processor (DSP) with variable instruction length, offering both high code density and easy programming. Architecture and instruction set are optimized for low power consumption and high efficiency execution of DSP algorithms, such as for wireless telephones, as well as pure control tasks. The processor includes an instruction buffer unit (106), a program flow control unit (108), an address / data flow unit (110), a data computation unit (112), and multiple interconnecting busses. Dual multiply-accumulate blocks improve processing performance. A memory interface unit (104) provides parallel access to data and instruction memories. The instruction buffer is operable to buffer single and compound instructions pending execution thereof. A decode mechanism is configured to decode instructions from the instruction buffer. The use of compound instructions enables effective use of the bandwidth available within the processor. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. Instructions can be conditionally executed or repeatedly executed. Bit field processing and various addressing modes, such as circular buffer addressing, further support execution of DSP algorithms. The processor includes a multistage execution pipeline with pipeline protection features. Various functional modules can be separately powered down to conserve power. The processor includes emulation and code debugging facilities with support for cache analysis.

Owner:TEXAS INSTR INC

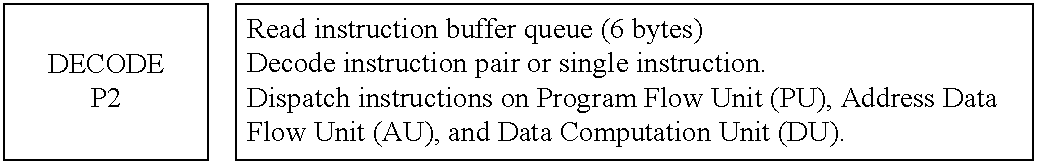

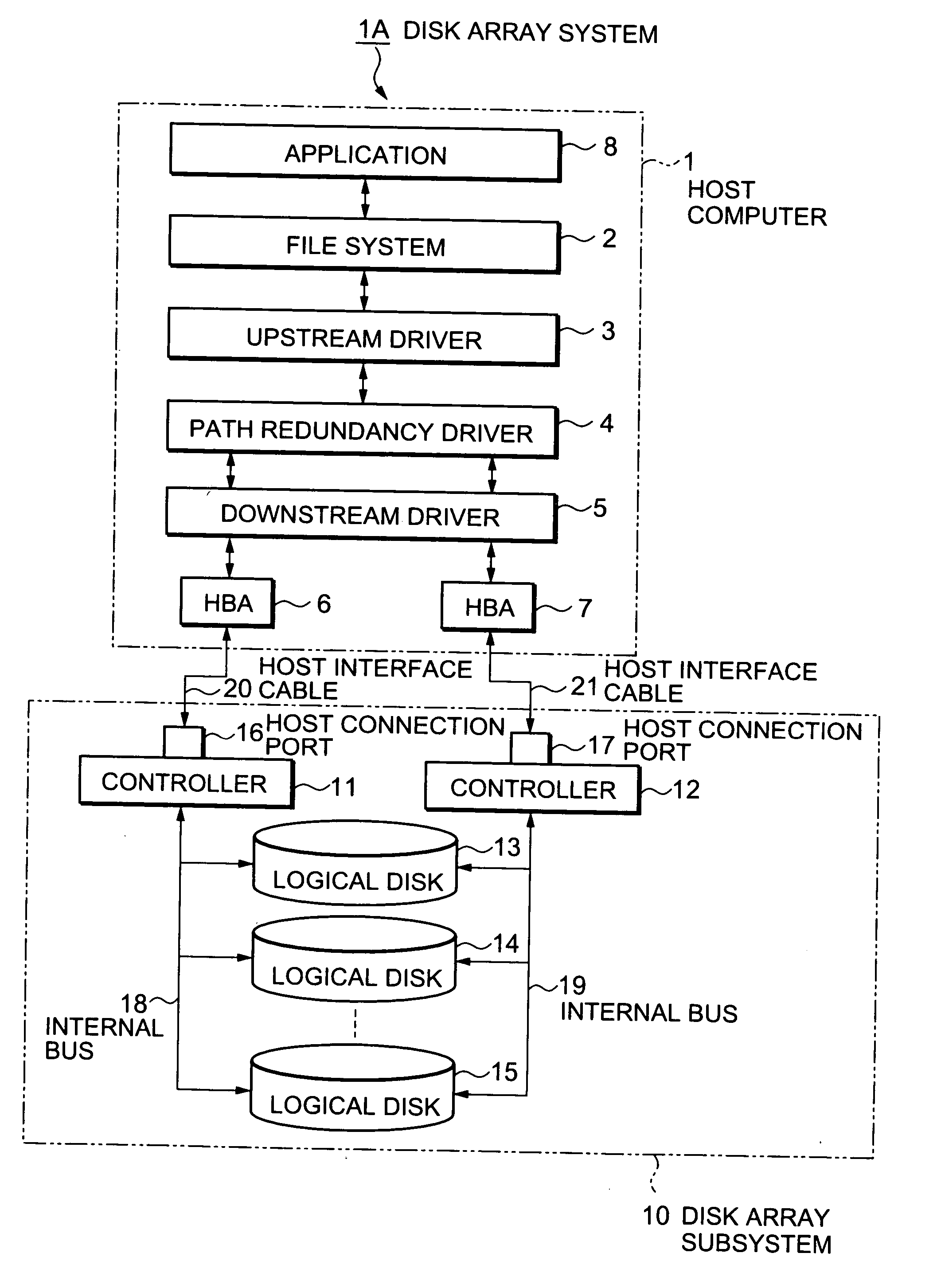

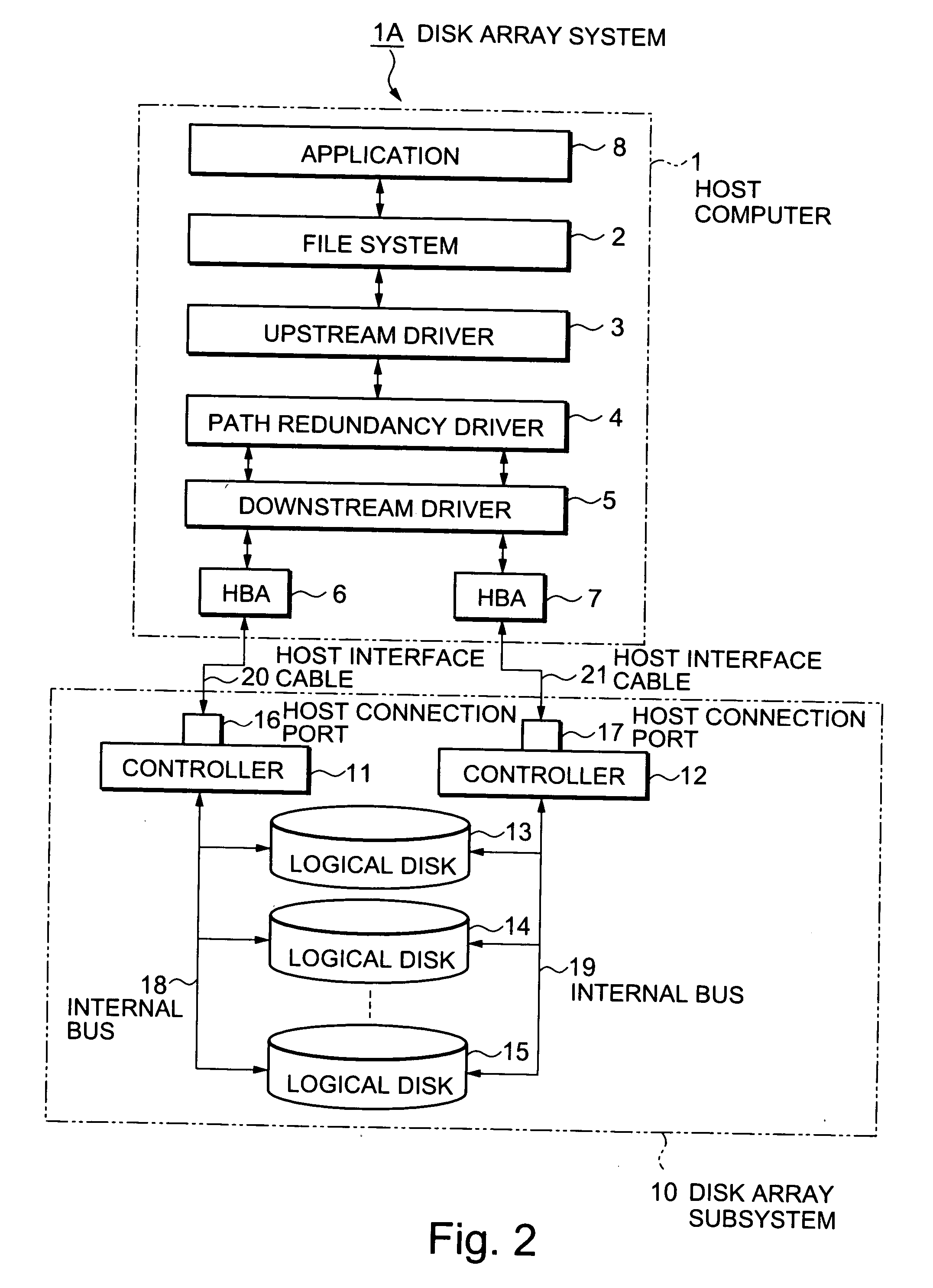

Path control device, system, cluster, cluster system, method and computer readable medium embodying program

InactiveUS20070022227A1Adequate exerciseImprove access performanceError detection/correctionInput/output processes for data processingCluster systemsEmbedded system

A path control device that controls first and second paths for accessing a peripheral subsystem, includes a command substituting unit that substitutes a first reserve command that allows an access through the first path, with a second reserve command that allows both of accesses through both of the first path and the second path.

Owner:NEC CORP

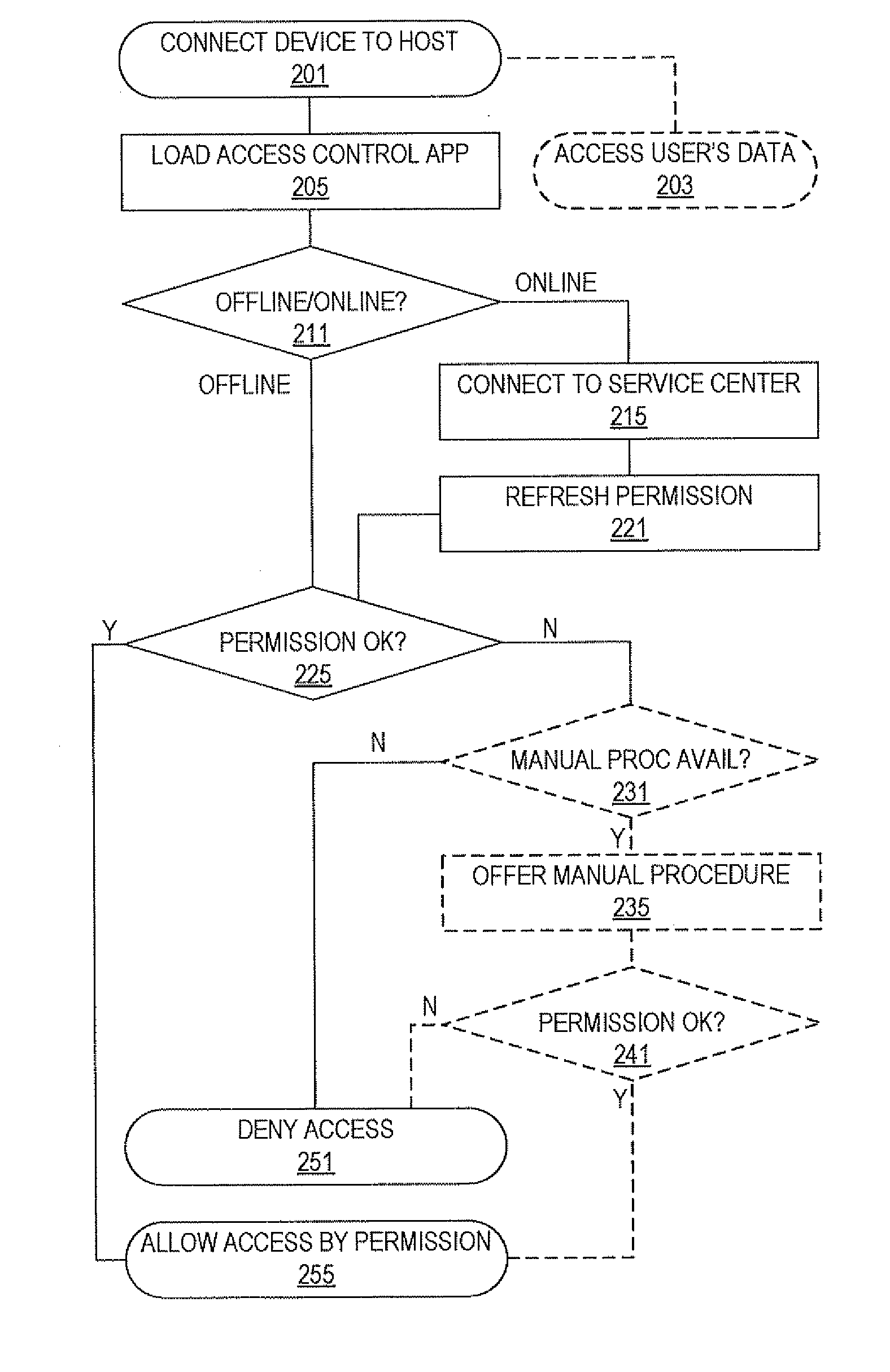

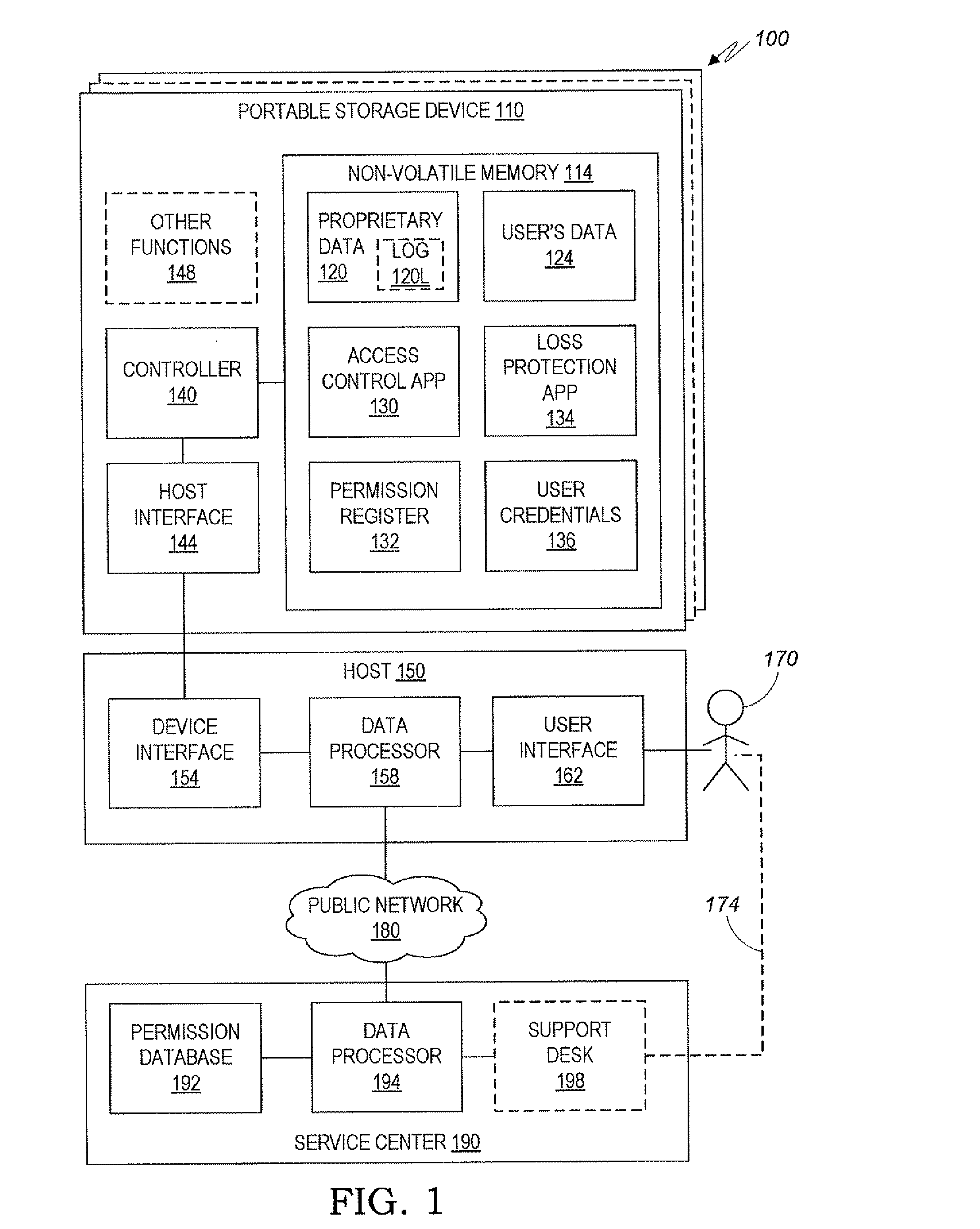

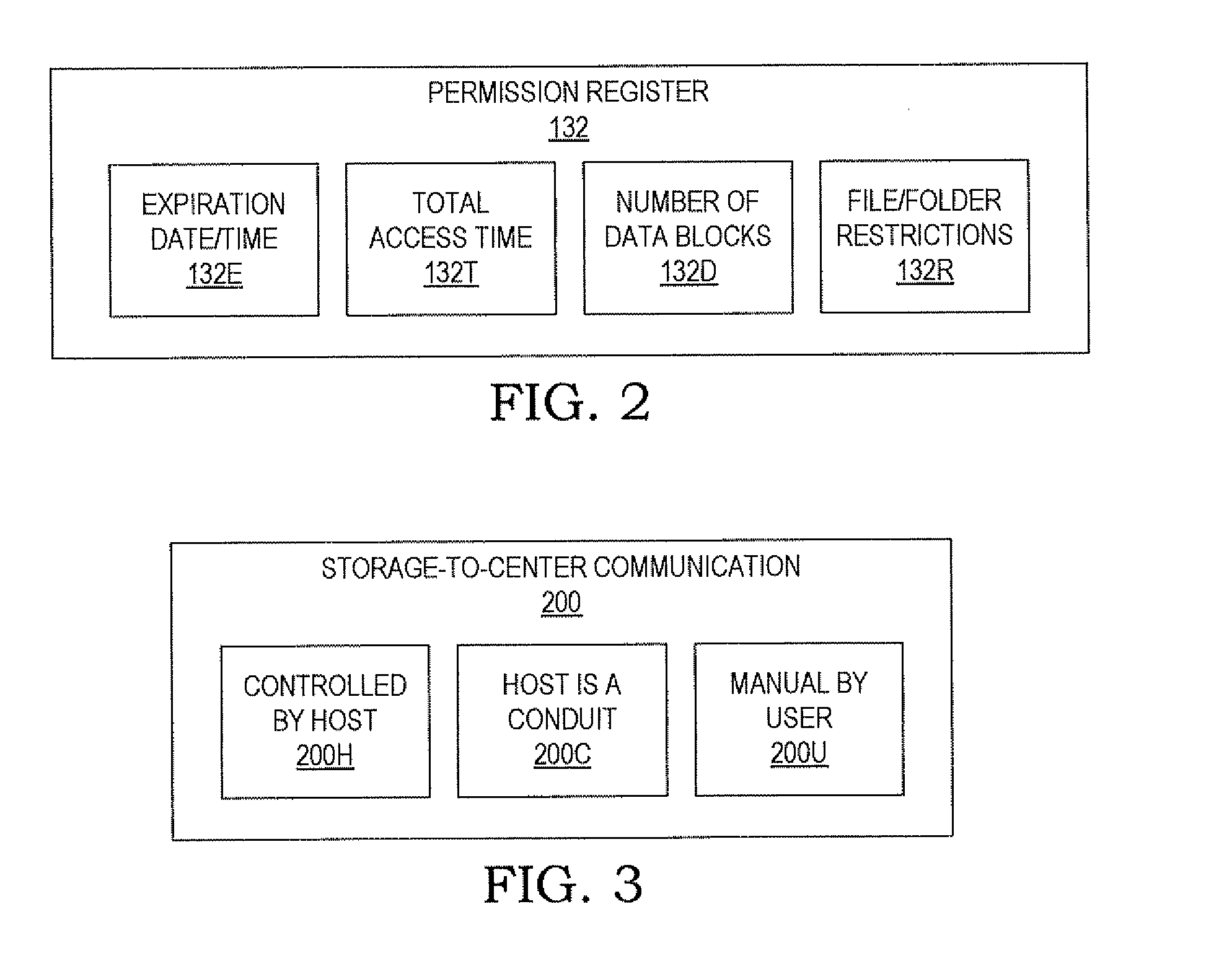

Portable Storage Device With Updatable Access Permission

ActiveUS20080059743A1Unauthorized memory use protectionInternal/peripheral component protectionCouplingProcessor register

Owner:WESTERN DIGITAL ISRAEL LTD

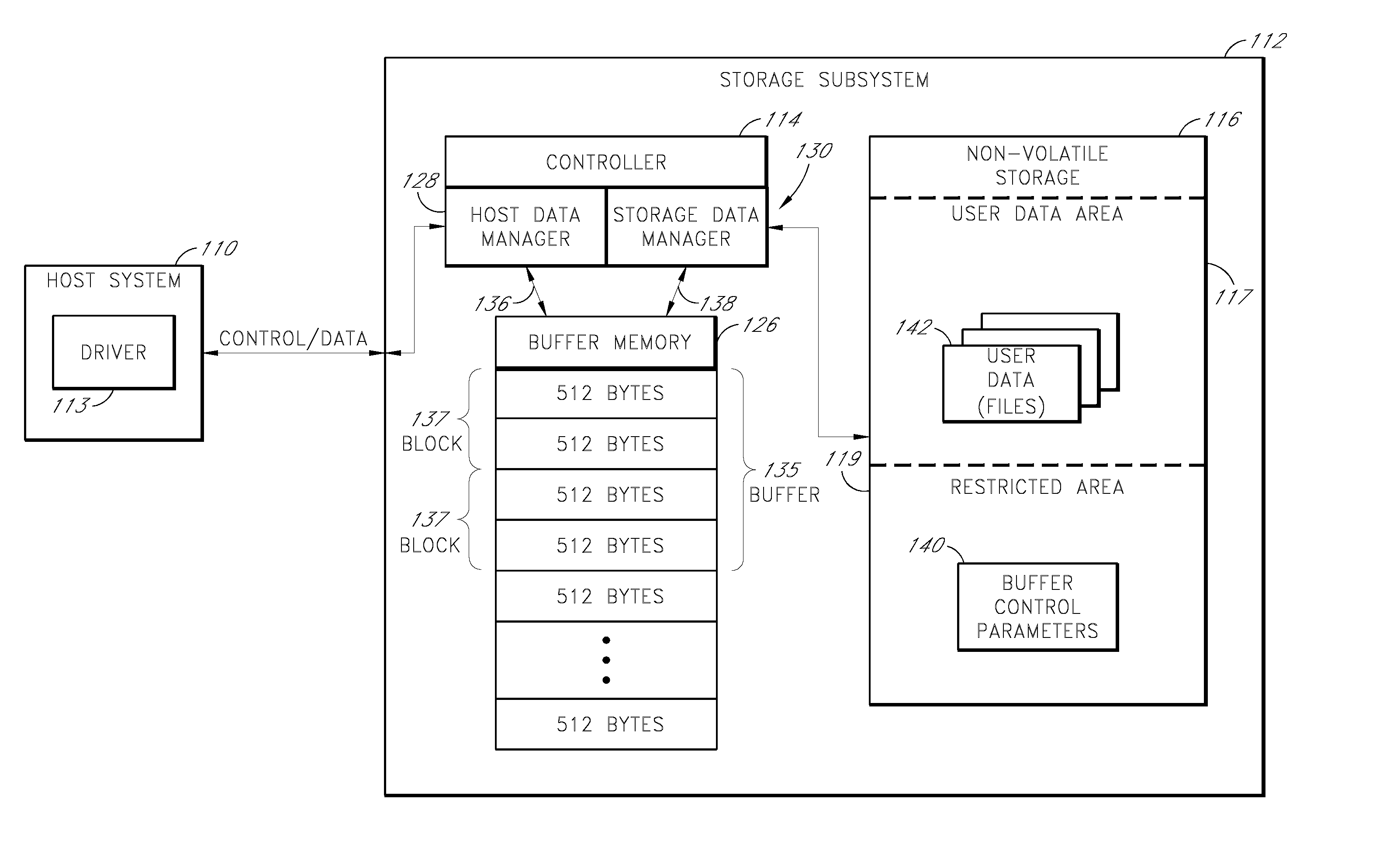

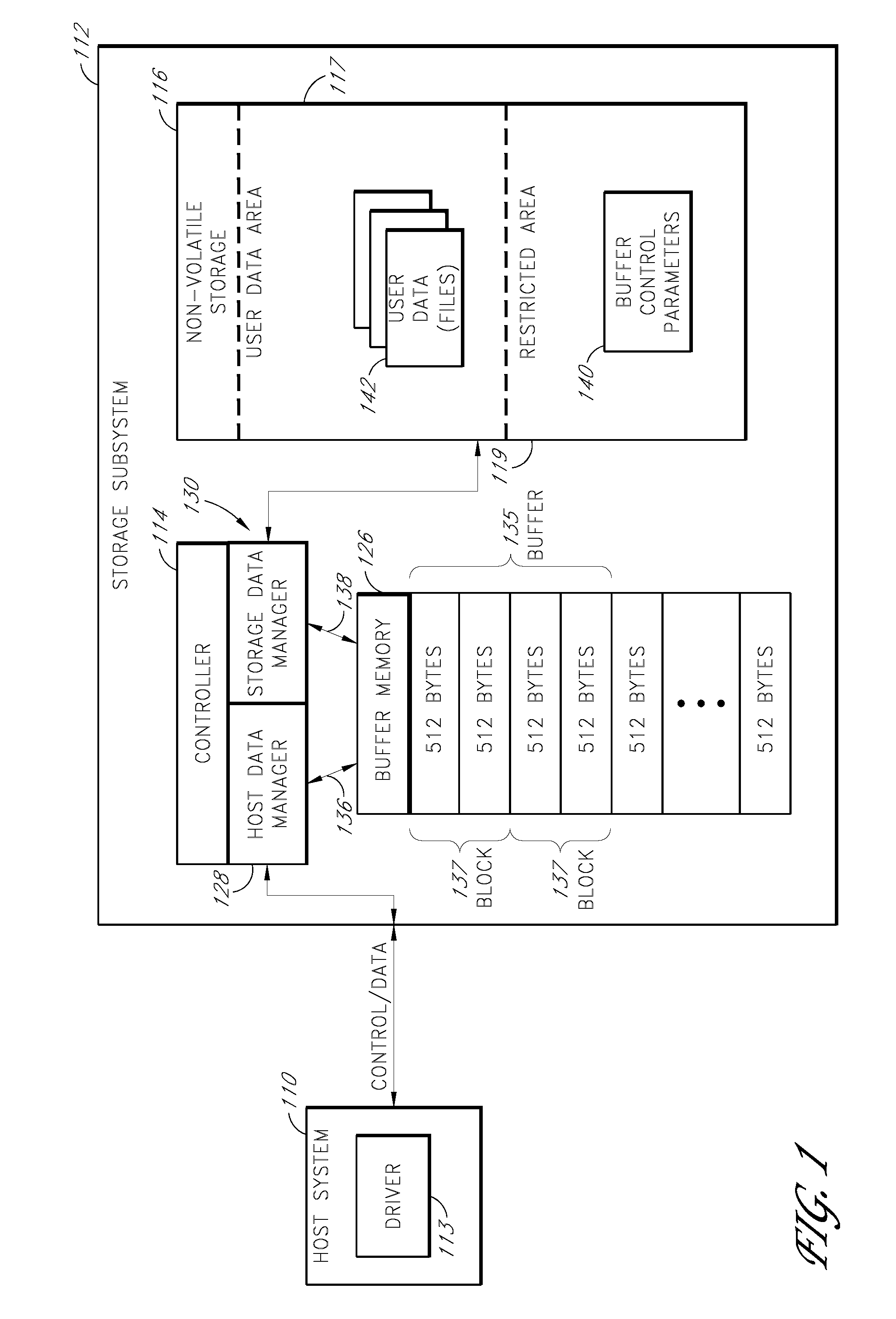

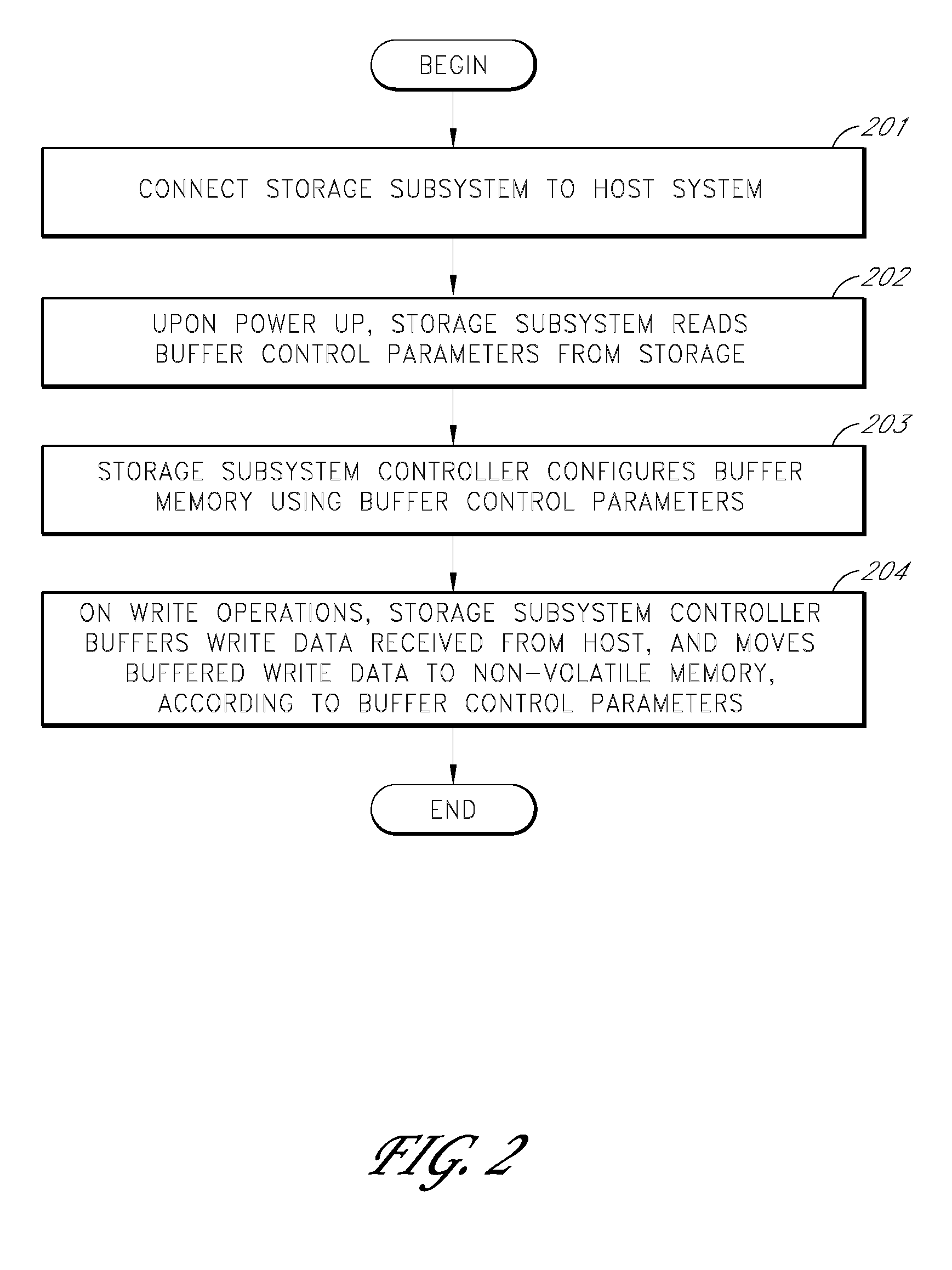

Storage subsystem with configurable buffer

ActiveUS7596643B2Reduce riskImprove performanceRecord information storageInput/output processes for data processingWrite bufferData loss

Owner:WESTERN DIGITAL TECH INC

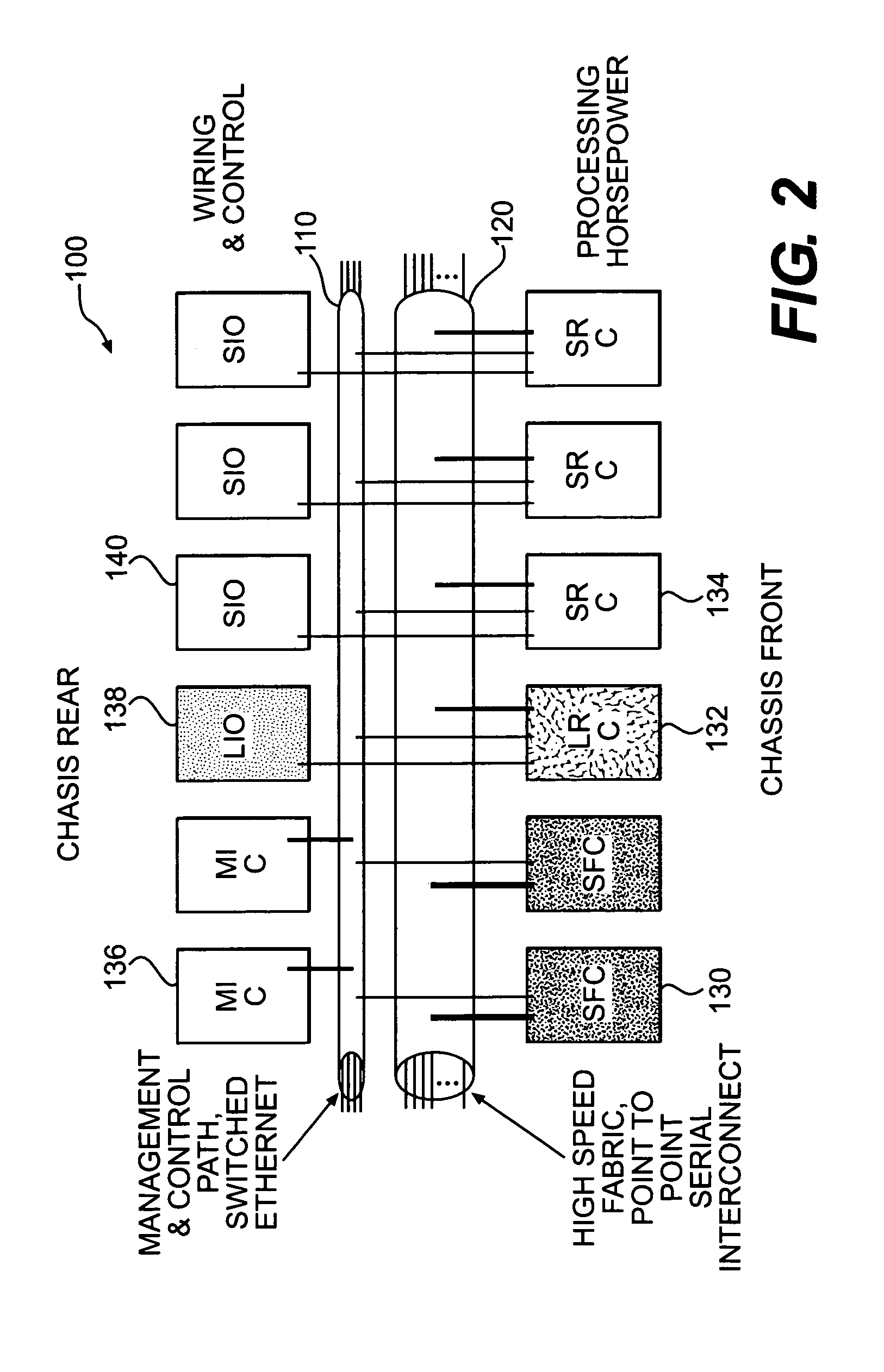

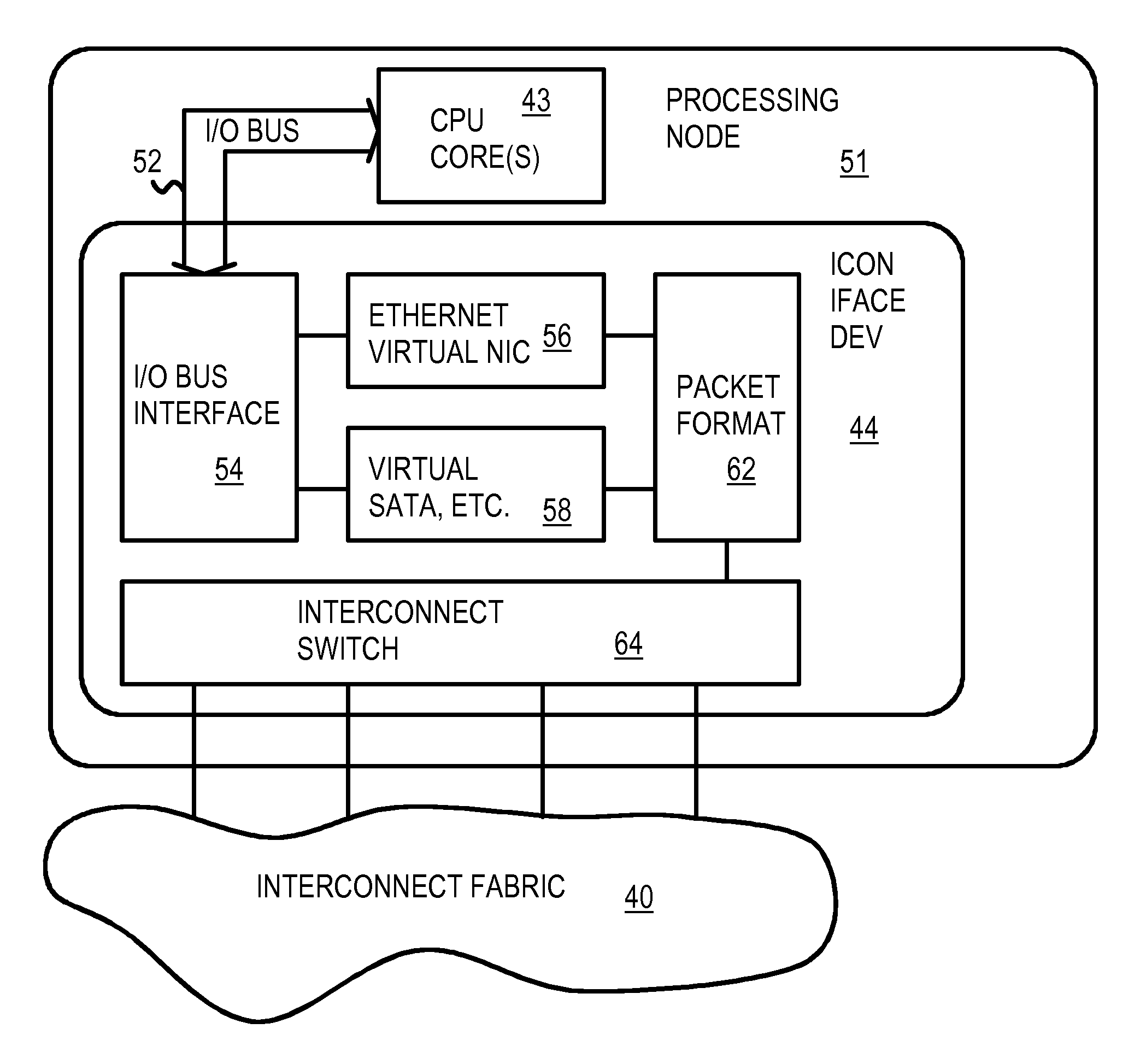

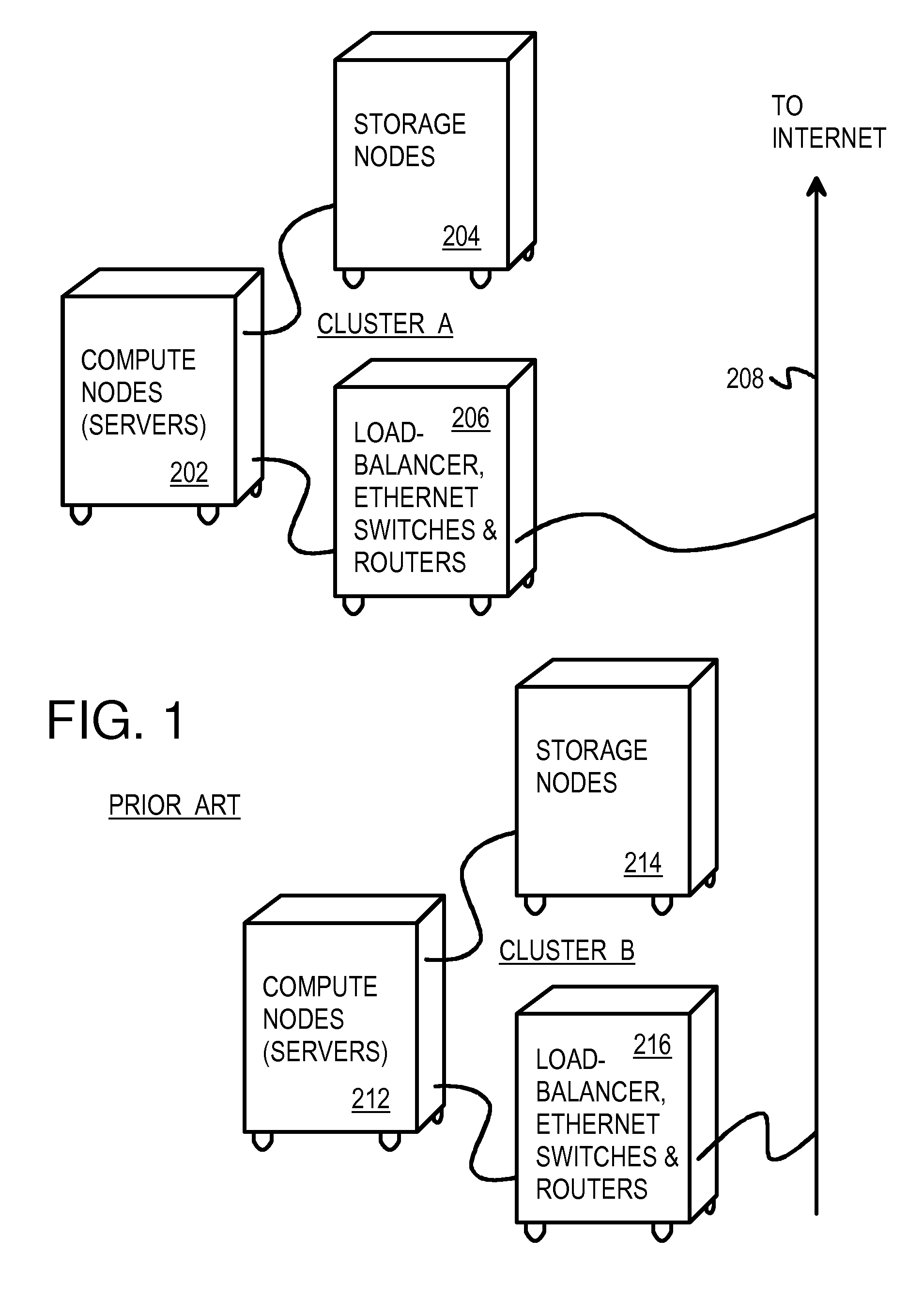

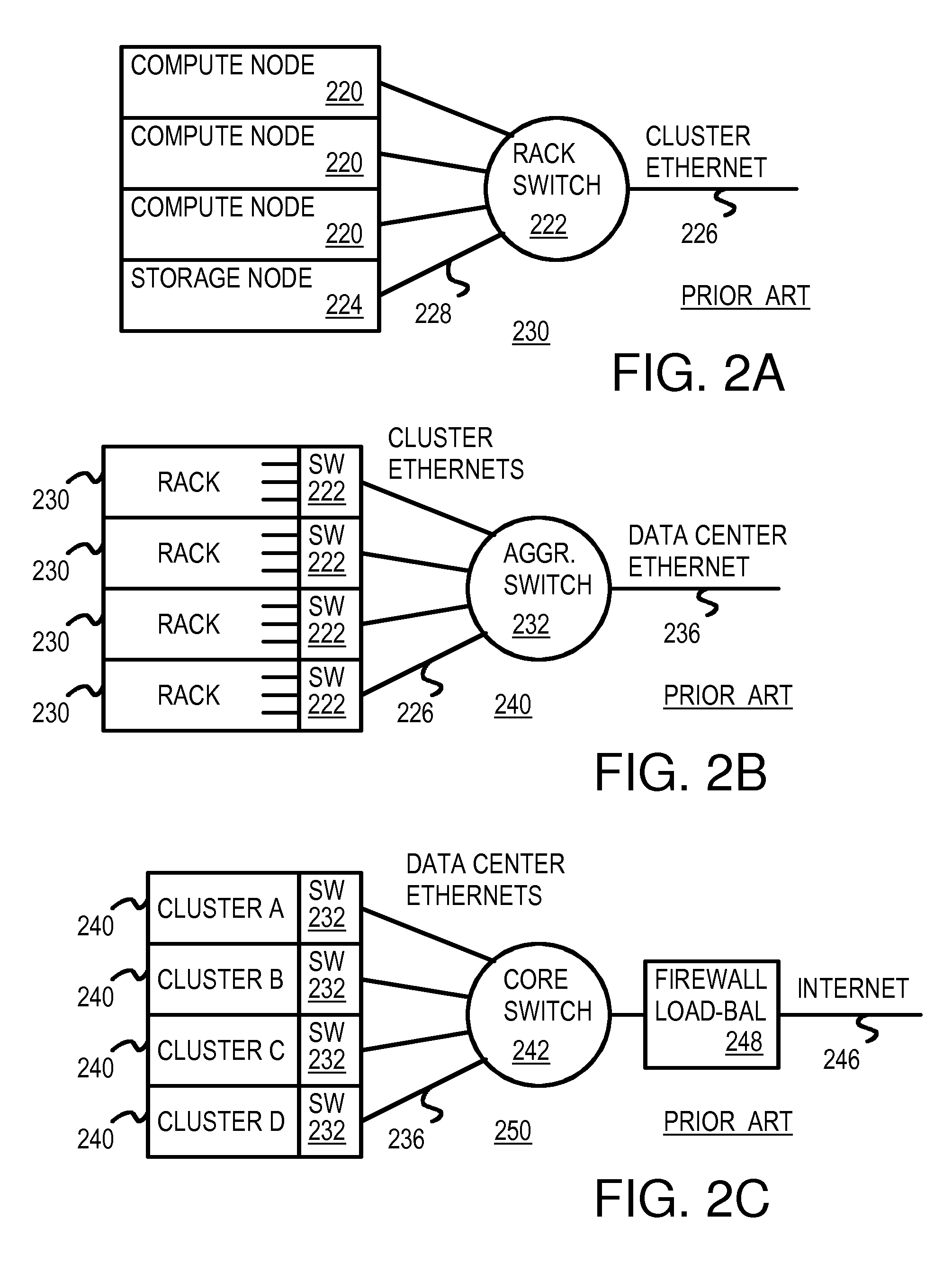

Dis-Aggregated and Distributed Data-Center Architecture Using a Direct Interconnect Fabric

ActiveUS20090216920A1Computer security arrangementsMultiple digital computer combinationsOperational systemData center

A data center has several dis-aggregated data clusters that connect to the Internet through a firewall and load-balancer. Each dis-aggregated data cluster has several dis-aggregated compute / switch / disk chassis that are connected together by a mesh of Ethernet links. Each dis-aggregated compute / switch / disk chassis has many processing nodes, disk nodes, and I / O nodes on node cards that are inserted into the chassis. These node cards are connected together by a direct interconnect fabric. Using the direct interconnect fabric, remote I / O and disk nodes appear to the operating system to be located on the local processor's own peripheral bus. A virtual Ethernet controller and a virtual generic peripheral act as virtual endpoints for the local processor's peripheral bus. I / O and disk node peripherals are virtualized by hardware without software drivers. Rack and aggregation Ethernet switches are eliminated using the direct interconnect fabric, which provides a flatter, dis-aggregated hierarchy.

Owner:SEAMICRO

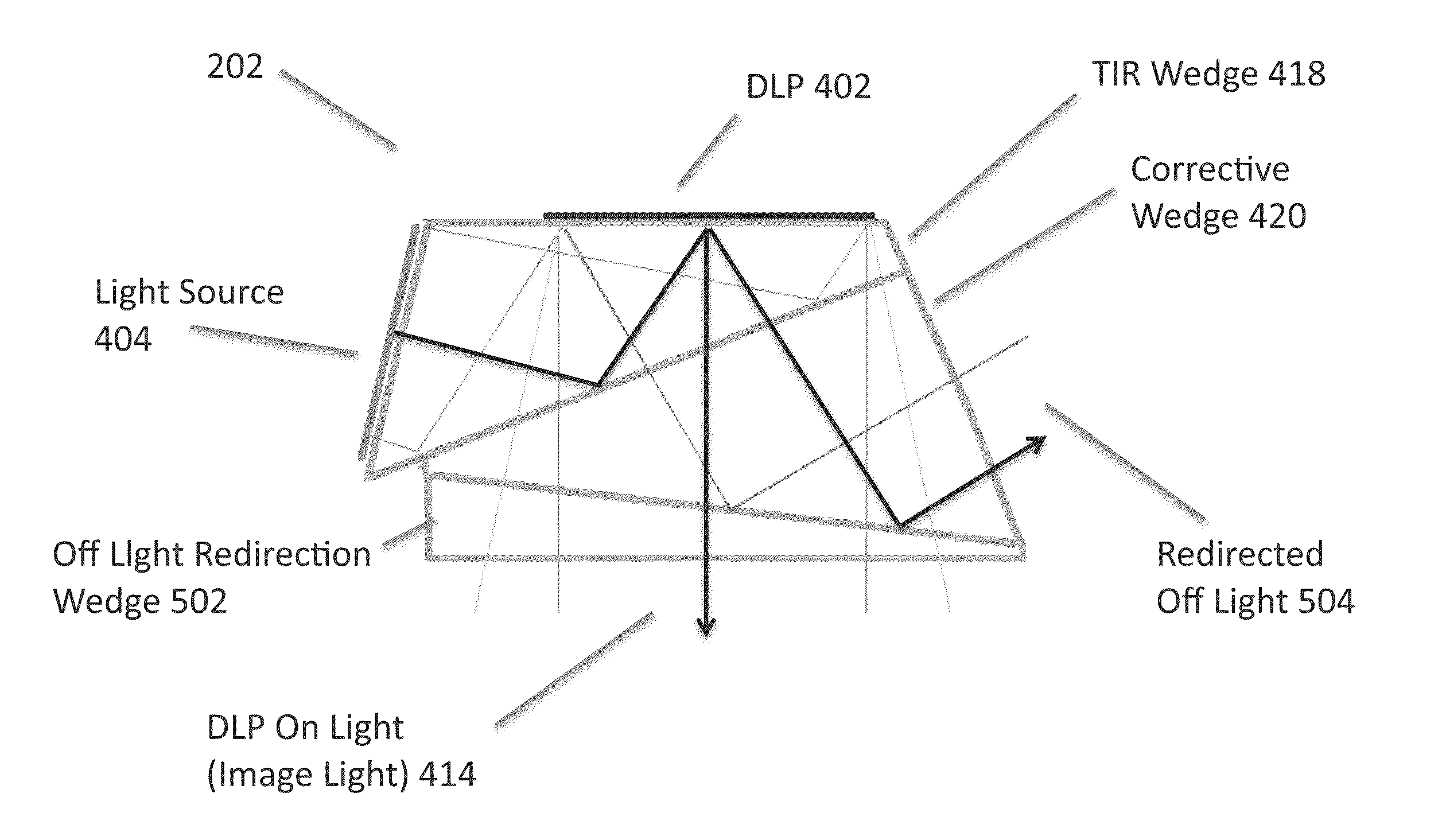

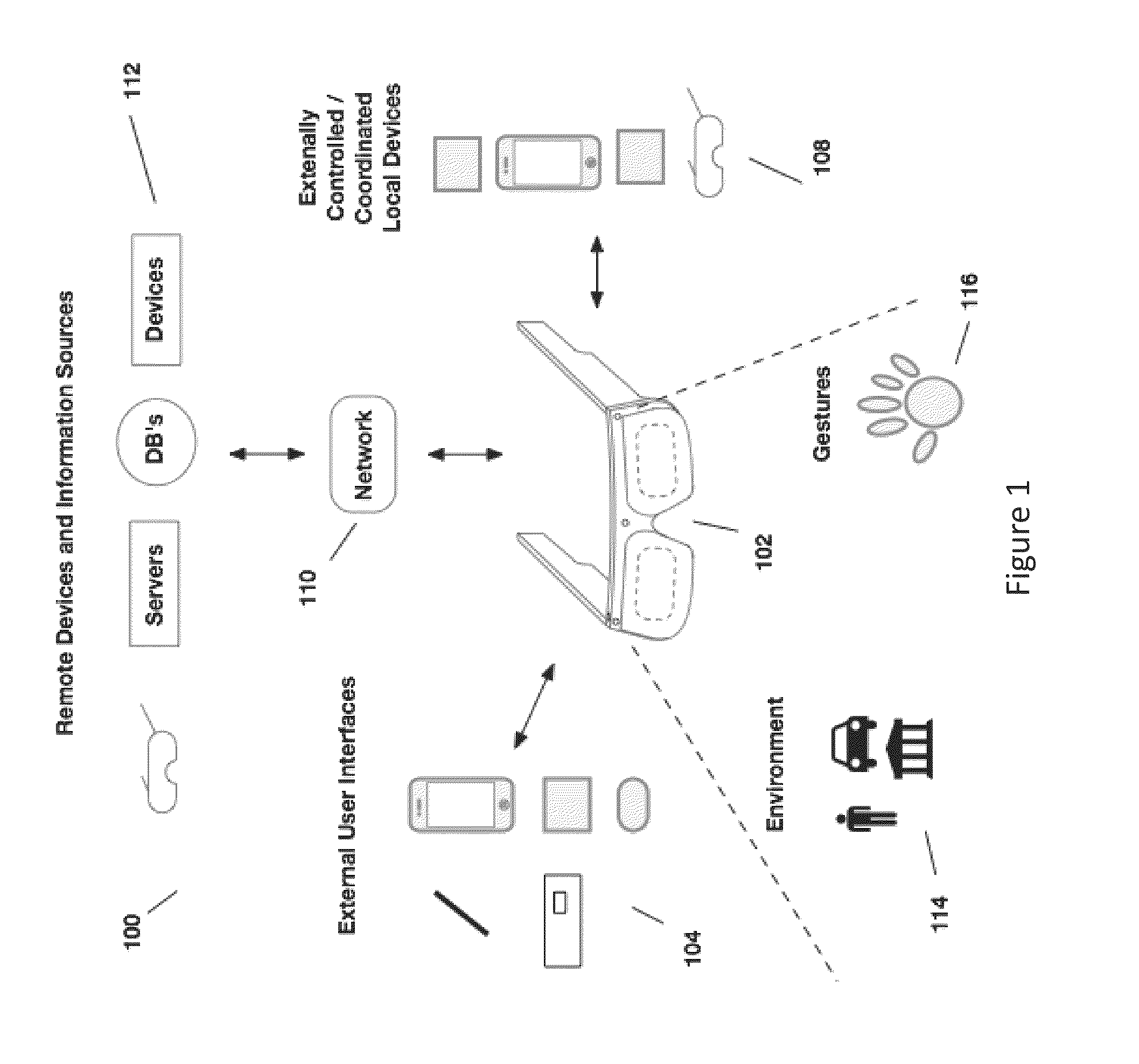

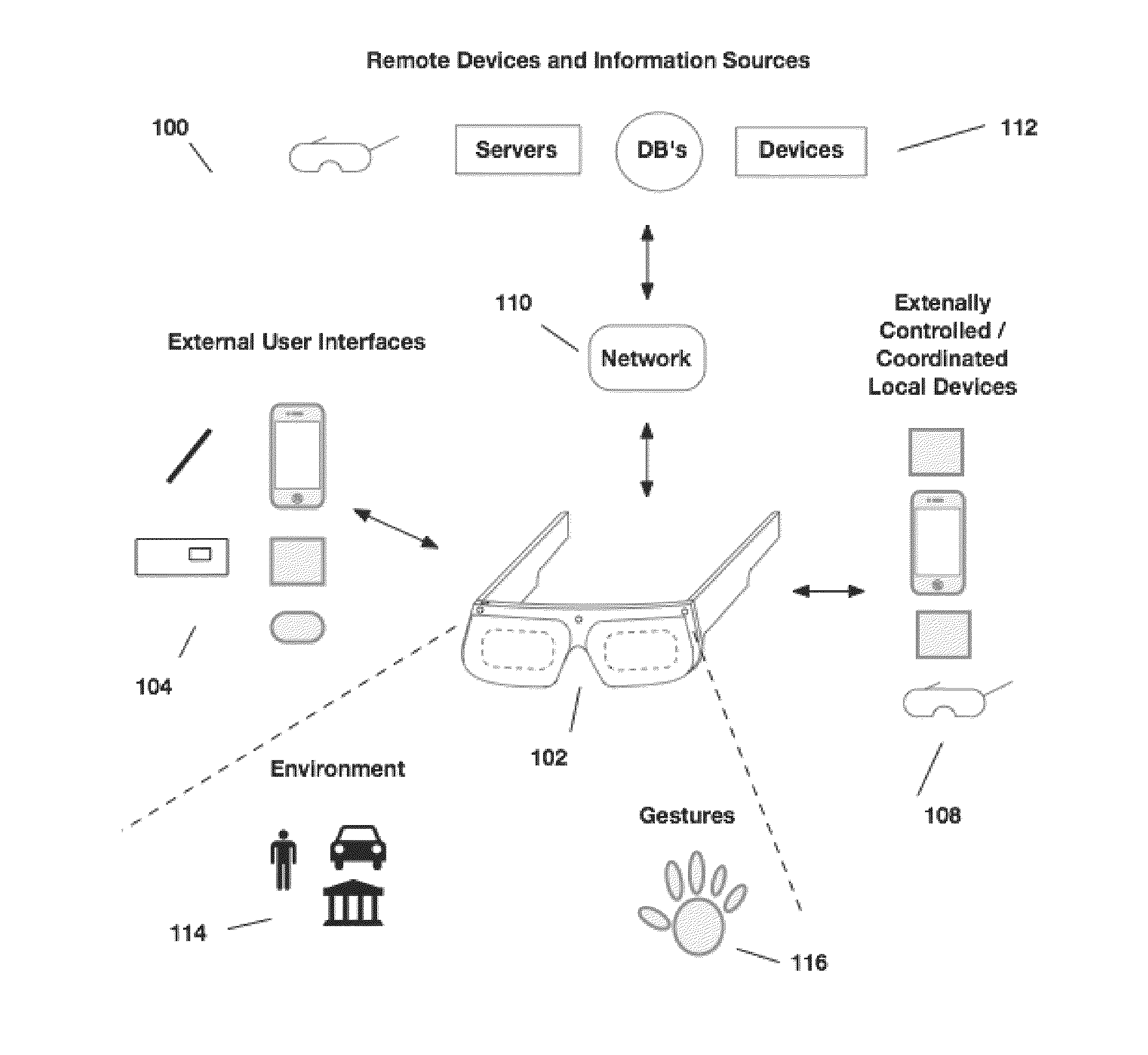

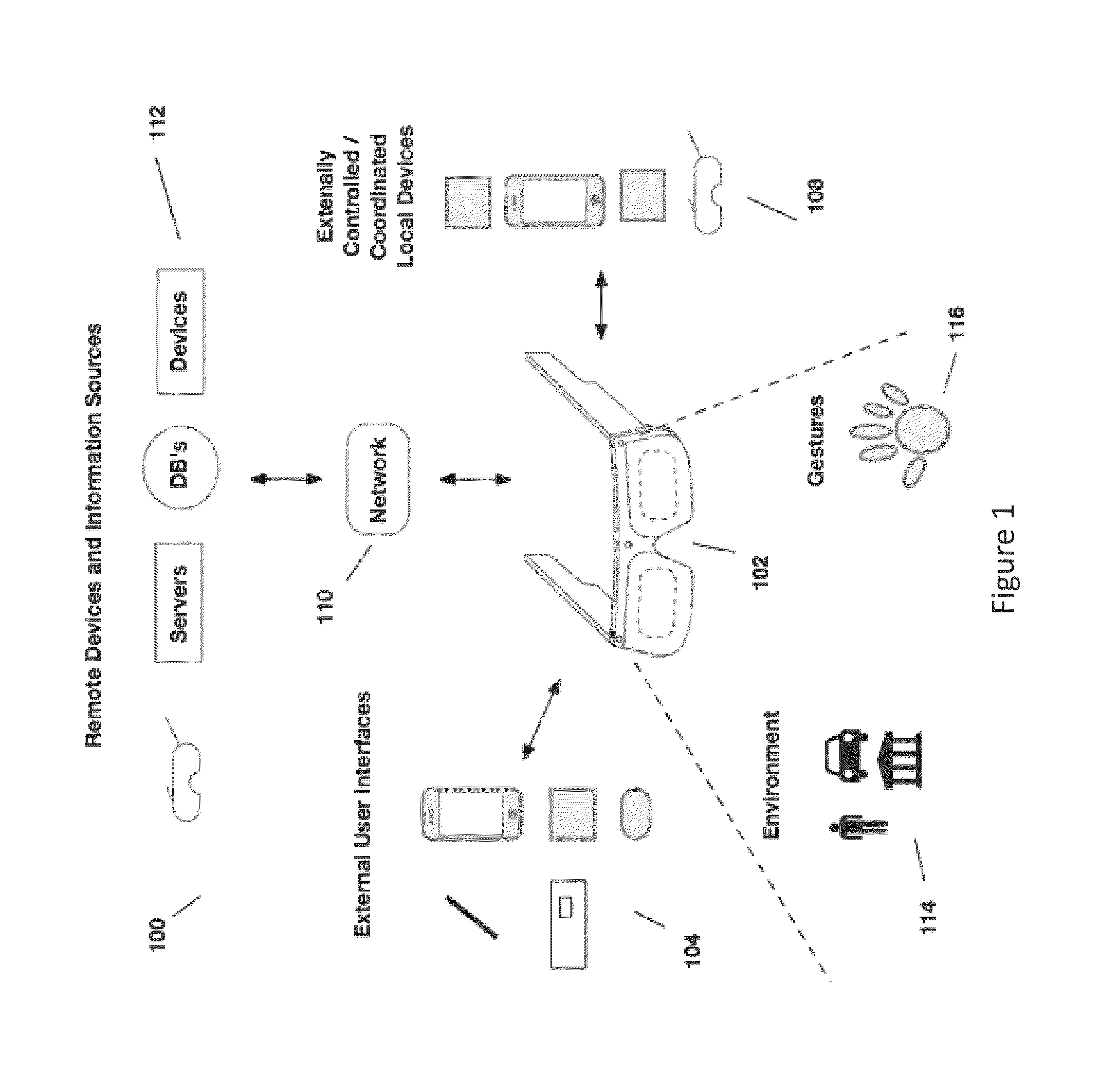

See-through computer display systems

Aspects of the present invention relate to methods and systems for the see-through computer display systems with a wide field of view.

Owner:MENTOR ACQUISITION ONE LLC

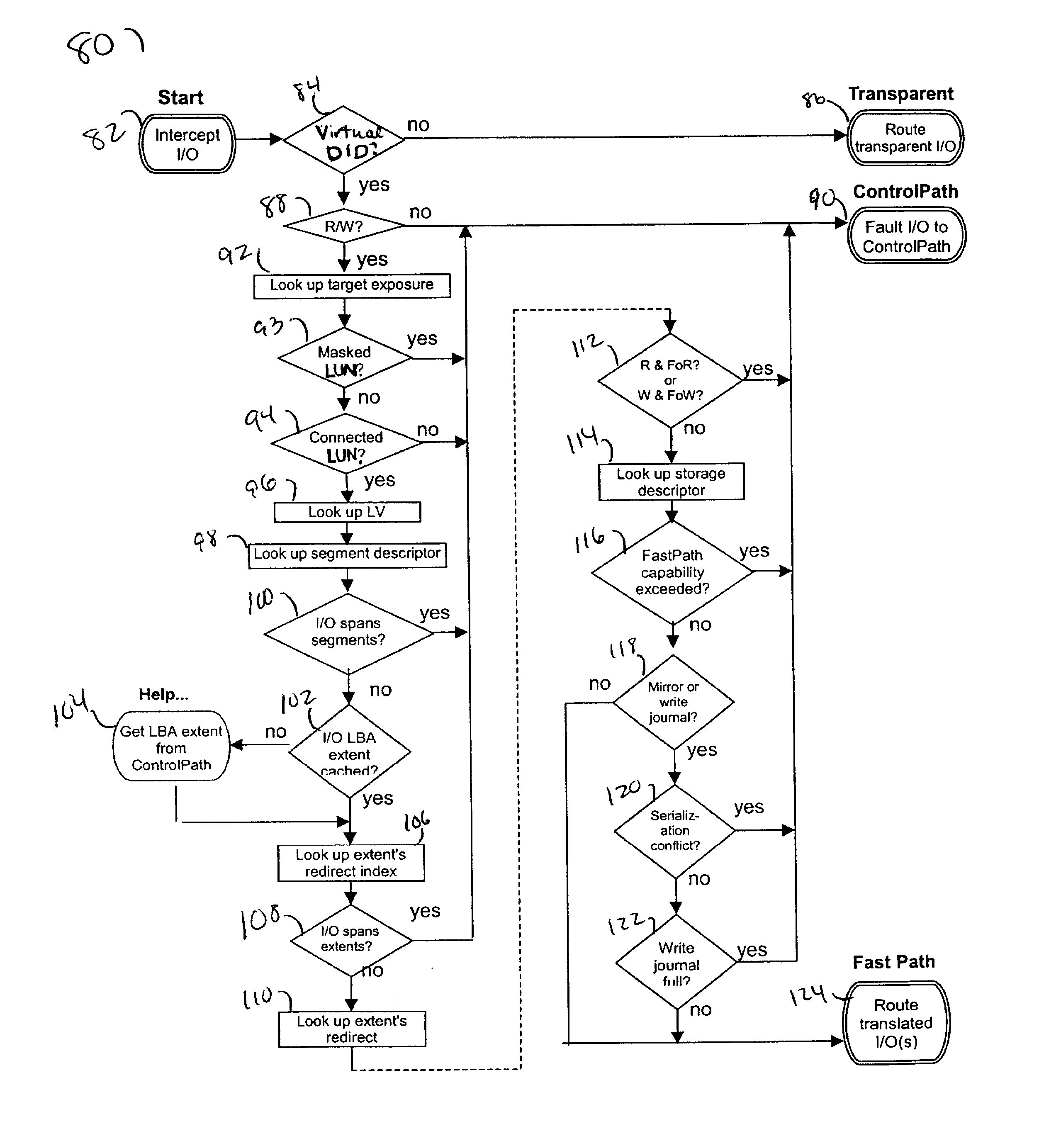

Fast path caching

InactiveUS20030140209A1Input/output to record carriersMemory adressing/allocation/relocationFast pathData operations

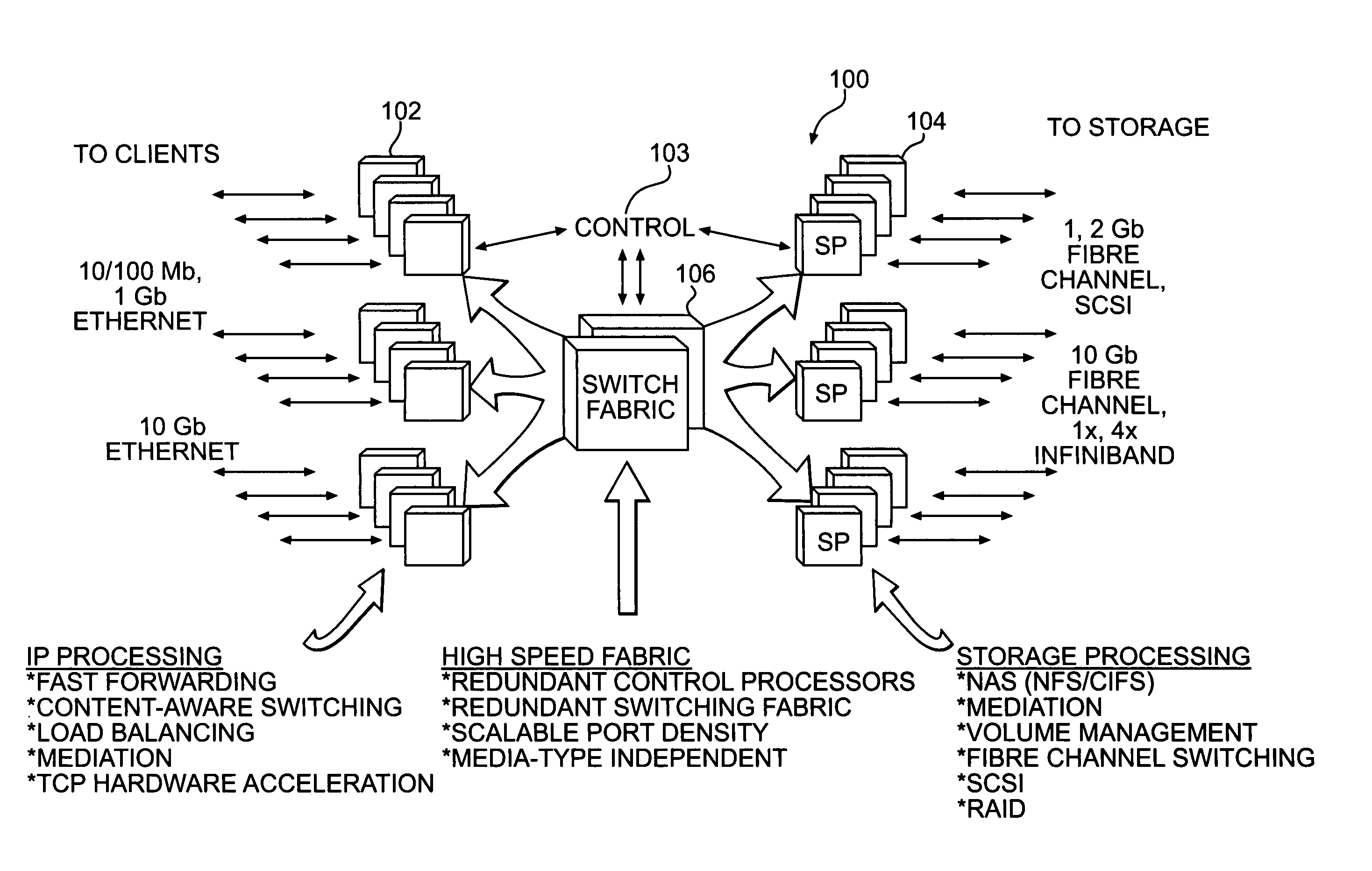

Described are techniques used in a computer system for handling data operations to storage devices. A switching fabric includes one or more fast paths for handling lightweight, common data operations and at least one control path for handling other data operations. A control path manages one or more fast paths. The fast path and the control path are utilized in mapping virtual to physical addresses using mapping tables. The mapping tables include an extent table of one or more entries corresponding to varying address ranges. The size of an extent may be changed dynamically in accordance with a corresponding state change of physical storage. The fast path may cache only portions of the extent table as needed in accordance with a caching technique. The fast path may cache a subset of the extent table stored within the control path. A set of primitives may be used in performing data operations. A locking mechanism is described for controlling access to data shared by the control paths.

Owner:IBM CORP

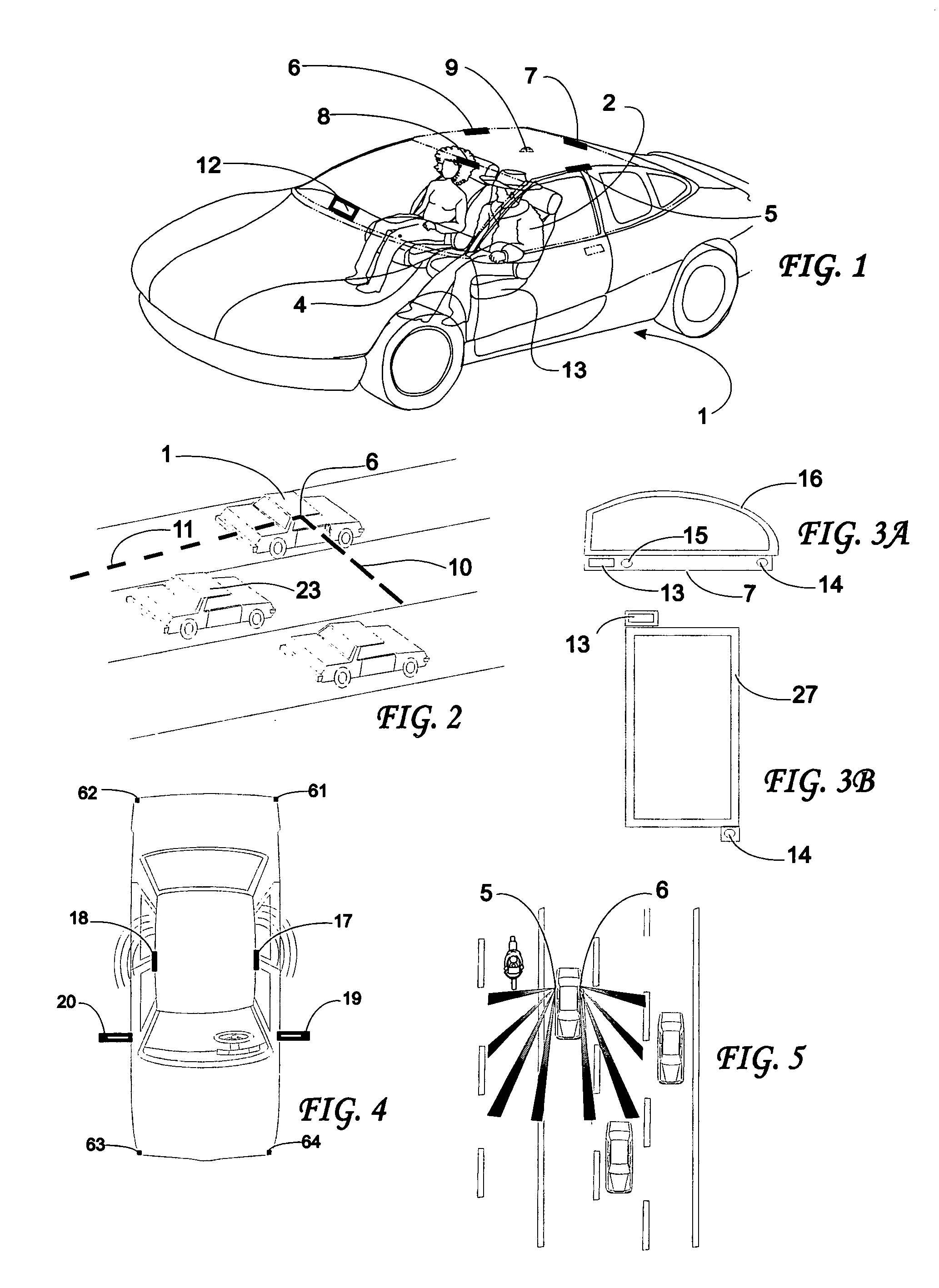

Vehicular impact reactive system and method

InactiveUS20050278098A1Reduce number and severityDigital data processing detailsAnti-collision systemsEngineeringReactive system

System and method for reacting to an expected impact involving a vehicle including an anticipatory sensor system for determining that an impact involving the vehicle is about to occur prior to the impact and an impact responsive system coupled to the sensor system and actuated after its determination of the expected impact. The sensor system includes wave receivers spaced apart from one another, each receiving waves generated by, modified by, or reflected from a common object exterior of the vehicle. The impact responsive system attempts to reduce the potential harm resulting from the impact and can be a protection apparatus which protects a vehicular occupant or a pedestrian, such as one including an airbag and an inflator for inflating the airbag.

Owner:AMERICAN VEHICULAR SCI

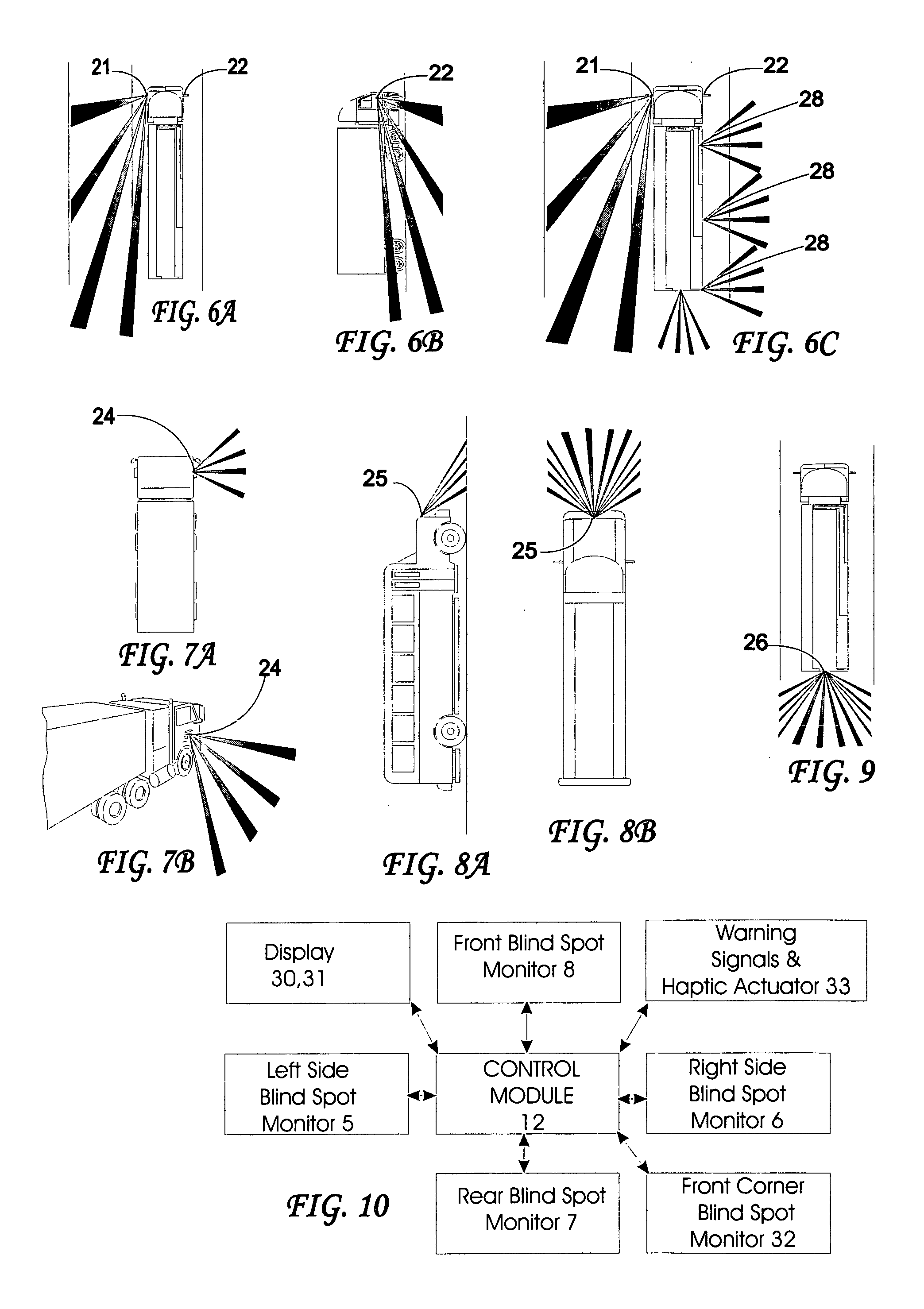

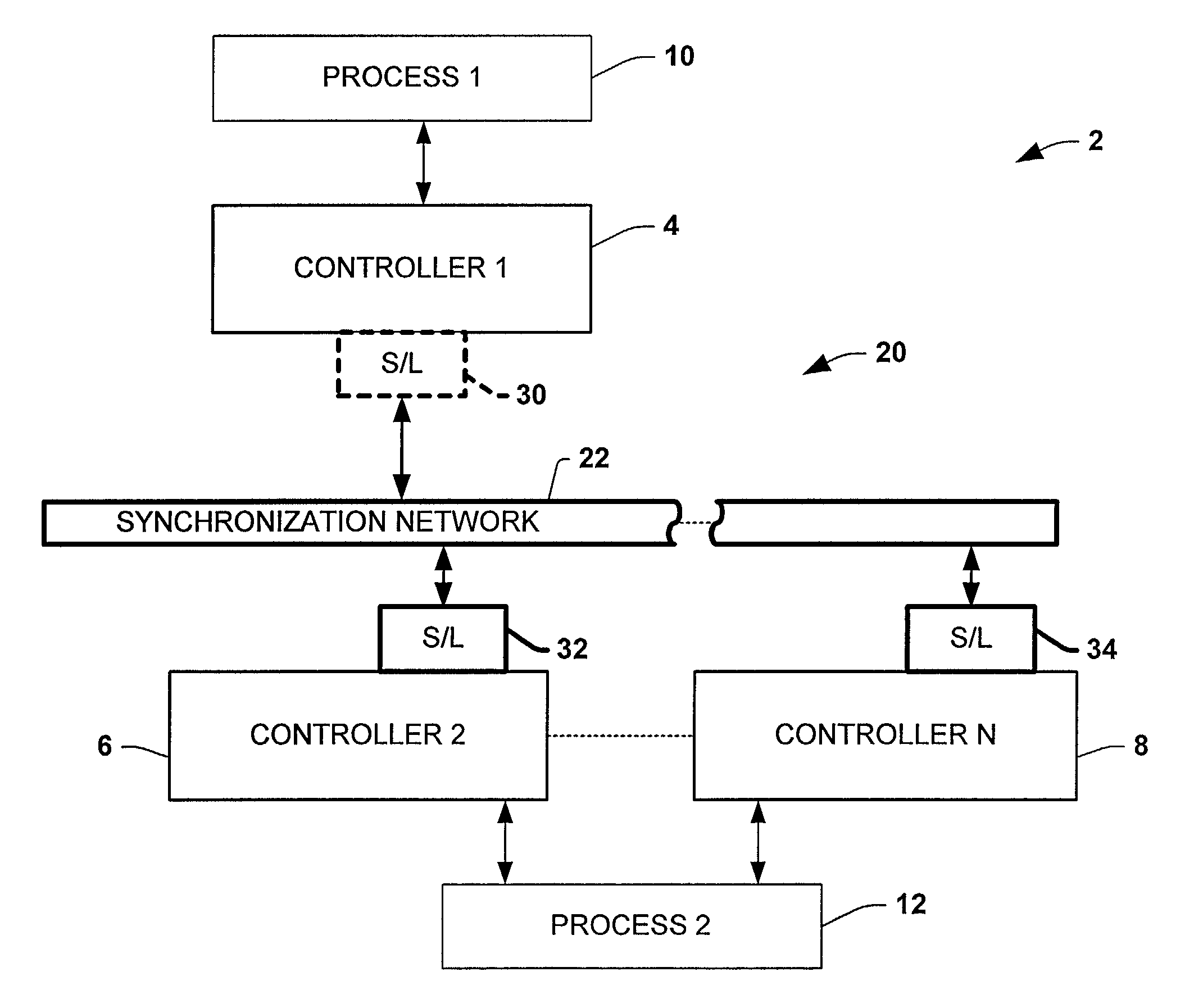

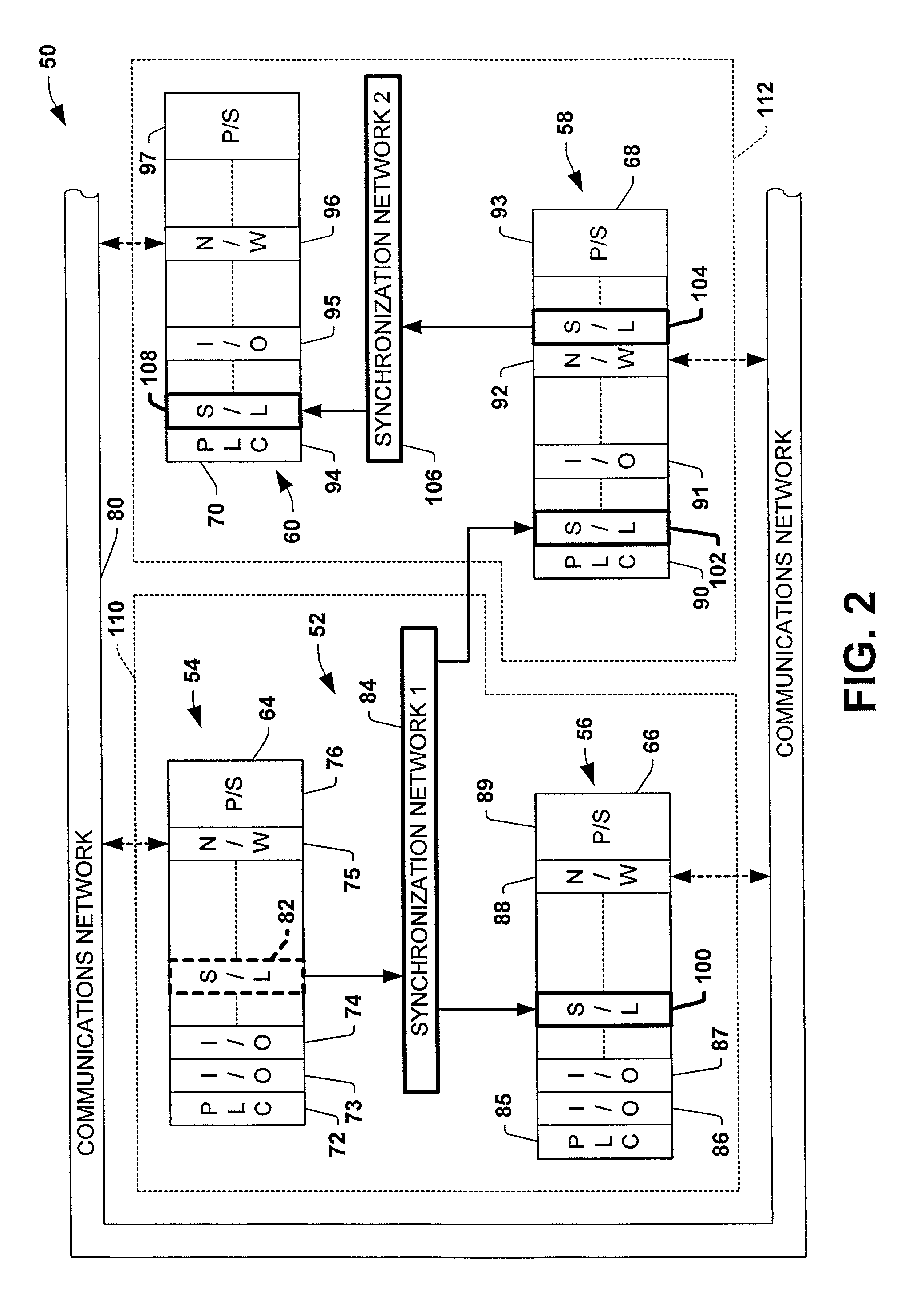

Protocol and method for multi-chassis configurable time synchronization

ActiveUS7007106B1Data representation error detection/correctionCode conversionSynchronous controlControl system

Systems and methods are disclosed for time synchronization of operations in a control system. Synchronization networks and devices are provided for transferring synchronization information between controllers in a distributed or localized control system, which is employed in order to allow operation of such controllers to be synchronized with respect to time. Also disclosed are synchronization protocols and hardware apparatus employed in synchronizing control operations in a control system.

Owner:ROCKWELL TECH

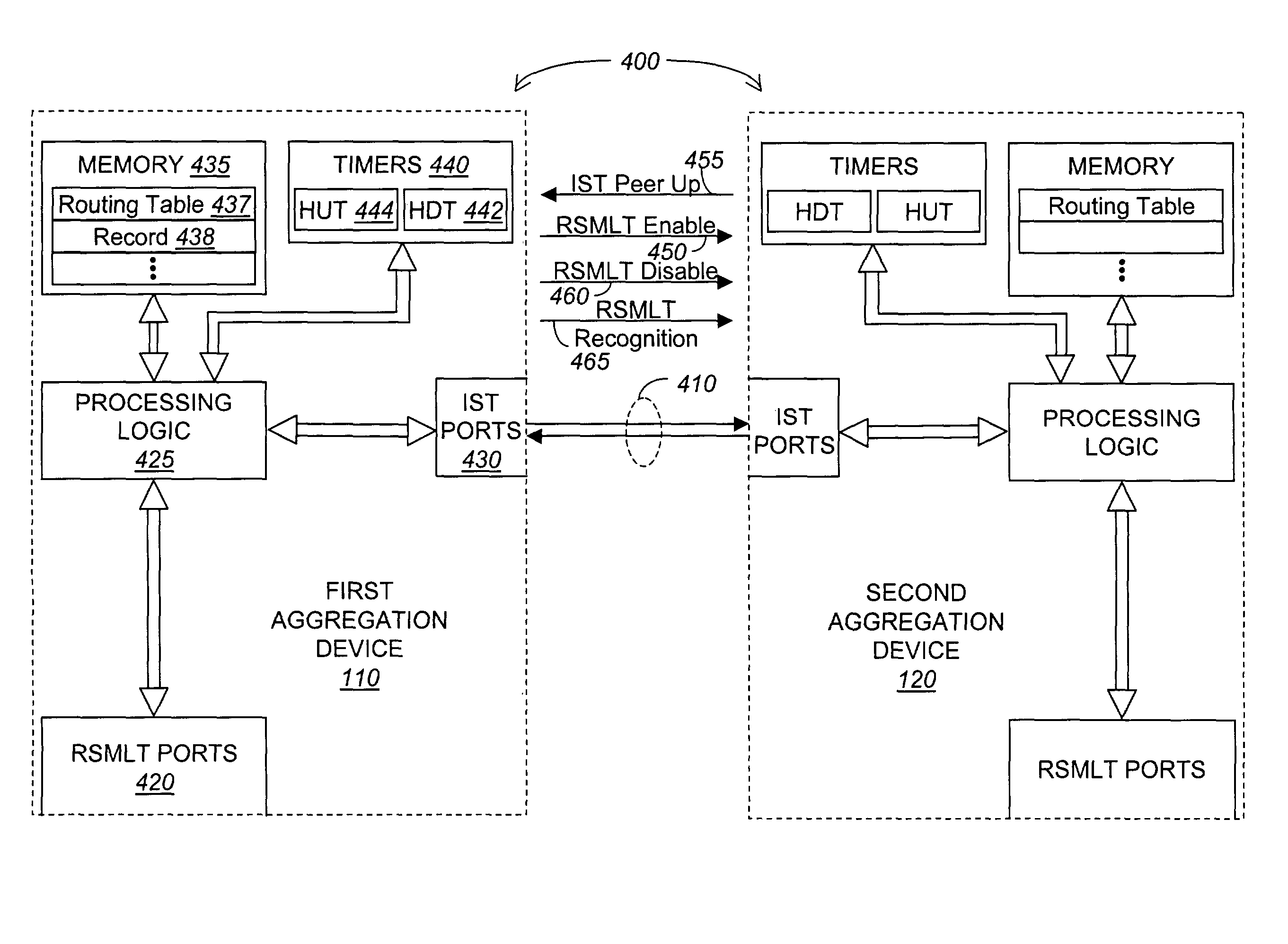

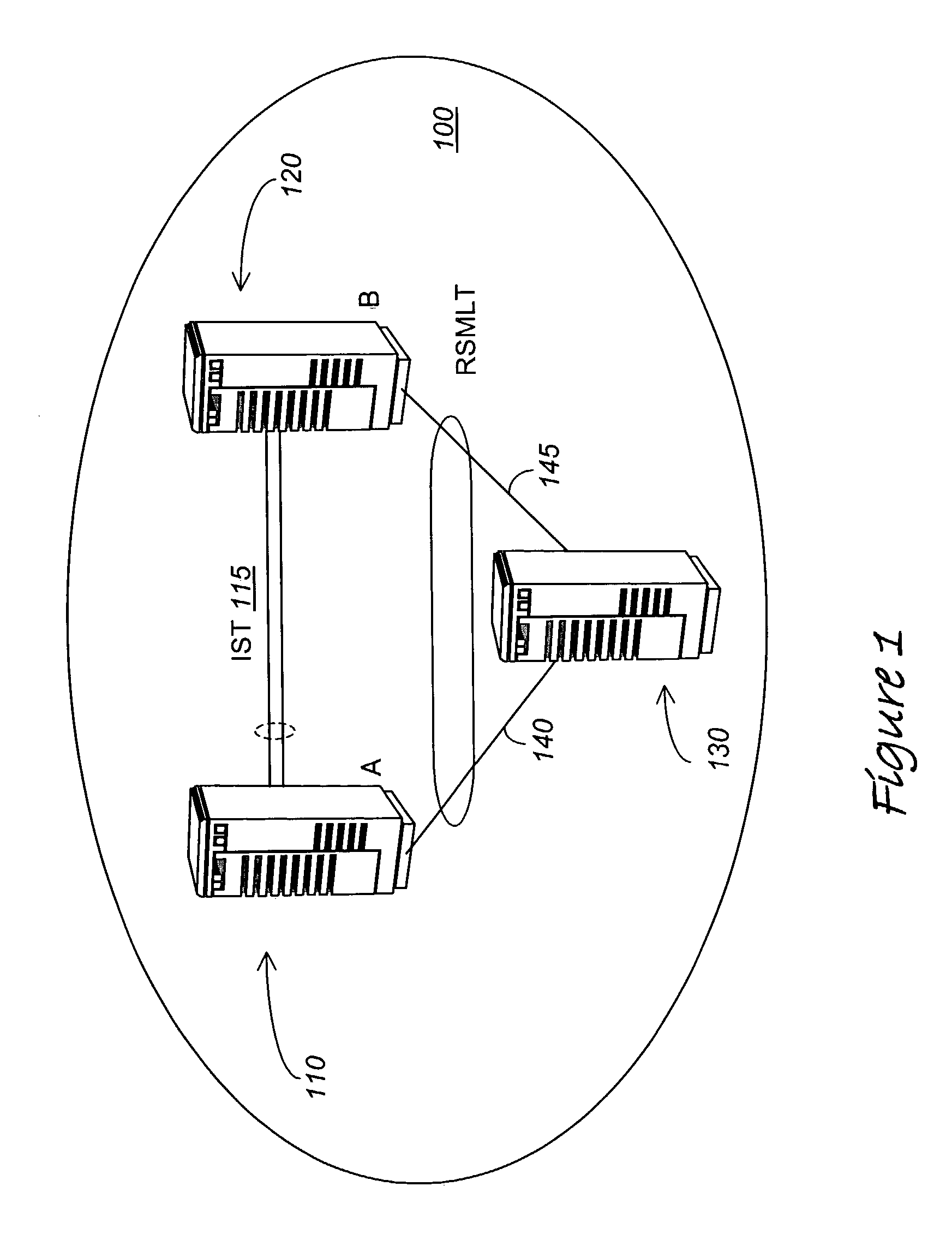

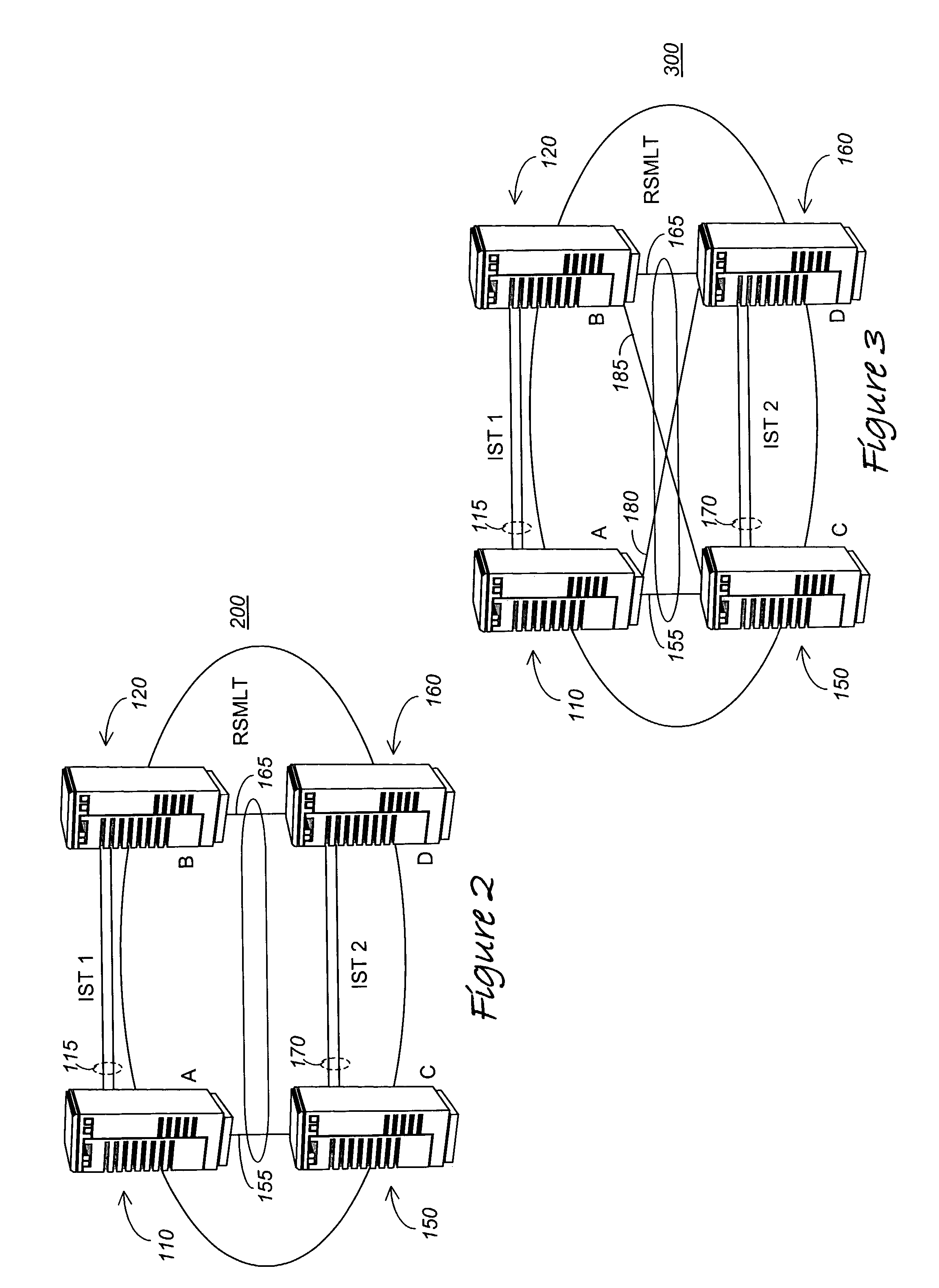

Routed split multilink trunking

In one embodiment, the invention relates to a method in which at least two aggregation devices, which logically operate as a single device, are interconnected by an Inter Switch Trunk (IST) link. Thereafter, forwarding records of local routing instances between the at least two aggregation devices are synchronized to enable one aggregation device to support data traffic for the other aggregation device if it has failed or a link to the aggregation device has failed.

Owner:AVAYA MANAGEMENT LP

See-through computer display systems

InactiveUS20160018645A1Input/output for user-computer interactionPolarising elementsExtended field of viewComputer engineering

Aspects of the present invention relate to methods and systems for the see-through computer display systems with an extended field of view.

Owner:OSTERHOUT GROUP INC

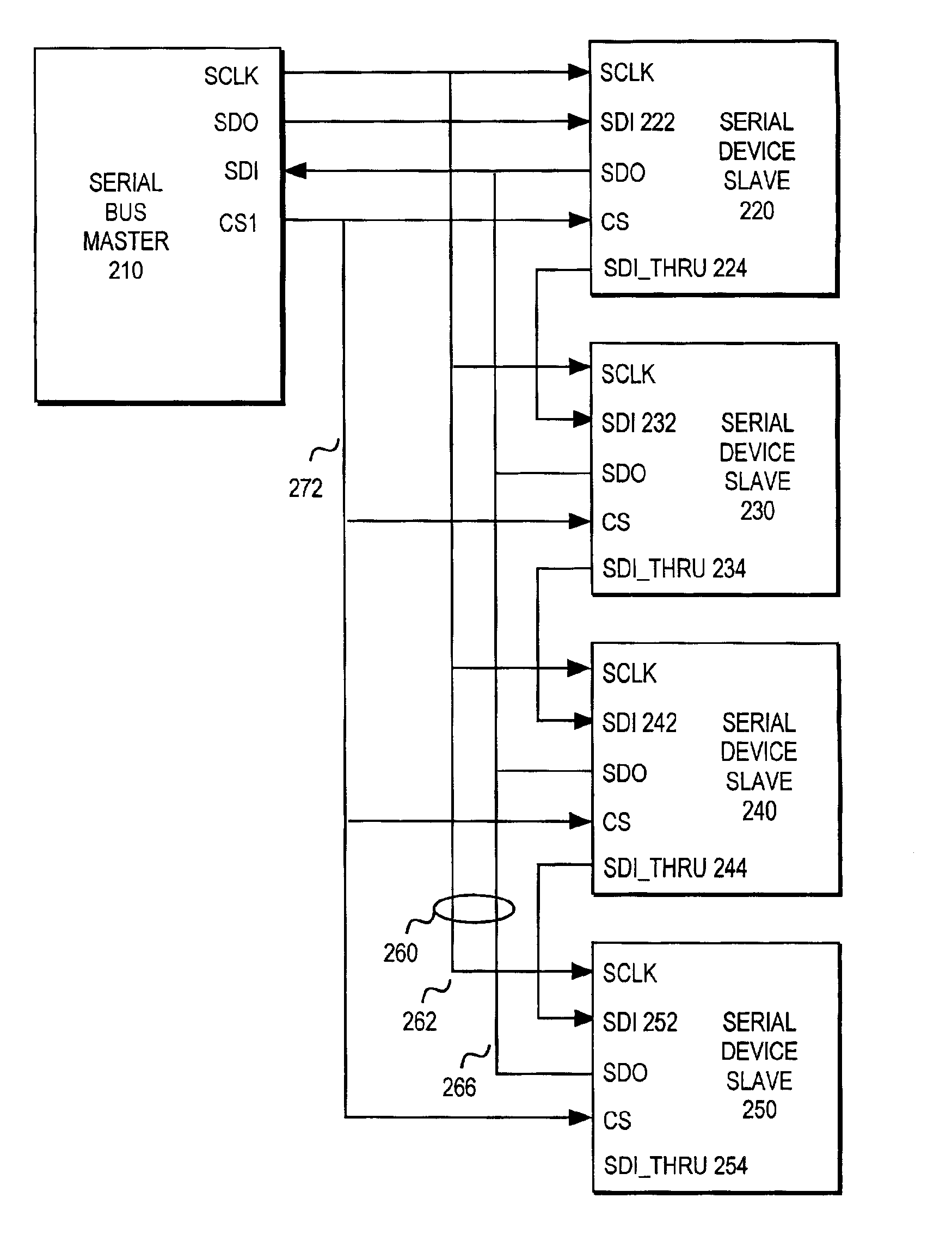

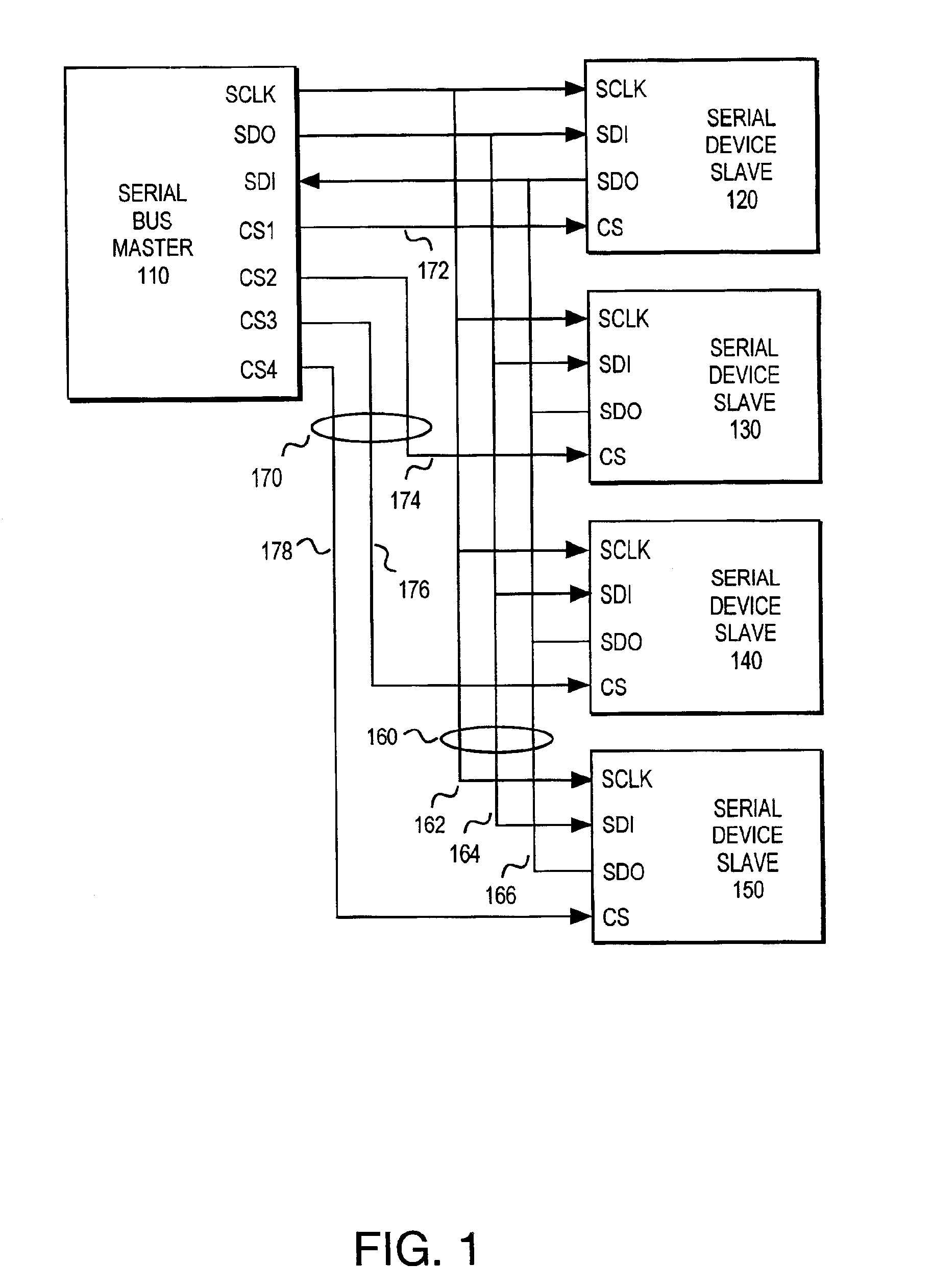

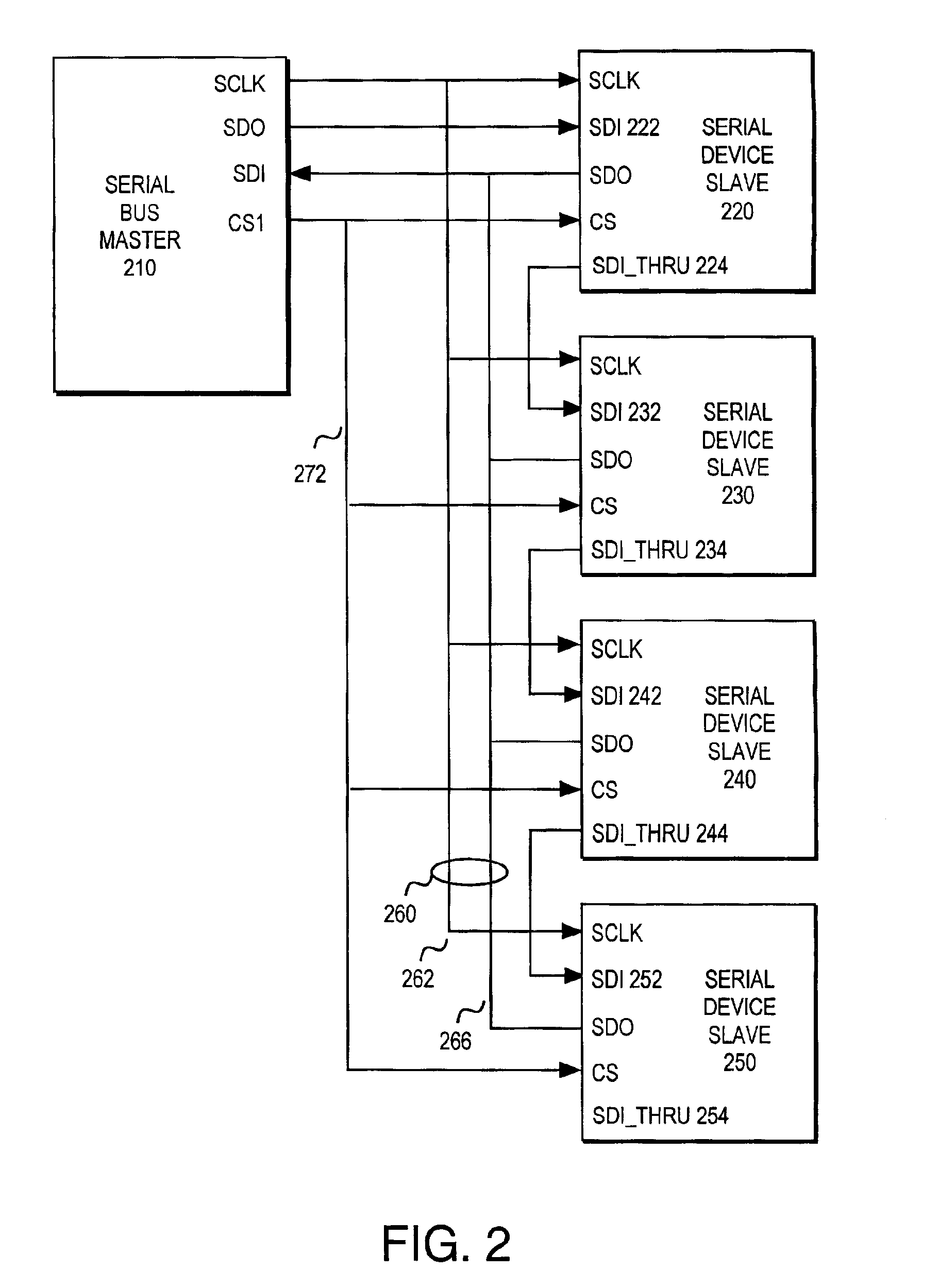

Serial device daisy chaining method and apparatus

InactiveUS6928501B2Data switching by path configurationInput/output processes for data processingComputer scienceEmbedded system

Methods and apparatus associated with a plurality of serial devices designed to communicate with a bus master in either a daisy chain or a normal configuration are provided. One method includes the step of serially providing a command sequence having a channel identifier to a given device of a plurality of daisy chained devices. The channel identifier is modified as it passes thru each daisy chained device. A specific device is identified or enabled when the channel identifier it receives matches a pre-determined value.

Owner:SKYWORKS SOLUTIONS INC

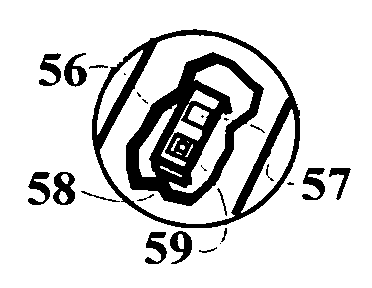

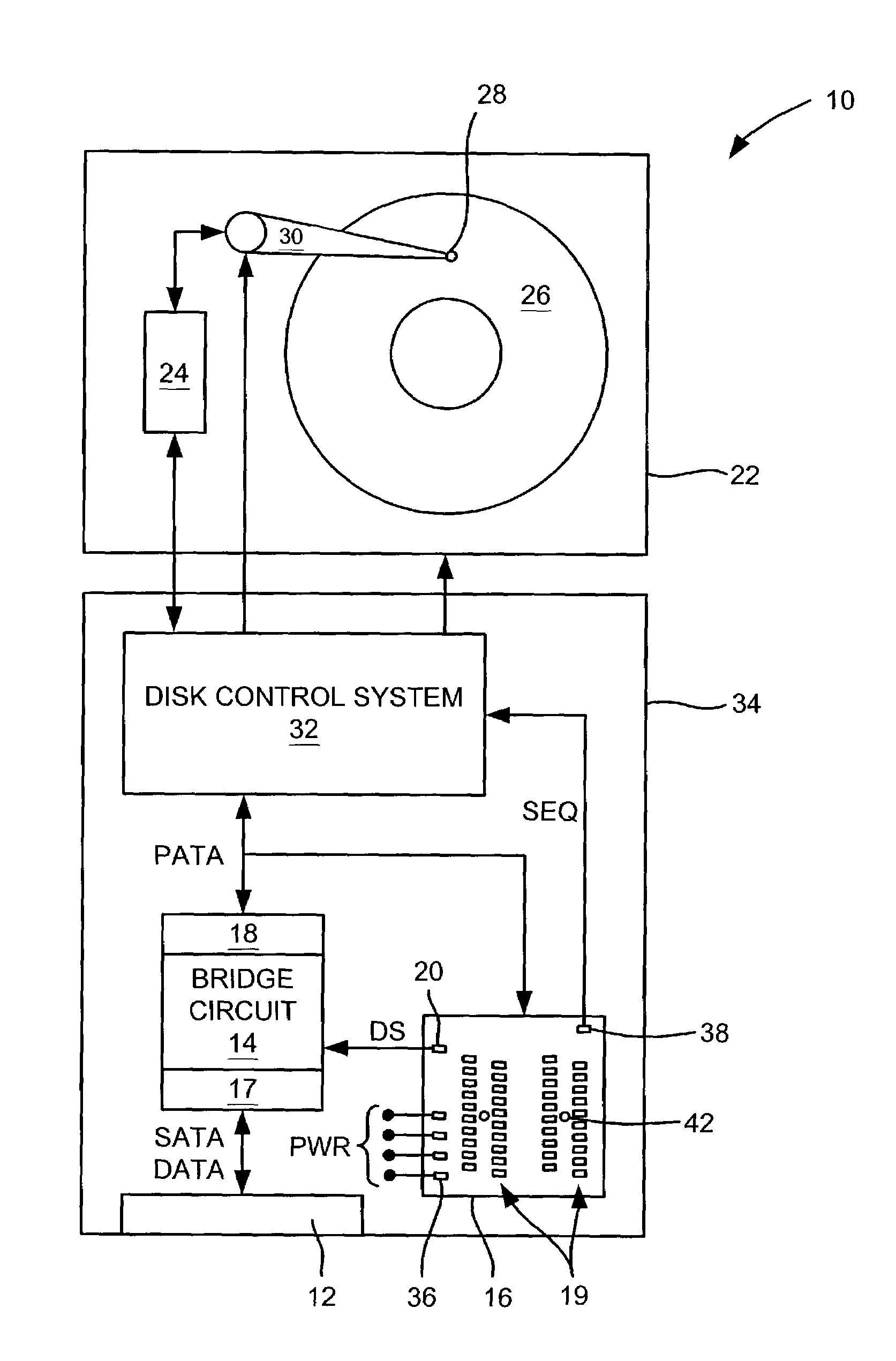

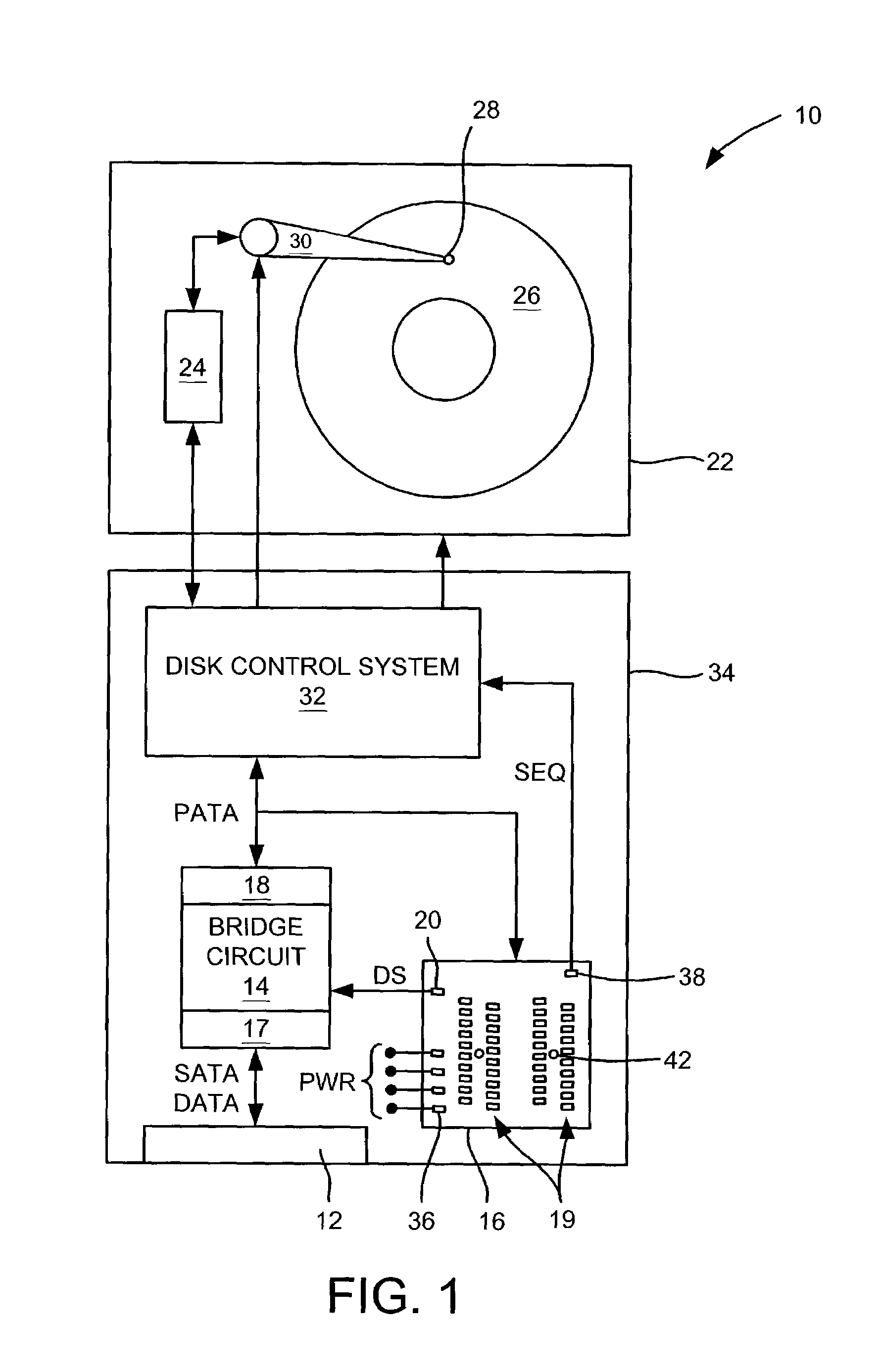

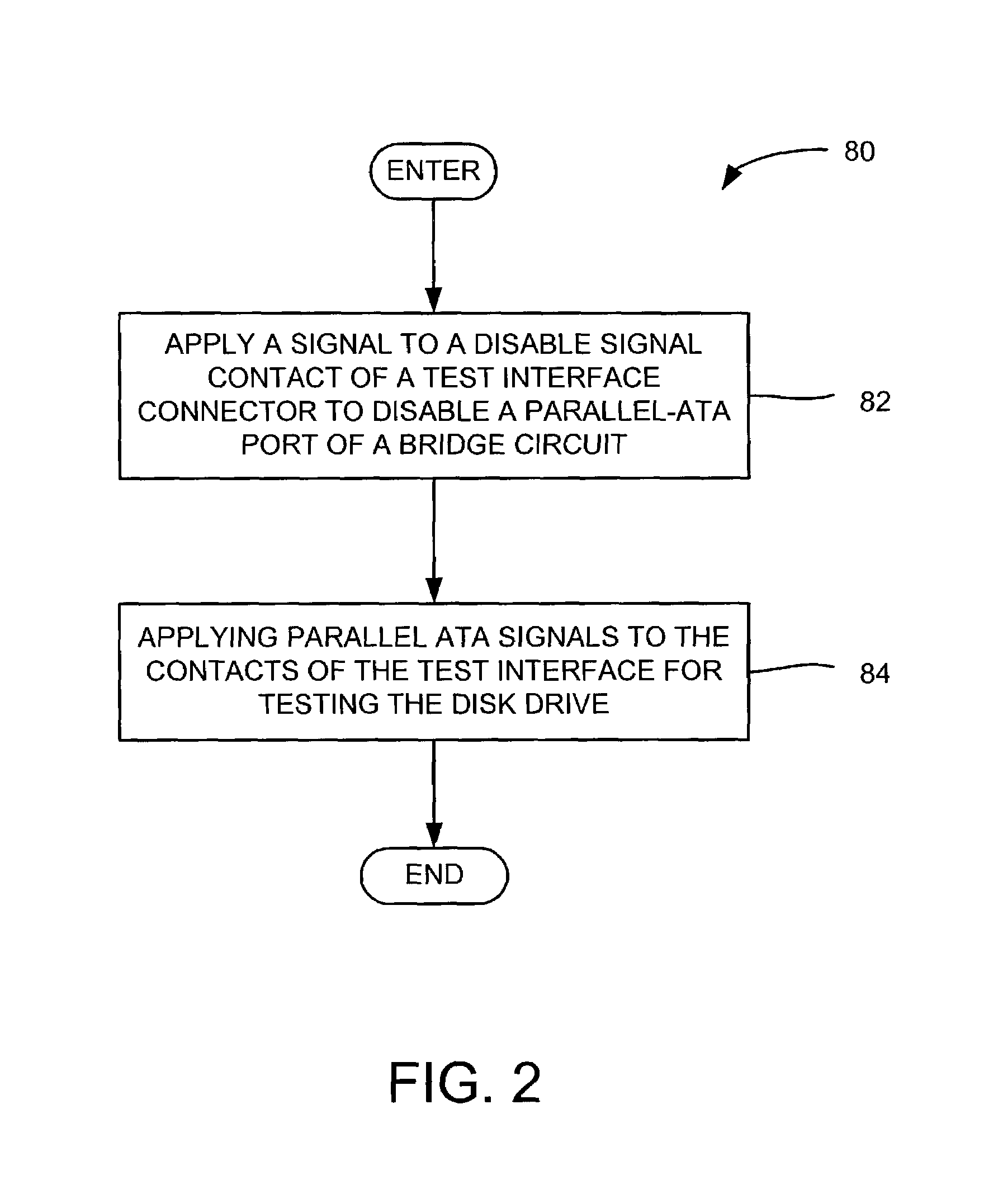

Serial ATA disk drive having a parallel ATA test interface and method

ActiveUS6976190B1Error detection/correctionInput/output processes for data processingParallel ATASignal transition

A serial ATA disk drive having a parallel ATA test interface is disclosed. A bridge circuit has a serial ATA port that is coupled to a serial ATA interface for receiving and transmitting serial ATA data signals, a parallel ATA port for receiving and transmitting parallel ATA signals, and a disable input for selectably disabling the parallel ATA port. The bridge circuit performs signal conversions between the ports. The test interface is for coupling the disk drive to a disk-drive test system. The test interface includes a connector having contacts for parallel ATA signals, and having a contact for a disable signal coupled to the disable input. The connector may be a pad pattern on a printed circuit of the disk drive. The disk drive may have an industry standard form factor, and the connector may be configured such that it lies within the disk drive's form factor.

Owner:WESTERN DIGITAL TECH INC

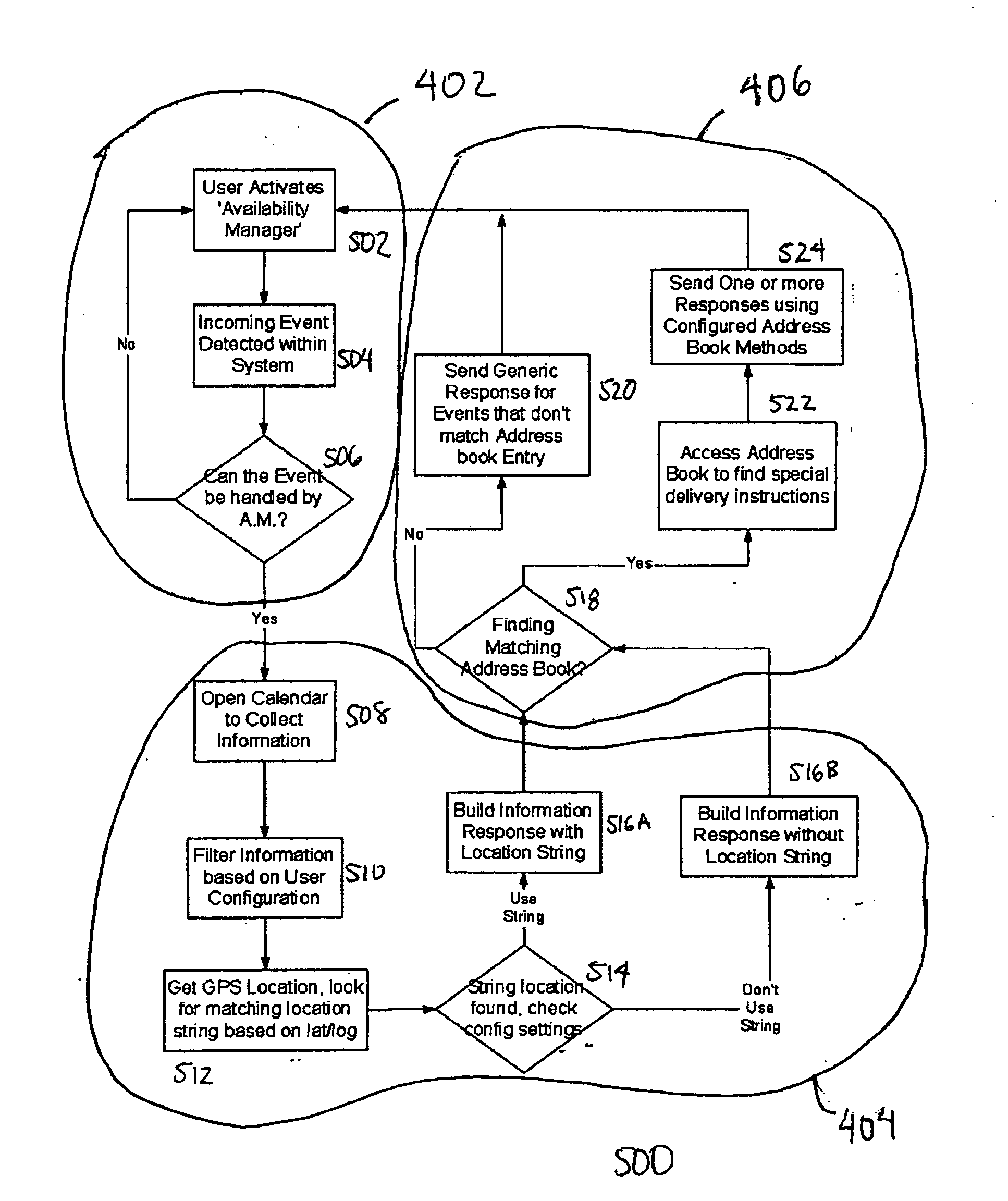

System and method for automatically responding to a received communication

ActiveUS20070011367A1Multiple digital computer combinationsSubstation equipmentComputer scienceCommunication device

A device and a method of responding to a received interrupt event received by a communication device is provided. The method comprises accessing data associated with a calendar application and / or a location application to determine a current state of availability of a user of the device using data; determining whether a response action is to be sent in response to the event when the device is note available; and sending the response action. The device incorporates modules to perform the method.

Owner:MALIKIE INNOVATIONS LTD

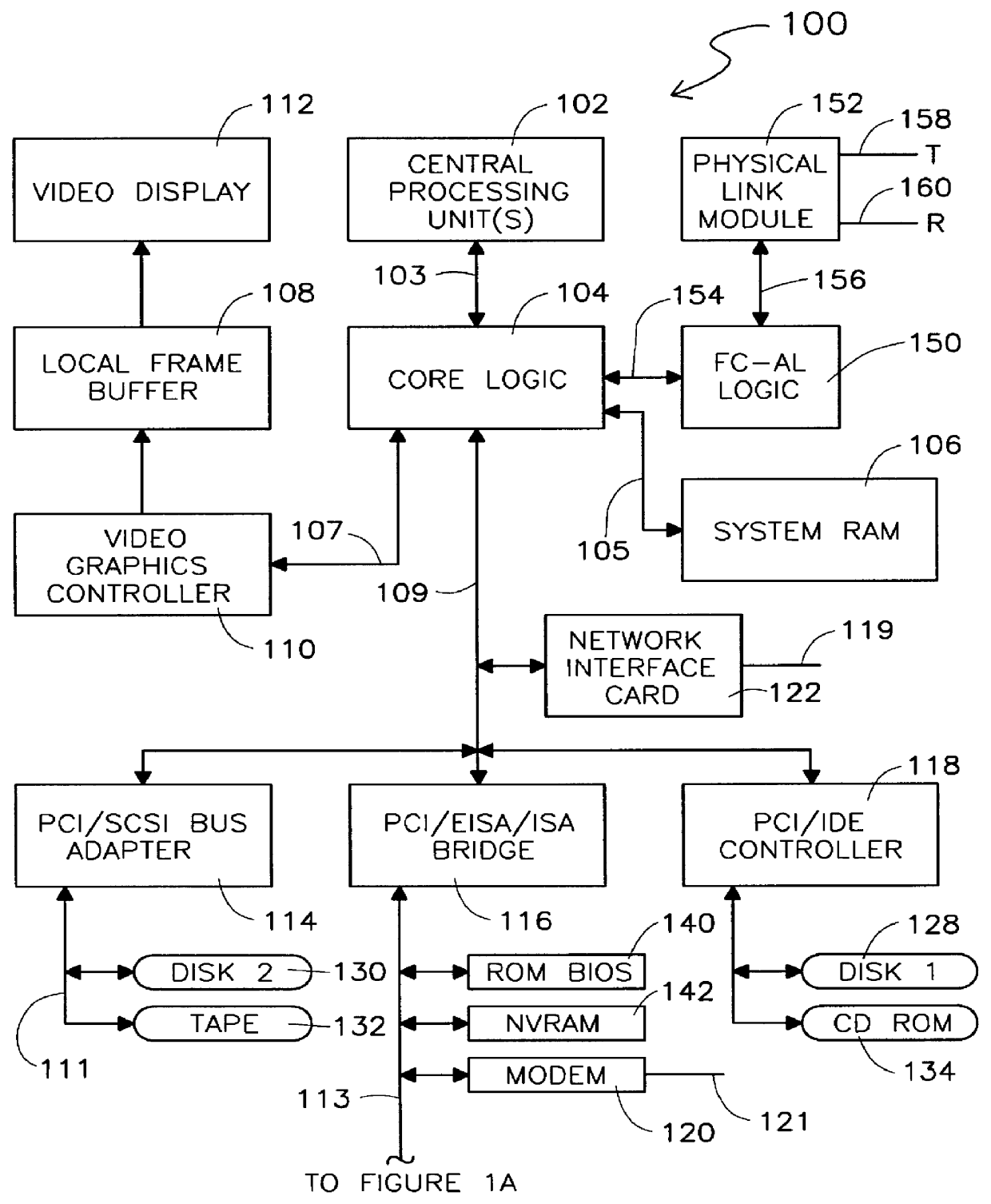

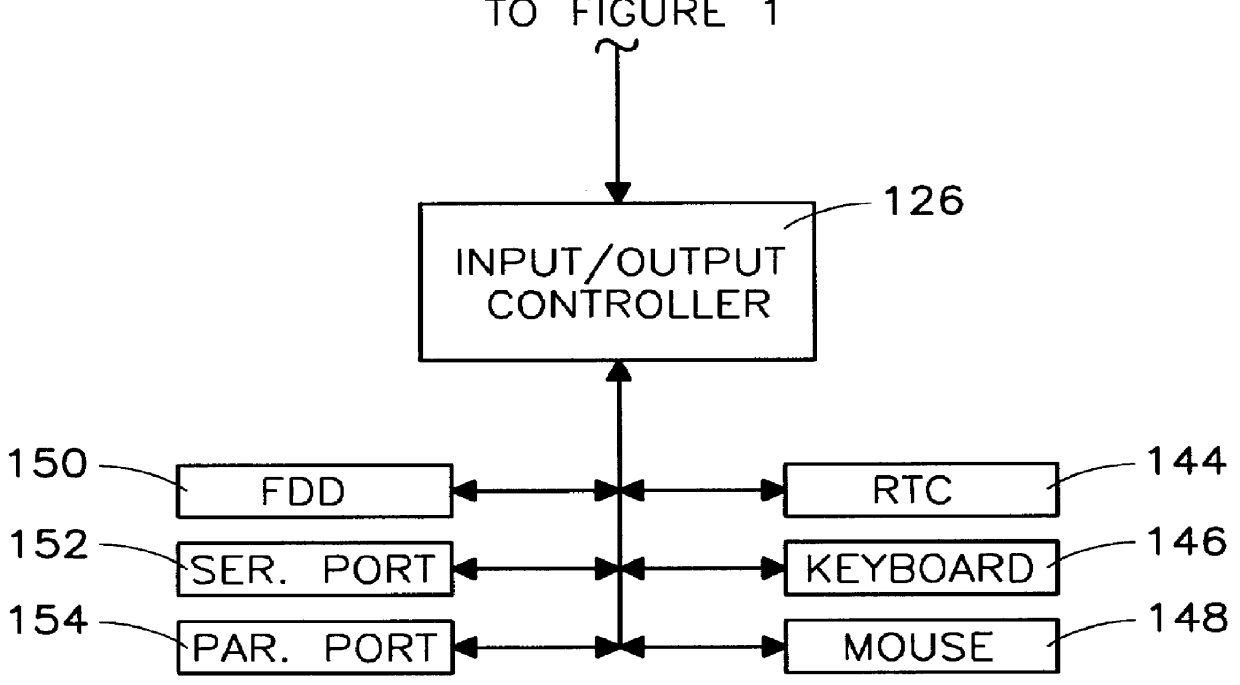

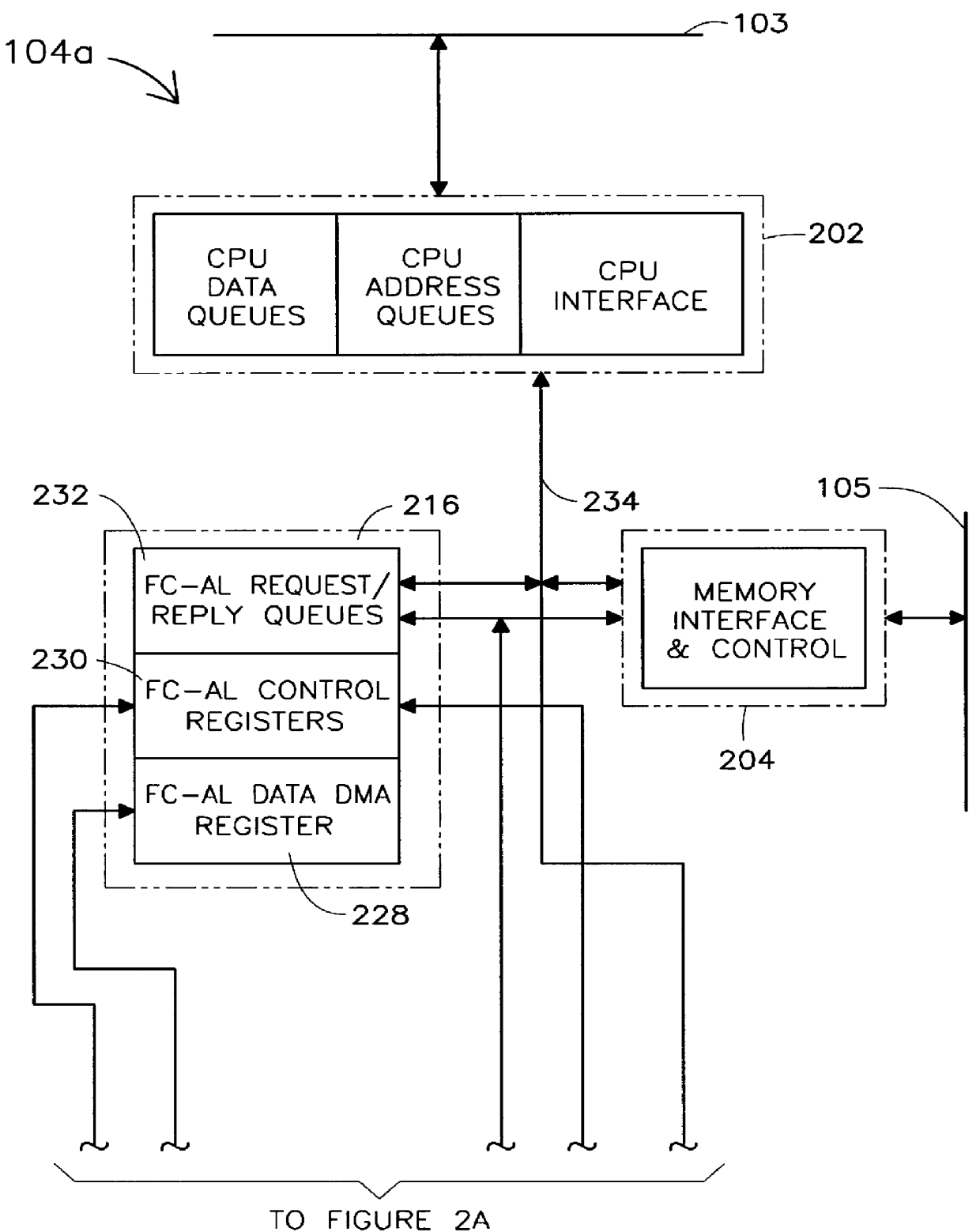

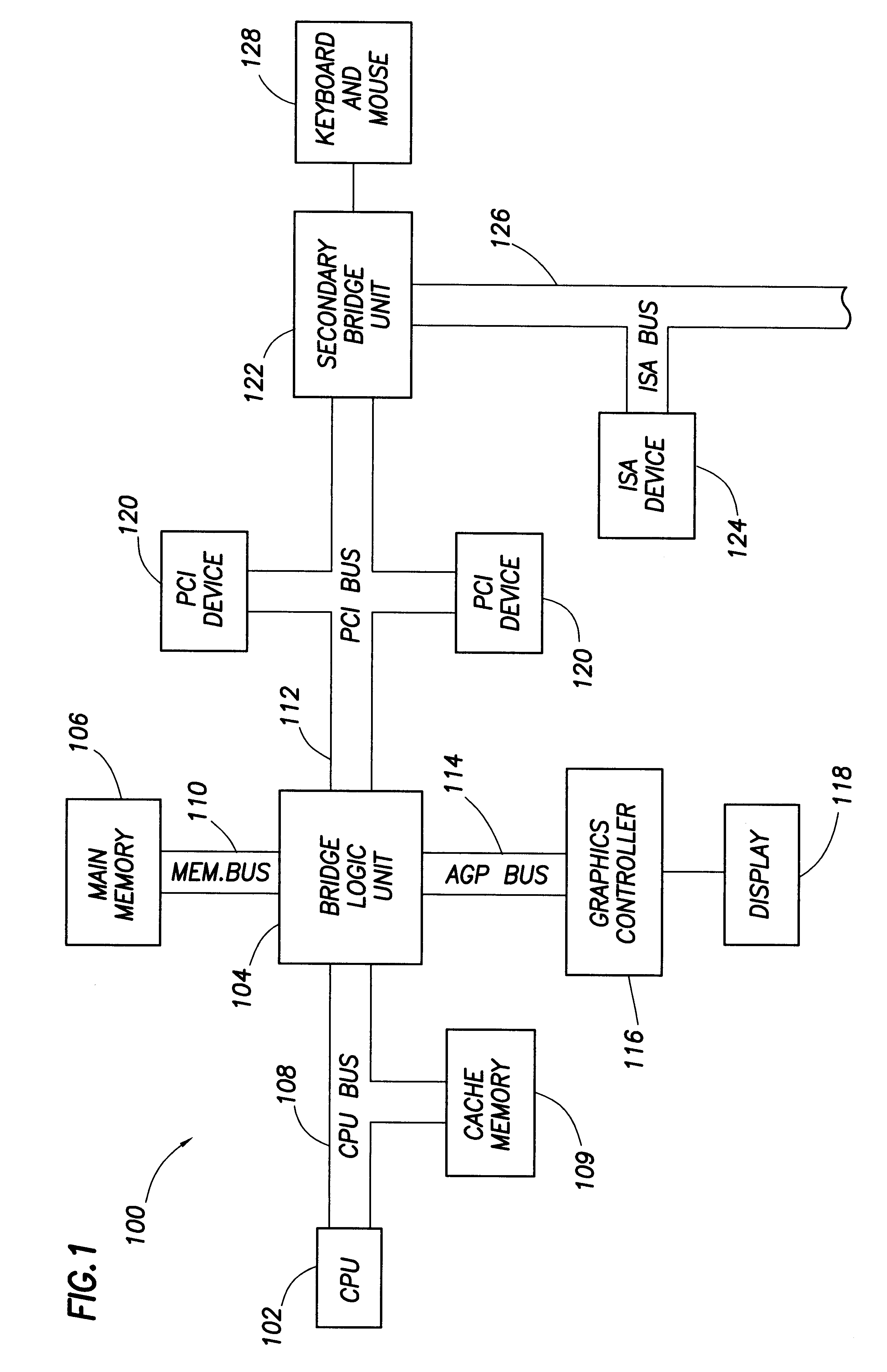

Dual purpose apparatus, method and system for accelerated graphics port and fibre channel arbitrated loop interfaces

InactiveUS6057863ALow costIncrease the number ofDigital computer detailsImage data processing detailsFiberComputer hardware

A multiple use core logic chipset is provided in a computer system that may be configured either as a bridge between an accelerated graphics port ("AGP") bus and host and memory buses, or as an interface bridge between a Fibre Channel Arbitrated Loop ("FC-AL") interface and the host and memory buses. The function of the multiple use chipset is determined at the time of manufacture of the computer system or in the field whether an AGP bus bridge or an FC-AL bridge interface is to be implemented. Selection of the type of bus bridge (AGP or FC-AL bridge interface) in the multiple use core logic chipset may be made by a hardware signal input, or by software during computer system configuration or power on self test ("POST"). Software configuration may also be determined upon detection of either an AGP or a FC-AL bridge interface device connected to the common AGP / FC-AL bus. FC-AL information may be stored in the computer system main memory using the high speed FC-AL bridge interface.

Owner:HEWLETT PACKARD DEV CO LP +1

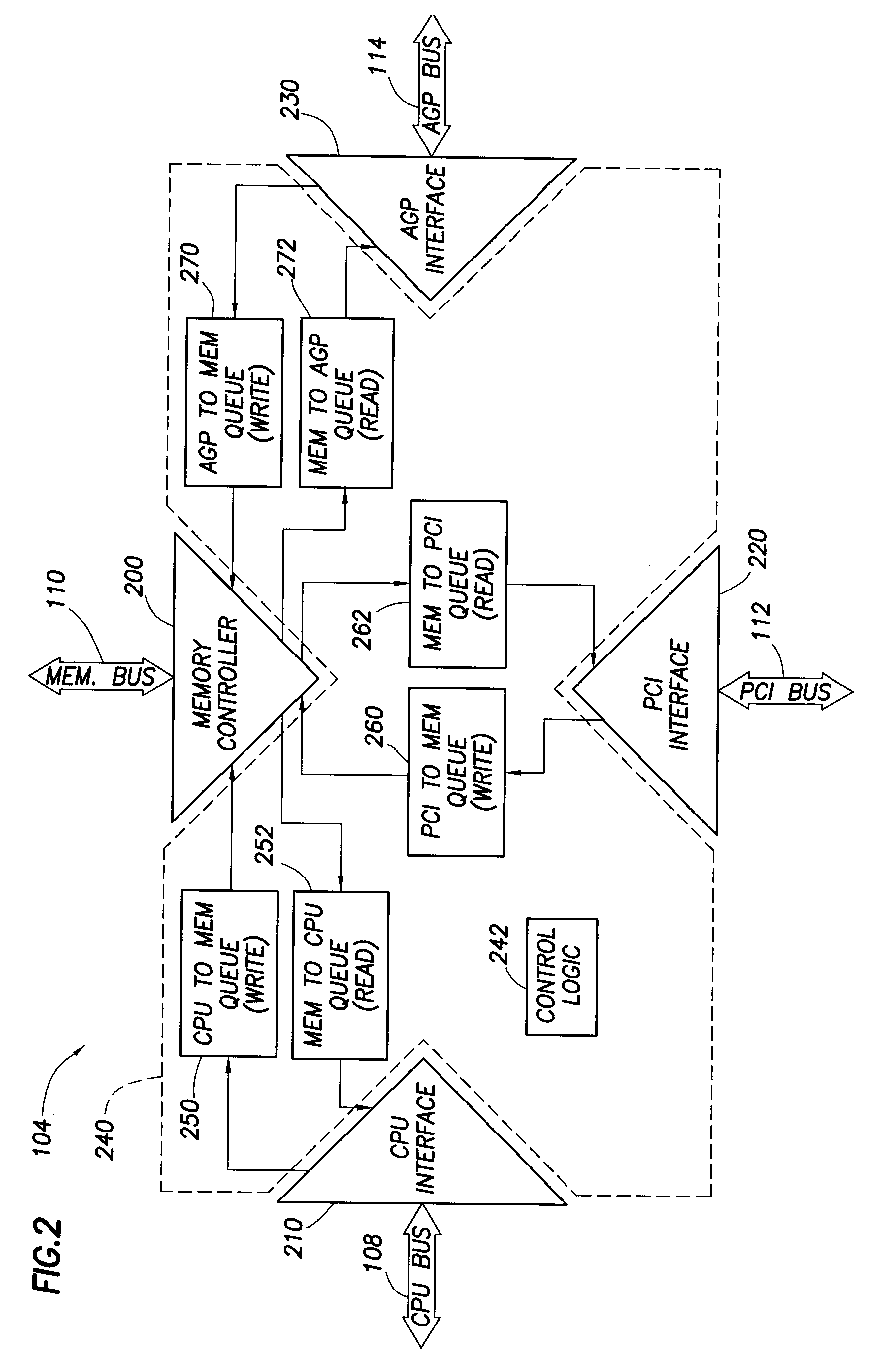

Techniques for processing out-of -order requests in a processor-based system

InactiveUS20030093630A1Memory systemsInput/output processes for data processingShift registerProcessor register

A mechanism for executing requests in a system. More specifically, a technique for processing requests to a memory system is provided. A shift register may be used to store an index associated with requests, such as read and write requests, to a memory system. Each request is stored in a respective queue depending on the source of the request and the request type (e.g. read or write). Each request includes flags which may be set to determine the processing order of the requests, such that out-of-order processing is feasible. An index corresponding to each of the requests is stored in an index shifter to facilitate the out-of-order processing of the requests. Alternatively, a shift register may be used to store each of the requests. Rather than shifting the indices to facilitate the out-of-order processing of requests, depending on the state of the corresponding request flags, the entire entry may be shifted.

Owner:VALTRUS INNOVATIONS LTD +1

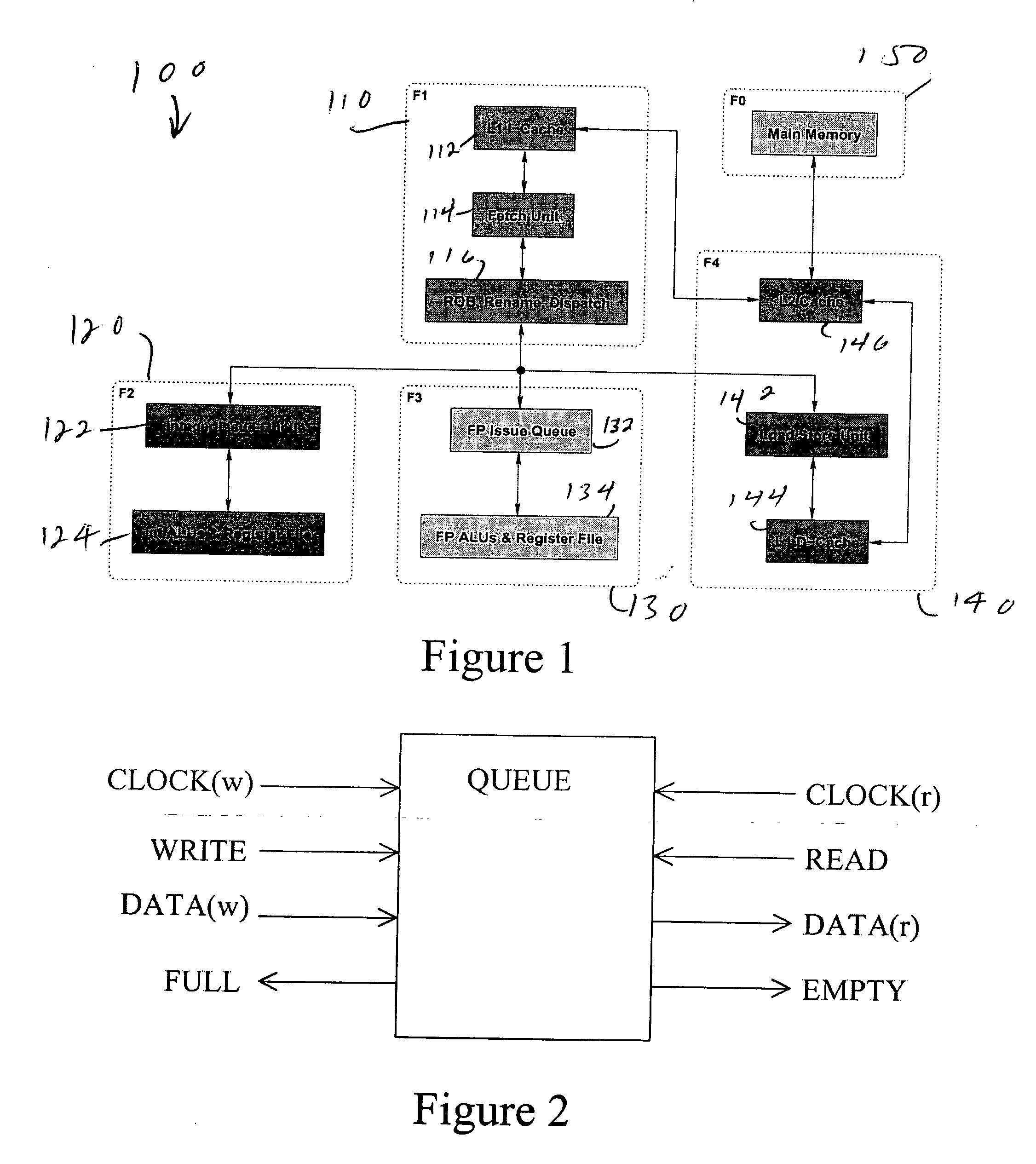

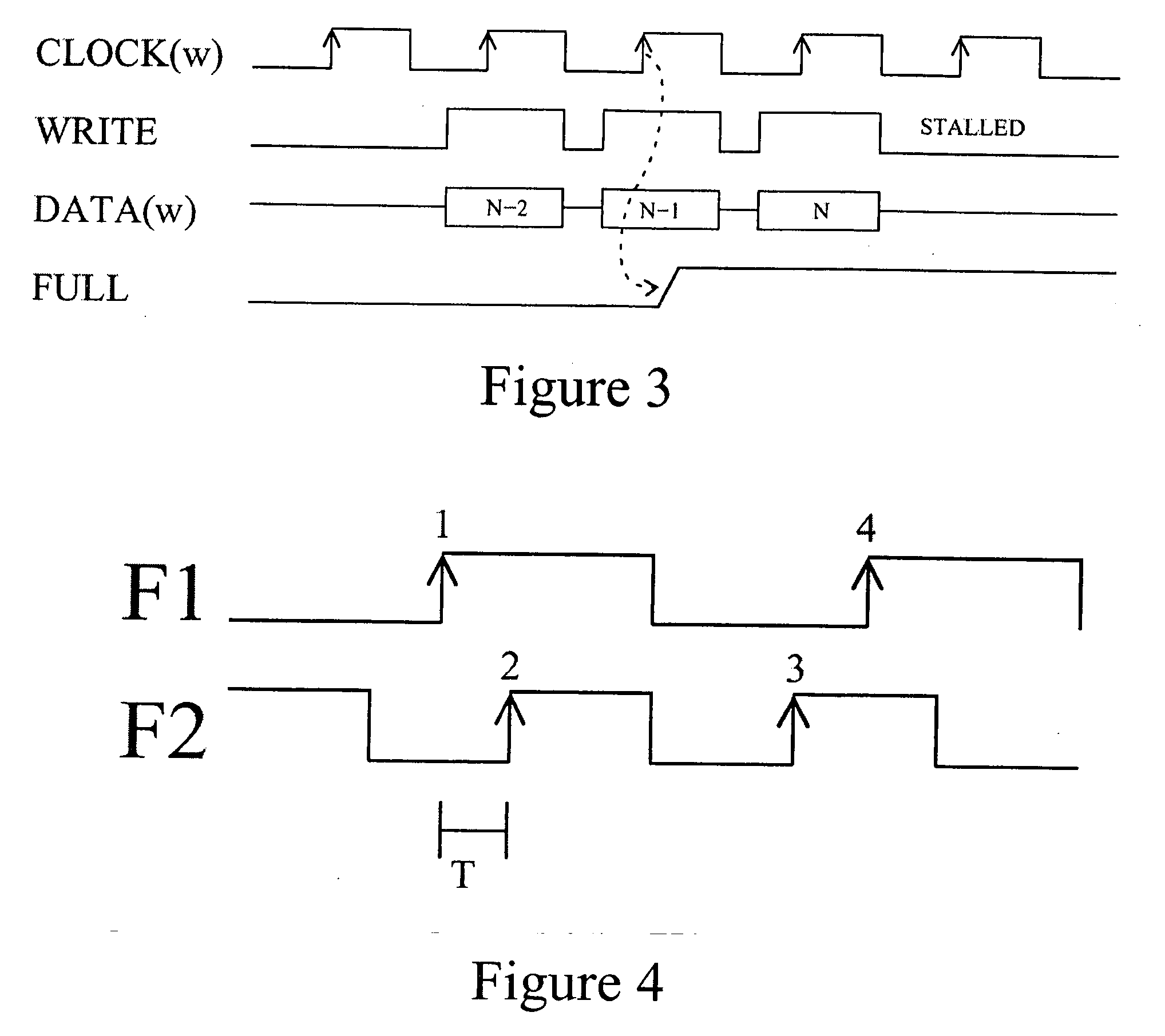

Multiple clock domain microprocessor

ActiveUS20070016817A1High frequencyImprove good performanceEnergy efficient ICTPower supply for data processingComputer scienceInter-domain

A multiple clock domain (MCD) microarchitecture uses a globally-asynchronous, locally-synchronous (GALS) clocking style. In an MCD microprocessor each functional block operates with a separately generated clock, and synchronizing circuits ensure reliable inter-domain communication. Thus, fully synchronous design practices are used in the design of each domain.

Owner:ALBONESI DAVID +5

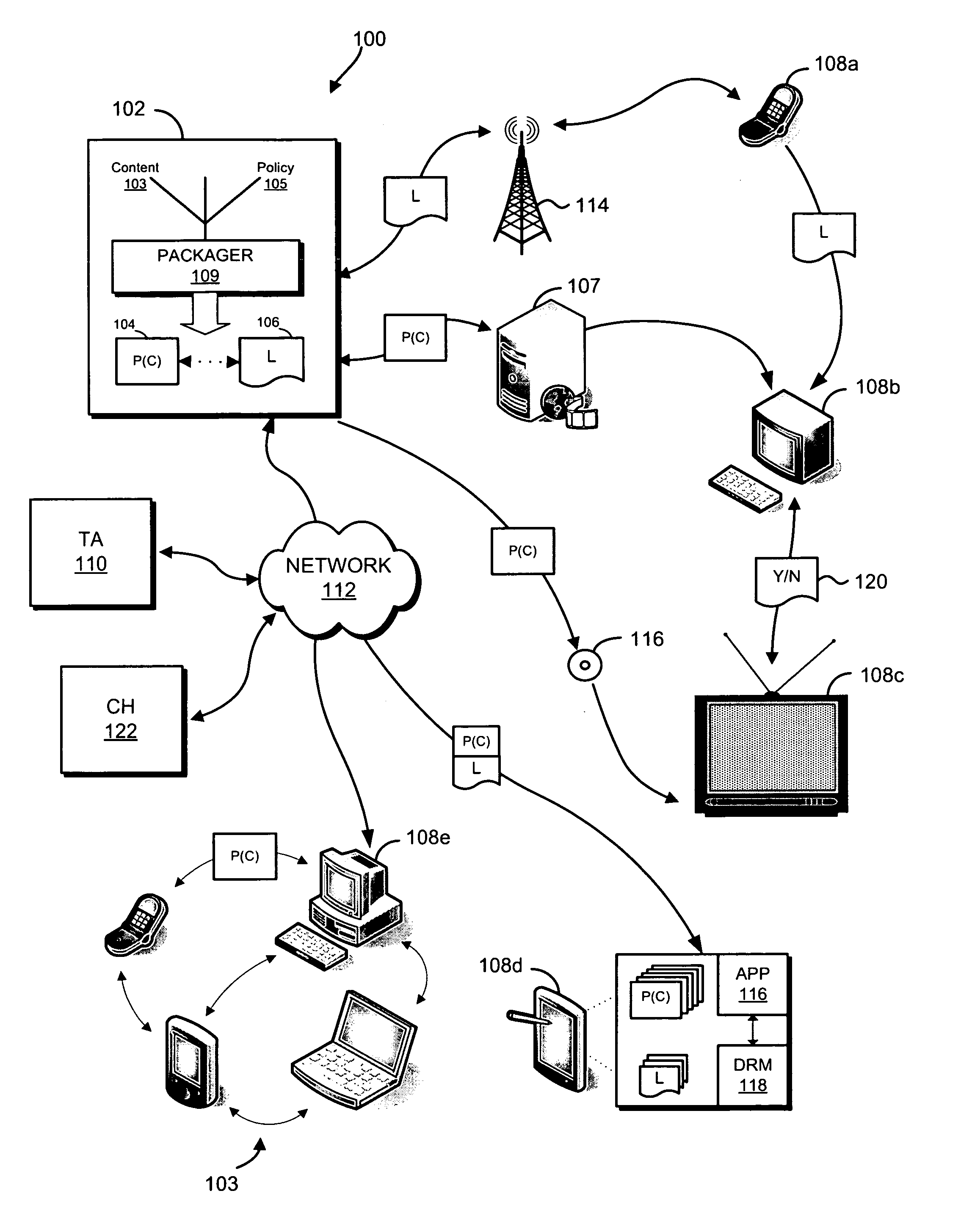

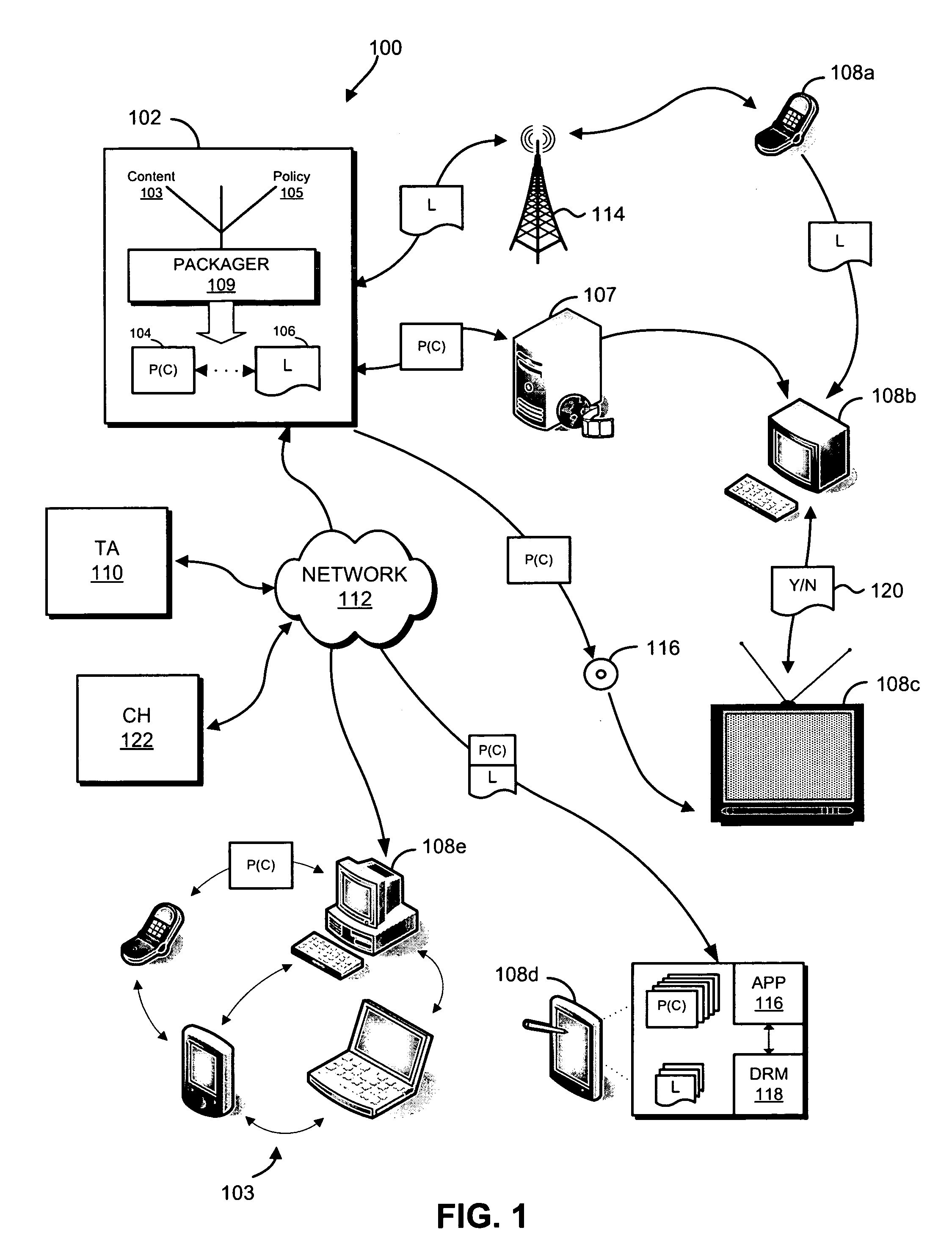

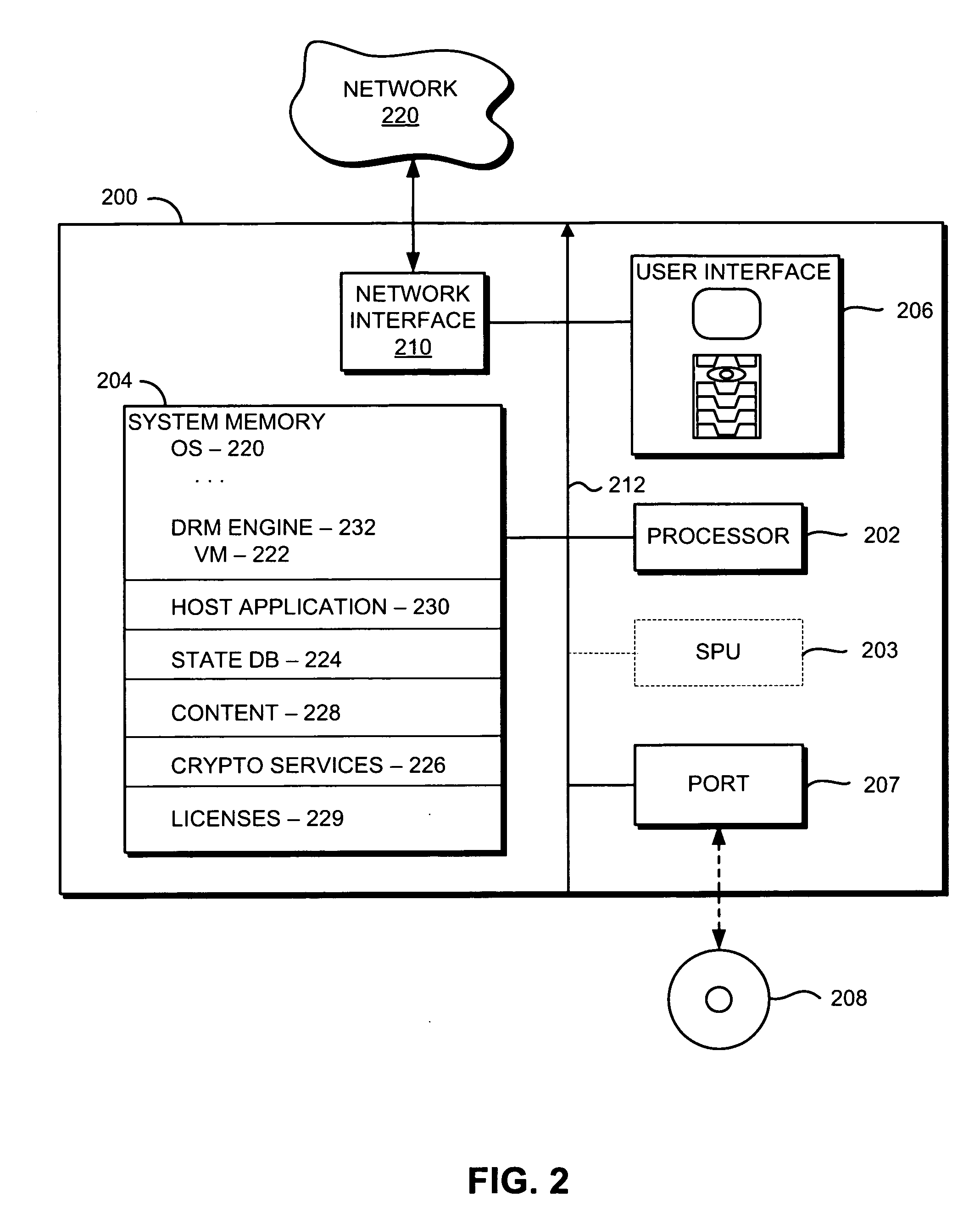

Digital rights management engine systems and methods

InactiveUS20070204078A1Limited accessValidity is limitedDigital data protectionProgram/content distribution protectionDigital rights managementLicense

In one embodiment, a digital rights management engine is provided that evaluates license associated with protected content to determine if a requested access or other use of the content is authorized. In some embodiments, the licenses contain control programs that are executable by the digital rights management engine.

Owner:INTERTRUST TECH CORP

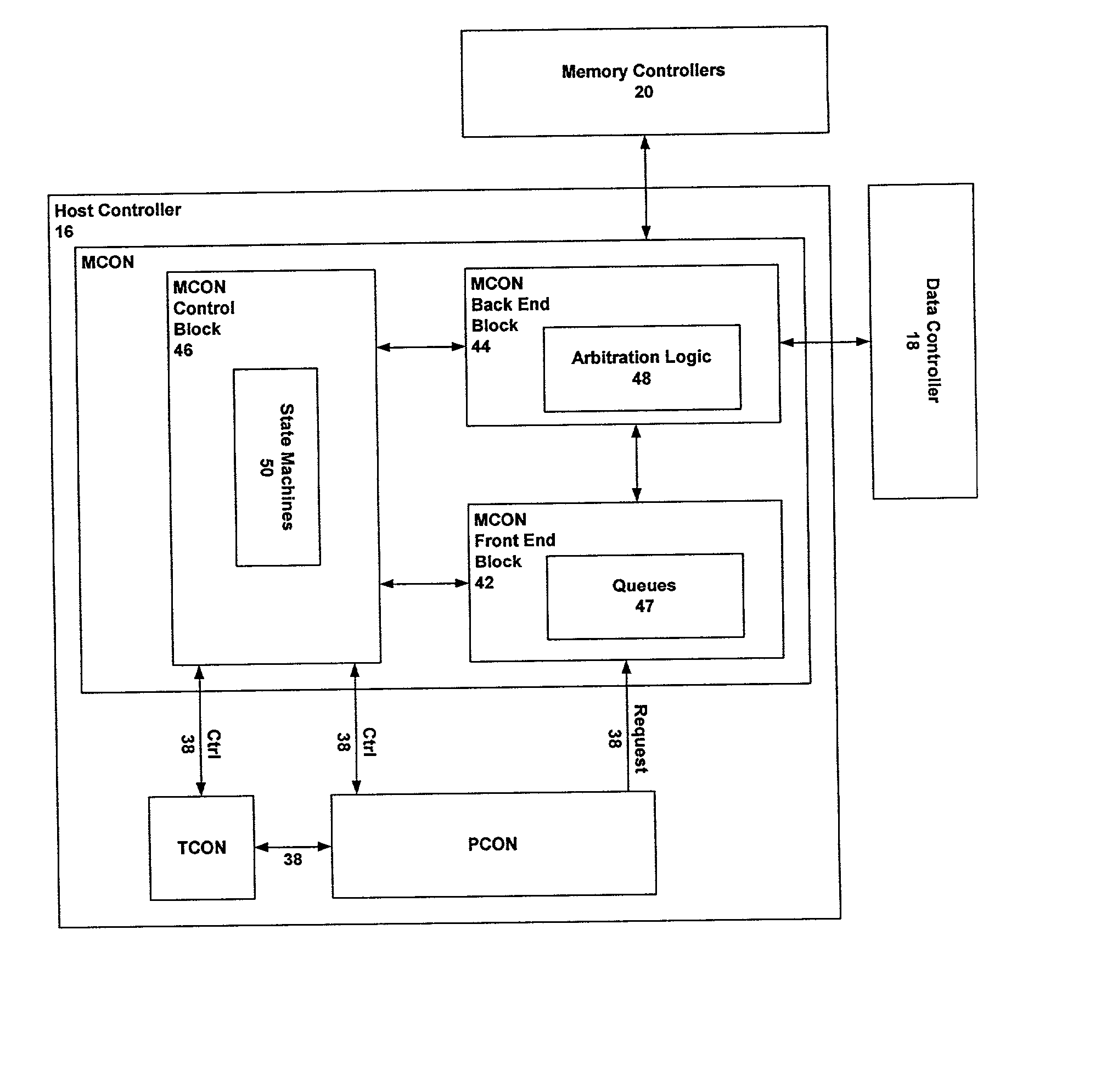

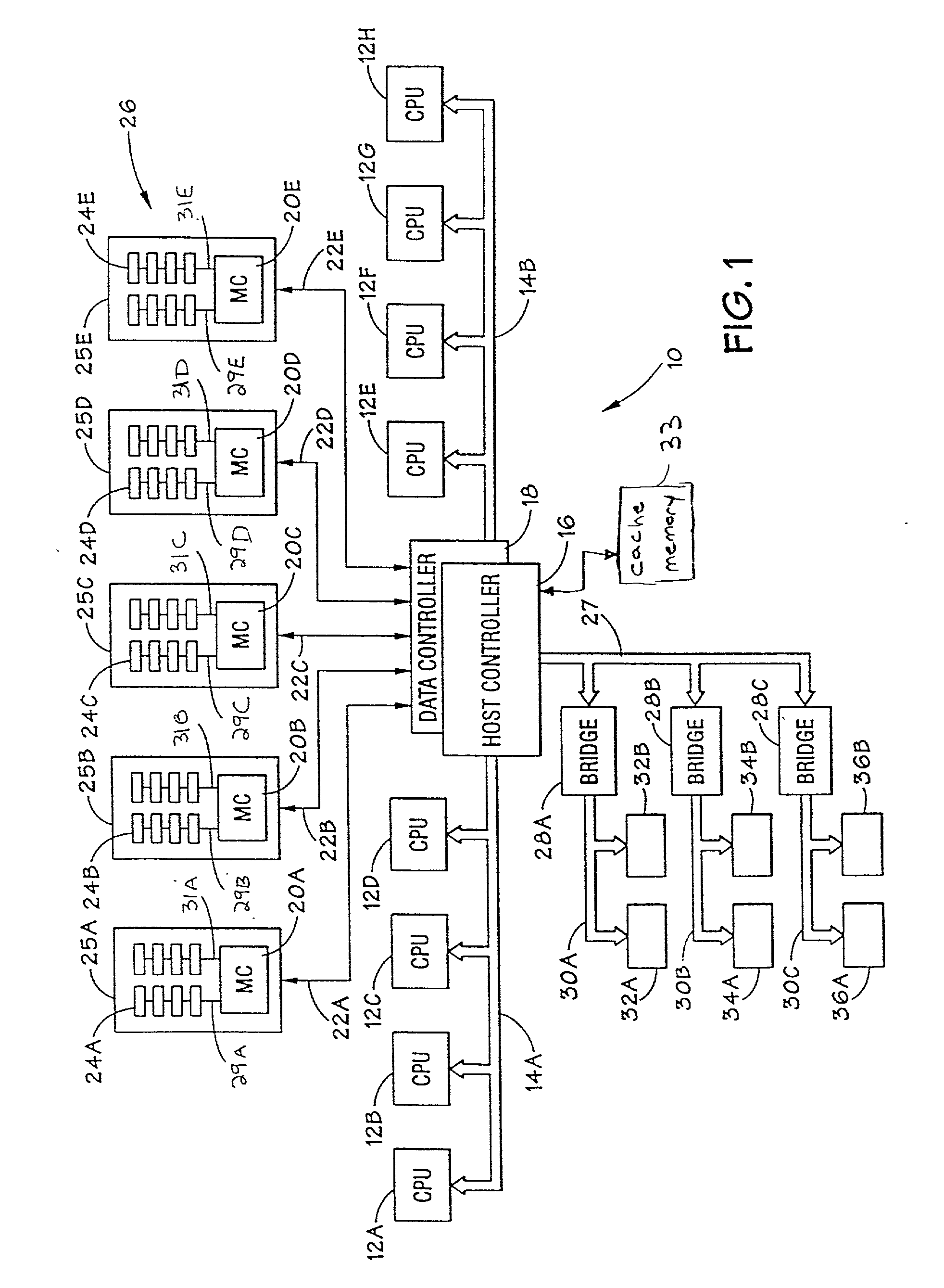

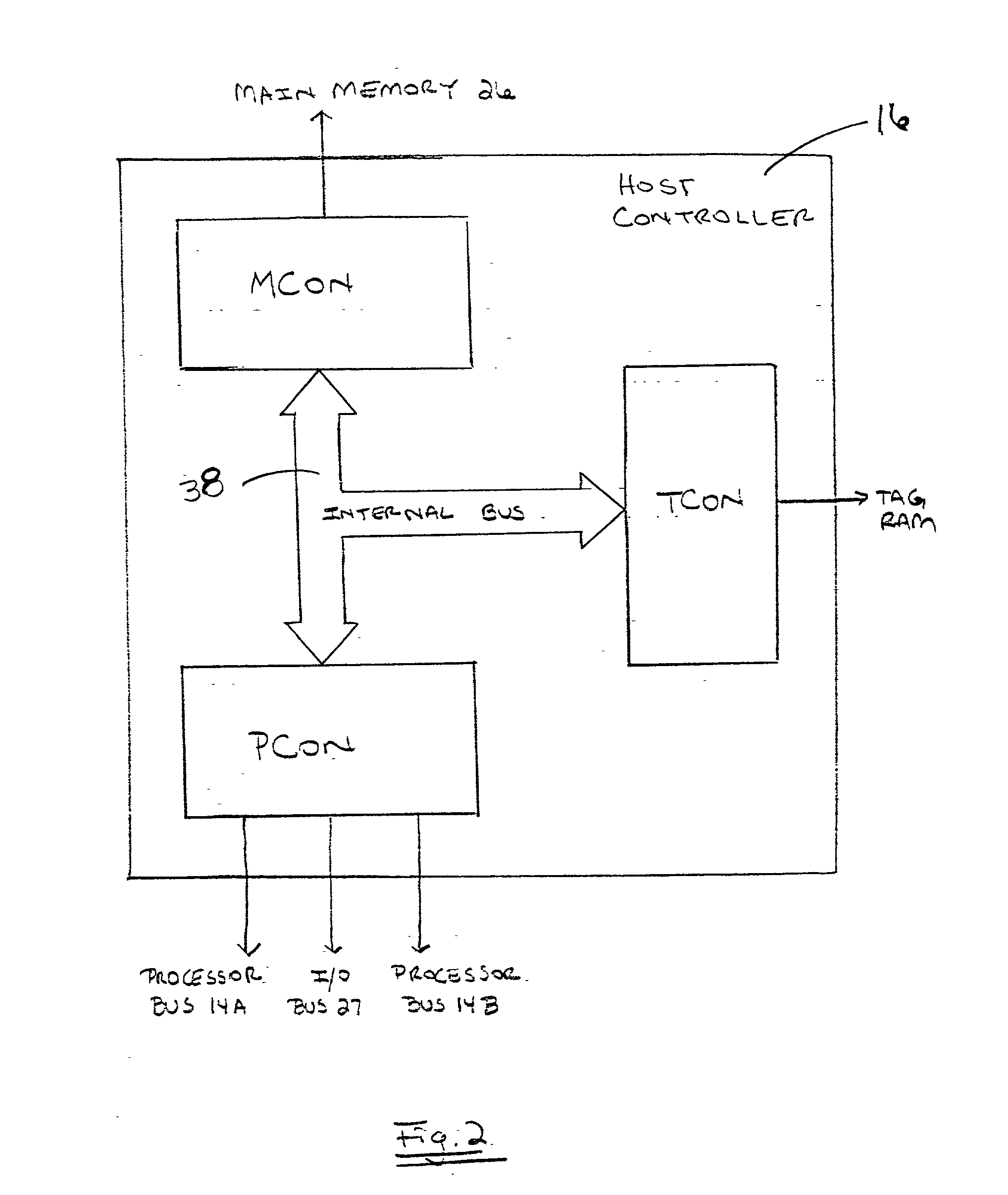

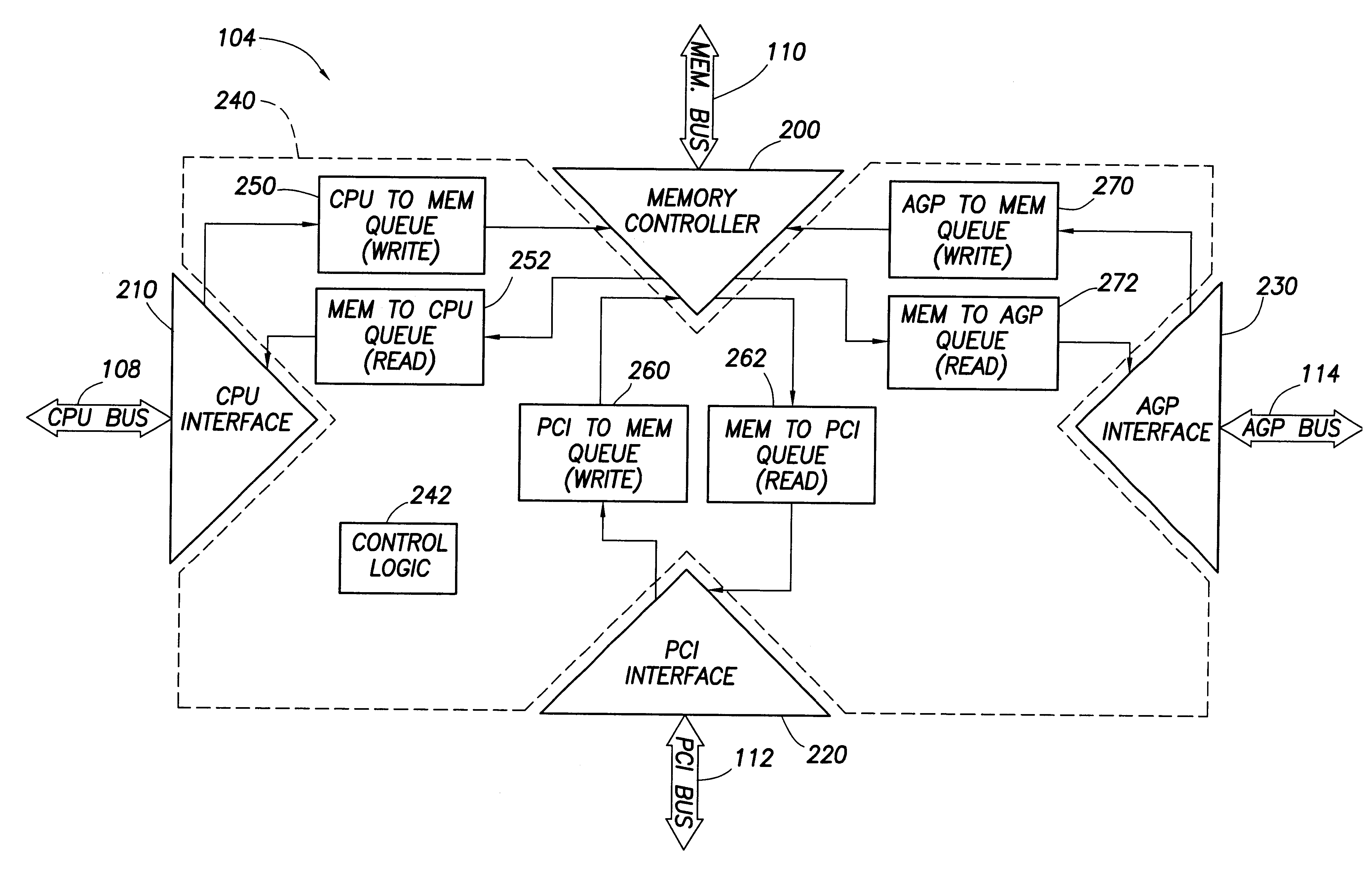

Computer system with adaptive memory arbitration scheme

InactiveUS6286083B1Raise priorityAvoid accessMemory systemsInput/output processes for data processingOut of memoryParallel computing

A computer system includes an adaptive memory arbiter for prioritizing memory access requests, including a self-adjusting, programmable request-priority ranking system. The memory arbiter adapts during every arbitration cycle, reducing the priority of any request which wins memory arbitration. Thus, a memory request initially holding a low priority ranking may gradually advance in priority until that request wins memory arbitration. Such a scheme prevents lower-priority devices from becoming "memory-starved." Because some types of memory requests (such as refresh requests and memory reads) inherently require faster memory access than other requests (such as memory writes), the adaptive memory arbiter additionally integrates a nonadjustable priority structure into the adaptive ranking system which guarantees faster service to the most urgent requests. Also, the adaptive memory arbitration scheme introduces a flexible method of adjustable priority-weighting which permits selected devices to transact a programmable number of consecutive memory accesses without those devices losing request priority.

Owner:HEWLETT PACKARD DEV CO LP

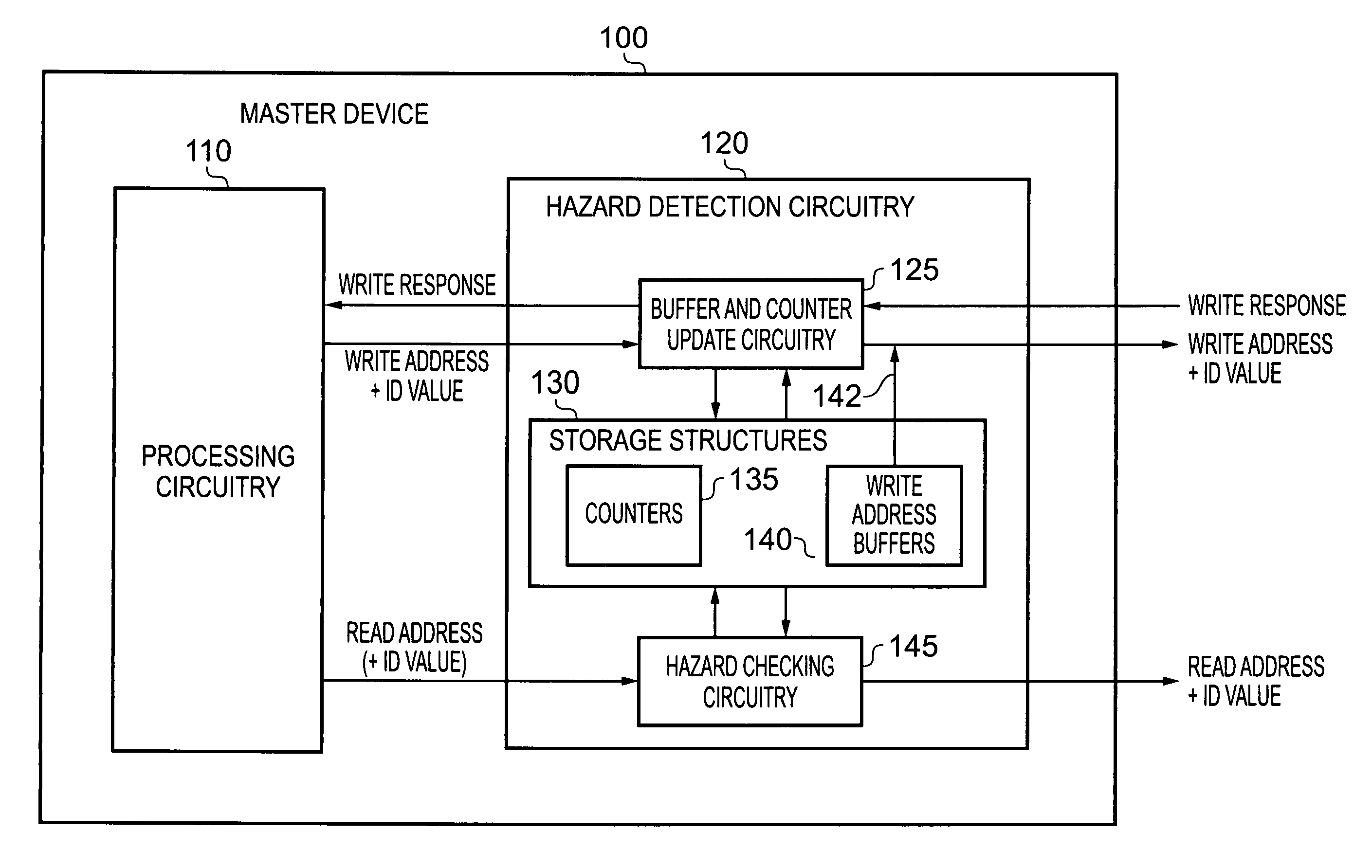

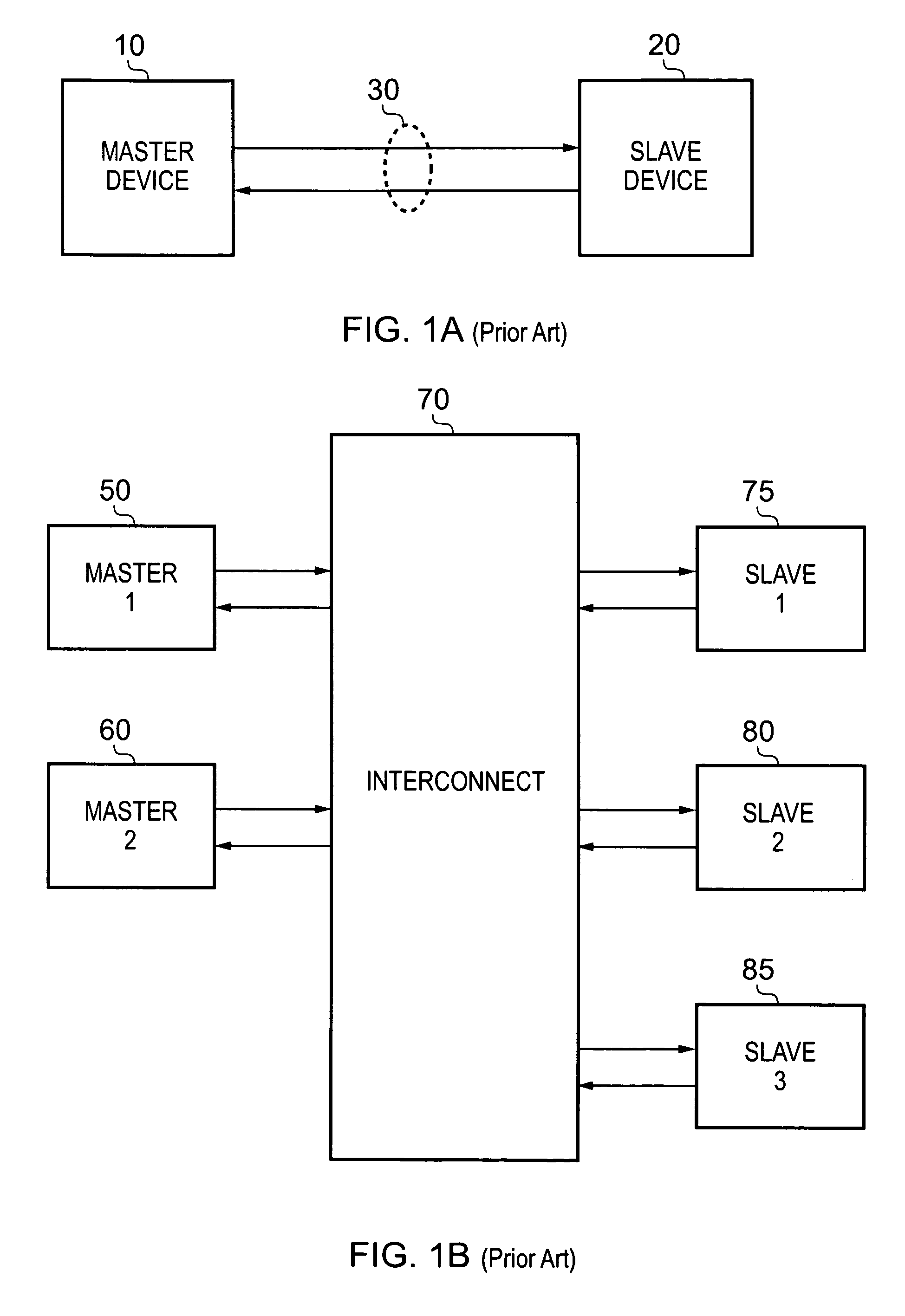

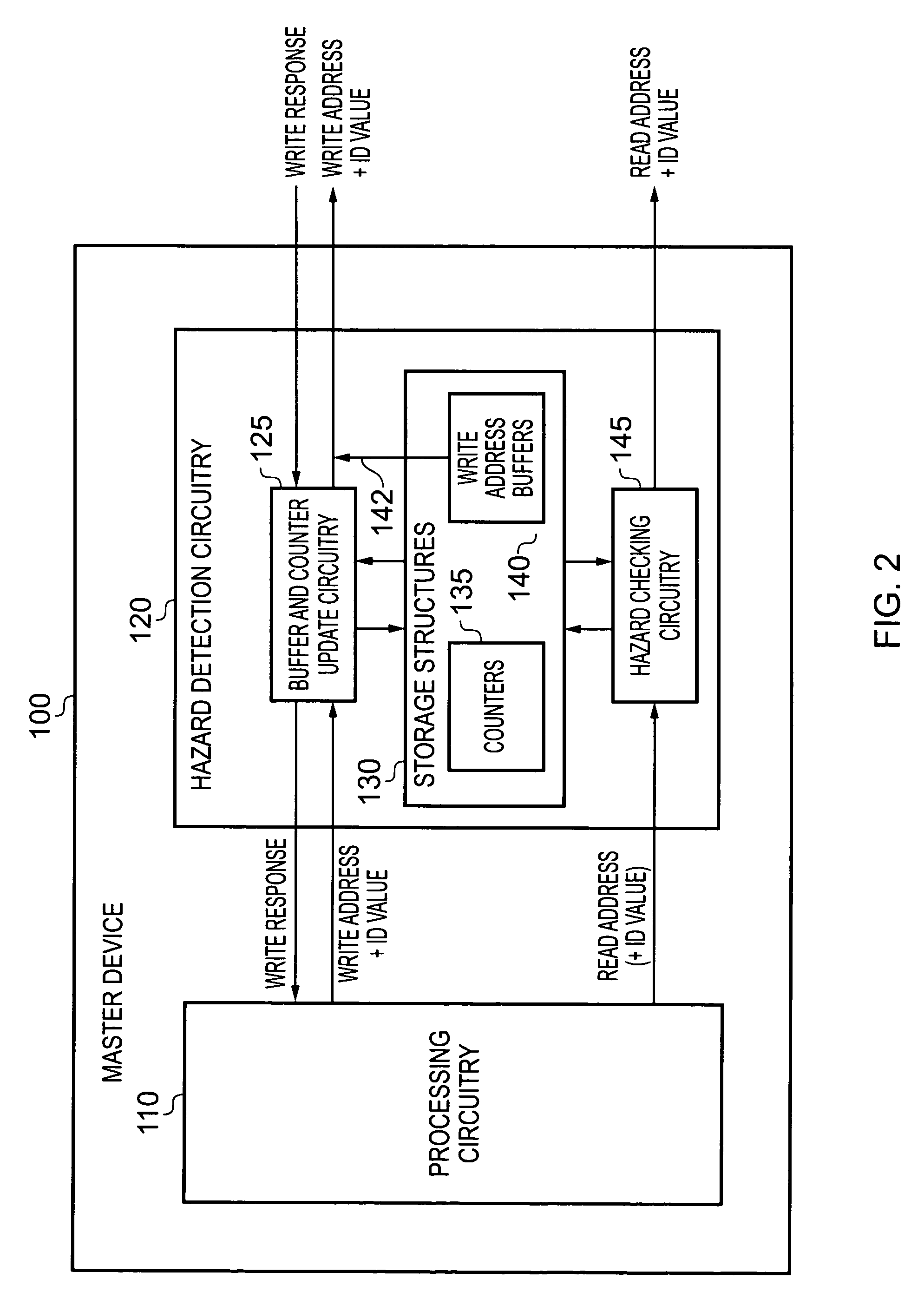

Data processing apparatus and method for performing hazard detection

ActiveUS20100250802A1Avoid possibilityAvoiding WAW hazardMemory systemsInput/output processes for data processingAccess historyData buffer

A data processing apparatus and method are provided for performing hazard detection in respect of a series of access requests issued by processing circuitry for handling by one or more slave devices. The series of access requests include one or more write access requests, each write access request specifying a write operation to be performed by an addressed slave device, and each issued write access request being a pending write access request until the write operation has been completed by the addressed slave device. Hazard detection circuitry comprises a pending write access history storage having at least one buffer and at least one counter for keeping a record of each pending write access request. Update circuitry is responsive to receipt of a write access request to be issued by the processing circuitry, to perform an update process to identify that write access request as a pending write access request in one of the buffers, and if the identity of another pending write access request is overwritten by that update process, to increment a count value in one of the counters. On completion of each write access request by the addressed slave device, the update circuitry performs a further update process to remove the record of that completed write access request from the pending write access history storage. Hazard checking circuitry is then responsive to at least a subset of the access requests to be issued by the processing circuitry, to reference the pending write access history storage in order to determine whether a hazard condition occurs. The manner in which the update circuitry uses a combination of buffers and counters to keep a record of each pending write access request provides improved performance with respect to known prior art techniques, without the hardware cost that would be associated with increasing the number of buffers.

Owner:ARM LTD

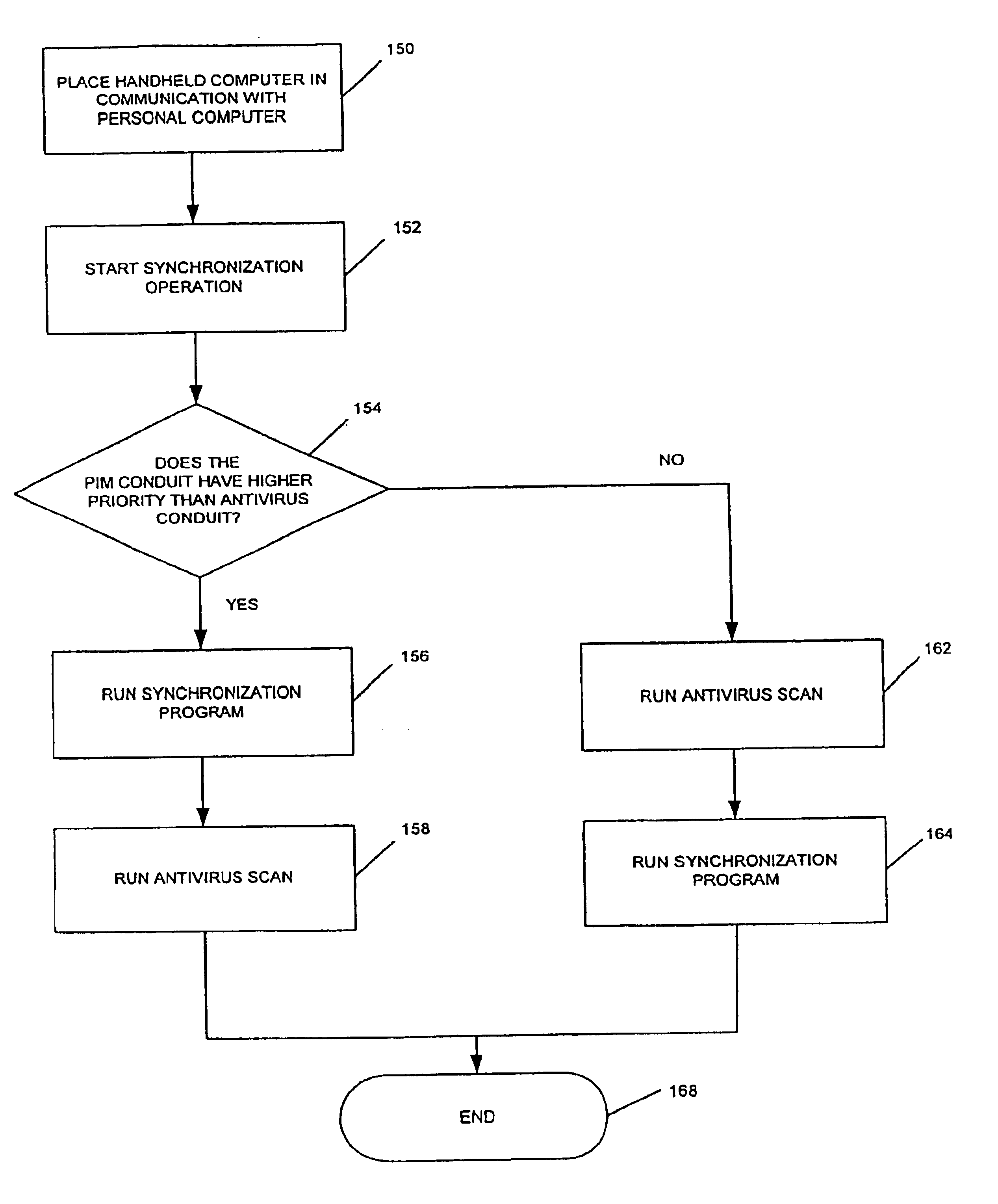

Method and system for detecting viruses on handheld computers

InactiveUS6842861B1Memory loss protectionUnauthorized memory use protectionComputerized systemHand Held Computer

A method and system for detecting viruses on handheld computers. The handheld computer is in communication with a computer system having a virus detection program. The method includes reading data from the handheld computer and writing the data at least temporarily to a database on the computer system. The data is scanned for viruses with the virus detection program. The method further includes updating data on the handheld computer based on results of the scanning.

Owner:MCAFEE INC

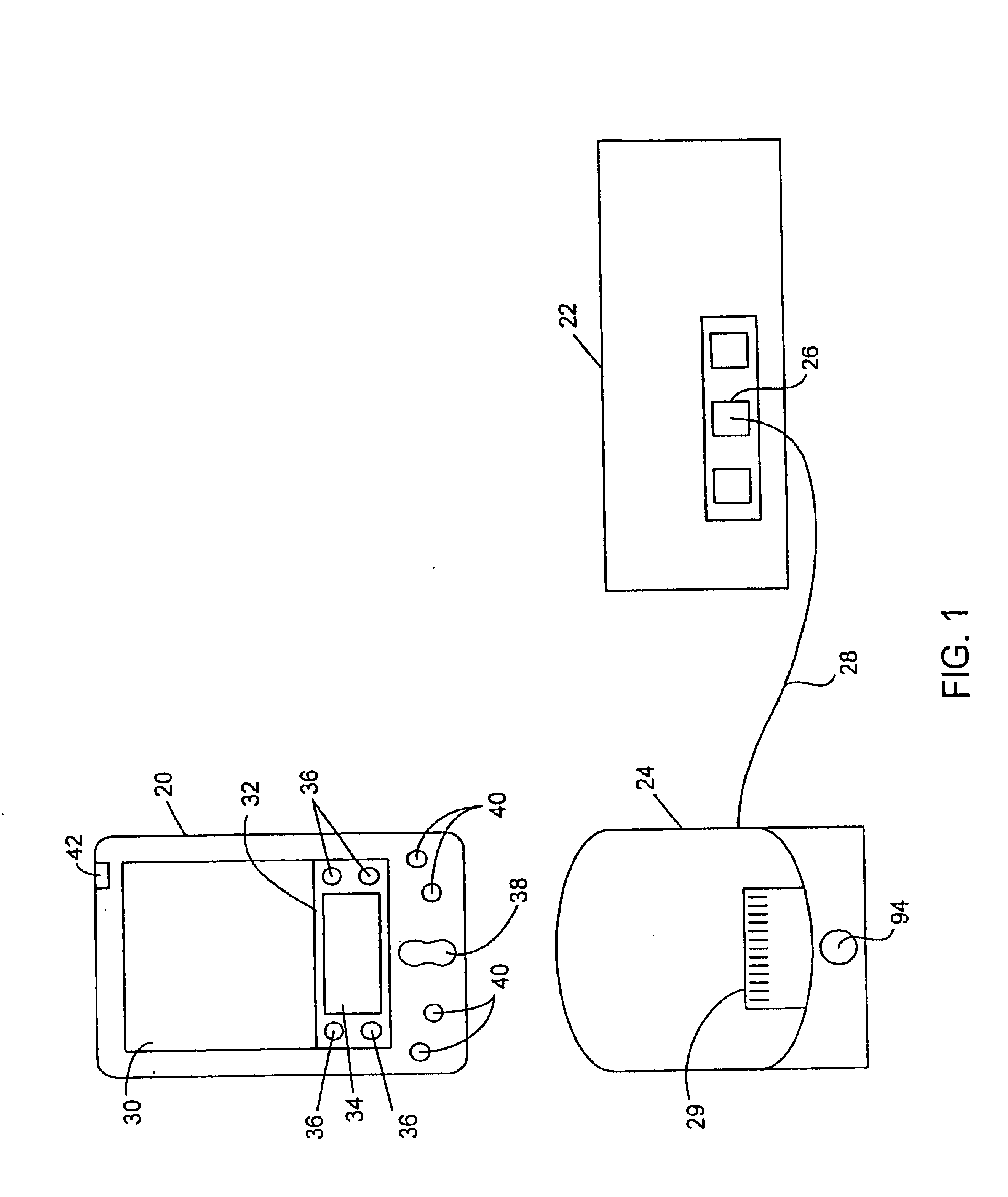

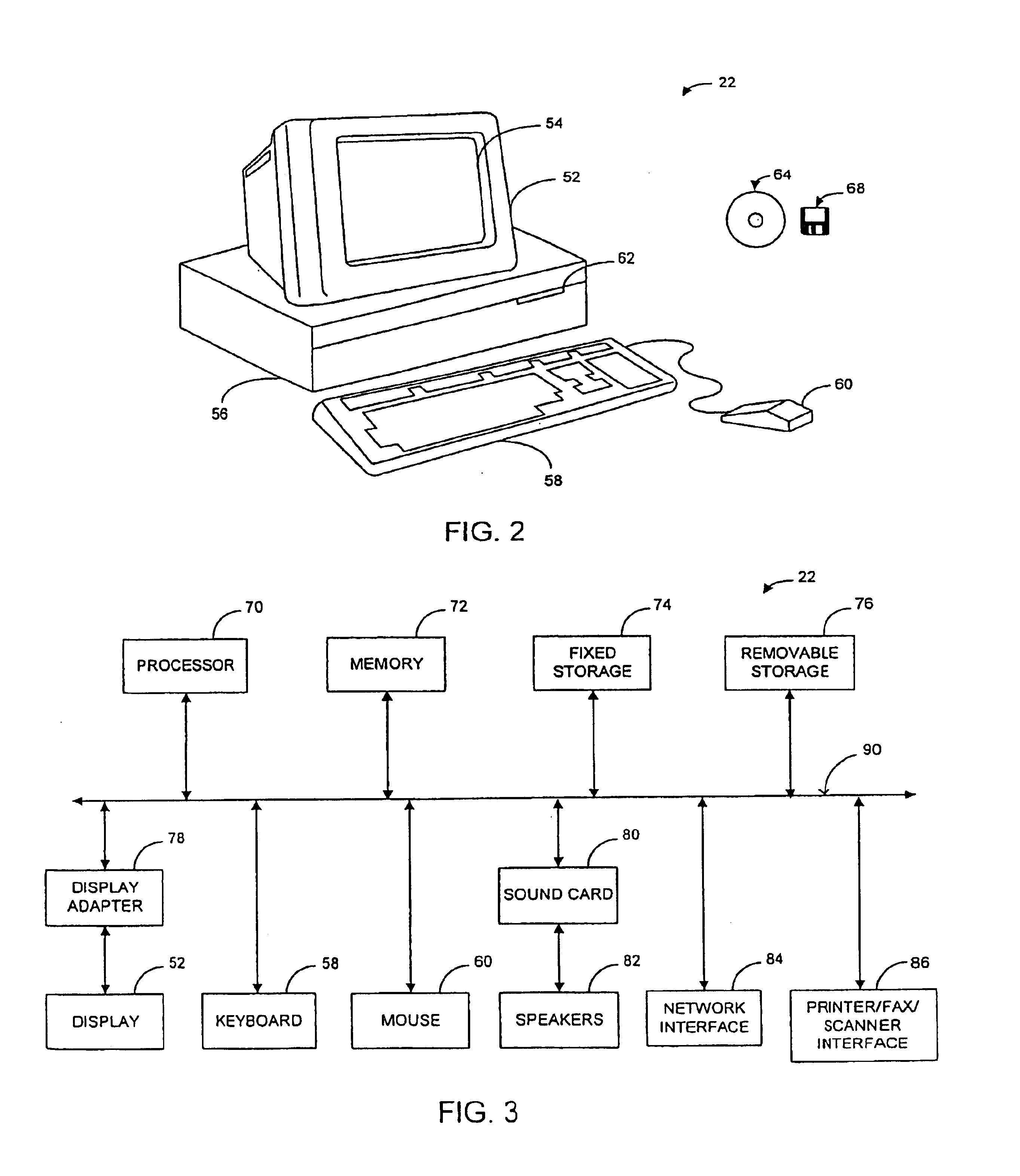

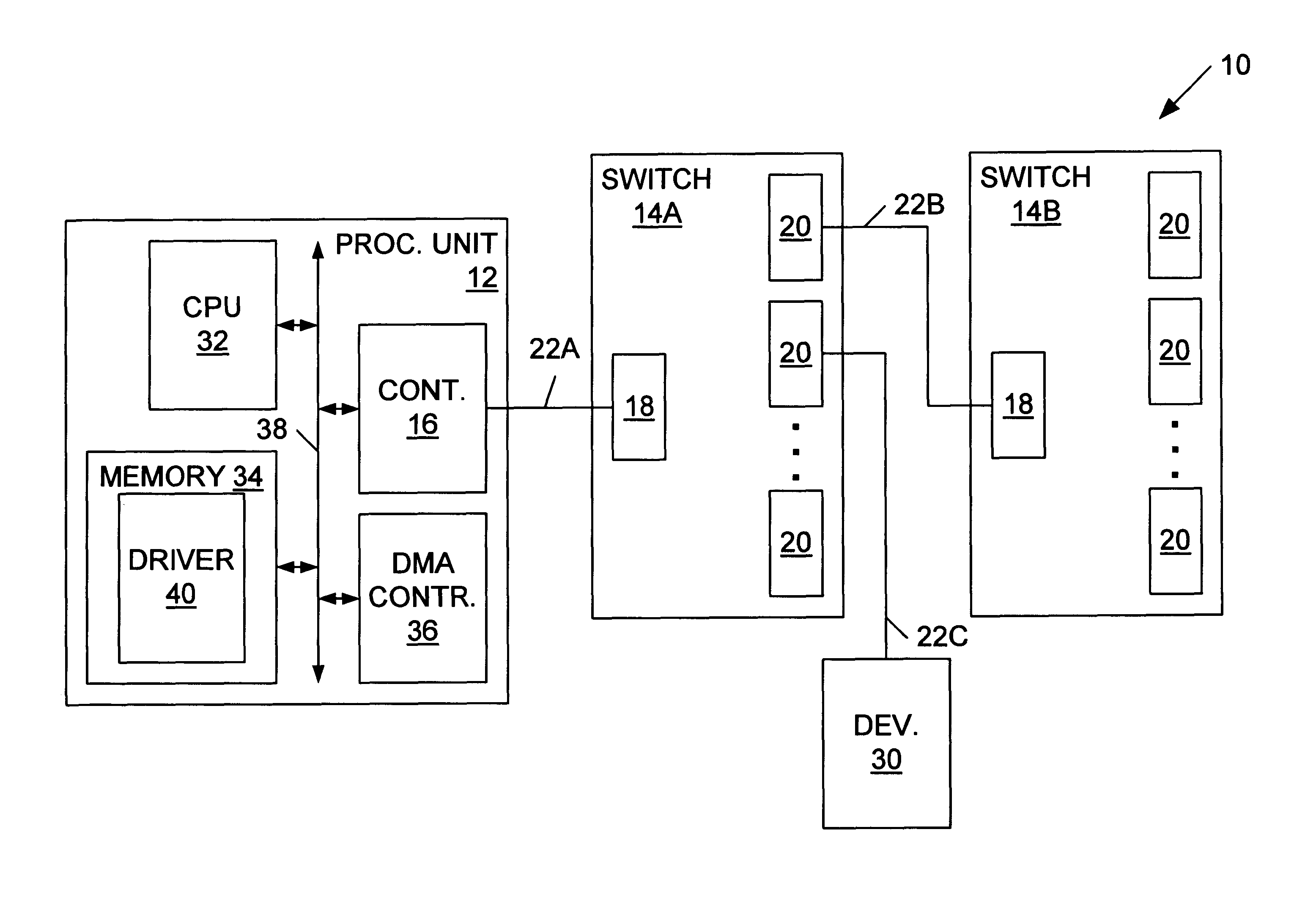

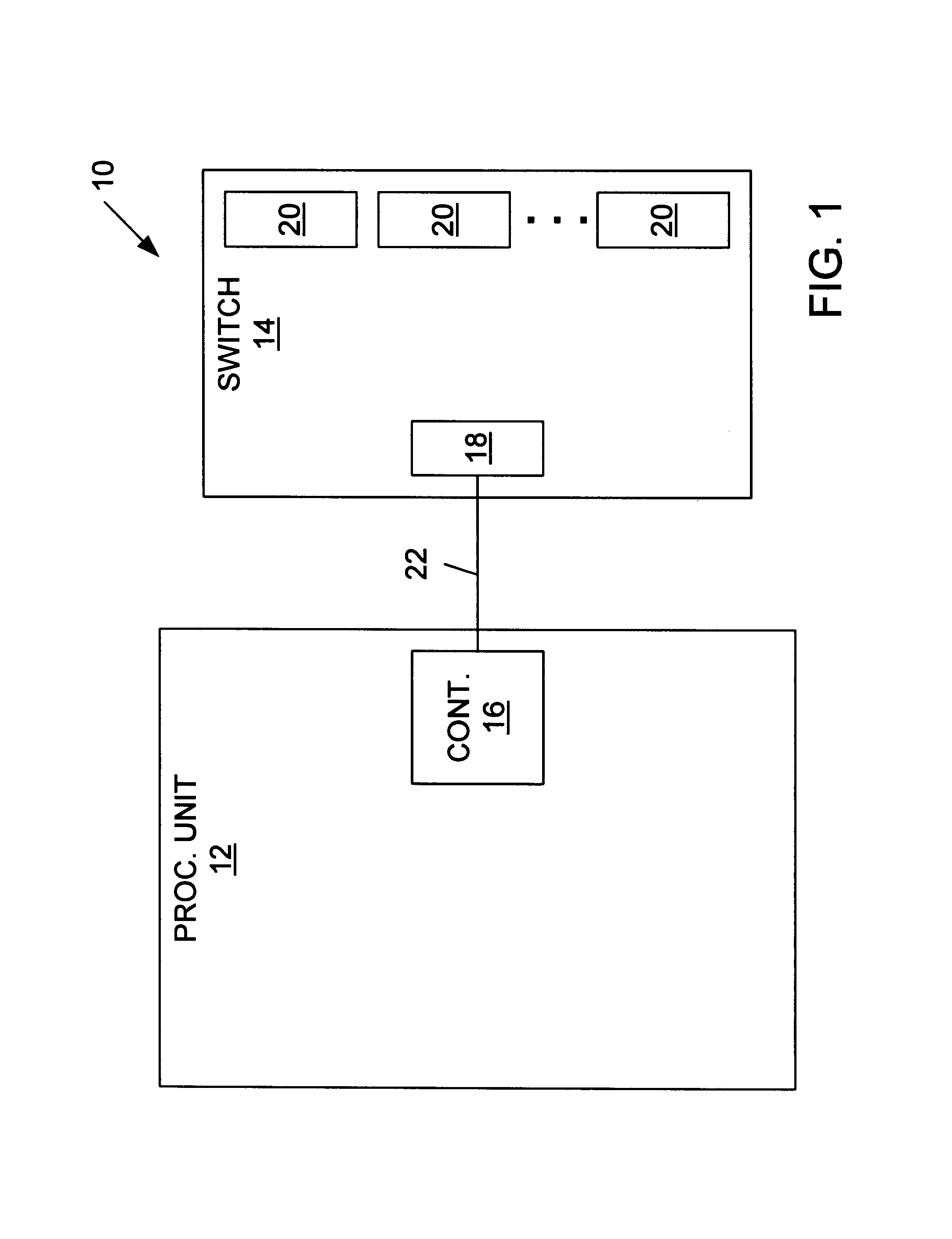

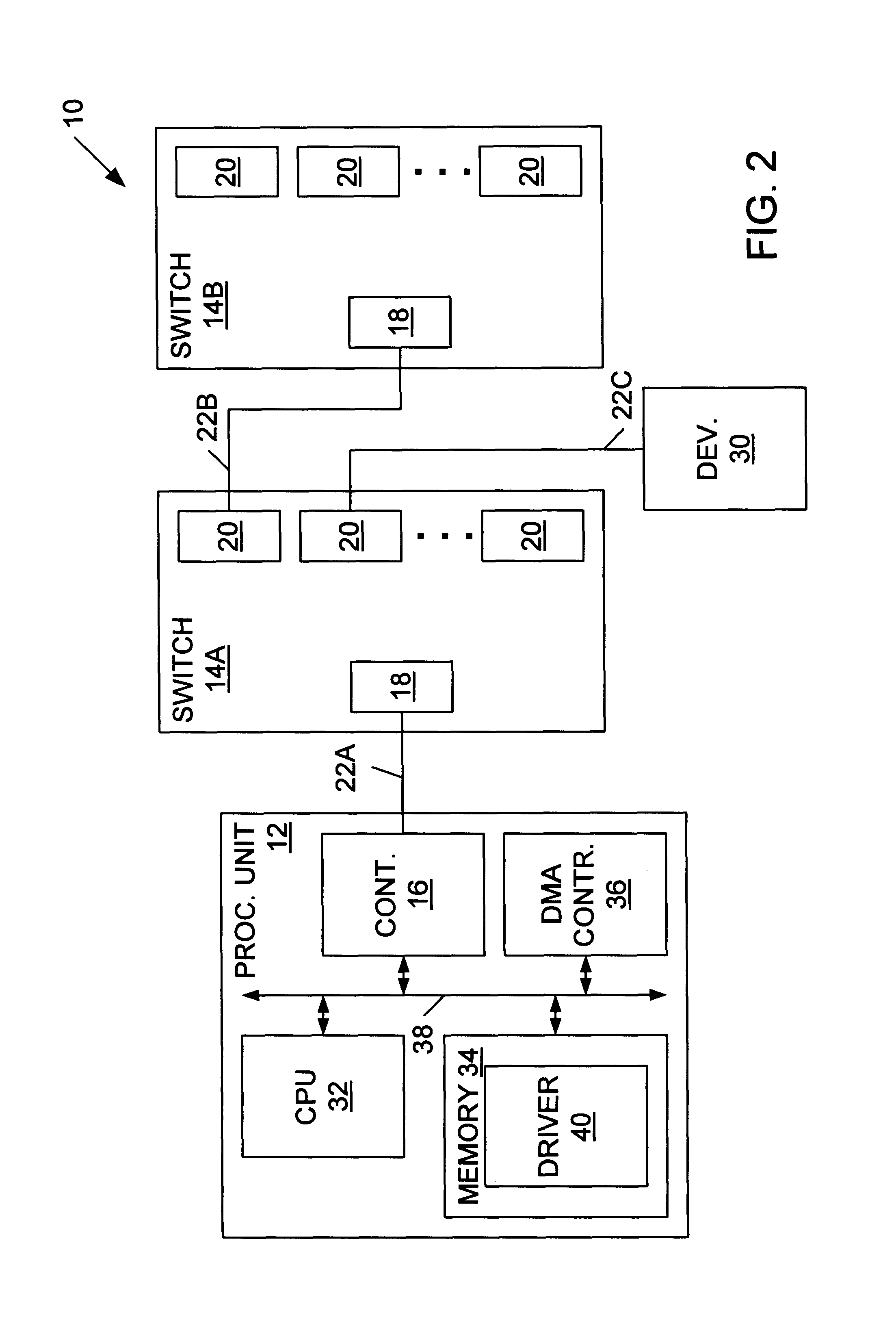

Data exchange methods for a switch which selectively forms a communication channel between a processing unit and multiple devices

InactiveUS6845409B1Reduce processing overheadReduce overheadMultiplex system selection arrangementsInput/output to record carriersMain processing unitDirect memory access

A switch is presented including a host input / output (I / O) port adapted for coupling to a controller, multiple device I / O ports each adapted for coupling to at least one device, and logic coupled between the host I / O port and the device I / O ports configured to selectively form a communication channel between the host I / O port and one of the device I / O ports. The switch may operate in a connected mode and a disconnected mode. When in the switch is in the disconnected mode, the logic may not form a communication channel between the host I / O port and any of the device I / O ports. In an ATA embodiment, the switch may comply with an AT attachment (ATA) standard, and thus be an ATA switch. The host I / O port may be adapted for coupling to an ATA controller, the device I / O ports may be adapted for coupling to at least one ATA device, and the logic may selectively form an ATA communication channel between the host I / O port and one of the device I / O ports. Several methods for exchanging data between a processing unit coupled to the host I / O port of the switch and one or more devices coupled to device I / O ports of the switch are described. Several methods for performing direct memory access (DMA) transfers to move data between a memory of the processing unit and one or more of the devices are also described.

Owner:ORACLE INT CORP

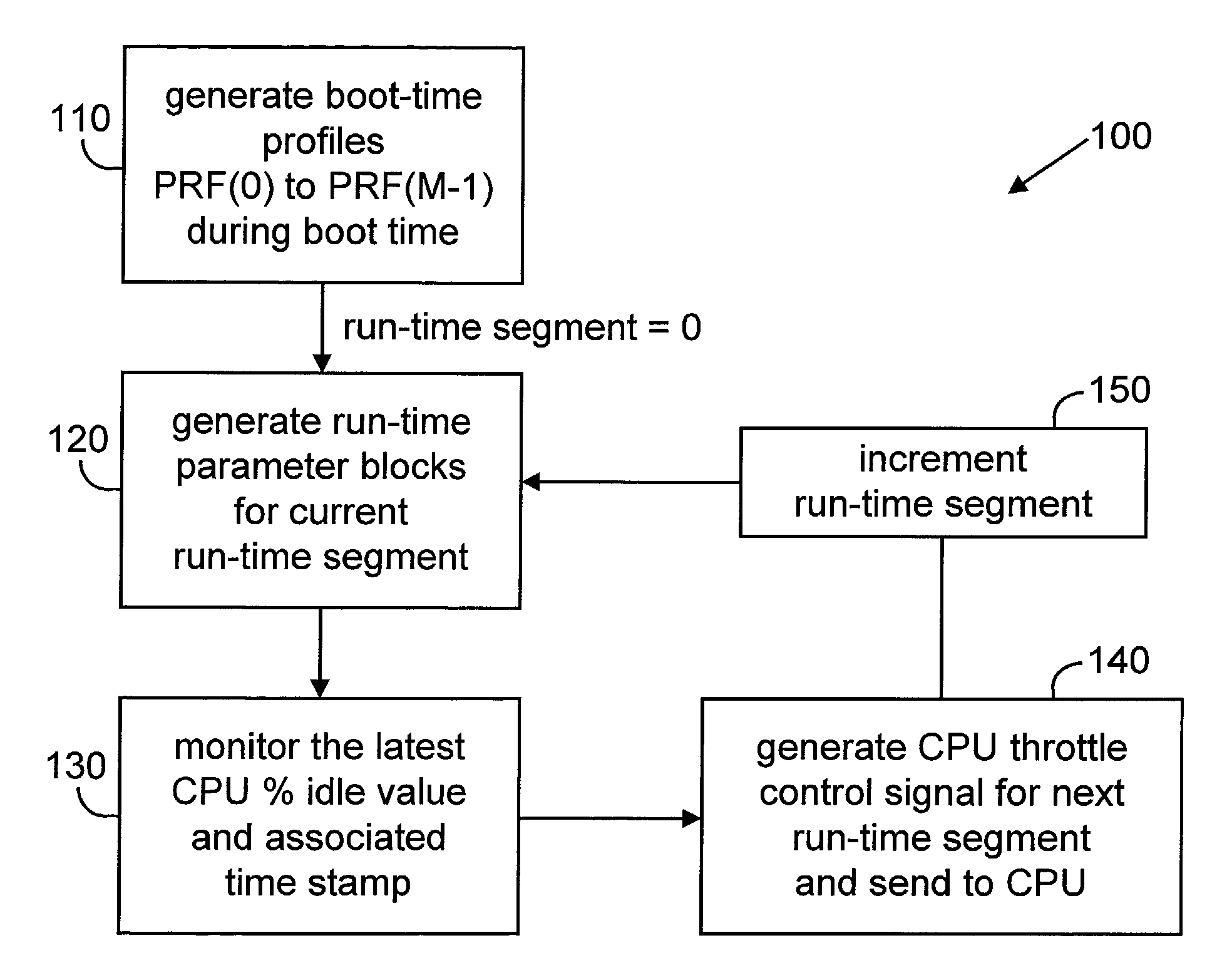

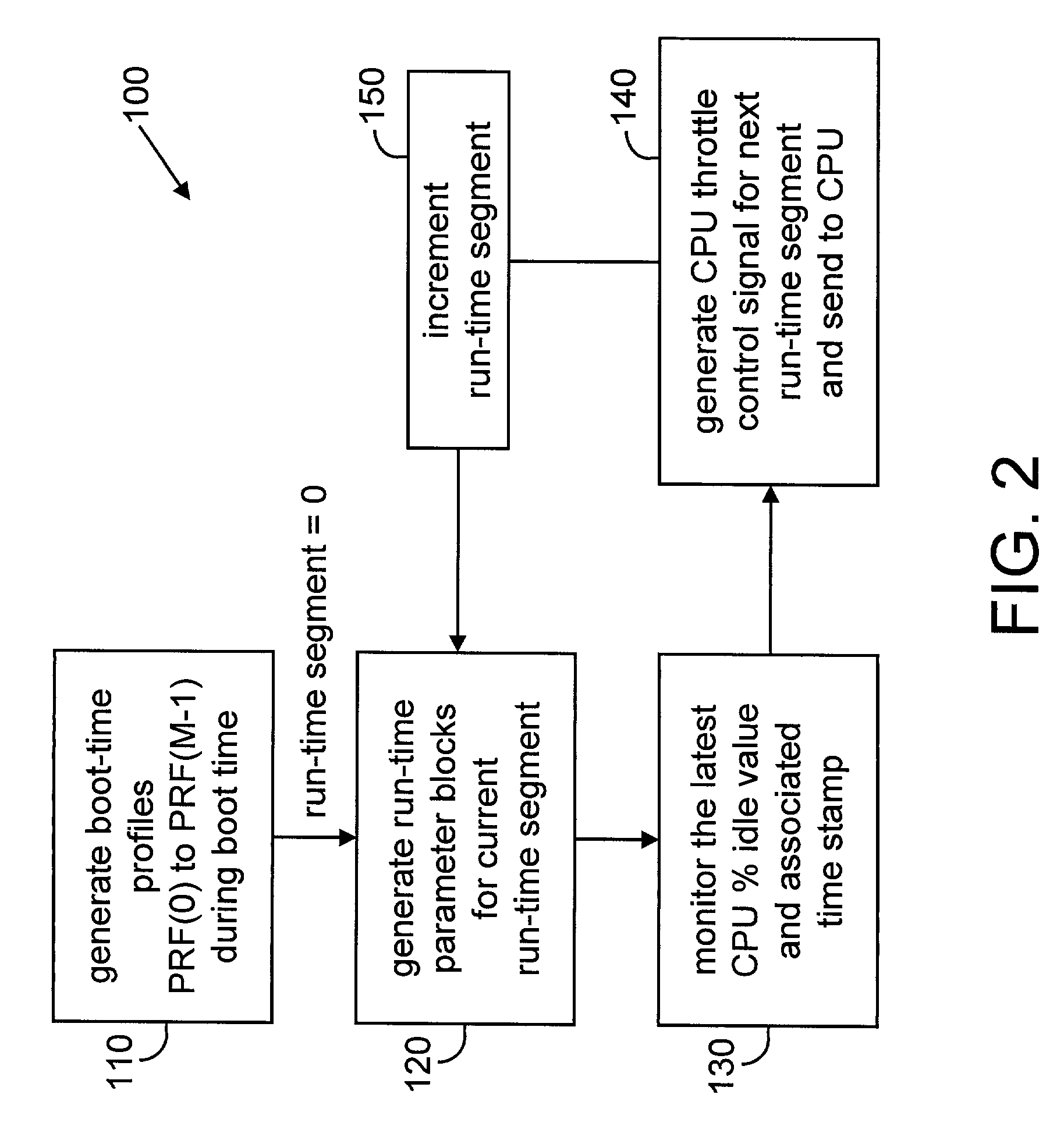

Method and apparatus for adaptive CPU power management

A method and apparatus are disclosed for performing adaptive run-time power management in a system employing a CPU and an operating system. A CPU cycle tracker (CCT) module monitors critical CPU signals and generates CPU performance data based on the critical CPU signals. An adaptive CPU throttler (THR) module uses the CPU performance data, along with a CPU percent idle value fed back from the operating system, to generate a CPU throttle control signal during predefined run-time segments of the CPU run time. The CPU throttle control signal links back to the CPU and adaptively adjusts CPU throttling and, therefore, power usage of the CPU during each of the run-time segments.

Owner:AVAGO TECH INT SALES PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com