Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2071 results about "Synchronizing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In telecommunication, the term synchronizing has the following meanings: Achieving and maintaining synchronism. In fax, achieving and maintaining predetermined speed relations between the scanning spot and the recording spot within each scanning line. In the civilian community, the noun "synchronization " is preferred to "synchronizing."

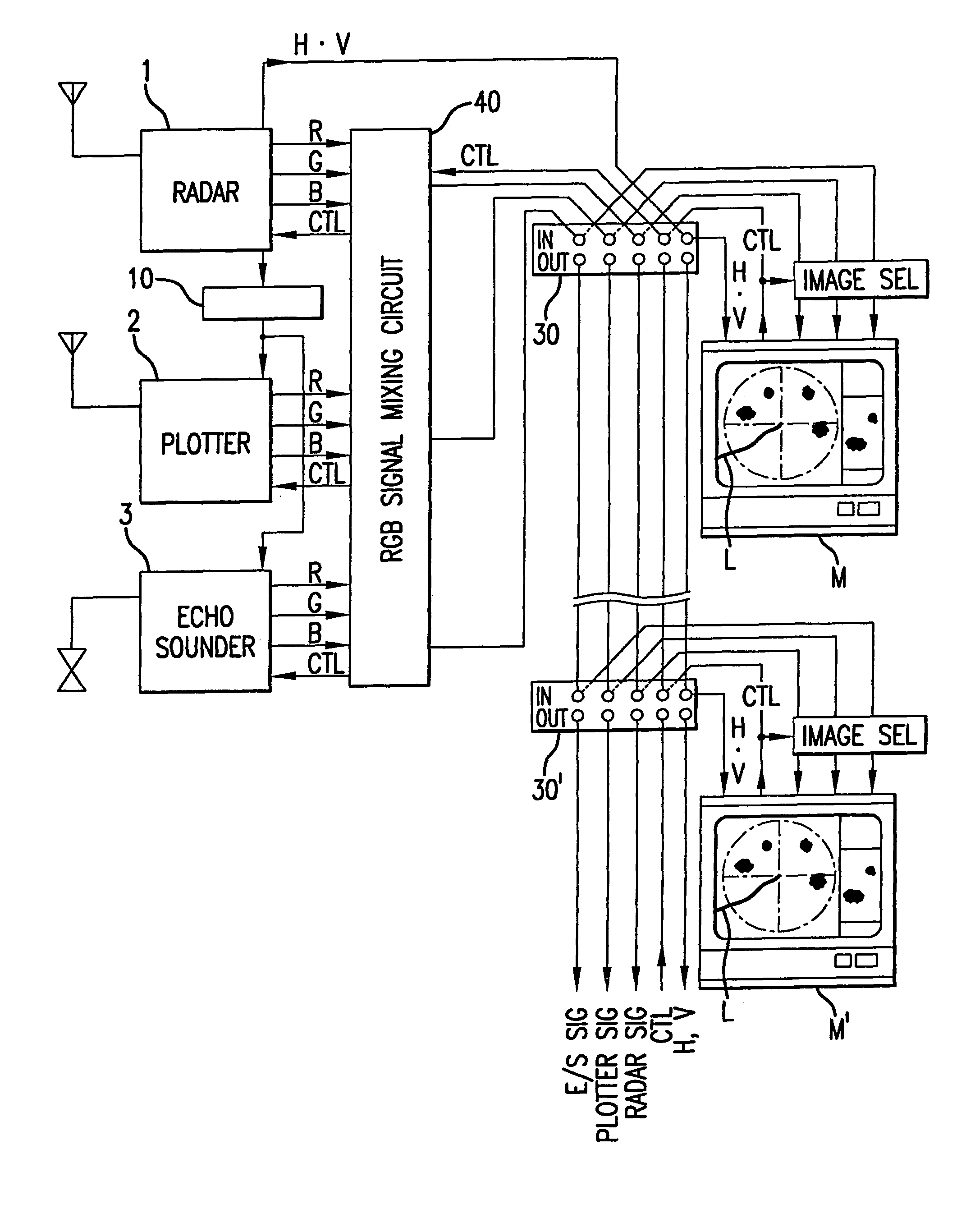

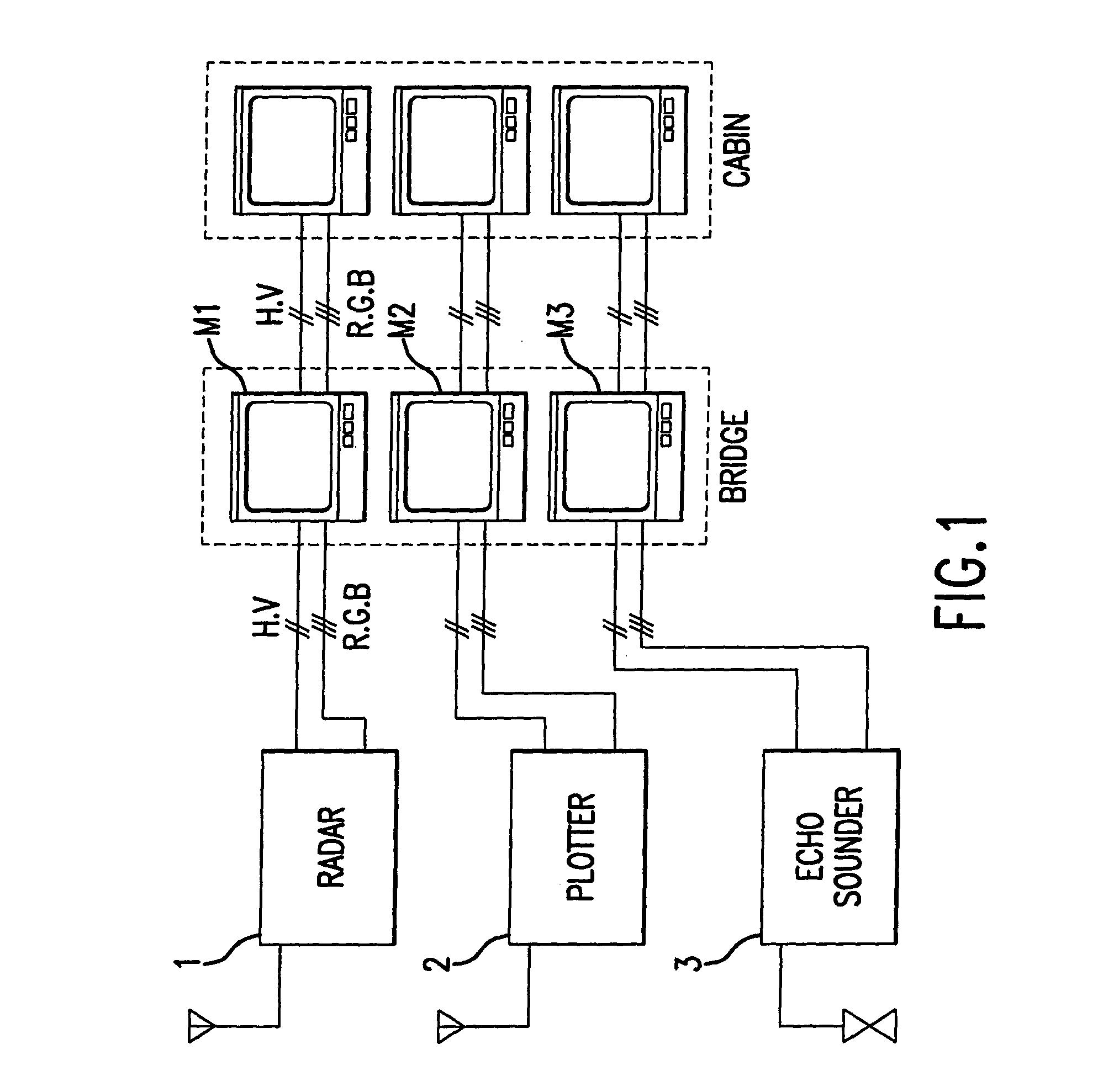

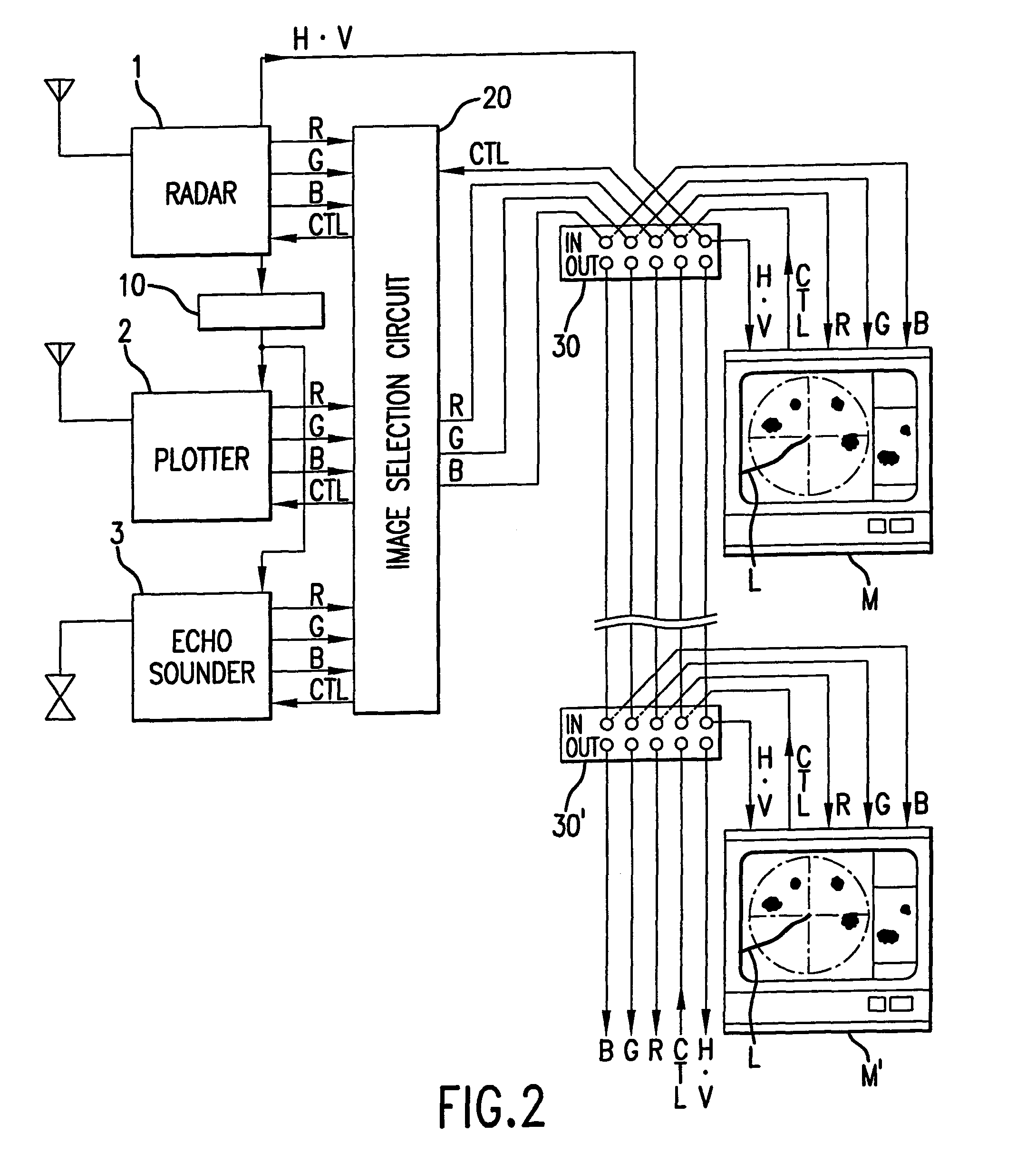

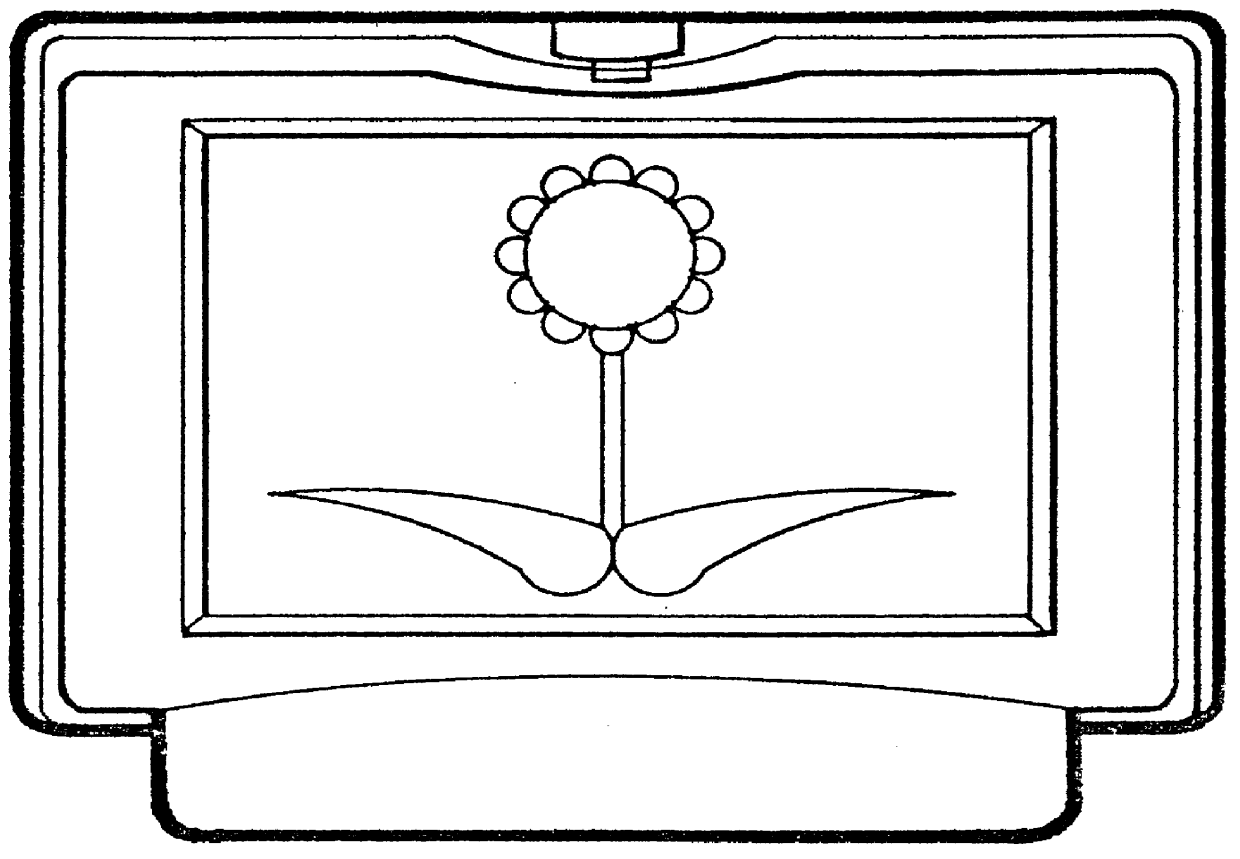

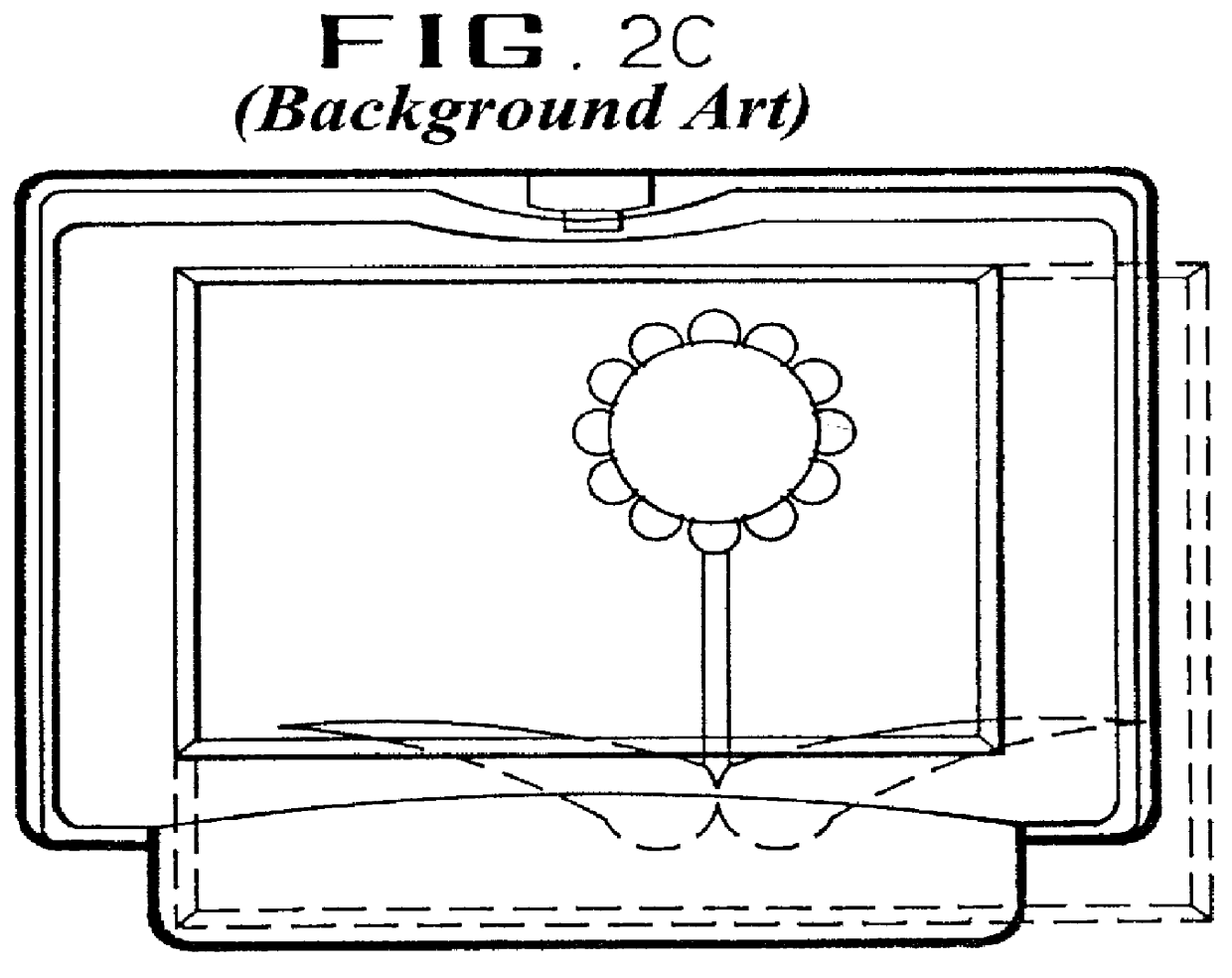

Display system

InactiveUS7161561B2Superfluous imageClearly presentedWave based measurement systemsCathode-ray tube indicatorsImage signalComputer science

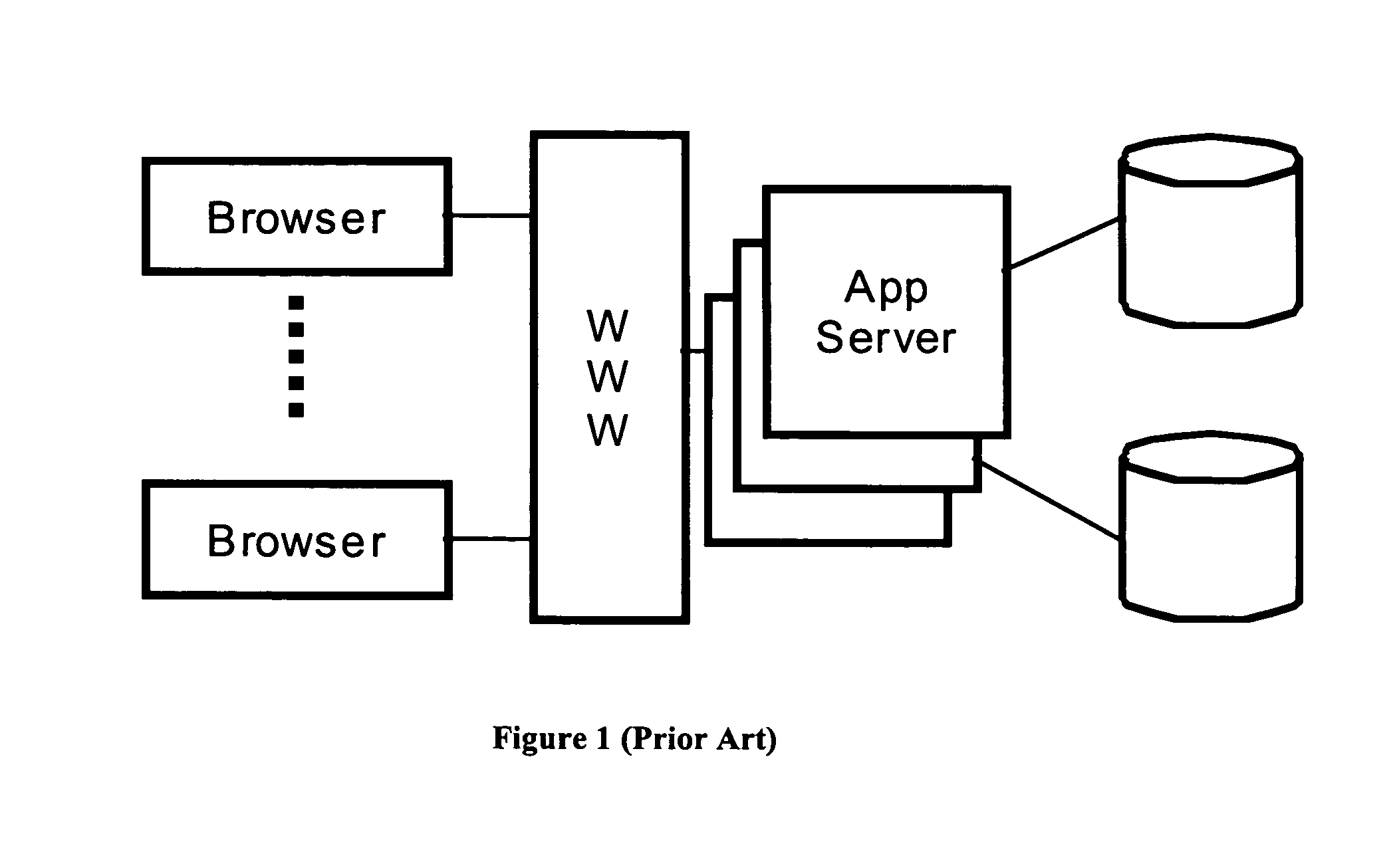

In a display system capable of displaying images fed from a plurality of sensing devices on an indicator, horizontal and vertical synchronizing signals of the individual measuring devices are synchronized with one another and desired image signals are selected for on-screen presentation during each successive horizontal scanning period, whereby operator-selected multiple images are displayed.

Owner:FURUNO ELECTRIC CO LTD

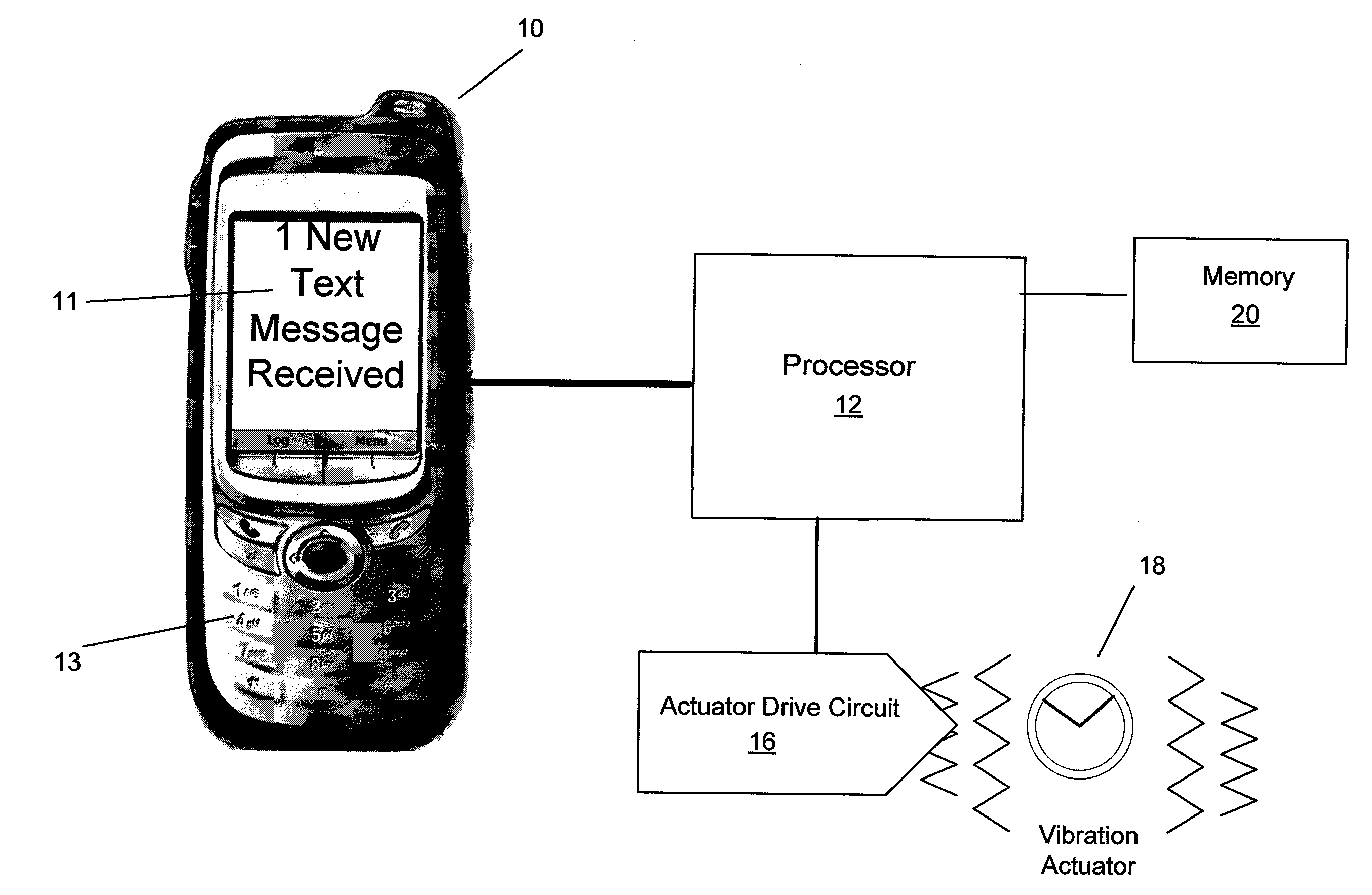

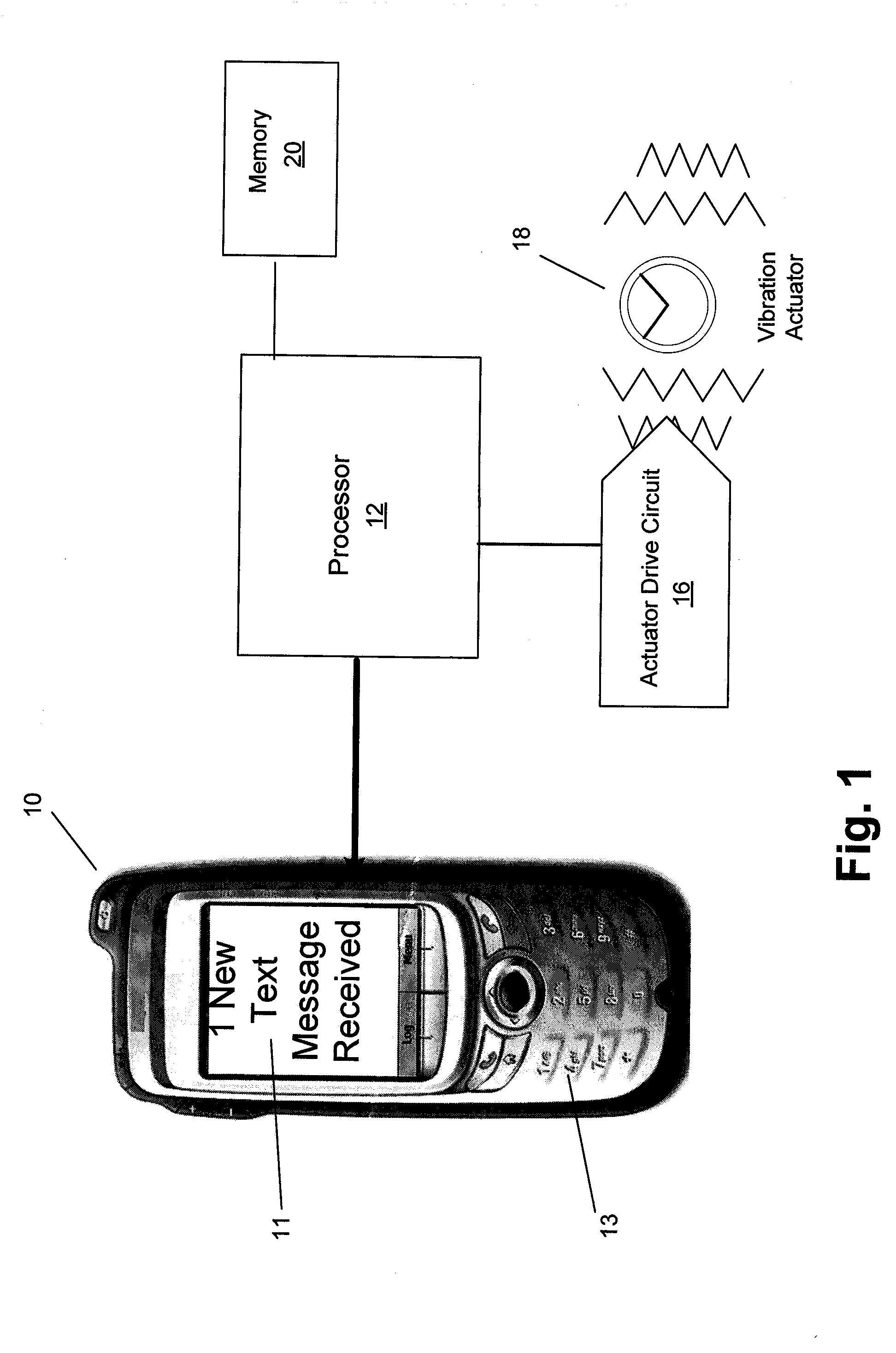

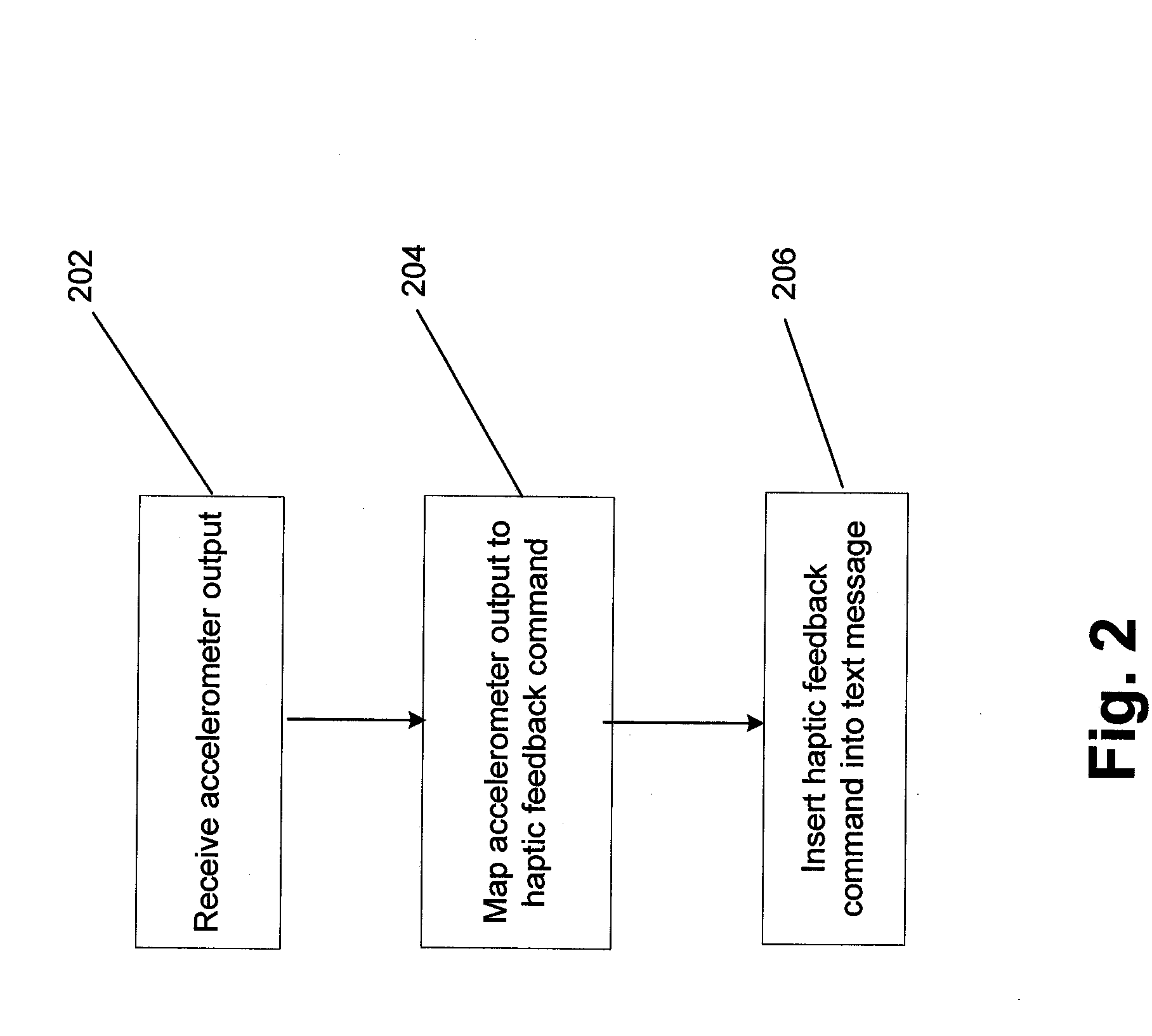

Haptically Enabled Messaging

ActiveUS20080287147A1Digital data processing detailsDevices with voice recognitionTerminal equipmentComputer terminal

A mobile terminal device receives a haptically enabled message that includes text and at least one haptic feedback command. The device determines the timing of the haptic feedback command within the message. When the device receives an indication that the message is being displayed by a user, the device synchronizes a haptic effect corresponding to the haptic feedback command. The synchronizing is based on the timing and the indication.

Owner:IMMERSION CORPORATION

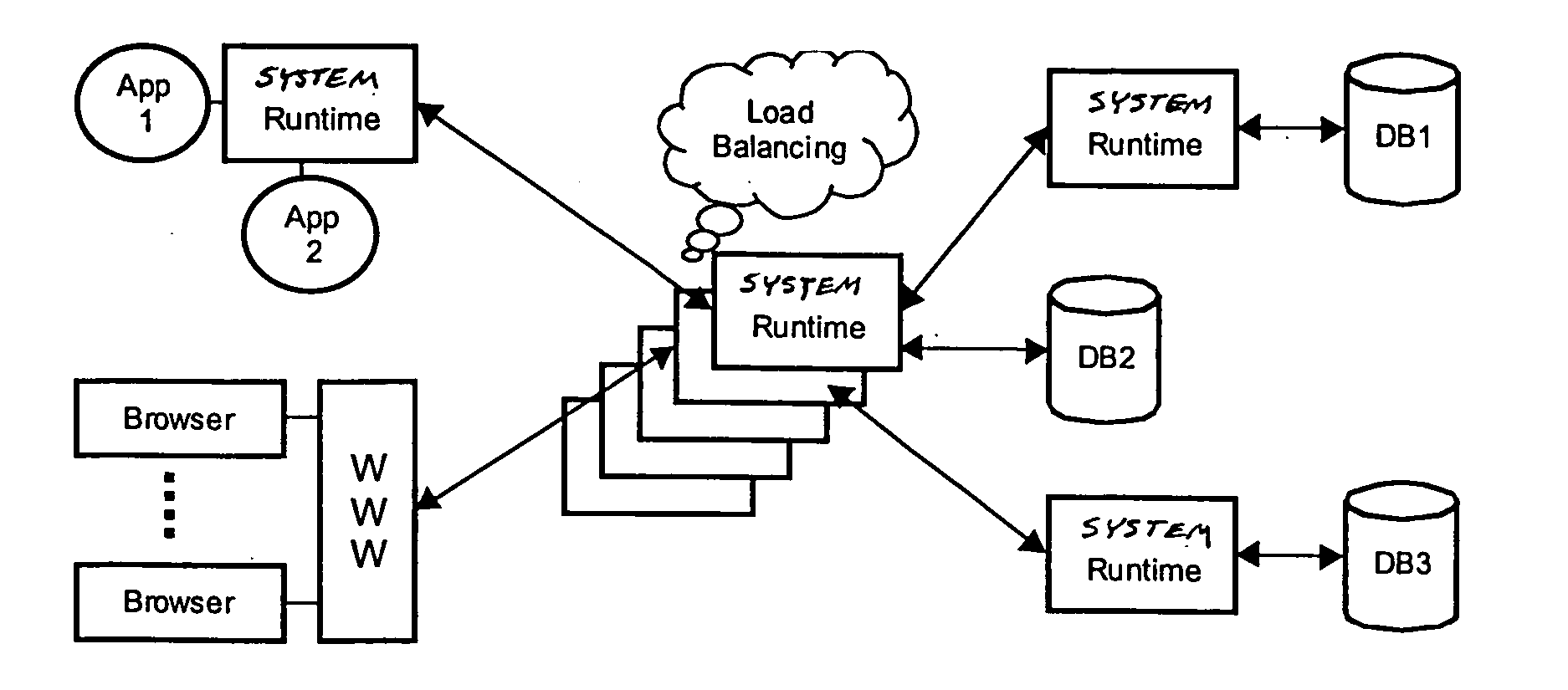

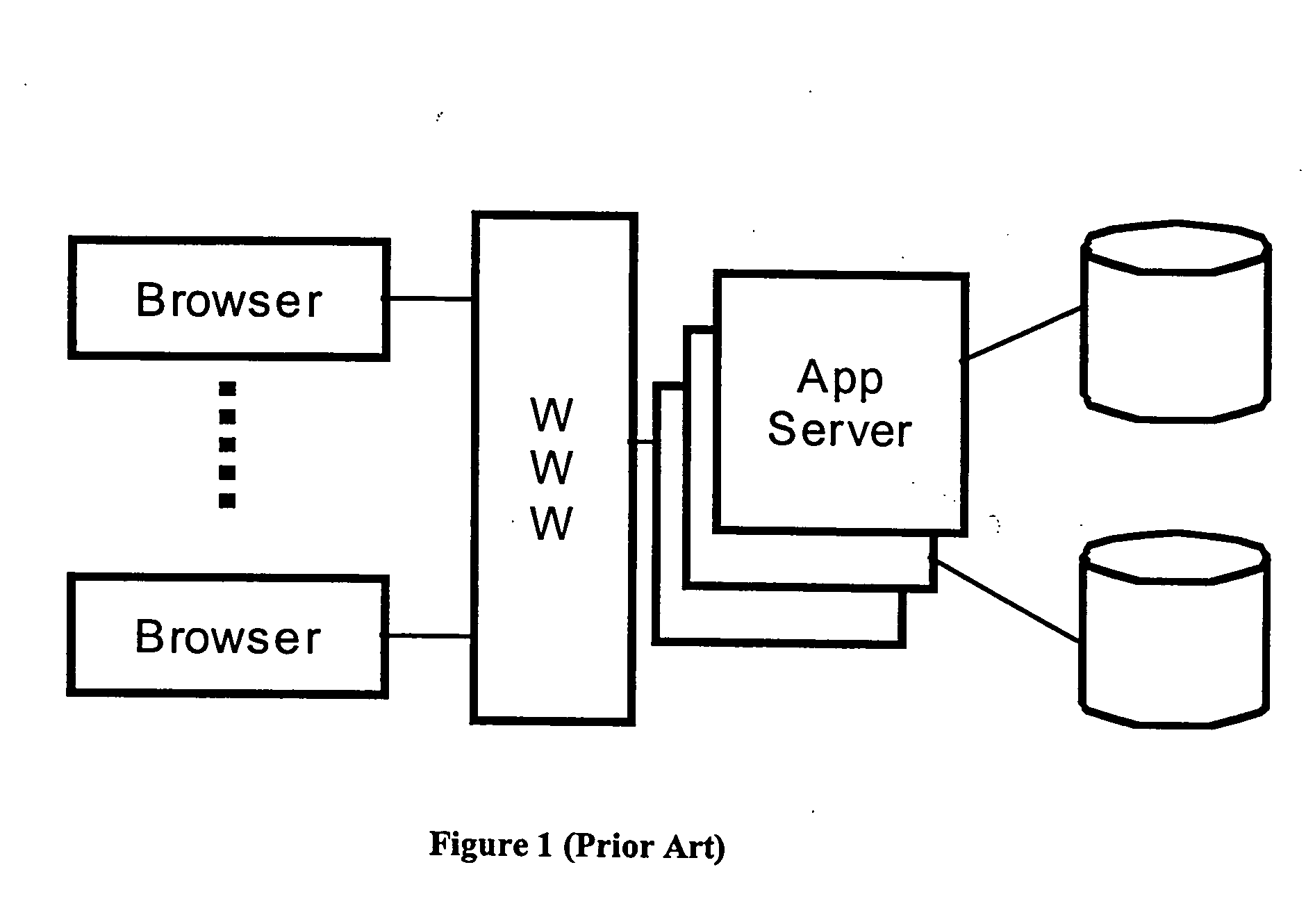

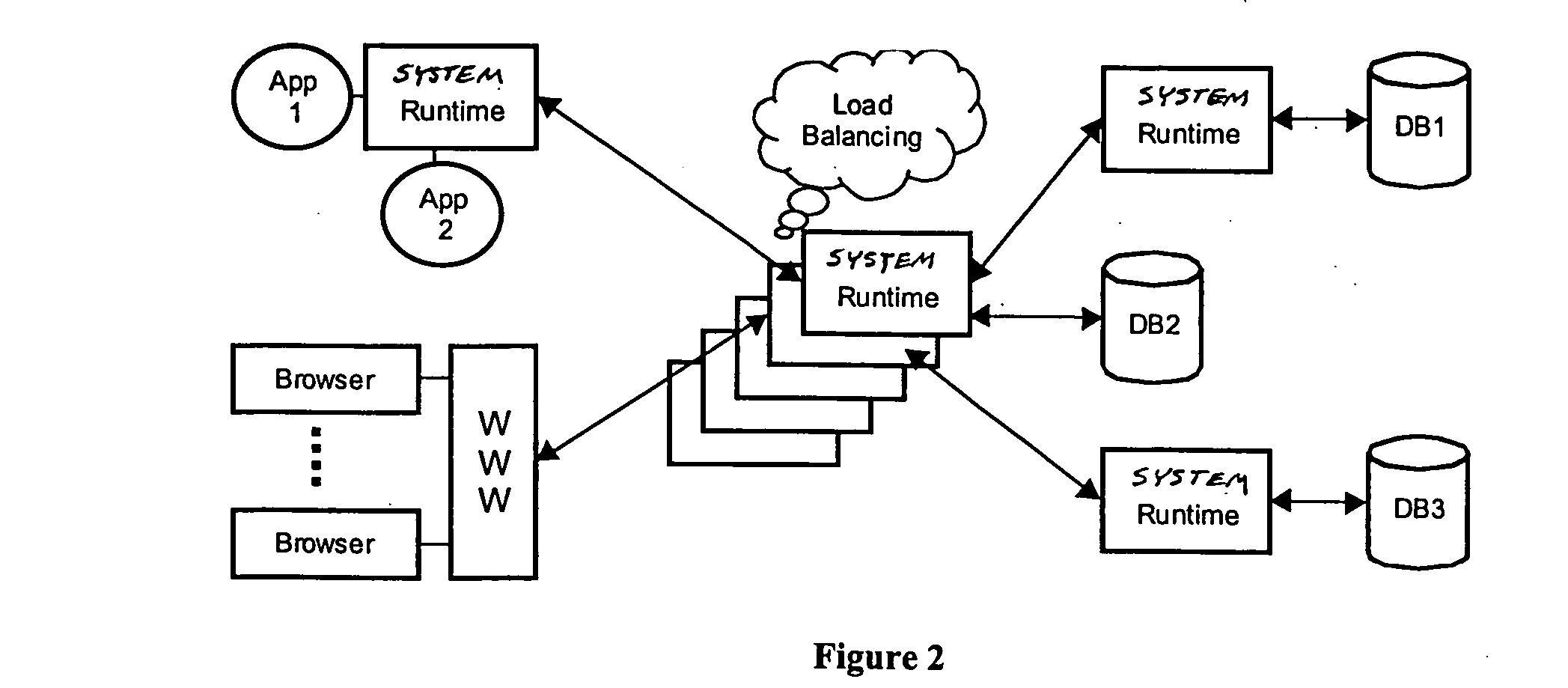

Method and apparatus for maintaining data integrity across distributed computer systems

InactiveUS20060143239A1Short response timeReduce network trafficDatabase distribution/replicationSpecial data processing applicationsData integrityComputerized system

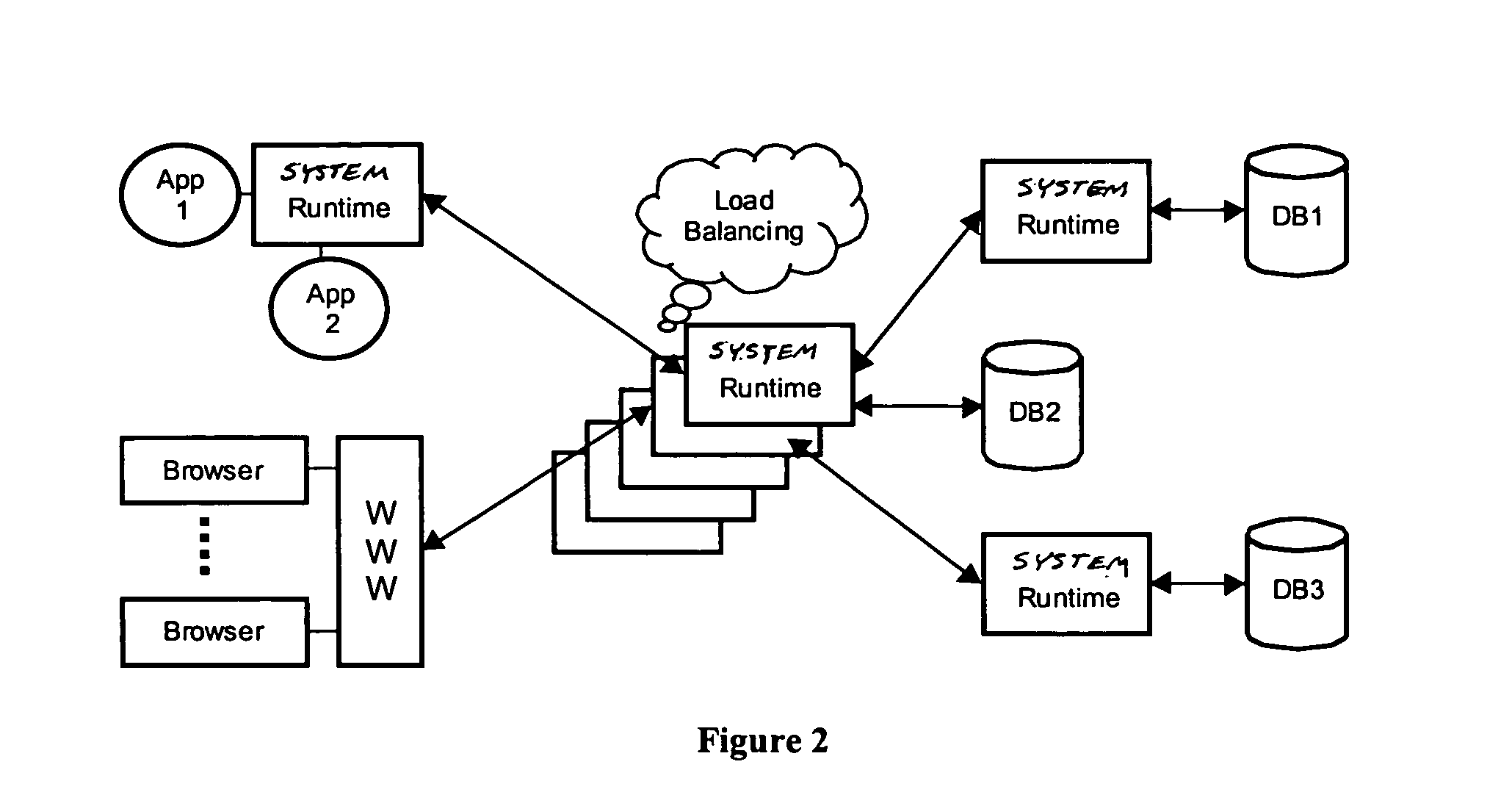

A method and apparatus are generally disclosed for maintaining data integrity across distributed computer systems. In one embodiment, the method of the invention includes the step of transmitting an object from a server application to a client application. The method also includes the step of transmitting an object state from the server application to the client application. The method further includes the steps of synchronizing the object and object state between the server application and the client application, and updating the object by invoking a server application method after the step of synchronizing. An apparatus and article of manufacture for carrying out the steps of the method are also disclosed.

Owner:COMP ASSOC THINK INC

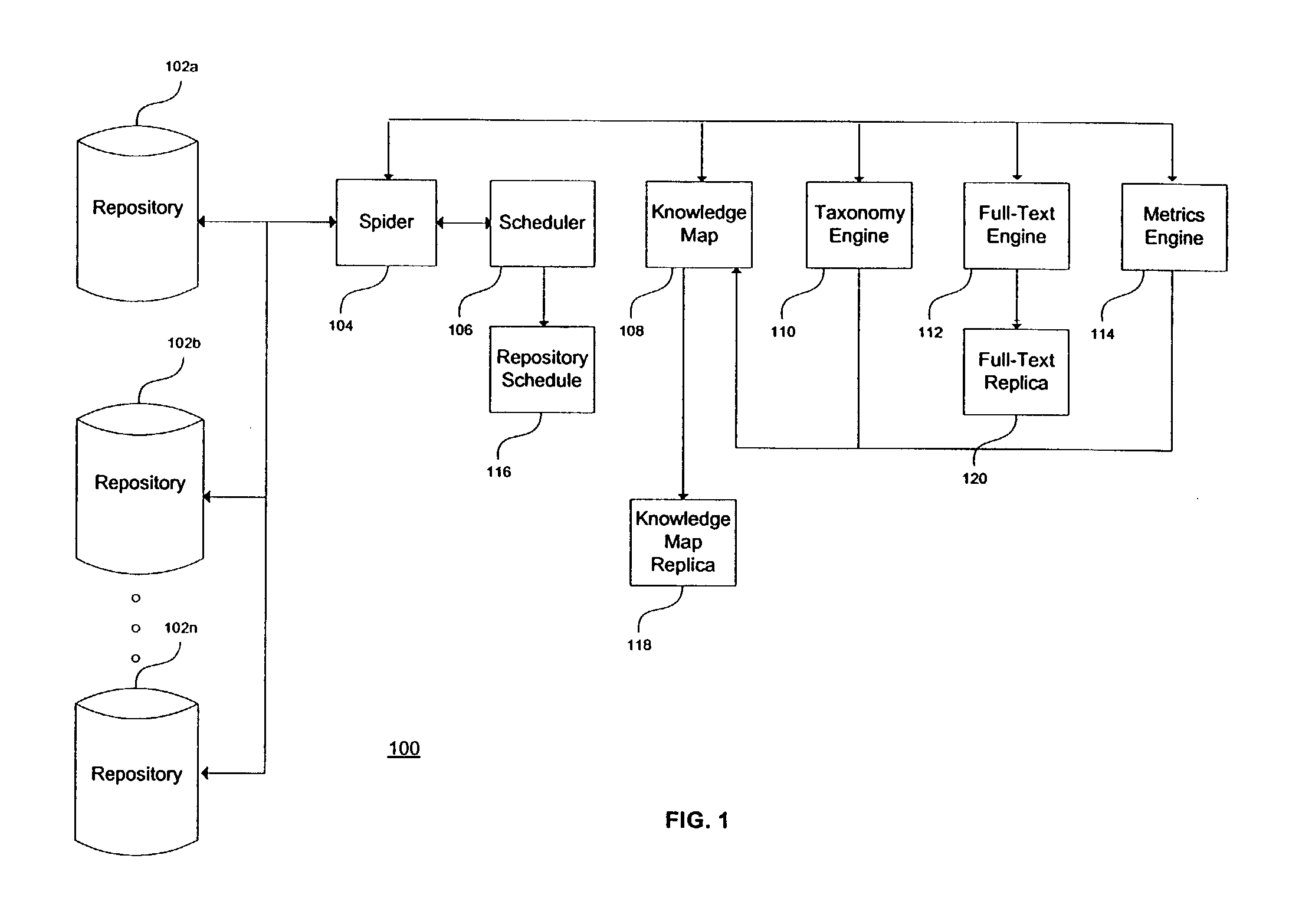

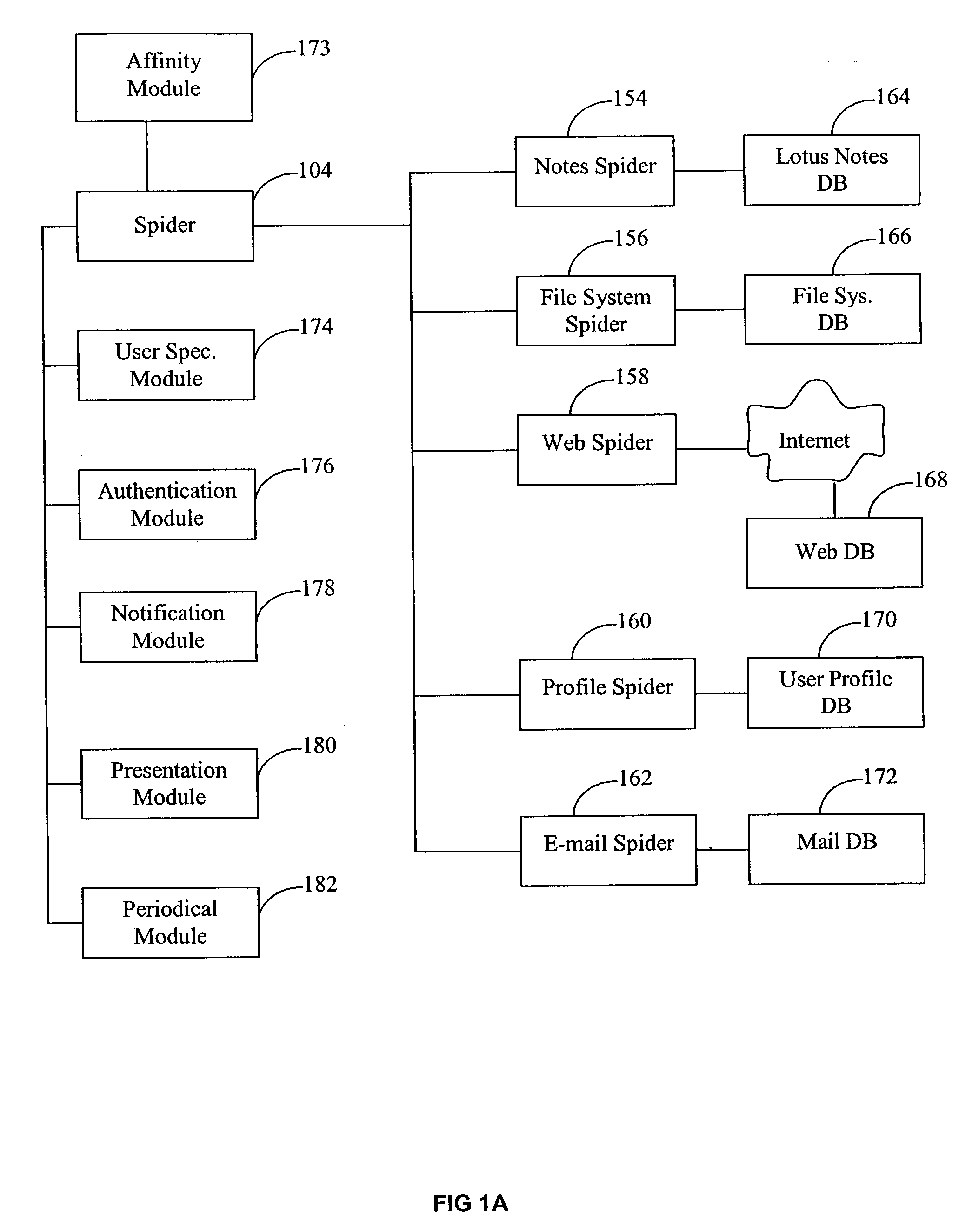

System for synchronizing of user's affinity to knowledge

A system and method for synchronizing profile data based on one or more changes in affinity to knowledge data in a system. The profile data may include at least an affinity of a person to knowledge data. In some embodiments, metadata information associated with stored content belonging to one or more topical categories of knowledge data may be provided. The metadata information may represent a history of the person's activities with the stored content. The affinity of the person to the one or more topical categories of knowledge data may be determined based at least in part on the metadata information. One or more changes in the affinity of the person to the one or more topical categories of knowledge data may be determined. The profile data may be synchronized to indicate the determined one or more changes.

Owner:BEIJING PIANRUOJINGHONG TECH CO LTD

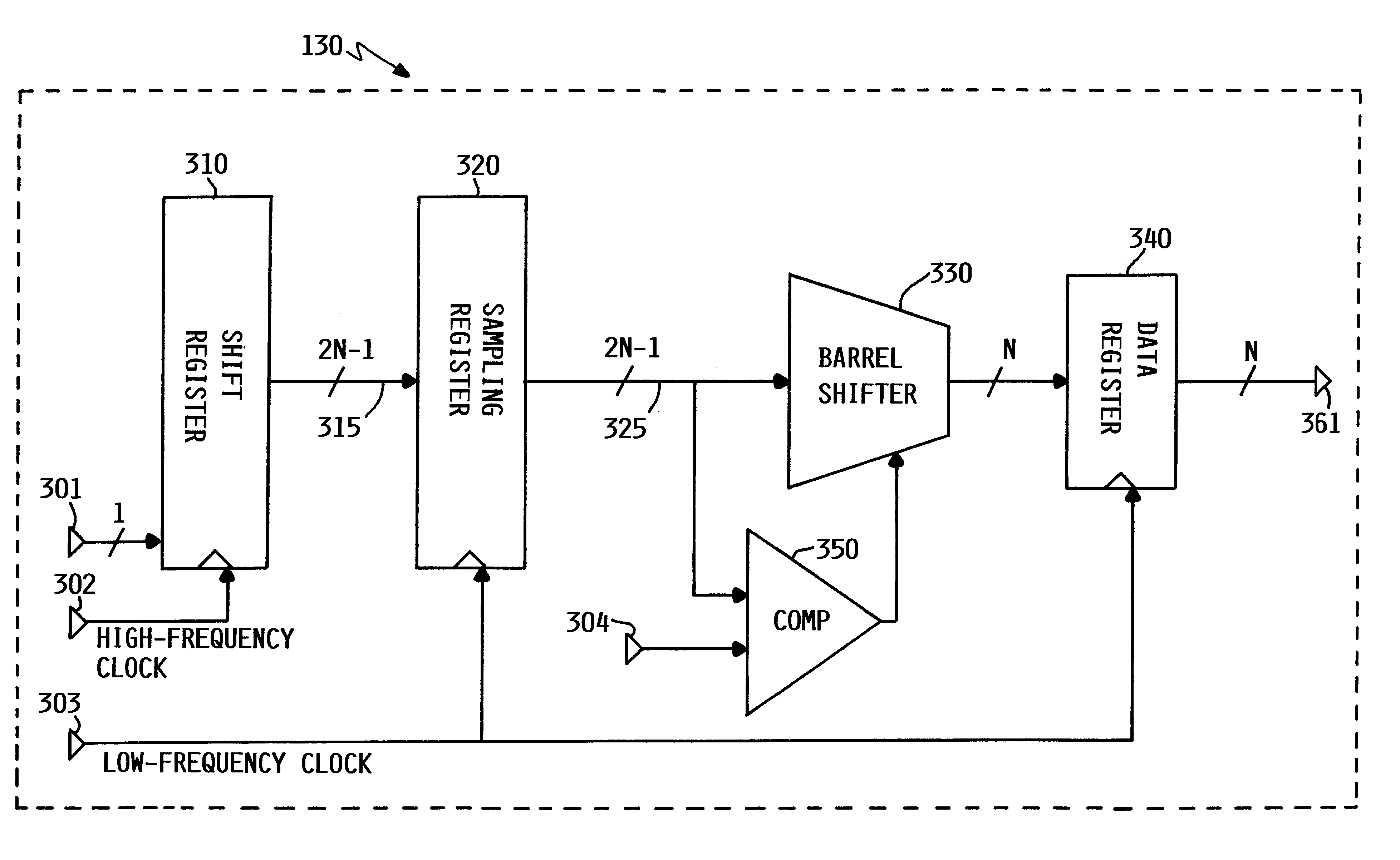

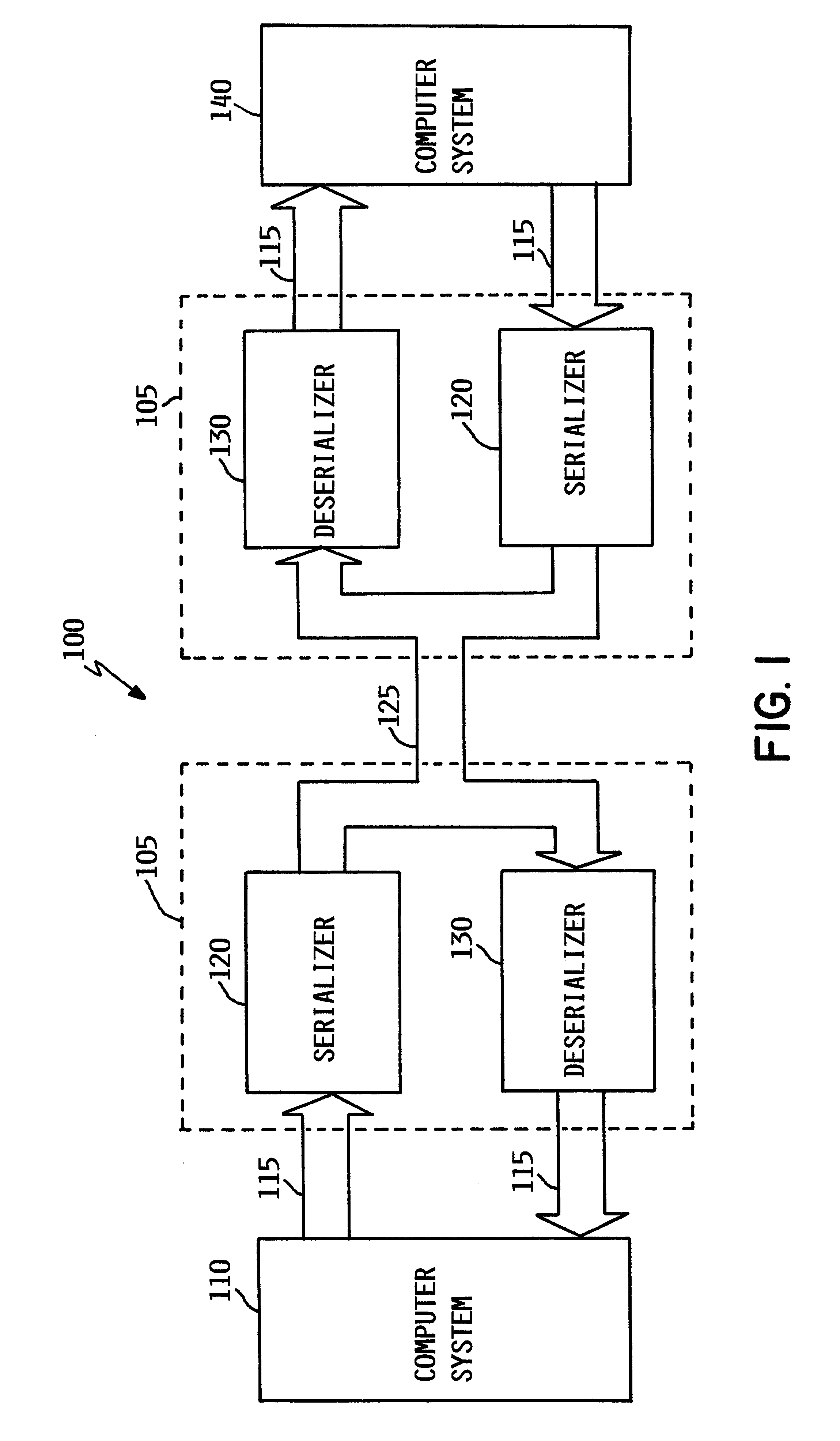

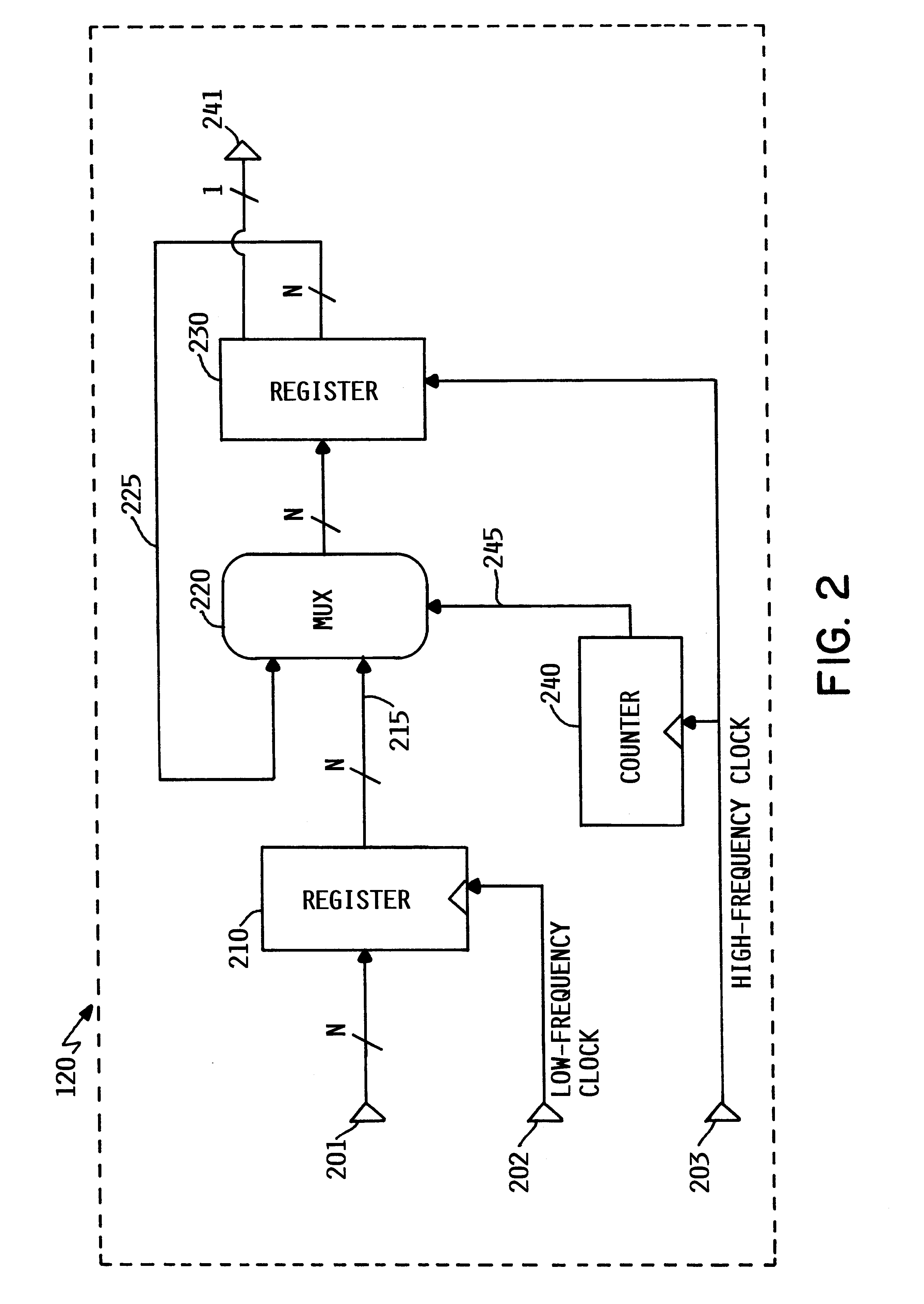

Apparatus and method for optimized self-synchronizing serializer/deserializer/framer

InactiveUS6459393B1Negatively impact design timeNegatively integrated circuit clock loadingParallel/series conversionViruses/bacteriophagesSerial transferTelecommunications link

An apparatus and method for improving the communication capabilities of computer systems is disclosed. The most preferred embodiments of the present invention use a series of data buffers and data registers to process an incoming high speed data signal. By using the buffers and registers, the incoming signal can be reformatted and manipulated at a much lower frequency than the original transmission frequency. The deserializer of the present invention also samples a greater portion of the incoming data signal than usual to further increase reliability. These various features of the invention provide for a more stable and reliable communication link and will also provide a less expensive solution for serialization / deserialization. The present invention includes a serializer that receives parallel data input from a computer and serializes the data for transmission over a high-speed serial communication link. On the receiving end, the present invention provides a deserializer that can quickly and efficiently transform the serial data back into parallel form for use within the computer system on the receiving end. By utilizing two related clock signals, one clock signal being an integer multiple of the other, a self-synchronizing serializer / deserializer can be created. In addition, by increasing the size of the data sample on the receiving end, the comparisons necessary to retrieve a parallel signal from a serial transmission can occur at a much lower frequency than the frequency of the serial transmission. In the most preferred embodiment, the invention is provided as a integrated solution manufactured on a Peripheral Component Interconnect (PCI) card, thereby allowing the present invention to be easy installed into existing computer systems.

Owner:MEDIATEK INC

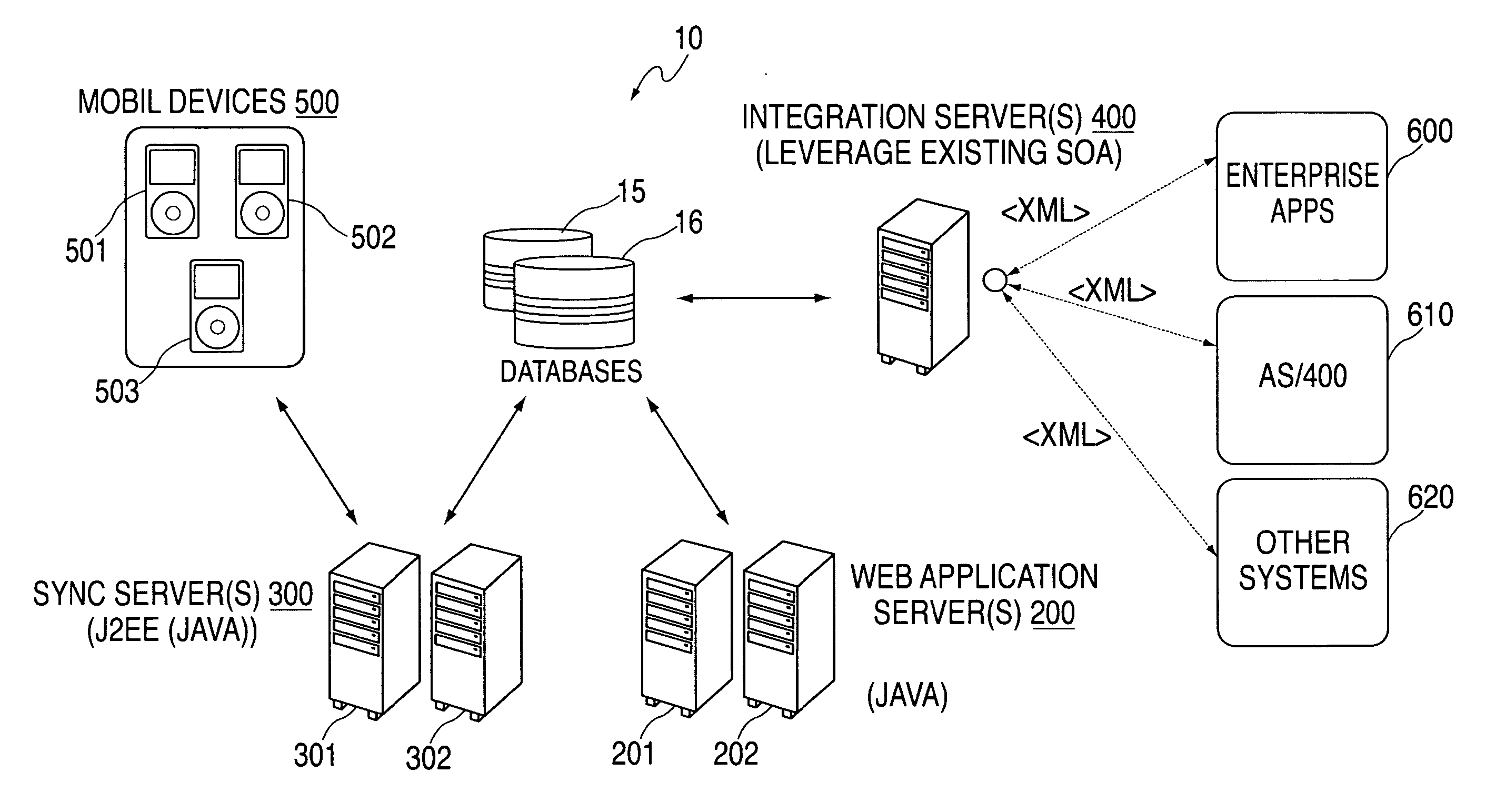

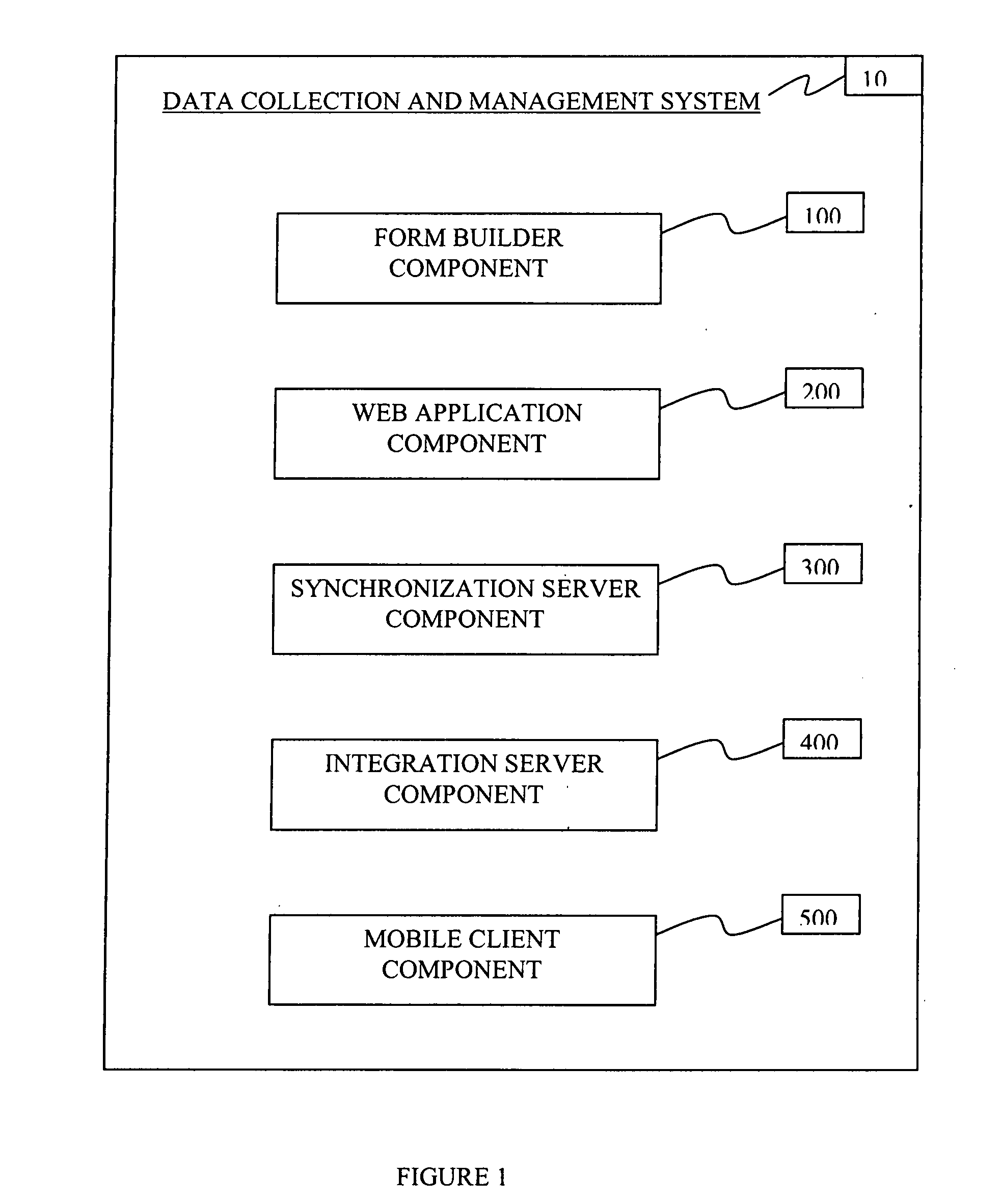

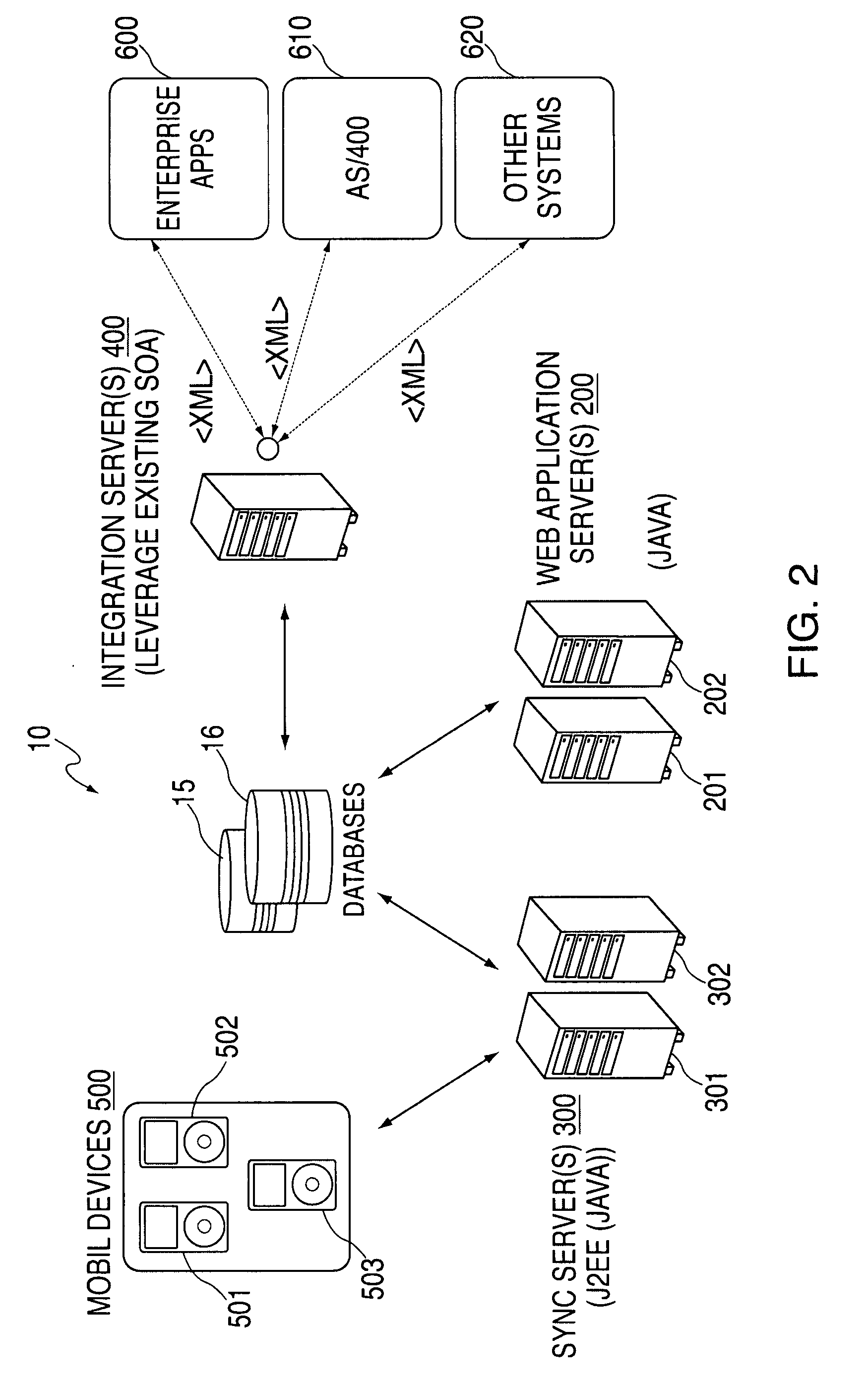

Method and apparatus for mobile data collection and management

InactiveUS20070260475A1Reduce costs and risksDigital data processing detailsMarketingData synchronizationTablet computer

A method and apparatus for a middleware approach to initializing and updating required data entry fields, pushing such required data entry fields to mobile devices and applications, collecting entered data from such mobile devices, and the synchronizing and integrating of the data is presented. A “form builder” software component of the present invention allows for the creation of easy to read and use data entry forms by company management. A “web application” software component of the present invention allows for the forms to then be distributed via electronic and / or wireless means to mobile client devices, such as PDA's, Tablets, and Laptops, and to Desktop computers. The mobile client devices run applications to utilize the data entry forms and are that into which collected data can be entered. A “synchronization server” software component of the present invention then allows for two-way communication, storage and conflict resolution (versioning) of the collected data. An “integration server” software component of the present invention allows for external access to the collected and versioned data and modeling / mapping of such data. Thus seamless data entry, collection, updating, conflict resolution, versioning, storage, access and utilization is available.

Owner:VERIFONE INC

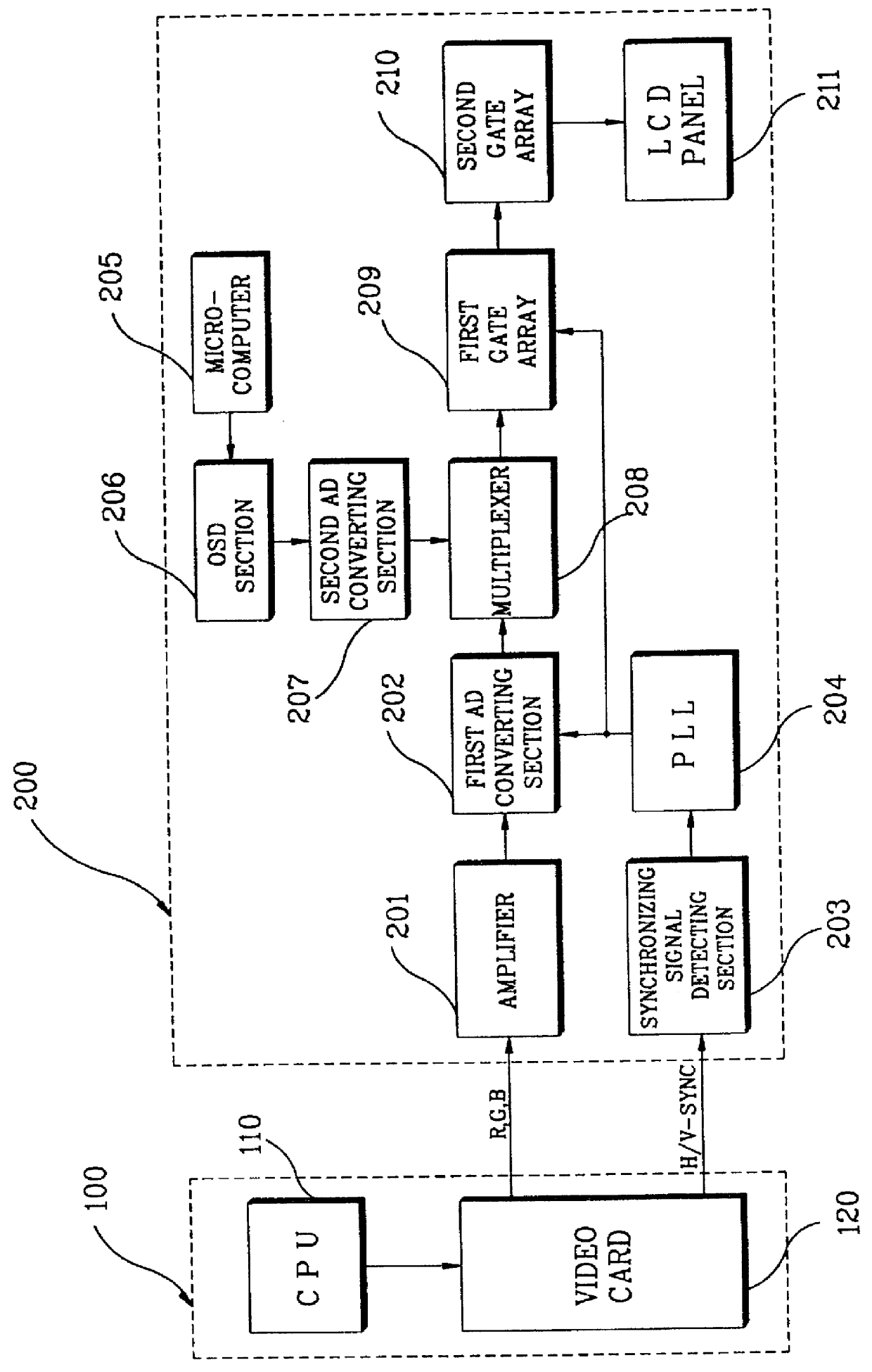

Format converter

InactiveUS6097437ATelevision system detailsTelevision system scanning detailsMicrocomputerDigital pictures

A format converter includes: a microcomputer for receiving horizontal and vertical synchronizing signals from a host, determining a video mode, and generating data that indicates the number of dots per a period of a horizontal output signal; a W-PLL and time generator for receiving the data from the microcomputer, and generating a write clock signal; an R-PLL and time generator for receiving the data and the horizontal synchronizing signal respectively generated by the microcomputer and the host, and generating a read clock signal; an AD converting section for sampling an analog picture signal received from the host according to the write clock signal of the W-PLL and time generator, and converting it to a digital picture signal; and a format converting section for storing the picture signal received from the AD converter according to the period of the write clock signal of the W-PLL and time generator, and converting the format of the stored picture signal according to the read clock signal received from the R-PLL and time generator.

Owner:SAMSUNG ELECTRONICS CO LTD

A/b/c phase determination and synchrophasor measurement using common electric smart meters and wireless communications

ActiveUS20130241746A1Electric signal transmission systemsTariff metering apparatusPower gridTime standard

Phasor Measurement Units (PMUs) tend to be specialized and expensive—relegated to only key points in power distribution networks, and are generally reliant on GPS technology. The present disclosure details how any smart meter—using wireless communication—can perform sub-microsecond-grade synchrophasor measurements. Other aspects concern smart meter-based determination of A, B or C phase of the tri-phase power network. This can involve count-stamp enabling message packets sent to and / or from a smart meter, and then associating such count-stamps to local measurements of power phase by a metrology unit. Once a network of such enabled smart meters and other devices is formed, sub-microsecond metropolitan-wide and entire region-wide synchronizing time standard can calibrate local measurements of power phase, where simple A, B and C phase determination is one low hanging fruit application of such. Low cost aggregate monitoring of metropolitan-wide synchrophasors promises a next chapter of importance for that relatively recent art.

Owner:DIGIMARC CORP

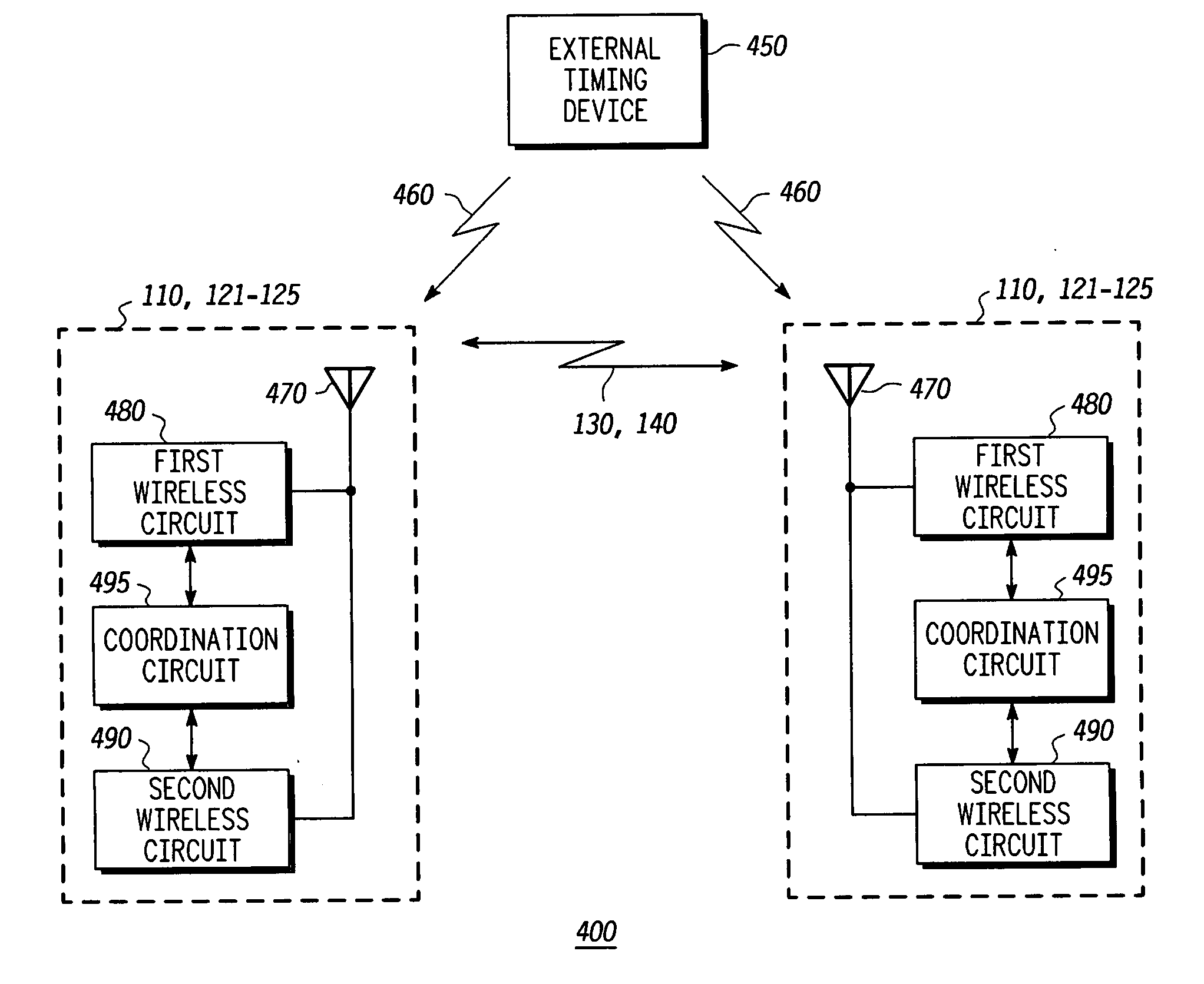

Method of synchronizing a wireless device using an external clock

A method is provided for operating a dual-use wireless device. The method includes: receiving an external timing signal (460) at a first wireless circuit (480) in the device (605); synchronizing a first clock in the first wireless circuit with the external timing signal (610); sending a first internal timing signal (570) from the first wireless circuit to a second wireless circuit in the device, after the synchronizing (615); and listening for a remote periodic control signal at the second wireless circuit for a set monitoring time, a start of the monitoring time being based on the first internal timing signal (865). The second wireless circuit sends an association request if the second wireless circuit hears the remote periodic control signal within the monitoring time (875), and sends a local periodic control signal if the second wireless circuit does not hear the remote periodic control signal within the monitoring time (625).

Owner:NORTH STAR INNOVATIONS

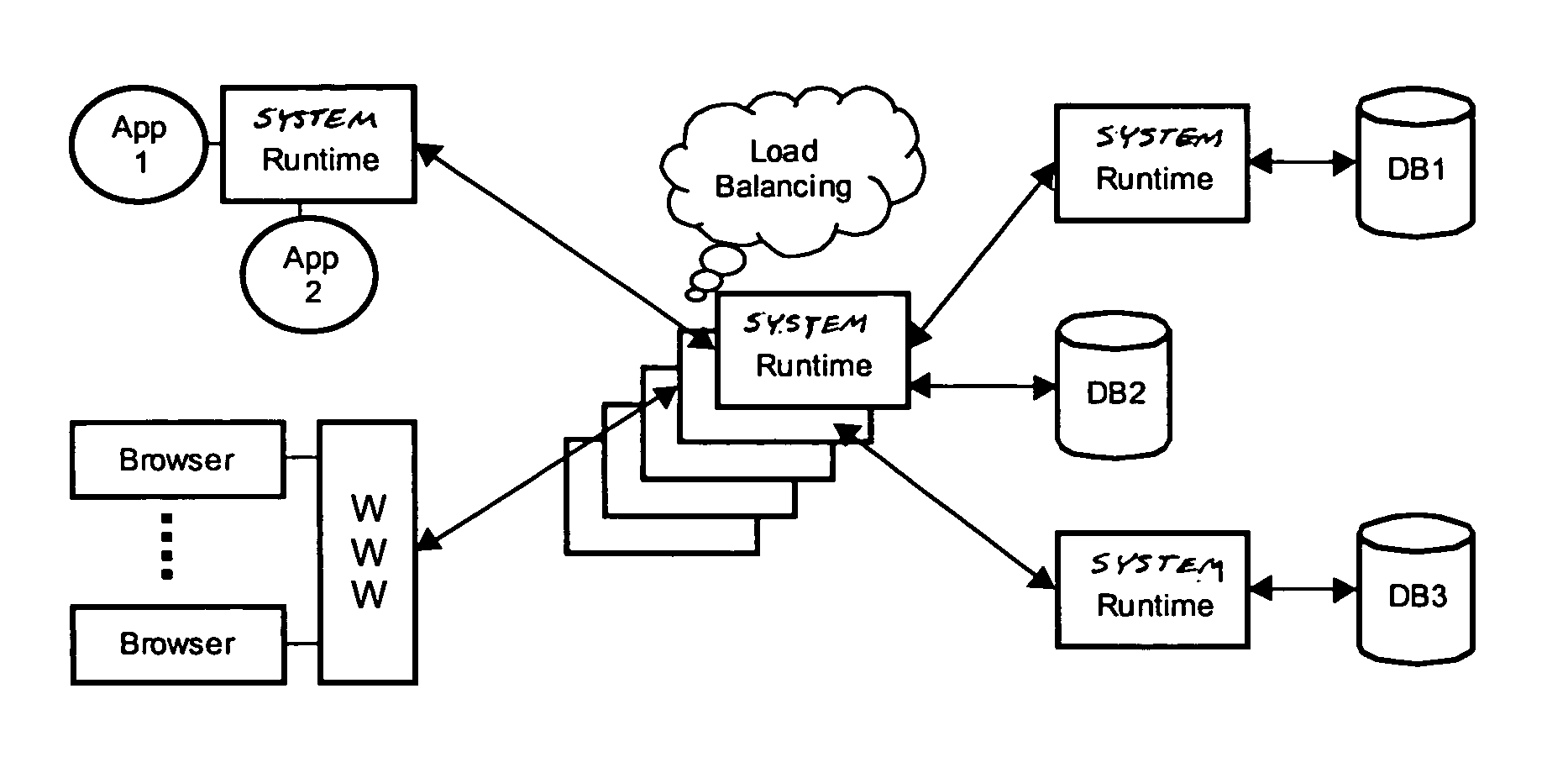

Method and apparatus for maintaining data integrity across distributed computer systems

InactiveUS7003587B1Reduce the possibilityShort response timeMultiple digital computer combinationsTransmissionData integrityComputerized system

A method and apparatus are generally disclosed for maintaining data integrity across distributed computer systems. In one embodiment, the method of the invention includes the step of transmitting an object from a server application to a client application. The method also includes the step of transmitting an object state from the server application to the client application. The method further includes the steps of synchronizing the object and object state between the server application and the client application, and updating the object by invoking a server application method after the step of synchronizing. An apparatus and article of manufacture for carrying out the steps of the method are also disclosed.

Owner:COMP ASSOC THINK INC

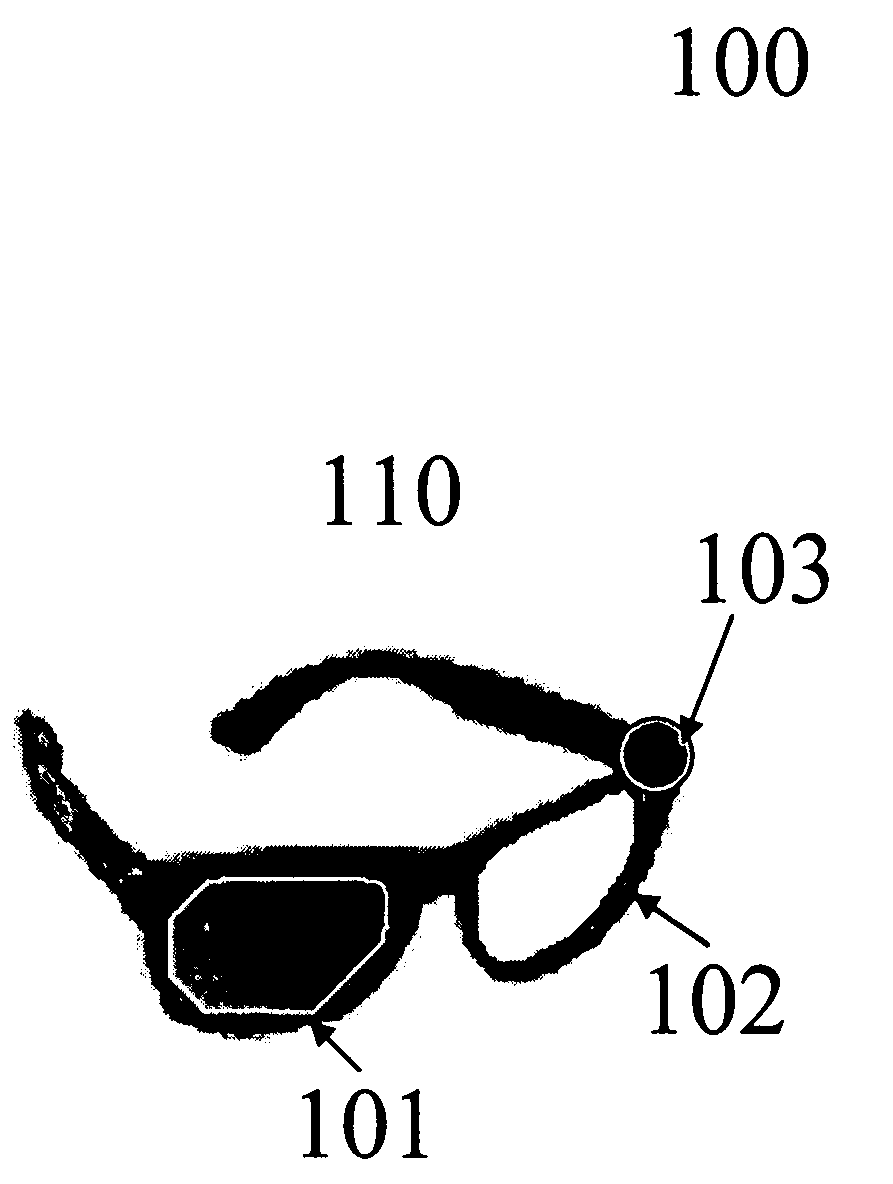

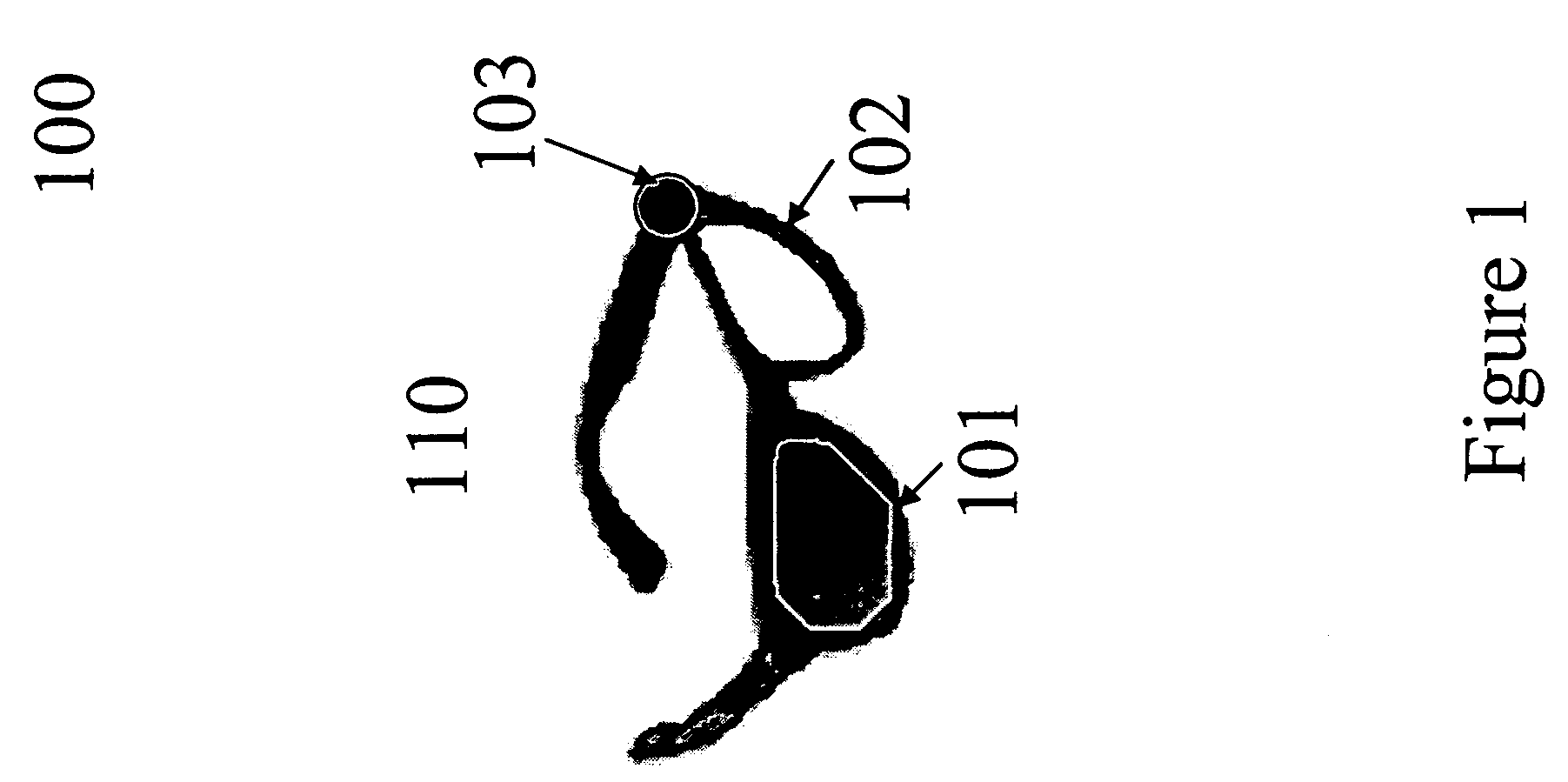

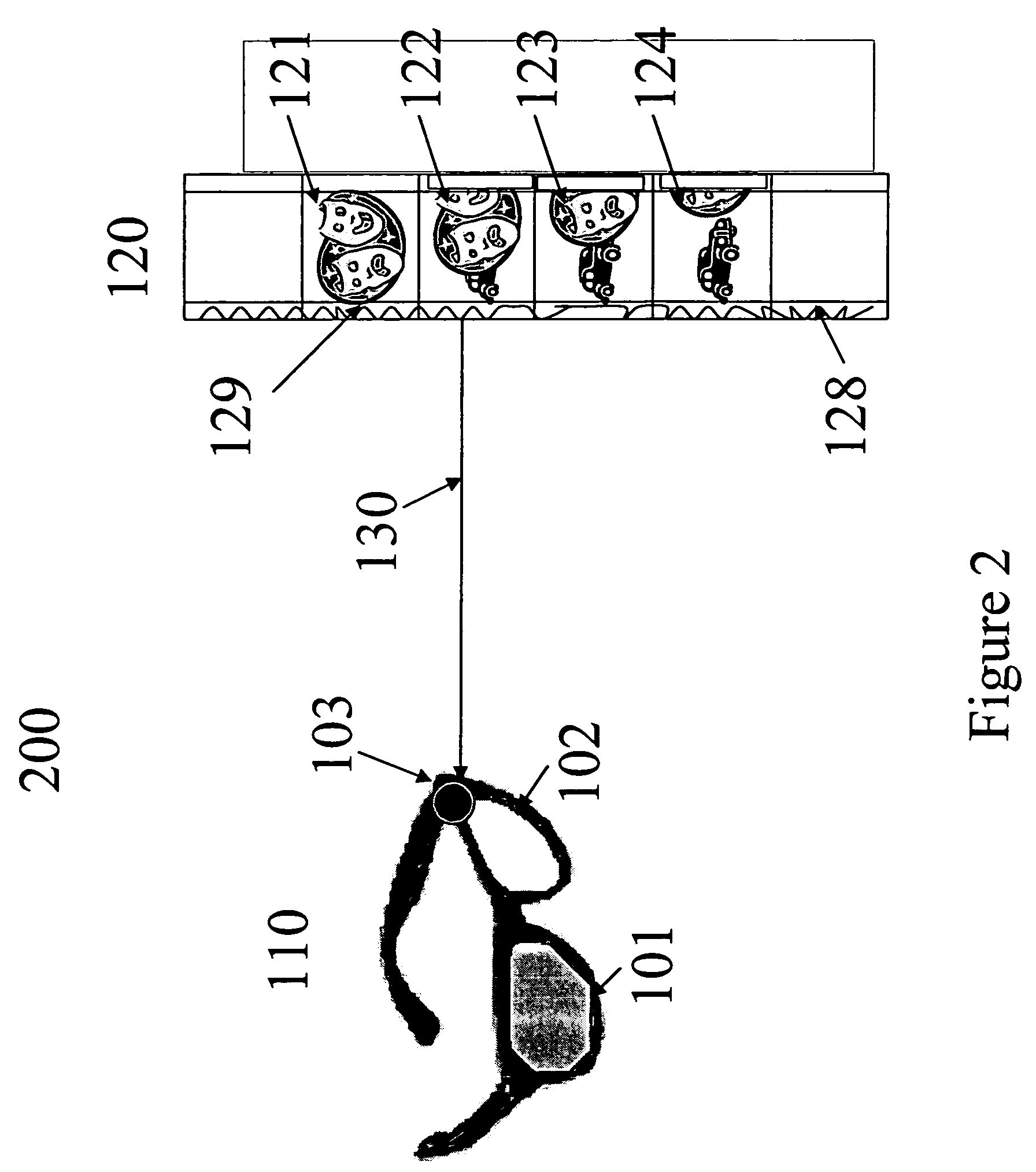

System and method for Pulfrich Filter Spectacles

InactiveUS7405801B2Overcome problemsProjectorsColor television detailsComputer graphics (images)Eyewear

Pulfrich Filter Spectacles to view a 2-dimensional motion picture with 3-dimensional visual effects are disclosed. A method for synchronizing the Puifrich filter spectacles and a method of displaying 2-dimensional motion pictures as 3-dimensional pictures using the spectacles are also disclosed. The Puifrich spectacles and its synchronizing method and displaying method will allow almost any motion picture to be viewed effortlessly by the viewer with the visual effect of 3-dimensions.

Owner:VDPP LLC +1

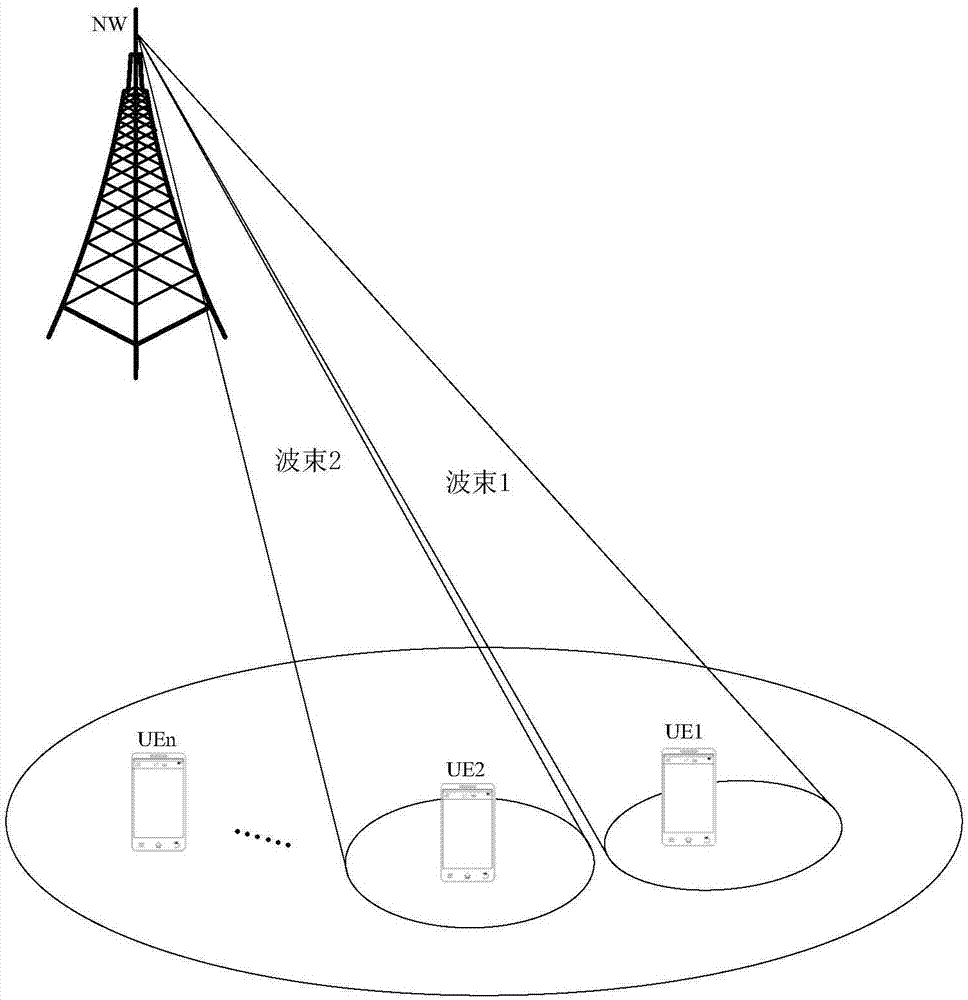

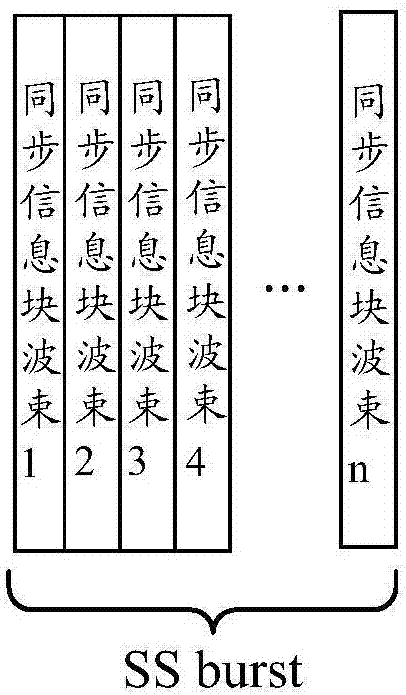

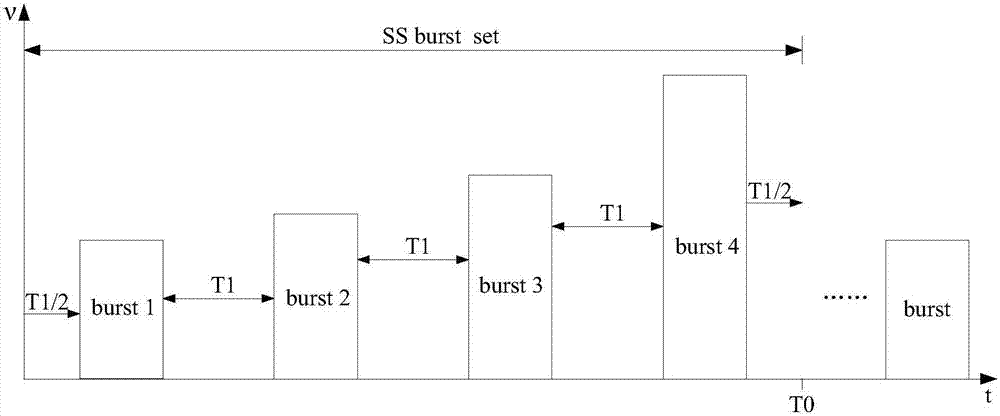

Method and device of transmitting and acquiring synchronous information blocks

ActiveCN107278383AAccurate acquisitionAccurately calculate estimated time of arrivalSynchronisation arrangementAssess restrictionG-networkUser equipment

The invention provides a method and a device of transmitting and acquiring synchronous information blocks. The method comprises steps that according to a synchronous information block set SS burst Set mode, target mode index information is determined; the target mode index information is stored in every synchronous information block SS block, and the to-be-transmitted synchronous information block is acquired; by adopting a high frequency wave beam, user equipment in a target cell is periodically transmitted to the target synchronous information block; every SS burst Set comprises periodically transmitted synchronously burst SS burst of a first preset number; every SS burst comprises target synchronous information blocks of a second preset number are transmitted according to a space sequence. By adopting the method provided by the invention, the cell signal synchronizing of the user equipment in a 5G network is realized accurately and quickly.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

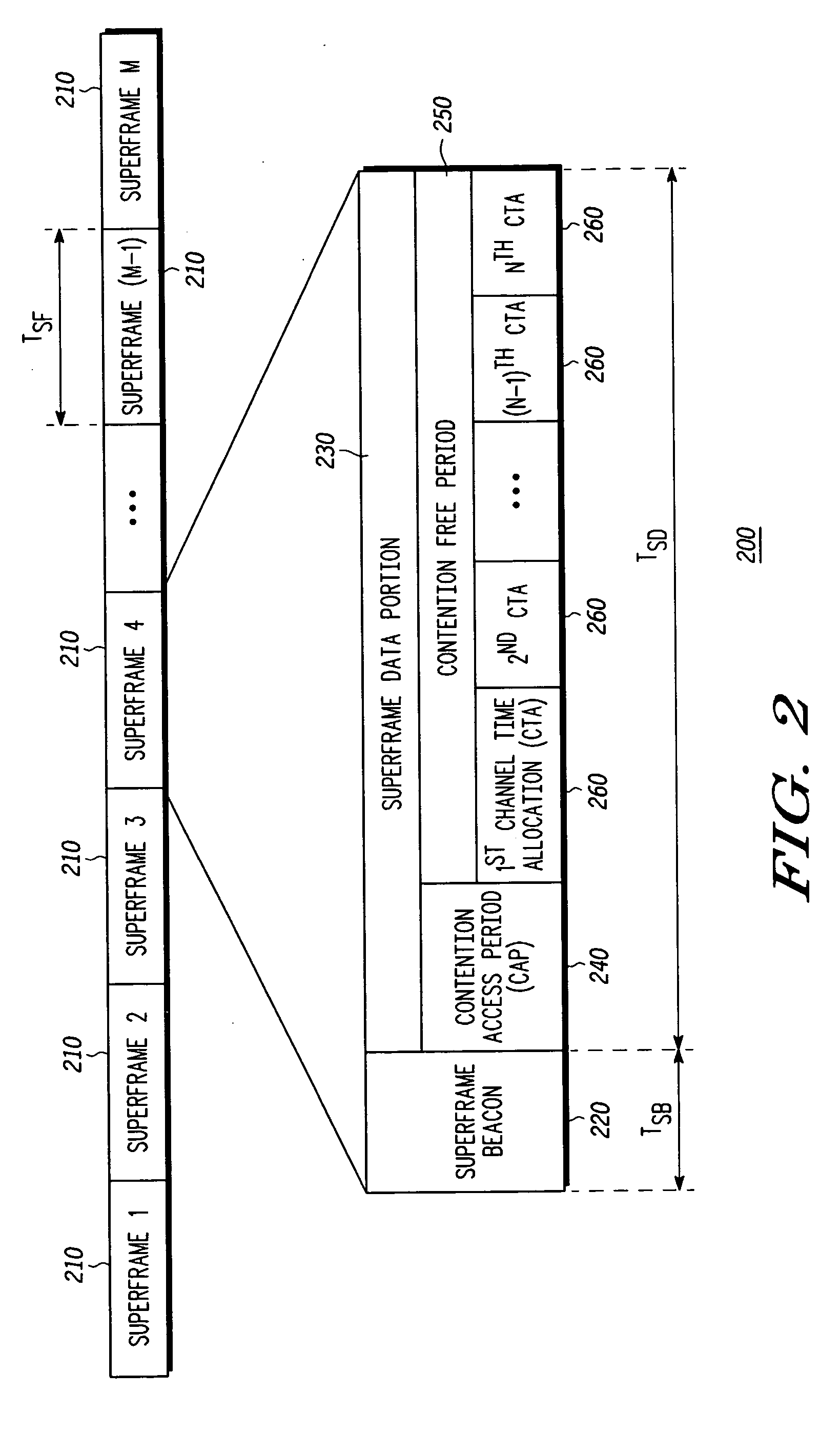

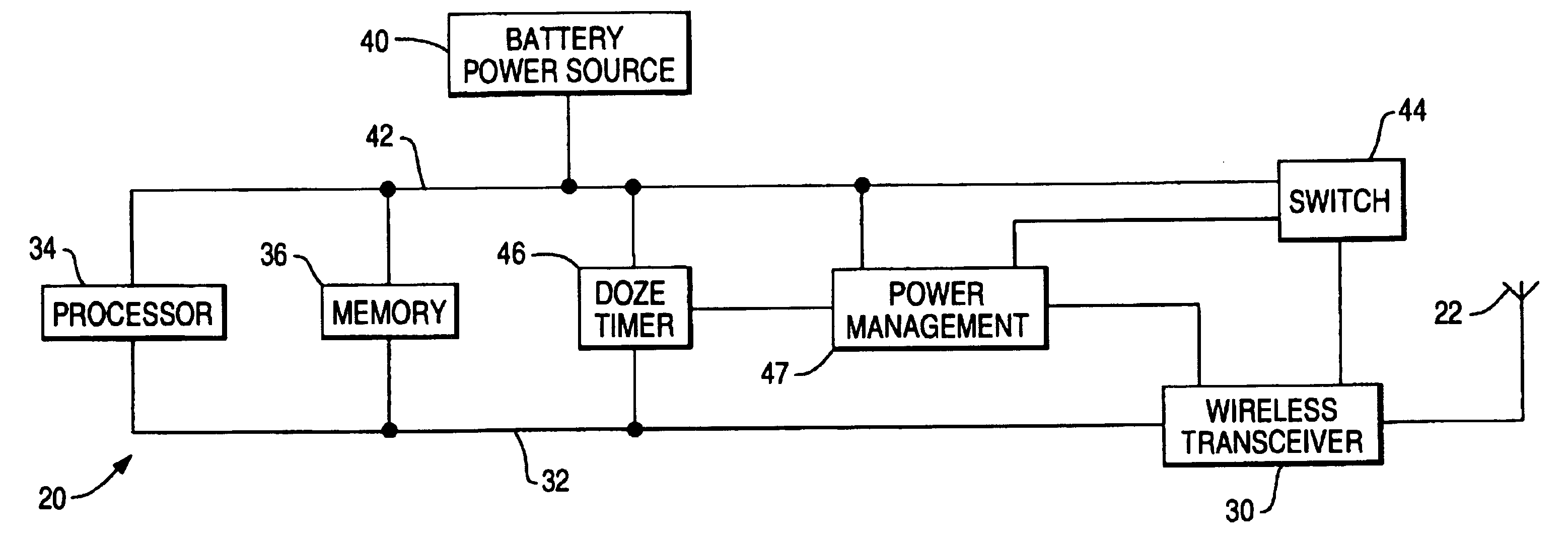

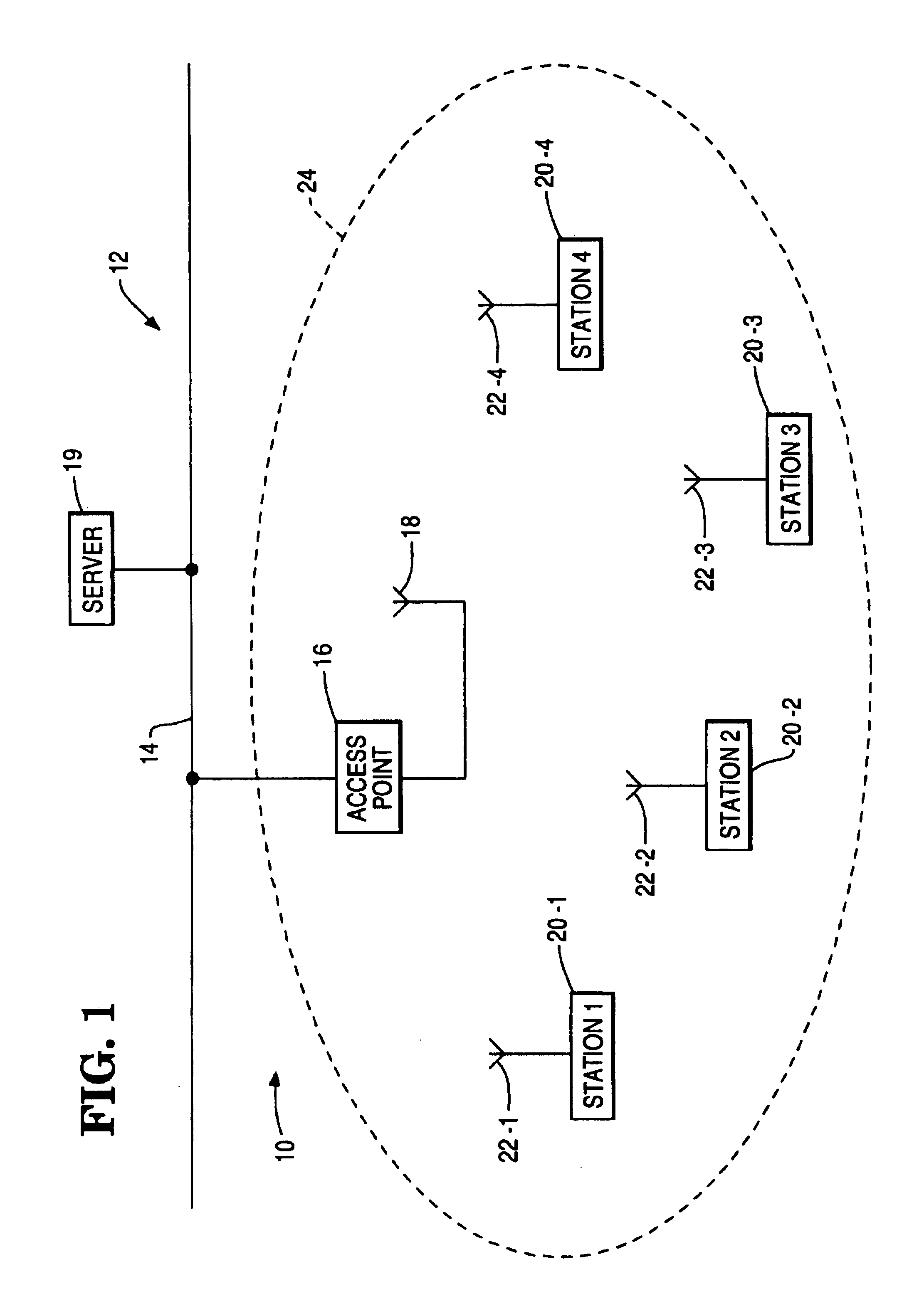

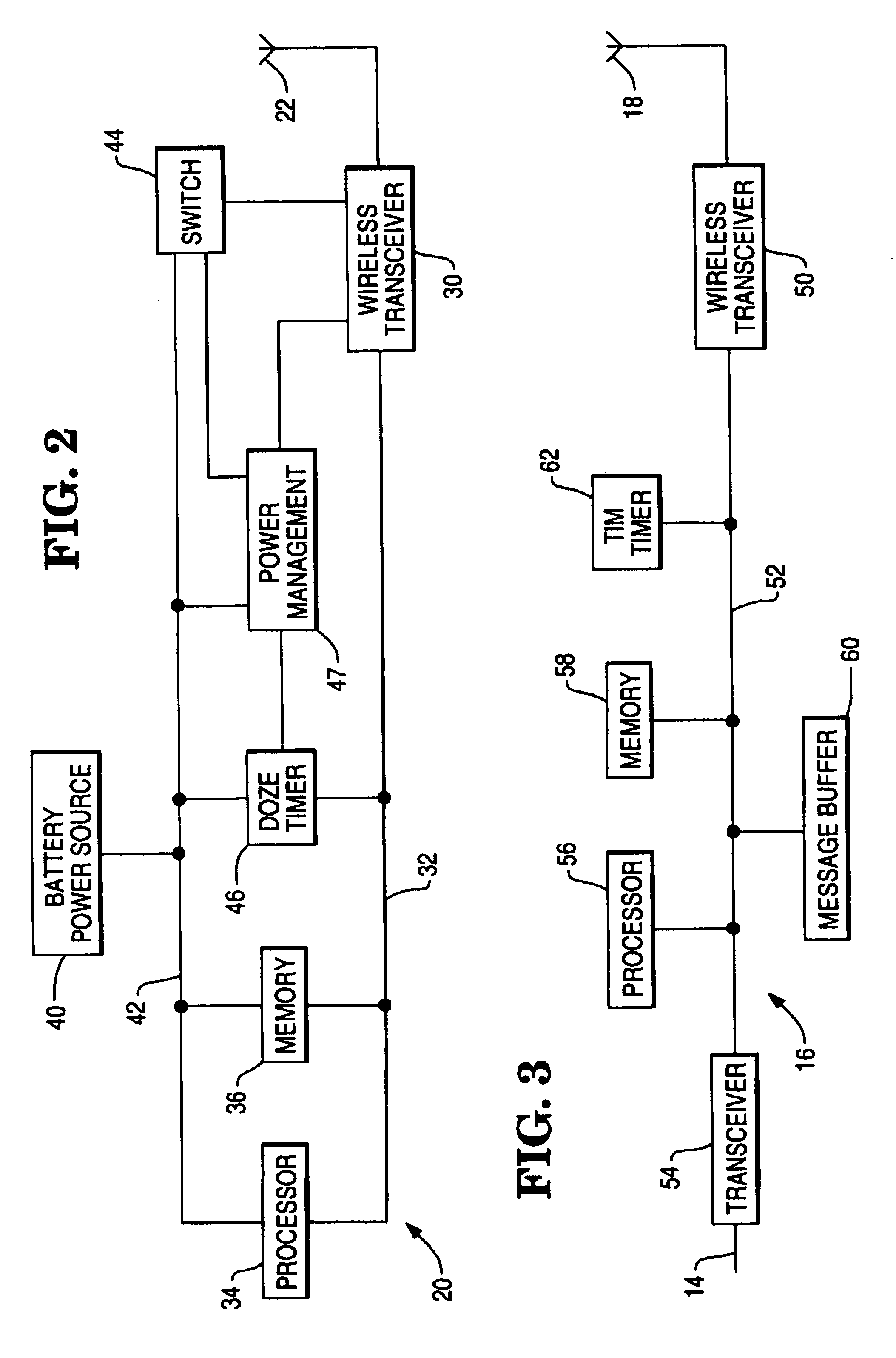

Wireless data communication system having power saving function

InactiveUSRE40032E1Easy to useMore power efficientPower managementTransmission systemsCommunications systemMaster station

A wireless data communication system is operable in a power saving mode wherein stations are synchronized to be in an awake state to receive synchronizing messages (TIM, PSYNC) and traffic indicator information and are changed to a doze state if they are not to receive data messages. In one embodiment all stations (20) communicate via a base station access point (16), which broadcasts synchronizing messages (TIM) at regular intervals identifying stations (20) that are to receive data messages. In another embodiment all stations (220) communicate directly with one another, one station assumes the role of a master station and broadcasts synchronizing messages (PSYNC), and stations (220) desiring to transmit data messages transmit traffic indicator messages (PTIM) to the appropriate destination stations (220), in a synchronized awake period just before the next synchronizing message (PSYNC) is expected to arrive.

Owner:AGERE SYST INC

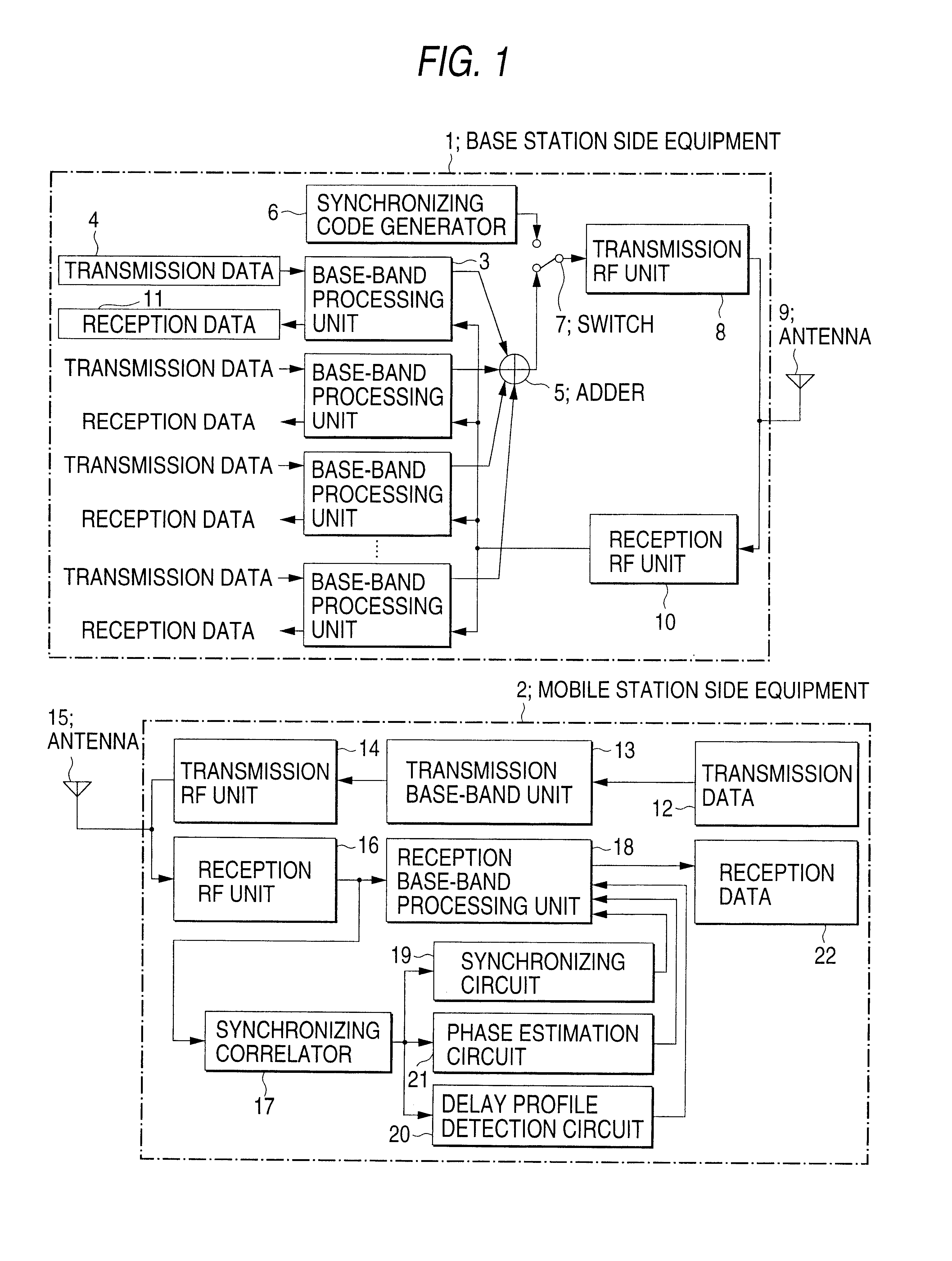

Spectrum spread communication system

InactiveUS6765895B1Easy accessReduce integration timeSynchronisation arrangementSynchronisation signal speed/phase controlFrequency spectrumCommunications system

In base station side equipment, a control channel for transmitting control information and a communication channel for transmitting information to each mobile station are spread with different synchronizing codes before being superposed by operating a switch to switch the output of an adder over to the output of a synchronizing code generator. Further, a synchronizing code is periodically inserted in a signal by one symbol length and the signal is transmitted over the superposed channel. In a plurality of base station side equipment, moreover, the synchronizing code and its transmission period are equal and the transmission timing is asynchronous and independent. A synchronizing correlator in mobile station side equipment obtains the correlation value of the whole chip phase in a synchronizing code transmission period using the synchronizing code and decides a base station which is transmitting the synchronizing code at the greatest correlating peak position to the closest one and further extracts symbol timing from the peak position.

Owner:PANASONIC CORP

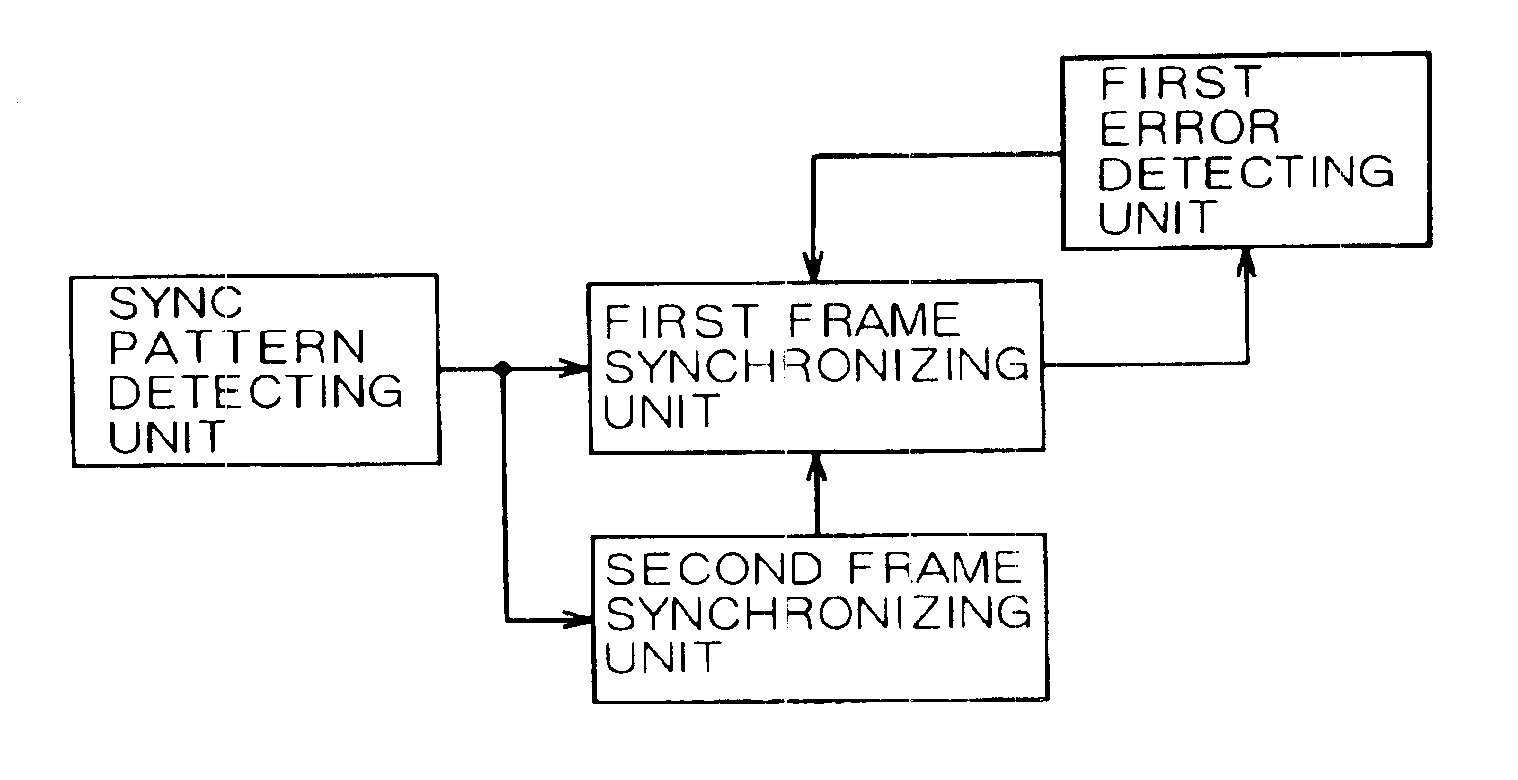

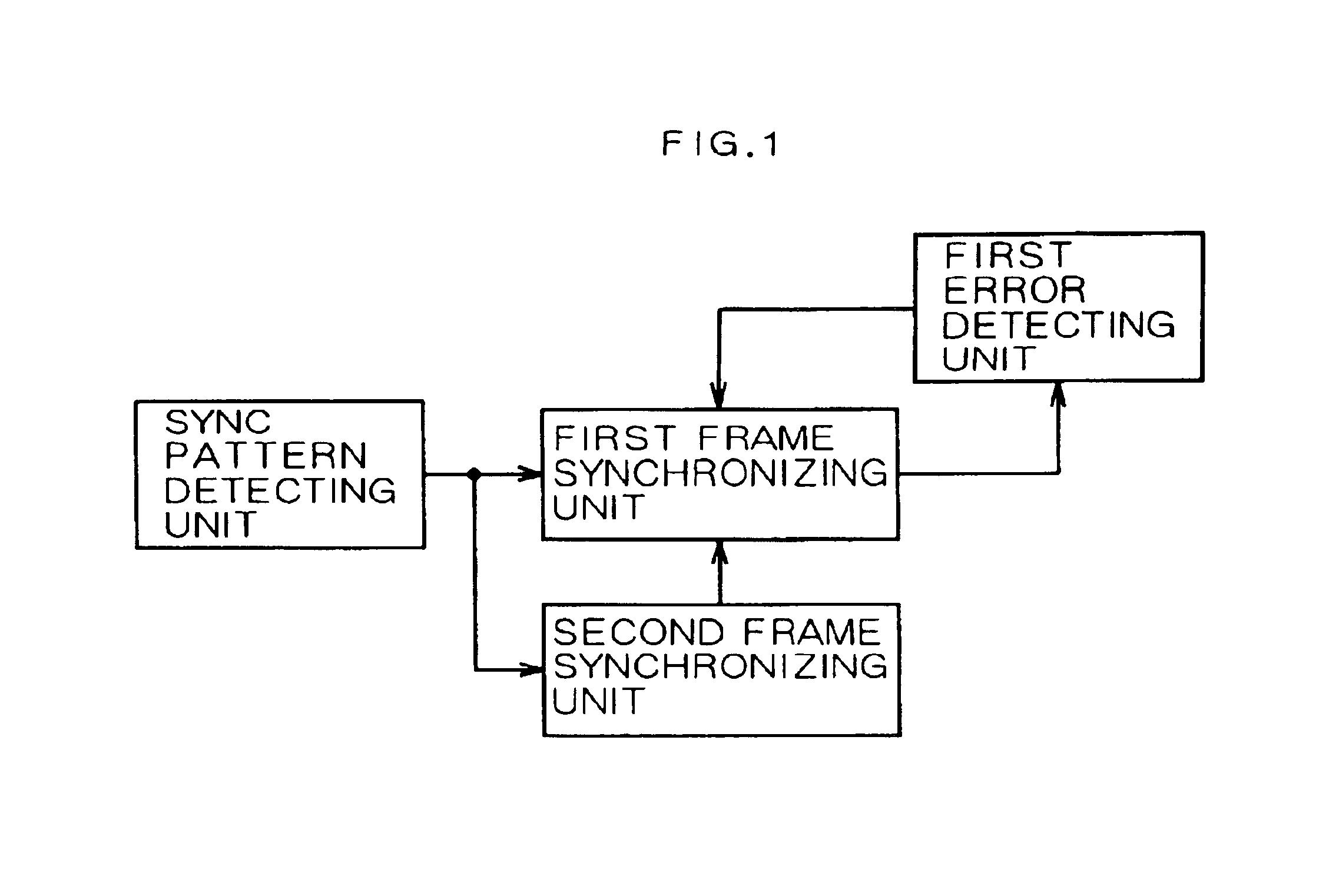

Frame synchronizing circuit

InactiveUS6865240B1Shorten the timeData representation error detection/correctionError detection/correctionSynchronizingReal-time computing

The frame synchronizing circuit establishes frame synchronization by detecting a sync pattern laid in an incoming frame. The frame synchronization circuit comprises a first frame synchronizing unit and a second frame synchronizing unit. The first and second synchronizing units synchronize with a first pattern, a second pattern at a first position and a second position, respectively. Thereafter, when the first position used for the synchronization by the first frame synchronizing unit is found to be in error, the first frame synchronizing unit synchronizes with the second pattern at the second position used by the second frame synchronization unit.

Owner:FUJITSU LTD

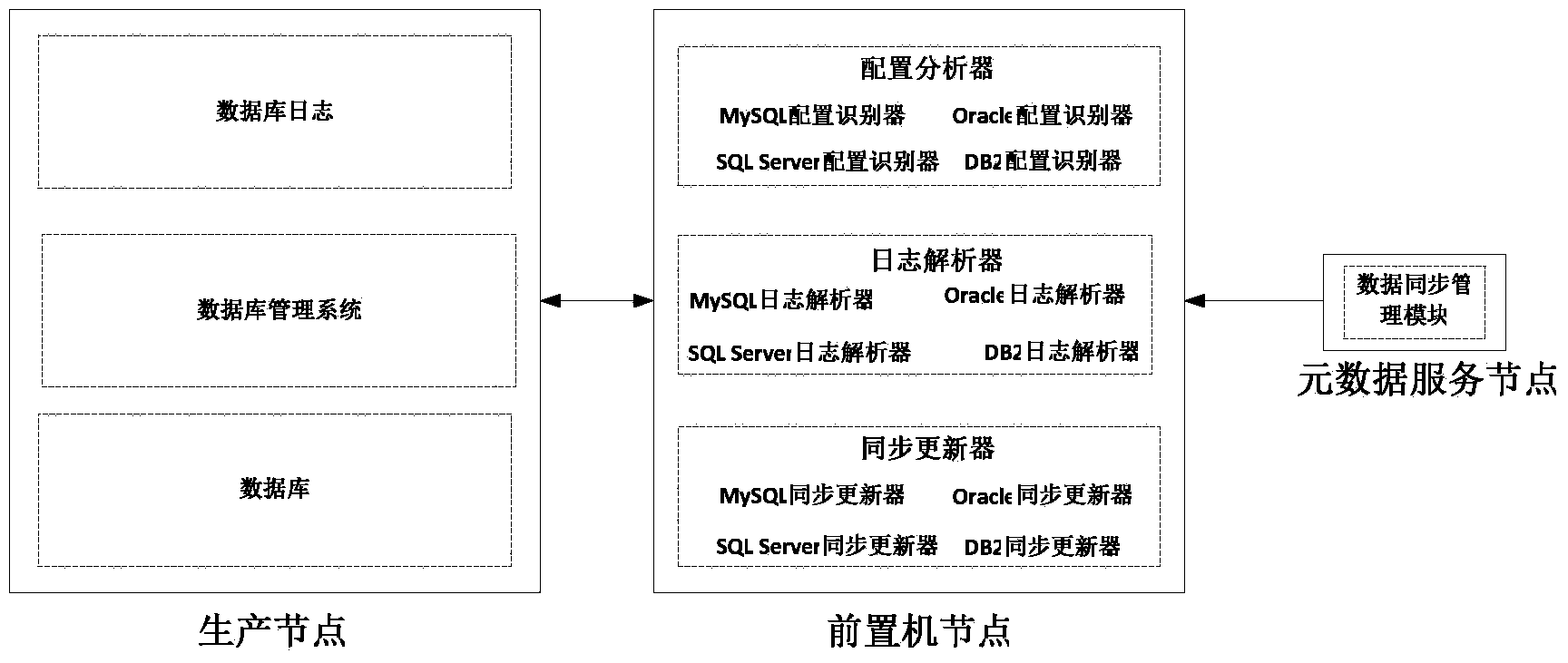

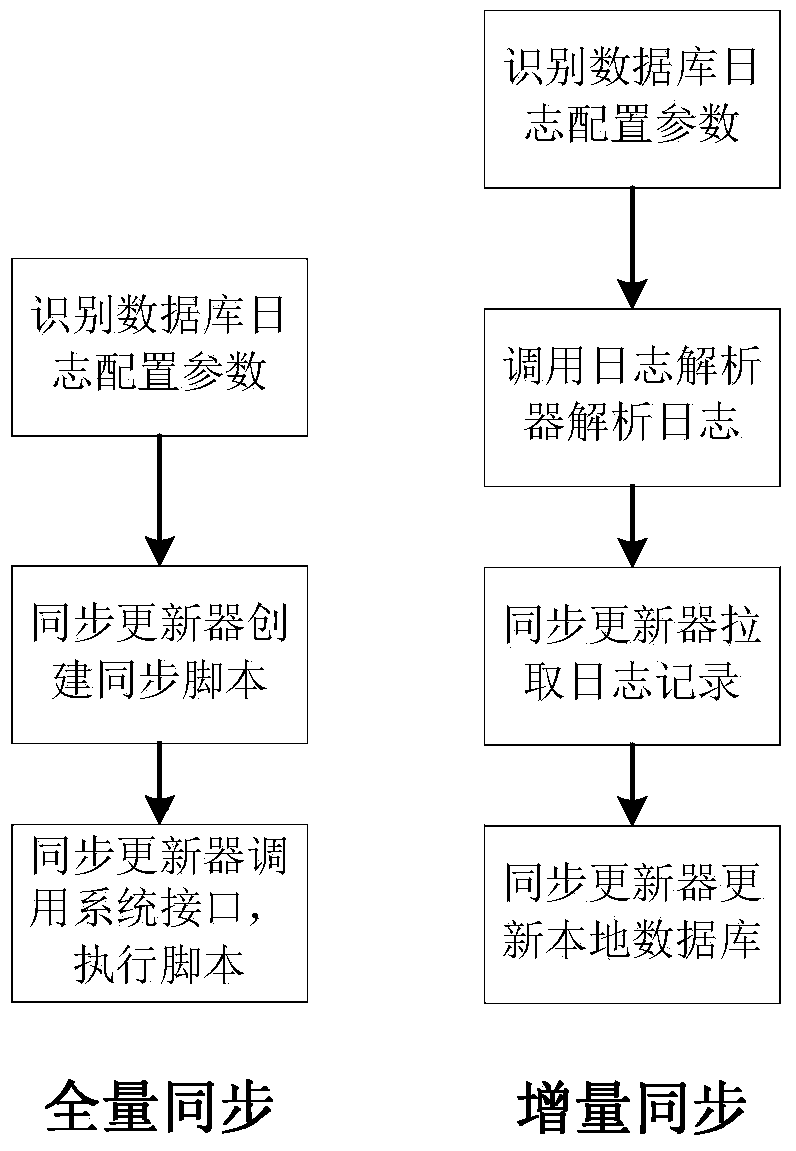

Method for achieving automatic synchronization of multi-source heterogeneous data resources

ActiveCN103617176AAchieve synchronizationReduce configuration difficultySpecial data processing applicationsData synchronizationComputer science

The invention relates to a method for achieving automatic synchronization of multi-source heterogeneous data resources. A metadata service node, a service node and a production node are related in the method, the metadata service node is responsible for storing a data dictionary in a distributed heterogeneous database system, the service node is responsible for analyzing user requests in the distributed heterogeneous database system and carrying out synchronization with a database on the production node periodically, and the production node is responsible for requests such as inquiring and updating in a corresponding production application system, wherein the service node is formed by a configuration recognizer, a blog parser and a data synchronizer, the configuration recognizer is used for analyzing the configuration of a source database on the production node and selecting a feasible synchronizing mode, the blog parser is used for analyzing blogs of different dataset systems and is a component for first-phase preparing work of an increment synchronization mode, and the data synchronizer carries out data synchronization according to the synchronizing mode of the configuration recognizer. The method for achieving the automatic synchronization of the multi-source heterogeneous data resources enables the automatic synchronization of the multi-source heterogeneous data resources to be achieved, and can be used in data resource processing.

Owner:GUANGDONG ELECTRONICS IND INST

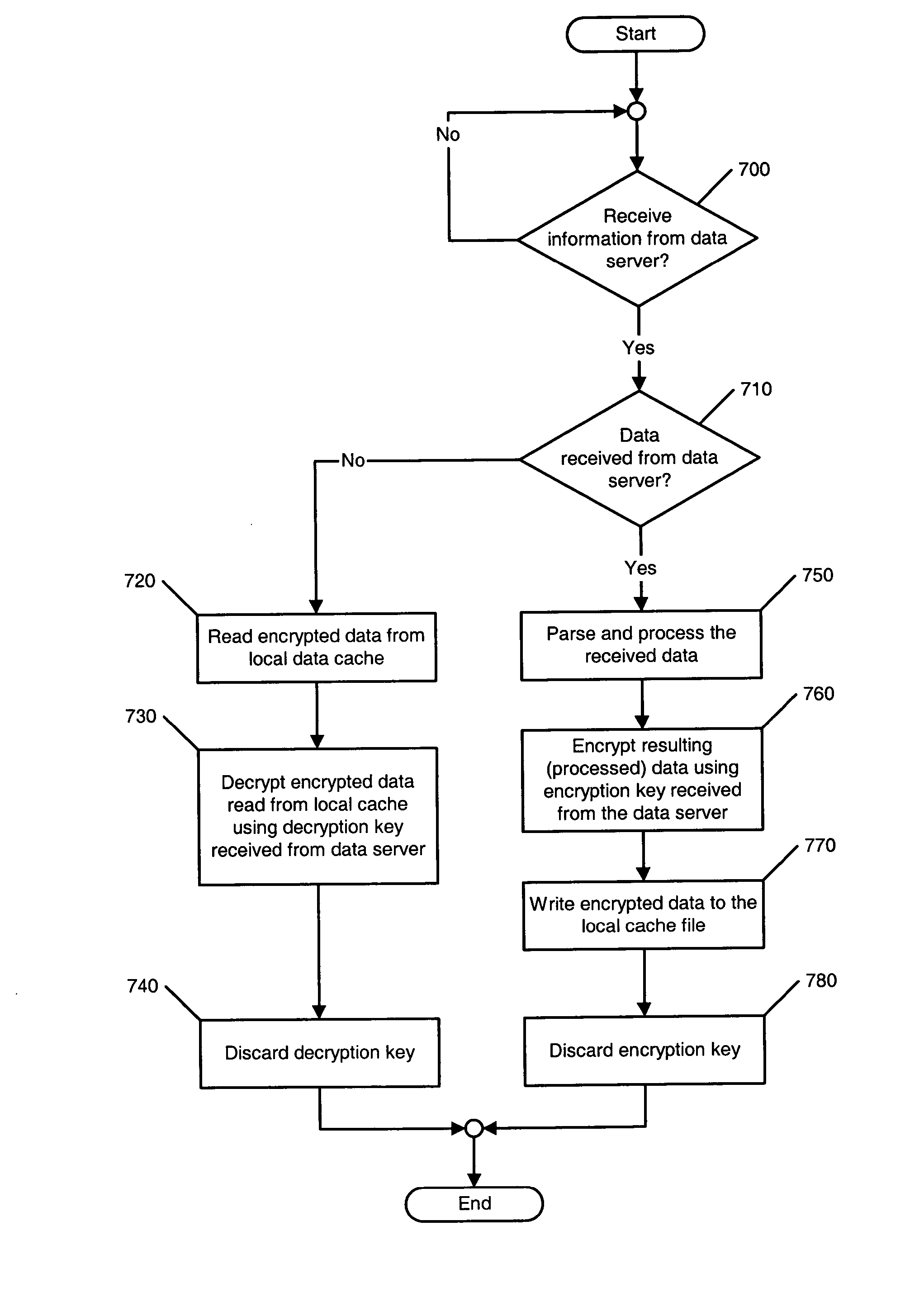

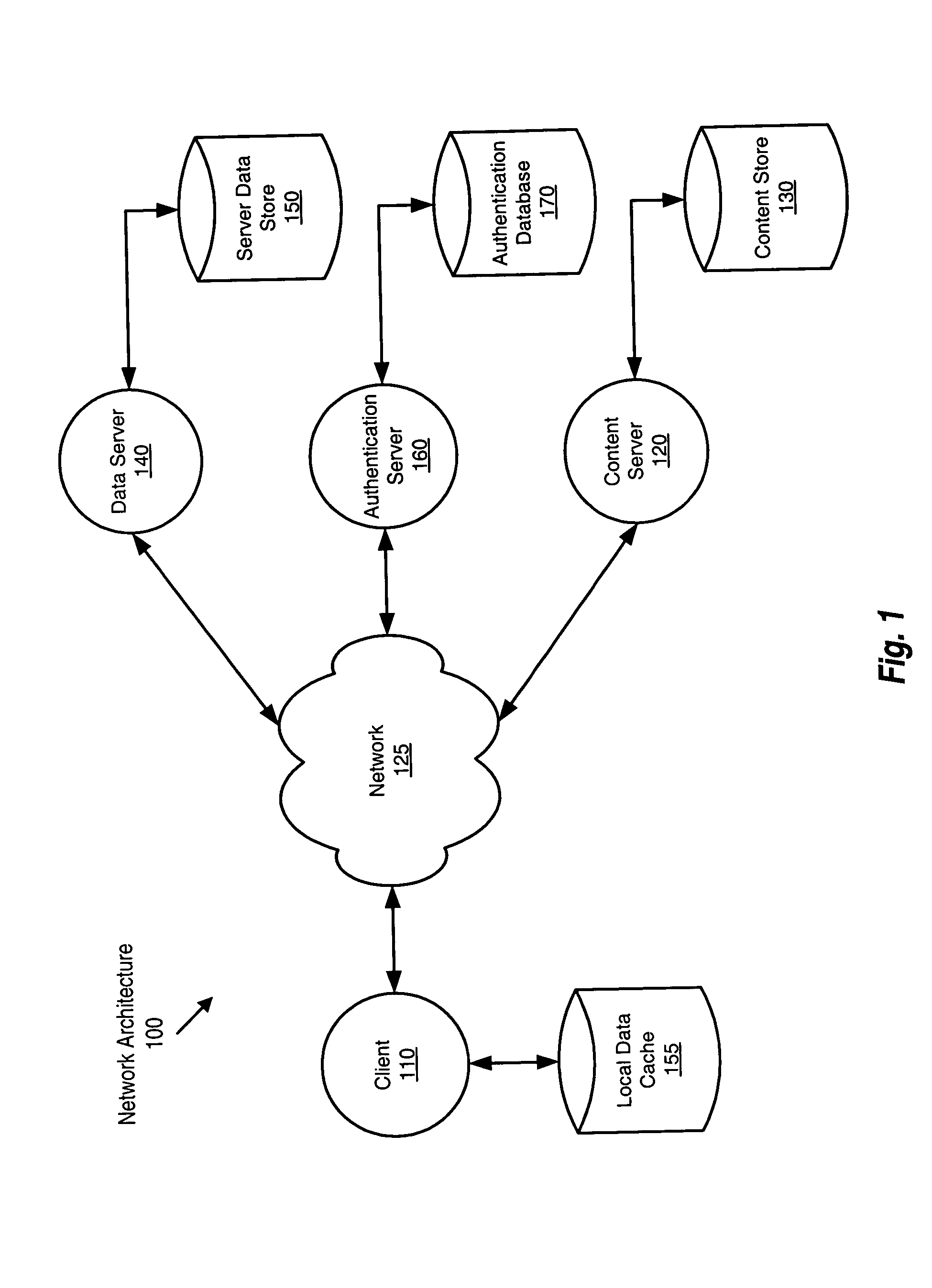

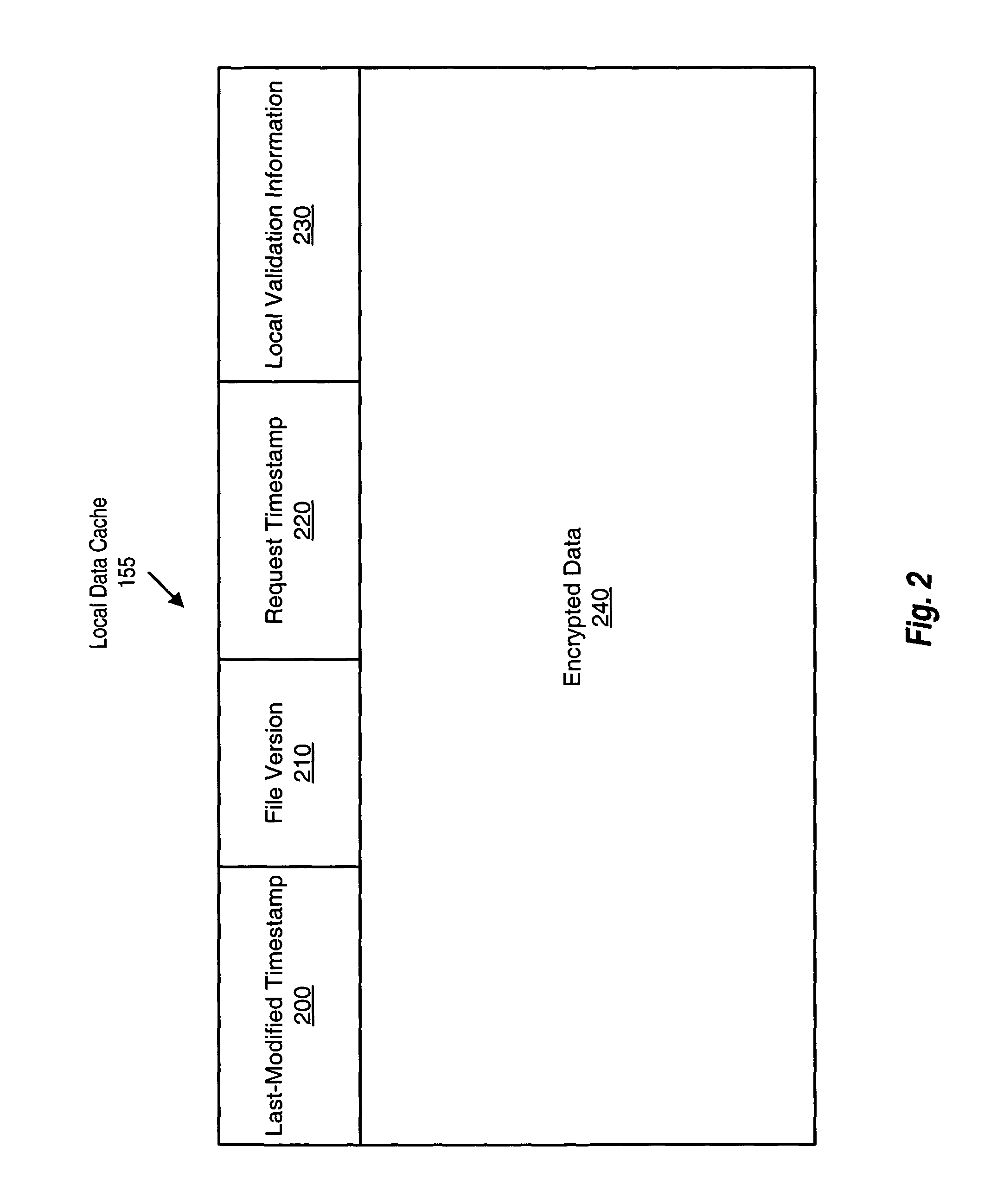

Method and system for maintaining synchronization between a local data cache and a data store

ActiveUS20050050067A1Quick and efficient accessAdversely impacting network resourceData processing applicationsDigital data information retrievalData memoryData storing

A method and system for maintaining synchronization between a local data cache and a data store is disclosed. The method includes comparing first validation information and second validation information, and synchronizing first data stored in a local data cache with second data stored in a data store, if the comparison indicates that the synchronizing is needed.

Owner:ENERGETIC POWER INVESTMENT

Safe start-up of a network

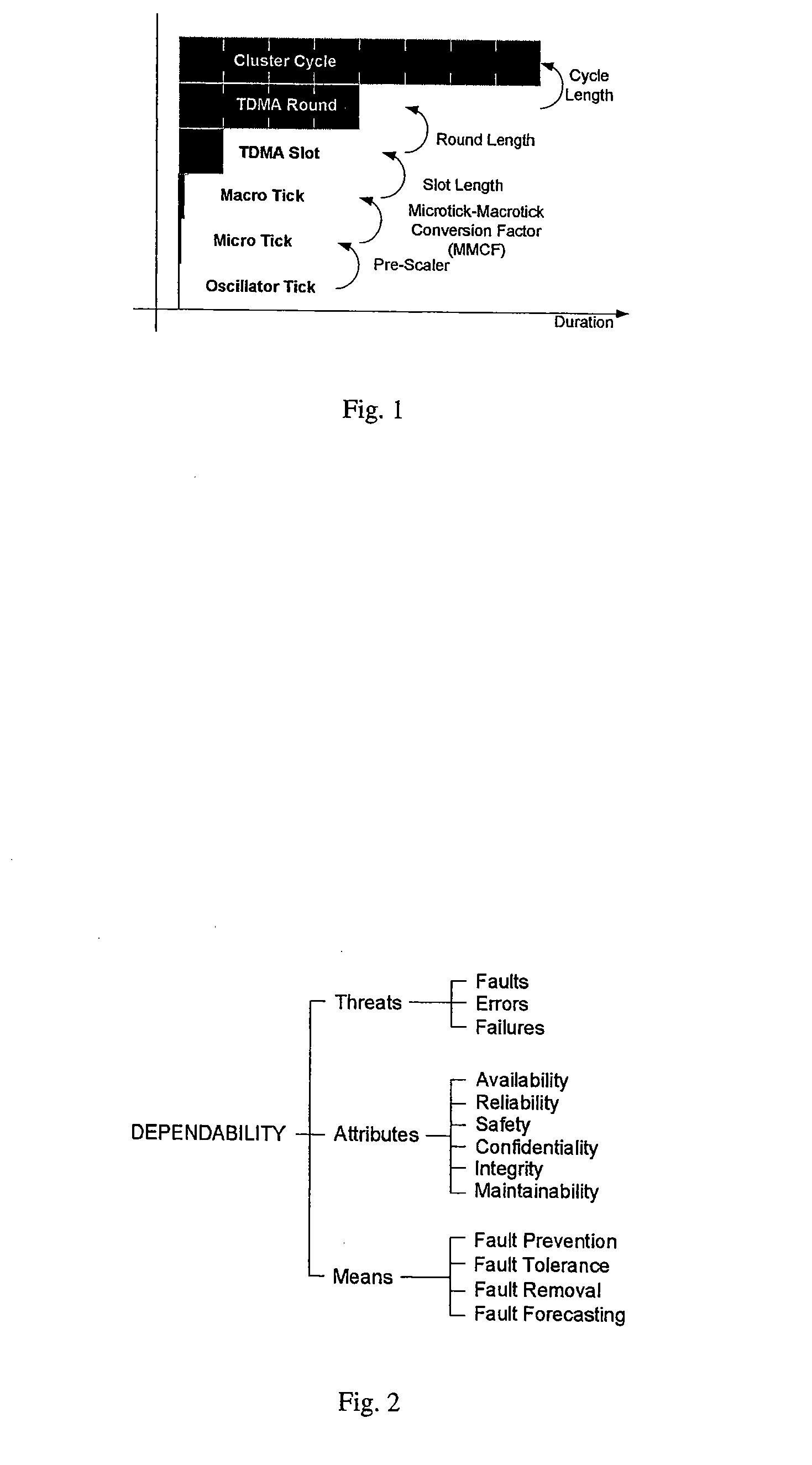

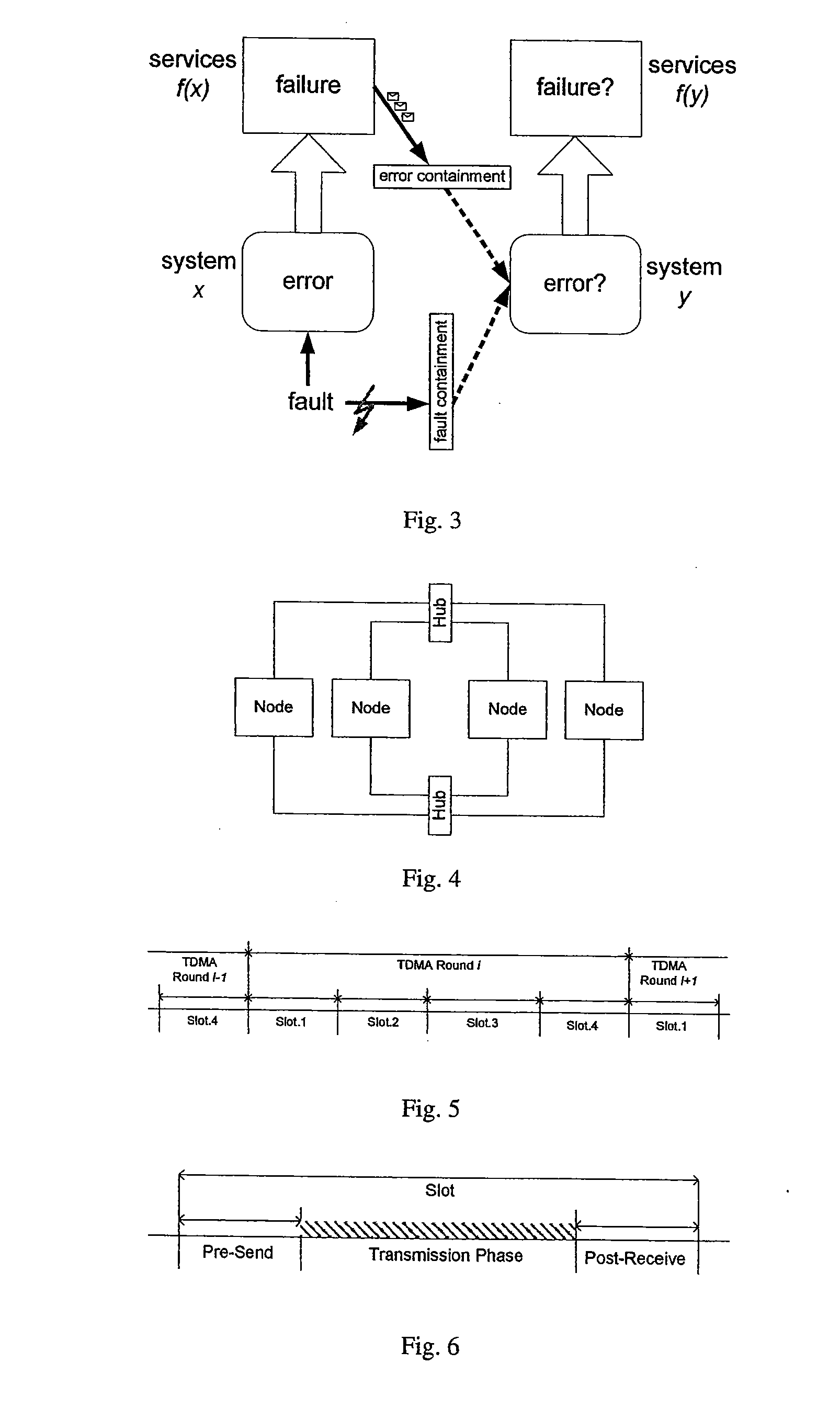

ActiveUS20090122812A1Time-division multiplexSynchronisation signal speed/phase controlStart upSynchronizing

A method for start-up of a network, including a number of nodes, which are connected via channels. The nodes exchange information in the form of messages via the channels. The transition phase of a synchronizing node from its initial phase to a synchronized phase is separated in a first integration phase and a second subsequent cold-start phase. A synchronizing node in the integration phase listens to messages being sent from nodes in the synchronized phase and only reacts to an integration message (i-frame) if the integration message is a valid message. Furthermore, a synchronizing node, wherein integration of the synchronizing node to a set of already synchronized nodes was not successful after a specifiable period, changes into the cold-start phase, in which a cold-start procedure of the node is extracted, wherein in the cold-start phase the node does not react to integration messages of a node in the synchronized phase.

Owner:HONEYWELL INT INC

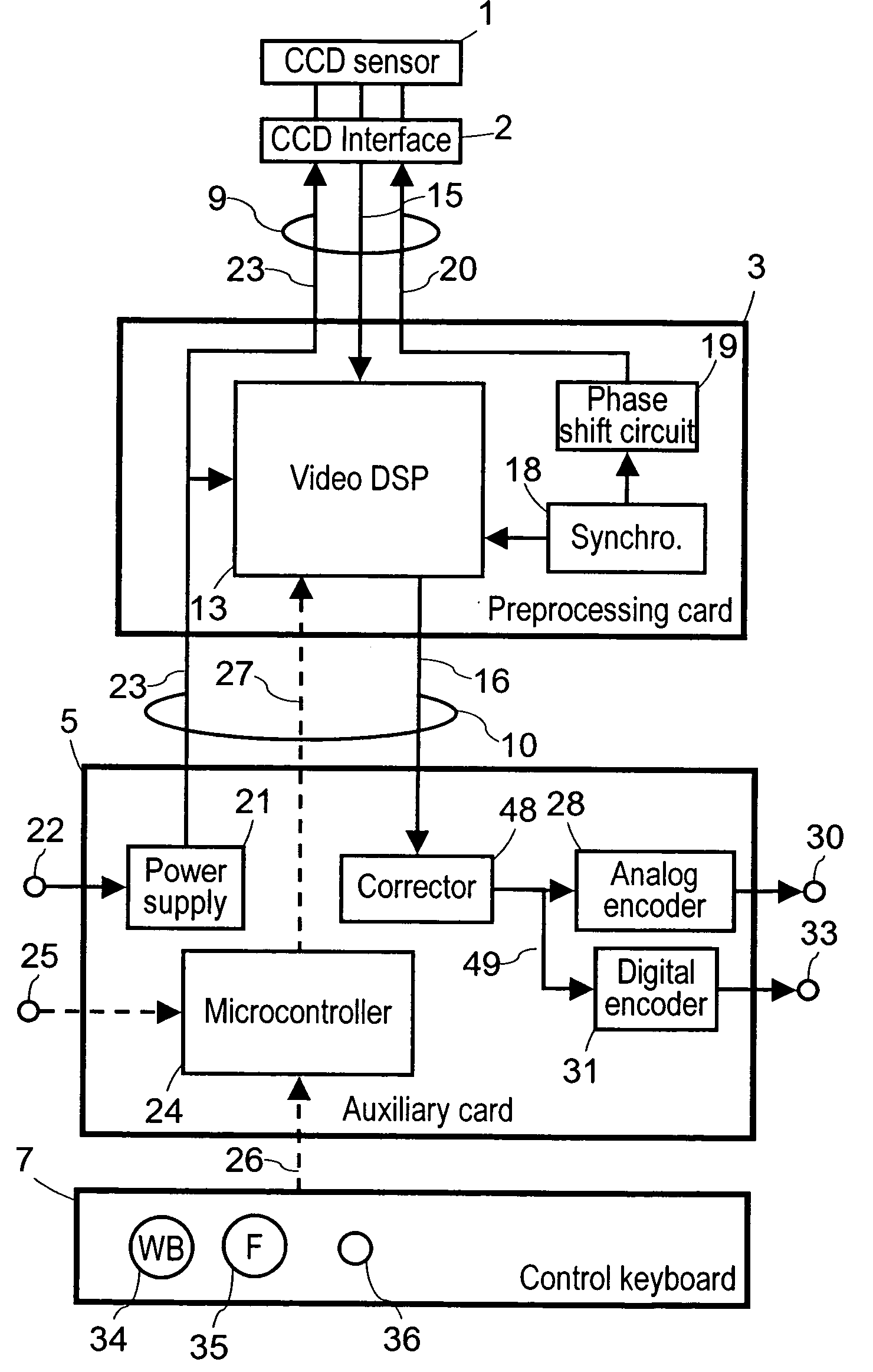

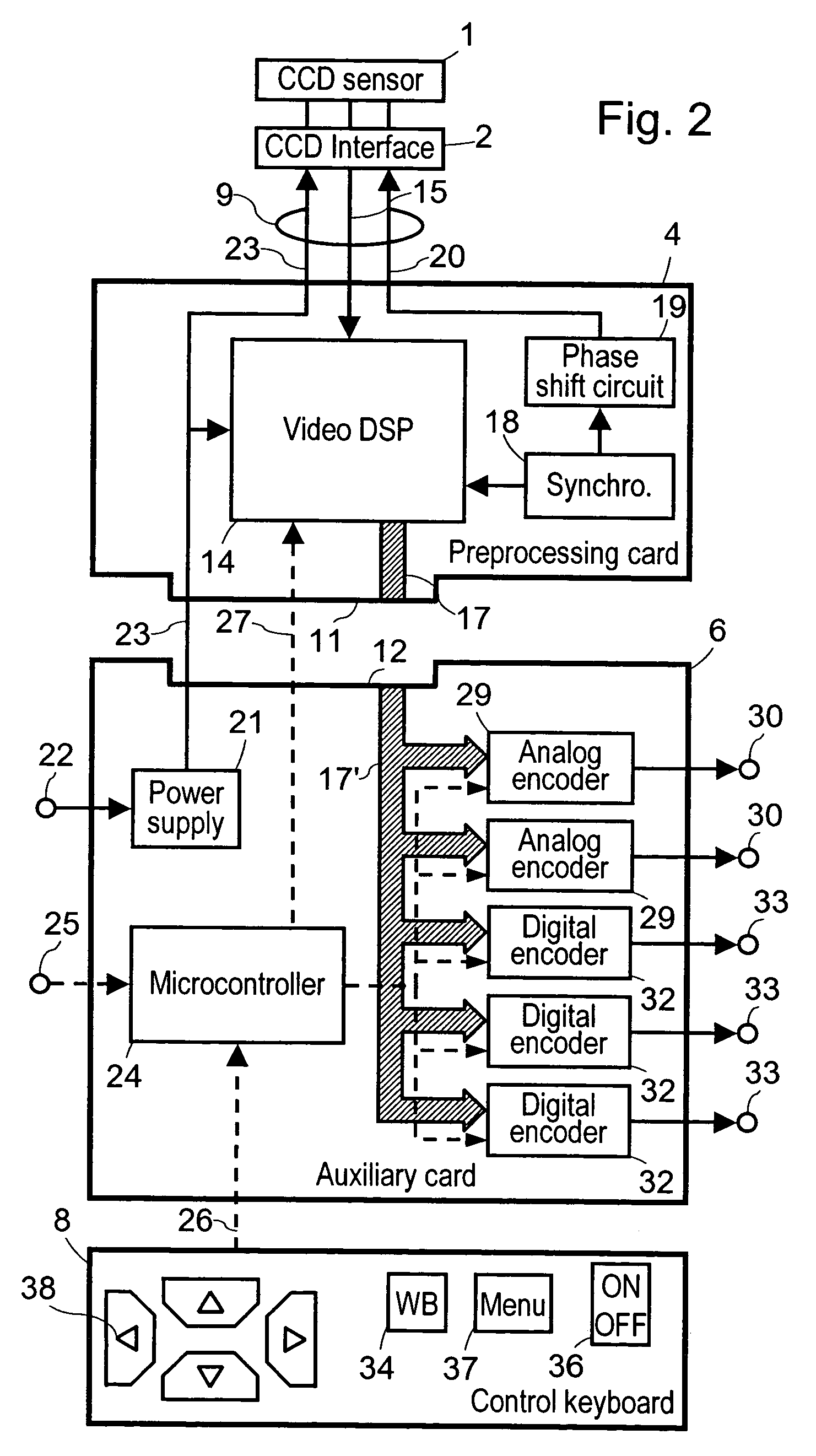

Video processor for endoscopy

InactiveUS20050018042A1Improve immunityEndoscopesColor television detailsFlexible endoscopeEndoscopic camera

A video processor for endoscopic camera or for videoendoscopic probe associated with a color video sensor, the video processor comprising: a signal preprocessing circuit designed to be remotely connected to the video sensor through an electrical link without any intermediate connection device, the preprocessing circuit comprising a first signal processor for generating from image signals output by the video sensor raw video signals comprising a brightness signal and a color signal, these signals being not usable directly because they are phase shifted and are noisy due to synchronization residues, and a synchronizing circuit for synchronizing the video sensor and the first signal processor; and a remote auxiliary circuit comprising a second signal processor connected to the first signal processor through a low impedance electrical link providing good immunity to interference, the second signal processor generating from said raw video brightness and color signals at least one useful video signal according to an international video standard.

Owner:TOKENDO

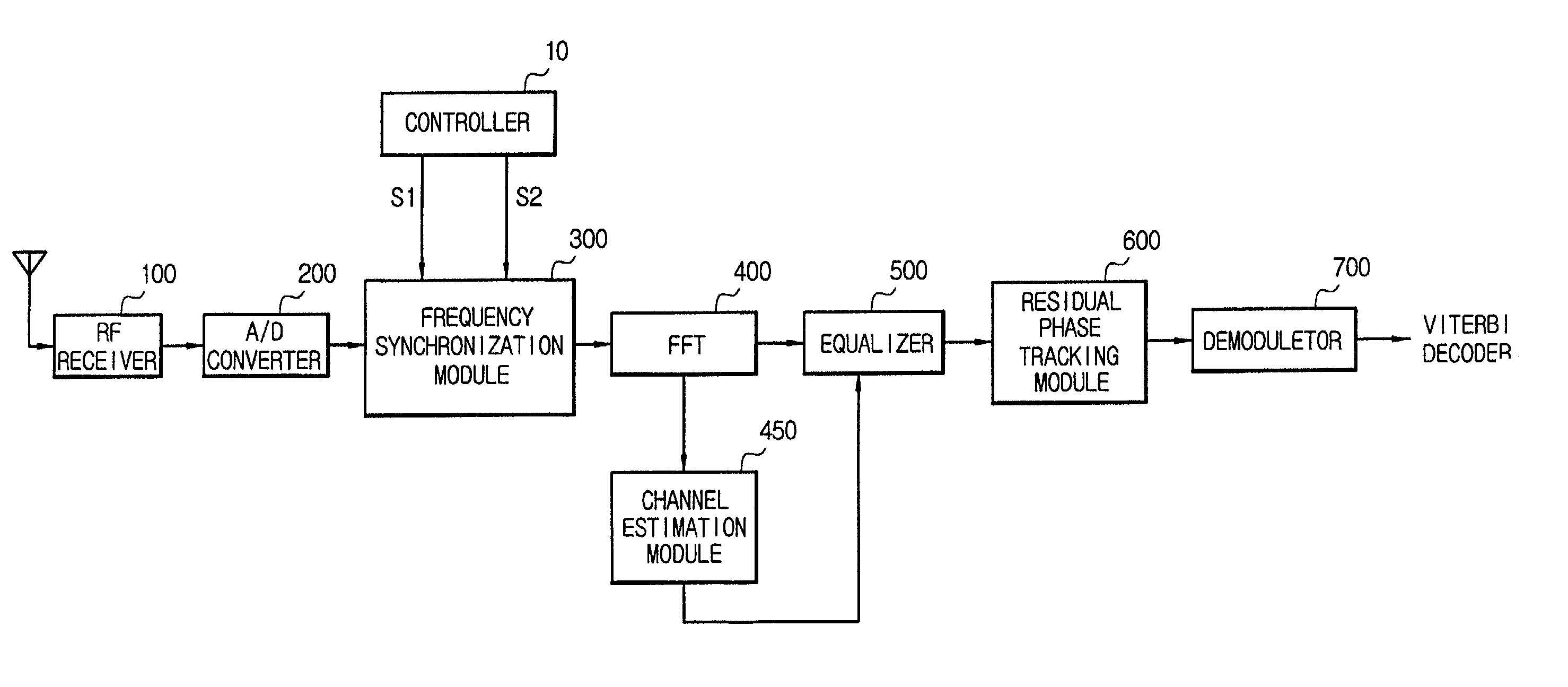

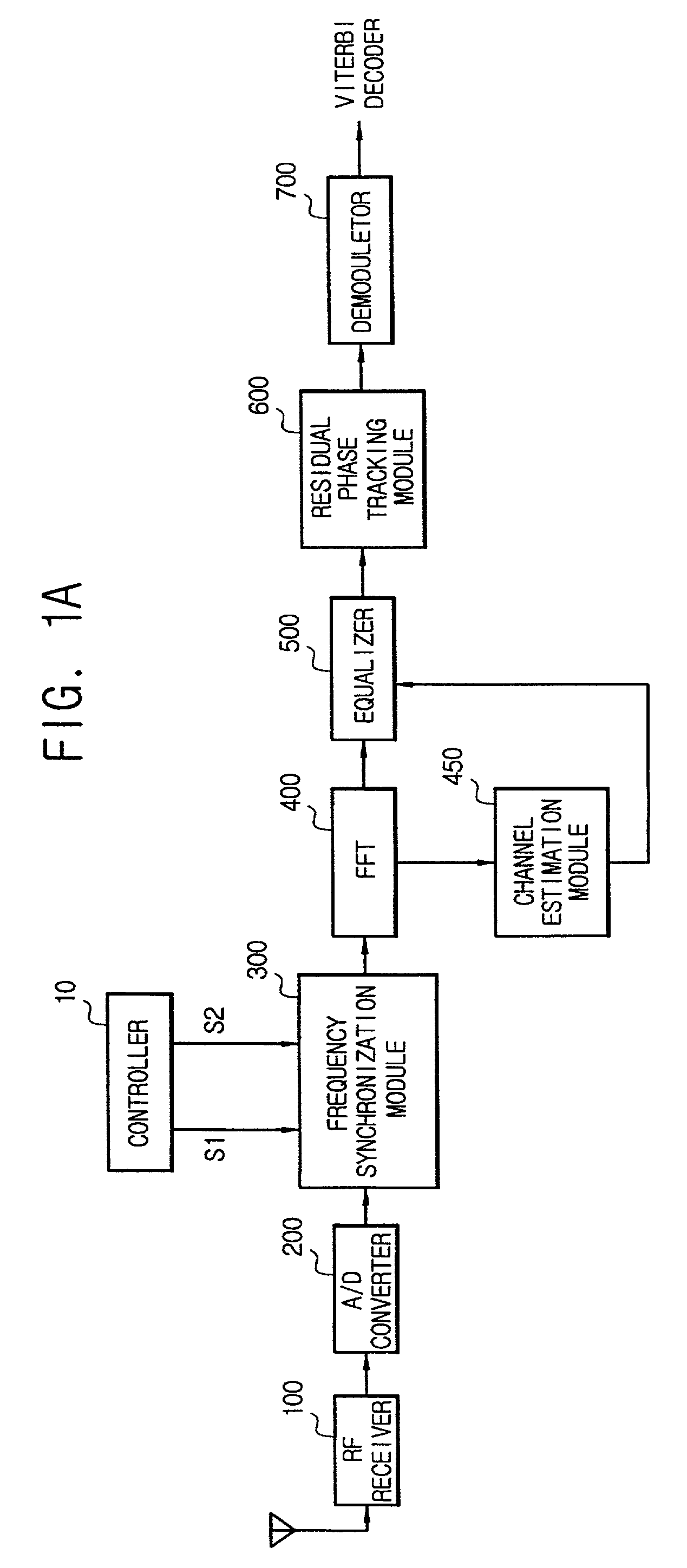

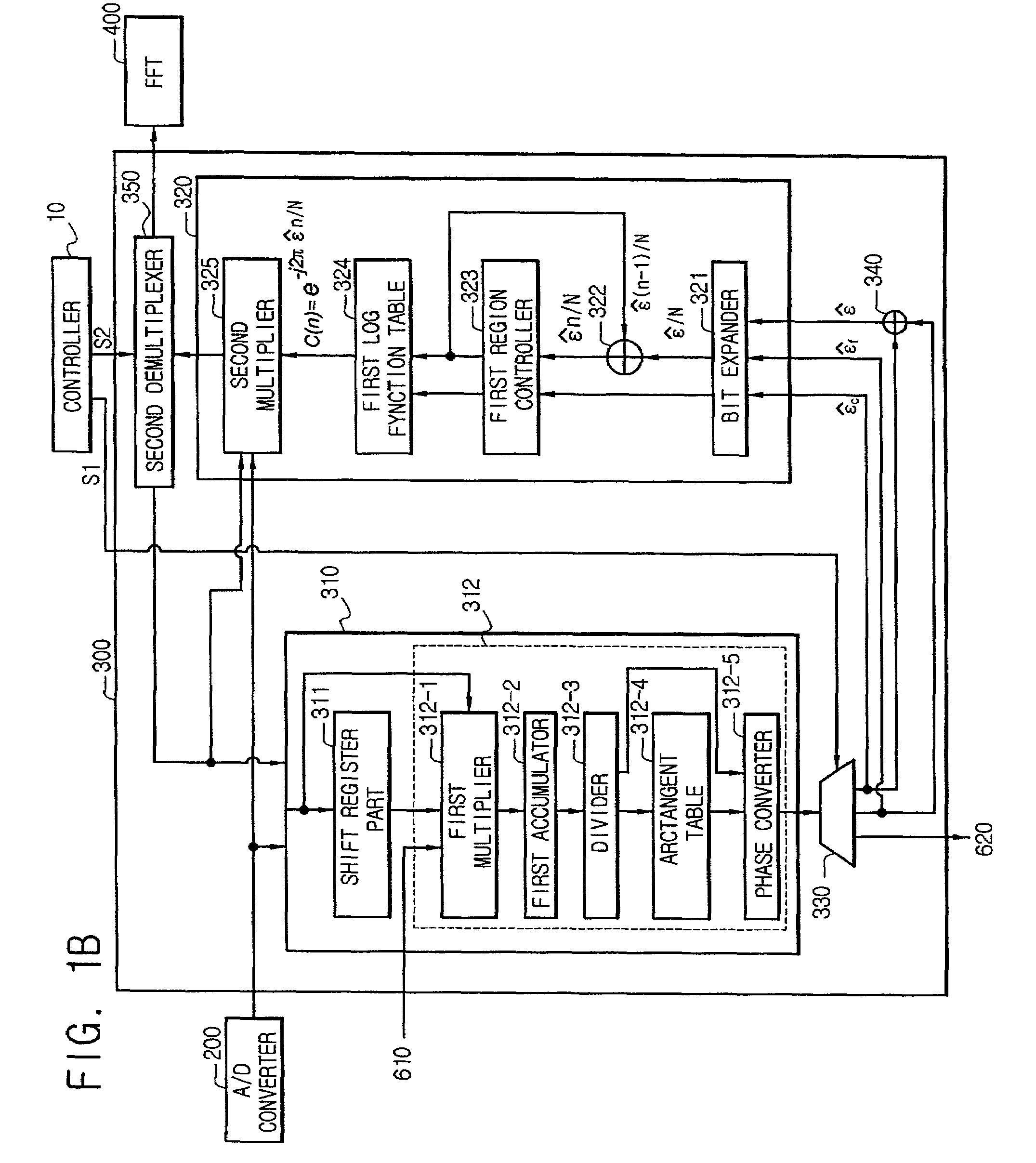

Apparatus and method for synchronizing frequency in orthogonal frequency division multiplexing communication system

InactiveUS7068593B2Accurate estimateImprove accuracyAmplitude-modulated carrier systemsSecret communicationFast Fourier transformCommunications system

A frequency synchronization apparatus for an orthogonal frequency division multiplexing (OFDM) communication system includes a radio frequency (RF) receiving module for receiving OFDM signal, an analog / digital (A / D) converter connected to the RF receiving module, the A / D converter converting the OFDM signal into a digital signal, a frequency synchronization module connected to the A / D converter, the frequency synchronization module synchronizing carrier frequency, a Fast Fourier Transformer (FFT) connected to the frequency synchronization module, the FFT performing fast Fourier transformation to symbols from the frequency synchronization module, a channel estimation module connected to the FFT, the channel estimation module estimating channel response, an equalizer connected to the FFT and the channel estimation module, the equalizer equalizing channel, a residual phase tracking module connected to the equalizer, the residual phase tracking module tracking residual phase, a demodulator connected to the residual phase tracking module, the demodulator demodulating, and a controller connected to the frequency synchronization module, the controller controlling the frequency synchronization module.

Owner:CHUNG ANG UNIV IND ACADEMIC COOP FOUND

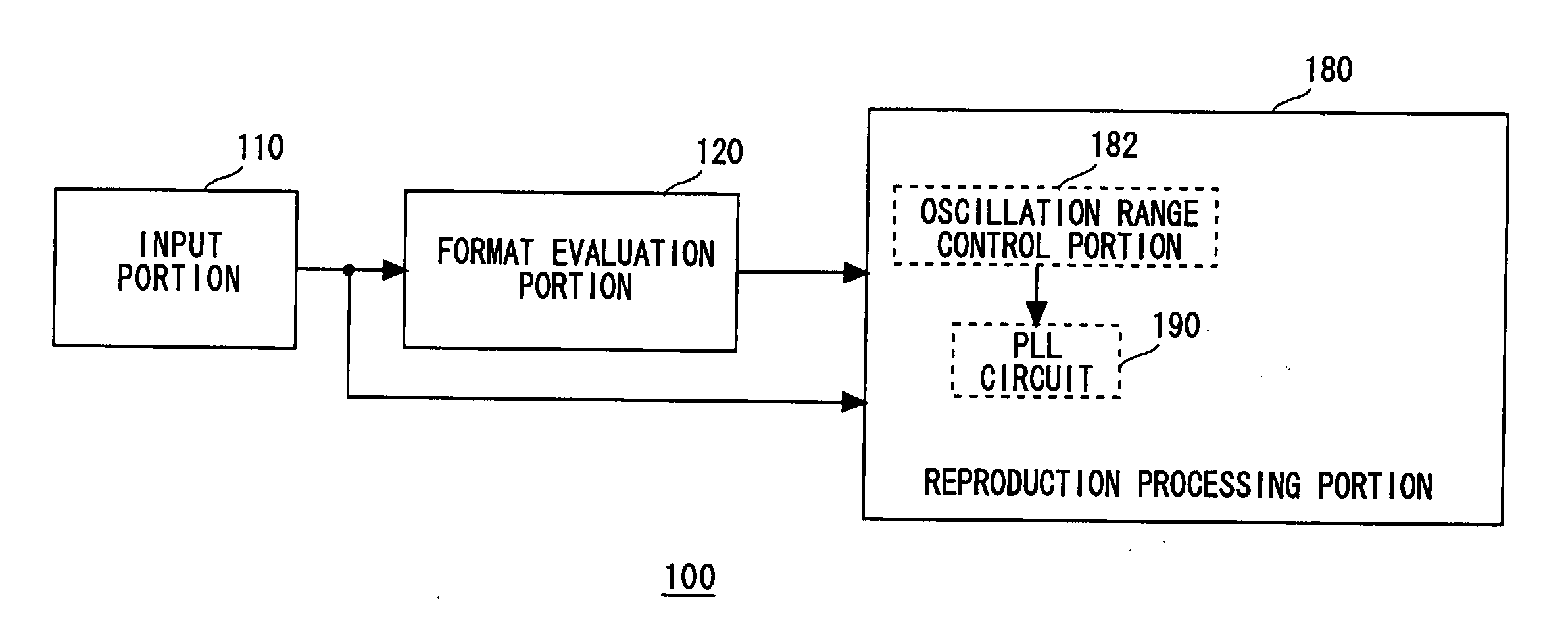

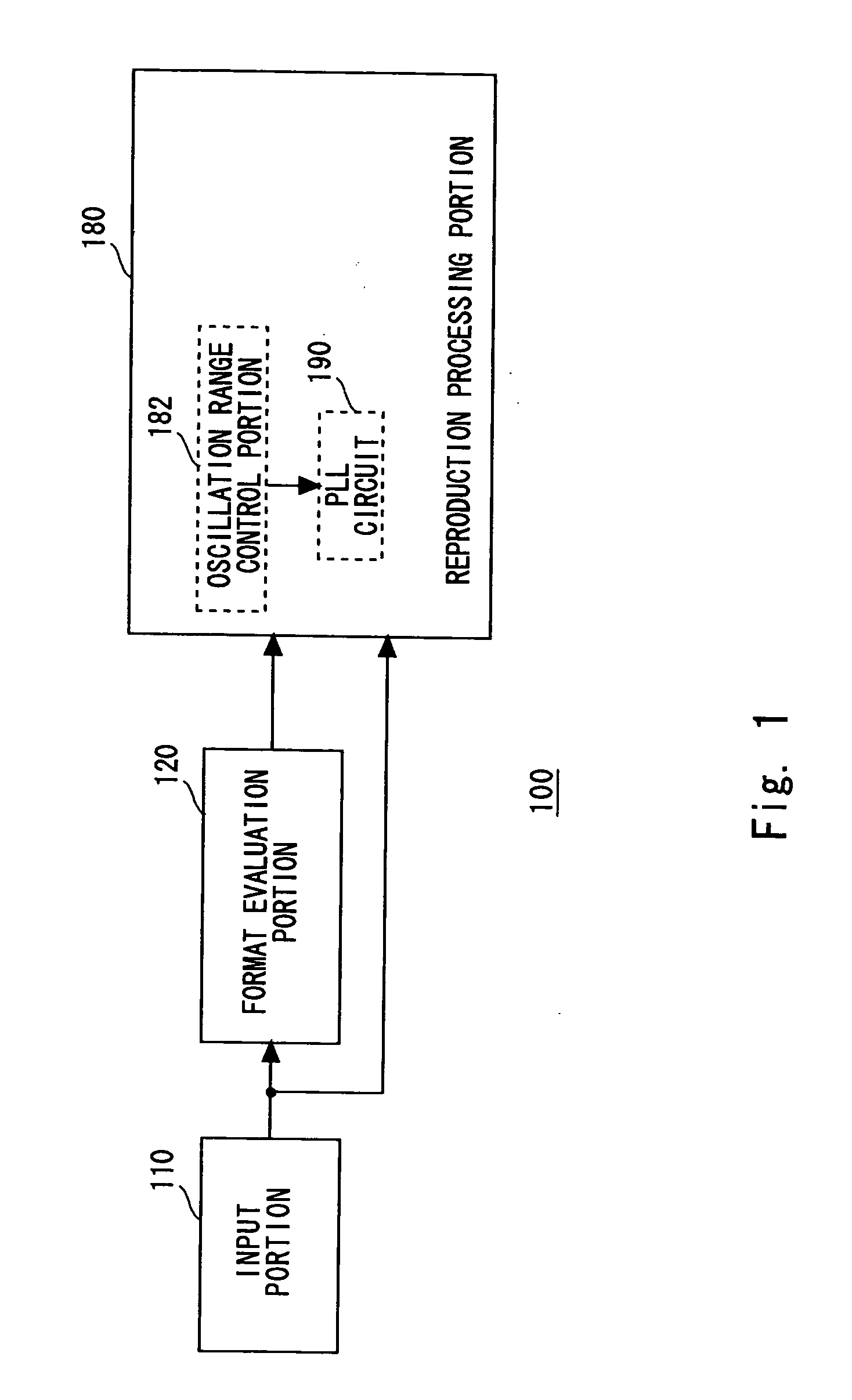

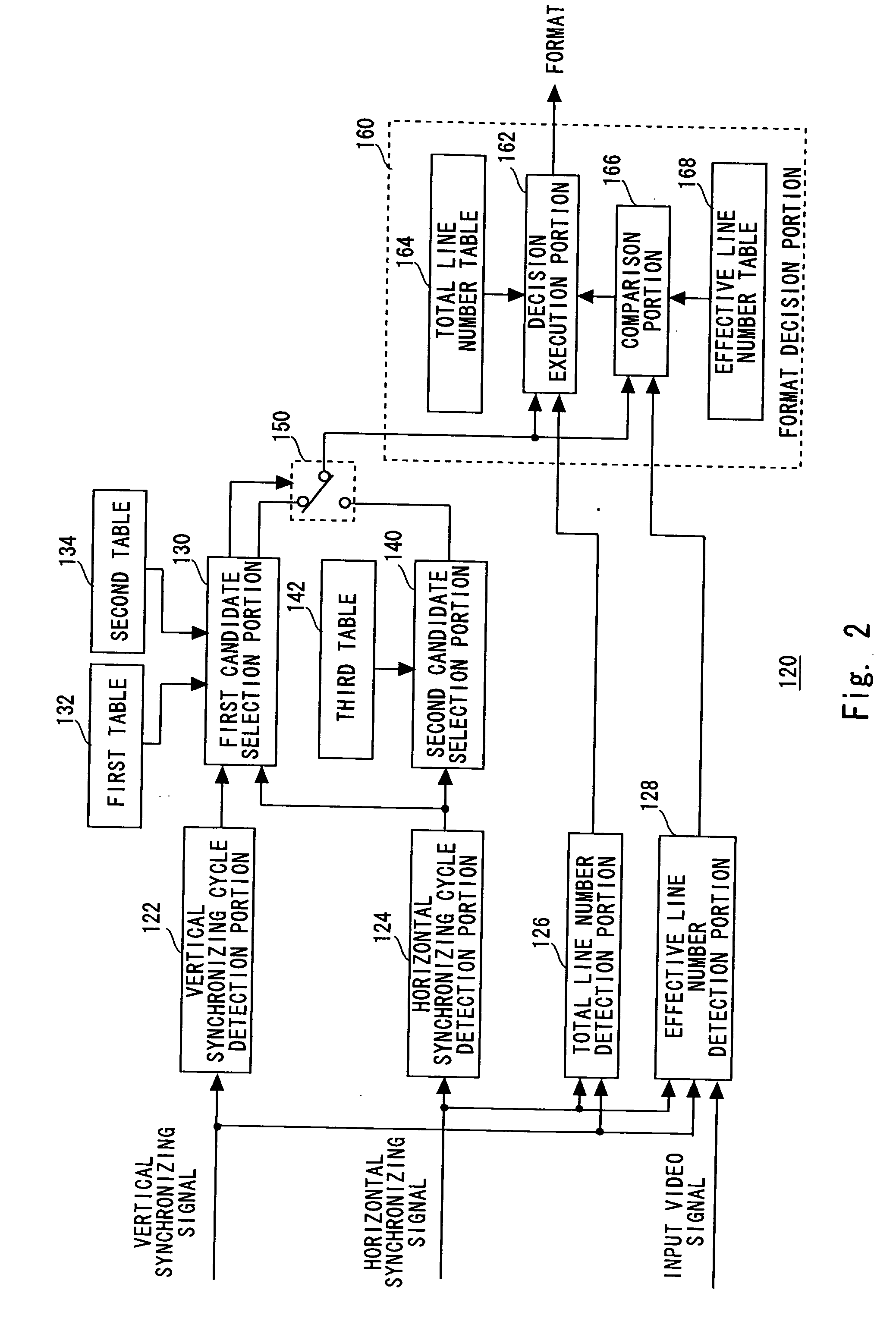

Signal processing device

InactiveUS20090079870A1Efficiently signaledTelevision system detailsTelevision system scanning detailsComputer graphics (images)Signal processing

A first candidate selection portion 130 selects format candidates based on the horizontal synchronizing cycle and the vertical synchronizing cycle of an input video signal. A second candidate selection portion 140 selects formats having the tolerance ranges for the horizontal synchronizing cycles within which the horizontal synchronizing cycle of the input video signal falls as format candidates. A format decision portion 160 determines the format of the input video signal from format candidates from the first candidate selection portion 130 when format candidate(s) is obtained by the first candidate selection portion 130, and determines the format of the input video signal from format candidates selected by the second candidate selection portion 140 when no format candidate is obtained by the first candidate selection portion 130.

Owner:NEC ELECTRONICS CORP

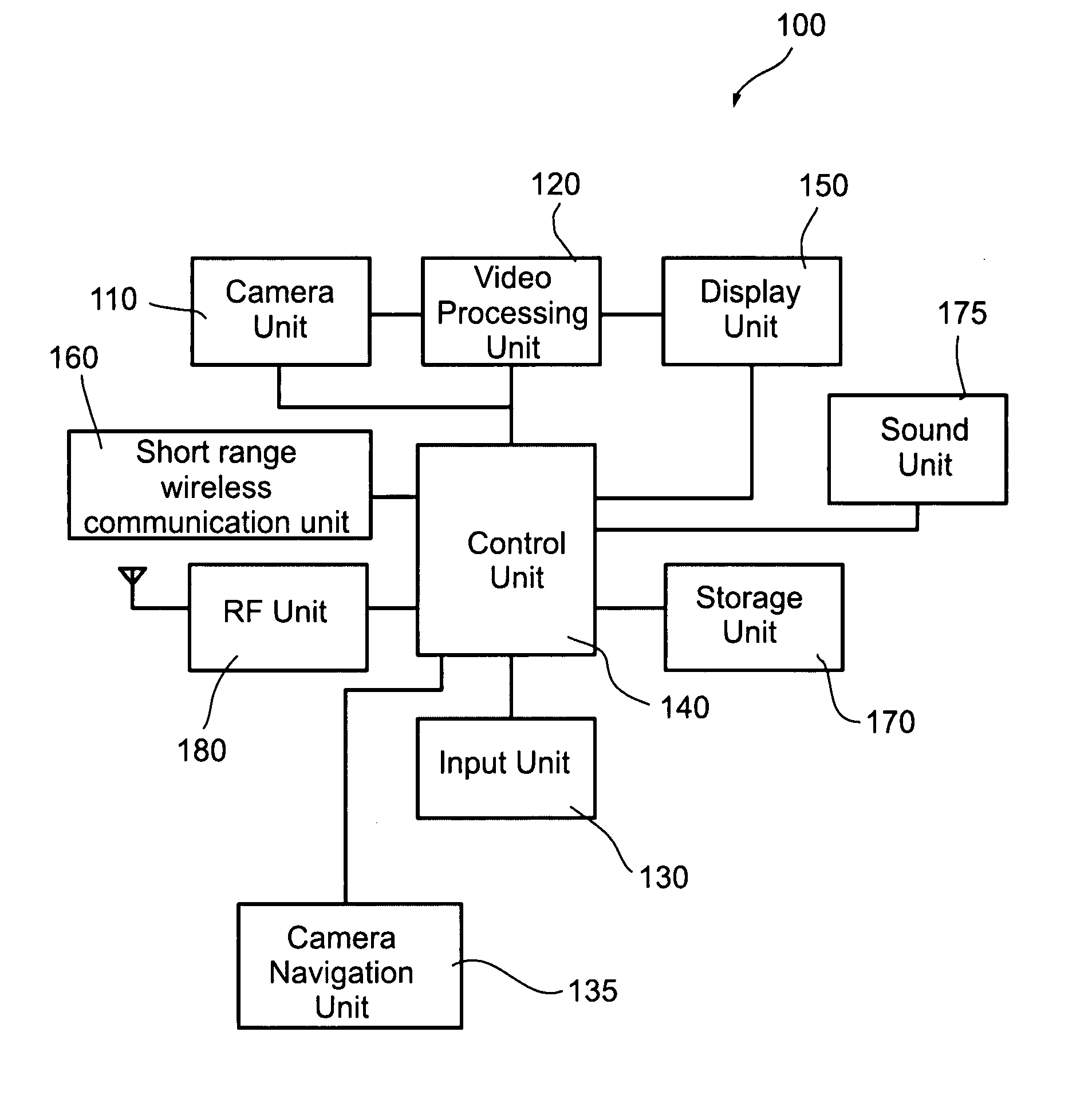

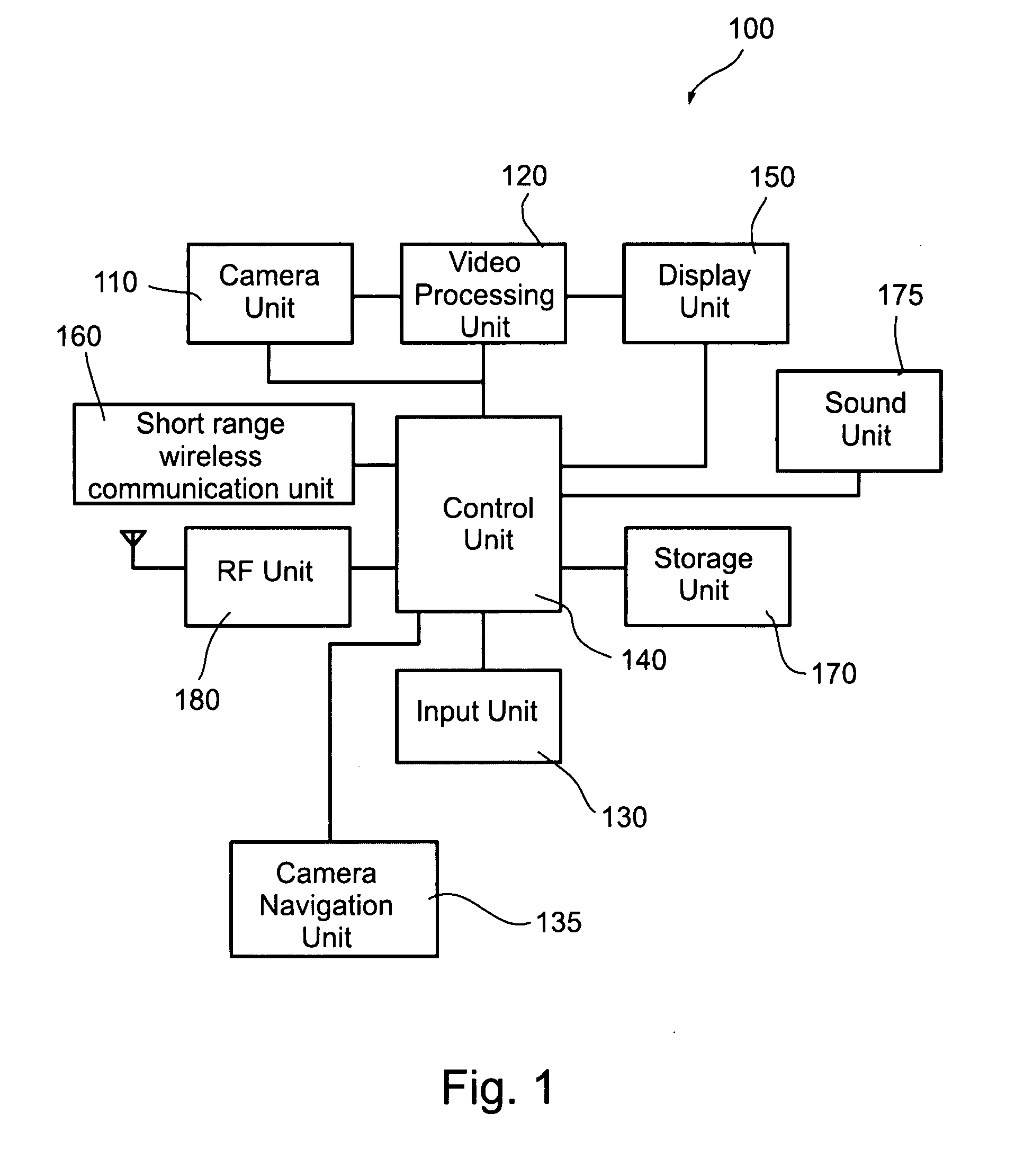

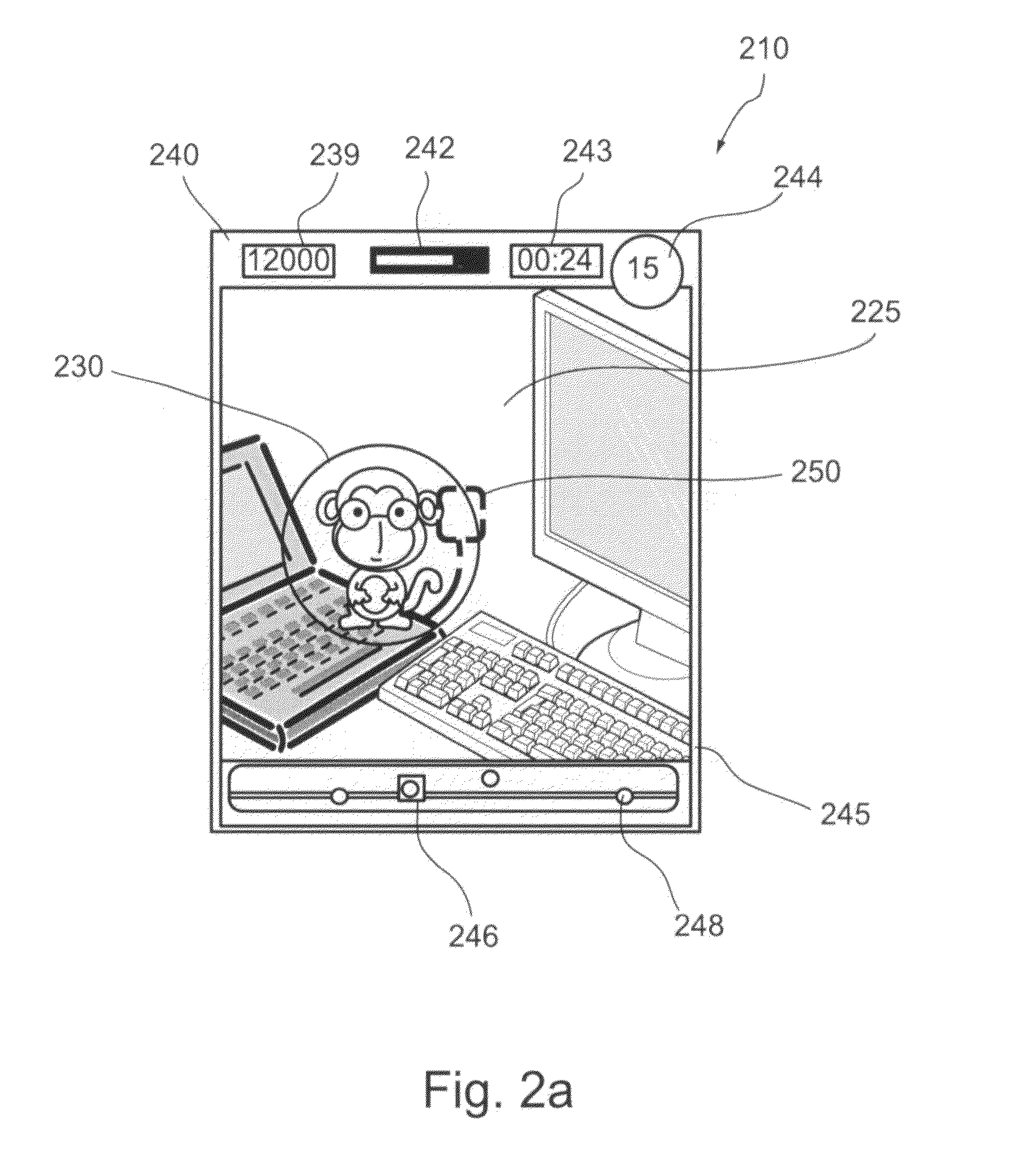

Wireless gaming method and wireless gaming-enabled mobile terminal

InactiveUS20080280676A1Without additional communication costData switching by path configurationApparatus for meter-controlled dispensingComputer terminalBackground image

A wireless gaming method and wireless gaming-enabled mobile terminal are provided for enabling a number of players to participate simultaneously in a game using their mobile terminals. A wireless gaming method of the present invention includes inviting, if a multi-player gaming mode for a game is activated, at least one counterpart terminal on a short range wireless communication network by transmitting a multi-player gaming mode request message; synchronizing, if an acknowledge message is received in response to the multi-player gaming mode request message, game data with the counterpart terminal transmitted the acknowledge message; and generating a game screen with an image taken by the camera as a background image after the game is synchronized; and starting the game with the game screen.

Owner:SAMSUNG ELECTRONICS CO LTD

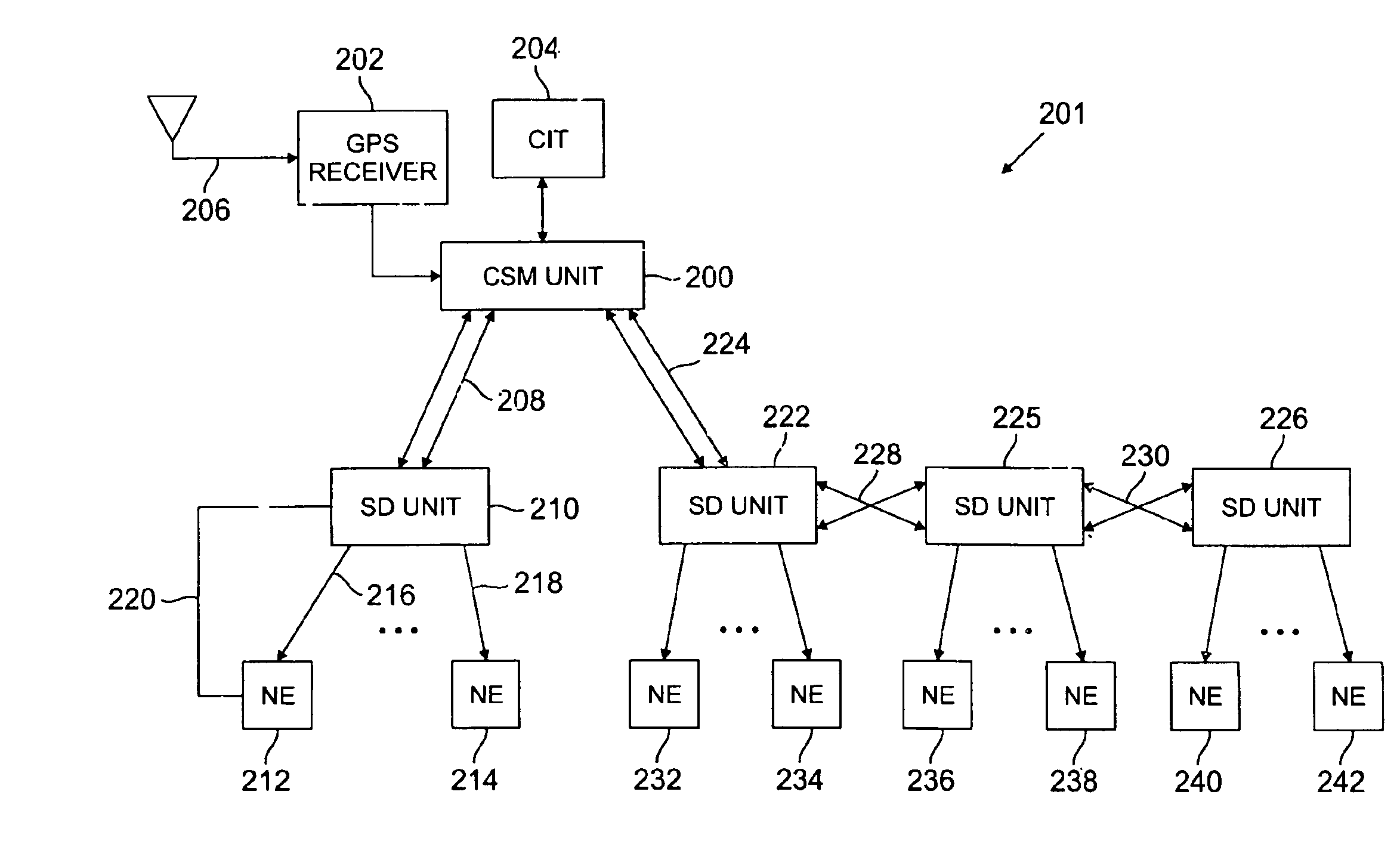

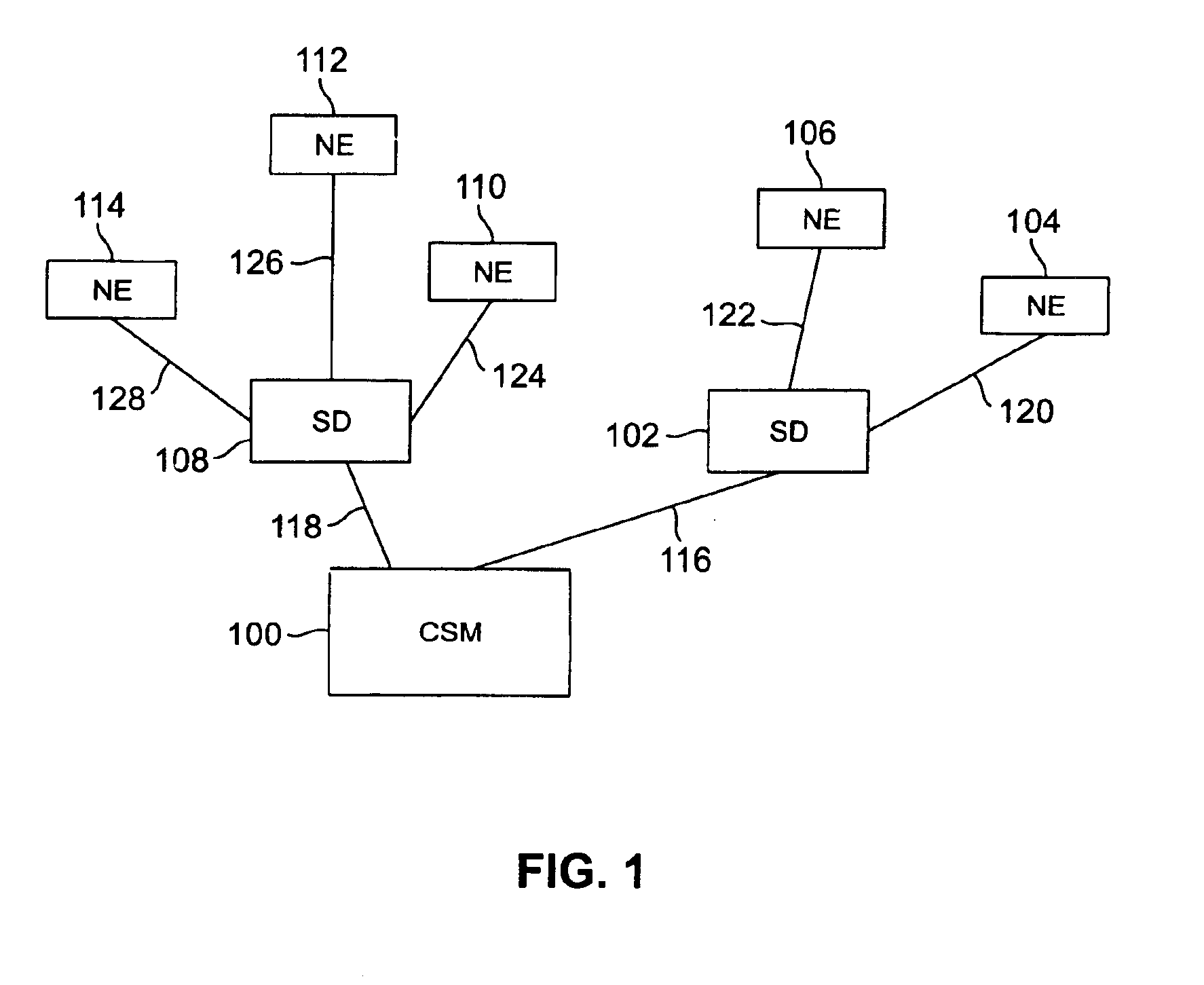

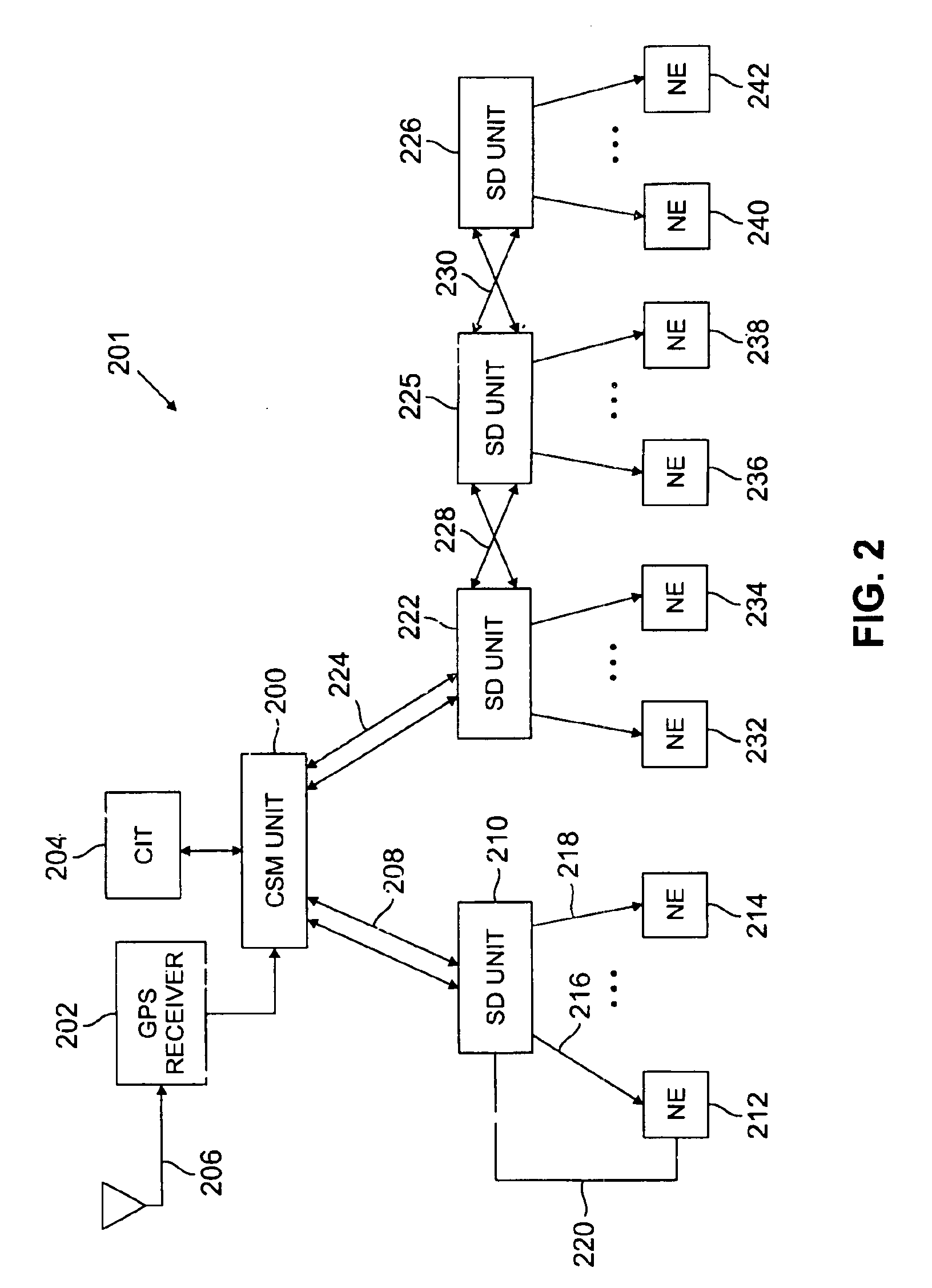

Optical synchronization system

InactiveUS6895189B1Ensure viabilityLow costTime-division optical multiplex systemsTime-division multiplexManagement unitSynchronization system

A synchronization system in accordance with the principles of the invention includes a central synchronizing management unit, at least one synchronization distribution unit, and at least one network element. Each synchronization distribution unit receives synchronization and management information from the central synchronization management unit. This information may be transmitted directly from the central synchronization management unit, or it may be transmitted though another synchronization distribution unit in a group of a daisy-chained synchronization distribution units. The daisy-chained arrangement employs both active and passive optical paths. The central synchronizing management unit may query any synchronization distribution unit within the system to obtain performance statistics. Additionally, the central synchronizing management unit may detect faults within the system by setting performance monitoring thresholds and interrogating a synchronization distribution unit to determine whether a threshold has been exceeded. The synchronization distribution units are physically located in close proximity to the network elements they serve. Additionally, the management and synchronization information exchanged between the central synchronization unit and a synchronization distribution unit is carried over a bidirectional optical link.

Owner:LUCENT TECH INC

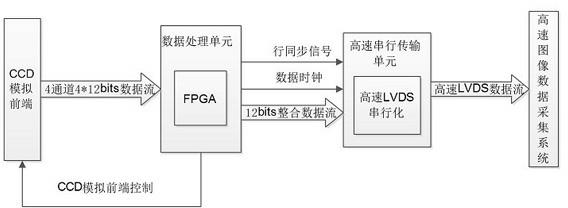

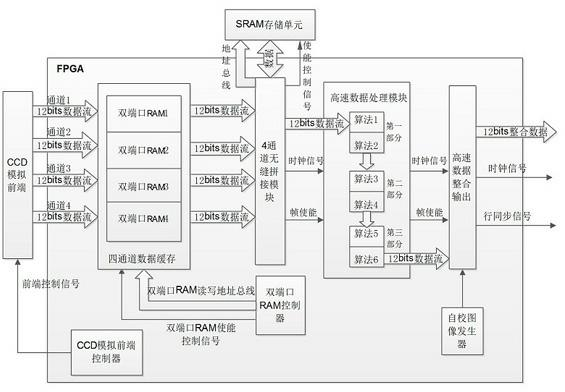

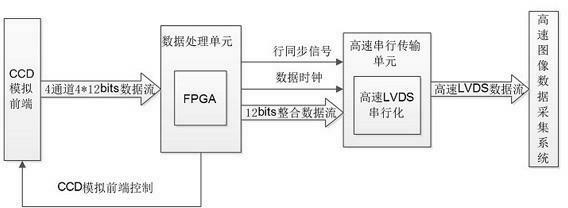

Data processing and transmitting system of high-speed multichannel CCD (charge-coupled device)

InactiveCN102638661AReal-time processingReduce in quantityTelevision system detailsPulse modulation television signal transmissionSerial transferData stream

The invention discloses a data processing and transmitting system of high-speed multichannel CCD (charge-coupled device), which comprises a CCD analog front end, a data processing unit, a high-speed serial transmission unit and a high-speed image data collection system which are sequentially connected. The CCD analog front end is used for converting an analog signal output by a CCD detector and subjected to sampling and pulse control into n channels of digital image data via n A / D (analog / digital) converters, transmitting the digital image data to the data processing unit, and acquiring data of each channel at the same time. The data processing unit is used for transmitting single-channel high-speed data streams, a data transmitter clock and a horizontal synchronizing signal acquired from integration of the digital image data to the high-speed serial transmission unit. The high-speed serial transmission unit is used for converting single-channel high-speed data streams via LVDS (low-voltage differential signaling) serial chips into high-speed LVDS data streams for transmitting. The high-speed image data collection system is used for collecting the high-speed serial LVDS data streams and realizing real-time storing and displaying of the image data.

Owner:NANJING UNIV OF SCI & TECH

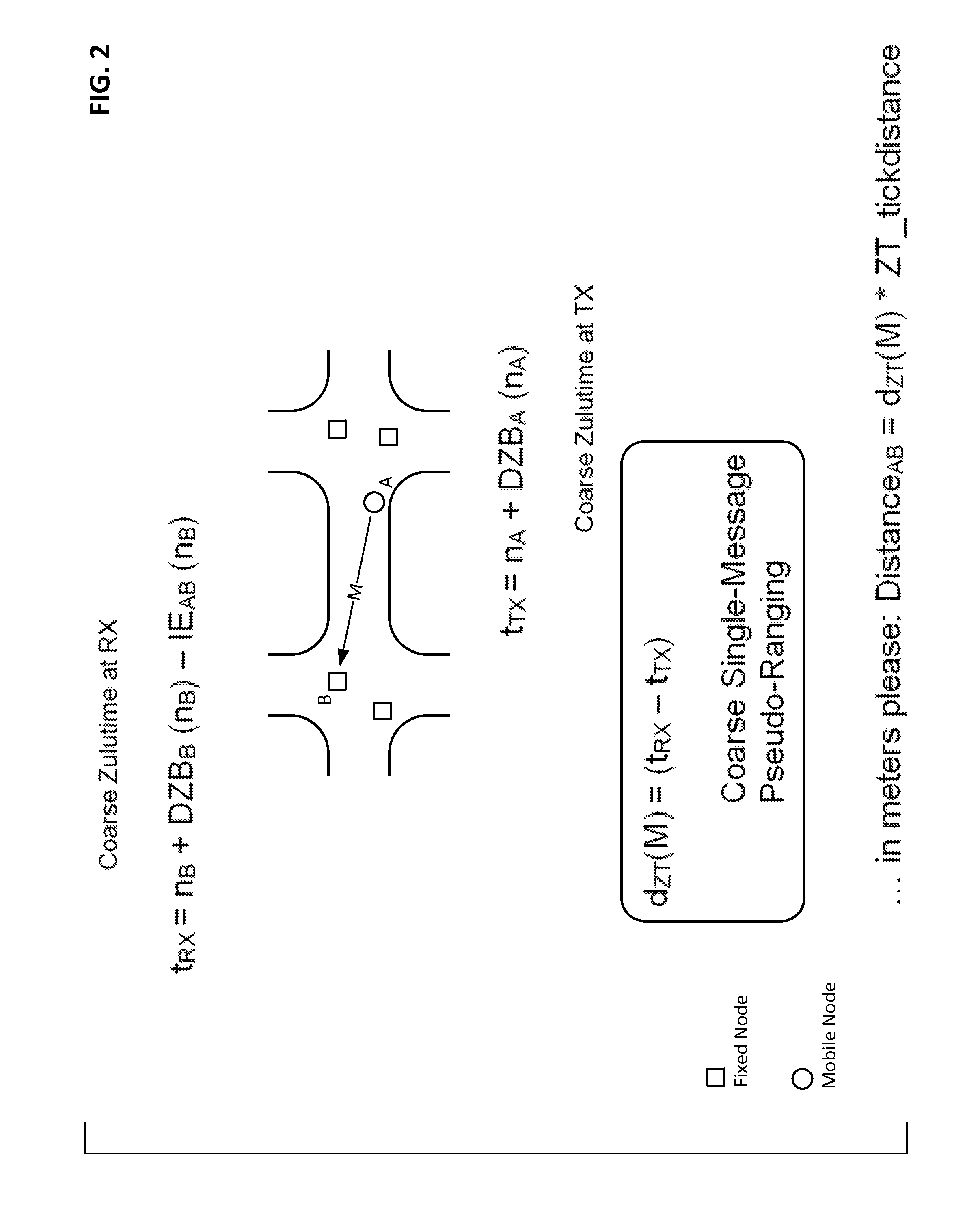

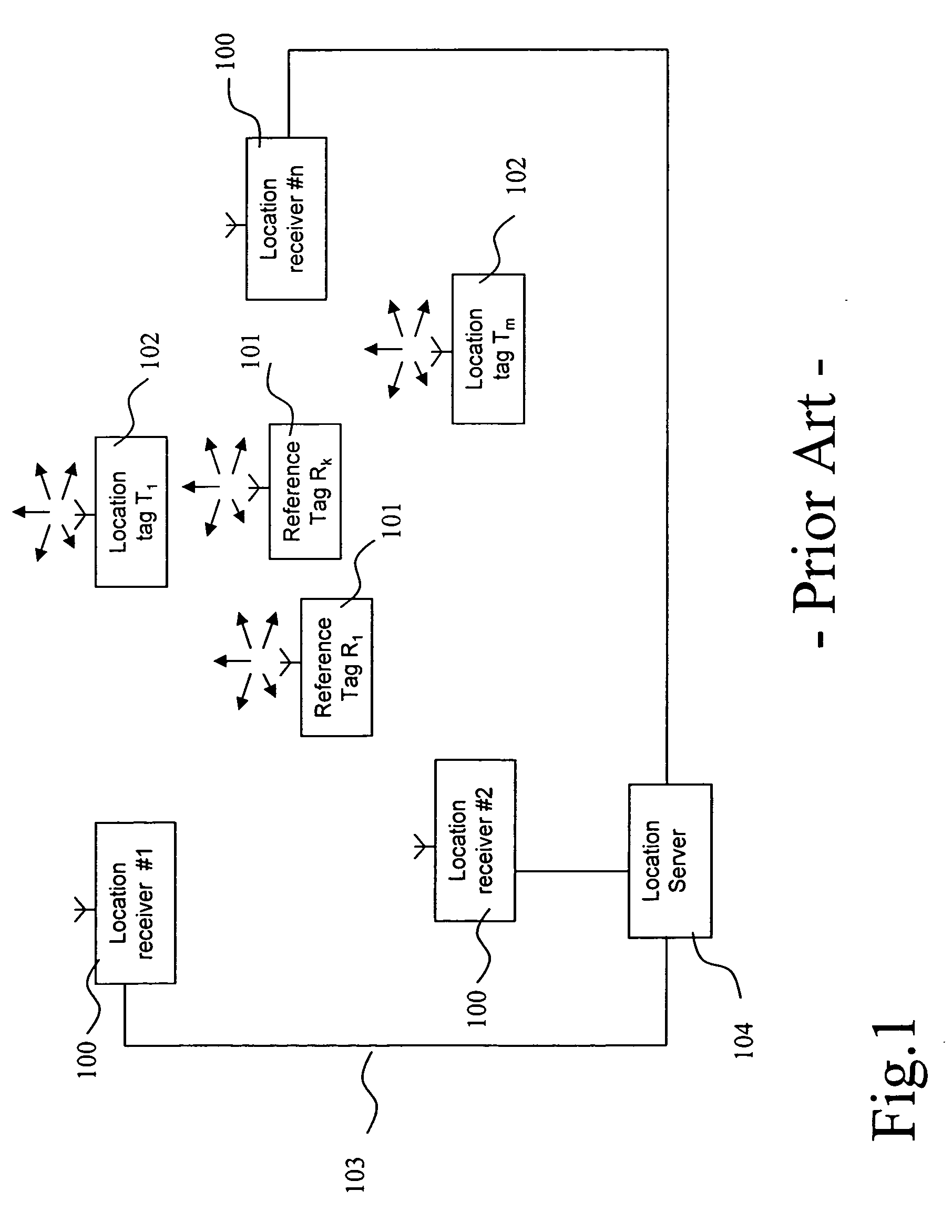

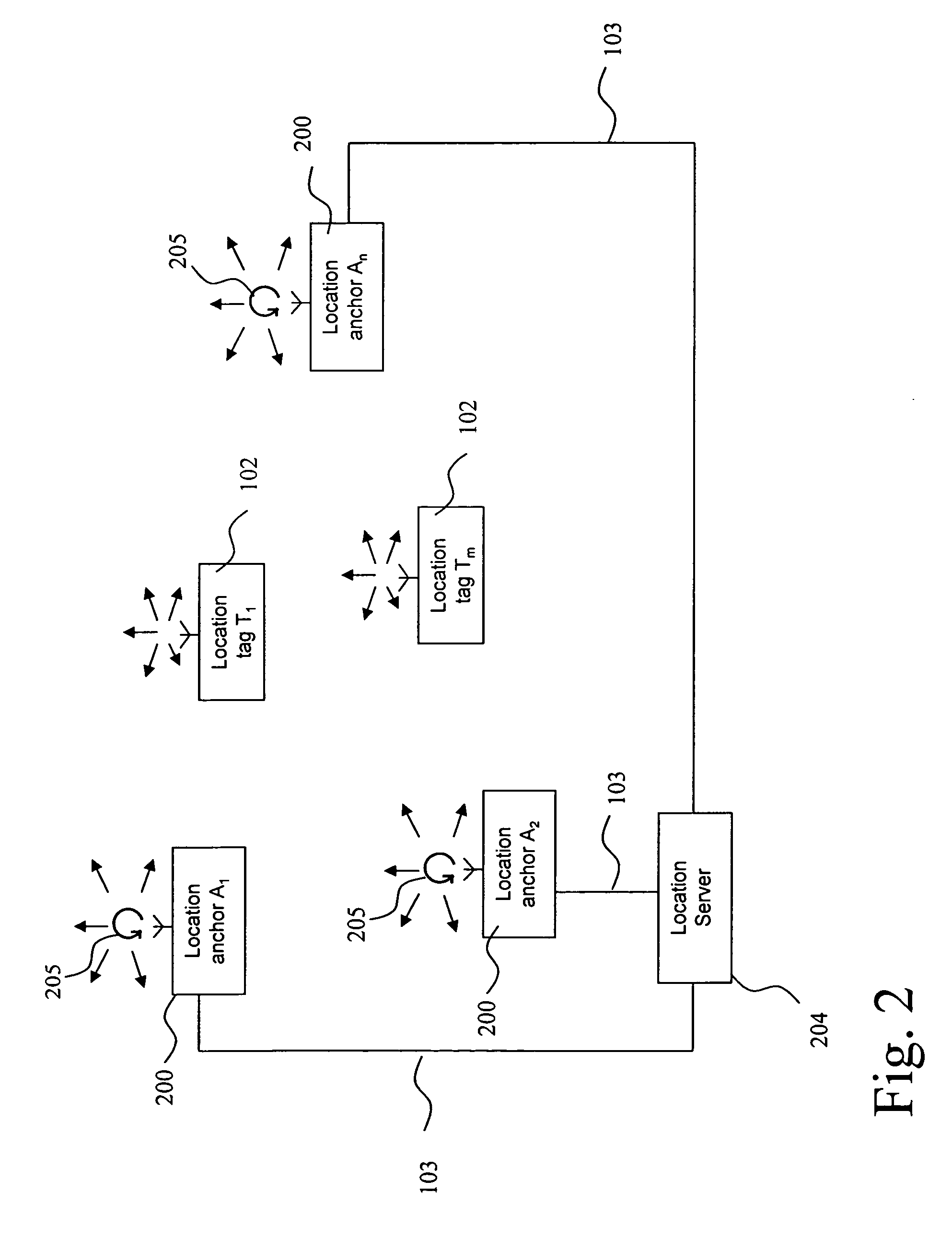

Method and System for Multipath Reduction for Wireless Synchronizing and/or Locating

ActiveUS20130021206A1Minimize air timeMaximize capacityDirection finders using radio wavesPosition fixationBroadcast transmissionSynchronizing

A method for determining an instantaneous phase difference between time bases of at least two location anchors for a desired point in time (t), each of the location anchors having transmitting and receiving access to a joint broadcast transmission medium and a respective time base for measuring time, wherein a first of the location anchors broadcasts a first broadcast message at least twice; the first location anchor and at least a second of the location anchors receive the first broadcast messages; the second location anchor broadcasting a second broadcast message at least twice; and the second location anchor and at least the first location anchor receive the second broadcast messages. The location server calculates the instantaneous phase difference from a determined first and second clock model functions and from a time elapsed between a reference point in time and the desired point in time t.

Owner:NANOTRON GES FUR MIKROTECHN

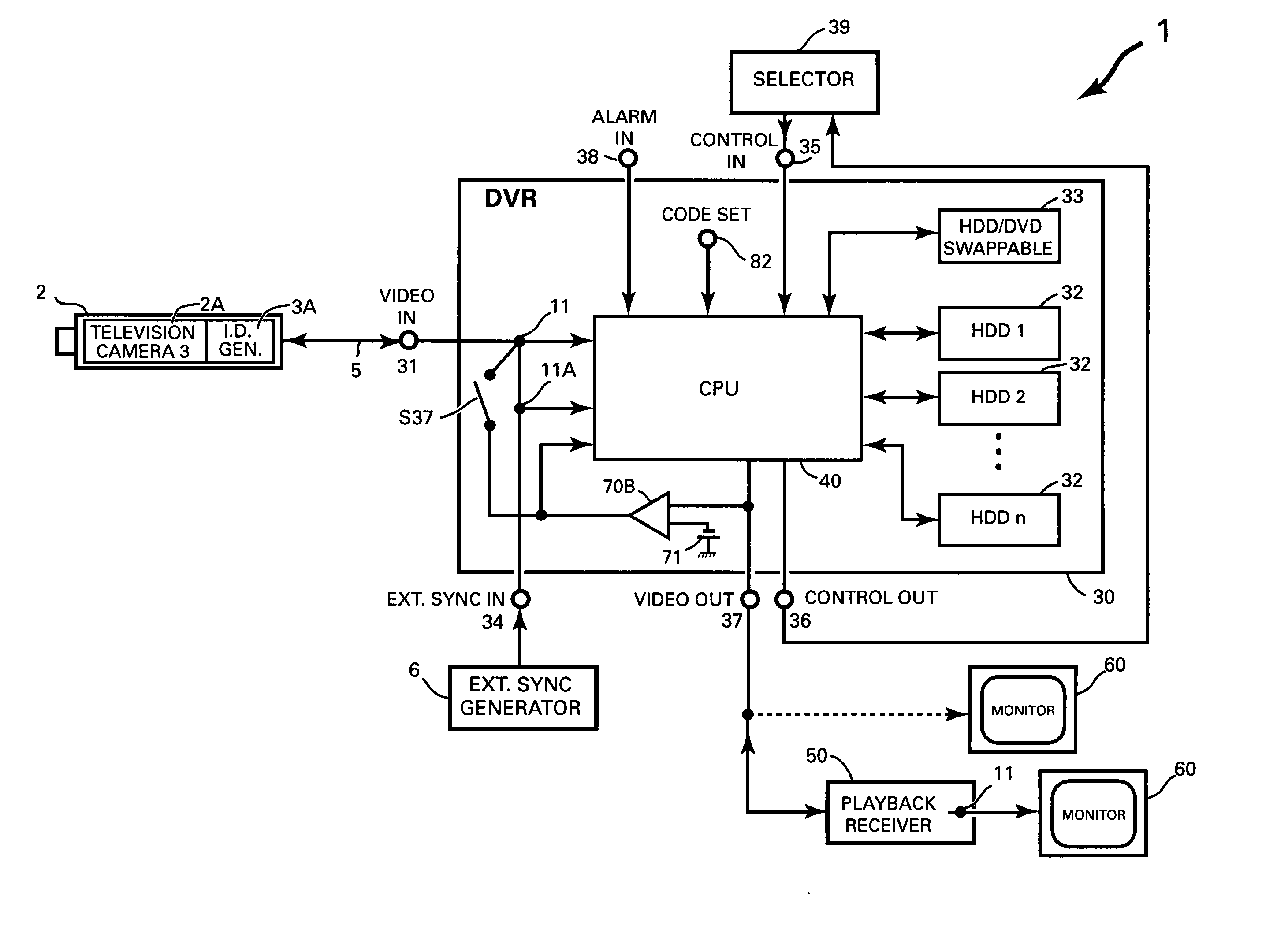

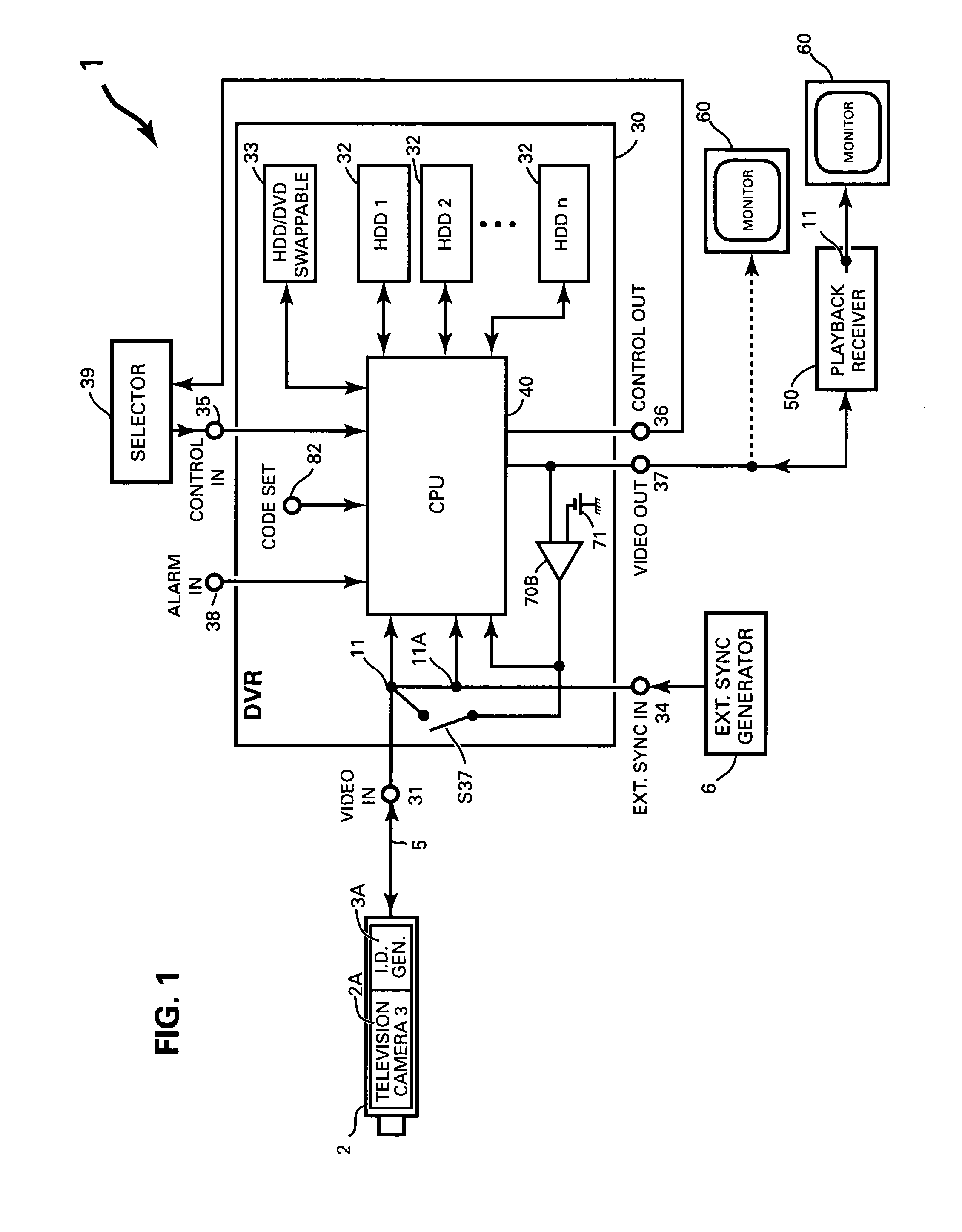

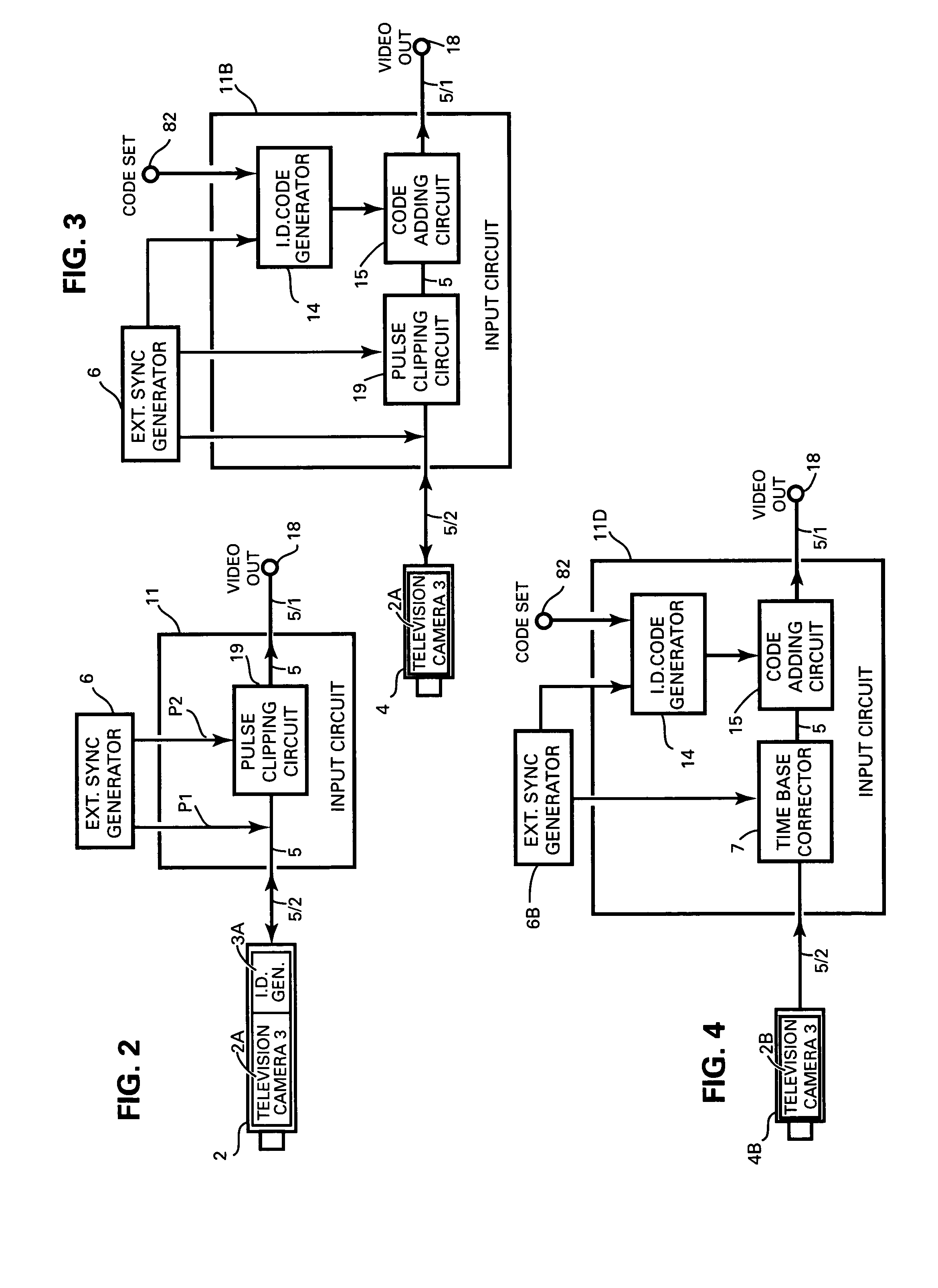

Method and apparatus for digitally recording and synchronously retrieving a plurality of video signals

InactiveUS20050094966A1Firmly connectedSimple addressingTelevision system detailsPicture reproducers using cathode ray tubesDigital videoVideo sender

A method and apparatus for connecting a plurality of digital video recorders to a plurality of video transmitters via first transmission lines and for connecting the plurality of digital video recorders to a playback receiver via second transmission lines. The playback receiver incorporates an external synchronizing generator for externally synchronizing the plurality of the digital video recorders and the video transmitters. The recorders receiving the video signals generate and inject into the output signals a signal corresponding to identification codes allotted to each video signals. The playback receiver has a selection control circuit receiving selectively and synchronously any individually coded playback or monitored signal, or multiple playback or monitored signals which are displayed individually or in a split screen, respectively. The digital video recorder includes a time-date signal generator and a processing circuit compressing the video signals and outputting them with an injected identification code and time and date of the recorded signals and storing the signal into at least one memory device in an endless rotation, wherein freshly stored signals replace the oldest stored signals.

Owner:ELBEX VIDEO LTD

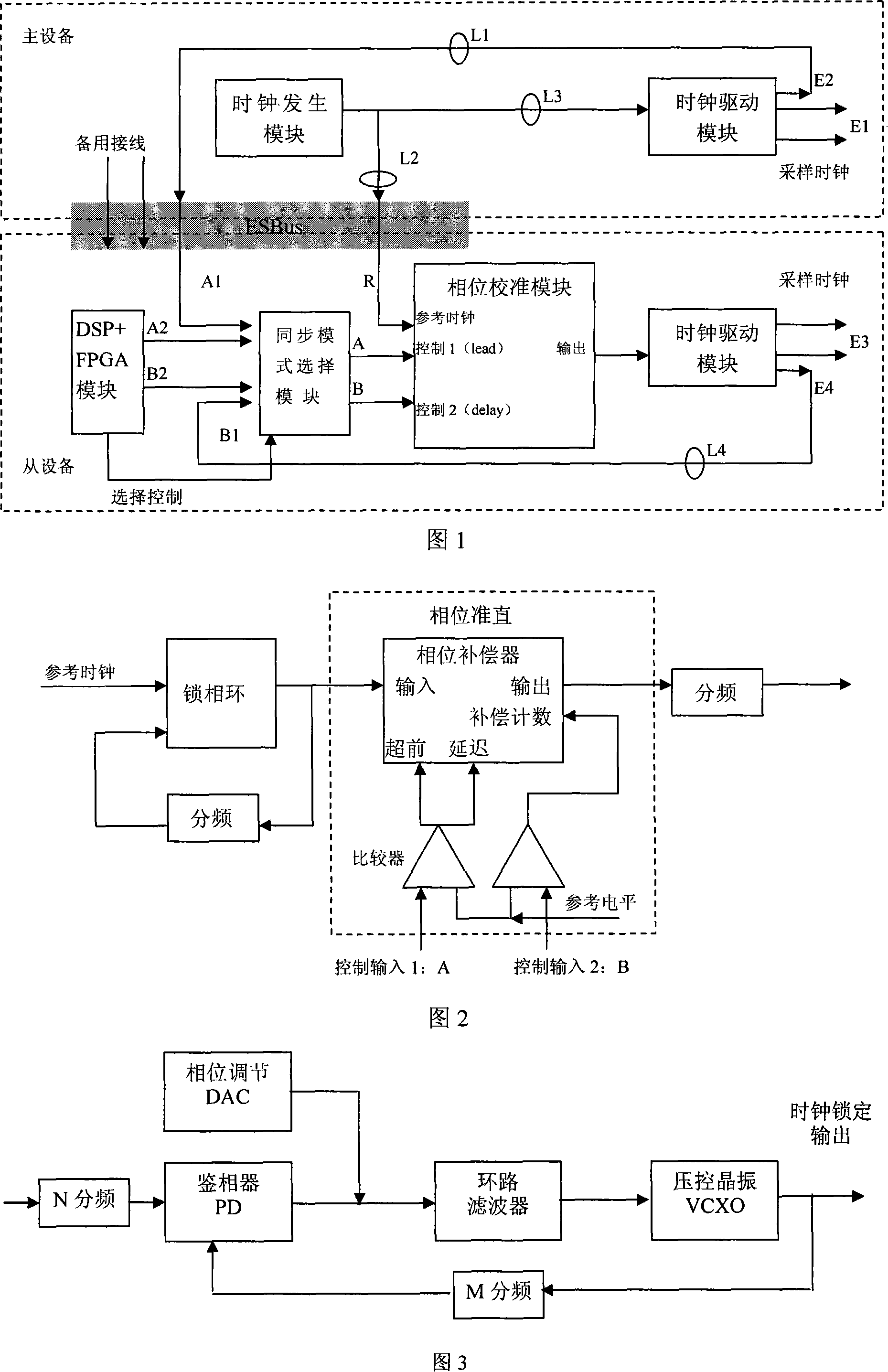

A multi-channel clock synchronization method and system

InactiveCN101150316AClock Precise SynchronizationPulse automatic controlAutomatic controlPhase difference

This invention provides a multi-channel clock synchronizing method and a system, in which, a phase calibration theory is used and a phase calibration module takes received sampling clocks of a main device and a path of sampling clocks output by a drive module of a slave device as the phase calibration automatic control input signal to regulate the phase of a reference clock of the main device so as to realize accurate synchronizatin of main and slave devices, and the system includes a main device and at least one slave device and provides a DSP+FPGA module used in generating active synchronous signals and a control mode selecting module used in realizing selection of active and automatic modes, which can realize accurate synchronization of multi-channel clocks, and an operator can regulate phase difference of main and slave device actively when the clock system is lost at automatic synchronization to realize synchronization again.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

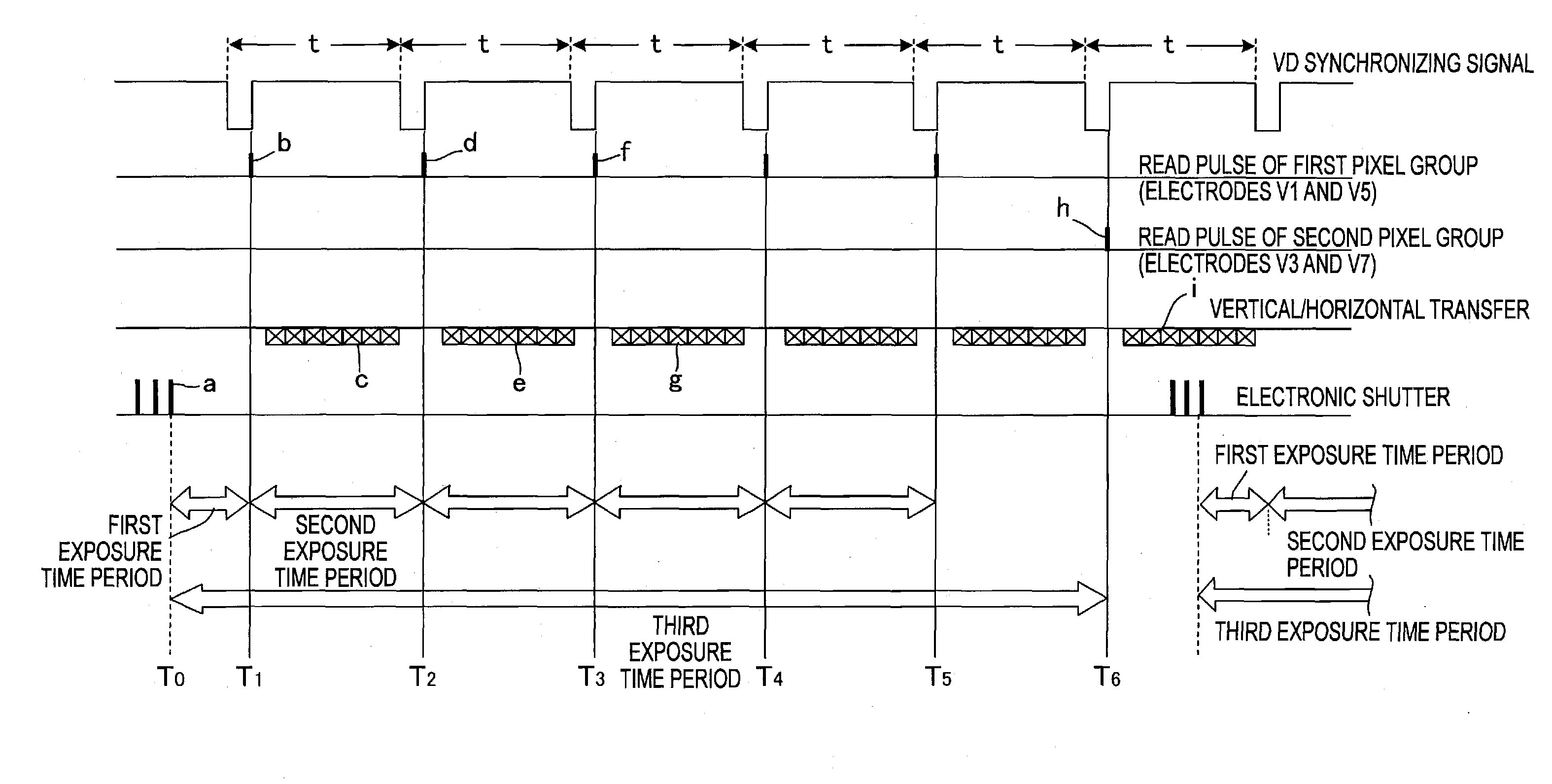

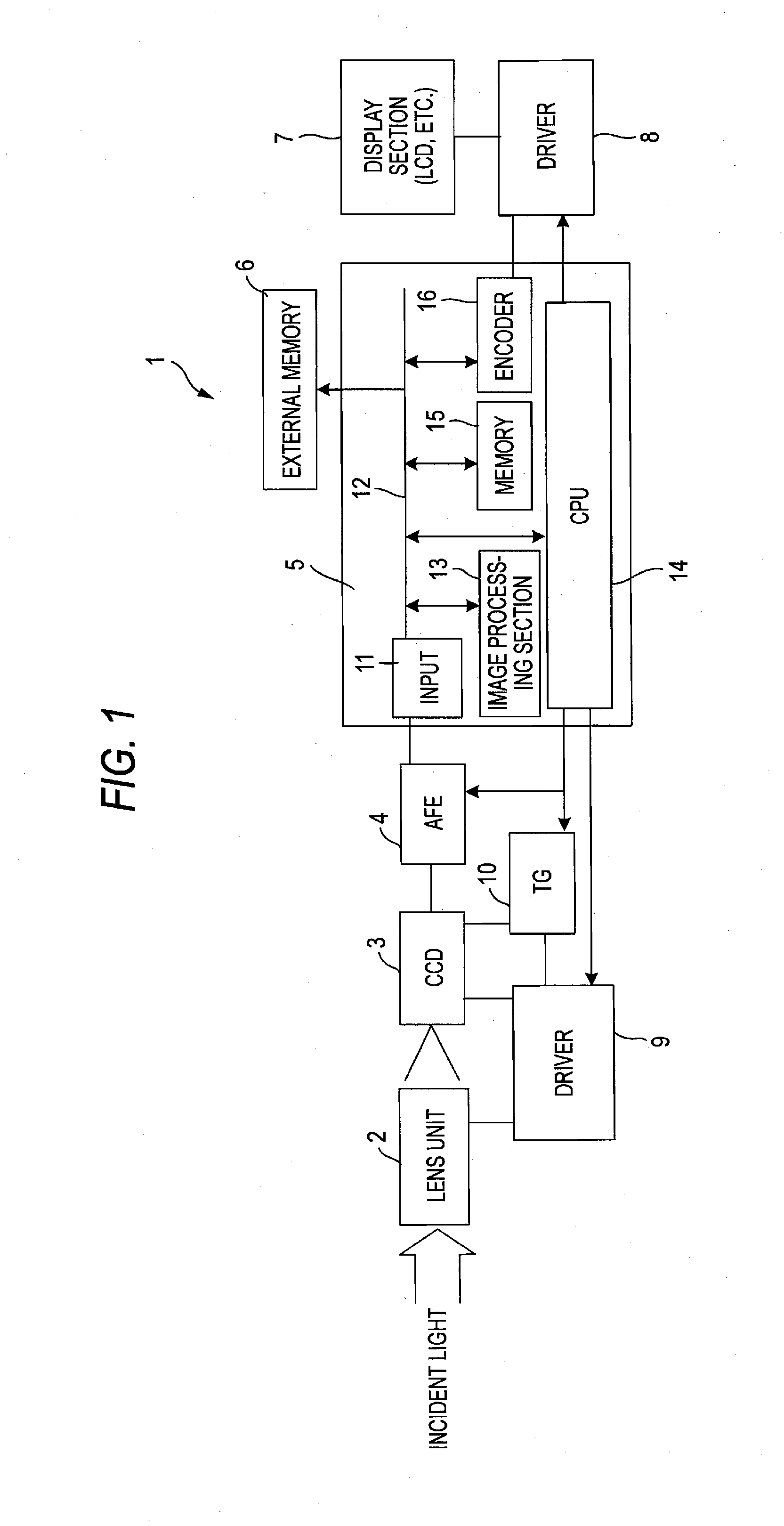

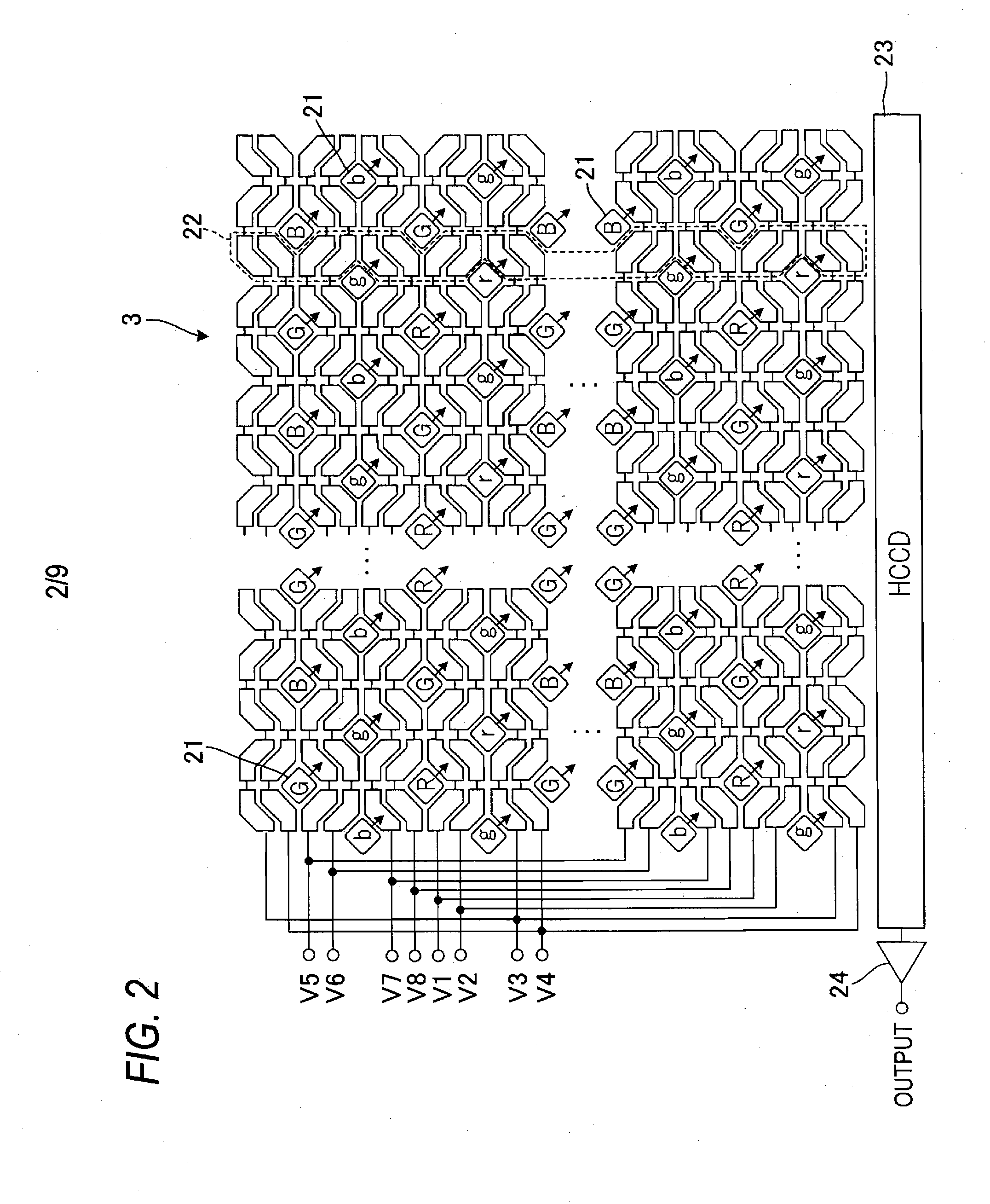

Imaging pickup device and image pickup method

InactiveUS20110096216A1Television system detailsTelevision system scanning detailsImage signalSubstrate surface

An image pickup device includes an image sensing device and a driving unit. The image sensing device includes a first pixel group and a second pixel group. The first pixel group includes a plurality of pixels arranged as a two-dimensional array in a semiconductor substrate surface portion that receives incidence light from a subject. The second pixel group includes a plurality of pixels arranged as a two-dimensional array in the semiconductor substrate surface portion in an area overlapping the first pixel group while the pixels in the first pixel group do not disposed in the same positions as the pixels in the second pixel group. The driving unit outputs a picked-up image signal of one frame from the first pixel group exposed over one vertical synchronizing time period for each vertical synchronizing signal.

Owner:FUJIFILM CORP

Clock synchronizing method for wireless sensor network

InactiveCN101588628ASynchronisation arrangementRadio transmission for post communicationTime informationWireless mesh network

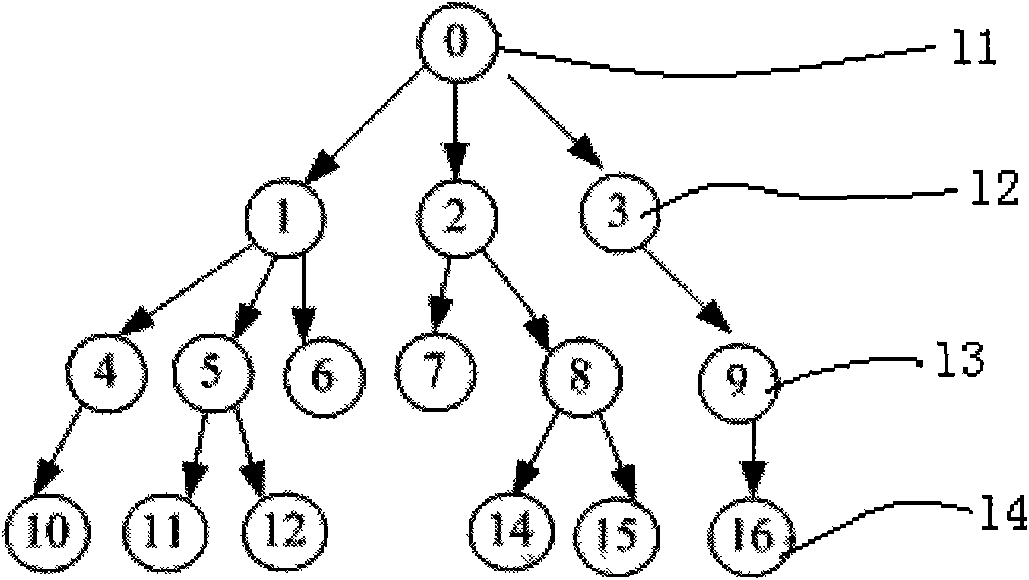

The invention discloses a clock synchronizing method for a wireless sensor network. The clock synchronizing method for the wireless sensor network comprises the following steps: firstly, constructing the wireless sensor network into a tree network topology, using the time value of a root node as a reference time, and synchronizing the root node and a base station of the network through pair-wise algorithm; then, broadcasting a synchronous data packet containing time information of the root node along each subtree by the root node, and synchronizing a father node of each subtree and a child node thereof through the pair-wise algorithm; and finally synchronizing layers of each subtree till each node of the tree network has a unified time signal. Based on the technical proposal, the clock synchronizing method for the wireless sensor network can improve the transmission capacity of the data packet and effectively improve the synchronizing precision.

Owner:SHANDONG COMP SCI CENTNAT SUPERCOMP CENT IN JINAN

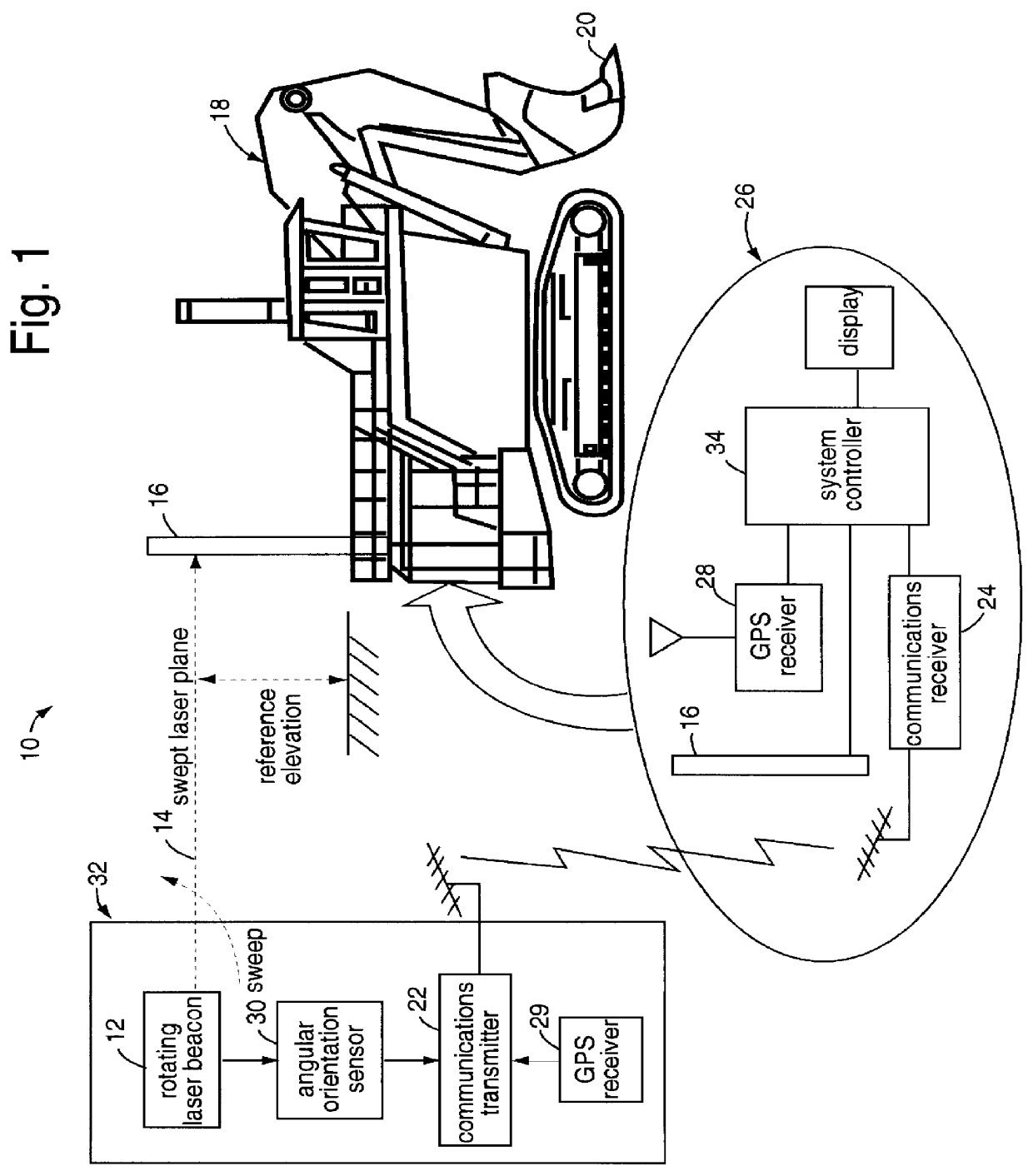

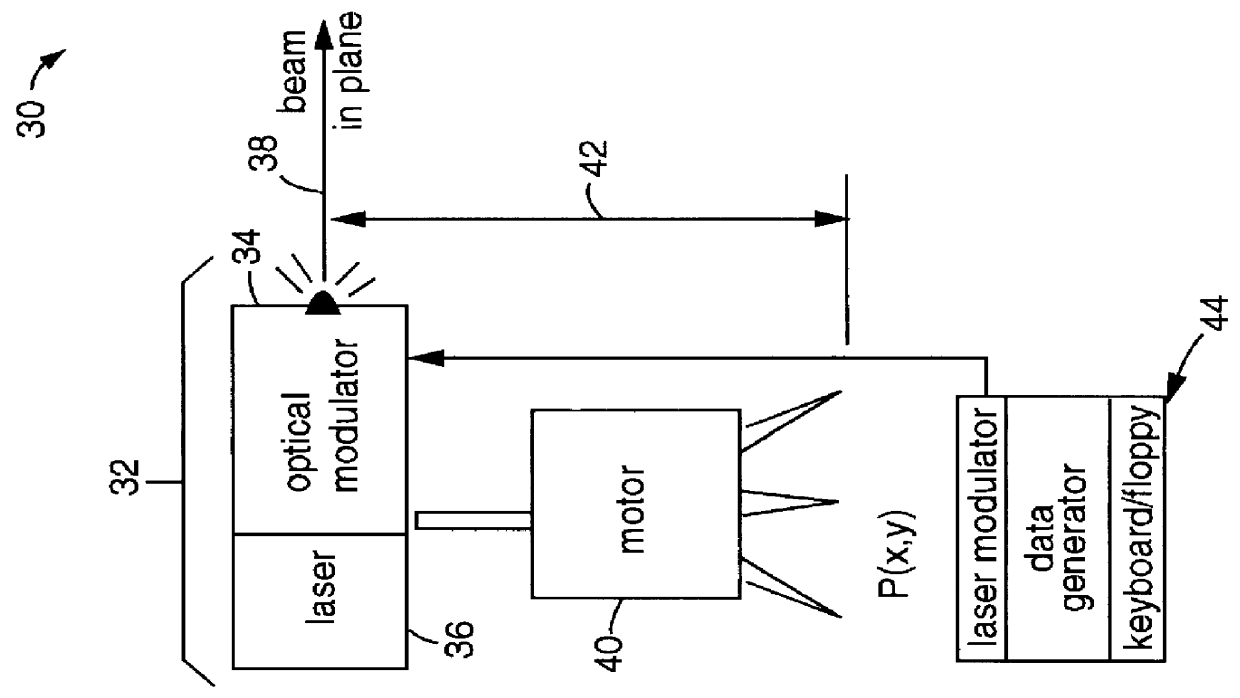

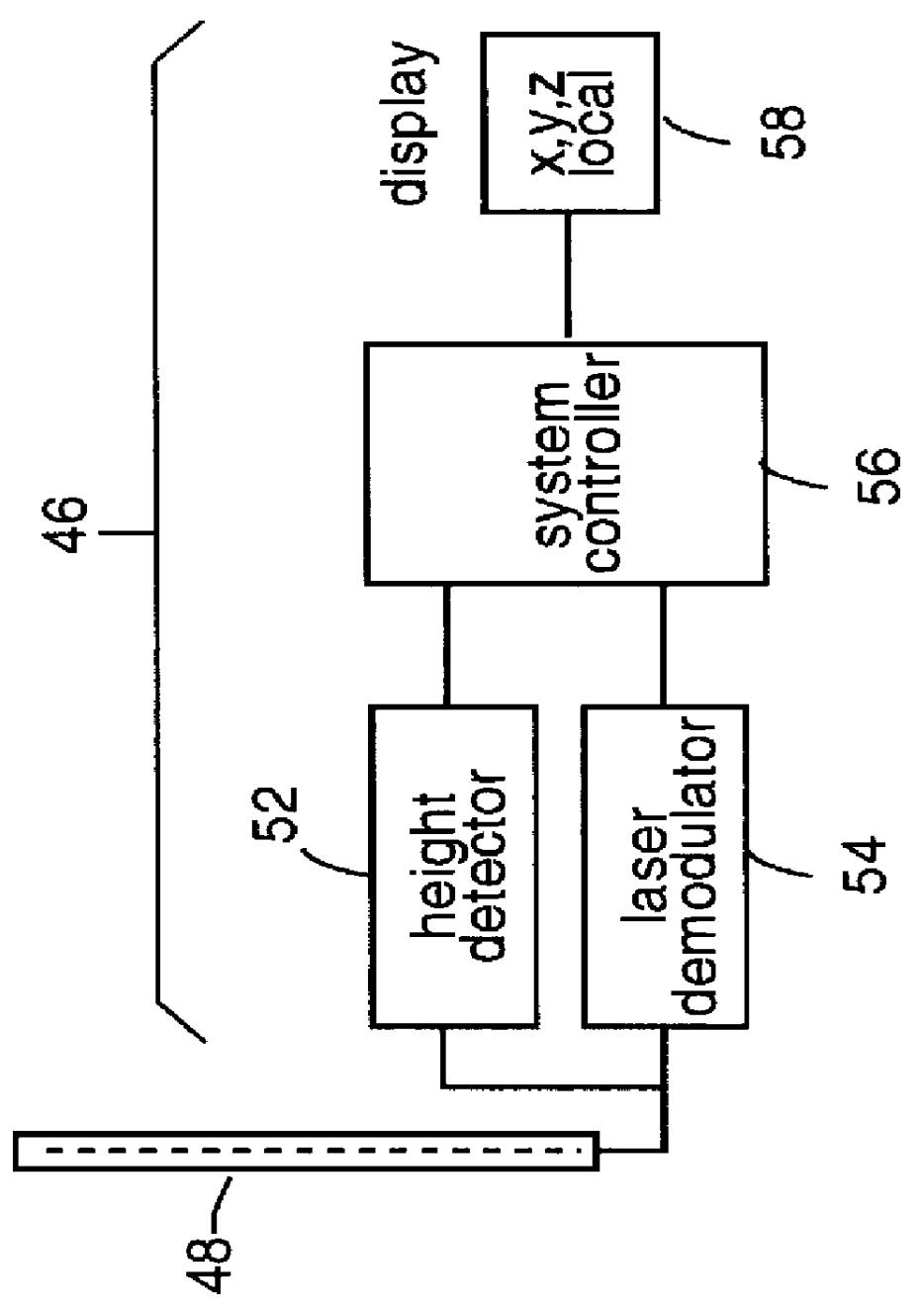

Multiple simultaneous laser-reference control system for construction equipment

A number of laser beam stations emit vertically separated parallel planes and / or ray-planes of laser light that can be discriminated by their respective plane elevations, modulation of the laser light, time synchronizing, etc. Identifying the laser plane would also imply an identification of the source laser beam station, and thus a precise indication of the elevation at the point of optical intercept. Alternatively, a single laser beam station is used that can emit several different monochromatic color planes and / or ray-planes of laser light. Monochromatic laser diodes, for example, are used for point-light sources and rotating or on-end conical mirrors are used to convert the diode laser light to the required monochromatic color planes and / or ray-planes of laser light. Receivers, generally held on masts attached to motor grader, bulldozer, loader, and excavator machines are used to sense the vertical reference position of the monochromatic color planes and / or ray-planes of laser light, relative to the earth cutting blade of the machine. Fixed-color filters, color filter wheels, and / or linear array photodetectors are used to discriminate amongst the colors and to exactly sense the plane of intersection with the machine. The results of the sensing are either displayed to an equipment operator for manual adjustment of the blade to an automatic servo control system connected to hydraulically control the blade.

Owner:TRIMBLE NAVIGATION LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com