Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1276 results about "Analog front-end" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An analog front-end (AFE or analog front-end controller AFEC) is a set of analog signal conditioning circuitry that uses sensitive analog amplifiers, often operational amplifiers, filters, and sometimes application-specific integrated circuits for sensors, radio receivers, and other circuits to provide a configurable and flexible electronics functional block, needed to interface a variety of sensors to an, antenna, analog to digital converter or in some cases to a microcontroller.

Systems and methods for extending dynamic range of imager arrays by controlling pixel analog gain

InactiveUS20130147979A1Improve dynamic rangeAdvanced image informationTelevision system detailsSolid-state device signal generatorsAnalog front-endDigital image data

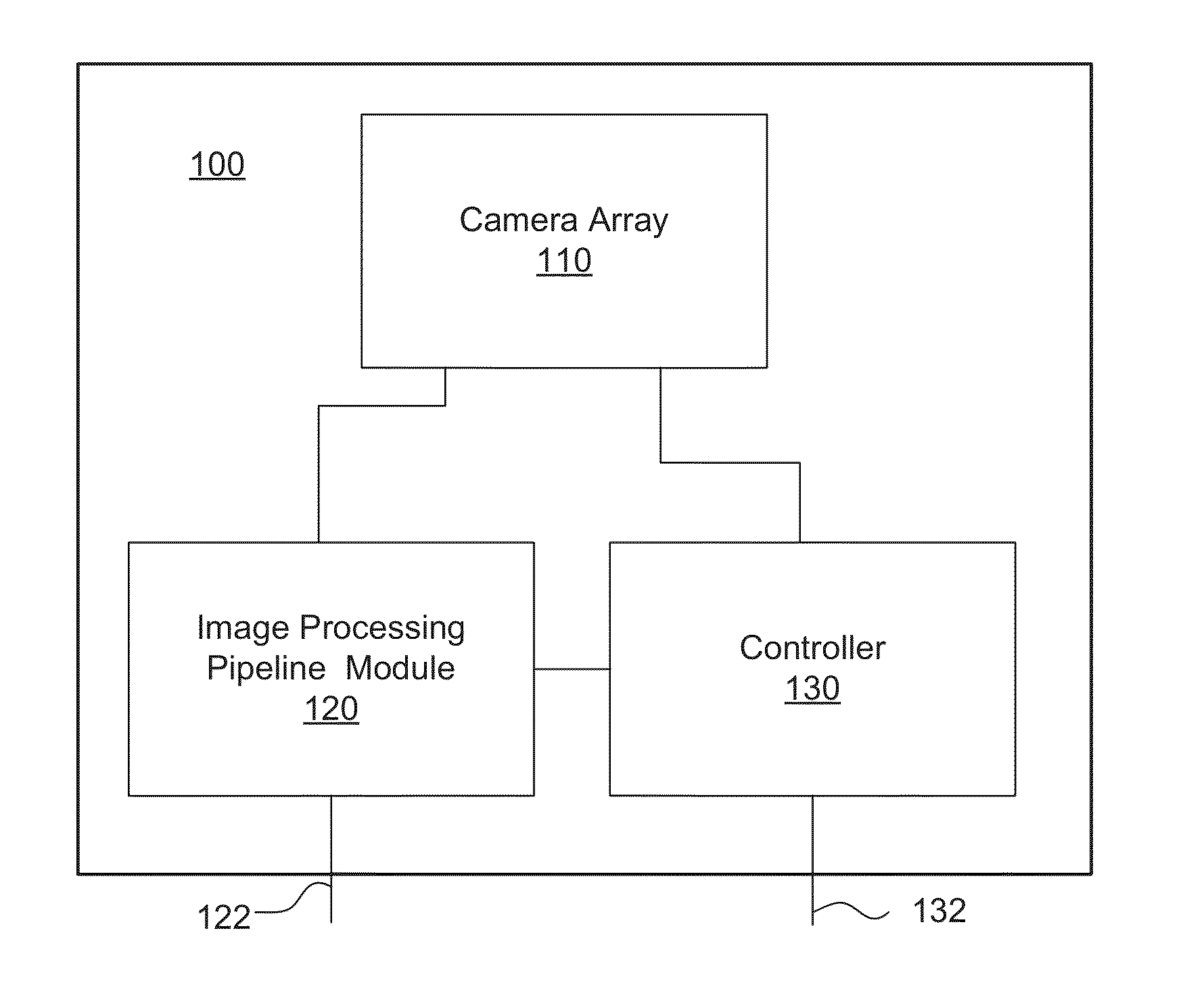

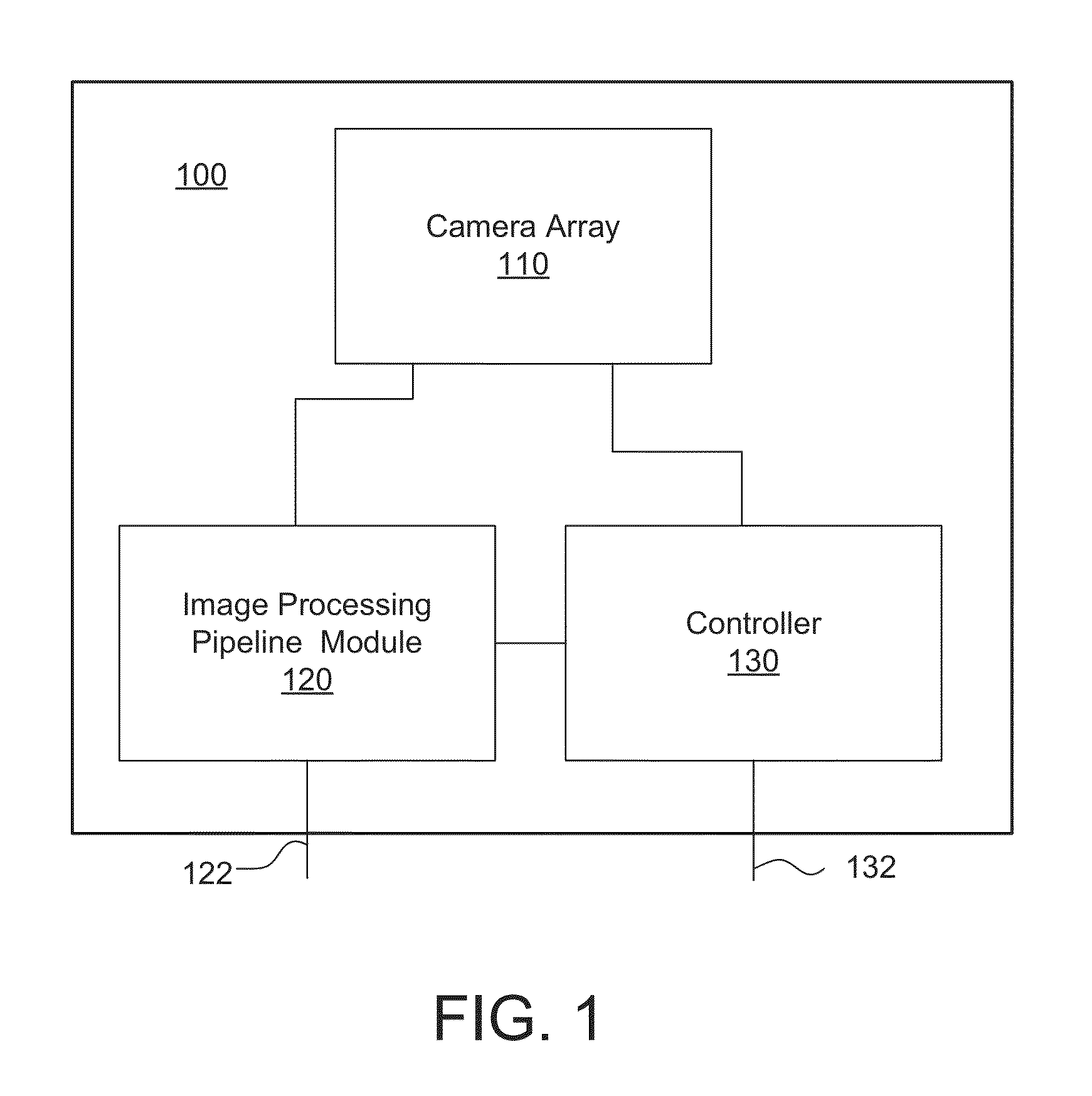

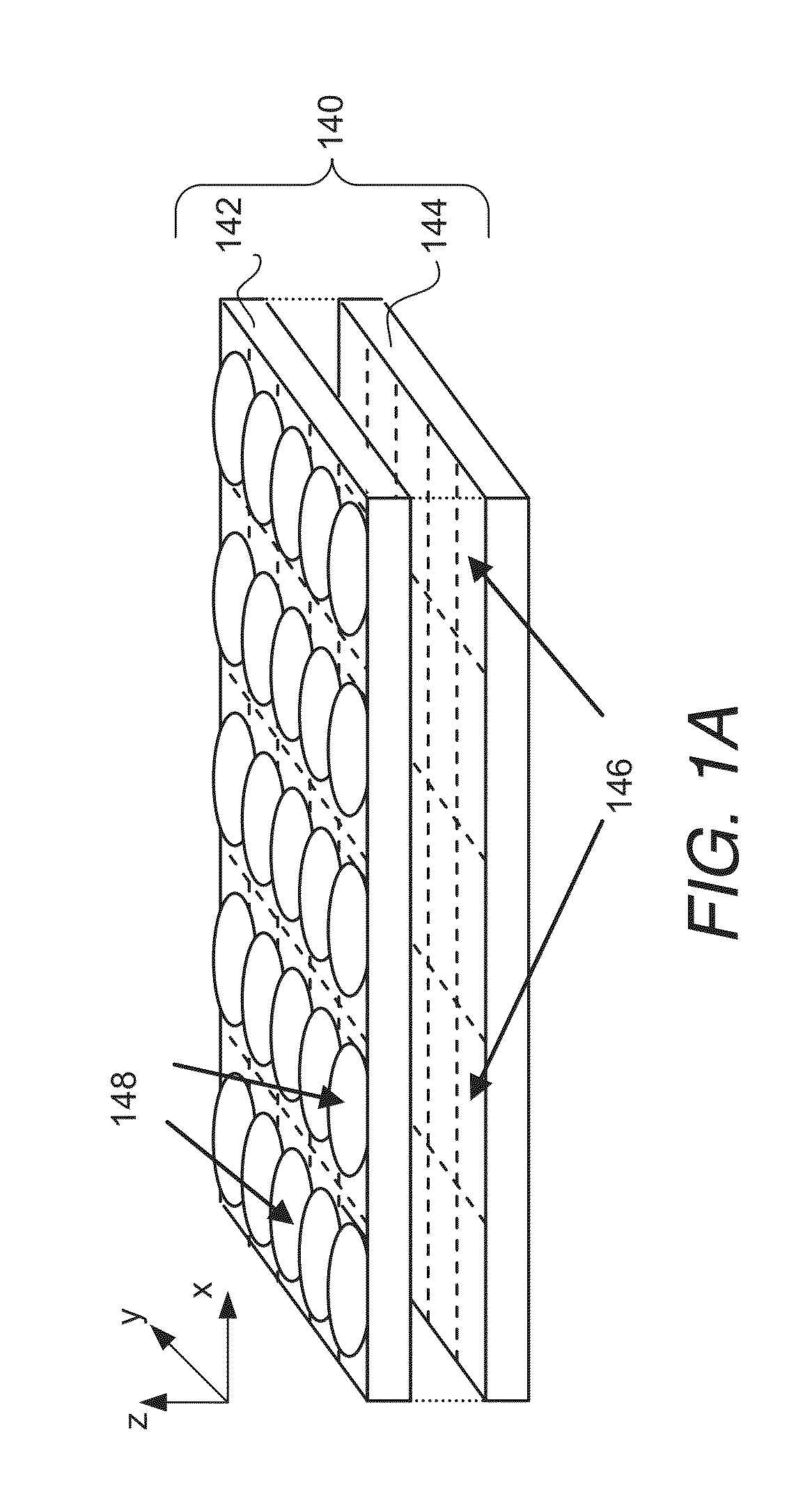

Array cameras and imager arrays configured to capture high dynamic range light field image data and methods of capturing high dynamic range light field image data in accordance with embodiments of the invention are disclosed. Imager arrays in accordance with many embodiments of the invention include multiple focal planes with associated read out and sampling circuitry. The sampling circuitry controls the conversion of the analog image information into digital image data. In certain embodiments, the sampling circuitry includes an Analog Front End (AFE) and an Analog to Digital Converter (ADC). In several embodiments, the AFE is used to apply different amplification gains to analog image information read out from pixels in a given focal plane to provide increased dynamic range to digital image data generated by digitizing the amplified analog image information. The different amplifications gains can be applied in a predetermined manner or on a pixel by pixel basis.

Owner:FOTONATION CAYMAN LTD

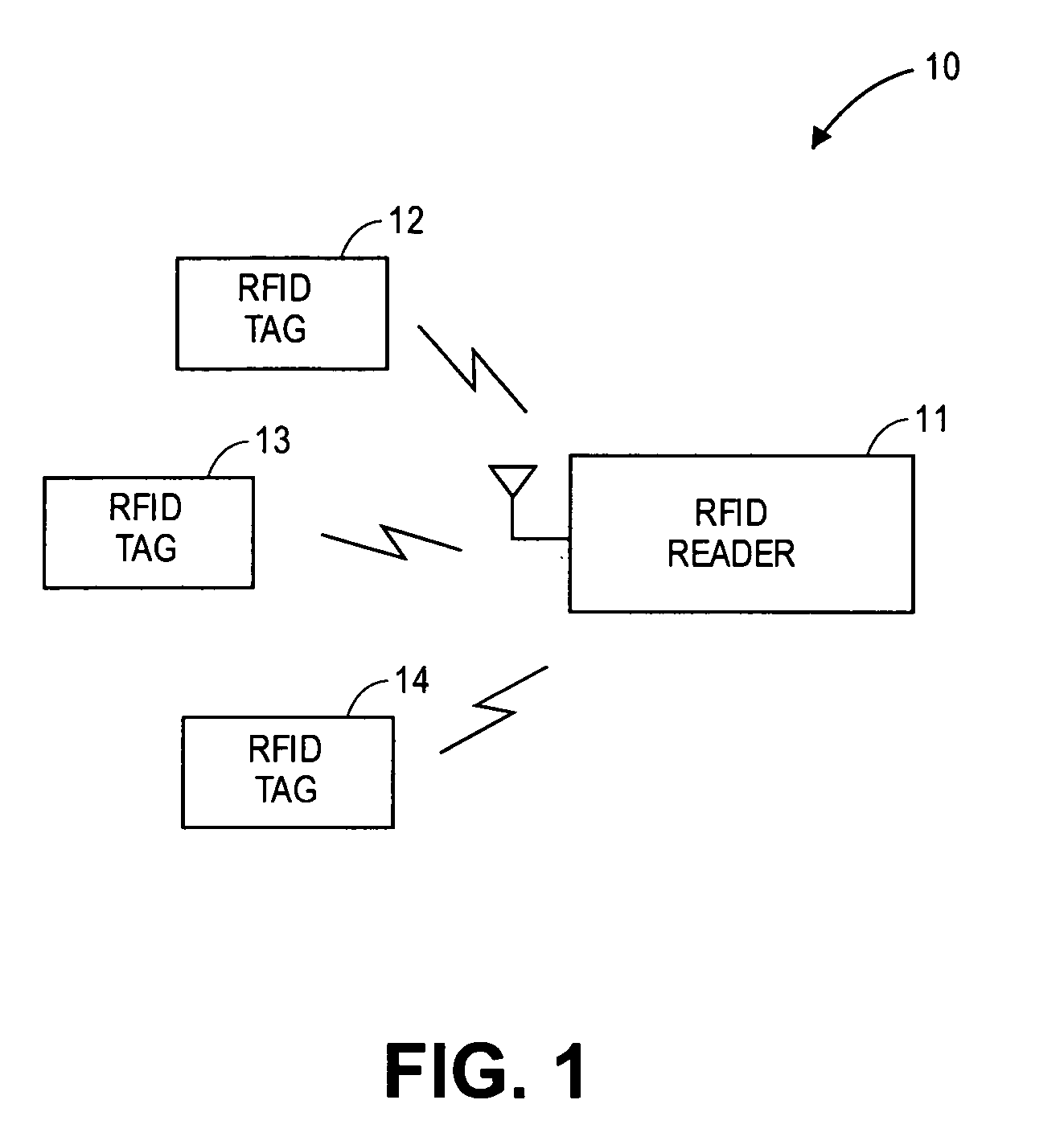

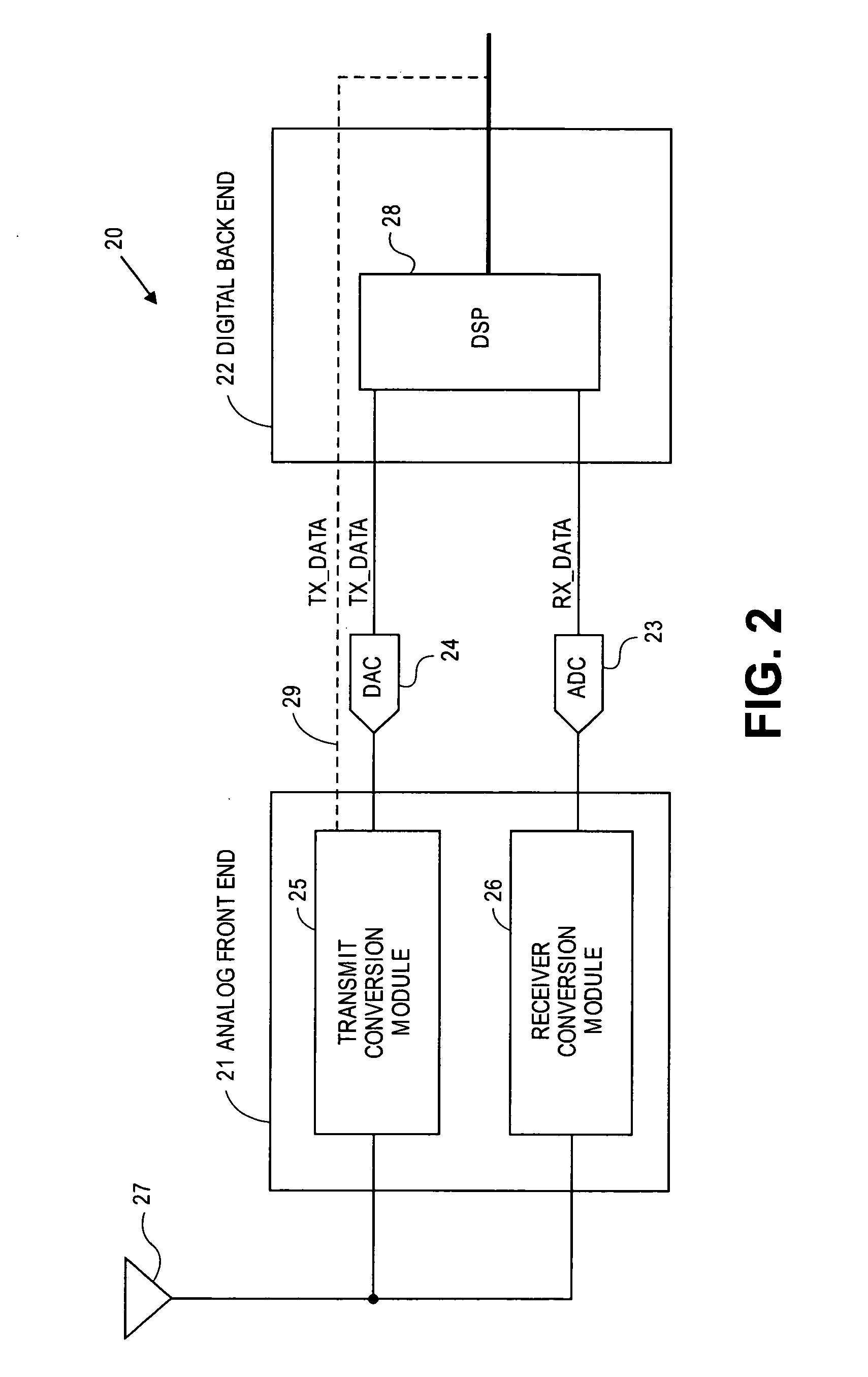

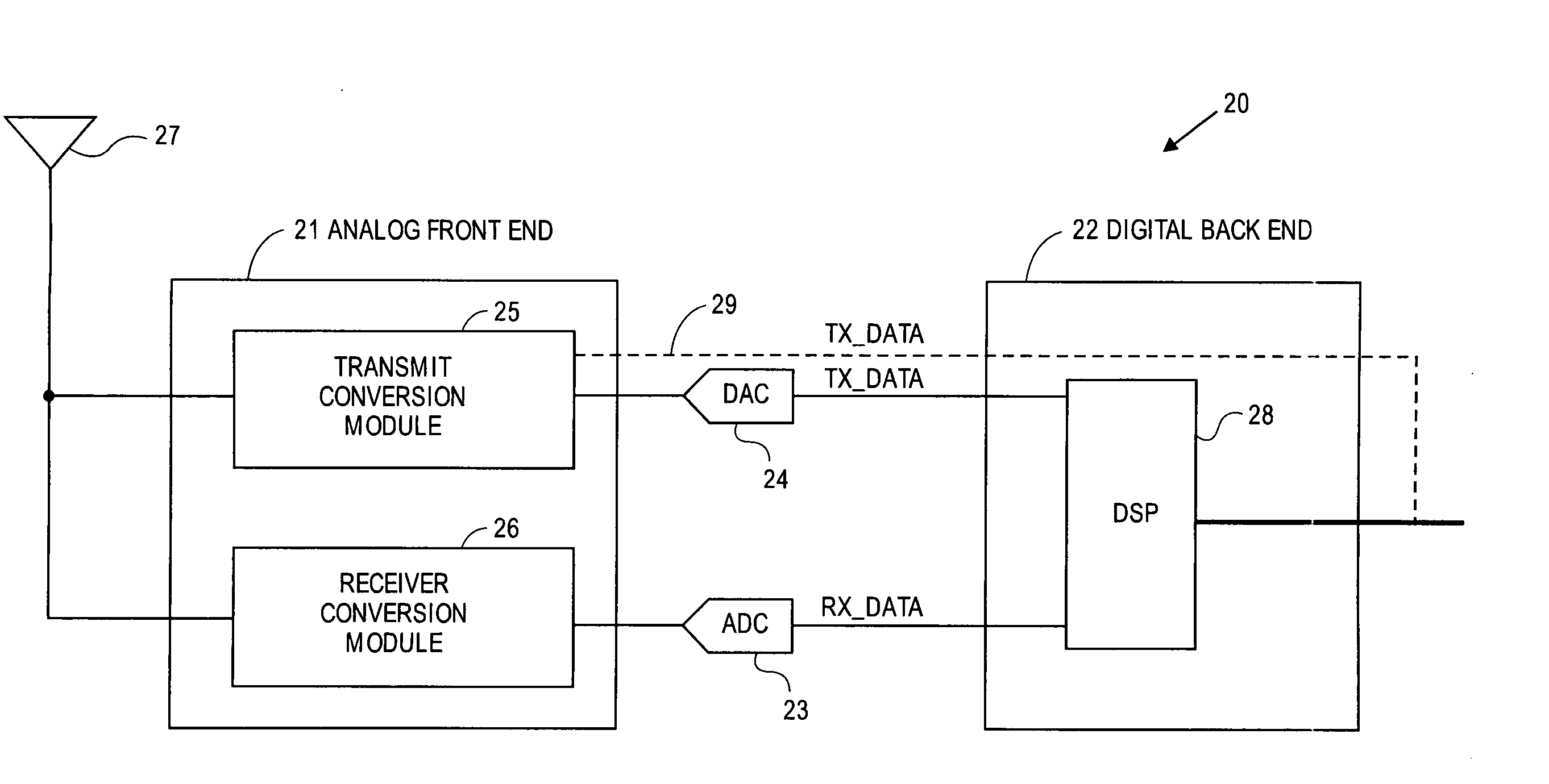

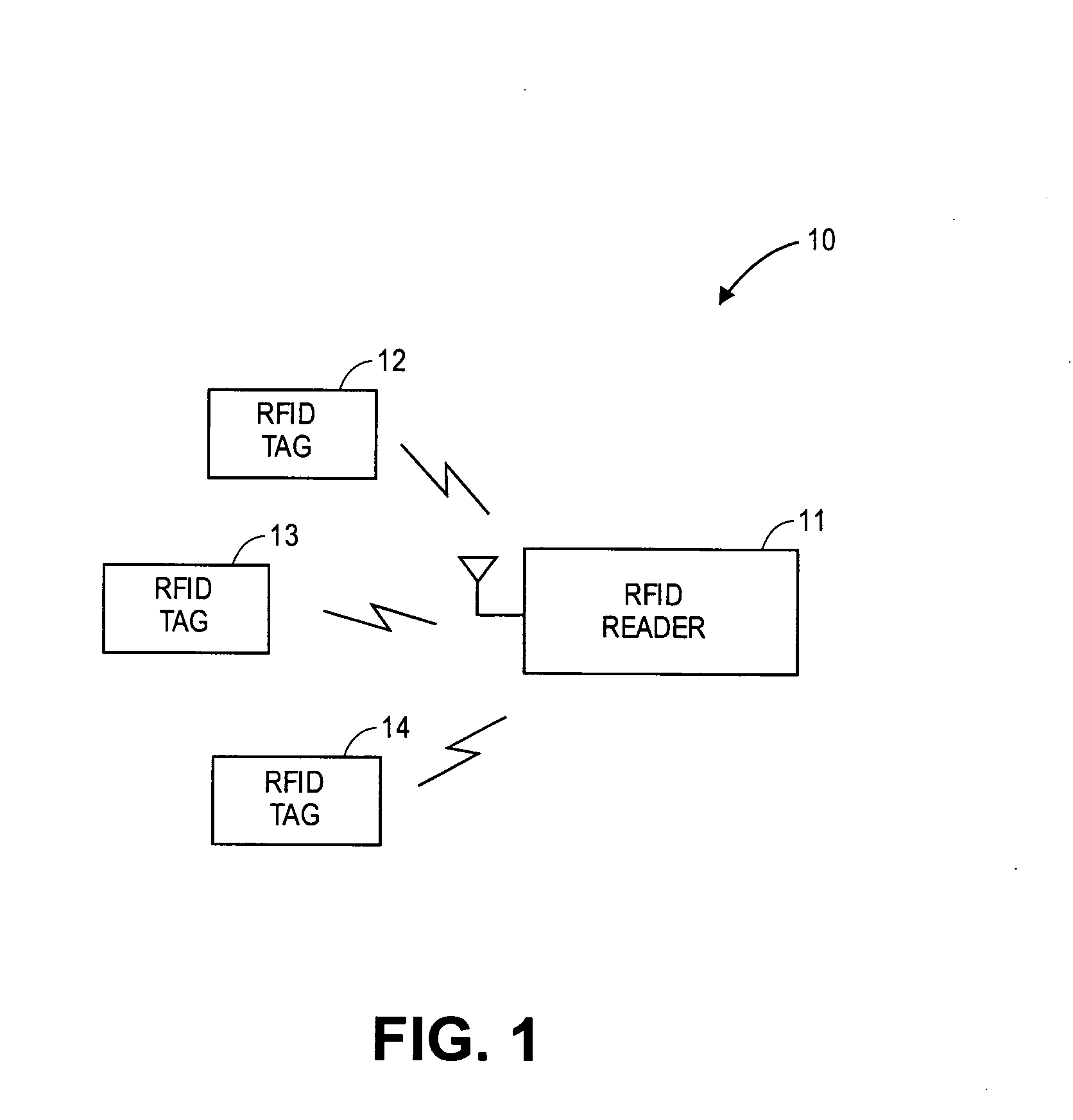

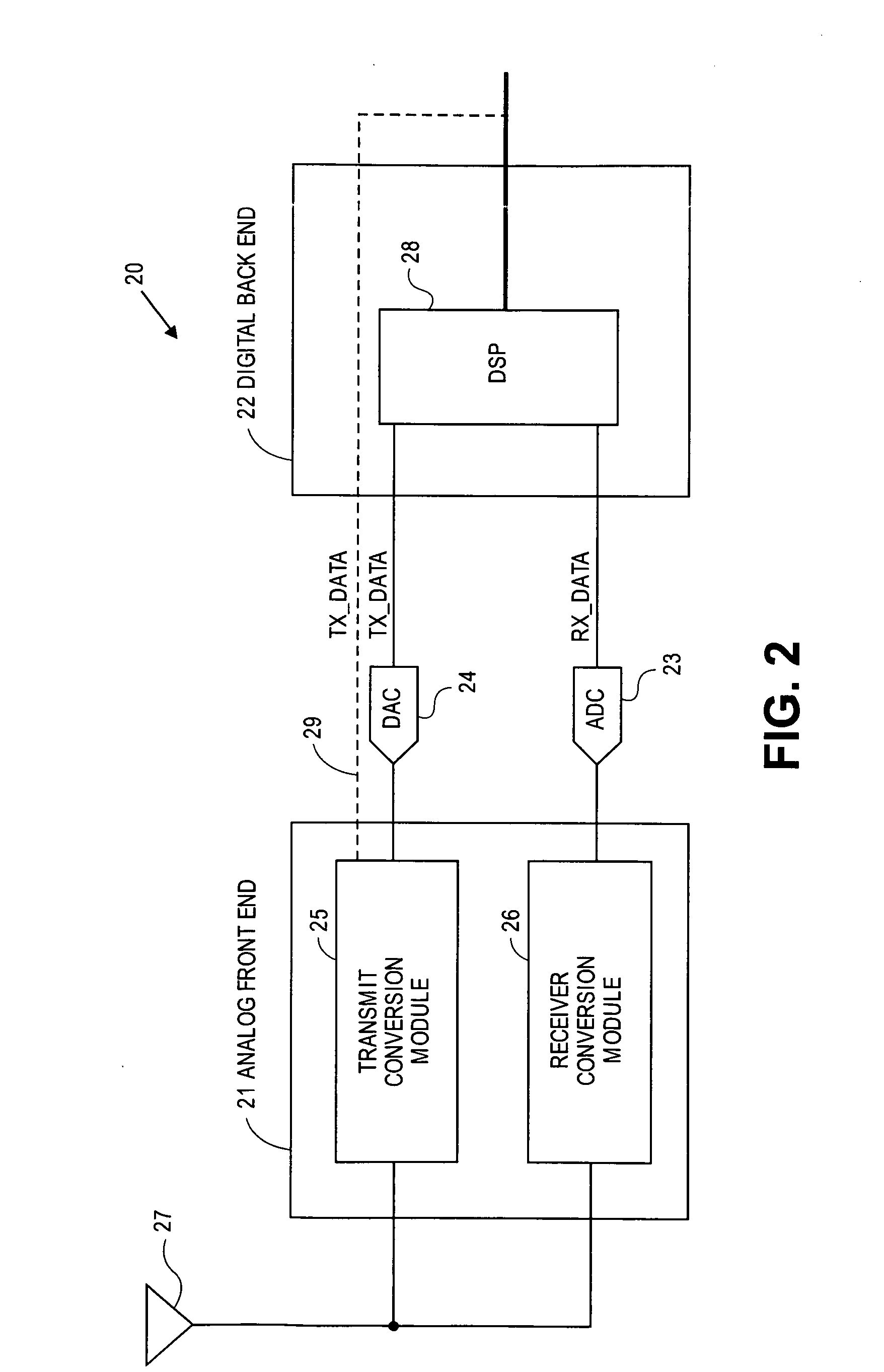

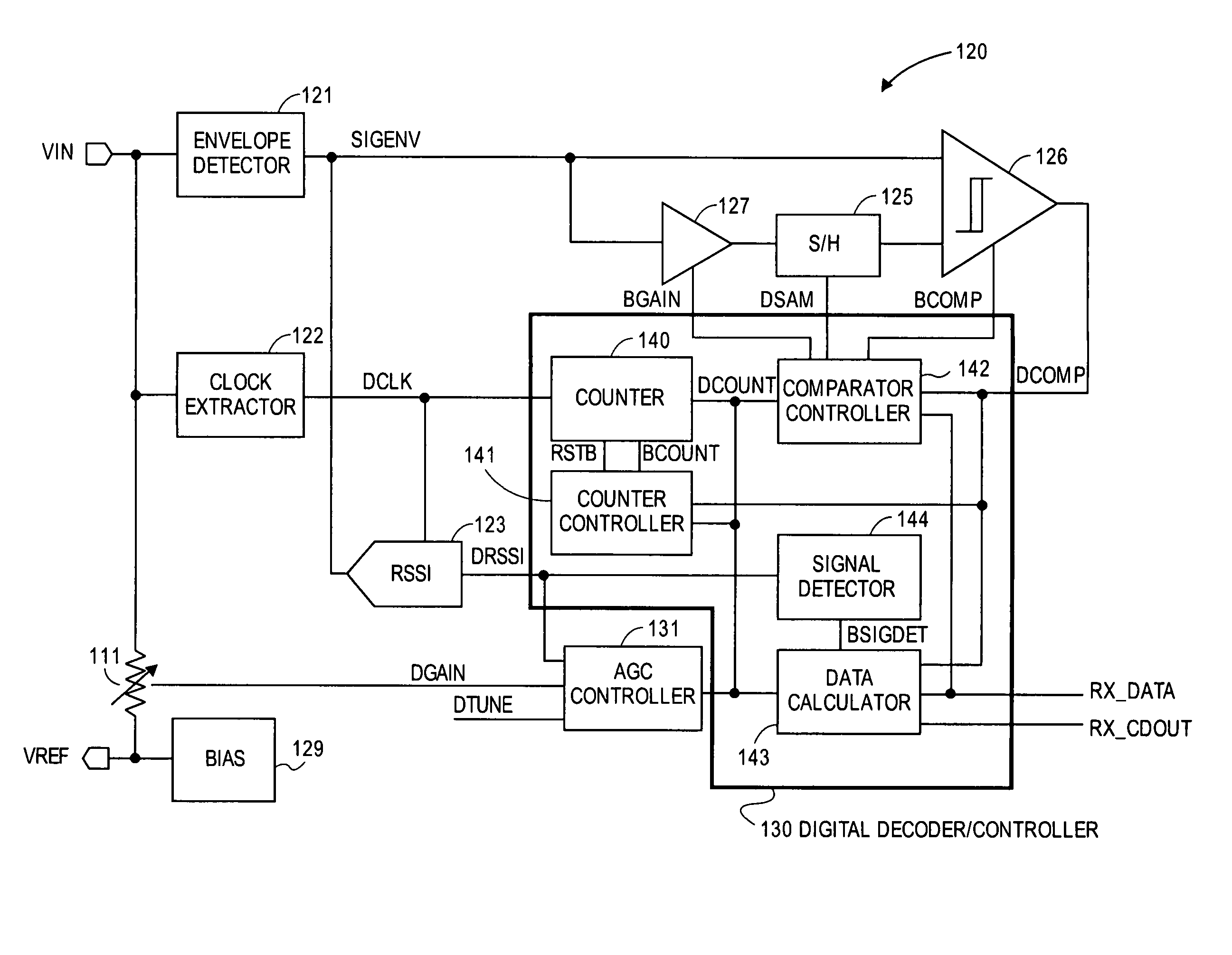

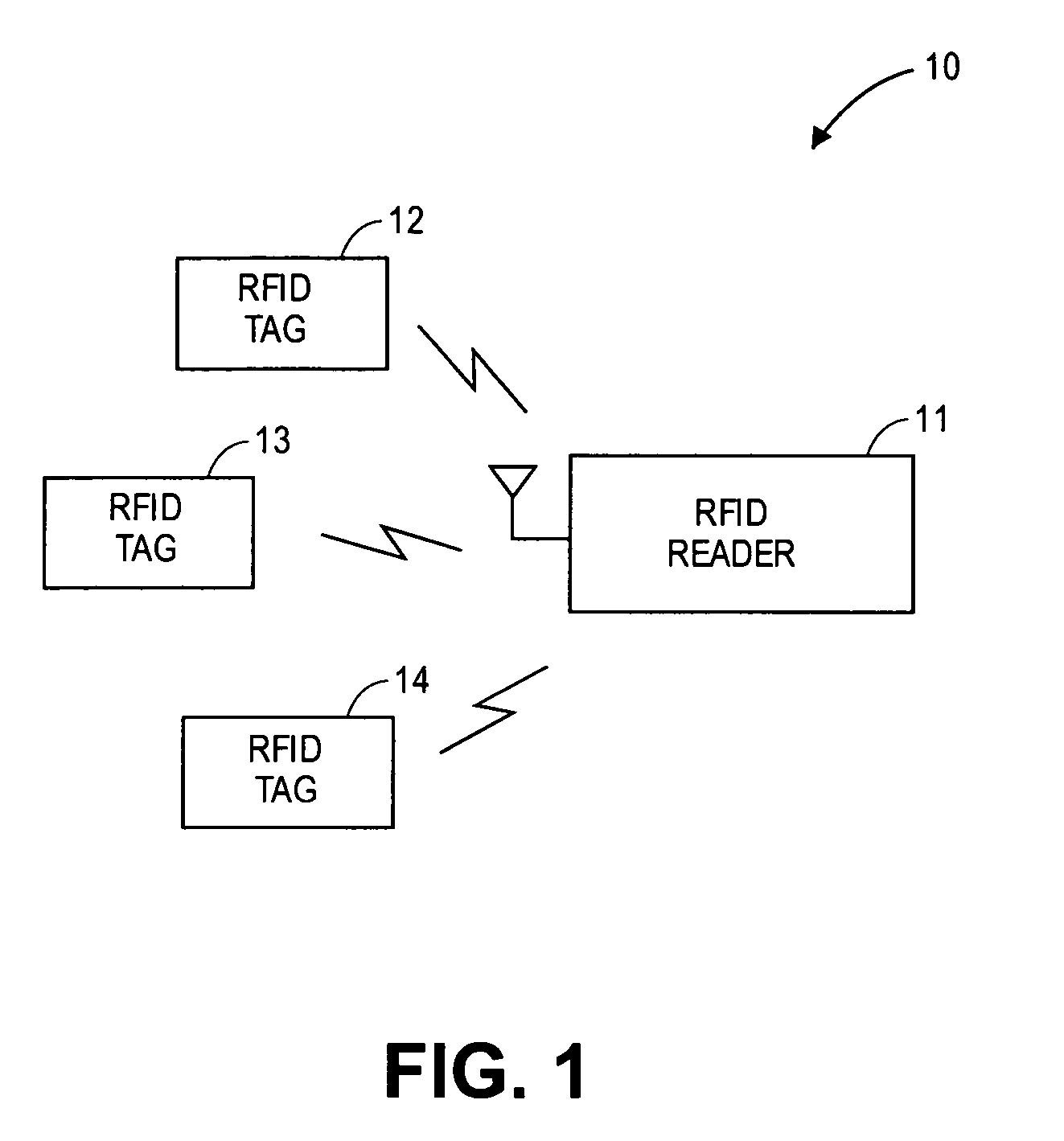

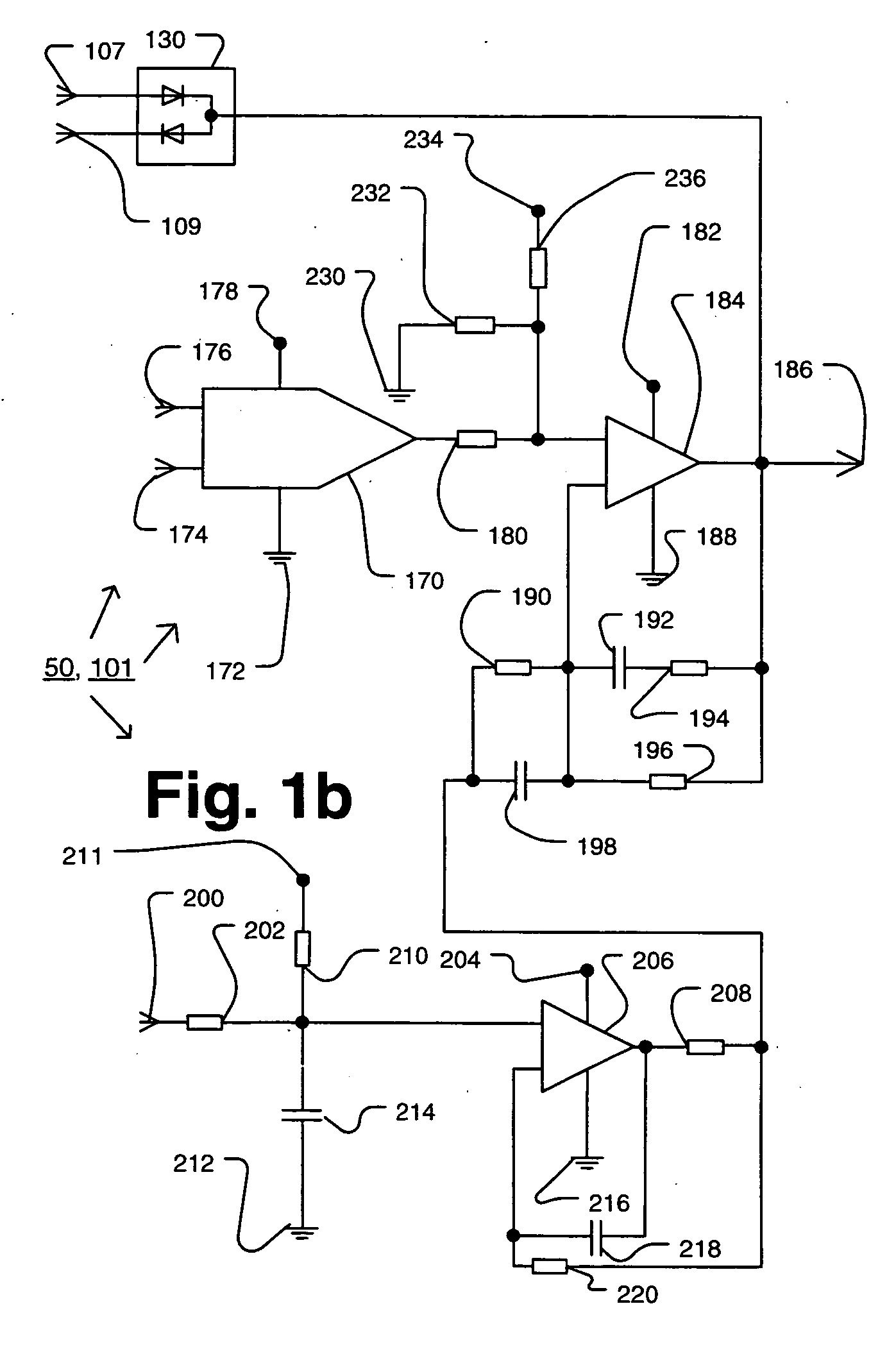

Multi-protocol radio frequency identification transponder transceiver

ActiveUS20060238301A1Memory record carrier reading problemsNear-field in RFIDTransceiverIn-phase and quadrature components

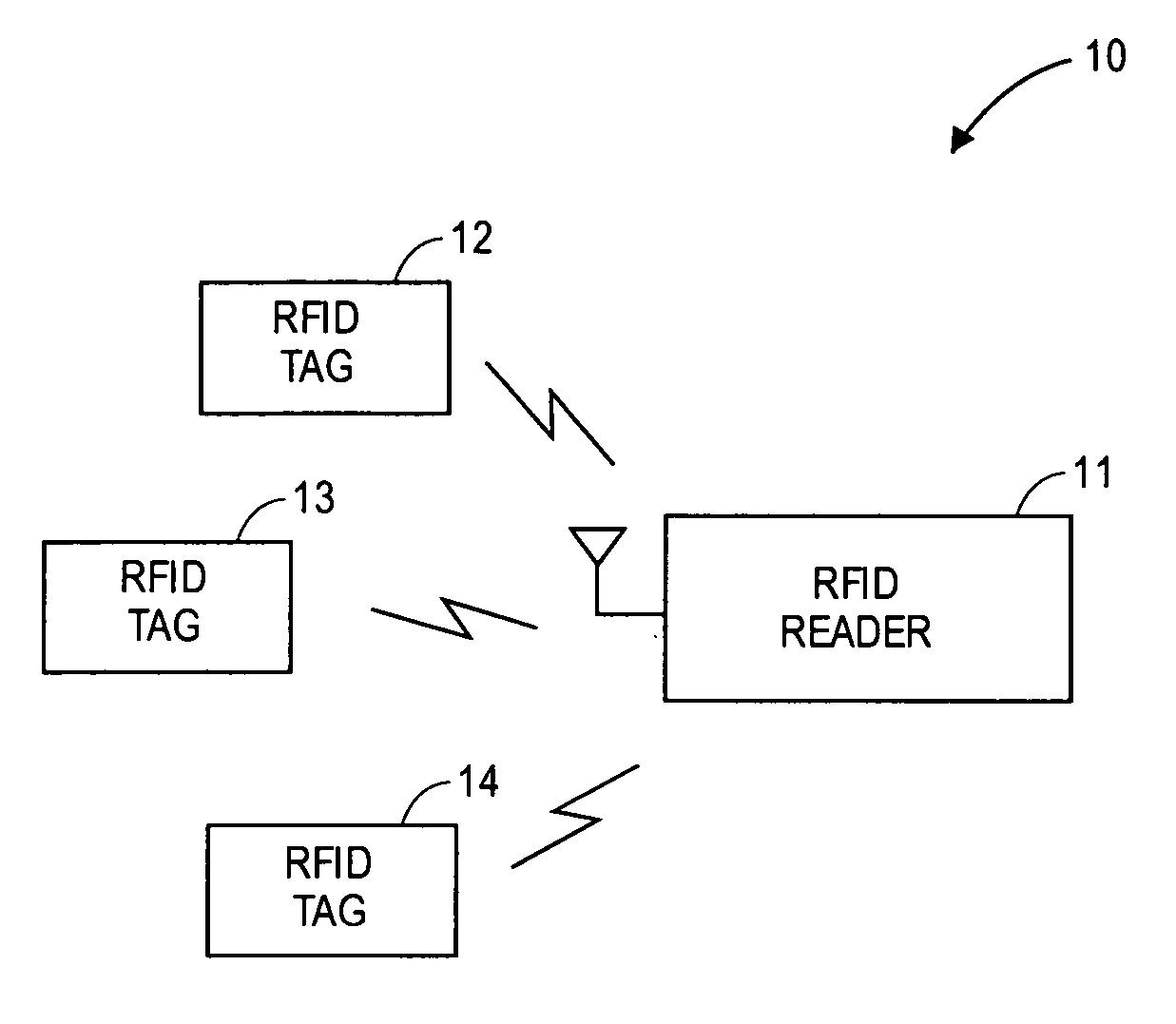

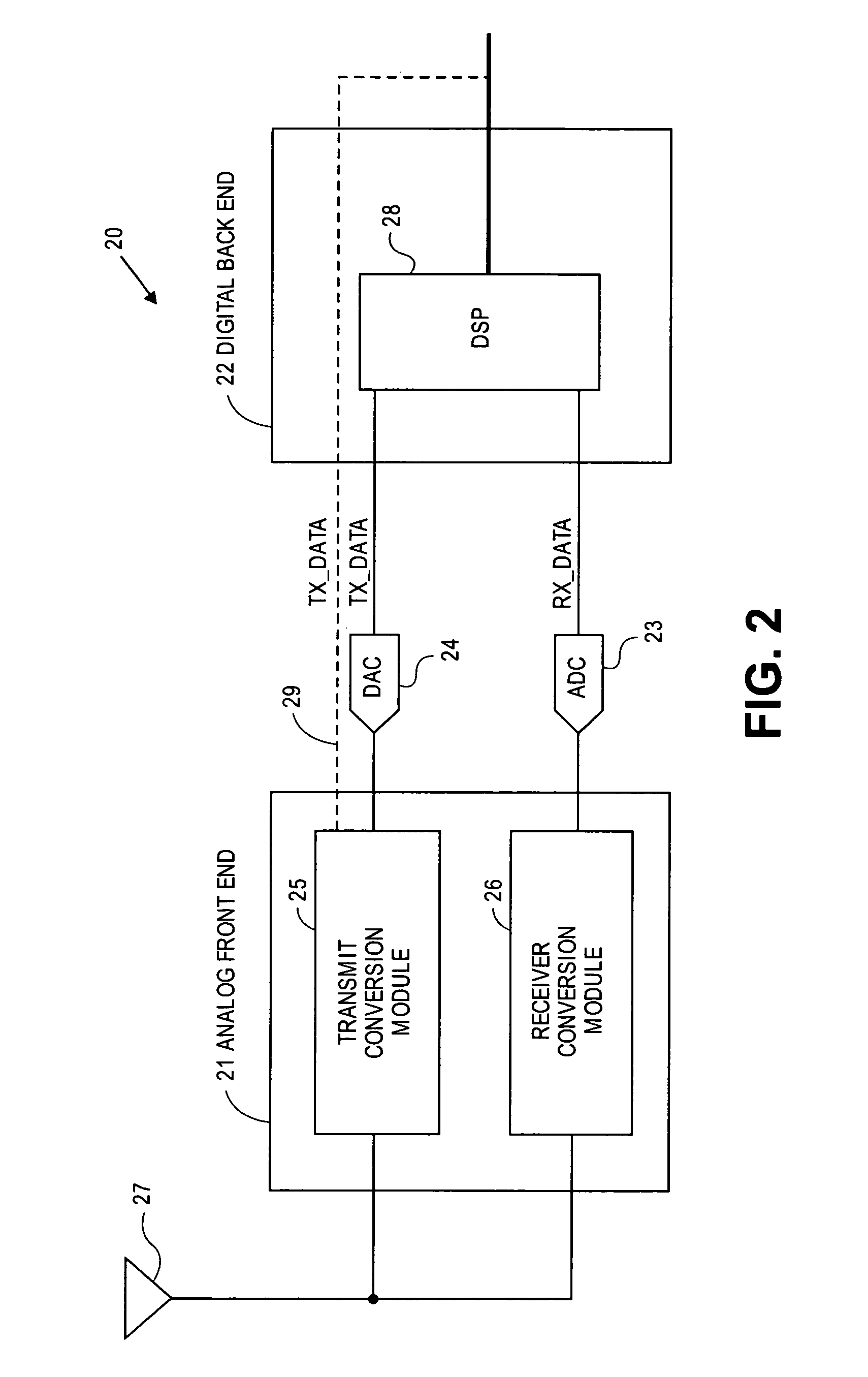

A transceiver for a RFID reader and a transceiver for a RFID transponder (tag) allow communication between the two devices. The RFID reader utilizes an analog front end and a digital backend. In the receiver portion of the transceiver, the front end of the RFID reader uses a pair of down-conversion mixers to demodulate a received signal into in-phase (I) and quadrature (Q) components and analog-to-digital converters (ADC) digitize the signal. A digital signal processor (DSP) in the back end processes the digital signal and uses a matched filter for data detection. The RFID tag receives an inductively coupled signal from the reader and the receiver portion of the tag uses a pulse / level detector that employs an analog comparator and a sample and hold circuit to detect the received signal. A digital decoder / controller is used to decode the incoming data and to establish a sampling clock for the pulse / level detector. An automatic gain control (AGC) circuit adjusts a receiver gain according to the received signal strength and controls tuning of magnetic coupling circuitry.

Owner:NXP USA INC

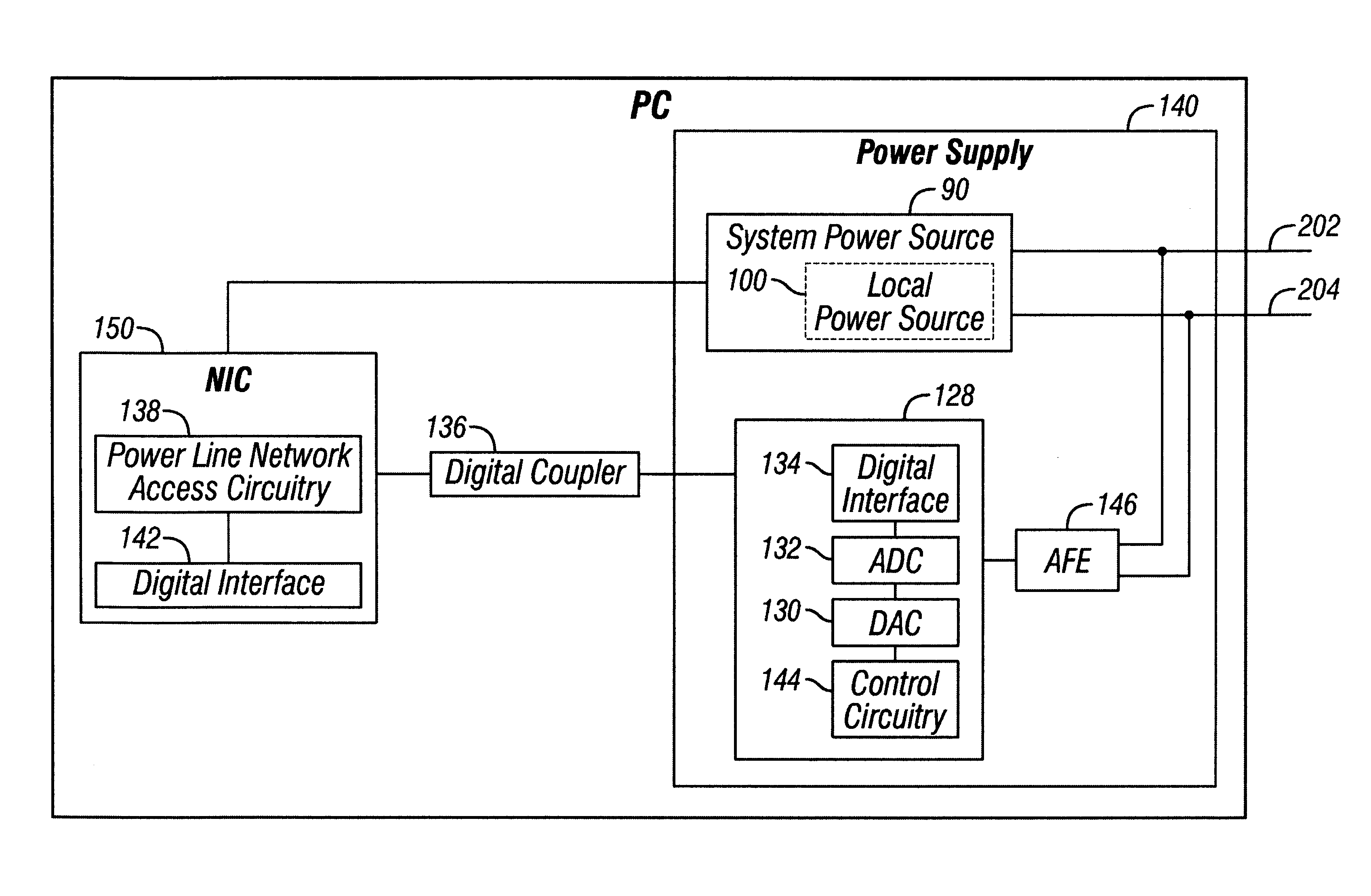

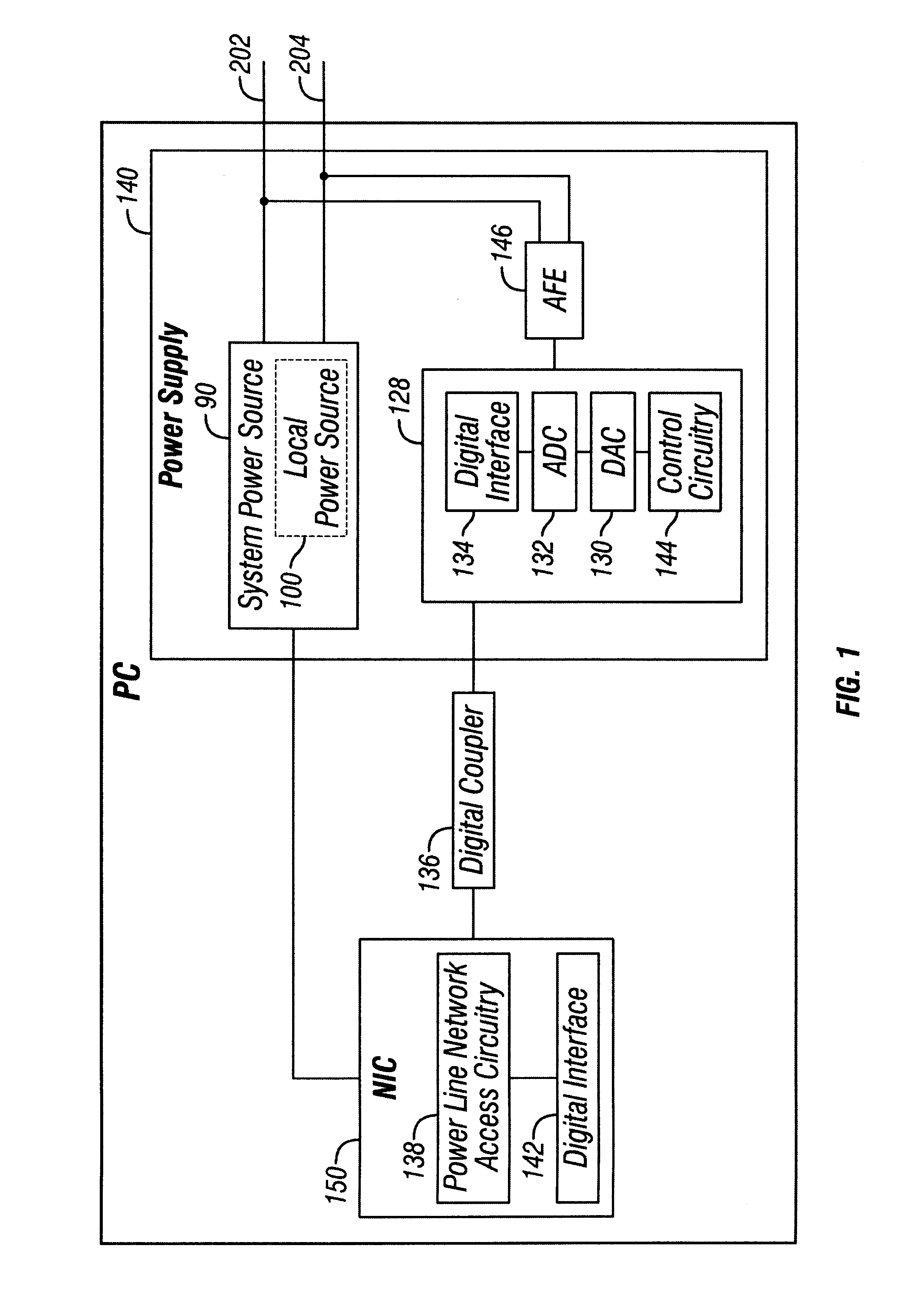

Power supply with digital data coupling for power-line networking

InactiveUS6373377B1Electric signal transmission systemsPower distribution line transmissionDigital dataPower line network

A power supply provides digital data coupling for power-line networking. The power supply includes a power supply side digital interface to transmit and receive a digital data passed through a digital coupler to and from a power-line network access circuitry side digital interface of power-line network access circuitry. The power supply further includes a digital-to-analog converter to process digital data into a high-frequency analog data carrier to provide to a power line of a power-line network. An analog-to-digital converter of the power supply converts a high-frequency analog data carrier from the power line into digital data for the power-line network access circuitry. A power-line analog front end of the power supply transmits and receives the high-frequency analog data carrier to and from the power line. Digital data exchanged between the power supply and the network access circuitry may include control signals for a control circuitry of the power supply. Control circuitry of the power supply may handle control of the digital-to-analog converter, the analog-to-digital converter and the analog front end.

Owner:SYNAPTICS INC

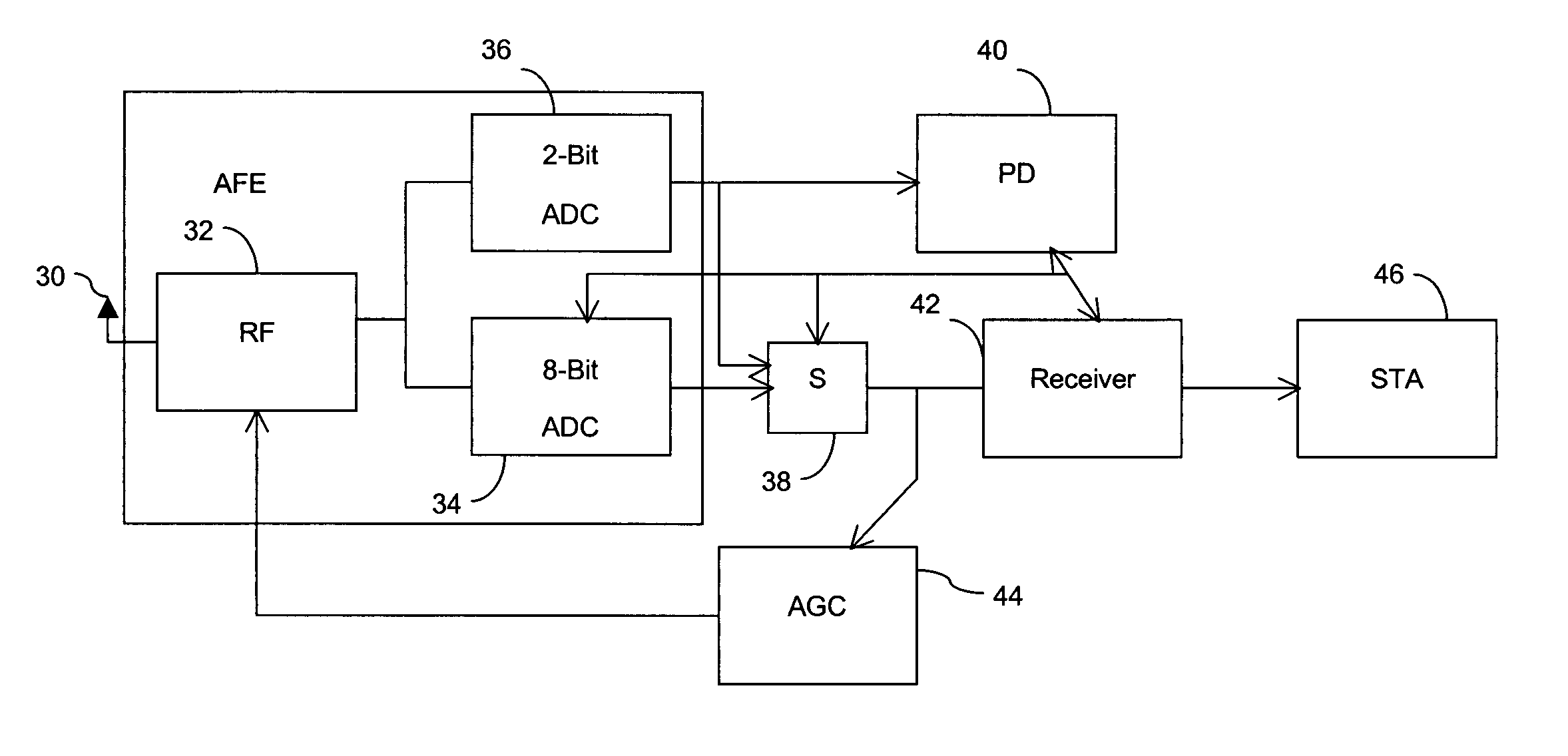

Multi-protocol radio frequency identification reader transceiver

ActiveUS20060186995A1Electric signal transmission systemsError preventionTransceiverDown conversion mixer

A transceiver for a RFID reader and a transceiver for a RFID transponder (tag) allow communication between the two devices. The RFID reader utilizes an analog front end and a digital backend. In the receiver portion of the transceiver, the front end of the RFID reader uses a pair of down-conversion mixers to demodulate a received signal into in-phase (I) and quadrature (Q) components and analog-to-digital converters (ADC) digitize the signal. A digital signal processor (DSP) in the back end processes the digital signal and uses a matched filter for data detection. The RFID tag receives an inductively coupled signal from the reader and the receiver portion of the tag uses a pulse / level detector that employs an analog comparator and a sample and hold circuit to detect the received signal. A digital decoder / controller is used to decode the incoming data and to establish a sampling clock for the pulse / level detector. An automatic gain control (AGC) circuit adjusts a receiver gain according to the received signal strength and controls tuning of magnetic coupling circuitry.

Owner:NXP USA INC

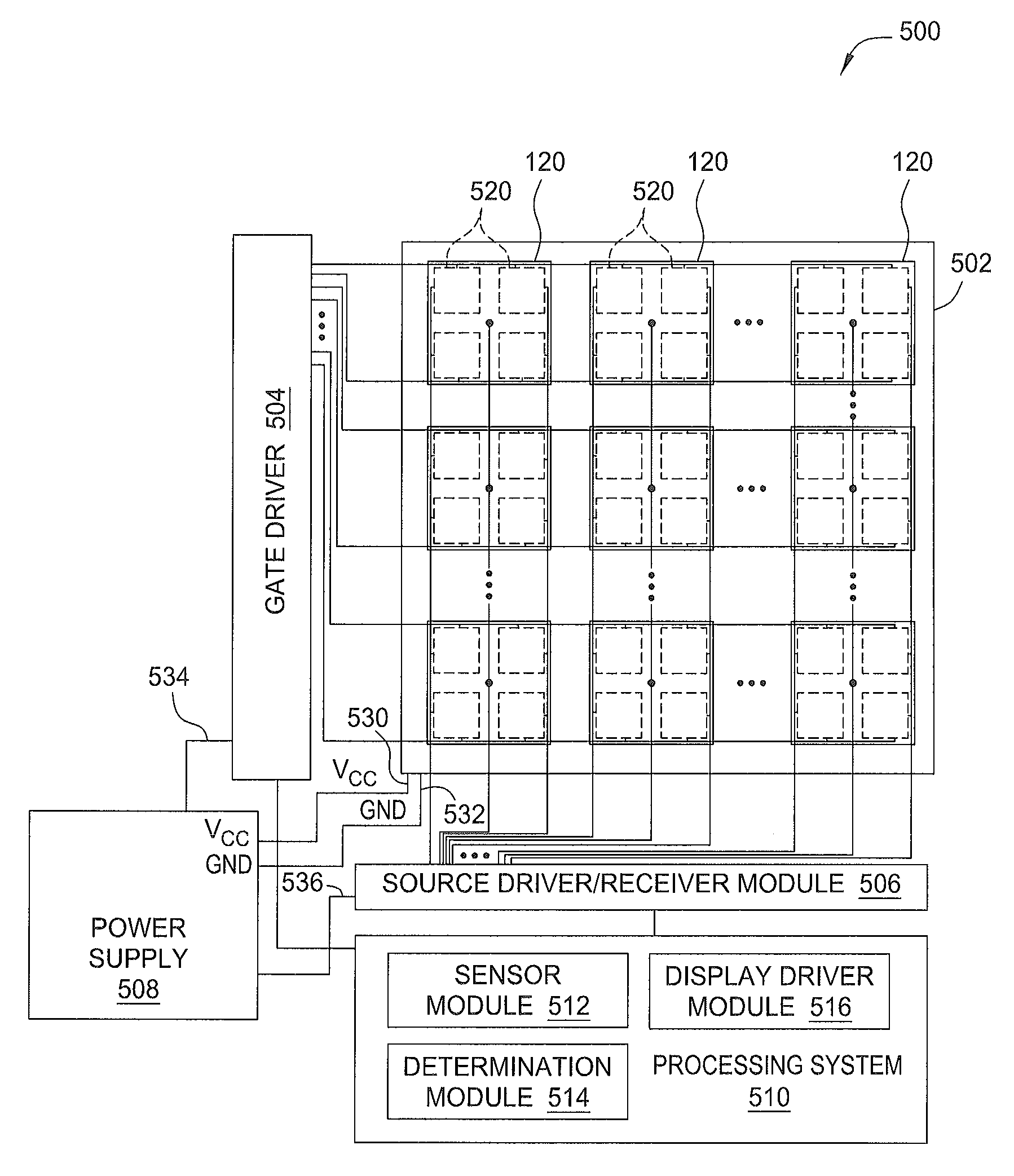

Modulated power supply for reduced parasitic capacitance

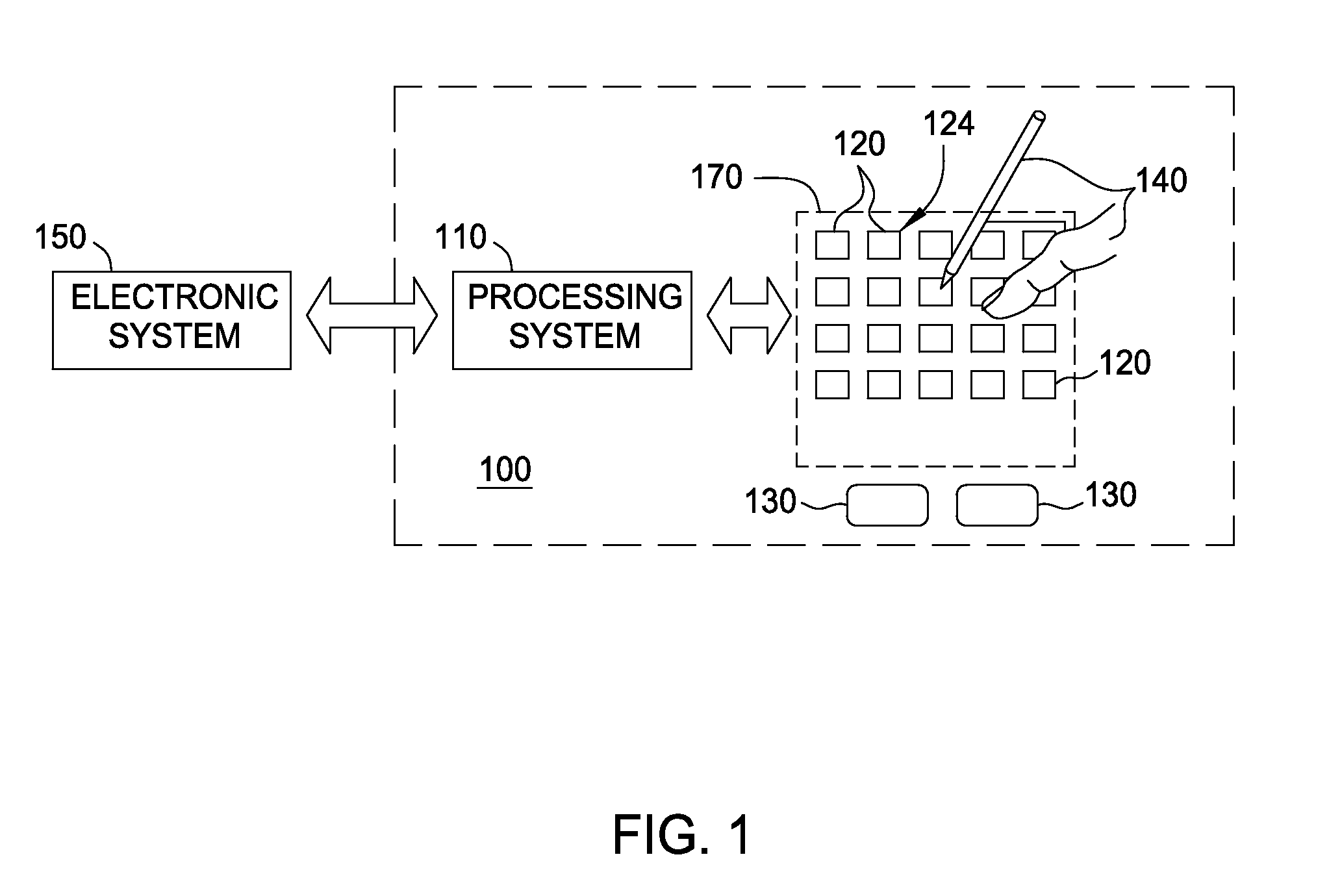

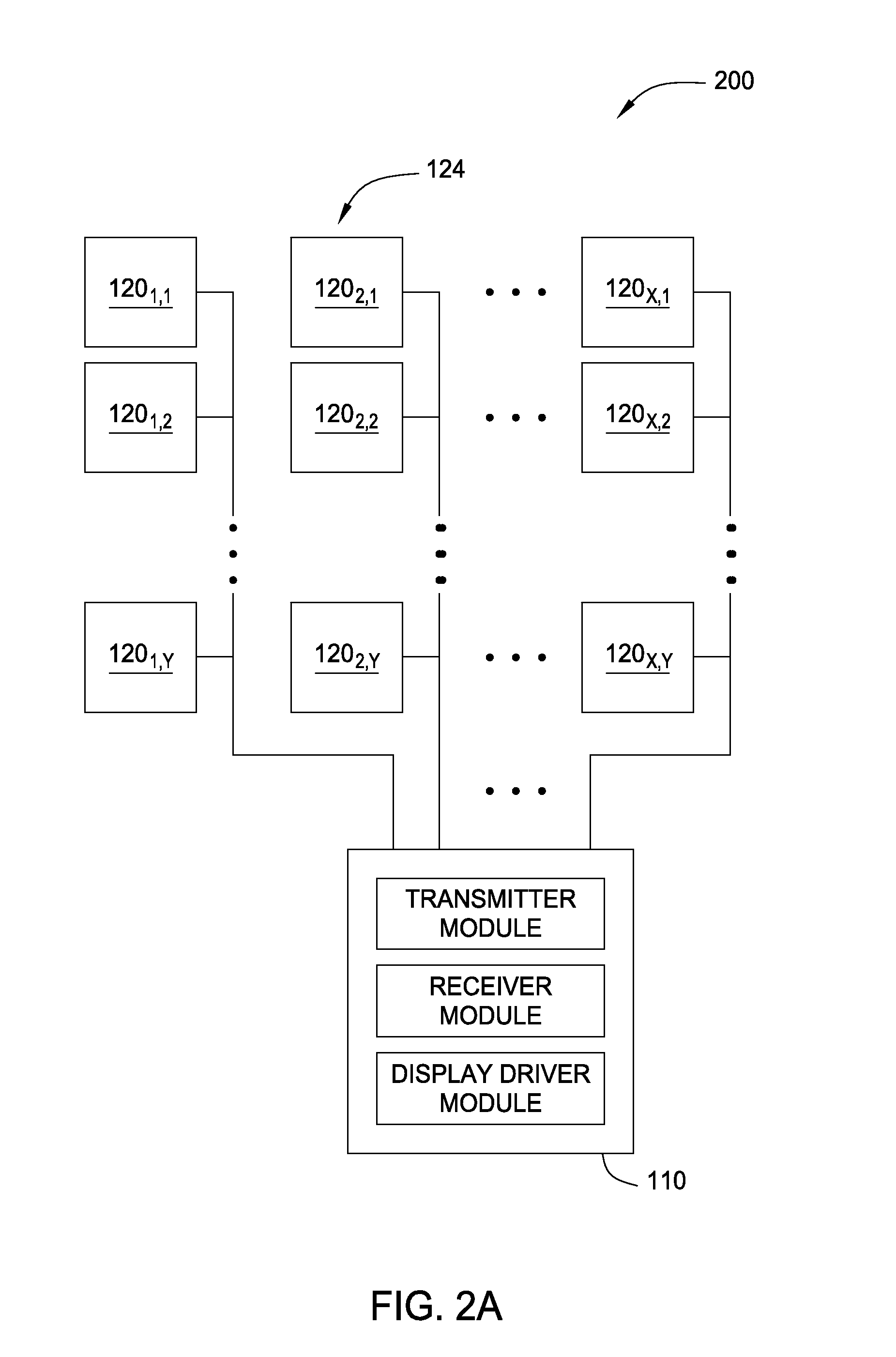

ActiveUS8766950B1Non-linear opticsInput/output processes for data processingParasitic capacitanceComputer module

Embodiments described herein include an input device for capacitive sensing. The input device includes a plurality of sensor electrodes, a modulated power supply, a plurality of analog front end channels, and a sensor module. The modulated power supply is configured to generate a modulated reference signal. The plurality of analog front end channels are coupled to the plurality of sensor electrodes and to the modulated power supply and are configured to flow charge in response to an input object in a sensing area associated with the plurality of sensor electrodes. The sensor module comprises transmitter circuitry that is coupled to the plurality of sensor electrodes and to the plurality of analog front end channels. The sensor module is configured to drive the plurality of sensor electrodes with a modulated sensor electrode signal that is based on the modulated reference signal, via the plurality of analog front end channels.

Owner:SYNAPTICS INC

Correction system and method of analog front end

InactiveUS20050007461A1Television system detailsPicture signal generatorsSoftware engineeringAnalog front-end

The present invention is a correction system applying in an analog front end(AFE). The correction system comprises a correction module, a first digital to analog converter(DAC1) and a second digital to analog converter(DAC2). The correction is used to generate a gain error correction and black pixel signal error correction when the black pixel signal is inputted into the AFE. The correction module corrects the digital output signals generated by the AFE according to the gain error correction. The correction module input the black pixel signal error correction to the DAC1 to generate a first analog correction signal to correct the signal inputted into the AFE. The present invention effectively corrects the signal error generated by the AFE to make the AFE output the corrected digital output signal.

Owner:NOVATEK MICROELECTRONICS CORP

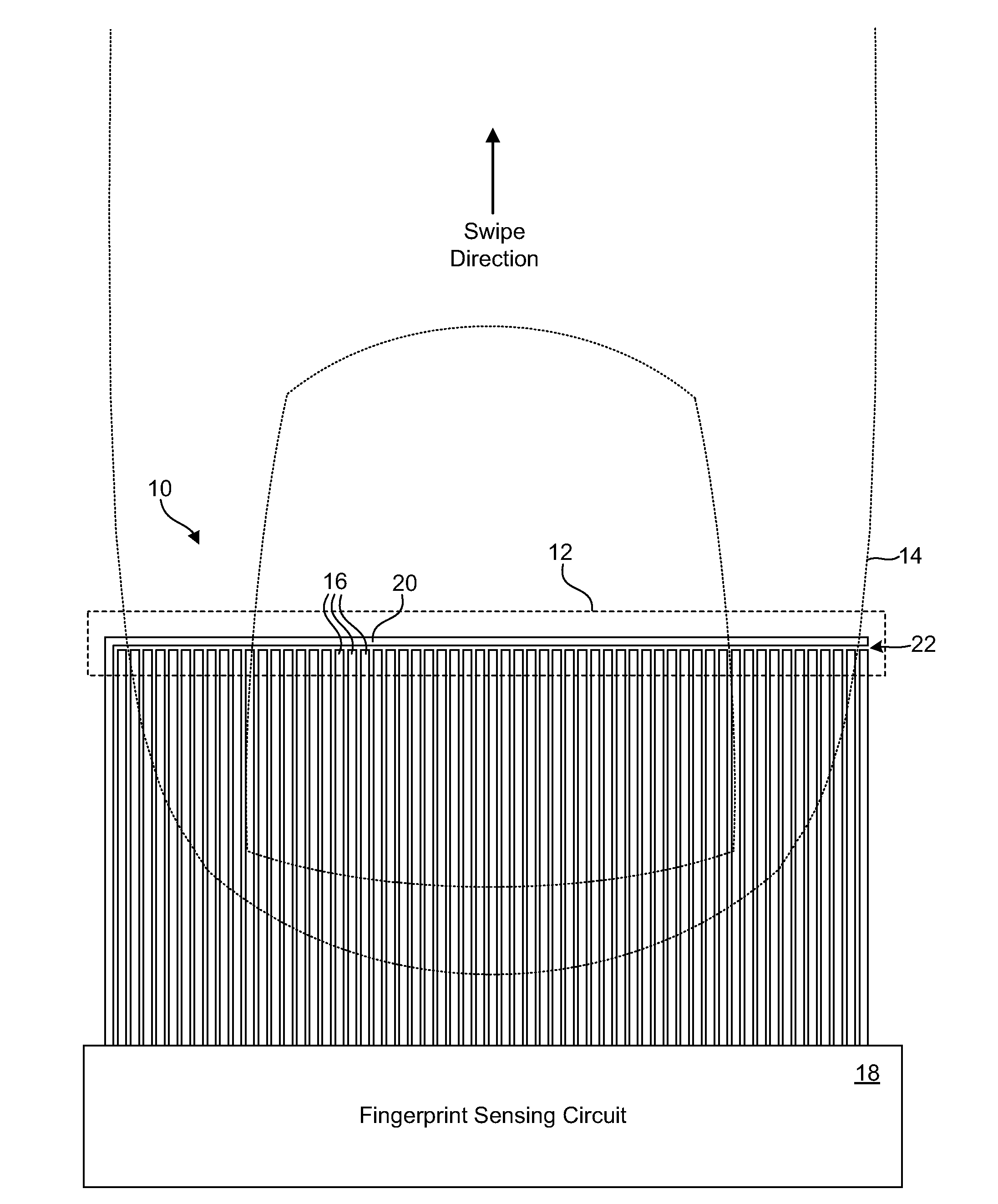

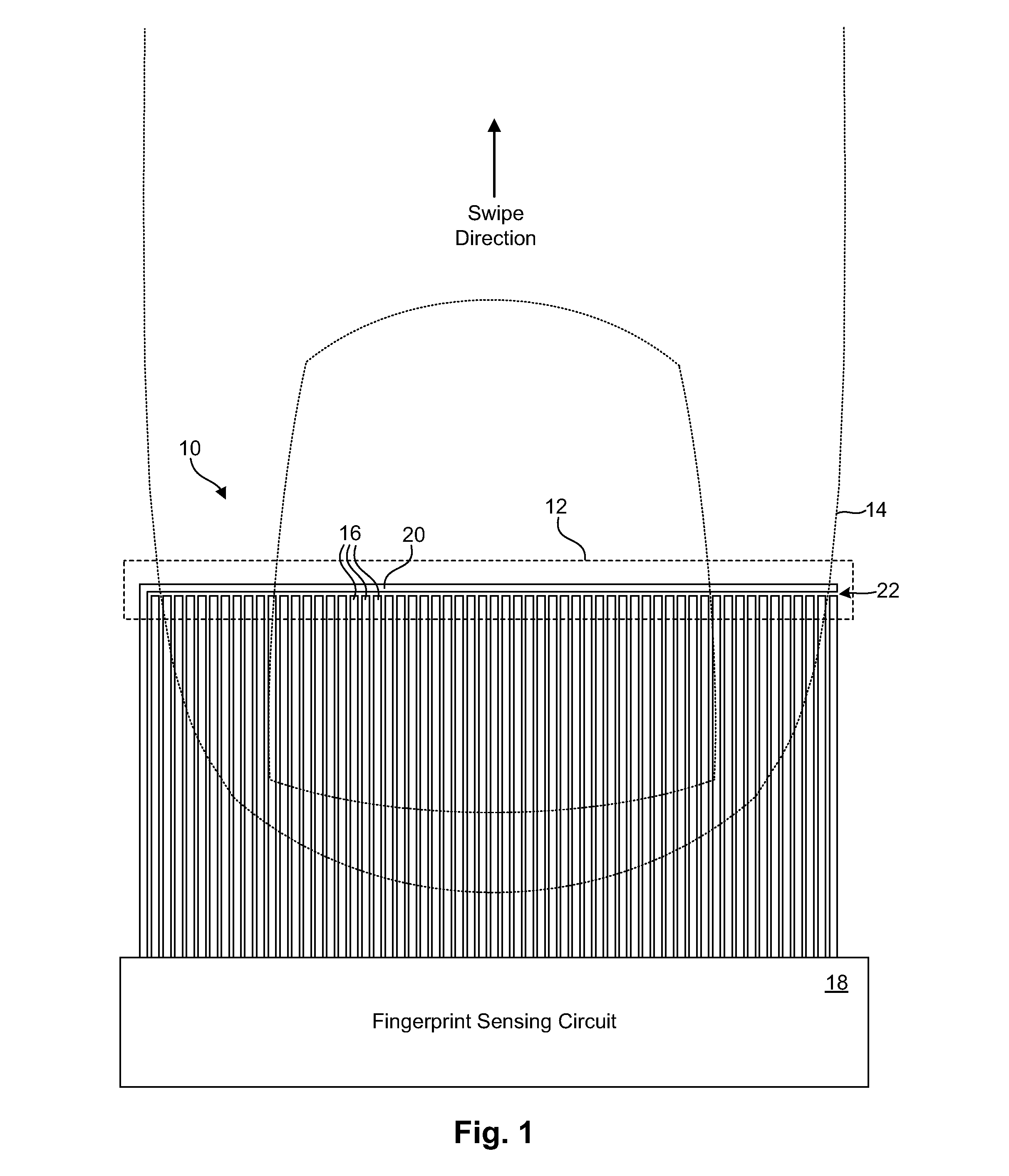

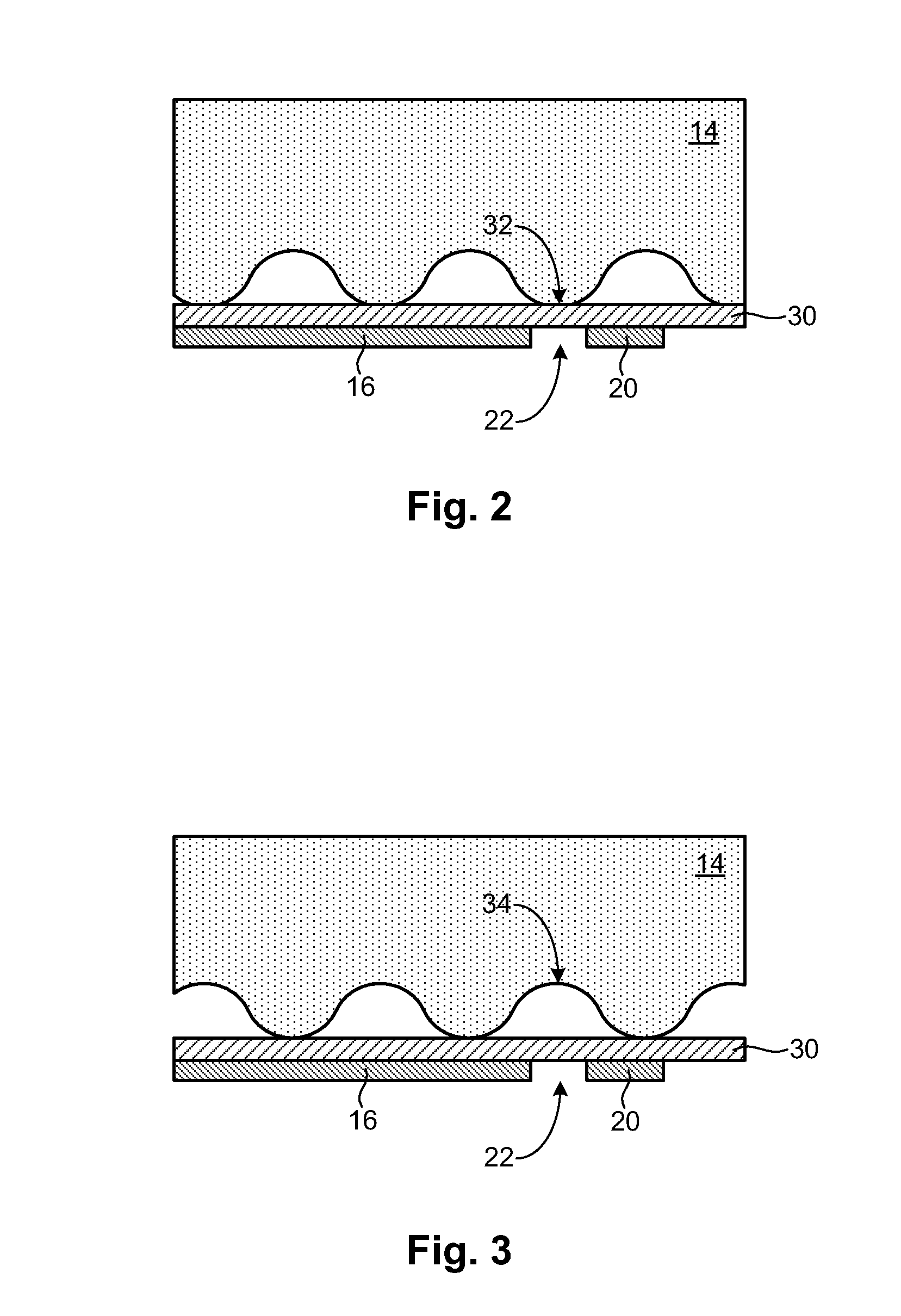

Apparatus and Method for Reducing Noise In Fingerprint Sensing Circuits

ActiveUS20090252385A1Reduce noiseReduce the amount requiredPrint image acquisitionEngineeringAnalog front-end

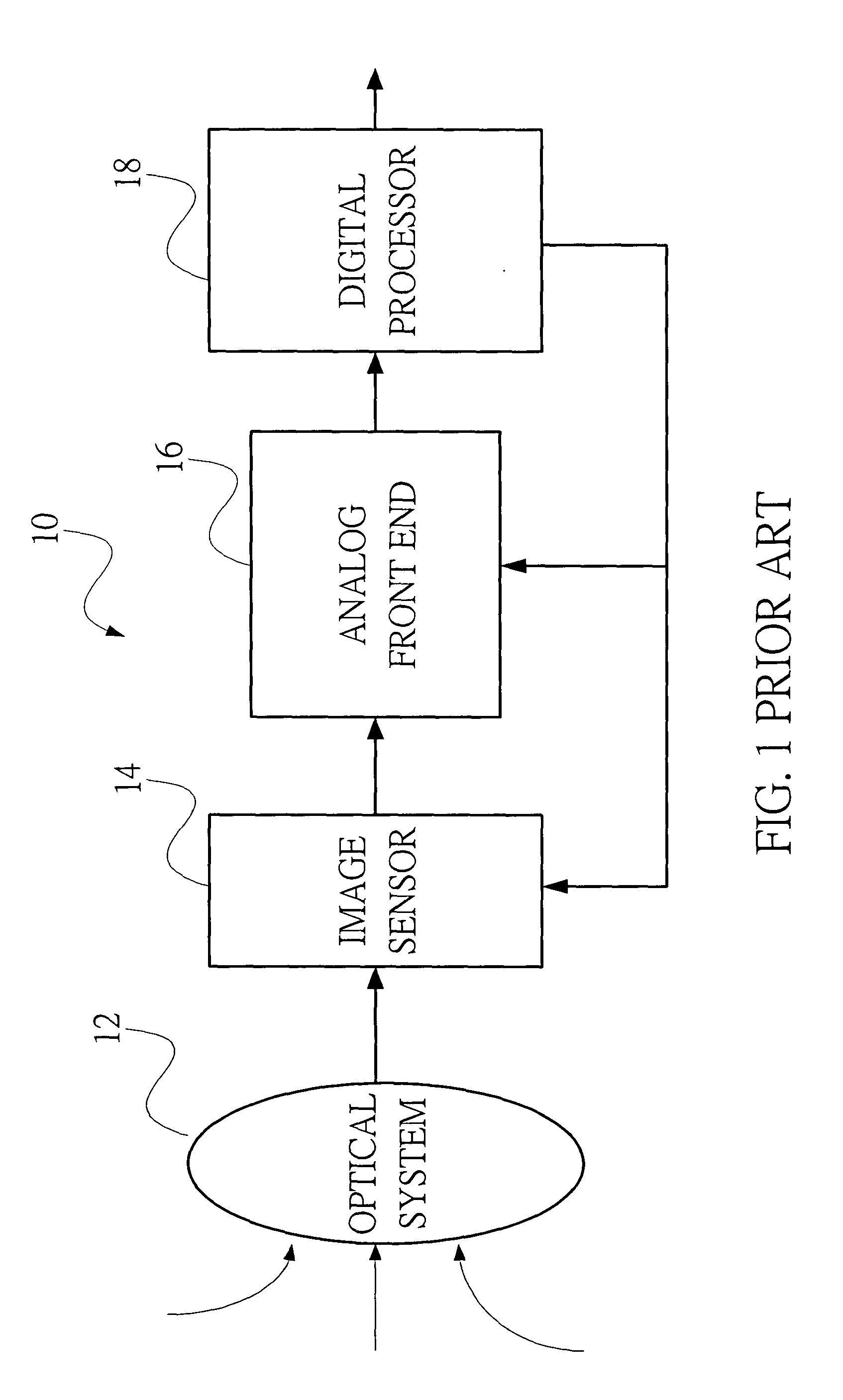

An apparatus for reducing noise in fingerprint sensing circuits is disclosed in one embodiment of the invention as including a fingerprint sensing area onto which a user can apply a fingerprint. An analog front end is coupled to the fingerprint sensing area and is configured to generate an analog response signal. An analog-to-digital converter (ADC) samples the analog response signal and converts the sample to a digital value, which may be received by a digital device such as a processor or CPU. To reduce the amount of the noise that is present in the analog response signal and therefore reflected in the digital value, the digital device may be shut down while the ADC is sampling the analog response signal.

Owner:SYNAPTICS INC

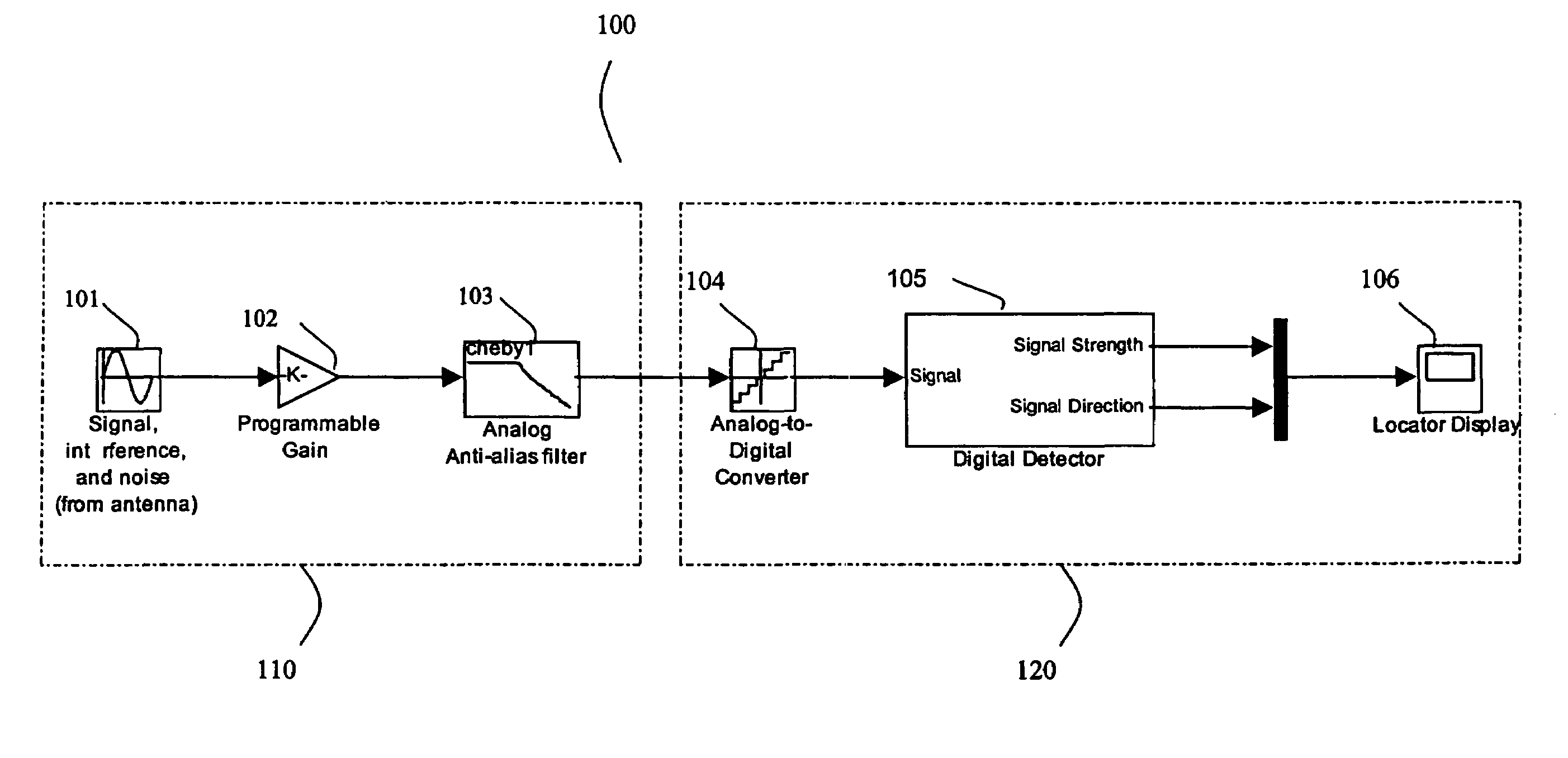

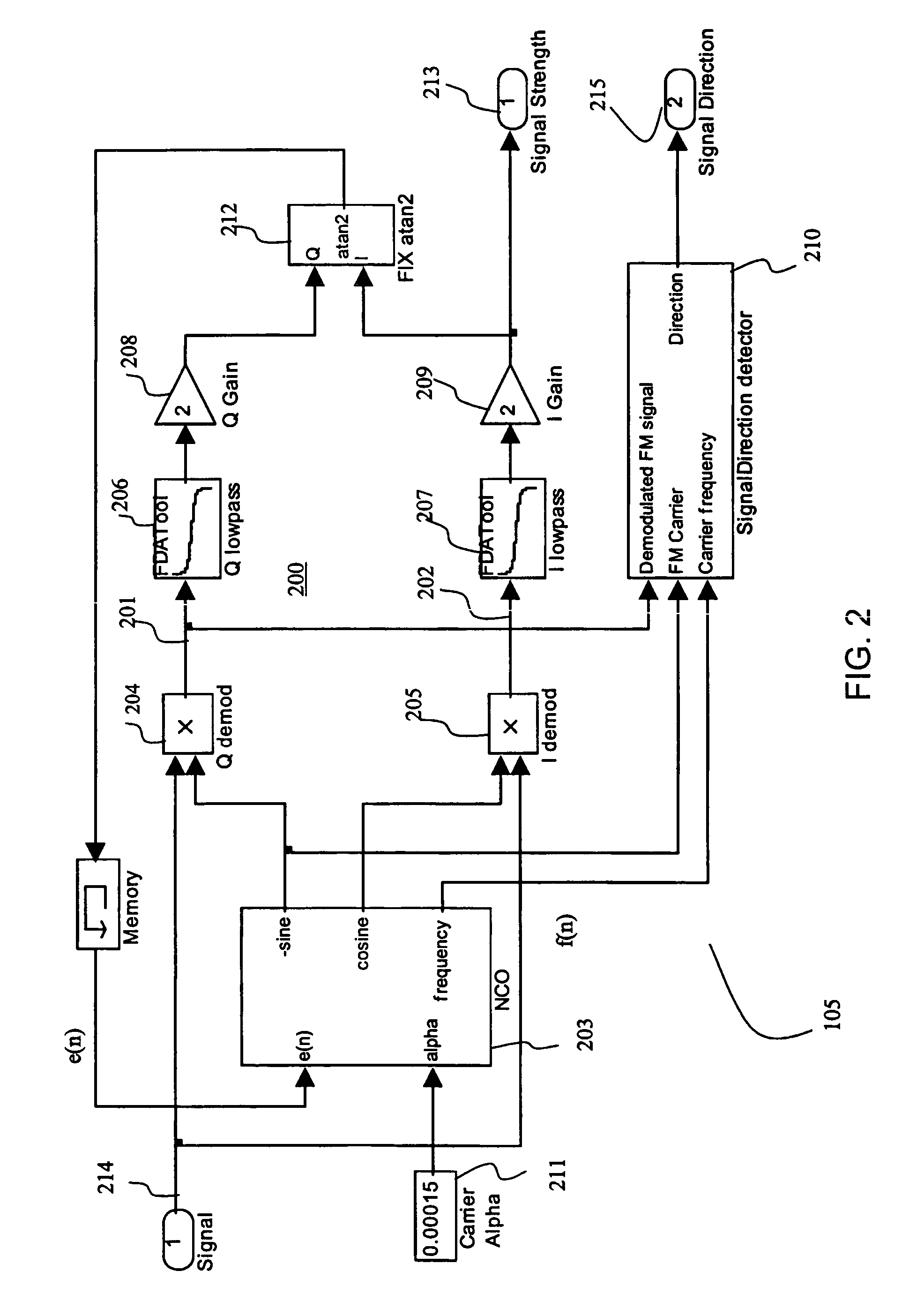

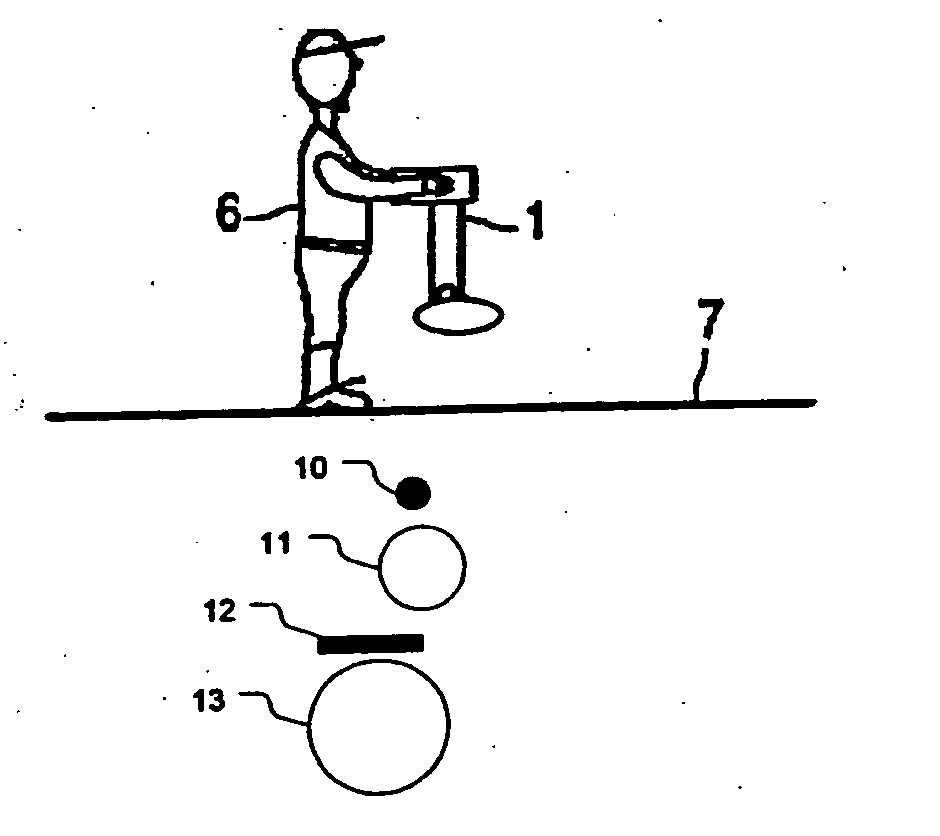

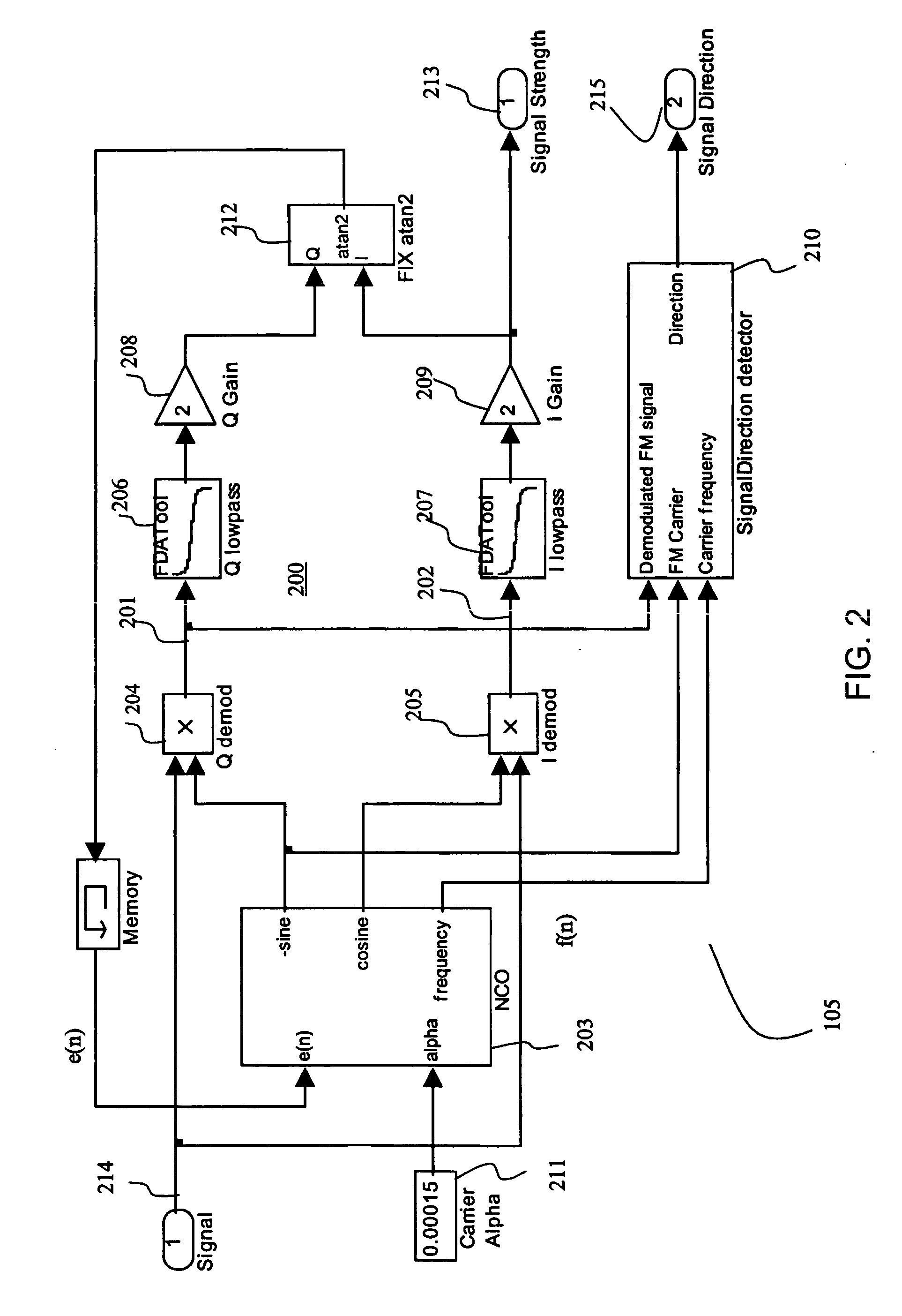

Method and apparatus for digital detection of electromagnetic signal strength and signal direction in metallic pipes and cables

InactiveUS7062414B2Low hardware requirementsWide resistance to component tolerancesAmplifier modifications to reduce noise influenceDigital computer detailsDigital signal processingCarrier signal

A new digital architecture for metallic pipe and cable locators, providing accurate estimation of the fundamental locate parameters, electromagnetic signal strength and signal direction, and utilizing a nested Digital Phase-Locked Loop (DPLL) structure is disclosed. The obstacles to signal direction measurement in low SINR environments using the signal select method are overcome and a more precise phase comparison between the carrier and the FM modulation signals is obtained. The architecture further significantly reduces analog front-end hardware requirements, offers wider resistance to component tolerances, lower calibration and test time, and provides flexible frequency selectivity. Locators according to the present invention provide accurate estimation of the fundamental physical parameters of line location (electromagnetic signal strength and signal direction) in extremely noisy environments, using Digital Signal Processing (DSP) methods.

Owner:BUSAN TRANSPORTATION CORPORATION

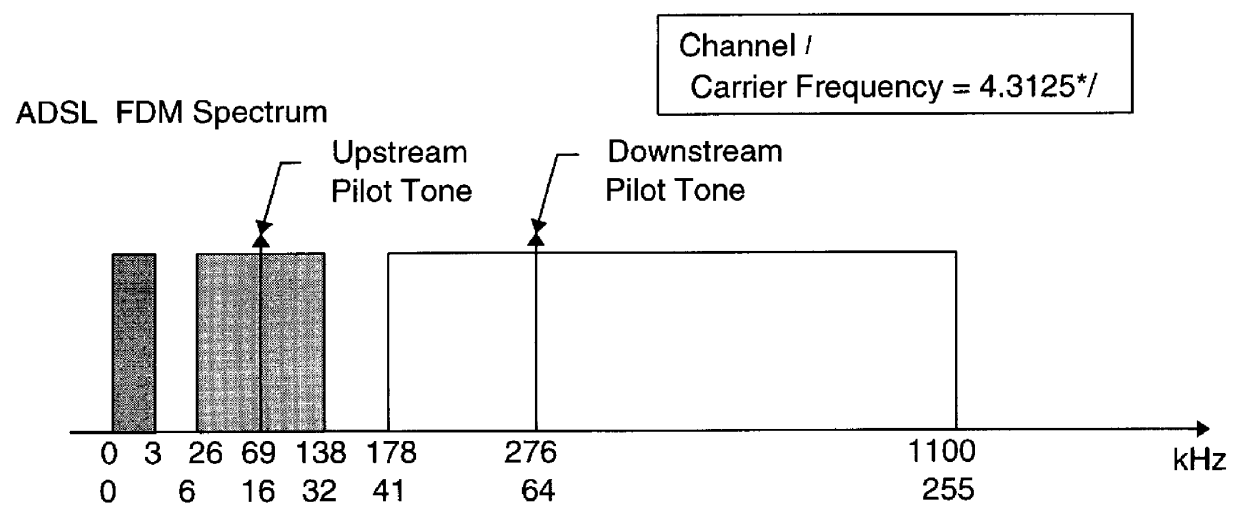

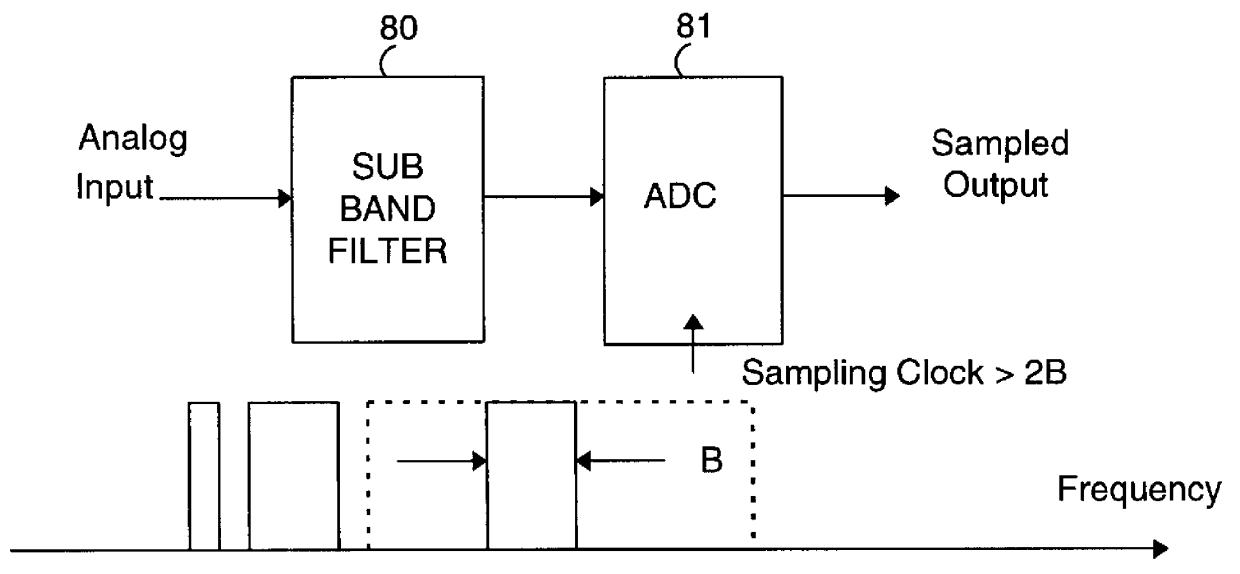

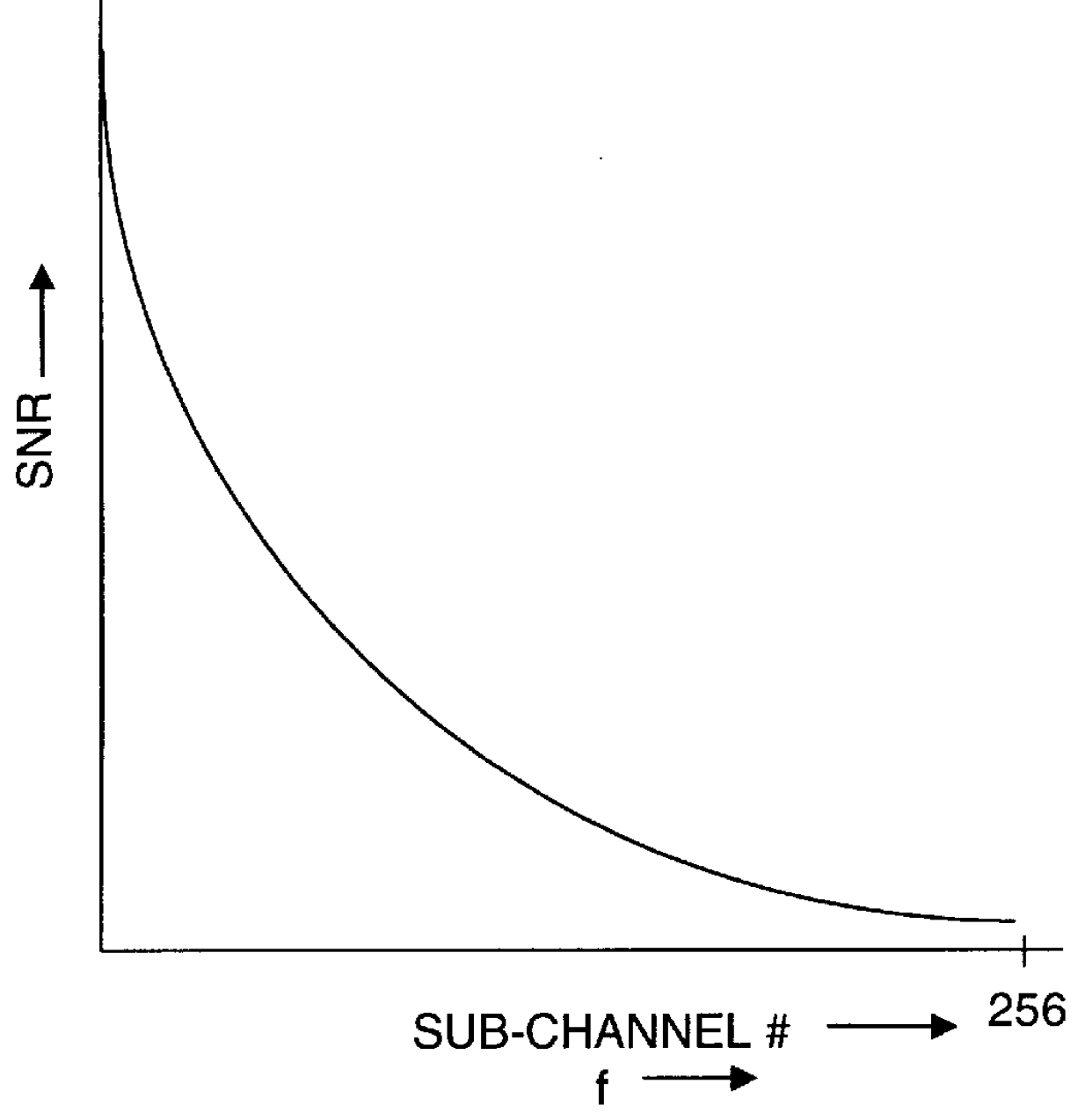

Program for controlling DMT based modem using sub-channel selection to achieve scaleable data rate based on available signal processing resources

InactiveUS6073179ALow costReduce complexityTelephonic communicationTime-division multiplexModem deviceData rate

An applications program is provided for permitting a user of a host processing system to dynamically control a modem having forward compatible and expandable functionality. In a preferred embodiment, the applications program is designed to run on a personal computer running the Windows.RTM. shell, and the modem is compatible with ADSL promulgated standards. As part of such program, initialization and detection routines determine the capabilities of an ADSL modem, including whether the same has been upgraded to have enhanced data throughput. A calibration routine measures the computing power available to the host processor, and based on this information and other relevant parameters determines nominal setup parameters for the modem. These parameters are stored in a Device Parameter Table so that they can be accessed by various application programs that may make use of such modem. A user of such program can at that time or thereafter alter the characteristics of the ADSL modem (including a target data rate) subject to availability of sufficiently powerful analog front end sampling circuitry and processing power.

Owner:REALTEK SEMICON CORP +1

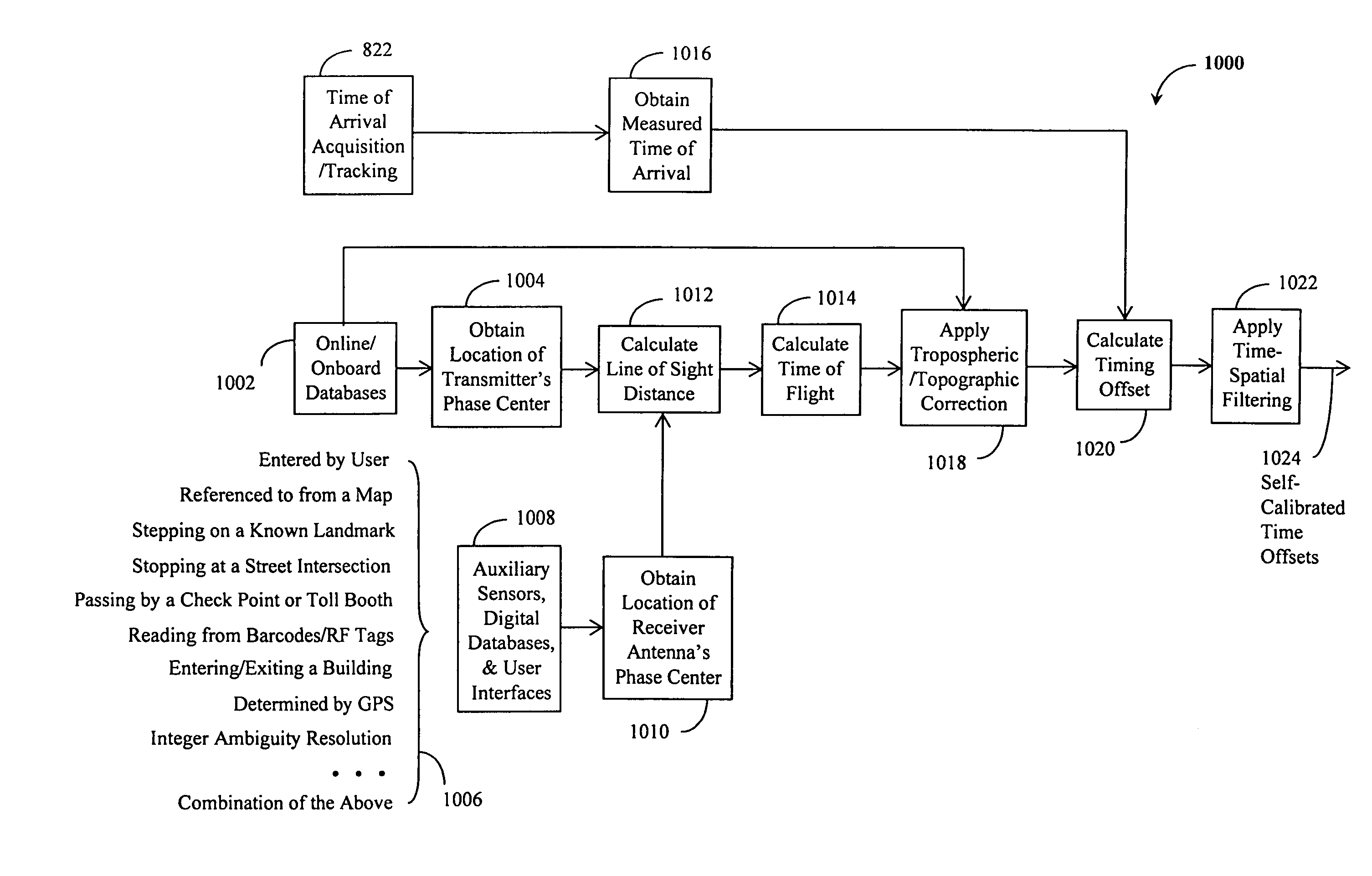

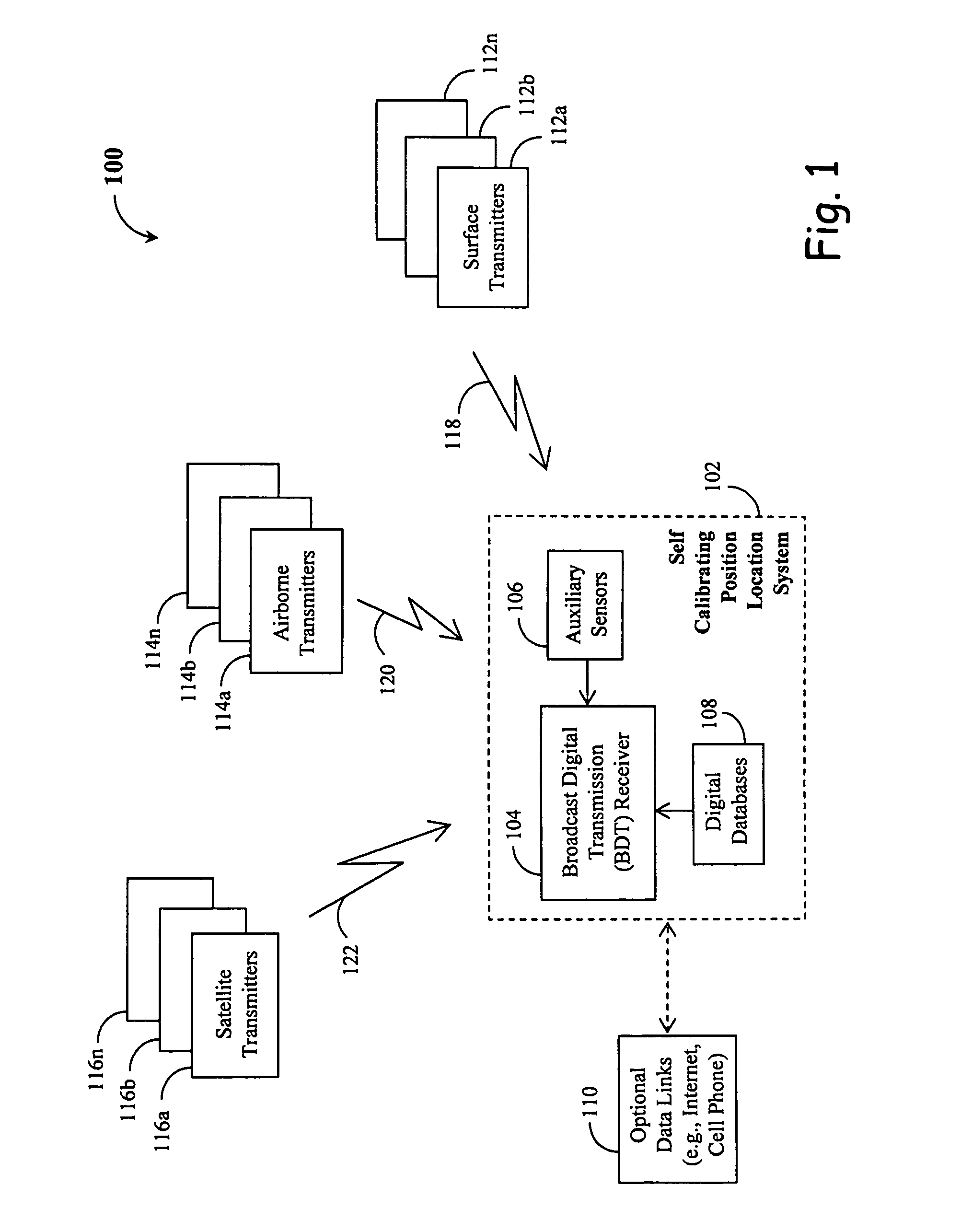

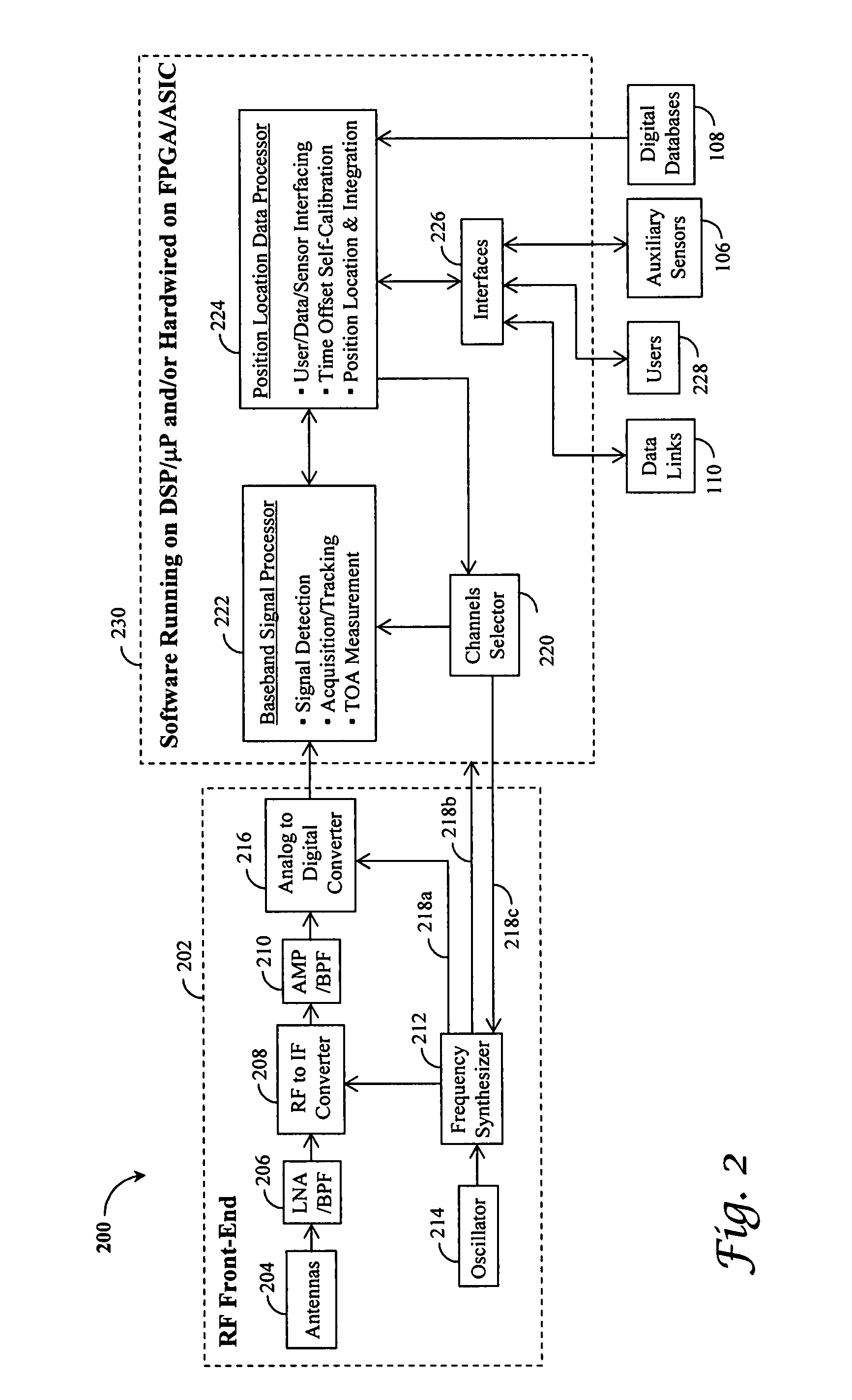

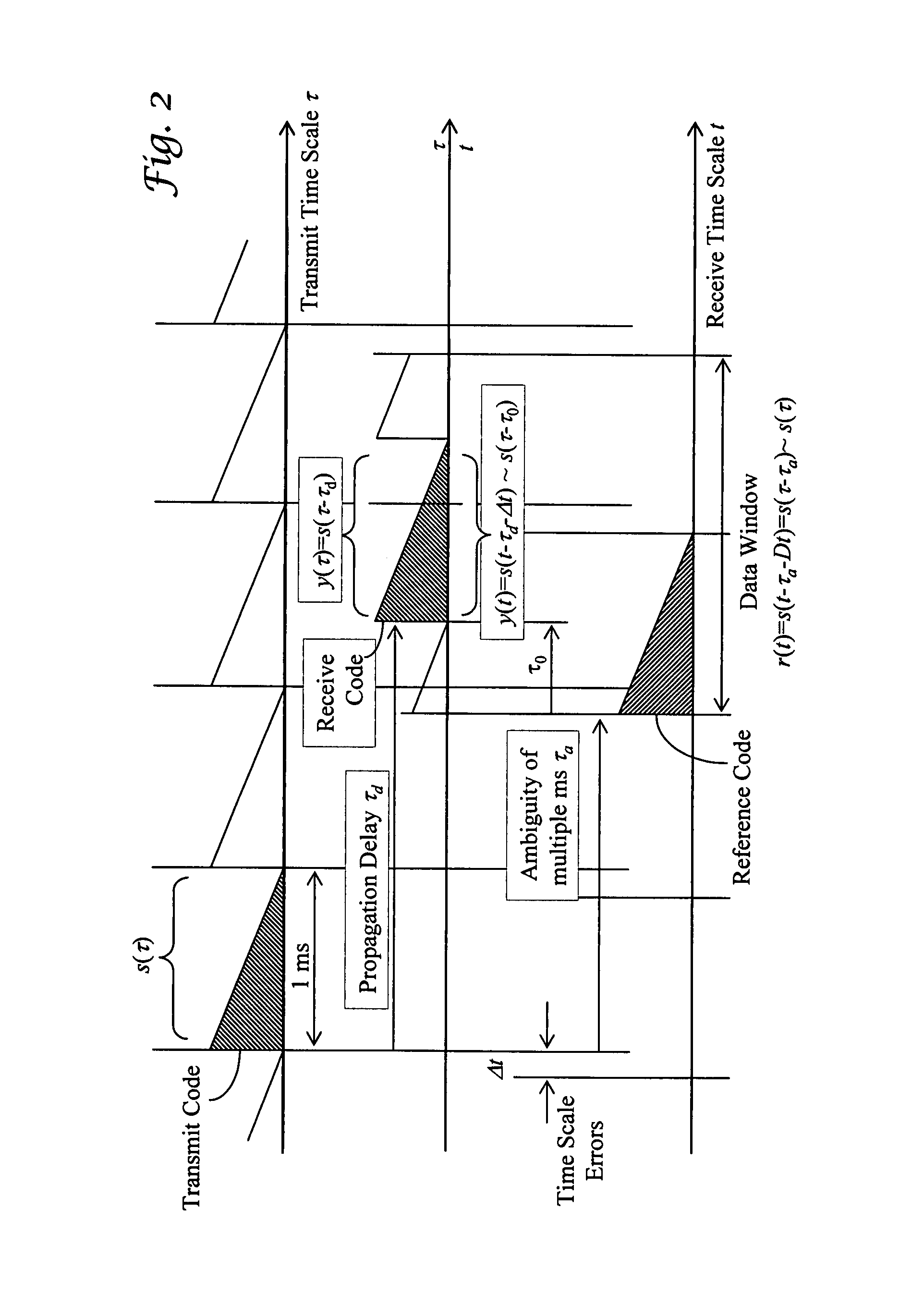

Self-calibrating position location using periodic codes in broadcast digital transmissions

InactiveUS7388541B1Convenient to accommodateOptimize timingDirection finders using radio wavesPosition fixationDigital dataEngineering

A broadcast digital transmission (BDT) receiver, computer-readable media, and associated method for receiving and processing of BDT signals from a plurality of transmitters. A BDT receiver includes an antenna to intercept broadcast radio signals and an analog front-end to down-convert it to a suitable frequency for digitization. A baseband signal processor acquires and tracks designated codes in BDT signals using a generalized correlator to produce time of arrival measurements thereof. A data processor, coupled to the baseband signal processor and with input from an auxiliary sensor and a digital database, first calibrates time offsets of said transmitters relative to the BDT receiver's time base and then operates on offset-adjusted time of arrival measurements to produce a position solution.

Owner:YANG CHUN

Method and apparatus for digital detection of electronic markers using frequency adaptation

ActiveUS20070040558A1High-precision identificationReliable discriminationPipe laying and repairElectric/magnetic detectionTested timeAnalog front-end

Owner:BUSAN TRANSPORTATION CORPORATION

Reducing false wake-up in a low frequency transponder

InactiveUS20050237160A1Eliminating false wake-upShortened battery lifeElectric signal transmission systemsDigital data processing detailsMicrocontrollerEngineering

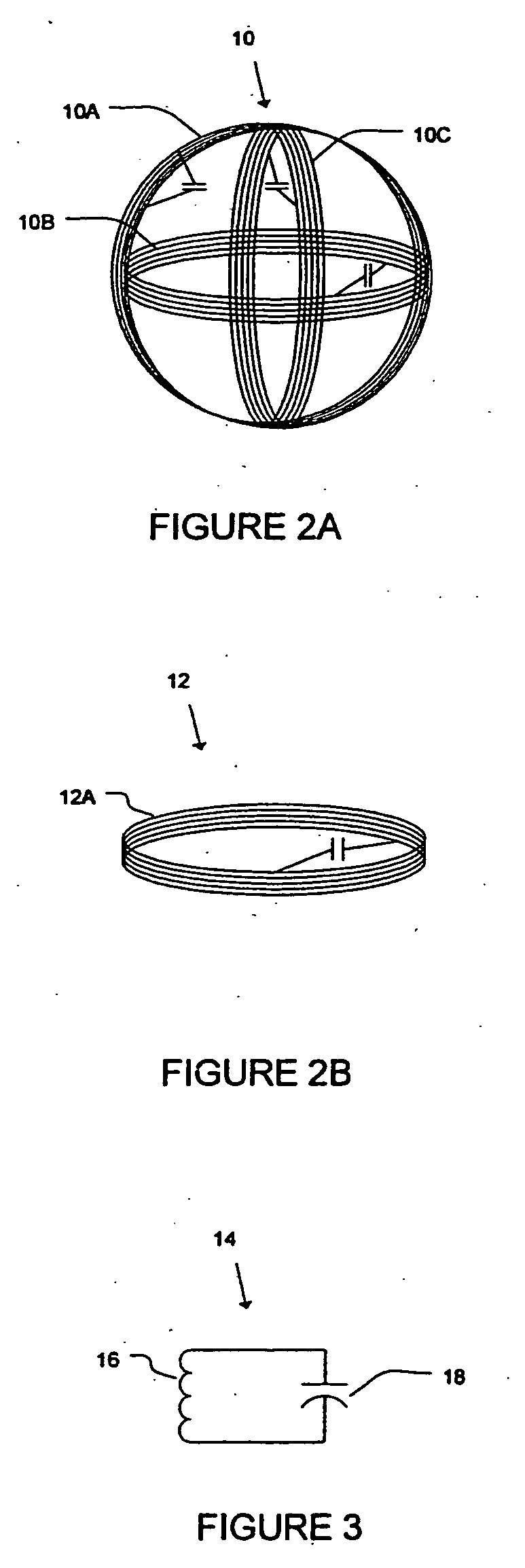

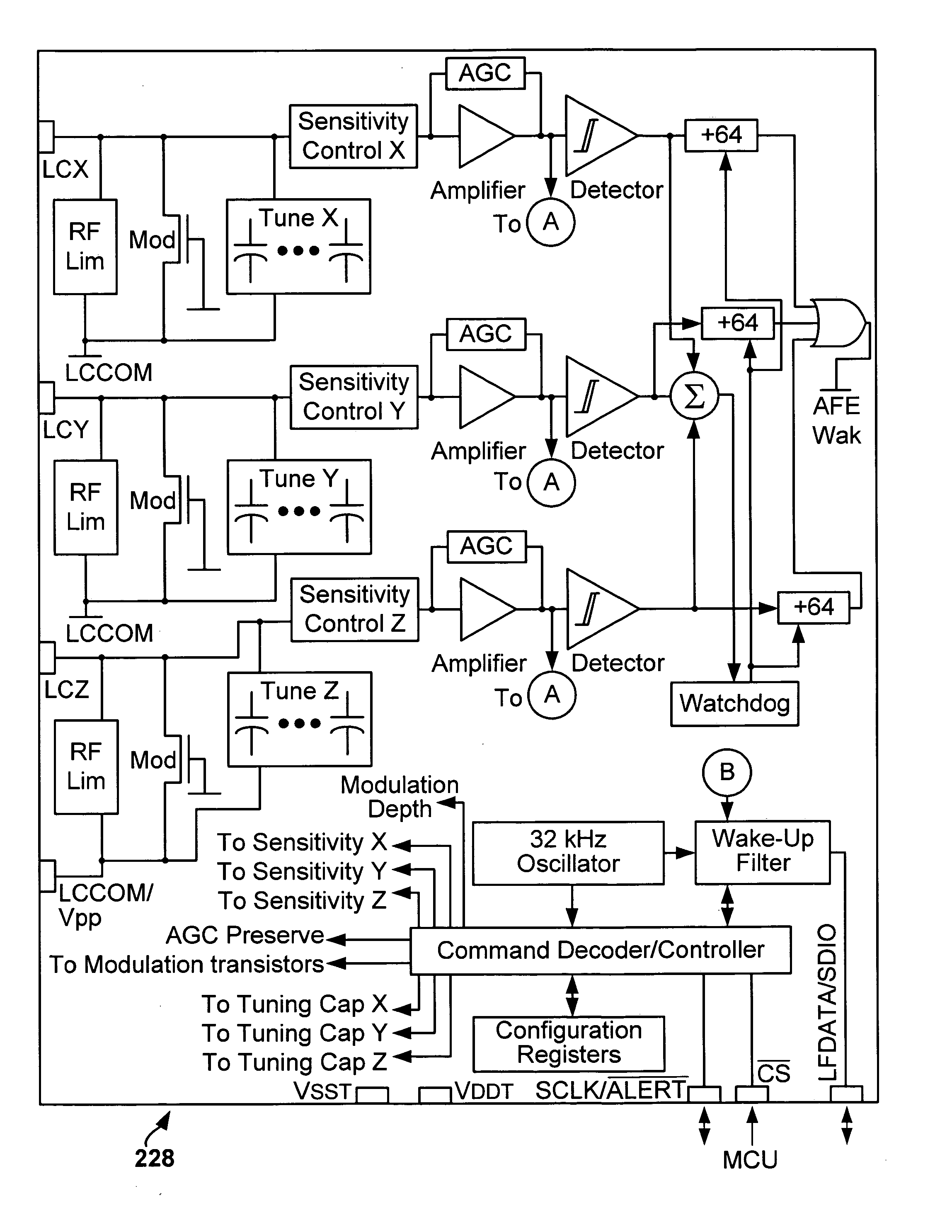

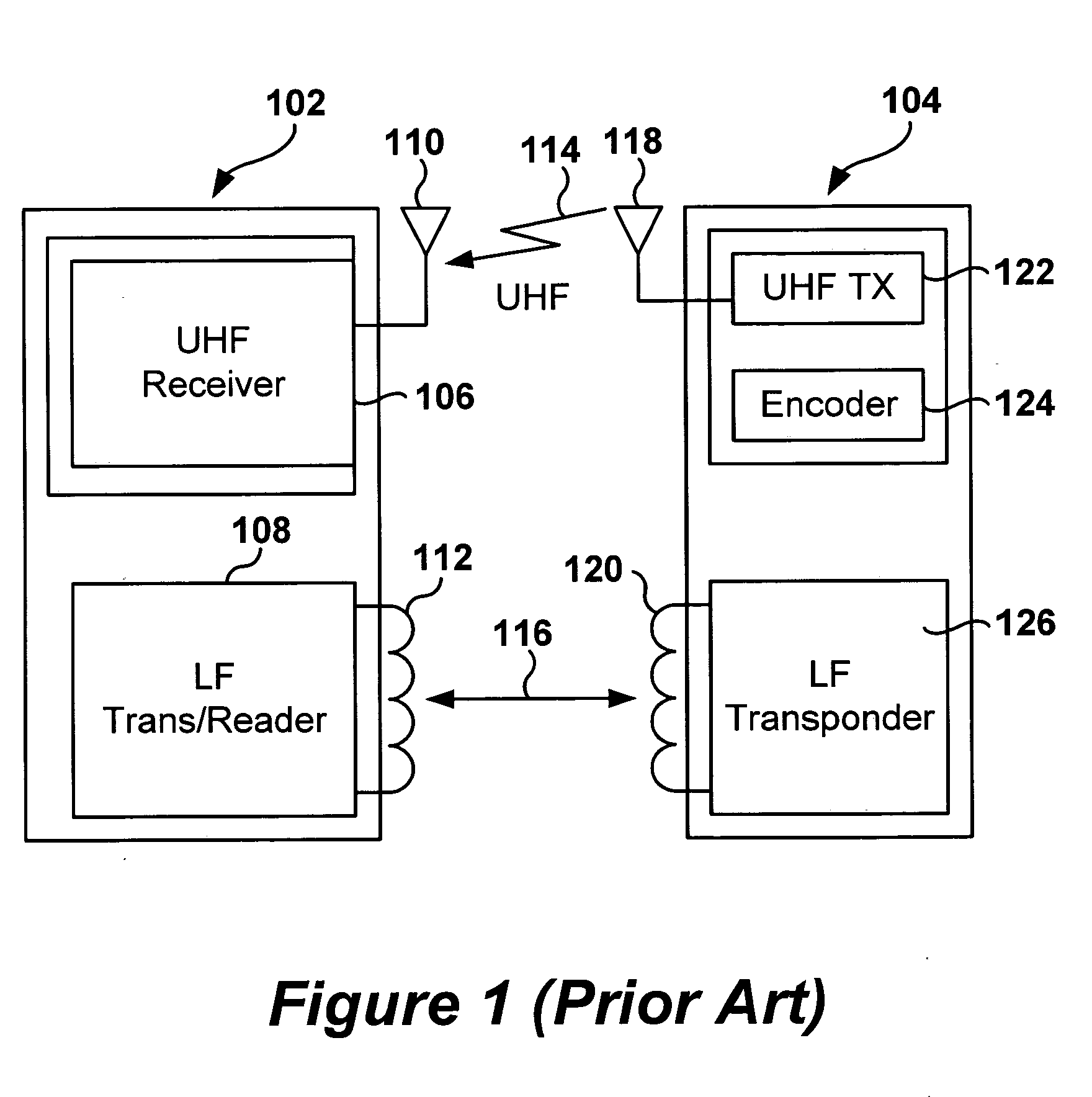

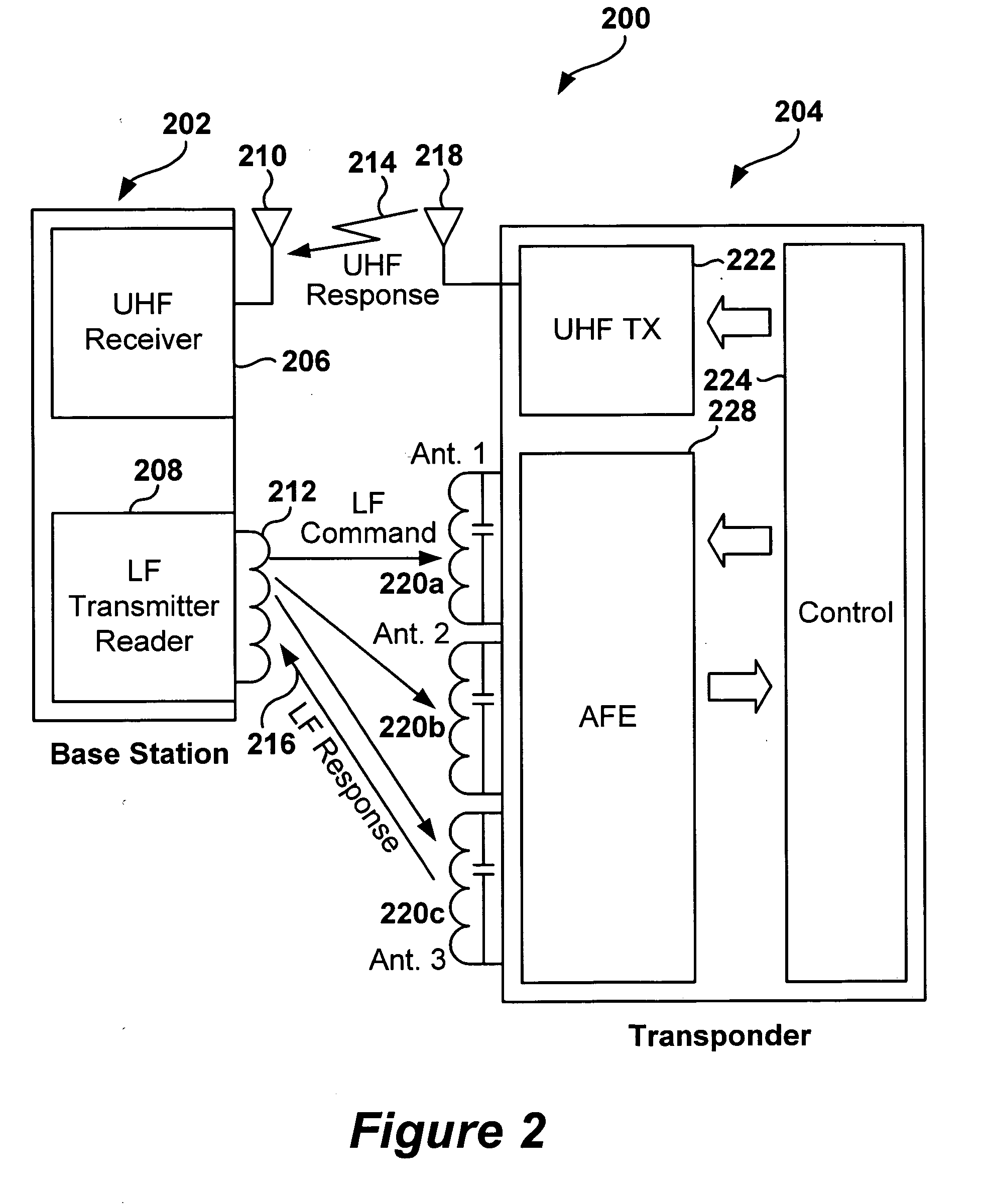

A bidirectional remote keyless entry (RKE) transponder comprises an analog front-end (AFE) having a programmable wake-up filter that predefines the waveform timing of the desired input signal, minimum modulation depth requirement of input signal, and independently controllable channel gain reduction of each of its three channels, X, Y, and Z. The wake-up filter parameters are the length of high and low durations of wake-up pulses that may be programmed in a configuration register. The wake-up filter allows the AFE to output demodulated data if the input signal meets its wake-up filter requirement, but does not output the demodulated data otherwise. The AFE output pin is typically connected to an external device for control, such as a microcontroller (MCU). The external device typically stays in low current sleep (or standby) mode when the AFE has no output and switches to high current wake-up (or active) mode when the AFE has output. Therefore, in order to keep the external control device in the low current sleep mode when there is no desired input signal, it is necessary to keep no output at the AFE output pin. This can be achieved by controlling the wake-up filter parameters, minimum modulation depth requirement of input signal, and channel gains of the AFE device. These features can reduce false-wake up of the bidirectional RKE transponder due to undesired input signals such as noise signals.

Owner:MICROCHIP TECH INC

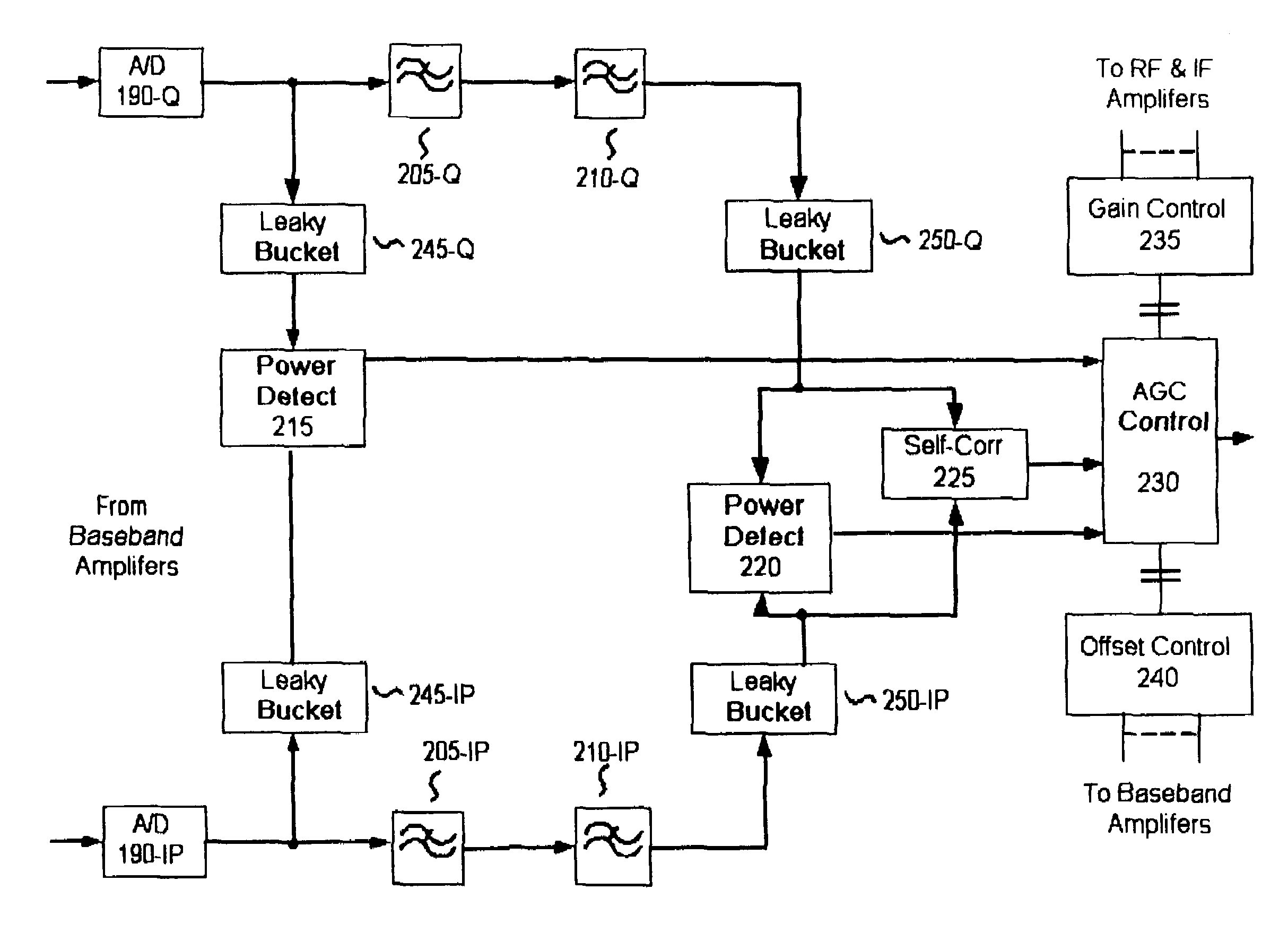

Method and system for noise floor calibration and receive signal strength detection

A system for detecting the level of the noise floor due to circuit noise as seen at the ADC for a wireless receiver. The system measures power after digitizing and filtering, and subtracts off any variable gain used in the analog front end to determine differentially the size of the signal at the antenna. The system further differentially detects the signal size of any incoming signal at the antenna in a similar fashion, and determines its size relative to the measured noise floor. If the level of the circuit noise of the receiver is known absolutely, the absolute signal size of the incoming signal can likewise be determined with this inventive method and system.

Owner:QUALCOMM INC

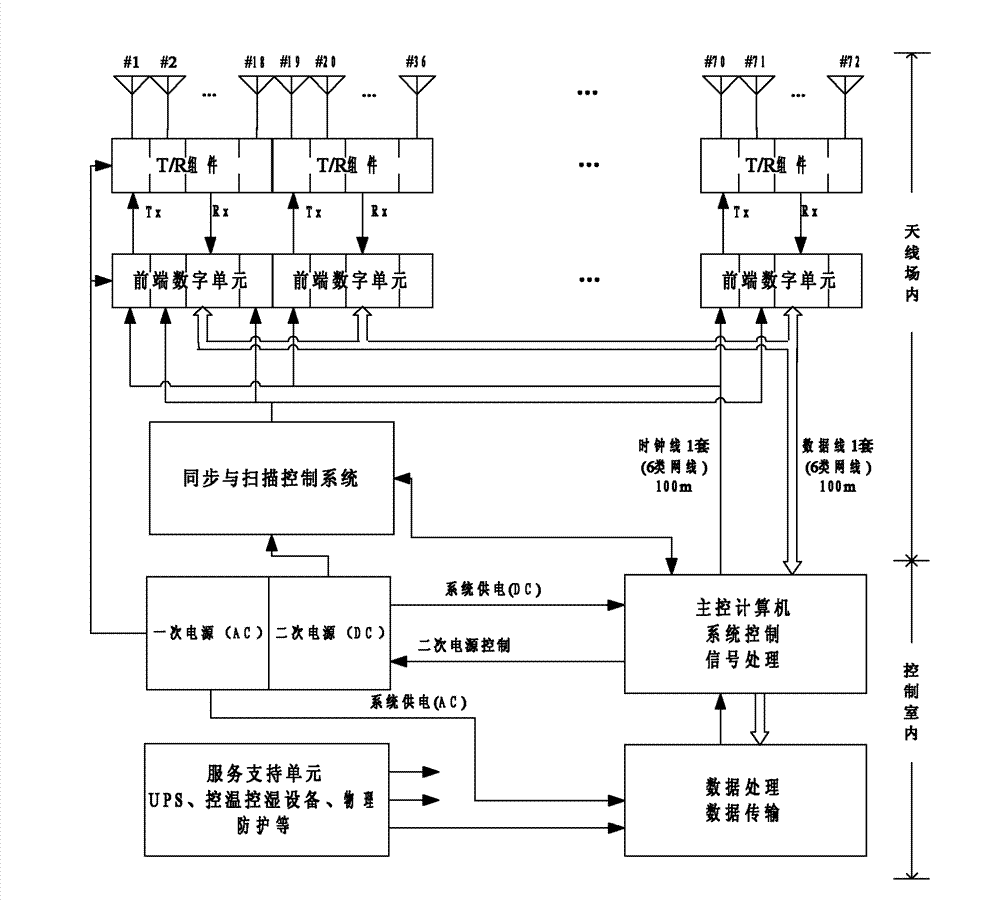

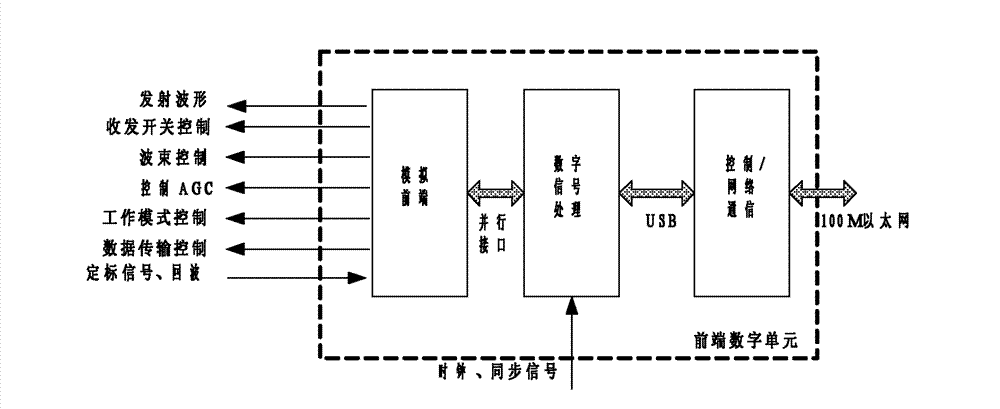

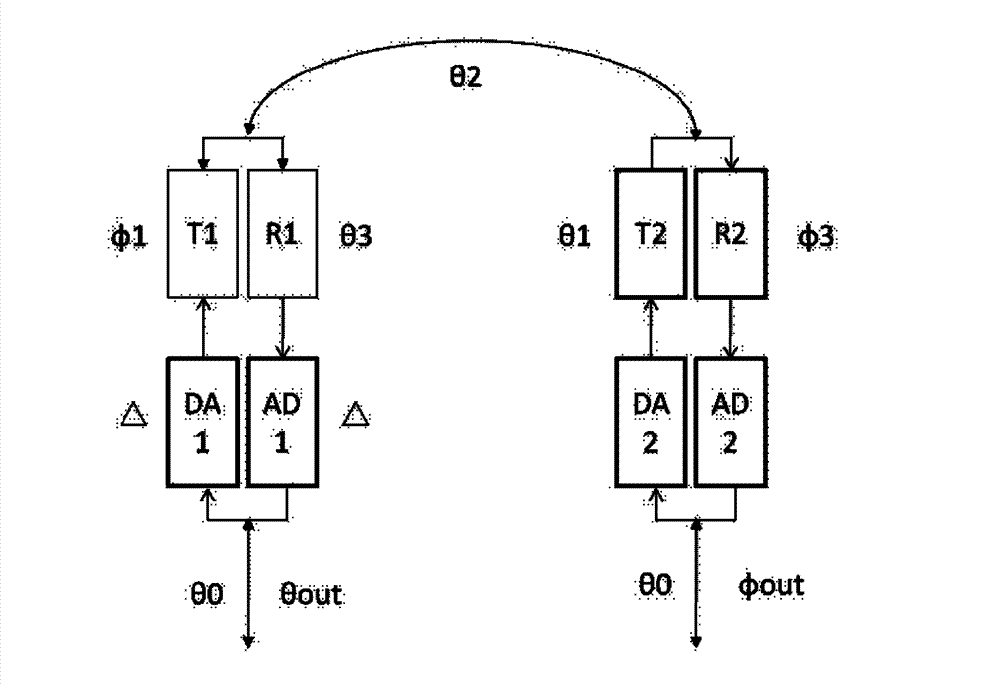

Distributed active phased array radar and beam forming method thereof

ActiveCN102955155AImprove radar performanceRealize real-time compensationRadio wave reradiation/reflectionLow noiseClock network

The invention relates to distributed active phased array radar and a beam forming method thereof. A transceiving component array consists of digital transceiving components which comprise analog front ends, power amplifiers, low-noise amplifiers and front-end digital units. The distributed active phased array radar further comprises a central processor, the central processor is connected with the multiple front-end digital units through a local area network by means of the hierarchical distributed processing technology, and used for setting operating modes of all of the front-end digital units and waveform data and receiving baseband data to guarantee reliability of target echo data subjected to digital synthesis and sending public clock signals to the front-end digital units through a clock network to guarantee synchronization of clock signals of each port. The multiple front-end digital units are correspondingly distributed in an antenna array, and each front-end digital unit is matched with one transceiving component. The distributed active phased array radar and the beam forming method thereof have the advantages of high flexibility, flexibility in data processing mode and improvement of phased array radar performances.

Owner:NAT SPACE SCI CENT CAS

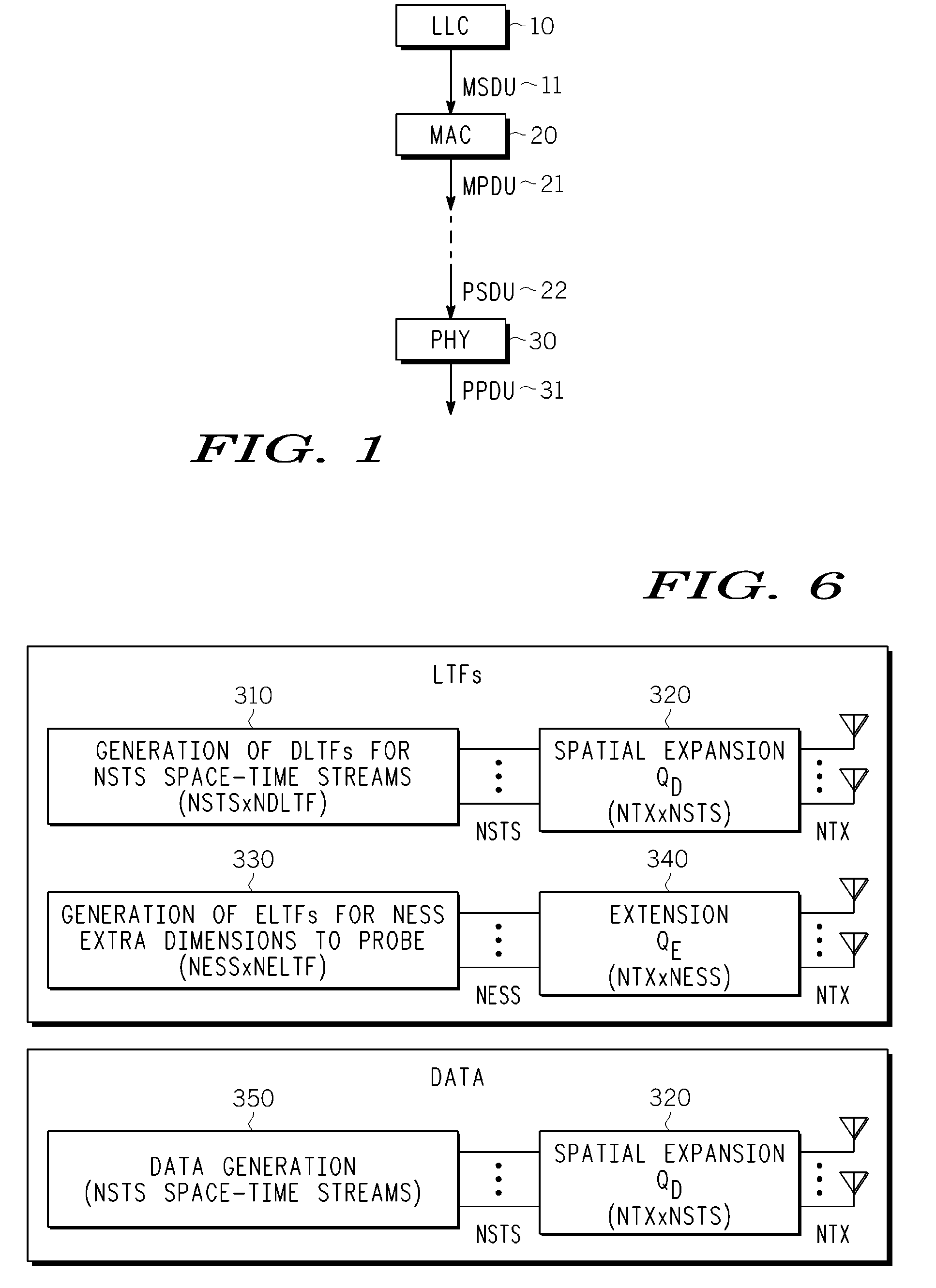

METHOD AND APPARATUS USING SOUNDING PPDUs TO PROVIDE RANGE EXTENSION TO IEEE 802.11n SIGNALS

InactiveUS20100111220A1Modulated-carrier systemsDiversity/multi-antenna systemsSpatial mappingCarrier signal

A wireless transmitter includes a stream parser for generating a plurality of spatial streams from a digital signal and a space time block coder (STBC) for mapping each of the spatial streams to a plurality of space-time streams that each include data and a preamble for estimating a channel transfer function. The transmitter also includes a spatial mapper for spatially expanding each of the space-time streams by applying a spatial expansion matrix to data and to first training symbols used in the preamble to probe a channel experienced by the data and by applying an extension matrix to second training symbols used in the preamble to probe at least one additional dimension of the channel to enable use of beamforming to achieve range extension The spatial expansion matrix and the extension matrix form an overall matrix that has at least two orthogonal columns with different norms. The wireless transmitter also includes an analog front end for modulating the spatially expanded space-time streams onto a wireless carrier.

Owner:GOOGLE TECH HLDG LLC

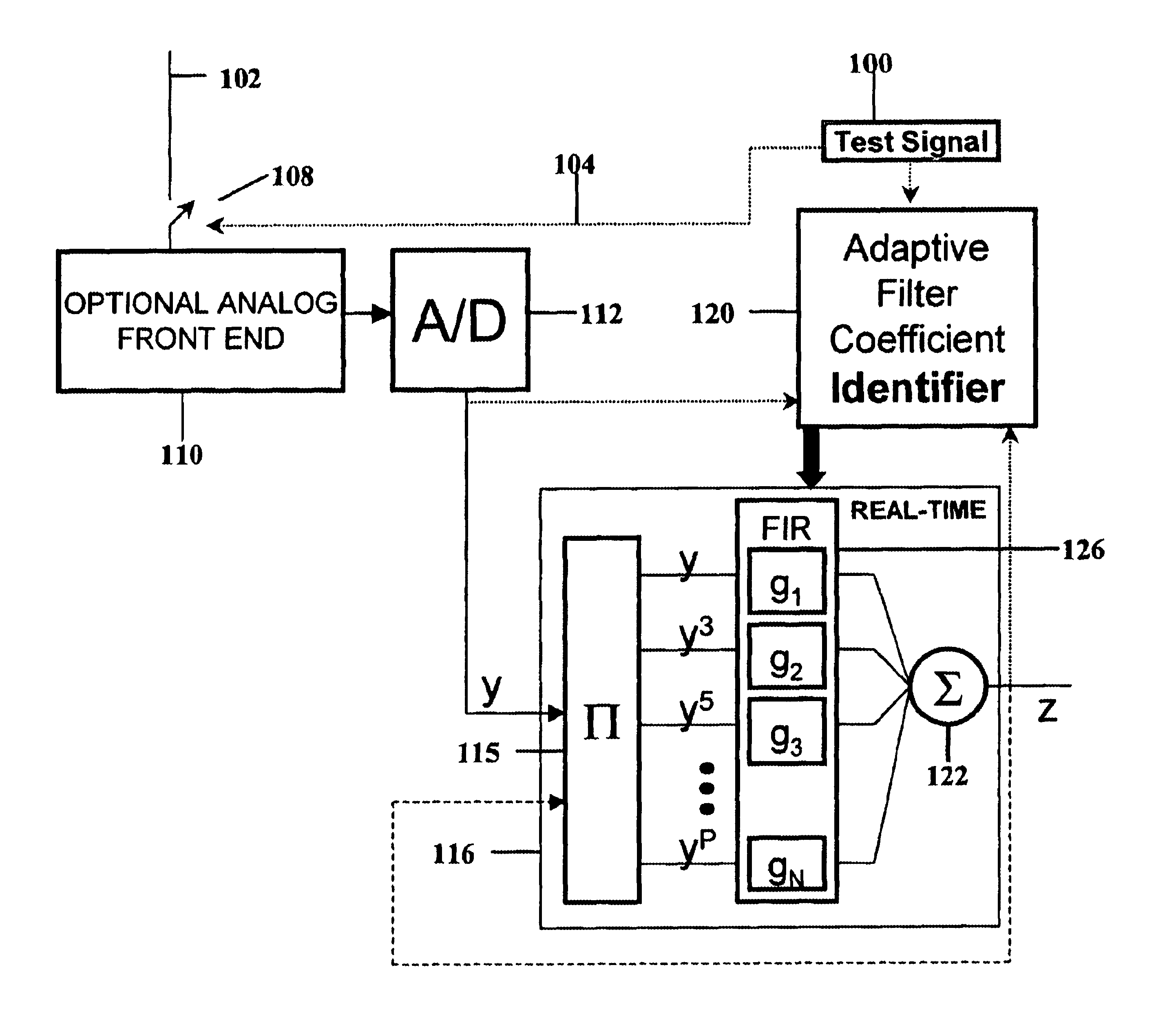

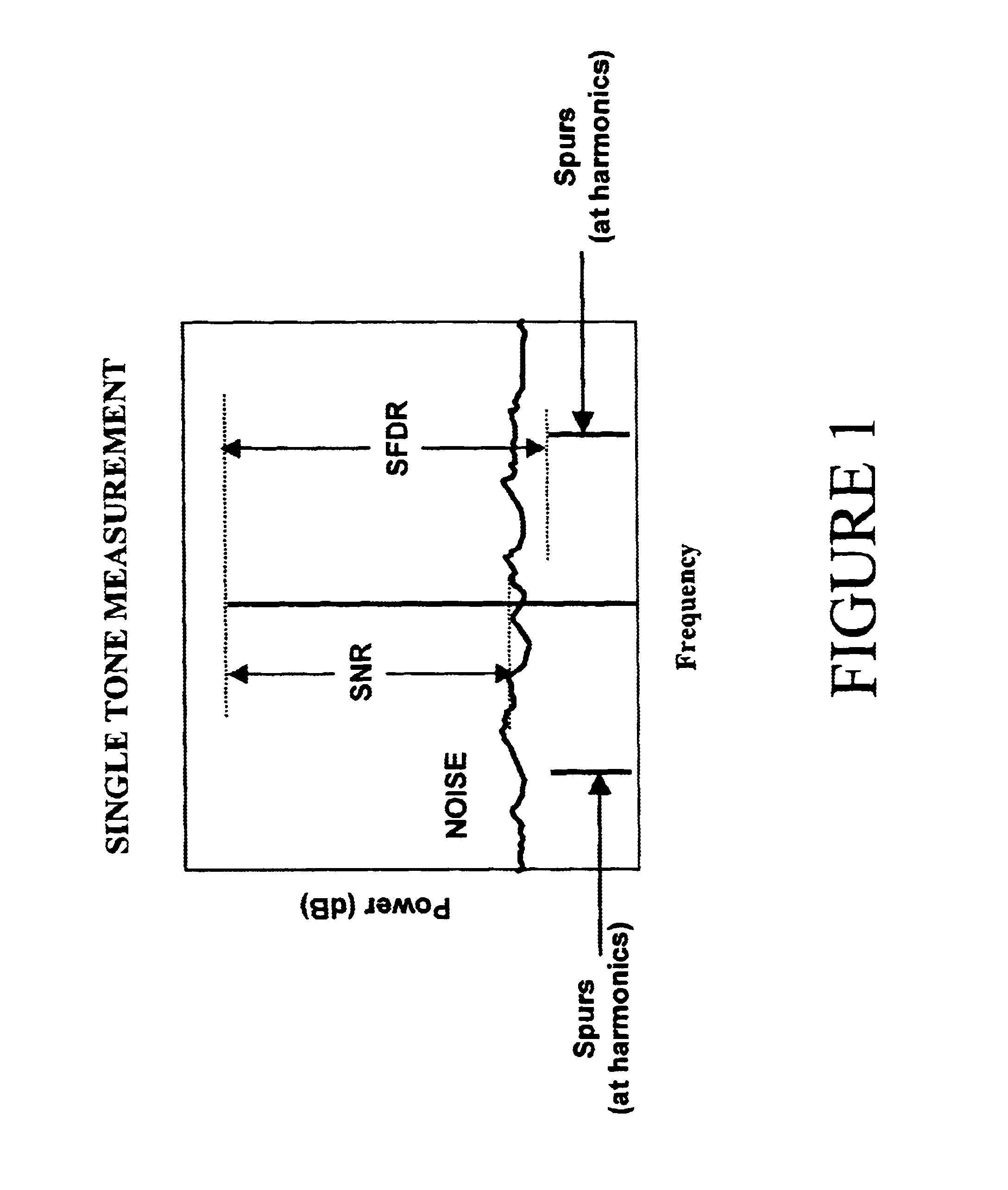

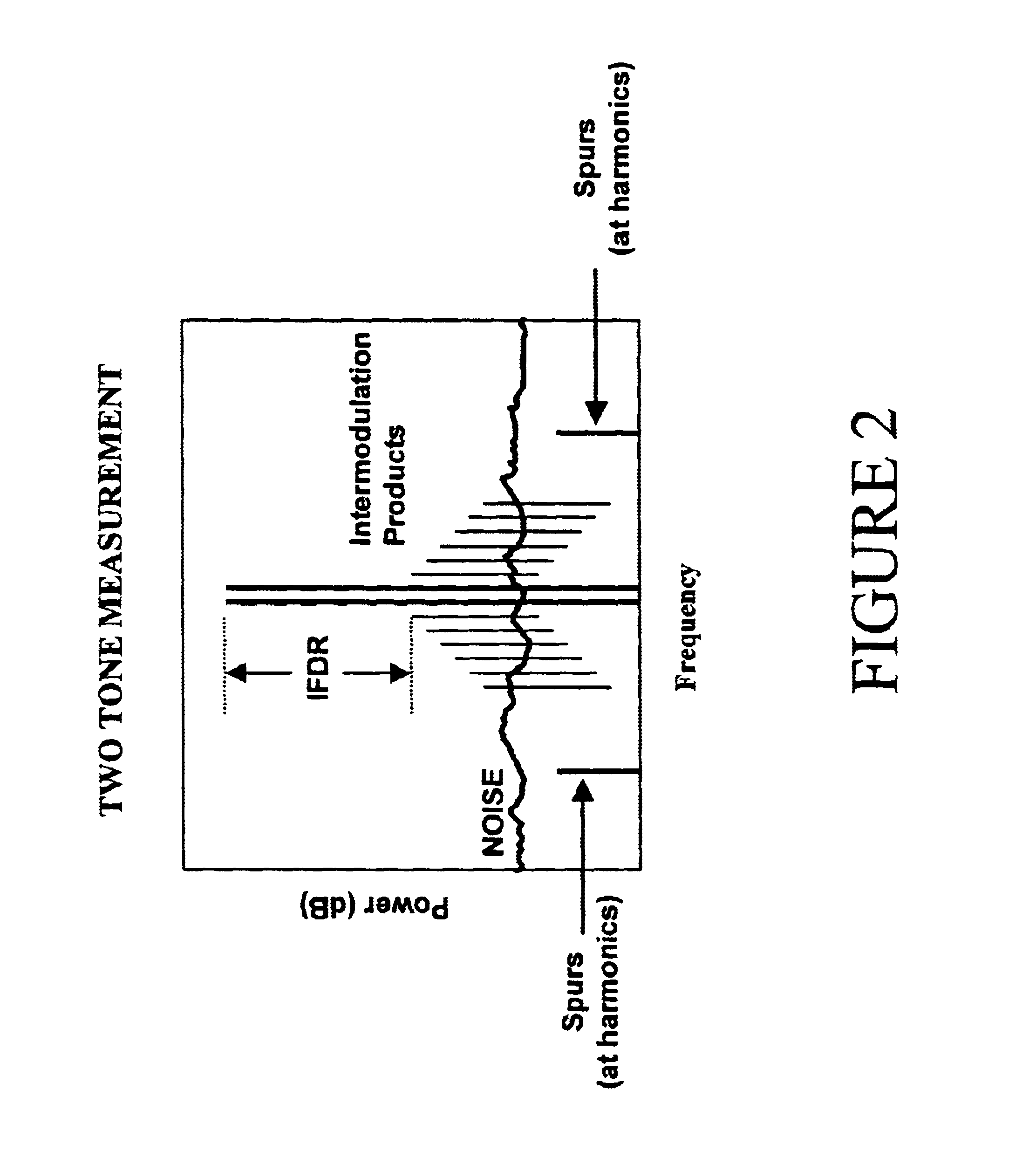

Highly linear analog-to-digital conversion system and method thereof

InactiveUS6639537B1Reduce nonlinear distortionMinimizes non-linear distortionElectric signal transmission systemsAnalogue conversionFinite impulse responseNonlinear distortion

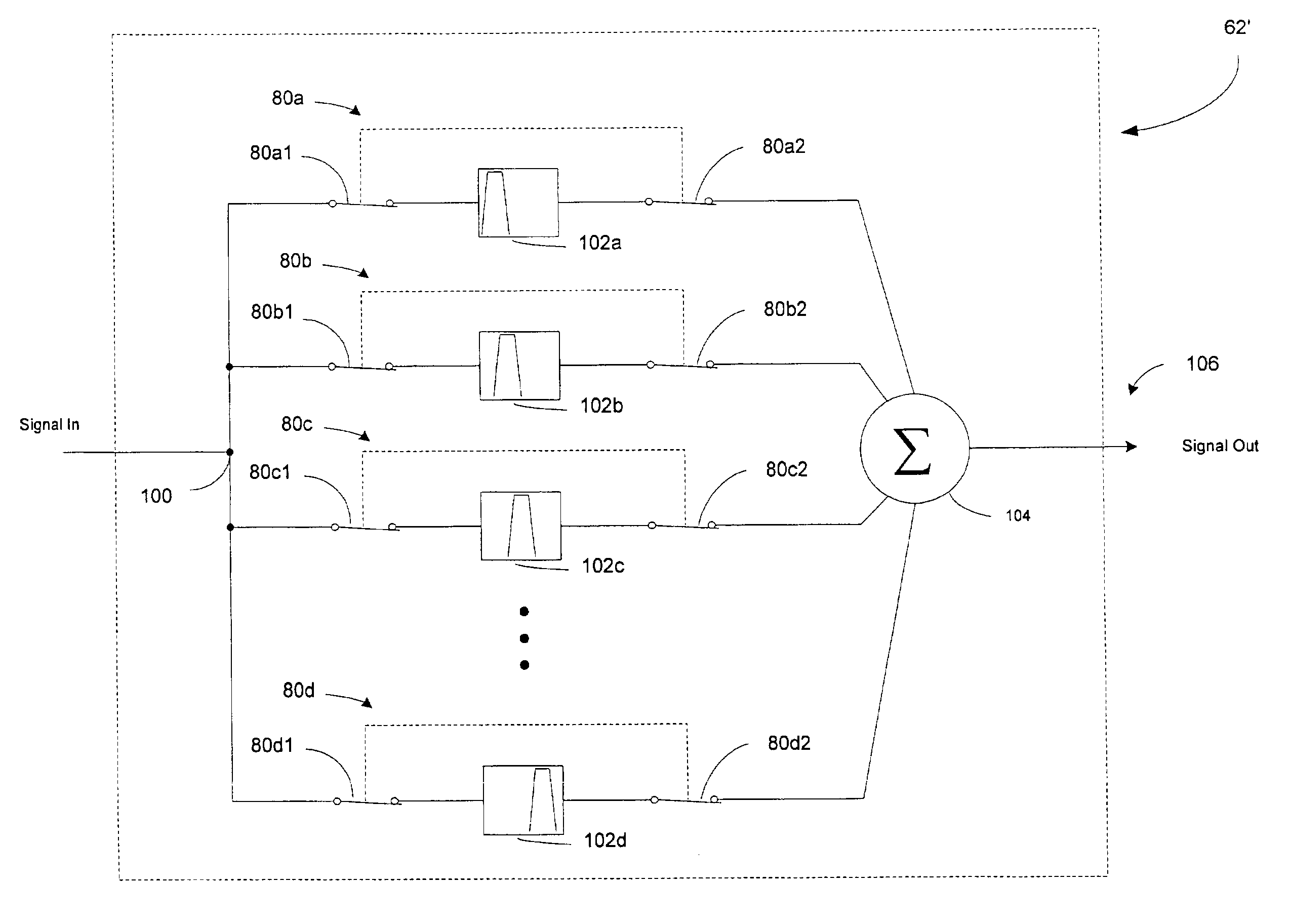

A highly linear analog-to-digital (ADC) conversion system has an analog front-end device in cascade with a standard ADC converter, and a tunable digital non-linear equalizer. The equalizer corrects the quantization distortion, deviations from ideal response, and additive noises generated by the analog front-end device and ADC converter. The equalizer is formed by three main parts: Generate Function Streams Unit, Finite Impulse Response FIR filters and a summer. The equalizer receives the unequalized output from the ADC converter and generates a plurality of monomial streams in a systolic fashion. Each of the monomial streams is passed through a corresponding linear finite impulse response FIR filter. A convolution sum of all outputs from the FIR filters produces a unique equalized output with the non-linear distortion reduced to a satisfactory level. The FIR filter coefficients are determined by an Identity Equalizer Coefficient Unit, and a Test Signal Generator with different types of test signals. The FIR filter coefficients are set to minimize an error function.

Owner:MASSACHUSETTS INST OF TECH

Multi-protocol radio frequency identification transponder transceiver

ActiveUS7689195B2Electric signal transmission systemsMemory record carrier reading problemsDigital signal processingTransceiver

A transceiver for a RFID reader and a transceiver for a RFID transponder (tag) allow communication between the two devices. The RFID reader utilizes an analog front end and a digital backend. In the receiver portion of the transceiver, the front end of the RFID reader uses a pair of down-conversion mixers to demodulate a received signal into in-phase (I) and quadrature (Q) components and analog-to-digital converters (ADC) digitize the signal. A digital signal processor (DSP) in the back end processes the digital signal and uses a matched filter for data detection. The RFID tag receives an inductively coupled signal from the reader and the receiver portion of the tag uses a pulse / level detector that employs an analog comparator and a sample and hold circuit to detect the received signal. A digital decoder / controller is used to decode the incoming data and to establish a sampling clock for the pulse / level detector. An automatic gain control (AGC) circuit adjusts a receiver gain according to the received signal strength and controls tuning of magnetic coupling circuitry.

Owner:NXP USA INC

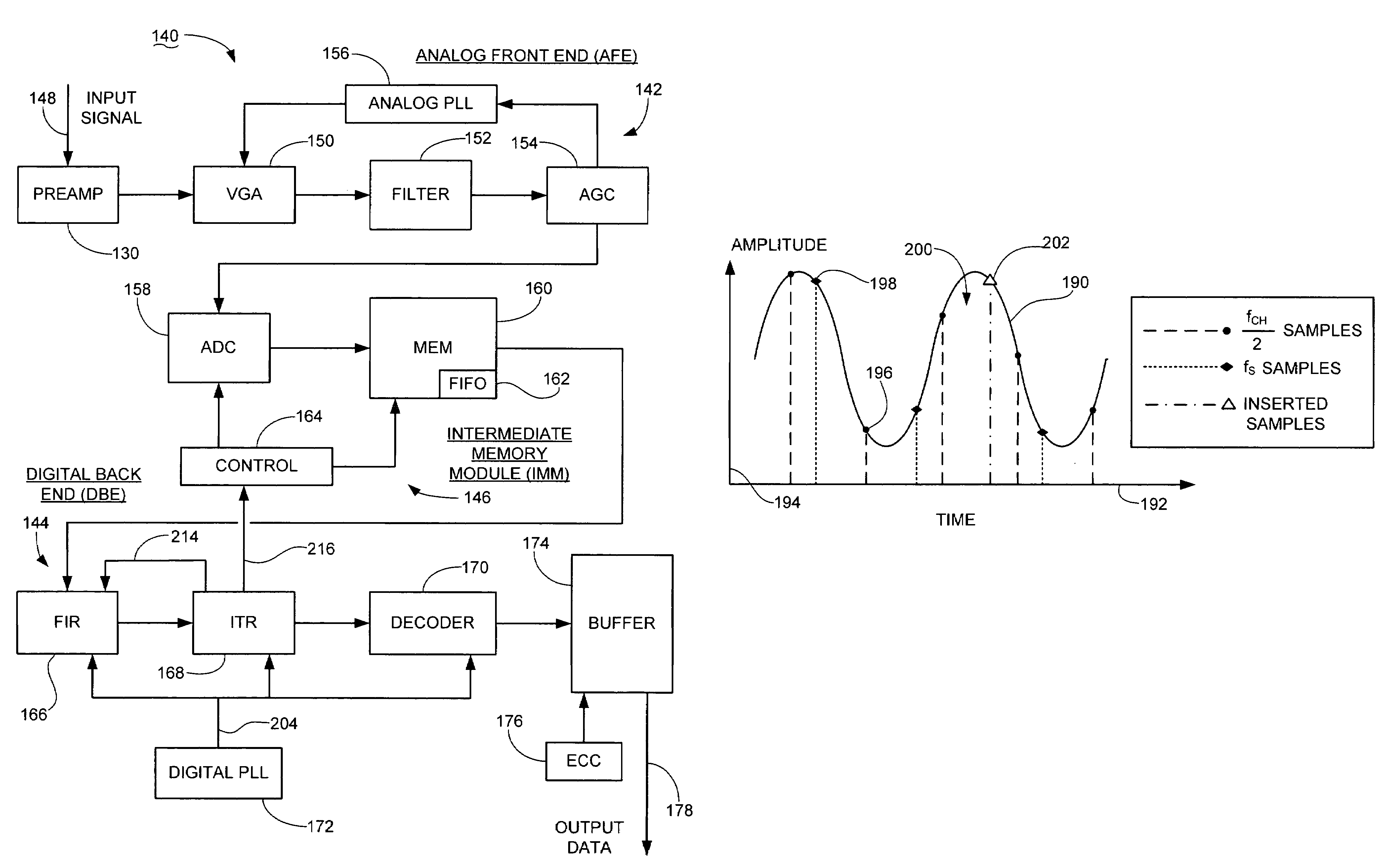

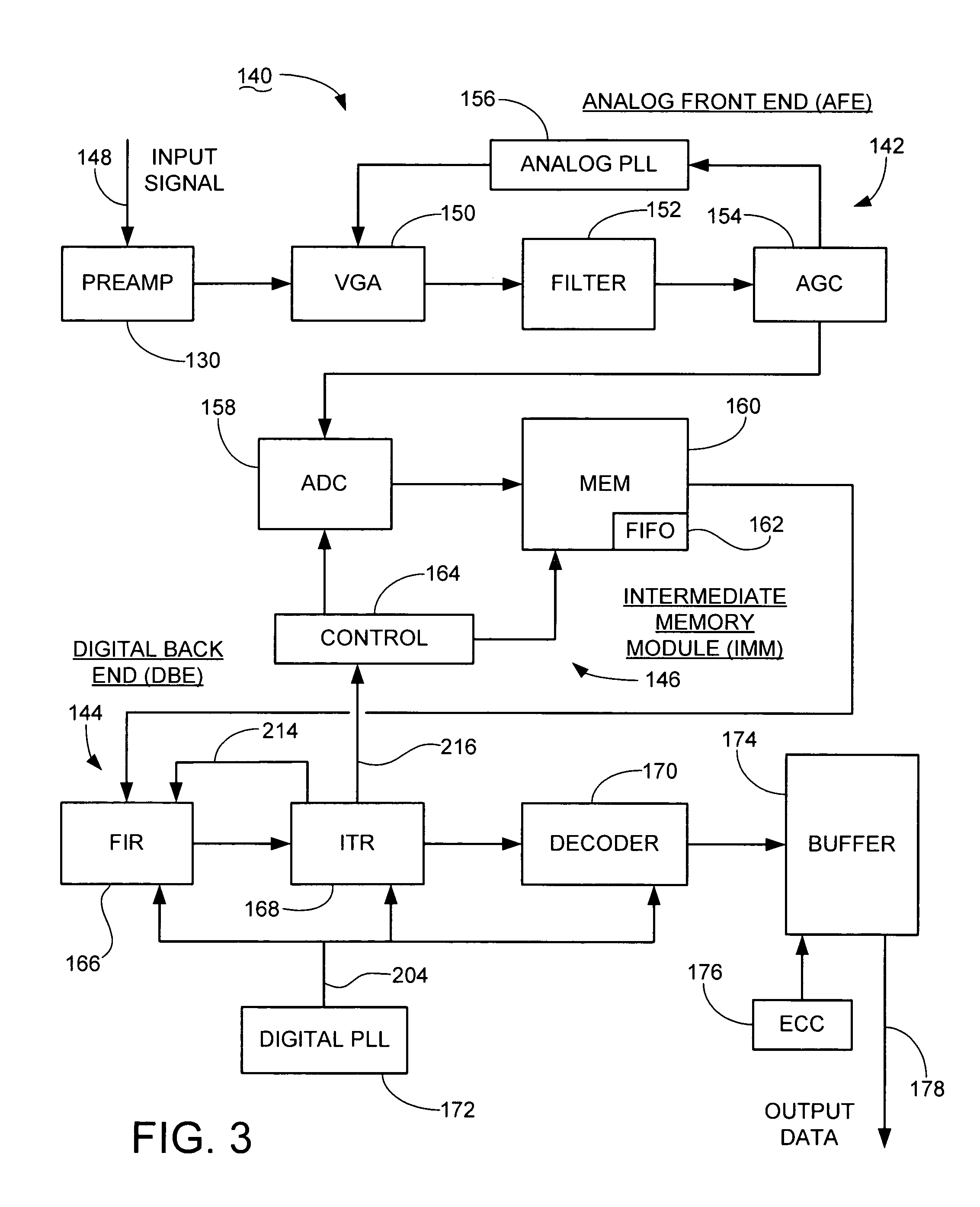

Communication channel with undersampled interpolative timing recovery

InactiveUS7365671B1Improve efficiencyElectric signal transmission systemsModification of read/write signalsRecovery methodContinuous signal

Method and apparatus for processing transmitted data. A sampling circuit preferably performs lossy sampling of a continuous signal to provide a corresponding sequence of discrete samples at a sampling rate less than a Nyquist rate of the continuous signal. A processing circuit reconstructs an informational content of the continuous signal from the discrete samples, and operates to periodically insert additional samples into the sequence, which preferably increases an effective rate of said sampling to match or exceed the Nyquist rate. Preferably, the lossy discrete samples are temporarily stored in a memory space prior to reconstruction by the processing circuit. The sampling circuit preferably comprises an analog-to-digital converter (ADC) of an analog front end (AFE). The processing circuit preferably comprises a digital back end (DBE) employing partial-response, maximum-likelihood (PRML) detection. The additional samples are preferably provided by an iterative timing recovery (ITR) block of the DBE.

Owner:SEAGATE TECH LLC

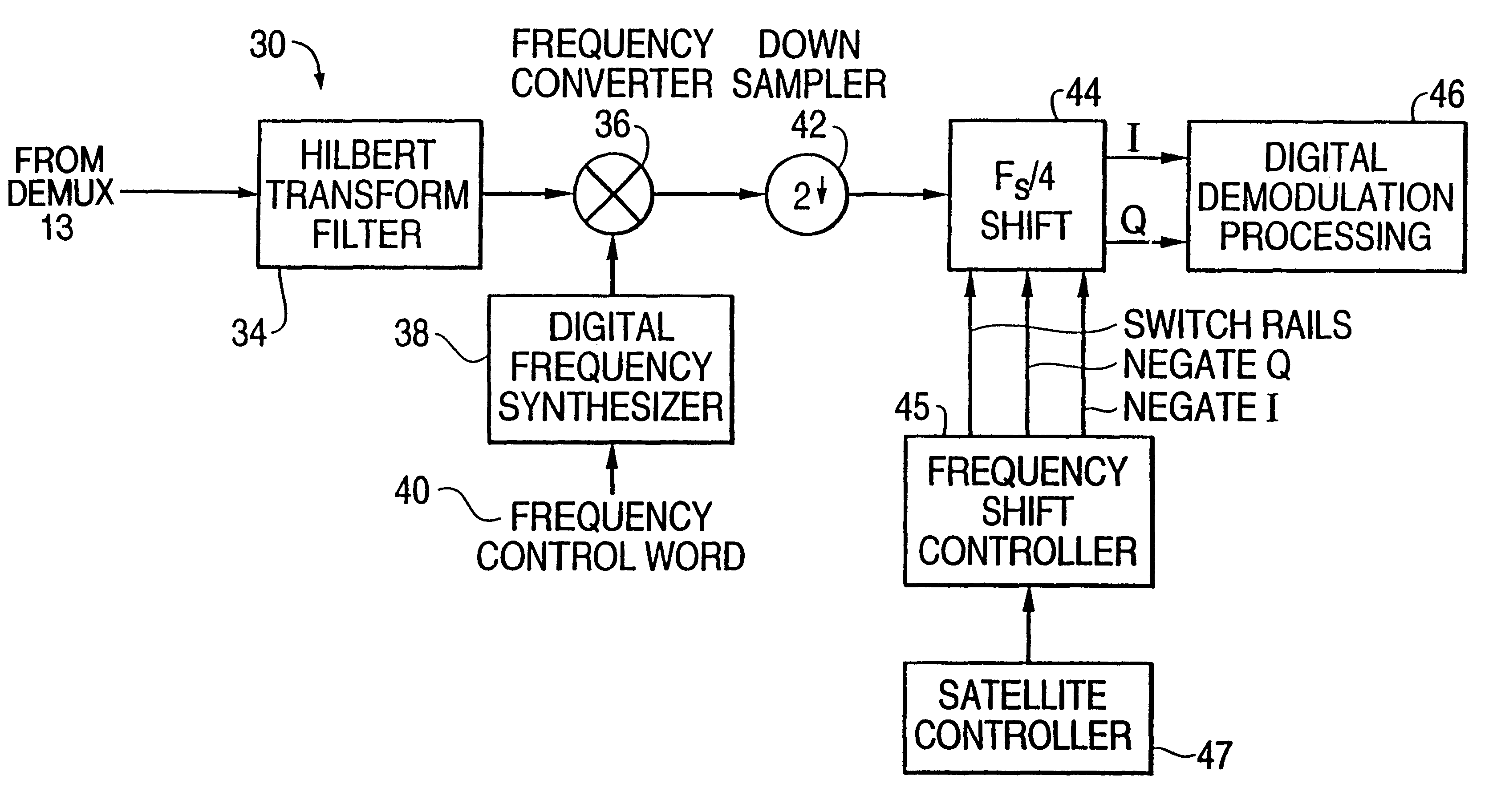

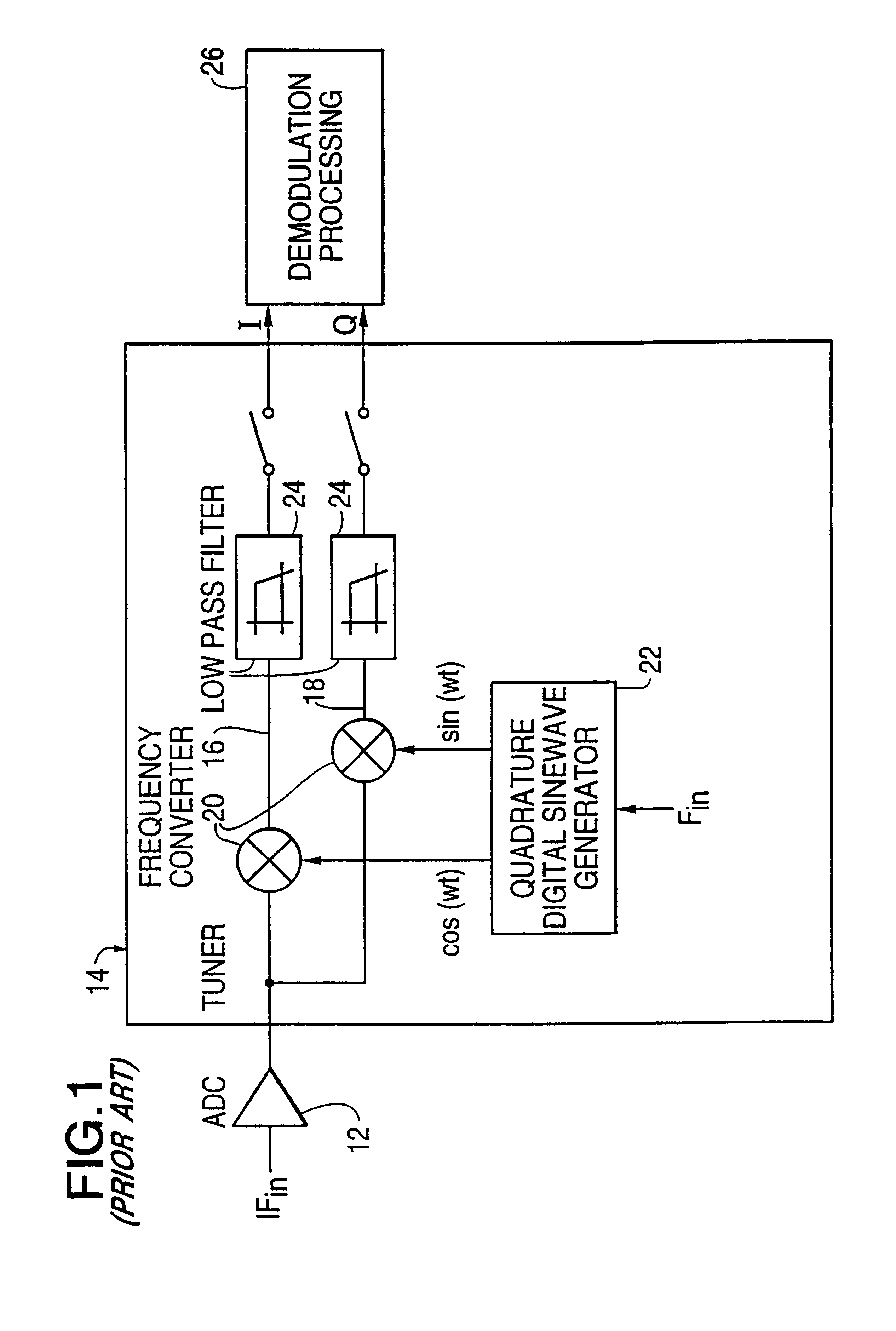

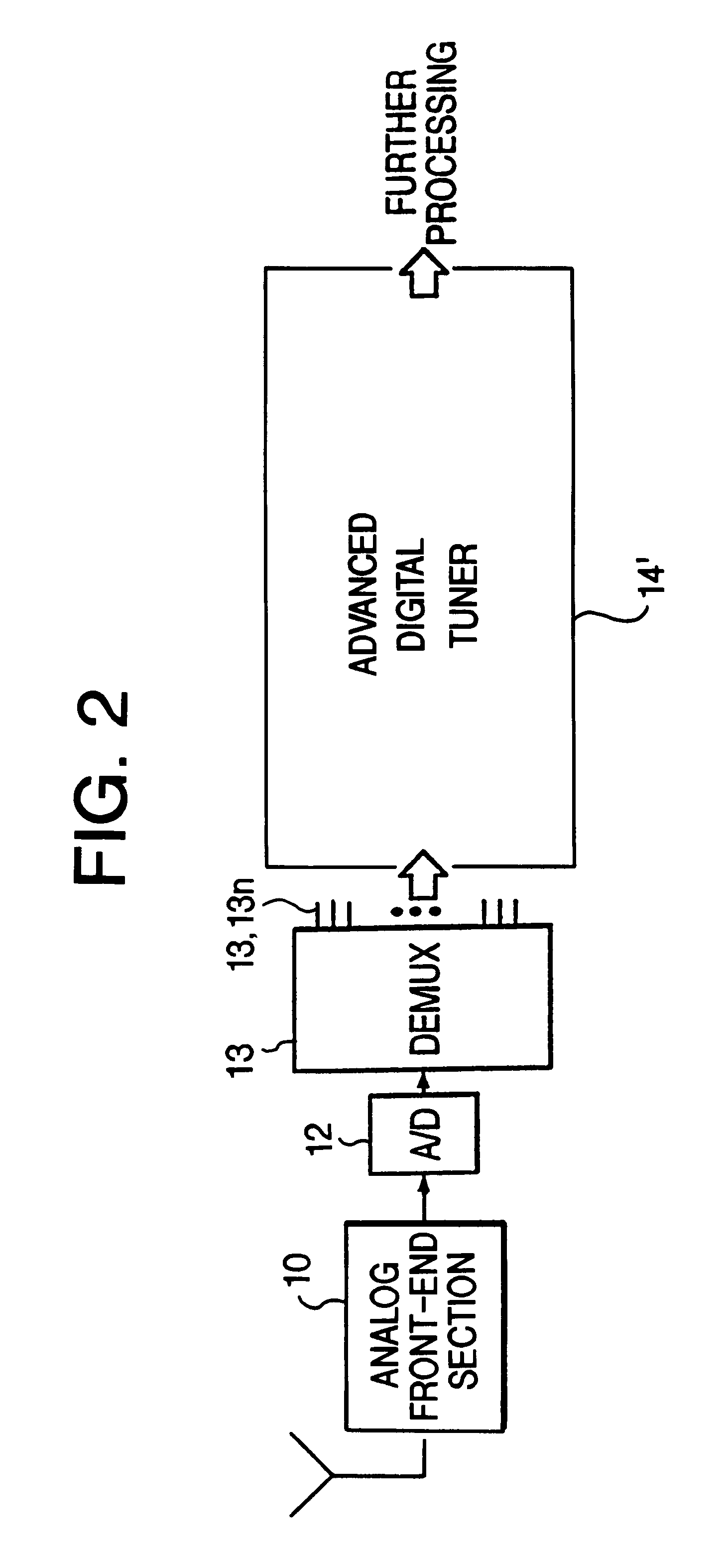

Wideband parallel processing digital tuner

InactiveUS6263195B1High speed data rateAvoid disadvantagesPolarisation/directional diversityPhase-modulated carrier systemsDigital dataFrequency spectrum

A wideband digital tuner (14') has an analog front-end section (10), a high speed analog-to-digital converter (12), demultiplexer (13) and a plurality of filters (341-342) arranged in a parallel input architecture to process wideband digital data received at extremely high sampling rates, such as at 2 Gsps (giga-samples per second). The tuner greatly attenuates an undesired spectral half of the wide bandwidth digital spectrum of the incoming digital signal using a complex band-pass filter, such as a Hilbert Transform filter. The tuner places the remaining half of the wide bandwidth digital spectrum of the incoming digital signal at complex baseband and down samples by 2. The architecture of the tuner can be partitioned into two separate halves which are hardware copies of each other.

Owner:NORTHROP GRUMMAN SYST CORP

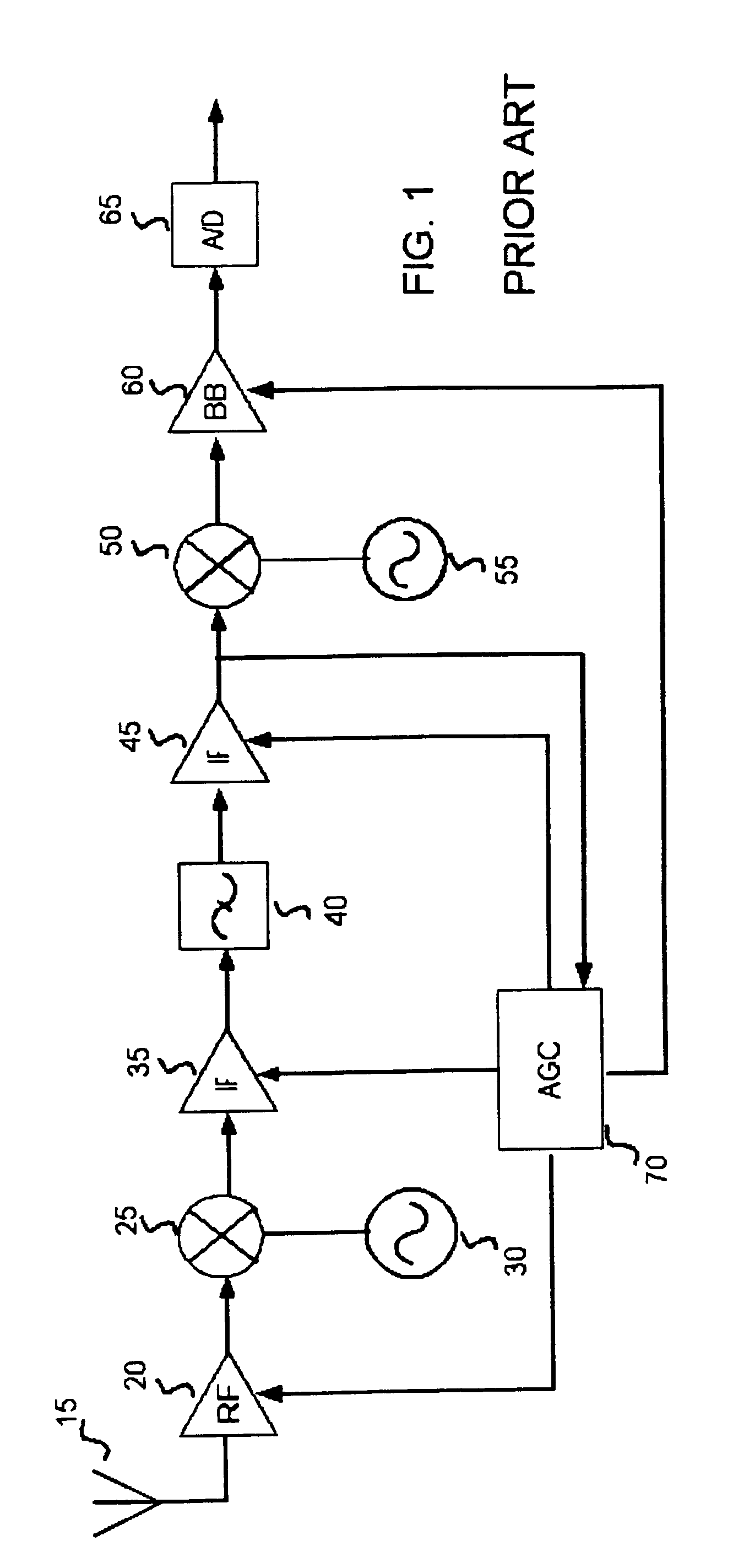

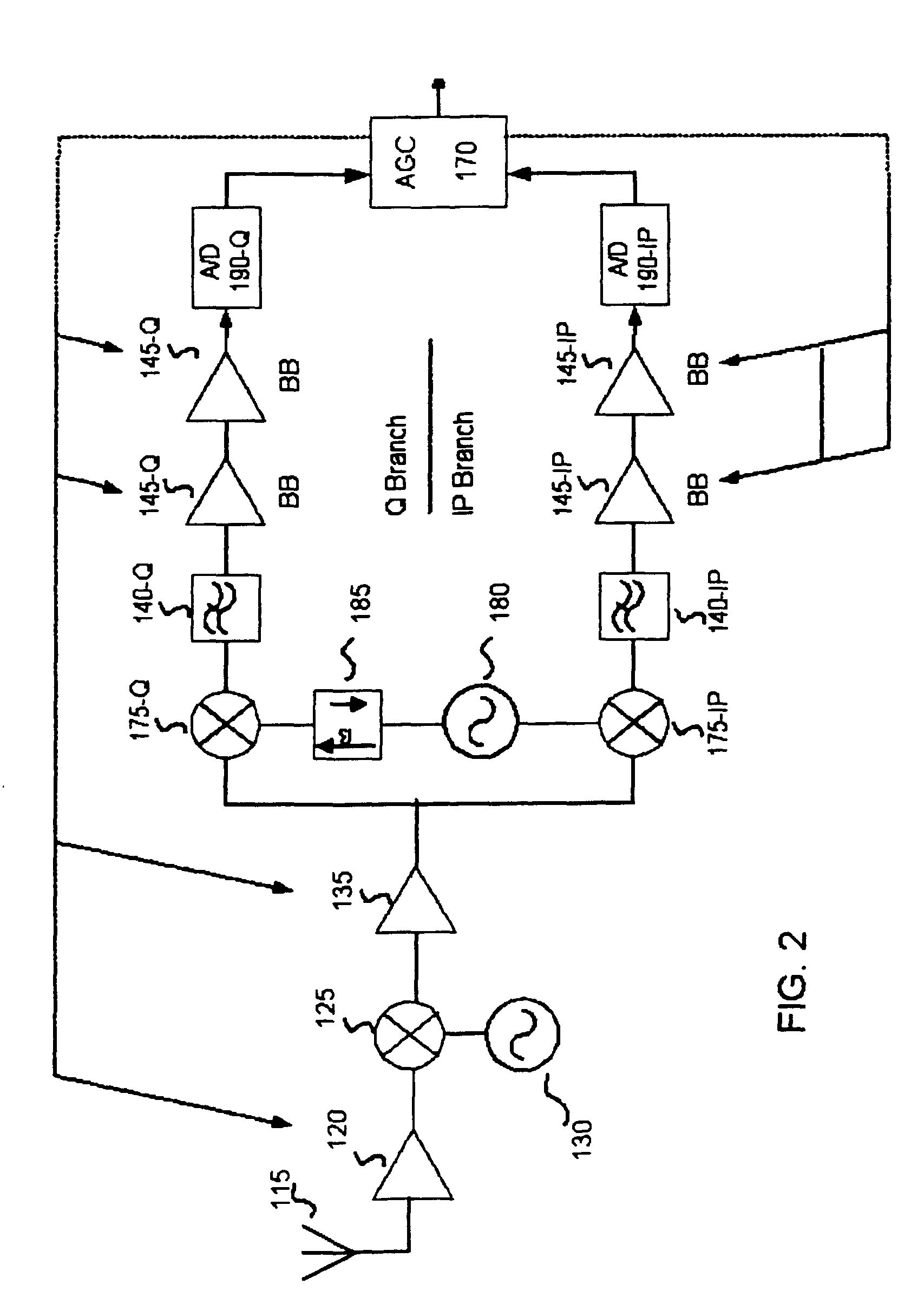

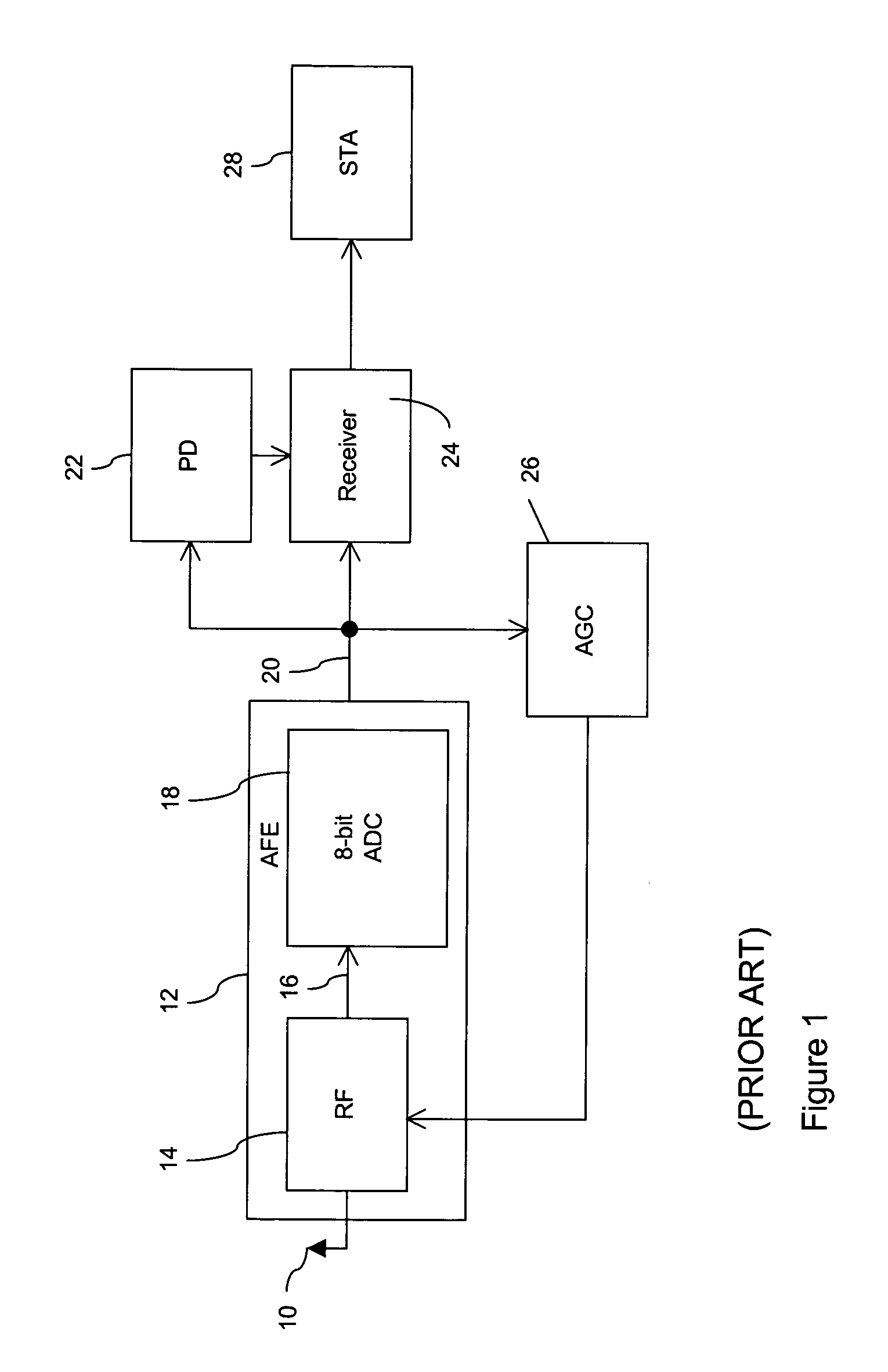

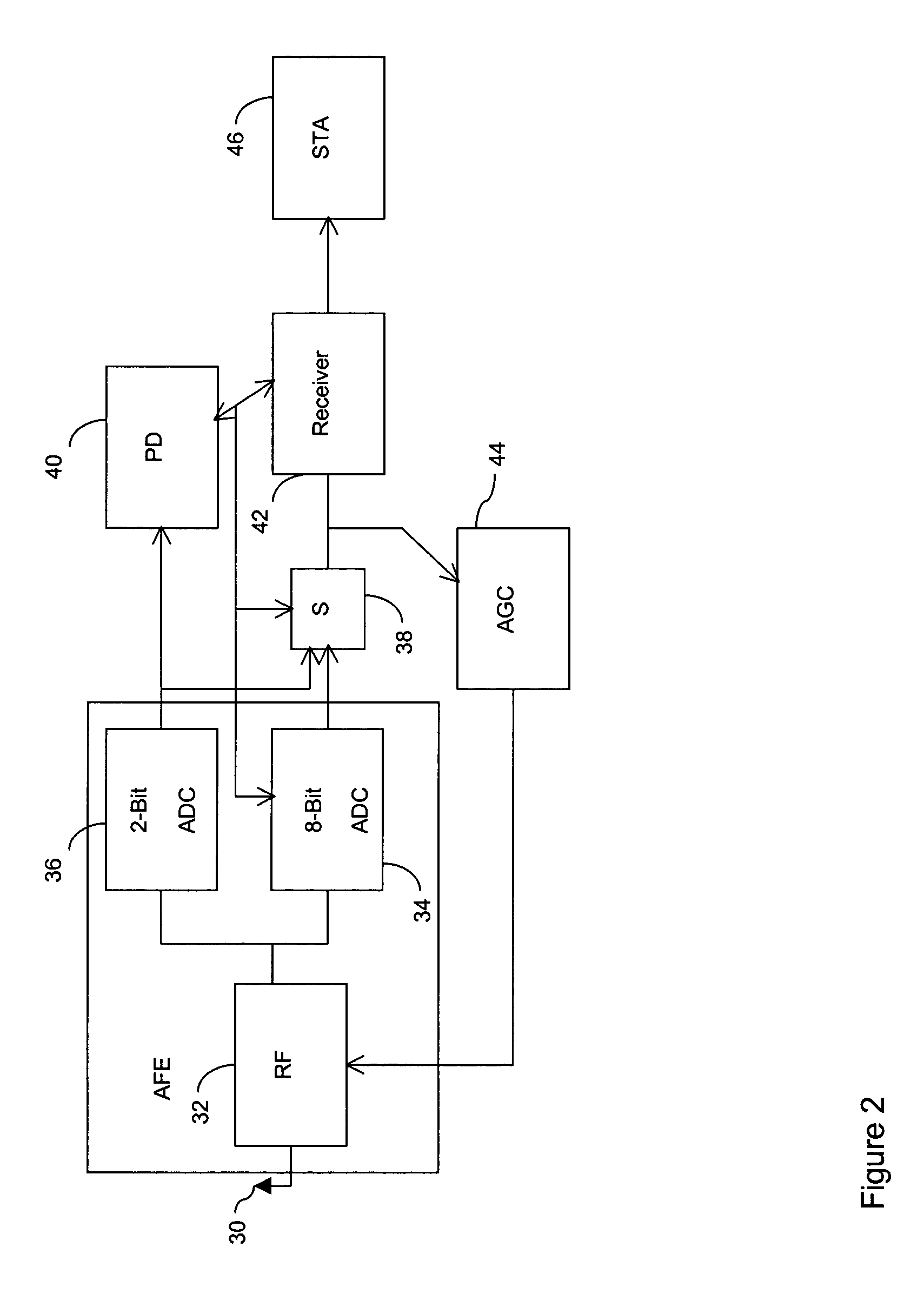

Receiver with low power listen mode in a wireless local area network

ActiveUS20050084037A1Reduce resolutionHigh resolutionEnergy efficient ICTPower managementBarker codeImage resolution

A receiver for a wireless local area network, WLAN, having a low power listening mode of operation. The receiver includes two separate paths in the analog front end, AFE. One path includes a low resolution and low power analog to digital converter, ADC. The other path includes a high resolution and high power ADC. In listen mode, only the low resolution ADC is powered and provides inputs to a packet detector for identifying a barker code. When the correct barker code is received, the high resolution ADC is enabled and coupled to a receiver for receiving a payload in the data packet.

Owner:TEXAS INSTR INC

Current prediction in a switching power supply

ActiveUS20060119331A1Reliable supplyReduces and eliminates switchingTransistorEfficient power electronics conversionMicrocontrollerCapacitance

A high efficiency switching power supply including an analog front end, a battery control circuitry portion, a display and equalization circuitry portion, field effect transistor (FET) drivers, an isolated power supply transformer circuitry (and three associated sets of tap circuitry), microcontroller circuitry, oscillator circuitry, overcharge protection circuitry, programmable logic circuitry portion, and a zero current predictor. Overbiasing of the FET power supply switches, and / or other various circuitry features disclosed herein, helps achieve electrical power efficiencies of preferably greater than 95%, even more preferably greater than 98% and even more preferably greater than 99%. Preferably, the switching power supply has one or more of the following: (1) high electrical power efficiency (>95%. >98%, >99%); (2) overbiasing of a gate of a power supply switch; (3) a power supply switch with a low gate capacitance ratio; (4) multiple modes of operation; and (5) current prediction wherein an inductor voltage is used to control a constant current capacitor whose voltage indicates the level of current in the inductor.

Owner:ELECTROVAYA

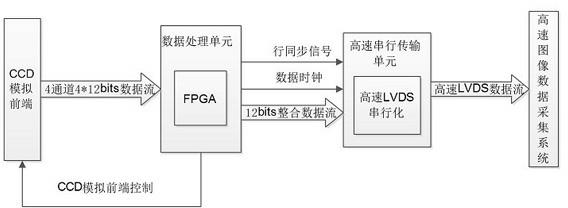

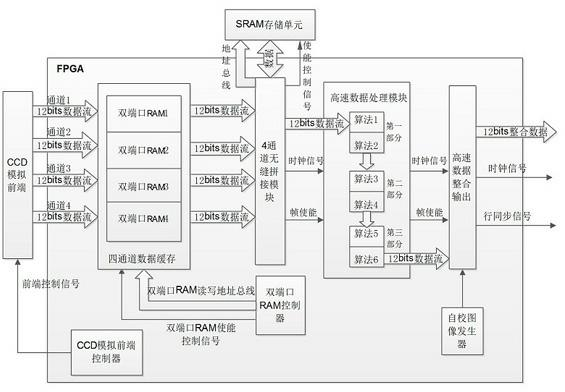

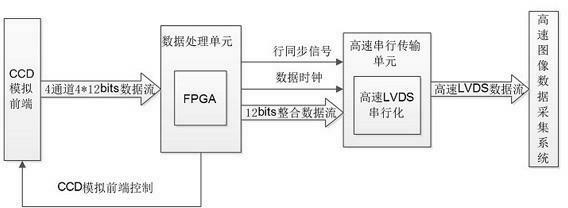

Data processing and transmitting system of high-speed multichannel CCD (charge-coupled device)

InactiveCN102638661AReal-time processingReduce in quantityTelevision system detailsPulse modulation television signal transmissionSerial transferData stream

The invention discloses a data processing and transmitting system of high-speed multichannel CCD (charge-coupled device), which comprises a CCD analog front end, a data processing unit, a high-speed serial transmission unit and a high-speed image data collection system which are sequentially connected. The CCD analog front end is used for converting an analog signal output by a CCD detector and subjected to sampling and pulse control into n channels of digital image data via n A / D (analog / digital) converters, transmitting the digital image data to the data processing unit, and acquiring data of each channel at the same time. The data processing unit is used for transmitting single-channel high-speed data streams, a data transmitter clock and a horizontal synchronizing signal acquired from integration of the digital image data to the high-speed serial transmission unit. The high-speed serial transmission unit is used for converting single-channel high-speed data streams via LVDS (low-voltage differential signaling) serial chips into high-speed LVDS data streams for transmitting. The high-speed image data collection system is used for collecting the high-speed serial LVDS data streams and realizing real-time storing and displaying of the image data.

Owner:NANJING UNIV OF SCI & TECH

Method and apparatus for digital detection of electromagnetic signal strength and signal direction in metallic pipes and cables

ActiveUS20050096879A1Reduced analog front-end hardware requirementWide resistance to componentAmplifier modifications to reduce noise influenceDigital computer detailsDigital signal processingCarrier signal

A new digital architecture for metallic pipe and cable locators, providing accurate estimation of the fundamental locate parameters, electromagnetic signal strength and signal direction, and utilizing a nested Digital Phase-Locked Loop (DPLL) structure is disclosed. The obstacles to signal direction measurement in low SINR environments using the signal select method are overcome and a more precise phase comparison between the carrier and the FM modulation signals is obtained. The architecture further significantly reduces analog front-end hardware requirements, offers wider resistance to component tolerances, lower calibration and test time, and provides flexible frequency selectivity. Locators according to the present invention provide accurate estimation of the fundamental physical parameters of line location (electromagnetic signal strength and signal direction) in extremely noisy environments, using Digital Signal Processing (DSP) methods.

Owner:BUSAN TRANSPORTATION CORPORATION

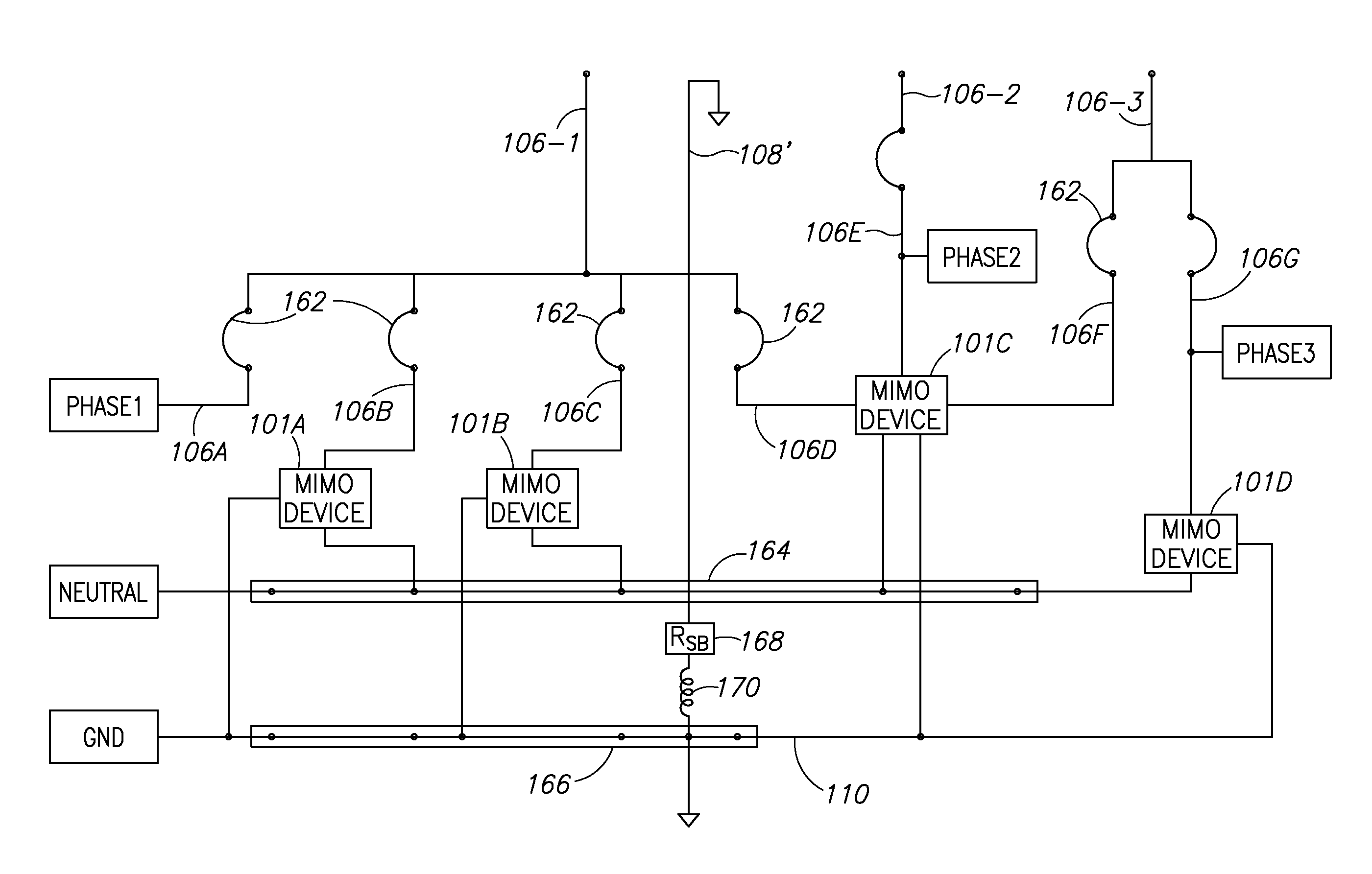

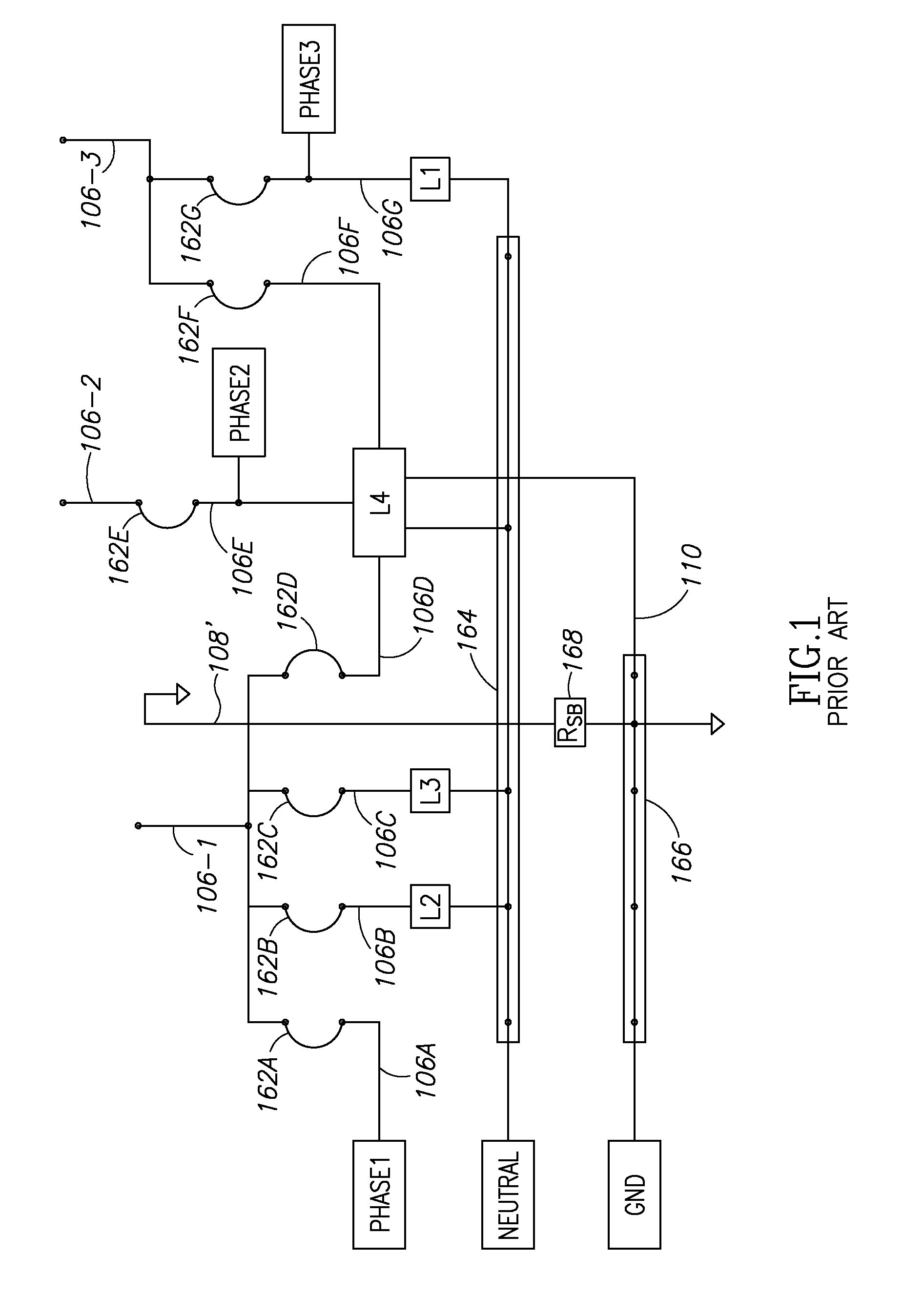

Multiple input, multiple output (MIMO) communication system over in-premises wires

ActiveUS20080273613A1Reduce the required powerPolarisation/directional diversityPower distribution line transmissionCommunication unitCommunications system

A multiple input, multiple output (MIMO) communications unit includes a multiplicity of analog front ends and a MIMO processor. Each analog front end is connectable to a different two of the wires in a subscriber premises and each handles data of one channel. The MIMO processor processes together the data of the channels. In one embodiment, the wires are the power line wires in a subscriber premises, including the phase, neutral and ground power line wires. In another embodiment, the wires are pairs of telephony wires.

Owner:SIGMA DESIGNS ISRAEL S D I

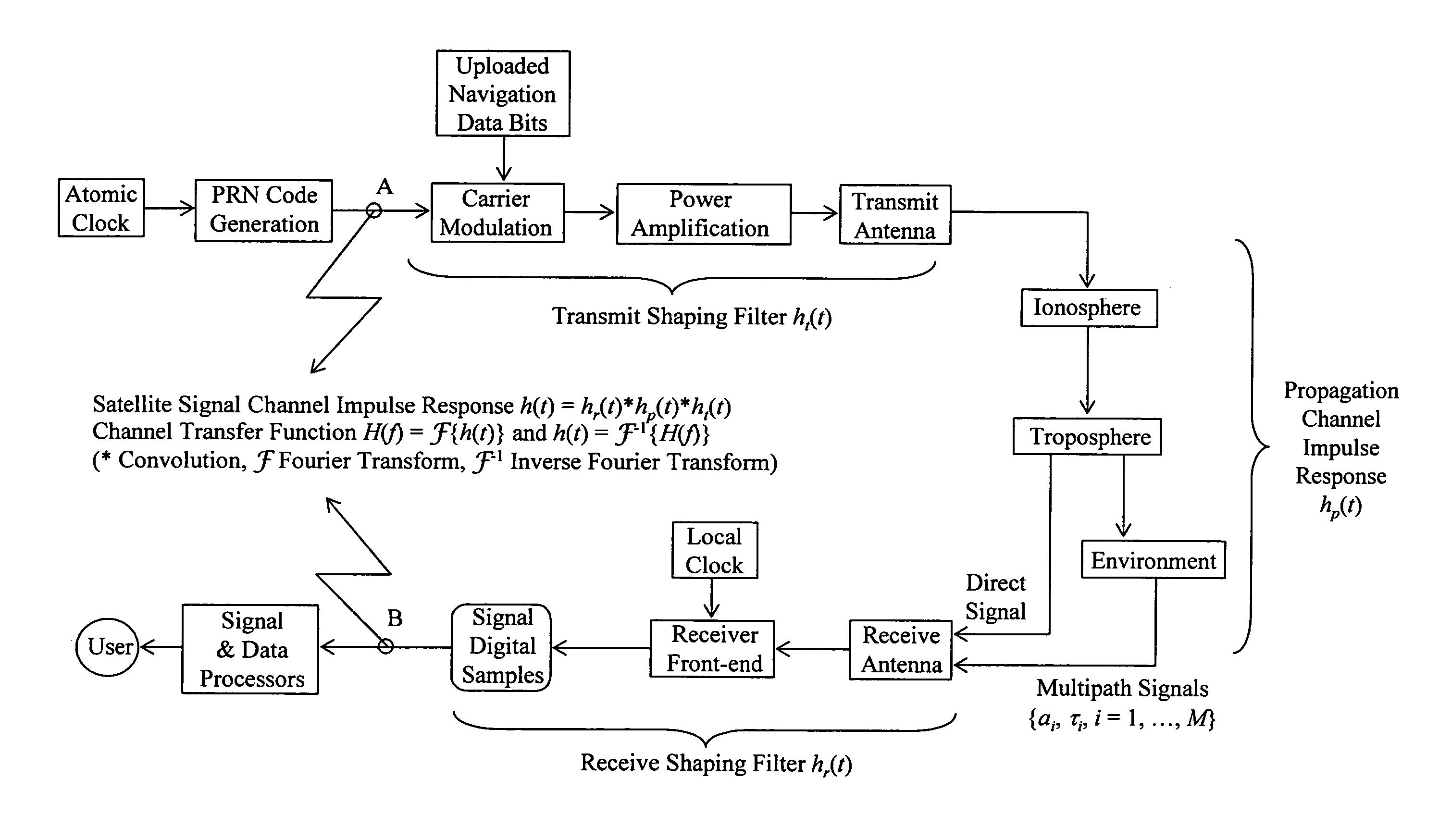

Global navigation satellite system (GNSS) receivers based on satellite signal channel impulse response

A Global Navigation Satellite System (GNSS) receiver and associated method for the reception and processing of GNSS signals. The GNSS receiver includes an antenna and an analog front-end to intercept the incoming radio-frequency signal and to convert it to an appropriate intermediate frequency for digital sampling. A baseband signal processor is organized into functionally identical channels, each dynamically assigned to a different satellite visible. The baseband signal processor processes the signal samples to generate the satellite signal channel impulse response for a number of Doppler frequency shifts. This results in a two-dimensional delay-Doppler map of satellite signal responses from which the baseband signal processor extracts the code time and carrier phase and frequency parameters as well as navigation data for timing, positioning, and environment mapping in the data processor.

Owner:YANG CHUN

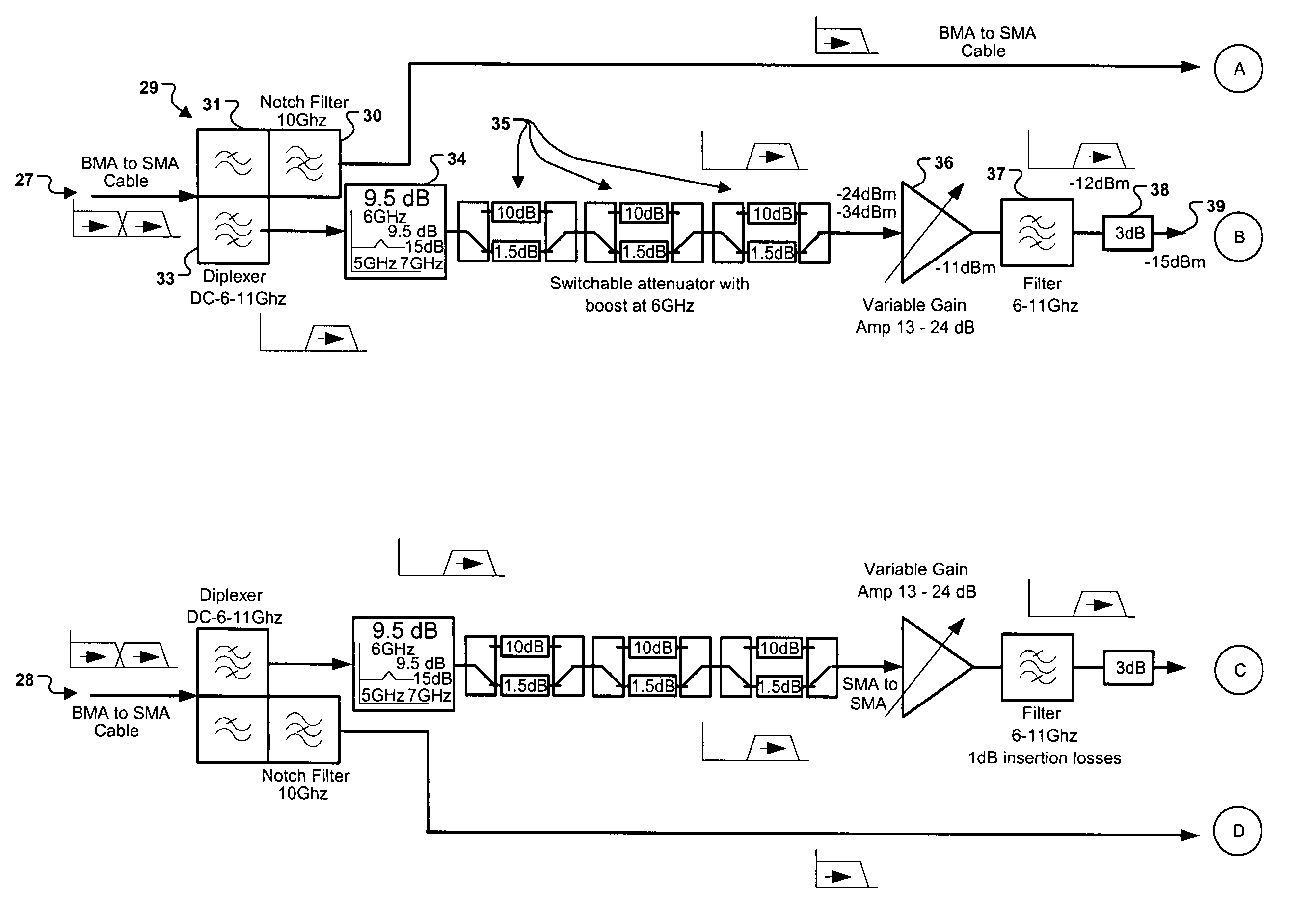

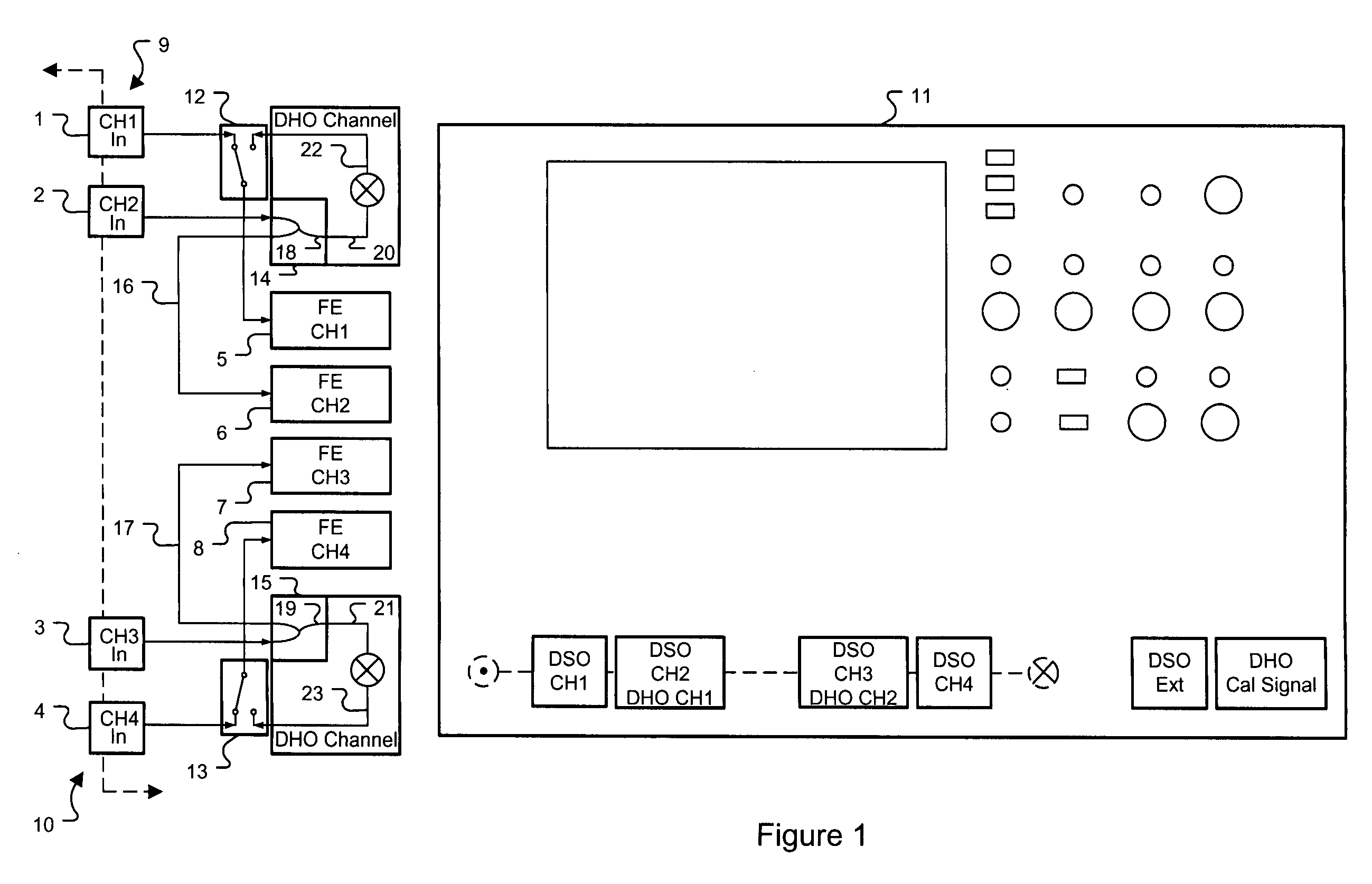

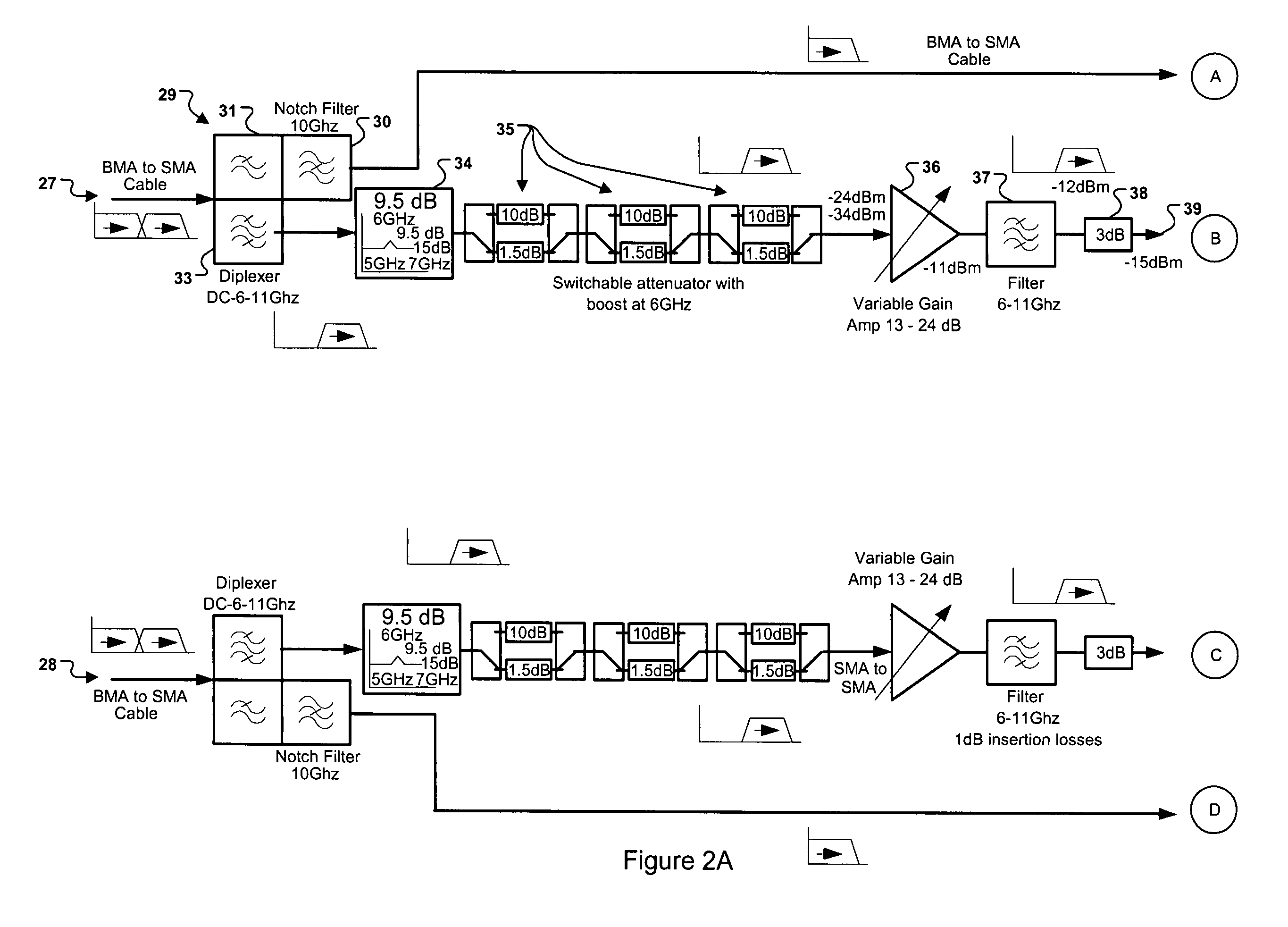

High bandwidth oscilloscope

InactiveUS7219037B2High bandwidthEliminate artifactsSpectral/fourier analysisDigital variable displayUp conversionDigitization

A method for improving bandwidth of an oscilloscope involves, in preferred embodiments, the use of frequency up-conversion and down-conversion techniques. In an illustrative embodiment the technique involves separating an input signal into a high frequency content and a low frequency content, down-converting the high frequency content in the analog domain so that it may be processed by the oscilloscope's analog front end, digitizing the low frequency content and the down-converted high frequency content, and forming a digital representation of the received analog signal from the digitized low frequency content and high frequency content.

Owner:TELEDYNE LECROY

Mixed technology MEMS/SiGe BiCMOS digitalized analog front end with direct RF sampling

A digitizing analog front end (DAFE) using mixed technology on a single substrate is described. SiGe BiCMOS technology is implemented for the semiconductor components, which include a low noise amplifier and an analog-to-digital converter. Micro Electro Mechanical System (MEMS) switches are used to change the filtering characteristics of several filters, including an anti-aliasing filter and a pre-select and anti-jamming filter.

Owner:RAYTHEON CO

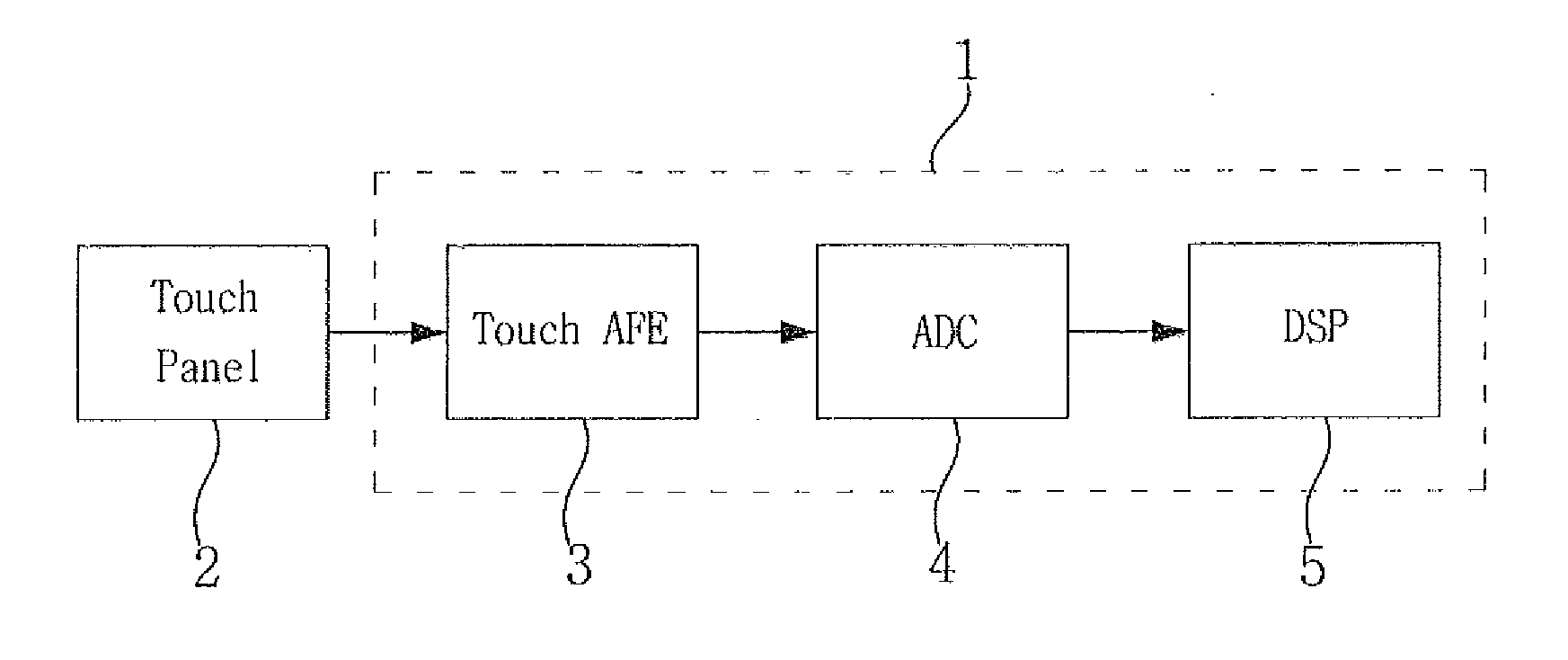

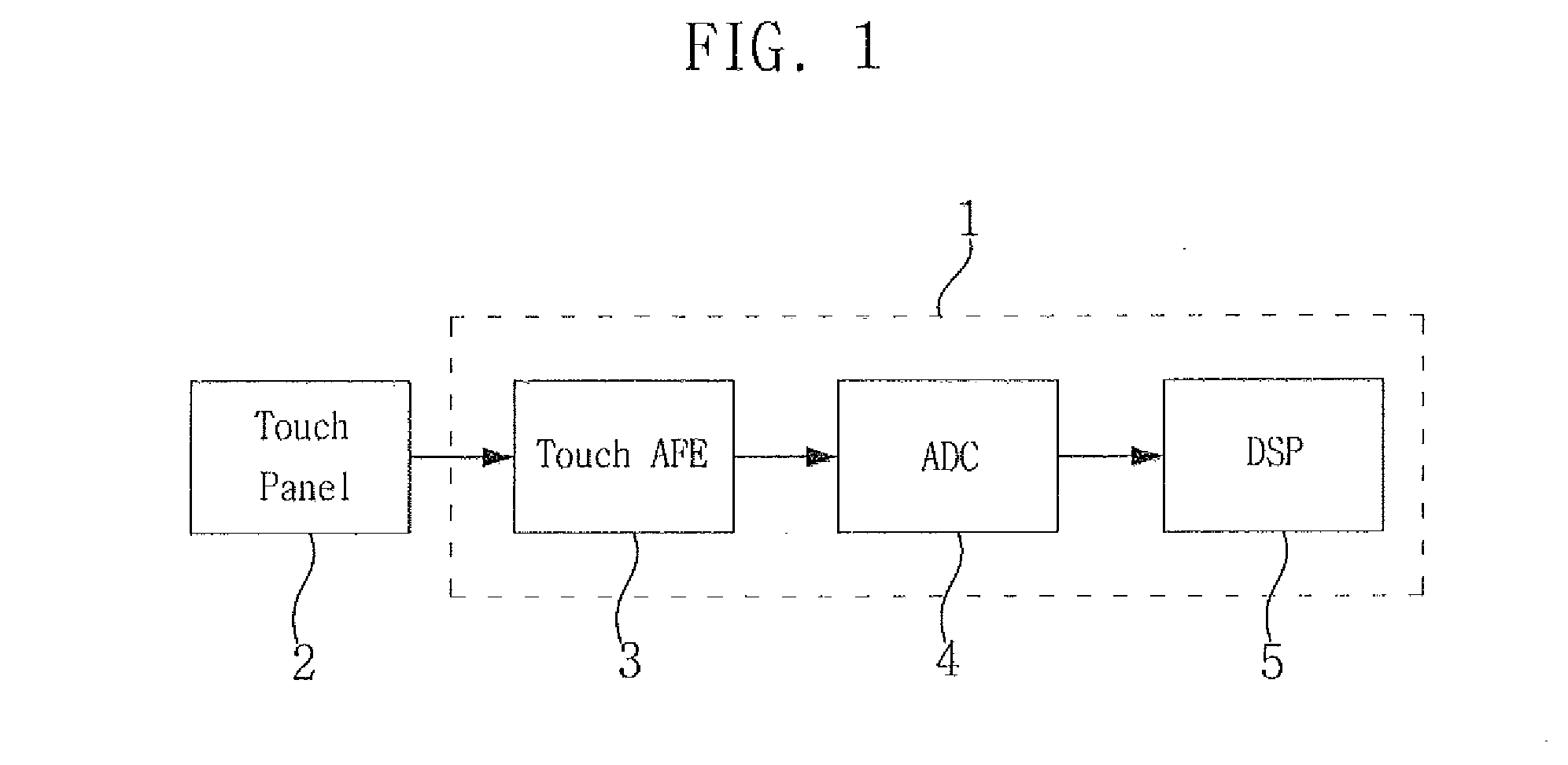

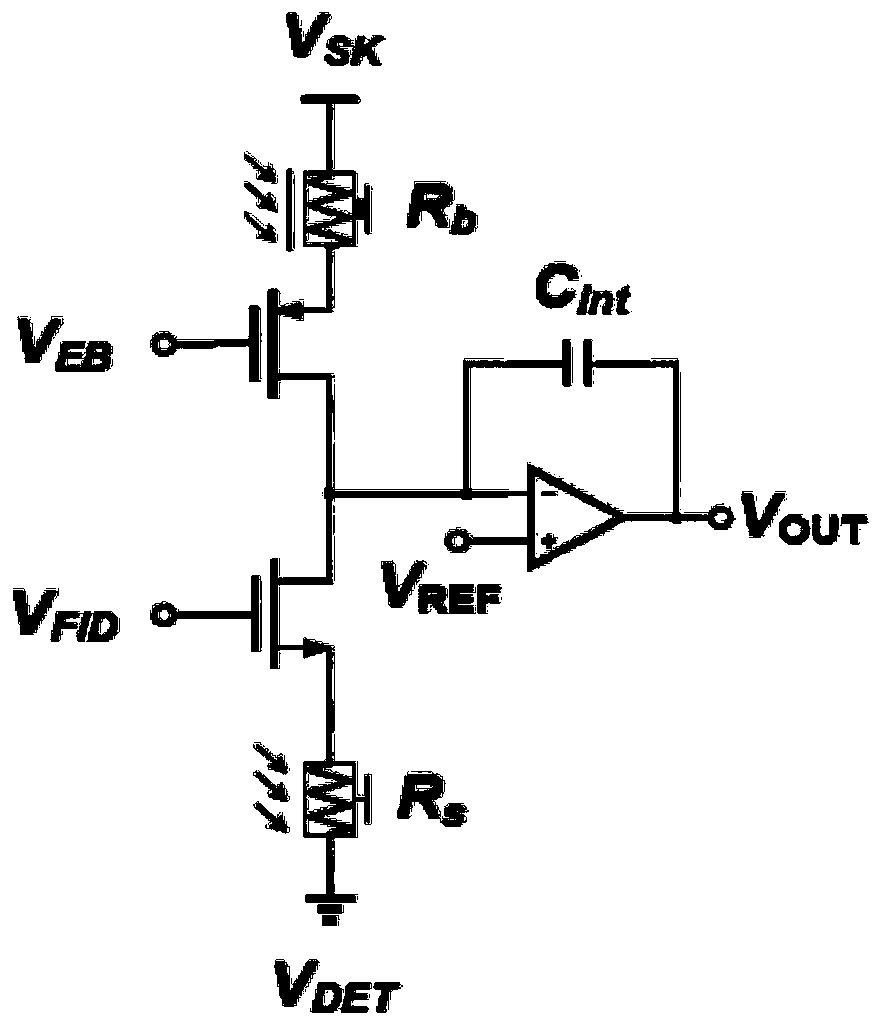

Touch analog front end and touch sensor controller having the same

ActiveUS20160124544A1Eliminate low frequency noiseDoubling sensitivity of a touch inputDetails for portable computersInput/output processes for data processingCapacitanceIntegrator

A touch analog front-end (AFE) for a touch sensitive screen may include a transmitter configured to charge a touch panel and a receiver configured to sense the touch panel. The receiver may include a charge-to-voltage (C2V) converter configured to convert a change of capacitance received from the touch panel into a voltage signal, a correlated double sampling (CDS) block configured to convert the voltage signal into a differential signal and to sample each of the positive and the negative signals of the differential signal, and an integrator configured to accumulate a difference between the sampled positive and negative signals.

Owner:SAMSUNG ELECTRONICS CO LTD

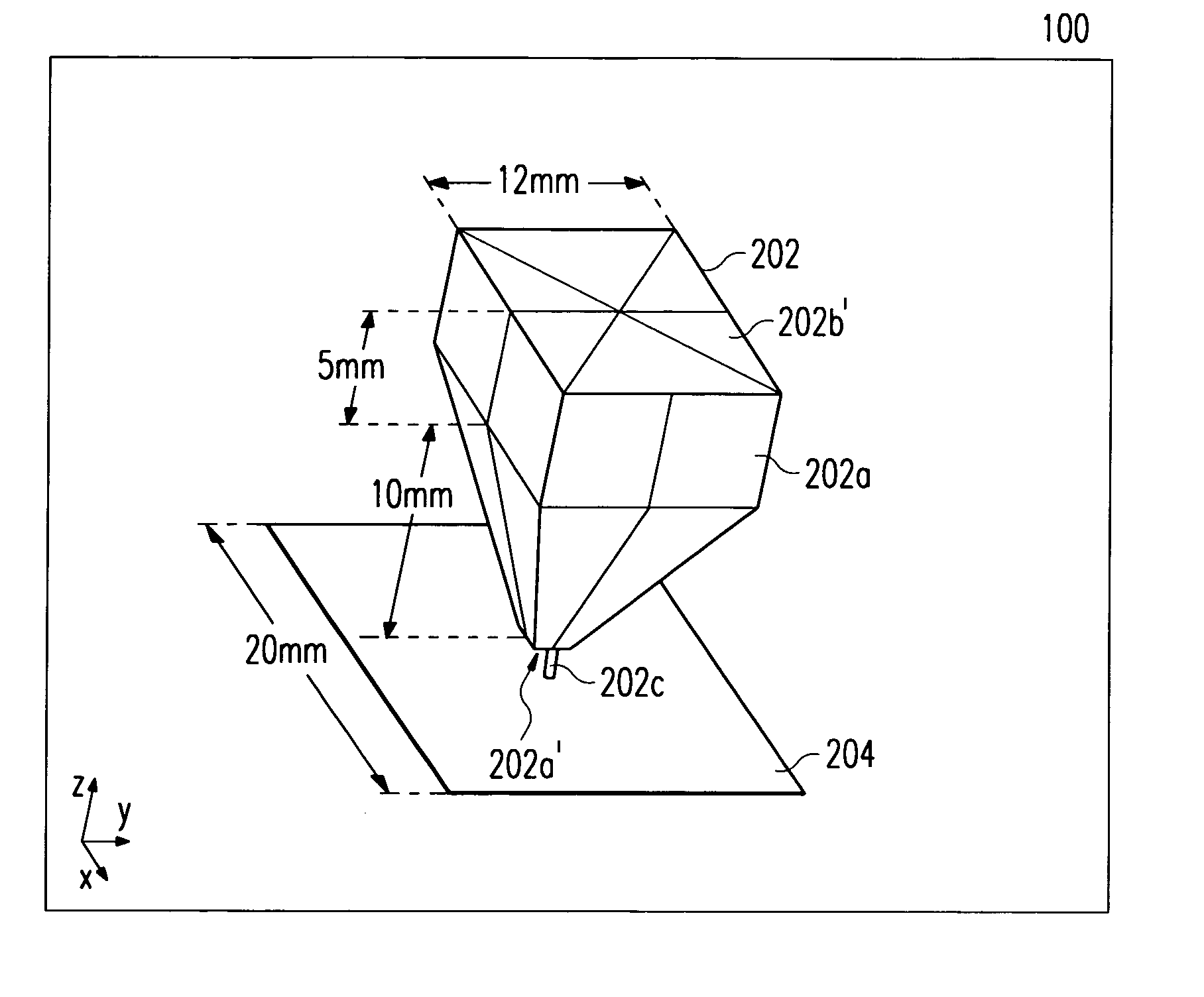

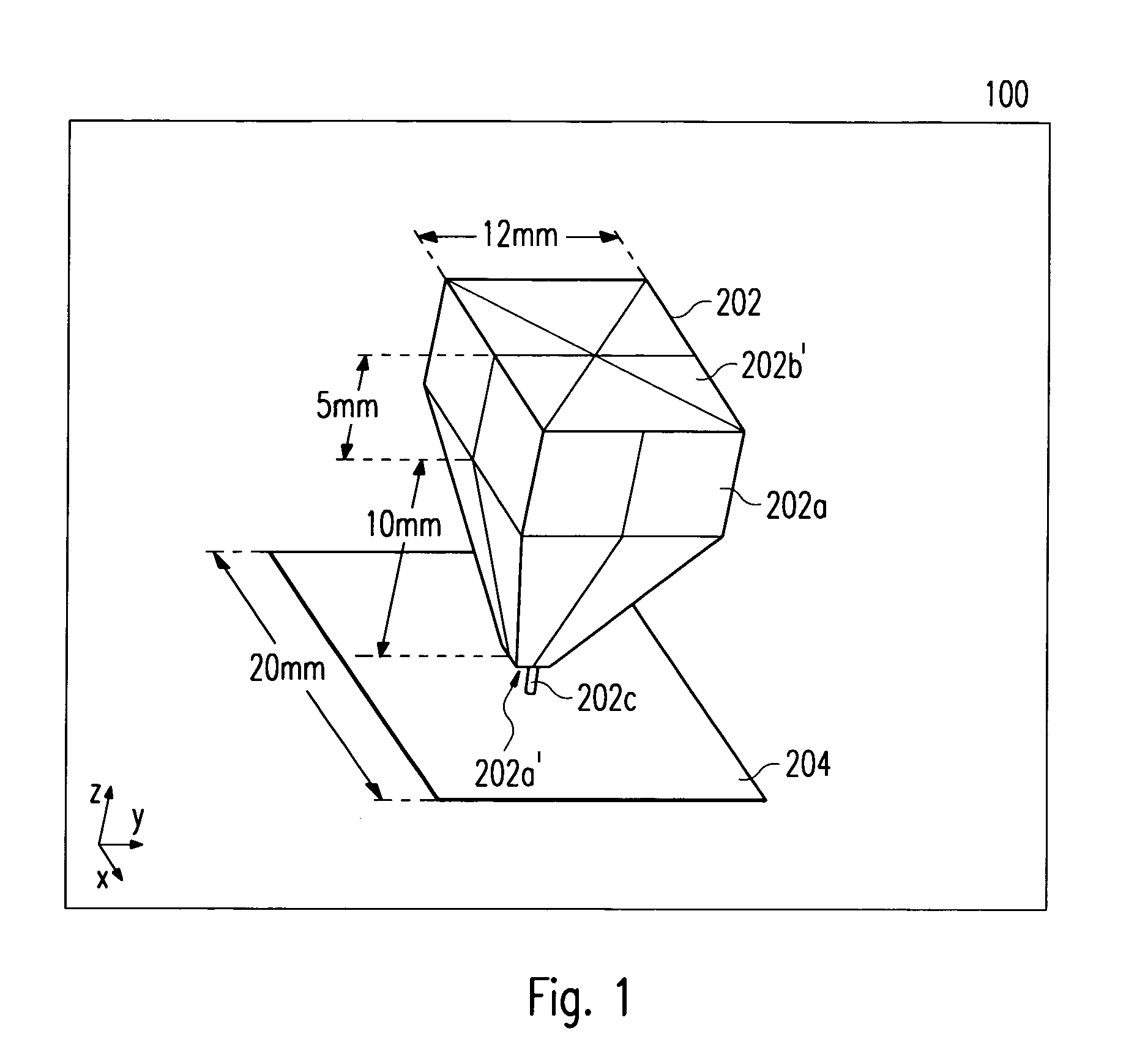

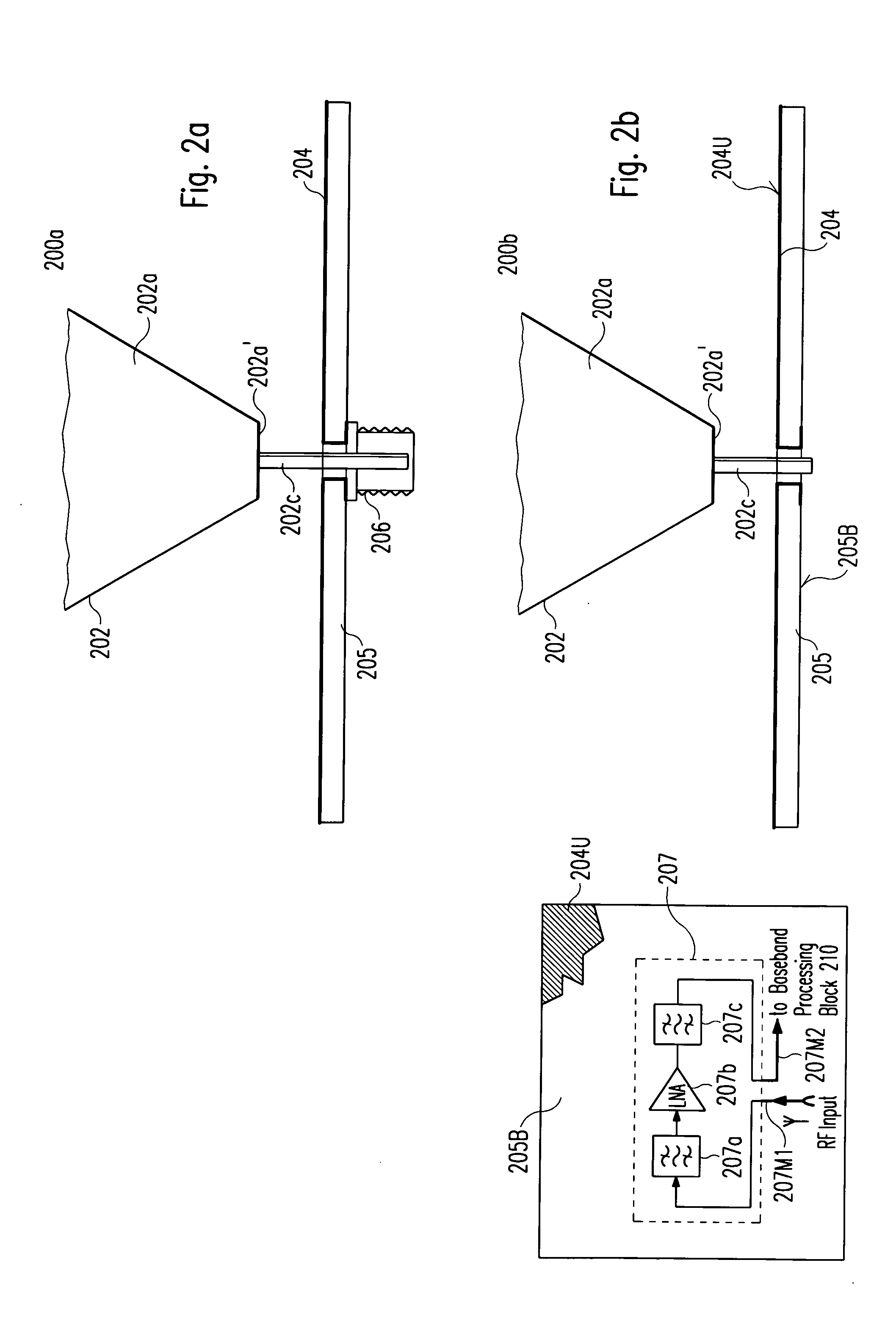

Three-dimensional omni-directional antenna designs for ultra-wideband applications

InactiveUS20050156804A1Easy to integrateElongated active element feedAntenna feed intermediatesUltra-widebandDielectric substrate

The present invention generally relates to the field of microwave antennas, and, more particularly, to a number of three-dimensional designs for the radiation element of an ultra-wideband monopole antenna with a symmetrical omni-directional radiation pattern operated in the frequency range between 3.1 GHz and 10.6 GHz. Said antenna is connected to the analog front-end circuitry of a wireless communication device used for transmitting and / or receiving microwave signals and meets the FCC requirements in terms of antenna gain, radiation pattern, polarization, frequency bandwidth, group delay, and size. It comprises a radiation element consisting of an air- and / or dielectric-filled cavity structure with a base plane and a radiator plane. A metallic ground plane having a relatively high surface impedance to electromagnetic waves within said frequency range, which is printed on a dielectric substrate, serves as a reflector. The monopole antenna further comprises an antenna feeding circuitry used for electronically steering the symmetrical omni-directional radiation pattern and a feeding line connecting the antenna feeding circuitry with the base plane of the radiation element. Thereby, parts of the analog front-end circuitry can optionally be placed within the air-filled part of the radiation element of the antenna. The proposed designs include a radiation element having the form of a truncated right circular cone, rotational-symmetric radiation elements with a convexly- or concavely-shaped 3D surface, respectively, a radiation element in the form of a truncated right regular pyramid with a square base plane, and radiation elements with a combined structure comprising a conical, pyramidal, convexly- or concavely-shaped first part and a closed cylindrical or cuboidal second part whose top plane is arranged on top of the congruent base plane of said first part. Further embodiments include radiation elements with the form of a radially notched cylinder or hemisphere as well as combined structures consisting of at least two convexly-shaped elements or two conical parts, respectively, stacked on top of each other.

Owner:SONY DEUT GMBH

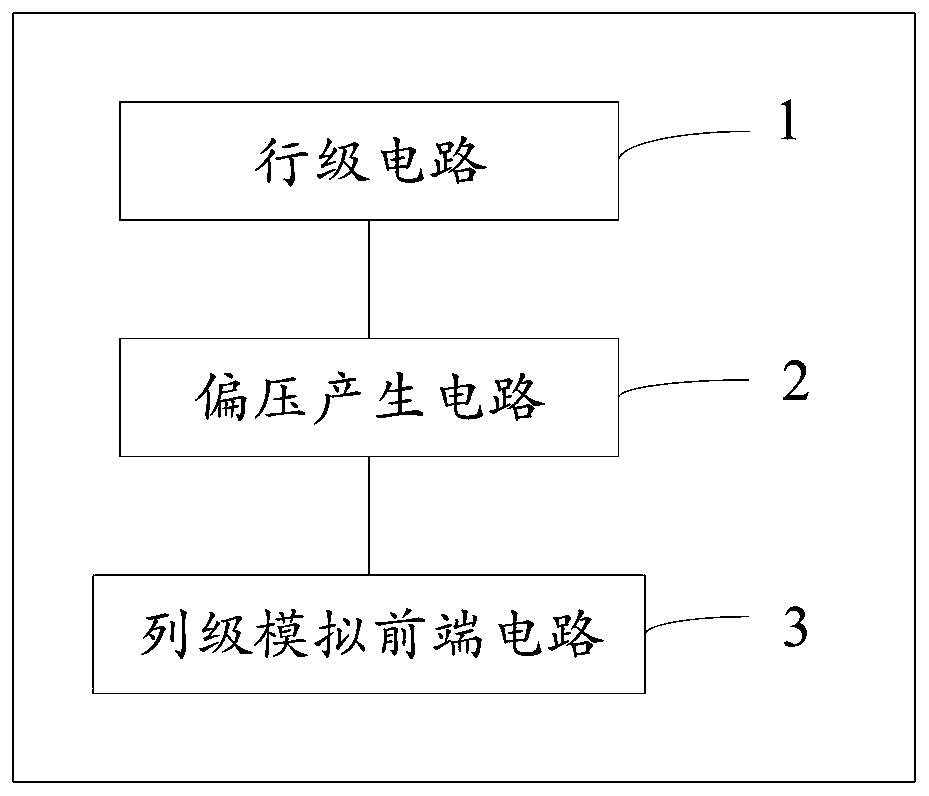

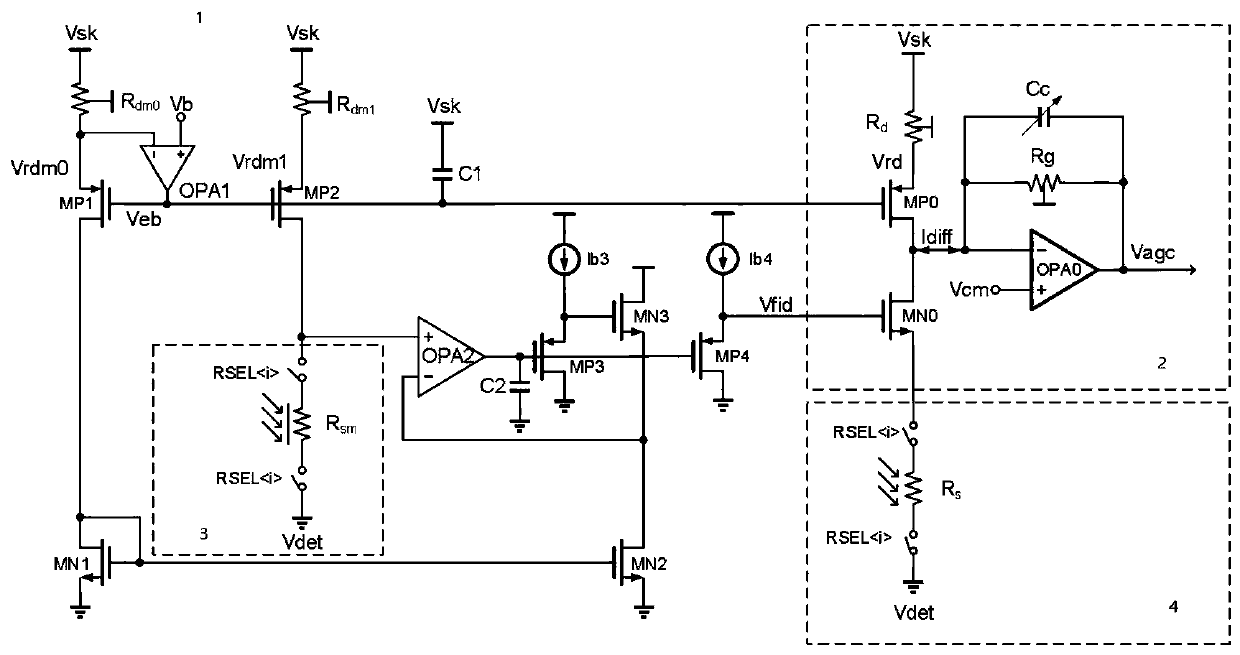

TEC(thermoelectric cooler)-free uncooled infrared focal plane array reading circuit

ActiveCN110006538AImprove stabilityReduce noisePyrometry using electric radation detectorsAnalog front-endMirror image

The invention discloses a TEC(thermoelectric cooler)-free uncooled infrared focal plane array reading circuit, and relates to the technical field of uncooled infrared focal plane array. A reading circuit comprises a bias generation circuit, a column-level analog front-end circuit, and a row-level circuit; the row-level circuit comprises a row-level mirror image pixel, is controlled by a row selection switch,and can output a third bias voltage; the bias generation circuit is connected with the row-level circuit, the input end of the bias generation circuit is connected with the output end of the row-level circuit; a first bias voltage and a second bias voltage are generated and outputtedbased onan inputted constant voltage and a third bias voltage; the column-level analog front-end circuitcomprises a blind pixel; the column-level analog front-end circuit is electrically connected with the bias generation circuit, the input end of the column-level analog front-end circuit is connected with the output end of the bias generation circuit to obtain two currents, and the difference between the two currents generated is amplified in a transimpedance mode and outputted as a voltage. By adopting the technical scheme of theTEC(thermoelectric cooler)-free uncooled infrared focal plane array reading circuit, the circuit has a stable output point unaffected by the substrate temperature andthe self-heating effect, and the stability of the circuit is improved.

Owner:北京安酷智芯科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com