Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

224 results about "BiCMOS" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Bipolar CMOS (BiCMOS) is a semiconductor technology that integrates two formerly separate semiconductor technologies, those of the bipolar junction transistor and the CMOS (complementary metal-oxide-semiconductor) gate, in a single integrated circuit device.

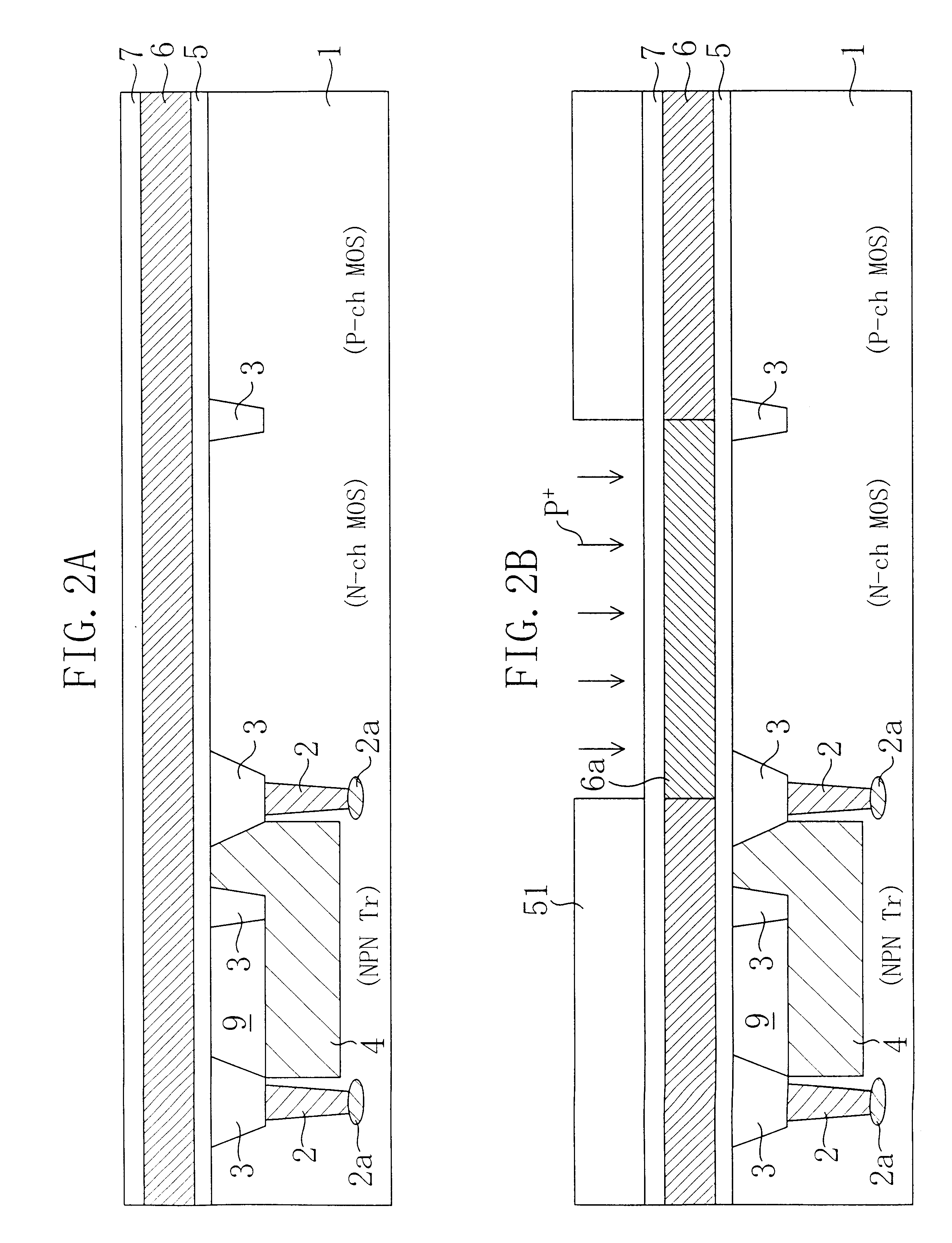

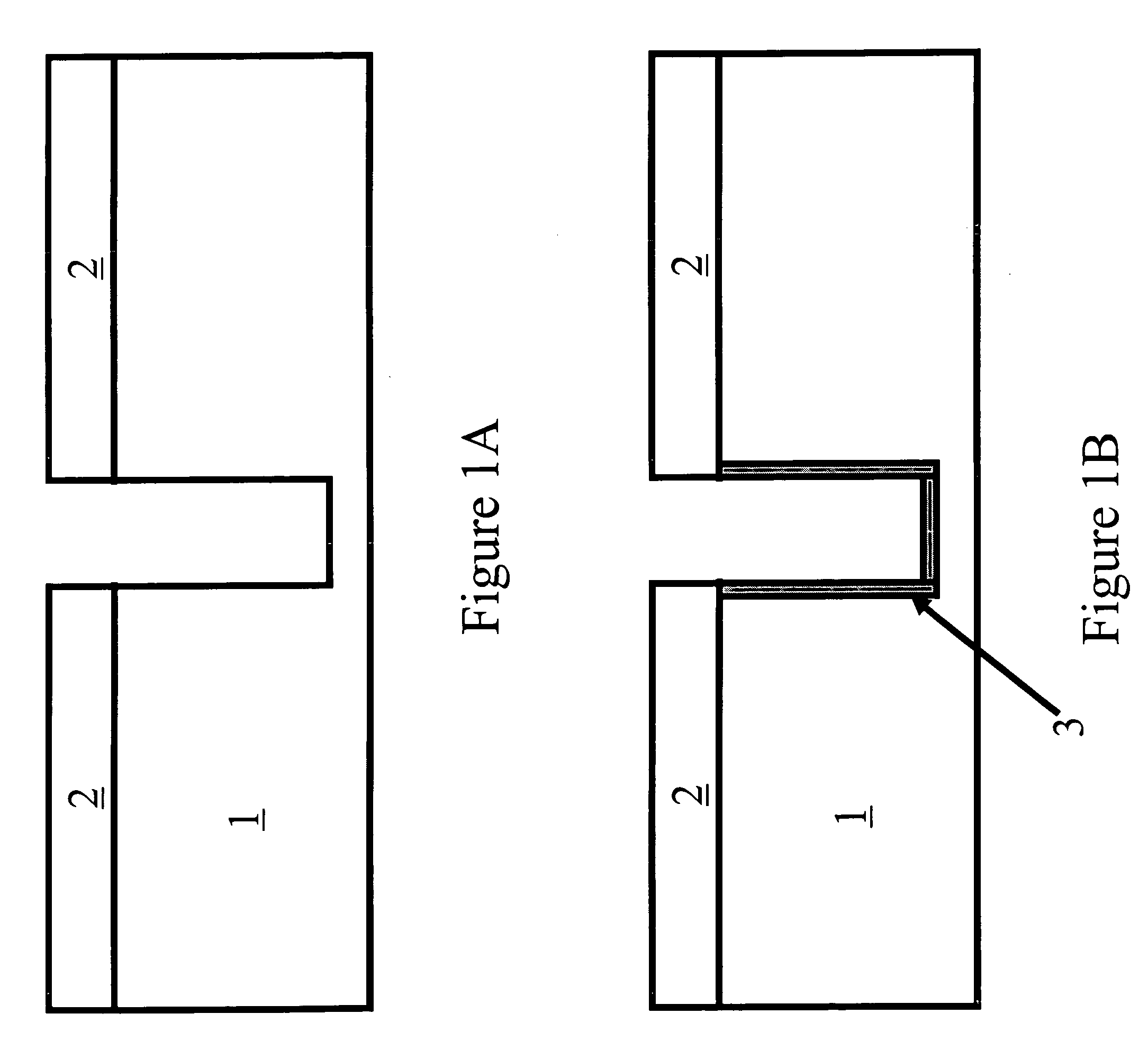

Semiconductor device and method for fabricating the same

InactiveUS6399993B1Reduce the number of stepsIncrease productivityTransistorSolid-state devicesCMOSThermal expansion

In a bipolar transistor block, a base layer (20a) of SiGe single crystals and an emitter layer (26) of almost 100% of Si single crystals are stacked in this order over a collector diffused layer (9). Over both edges of the base layer (20a), a base undercoat insulating film (5a) and base extended electrodes (22) made of polysilicon are provided. The base layer (20a) has a peripheral portion with a thickness equal to that of the base undercoat insulating film (5a) and a center portion thicker than the peripheral portion. The base undercoat insulating film (5a) and gate insulating films (5b and 5c) for a CMOS block are made of the same oxide film. A stress resulting from a difference in thermal expansion coefficient between the SiGe layer as the base layer and the base undercoat insulating film 5a can be reduced, and a highly reliable BiCMOS device is realized.

Owner:PANASONIC CORP

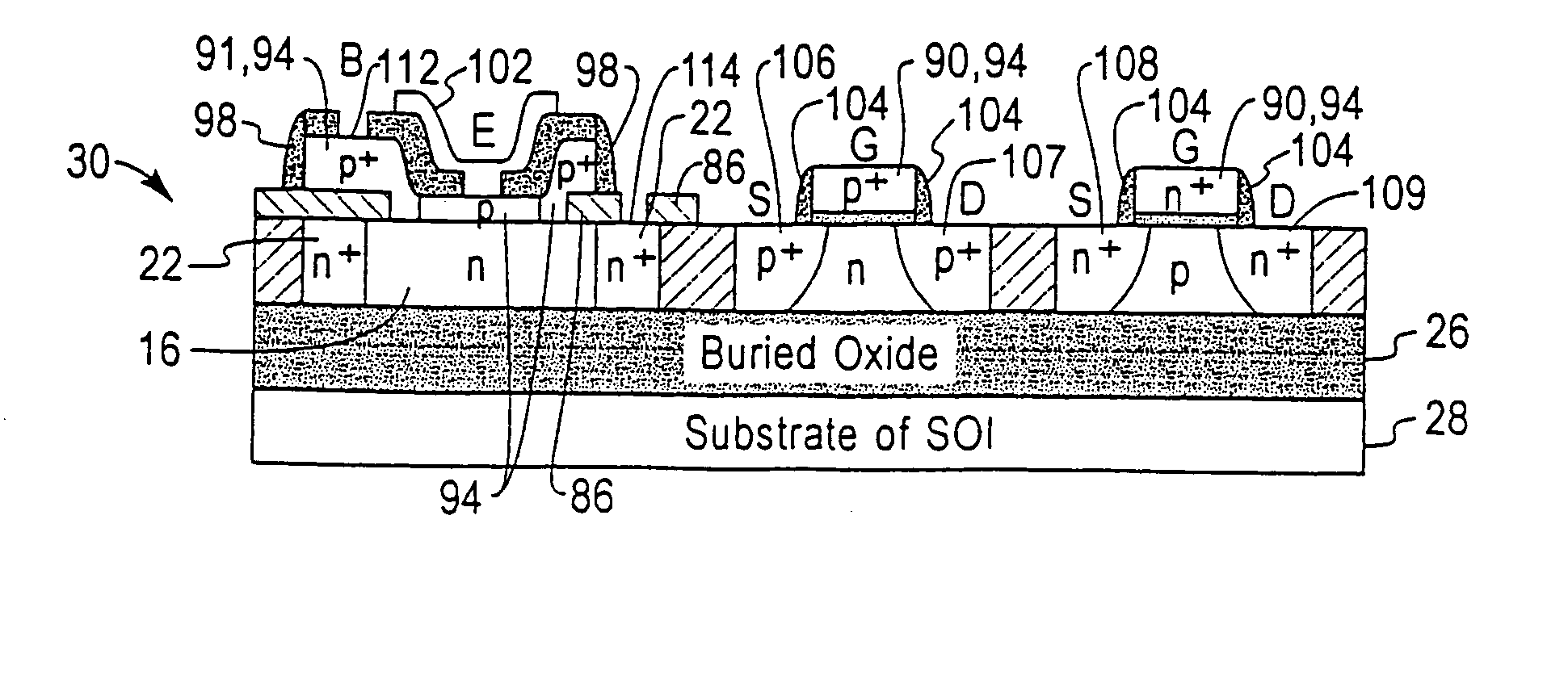

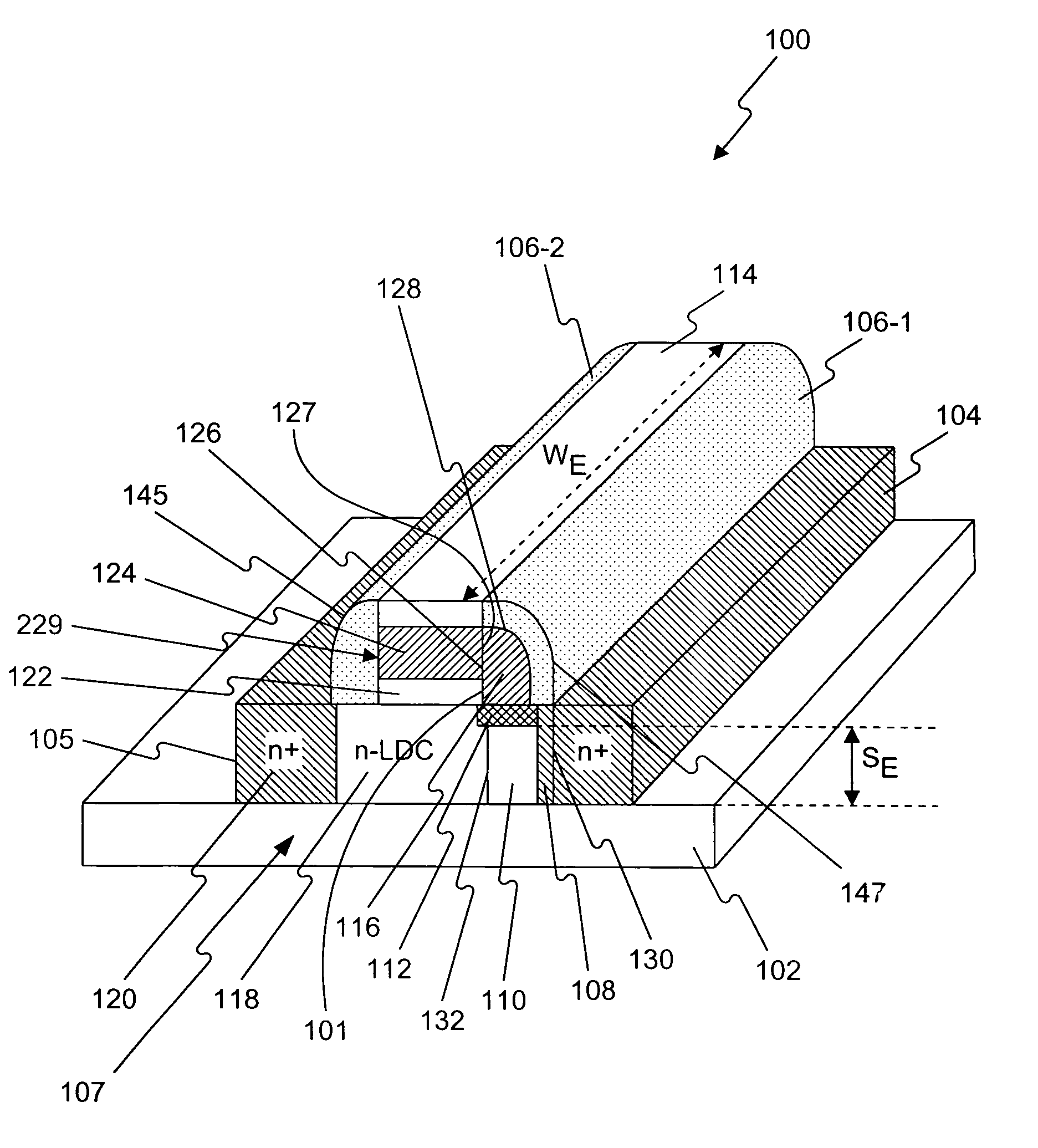

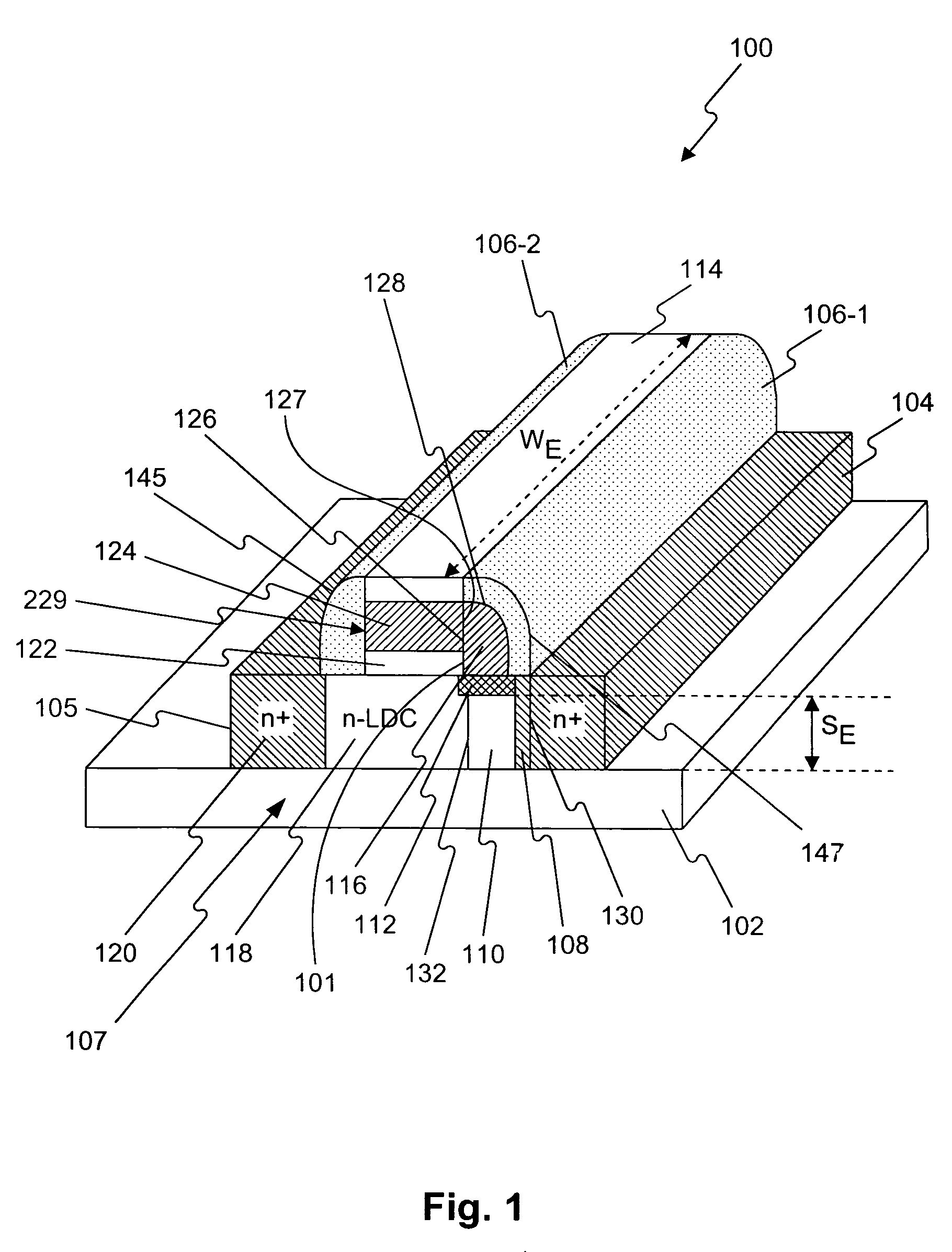

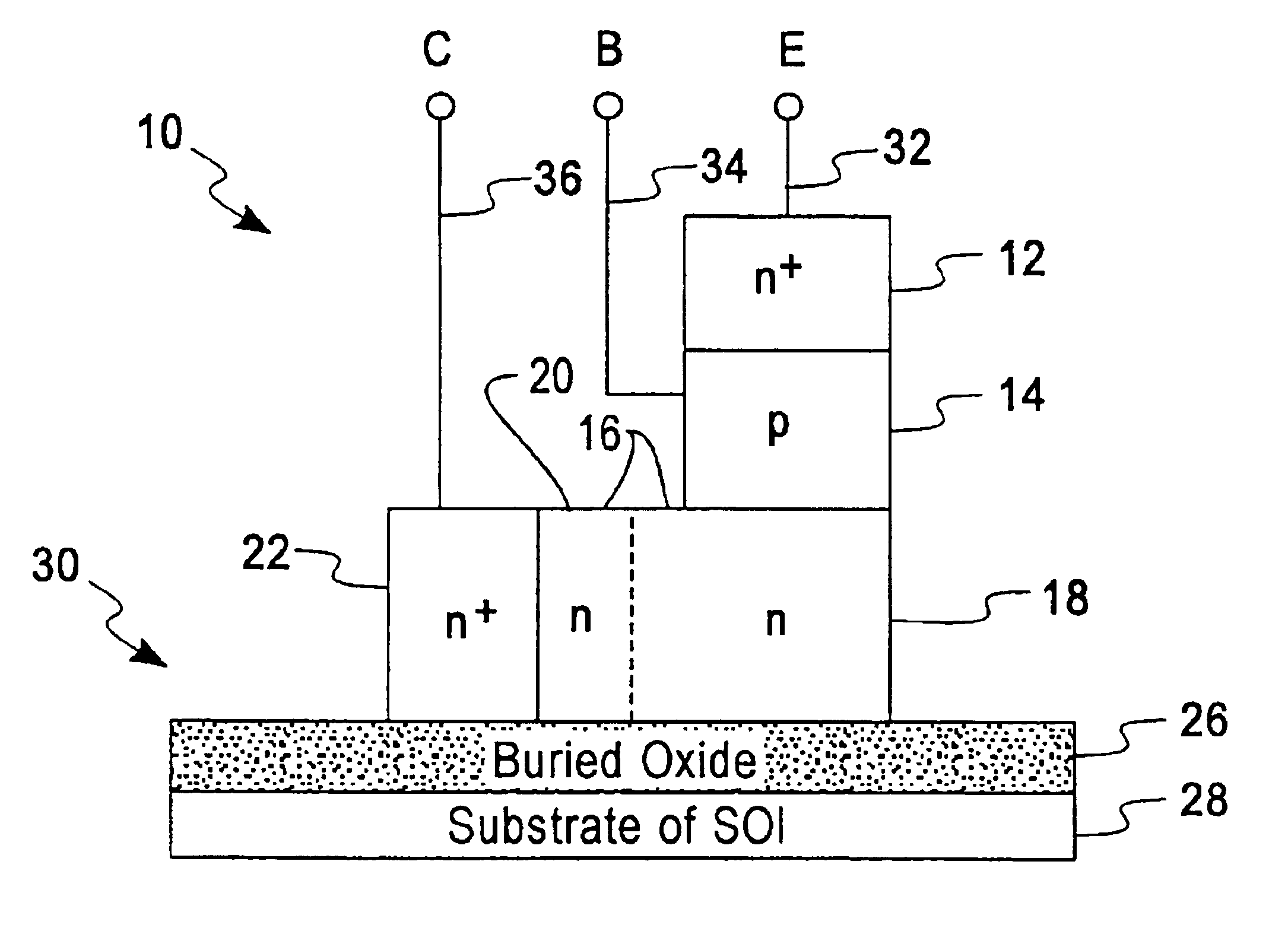

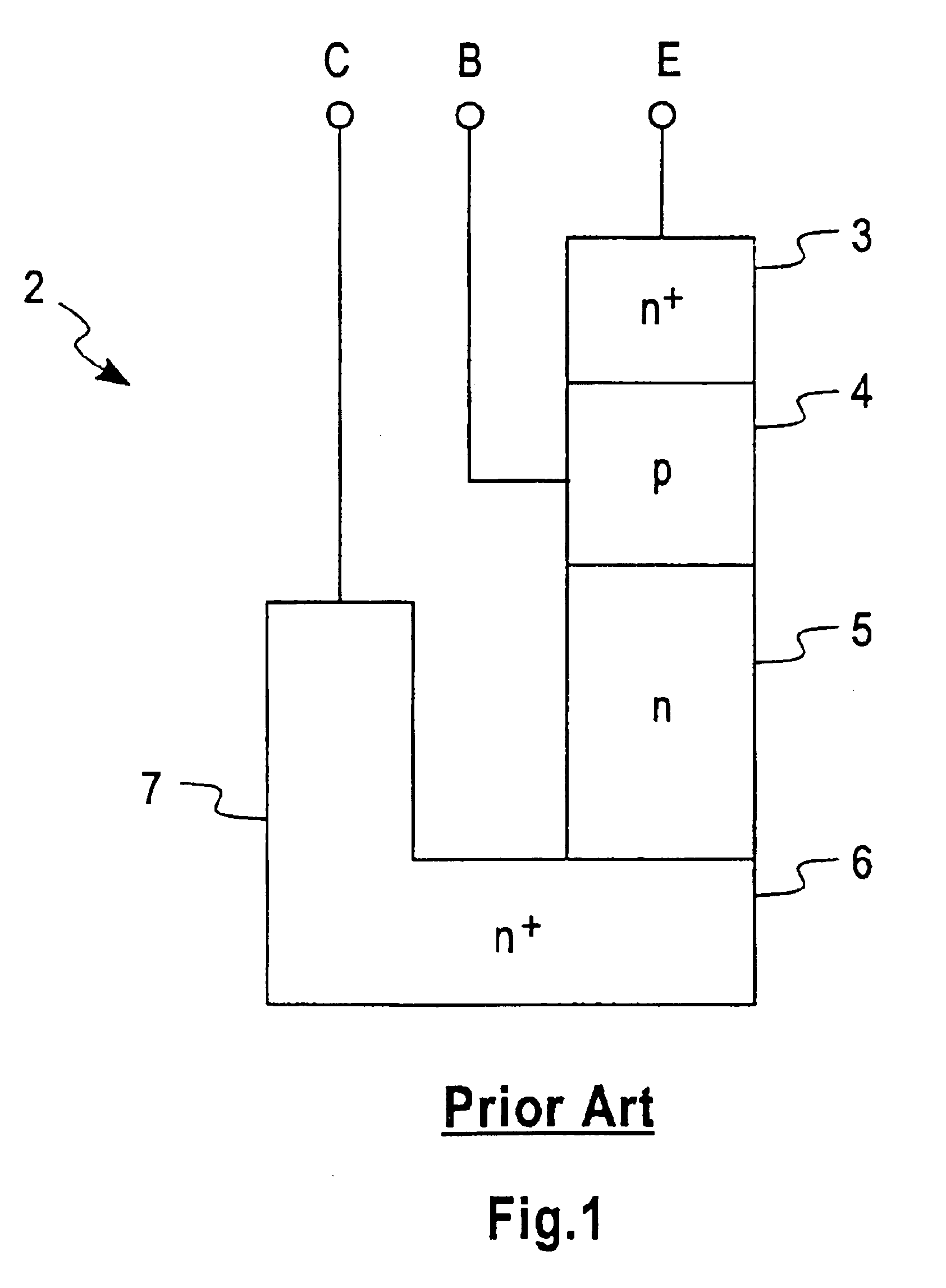

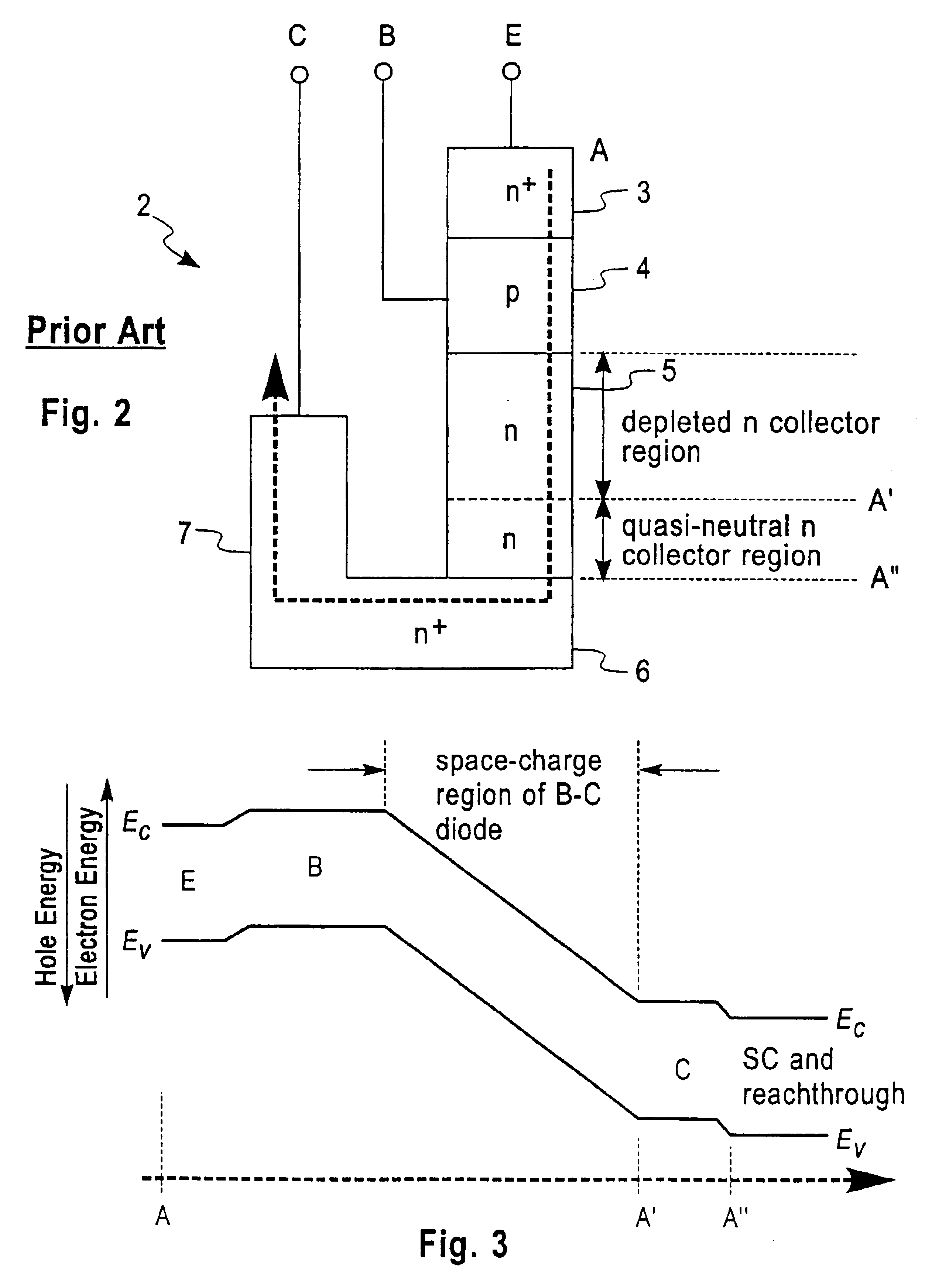

Fully-depleted-collector silicon-on-insulator (SOI) bipolar transistor useful alone or in SOI BiCMOS

InactiveUS20050087805A1Easy compatibilityTransistorSemiconductor/solid-state device detailsSemiconductor materialsEngineering

A bipolar transistor structure is described incorporating an emitter, base, and collector having a fully depleted region on an insulator of a Silicon-On-Insulator (SOI) substrate without the need for a highly doped subcollector to permit the fabrication of vertical bipolar transistors on semiconductor material having a thickness of 300 nm or less and to permit the fabrication of SOI BiCMOS. The invention overcomes the problem of requiring a thick semiconductor layer in SOI to fabricate vertical bipolar transistors with low collector resistance.

Owner:GLOBALFOUNDRIES US INC

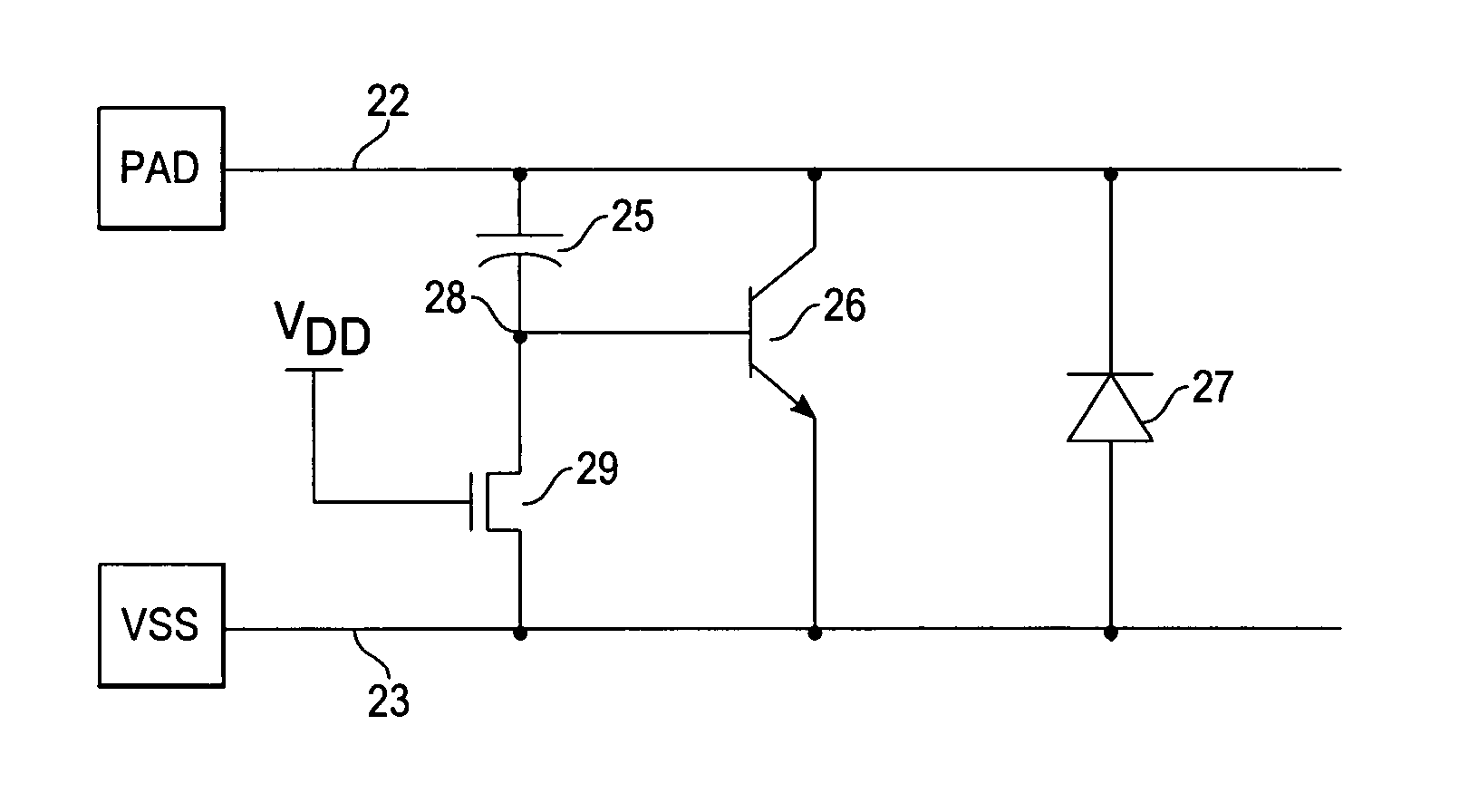

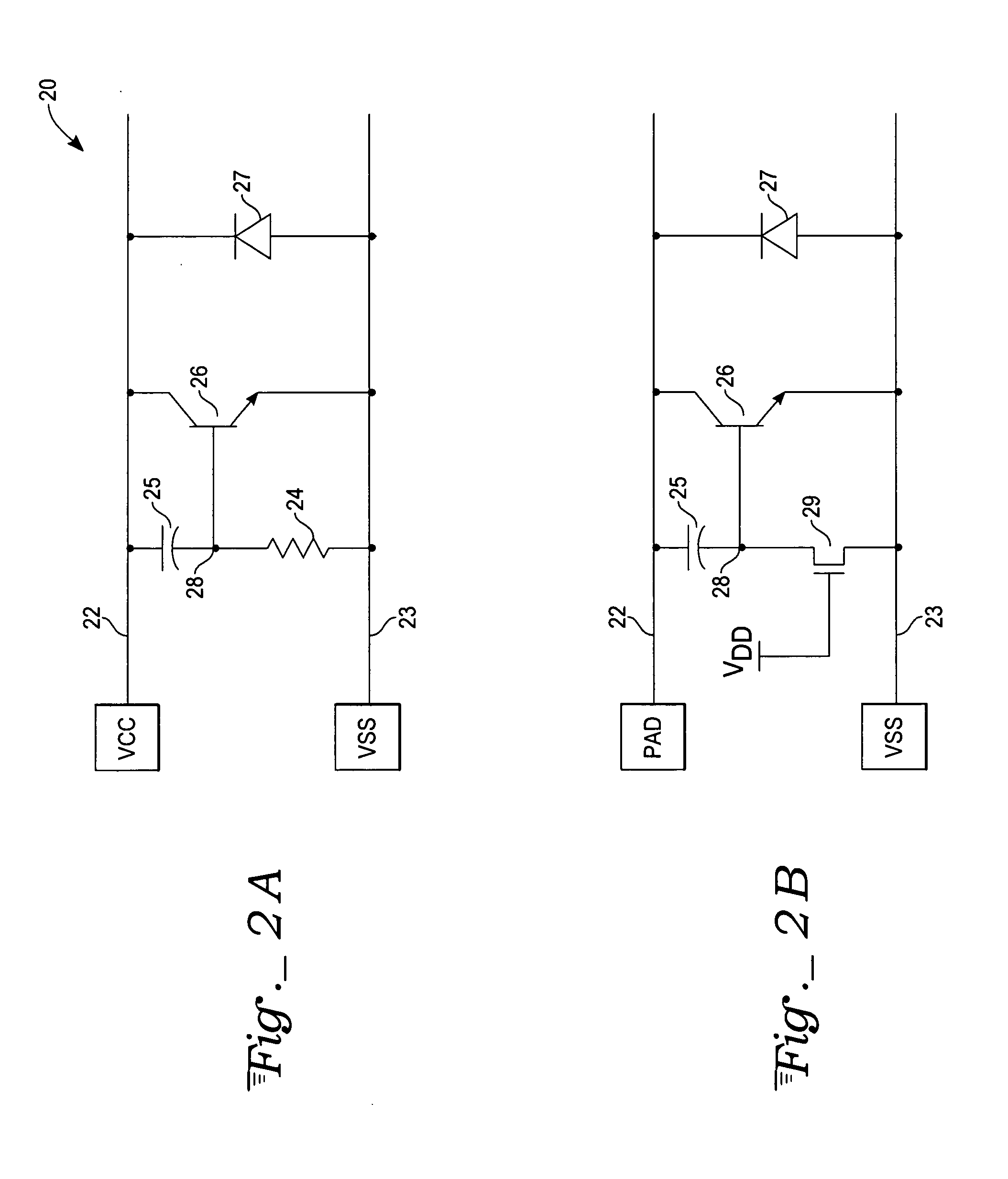

Transient pulse, substrate-triggered biCMOS rail clamp for ESD abatement

InactiveUS20060250732A1High currentLower clamping voltageTransistorEmergency protective arrangements for limiting excess voltage/currentVoltage pulseEngineering

A circuit for protecting a circuit device against electrostatic discharge (ESD), power line, and voltage supply line surges. A transistor, diode, resistor, and capacitor are configured to clamp voltage pulses between the power and ground lines. The circuit is constructed using a single bipolar npn transistor formed using an isolated p-well.

Owner:ATMEL CORP

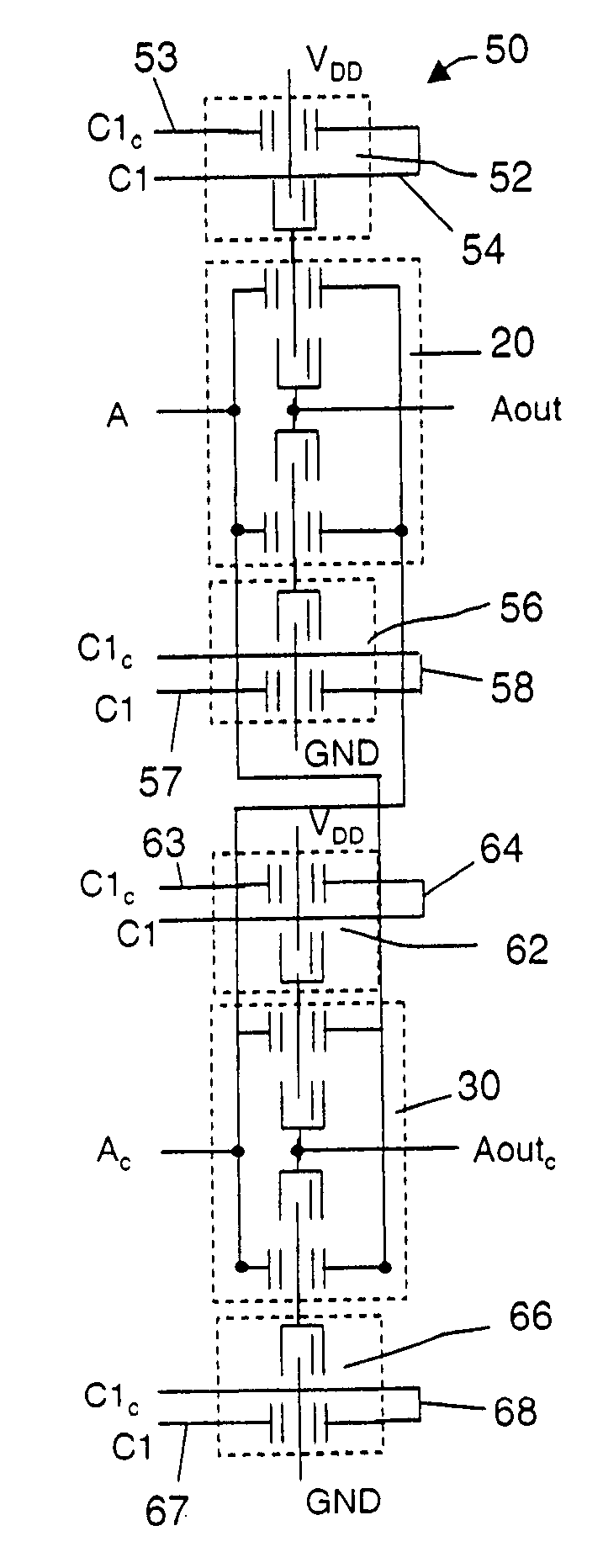

Tri-state circuit using nanotube switching elements

InactiveUS20060255834A1Logic circuits characterised by logic functionNanoelectromechanical switchesCMOSEngineering

Nanotube-based logic circuitry is disclosed. Tri-stating elements add an enable / disable function to the circuitry. The tri-stating elements may be provided by nanotube-based switching devices. In the disabled state, the outputs present a high impedance, i.e., are tri-stated, which state allows interconnection to a common bus or other shared communication lines. In embodiments wherein the components are non-volatile, the inverter state and the control state are maintained in the absence of power. Such an inverter may be used in conjunction with and in the absence of diodes, resistors and transistors or as part of or as a replacement to CMOS, biCMOS, bipolar and other transistor level technologies.

Owner:NANTERO

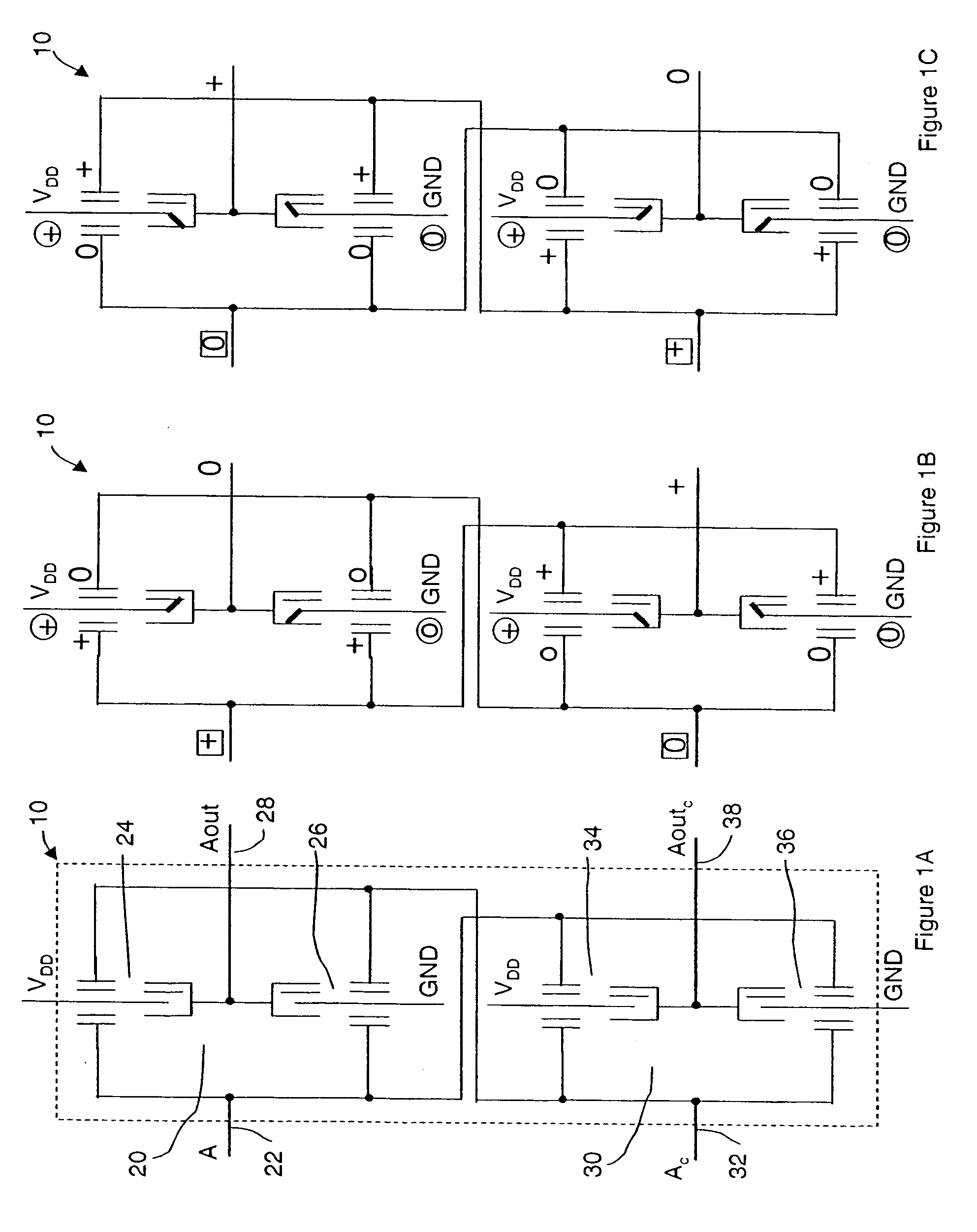

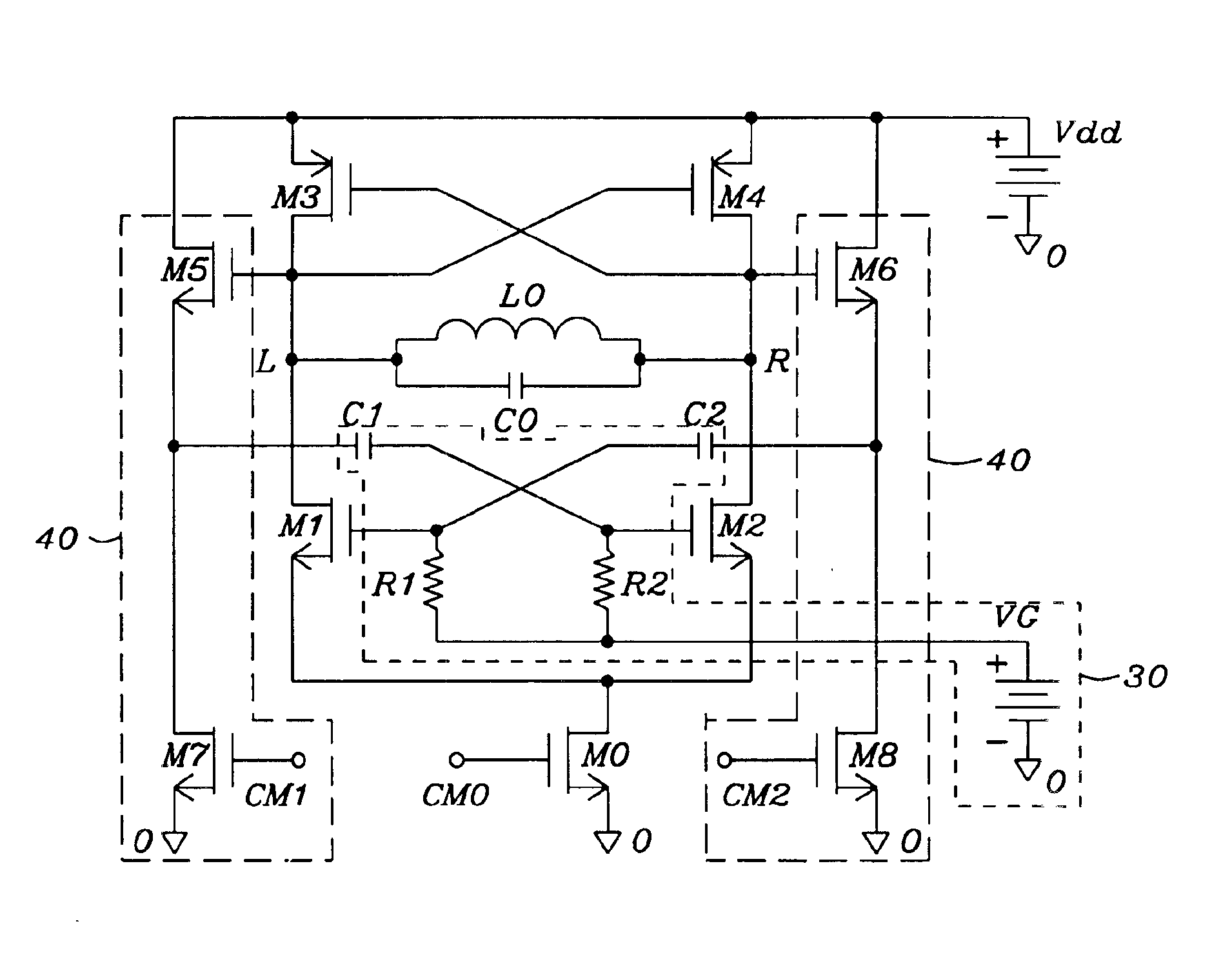

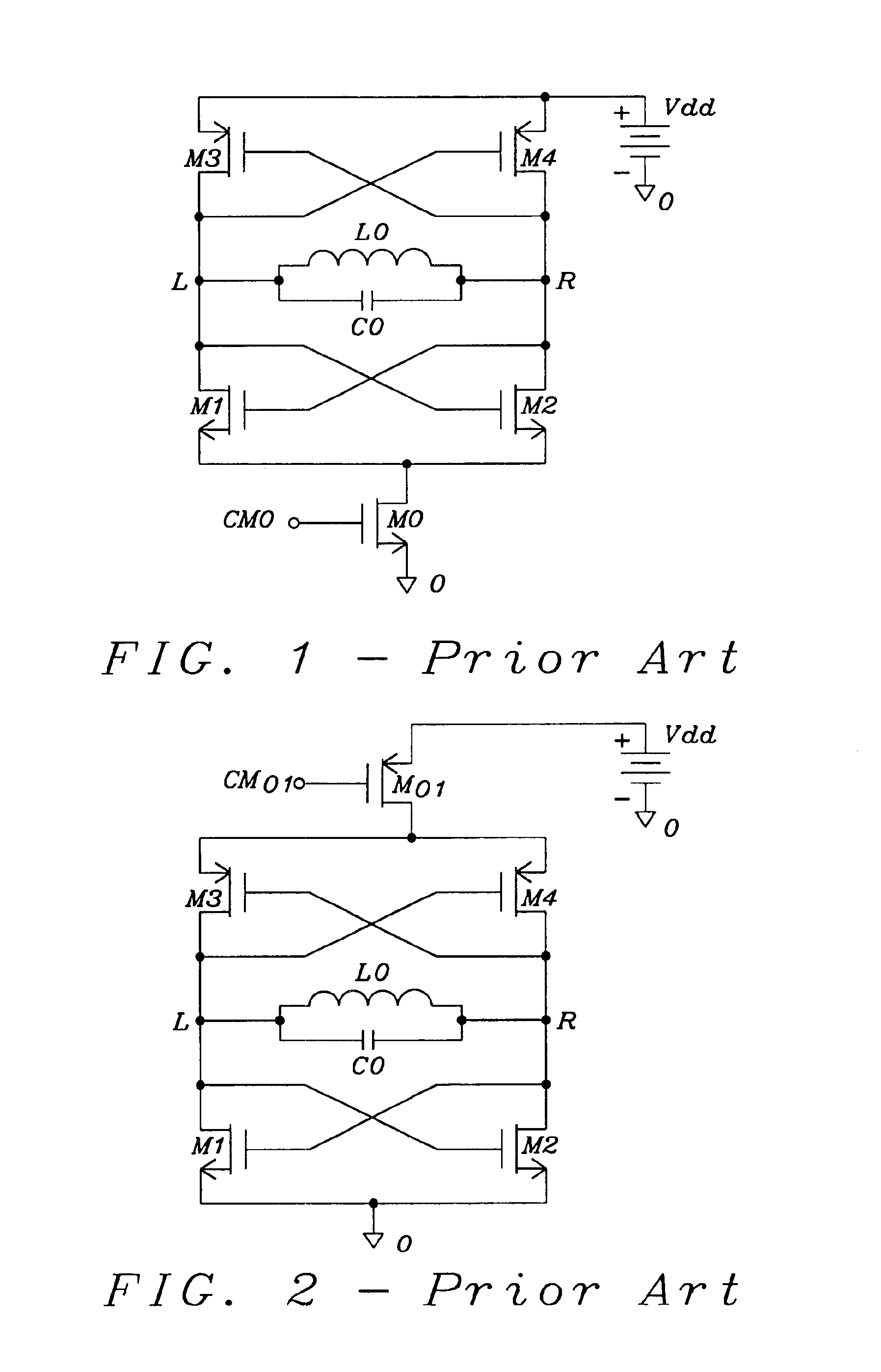

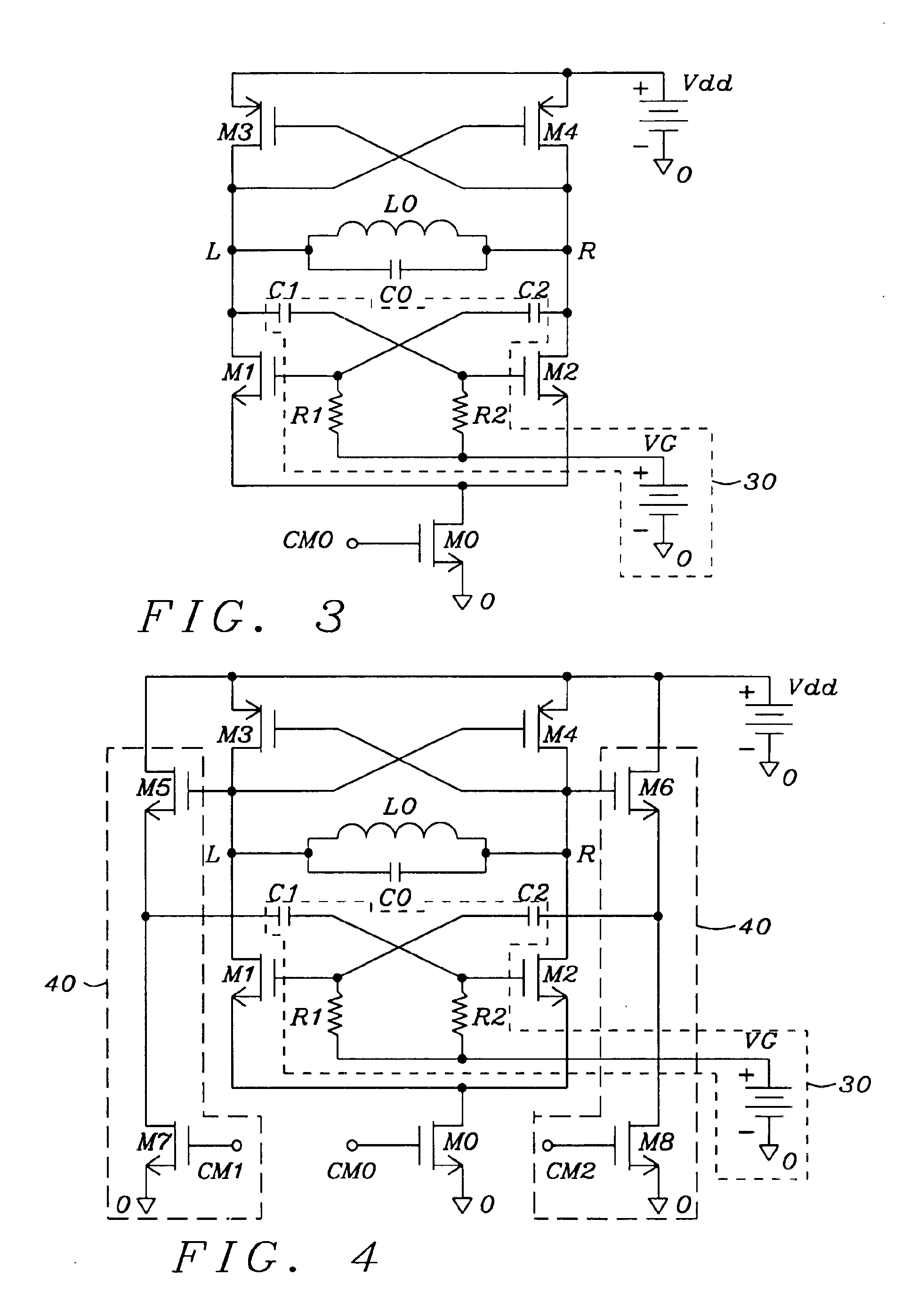

Enhanced architectures of voltage-controlled oscillators with single inductor (VCO-1L)

InactiveUS6867658B1Reduce phase noiseReduce power consumptionEnergy efficient ICTPulse automatic controlPhase noiseEngineering

Five circuit topologies of Voltage-Controlled Oscillators with Single Inductor (VCO-1L) are proposed. They offer lower power consumption, higher output amplitude, broader tuning range, cleaner s-rum and higher frequency stability seen as lower phase-noise. Most of the achievements are based on the development of active pull-down control circuitries of the timing and active charge dissipation in the transistors. The applications of the present invention are of critical importance for wireless communication systems not allowing any limitations in the frequency range. Among them are base stations and mobile terminals mobile phones, GSM, PCS / DCS, W-CDMA etc., as well BlueTooth, Wireless LAN, Automotive and ISM band etc. The advanced performance of the circuits is based on important architectural specifics and proven by simulation on advanced CMOS process. The architectures are not limited to use on CMOS; they can be efficiently used in any semiconductor process where complimentary polarity transistors are available, for example BiCMOS, SiGe / BiCMOS, GaAs etc.

Owner:DIALOG SEMICONDUCTOR GMBH

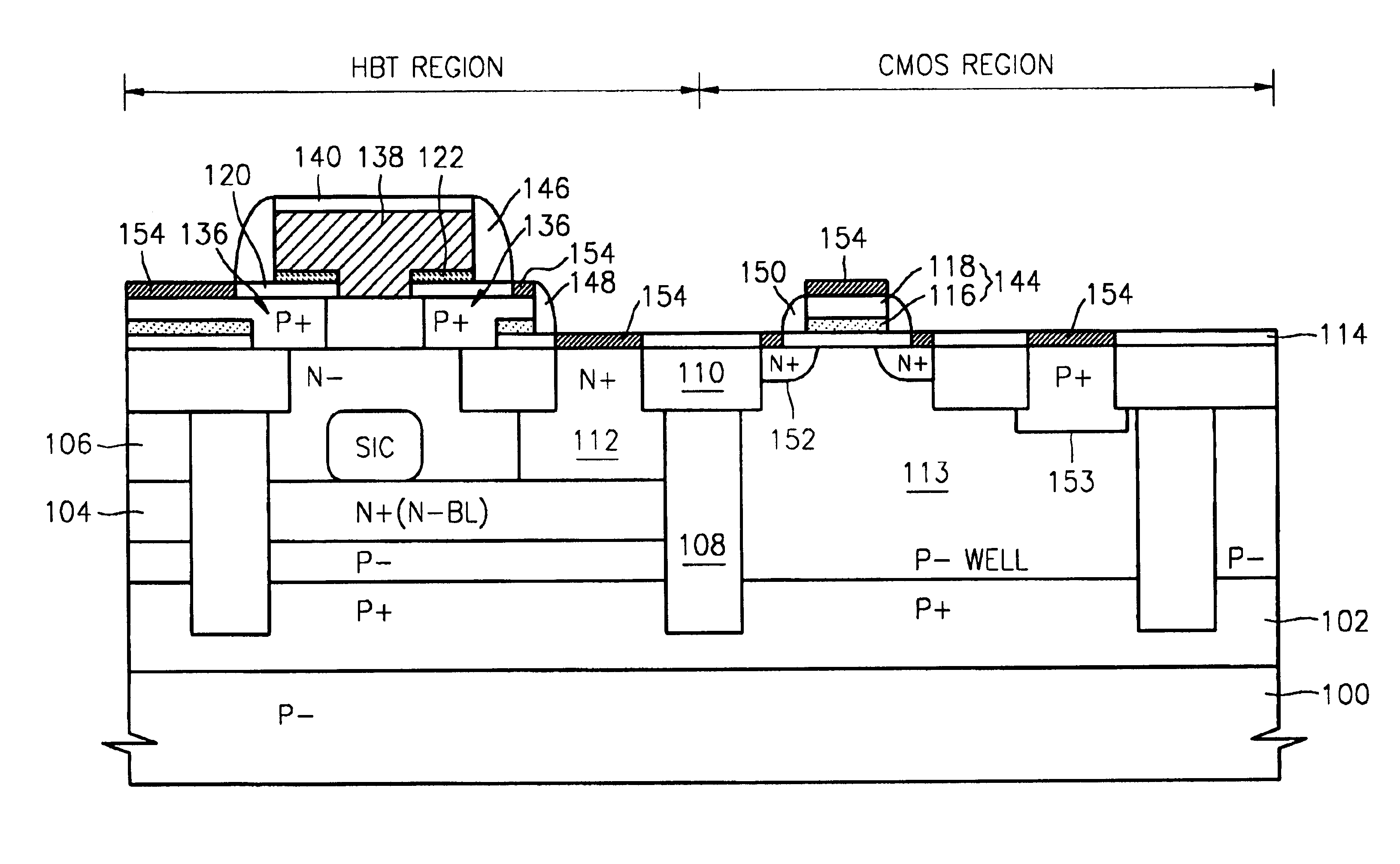

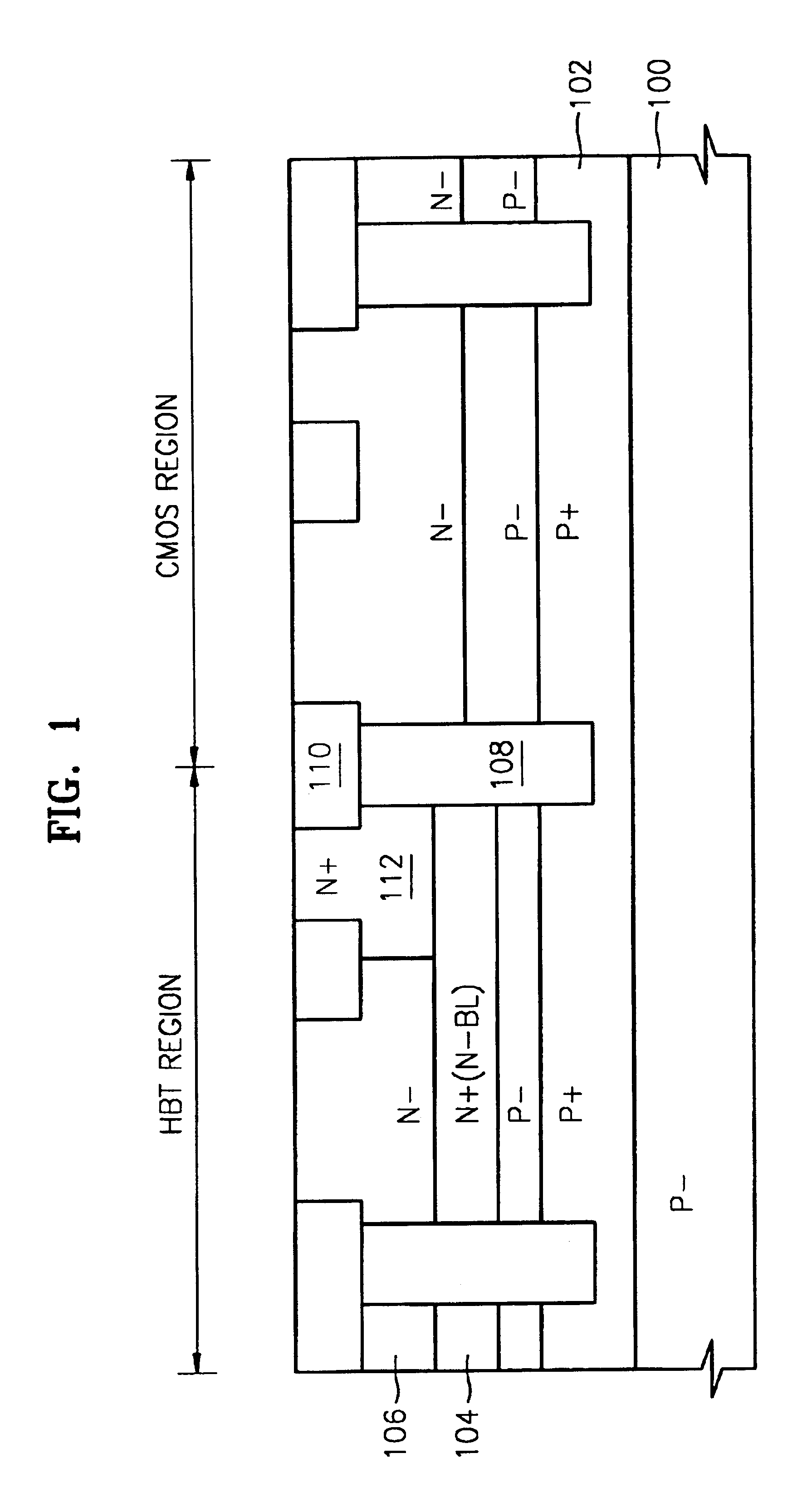

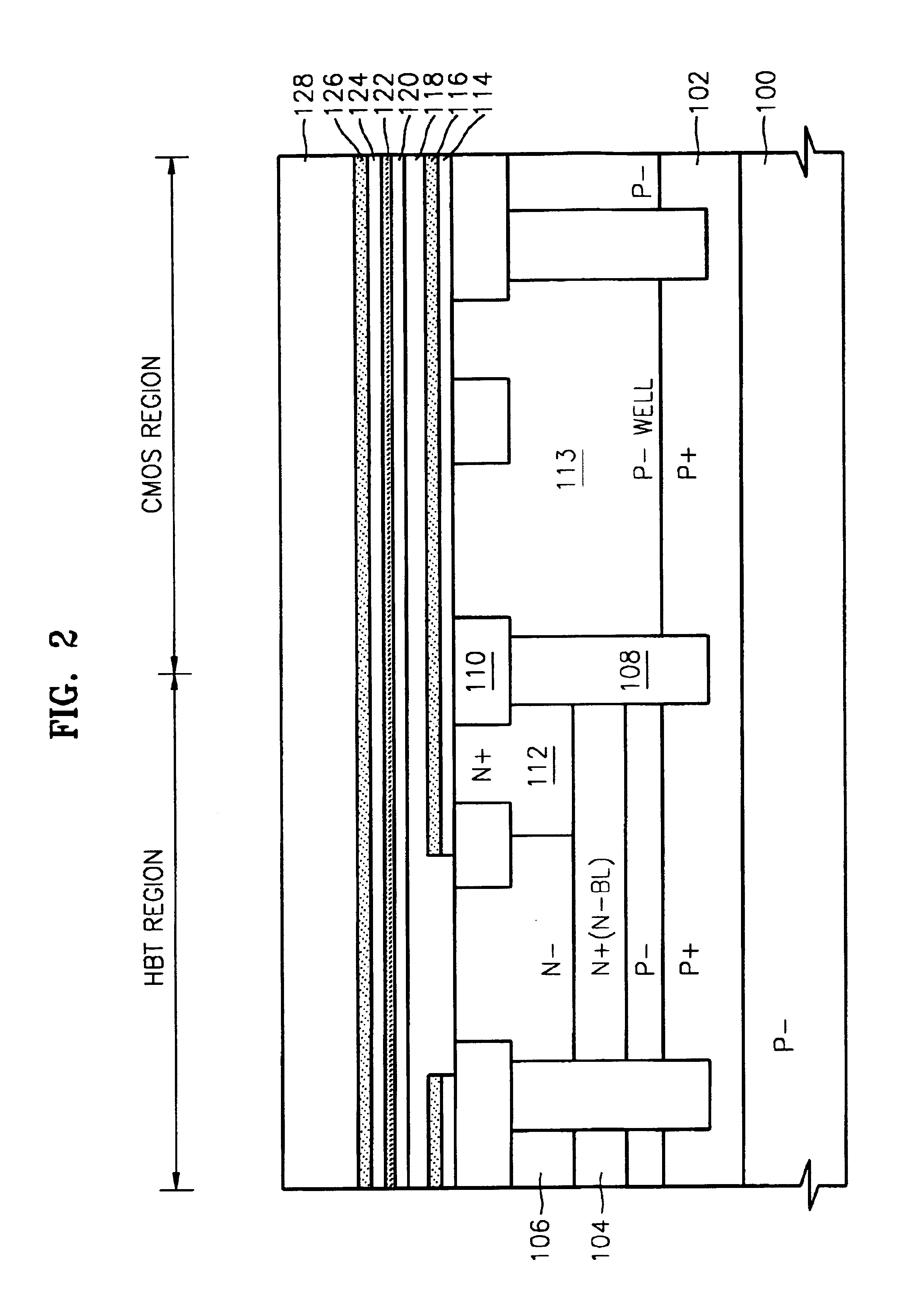

Method for manufacturing self-aligned BiCMOS

Provided is a method for manufacturing a self-aligned BiCMOS including a SiGe heterojunction bipolar transistor (HBT) for performing high-frequency operations. In this method, an extrinsic base and a selective ion-implanted collector (SIC) are formed by a self-alignment process.

Owner:SAMSUNG ELECTRONICS CO LTD

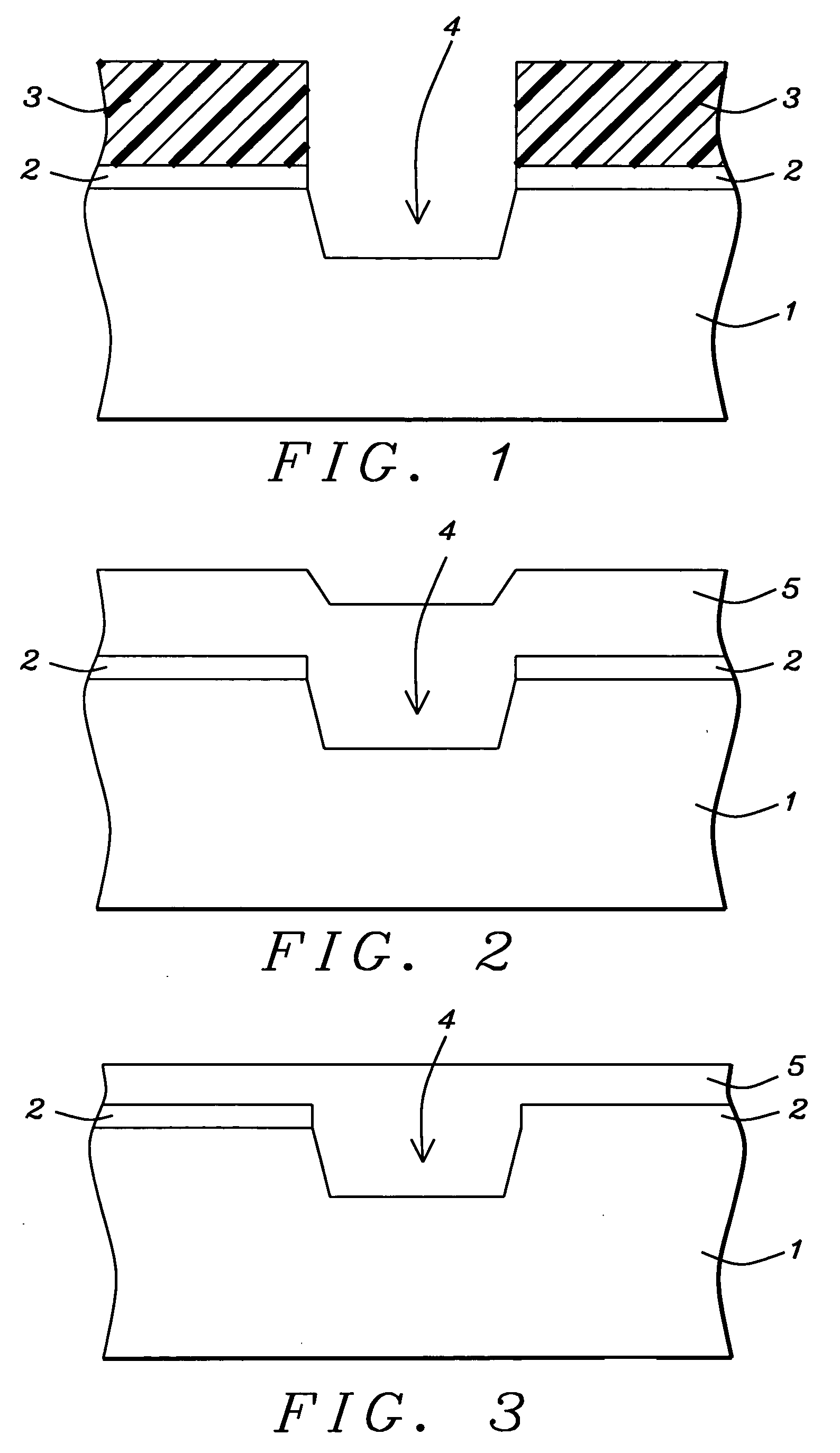

Formation of deep trench airgaps and related applications

ActiveUS20060131655A1Reduction of parasitic collector substrate perimeter capacitanceReduce widthSemiconductor/solid-state device detailsSolid-state devicesEngineeringBiCMOS

A method for forming deep trench or via airgaps in a semiconductor substrate is disclosed comprising the steps of patterning a hole in the substrate, partly fill said hole with a sacrificial material (e.g. poly-Si), depositing spacers on the sidewalls of the unfilled part of the hole (e.g. TEOS) to narrow the opening, removing through said narrowed opening the remaining part of the sacrificial material (e.g. by isotropic etching) and finally sealing the opening of the airgap by depositing a conformal layer (TEOS) above the spacers. The method of forming an airgap is demonstrated successfully for use as deep trench isolation structures in BiCMOS devices.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

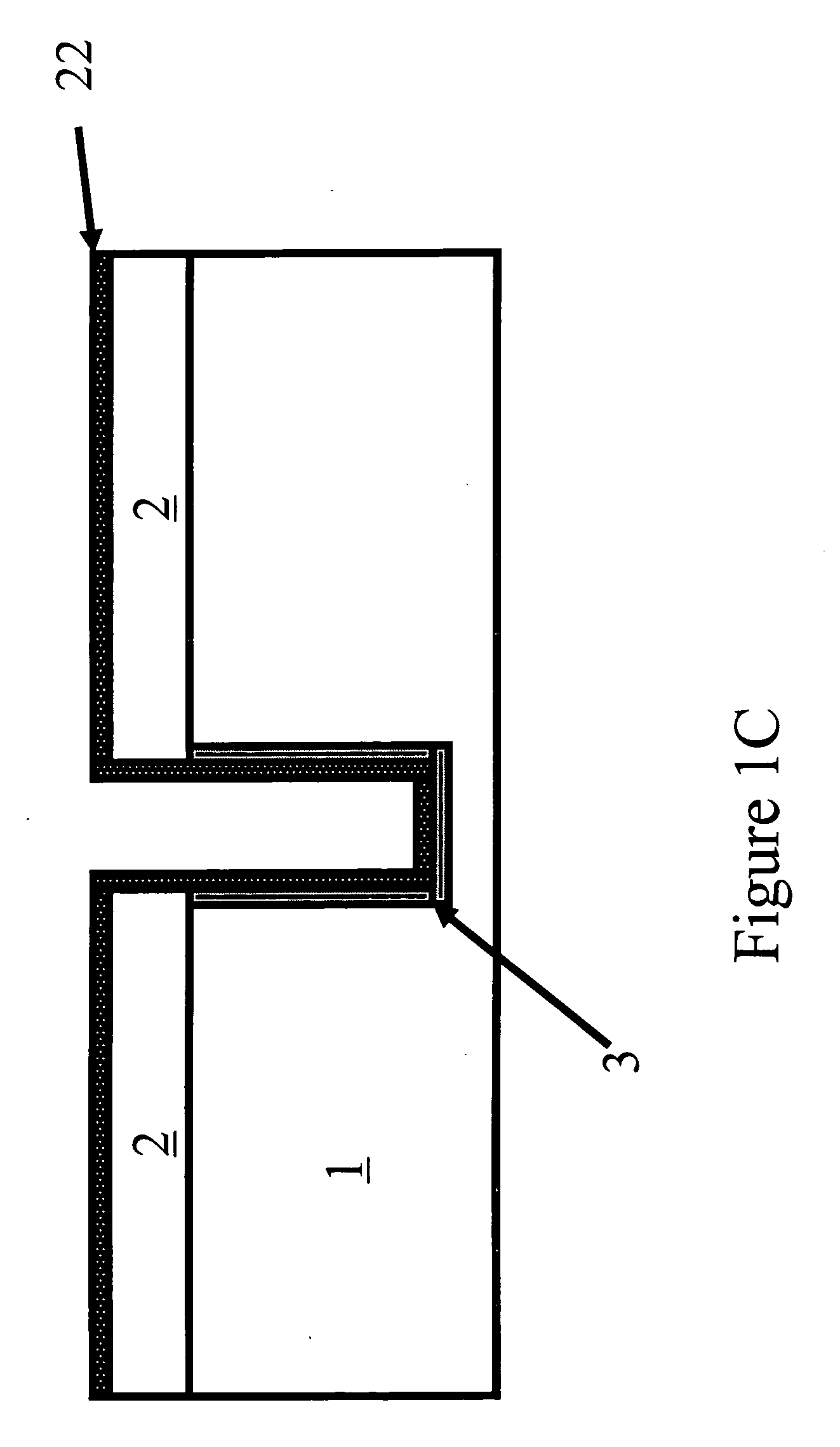

Background Limited Focal Plane Array Assembly

InactiveUS20130206990A1Improve the detection rateSolid-state devicesMaterial analysis by optical meansThermoelectric materialsLow noise

The thermoelectric detector comprises an infrared absorber pixel structure supported by two electrically connected beams made of a thermoelectric material. One end of the thermoelectric beam connects to the infrared absorber pixel structure; the other end connects to the substrate. The detector comprises a microlens for collecting and focusing infrared radiation on the detector. Infrared radiation is incident on the infrared absorber pixel structure results in a temperature gradient along the length of the thermoelectric legs, and generating an electrical voltage proportional to the gradient. A low noise SIGe BiCMOS readout integrated circuit is coupled to the detector to provide a background limited detector having improved detectivity.

Owner:PFG IP

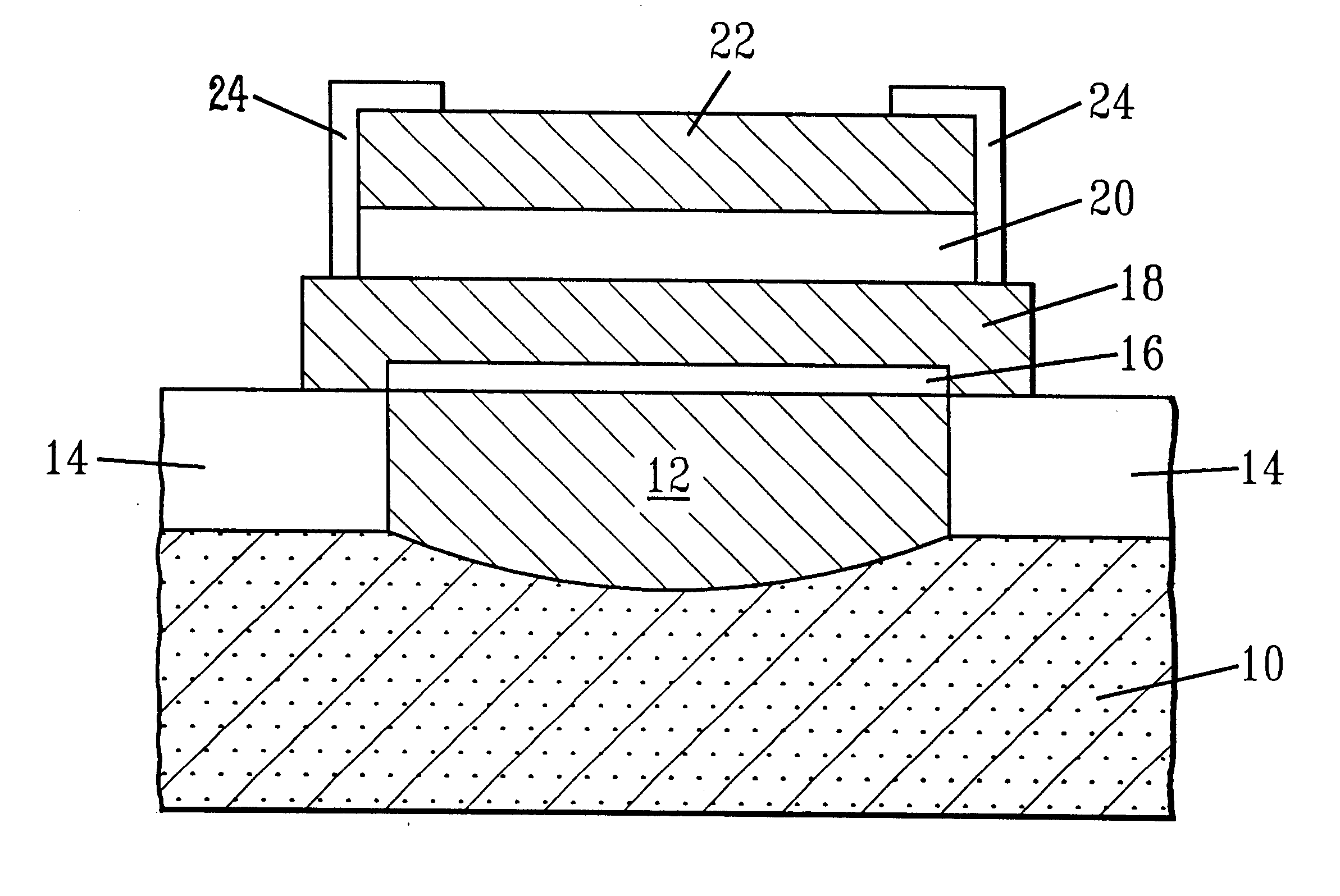

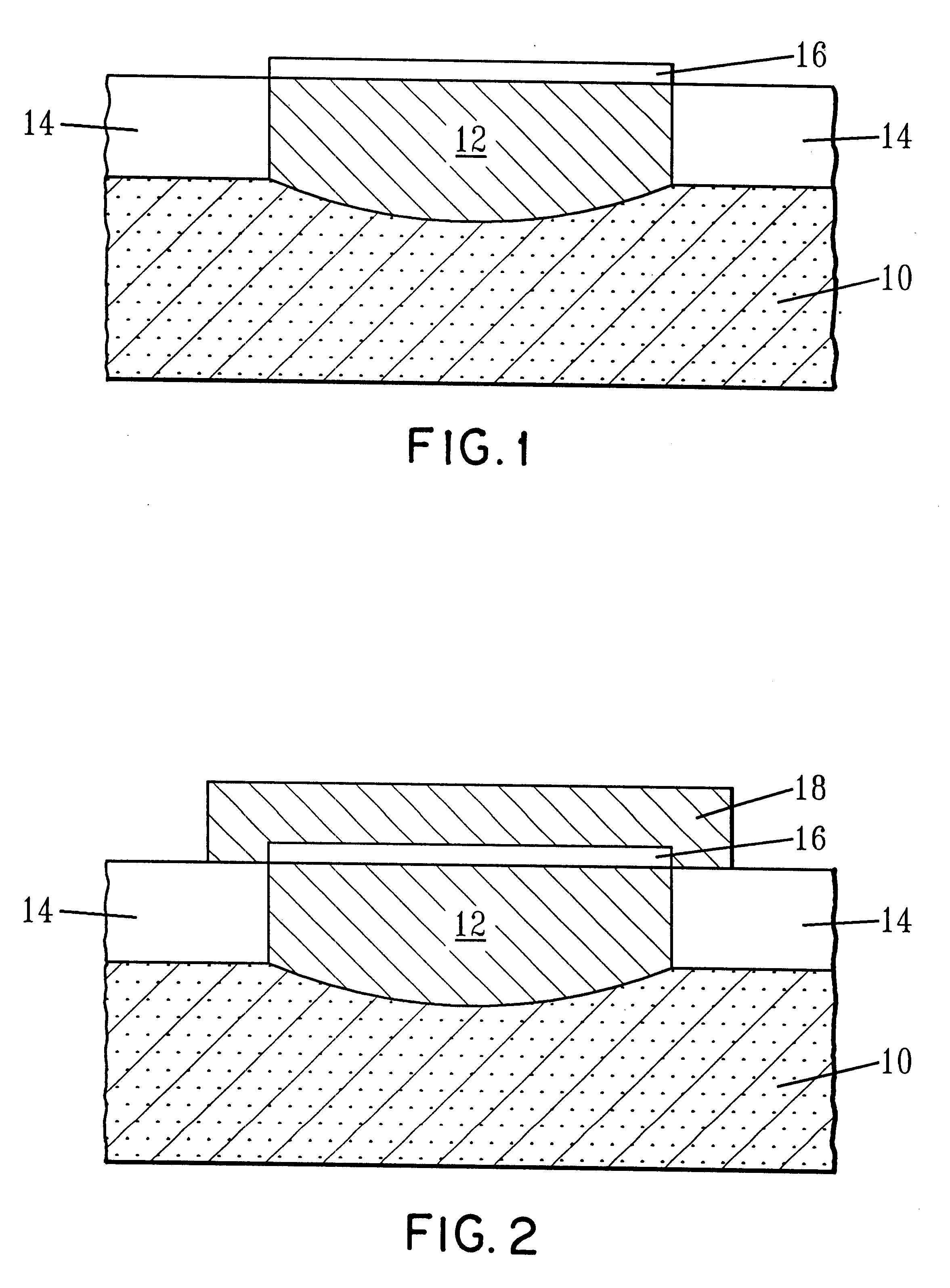

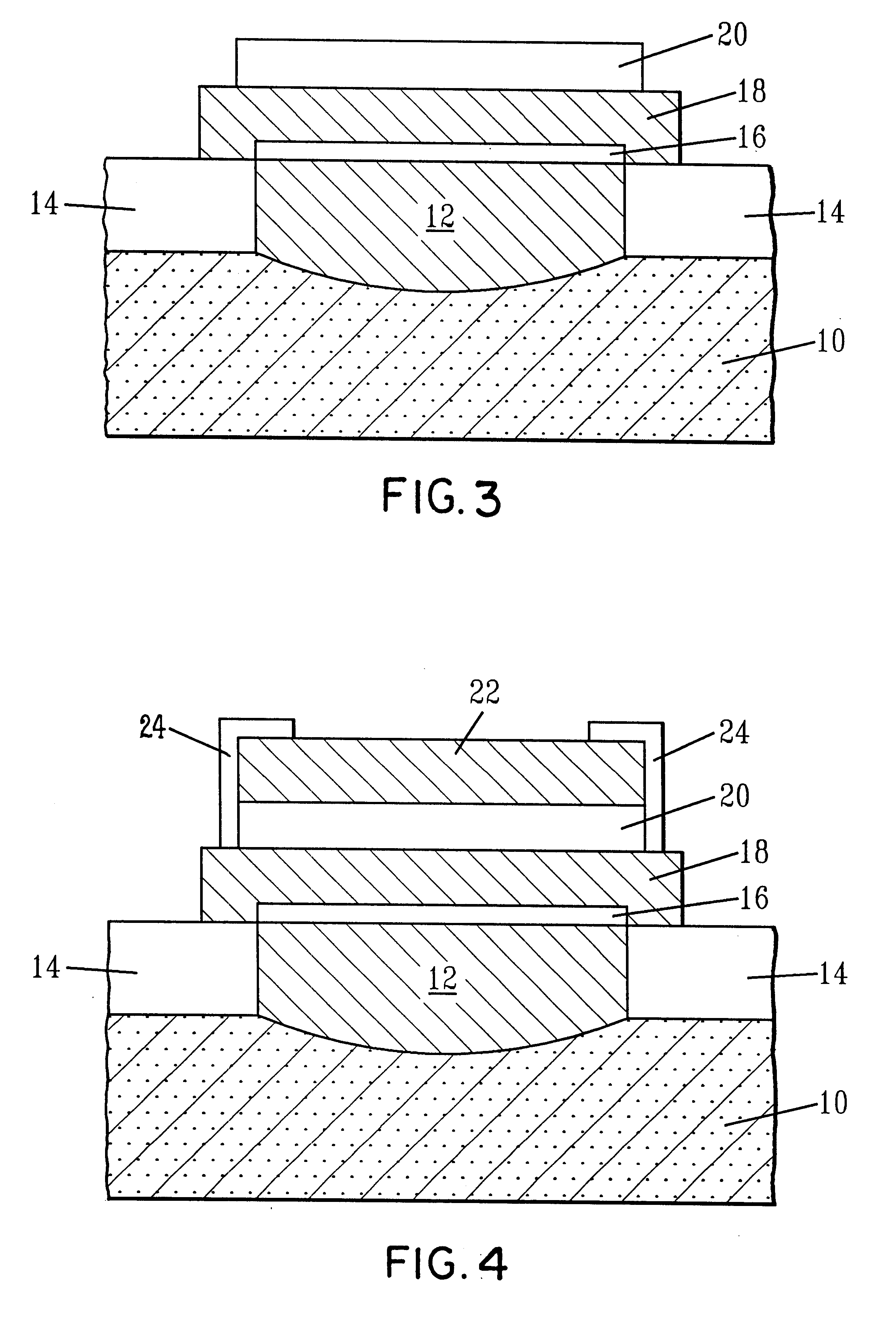

Polysilicon sidewall spacer lateral bipolar transistor on SOI

Consistent with an aspect of the present invention, a lateral bipolar transistor is provided that exhibits similar performance as that of high speed vertical bipolar junction transistors. The lateral bipolar transistor includes a polysilicon side-wall-spacer (PSWS) that forms a contact with the base of the transistor, and thus avoids the process step of aligning a contact mask to a relatively thin base region. The side wall spacer allows self-alignment of the base / emitter region, and has reduced base resistance and junction capacitance. Accordingly, improved cutoff frequency (fτ) and maximum oscillation frequency (fmax) can be achieved. Moreover, this novel topology enables the realization of Bipolar CMOS (BiCMOS) technology on insulating substrates, such as SOI.

Owner:ASAHI KASEI ELECTRONICS CO LTD

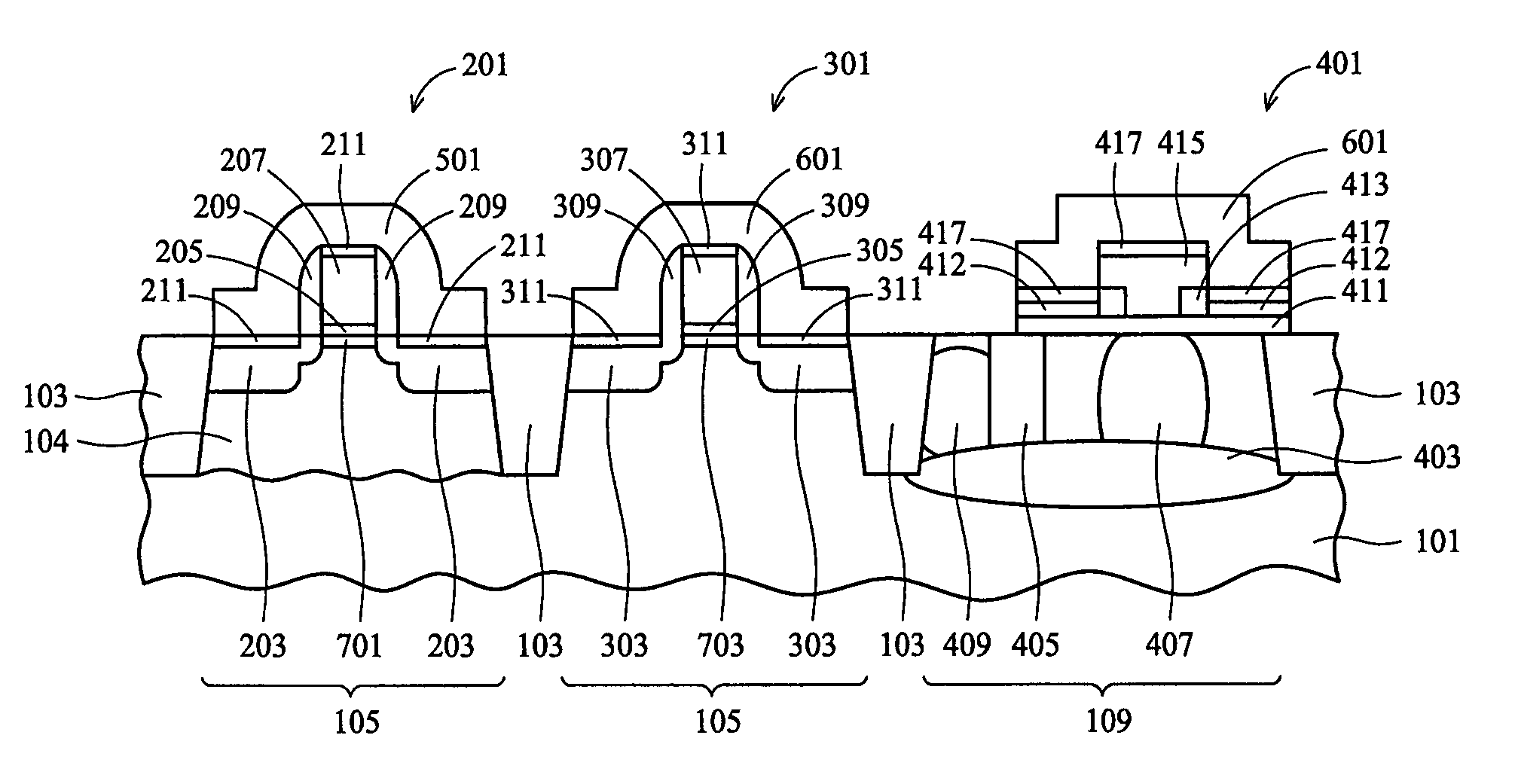

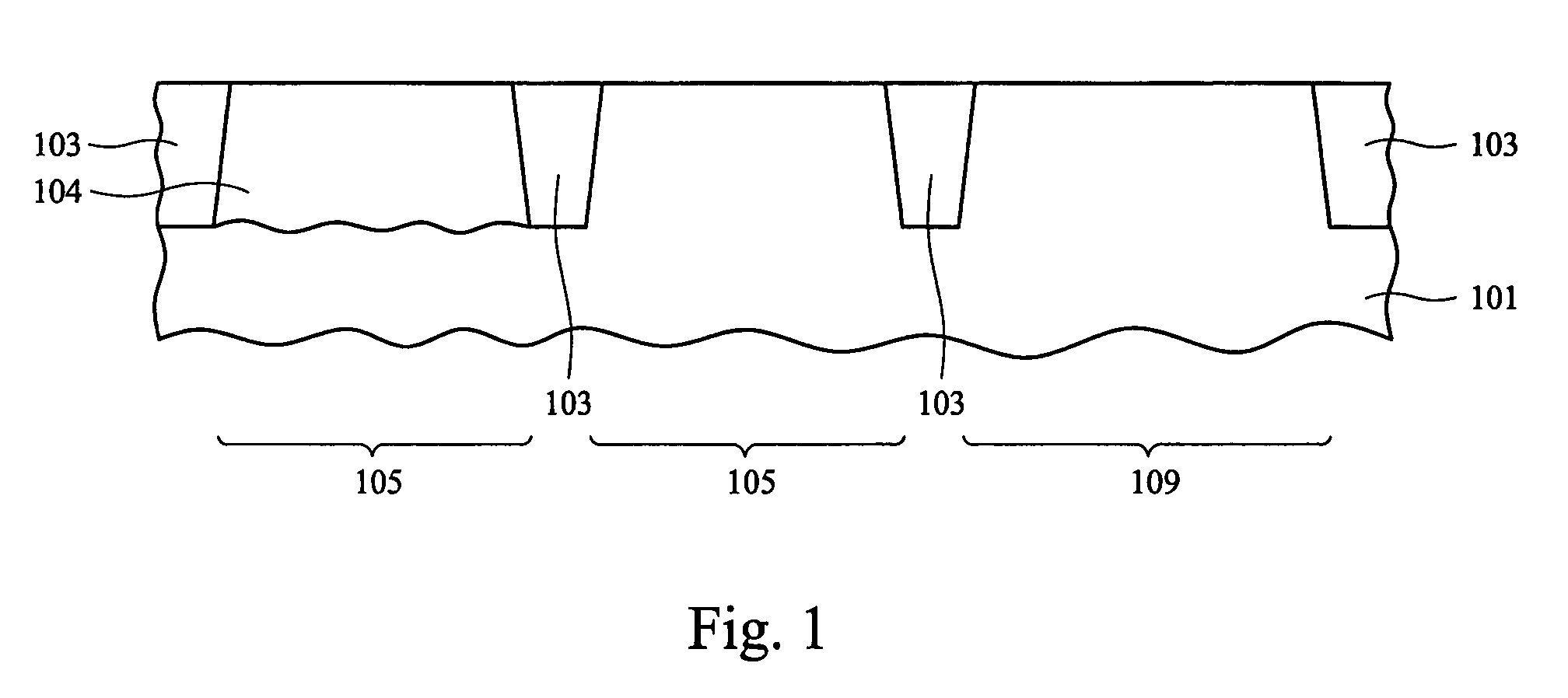

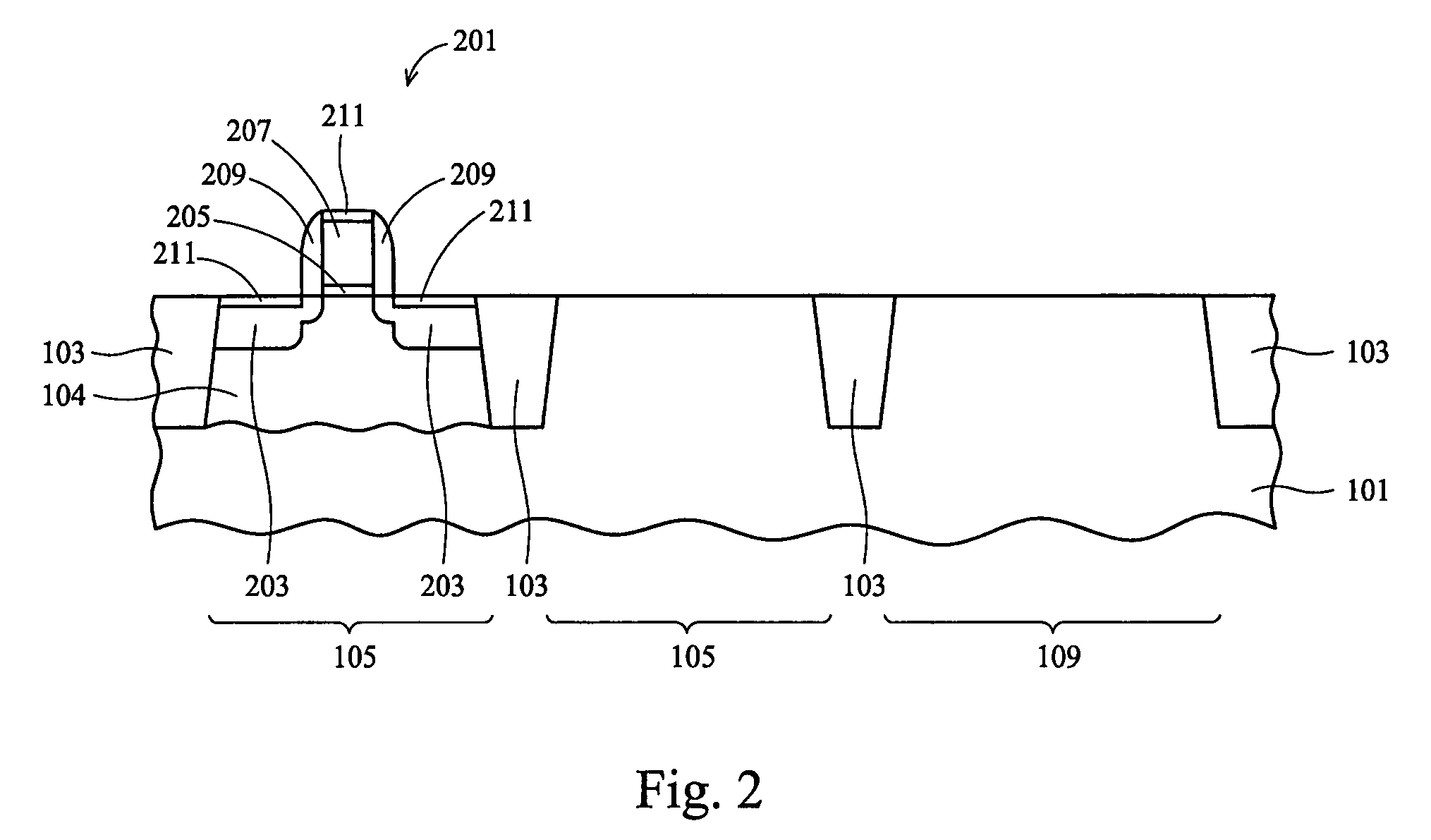

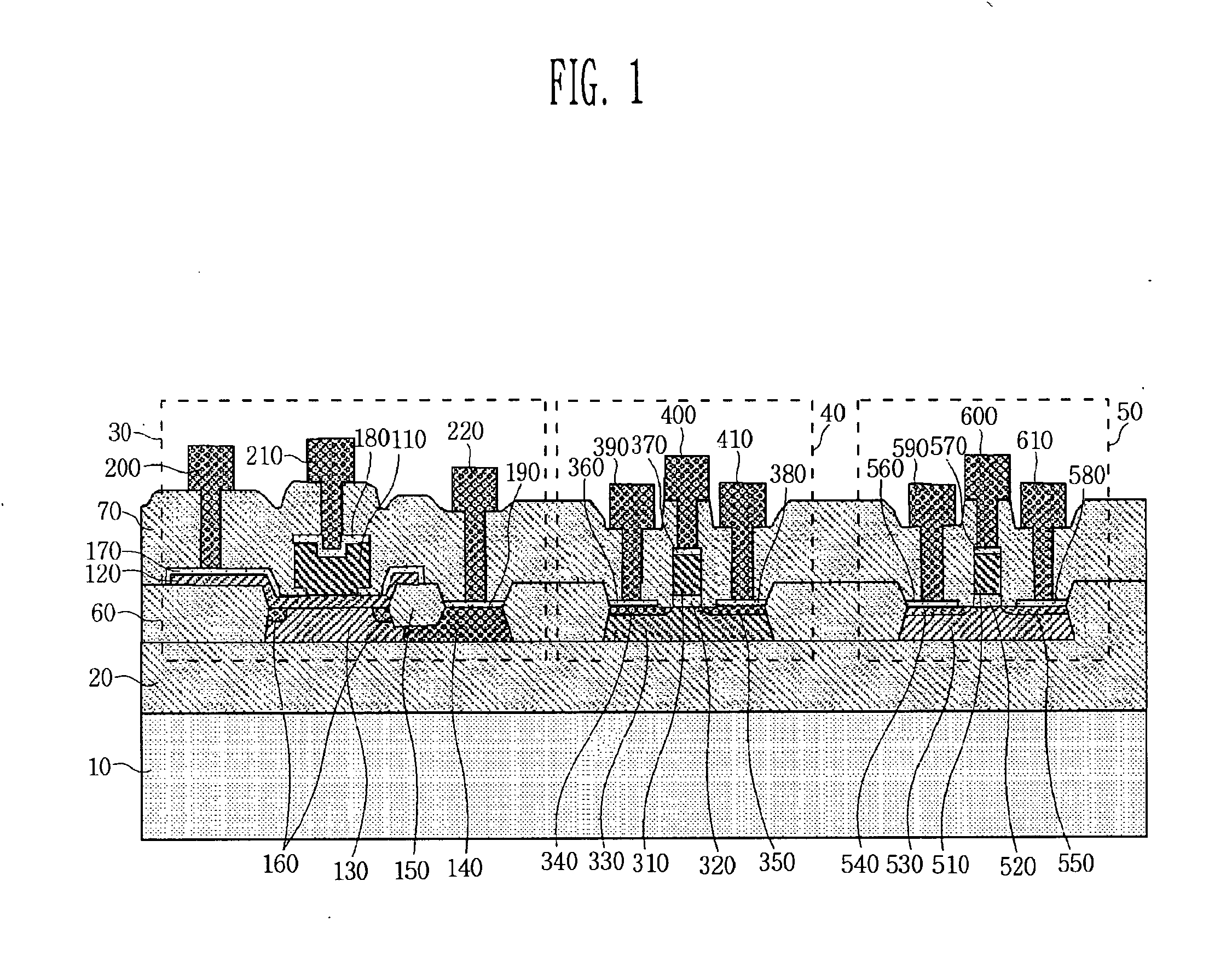

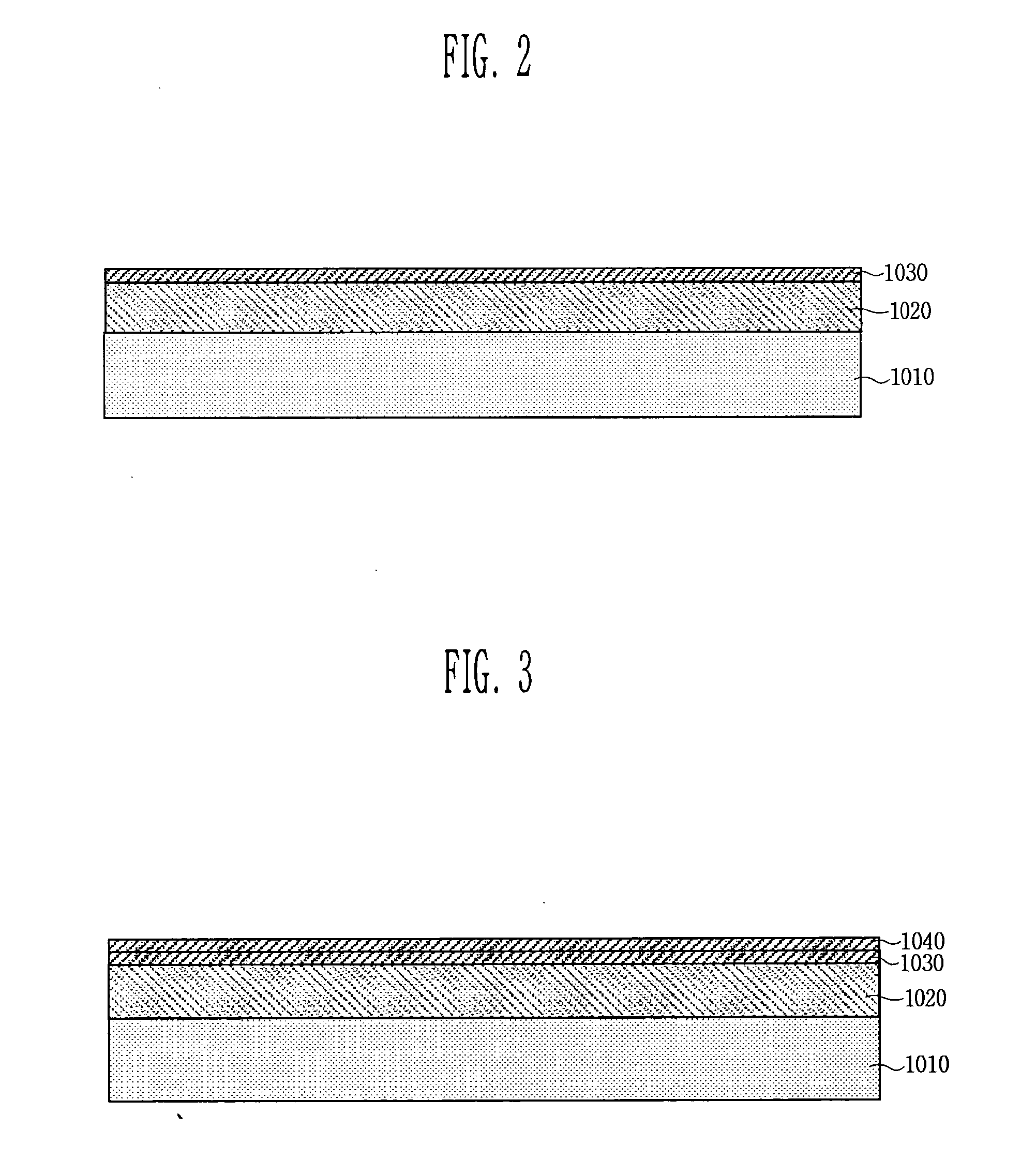

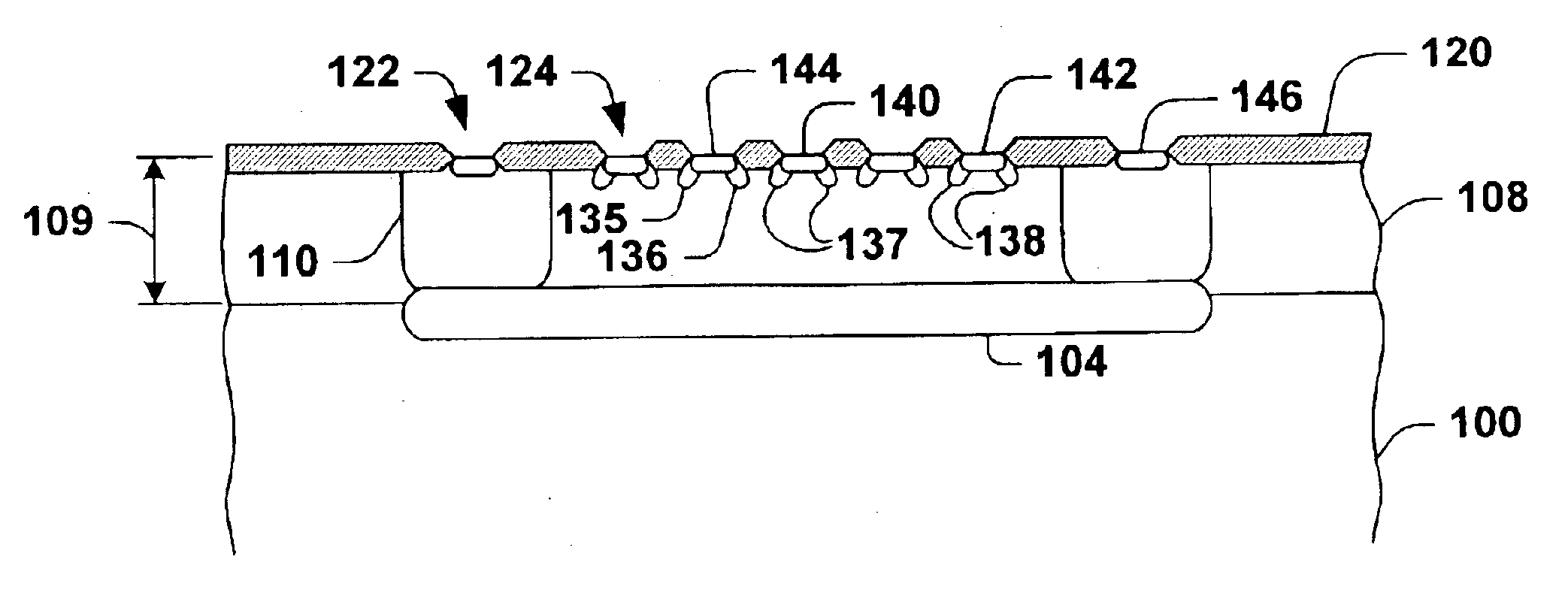

BiCMOS performance enhancement by mechanical uniaxial strain and methods of manufacture

A BiCMOS device with enhanced performance by mechanical uniaxial strain is provided. A first embodiment of the present invention includes an NMOS transistor, a PMOS transistor, and a bipolar transistor formed on different areas of the substrate. A first contact etch stop layer with tensile stress is formed over the NMOS transistor, and a second contact etch stop layer with compressive stress is formed over the PMOS transistor and the bipolar transistor, allowing for an enhancement of each device. Another embodiment has, in addition to the stressed contact etch stop layers, strained channel regions in the PMOS transistor and the NMOS transistor, and a strained base in the BJT.

Owner:TAIWAN SEMICON MFG CO LTD

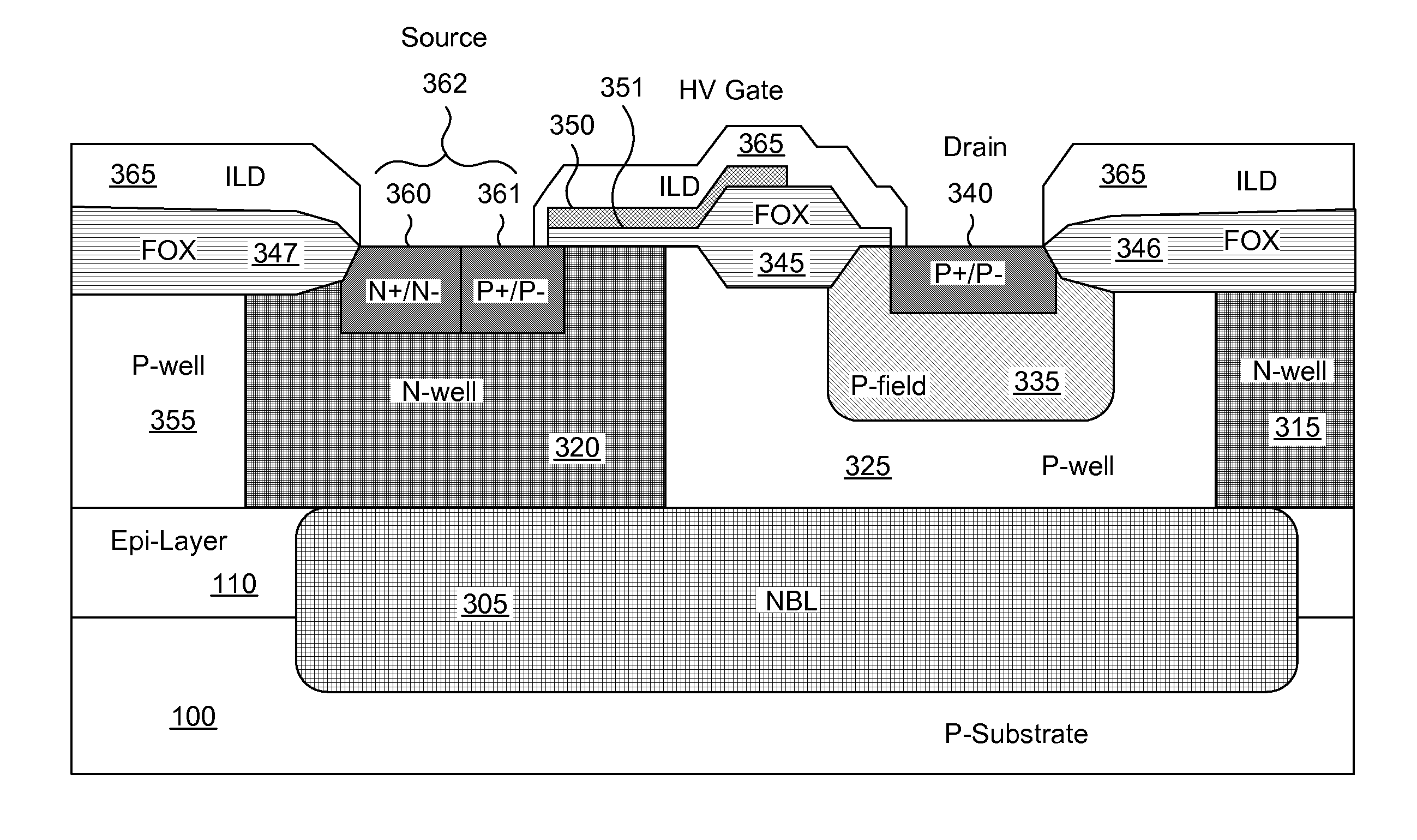

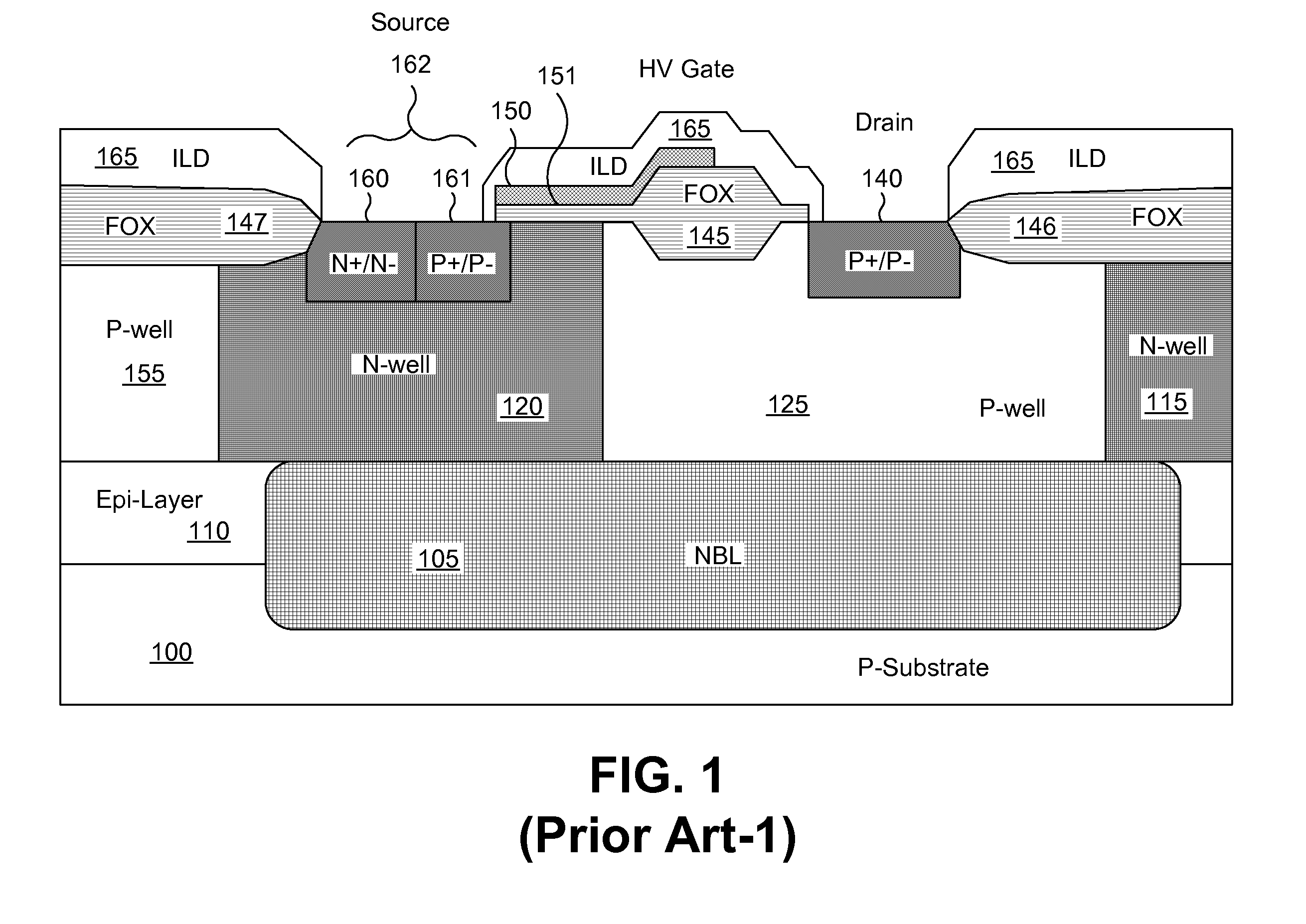

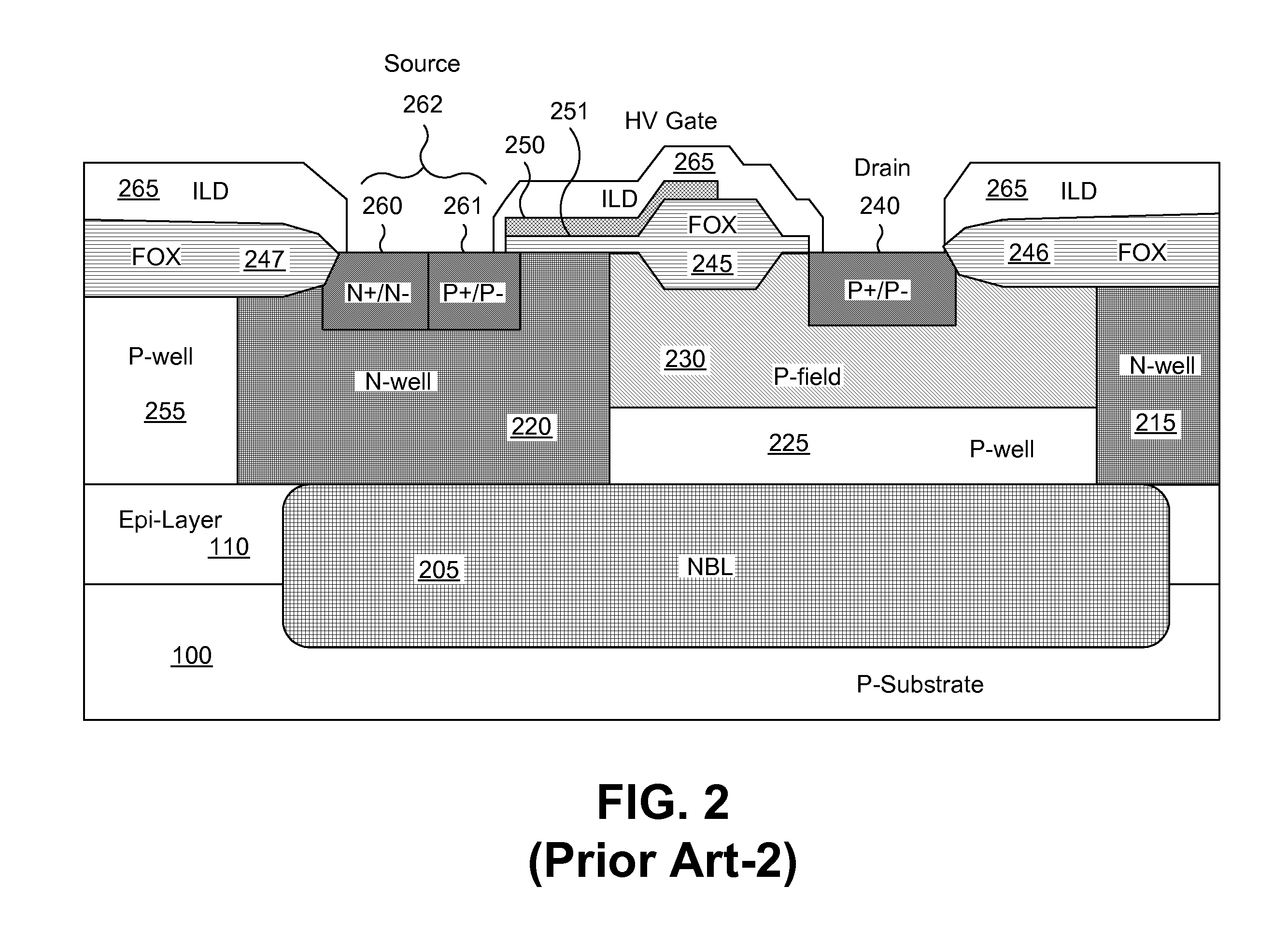

Ldpmos structure for enhancing breakdown voltage and specific on resistance in bicmos-DMOS process

ActiveUS20110303977A1TransistorSemiconductor/solid-state device manufacturingBiCMOSBreakdown voltage

An LDPMOS structure having enhanced breakdown voltage and specific on-resistance is described, as is a method for fabricating the structure. A P-field implanted layer formed in a drift region of the structure and surrounding a lightly doped drain region effectively increases breakdown voltage while maintaining a relatively low specific on-resistance.

Owner:MACRONIX INT CO LTD

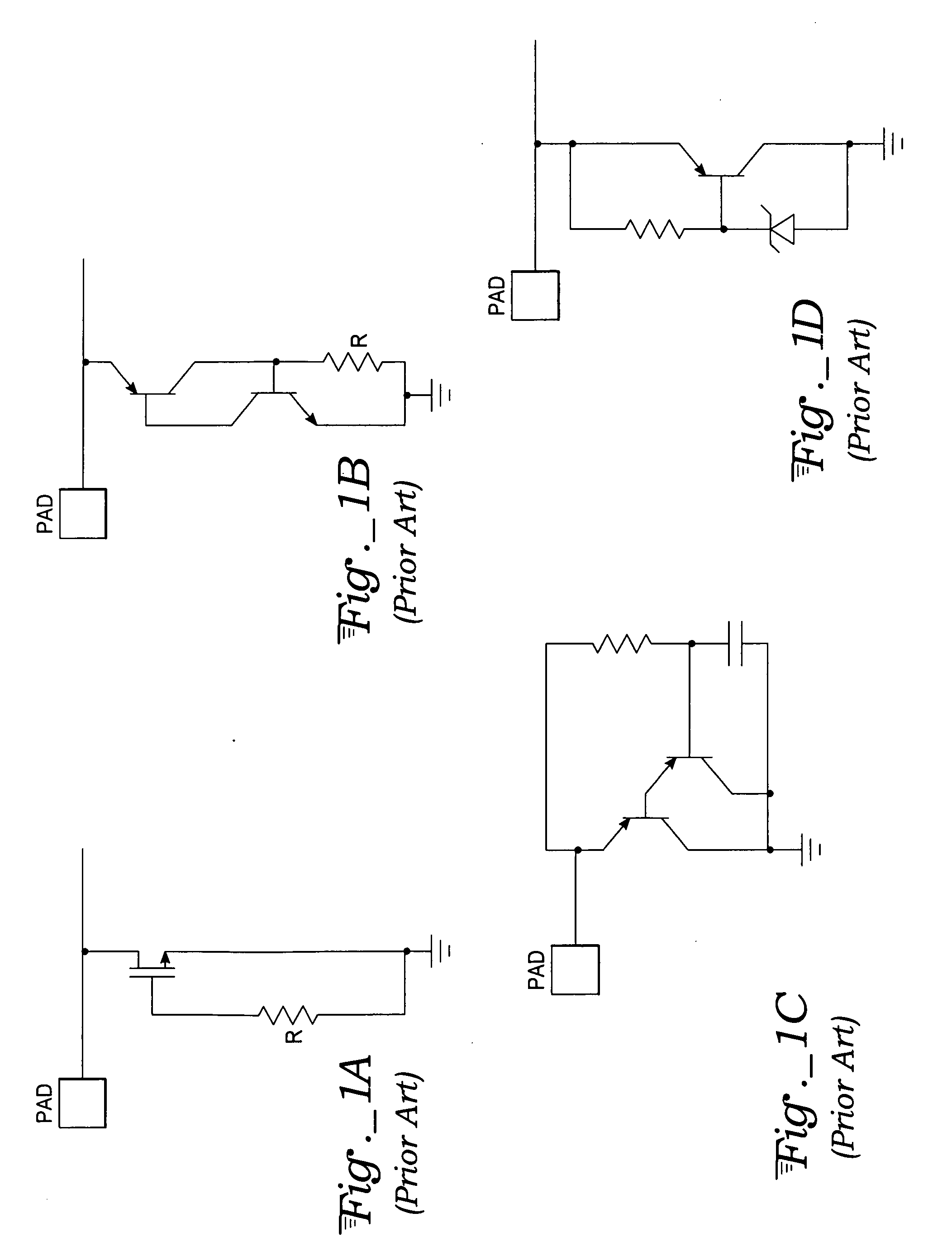

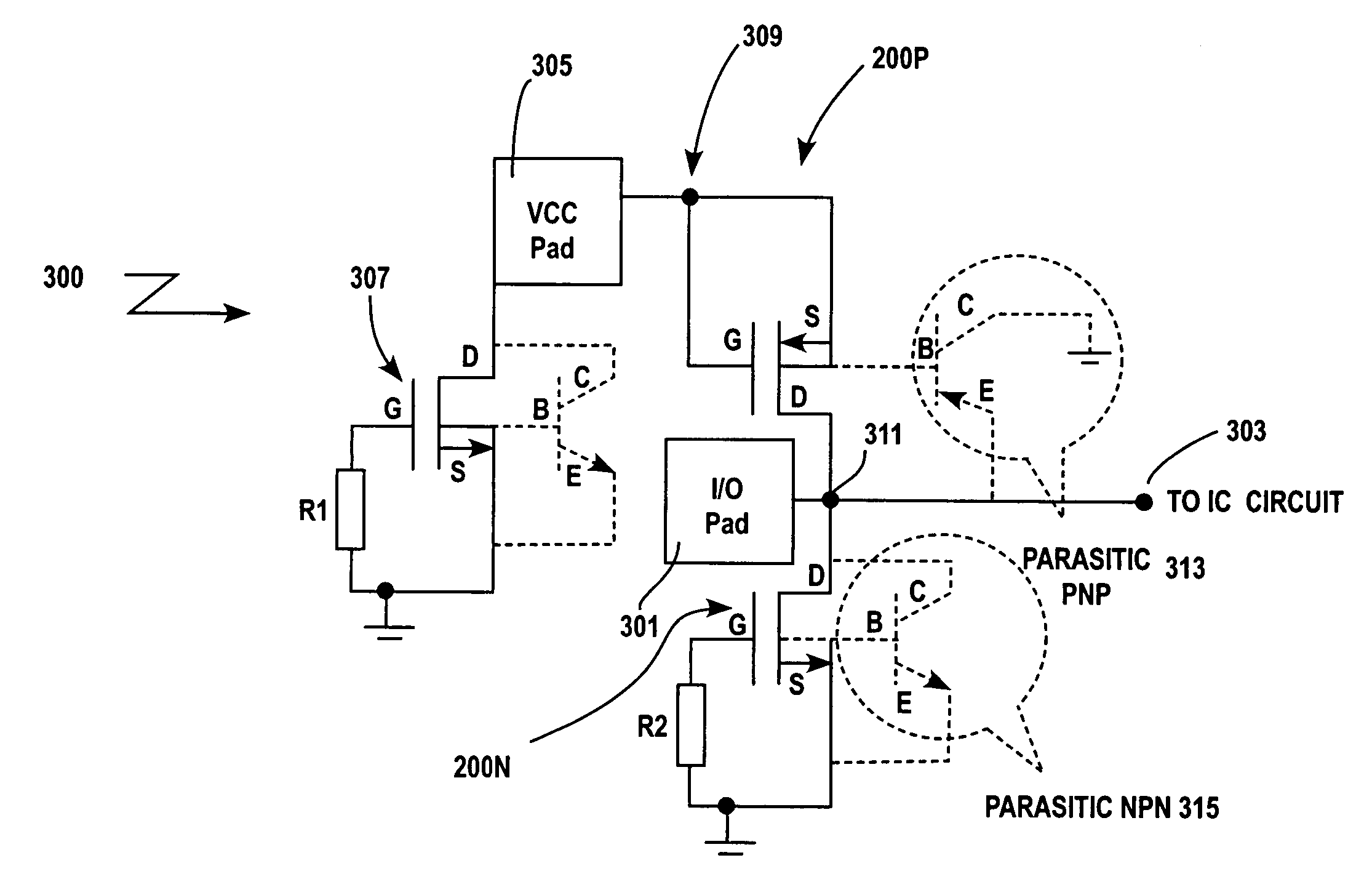

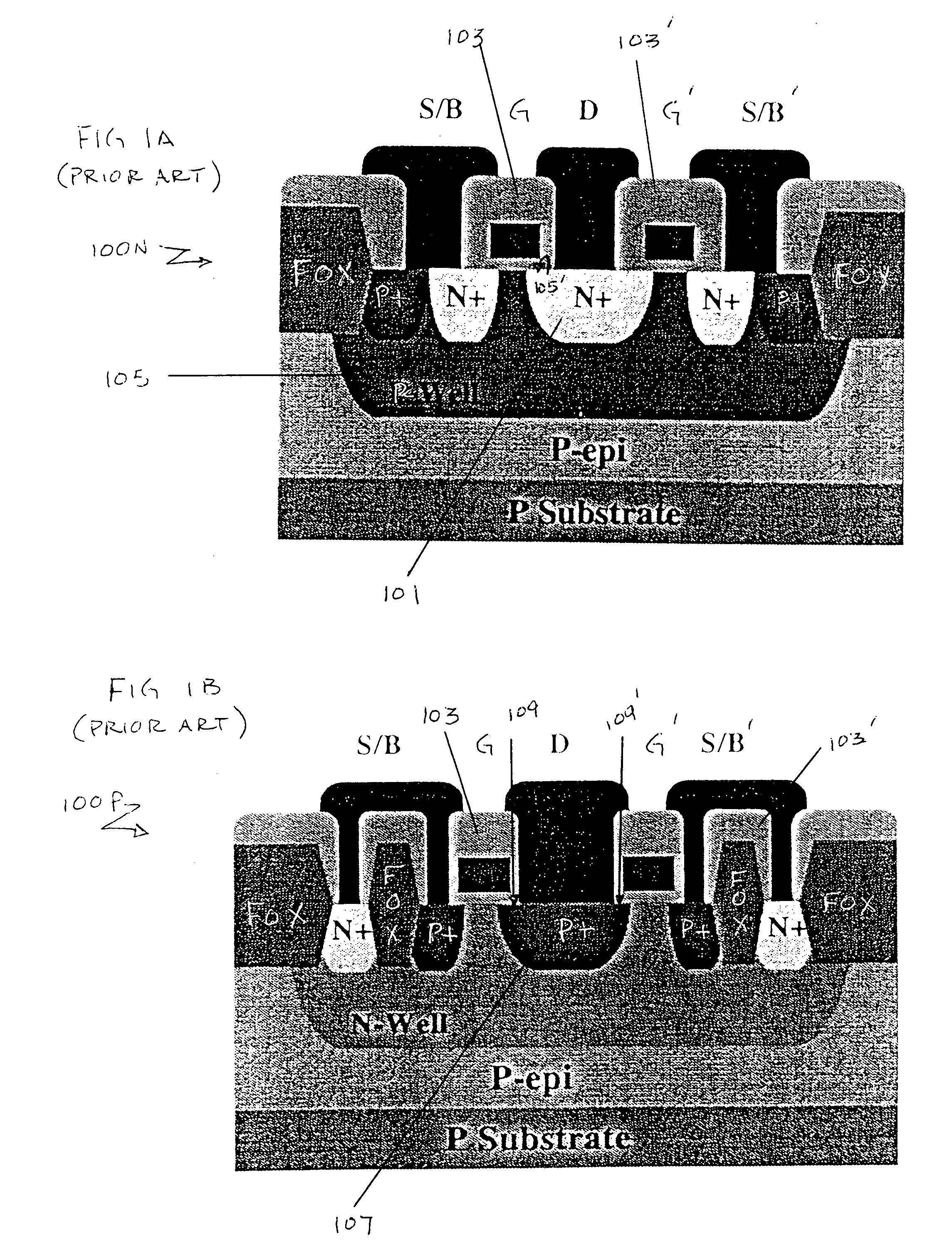

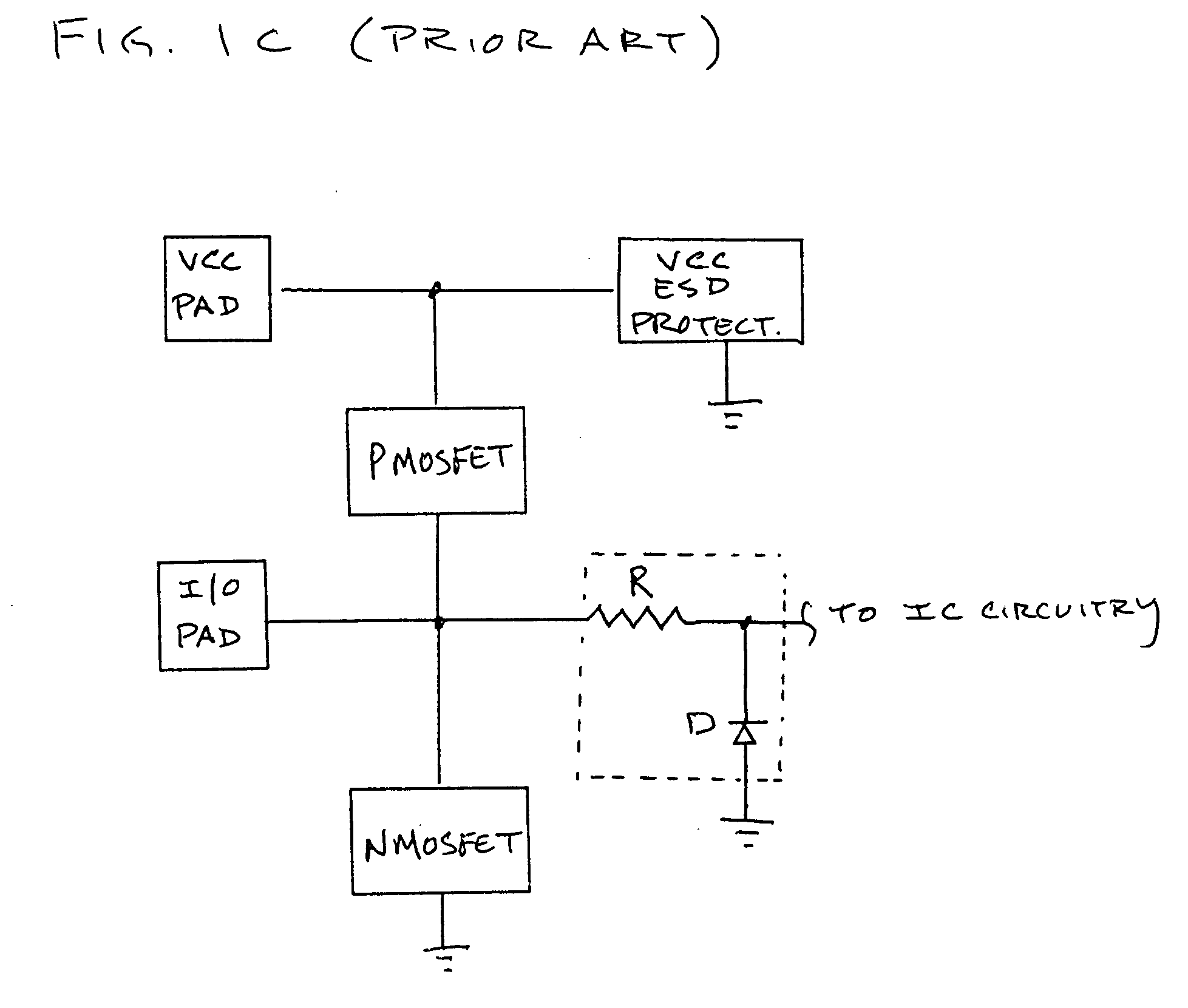

ESD protection for integrated circuits

InactiveUS20050275027A1Improve ESD toleranceSimple structureTransistorSemiconductor/solid-state device detailsCMOSMOSFET

Electrostatic discharge protection for integrated circuits, particularly for enhancing electrostatic discharge protection performance for Input-output cells and power supply clamps used in CMOS and BiCMOS IC technologies is described. A P-type, implantation region, or layer, referred to as “P-deep,” in both N-MOSFET and P-MOSFET devices is provided to enhance electrostatic discharge protection performance. Parasitic transistor gain is enhanced by providing the P-deep region subposing the drain contact. Exemplary embodiments for N-type and P-type MOSFETs, MOSFETs with surface diodes, MOSFETS with SCRs, and push-pull Input-output CMOS circuits are described.

Owner:MICREL

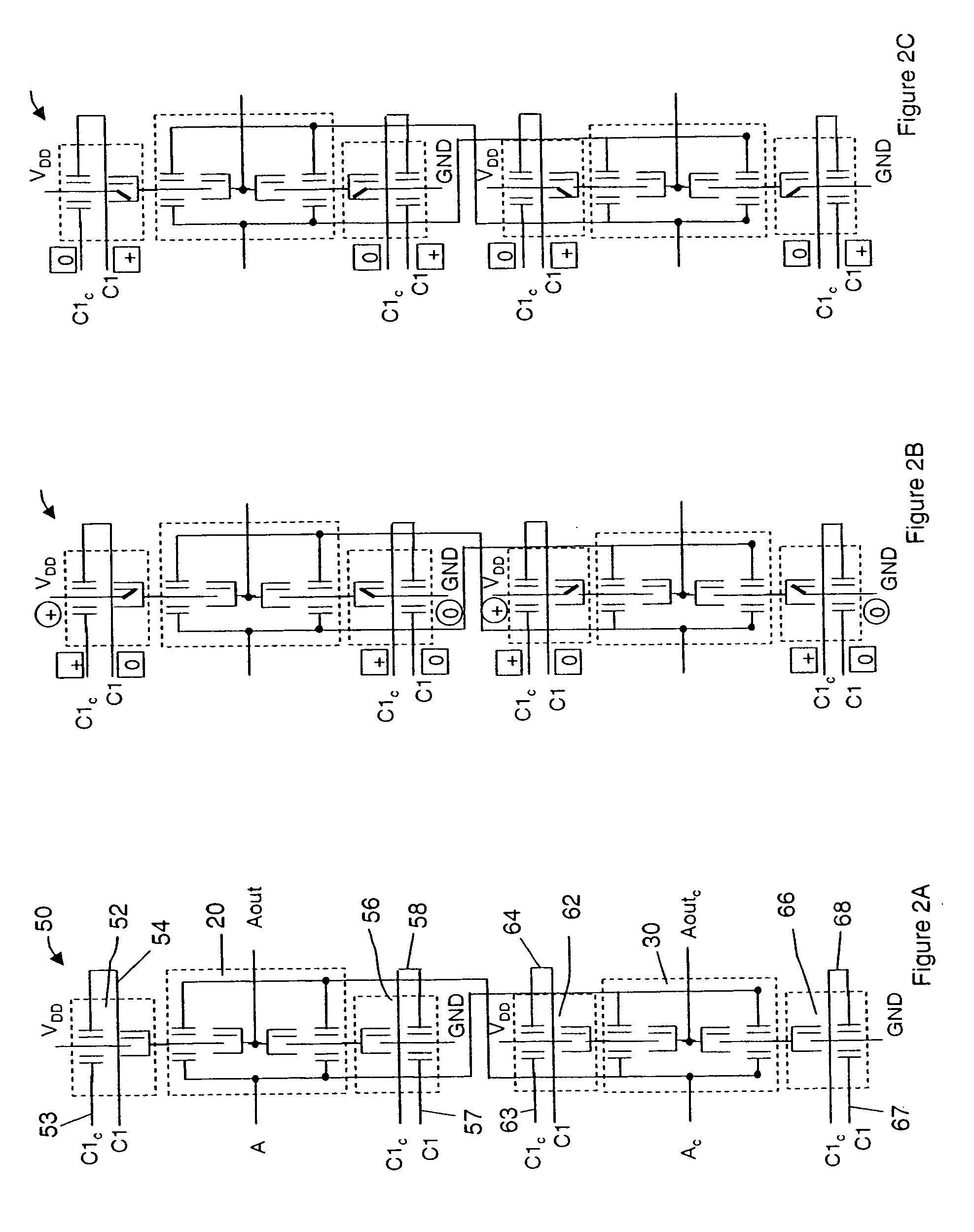

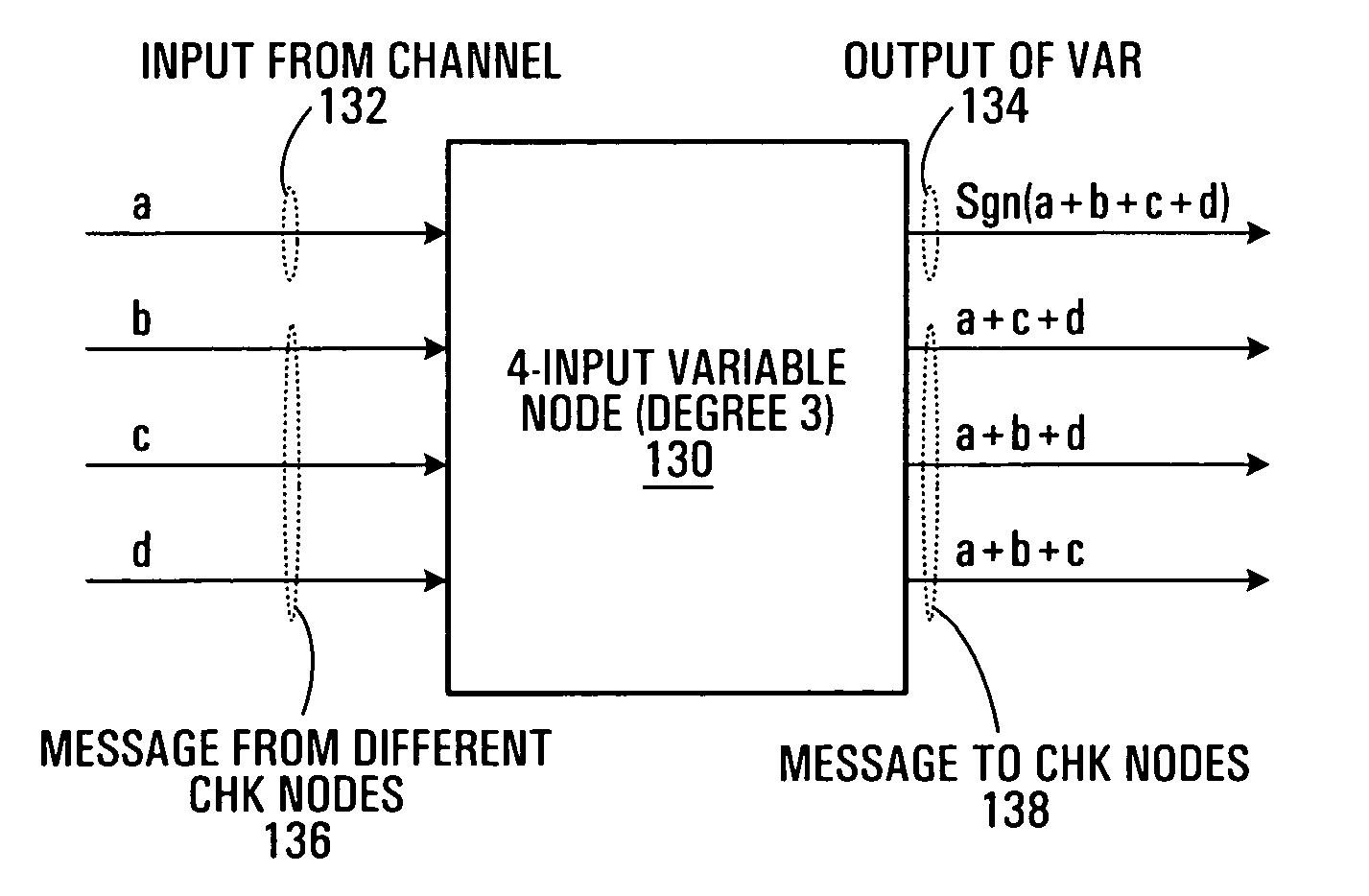

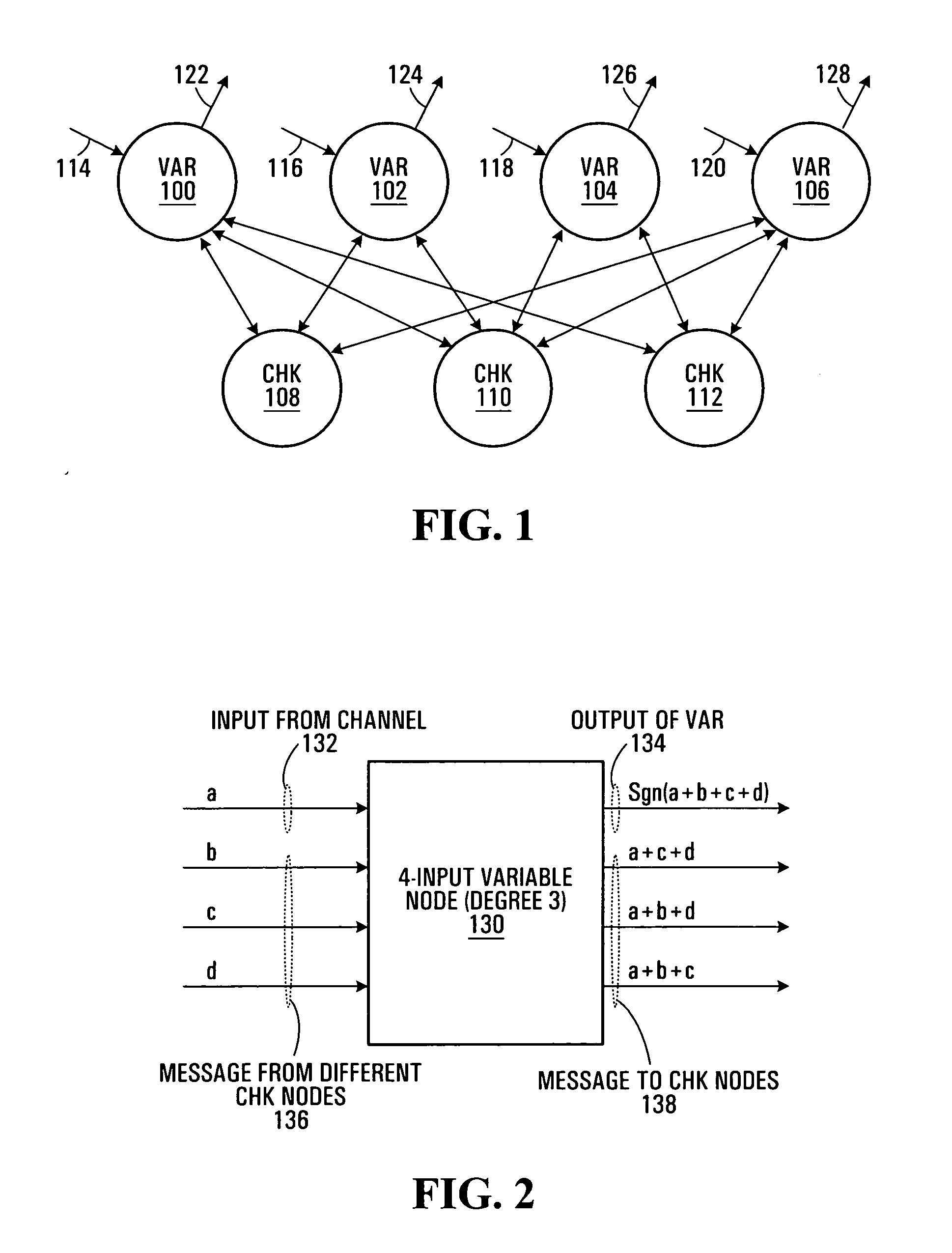

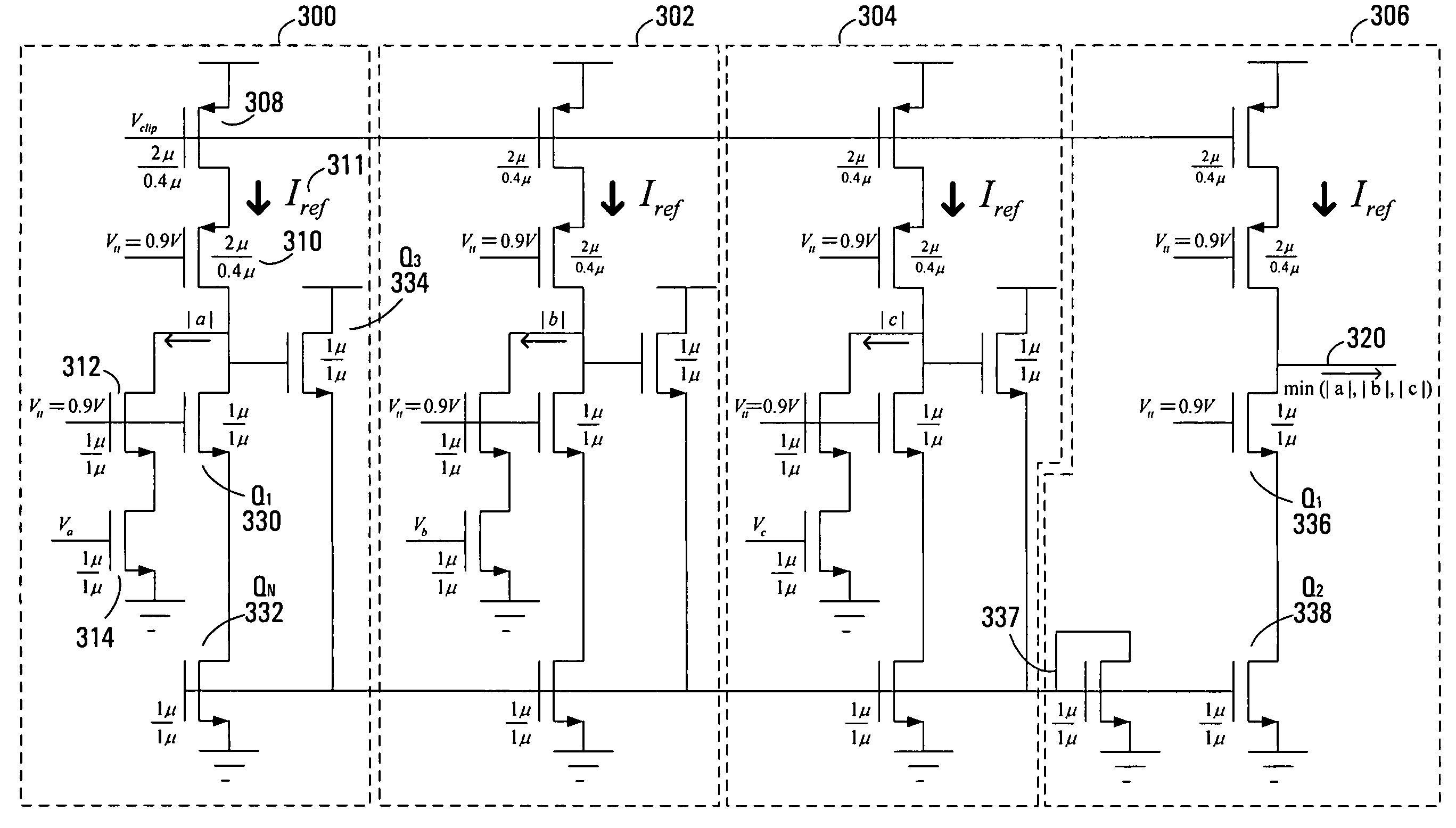

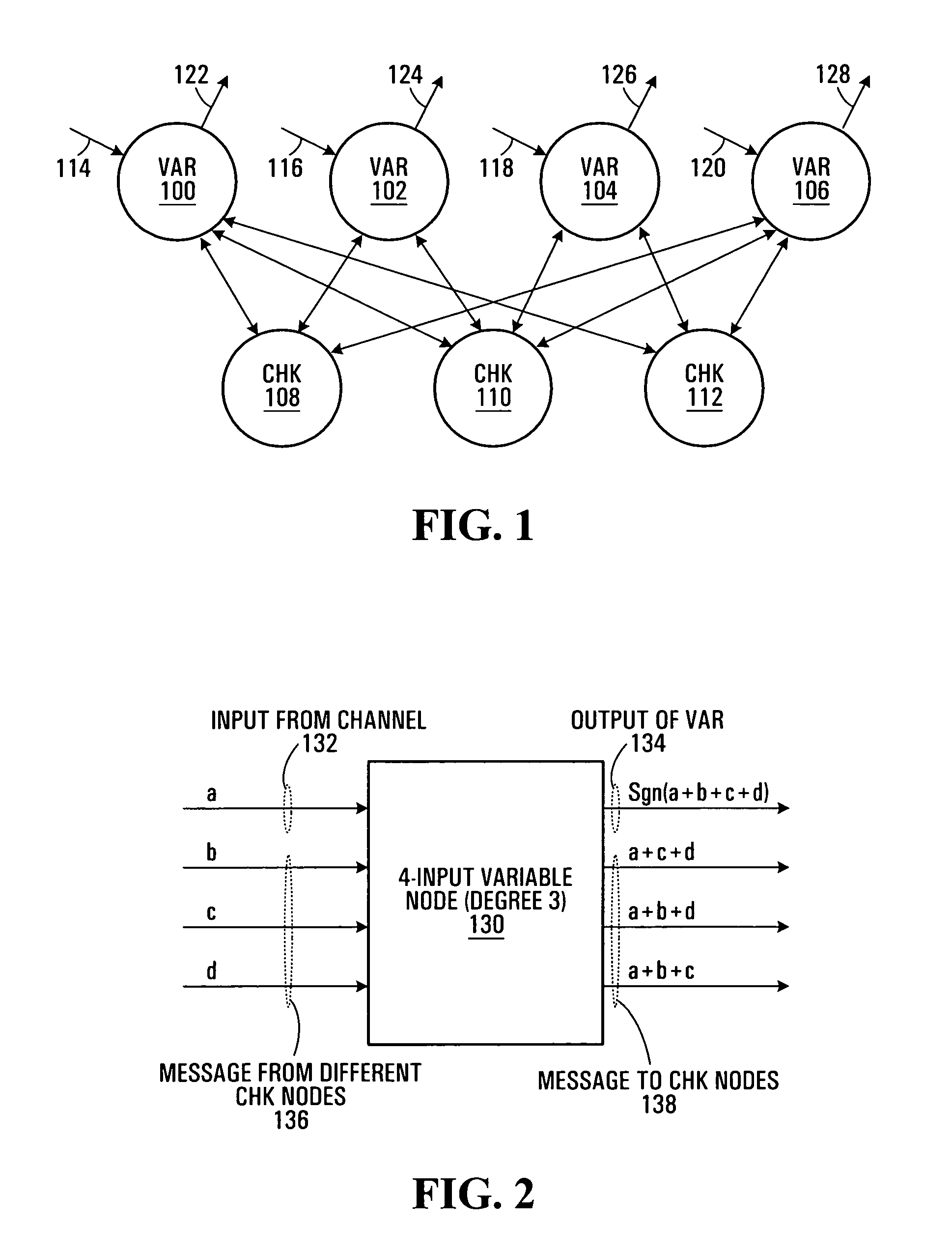

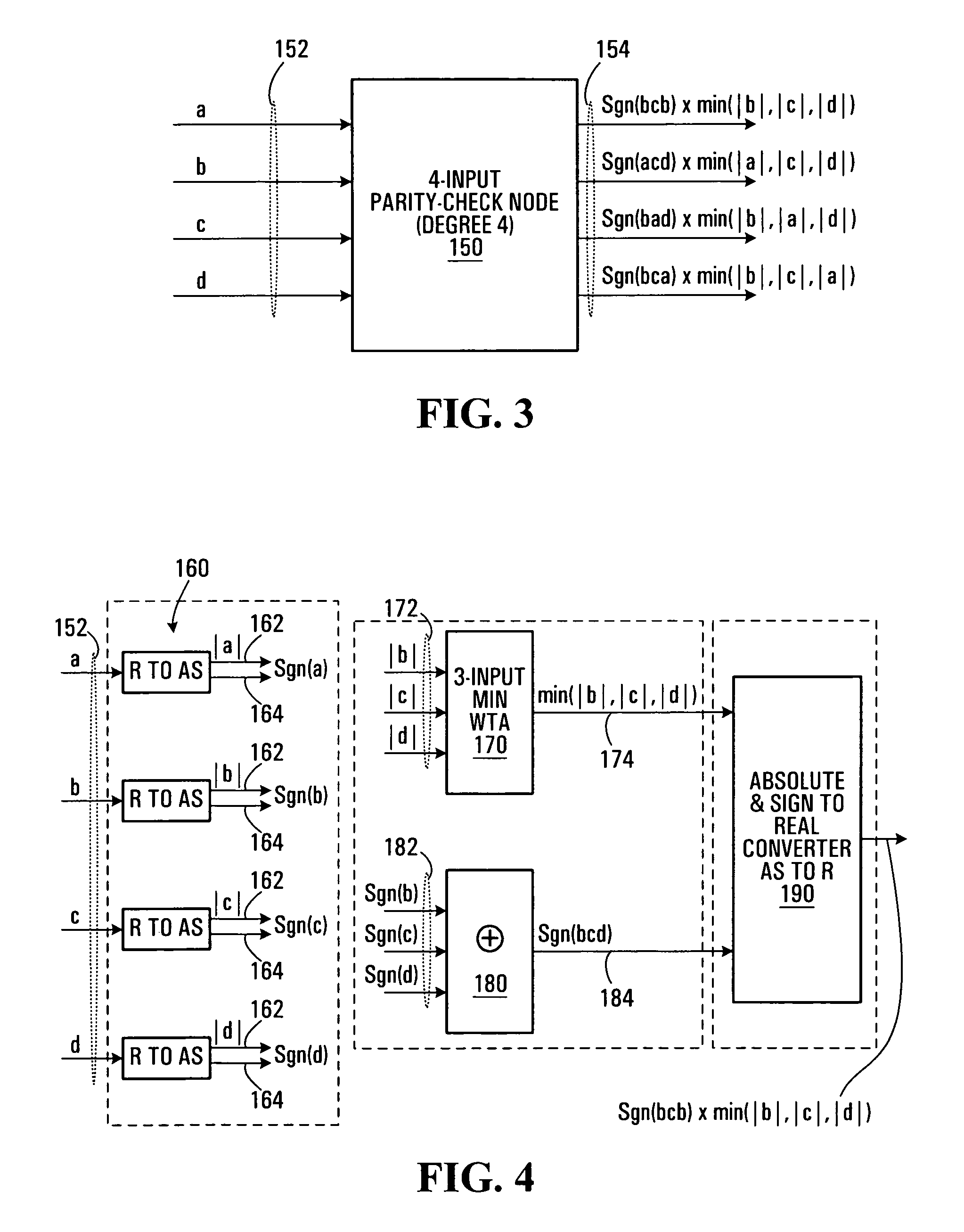

Full CMOS min-sum analog iterative decoders

InactiveUS20050240647A1Reduce manufacturing costSimple designDigital data processing detailsError correction/detection using multiple parity bitsMOSFETCMOS

Analog iterative decoders are provided that are based on the so-called min-sum algorithm (also referred to as max-sum or max-product, Max-Log-MAP or BP-based decoding) and can be used to decode powerful coding schemes such as low-density parity-check (LDPC) codes and turbo codes. The circuits can be implemented by standard CMOS technology, which means lower fabrication cost and / or simpler design compared to previously reported analog iterative decoders that are based on BiCMOS or sub-threshold CMOS technology. Soft information is passed among variable nodes and parity-check nodes. A low-voltage high-swing Max WTA circuit is also provided. The circuit can be implemented by short channel MOSFET transistors and yet provide a reasonably high degree of accuracy. Applications include soft computing, and analog signal processing, in general. A Min WTA circuit can also be built based on this circuit by subtracting the input currents from a large reference current.

Owner:BANIHASHEMI AMIR +1

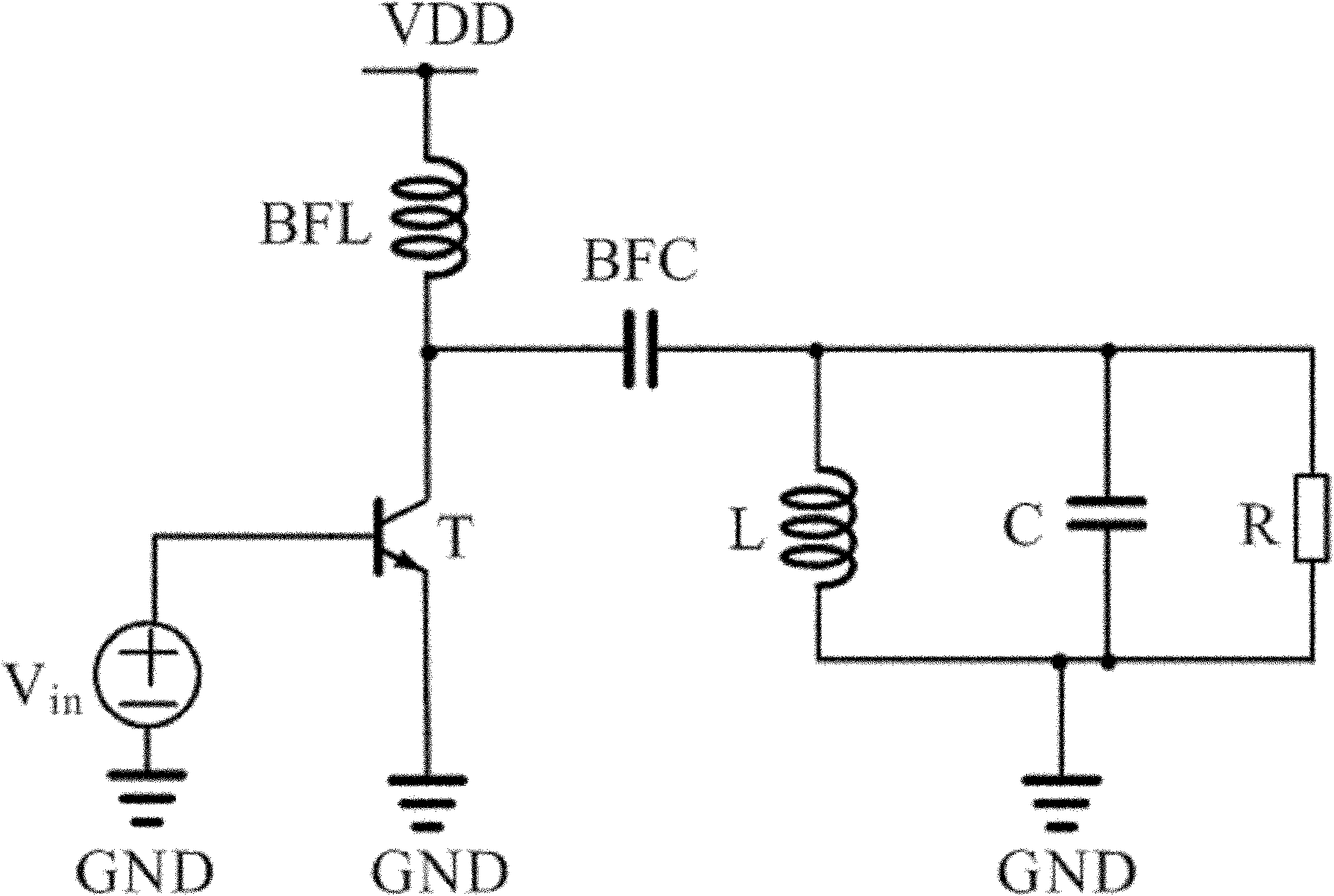

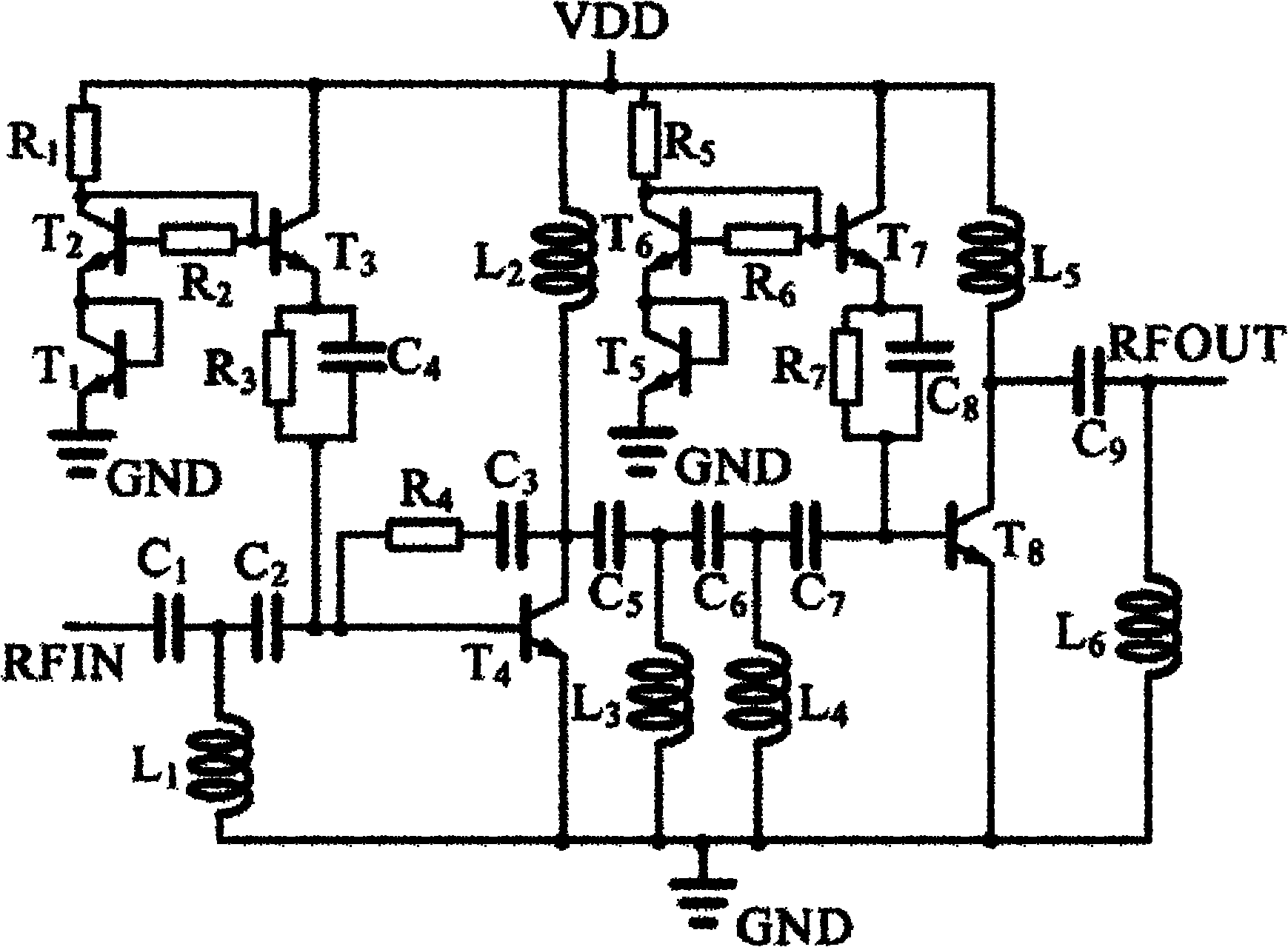

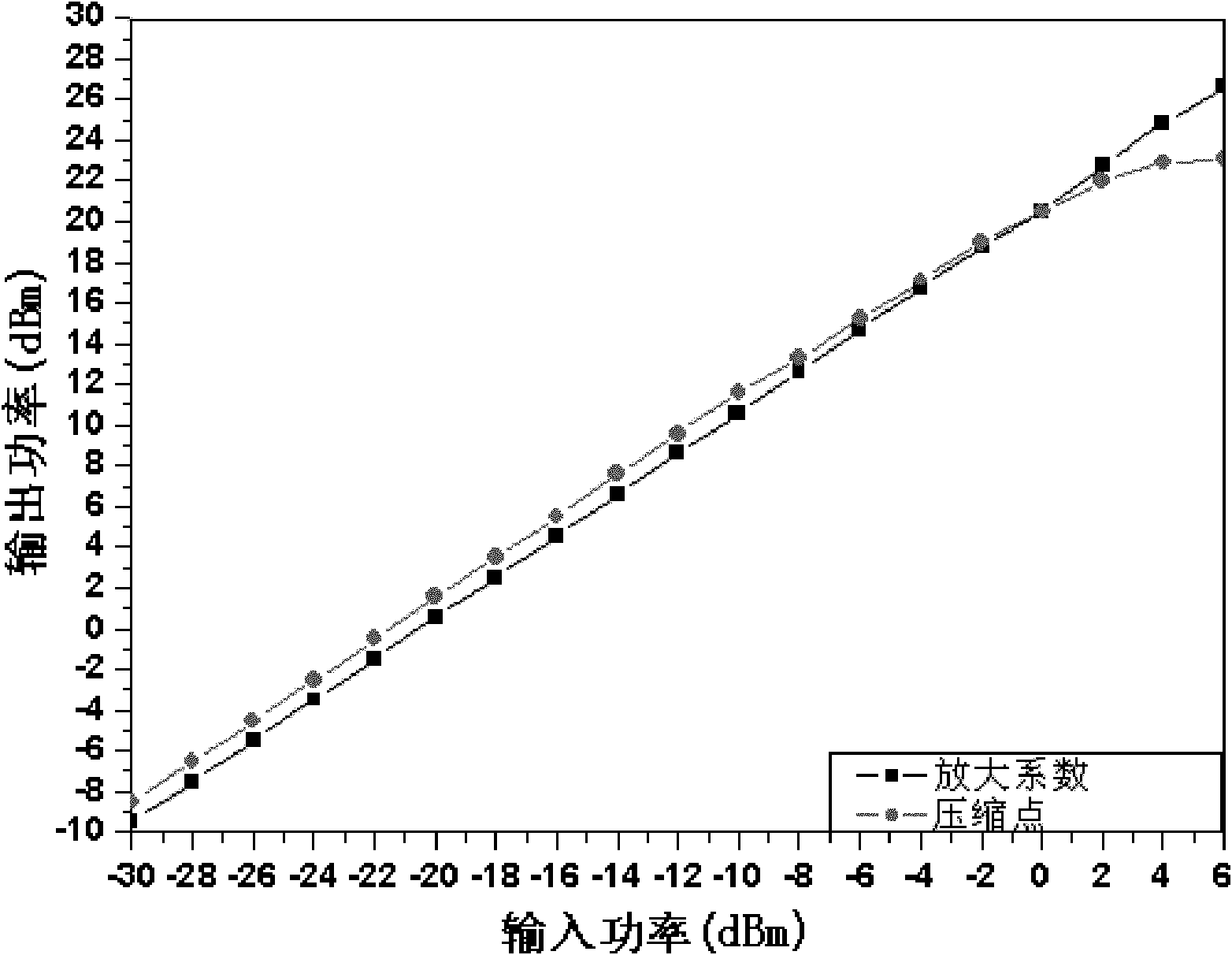

SiGe bipolar complementary metal oxide semiconductor (BiCMOS) radio-frequency power amplifier

InactiveCN102006015AImproved large signal performanceImprove breakdown voltageHigh frequency amplifiersPower amplifiersCapacitanceEngineering

The invention relates to a SiGe bipolar complementary metal oxide semiconductor (BiCMOS) radio-frequency power amplifier. The amplifier comprises a first-stage pre-amplification transistor, a second-stage power amplification transistor, a first-stage biasing circuit, a second-stage biasing circuit, an input matching network and an impedance conversion network. The circuit structure of the invention consists of a first-stage pre-amplification circuit and a second-stage power amplification circuit which are connected with each other through a coupling capacitor. The first-stage pre-amplification transistor is a standard SiGe transistor, and the linearity of the circuit is enhanced by a remote control (RC) serial feedback circuit; and the second-stage power amplification transistor is a high-voltage SiGe transistor and can reach relatively high output power. Both the first biasing circuit and the second biasing circuit have bipolar transistor current mirror structures, and temperature stability is enhanced by temperature negative feedback technology. The amplifier has high linearity and relatively high output power.

Owner:DONGHUA UNIV

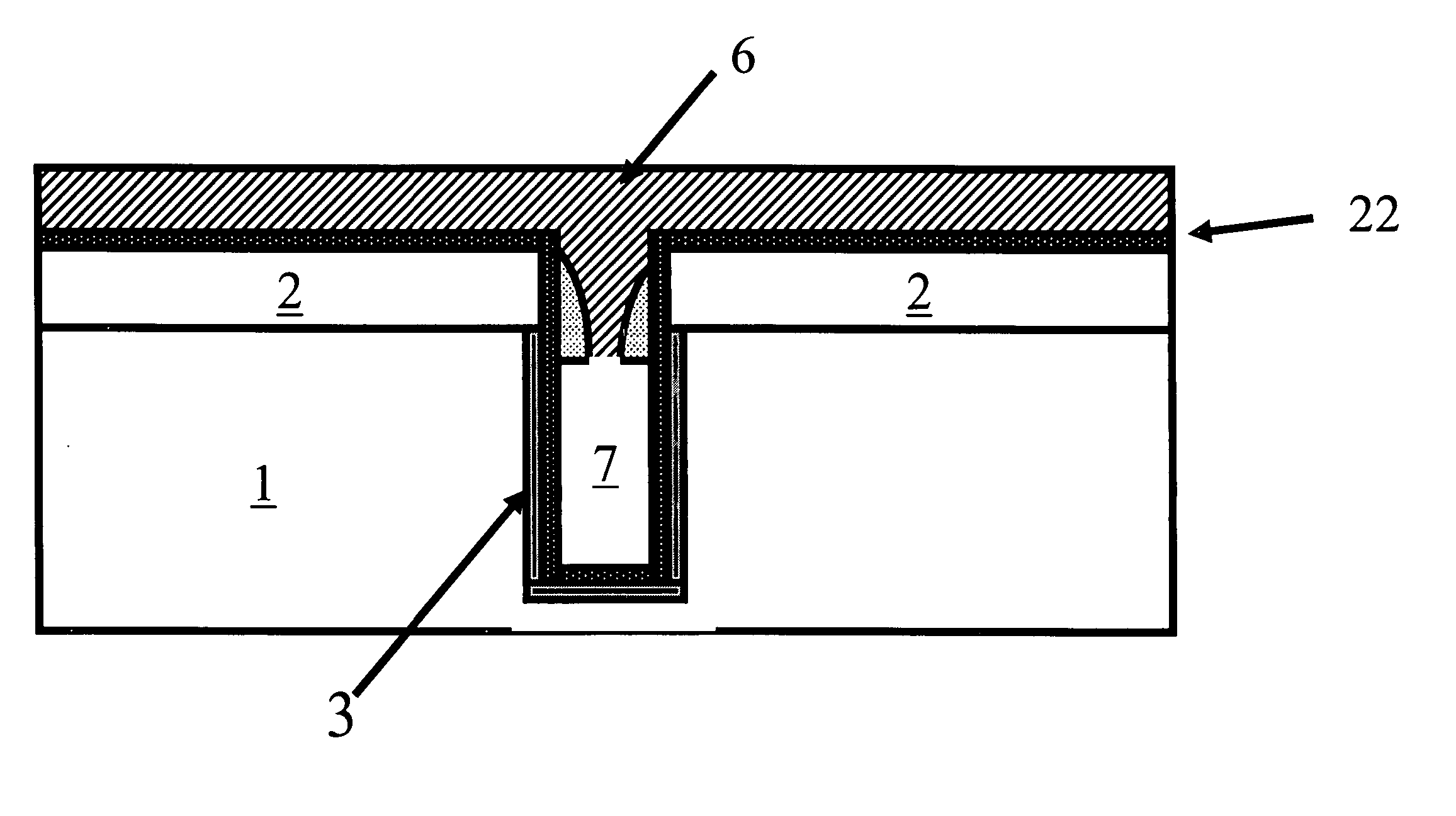

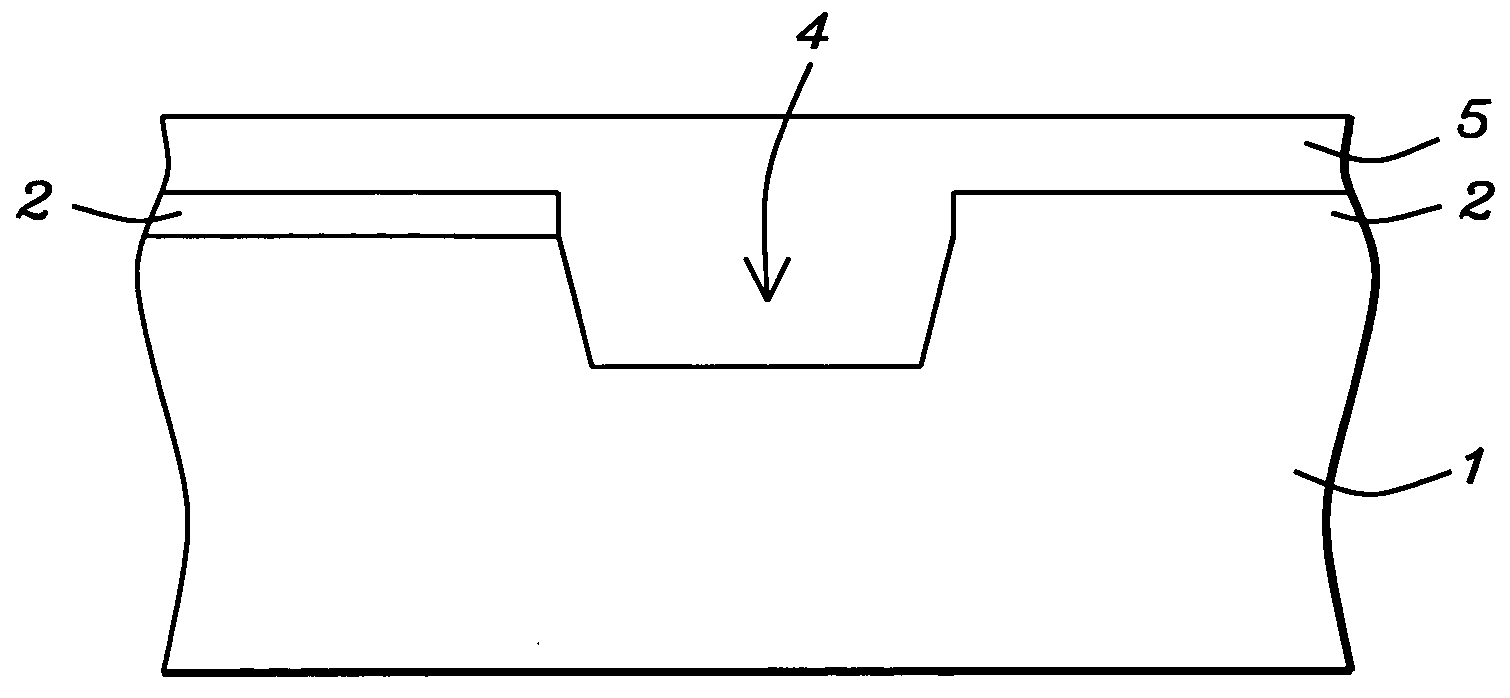

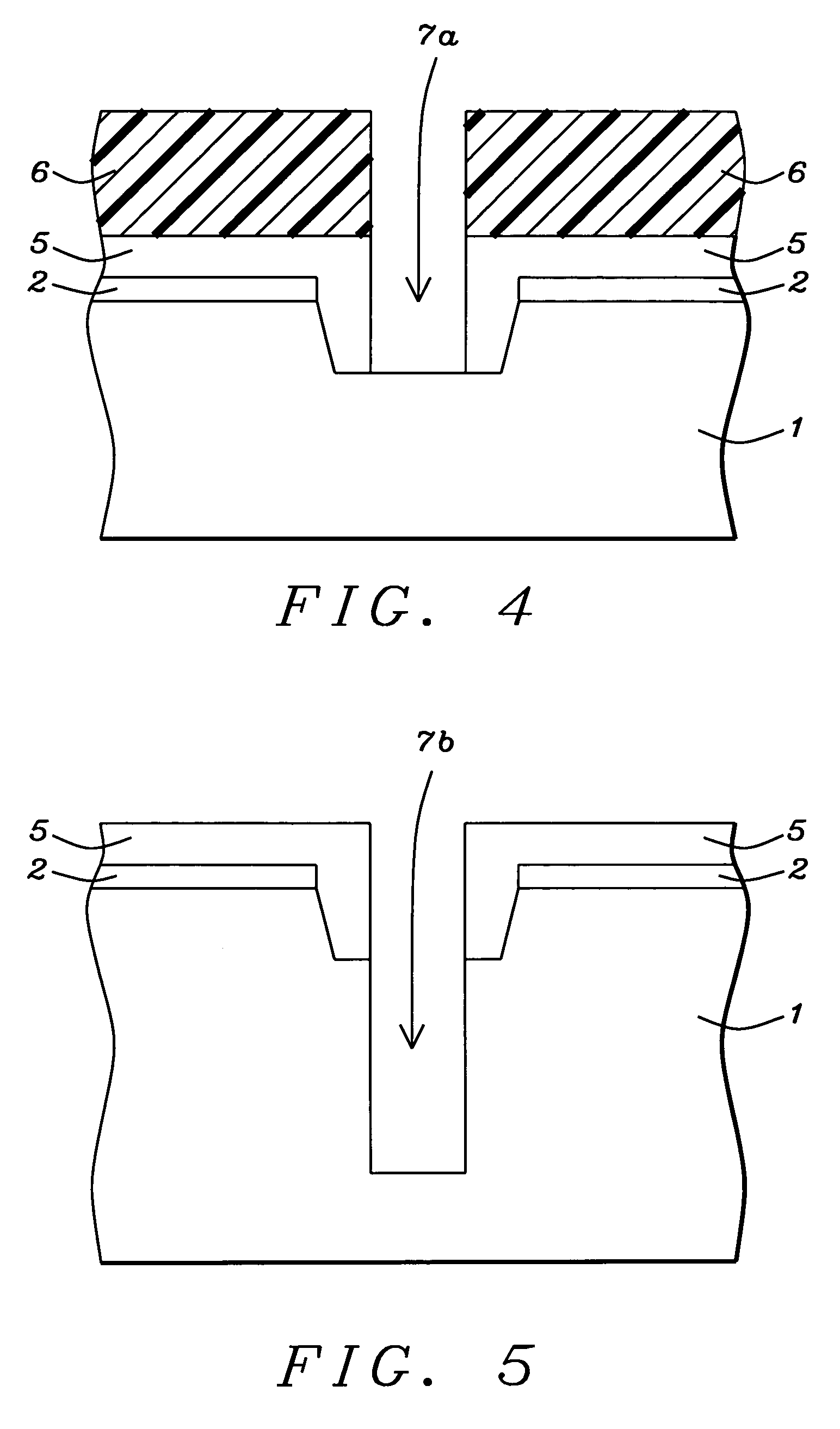

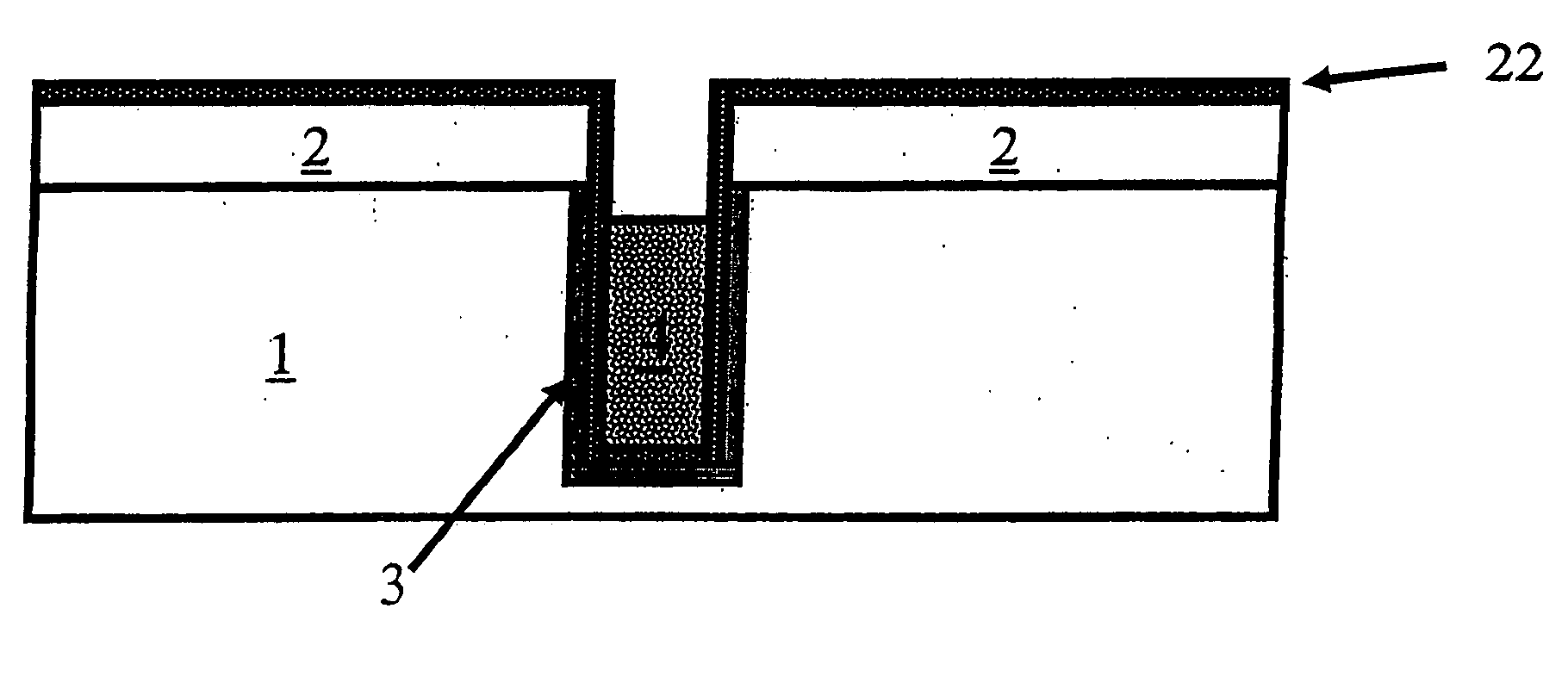

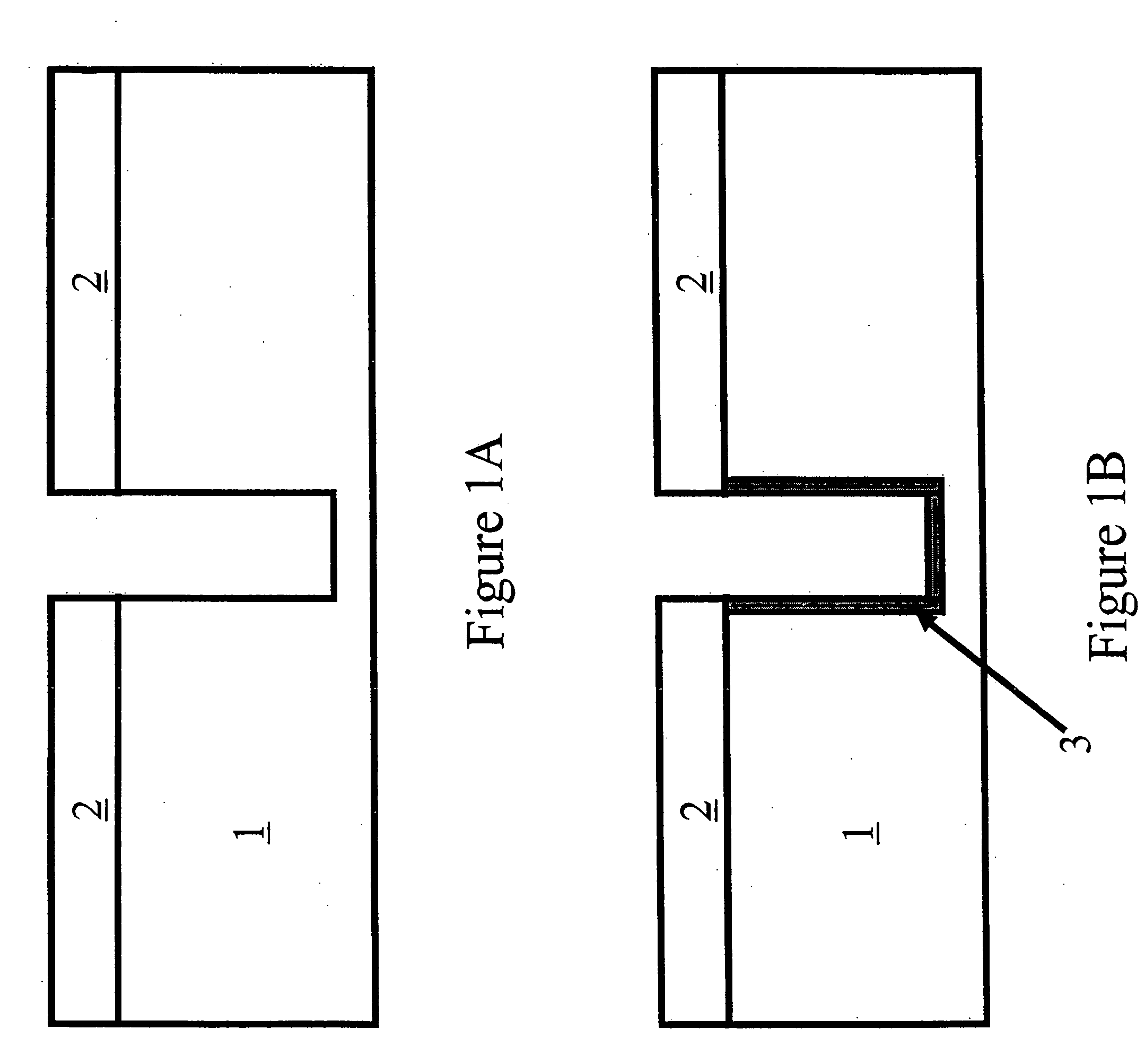

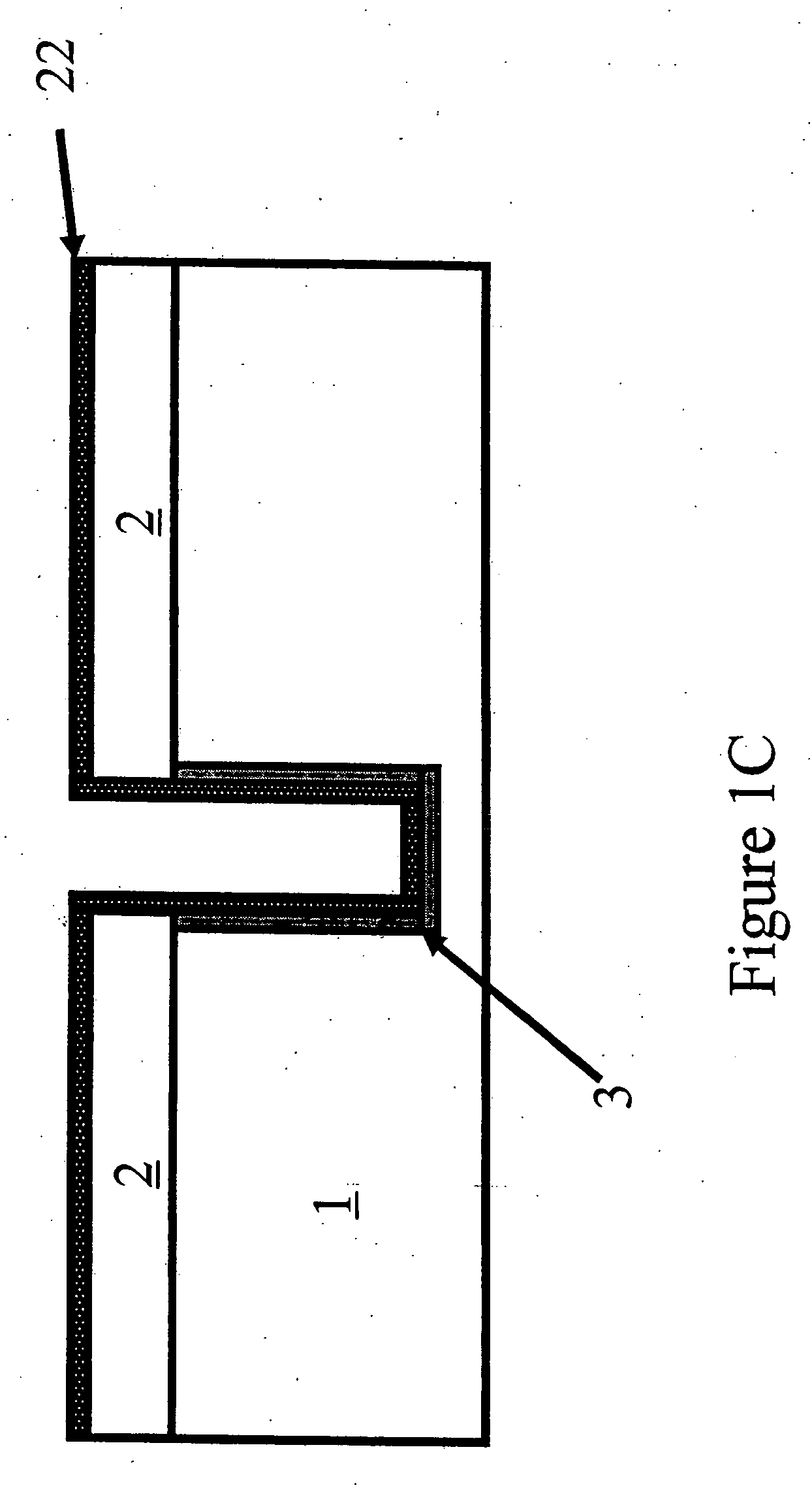

Method of forming a shallow trench-deep trench isolation region for a BiCMOS/CMOS technology

A process for forming an isolation region comprised of shallow trench-deep trench configuration, wherein a smooth top surface topography is obtained for the isolation region and for adjacent active device regions in the semiconductor substrate, has been developed. The process features initially forming an insulator filled shallow trench shape, planarized via a first chemical mechanical polishing procedure, allowing reduced complexity to be realized during the subsequent formation of a narrow diameter, deep trench opening, in the insulator filled shallow trench shape and in an underlying portion of semiconductor substrate. Formation of a recessed polysilicon plug located in the bottom portion of the deep trench opening is followed by formation of an insulator plug located in a top portion of the deep trench opening, overlying the recessed polysilicon plug. This is accomplished via photolithographic and selective dry definition procedures, and a second chemical mechanical polishing procedure, resulting in a filled, deep trench opening exhibiting a smooth top surface topography.

Owner:TAIWAN SEMICON MFG CO LTD

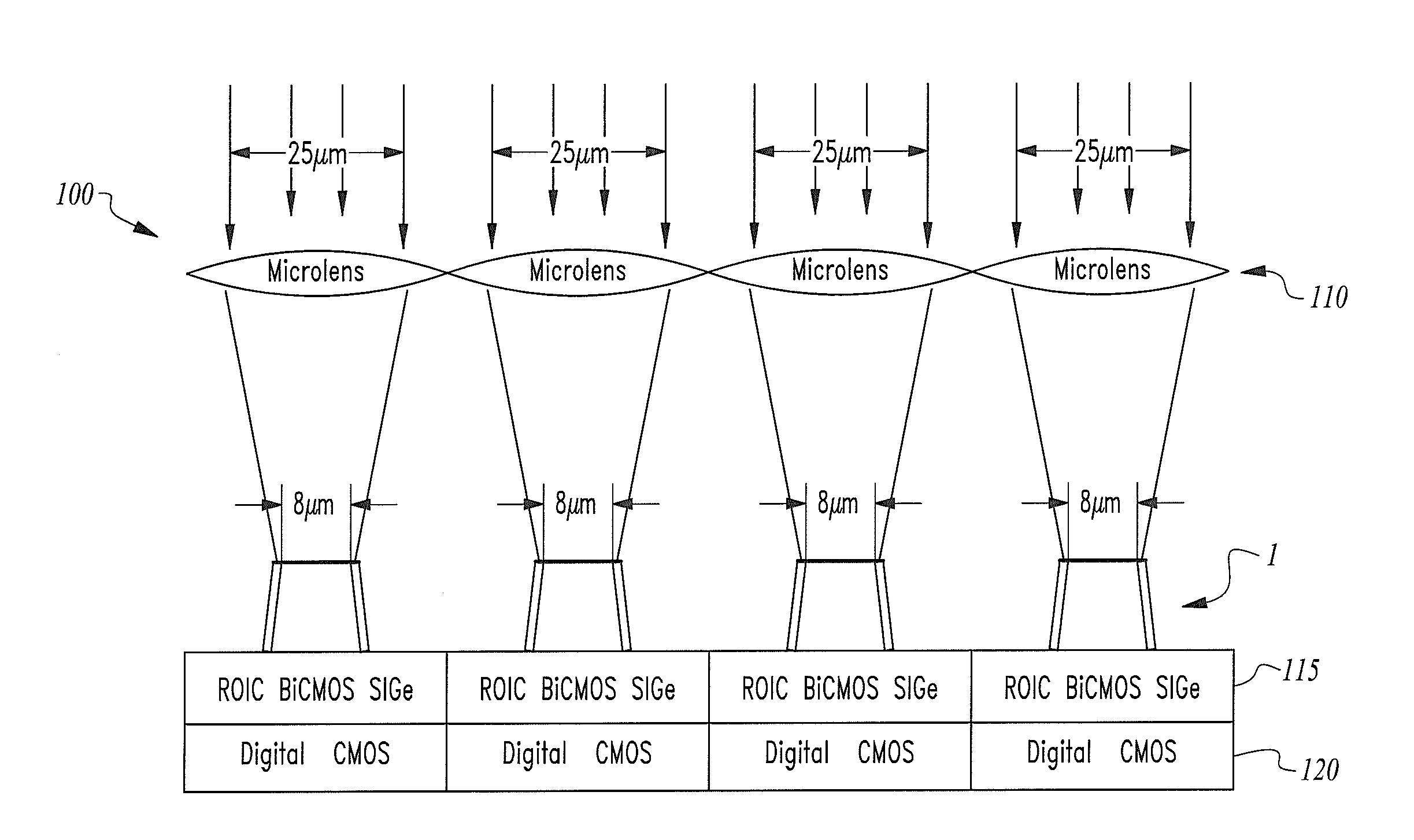

Method of making an integrated electromechanical switch and tunable capacitor

InactiveUS6969630B2Television system detailsPiezoelectric/electrostriction/magnetostriction machinesCMOSMicrowave

A monolithically integrated, electromechanical microwave switch, capable of handling signals from DC to millimeter-wave frequencies, and an integrated electromechanical tunable capacitor are described. Both electromechanical devices include movable beams actuated either by thermo-mechanical or by electrostatic forces. The devices are fabricated directly on finished silicon-based integrated circuit wafers, such as CMOS, BiCMOS or bipolar wafers. The movable beams are formed by selectively removing the supporting silicon underneath the thin films available in a silicon-based integrated circuit technology, which incorporates at least one polysilicon layer and two metallization layers. A cavity and a thick, low-loss metallization are used to form an electrode above the movable beam. A thick mechanical support layer is formed on regions where the cavity is located, or substrate is bulk-micro-machined, i.e., etched.

Owner:FOR NAT RES INITIATIVES

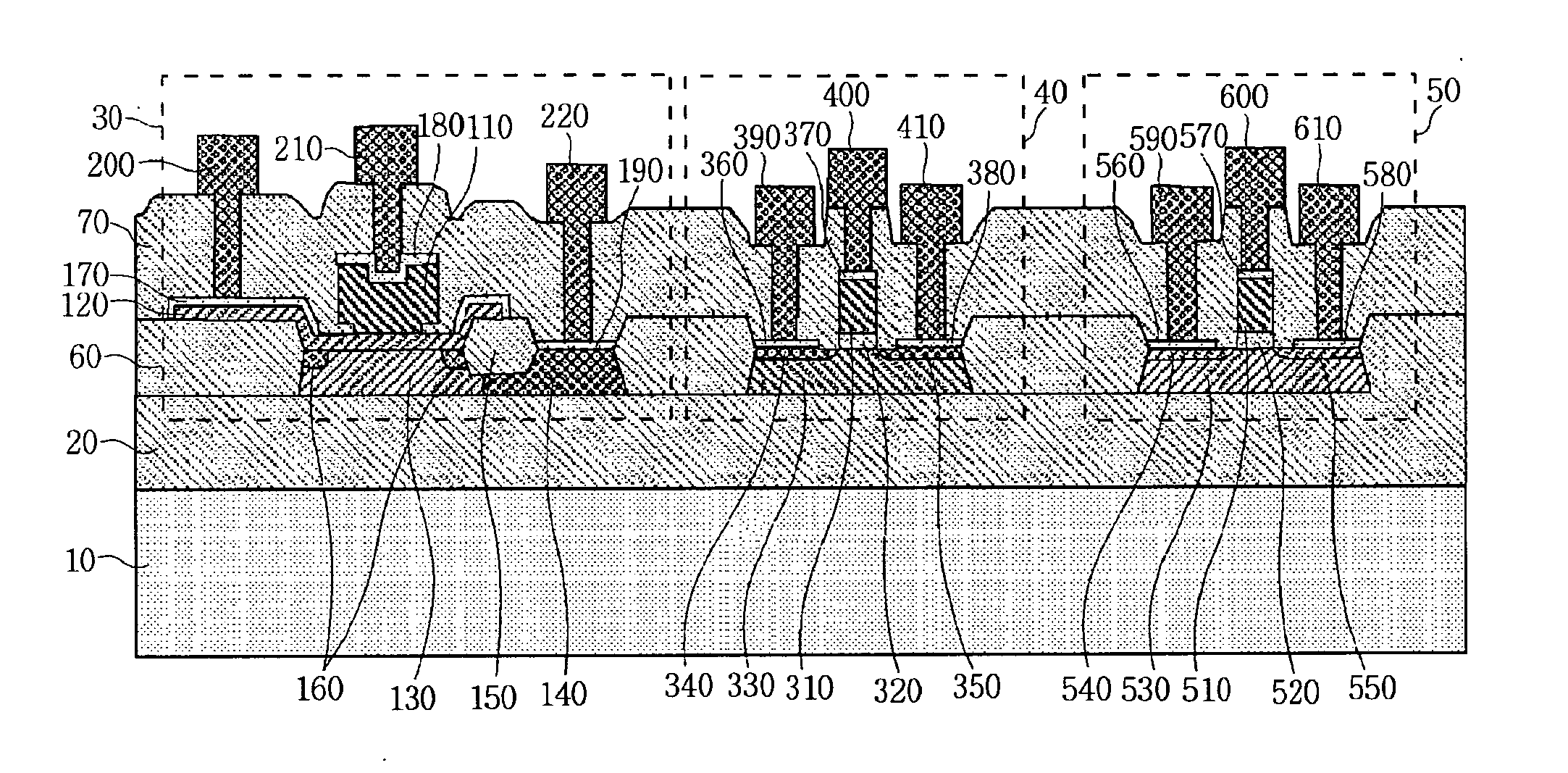

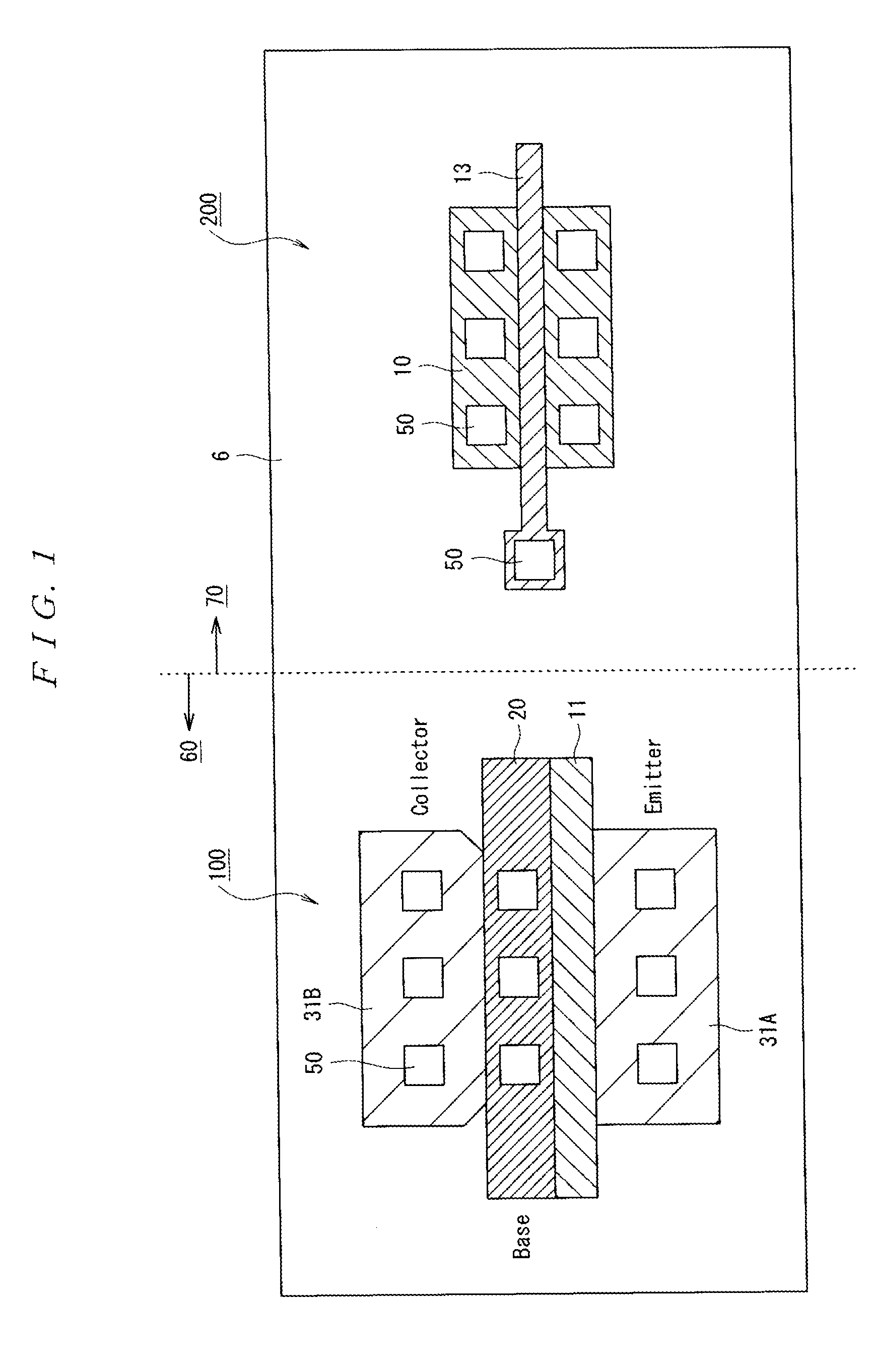

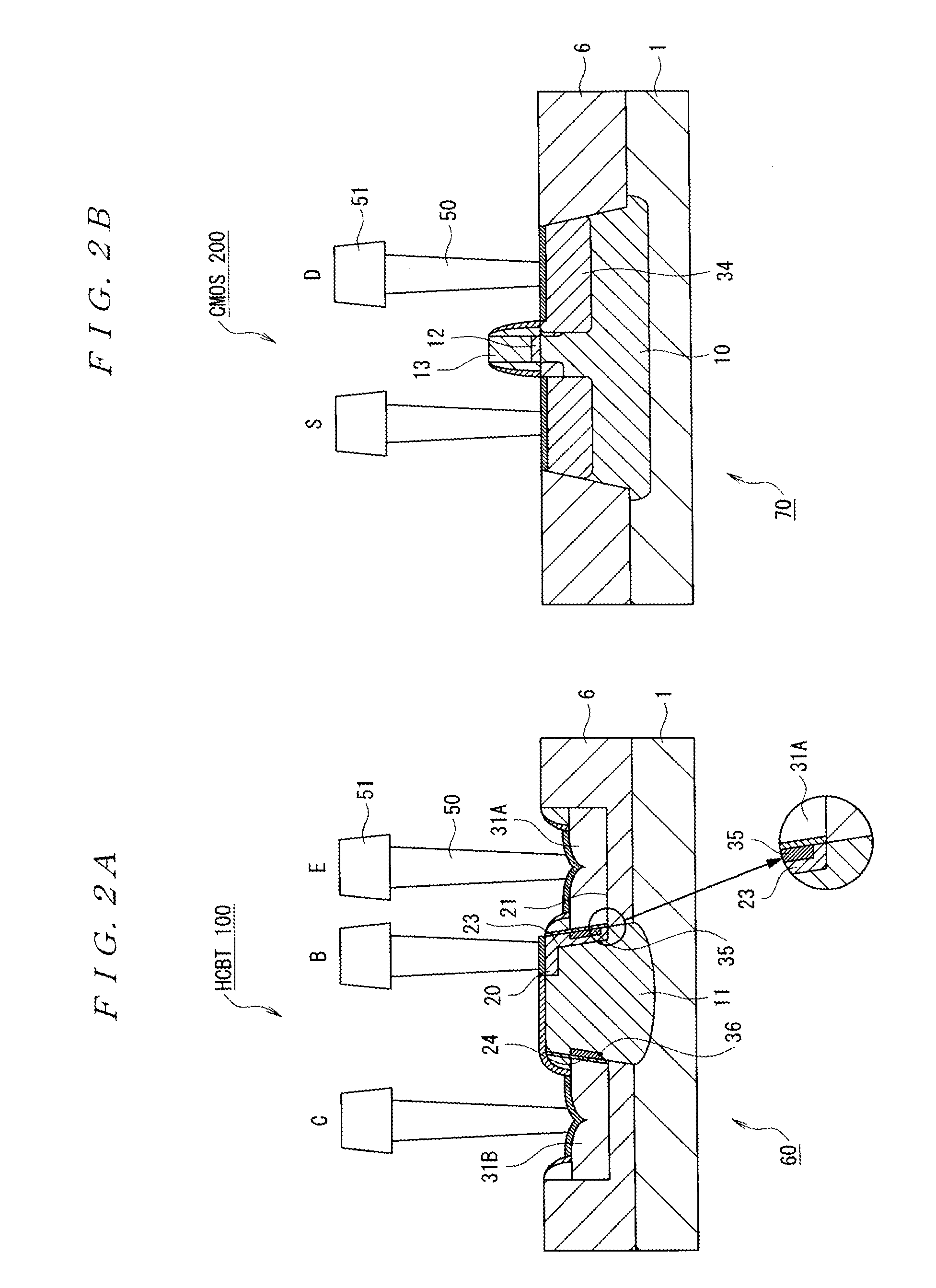

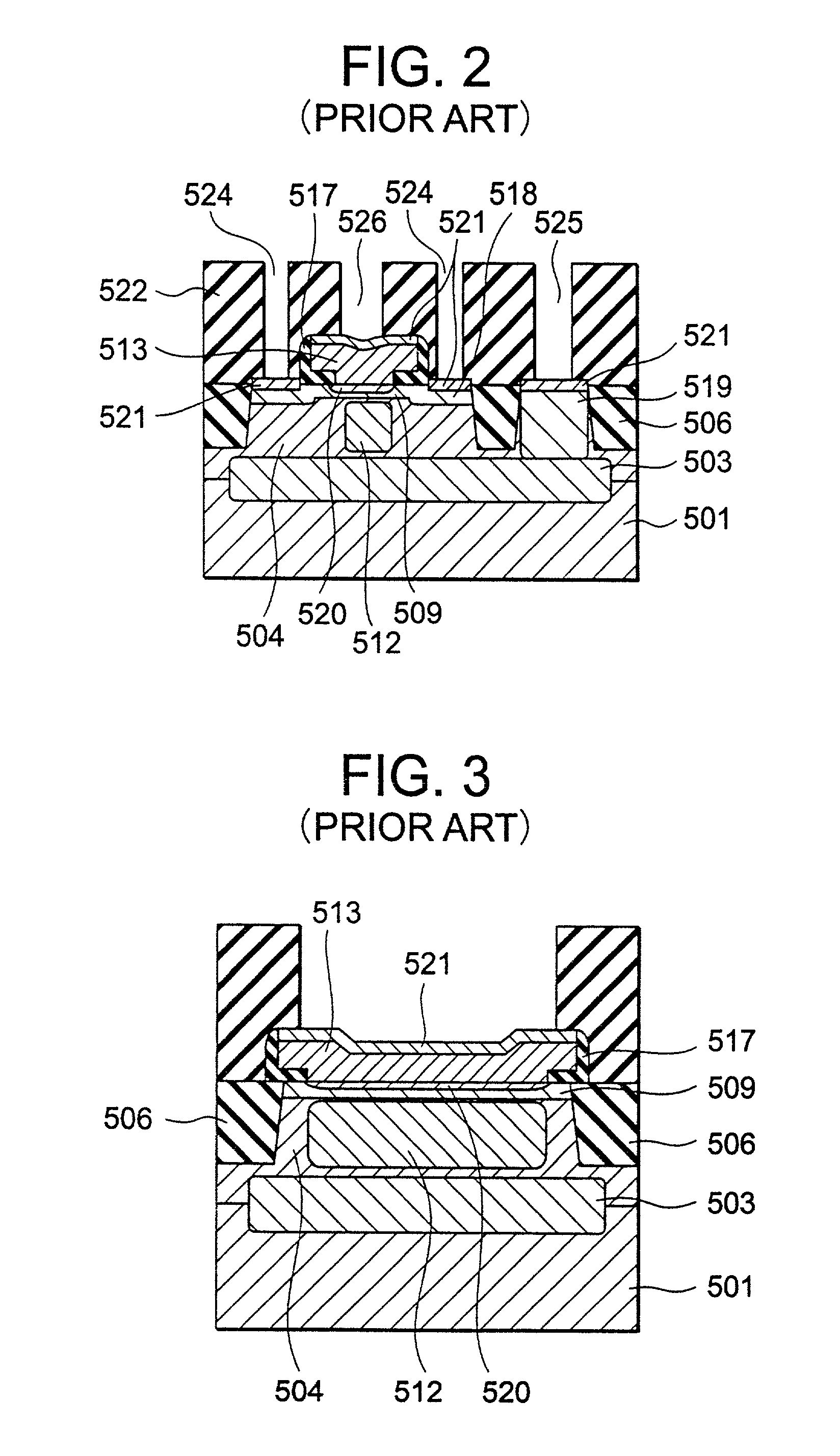

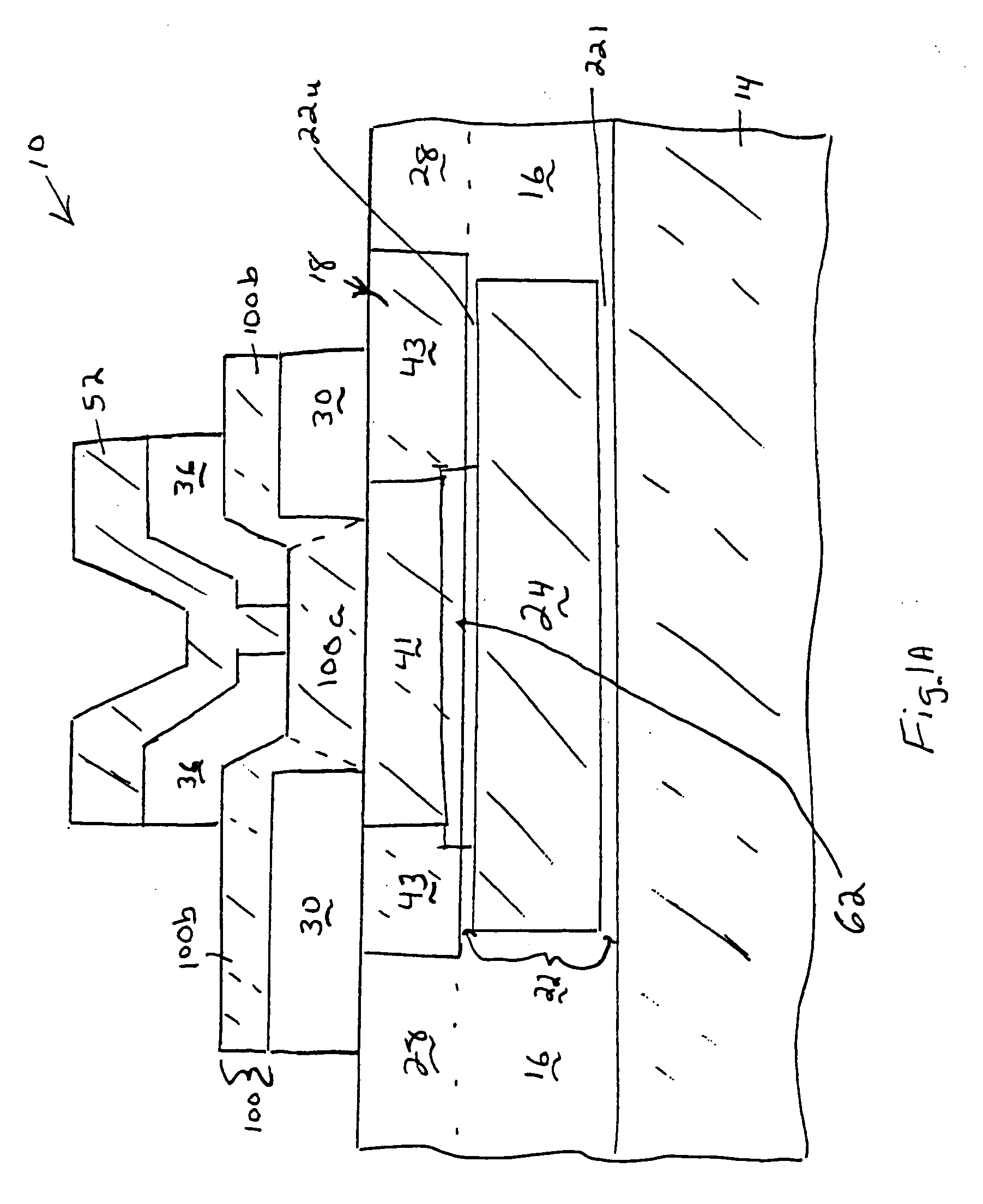

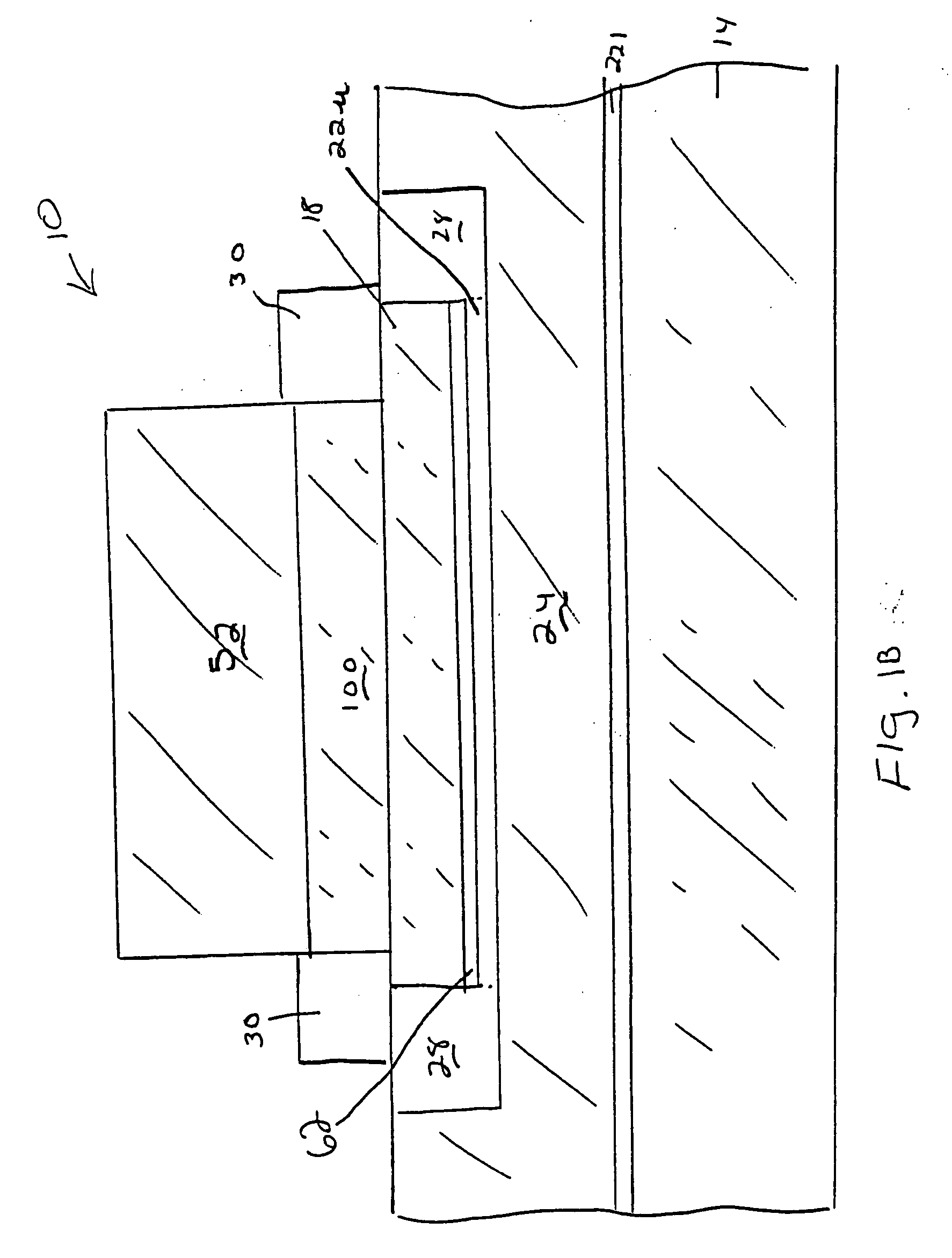

Bipolar transistor, BiCMOS device, and method for fabricating thereof

InactiveUS20050104127A1Reduce the numberReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosHigh density

Provided are bipolar transistor, BiCMOS device and method of fabricating thereof, in which an existing sub-collector disposed beneath a collector of a SiGe HBT is removed and a collector plug disposed at a lateral side of the collector is approached to a base when fabricating a Si-based very high-speed device, whereby it is possible to fabricate the SiGe HBT and an SOI CMOS on a single substrate, reduce the size of the device and the number of masks to be used, and implement the device of high density, low power consumption, and wideband performance.

Owner:ELECTRONICS & TELECOMM RES INST

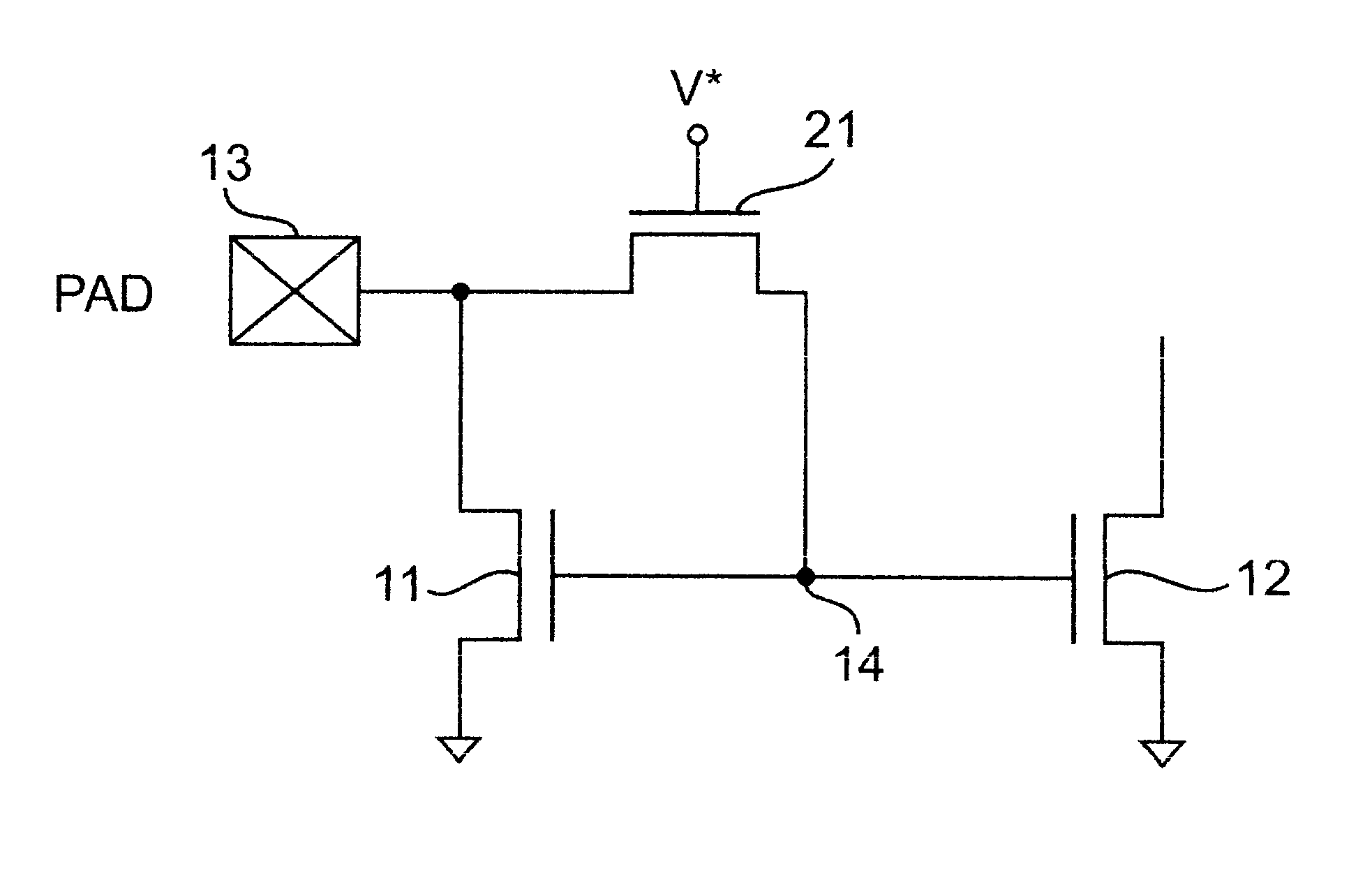

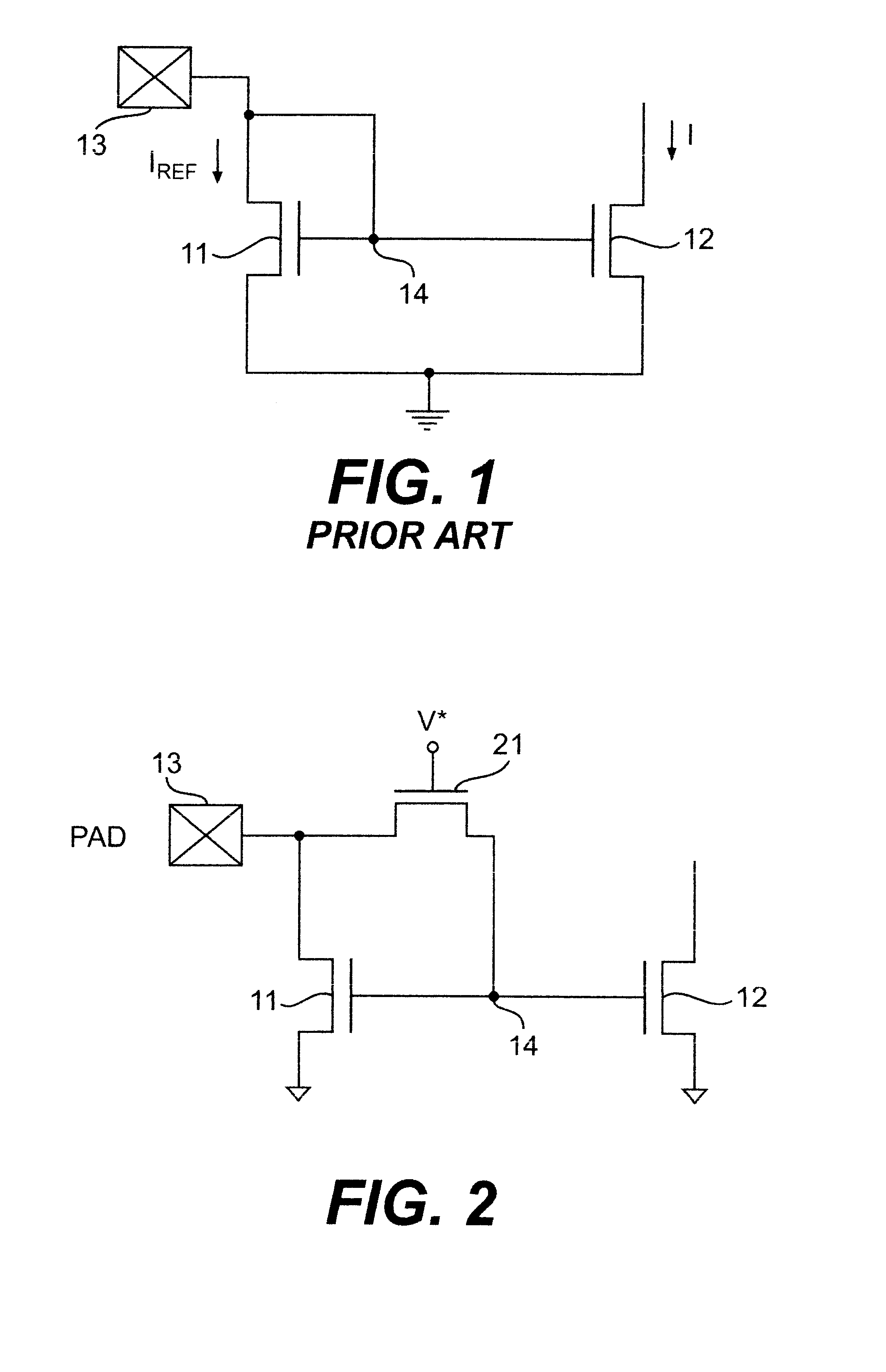

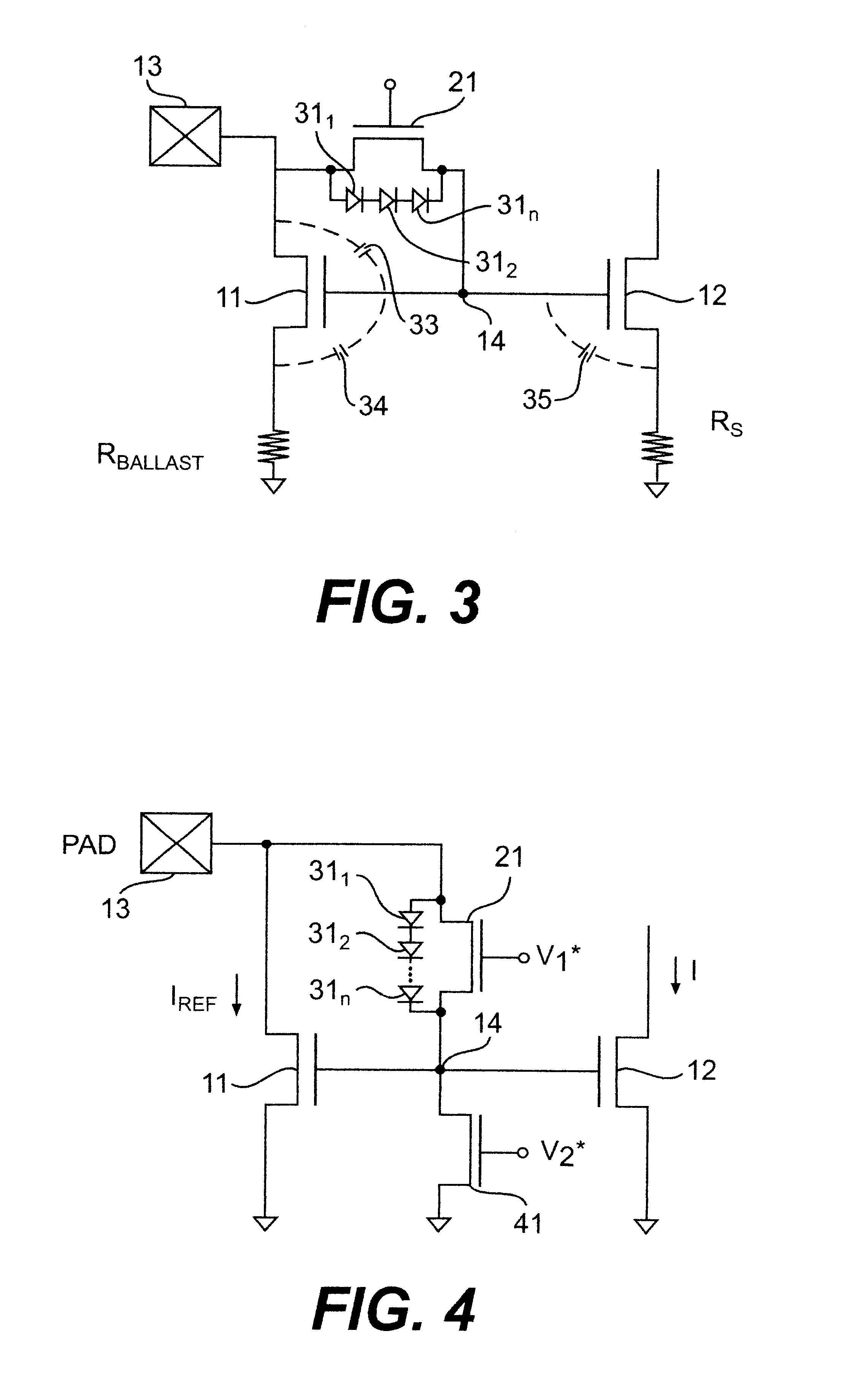

Modified current mirror circuit for BiCMOS application

ESD (Electrostatic Discharge) robust current mirror circuits incorporate circuitry for decoupling the gate when the chip is unpowered. Additional protection is provided by a second element which provides de-biasing to prevent Vgs from being established. A third element can be added between the gate and the ground potential on the current mirror gate node to prevent the gate of the current mirror from rising too high and allows the current to be discharged through the element instead of the current mirror.

Owner:IBM CORP

JFET structure for integrated circuit and fabrication method

InactiveUS6861303B2Improve Noise PerformanceReduce charge buildupTransistorSolid-state devicesBiCMOSHigh pressure

Junction field effect transistors (JFETs) can be fabricated with an epitaxial layer that forms a sufficiently thick channel region to enable the JFET for use in high voltage applications (e.g., having a breakdown voltage greater than about 20V). Additionally or alternatively, threshold voltage (VT) implants can be introduced at one or more of the gate, source and drain regions to improve noise performance of the JFET. Additionally, fabrication of such a JFET can be facilitated forming the entire JFET structure concurrently with a CMOS fabrication process and / or with a BiCMOS fabrication process.

Owner:TEXAS INSTR INC

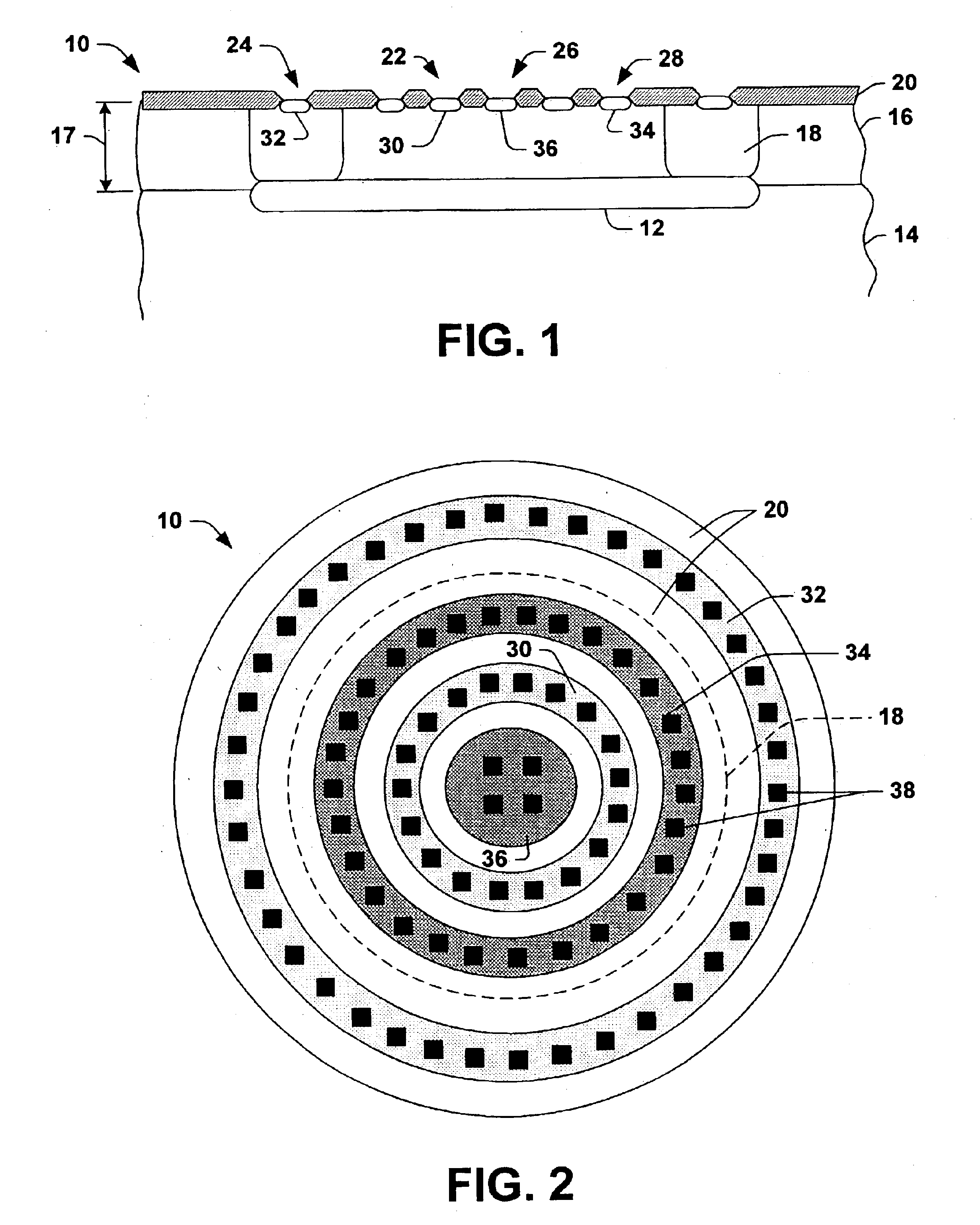

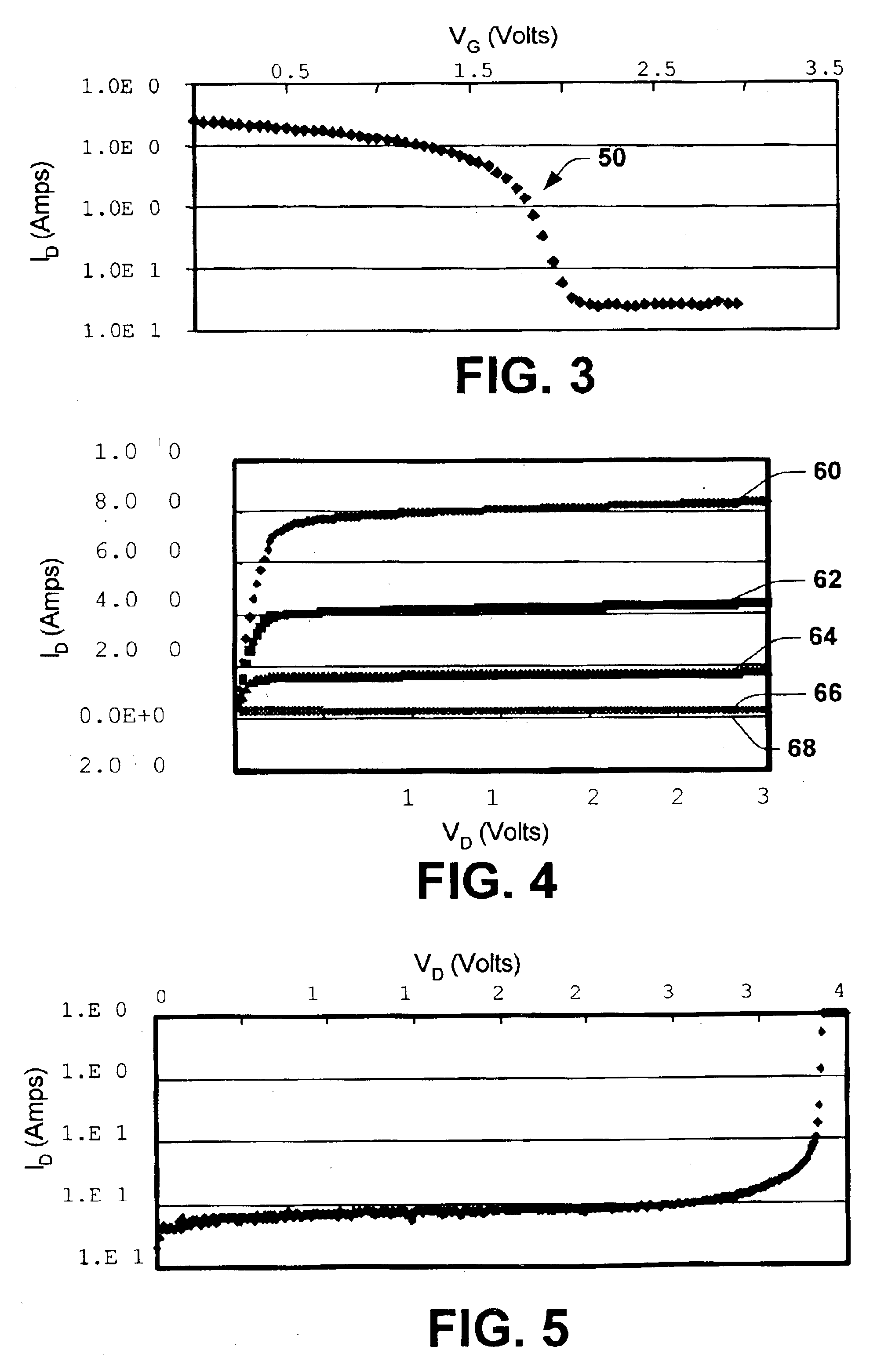

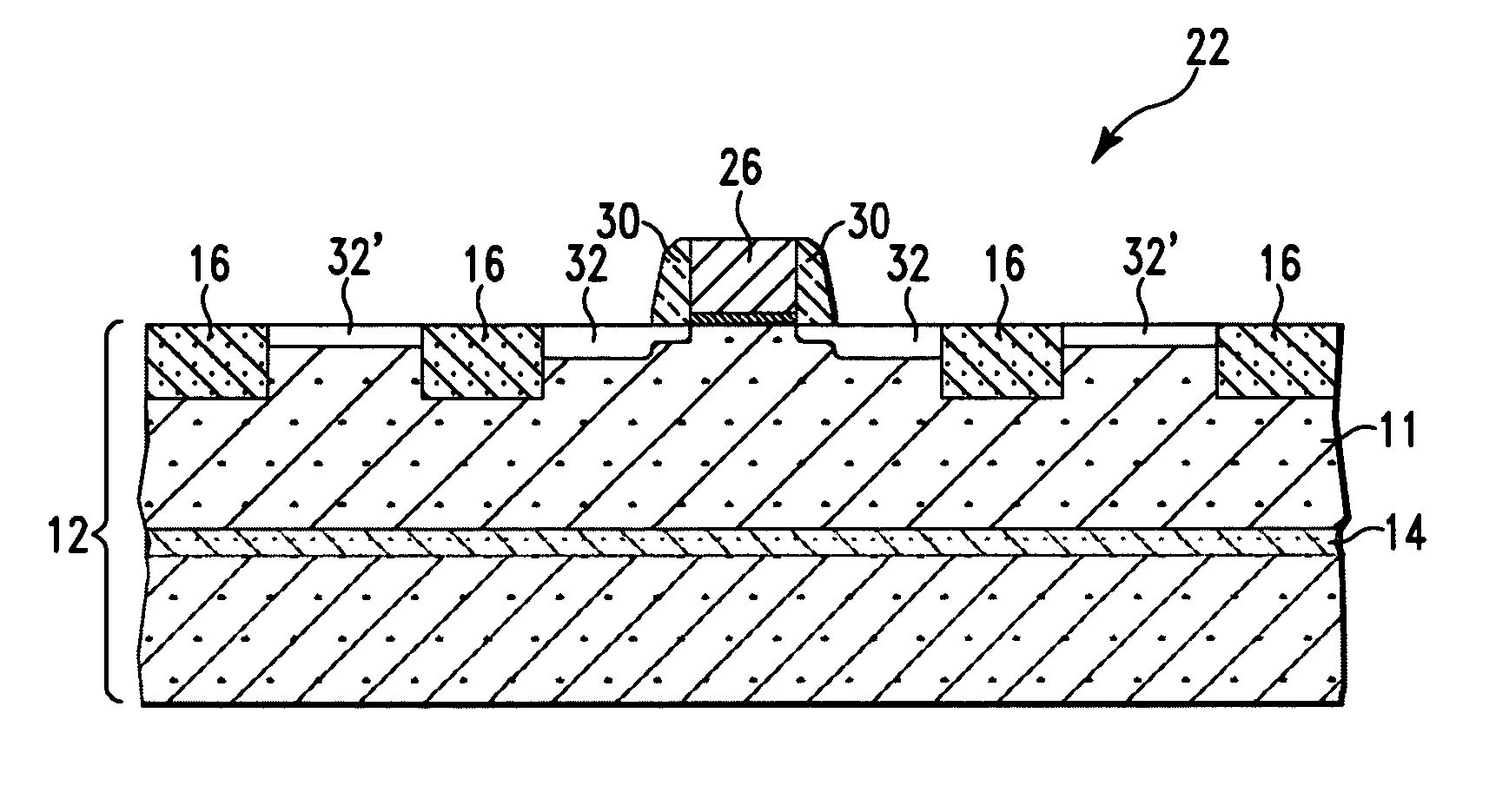

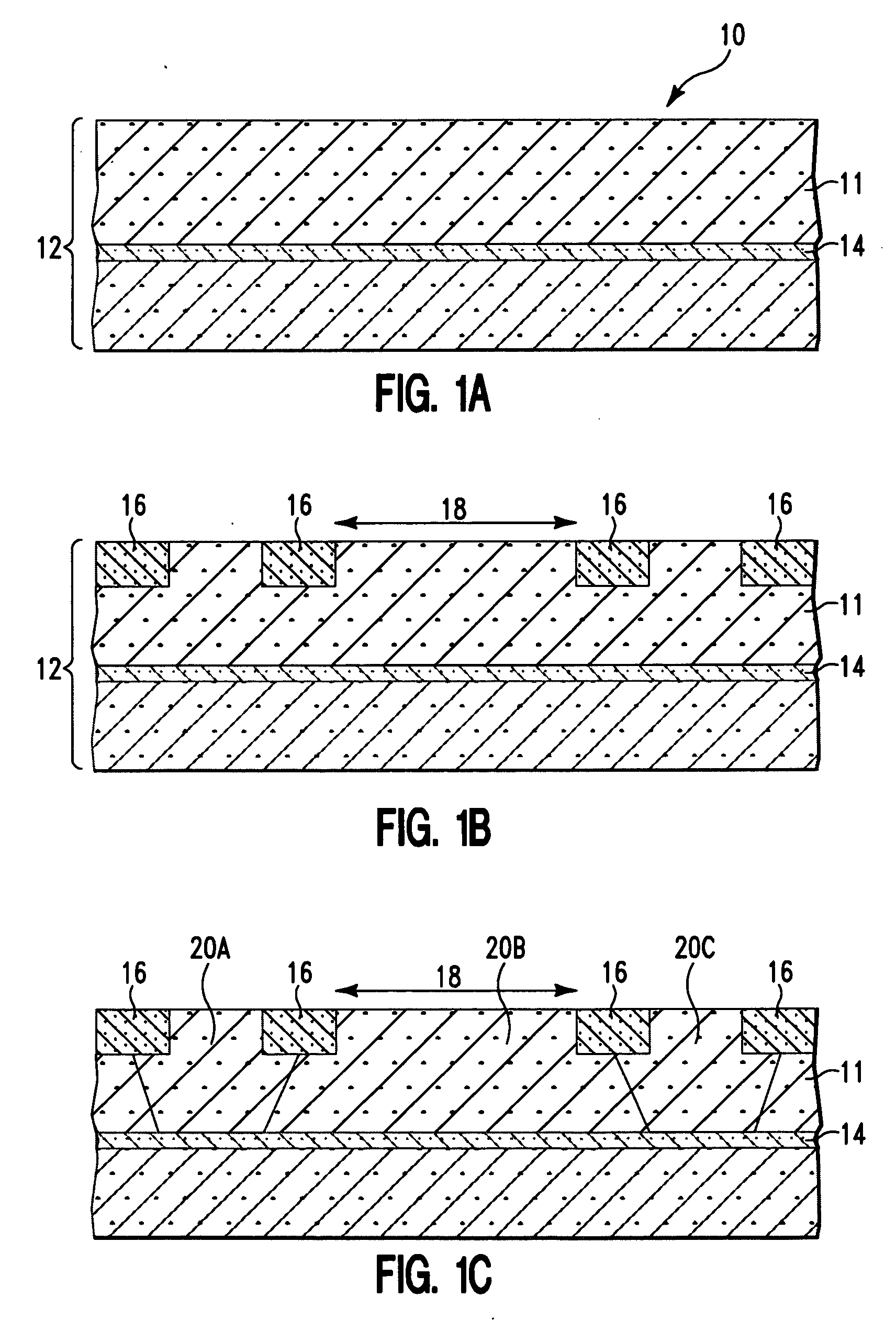

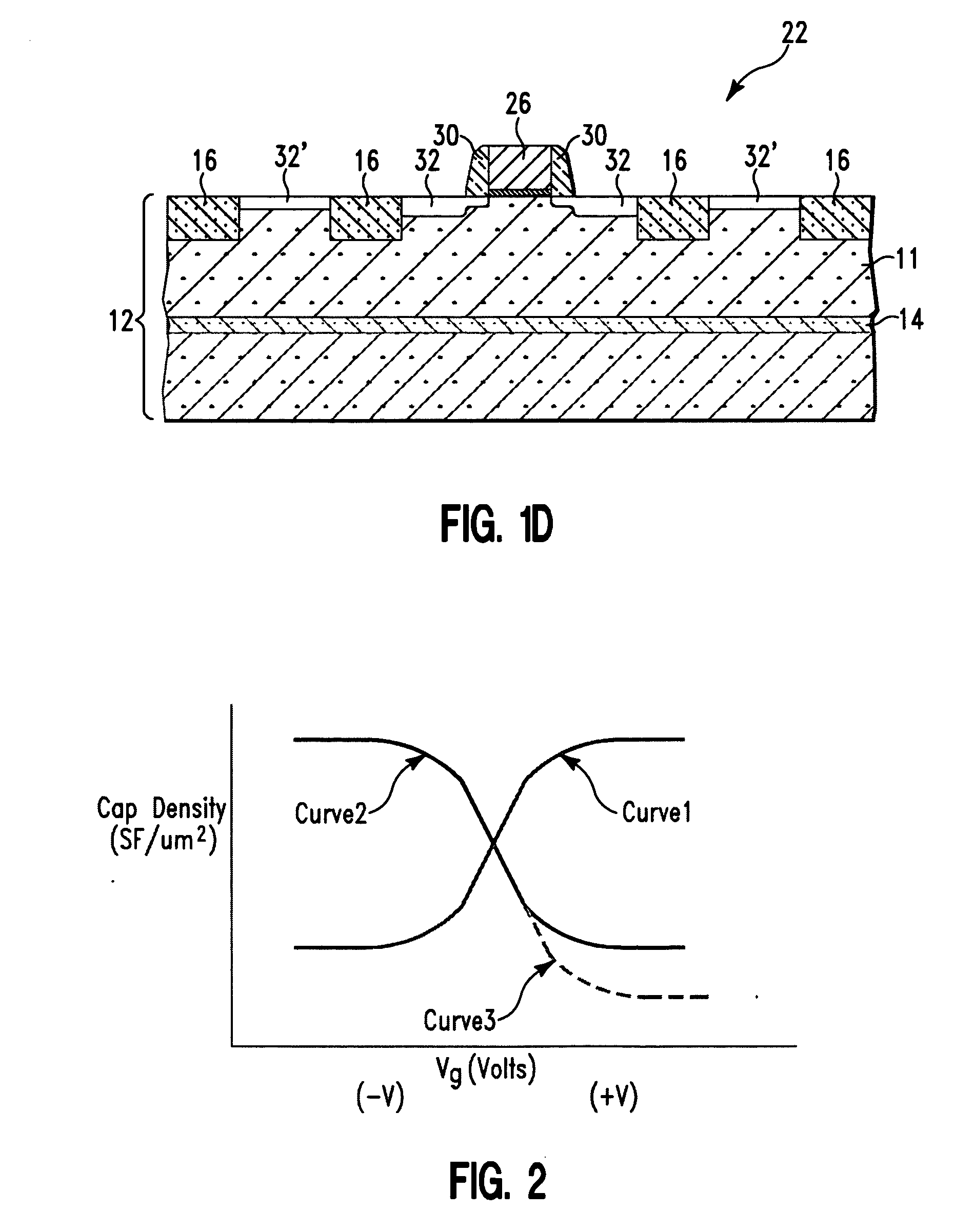

Mos varactor using isolation well

ActiveUS20060043454A1Improve adjustabilityHigh quality factorTransistorSolid-state devicesCMOSElectrical conductor

The present invention provides a varactor that has increased tunability and a high quality factor Q as well as a method of fabricating the varactor. The method of the present invention can be integrated into a conventional CMOS processing scheme or into a conventional BiCMOS processing scheme. The method includes providing a structure that includes a semiconductor substrate of a first conductivity type and optionally a subcollector or isolation well (i.e., doped region) of a second conductivity type located below an upper region of the substrate, the first conductivity type is different from said second conductivity type. Next, a plurality of isolation regions are formed in the upper region of the substrate and then a well region is formed in the upper region of the substrate. In some cases, the doped region is formed at this point of the inventive process. The well region includes outer well regions of the second conductivity type and an inner well region of the first conductivity type. Each well of said well region is separated at an upper surface by an isolation region. A field effect transistor having at least a gate conductor of the first conductivity type is then formed above the inner well region.

Owner:IBM CORP

Formation of deep trench airgaps and related applications

ActiveUS20060258077A1Reduce widthReduce capacitanceTransistorSemiconductor/solid-state device detailsEngineeringBiCMOS

A method for forming deep trench or via airgaps in a semiconductor substrate is disclosed comprising the steps of patterning a hole in the substrate, partly fill said hole with a sacrificial material (e.g. poly-Si), depositing spacers on the sidewalls of the unfilled part of the hole (e.g. TEOS) to narrow the opening, removing through said narrowed opening the remaining part of the sacrificial material (e.g. by isotropic etching) and finally sealing the opening of the airgap by depositing a conformal layer (TEOS) above the spacers. The method of forming an airgap is demonstrated successfully for use as deep trench isolation structures in BiCMOS devices.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

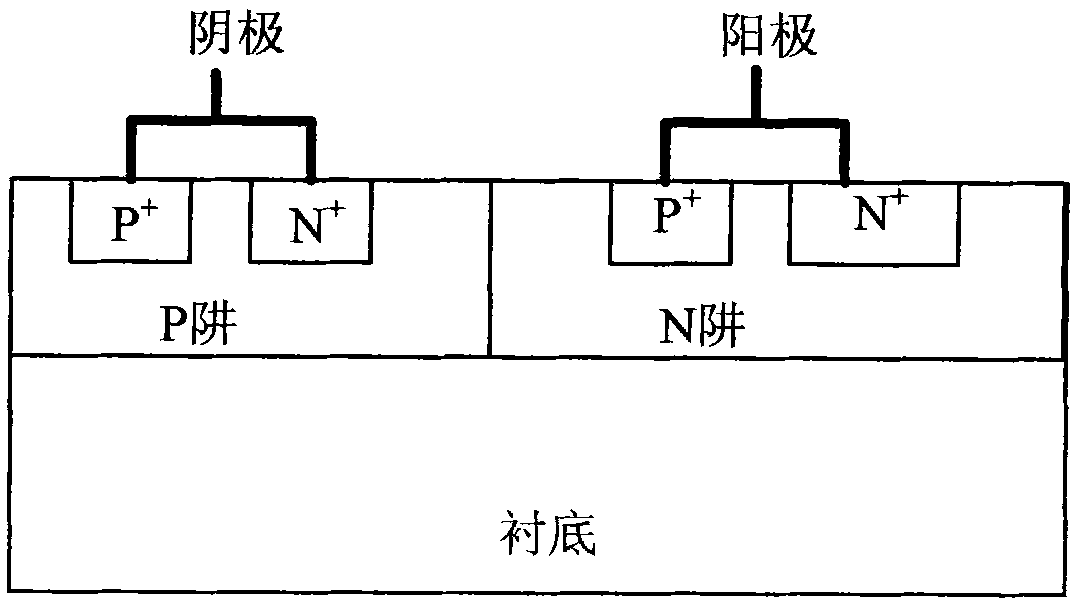

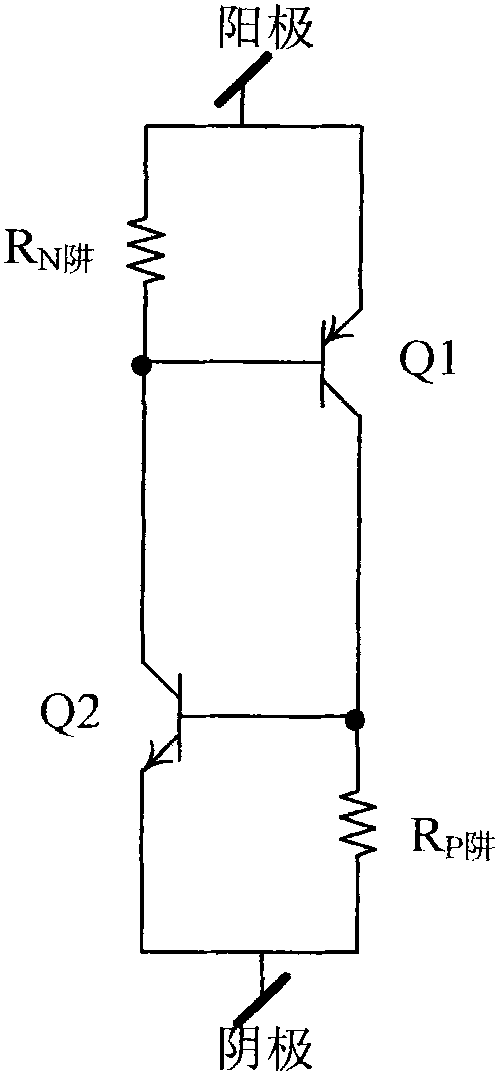

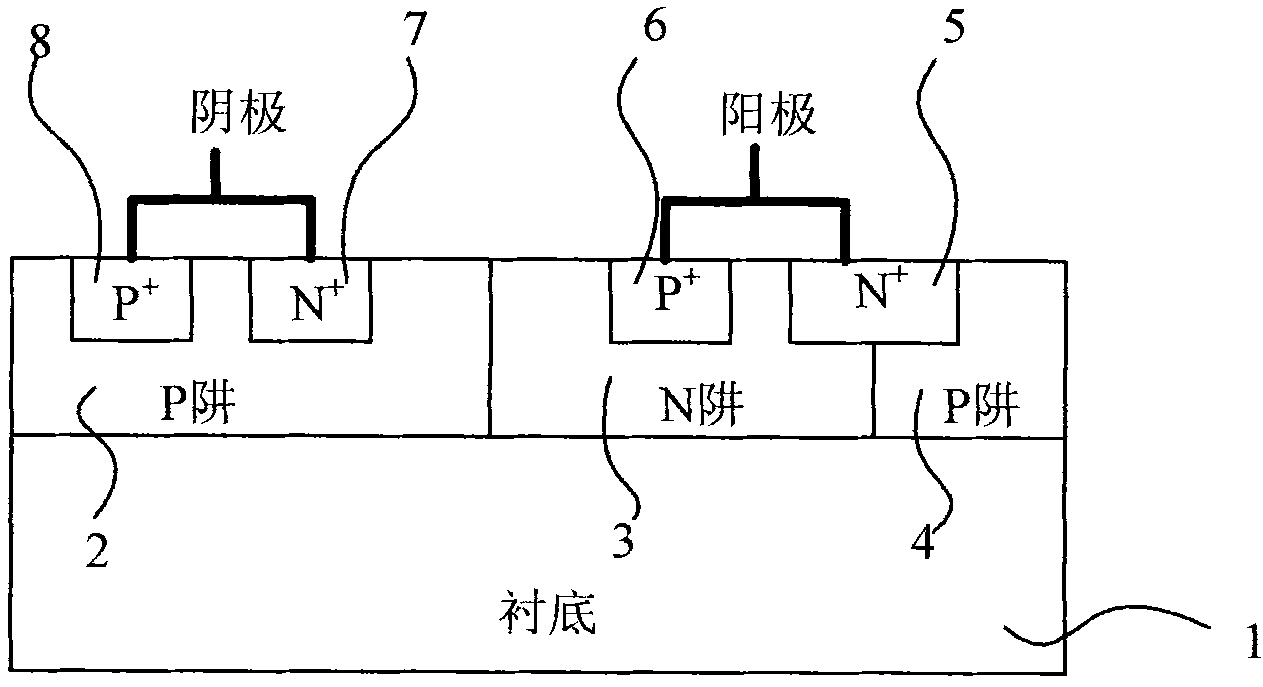

Silicon controlled rectifier electro-static discharge protective circuit structure triggered by diode

InactiveCN101840918ALower breakdown voltageEffective protectionThyristorSolid-state devicesSilicon-controlled rectifierEngineering

The invention relates to a silicon controlled rectifier (SCR) electro-static discharge (ESD) protective circuit structure triggered by a diode, which belongs to the technical field of the electron. The invention converts a trigger voltage of a conventional SCR ESD protective circuit structure into a N+ / P-well (or N-well / P+) junction breakdown voltage from a P-well / N-well junction breakdown voltage by integrating the diode with lower breakdown voltage so as to reduce the trigger voltage of the SCR ESD protective circuit structure and finally play a role of well protecting an internal circuit of a chip. Meanwhile, under the premise of not changing the trigger voltage, the silicon controlled rectifier (SCR) electro-static discharge (ESD) protective circuit structure can obtain an adjustable device maintaining voltage by simply adjusting size parameters of devices. The invention is compatible with a CMOS process, also can adopt processes of BiCMOS, BCD, SOI and the like, can connect the protective circuit structure provided by the invention between a power of an integrated circuit and the ground to serve as the ESD protection of a Power Clamp and also can connect the protective circuit structure among an input port and an output port of the integrated circuit and the power (the ground) to serve as the ESD protection of the input port and the output port.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

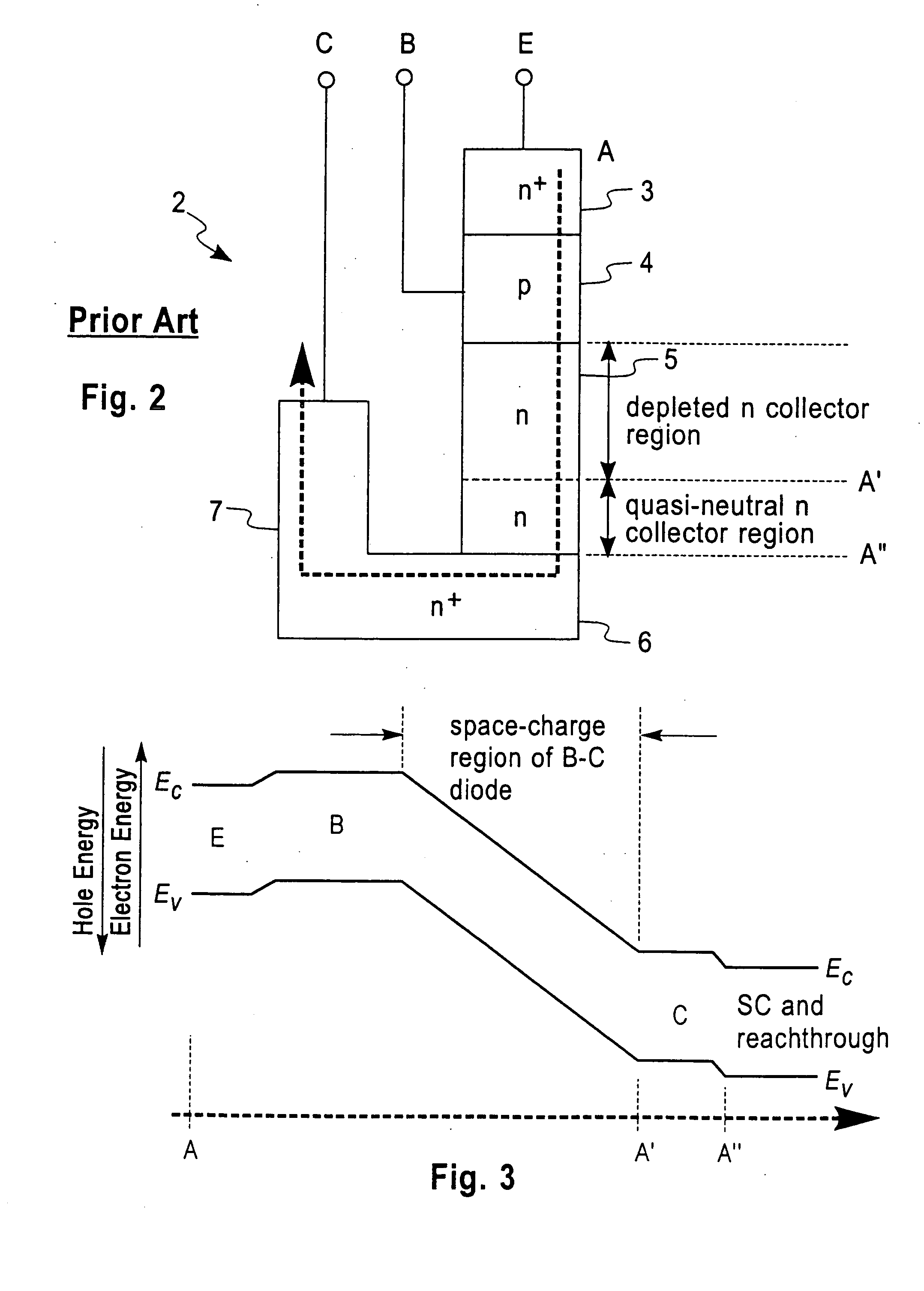

Fully-depleted-collector silicon-on-insulator (SOI) bipolar transistor useful alone or in SOI BiCMOS

InactiveUS6849871B2Easy compatibilityTransistorSemiconductor/solid-state device detailsSemiconductor materialsEngineering

A bipolar transistor structure is described incorporating an emitter, base, and collector having a fully depleted region on an insulator of a Silicon-On-Insulator (SOI) substrate without the need for a highly doped subcollector to permit the fabrication of vertical bipolar transistors on semiconductor material having a thickness of 300 nm or less and to permit the fabrication of SOI BiCMOS. The invention overcomes the problem of requiring a thick semiconductor layer in SOI to fabricate vertical bipolar transistors with low collector resistance.

Owner:GLOBALFOUNDRIES US INC

Quasi-vertical gated NPN-PNP ESD protection device

ActiveUS7968936B2TransistorSemiconductor/solid-state device manufacturingBiCMOSElectrostatic discharge

Fashioning a quasi-vertical gated NPN-PNP (QVGNP) electrostatic discharge (ESD) protection device is disclosed. The QVGNP ESD protection device has a well having one conductivity type formed adjacent to a deep well having another conductivity type. The device has a desired holding voltage and a substantially homogenous current flow, and is thus highly robust. The device can be fashioned in a cost effective manner by being formed during a BiCMOS or Smart Power fabrication process.

Owner:TEXAS INSTR INC

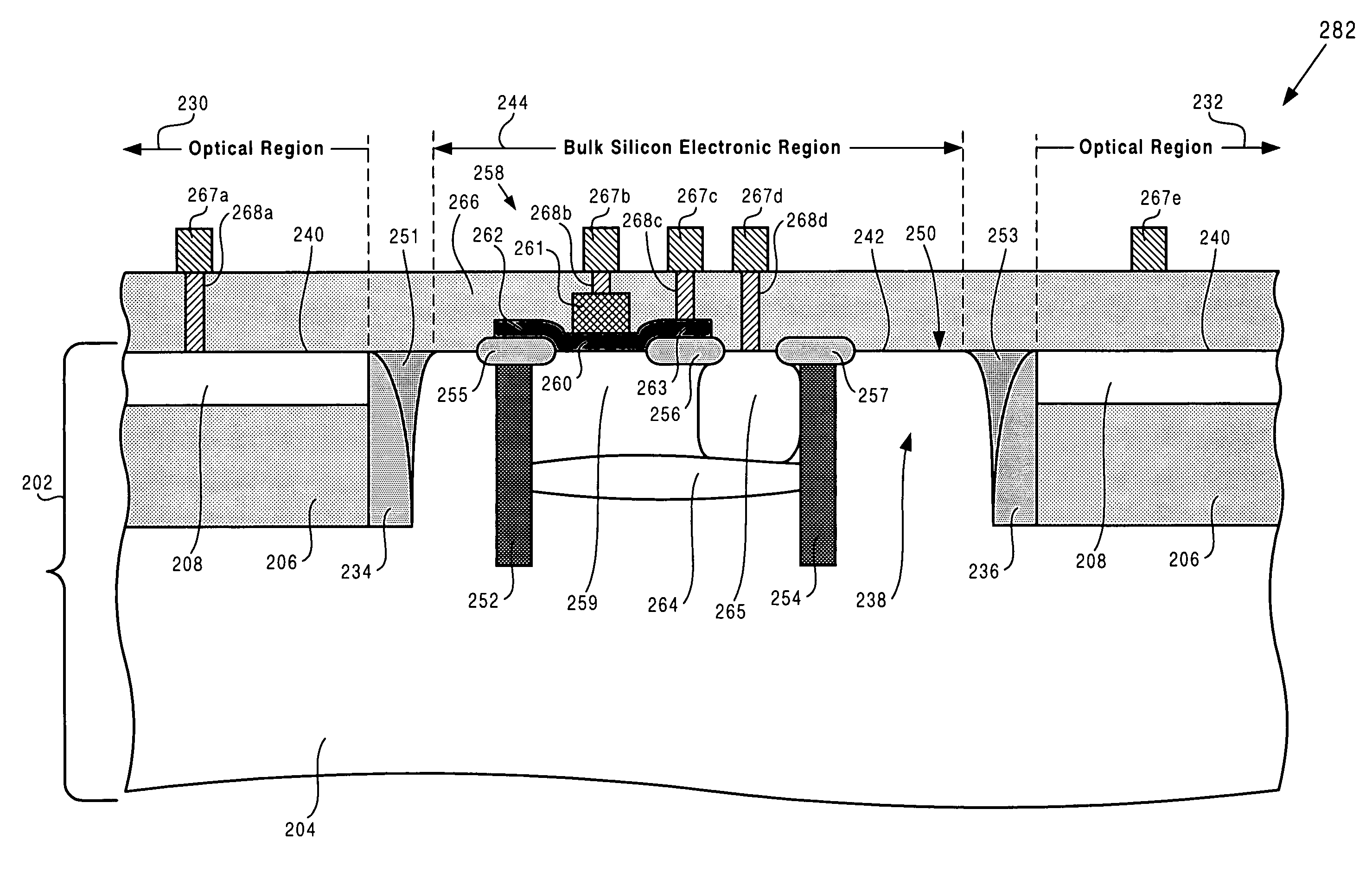

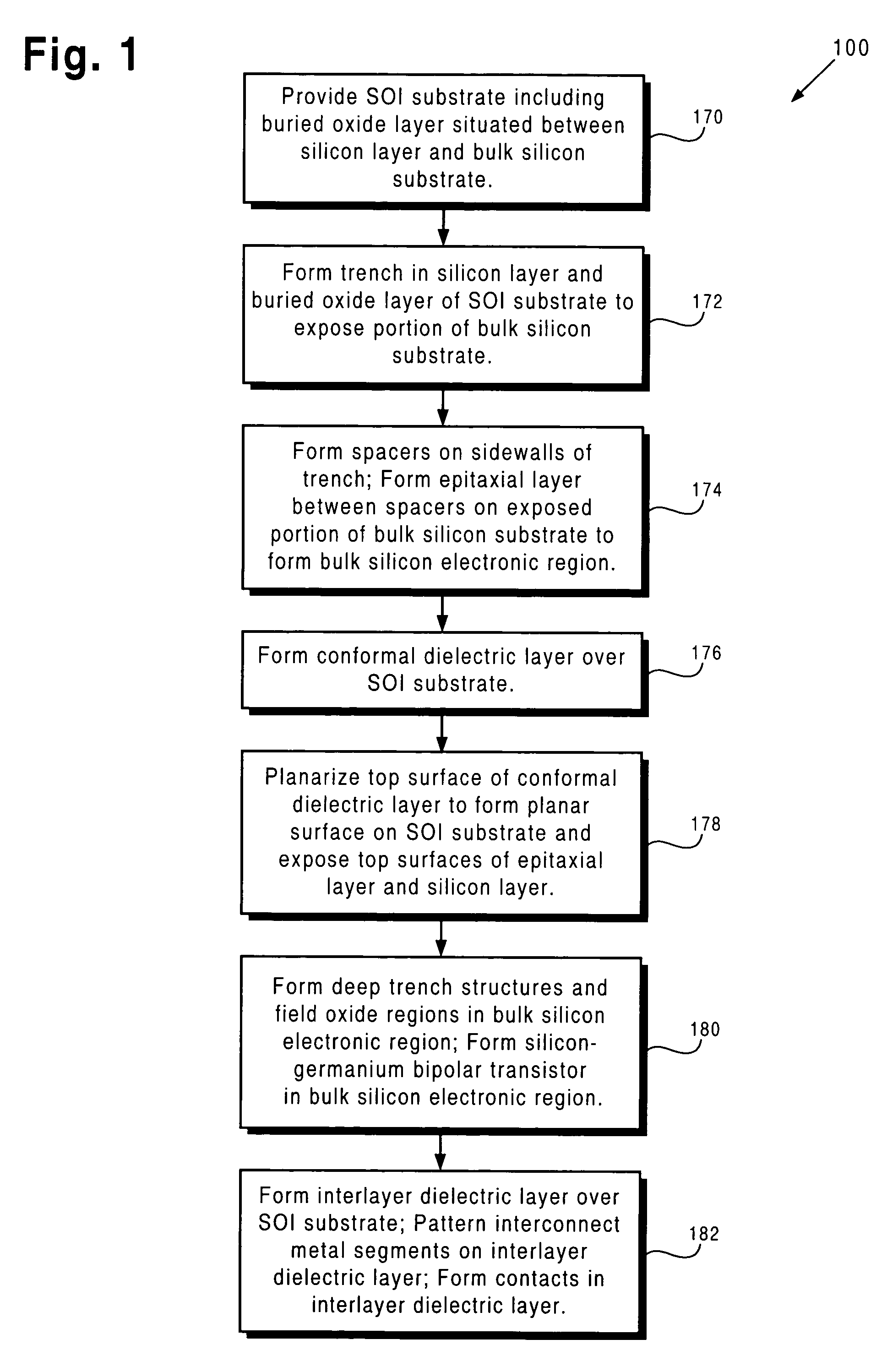

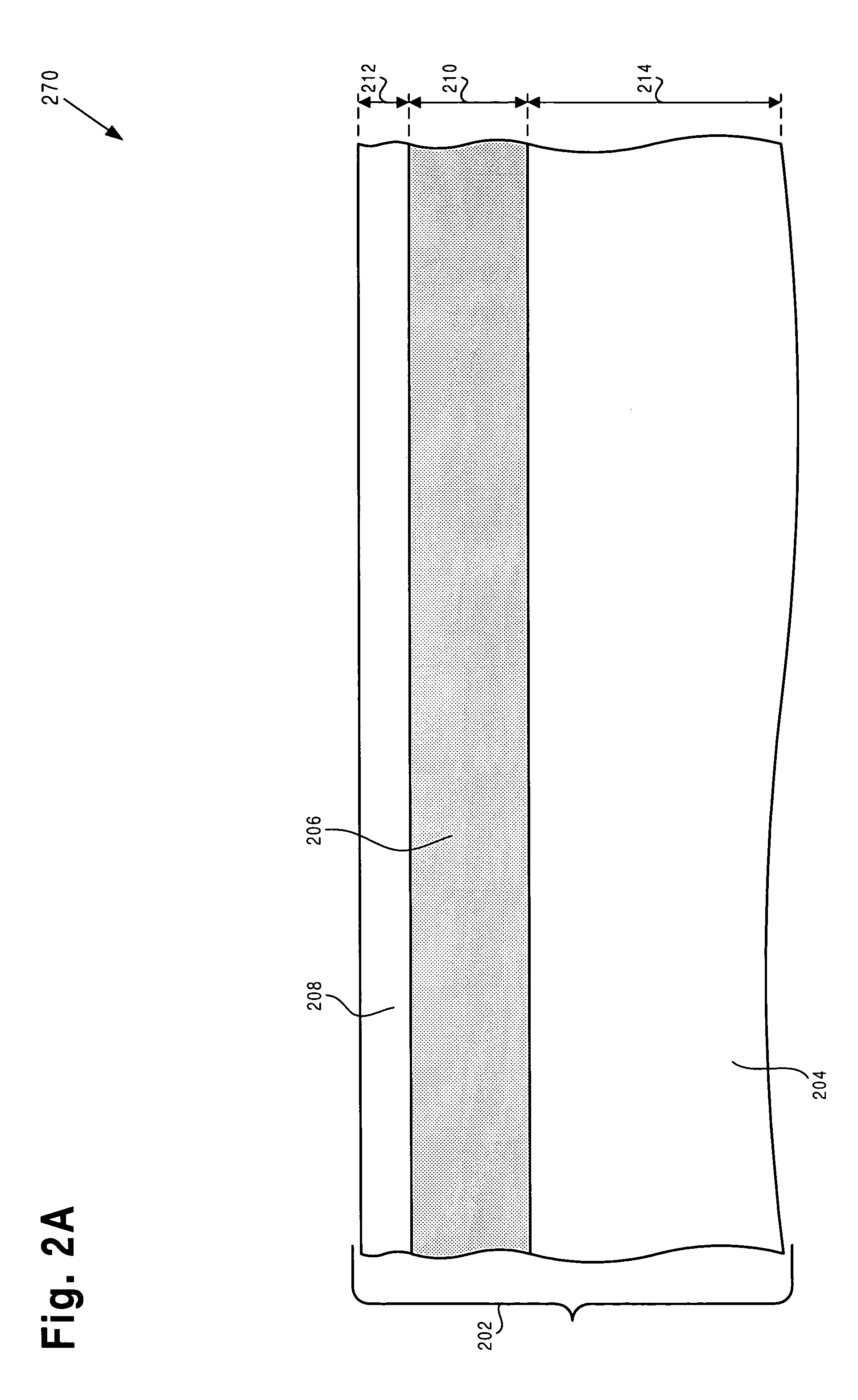

SOI substrate for integration of opto-electronics with SiGe BiCMOS

ActiveUS7339254B1Readily apparentTransistorSemiconductor/solid-state device testing/measurementBiCMOSSoi substrate

According to an exemplary embodiment, a structure includes a silicon-on-insulator substrate including a buried oxide layer situated over a bulk silicon substrate and a silicon layer situated over the buried oxide layer. The structure further includes a trench formed in the silicon layer and the buried oxide layer, where the trench has a bottom surface and a first and a second sidewall, and where the trench is situated adjacent to an optical region of the silicon-on-insulator substrate. According to this exemplary embodiment, the structure further includes an epitaxial layer situated in the trench and situated on the bulk silicon substrate, where the epitaxial layer and the bulk silicon substrate form a bulk silicon electronic region of the silicon-on-insulator substrate. The structure further includes a base of a bipolar transistor situated on the epitaxial layer, where the base can be silicon-germanium.

Owner:NEWPORT FAB

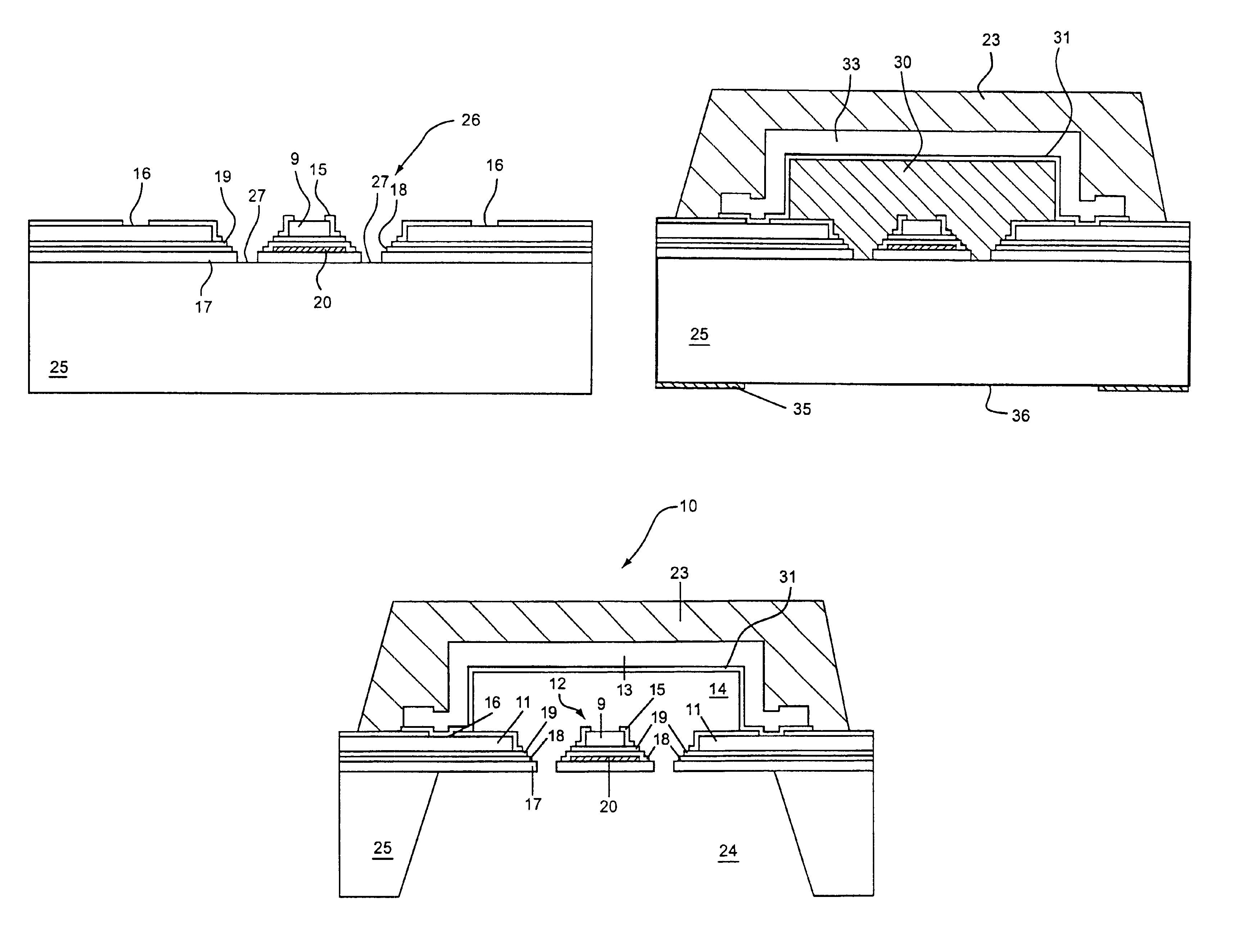

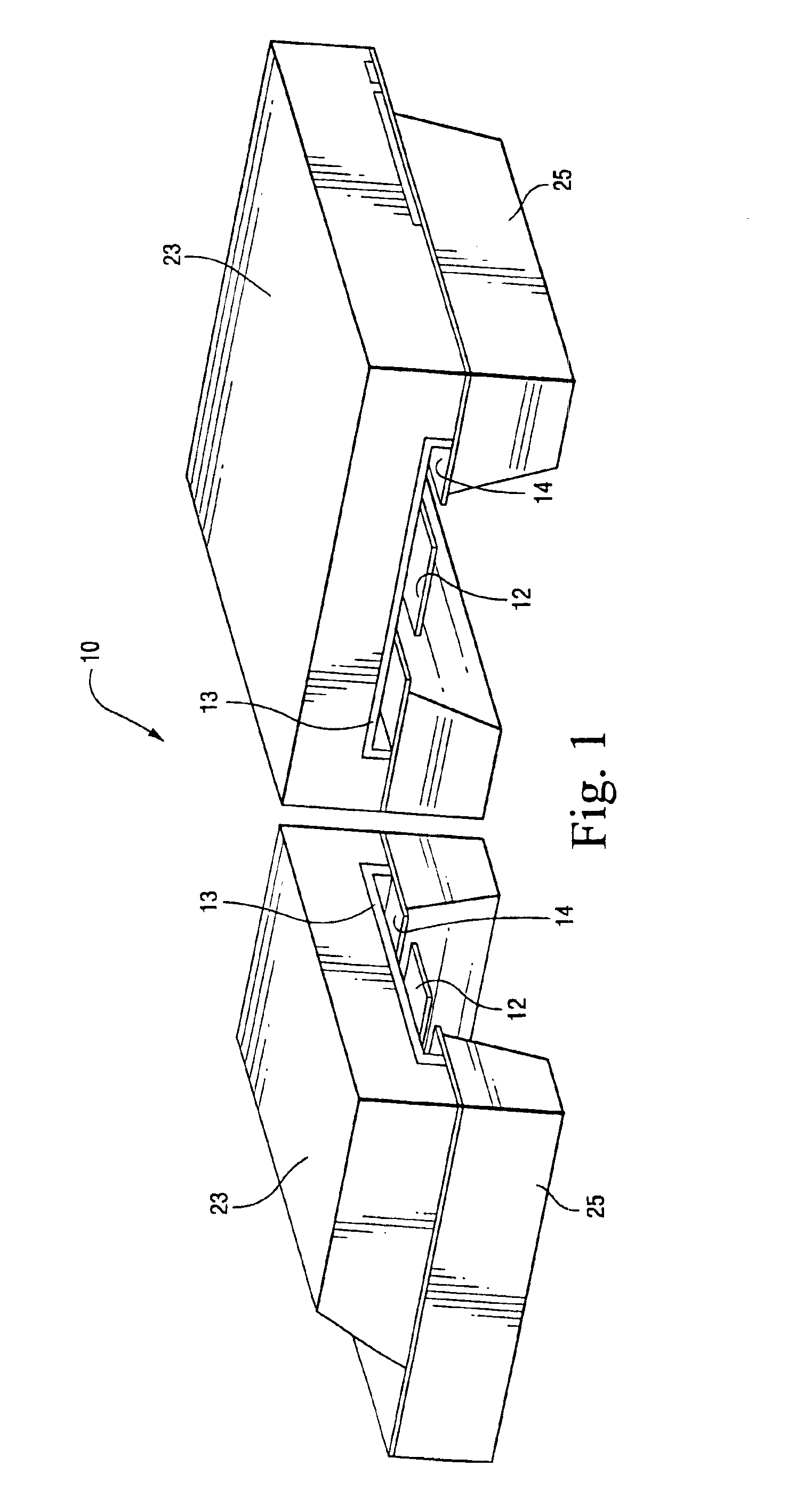

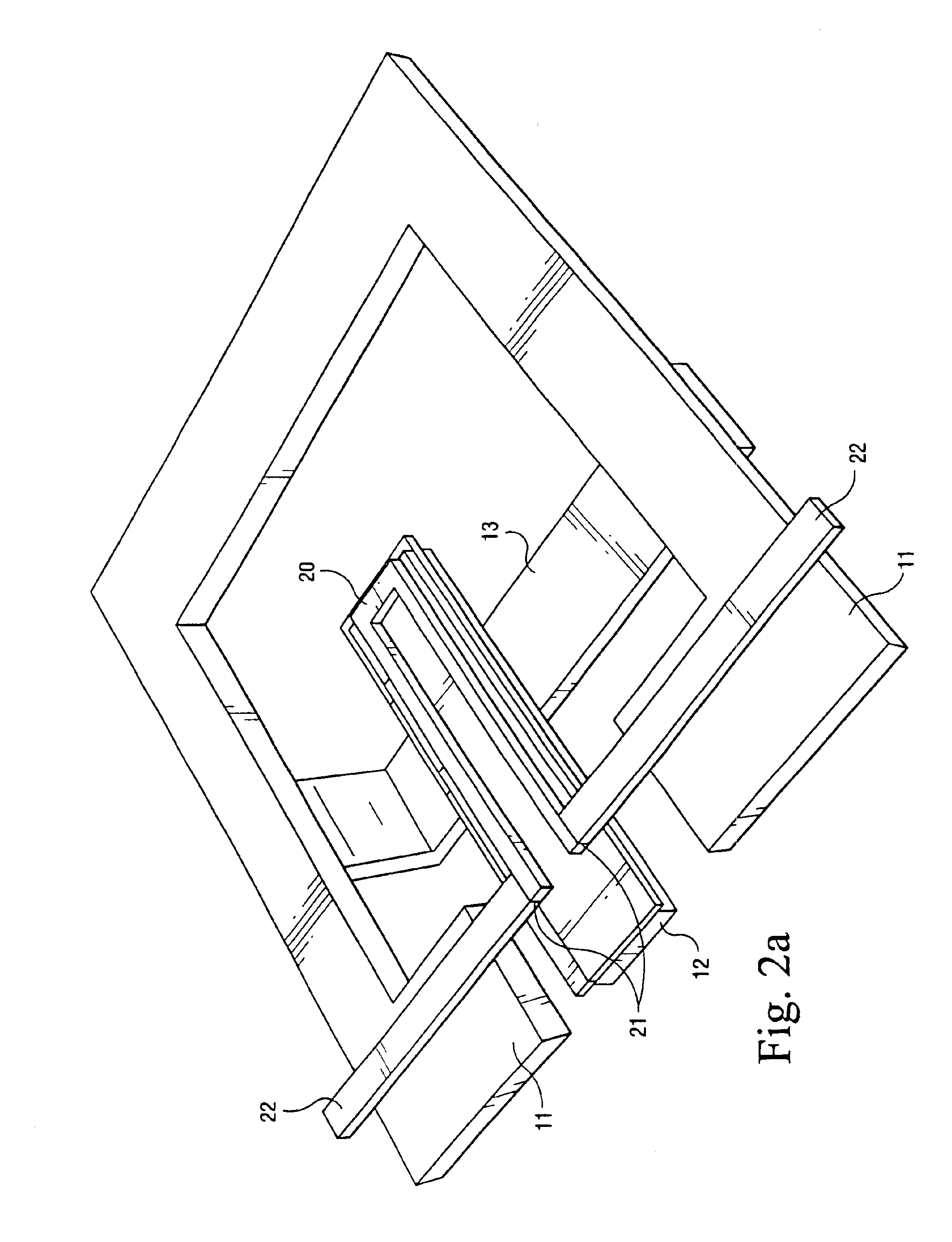

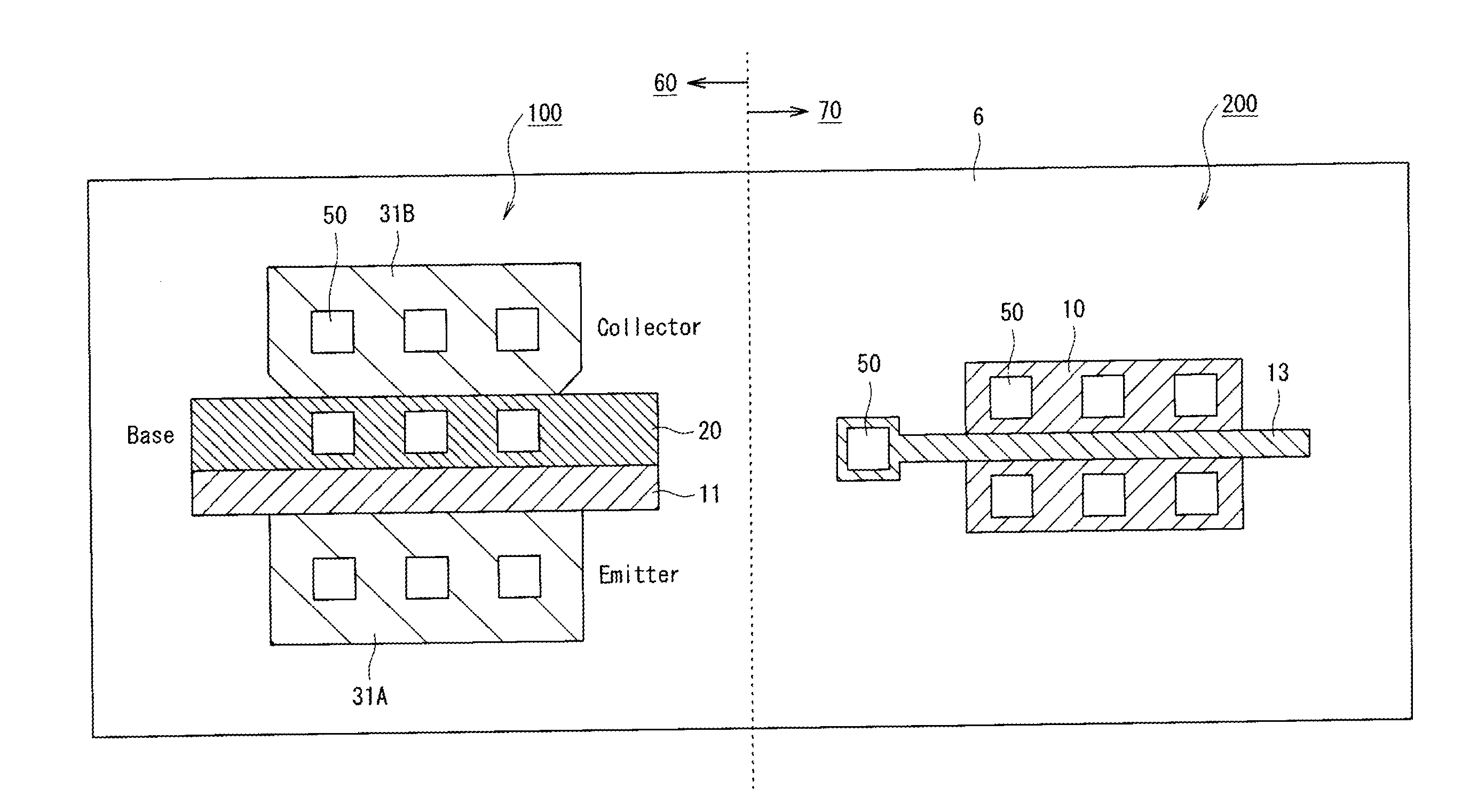

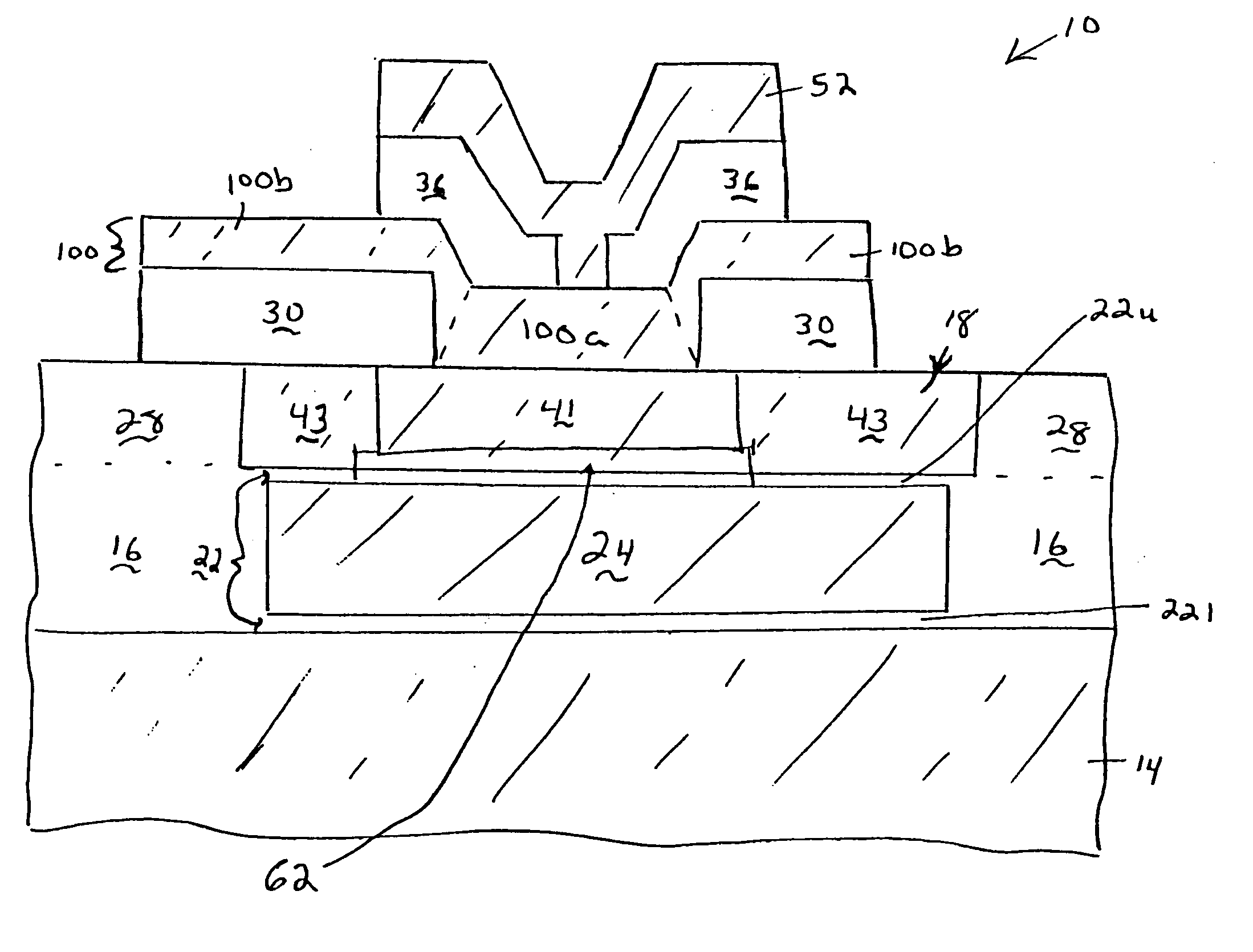

Semiconductor Device and Method for Manufacturing the Same

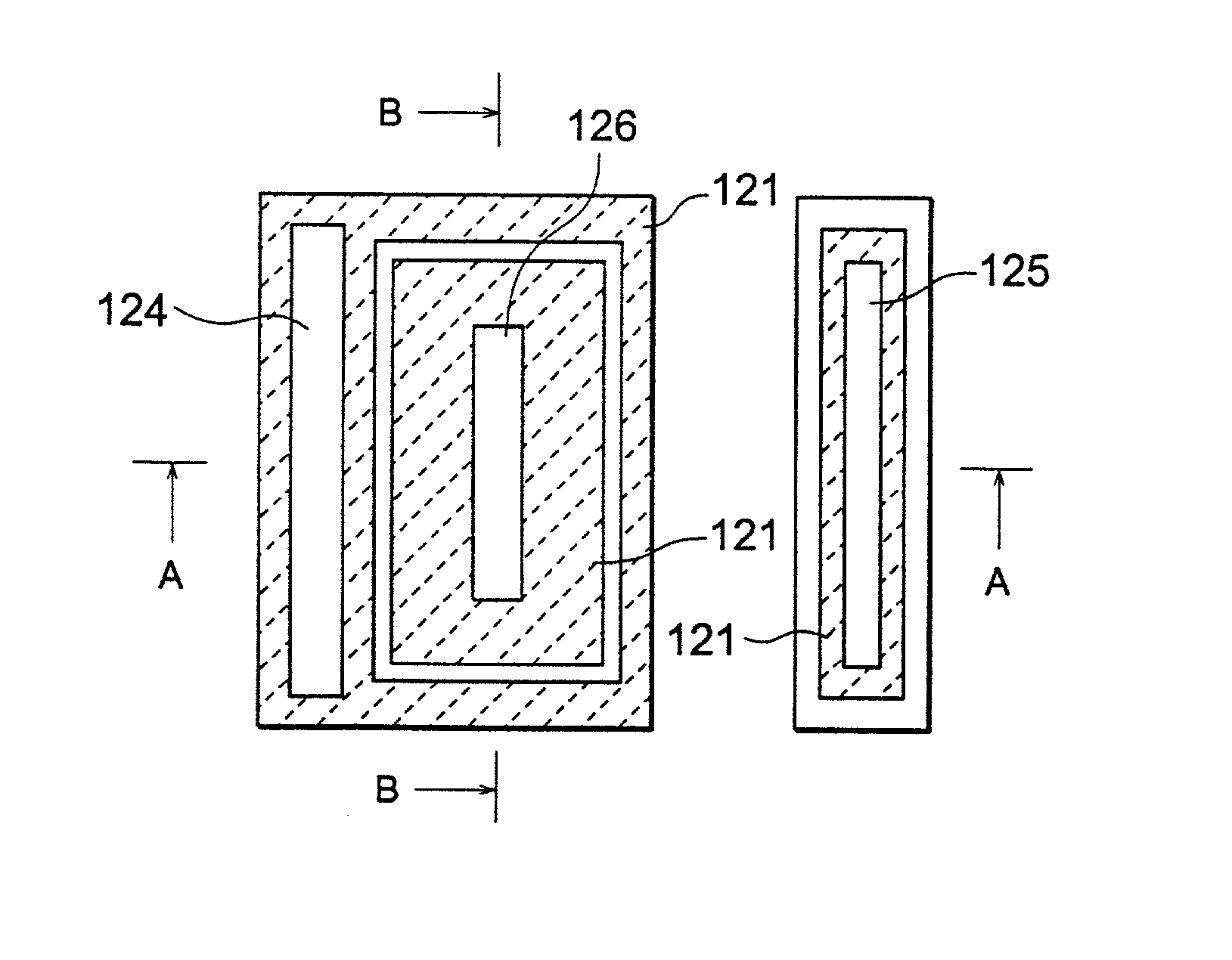

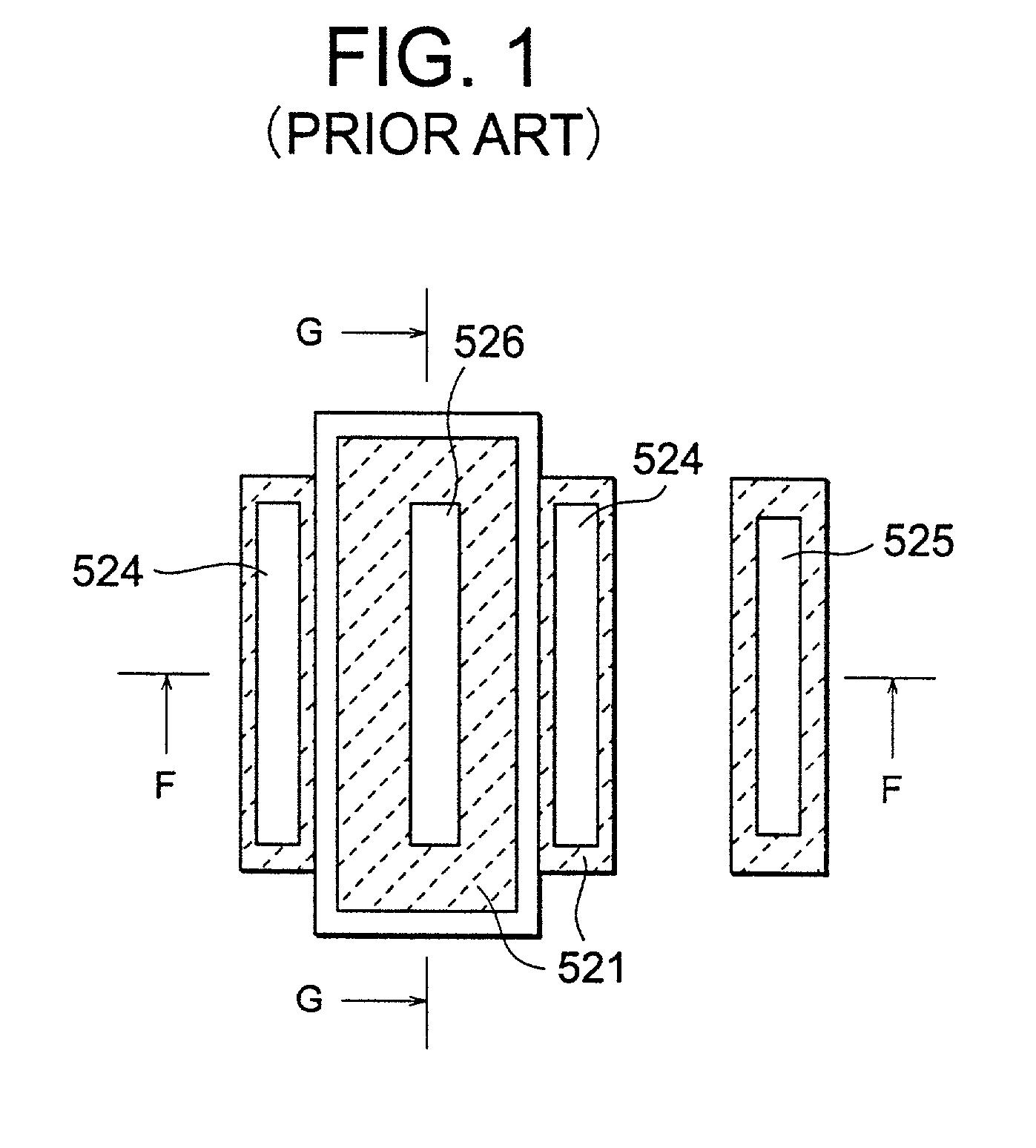

A configuration of a lateral transistor suited for the hybrid-integration (BiCMOS) of a high-performance lateral transistor (HCBT) and a CMOS transistor, and a method for manufacturing the lateral transistor are provided. A semiconductor device includes a HCBT 100 and a CMOS transistor 200 hybrid-integrated therein. The HCBT 100 has an open region 21 opened by etching a device isolating oxide film 6 surrounding an n-hill layer 11, an emitter electrode 31A and a collector electrode 31B each of which is formed in the open region 21 and is composed of a polysilicon film having such a thickness as to expose the n-hill layer 11 exposed by etching the device isolating oxide film, and an ultrathin oxide film 24 covering at least a part of the n-hill layer 11. The ultrathin oxide film 24 functions as a protective film for protecting the n-hill layer 11 from being etched when the polysilicon film is etched to form the emitter electrode 31A and the collector electrode 31B.

Owner:UNIV OF ZAGREB FACULTY OF ELECTRICAL ENG & COMPUTING

Bipolar/bicmos semiconductor device

An N type buried layer is buried in a P type silicon substrate. An N type epitaxial layer is formed on this buried layer. A P type intrinsic base region and an extrinsic base region are formed on the surface of the epitaxial layer. An N type emitter region is formed in the intrinsic base region. An emitter electrode is formed to contact the emitter region. A collector plug region is formed in an area separated from the extrinsic base region through a filed insulating film. A cobalt silicide film is formed on the extrinsic base region to surround the emitter electrode. An extrinsic base contact hole is formed at only one side of the emitter electrode. In the semiconductor device, the base resistance Rb and the collector-base capacity Ccb are reduced to make the maximum oscillation frequency fmax sufficiently large.

Owner:RENESAS ELECTRONICS CORP

Poly-poly/MOS capacitor having a gate encapsulating first electrode layer

A stacked Poly-Poly / MOS capacitor useful as a component in a BiCMOS device comprising a semiconductor substrate having a region of a first conductivity-type formed in a surface thereof; a gate oxide formed on said semiconductor substrate overlaying said region of first conductivity-type; a first polysilicon layer formed on at least said gate oxide layer, said first polysilicon layer being doped with an N or P-type dopant; a dielectric layer formed on said first polysilicon layer; and a second polysilicon layer formed on said dielectric layer, said second polysilicon layer being doped with the same or different dopant as the first polysilicon layer.

Owner:GLOBALFOUNDRIES INC

Full CMOS min-sum analog iterative decoders

InactiveUS7769798B2Reduce manufacturing costSimple designDigital data processing detailsError correction/detection using multiple parity bitsMOSFETLow voltage

Analog iterative decoders are provided that are based on the so-called min-sum algorithm (also referred to as max-sum or max-product, Max-Log-MAP or BP-based decoding) and can be used to decode powerful coding schemes such as low-density parity-check (LDPC) codes and turbo codes. The circuits can be implemented by standard CMOS technology, which means lower fabrication cost and / or simpler design compared to previously reported analog iterative decoders that are based on BiCMOS or sub-threshold CMOS technology. Soft information is passed among variable nodes and parity-check nodes. A low-voltage high-swing Max WTA circuit is also provided. The circuit can be implemented by short channel MOSFET transistors and yet provide a reasonably high degree of accuracy. Applications include soft computing, and analog signal processing, in general. A Min WTA circuit can also be built based on this circuit by subtracting the input currents from a large reference current.

Owner:BANIHASHEMI AMIR +1

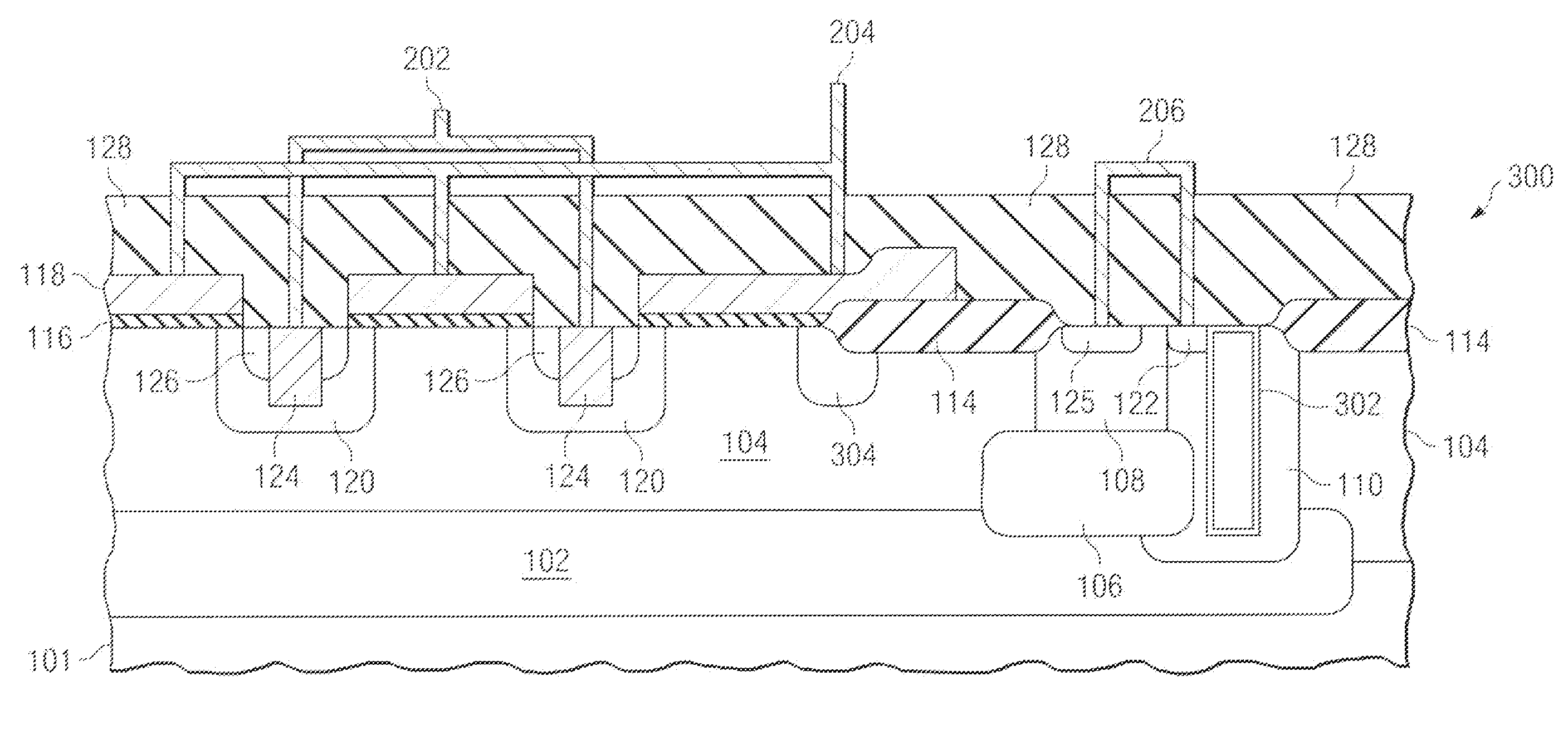

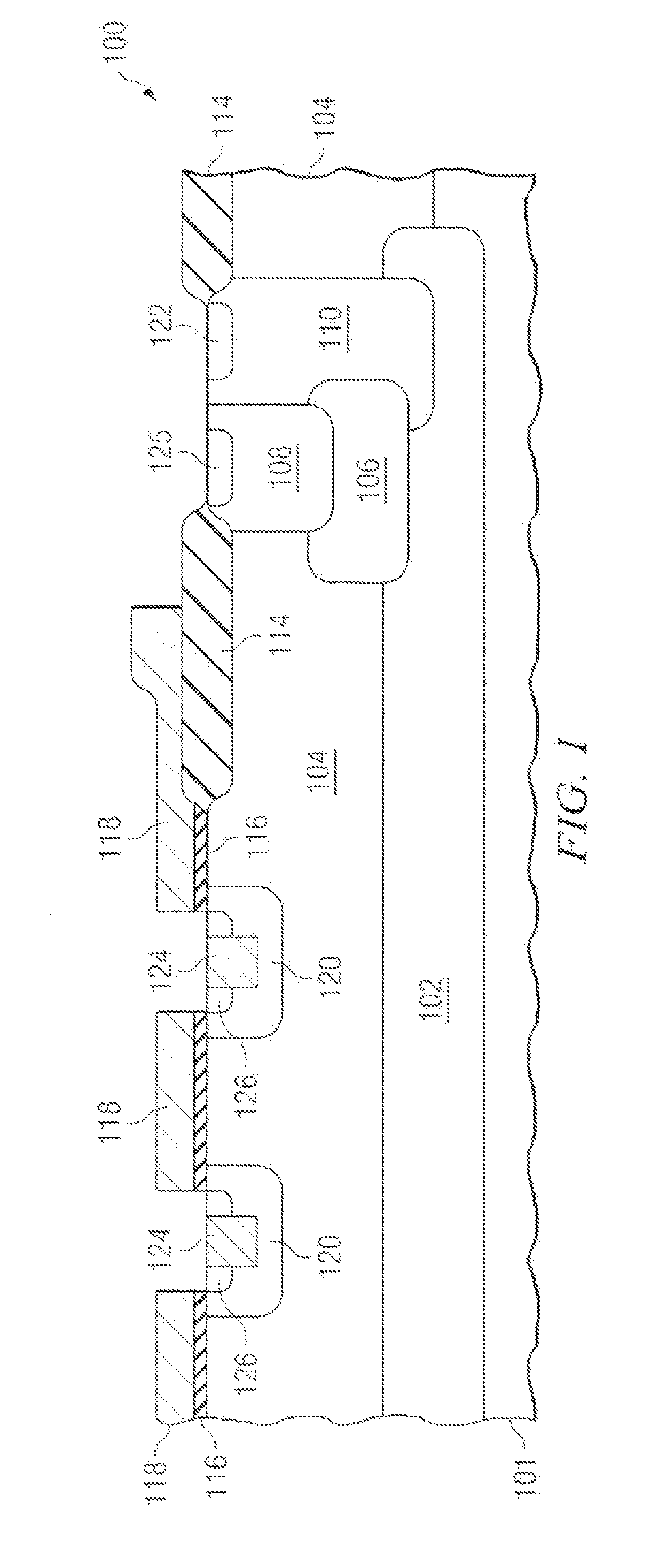

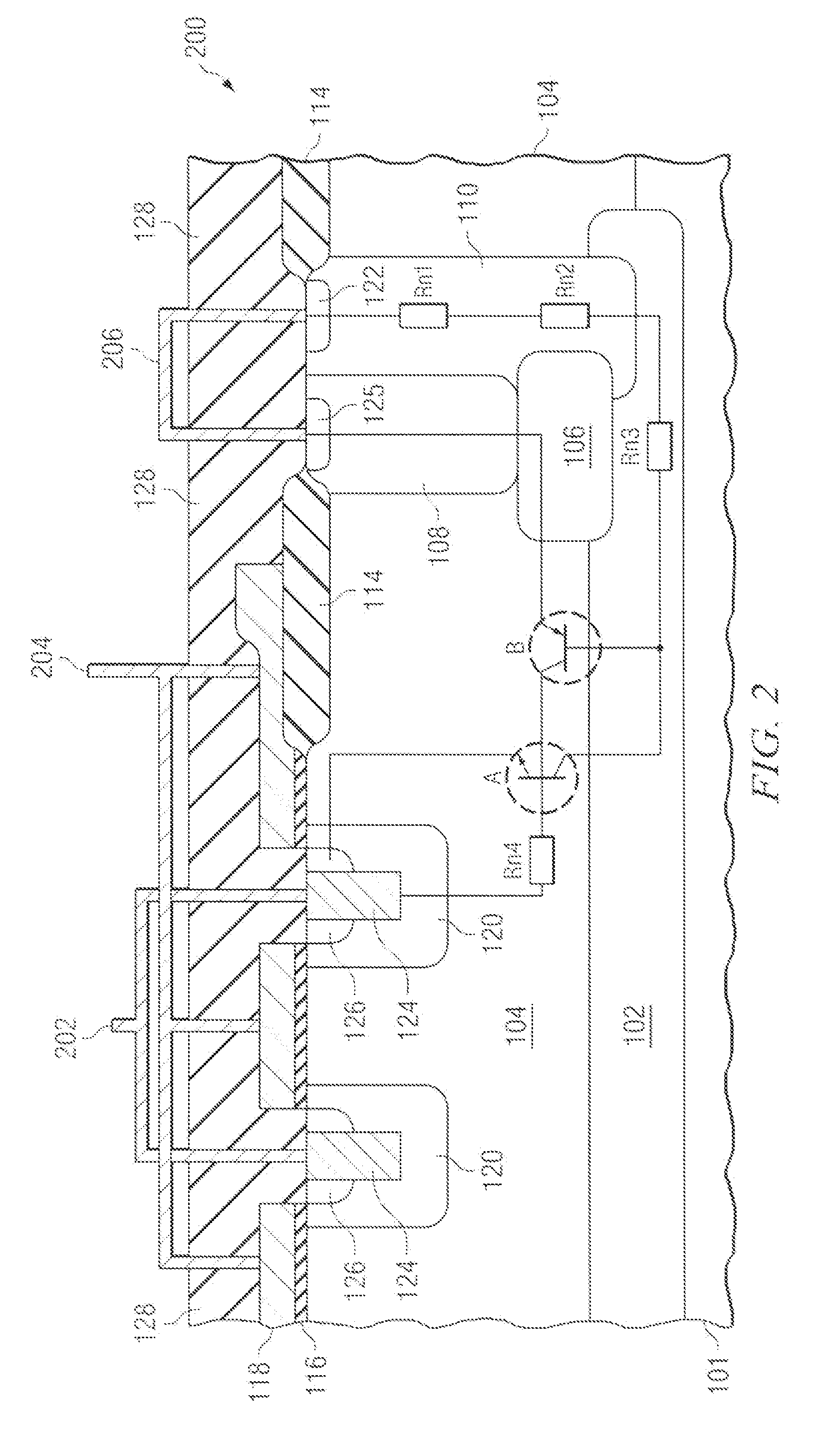

Vertical bipolar transistor with a majority carrier accumulation layer as a subcollector for SOI BiCMOS with reduced buried oxide thickness for low-substrate bias operation

InactiveUS20060043530A1Reduce thicknessReduced substrate biasSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing cost reductionCMOS

The present invention provides a “subcollector-less” silicon-on-insulator (SOI) bipolar junction transistor (BJT) that has no impurity-doped subcollector. Instead, the inventive vertical SOI BJT uses a back gate-induced, majority carrier accumulation layer as the subcollector when it operates. The SOI substrate is biased such that the accumulation layer is formed at the bottom of the first semiconductor layer. The advantage of such a device is its CMOS-like process. Therefore, the integration scheme can be simplified and the manufacturing cost can be significantly reduced. The present invention also provides a method of fabricating BJTs on selected areas of a very thin BOX using a conventional SOI starting wafer with a thick BOX. The reduced BOX thickness underneath the bipolar devices allows for a significantly reduced substrate bias compatible with the CMOS to be applied while maintaining the advantages of a thick BOX underneath the CMOS. A back-gated CMOS device is also provided.

Owner:GLOBALFOUNDRIES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com