Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3902results about How to "Improve breakdown voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

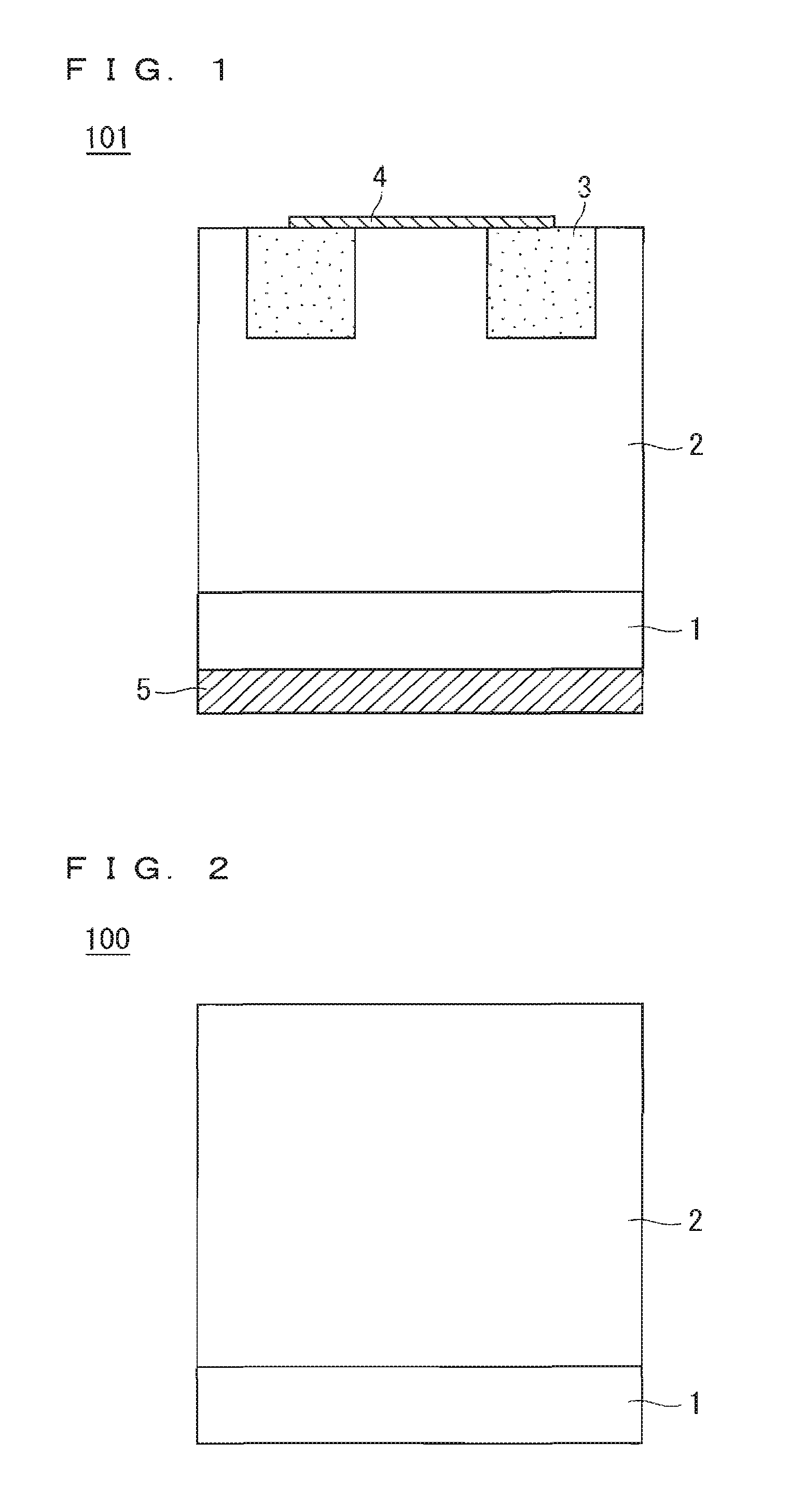

Silicon carbide semiconductor device and silicon carbide semiconductor device manufacturing method

ActiveUS20160336392A1Lower on-resistanceImprove breakdown voltageSemiconductor devicesDevice materialSemiconductor

A silicon carbide semiconductor device capable of achieving a decrease in ON resistance and an increase in breakdown voltage and a method for manufacturing a silicon carbide semiconductor device. A silicon carbide semiconductor device includes a silicon carbide substrate and a drift layer. The drift layer includes a breakdown voltage holding layer extending from a point where a doping concentration has a predetermined value to a surface of the drift layer. The doping concentration in the breakdown voltage holding layer continuously decreases from the point where the doping concentration has the predetermined value to a modulation point located further toward the surface of the drift layer than a midpoint in a film thickness direction of the breakdown voltage holding layer. The doping concentration in the breakdown voltage holding layer continuously increases from the modulation point to the surface of the drift layer.

Owner:MITSUBISHI ELECTRIC CORP

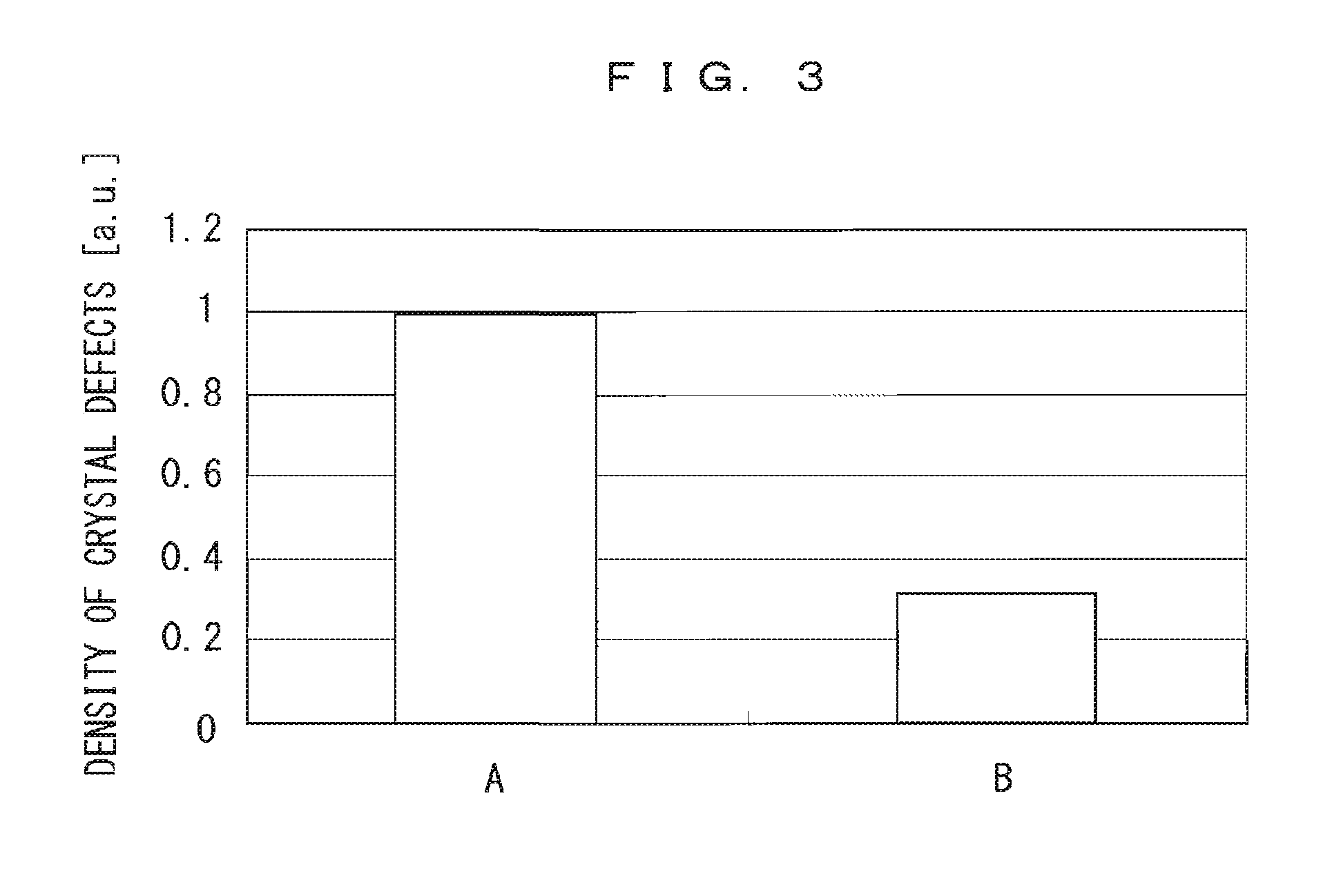

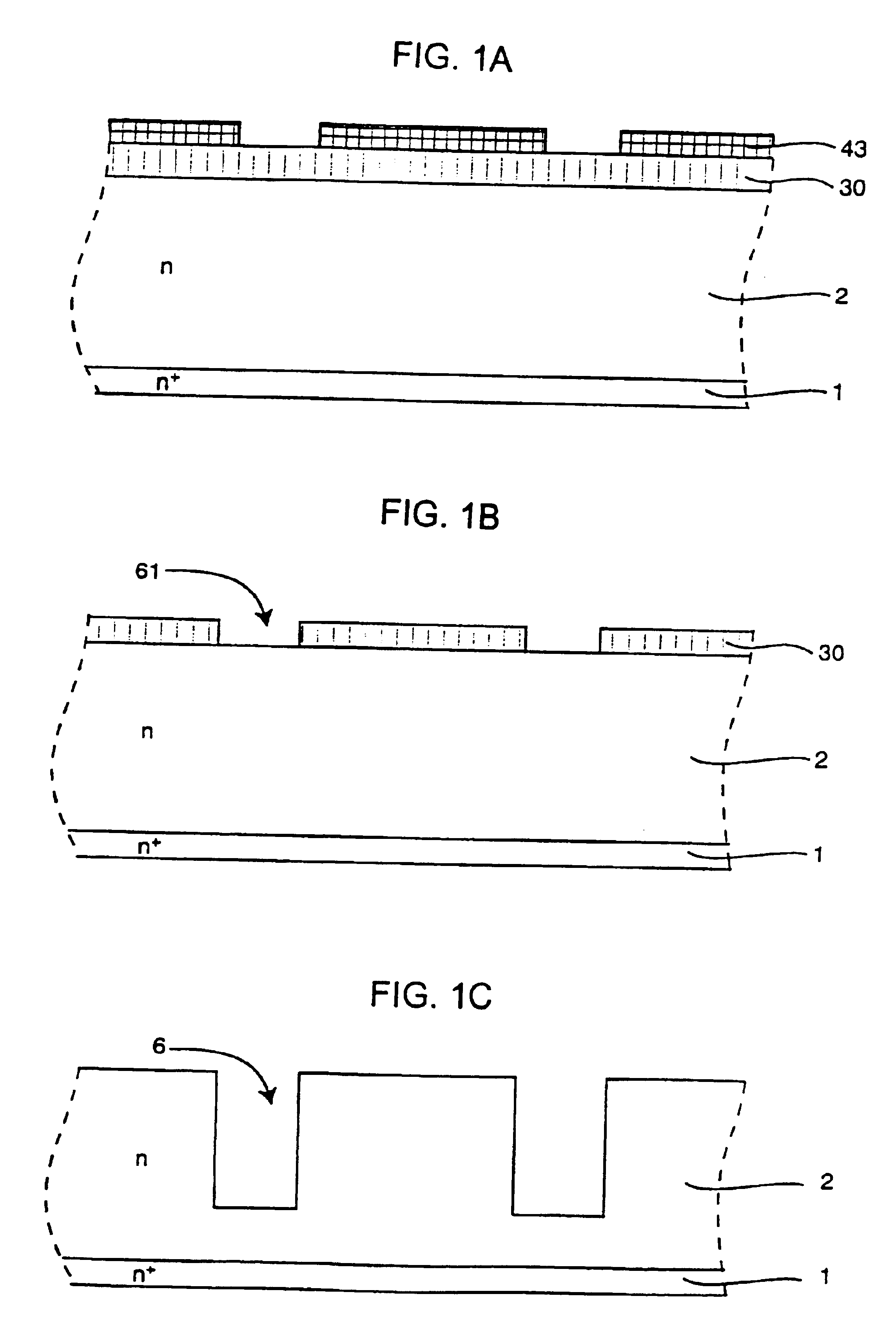

Manufacturing method of a silicon carbide semiconductor device

InactiveUS8071482B2Smooth curveImprove breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesSemiconductorDry etching

A manufacturing method for a silicon carbide semiconductor device is disclosed. It includes an etching method in which an Al film and Ni film are laid on an SiC wafer in this order and wet-etched, whereby a two-layer etching mask is formed in which Ni film portions overhang Al film portions. Mesa grooves are formed by dry etching by using this etching mask.

Owner:FUJI ELECTRIC CO LTD

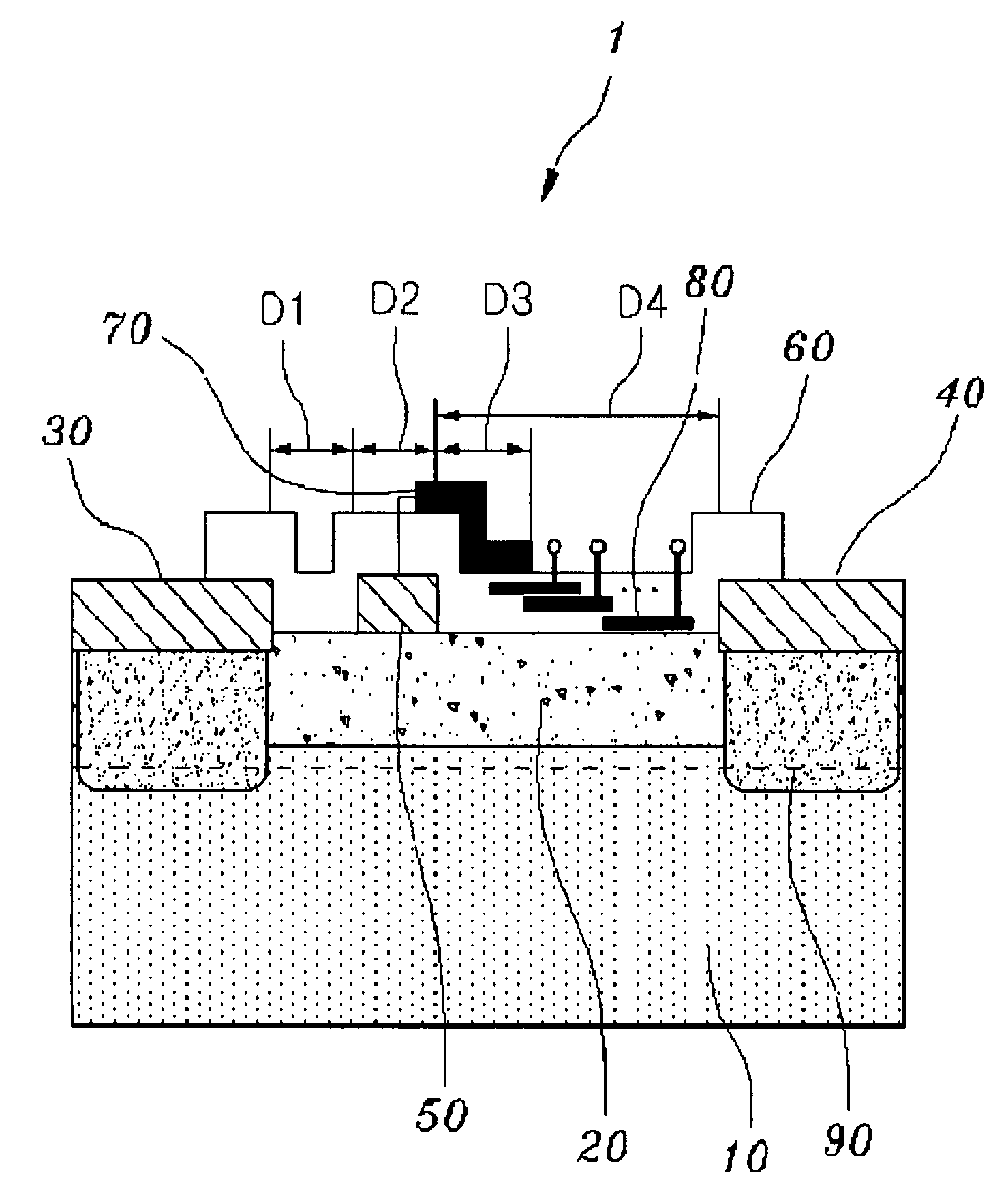

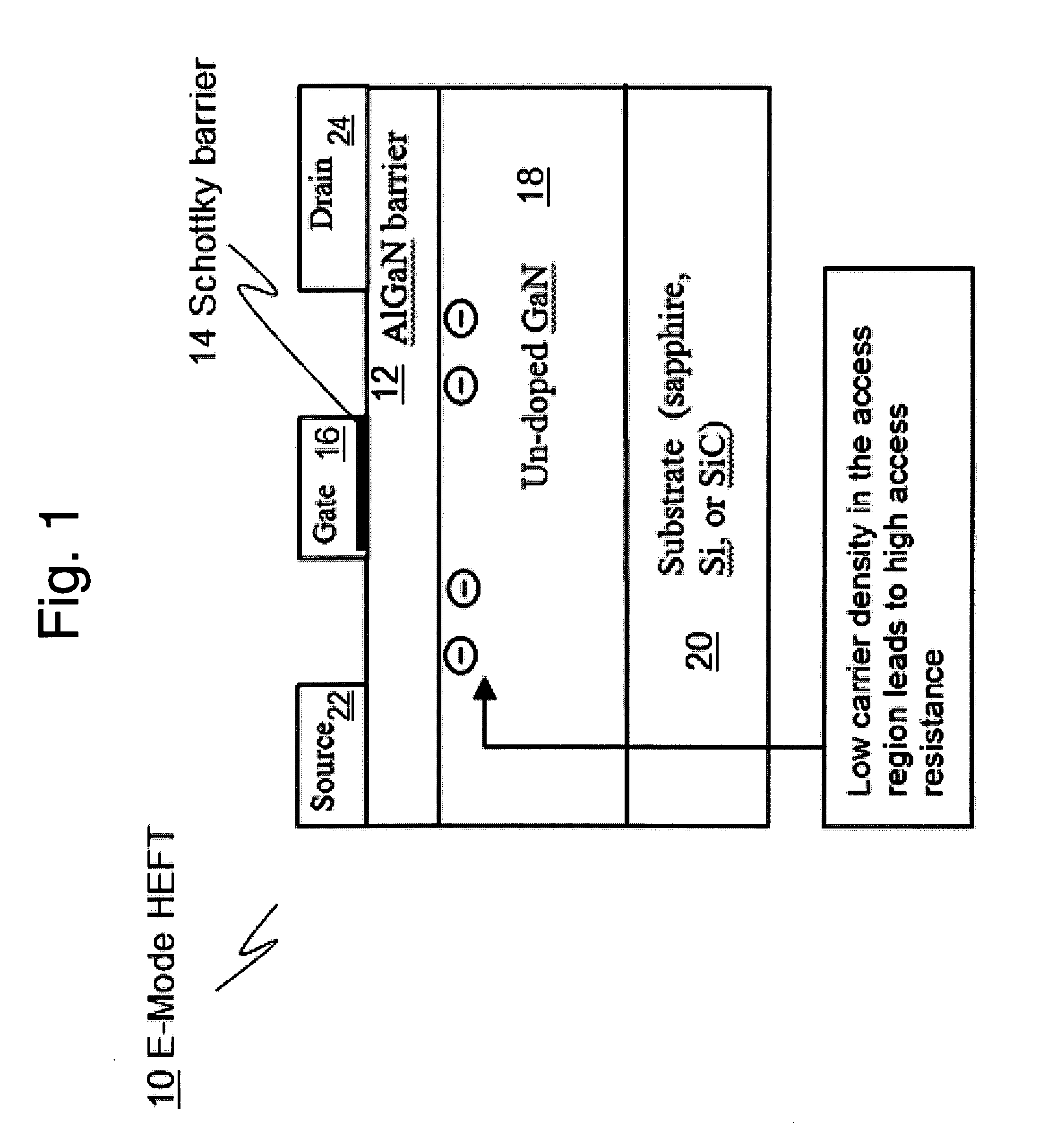

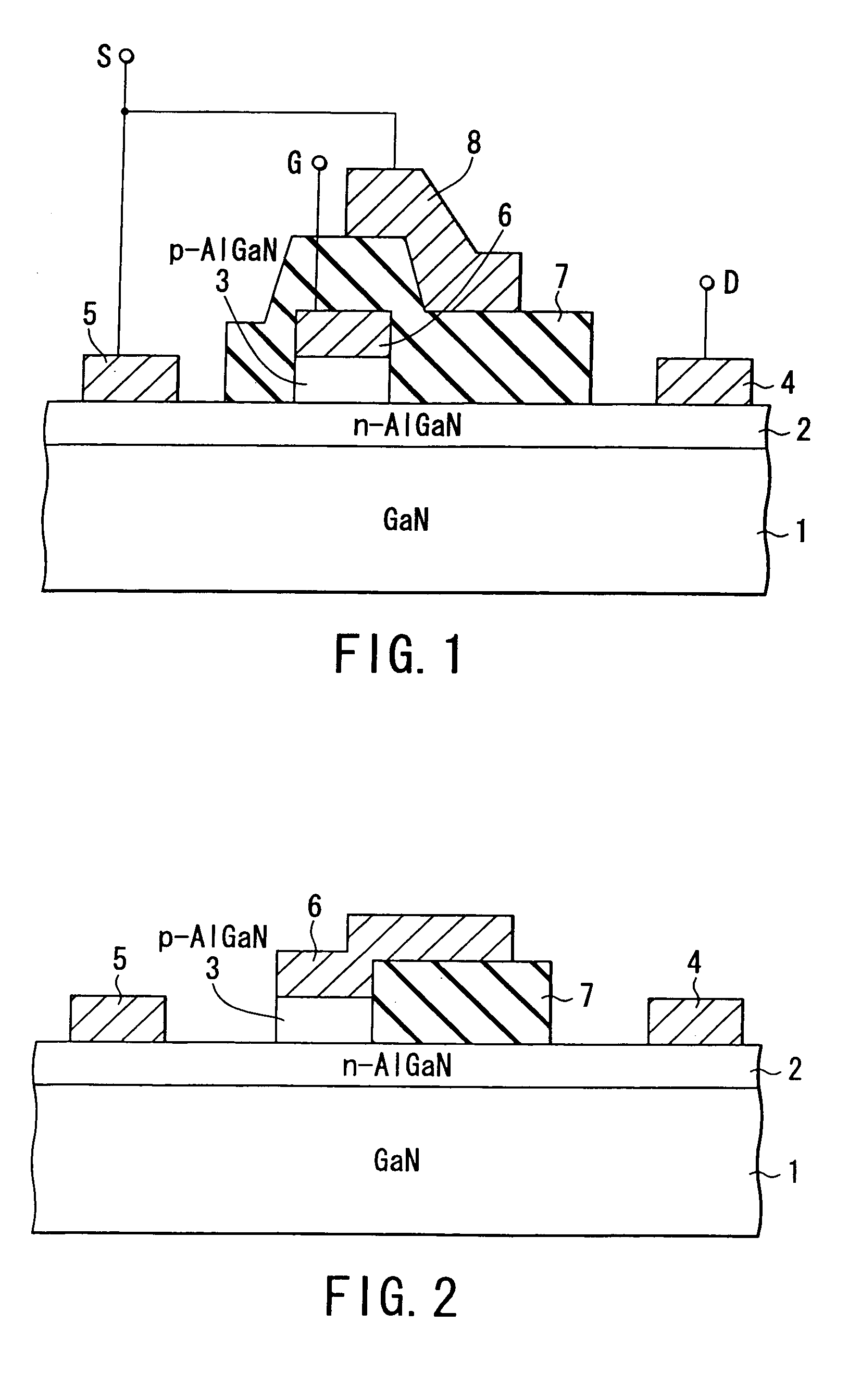

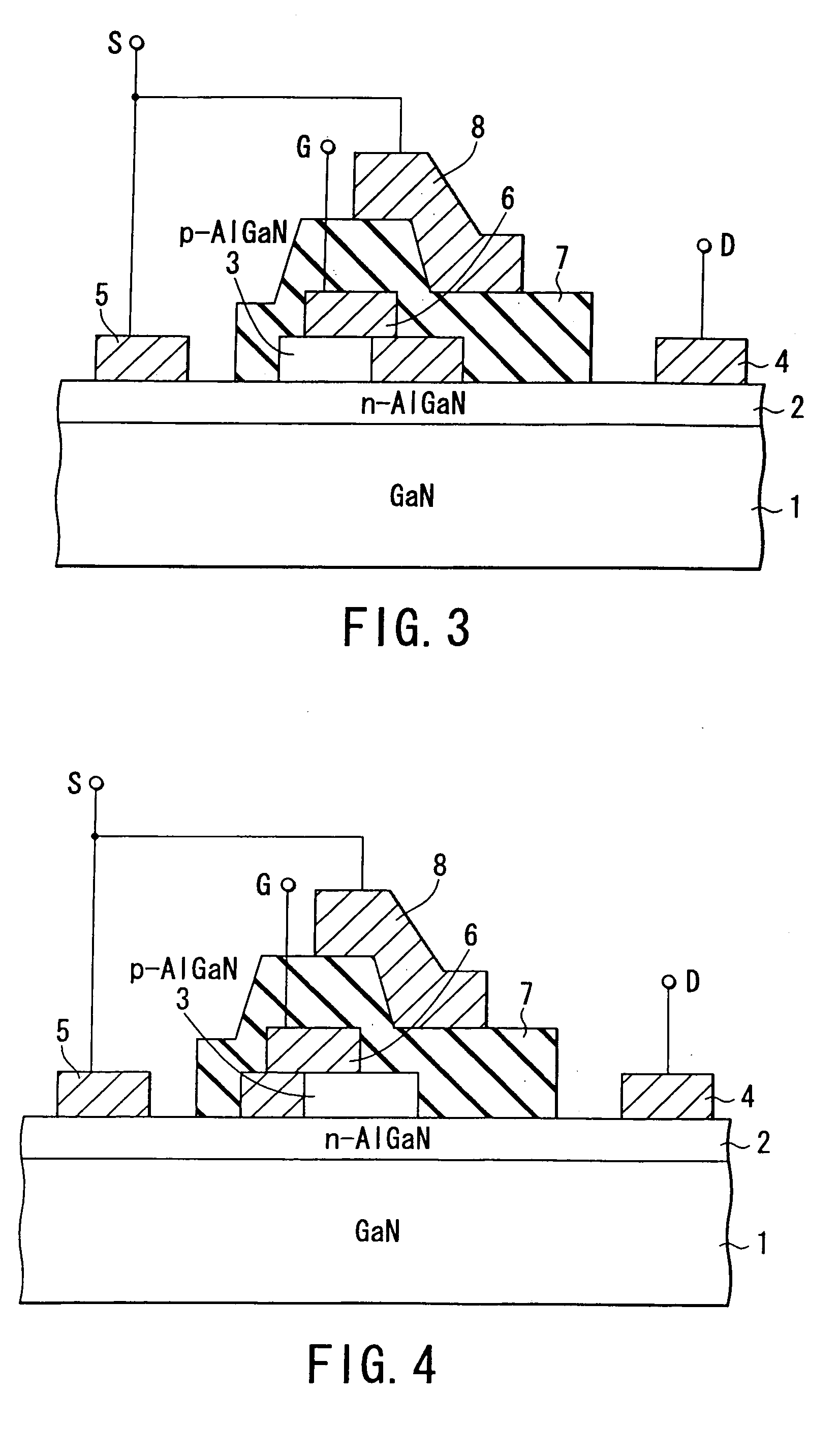

Field-effect transistor and method for fabricating the same

ActiveUS20060273347A1Small gateHigh currentSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactOptoelectronics

An AlN buffer layer, an undoped GaN layer, an undoped AlGaN layer, a p-type GaN layer and a heavily doped p-type GaN layer are formed in this order. A gate electrode forms an Ohmic contact with the heavily doped p-type GaN layer. A source electrode and a drain electrode are provided on the undoped AlGaN layer. A pn junction is formed in a gate region by a two dimensional electron gas generated at an interface between the undoped AlGaN layer and the undoped GaN layer and the p-type GaN layer, so that a gate voltage can be increased.

Owner:PANASONIC CORP

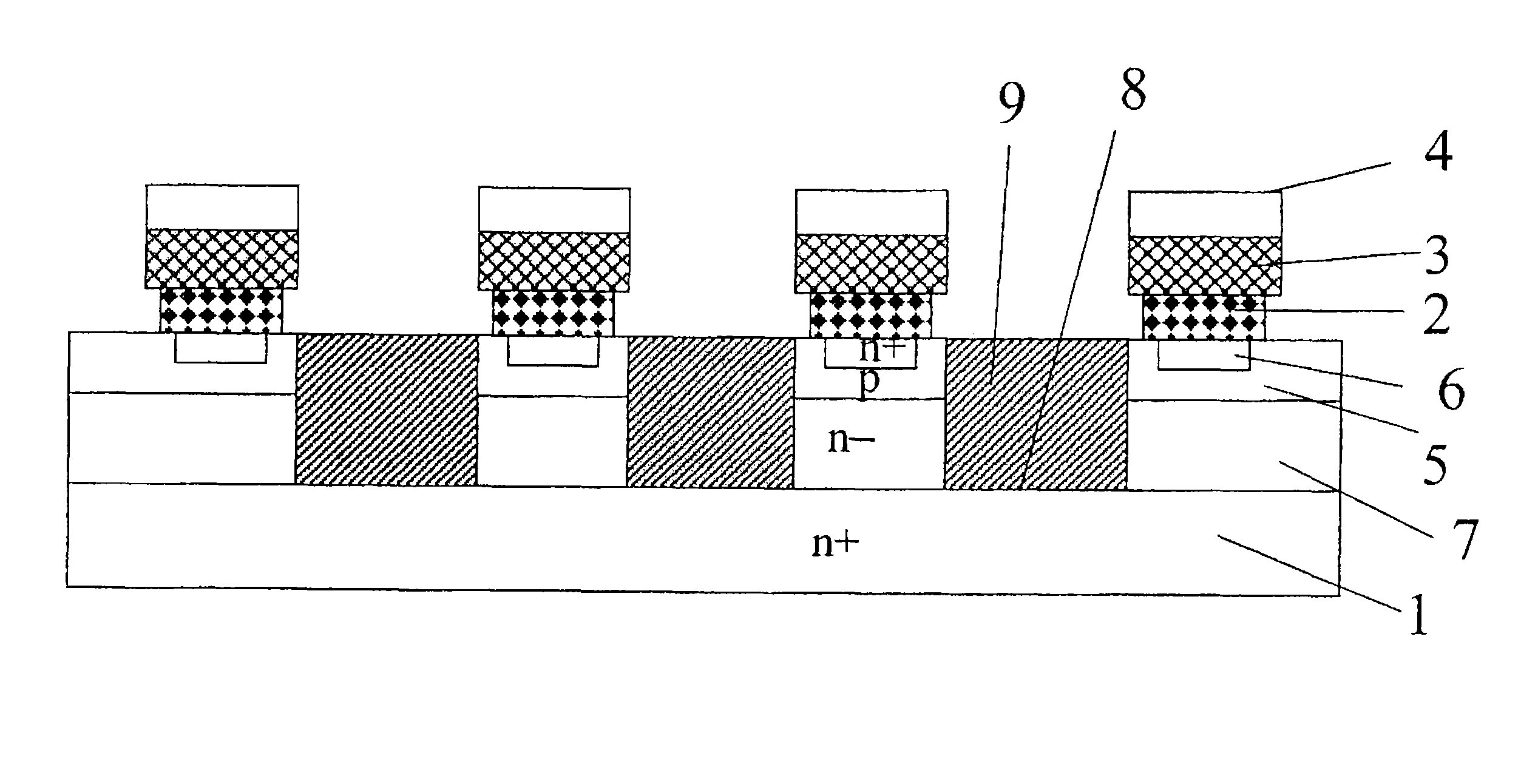

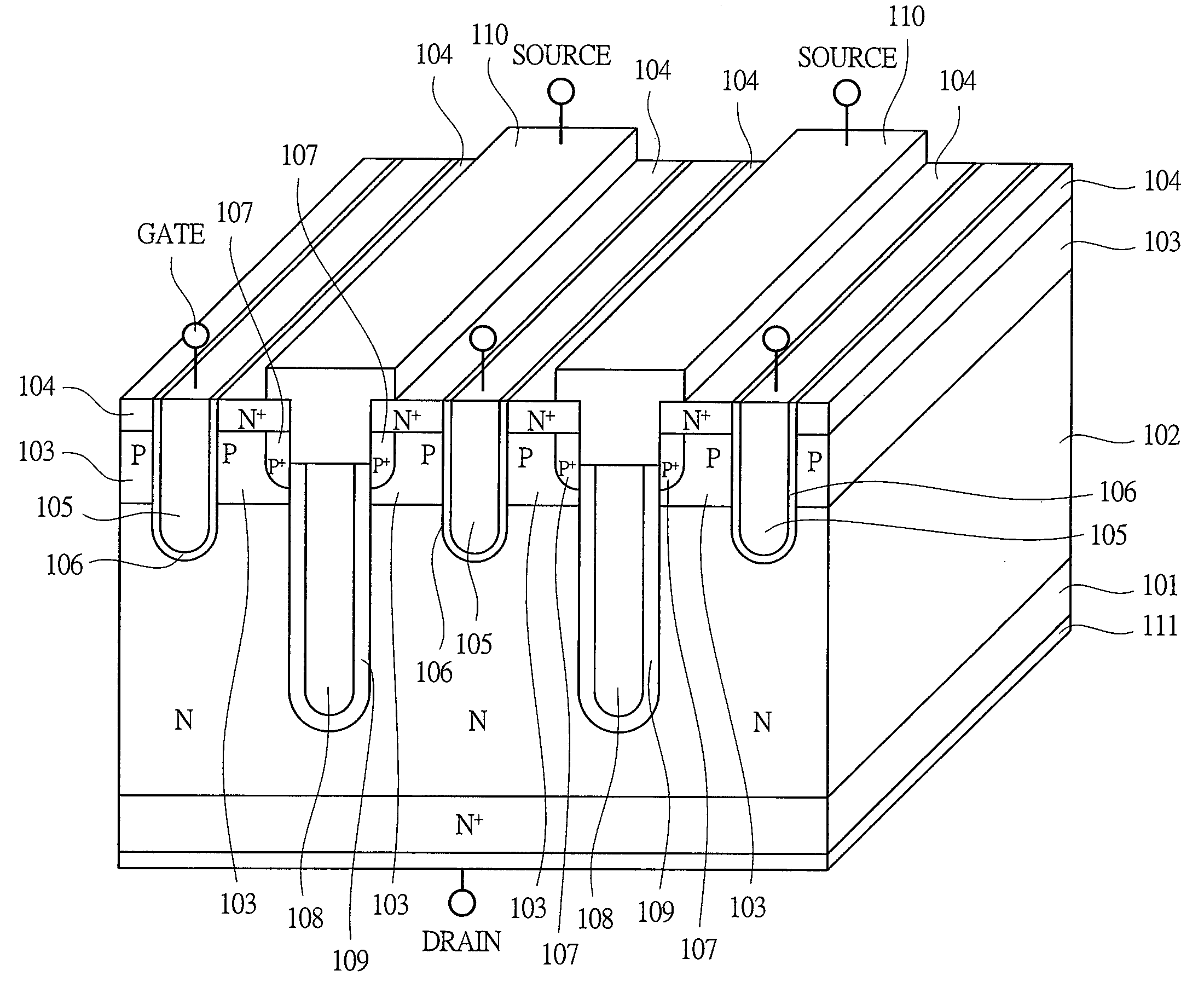

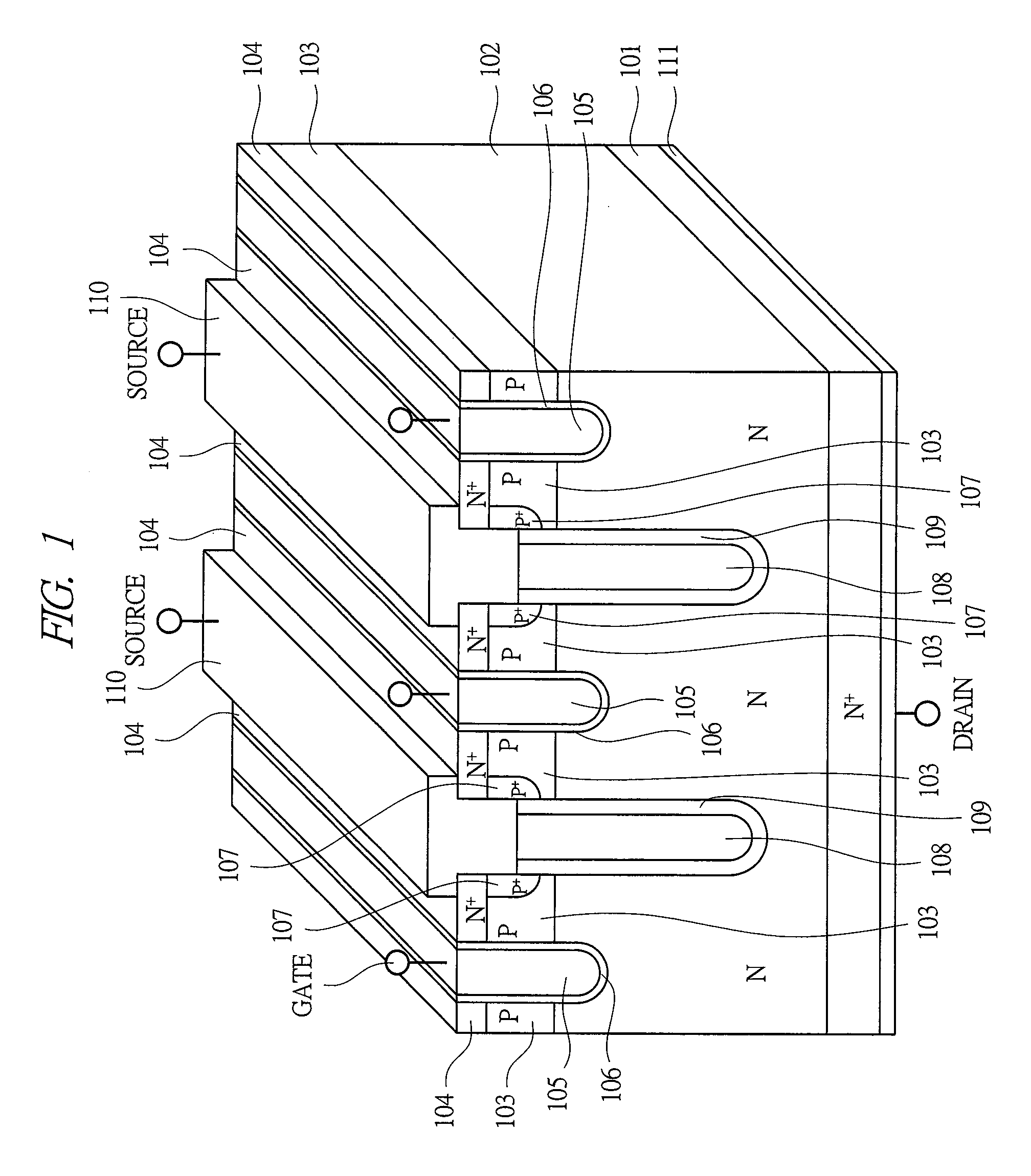

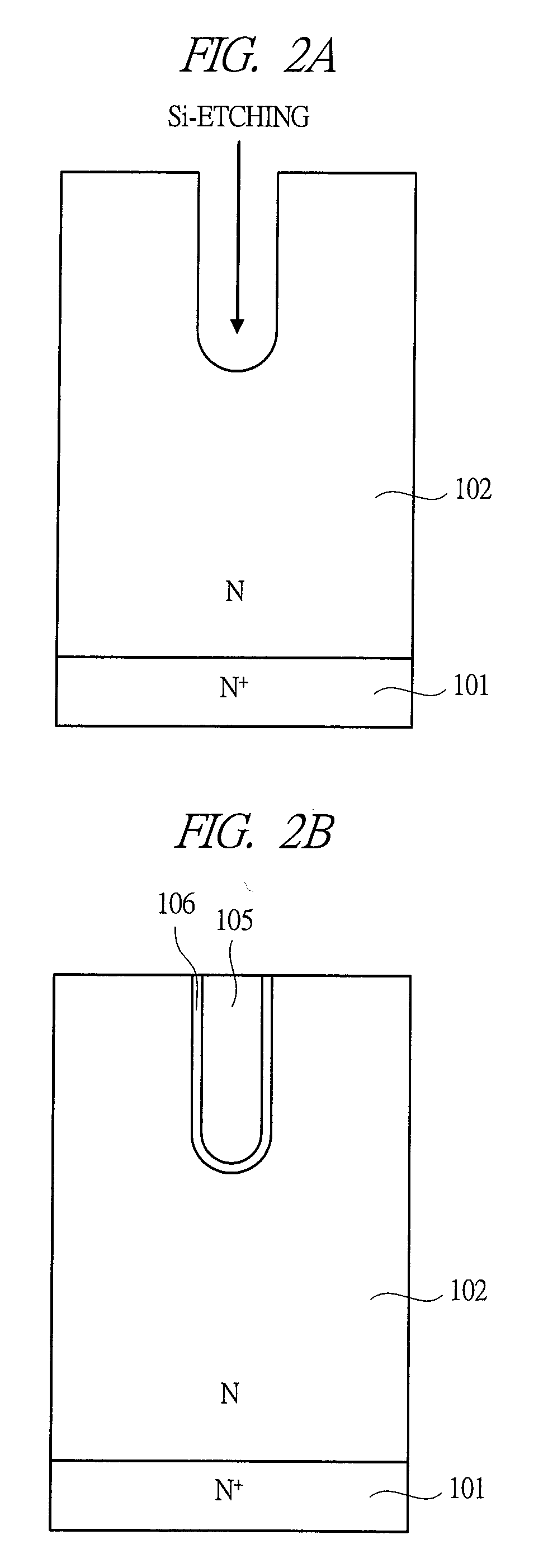

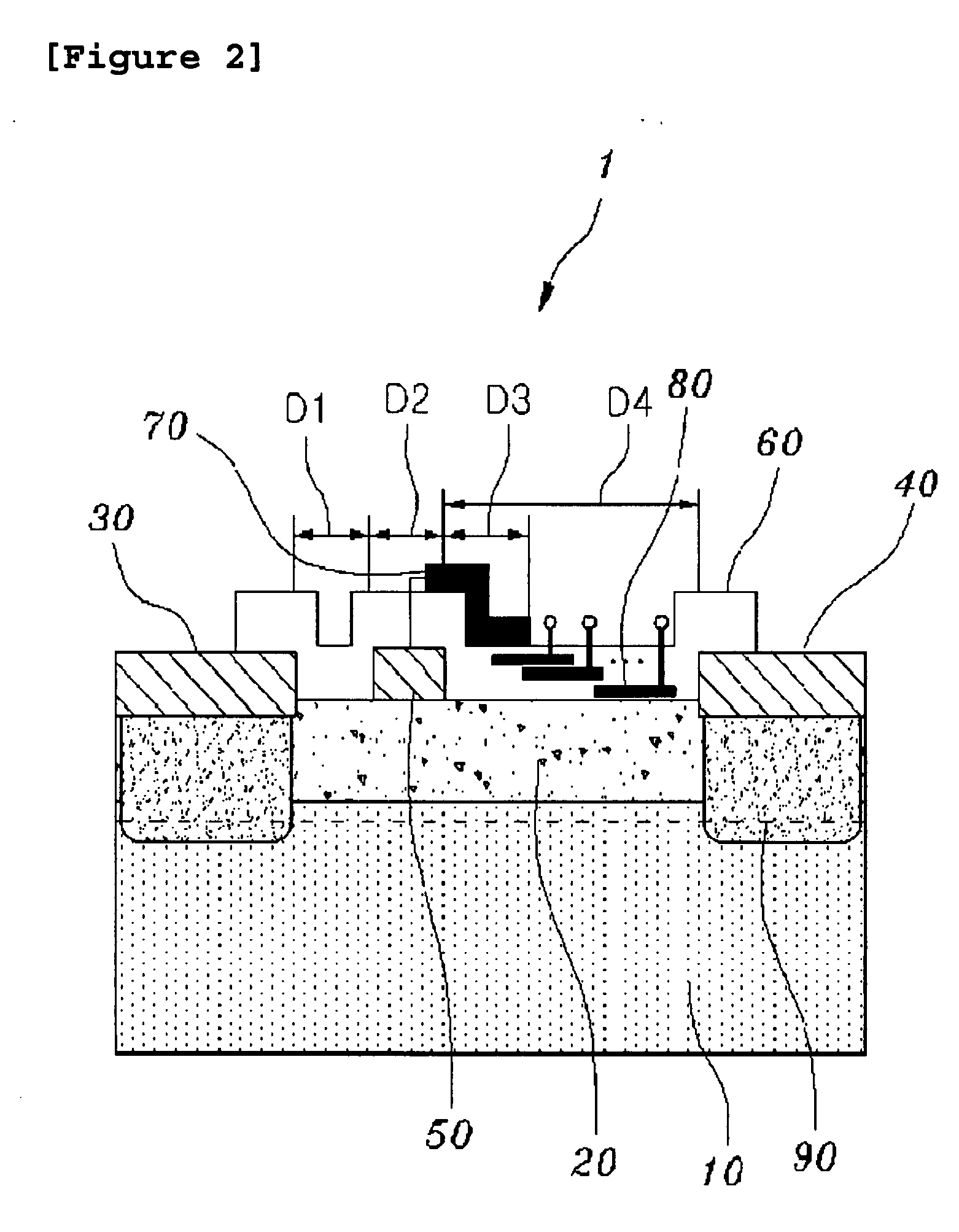

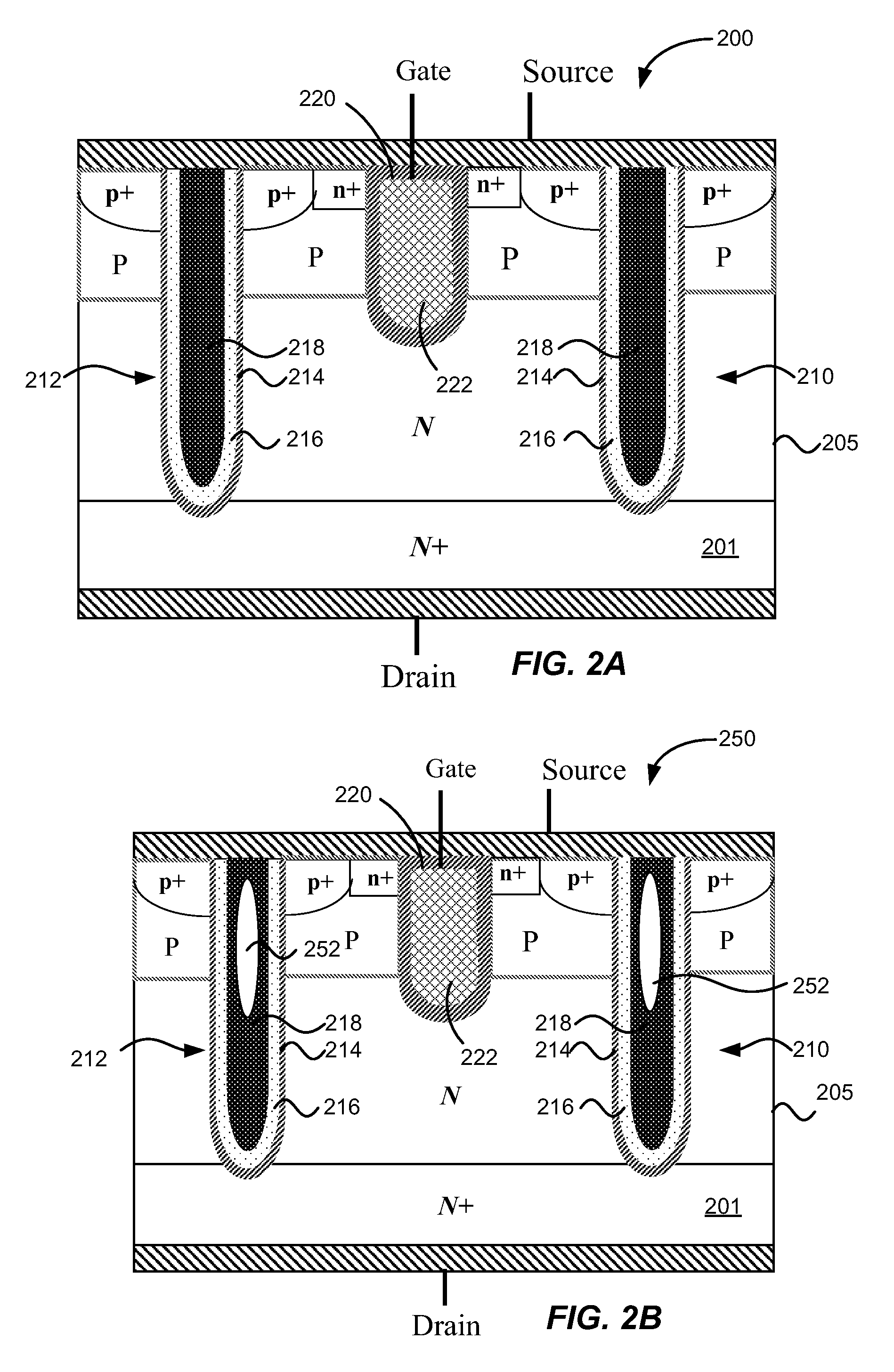

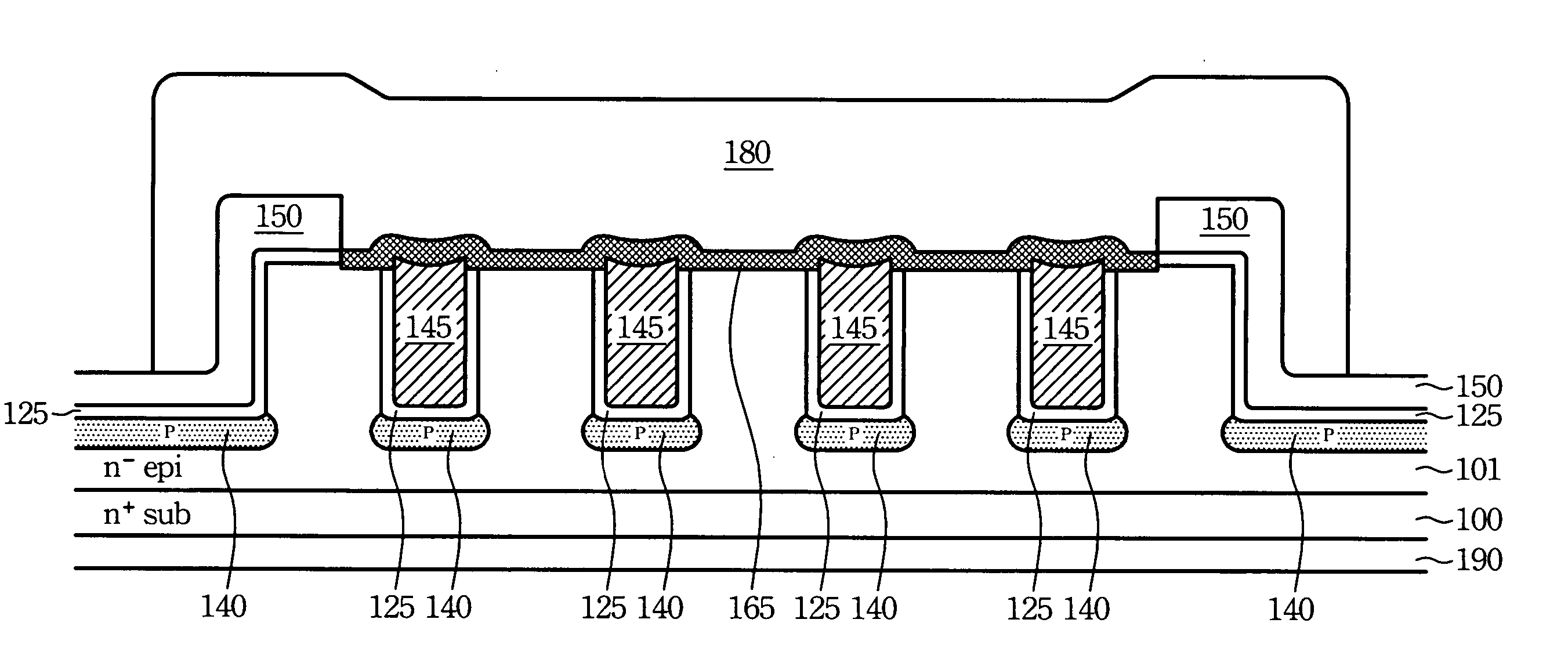

Semiconductor device and manufacturing method of the same

InactiveUS20090140327A1Increase impurity concentrationLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetElectrode Contact

The vertical trench MOSFET comprises: an N type epitaxial region formed on an upper surface of an N+ type substrate having a drain electrode on a lower surface thereof; a gate trench extending from a front surface into the N type epitaxial region; a gate electrode positioned in the gate trench so as to interpose an insulator; a channel region formed on the N type epitaxial region; a source region formed on the channel region; a source electrode formed on the source region; a source trench extending from the front surface into the N type epitaxial region; and a trench-buried source electrode positioned in the source trench so as to interpose an insulator, wherein the source electrode contacts with the trench-buried source electrode.

Owner:RENESAS ELECTRONICS CORP

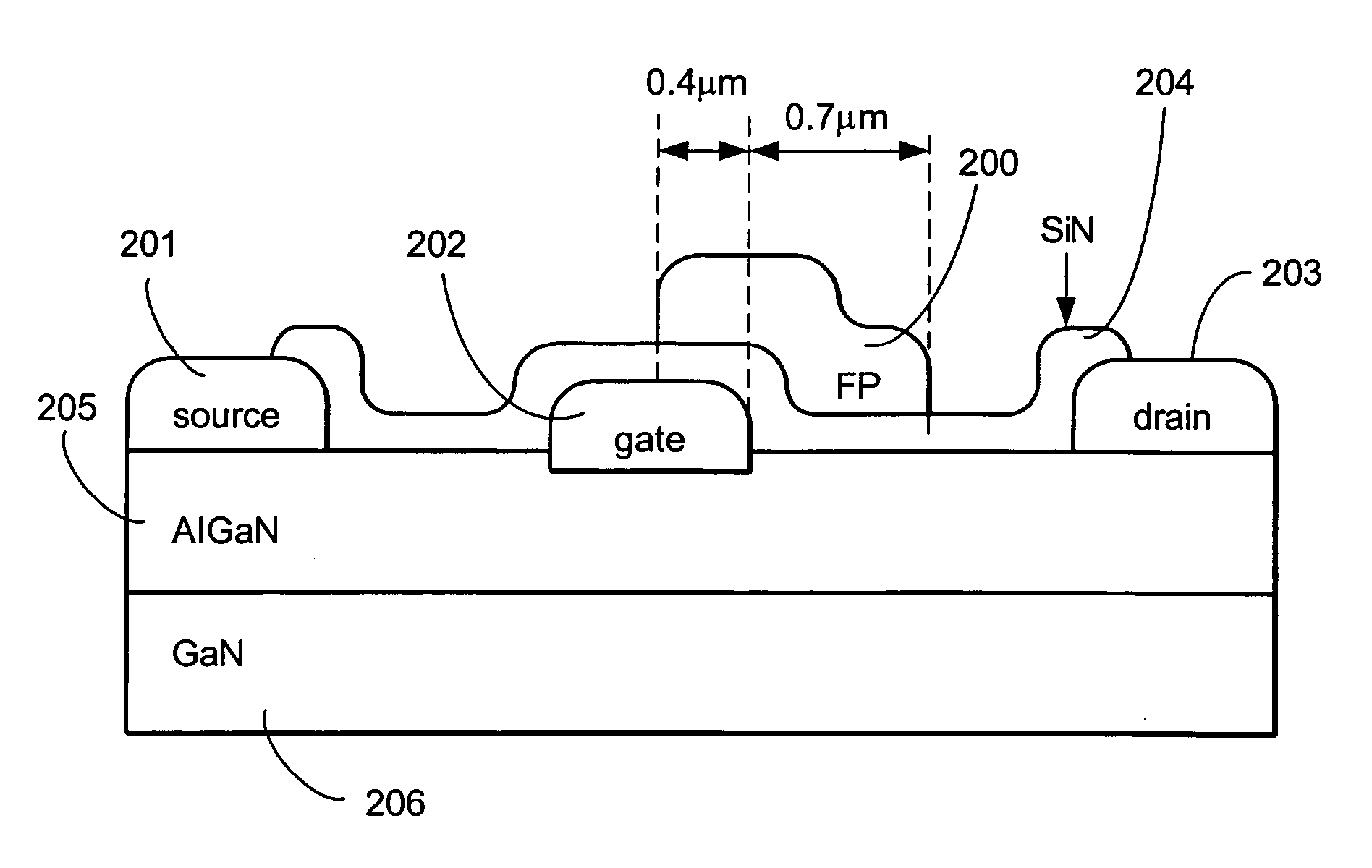

Methods to shape the electric field in electron devices, passivate dislocations and point defects, and enhance the luminescence efficiency of optical devices

ActiveUS20070224710A1Increase output powerReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueDislocation

A fluorine treatment that can shape the electric field profile in electronic devices in 1, 2, or 3 dimensions is disclosed. A method to increase the breakdown voltage of AlGaN / GaN high electron mobility transistors, by the introduction of a controlled amount of dispersion into the device, is also disclosed. This dispersion is large enough to reduce the peak electric field in the channel, but low enough in order not to cause a significant decrease in the output power of the device. In this design, the whole transistor is passivated against dispersion with the exception of a small region 50 to 100 nm wide right next to the drain side of the gate. In that region, surface traps cause limited amounts of dispersion, that will spread the high electric field under the gate edge, therefore increasing the breakdown voltage. Three different methods to introduce dispersion in the 50 nm closest to the gate are described: (1) introduction of a small gap between the passivation and the gate metal, (2) gradually reducing the thickness of the passivation, and (3) gradually reducing the thickness of the AlGaN cap layer in the region close the gate.

Owner:RGT UNIV OF CALIFORNIA

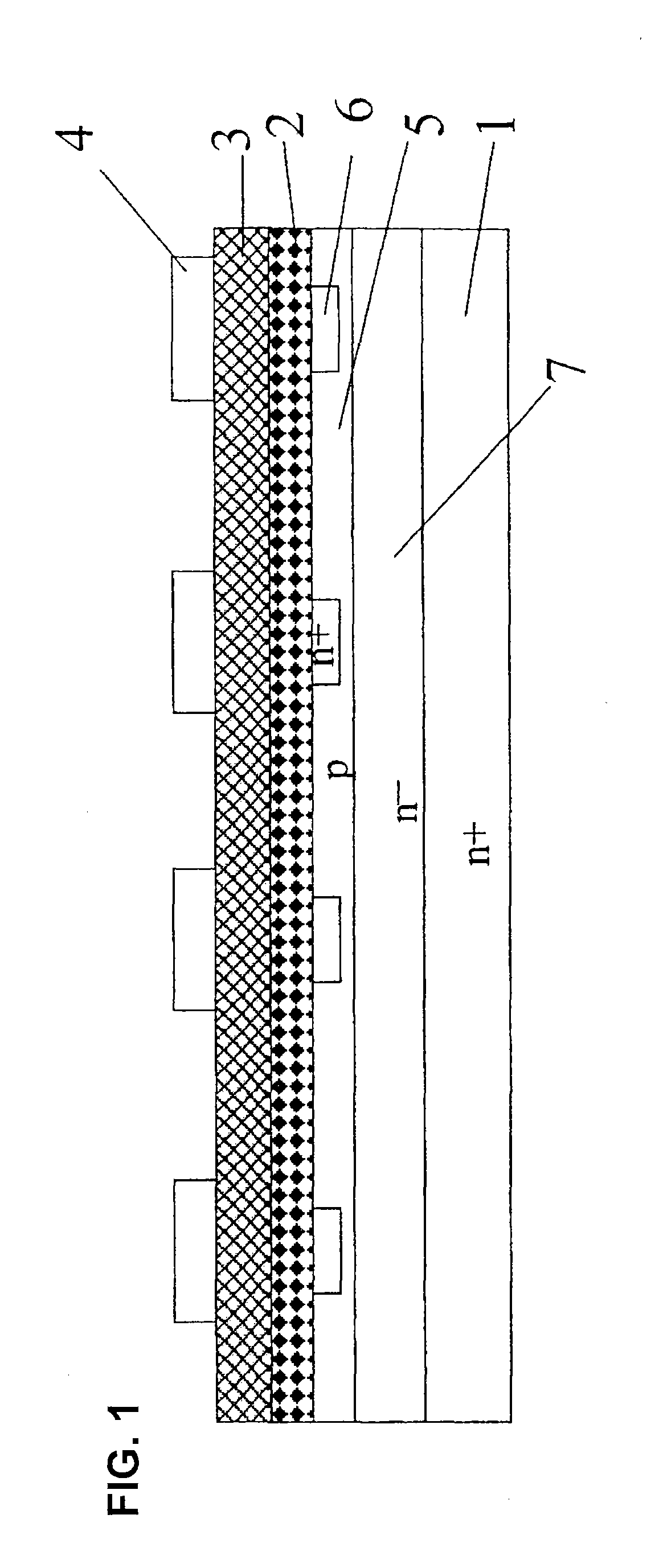

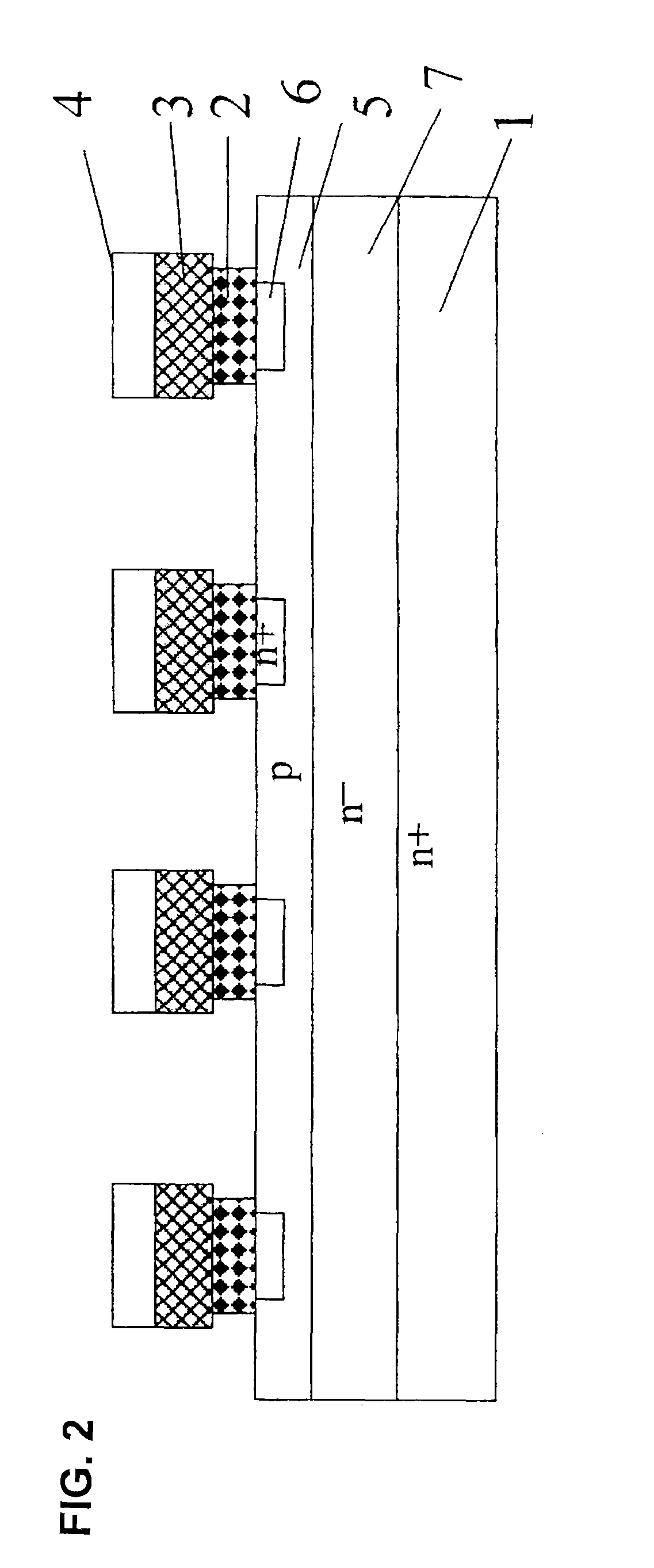

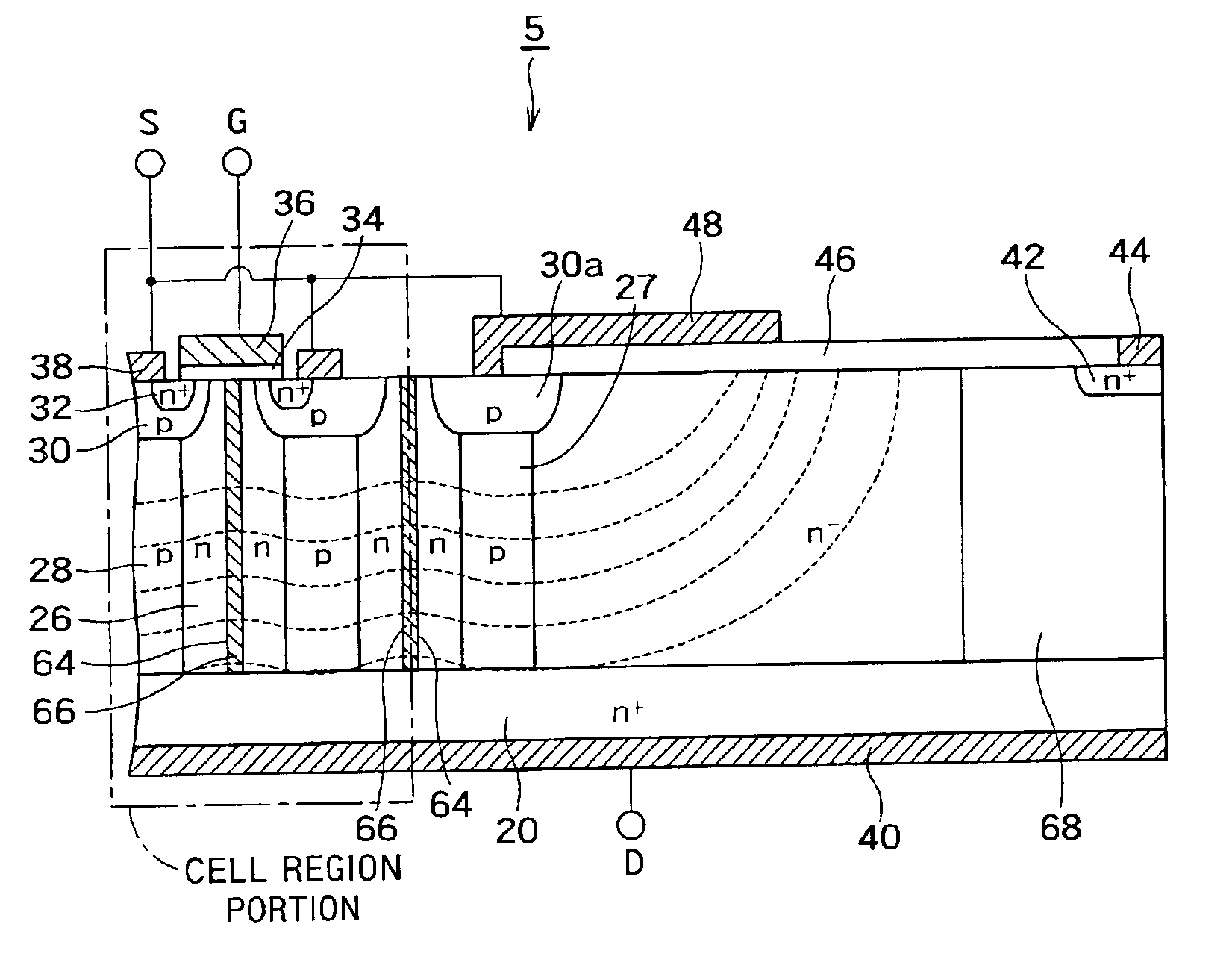

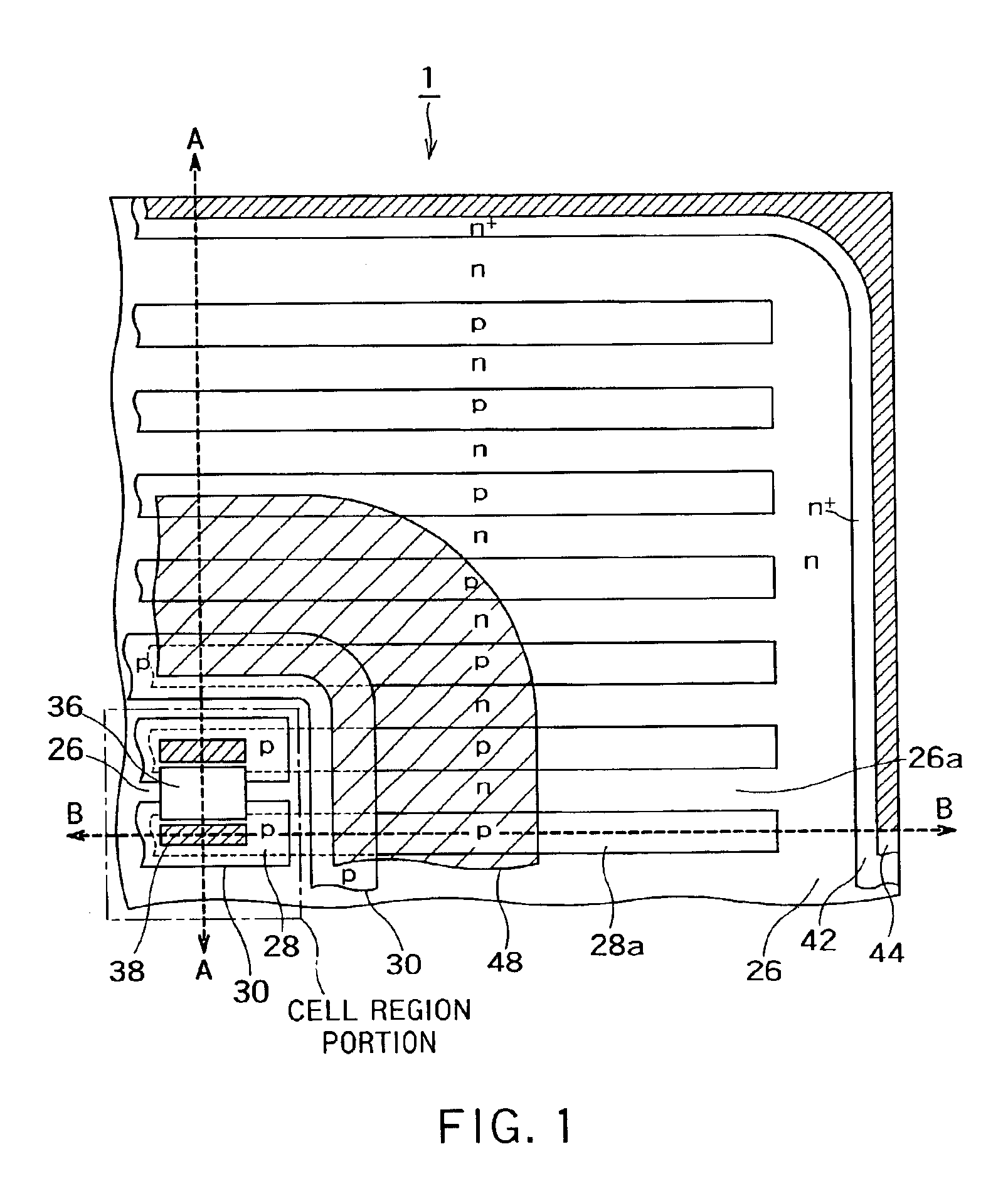

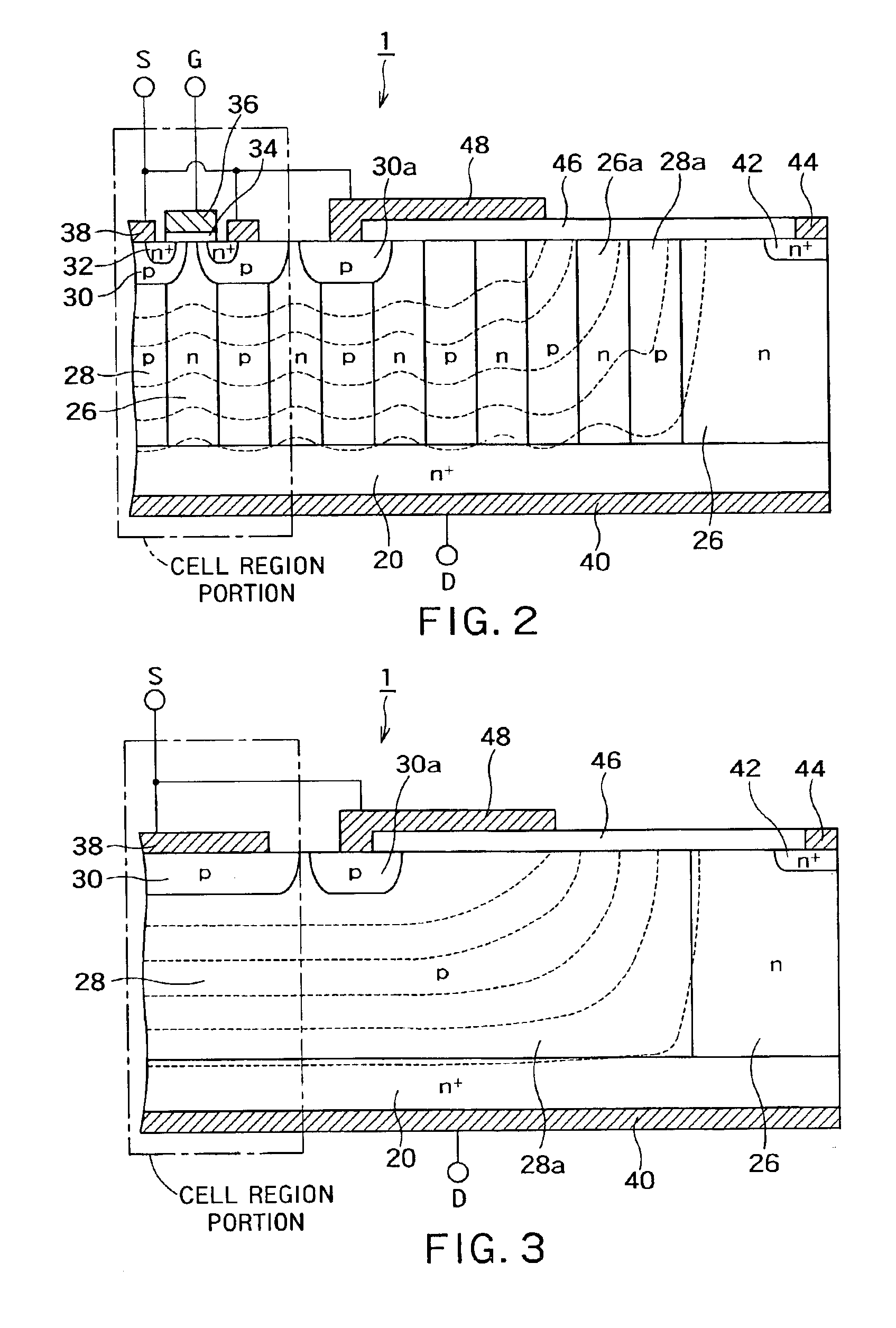

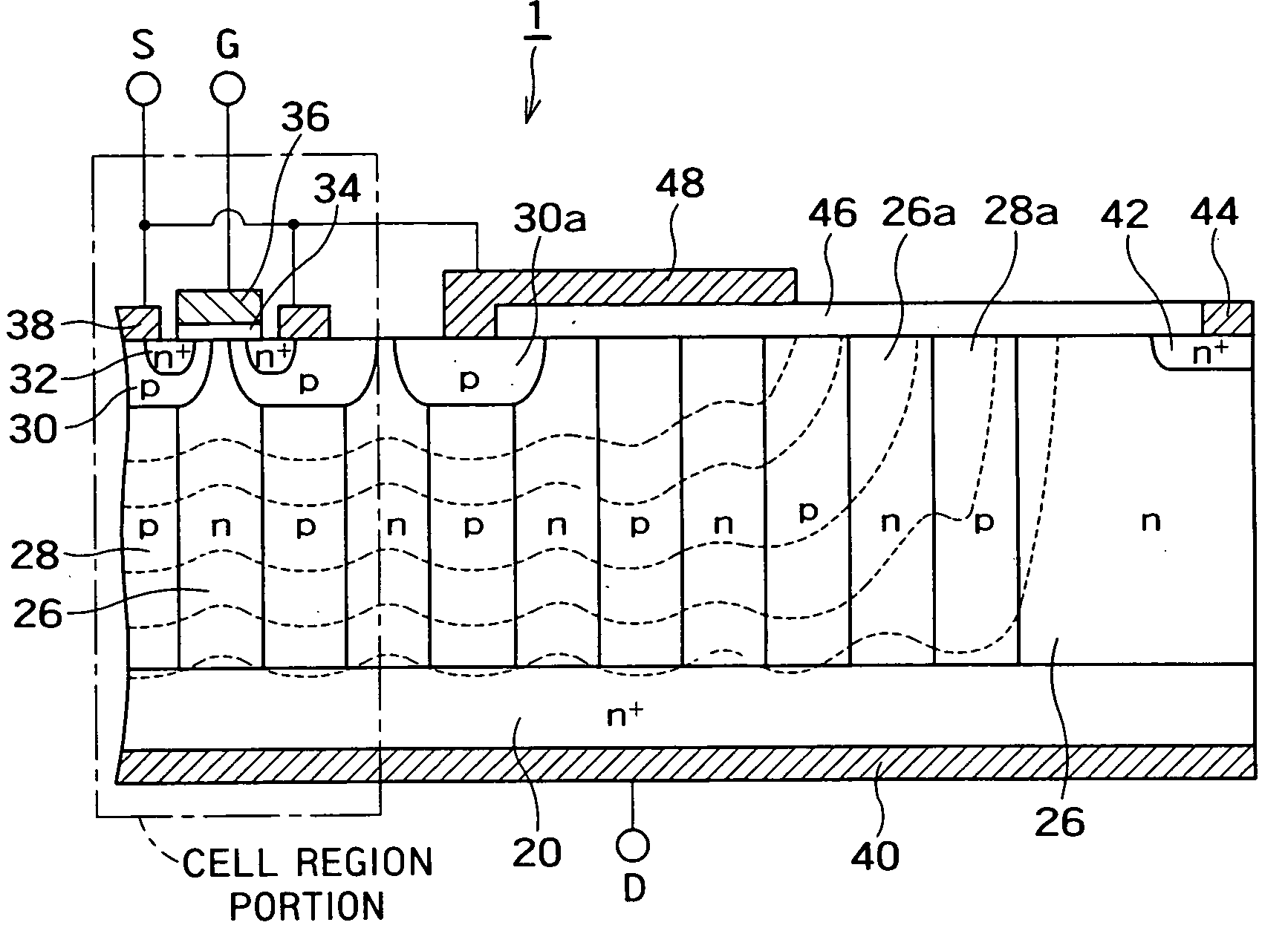

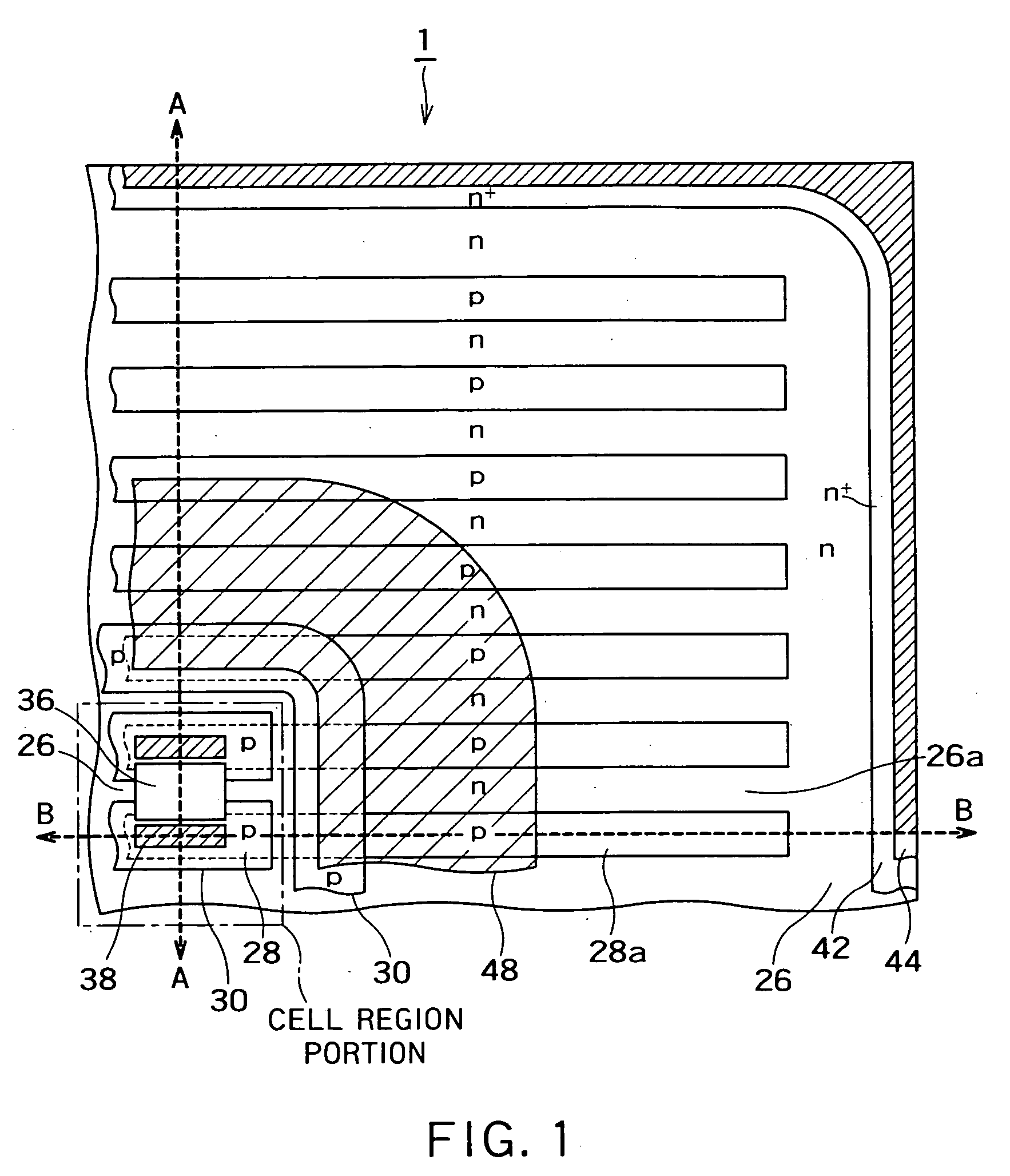

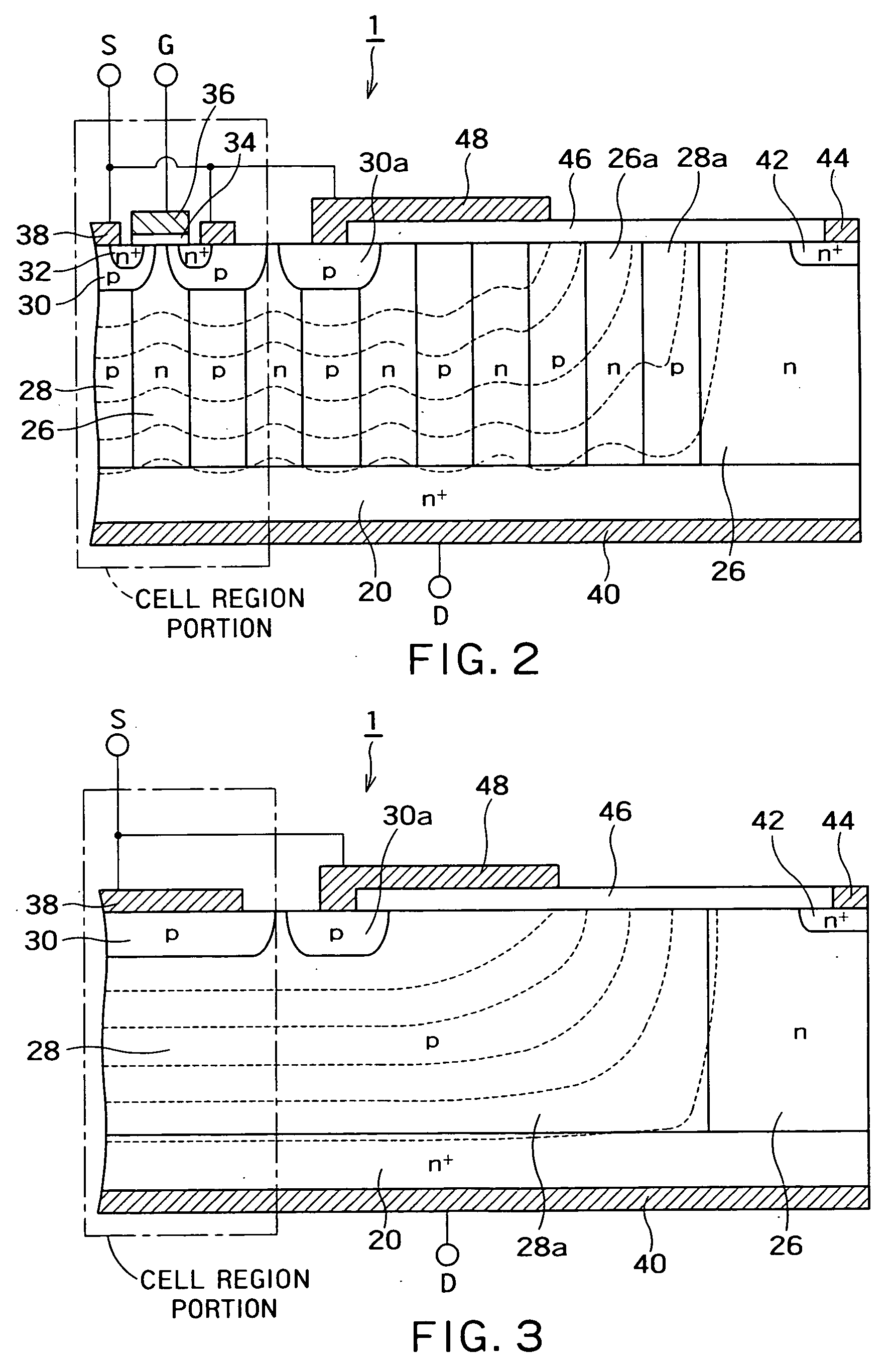

Semiconductor device with super junction region

InactiveUS6844592B2Improve breakdown voltageEfficiently obtainedSemiconductor/solid-state device manufacturingSemiconductor devicesCell regionSemiconductor

A semiconductor device includes a first-conductivity-type semiconductor layer which includes a cell region portion and a junction terminating region portion. The junction terminating region portion is a region portion which is positioned in an outer periphery of the cell region portion to maintain a breakdown voltage by extending a depletion layer to attenuate an electric field.

Owner:KK TOSHIBA

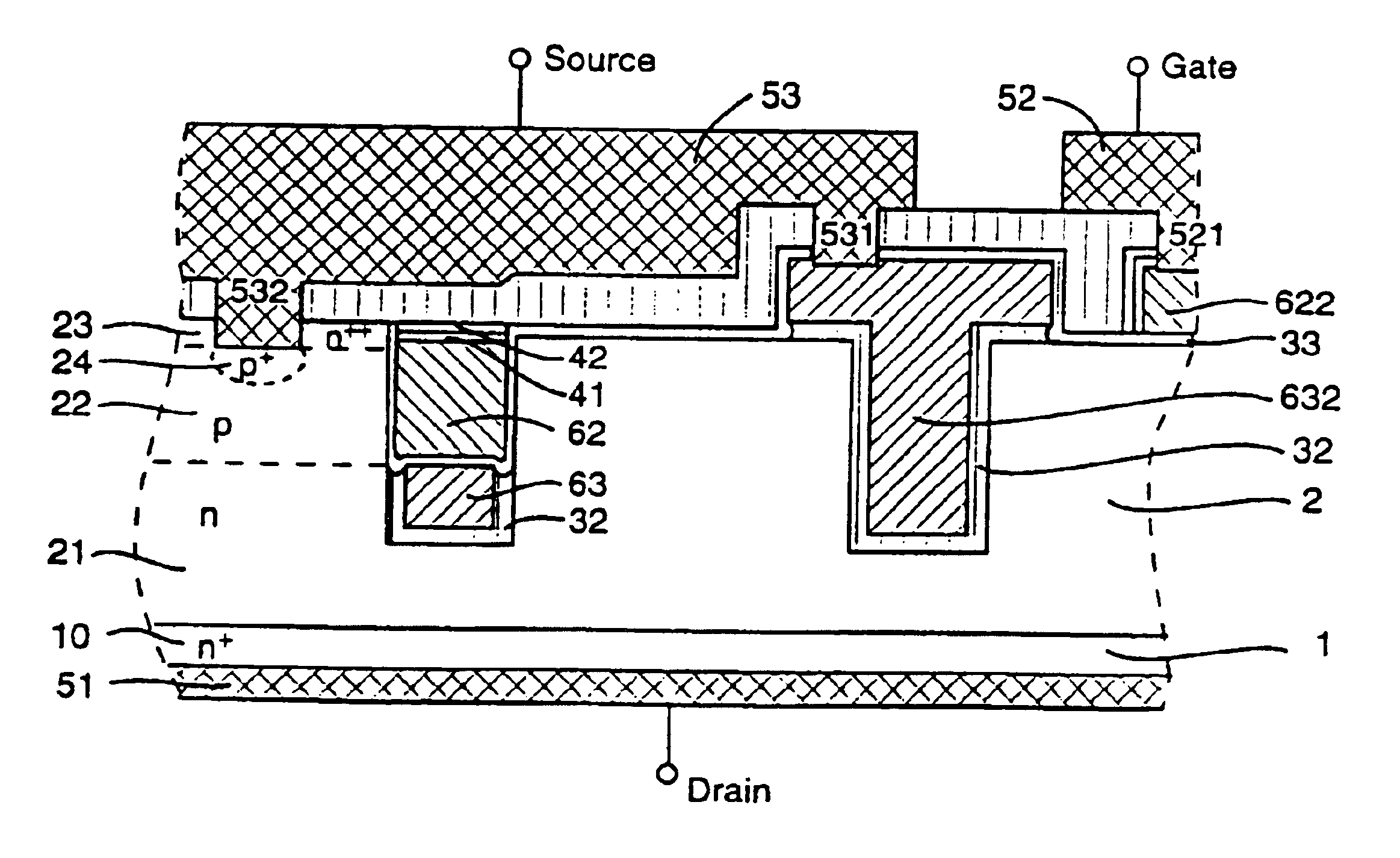

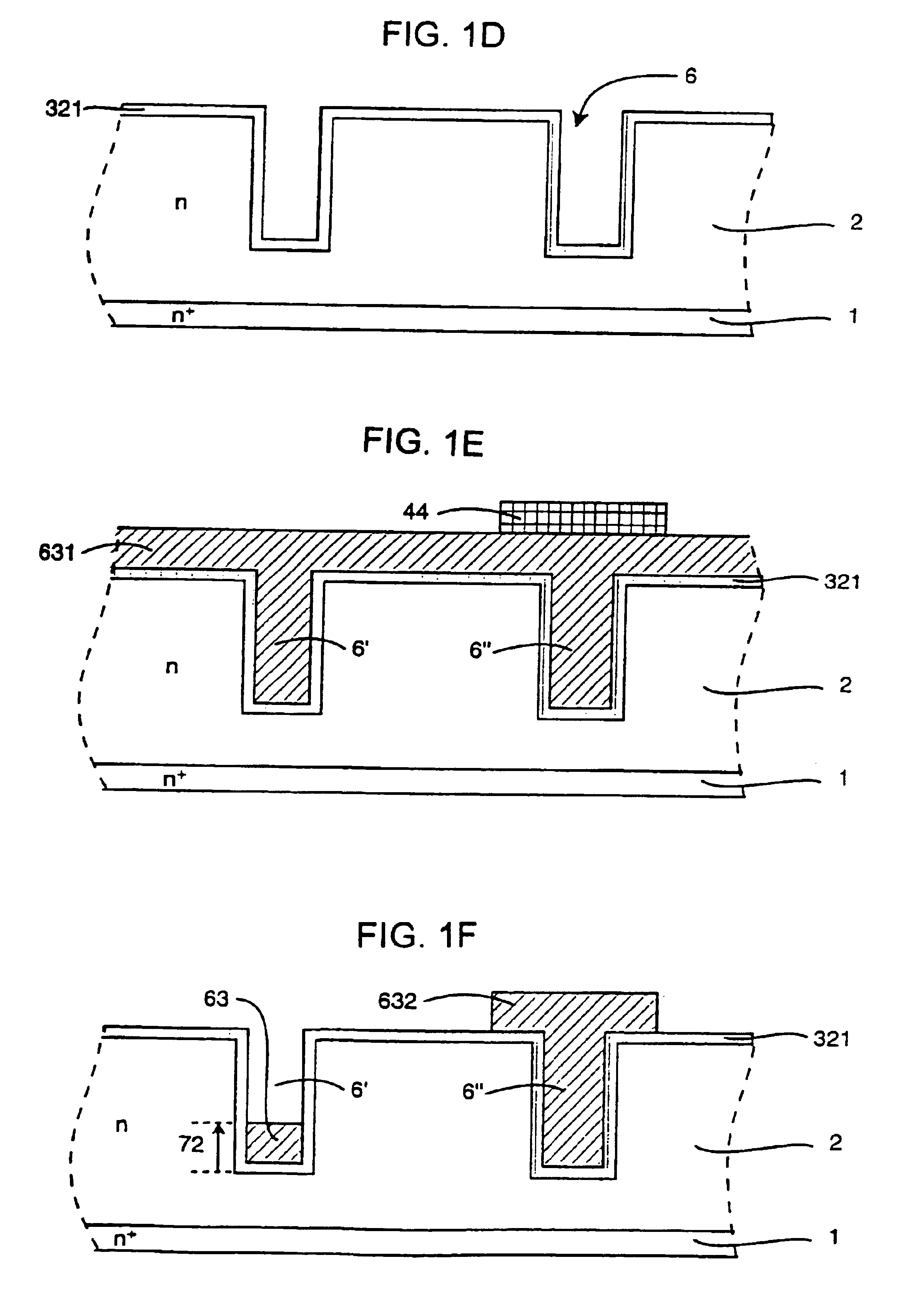

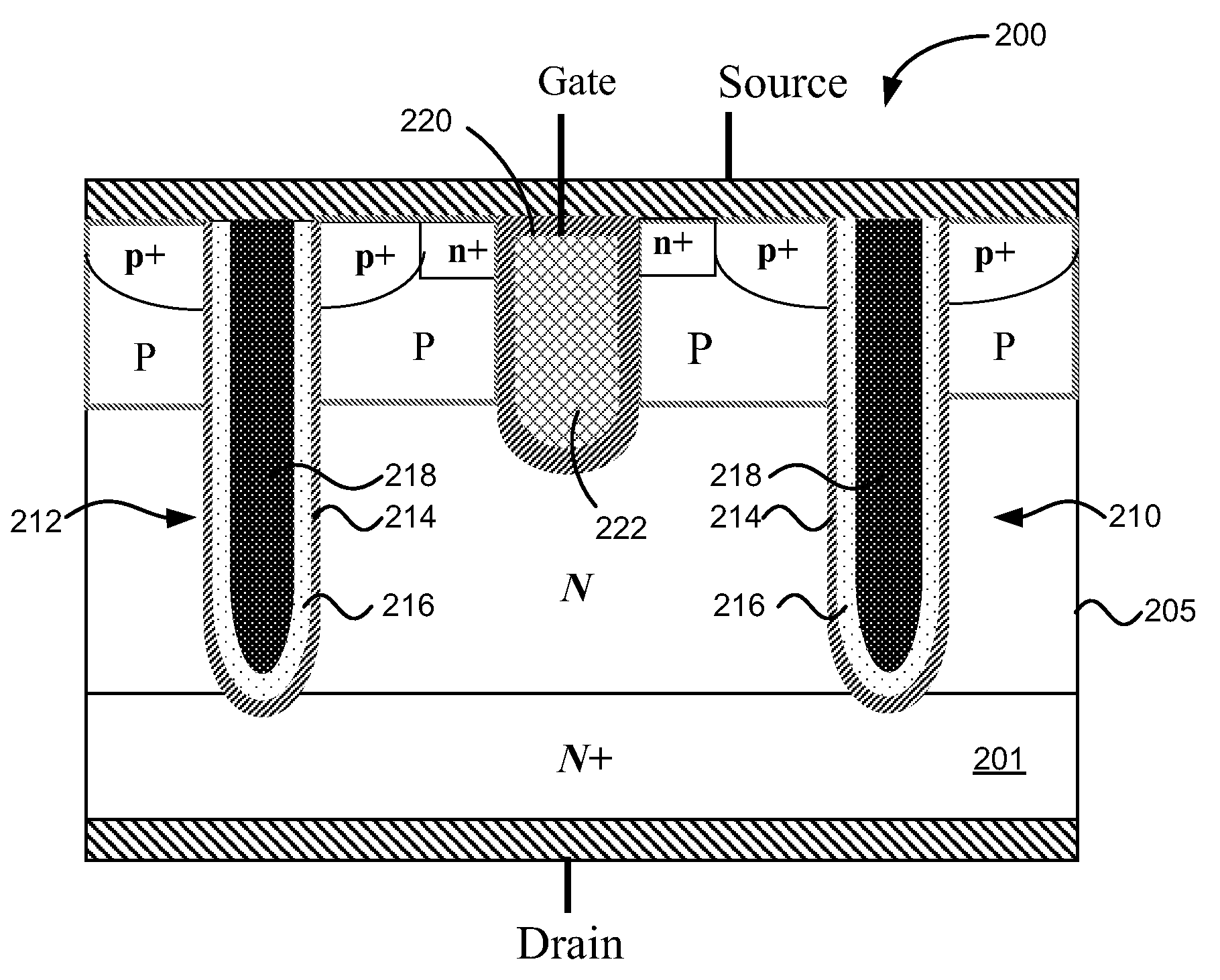

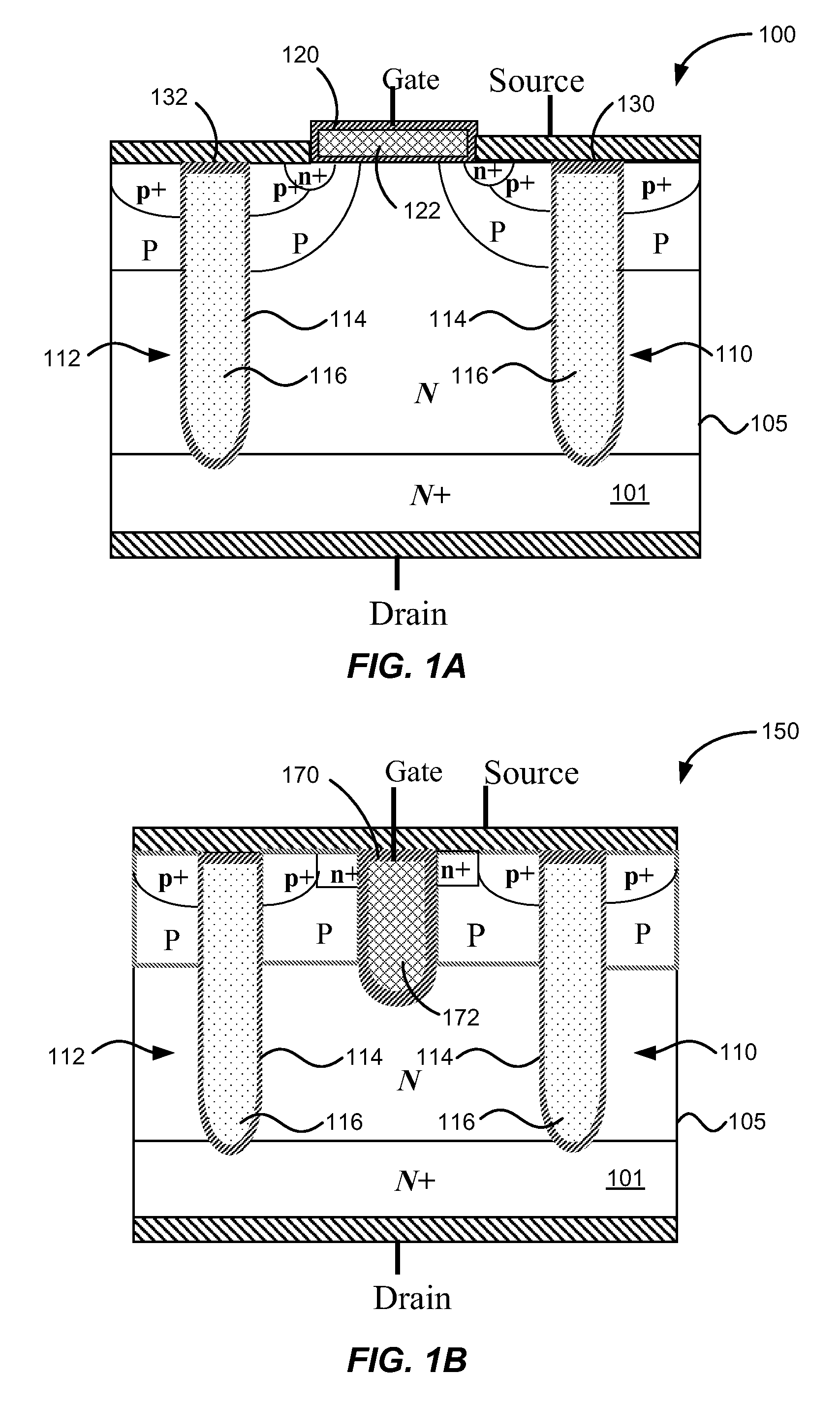

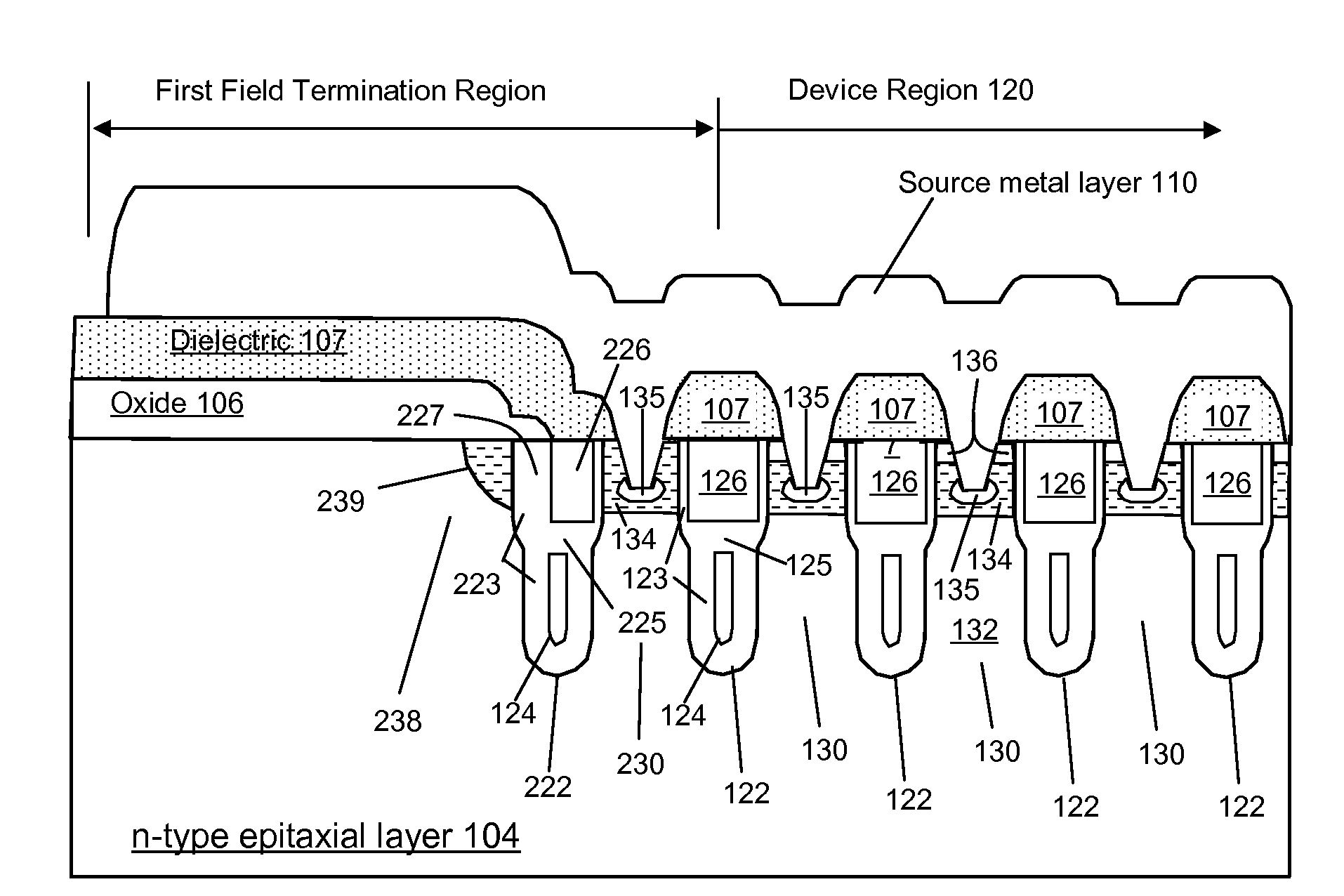

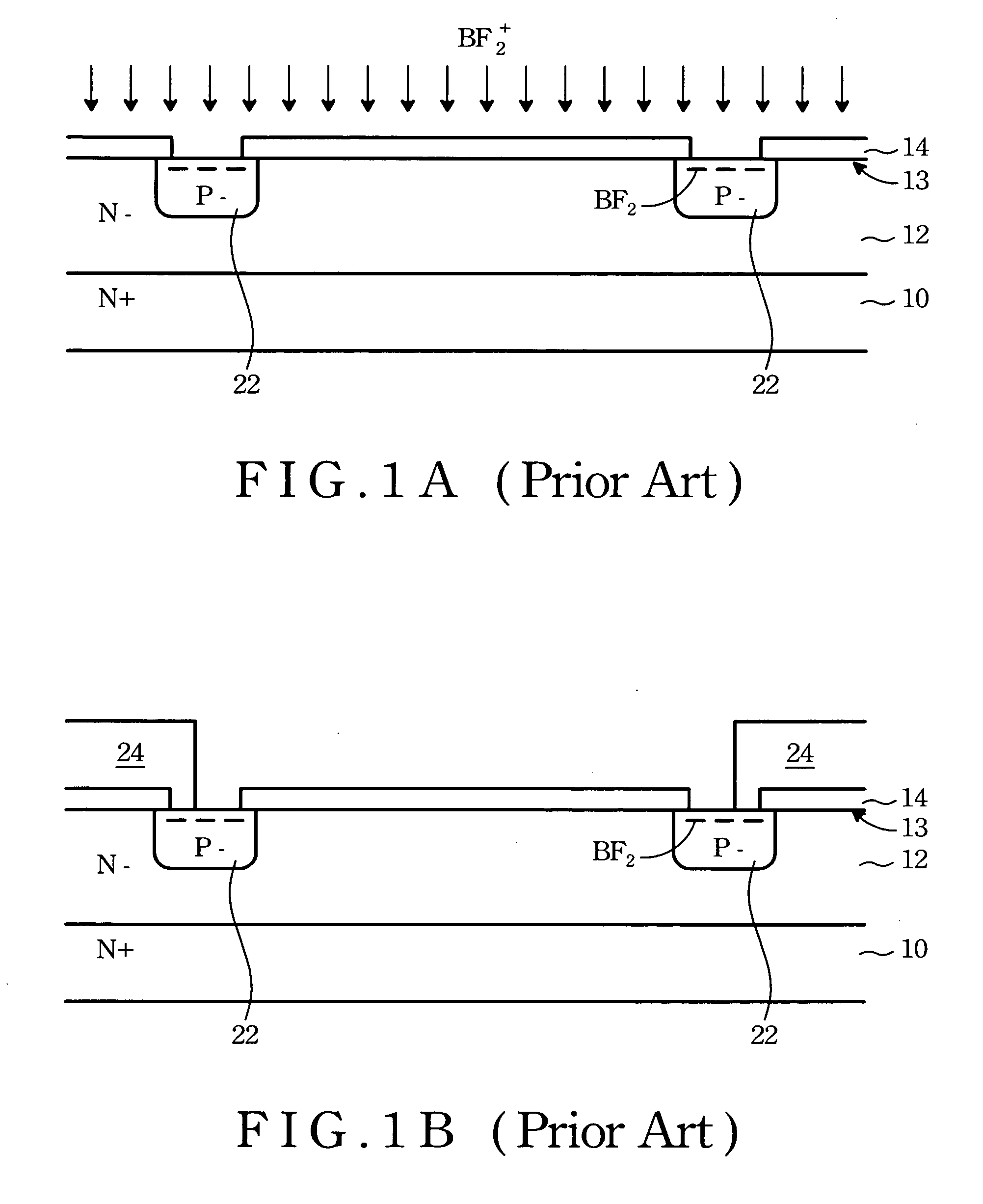

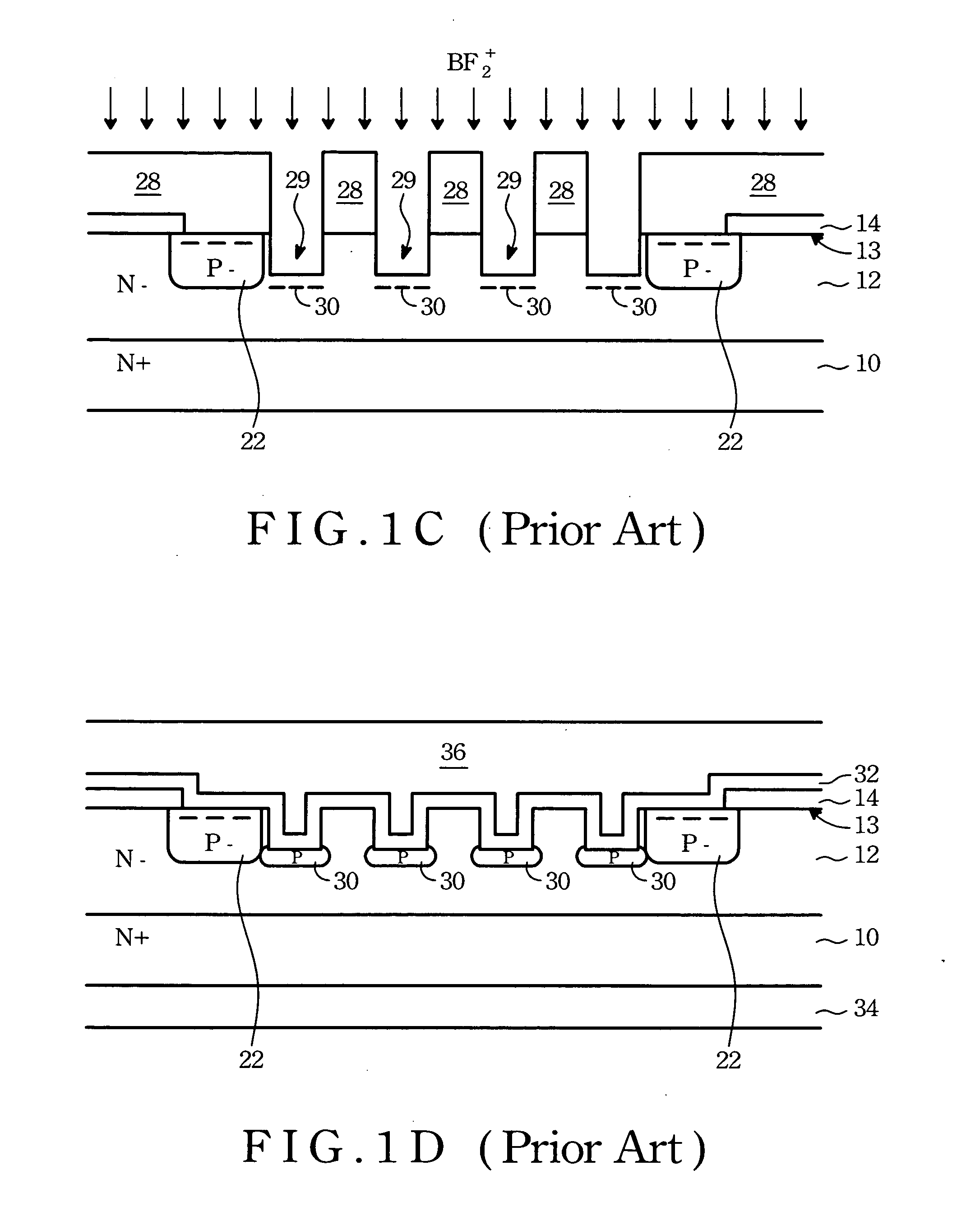

Power devices having trench-based source and gate electrodes

ActiveUS20060060916A1Improve breakdown voltageIncrease the on-resistanceSemiconductor/solid-state device manufacturingDiodePower semiconductor deviceDevice material

A power semiconductor device includes a plurality of trenches formed within a semiconductor body, each trench including one or more electrodes formed therein. In particular, according to embodiments of the invention, the plurality of trenches of a semiconductor device may include one or more gate electrodes, may include one or more gate electrodes or one or more source electrodes, or may include a combination of both gate and source electrodes formed therein. The trenches and electrodes may have varying depths within the semiconductor body.

Owner:INFINEON TECH AMERICAS CORP

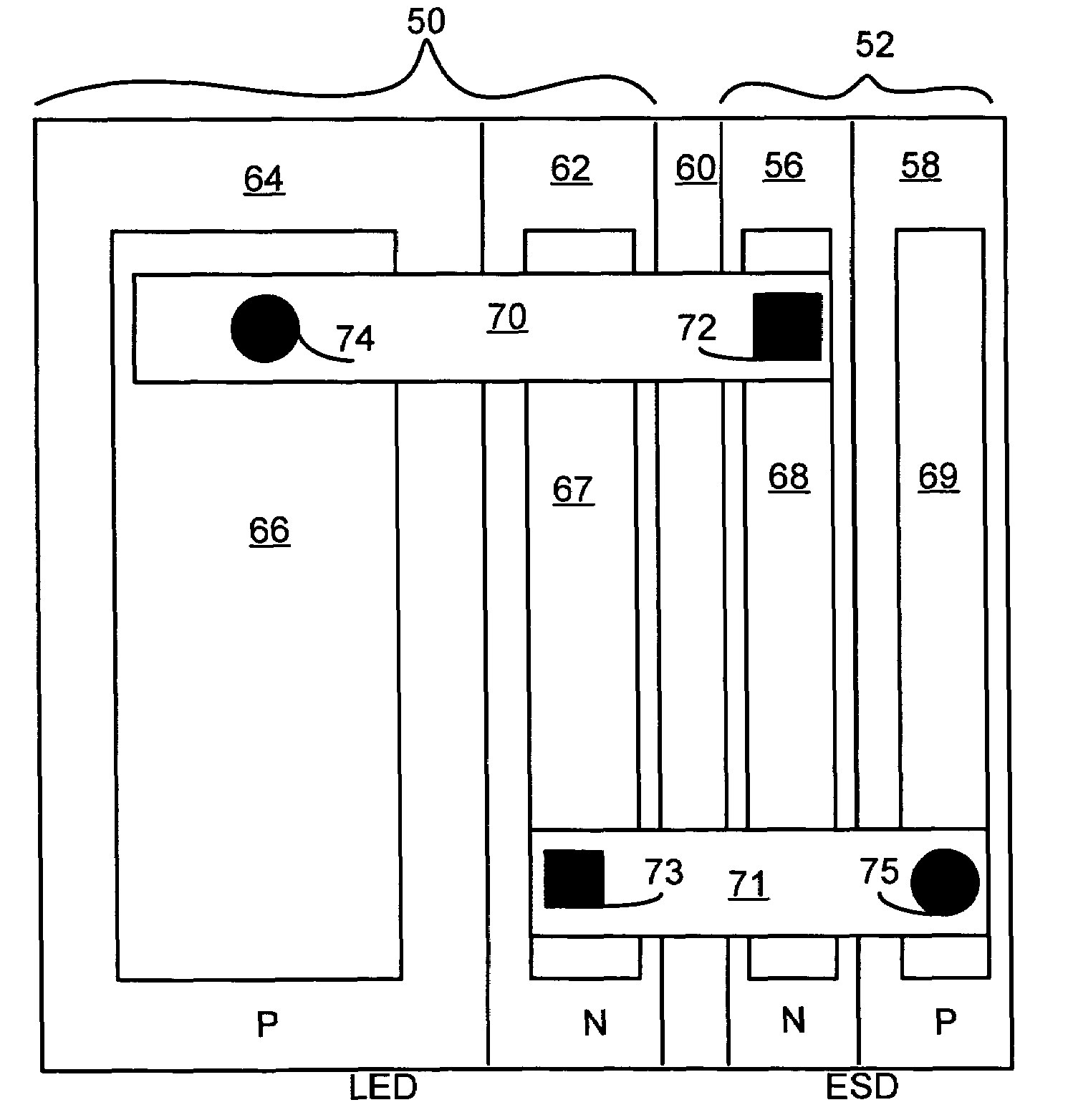

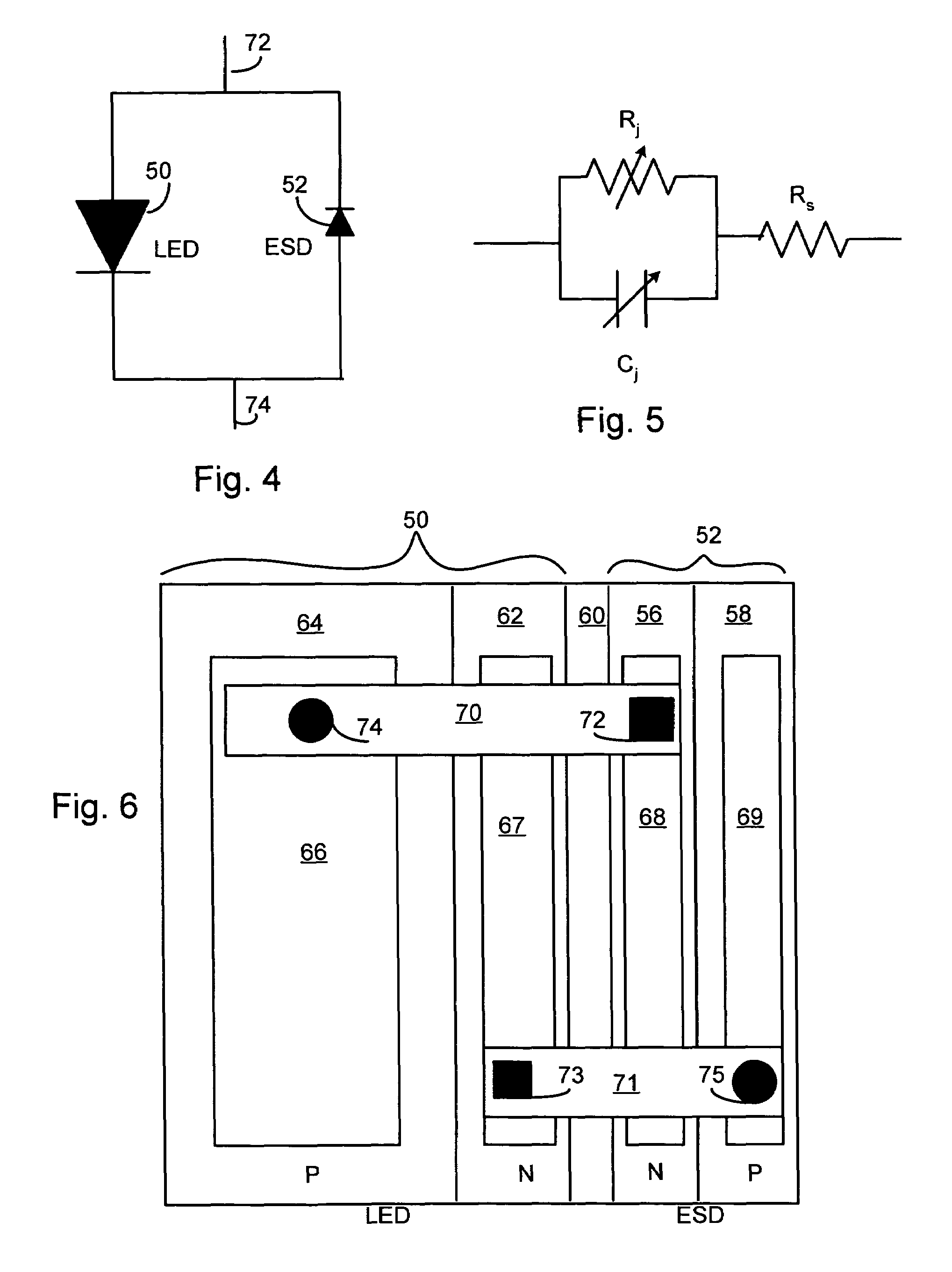

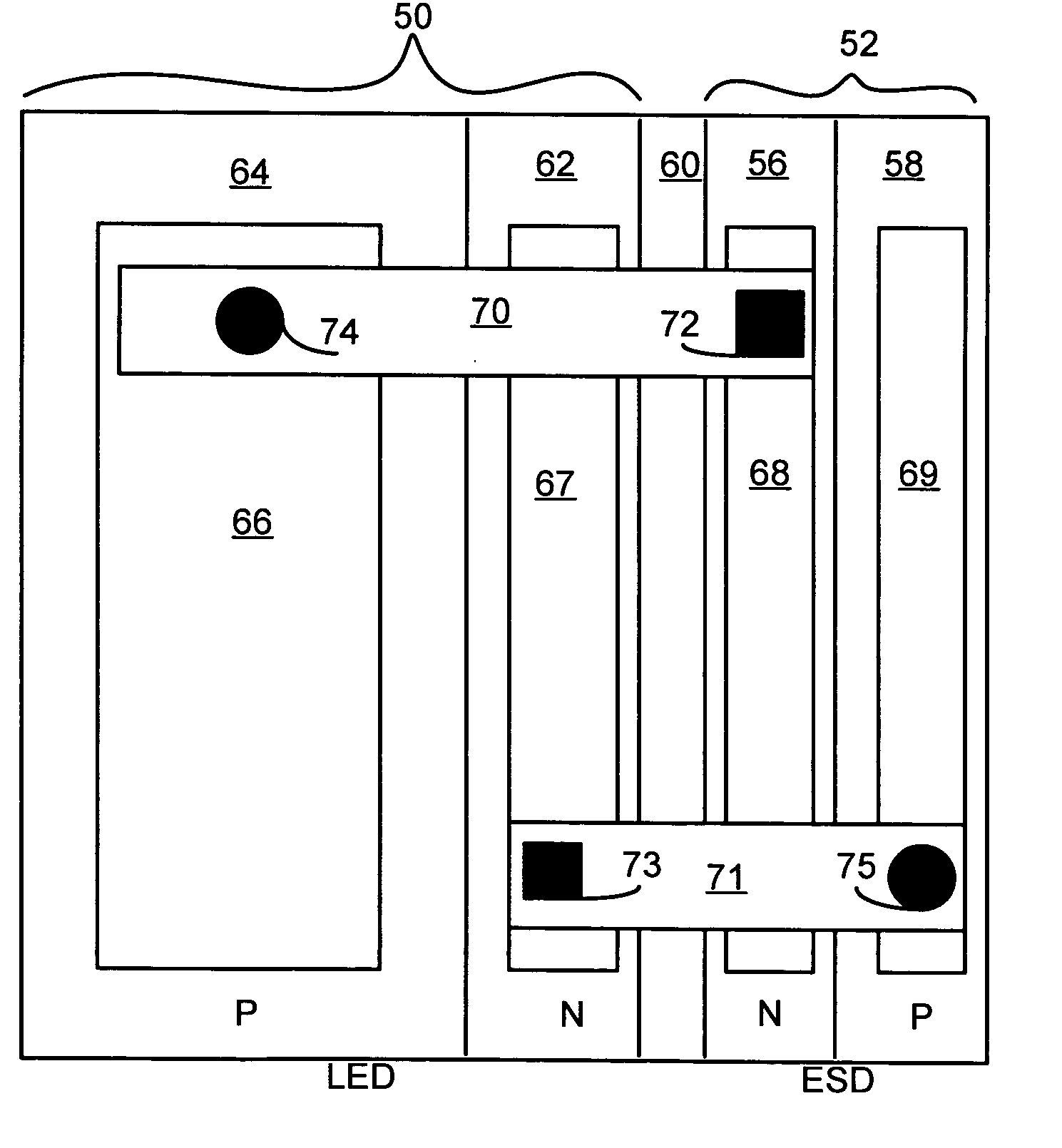

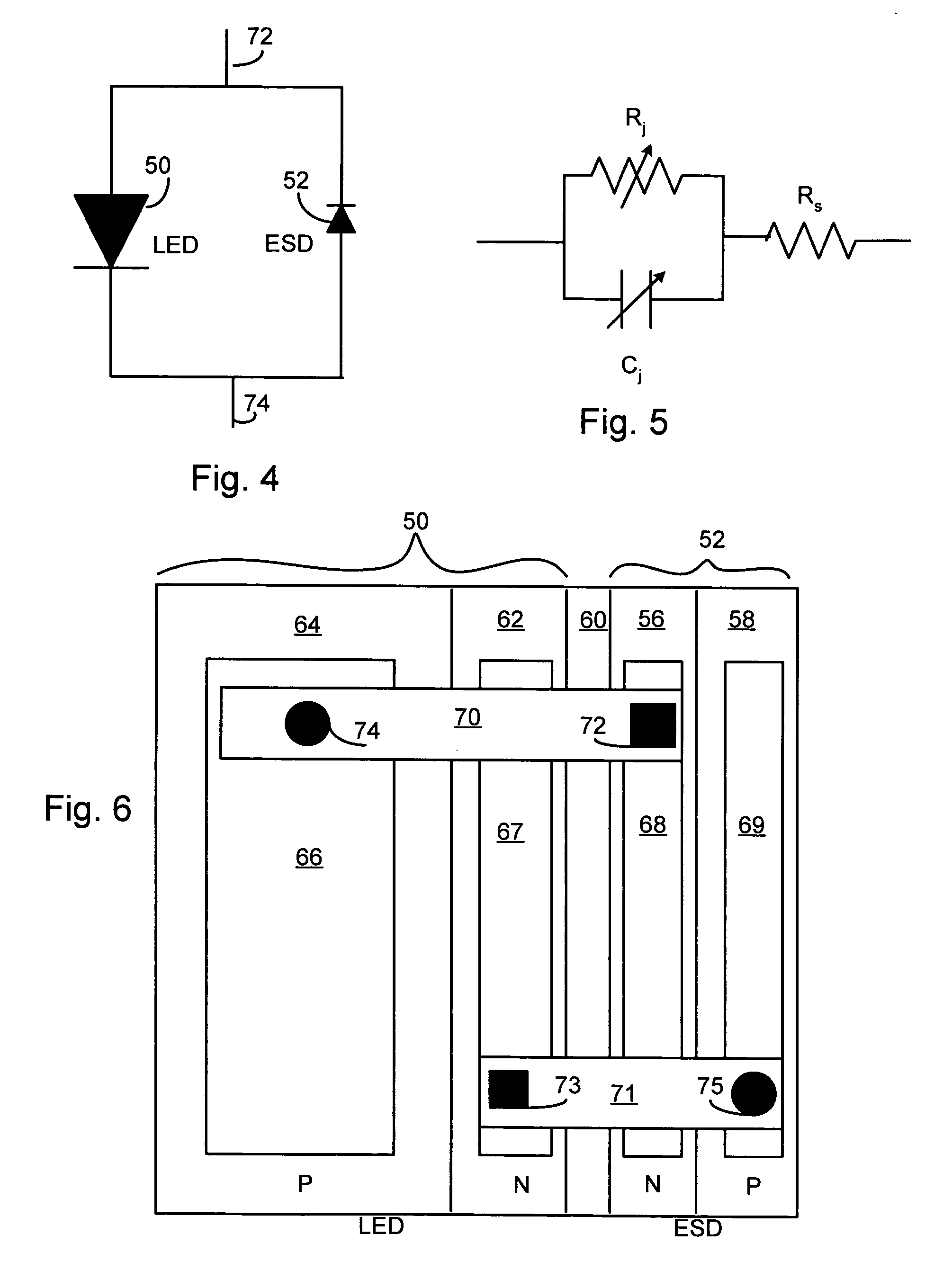

LED chip with integrated fast switching diode for ESD protection

ActiveUS7064353B2Reduced series resistanceIncrease widthSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsP–n junction

Owner:JANSSEN PHARMA NV +1

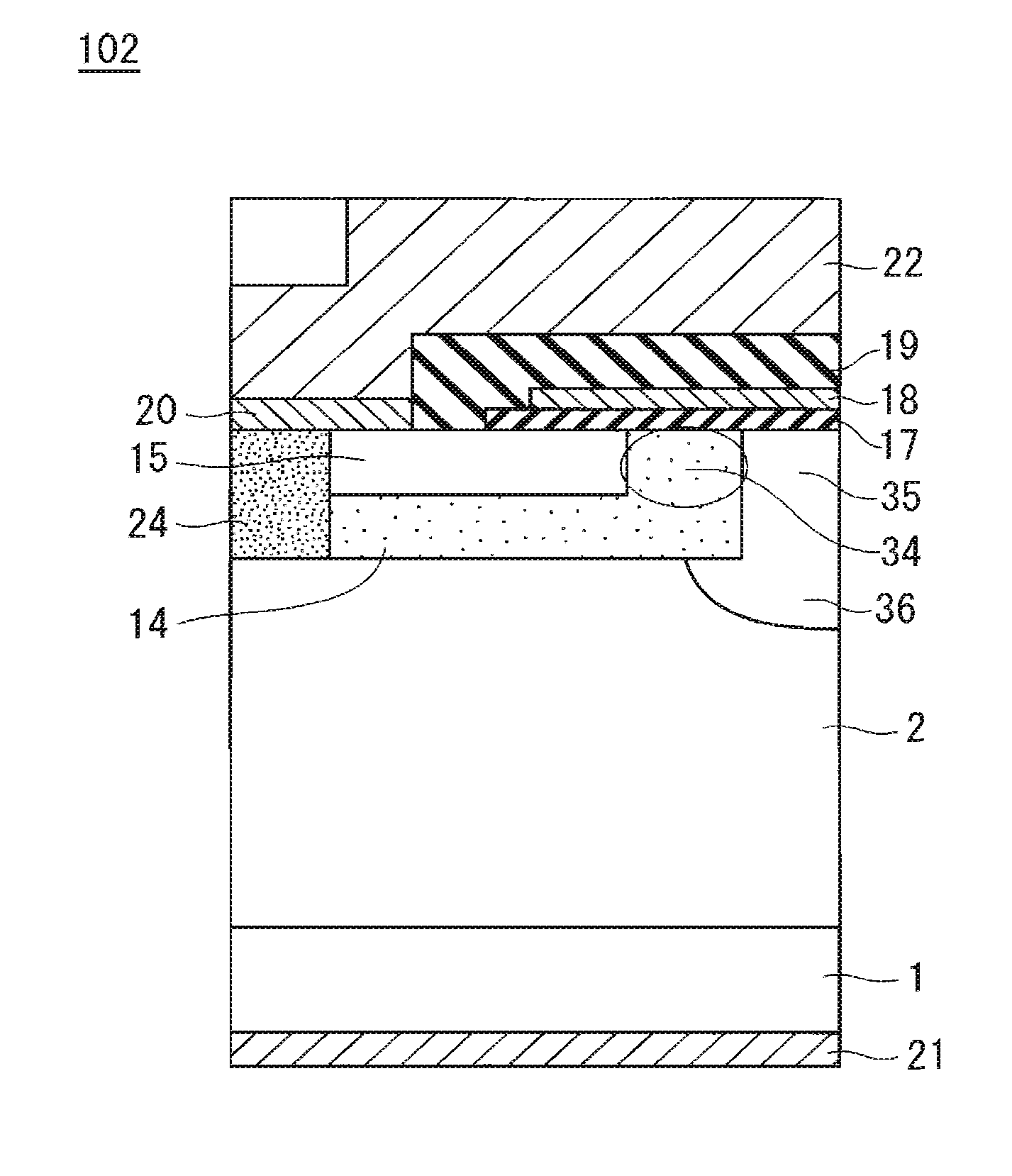

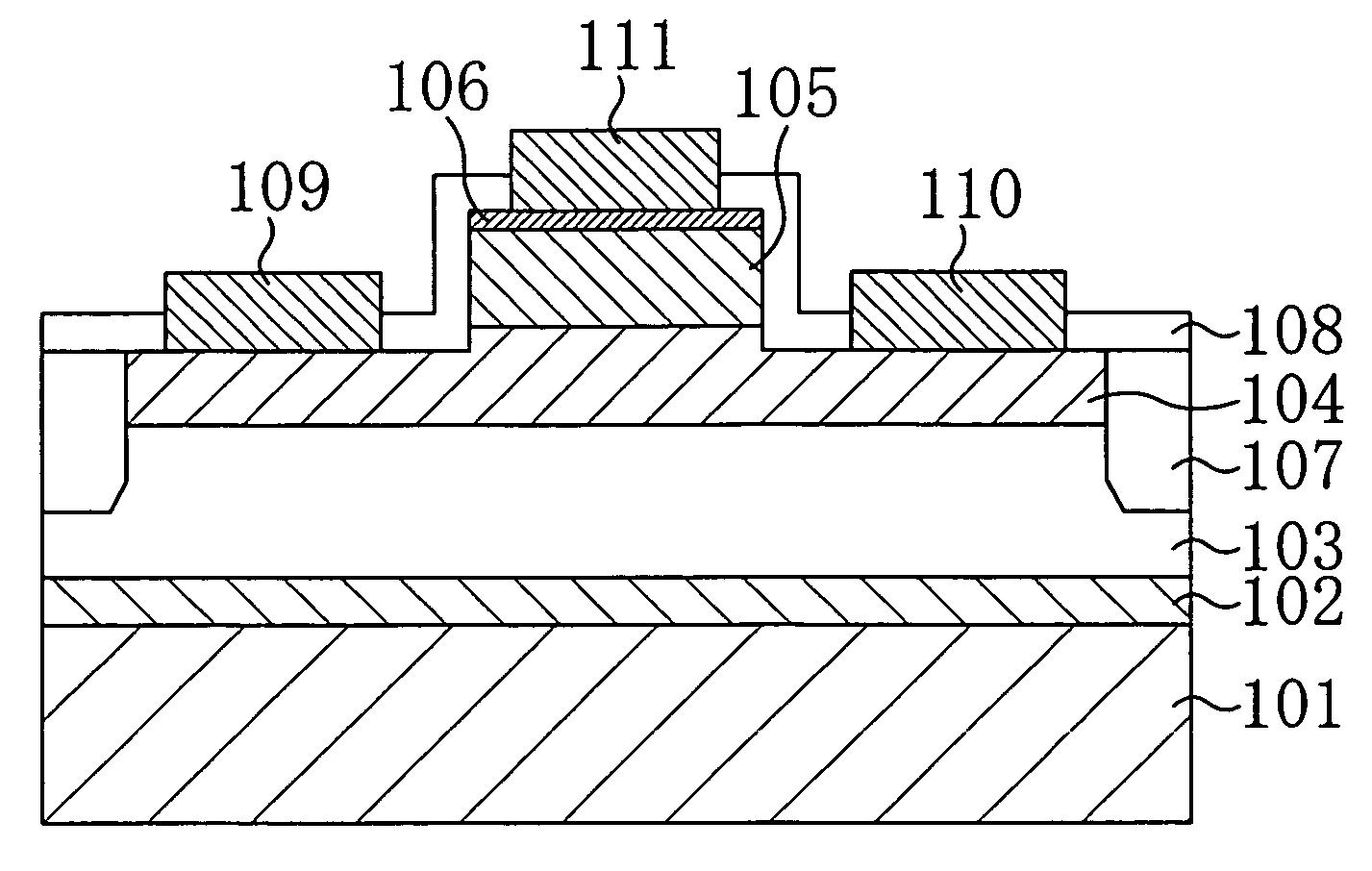

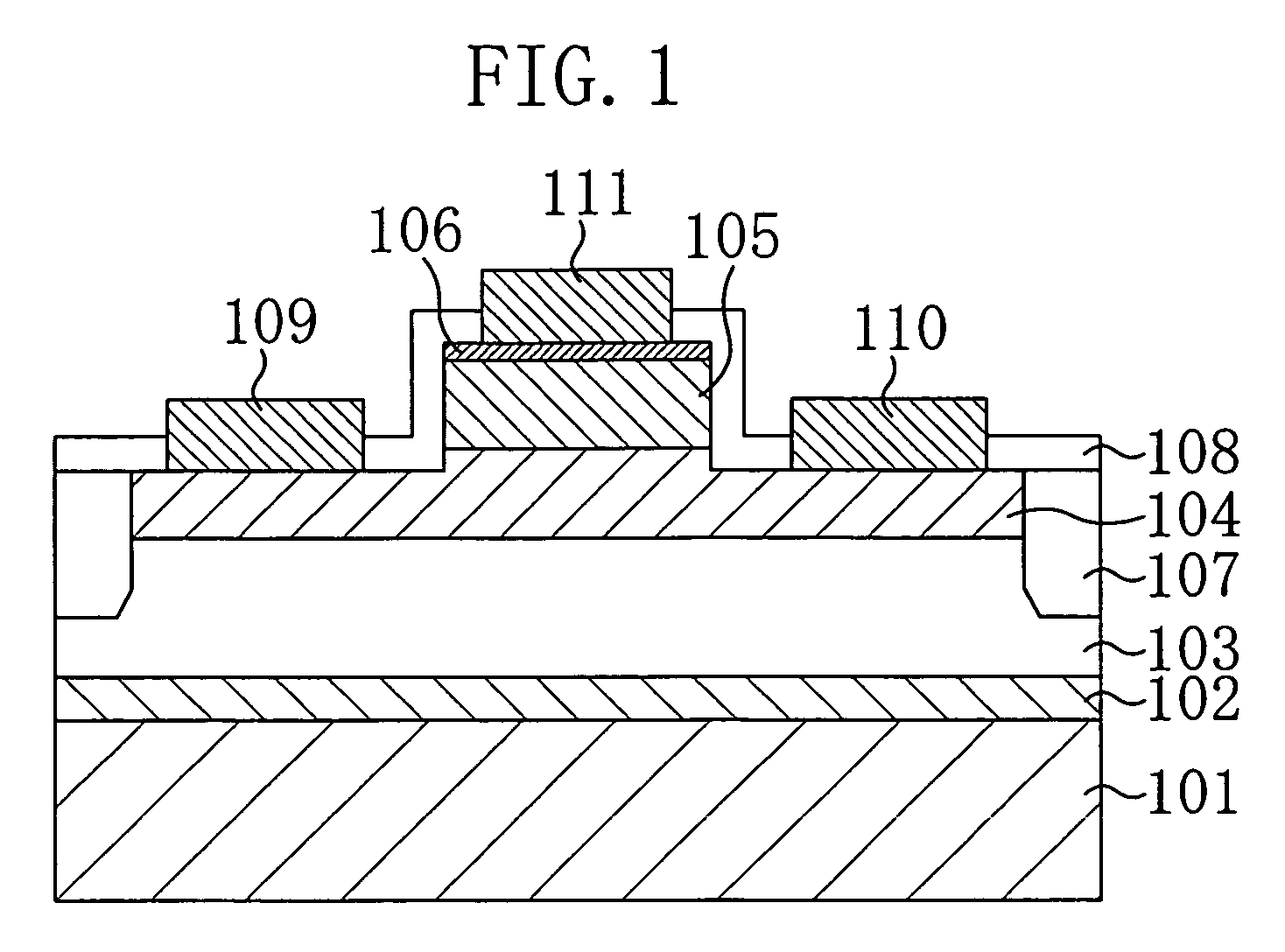

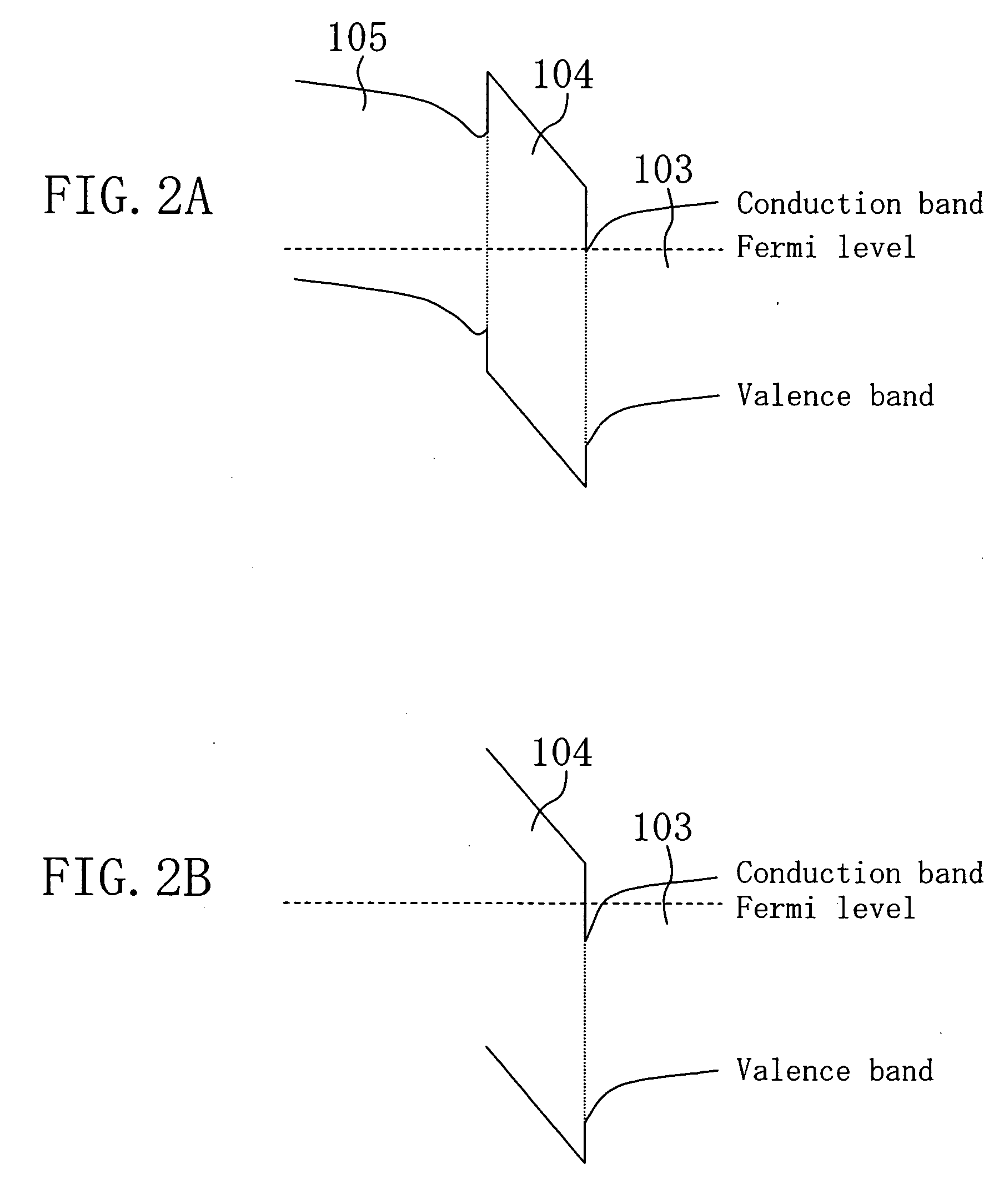

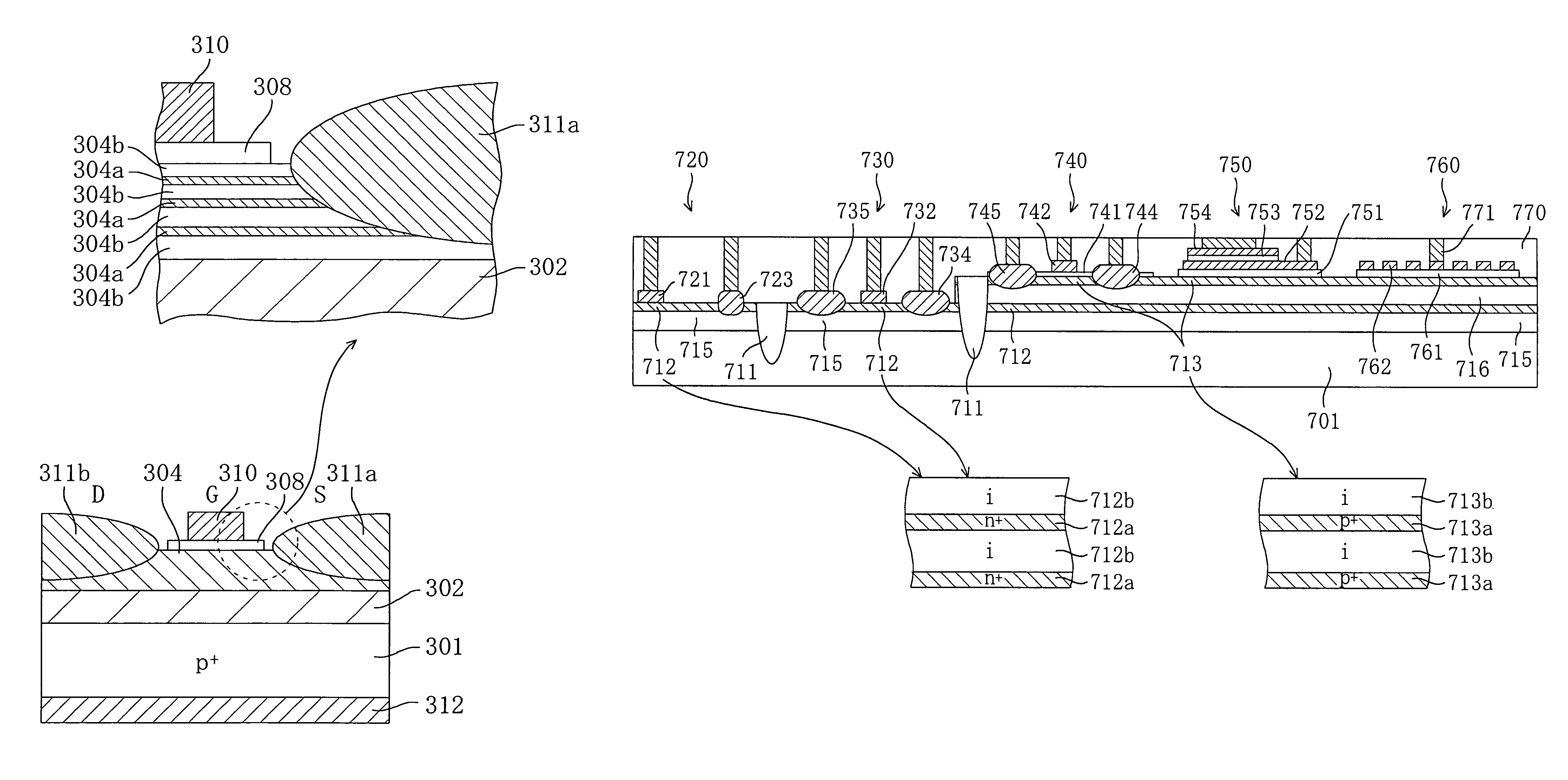

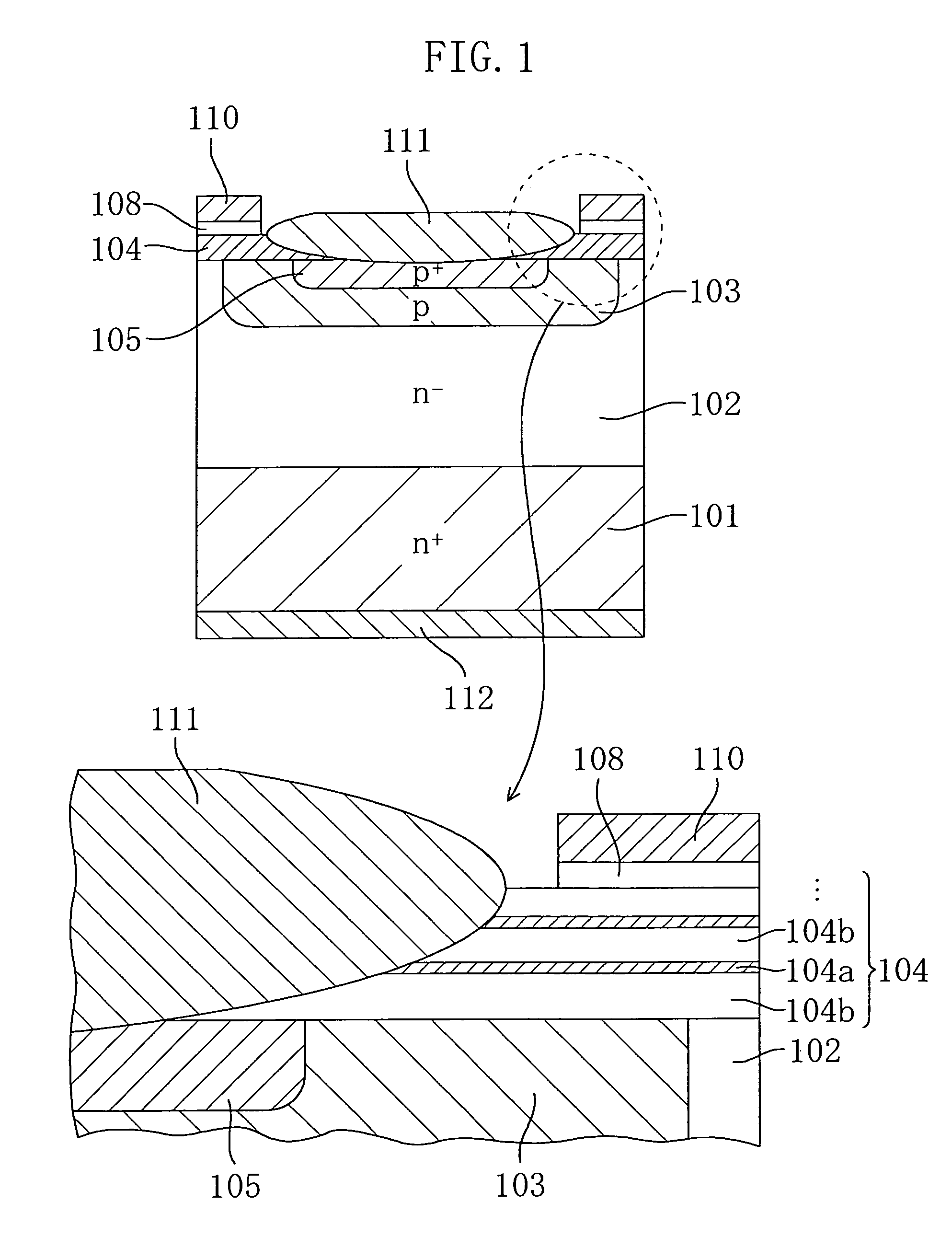

Semiconductor device and method for manufacturing same

InactiveUS7507999B2Improve breakdown voltageReduce lossTransistorSolid-state devicesHigh resistanceSic substrate

An accumulation-mode MISFET comprises: a high-resistance SiC layer 102 epitaxially grown on a SiC substrate 101; a well region 103; an accumulation channel layer 104 having a multiple δ-doped layer formed on the surface region of the well region 103; a contact region 105; a gate insulating film 108; and a gate electrode 110. The accumulation channel layer 104 has a structure in which undoped layers 104b and δ-doped layers 104a allowing spreading movement of carriers to the undoped layers 104b under a quantum effect are alternately stacked. A source electrode 111 is provided which enters into the accumulation channel layer 104 and the contact region 105 to come into direct contact with the contact region 105. It becomes unnecessary that a source region is formed by ion implantation, leading to reduction in fabrication cost.

Owner:PANASONIC CORP

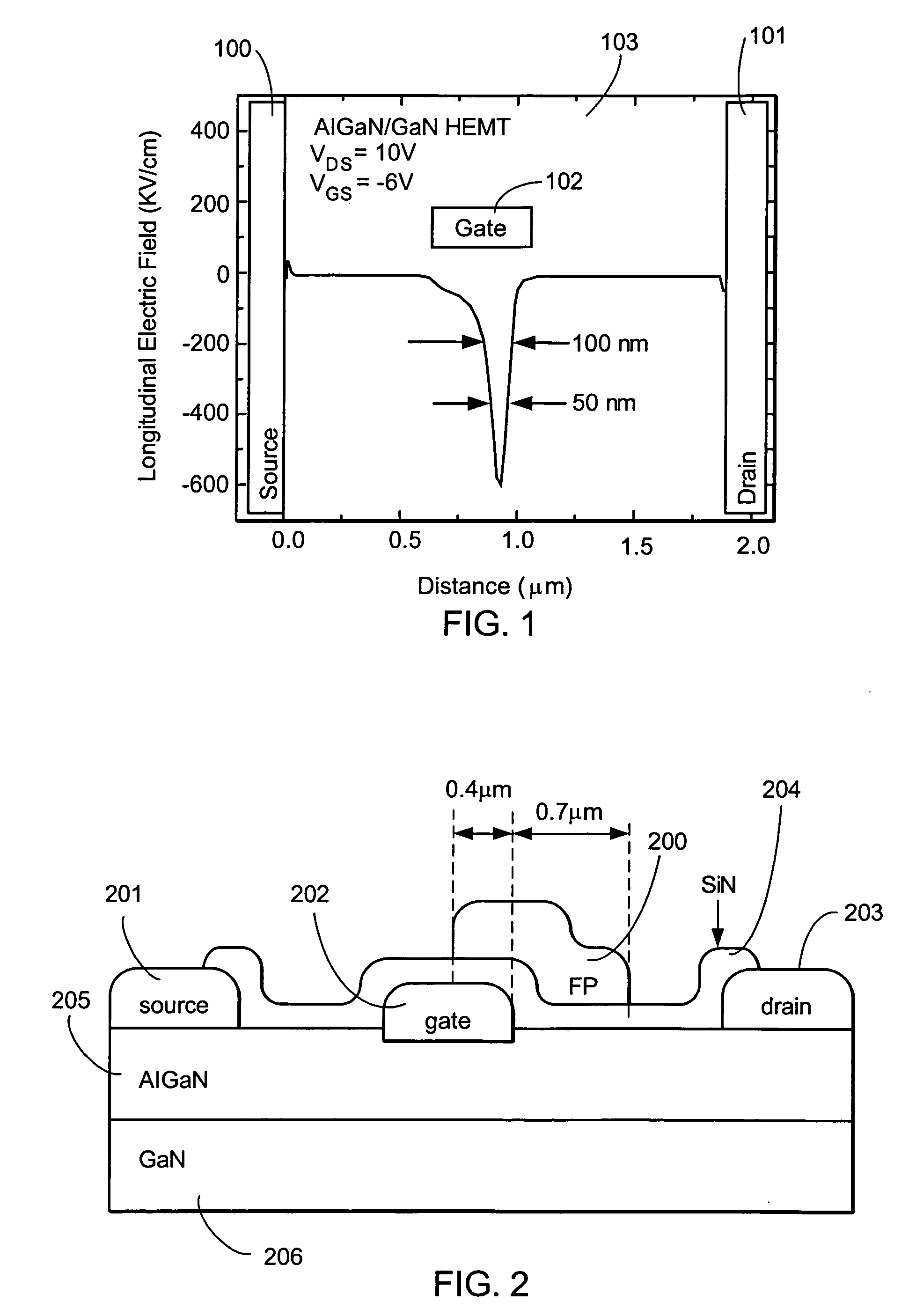

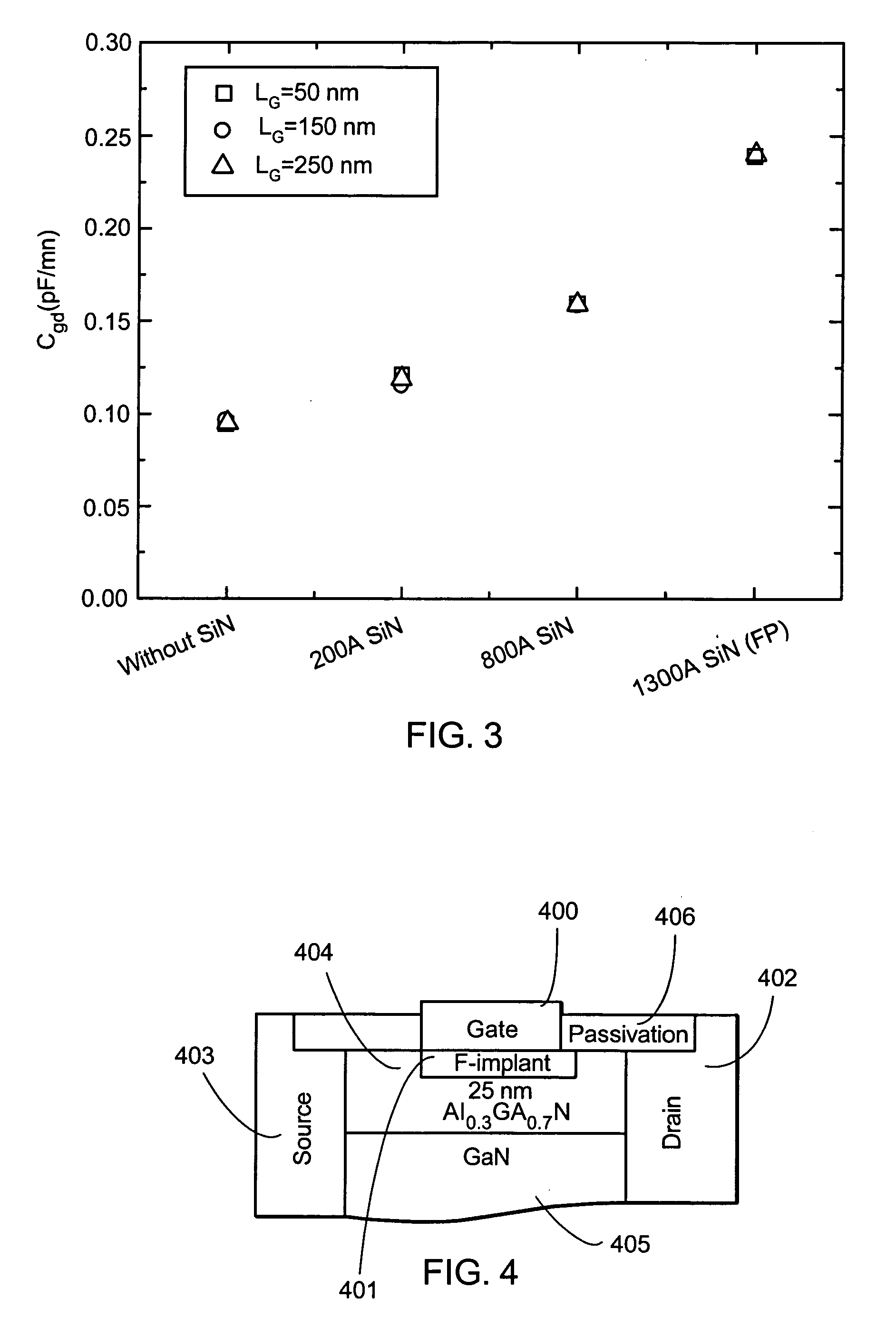

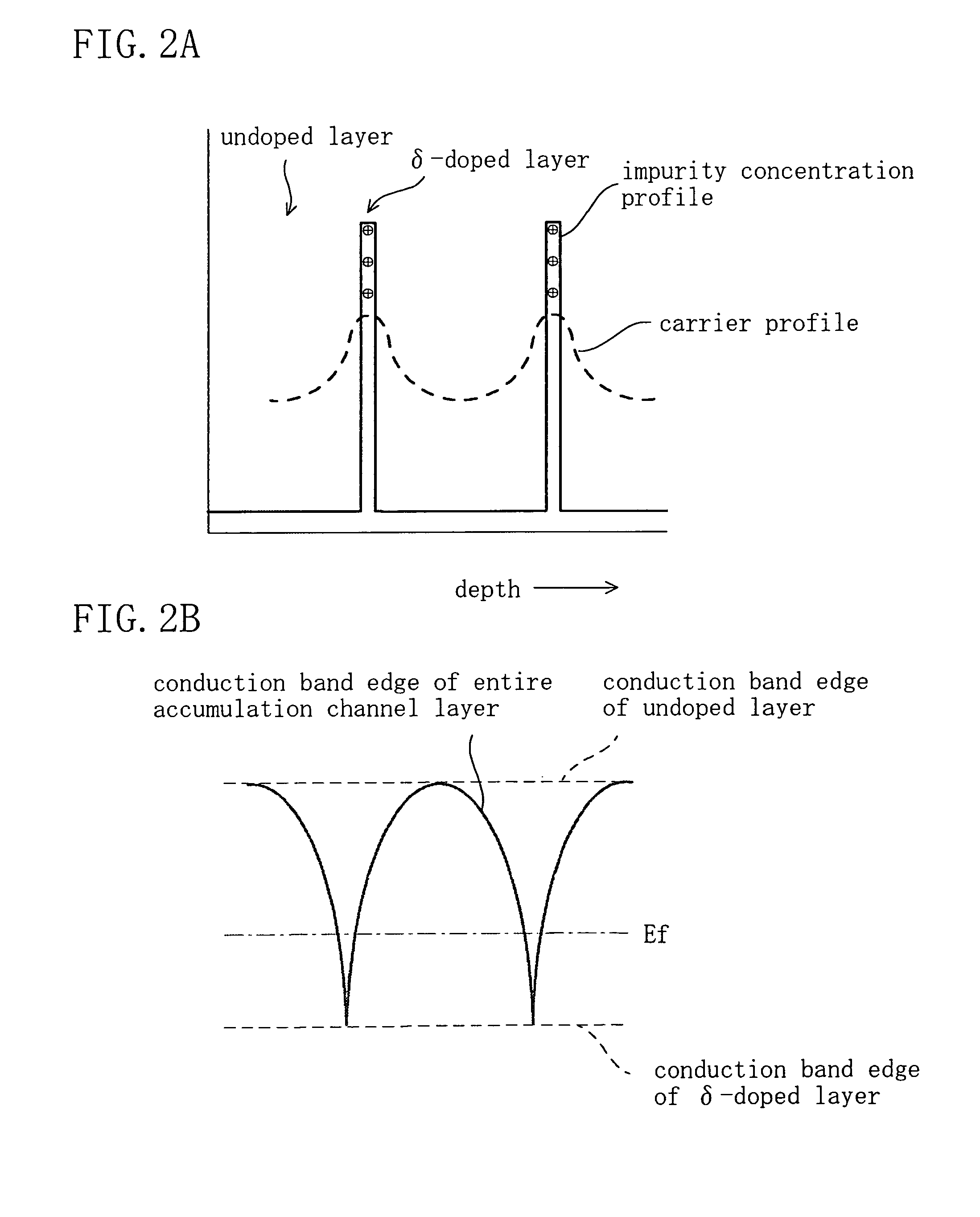

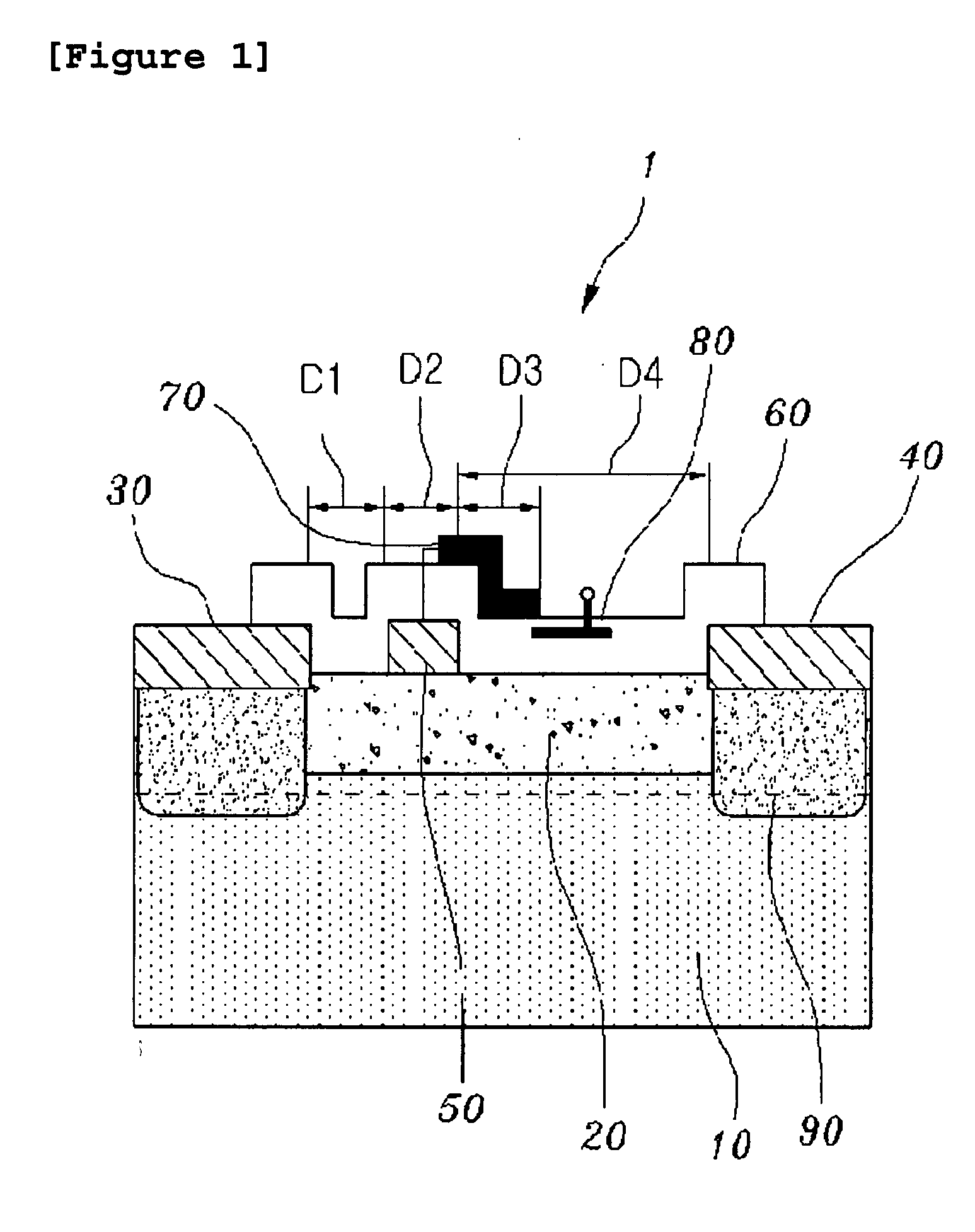

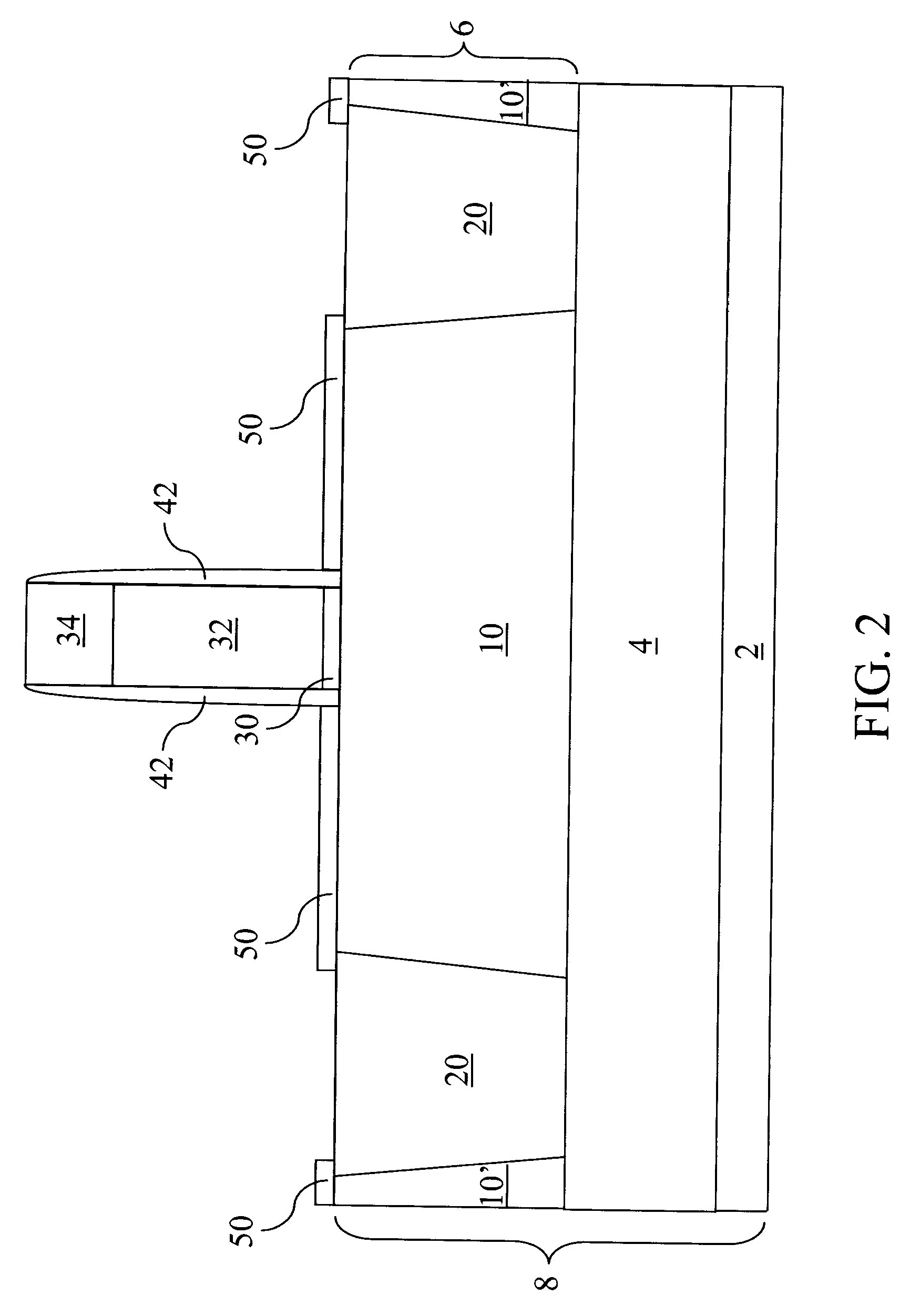

Gallium nitride high electron mobility transistor having inner field-plate for high power applications

InactiveUS20080073670A1Reduce peak valueHigh frequency performanceSemiconductor devicesPhysicsCapacitance

A gallium nitride high electron mobility transistor, in which an inner field-plate is disposed between the gate and drain of the high electron mobility transistor, so that an electric field is distributed between gate and drain regions to reduce a peak value and to reduce gate leakage current while maintaining high frequency performance, thus obtaining a high breakdown voltage, reducing the capacitance between the gate and the drain attributable to a shielding effect, and improving linearity and high power and high frequency characteristics through variation in the input voltage of the inner field-plate. The gallium-nitride high electron mobility transistor includes a gallium nitride buffer layer. An aluminum gallium-nitride barrier layer is formed on the buffer layer. A source electrode is placed on the barrier layer. A drain electrode is placed on the barrier layer to be spaced apart from the source electrode. A gate electrode is placed on a top of the barrier layer to be spaced apart from the source electrode and the drain electrode. A dielectric layer is deposited on the top of the barrier layer. An electric field electrode is formed on the dielectric layer located on the gate electrode. An inner field-plate is formed in the dielectric layer to be spaced apart from the gate electrode and the drain electrode.

Owner:KOREA ADVANCED INST OF SCI & TECH

Method for fabricating a transistor configuration including trench transistor cells having a field electrode, trench transistor, and trench configuration

ActiveUS7005351B2Increase variabilityReduce capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A method for fabricating a transistor configuration including at least one trench transistor cell has a gate electrode and a field electrode disposed in a trench below the gate electrode. The trenches are formed in a semiconductor substrate. A drift zone, a channel zone, and a source zone are in each case provided in the semiconductor substrate. According to the invention, the source zone and / or the channel zone are formed at the earliest after the introduction of the trenches into the semiconductor substrate by implantation and diffusion.

Owner:INFINEON TECH AG

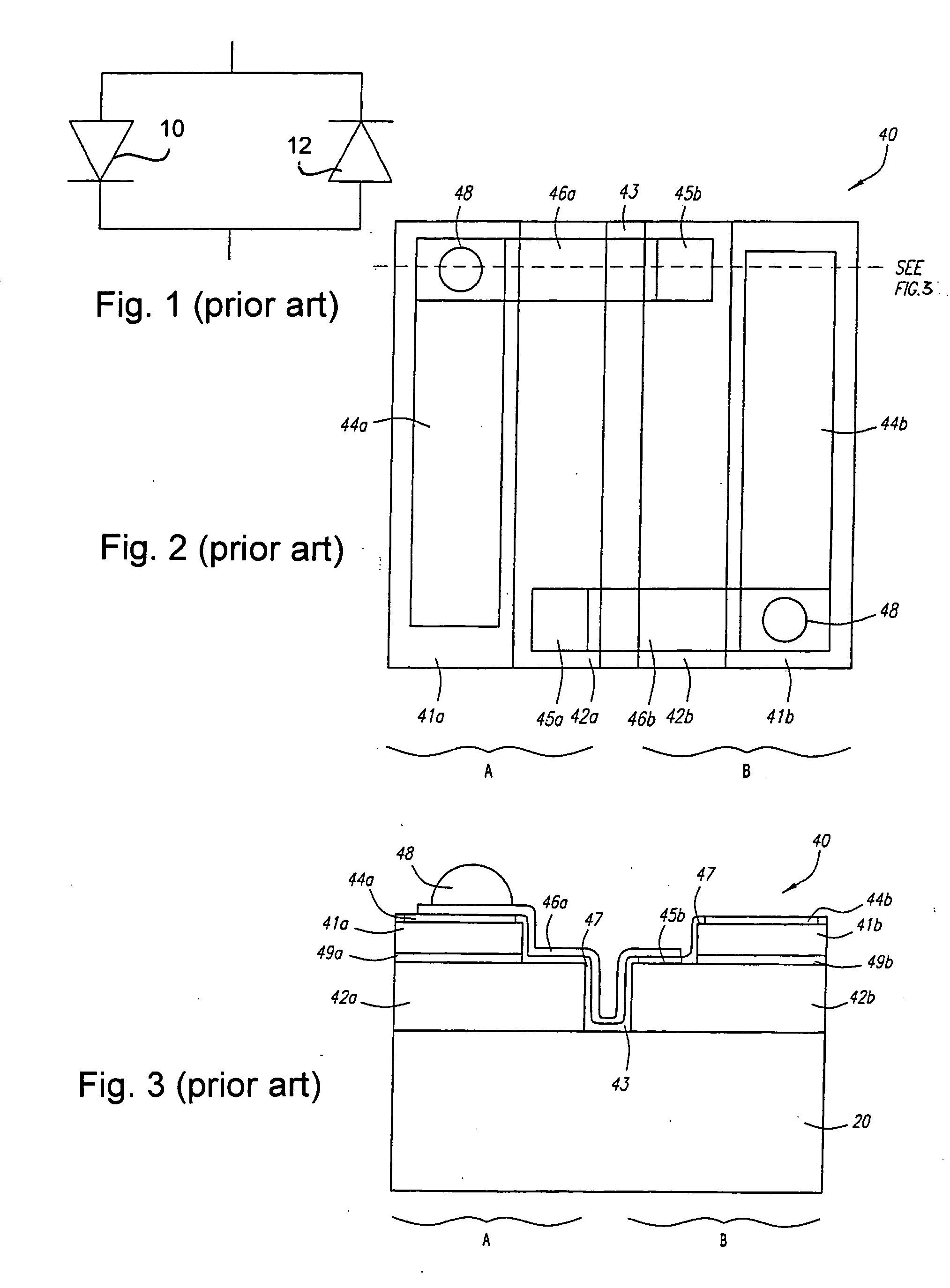

LED chip with integrated fast switching diode for ESD protection

ActiveUS20050274956A1Reduced series resistanceImprove breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsLight-emitting diode

A relatively small ESD protection diode is formed on the same chip as a light emitting diode. In one embodiment, the ESD diode is a mesa-type diode isolated from the light emitting diode by a trench. To reduce the series resistance of the ESD diode, the PN junction and metal contact to the semiconductor material is made long and expands virtually the width of the chip. Various configurations of the PN junction and the N and P metal contacts for the ESD diode are described for increasing the breakdown voltage and for improved testing.

Owner:JANSSEN PHARMA NV +1

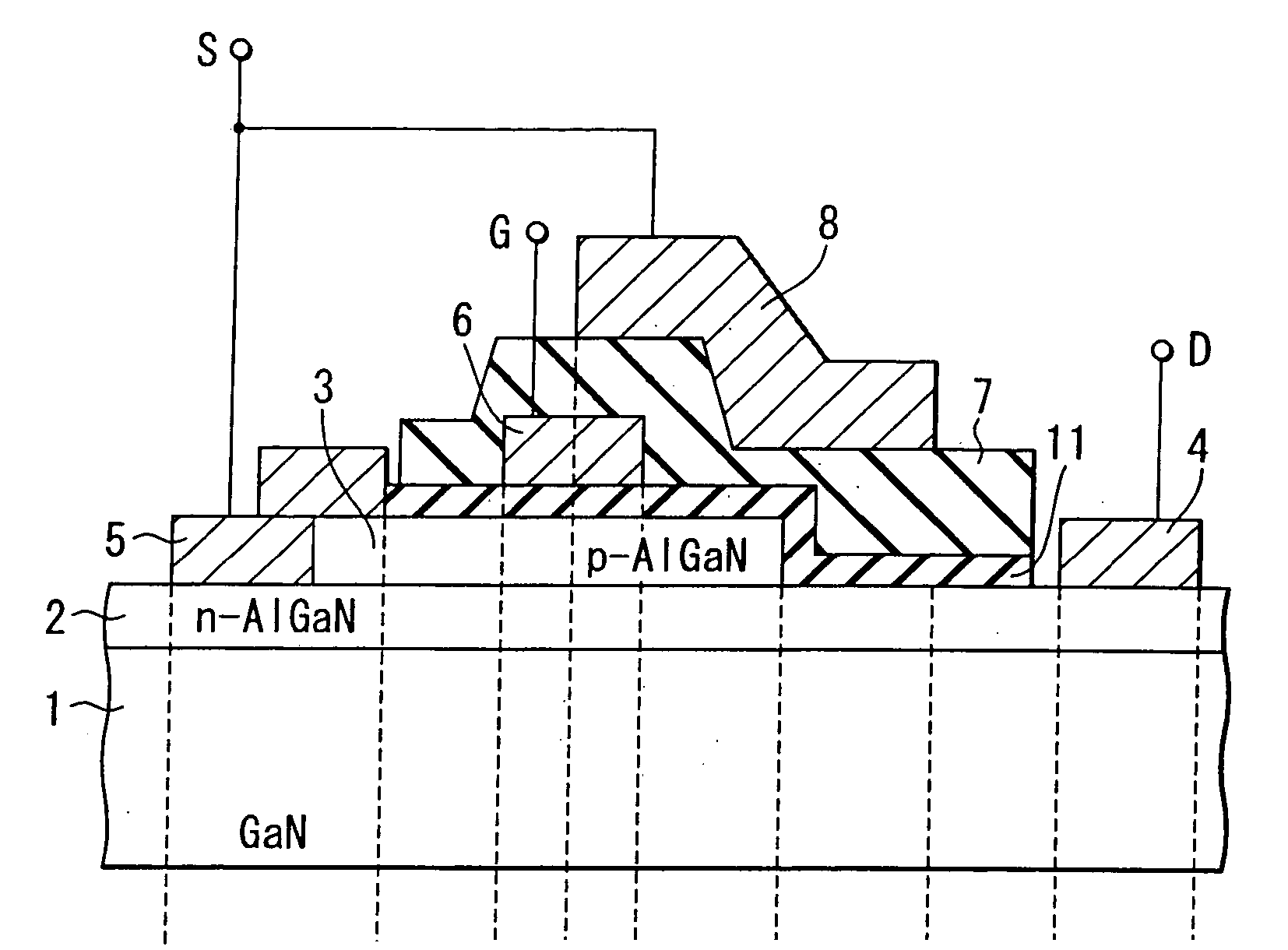

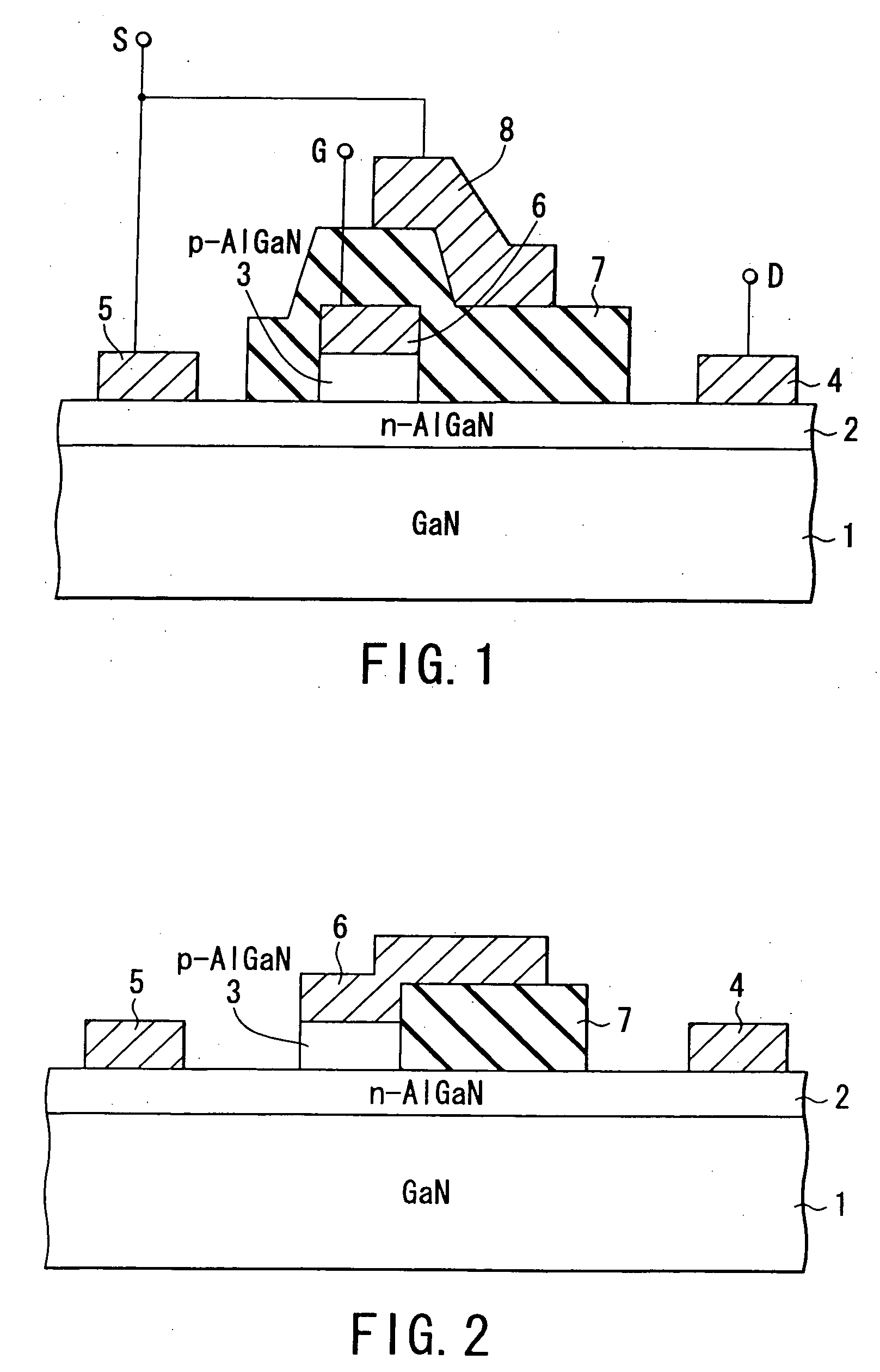

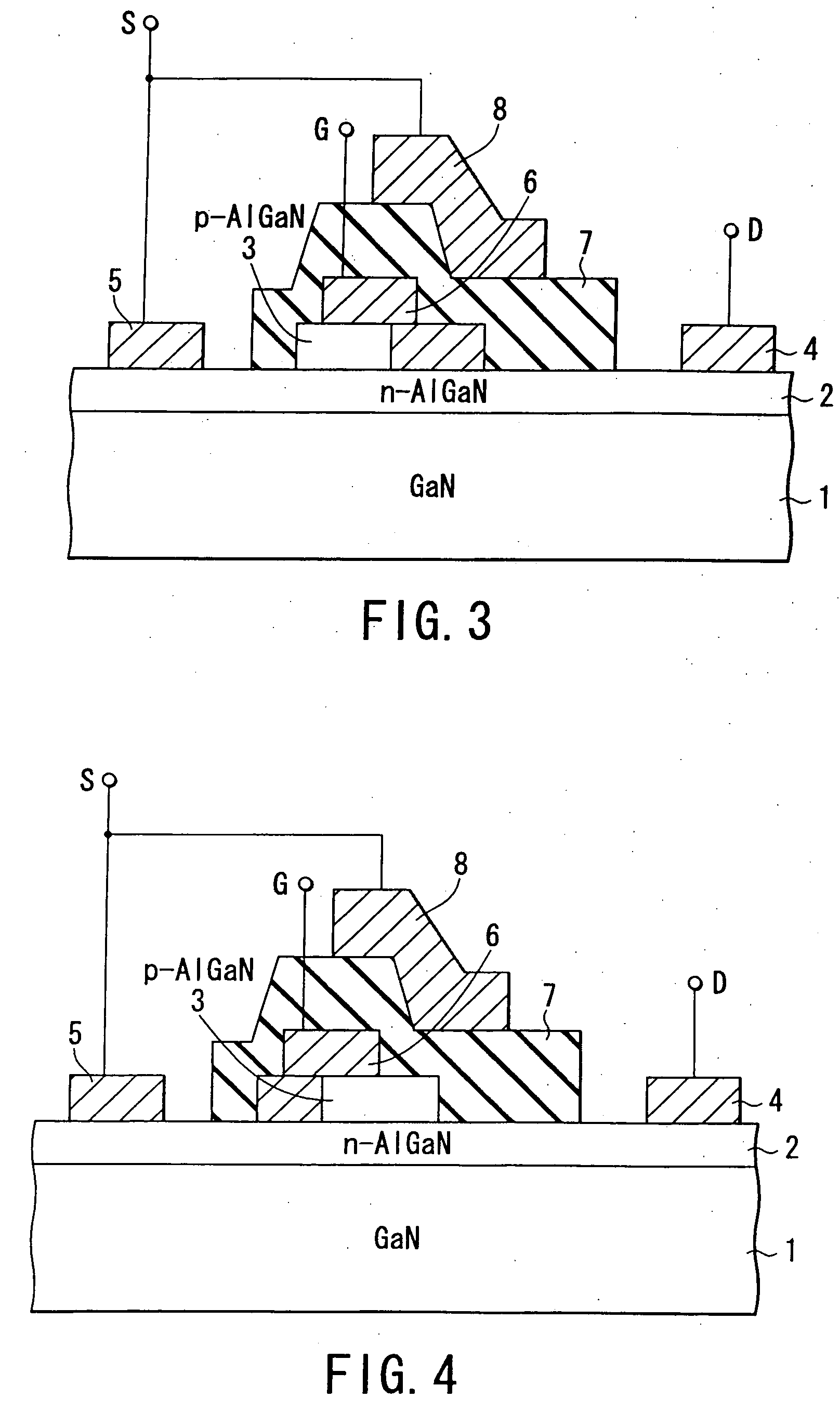

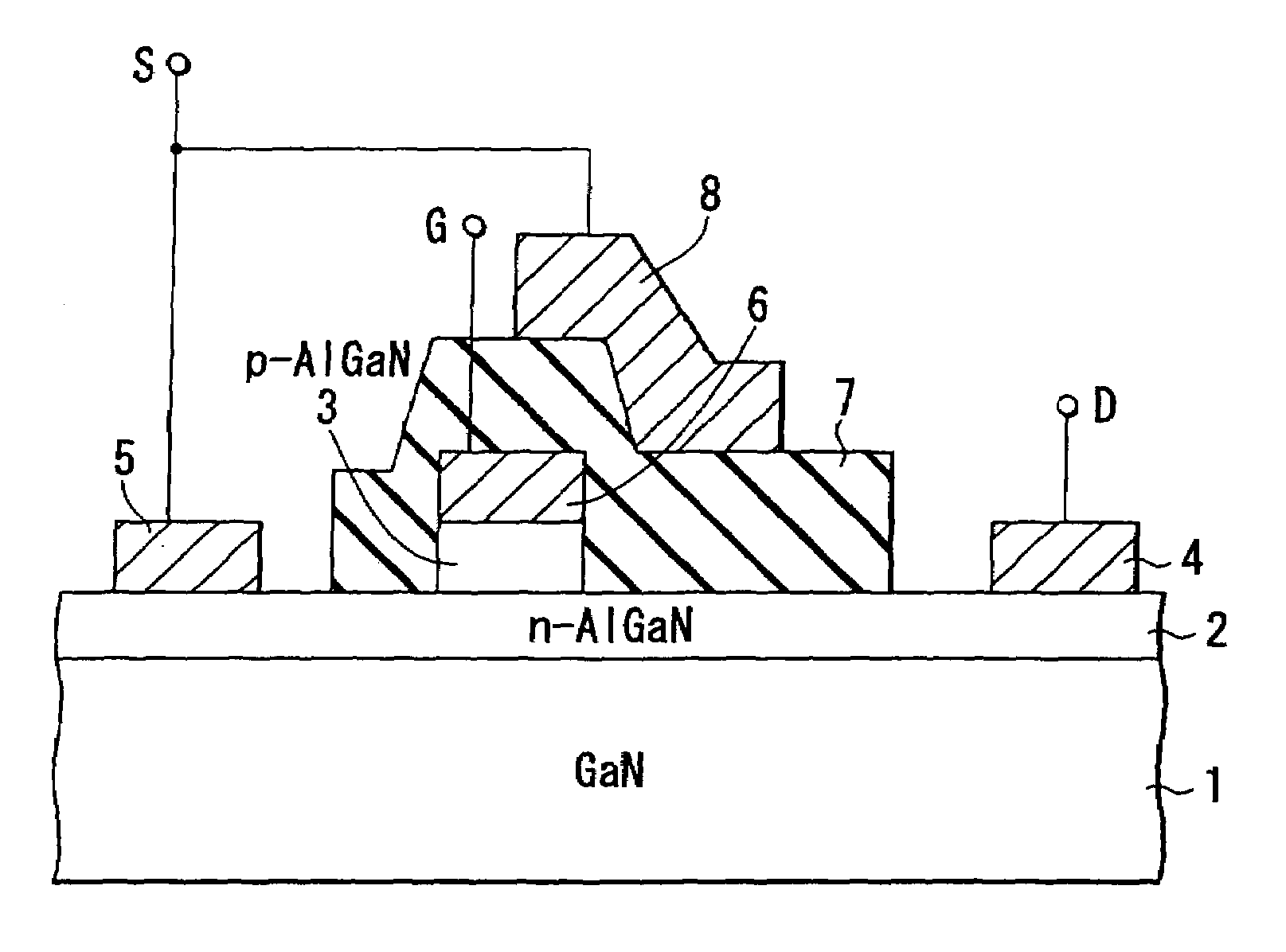

Power semiconductor device

InactiveUS20050110042A1Improve rendering capabilitiesResistanceTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceNon doped

A power semiconductor device including a non-doped GaN channel layer, an n-type Al0.2Ga0.8N barrier layer formed on the channel layer, a p-type Al0.1Ga0.9N semiconductor layer selectively formed on the barrier layer, a drain electrode positioned at one of both sides of the semiconductor layer and formed on the barrier layer, an insulating film formed on the barrier layer adjacent to the semiconductor layer between at least semiconductor layer and drain electrode, and a field plate electrode formed on the insulating film.

Owner:KK TOSHIBA

Semiconductor device and method of manufacturing semiconductor device

InactiveUS20050098826A1Improve breakdown voltageEfficiently obtainedSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

A method of manufacturing a semiconductor device in which a trench groove is formed in a first conductivity type semiconductor layer, and a second conductivity type semiconductor layer is epitaxially grown so as to bury the trench groove. The second conductivity type semiconductor layer is then removed until a surface of the first conductivity type semiconductor layer is exposed. The first conductivity type semiconductor layer is epitaxially grown on the first conductivity type semiconductor layer and the second conductivity type semiconductor layer such that the thickness of the first conductivity type semiconductor layer increases by a length which is substantially the same as a depth of the trench groove. The first conductivity type semiconductor layer is selectively removed such that the second conductivity type semiconductor layer is exposed, and the epitaxially growing of the second conductivity type semiconductor layer is repeated through selectively removing the first conductivity type semiconductor layer.

Owner:KK TOSHIBA

Semiconductor device

ActiveUS20080164516A1Improve switching performanceReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor deviceImpurity

A semiconductor device includes a semiconductor layer of a first conductivity type and a semiconductor layer of a second conductivity type formed thereon. The semiconductor device also includes a body layer extending a first predetermined distance into the semiconductor layer of the second conductivity type and a pair of trenches extending a second predetermined distance into the semiconductor layer of the second conductivity type. Each of the pair of trenches consists essentially of a dielectric material disposed therein and a concentration of doping impurities present in the semiconductor layer of the second conductivity type and a distance between the pair of trenches define an electrical characteristic of the semiconductor device. The semiconductor device further includes a control gate coupled to the semiconductor layer of the second conductivity type and a source region coupled to the semiconductor layer of the second conductivity type.

Owner:MAXPOWER SEMICON INC

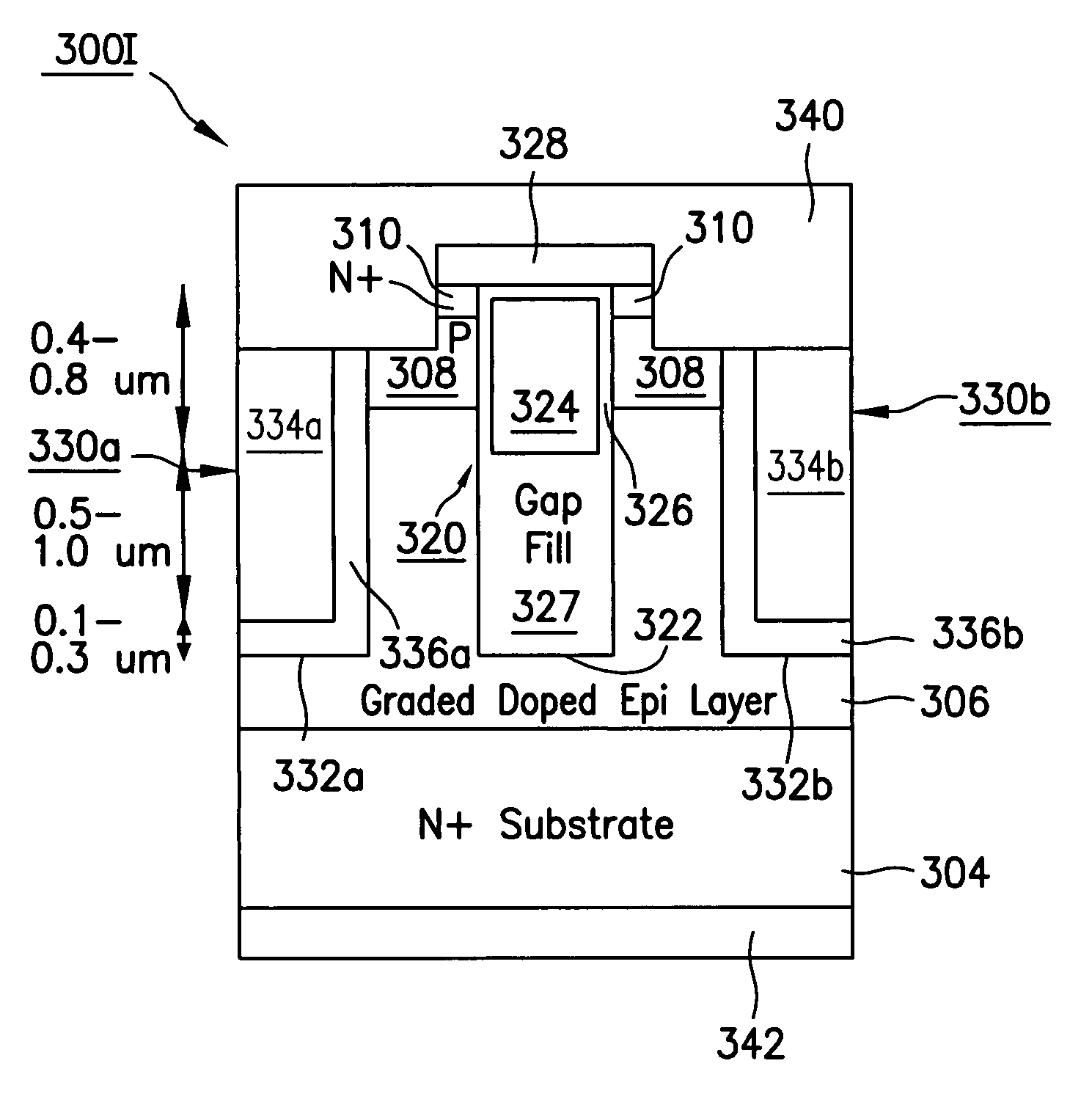

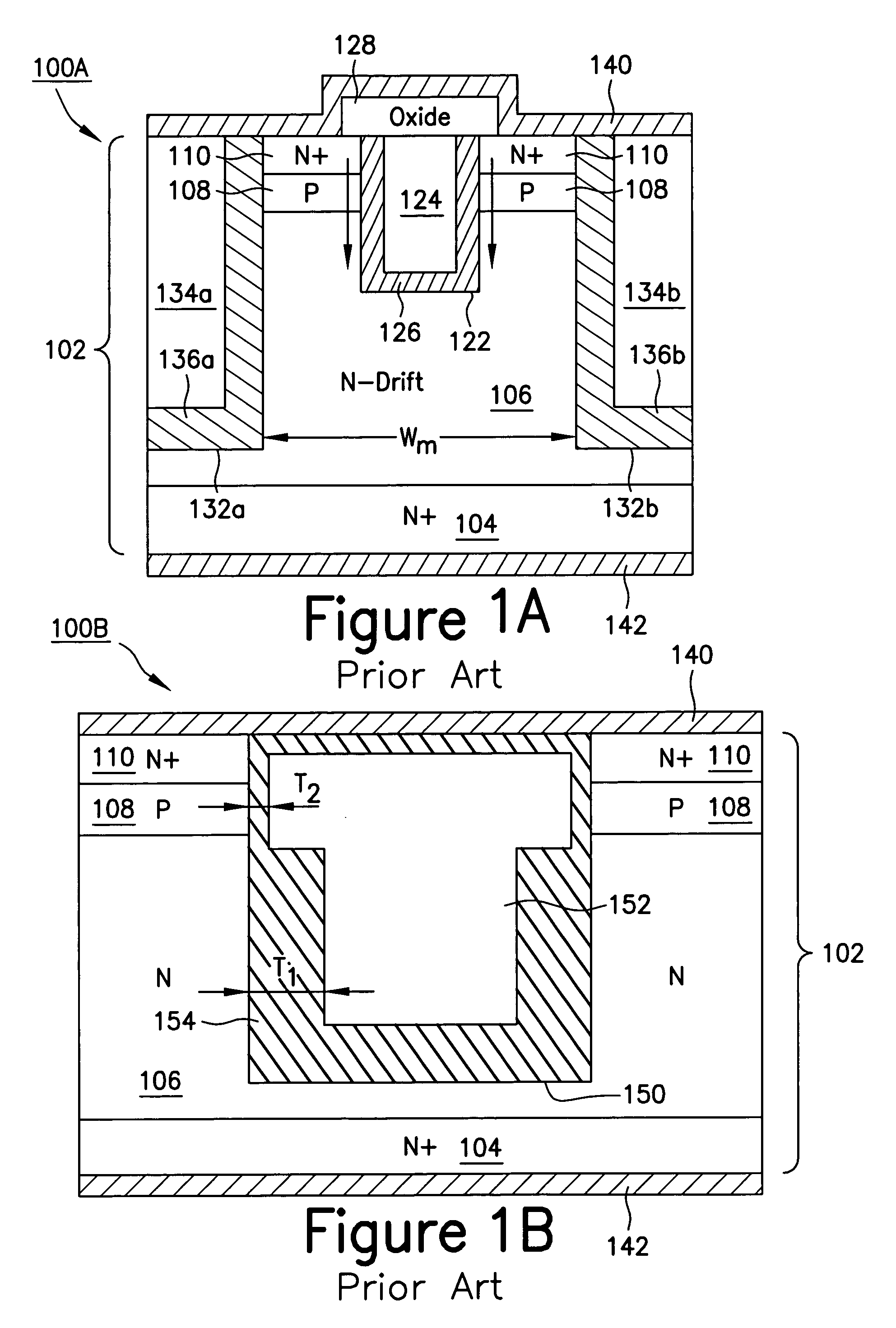

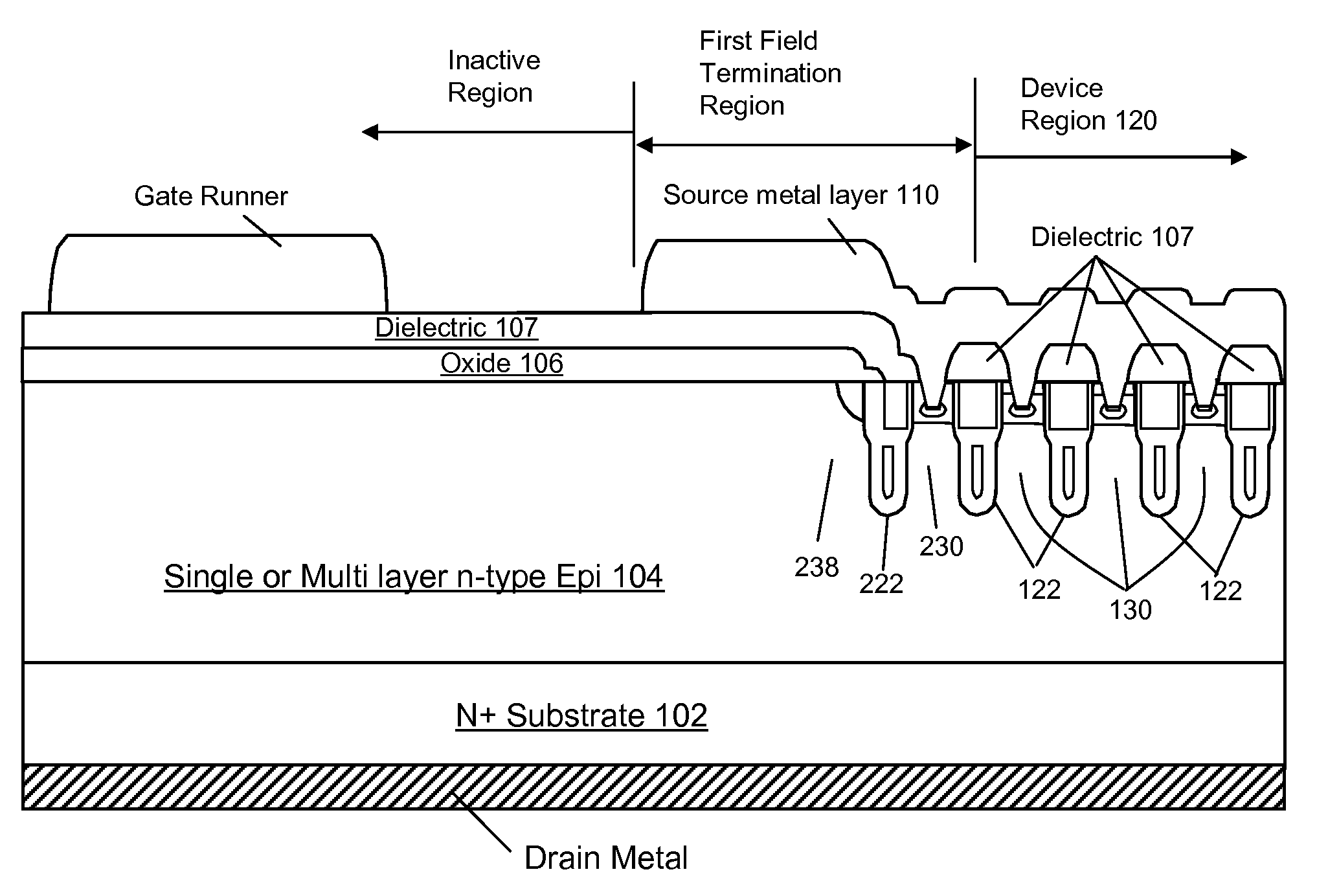

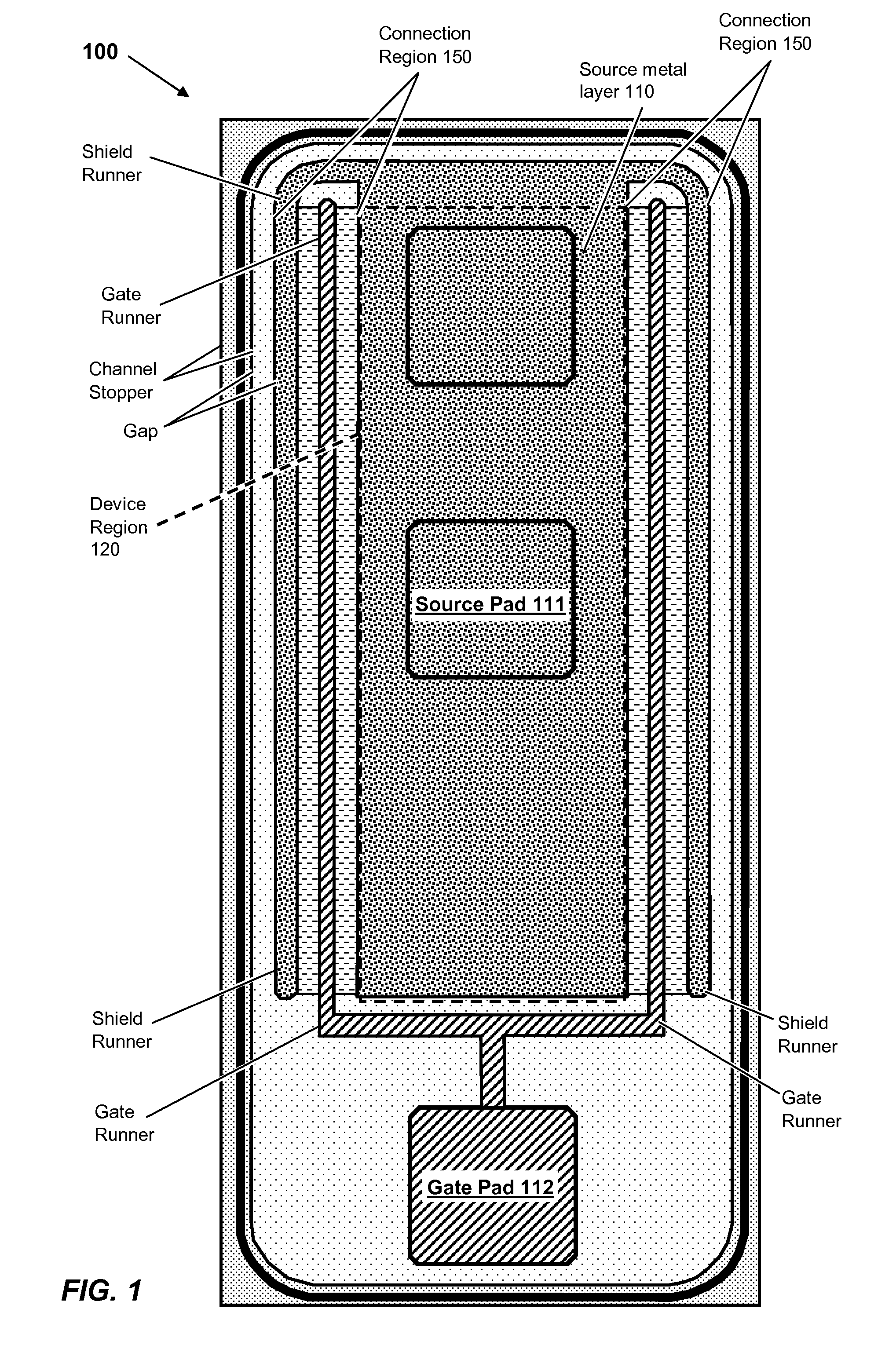

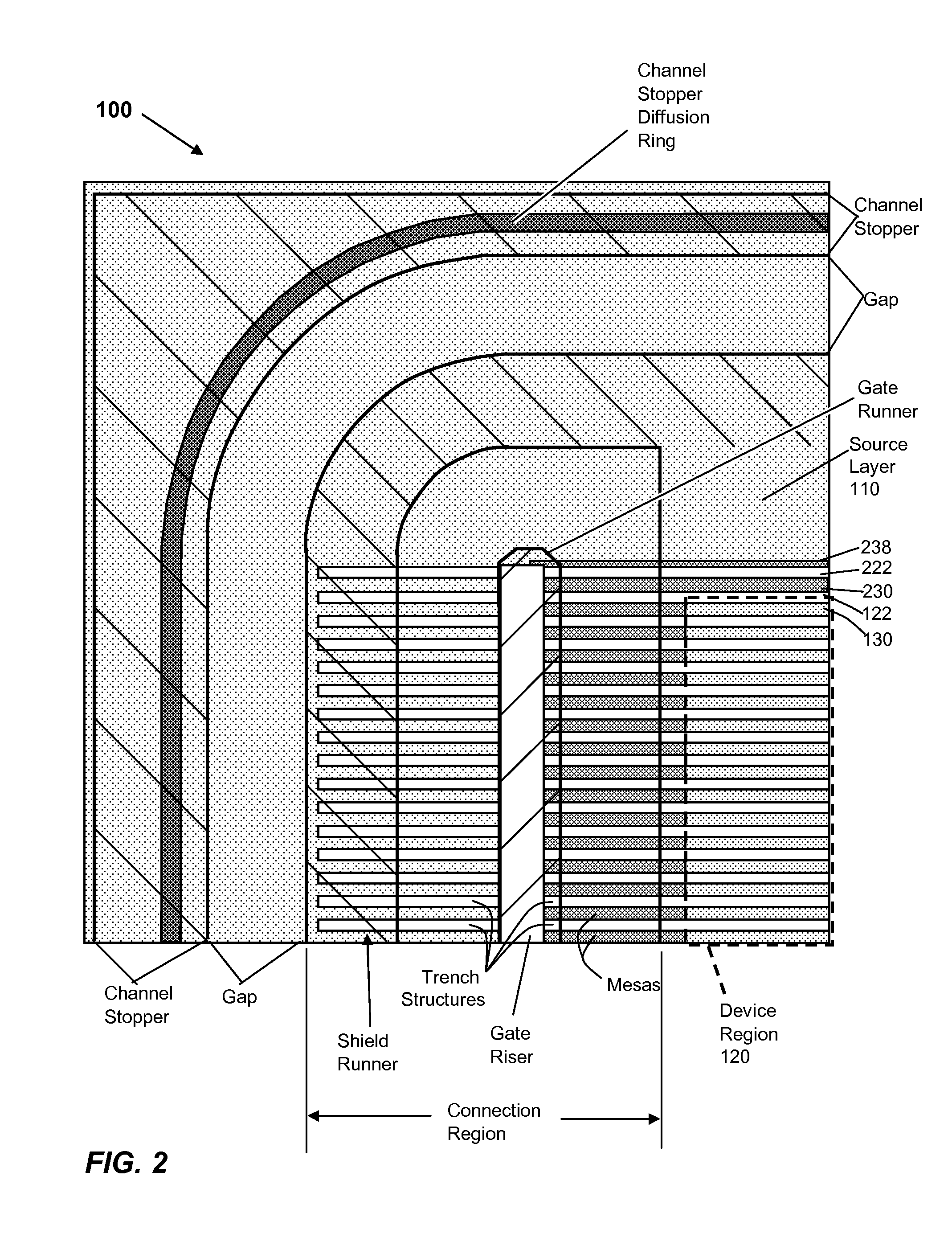

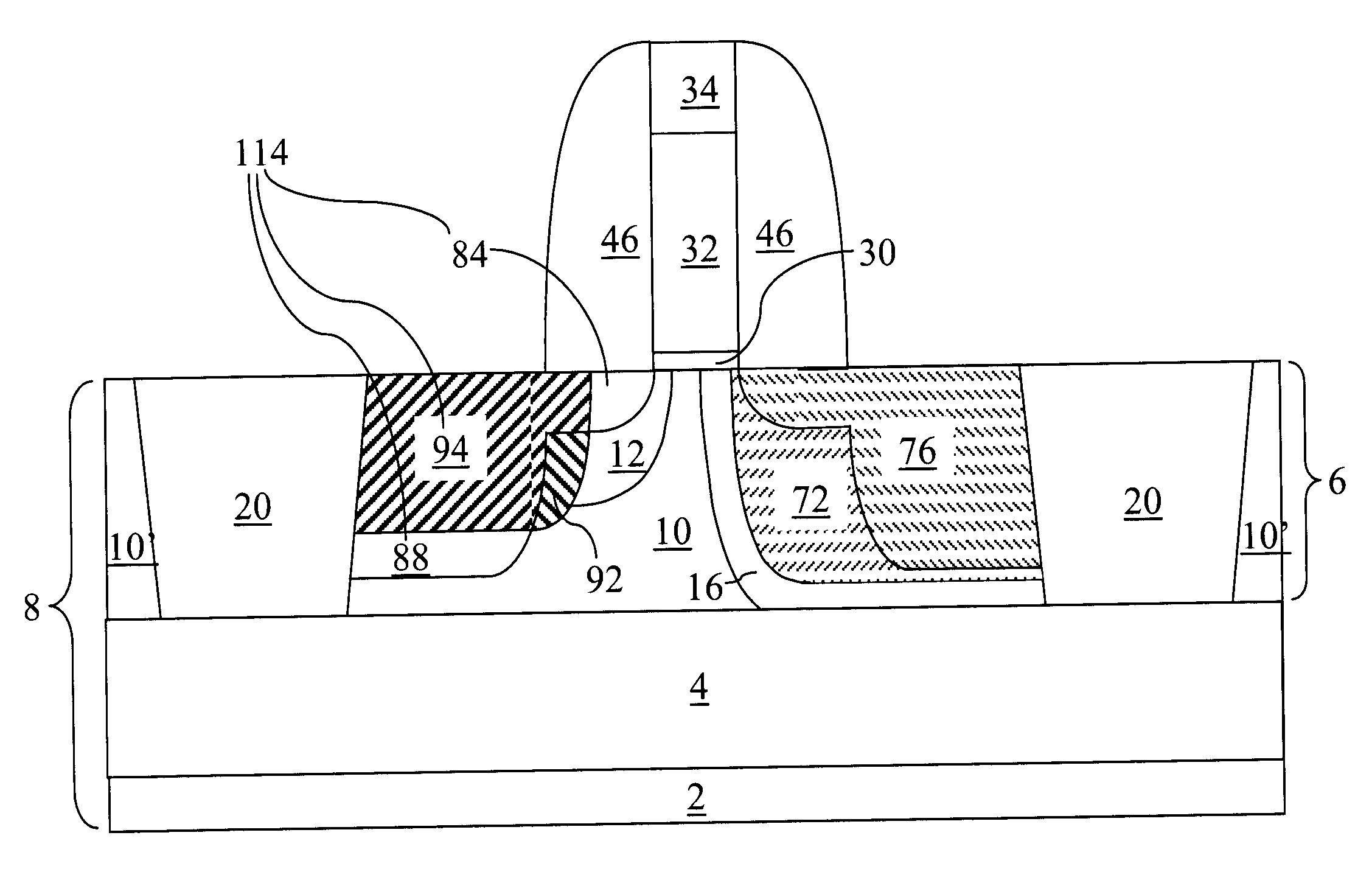

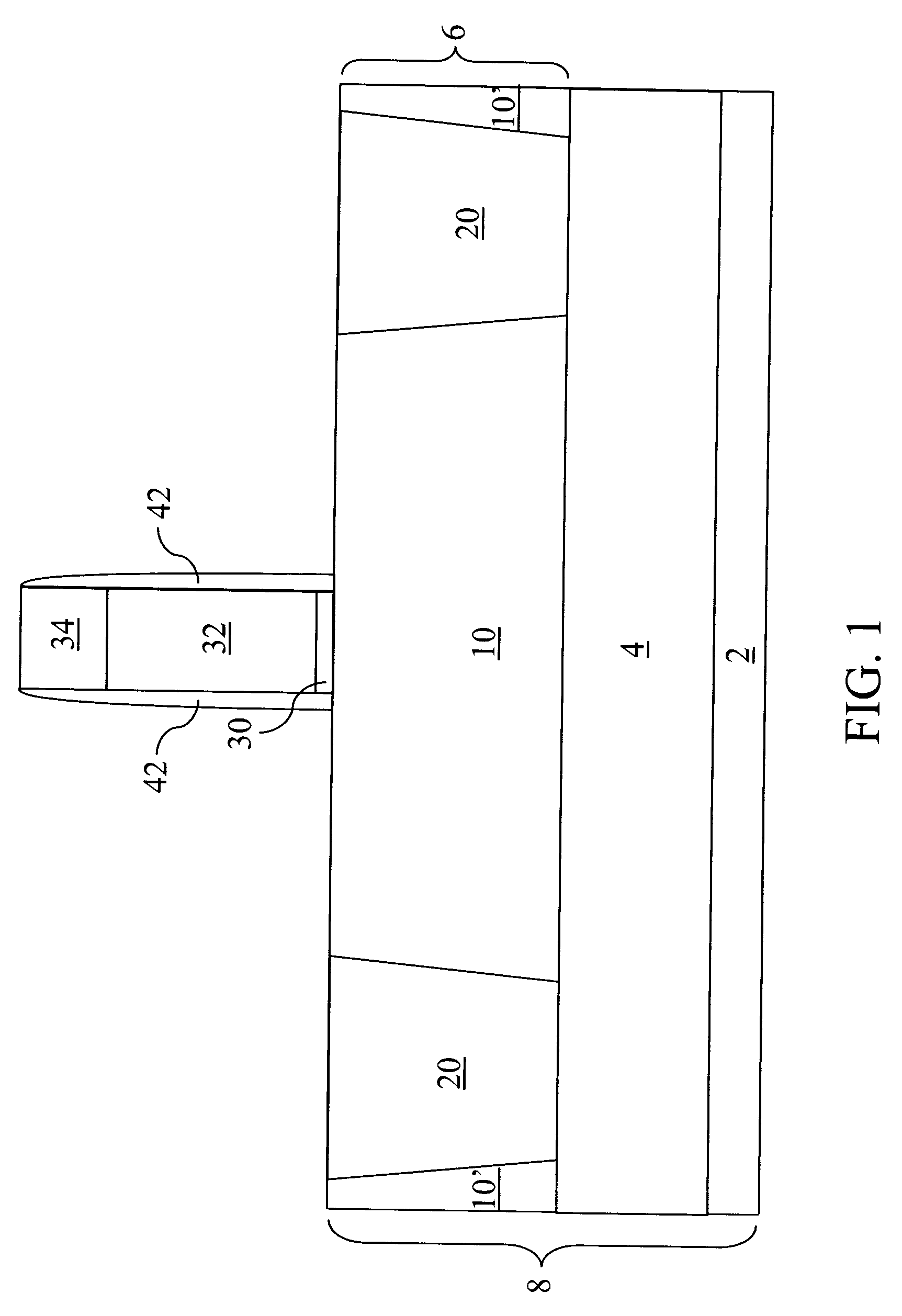

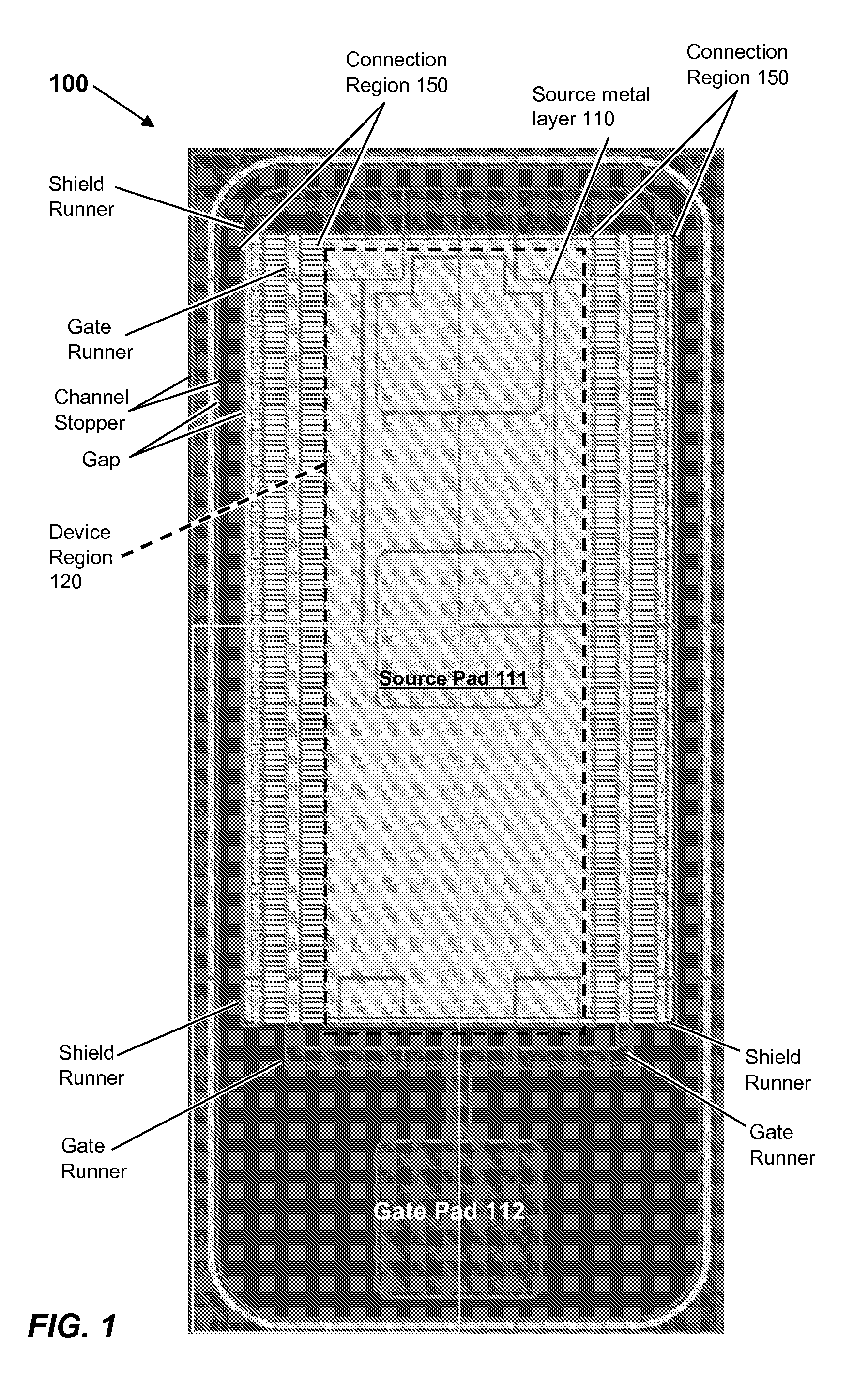

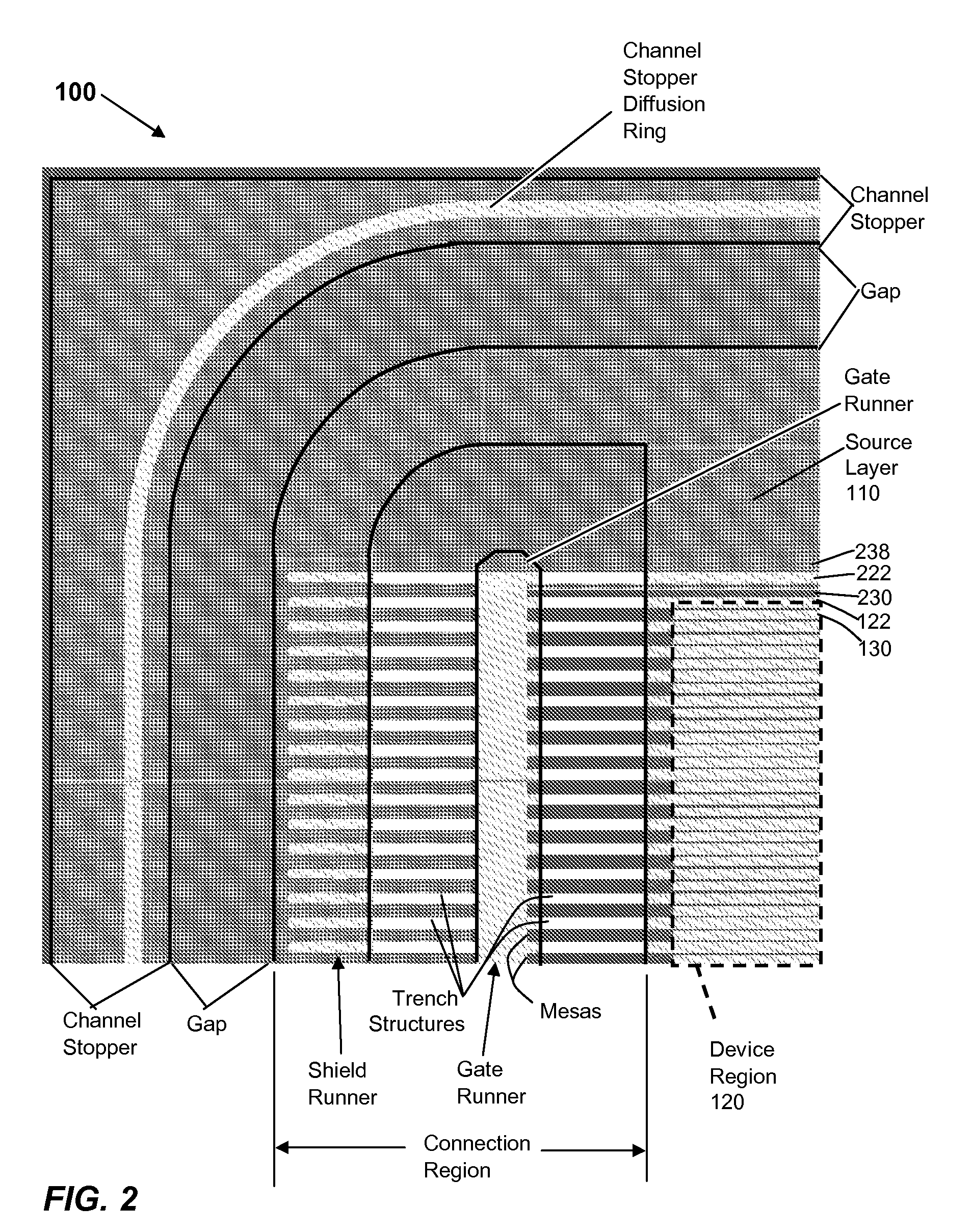

Trench-Based Power Semiconductor Devices with Increased Breakdown Voltage Characteristics

ActiveUS20100140689A1Improve breakdown voltageSolid-state devicesSemiconductor devicesPower semiconductor deviceSemiconductor

Exemplary power semiconductor devices with features providing increased breakdown voltage and other benefits are disclosed.

Owner:SEMICON COMPONENTS IND LLC

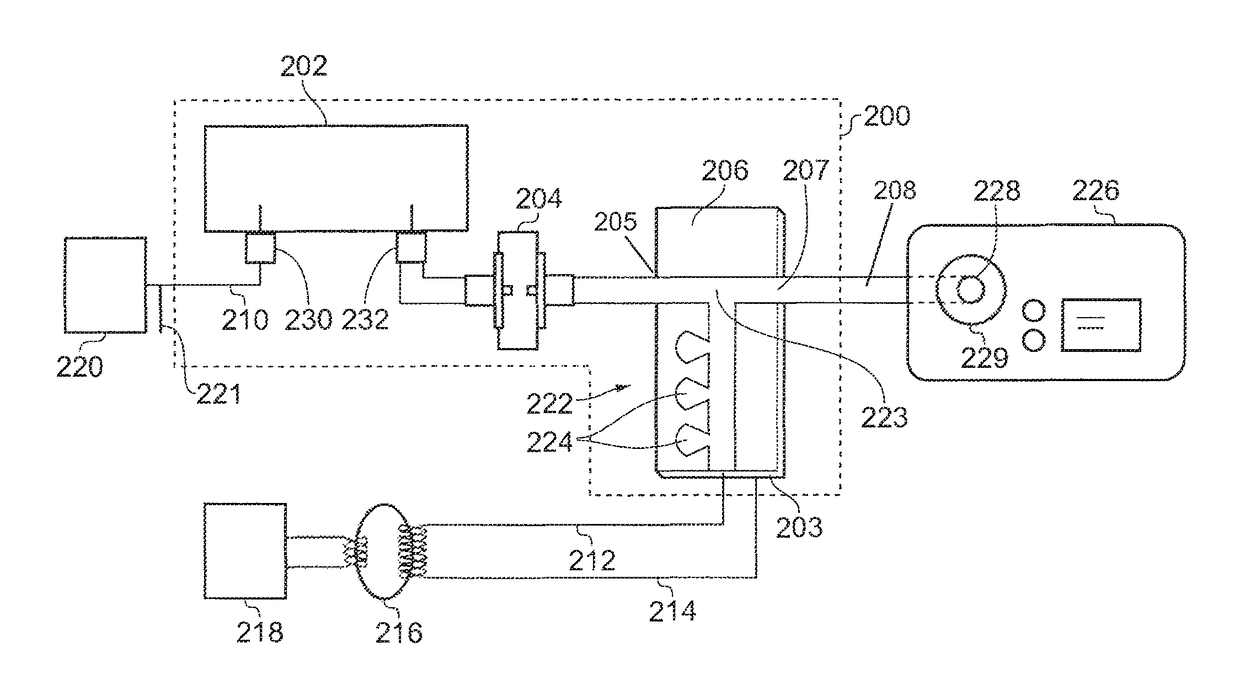

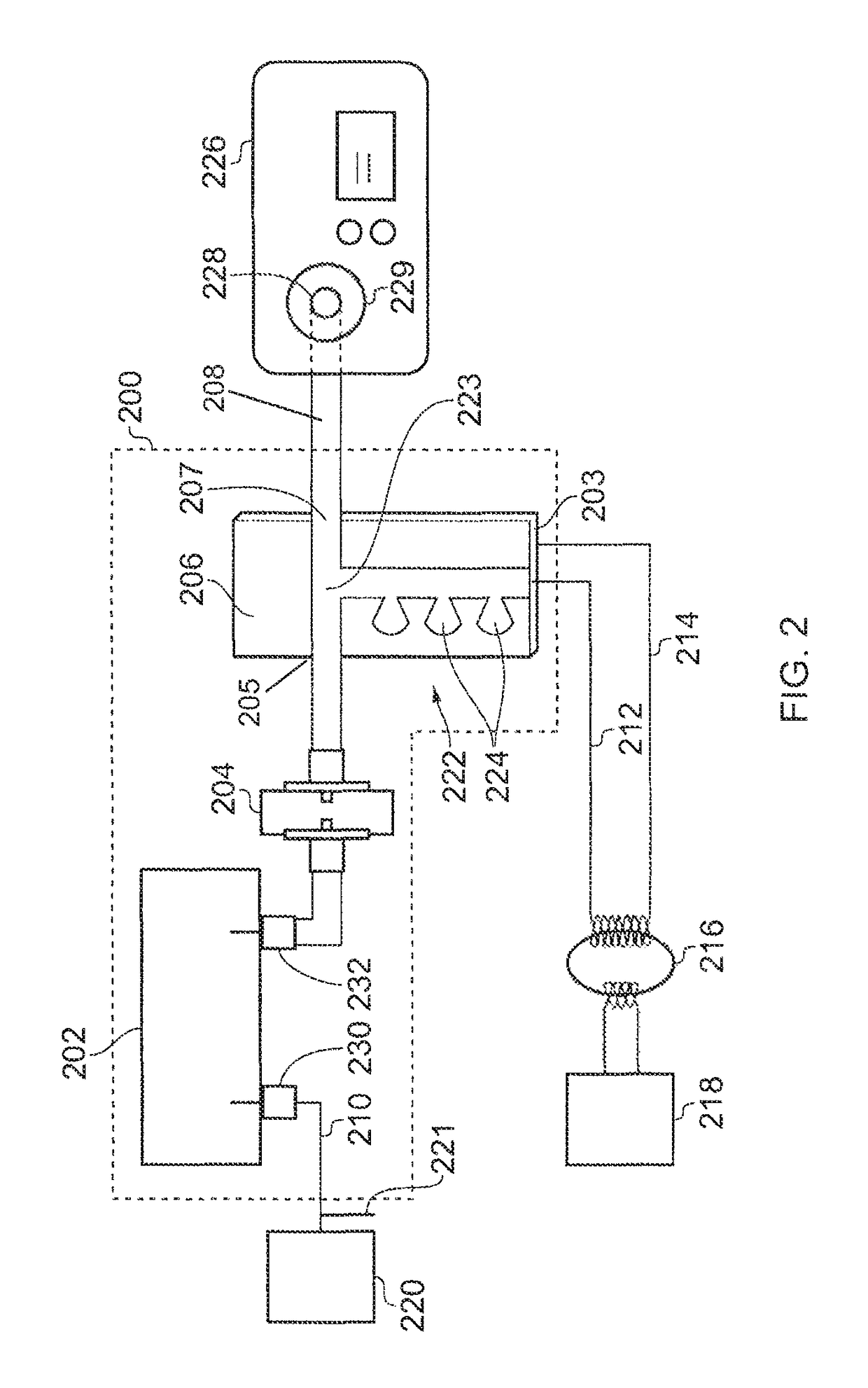

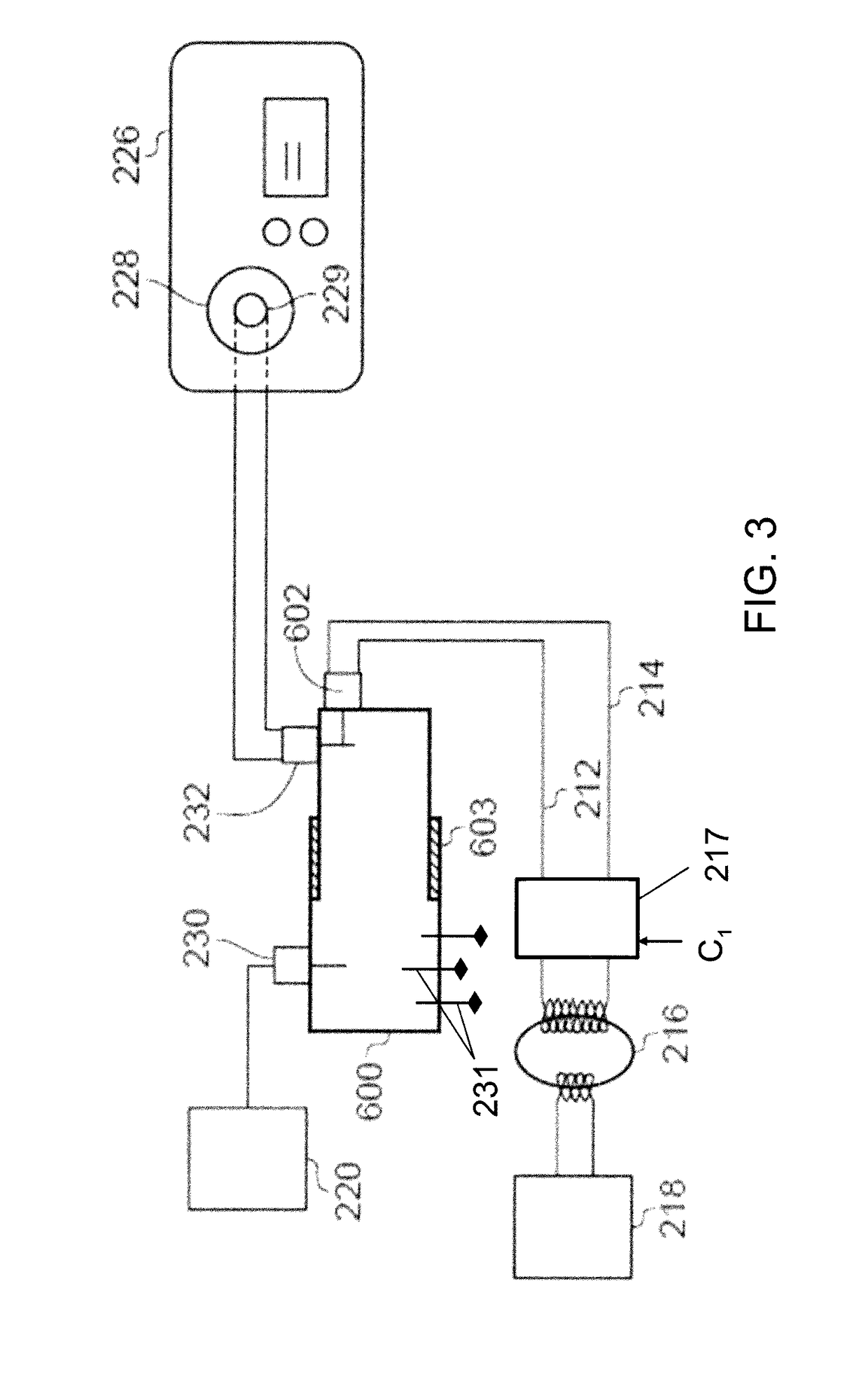

Electrosurgical apparatus

ActiveUS10080609B2Improve breakdown voltageReduce couplingSurgical instruments for heatingSurgical instruments using microwavesSignal generatorMicrowave signals

An electrosurgical apparatus having a feed structure comprising a radiofrequency (RF) channel for conveying RF electromagnetic (EM) radiation from an RF signal generator to a probe and a microwave channel for conveying microwave EM radiation from a microwave signal generator to the probe, wherein the RF channel and microwave channel comprise physically separate signal pathways, wherein the feed structure includes a combining circuit having an input connected to the signal pathway on the RF channel, another input connected to the signal pathway on the microwave channel, and an output connected to a common signal pathway for conveying the RE EM radiation and EM radiation separately or simultaneously to the probe, and wherein the microwave channel includes a waveguide isolator connected to isolate the signal pathway on the microwave channel from the RF EM radiation.

Owner:CREO MEDICAL LTD

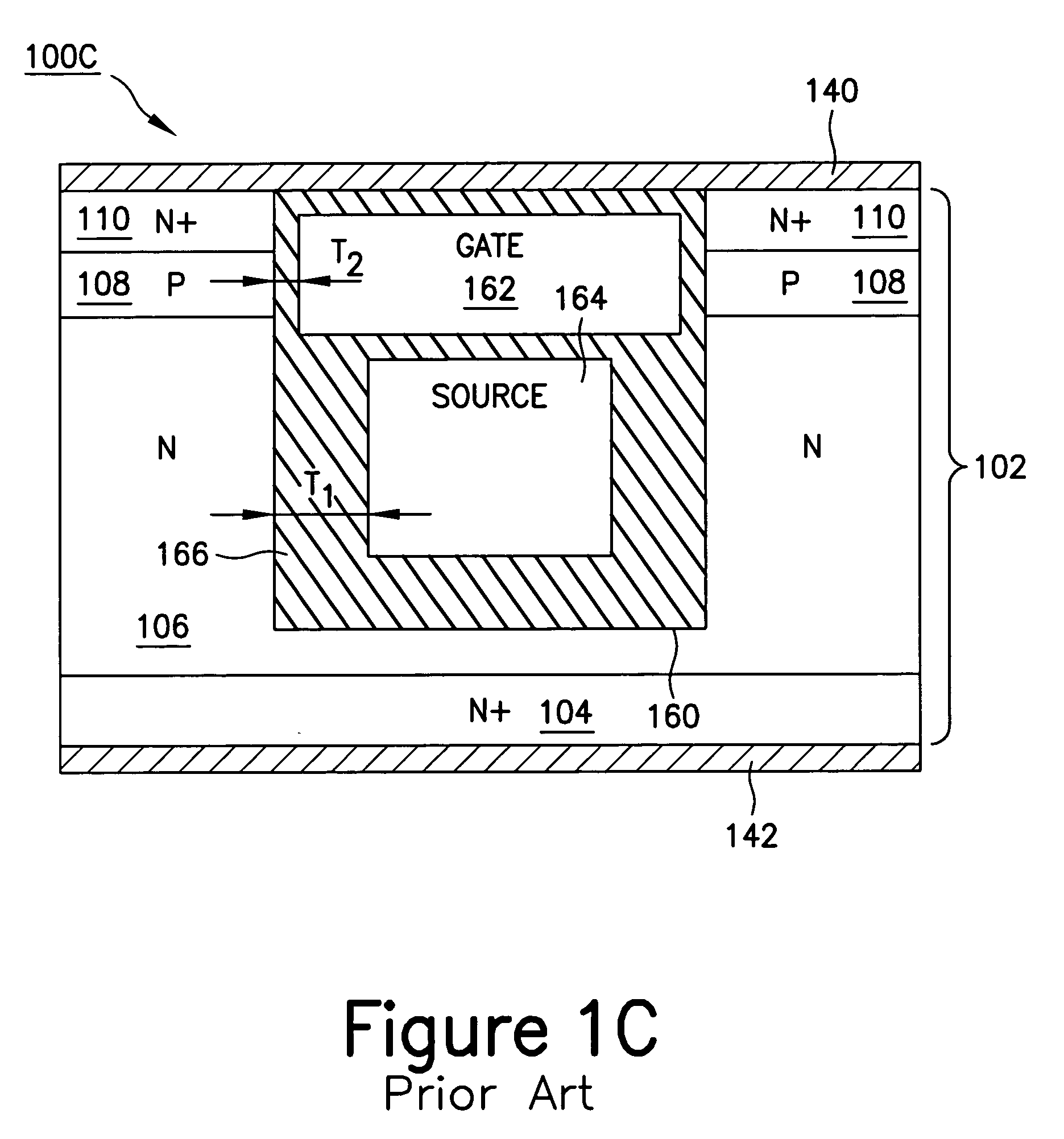

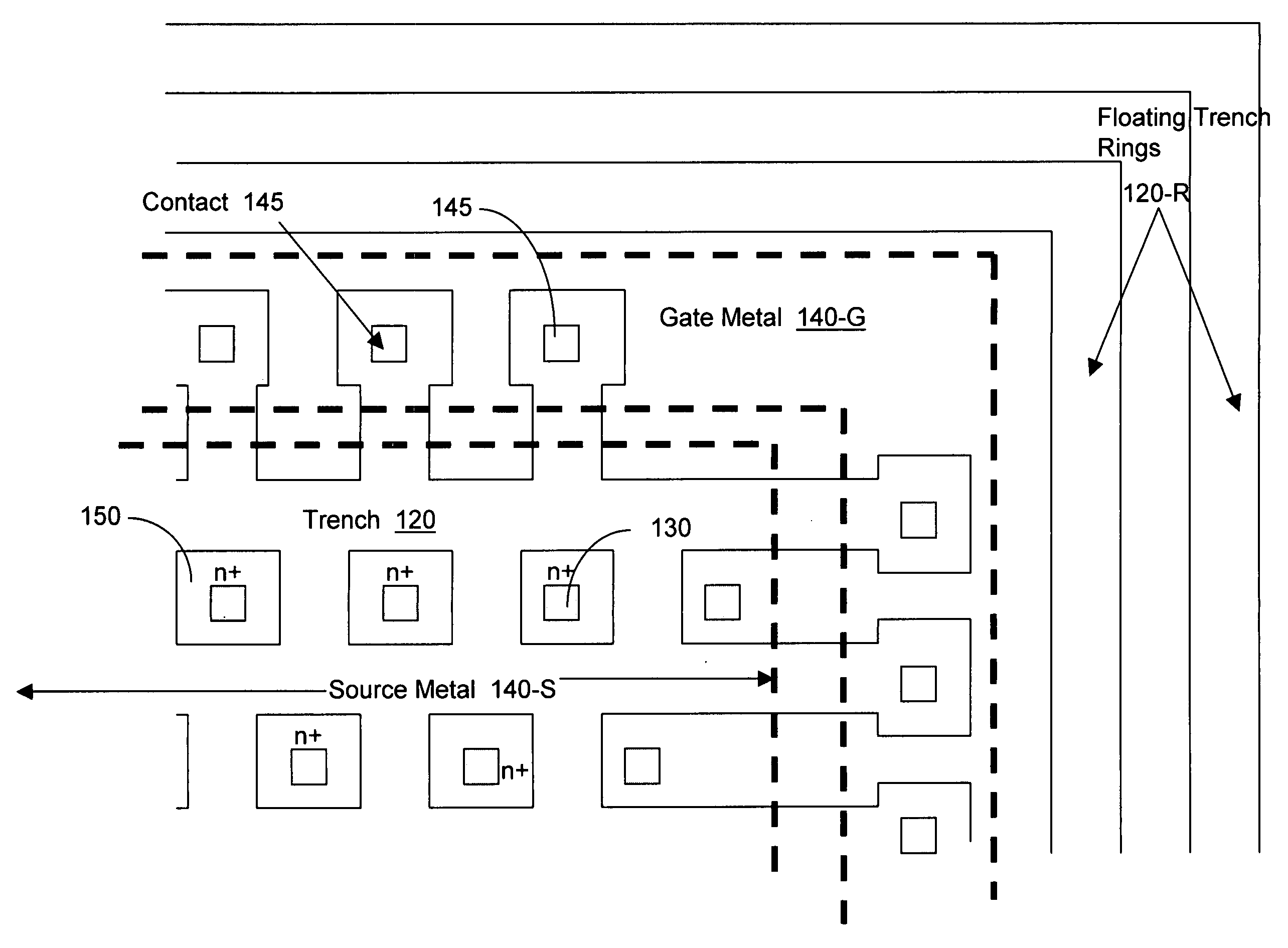

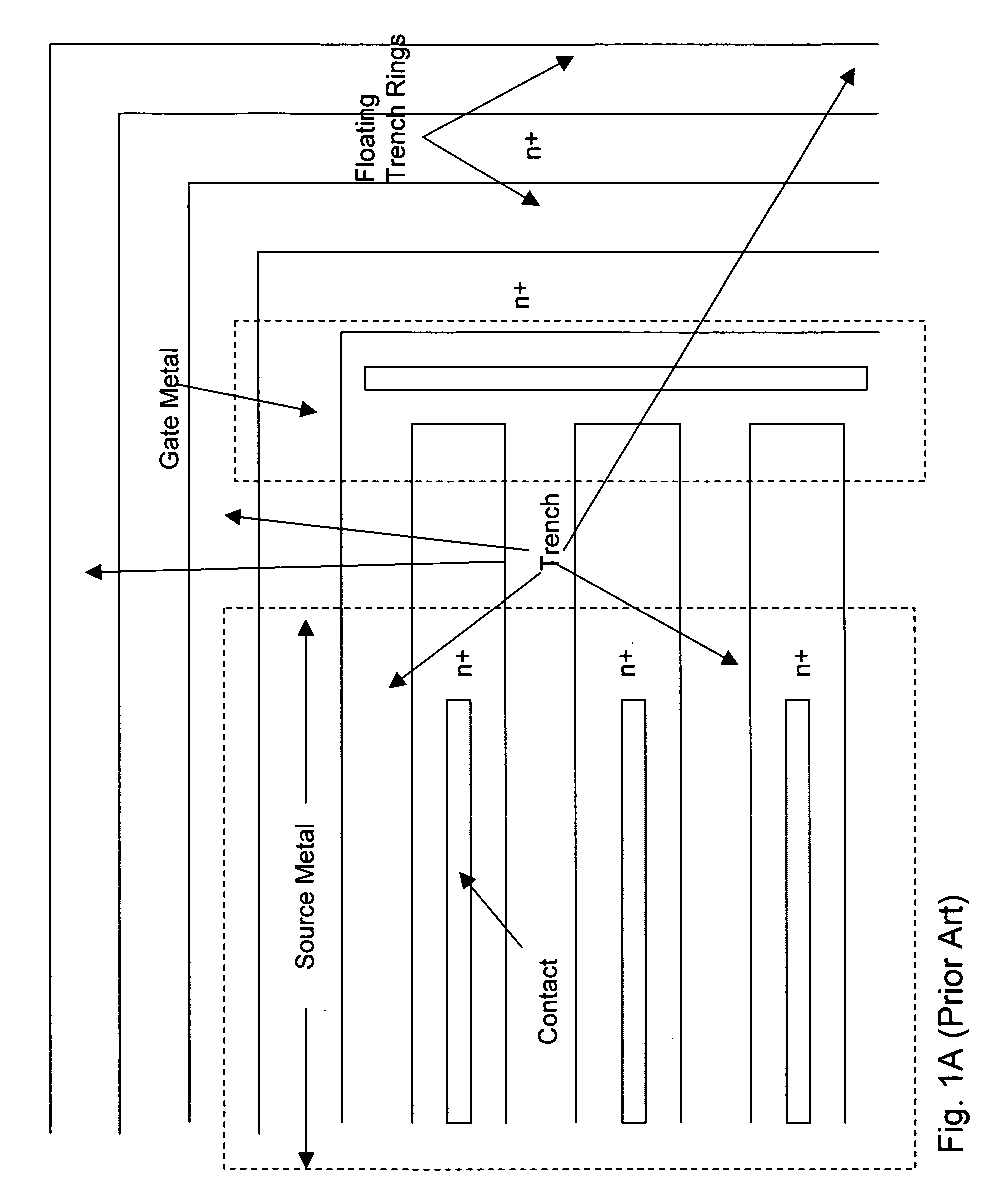

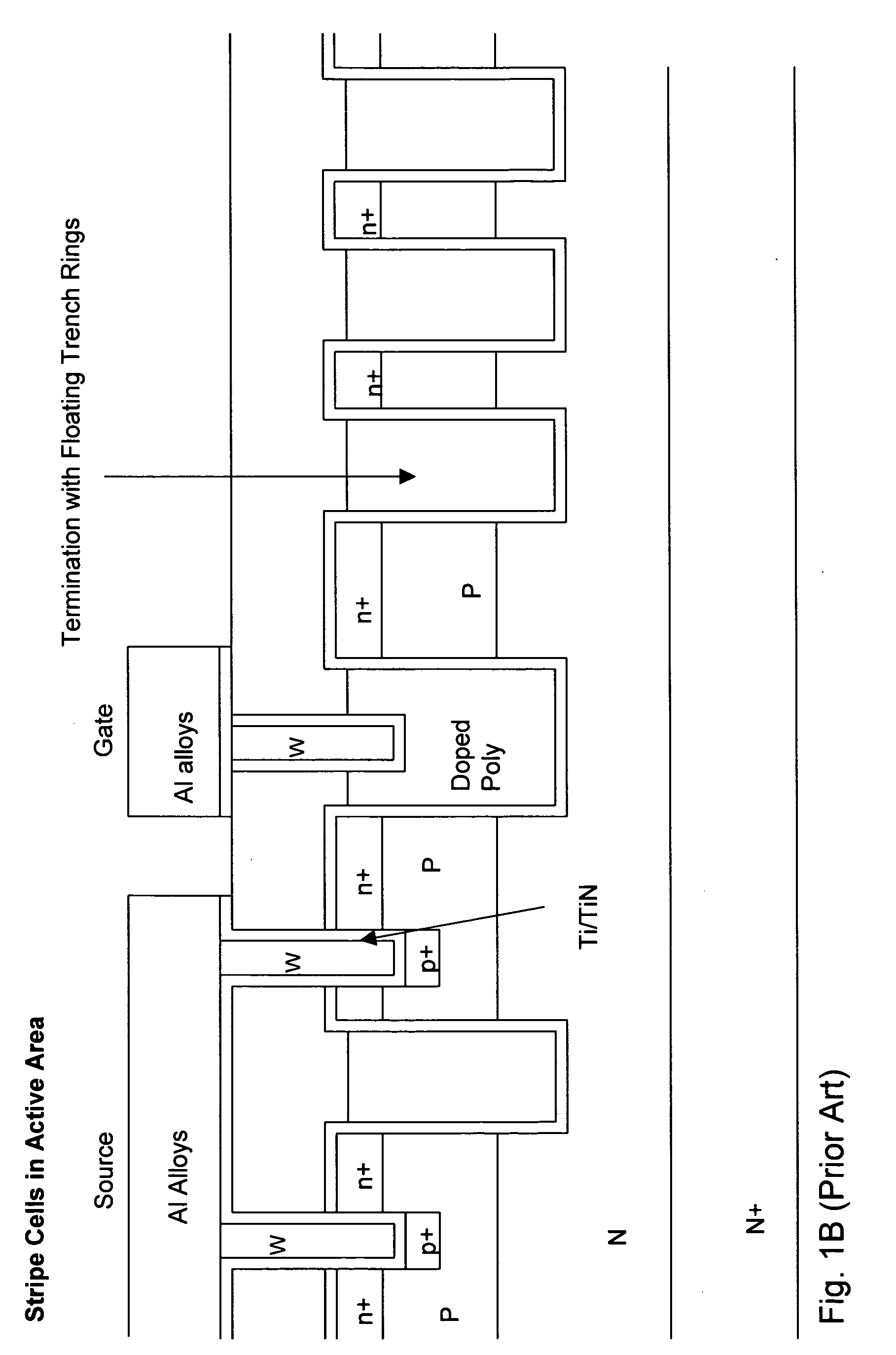

Closed trench MOSFET with floating trench rings as termination

ActiveUS20080179662A1Increased durabilityImprove breakdown voltageTransistorSolid-state devicesTrench mosfetTrench gate

A semiconductor power device includes a plurality of closed N-channel MOSFET cells surrounded by trenched gates constituting substantially a square or rectangular cell. The trenched gates are further extended to a gate contact area and having greater width as wider trenched gates for electrically contacting a gate pad wherein the semiconductor power device further includes a source region disposed only in regions near the trenched gates in the closed N-channel MOSFET cells and away from regions near the wider trenched gate whereby a device ruggedness is improved. The source region is further disposed at a distance away from a corner or an edge of the semiconductor power device and away from a termination area. The semiconductor device further includes multiple trenched rings disposed in a termination area opposite the active area and the trenched rings having a floating voltage. The closed N-channel MOSFET cells are further supported on a red phosphorous substrate.

Owner:FORCE MOS TECH CO LTD

Field effect transistor containing a wide band gap semiconductor material in a drain

InactiveUS20090121258A1Suppress impact ionizationLarge band gapTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsGate dielectric

A field effect transistor comprising a silicon containing body is provided. After formation of a gate dielectric, gate electrode, and a first gate spacer, a drain side trench is formed and filled with a wide band gap semiconductor material. Optionally, a source side trench may be formed and filled with a silicon germanium alloy to enhance an on-current of the field effect transistor. Halo implantation and source and drain ion implantation are performed to form various doped regions. Since the wide band gap semiconductor material as a wider band gap than that of silicon, impact ionization is reduced due to the use of the wide band gap semiconductor material in the drain, and consequently, a breakdown voltage of the field effect transistor is increased compared to transistors employing silicon in the drain region.

Owner:GLOBALFOUNDRIES INC

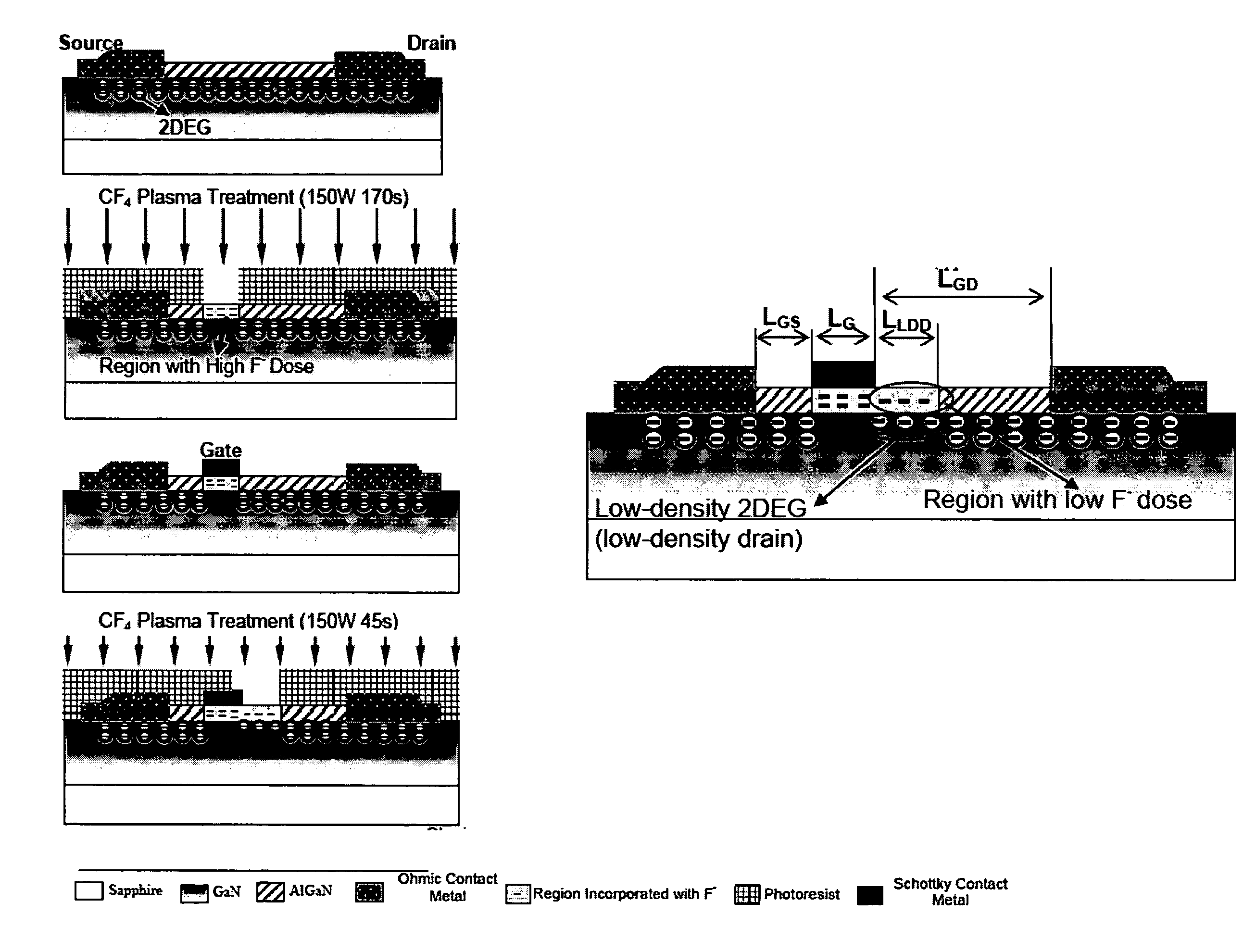

Low Density Drain HEMTs

ActiveUS20070295993A1Simple circuit configurationFavorable operating condition for device safetySemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationBreakdown voltage

Methods and devices for fabricating AlGaN / GaN normally-off high electron mobility transistors (HEMTs). A fluorine-based (electronegative ions-based) plasma treatment or low-energy ion implantation is used to modify the drain-side surface field distribution without the use of a field plate electrode. The off-state breakdown voltage can be improved and current collapse can be completely suppressed in LDD-HEMTs with no significant degradation in gains and cutoff frequencies.

Owner:THE HONG KONG UNIV OF SCI & TECH

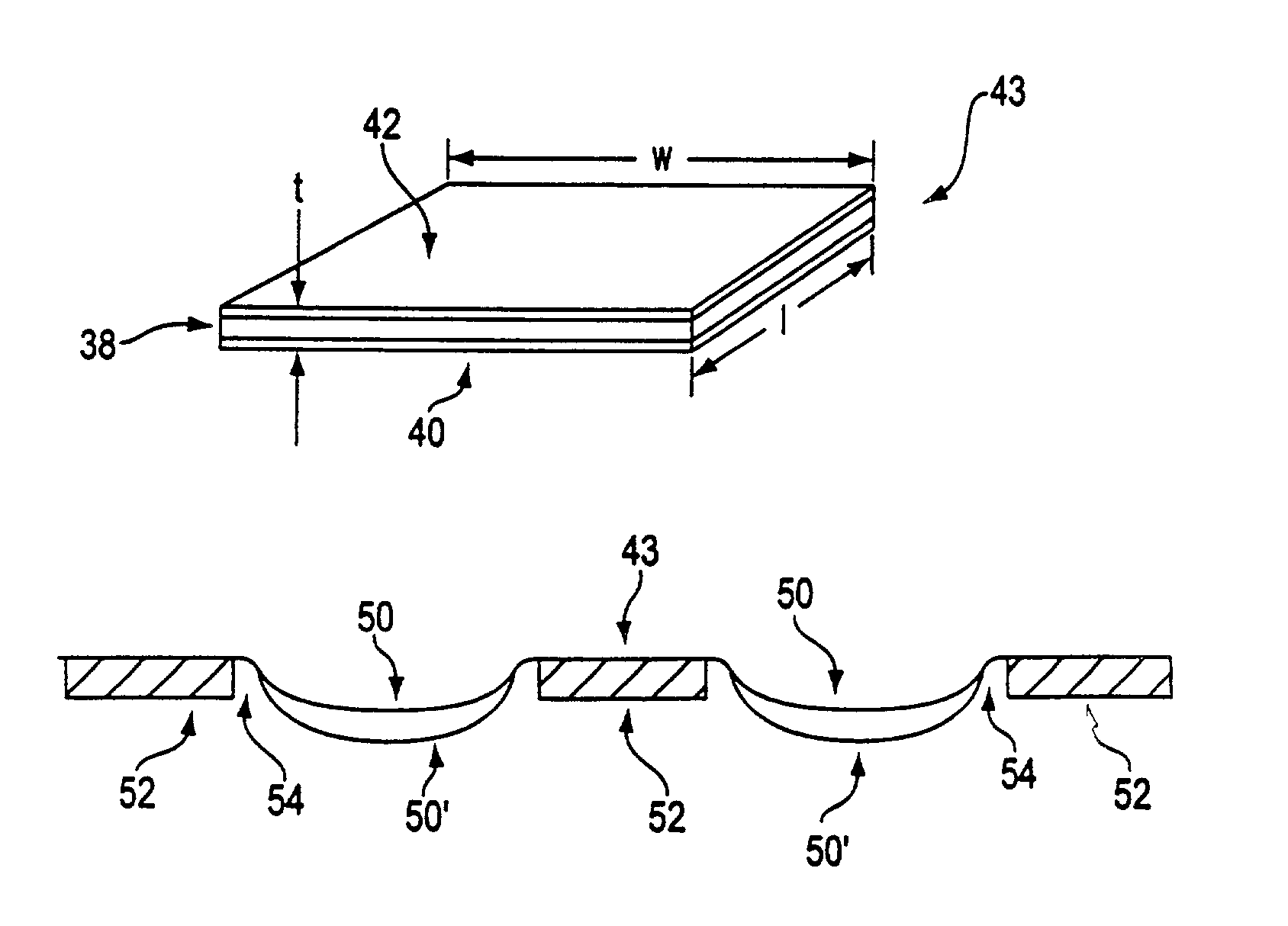

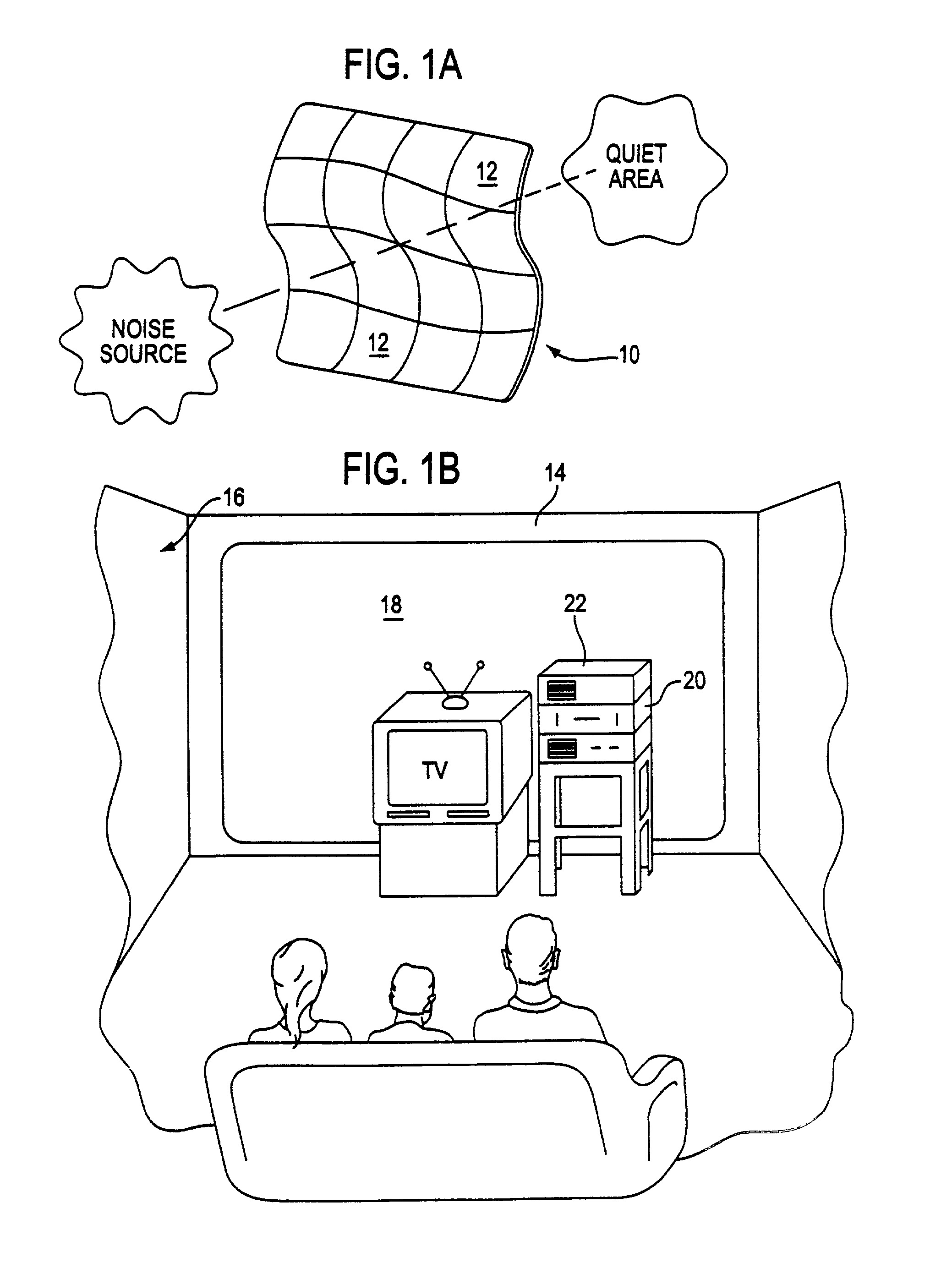

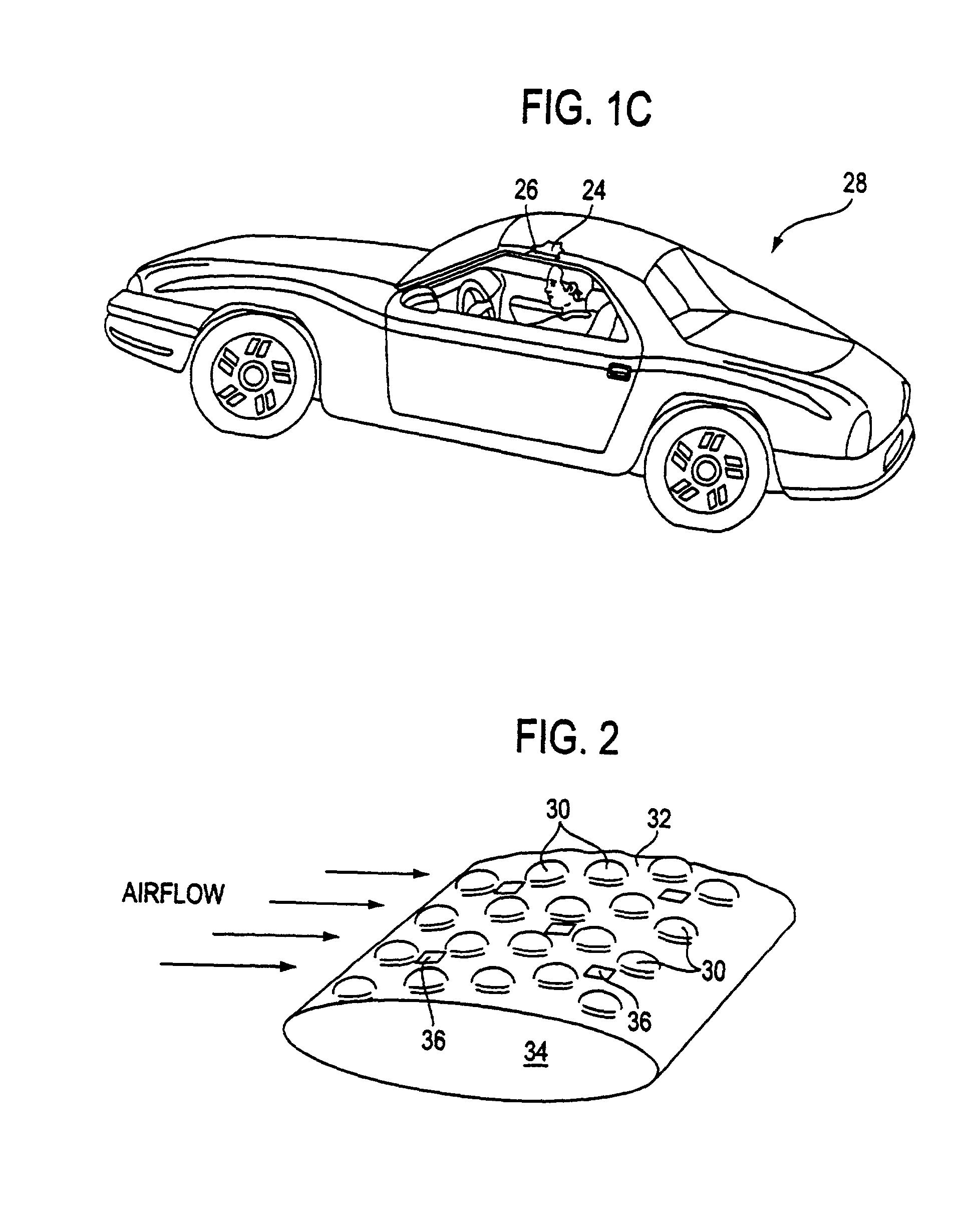

Elastomeric dielectric polymer film sonic actuator

InactiveUS7062055B2Optimize power outputLow working voltagePiezoelectric/electrostrictive gramophone pickupsStirling type enginesDielectricConductive polymer

A sonic actuator including a multi-layer membrane having a non-metallic elastomeric dielectric polymer layer with a first surface and a second surface, a first compliant electrode layer contacting the first surface of the polymer layer, and a second compliant electrode layer contacting the second surface of the polymer layer. The actuator further includes a support structure in contact with the sonic actuator film. Preferably, the non-metallic dielectric polymer is selected from the group consisting essentially of silicone, fluorosilicone, fluoroelastomer, natural rubber, polybutadiene, nitrile rubber, isoprene, and ethylene propylene diene. Also preferably, the compliant electrode layer is made from the group consisting essentially of graphite, carbon, and conductive polymers. The support structure can take the form of grid having a number of circular apertures. When a voltage is applied to the electrodes, portions of the film held at the aperture of the support structure can bulge due to the electrostriction phenomenon. The resultant “bubbles” can be modulated to generate sonic vibrations, or can be used to create a variable surface for airflow control.

Owner:SRI INTERNATIONAL

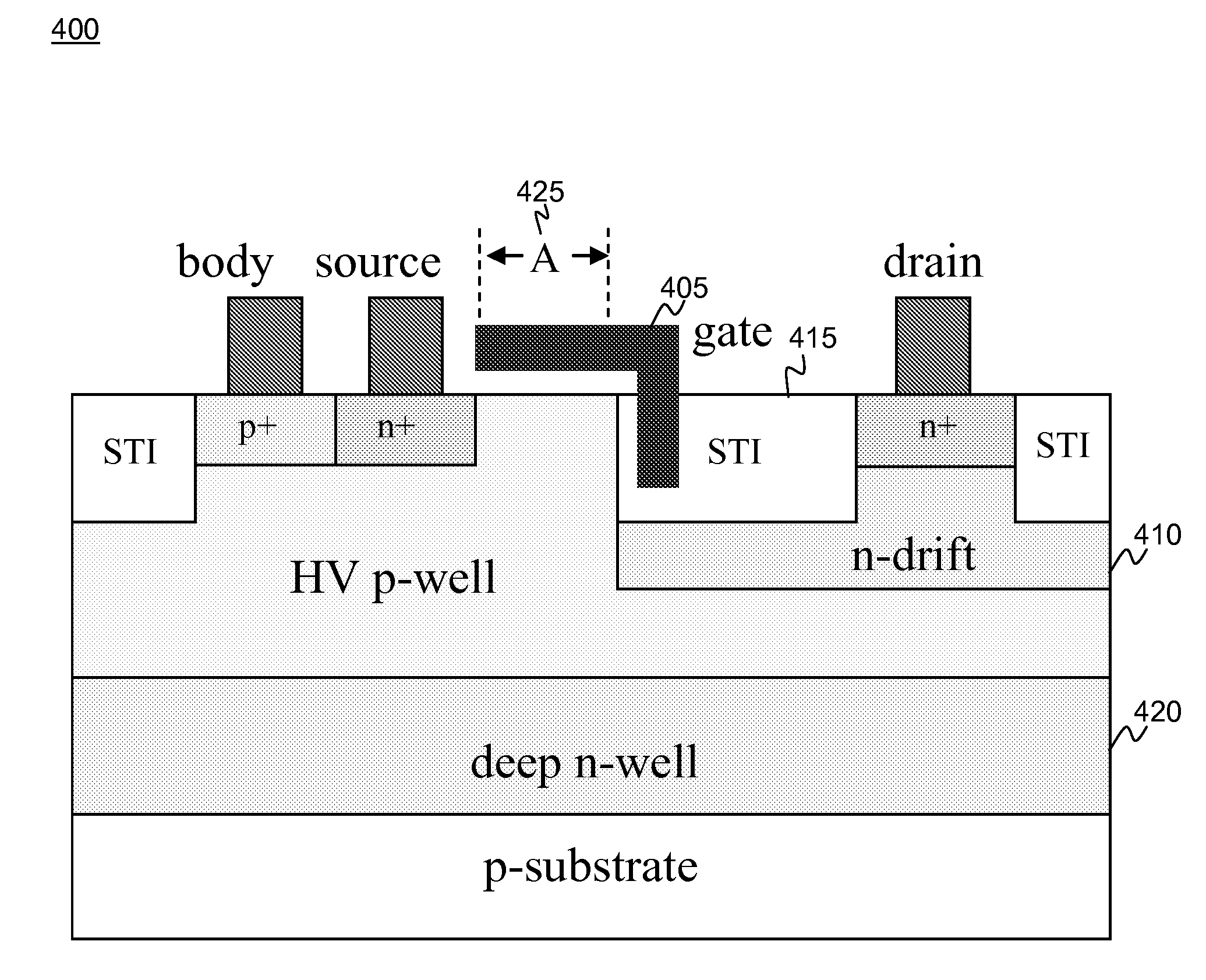

High speed orthogonal gate edmos device and fabrication

InactiveUS20090283825A1Reduce gate-to-drain capacitanceMinimizesSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

An orthogonal gate extended drain MOSFET (EDMOS) structure provides a low gate-to-drain capacitance (CGD) and exhibits increased reliability. It has a gate electrode that is folded into the shallow trench isolation (STI) oxide region. Horizontal and vertical gate electrode segments provide gate control. It accommodates both high voltage devices and standard CMOS components on the same substrate. Reduced surface field (RESURF) technology is employed to optimize tradeoffs between high breakdown voltage and specific on-resistance. Device fabrication steps are compatible with standard CMOS flow and process modules can be added or removed from baseline CMOS technology.

Owner:ASAHI KASEI ELECTRONICS CO LTD

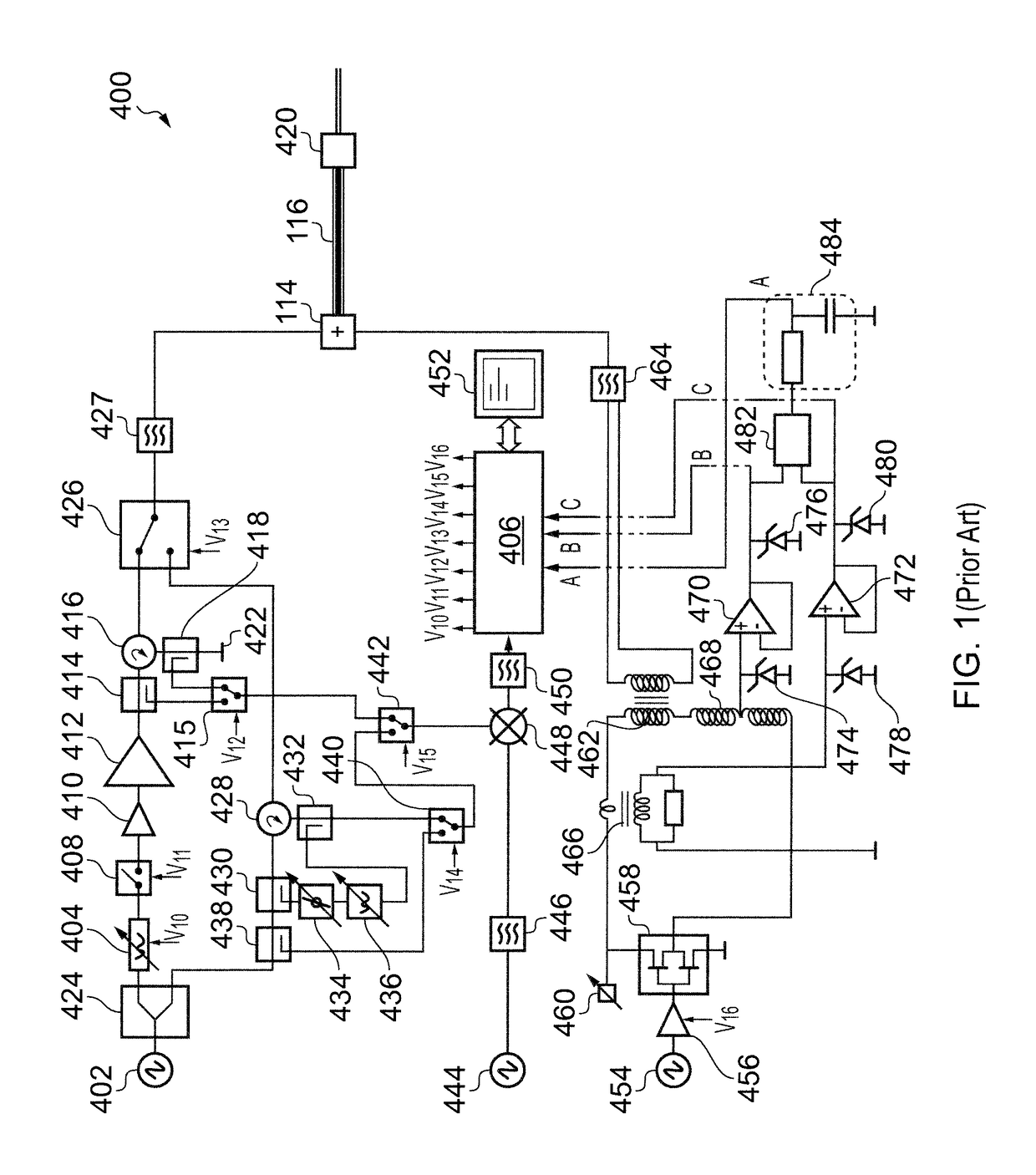

Electrosurgical apparatus for generating radiofrequency energy and microwave energy for delivery into biological tissue

ActiveUS10188455B2Improve accuracyReduced insertion lossCatheterSurgical instruments for heatingCapacitanceElectrical conductor

An isolating circuit for an electrosurgical generator arranged to produce radiofrequency (RF) energy and microwave energy for treating biological tissues is provided. The generator has an RF channel and a microwave channel which are combined at a signal combiner to enable the RF energy and microwave energy to be delivered into tissues along a common feed path. The isolating circuit includes a tunable wavelength isolator at a junction between the microwave channel and the signal combiner, and can include a capacitive structure between a ground conductor of the signal combiner and a conductive input section of the waveguide isolator to inhibit coupling of the RF energy and leakage of the microwave energy. The isolating circuit can combine into a single tunable unit all the necessary components to isolate the microwave and RF channels from one another while providing a high withstanding voltage.

Owner:CREO MEDICAL LTD

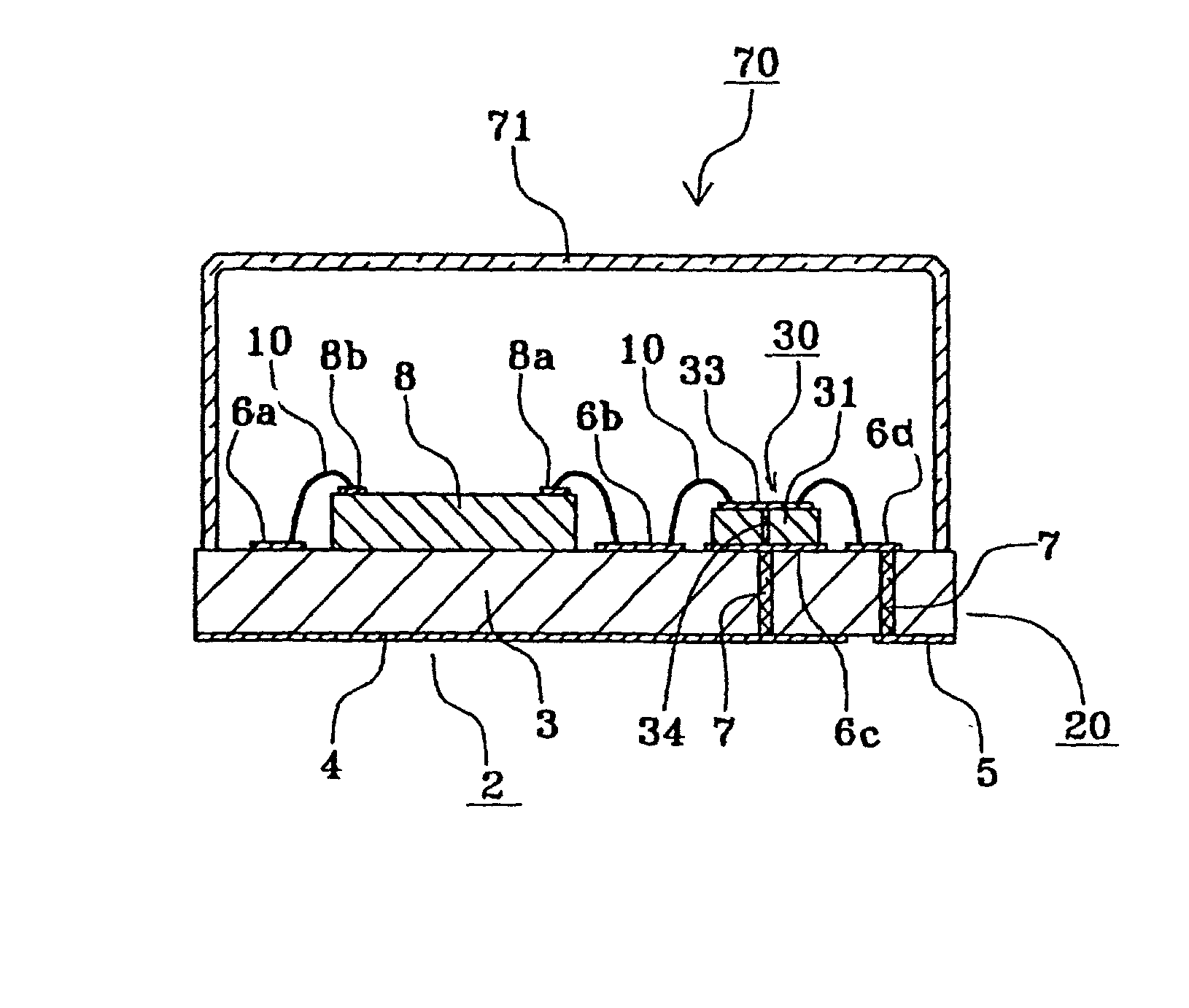

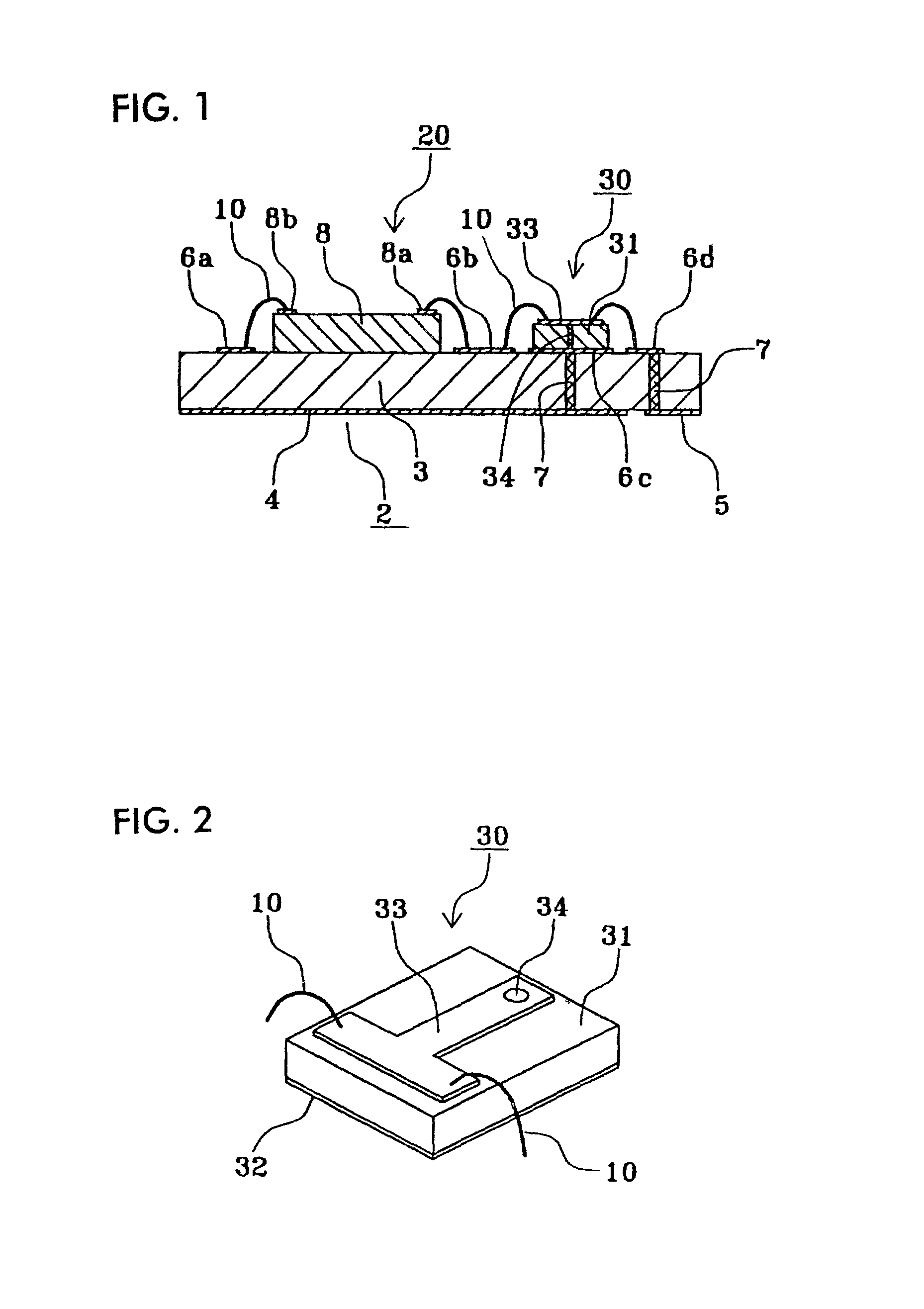

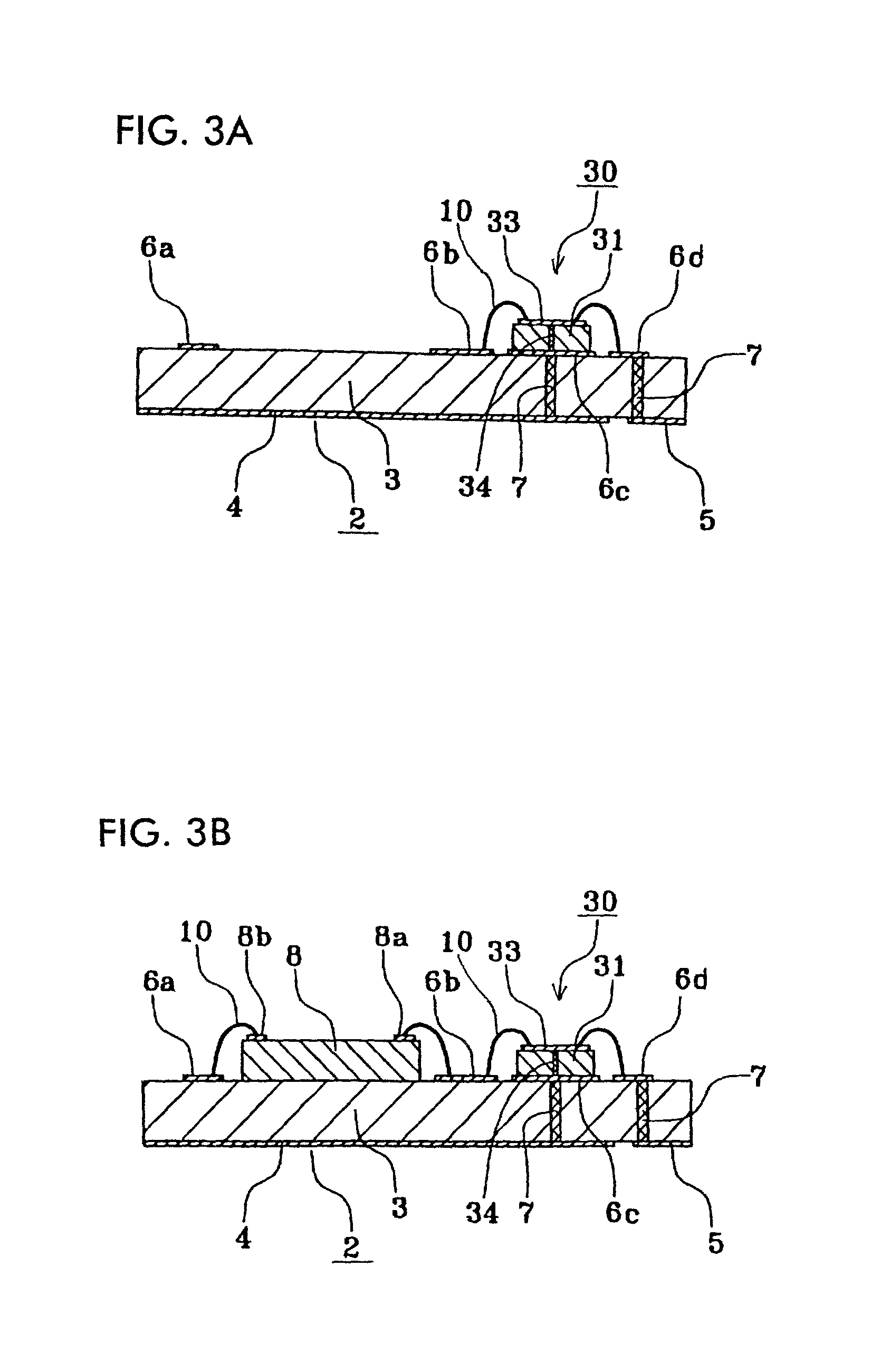

High-frequency circuit board unit, high frequency module using the same unit, electronic apparatus using the same module, and manufacturing method for the high-frequency circuit board unit

InactiveUS20020072147A1Improve breakdown voltageImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDielectric substrateSemiconductor

A ground electrode and a terminal electrode are formed on a first main surface of dielectric substrate forming a circuit board. Wiring electrodes are formed on a second main surface of the dielectric substrate. A semiconductor device and a filter are mounted on the wiring electrodes. A strip line electrode of the filter is connected to the ground electrode of the circuit board for conducting direct current, via a through-hole provided in the filter, a ground electrode of the filter, the wiring electrode, and a through-hole provided in the circuit board. With this arrangement, the terminal electrode is connected to a high-frequency signal terminal of the semiconductor device via the filter.

Owner:MURATA MFG CO LTD

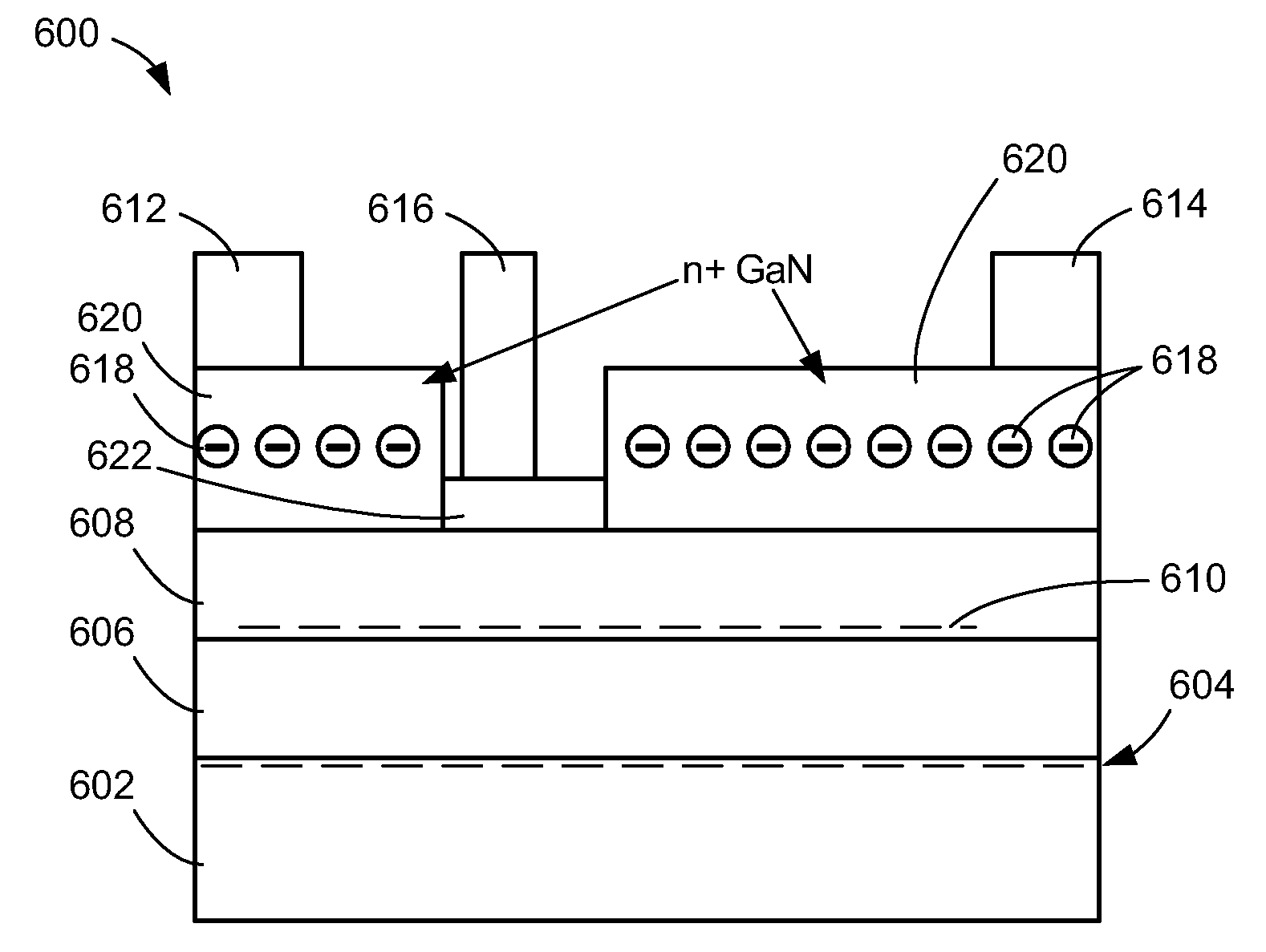

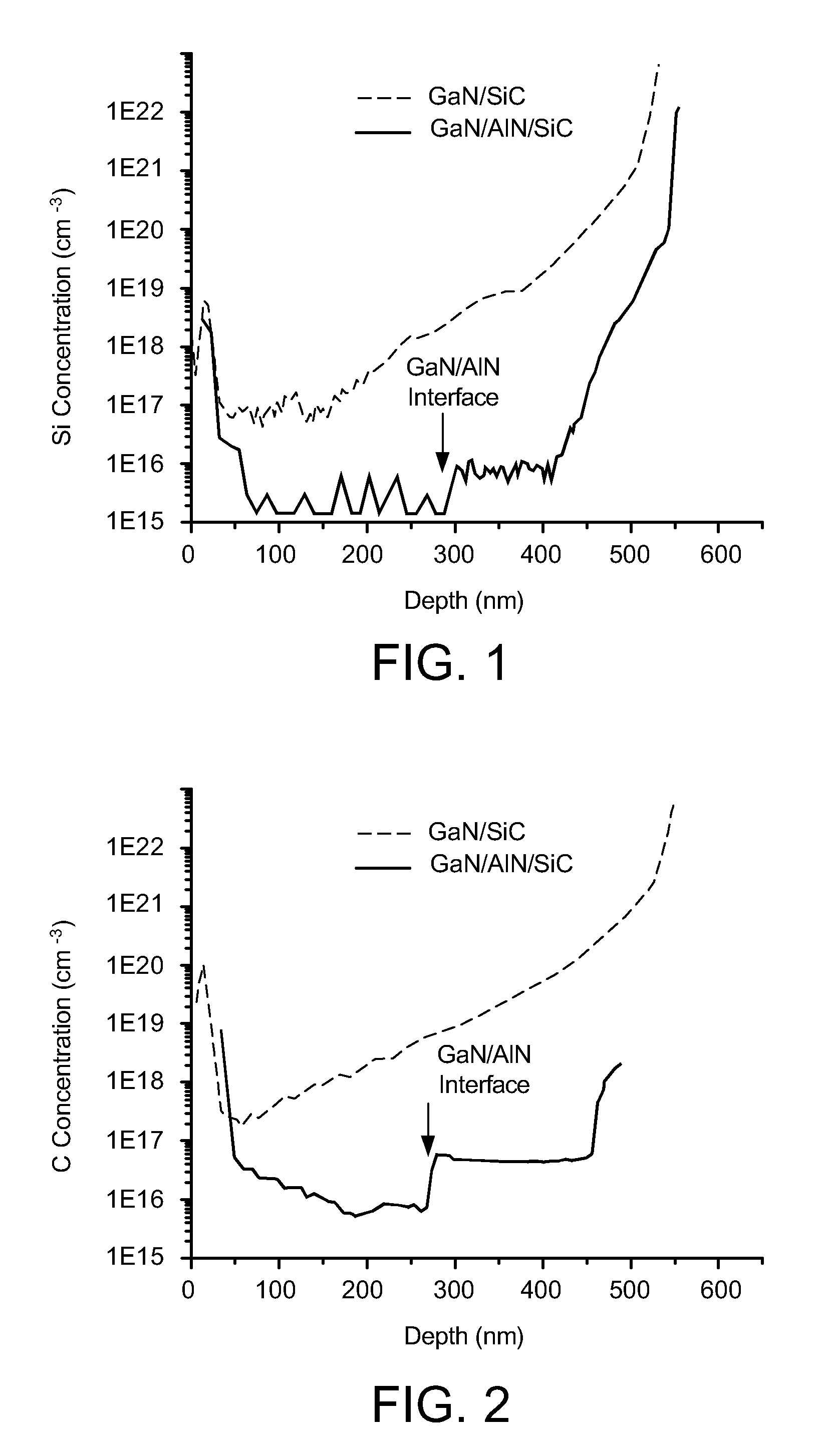

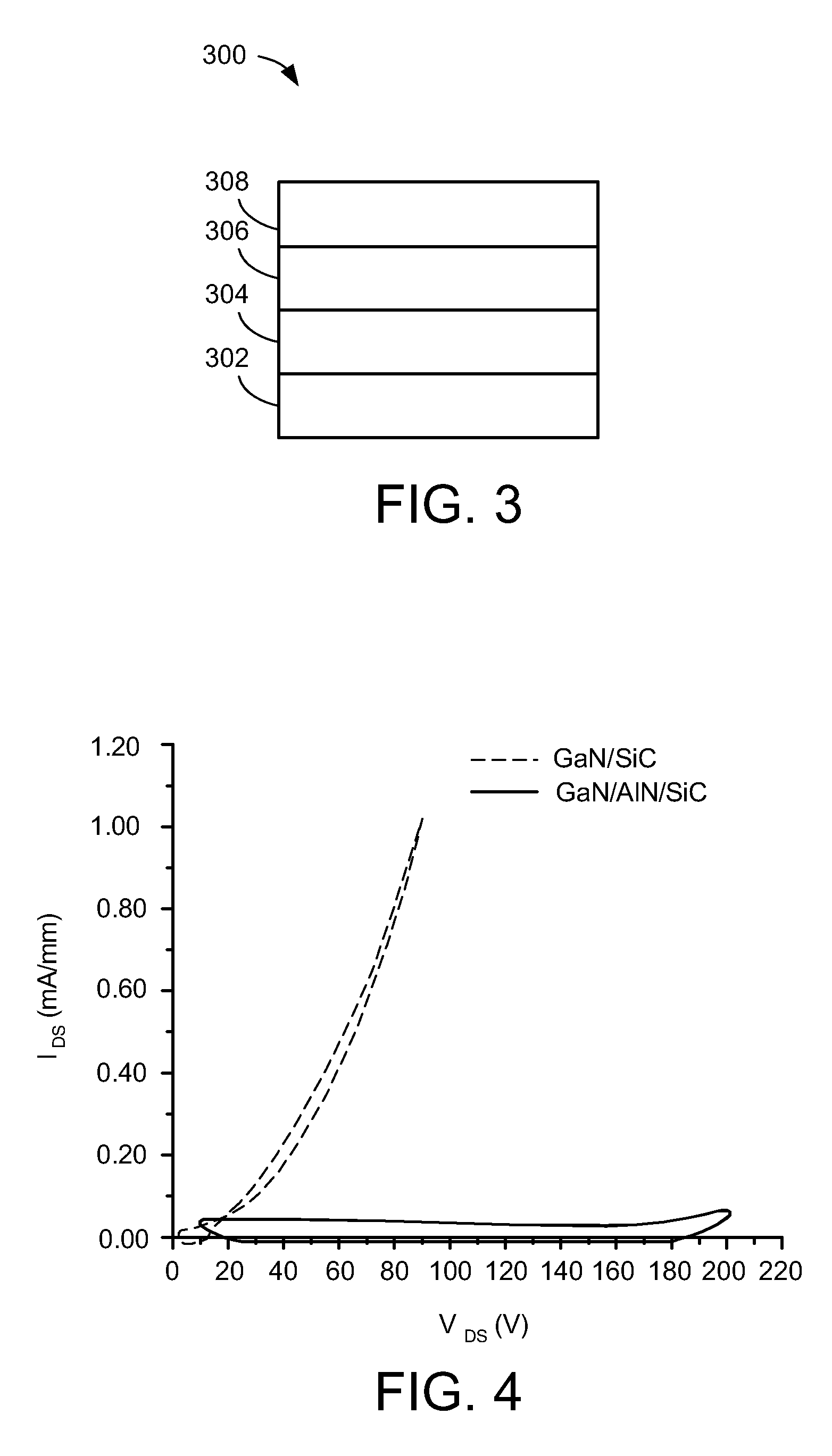

N-face high electron mobility transistors with low buffer leakage and low parasitic resistance

InactiveUS20080237640A1Enhance DEG mobilityIncrease electron velocitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh-electron-mobility transistorNitrogen

A method for fabricating nitrogen-face (N-face) nitride-based electronic devices with low buffer leakage, comprising isolating a buffer from a substrate with an AlGaInN nucleation layer to suppress impurity incorporation from the substrate into the buffer. A method for fabricating N-face nitride-based electronic devices with low parasitic resistance and high breakdown, comprising capping a device structure with a conductive layer to provide extremely low access and / or contact resistances, is also disclosed.

Owner:RGT UNIV OF CALIFORNIA

Trench-Based Power Semiconductor Devices With Increased Breakdown Voltage Characteristics

ActiveUS20100140695A1Improve breakdown voltageTransistorSolid-state devicesPower semiconductor deviceSemiconductor

Exemplary power semiconductor devices with features providing increased breakdown voltage and other benefits are disclosed.

Owner:SEMICON COMPONENTS IND LLC

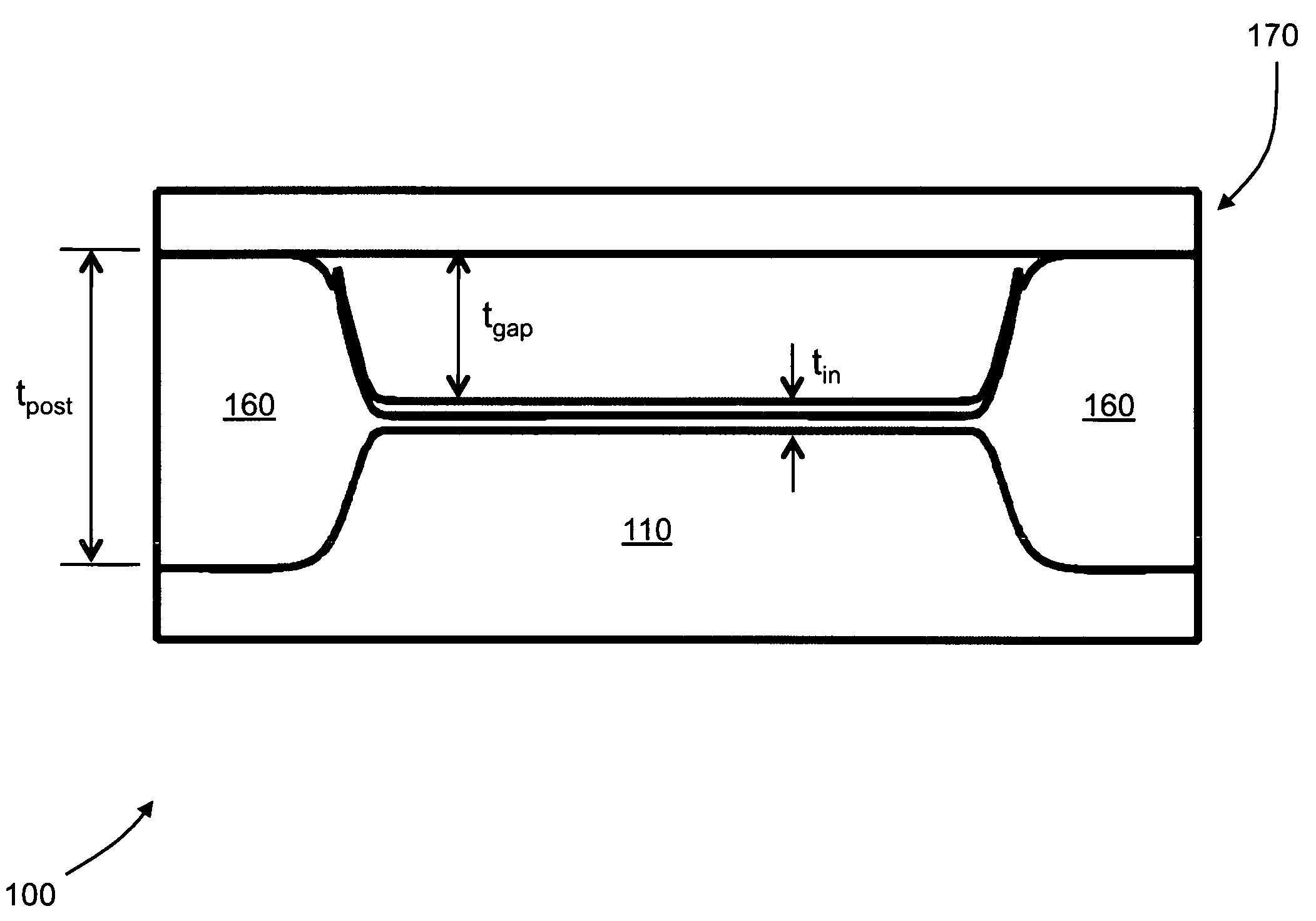

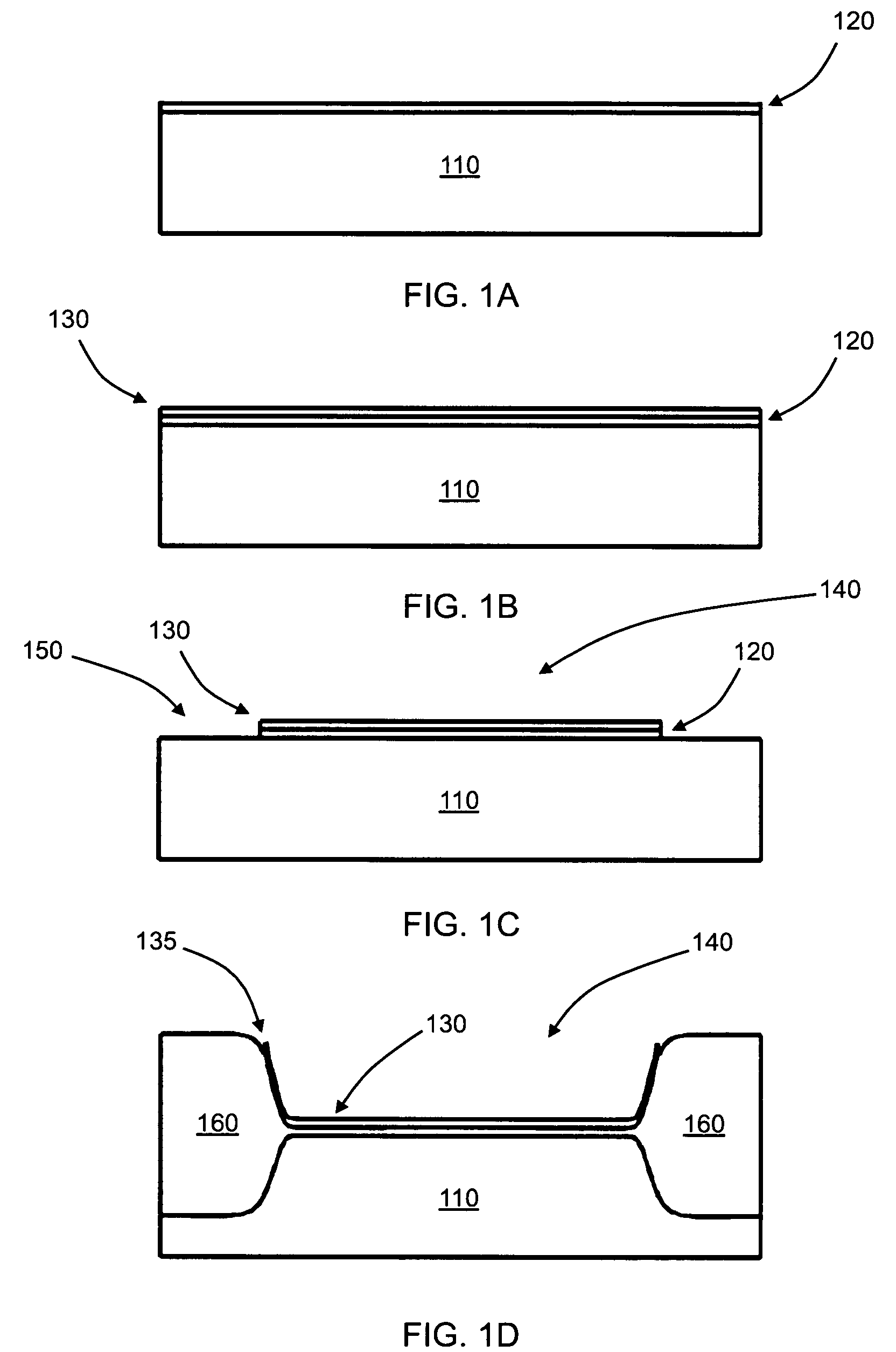

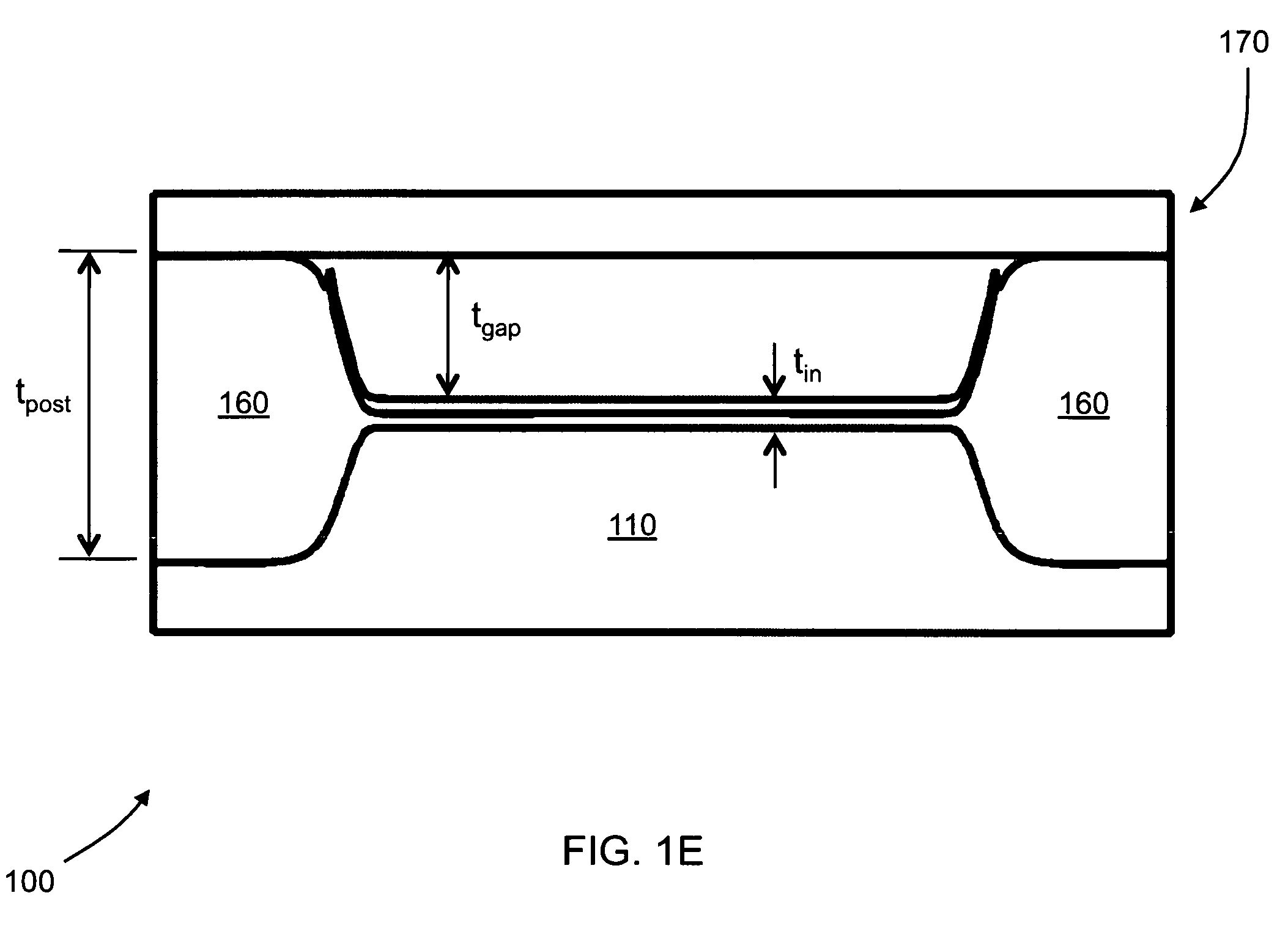

Fabrication of capacitive micromachined ultrasonic transducers by local oxidation

ActiveUS7745248B2Reduce parasitic capacitanceImprove breakdown voltageSemiconductor/solid-state device manufacturingMechanical vibrations separationCapacitanceCapacitive micromachined ultrasonic transducers

The current invention provides methods of fabricating a capacitive micromachined ultrasonic transducer (CMUT) that includes oxidizing a substrate to form an oxide layer on a surface of the substrate having an oxidation-enabling material, depositing and patterning an oxidation-blocking layer to form a post region and a cavity region on the substrate surface and remove the oxidation-blocking layer and oxide layer at the post region. The invention further includes thermally oxidizing the substrate to grow one or more oxide posts from the post region, where the post defines the vertical critical dimension of the device, and bonding a membrane layer onto the post to form a membrane of the device. A maximum allowed second oxidation thickness t2 can be determined, that is partially based on a desired step height and a device size, and a first oxidation thickness t1 can be determined that is partially based on the determined thickness t2.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

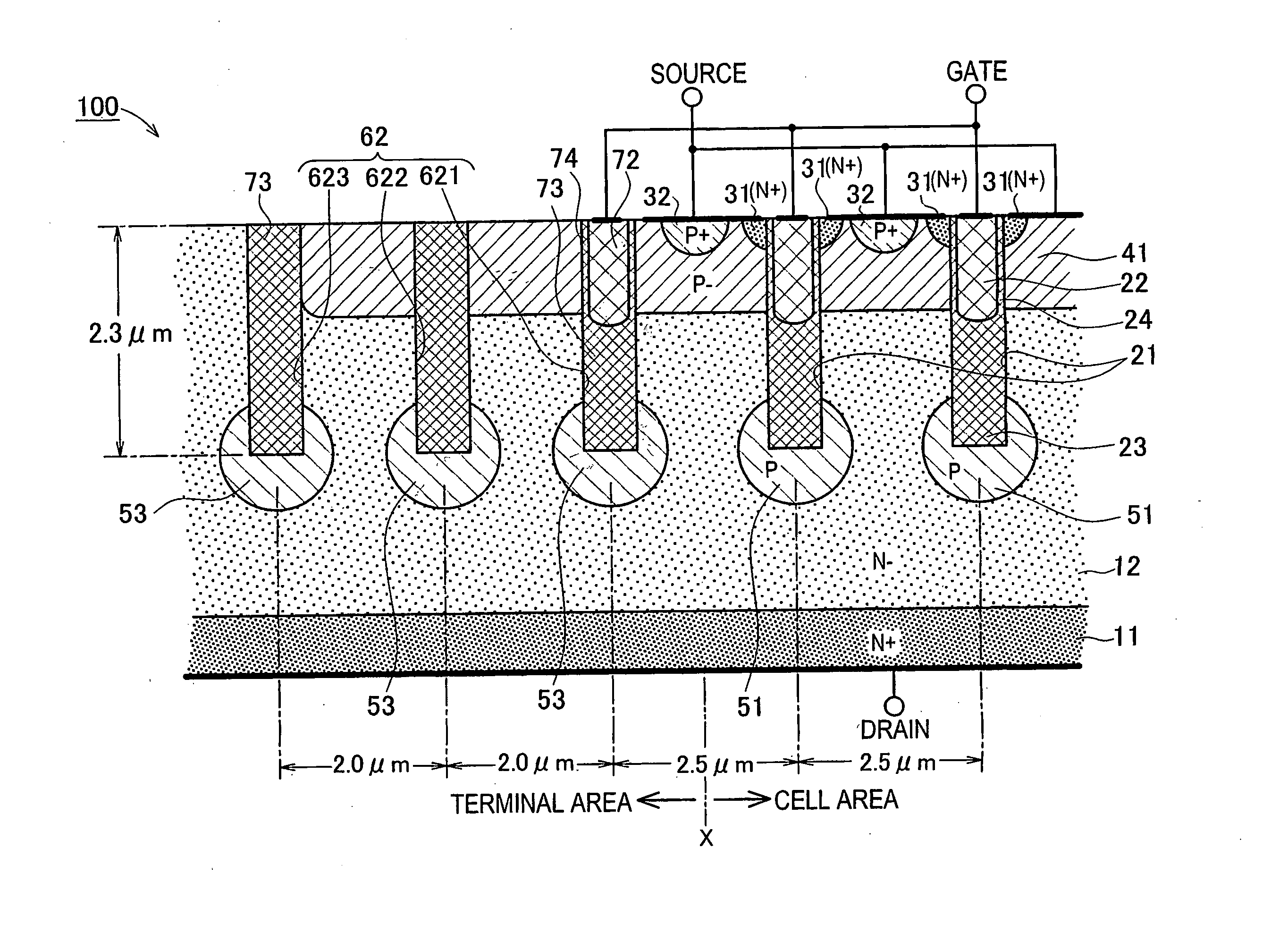

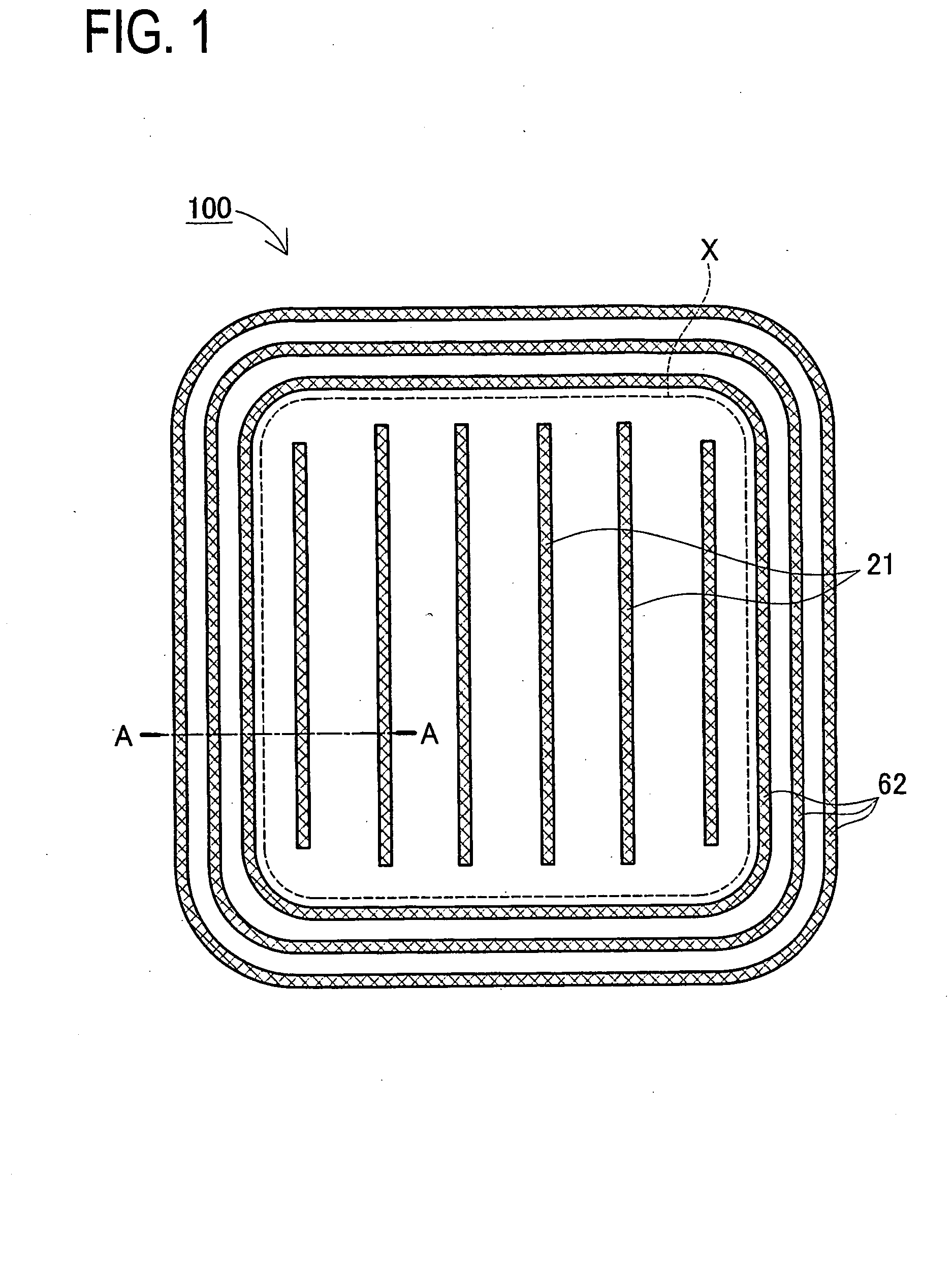

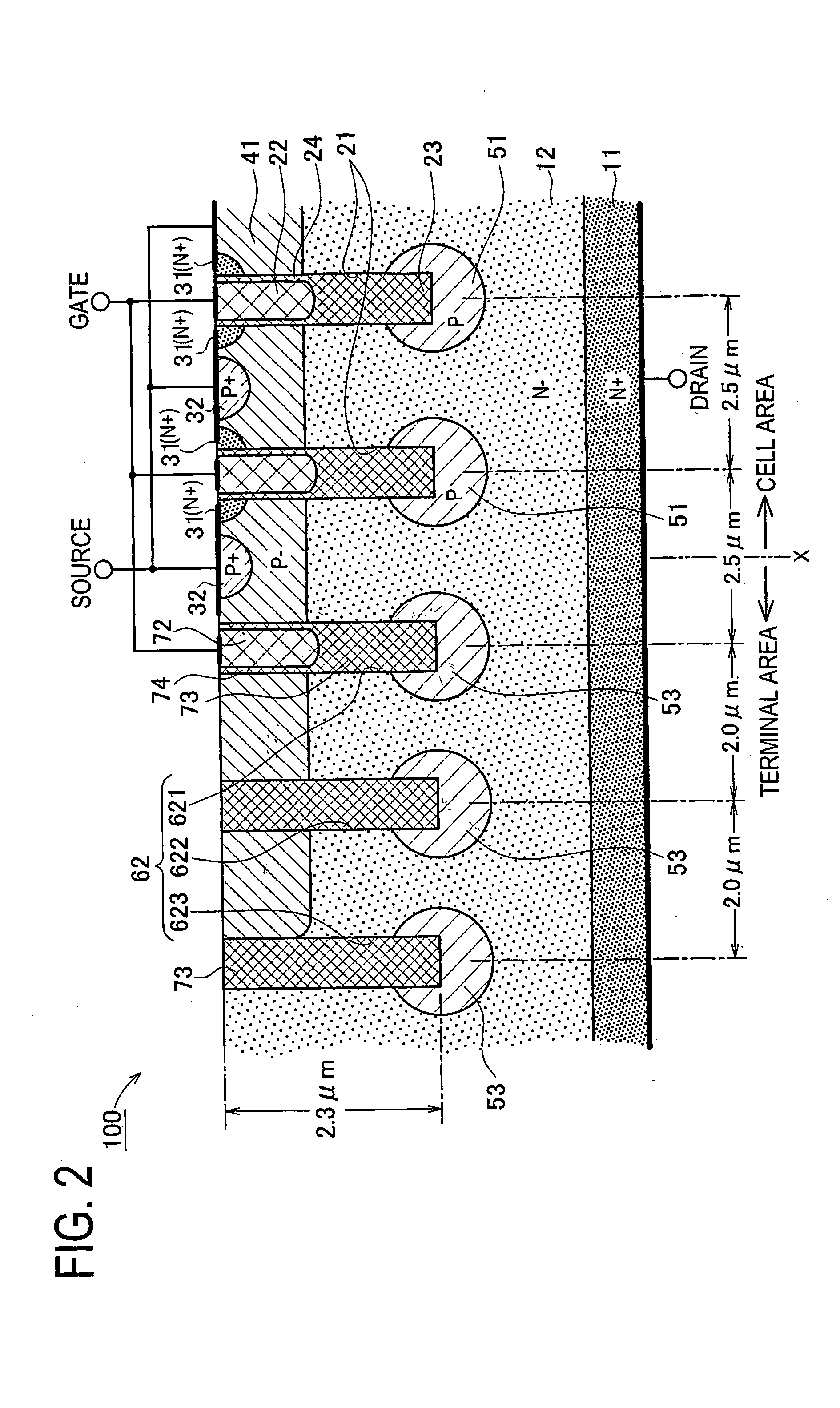

Insulated Gate Semiconductor Device and Method for Producing the Same

ActiveUS20080087951A1Firmly connectedImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The invention has an object to provide an insulation gate type semiconductor device and a method for producing the same in which high breakdown voltage and compactness are achieved. The semiconductor device has a gate trench and a P floating region formed in the cell area and has a terminal trench and a P floating region formed in the terminal area. In addition, a terminal trench of three terminal trenches has a structure similar to that of the gate trench, and the other terminal trenches have a structure in which an insulation substance such as oxide silicon is filled. Also, the P floating region 51 is an area formed by implanting impurities from the bottom surface of the gate trench, and the P floating region is an area formed by implanting impurities from the bottom surface of the terminal trench.

Owner:DENSO CORP +1

Schottky barrier diode and method of making the same

ActiveUS20050230744A1Improve breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesSchottky barrierReverse current

A power Schottky rectifier device having a plurality of first trenches filled in with an un-doped polycrystalline silicon layer and each first trenches also has a p-region beneath the bottom of said first trenches to block out reverse current while a reverse biased is applied and to reduce minority carrier while forward biased is applied. Thus, the power Schottky rectifier device can provide first fast switch speed. The power Schottky rectifier device is formed with termination region at an outer portion of the substrate. The manufacture method is also provided.

Owner:WU SHYE LIN +1

Power semiconductor device

InactiveUS6933544B2Improve rendering capabilitiesResistanceTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceNon doped

A power semiconductor device including a non-doped GaN channel layer, an n-type Al0.2Ga0.8N barrier layer formed on the channel layer, a p-type Al0.1Ga0.9N semiconductor layer selectively formed on the barrier layer, a drain electrode positioned at one of both sides of the semiconductor layer and formed on the barrier layer, an insulating film formed on the barrier layer adjacent to the semiconductor layer between at least semiconductor layer and drain electrode, and a field plate electrode formed on the insulating film.

Owner:KK TOSHIBA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com