Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

383 results about "Surface field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

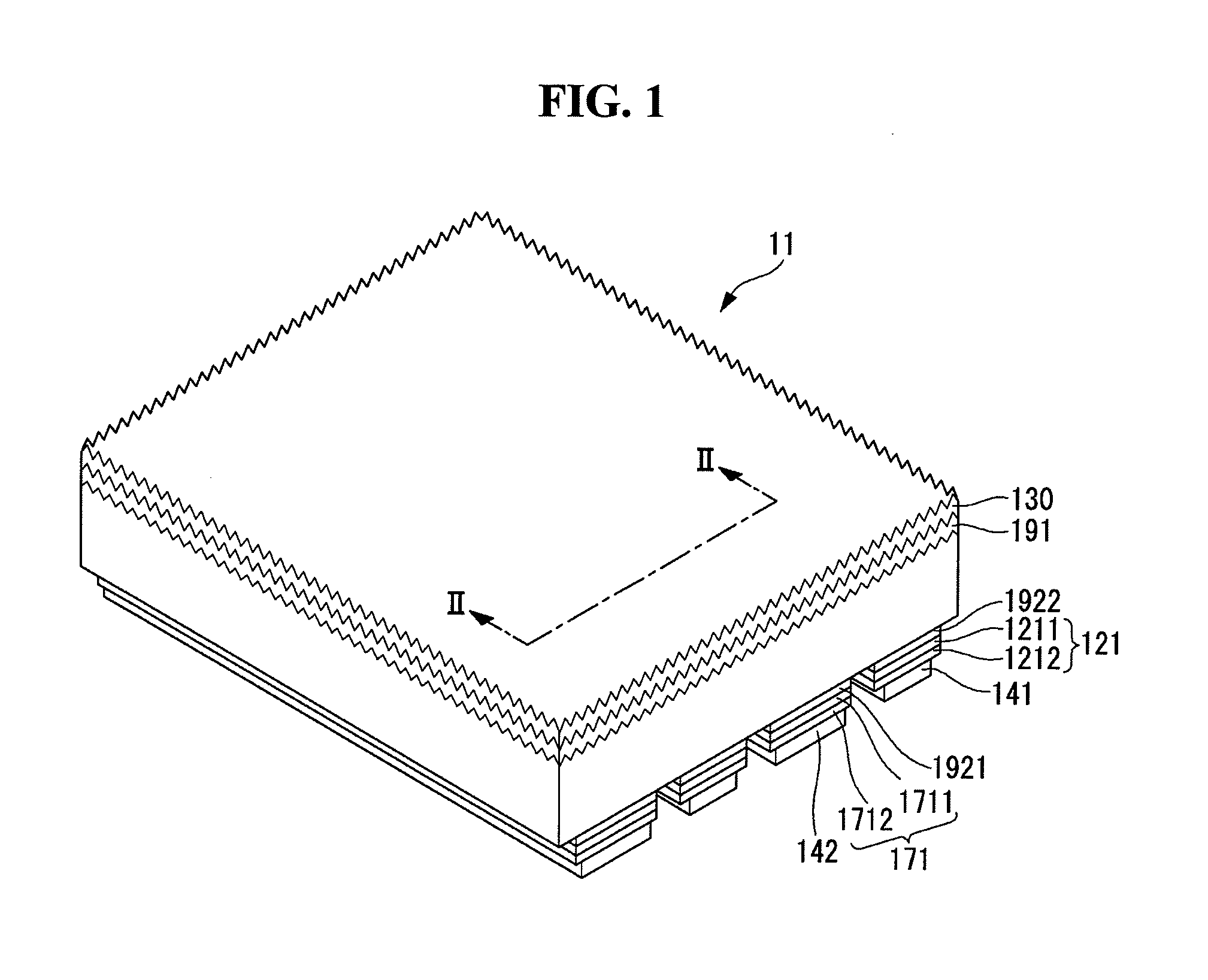

Back junction solar cell with tunnel oxide

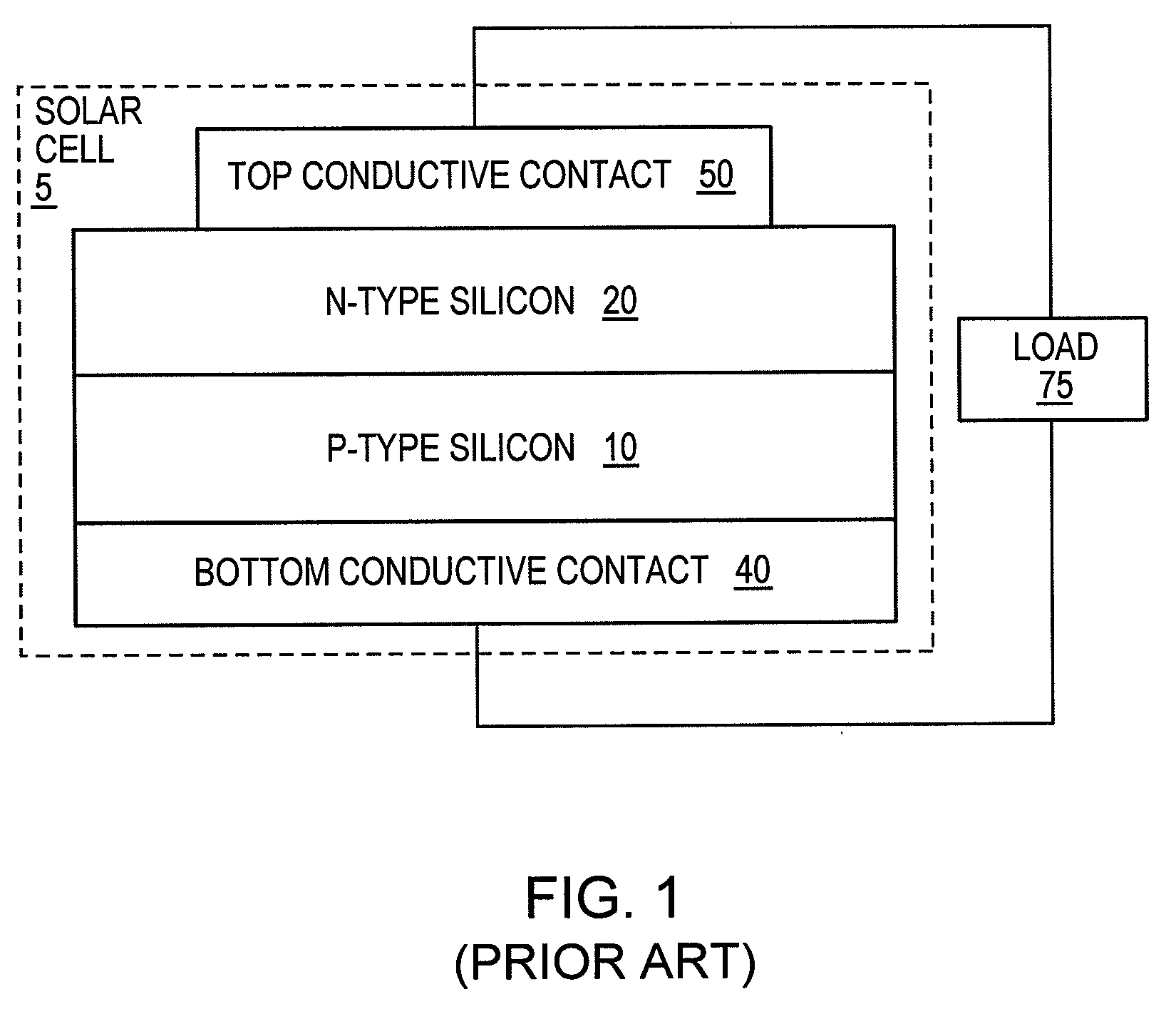

InactiveUS20120318340A1Final product manufactureSemiconductor/solid-state device manufacturingSolar cellSurface field

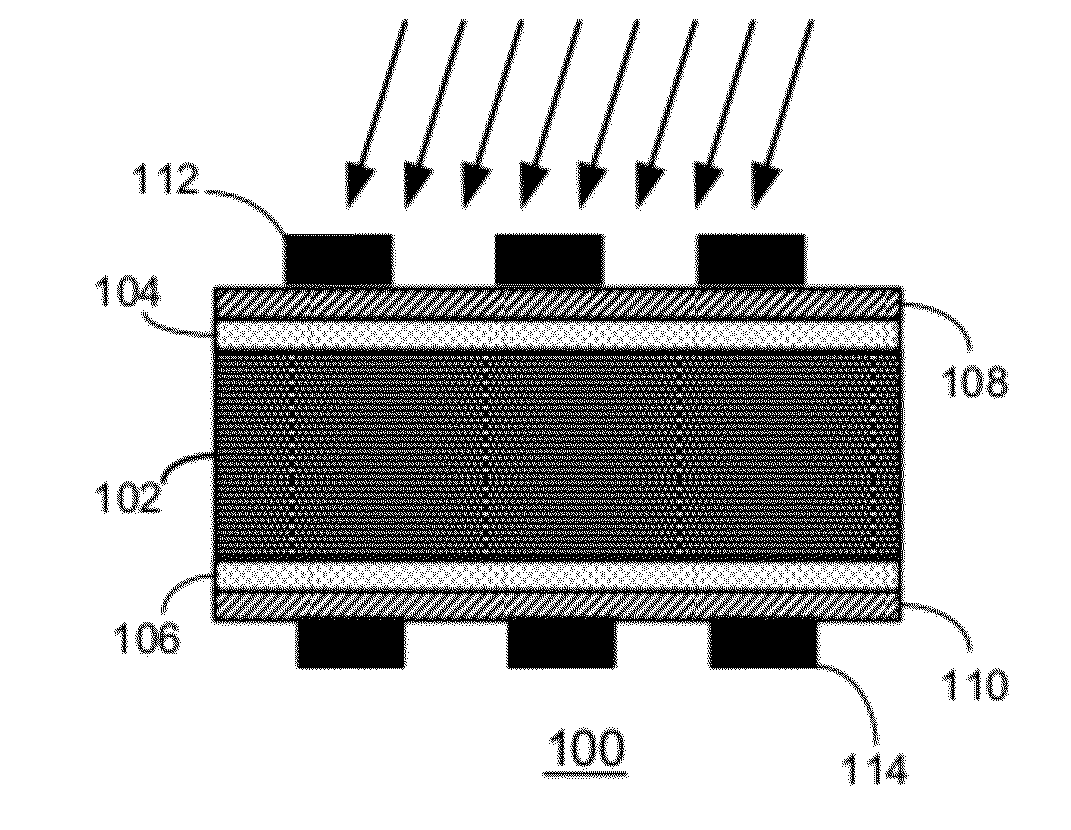

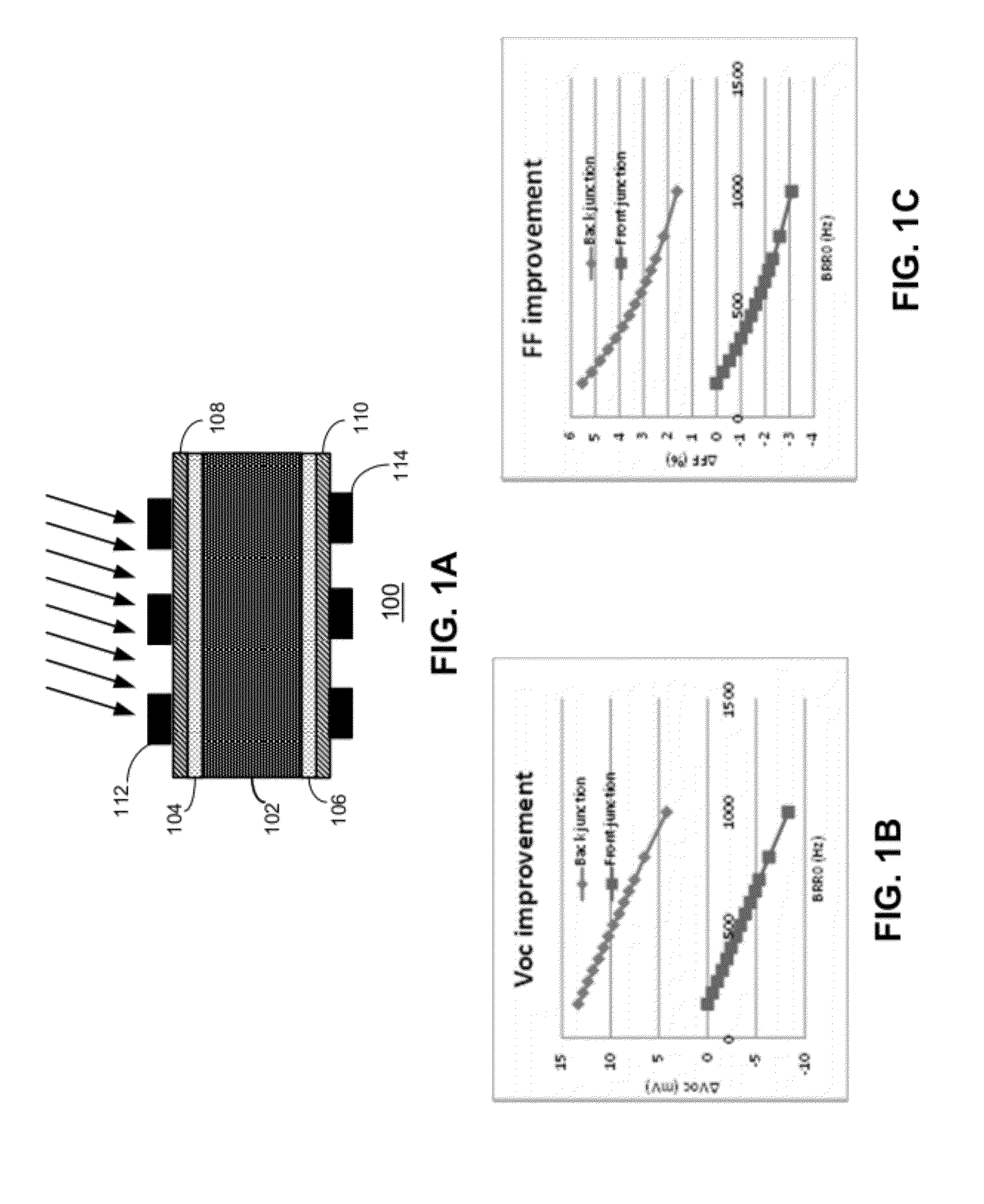

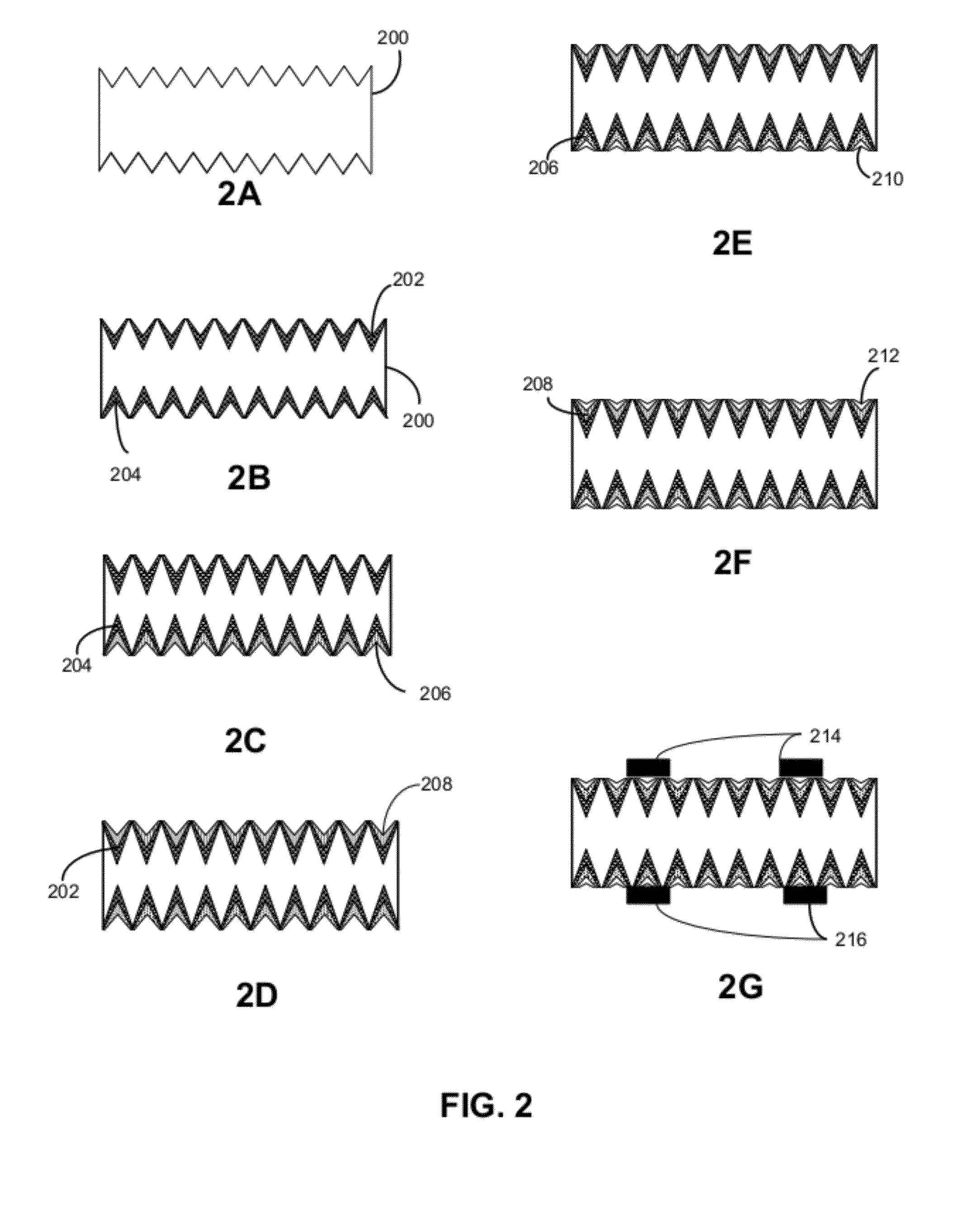

One embodiment of the present invention provides a back junction solar cell. The solar cell includes a base layer, a quantum-tunneling-barrier (QTB) layer situated below the base layer facing away from incident light, an emitter layer situated below the QTB layer, a front surface field (FSF) layer situated above the base layer, a front-side electrode situated above the FSF layer, and a back-side electrode situated below the emitter layer.

Owner:SOLARCITY

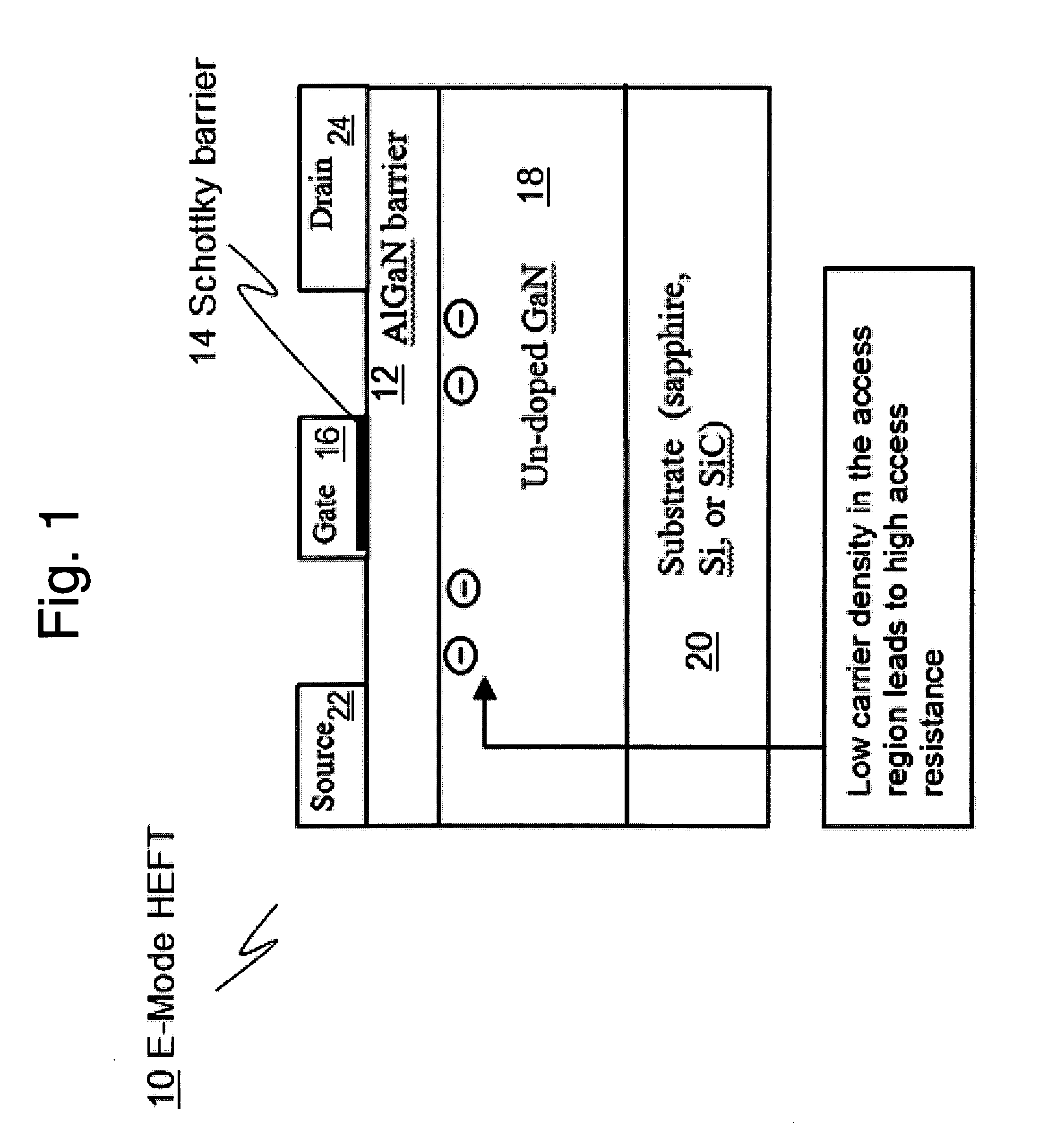

Low Density Drain HEMTs

ActiveUS20070295993A1Simple circuit configurationFavorable operating condition for device safetySemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationBreakdown voltage

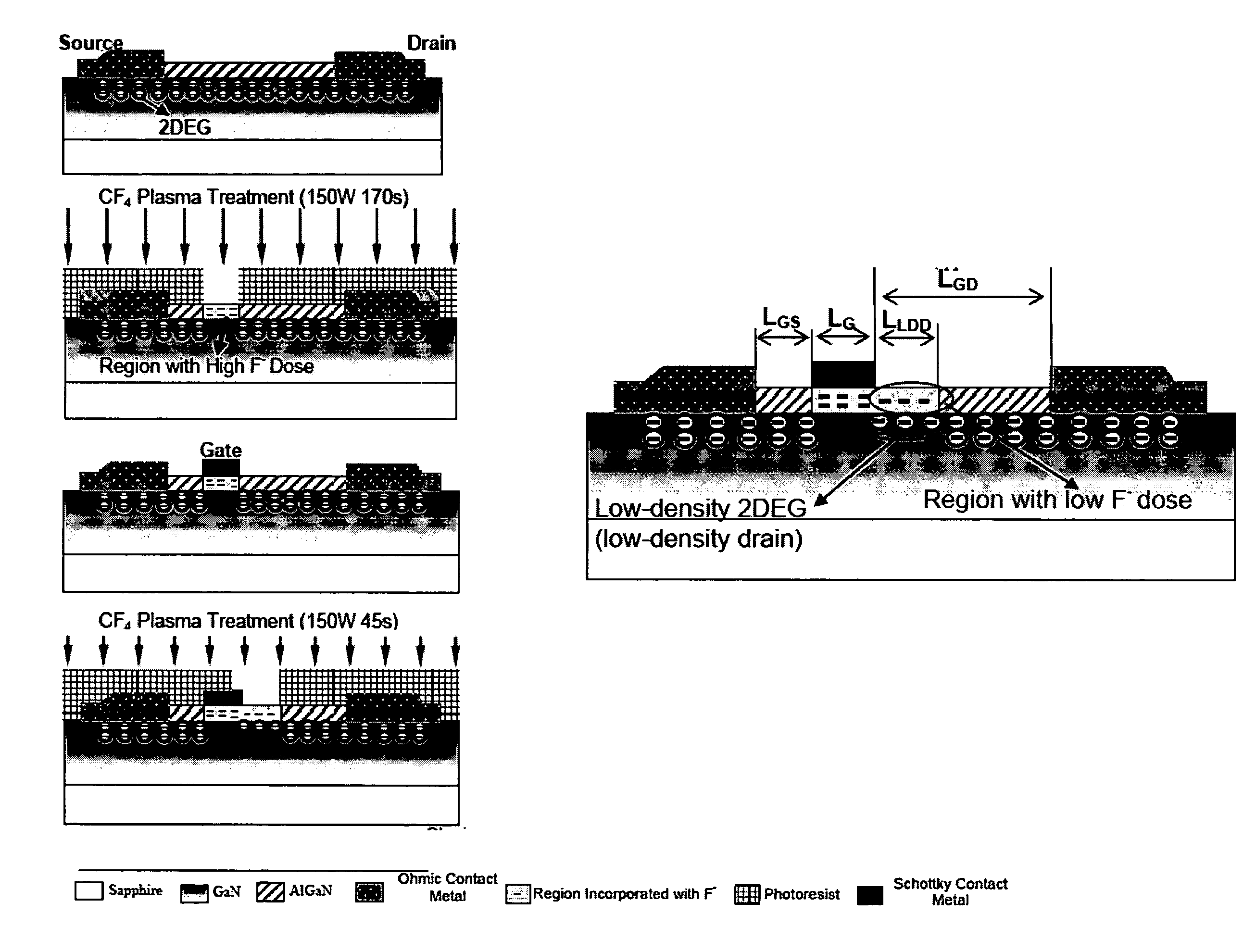

Methods and devices for fabricating AlGaN / GaN normally-off high electron mobility transistors (HEMTs). A fluorine-based (electronegative ions-based) plasma treatment or low-energy ion implantation is used to modify the drain-side surface field distribution without the use of a field plate electrode. The off-state breakdown voltage can be improved and current collapse can be completely suppressed in LDD-HEMTs with no significant degradation in gains and cutoff frequencies.

Owner:THE HONG KONG UNIV OF SCI & TECH

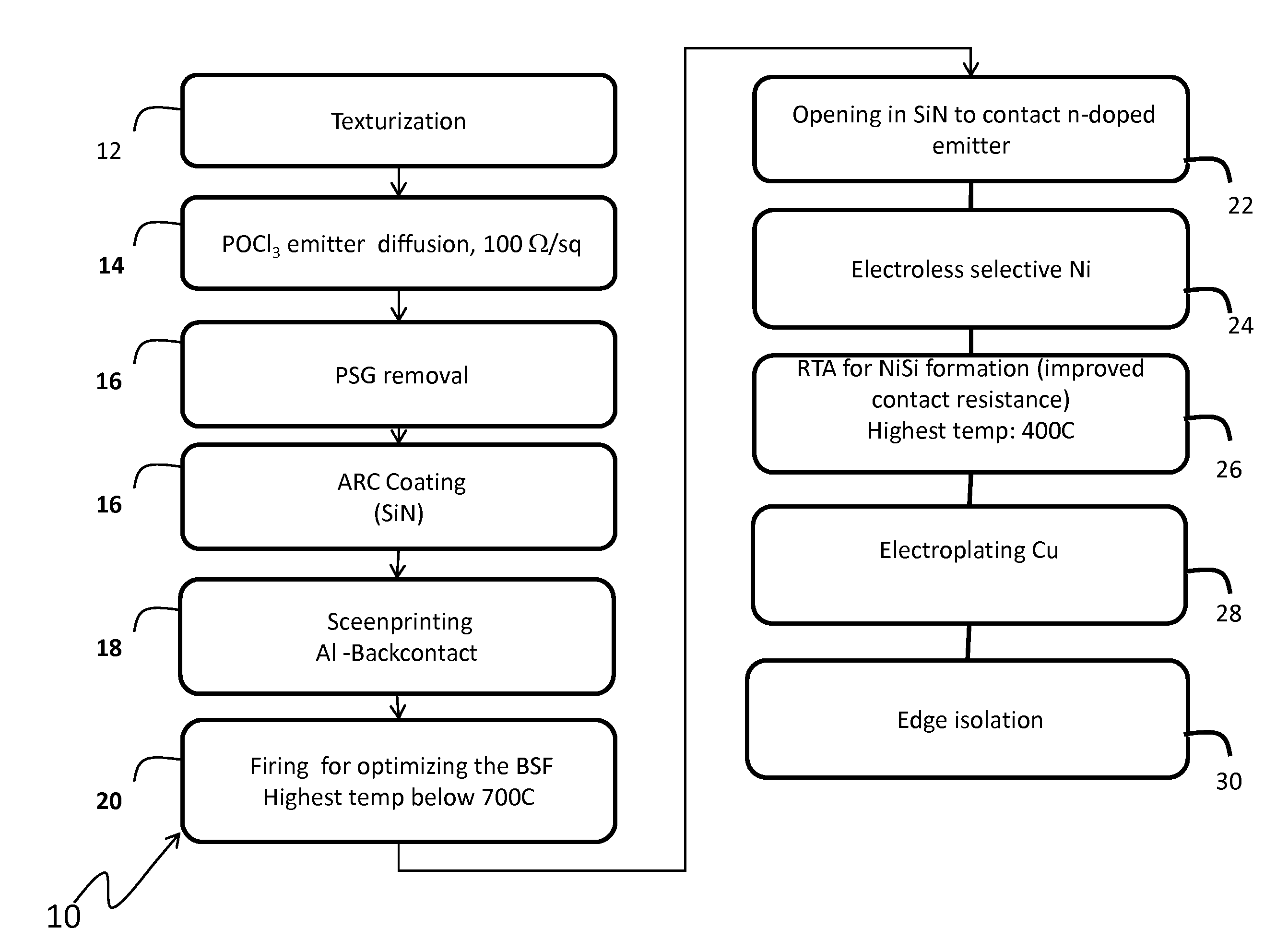

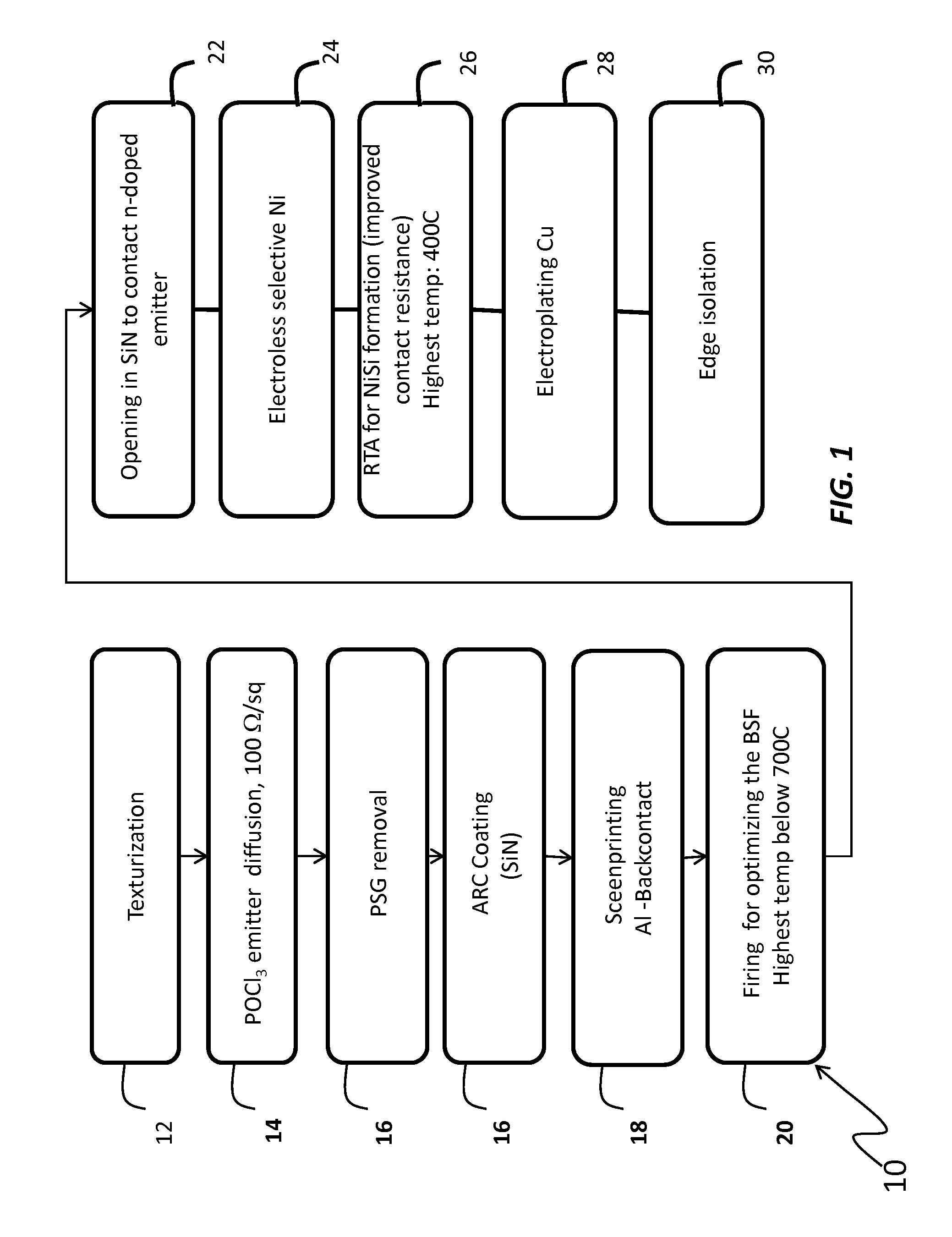

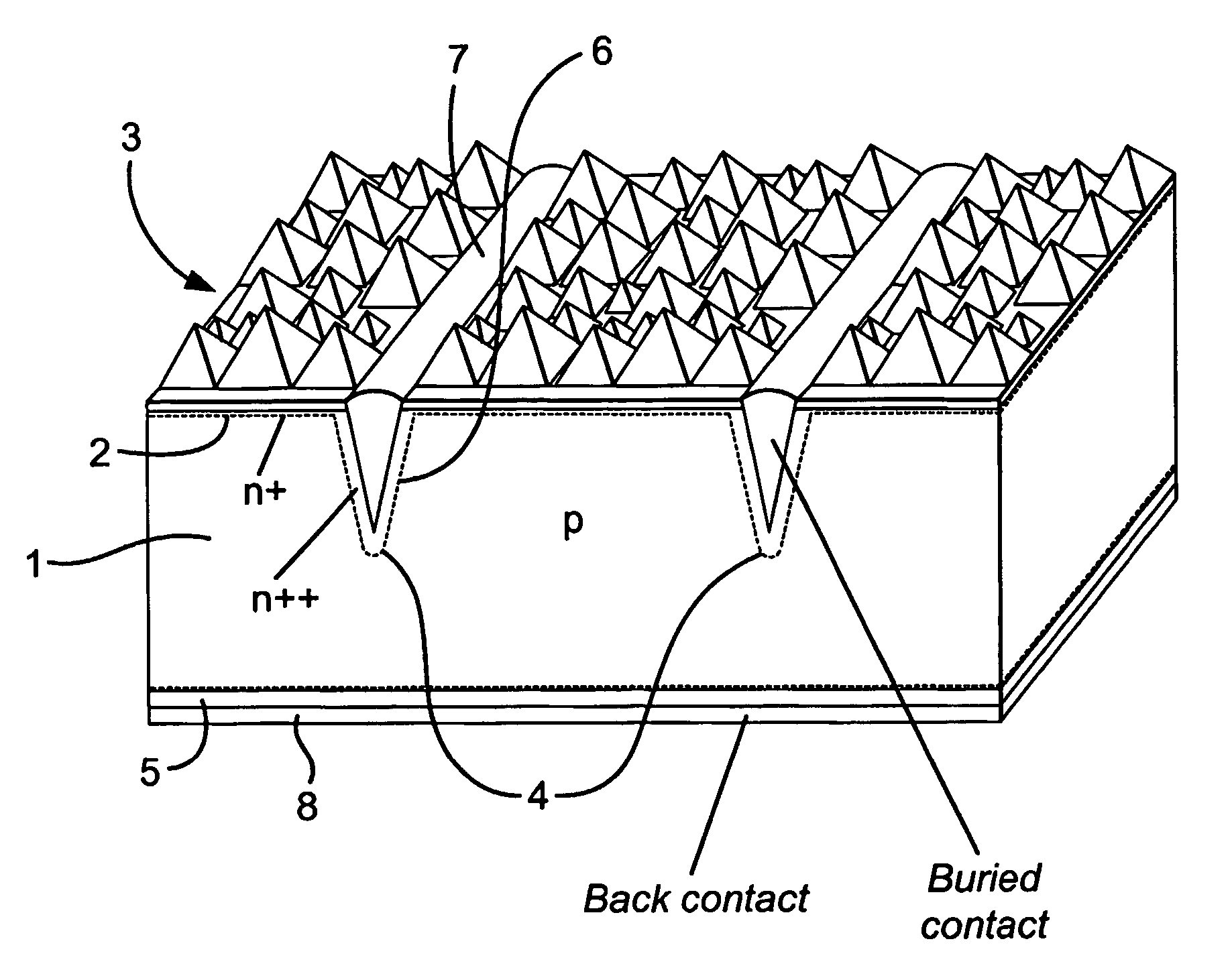

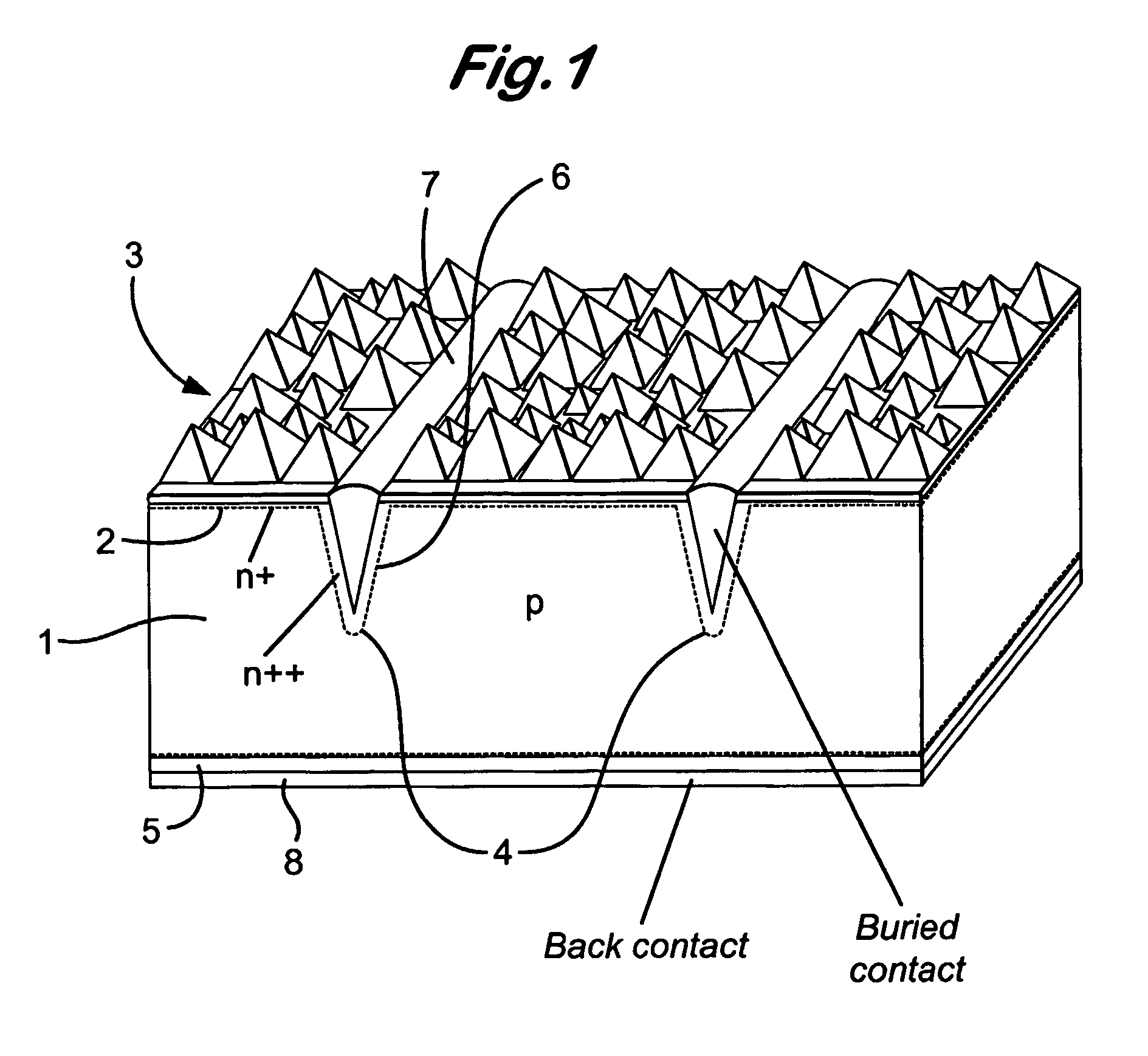

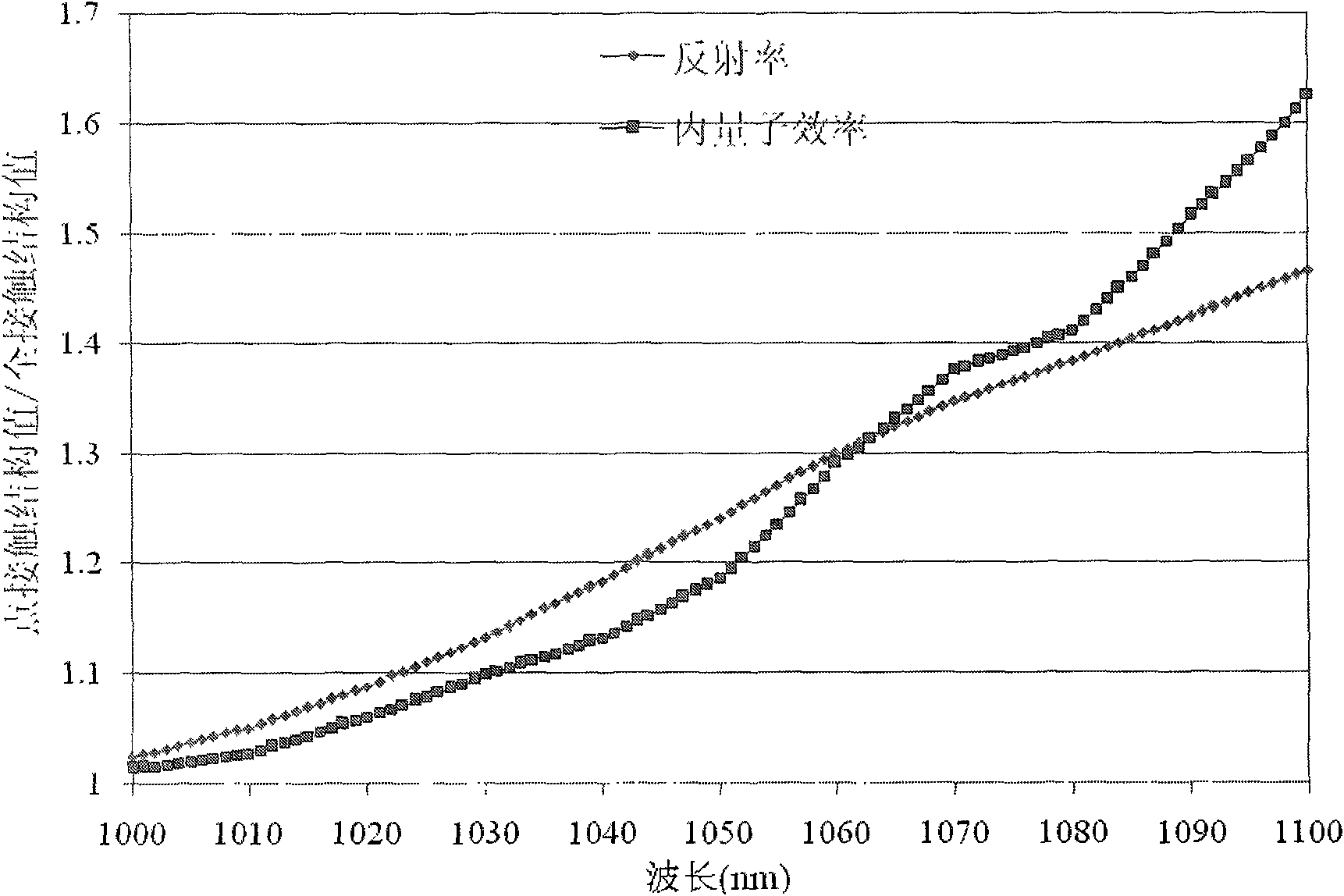

Solar cell and fabrication method using crystalline silicon based on lower grade feedstock materials

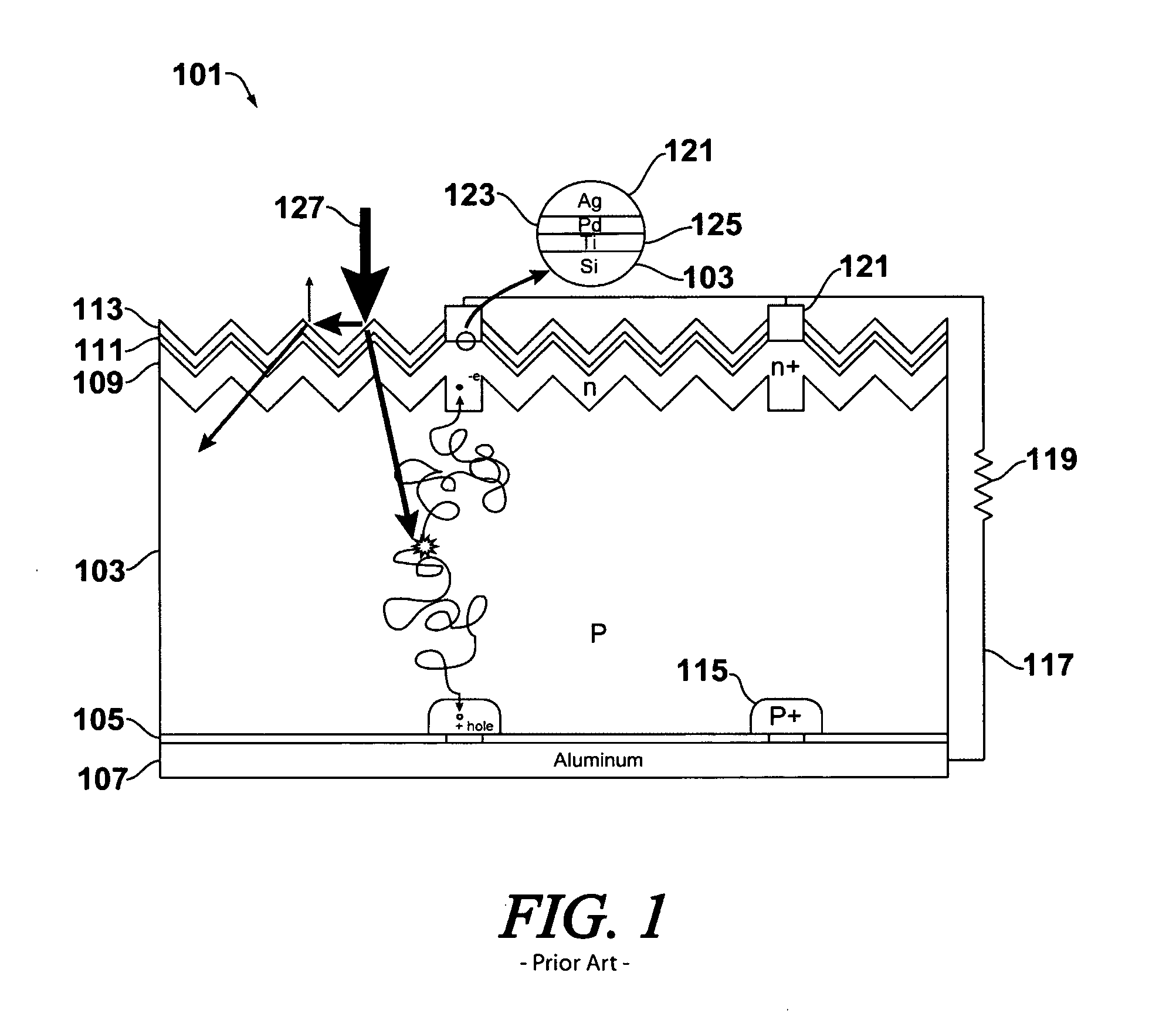

InactiveUS20090223549A1Lower resistanceGreat electrical outputPV power plantsFinal product manufactureAnti-reflective coatingElectrical resistance and conductance

Formation of a solar cell device from upgraded metallurgical grade silicon which has received at least one defect engineering process and including a low contact resistance electrical path. An anti-reflective coating is formed on an emitter layer and back contacts are formed on a back surface of the bulk silicon substrate. This photovoltaic device may be fired to form a back surface field at a temperature sufficiently low to avoid reversal of previous defect engineering processes. The process further forms openings in the anti-reflective coating and a low contact resistance metal layer, such as nickel layer, over the openings in the anti-reflective coating. The process may anneal the low contact resistance metal layer to form n-doped portion and complete an electrically conduct path to the n-doped layer. This low temperature metallization (e.g., <700° C.) supports the use of UMG silicon for the solar device formation without the risk of reversing earlier defect engineering processes.

Owner:SILICOR MATERIALS INC

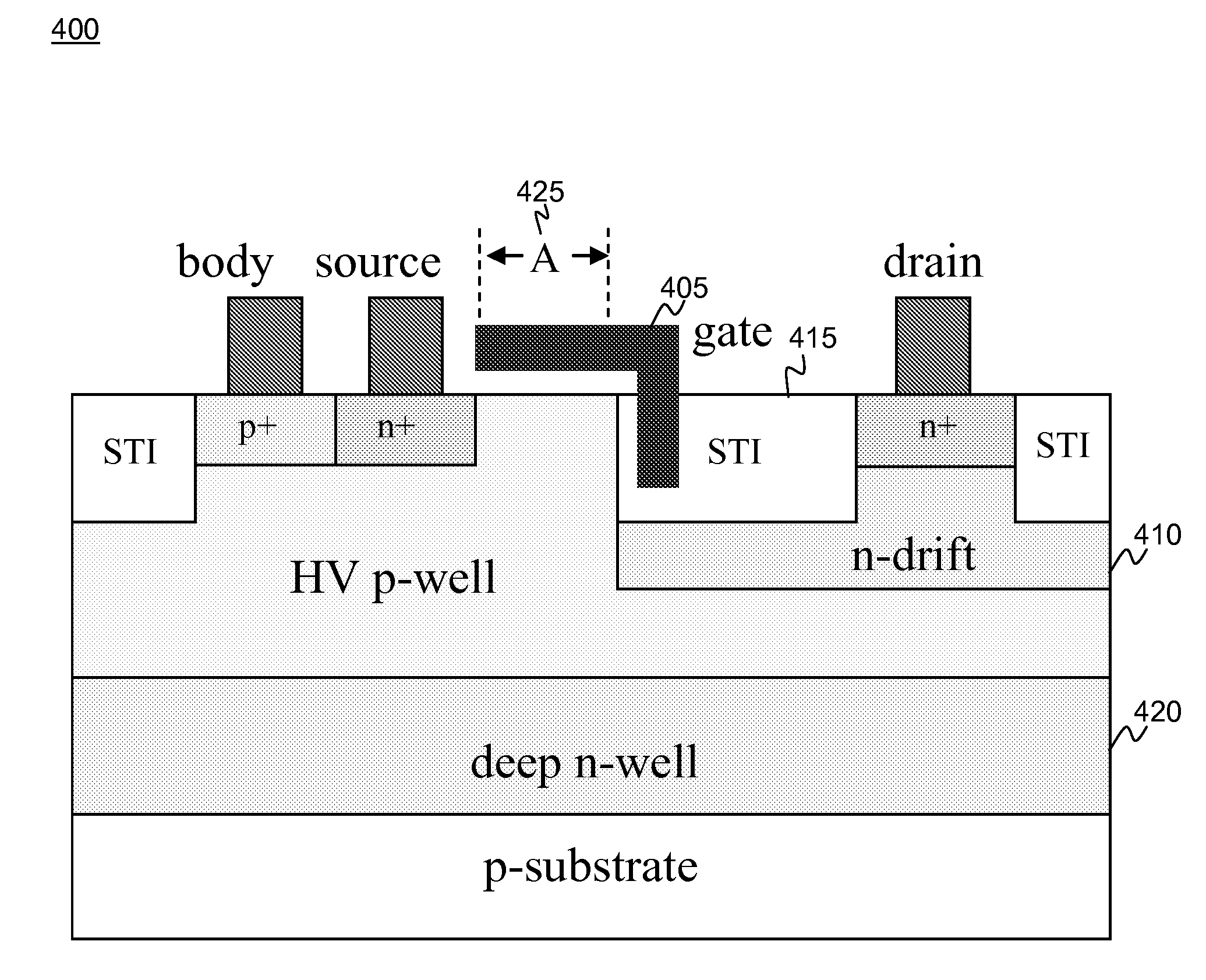

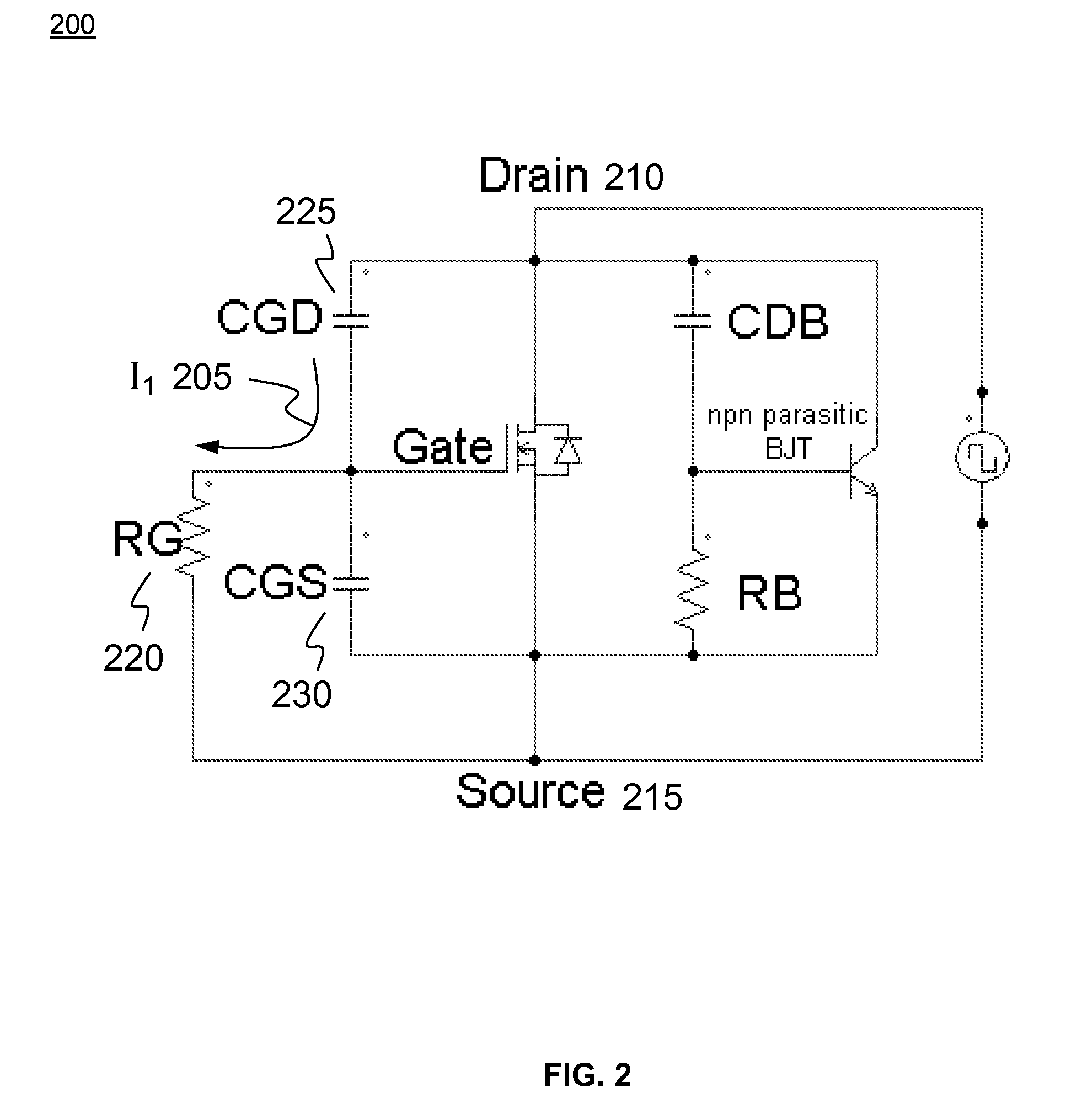

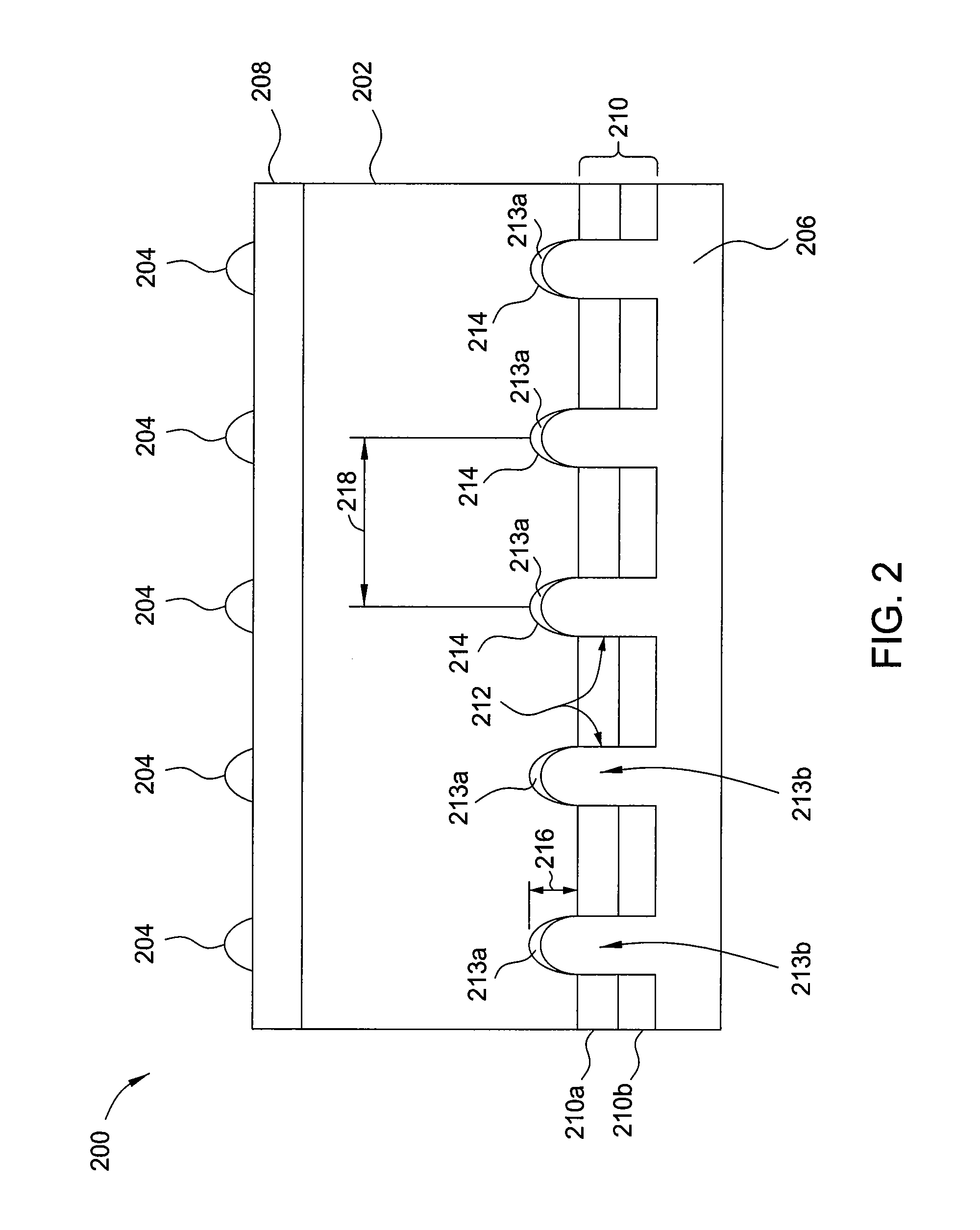

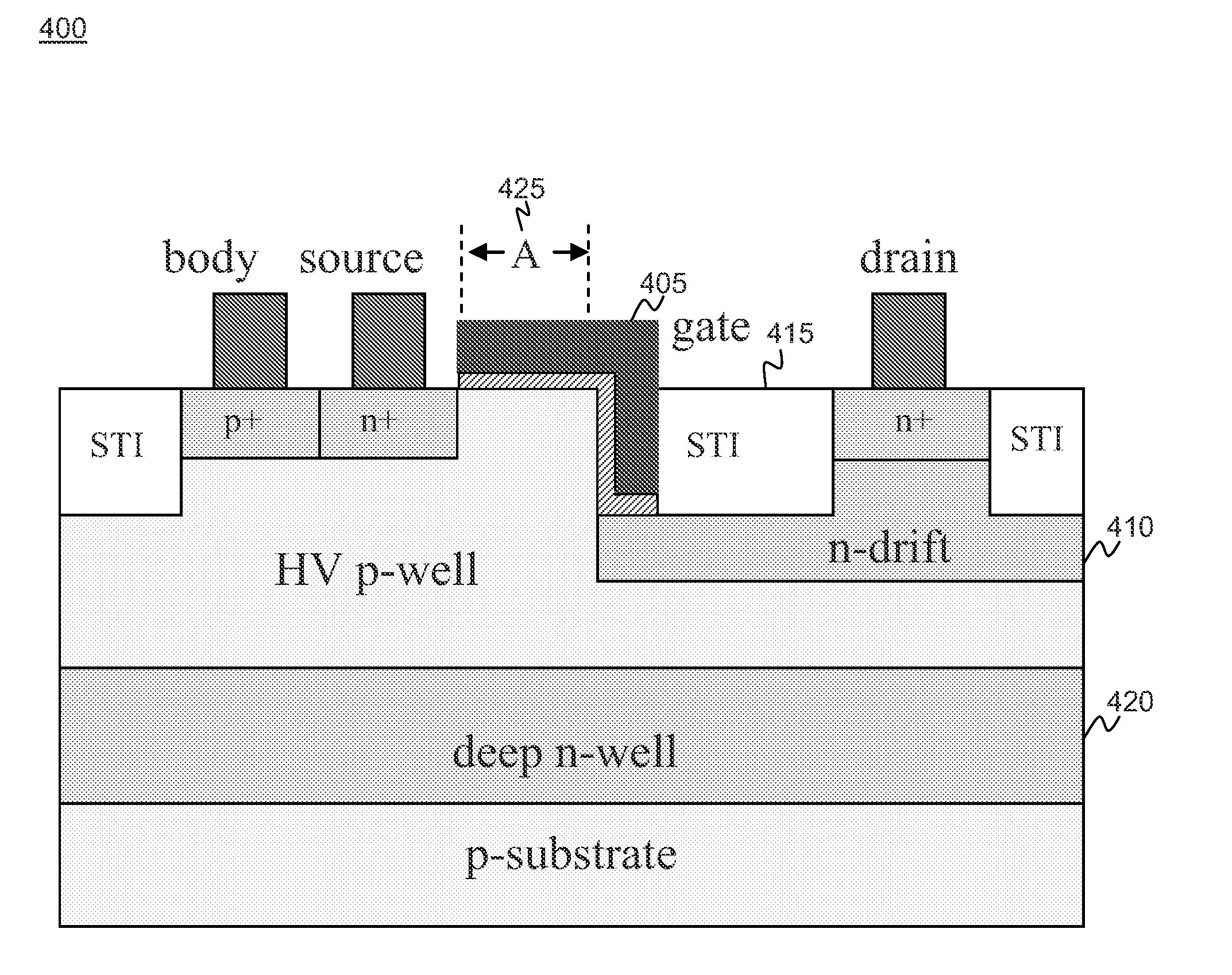

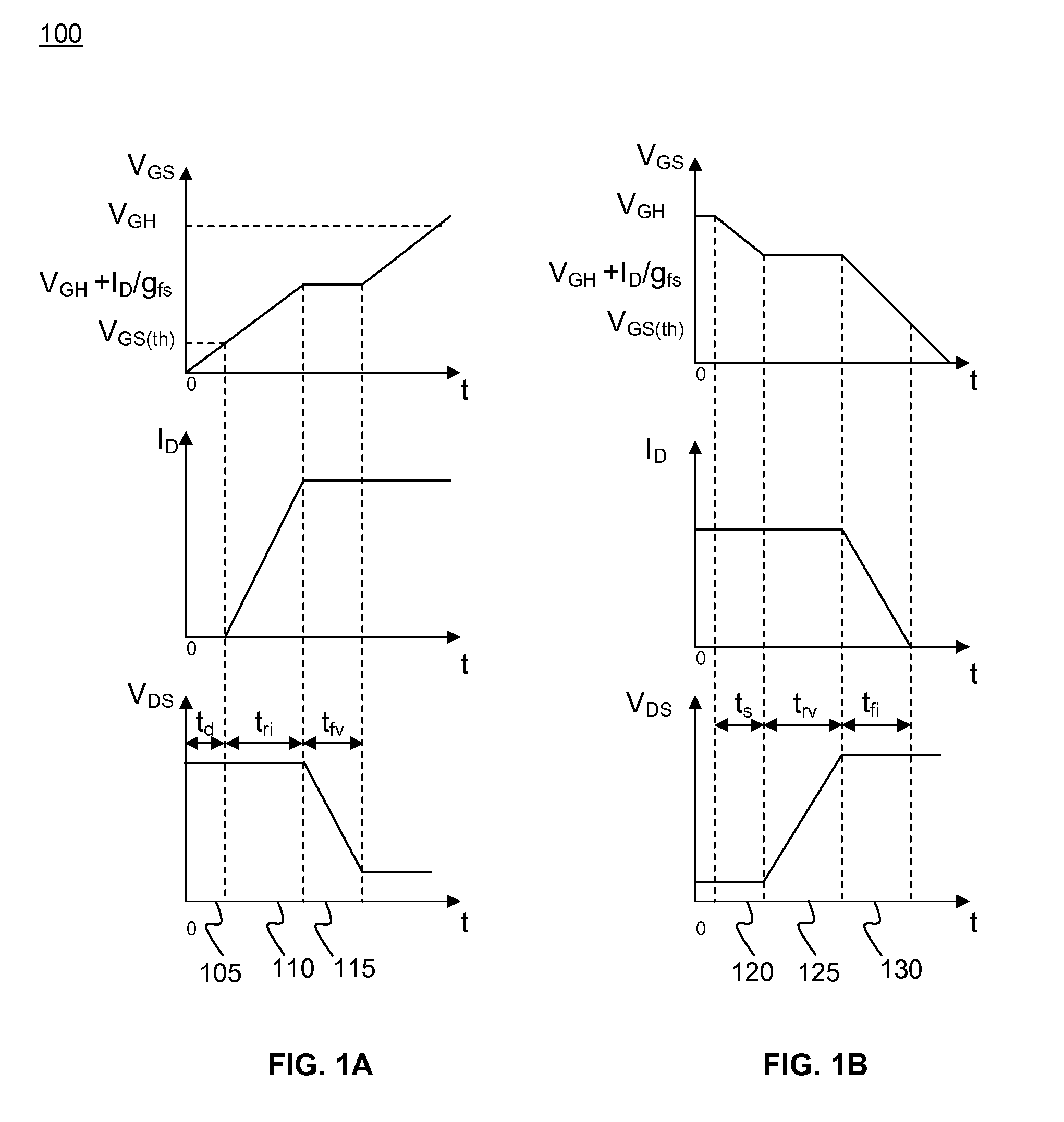

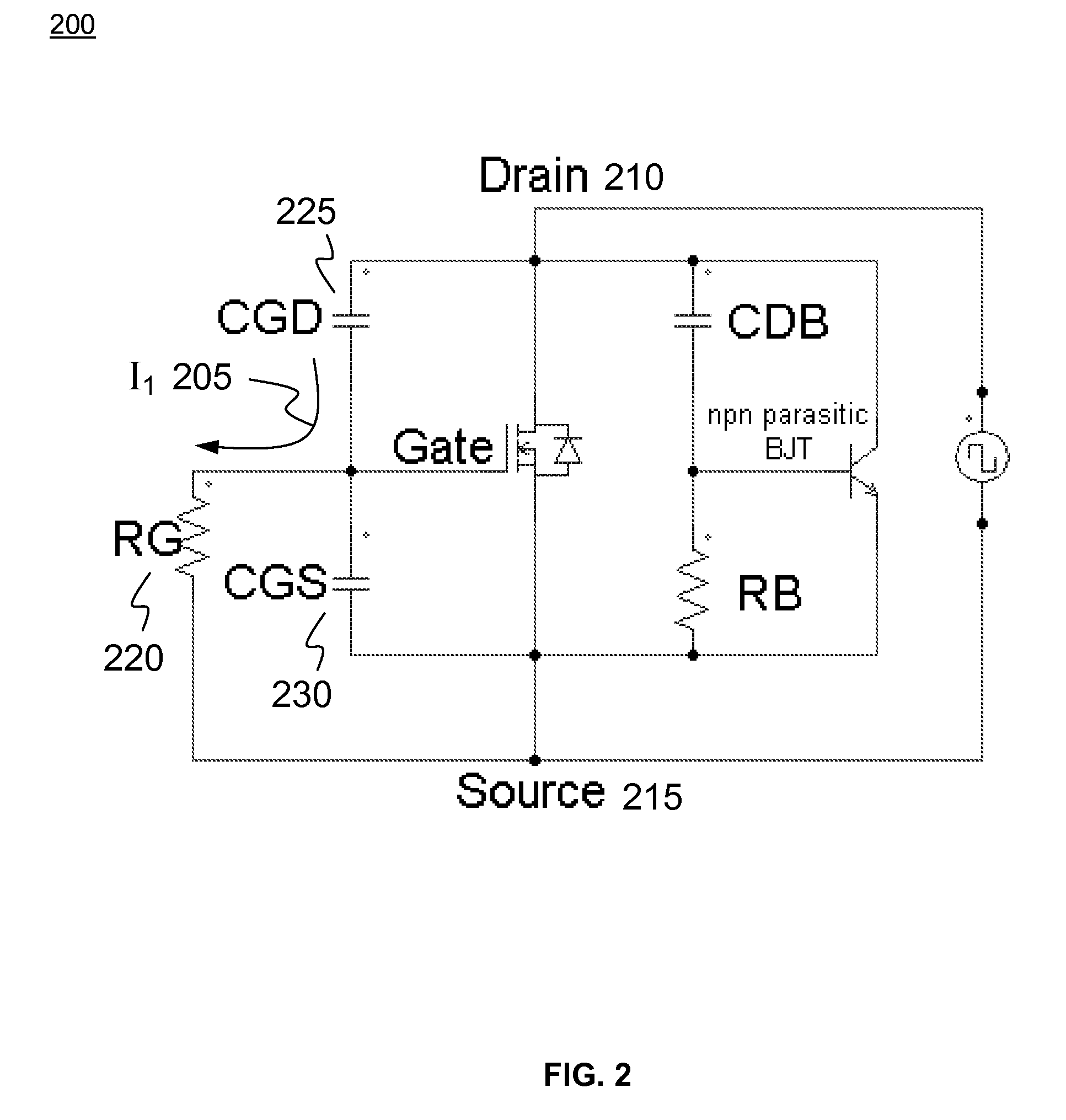

High speed orthogonal gate edmos device and fabrication

InactiveUS20090283825A1Reduce gate-to-drain capacitanceMinimizesSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

An orthogonal gate extended drain MOSFET (EDMOS) structure provides a low gate-to-drain capacitance (CGD) and exhibits increased reliability. It has a gate electrode that is folded into the shallow trench isolation (STI) oxide region. Horizontal and vertical gate electrode segments provide gate control. It accommodates both high voltage devices and standard CMOS components on the same substrate. Reduced surface field (RESURF) technology is employed to optimize tradeoffs between high breakdown voltage and specific on-resistance. Device fabrication steps are compatible with standard CMOS flow and process modules can be added or removed from baseline CMOS technology.

Owner:ASAHI KASEI ELECTRONICS CO LTD

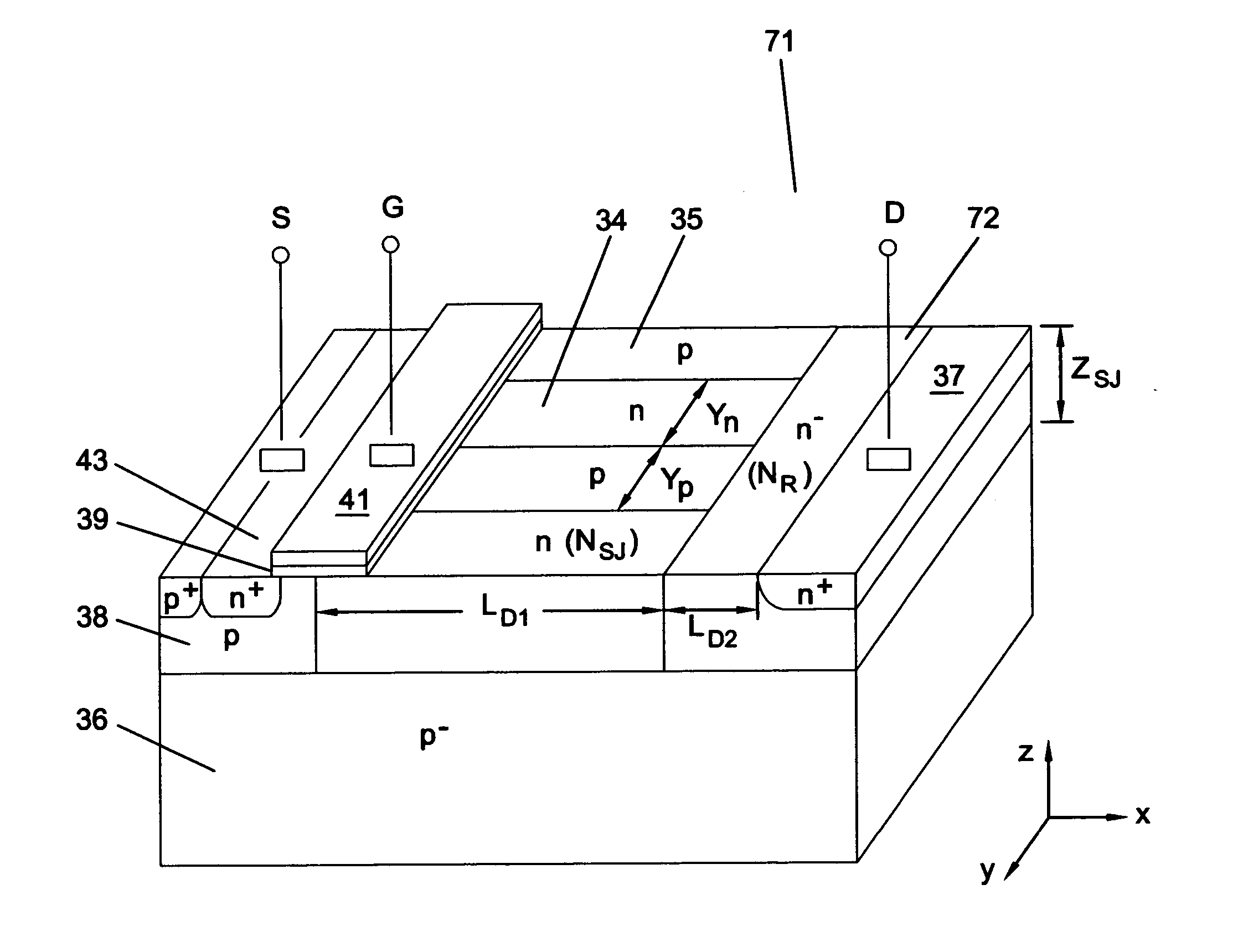

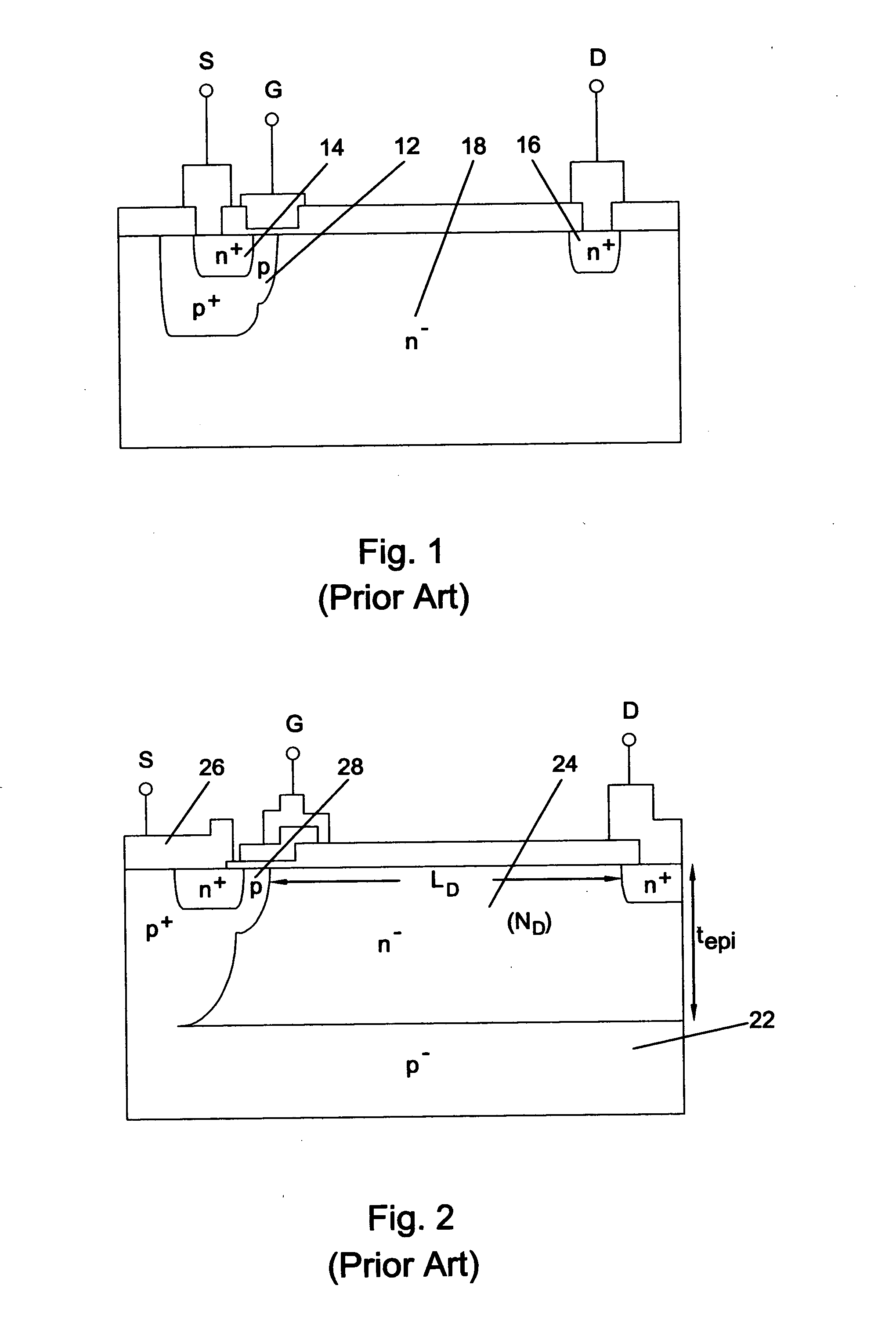

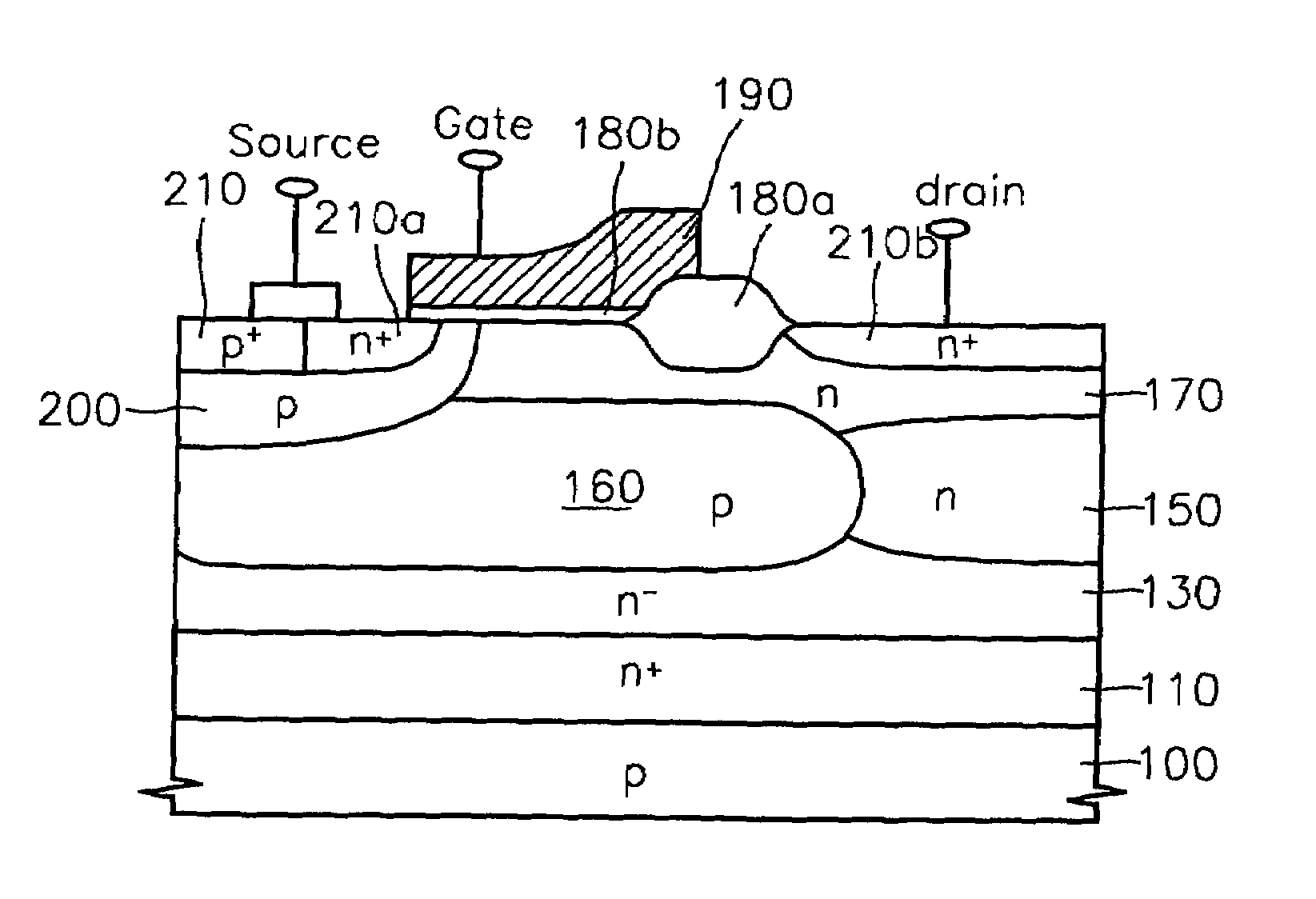

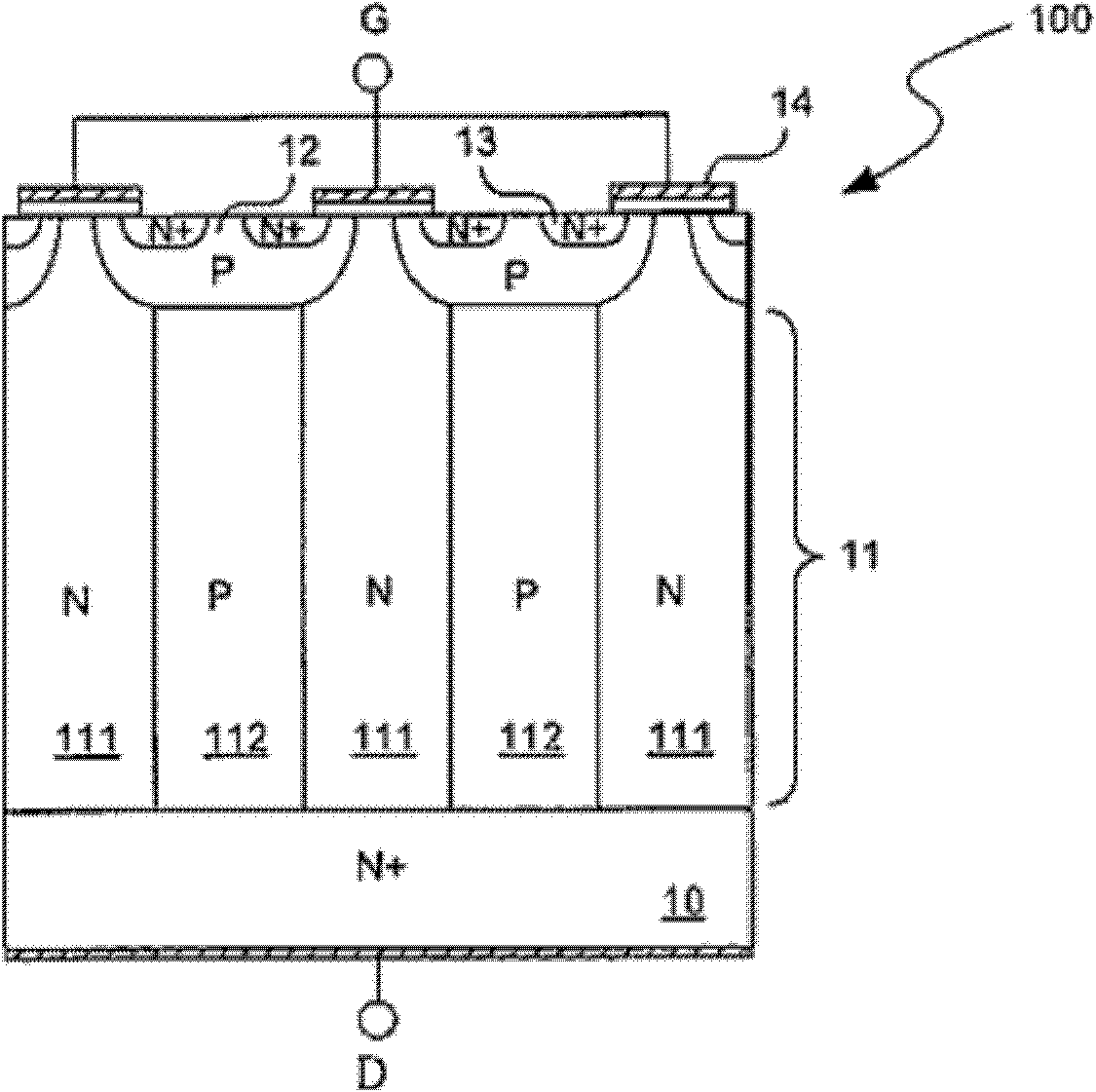

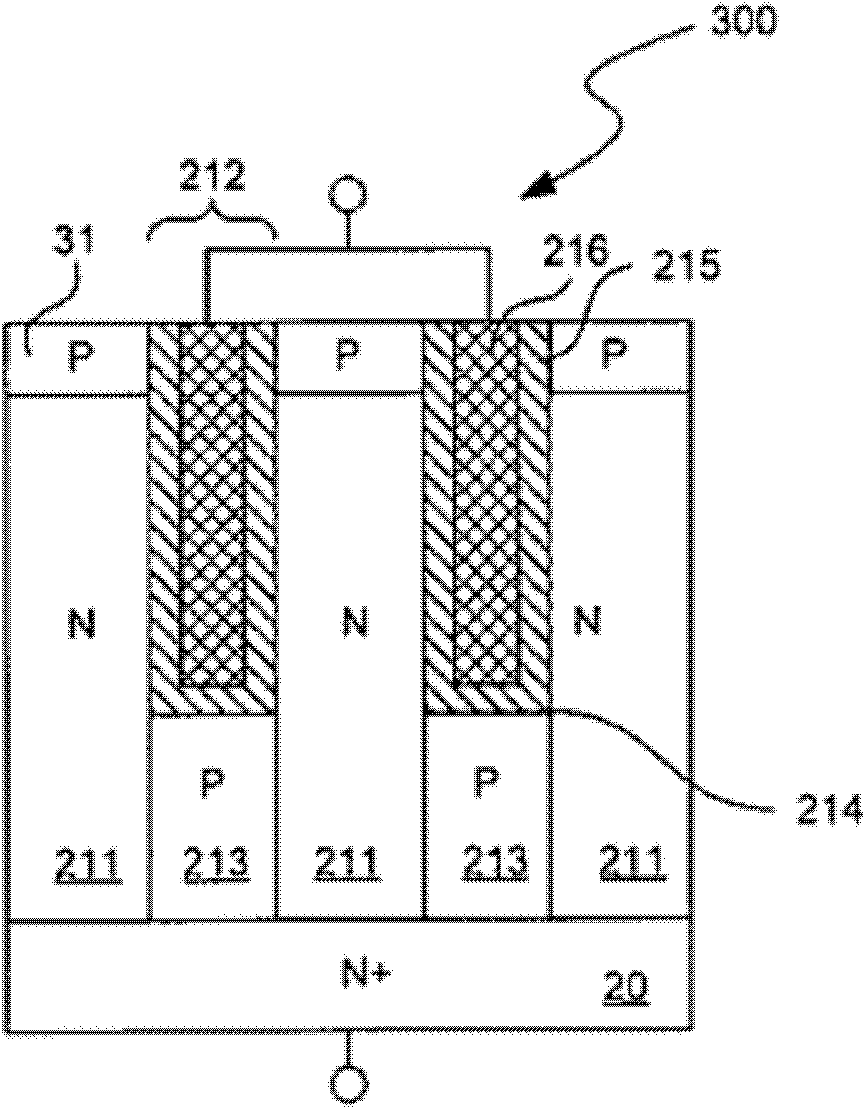

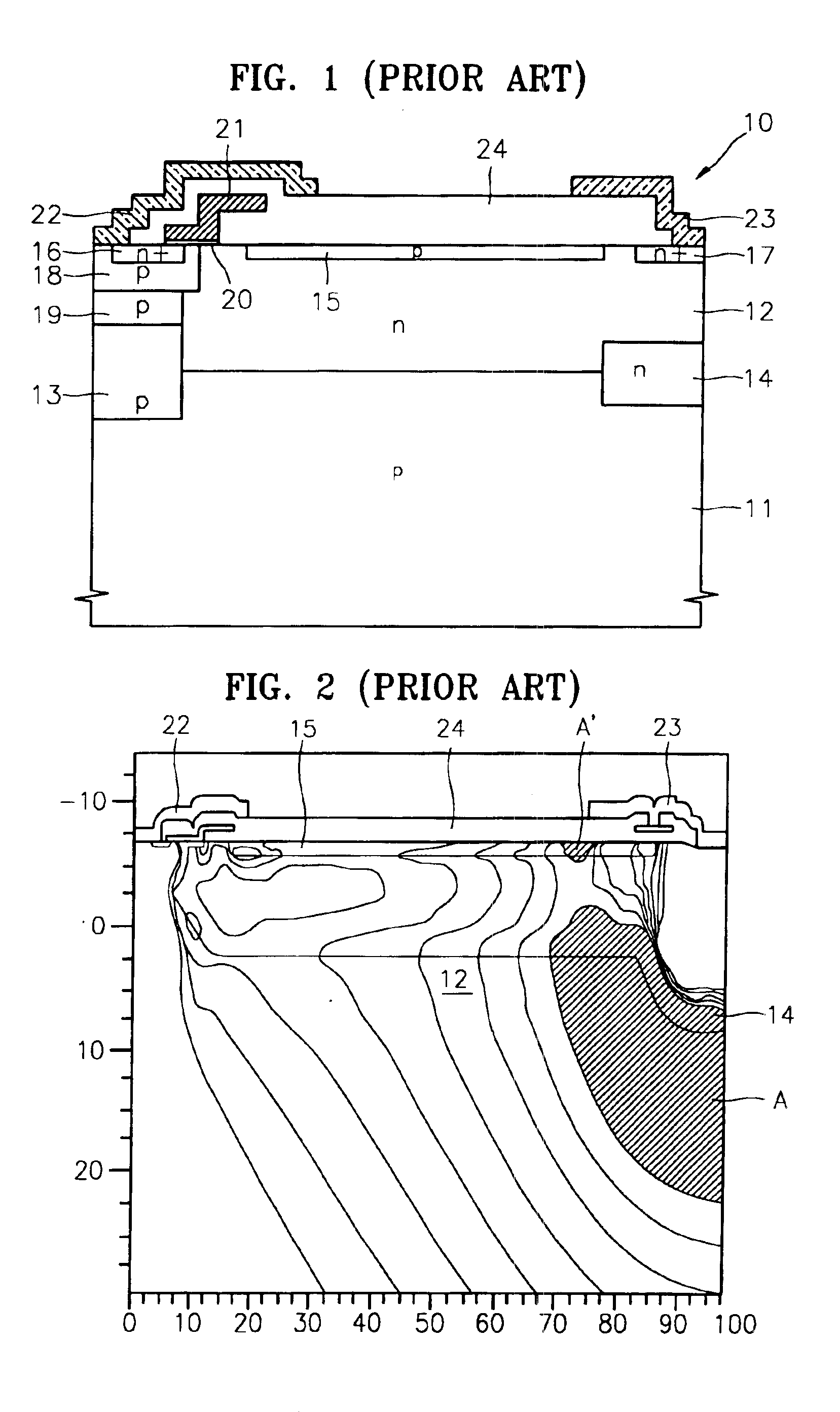

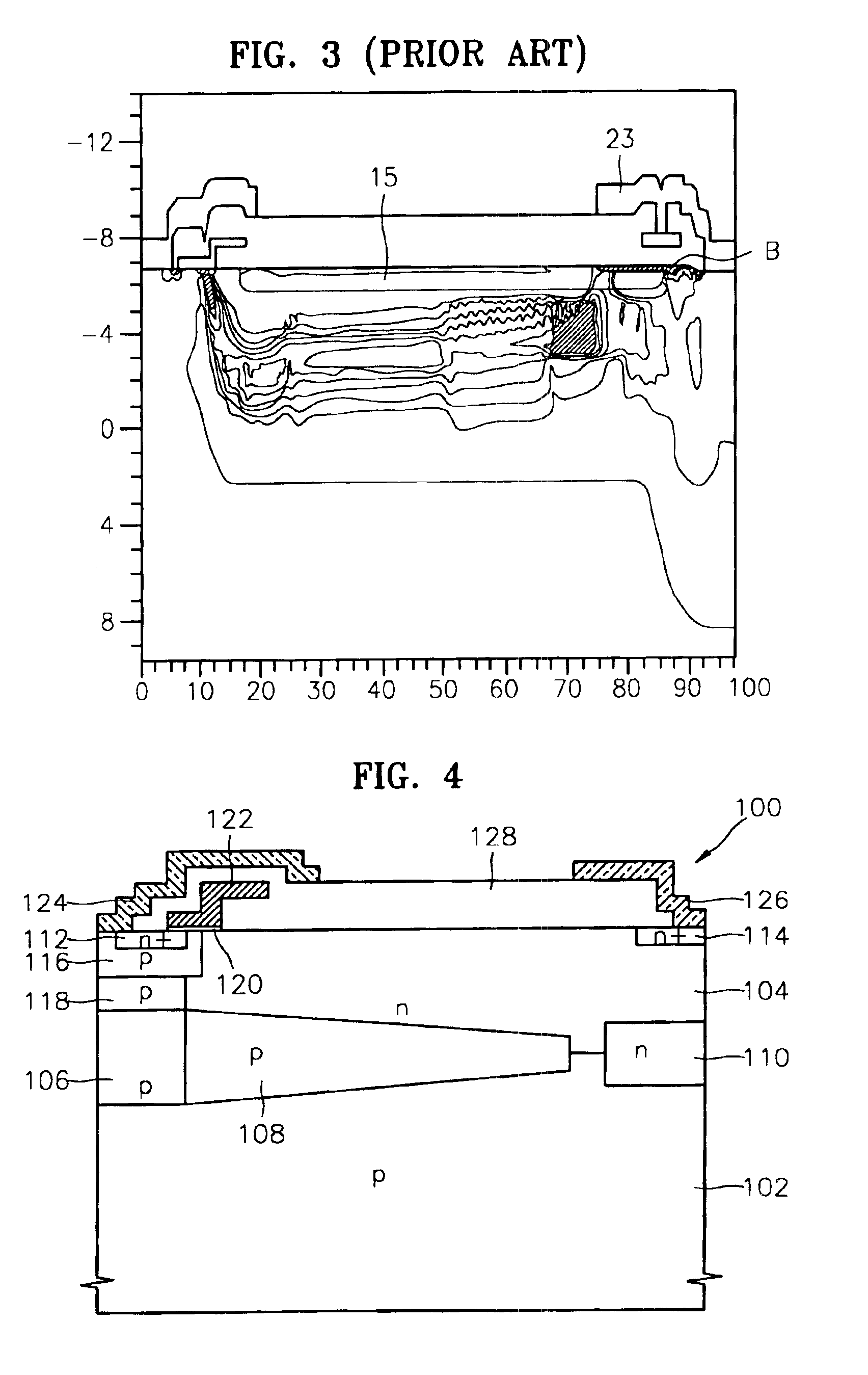

Super junction / resurf LDMOST (SJR-LDMOST)

InactiveUS7023050B2Reduce doping concentrationBreakdown voltage of deviceSemiconductor devicesMOSFETDisplay device

A lateral double diffused MOSFET (LDMOST) incorporates both the reduced surface field (RESURF) and super junction (SJ) in a split-drift region to significantly improve the on-state, off-state and switching characteristics in junction-isolated (JI) technology. The structure effectively suppresses substrate-assisted-depletion which is the main problem encountered when applying the SJ concept to lateral power devices. The device structure features a split-drift region formed of two parts: a SJ structure that extends over most of the drift region, and a terminating RESURF region occupying a portion of the drift region next to the drain. The structure offers improved breakdown voltage and reduced specific on resistance as compared to convention structures, and is useful in power integrated circuits suitable for a variety of applications including flat plasma panel display, automotive electronics, motor control, power supply and high voltage lamp ballasts.

Owner:SALAMA C ANDRE T +1

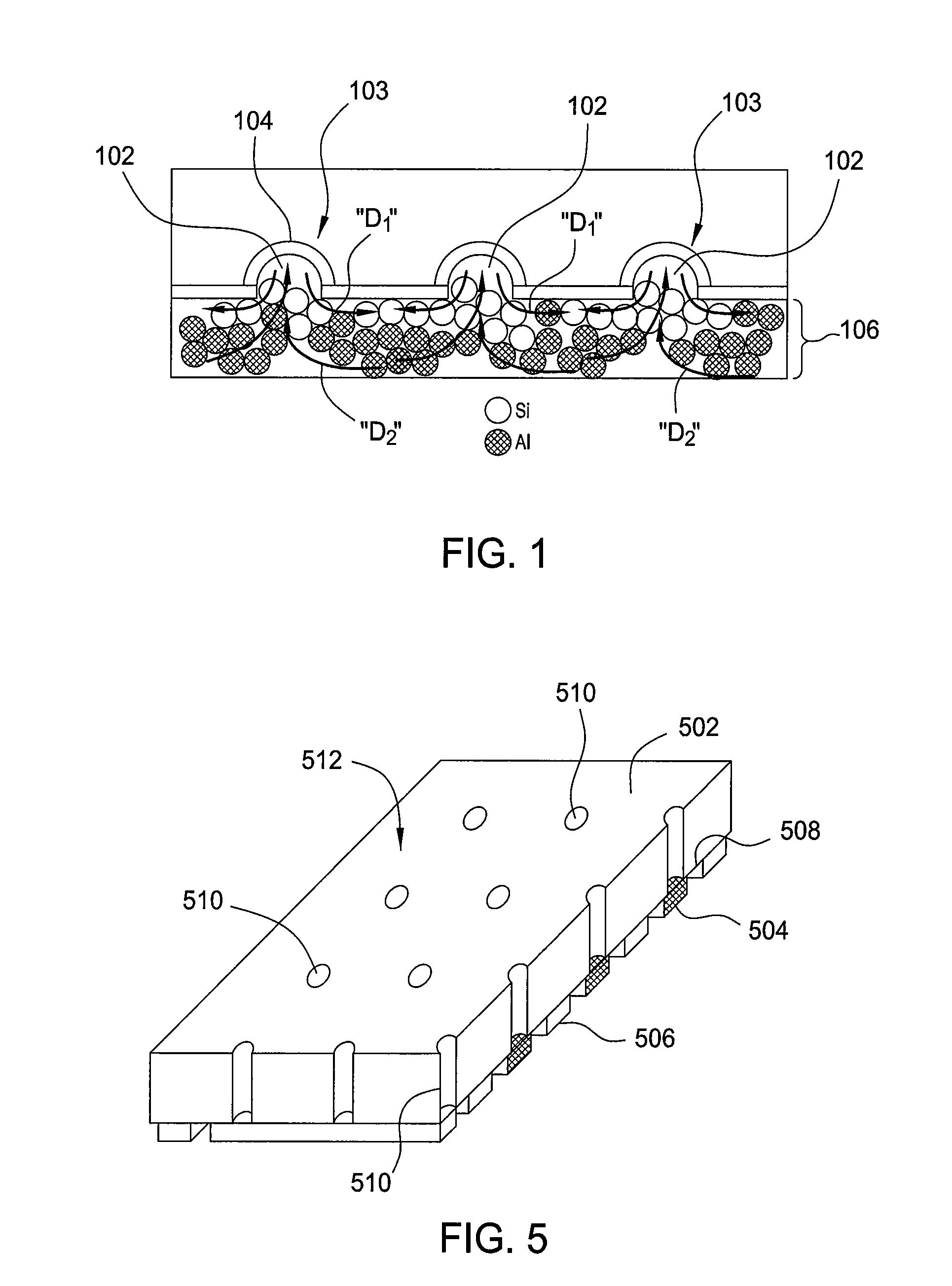

Process for manufacturing a solar cell

InactiveUS7071018B2Low costFinal product manufactureSemiconductor/solid-state device manufacturingBack surface fieldSilicon solar cell

Process for incorporating a back surface field into a silicon solar cell by depositing a layer of aluminium on the rear surface of the cell, sintering the aluminium at a temperature between 700 and 1000° C., exposing the cell to an atmosphere of a compound of Group V element and diffusing at a temperature of between 950 and 1000°C. so as to dope exposed p-type silicon surfaces with the Group V element. The step of exposing the cell to an atmosphere of a compound of a Group V element is carried separately from the step of sintering the aluminium layer, and subsequent to the step of depositing a layer of aluminium on the rear surface of the cell.

Owner:BP ALTERNATIVE ENERGY INT

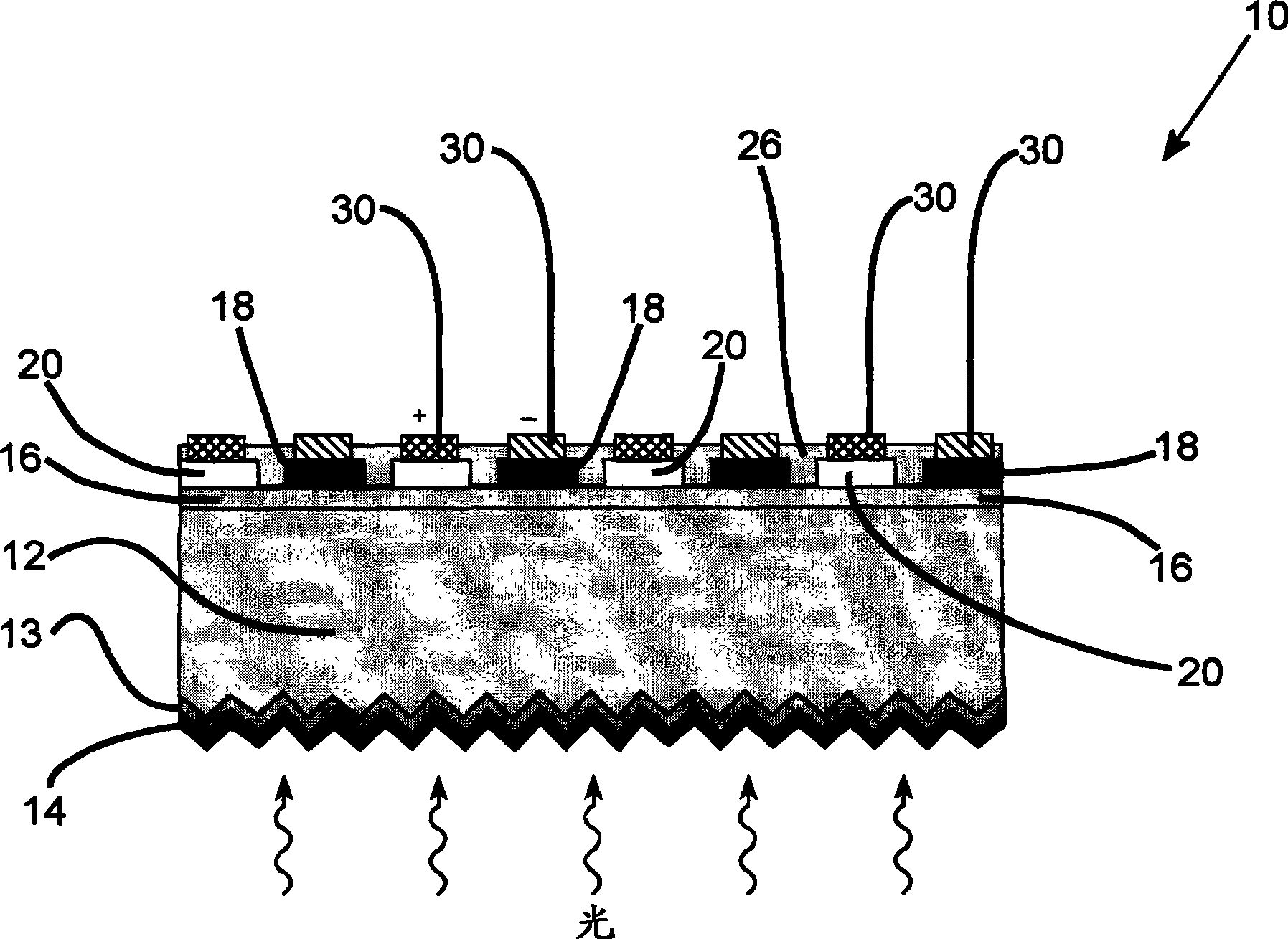

Solar cell

InactiveCN101401215APhotovoltaic energy generationSemiconductor devicesHeterojunctionBack surface field

The invention provides a thin film amorphous silicon-crystalline silicon back heterojunction and back surface field device configuration for a heterojunction solar cell. The configuration is attained by the formation of heterojunctions on the back surface of crystalline silicon at low temperatures. Low temperature fabrication allows for the application of low resolution lithography and / or shadow masking processes to produce the structures. The heterojunctions and interface passivation can be formed through a variety of material compositions and deposition processes, including appropriate surface restructing techniques. The configuration achieves separation of optimization requirements for light absorption and carrier generation at the front surface on which the light is incident, and in the bulk, and charge carrier collection at the back of the device. The shadowing losses are eliminated by positioning the electrical contacts at the back thereby removing them from the path of the incident light. Back contacts need optimization only for maximum charge carrier collection without bothering about shading losses. A range of elements / alloys may be used to effect band-bending.

Owner:ARISE TECH CORP

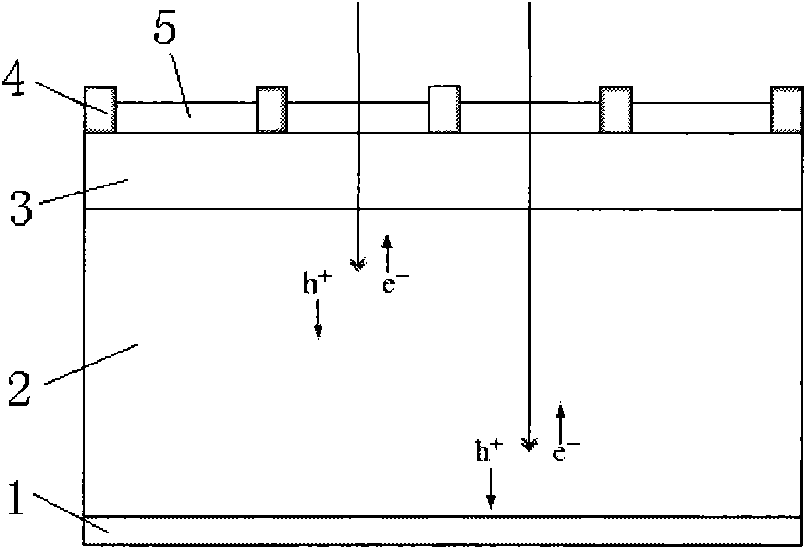

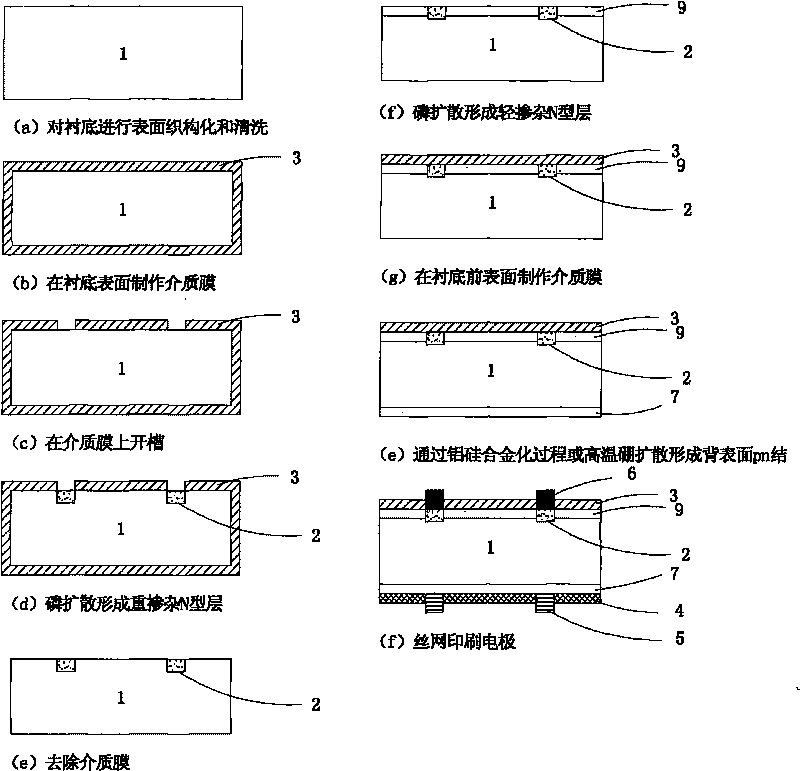

Method for preparing N-type crystalline silicon solar cell with aluminum-based local emitters on back side

InactiveCN101853897AAvoid damageAvoid Edge Leakage SituationsFinal product manufactureSemiconductor devicesP–n junctionMaterials science

The invention provides a method for preparing an N-type crystalline silicon solar cell with aluminum-based local emitters on the back side. The method comprises the following steps: firstly, selecting N-type silicon wafers to carry out the surface-textured etching process; further forming a front surface field through phosphorous diffusion; depositing a passivating film on the front surface after the phosphorosilicate glass is formed during the removal of diffused phosphorous; carrying out the back-side chemical polishing process on the silicon wafers to remove the N+ layer formed on the back side during the phosphorous diffusion; then, sequentially printing an aluminum layer or a silver-aluminum layer through the passivating film deposited on the back side, local holes or grooves on the back side and screens on the back side; then, printing silver paste on the front surface; and finally, carrying out the one-step sintering process to form a local P+ layer on the back side and allowing the P+ layer to coming into ohmic contact with the electrodes on the front and back surfaces. By using the N-type substrate, forming local aluminum-based P-N junctions on the back side and further using the back-side chemical polishing process to remove the edge junctions, the invention can substitute for the conventional stacking-type plasma etching process, simplify the technological procedures and further bring a series of performance improvement to cells.

Owner:JA YANGZHOU SOLAR PHOTOVOLTAIC ENG

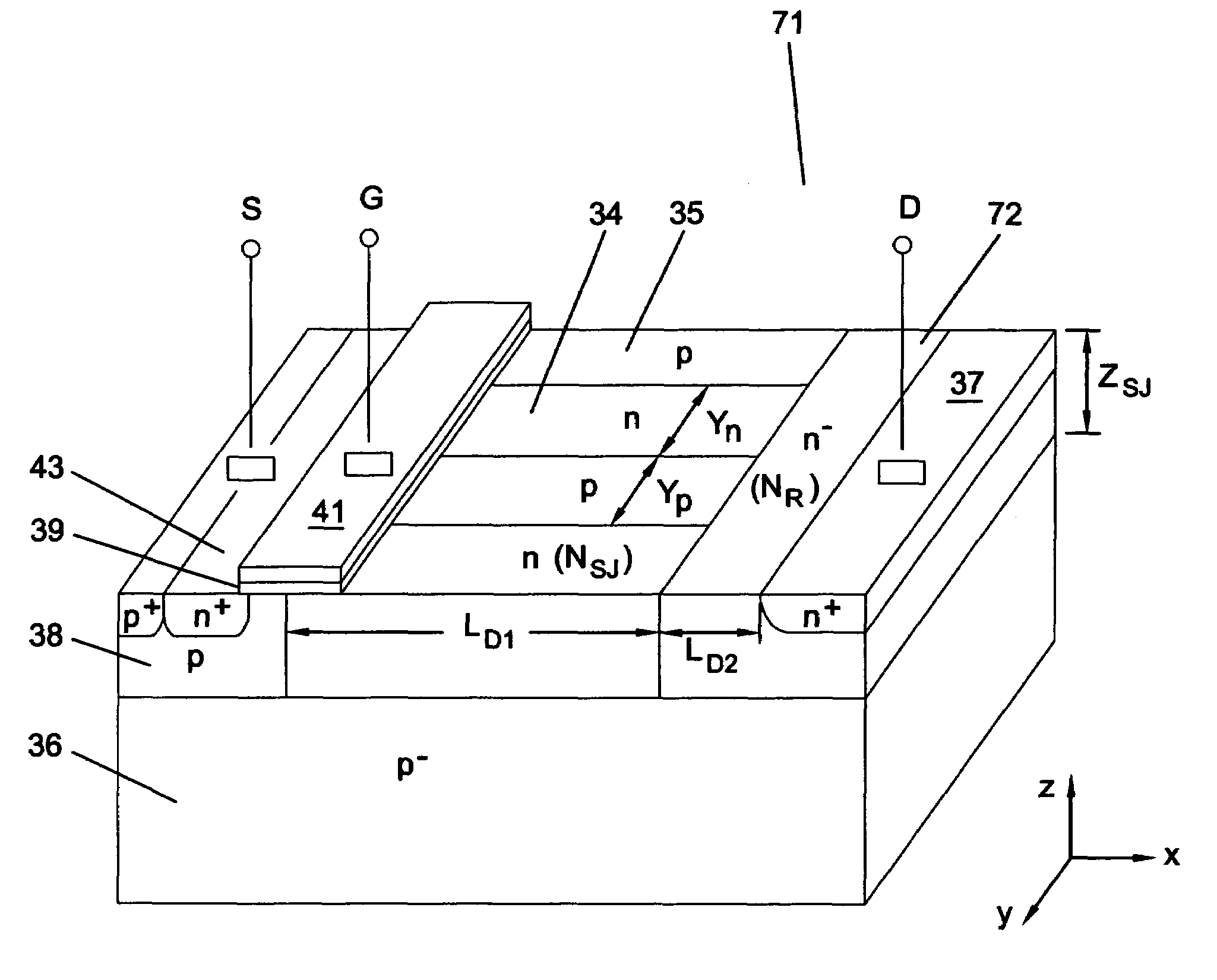

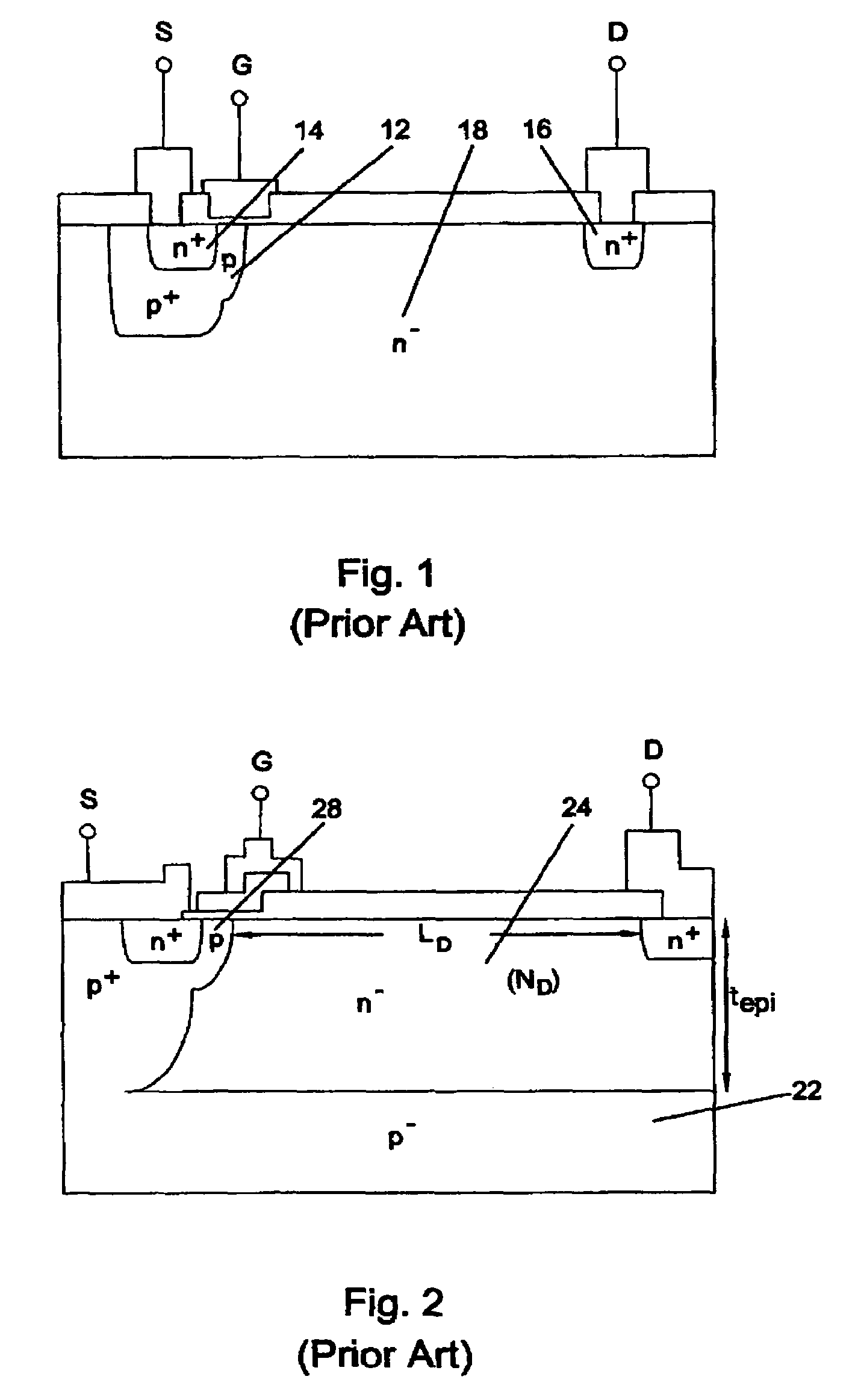

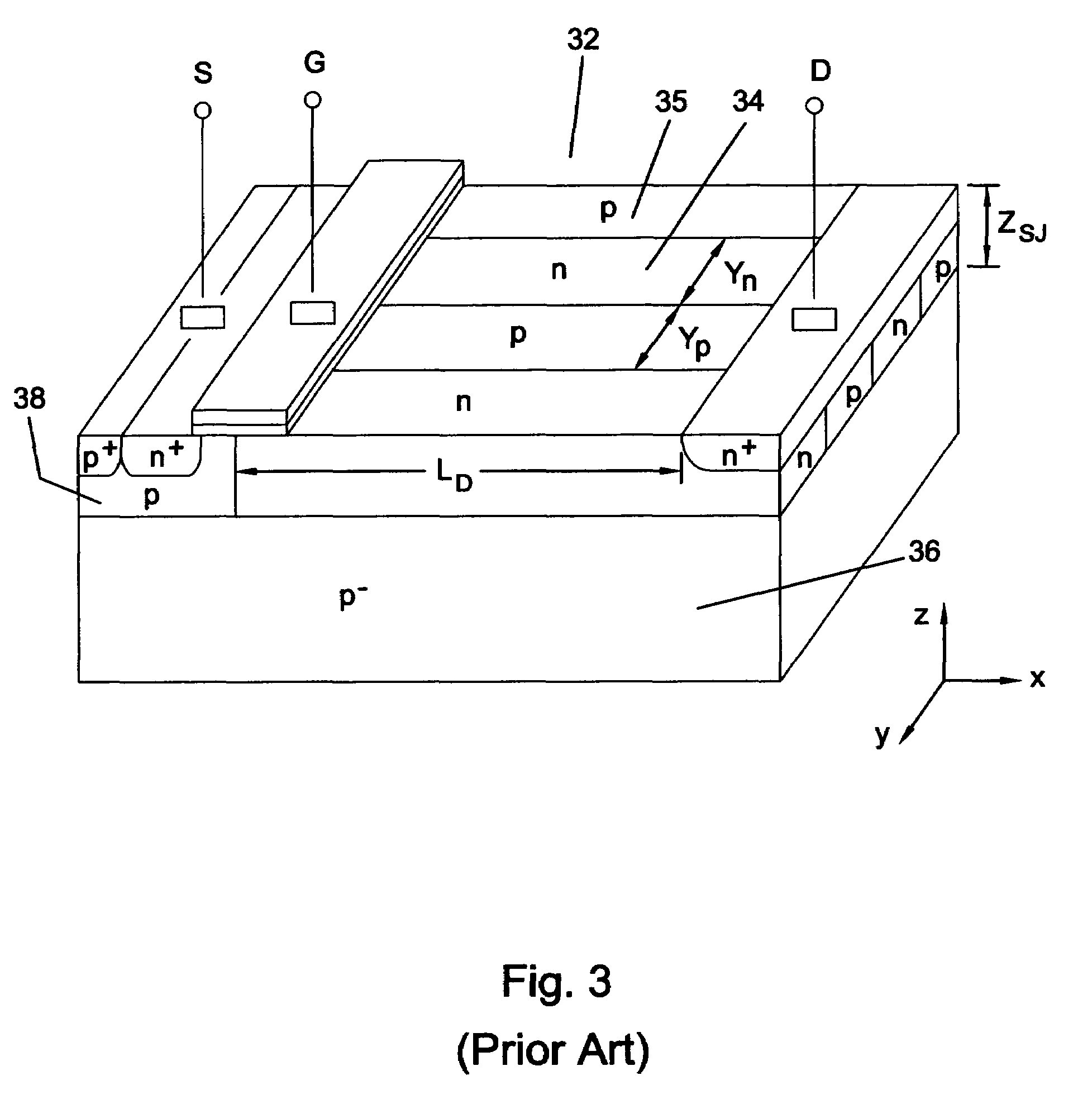

Super junction / resurf ldmost (sjr-LDMOST)

InactiveUS20050017300A1Reduce doping concentrationBreakdown voltage of deviceSemiconductor devicesMOSFETElectrical ballast

A lateral double diffused MOSFET (LDMOST) incorporates both the reduced surface field (RESURF) and super junction (SJ) in a split-drift region to significantly improve the on-state, off-state and switching characteristics in junction-isolated (JI) technology. The structure effectively suppresses substrate-assisted-depletion which is the main problem encountered when applying the SJ concept to lateral power devices. The device structure features a split-drift region formed of two parts: a SJ structure that extends over most of the drift region, and a terminating RESURF region occupying a portion of the drift region next to the drain. The structure offers improved breakdown voltage and reduced specific on resistance as compared to convention structures, and is useful in power integrated circuits suitable for a variety of applications including flat plasma panel display, automotive electronics, motor control, power supply and high voltage lamp ballasts.

Owner:SALAMA C ANDRE T +1

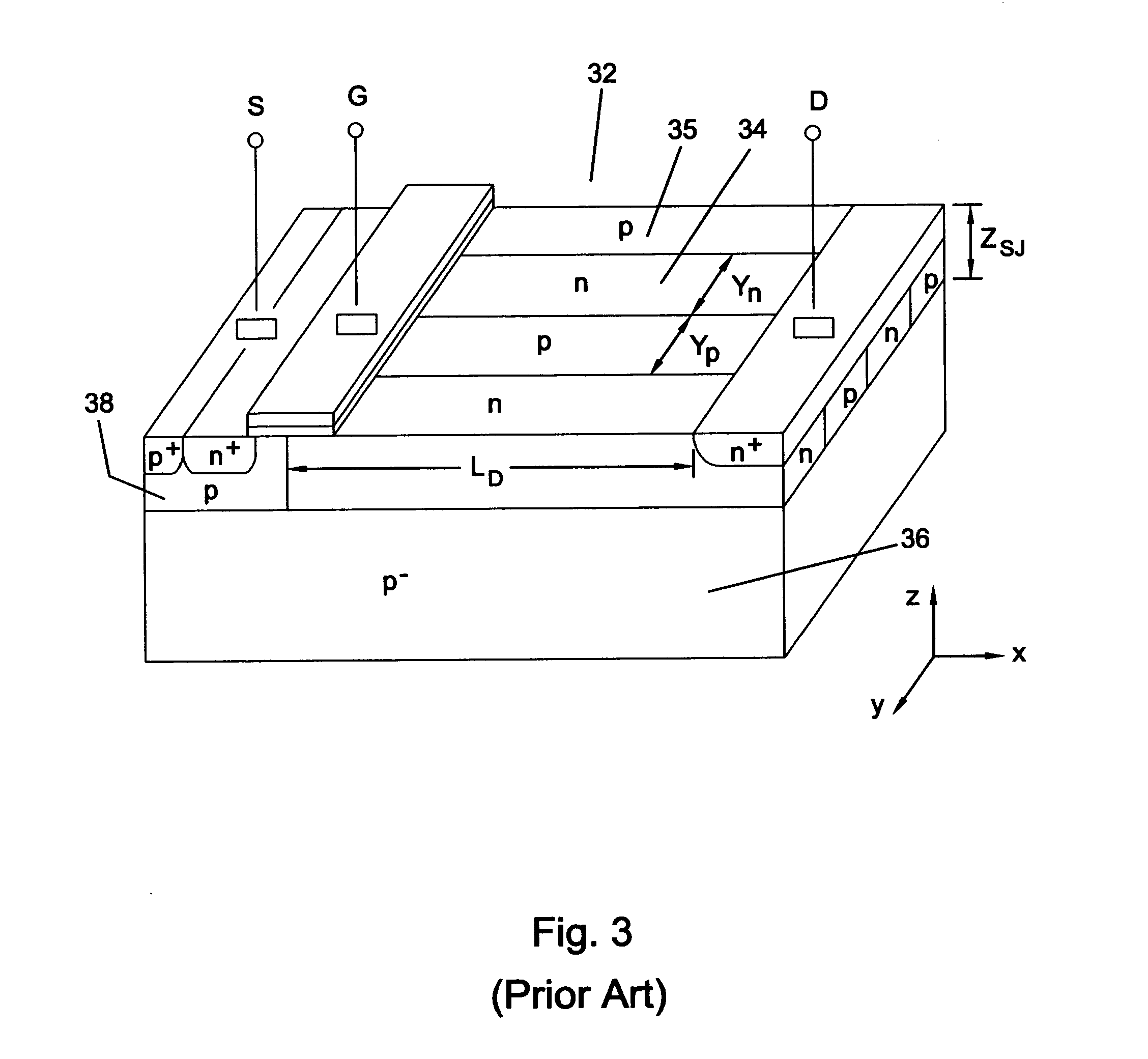

Forming jfet and ldmos transistor in monolithic power integrated circuit using deep diffusion regions

ActiveUS20150380398A1Solid-state devicesSemiconductor/solid-state device manufacturingLDMOSDevice form

A power integrated circuit includes a junction field effect transistor (JFET) device formed in a first portion of a semiconductor layer with a gate region being formed using a first body region, and a double-diffused metal-oxide-semiconductor (LDMOS) transistor formed in a second portion of the semiconductor layer with a channel being formed in a second body region. The power integrated circuit includes a first deep diffusion region formed under the first body region and in electrical contact with the first body region where the first deep diffusion region together with the firs body region establish a pinch off voltage of the JFET device; and a second deep diffusion region formed under the second body region and in electrical contact with the second body region where the second deep diffusion region forms a reduced surface field (RESURF) structure in the LDMOS transistor.

Owner:ALPHA & OMEGA SEMICON INC

Semiconductor device and method of manufacturing the same

InactiveUS20100032791A1Simple processStable enhancement of withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A semiconductor device includes: a first semiconductor region of a first conductivity type disposed on the side of a first electrode; and a second semiconductor region having first pillar regions of the first conductivity type and second pillar regions of a second conductivity type, the first pillar regions and the second pillar regions being provided in paired state and alternately, in a device portion and a terminal portion surrounding the device portion, along a surface on the side of a second electrode disposed on the opposite side of the first semiconductor region from the first electrode. The semiconductor device further includes a lateral RESURF (reduced surface field) region of the second conductivity type disposed at a surface portion, on the opposite side from the first semiconductor region, of the second semiconductor region in the terminal portion.

Owner:SONY CORP

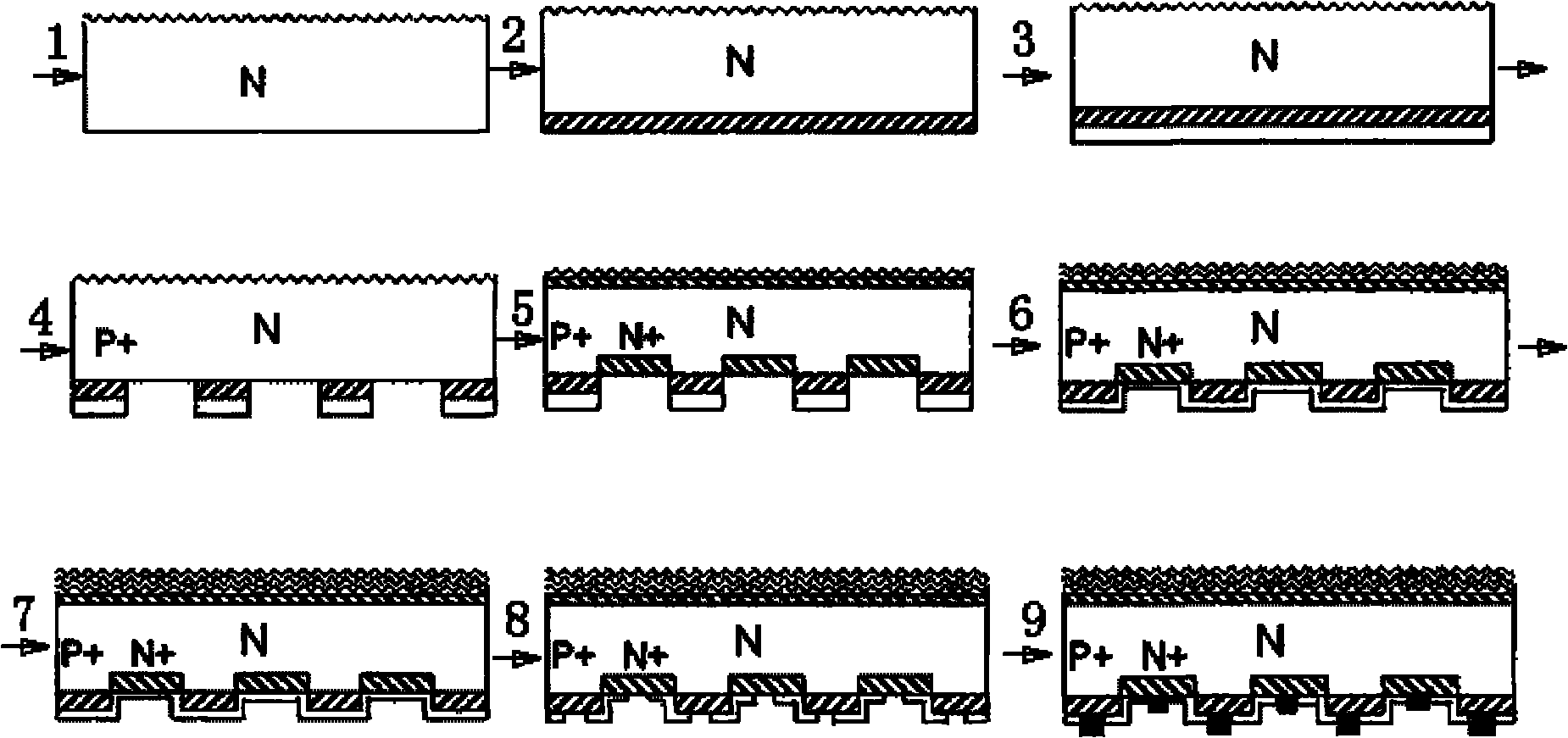

Method for manufacturing back contact solar energy batteries

ActiveCN101777603ASimple processEasy to implementFinal product manufactureSemiconductor devicesNon dopedSolar cell

The invention discloses a method for manufacturing back contact solar energy batteries, comprises the following steps of: firstly growing a P type doped silicon dioxide layer on an N type silicon chip; then growing a non-doped silicon dioxide layer on a P type doped layer; after that, printing a corrosive agent or an anti corrosive agent on the non-doped silicon dioxide layer to corrode the P type doped silicon dioxide layer and the non-doped silicon dioxide layer so as to form required patterns; and finally carrying out N type adulteration on the back face and the front face of the silicon chip to form an N type doped layer. The P type doped layer is protected by the non-doped silicon dioxide layer, and an N front surface field on the front face of the battery and a PN alternating doped layer on the back face of the battery are realized in the N type doped step at the same time, thereby reducing the diffusion step, reducing the cost and simplifying the process.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

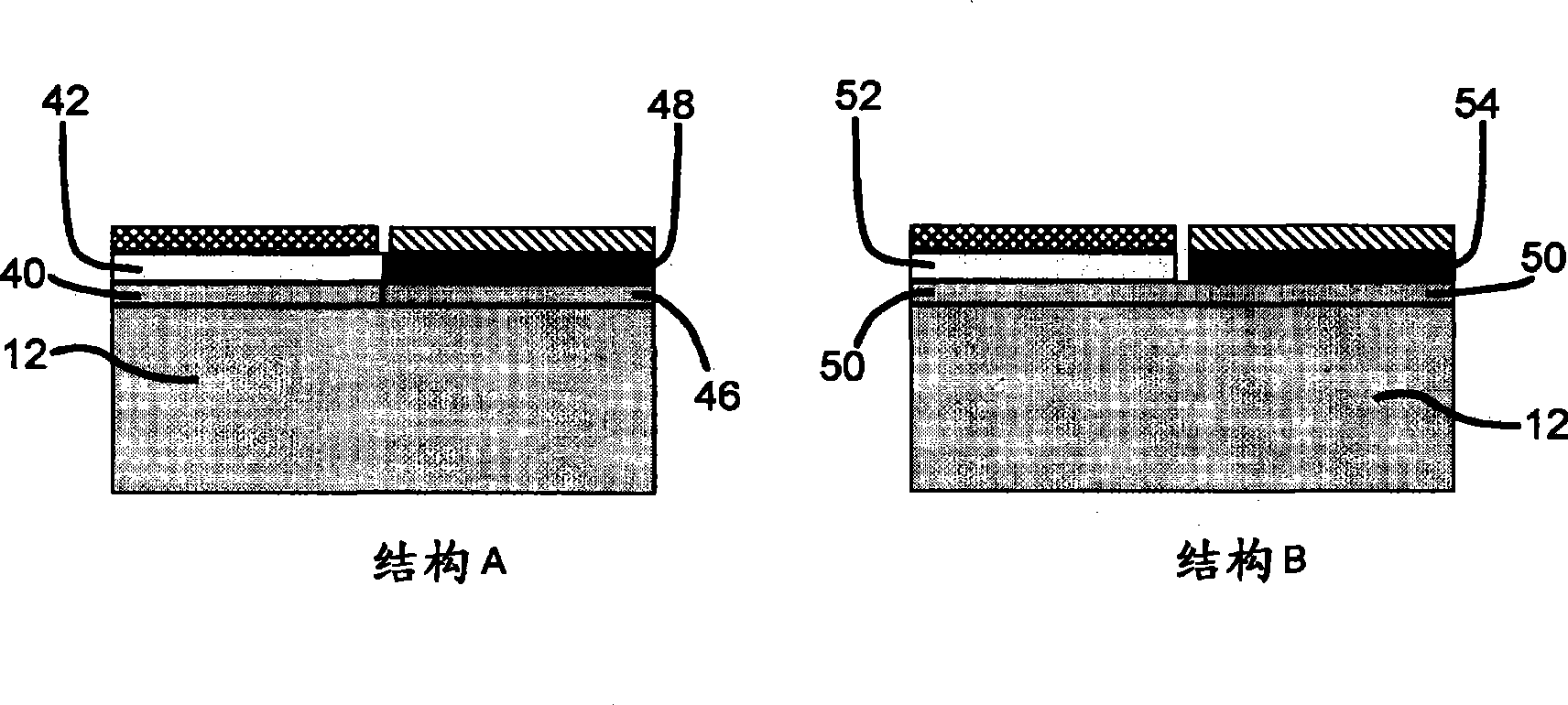

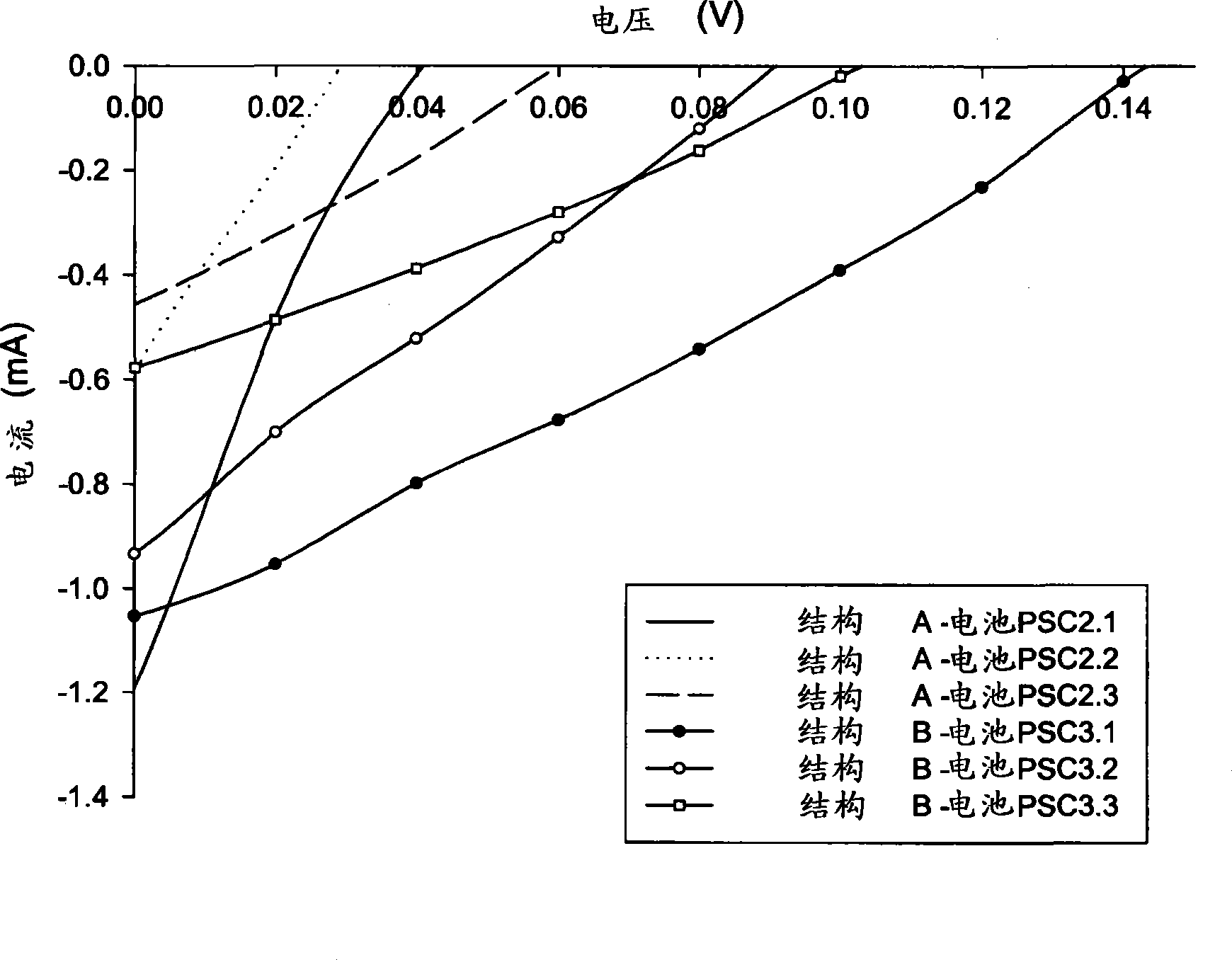

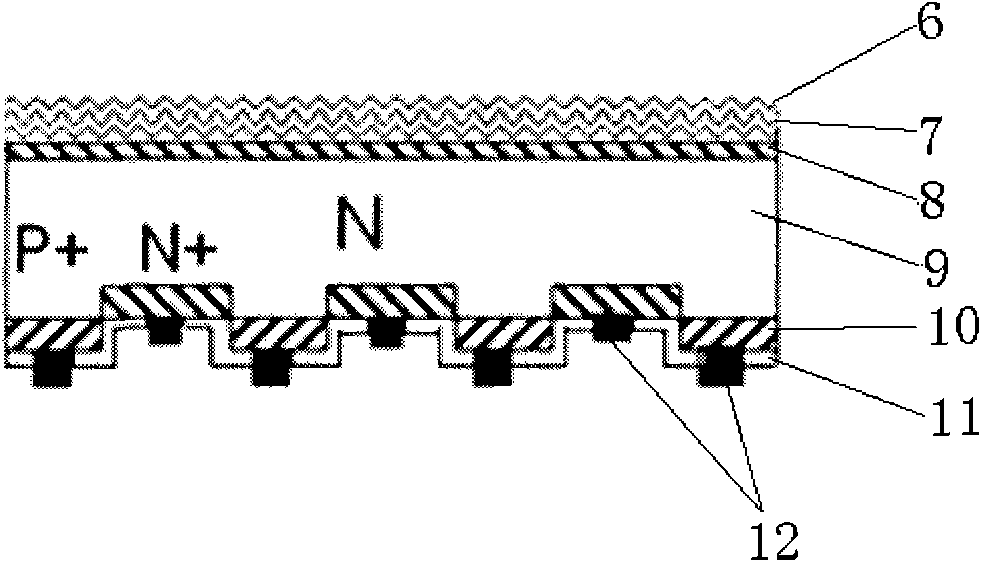

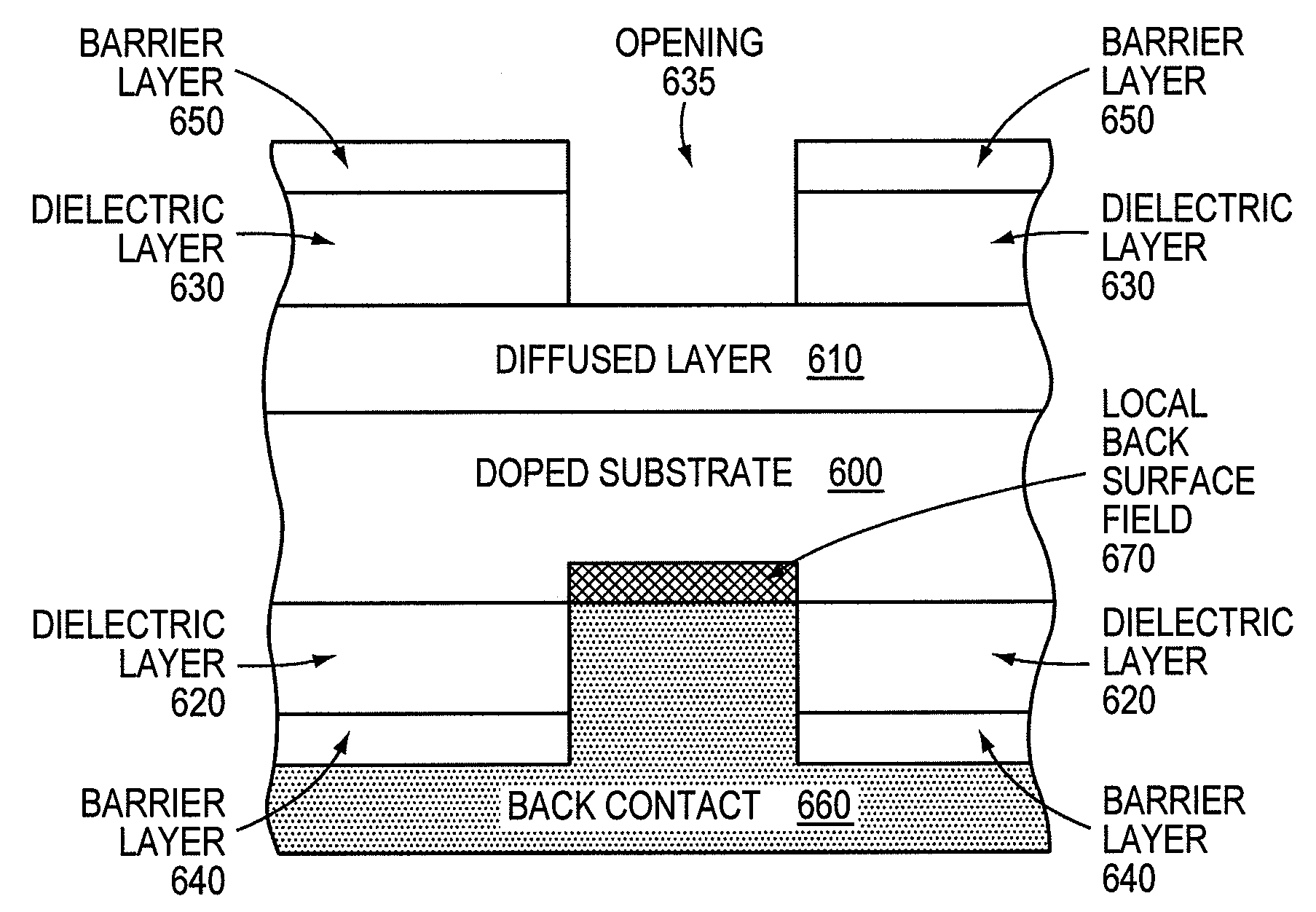

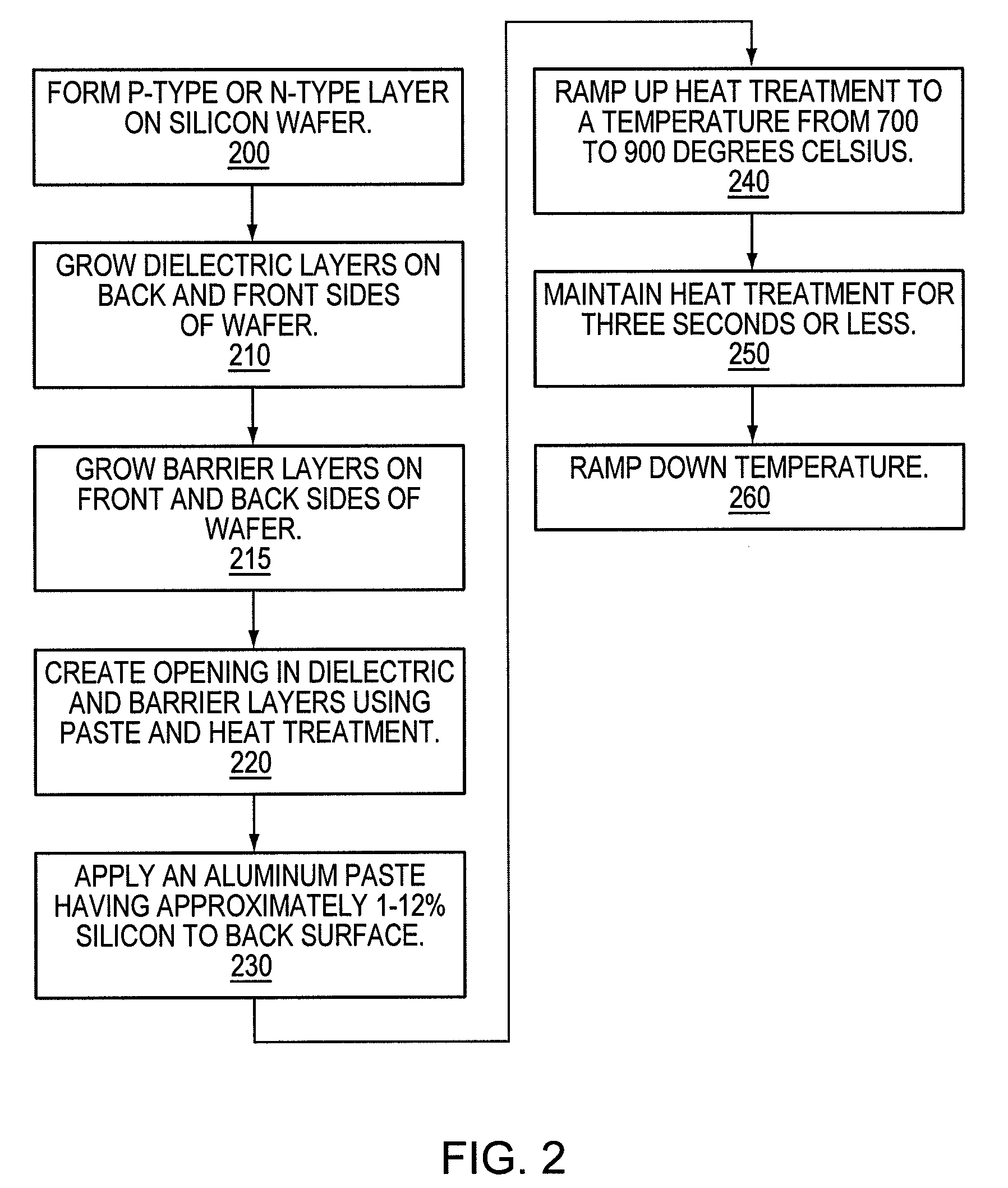

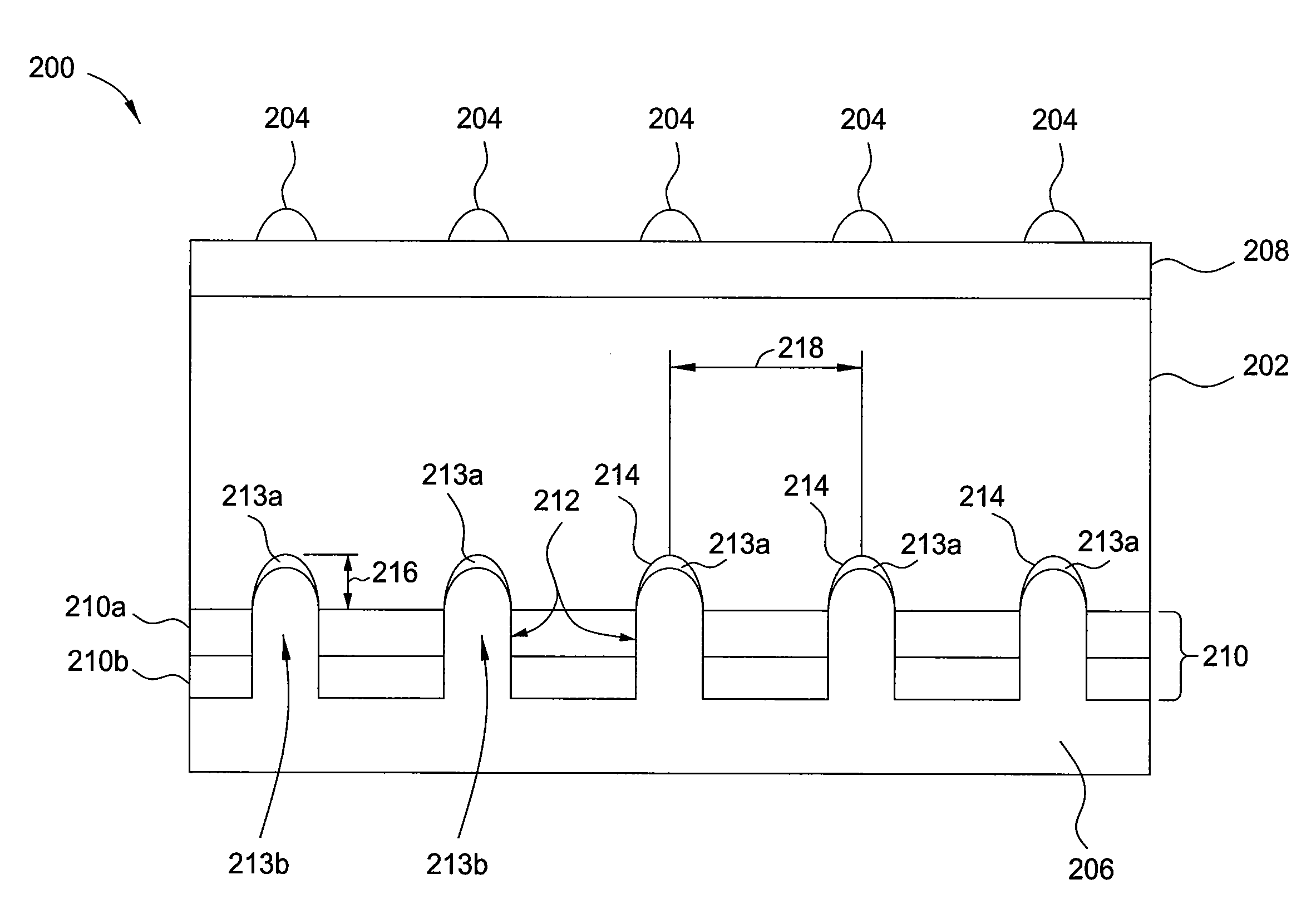

Solar cell having high quality back contact with screen-printed local back surface field

InactiveUS20090025786A1Final product manufacturePhotovoltaic energy generationScreen printingCelsius Degree

A thin silicon solar cell having a back dielectric passivation and rear contact with local back surface field is described. Specifically, the solar cell may be fabricated from a crystalline silicon wafer having a thickness from 50 to 500 micrometers. A barrier layer and a dielectric layer are applied at least to the back surface of the silicon wafer to protect the silicon wafer from deformation when the rear contact is formed. At least one opening is made to the dielectric layer. An aluminum contact that provides a back surface field is formed in the opening and on the dielectric layer. The aluminum contact may be applied by screen printing an aluminum paste having from one to 12 atomic percent silicon and then applying a heat treatment at 750 degrees Celsius.

Owner:GEORGIA TECH RES CORP

Manufacture method of selective front surface field N-type solar cell

InactiveCN101764179ASimple processLow costFinal product manufactureSemiconductor devicesChemical platingSilicon alloy

The invention discloses a manufacture method of a selective front surface field N-type solar cell, which is characterized in that a back surface p-n junction is formed by utilizing an aluminum-silicon alloying process and a high-temperature boron diffusion process, a front surface lightly doped N-type layer is formed by high-temperature phosphorous diffusion, a front surface local heavily doped N-type region is formed by laser doping, and a front electrode is manufactured on the heavily doped N-type region by utilizing a chemical plating method or an electroplating method. Compared with the traditional manufacture process, the invention has the advantages of simple process and low cost and does not need secondary contraposition.

Owner:SUN YAT SEN UNIV

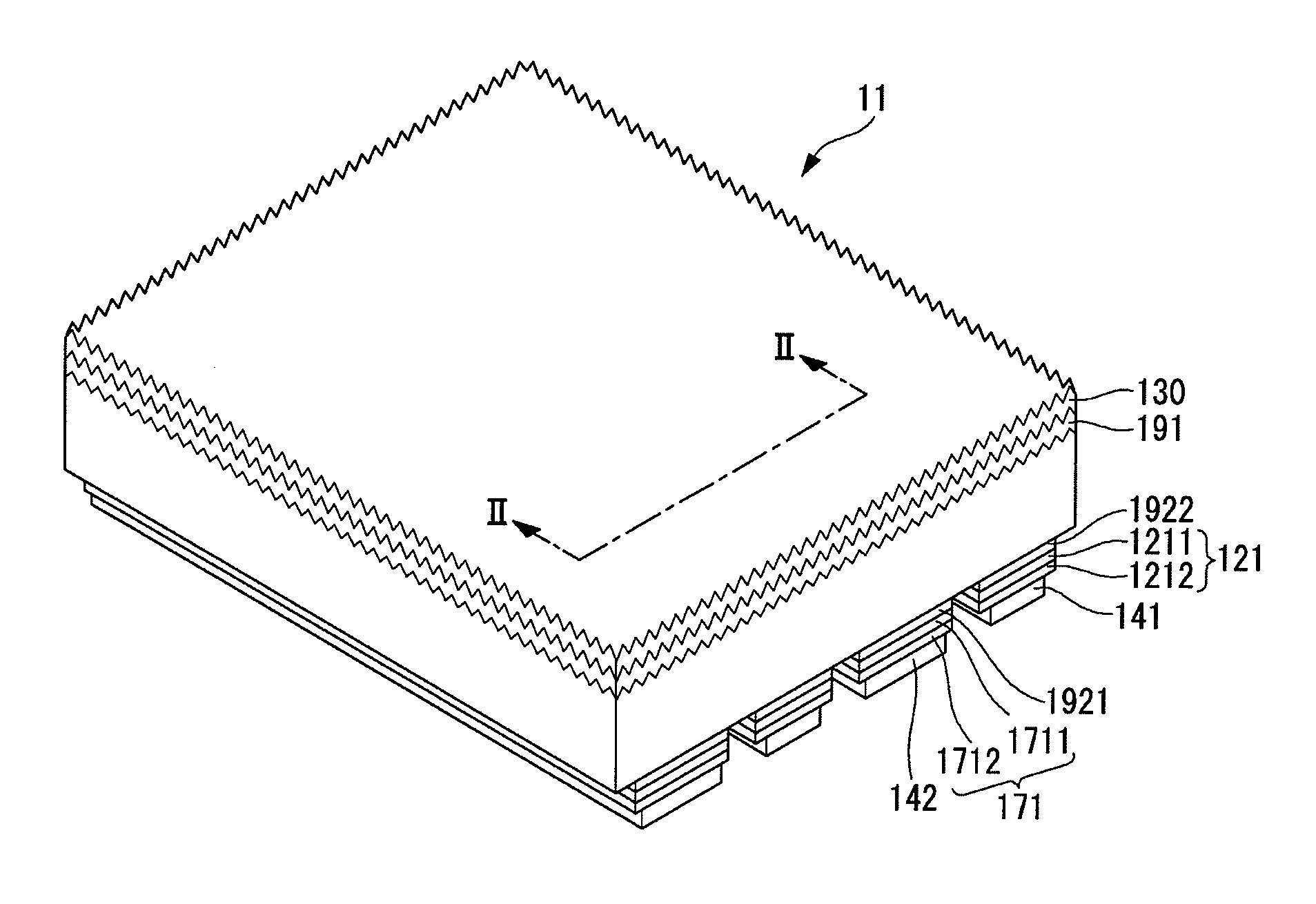

Solar cell

A solar cell is discussed. The solar cell includes a substrate having a first conductivity type and made of a crystalline semiconductor; an emitter region having a second conductivity type opposite the first conductivity type, and forming a p-n junction with the substrate; a surface field region having the first conductivity type and being separated from the emitter region; a first electrode connected to the emitter region; and a second electrode connected to the surface field region, wherein at least one of the emitter region and the surface field region includes a plurality of semiconductor portions, and at least one of the plurality of semiconductor portion is a crystalline semiconductor portion.

Owner:LG ELECTRONICS INC

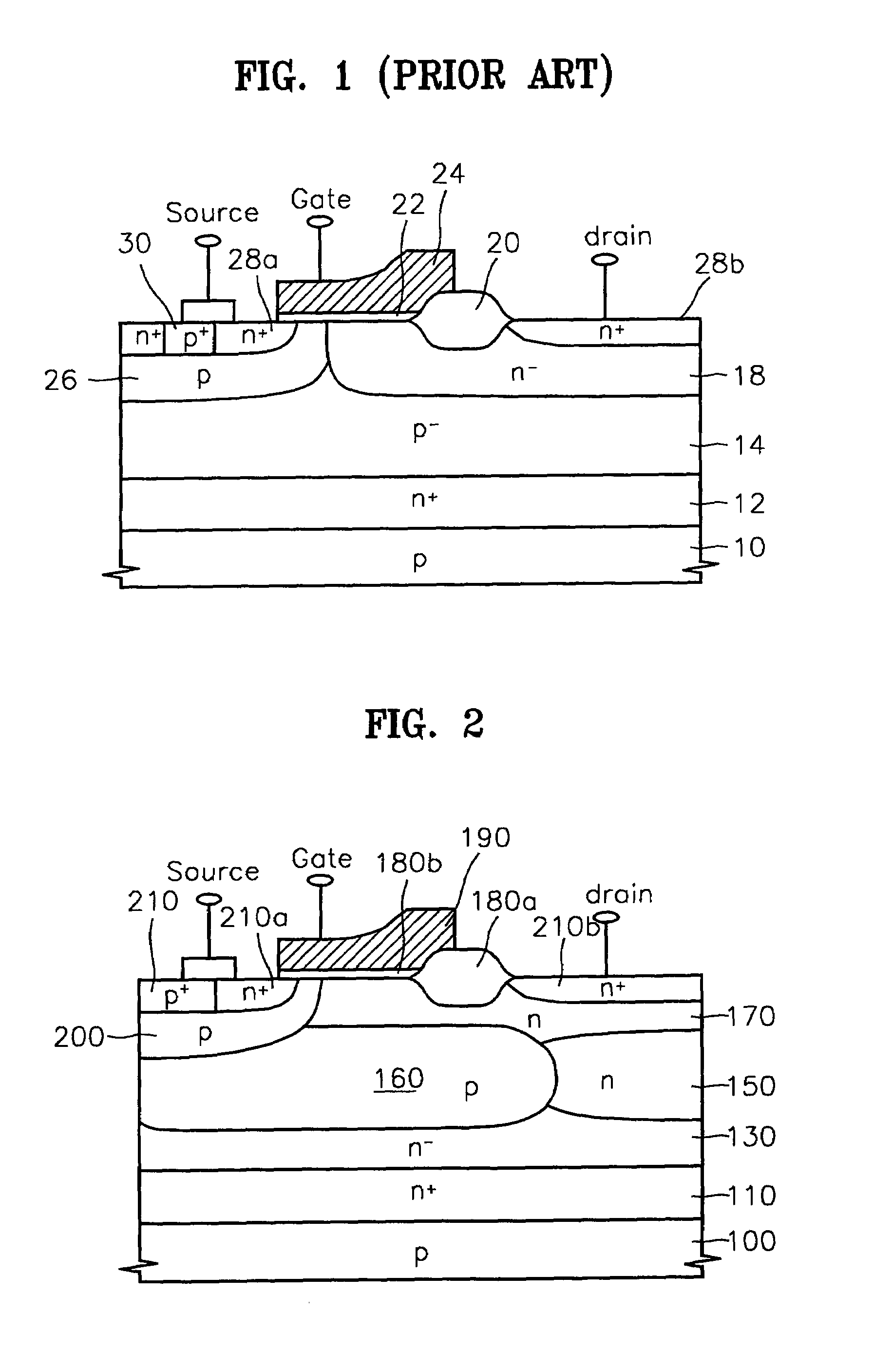

Reduced surface field technique for semiconductor devices

A power device and a method for manufacturing the same are provided. The power device comprises a first conductive semiconductor substrate; a second conductive buried layer formed to a certain depth within the semiconductor substrate; a second conductive epitaxial layer formed on the conductive buried layer; a first conductive well formed within the conductive epitaxial layer; a second conductive well formed within the second conductive epitaxial layer, on both sides of the first conductive well; a second conductive drift region formed in predetermined portions on the first and the second conductive well; and a lateral double diffused MOS transistor formed in the second conductive drift region. The breakdown voltage of the power device is controlled according to a distance between the first conductive well and the second conductive buried layer.

Owner:SEMICON COMPONENTS IND LLC

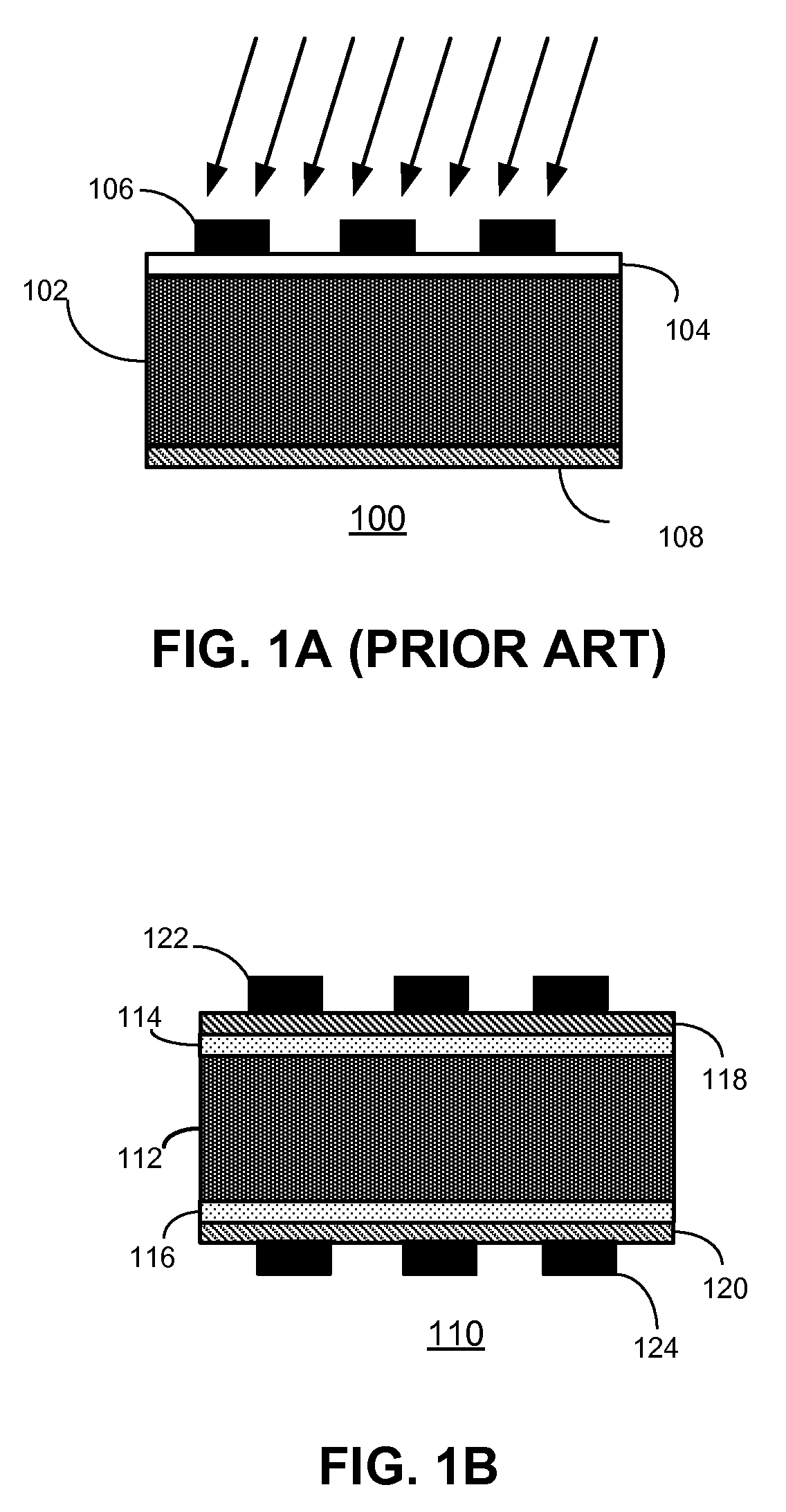

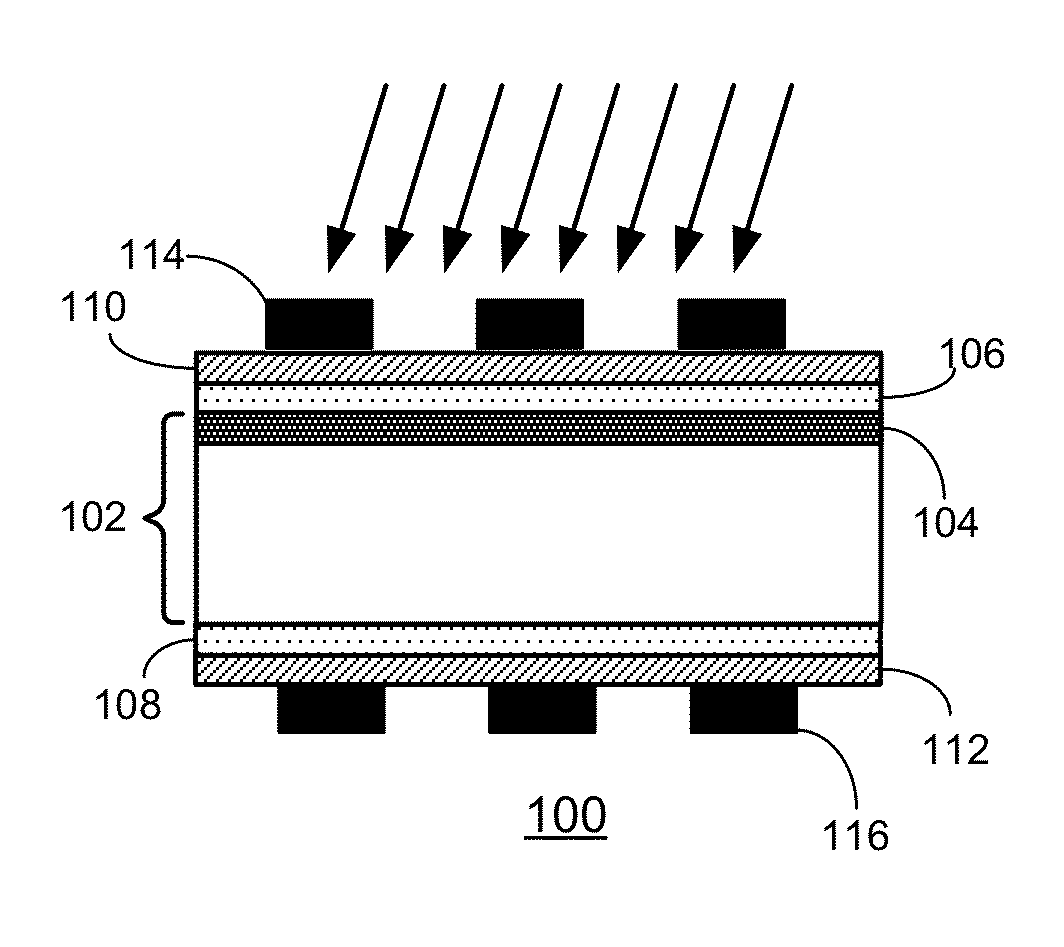

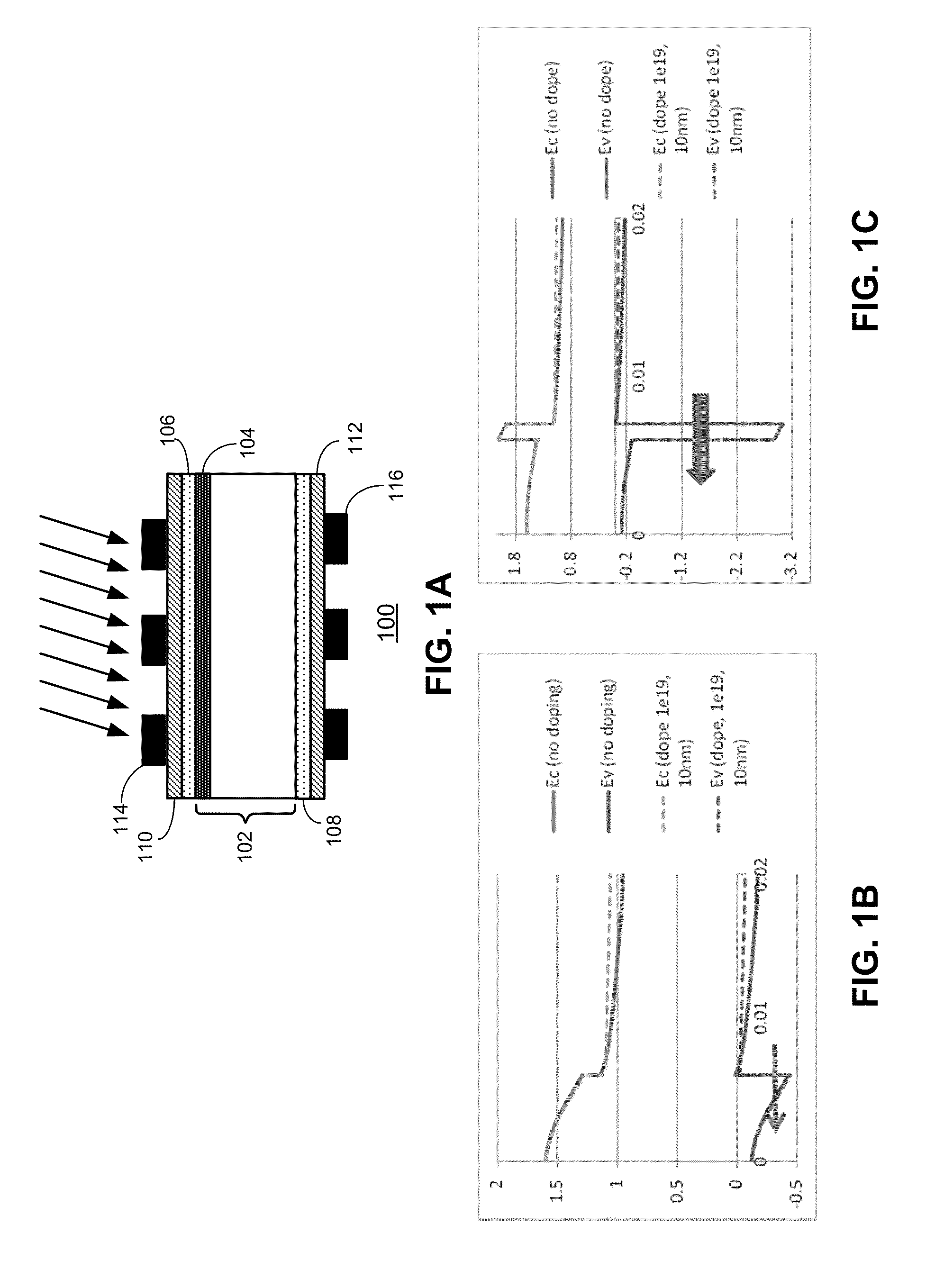

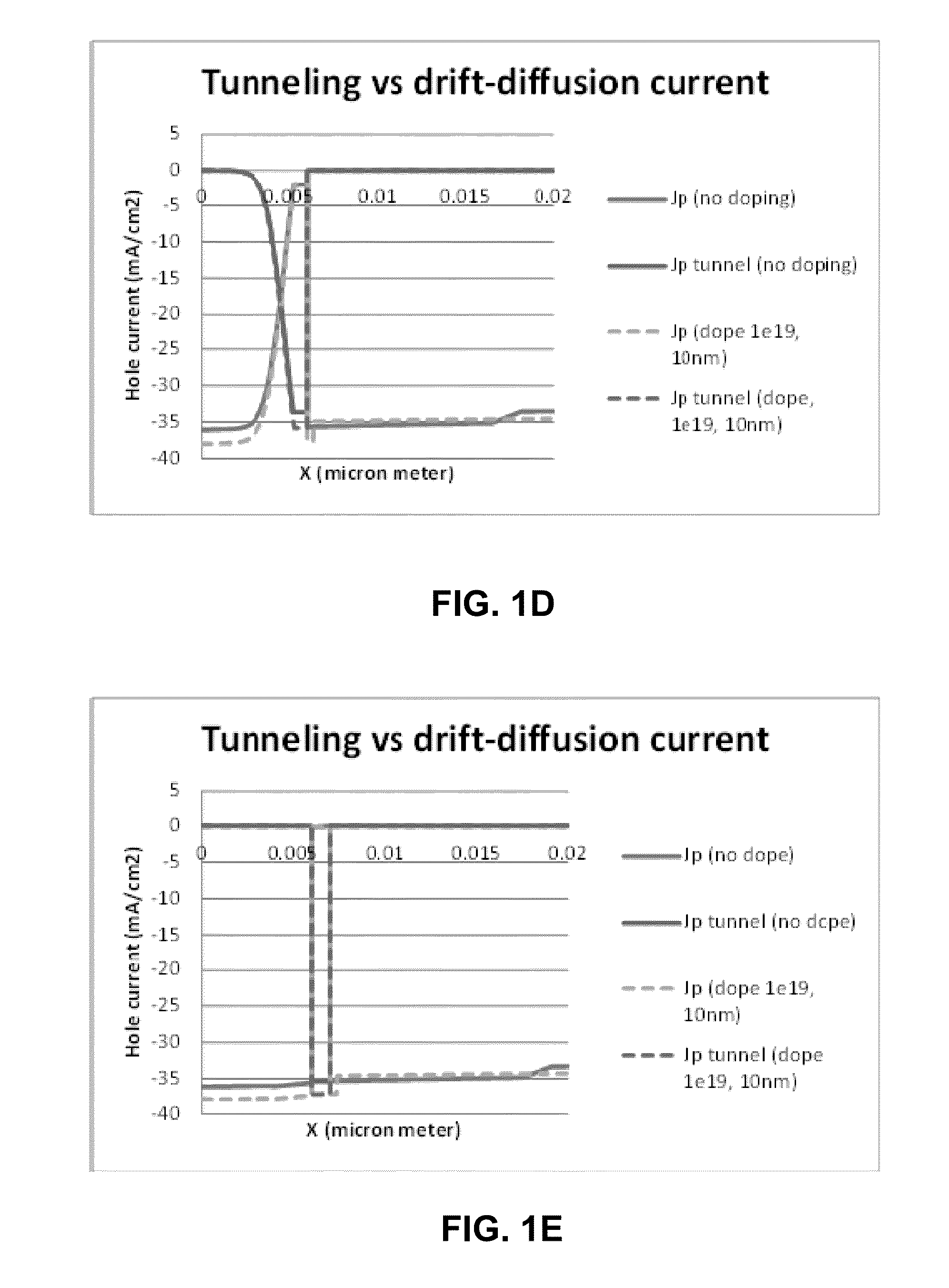

Solar cell with oxide tunneling junctions

ActiveUS8686283B2Final product manufactureSemiconductor/solid-state device manufacturingSolar cellTunnel junction

One embodiment of the present invention provides a tunneling junction based solar cell. The solar cell includes a base layer; a quantum-tunneling-barrier (QTB) layer situated adjacent to the base layer; an emitter; a surface field layer; a front-side electrode; and a back-side electrode.

Owner:TESLA INC

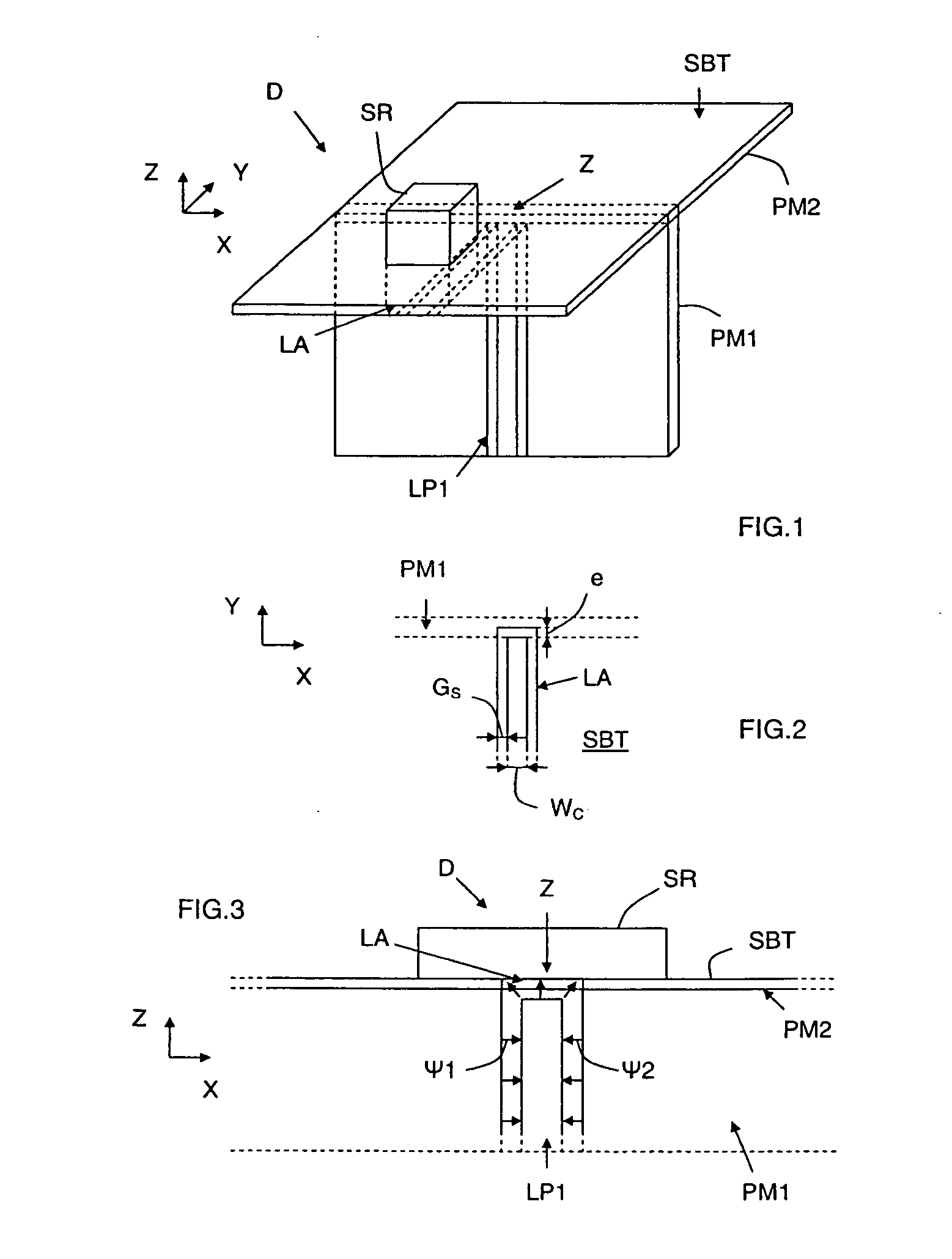

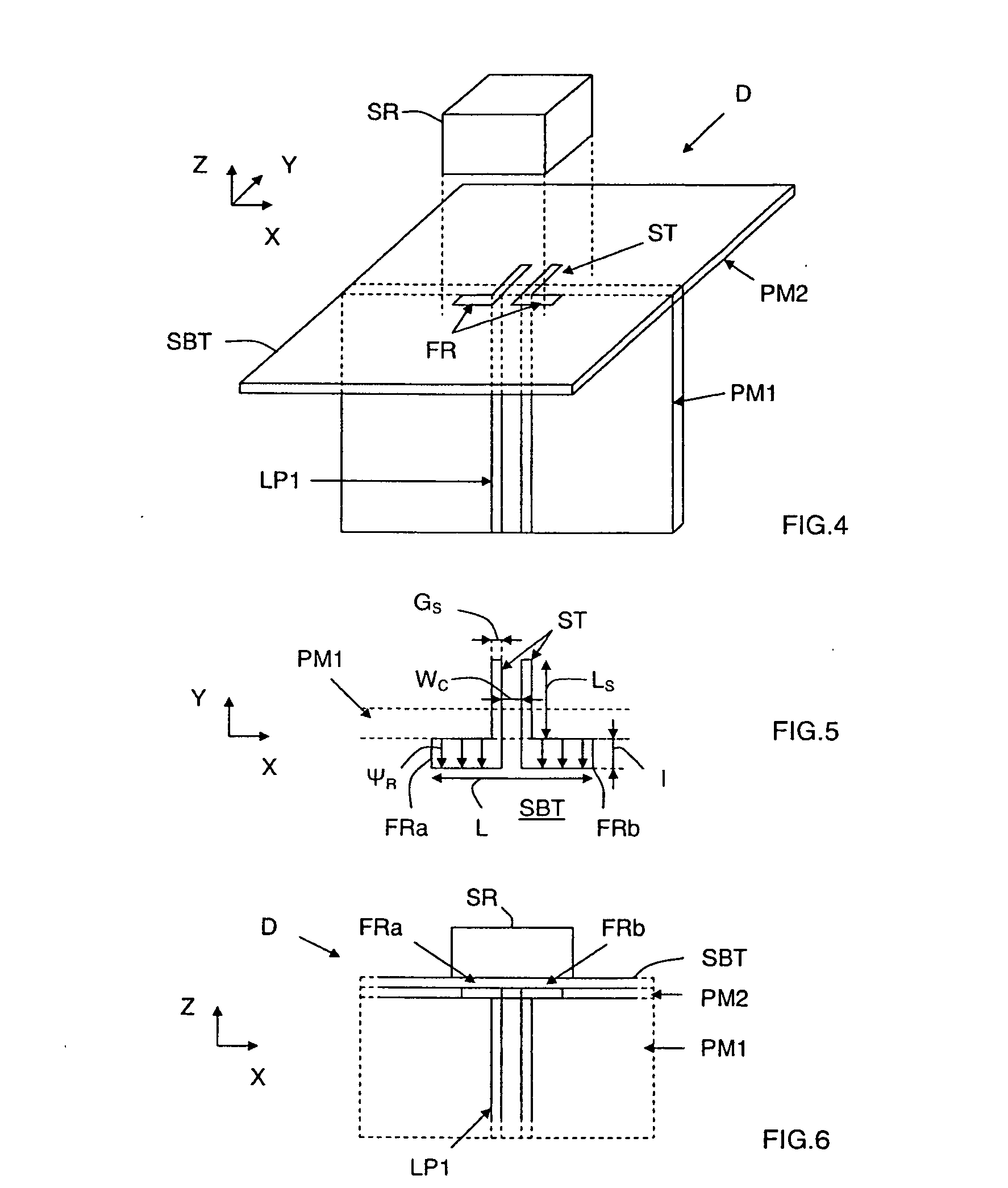

Multipolarization radiating device with orthogonal feed via surface field line(S)

InactiveUS20050179598A1Particular array feeding systemsSimultaneous aerial operationsElectromagnetic couplingGround plane

A radiating device for an antenna comprises a first ground plane comprising a surface electric field main feed line, a second ground plane substantially perpendicular to the first ground plane and comprising electromagnetic coupling means fed orthogonally by a first end of the main feed line, and a resonant structure adapted to radiate energy in the event of excitation by electromagnetic coupling at the first end of the main feed line via the coupling means.

Owner:THALES SA

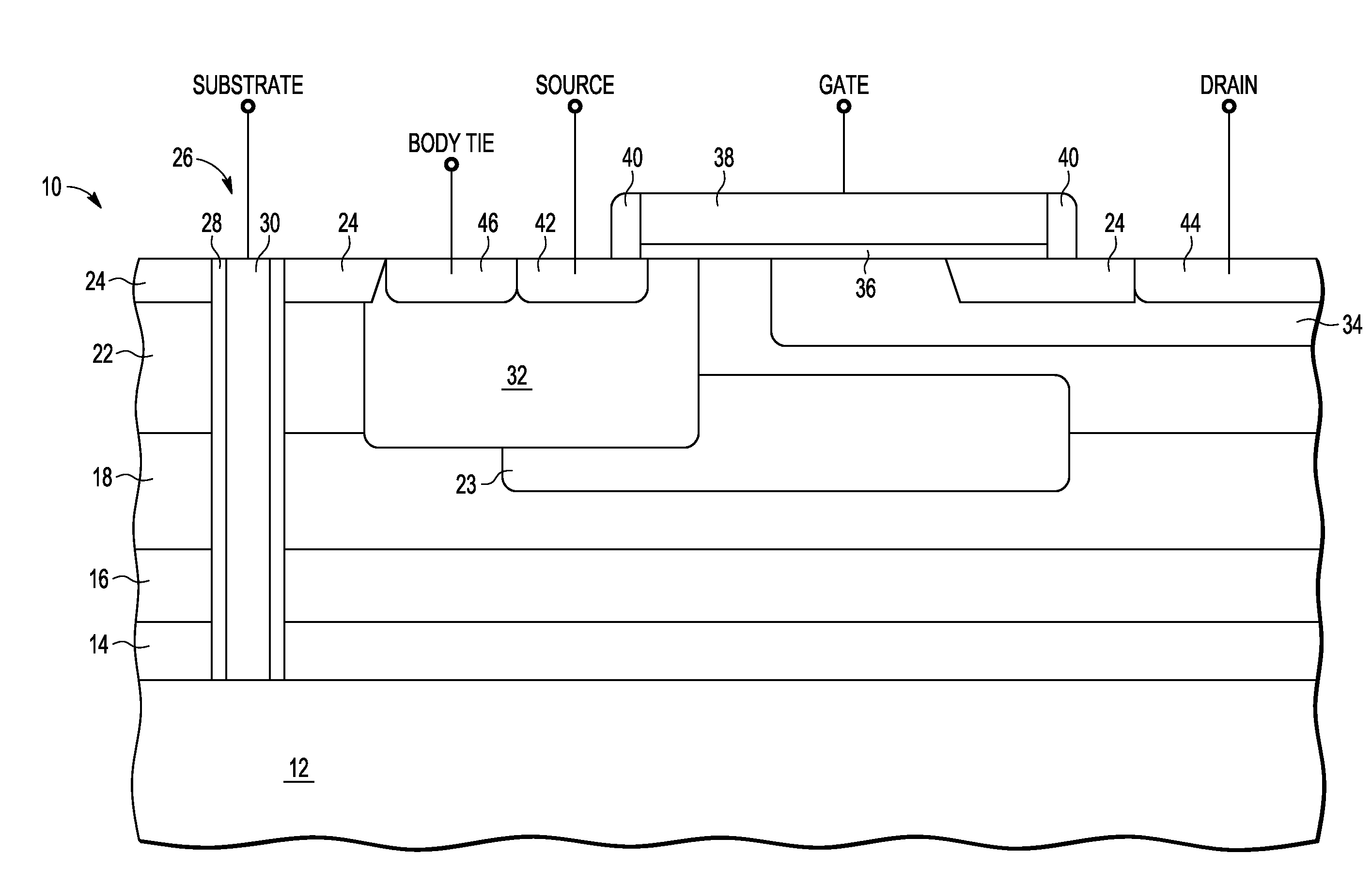

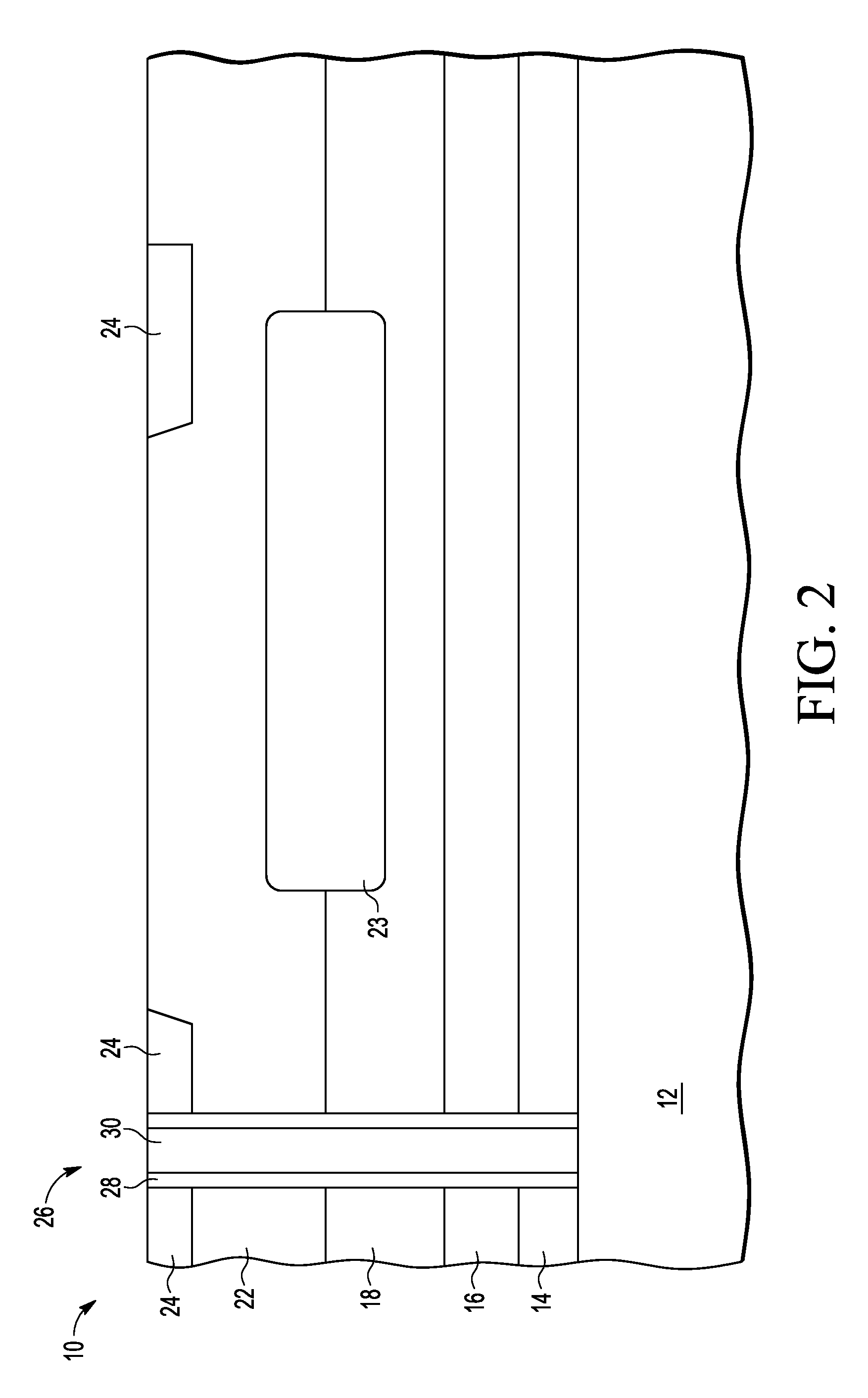

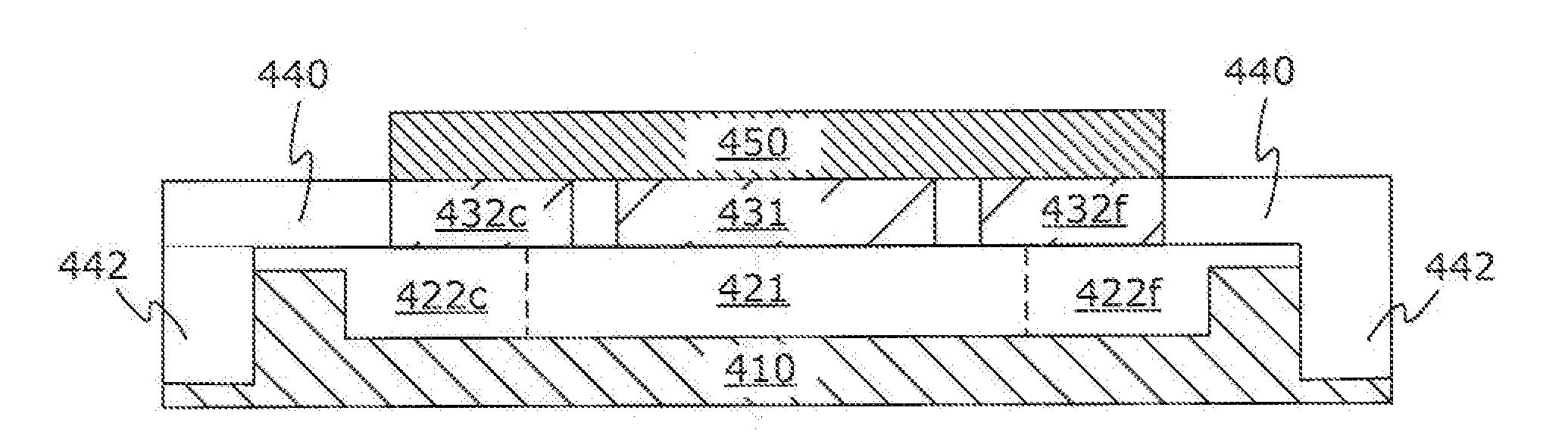

Laterally double diffused metal oxide semiconductor transistor having a reduced surface field structure and method therefor

ActiveUS20110309442A1Semiconductor/solid-state device manufacturingSemiconductor devicesLDMOSSemiconductor materials

An LDMOS transistor includes a substrate of semiconductor material, an insulator layer overlying the substrate, a semiconductor layer overlying the insulator layer, a RESURF region, and a gate. The semiconductor layer includes a first conductivity type well region, a second conductivity type source region in contact with the first conductivity type well region, a second conductivity type drain region. The RESURF region includes at least one first conductivity type material portion, and at least one portion of the at least one first conductivity type material portion electrically coupled to the first conductivity type well region. A semiconductor material having a second conductivity type is located below the RESURF region. The second conductivity type semiconductor material is also located over a part of the RESURF region. The gate is located over the first conductivity type well region and over the RESURF region.

Owner:NXP USA INC

Doped ai paste for local alloyed junction formation with low contact resistance

InactiveUS20130255765A1Reduce carrier recombinationReduces cost-per-wattSemiconductor/solid-state device manufacturingPhotovoltaic energy generationJunction formationCharge carrier

Embodiments of the invention generally relate to solar cells having reduced carrier recombination and methods of forming the same. The solar cells have eutectic local contacts and passivation layers which reduce recombination by facilitating formation of a back surface field (BSF). A patterned aluminum back contact doped with a Group III element is disposed on the passivation layer for removing current form the solar cell. The methods of forming the solar cells include depositing a passivation layer including aluminum oxide and silicon nitride on a back surface of a solar cell, and then forming openings through the passivation layer. An aluminum back contact doped with a Group III element is disposed on the passivation layer in a pattern covering the holes, and thermally processed to form a silicon-aluminum eutectic within the openings.

Owner:APPLIED MATERIALS INC

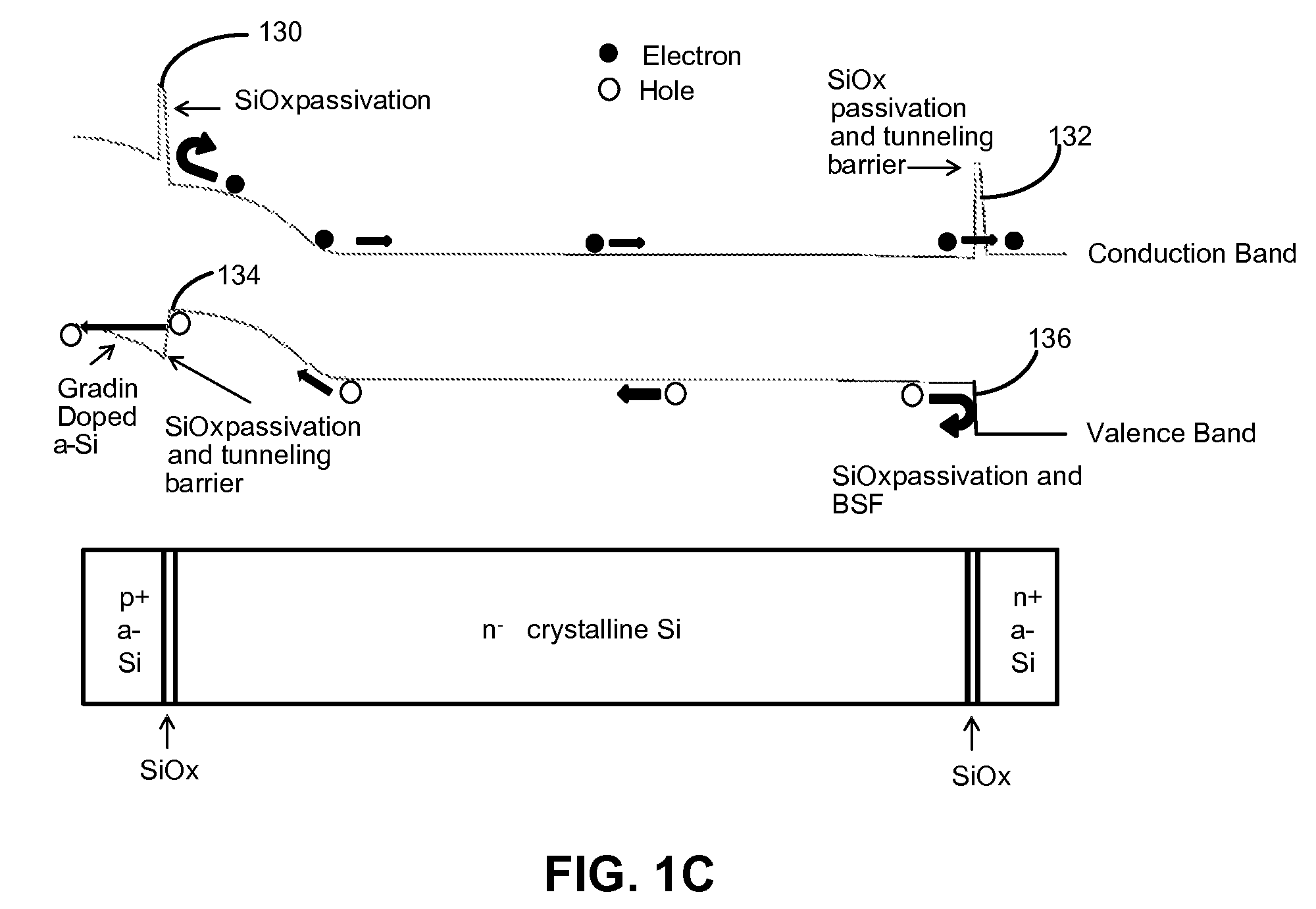

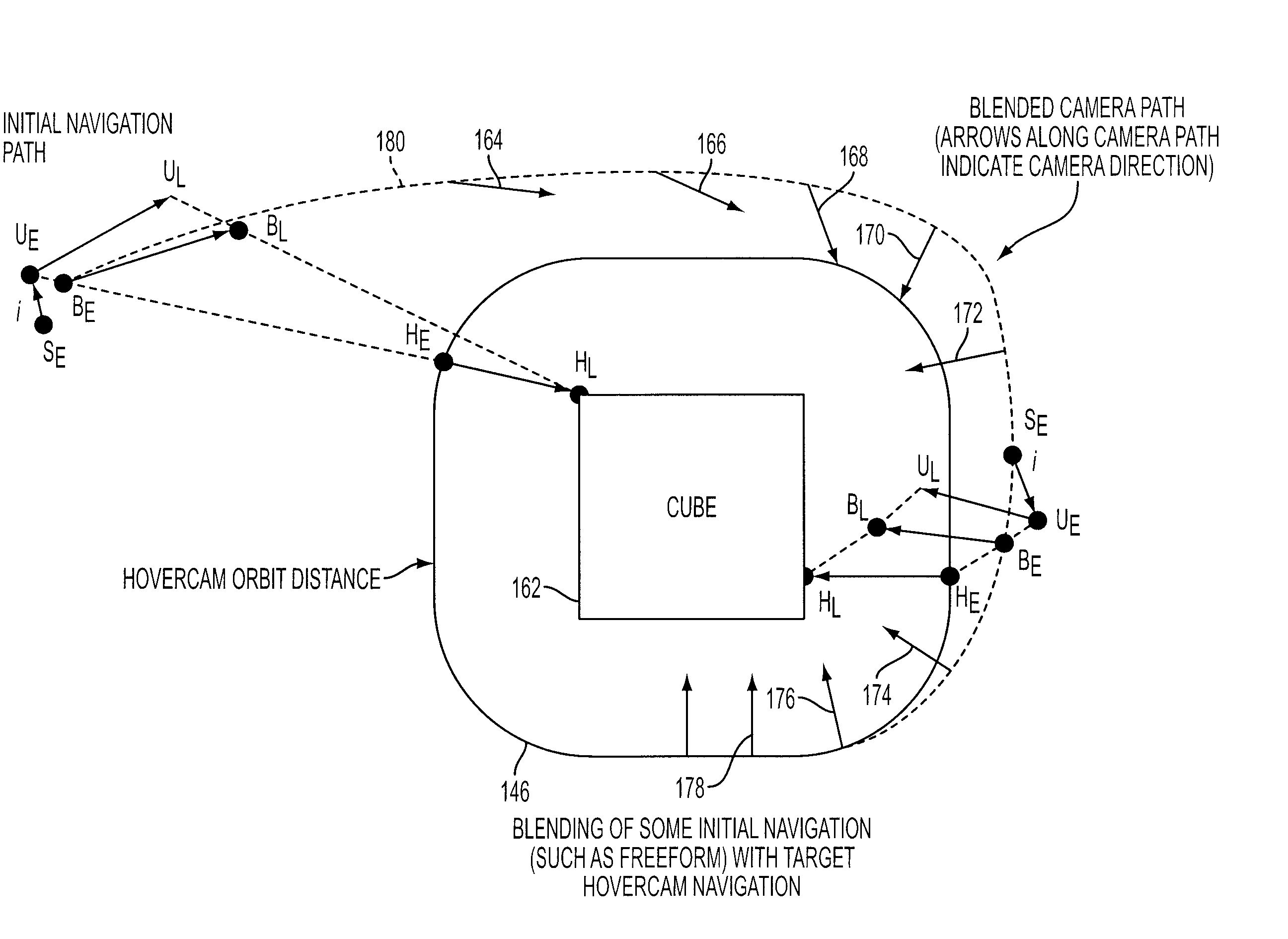

System for interactive 3D navigation for proximal object inspection

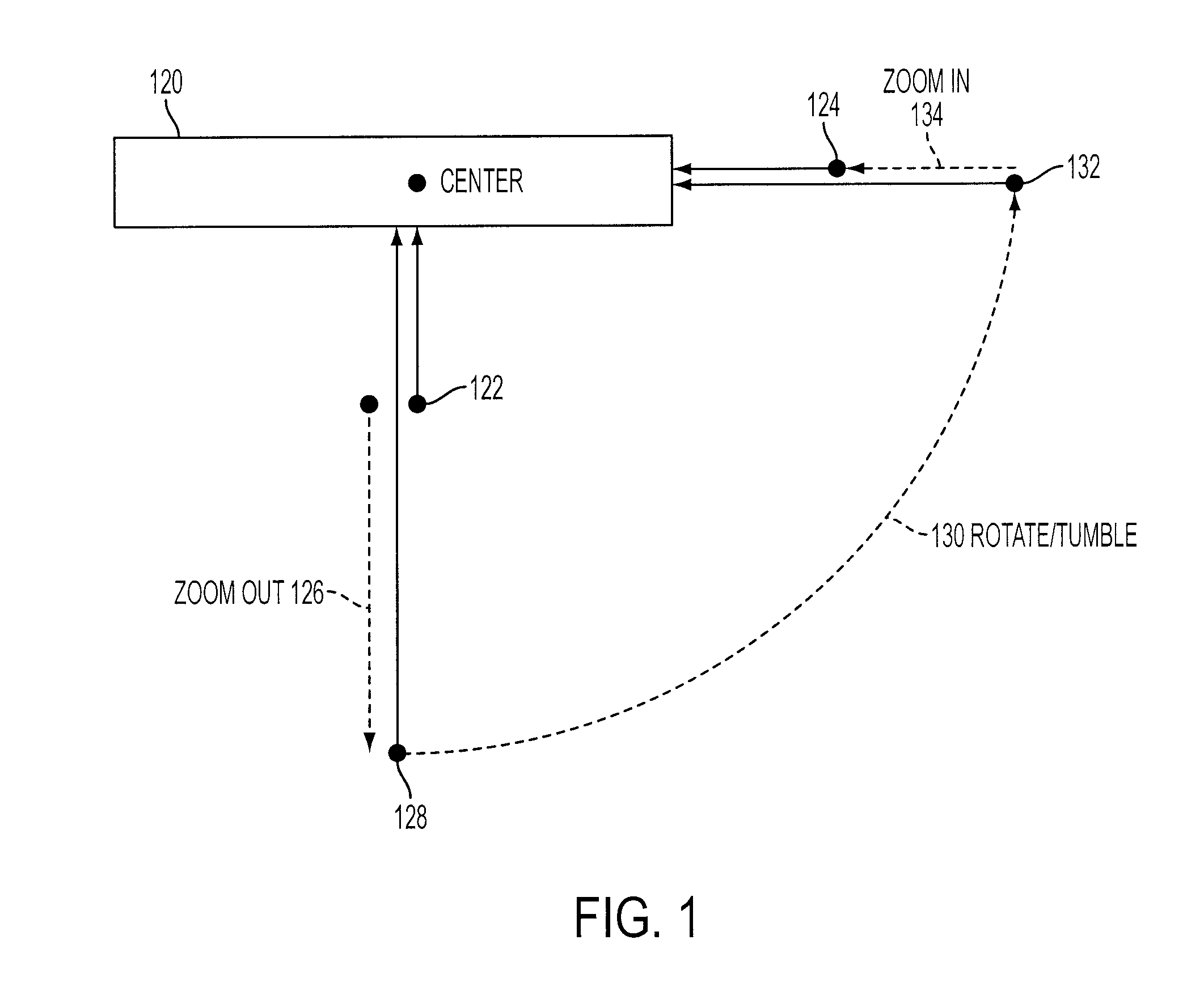

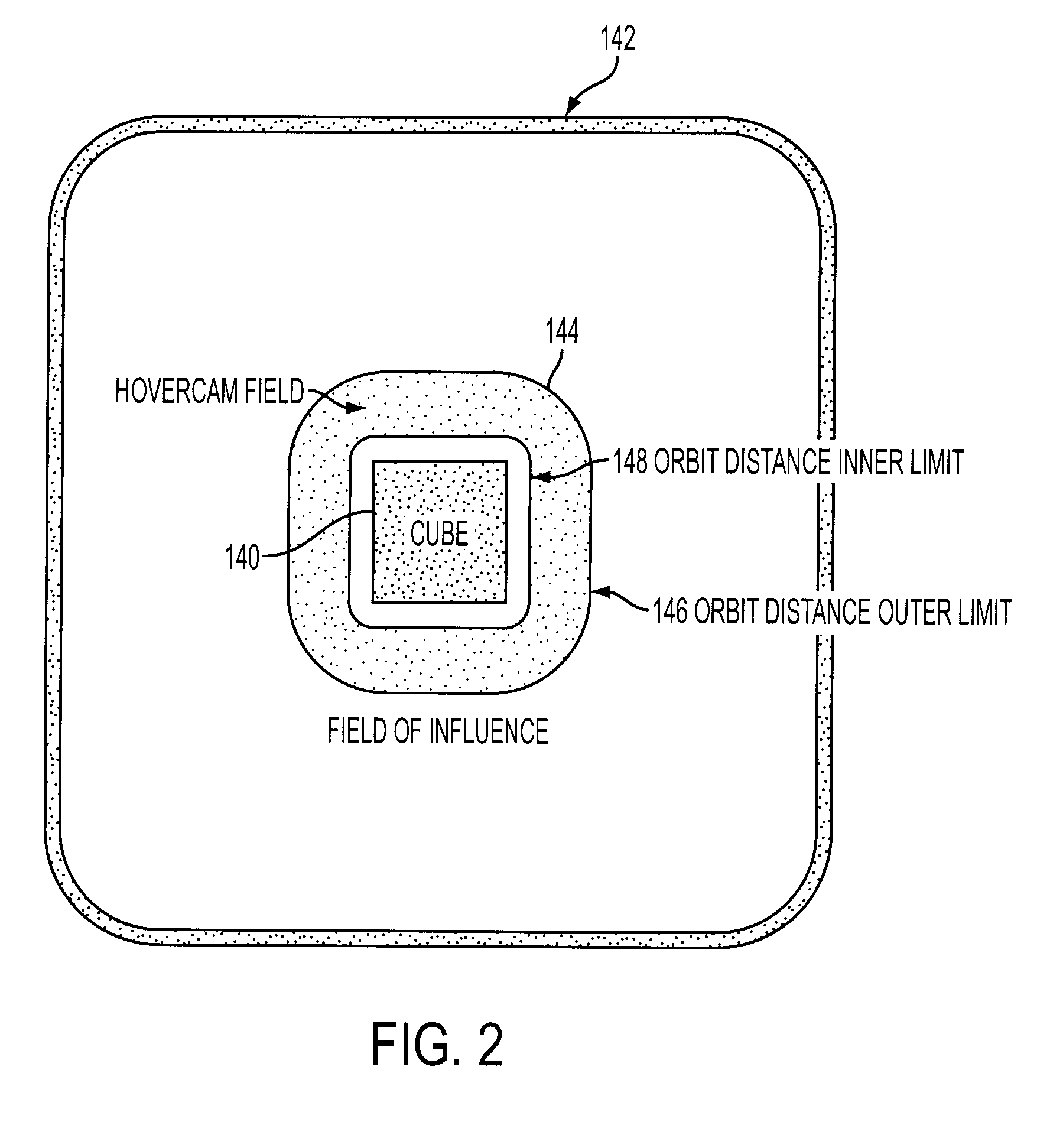

ActiveUS20060227134A1Reduce processing timeGeometric image transformationCathode-ray tube indicatorsClosest pointProximal point

A system that transitions from freeform camera motion to surface following motion as a surface of an object is approached by clipping the vectors for closest point and look-at point. When the surface is reached and while following the surface the user can designate an up model that sets an up vector to conform the view to a users expectations while the system operates using a local up vector for computations. A restricted surface field of view along with an obstacle field of view can be used by the system to allow the view to traverse cavities and maintain a specified surface following distance from an obstacle, from a wall and from a floor.

Owner:AUTODESK INC

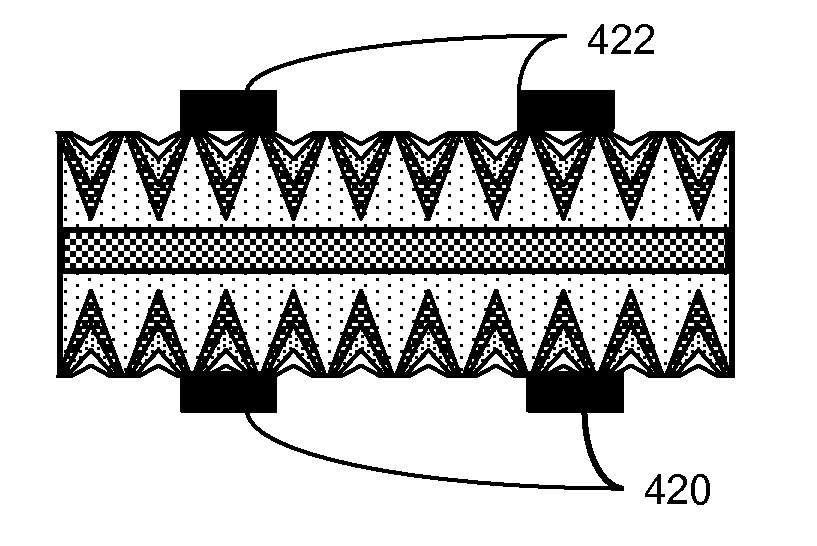

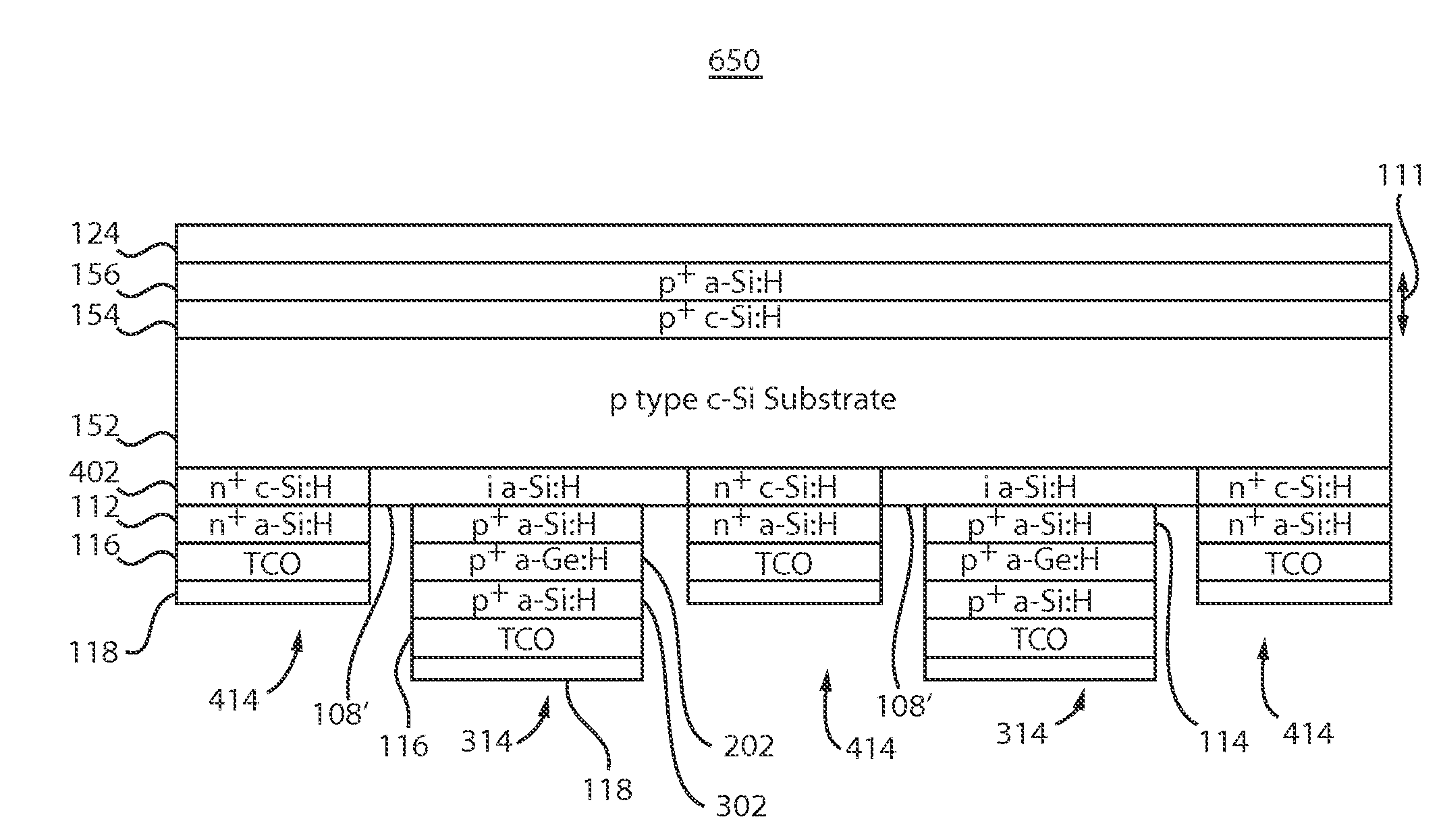

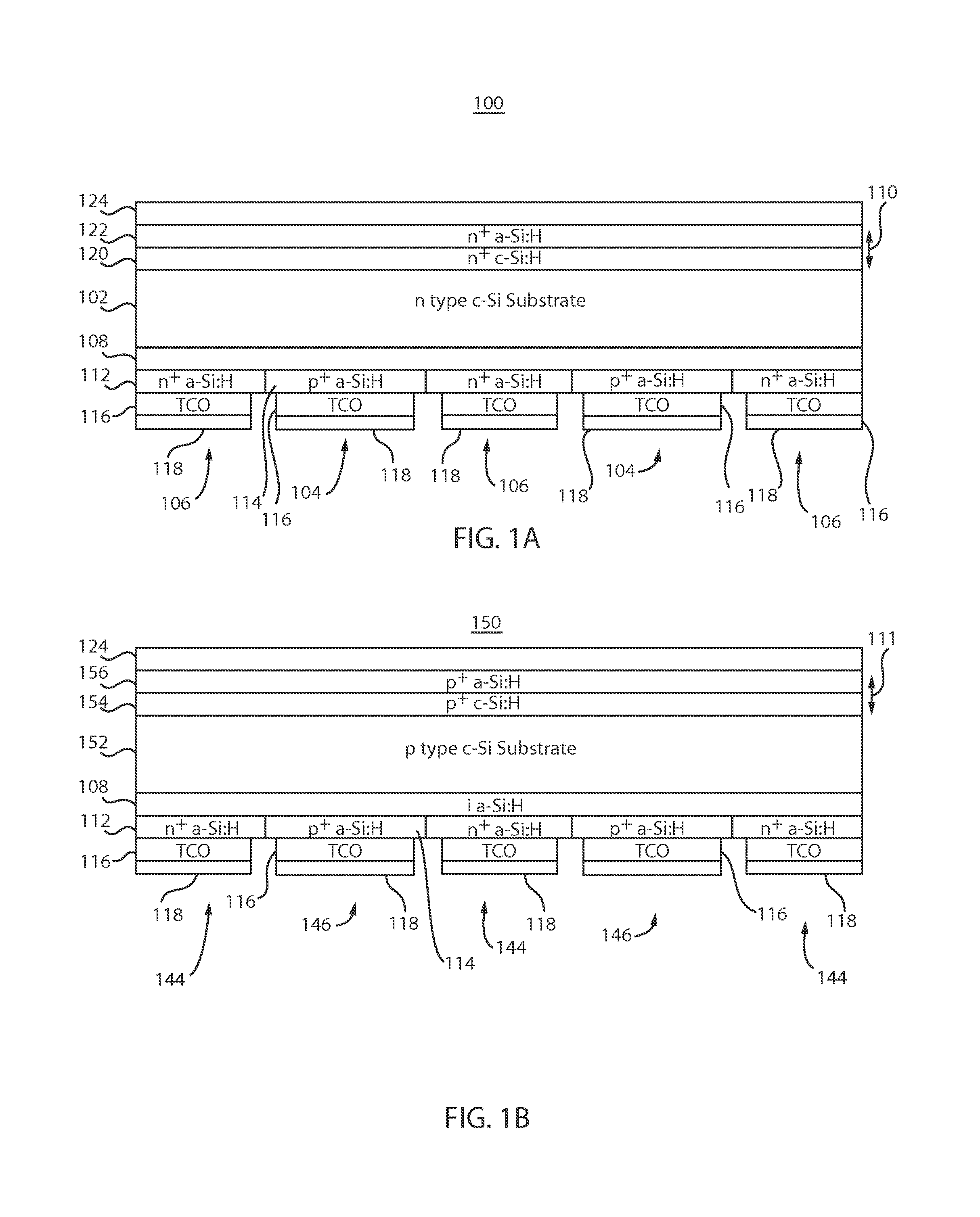

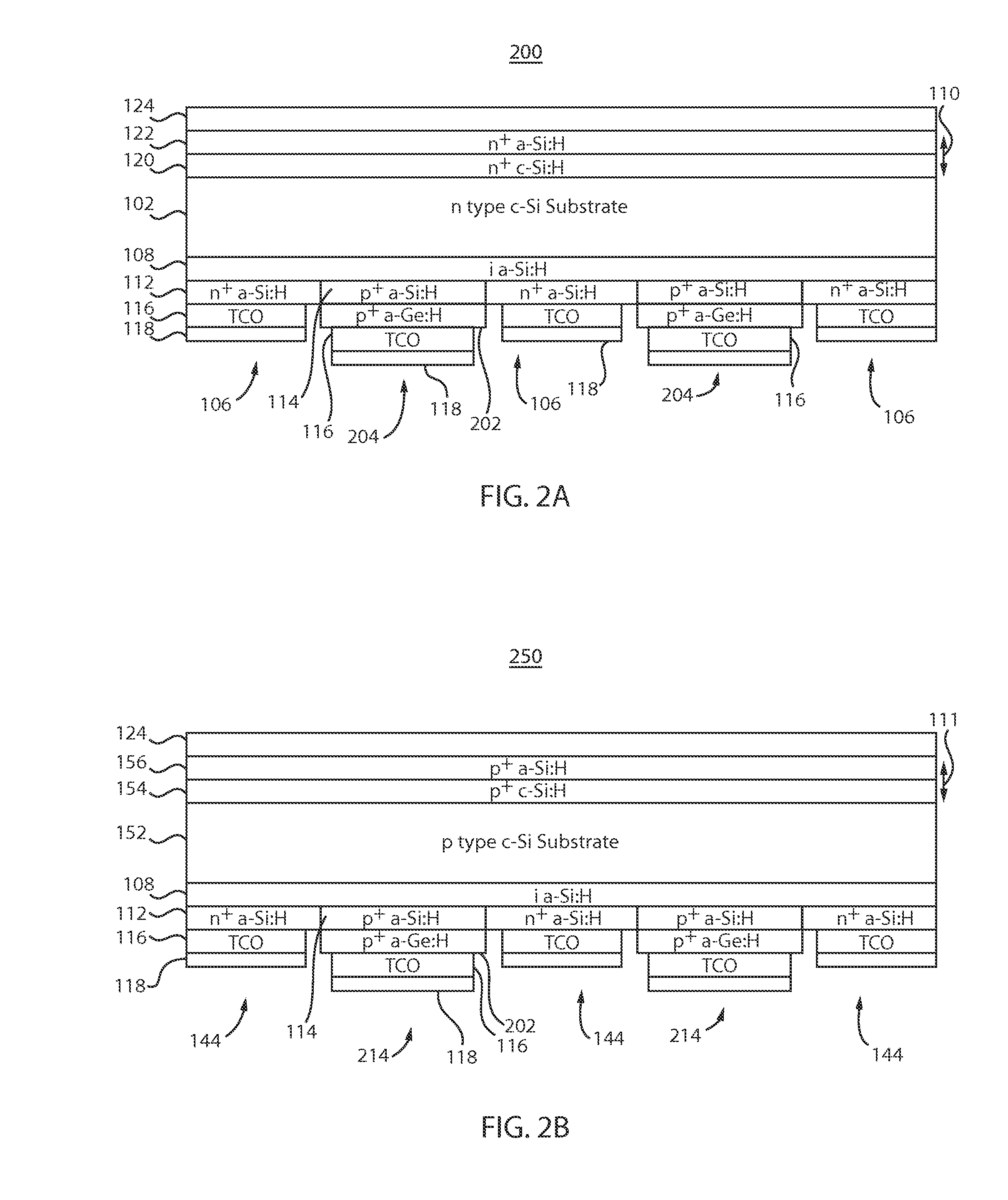

Interdigitated back contact heterojunction photovoltaic device

InactiveUS20140224307A1Less thicknessSemiconductor/solid-state device manufacturingPhotovoltaic energy generationHeterojunctionDopant

A photovoltaic device includes a crystalline substrate having a first dopant conductivity, an interdigitated back contact and a front surface field structure. The front surface field structure includes a crystalline layer formed on the substrate and a noncrystalline layer formed on the crystalline layer. The crystalline layer and the noncrystalline layer are doped with dopants having a same dopant conductivity as the substrate. Methods are also disclosed.

Owner:IBM CORP

Method for passivating P-type doping layer of N-type silicon solar cell and cell structure

ActiveCN102169923ASuitable for large-scale industrial productionFinal product manufacturePhotovoltaic energy generationSilicon matrixMetal grid

The invention relates to a method for passivating a P-type doping layer of an N-type silicon solar cell and a cell structure. An emitter of a non-metal contact region of a P-type emitter junction at the back of an N-type czochralski silicon matrix forms a floating junction through a phosphorus diffusion layer, the floating junction is isolated from a back metal grid line through a dielectric film, and a passivating film is formed on the surface of the floating junction. An N-type front surface field is formed on the front of the matrix, a pyramid suede structure is formed on the front of the N-type front surface field, a SiNx layer with a passivating N-type surface field is arranged on the surface of the N-type front surface, and metal grid lines are arranged on the front and the back of a battery cell. A boron-doped layer is passivated by using the floating junction, and needs not to be subjected to production line reconstruction compared with a mode of passivating by using Al2O3, thus the method is suitable for massive industrialized production and has an efficiency reaching 19 percent proved by tests.

Owner:TRINA SOLAR CO LTD

Tunneling-junction solar cell with shallow counter doping layer in the substrate

InactiveUS20130298973A1Final product manufactureSemiconductor/solid-state device manufacturingSolar cellTunnel junction

One embodiment of the present invention provides a tunneling junction solar cell. The solar cell includes a base layer, an emitter layer situated adjacent to the shallow counter doping layer, a surface field layer situated adjacent to a side of the base layer opposite to the shallow counter doping layer, a front-side electrode, and a back-side electrode. The base layer includes a shallow counter doping layer having a conduction doping type that is opposite to a remainder of the base layer. The emitter layer has a bandgap that is wider than that of the base layer.

Owner:SOLARCITY

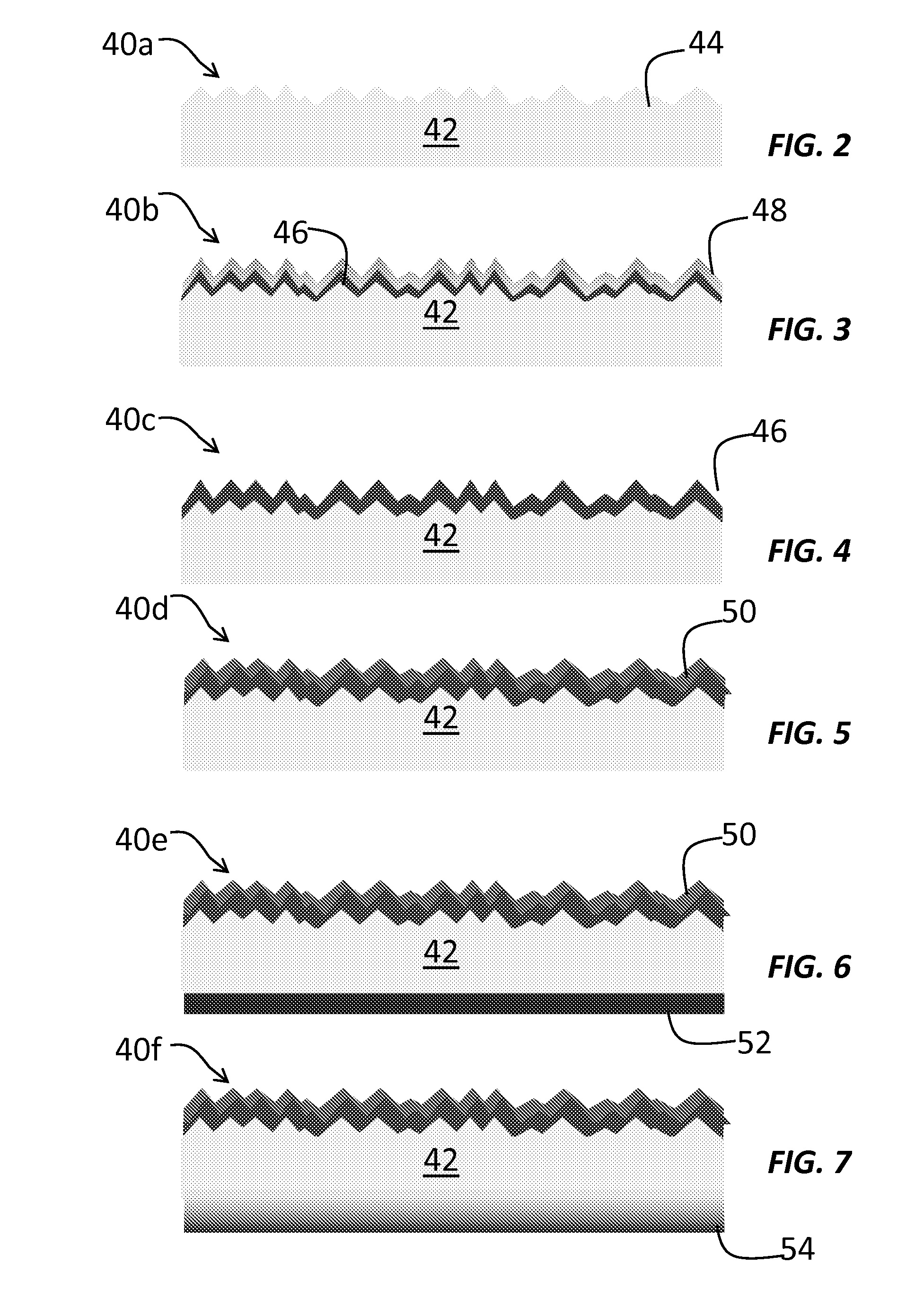

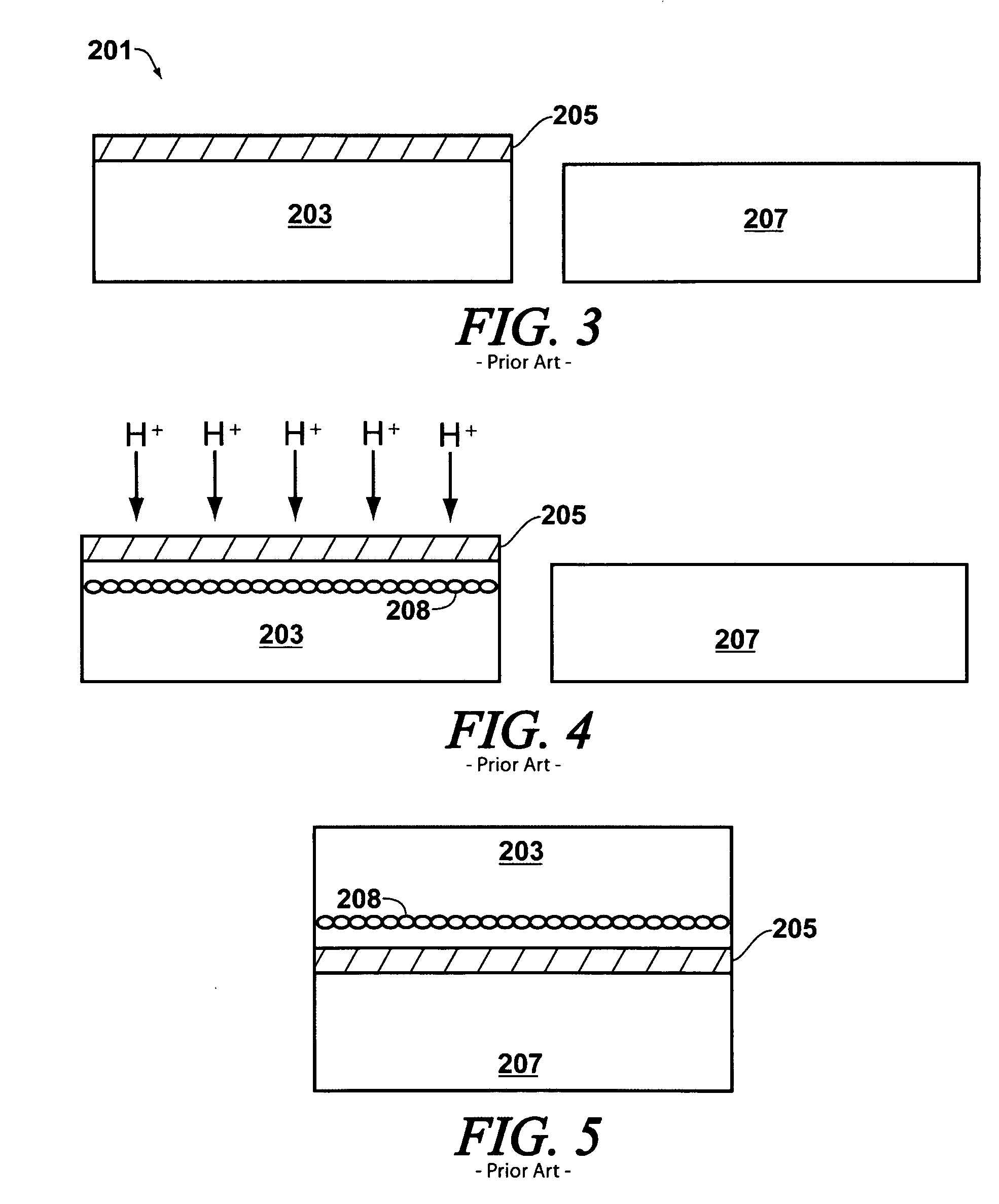

Photovoltaic device having a textured metal silicide layer

A semiconductor device is formed on a low cost substrate 312 onto which is deposited a metal film 314 that serves as an intermediate bonding layer with a transferred film 324 of semiconducting material from a bulk semiconductor substrate 322. The metal film forms an intermetallic compound such as a silicide 316 and functions as a bonding agent between the low cost substrate and the semiconducting substrate, as a back surface field for reflection of minority carriers, and as a textured optical reflector of photons. The silicide also forms a low resistivity back-side ohmic contact with the semiconductor layer. This results in a low cost, flexible, high efficiency, thin film solar cell device.

Owner:WOODSIDE GRP PTE LTD THE

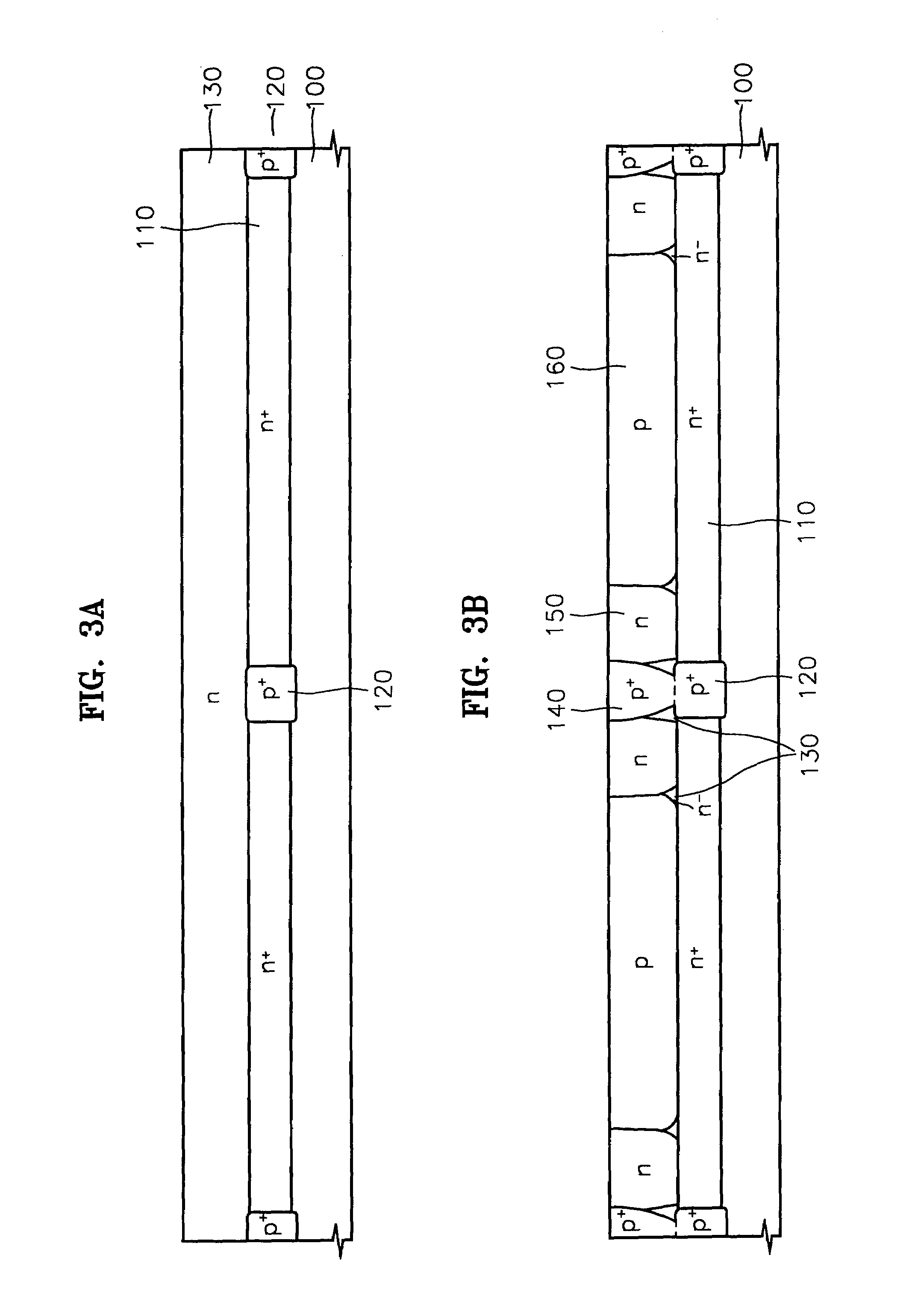

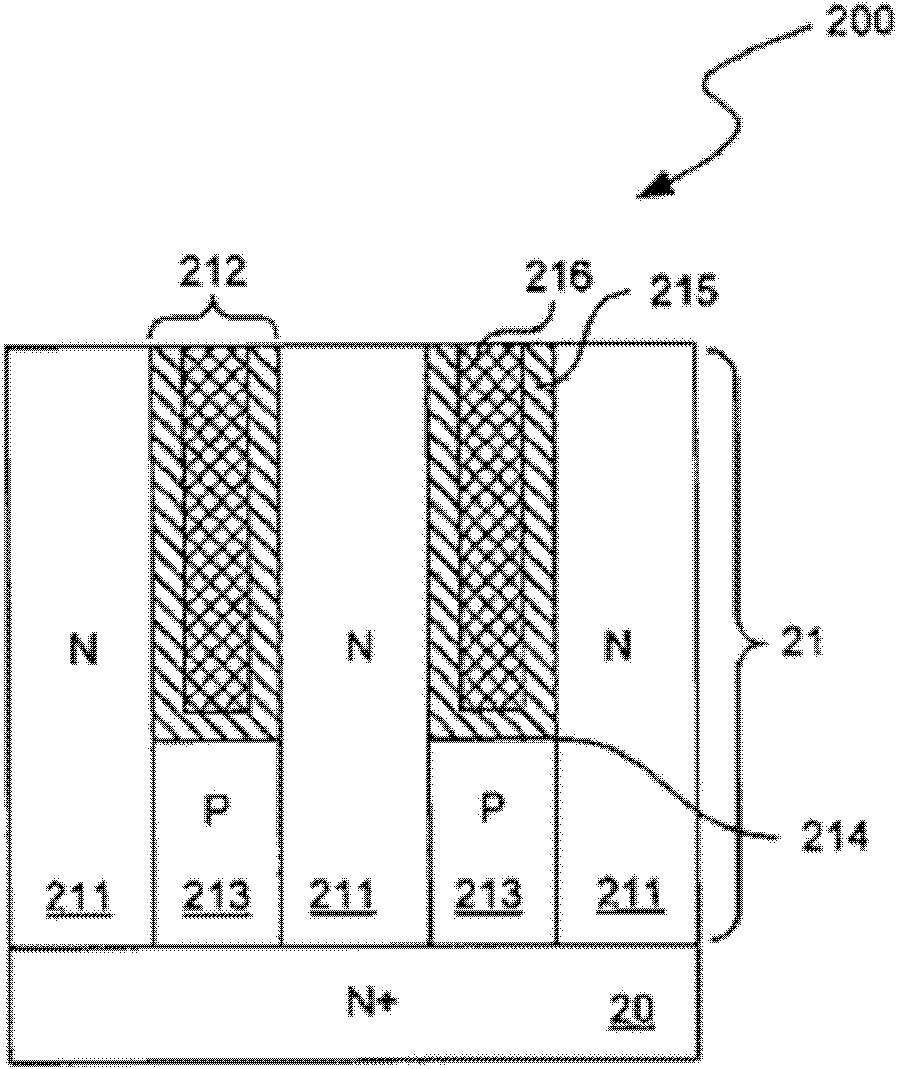

Super junction device with deep trench and implant

ActiveCN102169902ALower on-resistanceEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

The invention discloses a semiconductor device which has the effect of RESURF (Reduced Surface Field) and comprises deep trenches and relatively deep implants). Also, methods of fabricating such devices are described herein. A RESURF effect device may include alternating regions of first and second conductivity types where each of the second regions includes an implant region formed into a trench region of the second region. The device can ensure quite a low conduction resistance at quite a high withstand voltage and a easy producing.

Owner:CHENGDU MONOLITHIC POWER SYST

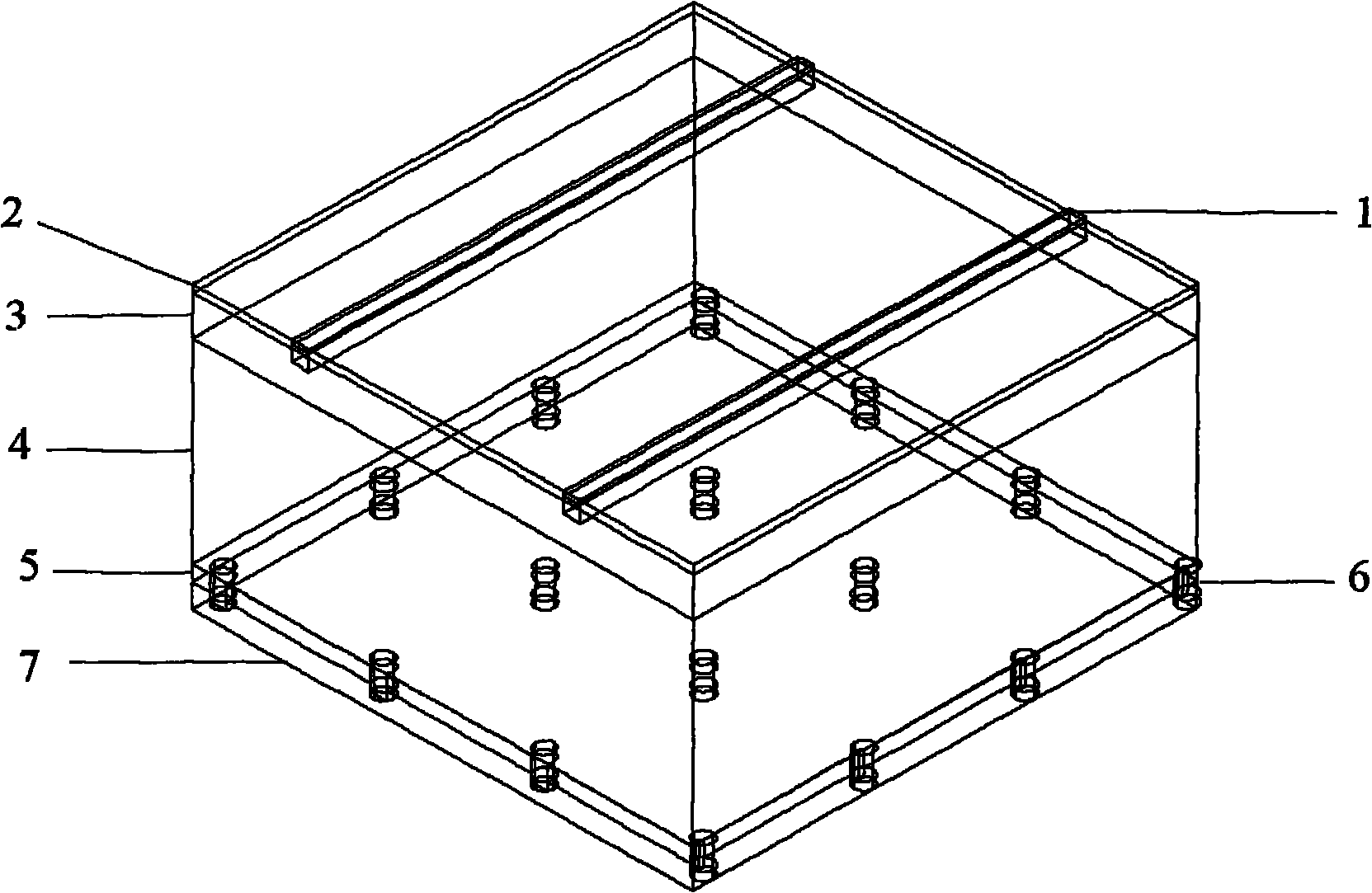

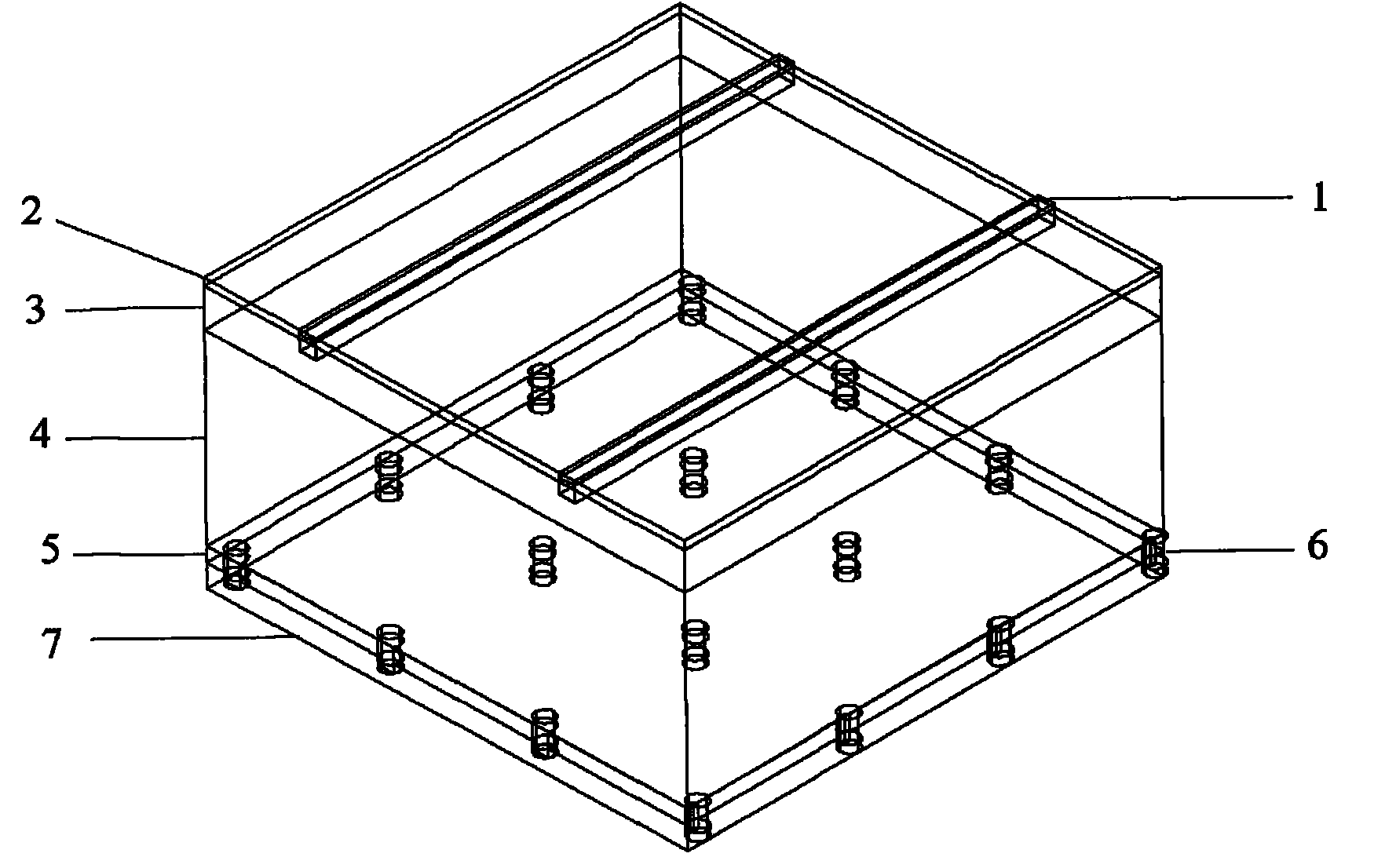

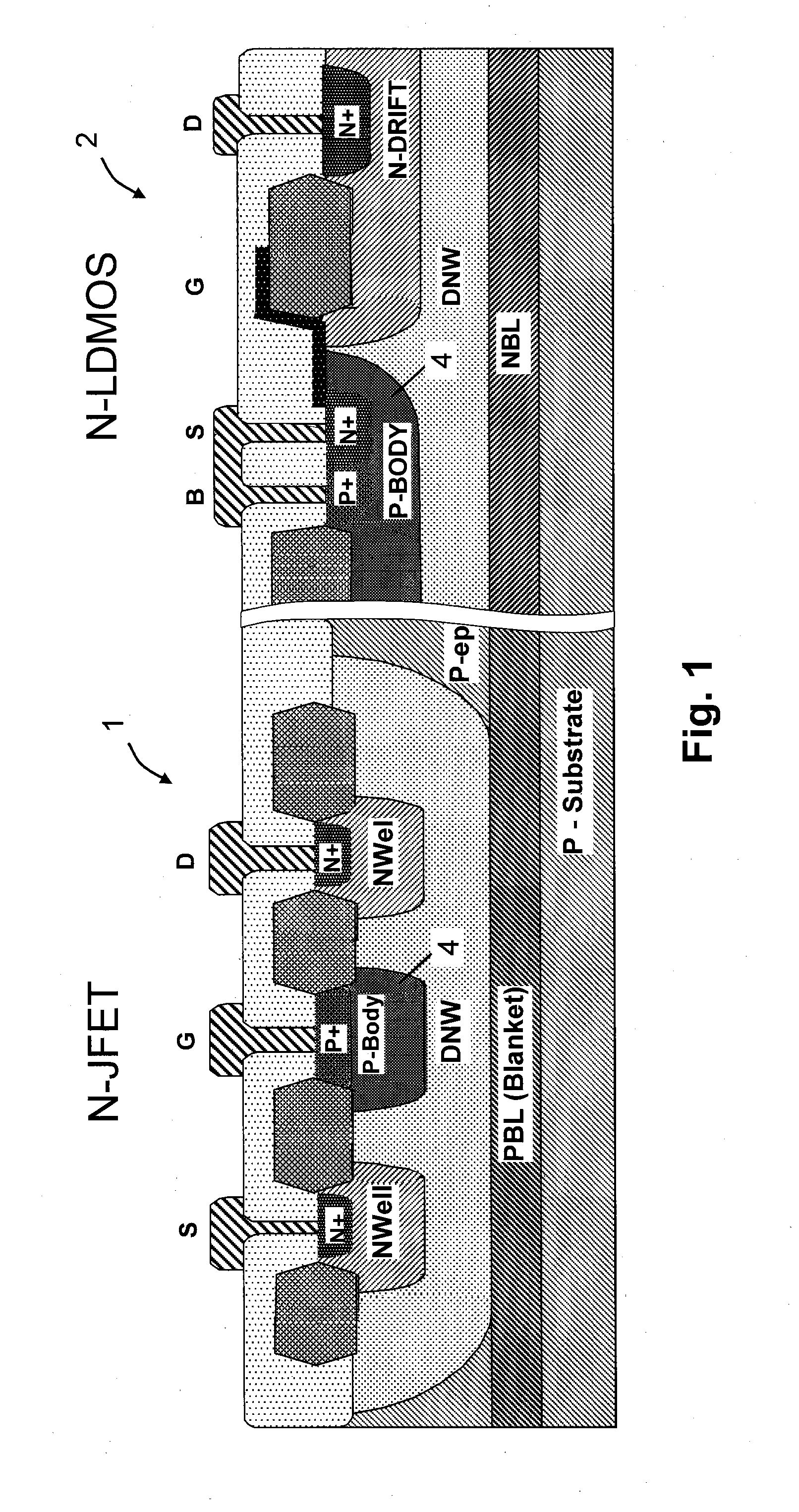

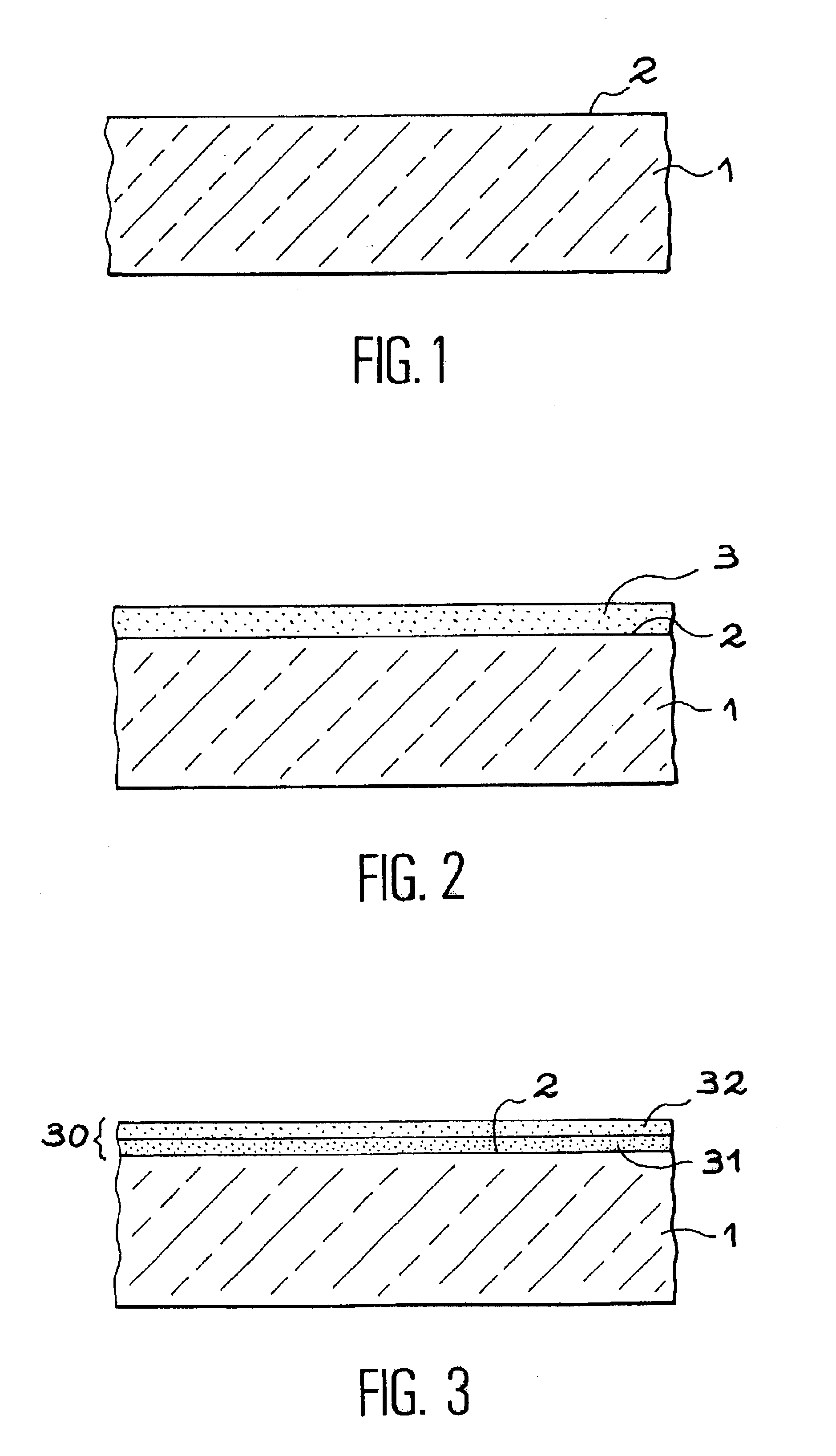

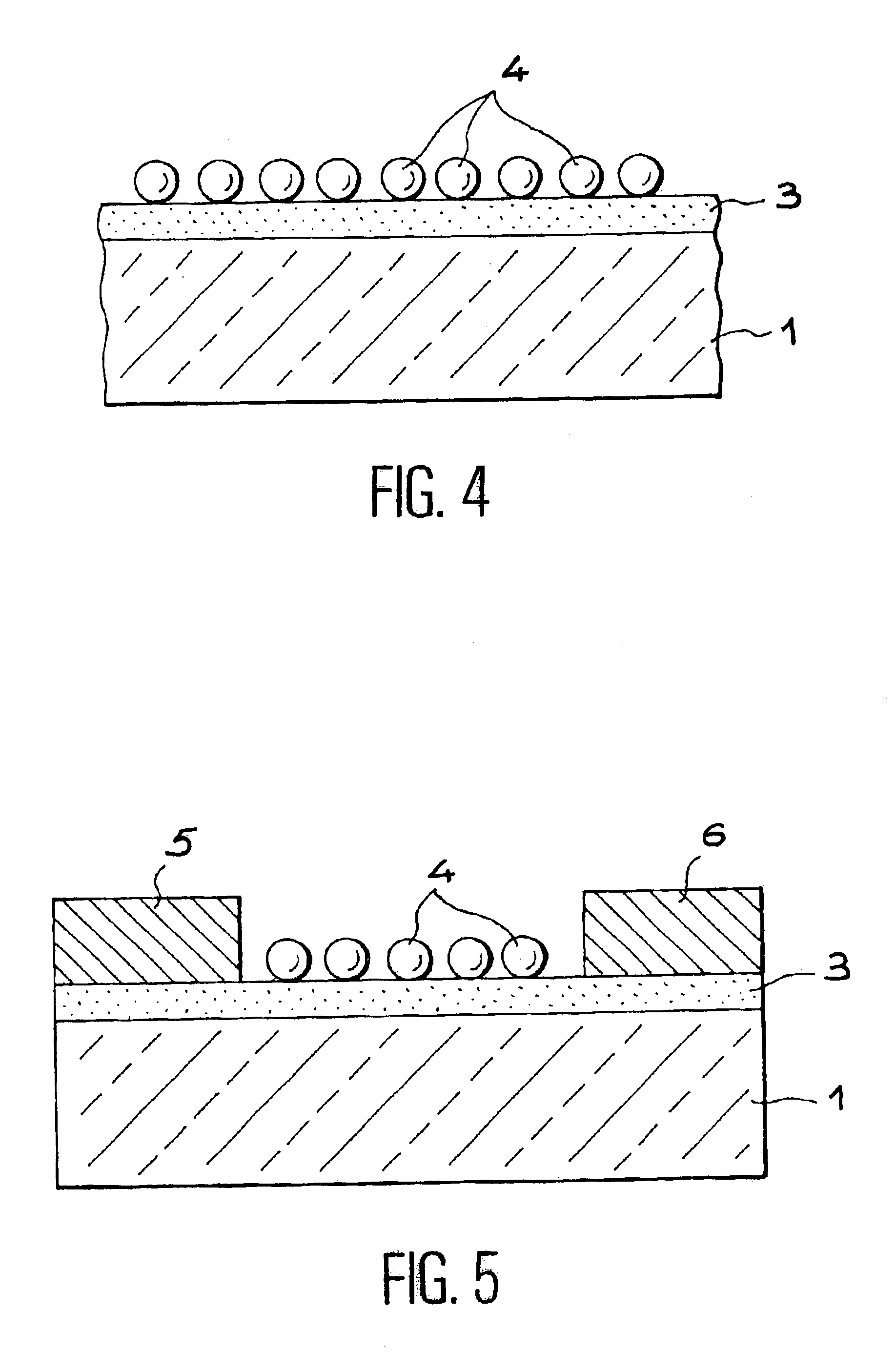

Method for automatic organization of microstructures or nanostructures and related device obtained

InactiveUS6724017B2Avoid pollutionFacilitate putting nanostructures into orderPolycrystalline material growthVacuum evaporation coatingInter layerCrystalline materials

The invention relates to a device comprising microstructures or nanostructures on a support, characterized in that the support comprises:a) a substrate (1) comprising at least one part composed of a crystalline material, this part having a surface (2) with a stress field or a topology associated with a stress field, the stress field being associated with dislocations,b) an intermediate layer (3) bonded to the surface (2), and having a thickness and / or composition and / or a surface state enabling transmission of said stress field through this layer as far as its free face that supports microstructures or nanostructures (4).

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

High speed orthogonal gate EDMOS device and fabrication

InactiveUS8357986B2Minimizes the gate to drain overlapLow technical requirementsSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

An orthogonal gate extended drain MOSFET (EDMOS) structure provides a low gate-to-drain capacitance (CGD) and exhibits increased reliability. It has a gate electrode that is folded into the shallow trench isolation (STI) oxide region. Horizontal and vertical gate electrode segments provide gate control. It accommodates both high voltage devices and standard CMOS components on the same substrate. Reduced surface field (RESURF) technology is employed to optimize tradeoffs between high breakdown voltage and specific on-resistance. Device fabrication steps are compatible with standard CMOS flow and process modules can be added or removed from baseline CMOS technology.

Owner:ASAHI KASEI ELECTRONICS CO LTD

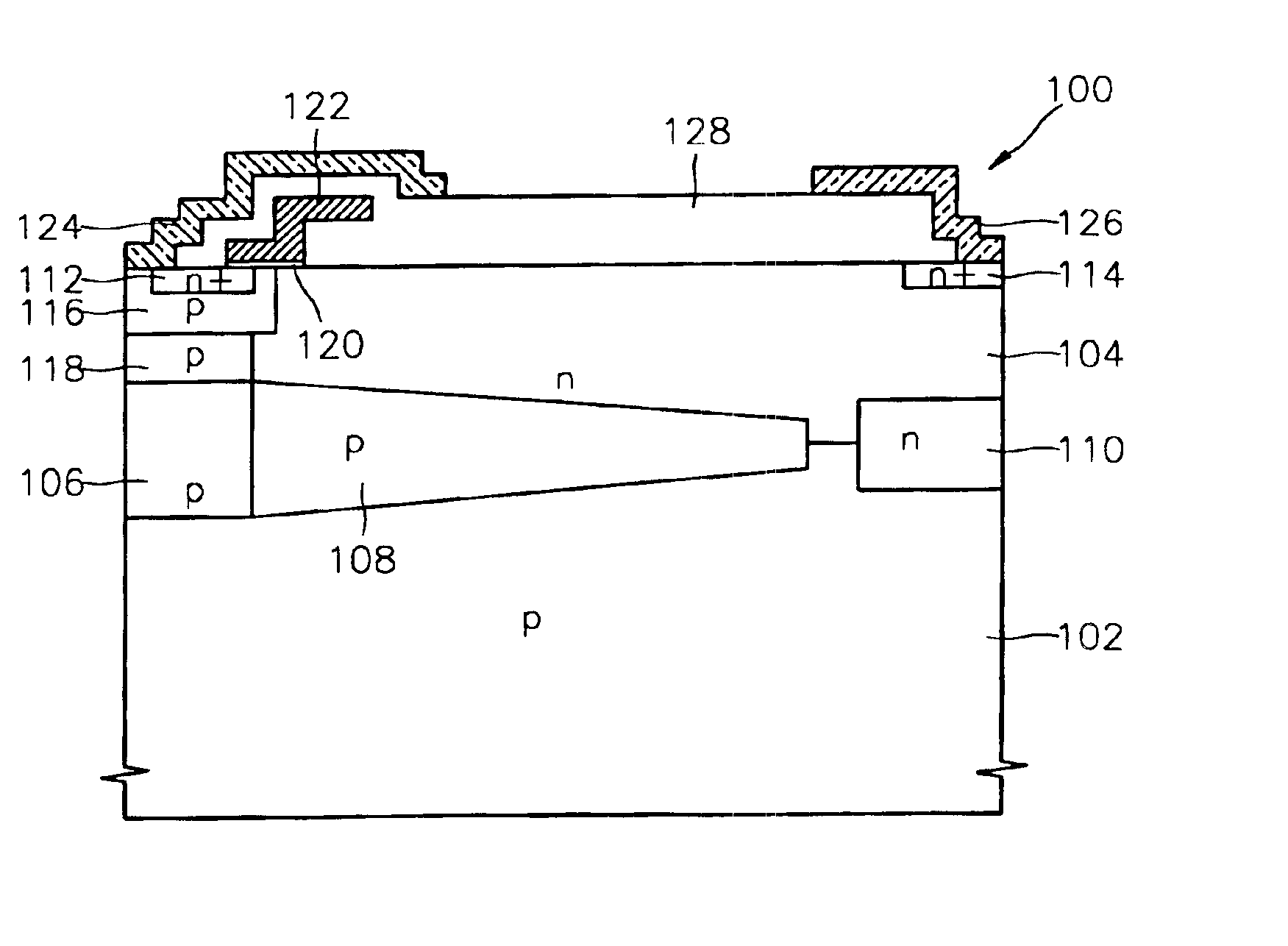

Lateral DMOS transistor having reduced surface field

InactiveUS6888210B2Semiconductor/solid-state device detailsSolid-state devicesBody regionSemiconductor

In accordance with the present invention, a metal oxide semiconductor (MOS) transistor has a substrate of a first conductivity type. A drift region of a second conductivity type is formed over the substrate. A body region of the first conductivity type is formed in the drift region. A source region of the second conductivity is formed in the body region. A gate extends over a surface portion of the body region and overlaps each of the source region and the body region such that the surface portion of the body region forms a channel region of the transistor. A drain region of the second conductivity type is formed in the drift region. The drain region is laterally spaced from the source region a first predetermined distance. A first buried layer of the first conductivity type extends into the substrate and the drift region. The first buried layer laterally extends between the source and drain regions.

Owner:SEMICON COMPONENTS IND LLC

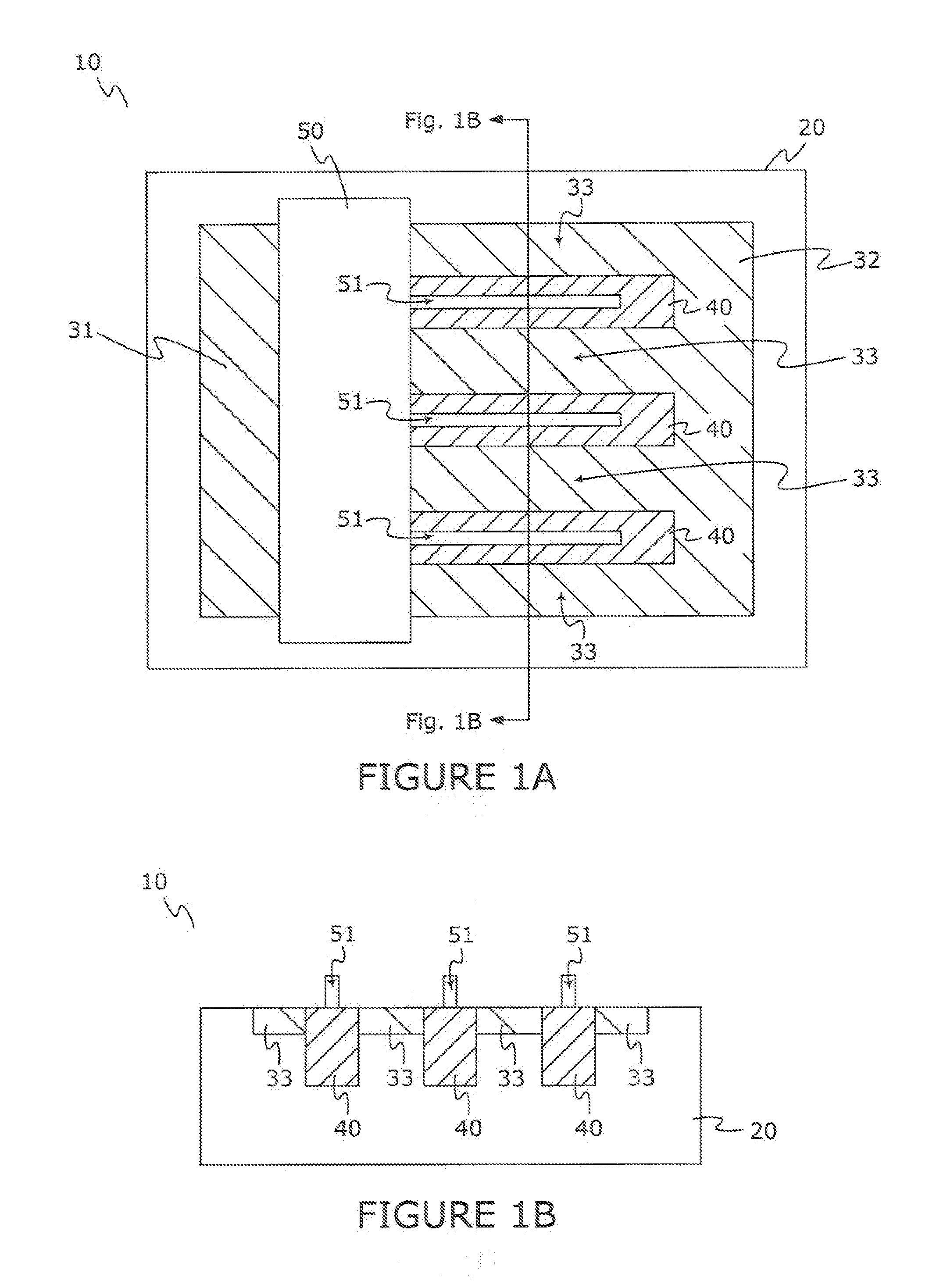

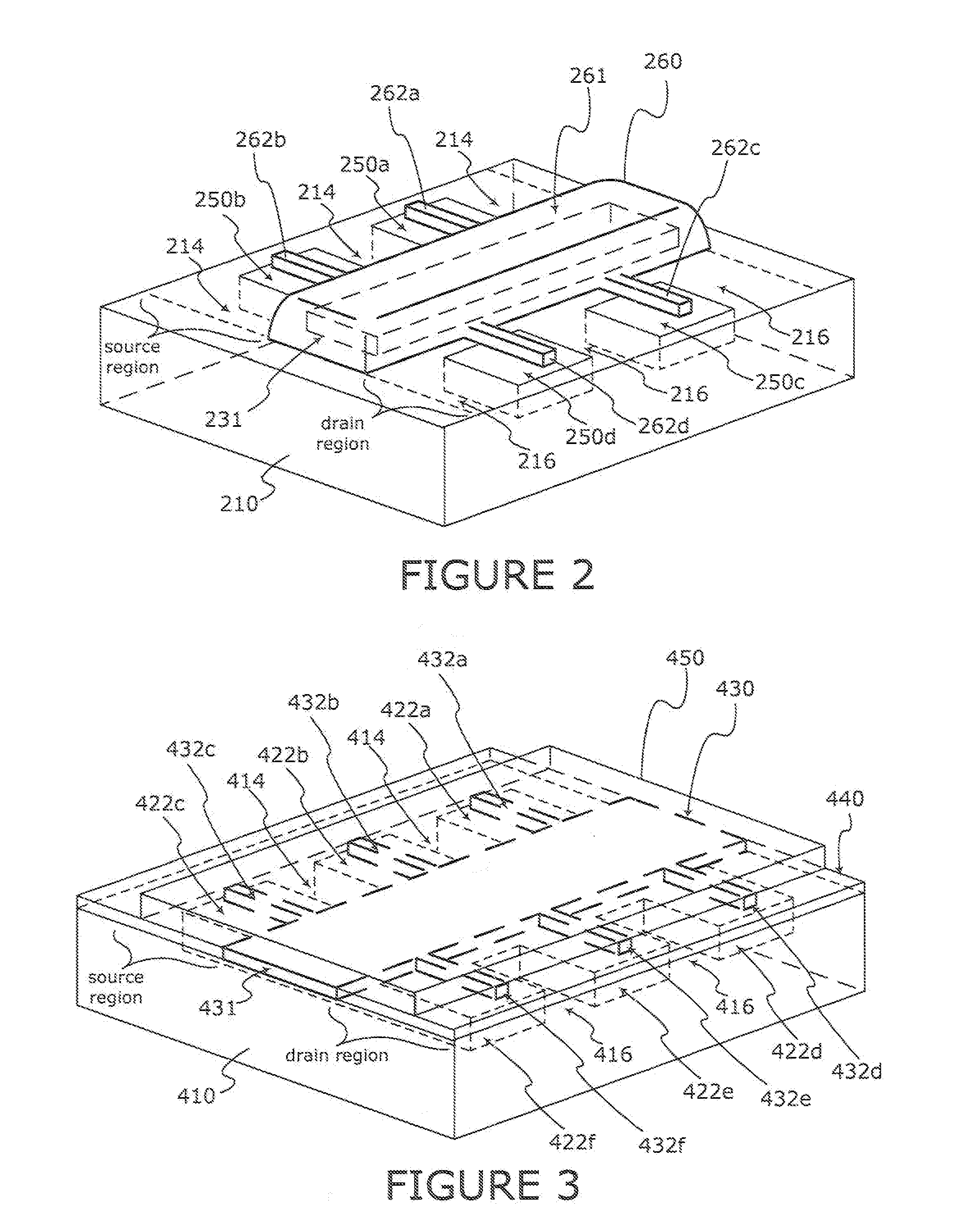

Semiconductor device with reduced surface field effect and methods of fabrication the same

ActiveUS20110147844A1Semiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCapacitive coupling

Embodiments of the present invention describe a semiconductor device implementing the reduced-surface-field (RESURF) effect. The semiconductor device comprises a source / drain region having a plurality of isolation regions interleaved with source / drain extension regions. A gate electrode is formed on the semiconductor device, where the gate electrode includes gate finger elements formed over the isolation regions to induce capacitive coupling. The gate finger elements enhance the depletion of the source / drain extension regions, thus inducing a higher breakdown voltage.

Owner:INTEL NDTM US LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com