Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

13203 results about "Ion implantation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Ion implantation is a low-temperature process by which ions of one element are accelerated into a solid target, thereby changing the physical, chemical, or electrical properties of the target. Ion implantation is used in semiconductor device fabrication and in metal finishing, as well as in materials science research. The ions can alter the elemental composition of the target (if the ions differ in composition from the target) if they stop and remain in the target. Ion implantation also causes chemical and physical changes when the ions impinge on the target at high energy. The crystal structure of the target can be damaged or even destroyed by the energetic collision cascades, and ions of sufficiently high energy (10s of MeV) can cause nuclear transmutation.

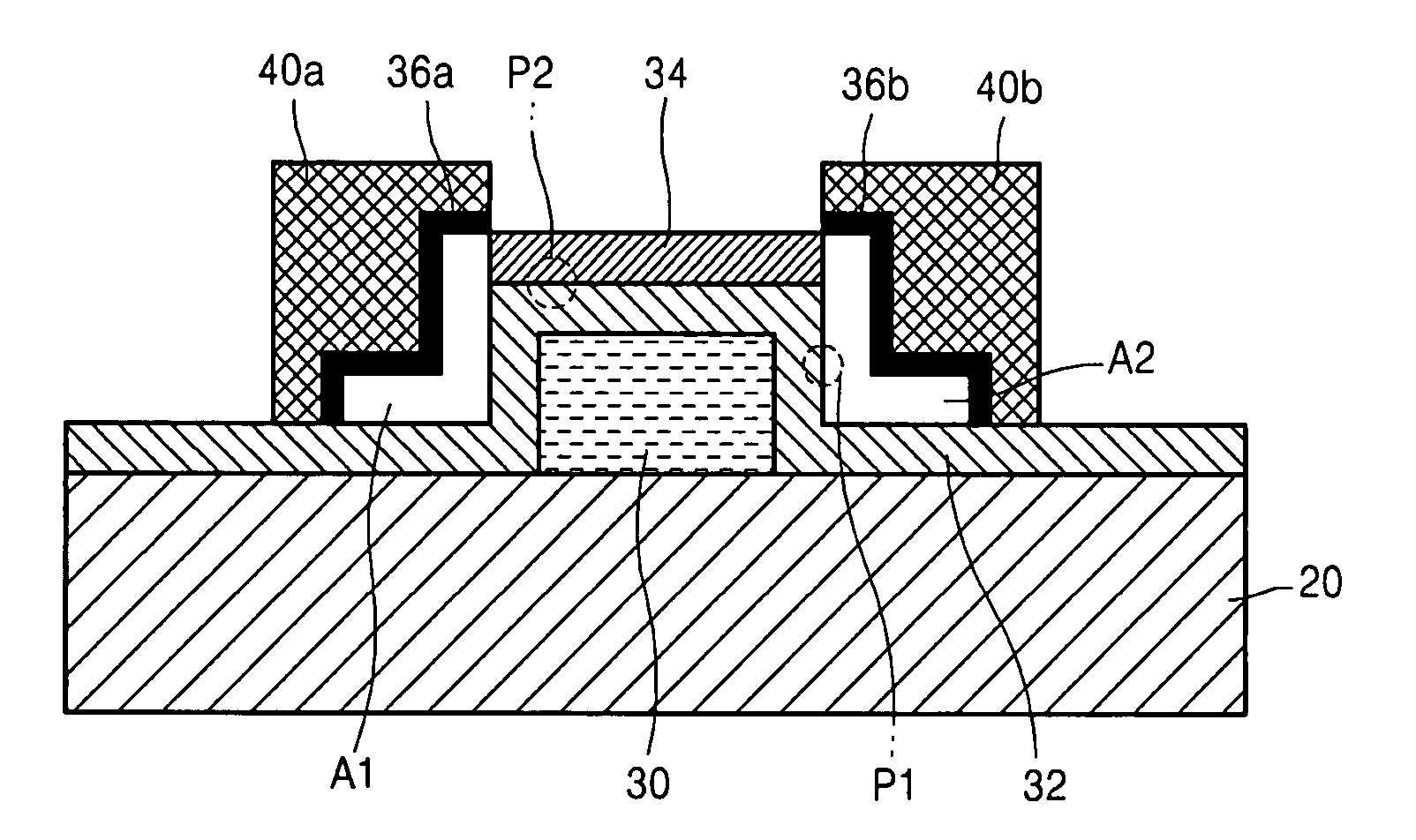

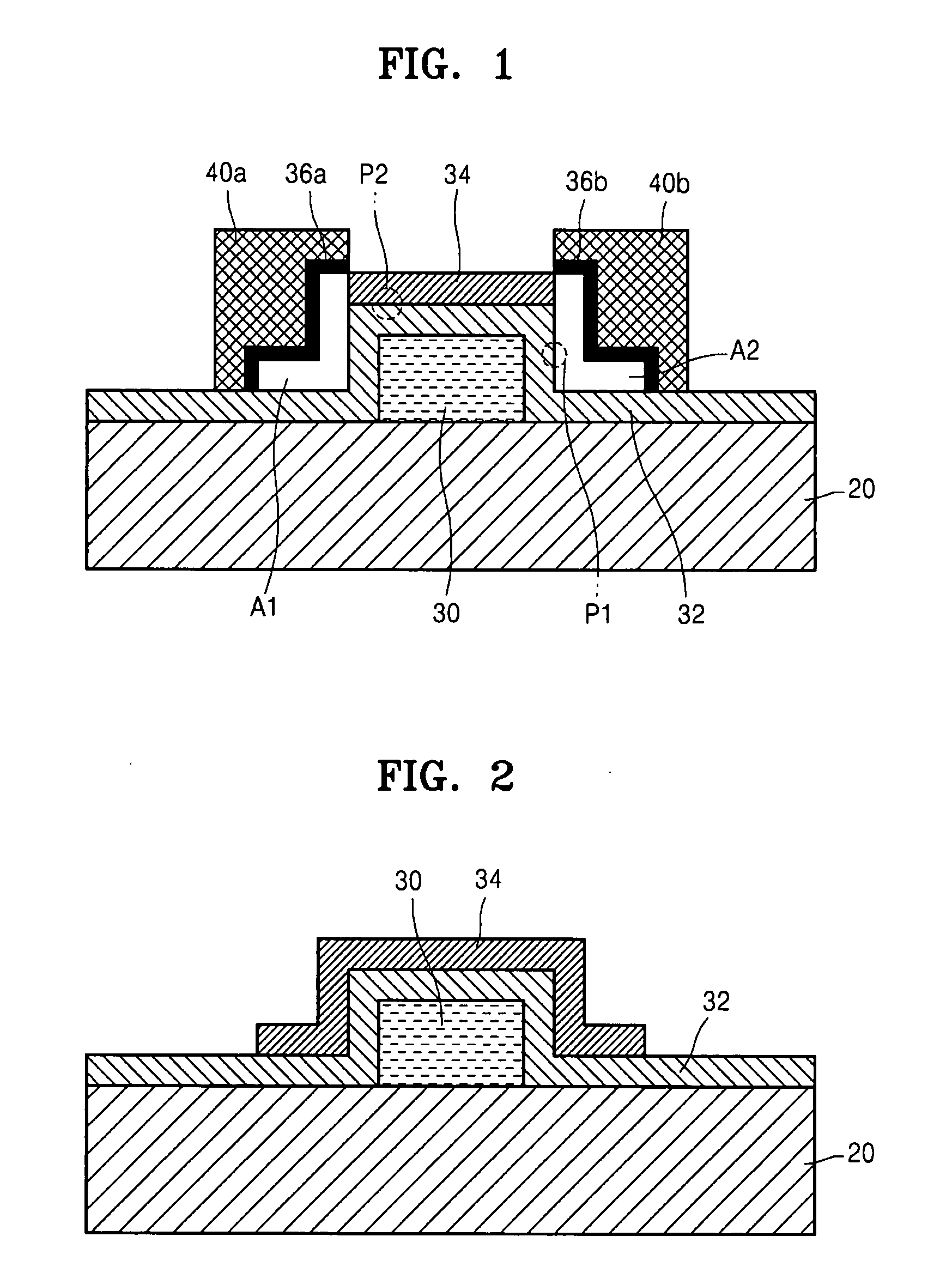

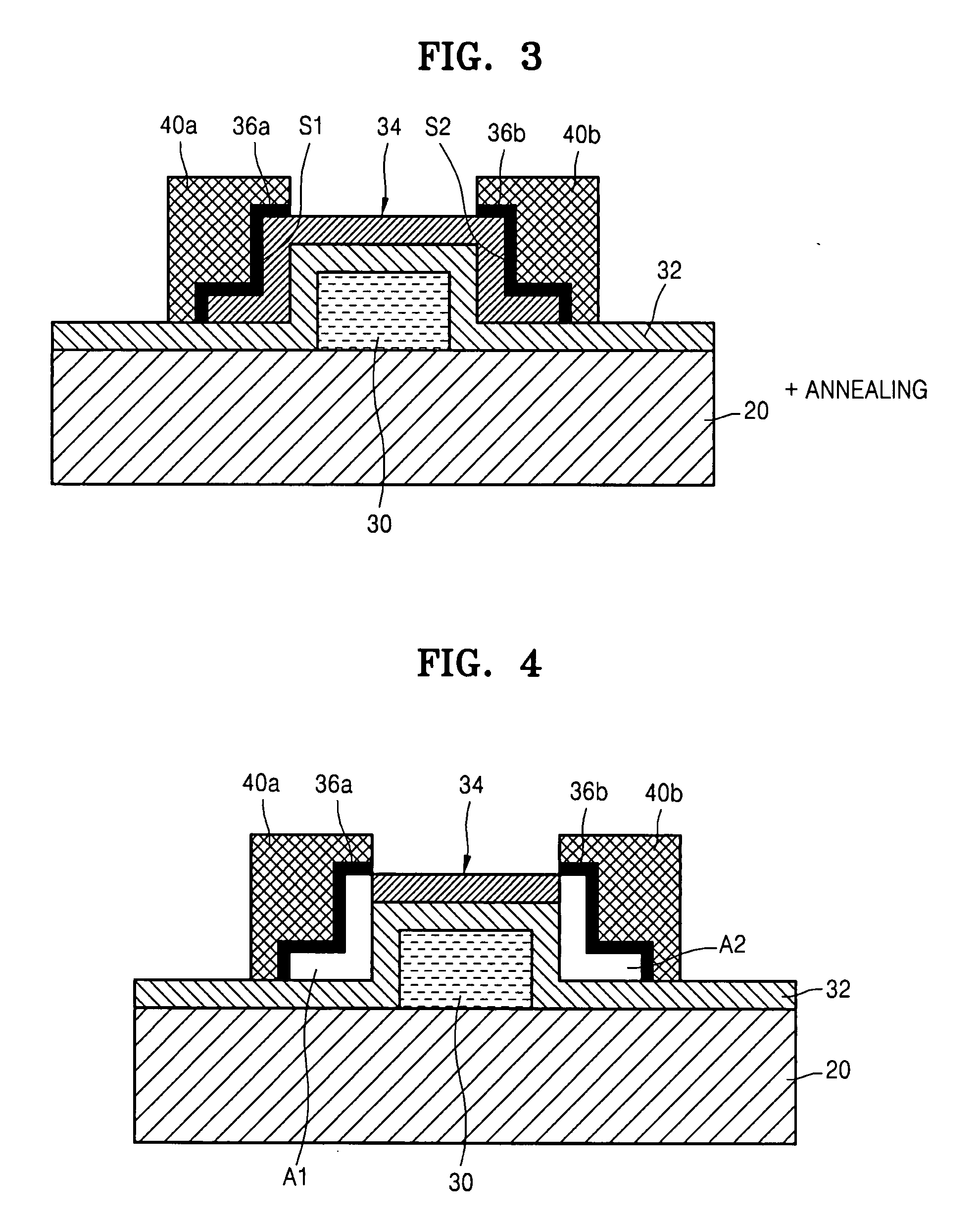

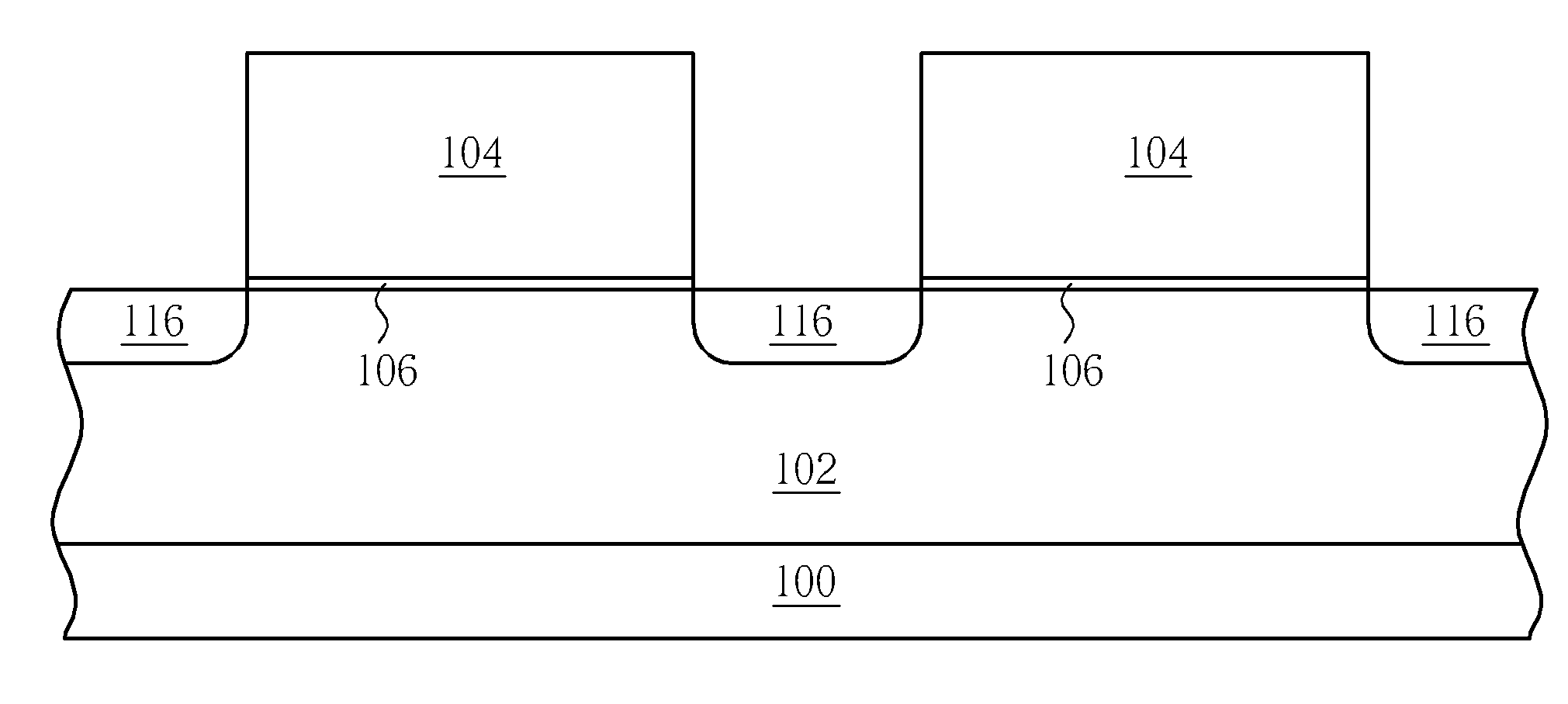

Thin film transistor including selectively crystallized channel layer and method of manufacturing the thin film transistor

ActiveUS20080258140A1Stable contact characteristicHigh carrier mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringIon implantation

Provided are a thin film transistor (TFT) including a selectively crystallized channel layer, and a method of manufacturing the TFT. The TFT includes a gate, the channel layer, a source, and a drain. The channel layer is formed of an oxide semiconductor, and at least a portion of the channel layer contacting the source and the drain is crystallized. In the method of manufacturing the TFT, the channel layer is formed of an oxide semiconductor, and a metal component is injected into the channel layer so as to crystallize at least a portion of the channel layer contacting the source and the drain. The metal component can be injected into the channel layer by depositing and heat-treating a metal layer or by ion-implantation.

Owner:SAMSUNG ELECTRONICS CO LTD

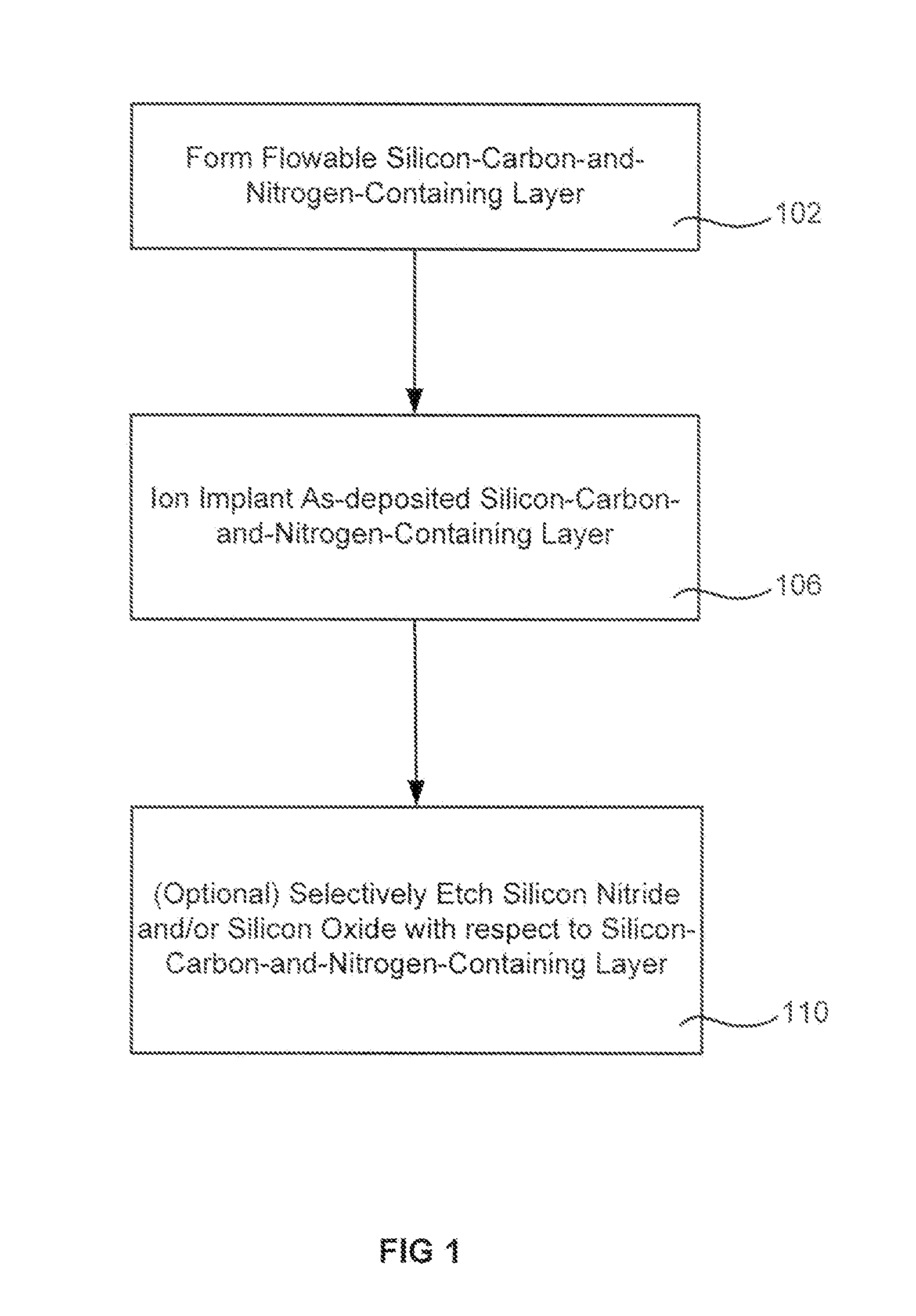

Doping of dielectric layers

InactiveUS20130217243A1Increase etch tolerancePrevent shrinkageSemiconductor/solid-state device manufacturingDeposition temperaturePhysical chemistry

Methods are described for forming and treating a flowable silicon-carbon-and-nitrogen-containing layer on a semiconductor substrate. The silicon and carbon constituents may come from a silicon-and-carbon-containing precursor while the nitrogen may come from a nitrogen-containing precursor that has been activated to speed the reaction of the nitrogen with the silicon-and-carbon-containing precursor at lower deposition temperatures. The initially-flowable silicon-carbon-and-nitrogen-containing layer is ion implanted to increase etch tolerance, prevent shrinkage, adjust film tension and / or adjust electrical characteristics. Ion implantation may also remove components which enabled the flowability, but are no longer needed after deposition. Some treatments using ion implantation have been found to decrease the evolution of properties of the film upon exposure to atmosphere.

Owner:APPLIED MATERIALS INC

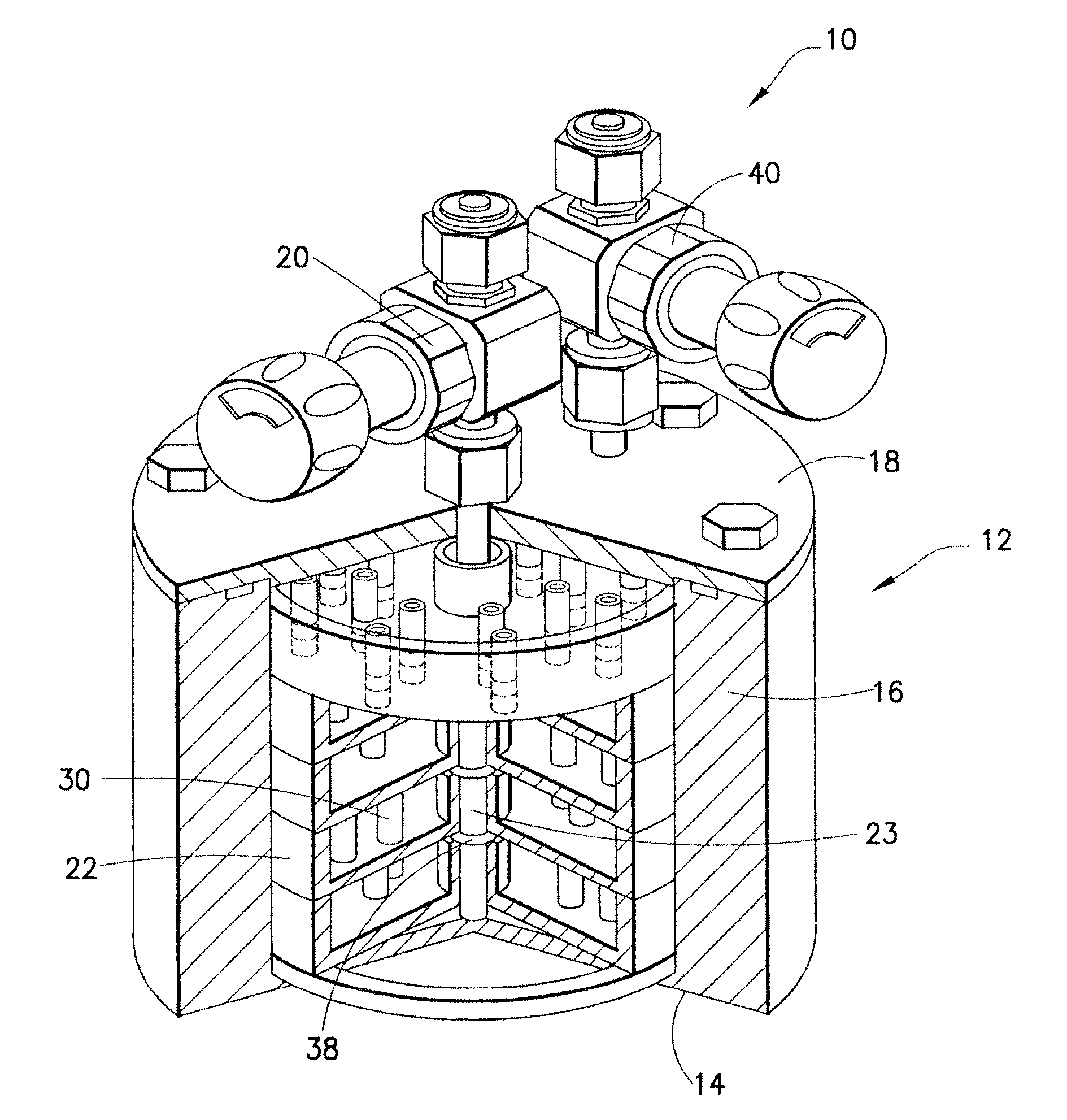

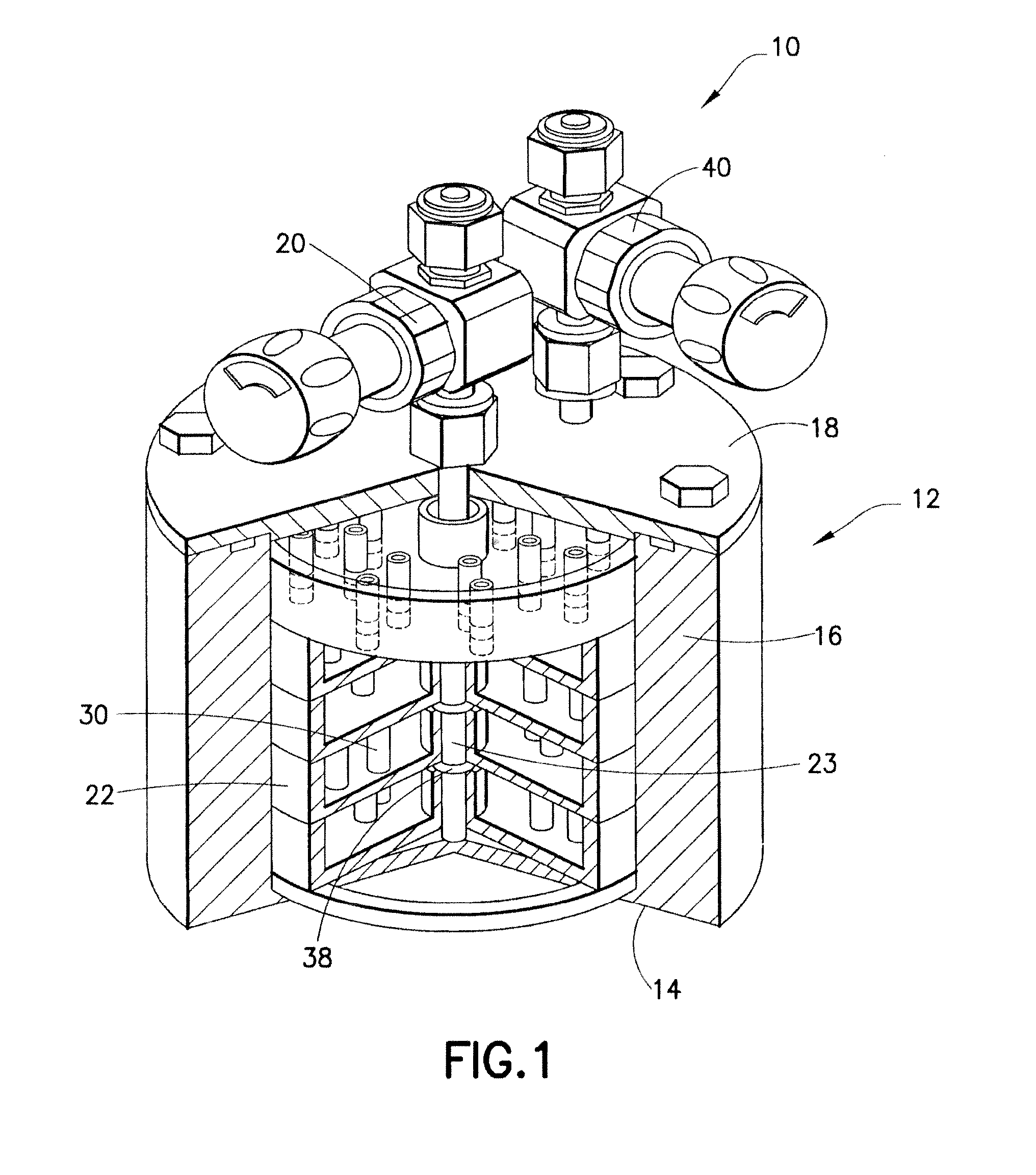

Solid precursor-based delivery of fluid utilizing controlled solids morphology

ActiveUS20100255198A1Vacuum evaporation coatingSputtering coatingMetal halidesAtomic layer deposition

Apparatus and method for volatilizing a source reagent susceptible to particle generation or presence of particles in the corresponding source reagent vapor, in which such particle generation or presence is suppressed by structural or processing features of the vapor generation system. Such apparatus and method are applicable to liquid and solid source reagents, particularly solid source reagents such as metal halides, e.g., hafnium chloride. The source reagent in one specific implementation is constituted by a porous monolithic bulk form of the source reagent material. The apparatus and method of the invention are usefully employed to provide source reagent vapor for applications such as atomic layer deposition (ALD) and ion implantation.

Owner:ENTEGRIS INC

Method for ion implanting insulator material to reduce dielectric constant

InactiveUS20050191828A1Low dielectric constantElectric discharge tubesSemiconductor/solid-state device manufacturingMicroelectronic circuitsIon implantation

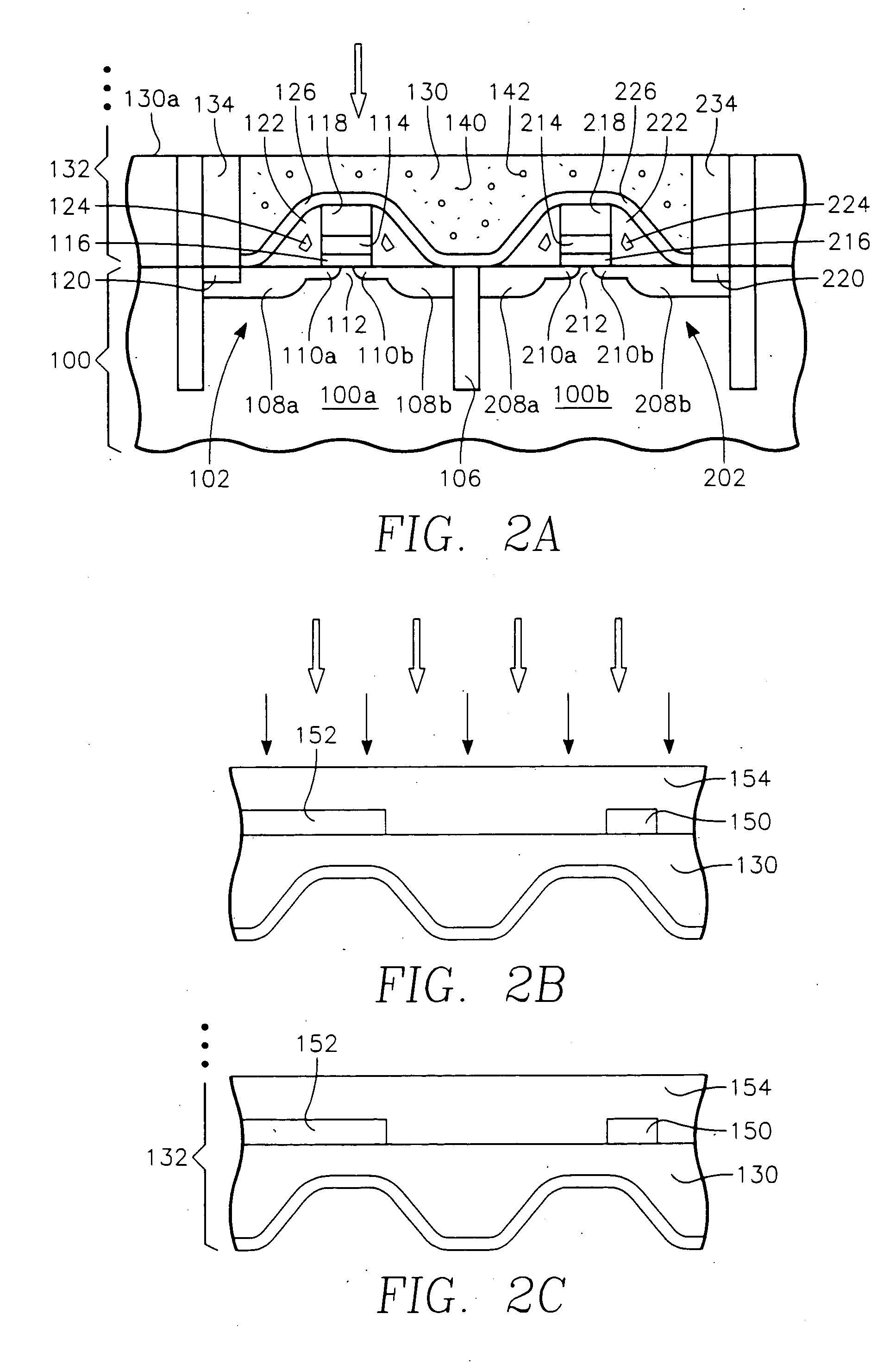

An integrated microelectronic circuit has a multi-layer interconnect structure overlying the transistors consisting of stacked metal pattern layers and insulating layers separating adjacent ones of said metal pattern layers. Each of the insulating layers is a dielectric material with plural gas bubbles distributed within the volume of the dielectric material to reduce the dielectric constant of the material, the gas bubbles being formed by ion implantation of a gaseous species into the dielectric material.

Owner:APPLIED MATERIALS INC

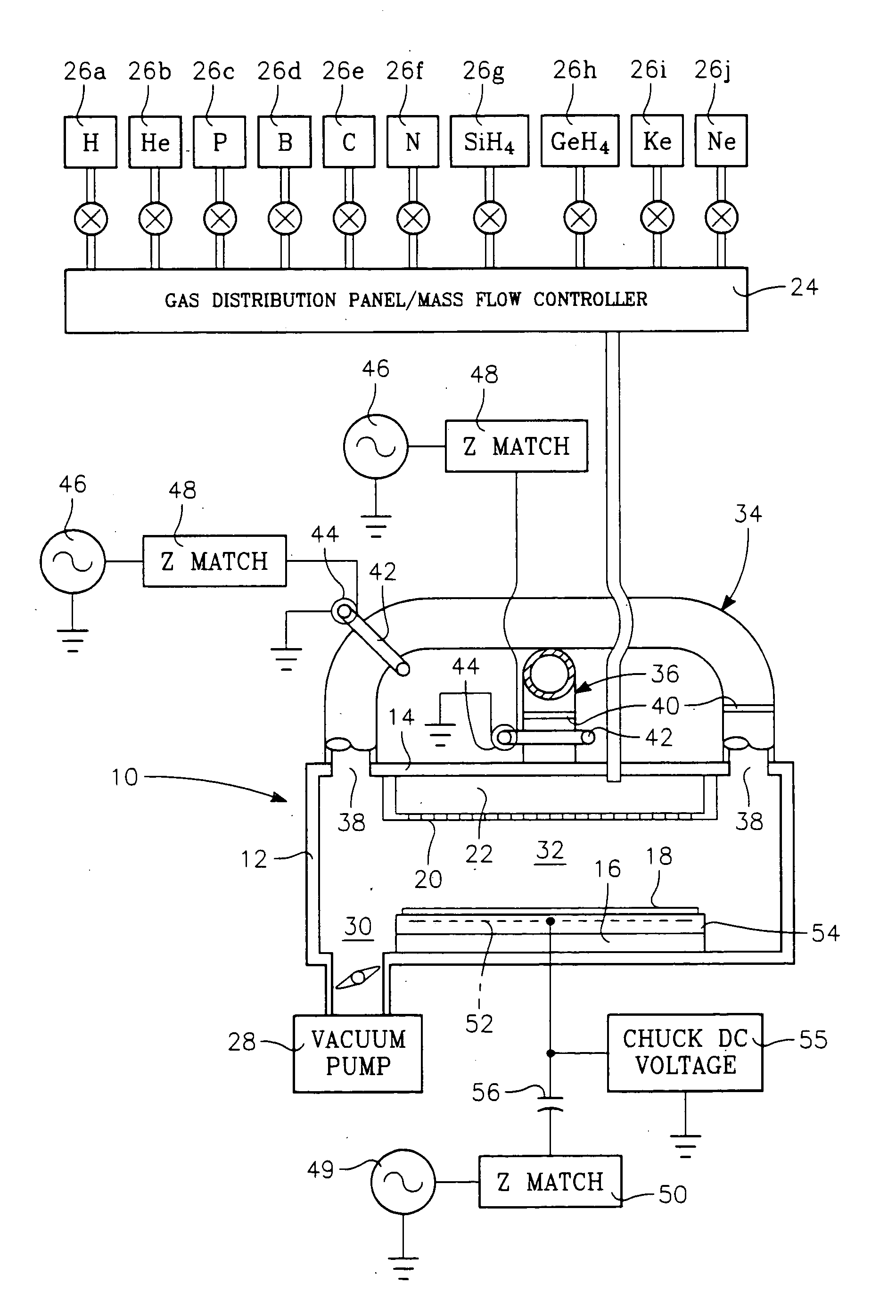

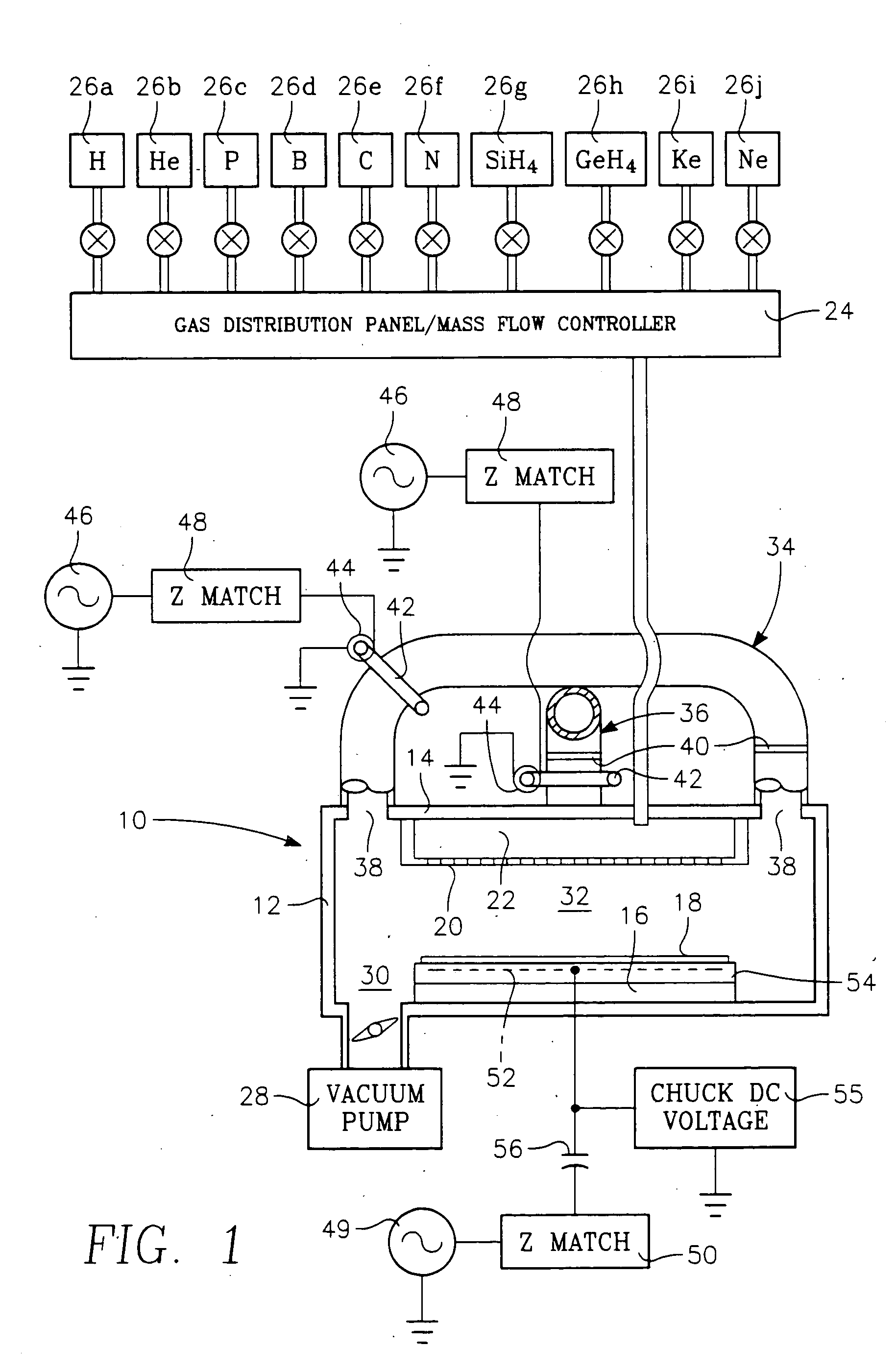

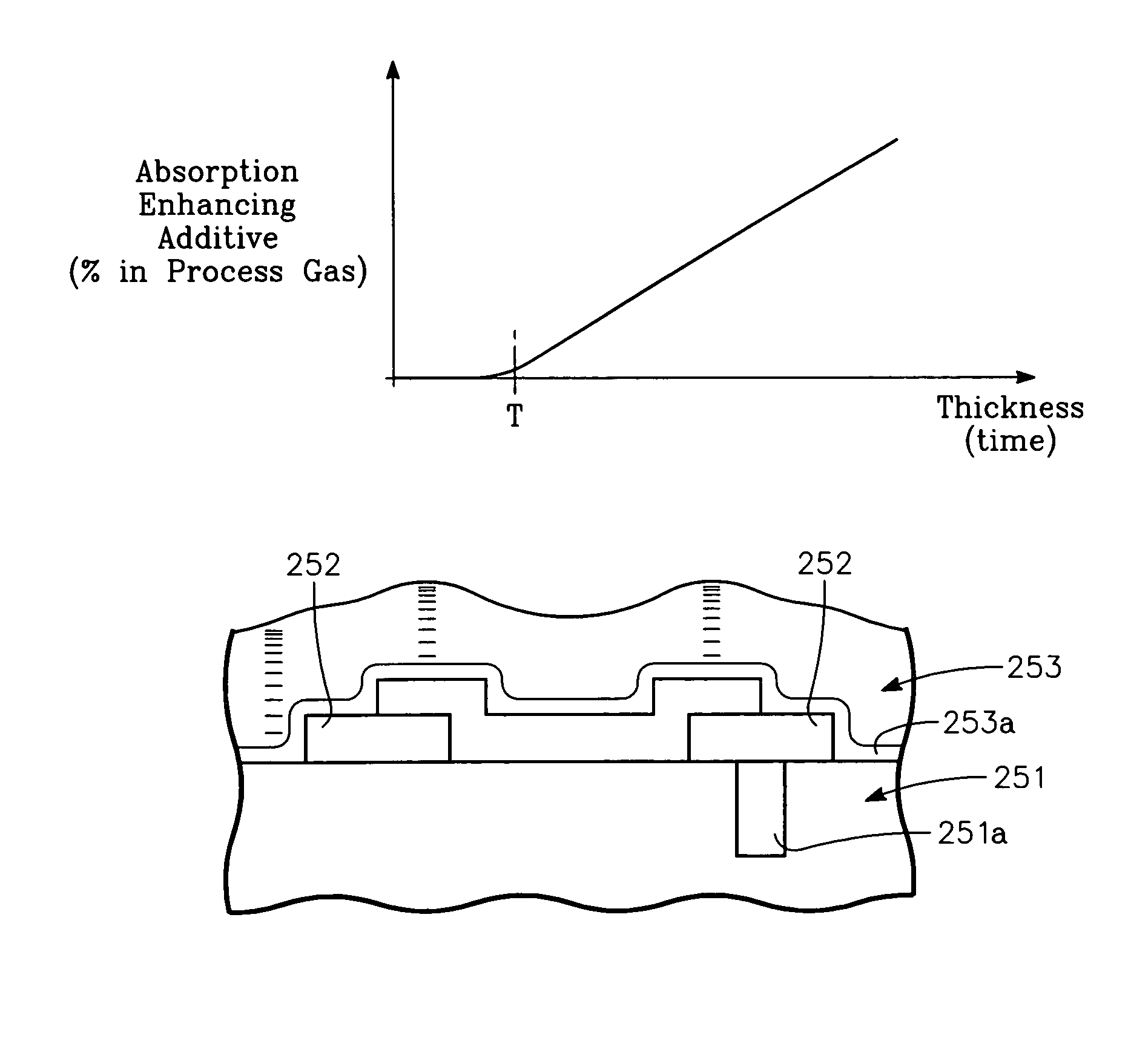

Semiconductor junction formation process including low temperature plasma deposition of an optical absorption layer and high speed optical annealing

A method of forming semiconductor junctions in a semiconductor material of a workpiece includes ion implanting dopant impurities in selected regions of the semiconductor material, introducing an optical absorber material precursor gas into a chamber containing the workpiece, generating an RF oscillating toroidal plasma current in a reentrant path that includes a process zone overlying the workpiece by applying RF source power, so as to deposit a layer of an optical absorber material on the workpiece, and optically annealing the workpiece so as to activate dopant impurities in the semiconductor material.

Owner:APPLIED MATERIALS INC

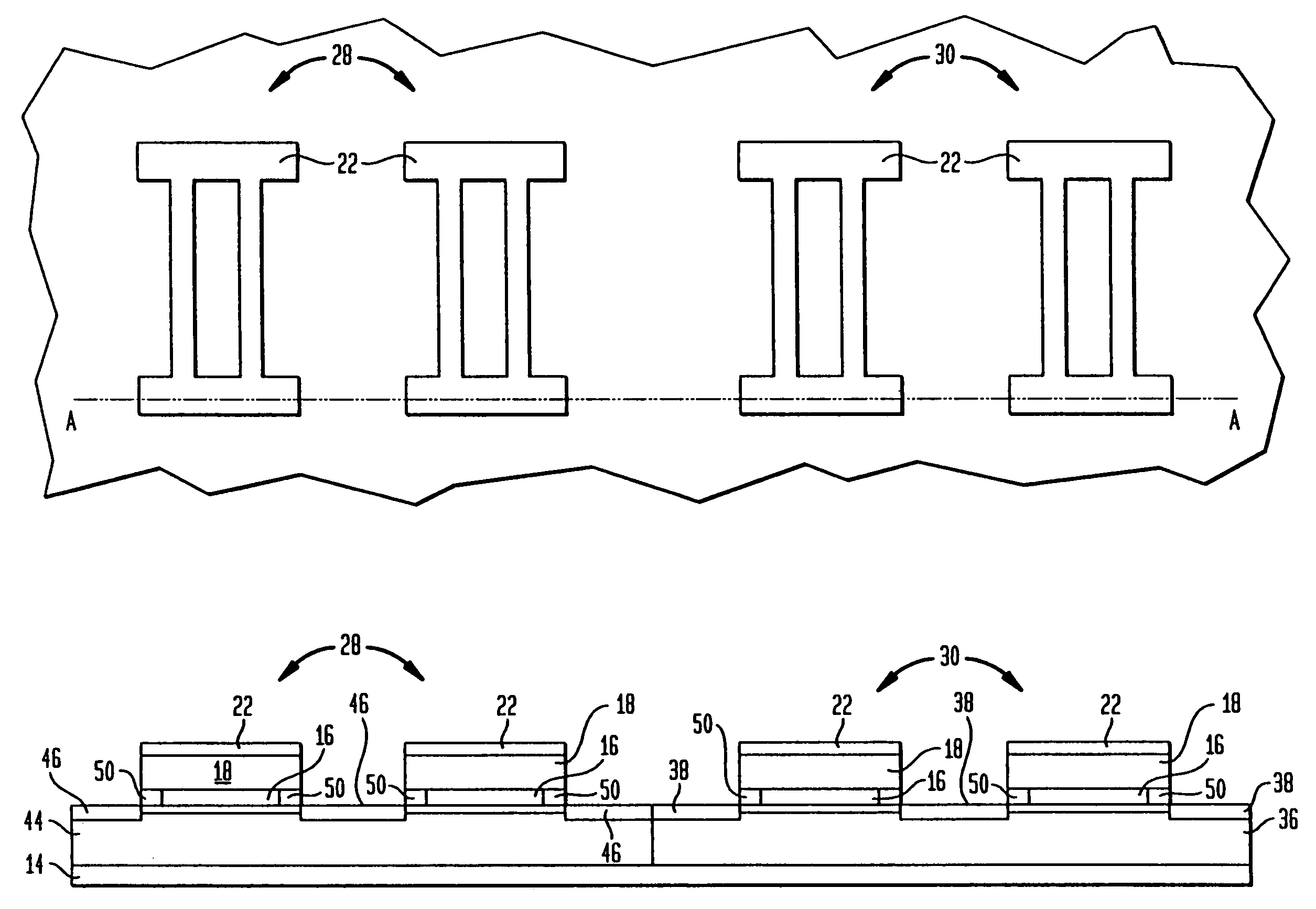

Low capacitance junction-isolation for bulk FinFET technology

ActiveUS7101763B1Good junction isolationLow capacitance benefitSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricCapacitance

The present invention provides a SiGe-based bulk integration scheme for generating FinFET devices on a bulk Si substrate in which a simple etch, mask, ion implant set of sequences have been added to accomplish good junction isolation while maintaining the low capacitance benefits of FinFETs. The method of the present invention includes providing a structure including a bottom Si layer and a patterned stack comprising a SiGe layer and a top Si layer on the bottom Si layer; forming a well region and isolation regions via implantation within the bottom Si layer; forming an undercut region beneath the top Si layer by etching back the SiGe layer; and filling the undercut with a dielectric to provide device isolation, wherein the dielectric has an outer vertical edge that is aligned to an outer vertical edge of the top Si layer.

Owner:GLOBALFOUNDRIES US INC

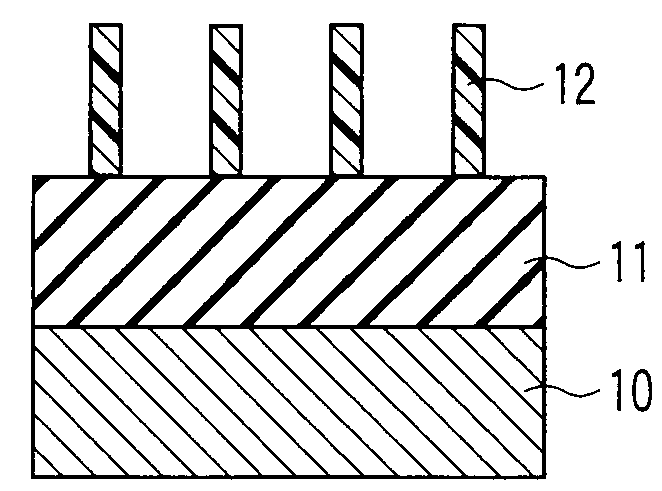

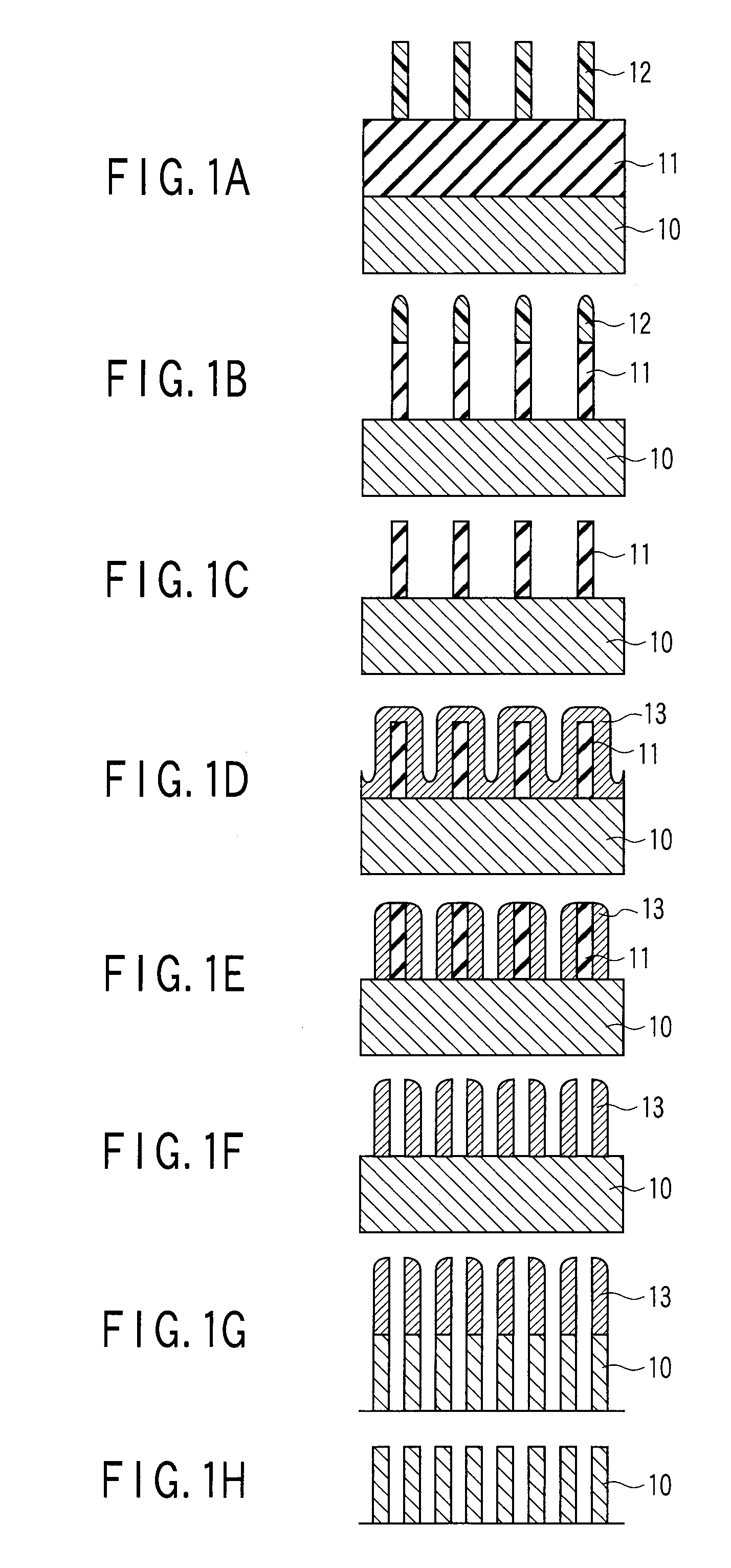

Pattern forming method using relacs process

InactiveUS20080305443A1Semiconductor/solid-state device manufacturingOriginals for photomechanical treatmentResistOrganic film

A resist pattern is formed on a to-be-processed film. Ions are implanted in the upper surface of the resist pattern. After ion implantation, an organic film is formed to cover the resist pattern and heated. A crosslinked resin film made of the organic film which has crosslinked is formed on the sidewall of the resist pattern by developing the organic film after heating. After formation of the crosslinked resin film, the resist pattern is removed. The to-be-processed film is processed using the crosslinked resin film as a mask.

Owner:KK TOSHIBA

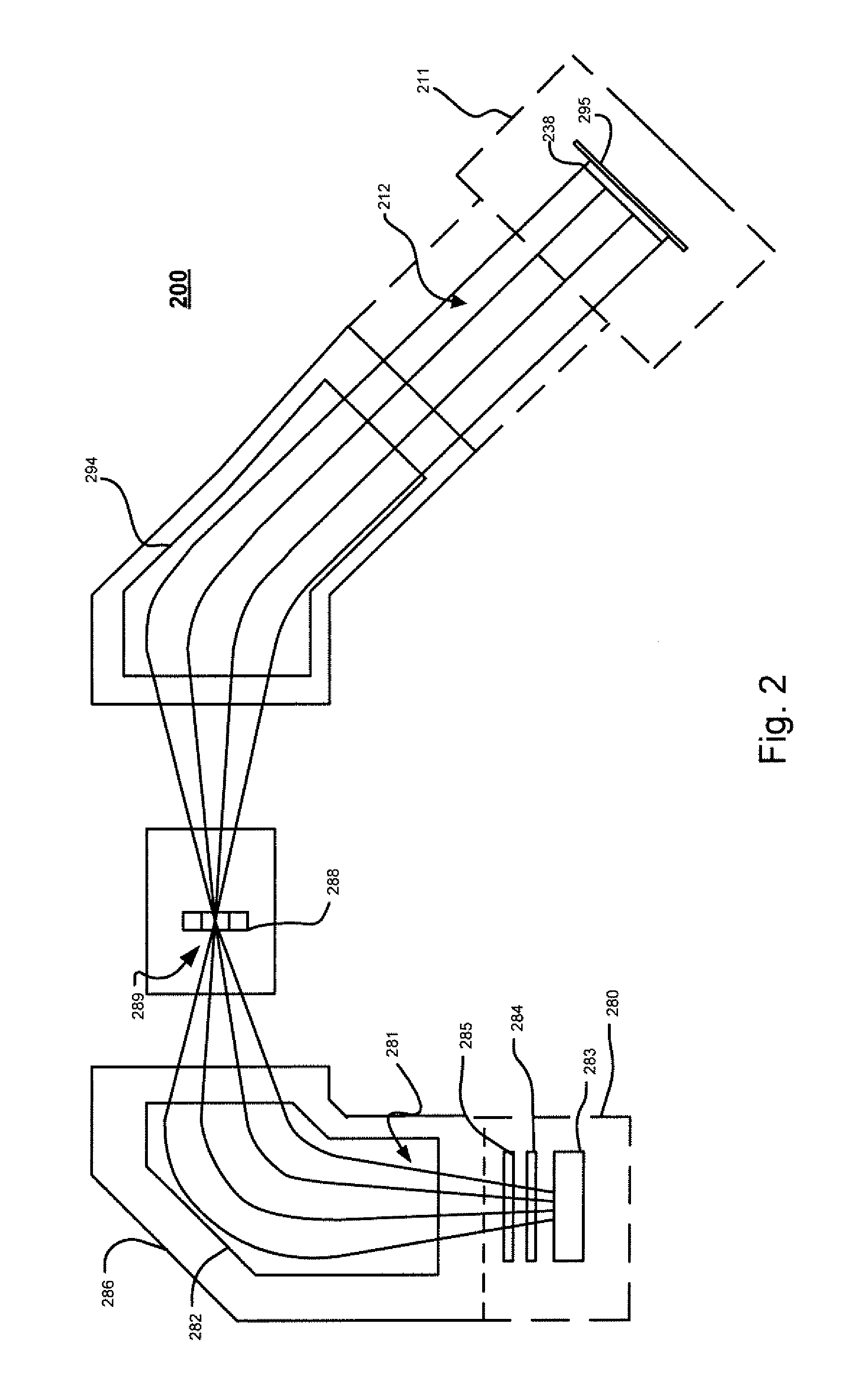

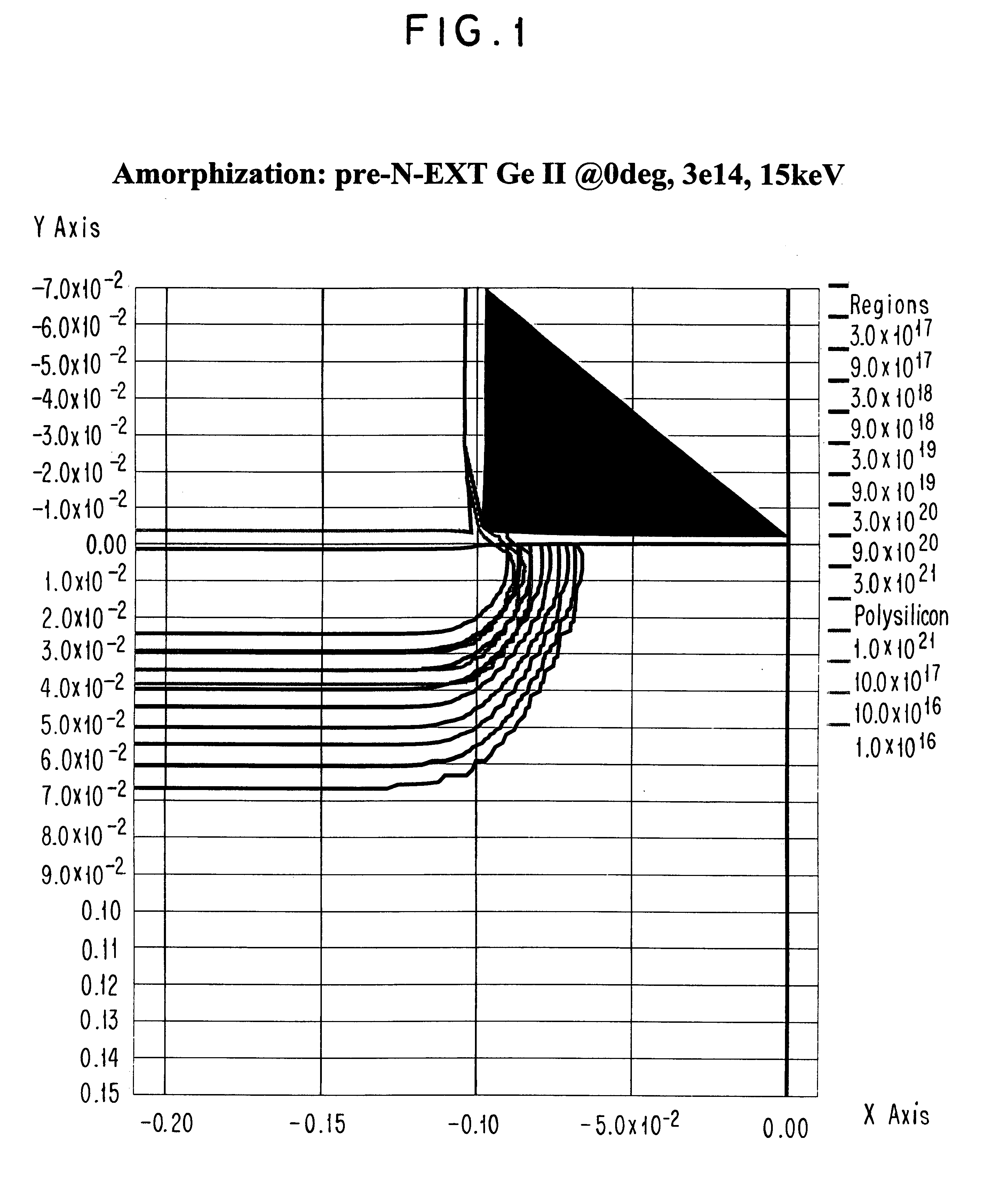

Techniques for cold implantation of carbon-containing species

InactiveUS20090200494A1Increase strainElectric discharge tubesSemiconductor/solid-state device manufacturingIon implantationMaterials science

Techniques for cold implantation of carbon-containing species are disclosed. In one particular exemplary embodiment, the techniques may be realized as an apparatus for ion implantation including a cooling device for cooling a target material to a predetermined temperature, and an ion implanter for implanting the target material with a carbon-containing species at the predetermined temperature to improve at least one of strain and amorphization.

Owner:VARIAN SEMICON EQUIP ASSOC INC

Metal capacitor and method of making the same

ActiveUS8114734B2Increase capacitanceAvoid delaySemiconductor/solid-state device detailsSolid-state devicesCapacitanceInterconnection

A method of making a metal capacitor includes the following steps. A dielectric layer having a metal interconnection and a capacitor electrode is provided. Then, a treatment is performed to increase the dielectric constant of the dielectric layer surrounding the capacitor electrode. The treatment can be UV radiation, a plasma treatment or an ion implantation. Accordingly, the metal capacitor will have a higher capacitance and RC delay between the metal interconnection and the dielectric layer can be prevented.

Owner:MARLIN SEMICON LTD

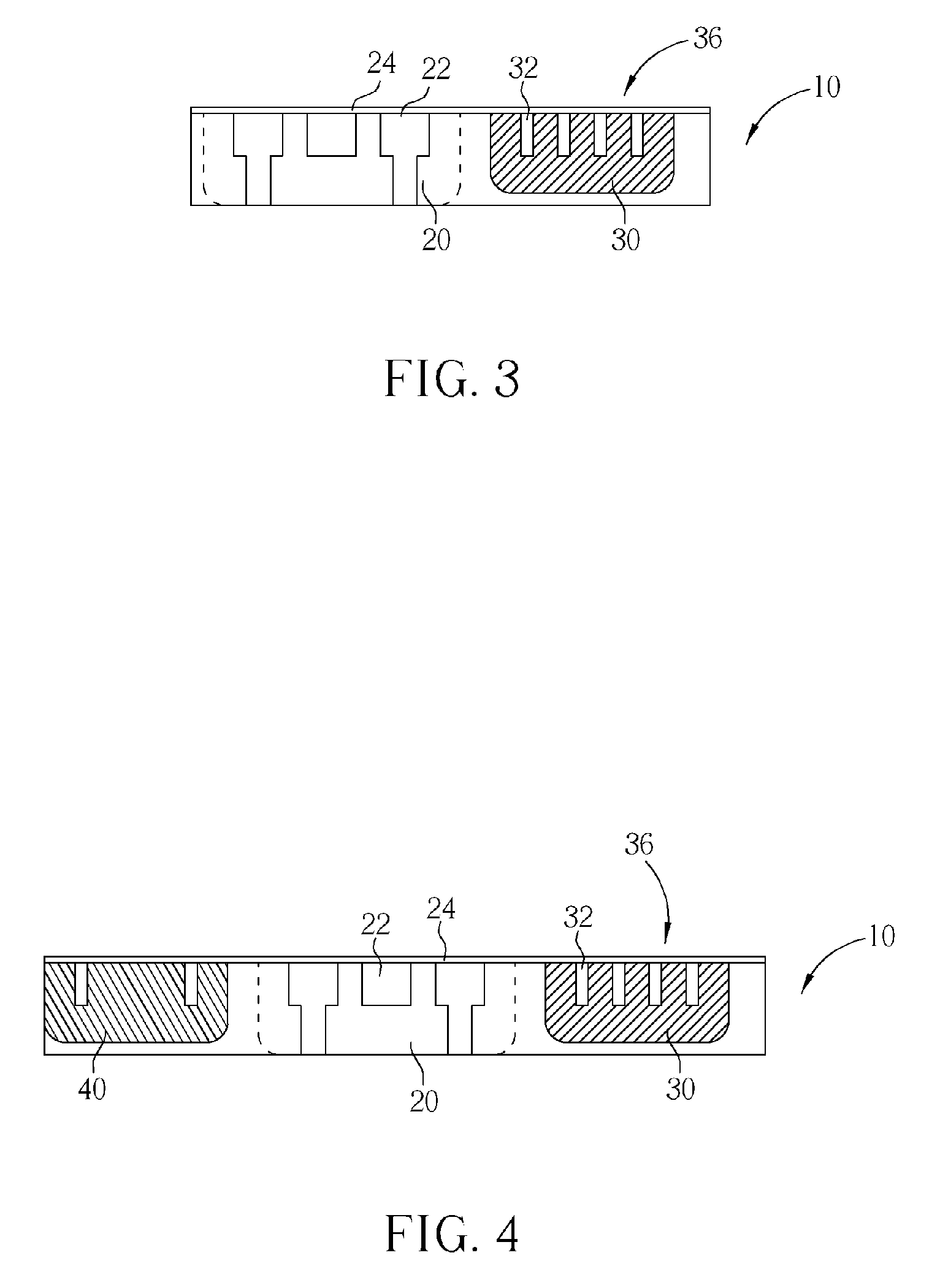

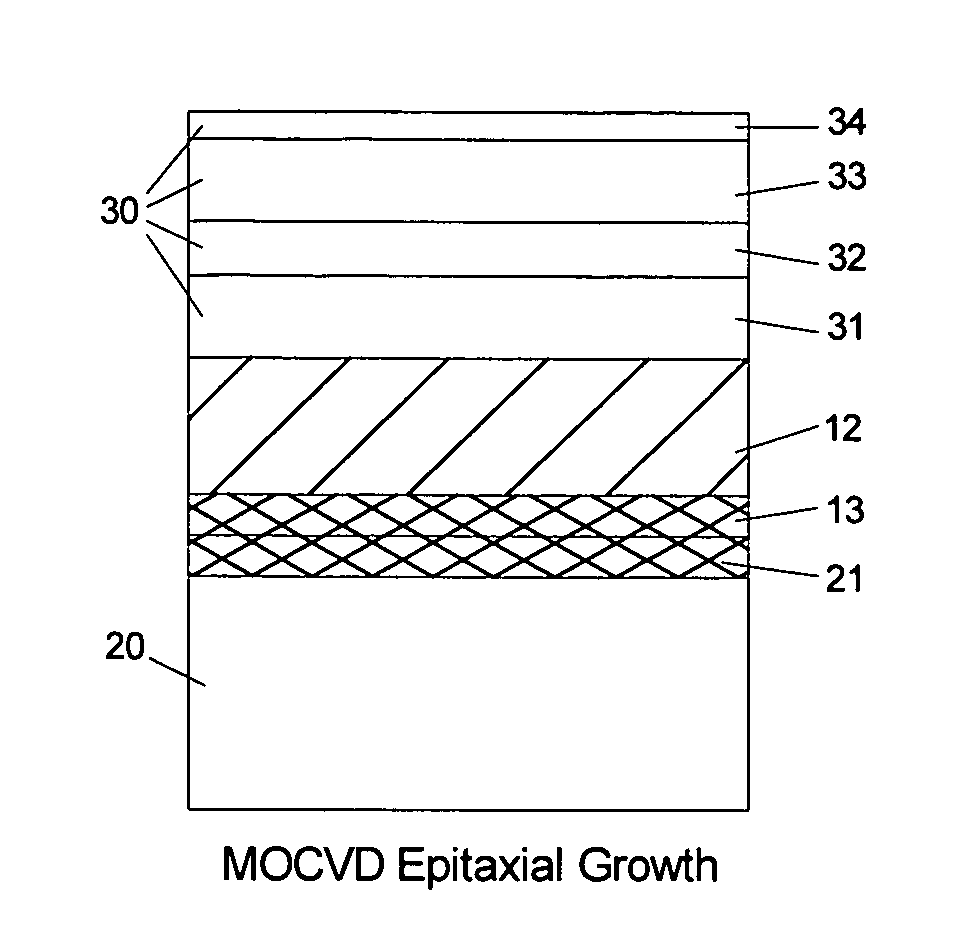

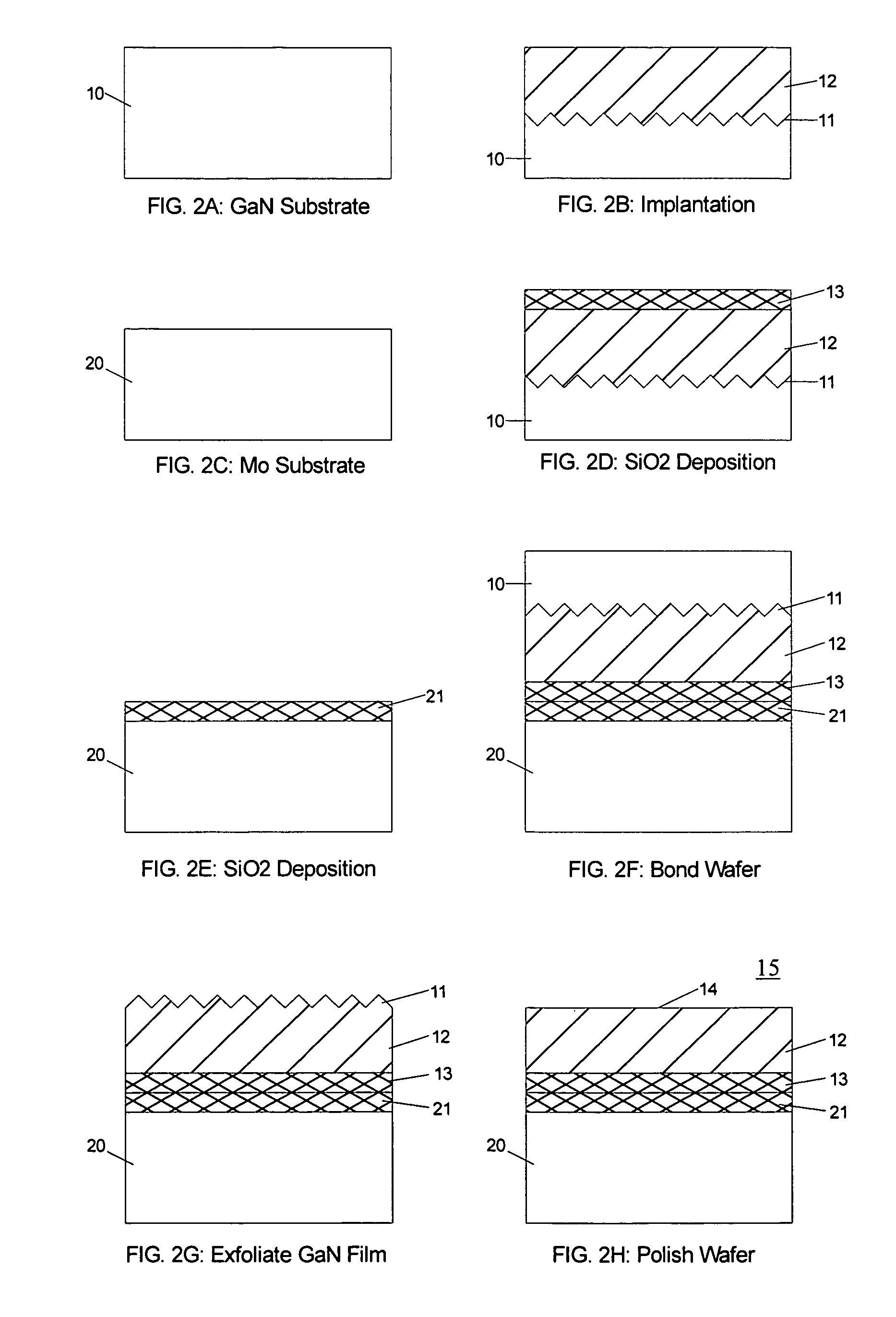

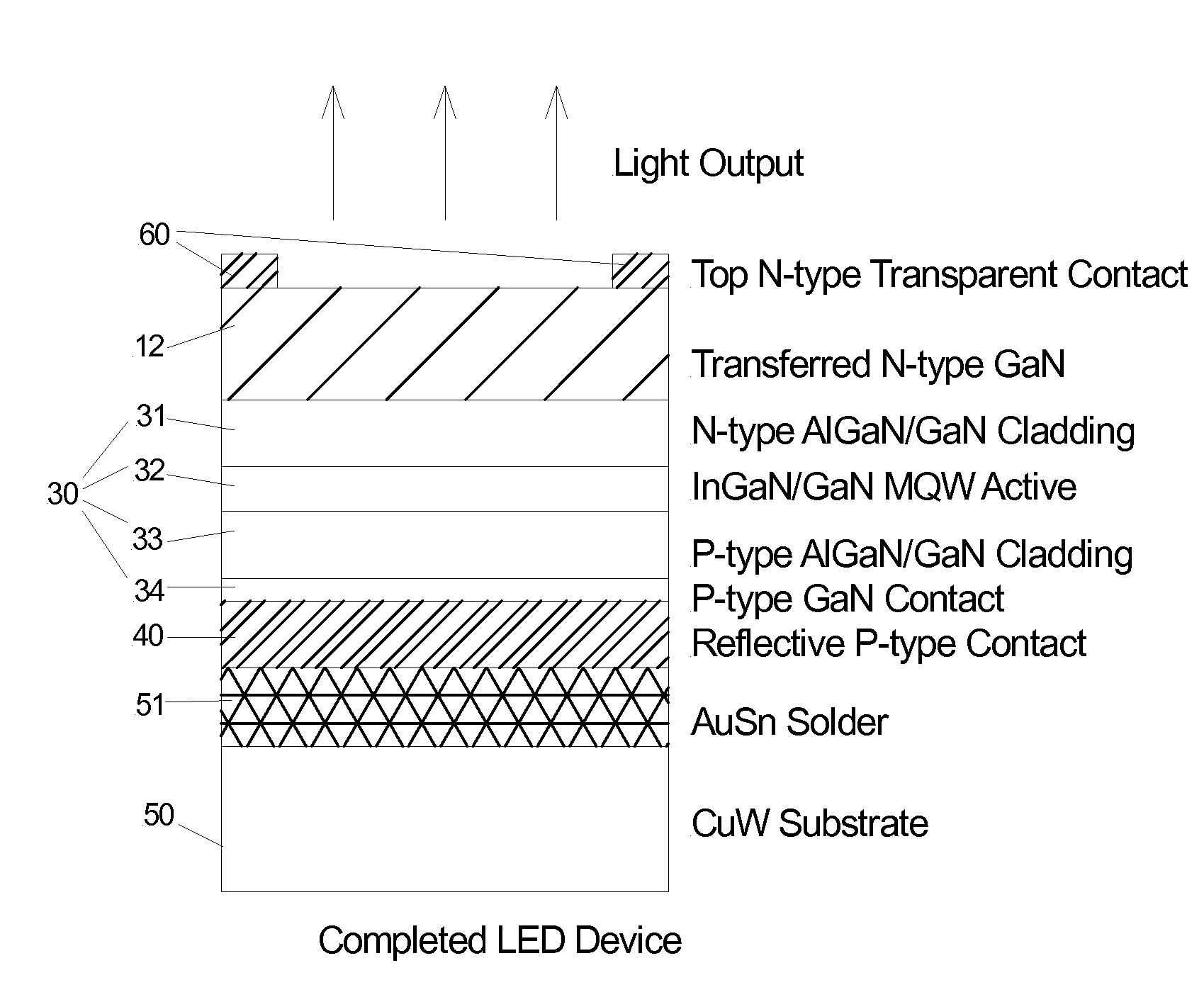

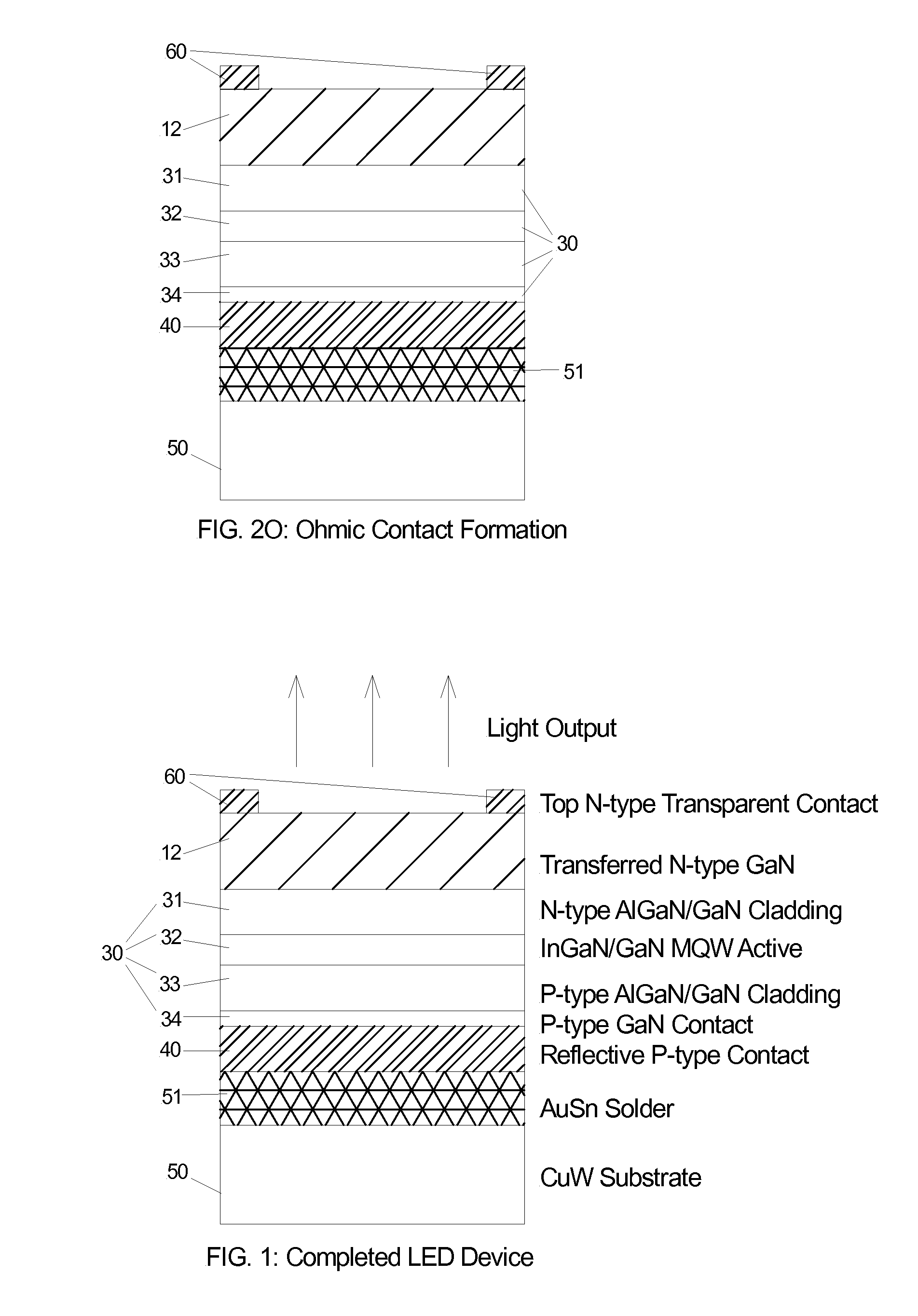

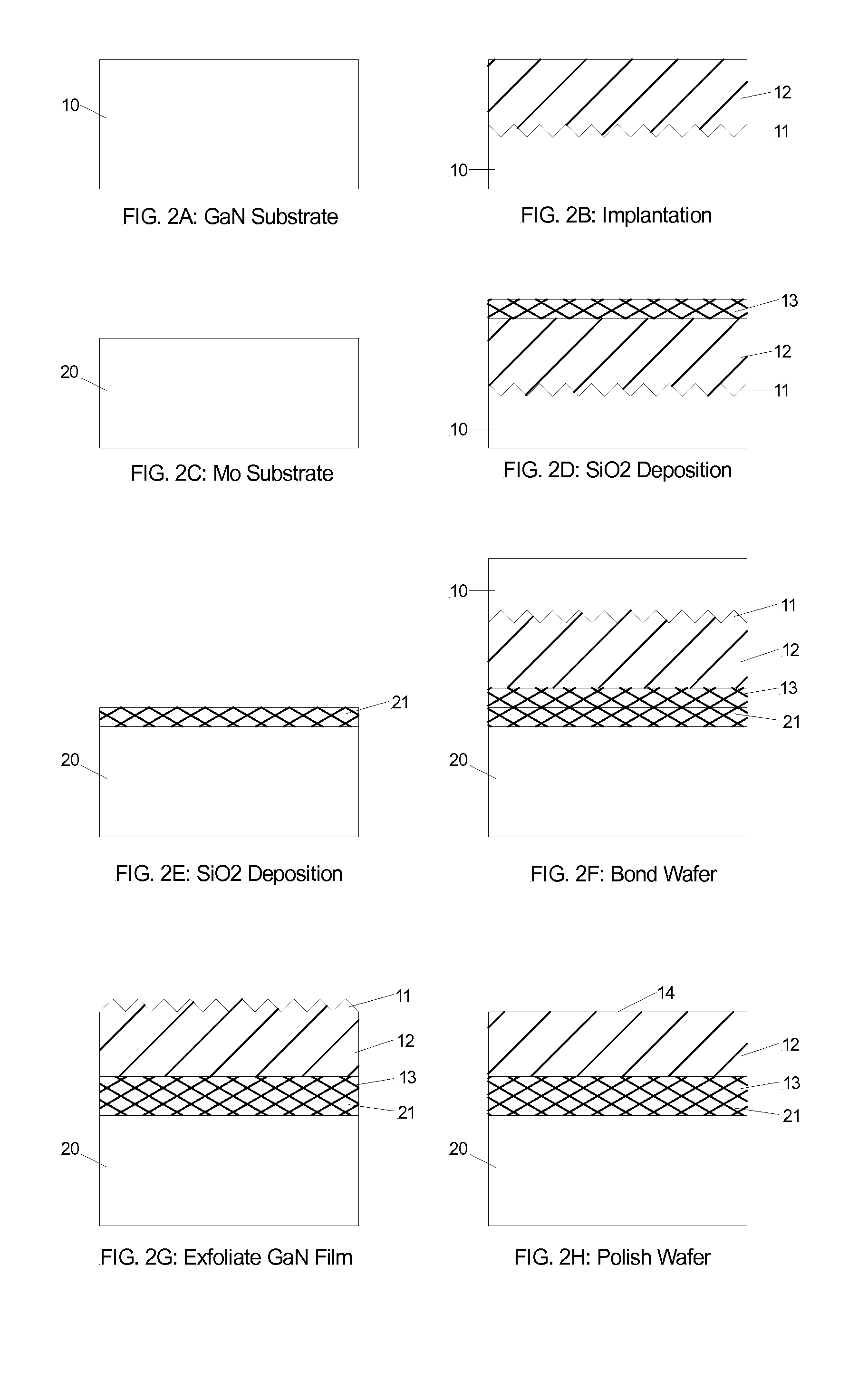

Bonded intermediate substrate and method of making same

ActiveUS7732301B1Solid-state devicesSemiconductor/solid-state device manufacturingNitrogenSingle crystal

A method of making a bonded intermediate substrate includes forming a weak interface in a GaN source substrate by implanting ions into an N-terminated surface of the GaN source substrate, bonding the N-terminated surface of the GaN source substrate to a handle substrate, and exfoliating a thin GaN single crystal layer from the source substrate such that the thin GaN exfoliated single crystal layer remains bonded to the handle substrate and a Ga-terminated surface of the thin GaN single crystal layer is exposed. The method further includes depositing a capping layer directly onto the exposed surface of the thin GaN single crystal layer, and annealing the thin GaN single crystal layer in a nitrogen containing atmosphere after depositing the capping layer. The in-plane strain present in the thin GaN single crystal layer after the annealing is reduced relative to an in-plane strain present in said layer prior to the annealing.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

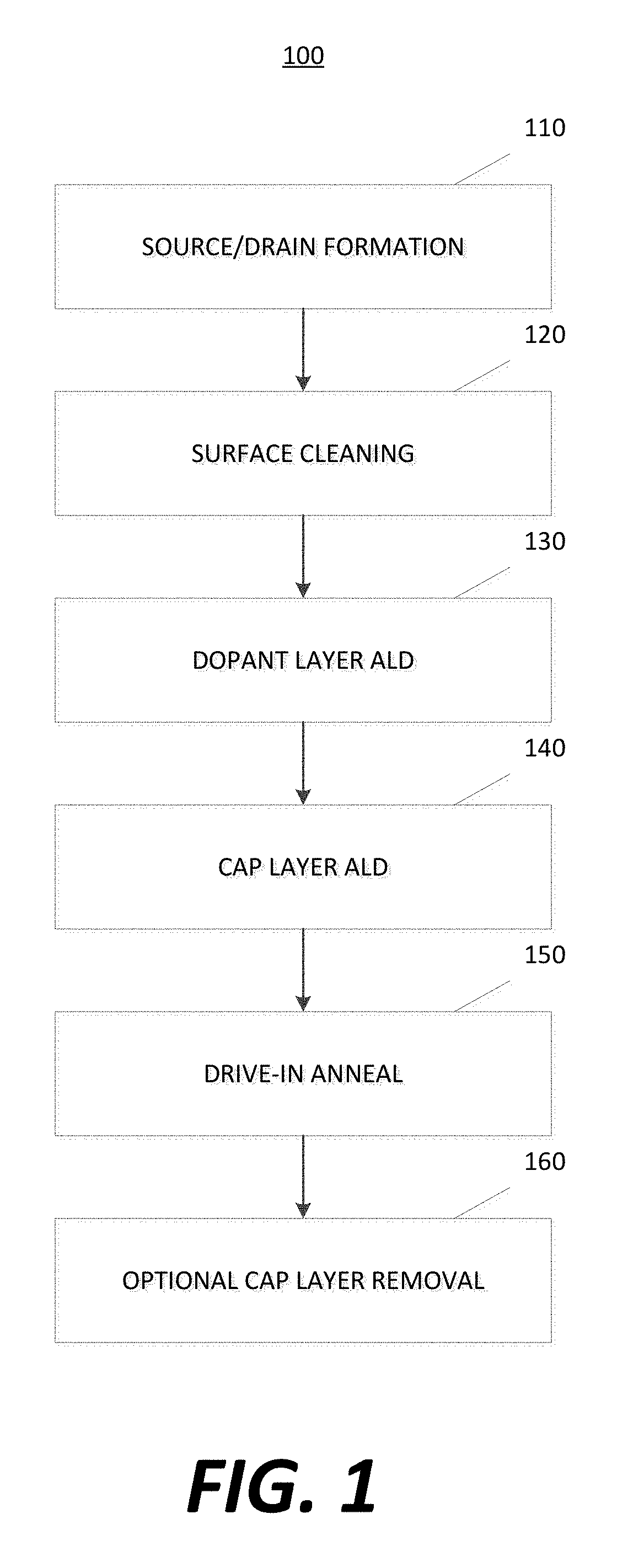

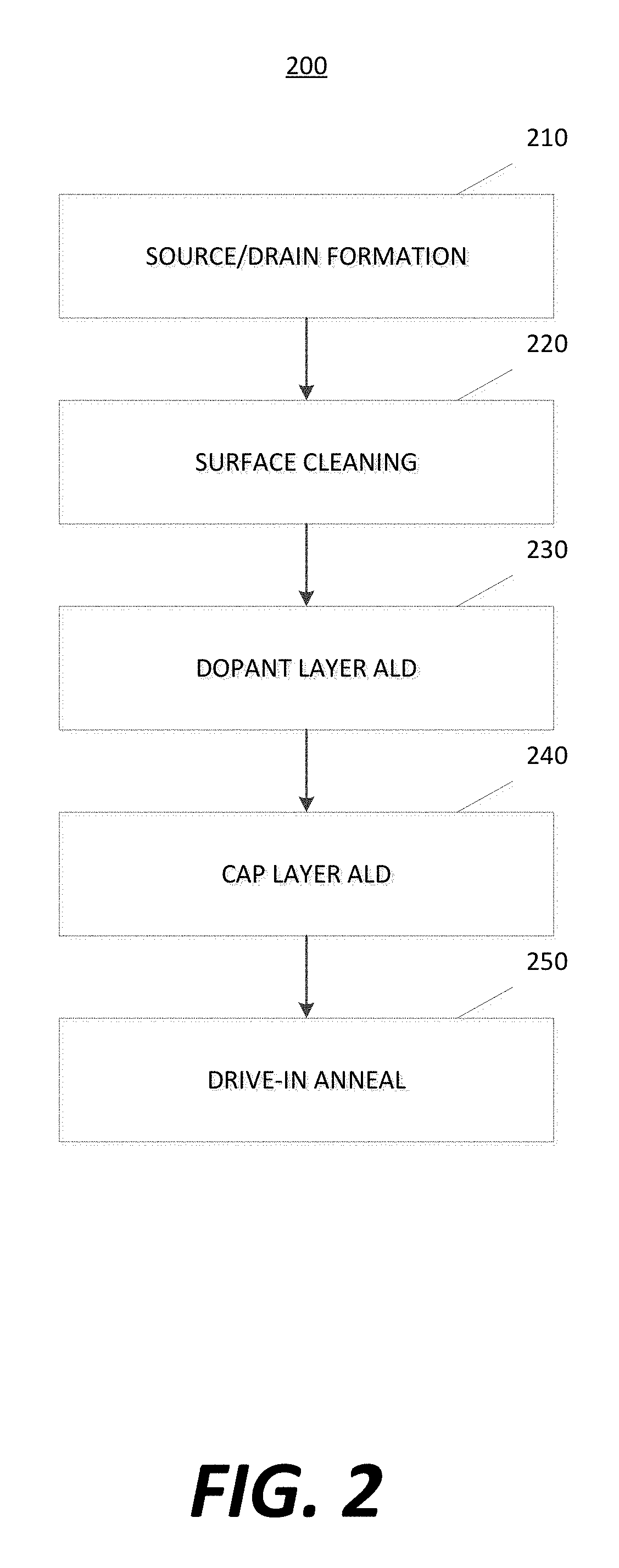

Source/drain performance through conformal solid state doping

ActiveUS10032628B2TransistorSemiconductor/solid-state device manufacturingAtomic layer depositionIon implantation

Owner:ASM IP HLDG BV

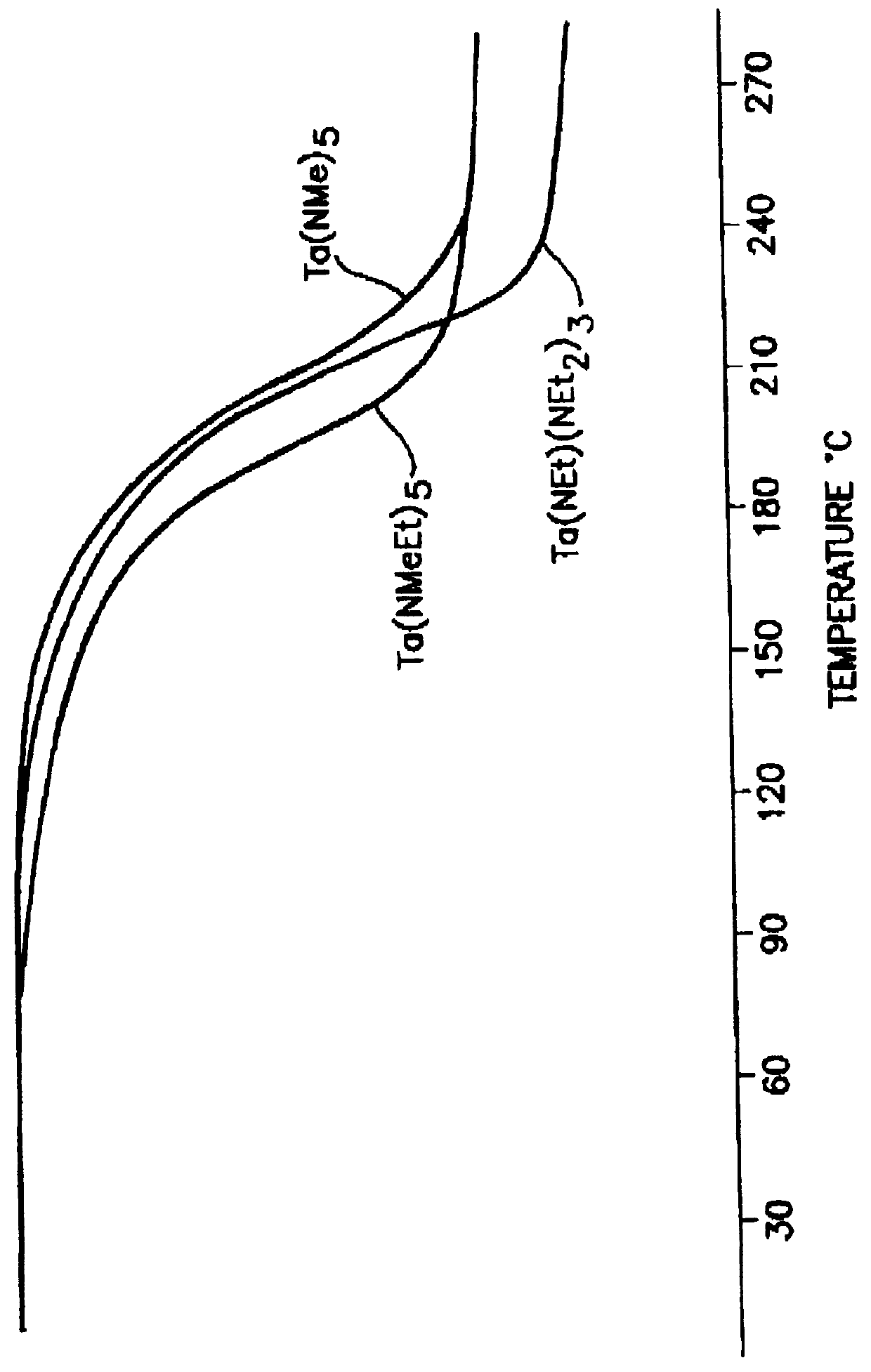

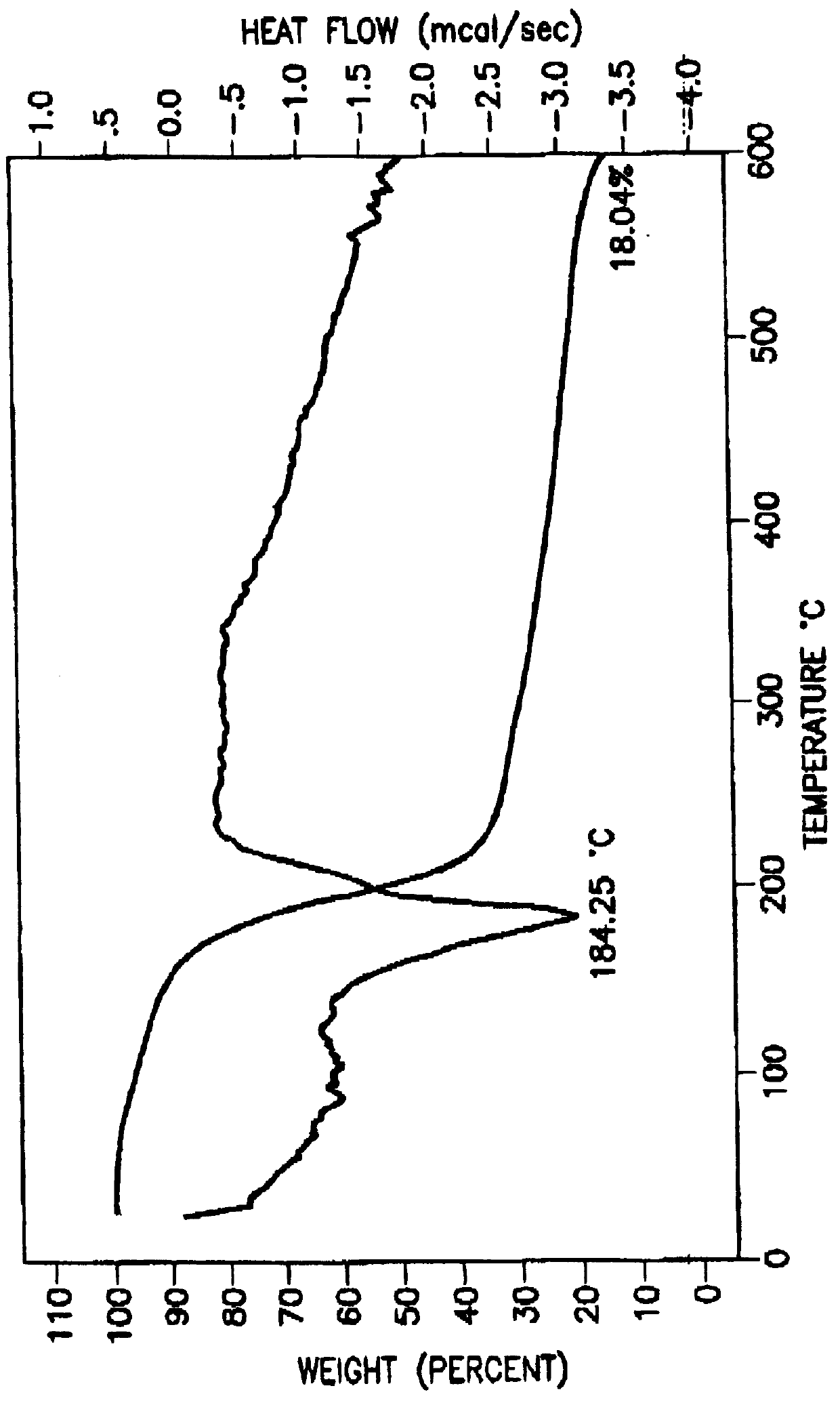

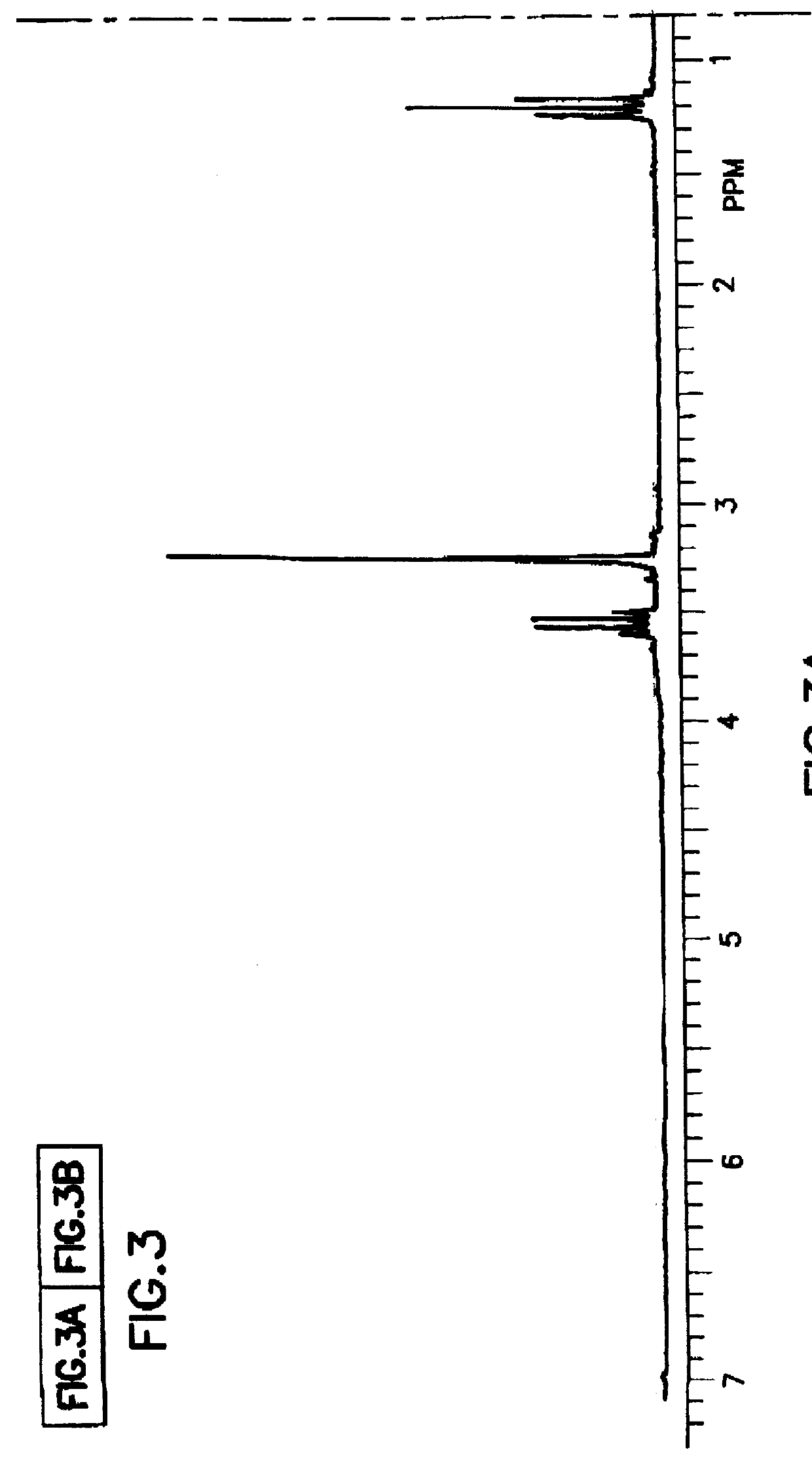

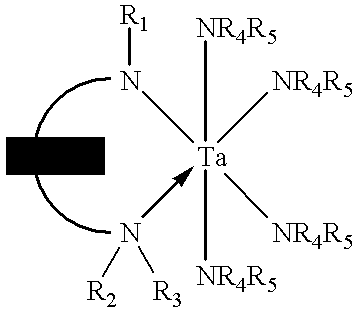

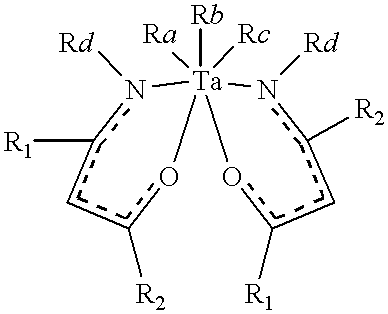

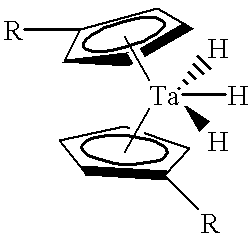

Tantalum amide precursors for deposition of tantalum nitride on a substrate

InactiveUS6015917ARapid heat treatmentSilicon organic compoundsPolycrystalline material growthFerroelectric thin filmsChemical vapor deposition

Tantalum and titanium source reagents are described, including tantalum amide and tantalum silicon nitride precursors for the deposition of tantalum nitride material on a substrate by processes such as chemical vapor deposition, assisted chemical vapor deposition, ion implantation, molecular beam epitaxy and rapid thermal processing. The precursors may be employed to form diffusion barrier layers on microlectronic device structures enabling the use of copper metallization and ferroelectric thin films in device construction.

Owner:ENTEGRIS INC

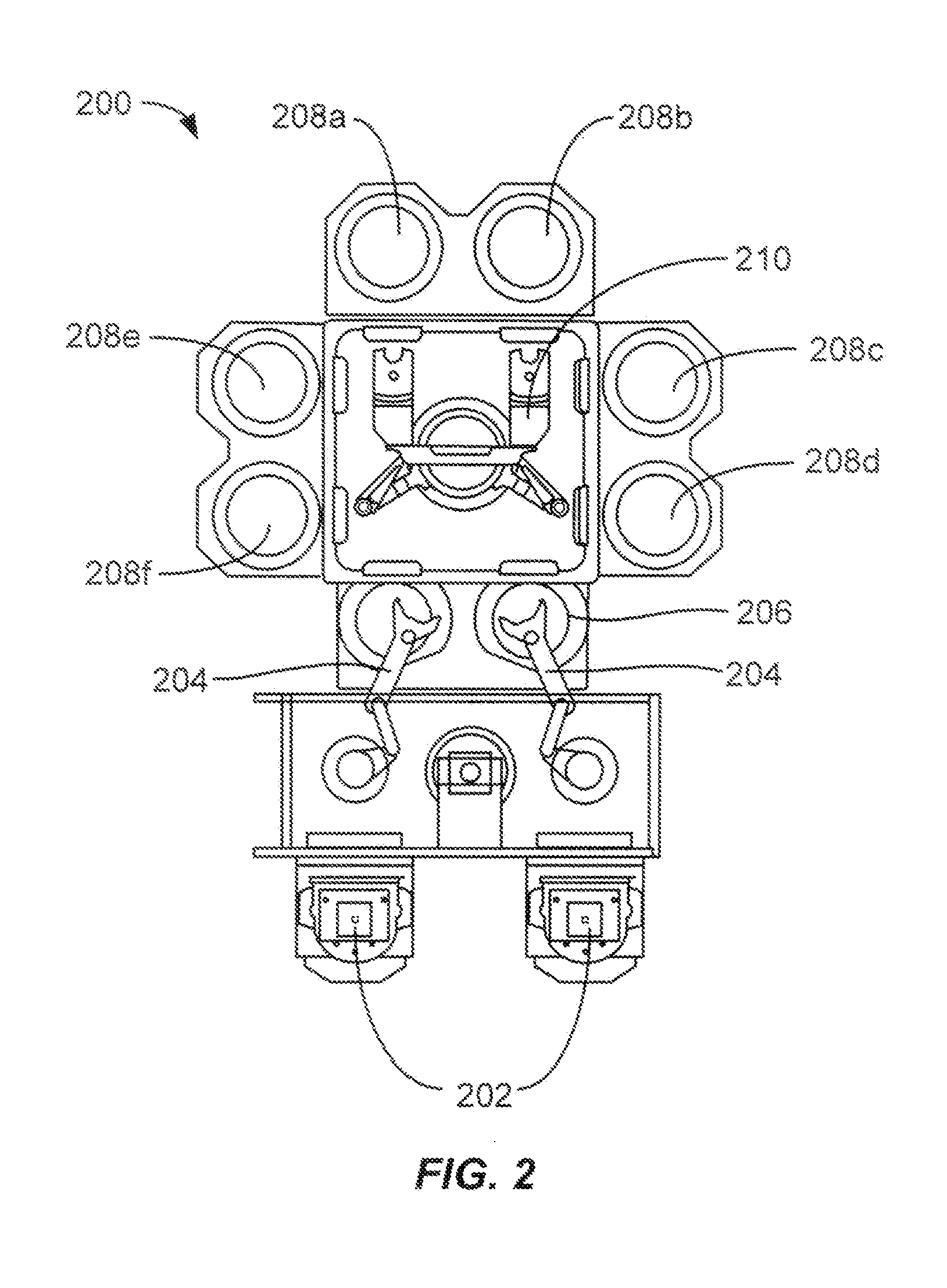

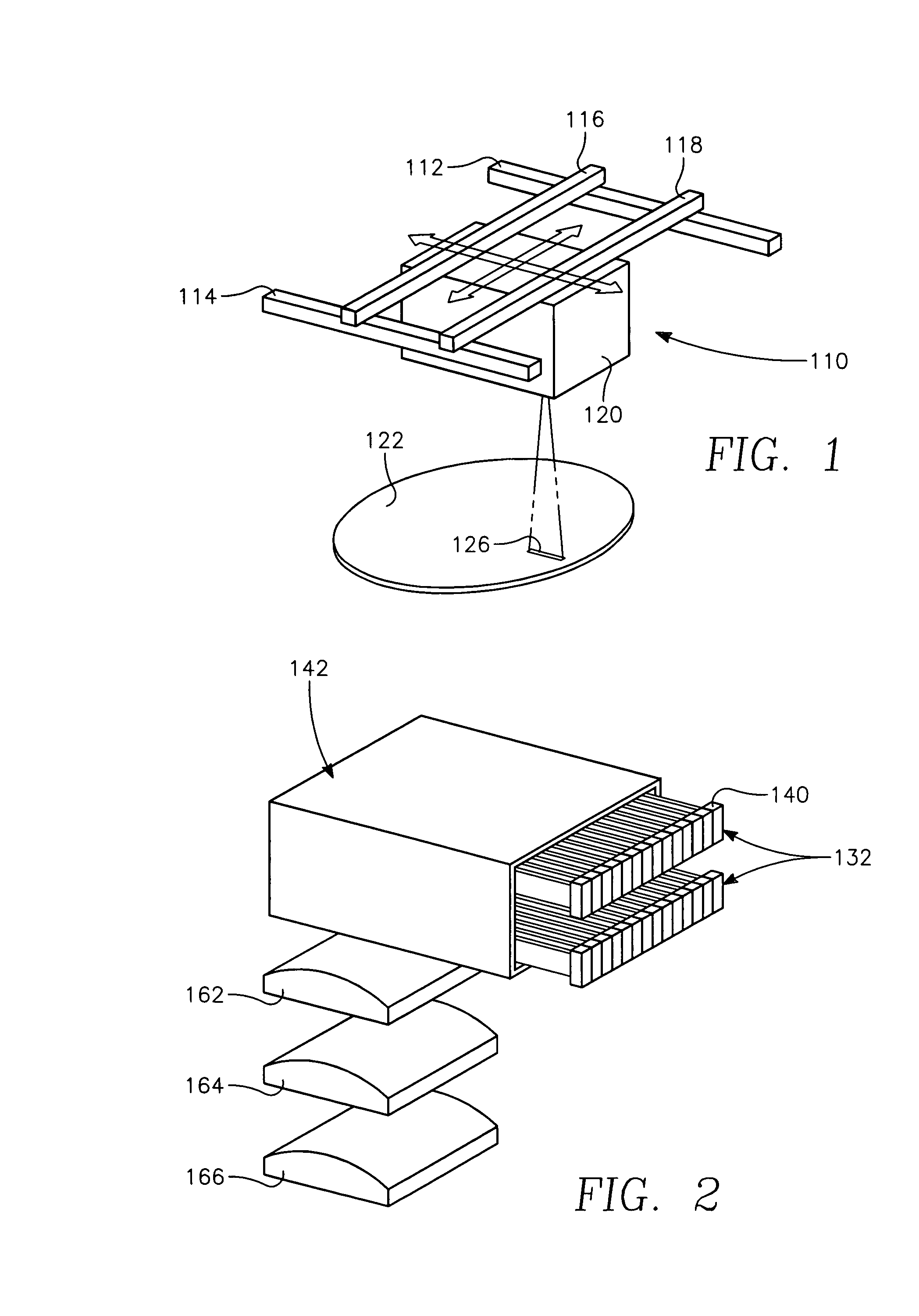

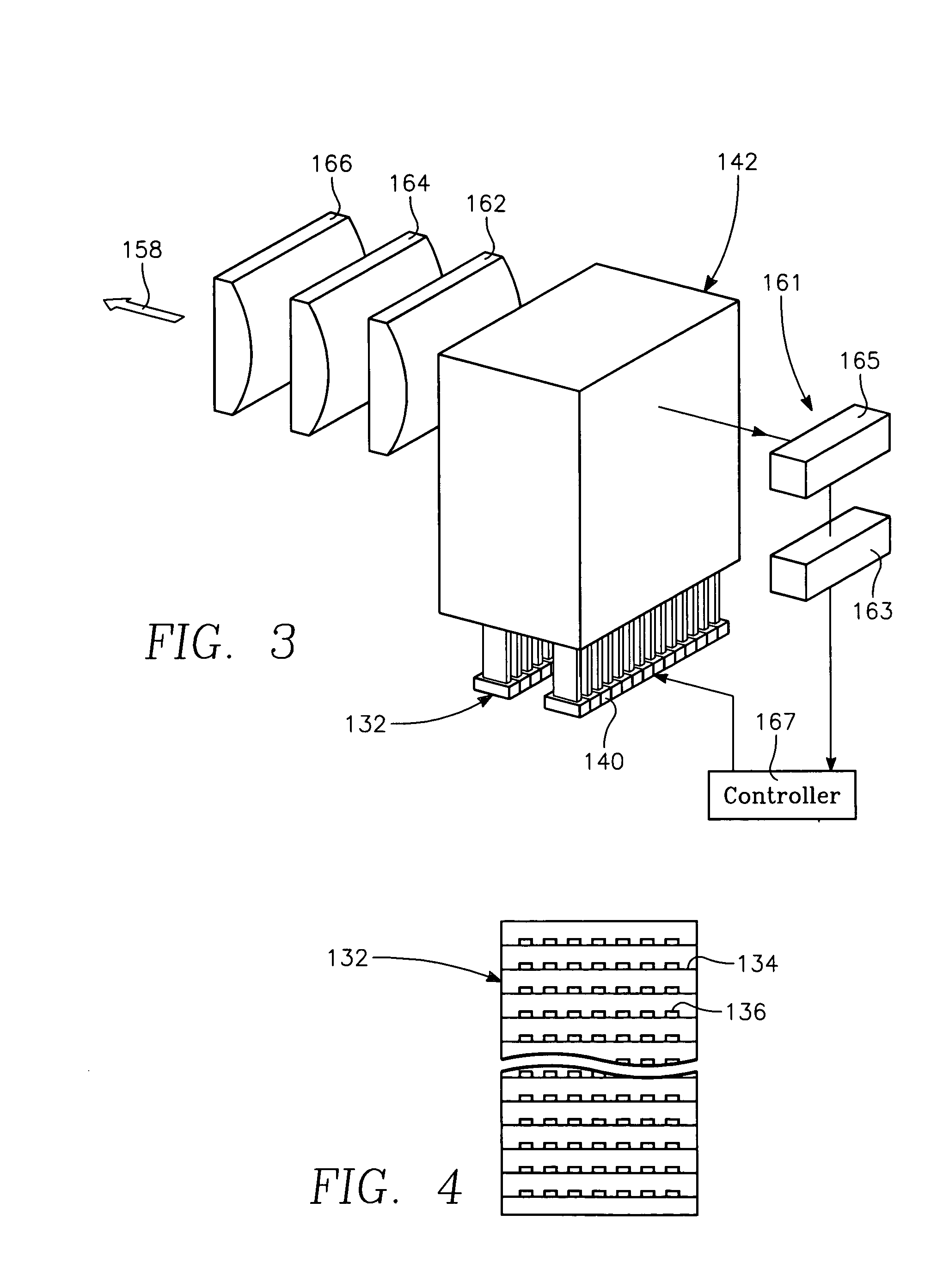

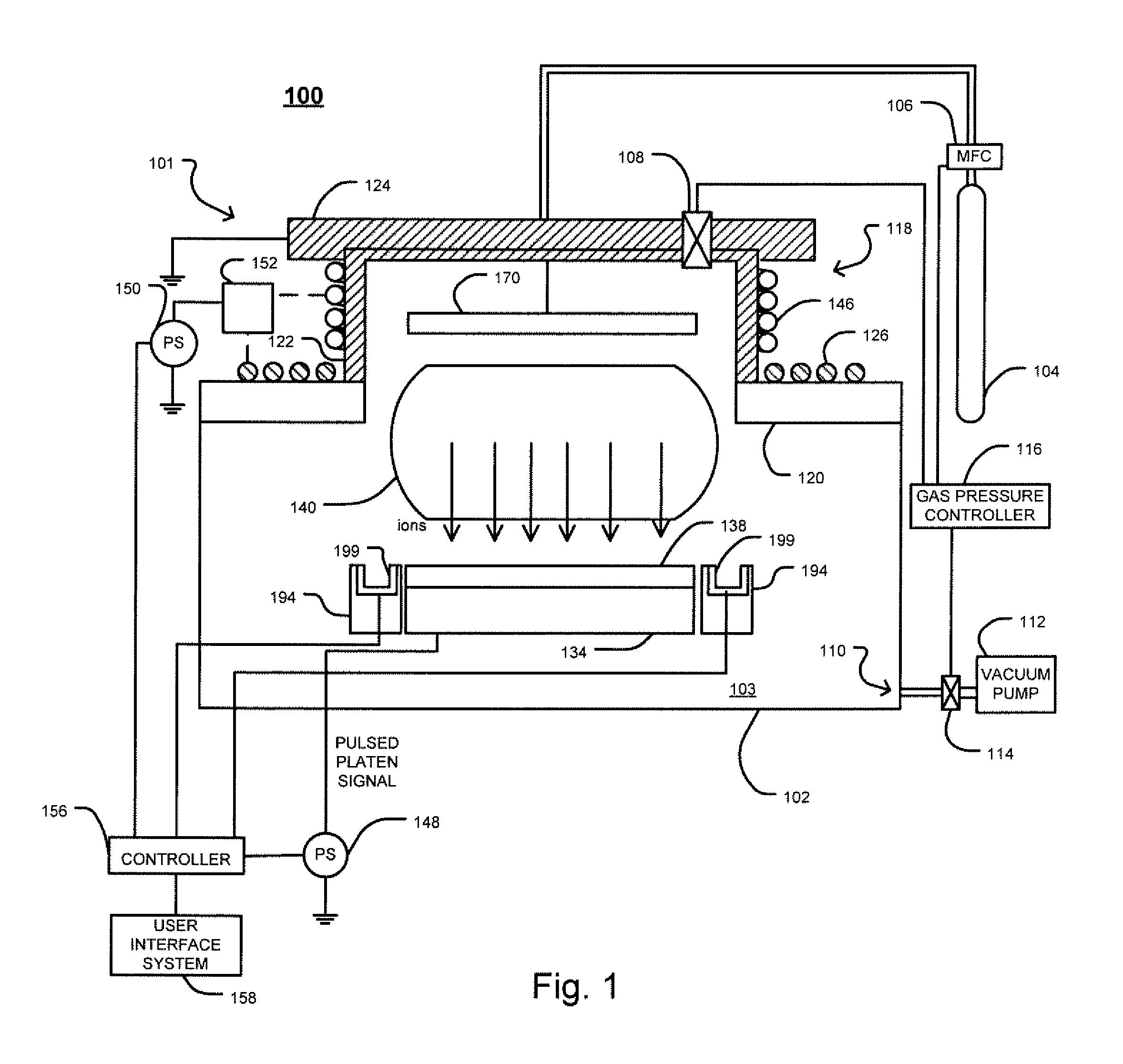

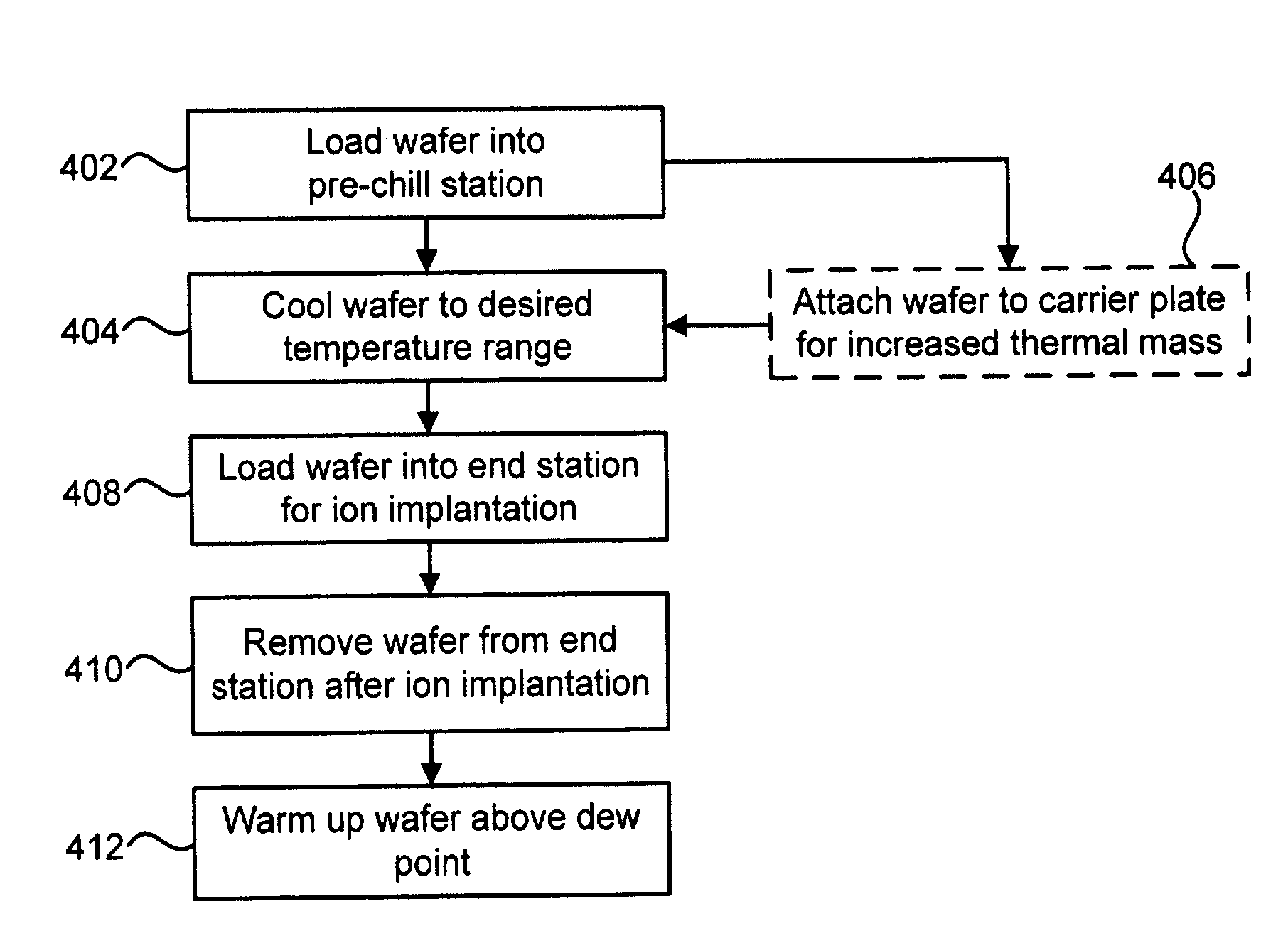

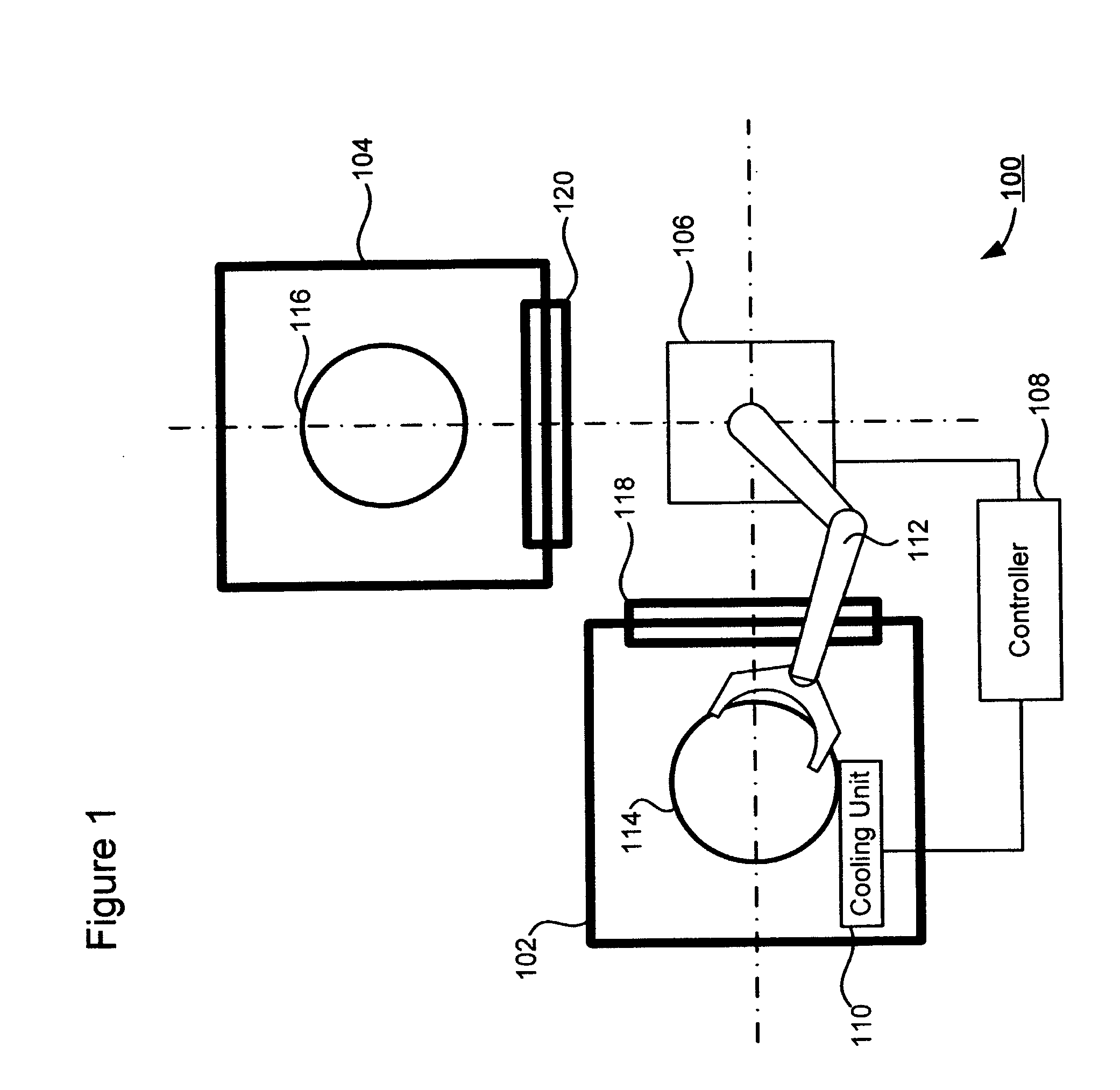

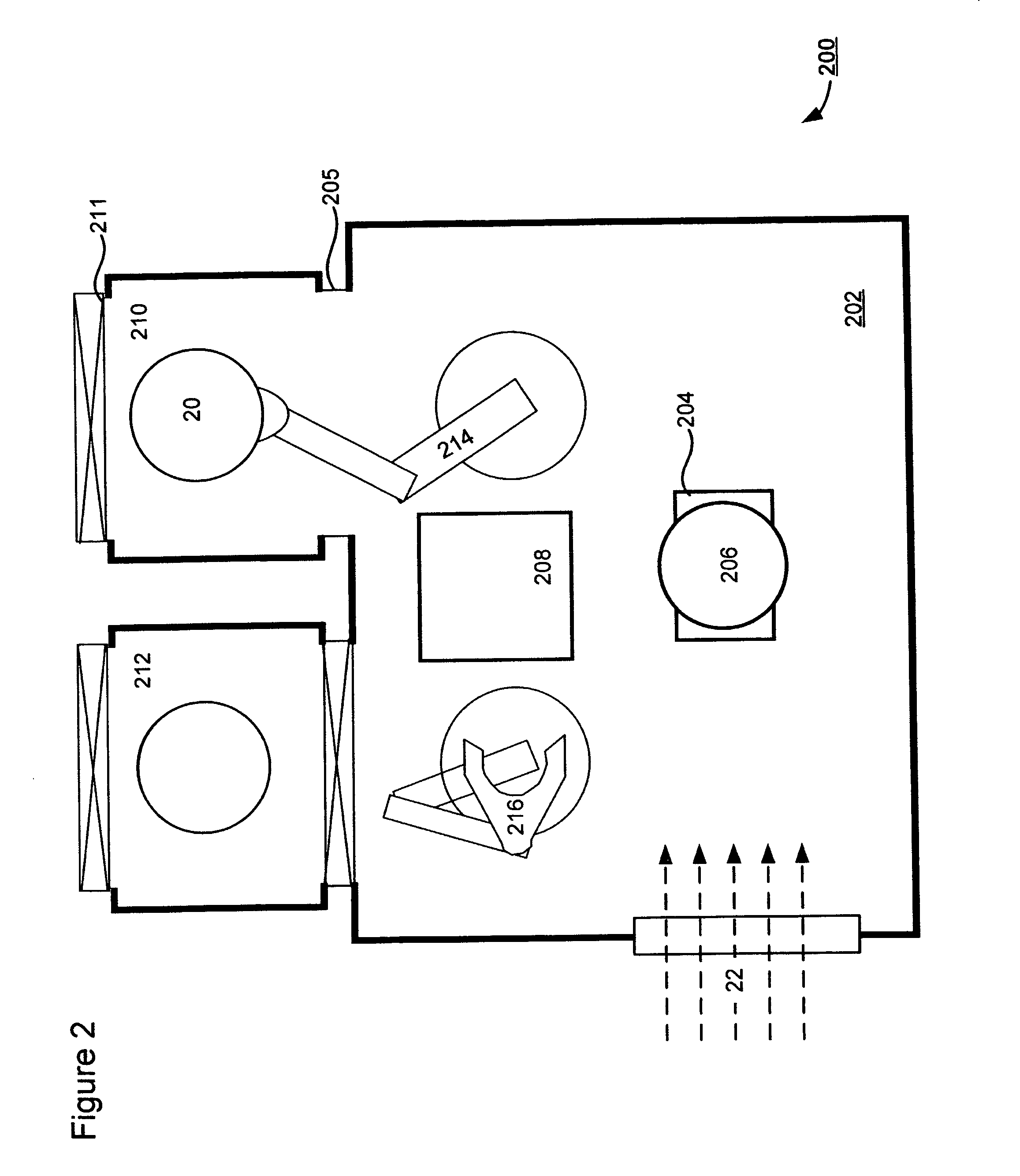

Technique for low-temperature ion implantation

ActiveUS20080044938A1Avoid overall overheatingFacilitate tilting and rotationMaterial analysis using wave/particle radiationElectric discharge tubesEngineeringIon implantation

A technique for low-temperature ion implantation is disclosed. In one particular exemplary embodiment, the technique may be realized as an apparatus for low-temperature ion implantation. The apparatus may comprise a pre-chill station located in proximity to an end station in an ion implanter. The apparatus may also comprise a cooling mechanism within the pre-chill station. The apparatus may further comprise a loading assembly coupled to the pre-chill station and the end station. The apparatus may additionally comprise a controller in communication with the loading assembly and the cooling mechanism to coordinate loading a wafer into the pre-chill station, cooling the wafer down to a predetermined temperature range, and loading the cooled wafer into the end station where the cooled wafer undergoes an ion implantation process.

Owner:VARIAN SEMICON EQUIP ASSOC INC

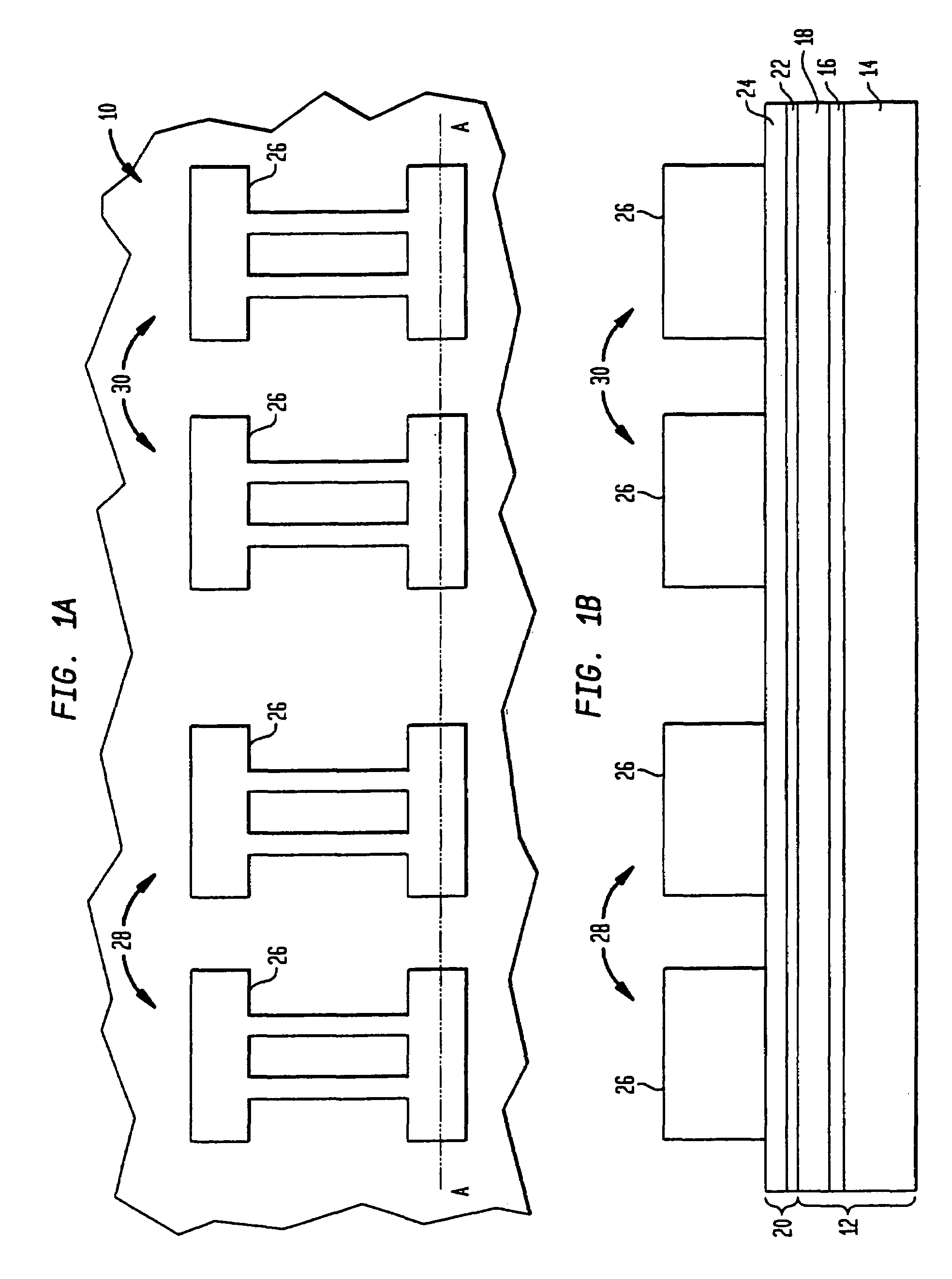

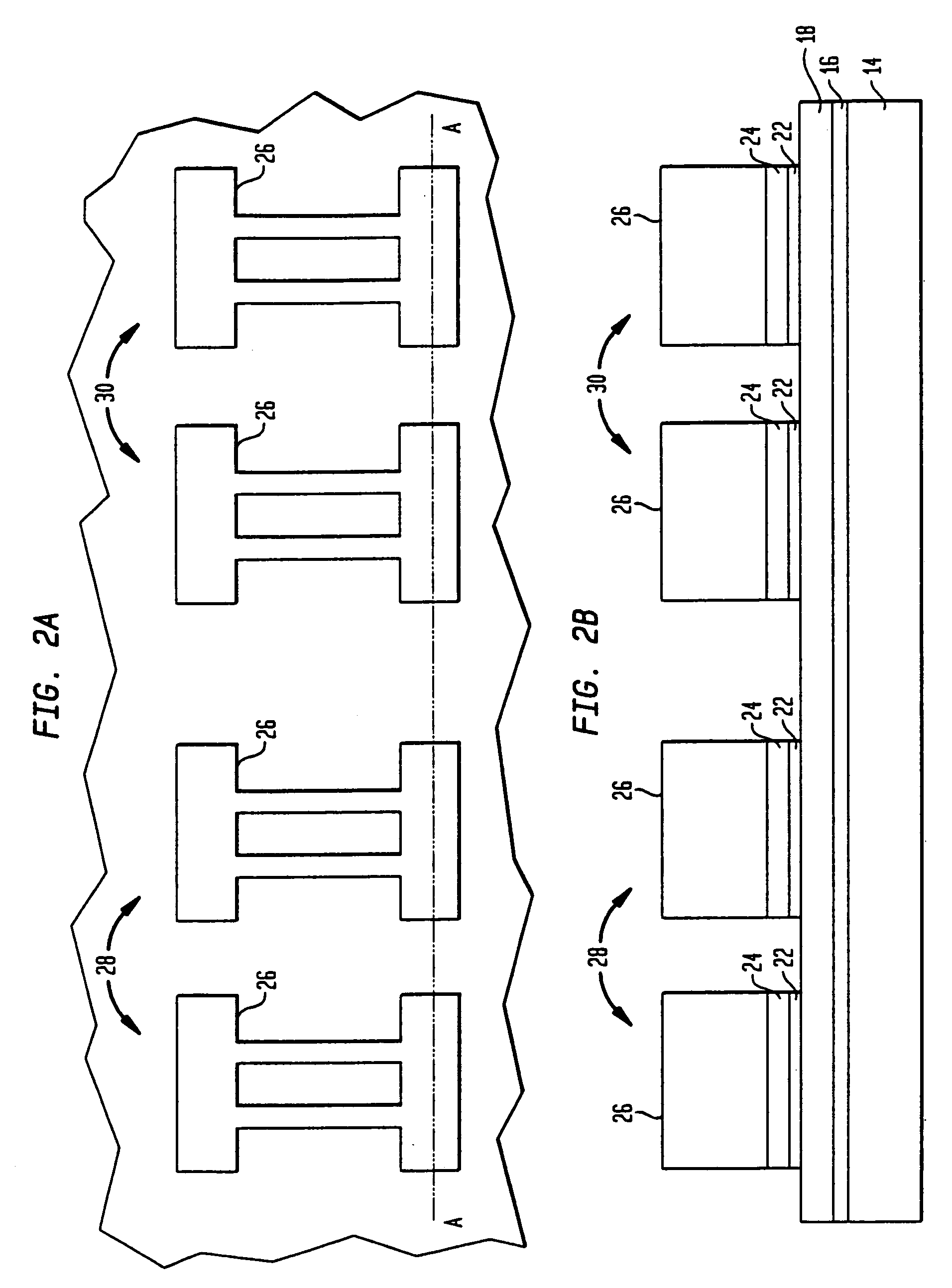

Method of manufacturing a split-gate flash memory device

ActiveUS20060154424A1Improve reliabilityHigh yieldSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringDielectric layer

A method of manufacturing a split-gate flash memory device is disclosed. On a semiconductor substrate having a plurality of parallel conductive lines, a plurality of doped regions are formed by an ion implantation using the conductive lines as mask. Then, the conductive lines are trimmed for thinning the cover area. Afterward, a composite dielectric layer is formed on the substrate and covers the conductive lines. Finally, a plurality of word lines are formed on the composite dielectric layer.

Owner:UNITED MICROELECTRONICS CORP

Bonded intermediate substrate and method of making same

InactiveUS20090278233A1Quality improvementSolid-state devicesSemiconductor/solid-state device manufacturingNitrideIon implantation

A method includes growing a first epitaxial layer of III-nitride material, forming a damaged region by implanting ions into an exposed surface of the first epitaxial layer, and growing a second epitaxial layer of III-nitride material on the exposed surface of the first epitaxial layer. A level of defects present in the second epitaxial layer is less than a level of defects present in the first epitaxial layer.

Owner:AMBERWAVE SYST

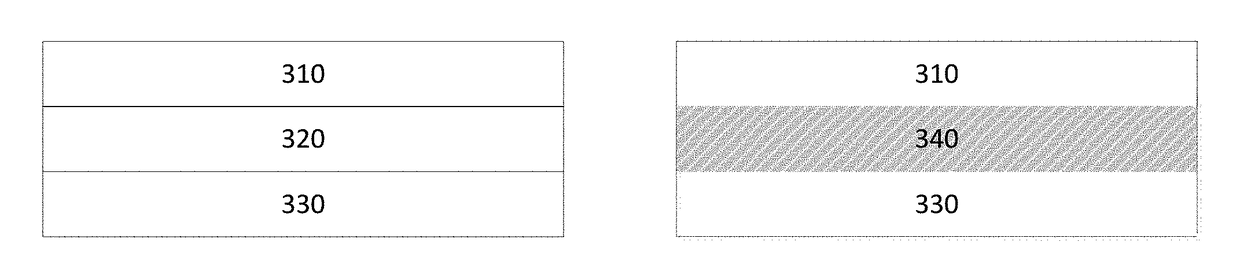

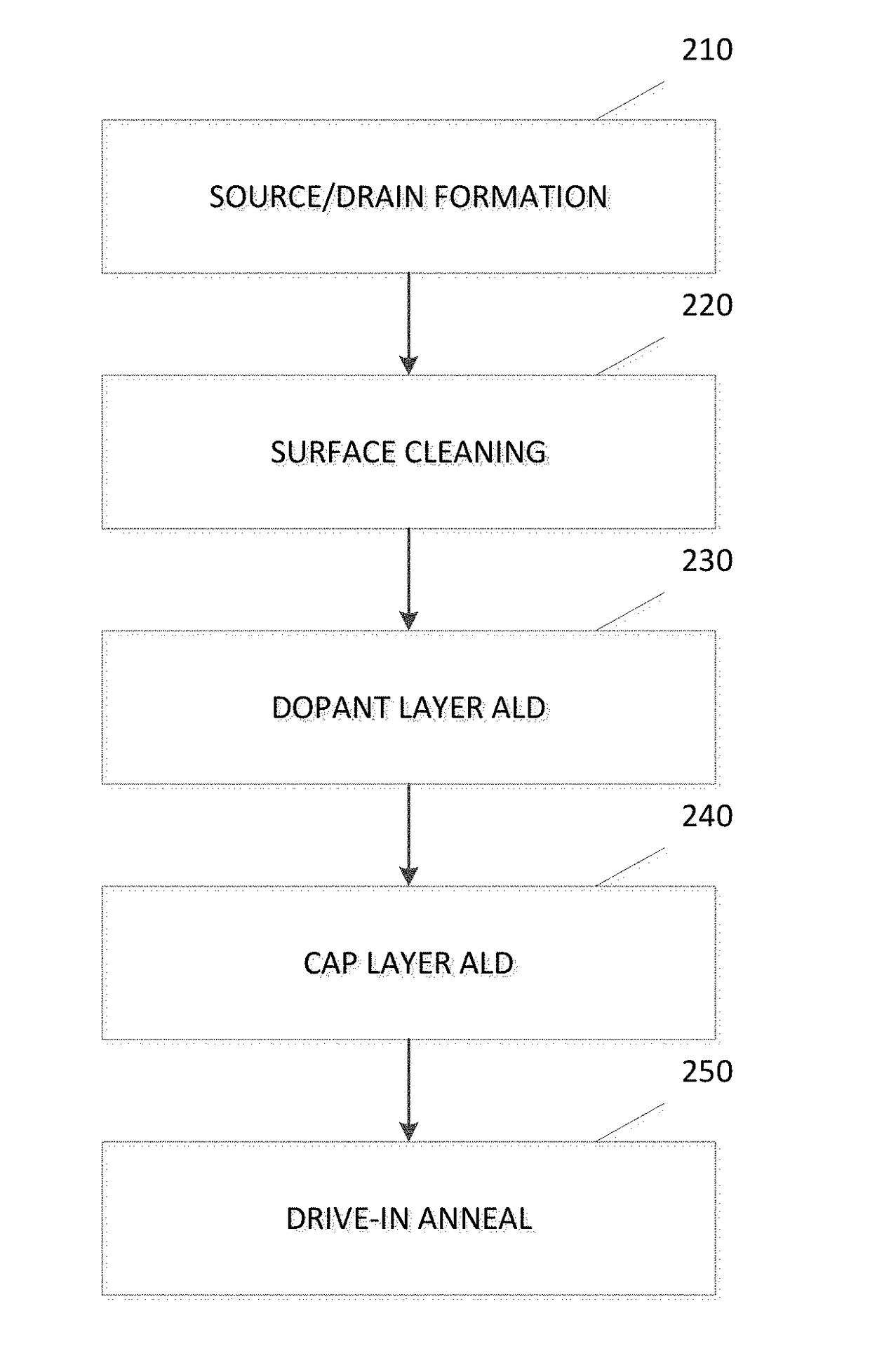

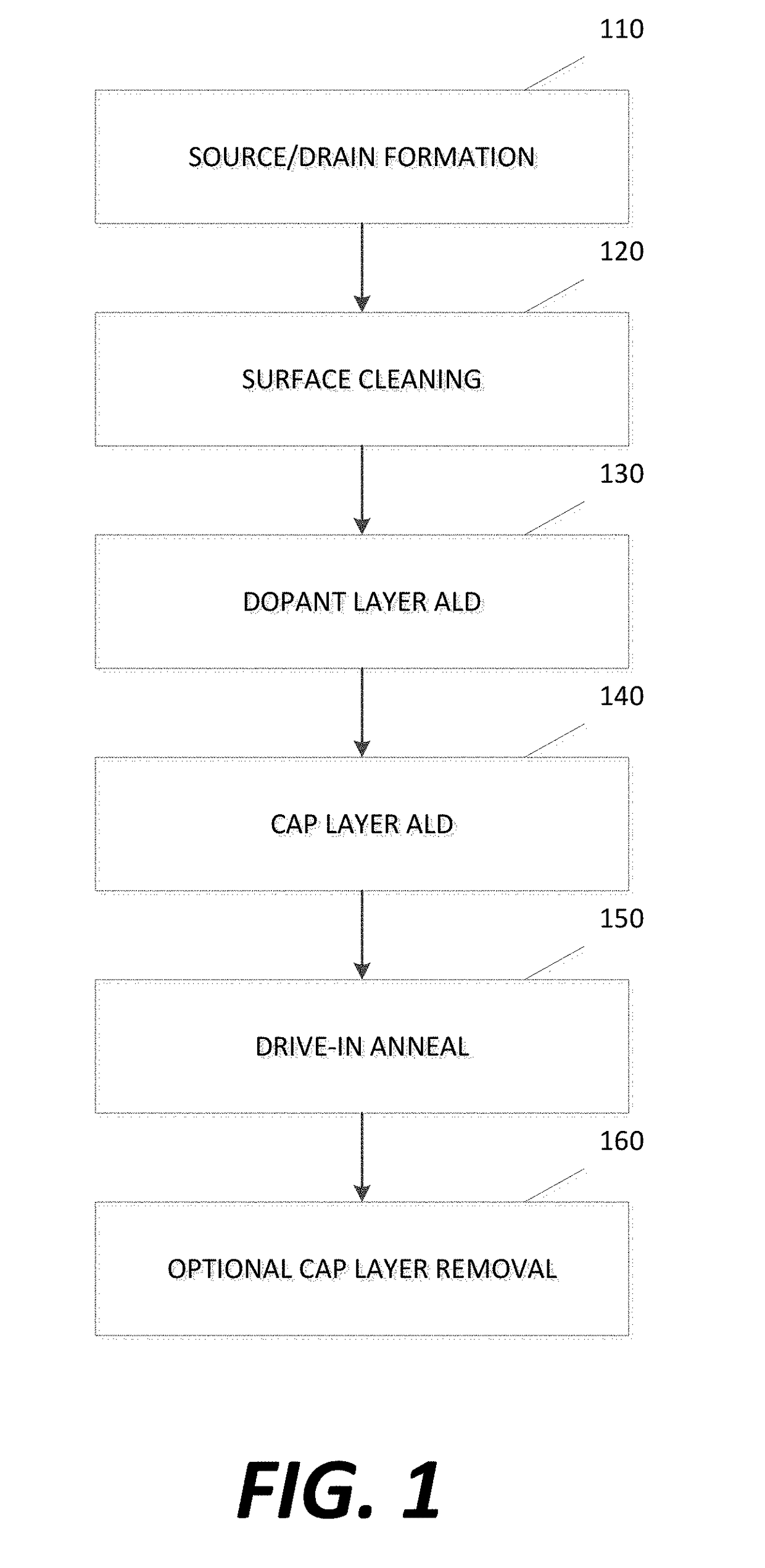

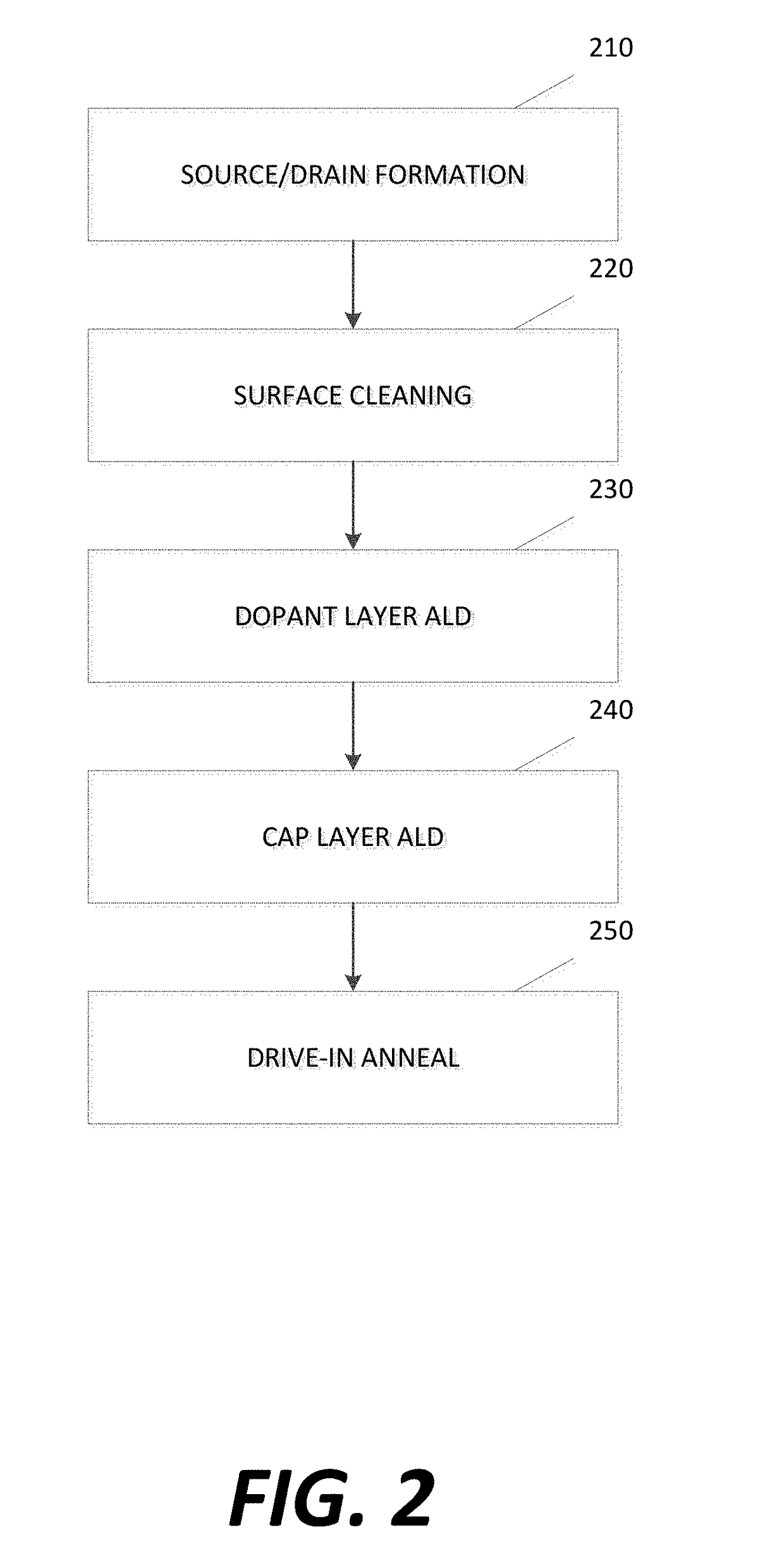

Source/drain performance through conformal solid state doping

ActiveUS20170316933A1TransistorSemiconductor/solid-state device manufacturingAtomic layer depositionIon implantation

A method for improving source / drain performance through conformal solid state doping and its resulting device are disclosed. Specifically, the doping takes place through an atomic layer deposition of a dopant layer. Embodiments of the invention may allow for an increased doping layer, improved conformality, and reduced defect formation, in comparison to alternate doping methods, such as ion implantation or epitaxial doping.

Owner:ASM IP HLDG BV

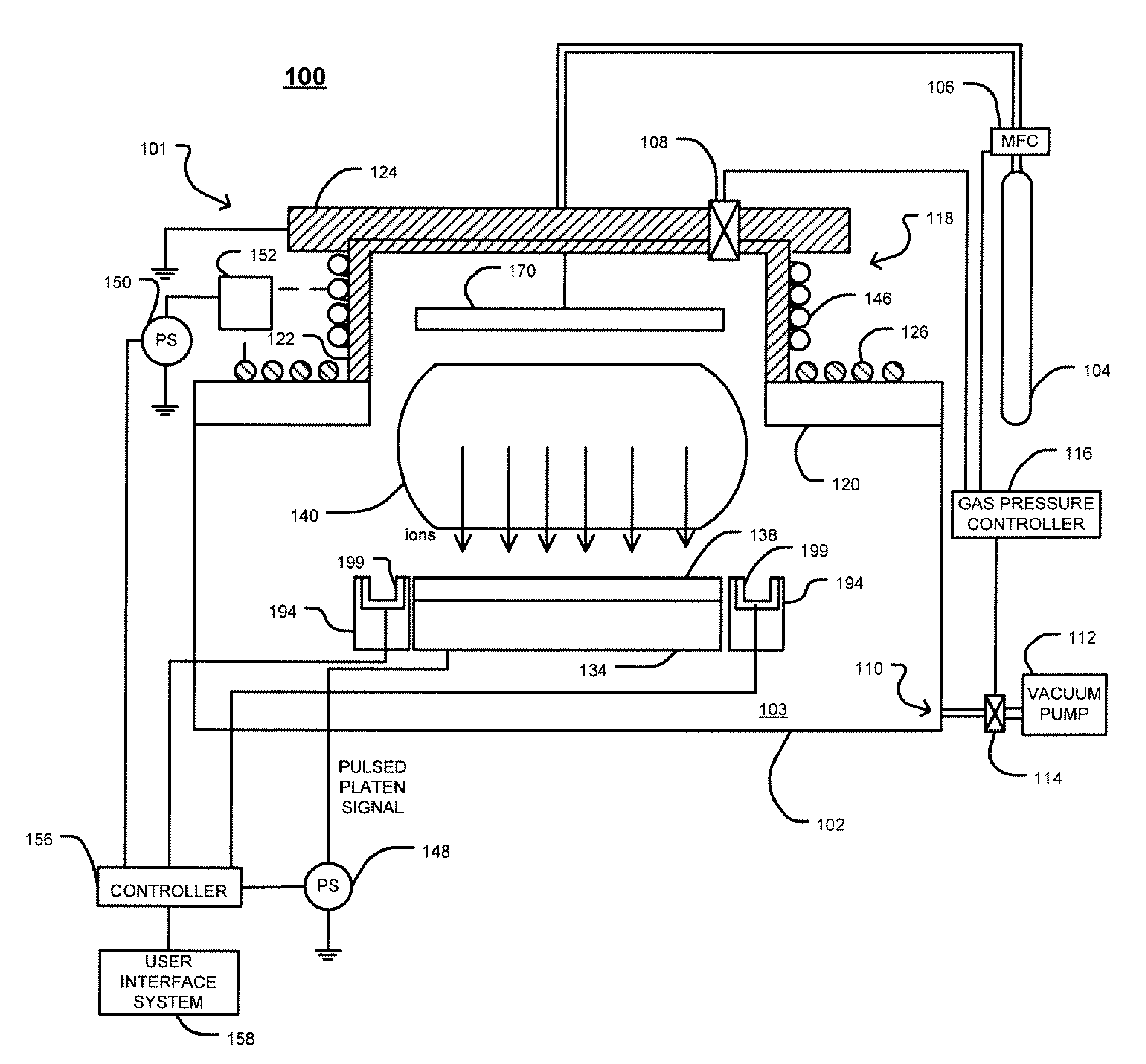

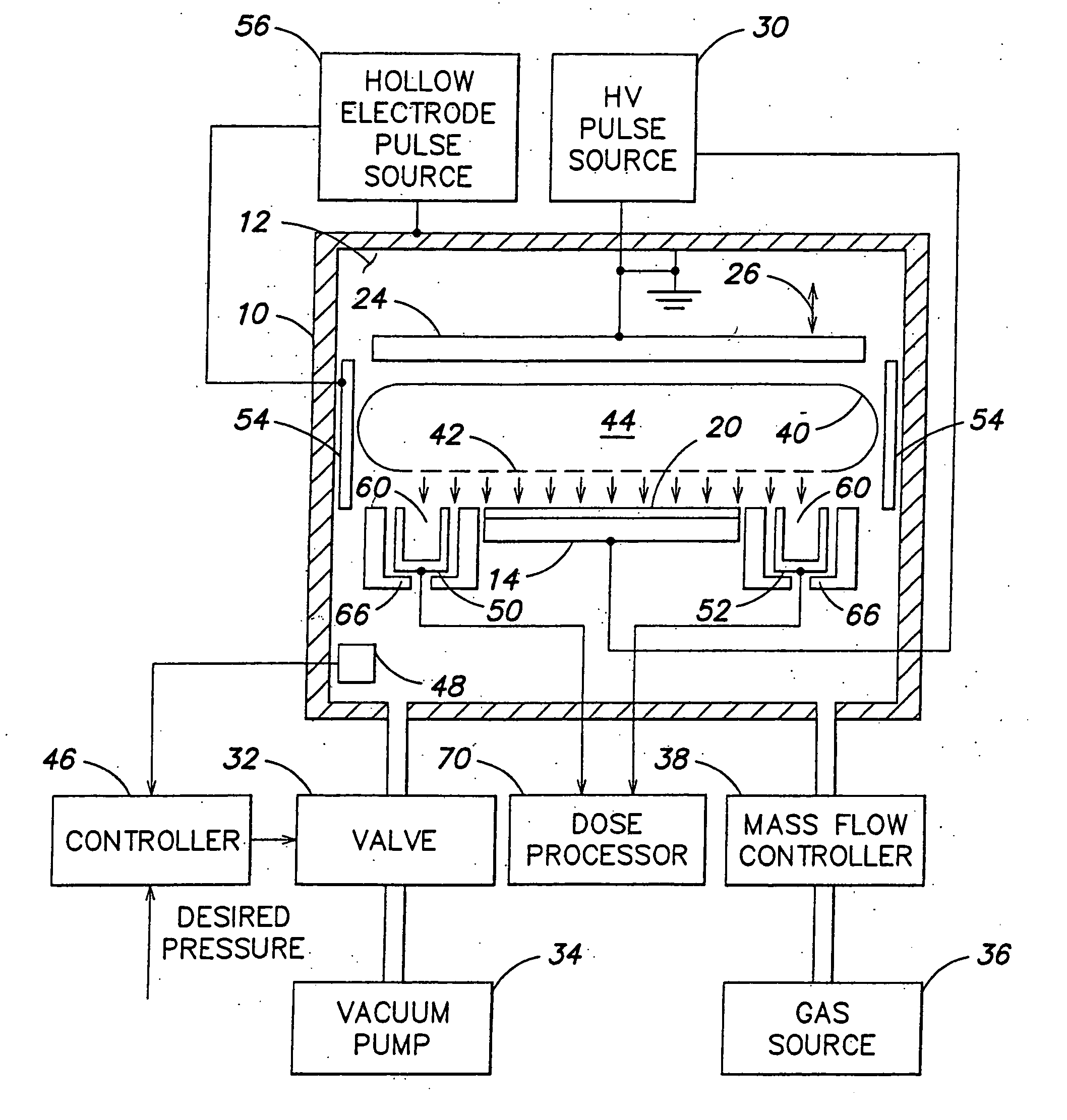

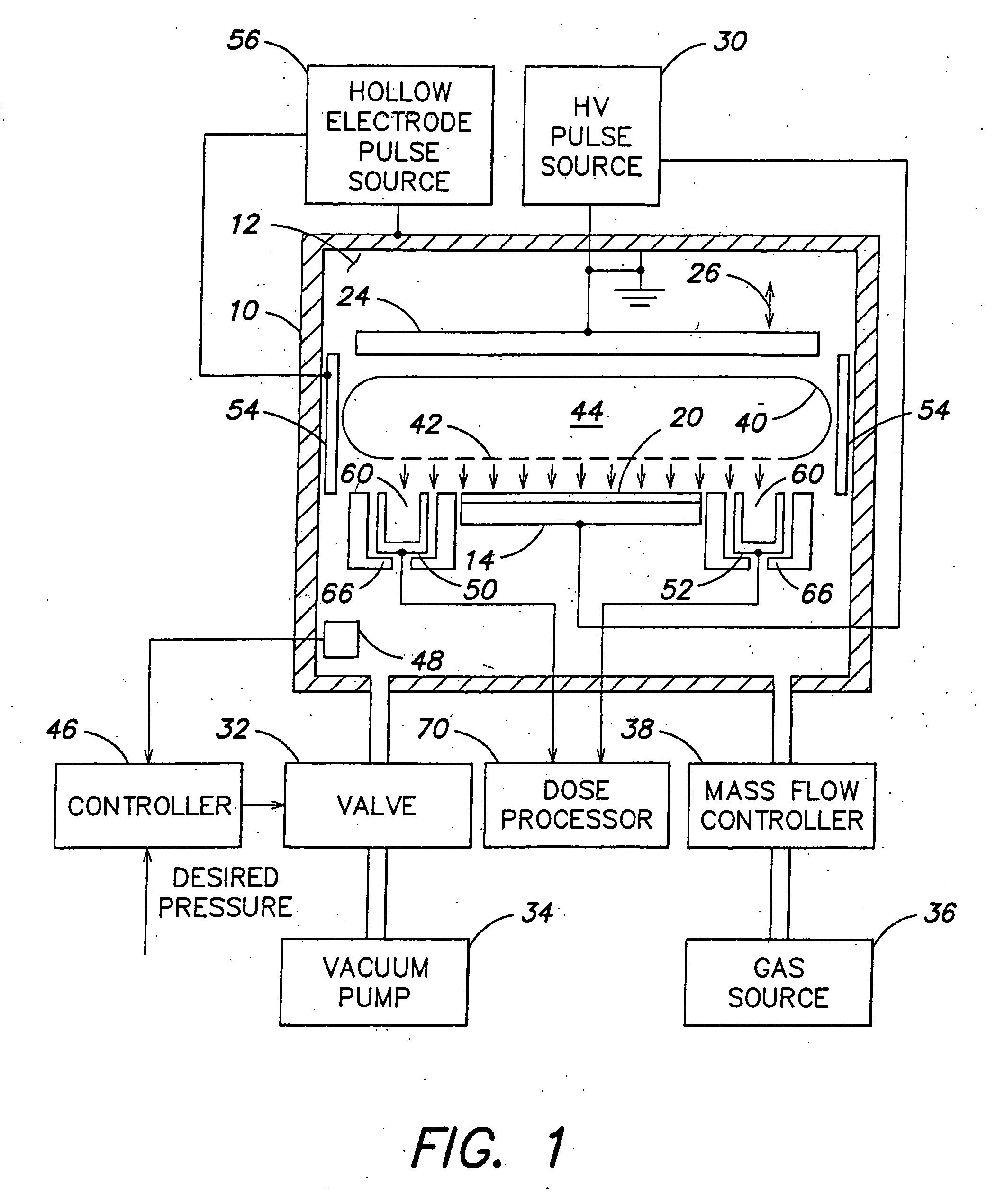

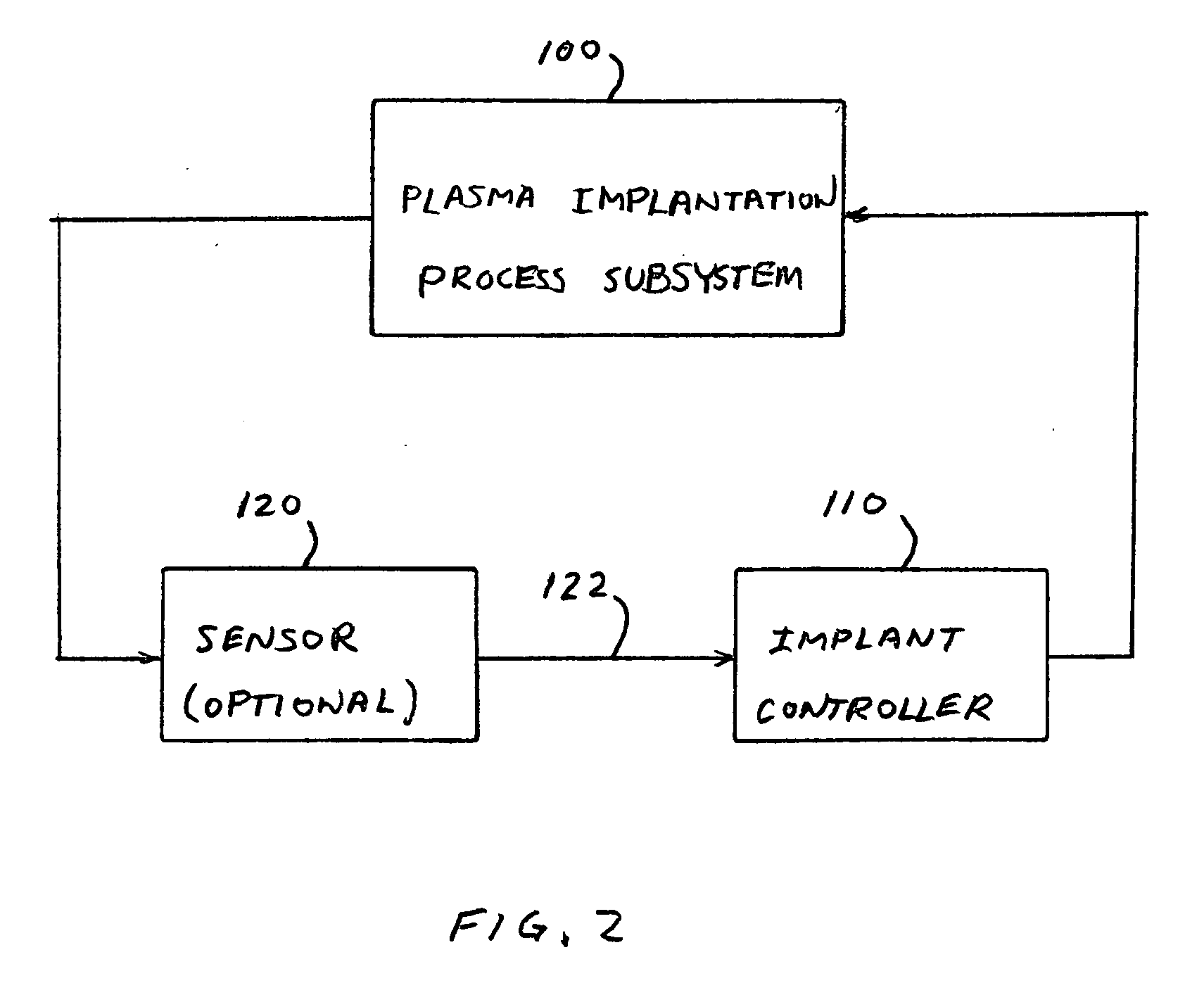

Methods for stable and repeatable ion implantation

A method for plasma ion implantation of a substrate includes providing a plasma ion implantation system having a process chamber, a source for producing a plasma in the process chamber, a platen for holding a substrate in the process chamber, an anode spaced from the platen, and a pulse source for generating implant pulses for accelerating ions from the plasma into the substrate. In one aspect, a parameter of an implant process is varied to at least partially compensate for undesired effects of interaction between ions being implanted and the substrate. For example, dose rate, ion energy, or both may be varied during the implant process. In another aspect, a pretreatment step includes accelerating ions from the plasma to the anode to cause emission of secondary electrons from the anode, and accelerating the secondary electrons from the anode to a substrate for pretreatment of the substrate.

Owner:VARIAN SEMICON EQUIP ASSOC INC

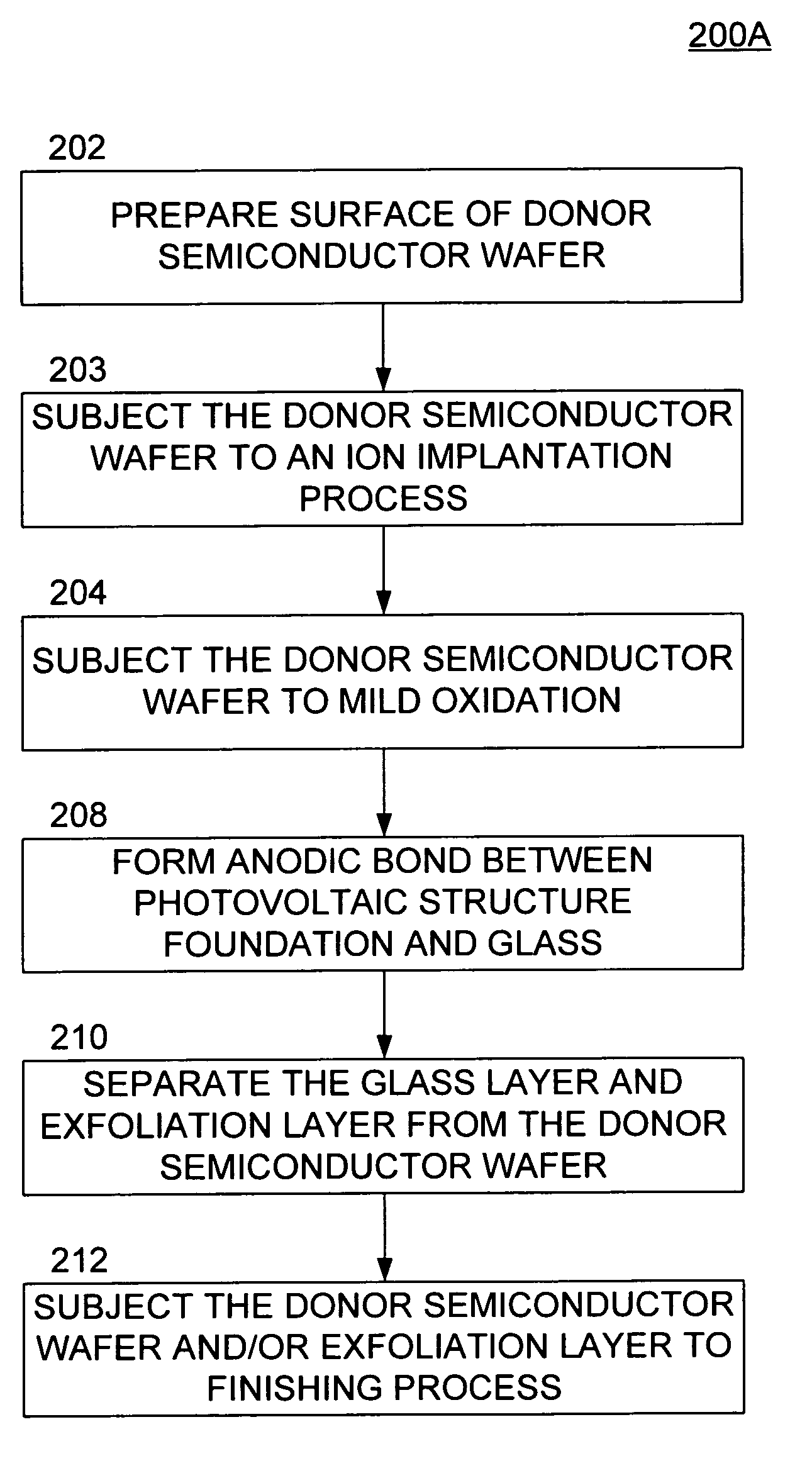

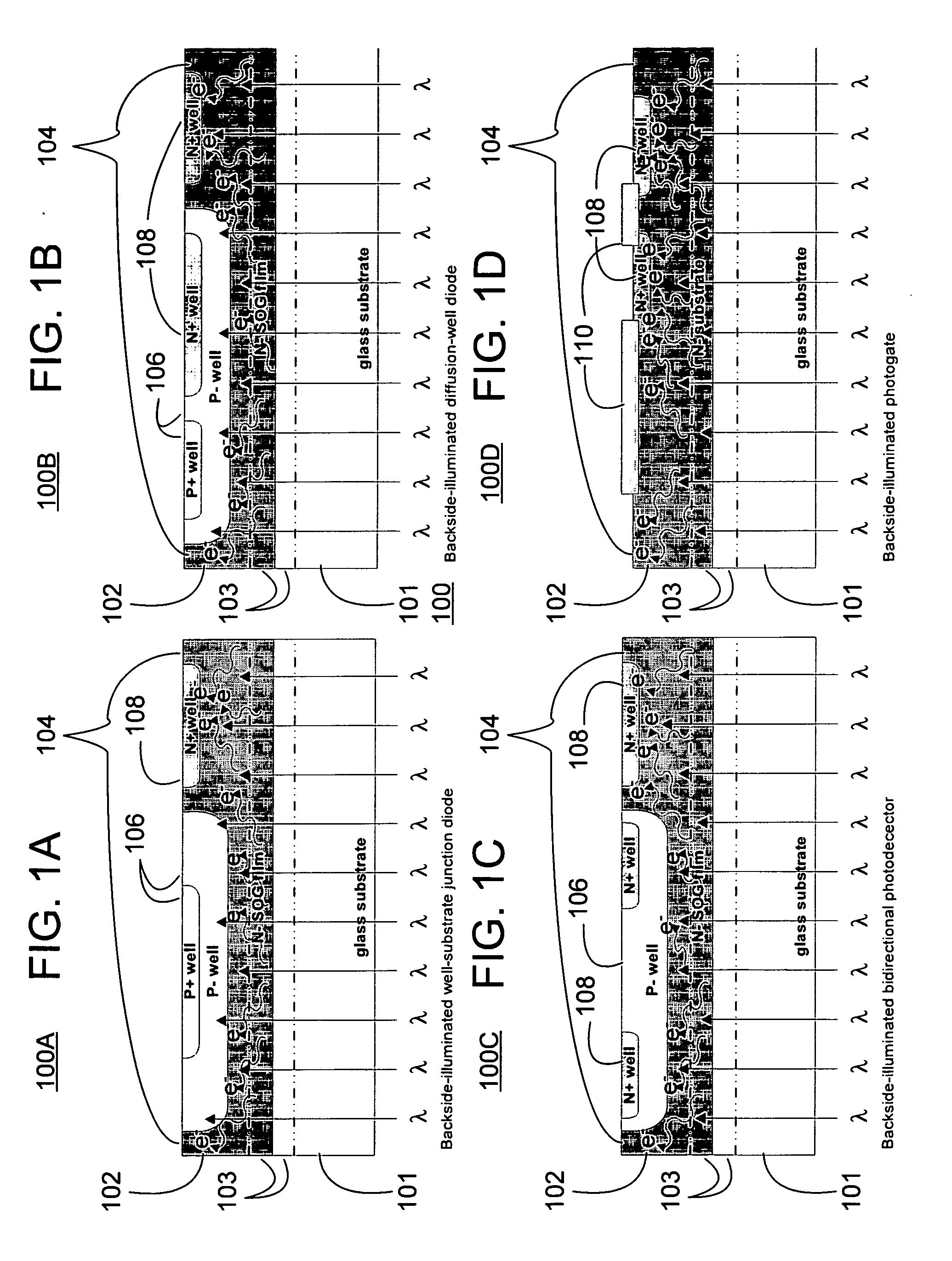

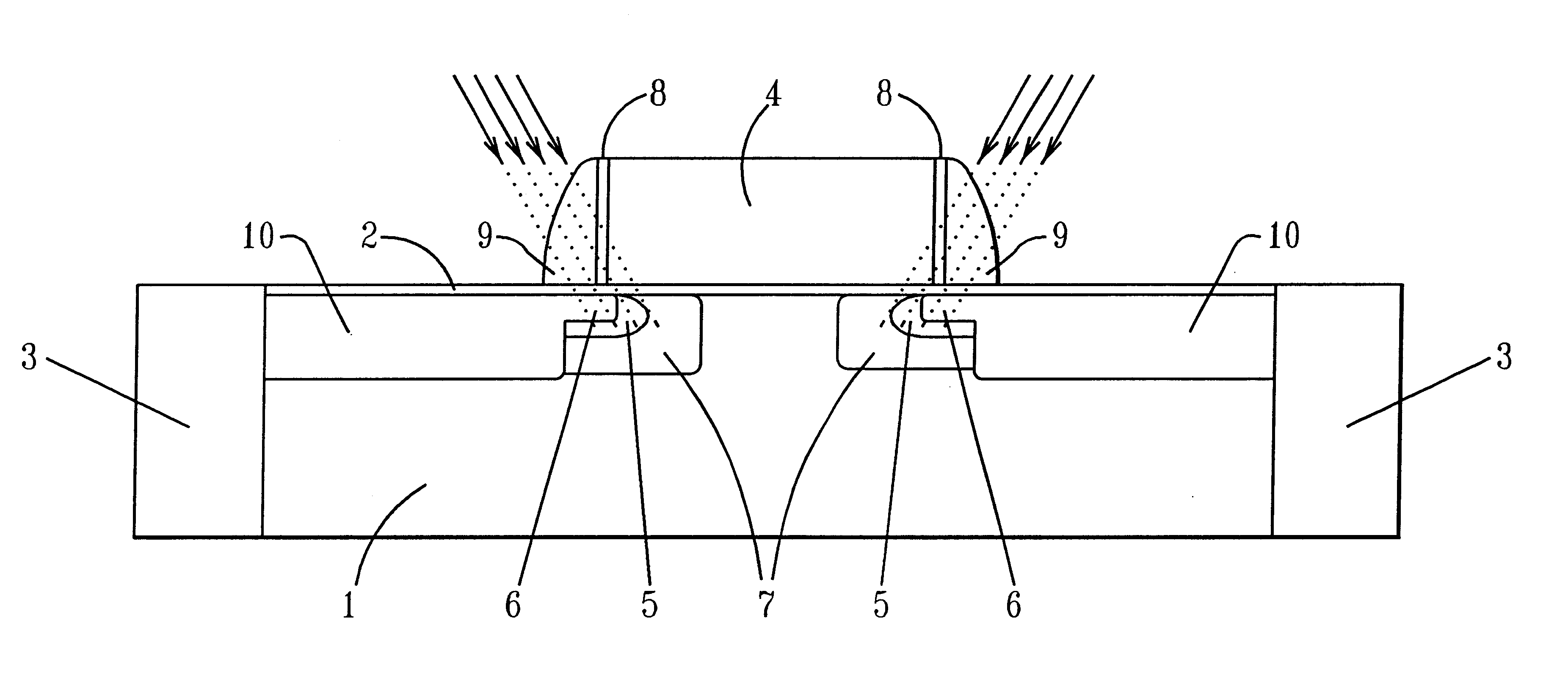

Image sensor using thin-film SOI

InactiveUS20080070340A1Faster throughputImage degradationSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalThin film soi

Systems and methods related to an image sensor of one or more embodiments include subjecting a donor semiconductor wafer to an ion implantation process to create an exfoliation layer of semiconductor film on the donor semiconductor wafer, forming an anodic bond between the exfoliation layer and an insulator substrate by means of electrolysis; separating the exfoliation layer from the donor semiconductor wafer to transfer the exfoliation layer to the insulator substrate; and creating a plurality of image sensor features proximate to the exfoliation layer. Forming the anodic bonding by electrolysis may include the application of heat, pressure and voltage to the insulator structure and the exfoliation layer attached to the donor semiconductor wafer. Image sensor devices include an insulator structure, a semiconductor film, an anodic bond between them, and a plurality of image sensor features. The semiconductor film preferably comprises an exfoliation layer of a substantially single-crystal donor semiconductor wafer.

Owner:CORNING INC

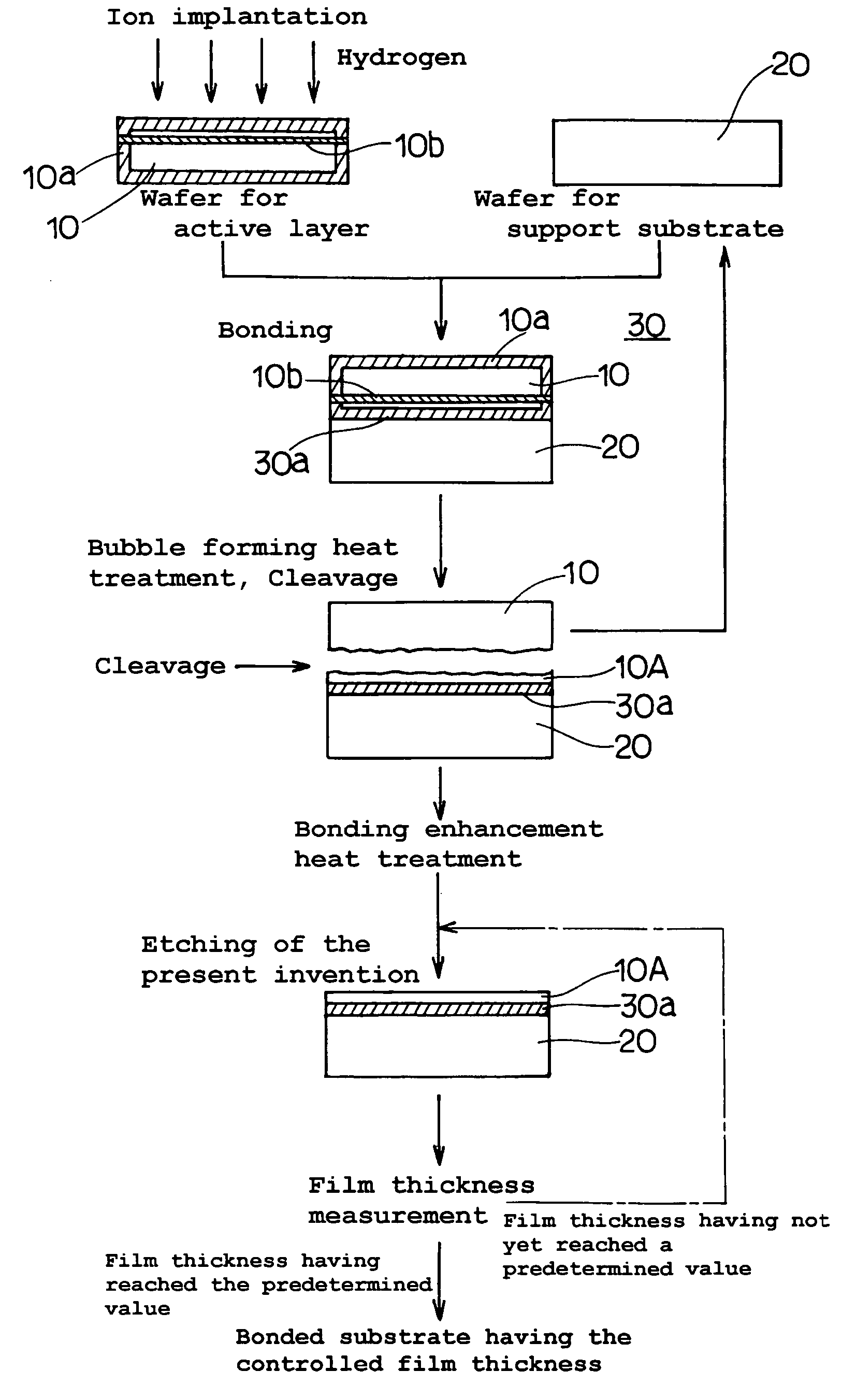

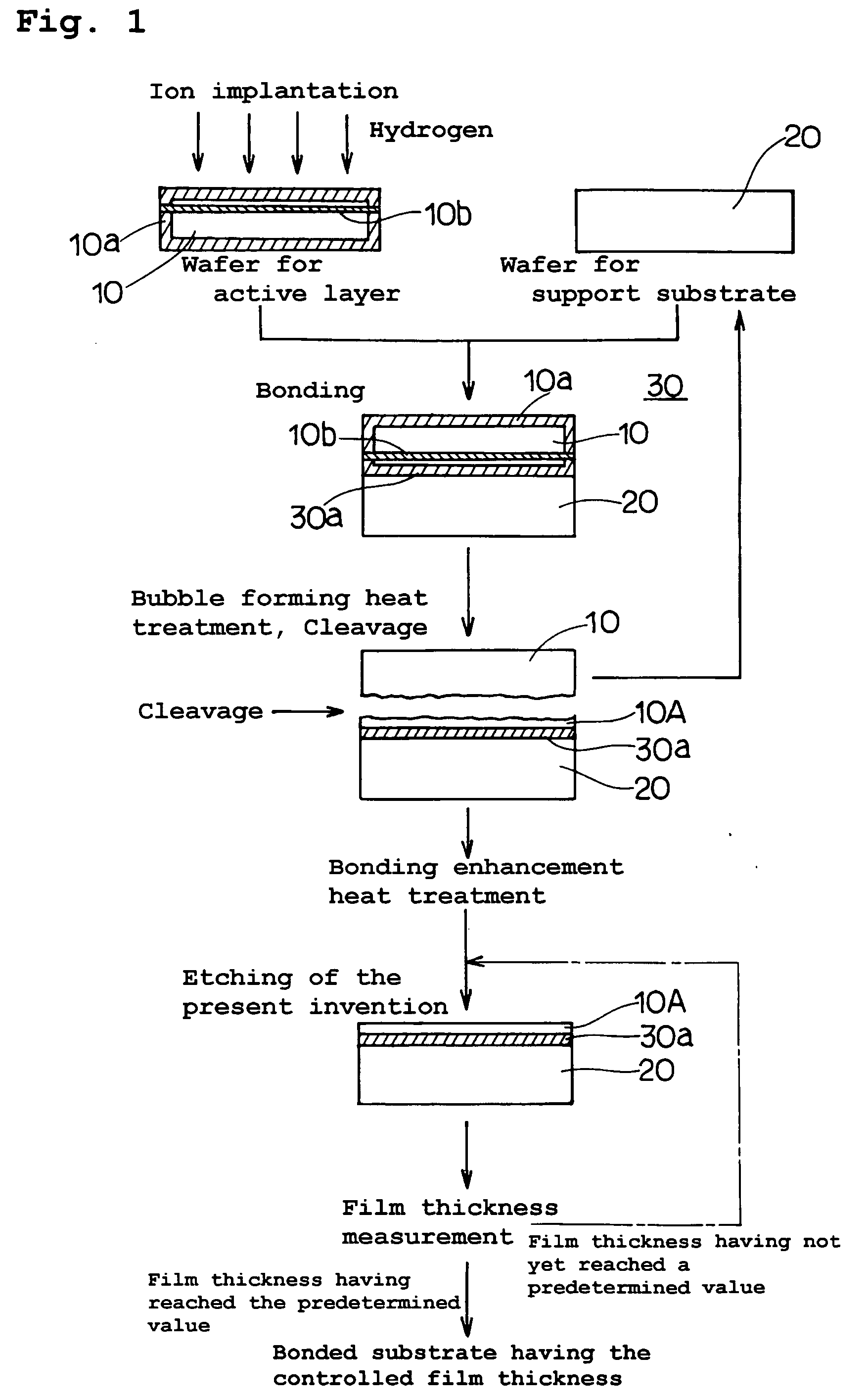

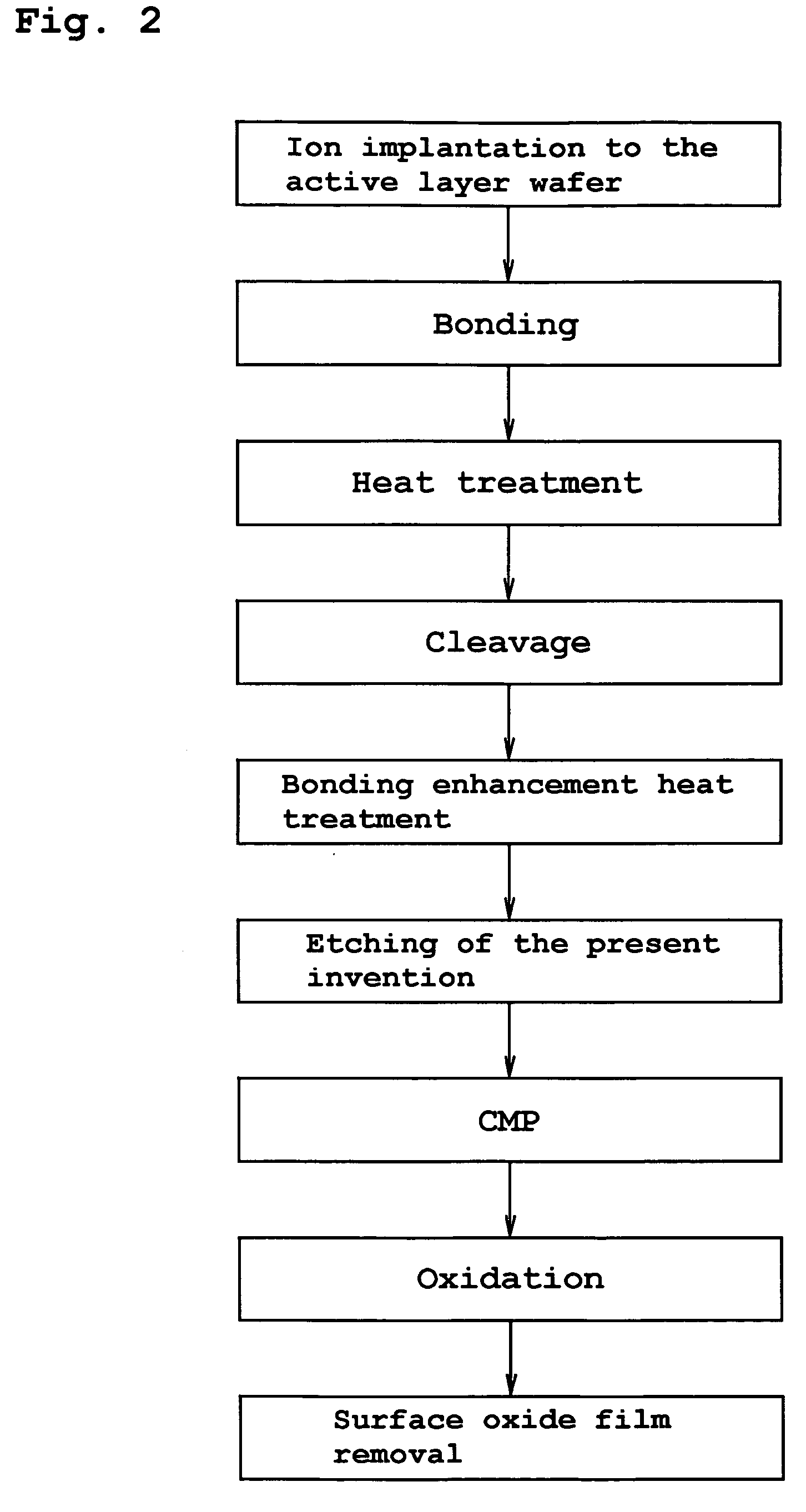

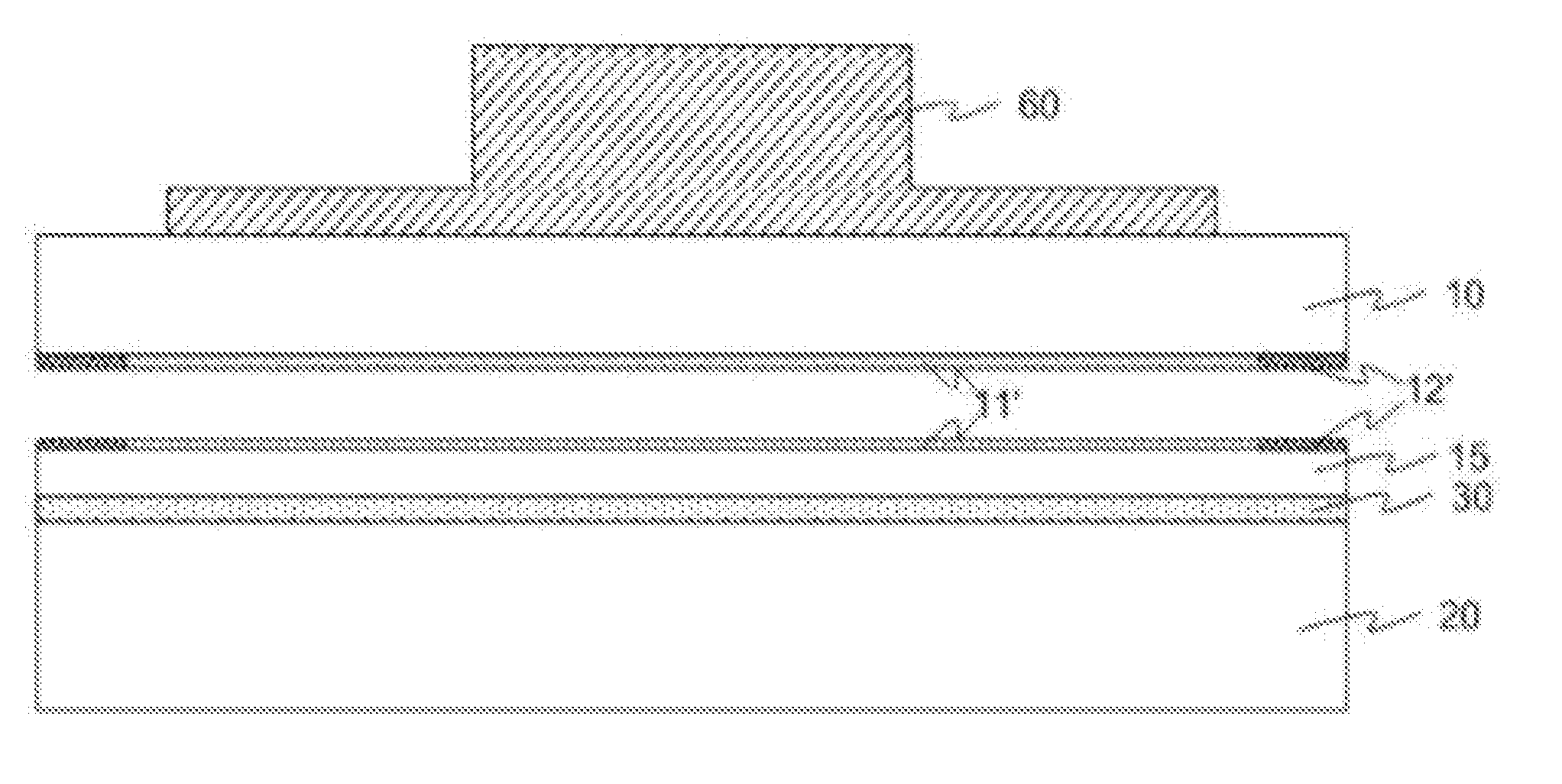

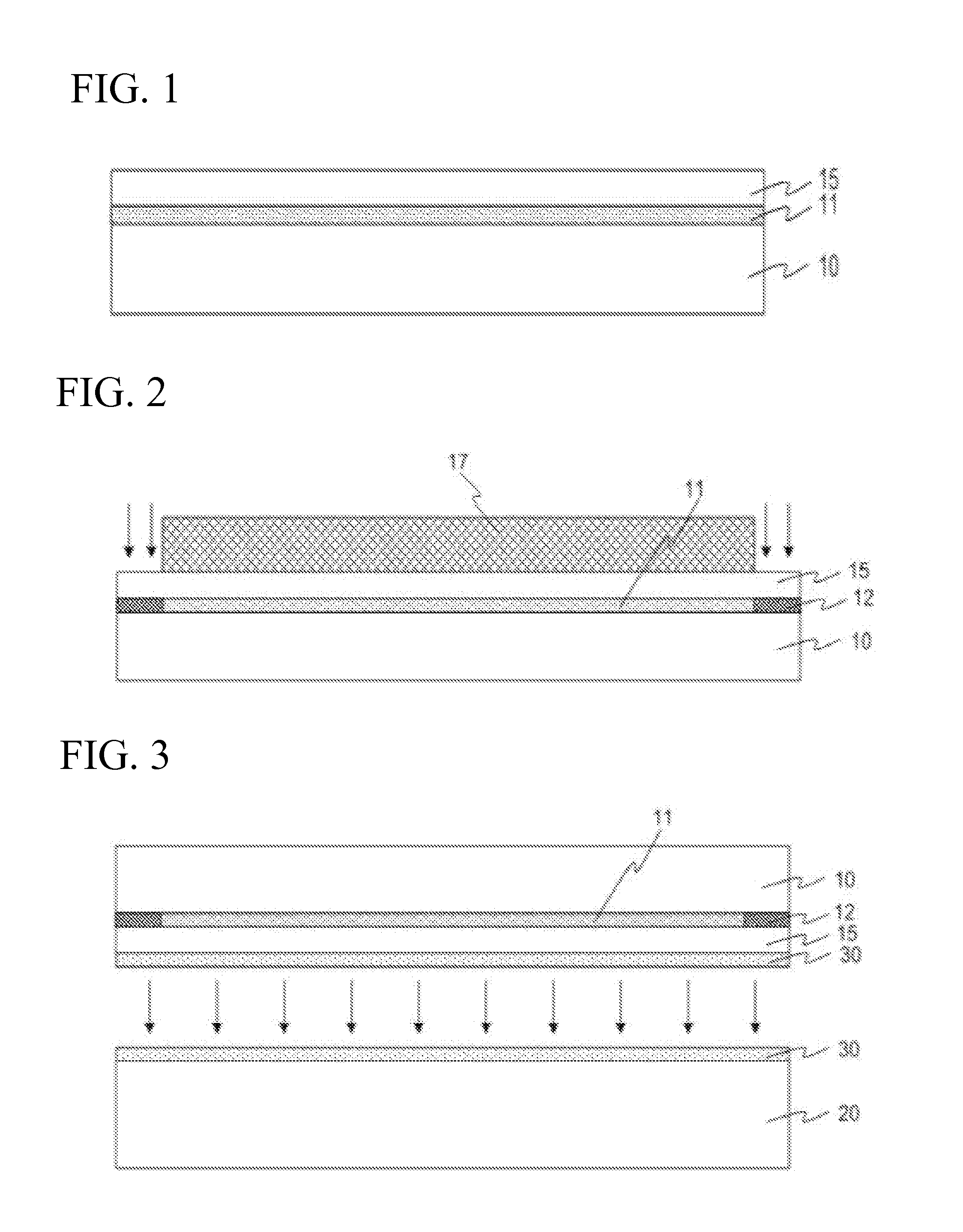

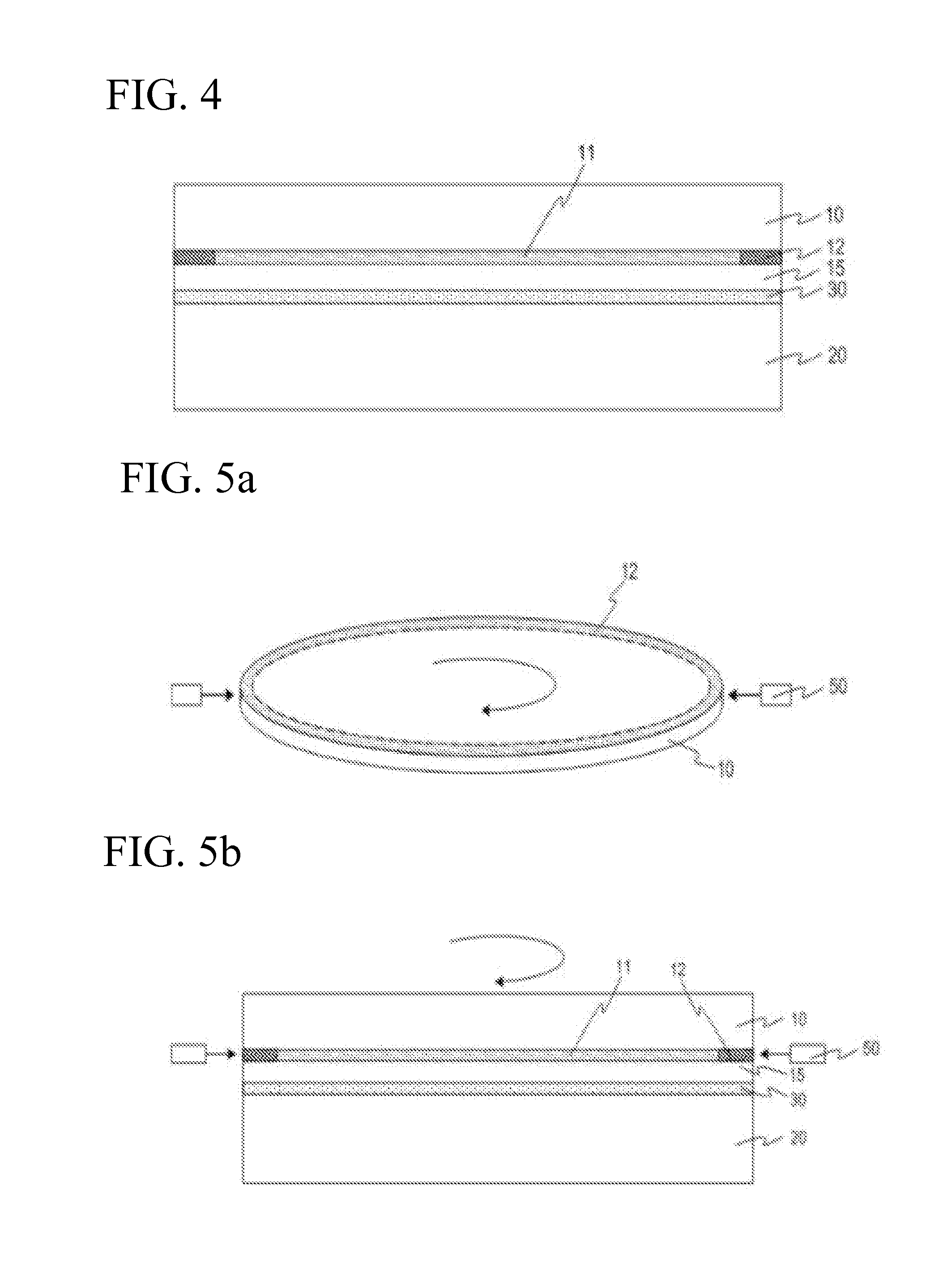

Laminated semiconductor substrate process for producing the same

InactiveUS20060118935A1Simple processReduce surface roughnessDecorative surface effectsSemiconductor/solid-state device detailsEtchingSurface roughness

The present invention provides a bonded substrate fabricated to have its final active layer thickness of 200 nm or lower by performing the etching by only 1 nm to 1 μm with a solution having an etching effect on a surface of an active layer of a bonded substrate which has been prepared by bonding two substrates after one of them having been ion-implanted and then cleaving off a portion thereof by heat treatment. SC-1 solution is used for performing the etching. A polishing, a hydrogen annealing and a sacrificial oxidation may be respectively applied to the active layer before and / or after the etching. The film thickness of this active layer can be made uniform over the entire surface area and the surface roughness of the active layer can be reduced as well.

Owner:SUMCO CORP +1

Semiconductor structure and method of fabricating the same

InactiveUS20120003815A1Semiconductor/solid-state device manufacturingSemiconductor structureIon implantation

A method of fabricating a semiconductor substrate includes providing a first semiconductor substrate, which includes a detaching layer spaced from an upper surface of the first semiconductor substrate; forming an ion-implanted layer proximate to an edge of the detaching layer; bonding a second semiconductor substrate to the first semiconductor substrate; forming a crack in the ion-implanted layer in response to applying stress to the ion-implanted layer; and detaching a portion of the first semiconductor substrate in response to cleaving through the crack.

Owner:BESANG

Tantalum amide precursors for deposition of tantalum nitride on a substrate

InactiveUS6379748B1Rapid heat treatmentSilicon organic compoundsPolycrystalline material growthFerroelectric thin filmsChemical vapor deposition

Tantalum and titanium source reagents are described, including tantalum amide and tantalum silicon nitride precursors for the deposition of tantalum nitride material on a substrate by processes such as chemical vapor deposition, assisted chemical vapor deposition, ion implantation, molecular beam epitaxy and rapid thermal processing. The precursors may be employed to form diffusion barrier layers on microelectronic device structures enabling the use of copper metallization and ferroelectric thin films in device construction.

Owner:ADVANCED TECH MATERIALS INC

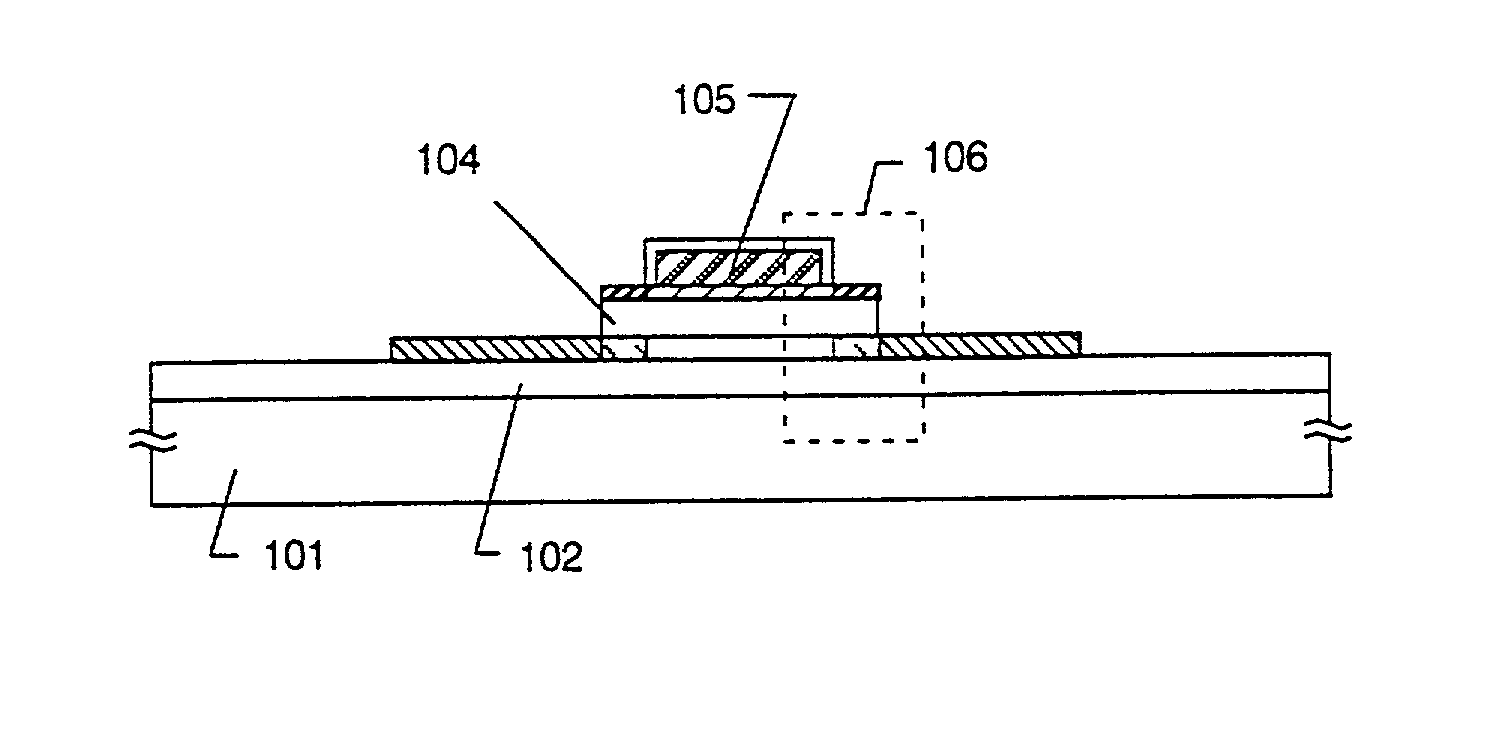

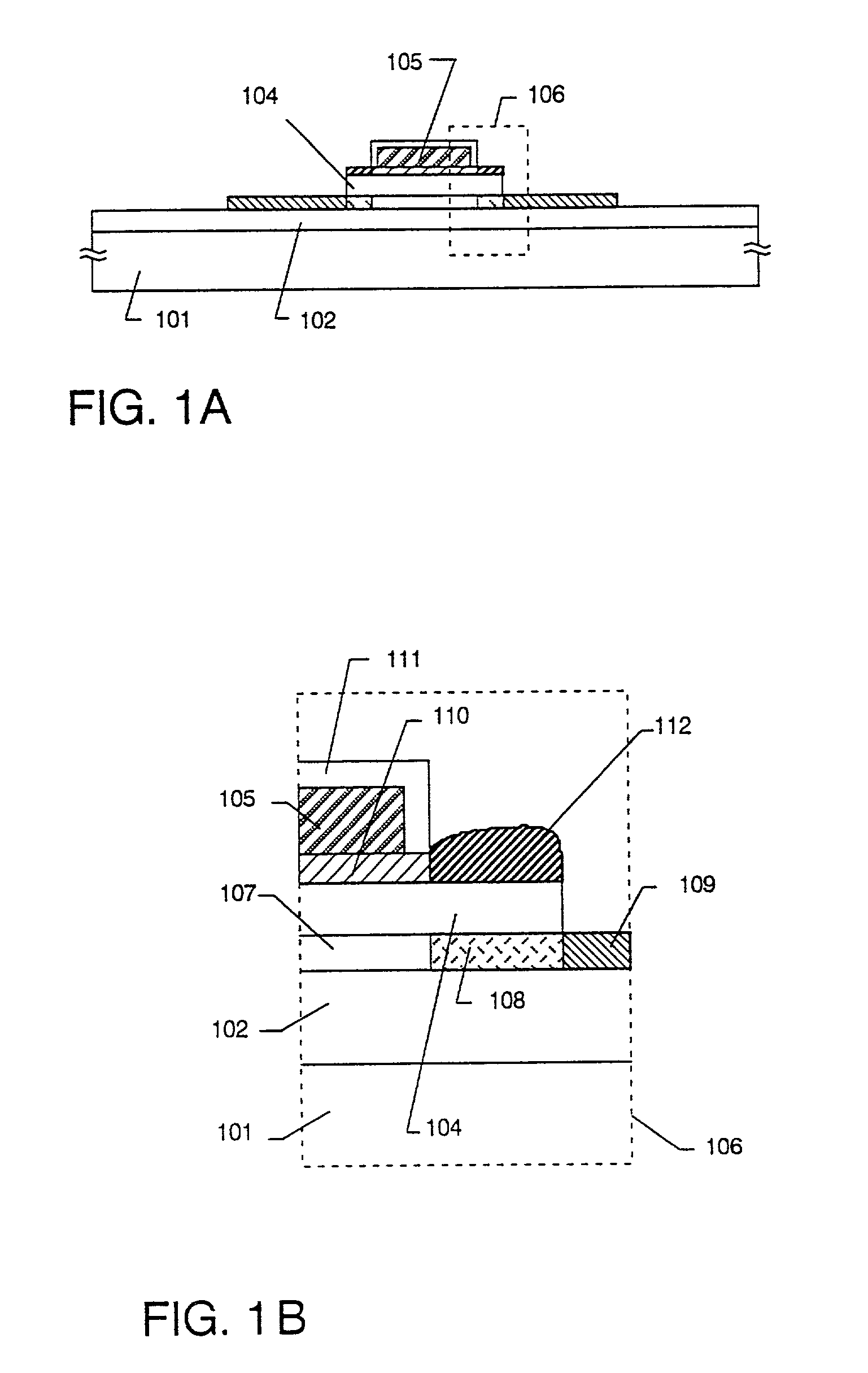

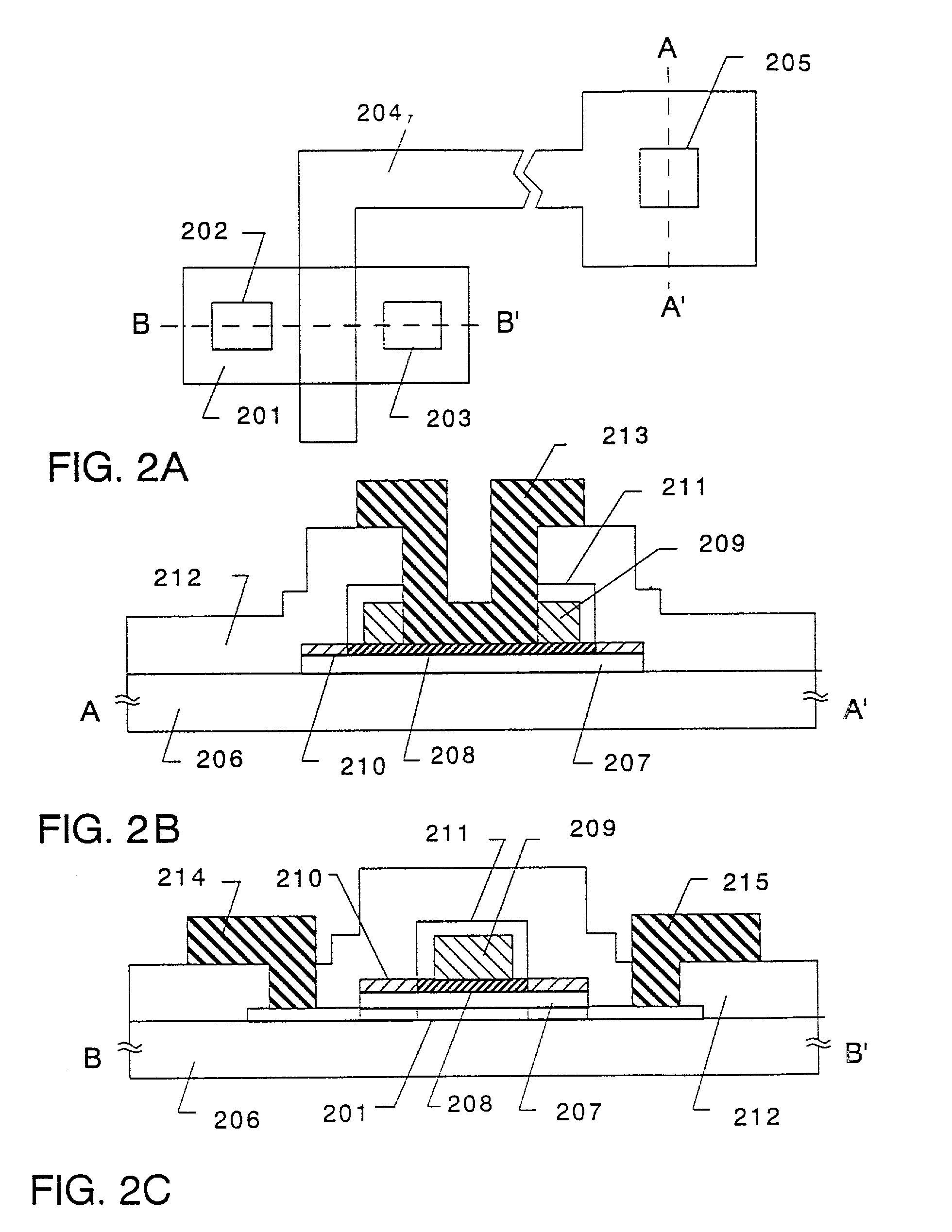

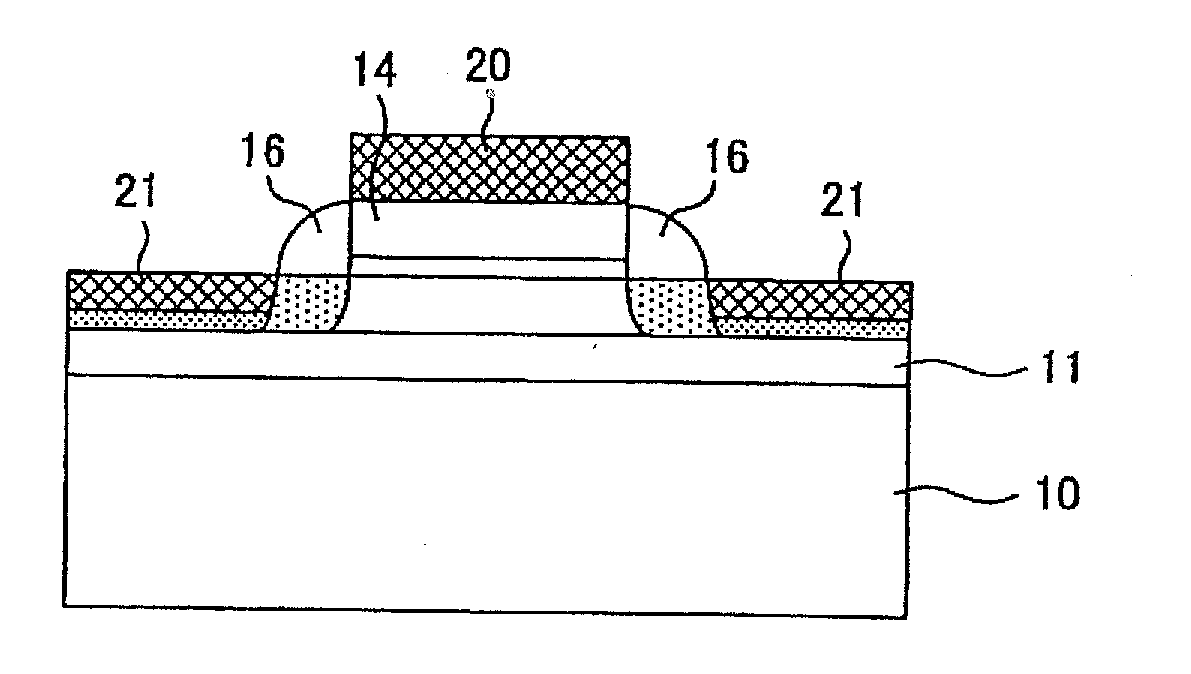

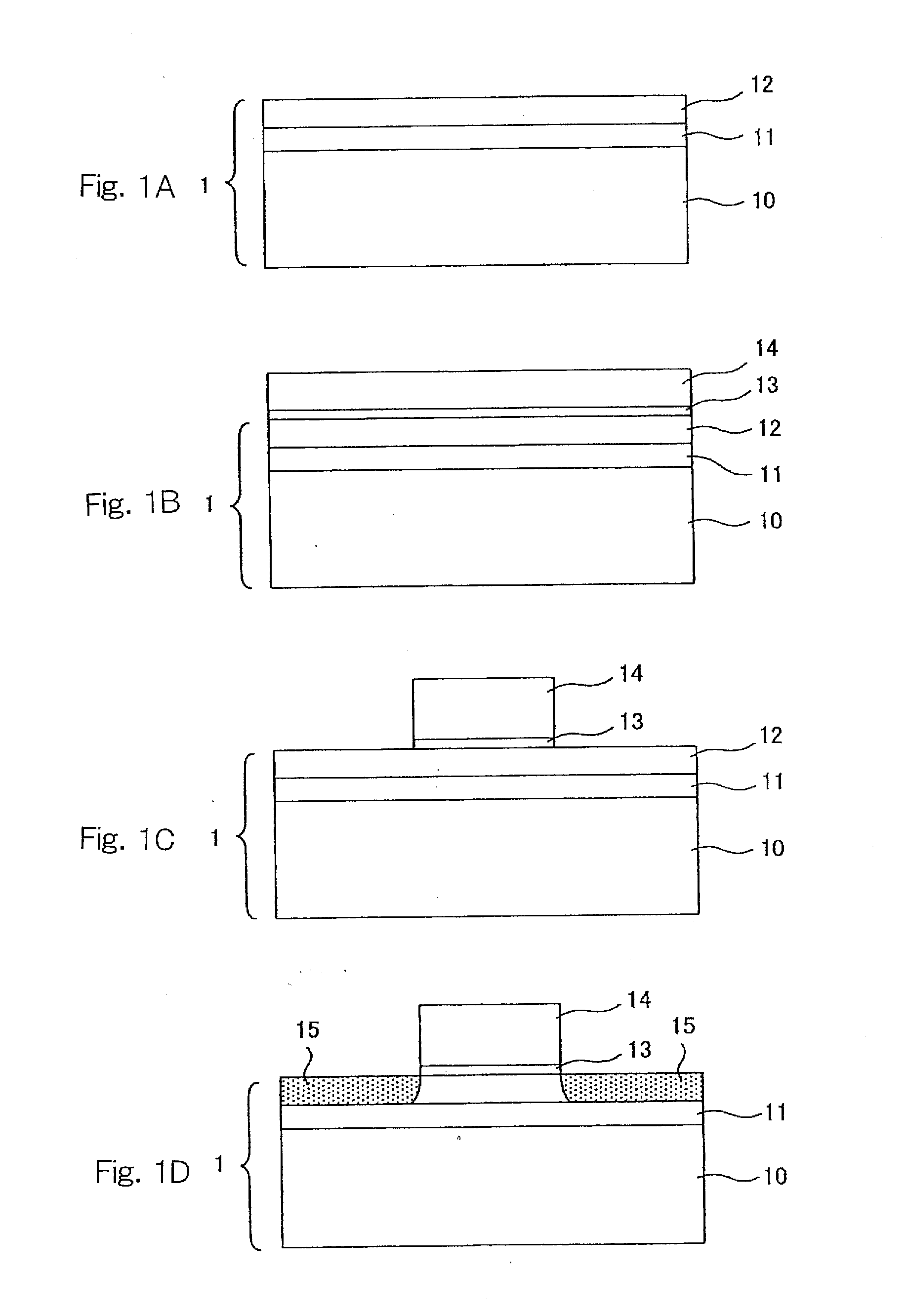

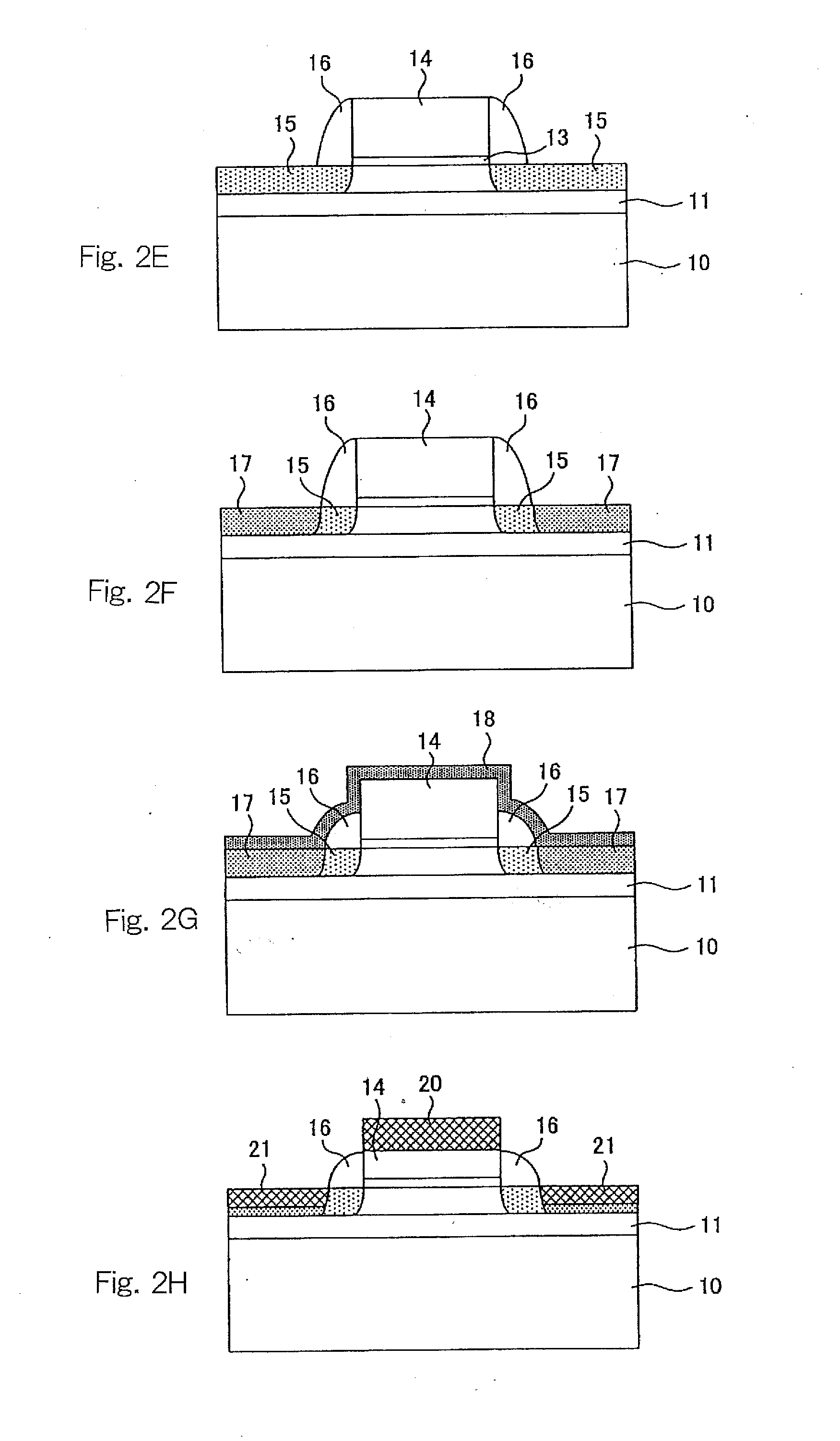

Semiconductor device and method of manufacturing the semiconductor device

InactiveUS20020096681A1TransistorSemiconductor/solid-state device manufacturingActive layerIon implantation

A TFT using an aluminum material for a gate electrode is manufactured at a high yield factor. The gate electrode provided over an active layer and a gate insulating film is constituted by a lamination film of a tantalum layer and an aluminum layer. In this structure, the tantalum layer functions as a stopper, so that it is possible to prevent a constituent material of the aluminum layer from intruding into the gate insulating film. An end portion of the tantalum layer is transformed into tantalum oxide, which has an effect to lower damage at ion implantation to the gate insulating film in the formation of an LDD region.

Owner:SEMICON ENERGY LAB CO LTD

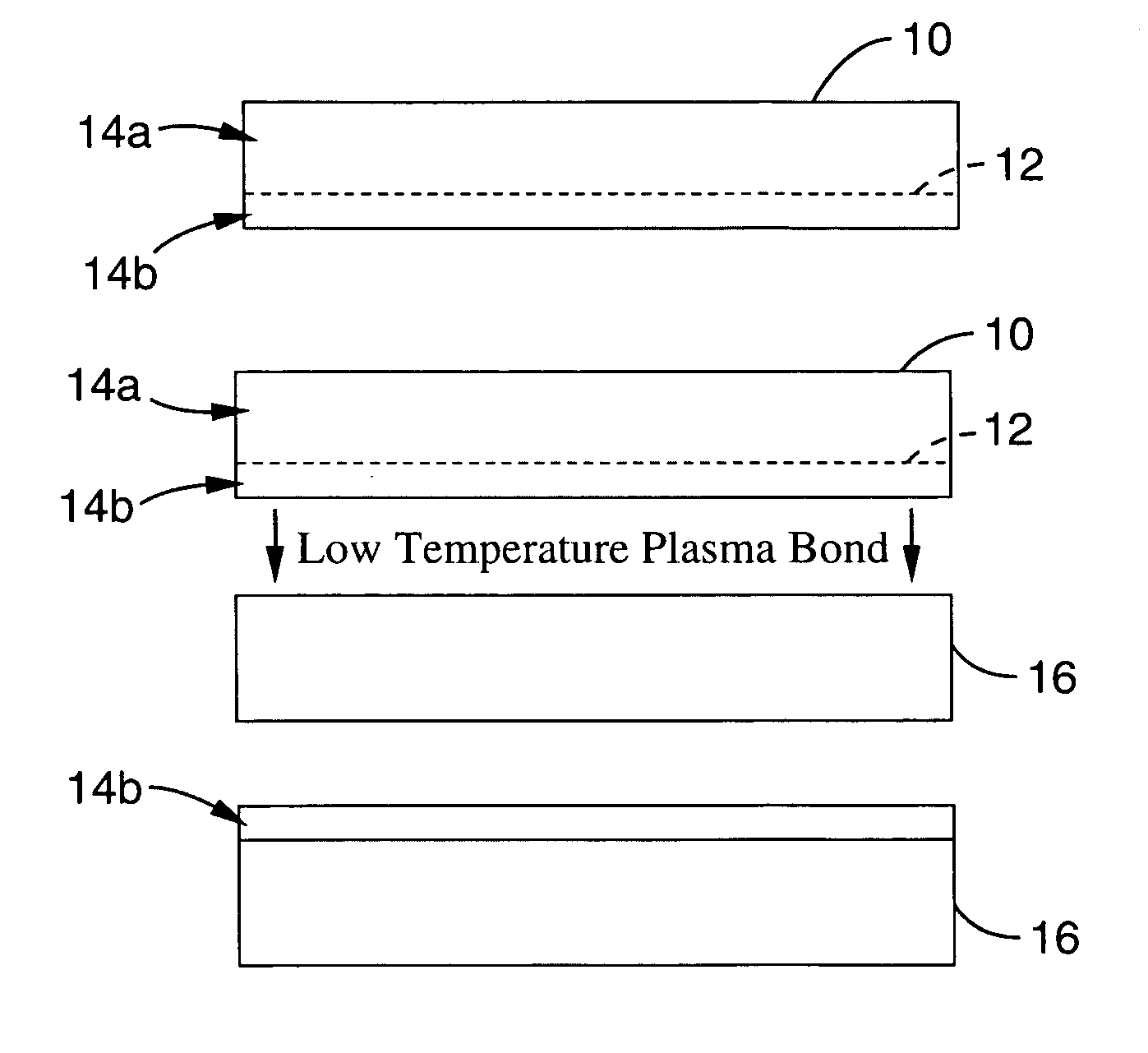

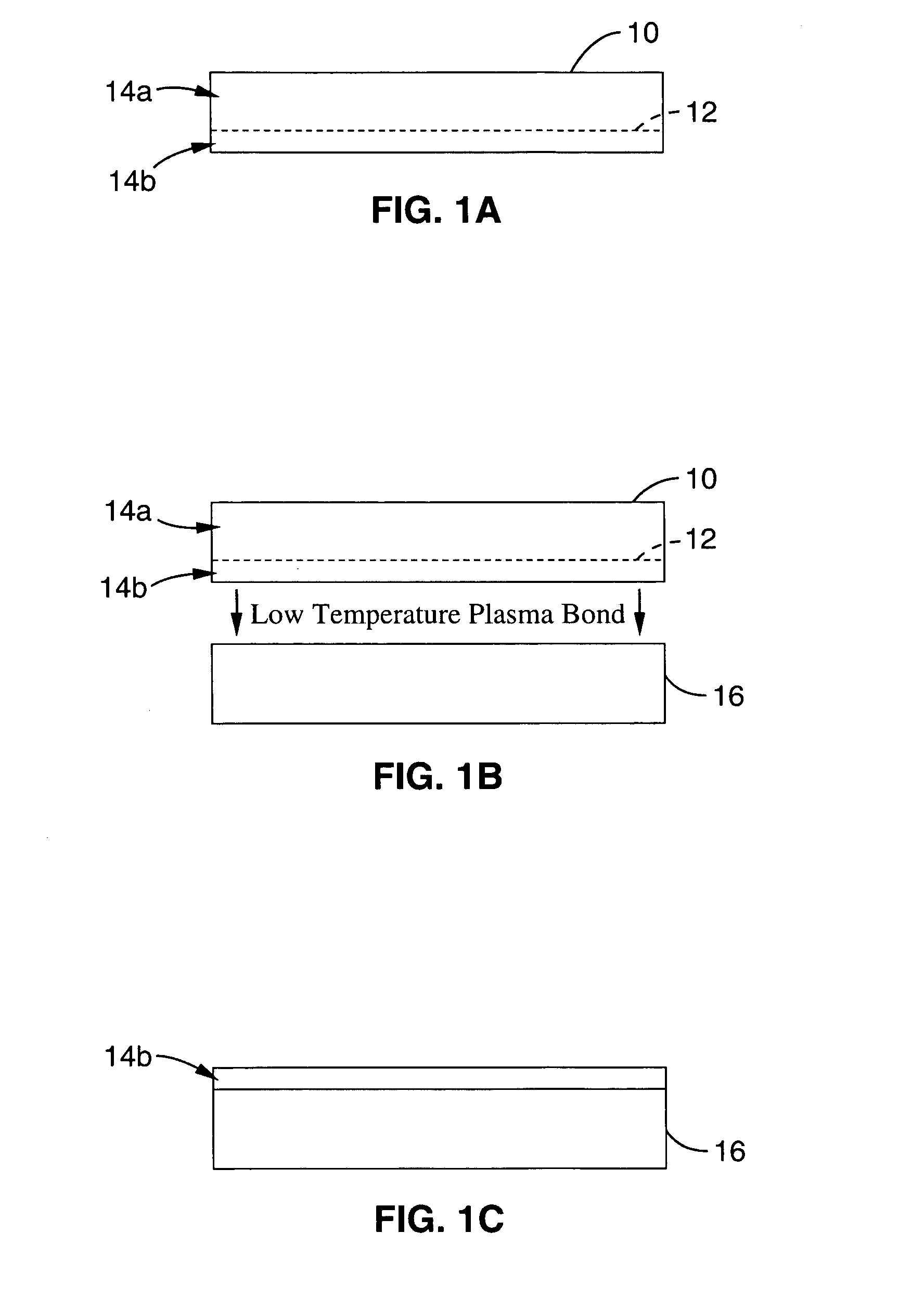

Smooth thin film layers produced by low temperature hydrogen ion cut

A method for producing wafer splitting from ion implantation into silicon after low temperature direct bonding with surface roughness that is ˜1 nm (RMS). This result is an order of magnitude smoother than the previous work (˜10 nm RMS). The key improvement in this work is the use of a low temperature bond resulting in a strong bond before the material is cut. The smooth as-split surfaces produced using a low temperature bond are very important for creation of very thin (<50 nm) silicon-on-insulator (SOI), three-dimensional bonded structures and nanostructures that are split after processing.

Owner:EPIR TECH INC

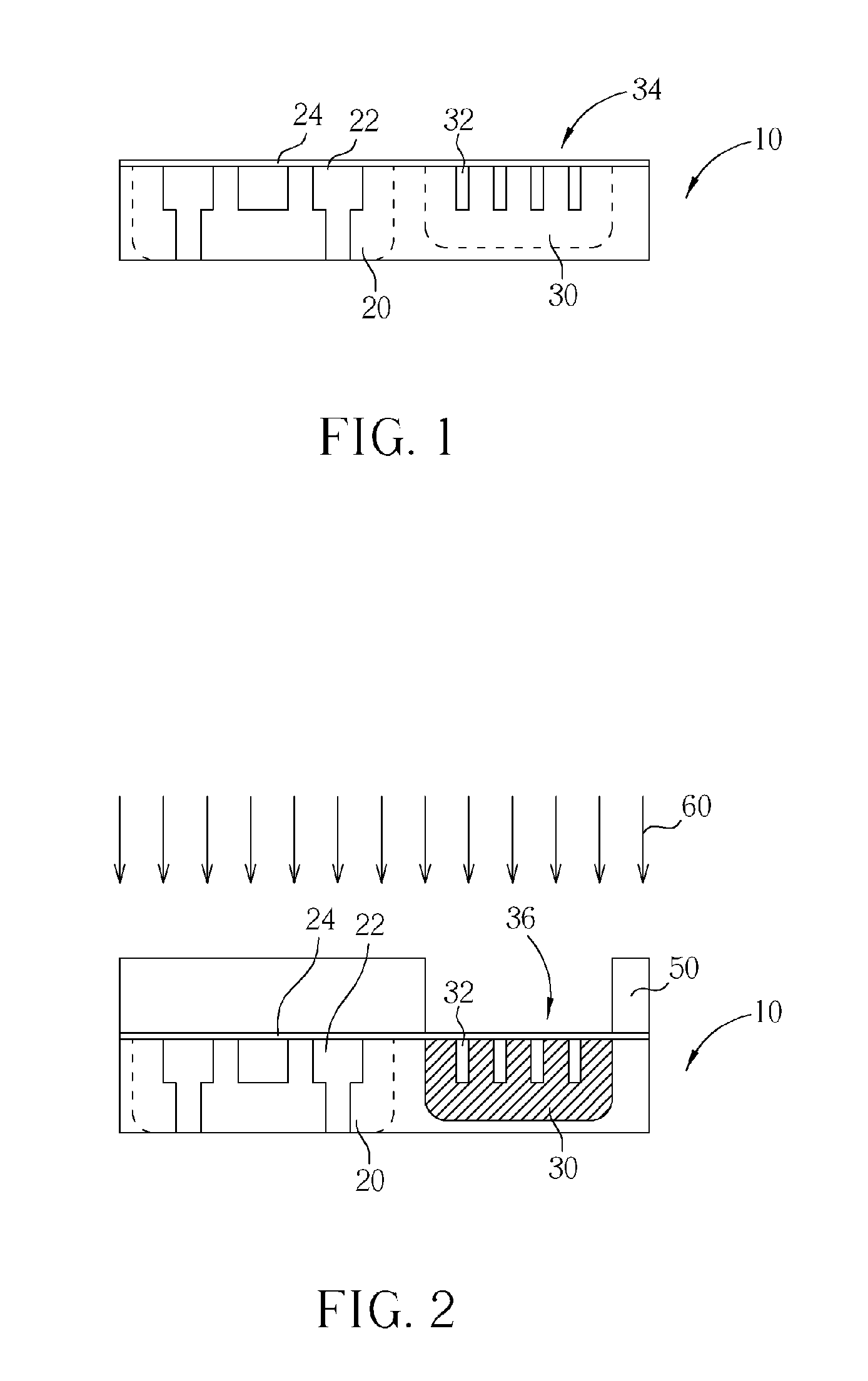

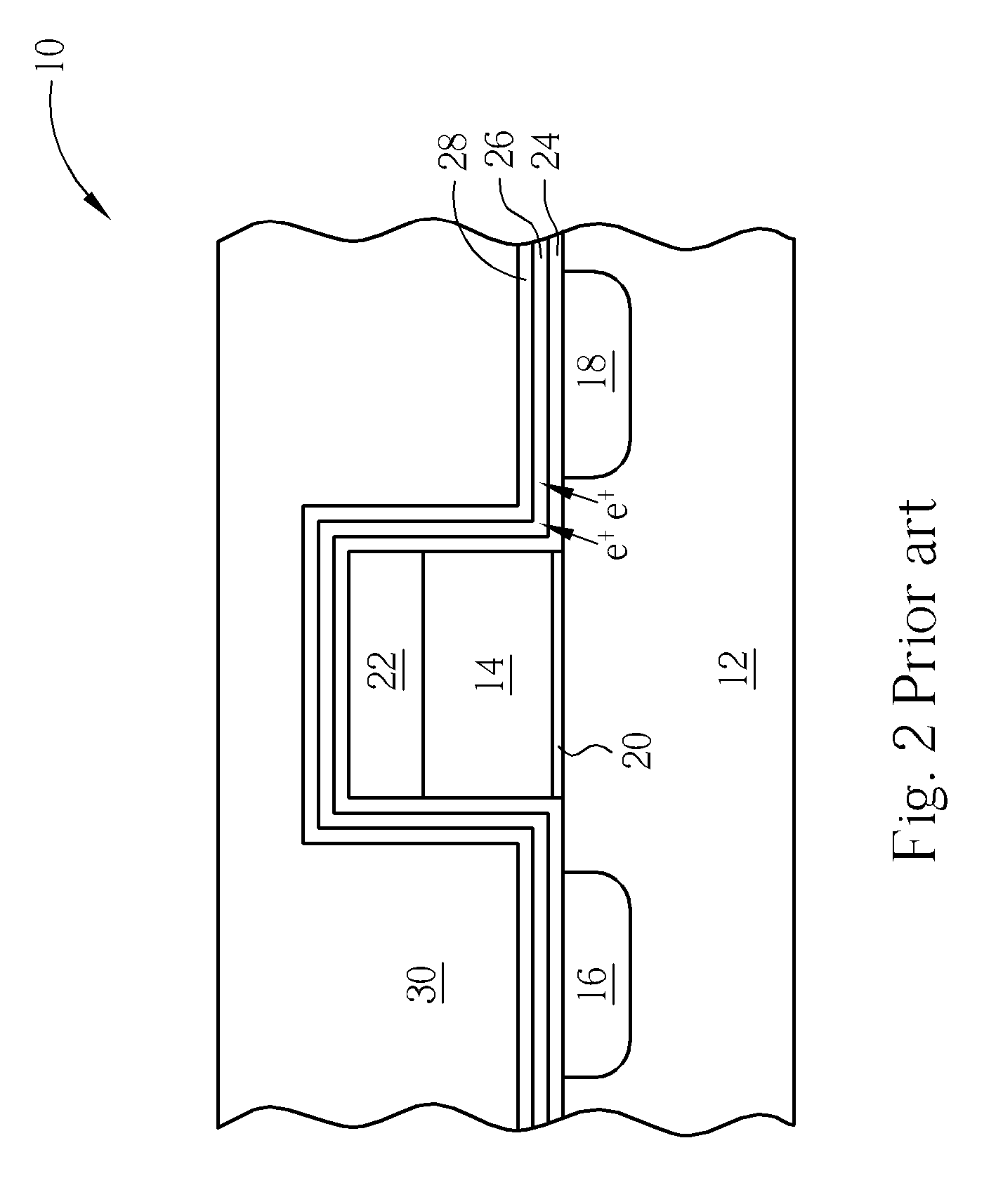

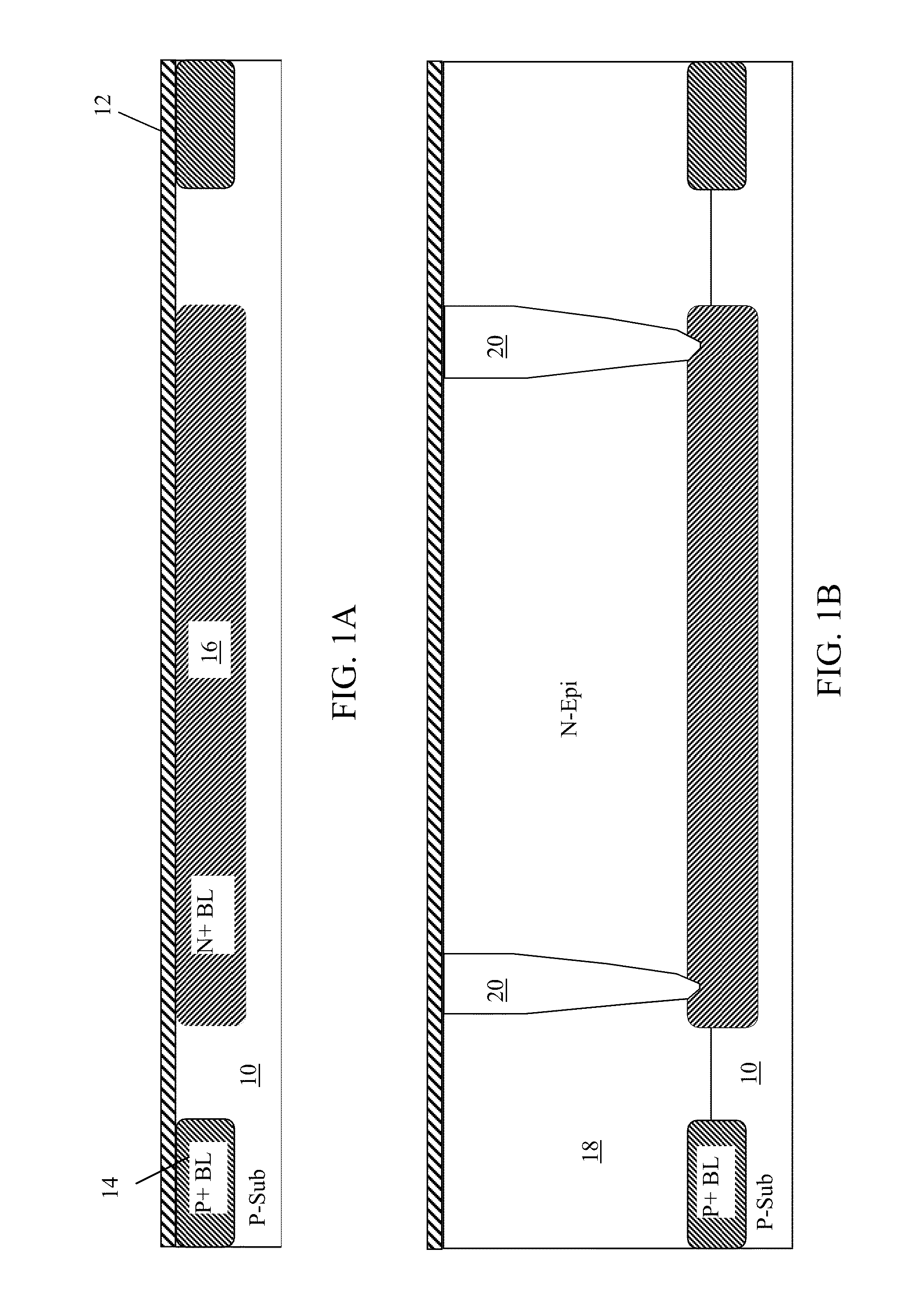

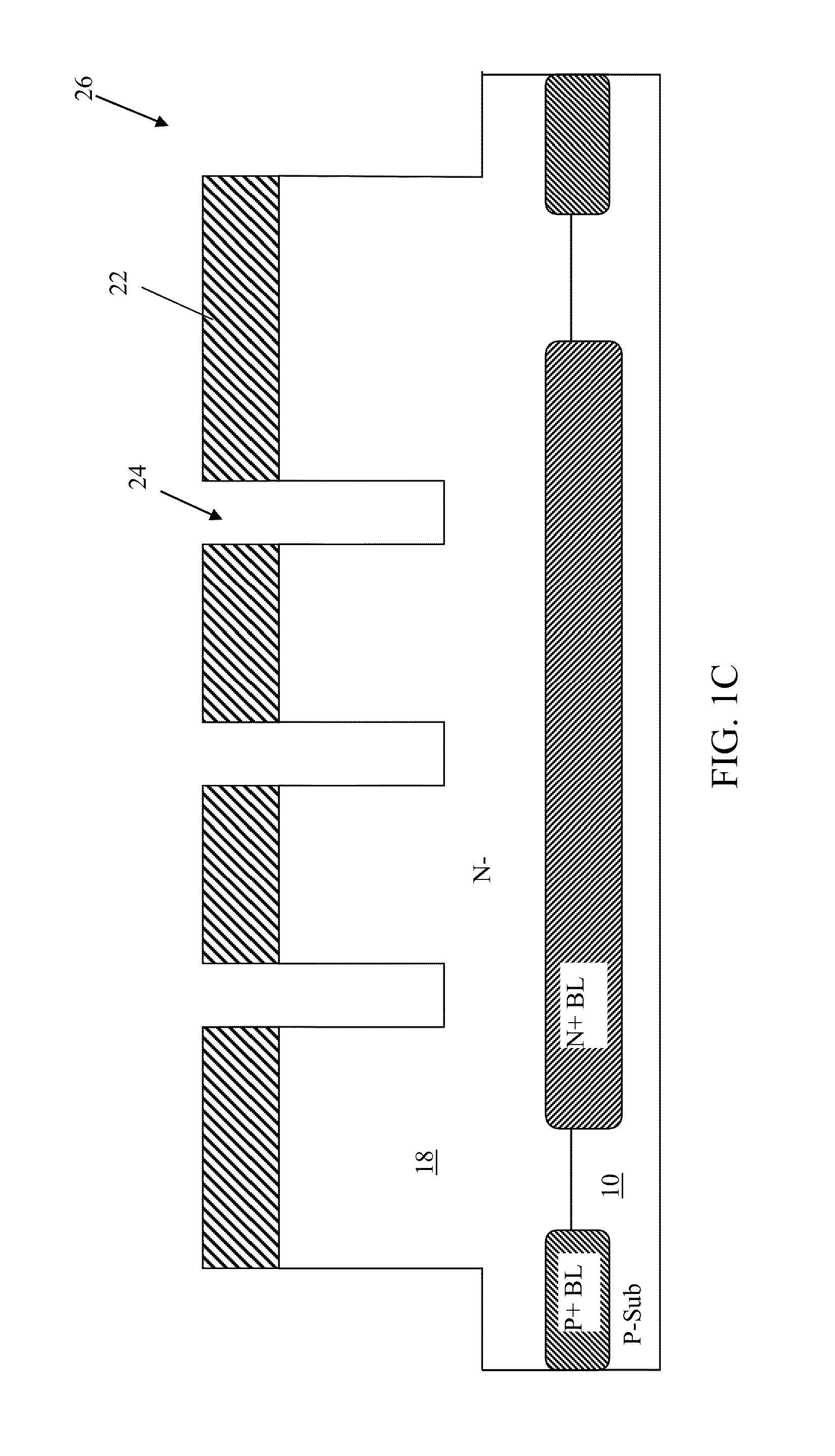

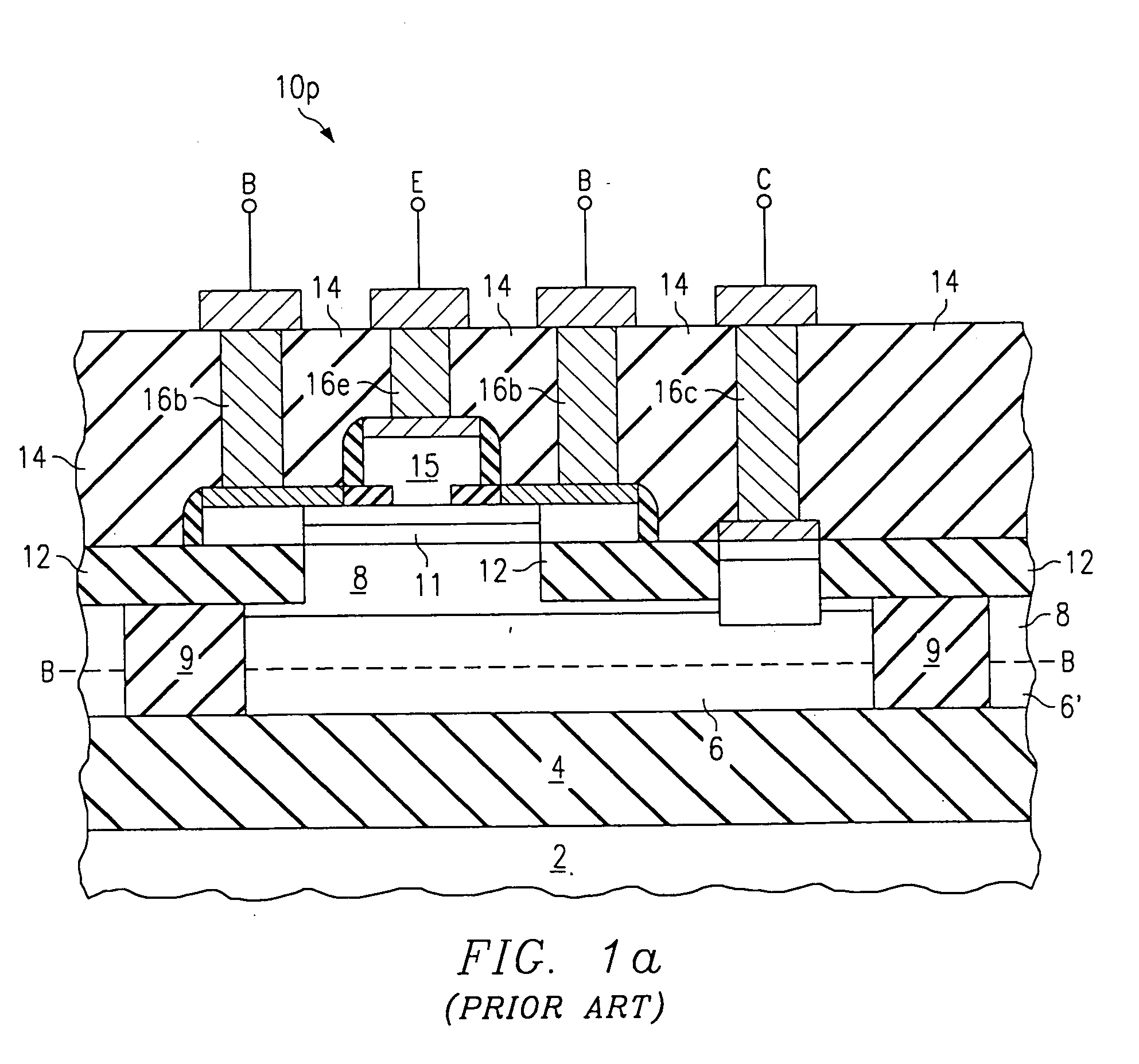

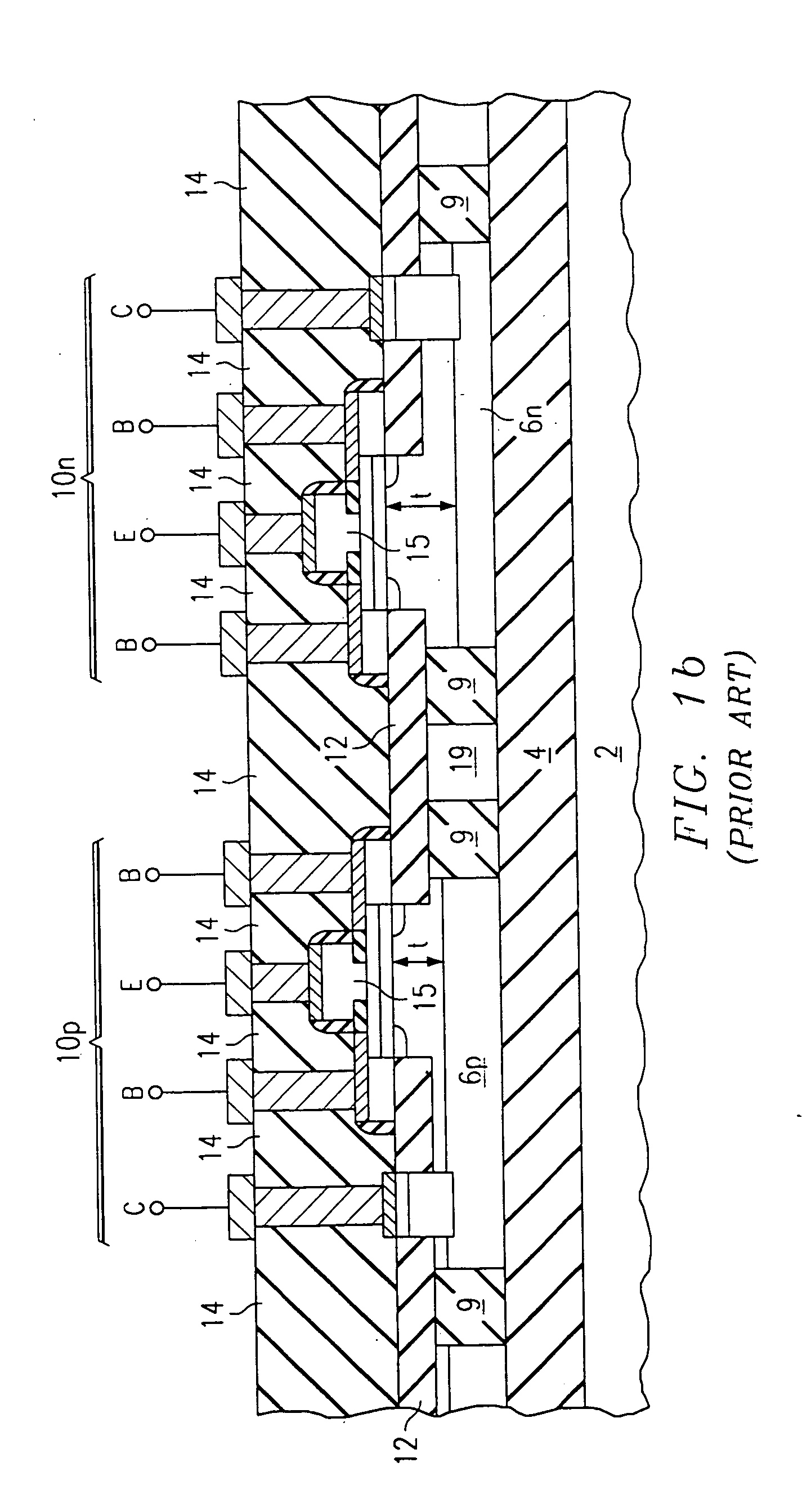

Lateral PNP Bipolar Transistor with Narrow Trench Emitter

ActiveUS20130075746A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantEngineering

A lateral bipolar transistor includes trench emitter and trench collector regions to form ultra-narrow emitter regions, thereby improving emitter efficiency. The same trench process is used to form the emitter / collector trenches as well as the trench isolation structures so that no additional processing steps are needed to form the trench emitter and collector. In embodiments of the present invention, the trench emitter and trench collector regions may be formed using ion implantation into trenches formed in a semiconductor layer. In other embodiments, the trench emitter and trench collector regions may be formed by out-diffusion of dopants from heavily doped polysilicon filled trenches.

Owner:ALPHA & OMEGA SEMICON INC

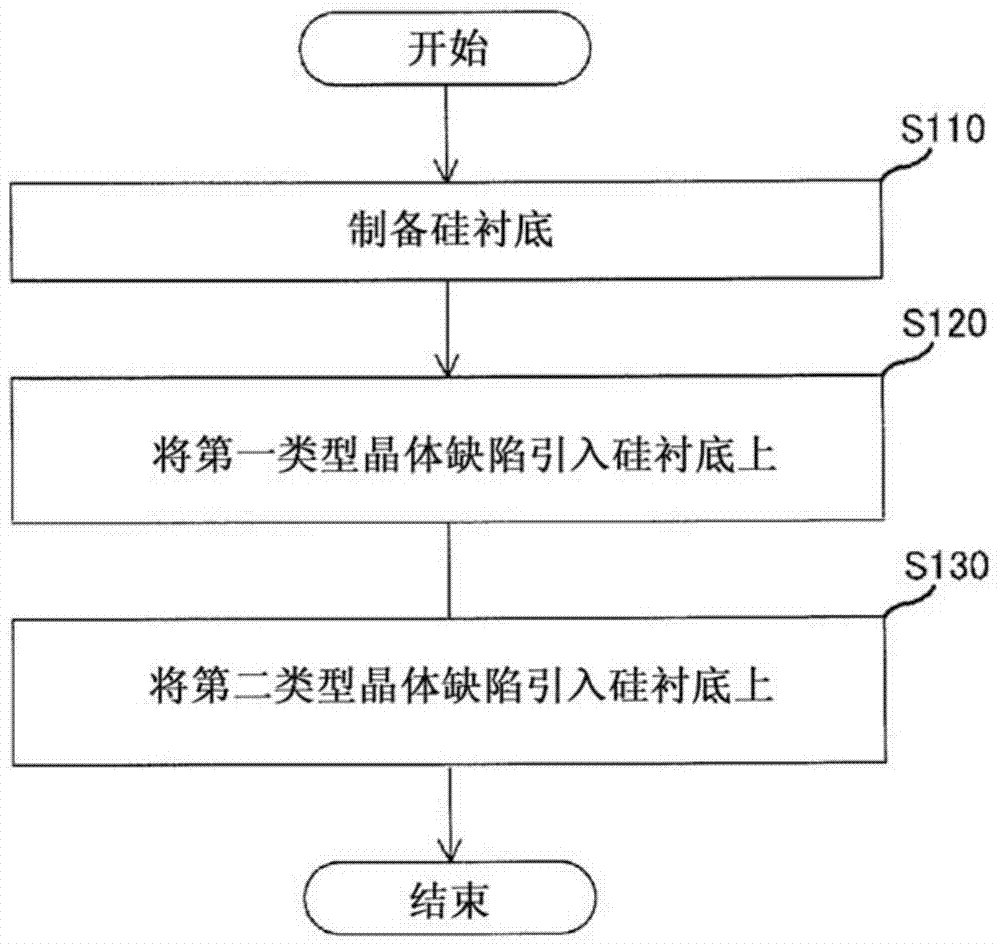

Semiconductor device, method of manufacturing semiconductor device, and antenna switch module

ActiveCN103811474ASemiconductor/solid-state device detailsSolid-state devicesEngineeringCrystallographic defect

The invention relates to a semiconductor device, a method of manufacturing semiconductor device, and an antenna switch module. Disclosed is a semiconductor device having a radio frequency switch. Also disclosed are an antenna switch module and a method of manufacturing the semiconductor device. The semiconductor device includes a metal wiring insulating film bonded to a silicon substrate. In the semiconductor device, a crystal defect layer extends into the silicon substrate from a surface of the silicon substrate. Crystal defects are throughout the crystal defect layer. The semiconductor device and an integrated circuit are in the antenna switch module. The integrated circuit in the antenna switch module is mounted with the radio-frequency switch device and the silicon substrate. The method of manufacturing the semiconductor device includes a step of forming crystal defects throughout a silicon substrate. Radiation or a diffusion is used to form the crystal defects. After the step of forming the crystal defects, the method includes a step of implanting ions into a surface of the silicon substrate to form a crystal defect layer.

Owner:SONY CORP

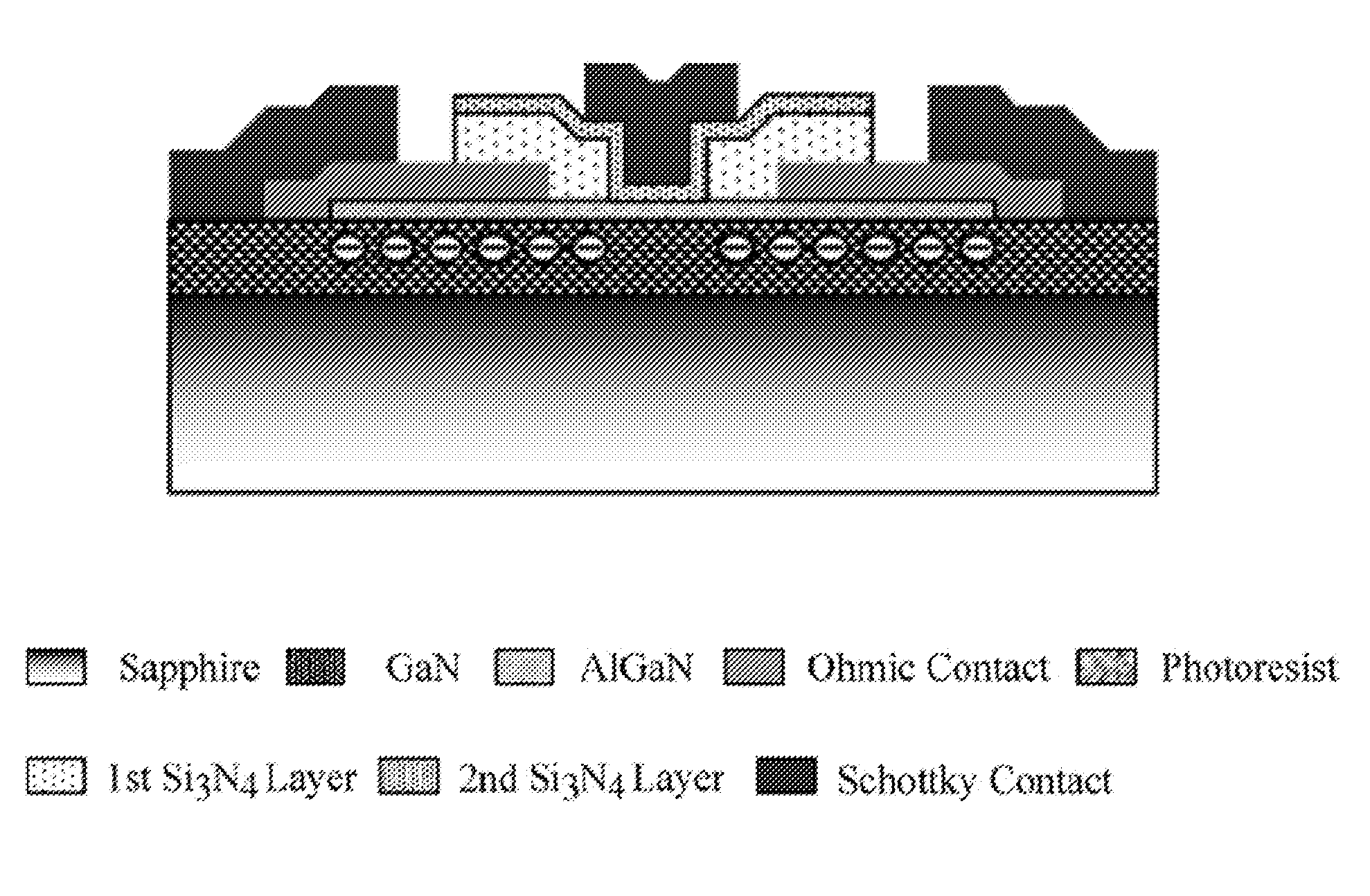

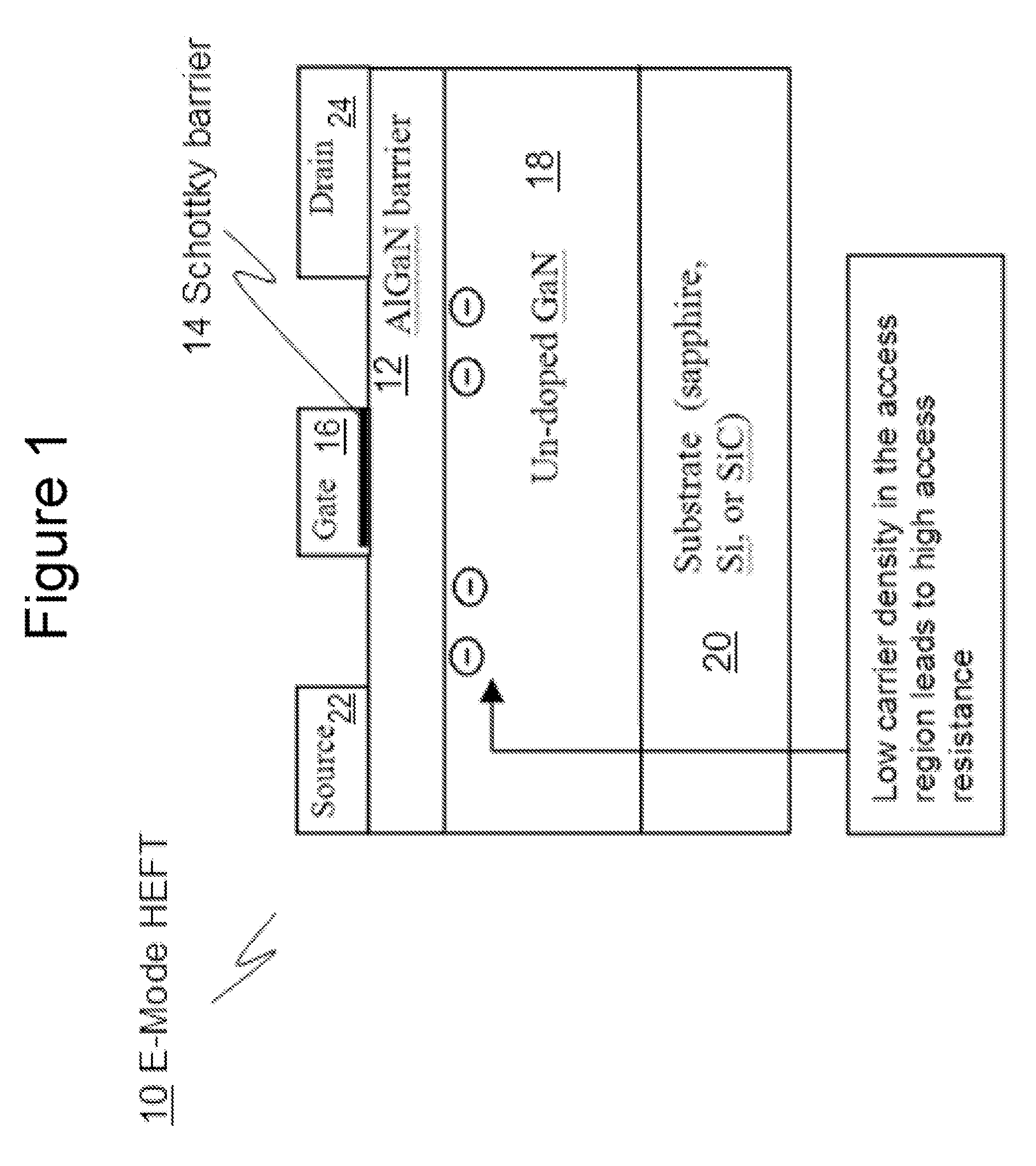

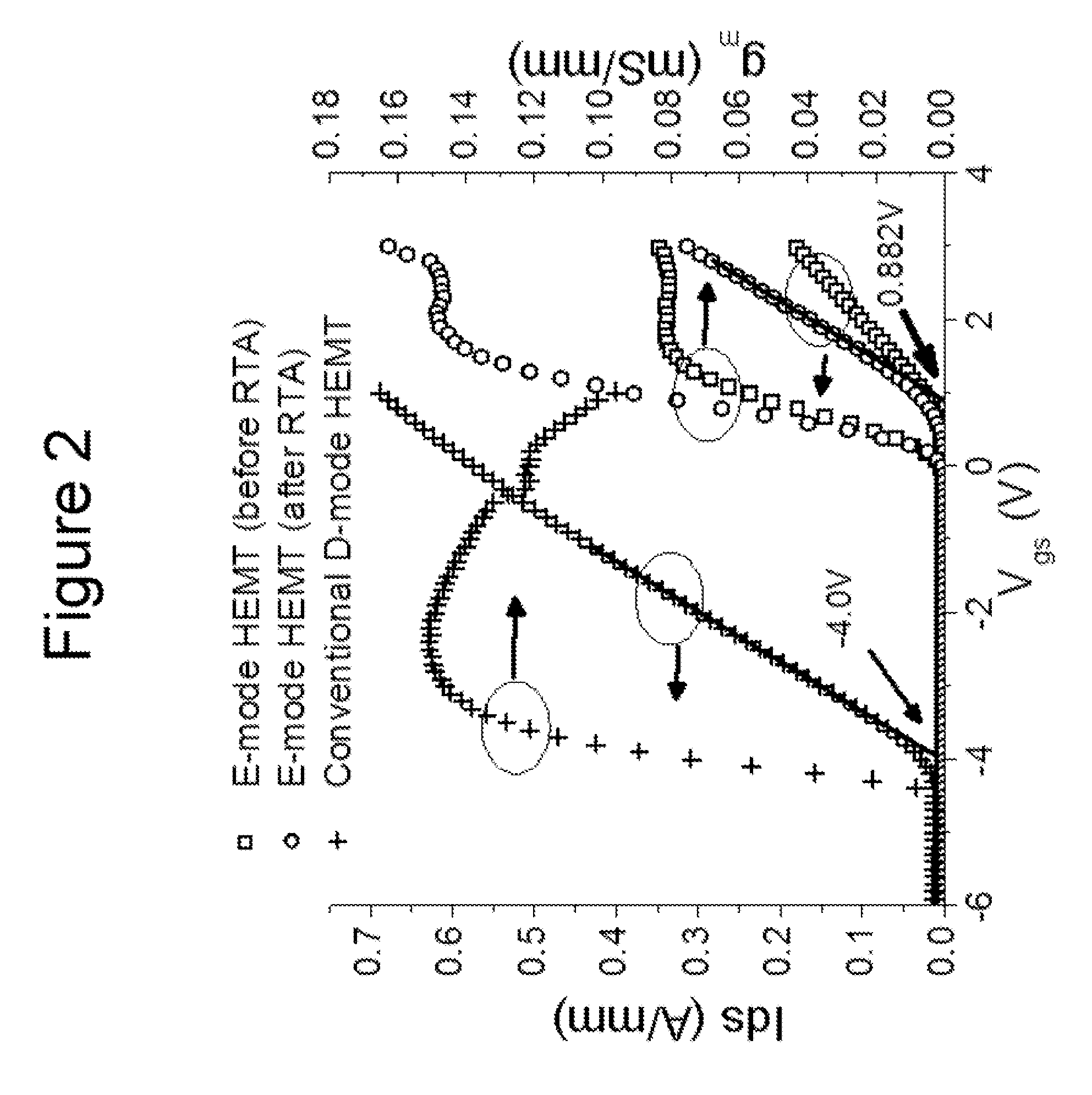

Enhancement-Mode III-N Devices, Circuits, and Methods

ActiveUS20070278518A1High breakdown fieldHigh Power Handling CapabilitySemiconductor devicesPhotoresistIon implantation

A method of fabricating AlGaN / GaN enhancement-mode heterostructure field-effect transistors (HFET) using fluorine-based plasma immersion or ion implantation. The method includes: 1) generating gate patterns; 2) exposing the AlGaN / GaN heterostructure in the gate region to fluorine-based plasma treatment with photoresist as the treatment mask in a self-aligned manner; 3) depositing the gate metal to the plasma treated AlGaN / GaN heterostructure surface; 4) lifting off the metal except the gate electrode; and 5) high temperature post-gate annealing of the sample. This method can be used to shift the threshold voltage of a HFET toward a more positive value, and ultimately convert a depletion-mode HFET to an enhancement-mode HFET (E-HFET).

Owner:THE HONG KONG UNIV OF SCI & TECH

Method of manufacturing semiconductor device

InactiveUS20090317950A1Reduce parasitic resistanceImprove leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageSoi substrate

A semiconductor device manufacturing method which sequentially forms a gate oxide film and gate electrode material over a semiconductor layer of an SOI substrate and patterns the material into gate electrodes. The method further comprises the steps of forming sidewalls made of an insulator to cover side surfaces of the gate electrode; ion-implanting into the semiconductor layer on both sides of the gate electrode to form drain / source regions; partially etching the sidewalls to expose upper parts of the side surfaces of the gate electrode; depositing a metal film to cover the tops of the drain / source regions and of the gate electrode and the exposed upper parts of the side surfaces of the gate electrode; and performing heat treatment on the SOI substrate to form silicide layers respectively in the surfaces of the gate electrode and of the drain / source regions.

Owner:LAPIS SEMICON CO LTD

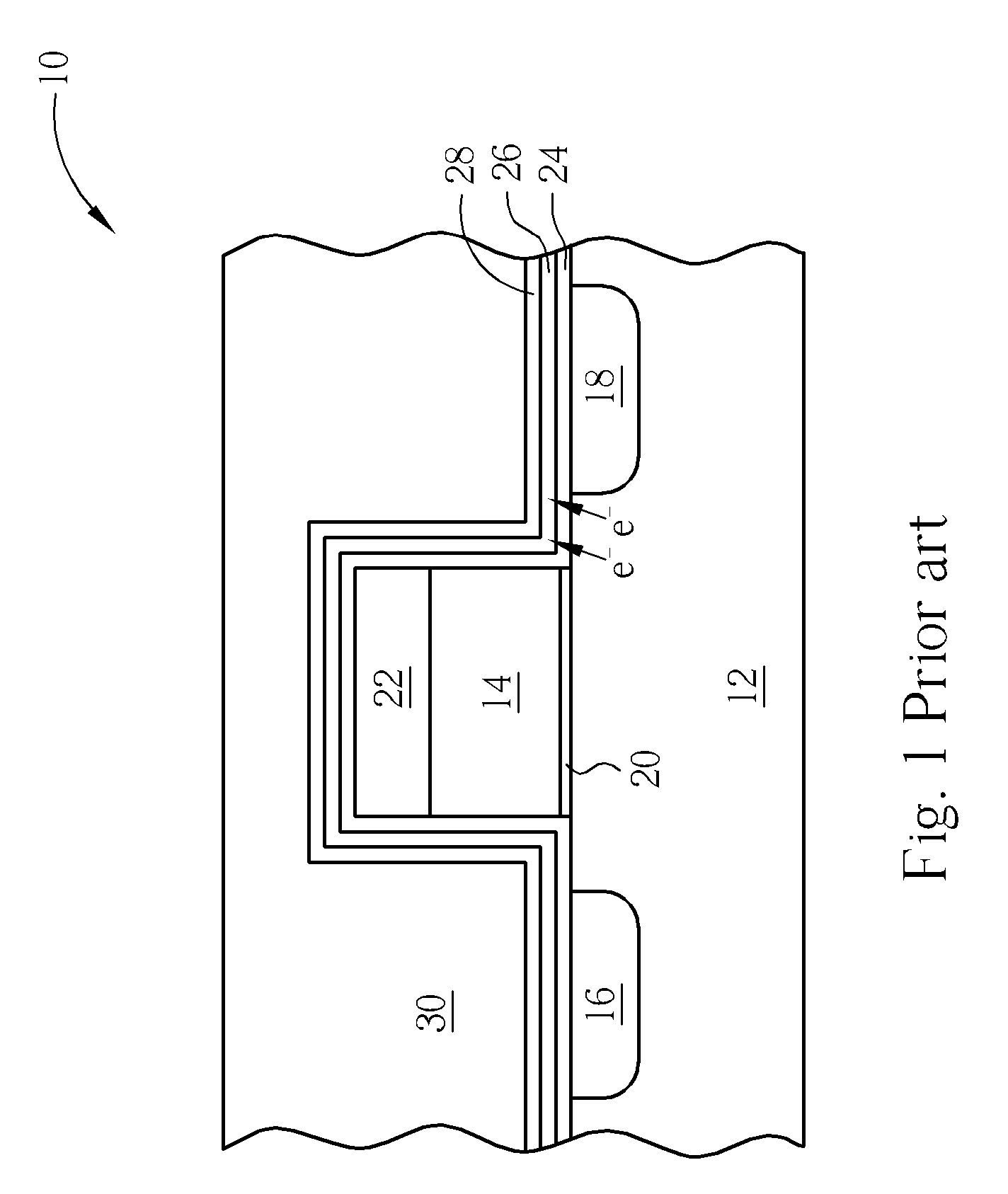

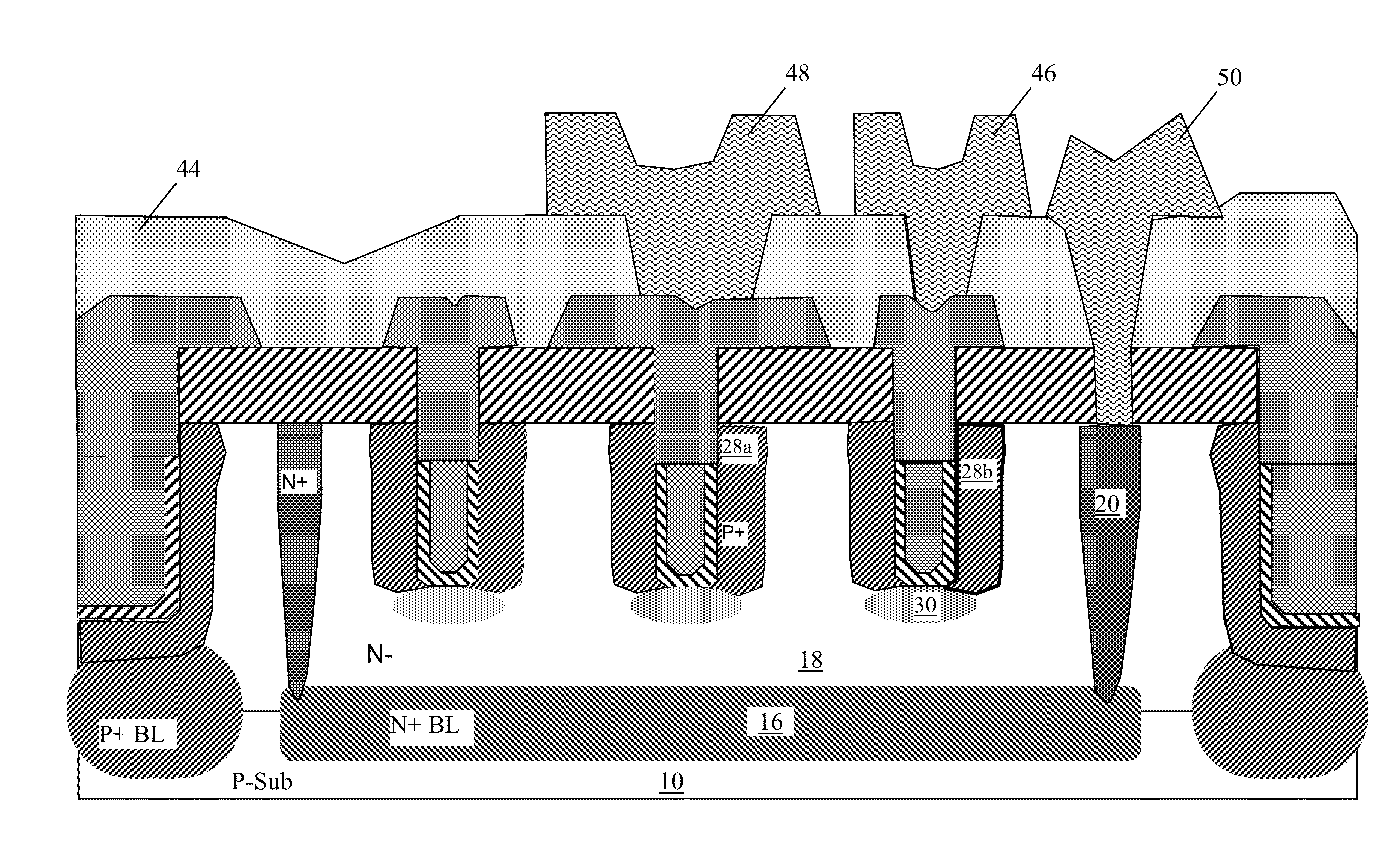

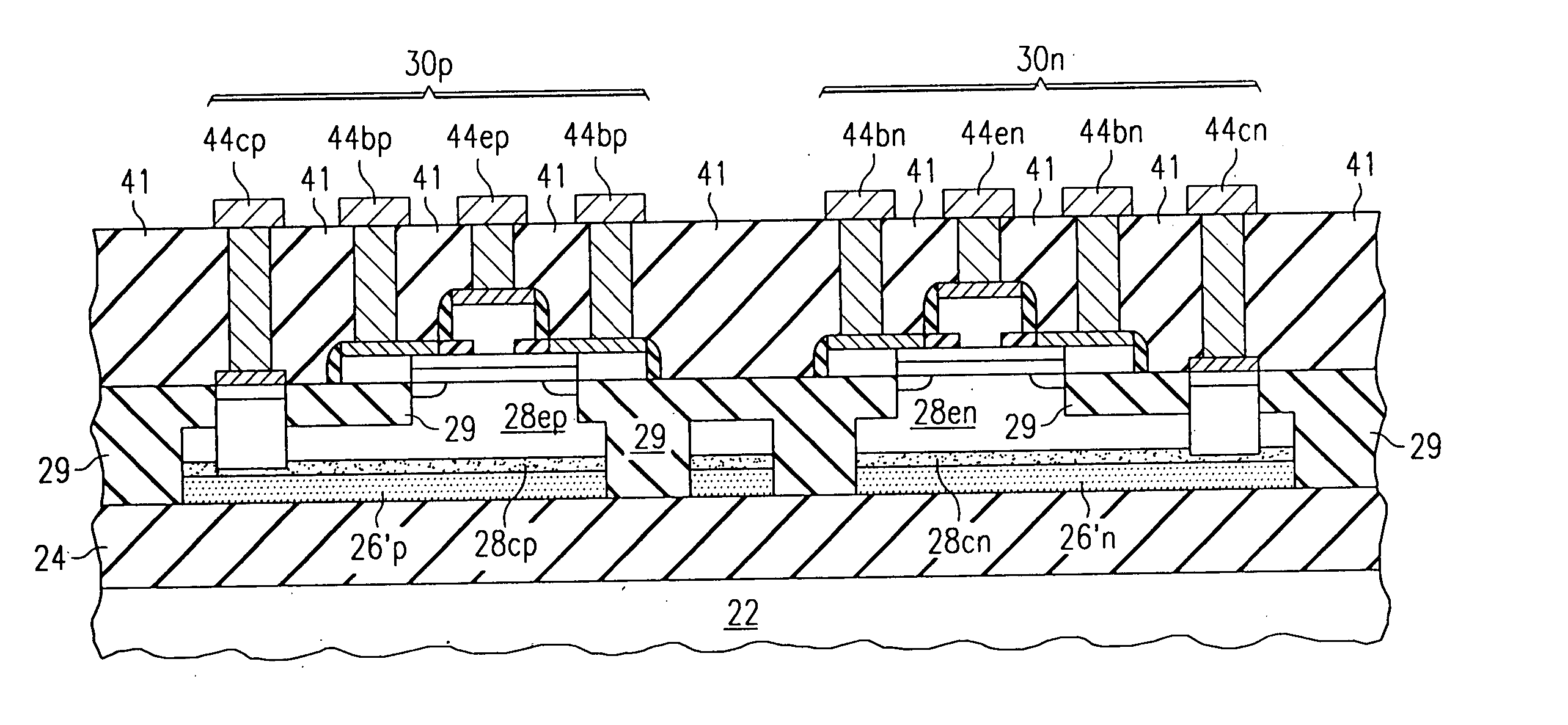

Control of dopant diffusion from buried layers in bipolar integrated circuits

InactiveUS20050250289A1Mitigating dopant diffusionReduce diffuseTransistorSemiconductor/solid-state device manufacturingDopantDiffusion

An integrated circuit and method of fabricating the integrated circuit is disclosed. The integrated circuit includes vertical bipolar transistors (30, 50, 60), each having a buried collector region (26′). A carbon-bearing diffusion barrier (28c) is disposed over the buried collector region (26′), to inhibit the diffusion of dopant from the buried collector region (26′) into the overlying epitaxial layer (28). The diffusion barrier (28c) may be formed by incorporating a carbon source into the epitaxial formation of the overlying layer (28), or by ion implantation. In the case of ion implantation of carbon or SiGeC, masks (52, 62) may be used to define the locations of the buried collector regions (26′) that are to receive the carbon; for example, portions underlying eventual collector contacts (33, 44c) may be masked from the carbon implant so that dopant from the buried collector region (26′) can diffuse upward to meet the contact (33). MOS transistors (70, 80) including the diffusion barrier (28) are also disclosed.

Owner:BABCOCK JEFFREY A +5

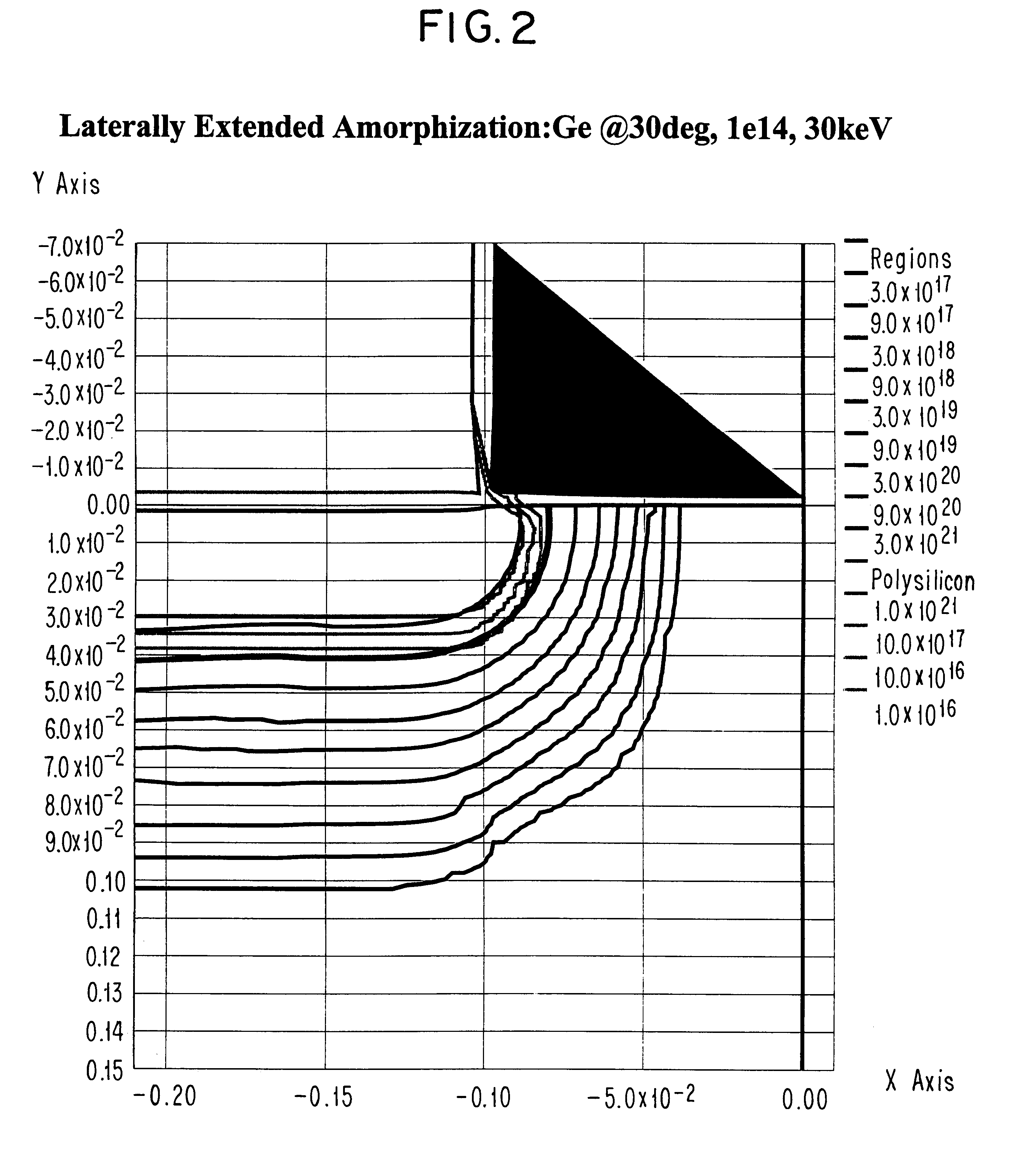

Forming steep lateral doping distribution at source/drain junctions

InactiveUS6268640B1Improved short channel characteristicGood scalabilityTransistorSemiconductor/solid-state device manufacturingIonDopant

A semiconductor device is fabricated by implanting into a semiconductor substrate non-doping ions at a tilt angle of at least about 10° to laterally extend preamorphization of the substrate portion and then implanting into the substrate dopants for providing source / drain extensions or halo doping or both.

Owner:IBM CORP

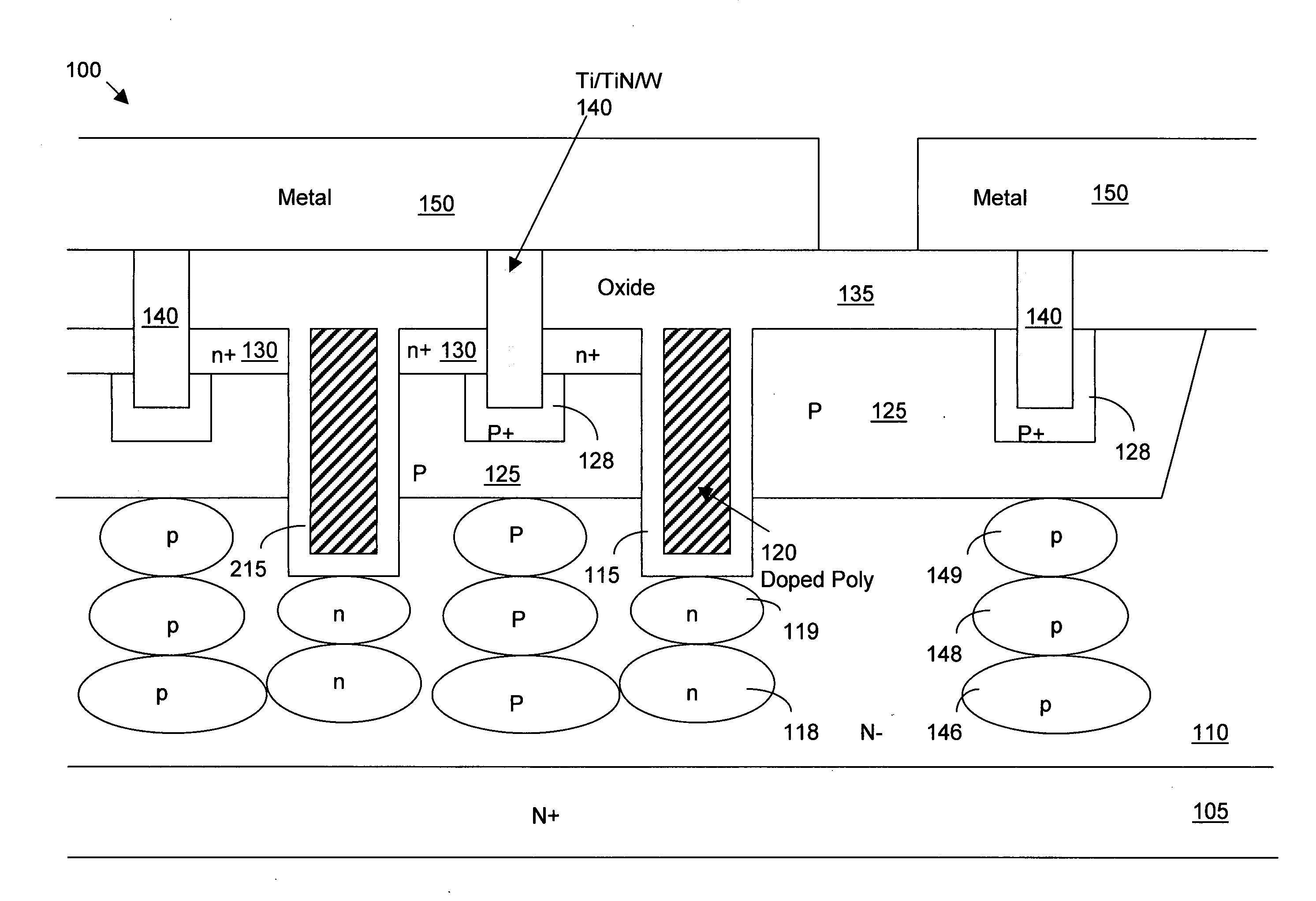

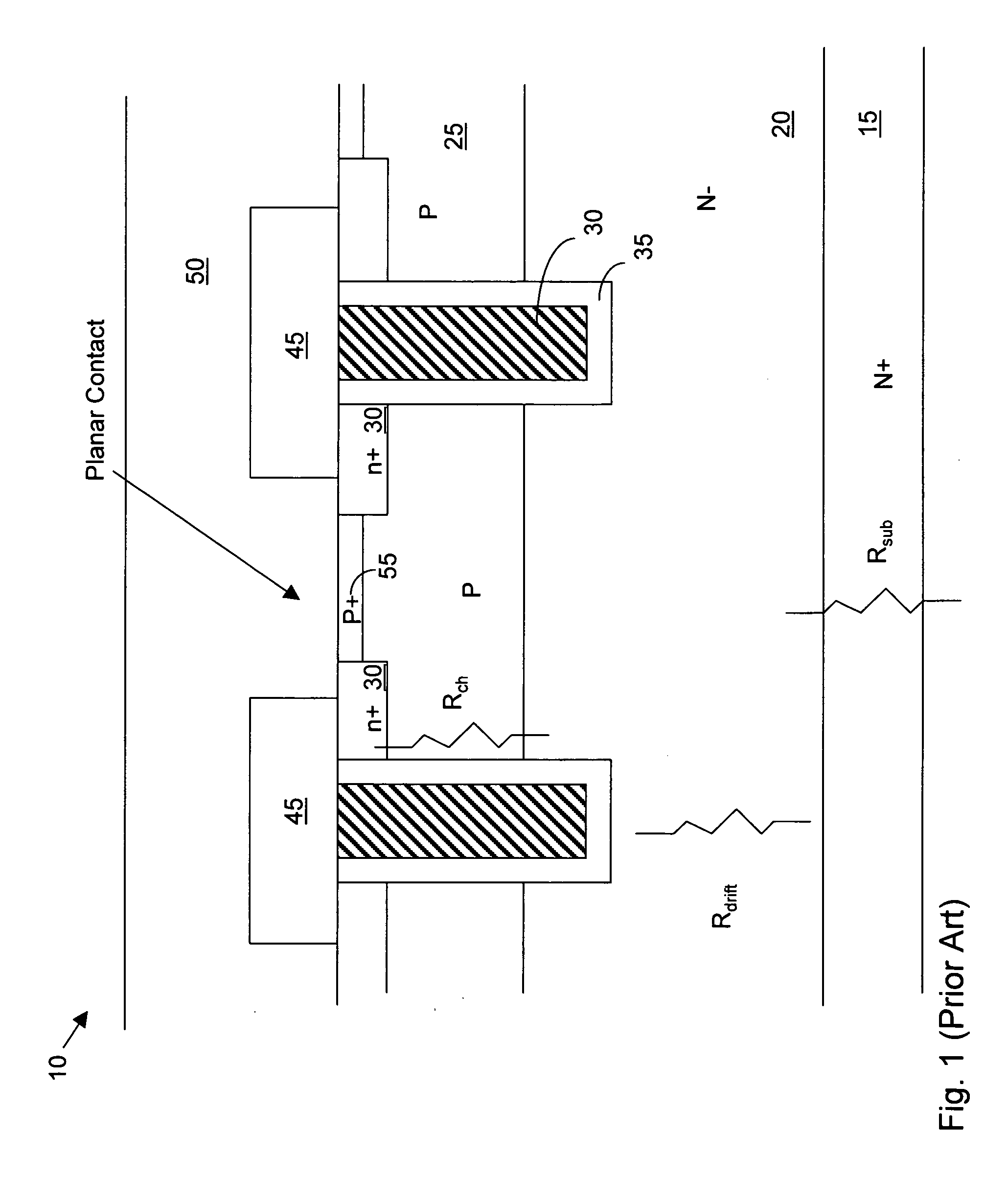

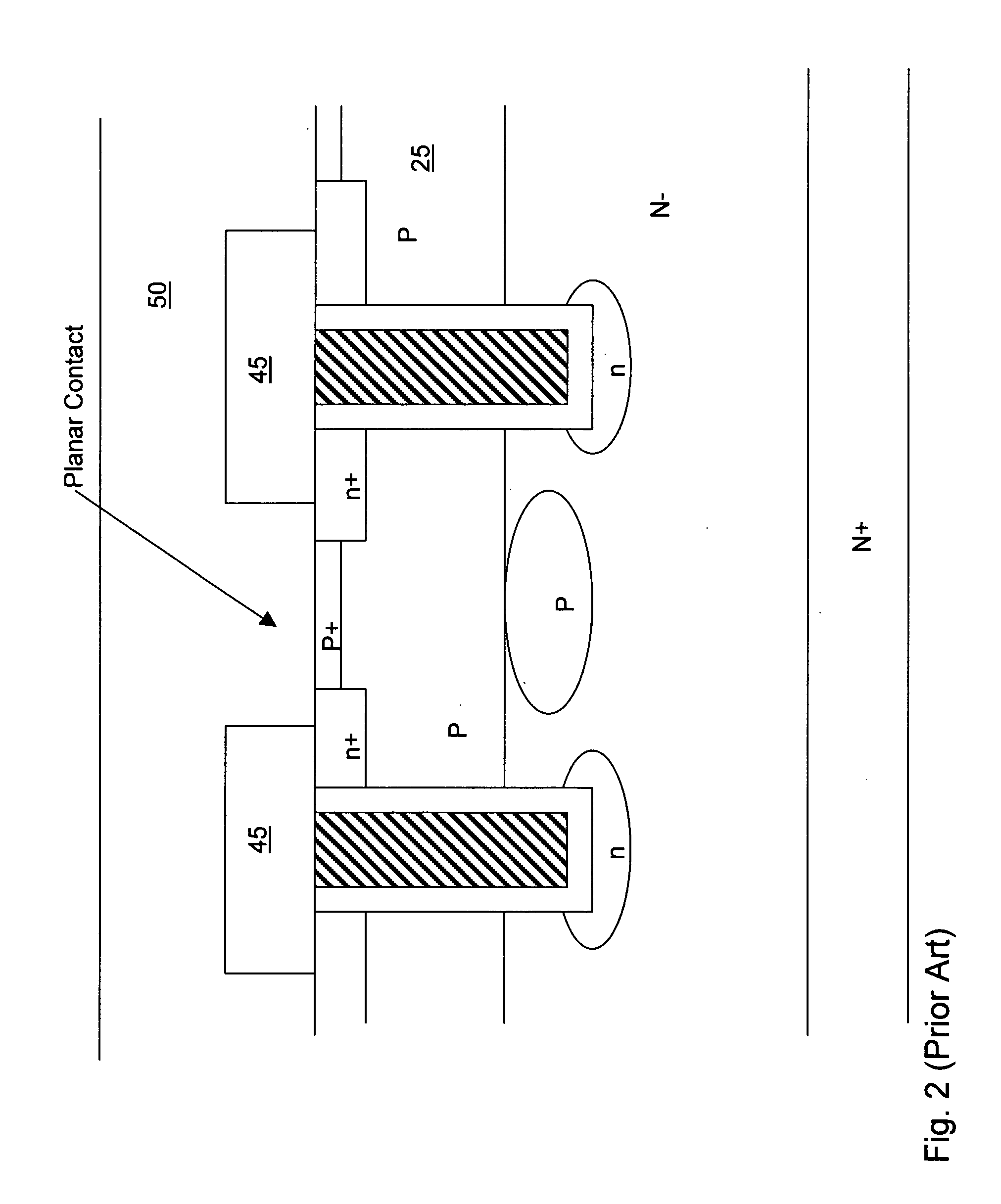

High density trench MOSFET with reduced on-resistance

InactiveUS20070114599A1Reduce resistanceImprove breakdown voltageSemiconductor devicesInsulation layerBody contact

Owner:M MOS SEMICON

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com