Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

92 results about "Junction isolation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

P–n junction isolation. Jump to navigation Jump to search. p–n junction isolation is a method used to electrically isolate electronic components, such as transistors, on an integrated circuit (IC) by surrounding the components with reverse biased p–n junctions.

Low capacitance junction-isolation for bulk FinFET technology

ActiveUS7101763B1Good junction isolationLow capacitance benefitSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricCapacitance

The present invention provides a SiGe-based bulk integration scheme for generating FinFET devices on a bulk Si substrate in which a simple etch, mask, ion implant set of sequences have been added to accomplish good junction isolation while maintaining the low capacitance benefits of FinFETs. The method of the present invention includes providing a structure including a bottom Si layer and a patterned stack comprising a SiGe layer and a top Si layer on the bottom Si layer; forming a well region and isolation regions via implantation within the bottom Si layer; forming an undercut region beneath the top Si layer by etching back the SiGe layer; and filling the undercut with a dielectric to provide device isolation, wherein the dielectric has an outer vertical edge that is aligned to an outer vertical edge of the top Si layer.

Owner:GLOBALFOUNDRIES US INC

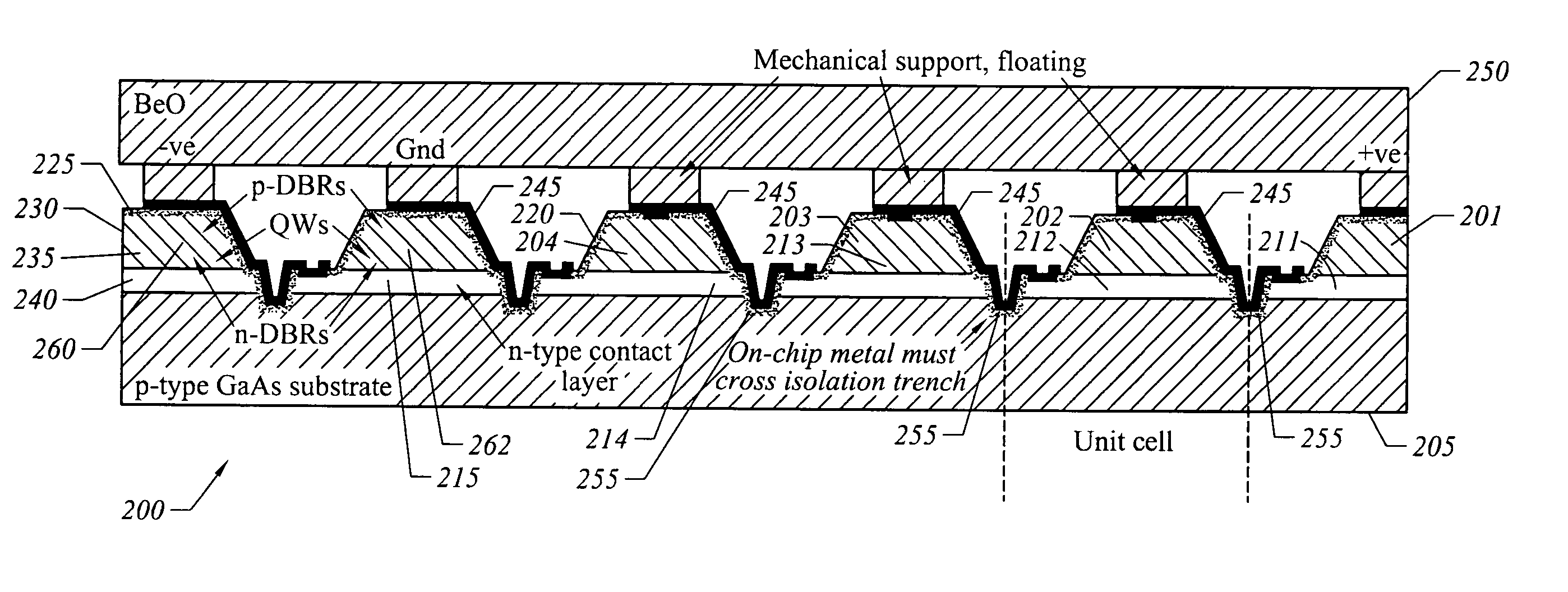

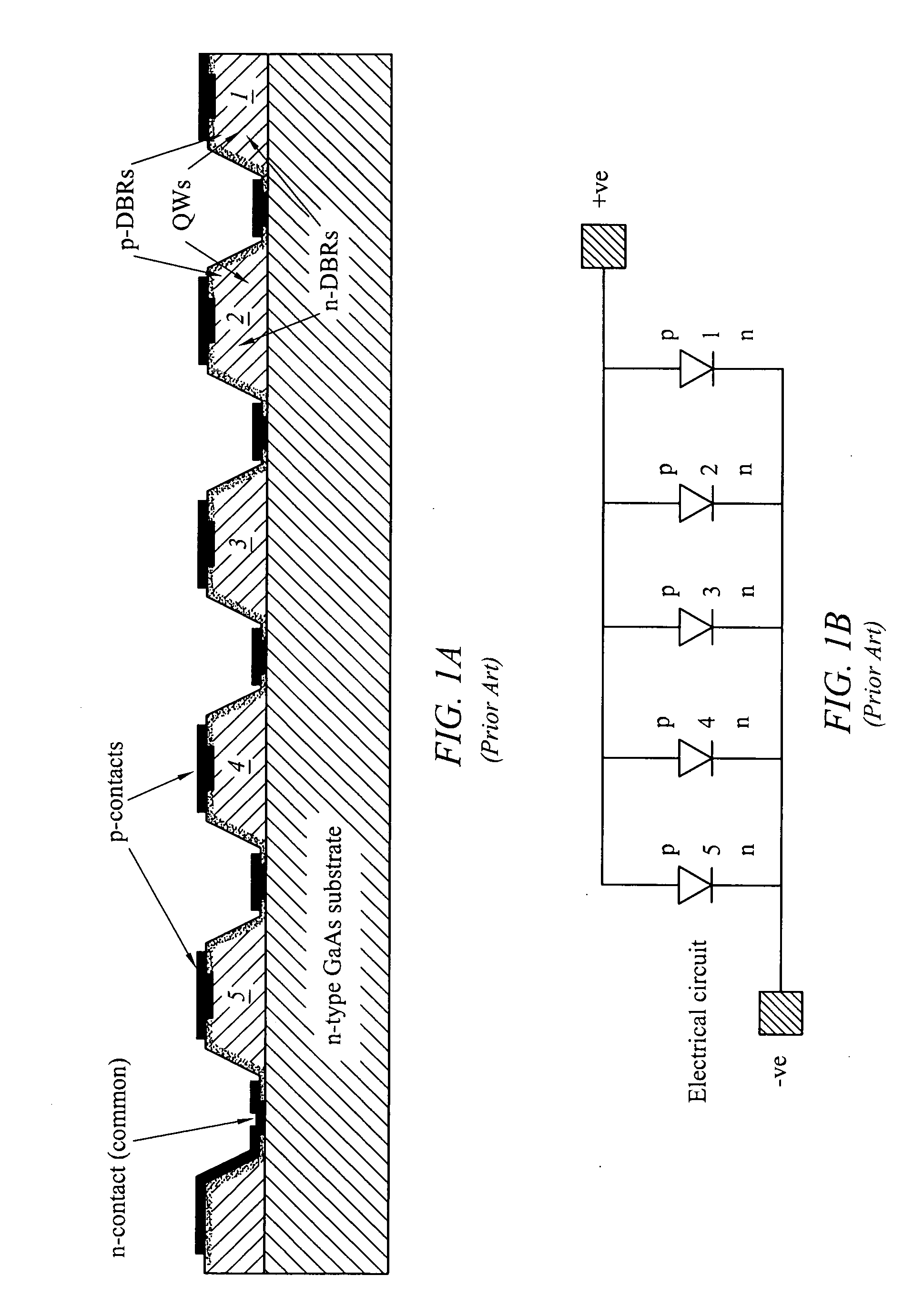

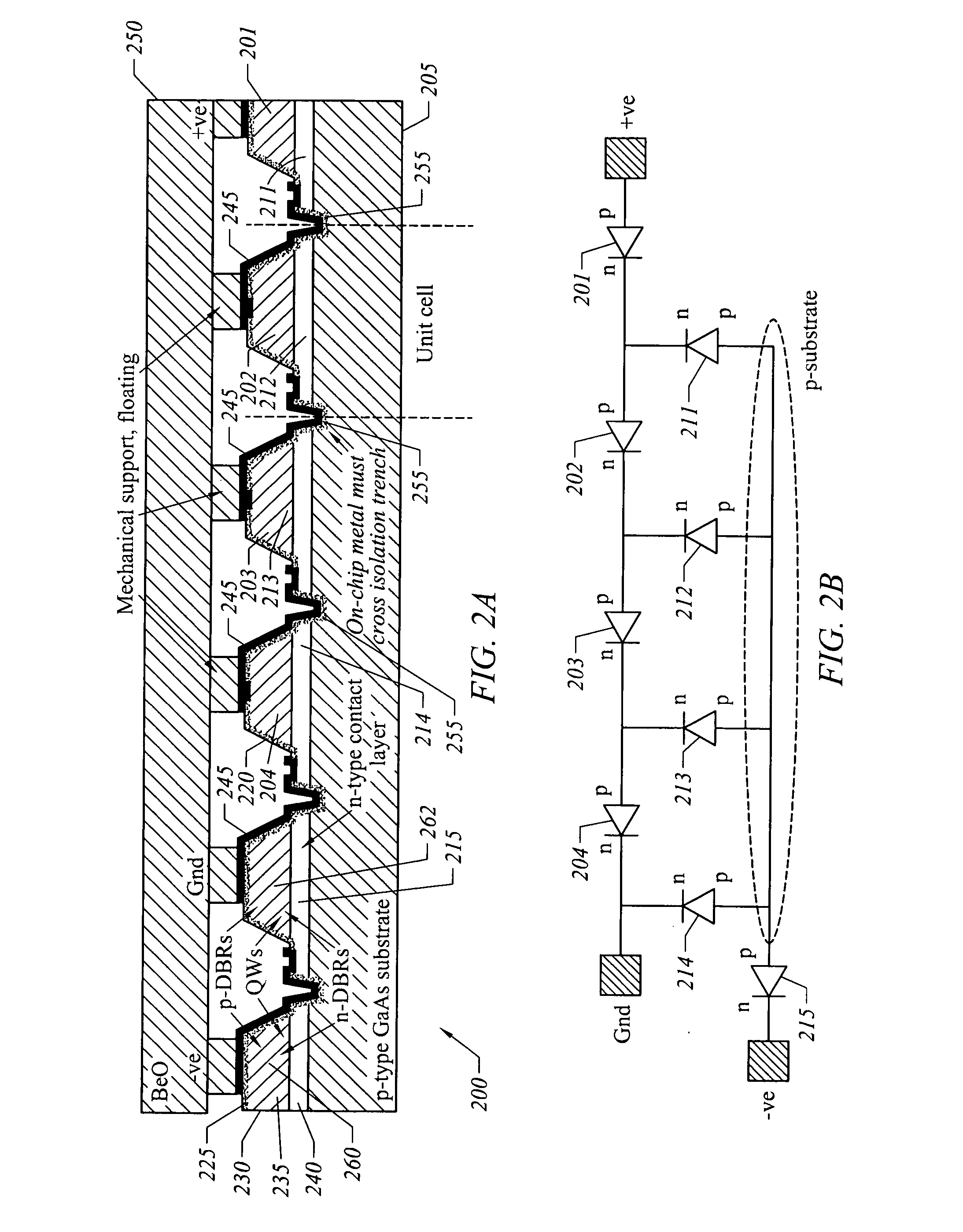

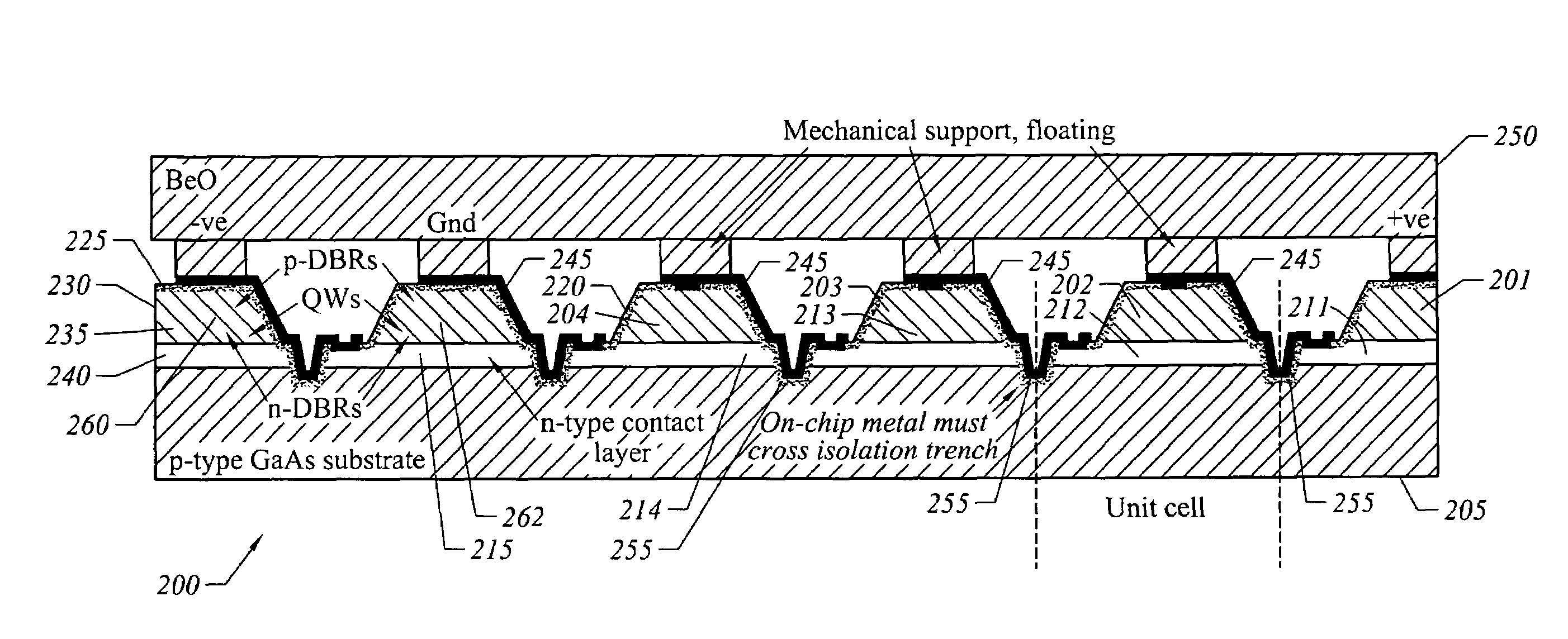

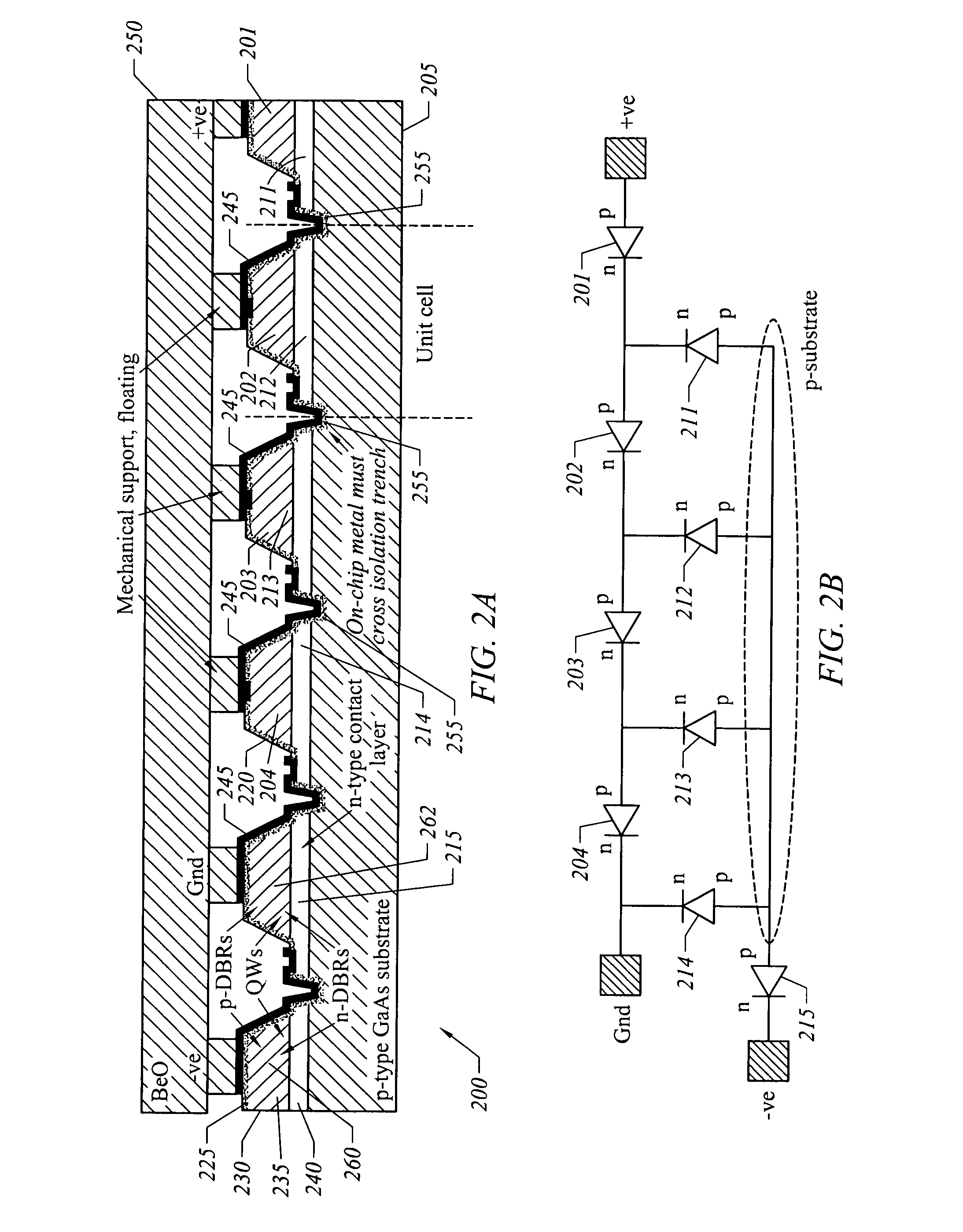

Apparatus, system, and method for junction isolation of arrays of surface emitting lasers

An array of surface emitting laser diodes has a series electrical connection of laser diodes. Junction isolation is used to isolate laser diodes in the array.

Owner:NECSEL INTPROP +1

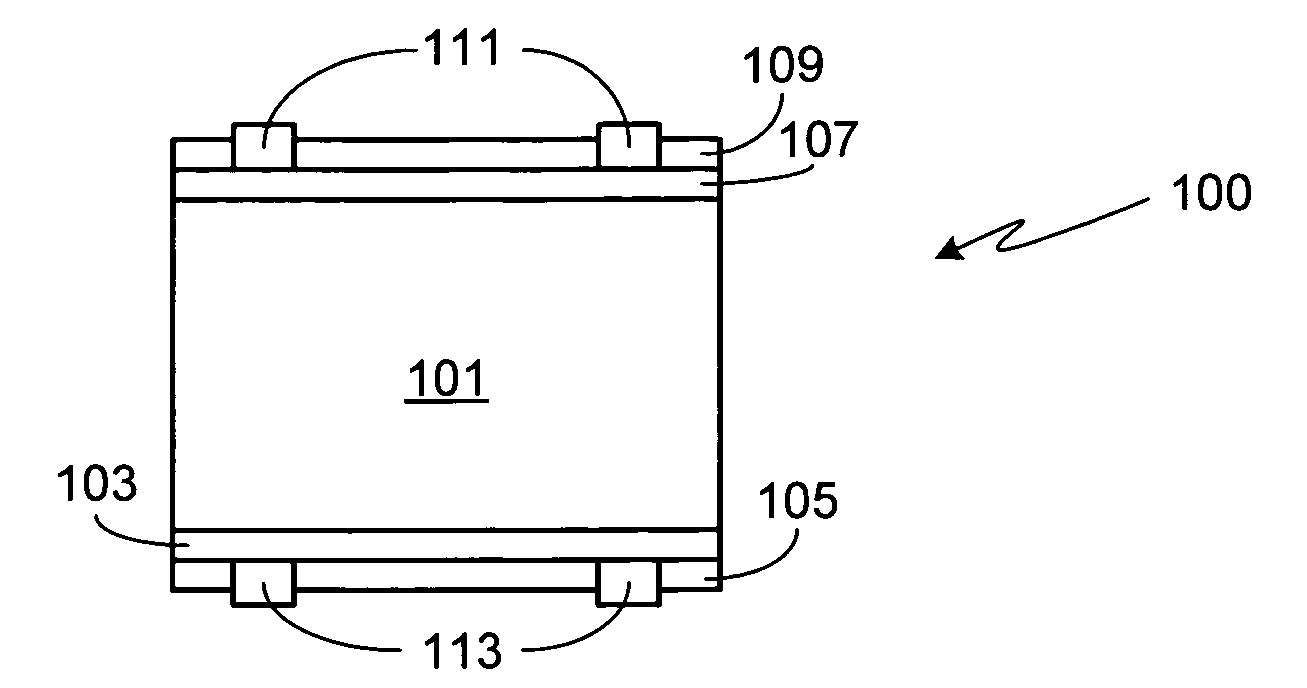

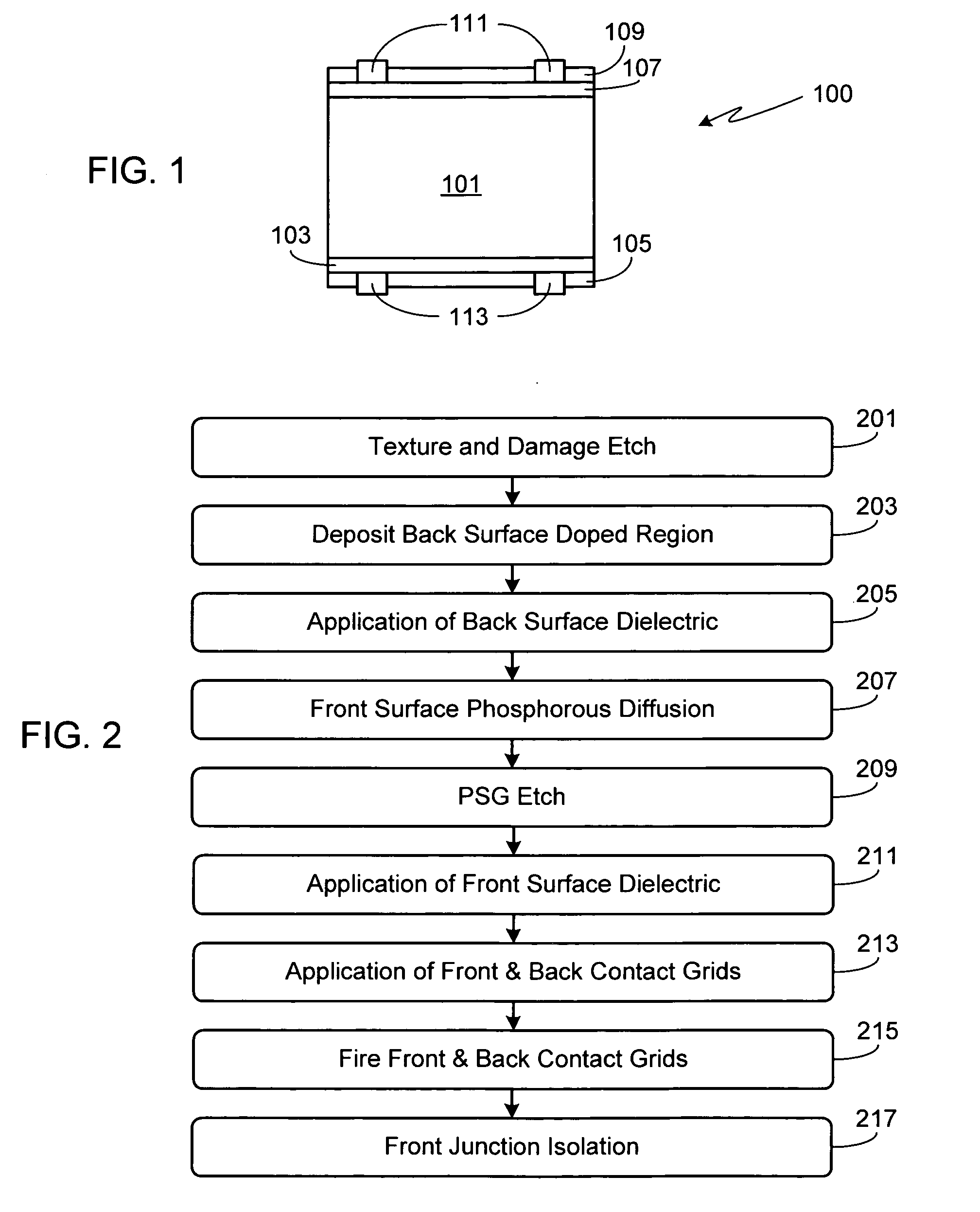

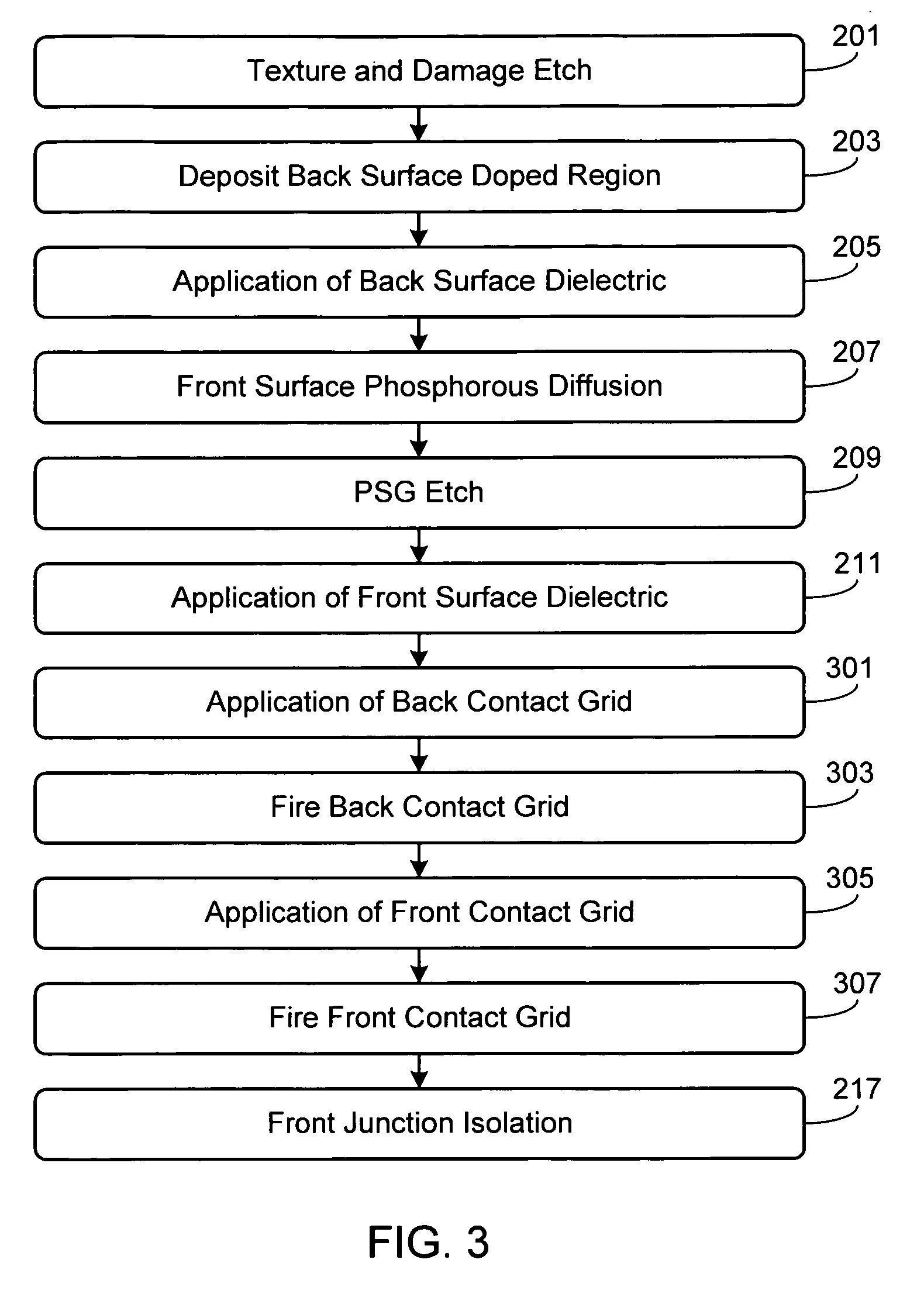

Bifacial solar cells with back surface doping

InactiveUS20100275984A1Simple manufacturing processReduce manufacturing costFinal product manufactureSemiconductor/solid-state device manufacturingScreen printingEngineering

A simplified manufacturing process and the resultant bifacial solar cell (BSC) are provided, the simplified manufacturing process reducing manufacturing costs. The BSC includes an active region located on the front surface of the substrate, formed for example by a phosphorous diffusion step. The back surface includes a doped region, the doped region having the same conductivity as the substrate but with a higher doping level. Contact grids are formed, for example by screen printing. Front junction isolation is accomplished using a laser scribe.

Owner:HIGHLAND MATERIALS INC

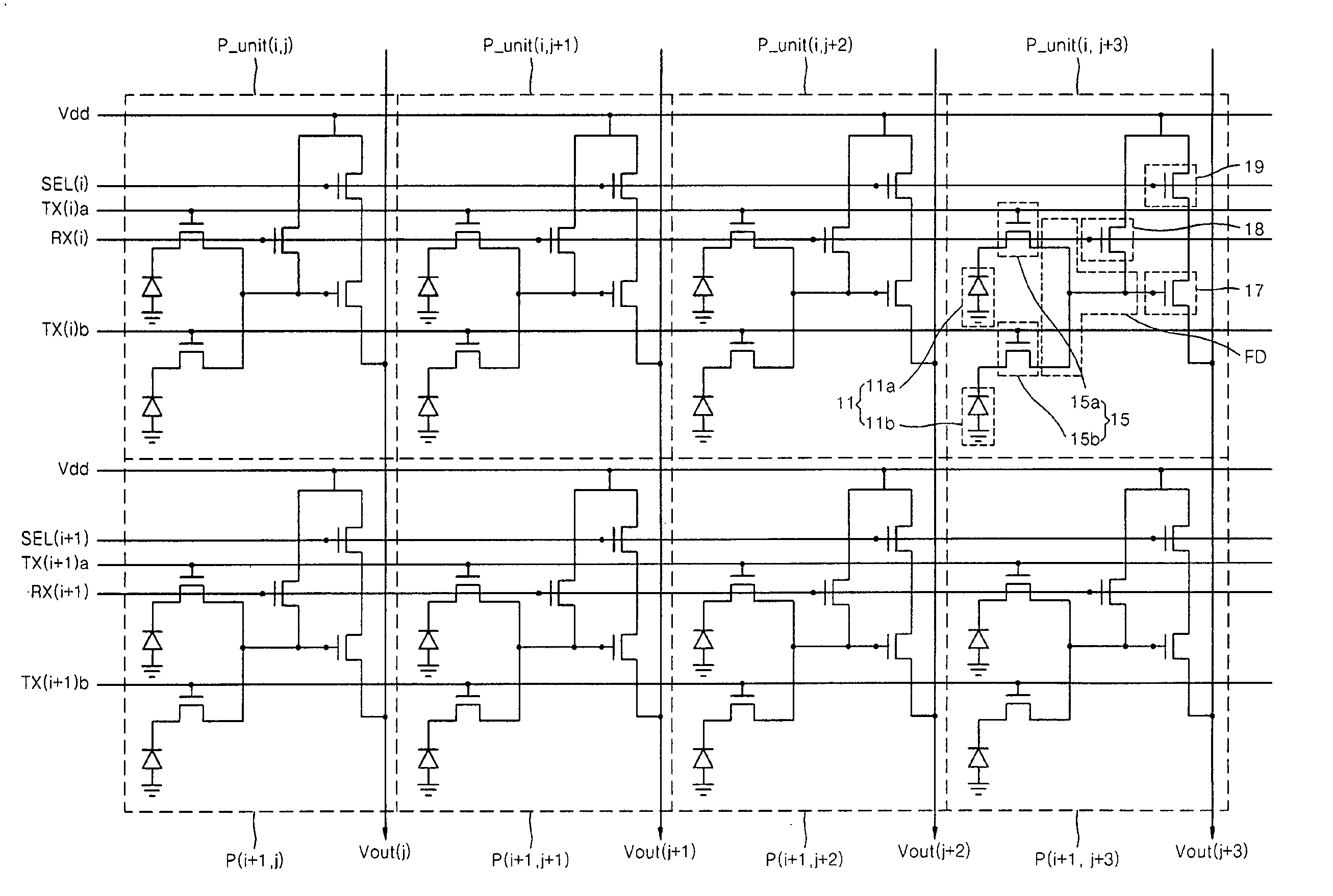

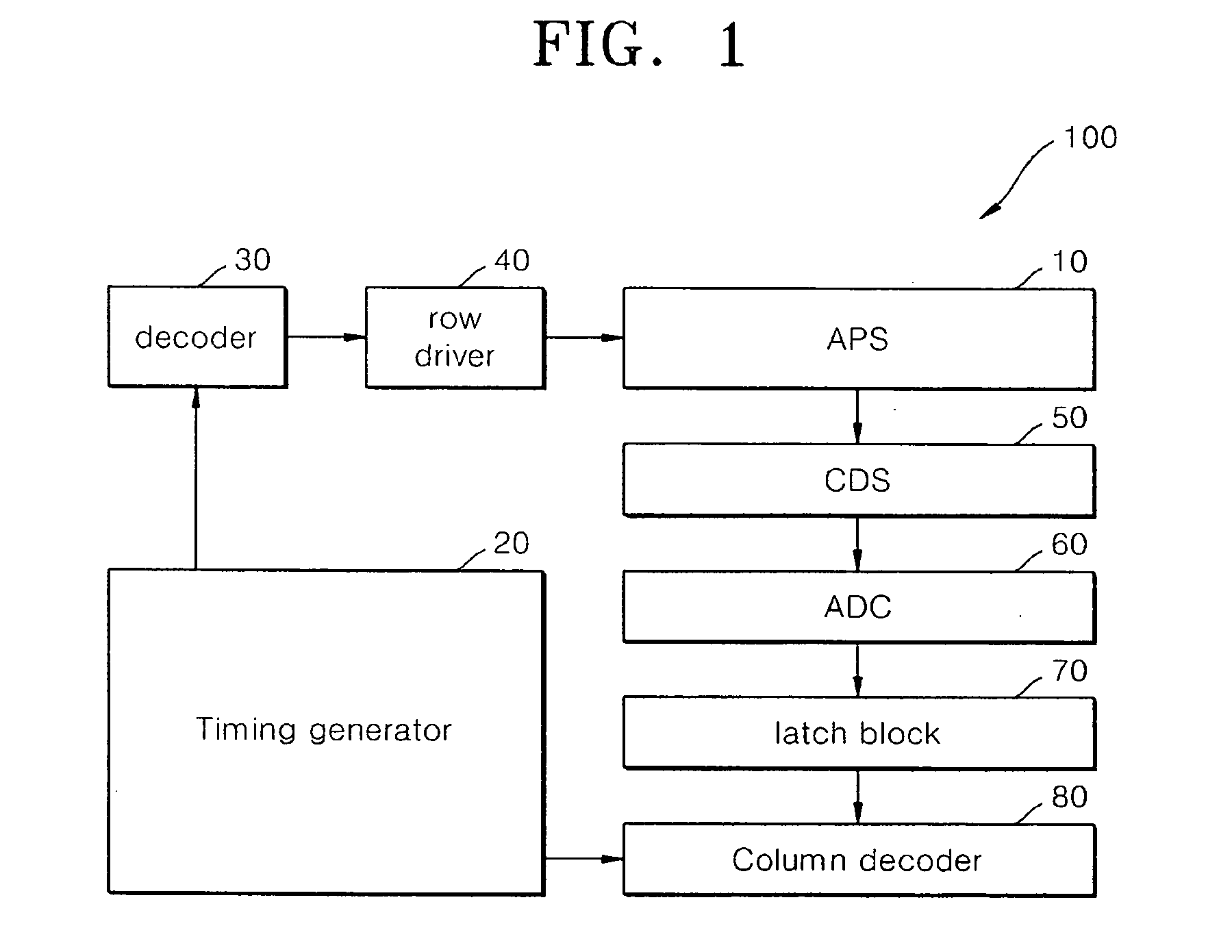

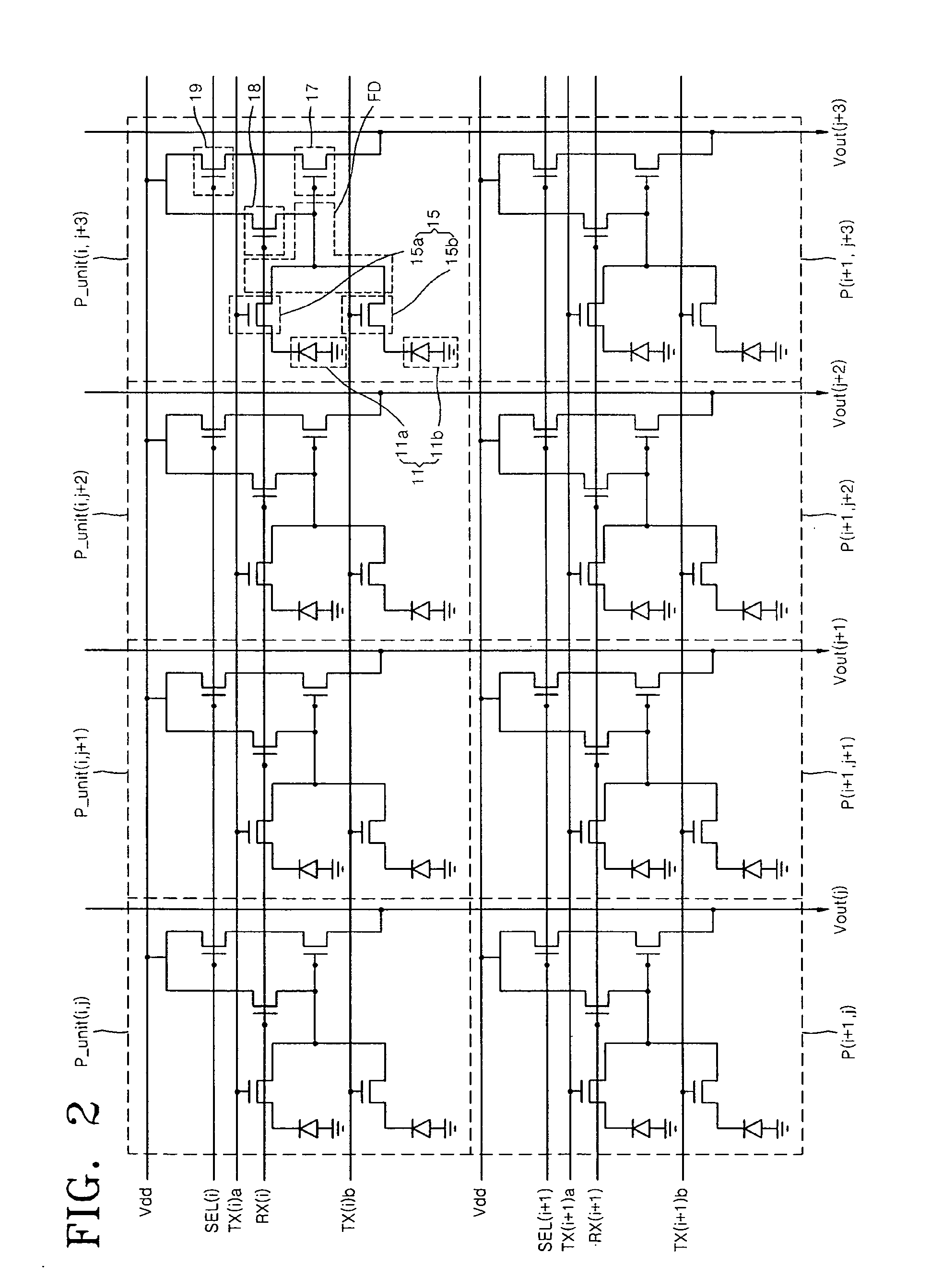

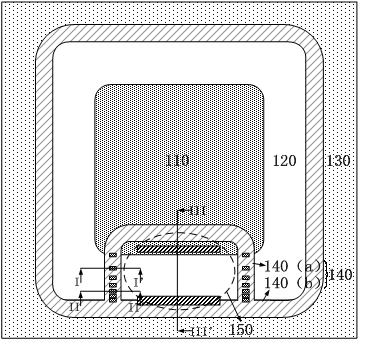

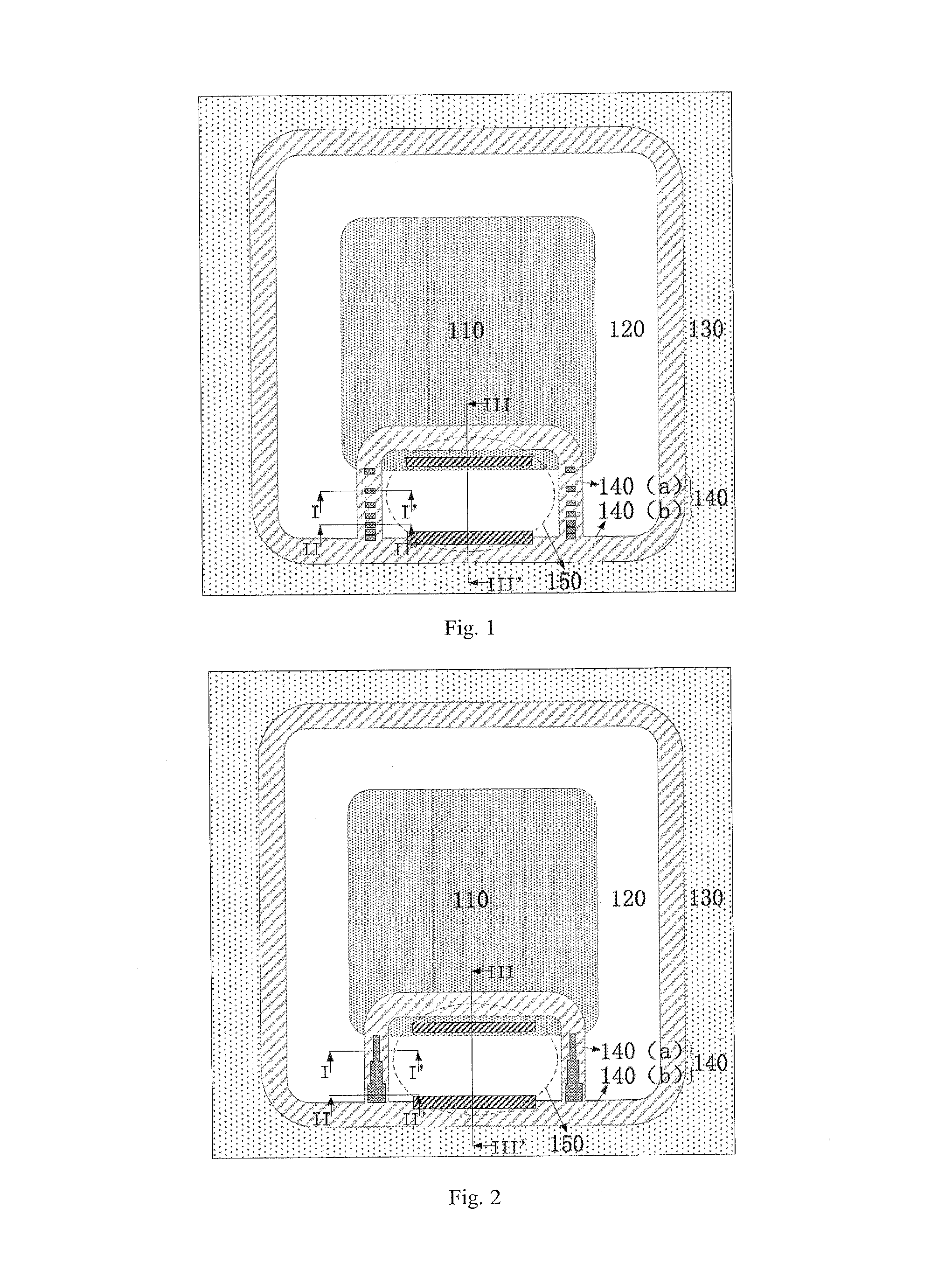

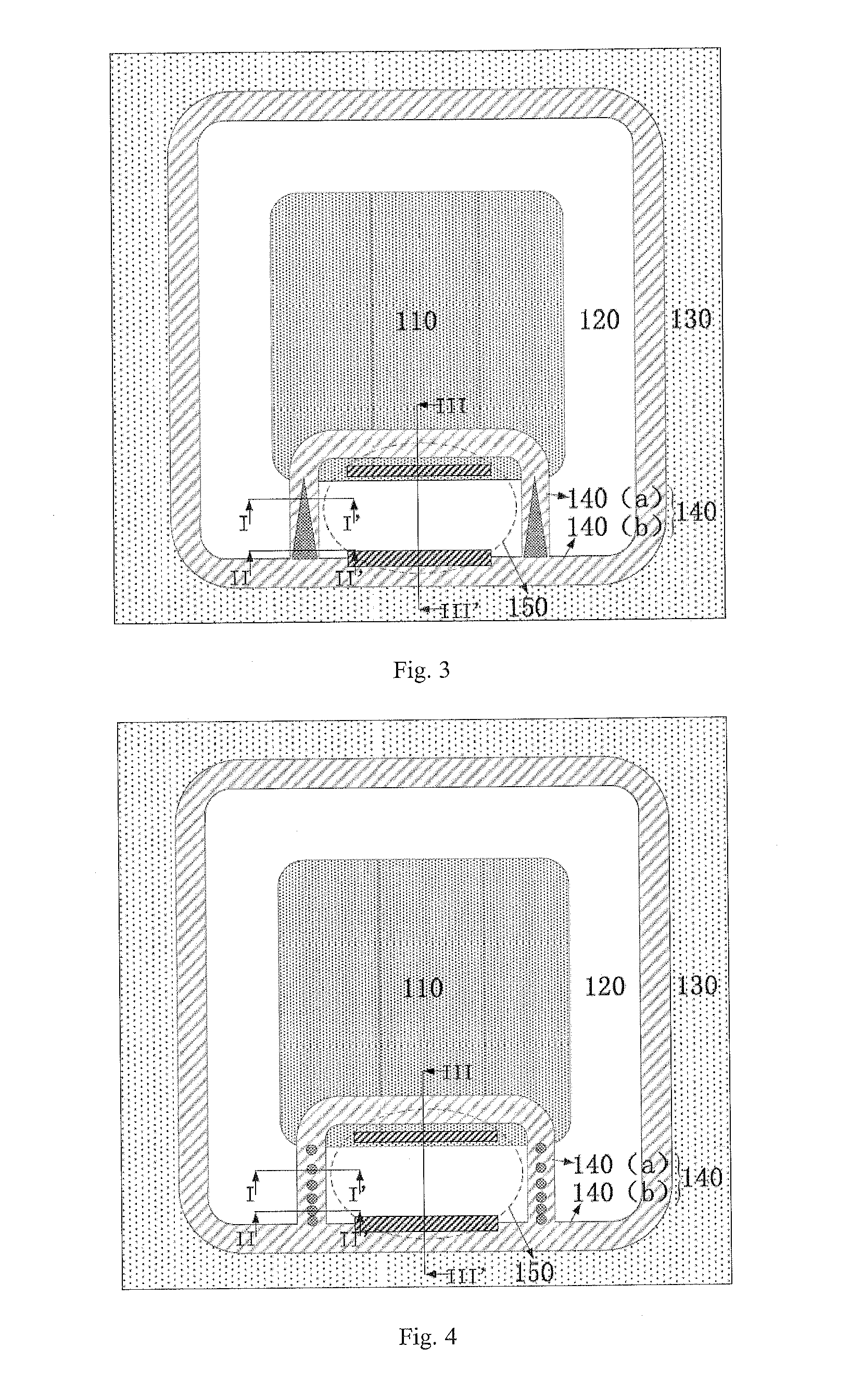

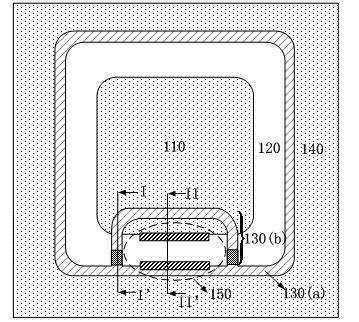

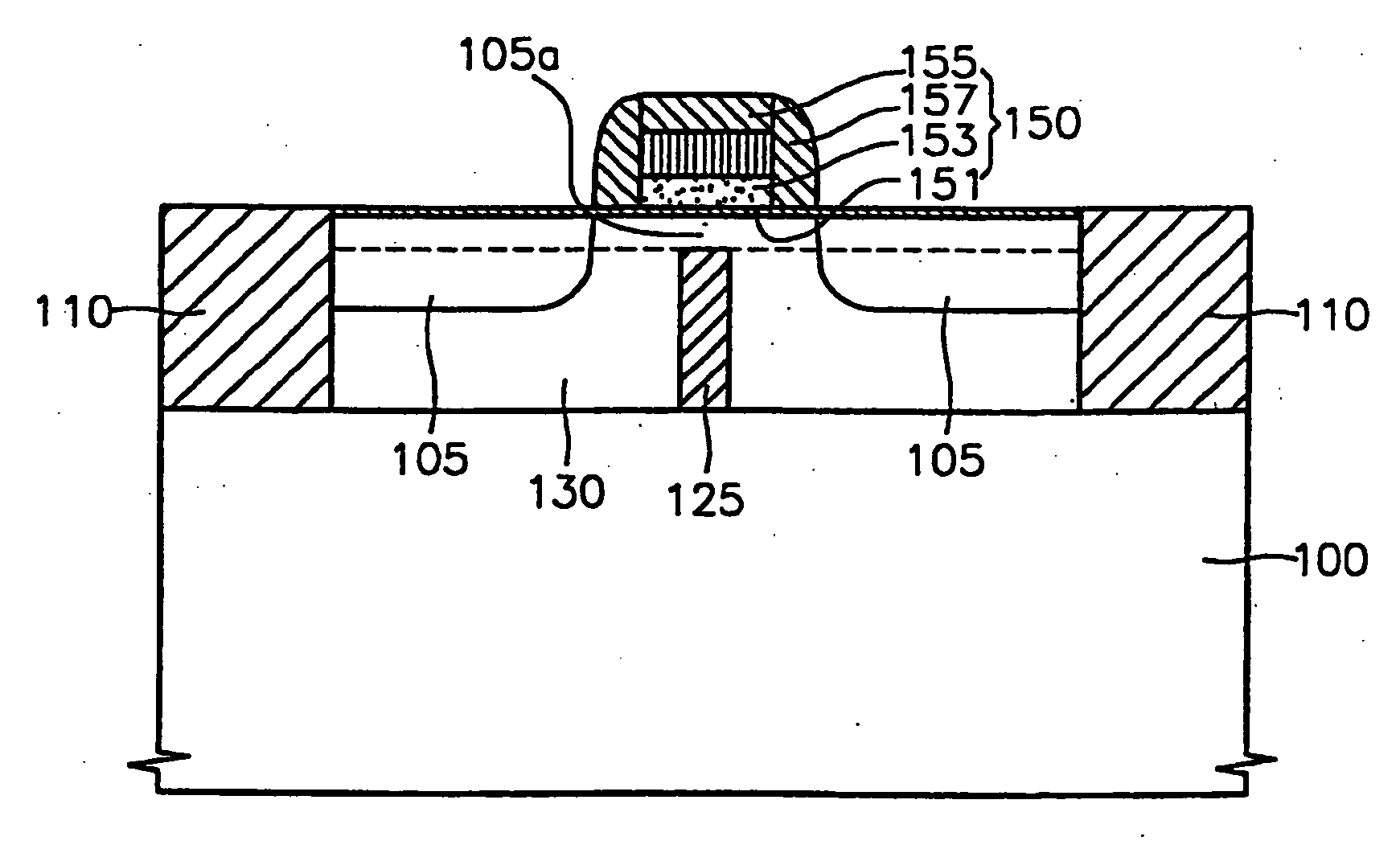

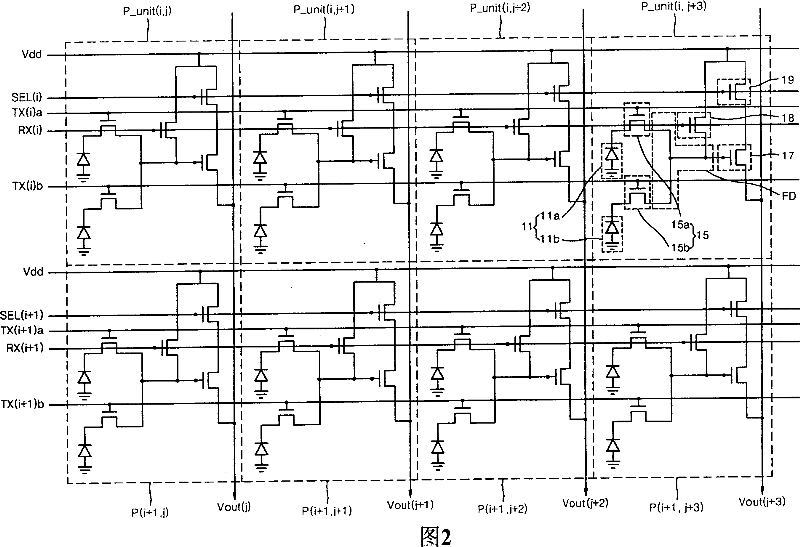

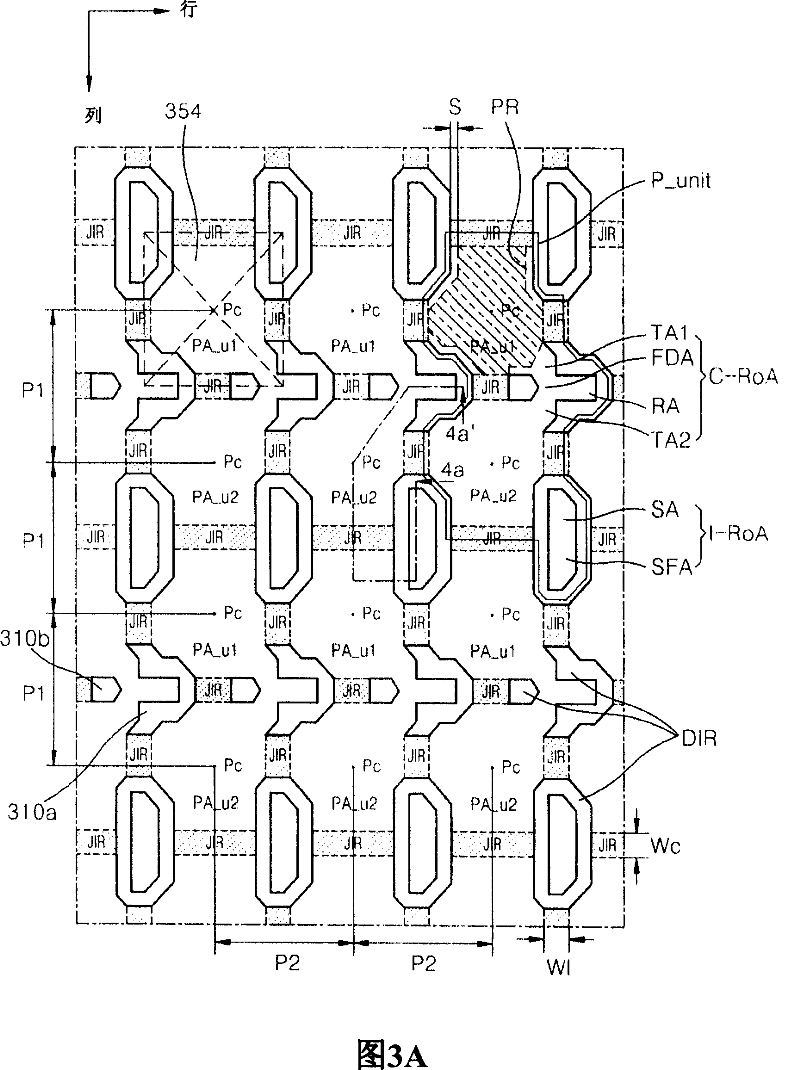

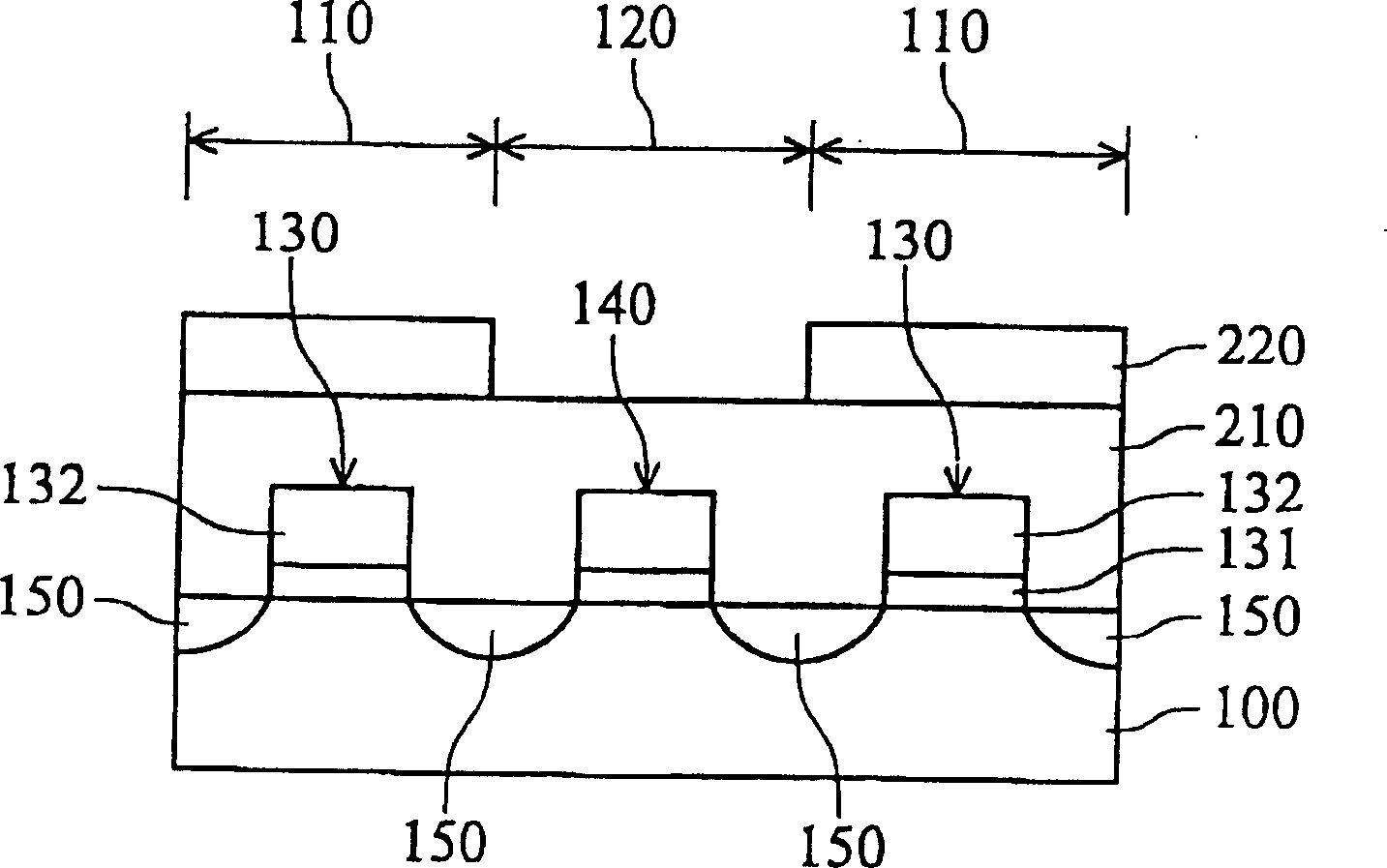

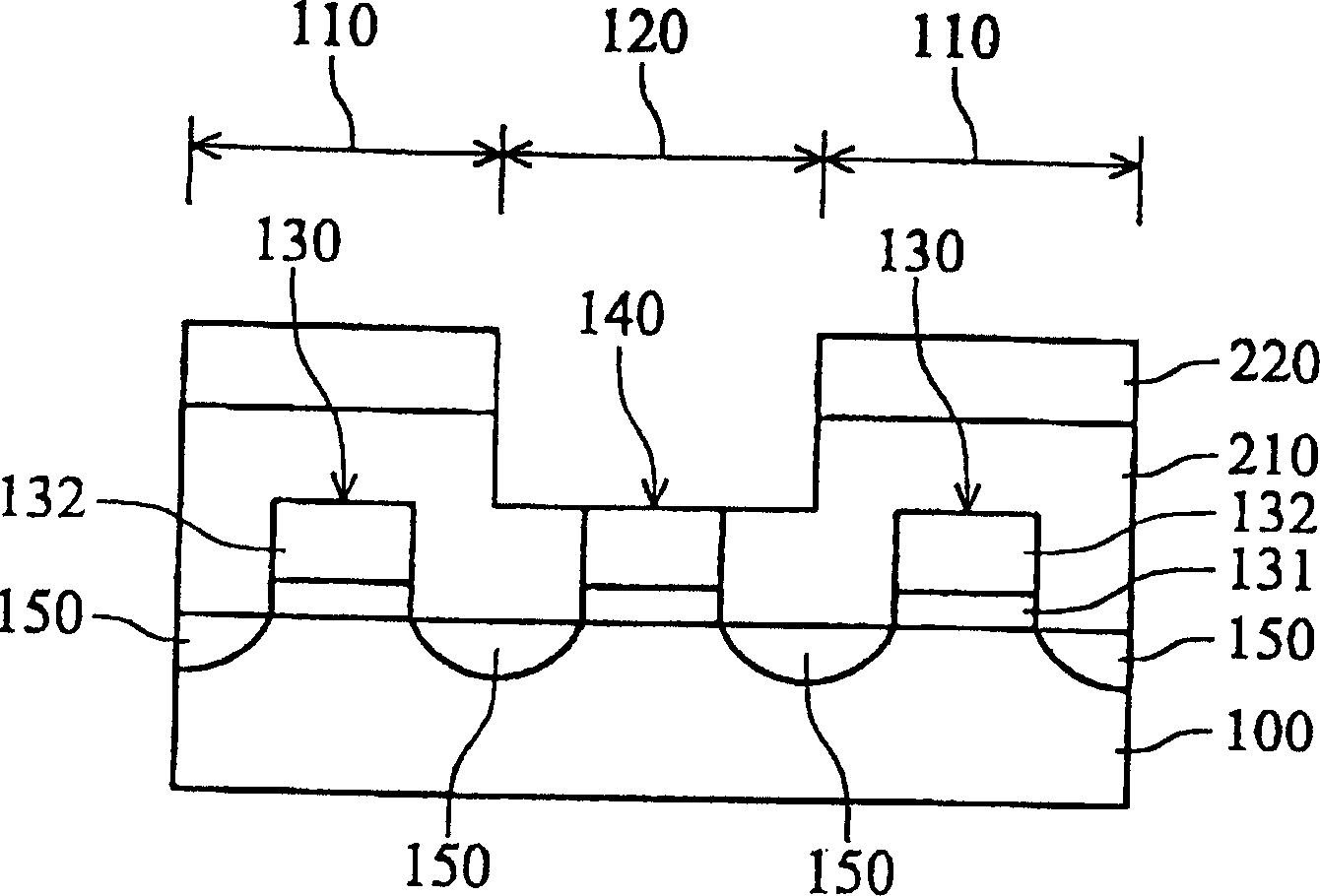

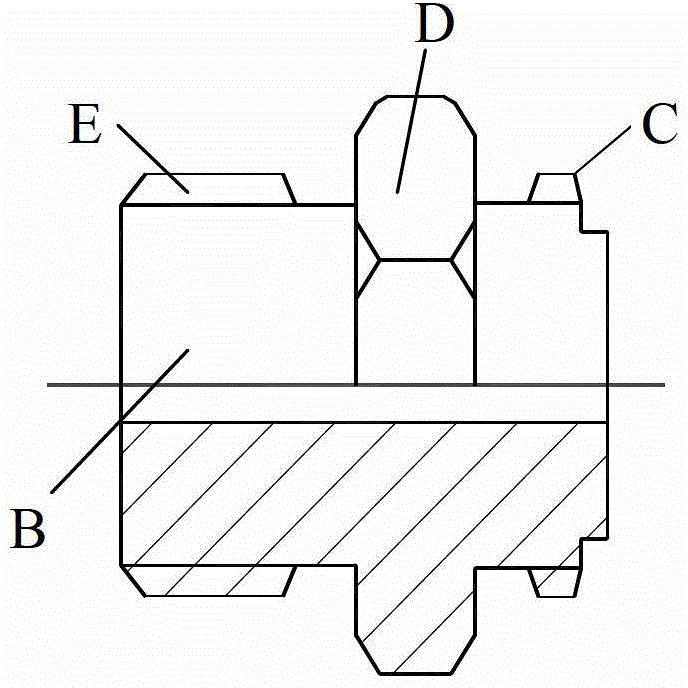

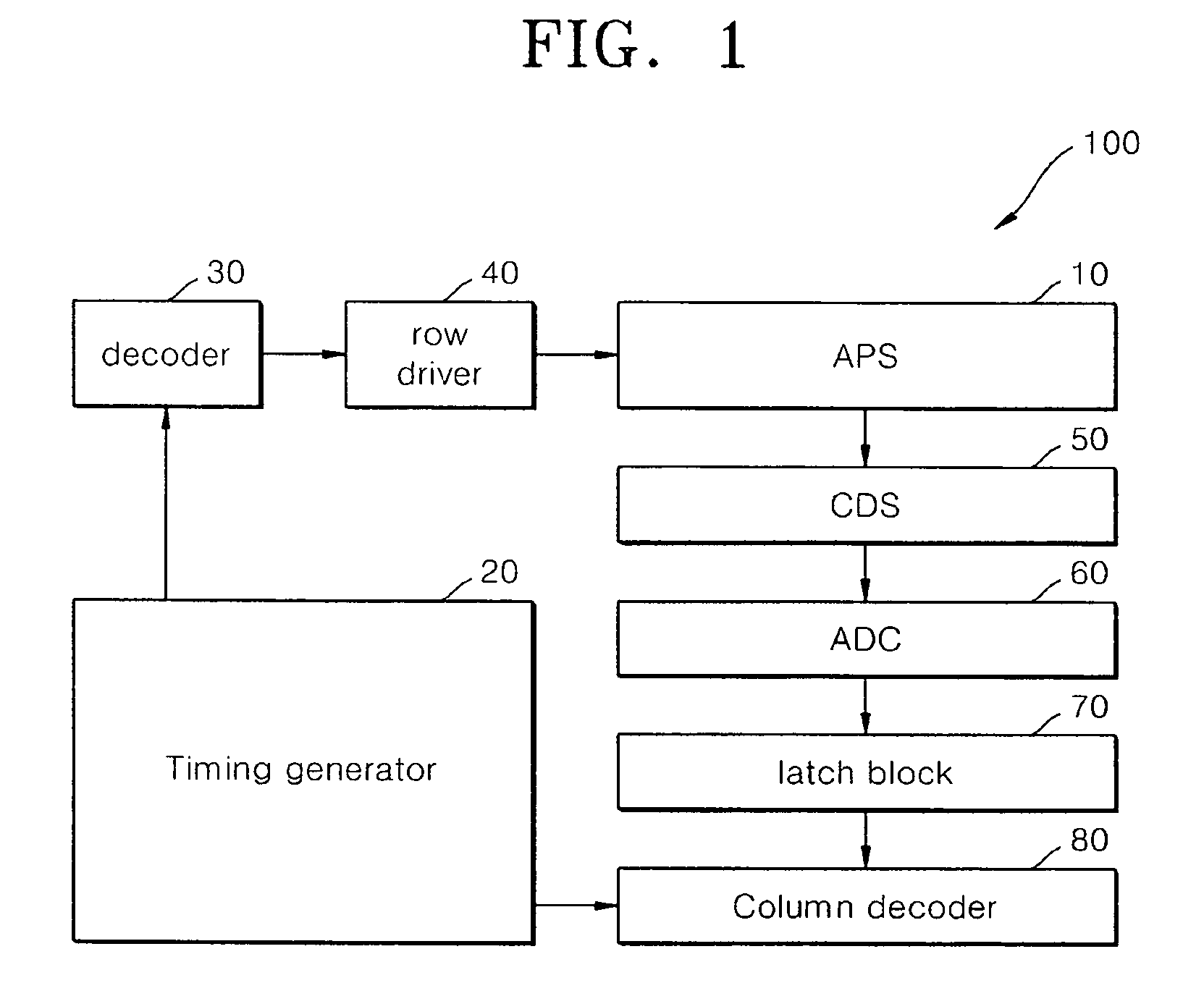

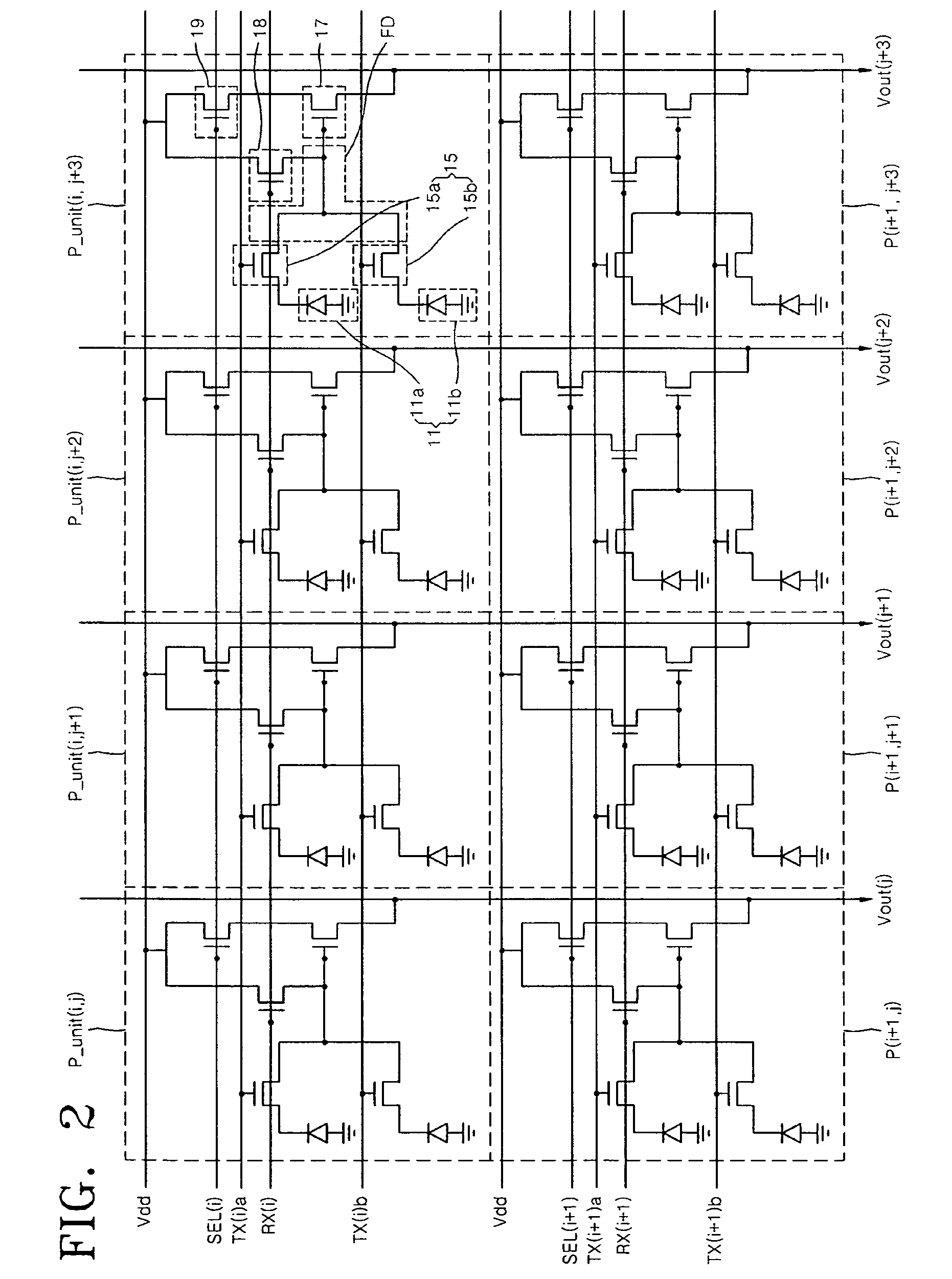

Image sensor with high fill factor pixels and method for forming an image sensor

ActiveUS20070210239A1Improve fill factorTelevision system detailsSolid-state devicesFill factorEngineering

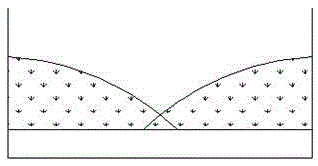

An image sensor comprises: an array of photoelectric conversion elements in a substrate, the photoelectric conversion elements being arranged in rows and columns extending in a first direction and a second direction respectively; a plurality of first junction isolation regions in the substrate that each isolate side portions of neighboring photoelectric conversion elements of a common row, and a plurality of second junction isolation regions in the substrate that each isolate side portions of neighboring photoelectric conversion elements of a common column; and a plurality of dielectric isolation regions in the substrate, that each isolate corner portions of neighboring photoelectric conversion elements. In one embodiment, the photoelectric conversion elements have a first pitch in the first direction and have a second pitch in the second direction and the first pitch is substantially equal for the photoelectric conversion elements of a common row, and the second pitch is substantially equal for the photoelectric conversion elements of a common column.

Owner:SAMSUNG ELECTRONICS CO LTD

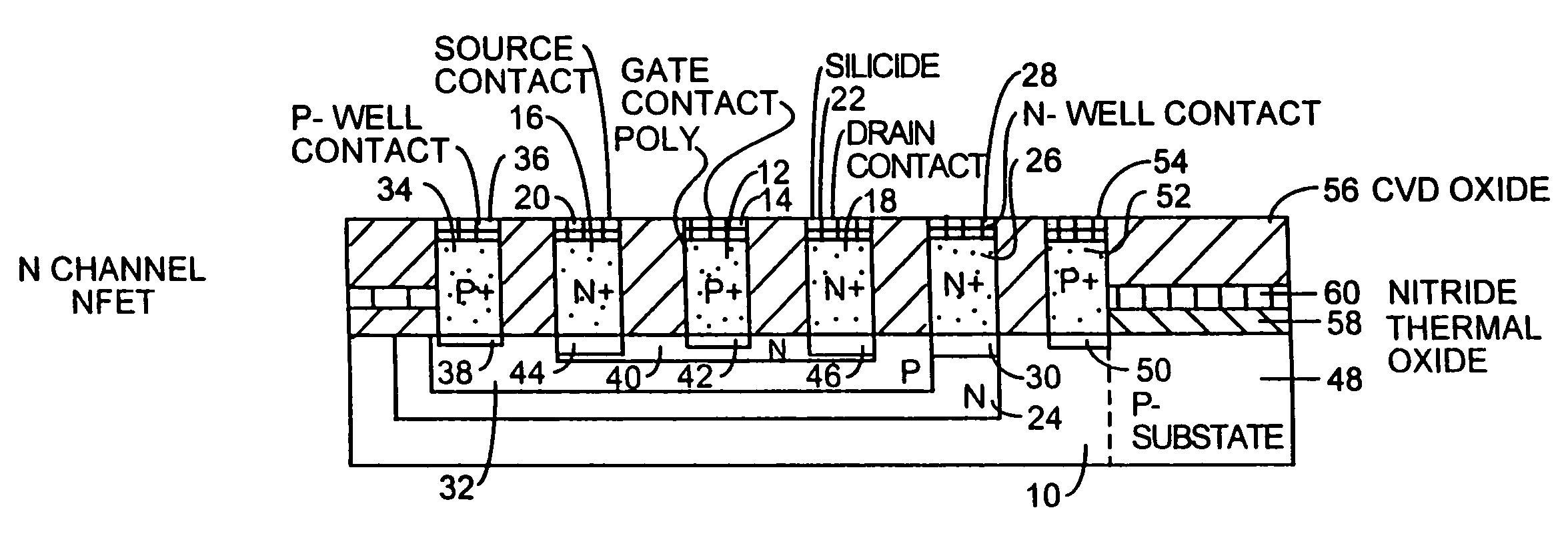

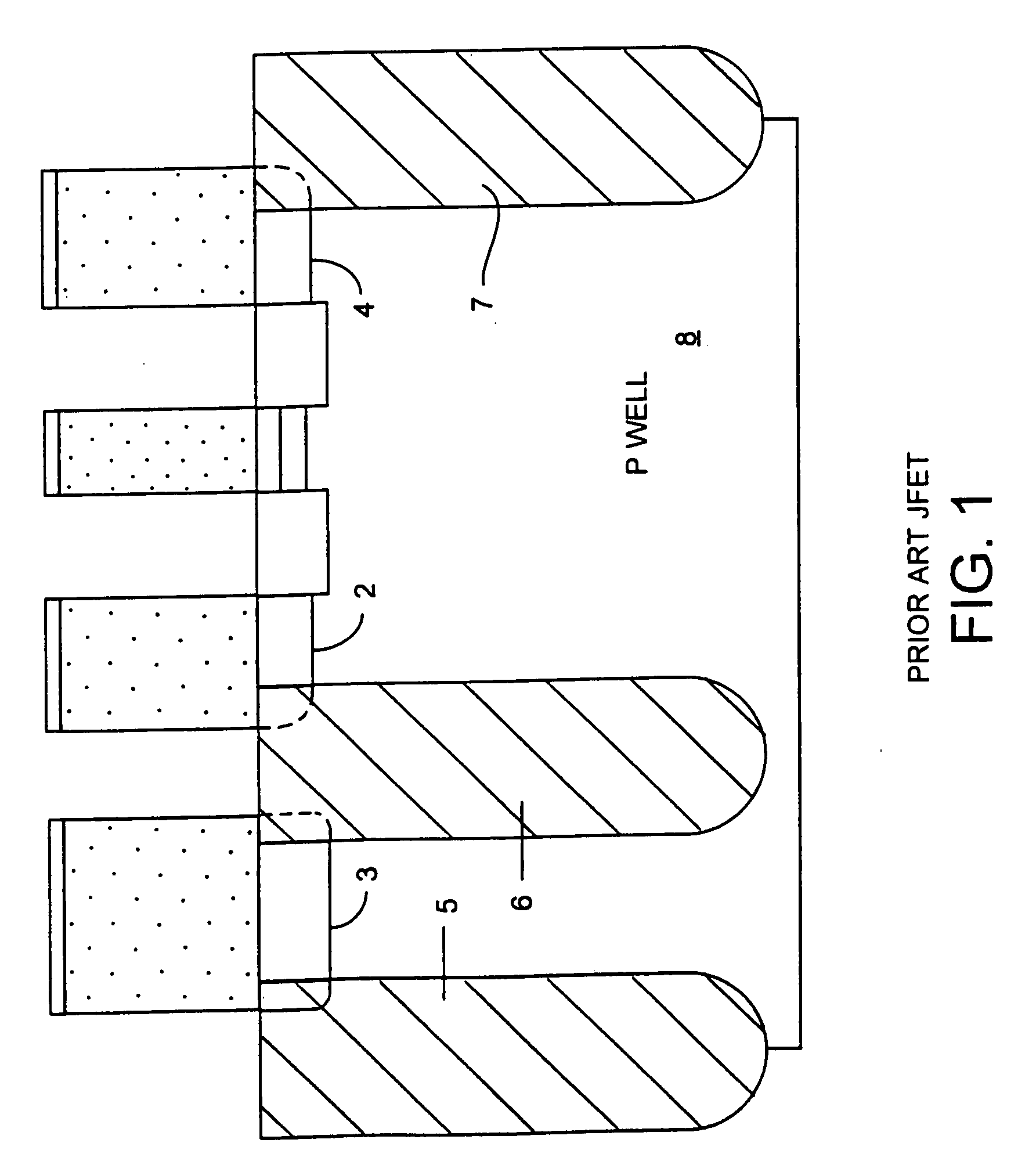

Junction isolated poly-silicon gate JFET

InactiveUS20080128762A1Avoid problemsTransistorSemiconductor/solid-state device manufacturingReverse biasJFET

An integrated Junction Field Effect Transistor is disclosed which is much smaller and much less expensive to fabricate because it does not use Shallow Trench Isolation or field oxide in the semiconductor substrate to isolate separate transistors. Instead, a layer of insulating material is formed on the top surface of said substrate, and interconnect trenches are etched in said insulating layer which do not go all the way down to the semiconductor substrate. Contact openings are etched in the insulating layer all the way down to the semiconductor layer. Doped poly-silicon is formed in the contact openings and interconnect trenches and silicide is formed on tops of the poly-silicon. This contact and interconnect structure applies to any integrated transistor. The integrated JFET disclosed herein does not use STI or field oxide and uses junction isolation. A conventional JFET is built in a P-well. The P-well is encapsulated in an N-well which is implanted into the substrate. Separate contacts to the P-well, N-well and substrate are formed as well as to the source, drain and gate so that the device can be isolated by reverse-biasing a PN junction. Operating voltage is restricted to less than 0.7 volts to prevent latching.

Owner:DSM SOLUTIONS

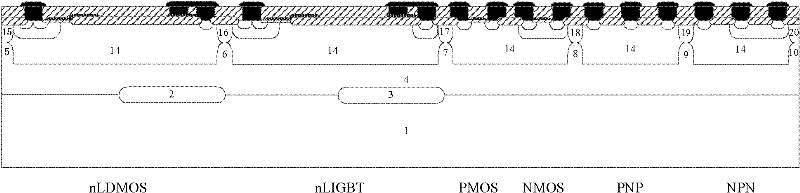

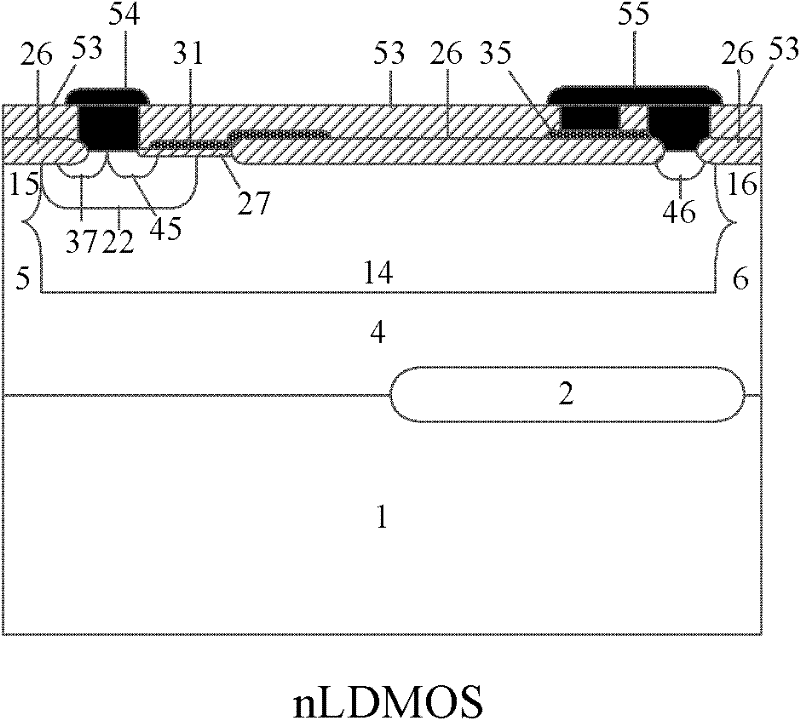

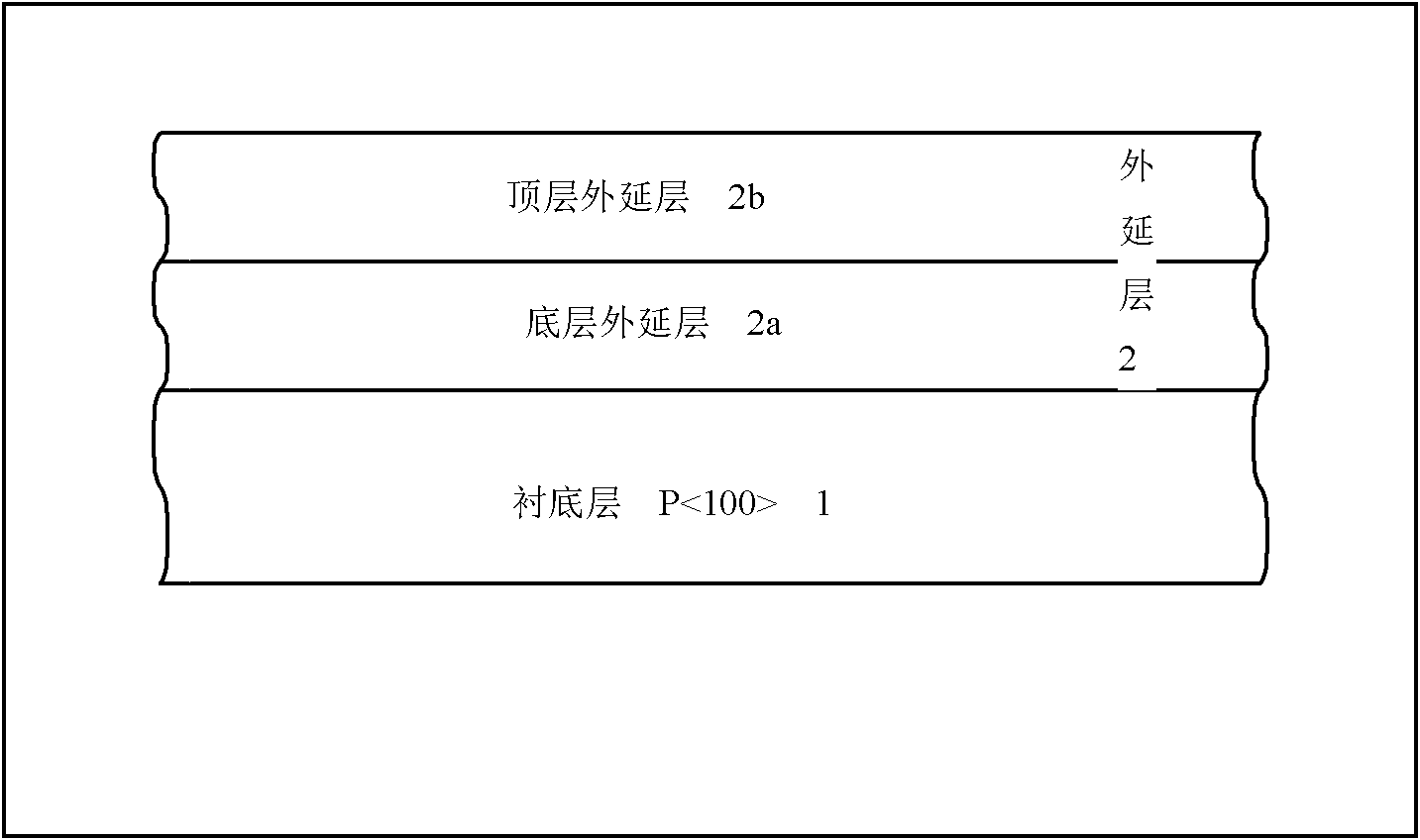

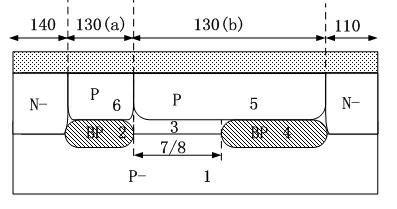

Bipolar CMOS DMOS (BCD) integrated device based on N type extension layer and manufacture method thereof

InactiveCN102201406AIncrease manufacturing costReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingCMOSLow voltage

A bipolar CMOS DMOS (BCD) integrated device based on a N type extension layer and a manufacture method thereof, which belongs to the semiconductor power device technology field, are disclosed. In the invention, a high voltage nLDMOS device, a high voltage nLIGB device, a low voltage PMOS device, a low voltage NMOS device, a low voltage PNP device and a low voltage NPN device are integrated on a same substrate. All devices are made in an N type extension layer arranged on a surface of a P type extension layer which is on a surface of a P type substrate. And junction isolations of the devices are realized through P<+> isolation regions. N type buried layers are arranged between the P type substrate and the P type extension layer, wherein the P type substrate and the P type extension layer are under the high voltage devices. N type buried layers are / are not arranged between the P type extension layer and the N type extension layer, wherein the P type extension layer and the N type extension layer are under the low voltage devices. The N type buried layers are introduced in the invention to realize that silicon chips with lower resistivity can be used as the substrate at a same breakdown voltage. In the prior art, float-zone technique is adopted to manufacture monocrystalline silicon pieces, which can increase the chip manufacturing costs. In the invention, the float-zone technique is not used so that the chip manufacturing costs can be reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

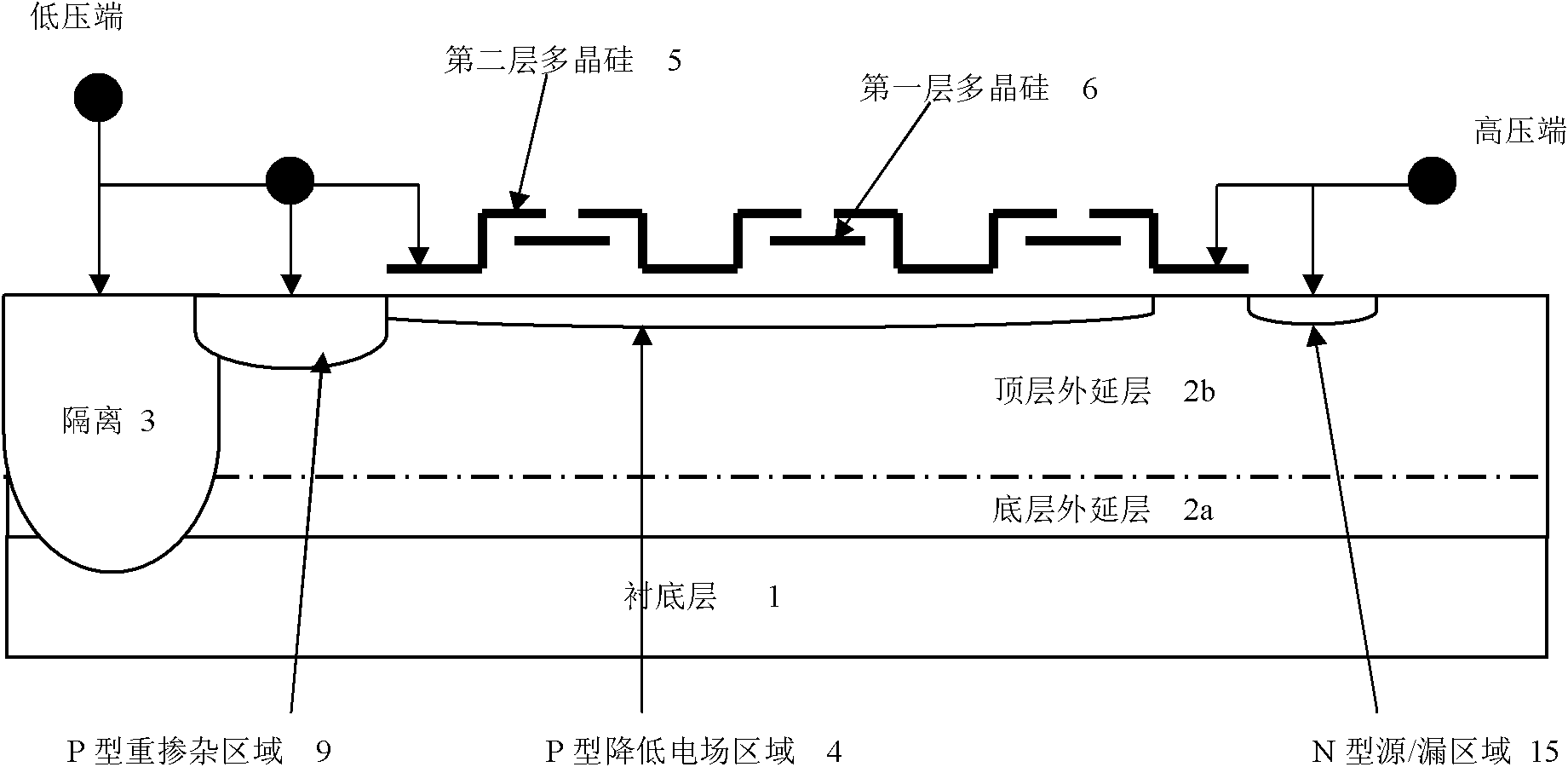

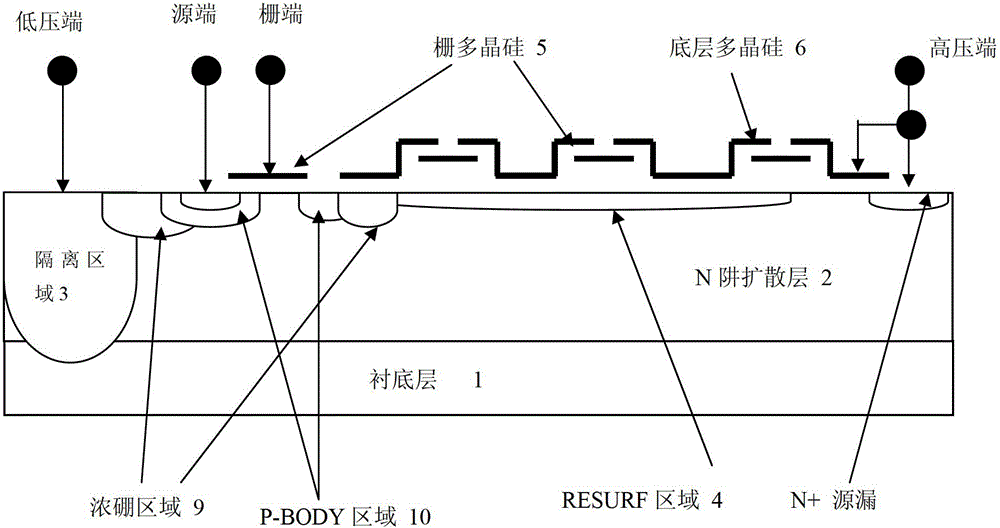

Method for producing high-voltage grid drive chip for directly driving power device

ActiveCN102130060AReduce lateral spreadHigh energySemiconductor/solid-state device manufacturingSemiconductor devicesCMOSLow voltage

The invention discloses a method for producing a high-voltage grid drive chip for directly driving a power device. By adopting a high-voltage junction isolating process, a high-voltage side drive control module is isolated from a low-voltage side drive control module; on the basis of the PN junction isolation in the conventional CMOS (Complementary Metal-Oxide-Semiconductor Transistor) transistorprocess, a surface electric field reducing region is formed on the surface of a PN junction; a capacitive voltage divider is formed by using two layers of polysilicon; the distribution of an electricfield on the surface of the PN junction is effectively changed; the high-voltage isolation of a high-voltage transverse DMOS (Double-Diffused Metal Oxide Semiconductor) transistor is formed; and a high-voltage N type DMOS transistor is obtained by forming a P type lightly-doped region. Compared with the conventional transverse DMOS transistor, the voltage resistant requirement of over 700V can bemet by additionally arranging a P type surface electric field reducing region structure and a dual-layer polysilicon capacitor structure; and meanwhile, the production method has concise work procedures and lower cost; and a high-voltage grid drive circuit device for directly driving the power device can be formed by only needing 13 structure levels.

Owner:NINGBO SEMICON INT CORP

Apparatus, system, and method for junction isolation of arrays of surface emitting lasers

Owner:NECSEL INTPROP +1

Isolation structure of high voltage driver circuit

InactiveCN102306656AImprove breakdown voltageEffective isolationSemiconductor/solid-state device manufacturingSemiconductor devicesDriver circuitLow voltage

The invention relates to an isolation structure of a high voltage driver circuit. The isolation structure is characterized in that: the structure comprises a P type substrate and a P type epitaxial layer; a high voltage area, a low voltage area and a high and low voltage junction terminal area are arranged on the P type epitaxial layer; a first P type junction isolation area is arranged between the high and low voltage junction terminal area and the low voltage area as well as a high voltage insulated gate field effect tube is arranged between the high voltage area and the low voltage area; two sides of the high voltage insulated gate field effect tube and an isolation structure between the high voltage insulated gate field effect tube and a high side area are formed into a second P type junction isolation area.

Owner:SOUTHEAST UNIV

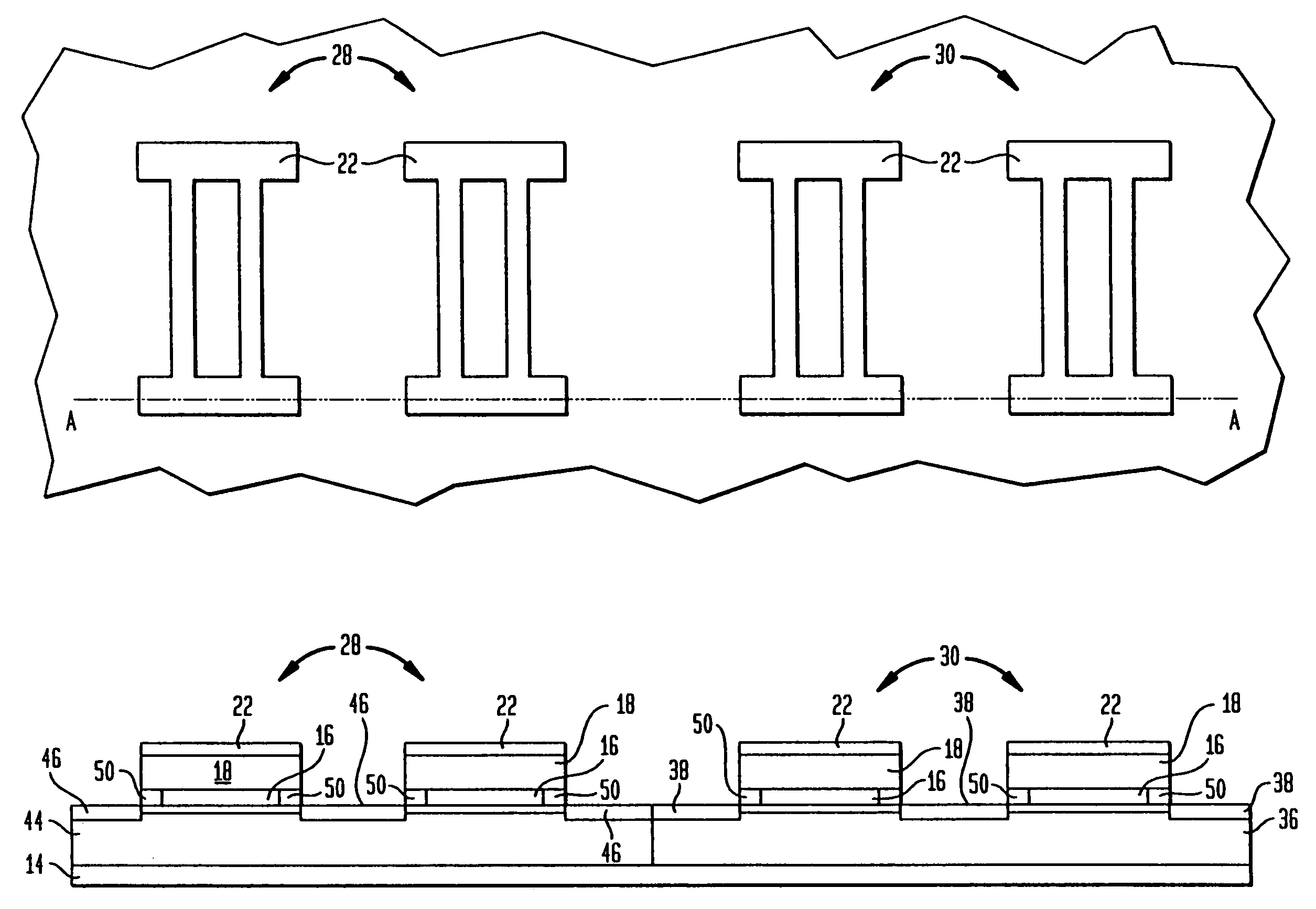

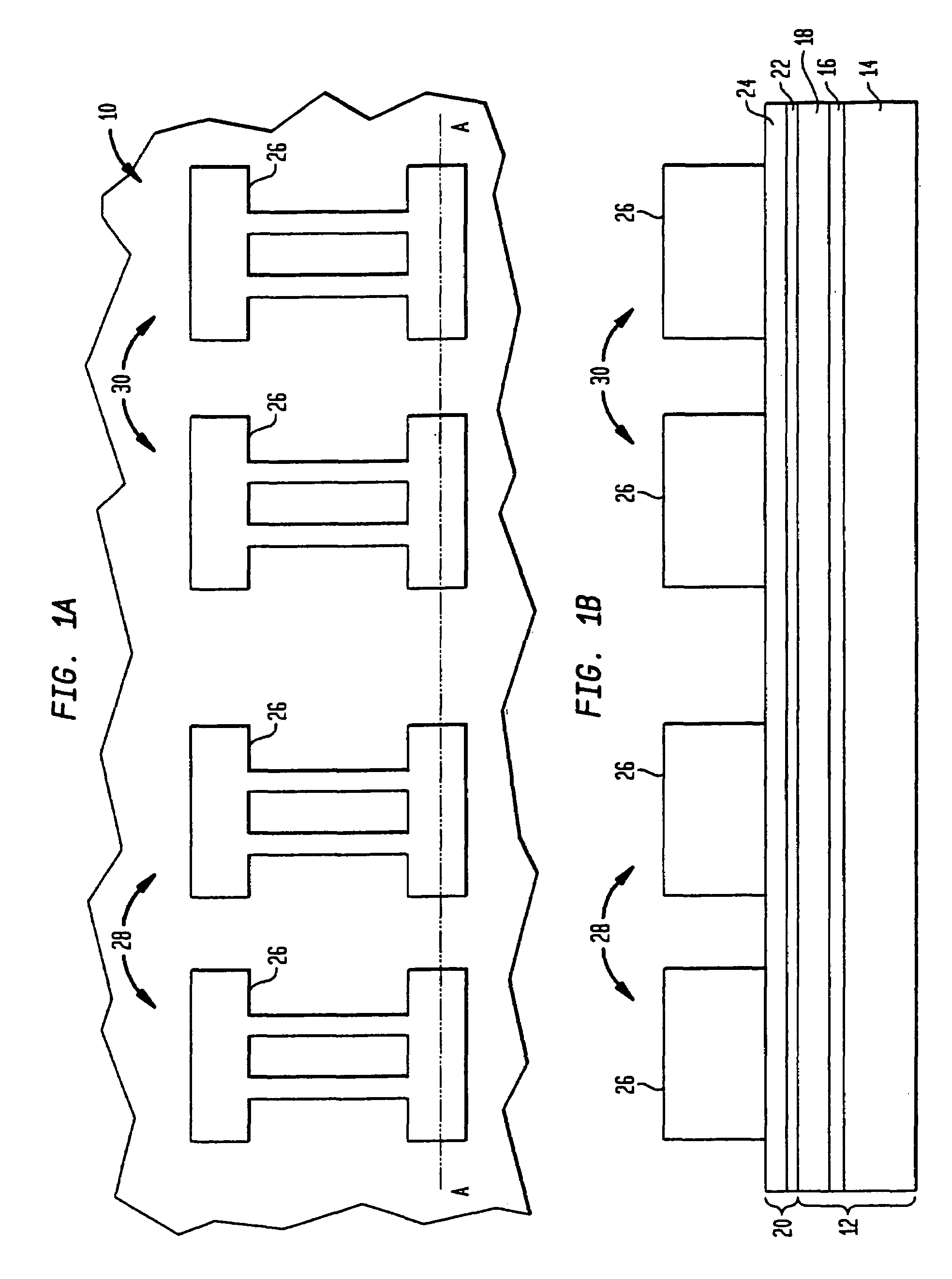

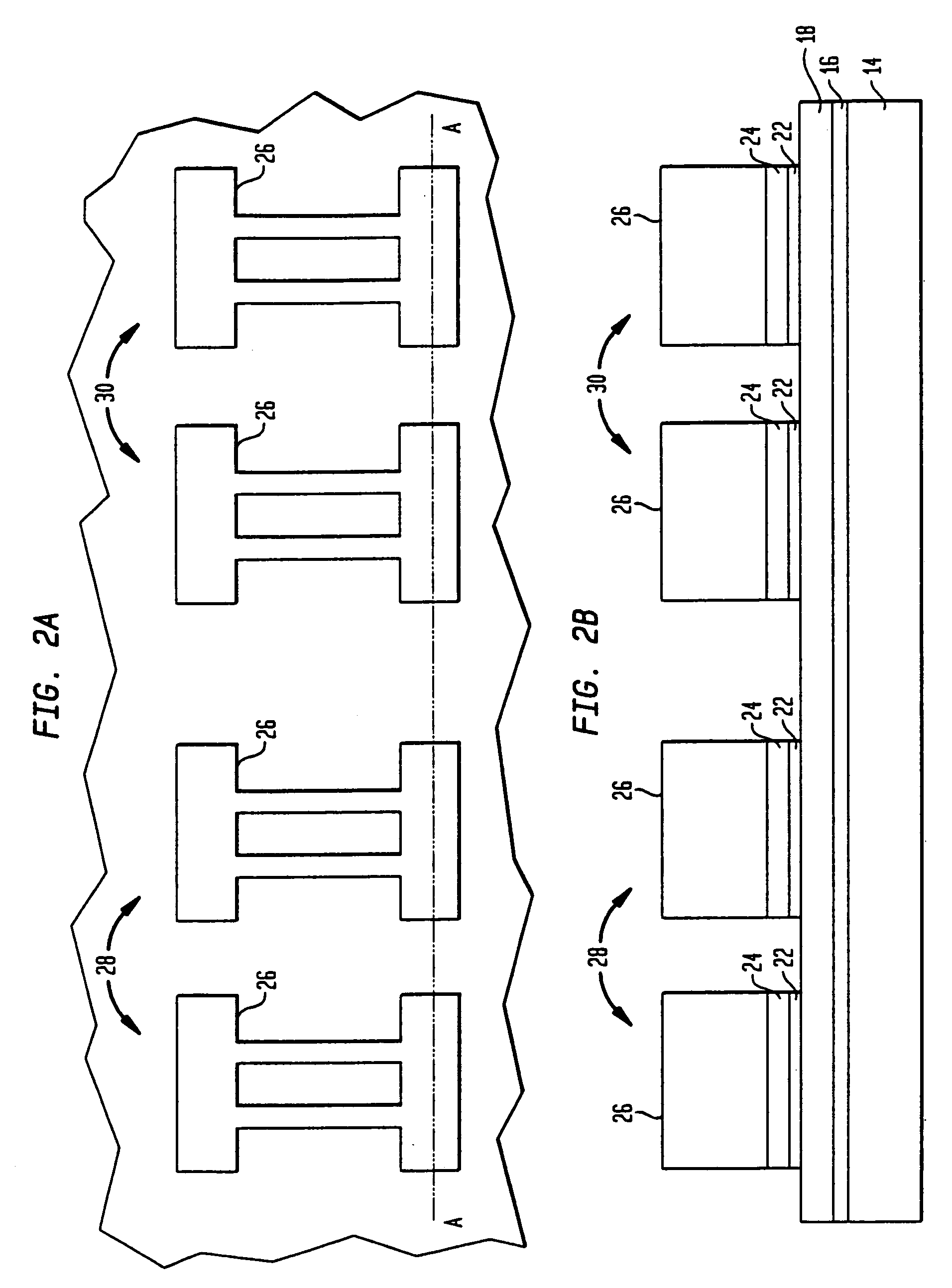

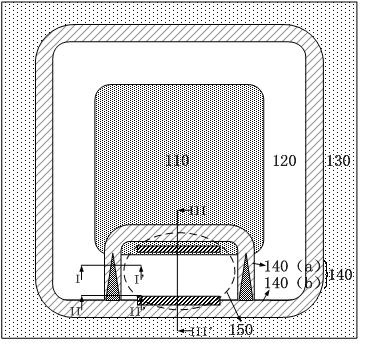

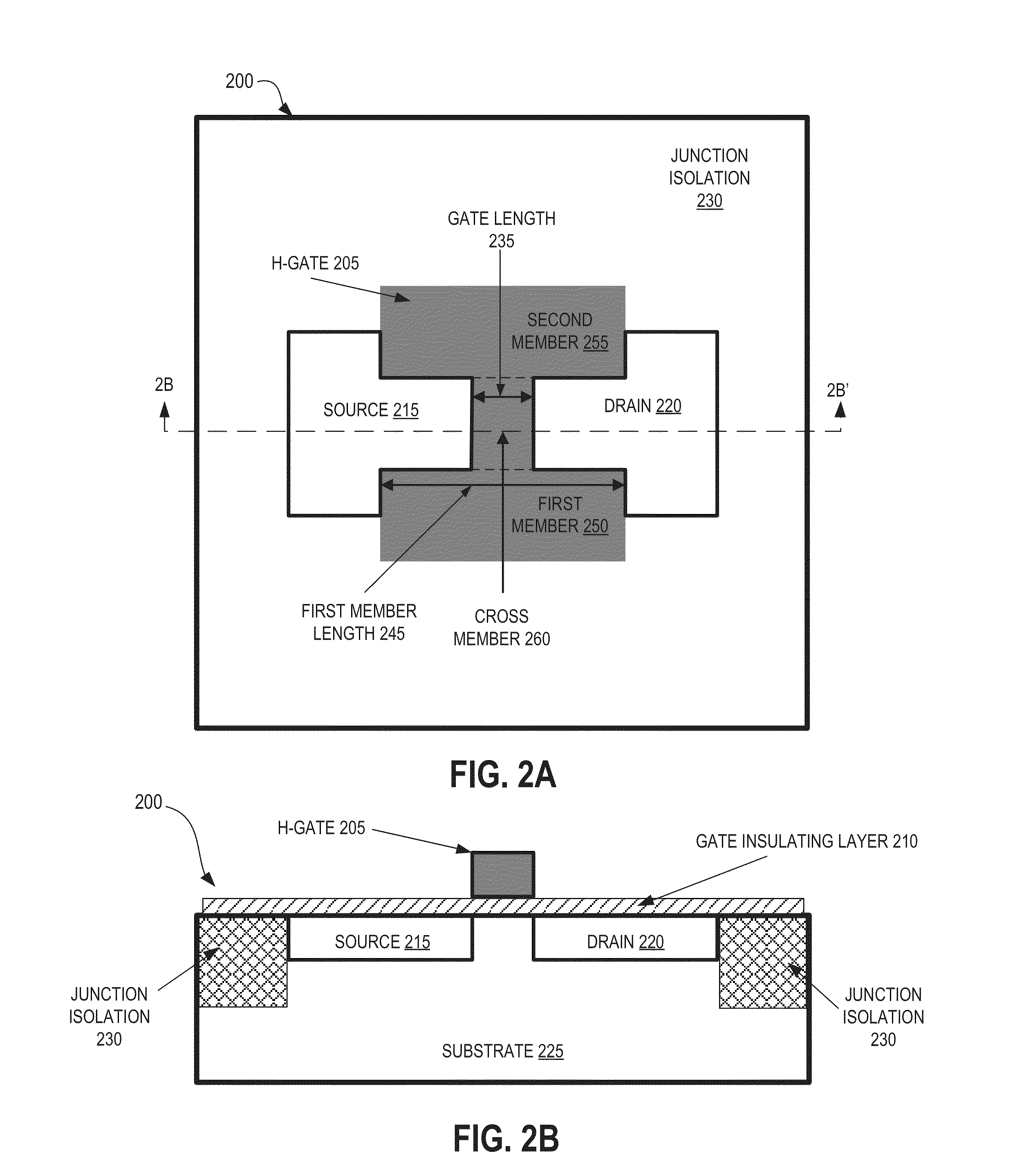

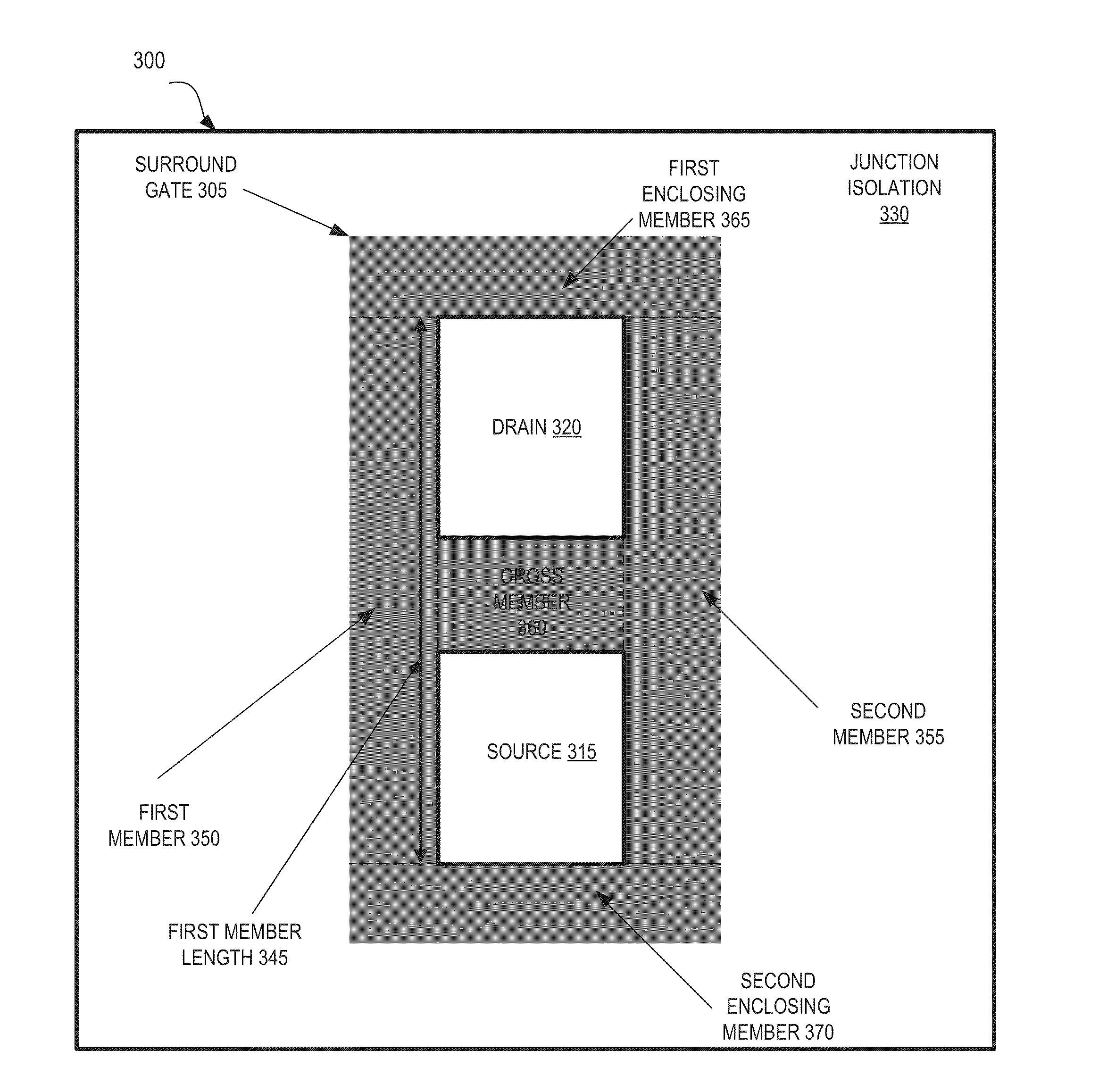

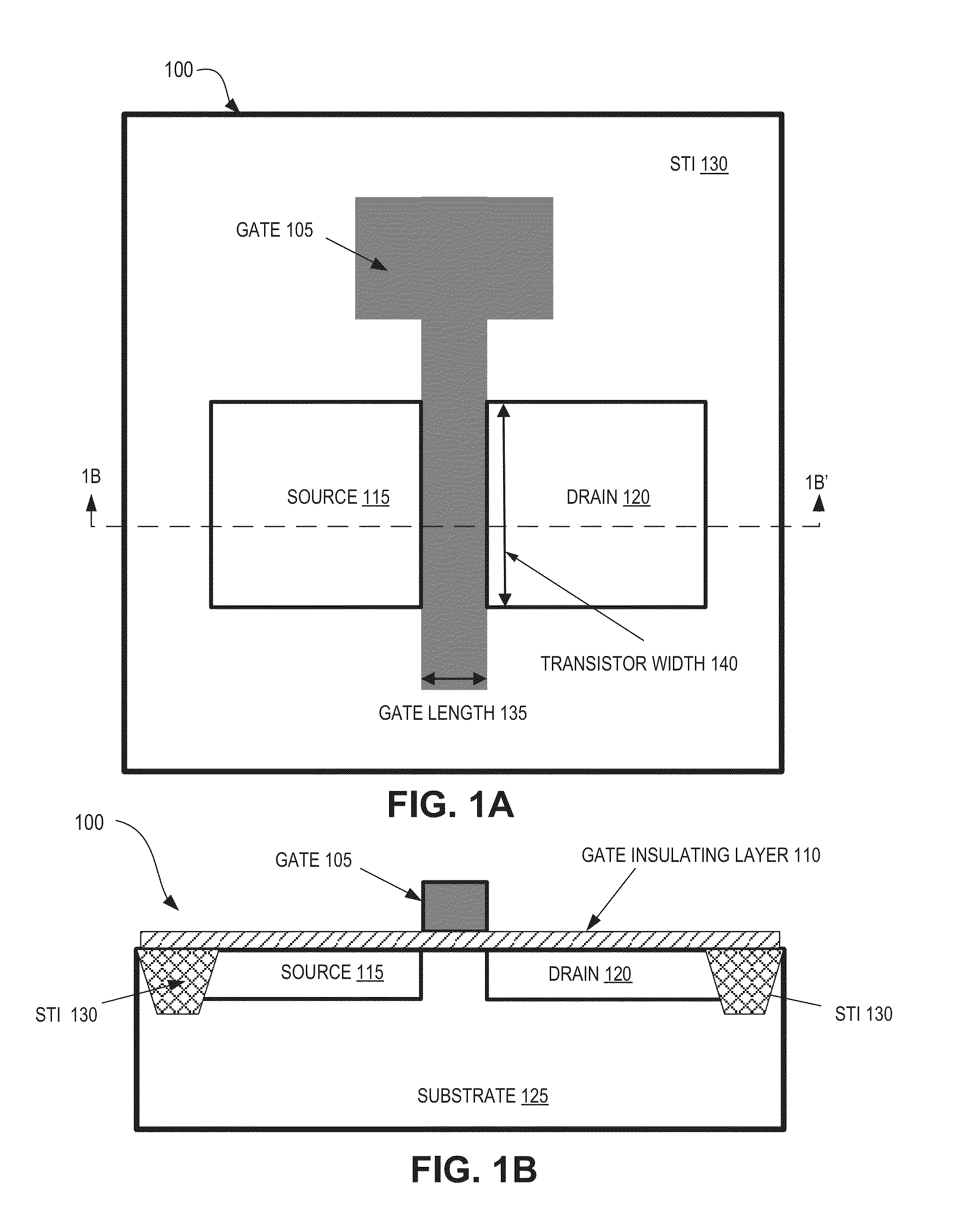

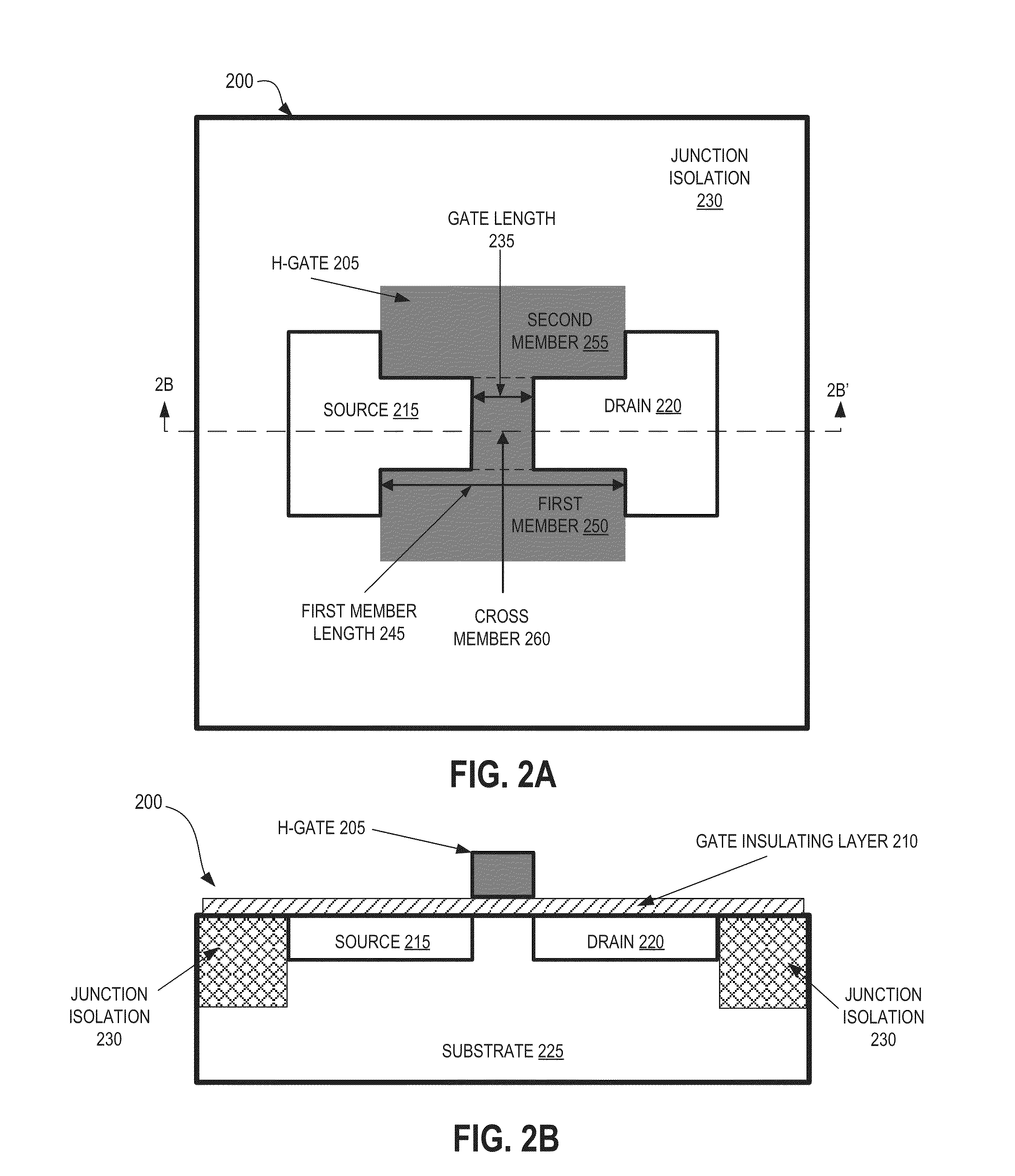

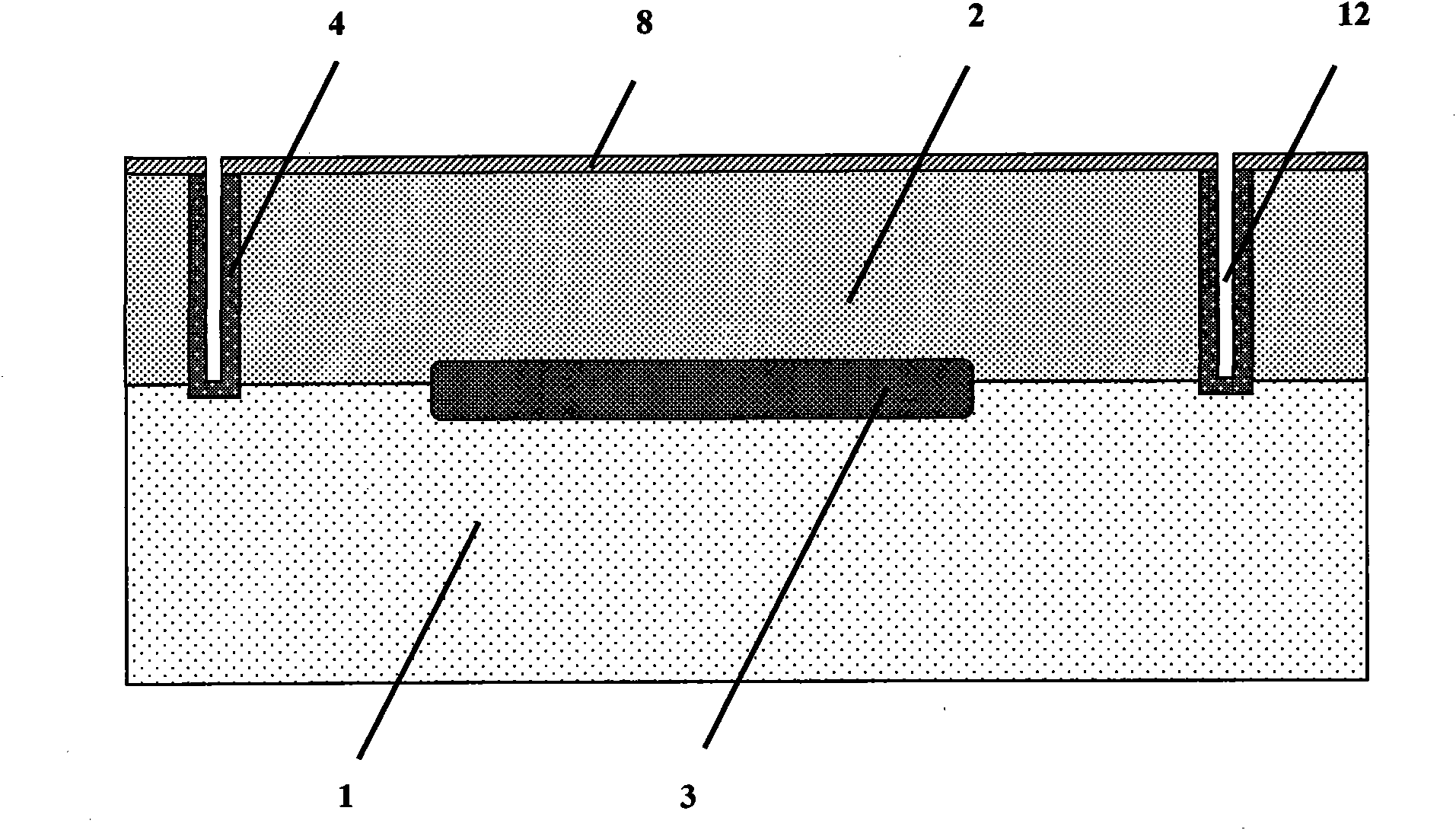

Transistor with self-aligned channel width

A device includes a transistor including a source and a drain disposed in a substrate and a gate disposed above the substrate. The gate includes a first longitudinal member disposed above the source and the drain and running substantially parallel to a channel of the transistor. The first longitudinal member is disposed over a first junction isolation area. The gate also includes a second longitudinal member disposed above the source and the drain and running substantially parallel to the channel of the transistor. The second longitudinal member is disposed over a second junction isolation region. The gate also includes a cross member running substantially perpendicular to the channel of the transistor and connecting the first longitudinal member to the second longitudinal member. The cross member is disposed above and between the source and the drain.

Owner:OMNIVISION TECH INC

Semiconductor device and method for fabricating the same

InactiveUS20060160295A1Excellent electrical propertiesEffective preventionTransistorSemiconductor/solid-state device detailsDevice materialSemiconductor

A semiconductor device and a method for fabricating the same are provided. The provided semiconductor device includes a field oxide layer formed in a semiconductor substrate to define an active region; gate structures formed on the active region; source / drain junctions formed on either side of the gate structures on the semiconductor substrate; a channel silicon layer arranged under the gate insulating layer to operate as a channel for connecting sources and drains; and buried junction isolation insulating layers under the channel silicon layer. The buried junction isolation insulating layers isolate source / drain junction regions of a MOS transistor, so that a short circuit in a bulk region under the channel of a transistor due to the high-integration of the device can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

Transistor with self-aligned channel width

A device includes a transistor including a source and a drain disposed in a substrate and a gate disposed above the substrate. The gate includes a first longitudinal member disposed above the source and the drain and running substantially parallel to a channel of the transistor. The first longitudinal member is disposed over a first junction isolation area. The gate also includes a second longitudinal member disposed above the source and the drain and running substantially parallel to the channel of the transistor. The second longitudinal member is disposed over a second junction isolation region. The gate also includes a cross member running substantially perpendicular to the channel of the transistor and connecting the first longitudinal member to the second longitudinal member. The cross member is disposed above and between the source and the drain.

Owner:OMNIVISION TECH INC

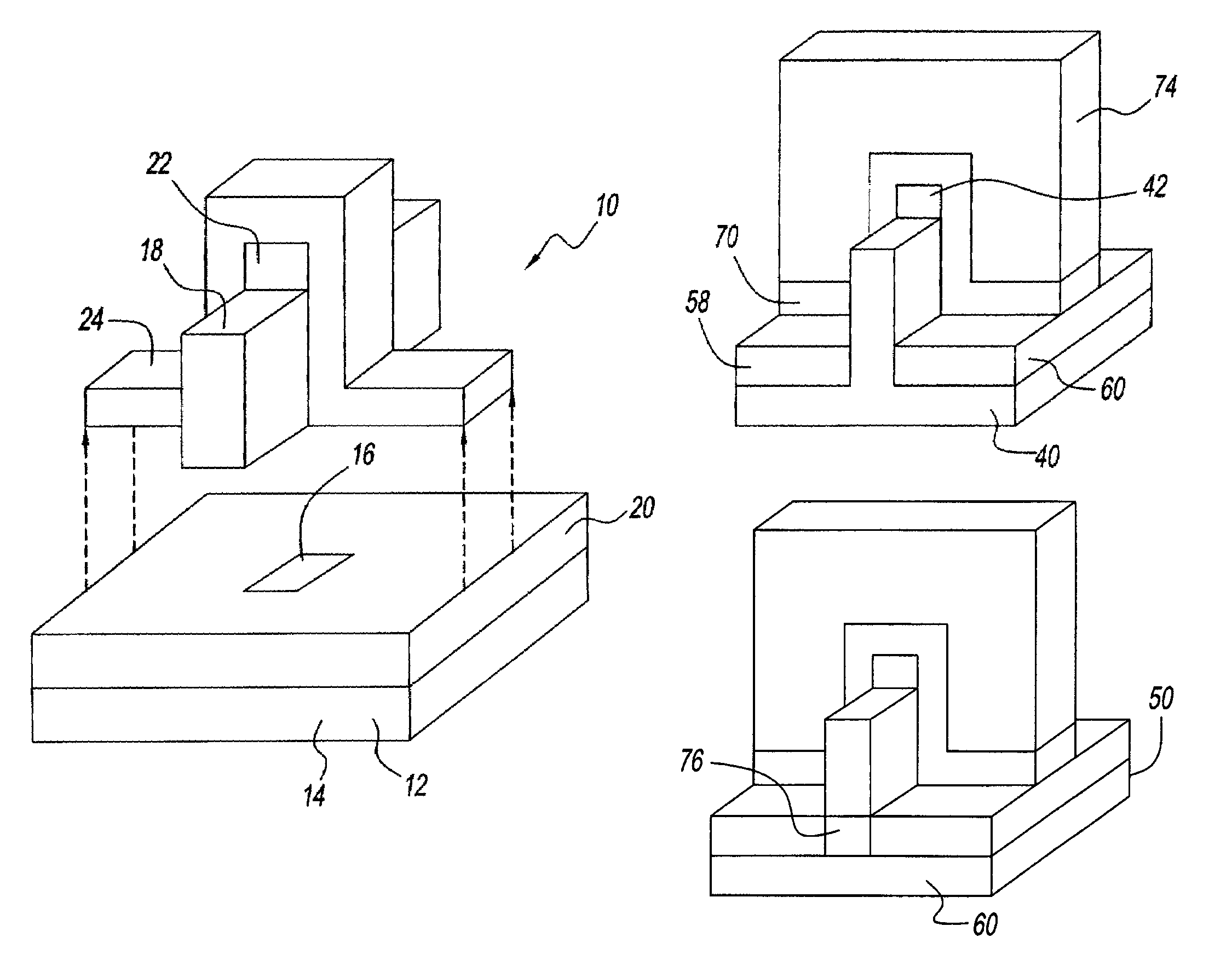

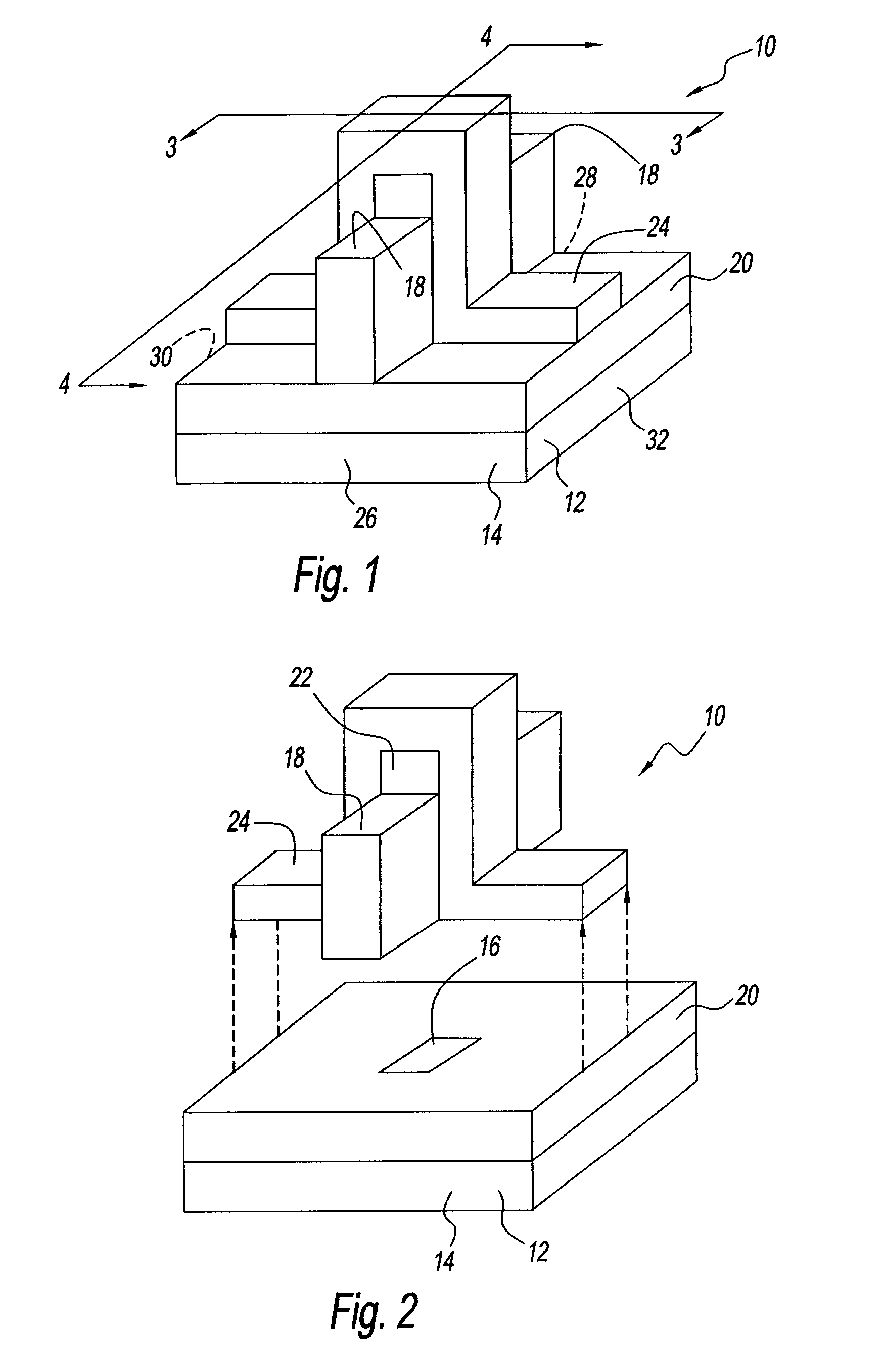

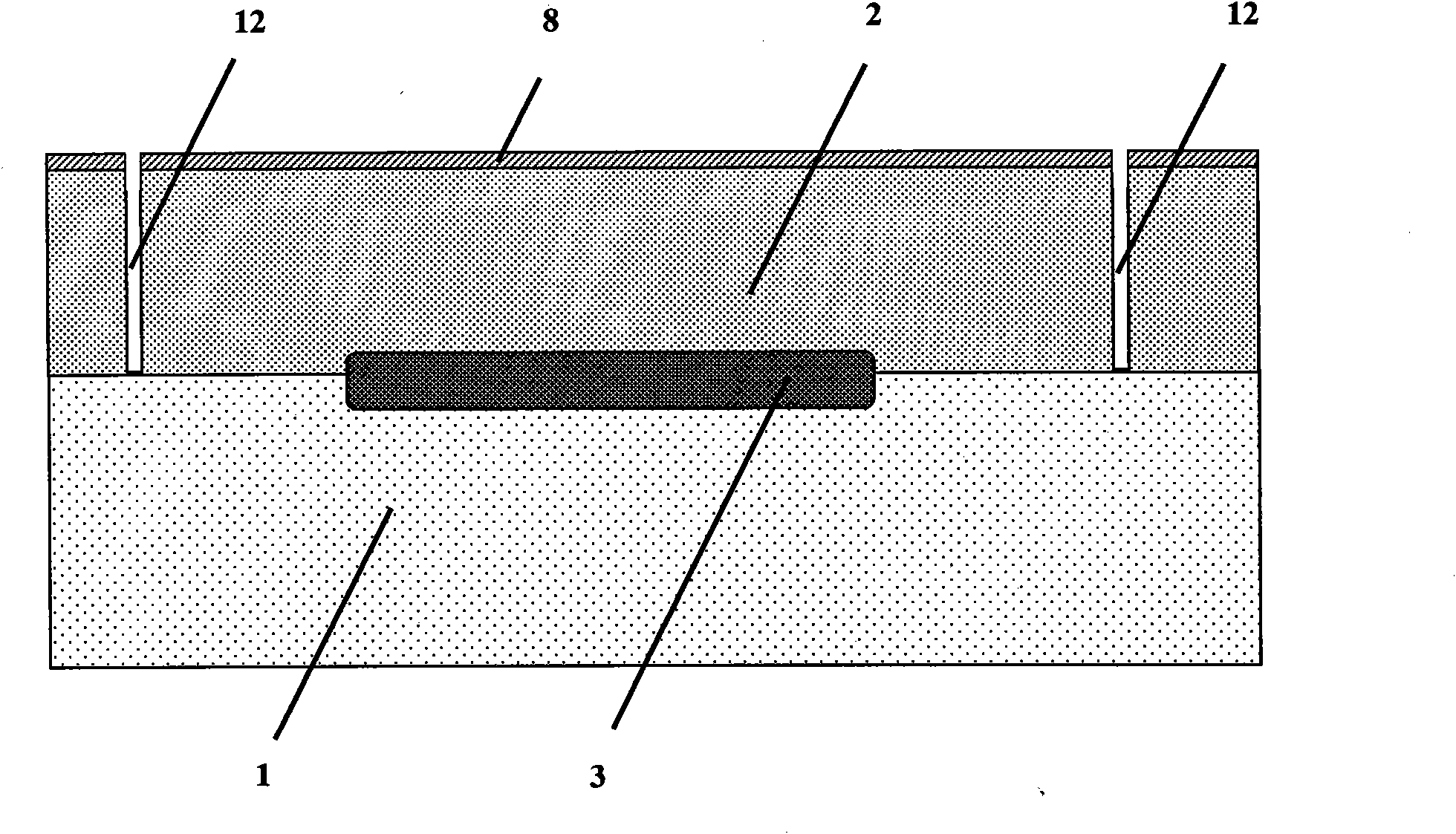

Process for making finfet device with body contact and buried oxide junction isolation

InactiveUS20080224213A1Solid-state devicesSemiconductor/solid-state device manufacturingBody contactEngineering

There is a FinFET device. The device has a silicon substrate, an oxide layer, and a polysilicone gate. The silicon substrate defines a planar body, a medial body, and a fin. The planar body, the medial body, and the fin are integrally connected. The medial body connects the planar body and the fine. The planar body extends generally around the medial body. The fin is situated to extend substantially from a first side of the substrate to an opposing second side of the substrate. The fin is substantially perpendicularly disposed with respect to the planar body. The first oxide layer is situated on the planar body between the planar body and the fine. The oxide layer extends substantially around the medial body. The polysilicone gate is situated on the oxide layer to extend substantially from a third side to an opposing fourth side of the substrate. The gate is situated to extend across the fin proximal to a medial portion of an upper surface of the fine. There is also a process for making a FinFET device.

Owner:GLOBALFOUNDRIES INC

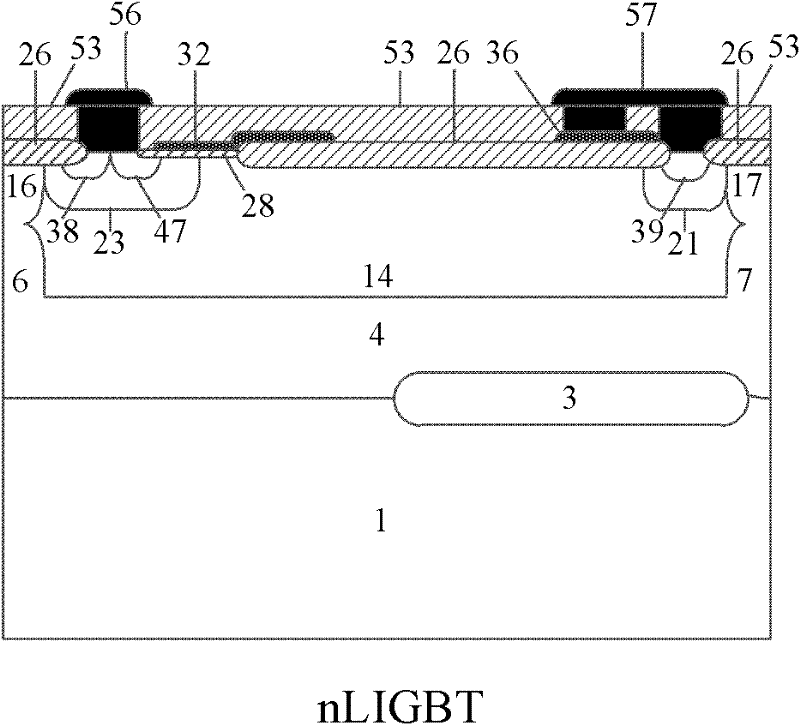

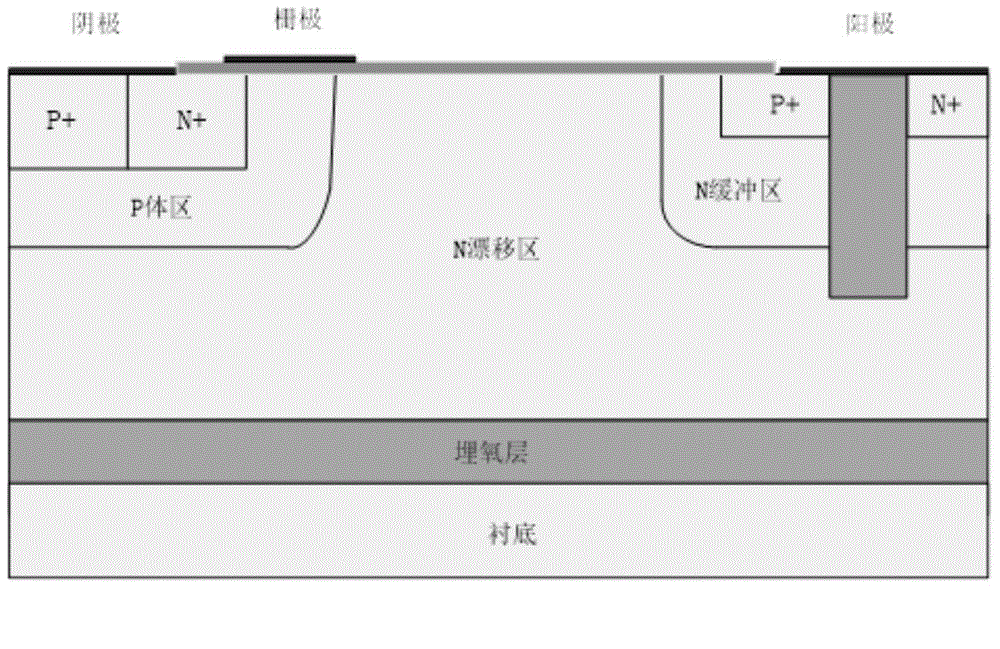

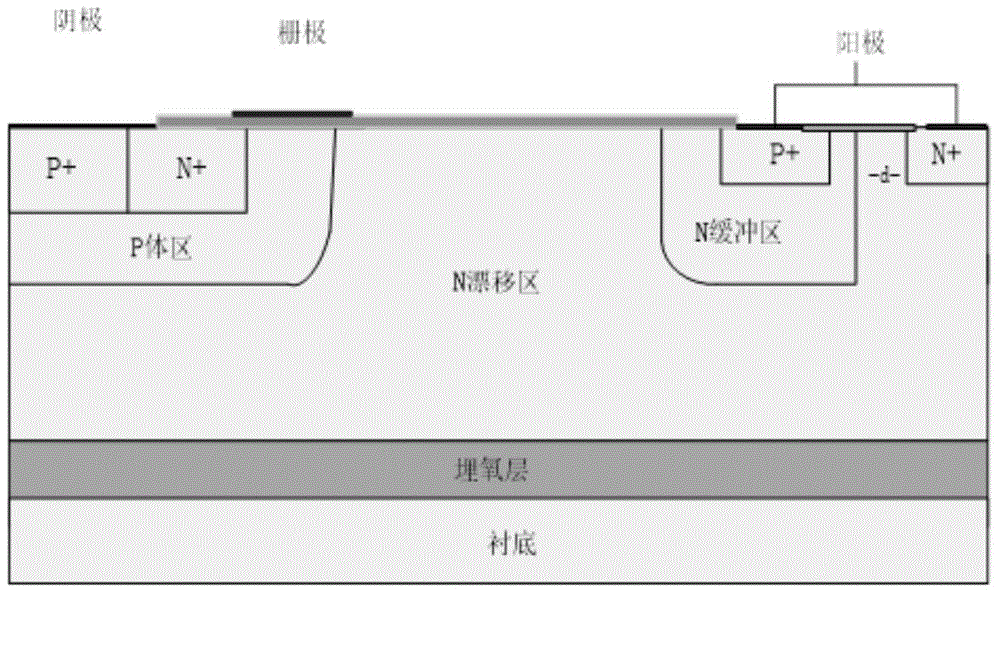

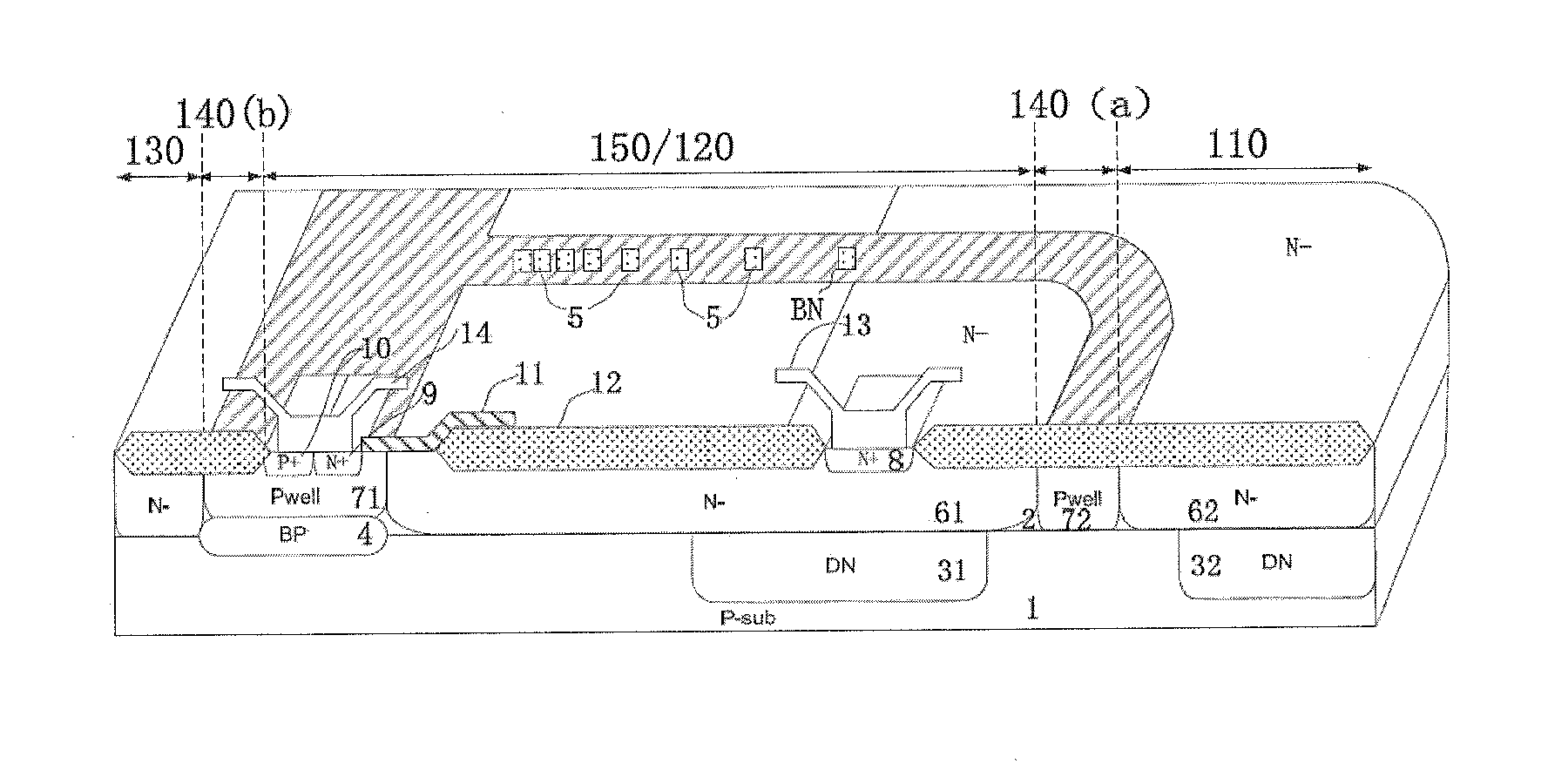

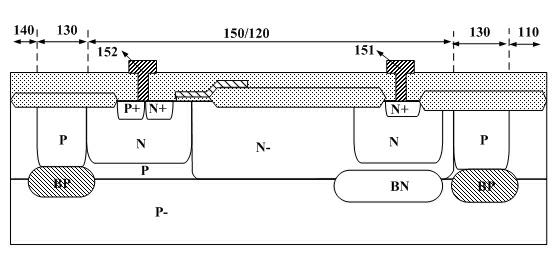

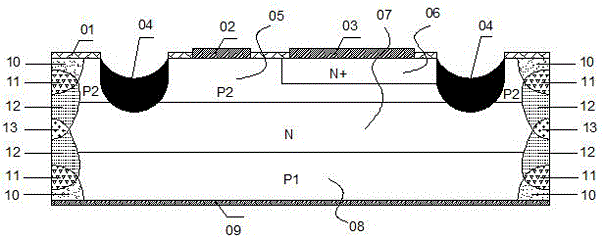

Dielectric isolation and junction isolation combined LIGBT (Lateral Insulated Gate Bipolar Transistor) device and manufacturing method

InactiveCN104637995AReduce depthLower requirementSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectron

The invention relates to a dielectric isolation and junction isolation combined LIGBT (Lateral Insulated Gate Bipolar Transistor) device and a manufacturing method and belongs to the technical field of electronics. According to the LIGBT device, for an anode area of the traditional short-circuit LIGBT, a dielectric isolation and junction isolation combined structure is adopted, dielectric isolation is adopted between N+ and P+ of an anode, and junction isolation is adopted below N+. According to the novel dielectric isolation and junction isolation combined structure, on one hand, on the basis that shorter off time of the device is guaranteed, during conduction, the negative resistance effect of the negative resistance effect can be eliminated and the performance and the stability of the device are improved, and on the other hand, the size area of the device can also be reduced.

Owner:NANJING UNIV OF POSTS & TELECOMM

Method for making high-voltage high-power low differential pressure linear integrated regulated power supply circuit

InactiveCN1670946AReduce areaEliminate the shortcomings that cannot meet the needs of special occasionsSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageDifferential pressure

This invention refers to a method for making the circuit of high voltage high power low voltage difference linear integrated stabilized voltage supply, which contains obtaining SOI chip by silicon / silicon bonding and thickness-reducing polishing technology, deep groove etching on SOI, polysilicon back filling dielectric isolation and longitudinal PNP and longitudinal NPN compatible bipolar technology. Said method reduces the device isolated distance and chip area and raises chip yield.

Owner:NO 24 RES INST OF CETC

Polysilicon selective emitter solar cell manufacture process

InactiveCN101916797AHigh Surface Phosphorus ConcentrationLow surface phosphorus concentrationFinal product manufactureSemiconductor devicesBack surface fieldEngineering

The invention discloses a polysilicon selective emitter solar cell manufacture process, which comprises the steps of: carrying out surface damage removal, etching treatment and diffusion knotting on a polycrystalline silicon wafer; carrying out screen printing on an emitting layer with etching-back blocking slurry according to a metallization pattern area and prebaking; carrying out local wet chemical etching back after phosphorosilicate glass removal is carried out on local wafer with etching-back blocking slurry printed on the metallization area; removing the etching-back blocking slurry; carrying out pn junction isolation while removing the phosphorosilicate glass; depositing an SiNx or SiO2 / SiNx film on the surface and carrying out surface passivation; and printing a back surface electrode and an aluminum back surface field to form a front surface metallization electrode, and sintering to form a finished product of the polysilicon selective emitter solar cell. In the invention, a mixed solution of hydrofluoric acid and nitric acid is adopted for etching back, porous silicon is not generated on the surface after etching back, and the surface topography is not changed; and because only one high temperature process is needed, the invention has simple process, high production efficiency and low energy consumption and is applicable to large-scale industrial production.

Owner:江苏韩华太阳能电池及应用工程技术研究中心有限公司

Isolation structure of high-voltage driving circuit

ActiveUS20140203406A1Reduce withstand voltageVoltage breakdownSemiconductor/solid-state device manufacturingSemiconductor devicesLow voltageField-effect transistor

An isolation structure of a high-voltage driving circuit includes a P-type substrate and a P-type epitaxial layer; a high voltage area, a low voltage area and a high and low voltage junction terminal area are arranged on the P-type epitaxial layer; a first P-type junction isolation area is arranged between the high and low voltage junction terminal area and the low voltage area, and a high-voltage insulated gate field effect tube is arranged between the high voltage area and the low voltage area; two sides of the high-voltage insulated gate field effect tube and an isolation structure between the high-voltage insulated gate field effect tube and a high side area are formed as a second P-type junction isolation area.

Owner:SOUTHEAST UNIV

Isolation structure of high-voltage driving circuit

InactiveCN102208450AImprove breakdown voltageProne to partial breakdownSolid-state devicesSemiconductor devicesLDMOSLow voltage

The invention discloses an isolation structure of a high-voltage driving circuit, and the isolation structure comprises a P-type substrate on which a P-type epitaxial layer is arranged, wherein a high-voltage region, a low-voltage region, a high-low-voltage junction terminal region, a first P-type junction isolation region and a half-ring P-type junction isolation region are arranged on the P-type epitaxial layer, and both ends of the half-ring P-type junction isolation region are connected with the first P-type junction isolation region. The isolation structure provided by the invention is characterized in that the half-ring P-type junction isolation region is composed of a half-ring P-type buried layer and a half-ring P-type well region, the half-ring P-type well region is positioned above the half-ring P-type buried layer; a first slot and a second slot are respectively arranged between two ends of the half-ring P-type buried layer and the first P-type junction isolation region, and the P-type substrate and the P-type epitaxial extend towards and fill the first slot and the second slot. The problem of localized breakdown in the high-low-voltage junction terminal region caused by the P-type buried layer is solved by using the isolation structure; therefore, an LDMOS (laterally-diffused metal oxide semiconductor) is effectively isolated from peripheral parts.

Owner:SOUTHEAST UNIV

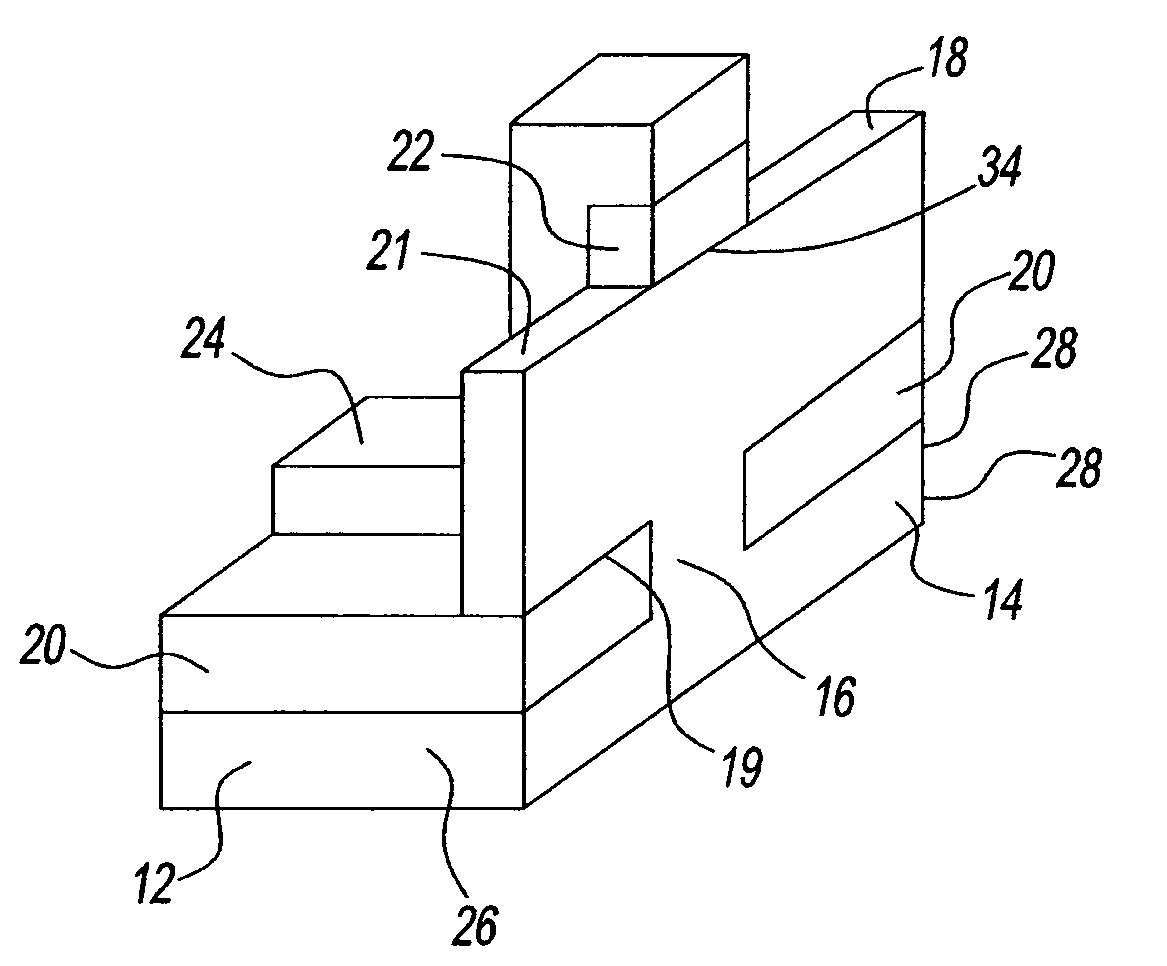

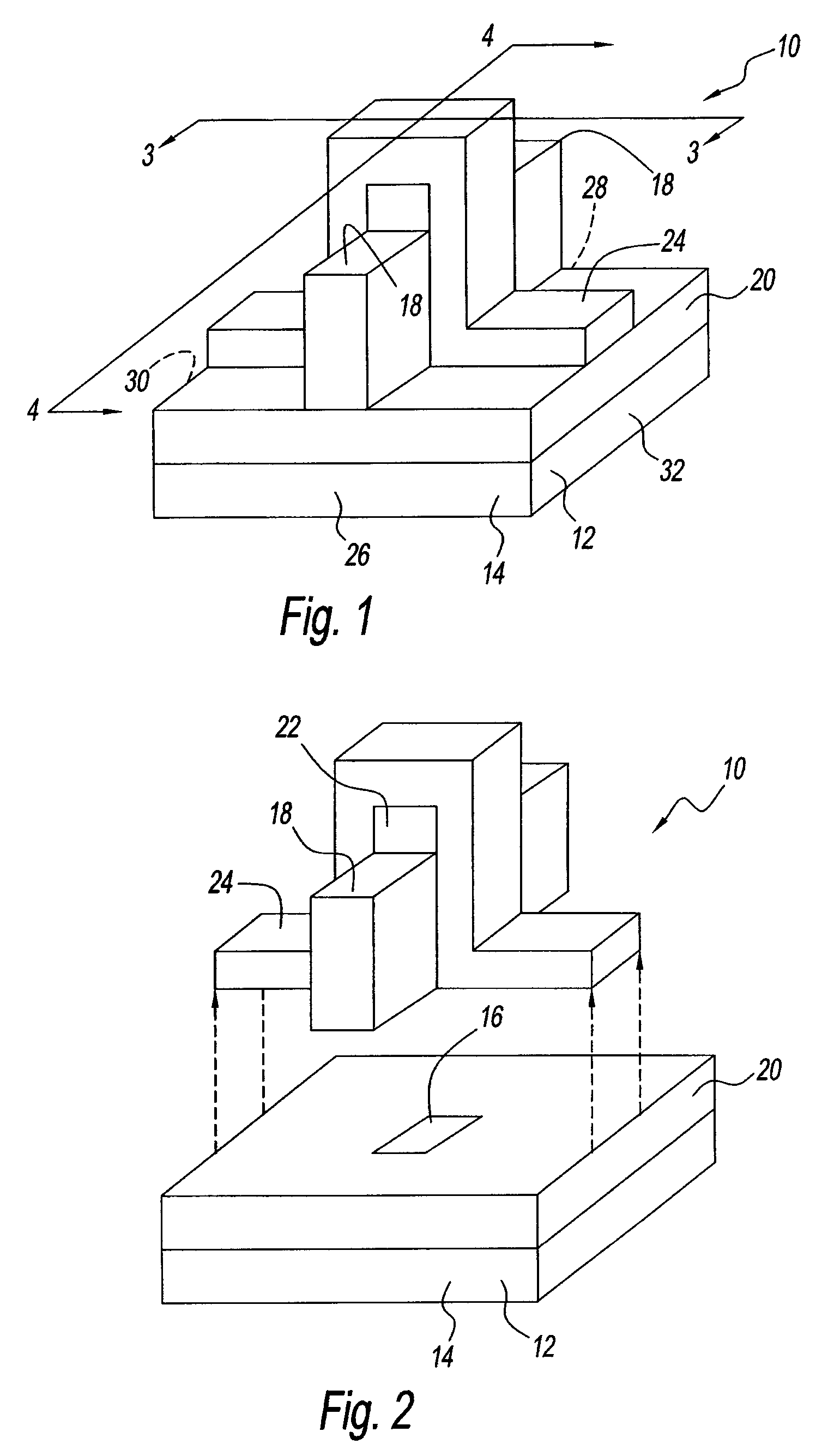

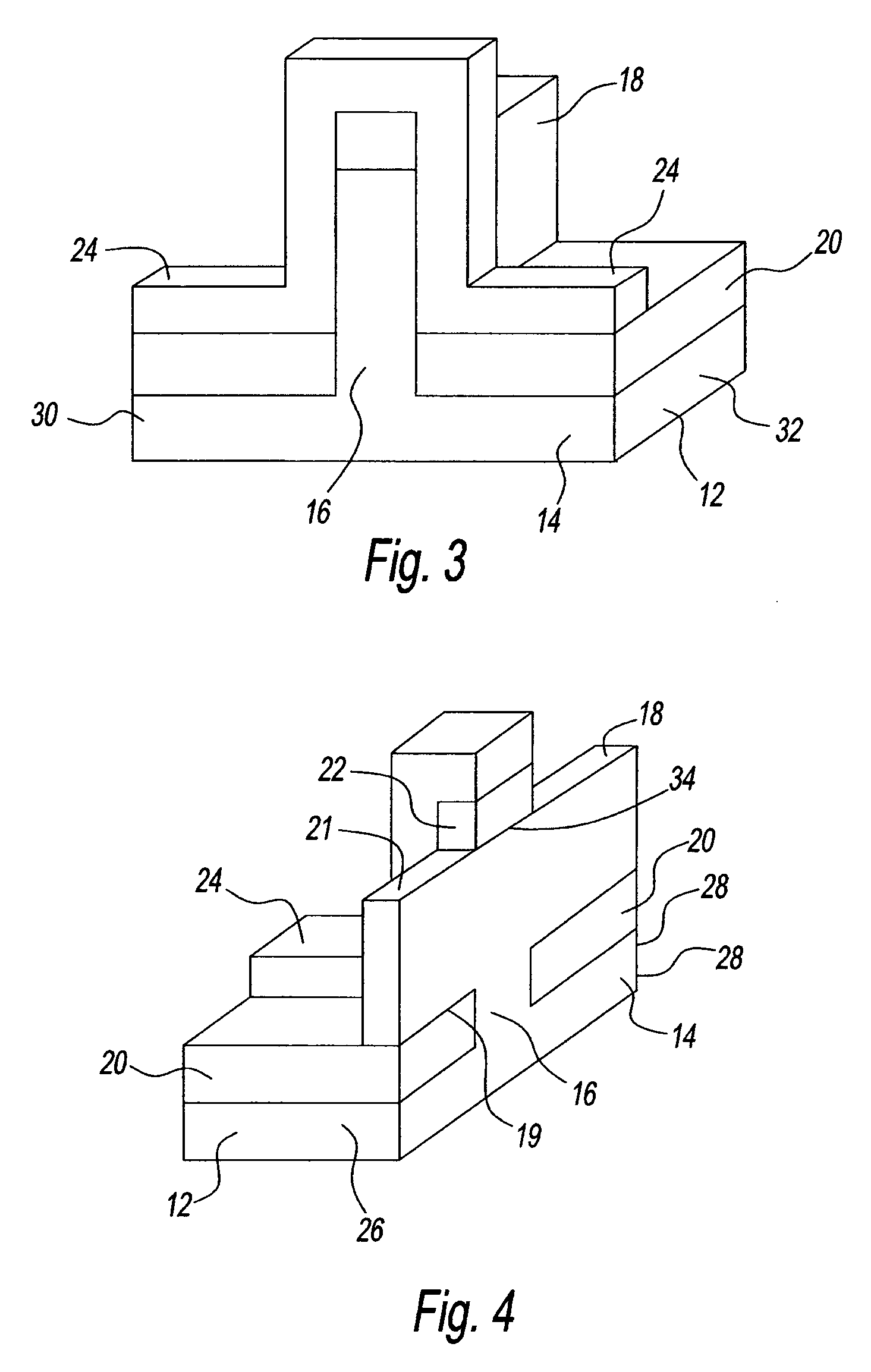

Process for making FinFET device with body contact and buried oxide junction isolation

InactiveUS7452758B2Solid-state devicesSemiconductor/solid-state device manufacturingBody contactEngineering

There is a FinFET device. The device has a silicon substrate, an oxide layer, and a polysilicone gate. The silicon substrate defines a planar body, a medial body, and a fin. The planar body, the medial body, and the fin are integrally connected. The medial body connects the planar body and the fin. The planar body extends generally around the medial body. The fin is situated to extend substantially from a first side of the substrate to an opposing second side of the substrate. The fin is substantially perpendicularly disposed with respect to the planar body. The first oxide layer is situated on the planar body between the planar body and the fin. The oxide layer extends substantially around the medial body. The polysilicone gate is situated on the oxide layer to extend substantially from a third side to an opposing fourth side of the substrate. The gate is situated to extend across the fin proximal to a medial portion of an upper surface of the fin. There is also a process for making a FinFET device.

Owner:GLOBALFOUNDRIES INC

Semiconductor device and method for manufacturing the same

InactiveUS20050064640A1Reduction in design ruleDistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialGate stack

Provided are a semiconductor device and a method for manufacturing the semiconductor device. The semiconductor device includes an isolation insulating film, an epitaxial silicon layer, a junction blocking insulating film, a gate stack, and source and drain junctions. The isolation insulating film is formed on a semiconductor substrate to define an active area. The epitaxial silicon layer is formed in the active area of the semiconductor substrate and surrounded by the isolation insulating film. The junction blocking insulating film is formed in the epitaxial silicon layer. The gate stack is formed over the epitaxial silicon layer so that the junction blocking insulating film is buried under approximately the center of the gate stack. The source and drain junctions are formed adjacent the sidewalls of the gate stack. Accordingly, a short circuit between source / drain junctions in a bulk area caused by the unwanted diffusion of the junctions can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

Image sensor with high fill factor pixels and method for forming an image sensor

ActiveCN101038927AImprove resolutionImprove fill factorSolid-state devicesSemiconductor/solid-state device manufacturingFill factorEngineering

An image sensor comprises: an array of photoelectric conversion elements in a substrate, the photoelectric conversion elements being arranged in rows and columns extending in a first direction and a second direction respectively; a plurality of first junction isolation regions in the substrate that each isolate side portions of neighboring photoelectric conversion elements of a common row, and a plurality of second junction isolation regions in the substrate that each isolate side portions of neighboring photoelectric conversion elements of a common column; and a plurality of dielectric isolation regions in the substrate, that each isolate corner portions of neighboring photoelectric conversion elements. In one embodiment, the photoelectric conversion elements have a first pitch in the first direction and have a second pitch in the second direction and the first pitch is substantially equal for the photoelectric conversion elements of a common row, and the second pitch is substantially equal for the photoelectric conversion elements of a common column.

Owner:SAMSUNG ELECTRONICS CO LTD

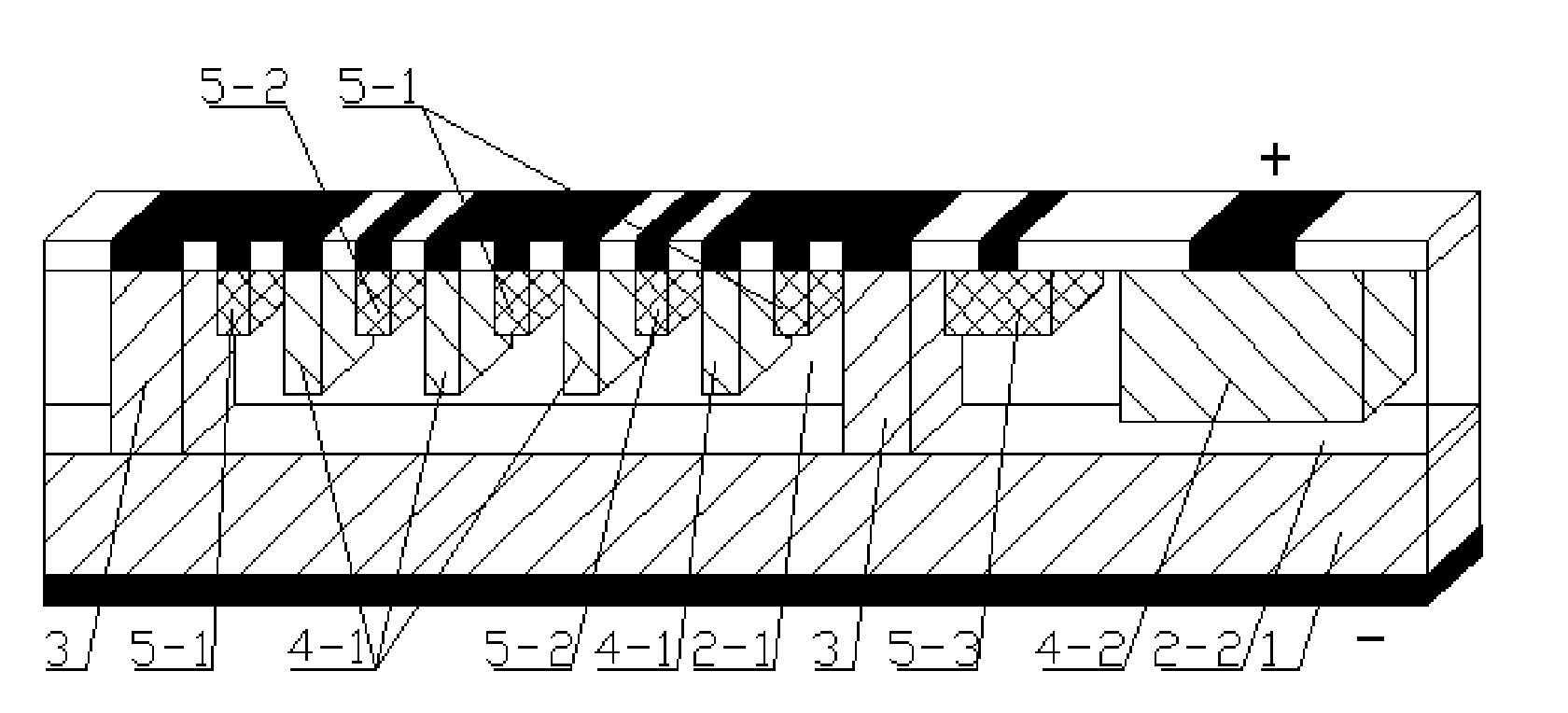

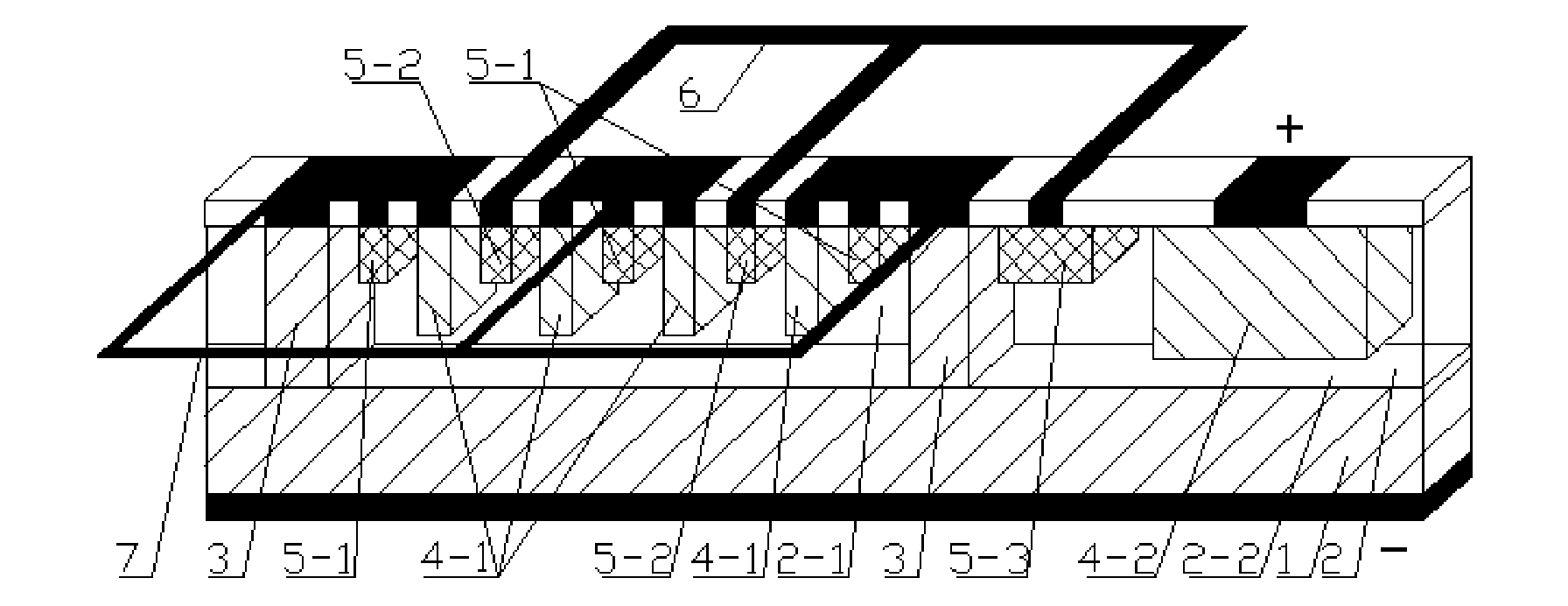

Multichannel current extended type semiconductor constant-current diode

The invention discloses a multichannel current extended type semiconductor constant-current diode which is characterized in that a N type semiconductor area (2) and a P+ type semiconductor area (3) are extended outwards on a P+ type semiconductor substrate (1); the P+ type semiconductor area (3) divides the N type semiconductor area (2) into two PN junction isolation areas; upper grids of the isolation areas are dispersed with a first P+ semiconductor area (4-1), a second P+ semiconductor area (4-2), a first N+ semiconductor area (5-1), a second N+ semiconductor area (5-2) and a third N+ semiconductor area (5-3); and a multichannel N-JFET and PNP transistor composite structure is formed. The diode connects the positive electrode of a power supply to the positive electrode of a device, connects the negative electrode of the power supply to the negative electrode of the device (also can be connected to the negative electrode by load), and can realize constant-current characteristics in a fundamental circuit. The size of the constant-current value can be realized by designing the N-JFET channel quantity and current gain of PNP. The structure can reach output constant current of 20mA-100mA series.

Owner:GUIZHOU UNIV

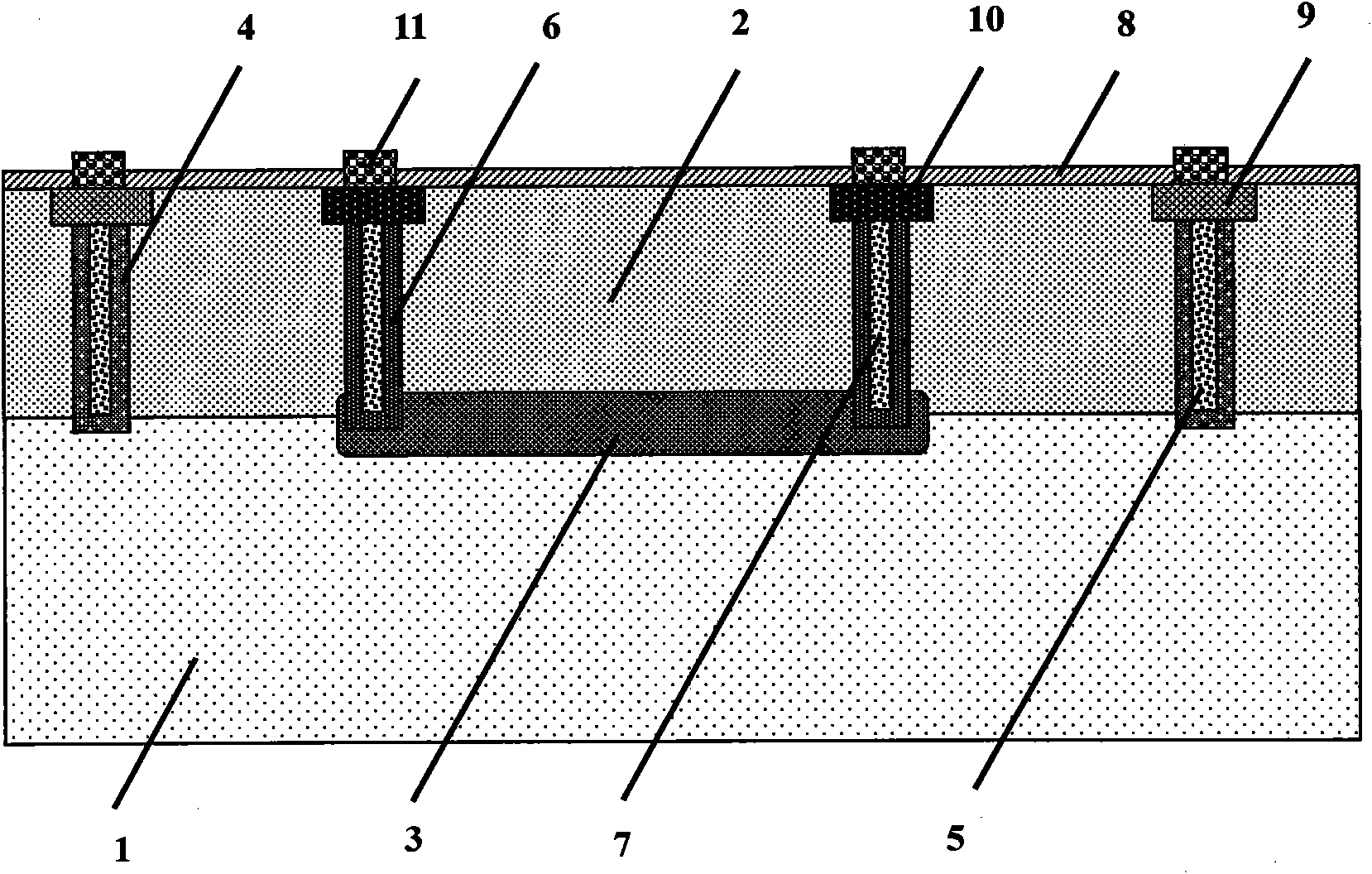

Preparation method of N-trap high-voltage gate driving chip for directly driving power device

ActiveCN102723304AReduce manufacturing costLow costSemiconductor/solid-state device manufacturingCapacitanceLow voltage

The invention discloses a preparation method of an N-trap high-voltage gate driving chip for directly driving a power device. A high-voltage side driving control module and a low-voltage side driving control module are separated through a way of directly injecting N-type impurities on a polished silicon wafer, through a trap pushing way and by adopting a high-pressure junction isolation technology; and a capacitive voltage divider is formed by utilizing two layers of polysilicons by forming an RESURF (Reducing Surface Electric Field) area on a PN (Positive Negative) junction surface on the basis of PN junction isolation of the conventional CMOS (Complementary Metal Oxide Semiconductor) tube technology, the electric field distribution on the PN junction surface is effectively changed, the high-voltage isolation of a high-voltage LDMOS (Laterally Diffused Metal Oxide Semiconductor) tube is formed, and a high-voltage N-type LDMOS tube is prepared and obtained by forming a P-BODY area. Compared with the conventional LDMOS tube, the voltage resistance requirement with the voltage being more than 700V can be achieved by adding an RESURF area structure and a double-layer polysilicon capacitance structure; and simultaneously, the working procedure of the preparation method is simple and compact, the cost is lower, and a high-voltage gate driving circuit device which is used for directly driving the power device can be formed by only 14 structural layers.

Owner:NINGBO SEMICON INT CORP

Method of forming junction isolation active assembly

The invention provides a shaping method of the junction insulation active blocks. The fundus of the semiconductor has several preconcerted active regions and there is at least one preconcerted isolation region between the two active regions. It forms the first grid structure on part of the fundus of the active regions as well as the second grid structure on the fundus of the isolation regions, engenders the first ion adulterating region in the funduses of the two sides of the first and second grid structures, forms the antireflection coatings on the fundus and the first and second grid structures, gets rid of part of the antireflection coating to reveal the second grid structure, then get rid of the second grid structure to reveal the fundus, forms the second ion adulterating region in the fundus of the isolation area and gets rid of the antireflection coatings.

Owner:MACRONIX INT CO LTD

Semiconductor structure for increasing integration density of high-voltage integrated circuit device and manufacturing method

ActiveCN101976680AImprove integration densityLower process temperatureSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

The invention relates to a semiconductor structure for increasing integration density of a high-voltage integrated circuit device and a manufacturing method. Aiming at the problems of large occupation area of PN junction isolation and penetration diffusion adopted in a high-voltage integrated circuit and high step, high electric field, high stress and poor clamping hidden trouble of conventional deep slot isolation, a deep slot diffusion isolation and deep slot penetration diffusion structure is adopted to realize improvement on the integration density of the high-voltage device and promotion on the performance of the device. The method can reduce over 35 percent of high-voltage integrated circuit area at most, improve the integration density of the high-voltage integrated circuit, thin the thickness of an epitaxial layer compared with the common penetration structure, simplify the process design of the high-voltage integrated circuit device structure and effectively solve the high step, high electric field, high stress and poor clamping hidden trouble of the conventional deep slot isolation structure. The method is applied in the fields of structure design and manufacture of high-voltage semiconductor devices and integrated circuits.

Owner:NO 24 RES INST OF CETC

High-temperature impact-pressure-resistant sensor and production method thereof

InactiveCN102980692AImprove reliabilityReduce pollutionFluid pressure measurement using piezo-electric devicesSemiconductor/solid-state device manufacturingDiffusionInsulation layer

The invention discloses a high-temperature impact-pressure-resistant sensor and a production method thereof. The high-temperature impact-pressure-resistant sensor comprises a metal sleeve and a core body sleeved in the metal sleeve, wherein threads are arranged on the connection portion of the core body and the metal sleeve, and the core body and the metal sleeve are integrally connected through the threads in laser soldering mode. The core body comprises a cylindrical casing, a horizontal groove is arranged at the upper end of the casing, and a silicon on insulator (SOI) chip is arranged in the horizontal groove. A lead electrode is arranged in the casing, and a pad electrode of the SOI chip is connected with the lead electrode arranged in the casing through a gold wire. The lead electrode arranged in the casing is led out to form an internal lead, and the internal lead is connected onto an external lead through a clamp. According to the high-temperature impact-pressure-resistant sensor, the diffusion silicon PN junction isolation process design scheme is improved to be the insulation layer isolation SOI process scheme. The temperature of the high-temperature impact-pressure-resistant sensor can reach 300 DEG C, and the problem that the sensor cannot work due to overlarge current leakage at high temperature when PN junction isolation is adopted is solved.

Owner:西安微纳传感器研究所有限公司

Image sensor with high fill factor pixels and method for forming an image sensor

ActiveUS7667183B2Improve fill factorTelevision system detailsSolid-state devicesFill factorEngineering

An image sensor comprising an array of photoelectric conversion elements in a substrate, the photoelectric conversion elements being arranged in rows and columns extending in a first direction and a second direction respectively, a plurality of first junction isolation regions in the substrate that each isolate side portions of neighboring photoelectric conversion elements of a common row, and a plurality of second junction isolation regions in the substrate that each isolate side portions of neighboring photoelectric conversion elements of a common column, and a plurality of dielectric isolation regions in the substrate, that each isolate corner portions of neighboring photoelectric conversion elements. In one embodiment, the photoelectric conversion elements have a first pitch in the first direction and have a second pitch in the second direction and the first pitch is substantially equal for the photoelectric conversion elements of a common row, and the second pitch is substantially equal for the photoelectric conversion elements of a common column.

Owner:SAMSUNG ELECTRONICS CO LTD

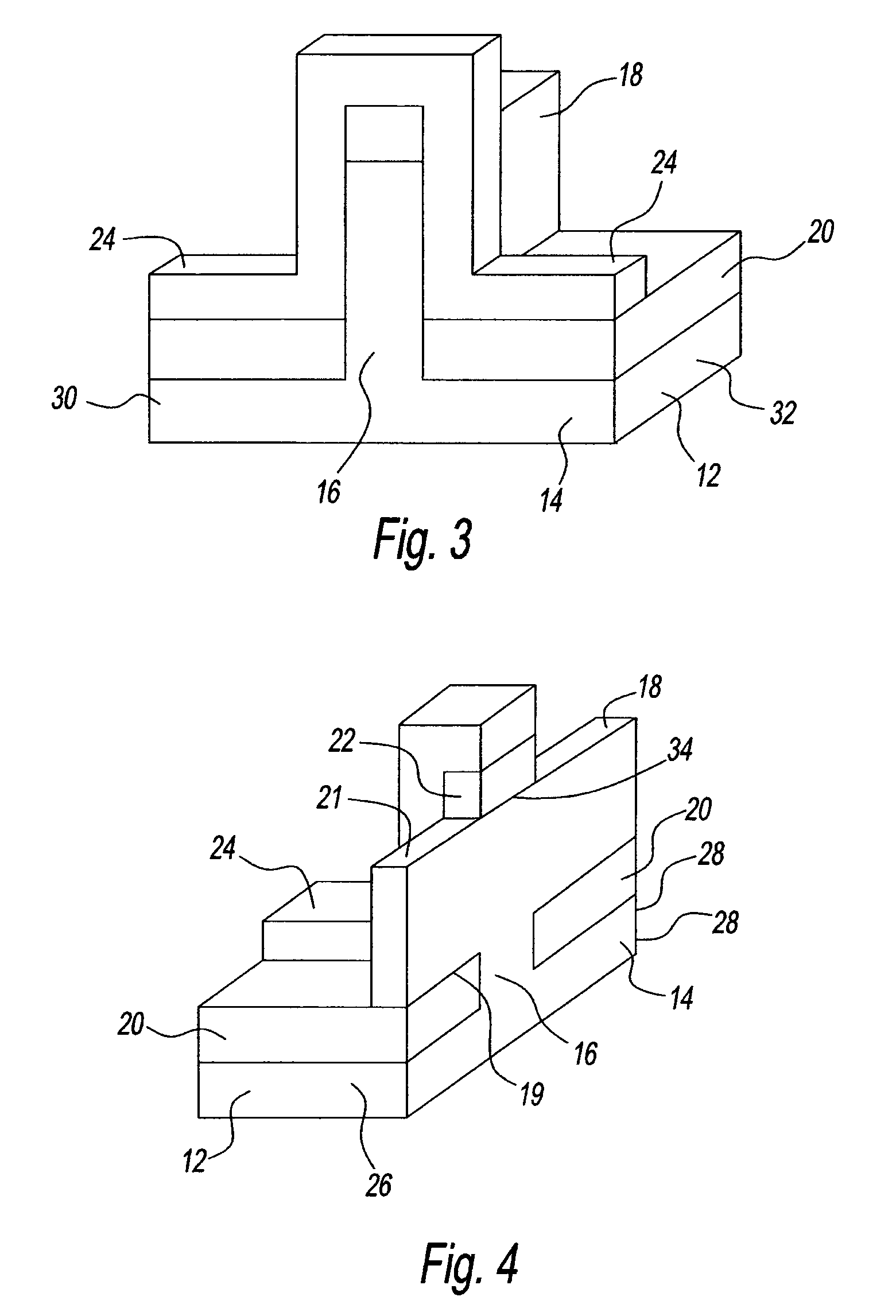

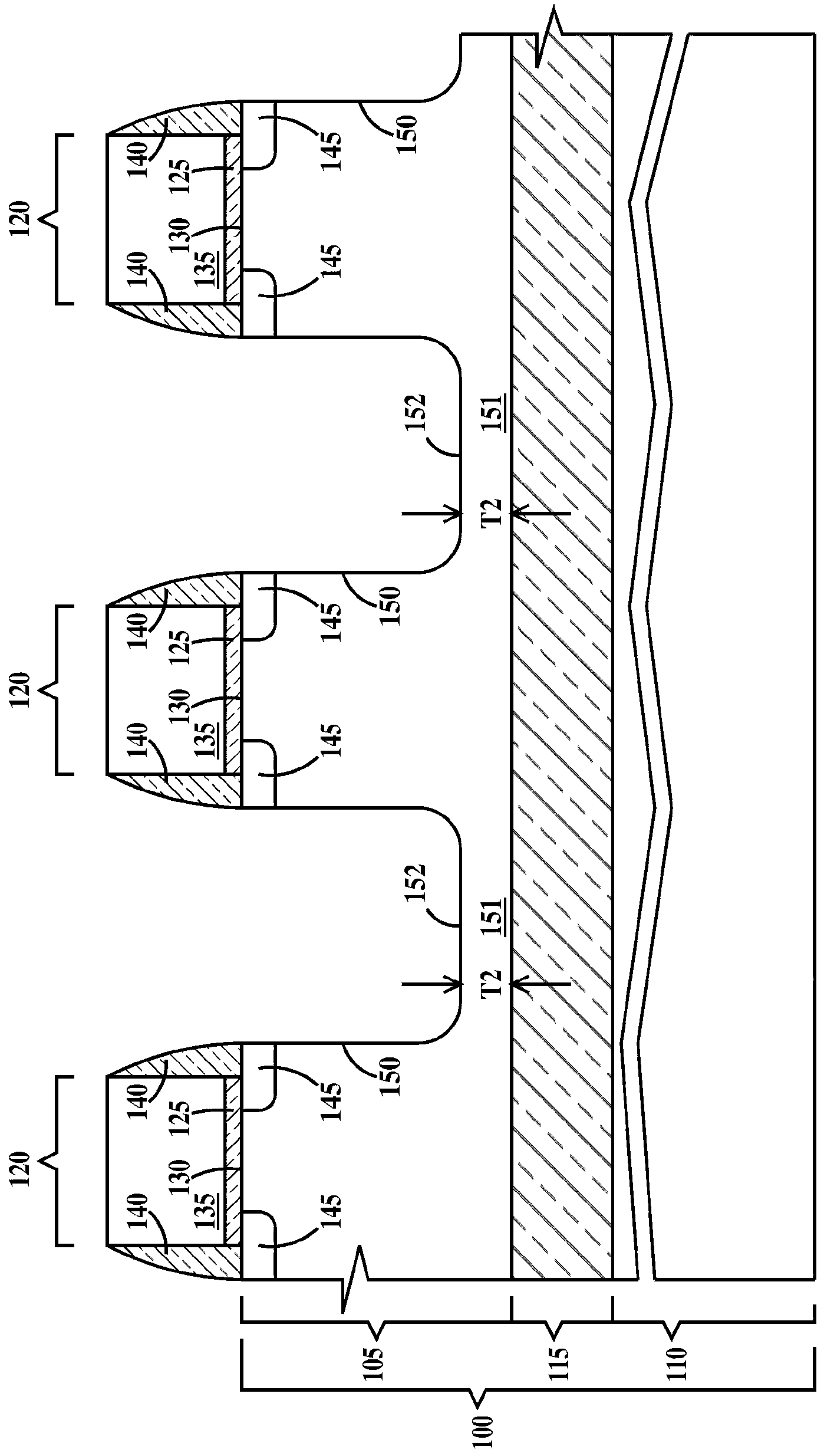

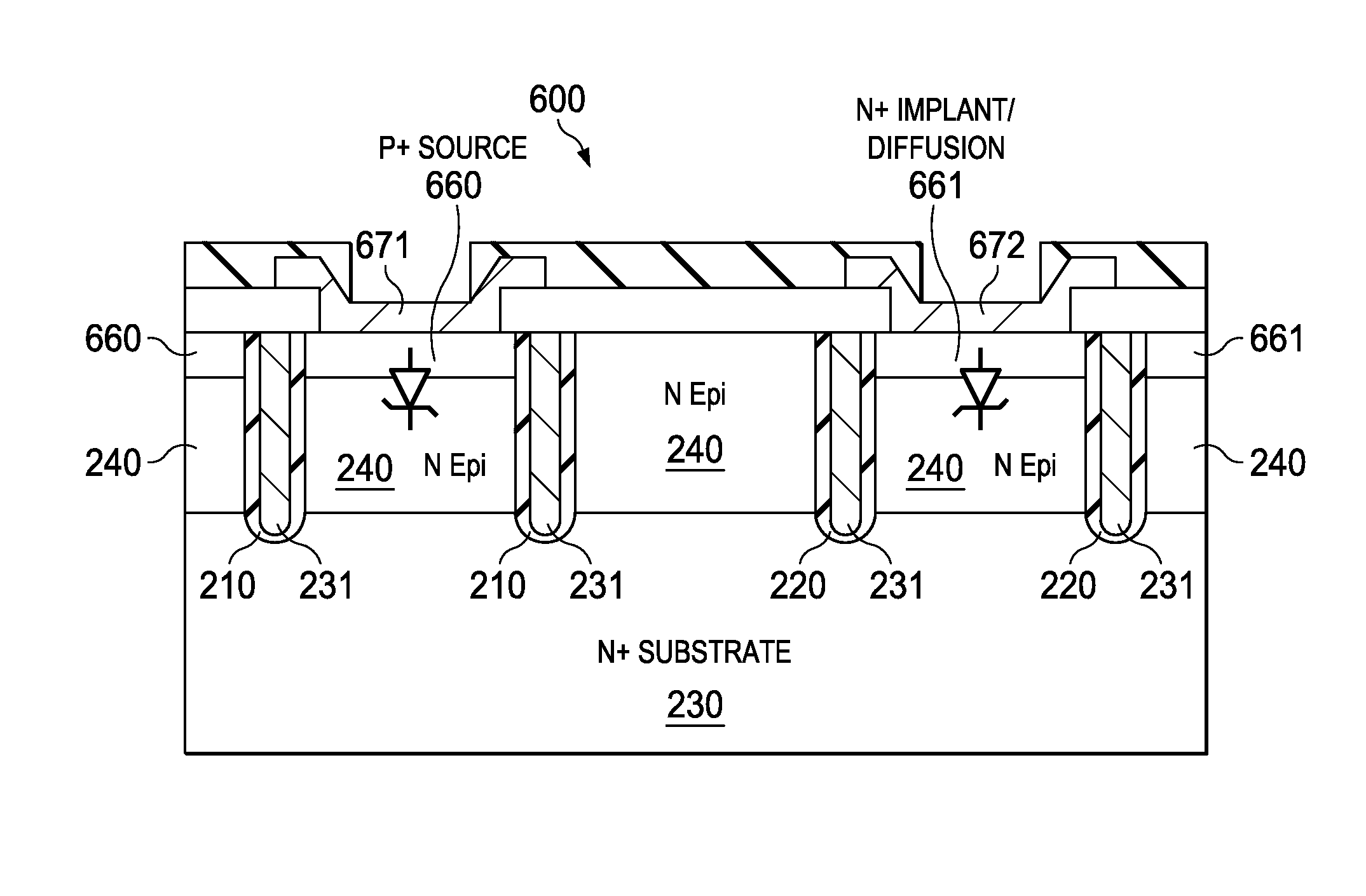

Butted SOI junction isolation structures and devices and method of fabrication

ActiveCN103210493ASolid-state devicesSemiconductor/solid-state device manufacturingDopantJunction isolation

A structure, a FET, a method of making the structure and of making the FET. The structure including: a silicon layer (105; Fig. 5) on a buried oxide (BOX) layer (115) of a silicon-on-insulator substrate (100); a trench in the silicon layer extending from a top surface of the silicon layer into the silicon layer, the trench not extending to the BOX layer (160, 165, and 170), a doped region (155) in the silicon layer between and abutting the BOX layer and a bottom of the trench, the first doped region doped to a first dopant concentration; a first epitaxial layer (160), doped to a second dopant concentration, in a bottom of the trench; a second epitaxial layer (165), doped to a third dopant concentration, on the first epitaxial layer in the trench; ; and wherein the third dopant concentration is greater than the first and second dopant concentrations and the first dopant concentration is greater than the second dopant concentration.

Owner:TAIWAN SEMICON MFG CO LTD

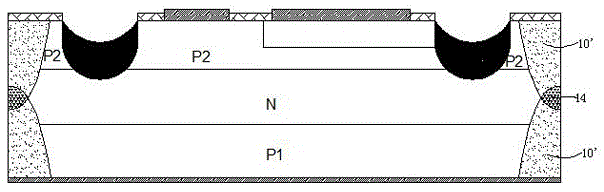

Thyristor chip with seven-layer p-n junction isolation structure and preparation method of thyristor chip

ActiveCN105633129AImprove completenessReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon-controlled rectifierEngineering

The invention discloses a thyristor chip with a seven-layer p-n junction isolation structure and a preparation method of the thyristor chip. The thyristor chip comprises an anode region P1, an N-type long base region, a short base region P2, an N<+>-type cathode region, a front oxidation film, a front gate metal electrode, a front cathode metal electrode, a back anode metal electrode, an annular passivation groove and an isolation ring of the seven-layer p-n junction isolation structure, wherein the isolation ring of the seven-layer p-n junction isolation structure comprises a boron impurity region, a boron-aluminum mixed impurity region, an aluminum impurity region, an aluminum-aluminum overlapping impurity region, an aluminum impurity region, the boron-aluminum mixed impurity region and the boron impurity region from top to bottom; and the isolation ring of the seven-layer p-n junction isolation structure is arranged between the front oxidation film and the back anode metal electrode along the vertical direction and surrounds the peripheries of the anode region P1, the N-type long base region and the short base region P2. The thyristor chip is short in diffusion time, low in production energy consumption, high in efficiency, high in silicon wafer integrity rate, little in transverse diffusion of the isolation region surface and small in isolation region width, and saves the area of the silicon wafer.

Owner:JIANGSU JIEJIE MICROELECTRONICS

Semiconductor diode assembly

ActiveUS20140167204A1Less complicatedLow costSemiconductor/solid-state device manufacturingDiodeJunction formationEngineering physics

TSV devices with p-n junctions that are planar have superior performance in breakdown and current handling. Junction diode assembly formed in enclosed trenches occupies less chip area compared with junction-isolation diode assembly in the known art. Diode assembly fabricated with trenches formed after the junction formation reduces fabrication cost and masking steps increase process flexibility and enable asymmetrical TSV and uni-directional TSV functions.

Owner:DIODES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com