Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

982 results about "JFET" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

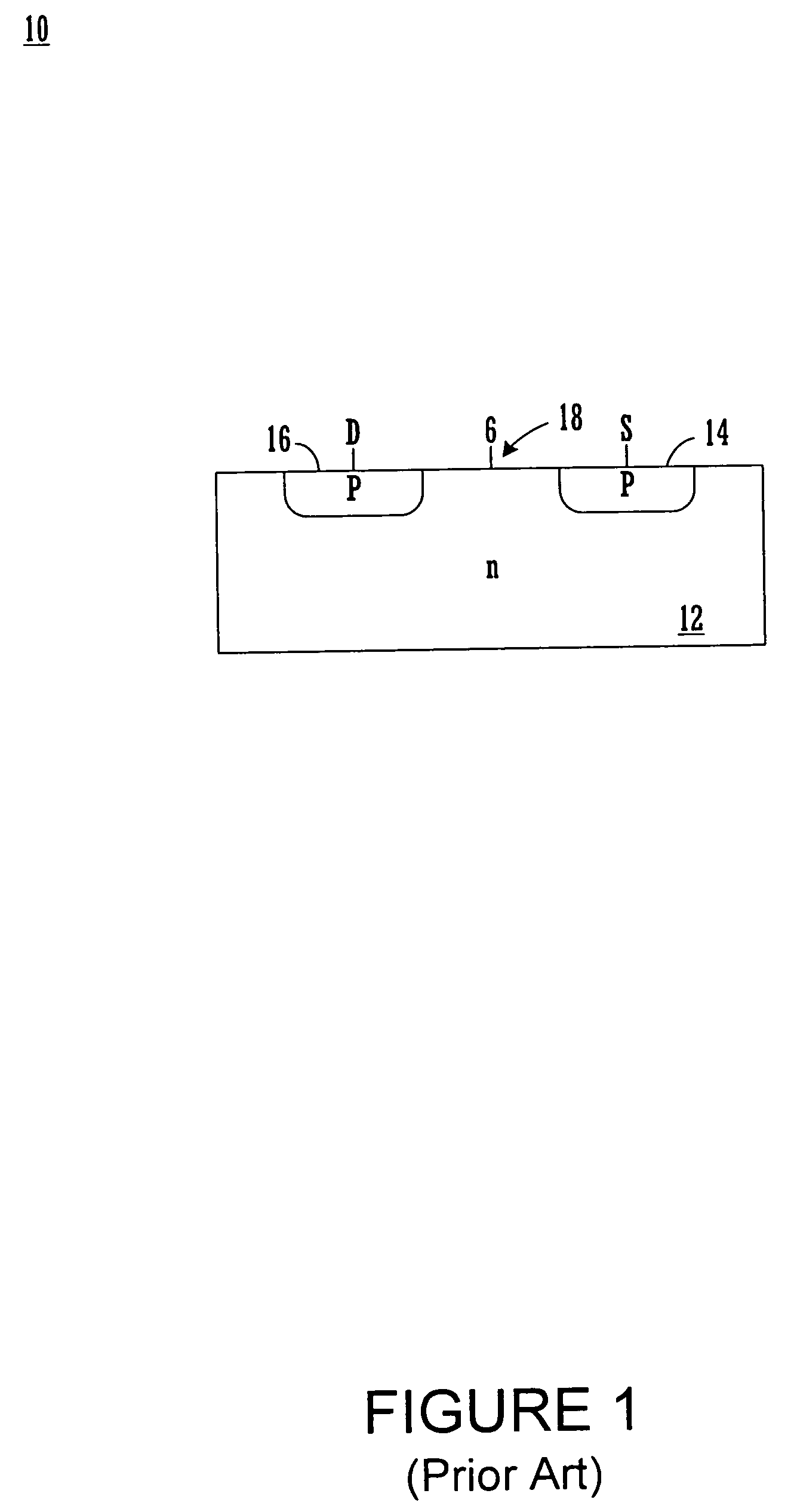

The junction gate field-effect transistor (JFET or JUGFET) is one of the simplest types of field-effect transistor. JFETs are three-terminal semiconductor devices that can be used as electronically-controlled switches, amplifiers, or voltage-controlled resistors.

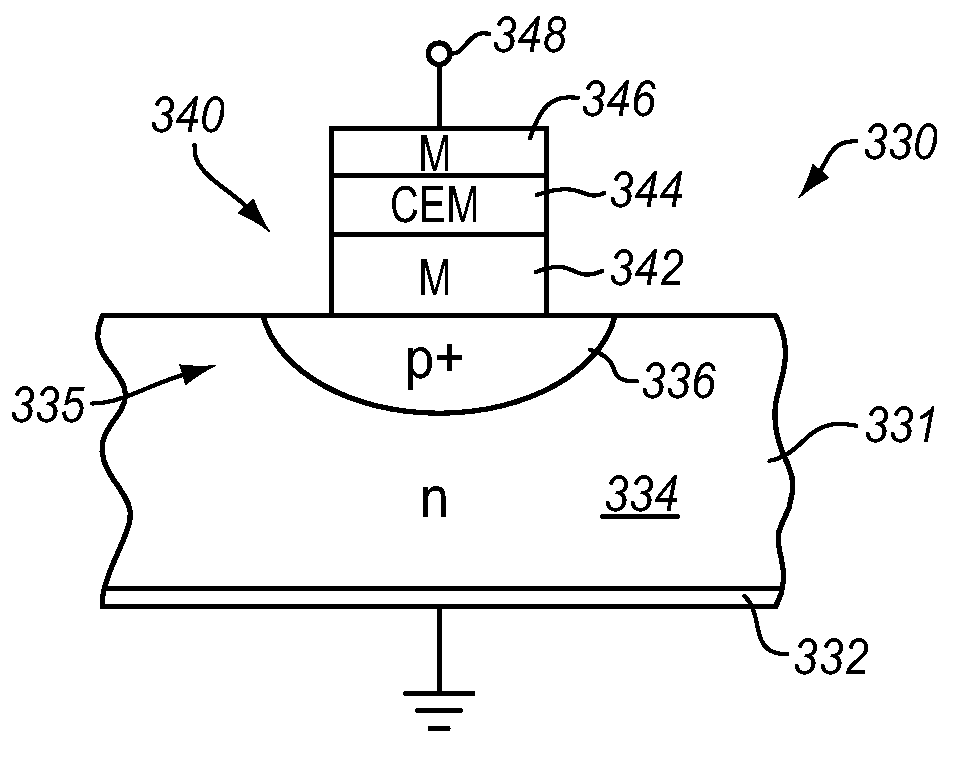

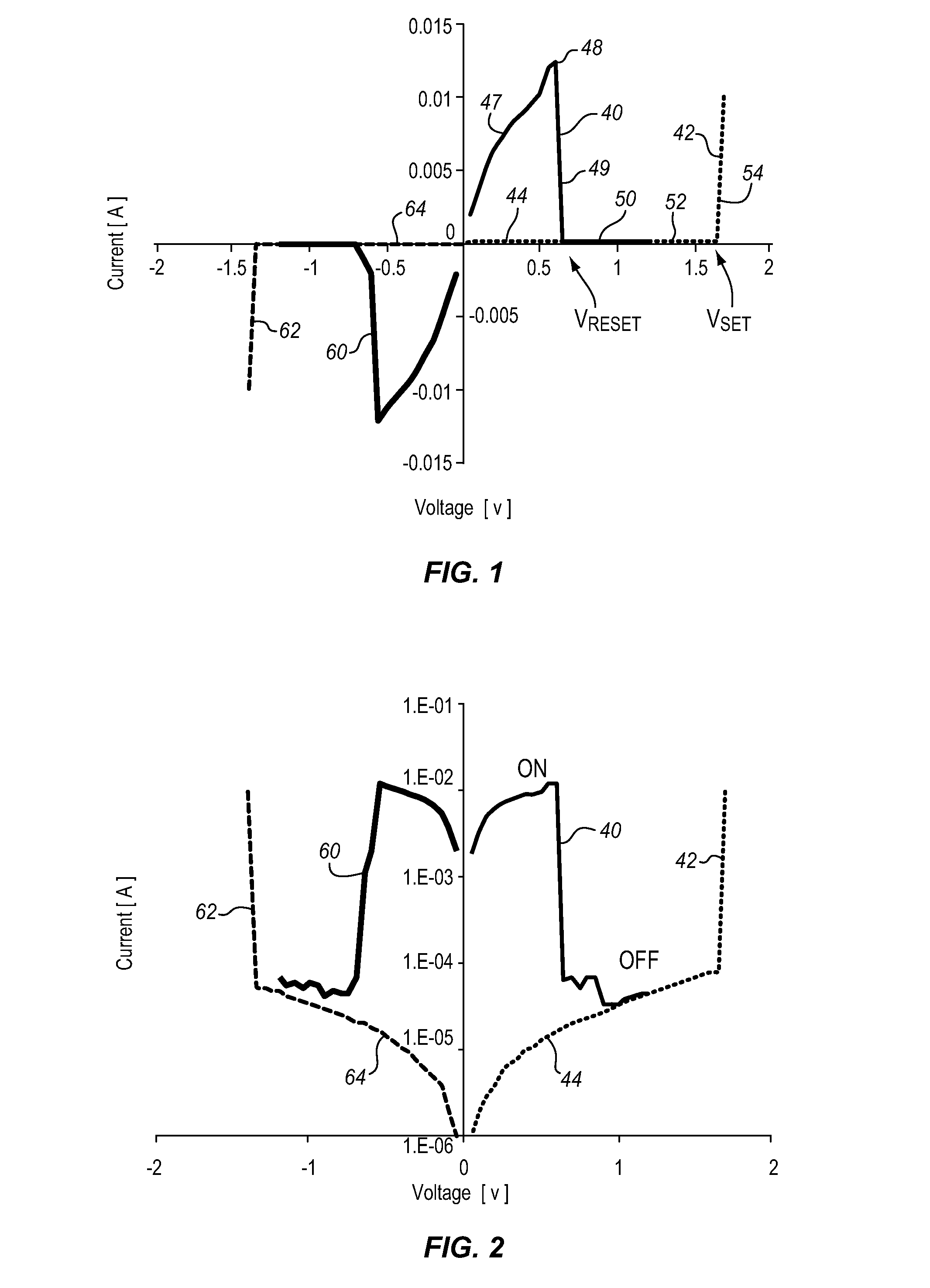

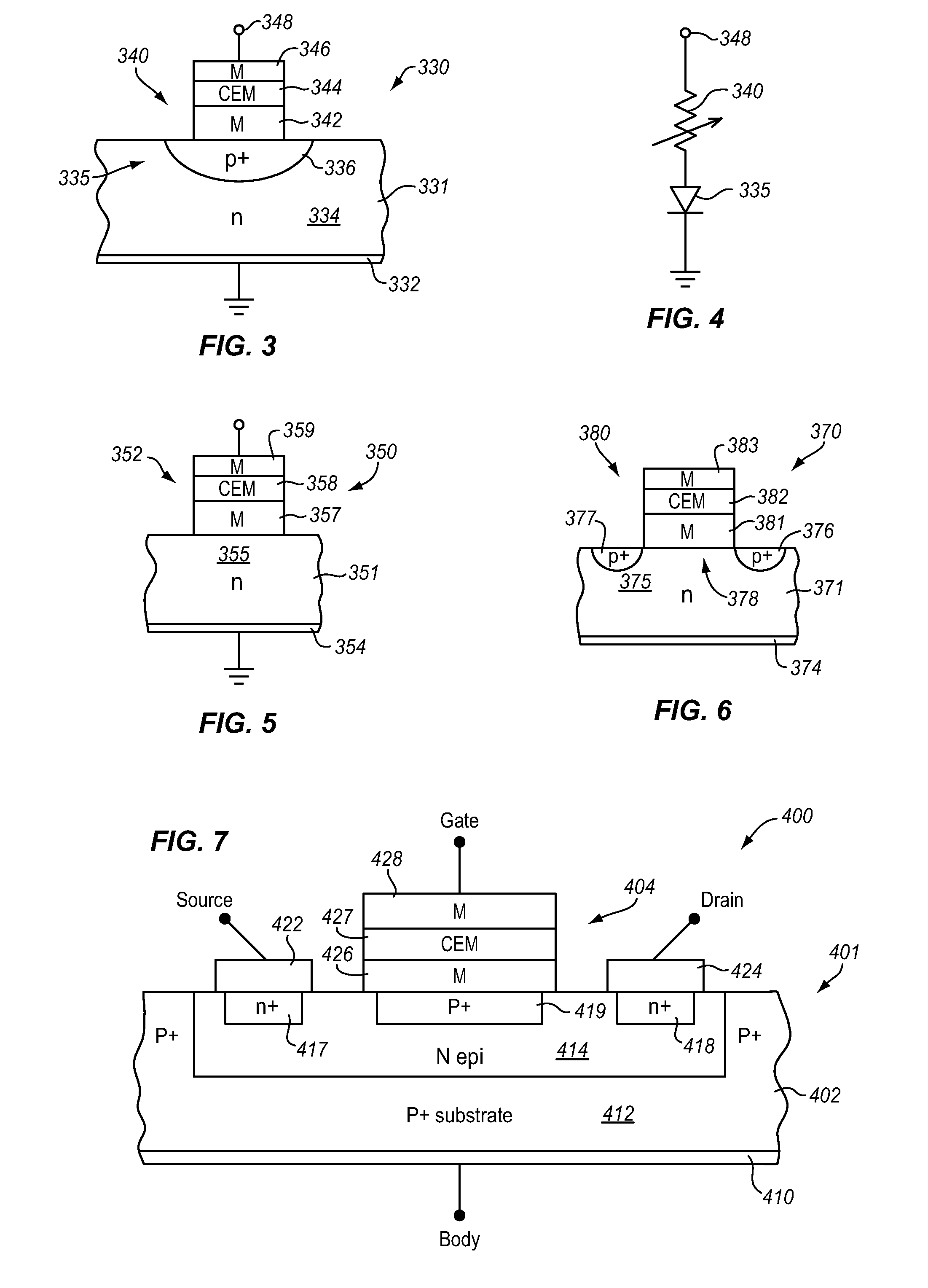

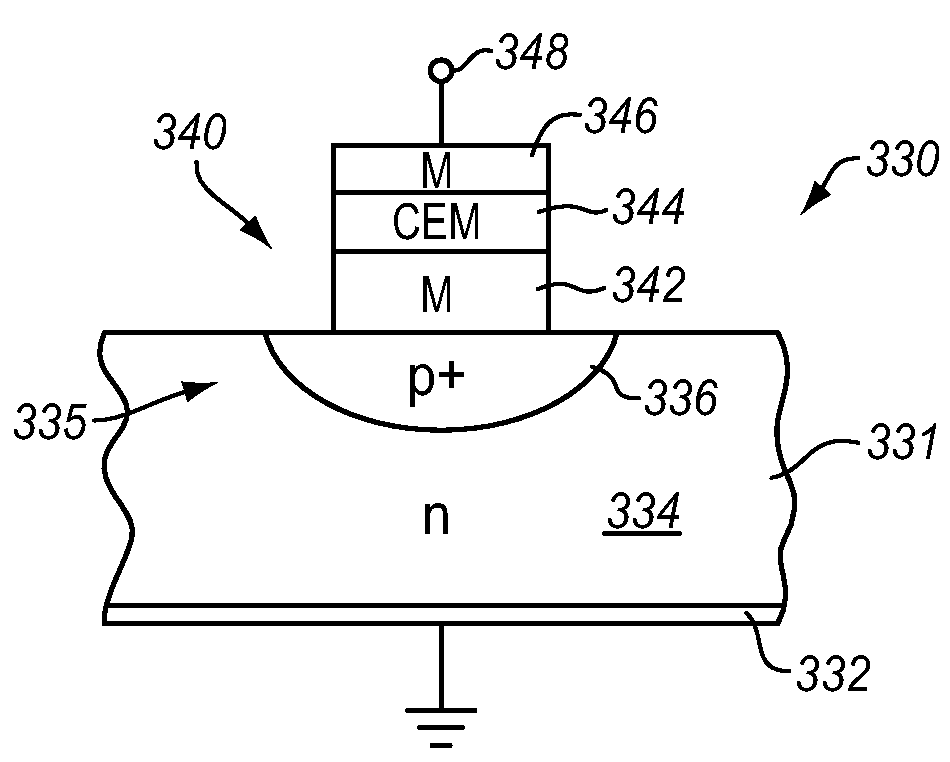

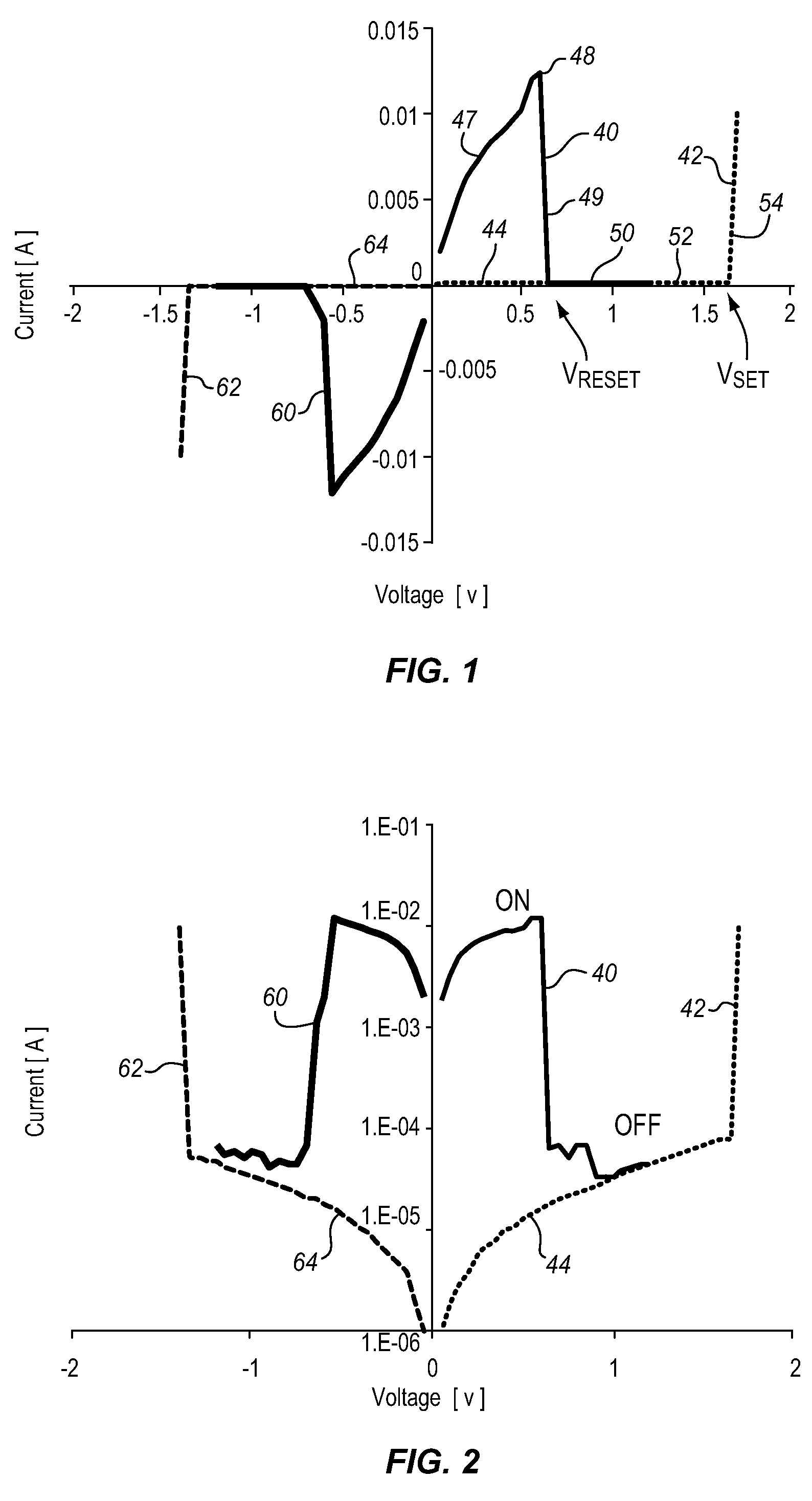

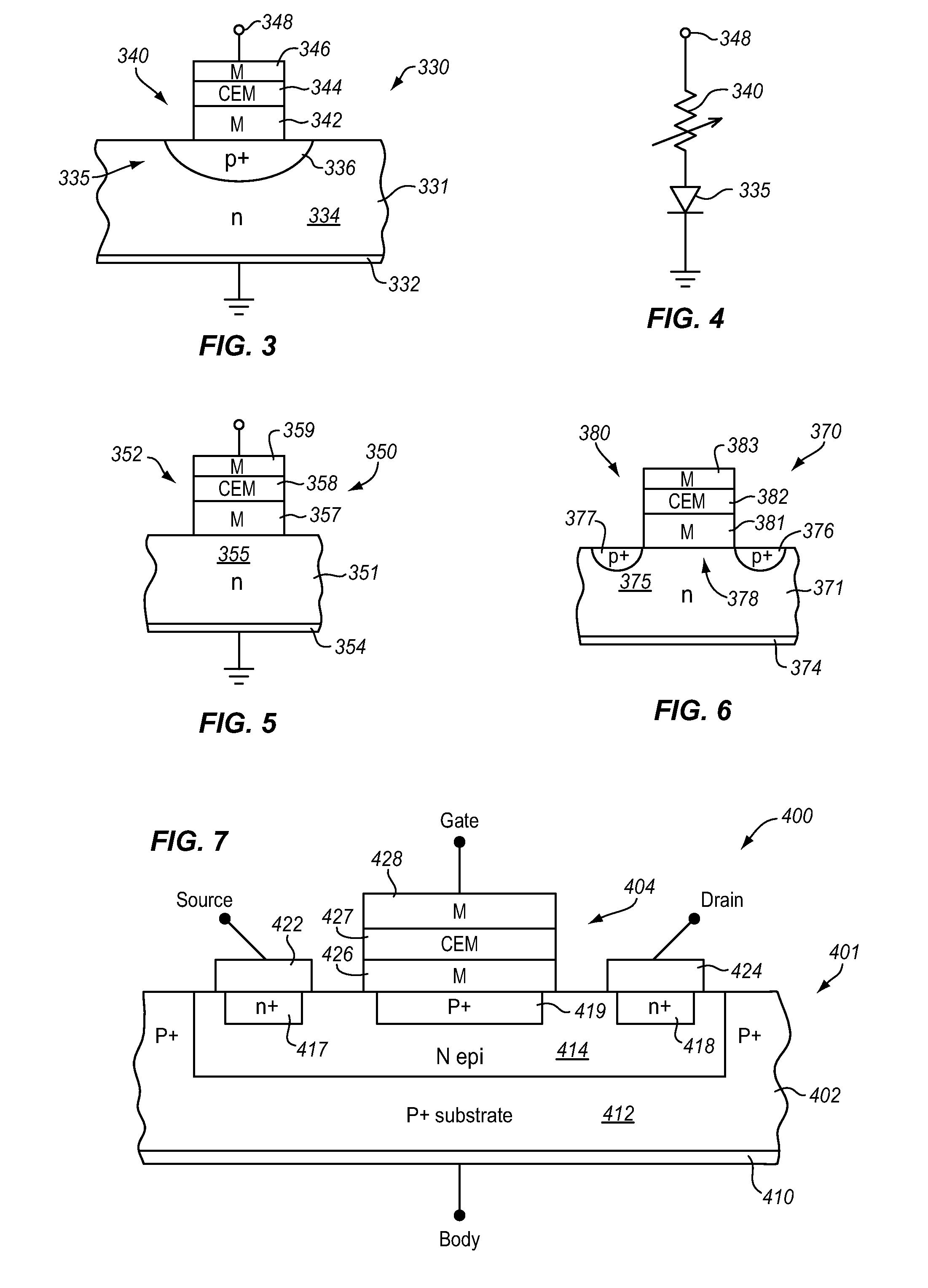

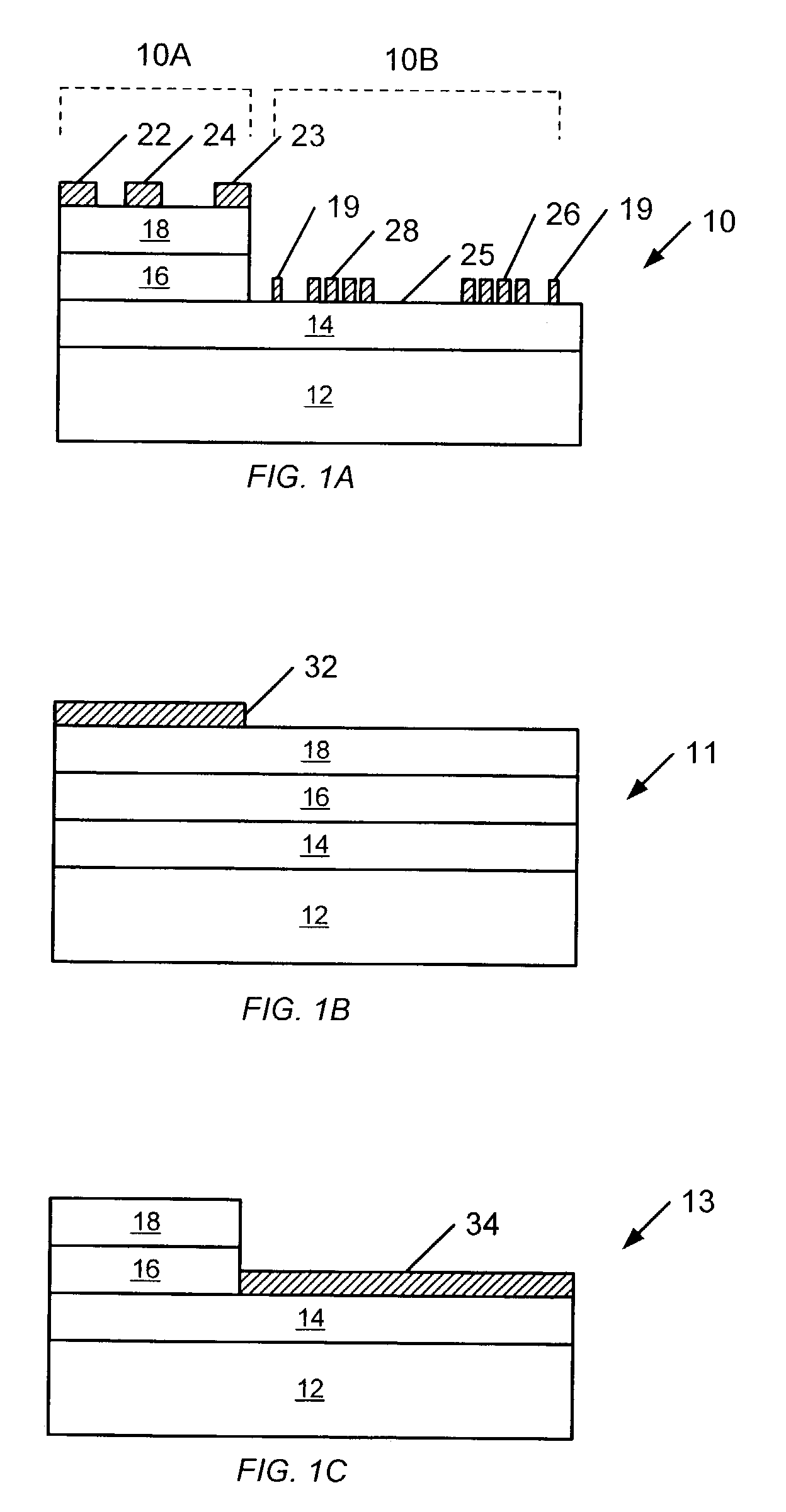

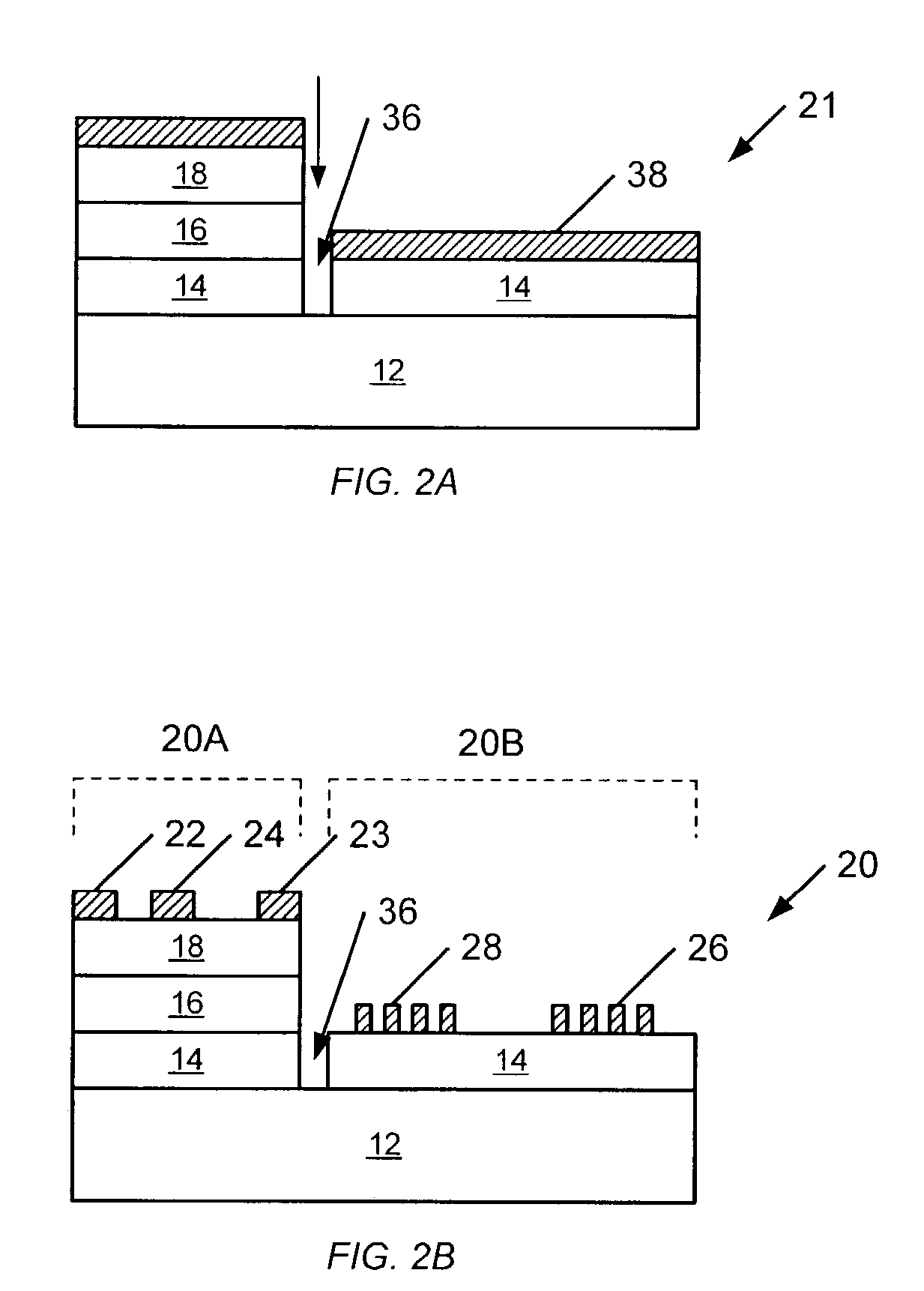

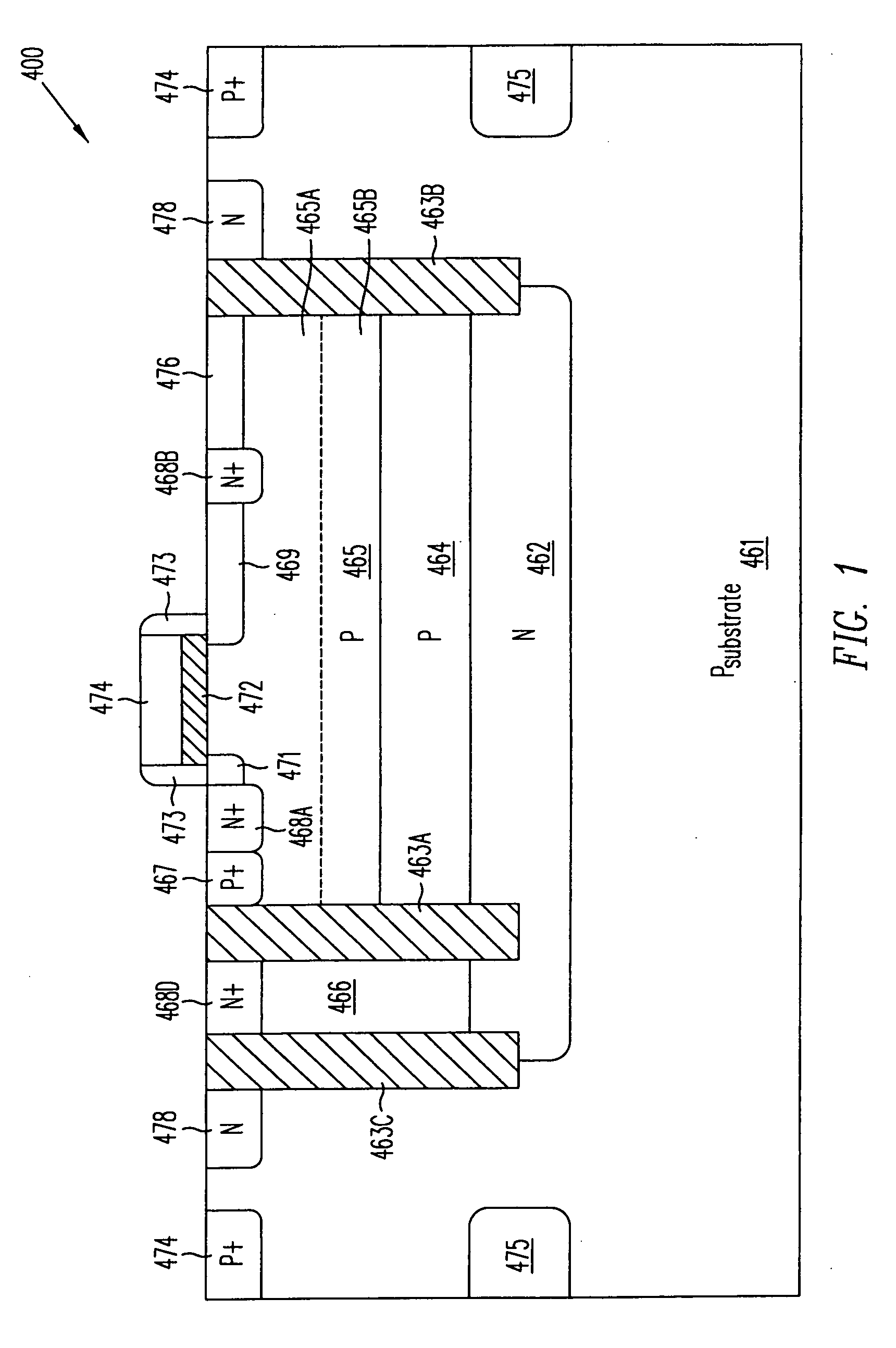

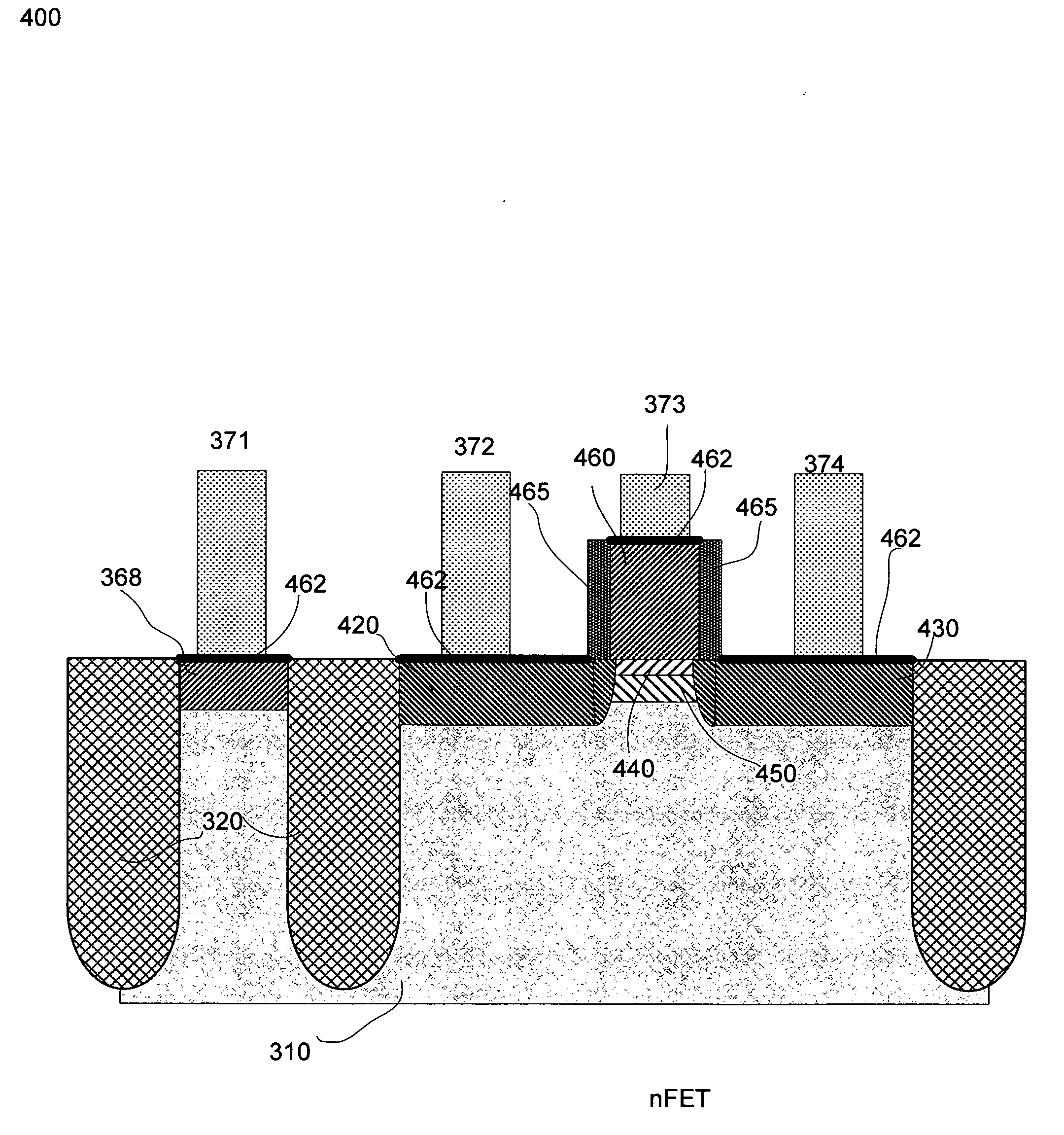

Non-volatile resistance switching memories and methods of making same

An integrated circuit memory cell including: a semiconductor having a first active area, a second active area, and a channel between the active areas; and a layer of a variable resistance material (VRM) directly above the channel. In one embodiment, there is a first conductive layer between the VRM and the channel and a second conductive layer directly above the VRM layer. The VRM preferably is a correlated electron material (CEM). The memory cell comprises a FET, such as a JFET or a MESFET. In another embodiment, there is a layer of an insulating material between the VRM and the channel. In this case, the memory cell may include a MOSFET structure.

Owner:SYMETRIX MEMORY

Non-volatile resistance switching memories and methods of making same

An integrated circuit memory cell including: a semiconductor having a first active area, a second active area, and a channel between the active areas; and a layer of a variable resistance material (VRM) directly above the channel. In one embodiment, there is a first conductive layer between the VRM and the channel and a second conductive layer directly above the VRM layer. The VRM preferably is a correlated electron material (CEM). The memory cell comprises a FET, such as a JFET or a MESFET. In another embodiment, there is a layer of an insulating material between the VRM and the channel. In this case, the memory cell may include a MOSFET structure.

Owner:SYMETRIX MEMORY

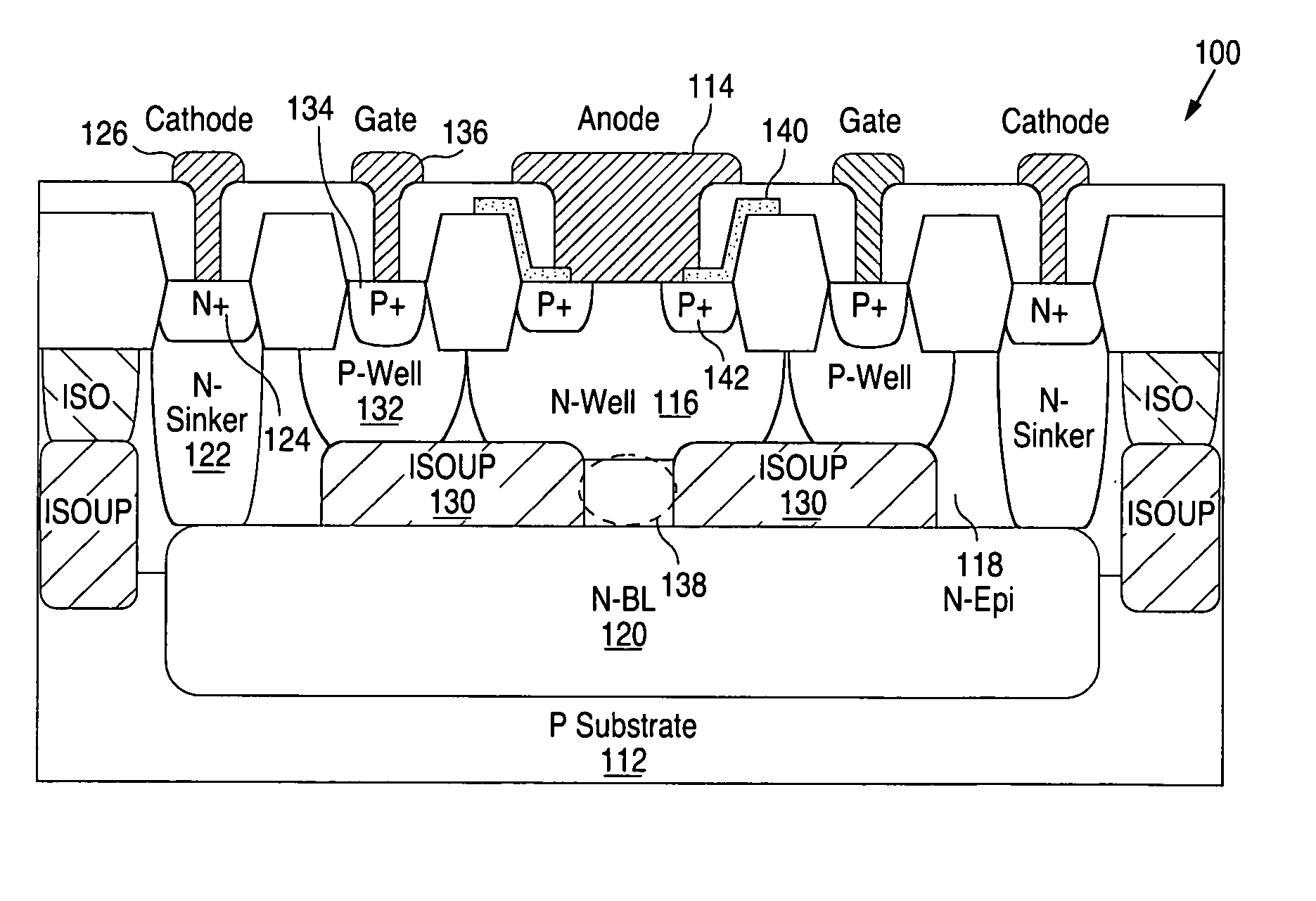

High-voltage bipolar-CMOS-DMOS integrated circuit devices and modular methods of forming the same

InactiveUS20070278568A1Eliminate needReduce seizuresTransistorSolid-state devicesCMOSDevice material

All low-temperature processes are used to fabricate a variety of semiconductor devices in a substrate the does not include an epitaxial layer. The devices include a non-isolated lateral DMOS, a non-isolated extended drain or drifted MOS device, a lateral trench DMOS, an isolated lateral DMOS, JFET and depletion-mode devices, and P-N diode clamps and rectifiers and junction terminations. Since the processes eliminate the need for high temperature processing and employ “as-implanted” dopant profiles, they constitute a modular architecture which allows devices to be added or omitted to the IC without the necessity of altering the processes used to produce the remaining devices.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED +1

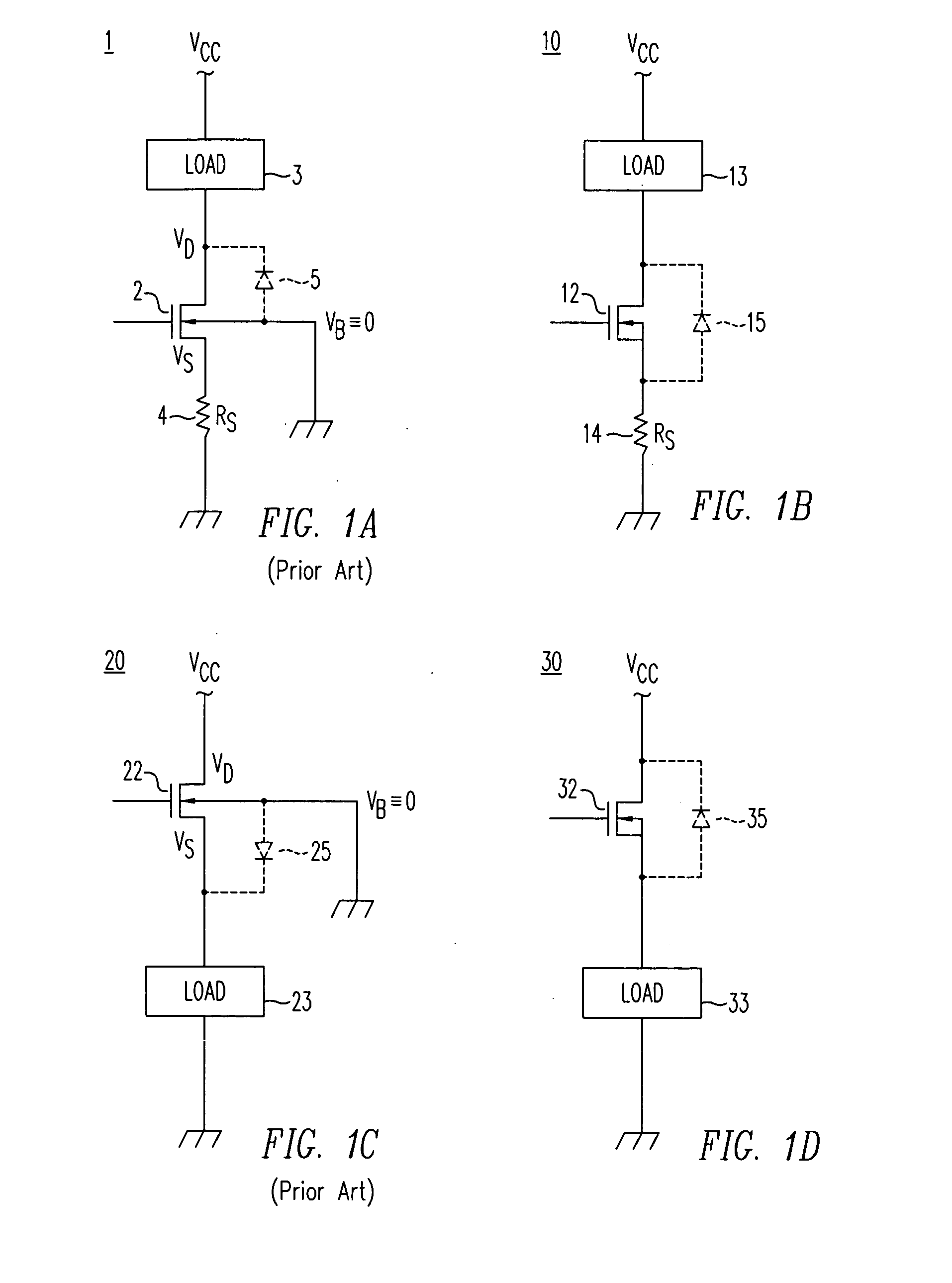

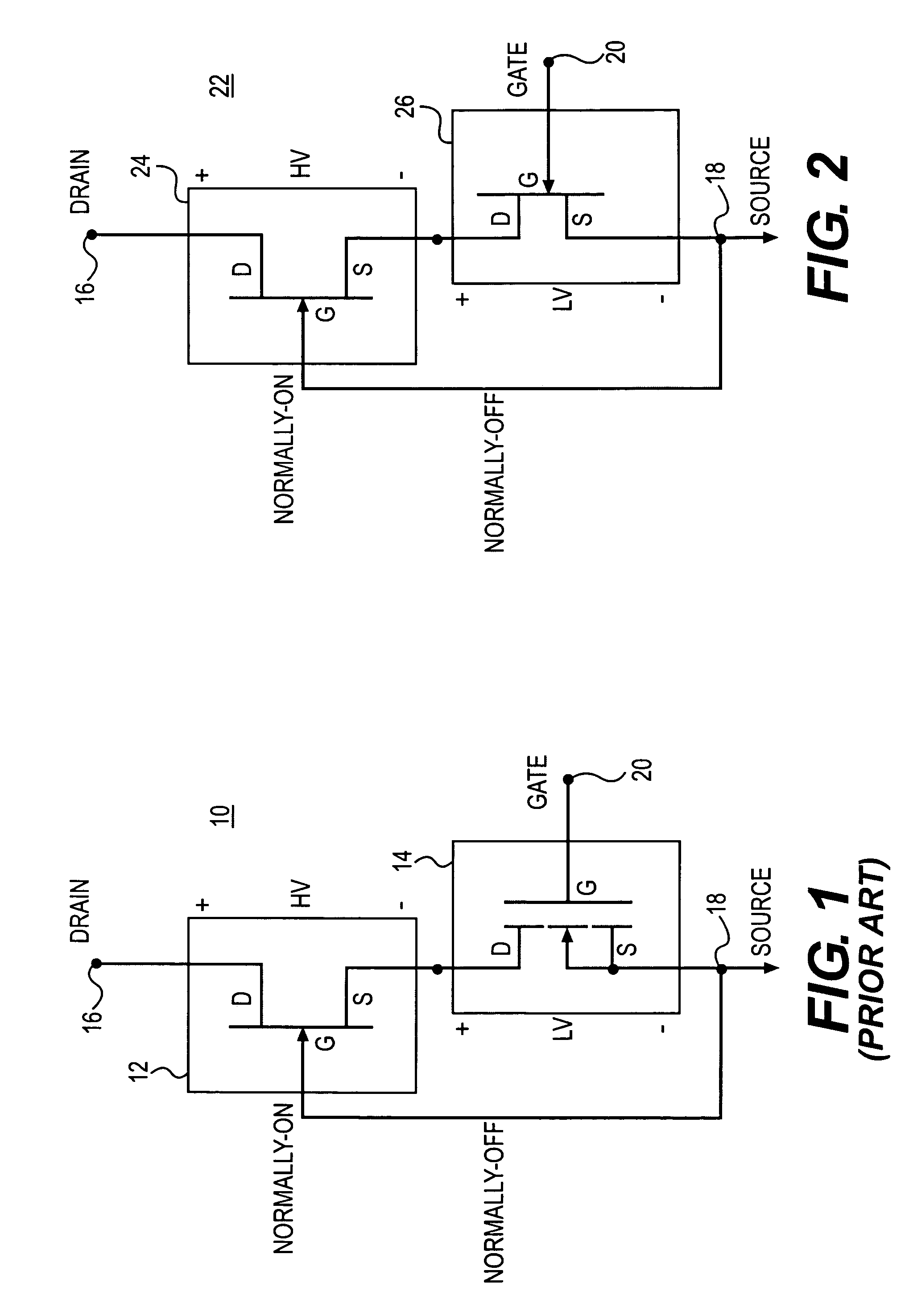

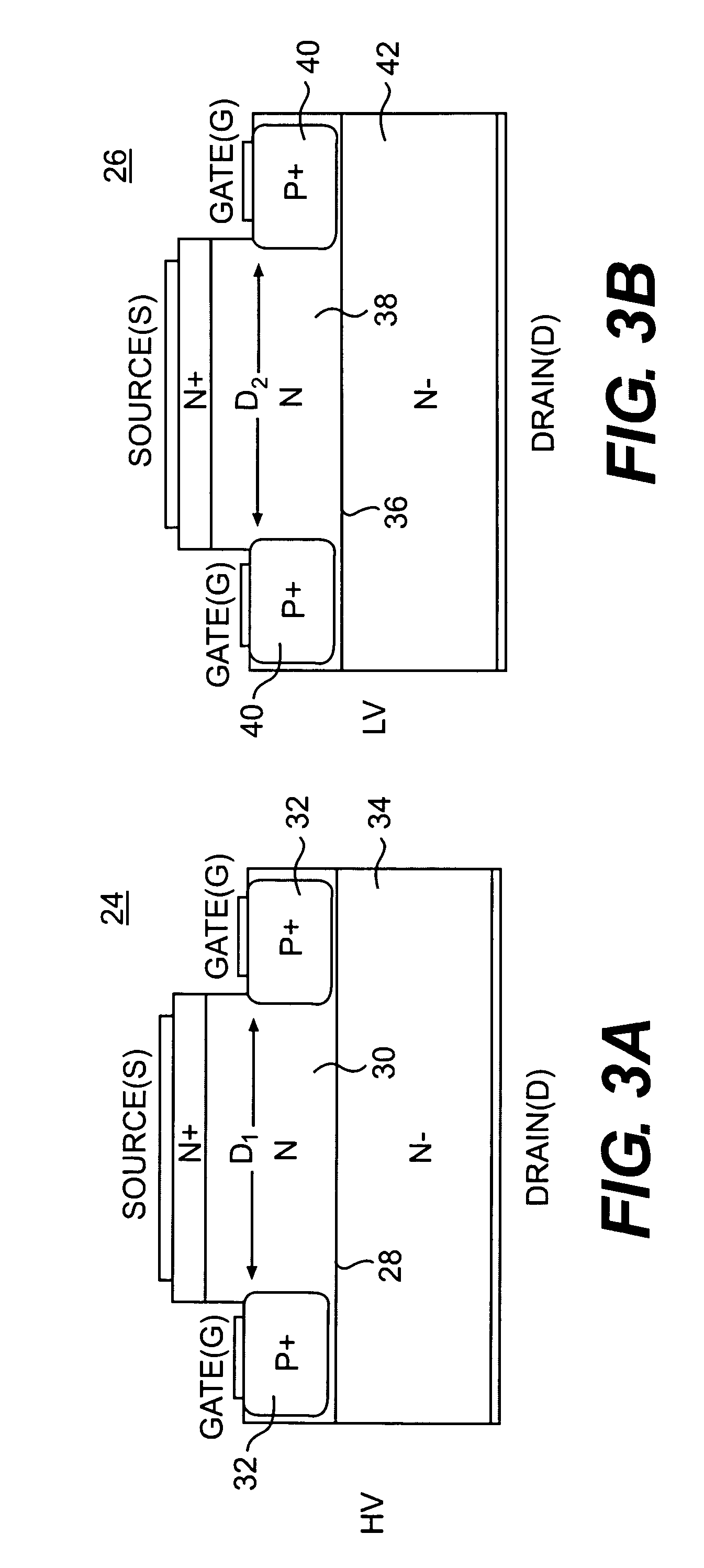

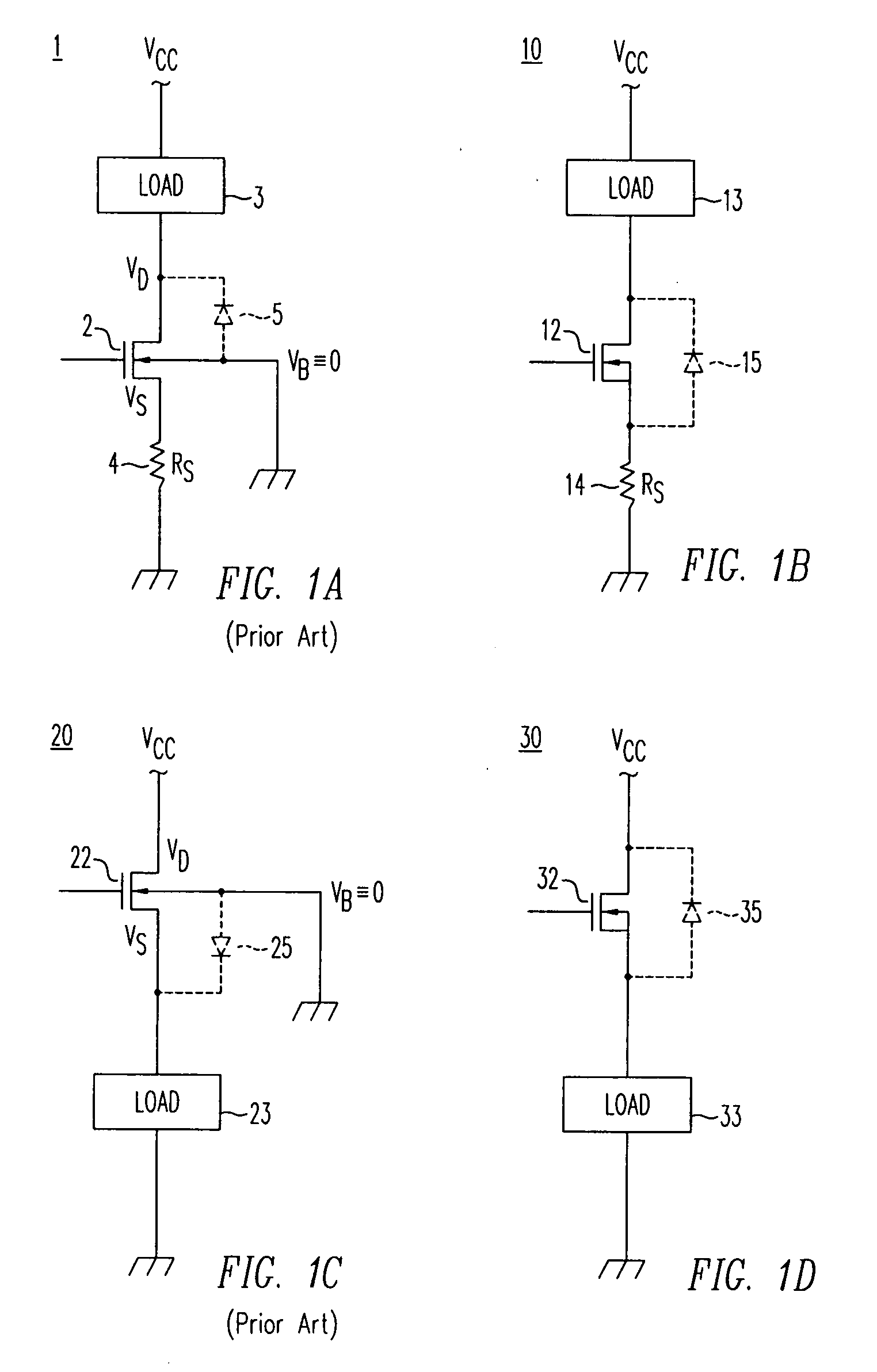

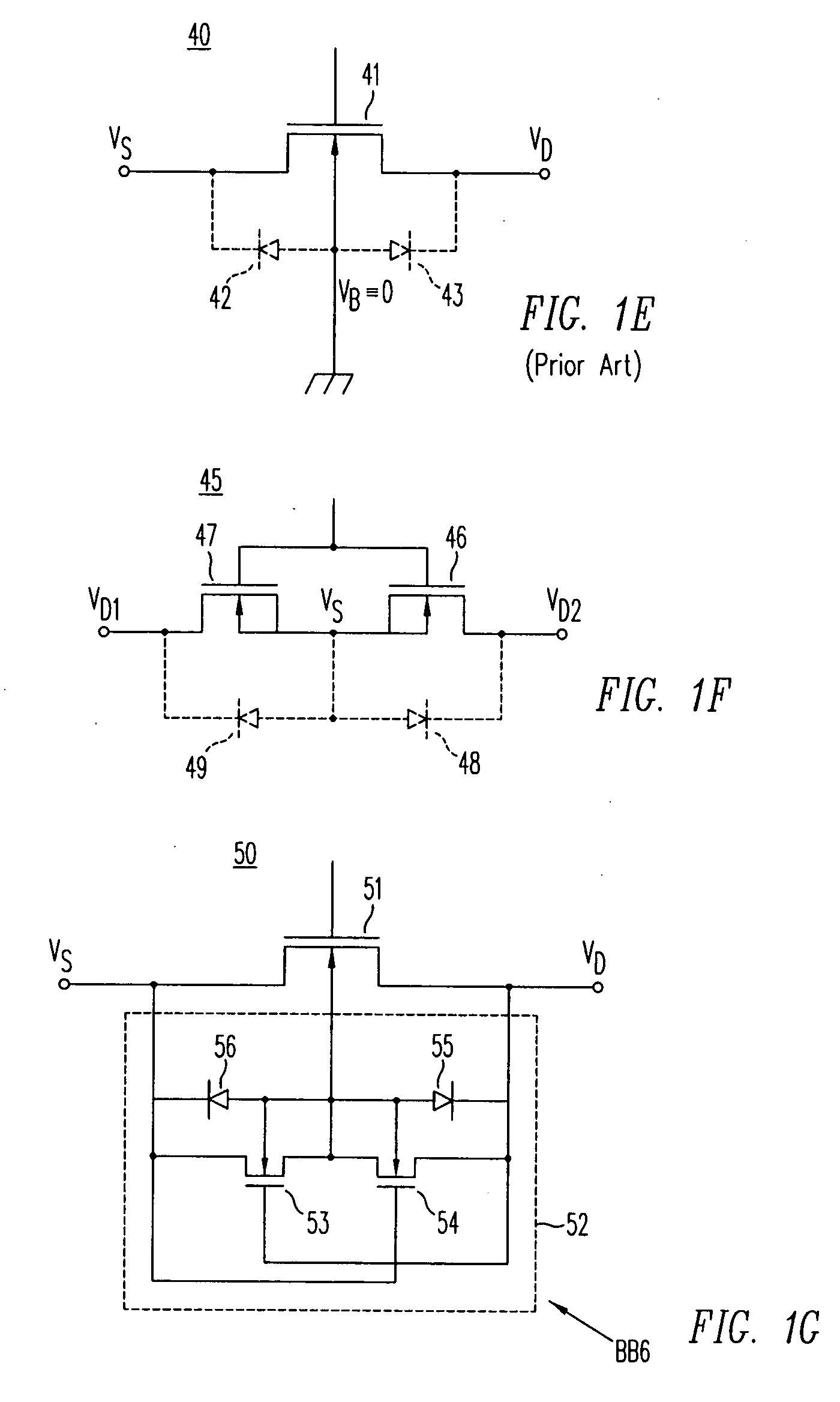

Cascode power switch topologies

ActiveUS7719055B1Increase temperatureHigh blocking voltageElectronic switchingSemiconductor devicesCascodeGallium nitride

A normally-off cascode power switch circuit is disclosed fabricated in wide bandgap semiconductor material such as silicon carbide or gallium nitride and which is capable of conducting current in the forward and reverse direction under the influence of a positive gate bias. The switch includes cascoded junction field effect transistors (JFETs) that enable increased gain, and hence blocking voltage, while minimizing specific on-resistance.

Owner:NORTHROP GRUMMAN SYST CORP

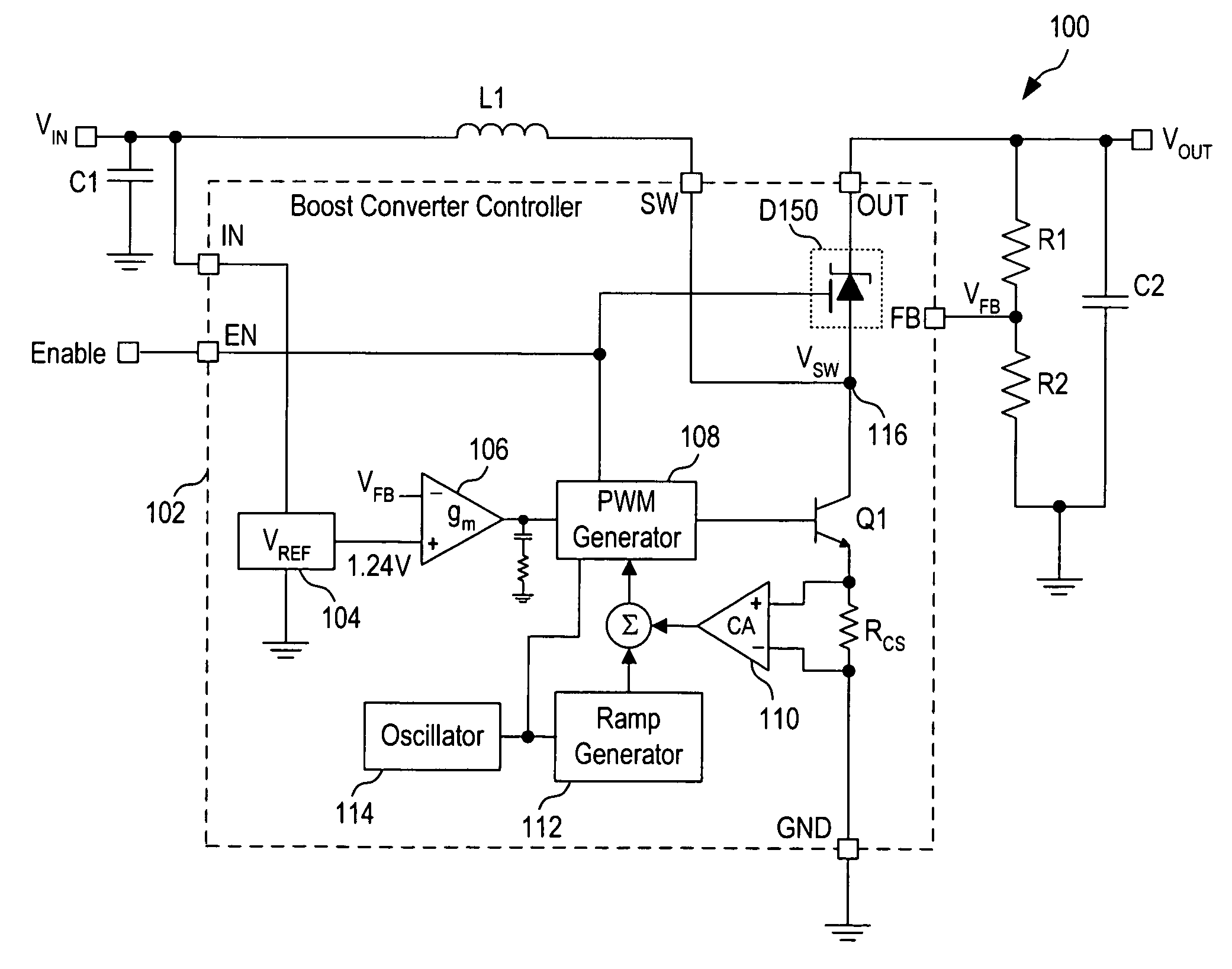

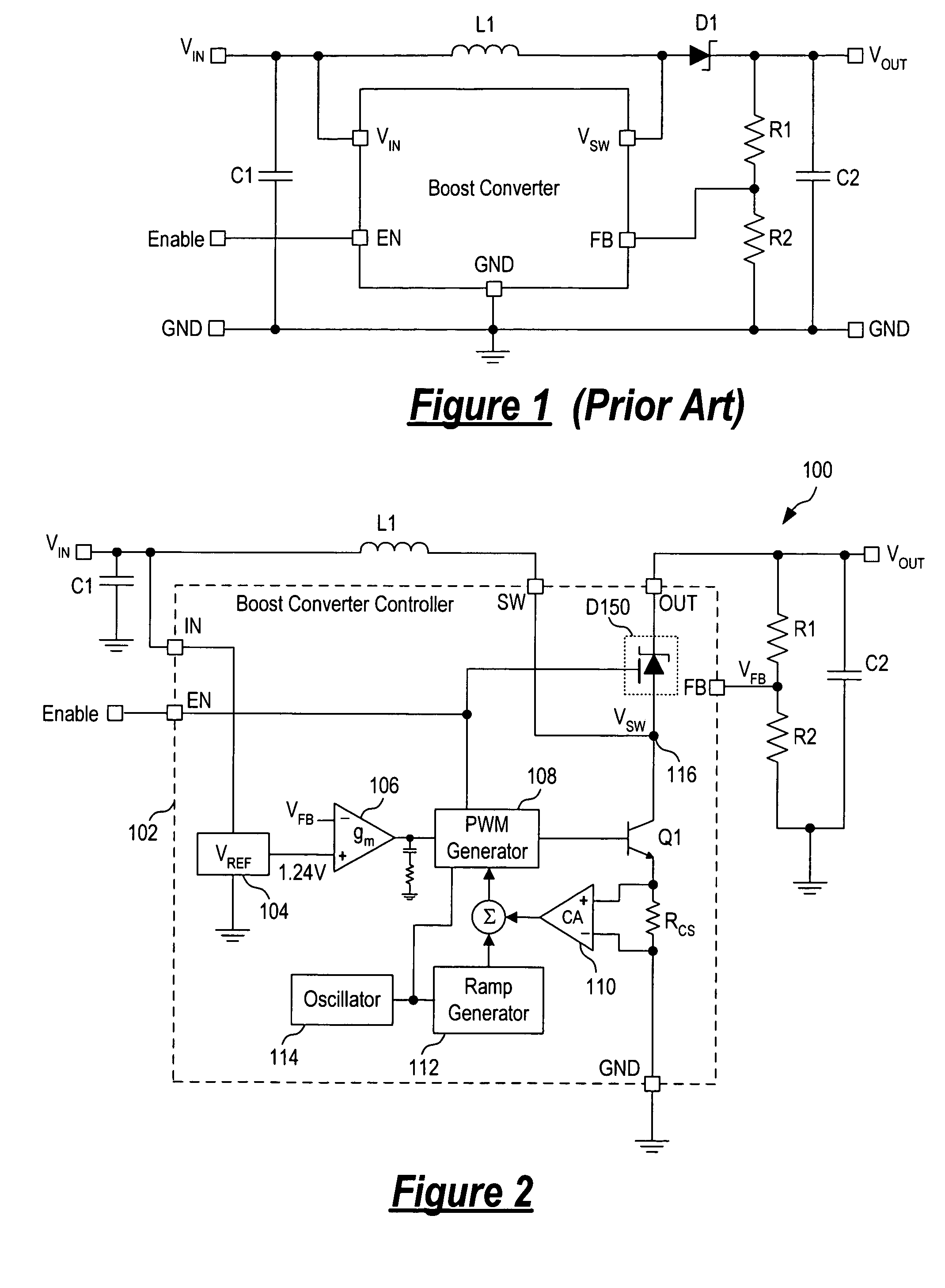

Non-synchronous boost converter including switched schottky diode for true disconnect

ActiveUS20060176029A1Avoid conductionTransistorEfficient power electronics conversionLDMOSControl signal

A non-synchronous boost converter includes a switched Schottky diode to rectify the switched output voltage of the boost converter where the switched Schottky diode has forward conduction blocking capability. The switched Schottky diode has an anode terminal coupled to receive the switched output voltage, a cathode terminal providing the output DC voltage, and a gate terminal coupled to receive a control signal. The control signal has a first state for turning the switched Schottky diode on where the switched Schottky diode conducts current when forward biased and a second state for turning the switched Schottky diode off where forward conduction of the switched Schottky diode is blocked even when the diode is forward biased. The switched Schottky diode can be a JFET controlled or an LDMOS gate controlled Schottky diode. Furthermore, the switched Schottky diode can be formed on-chip or off-chip of the controller circuit of the boost converter.

Owner:MICREL

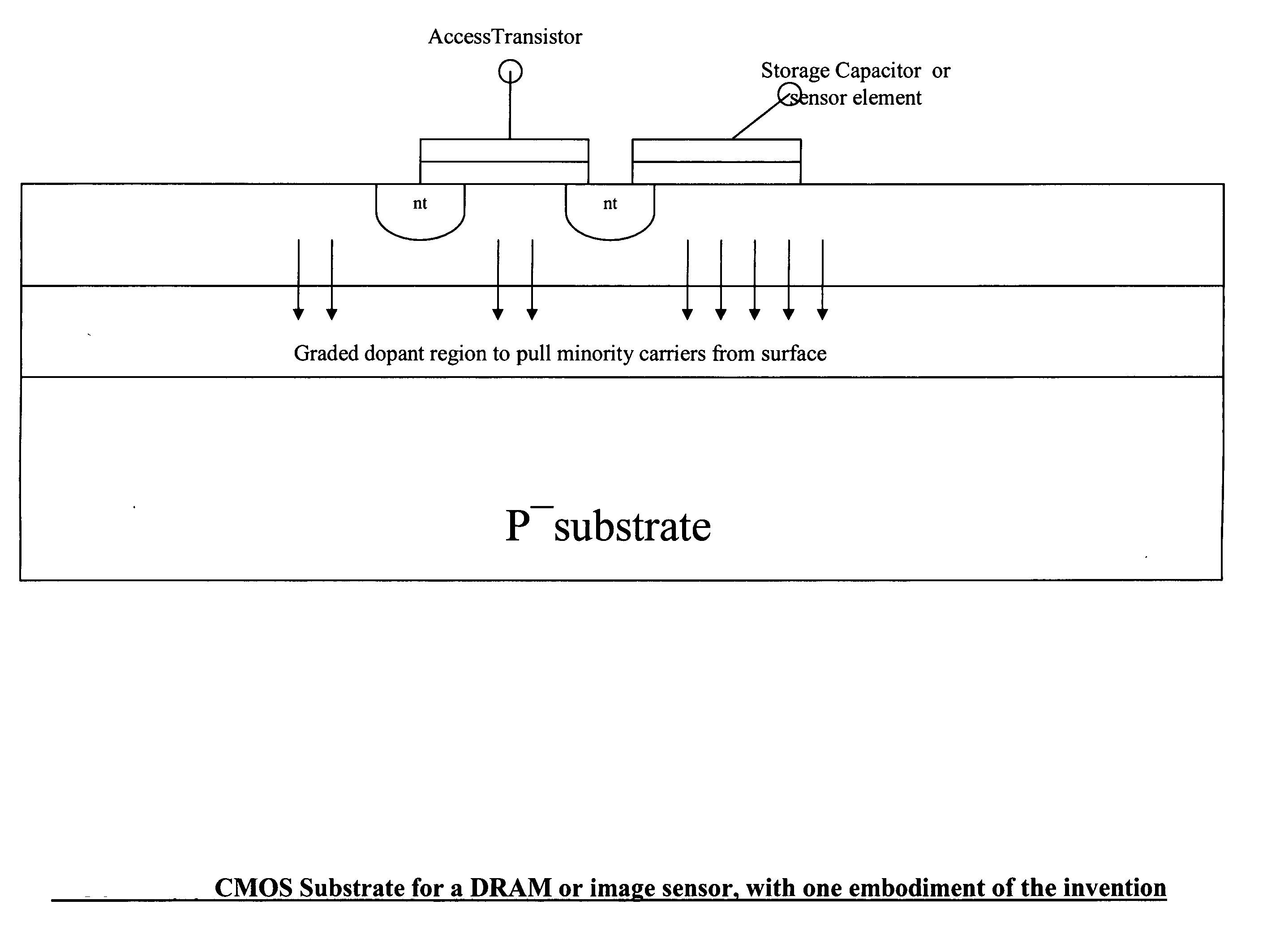

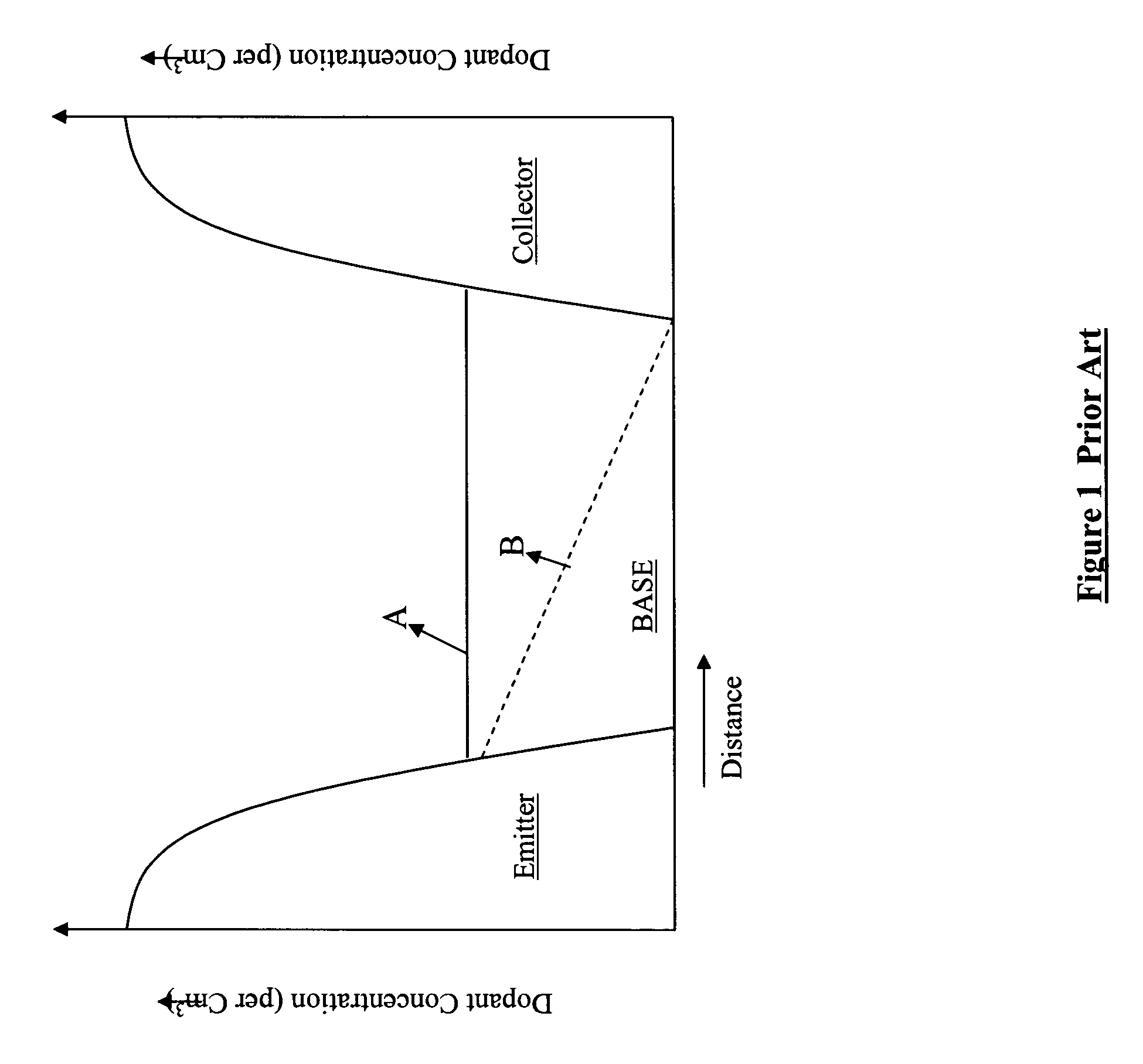

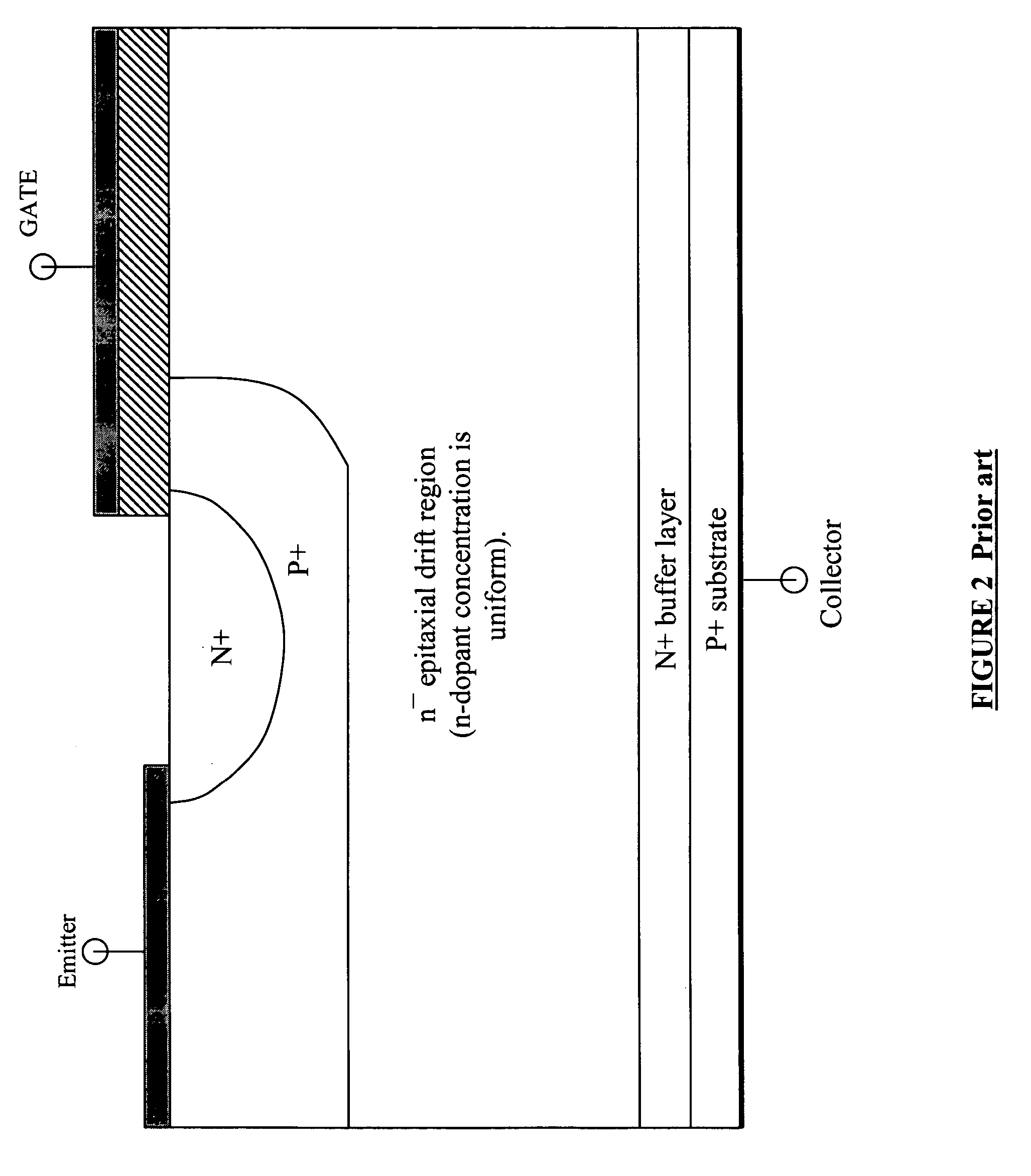

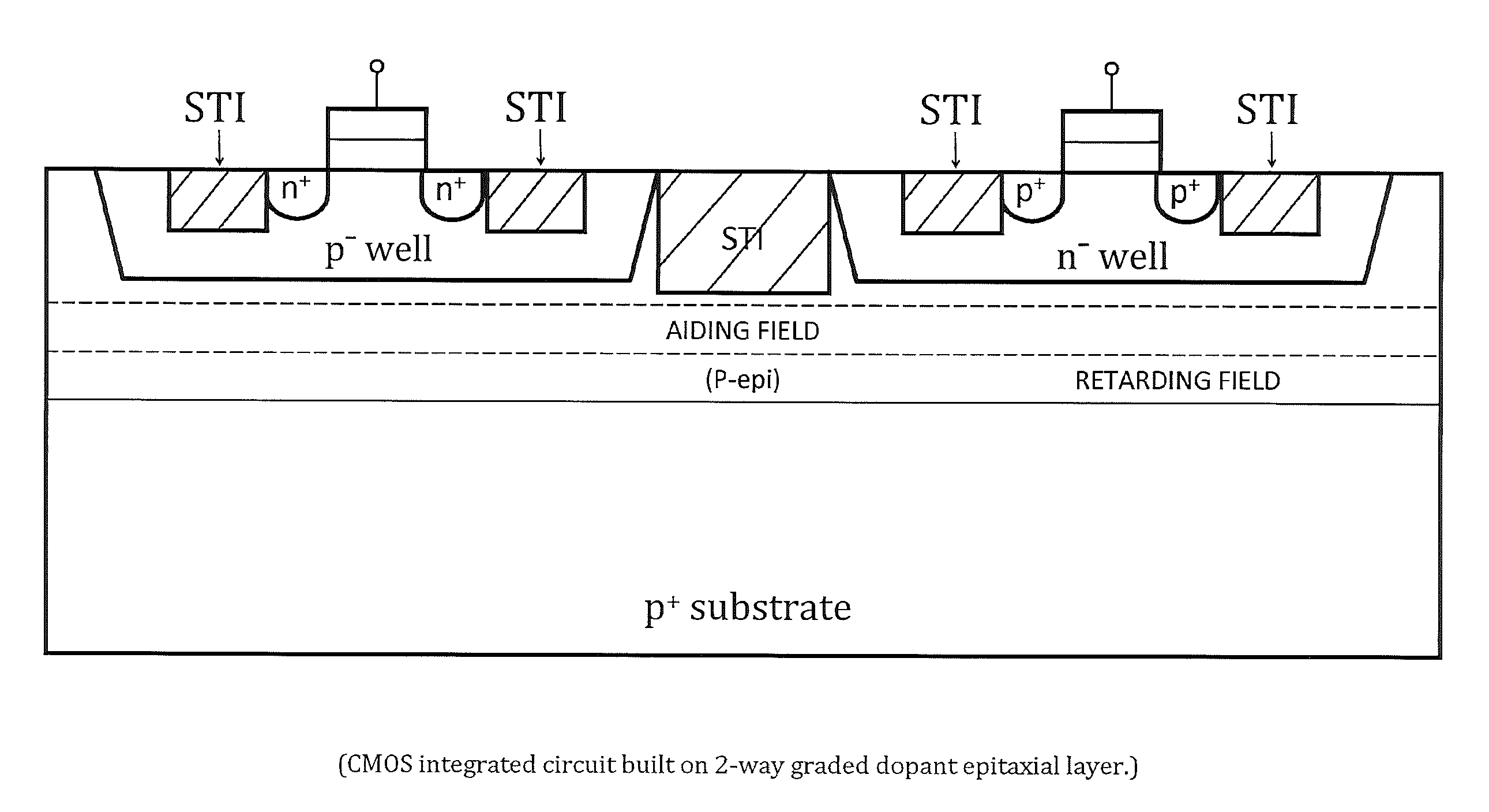

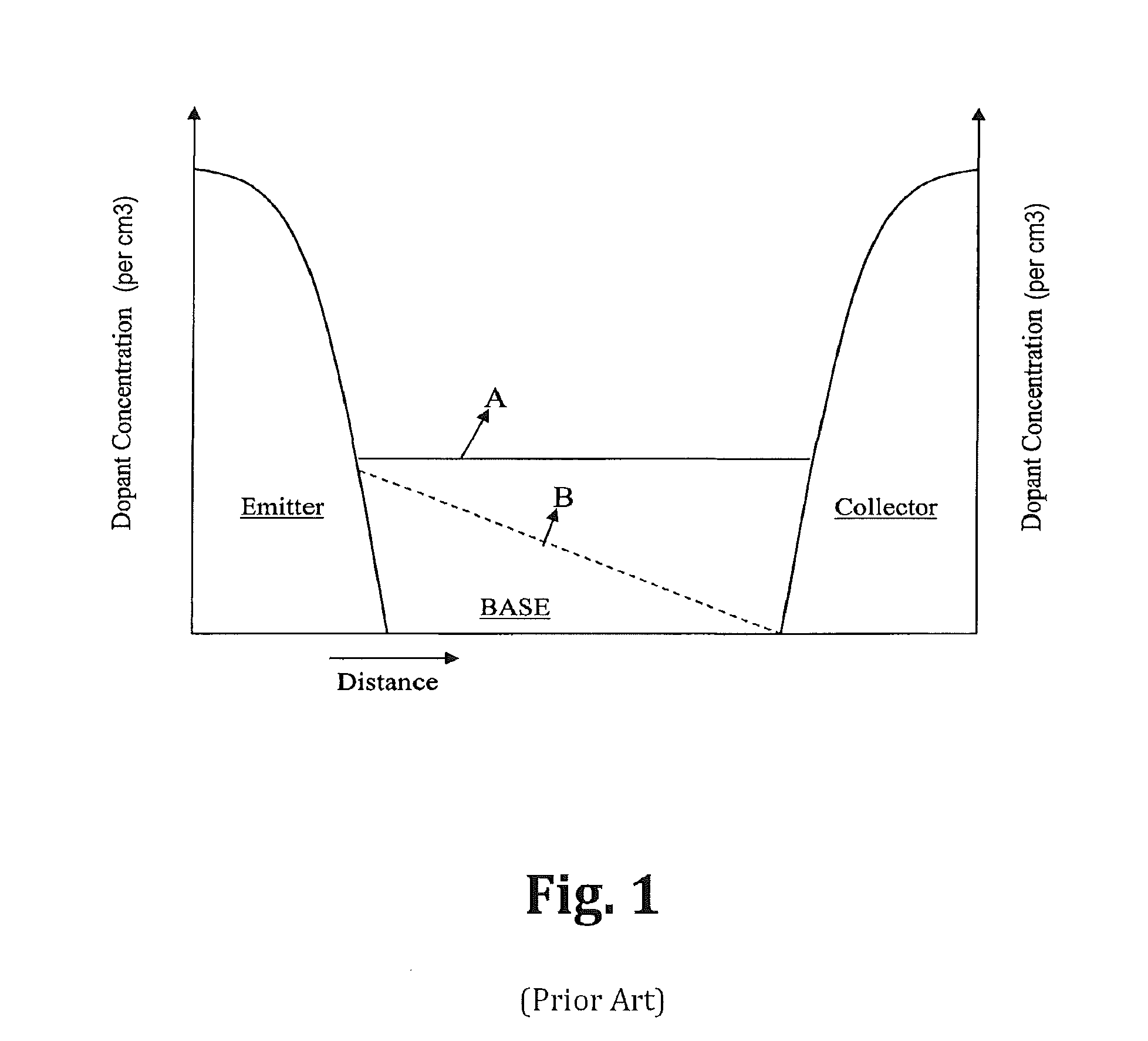

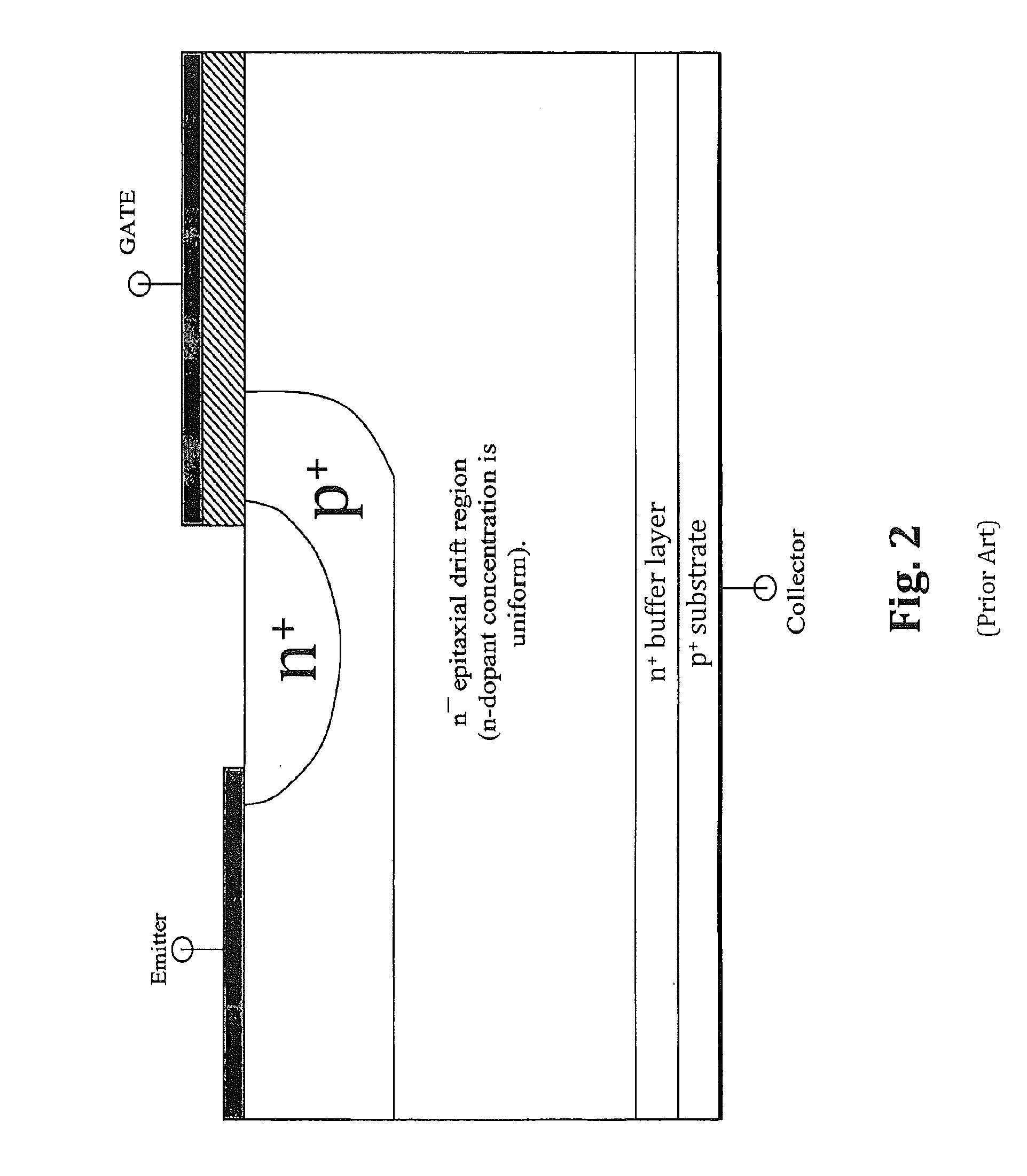

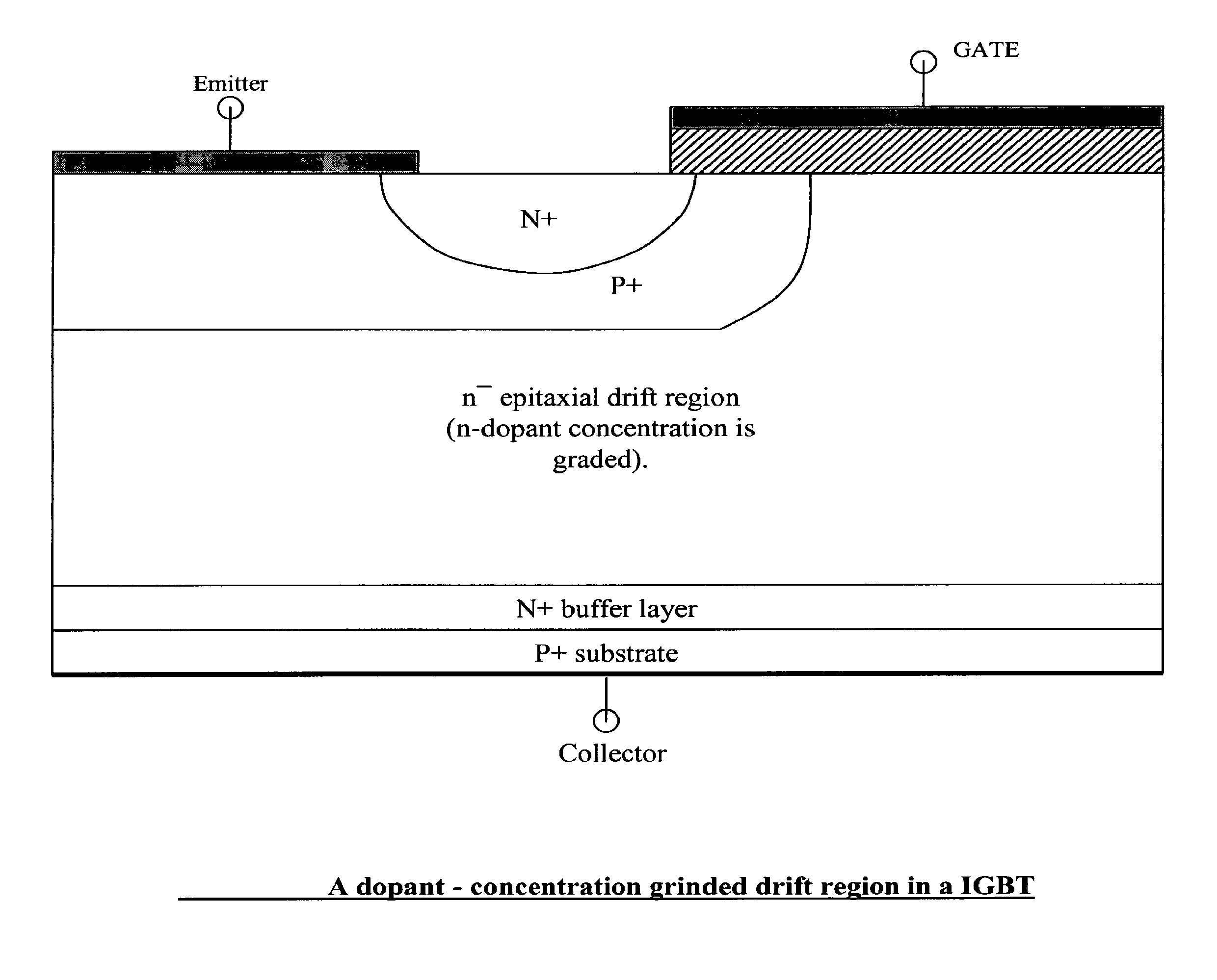

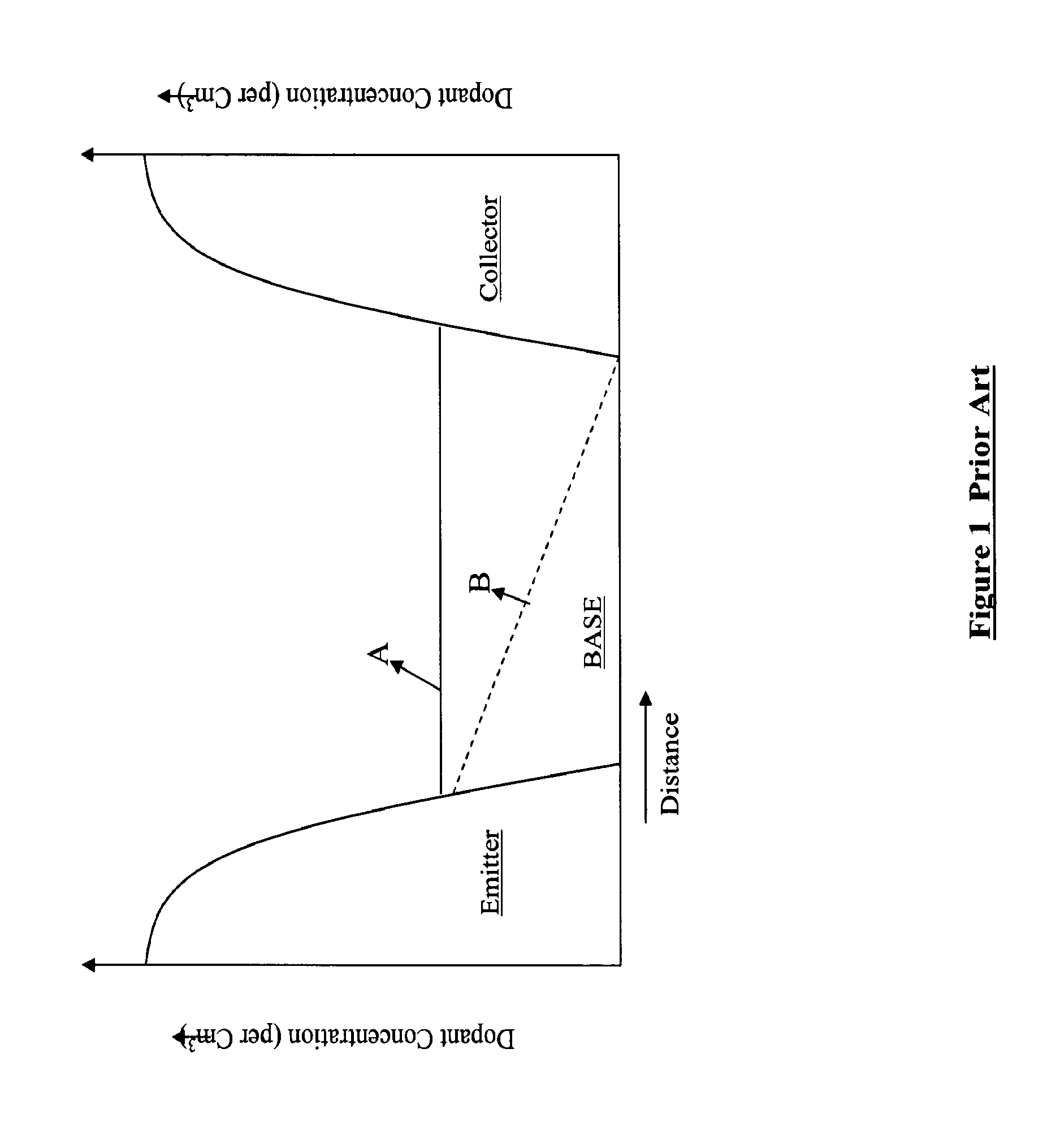

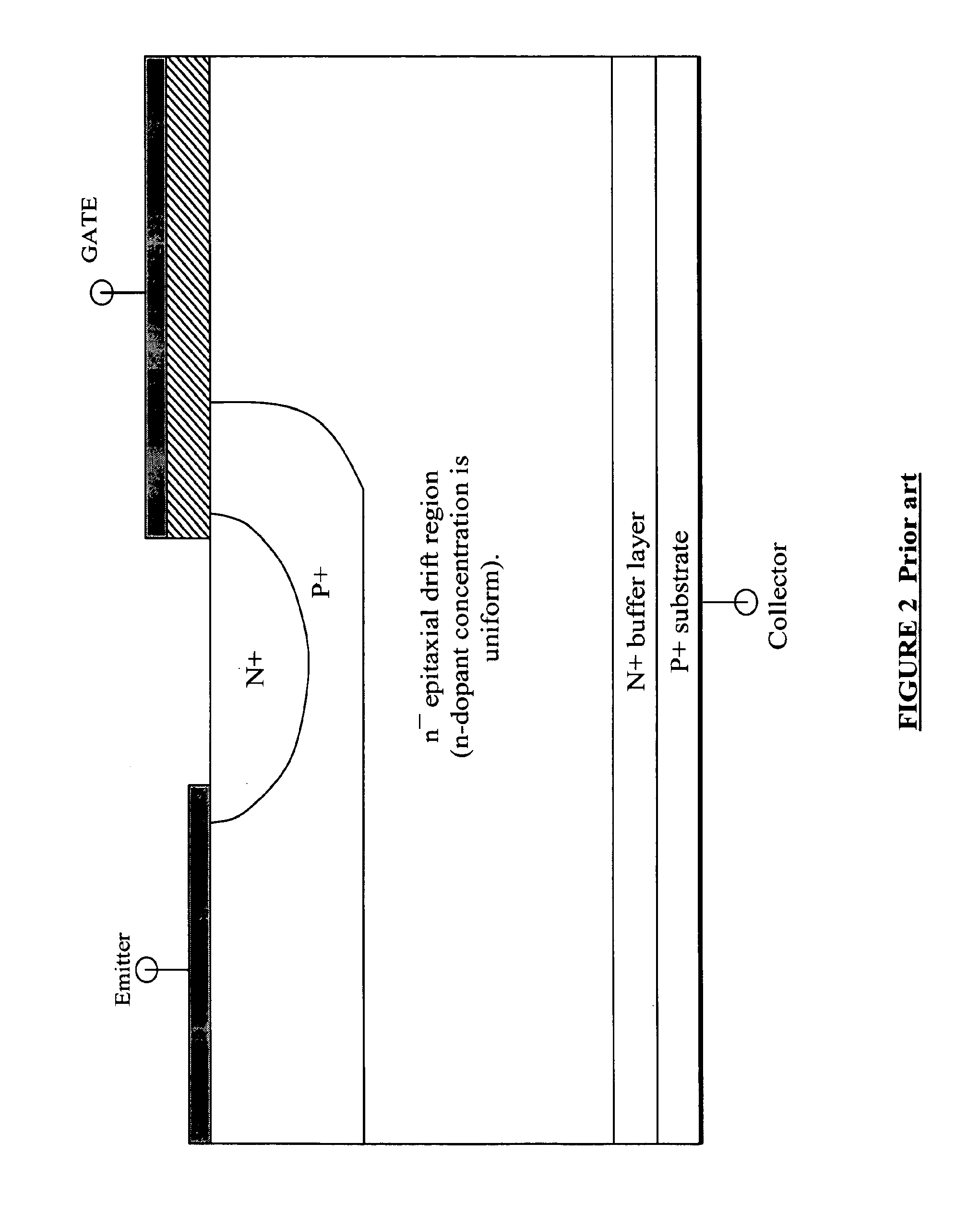

Semiconductor devices with graded dopant regions

Most semiconductor devices manufactured today, have uniform dopant concentration, either in the lateral or vertical device active (and isolation) regions. By grading the dopant concentration, the performance in various semiconductor devices can be significantly improved. Performance improvements can be obtained in application specific areas like increase in frequency of operation for digital logic, various power MOSFET and IGBT ICS, improvement in refresh time for DRAM's, decrease in programming time for nonvolatile memory, better visual quality including pixel resolution and color sensitivity for imaging ICs, better sensitivity for varactors in tunable filters, higher drive capabilities for JFET's, and a host of other applications.

Owner:GREENTHREAD

Solid-state imaging device

InactiveUS6046466ASharp image can be stably obtainedRealize automatic adjustmentTransistorTelevision system detailsSensor arrayMOSFET

A photoelectric conversion device suitable for use as an element of a photodetector array includes a photodiode for generating a first signal charge in response to incident light, an output unit including a JFET, and at least one transistor having an electrode that generates a second signal charge in response to incident light. The first and second signal charges may be output separately or combined. The second signal charge, or the first and second signal charges combined, may be monitored during an exposure time to determine the desired end of the exposure. An image sensor array may have one or more pixels with such light monitoring capability. The output signal for monitoring the light may be output over a reset drain interconnection, directly from the monitoring pixel or through other pixels via inter-pixel MOSFETS. Exposure time may be controlled, by timing a shutter or a strobe or the like, based on the monitored accumulation of signal charge during exposure. Microlenses may be provided on-chip to increase the effective aperture ratio of the array. The microlenses are designed to avoid interfering with the incident light used for monitoring. Resulting pixel-to-pixel variations in effective aperture ratio, if any, may be electronically compensated.

Owner:NIKON CORP

Semiconductor devices with graded dopant regions

ActiveUS8106481B2Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringPower MOSFET

Most semiconductor devices manufactured today, have uniform dopant concentration, either in the lateral or vertical device active (and isolation) regions. By grading the dopant concentration, the performance in various semiconductor devices can be significantly improved. Performance improvements can be obtained in application specific areas like increase in frequency of operation for digital logic, various power MOSFET and IGBT ICS, improvement in refresh time for DRAM's, decrease in programming time for nonvolatile memory, better visual quality including pixel resolution and color sensitivity for imaging ICs, better sensitivity for varactors in tunable filters, higher drive capabilities for JFET's, and a host of other applications.

Owner:GREENTHREAD

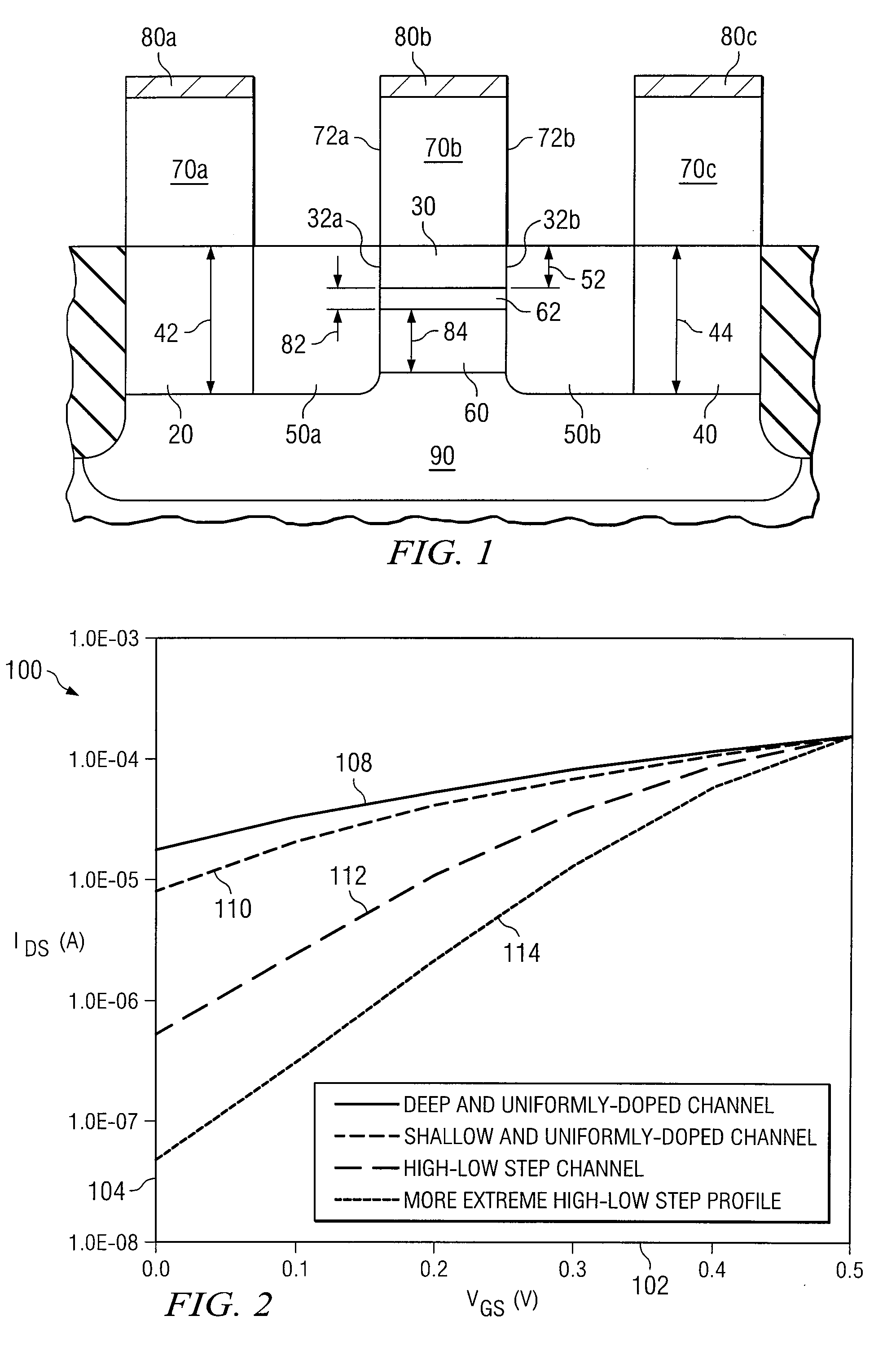

JFET Having a Step Channel Doping Profile and Method of Fabrication

InactiveUS20080272409A1Disadvantages and reduced eliminatedEffect reduced eliminatedTransistorSemiconductor/solid-state device manufacturingHigh concentrationJFET

A junction field effect transistor comprises a semiconductor substrate, a source region formed in the substrate, a drain region formed in the substrate and spaced apart from the source region, and a gate region formed in the substrate. The transistor further comprises a first channel region formed in the substrate and spaced apart from the gate region, and a second channel region formed in the substrate and between the first channel region and the gate region. The second channel region has a higher concentration of doped impurities than the first channel region.

Owner:DSM SOLUTIONS

Semiconductor devices with graded dopant regions

Most semiconductor devices manufactured today, have uniform dopant concentration, either in the lateral or vertical device active (and isolation) regions. By grading the dopant concentration, the performance in various semiconductor devices can be significantly improved. Performance improvements can be obtained in application specific areas like increase in frequency of operation for digital logic, various power MOSFET and IGBT ICS, improvement in refresh time for DRAM's, decrease in programming time for nonvolatile memory, better visual quality including pixel resolution and color sensitivity for imaging ICs, better sensitivity for varactors in tunable filters, higher drive capabilities for JFET's, and a host of other applications.

Owner:GREENTHREAD

Integrated nitride-based acoustic wave devices and methods of fabricating integrated nitride-based acoustic wave devices

ActiveUS7112860B2Reduce unwanted reflectionReduce reflectionPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostriction/magnetostriction machinesMOSFETMESFET

A monolithic electronic device includes a substrate, a semi-insulating, piezoelectric Group III-nitride epitaxial layer formed on the substrate, a pair of input and output interdigital transducers forming a surface acoustic wave device on the epitaxial layer and at least one electronic device (such as a HEMT, MESFET, JFET, MOSFET, photodiode, LED or the like) formed on the substrate. Isolation means are disclosed to electrically and acoustically isolate the electronic device from the SAW device and vice versa. In some embodiments, a trench is formed between the SAW device and the electronic device. Ion implantation is also disclosed to form a semi-insulating Group III-nitride epitaxial layer on which the SAW device may be fabricated. Absorbing and / or reflecting elements adjacent the interdigital transducers reduce unwanted reflections that may interfere with the operation of the SAW device.

Owner:CREE INC

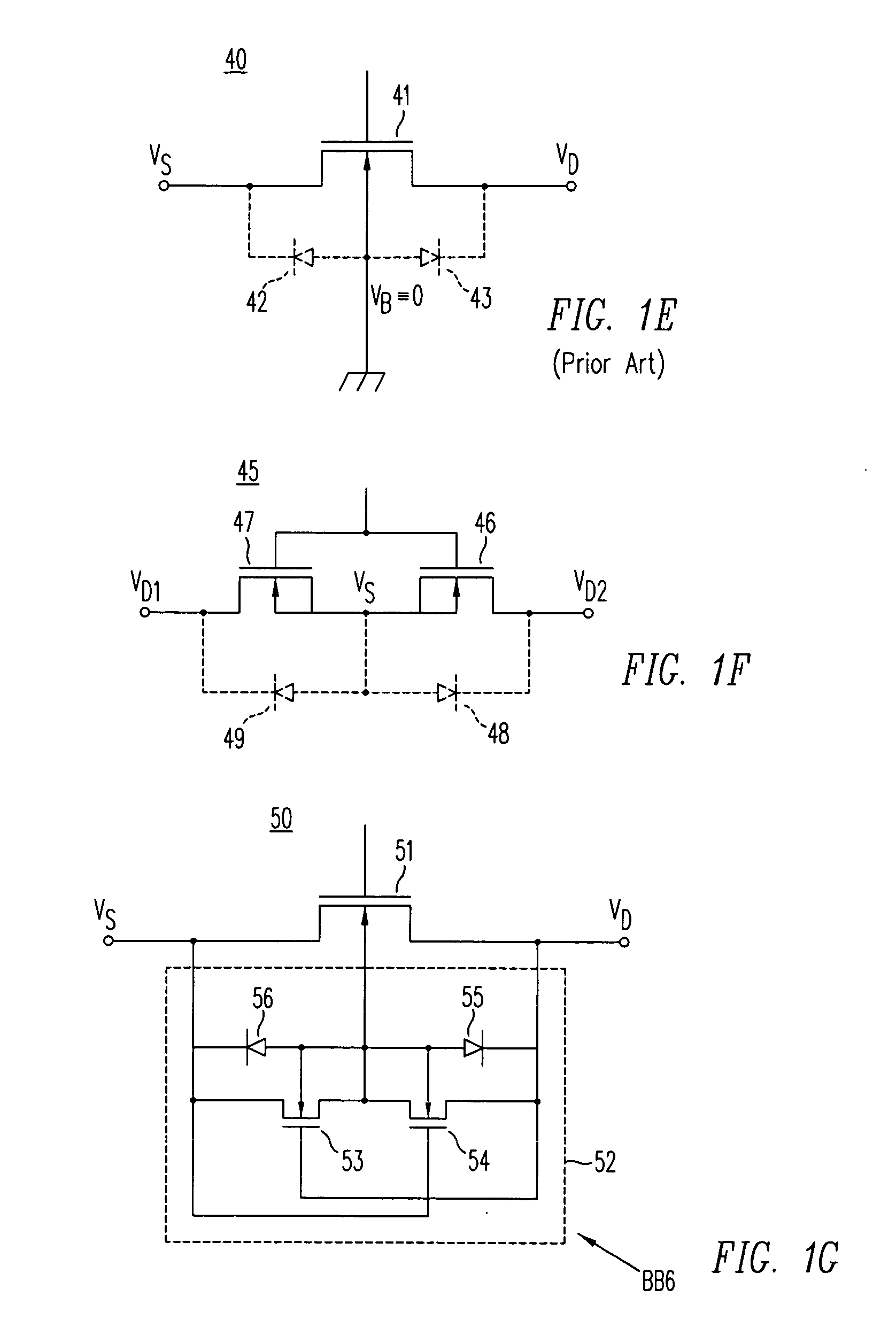

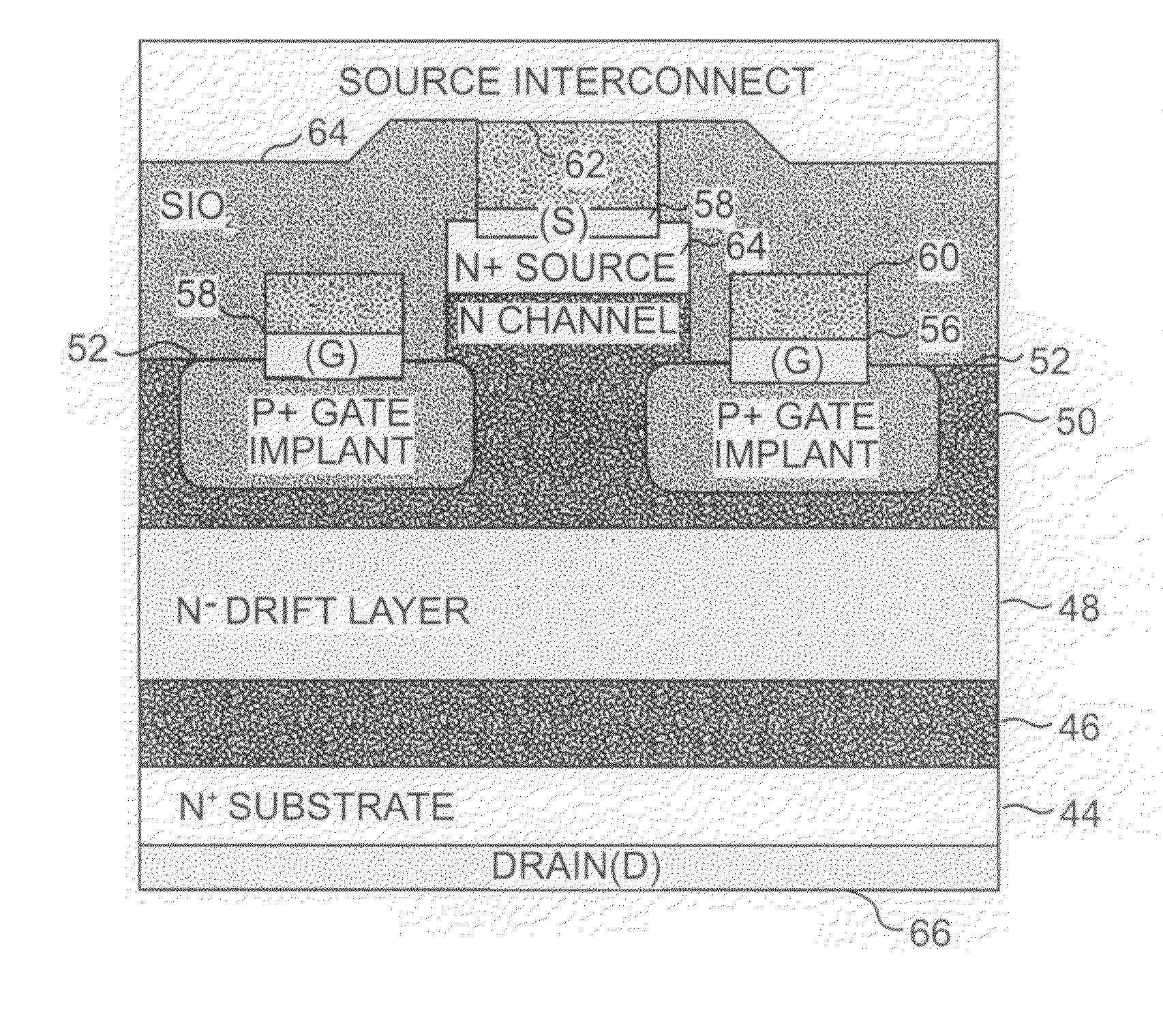

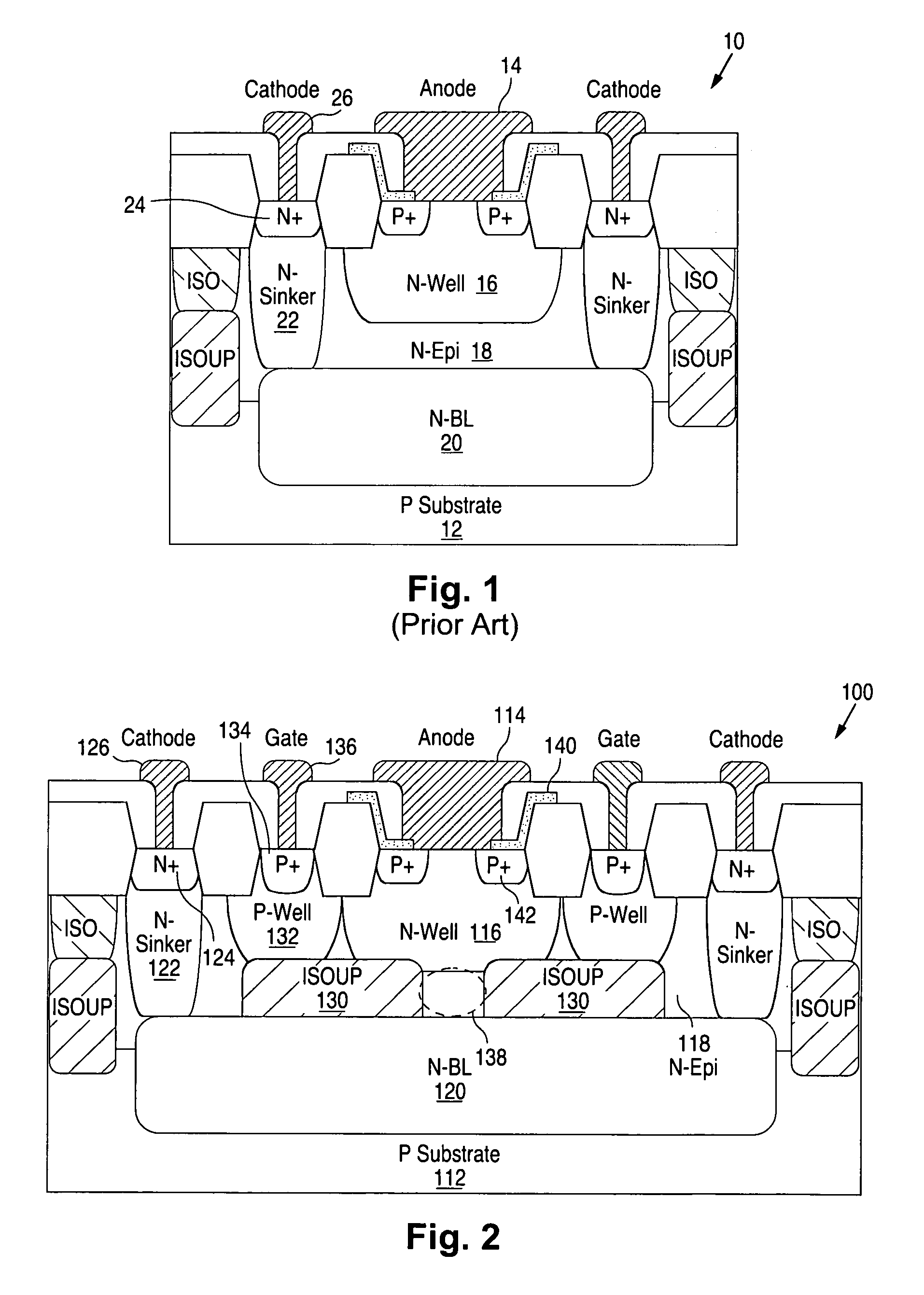

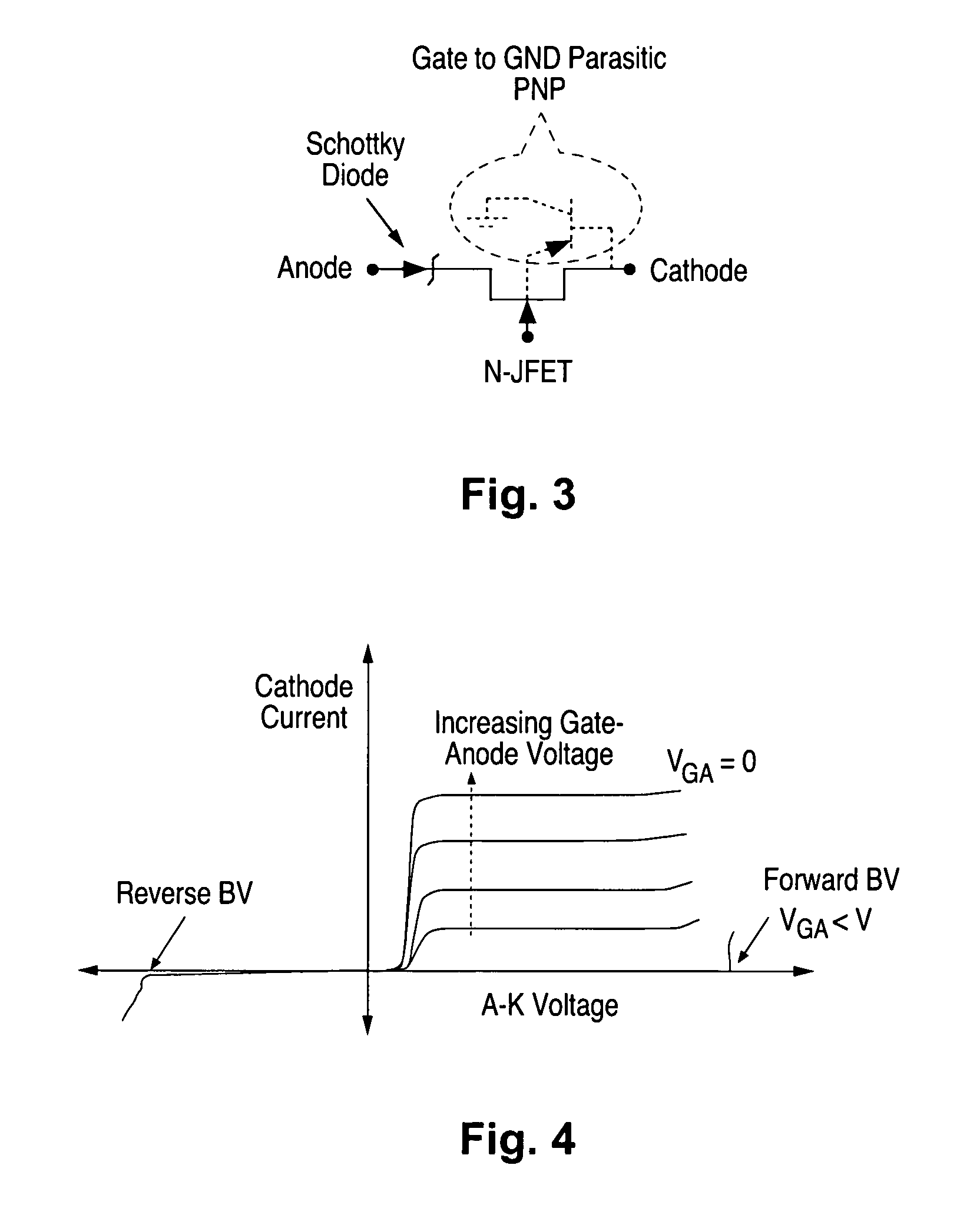

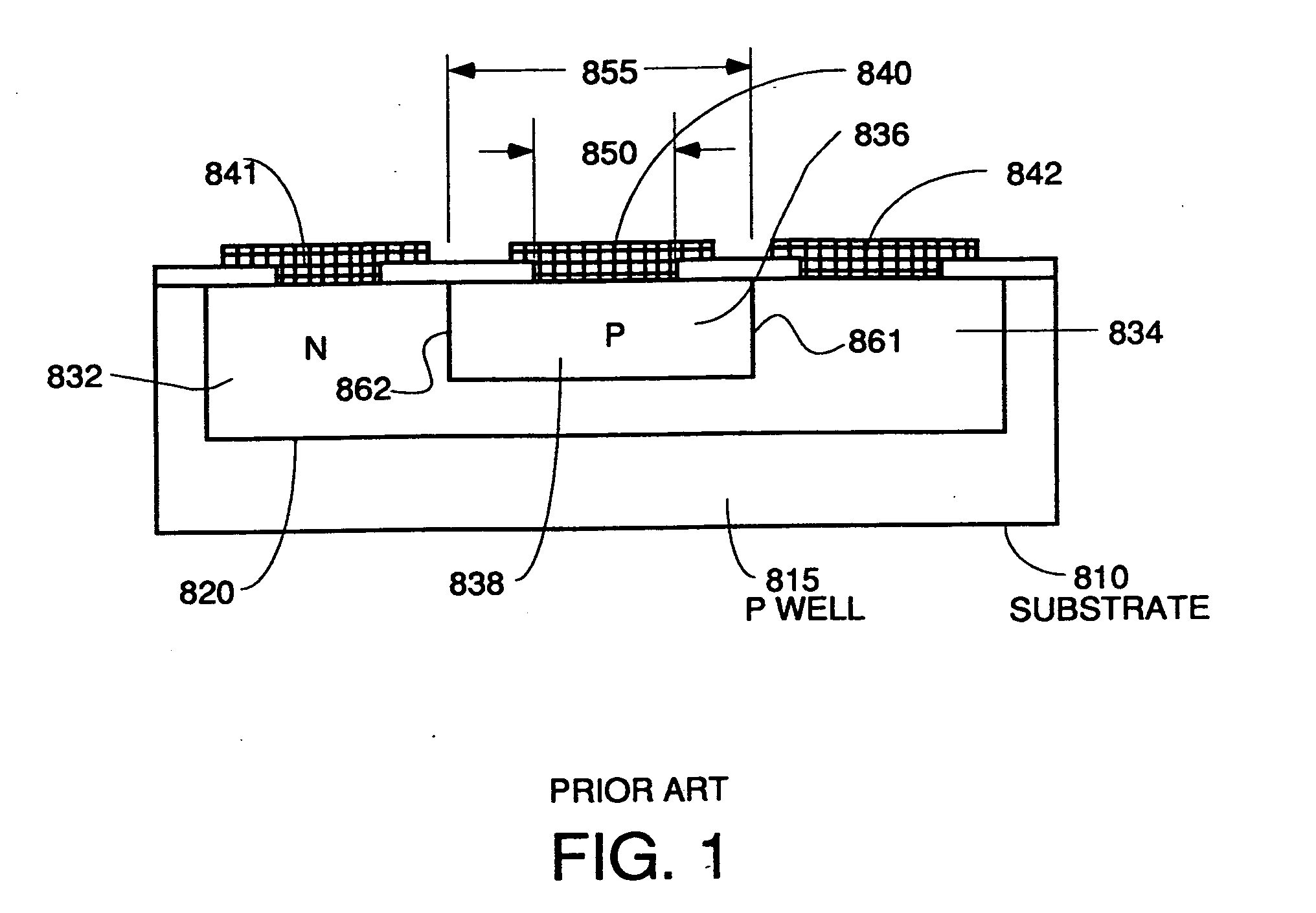

JFET controlled schottky barrier diode

A JFET controlled Schottky barrier diode includes a p-type diffusion region integrated into the cathode of the Schottky diode to form an integrated JFET where the integrated JFET provides on-off control of the Schottky barrier diode. The p-type diffusion region encloses a portion of the forward current path of the Schottky barrier diode where the p-type diffusion region forms the gate of the JFET and the enclosed portion of the forward current path forms the channel region of the JFET. By applying a reverse biased potential to the gate of the JEFT with respect to the anode of the Schottky diode, the forward current of the Schottky diode can be pinched off, thereby providing on-off control over the Schottky diode forward current.

Owner:MICREL

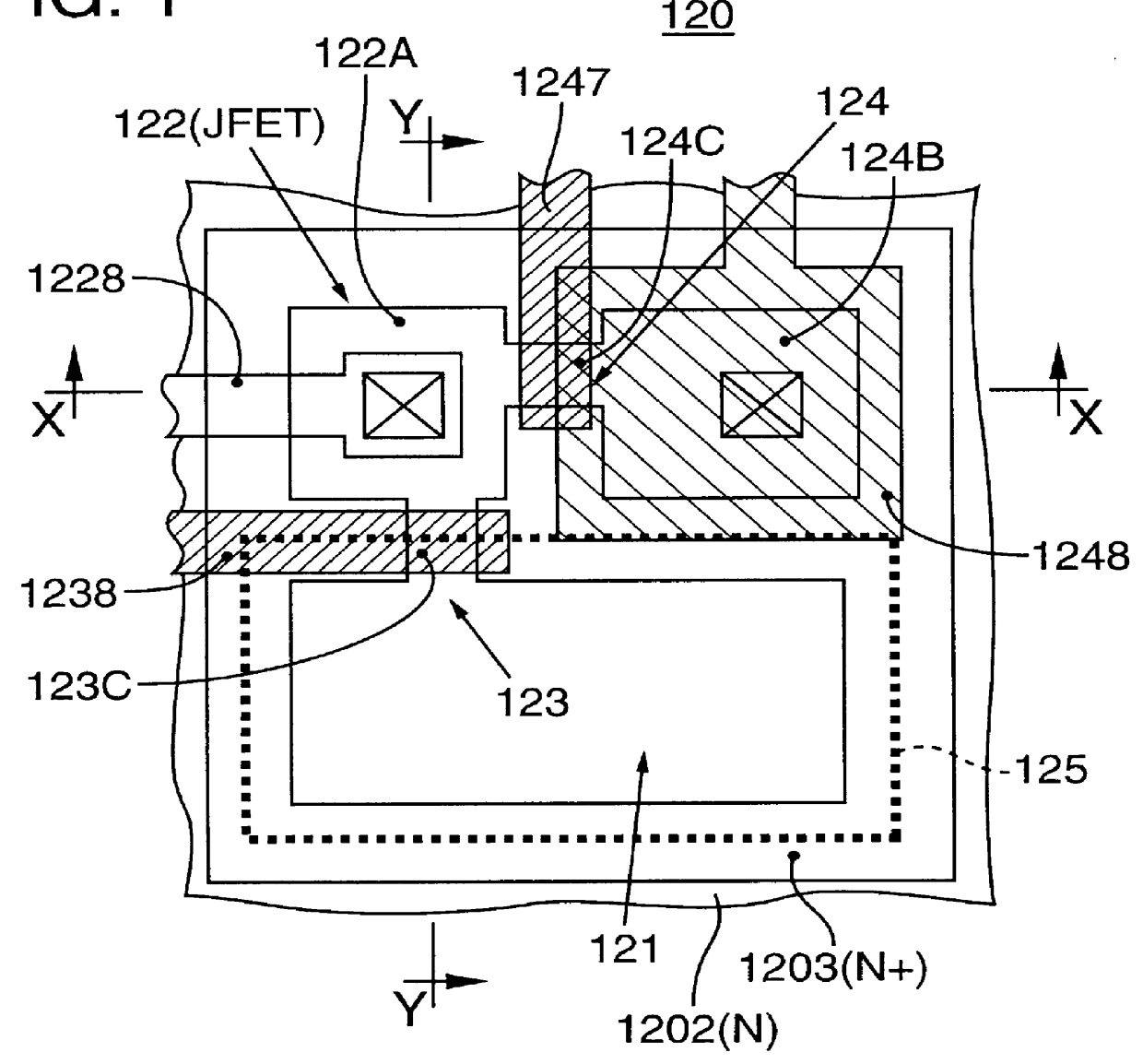

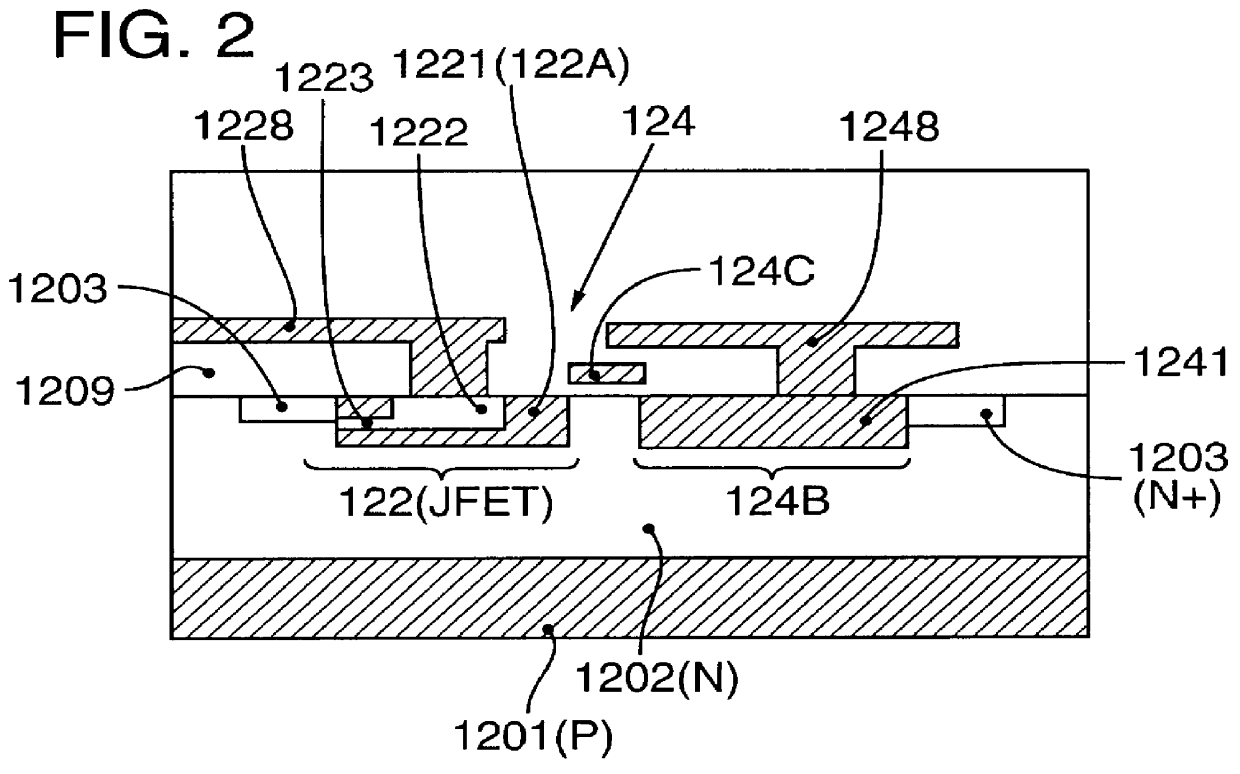

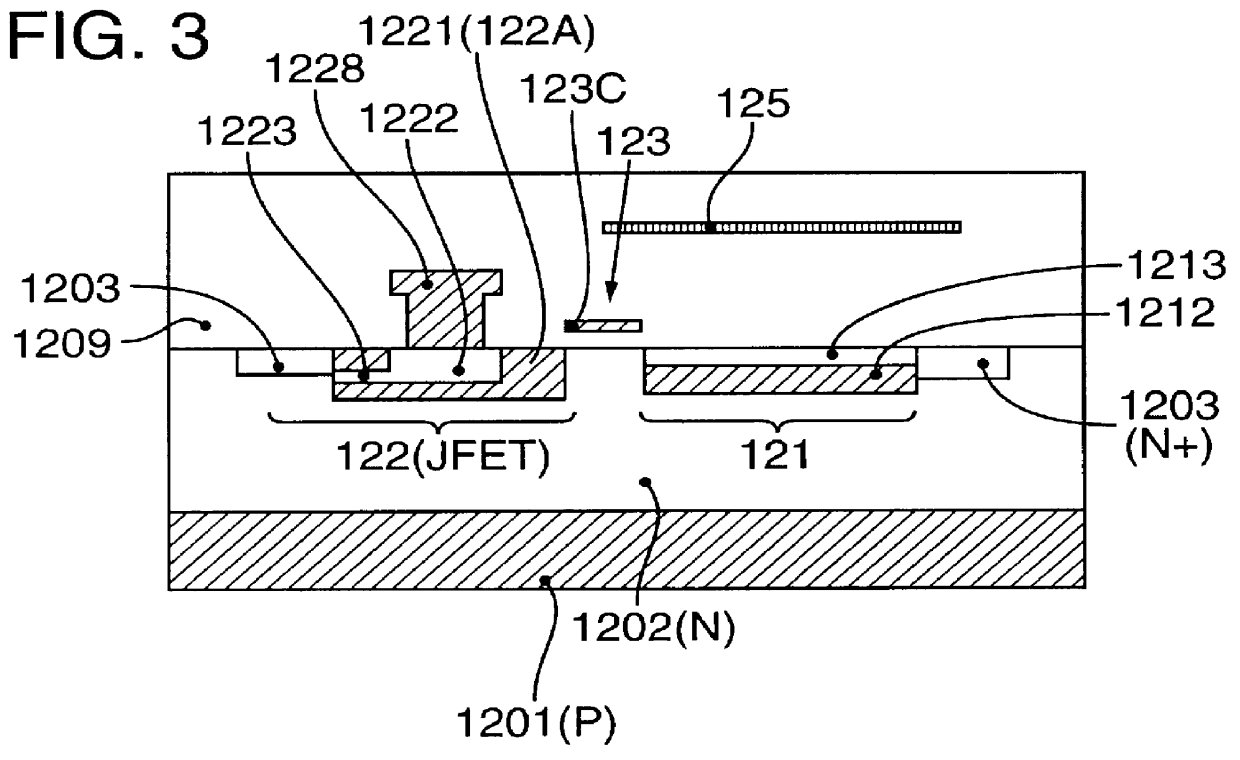

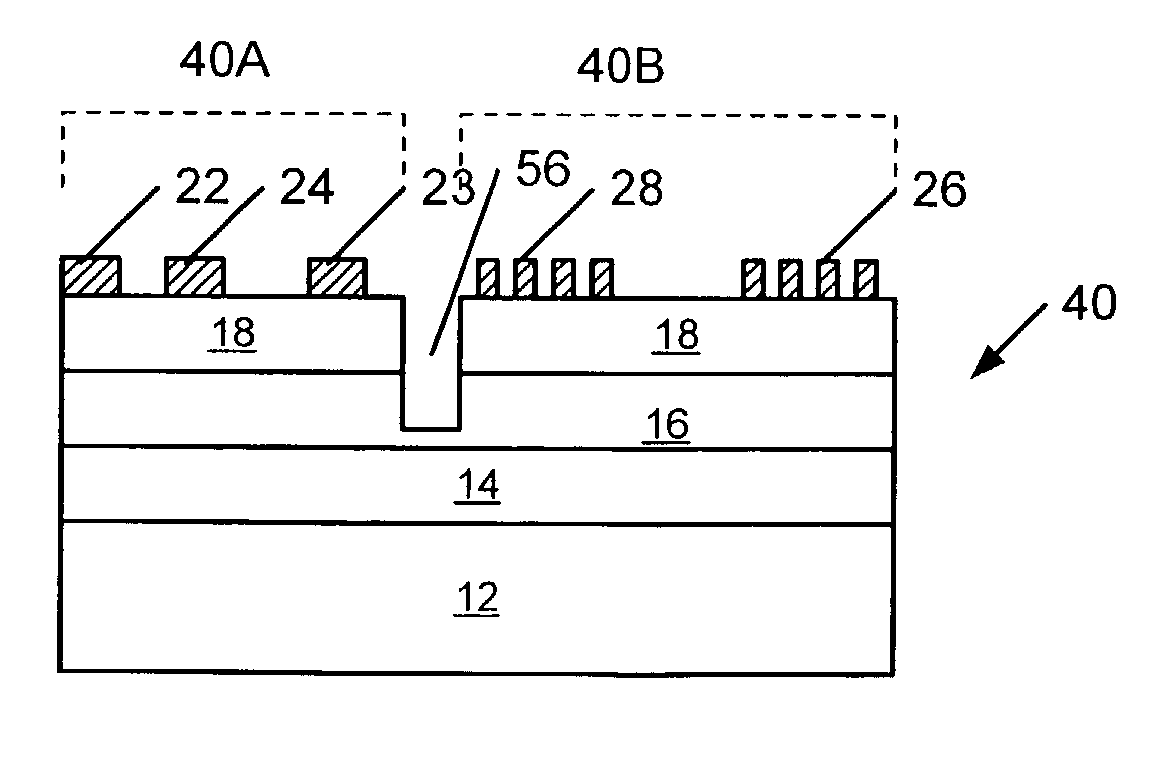

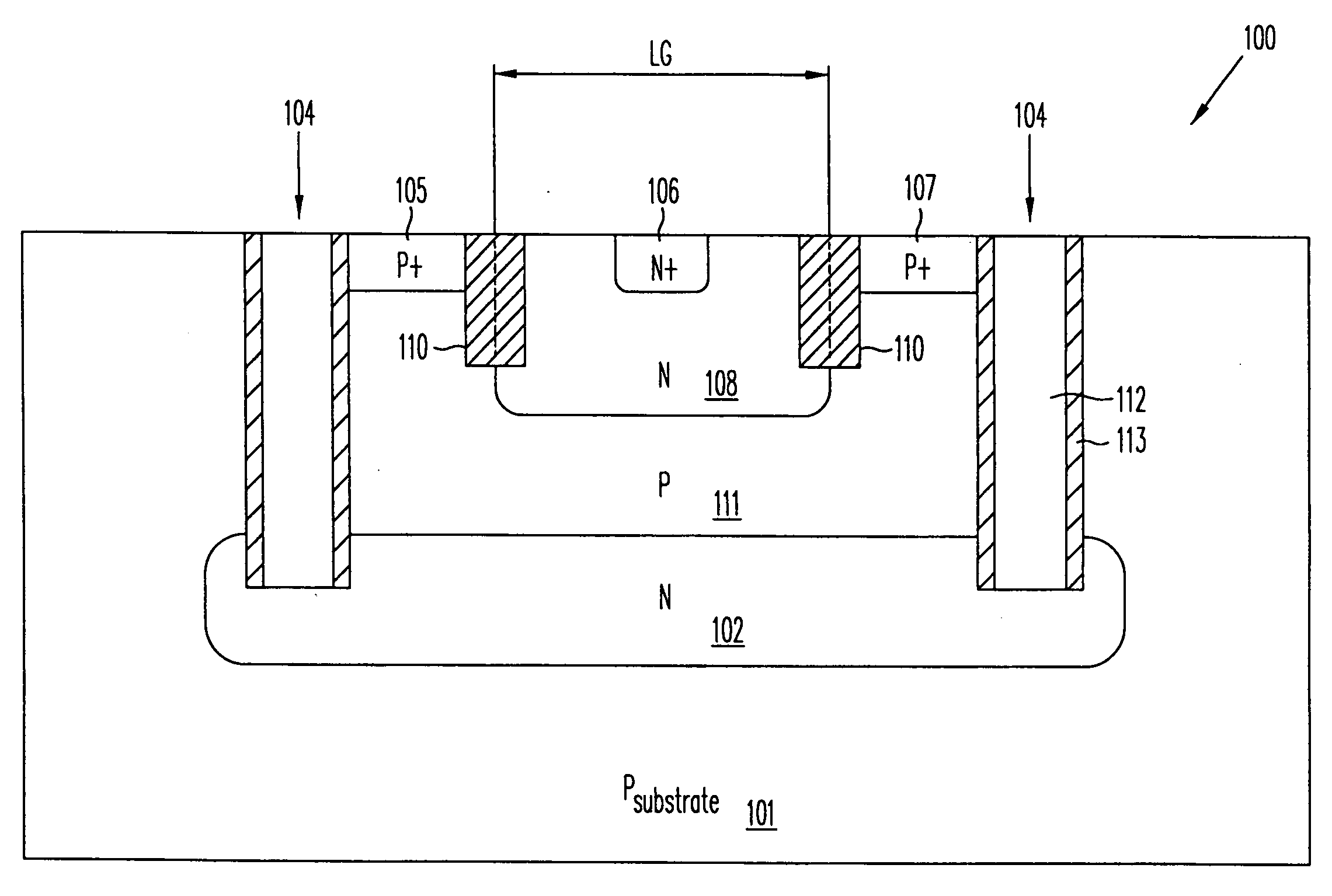

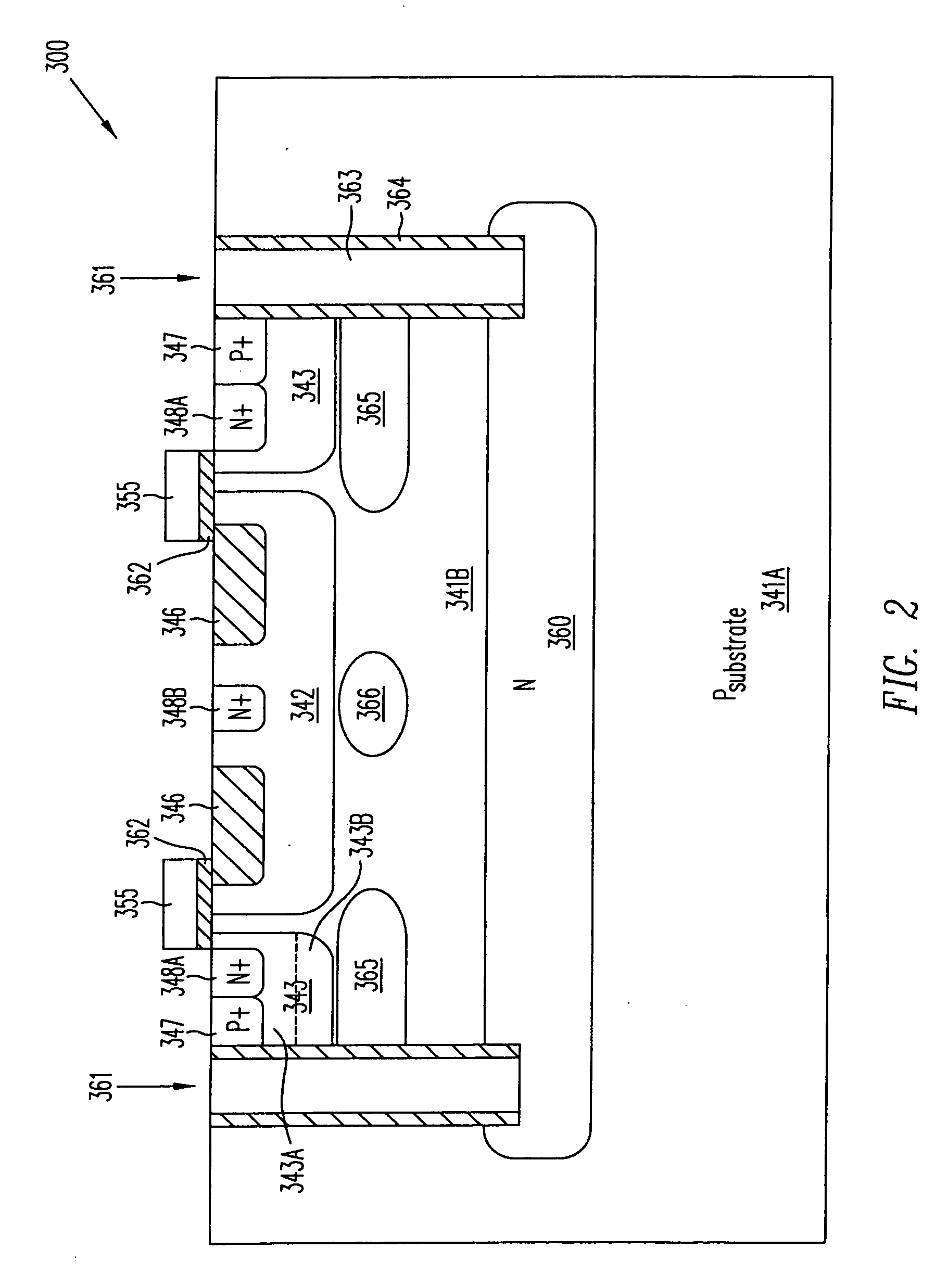

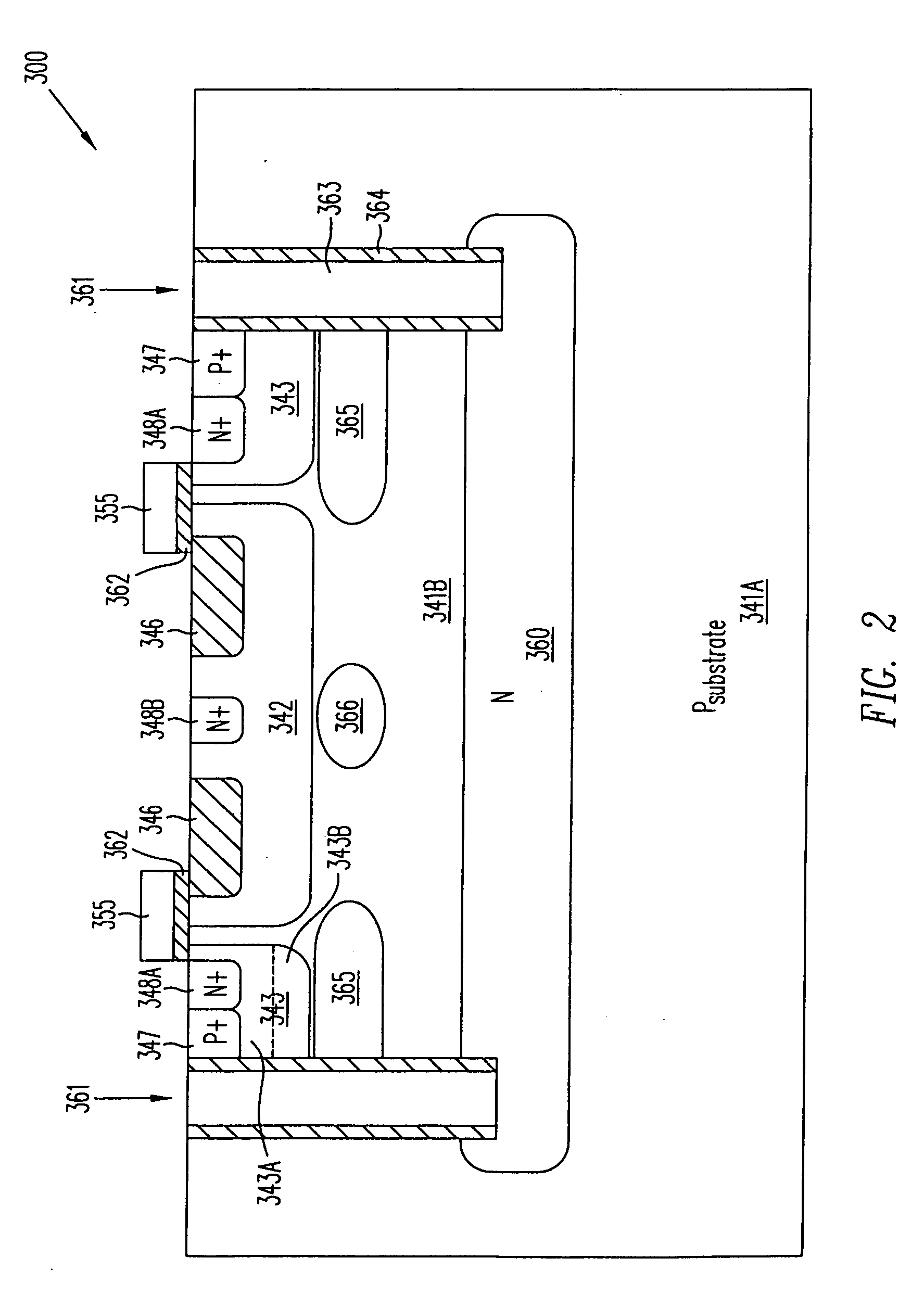

Isolated junction field-effect transistor

Various integrated circuit devices, in particular a junction field-effect transistor (JFET), are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

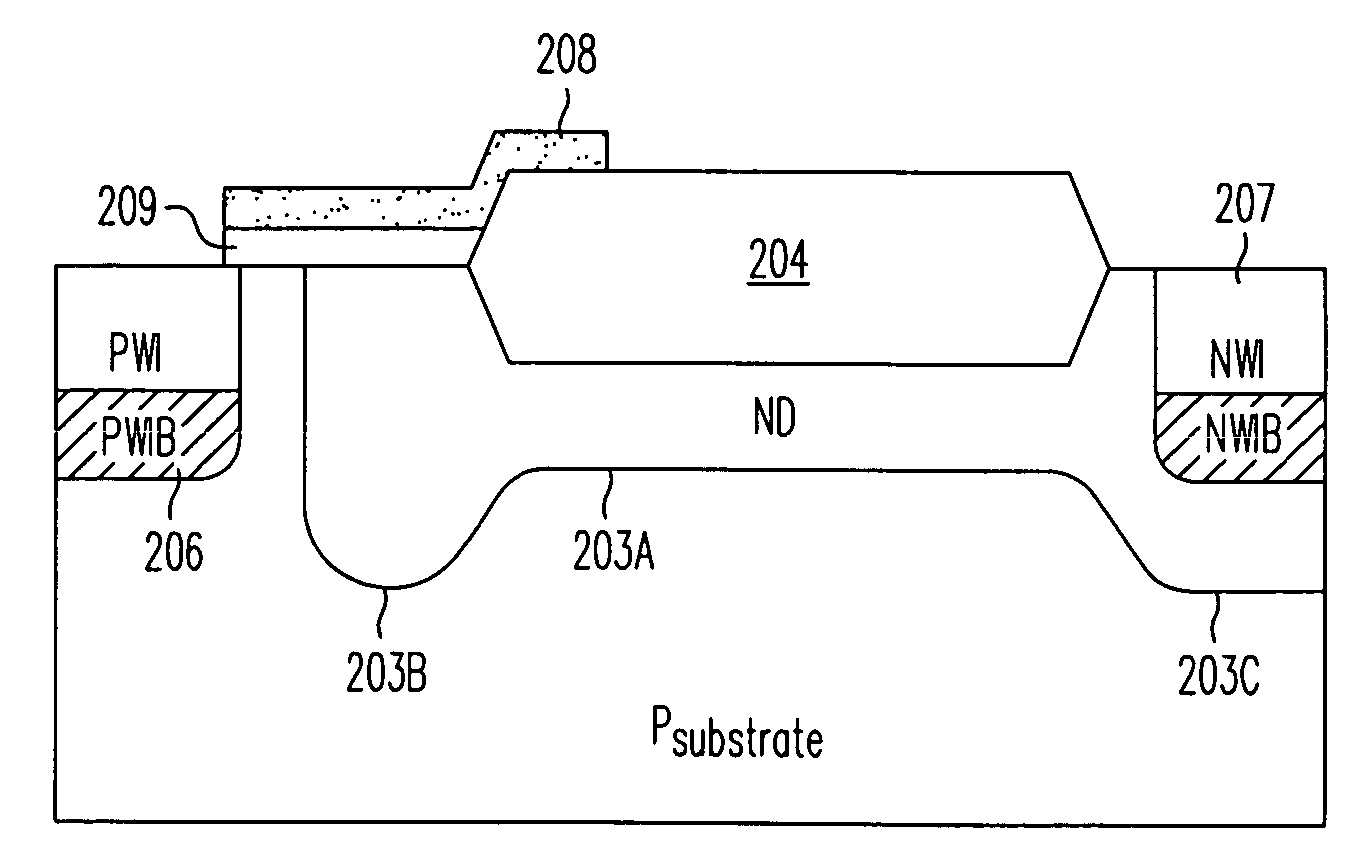

Isolation and termination structures for semiconductor die

InactiveUS20080197445A1Reduce chargeReducing other time-dependent surface-related phenomenonTransistorThyristorMOSFETSemiconductor chip

Various integrated circuit devices, including a lateral DMOS transistor, a quasi-vertical DMOS transistor, a junction field-effect transistor (JFET), a depletion-mode MOSFET, and a diode, are formed inside an isolation structure which includes a floor isolation region and a trench extending from the surface of the substrate to the floor isolation region. The trench may be filled with a dielectric material or may have a conductive material in a central portion with a dielectric layer lining the walls of the trench. Various techniques for terminating the isolation structure by extending the floor isolation region beyond the trench, using a guard ring, and a forming a drift region are described.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

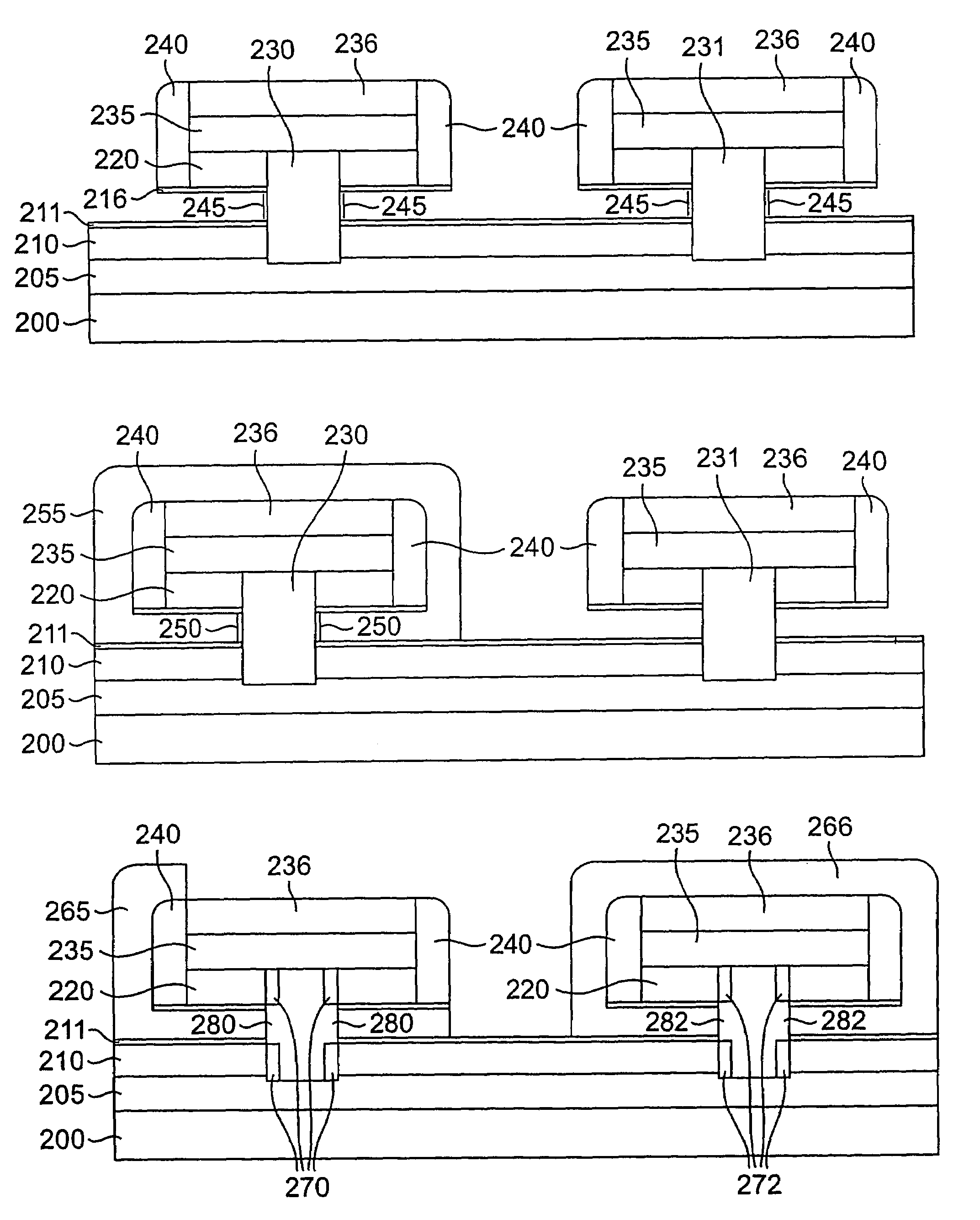

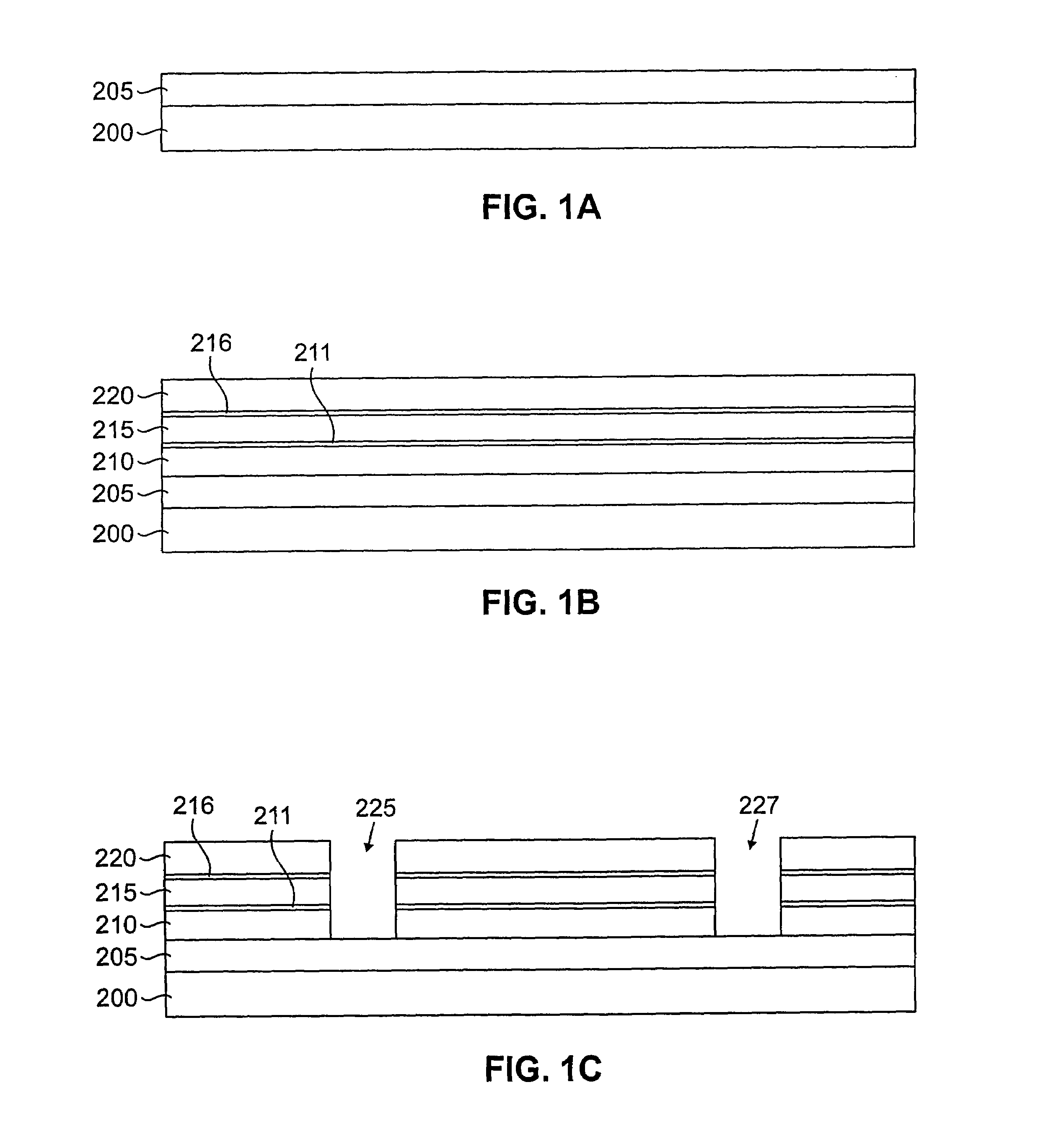

Vertical replacement-gate junction field-effect transistor

InactiveUS7033877B2Increase the doping concentrationUniform conditionsTransistorSolid-state devicesJFETSemiconductor

An architecture for creating a vertical JFET. Generally, an integrated circuit structure includes a semiconductor area with a major surface formed along a plane and a first source / drain doped region formed in the surface. A second doped region forming a channel of different conductivity type than the first region is positioned over the first region. A third doped region is formed over the second doped region having an opposite conductivity type with respect to the second doped region, and forming a source / drain region. A gate is formed over the channel to form a vertical JFET.In an associated method of manufacturing the semiconductor device, a first source / drain region is formed in a semiconductor layer. A field-effect transistor gate region, including a channel and a gate electrode, is formed over the first source / drain region. A second source / drain region is then formed over the channel having the appropriate conductivity type.

Owner:BELL SEMICON LLC

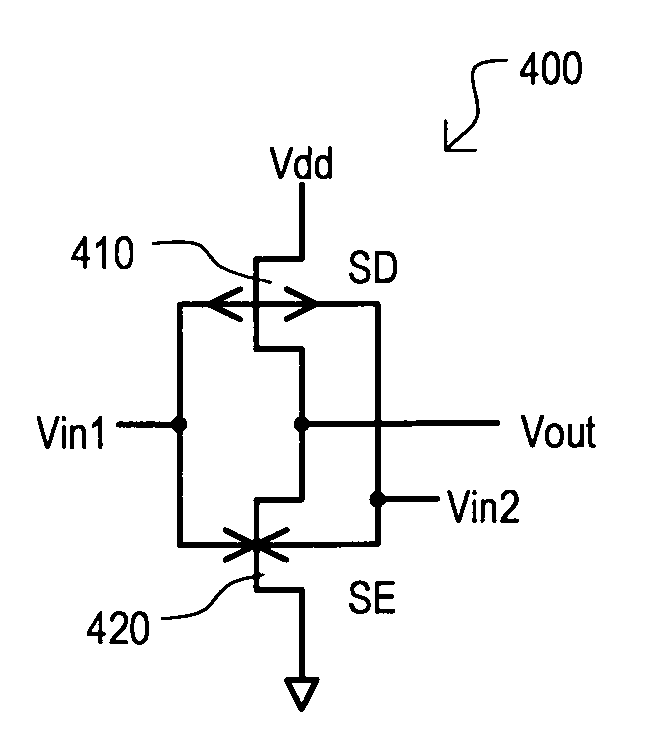

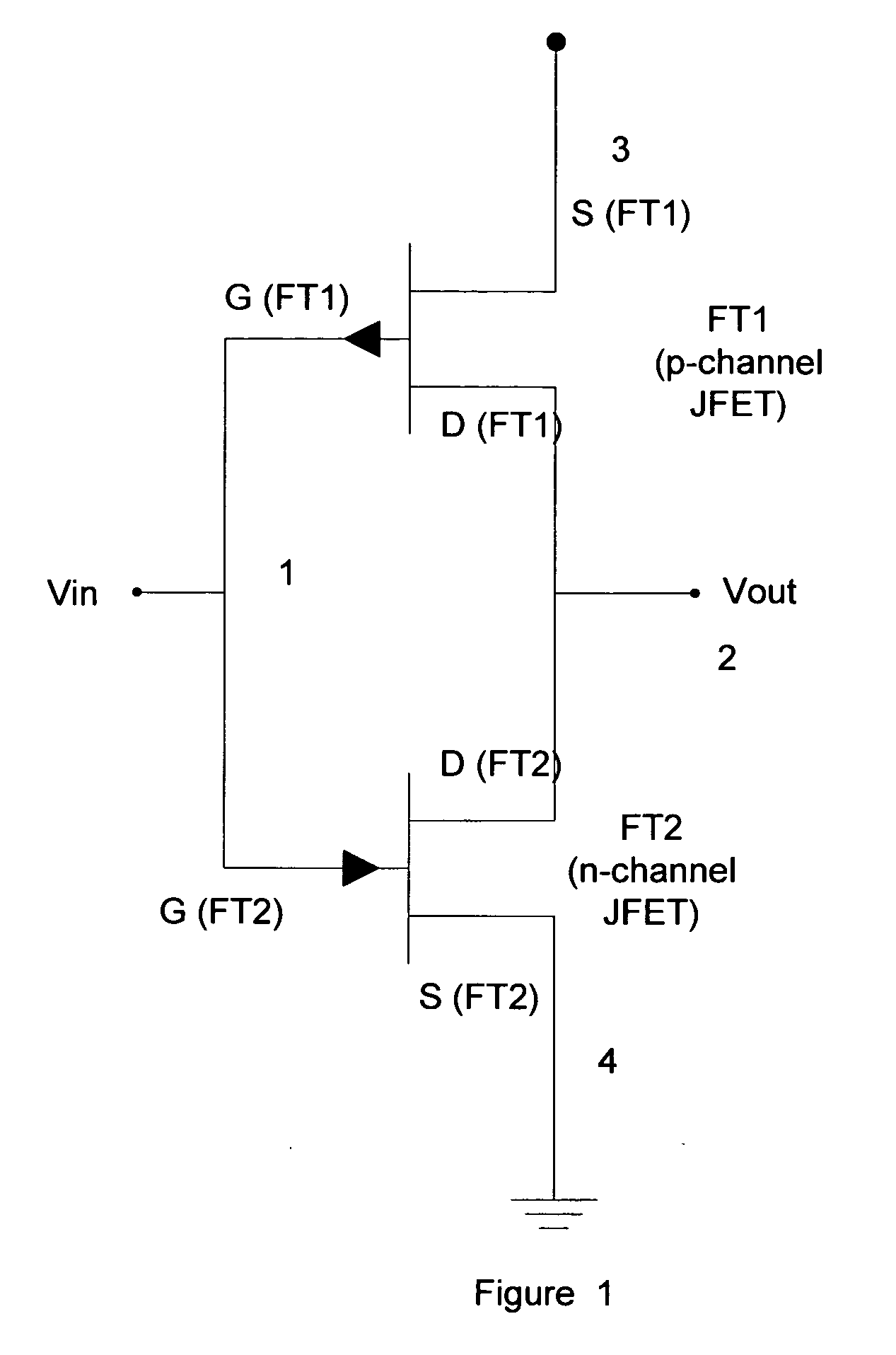

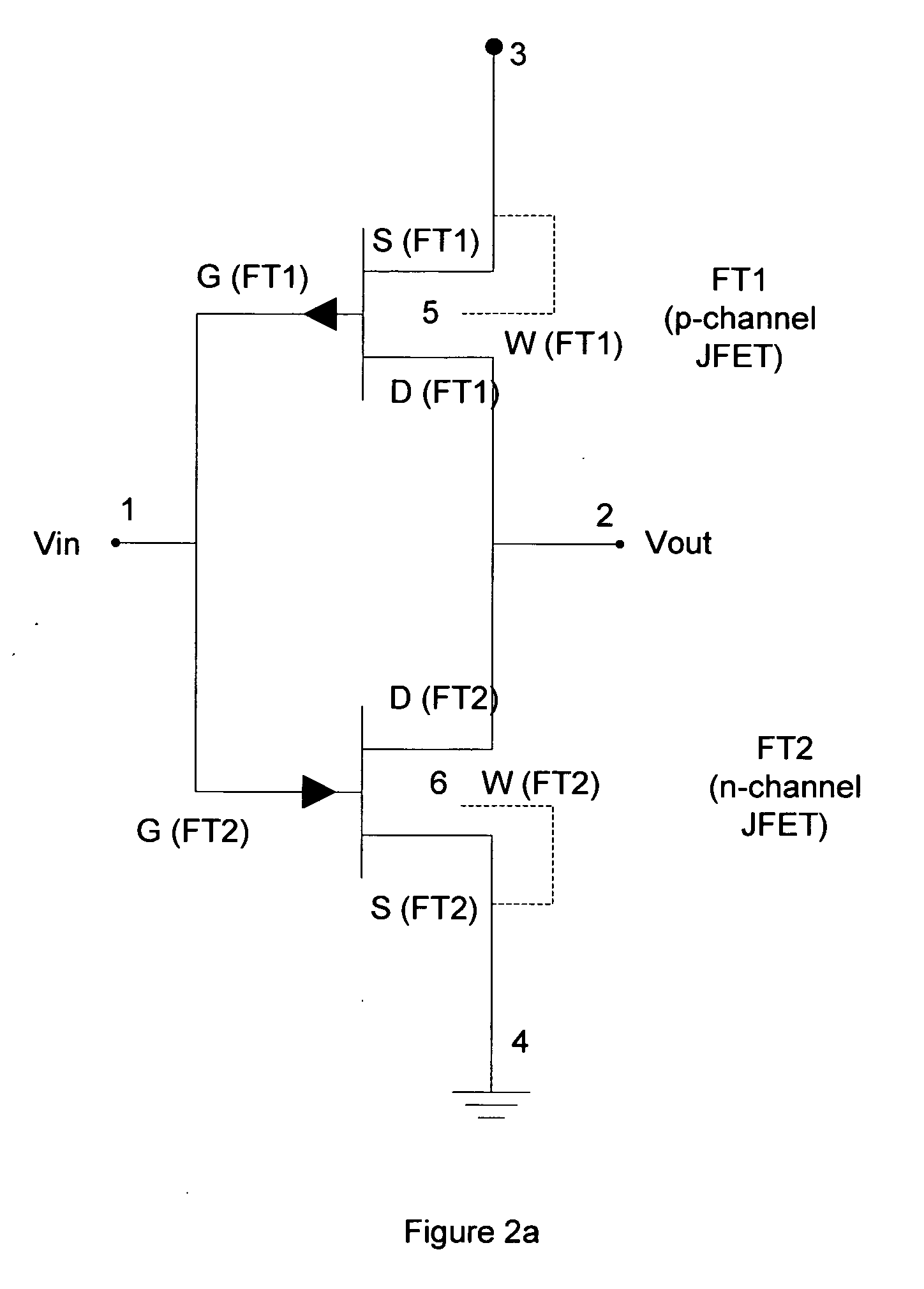

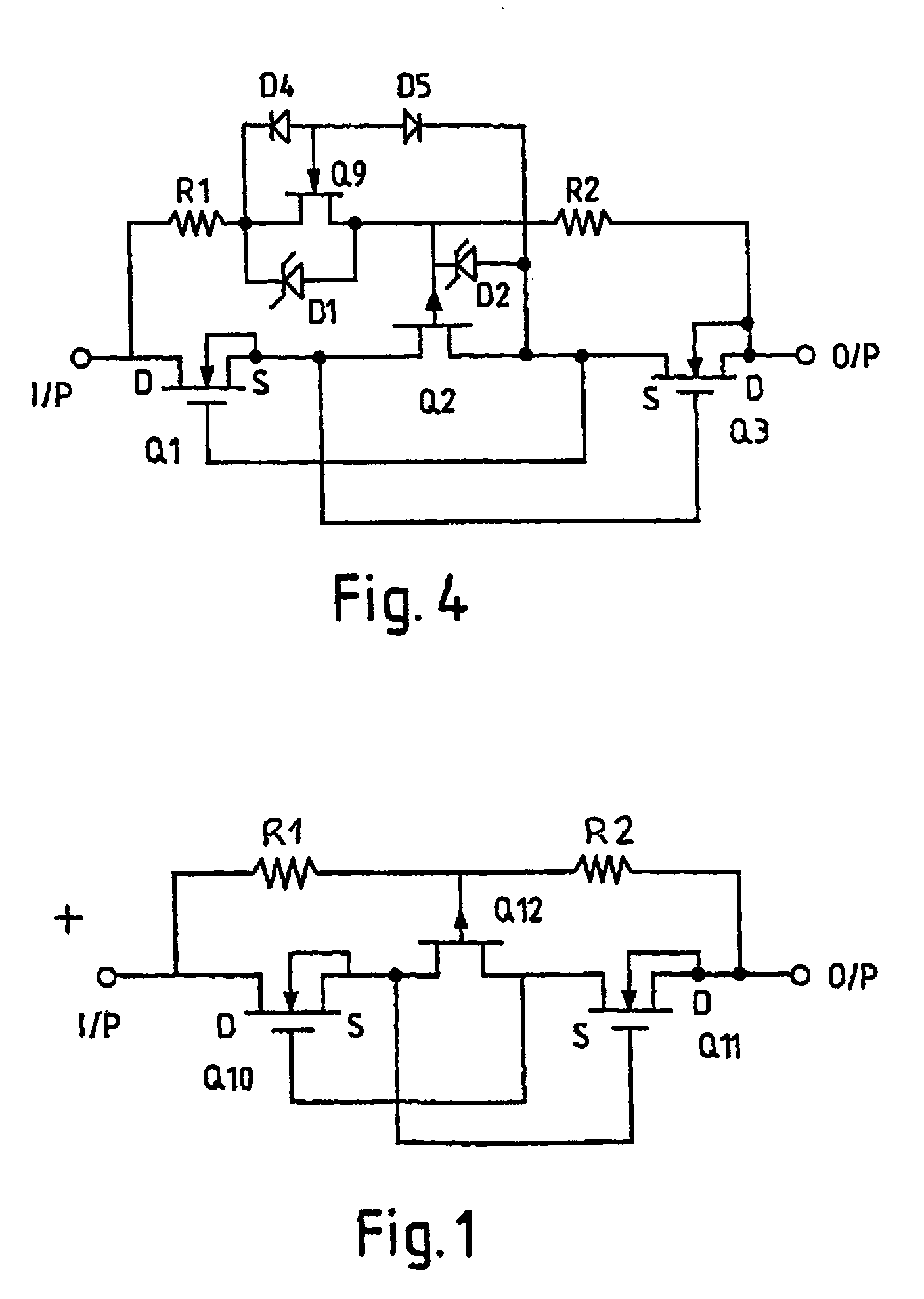

Circuit configurations having four terminal JFET devices

InactiveUS20070262793A1Logic circuits characterised by logic functionSolid-state devicesPhase detectorMultiplexer

Circuits using four terminal junction field effect transistors (JFETs) are disclosed. Such circuits can include various static and dynamic logic circuits, flip-flops, multiplexer, tri-state driver, phase detector, logic having variable speeds of operation, and / or analog circuit with such four terminal JFETs operating in a linear or nonlinear mode.

Owner:MIE FUJITSU SEMICON

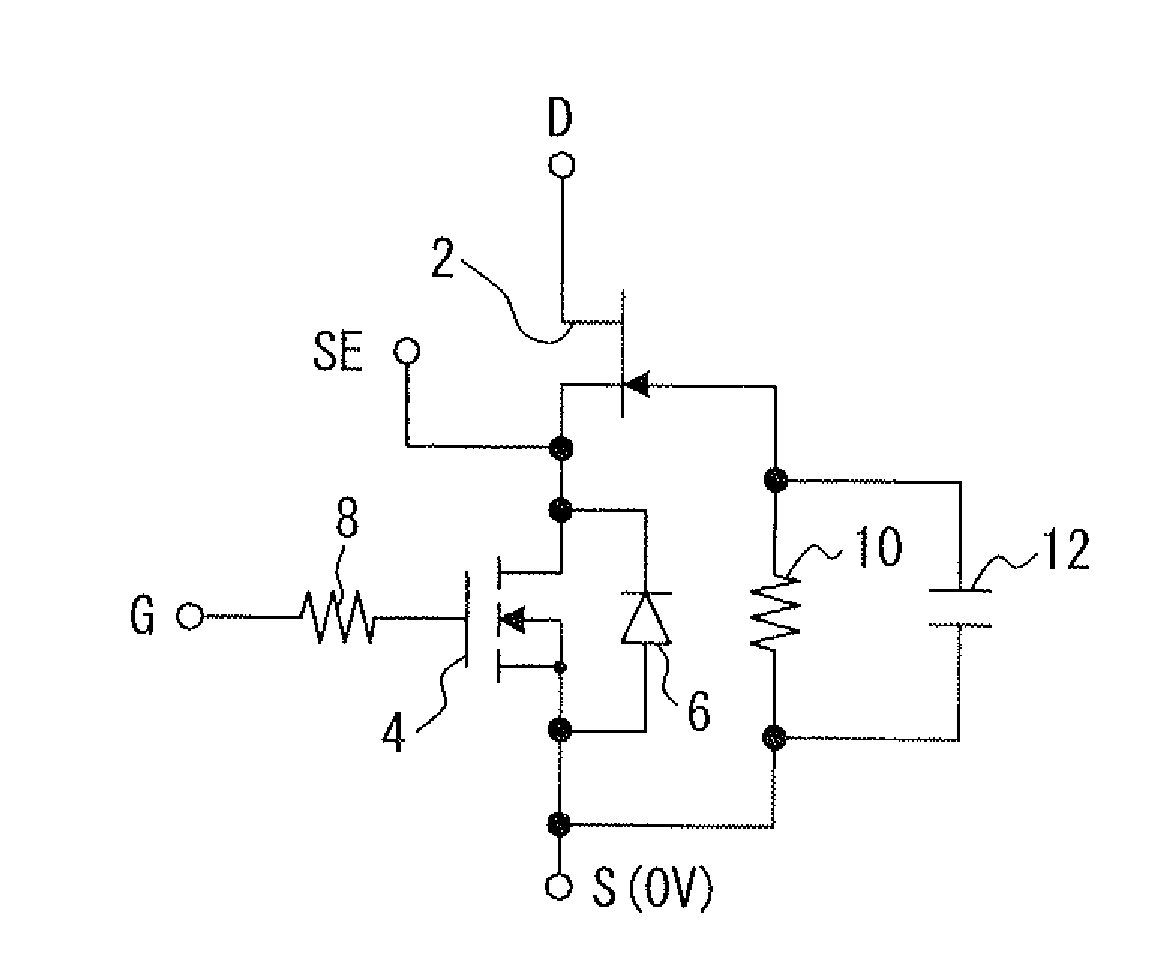

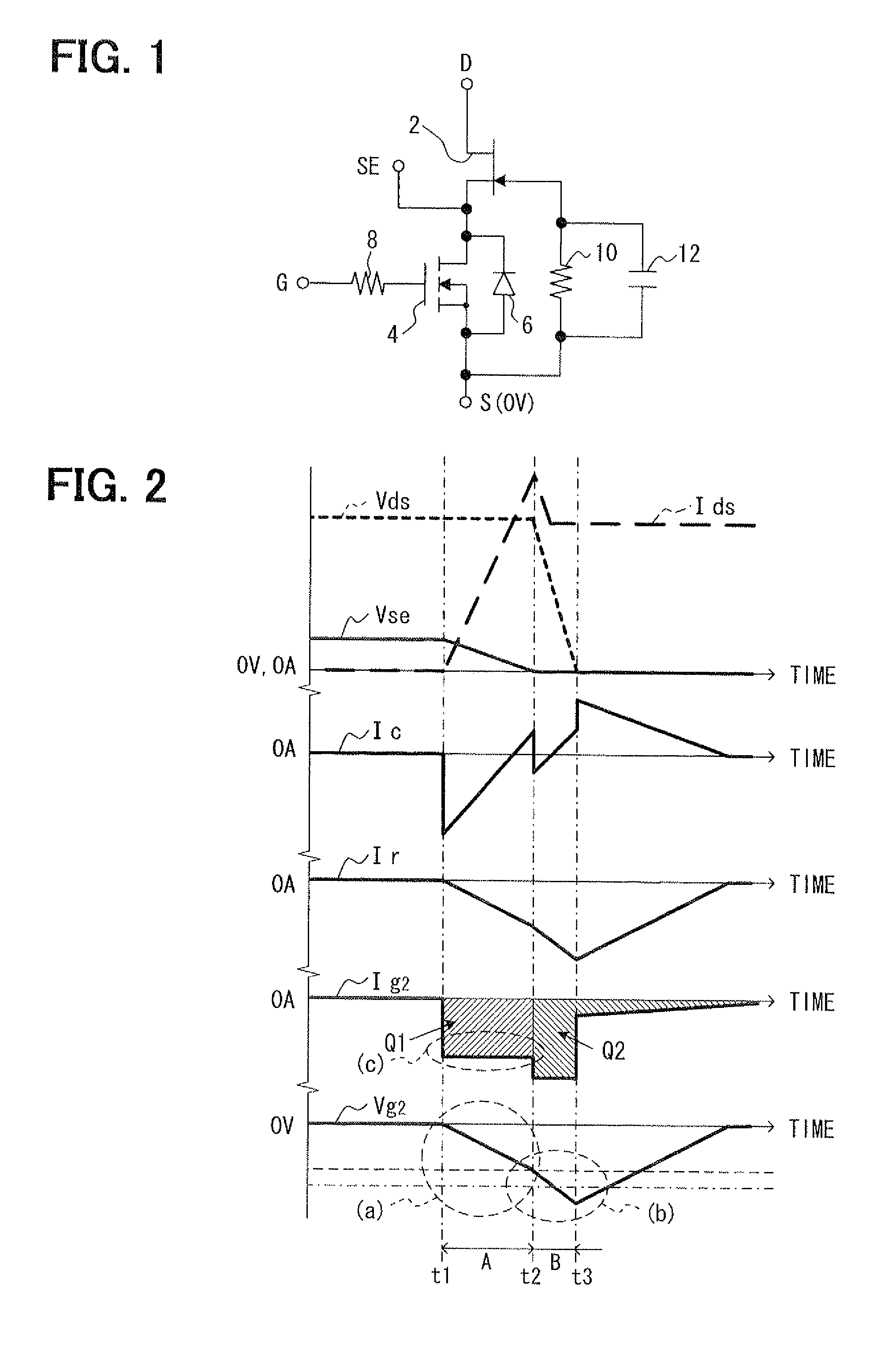

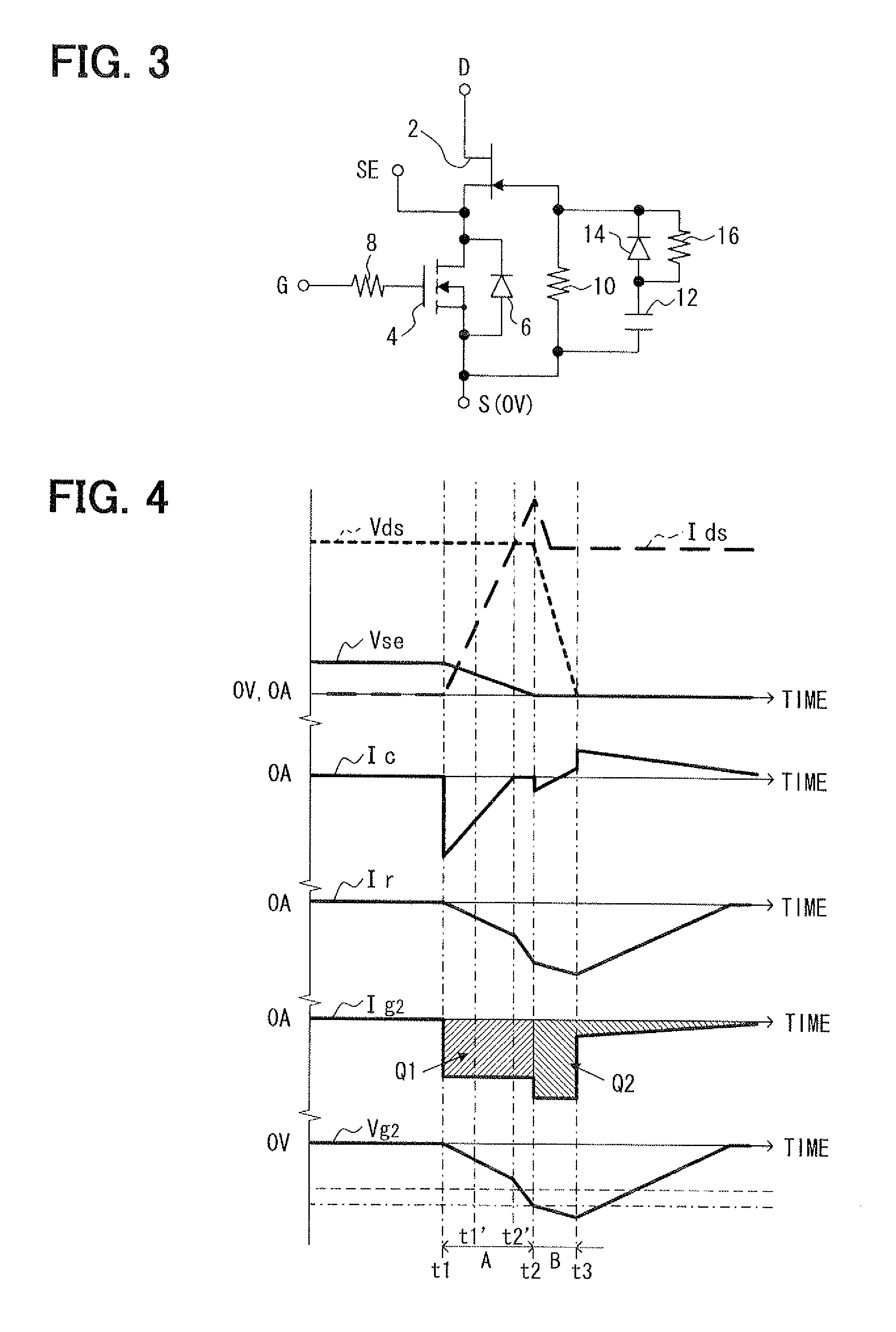

Hybrid power device

ActiveUS20110199148A1Suppress resonanceReduce switching lossesElectronic switchingElectric pulse generatorMOSFETCascode

A hybrid power device is formed of a normally-on type SiC-JFET and a normally-off type Si-MOSFET, which are connected in cascode with a source of the SiC-JFET and a drain of the Si-MOSFET being connected to each other thereby forming a hybrid power FET. A gate of the SiC-JFET and a source of the Si-MOSFET are connected via a switching speed regulating resistor. A capacitor is connected to the switching speed regulating resistor in parallel to control a switching speed to a first speed in a former part of the switching period of the hybrid power FET and to a second switching speed in a latter part of the switching period. The second switching speed is lower than the first switching speed.

Owner:DENSO CORP

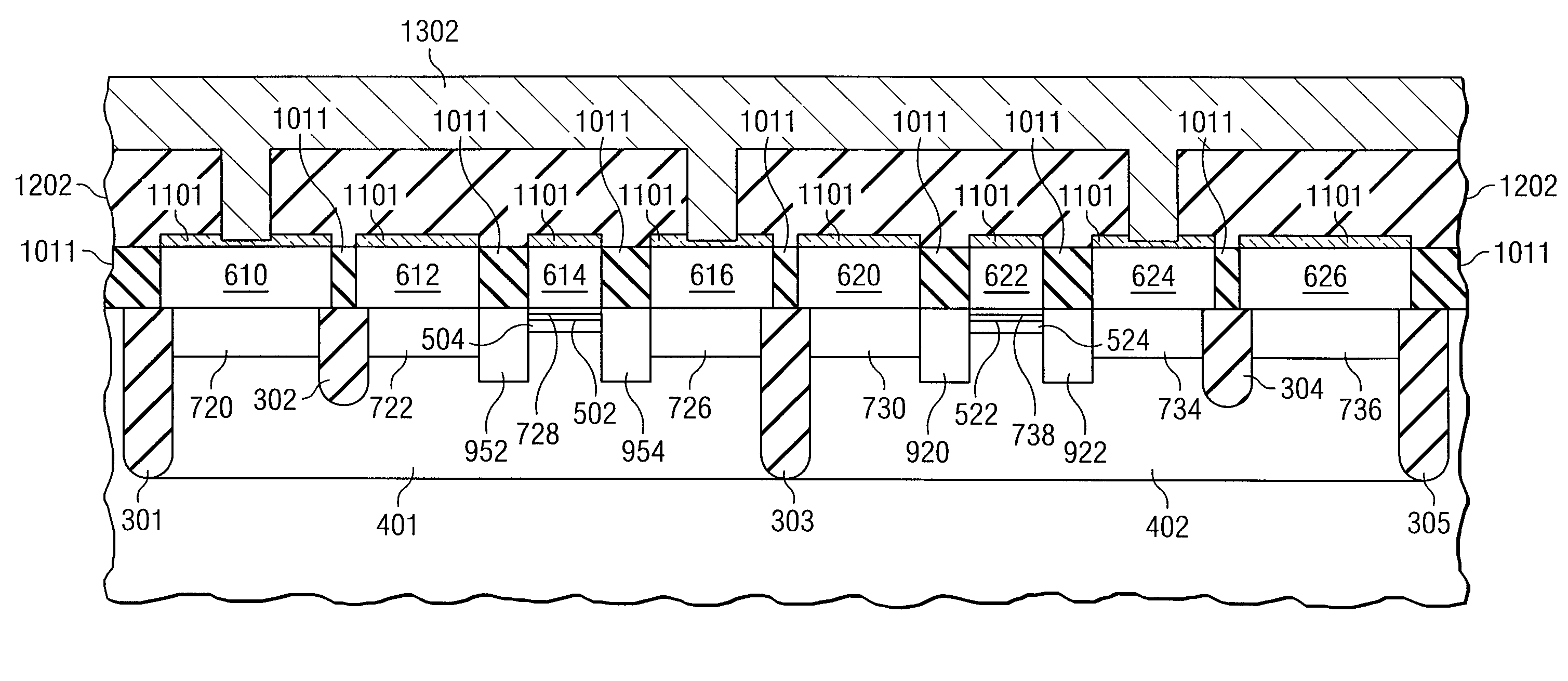

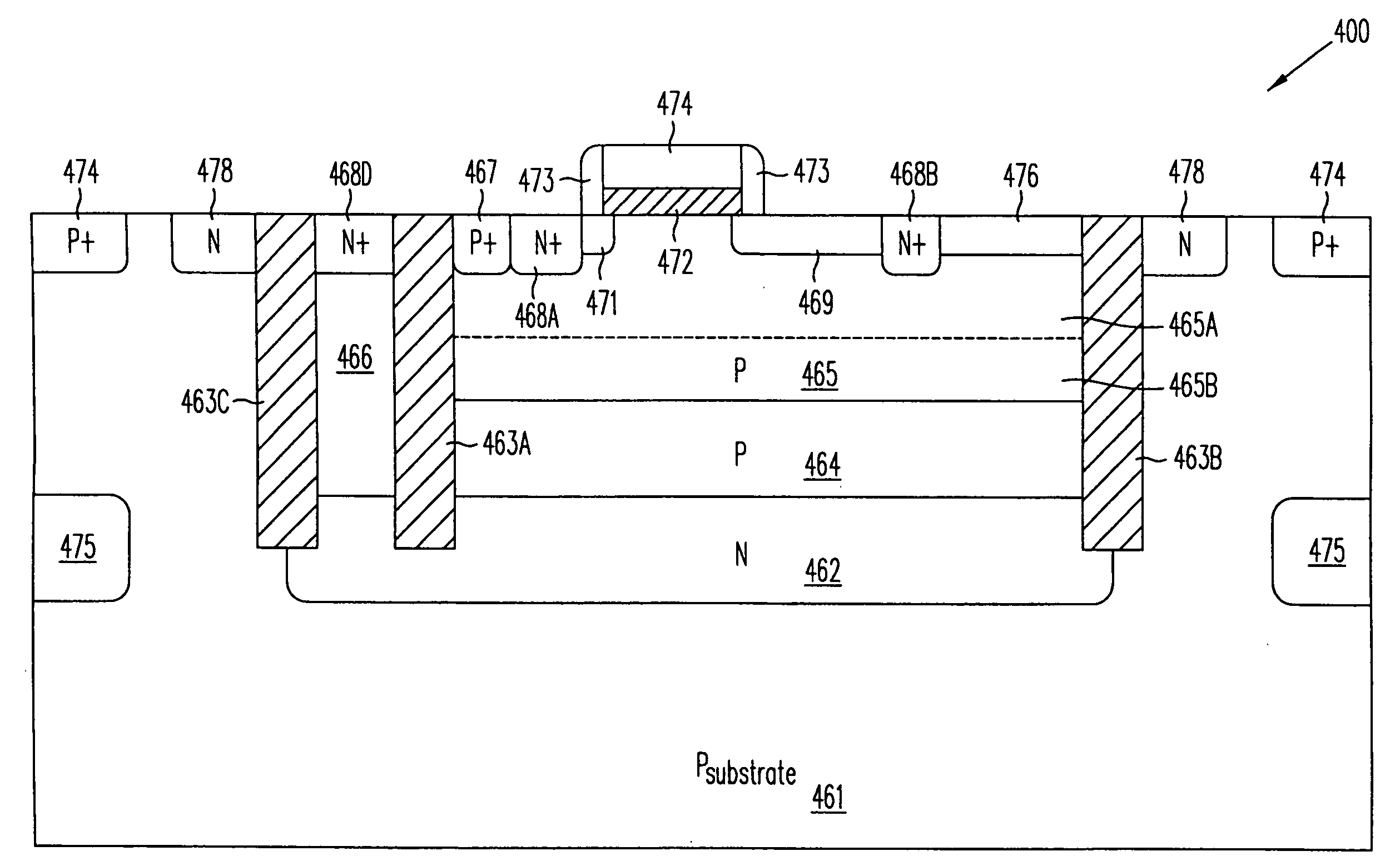

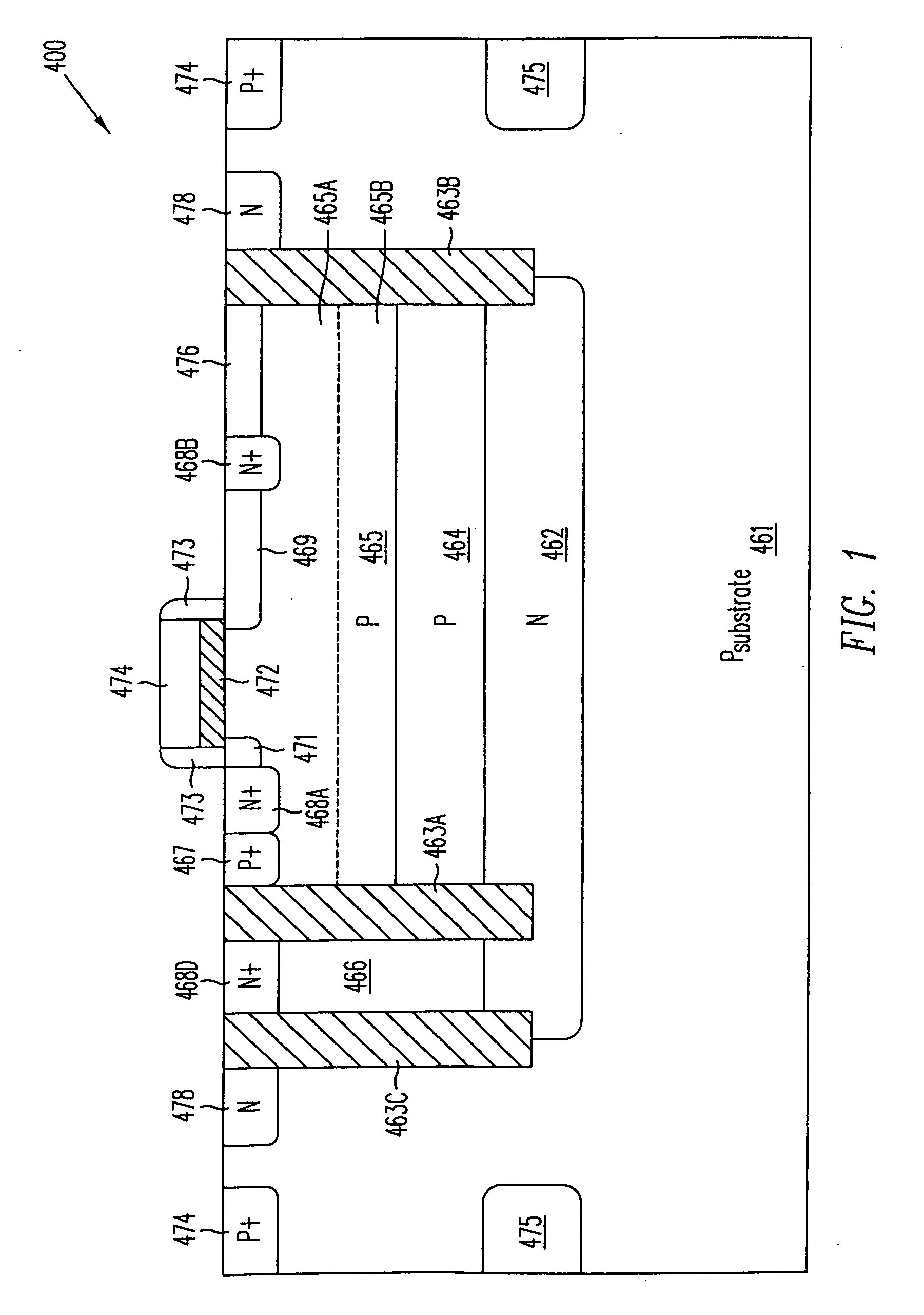

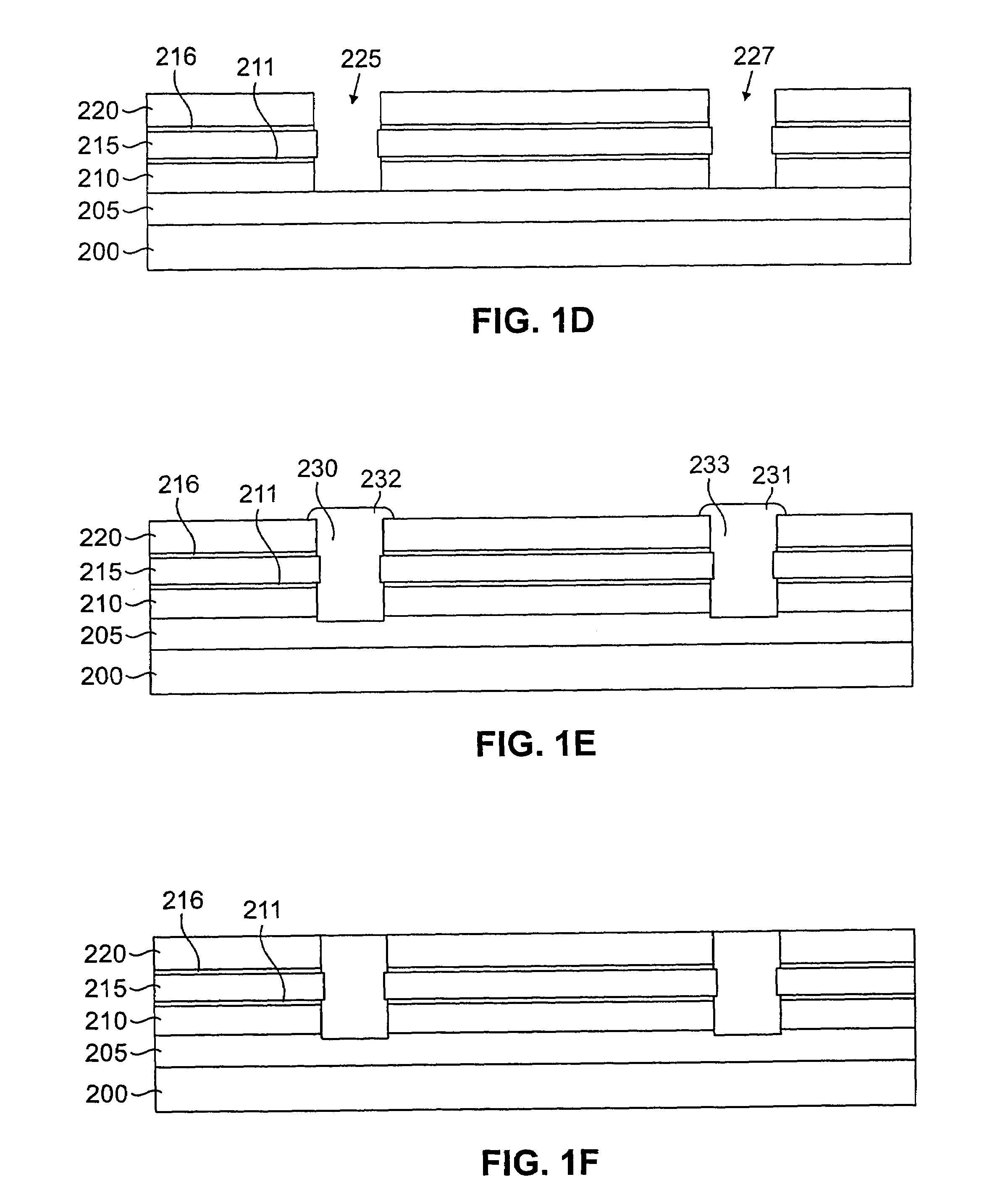

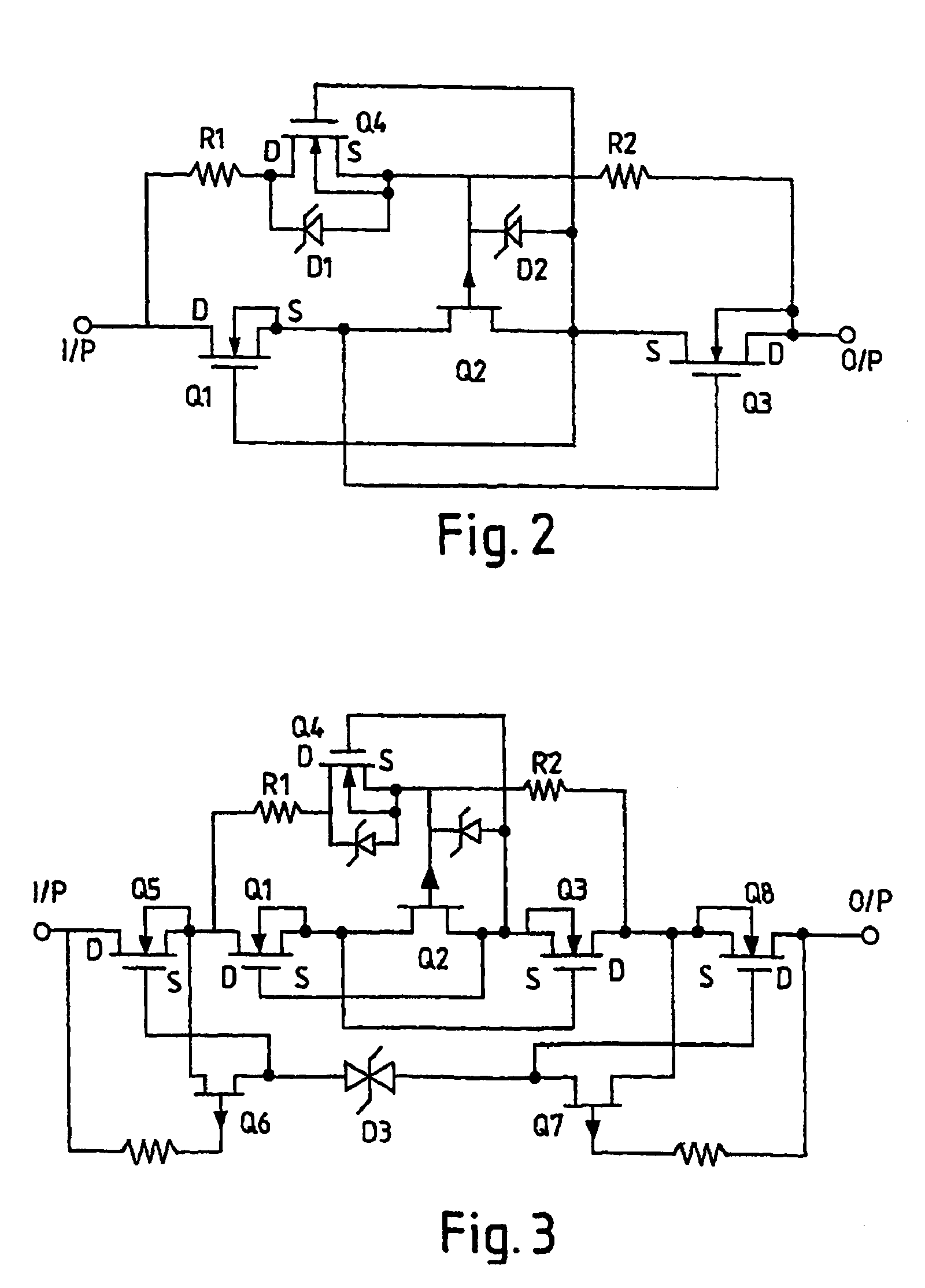

Integrated circuit using complementary junction field effect transistor and MOS transistor in silicon and silicon alloys

InactiveUS20070096144A1Reduce power consumptionReduce gate capacitanceTransistorSolid-state devicesCMOSSilicon alloy

This invention describes a method of building complementary logic circuits using junction field effect transistors in silicon. This invention is ideally suited for deep submicron dimensions, preferably below 65 nm. The basis of this invention is a complementary Junction Field Effect Transistor which is operated in the enhancement mode. The speed-power performance of the JFETs becomes comparable with the CMOS devices at sub-70 nanometer dimensions. However, the maximum power supply voltage for the JFETs is still limited to below the built-in potential (a diode drop). To satisfy certain applications which require interface to an external circuit driven to higher voltage levels, this invention includes the structures and methods to build CMOS devices on the same substrate as the JFET devices.

Owner:MIE FUJITSU SEMICON

Self aligned gate JFET structure and method

A JFET integrated onto a substrate having a semiconductor layer at least and having source and drain contacts over an active area and made of first polysilicon (or other conductors such as refractive metal or silicide) and a self-aligned gate contact made of second polysilicon which has been polished back to be flush with a top surface of a dielectric layer covering the tops of the source and drain contacts. The dielectric layer preferably has a nitride cap to act as a polish stop. In some embodiments, nitride covers the entire dielectric layer covering the source and drain contacts as well as the field oxide region defining an active area for said JFET. An embodiment with an epitaxially grown channel region formed on the surface of the substrate is also disclosed.

Owner:MIE FUJITSU SEMICON

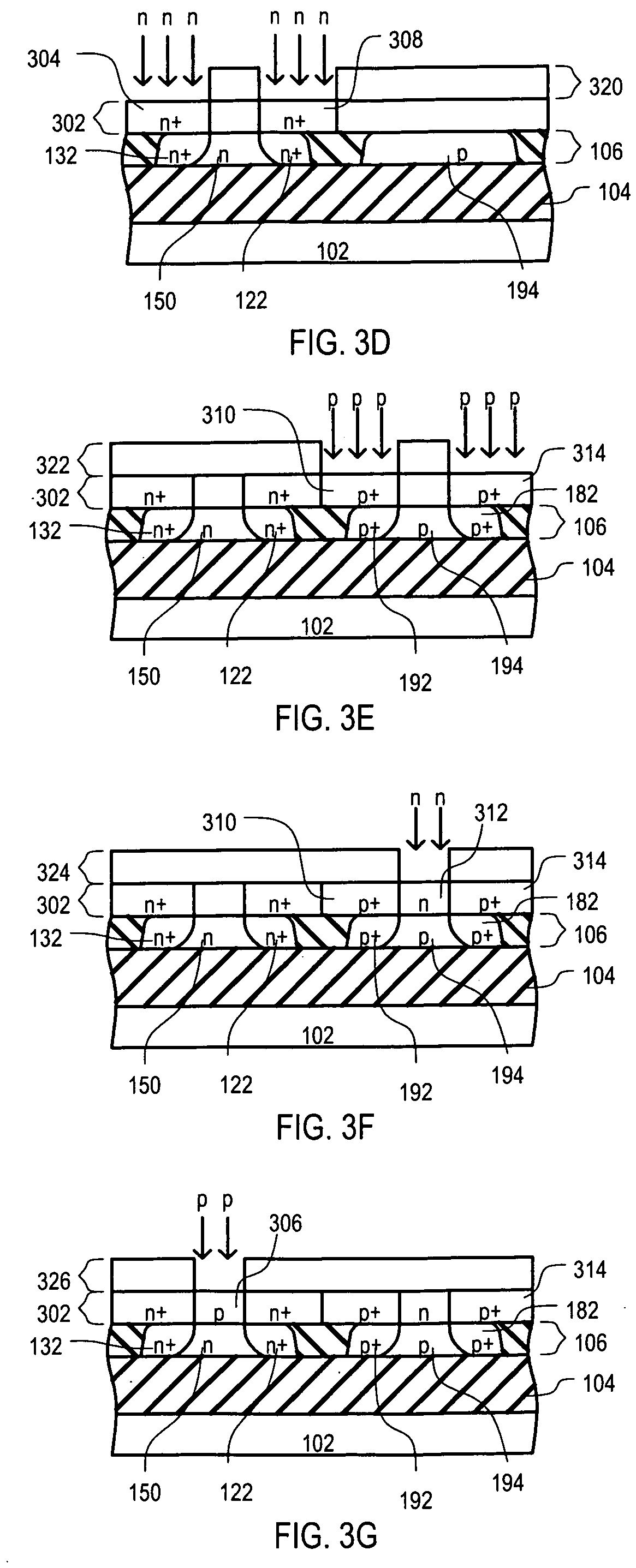

High-voltage bipolar-CMOS-DMOS integrated circuit devices and modular methods of forming the same

All low-temperature processes are used to fabricate a variety of semiconductor devices in a substrate the does not include an epitaxial layer. The devices include a non-isolated lateral DMOS, a non-isolated extended drain or drifted MOS device, a lateral trench DMOS, an isolated lateral DMOS, JFET and depletion-mode devices, and P-N diode clamps and rectifiers and junction terminations. Since the processes eliminate the need for high temperature processing and employ “as-implanted” dopant profiles, they constitute a modular architecture which allows devices to be added or omitted to the IC without the necessity of altering the processes used to produce the remaining devices.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

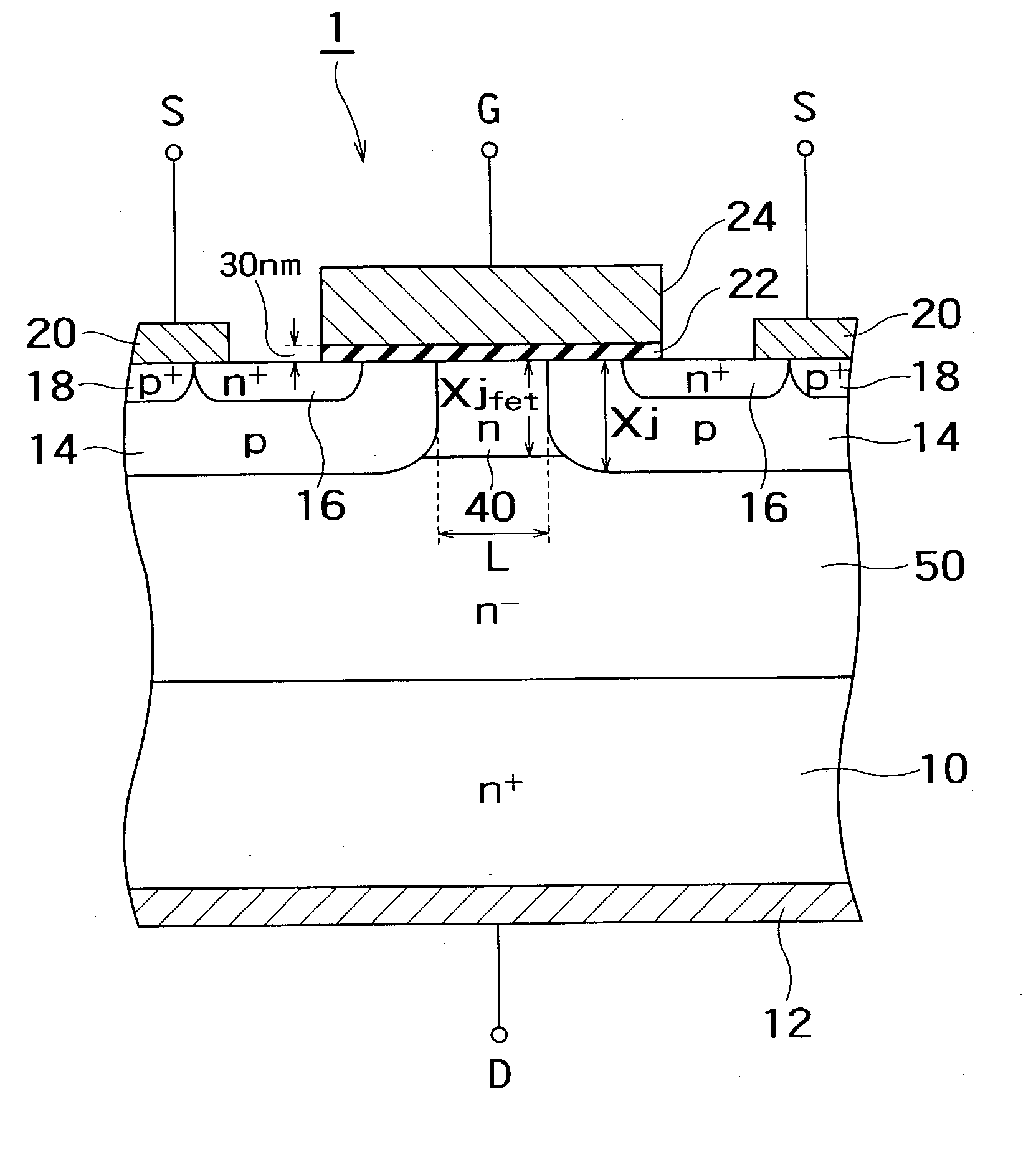

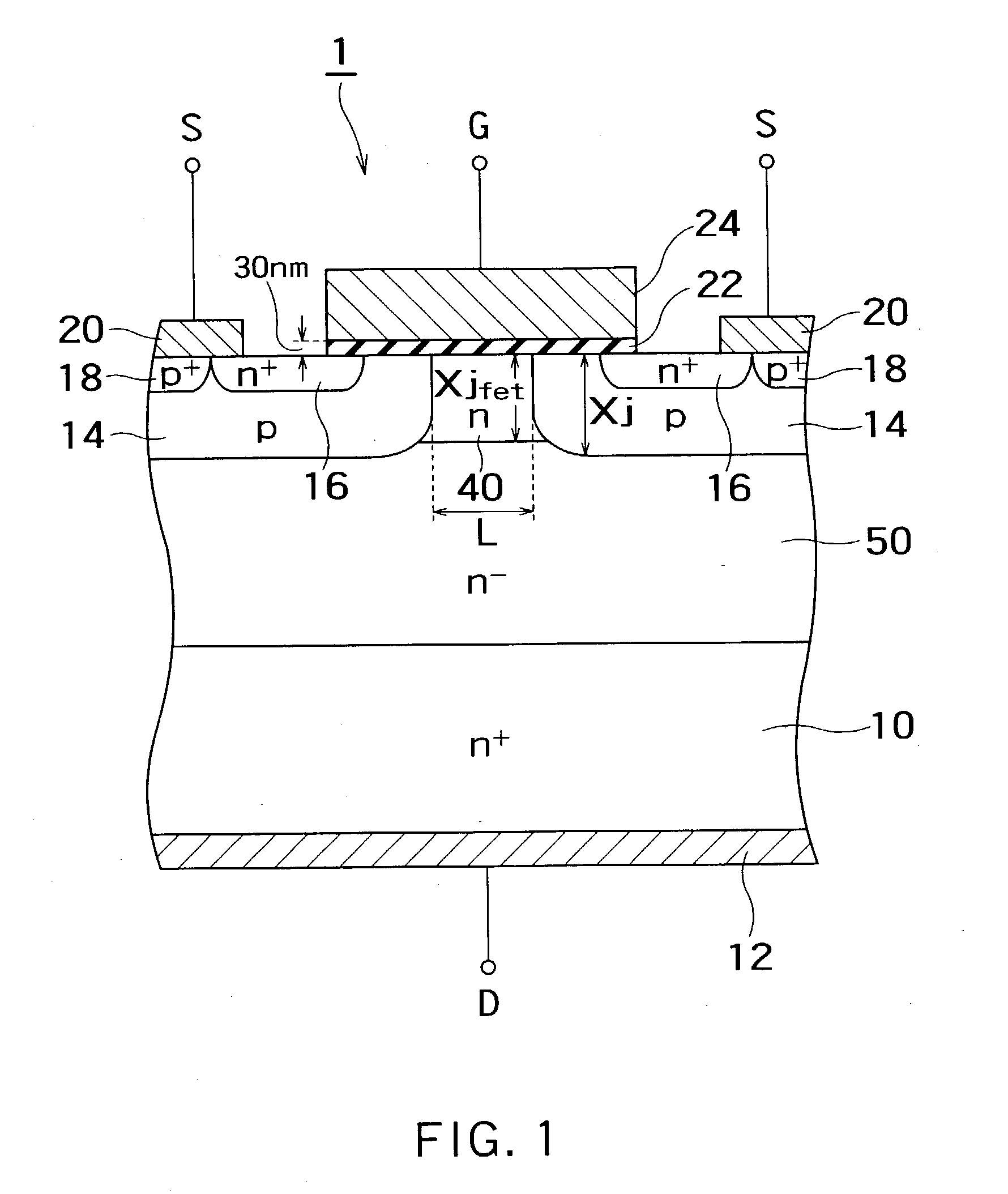

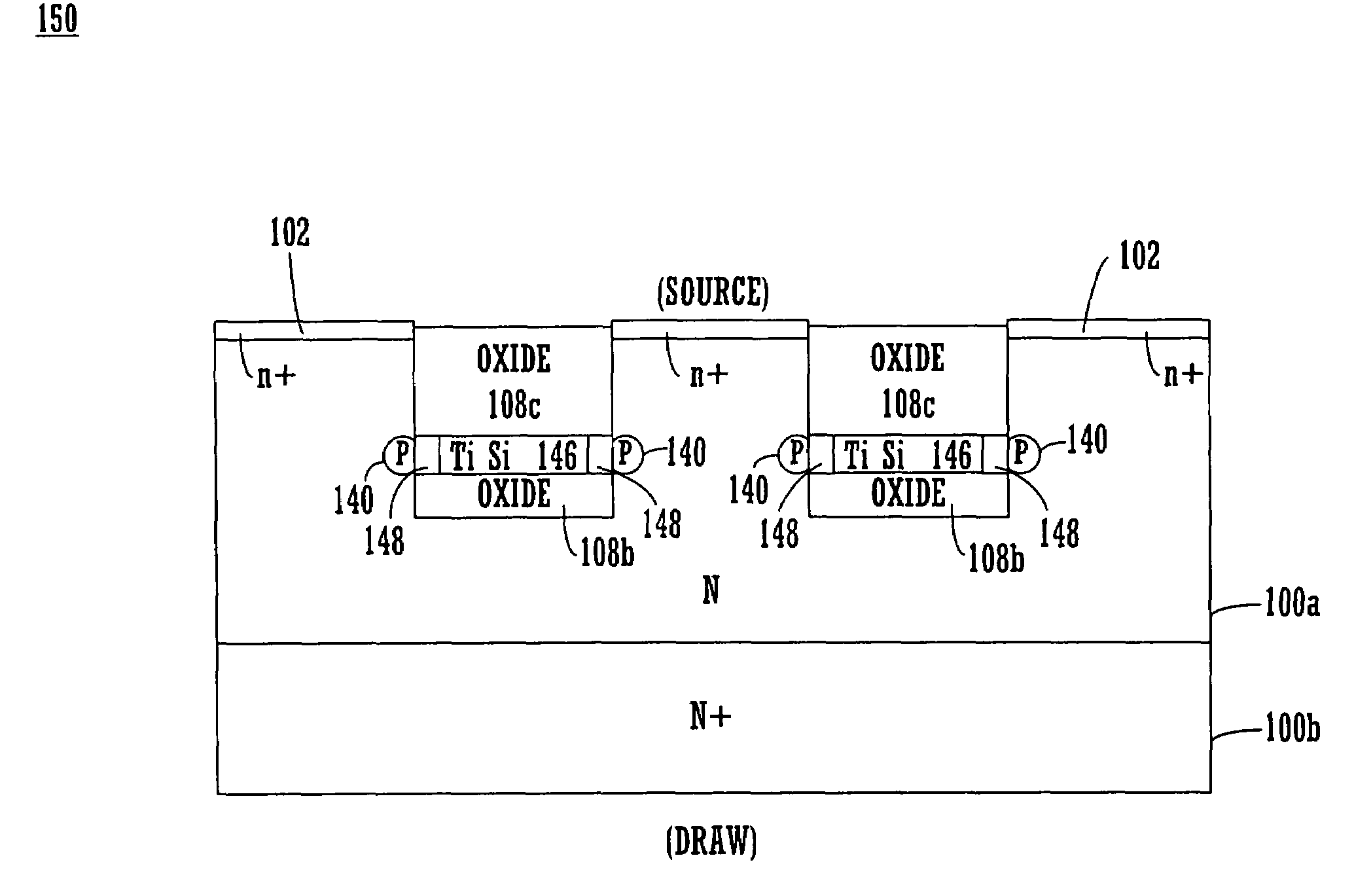

Semiconductor device

InactiveUS20030227052A1Semiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceHigh resistance

A semiconductor device includes: a semiconductor substrate, at least a surface portion thereof serving as a low-resistance drain layer of a first conductivity type; a first main electrode connected to the low-resistance drain layer; a high-resistance epitaxial layer of a second-conductivity type formed on the low-resistance drain layer; a second-conductivity type base layer selectively formed on the high-resistance epitaxial layer; a first-conductivity type source layer selectively formed in a surface portion of the second-conductivity type base layer; a trench formed in a region sandwiched by the second-conductivity type base layers with a depth extending from the surface of the high-resistance epitaxial layer to the semiconductor substrate; a jfet layer of the first conductivity type formed on side walls of the trench; an insulating layer formed in the trench; an LDD layer of the first-conductivity type formed in a surface portion of the second-conductivity type base layer so as to be connected to the first-conductivity type jfet layer around a top face of the trench; a control electrode formed above the semiconductor substrate so as to be divided into a plurality of parts, and formed on a gate insulating film formed on a part of the surface of the LDD layer, on surfaces of end parts of the first-conductivity type source layer facing each other across the trench, and on a region of the surface of the second-conductivity type base layer sandwiched by the LDD layer and the first-conductivity type source layer; and a second main electrode in ohmic contact with the first-conductivity type source layer and the second-conductivity type base layer so as to sandwich the control electrode.

Owner:KK TOSHIBA

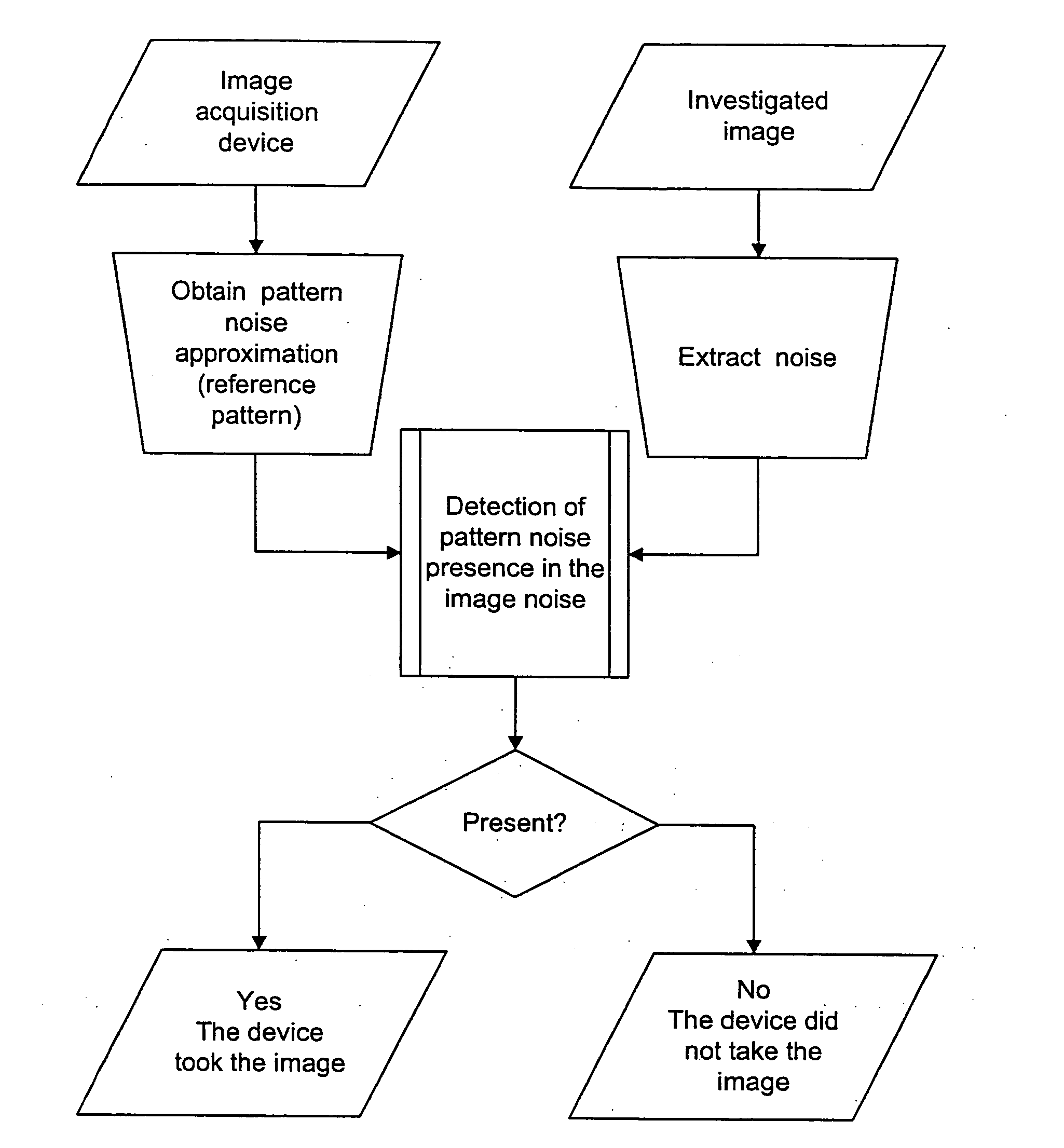

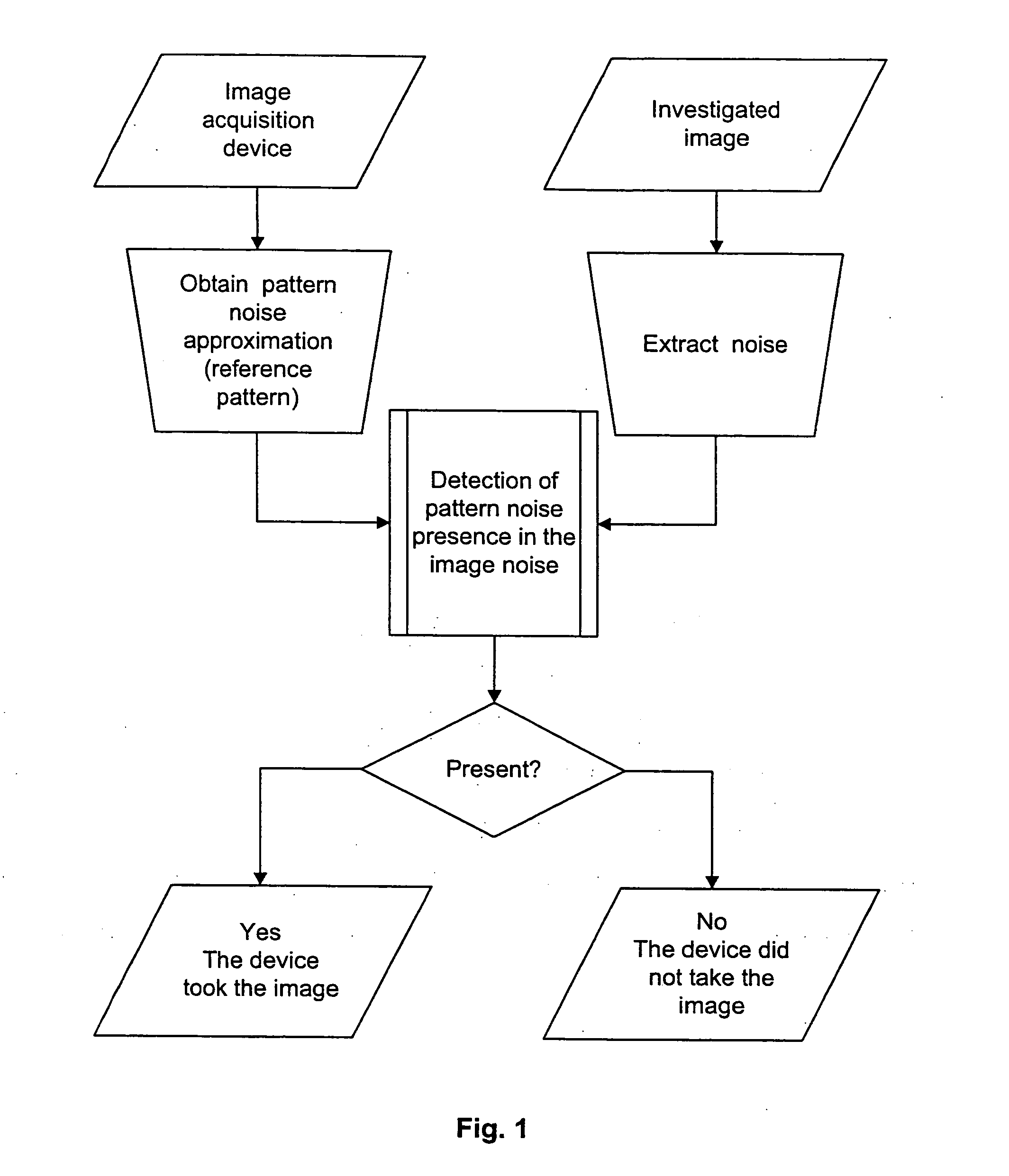

Method and apparatus for identifying an imaging device

InactiveUS20090257671A1Reliable matchReliable identificationTelevision system detailsCharacter and pattern recognitionCMOSPattern recognition

A new technique for identifying from images a camera, or other imaging device such as a scanner, is based on the device's reference noise pattern, a unique stochastic characteristic of all common digital imaging sensors, including CCD, CMOS (Foveon™ X3), and JFET. First, one determines from images the sensor's reference pattern noise, which uniquely identifies each sensor. To identify the sensor from a given image, the presence or absence of the reference pattern noise in the image under examination is established using a correlation detector or other means.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

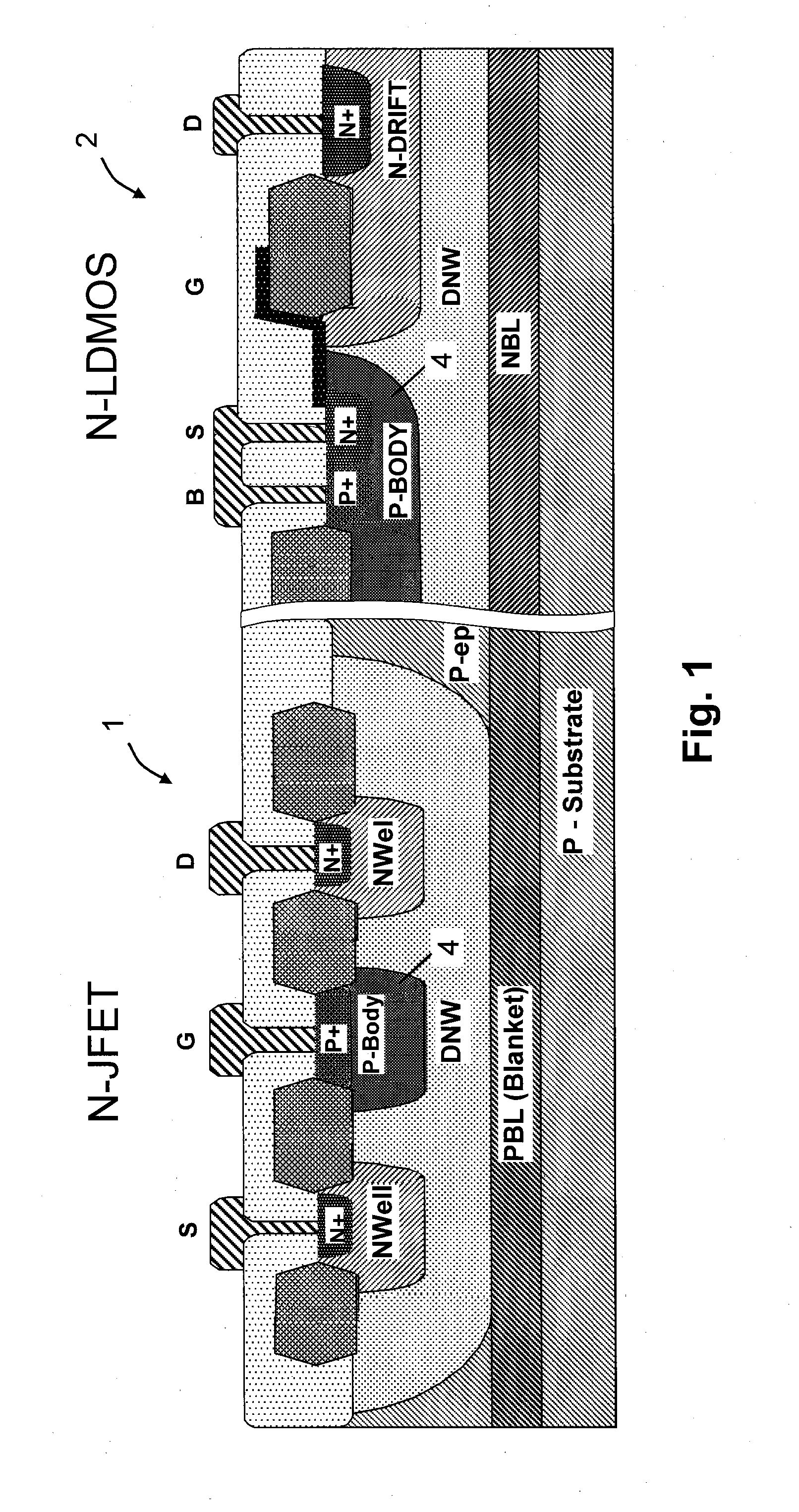

Forming jfet and ldmos transistor in monolithic power integrated circuit using deep diffusion regions

ActiveUS20150380398A1Solid-state devicesSemiconductor/solid-state device manufacturingLDMOSDevice form

A power integrated circuit includes a junction field effect transistor (JFET) device formed in a first portion of a semiconductor layer with a gate region being formed using a first body region, and a double-diffused metal-oxide-semiconductor (LDMOS) transistor formed in a second portion of the semiconductor layer with a channel being formed in a second body region. The power integrated circuit includes a first deep diffusion region formed under the first body region and in electrical contact with the first body region where the first deep diffusion region together with the firs body region establish a pinch off voltage of the JFET device; and a second deep diffusion region formed under the second body region and in electrical contact with the second body region where the second deep diffusion region forms a reduced surface field (RESURF) structure in the LDMOS transistor.

Owner:ALPHA & OMEGA SEMICON INC

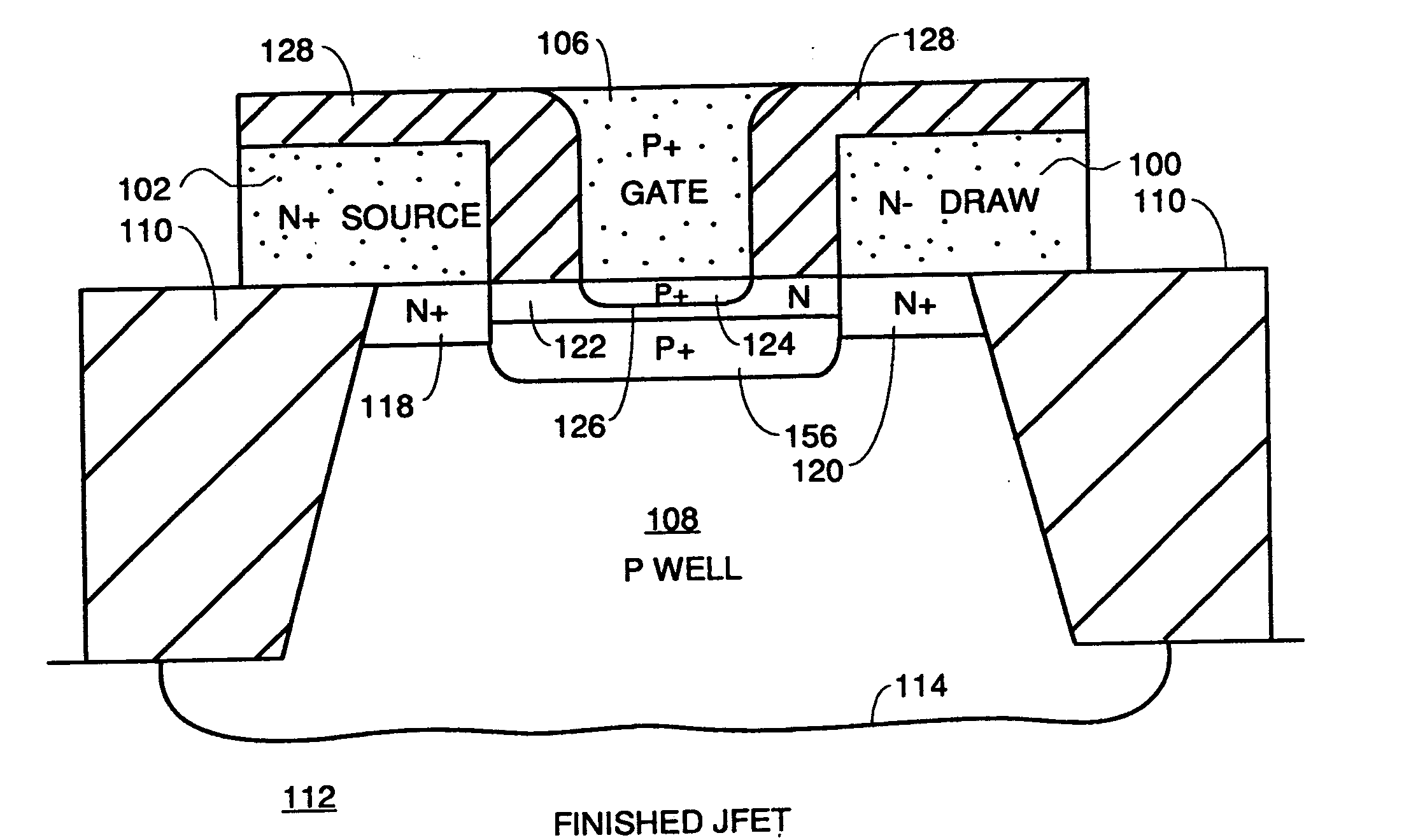

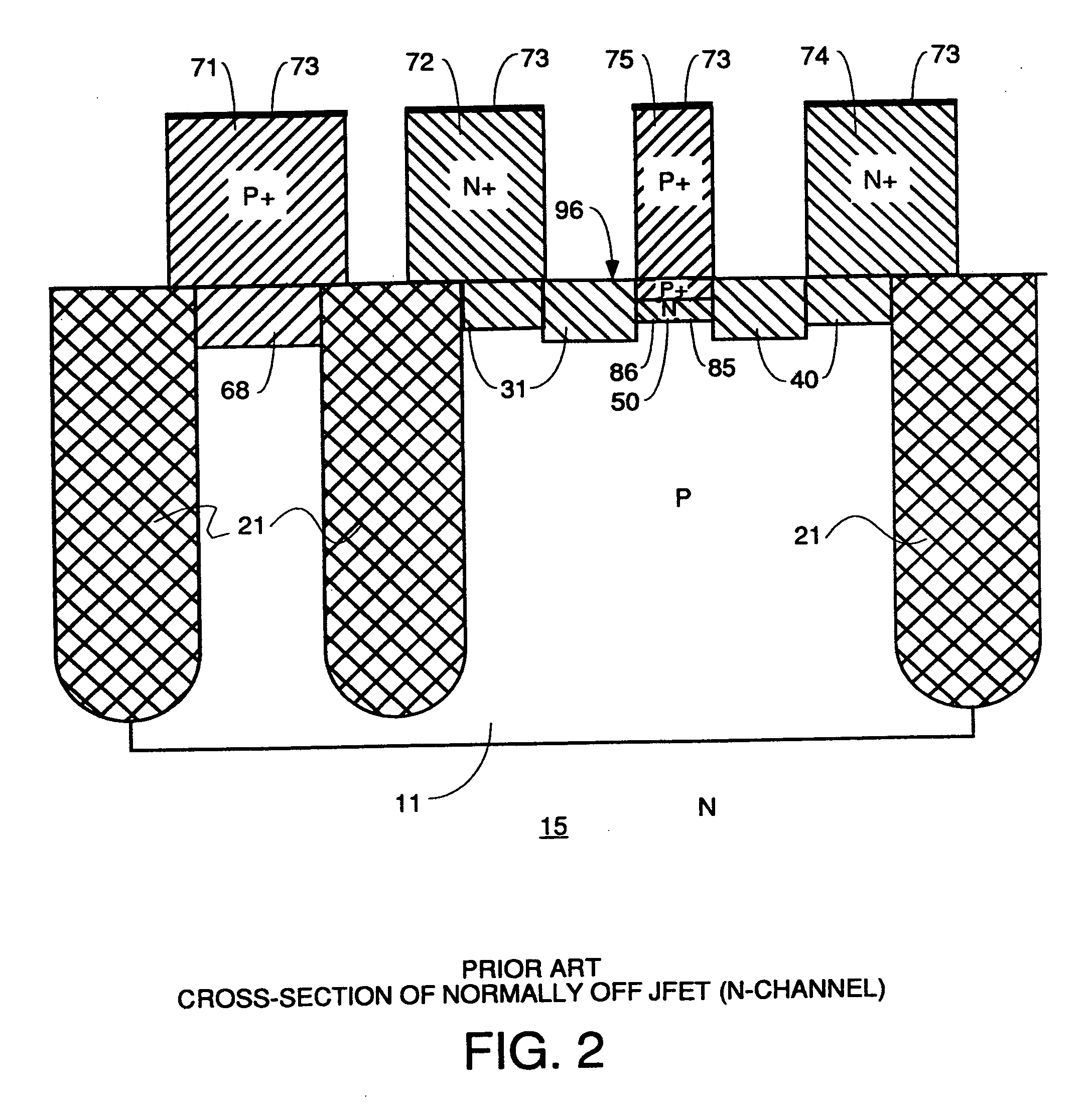

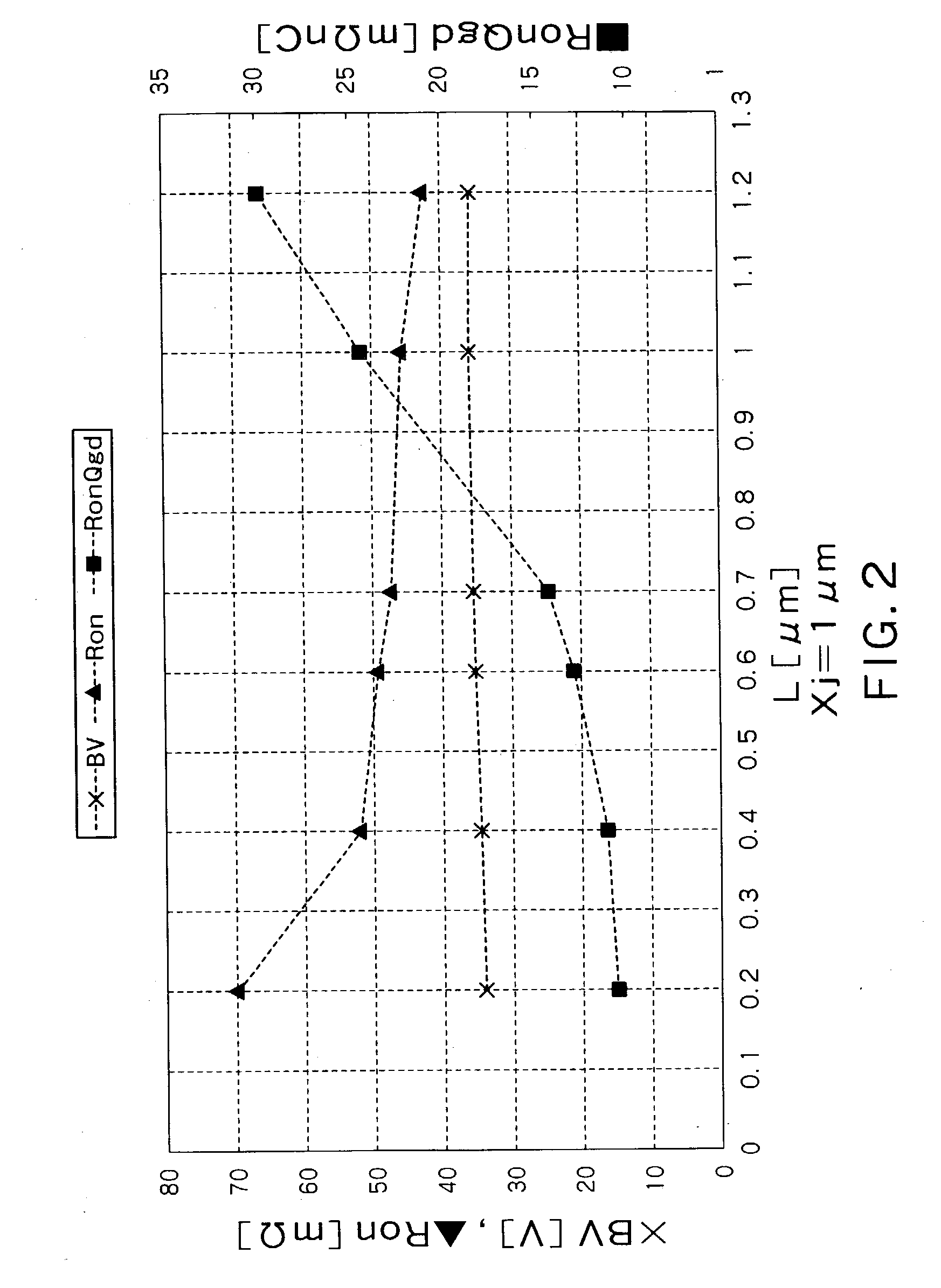

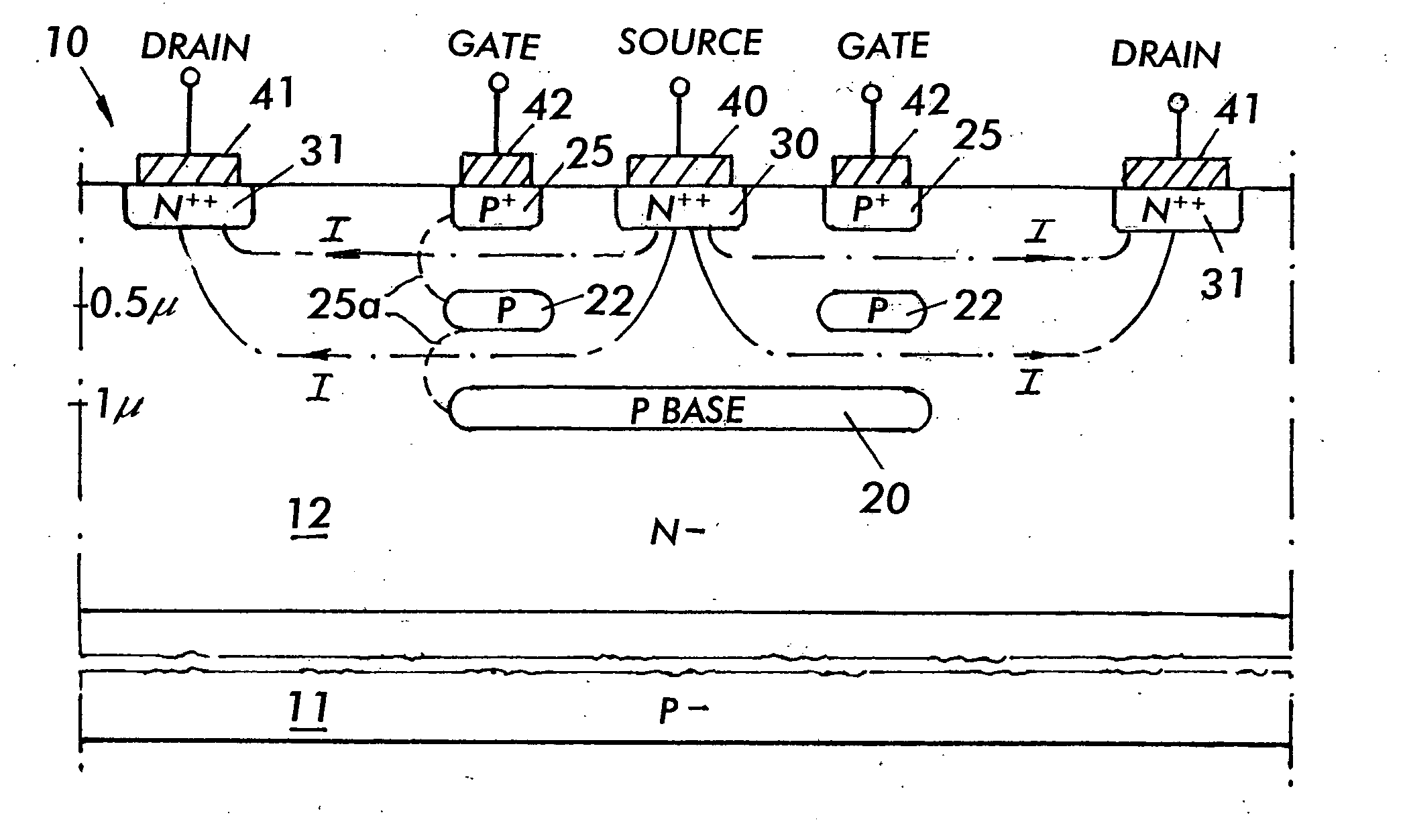

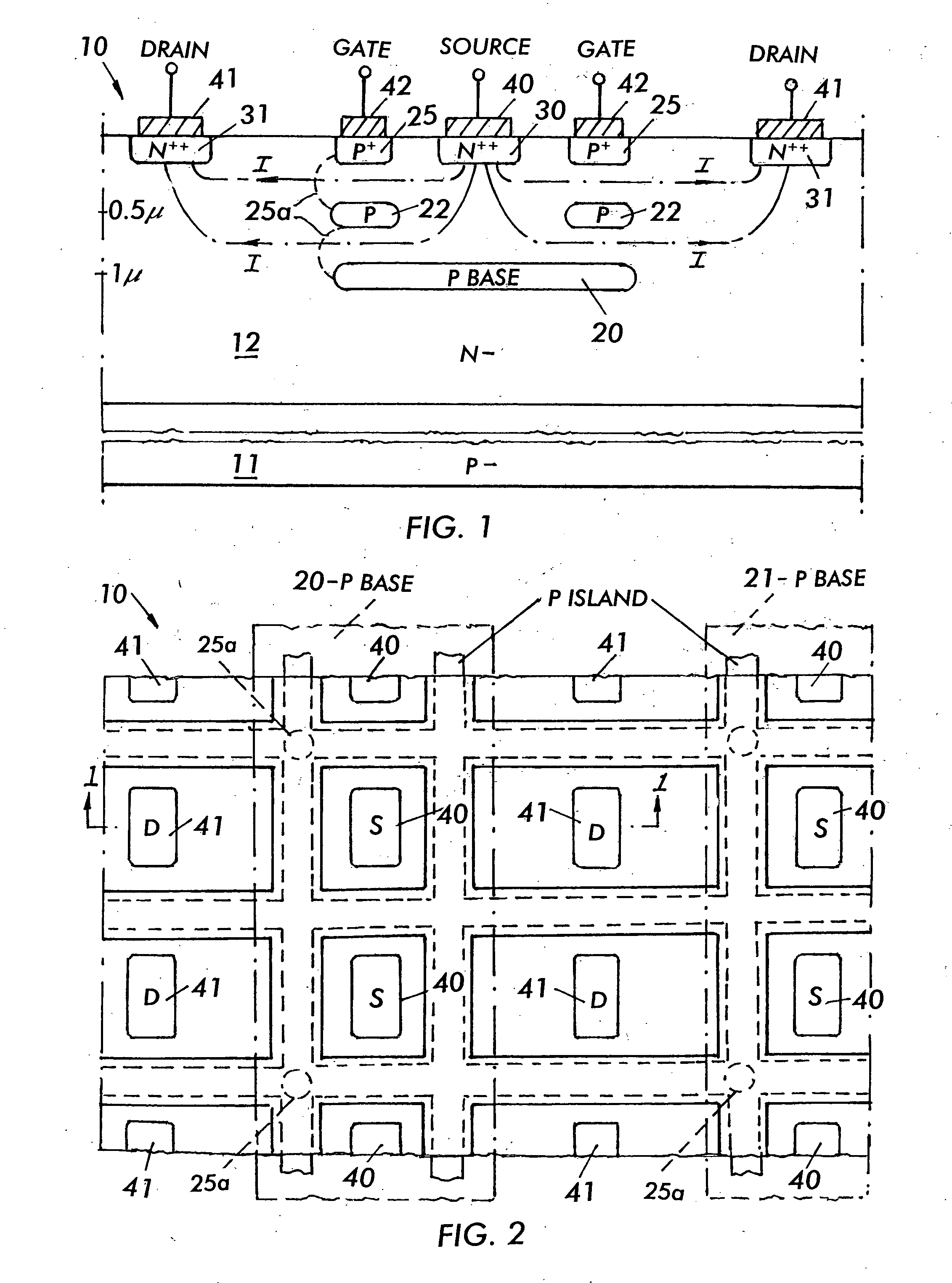

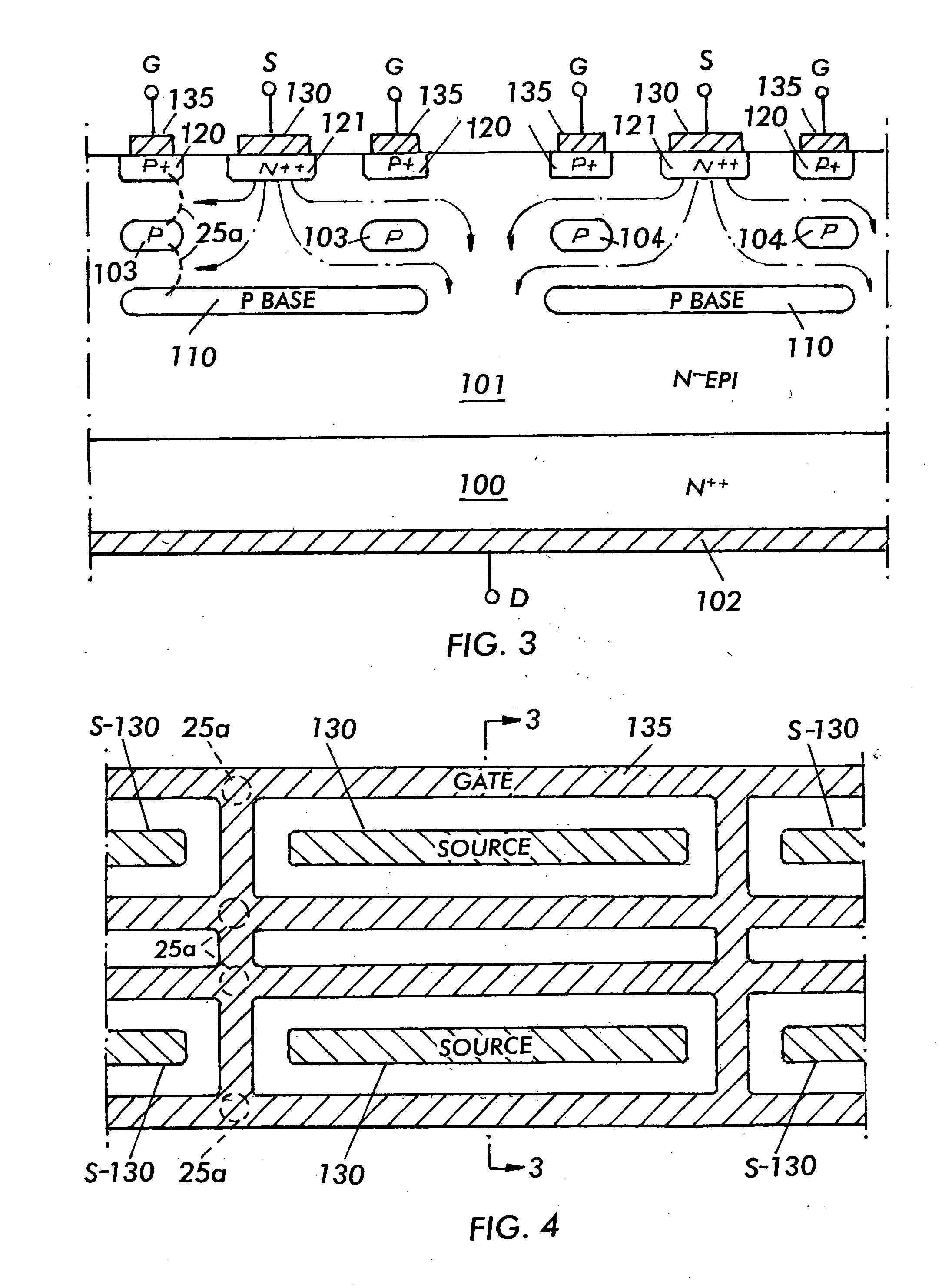

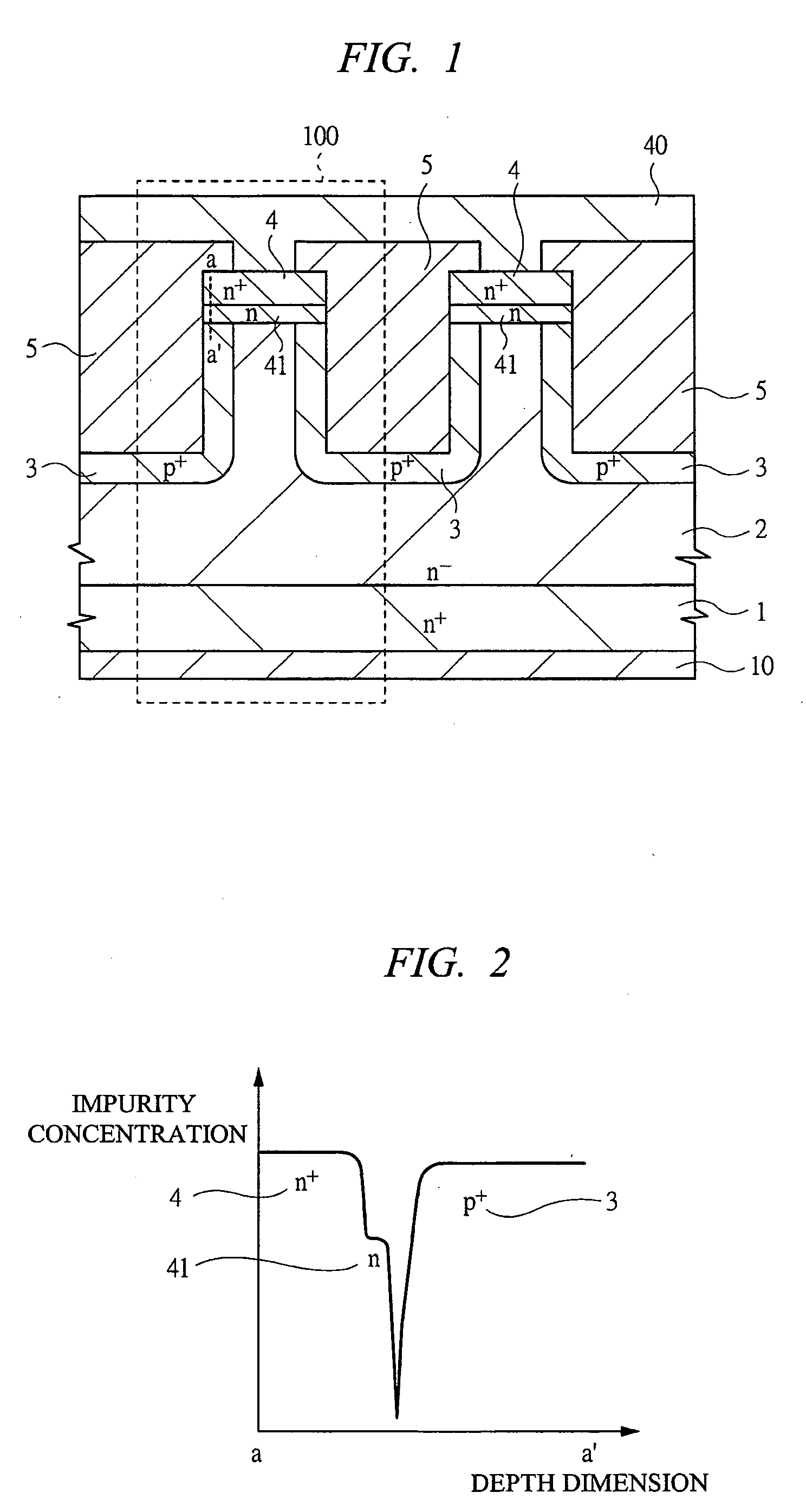

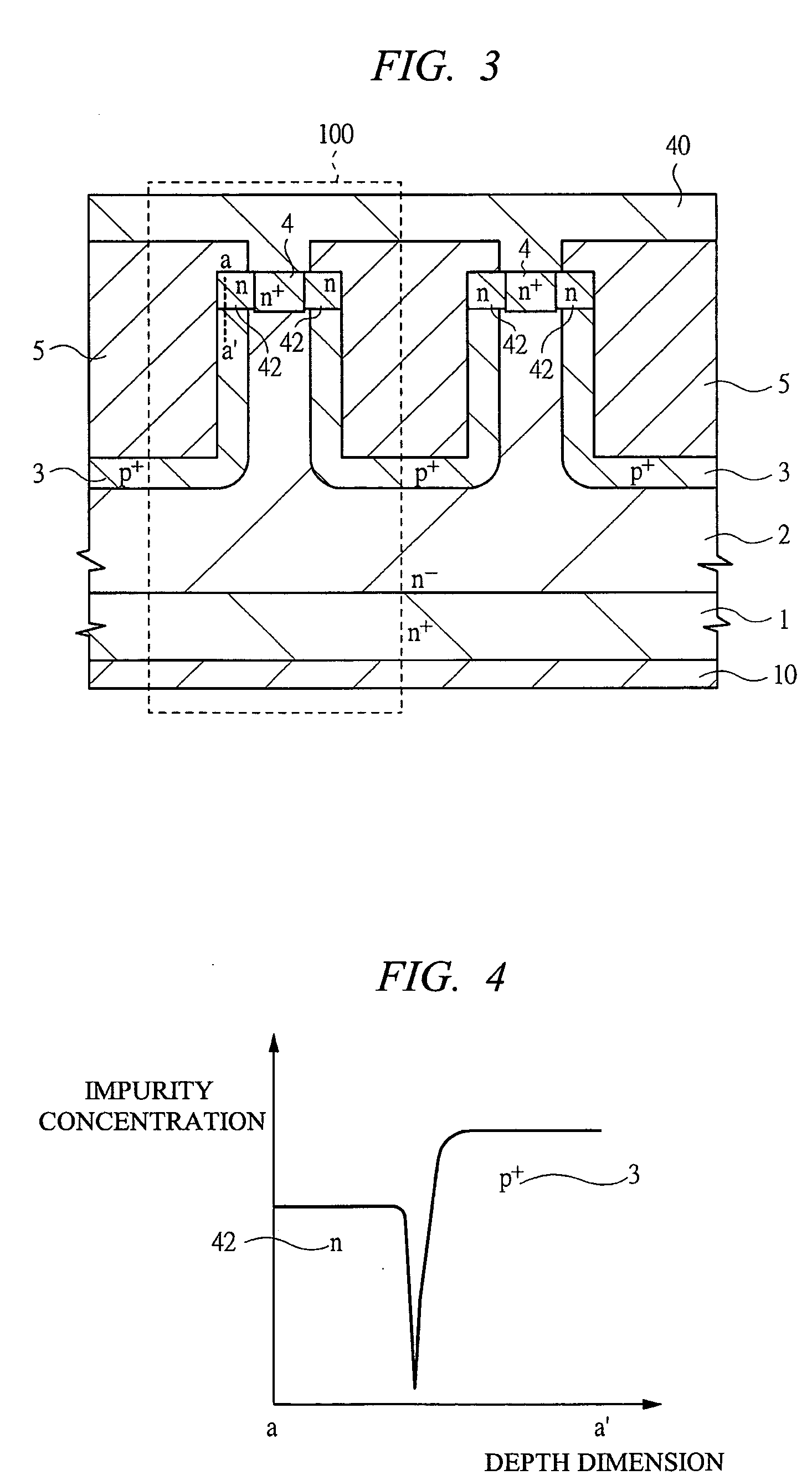

Normally off JFET

ActiveUS20050173726A1Reduce concentrationSimple processTransistorSemiconductor/solid-state device manufacturingJFETGate voltage

A normally off JFET is formed by the implantation of a P base; and a shallower P island atop the P base, forming a narrow lateral conduction channel between the two and a shallow gate implant in the device top surface which forms a second lateral conduction channel with the island. The two channels are each less than 0.5 microns thick and have an impurity concentration such that the channels are depleted at zero gate voltage and are turned on when the gate is forward biased. The gate surrounds a source implant region and a remote drain is provided which is connected to the top surface of the device for a lateral JFET or the bottom of the device for a vertical conduction JFET.

Owner:INFINEON TECH AMERICAS CORP

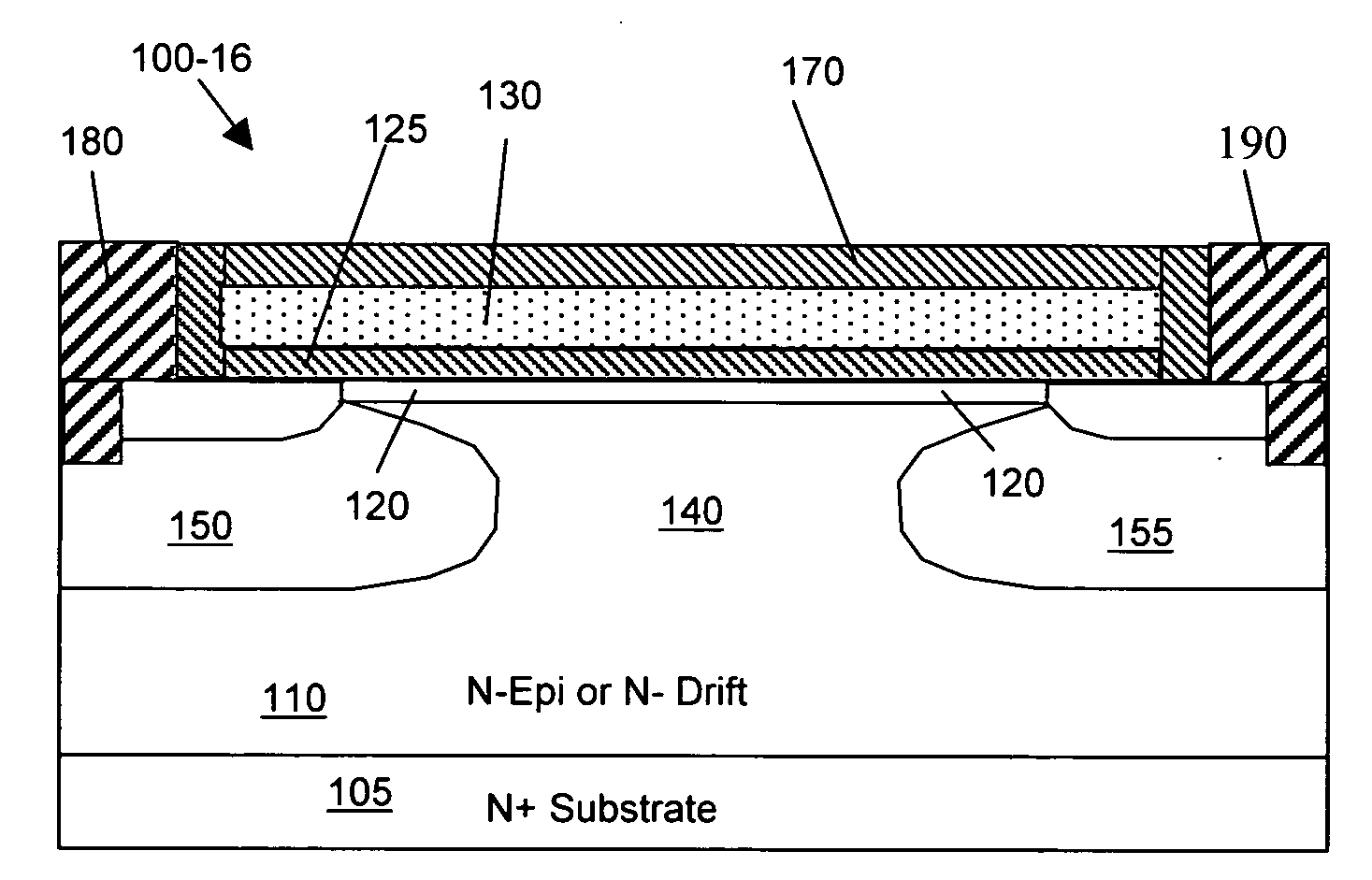

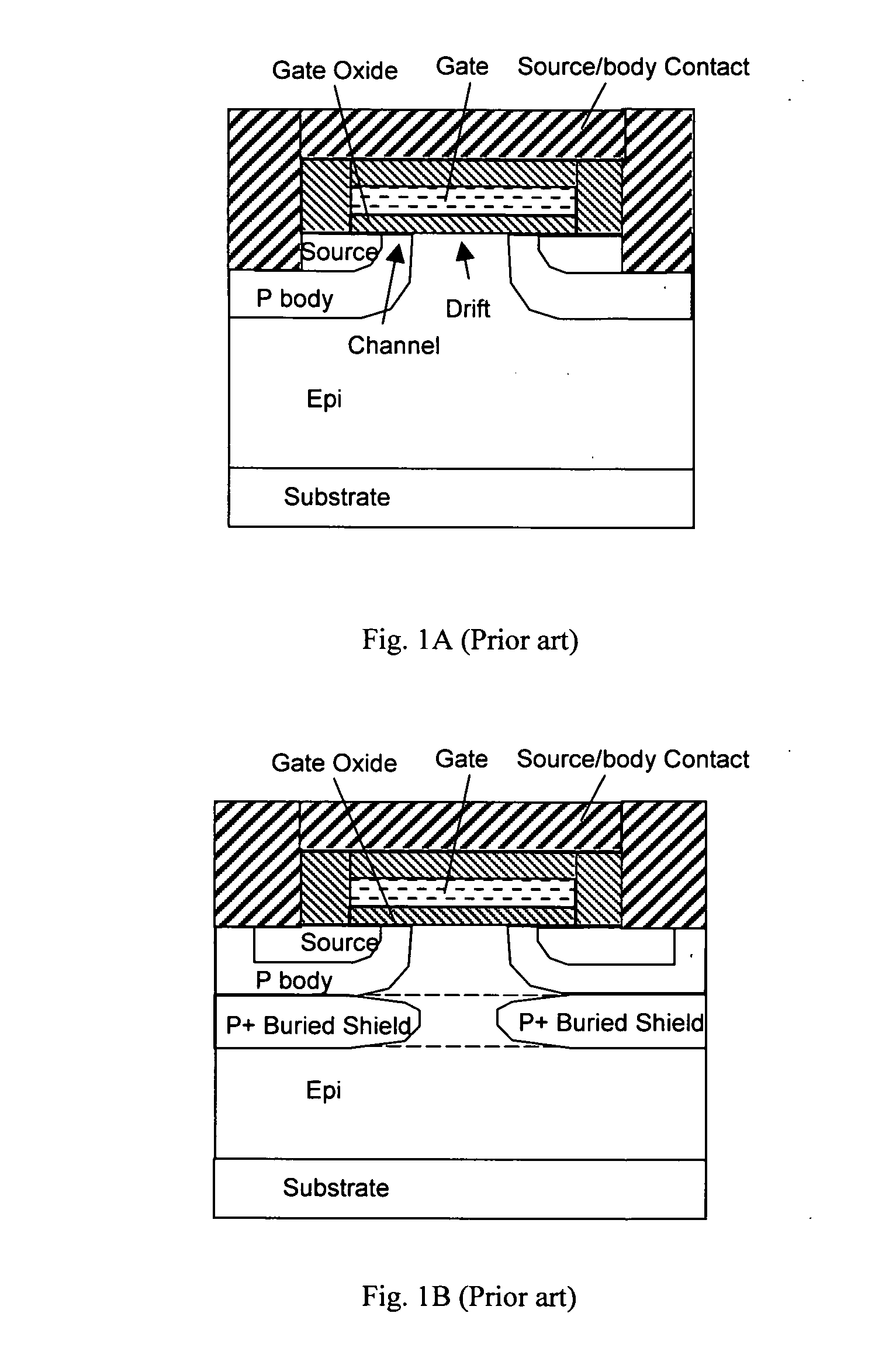

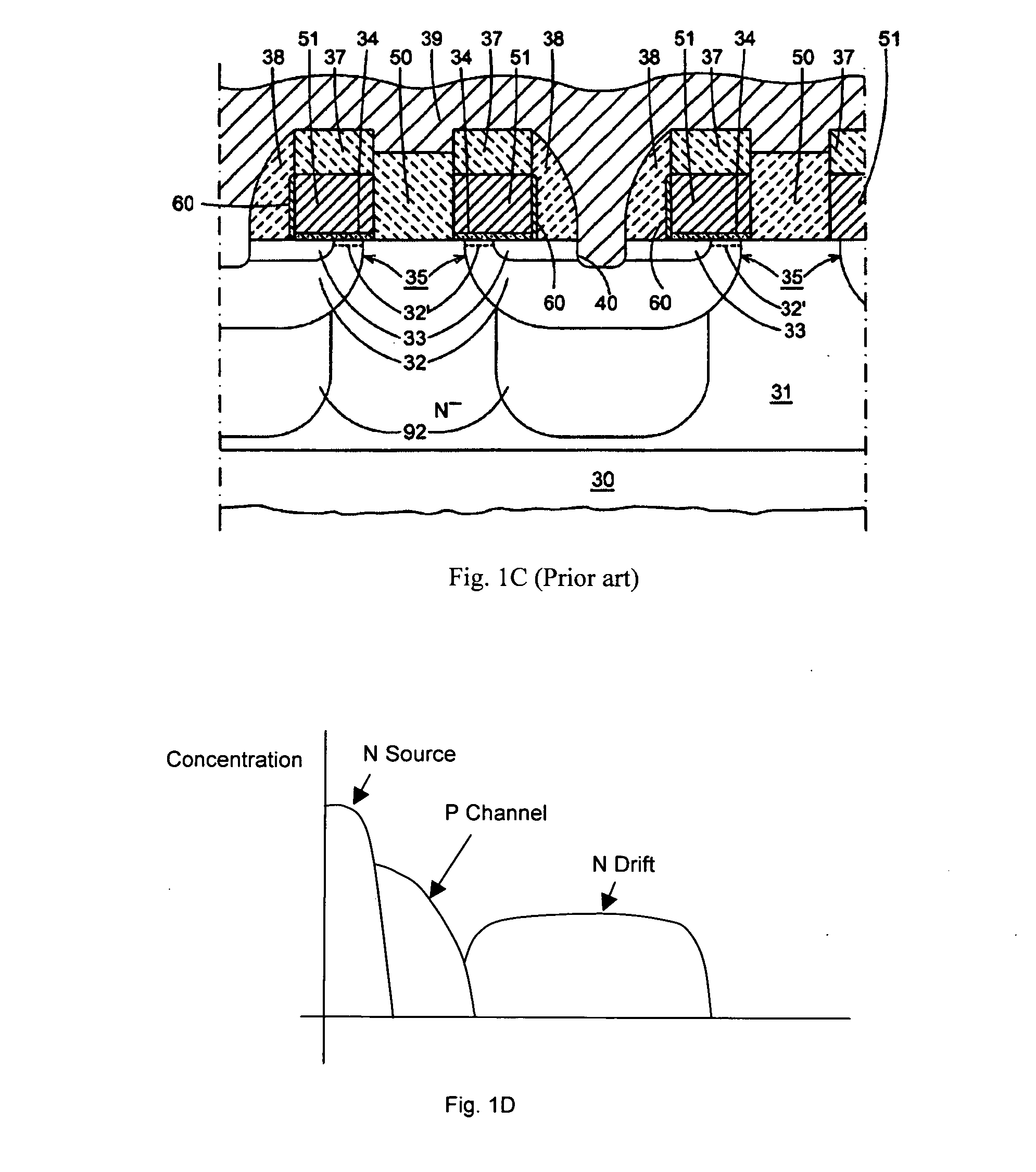

Planar split-gate high-performance MOSFET structure and manufacturing method

ActiveUS20070278571A1Unified controlIncrease the doping concentrationTransistorSemiconductor/solid-state device manufacturingMOSFETDopant

This invention discloses an improved semiconductor power device includes a plurality of power transistor cells wherein each cell further includes a planar gate padded by a gate oxide layer disposed on top of a drift layer constituting an upper layer of a semiconductor substrate wherein the planar gate further constituting a split gate including a gap opened in a gate layer whereby the a total surface area of the gate is reduced. The transistor cell further includes a JFET (junction field effect transistor) diffusion region disposed in the drift layer below the gap of the gate layer wherein the JFET diffusion region having a higher dopant concentration than the drift region for reducing a channel resistance of the semiconductor power device. The transistor cell further includes a shallow surface doped regions disposed near a top surface of the drift layer under the gate adjacent to the JFET diffusion region wherein the shallow surface doped region having a dopant concentration lower than the JFET diffusion region and higher than the drift layer.

Owner:ALPHA & OMEGA SEMICON LTD

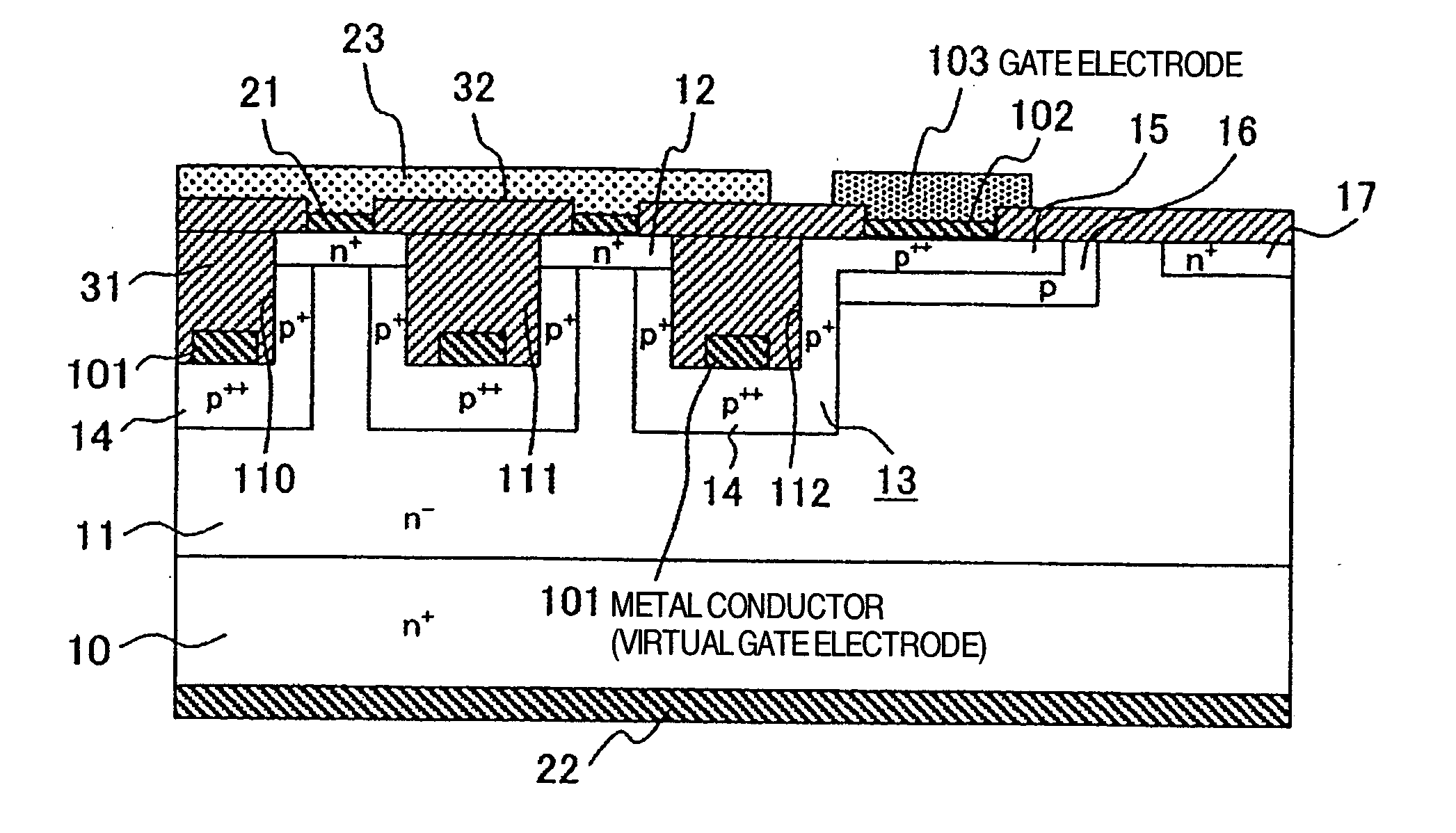

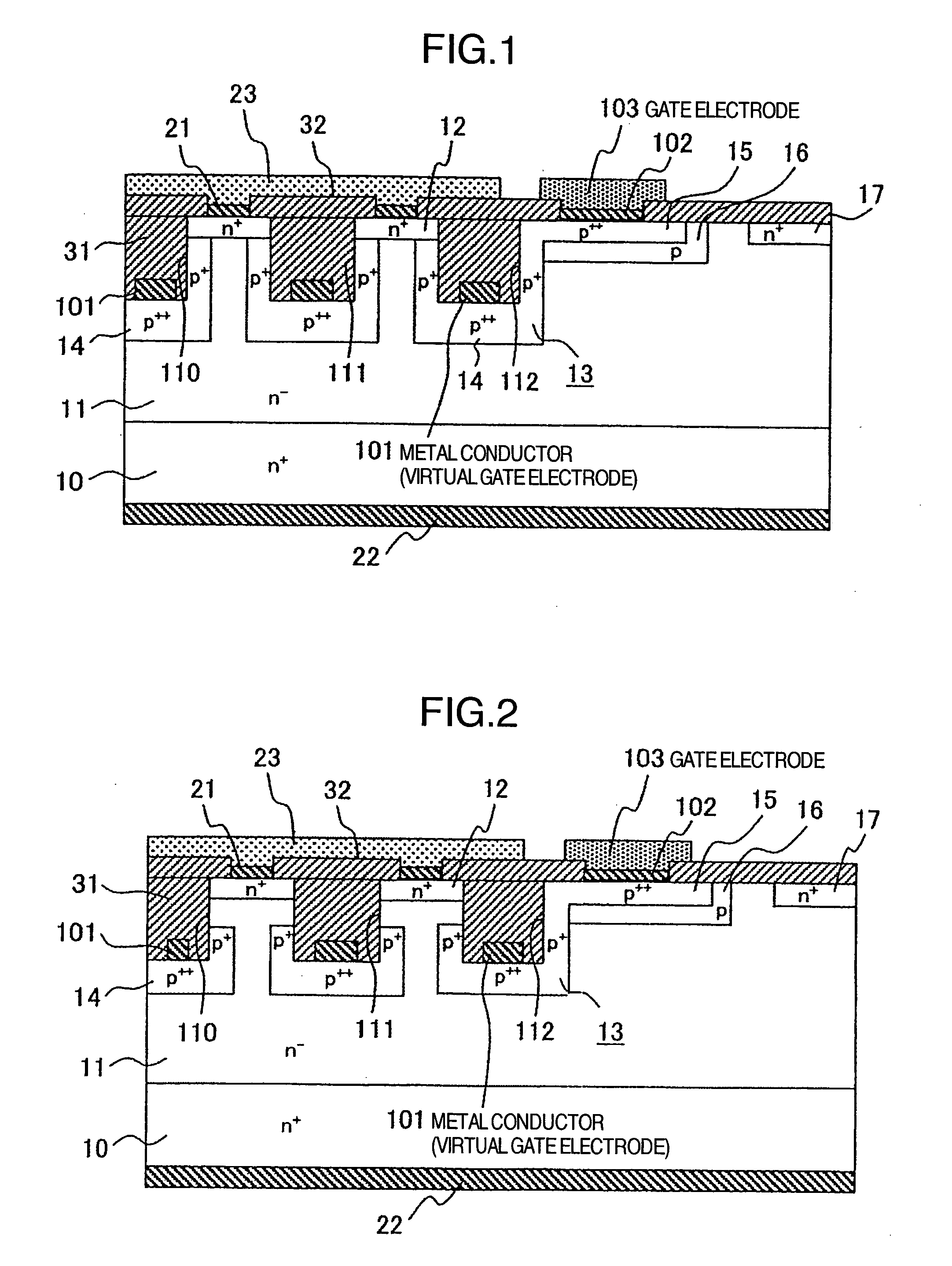

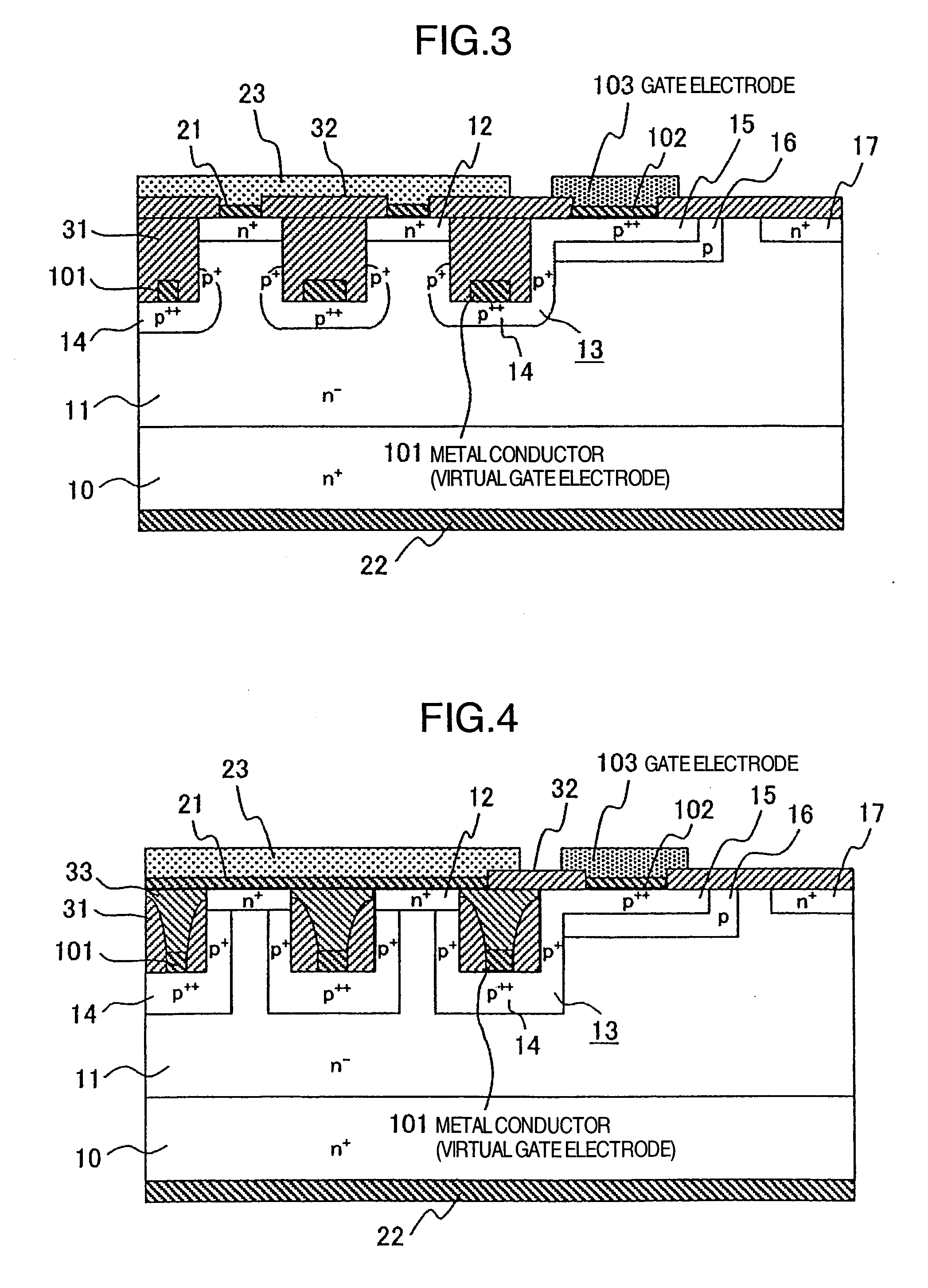

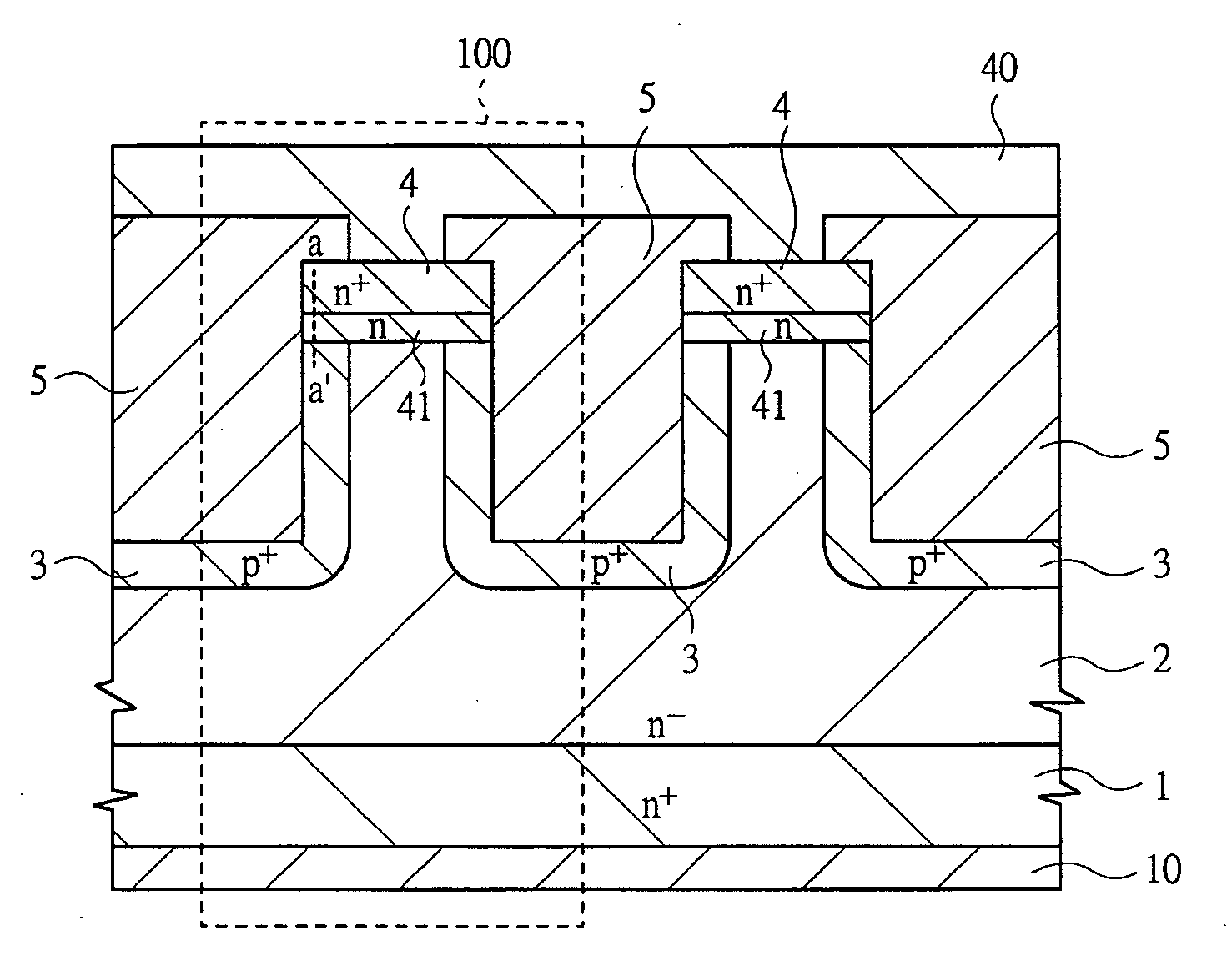

Semiconductor devices

InactiveUS20060060884A1Increase current densityLower gate resistanceThyristorElectrical conductorDevice material

A silicon carbide semiconductor device such as JFET, SIT and the like is provided for accomplishing a reduction in on-resistance and high-speed switching operations. In the JFET or SIT which turns on / off a current with a depletion layer extending in a channel between a gate region formed along trench grooves, a gate contact layer and a gate electrode, which can be supplied with voltages from the outside, are formed on one surface of a semiconductor substrate or on the bottom of the trench groove. A metal conductor (virtual gate electrode) is formed in ohmic contact with a p++ contact layer of the gate region on the bottom of the trench grooves independently of the gate electrode. The virtual gate electrode is electrically isolated from the gate electrode and an external wire.

Owner:DENSO CORP +1

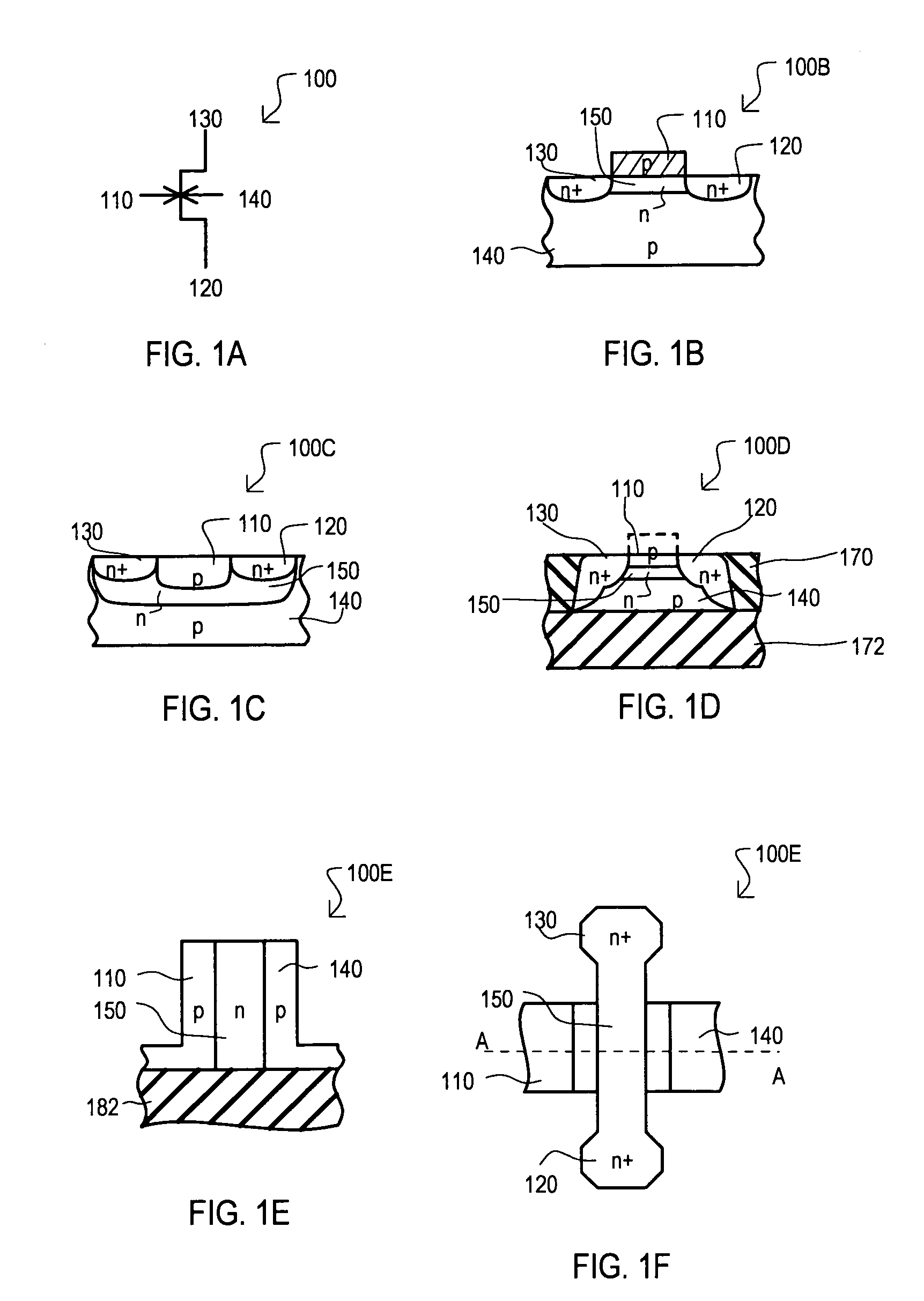

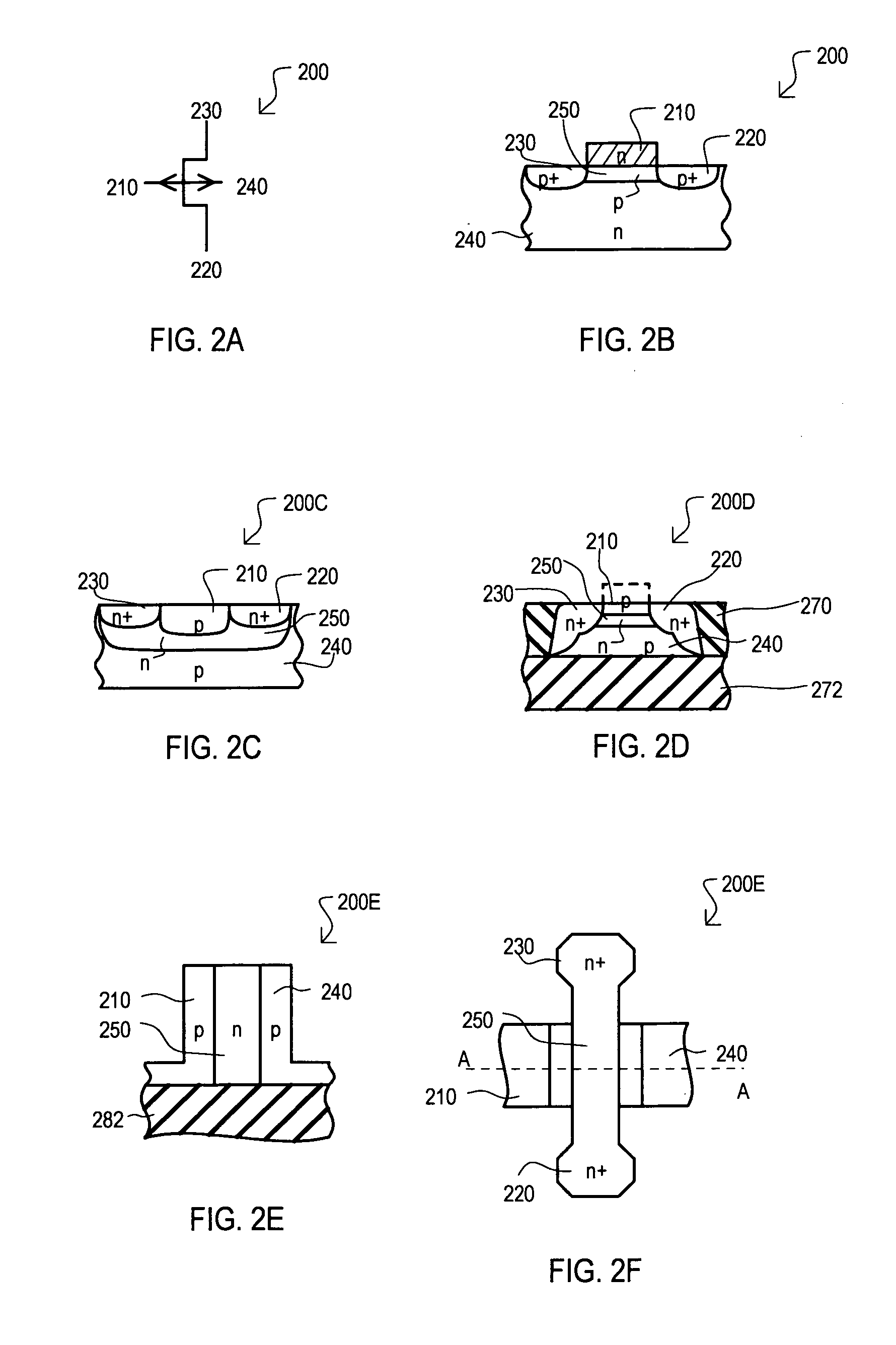

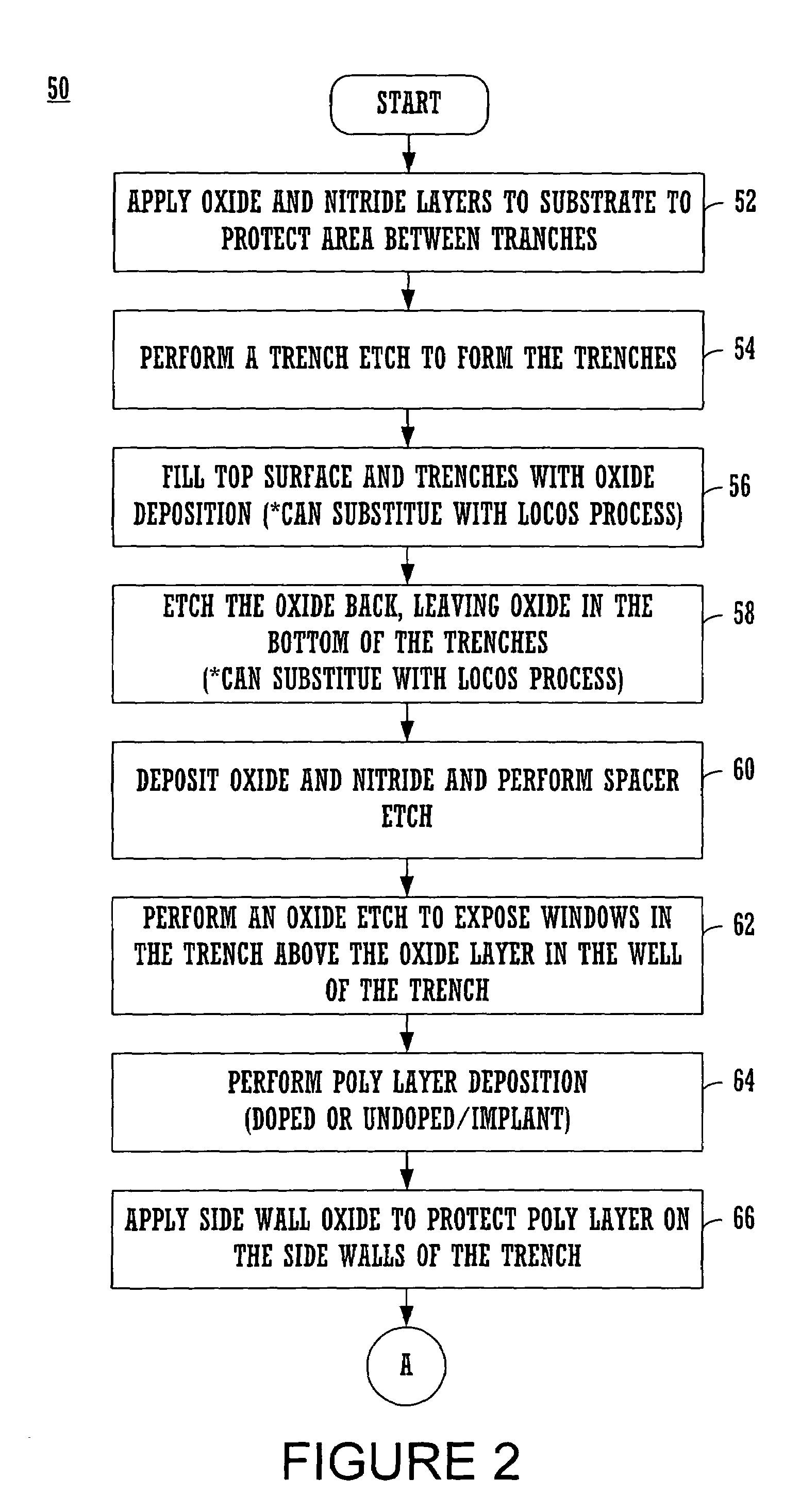

JFET and MESFET structures for low voltage high current and high frequency applications

InactiveUS7045397B1Easy to controlLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceLow voltage

JFET and MESFET structures, and processes of making same, for low voltage, high current and high frequency applications. The structures may be used in normally-on (e.g., depletion mode) or normally-off modes. The structures include an oxide layer positioned under the gate region which effectively reduces the junction capacitance (gate to drain) of the structure. For normally off modes, the structures reduce gate current at Vg in forward bias. In one embodiment, a silicide is positioned in part of the gate to reduce gate resistance. The structures are also characterized in that they have a thin gate due to the dipping of the spacer oxide, which can be below 1000 angstroms and this results in fast switching speeds for high frequency applications.

Owner:POWER INTEGRATIONS INC

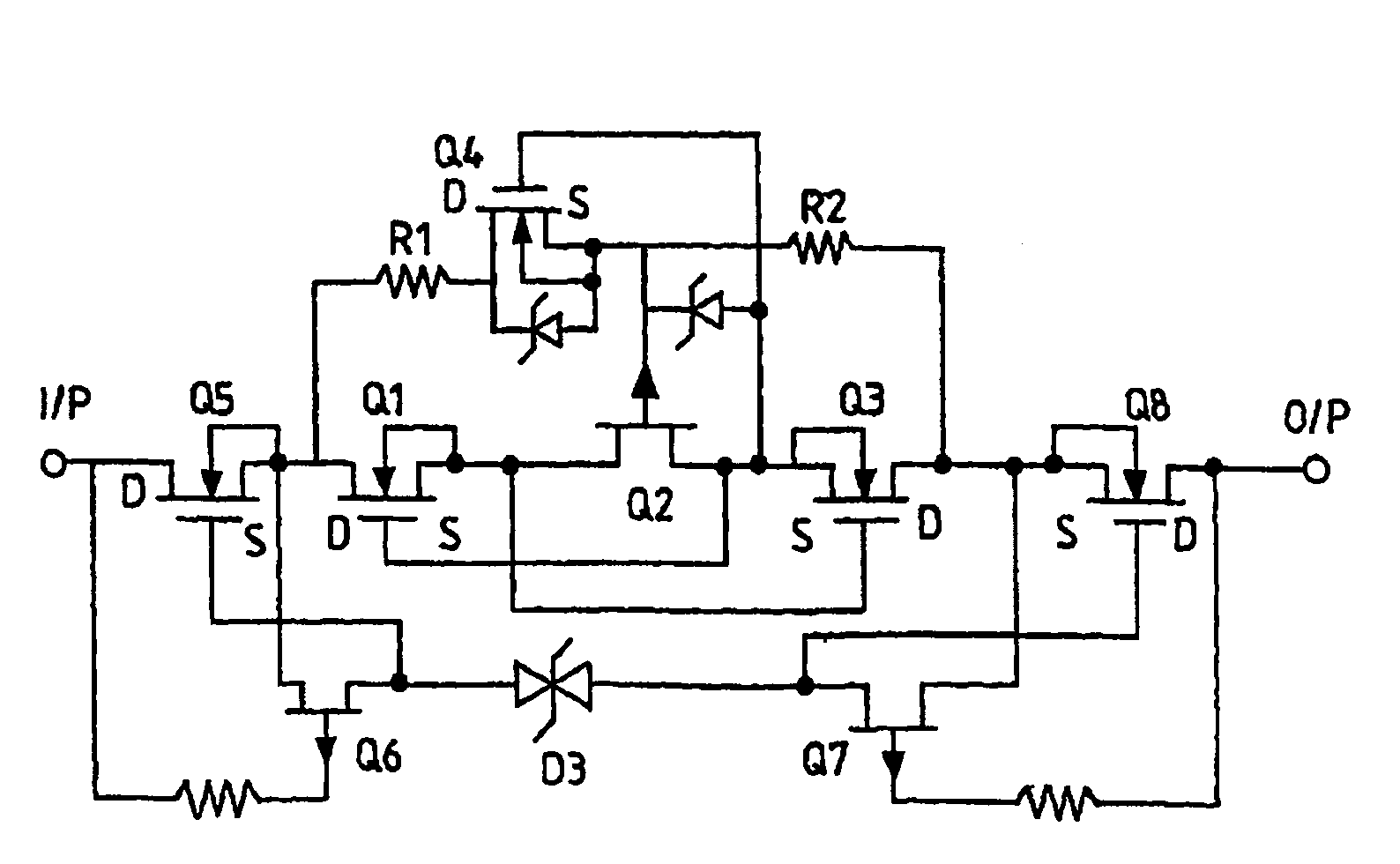

Protection device

A protection device is enclosed. The device has a first MOSFET (Q 10), a second MOSFET (Q 11) and a third JFET (Q 12) with their conductive paths in series with the JFET (Q 12) being located between the MOSFETS (Q 10, Q 11). The source of the first MOSFET (Q 10) is connected to the gate of the second MOSFET (Q 11) and the source of the second MOSFET (Q 11) is connected to the gate of the first MOSFET (Q 10). The MOSFETS (Q 10, Q 11) and JFET (Q 12) together form a variable resistance circuit block connectable between an input and an output The gate of the JFET (Q 12) being coupled to the input and the output by respective current sources.

Owner:BOURNS INC

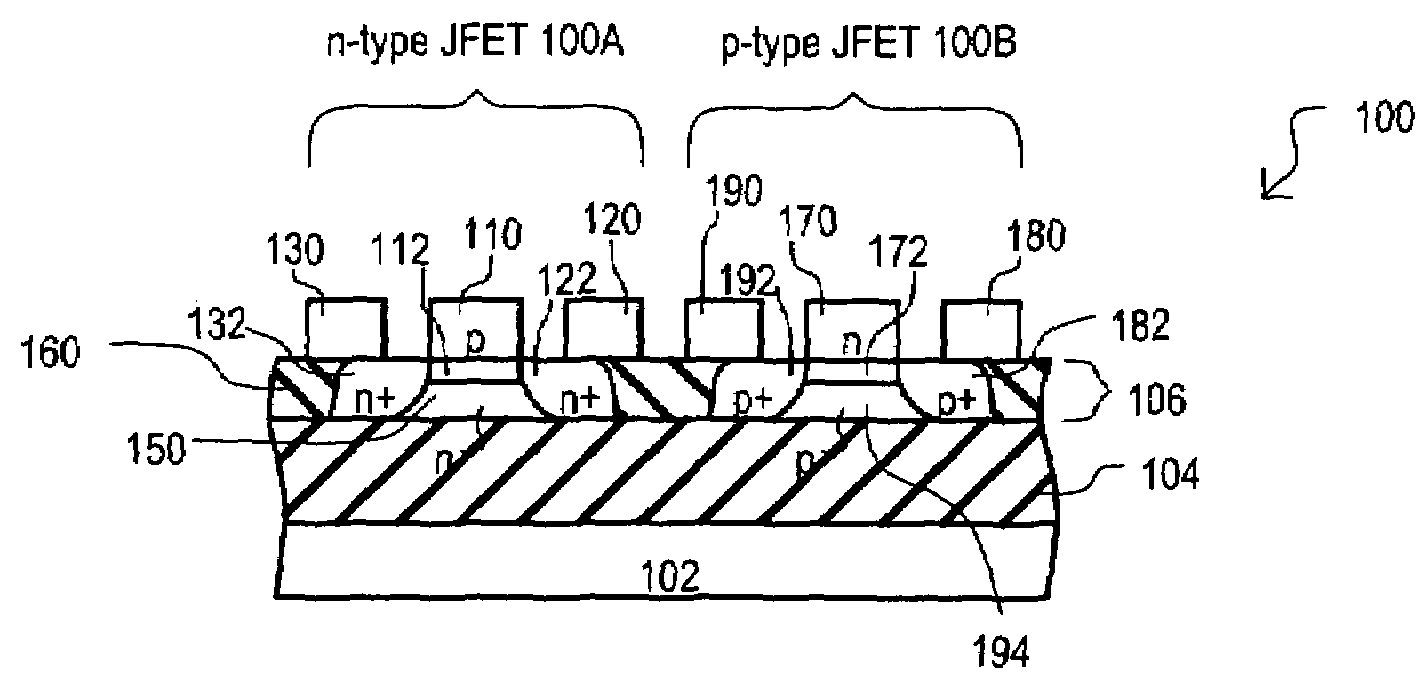

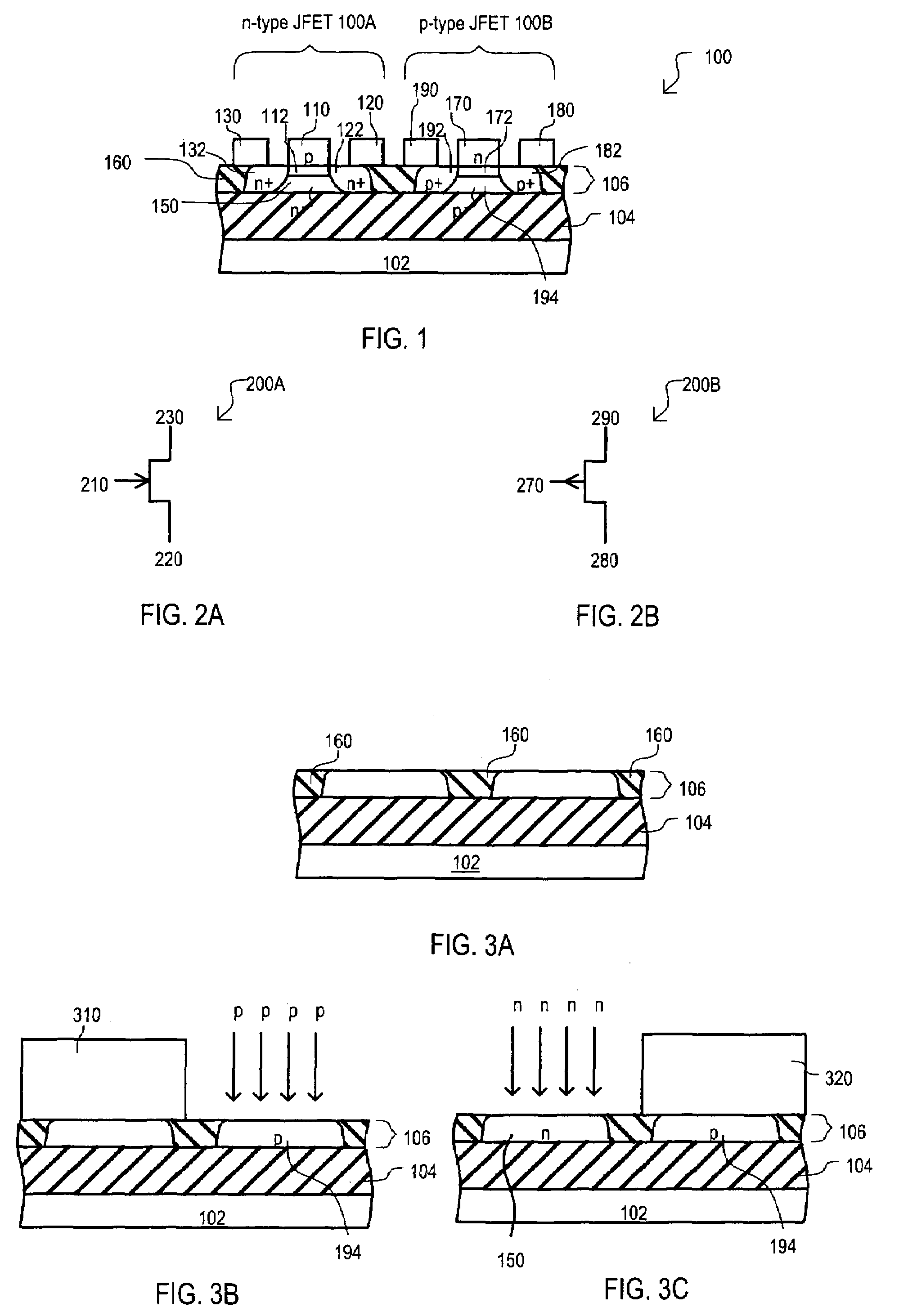

Silicon-on-insulator (SOI) junction field effect transistor and method of manufacture

A semiconductor device including complementary junction field effect transistors (JFETS) manufactured on a silicon on insulator (SOI) wafer is disclosed. A p-type JFET includes a control gate formed from n-type polysilicon and an n-type JFET includes a control gate formed from p-type polysilicon. The complementary JFETs may include four terminal JFETs having a back gate formed below a channel region. The back gate may be electrically connected to a control gate formed above a channel region via a cut region in an isolation structure. Furthermore, the complementary JFETs may be formed on strained silicon formed on a silicon germanium (SiGe) or silicon germanium carbon (SiGeC) layer, or the like.

Owner:DSM SOLUTIONS

Switching semiconductor devices and fabrication process

InactiveUS20070096145A1Avoid misuseImprove breakdown voltageSemiconductor devicesManufacturing technologyDevice material

A switching semiconductor device is provided, in which a negative gate voltage can be applied to the semiconductor device in an OFF state so as to increase a breakdown voltage of the gate junction without impairing a normally-off function of the semiconductor device and the ON-resistance. The switching semiconductor device is fabricated by using a semiconductor substrate with a band gap of 2.0 eV or more. In a JFET structure where a p+ type gate region and an n type source region are in contact so that a negative gate voltage can be applied, the p+ type gate region and an n+ type source region with a high impurity concentration are disposed with interposing an n type source region with an impurity concentration lower than that of the p+ type gate region and higher than that of a drift region of the JFET therebetween.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com