Semiconductor device

a technology of semiconductors and devices, applied in the direction of semiconductor devices, basic electric elements, electrical equipment, etc., can solve the problems of reducing the breakdown voltage of the device, increasing the on-state resistance ron of the device,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0036] (1) First Embodiment

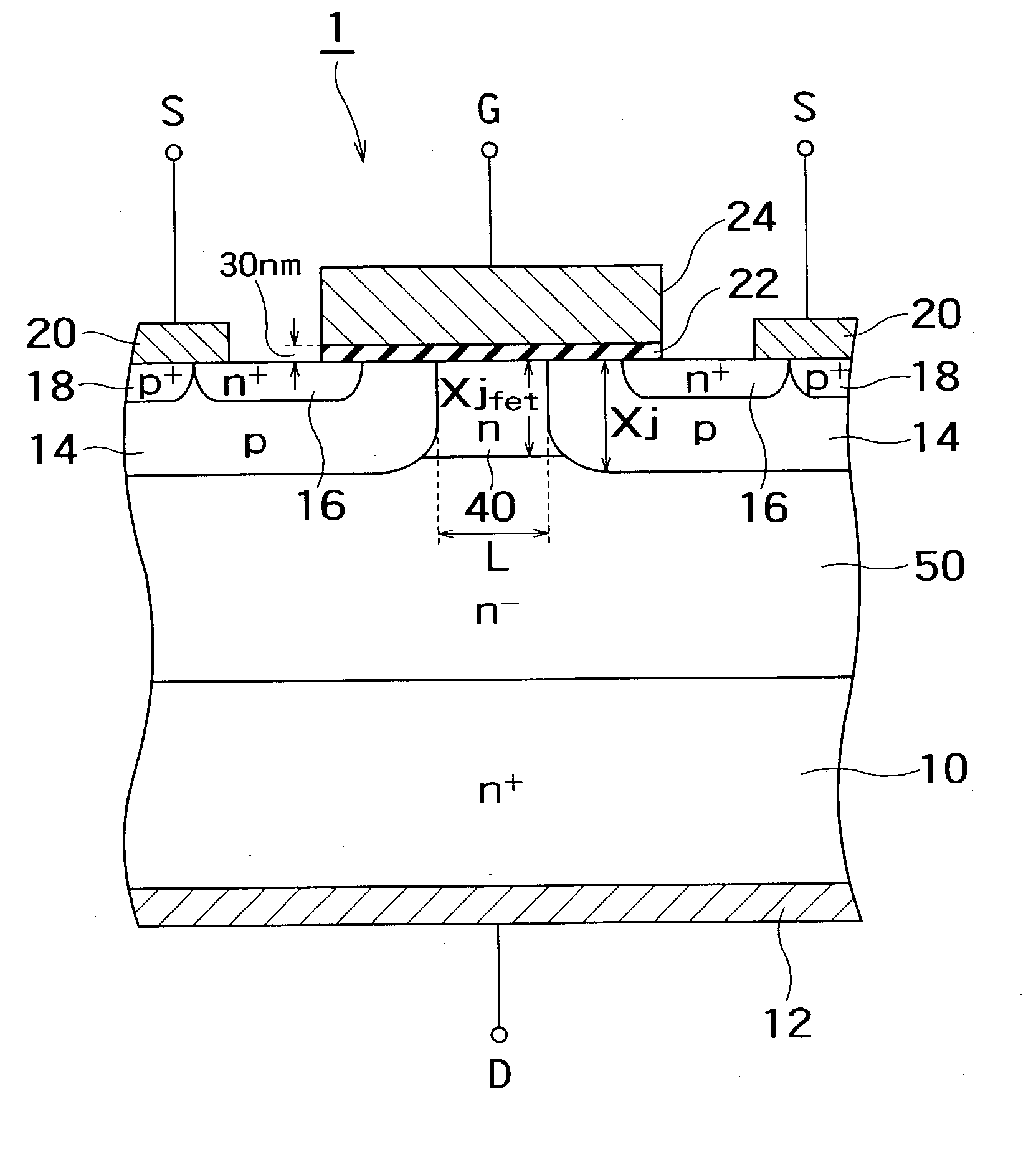

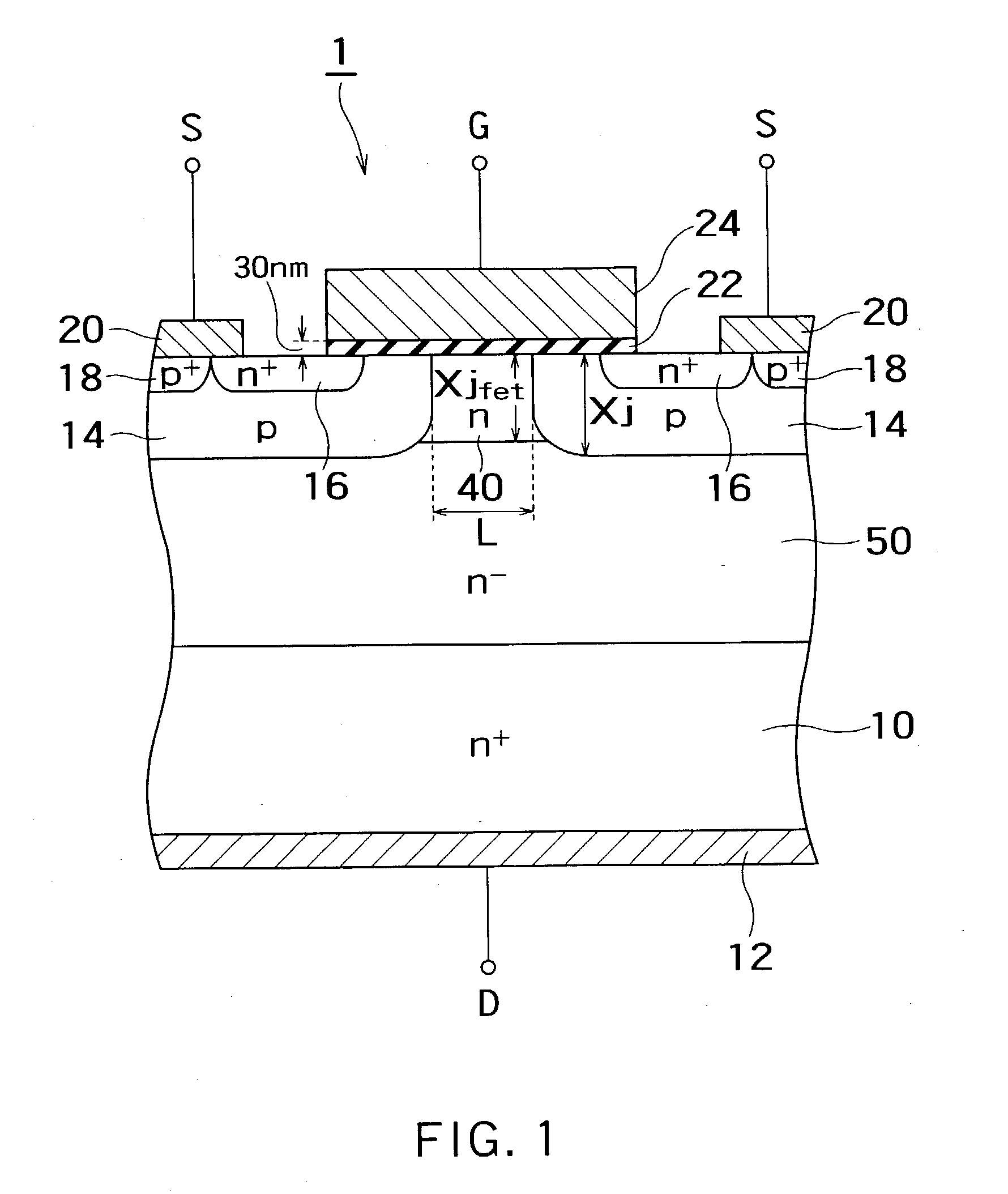

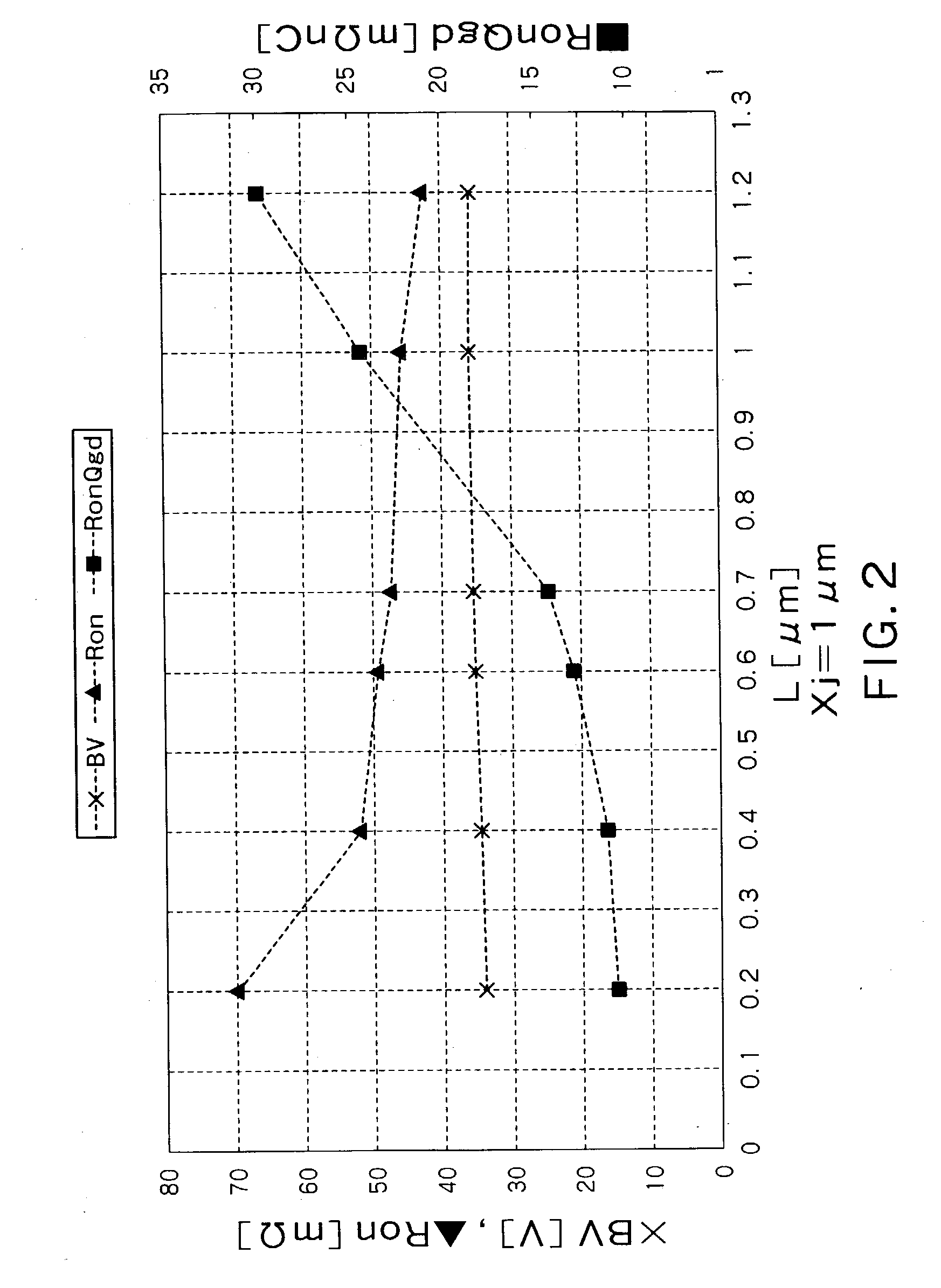

[0037] FIG. 1 is a schematic cross section showing a first embodiment of a semiconductor device according to the invention. The semiconductor device of the present embodiment is characterized in that an Njfet region 40 is formed in a narrow width at a high concentration. The structure of the semiconductor device of the embodiment will be described in more detail hereinbelow.

[0038] A power MOSFET 1 shown in FIG. 1 is a power MOSFET of a vertical type to which the invention is applied, and includes an n.sup.+ type low-resistance semiconductor substrate 10, a drain electrode 12, an n.sup.- type high-resistance epitaxial layer 50, a p type base layer 14, an n.sup.+ type source layer 16, the Njfet region 40, a gate electrode 24, and a source electrode 20.

[0039] The drain electrode 12 is provided on one of the surfaces (under face in FIG. 1) of the n.sup.+ type low-resistance semiconductor substrate 10, and the n.sup.- type high-resistance epitaxial layer 50 is ...

second embodiment

[0045] (2) Second Embodiment

[0046] FIG. 4 is a schematic cross section showing a second embodiment of a semiconductor device according to the invention. As obviously understood from comparison with FIG. 1, a power MOSFET 3 of the second embodiment is characterized in that a gate insulating film 23 is formed so as to be thicker in a region facing the Njfet region 40 as well as in that the Njfet region 40 is formed in narrow width and at high concentration. More specifically, a portion 23a of the gate insulating film 23 facing the Njfet region 40 has a thickness of about 90 nm whereas the other portion of the gate insulating film 23 is formed to have a thickness of about 30 nm. By the configuration, in the region facing the Njfet region 40, a gate electrode 25 can be further isolated from the Njfet region 40.

[0047] Since the Njfet region 40 is formed in narrow width and at high concentration, at the time of depleting the Njfet region 40, depletion from the p type base layer 14 becomes...

third embodiment

[0049] (3) Third Embodiment

[0050] FIG. 5 is a schematic cross section showing a third embodiment of a semiconductor device according to the invention. As obviously understood by comparison with FIG. 1, a power MOSFET 5 of the third embodiment is characterized in that a portion facing the Njfet region 40 in the gate electrode 28 is selectively removed.

[0051] By employing the structure in which the gate electrode 28 is divided as described above, the width L of the Njfet region 40 can be further narrowed, so that the gate-drain capacitance Q.sub.gd is further reduced and operation speed of the device is further increased. By implanting n-type impurities using the gate electrode 28 in the divisional structure as a mask, the Njfet region 40 can be formed in a self-aligned manner.

[0052] FIGS. 6 and 7 are diagrams for explaining reduction in the gate-drain capacitance Q.sub.gd according to the third embodiment. FIG. 6 shows electron density in the conventional power MOSFET 100 illustrated...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com