Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7859 results about "High resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

High Resistance is the passive ability to be resistant to attacks by weapons, or magic, or powers of other magical beings. This trait allows users to survive attacks that are otherwise lethal. It also grants users protection against their own powers. This ability is not as powerful as Immunity or Invincibility,...

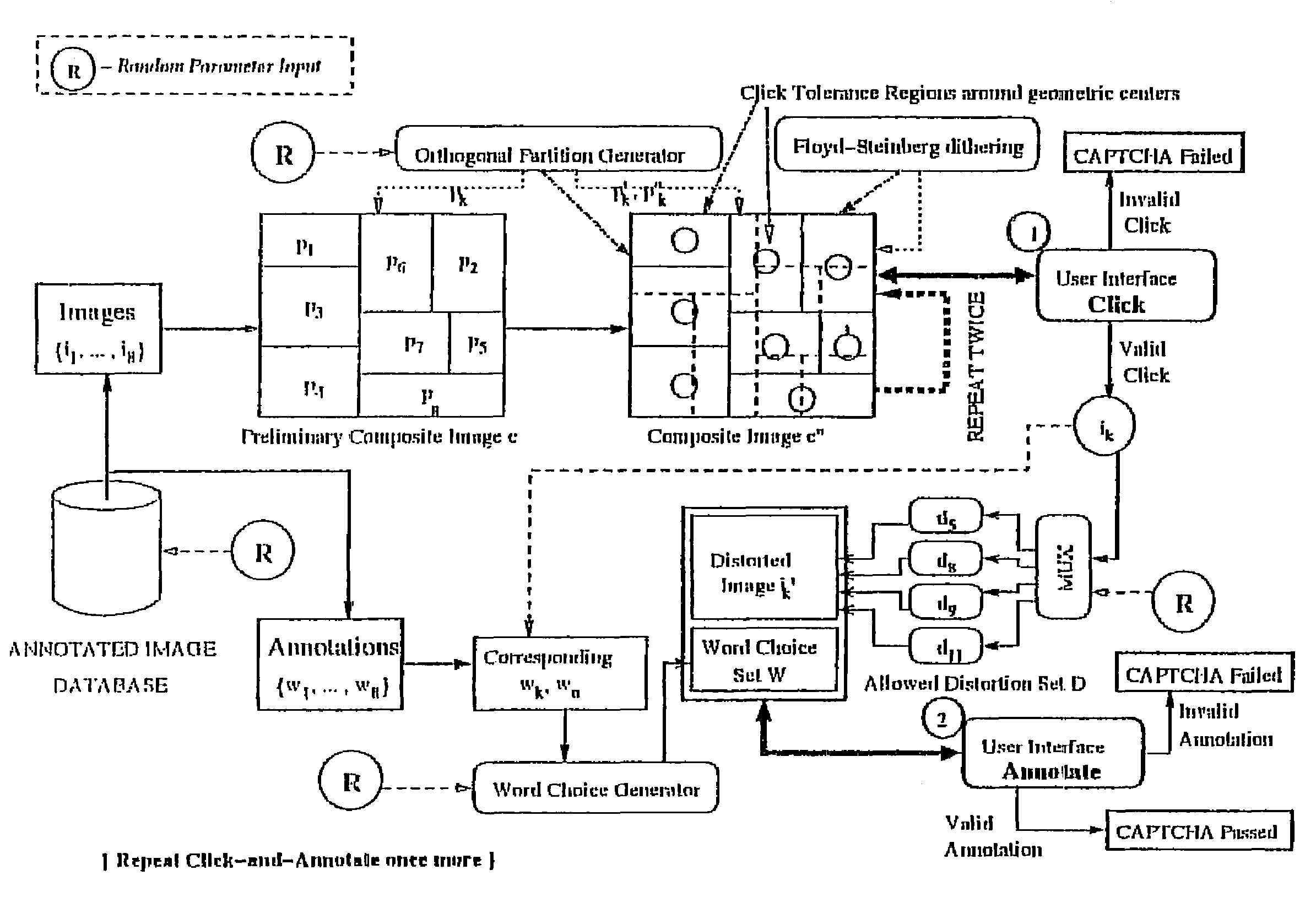

Image-based CAPTCHA generation system

InactiveUS7929805B2Digital data processing detailsUnauthorized memory use protectionHigh resistanceAmbiguity

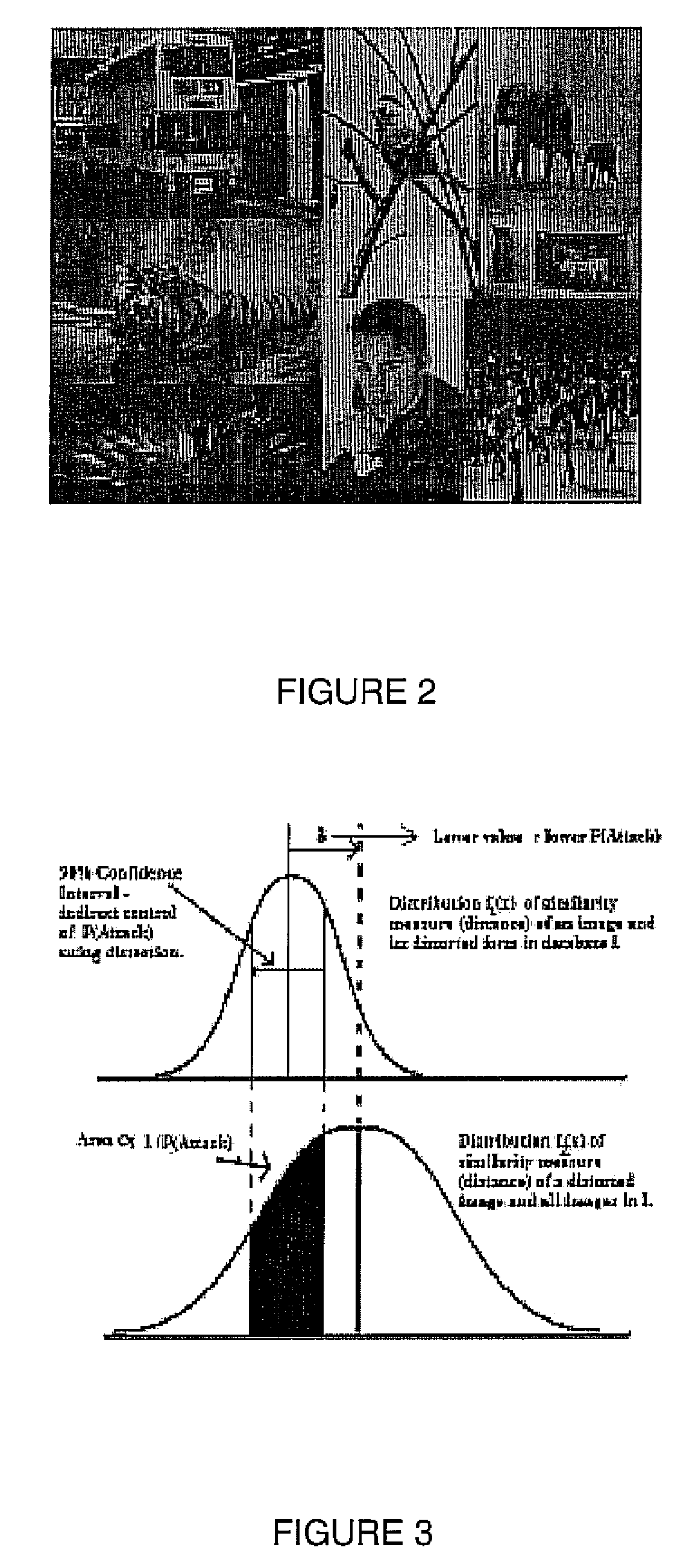

In a system and method for the generation of attack-resistant, user-friendly, image-based CAPTCHAs (Completely Automated Public test to Tell Computers and Humans Apart), controlled distortions are applied to randomly chosen images and presented to a user for annotation from a given list of words. An image is presented that contains multiple connected but independent images with the borders between them distorted or otherwise visually obfuscated in a way that a computer cannot distinguish the borders and a user selects near the center of one of the images. The distortions are performed in a way that satisfies the incongruous requirements of low perceptual degradation and high resistance to attack by content-based image retrieval systems. Word choices are carefully generated to avoid ambiguity as well as to avoid attacks based on the choices themselves.

Owner:PENN STATE RES FOUND

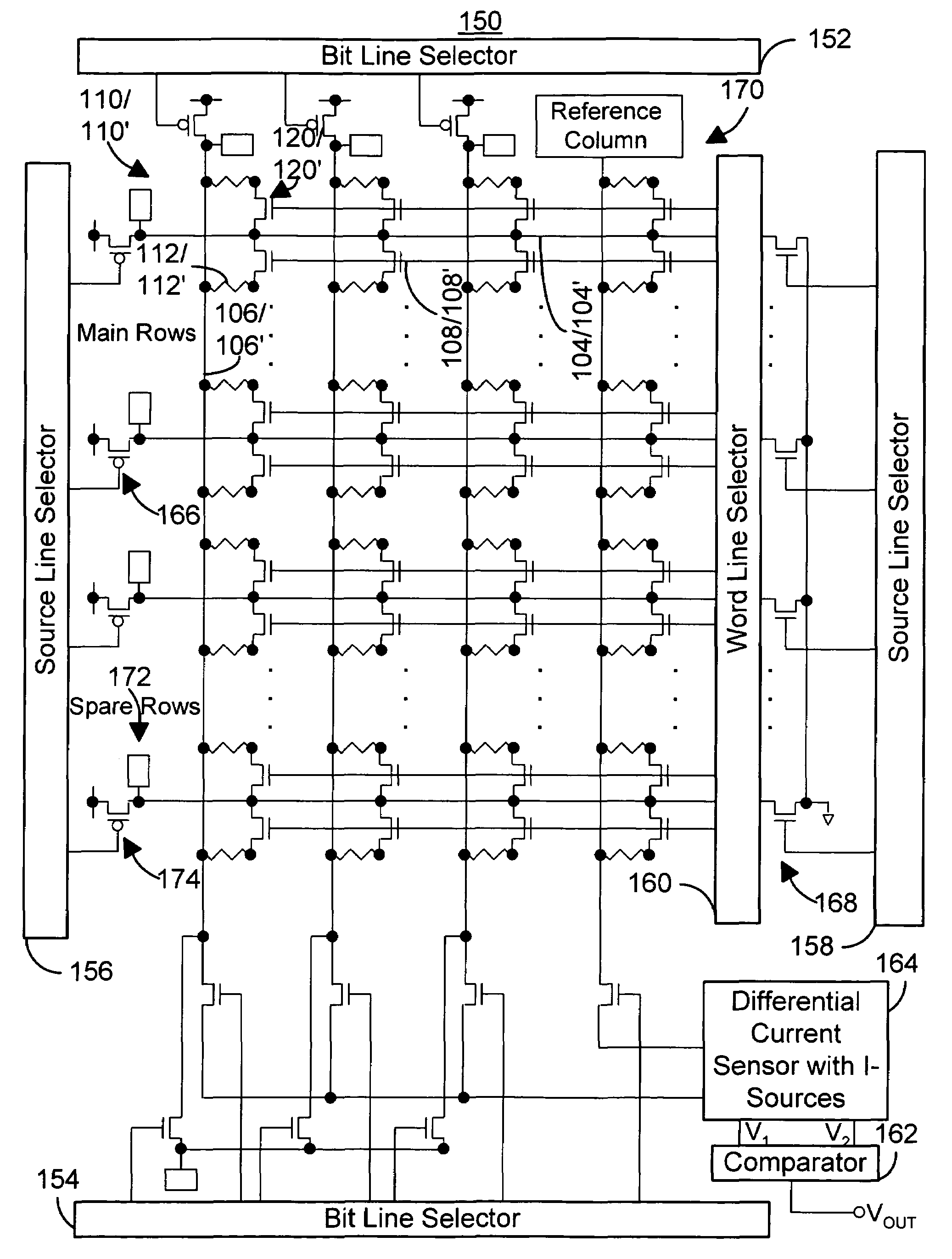

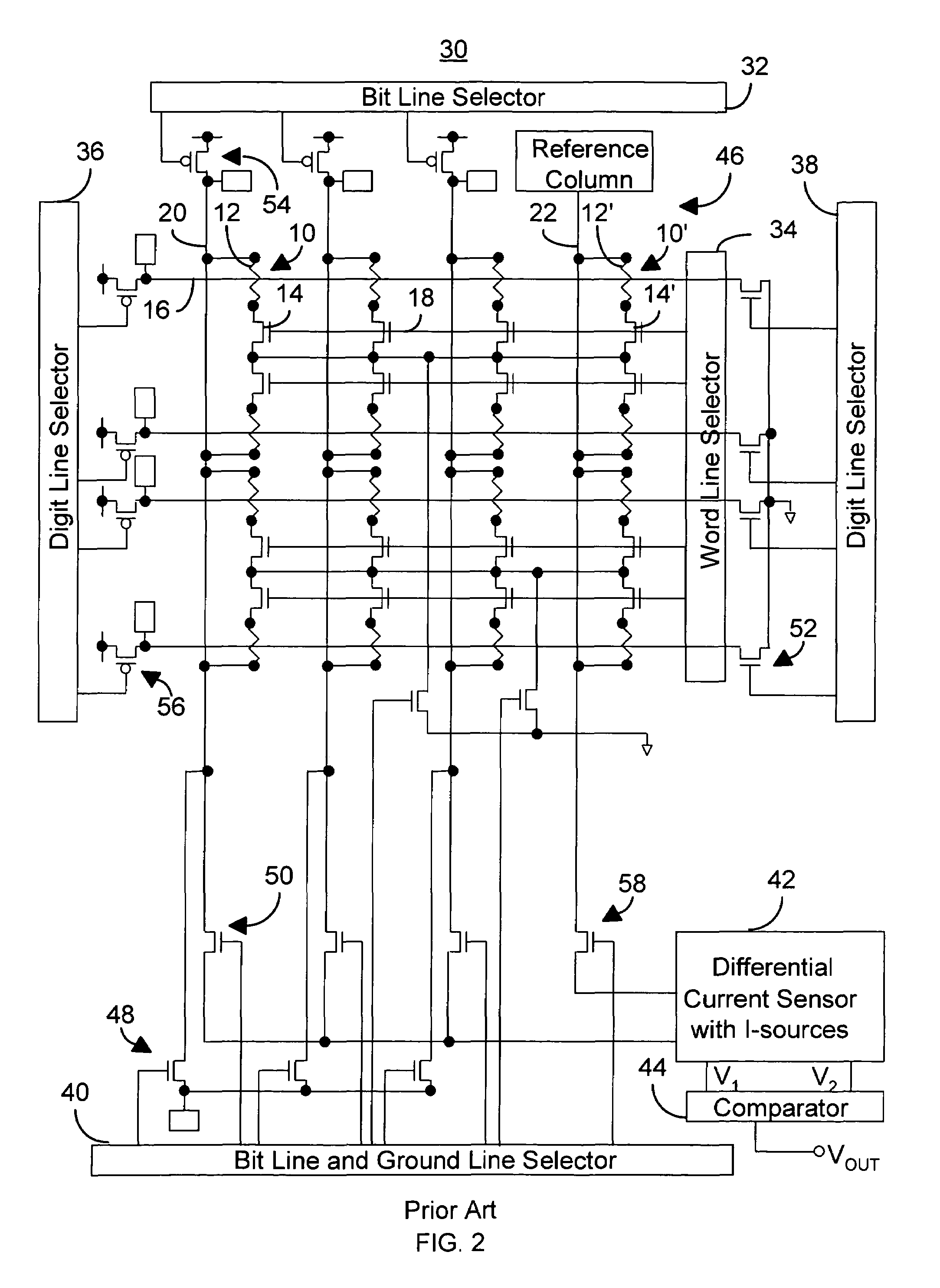

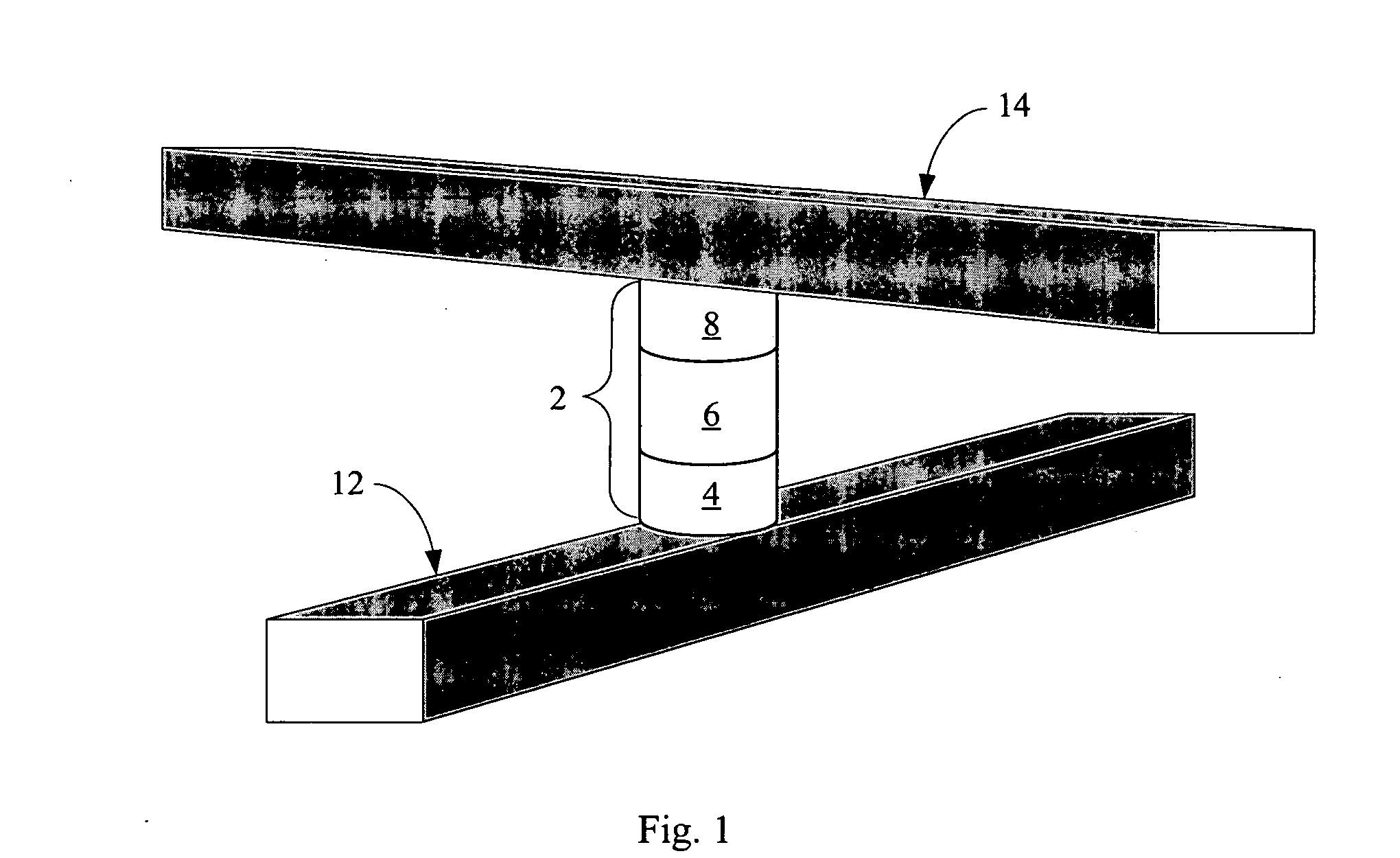

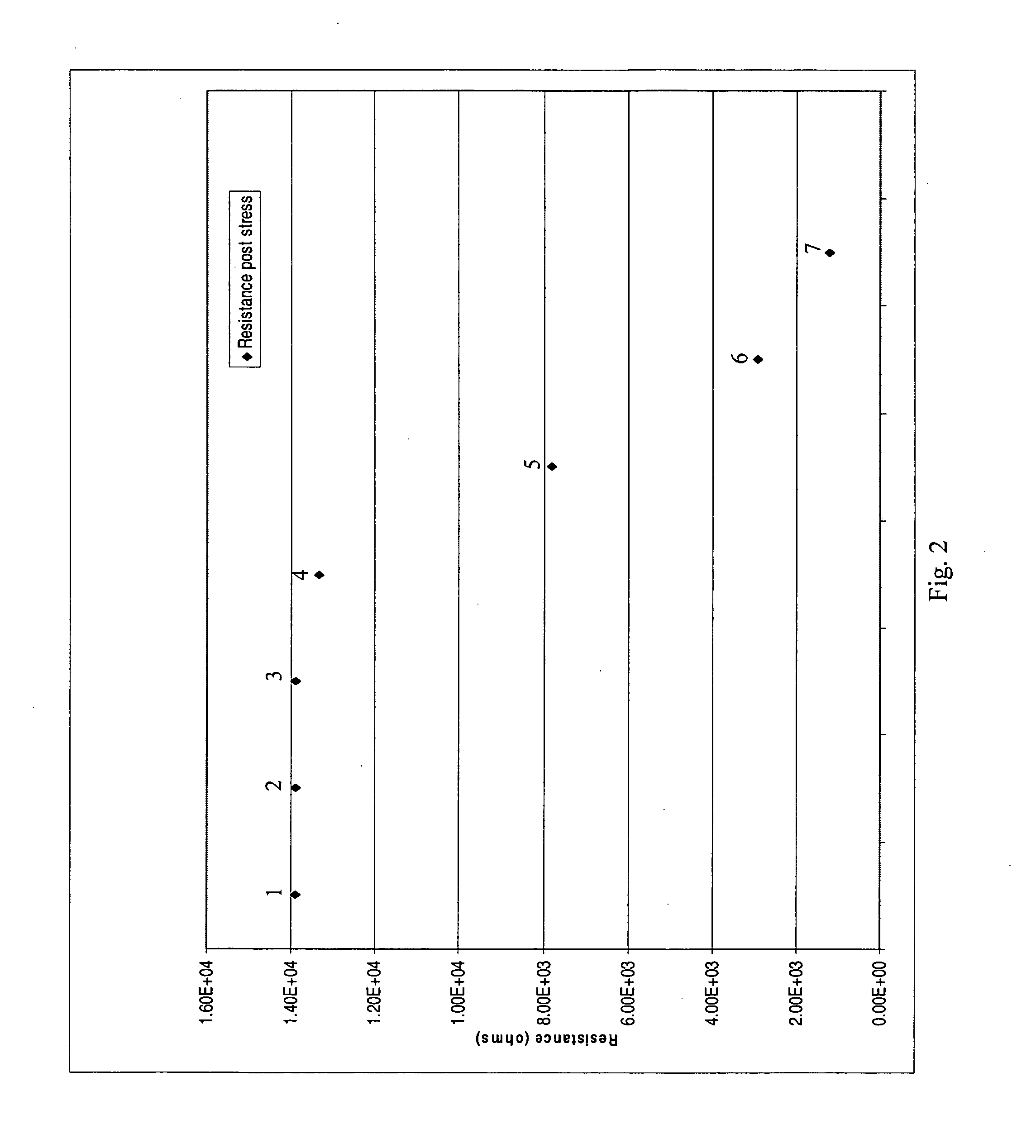

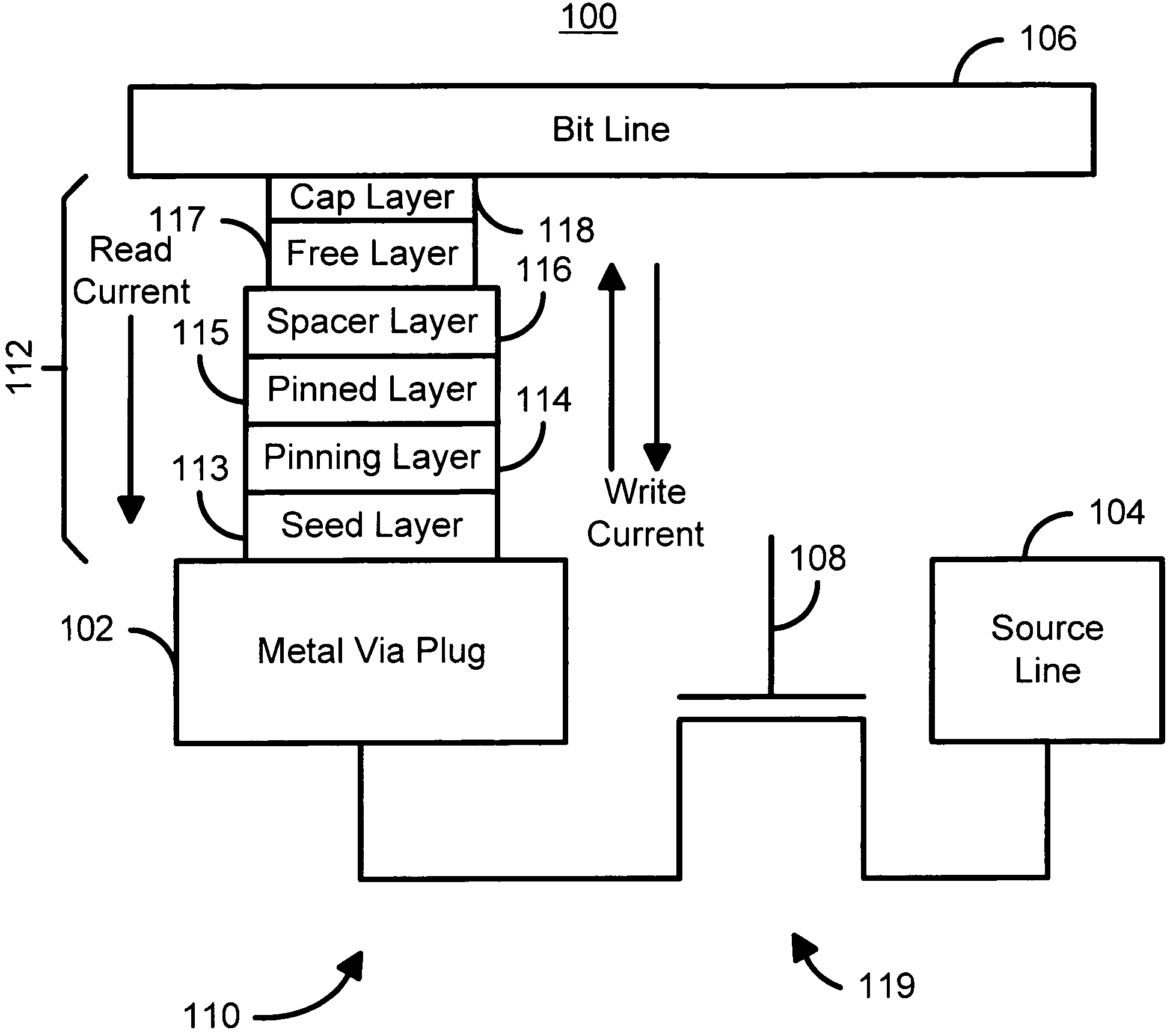

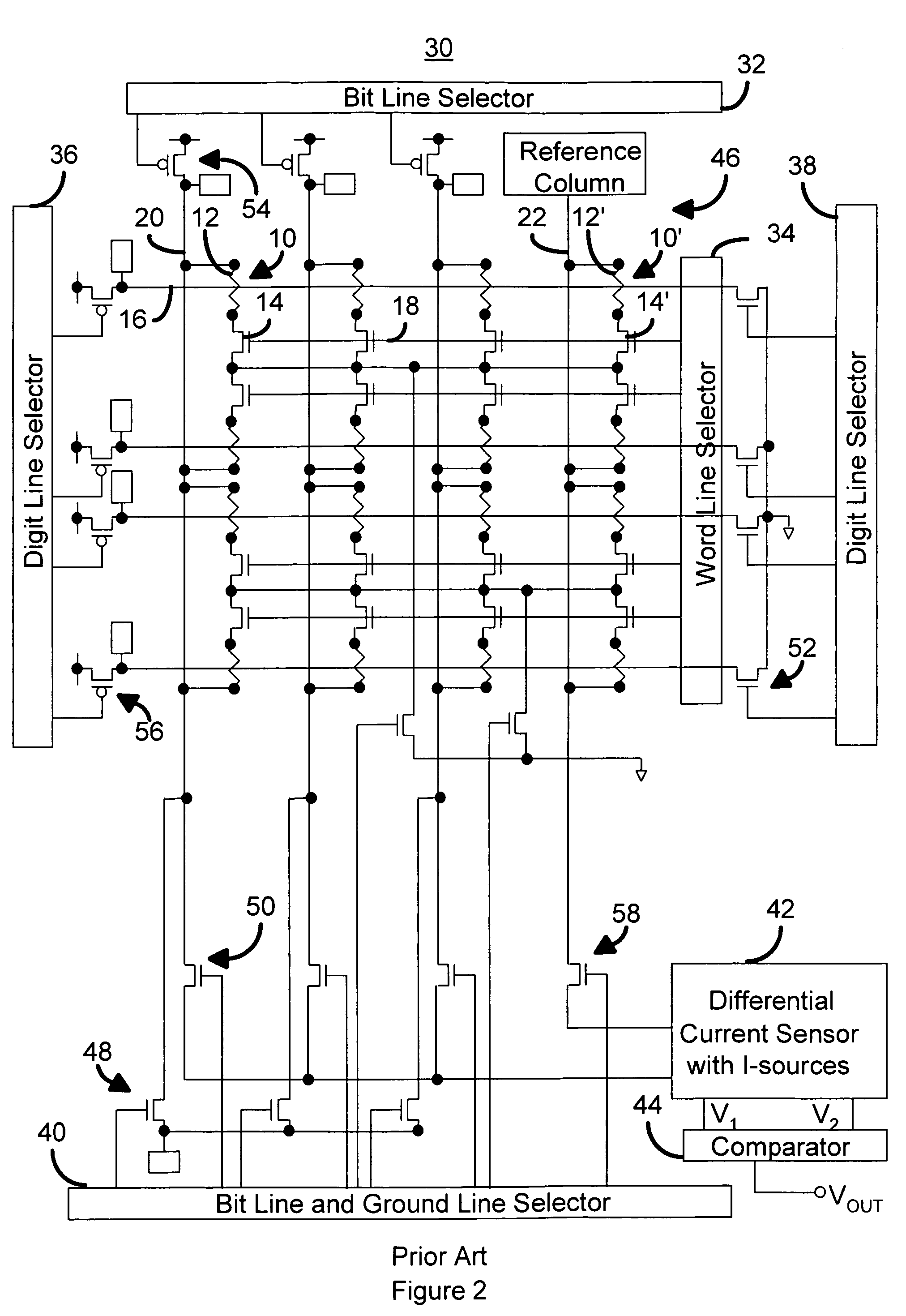

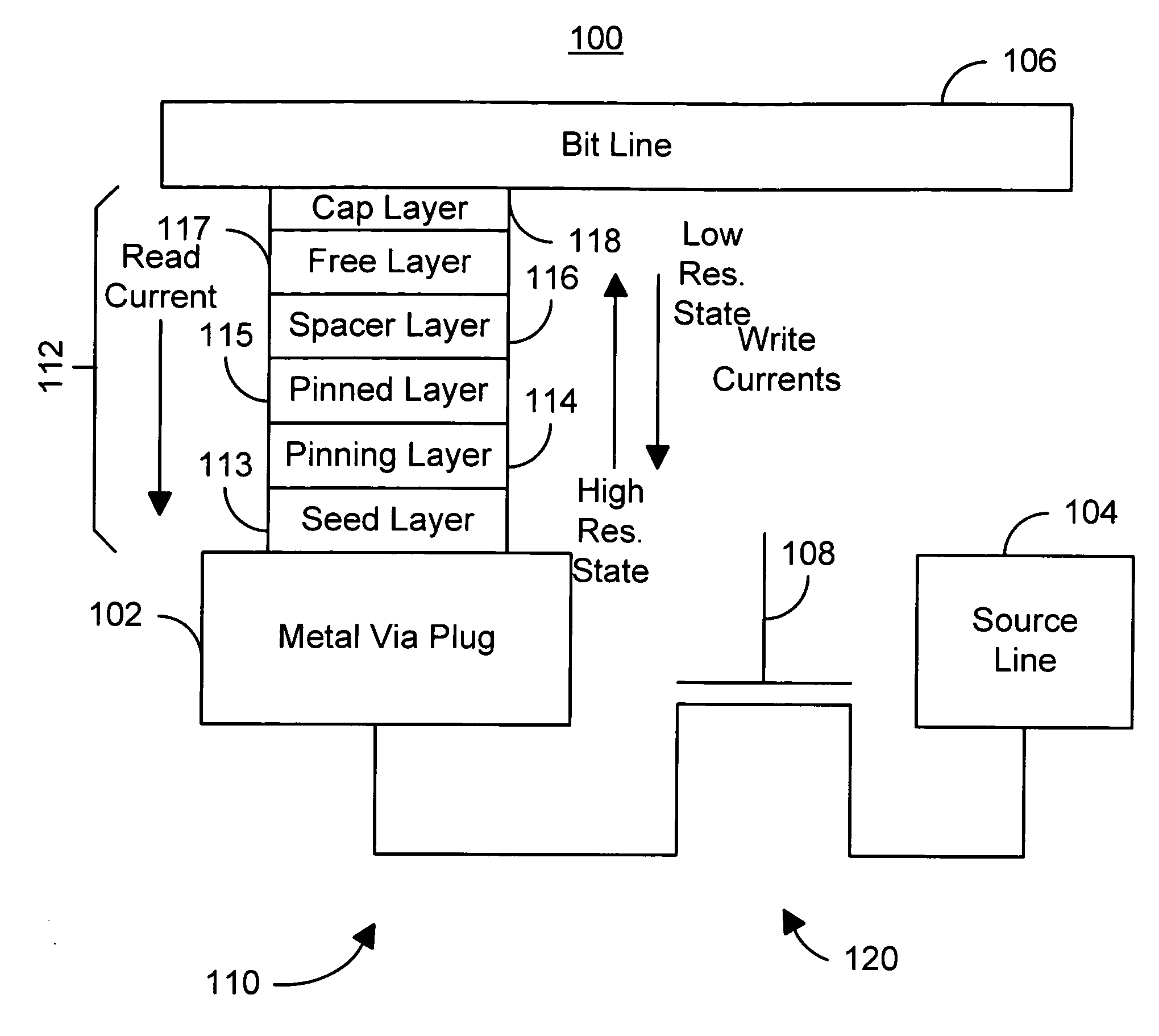

Current driven switching of magnetic storage cells utilizing spin transfer and magnetic memories using such cells having enhanced read and write margins

ActiveUS7379327B2Higher read and write marginDigital storageHigh resistanceElectrical resistance and conductance

A method and system for providing a magnetic memory. The magnetic memory includes magnetic storage cells in an array, bit lines, and source lines. Each magnetic storage cell includes at least one magnetic element. The magnetic element(s) are programmable by write currents driven through the magnetic element(s). Each magnetic element has free and pinned layer(s) and a dominant spacer. The magnetic memory is configured such that either the read current(s) flow from the free layer(s) to the dominant spacer if the maximum low resistance state read current divided by the minimum low resistance state write current is greater than the maximum high resistance state read current divided by the minimum high resistance state write current or the read current(s) flow from the dominant spacer to the free layer(s) if the maximum low resistance state read current divided by the minimum low resistance state write current is less than the maximum high resistance state read current divided by the minimum high resistance state write current.

Owner:SAMSUNG SEMICON +1

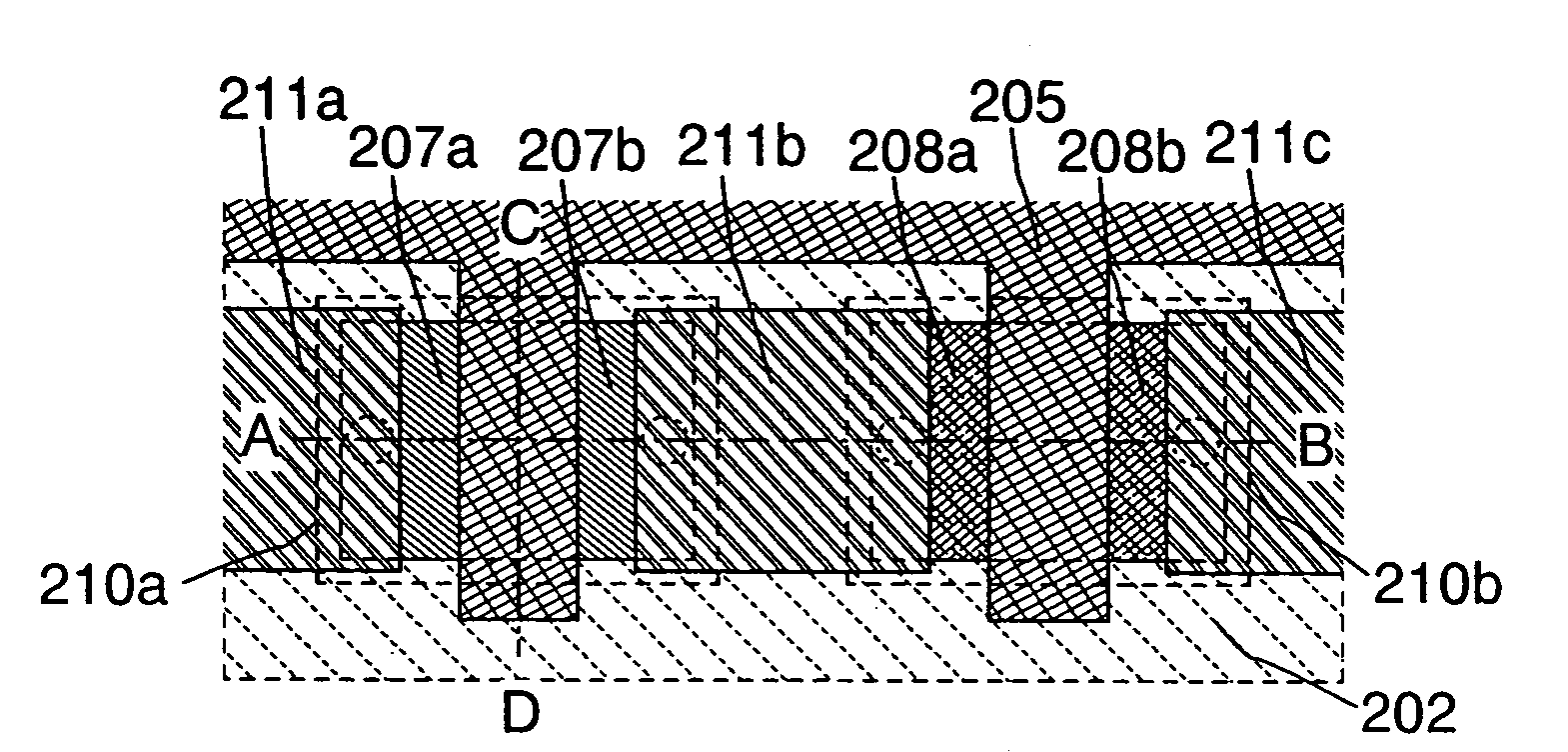

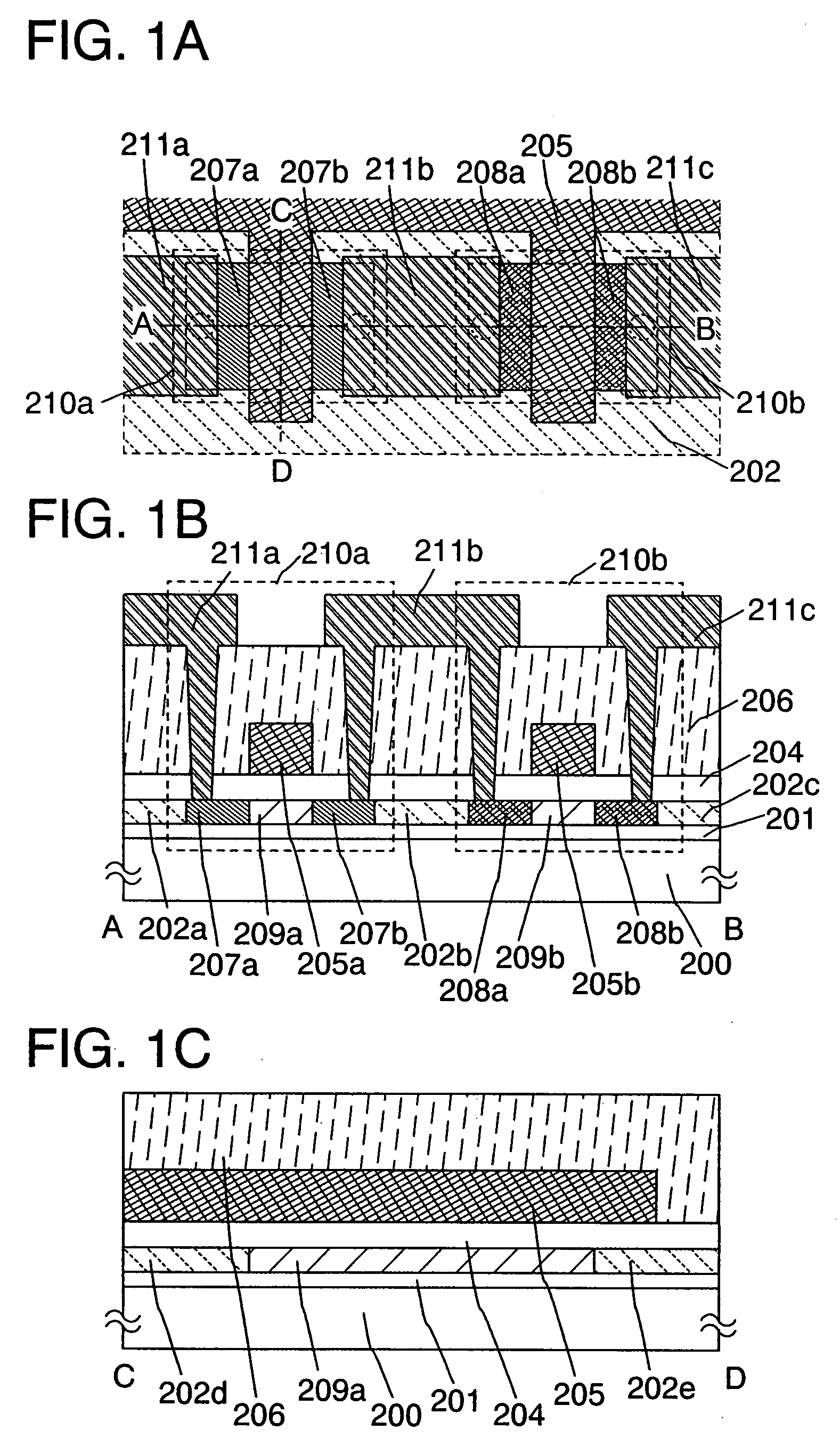

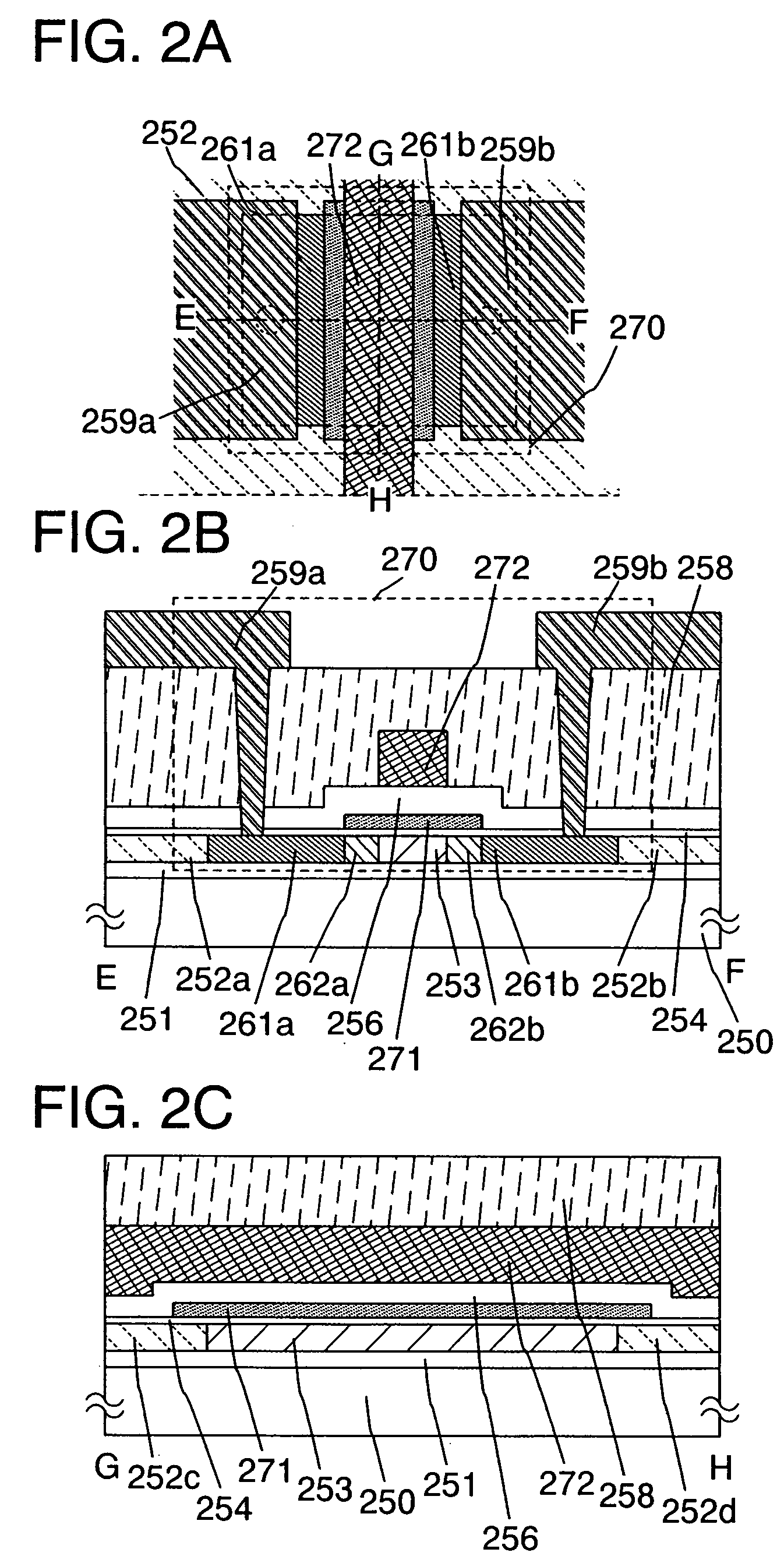

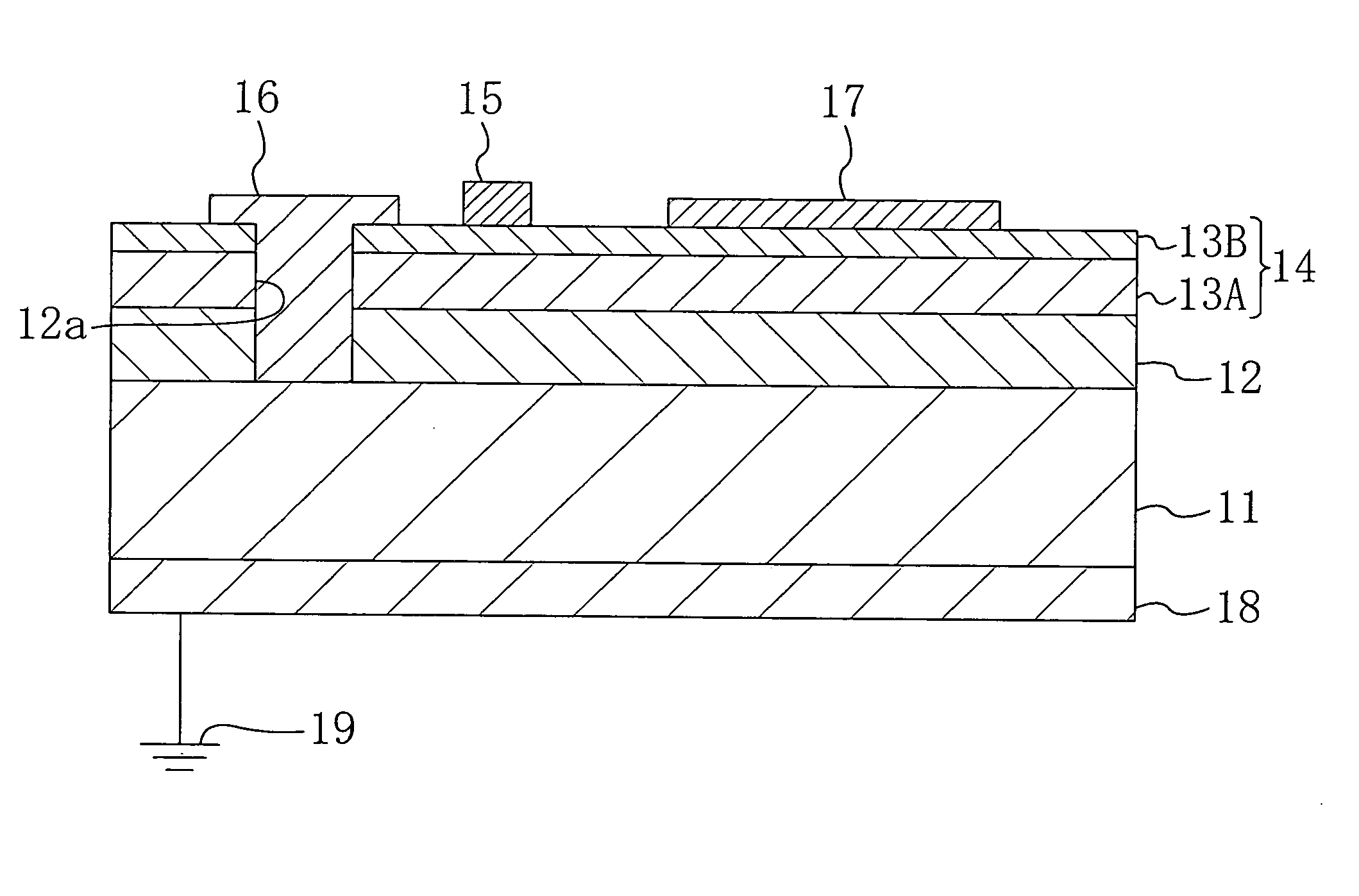

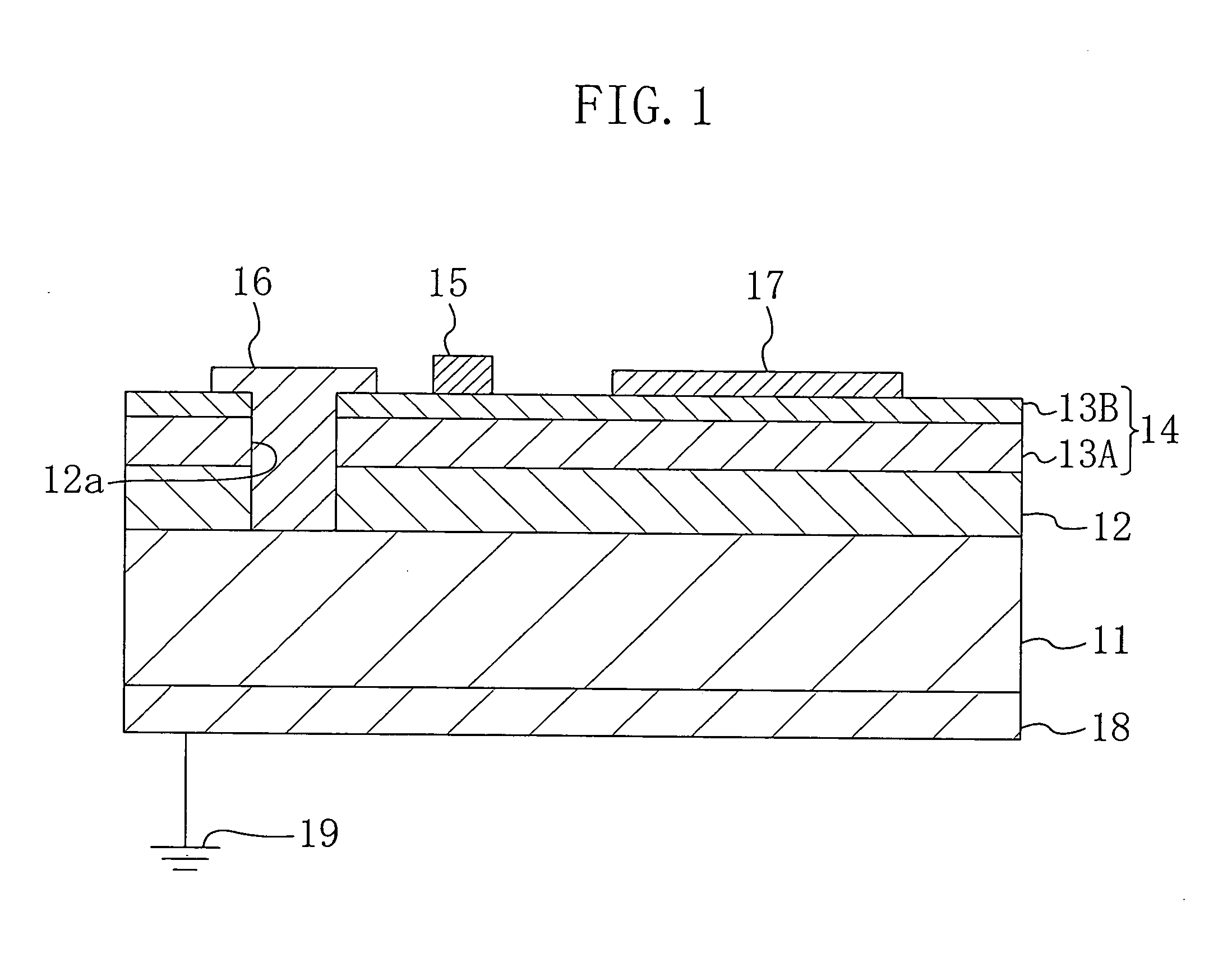

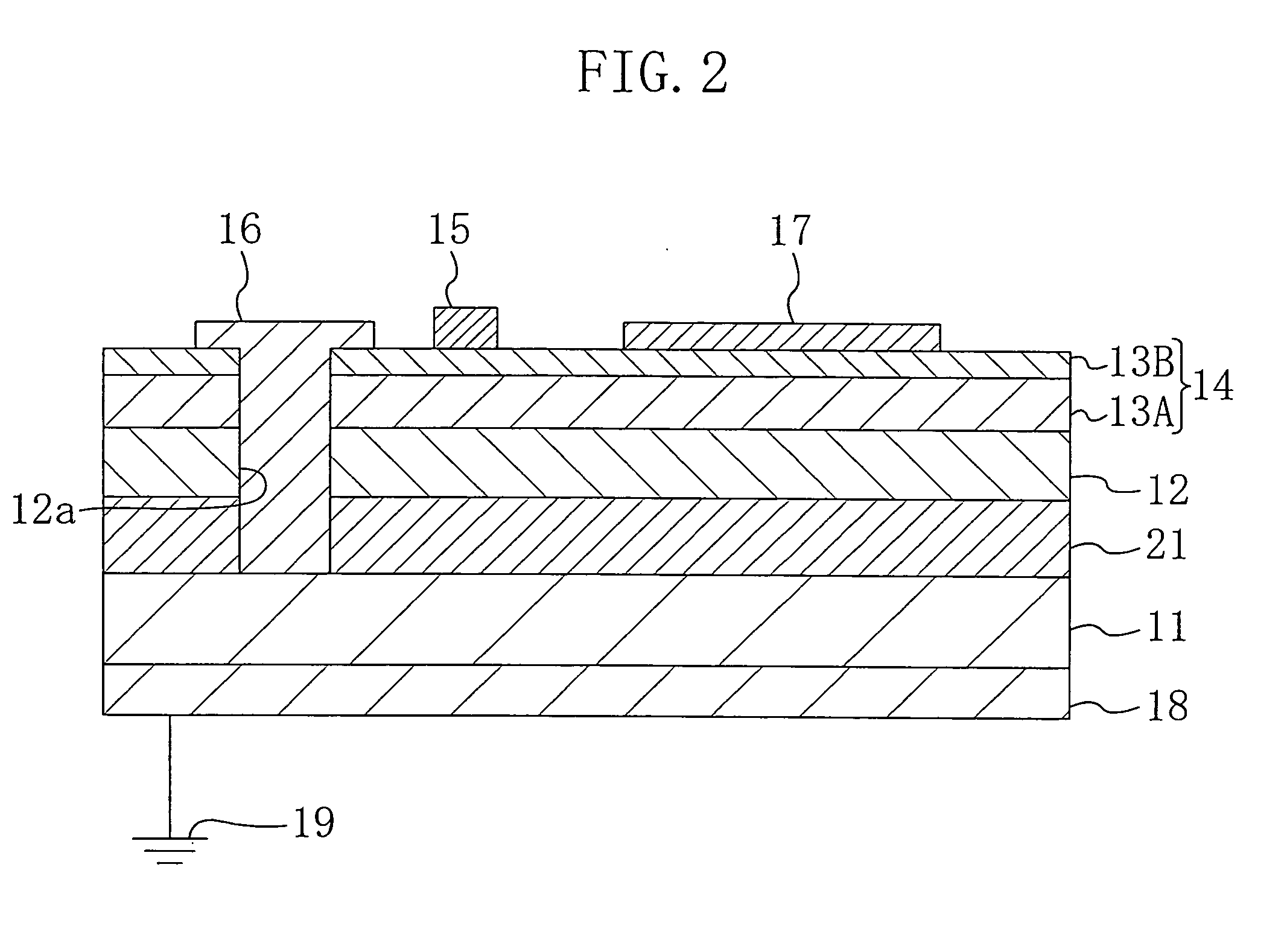

Semiconductor device and method for manufacturing the semiconductor device

InactiveUS20070252233A1Expand coverageEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingPhysicsHigh resistance

A semiconductor device is provided, which comprises a semiconductor layer over an insulating surface, and an insulating layer over the semiconductor layer. The semiconductor layer includes at least two element regions, and an element separation region. The element separation region is disposed between the two element regions. The element separation region includes at least one impurity element selected from the group consisting of oxygen, nitrogen, and carbon. The element separation region has higher resistance than a first source and drain regions included in one of the two element regions and a second source and drain regions included in the other of the two element regions.

Owner:SEMICON ENERGY LAB CO LTD

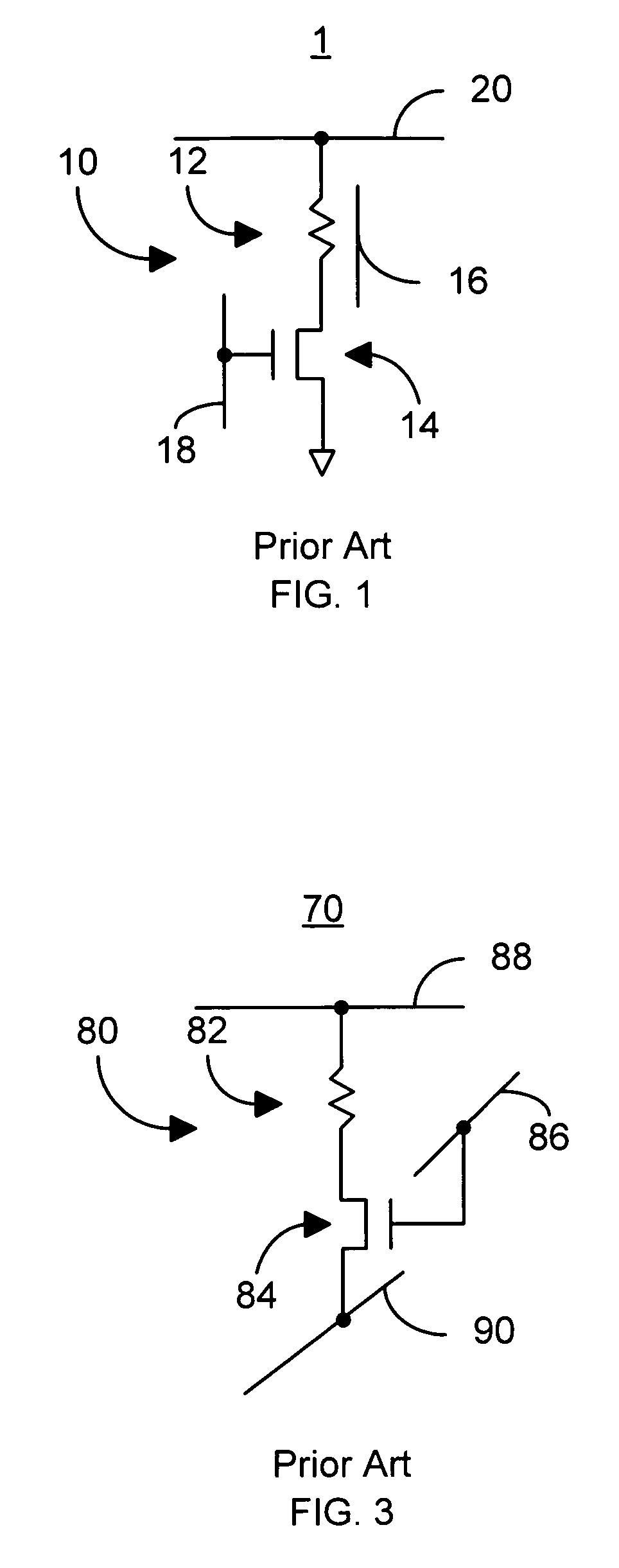

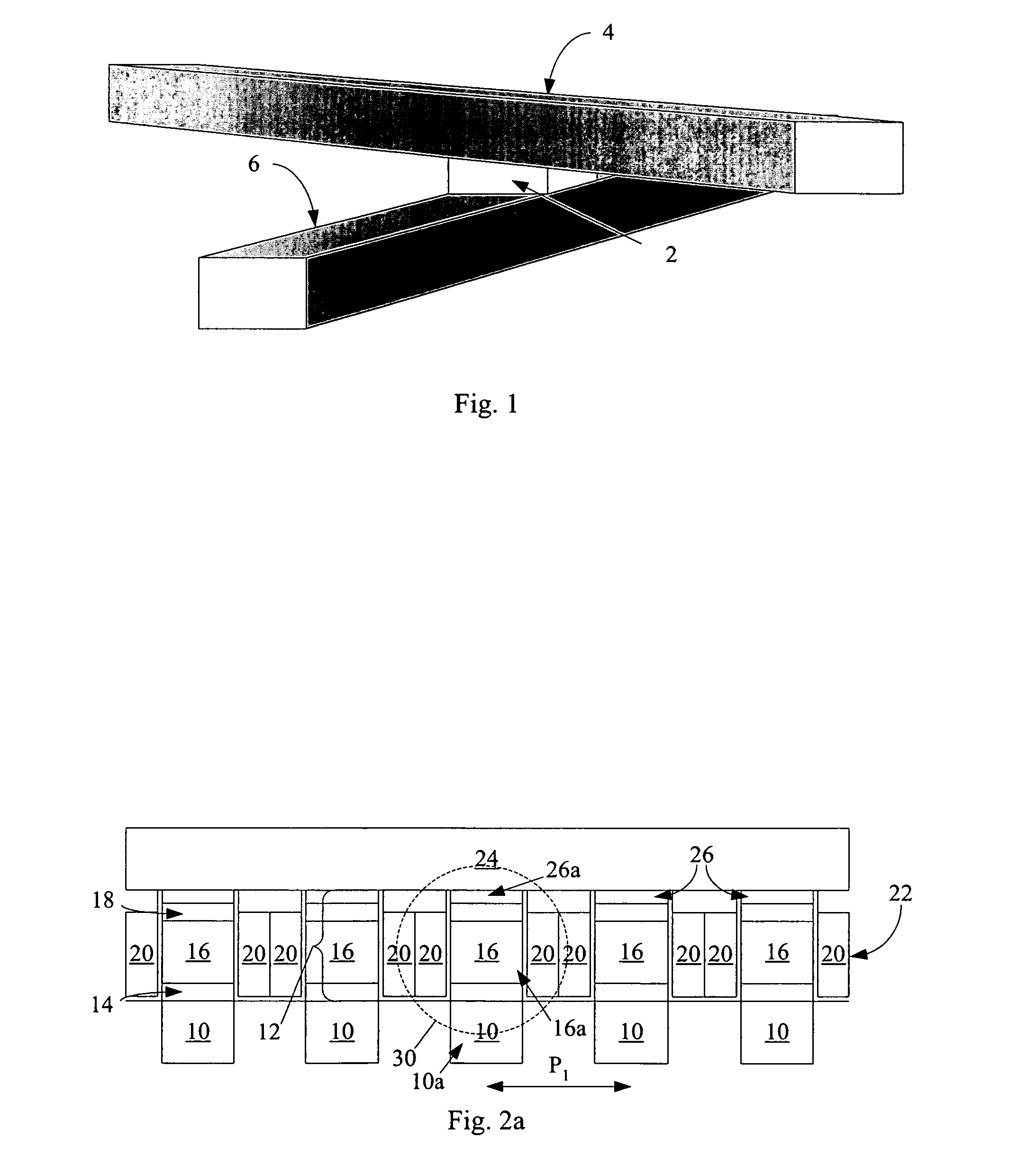

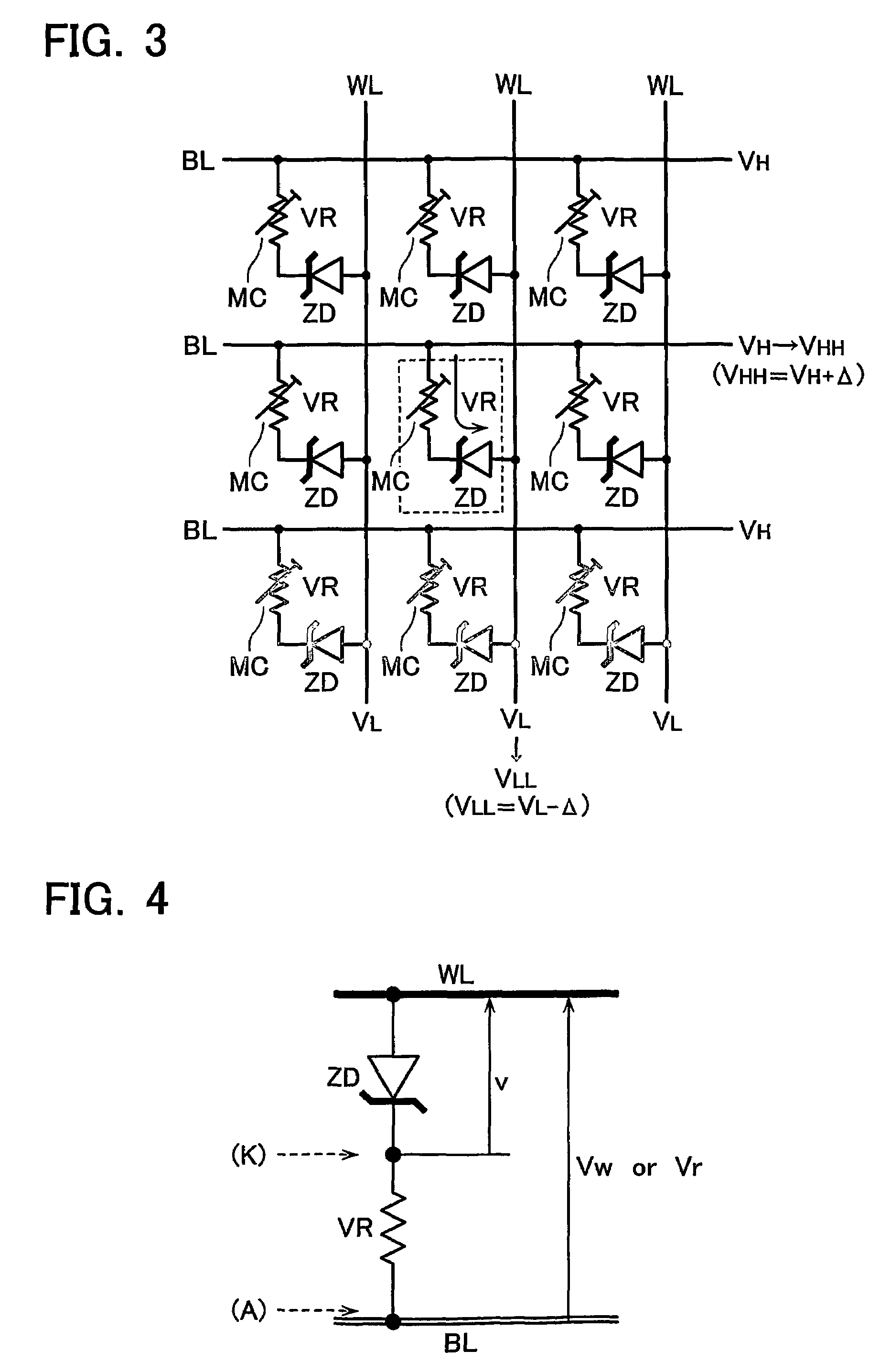

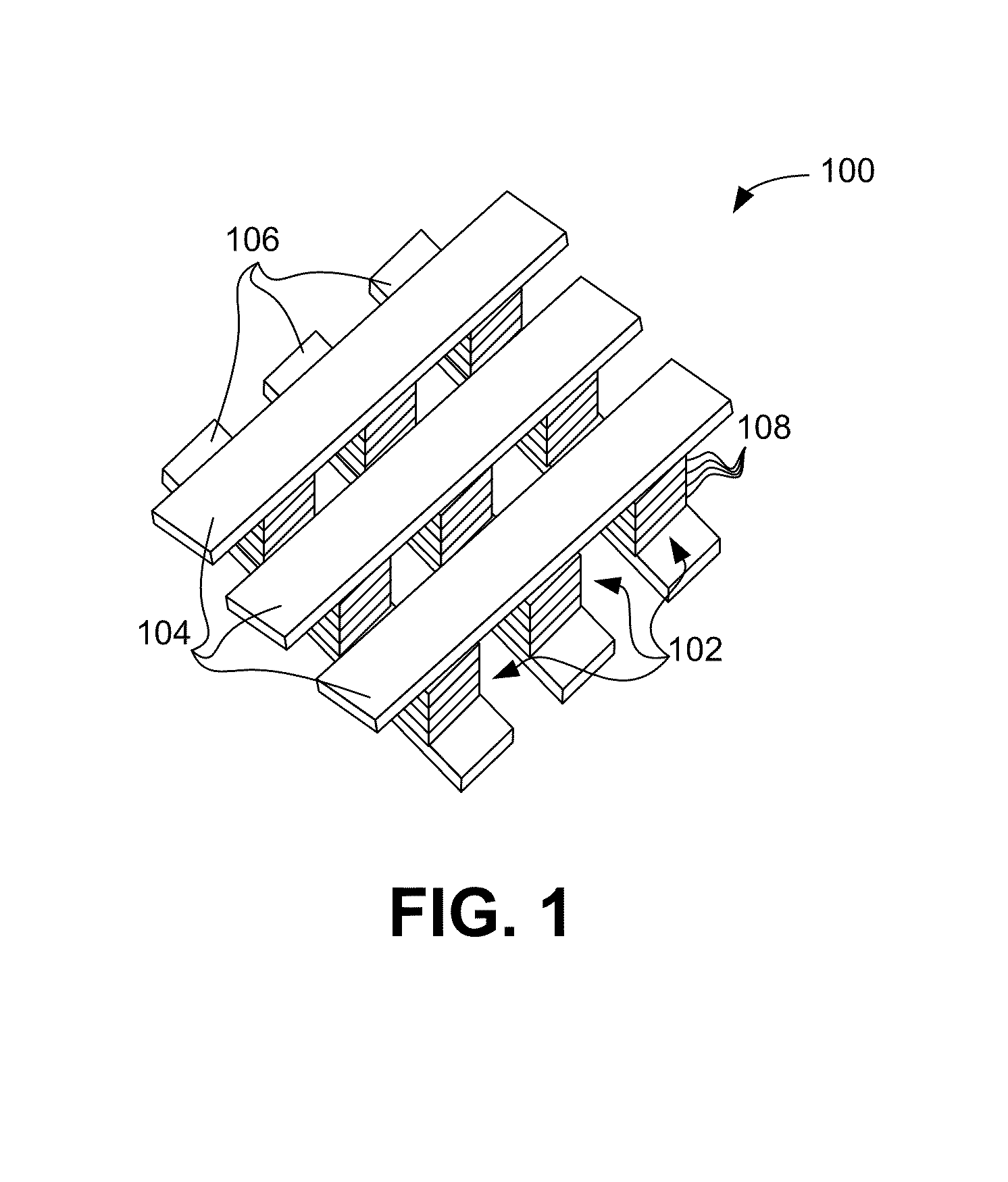

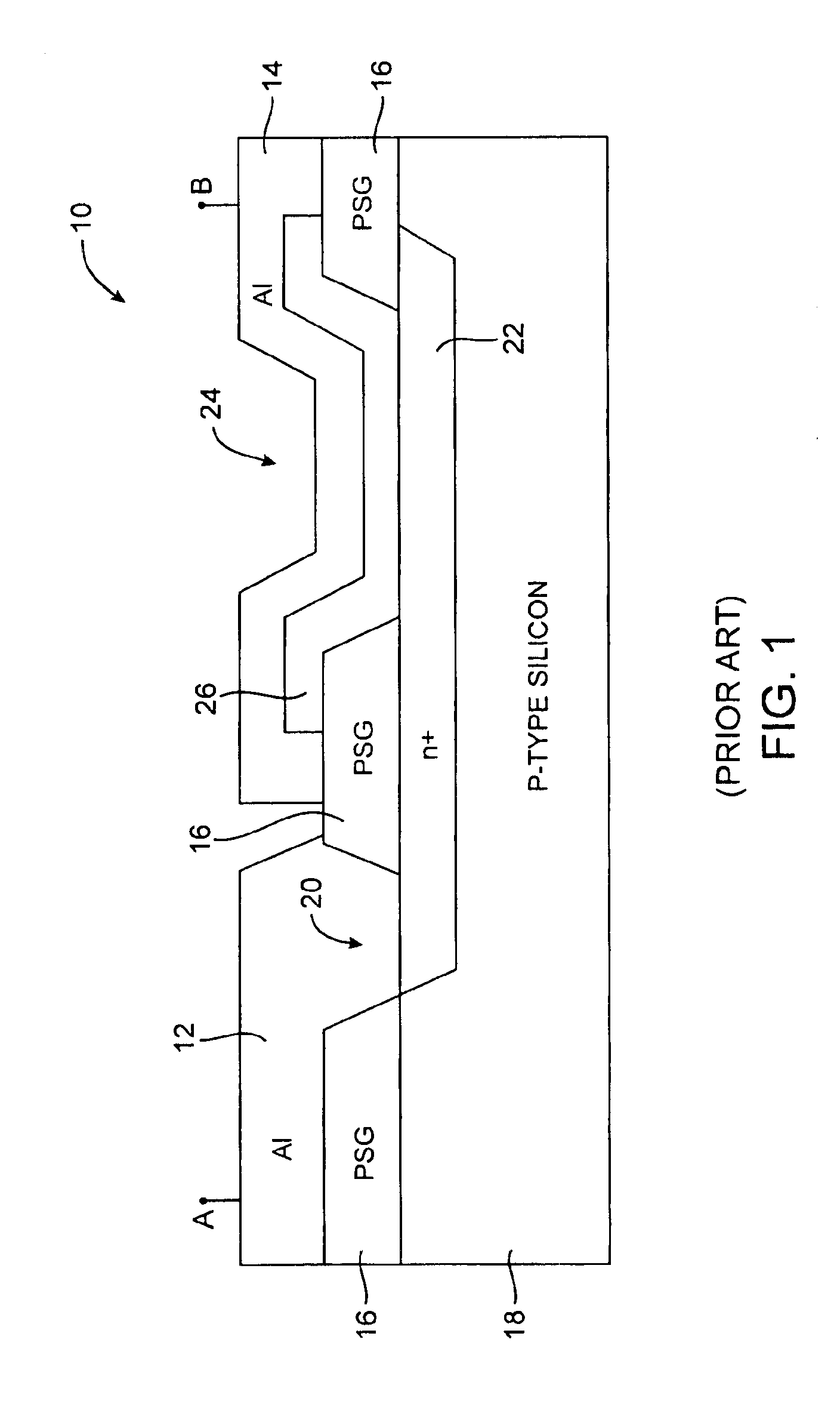

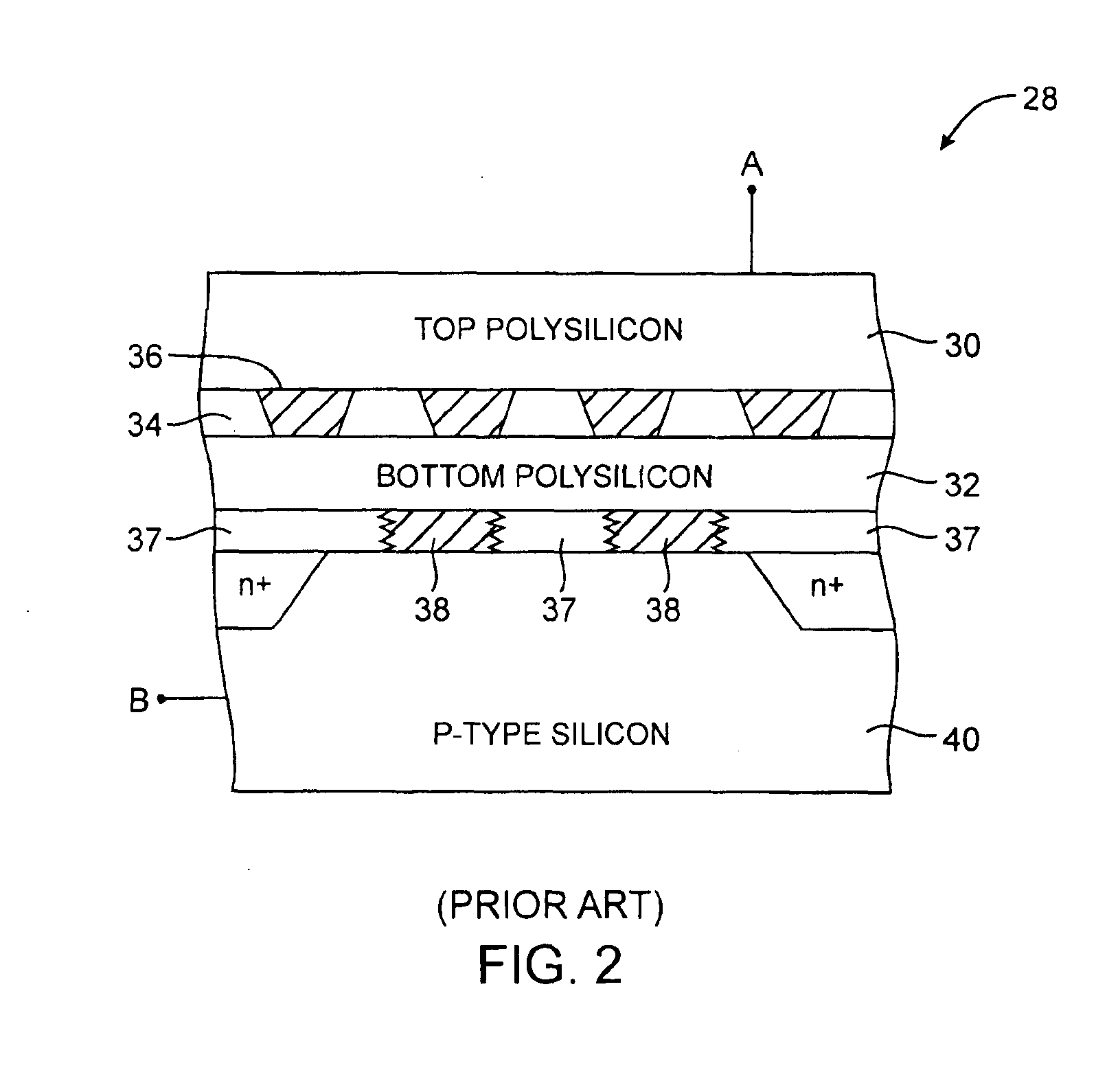

Rewriteable memory cell comprising a transistor and resistance-switching material in series

InactiveUS20060273298A1Solid-state devicesBulk negative resistance effect devicesHigh resistanceEngineering

A nonvolatile memory cell is provided, the cell comprising a transistor in series with resistance-switching material, which can be switched between at least two stable resistance states, for example a high-resistance state and a low-resistance state. In preferred embodiments the transistor is a TFT, having a channel region not formed in a monocrystalline wafer substrate. In preferred embodiments the transistor may have either a vertically oriented channel or a laterally oriented channel. Either embodiment can be formed in a monolithic three dimensional memory array in which multiple memory levels can be formed above a single substrate, forming a highly dense nonvolatile memory array.

Owner:SANDISK TECH LLC

Memory cell comprising switchable semiconductor memory element with trimmable resistance

ActiveUS20070090425A1Solid-state devicesRead-only memoriesHigh resistanceElectrical resistance and conductance

A nonvolatile memory cell comprising doped semiconductor material and a diode can store memory states by changing the resistance of the doped semiconductor material by application of a set pulse (decreasing resistance) or a reset pulse (increasing resistance.) Set pulses are of short duration and above a threshold voltage, while reset pulses are longer duration and below a threshold voltage. In some embodiments multiple resistance states can be achieved, allowing for a multi-state cell, while restoring a prior high-resistance state allows for an rewriteable cell. In some embodiments, the diode and a switchable memory formed of doped semiconductor material are formed in series, while in other embodiments, the diode itself serves as the semiconductor switchable memory element.

Owner:WODEN TECH INC

Current driven switched magnetic storage cells having improved read and write margins and magnetic memories using such cells

A method and system for providing a magnetic memory is described. The magnetic memory includes a plurality of magnetic storage cell and at least one bit line and a plurality of source lines corresponding to the plurality of magnetic storage cells. Each magnetic storage cell includes a magnetic element that is programmed to a high resistance state by a first write current driven through the magnetic element in a first direction and to a low resistance state by a second write current driven through the magnetic element in a second direction. The bit line(s) and the source lines are configured to drive the first write current through the magnetic element in the first direction, to drive the second write current through the magnetic element in the second direction, and to drive at least one read current through the magnetic element in a third direction that does not destabilize the low resistance state.

Owner:SAMSUNG SEMICON

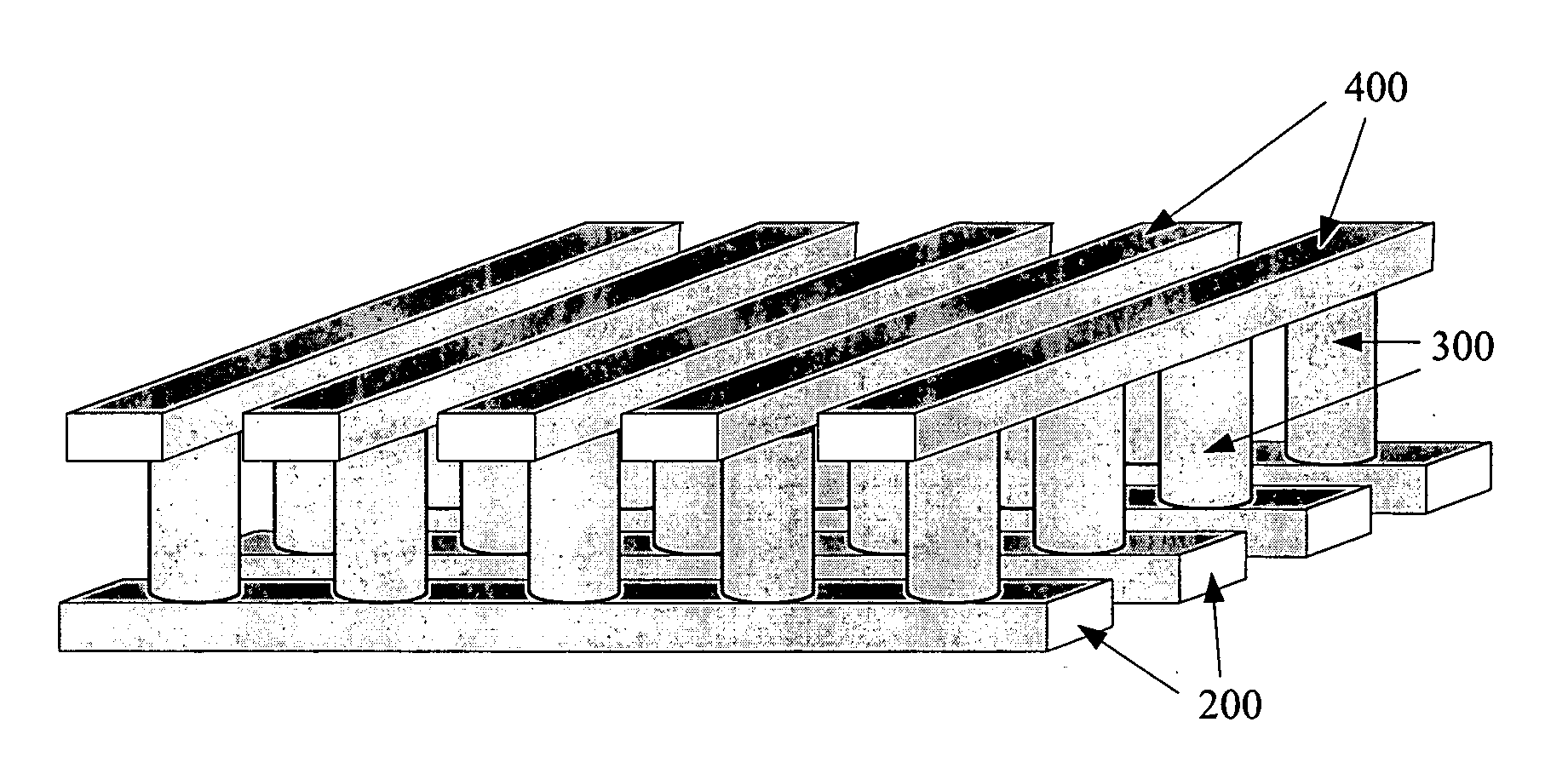

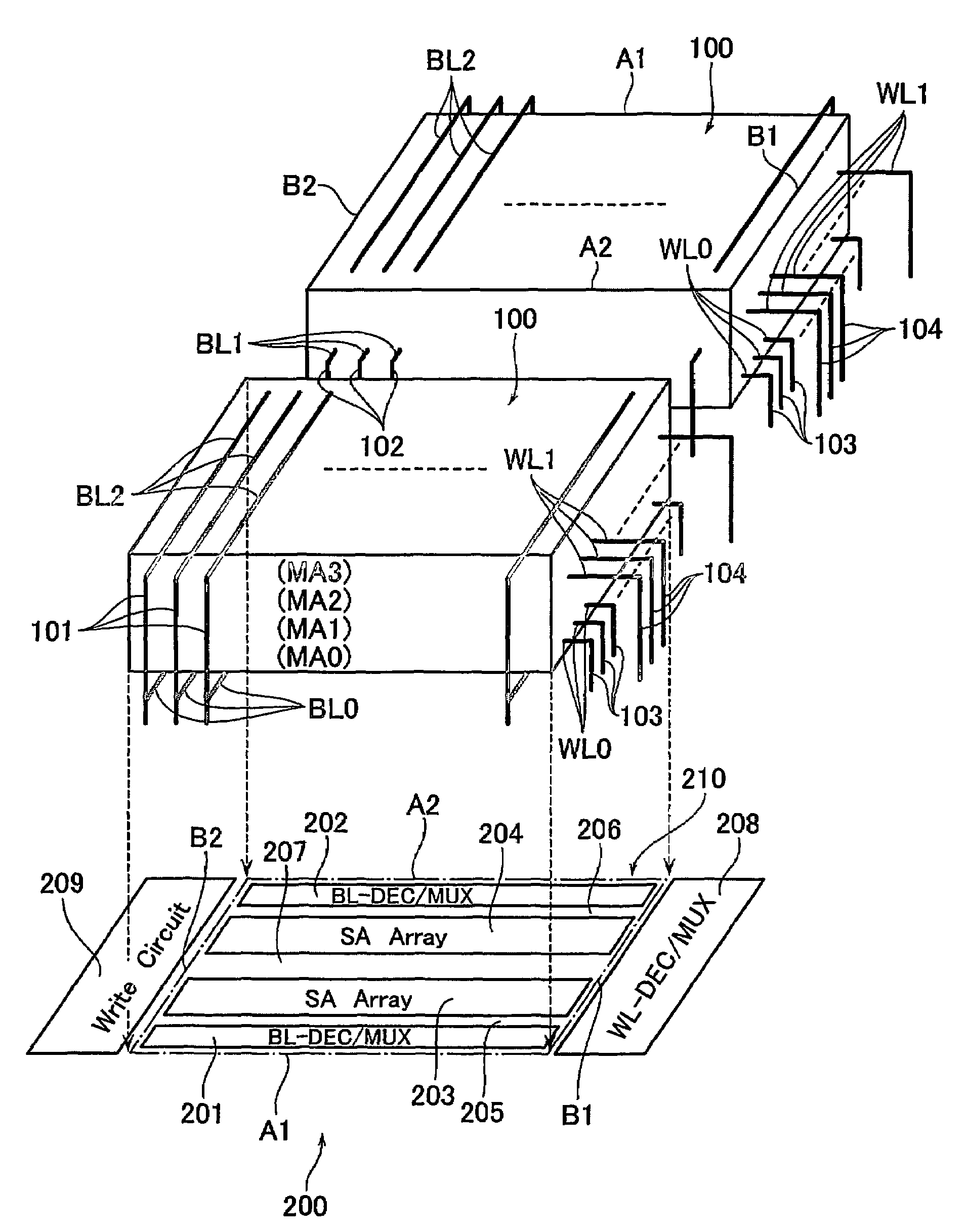

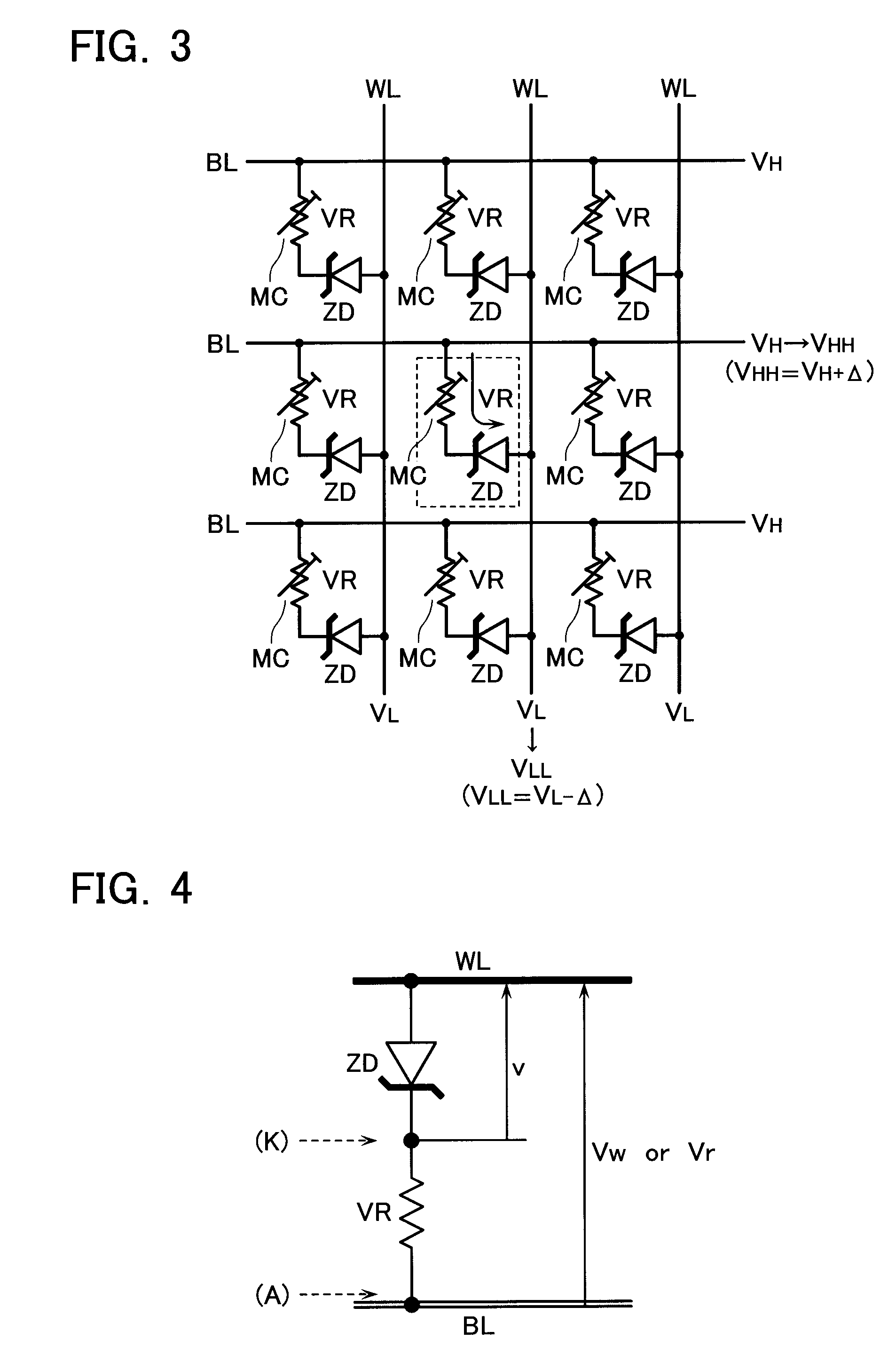

Three-dimensional programmable resistance memory device with a read/write circuit stacked under a memory cell array

A programmable resistance memory device includes a semiconductor substrate, at least one cell array, in which memory cells are arranged and formed above the semiconductor substrate. Each of the memory cells has a stack structure of a programmable resistance element and an access element, the programmable resistance element storing a high resistance state or a low resistance state based on the polarity of voltage application in a non-volatile manner. The access element has a resistance value in an off-state in a certain voltage range that is ten time or more as high as that in a select state. A read / write circuit is formed on the semiconductor substrate and underlying the cell array for data reading and data writing in communication with the cell array.

Owner:KIOXIA CORP

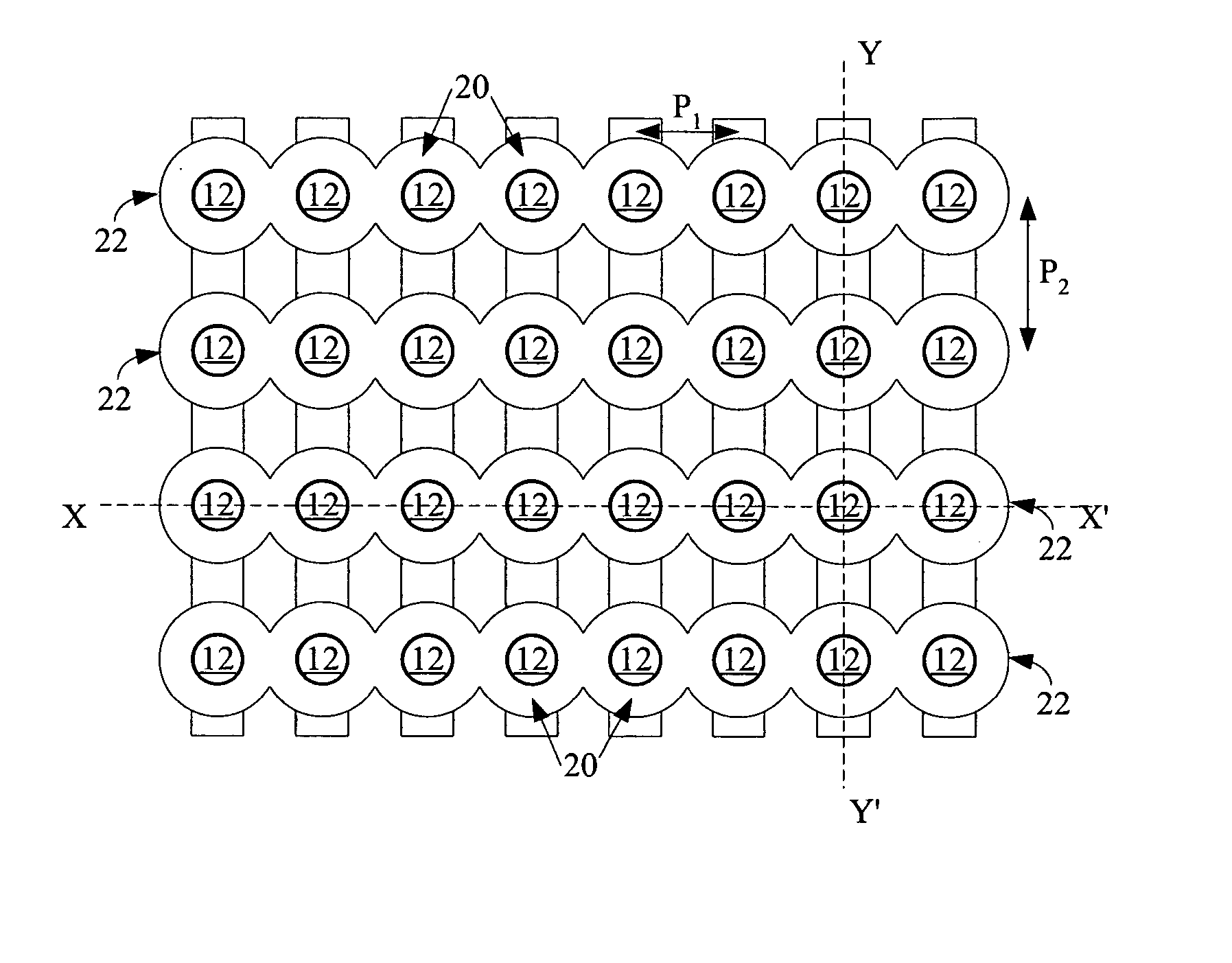

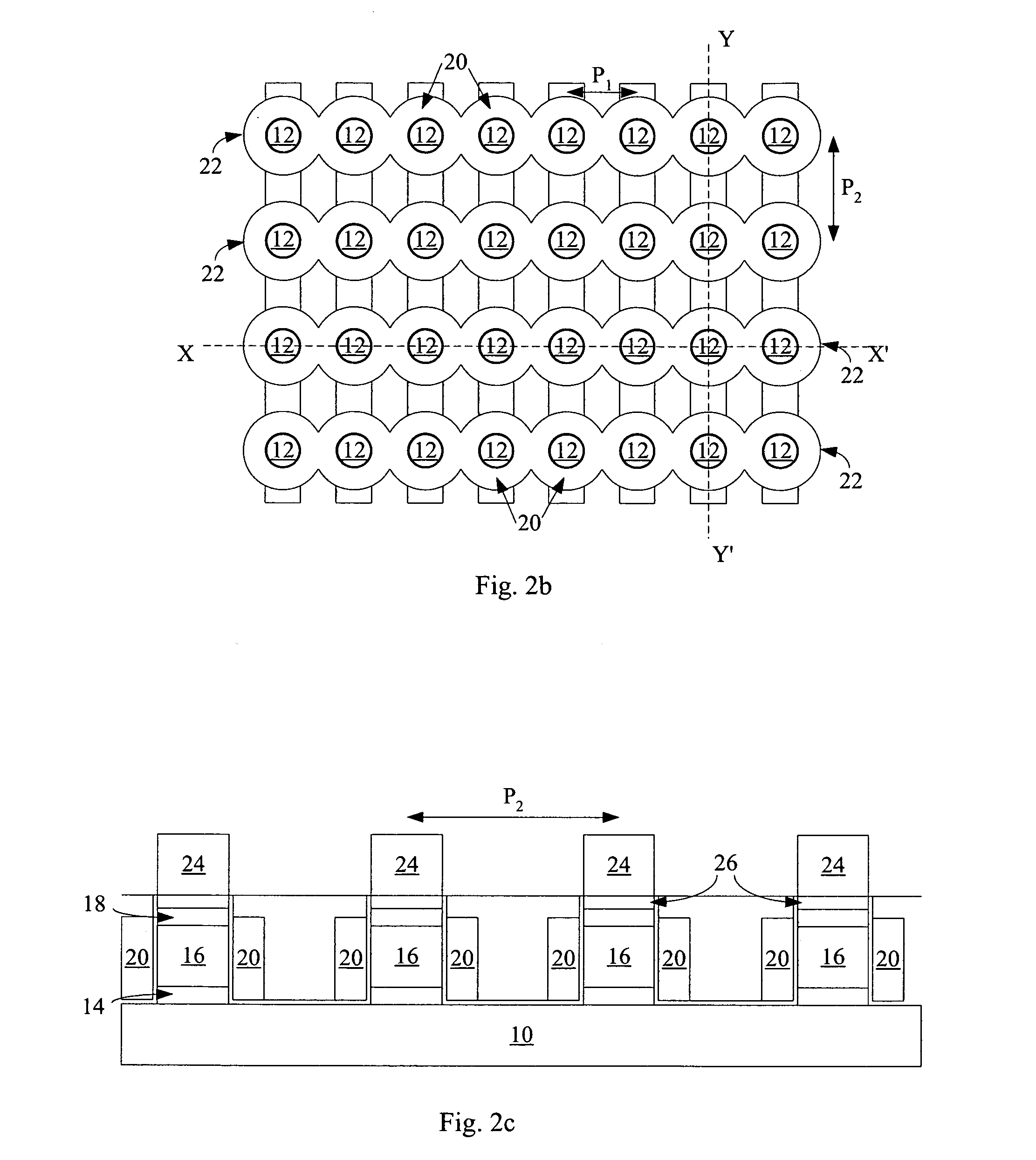

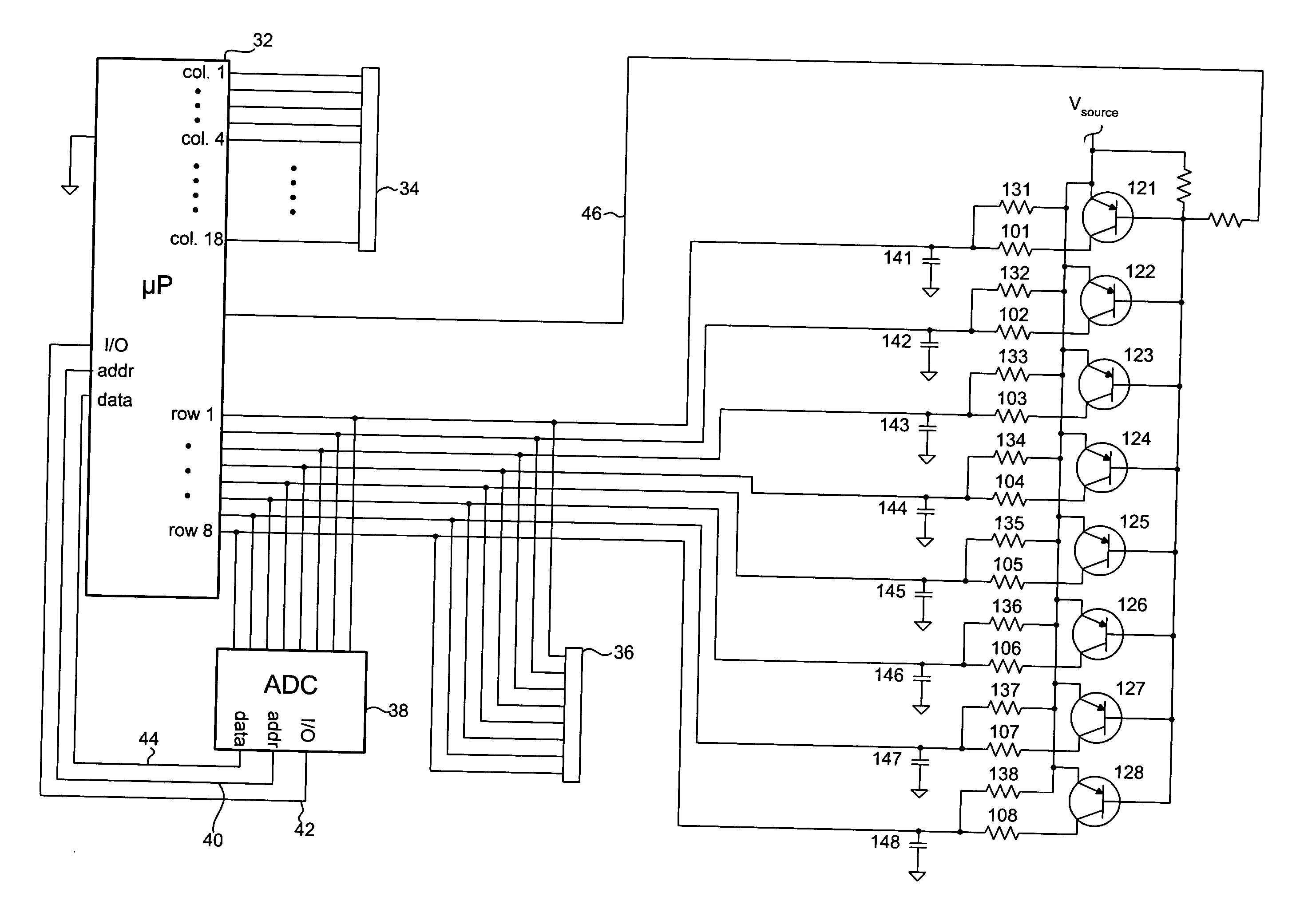

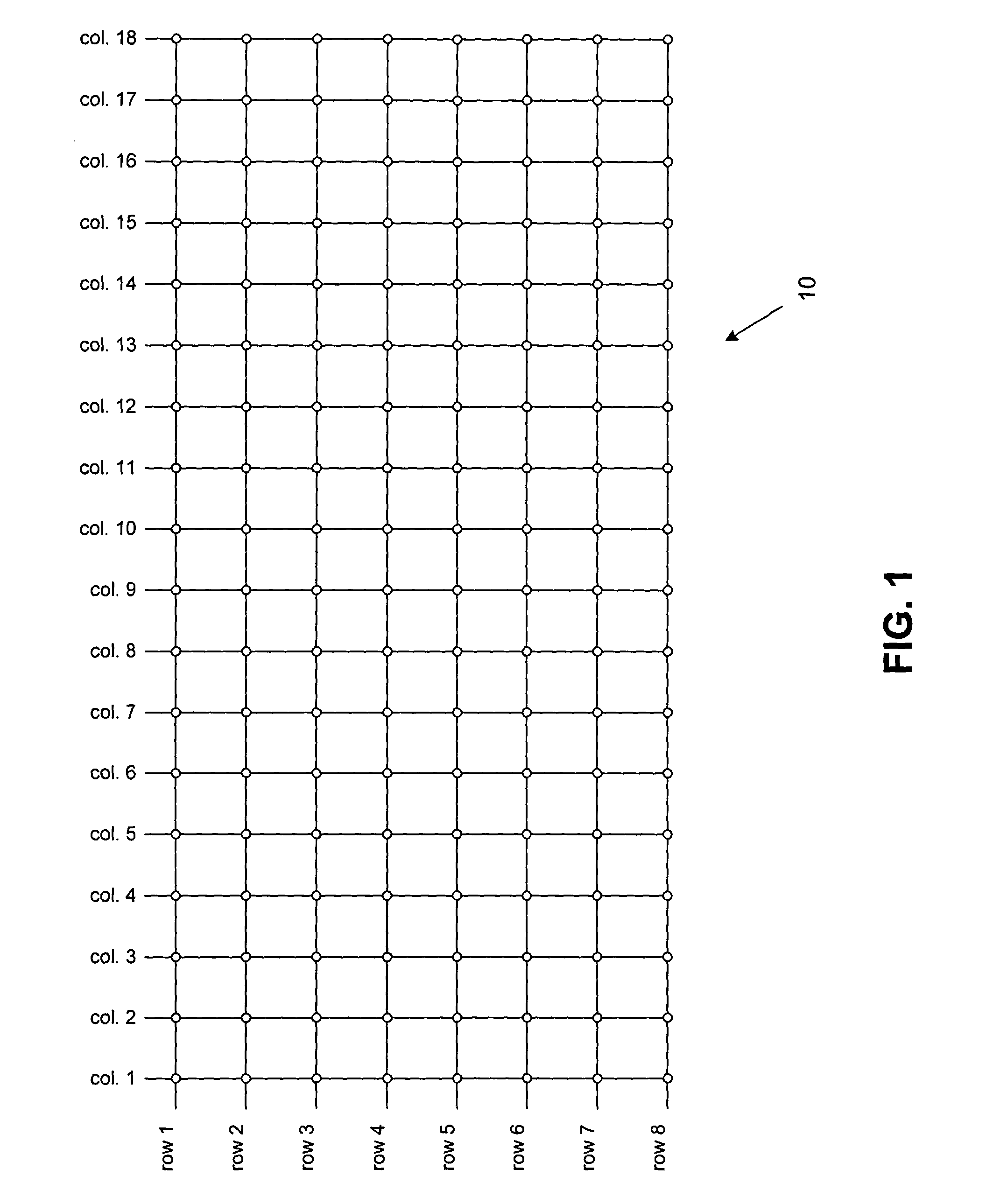

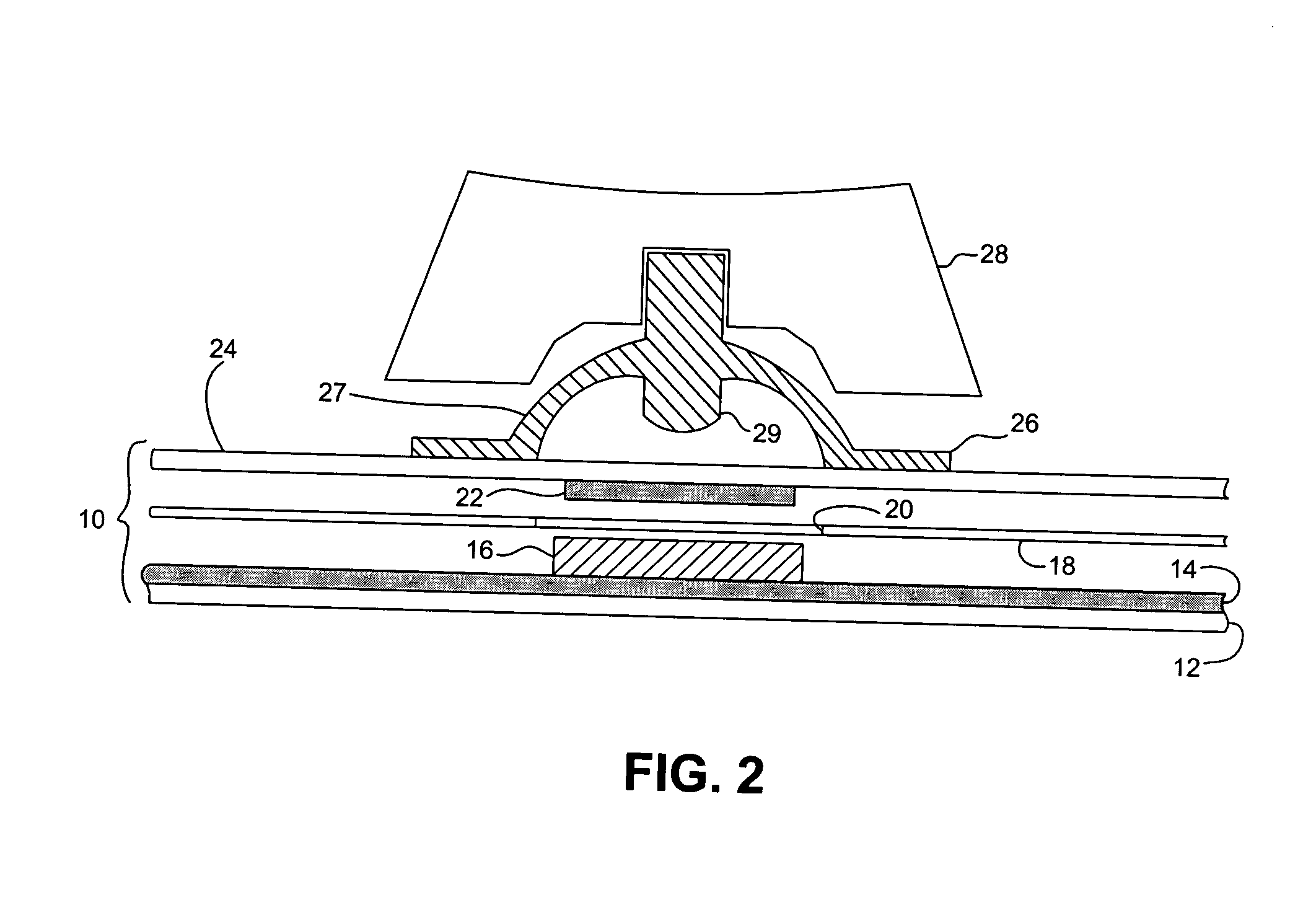

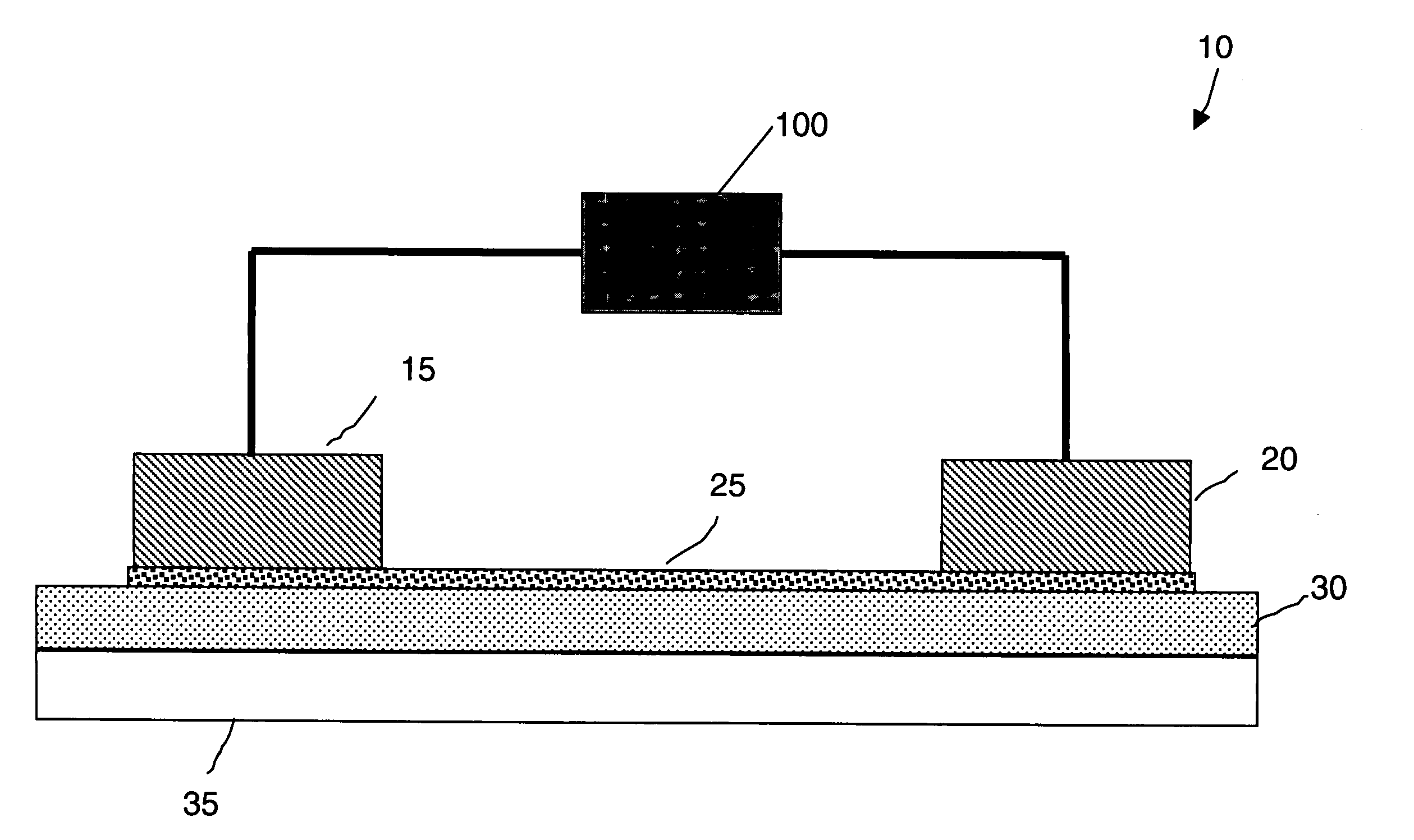

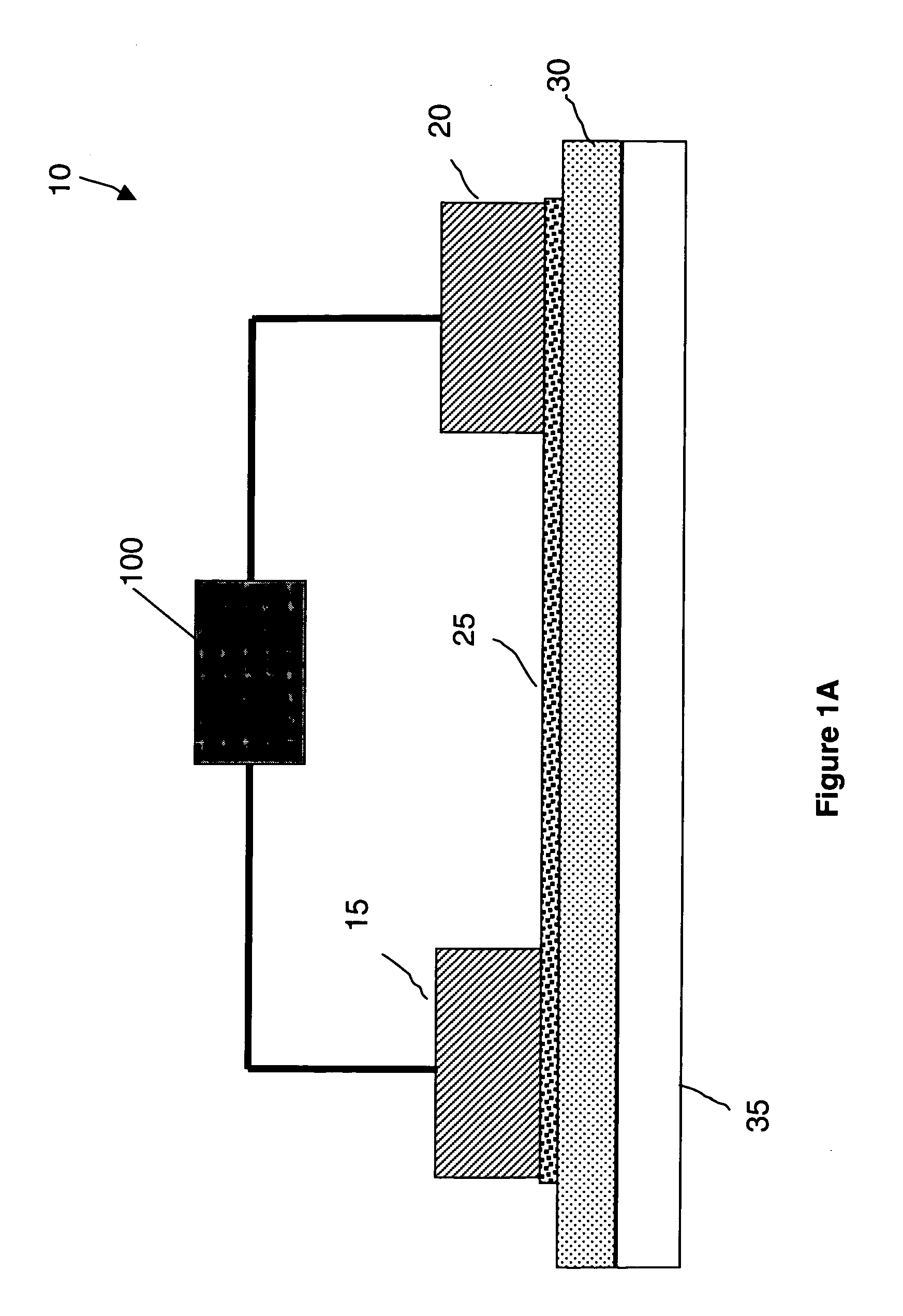

Computer keyboard with quantitatively force-sensing keys

ActiveUS20050057515A1Readily apparentInput/output for user-computer interactionCathode-ray tube indicatorsHigh resistanceElectrical resistance and conductance

A computer keyboard has a grid of conductors forming a plurality of intersections, with force-sensitive resistor (FSR) elements located between the conductors at the intersections. A plurality of keys are located above the intersections and exert force on the conductors and FSR elements during key presses. A resistor network sub-circuit is connected to some of the conductors, and is switchable between low and high resistance values. An Analog to Digital Converter (ADC) is coupled to the resistor network sub-circuit. A microprocessor grounds a conductor and tests another conductor for a threshold voltage level while the resistor network is switched to the high resistance value. The microprocessor switches the resistor network to the low resistance value upon detecting the threshold voltage level and subsequently receives from the ADC a digital value of a voltage on the tested conductor.

Owner:MICROSOFT TECH LICENSING LLC

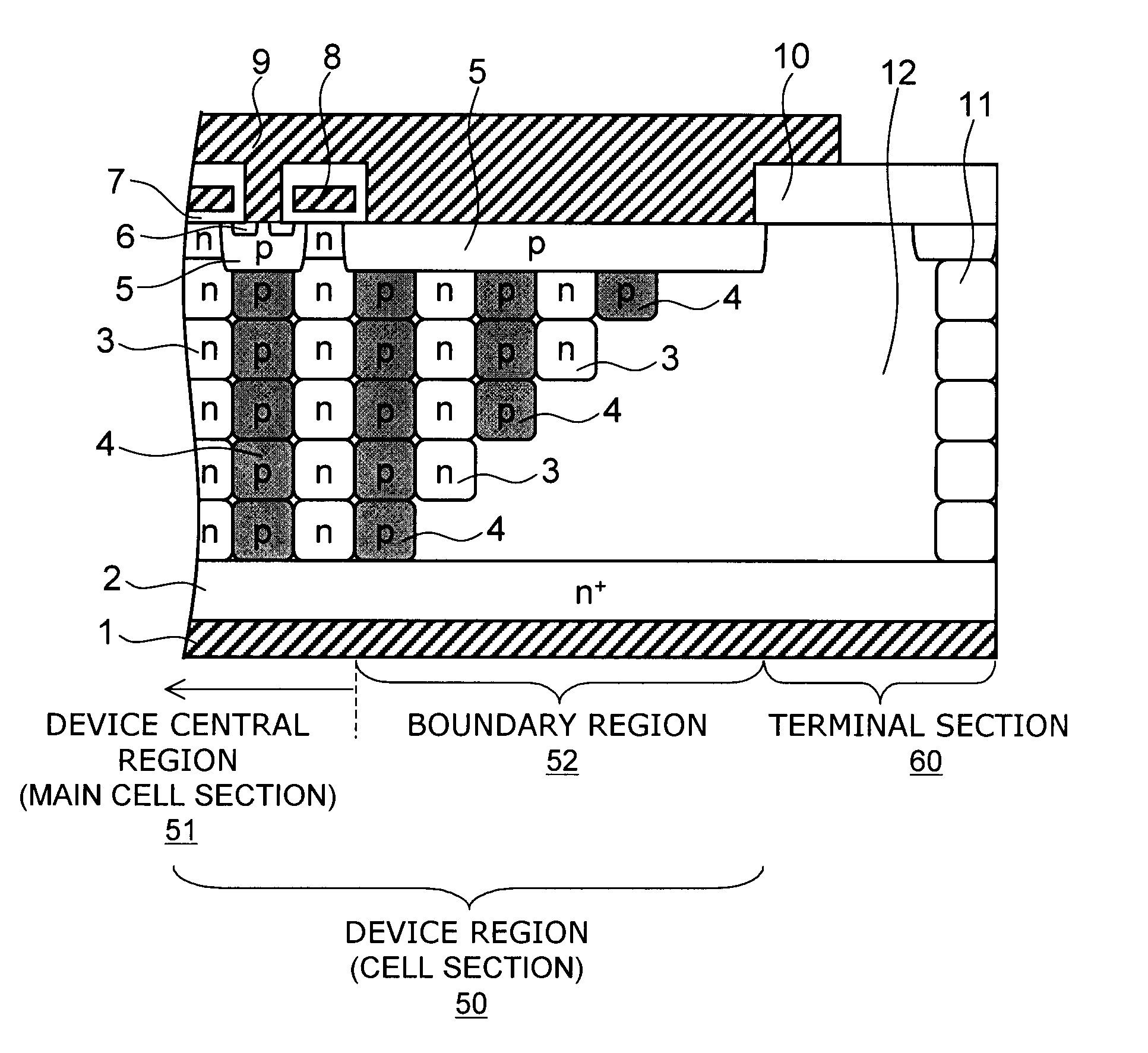

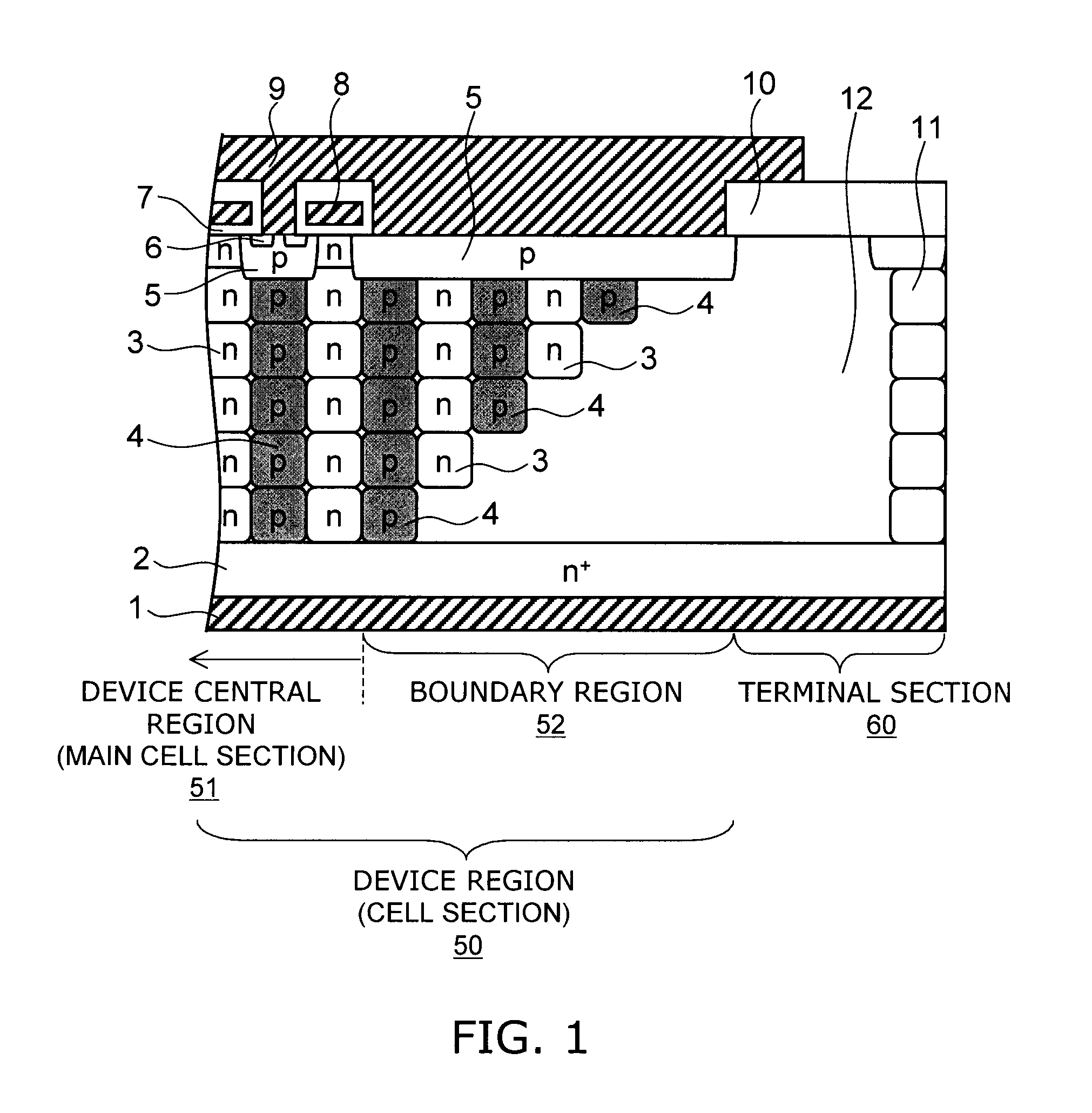

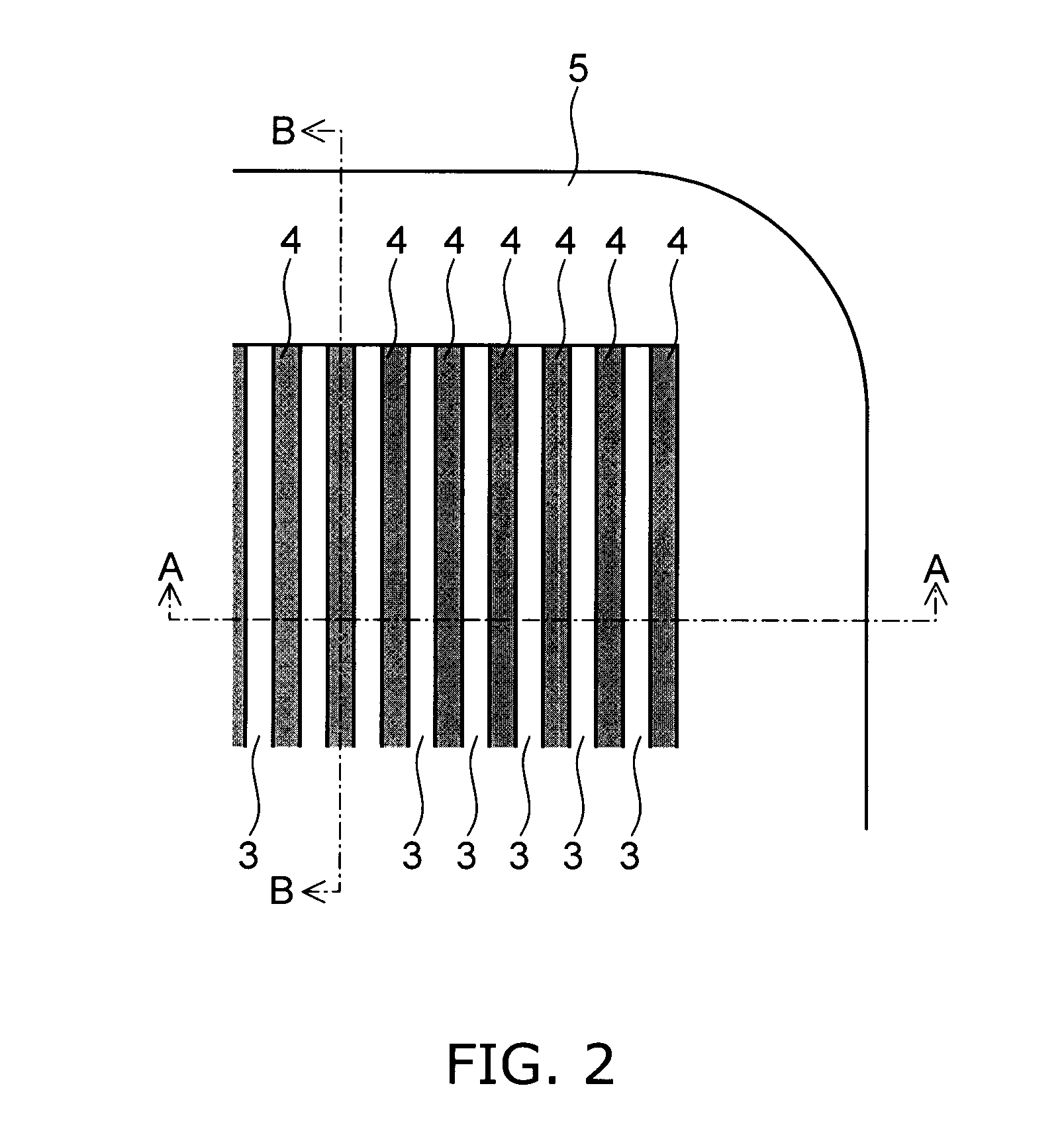

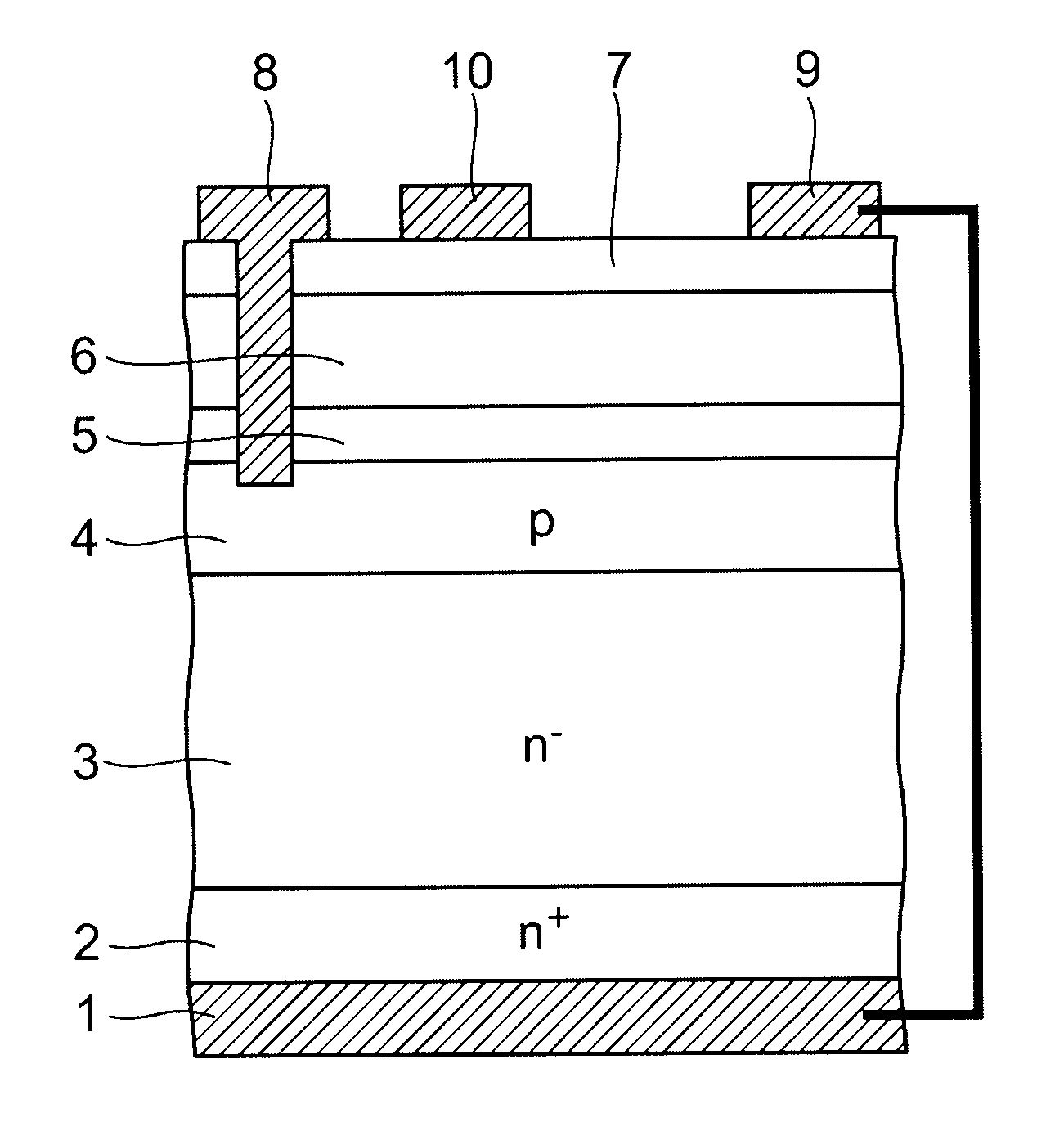

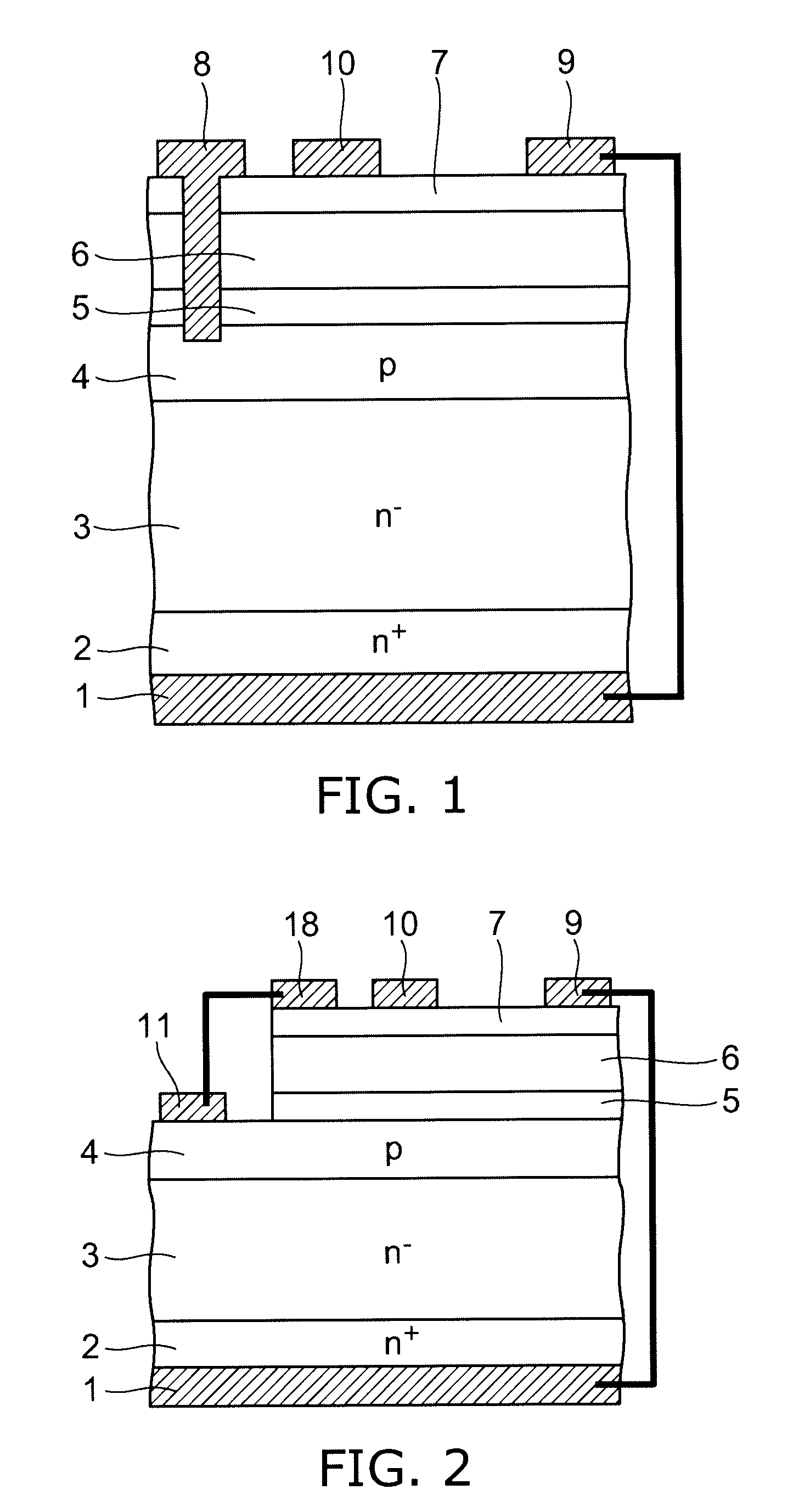

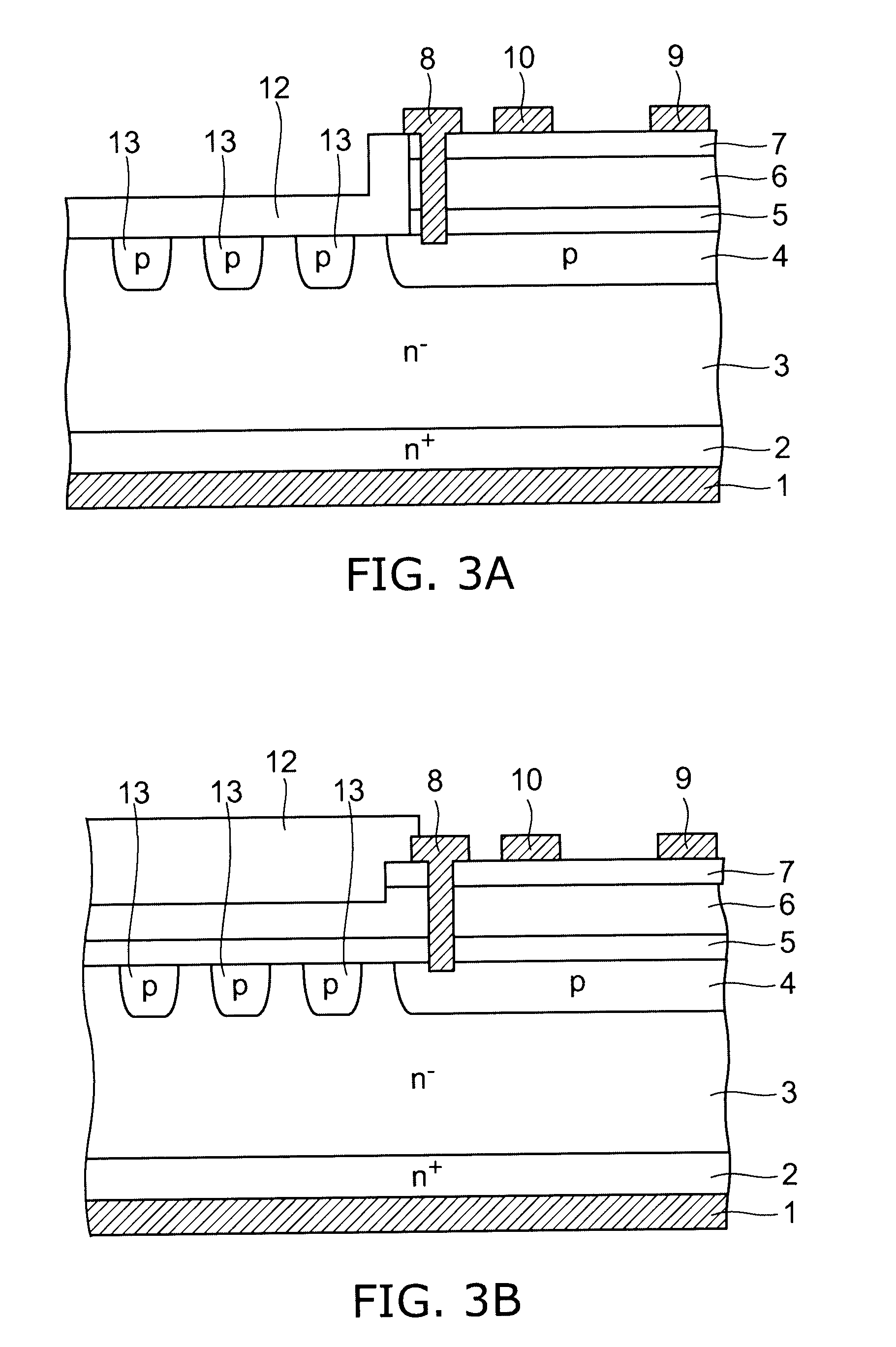

Semiconductor device

InactiveUS20070272979A1Reduce doping concentrationSemiconductor/solid-state device manufacturingDiodeHigh resistanceDopant

A semiconductor device includes: a semiconductor layer of a first conductivity type; a first semiconductor pillar region of the first conductivity type provided on a major surface of the semiconductor layer; a second semiconductor pillar region of a second conductivity type provided adjacent to the first semiconductor pillar region on the major surface of the semiconductor layer, the second semiconductor pillar region forming a periodic arrangement structure substantially parallel to the major surface of the semiconductor layer together with the first semiconductor pillar region; a first main electrode; a first semiconductor region of the second conductivity type; a second semiconductor region of the first conductivity type; a second main electrode; a control electrode; and a high-resistance semiconductor layer provided on the semiconductor layer in an edge termination section surrounding the first semiconductor pillar region and the second semiconductor pillar region. The high-resistance semiconductor layer has a lower dopant concentration than the first semiconductor pillar region. A boundary region is provided between a device central region and the edge termination section. The first semiconductor pillar region and the second semiconductor pillar region adjacent to the high-resistance semiconductor layer in the boundary region have a depth decreasing stepwise toward the edge termination section.

Owner:KK TOSHIBA

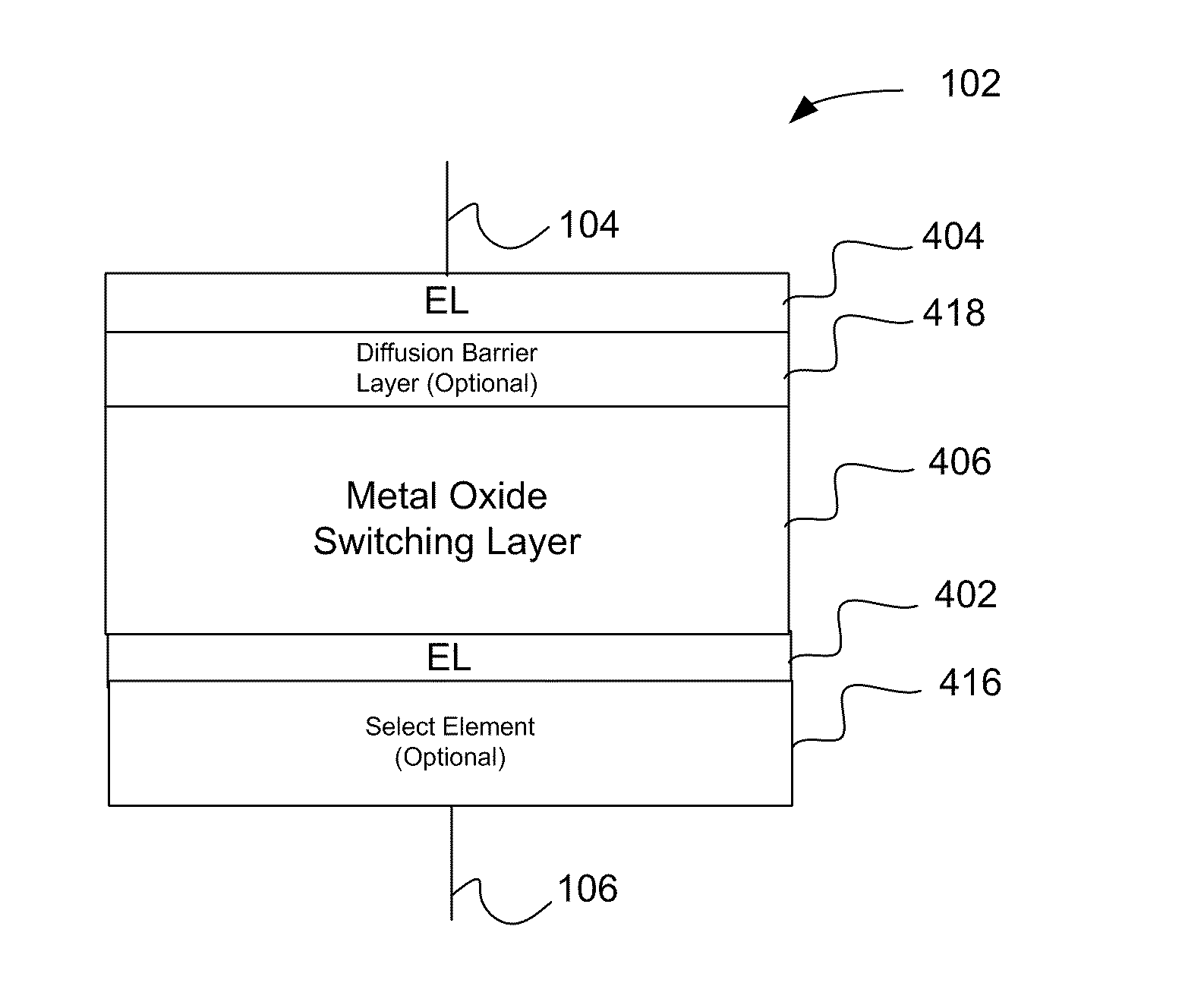

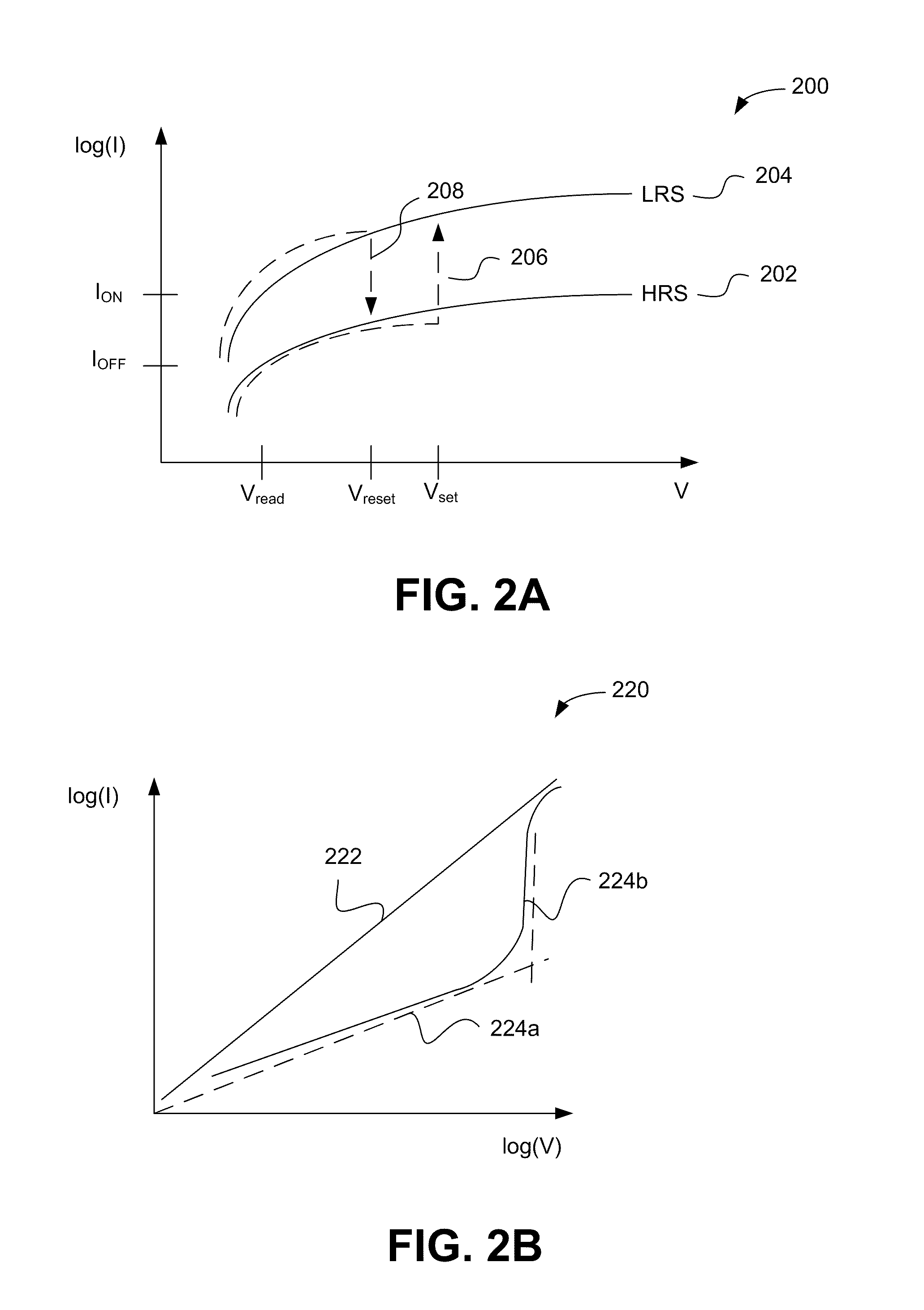

Resistive switching memory element including doped silicon electrode

A resistive switching memory element including a doped silicon electrode is described, including a first electrode comprising doped silicon having a first work function, a second electrode having a second work function that is different from the first work function by between 0.1 and 1.0 electron volts (eV), a metal oxide layer between the first electrode and the second electrode, the metal oxide layer switches using bulk-mediated switching and has a bandgap of greater than 4 eV, and the memory element switches from a low resistance state to a high resistance state and vice versa.

Owner:INTERMOLECULAR

Drillable drill bit nozzle

InactiveUS6848517B2Thin structureImprove corrosion resistanceDrill bitsDrilling rodsHigh resistanceRubber material

A drill bit nozzle providing a through bore for the passage of drilling fluid through a drill bit. The nozzle is made of a material or materials which can be drilled through by standard well bore drilling equipment. The material(s) are selected to provide a surface to the through bore which has a relatively high resistance to erosion to withstand the abrasive and corrosive impact of jetted drilling fluid. Embodiments are described using a hard chrome / copper combination and a single rubber material.

Owner:WEATHERFORD TECH HLDG LLC

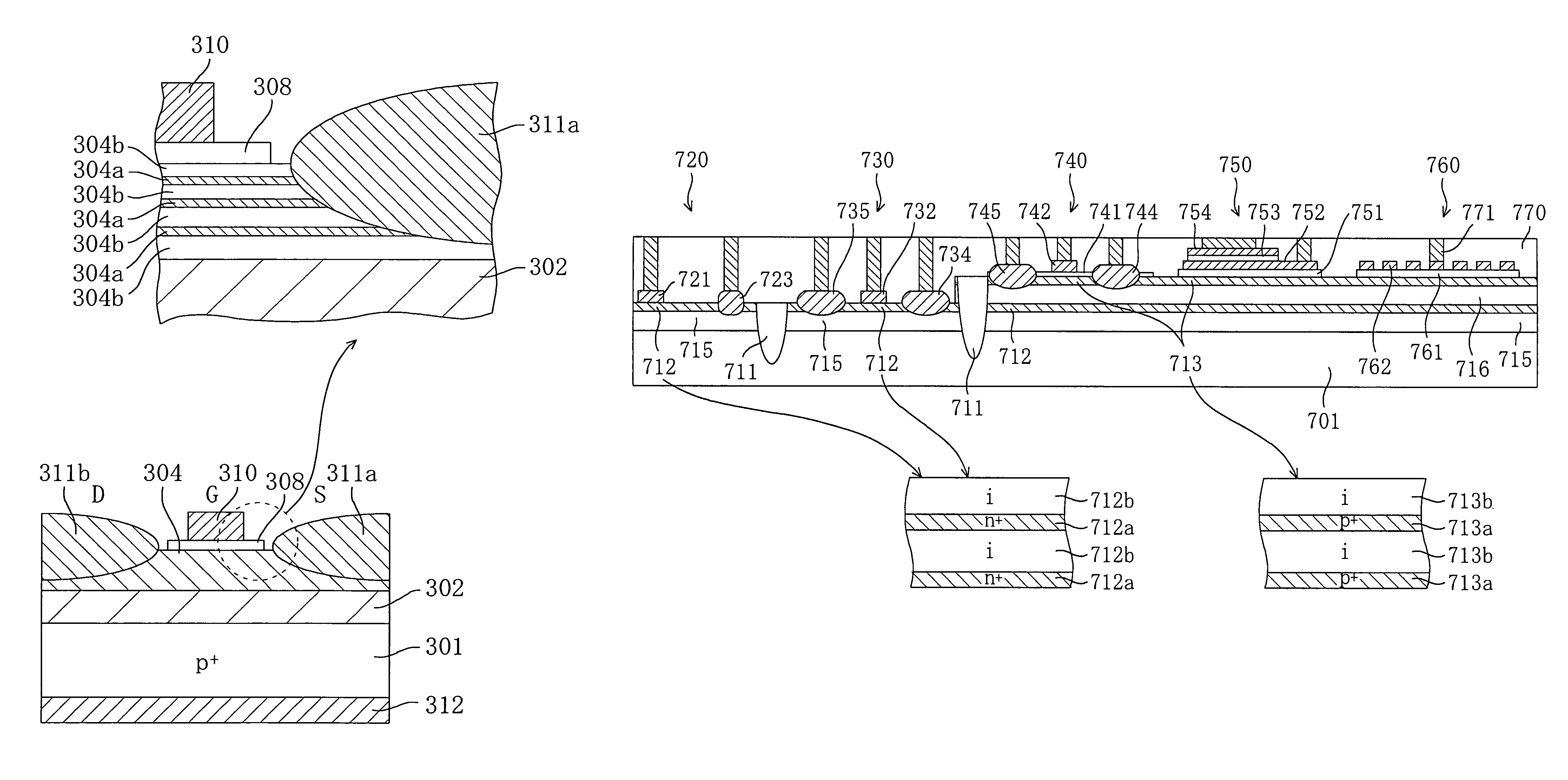

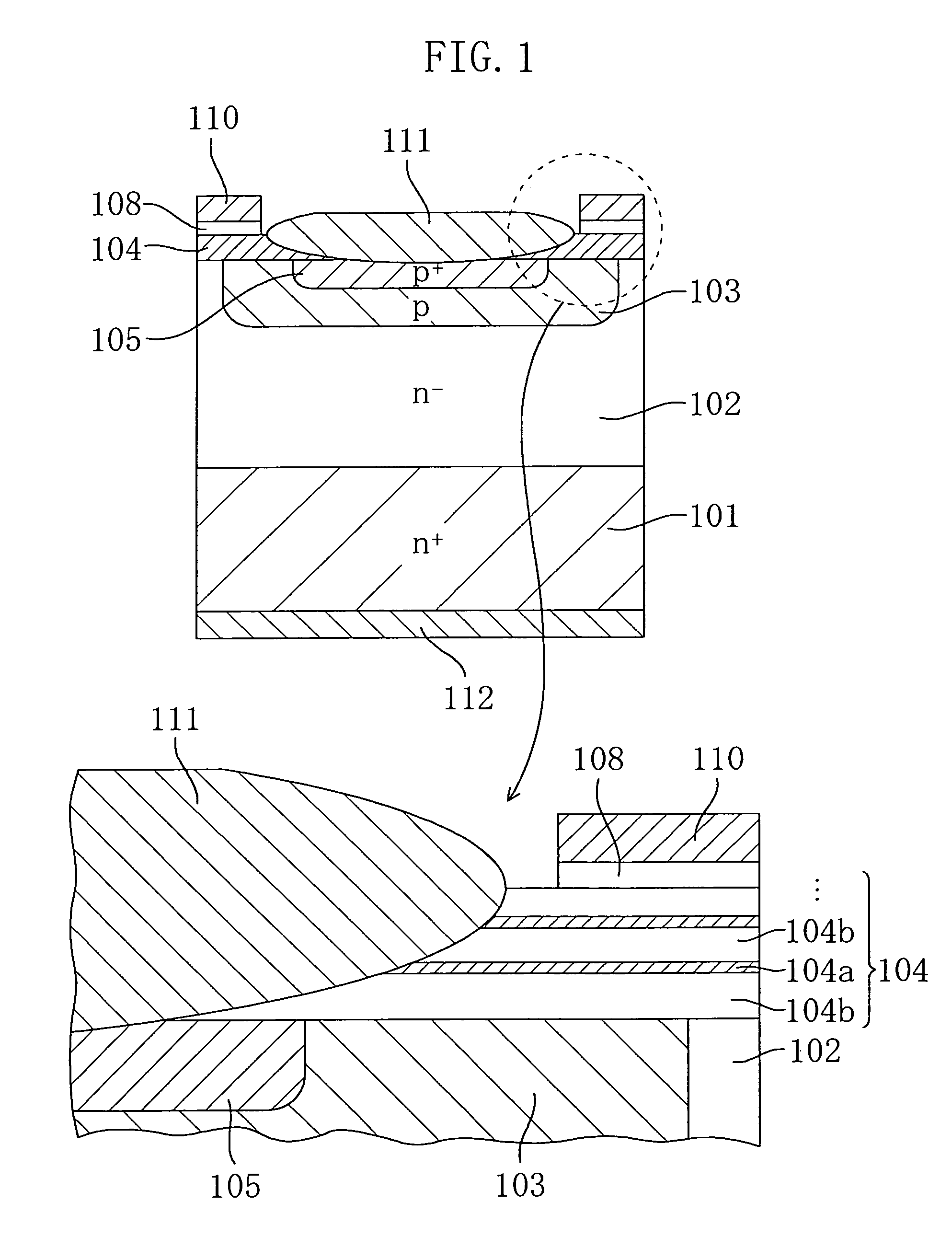

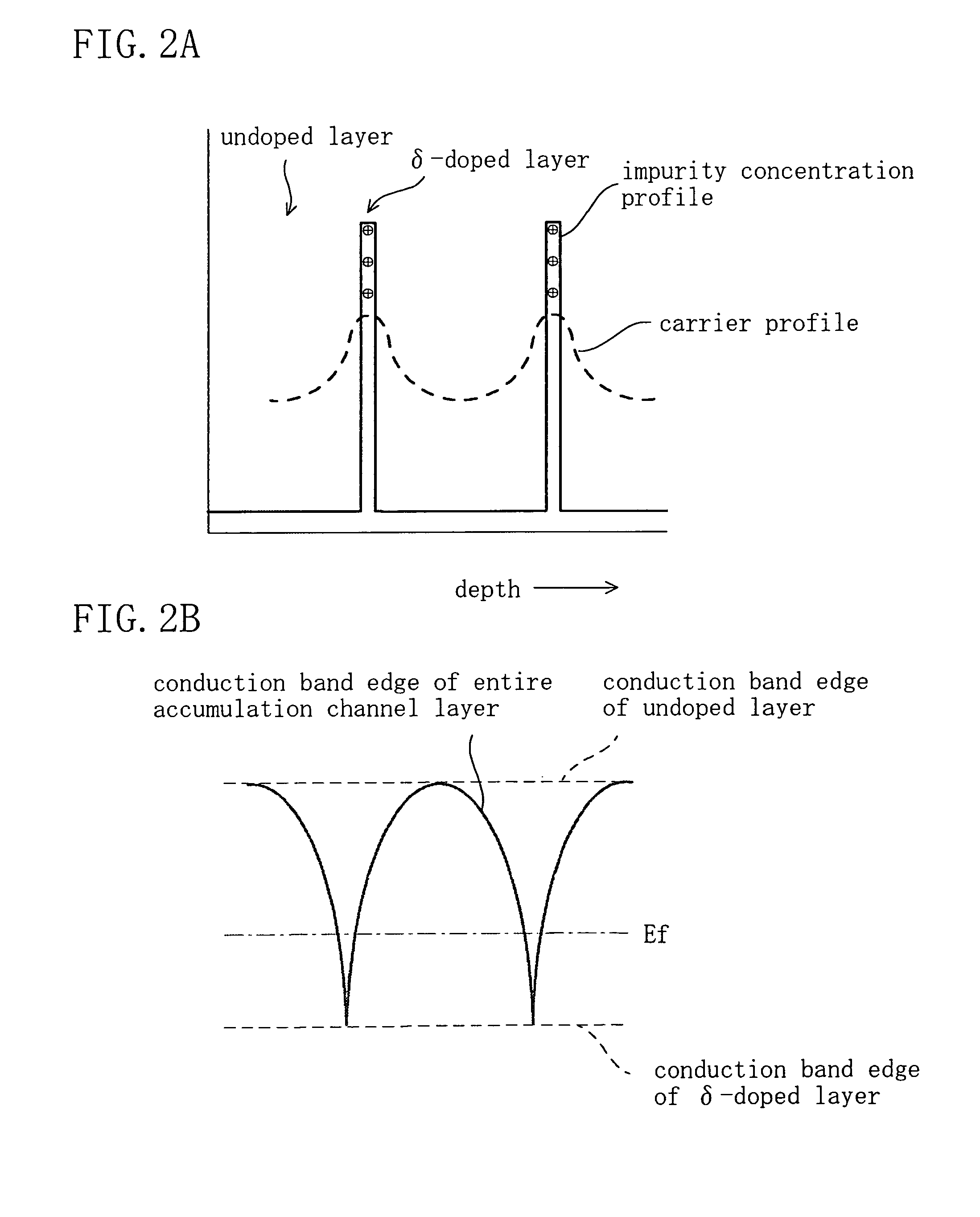

Semiconductor device and method for manufacturing same

InactiveUS7507999B2Improve breakdown voltageReduce lossTransistorSolid-state devicesHigh resistanceSic substrate

An accumulation-mode MISFET comprises: a high-resistance SiC layer 102 epitaxially grown on a SiC substrate 101; a well region 103; an accumulation channel layer 104 having a multiple δ-doped layer formed on the surface region of the well region 103; a contact region 105; a gate insulating film 108; and a gate electrode 110. The accumulation channel layer 104 has a structure in which undoped layers 104b and δ-doped layers 104a allowing spreading movement of carriers to the undoped layers 104b under a quantum effect are alternately stacked. A source electrode 111 is provided which enters into the accumulation channel layer 104 and the contact region 105 to come into direct contact with the contact region 105. It becomes unnecessary that a source region is formed by ion implantation, leading to reduction in fabrication cost.

Owner:PANASONIC CORP

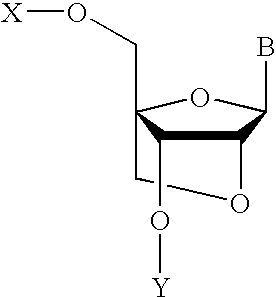

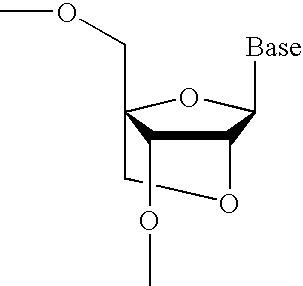

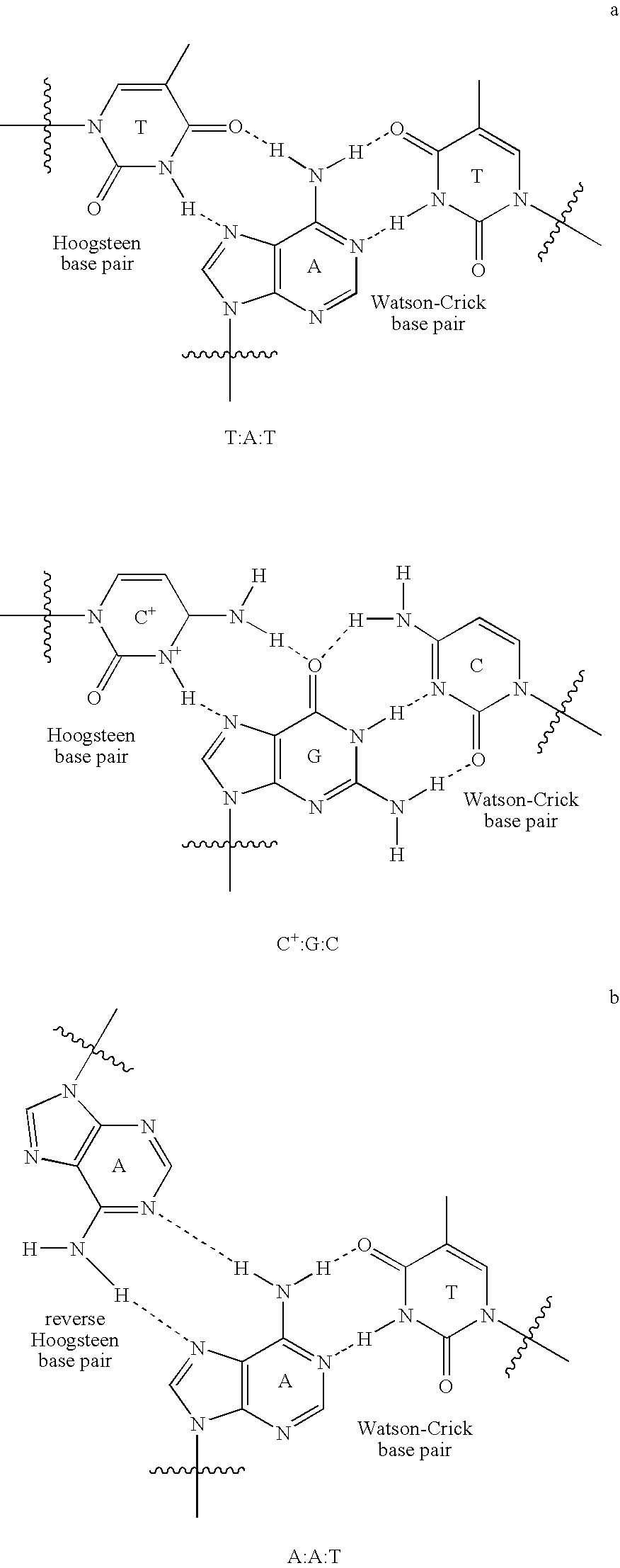

Nucleoside analogs and oligonucleotide derivatives containing these analogs

Nucleoside analogues expressed by the following general formula where B represents an aromatic base having carbonyl oxygen at the 2-position, or a 2-hydroxyphenyl group, or oligonucleotide derivatives containing one or more of the nucleoside analogues are provided.The oligonucleotide derivatives are triplex-forming oligonucleotide derivatives which bind specifically to target double-stranded DNA with high affinity in the antigene method to form triplexes, and can thereby control and inhibit the expression of relevant genes efficiently, and which show high resistance to nucleases.

Owner:IMANISHI TAKESHI

Two-terminal nanotube devices and systems and methods of making same

ActiveUS20080012047A1Minimize flow of heatImprove conductivityNanoinformaticsSolid-state devicesHigh resistanceNanotube

A two terminal switching device includes first and second conductive terminals and a nanotube article. The article has at least one nanotube, and overlaps at least a portion of each of the first and second terminals. The device also includes a stimulus circuit in electrical communication with at least one of the first and second terminals. The circuit is capable of applying first and second electrical stimuli to at least one of the first and second terminal(s) to change the relative resistance of the device between the first and second terminals between a relatively high resistance and a relatively low resistance. The relatively high resistance between the first and second terminals corresponds to a first state of the device, and the relatively low resistance between the first and second terminals corresponds to a second state of the device.

Owner:NANTERO

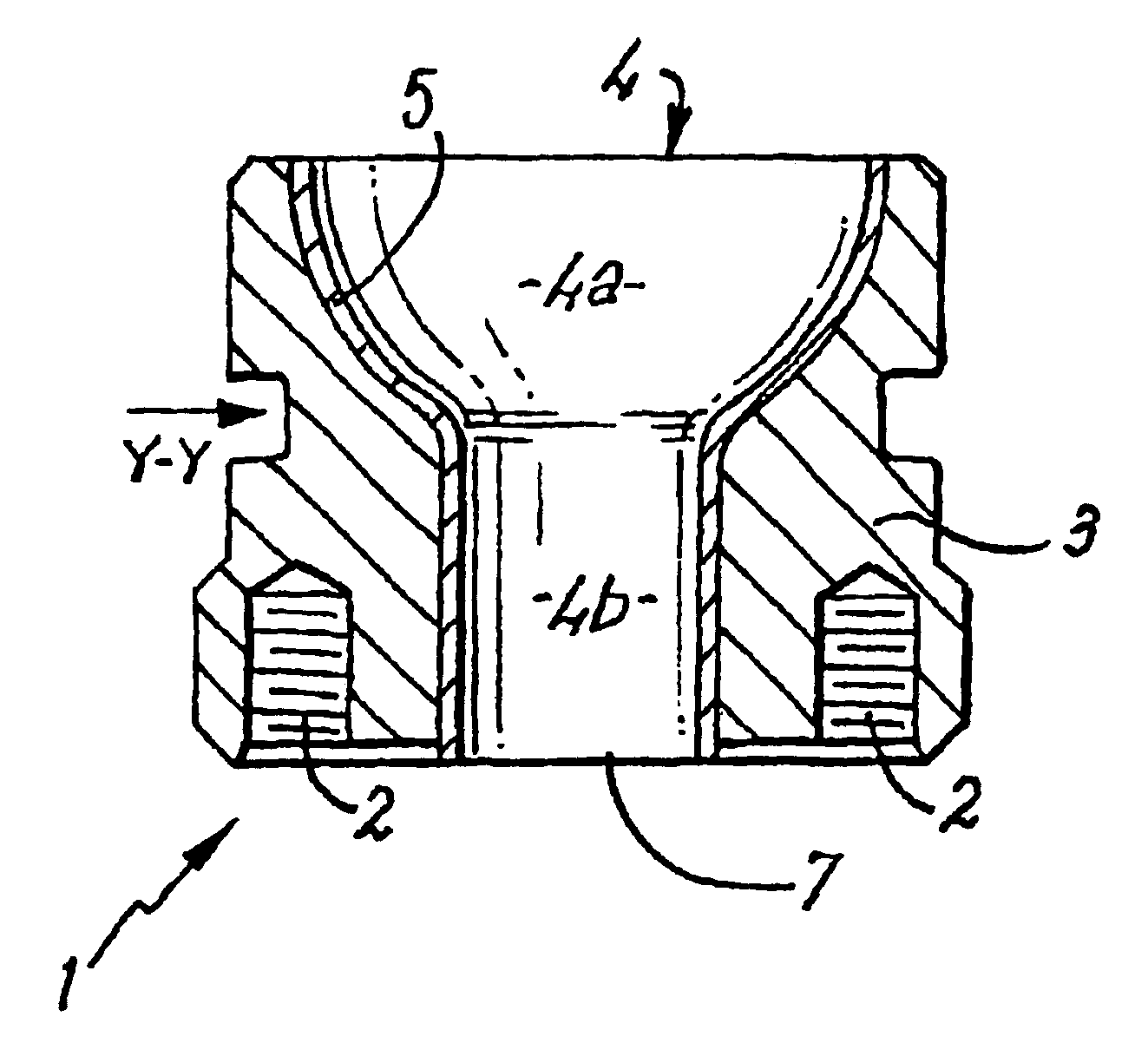

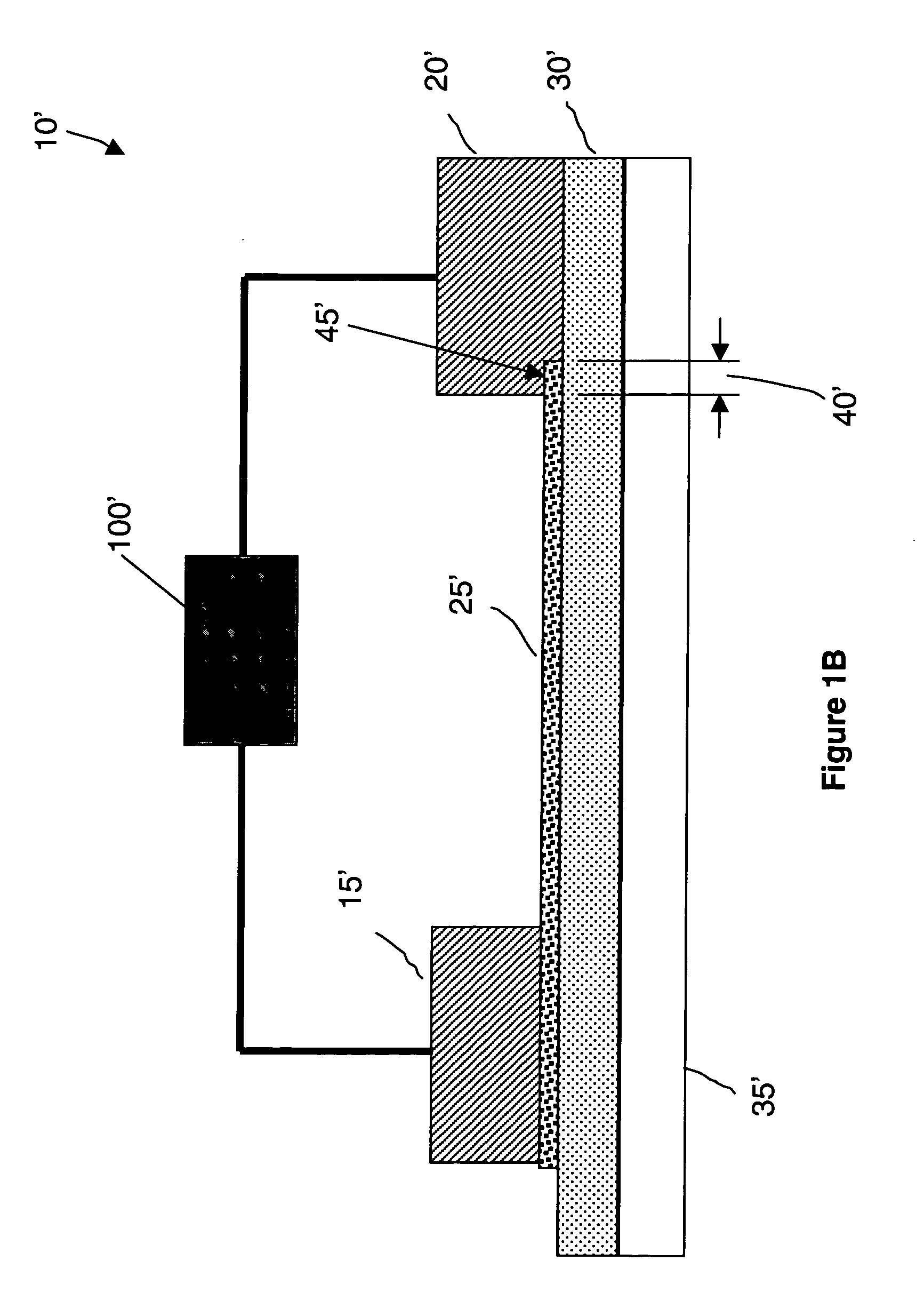

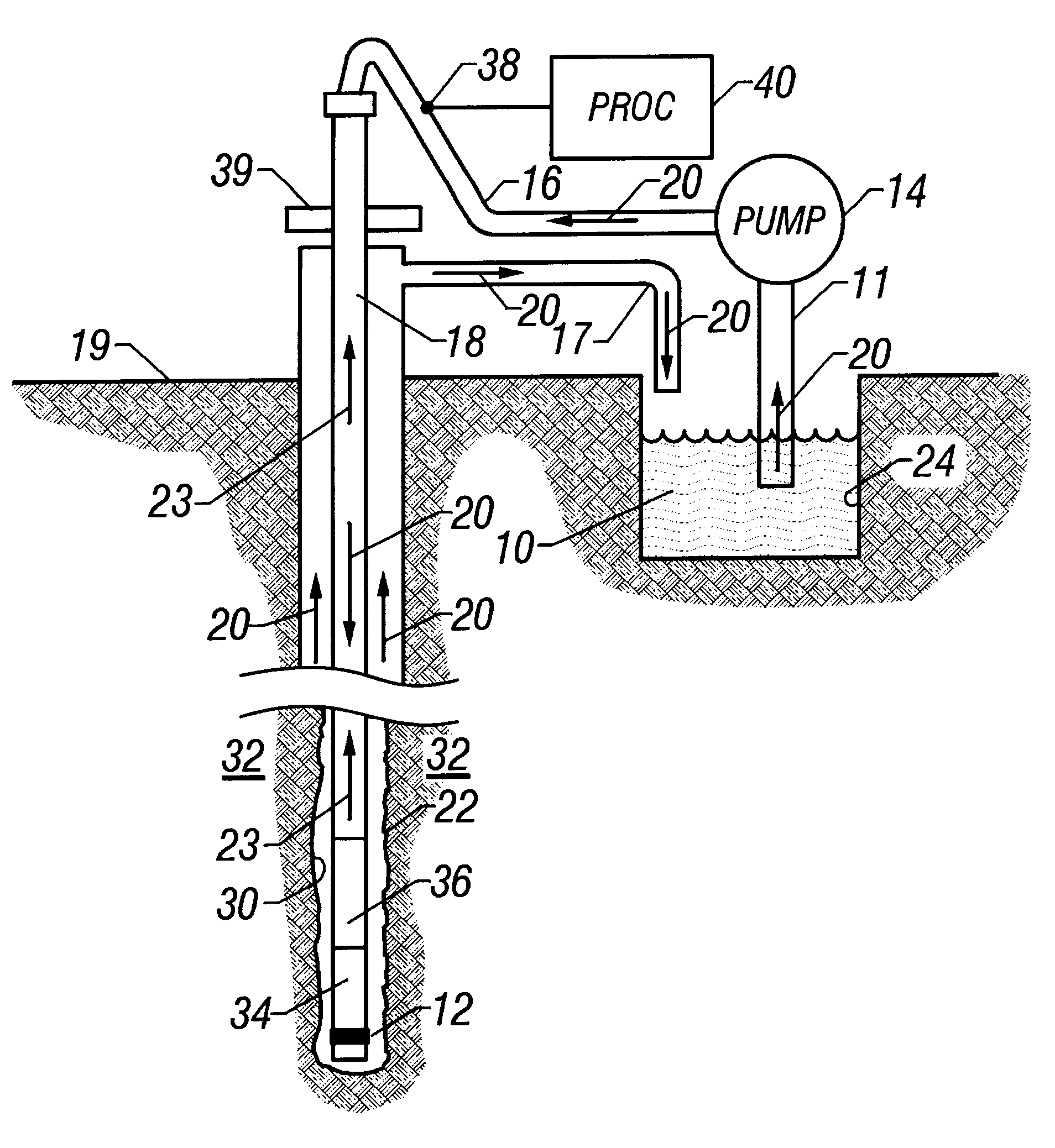

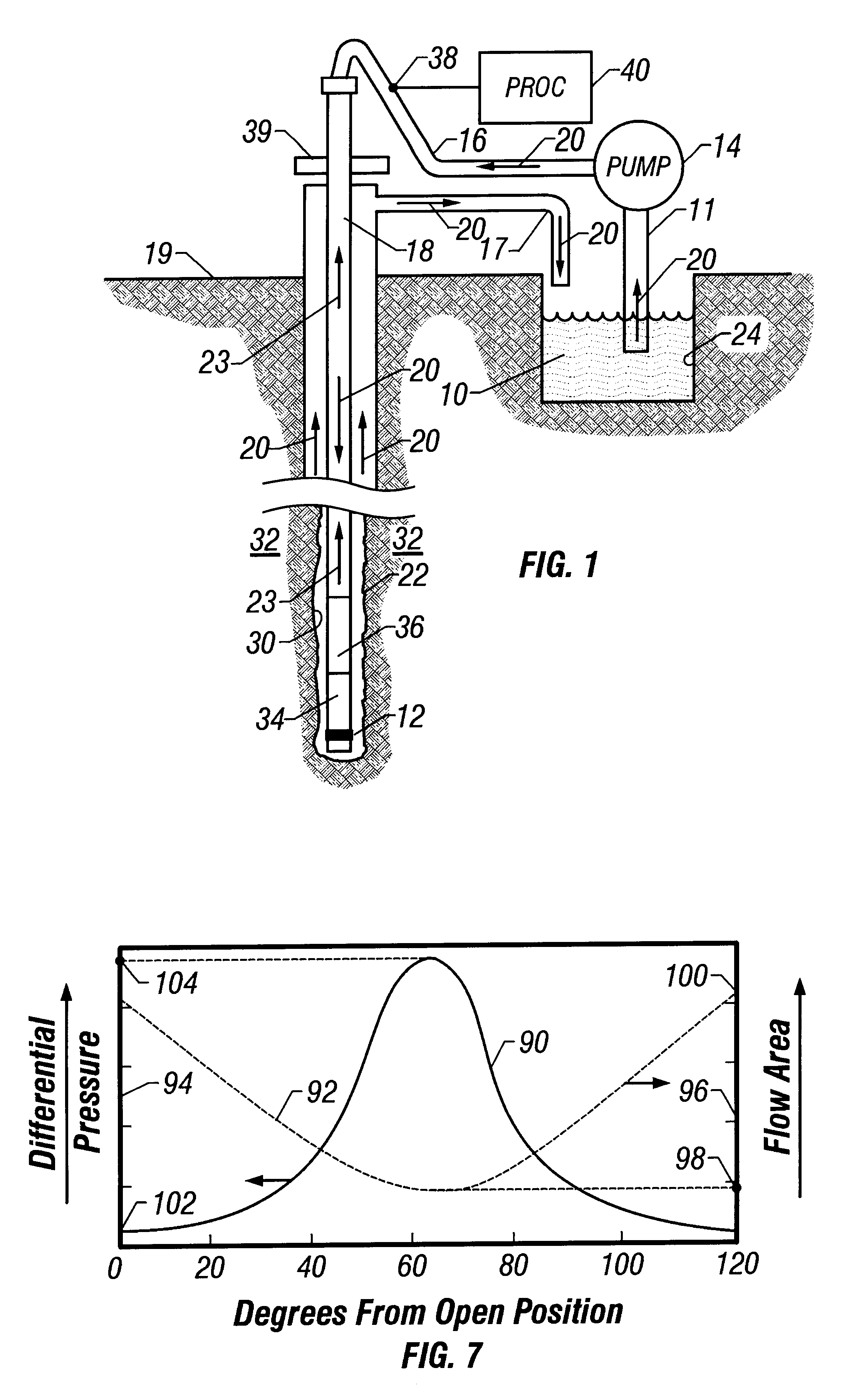

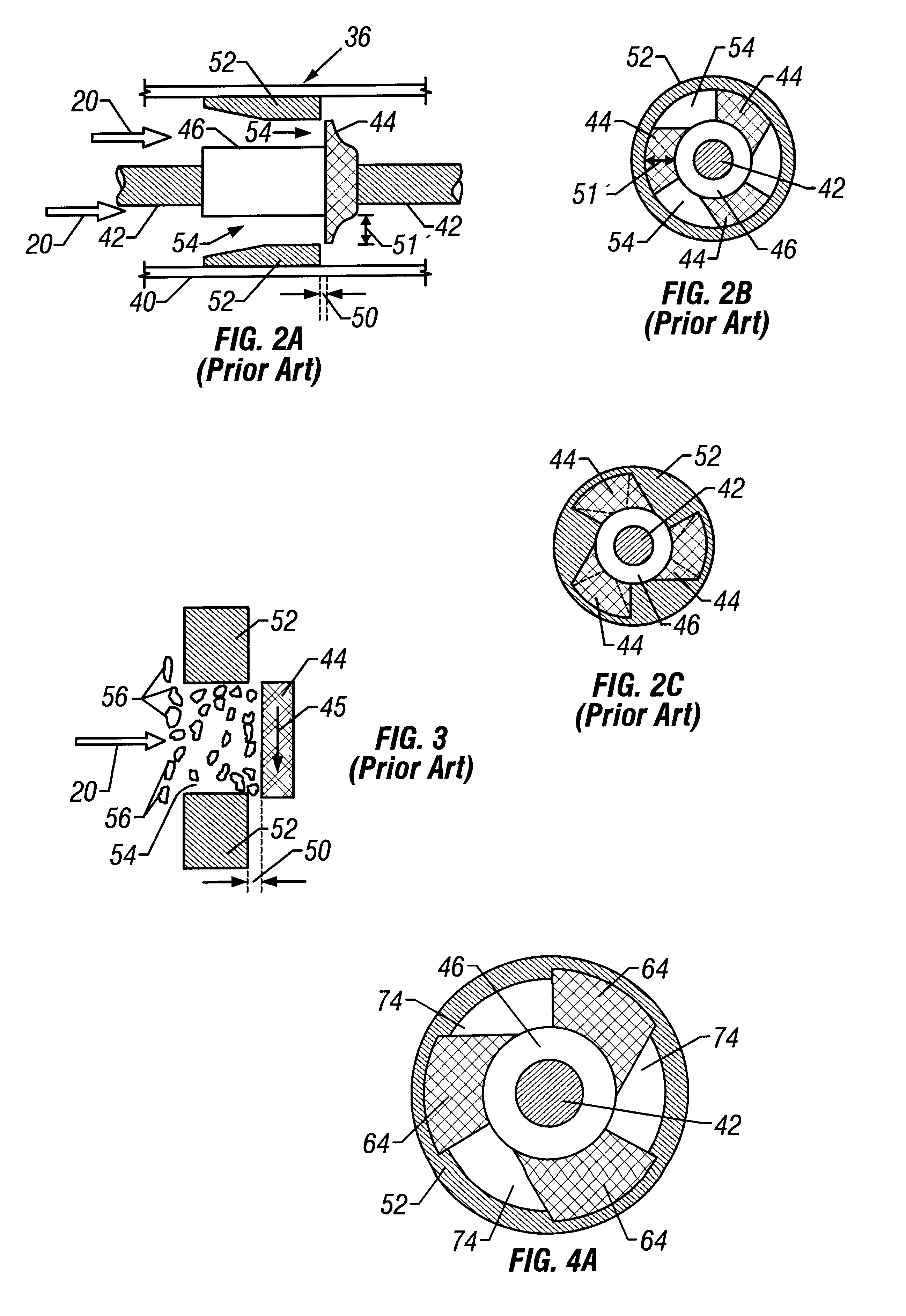

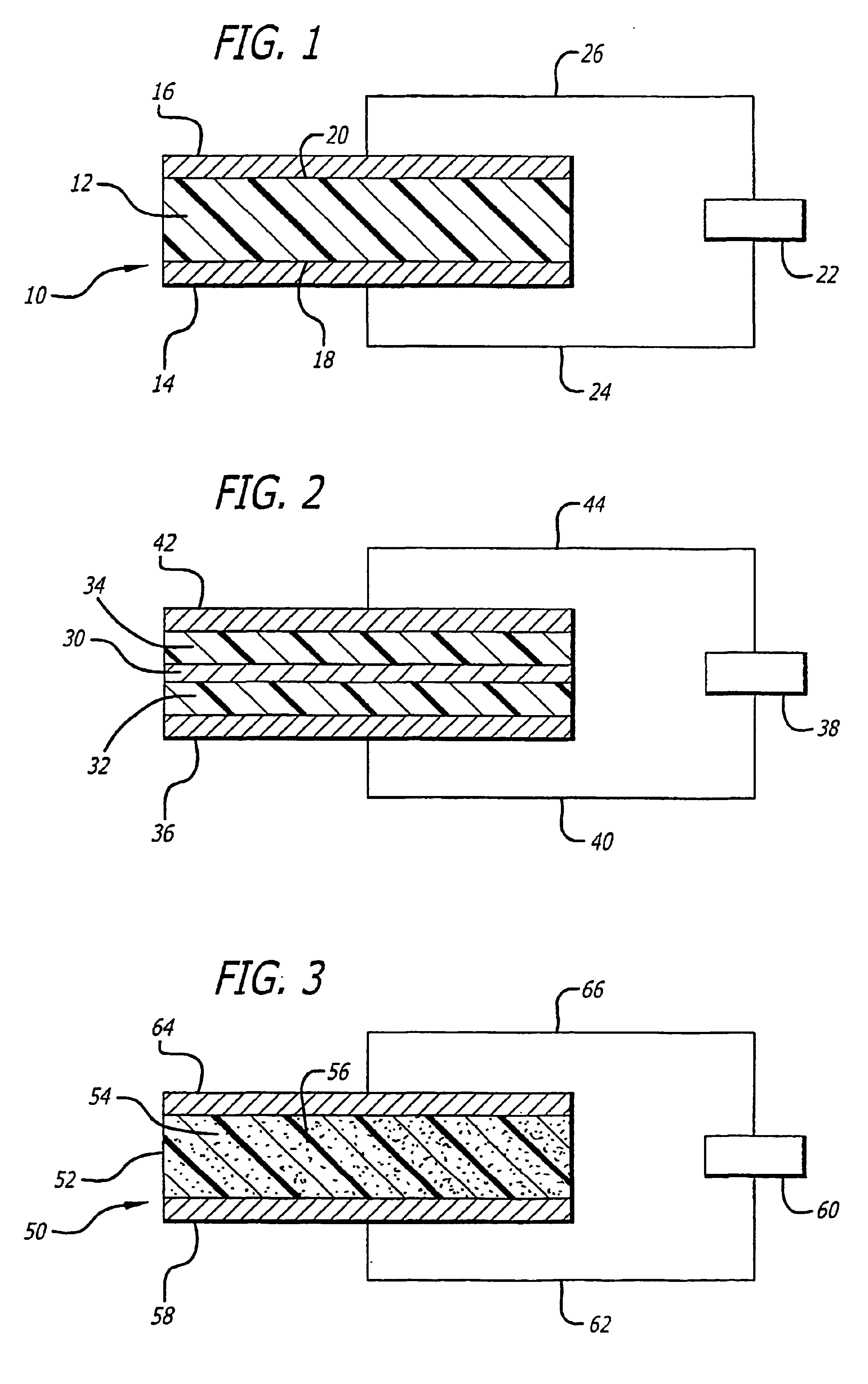

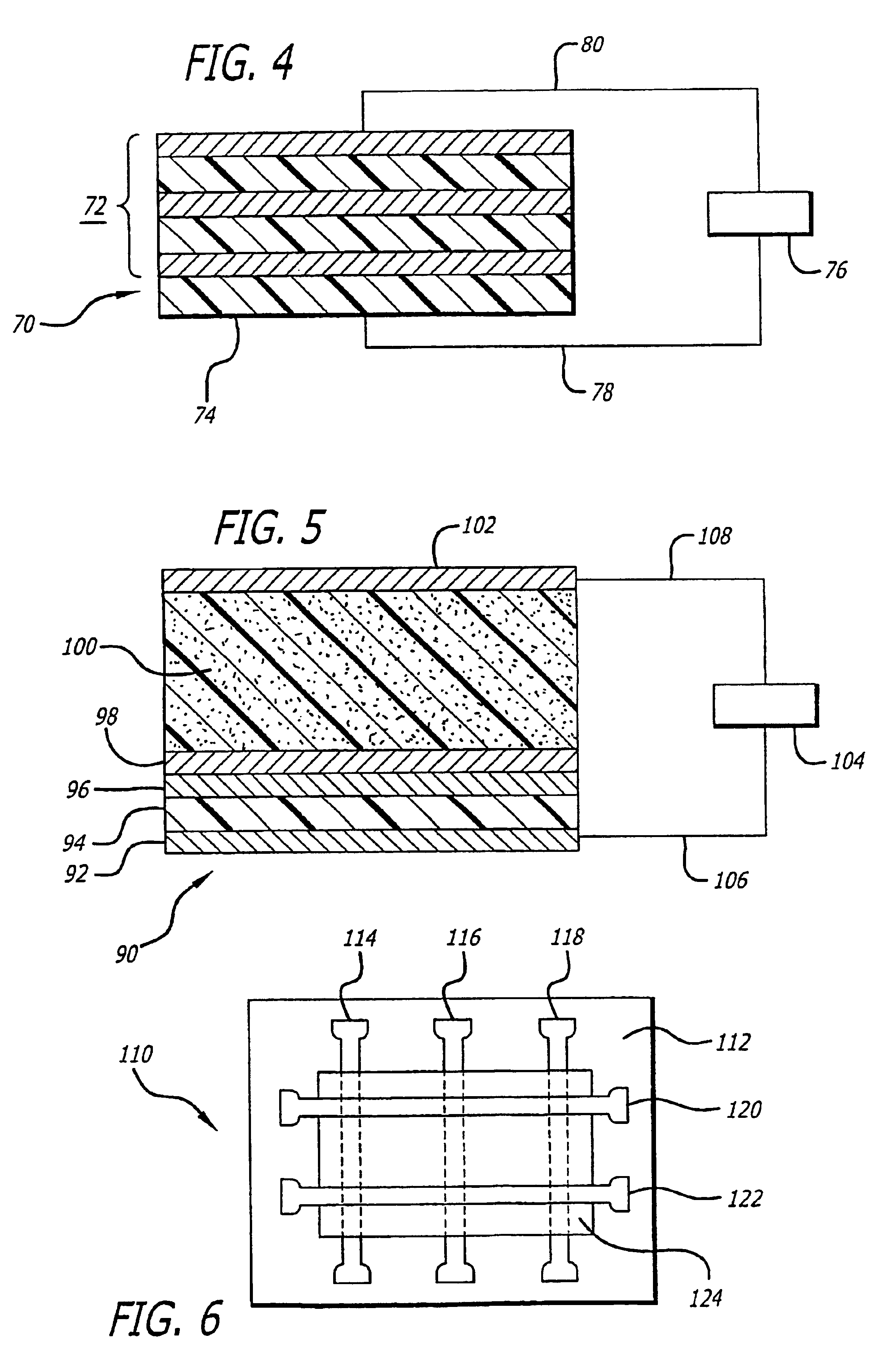

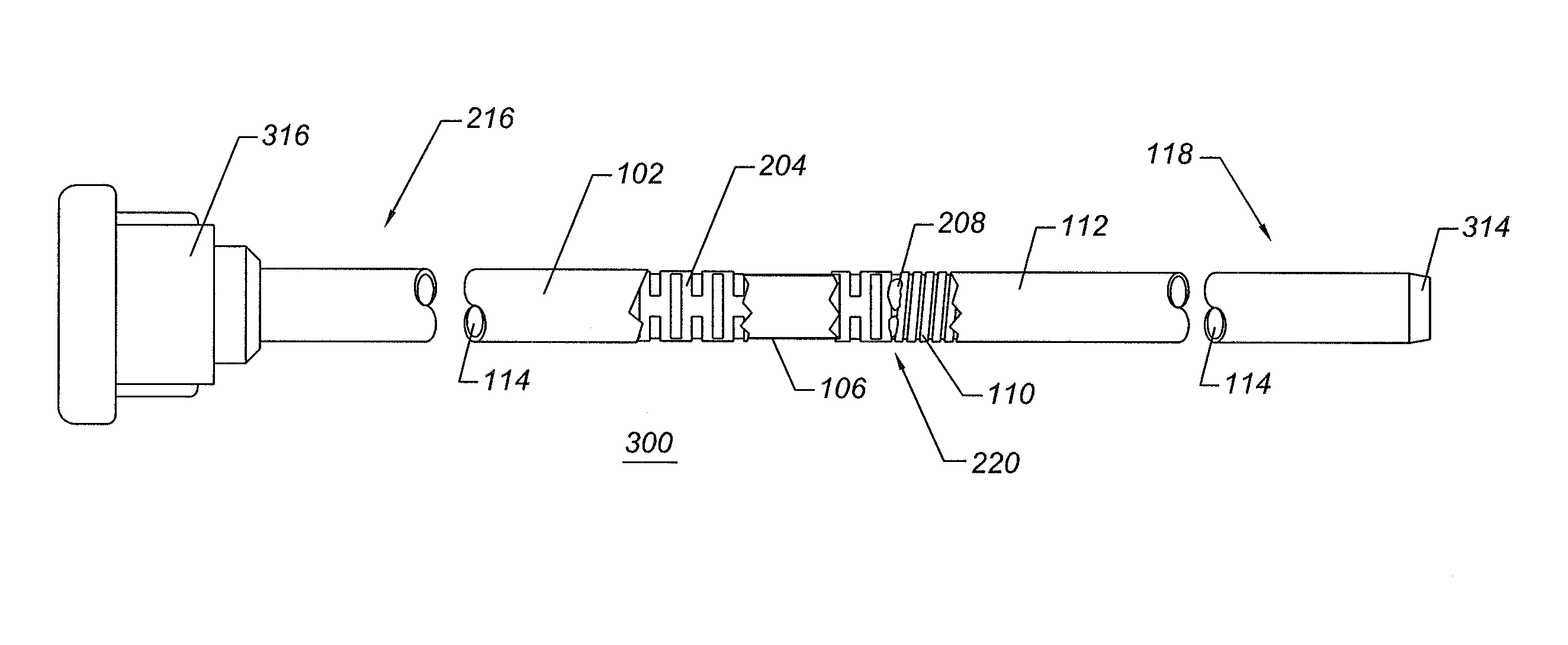

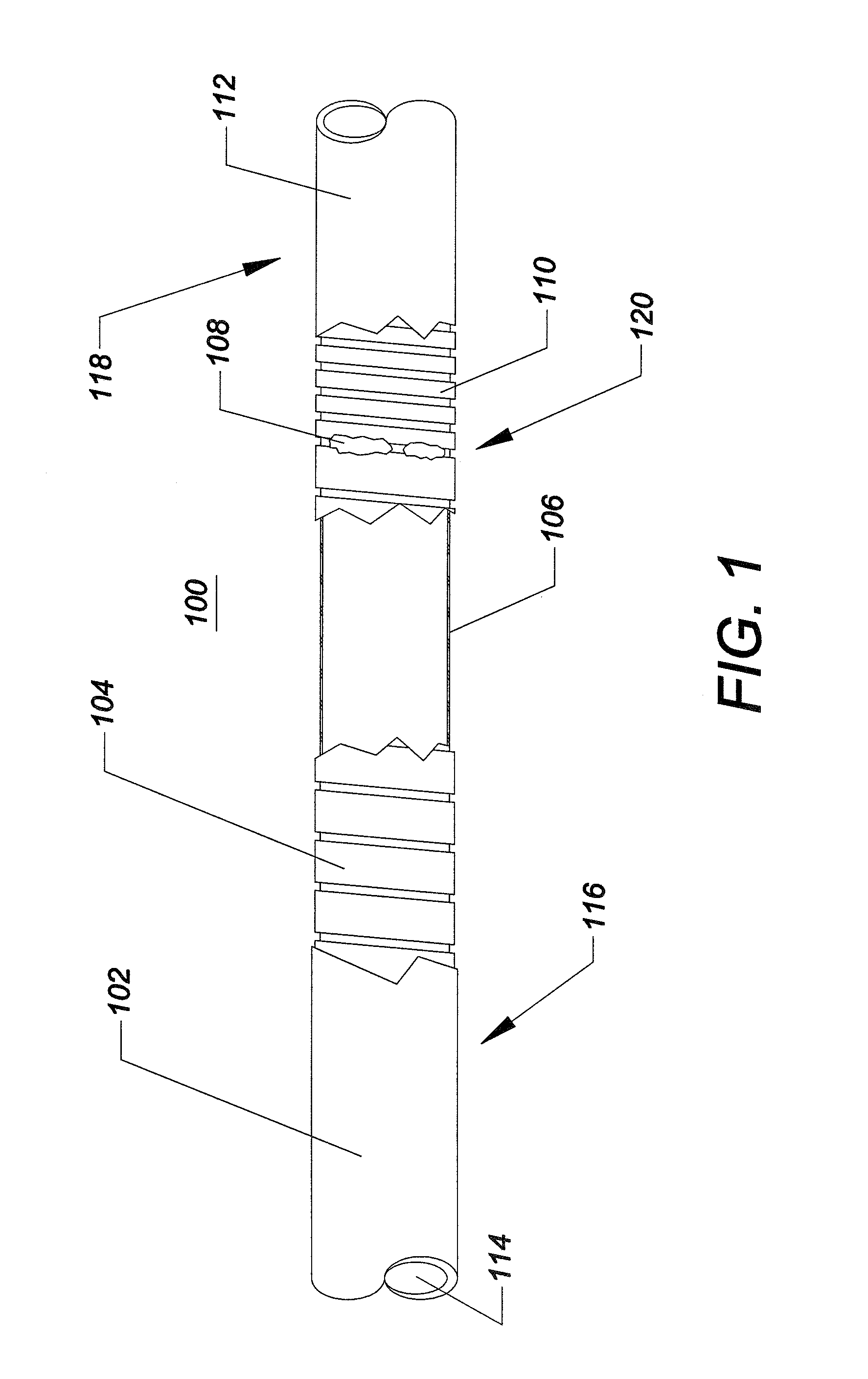

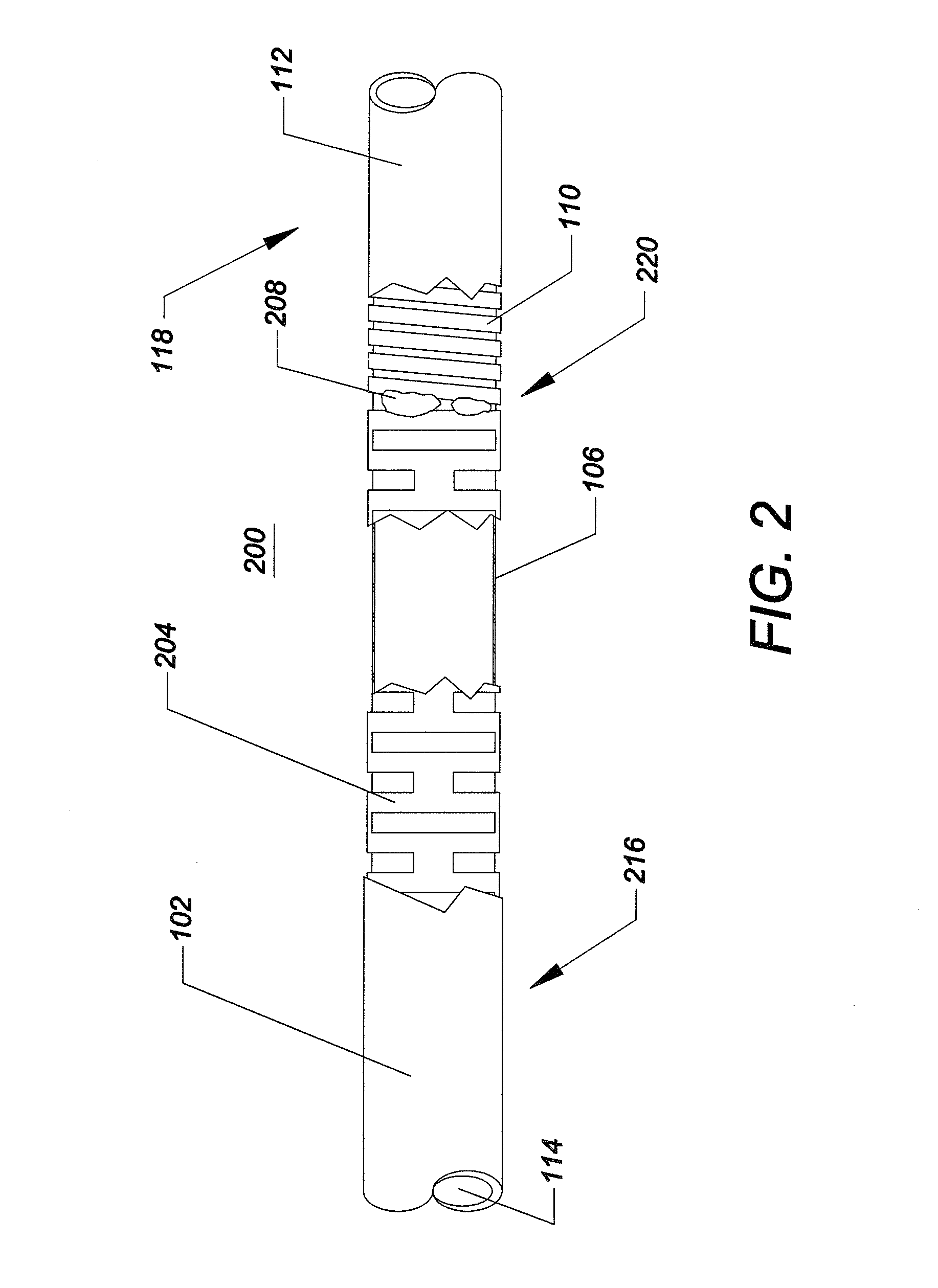

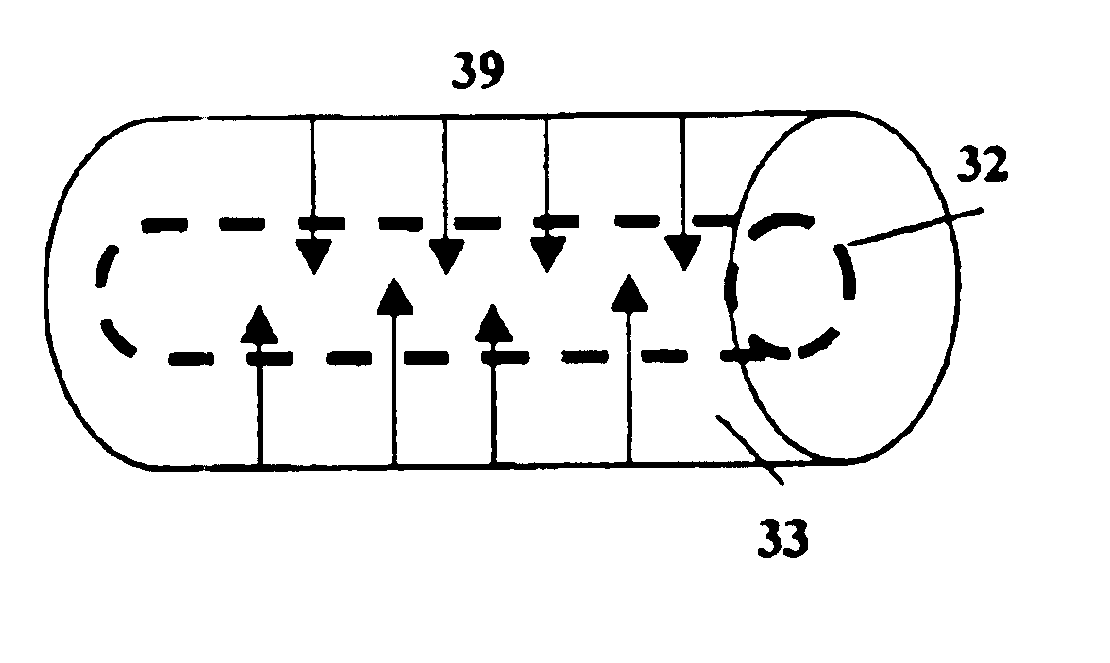

Pressure pulse generator for measurement-while-drilling systems which produces high signal strength and exhibits high resistance to jamming

InactiveUS6219301B1Easy to useIncrease signal strengthSurveyConstructionsHigh resistanceParticulates

A system is disclosed for generating and transmitting data signals to the surface of the earth while drilling a borehole, the system operating by generating pressure pulses in the drilling fluid filling the drill string. The system is designed to maximize signal strength while minimizing the probability of jamming by drilling fluid particulates. The system uses a rotary valve modulator consisting of a stator with flow orifices through which drilling fluid flows, and a rotor which rotates with respect to the stator thereby opening and restricting flow through the orifices and thereby generating pressure pulses. The flow orifices with the stator in a "closed" position are configured to reduce jamming, and to simultaneously minimize flow area in order to maximize signal strength. This is accomplished by imparting a shear to the fluid flow through the modulator, and minimizing the aspect ratio and maximizing the minimum principal dimension of the closed flow area. A preferred embodiment and three alternate embodiments of the modulator are disclosed.

Owner:SCHLUMBERGER TECH CORP

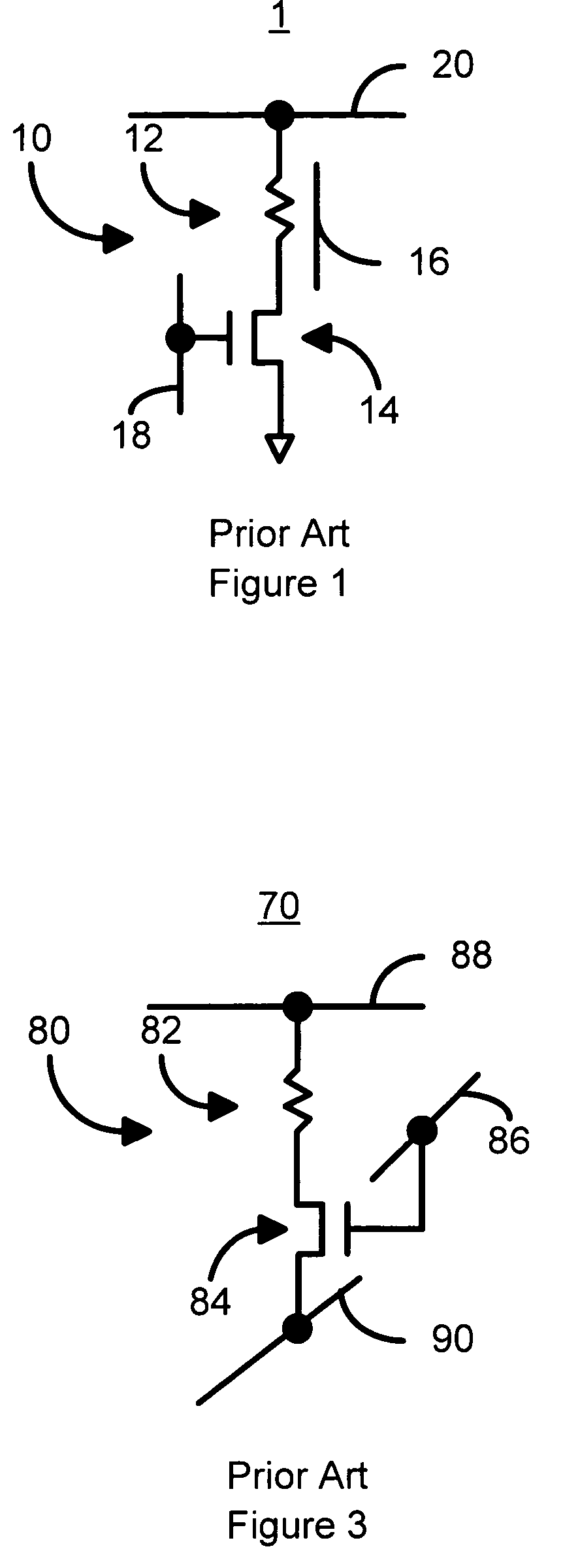

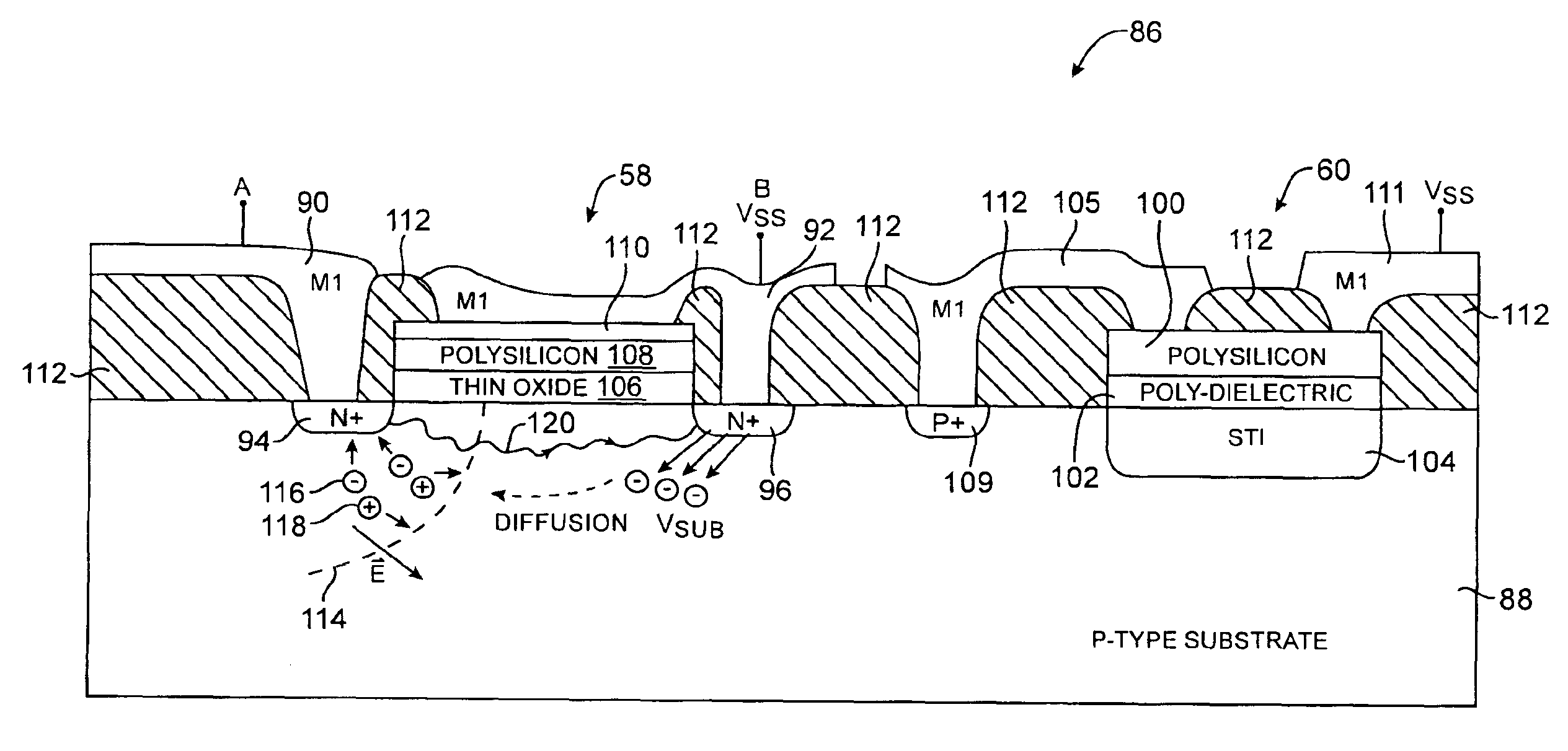

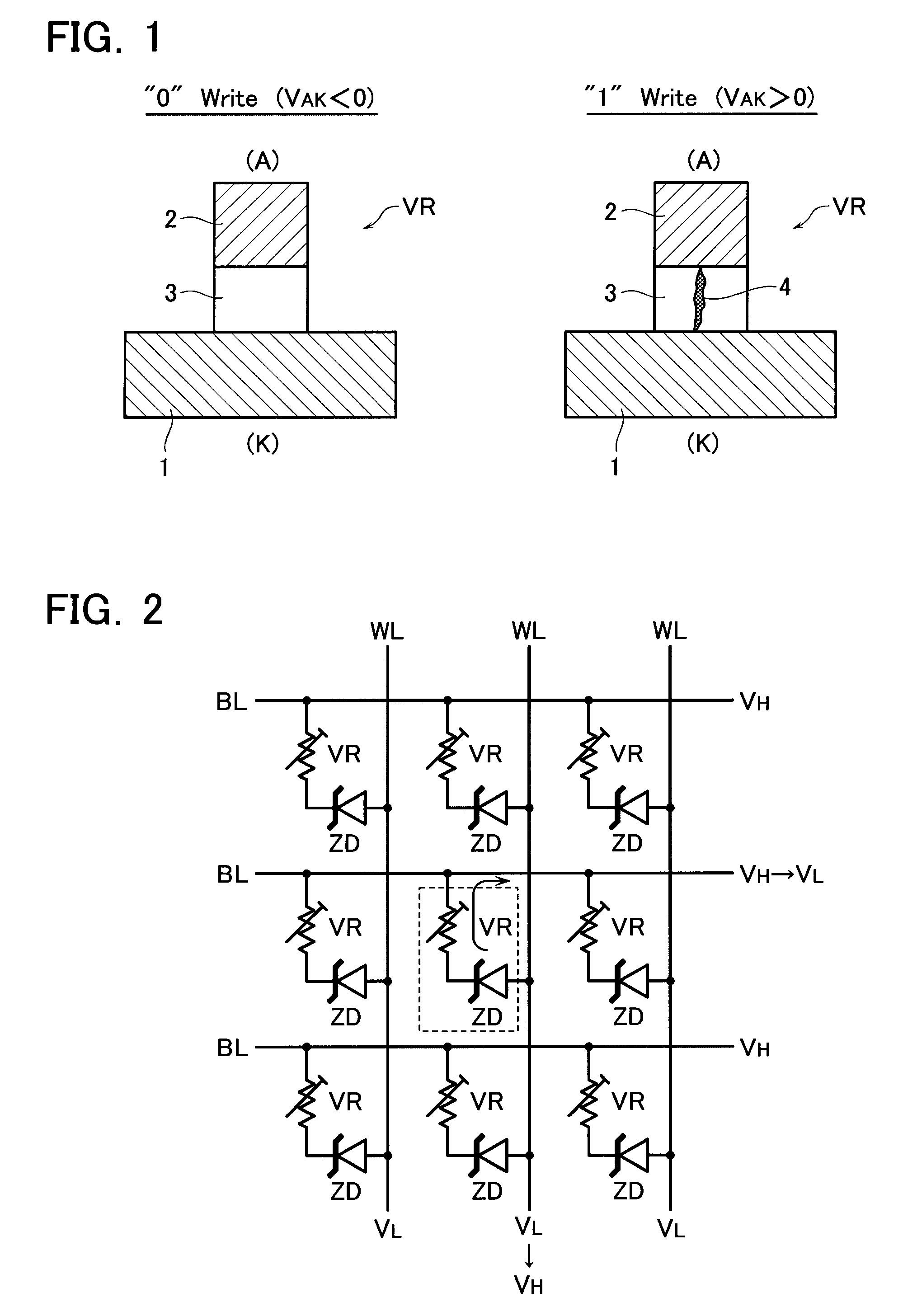

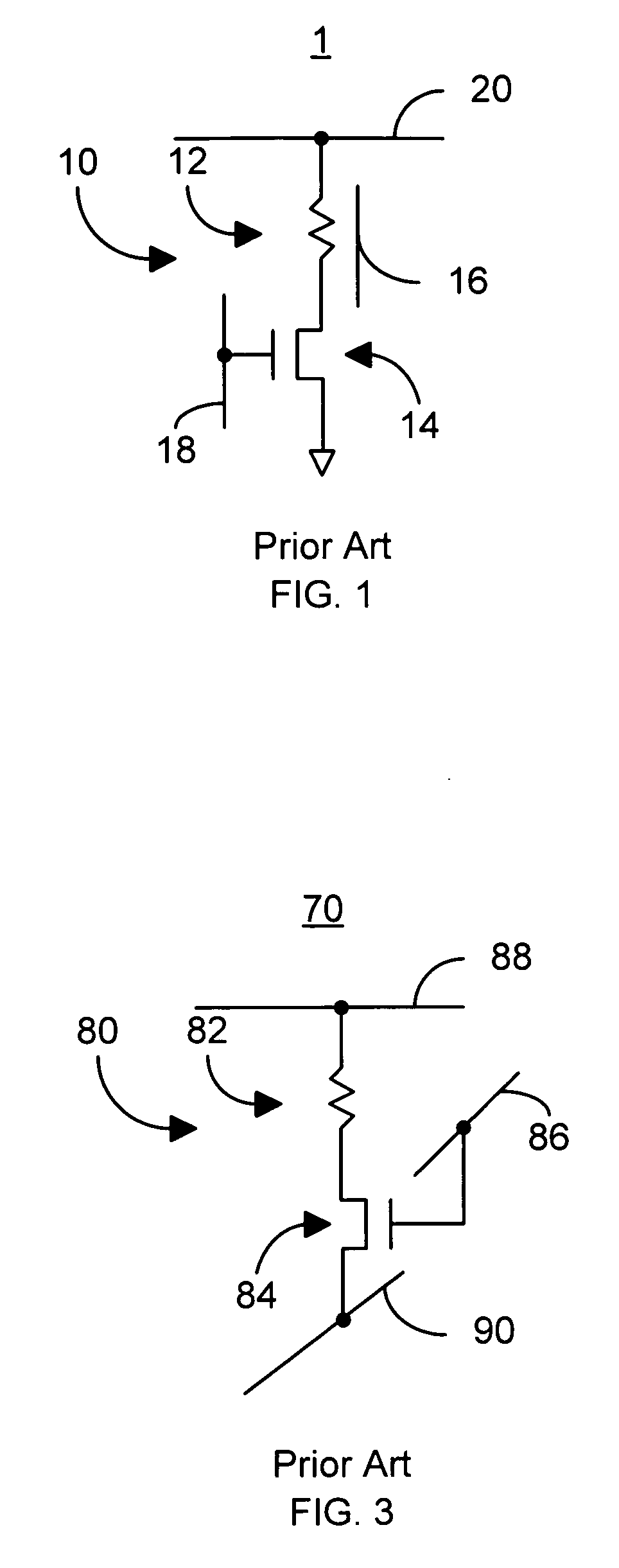

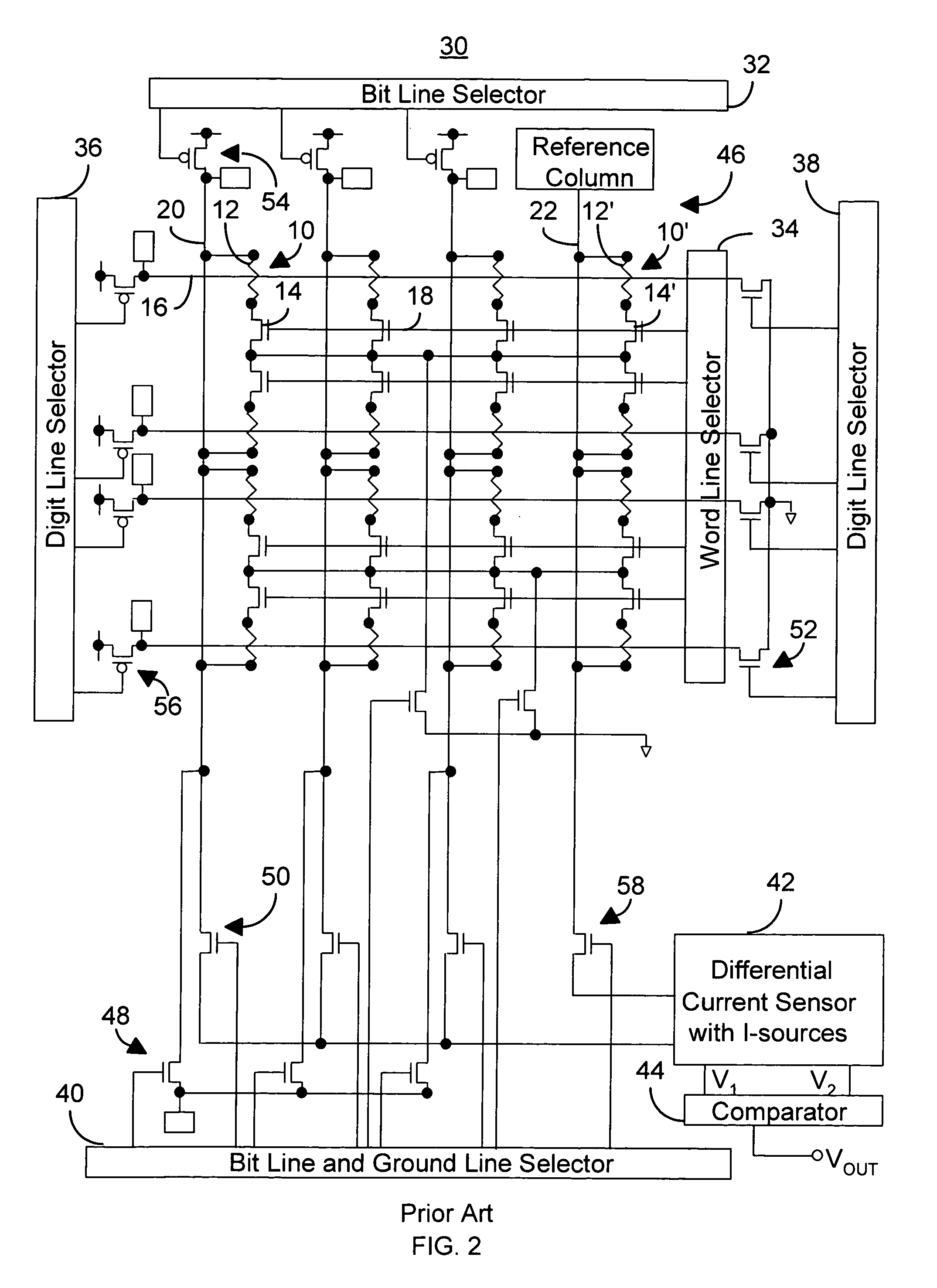

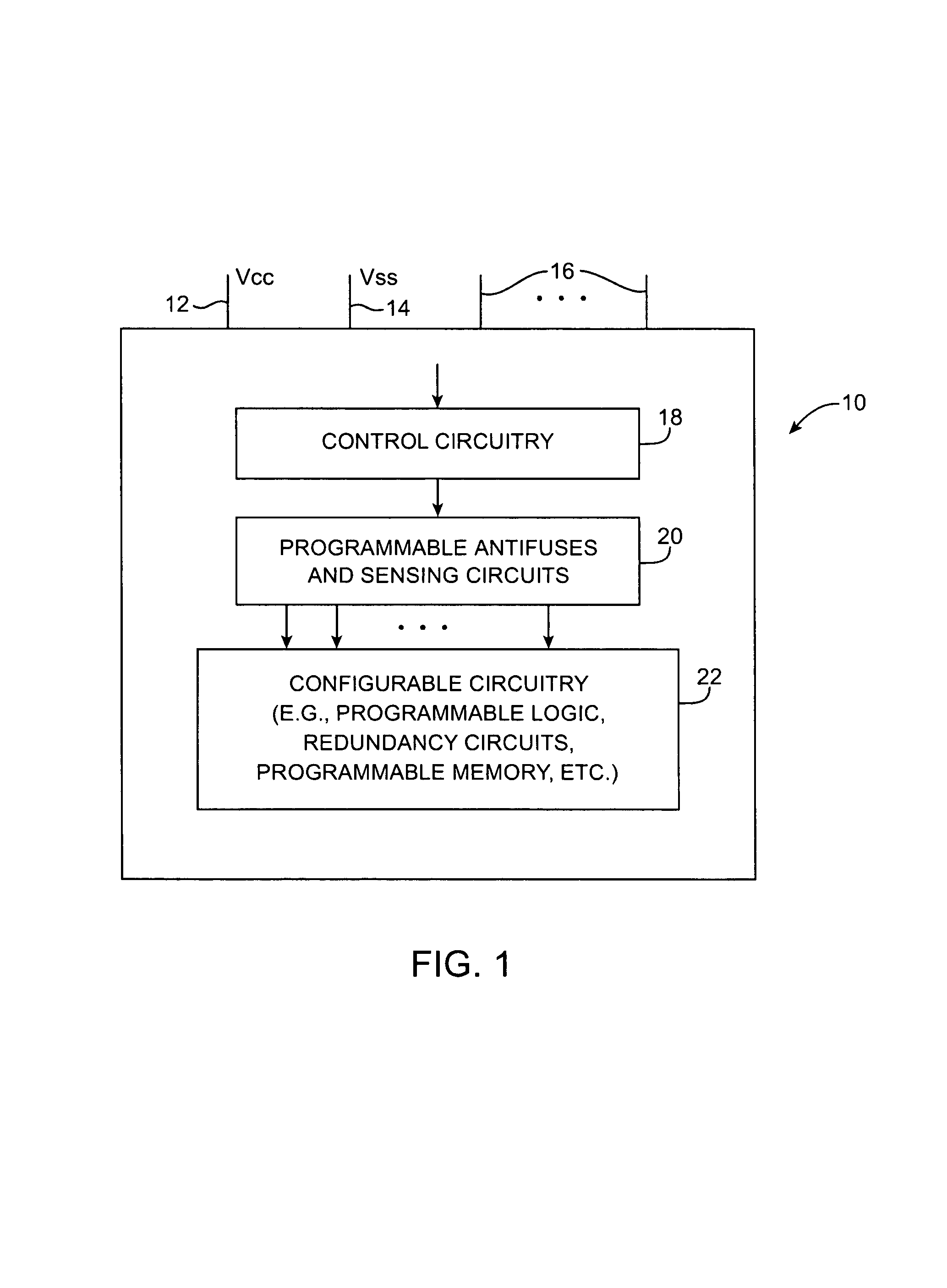

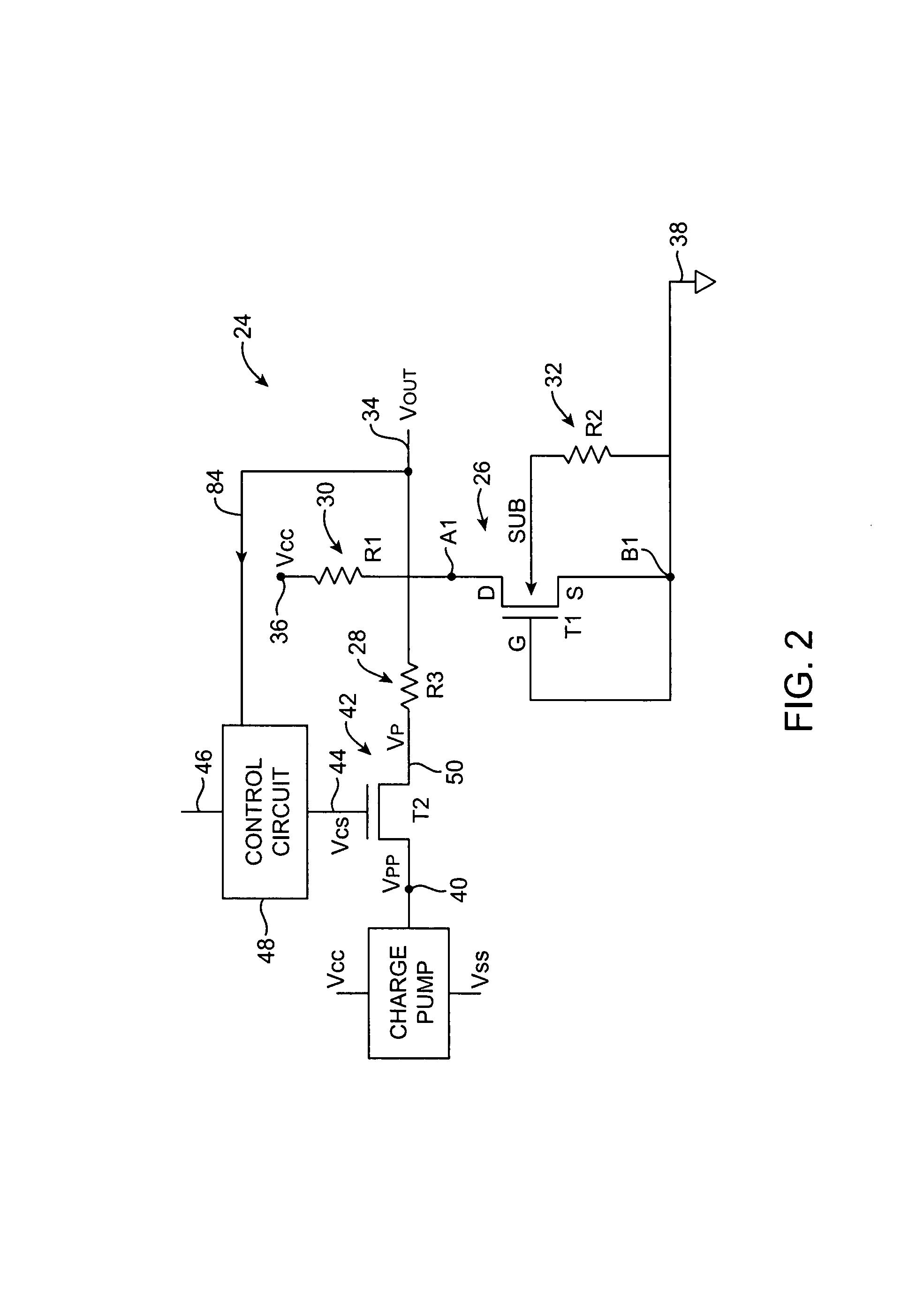

Electrically-programmable integrated circuit antifuses

InactiveUS6897543B1Reduces drain-to-source resistanceIncrease resistanceTransistorSemiconductor/solid-state device detailsHigh resistanceZener diode

Integrated circuit antifuse circuitry is provided. A metal-oxide-semiconductor (MOS) antifuse transistor serves as an electrically-programmable antifuse. In its unprogrammed state, the antifuse transistor is off and has a relatively high resistance. During programming, the antifuse transistor is turned on which melts the underlying silicon and causes a permanent reduction in the transistor's resistance. A sensing circuit monitors the resistance of the antifuse transistor and supplies a high or low output signal accordingly. The antifuse transistor may be turned on during programming by raising the voltage at its substrate relative to its source. The substrate may be connected to ground through a resistor. The substrate may be biased by causing current to flow through the resistor. Current may be made to flow through the resistor by inducing avalanche breakdown of the drain-substrate junction or by producing Zener breakdown of external Zener diode circuitry connected to the resistor.

Owner:TAHOE RES LTD

Organic bistable device and organic memory cells

A bistable electrical device (50) employing a bistable body (52) and a high conductivity material (54). A sufficient amount of high conductivity material (54) is included in the bistable body (52) to impart bistable between a low resistance state and a high resistance state by application of an electrical voltage (60).

Owner:RGT UNIV OF CALIFORNIA

Semiconductor apparatus

A semiconductor apparatus includes, a first silicon layer of a first conductivity type; a second silicon layer provided on the first silicon layer and having a higher resistance than the first silicon layer, a third silicon layer of a second conductivity type provided on the second silicon layer, a first nitride semiconductor layer provided on the third silicon layer, a second nitride semiconductor layer provided on the first nitride semiconductor layer and having a larger bandgap than the first nitride semiconductor layer, a first main electrode being in contact with a surface of the second nitride semiconductor layer and connected to the third silicon layer, a second main electrode being in contact with the surface of the second nitride semiconductor layer and connected to the first silicon layer, and a control electrode provided between the first main electrode and the second main electrode on the second nitride semiconductor layer.

Owner:KK TOSHIBA

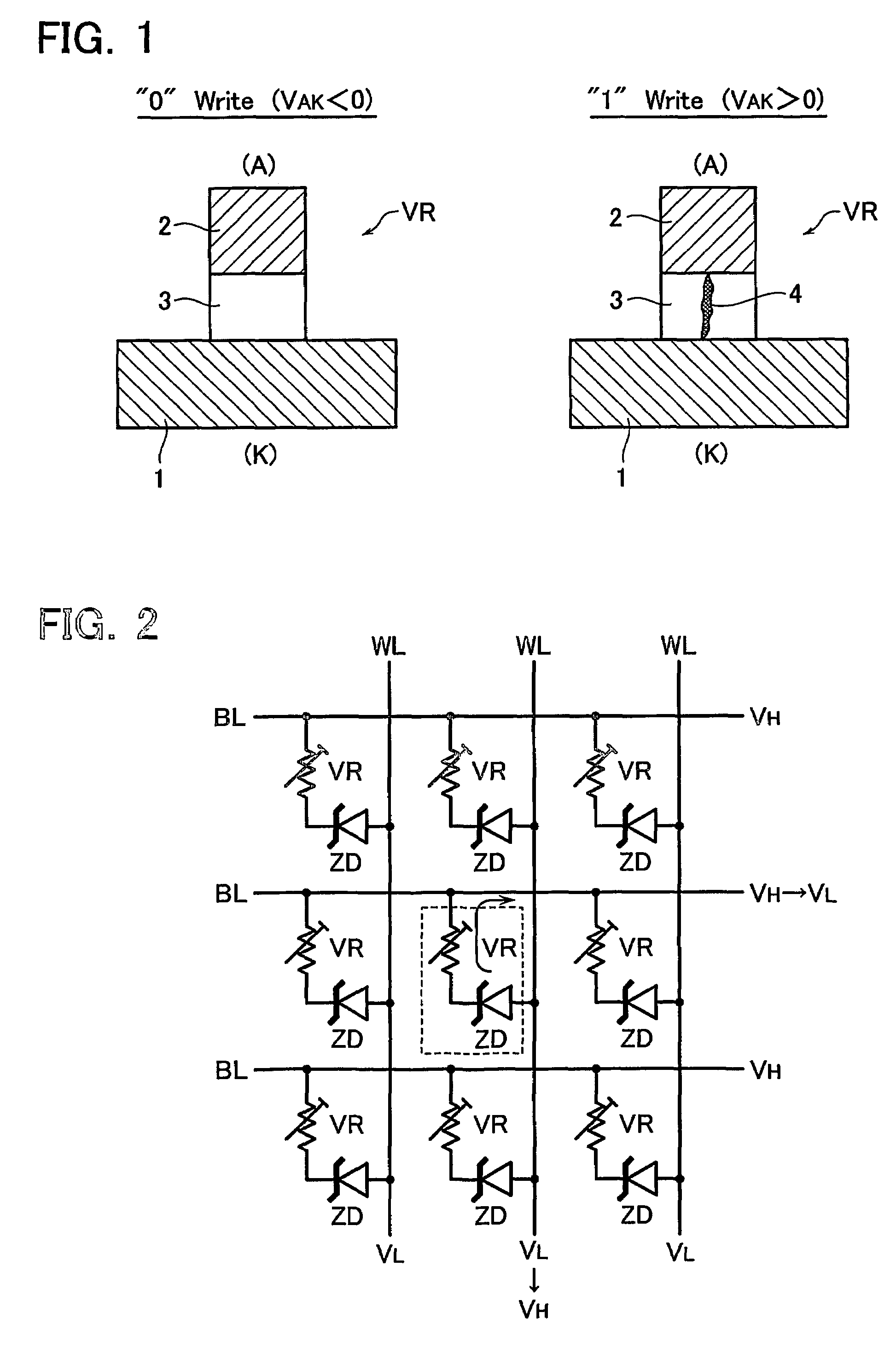

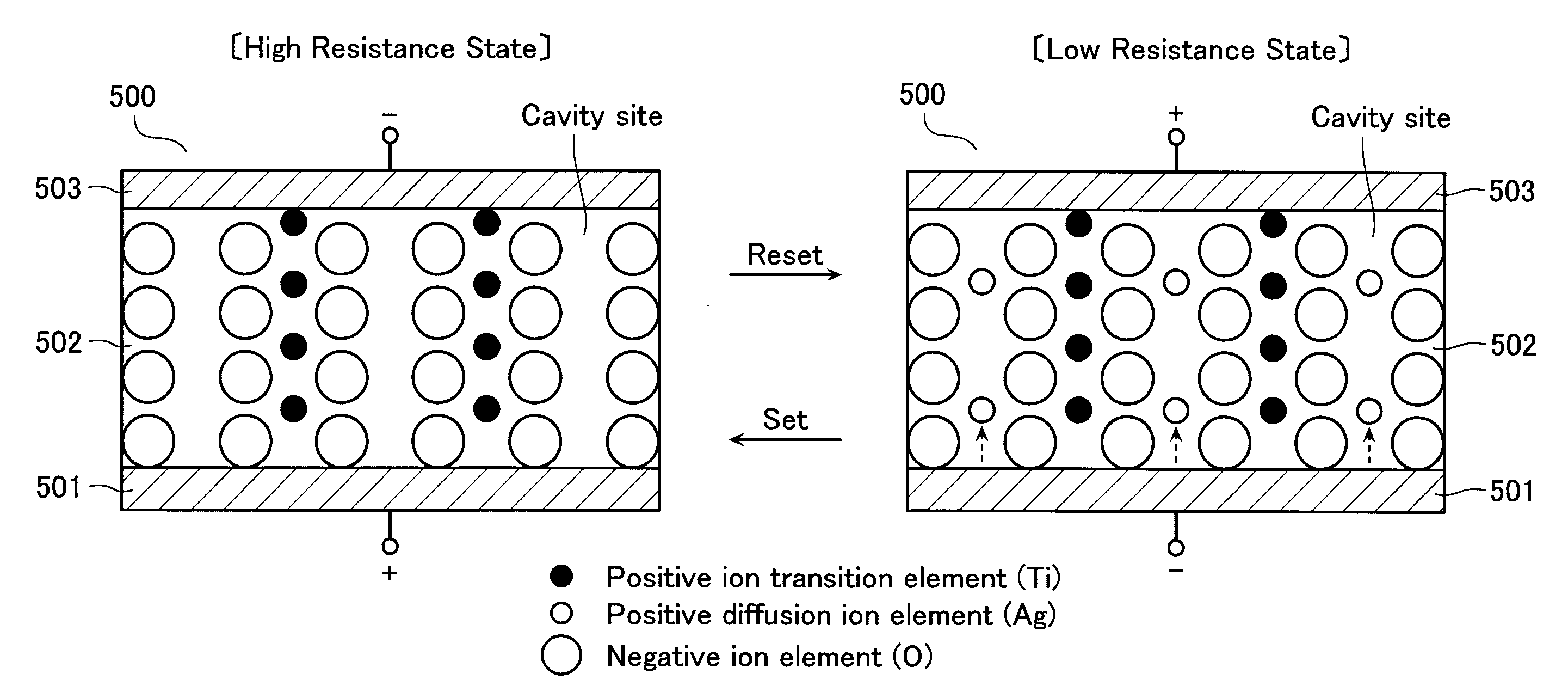

Resistance change memory device having a variable resistance element with a recording layer electrode served as a cation source in a write or erase mode

A resistance change memory device including: a semiconductor substrate; at least one cell array formed above the semiconductor substrate to have a stack structure of a variable resistance element and an access element, the variable resistance element storing a high resistance state or a low resistance state in a non-volatile manner, the access element having such an off-state resistance value in a certain voltage range that is ten times or more as high as that in a select state; and a read / write circuit formed on the semiconductor substrate, wherein the variable resistance element includes: a recording layer formed of a composite compound containing at least one transition element and a cavity site for housing a cation ion; and electrodes formed on the opposite sides of the recording layer, one of the electrodes serving as a cation source in a write or erase mode for supplying a cation to the recording layer to be housed in the cavity site.

Owner:TOSHIBA MEMORY CORP

Translation dilator and stand alone vascular guide catheter

Systems and methods for delivering implantable devices, catheters, or substances in or near and / or restoring flow through body lumens, such as blood vessel lumens are described. A catheter having a proximal portion of a first diameter and a distal portion of a second diameter (smaller than the first diameter) is advanced into a body lumen. The distal portion of the catheter is caused to expand to a diameter that is larger than the second diameter but no larger than the first diameter. A working device is then advanced out of the distal end of the catheter and used to remove obstructive matter, deliver an implantable device or substance and / or restore flow. The distal portion can be reduced in diameter prior to removal from the body. A stand alone, guide catheter is also disclosed possessing high resistance to kinking even with a very thin wall.

Owner:TYCO HEALTHCARE GRP LP

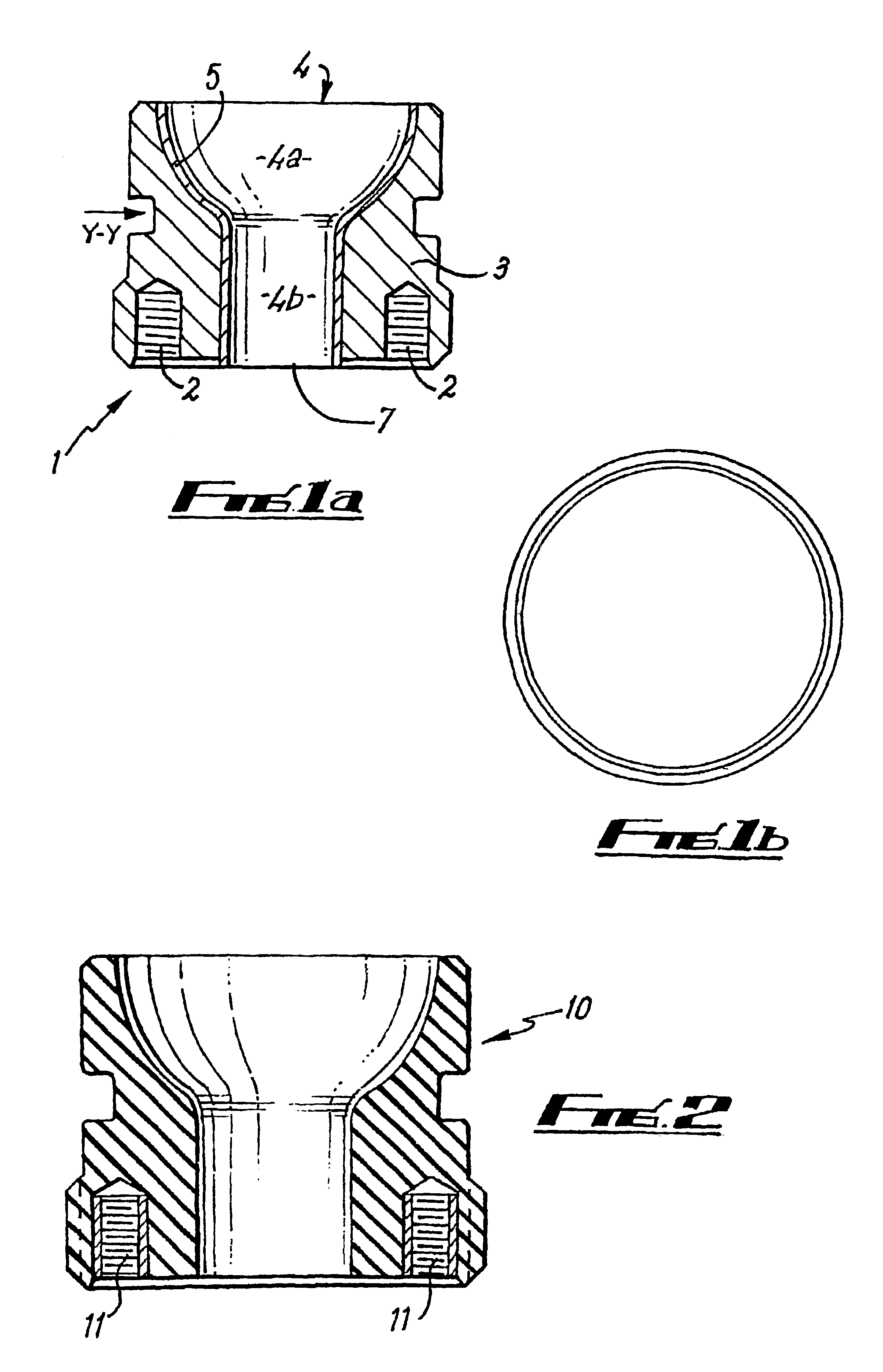

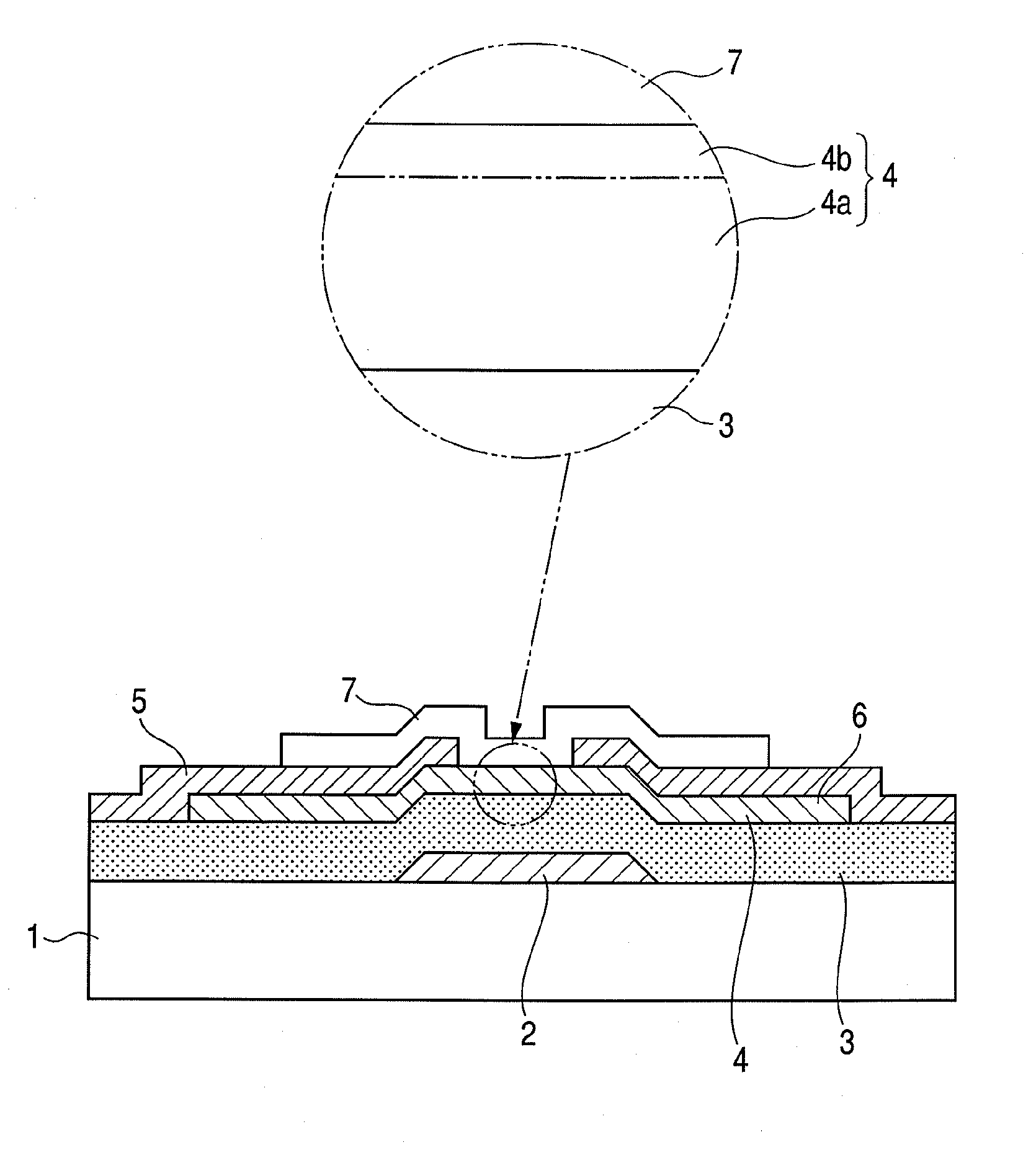

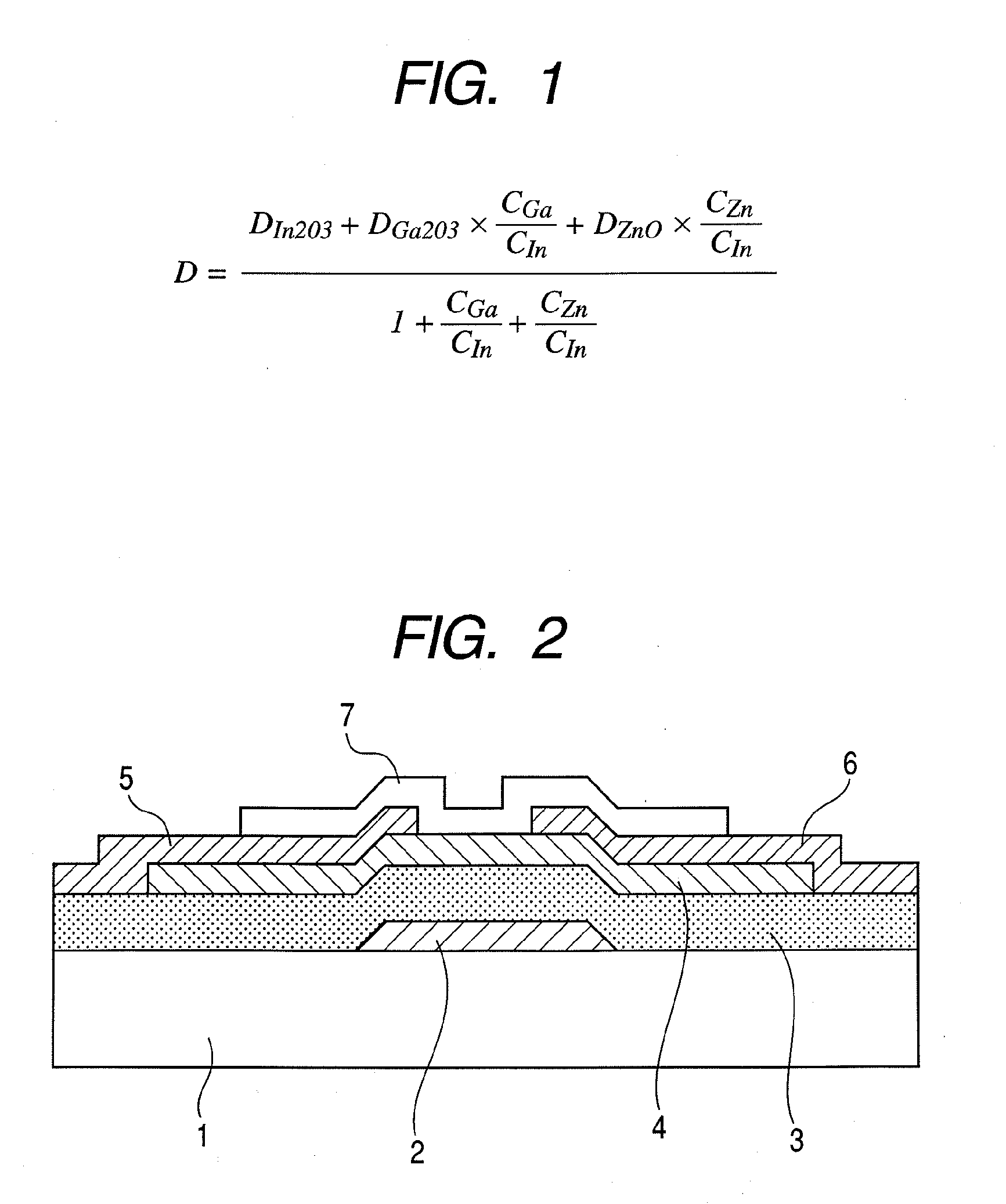

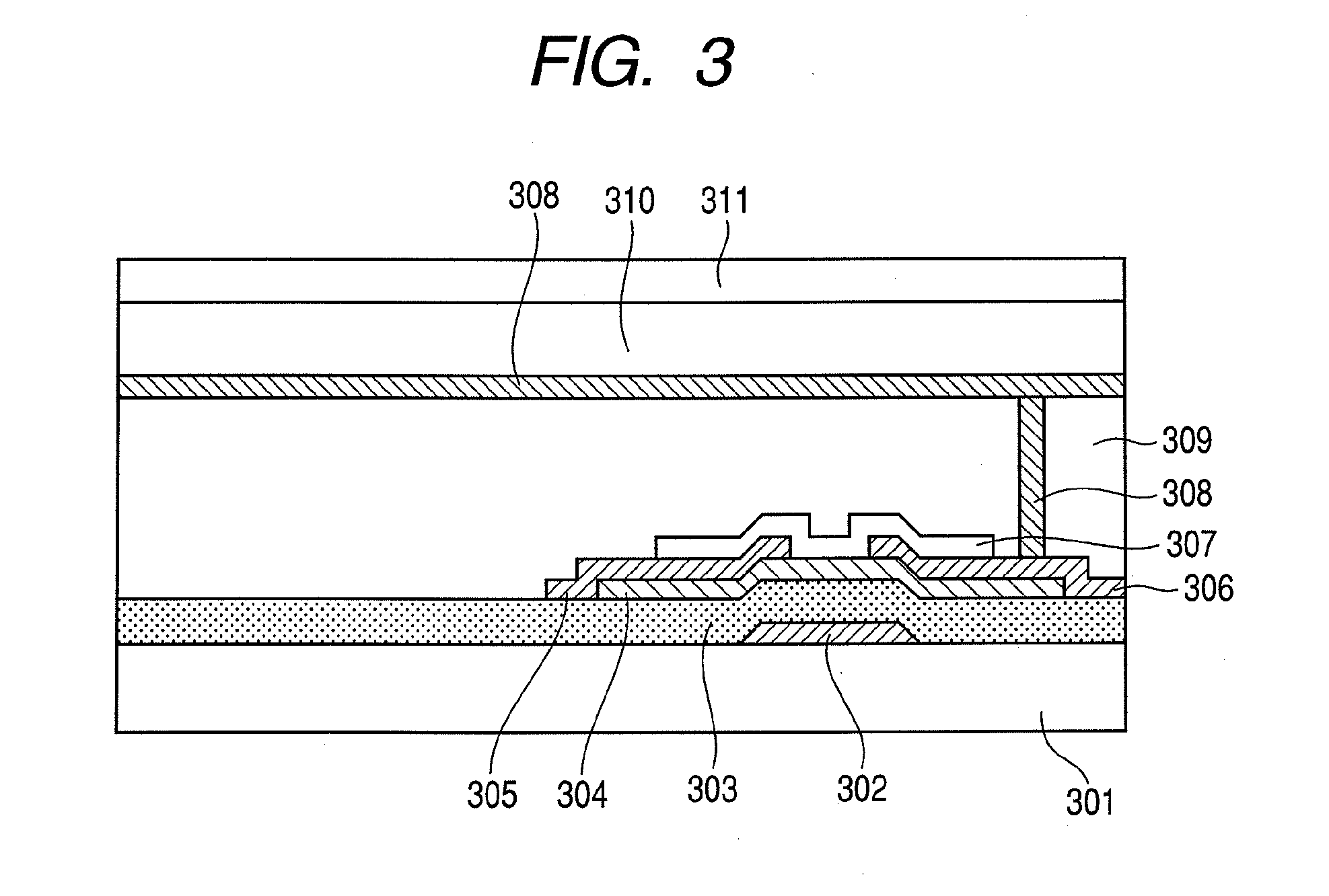

Thin film transistor having a two-layer semiconductor, manufacturing method therefor, and display apparatus using the same

InactiveUS20120132911A1Lower resistanceGood dispersionTransistorSemiconductor/solid-state device manufacturingHigh resistanceInsulation layer

A transistor is constituted of a gate electrode 2, a gate insulation layer 3, a semiconductor layer 4 formed of an amorphous oxide, a source electrode 5, a drain electrode 6 and a protective layer 7. The protective layer 7 is provided on the semiconductor layer 4 in contact with the semiconductor layer 4, and the semiconductor layer 4 includes a first layer at least functioning as a channel layer and a second layer having higher resistance than the first layer. The first layer is provided on the gate electrode 2 side of the semiconductor layer 4 and the second layer is provided on the protective layer 7 side of the semiconductor layer 4.

Owner:CANON KK

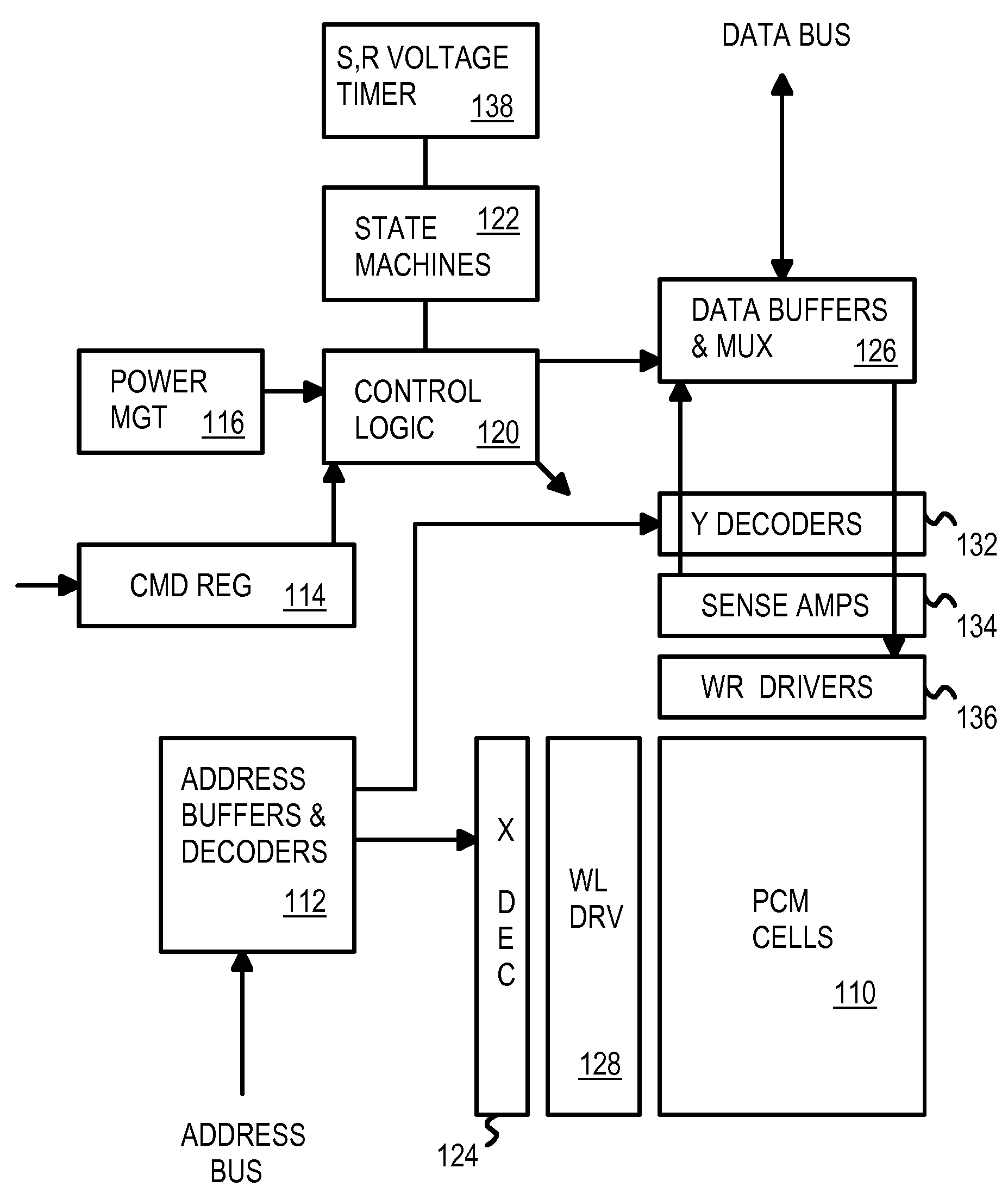

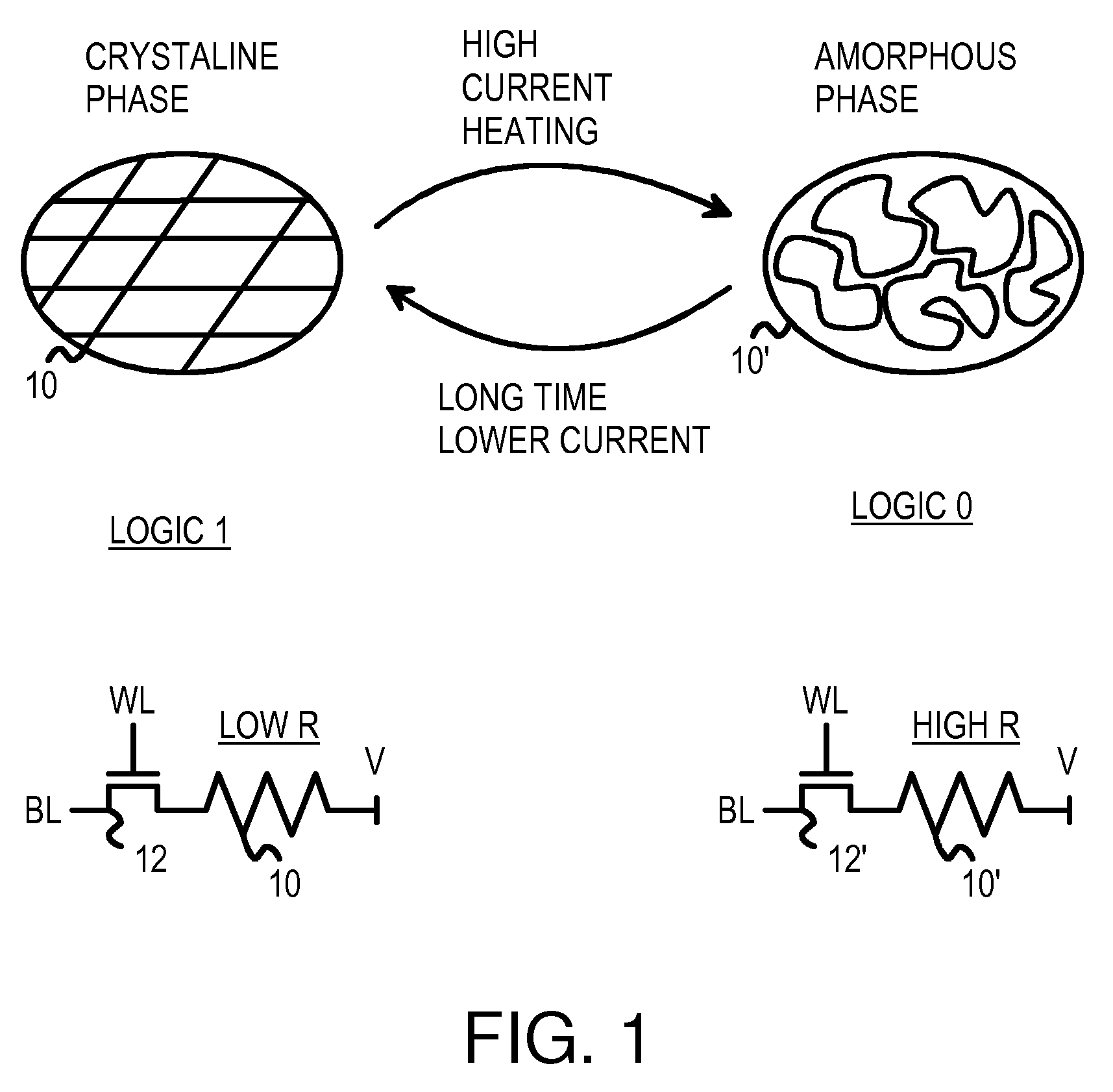

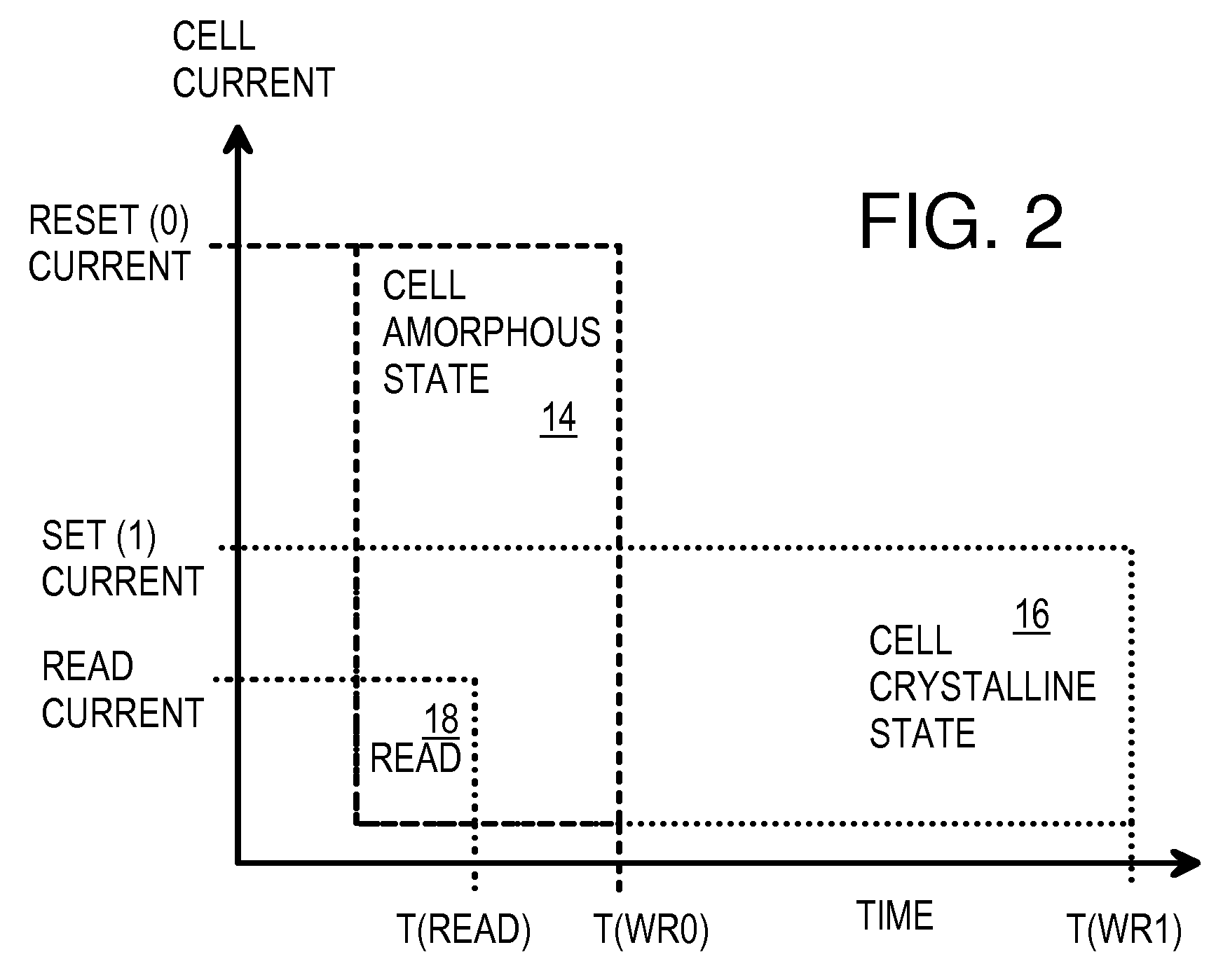

High-Speed Controller for Phase-Change Memory Peripheral Device

InactiveUS20070255891A1Memory architecture accessing/allocationDigital storageHigh resistancePhase-change memory

Peripheral devices store data in non-volatile phase-change memory (PCM). PCM cells have alloy resistors with high-resistance amorphous states and low-resistance crystalline states. The peripheral device can be a Multi-Media Card / Secure Digital (MMC / SD) card. A PCM controller accesses PCM memory devices. Various routines that execute on a CPU in the PCM controller are activated in response to commands in the host-bus transactions. The PCM system increases the throughput of one or more phase-change memory devices by performing one or more of a read-ahead memory operation, a write-ahead memory write operation, a larger page memory write operation, a wider data bus memory write operation, a multi-channel concurrent multi-bank interleaving memory read or write operation, a write-cache memory write operation, and any combination thereof.

Owner:SUPER TALENT TECH CORP

Self-hardening calcium phosphate materials with high resistance to fracture, controlled strength histories and tailored macropore formation rates

InactiveUS6955716B2Strong and tough self-hardeningHigh strengthPhosphatesOther chemical processesFiberHigh resistance

A bone replacement material and therapy comprises the combination of calcium phosphate compounds and two or more soluble fillers in the form of fibers, mesh or other materials which have the dual functions of reinforcing an in vivo implant while dissolving at a programmed rate to form macropores capable of receiving natural bone ingrowth.

Owner:ADA FOUND

Semiconductor device

ActiveUS20050001235A1Promote formationObstruction is producedLaser active region structureSemiconductor/solid-state device manufacturingHigh resistanceDevice material

A semiconductor device has: a buffer layer formed on a conductive substrate and made of AlxGa1-xN with a high resistance; an element-forming layer formed on the buffer layer, having a channel layer, and made of undoped GaN and N-type AlyGa1-yN; and a source electrode, a drain electrode and a gate electrode which are selectively formed on the element-forming layer. The source electrode is filled in a through hole provided in the buffer layer and the element-forming layer, and is thus electrically connected to the conductive substrate.

Owner:PANASONIC CORP

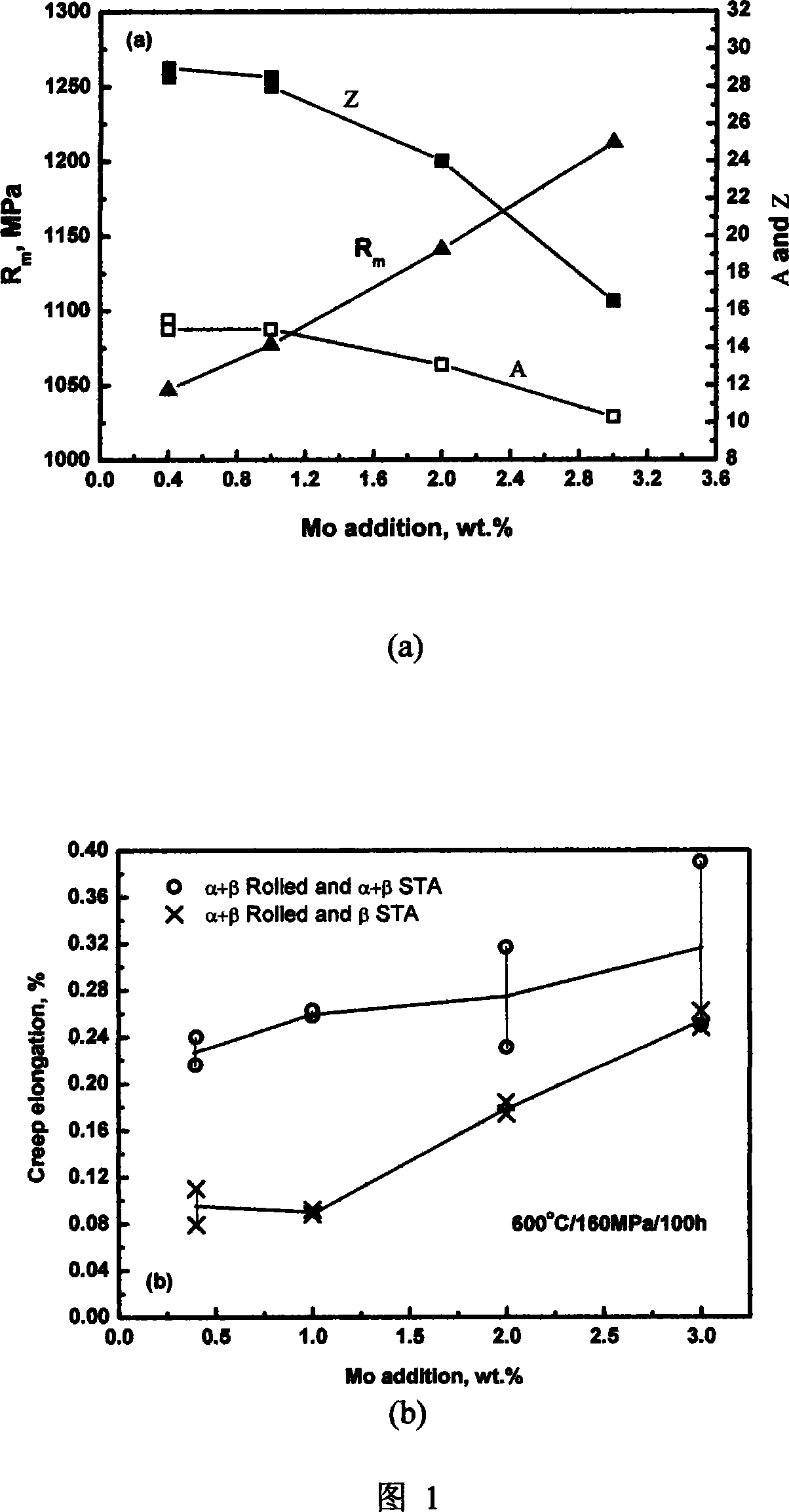

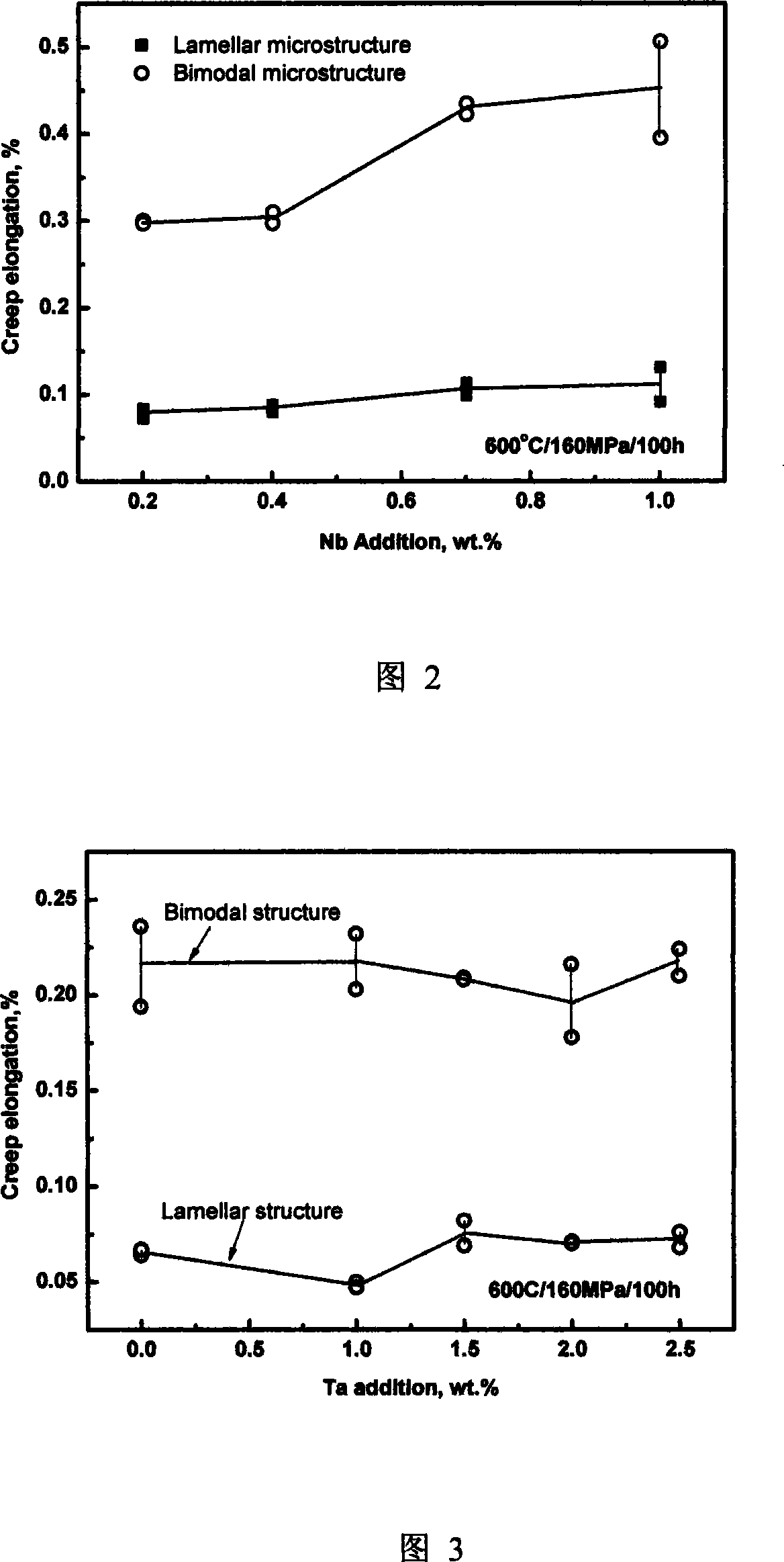

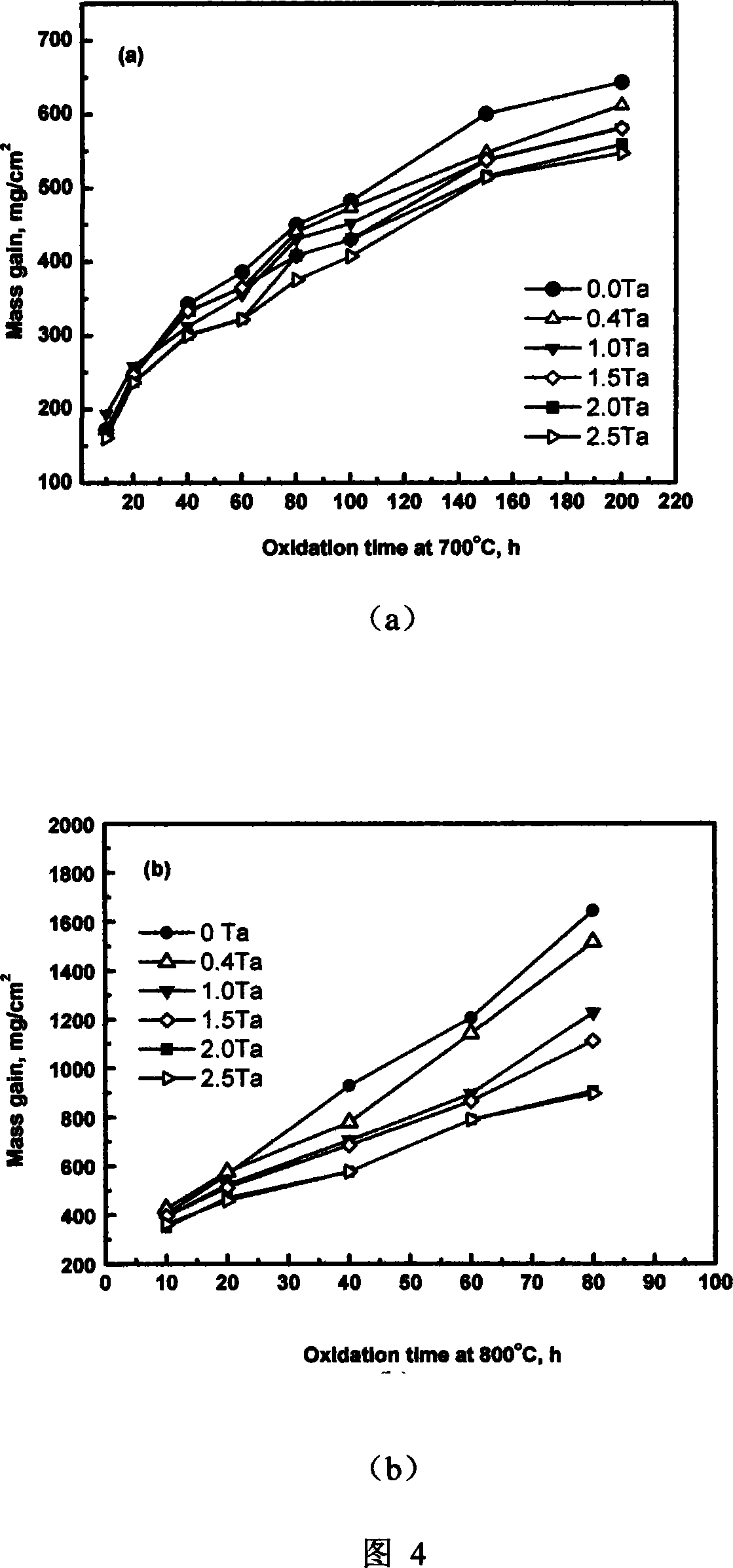

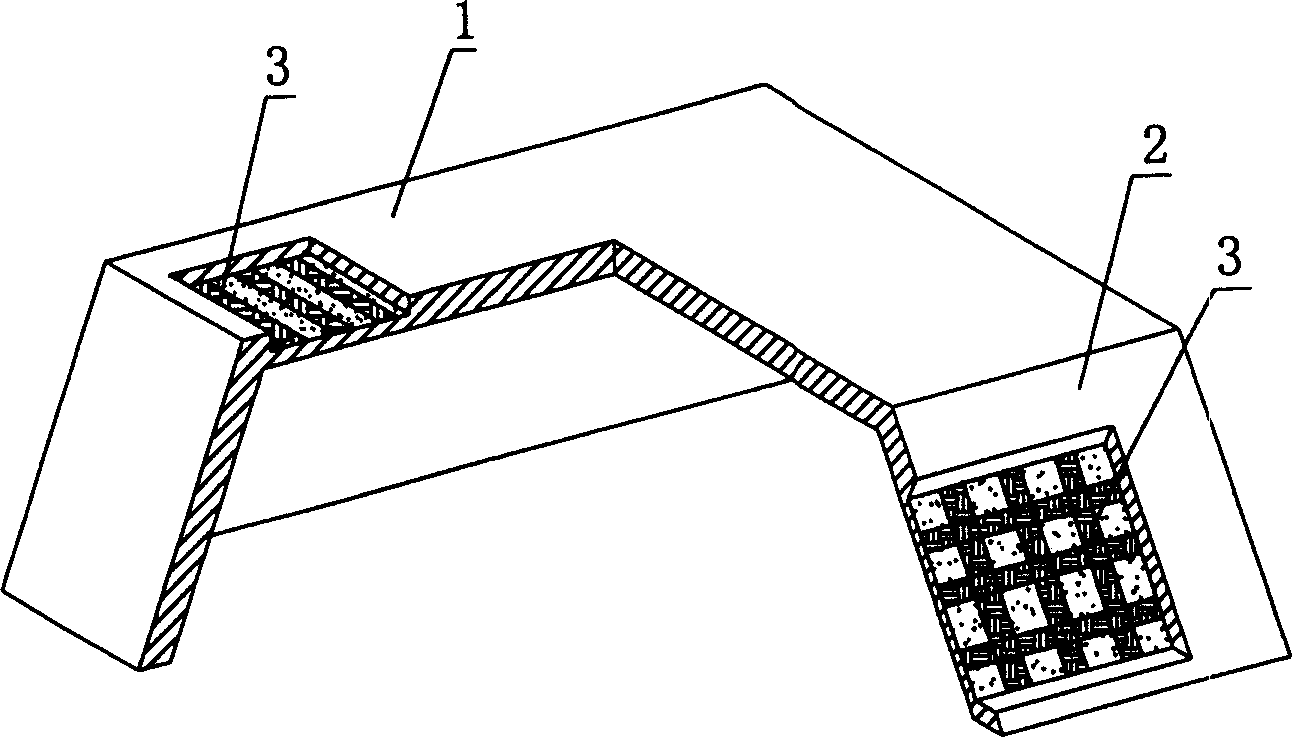

High-temperature titanium alloy with high heat resistance and high thermal stabilization

The invention provides a novel high-temperature Ti alloy with high heat resistance and high heat stability. The alloy contains eutectic Nb, Ta and Mo elements. Based on the appropriate proportion of these three elements, the alloy is superior in high resistance and stability to heat and good antioxidant effect. The alloy contains (by weight) Al 5.0-6.3 percent, Sn 3.0-5.0 percent, Zr 2.5-7.0 percent, Mo 0.2-1.5 percent, Si 0.20-0.55 percent, Nb 0.2-1.0 percent, Ta 0.2-3.0 percent, C 0.01-0.09 percent, and Ti and other inevitable impurities in balance. The alloy is an ideal alternative material for high-temperature parts of aircraft engine, such as wheel disk, drum barrel, barrel shaft and blade.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI +1

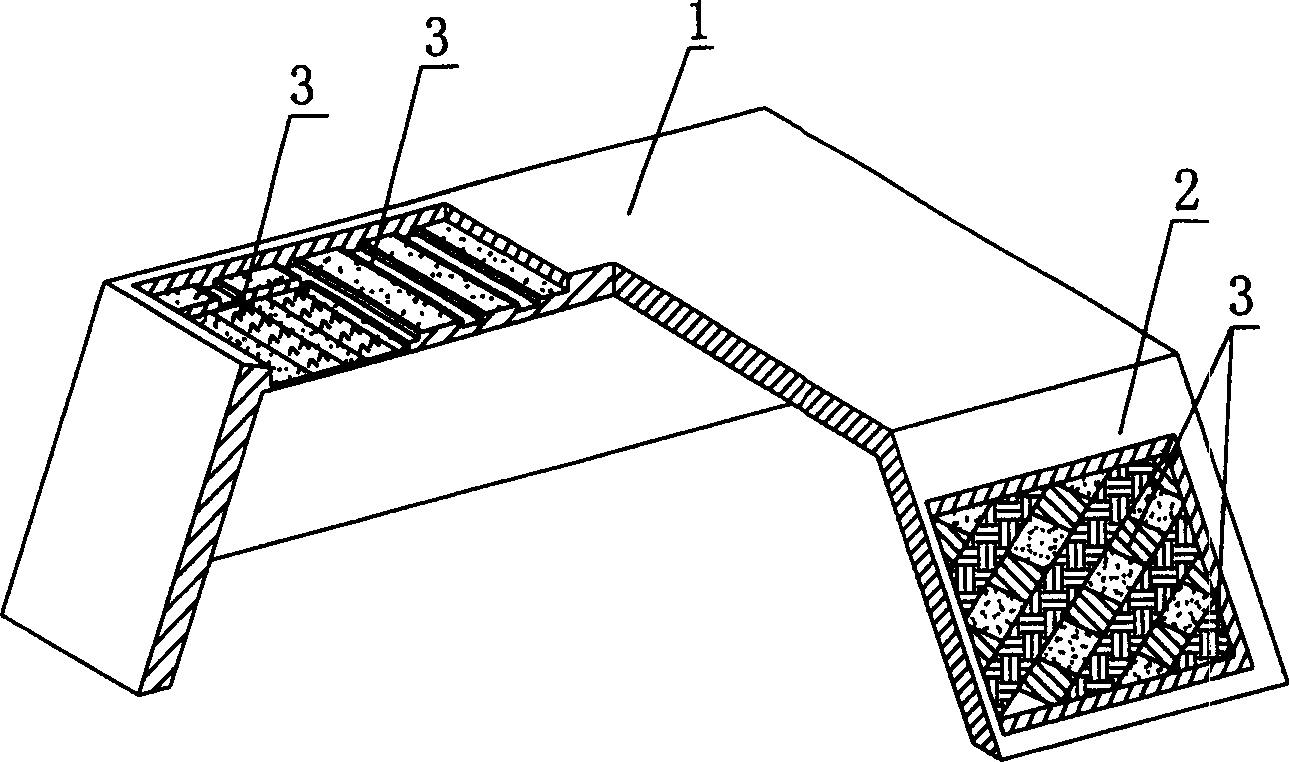

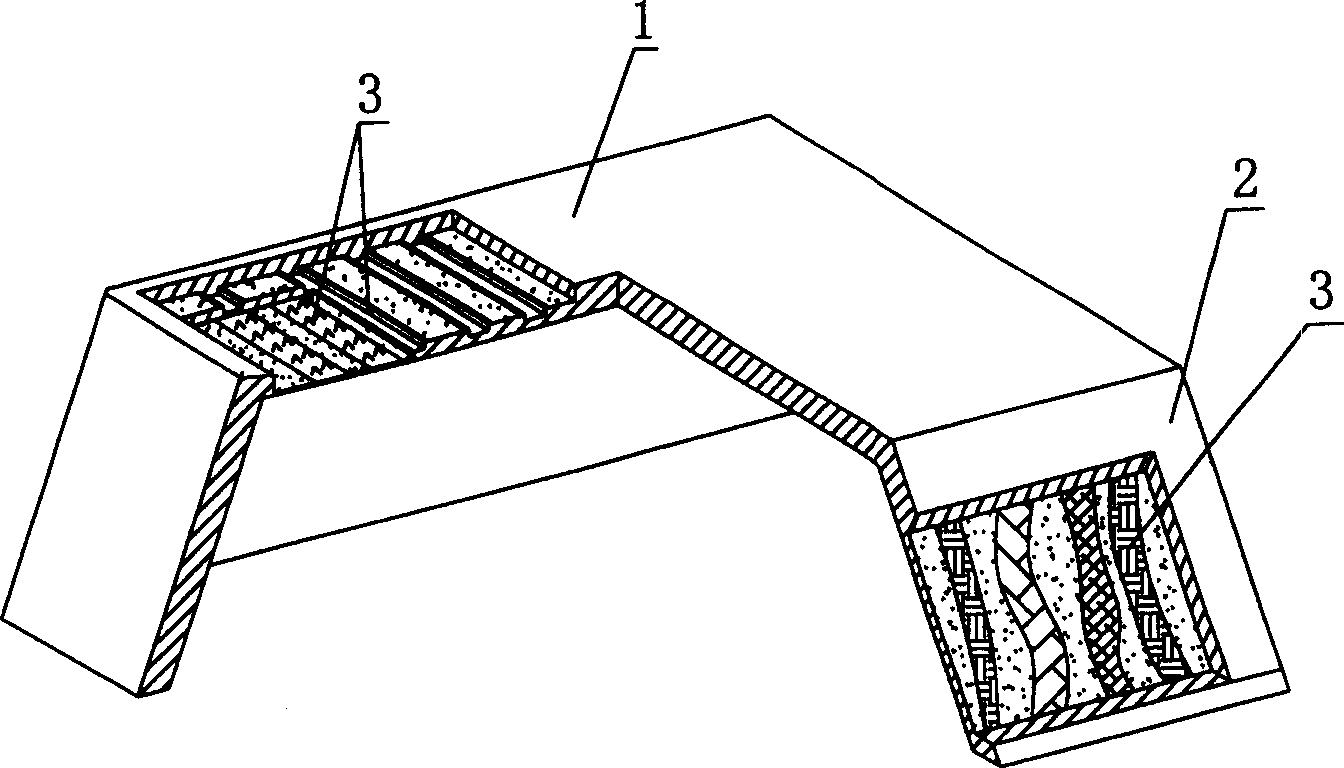

Thin-wall form for filling concrete

A thin-wall form for filling concrete in it to in-situ pour hollow non-beam floor is composed of top plate and peripheral wall, and is characterized by that at least one of said top plate and peripheral wall contains at least one thin strip for improving its resistance to impact and collision. Its advantages are simple structure and high resistance to deformation and vibration.

Owner:湖南邱则有专利战略策划有限公司

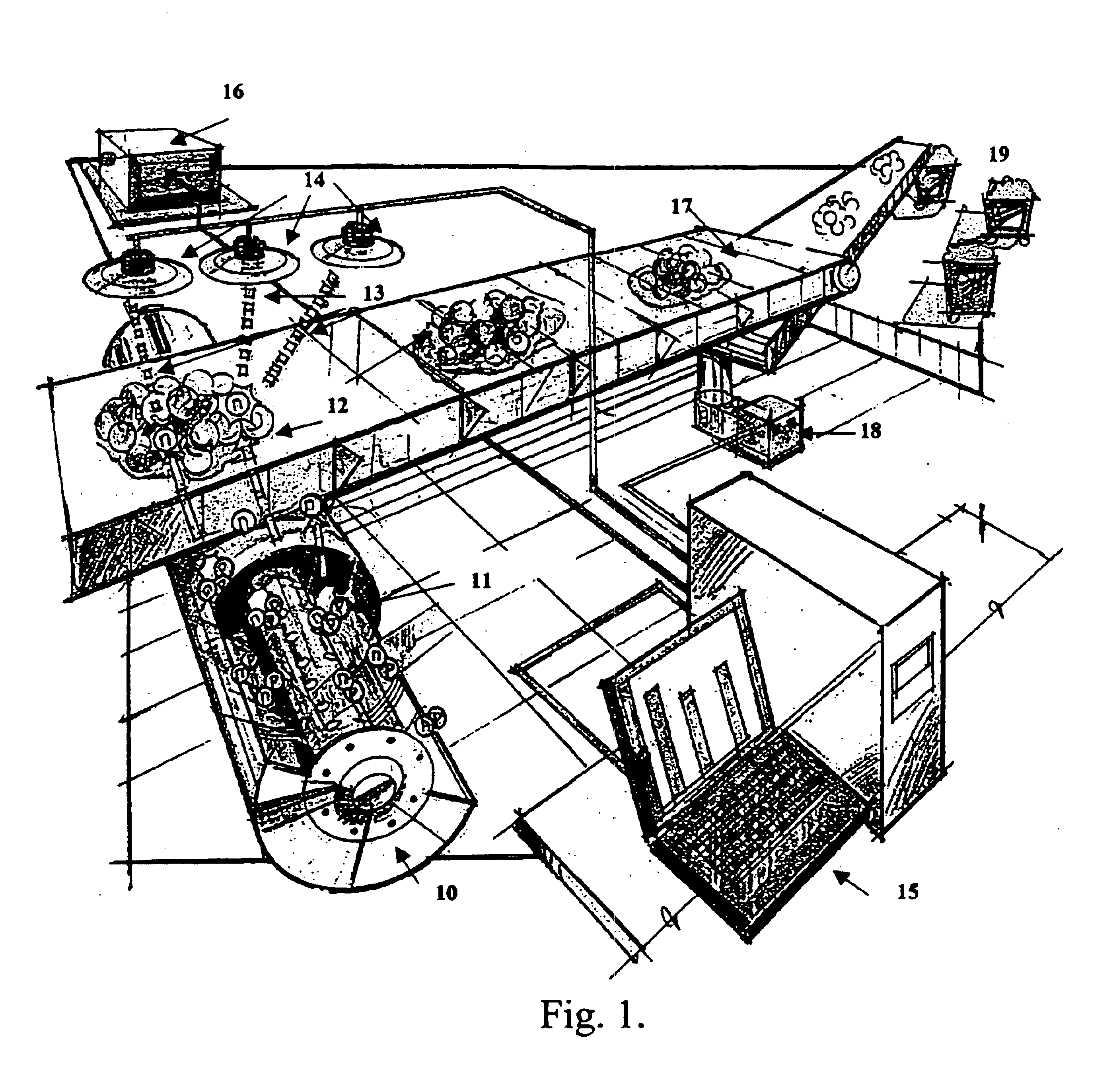

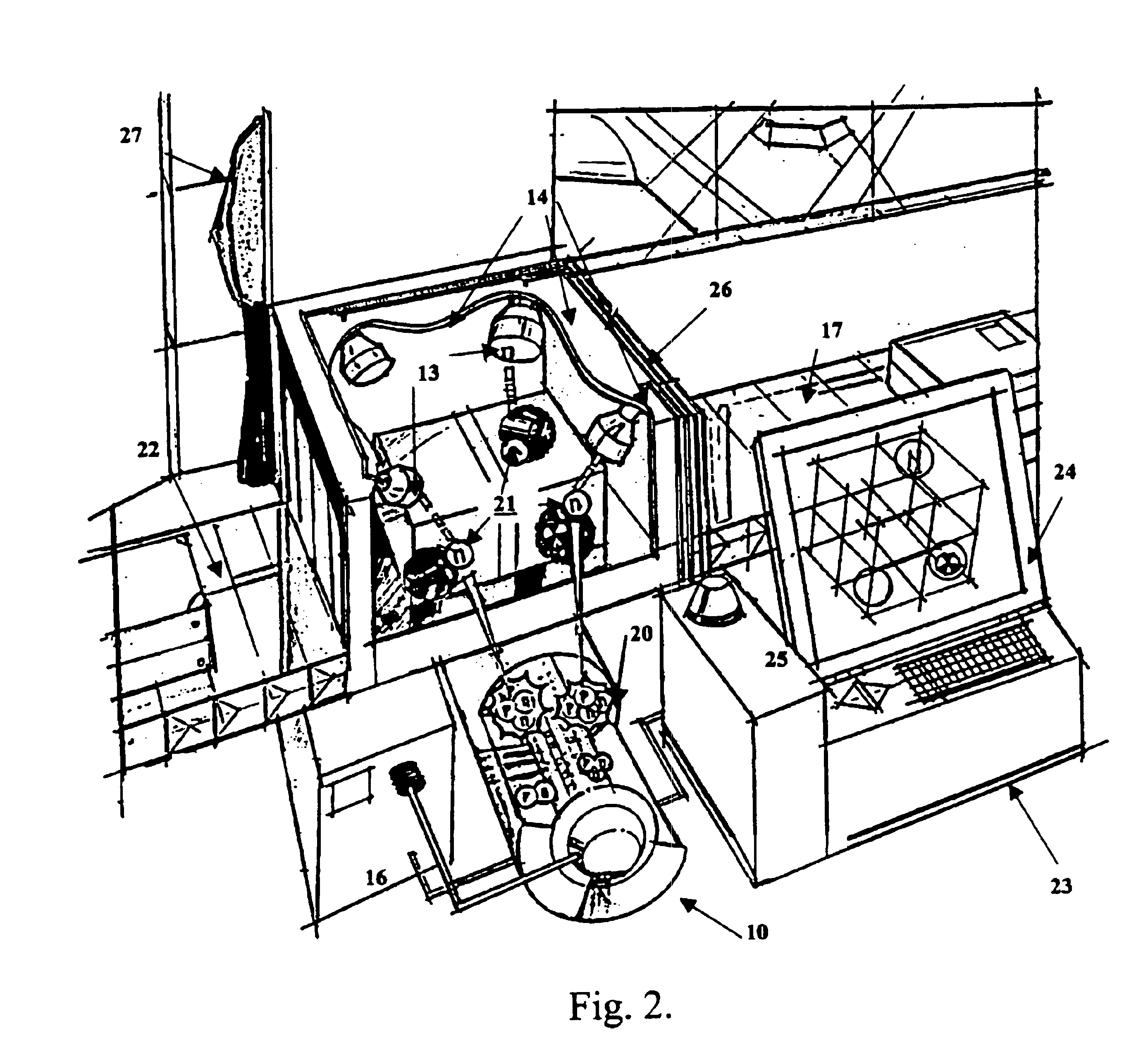

Gas-target neutron generation and applications

InactiveUS6922455B2Improve performanceMaximize productionNuclear energy generationX-ray tube electrodesHigh resistanceNeutron emission

Described herein are integrated systems for generating neutrons to perform a variety of tasks including: on-line analysis of bulk material and industrial process control (as shown in FIG. 1), security interrogation (as shown in FIG. 2), soil and environmental analysis, and medical diagnostic treatment. These systems are based on novel gas-target neutron generation which embodies the beneficial characteristics of replenishable fusible gas targets for very long lifetime, stability and continuous operation, combined with the advantageous features common to conventional accelerator neutron tubes including: on / off operation, hermetically sealed operation, and safe storage and transport. Innovative electron management techniques provide gas-target neutron production efficiencies that are comparable or surpass existing sources. The high-pressure high-resistance gaseous discharge is presented as a favorable gas-target neutron generator embodiment, combining ion source regions, accelerator regions, gas-target regions and electron management components within a single simple cost-effective device that is adaptable to various geometric configurations that provide specific neutron emission profiles for greater analysis capacity.

Owner:STARFIRE INDS MANAGEMENT

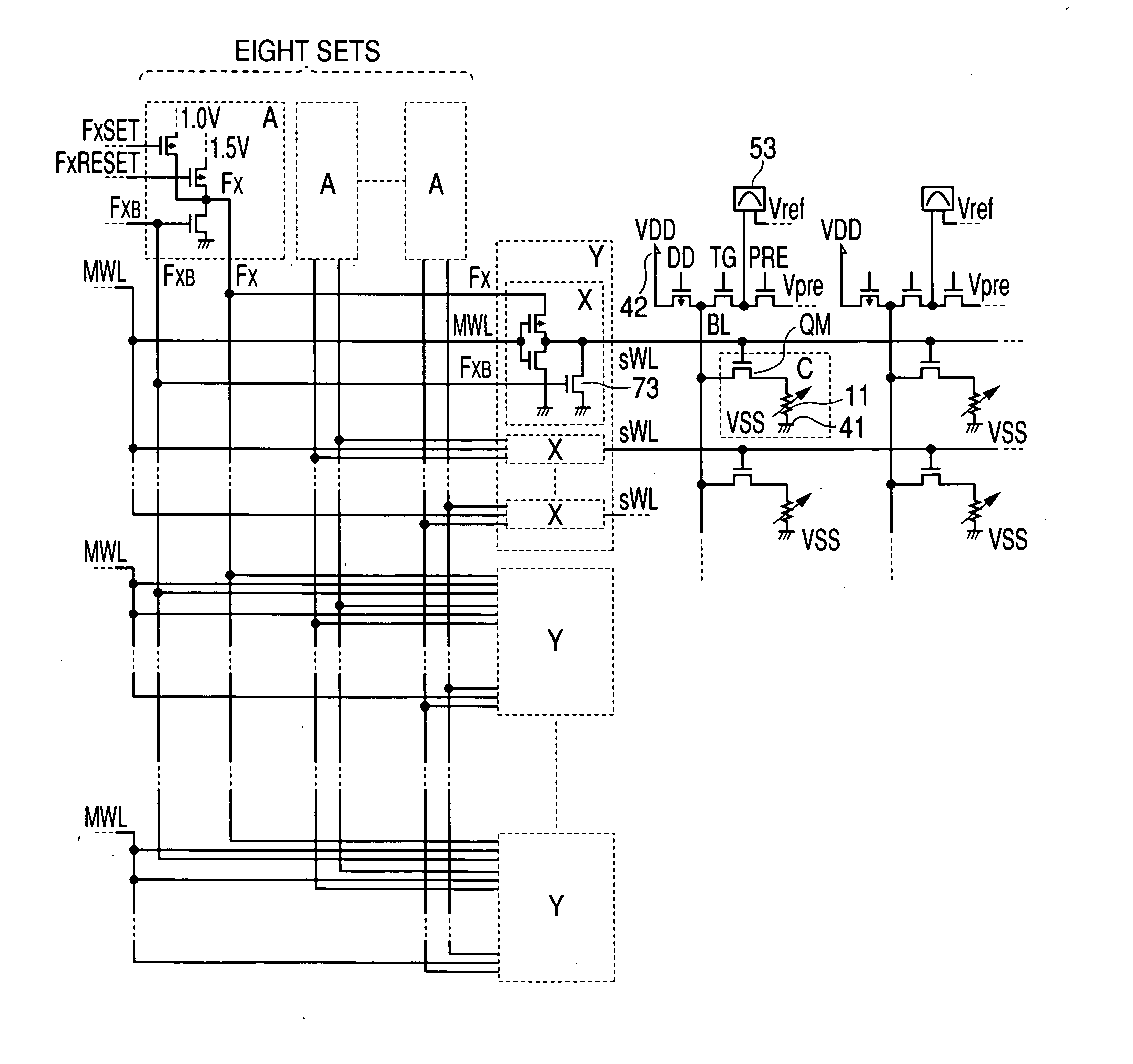

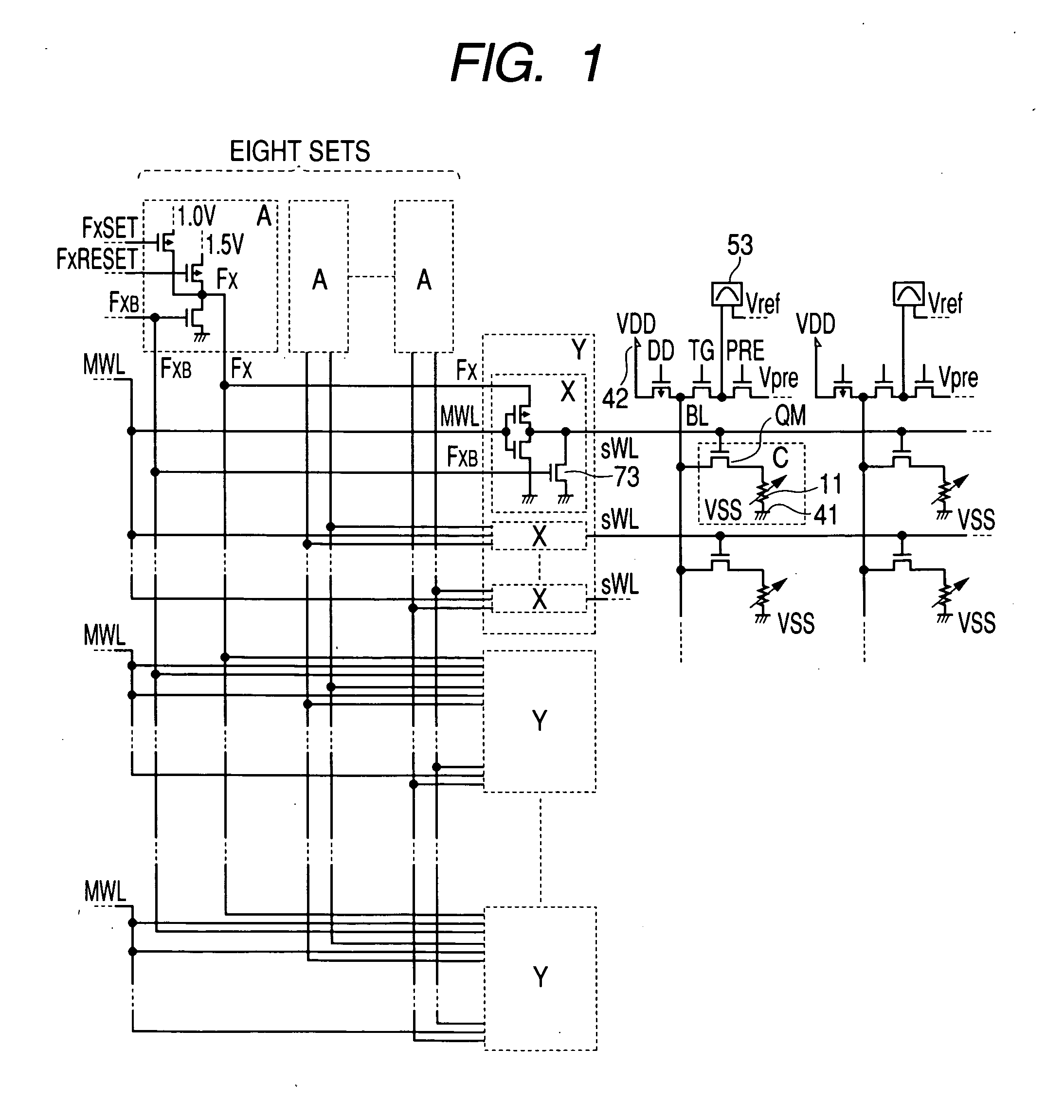

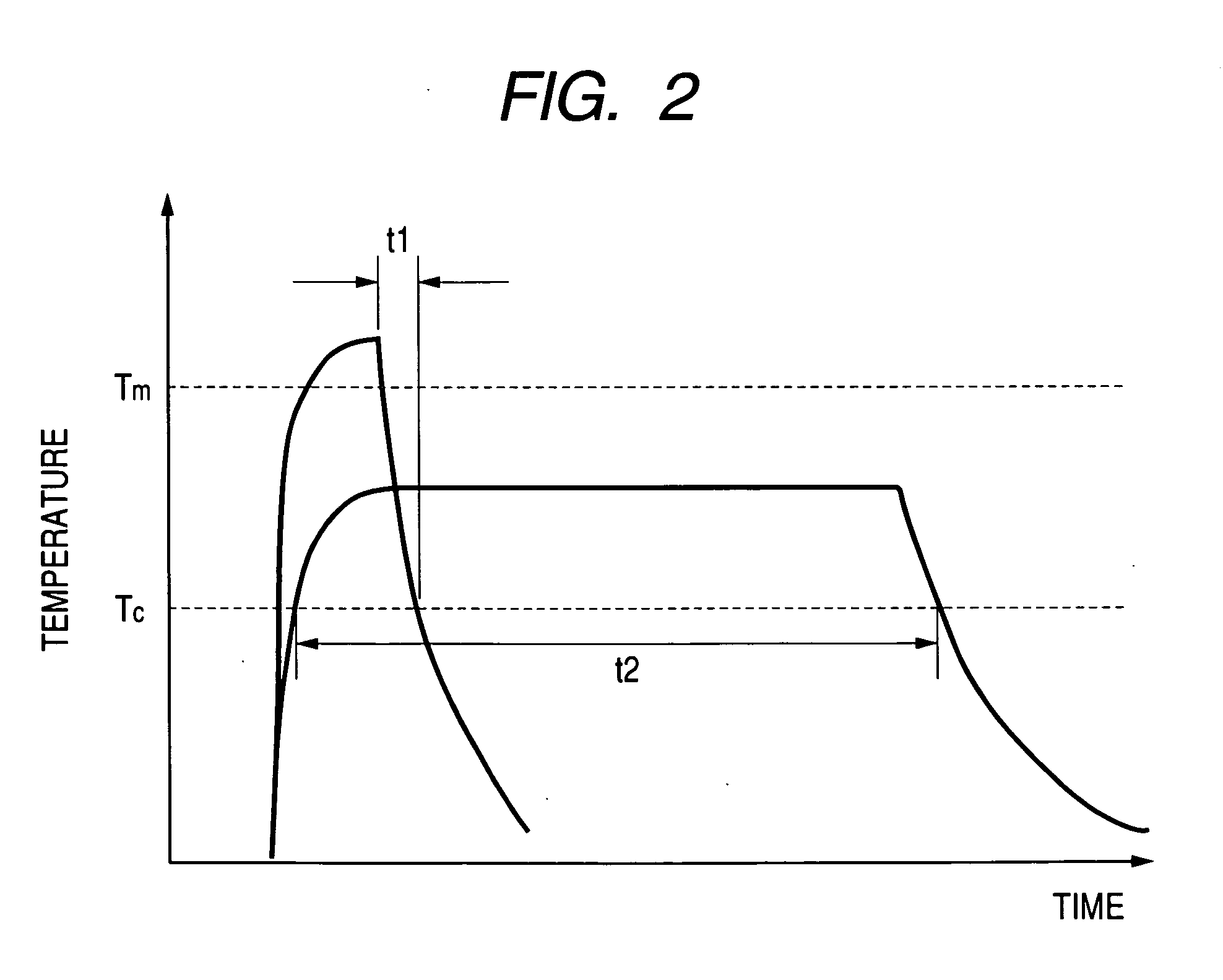

Semiconductor integrated circuit device

InactiveUS20050128799A1Improve reliabilityIncrease heightSolid-state devicesRead-only memoriesHigh resistanceElectrical resistance and conductance

In a non-volatile phase change memory, information is recorded by utilizing a change in resistance of a phase change portion. When the phase change portion is allowed to generate Joule's heat and is held at a specific temperature, it goes into a state of a low resistance. At this time, if a constant voltage source is used, not only the phase change portion assumes a state of a low resistance, but also a large current flows, so that a sample concerned is overheated and goes into a state of a high resistance. Thus, it is difficult to make the phase change portion low in resistance stably. When the gate voltage of a memory cell selection transistor QM is controlled with MISFET to afford a low resistance state, the maximum amount of current applied to the sample is limited by the application of a medium-state voltage.

Owner:RENESAS ELECTRONICS CORP

Current driven switching of magnetic storage cells utilizing spin transfer and magnetic memories using such cells having enhanced read and write margins

ActiveUS20070297223A1High readHigh write marginDigital storageHigh resistanceElectrical resistance and conductance

A method and system for providing a magnetic memory is described. The magnetic memory includes magnetic storage cells in an array, bit lines, and source lines. Each magnetic storage cell includes at least one magnetic element. The magnetic element(s) are programmable by write currents driven through the magnetic element(s). Each magnetic element has free and pinned layer(s) and a dominant spacer. The magnetic memory is configured such that either the read current(s) flow from the free layer(s) to the dominant spacer if the maximum low resistance state read current divided by the minimum low resistance state write current is greater than the maximum high resistance state read current divided by the minimum high resistance state write current or the read current(s) flow from the dominant spacer to the free layer(s) if the maximum low resistance state read current divided by the minimum low resistance state write current is less than the maximum high resistance state read current divided by the minimum high resistance state write current.

Owner:SAMSUNG SEMICON +1

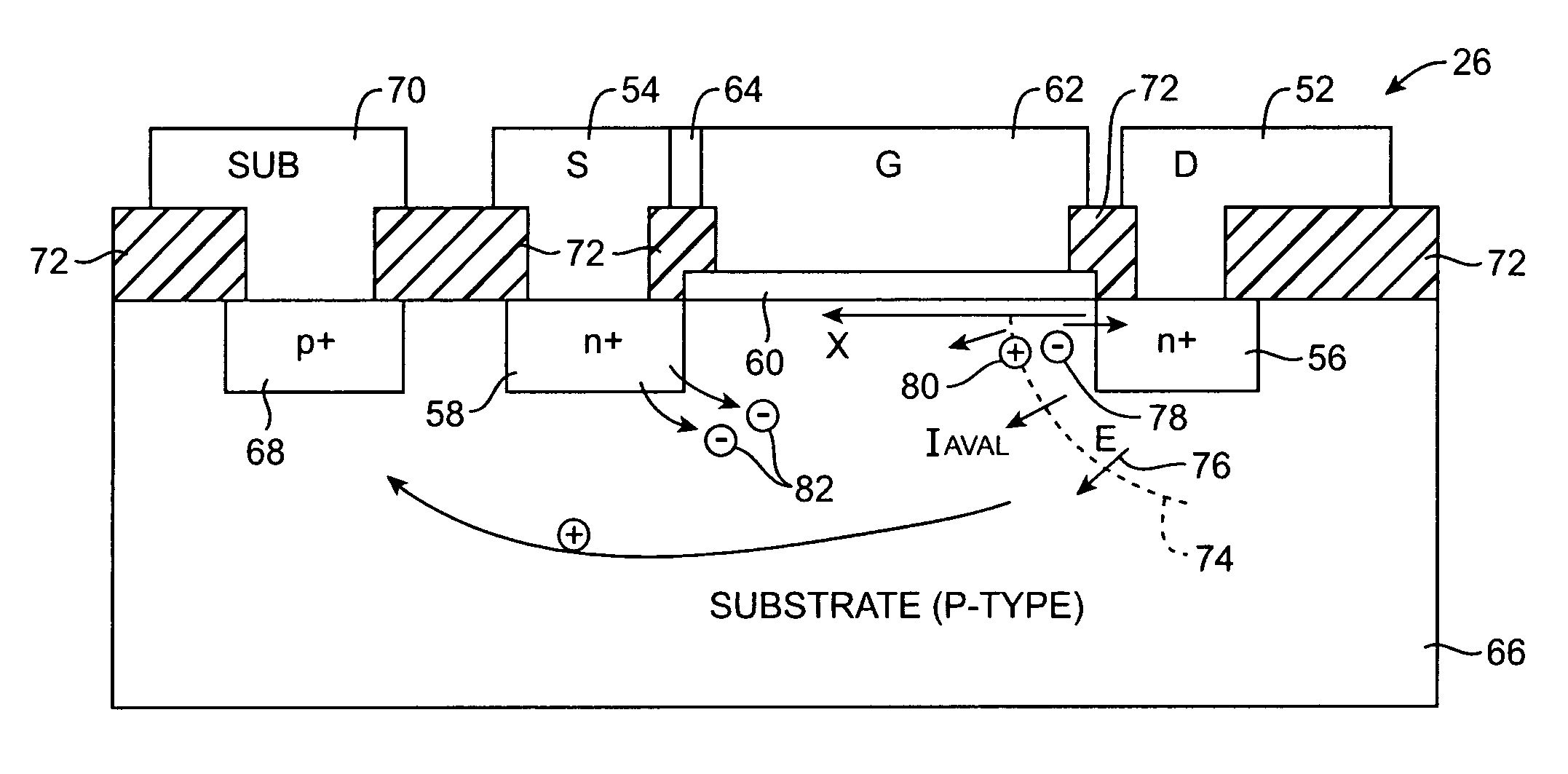

Electrically-programmable transistor antifuses

InactiveUS7157782B1Minimize powerMinimize timeTransistorSemiconductor/solid-state device detailsHigh resistanceEngineering

Integrated circuit antifuse circuitry is provided. A metal-oxide-semiconductor (MOS) transistor serves as an electrically-programmable antifuse. The antifuse transistor has source, drain, gate, and substrate terminals. The gate has an associated gate oxide. In its unprogrammed state, the gate oxide is intact and the antifuse has a relatively high resistance. During programming, the gate oxide breaks down, so in its programmed state the antifuse transistor has a relatively low resistance. The antifuse transistor can be programmed by injecting hot carriers into the substrate of the device in the vicinity of the drain. Because there are more hot carriers at the drain than at the substrate, the gate oxide is stressed asymmetrically, which enhances programming efficiency. Feedback can be used to assist in turning the antifuse transistor on to inject the hot carriers.

Owner:ALTERA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com