Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

767 results about "Antifuse" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An antifuse is an electrical device that performs the opposite function to a fuse. Whereas a fuse starts with a low resistance and is designed to permanently break an electrically conductive path (typically when the current through the path exceeds a specified limit), an antifuse starts with a high resistance and is designed to permanently create an electrically conductive path (typically when the voltage across the antifuse exceeds a certain level). This technology has many applications.

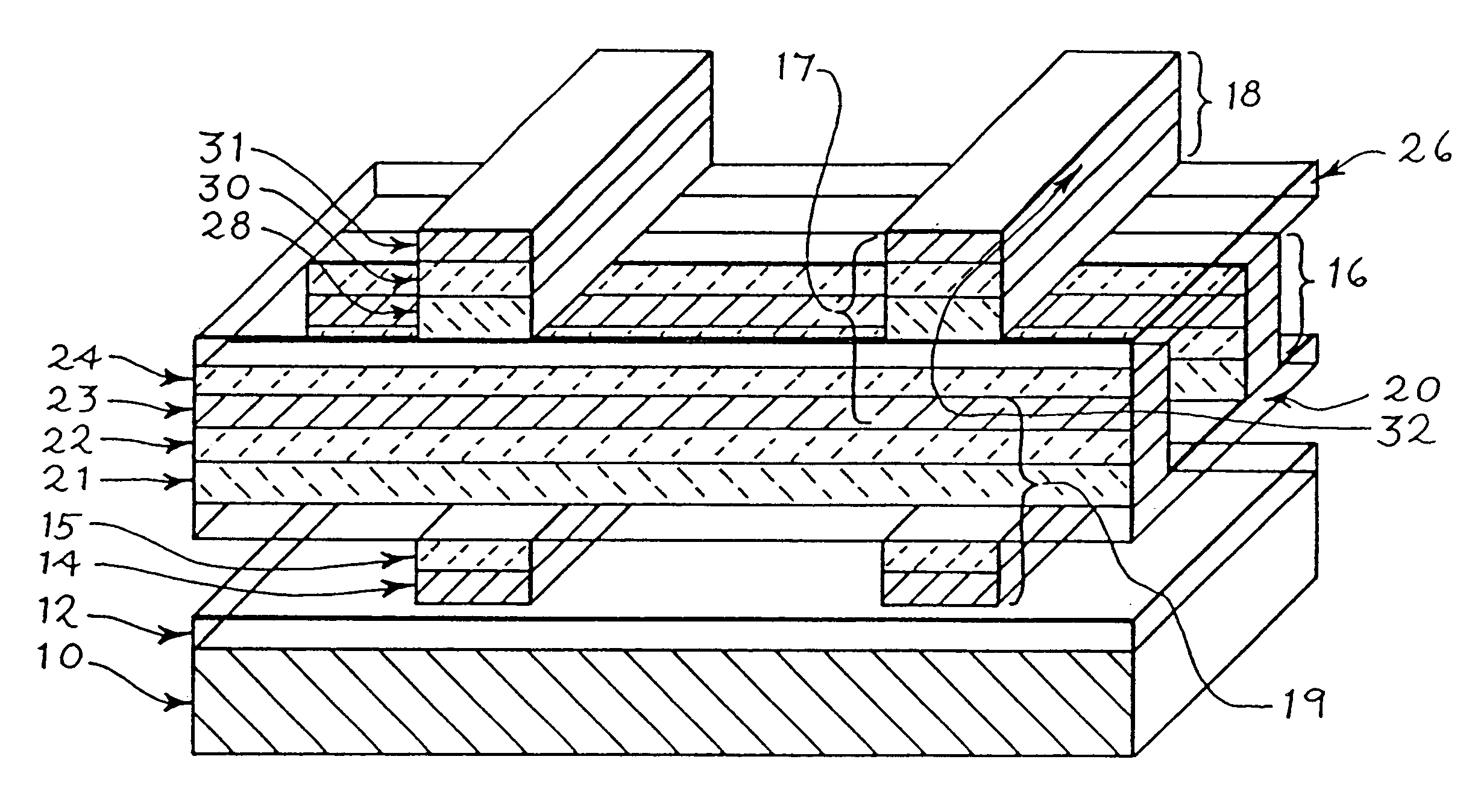

High-density three-dimensional memory cell

InactiveUS6952030B2High densityReduce the overall heightTransistorSemiconductor/solid-state device detailsElectrical conductorHigh density

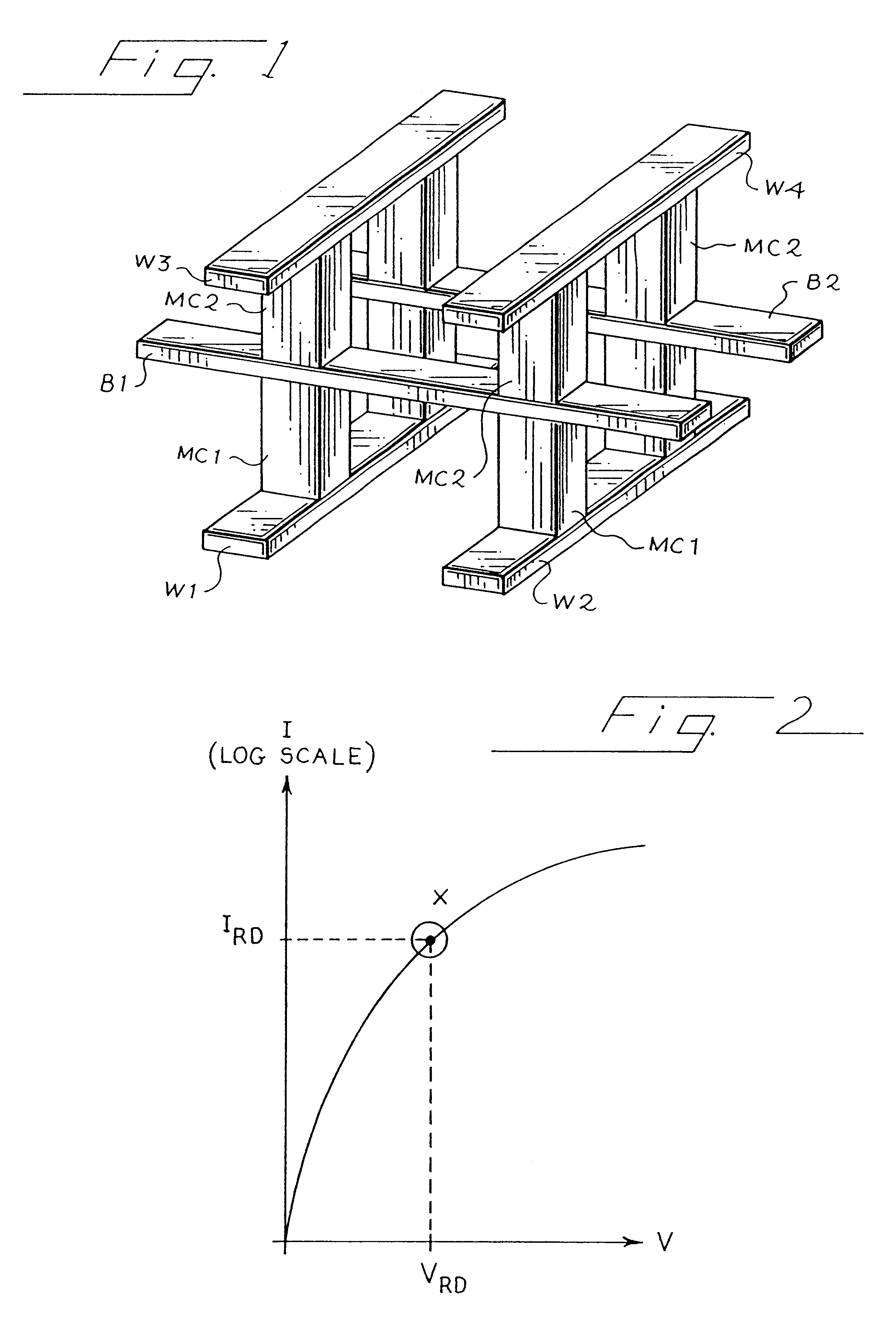

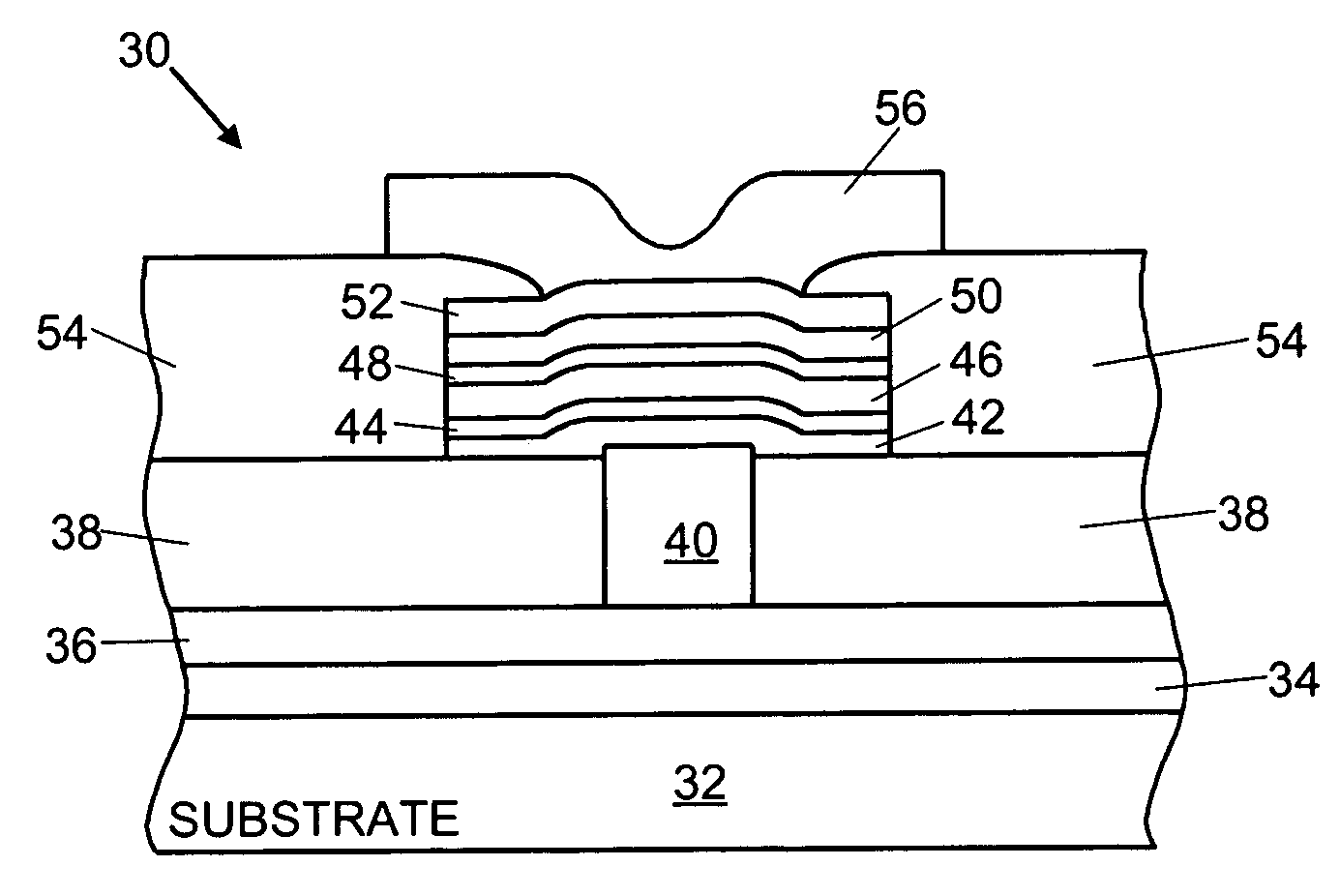

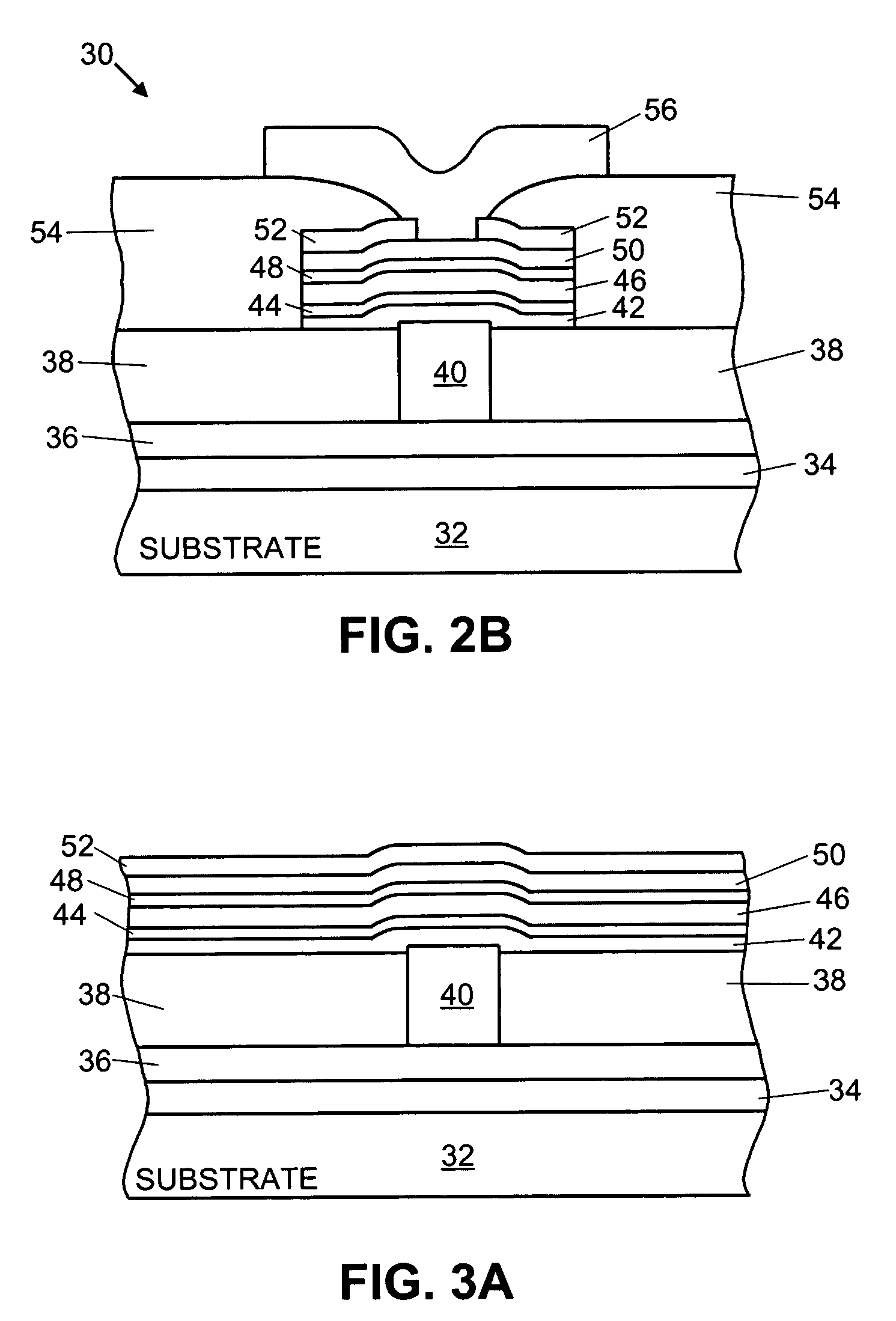

A three dimensional monolithic memory comprising a memory cell allowing for increased density is disclosed. In the memory cell of the present invention, a bottom conductor preferably comprising tungsten is formed. Above the bottom conductor a semiconductor element preferably comprises two diode portions and an antifuse. Above the semiconductor element are additional conductors and semiconductor elements in multiple stones of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

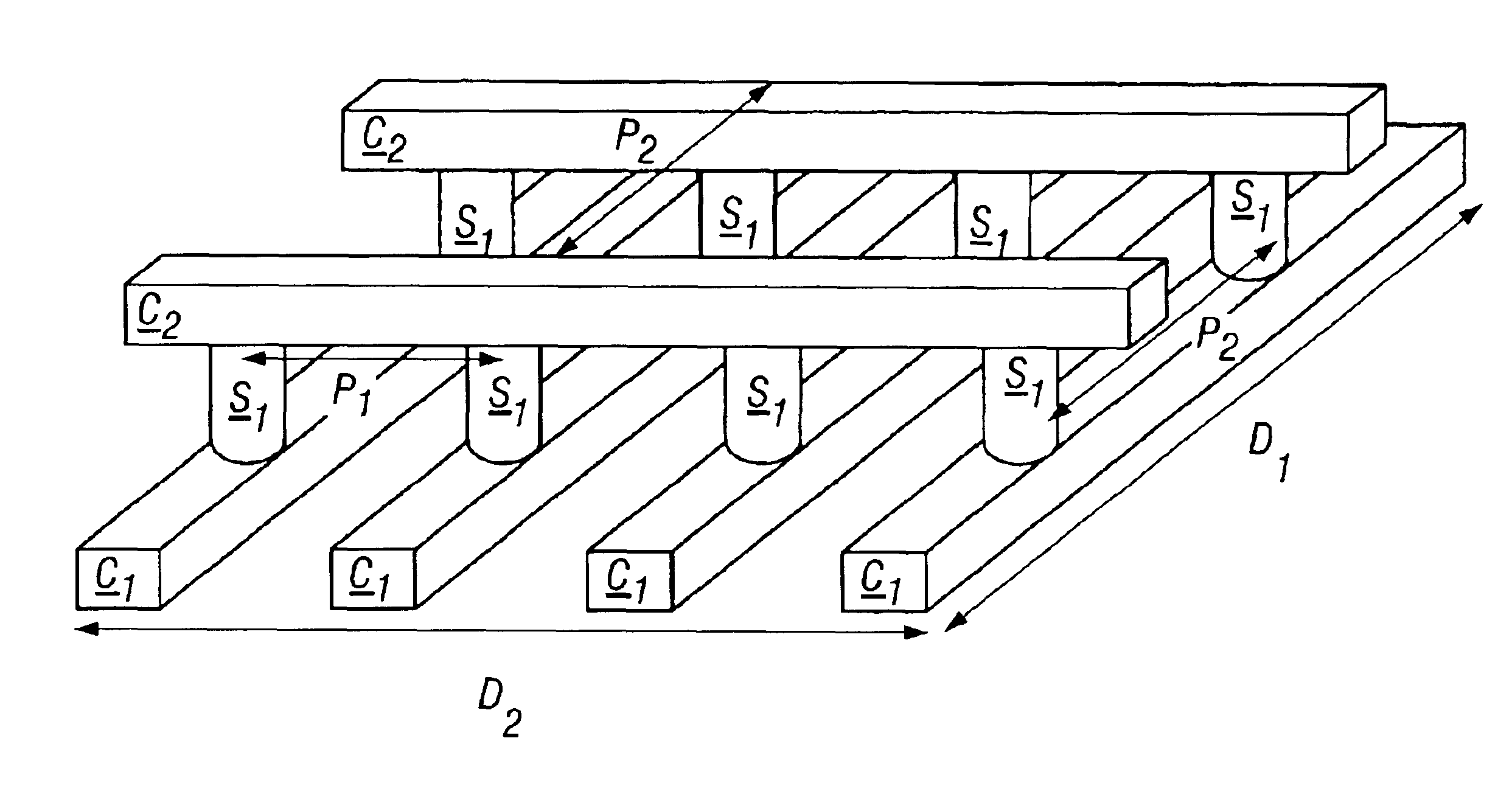

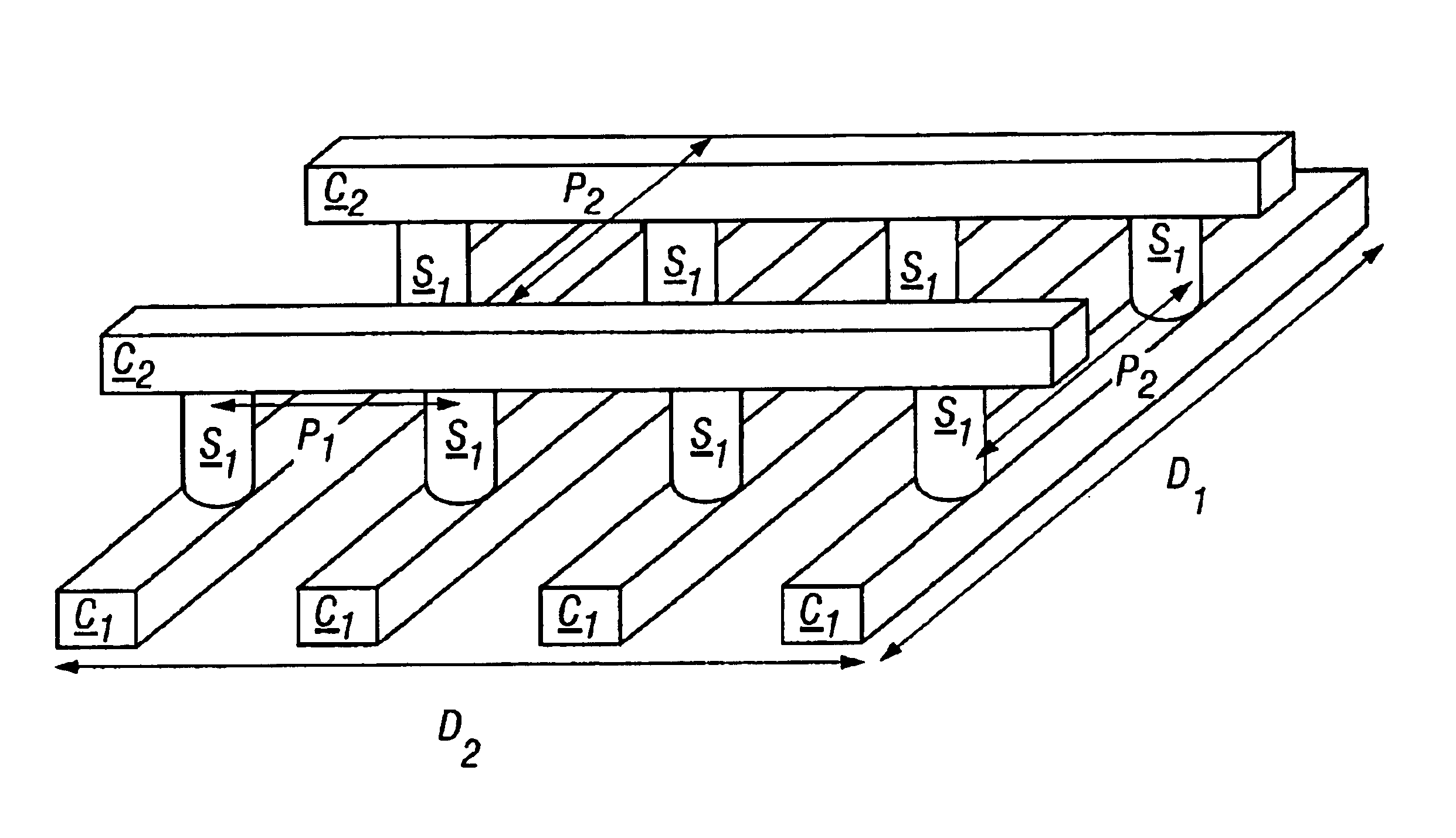

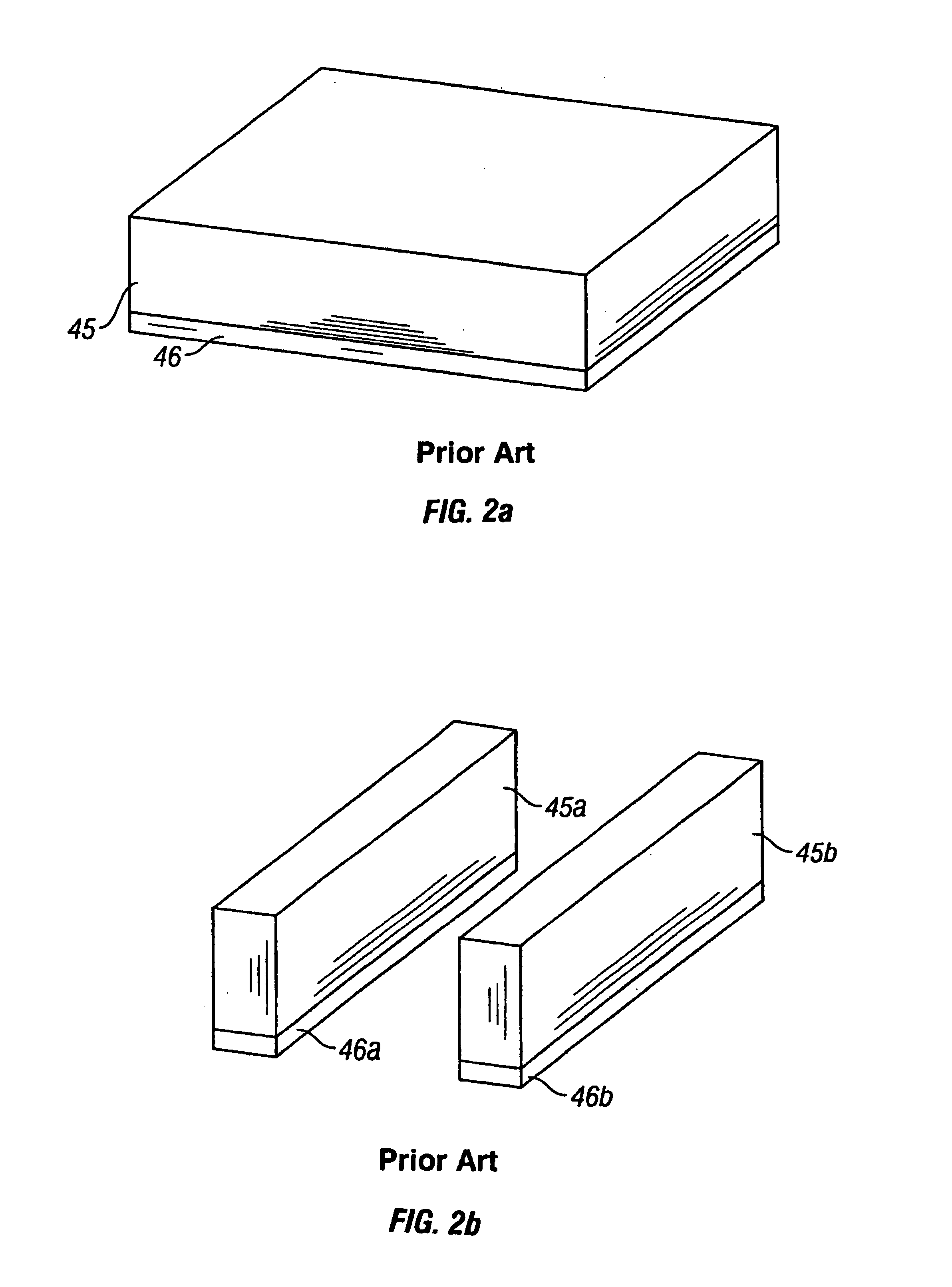

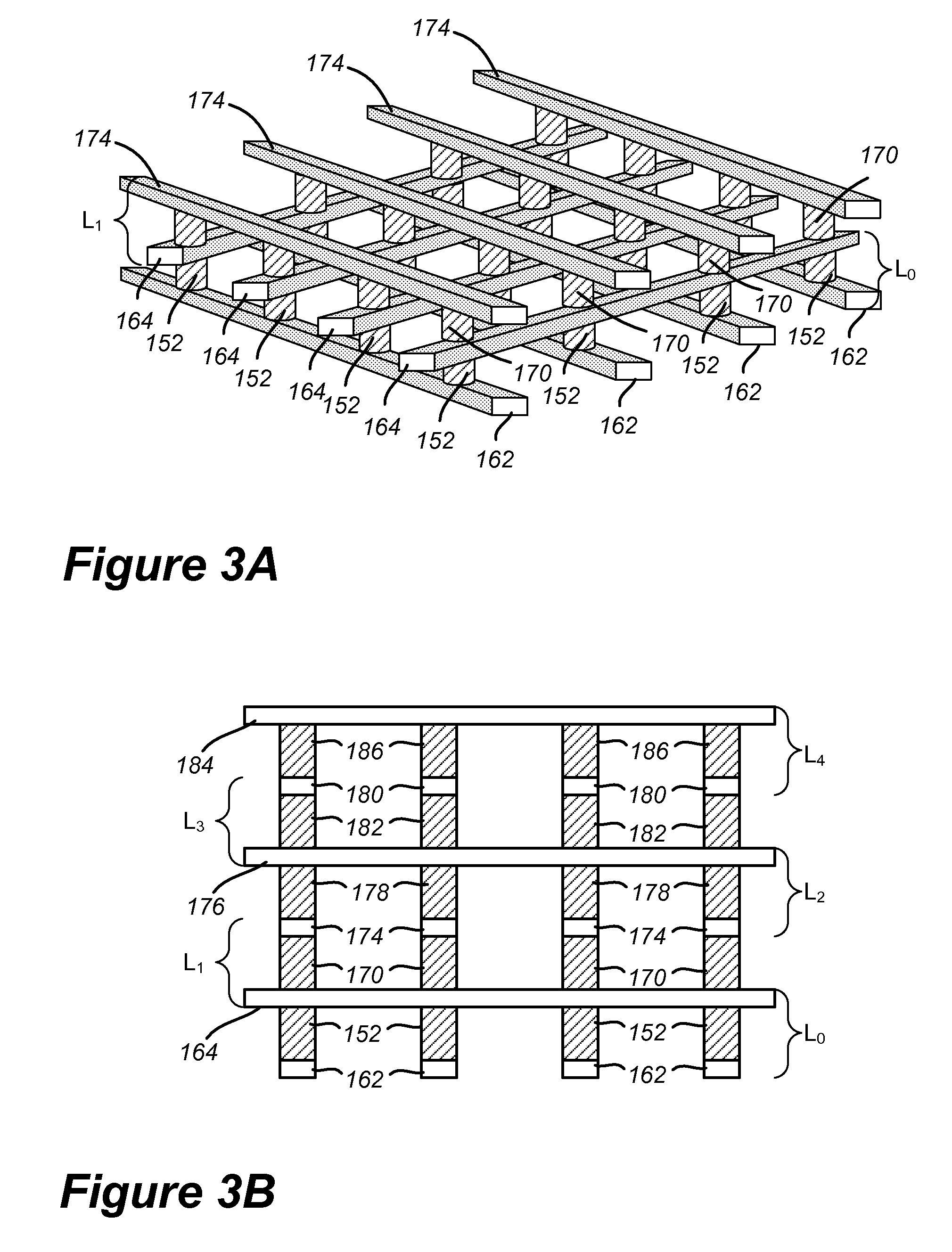

Low cost three-dimensional memory array

InactiveUS6515888B2Reduce areaReduce manufacturing costSolid-state devicesRead-only memoriesDopantAccess time

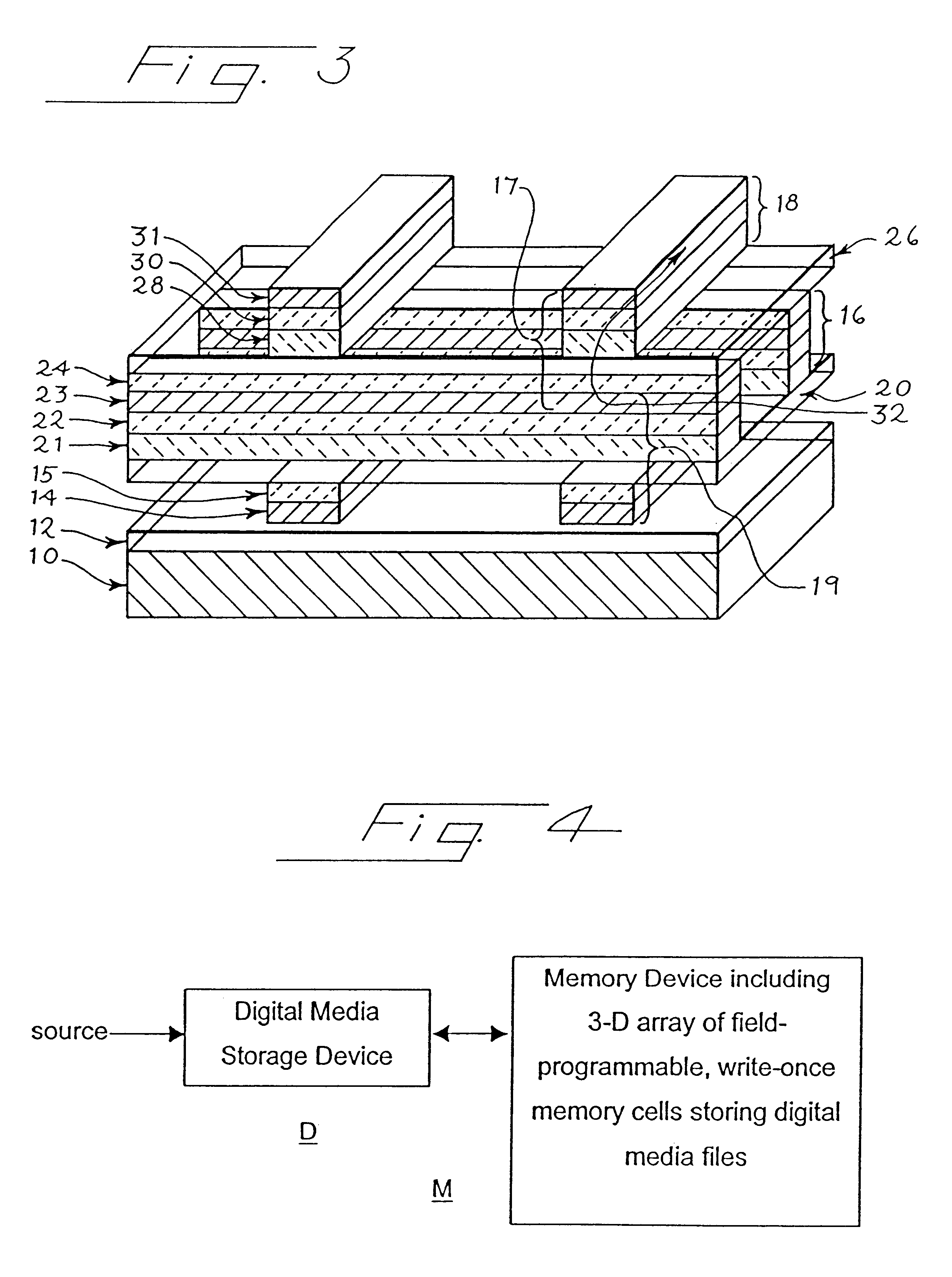

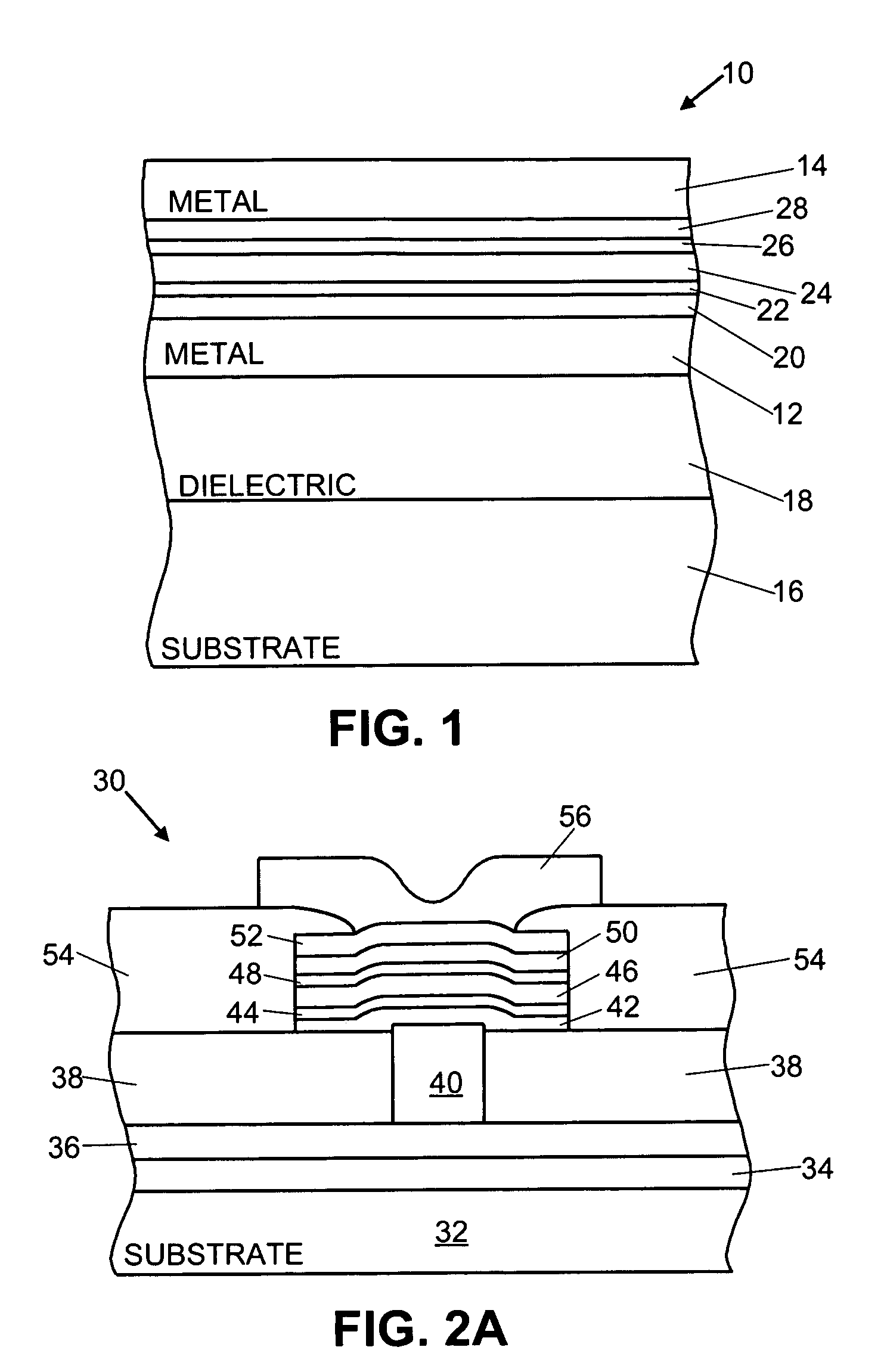

A low-cost memory cell array includes multiple, vertically-stacked layers of memory cells. In one form, each memory cell is characterized by a small cross-sectional area and a read current less than 6.3 microamperes. The resulting memory array has a slow access time and is well-suited for digital media storage, where access time requirements are low and the dramatic cost reductions associated with the disclosed memory arrays are particularly attractive. In another form, each memory cell includes an antifuse layer and diode components, wherein at least one diode component is heavily doped (to a dopant concentration greater than 1019 / cm3), and wherein the read current is large (up to 500 mA).

Owner:SANDISK TECH LLC

Reprogrammable metal-to-metal antifuse employing carbon-containing antifuse material

InactiveUS7459763B1Semiconductor/solid-state device detailsSolid-state devicesHydrogenMetal interconnect

A reprogrammable metal-to-metal antifuse is disposed between two metal interconnect layers in an integrated circuit. A lower barrier layer is formed from Ti. A lower adhesion-promoting layer is disposed over the lower Ti barrier layer. An antifuse material layer selected from a group comprising at least one of amorphous carbon and amorphous carbon doped with at least one of hydrogen and fluorine is disposed over the lower adhesion-promoting layer. An upper adhesion-promoting layer is disposed over the antifuse material layer. An upper Ti barrier layer is disposed over the upper adhesion-promoting layer.

Owner:MICROSEMI SOC

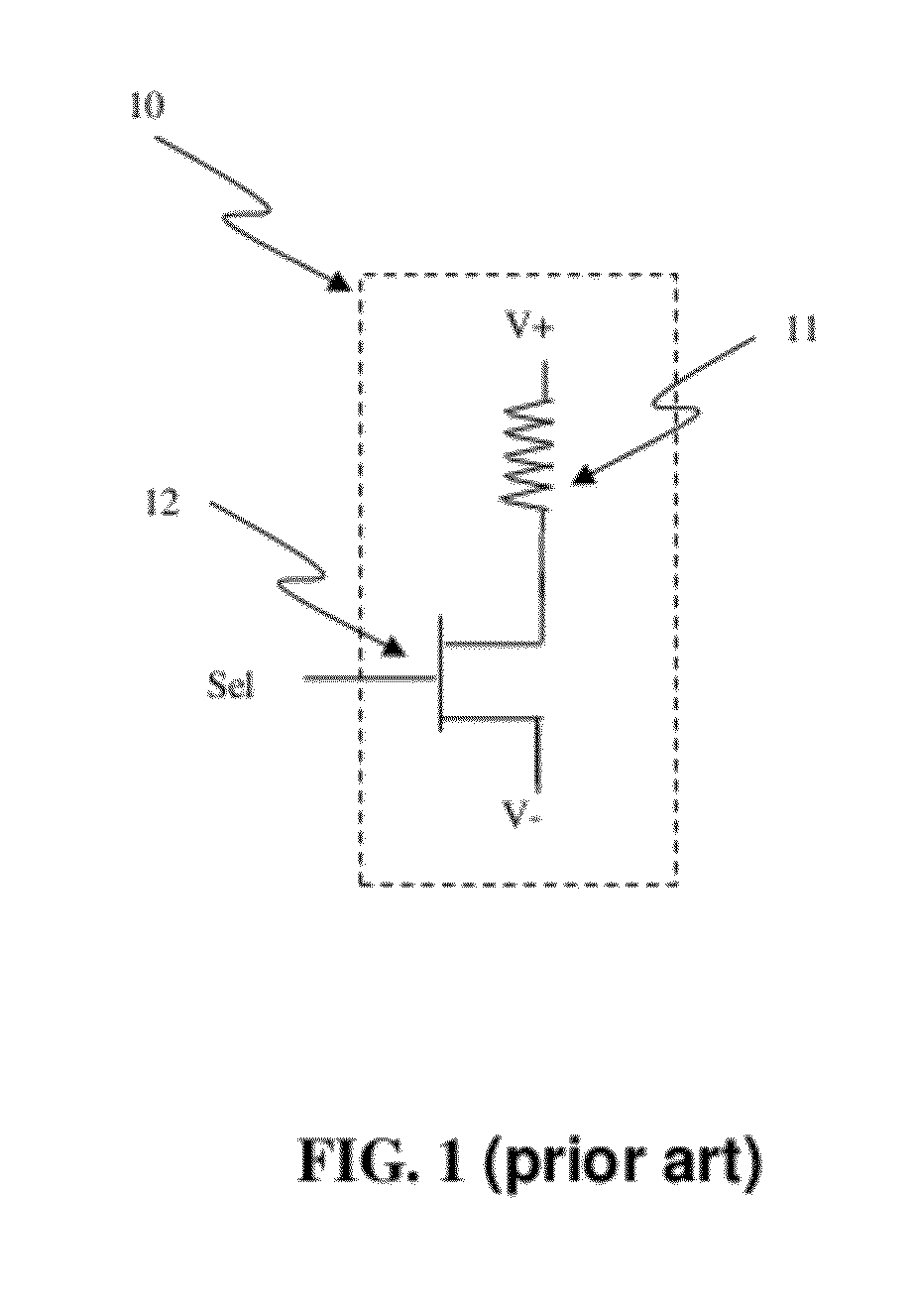

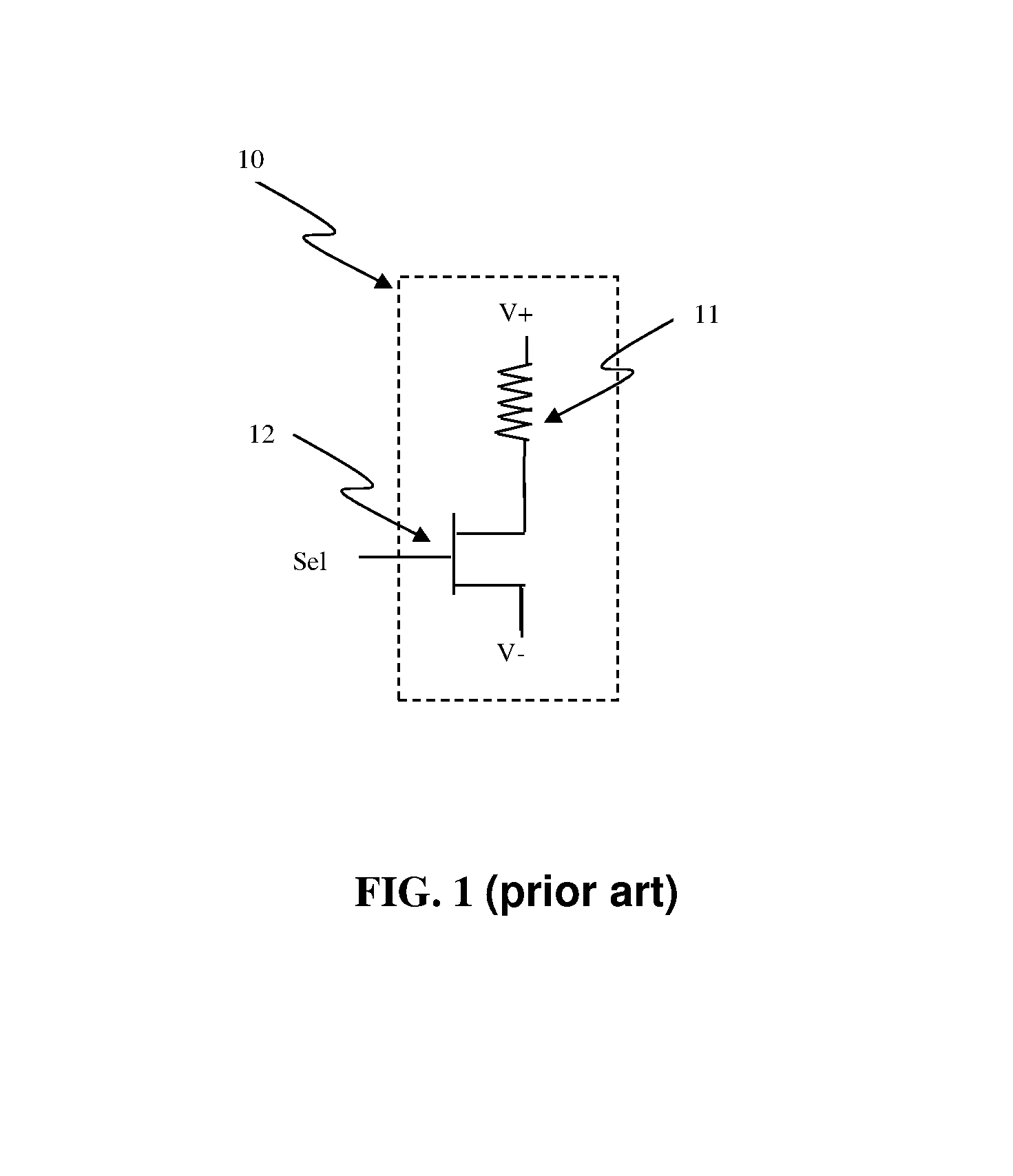

Split-channel antifuse array architecture

InactiveUS20060244099A1Limited over-voltage exposureSimplify and improve and accessTransistorSemiconductor/solid-state device detailsCMOSEngineering

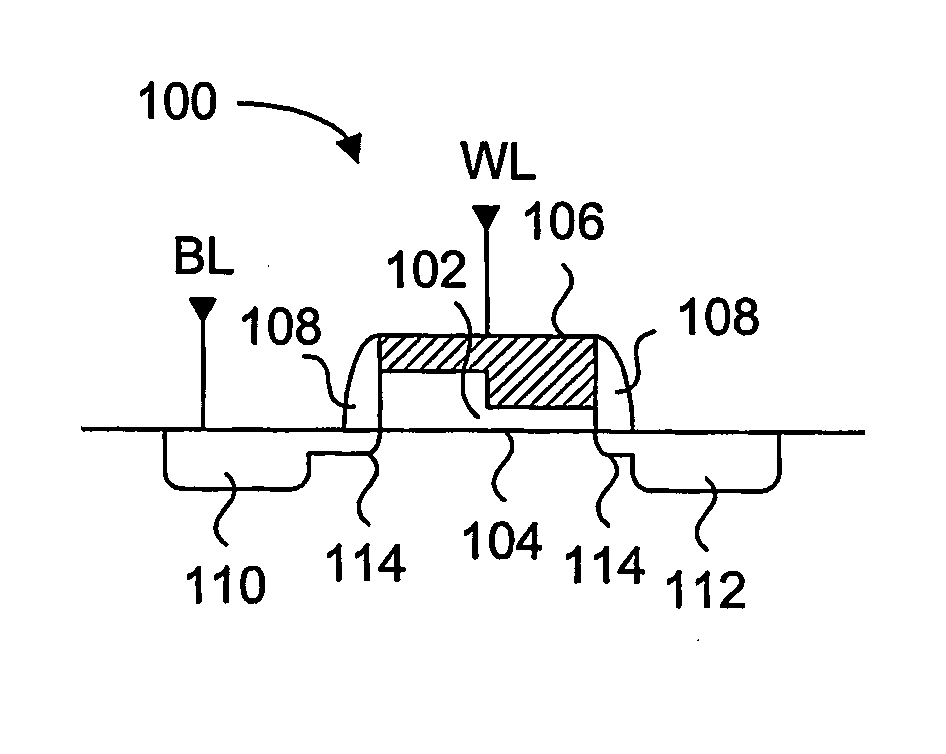

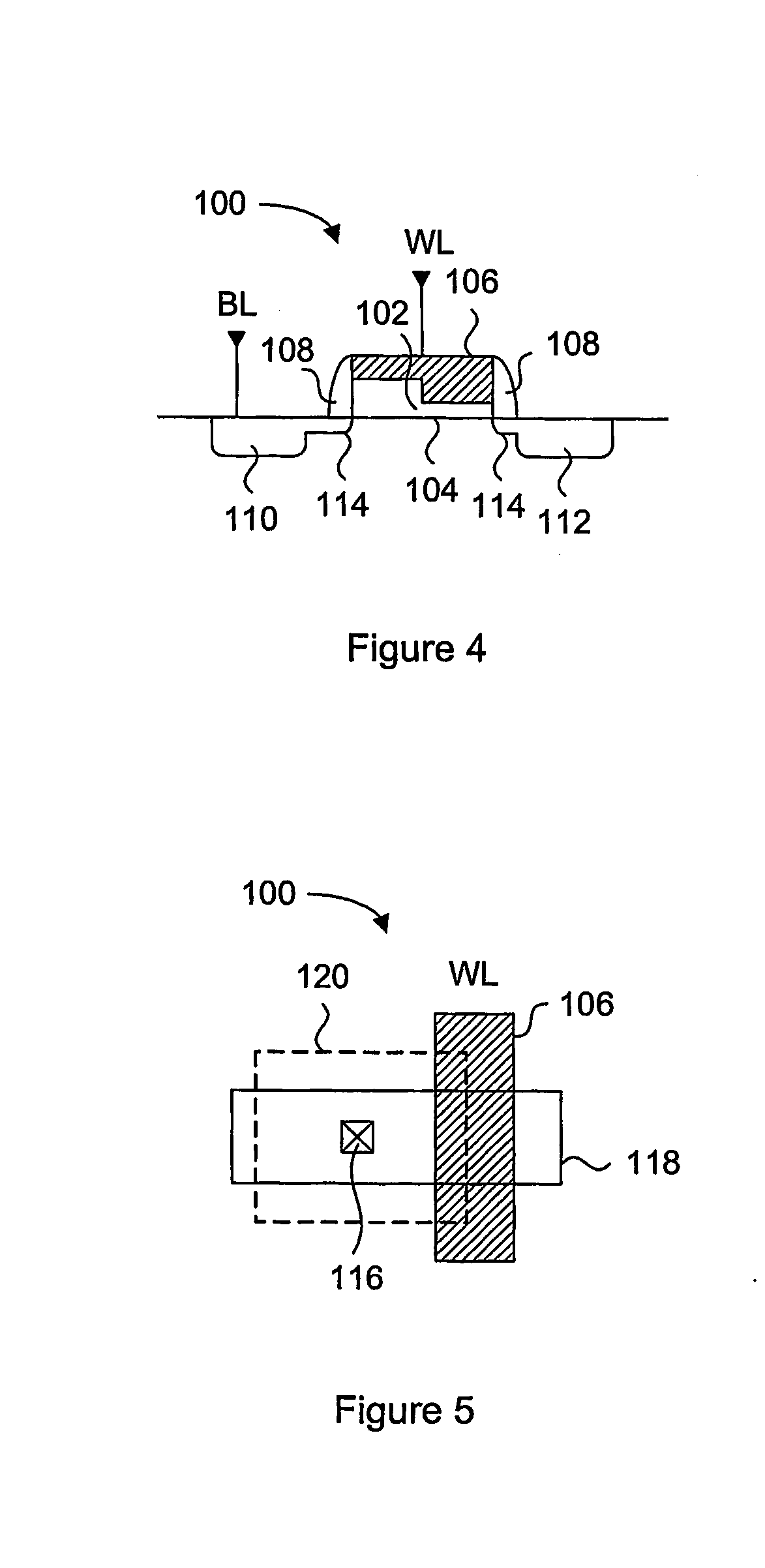

Generally, the present invention provides a variable thickness gate oxide anti-fuse transistor device that can be employed in a non-volatile, one-time-programmable (OTP) memory array application. The anti-fuse transistor can be fabricated with standard CMOS technology, and is configured as a standard transistor element having a source diffusion, gate oxide, polysilicon gate and optional drain diffusion. The variable gate oxide underneath the polysilicon gate consists of a thick gate oxide region and a thin gate oxide region, where the thin gate oxide region acts as a localized breakdown voltage zone. A conductive channel between the polysilicon gate and the channel region can be formed in the localized breakdown voltage zone during a programming operation. In a memory array application, a wordline read current applied to the polysilicon gate can be sensed through a bitline connected to the source diffusion, via the channel of the anti-fuse transistor. More specifically, the present invention provides an effective method for utilizing split channel MOS structures as an anti-fuse cell suitable for OTP memories.

Owner:SYNOPSYS INC

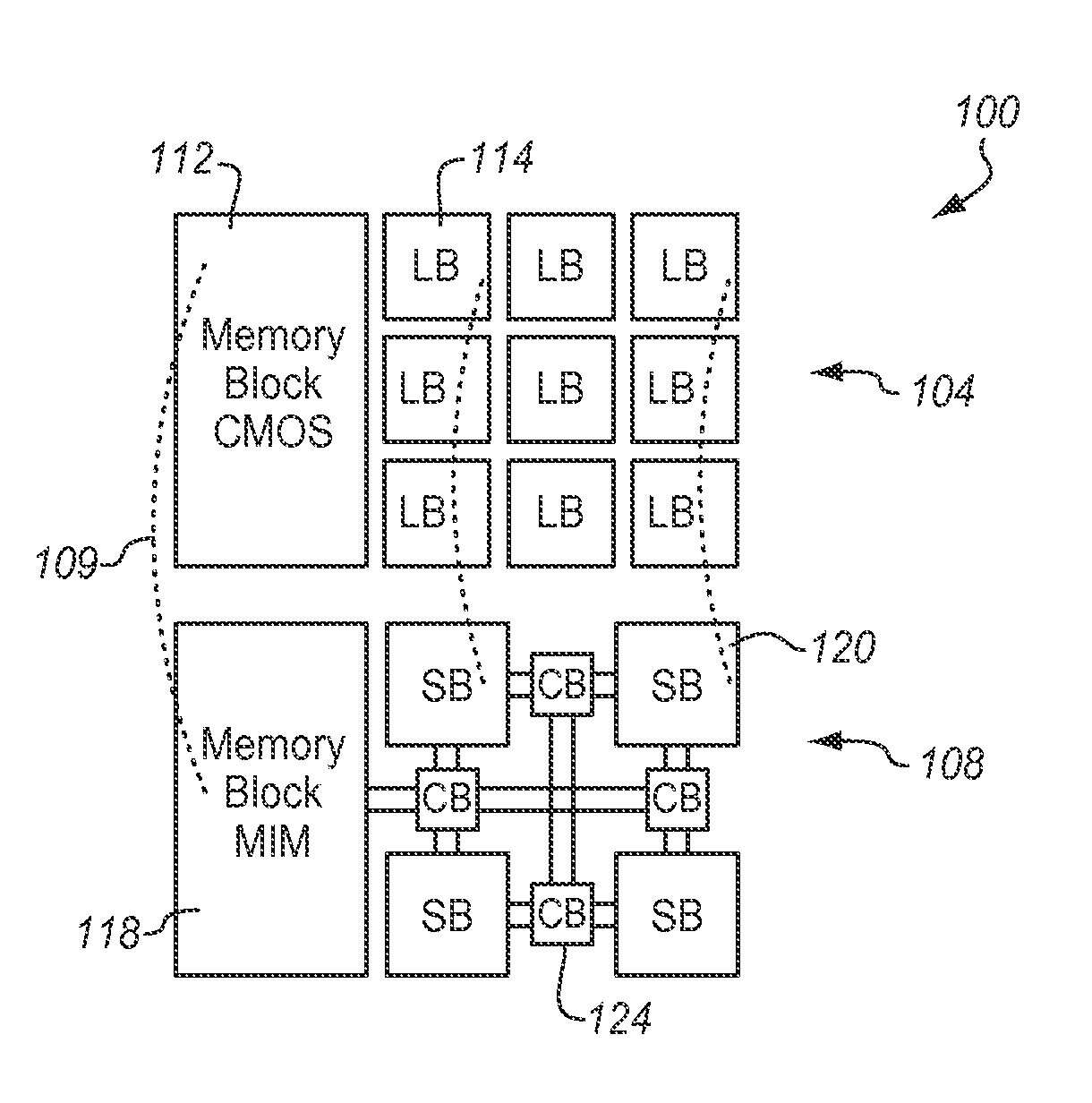

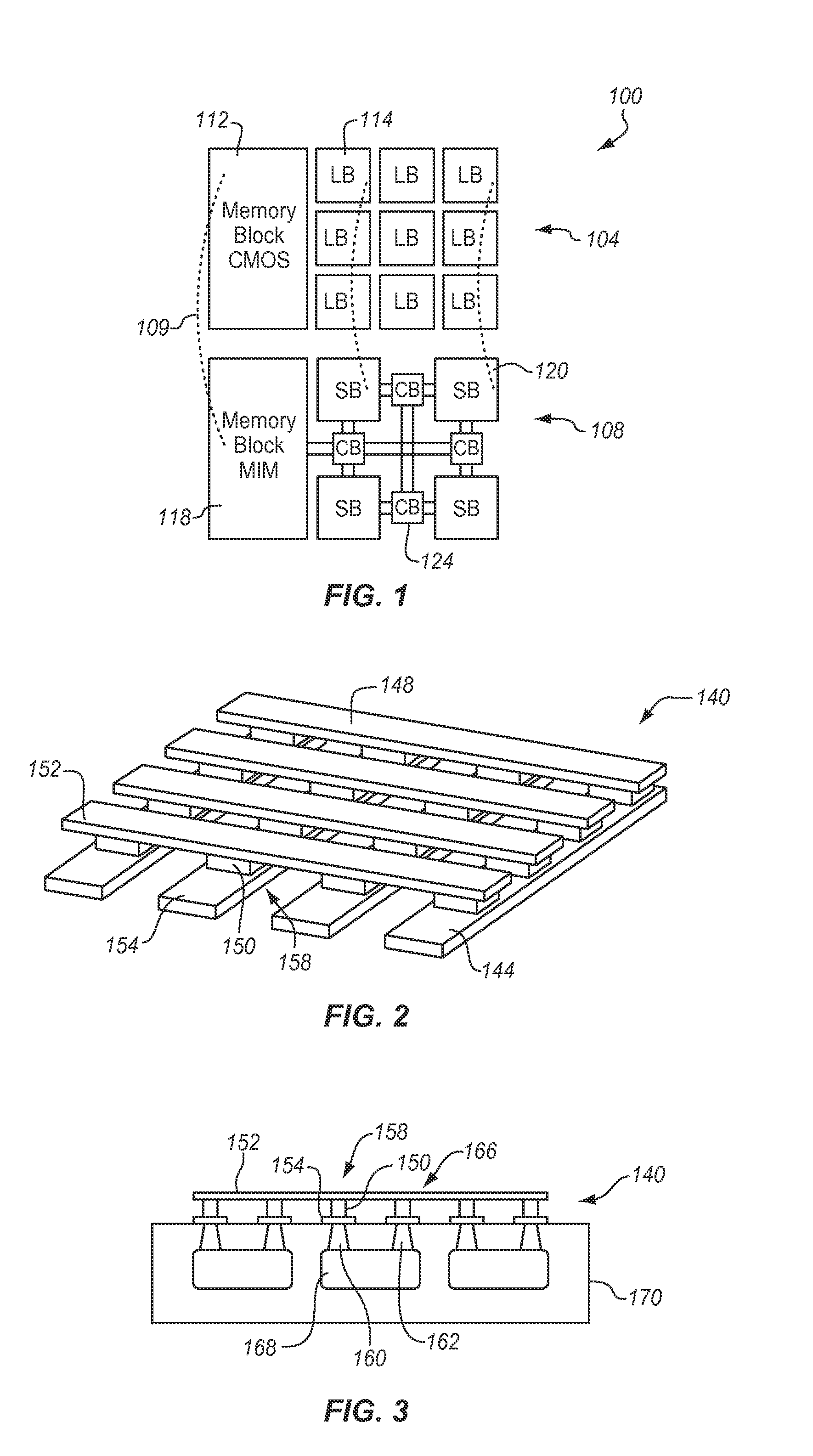

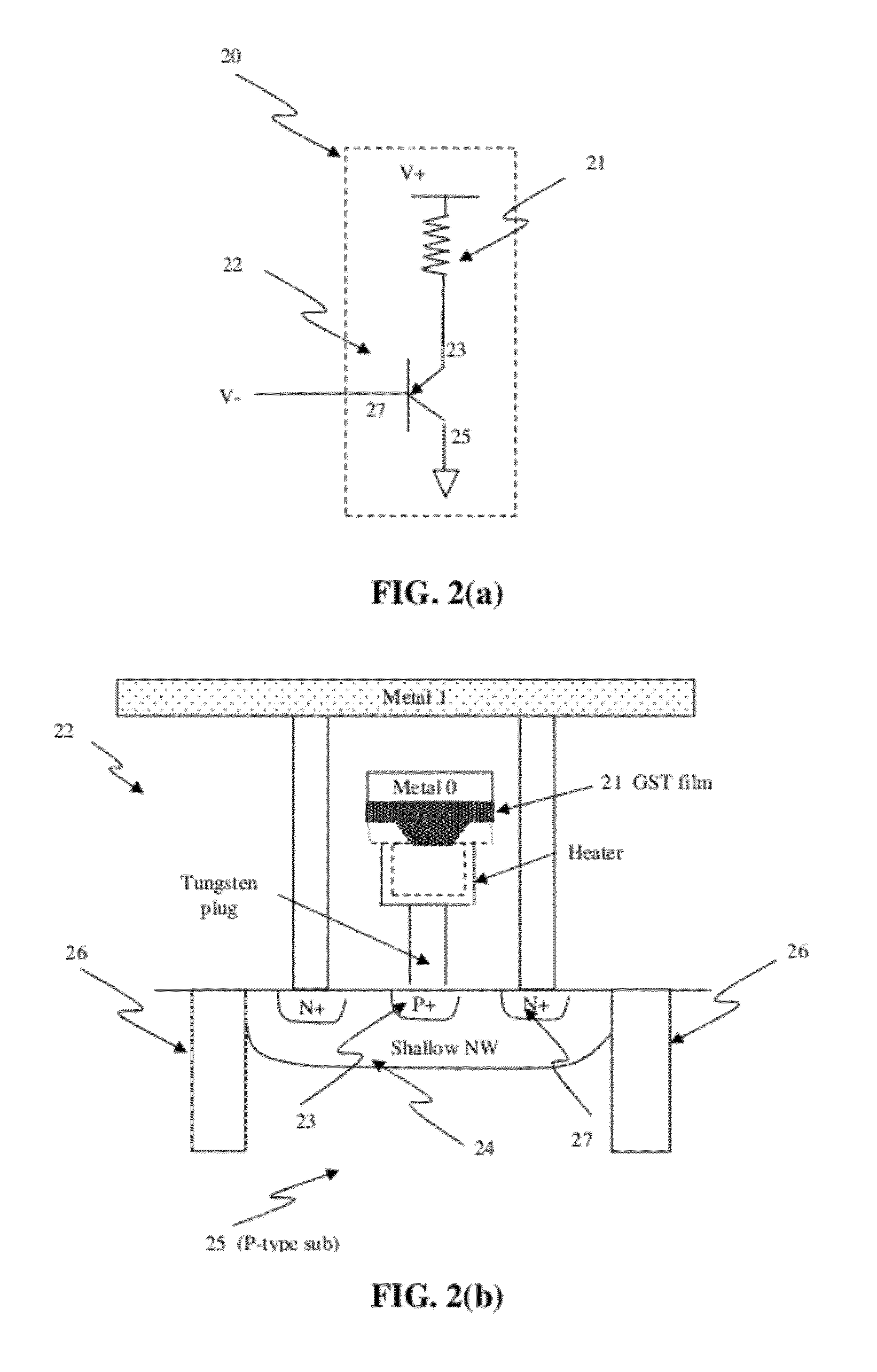

RE-PROGRAMMABLE ANTIFUSE FPGA UTILIZING RESISTIVE CeRAM ELEMENTS

ActiveUS20130285699A1Solid-state devicesRead-only memoriesElectrical resistance and conductanceResistive switching

A re-programmable antifuse field programmable gate array (FPGA) integrated circuit, the FPGA comprising: a plurality of CeRAM resistive switching elements forming a connection block, the switching elements capable of being switched from a conductive (ON) state to a non-conductive (OFF) state and back to a conductive (ON) state; a plurality of logic elements forming a logic block; and a programming circuit for turning the CeRAM switching elements OFF and ON to connect the logic elements to form the FPGA.

Owner:SYMETRIX MEMORY

Method for making high density nonvolatile memory

InactiveUS6984561B2High densityReduce the overall heightTransistorBeacon systems using ultrasonic/sonic/infrasonic wavesElectrical conductorHigh density

An improved method for fabricating a three dimensional monolithic memory with increased density. The method includes forming conductors preferably comprising tungsten, then filling and planarizing; above the conductors forming semiconductor elements preferably comprising two diode portions and an antifuse, then filling and planarizing; and continuing to form conductors and semiconductor elements in multiple stories of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

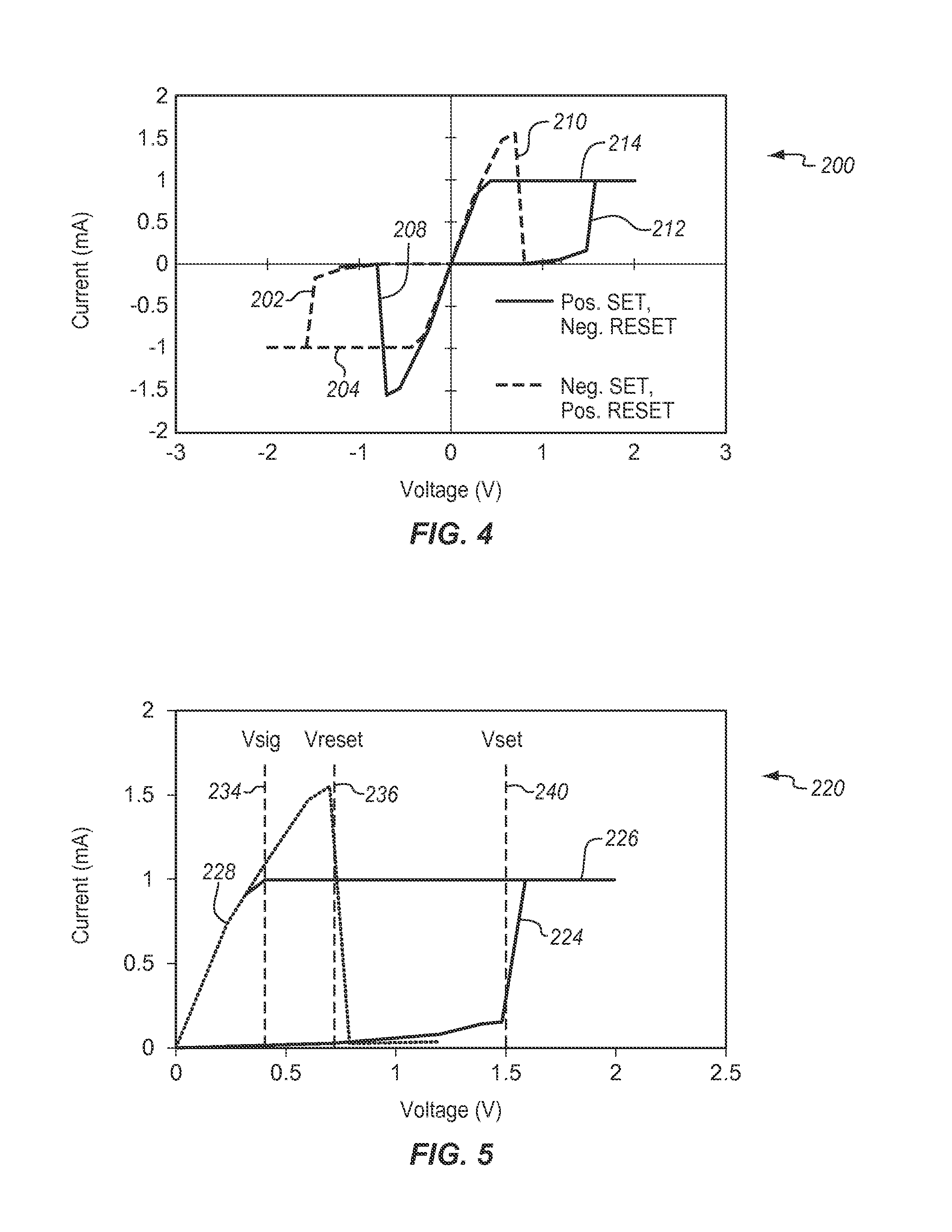

Nonvolatile rewritable memory cell comprising a resistivity-switching oxide or nitride and an antifuse

ActiveUS7829875B2Semiconductor/solid-state device detailsSolid-state devicesDielectricElectrical resistance and conductance

A memory cell is described, the memory cell comprising a dielectric rupture antifuse and a layer of a resistivity-switching material arranged electrically in series, wherein the resistivity-switching material is a metal oxide or nitride compound, the compound including exactly one metal. The dielectric rupture antifuse is ruptured in a preconditioning step, forming a rupture region through the antifuse. The rupture region provides a narrow conductive path, serving to limit current to the resistivity-switching material, and improving control when the resistivity-switching layer is switched between higher- and lower-resistivity states.

Owner:SANDISK TECH LLC

Electrically-programmable integrated circuit antifuses

InactiveUS6897543B1Reduces drain-to-source resistanceIncrease resistanceTransistorSemiconductor/solid-state device detailsHigh resistanceZener diode

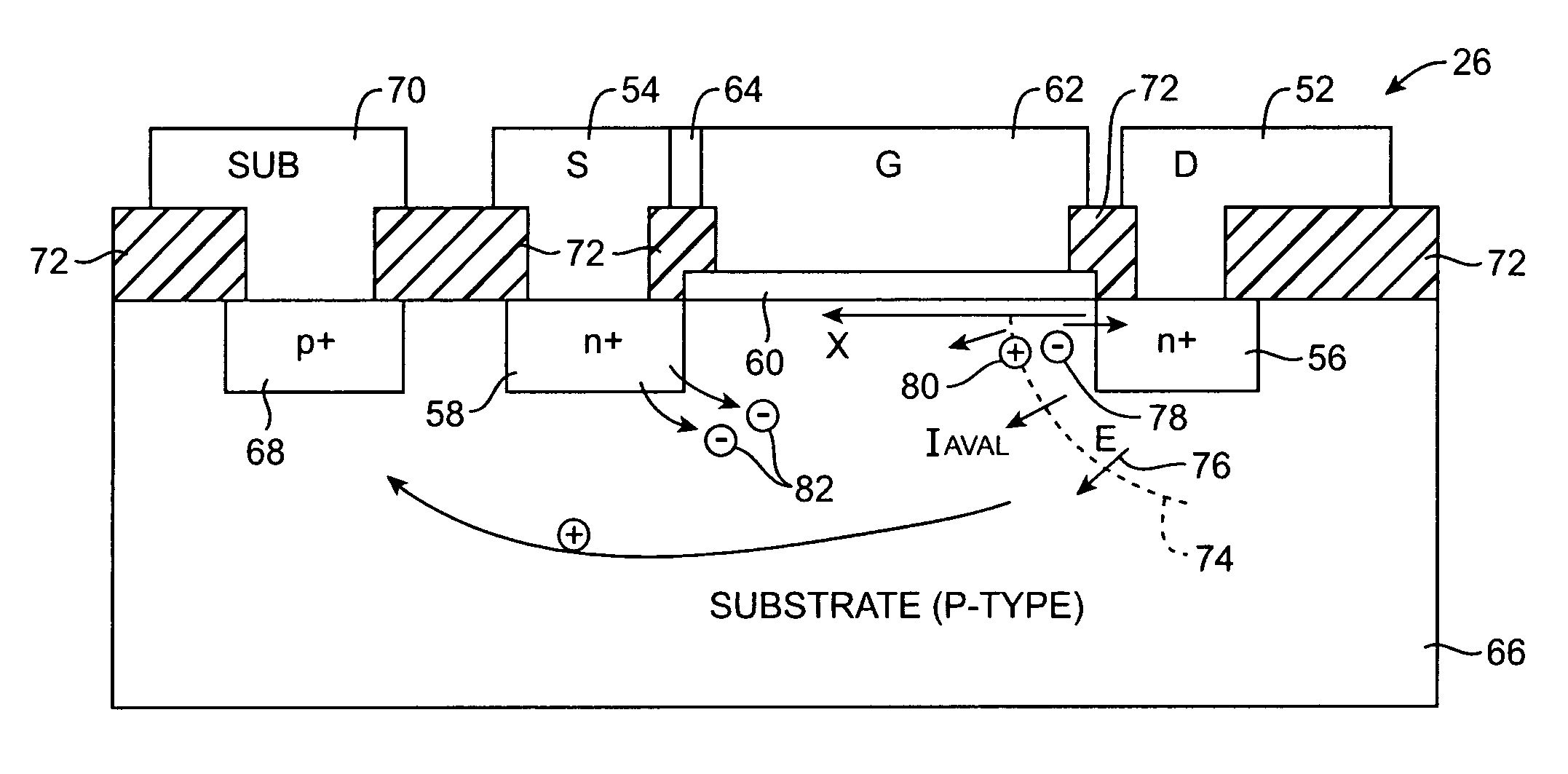

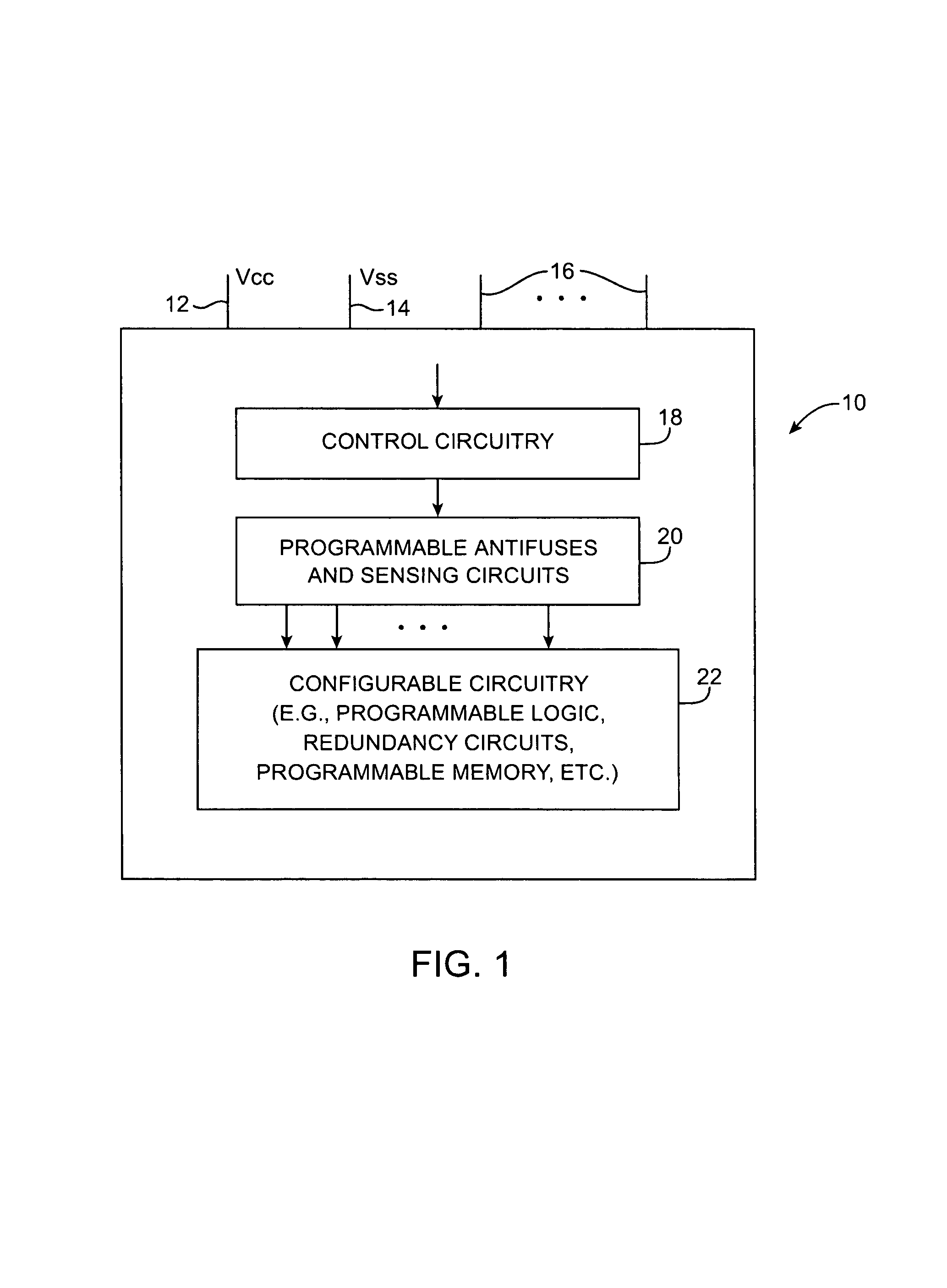

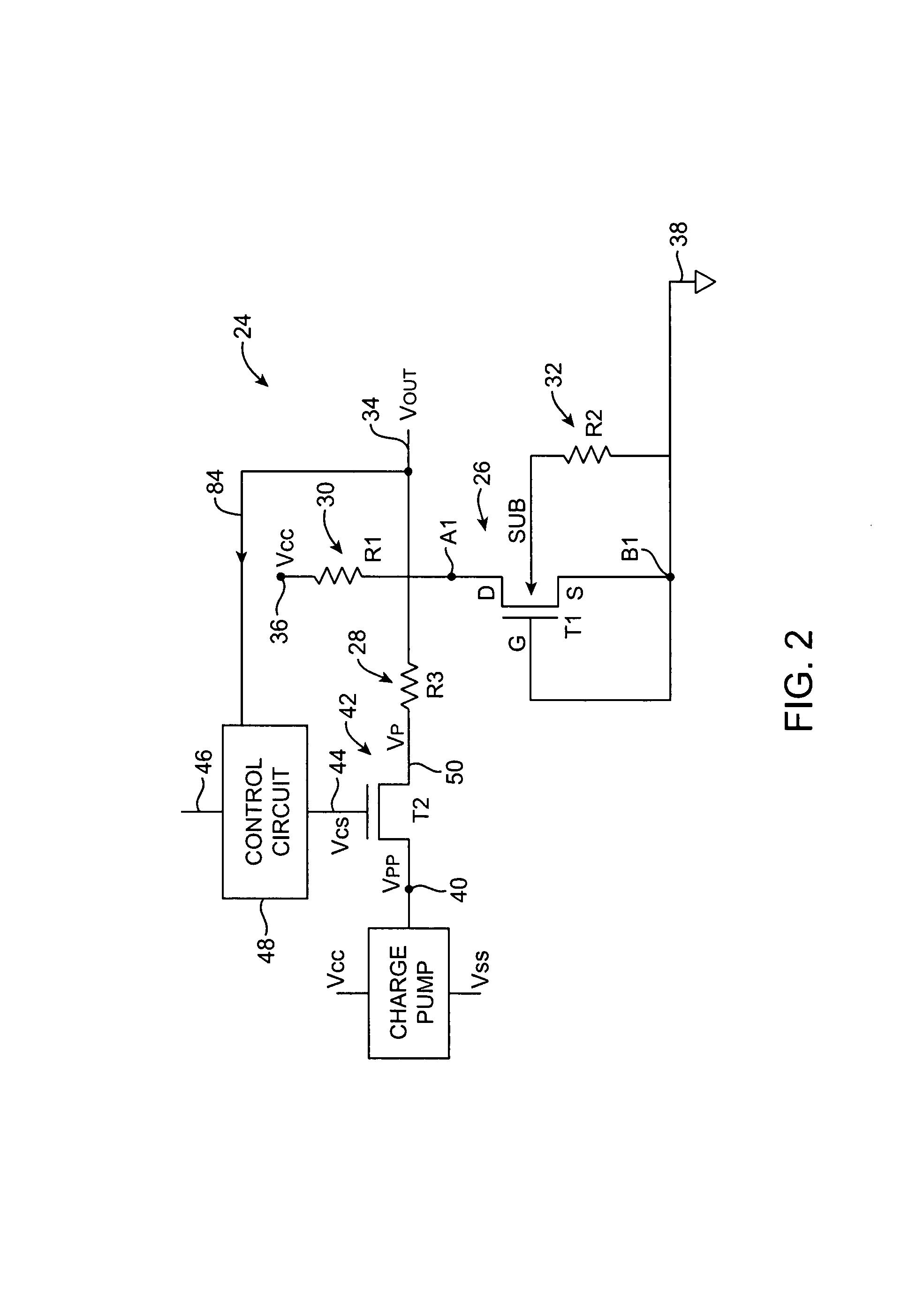

Integrated circuit antifuse circuitry is provided. A metal-oxide-semiconductor (MOS) antifuse transistor serves as an electrically-programmable antifuse. In its unprogrammed state, the antifuse transistor is off and has a relatively high resistance. During programming, the antifuse transistor is turned on which melts the underlying silicon and causes a permanent reduction in the transistor's resistance. A sensing circuit monitors the resistance of the antifuse transistor and supplies a high or low output signal accordingly. The antifuse transistor may be turned on during programming by raising the voltage at its substrate relative to its source. The substrate may be connected to ground through a resistor. The substrate may be biased by causing current to flow through the resistor. Current may be made to flow through the resistor by inducing avalanche breakdown of the drain-substrate junction or by producing Zener breakdown of external Zener diode circuitry connected to the resistor.

Owner:TAHOE RES LTD

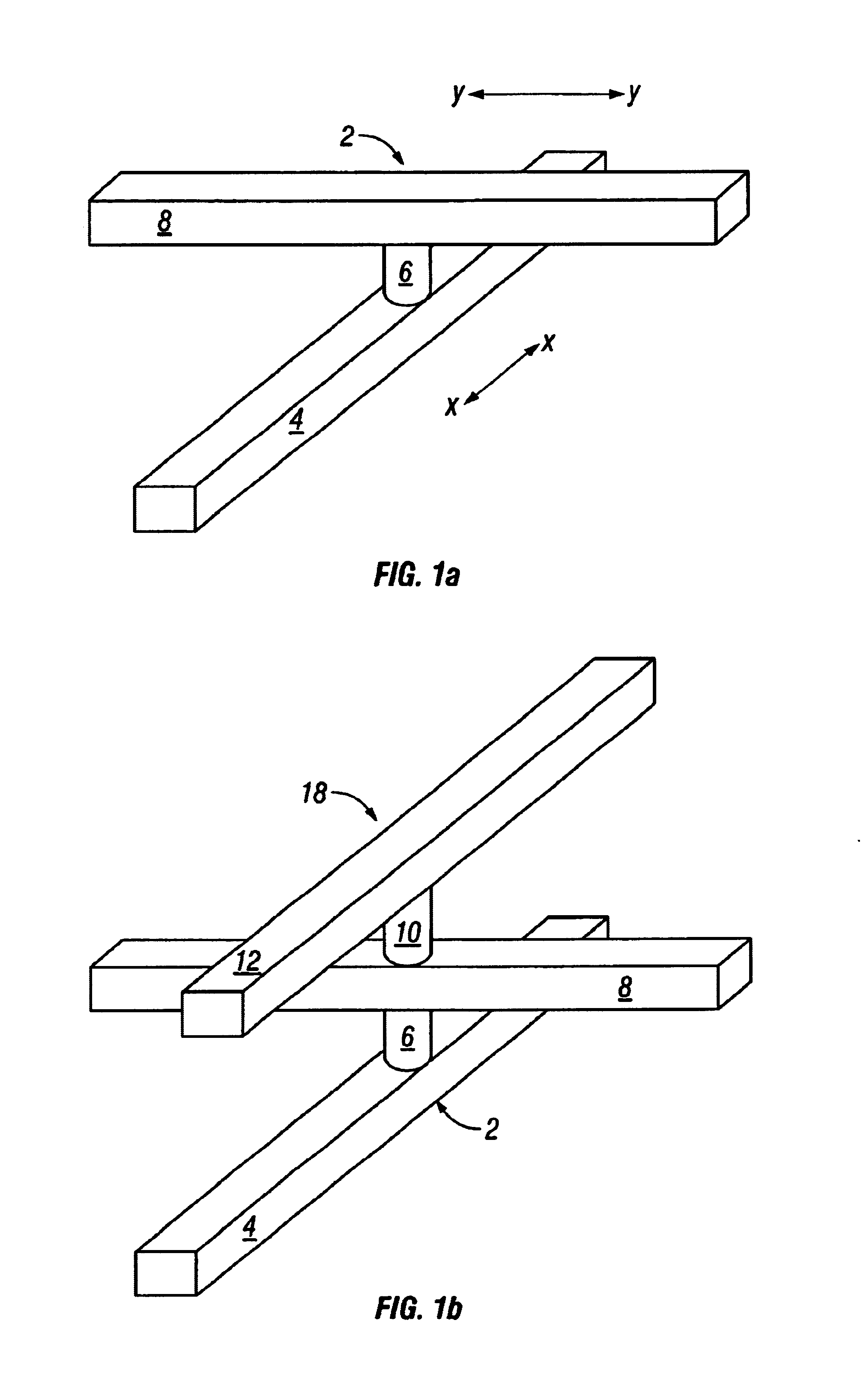

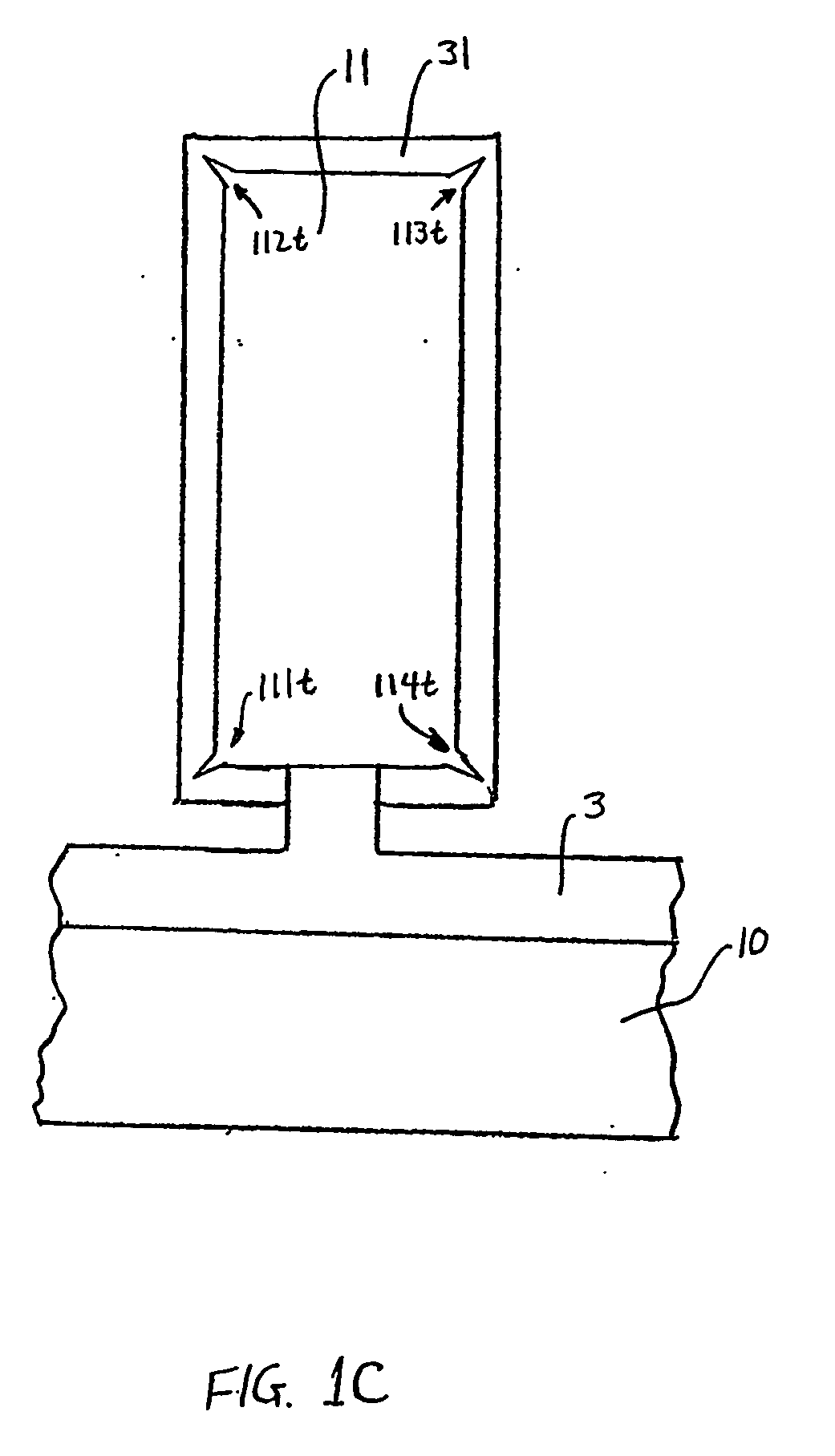

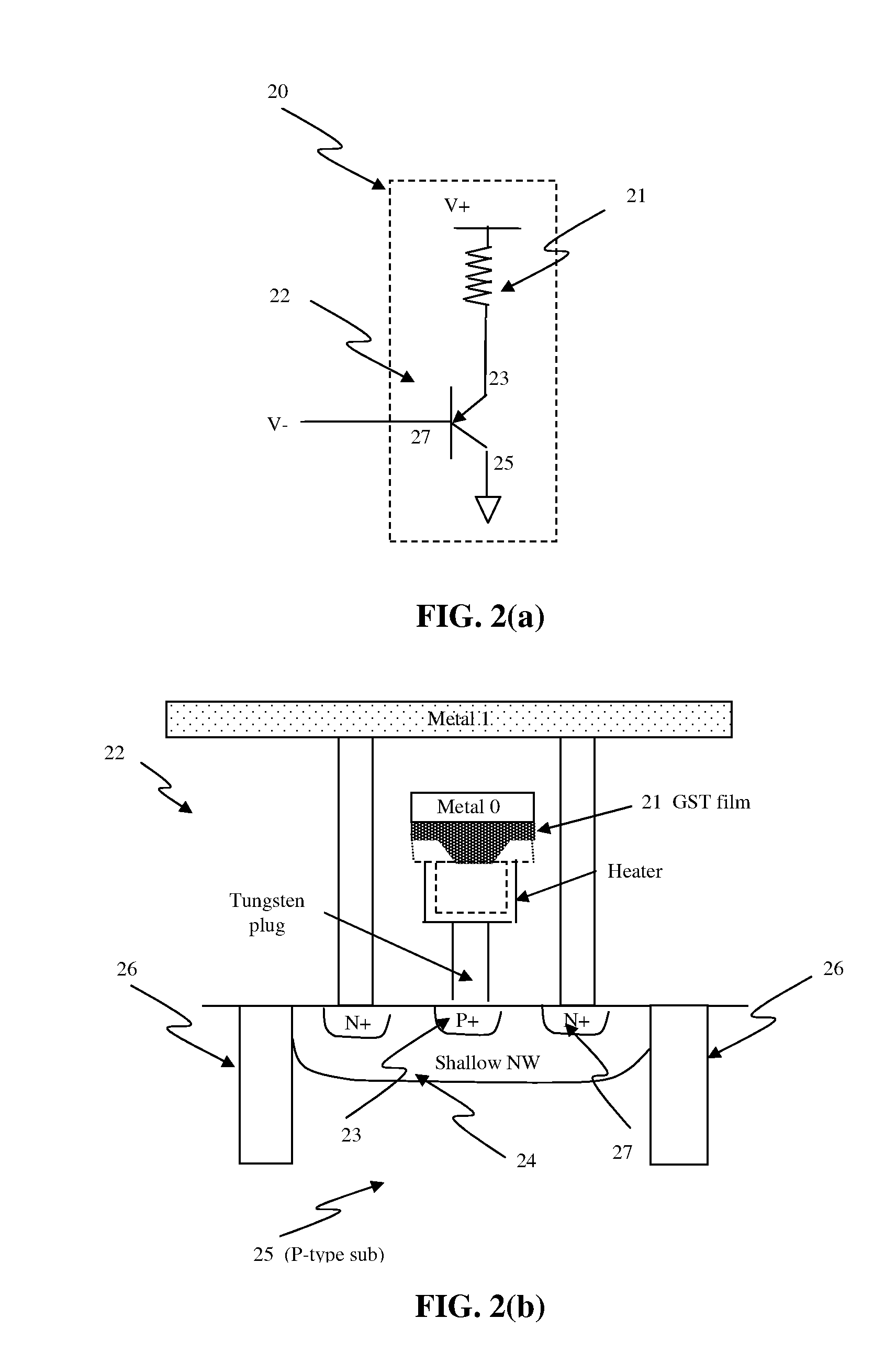

Circuit and system of a high density Anti-fuse

ActiveUS20120147653A1Eliminate needHigh voltageSemiconductor/solid-state device detailsSolid-state devicesThin oxideHigh density

A high density anti-fuse cell can be built at the cross points of two perpendicular interconnect lines, such as active region lines, active and polysilicon lines, active and metal lines, or polysilicon and metal lines. The cell size can be very small. At least one of the anti-fuse cells have a thin oxide fabricated before, after, or between a diode in at least one contact holes at the cross points of the interconnect lines. The thin oxide of the anti-fuse cells at the cross points can be selected for rupture by applying supply voltages in the two perpendicular lines. In some embodiments, a diode can be created after thin oxide is ruptured so that explicitly fabricating a diode or opening a contact hole at the cross-point may not be necessary.

Owner:ATTOPSEMI TECH CO LTD

Method for making high density nonvolatile memory

InactiveUS20050012119A1High densitySmall feature sizeTransistorSemiconductor/solid-state device detailsElectrical conductorHigh density

An improved method for fabricating a three dimensional monolithic memory with increased density. The method includes forming conductors preferably comprising tungsten, then filling and planarizing; above the conductors forming semiconductor elements preferably comprising two diode portions and an antifuse, then filling and planarizing; and continuing to form conductors and semiconductor elements in multiple stories of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

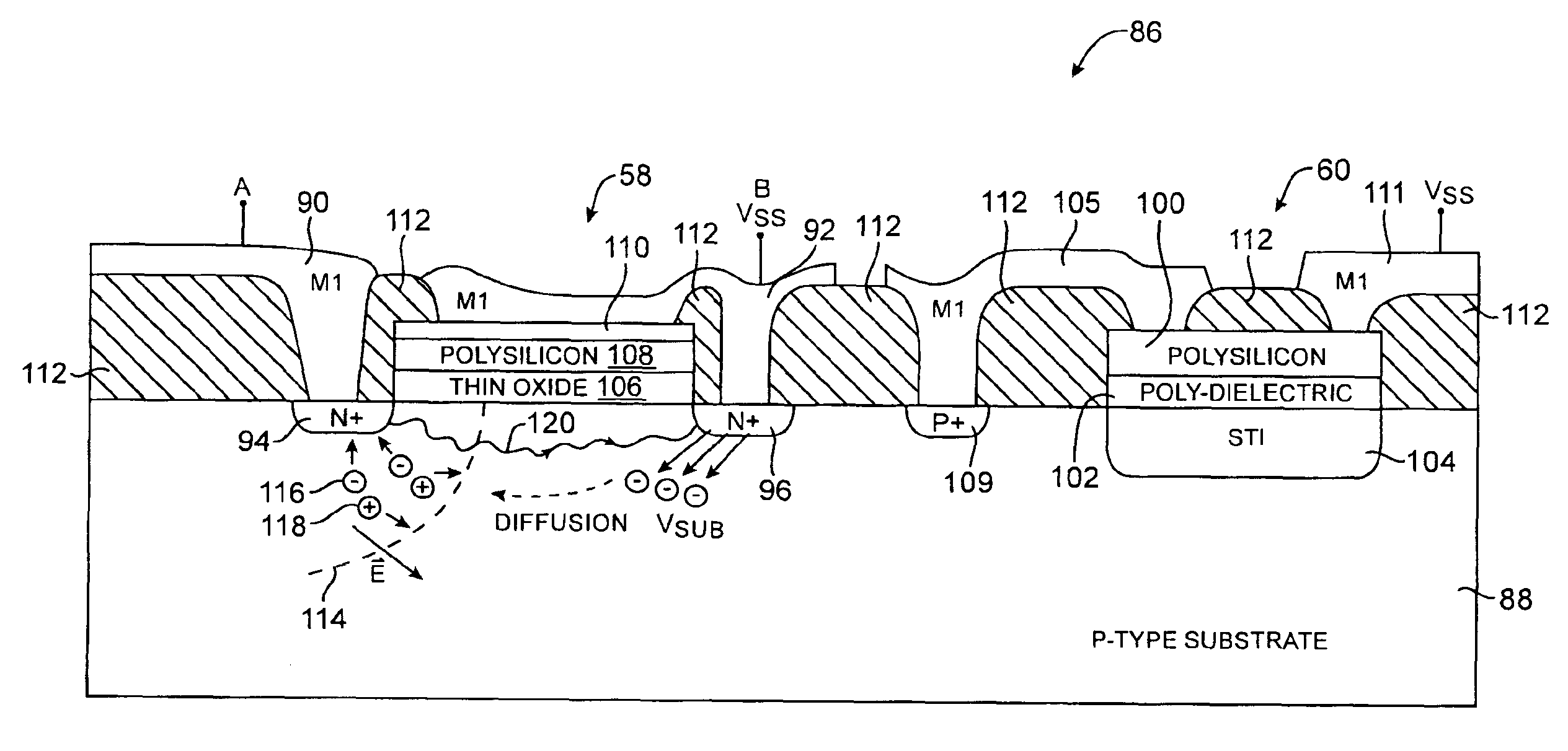

Electrically-programmable transistor antifuses

InactiveUS7157782B1Minimize powerMinimize timeTransistorSemiconductor/solid-state device detailsHigh resistanceEngineering

Integrated circuit antifuse circuitry is provided. A metal-oxide-semiconductor (MOS) transistor serves as an electrically-programmable antifuse. The antifuse transistor has source, drain, gate, and substrate terminals. The gate has an associated gate oxide. In its unprogrammed state, the gate oxide is intact and the antifuse has a relatively high resistance. During programming, the gate oxide breaks down, so in its programmed state the antifuse transistor has a relatively low resistance. The antifuse transistor can be programmed by injecting hot carriers into the substrate of the device in the vicinity of the drain. Because there are more hot carriers at the drain than at the substrate, the gate oxide is stressed asymmetrically, which enhances programming efficiency. Feedback can be used to assist in turning the antifuse transistor on to inject the hot carriers.

Owner:ALTERA CORP

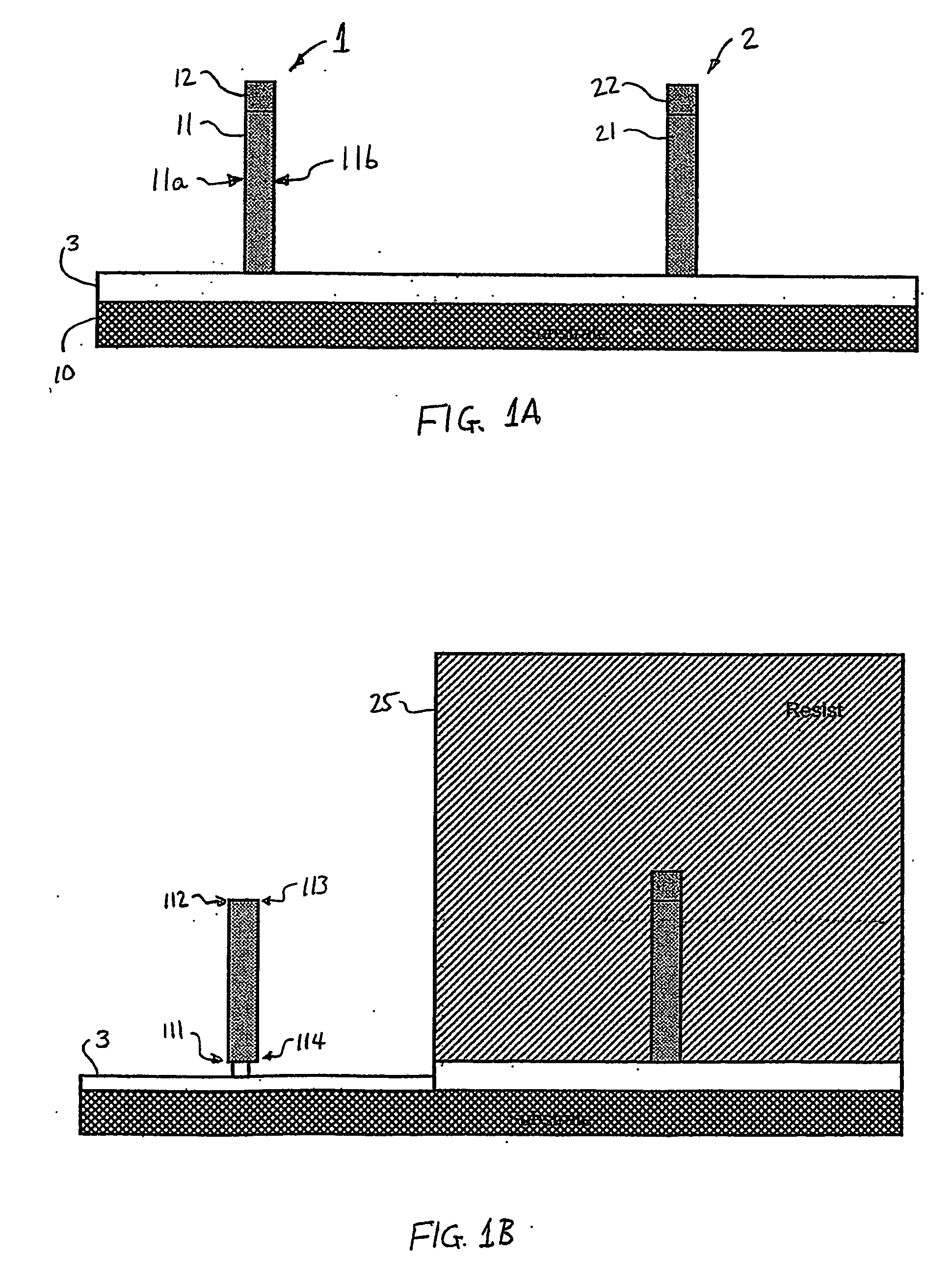

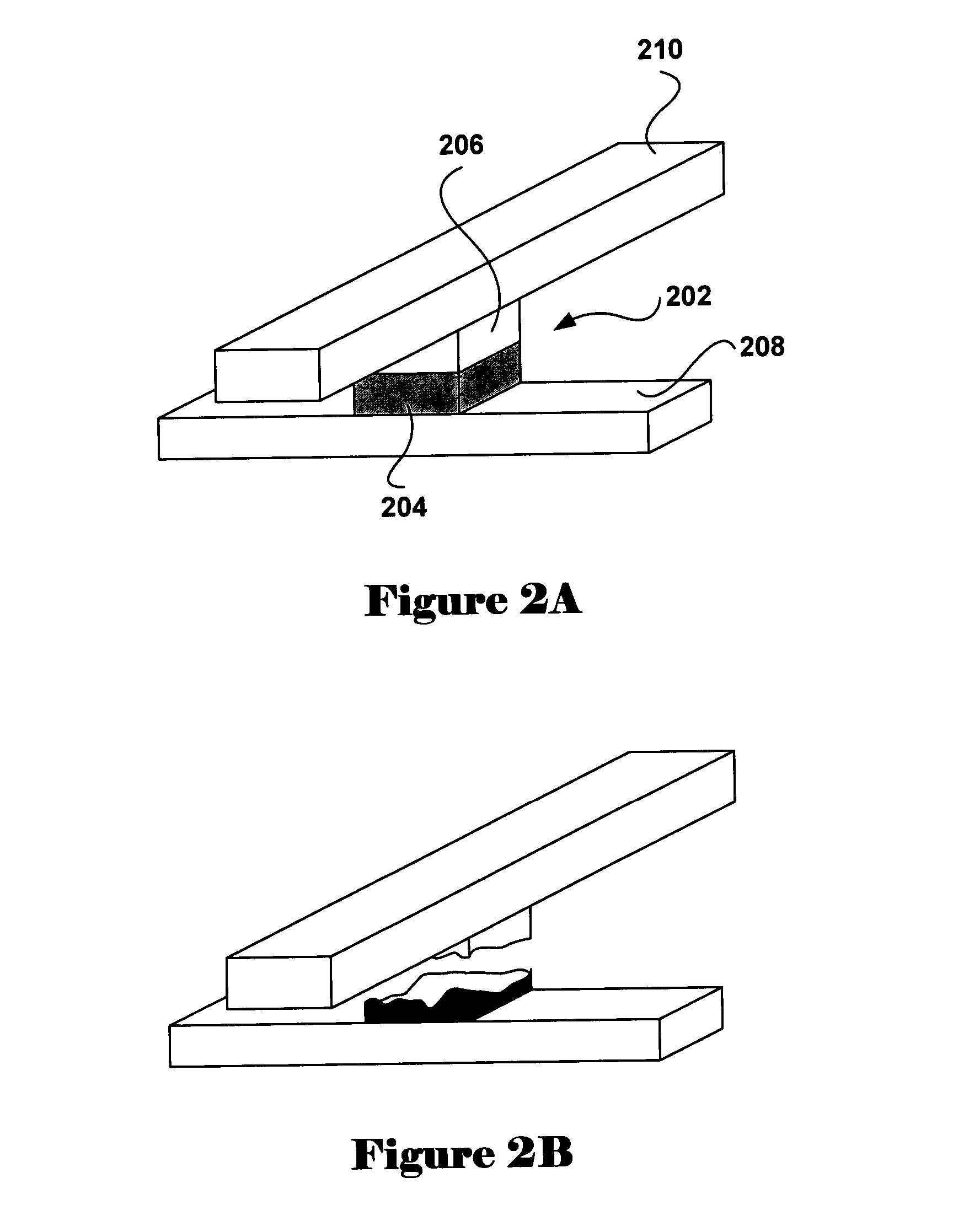

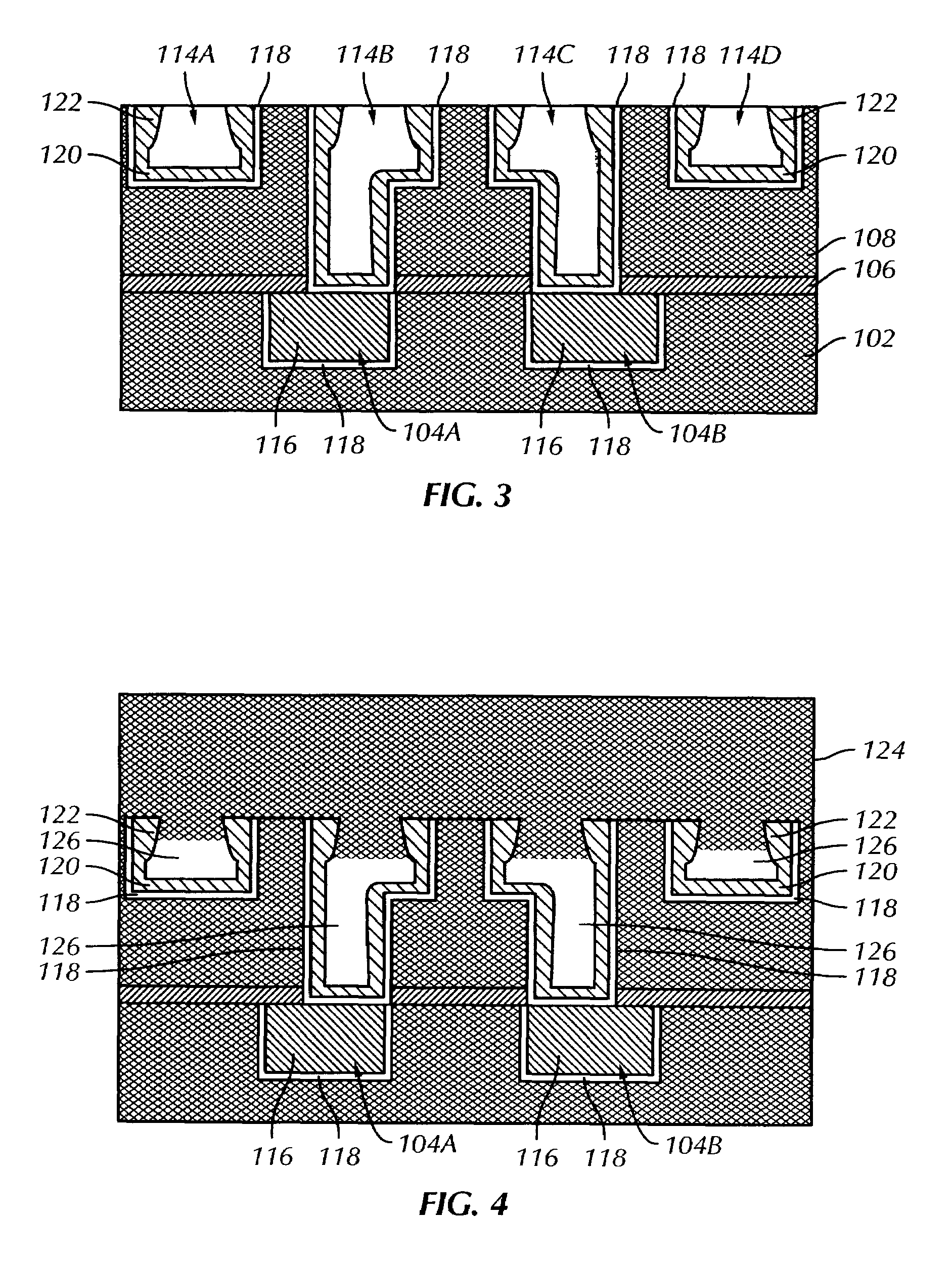

Integrated antifuse structure for finfet and cmos devices

InactiveUS20060128071A1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSSemiconductor materials

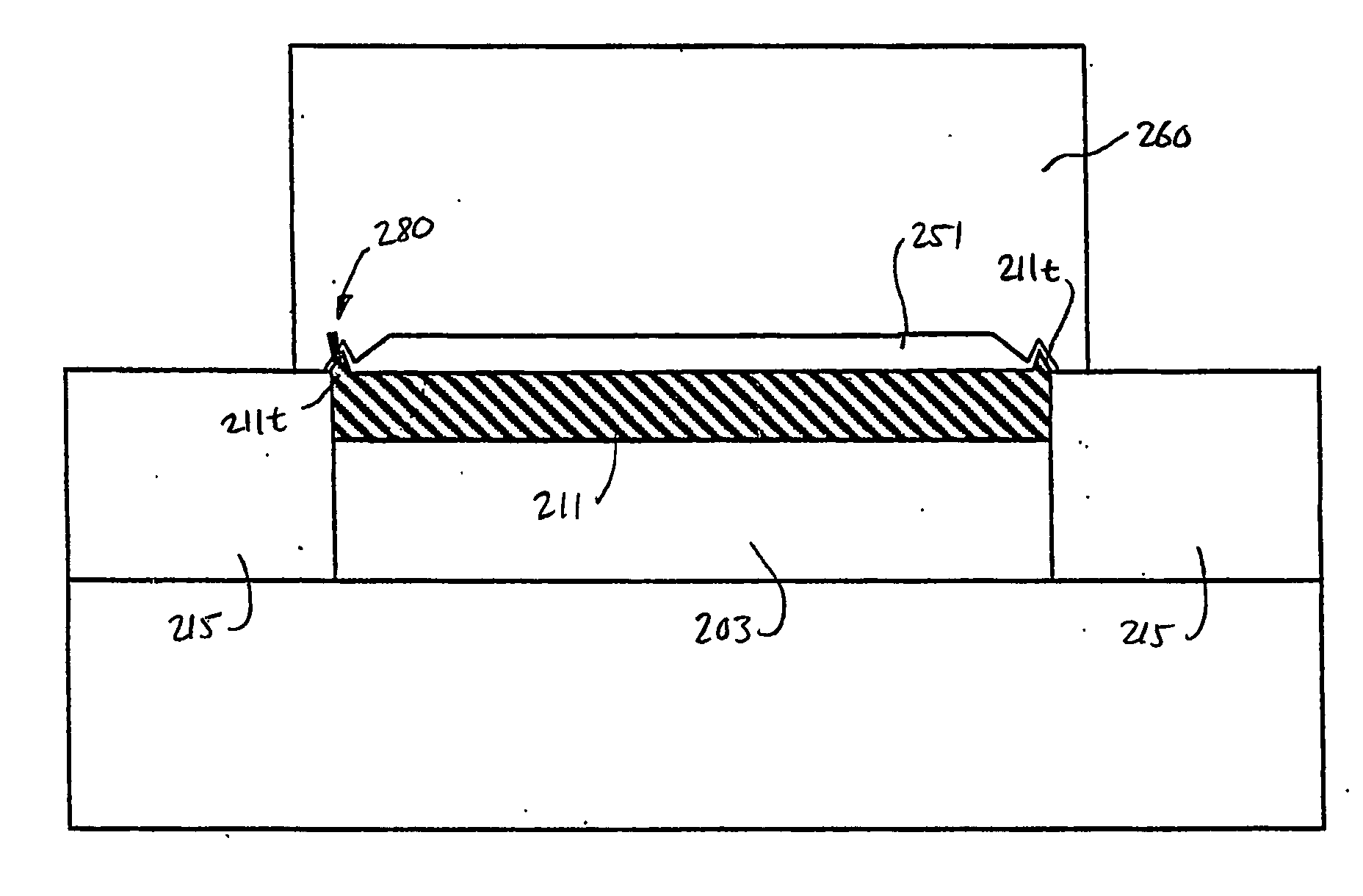

A method is described for fabricating and antifuse structure (100) integrated with a semiconductor device such as a FINFET or planar CMOS devise. A region of semiconducting material (11) is provided overlying an insulator (3) disposed on a substrate (10); an etching process exposes a plurality of corners (111-114) in the semiconducting material. The exposed corners are oxidized to form elongated tips (111t-114t) at the corners; the oxide (31) overlying the tips is removed. An oxide layer (51), such as a gate oxide, is then formed on the semiconducting material and overlying the corners; this layer has a reduced thickness at the corners. A layer of conducting material (60) is formed in contact with the oxide layer (51) at the corners, thereby forming a plurality of possible breakdown paths between the semiconducting material and the layer of conducting material through the oxide layer. Applying a voltage, such as a burn-in voltage, to the structure converts at least one of the breakdown paths to a conducting path (103, 280).

Owner:GLOBALFOUNDRIES US INC

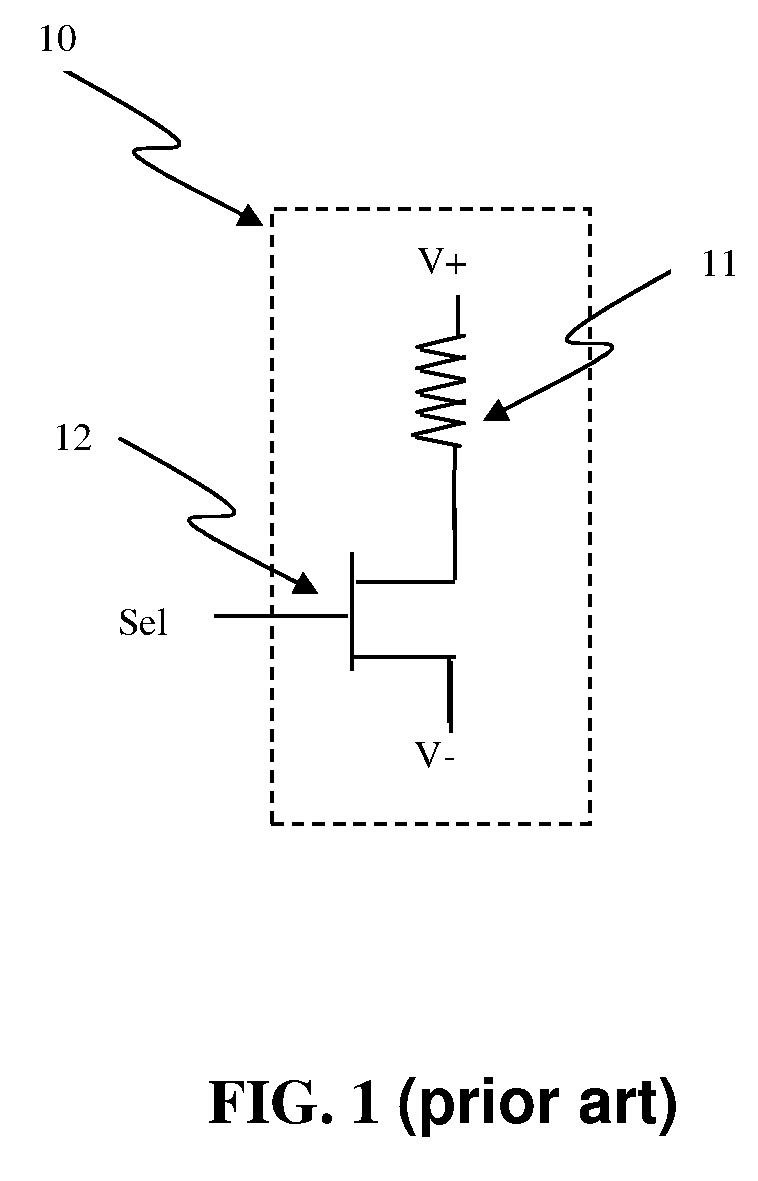

System for improving LED illumination reliability in projection display systems

InactiveUS20080007885A1Improve reliabilityNone of can remain in operationElectroluminescent light sourcesEmergency protective arrangements for automatic disconnectionAntifuseHolding current

System and method for increasing the reliability of LED illumination systems used in projection display systems. A preferred embodiment comprises a light source with one or more serially connected sequences of two or more light elements coupled to a power source. Each light element includes a light emitting diode and an antifuse coupled in parallel to the light emitting diode, wherein the antifuse short circuits if a current flowing through the antifuse exceeds a specified magnitude. The current exceeds the specified magnitude only if an open circuit type failure occurs in the light emitting diode and the short circuit of the antifuse creates a low-resistance current path, thereby preserving current flow through the serially connected sequence and keeping the remaining light elements illuminated.

Owner:TEXAS INSTR INC

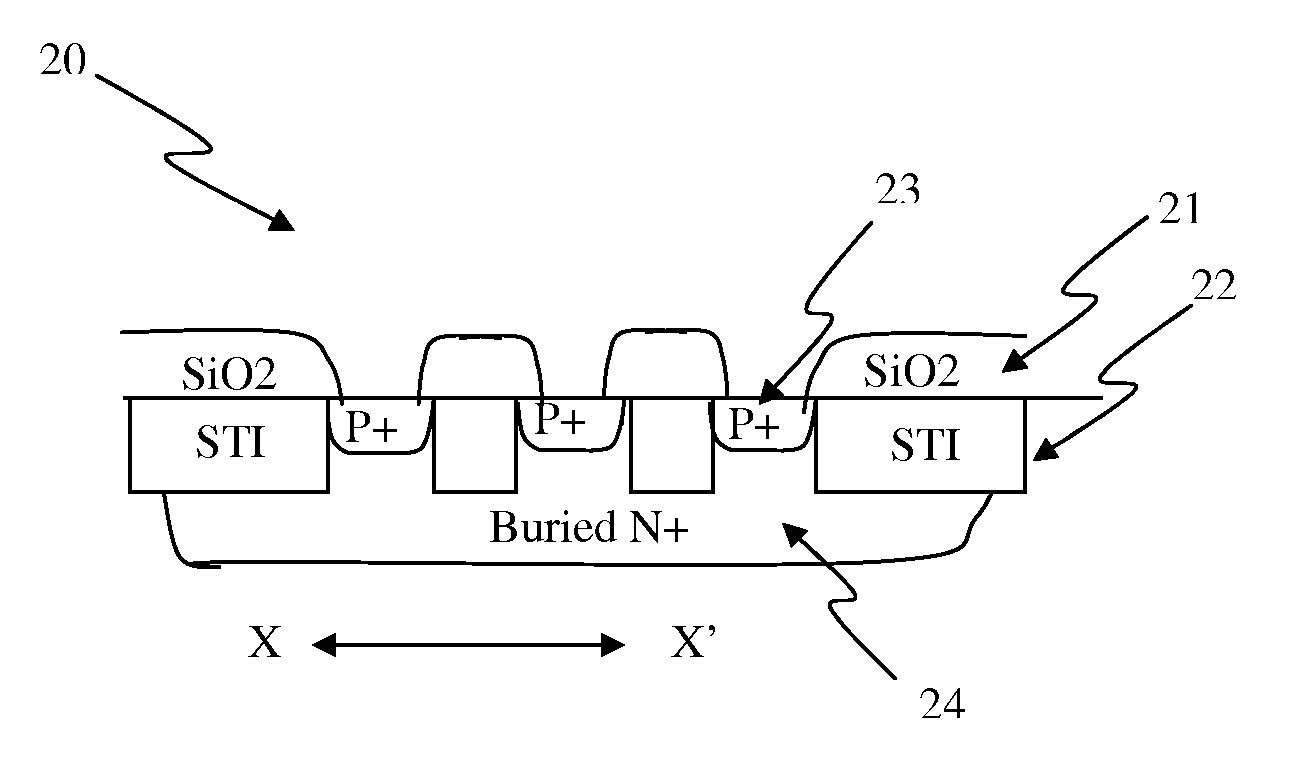

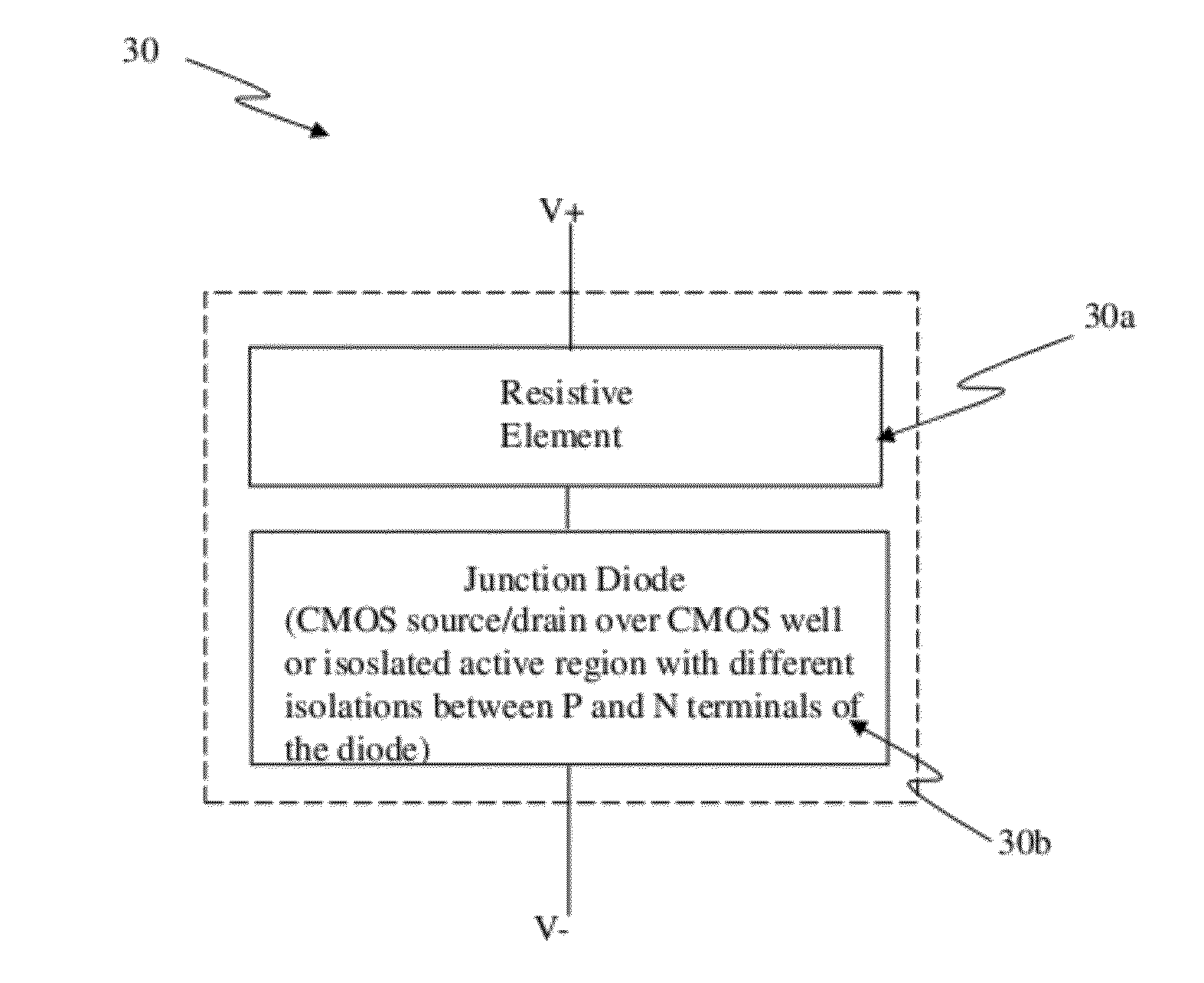

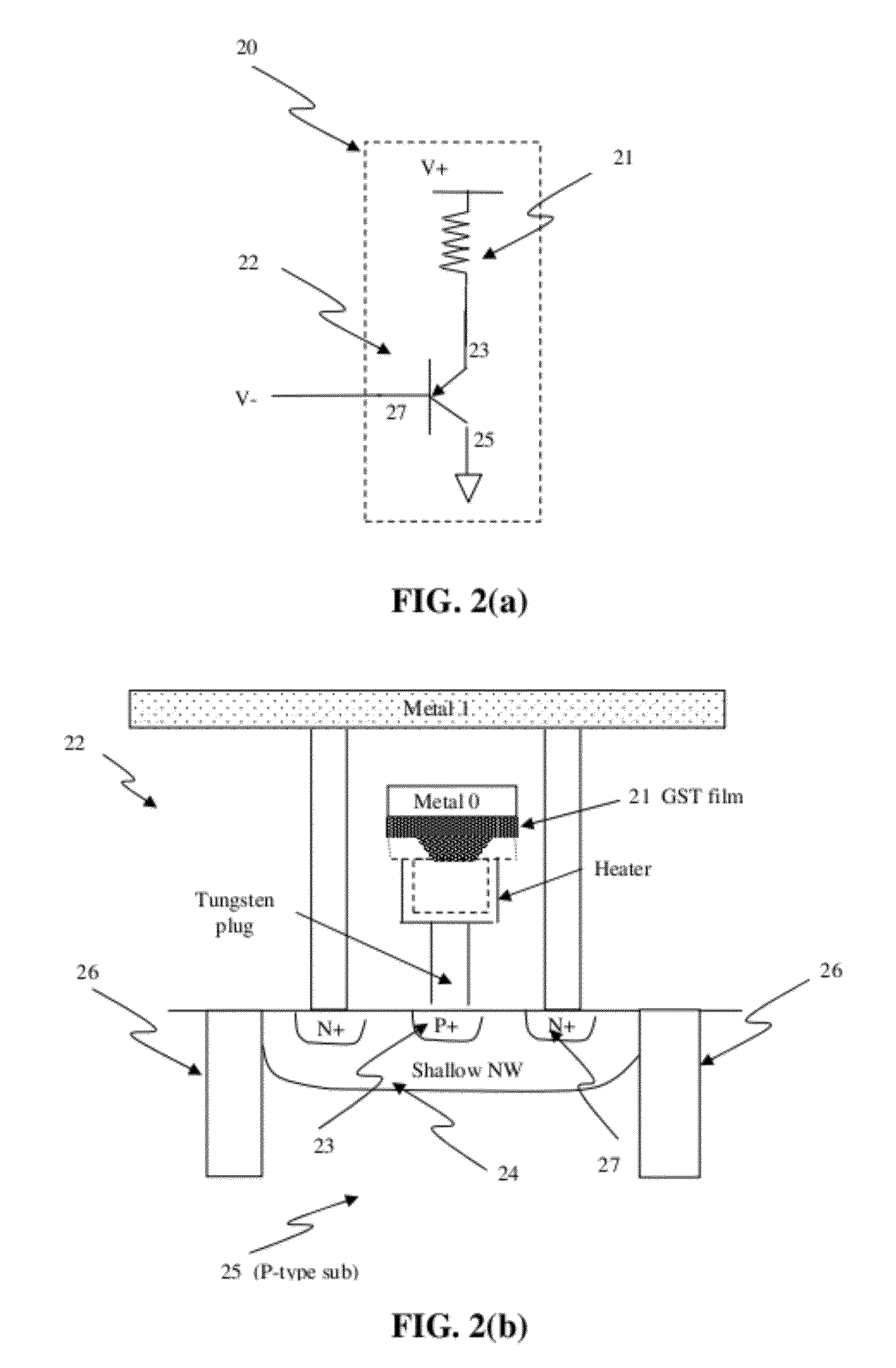

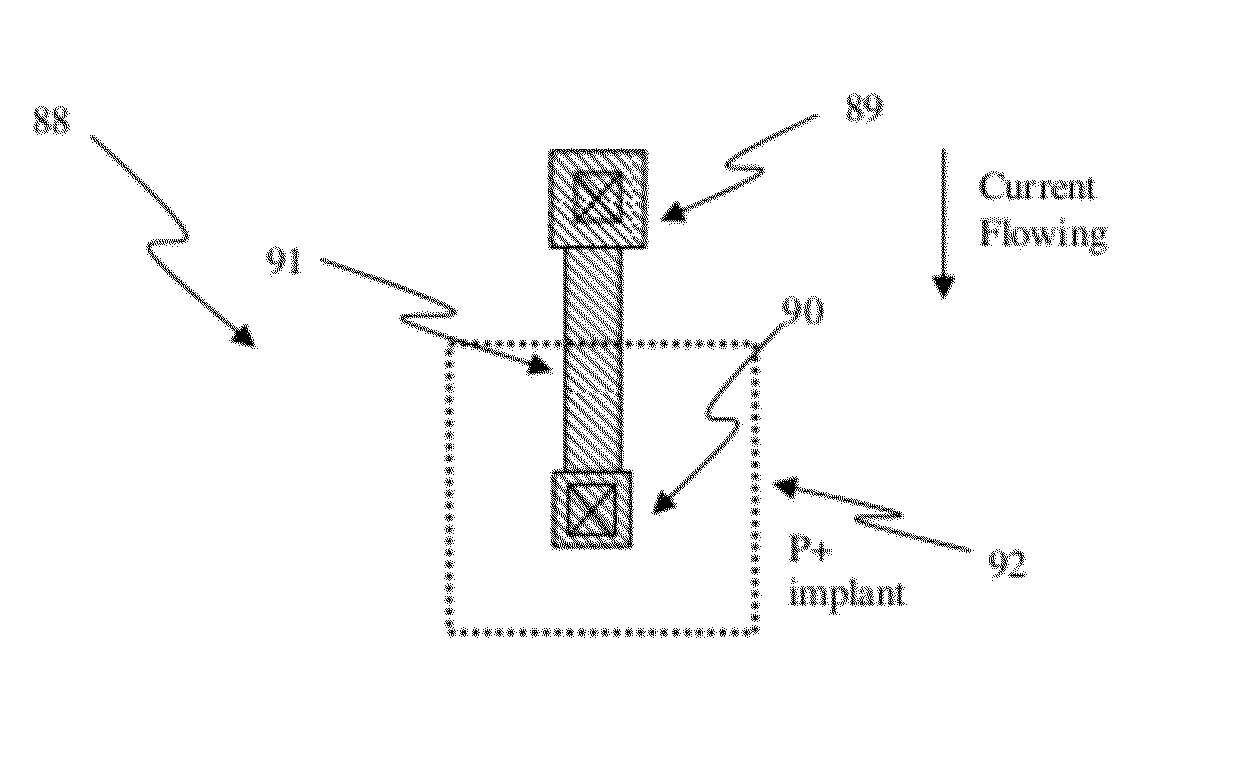

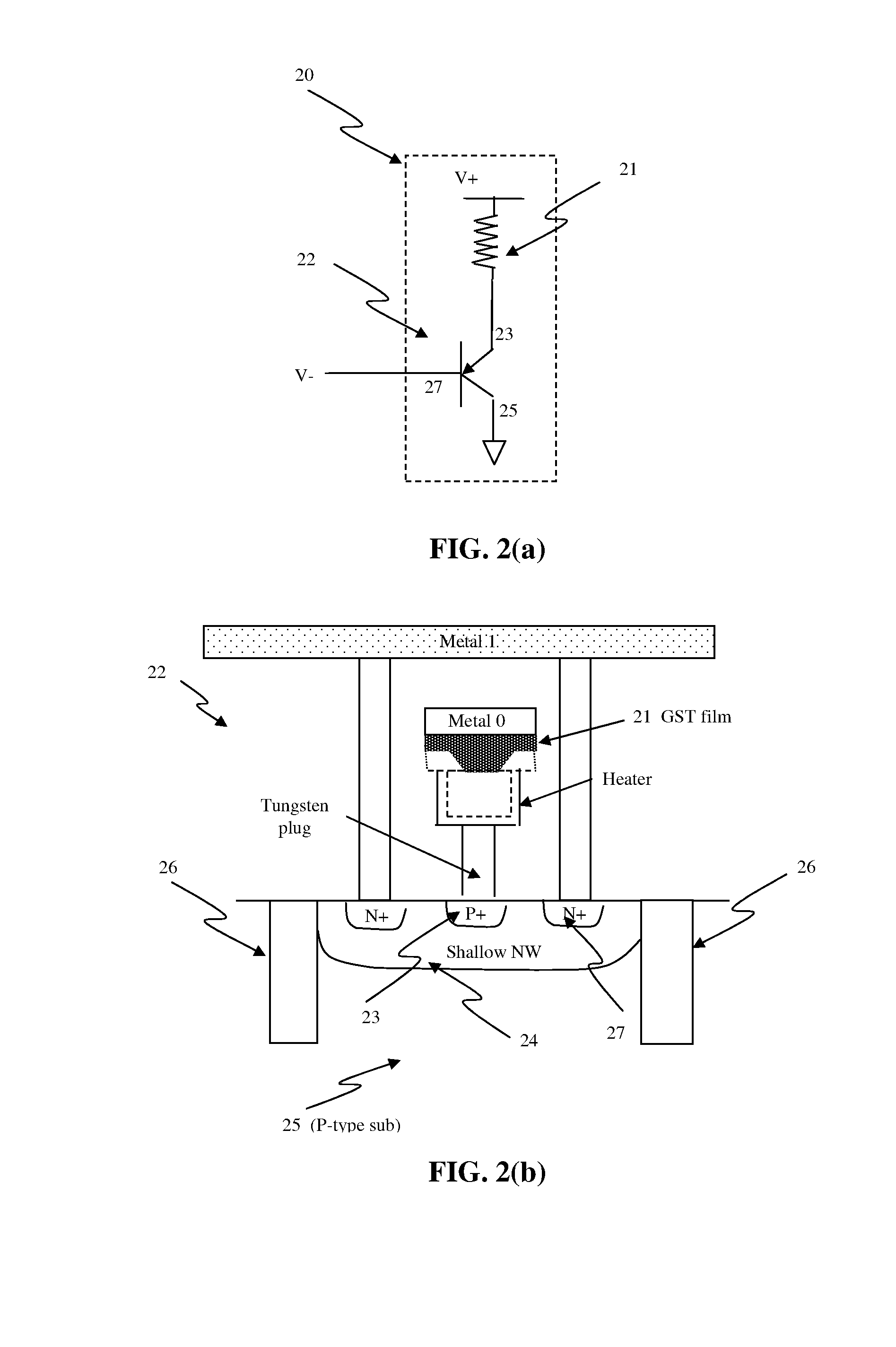

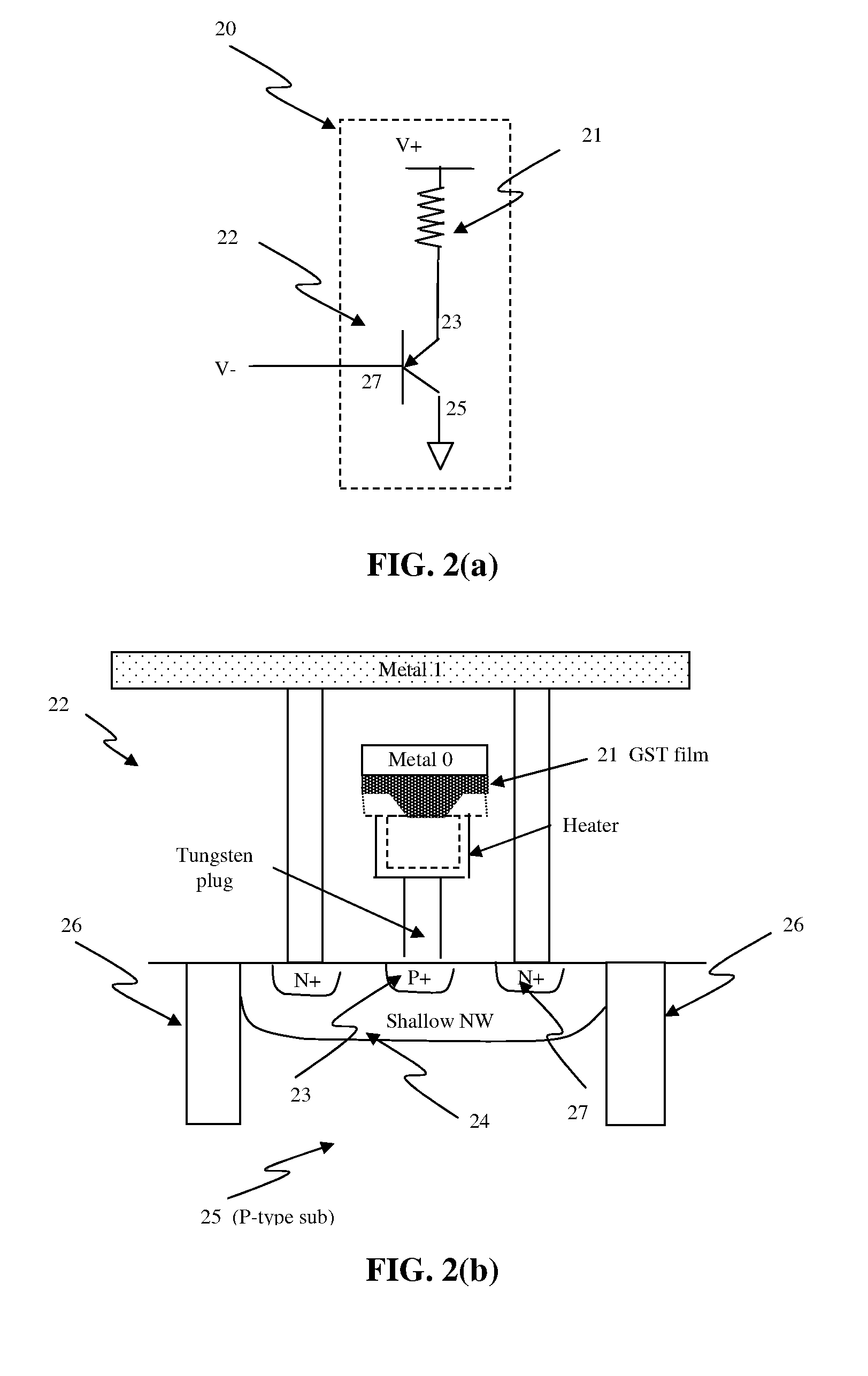

Circuit and system of using a junction diode as program selector for resistive devices

ActiveUS20120044746A1Low costSmall sizeSolid-state devicesRead-only memoriesCMOSElectrical resistance and conductance

Junction diodes fabricated in standard CMOS logic technologies can be used as program selectors for a programmable resistive device, such as electrical fuse, contact / via fuse, anti-fuse, or emerging nonvolatile memory such as MRAM, PCM, CBRAM, or RRAM. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. By applying a high voltage to the P terminal of a diode and switching the N terminal of a diode to a low voltage for proper duration of time, a current flows through a resistive element in series with the program selector may change the resistance state. The P+ active region of the diode can be isolated from the N+ active region in the N well by using dummy MOS gate, SBL, or STI isolations. If the resistive element is an interconnect fuse based on CMOS gate material, the resistive element can be coupled to the P+ active region by an abutted contact such that the element, active region, and metal can be connected in a single rectangular contact.

Owner:ATTOPSEMI TECH CO LTD

Nonvolatile rewritable memory cell comprising a resistivity-switching oxide or nitride and an antifuse

A memory cell is described, the memory cell comprising a dielectric rupture antifuse and a layer of a resistivity-switching material arranged electrically in series, wherein the resistivity-switching material is a metal oxide or nitride compound, the compound including exactly one metal. The dielectric rupture antifuse is ruptured in a preconditioning step, forming a rupture region through the antifuse. The rupture region provides a narrow conductive path, serving to limit current to the resistivity-switching material, and improving control when the resistivity-switching layer is switched between higher-and lower-resistivity states.

Owner:SANDISK TECH LLC

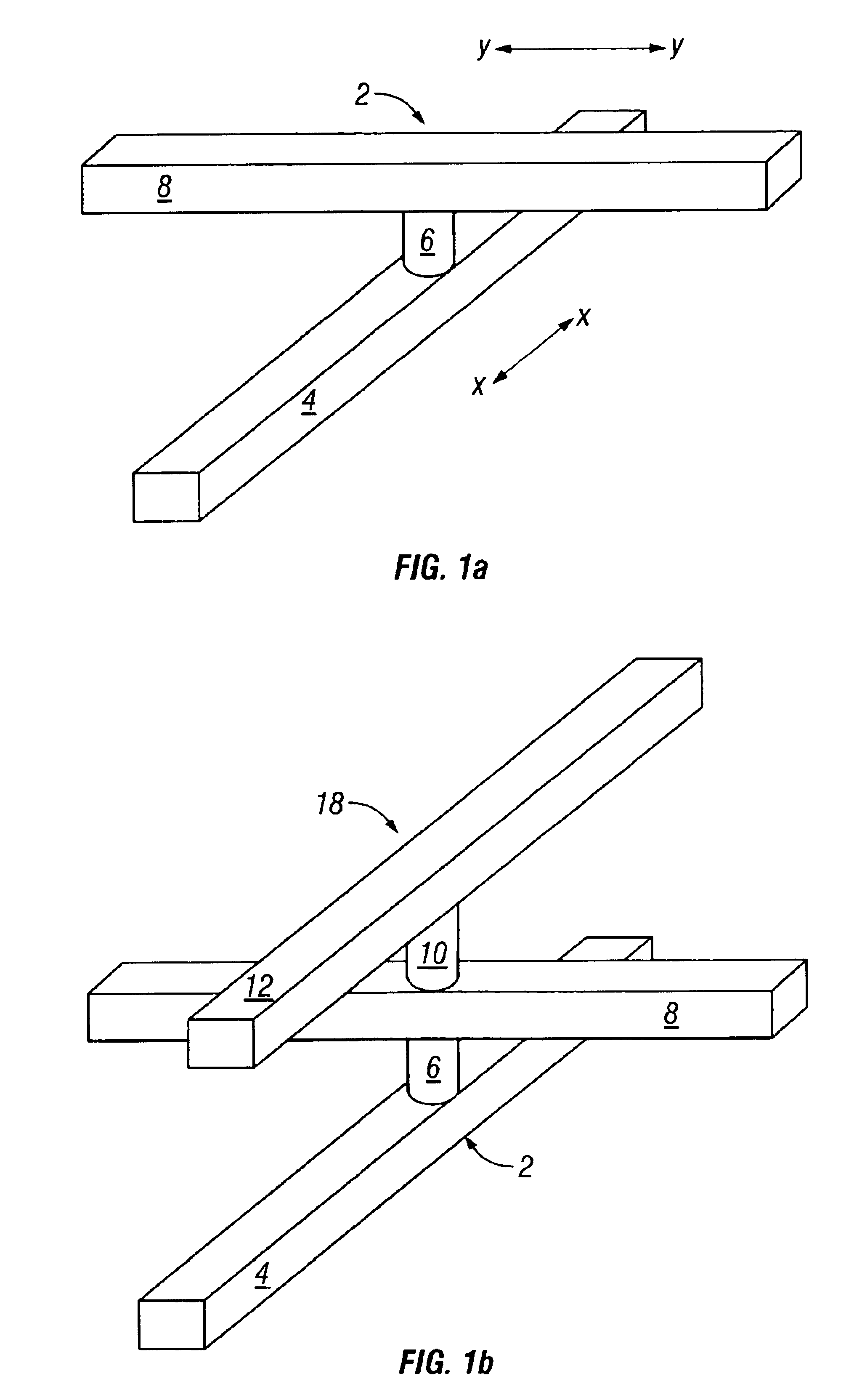

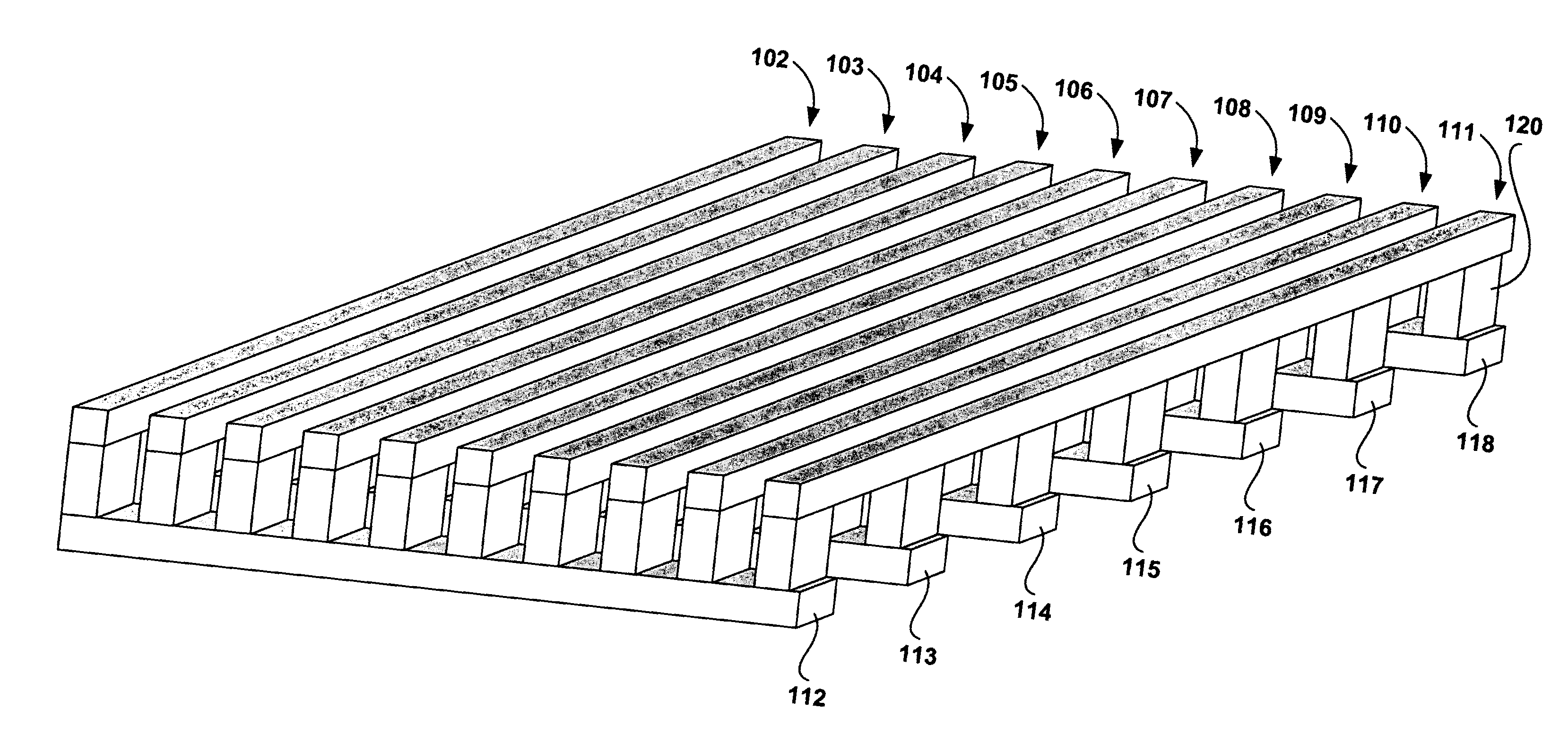

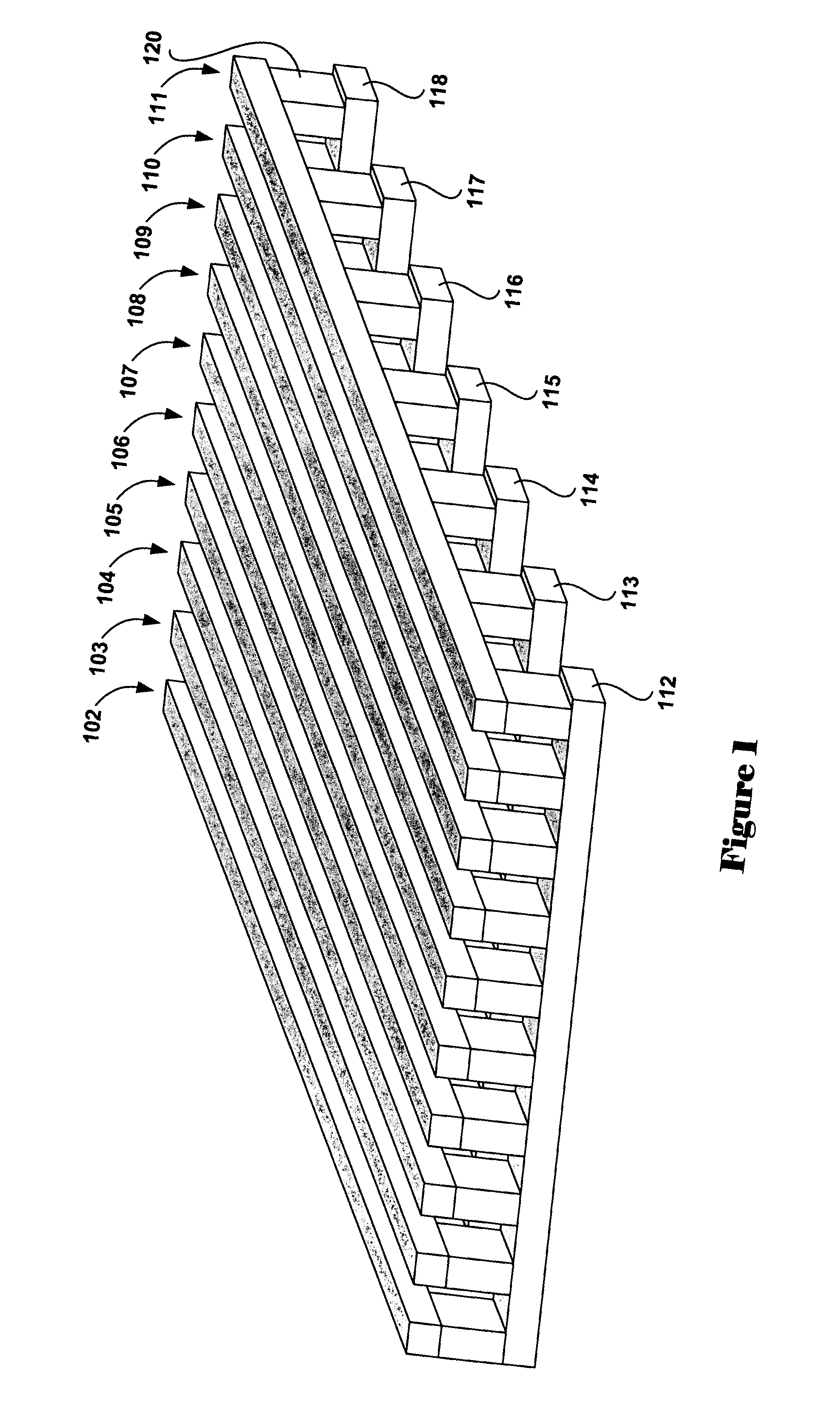

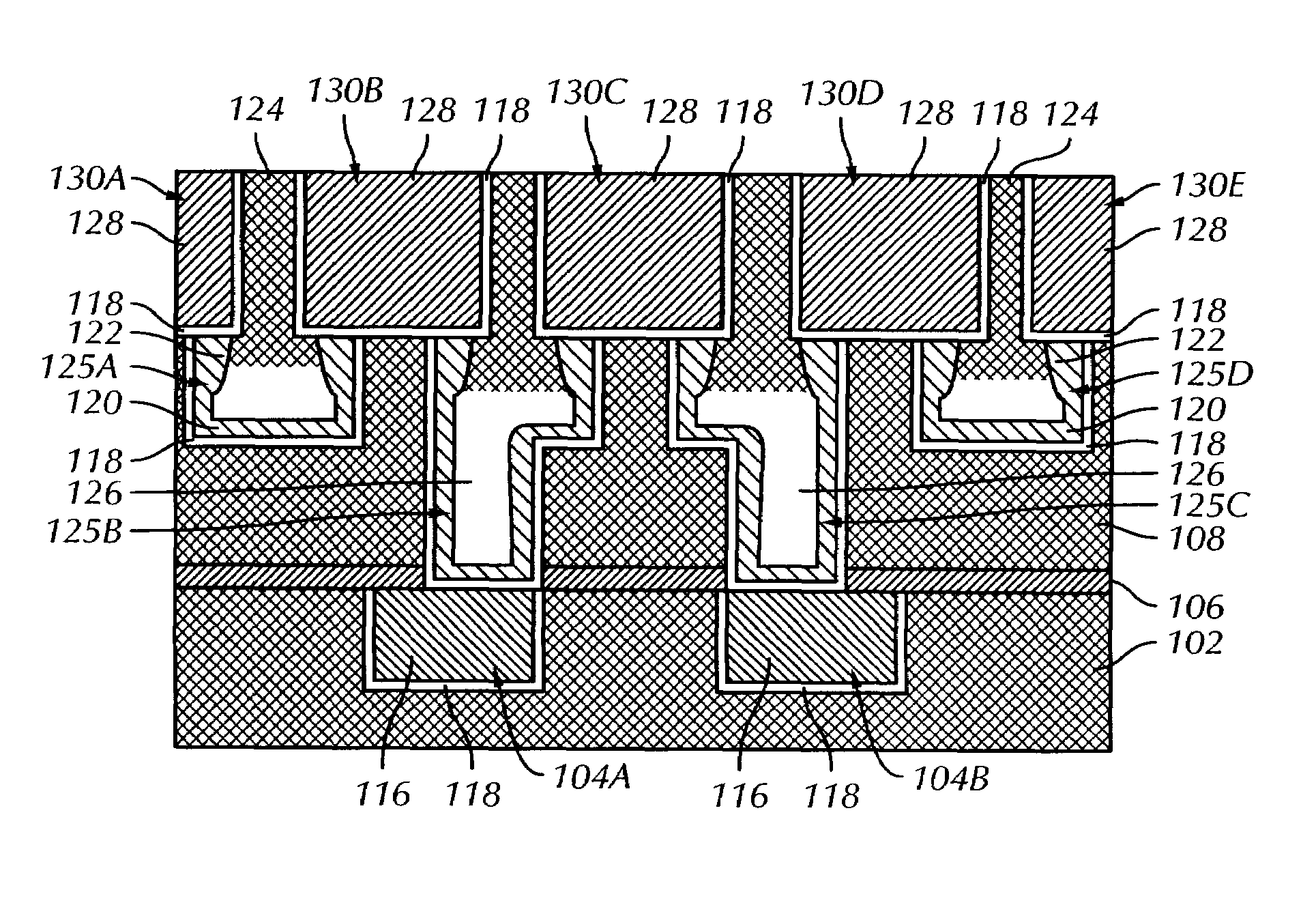

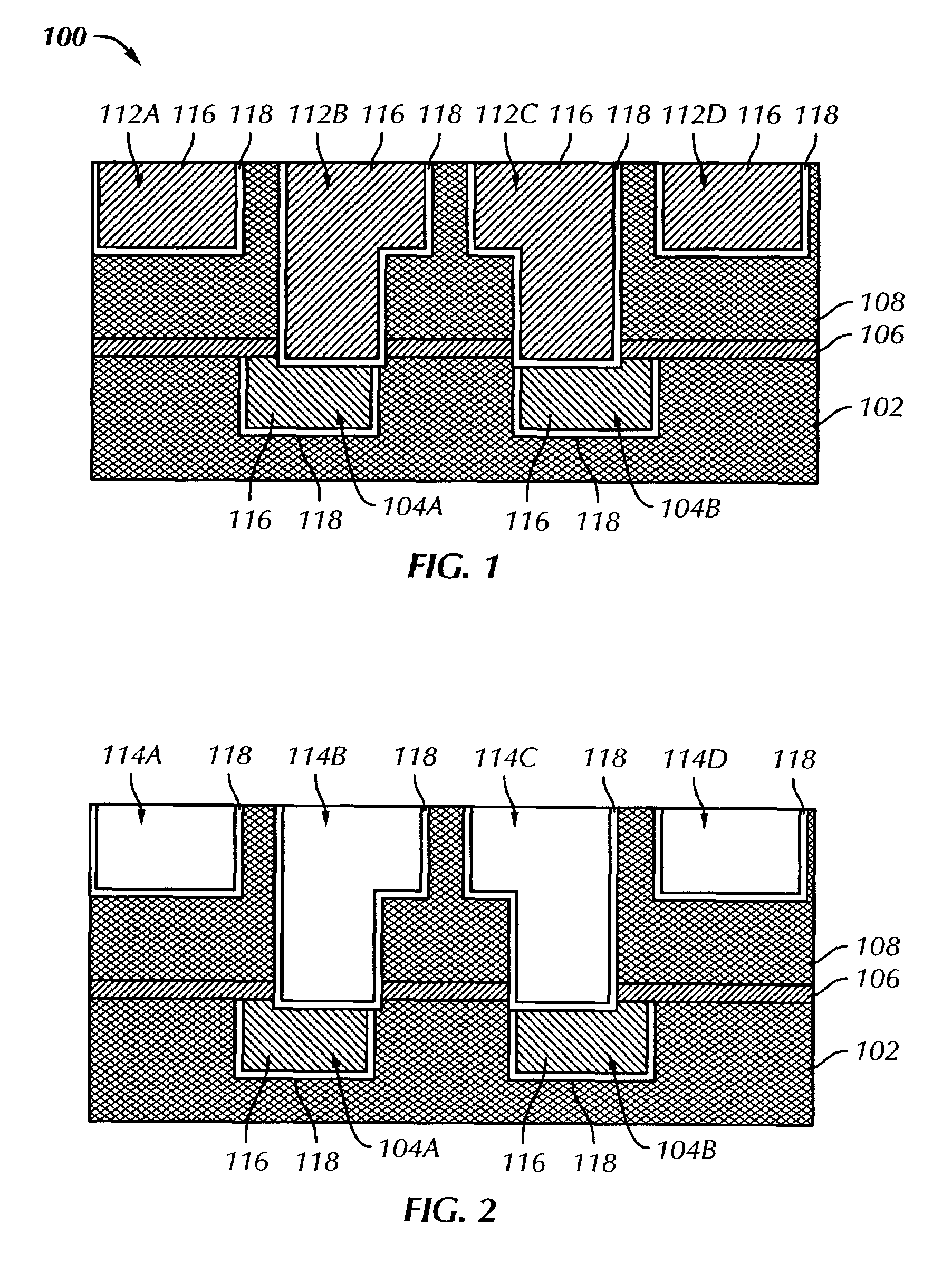

Non-Volatile Memory Arrays Comprising Rail Stacks with a Shared Diode Component Portion for Diodes of Electrically Isolated Pillars

ActiveUS20090309089A1Semiconductor/solid-state device manufacturingDiodeElectrical conductorTerminal equipment

An integrated circuit including vertically oriented diode structures between conductors and methods of fabricating the same are provided. Two-terminal devices such as passive element memory cells can include a diode steering element in series with an antifuse and / or other state change element. The devices are formed using pillar structures at the intersections of upper and lower sets of conductors. The height of the pillar structures are reduced by forming part of the diode for each pillar in a rail stack with one of the conductors. A diode in one embodiment can include a first diode component of a first conductivity type and a second diode component of a second conductivity type. A portion of one of the diode components is divided into first and second portions with one on the portions being formed in the rail stack where it is shared with other diodes formed using pillars at the rail stack.

Owner:SANDISK TECH LLC

Polymer-based memory element

InactiveUS20050006640A1Increase and decrease resistanceNanoinformaticsSolid-state devicesElectrical resistance and conductanceChemical compound

Fuse-type and antifuse-type semiconducting-organic-polymer-film-based memory elements for use in memory devices are disclosed. Various embodiments of the present invention employ a number of different techniques to alter the electrical conductance or, equivalently, the resistance, of organic-polymer-film memory elements in order to produce detectable memory-state changes in the memory elements. The techniques involve altering the electronic properties of the organic polymers by application of heat or electric fields, often in combination with additional chemical compounds, to either increase or decrease the resistance of the organic polymers.

Owner:HEWLETT PACKARD DEV CO LP

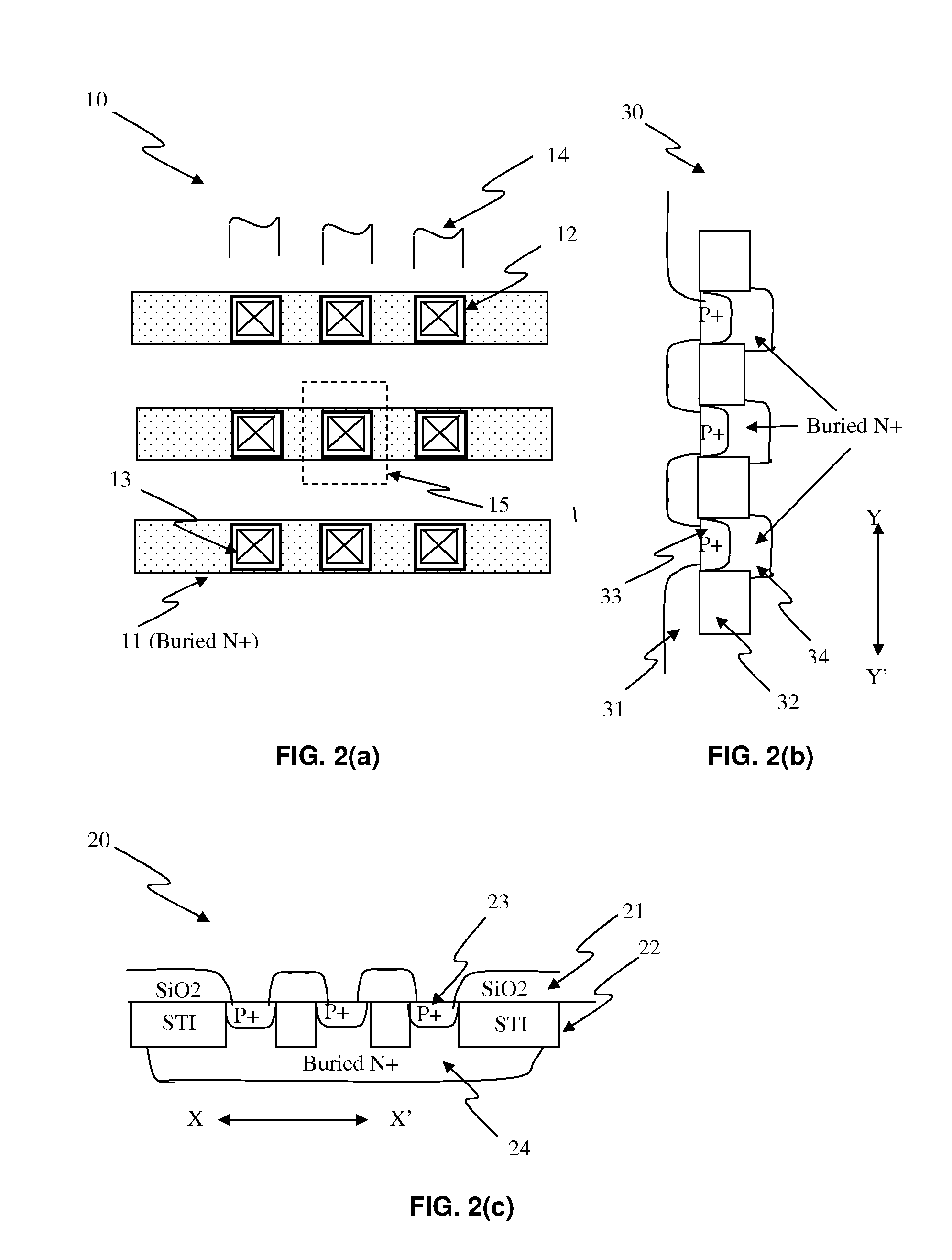

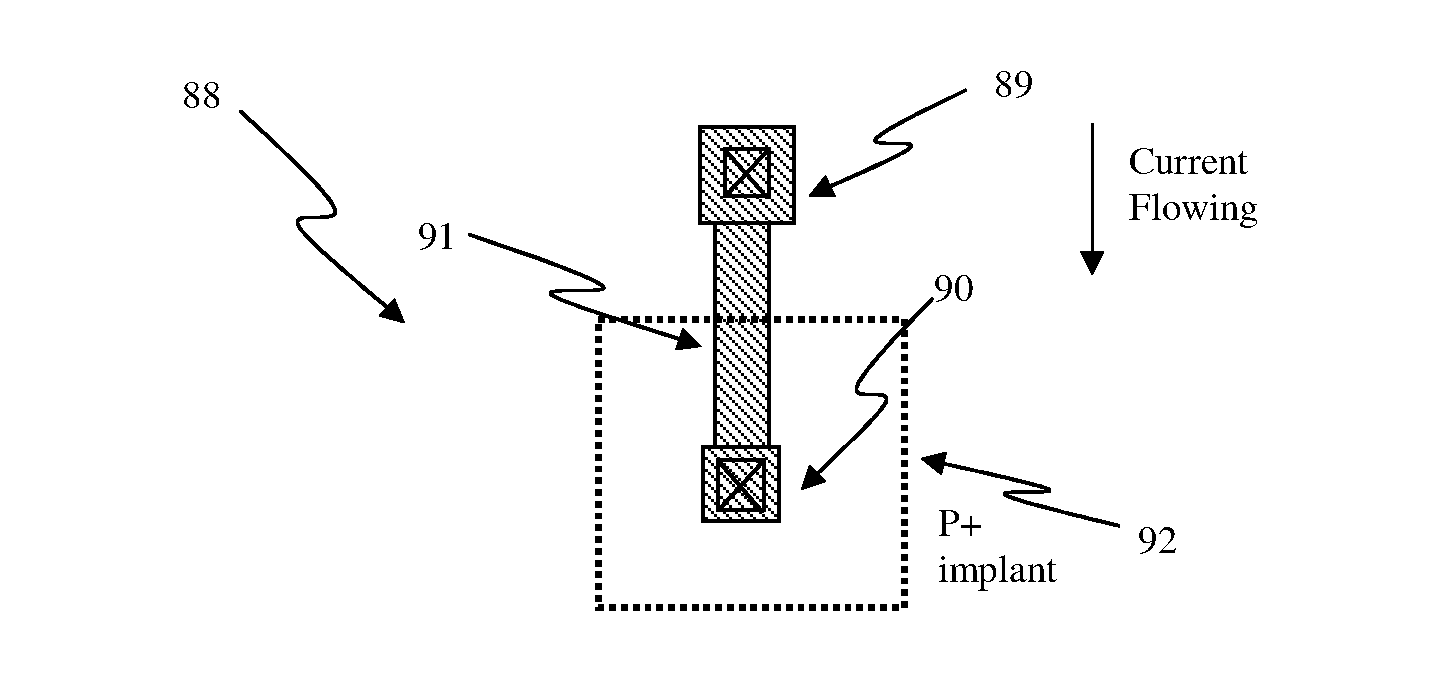

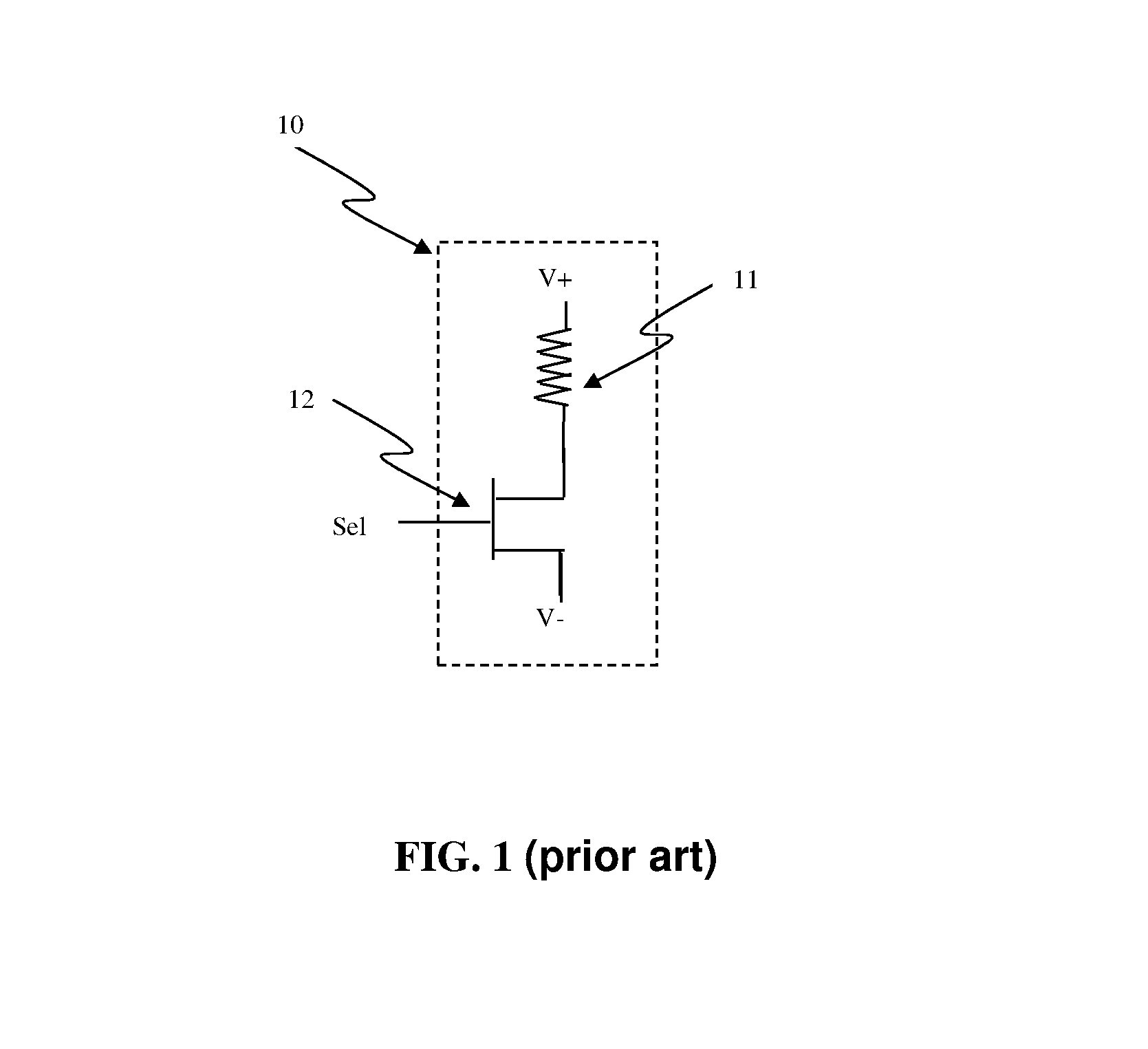

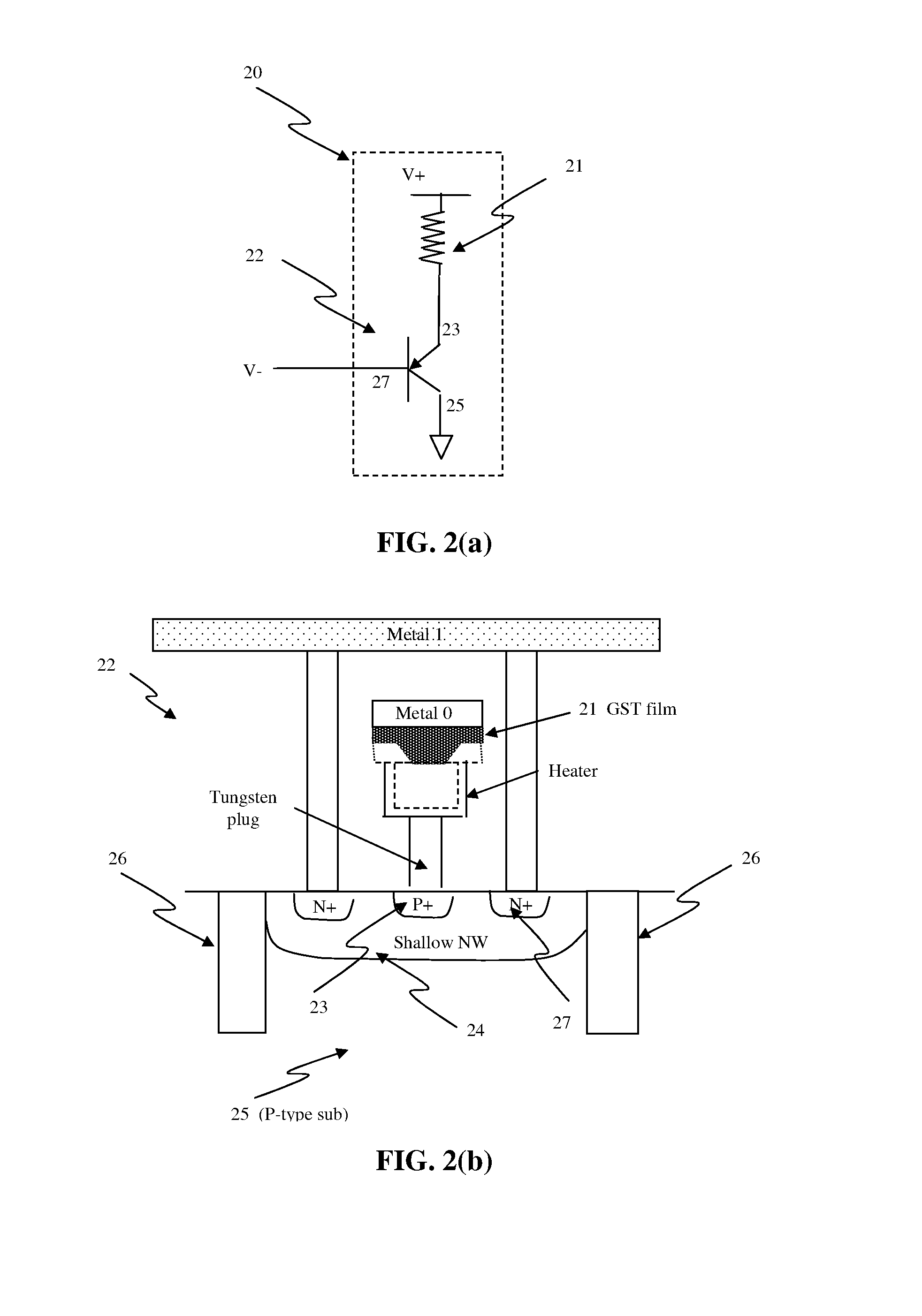

Circuit and System of Using Junction Diode as Program Selector for One-Time Programmable Devices

ActiveUS20120224406A1Small cell sizeLow costMagnetic-field-controlled resistorsSolid-state devicesHemt circuitsEngineering

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has at least one OTP element coupled to at least one diode in a memory cell. The diode can be constructed by P+ and N+ active regions in a CMOS N well, or on an isolated active region as the P and N terminals of the diode. The isolation between P+ and the N+ active regions of the diode in a cell or between cells can be provided by dummy MOS gate, SBL, or STI / LOCOS isolations. The OTP element can be polysilicon, silicided polysilicon, silicide, metal, metal alloy, local interconnect, thermally isolated active region, CMOS gate, or combination thereof.

Owner:ATTOPSEMI TECH CO LTD

Circuit and system of using junction diode as program selector for one-time programmable devices

ActiveUS20120044739A1Small cell sizeLow costSolid-state devicesRead-only memoriesElectrical resistance and conductanceCMOS

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has an OTP element coupled to a diode in a memory cell. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. By applying a high voltage to the P terminal of a diode and switching the N terminal of a diode to a low voltage for suitable duration of time, a current flows through an OTP element in series with the program selector may change the resistance state. The P+ active region of the diode can be isolated from the N+ active region in the N well by using dummy MOS gate, SBL, or STI / LOCOS isolations. If the resistive element is an interconnect fuse based on CMOS gate material, the resistive element can be coupled to the P+ active region by an abutted contact such that the element, active region, and metal are connected in a single rectangular contact.

Owner:ATTOPSEMI TECH CO LTD

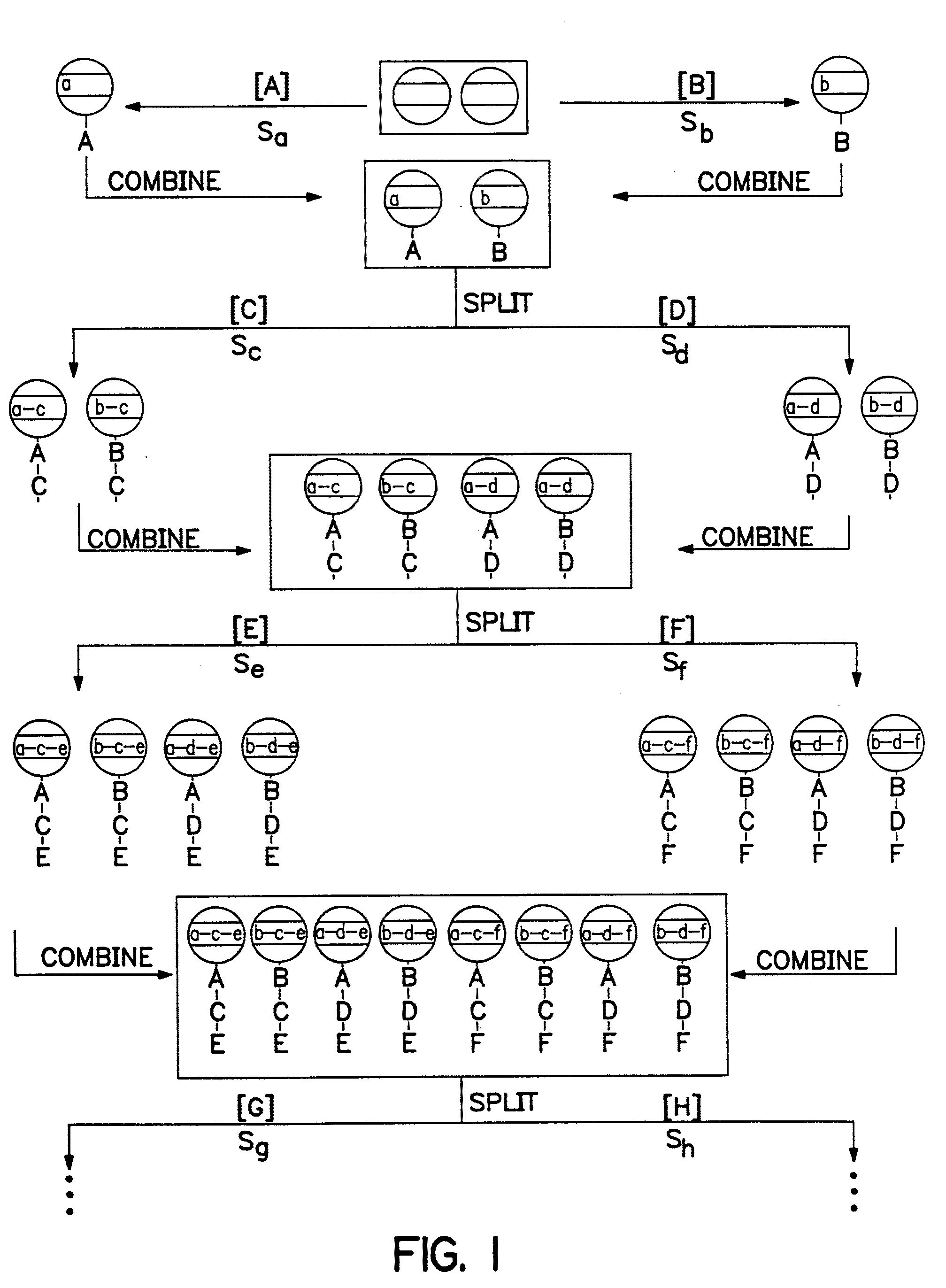

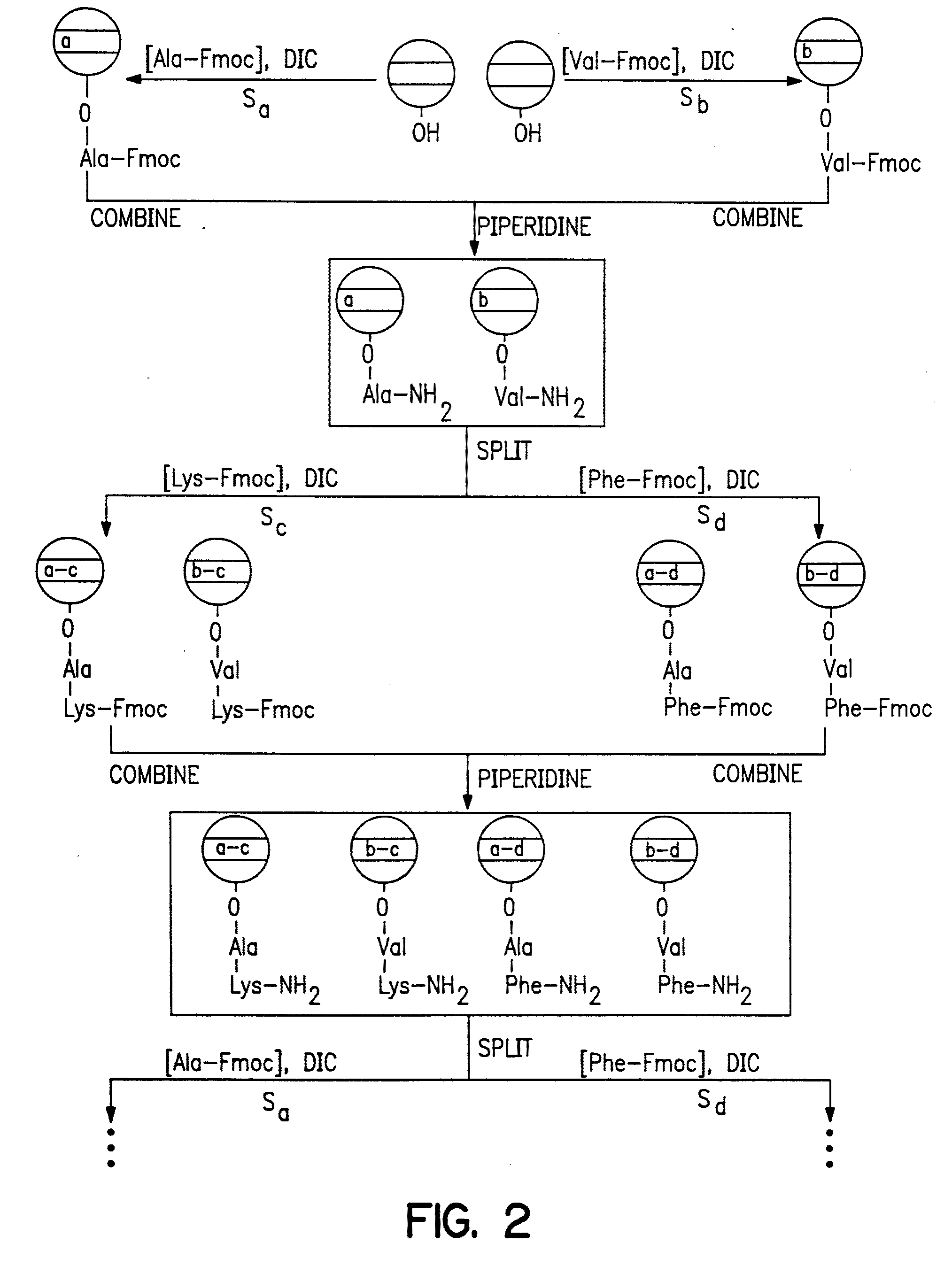

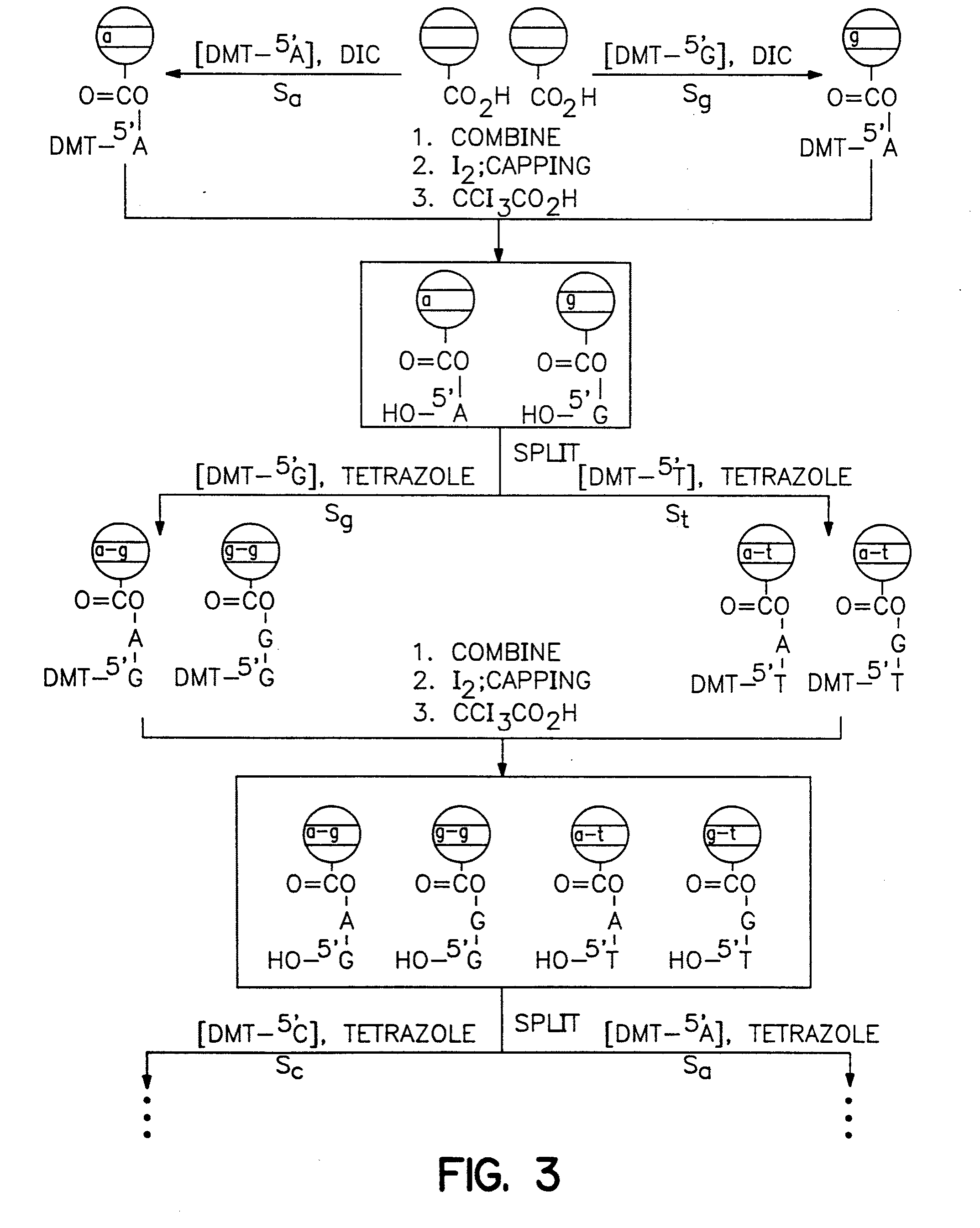

Encoded solid supports for biological processing and assays using same

InactiveUS20090226891A2Sequential/parallel process reactionsNon-electrical signal transmission systemsAntifuseSolid phases

Owner:IRORI TECH

Circuit and system of using polysilicon diode as program selector for one-time programmable devices

ActiveUS20120044737A1Avoid shortingSave extra spaceSolid-state devicesRead-only memoriesLow voltageHemt circuits

Polysilicon diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The OTP device has an OTP element coupled to a diode in a memory cell. The diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. By applying a high voltage to an OTP element coupled to the P-terminal of a diode and switching the N-terminal of a diode to a low voltage for suitable duration of time, a current flows through the OTP element may change the resistance state. On the polysilicon diode, the spacing and doping level of a gap between the P- and N-implants can be controlled for different breakdown voltages and leakage currents. The Silicide Block Layer (SBL) can be used to block silicide formation on the top of polysilicon to prevent shorting. If the OTP element is a polysilicon electrical fuse, the fuse element can be merged with the polysilicon diode in one piece to save area.

Owner:ATTOPSEMI TECH CO LTD

Circuit and system of using a polysilicon diode as program selector for resistive devices in CMOS logic processes

ActiveUS20120044743A1Small cell sizeLow costSolid-state devicesRead-only memoriesLow voltageEngineering

Polysilicon diodes fabricated in standard CMOS logic technologies can be used as program selectors for a programmable resistive device, such as electrical fuse, contact / via fuse, anti-fuse, or emerging nonvolatile memory such as MRAM, PCM, CBRAM, or RRAM. The diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. By applying a high voltage to a resistive element coupled to the P terminal of a diode and switching the N terminal of a diode to a low voltage for proper time, a current flows through a resistive element may change the resistance state. On the polysilicon diode, the spacing and doping level of a gap between the P+ and N+ implants can be controlled for different breakdown voltages and leakage currents. The Silicide Block Layer (SBL) can be used to block silicide formation on the top of polysilicon to prevent shorting. If the resistive element is a polysilicon electrical fuse, the fuse element can be merged with the polysilicon diode in one piece to save area.

Owner:ATTOPSEMI TECH CO LTD

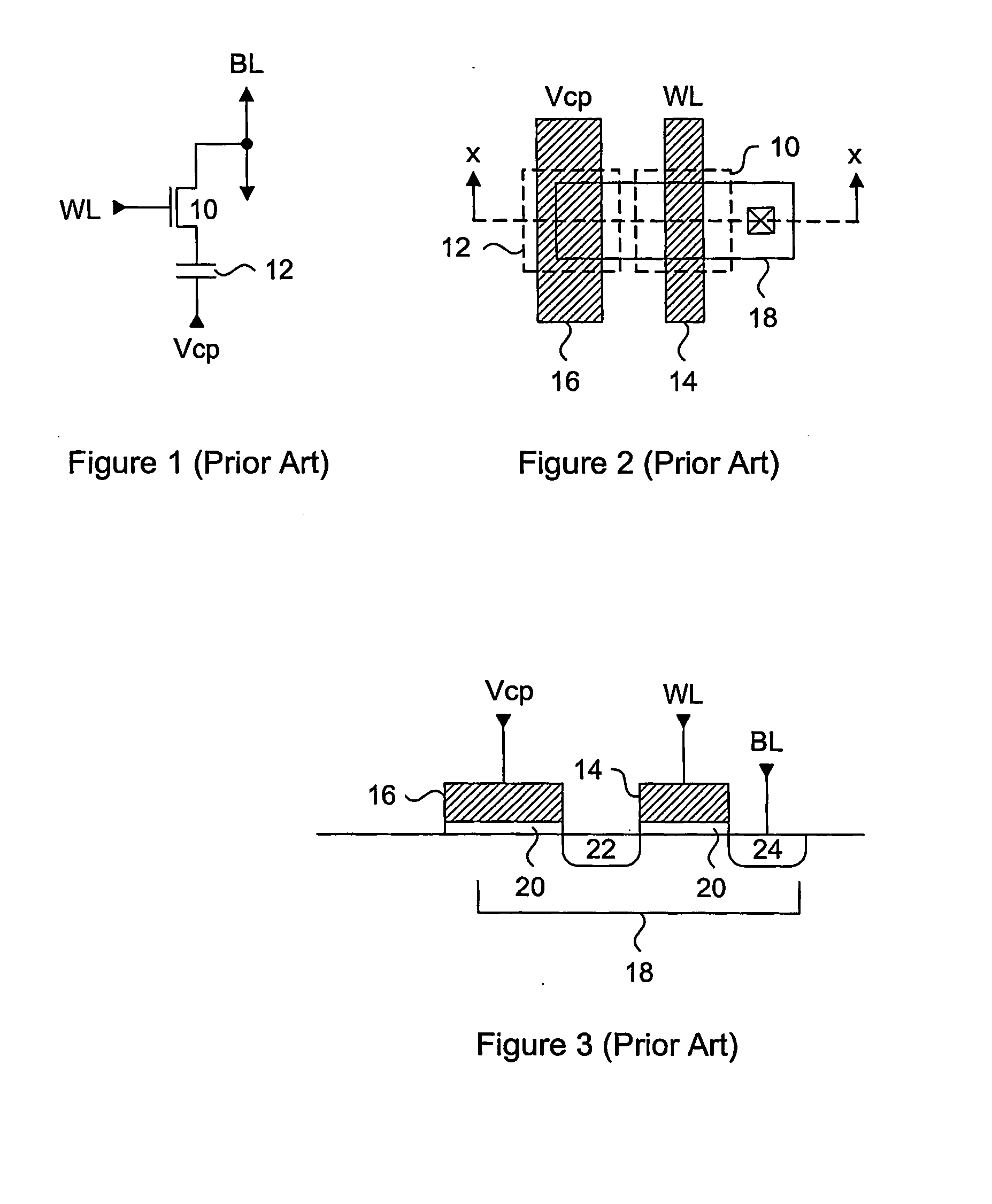

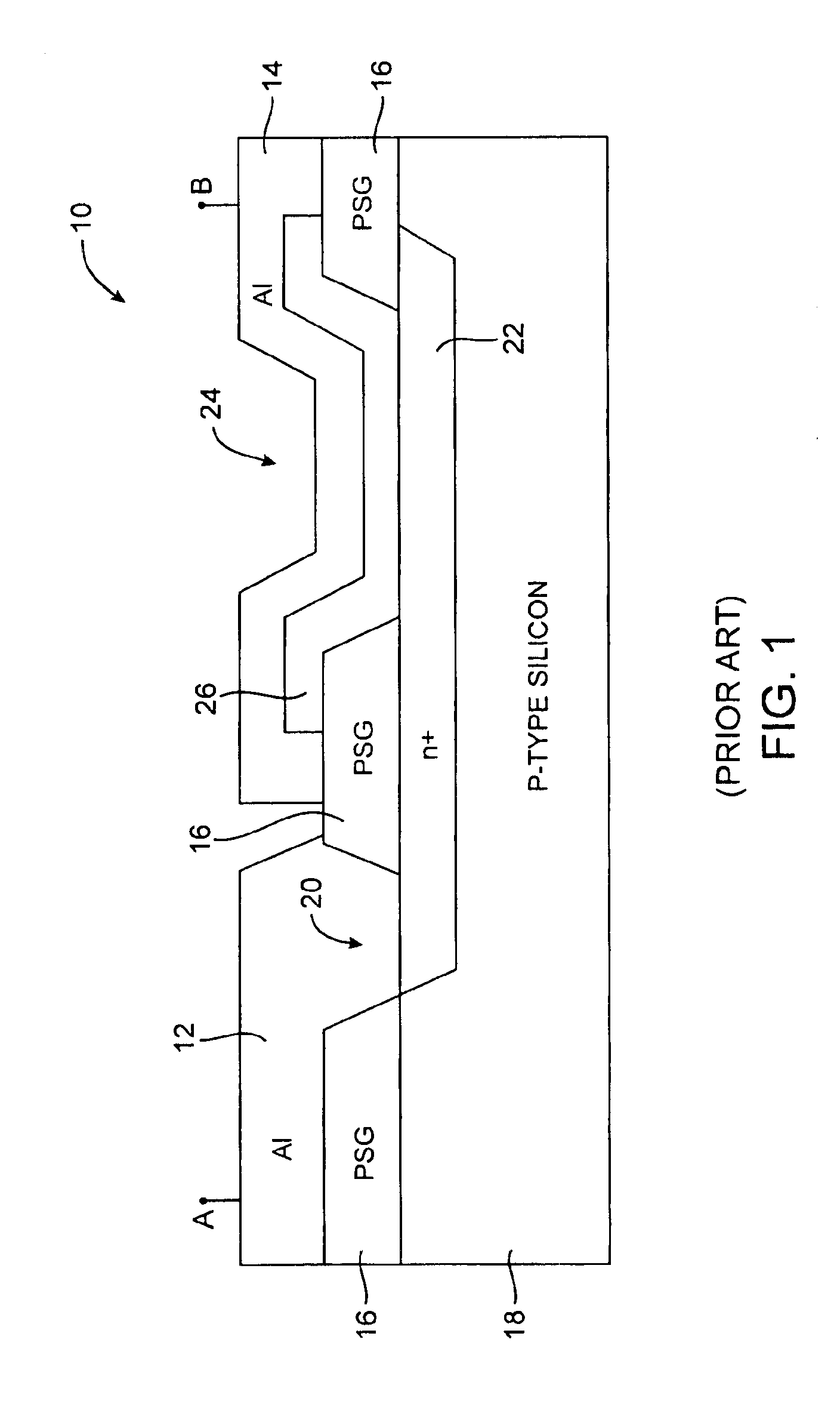

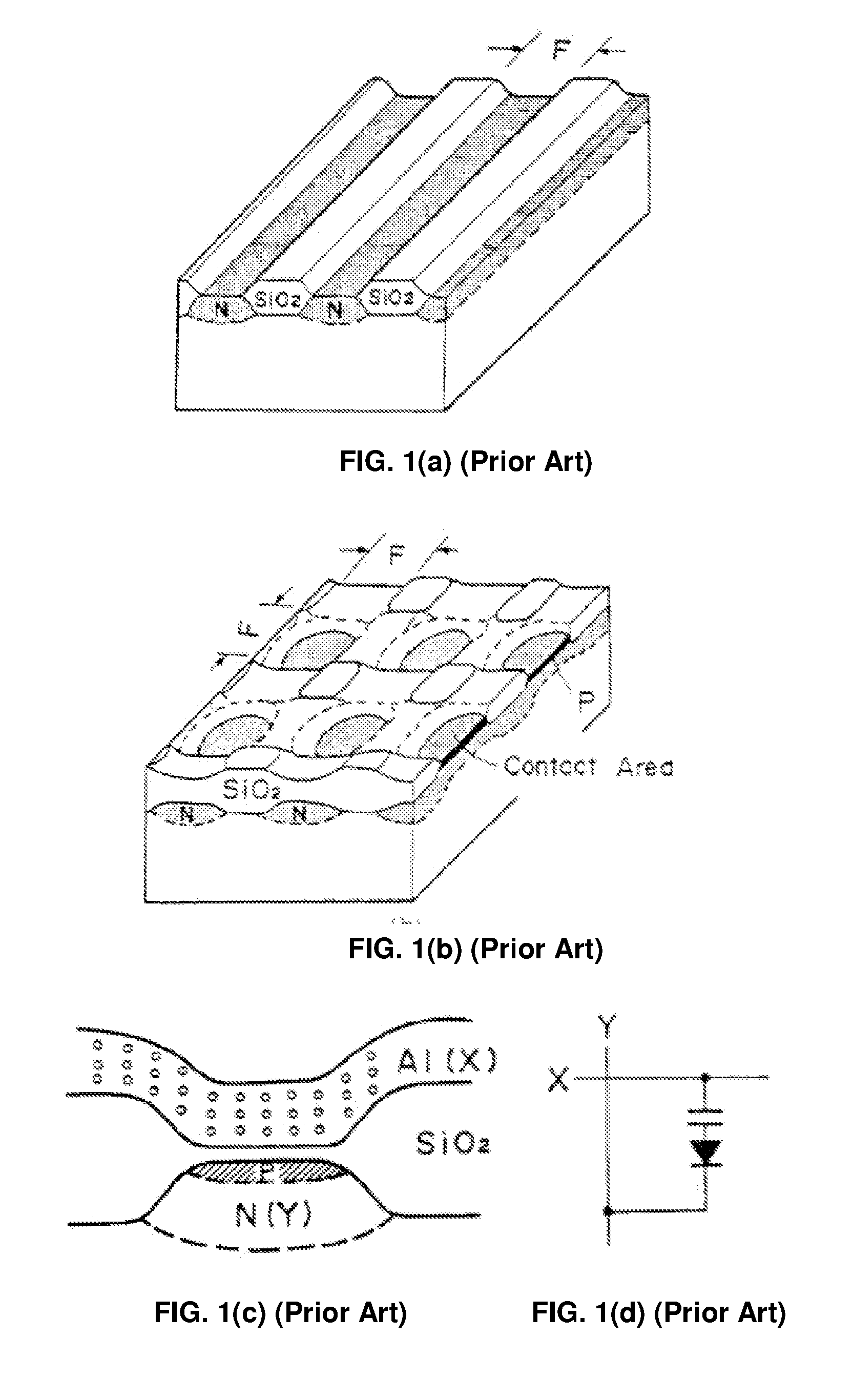

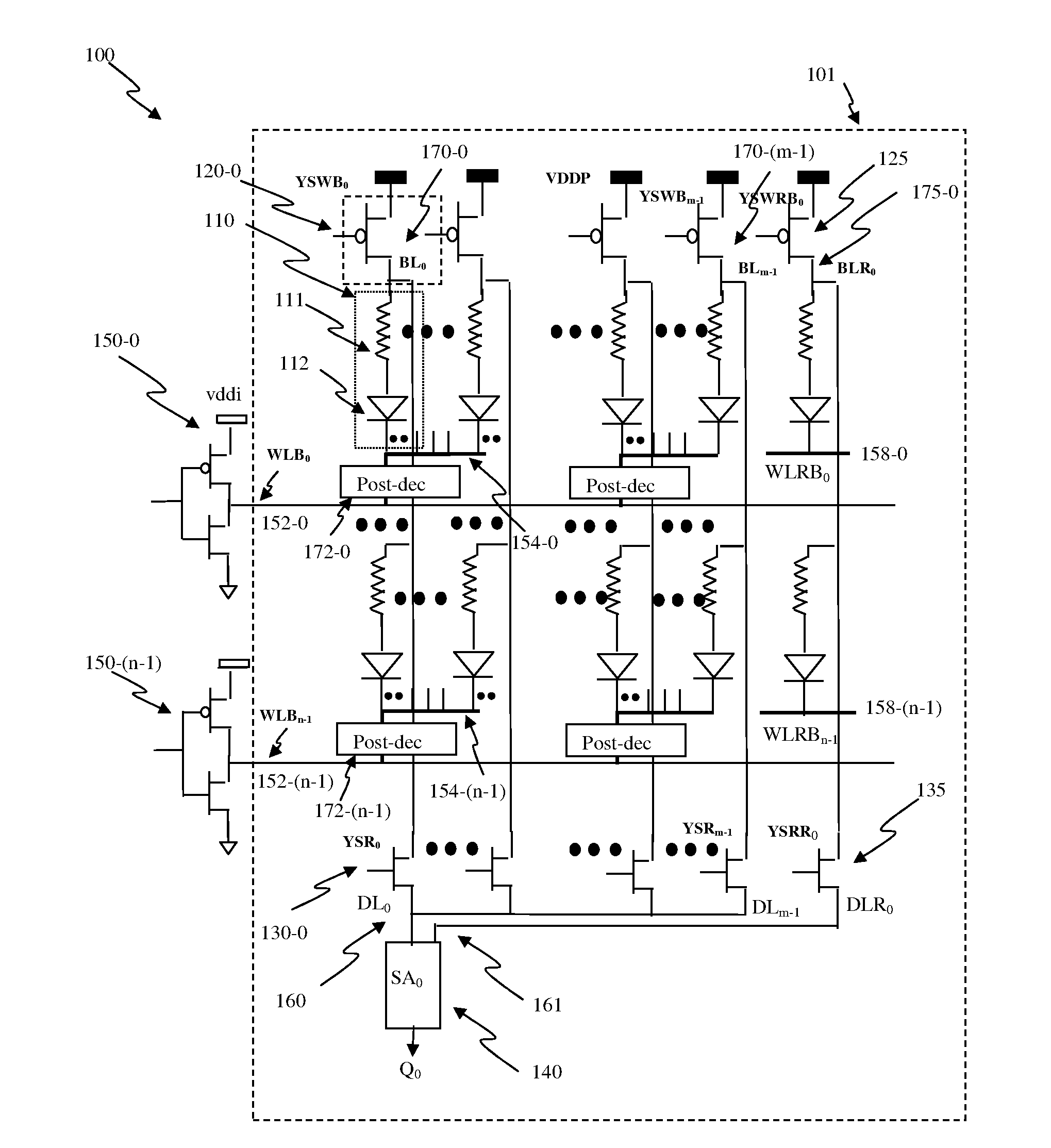

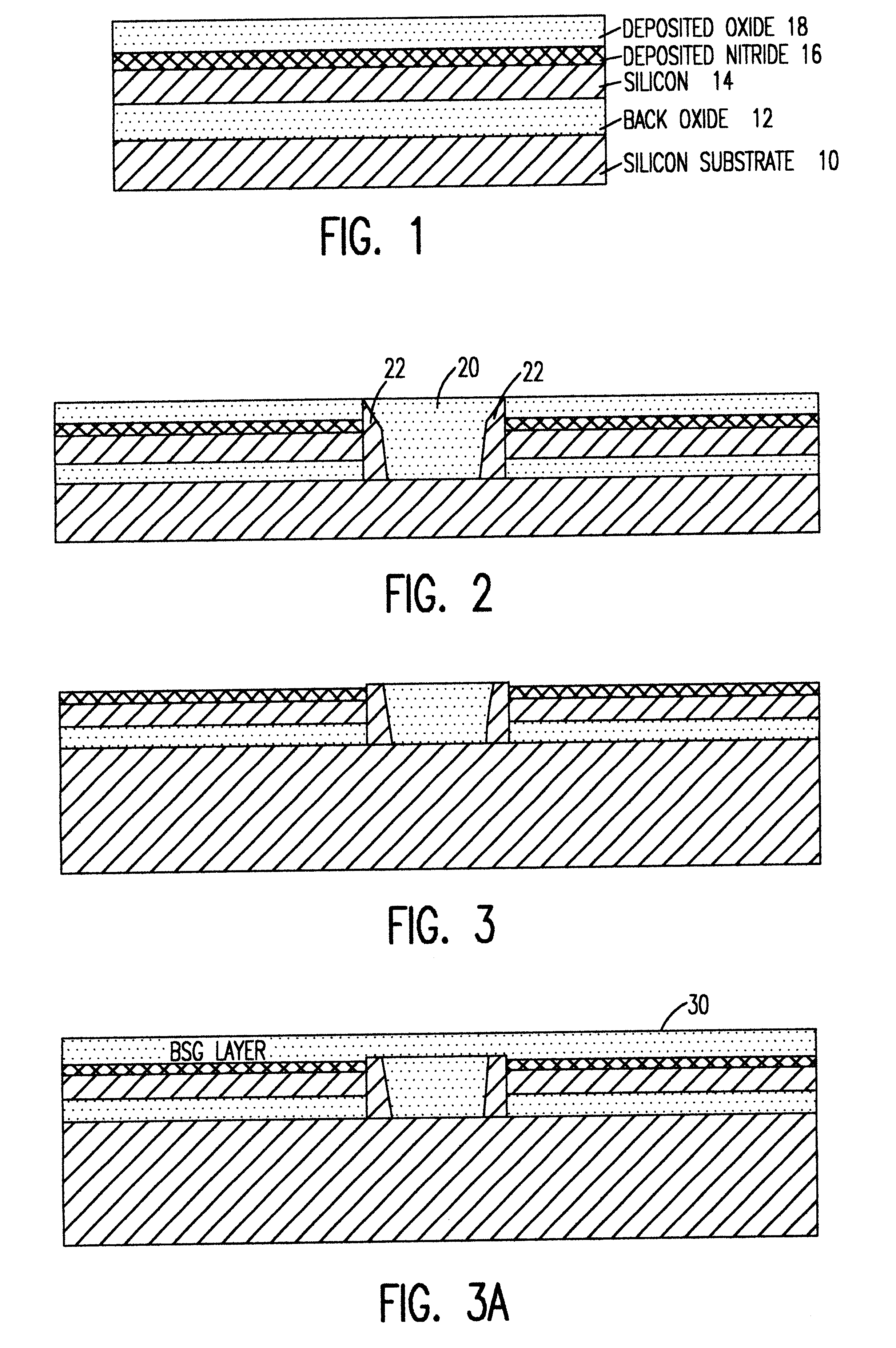

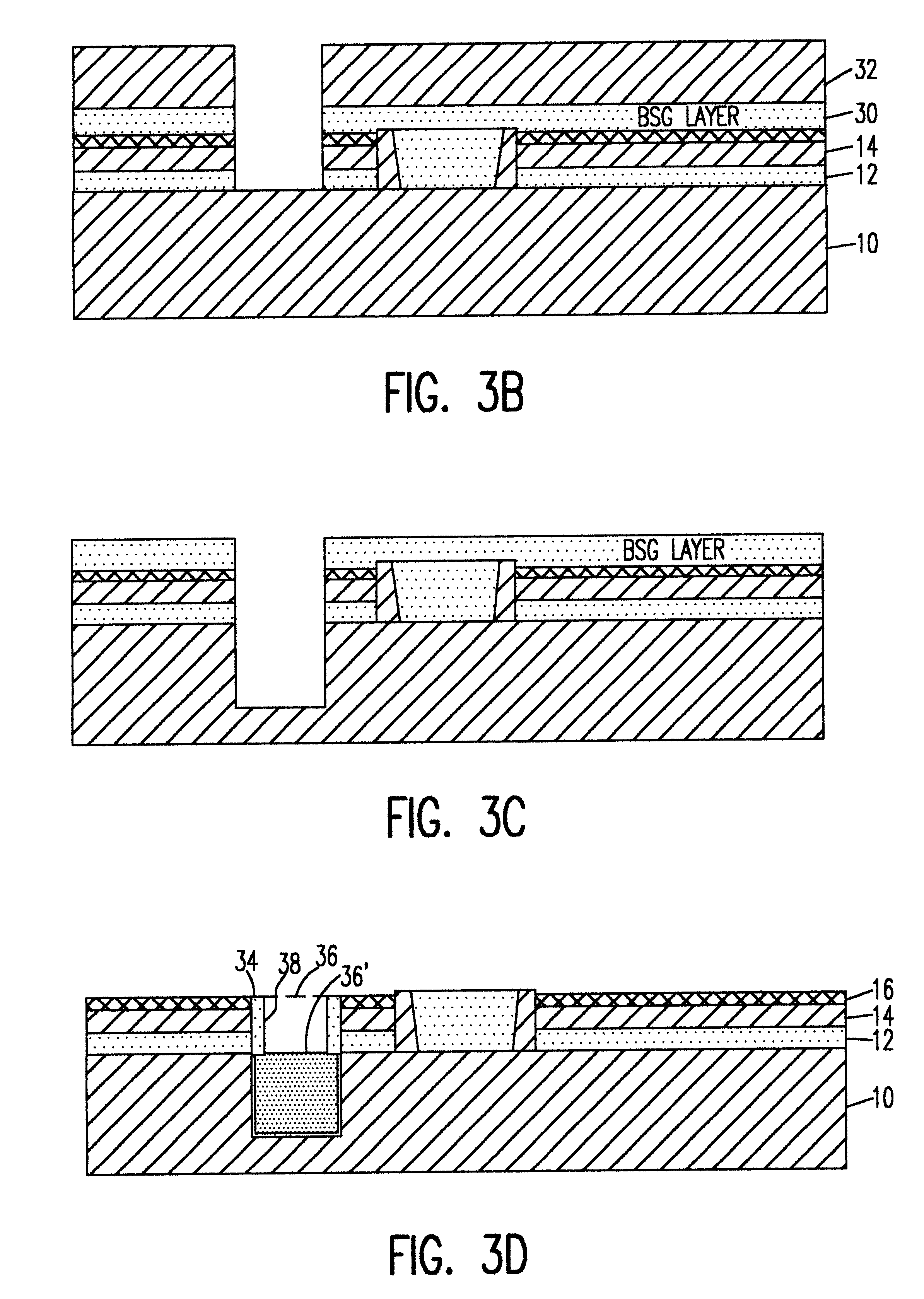

Silicon anti-fuse structures, bulk and silicon on insulator fabrication methods and application

A method and semiconductor structure that uses a field enhanced region where the oxide thickness is substantially reduced, thereby allowing antifuse programming at burn-in voltages which do not damage the standard CMOS logic. The semiconductor device comprises a substrate that has a raised protrusion terminating at a substantially sharp point, an insulator layer over the raised protrusion sufficiently thin to be breached by a breakdown voltage applied to the sharp point, a region comprised of a material on the insulator over the raised protrusion for becoming electrically coupled to the substrate after the insulator layer is breached by the breakdown voltage, and a contact for supplying the breakdown voltage to the substrate. In a second embodiment, the semiconductor device comprises a substrate having a trough formed in a top surface of the substrate, a relatively thick insulator layer over the top surface of the substrate, a relatively thin insulator layer over the trough that is breached by a breakdown voltage applied to the trough, a region comprised of a material on the relatively thin insulator layer over the trough for becoming electrically coupled to the substrate after the relatively thin insulator layer is breached by the breakdown voltage, and a contact for supplying the breakdown voltage to said substrate.

Owner:IBM CORP

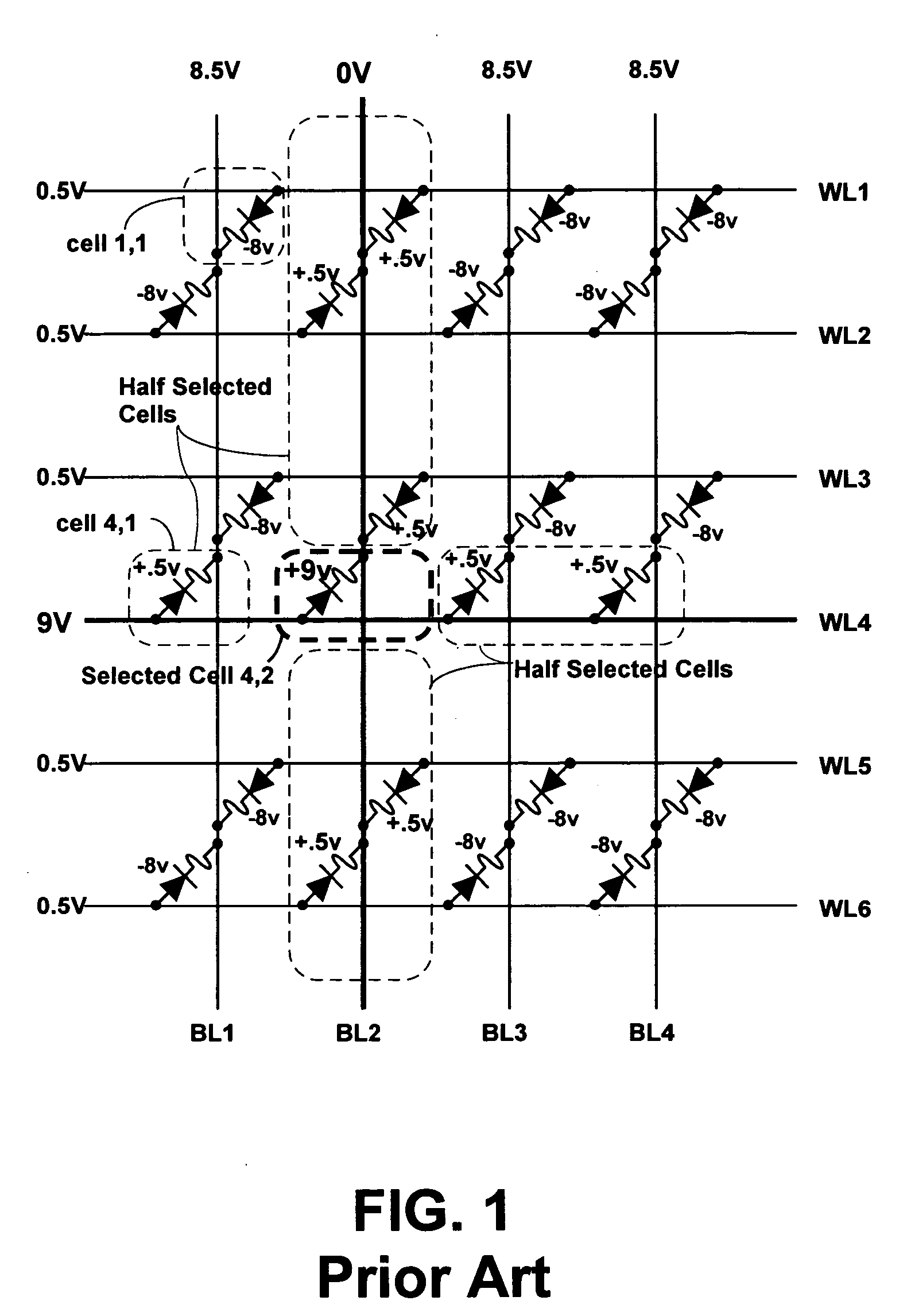

One-time programmable memories using junction diodes as program selectors

ActiveUS20120044740A1Small cell sizeLow costSolid-state devicesRead-only memoriesCMOSElectrical resistance and conductance

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, such as electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse, etc. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. The OTP device has an OTP element coupled to the diode. The OTP device can be used to construct a two-dimensional OTP memory with the N terminals of the diodes in a row connected as a wordline and the OTP elements in a column connected as a bitline. By applying a high voltage between a selected bitline and a selected wordline to turn on a diode in a selected cell for suitable duration of time, a current flows through an OTP element in series with the program selector may change the resistance state. The cell data in the OTP memory can also be read by turning on a selected wordline and to couple a selected bitline to a sense amplifier. The wordlines may have high-resistivity local wordlines coupled to low-resistivity global wordlines through conductive contact(s) or via(s).

Owner:ATTOPSEMI TECH CO LTD

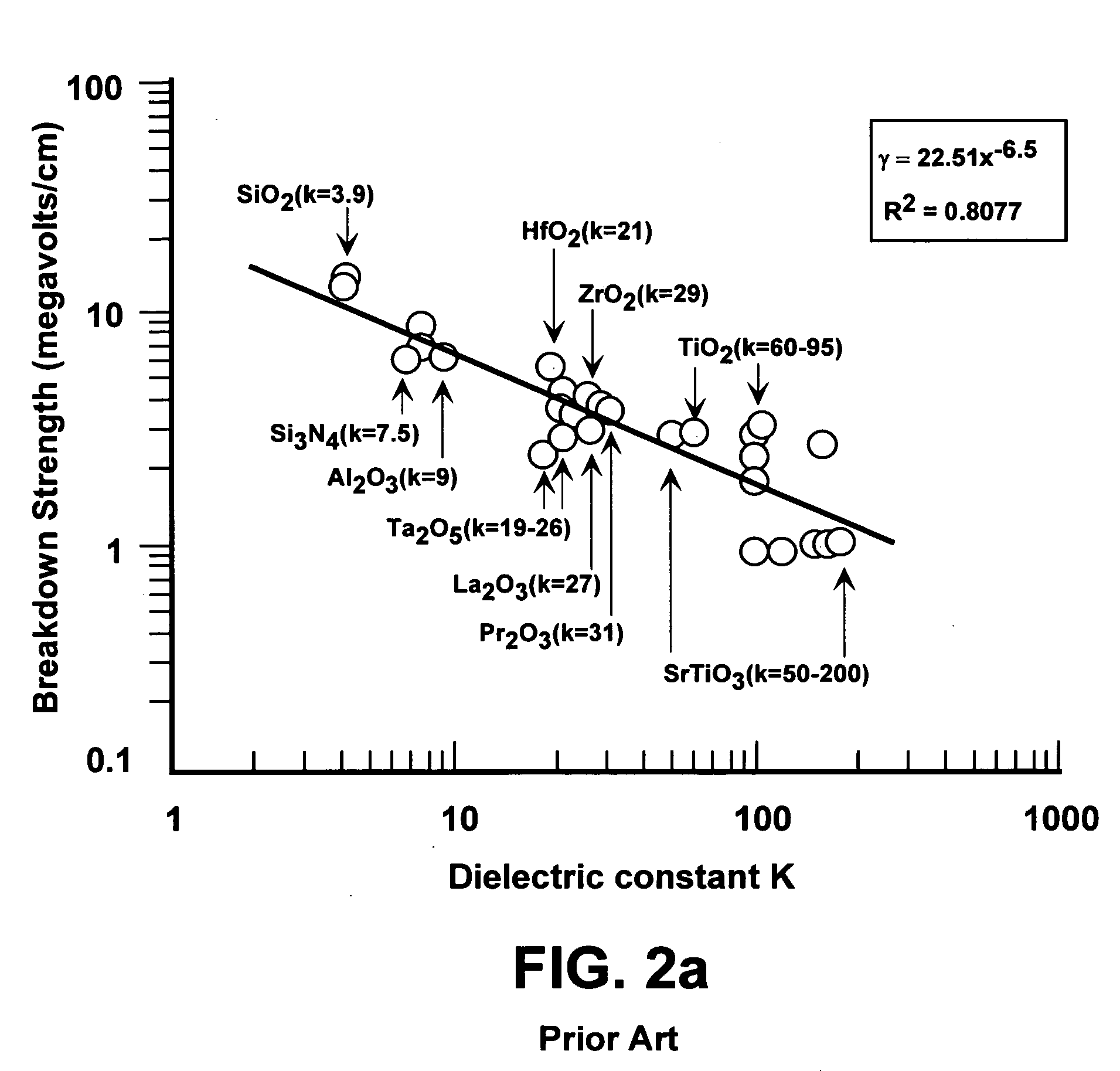

Memory with high dielectric constant antifuses and method for using at low voltage

InactiveUS20070069241A1Reliable readWrite reliablySemiconductor/solid-state device detailsSolid-state devicesLow voltageAlloy

A memory array having memory cells comprising a diode and an antifuse can be made smaller and programmed at lower voltage by using antifuse materials having higher dielectric constant and higher acceleration factor than silicon dioxide, and by using diodes having lower band gaps than silicon. Such memory arrays can be made to have long operating lifetimes by using the high acceleration factor and lower band gap materials. Antifuse materials having dielectric constants between 5 and 27, for example hafnium silicon oxynitride or hafnium silicon oxide are particularly effective. Diode materials with band gaps lower than silicon, such as germanium or a silicon-germanium alloy are particularly effective.

Owner:SANDISK TECH LLC

3-transistor OTP ROM using CMOS gate oxide antifuse

Owner:KOREA ADVANCED INST OF SCI & TECH

One-time programmable memories using polysilicon diodes as program selectors

ActiveUS20120044738A1Small cell sizeCost reductionSolid-state devicesRead-only memoriesSense amplifierHigh resistivity

Polysilicon diodes fabricated in standard CMOS logic processes can be used as program selectors for One-Time Programmable (OTP) devices, using electrical fuse, contact / via fuse, contact / via anti-fuse, or gate-oxide breakdown anti-fuse etc. as OTP element The diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. The OTP device has an OTP element coupled to a polysilicon diode. The OTP devices can be used to construct a two-dimensional OTP memory with the N-terminals of the diodes in a row connected as a wordline and the OTP elements in a column connected as a bitline. By applying a high voltage between a selected bitline and a selected wordline to turn on a diode in a selected cell for suitable duration of time, a current flows through an OTP element may change the resistance state. The cell data in the OTP memory can also be read by turning on a selected wordline and to couple a selected bitline to a sense amplifier. The wordlines may have high-resistivity local wordlines coupled to low-resistivity global wordlines through conductive contact(s) or via(s).

Owner:ATTOPSEMI TECH CO LTD

Reversible electric fuse and antifuse structures for semiconductor devices

ActiveUS7557424B2Improve electromigration problemsGood reversibilitySemiconductor/solid-state device detailsSolid-state devicesElectric fusesEngineering

A structure and method of fabricating reversible fuse and antifuse structures for semiconductor devices is provided. In one embodiment, the method includes forming at least one line having a via opening for exposing a portion of a plurality of interconnect features; conformally depositing a first material layer over the via opening; depositing a second material layer over the first material layer, wherein the depositing overhangs a portion of the second material layer on a top portion of the via opening; and depositing a blanket layer of insulating material, where the depositing forms a plurality of fuse elements each having an airgap between the insulating material and the second material layer. The method further includes forming a plurality of electroplates in the insulator material connecting the fuse elements. In another embodiment, the method includes depositing a first and a second material layer on a semiconductor substrate, wherein the second material layer having a higher electrical conductivity than the first material layer; selectively etching the first and second material layer to create at least one constricted region to facilitate electromigration of the second material; wherein the electromigration creates a plurality of micro voids; and forming a plurality of electrical contacts on the second material layer.

Owner:GLOBALFOUNDRIES U S INC

Inverse fuse wire and memory cell without ability to cause non-linear current after fusing

The anti-fuse is formed by a transistor of a channel with doping carriers, which can not lead to the nonlinear electric current after fusing and can be used for a memory cell of a memorizer for programming of expression of first degree. The memorizer for programming of expression of first degree adopts a P-shaped transistor and an N-shaped transistor for programming for the anti-fuse. As the anti-fuse is provided with the channel with doping carriers, after the anti-fuse is fused, the electric current can not flow through the P / N knob between two doping regions and basements to form a nonlinear electric current, thus leading the memory cell to be programmed correctly.

Owner:UNITED MICROELECTRONICS CORP

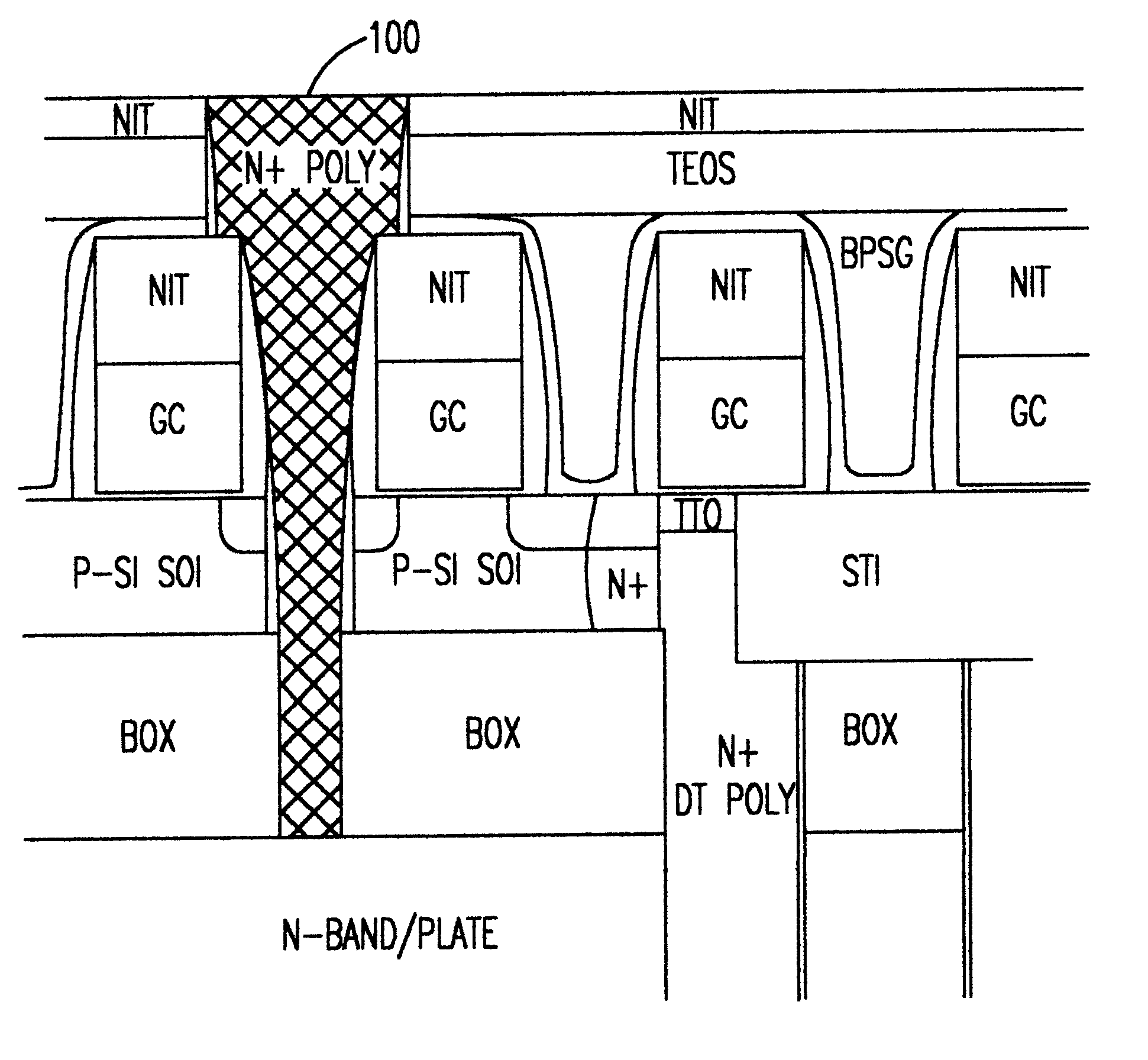

Structures and methods of anti-fuse formation in SOI

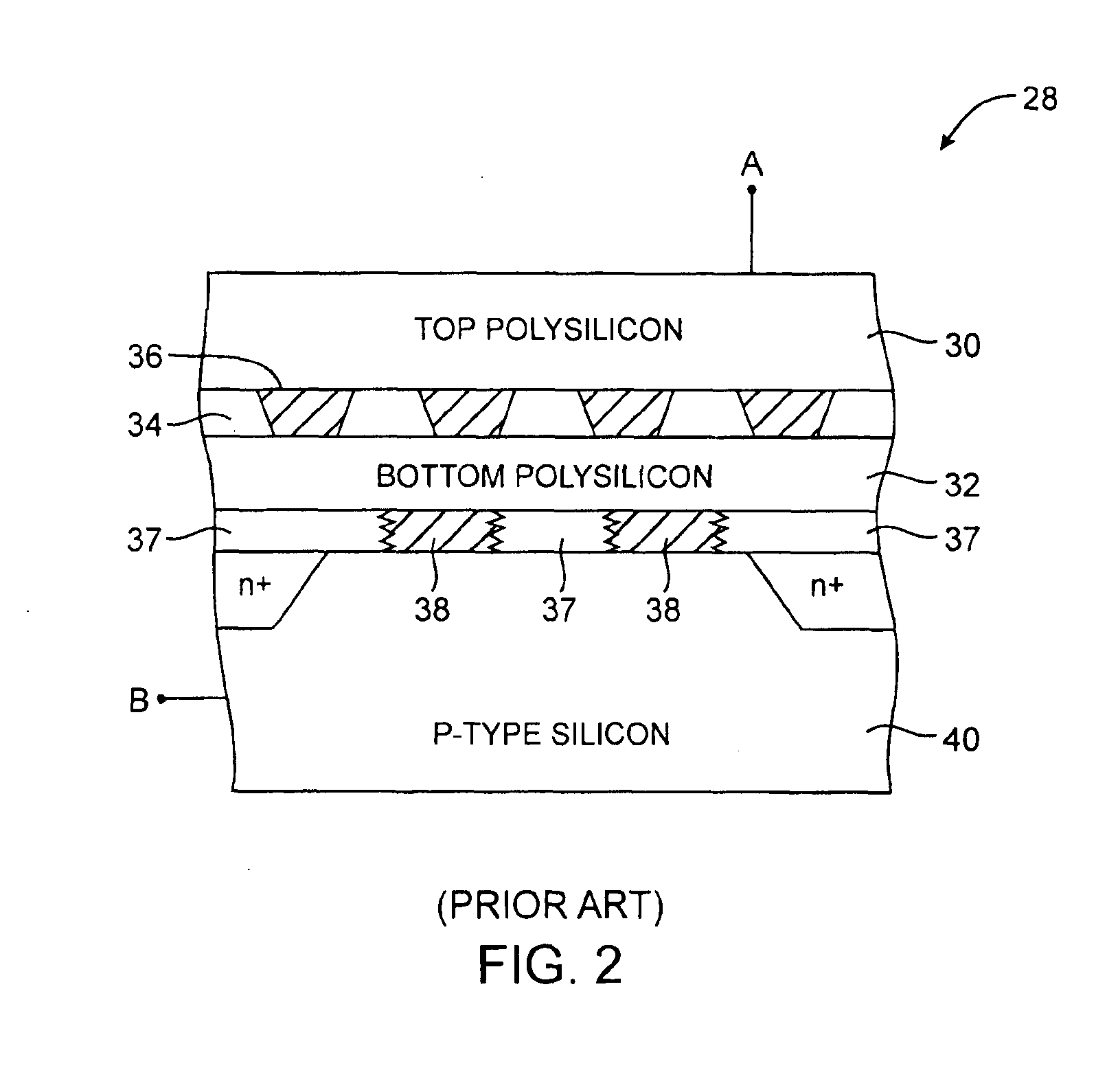

InactiveUS6396121B1Low programming voltage and currentReduce thermal effectsTransistorSemiconductor/solid-state device detailsDielectricElement space

An anti-fuse structure that can be programmed at low voltage and current and which potentially consumes very little chip spaces and can be formed interstitially between elements spaced by a minimum lithographic feature size is formed on a composite substrate such as a silicon-on-insulator wafer by etching a contact through an insulator to a support semiconductor layer, preferably in combination with formation of a capacitor-like structure reaching to or into the support layer. The anti-fuse may be programmed either by the selected location of conductor formation and / or damaging a dielectric of the capacitor-like structure. An insulating collar is used to surround a portion of either the conductor or the capacitor-like structure to confine damage to the desired location. Heating effects voltage and noise due to programming currents are effectively isolated to the bulk silicon layer, permitting programming during normal operation of the device. Thus the potential for self-repair without interruption of operation is realized.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com