Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

261results about How to "Small feature size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

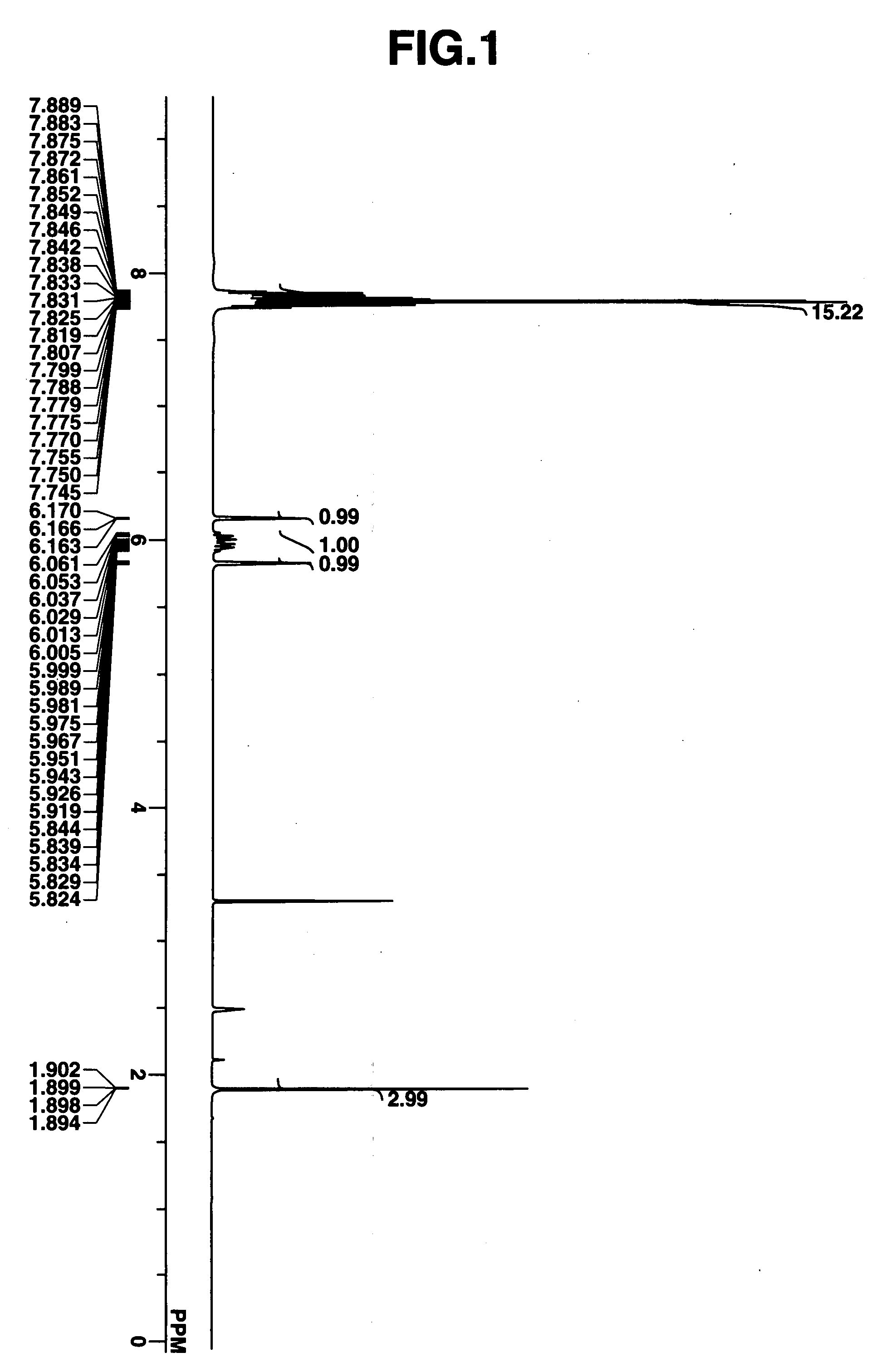

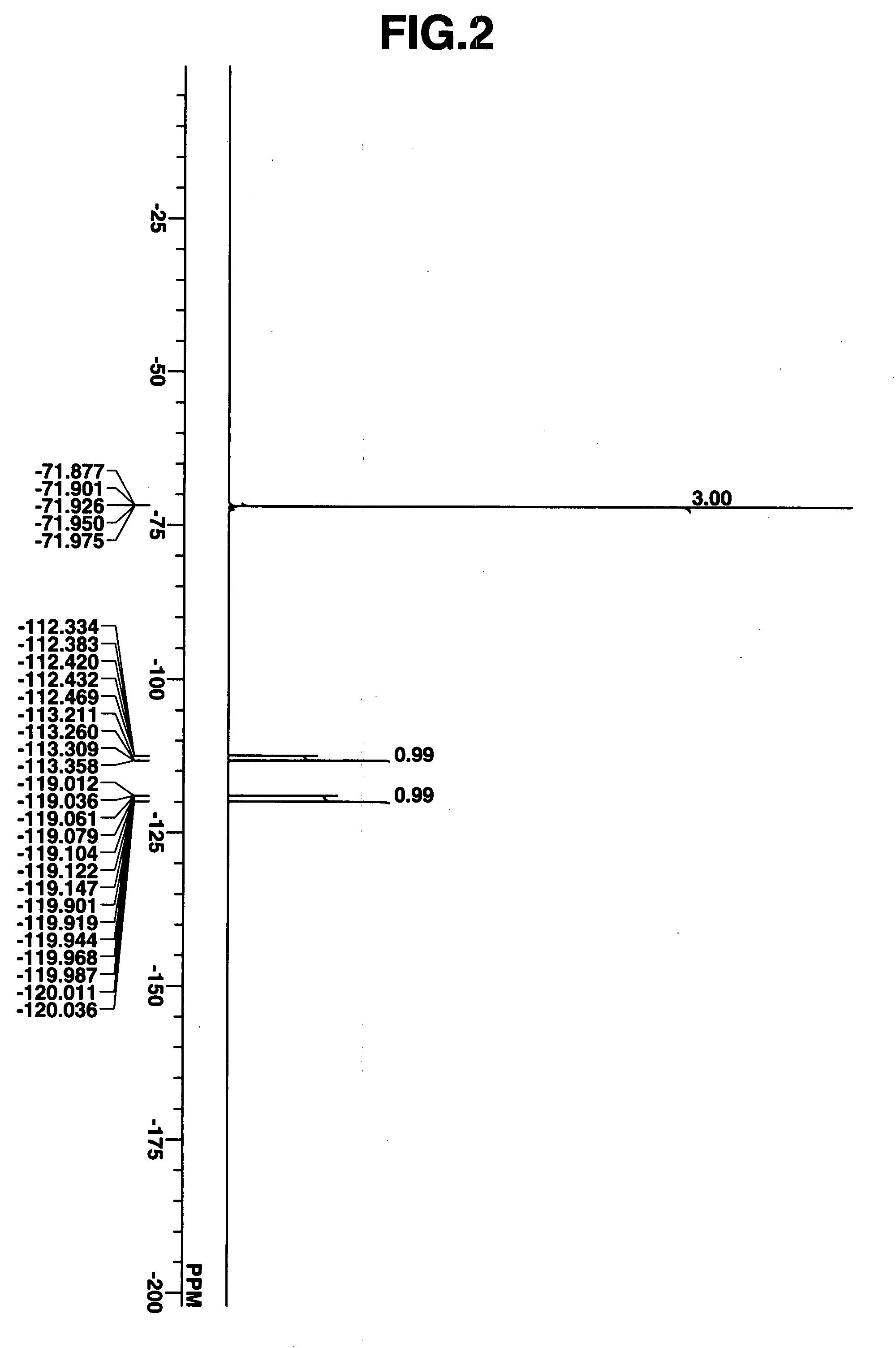

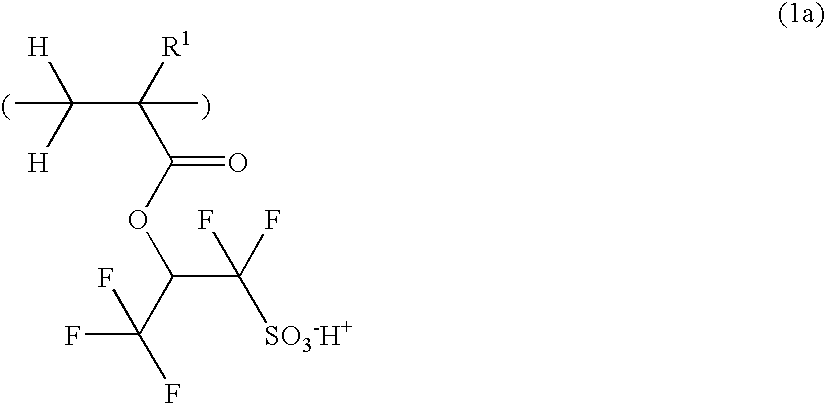

Sulfonium salt having polymerizable anion, polymer, resist composition, and patterning process

ActiveUS20080102407A1Feature size of to decreaseSmall feature sizeOrganic chemistryPhotosensitive materialsResistHigh energy

A sulfonium salt having a polymerizable anion generates a strong sulfonic acid upon exposure to high-energy radiation so that it facilitates effective scission of acid labile groups in chemically amplified resist compositions. It is useful as a monomer from which a base resin for use in radiation-sensitive resist compositions is derived.

Owner:SHIN ETSU CHEM IND CO LTD

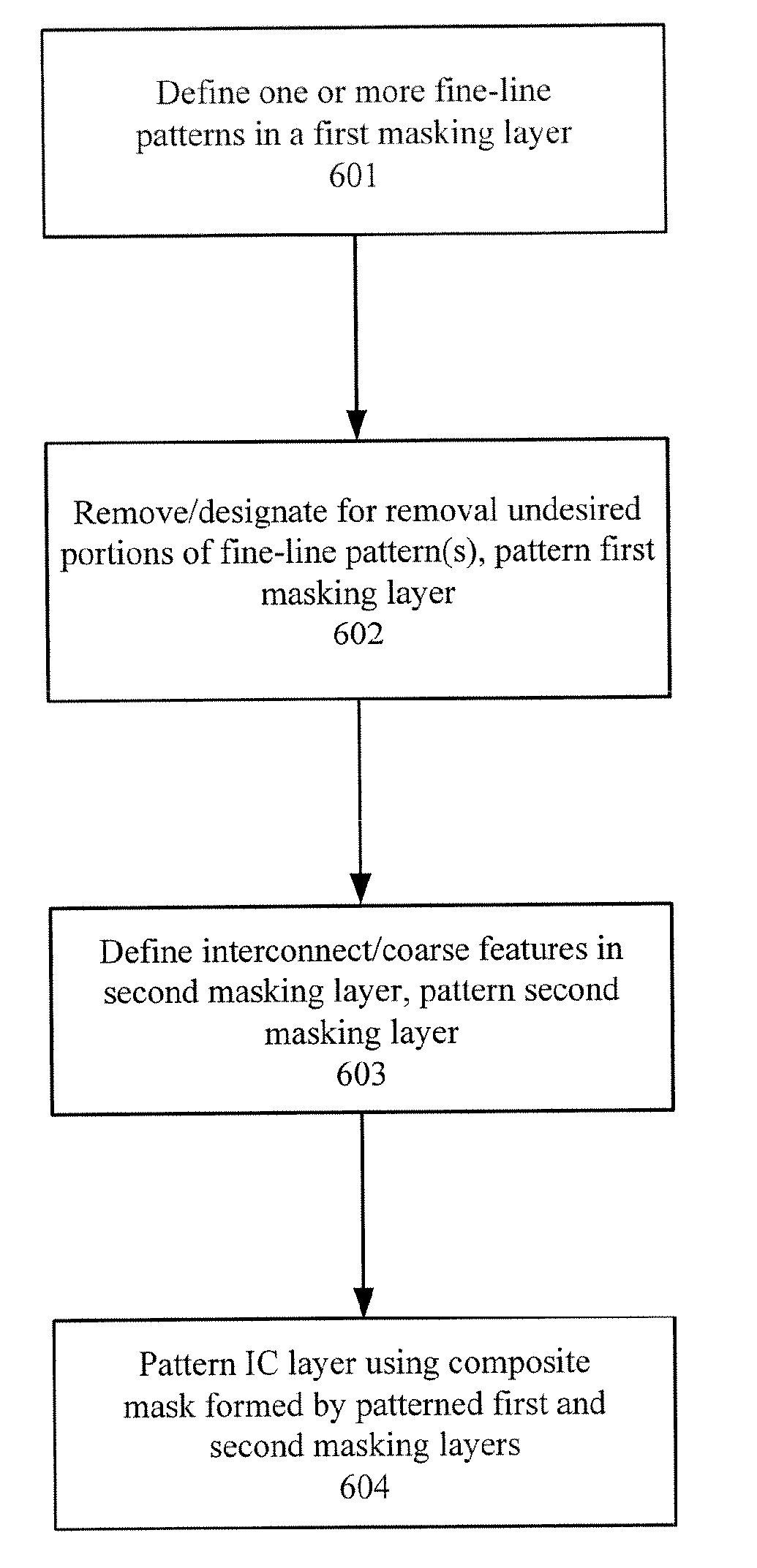

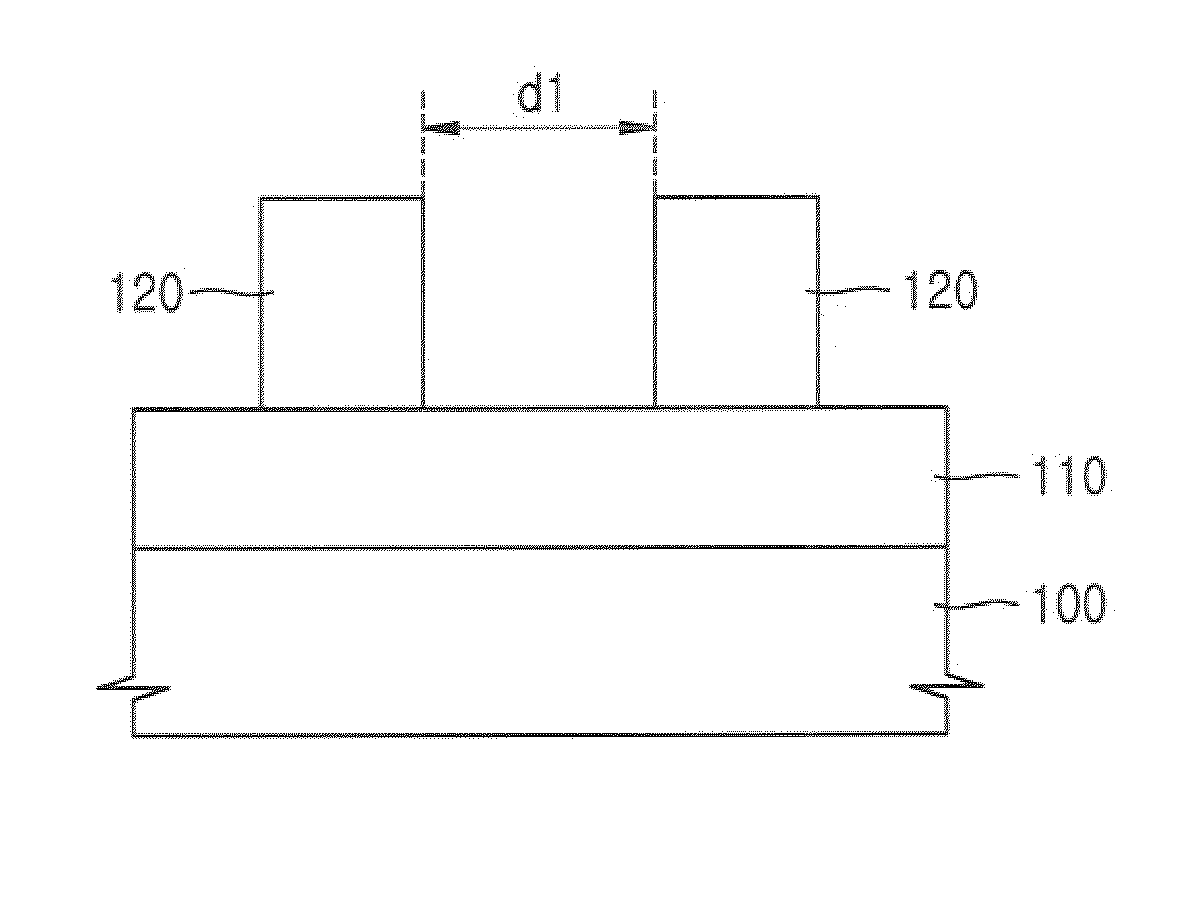

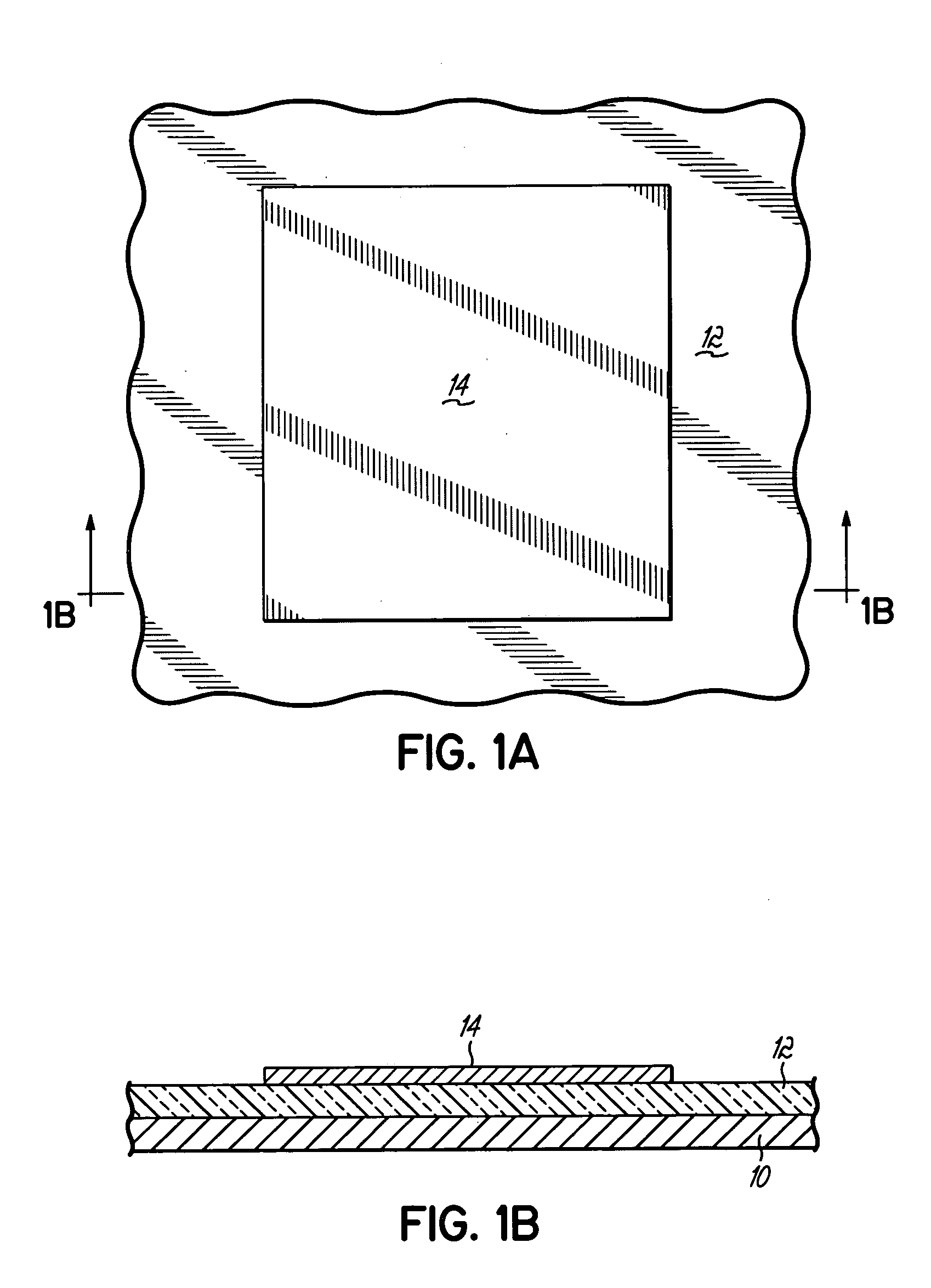

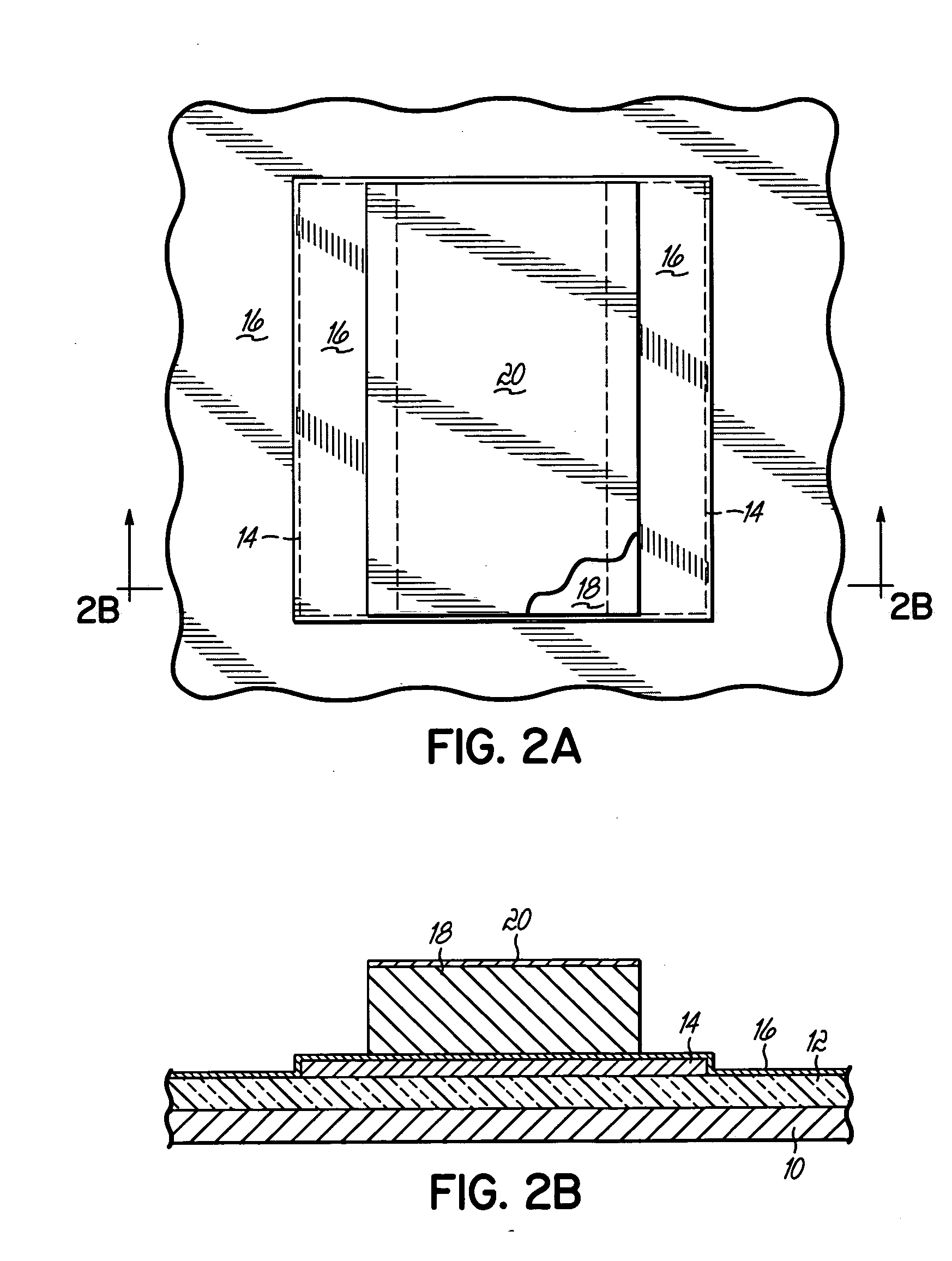

Patterning A Single Integrated Circuit Layer Using Multiple Masks And Multiple Masking Layers

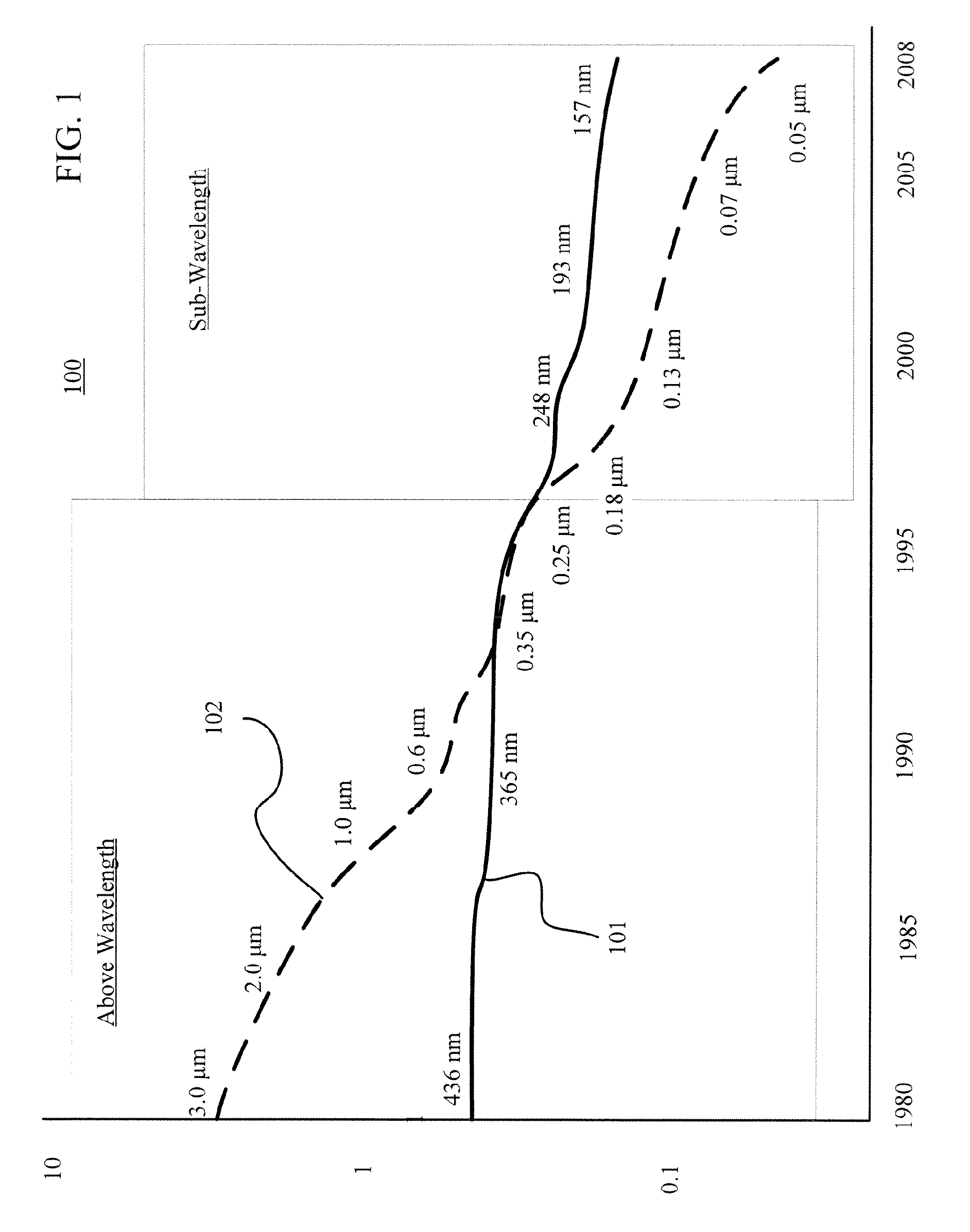

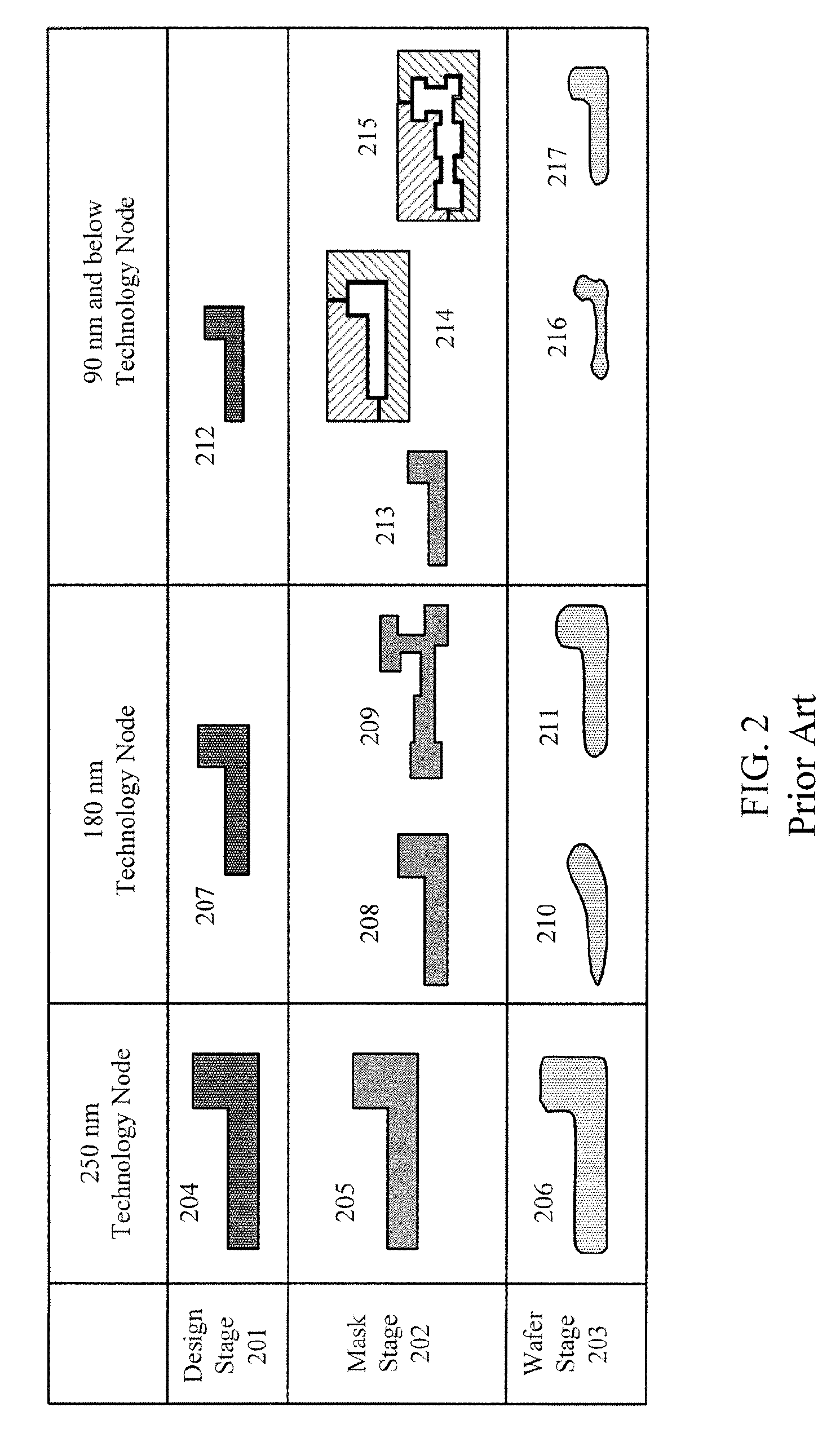

ActiveUS20070275309A1Increase productionEasy to useSemiconductor/solid-state device manufacturingPhotosensitive material processingResolution enhancement technologiesLength wave

A multiple mask and a multiple masking layer technique can be used to pattern a single IC layer. A resolution enhancement technique can be used to define one or more fine-line patterns in a first masking layer, wherein each fine-line feature is sub-wavelength. Moreover, the pitch of each fine-line pattern is less than or equal to that wavelength. The portions of the fine-line features not needed to implement the circuit design are then removed or designated for removal using a mask. After patterning of the first masking layer, another mask can then be used to define coarse features in a second masking layer formed over the patterned first masking layer. At least one coarse feature is defined to connect two fine-line features. The IC layer can be patterned using the composite mask formed by the patterned first and second masking layers.

Owner:SYNOPSYS INC

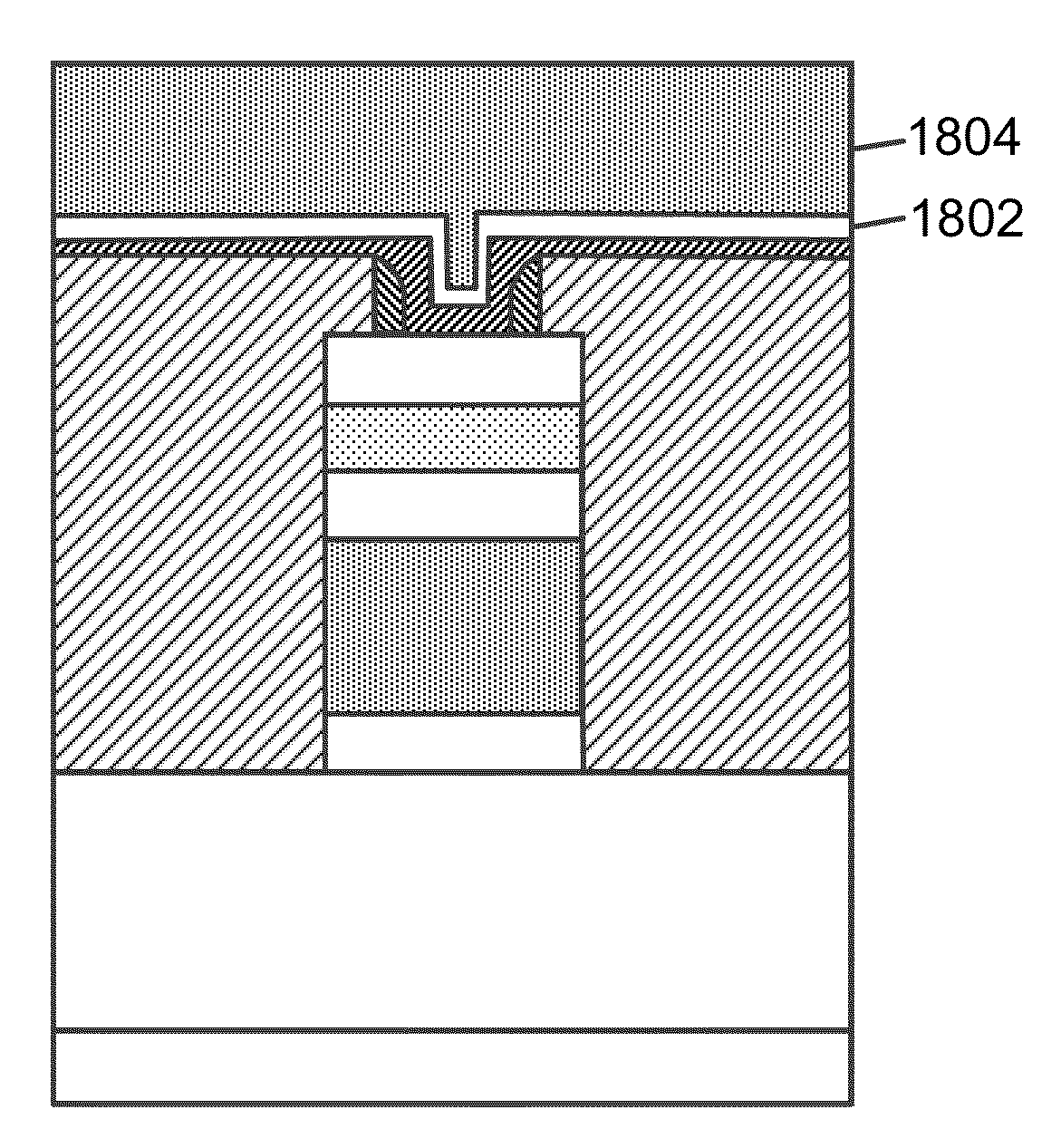

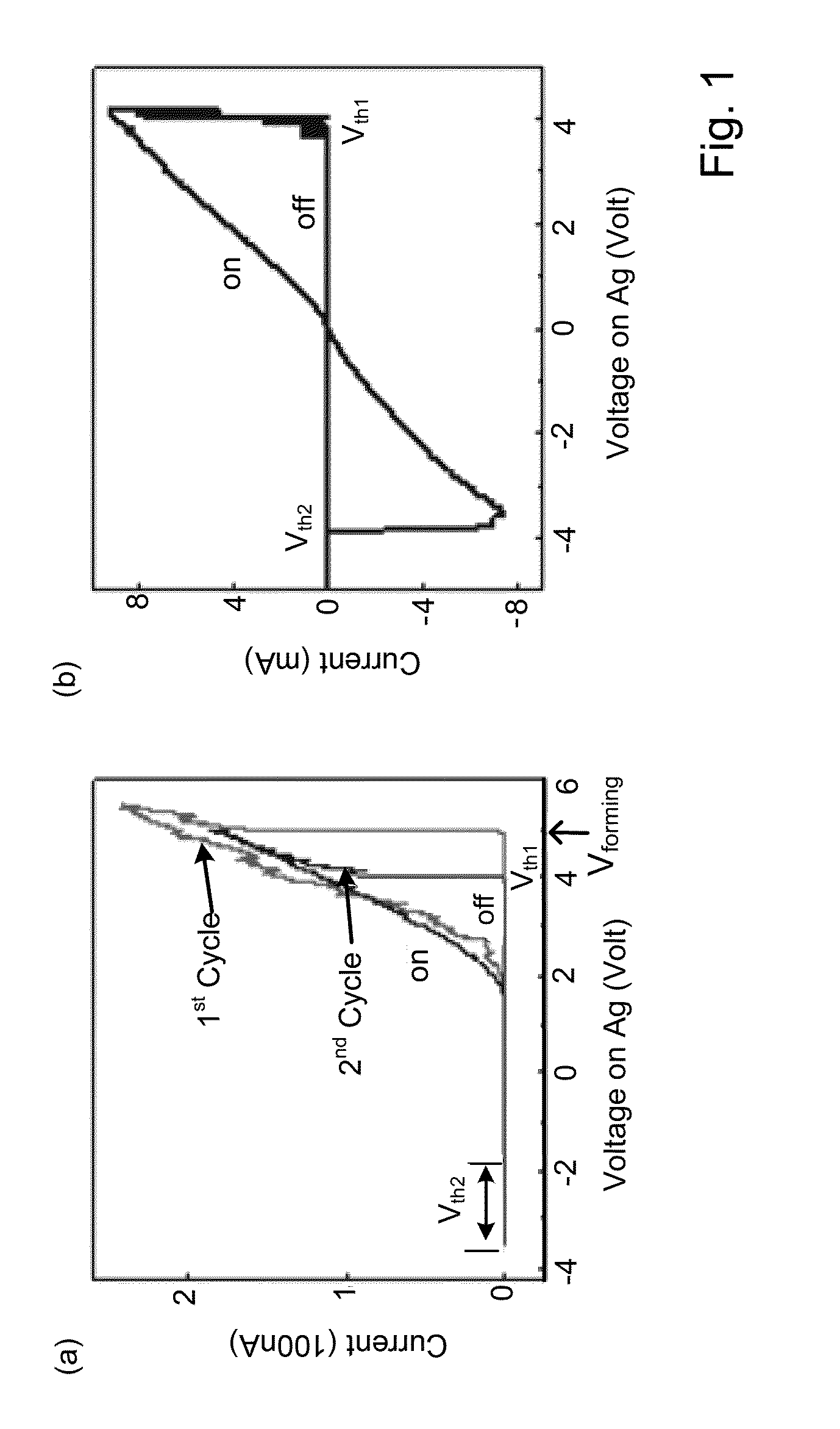

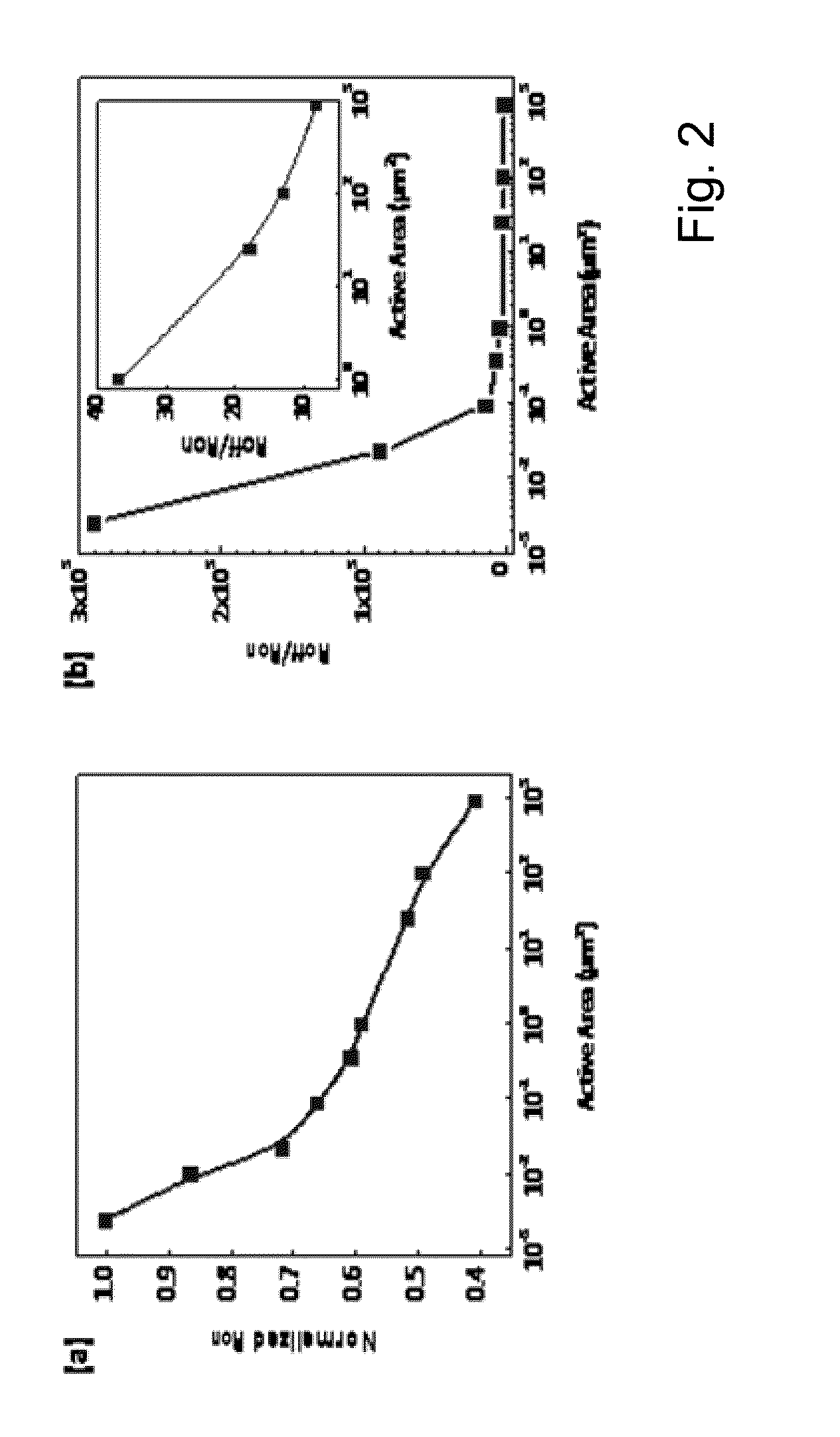

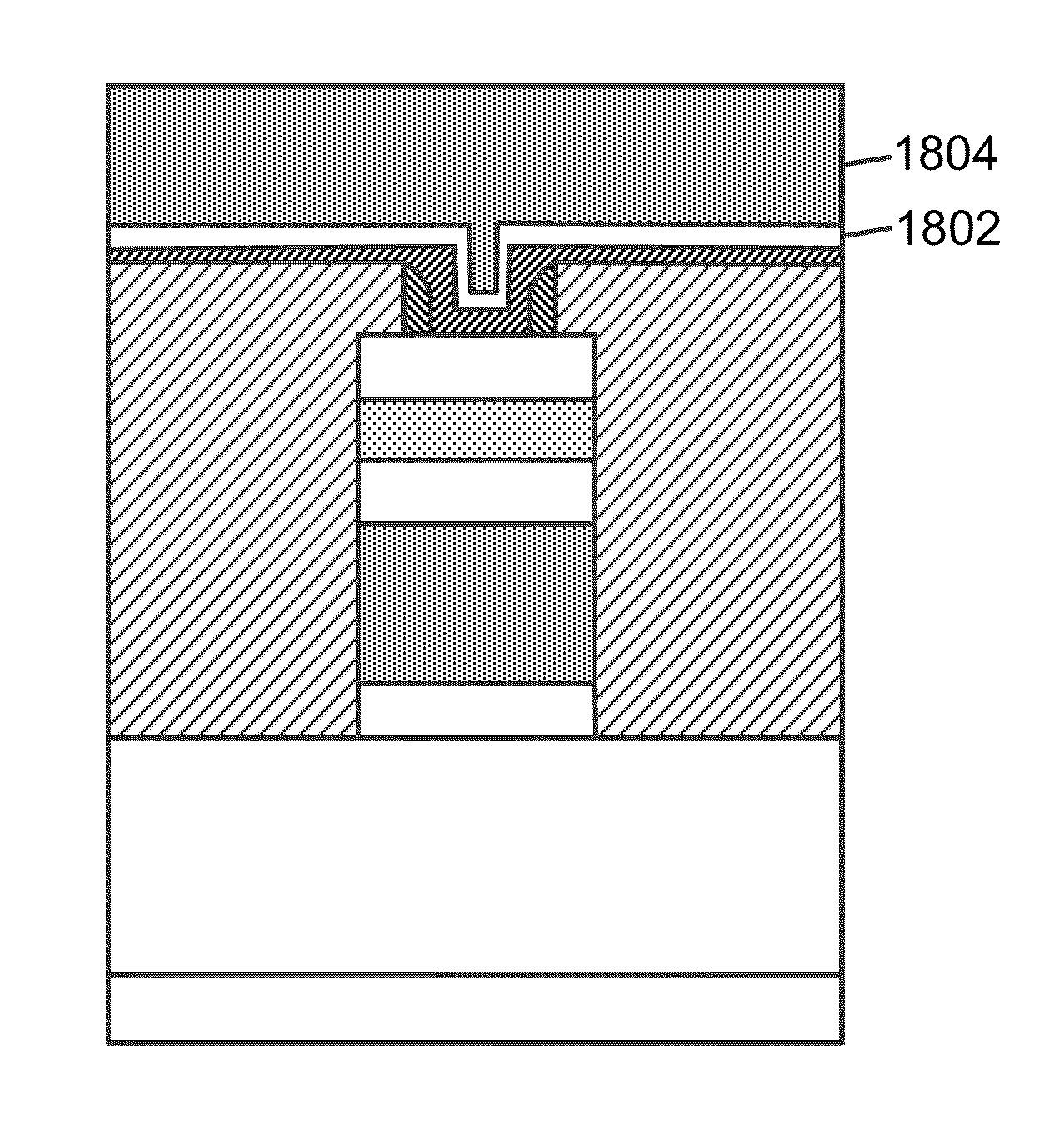

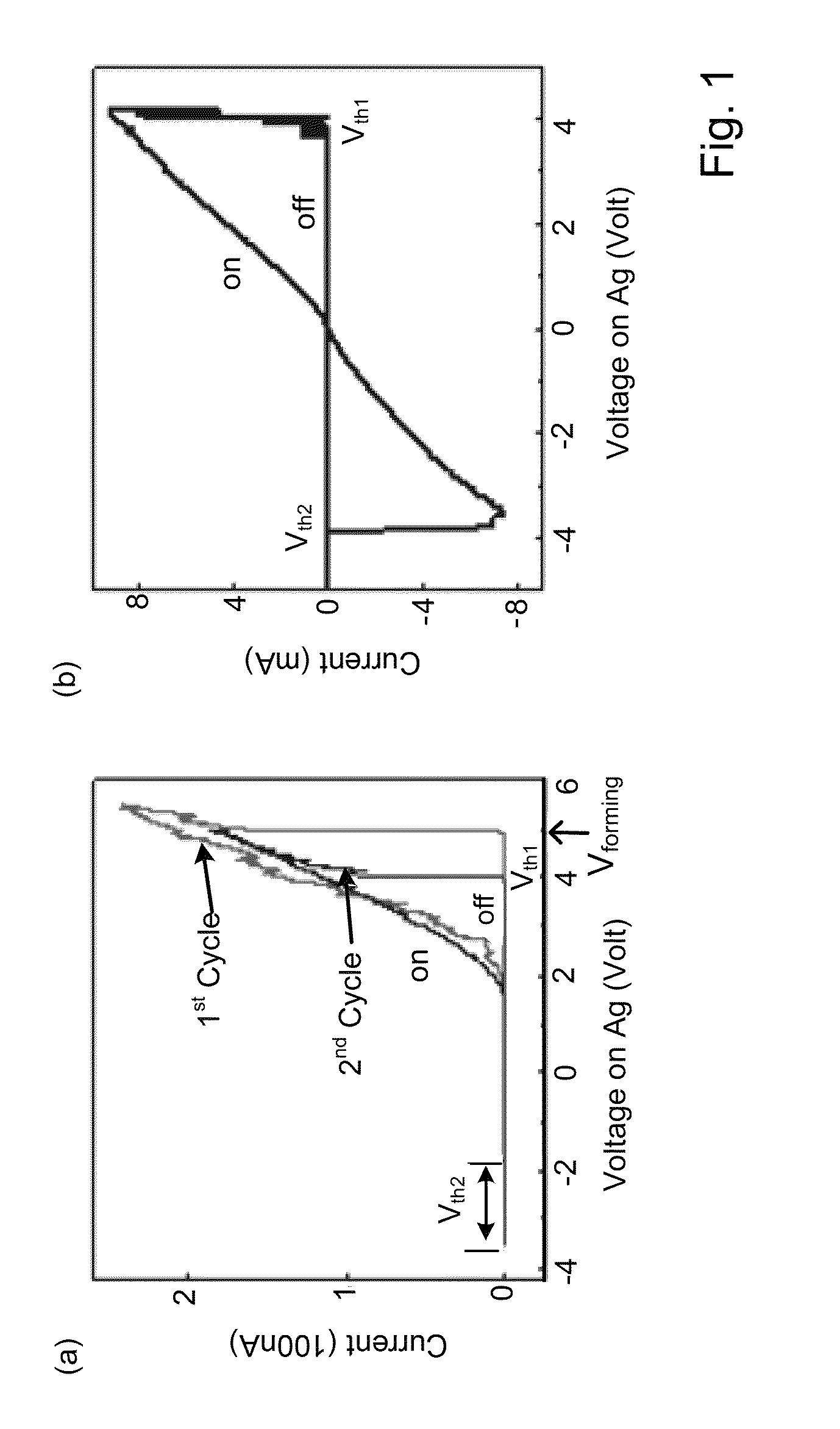

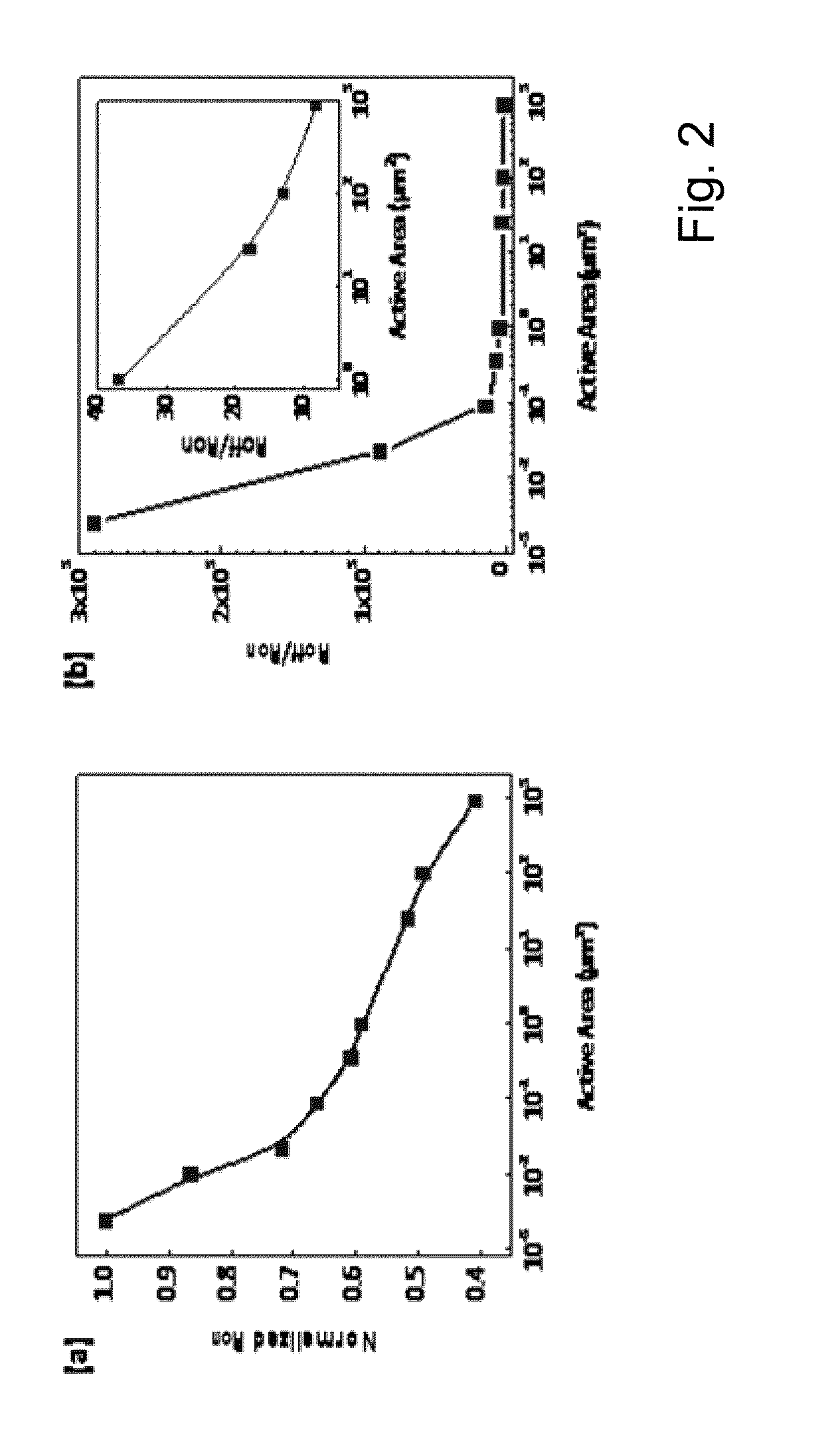

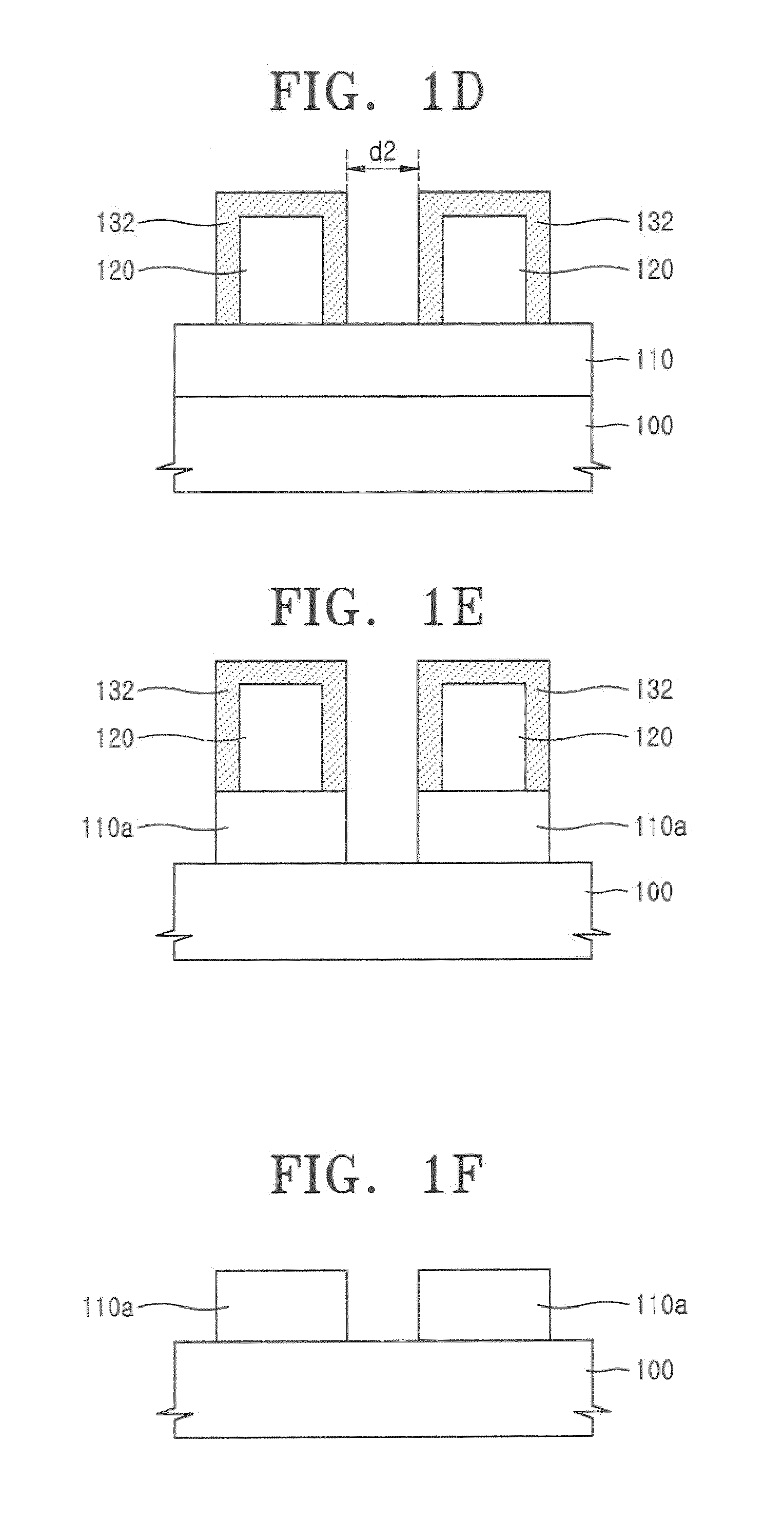

Improved on/off ratio for non-volatile memory device and method

ActiveUS20120012806A1Quick switchWide rangeSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesSwitched currentEngineering

This application describes a method of forming a switching device. The method includes forming a first dielectric material overlying a surface region of a substrate. A bottom wiring material is formed overlying the first dielectric material and a switching material is deposited overlying the bottom wiring material. The bottom wiring material and the switching material is subjected to a first patterning and etching process to form a first structure having a top surface region and a side region. The first structure includes at least a bottom wiring structure and a switching element having a top surface region including an exposed region of the switching element. A second dielectric material is formed overlying at least the first structure including the exposed region of the switching element. The method forms a first opening region in a portion of the second dielectric layer to expose a portion of the top surface region of the switching element. A dielectric side wall structure is formed overlying a side region of the first opening region. A top wiring material including a conductive material is formed overlying at lease the top surface region of the switching element such that the conductive material is in direct contact with the switching element. The side wall spacer reduces a contact area for the switching element and the conductive material and thus a reduced active device area for the switching device. In a specific embodiment, the reduced area provides for an increase in device ON / OFF current ratio.

Owner:CROSSBAR INC

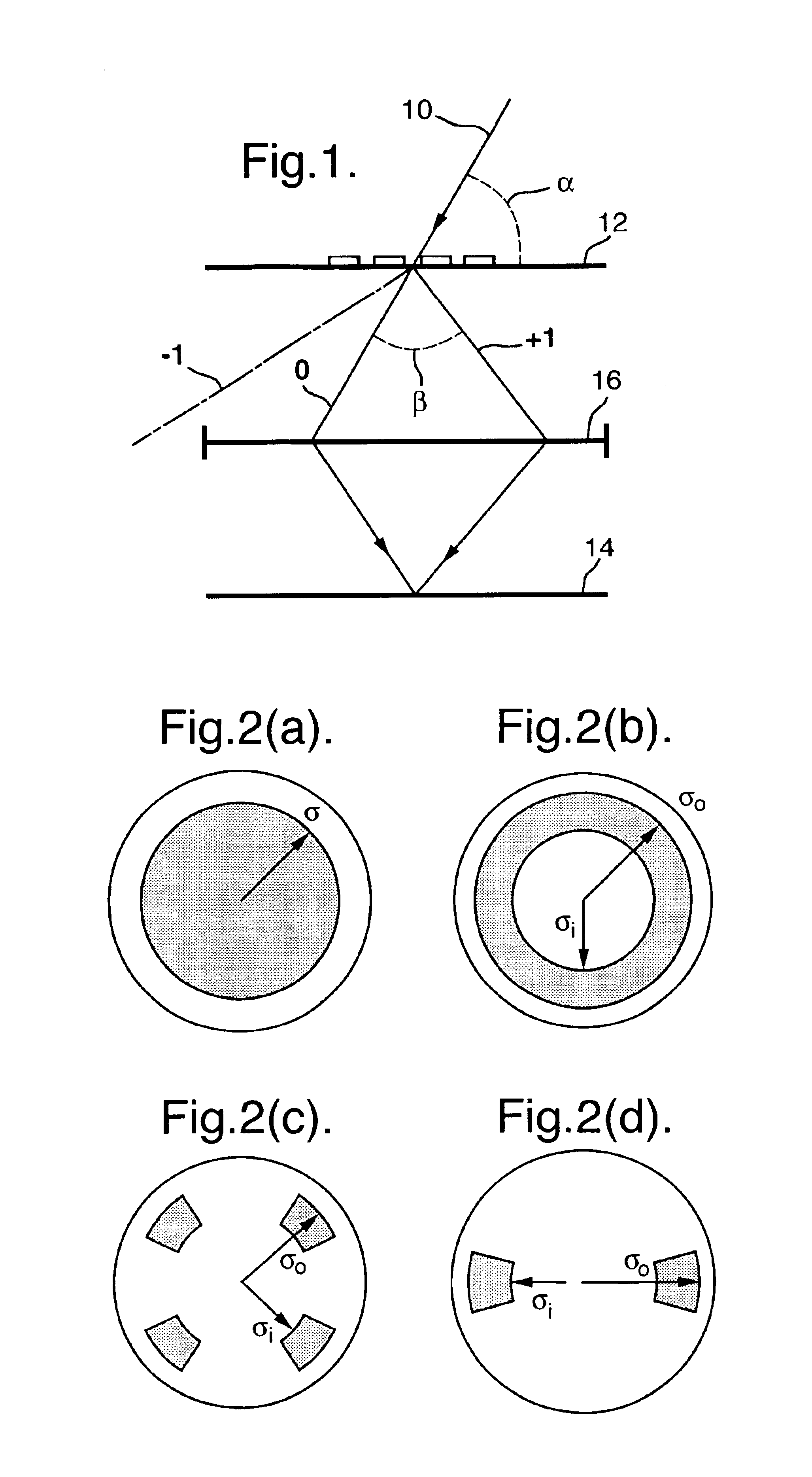

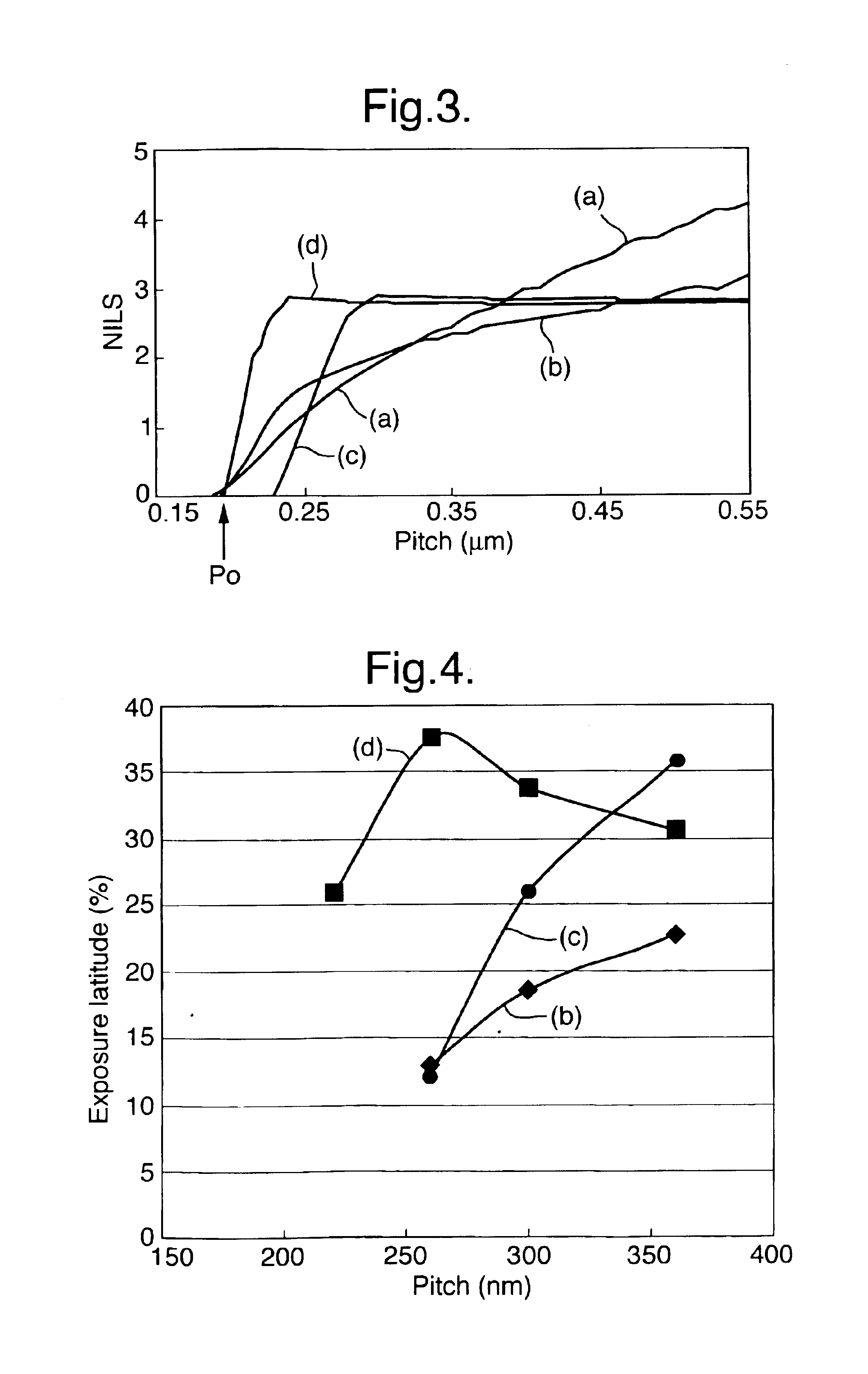

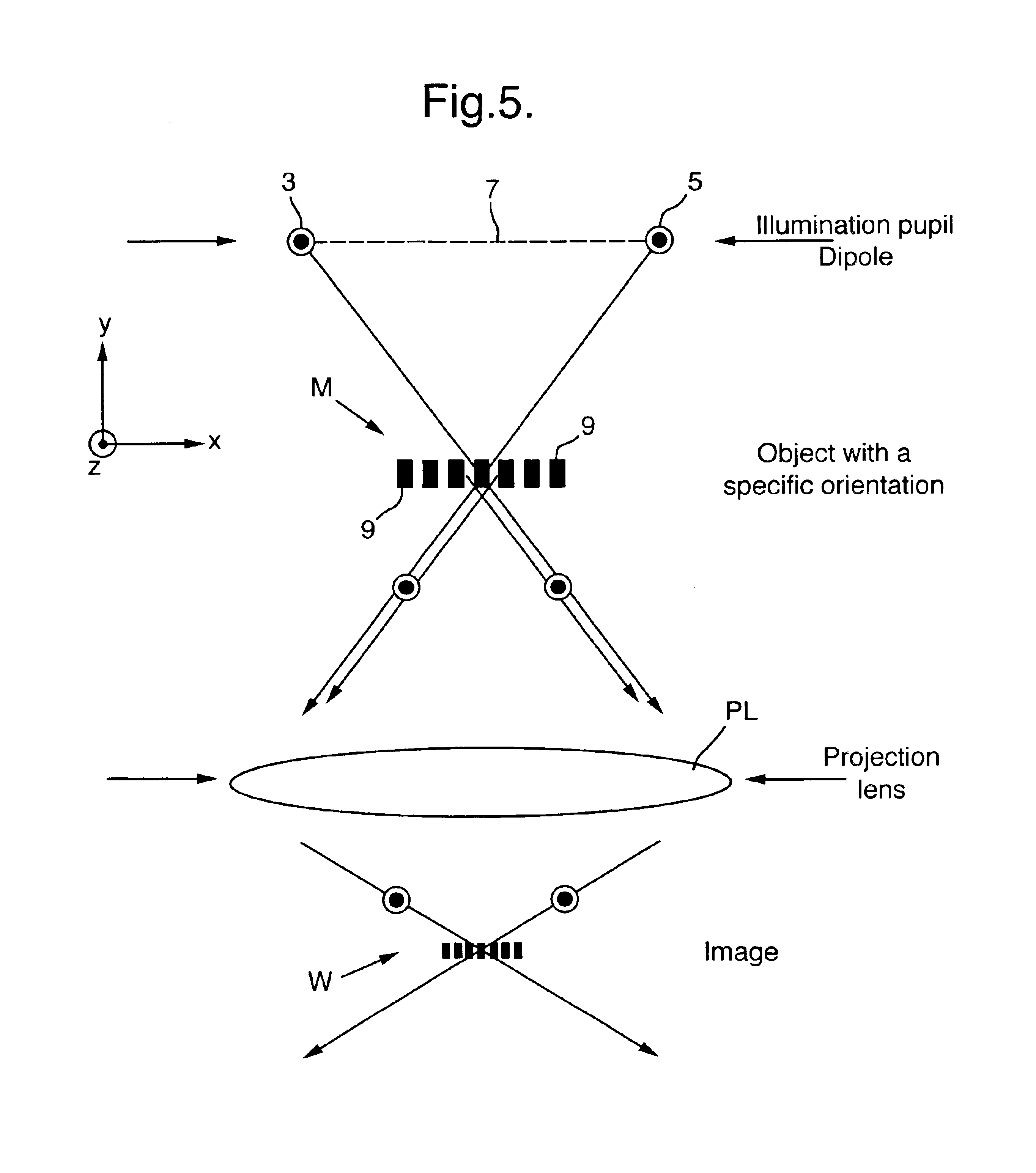

Lithographic method and apparatus

InactiveUS6855486B1Small feature sizeOptimizing Process ParametersPhoto-taking processesSemiconductor/solid-state device manufacturingSingle exposureMethod of images

A method of imaging a pattern in a microlithographic exposure apparatus includes performing two exposures, each with a different mask, the superposition of the images defined by the two masks produces the complete circuit pattern. A dipolar illumination mode is used for each exposure, the dipoles of the two exposures being mutually perpendicular. The dipolar illumination mode of the first exposure is used to image mask features parallel to a first direction, and the dipolar illumination mode of the second exposure is used to image mask features perpendicular to the first direction.

Owner:ASML NETHERLANDS BV

On/off ratio for non-volatile memory device and method

ActiveUS8168506B2Improve switching characteristicsLow yieldSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesPower flowConductive materials

This application describes a method of forming a switching device. The method includes forming a first dielectric material overlying a surface region of a substrate. A bottom wiring material is formed overlying the first dielectric material and a switching material is deposited overlying the bottom wiring material. The bottom wiring material and the switching material is subjected to a first patterning and etching process to form a first structure having a top surface region and a side region. The first structure includes at least a bottom wiring structure and a switching element having a top surface region including an exposed region of the switching element. A second dielectric material is formed overlying at least the first structure including the exposed region of the switching element. The method forms a first opening region in a portion of the second dielectric layer to expose a portion of the top surface region of the switching element. A dielectric side wall structure is formed overlying a side region of the first opening region. A top wiring material including a conductive material is formed overlying at lease the top surface region of the switching element such that the conductive material is in direct contact with the switching element. The side wall spacer reduces a contact area for the switching element and the conductive material and thus a reduced active device area for the switching device. In a specific embodiment, the reduced area provides for an increase in device ON / OFF current ratio.

Owner:CROSSBAR INC

Coating Compositions for Use in Forming Patterns and Methods of Forming Patterns

InactiveUS20080113300A2Increased durabilityReduce distortionSemiconductor/solid-state device manufacturingPhotosensitive material processingVinyl etherOrganic solvent

A coating composition for forming etch mask patterns may include a polymer and an organic solvent. The polymer may have an aromatic ring substituted by a vinyl ether functional group. The polymer may be, for example, a Novolak resin partially substituted by a vinyl ether functional group or poly(hydroxystyrene) partially substituted by a vinyl ether functional group.

Owner:SAMSUNG ELECTRONICS CO LTD

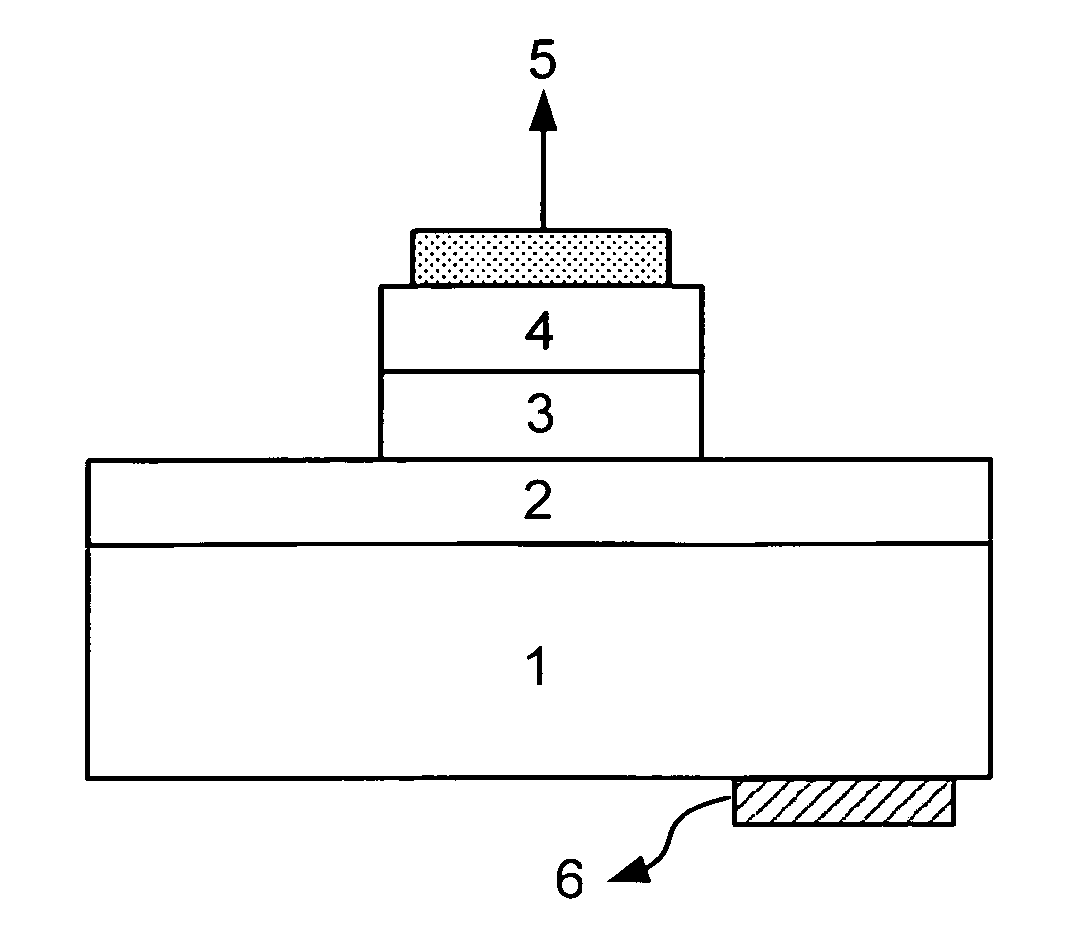

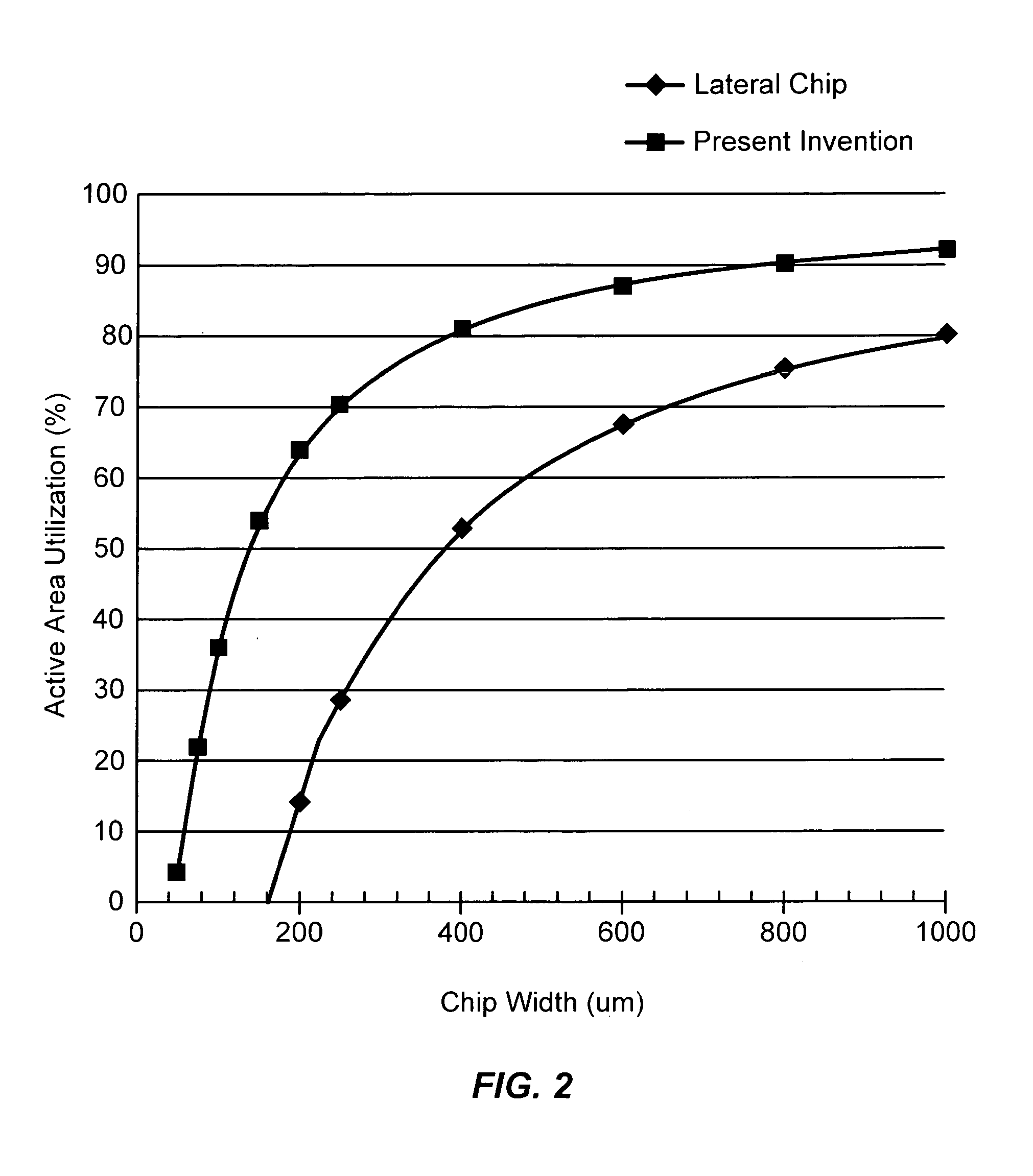

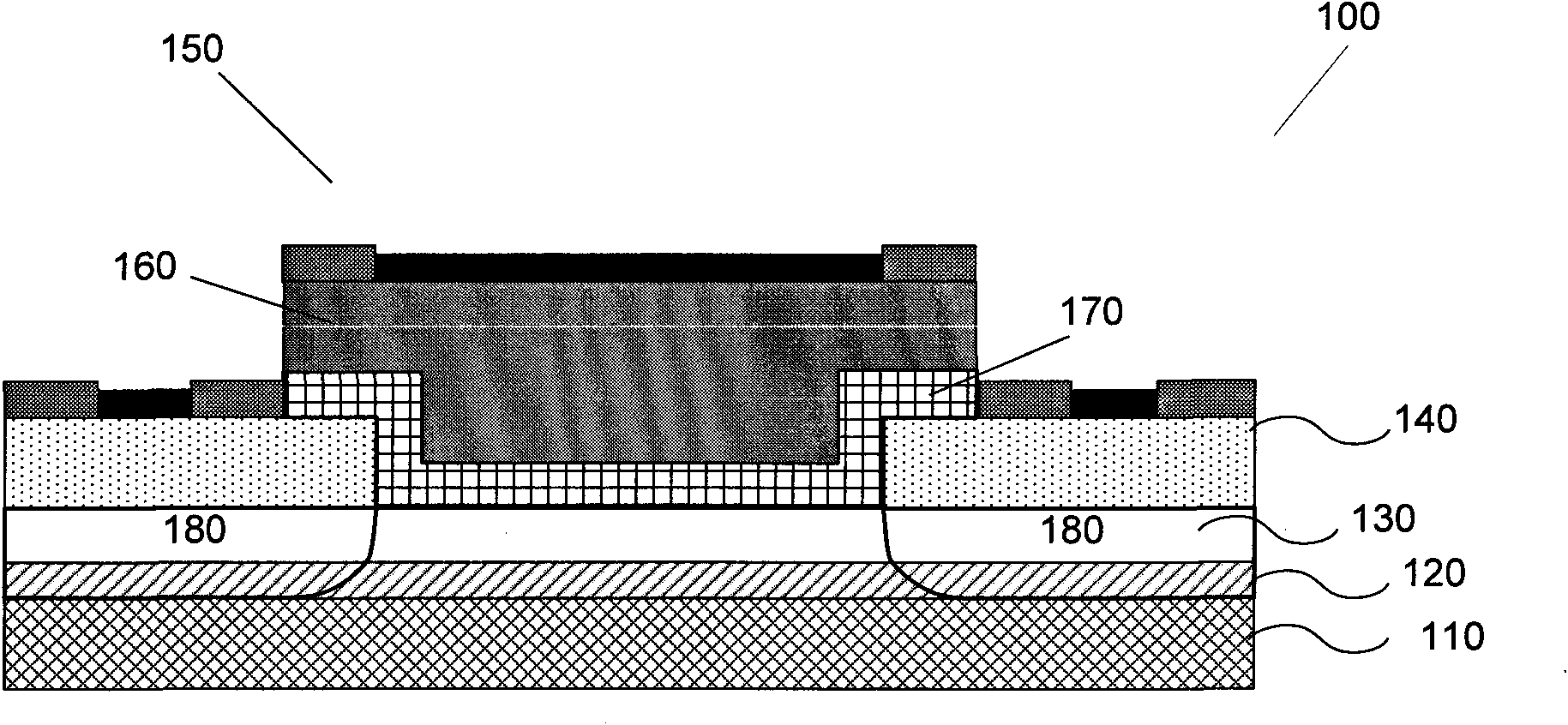

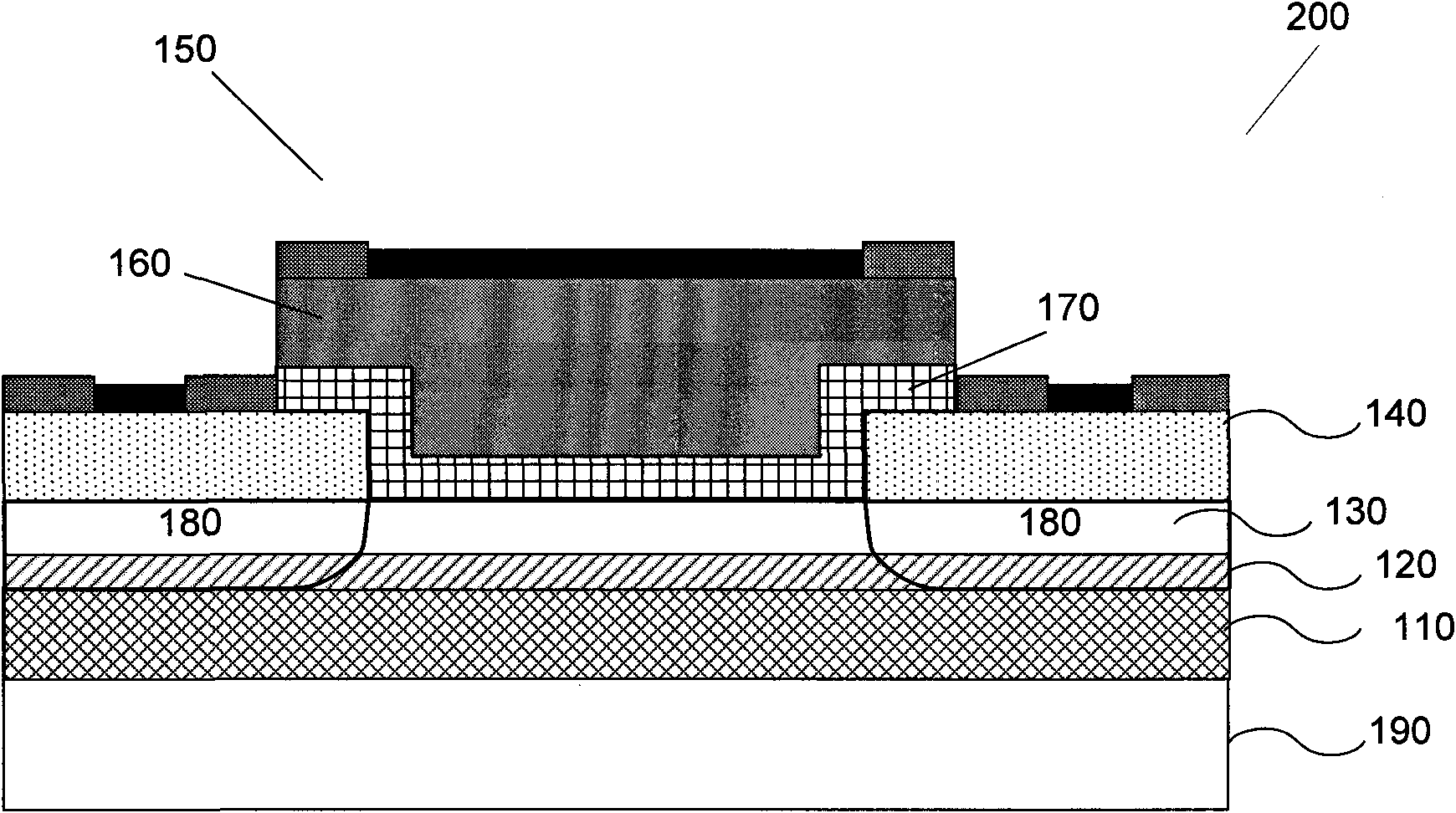

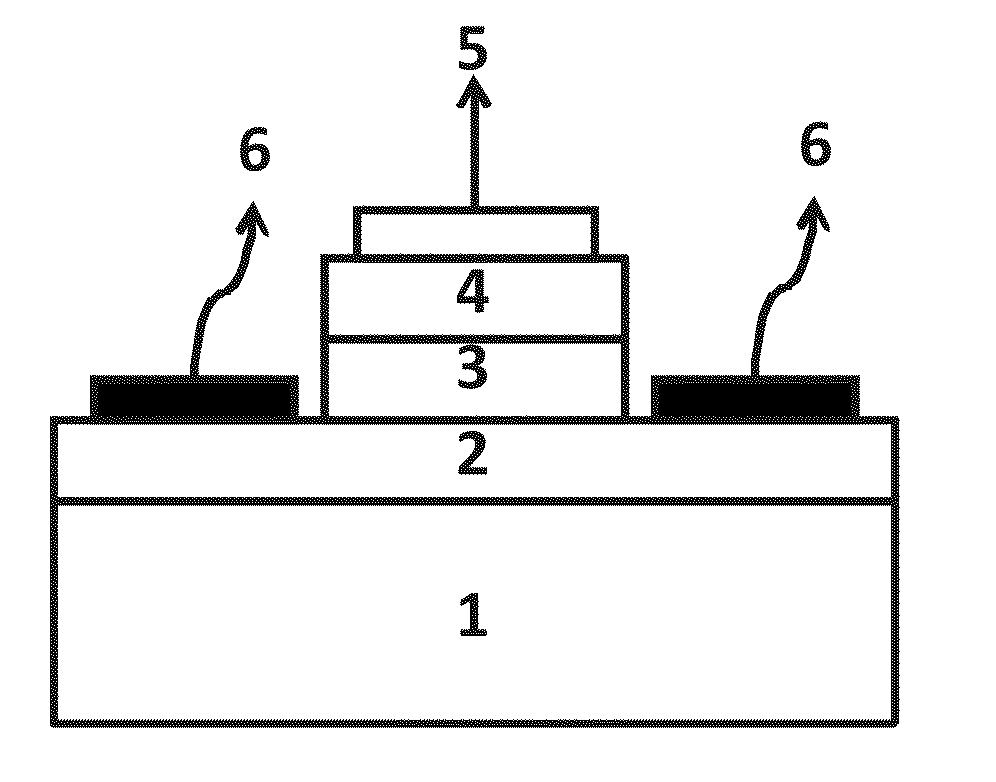

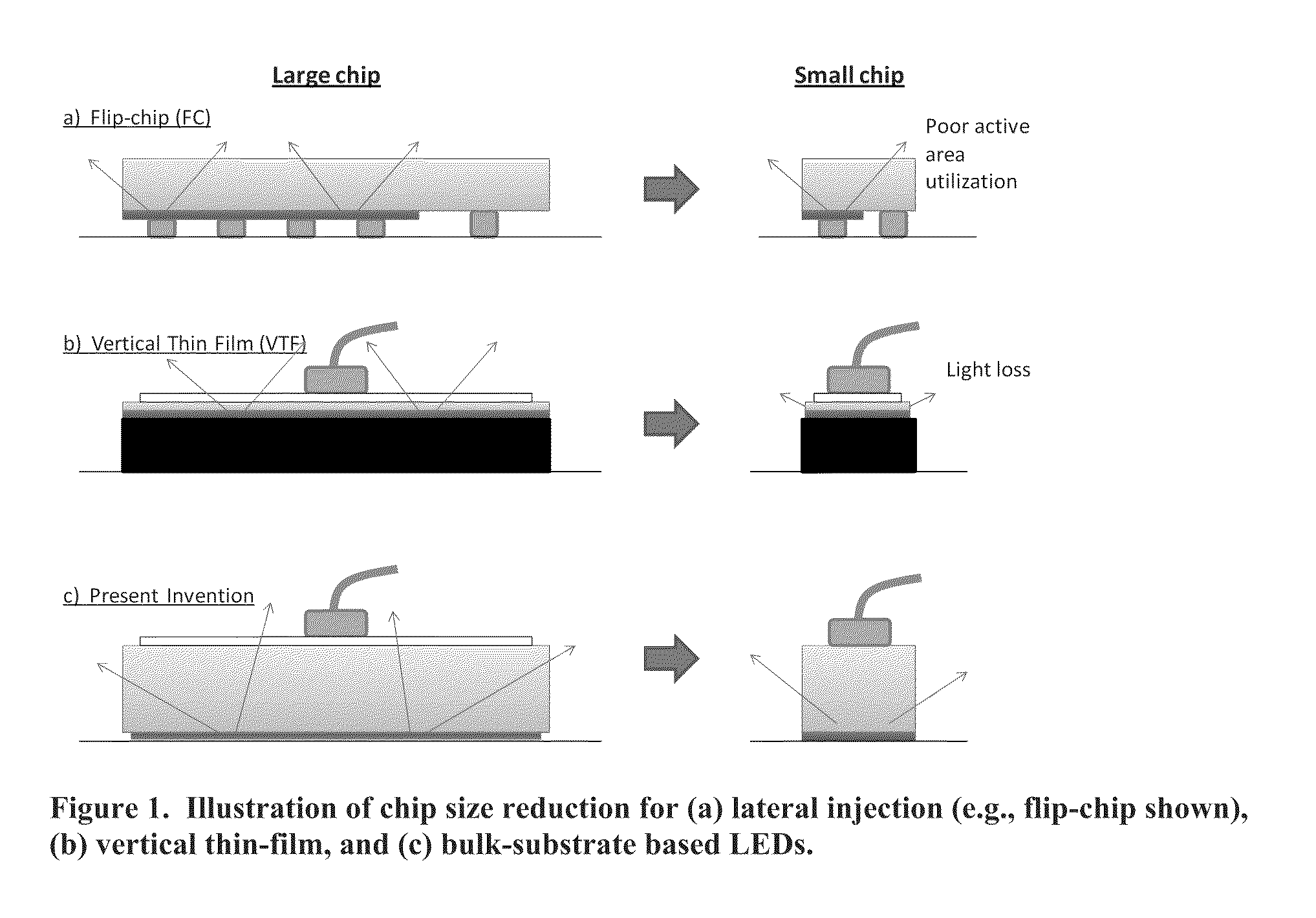

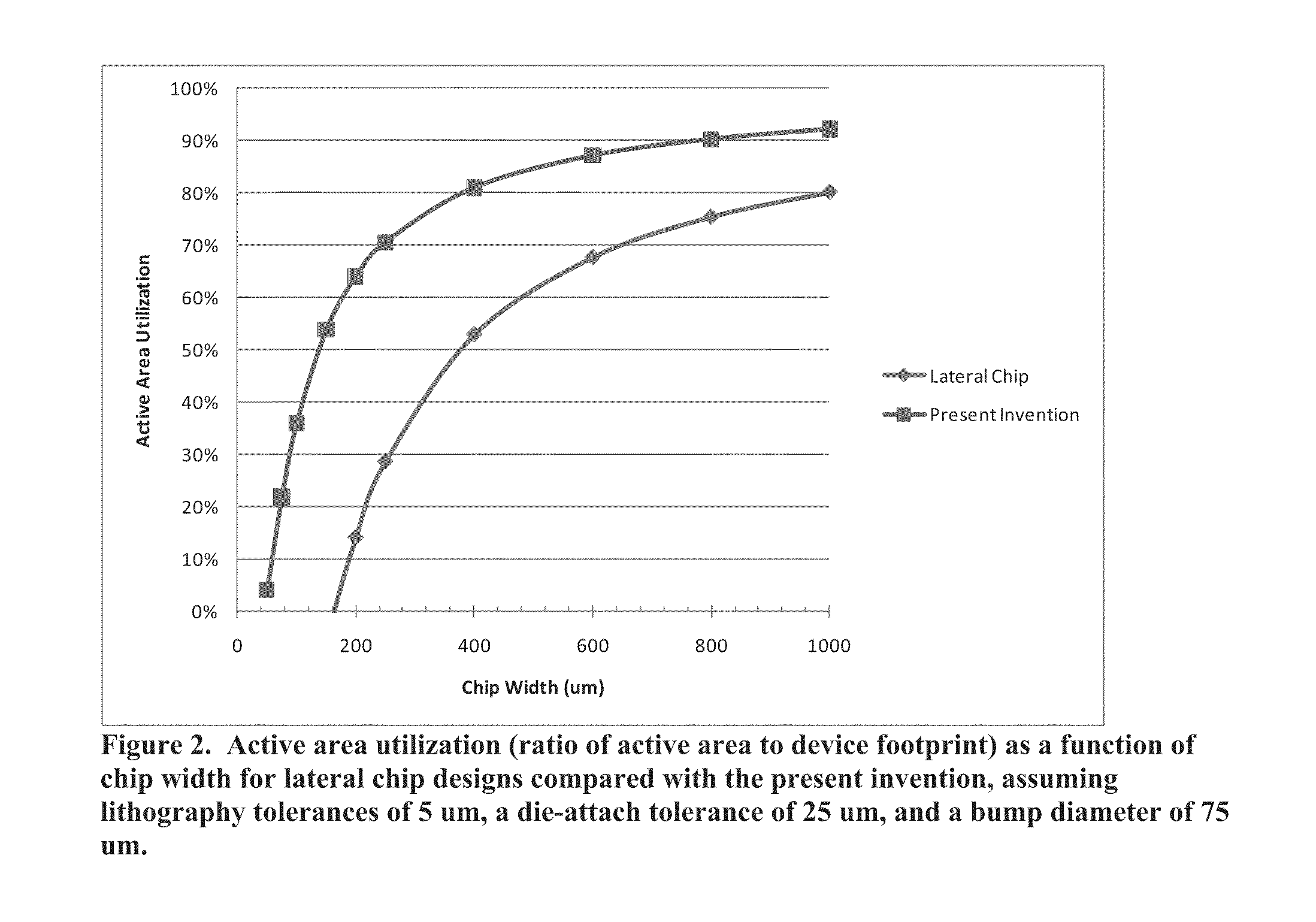

Power Light Emitting Diode and Method with Current Density Operation

ActiveUS20110279054A1Improve light extraction efficiencyReduce semiconductor areaSolid-state devicesSemiconductor/solid-state device manufacturingQuantum efficiencyNitrogen

A light emitting diode device emitting at a wavelength of 390-415 nm has a bulk gallium and nitrogen containing substrate with an active region. The device has a current density of greater than about 175 Amps / cm2 and an external quantum efficiency with a roll off of less than about 5% absolute efficiency.

Owner:KORRUS INC

Semiconductor device structure and forming method thereof

ActiveCN101834206AHigh speedSmall feature sizeSemiconductor/solid-state device manufacturingSemiconductor devicesCarbon layerMetal silicide

The invention provides a semiconductor device structure and a forming method thereof. The semiconductor device structure comprises a substrate layer, a silicon carbon layer, a carbon base material layer, a gate stacker, a source, a drain and a metal silicide layer, wherein the silicon carbon layer is formed on the substrate layer; the carbon base material layer is formed on the silicon carbon layer; the gate stacker is formed on the carbon base material layer; the source and the drain are formed in the carbon base material layer; and the metal silicide layer is formed on the source and the drain. In the invention, the carbon base material layer, such as graphene, is used as a channel layer, and therefore, the speed of the device is greatly increased.

Owner:TSINGHUA UNIV

Control of etch and deposition processes

InactiveUS20050042777A1Easy to controlIncrease depositionSemiconductor/solid-state device testing/measurementElectric discharge tubesDevice materialEngineering

This invention relates to the control of etch and deposition processes in the manufacture of semiconductor devices, microelectronic machines (MEMs), and waveguides.

Owner:BOC GRP INC

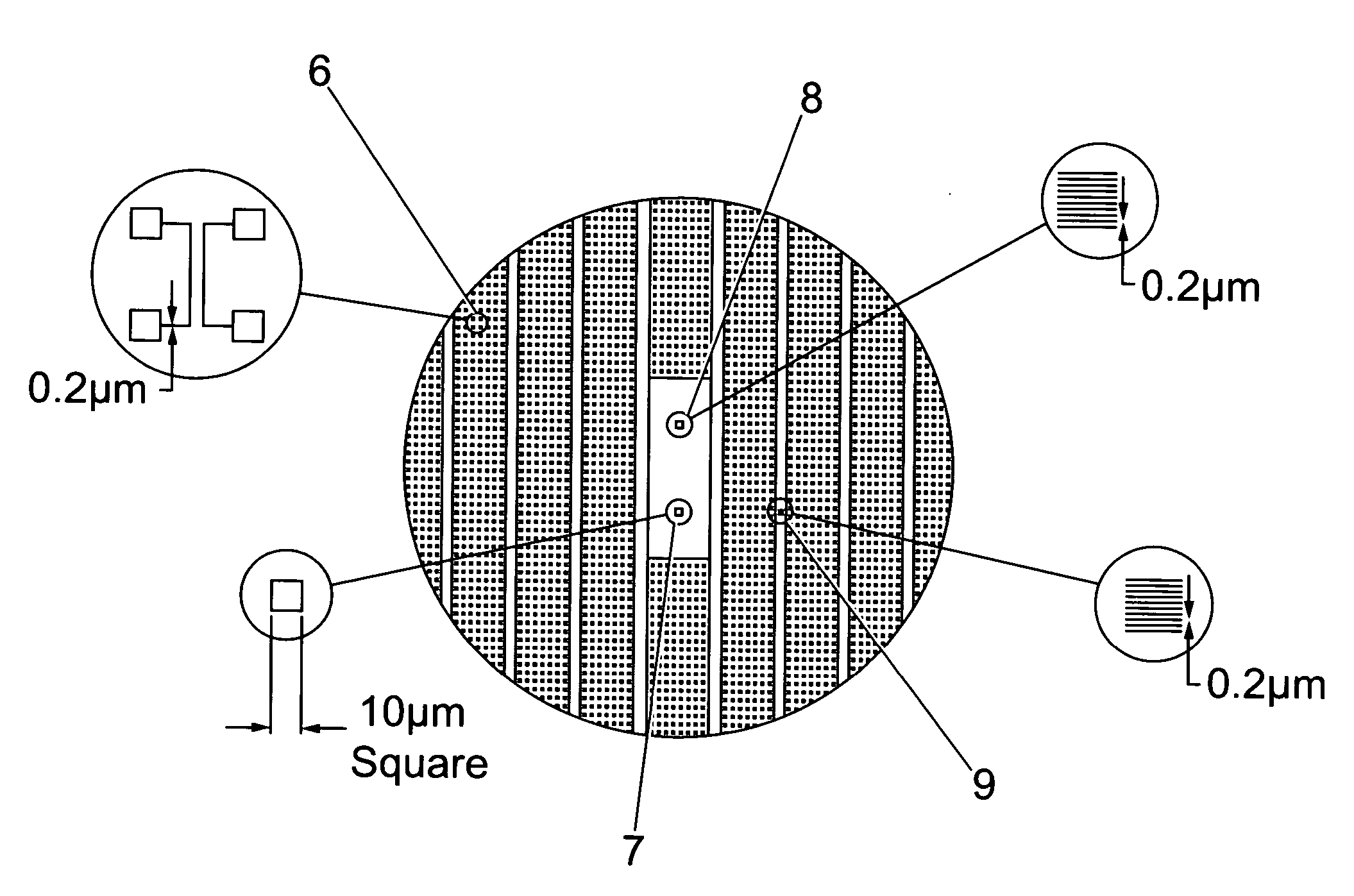

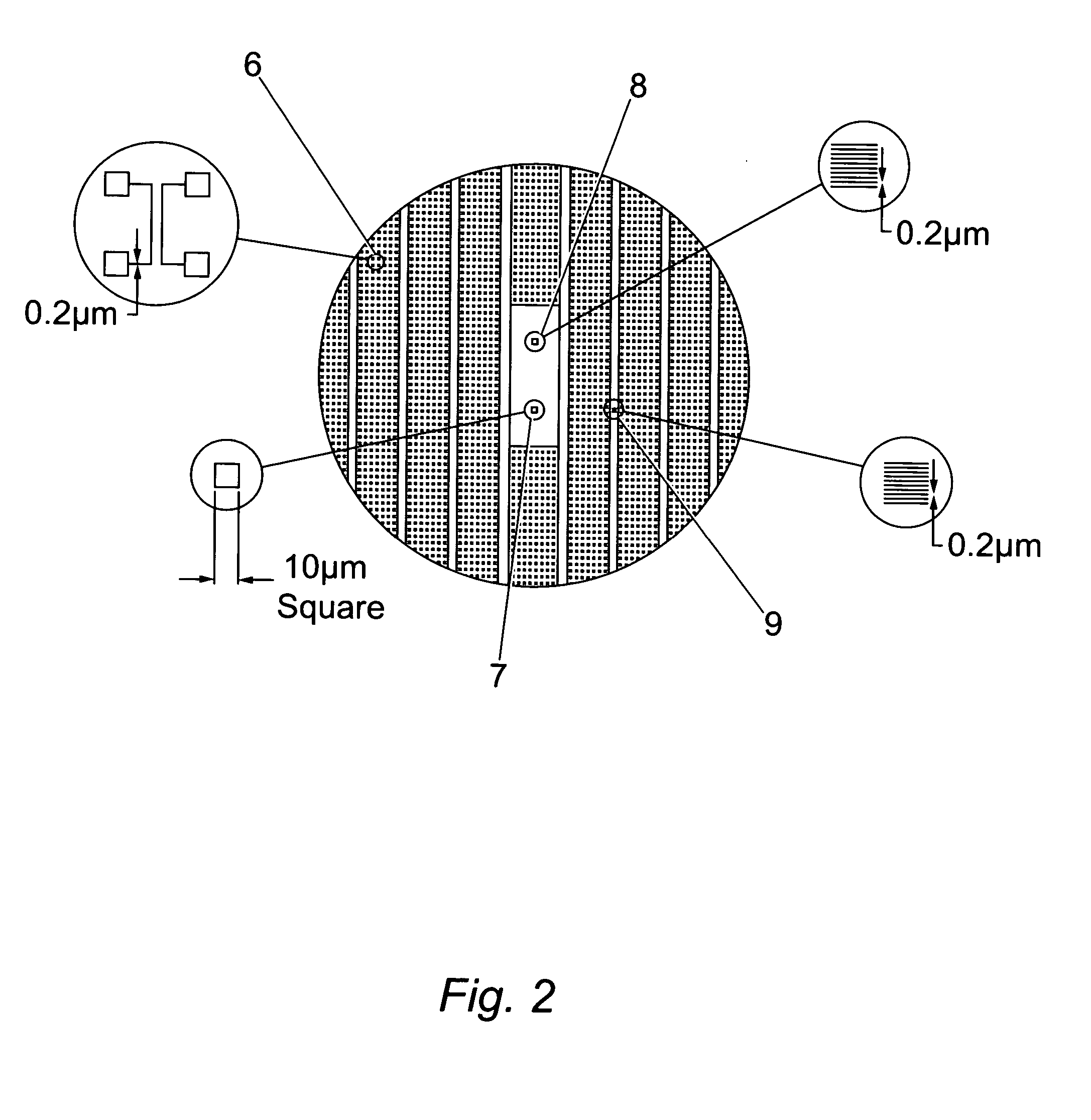

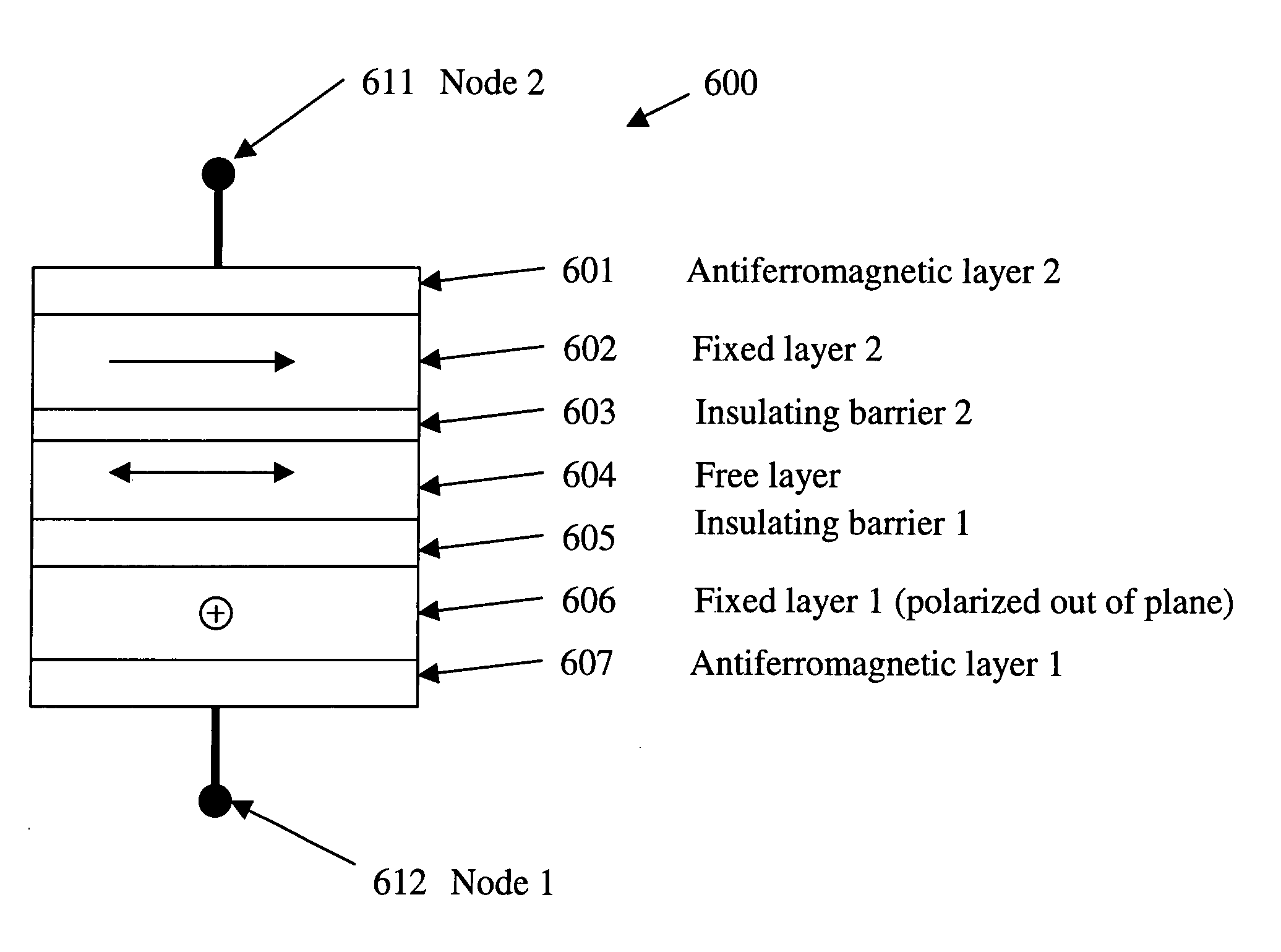

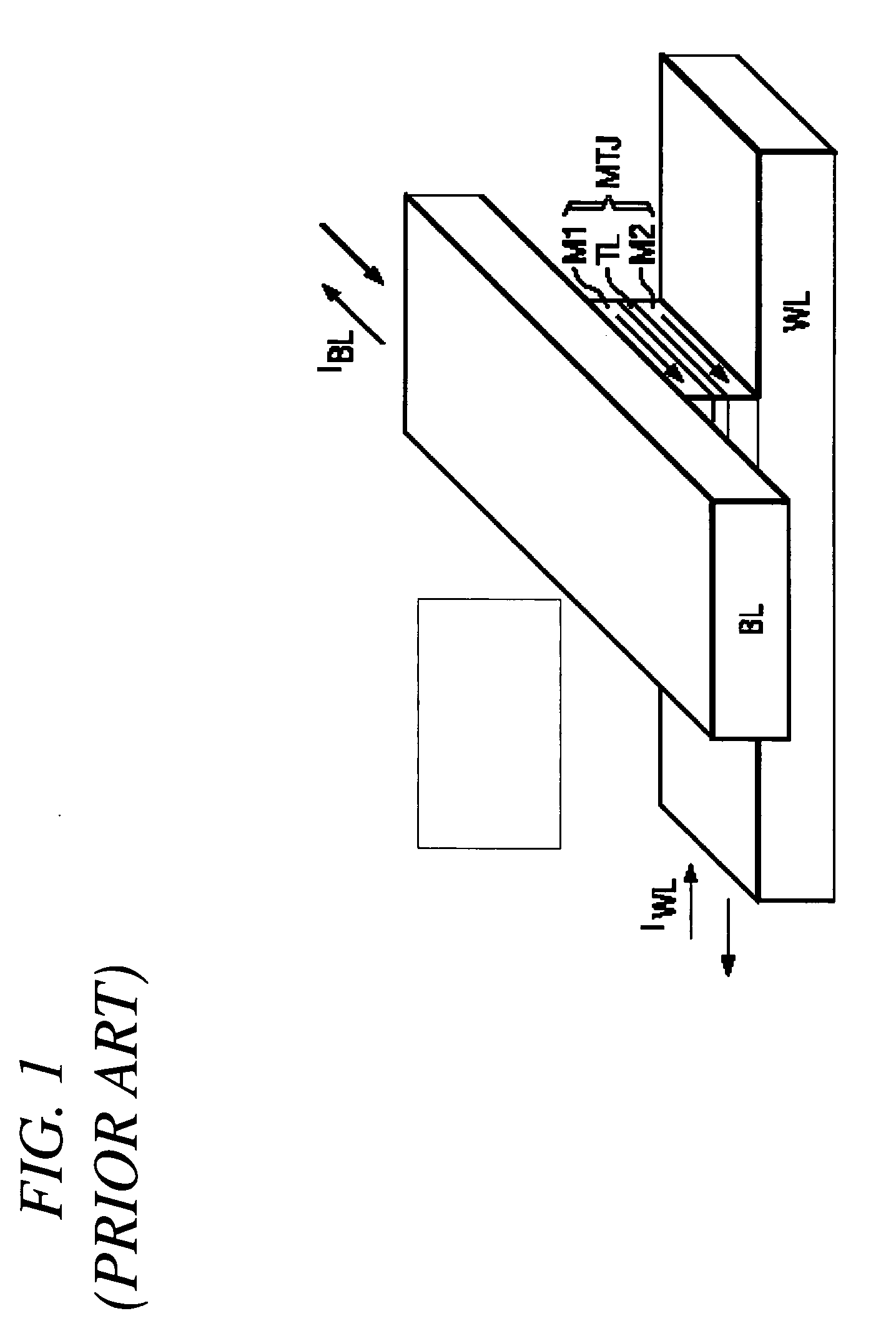

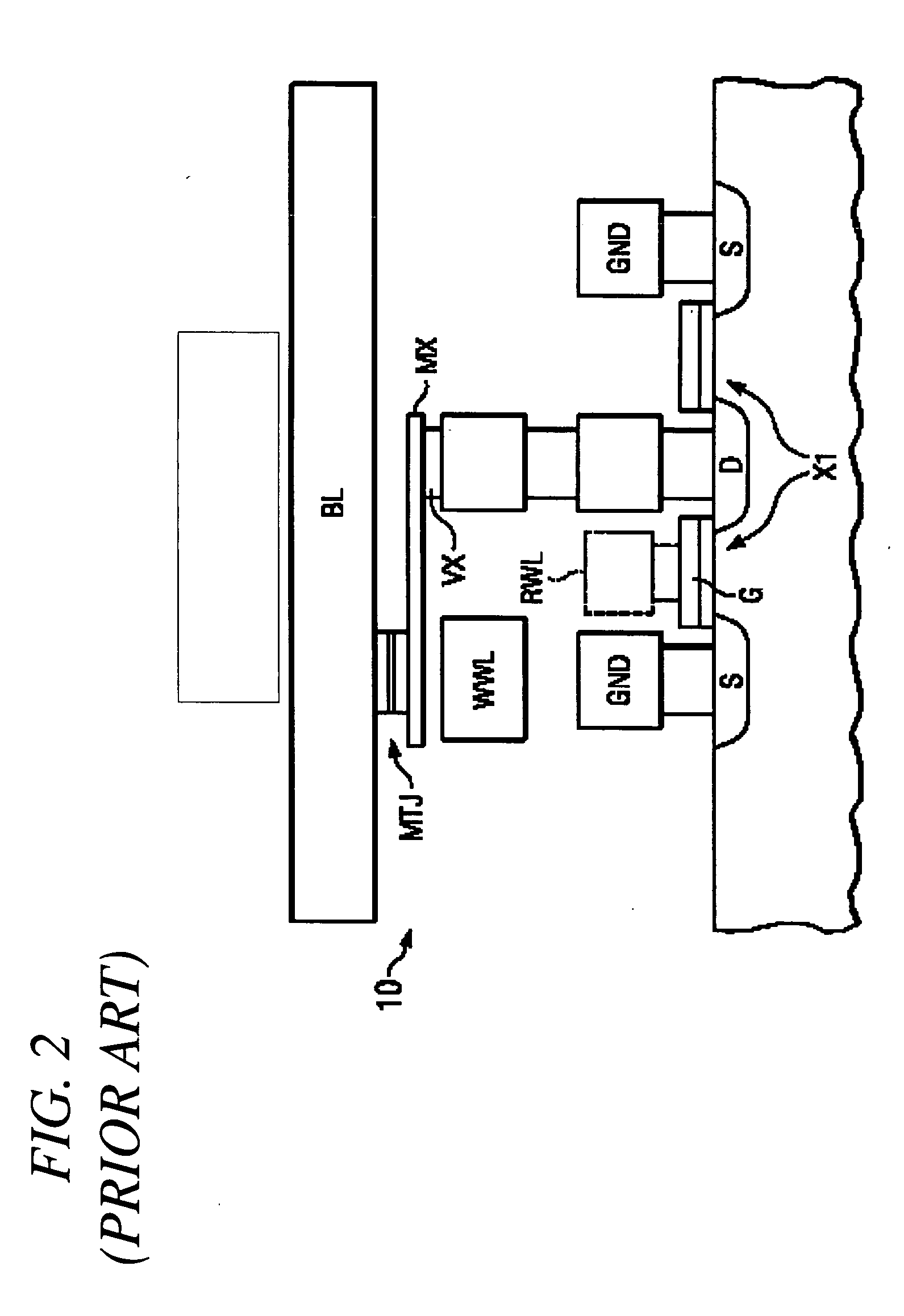

Read out scheme for several bits in a single MRAM soft layer

InactiveUS20060013039A1Increase memory densityReduce manufacturing costSemiconductor/solid-state device manufacturingDigital storageSoft layerElectrical resistance and conductance

A magnetic tunnel junction (MTJ) device is configured to store at least two bits of data in a single cell utilizing the variable resistance characteristic of a MTJ. The MTJ includes a soft and two fixed magnetic layers with fixed field directions oriented in perpendicular directions. The soft magnetic layer is separated from the fixed layers by insulating layers preferably with different thicknesses, or with different material compositions. The resulting junction resistance can exhibit at least four distinct resistance values dependent on the magnetic orientation of the free magnetic layer. The cell is configured using a pattern with four lobes to store two bits, and eight lobes to store three bits. The resulting cell can be used to provide a fast, non-volatile magnetic random access memory (MRAM) with high density and no need to rewrite stored data after they are read, or as a fast galvanic isolator.

Owner:INFINEON TECH AG

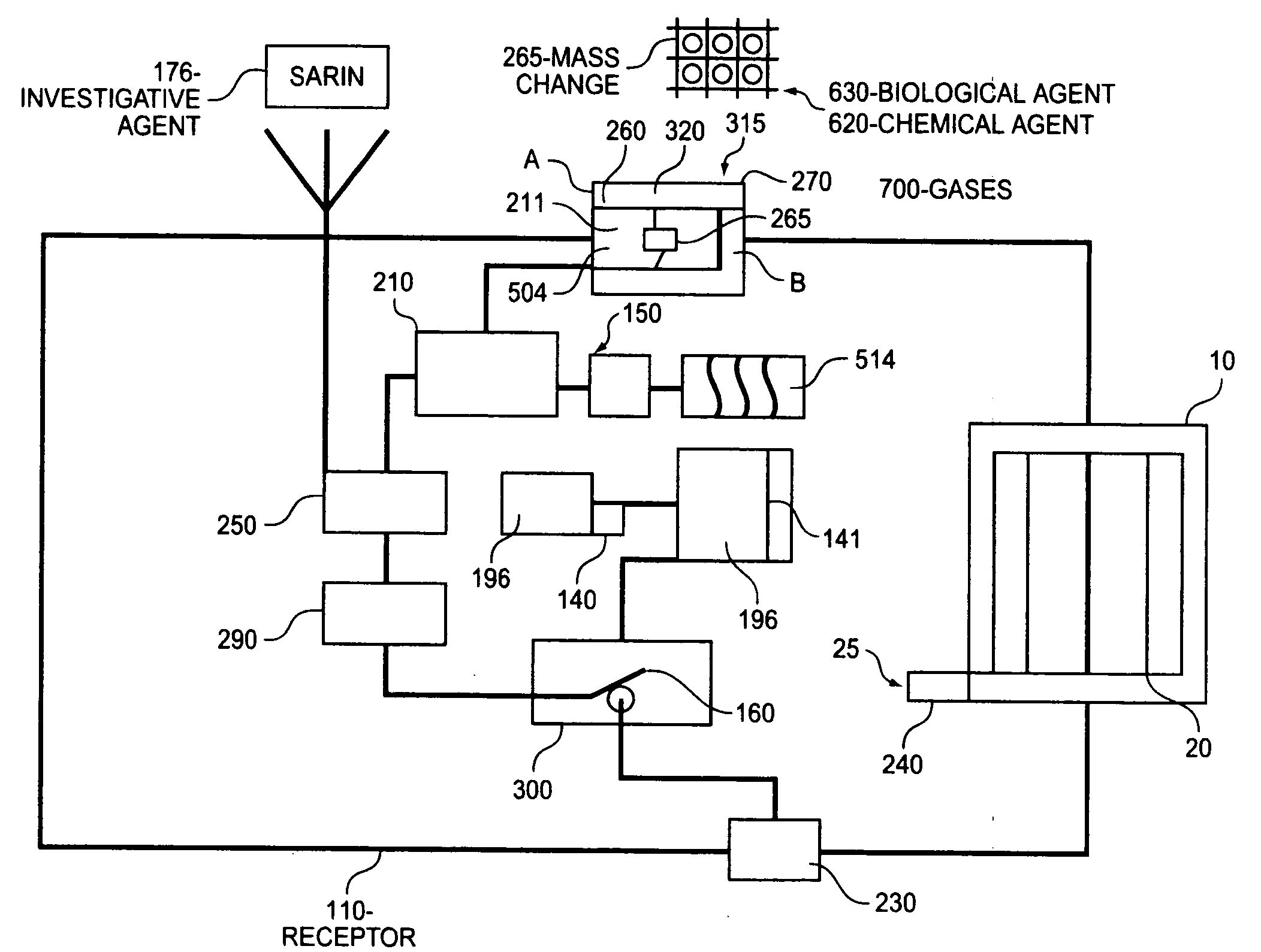

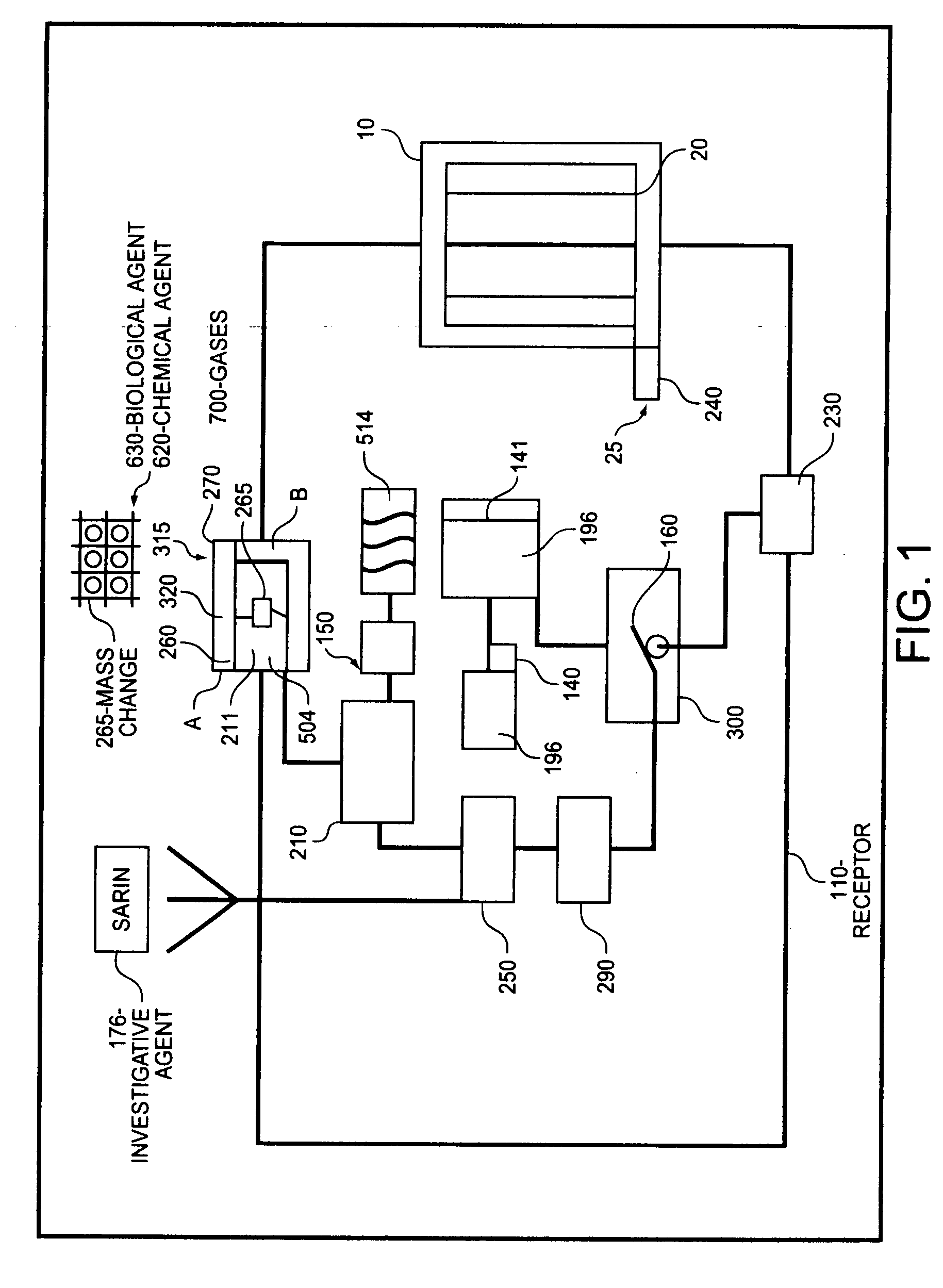

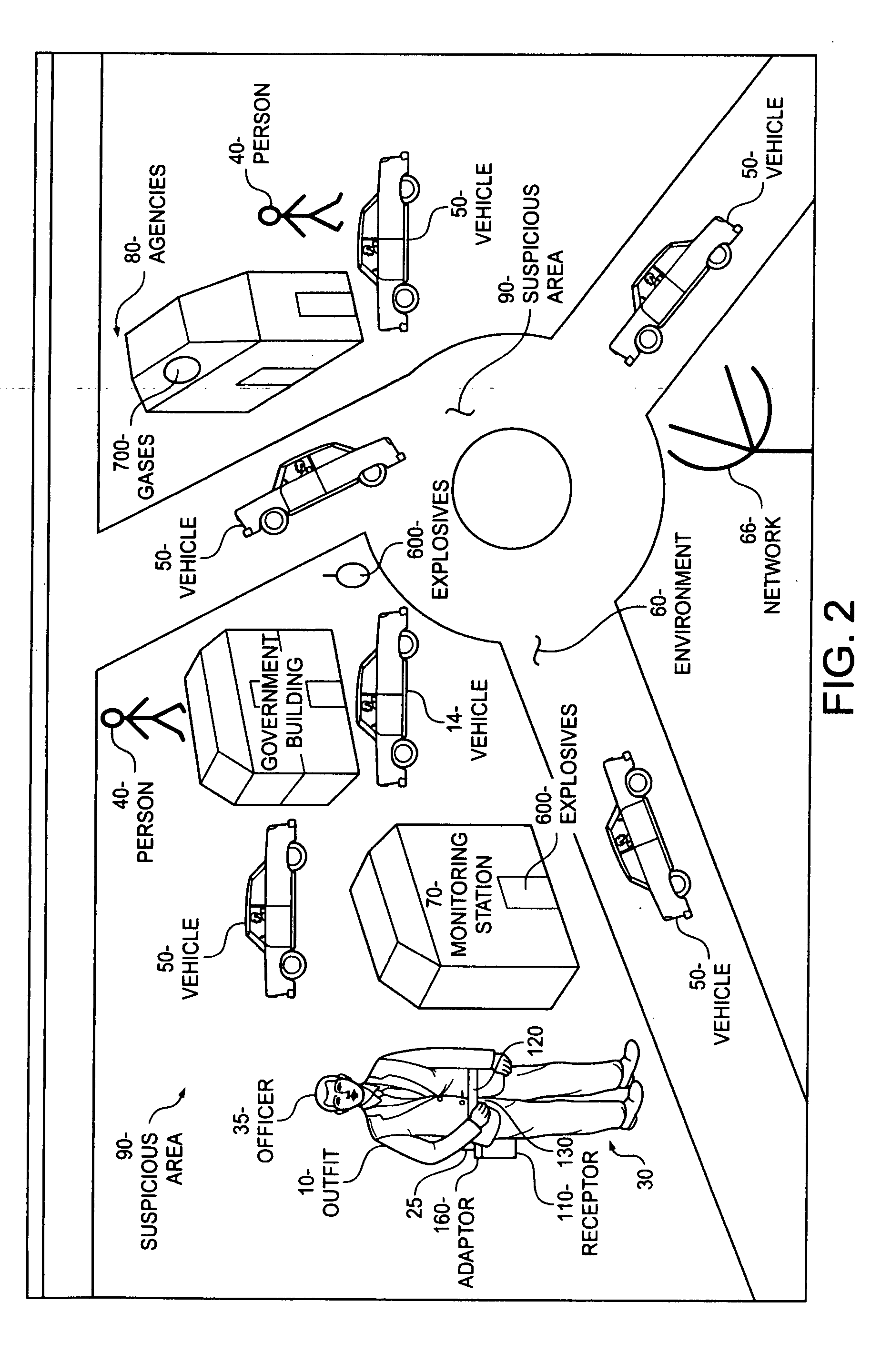

Homeland intelligence systems technology "H-List"

InactiveUS20090115603A1High detection sensitivityHigh selectivitySemiconductor/solid-state device detailsSurgeryFiberEngineering

Homeland Intelligence Systems Technology “H-LIST” comprises nano-sensors embedded in a silicon substrate and etched / fused in a micro-fibered material alloyed with miniaturized steel responsive to preventing bullet penetration and to enable effective detection platform on an outfit for monitoring suspicious terrorist activities and for tracking biological and chemical gases, and explosives, including weapons of mass destruction and physiological conditions of personnel. H-LIST comprises plurality sensors on an outfit worn by an officer, a security officer, a bus driver, hostesses, Doctors, civil establishment hospital patients and the like, for sensing deadly gases, explosives, and physiological conditions in a defined area A receptor is operatively configured and worn proximate to the outfit responsive for empowering the sensors and for receiving / analyzing detection signal communications wirelessly indicative of the presence of a sensed agent, whereby detected signals are transported wirelessly to a central security monitoring station, enabling communication with first responders and backup security personnel or agents to the vicinity of the detection. The sensors are multifunctional and coded to recognize wavelike pattern of gases and explosives traveling through the wave, enabling the outfit and the receptor to be operable and process the portion of the detection signal to determine the detection type and / or whether there is a concealed object by conducting a test in which a first characteristic of a first dielectric constant associated with a person is determined, and a second characteristic of a second dielectric constant associated with the concealed object and or weapons of mass destruction is determined to expedite data transmission and communication to first responders.

Owner:TABE JOSEPH AKWO

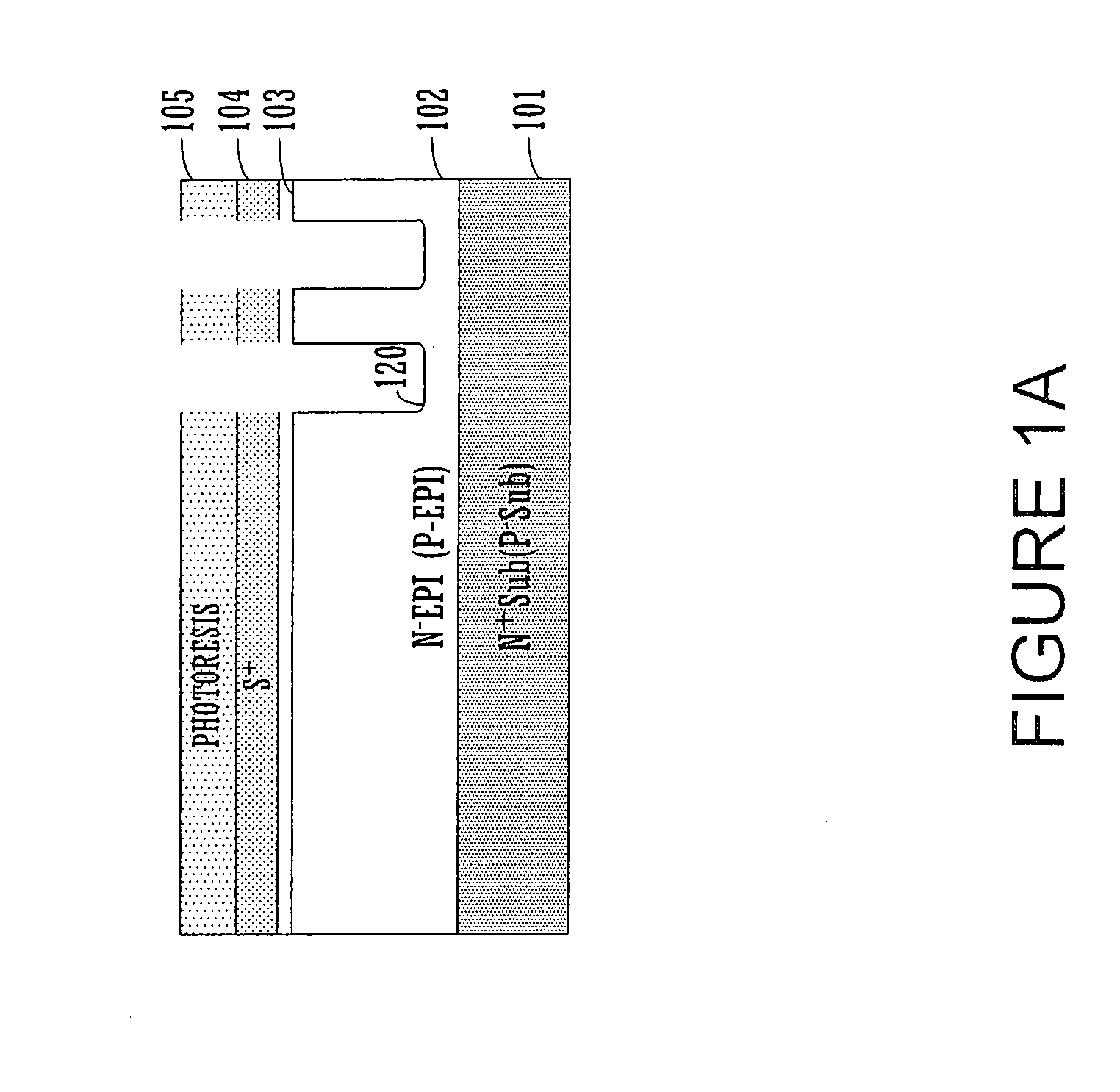

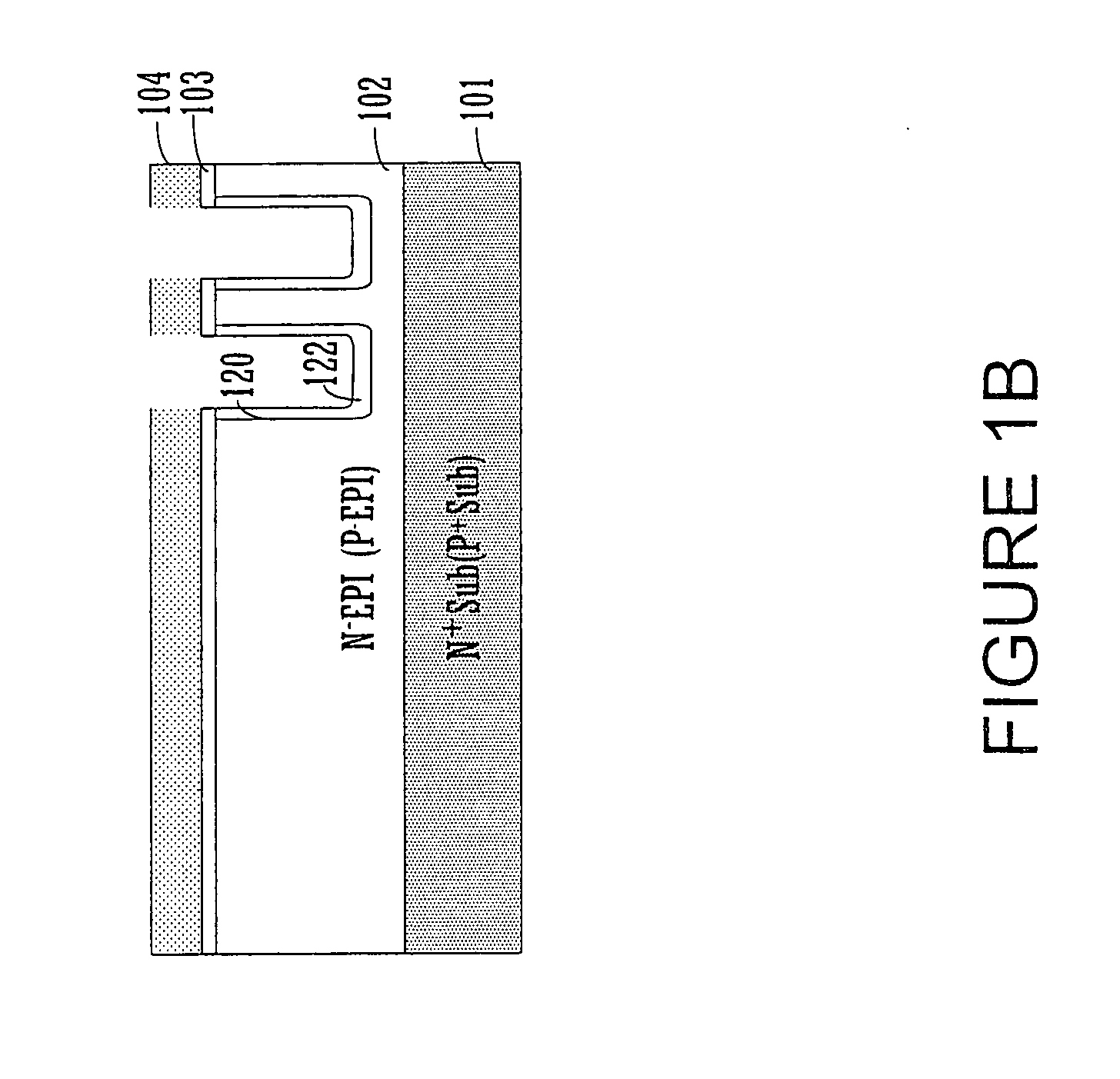

Trench polysilicon diode

ActiveUS20070145411A1Reduction in topologyOptimize topologyTransistorThyristorEngineeringPolycrystalline silicon

Embodiments of the present invention include a method of manufacturing a trench polysilicon diode. The method includes forming a N− (P−) type epitaxial region on a N+ (P+) type substrate and forming a trench in the N− (P−) type epitaxial region. The method further includes forming a insulating layer in the trench and filling the trench with polysilicon forming a top surface of the trench. The method further includes forming P+ (N+) type doped polysilicon region and N+ (P+) type doped polysilicon region in the trench and forming a diode in the trench wherein a portion of the diode is lower than the top surface of the trench.

Owner:VISHAY SILICONIX LLC

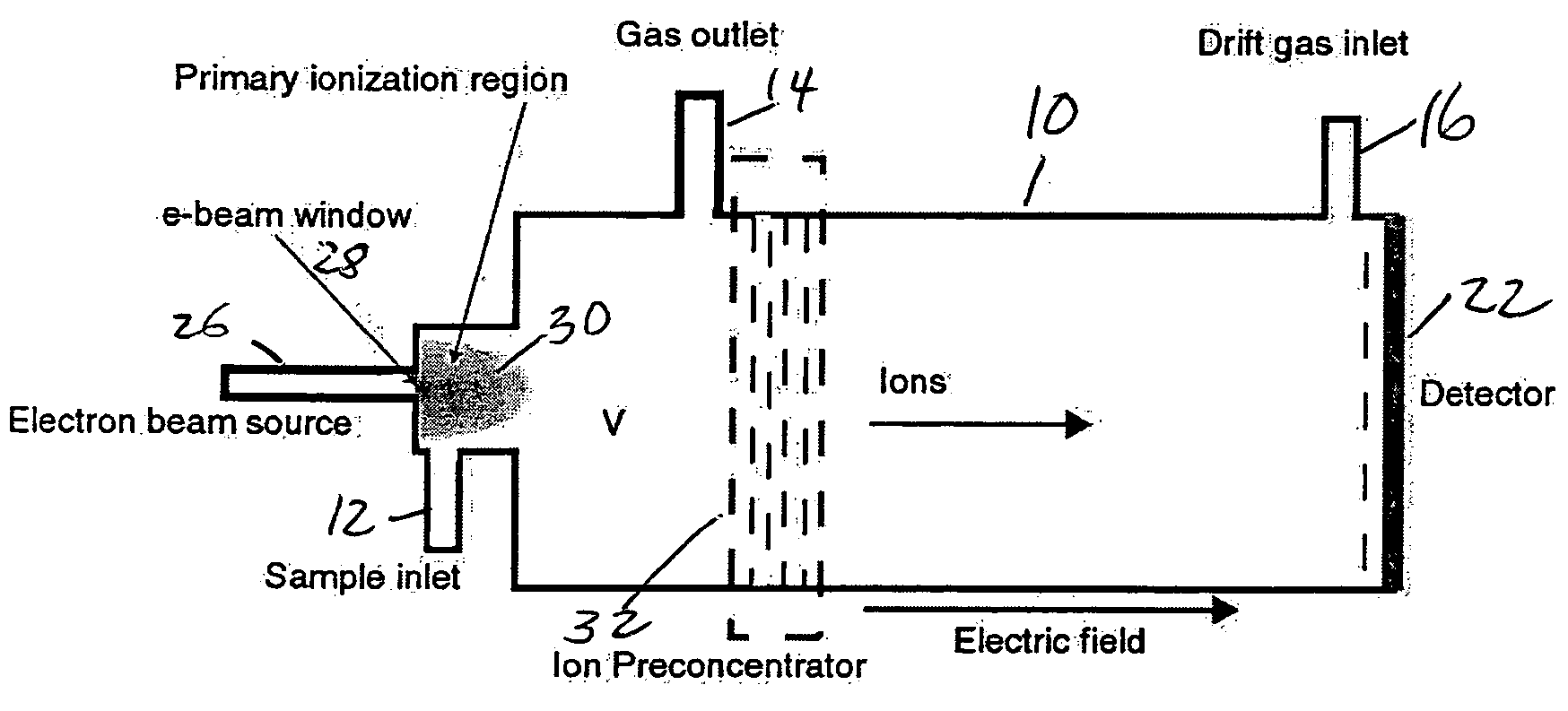

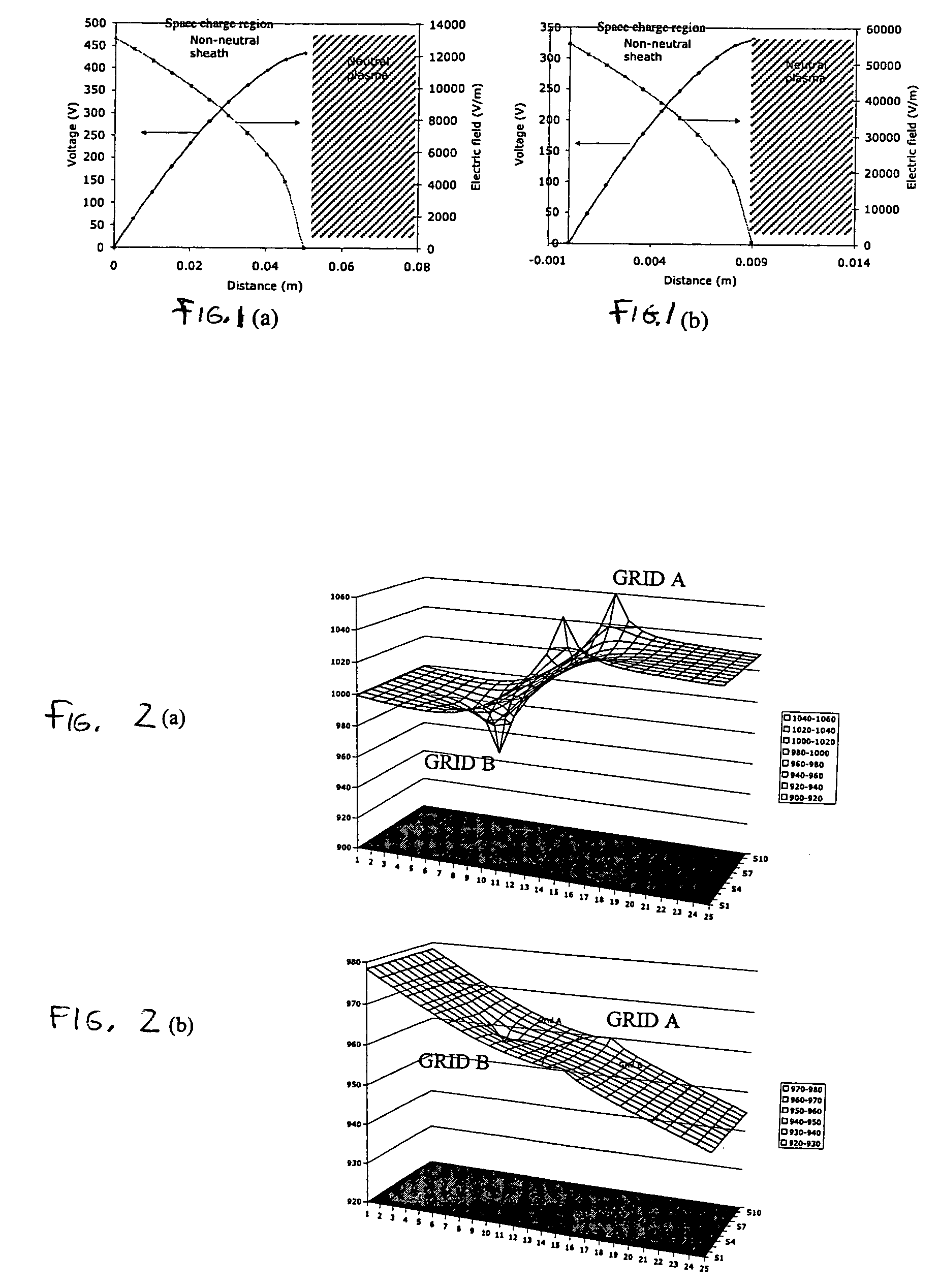

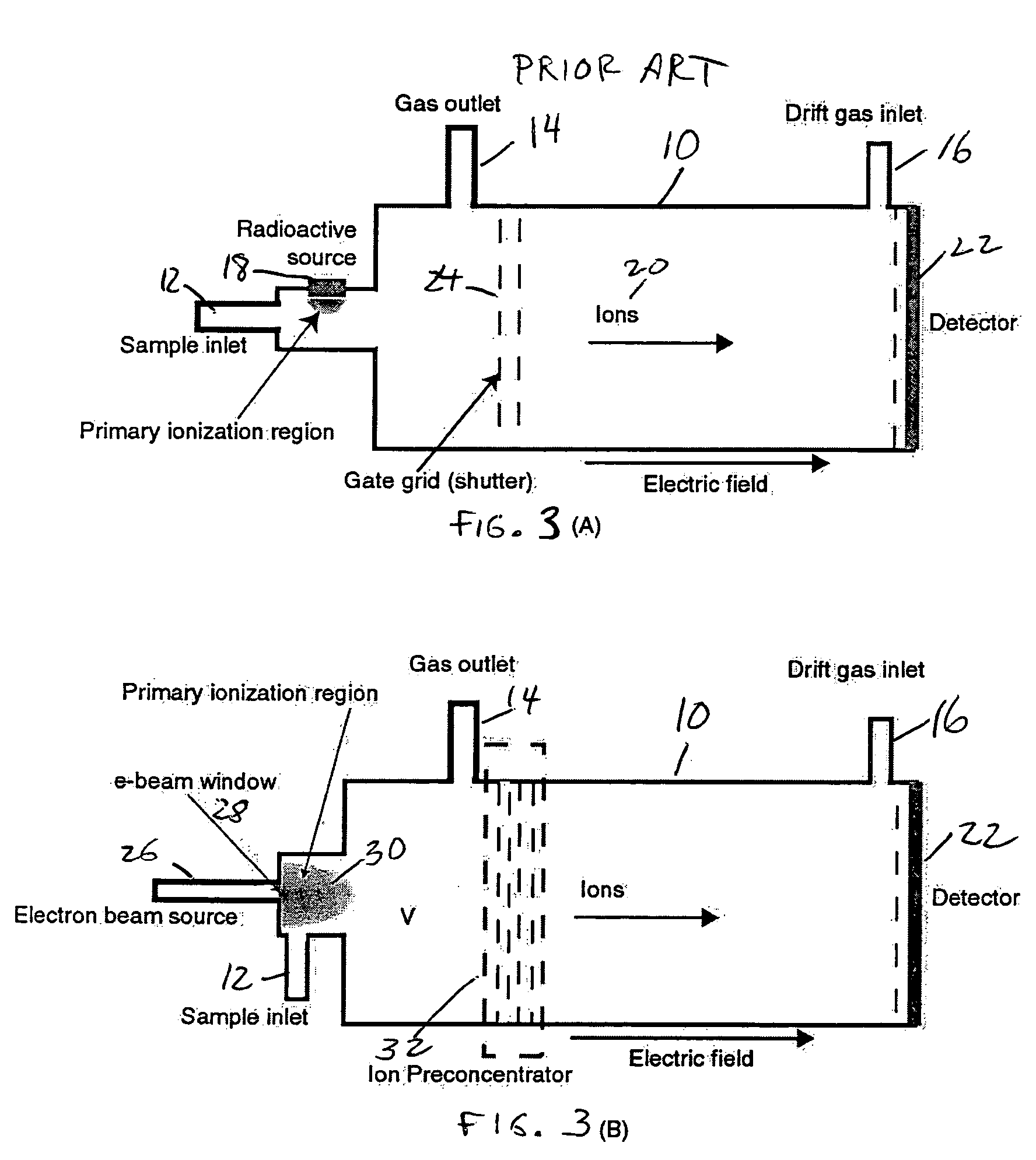

Plasma ion mobility spectrometer

InactiveUS20050205775A1Optimize ion preconcentrationReduce distortion problemsTime-of-flight spectrometersMaterial analysis by electric/magnetic meansIonizationSpectrometer

Ion mobility spectrometer. The spectrometer includes an enclosure for receiving a sample therewithin and an electron beam window admits an electron beam into the enclosure to ionize the sample in an ionization region. A shutter grid is spaced apart from the ionization region and means are provided for sample ion preconcentration upstream of the shutter grid. The ion preconcentration is effective to reduce space charge resulting in a lowered threshold detection level.

Owner:MASSACHUSETTS INST OF TECH

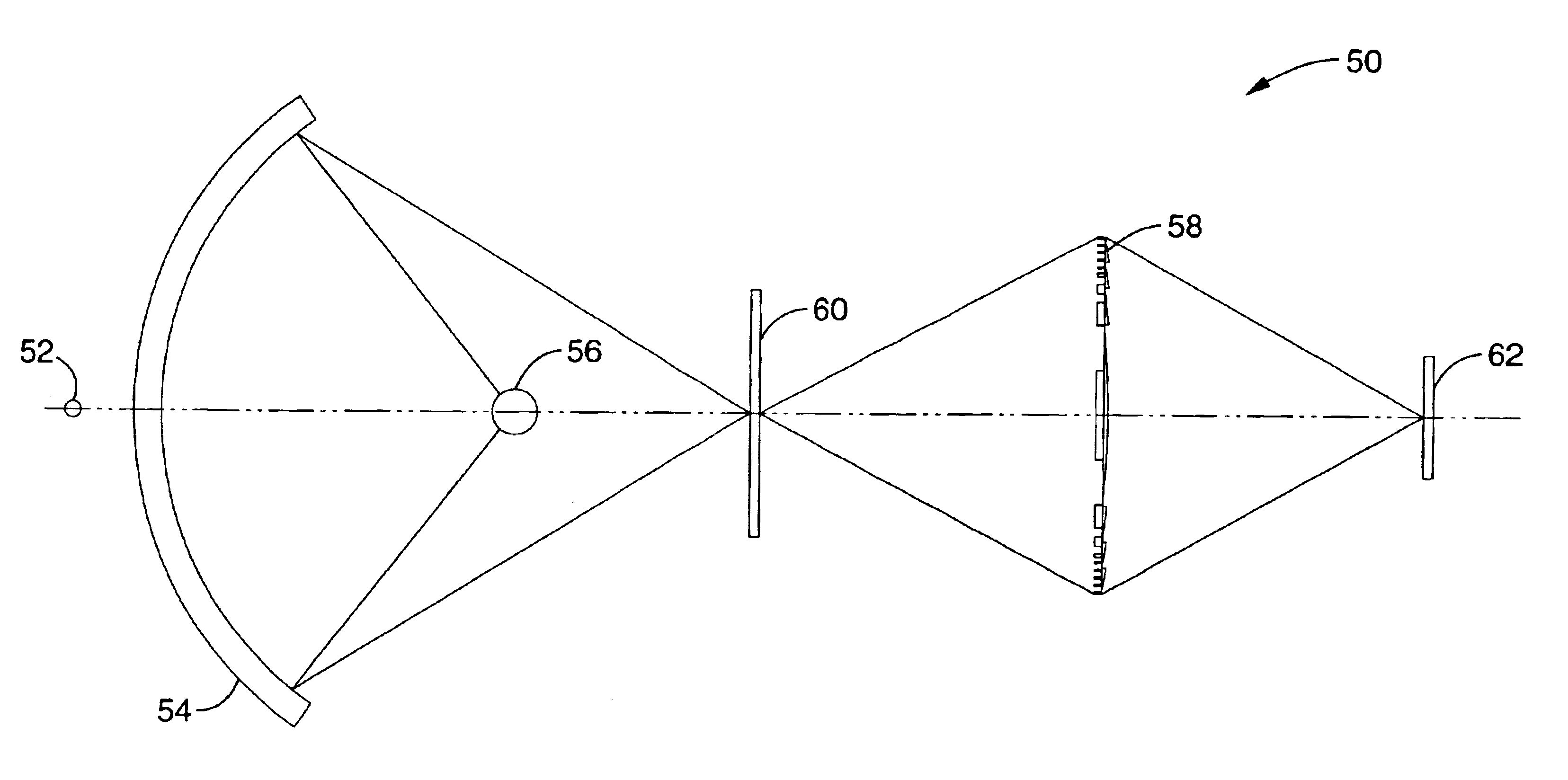

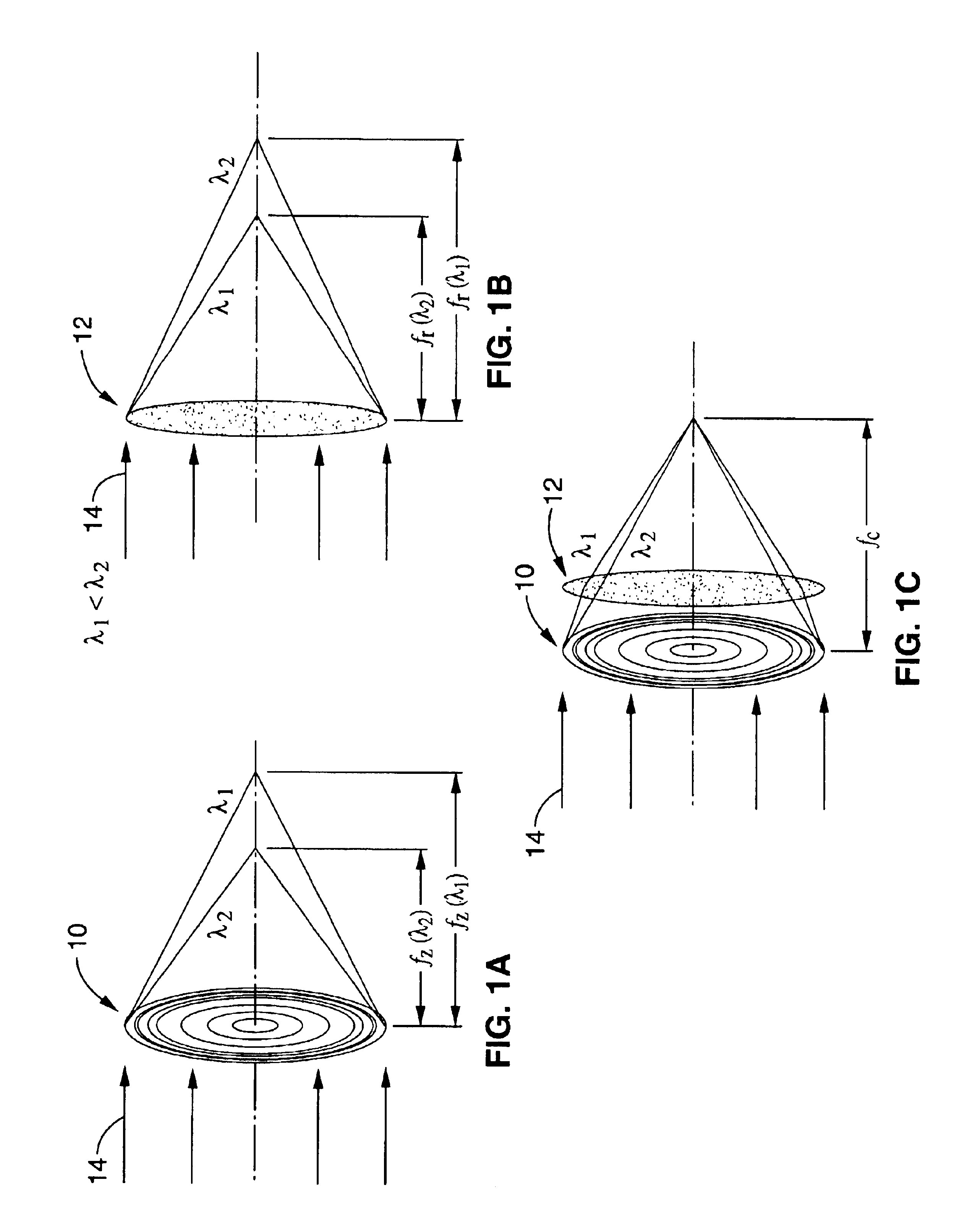

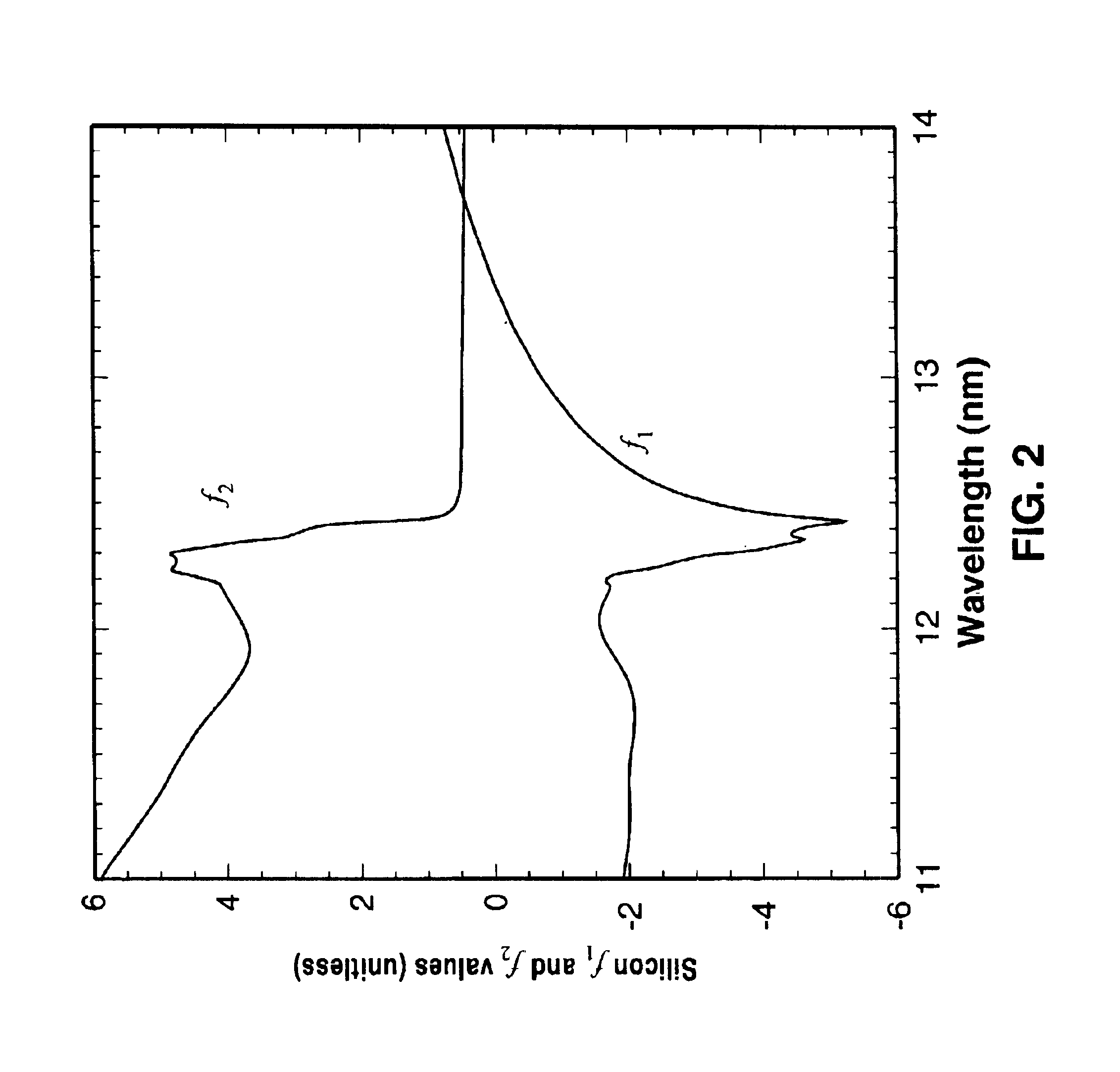

Achromatic fresnel optics based lithography for short wavelength electromagnetic radiations

InactiveUS6885503B2Simplify System DesignImprove system throughputMirrorsDiffraction gratingsRefractive indexElectromagnetic radiation

A lithography apparatus having achromatic Fresnel objective (AFO) that combines a Fresnel zone plate and a refractive Fresnel lens. The zone plate provides high resolution for imaging and focusing, while the refractive lens takes advantage of the refraction index change properties of appropriate elements near absorption edges to recombine the electromagnetic radiation of different energies dispersed by the zone plate. This compound lens effectively solves the high chromatic aberration problem of zone plates. The lithography apparatus allows the use of short wavelength radiation in the 1-15 nm spectral range to print high resolution features as small as 20 nm.

Owner:XRADIA

Power light emitting diode and method with current density operation

ActiveUS8502465B2Reduce chip areaLow costSolid-state devicesSemiconductor/solid-state device manufacturingQuantum efficiencyNitrogen

A light emitting diode device emitting at a wavelength of 390-415 nm has a bulk gallium and nitrogen containing substrate with an active region. The device has a current density of greater than about 175 Amps / cm2 and an external quantum efficiency with a roll off of less than about 5% absolute efficiency.

Owner:KORRUS INC

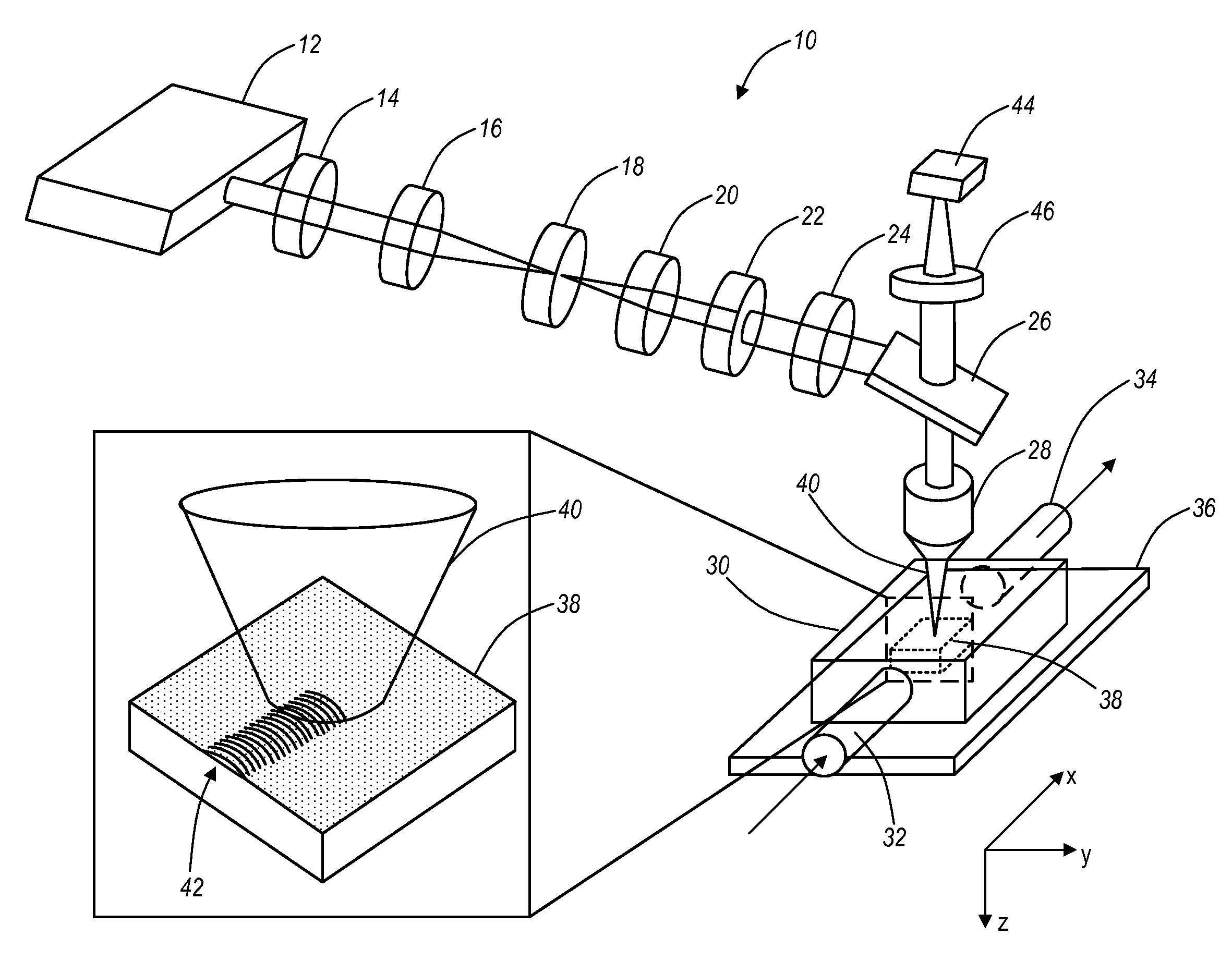

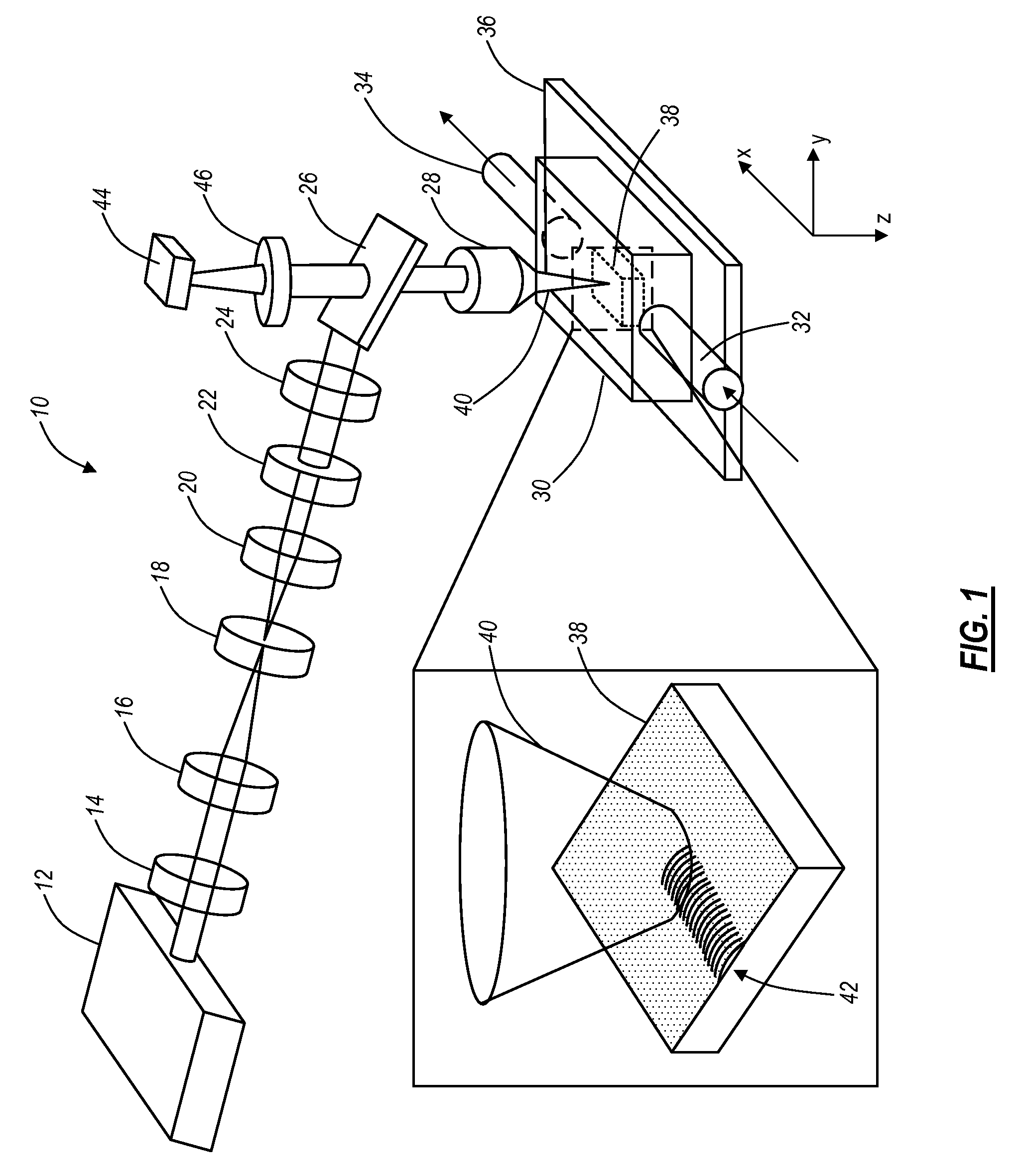

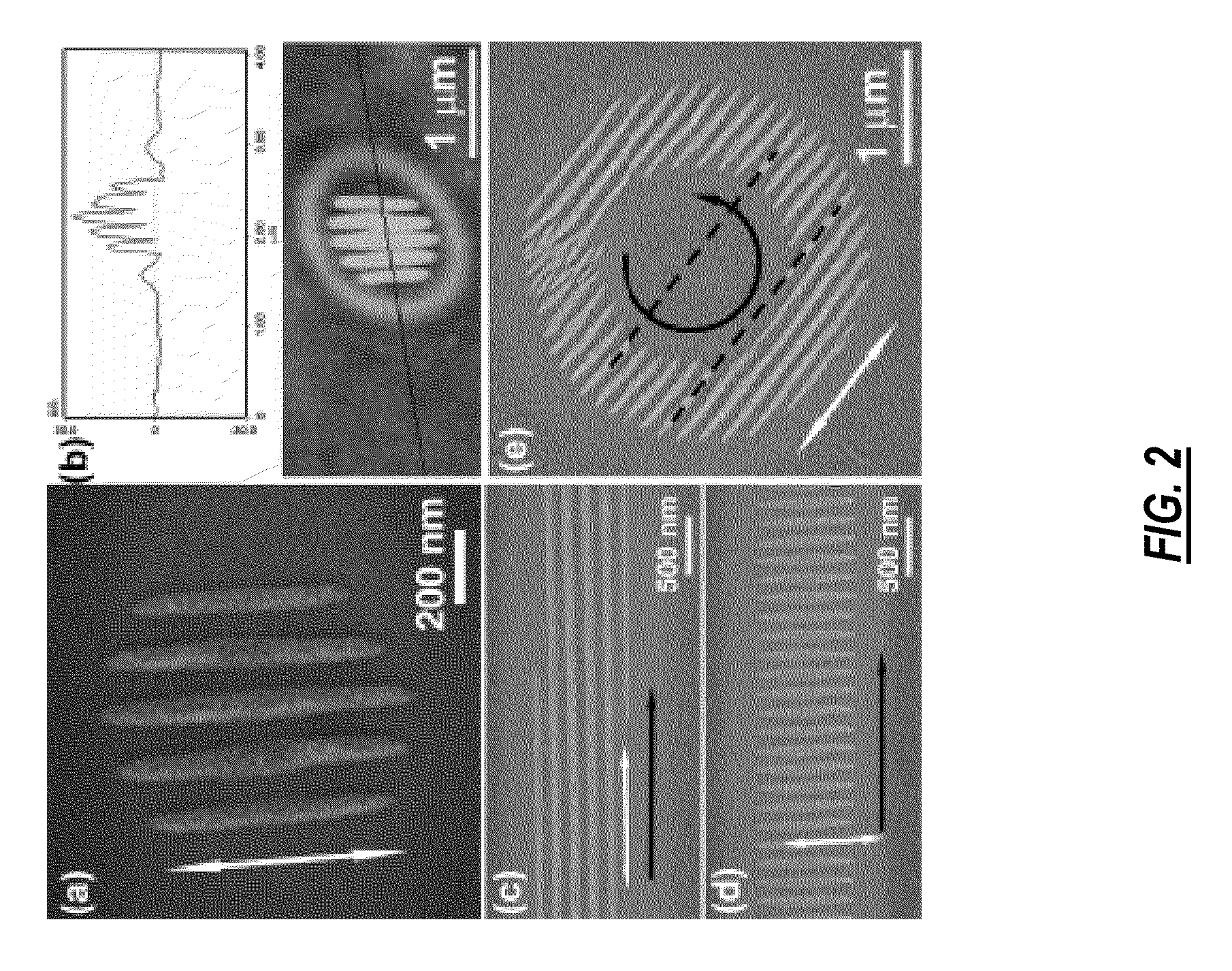

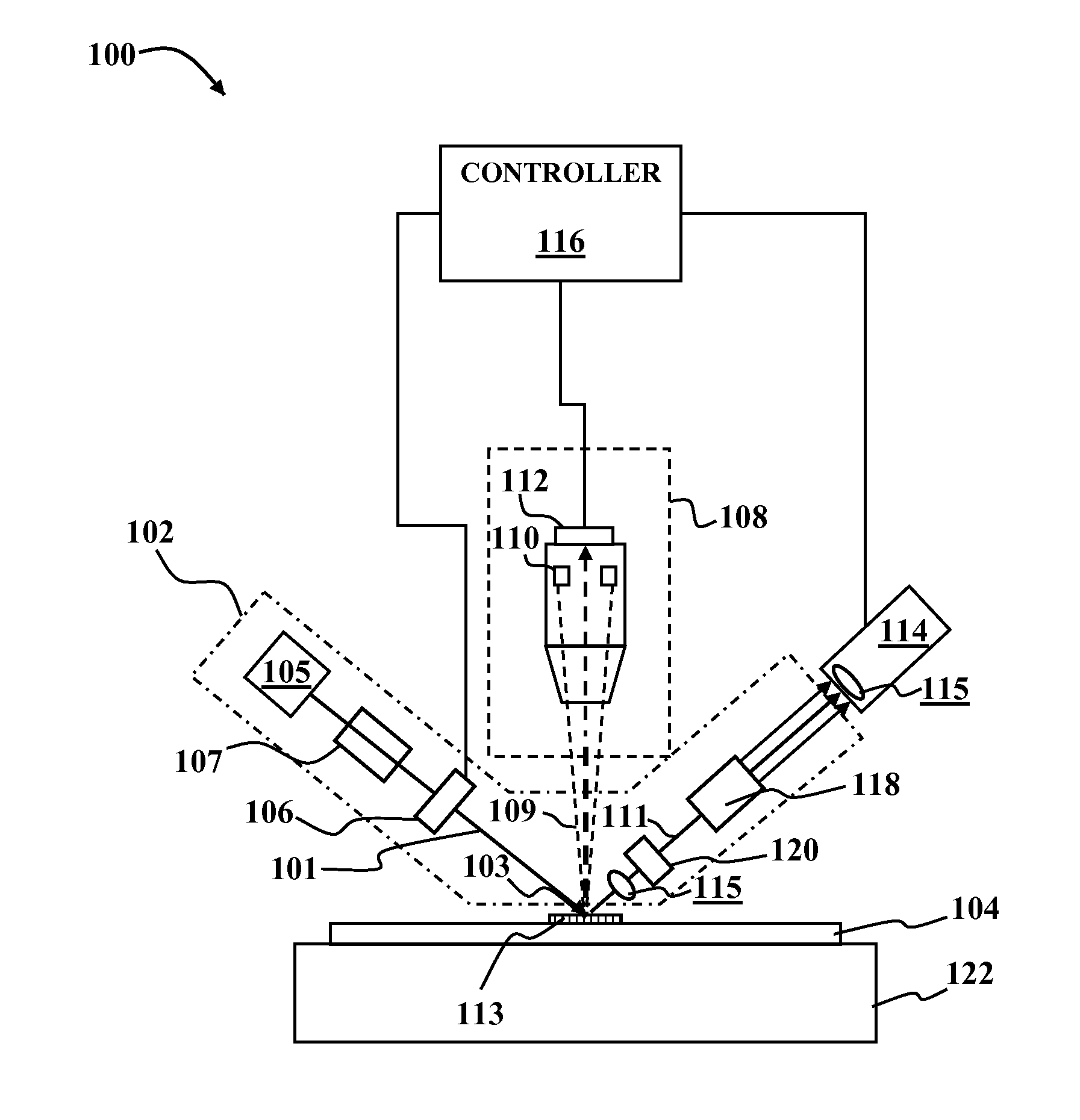

Light-induced directed self-assembly of periodic sub-wavelength nanostructures

ActiveUS20090214885A1Small feature sizeExcellent long-range orderCasting plantsNanoinformaticsWavelengthNanostructure

In various exemplary embodiments, the present invention provides a system for the light-induced directed self-assembly (LIDSA) of periodic sub-wavelength nanostructures, including: a light source for delivering a beam of photons; a reaction chamber disposed adjacent to the light source; a gas including one or more precursor materials disposed within the reaction chamber; and a substrate disposed within the reaction chamber, wherein the substrate is positioned and configured to receive the beam of photons; wherein the beam of photons causes a periodic sub-wavelength nanostructure of one or more constituents of the one or more precursor materials to form on a surface of the substrate. In various exemplary embodiments, the present invention also provides an associated method.

Owner:JUNIVERSITI OF NORT KAROLINA EHT SHARLOTT

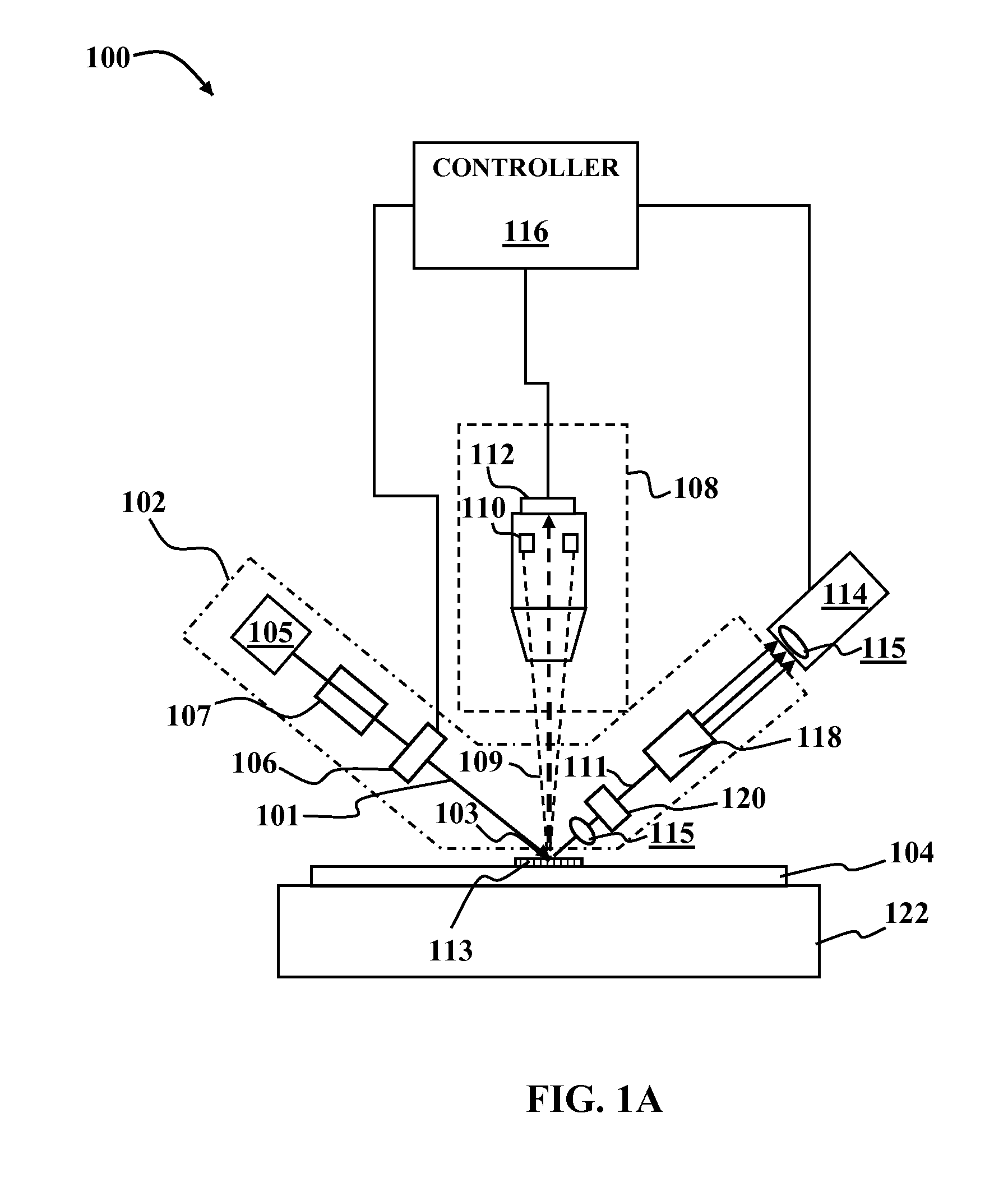

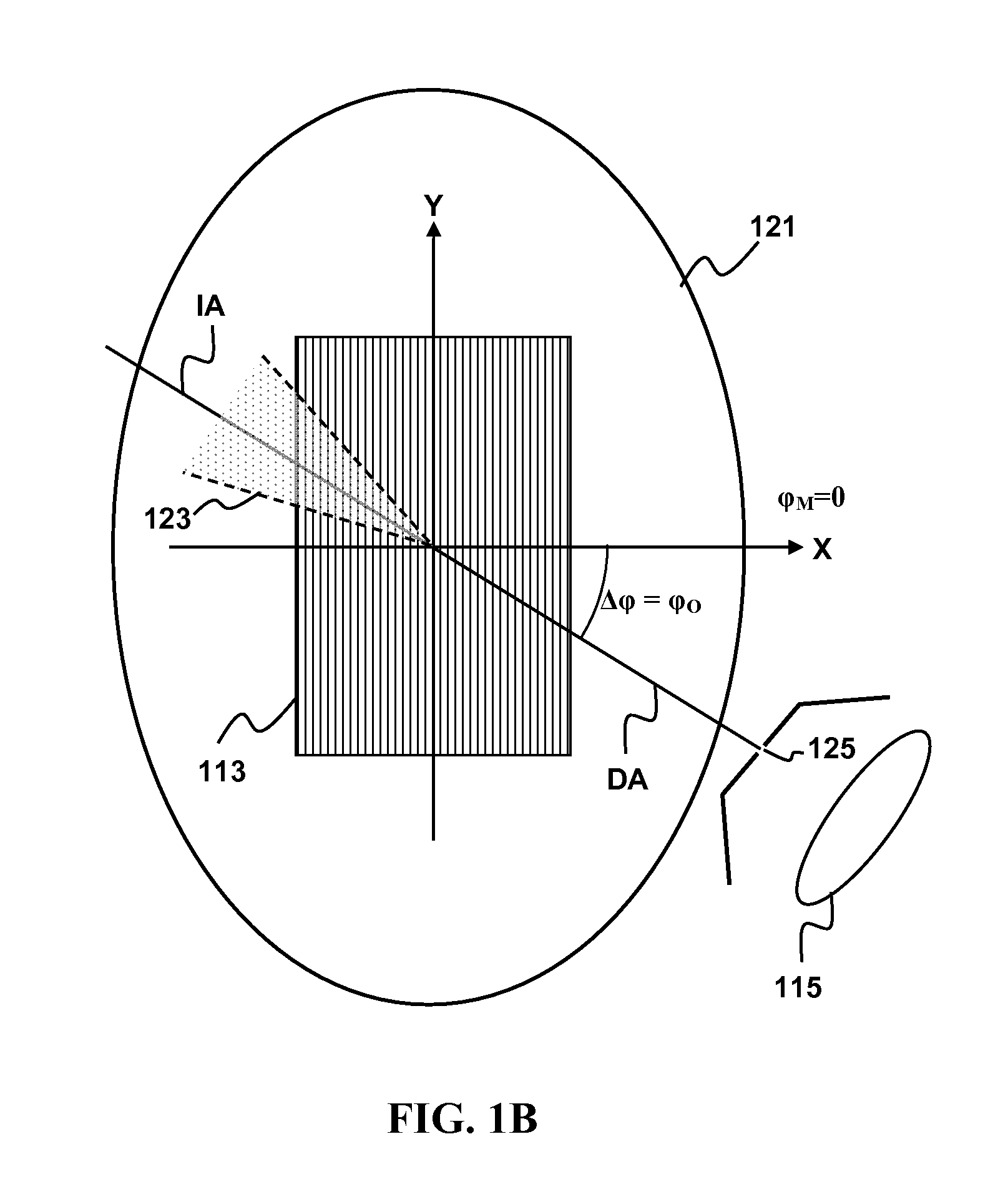

Azimuth angle measurement

ActiveUS8040511B1Improve accuracyImprove tool matchingMaterial analysis by optical meansUsing optical meansDiffraction orderGrating

Methods and apparatus for measuring an optical azimuth angle φO of a substrate relative to a plane of detection in scatterometry tools are disclosed. A grating target on a stage of a scatterometry tool may be illuminated and positions of the resulting diffraction orders may be observed. The optical azimuth angle may be determined from the positions of the diffraction orders. Alternatively, polarization-dependent signals of radiation scattered from a line grating may be measured for equal and opposite polarization angles +A and −A. A combination signal may be computed from the polarization-dependent signals obtained at +A and −A and a property of the combination signal may be calculated for several mechanical Azimuth angles φM. A relationship between the optical azimuth angle φO and the mechanical azimuth angle φM may be determined from a behavior of the property as a function of mechanical azimuth angle φM.

Owner:KLA TENCOR TECH CORP

Process for fabricating an MOS device having highly-localized halo regions

Owner:INT BUSINESS MASCH CORP

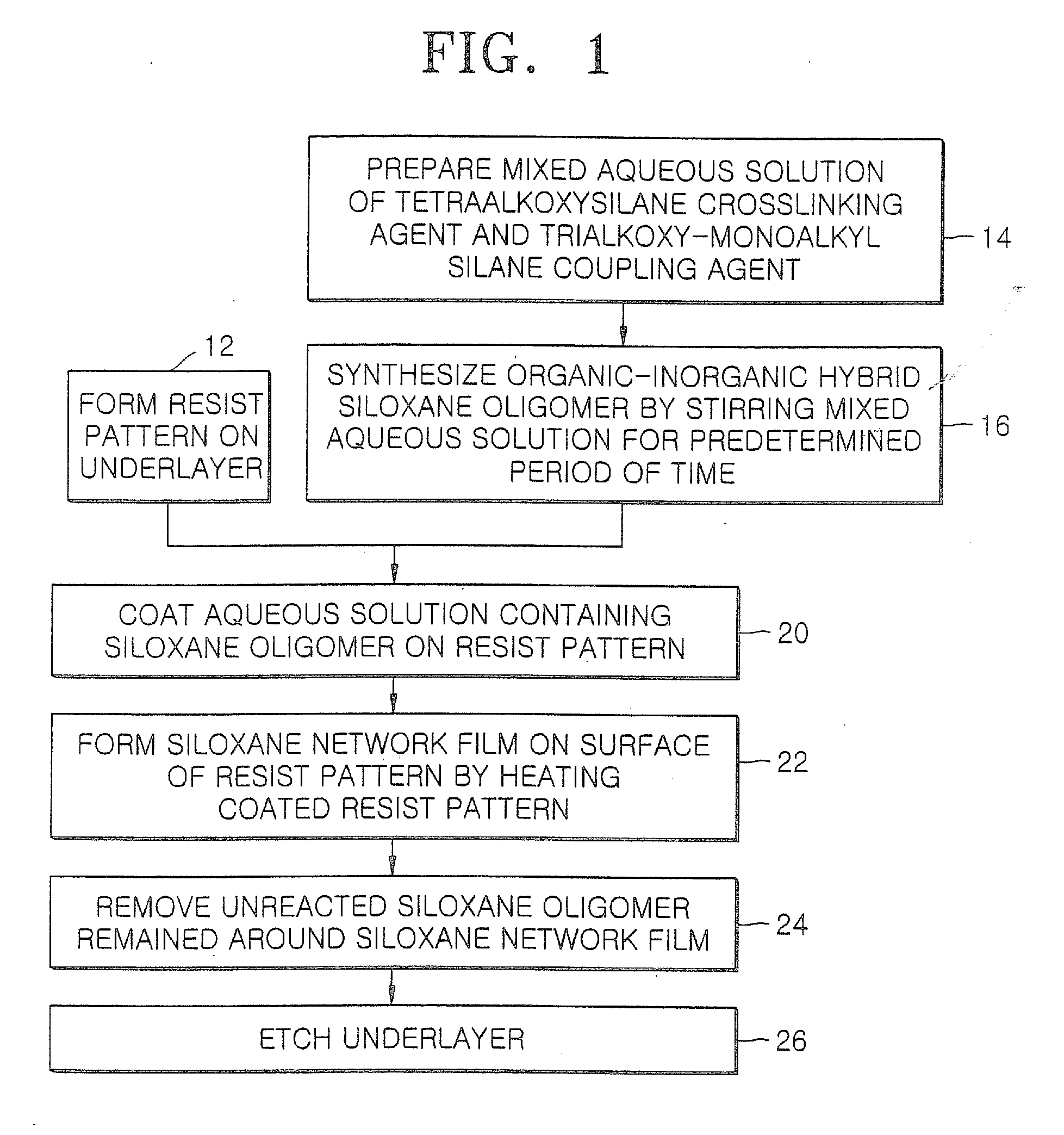

Mask Patterns for Semiconductor Device Fabrication and Related Methods and Structures

InactiveUS20080176152A1Simple and inexpensive processSolve the lack of resistanceElectric discharge tubesSemiconductor/solid-state device manufacturingResistEngineering

Methods of forming an integrated circuit device may include forming a resist pattern on a layer of an integrated circuit device with portions of the layer being exposed through openings of the resist pattern. An organic-inorganic hybrid siloxane network film may be formed on the resist pattern. Portions of the layer exposed through the resist pattern and the organic-inorganic hybrid siloxane network film may then be removed. Related structures are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

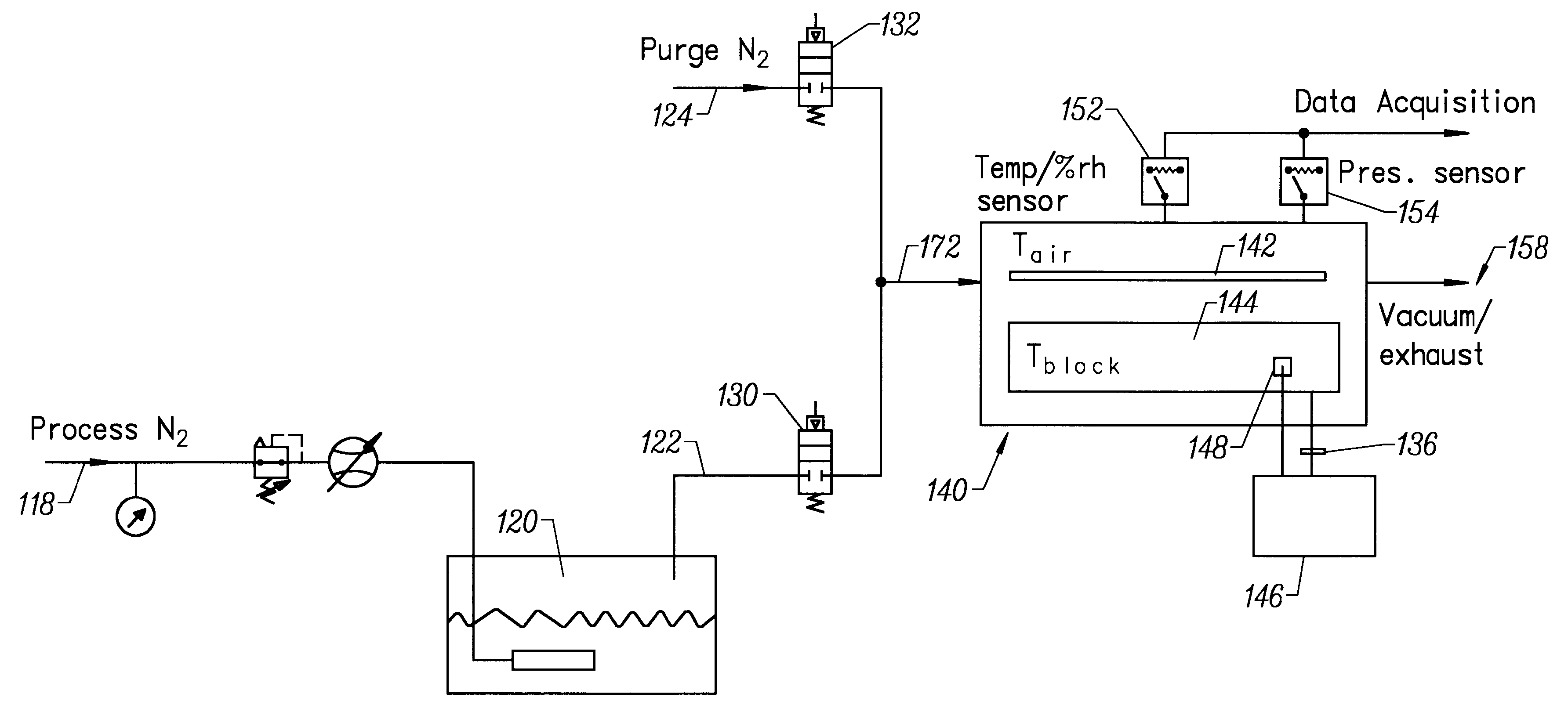

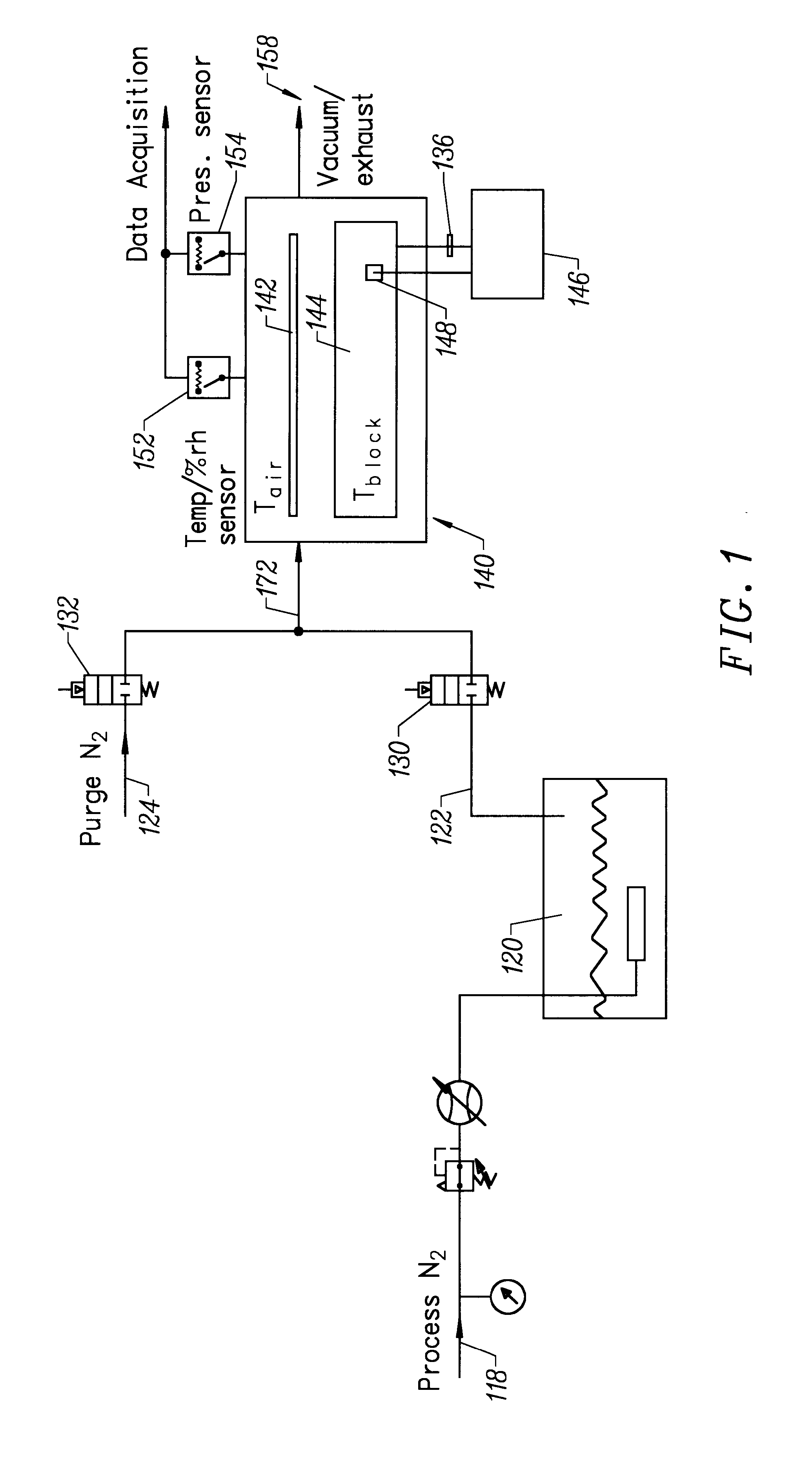

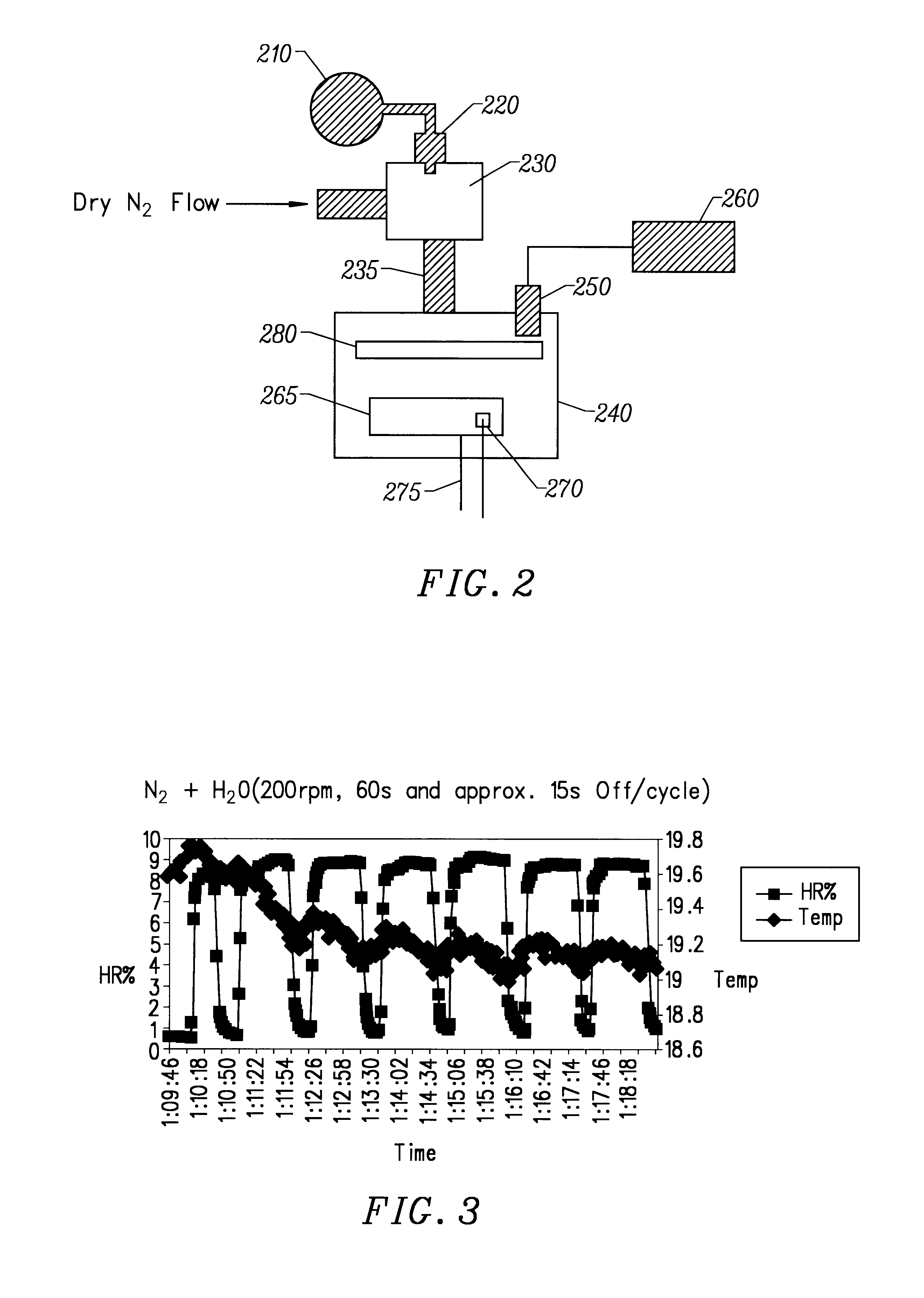

Environment exchange control for material on a wafer surface

InactiveUS6254936B1Avoid pollutionImproves mechanical and physical propertySemiconductor/solid-state device manufacturingPretreated surfacesSpinsEngineering

Systems and methods are described for environmental exchange control for a polymer on a wafer surface. An apparatus for controlling an exchange between an environment and a polymer on a surface of a wafer located in the environment includes: a chamber adapted to hold the wafer, define the environment, and maintain the polymer in an adjacent relationship with the environment; and a heater coupled to the chamber. A method for improving performance of a spin-on material includes: forming the spin-on material on a surface of a wafer; then locating the spin-on material in an environment so that said environment is adjacent said spin-on material; and then controlling an exchange between the spin-on material and said environment. The systems and methods provide advantages because inappropriate deprotection is mitigated by careful control of the environmental temperature and environmental species partial pressures (e.g. relative humidity).

Owner:ASML HLDG NV

Vertical field effect transistors incorporating semiconducting nanotubes grown in a spacer-defined passage

InactiveUS20050266627A1Efficient and effective introductionImprove directionNanoinformaticsSolid-state devicesGas phaseEngineering

Vertical field effect transistors having a channel region defined by at least one semiconducting nanotube and methods for fabricating such vertical field effect transistors by chemical vapor deposition using a spacer-defined channel. Each nanotube is grown by chemical vapor deposition catalyzed by a catalyst pad positioned at the base of a high-aspect-ratio passage defined between a spacer and a gate electrode. Each nanotube grows in the passage with a vertical orientation constrained by the confining presence of the spacer. A gap may be provided in the base of the spacer remote from the mouth of the passage. Reactants flowing through the gap to the catalyst pad participate in nanotube growth.

Owner:IBM CORP

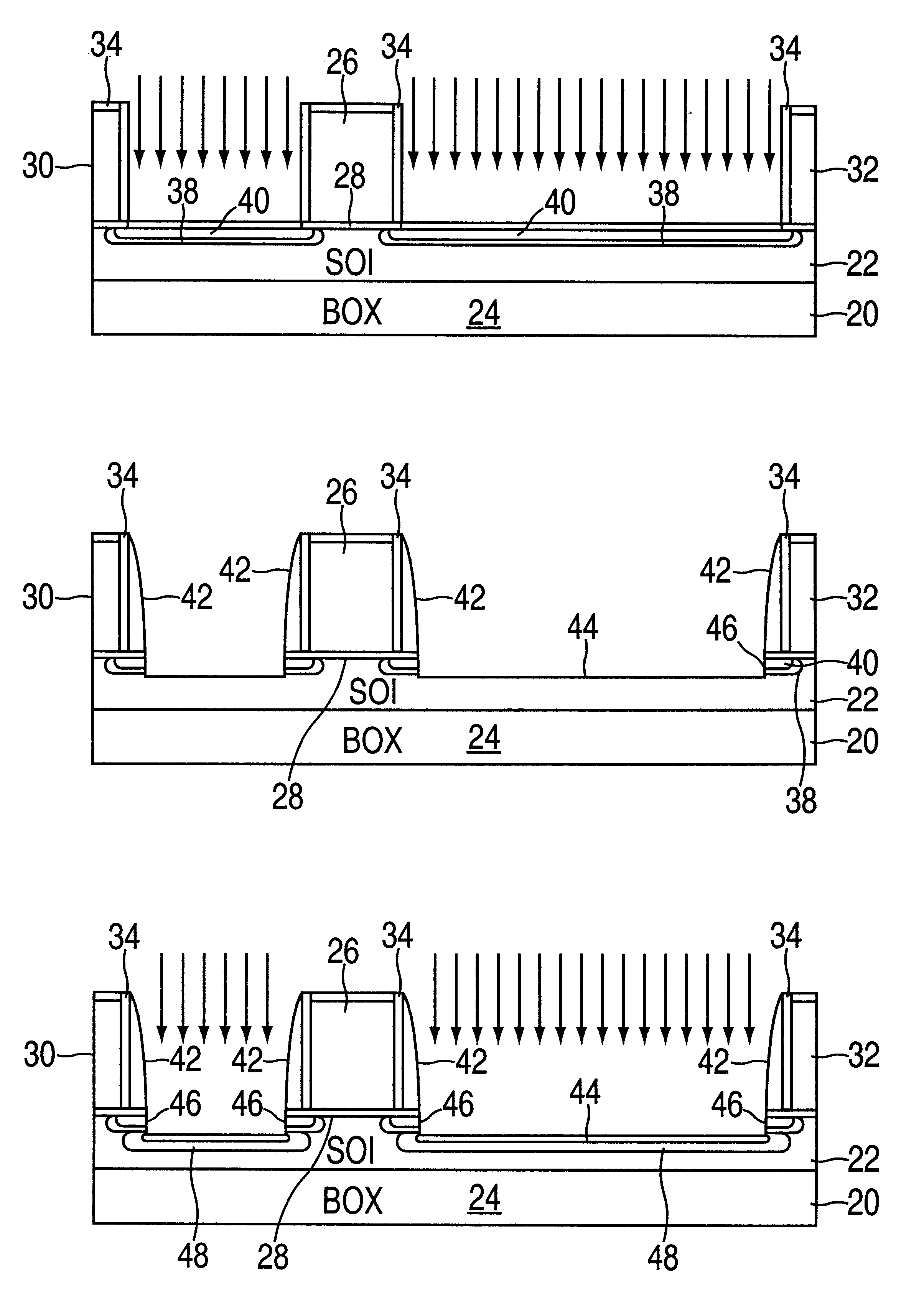

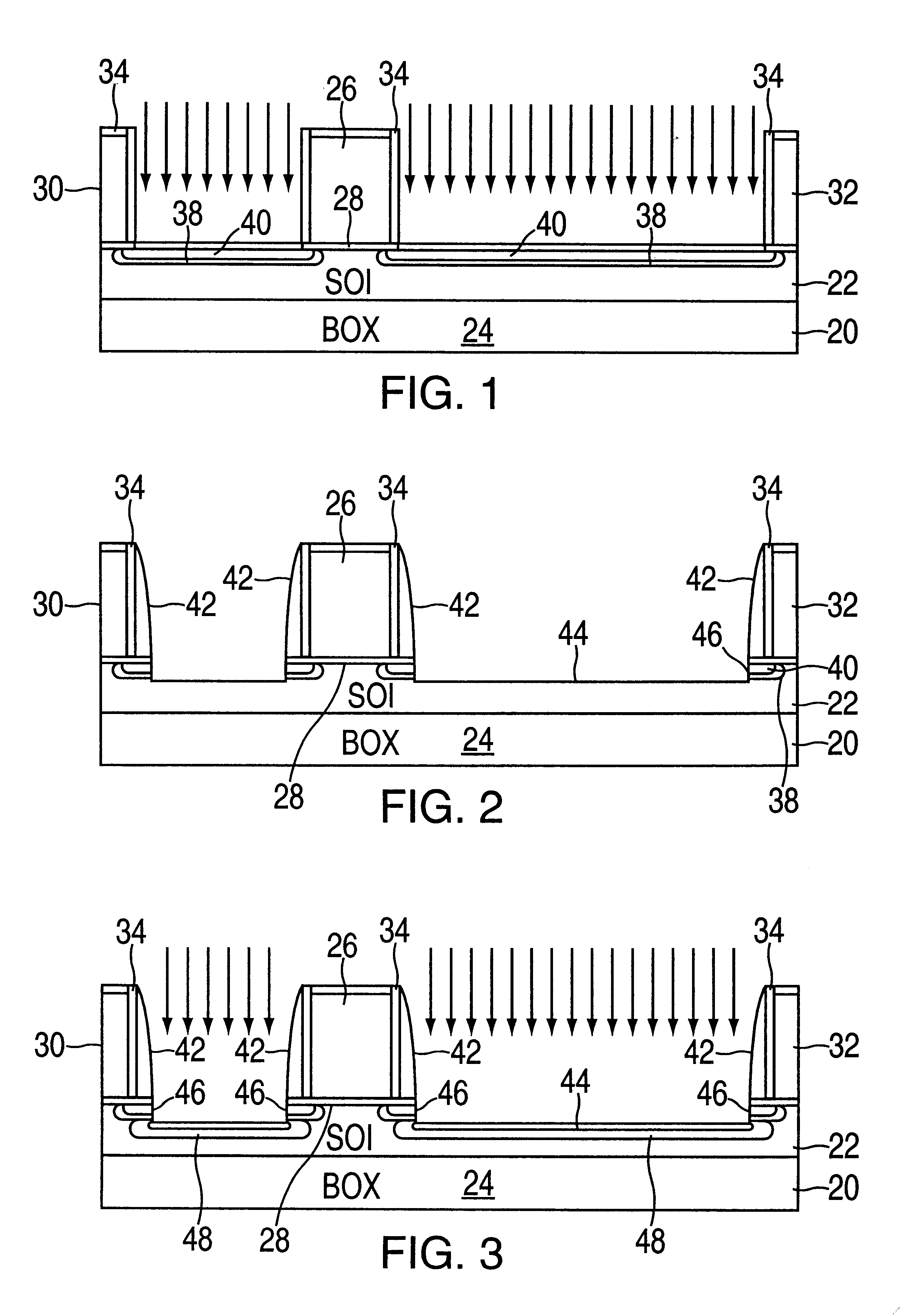

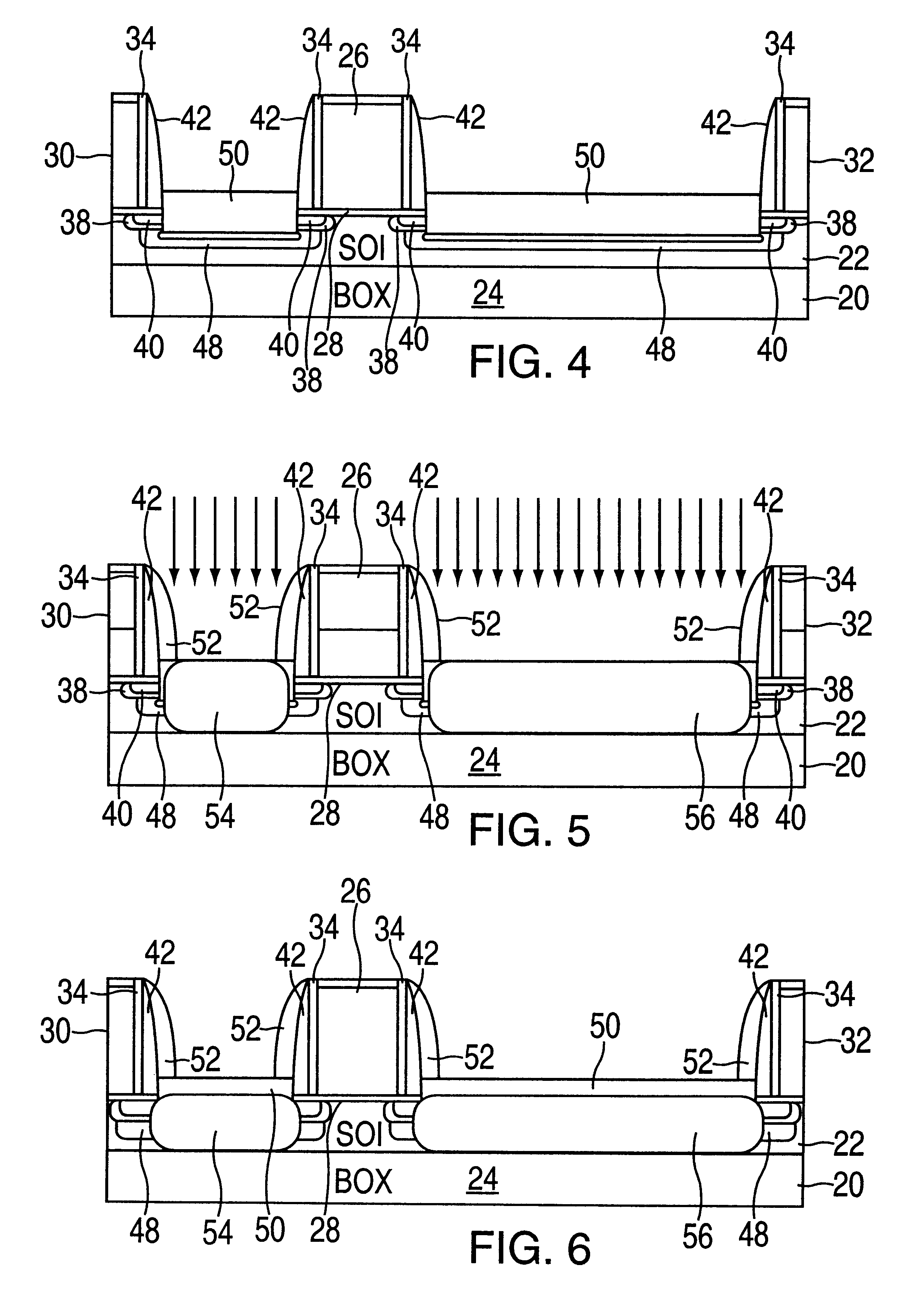

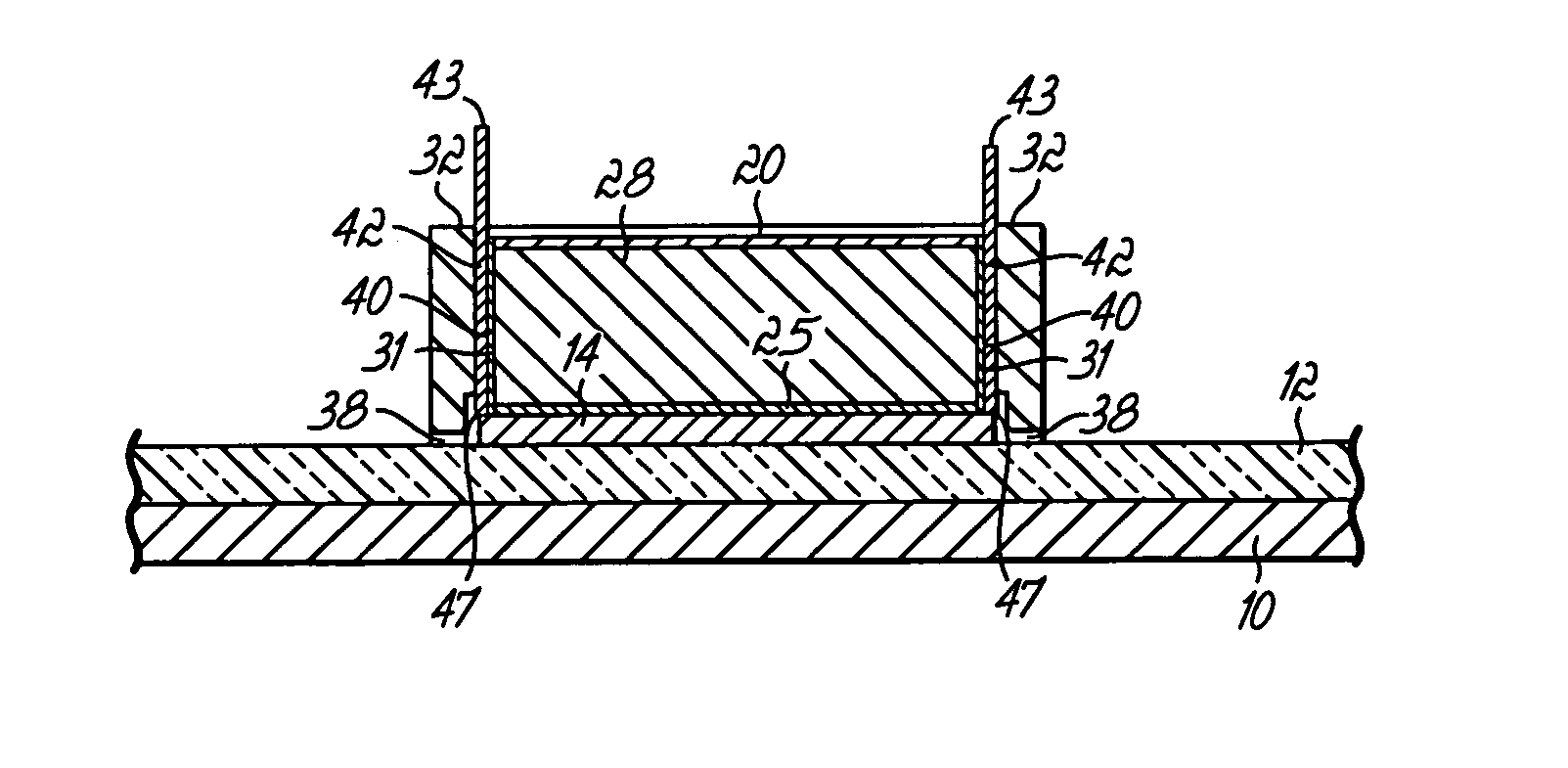

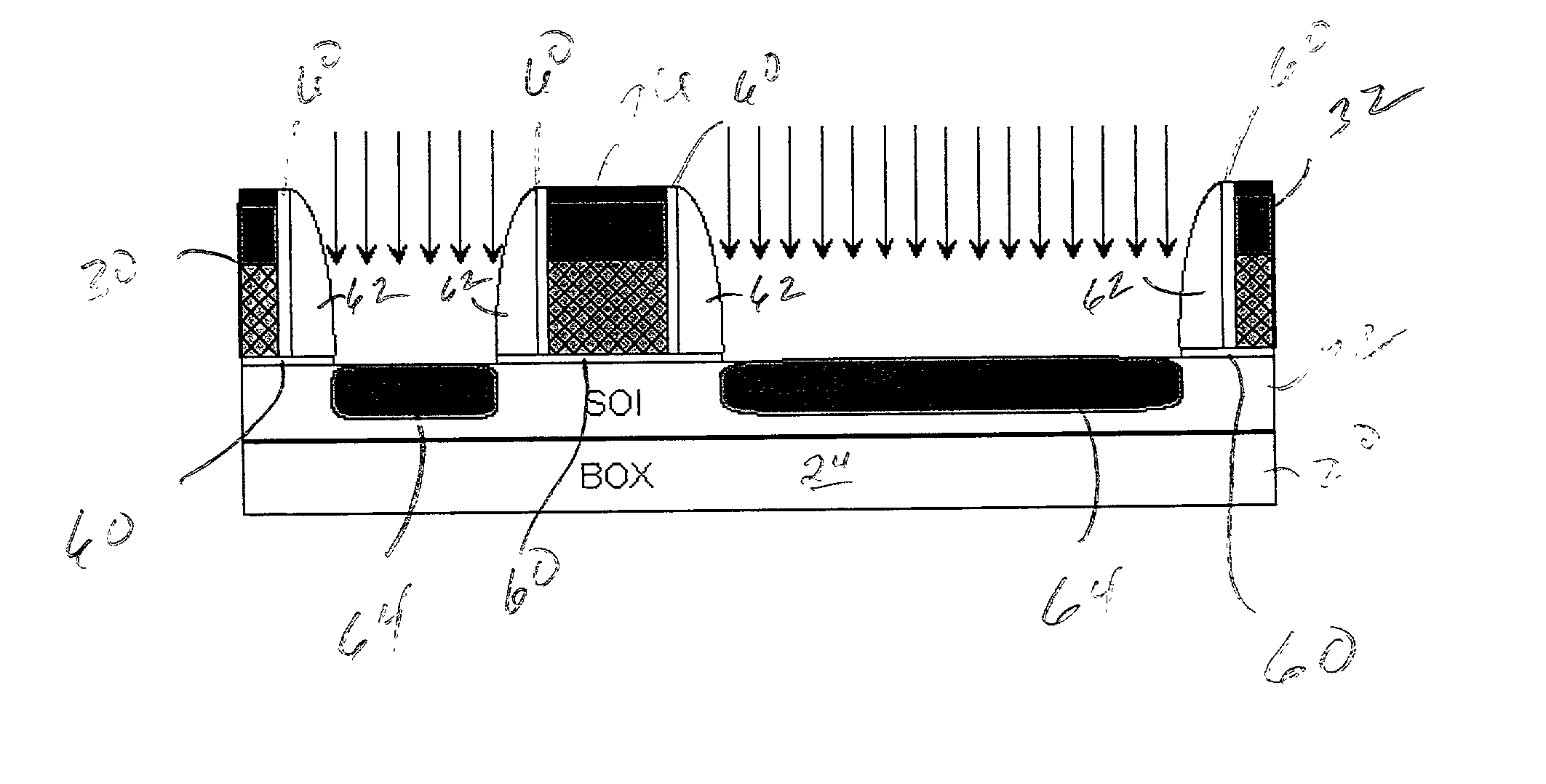

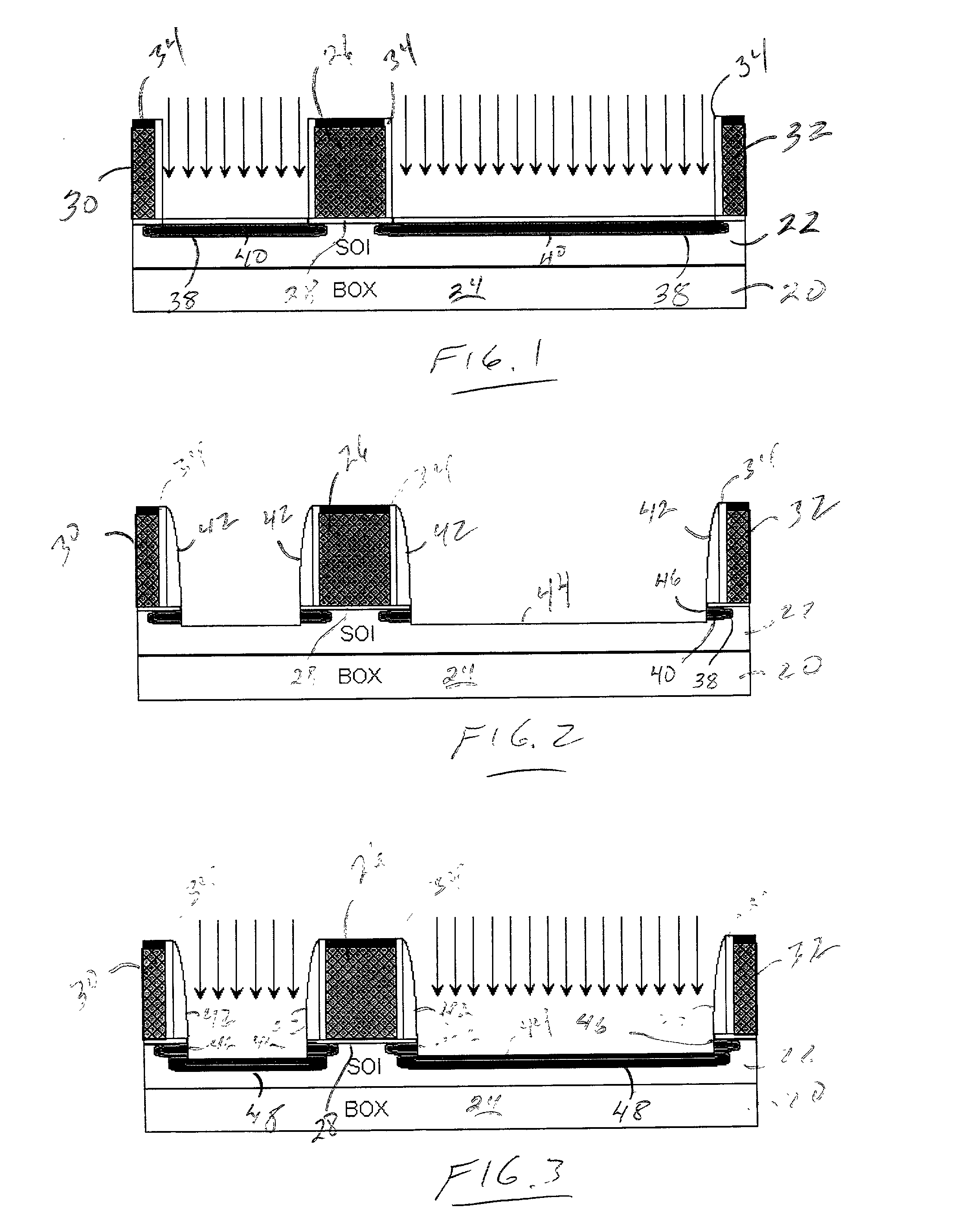

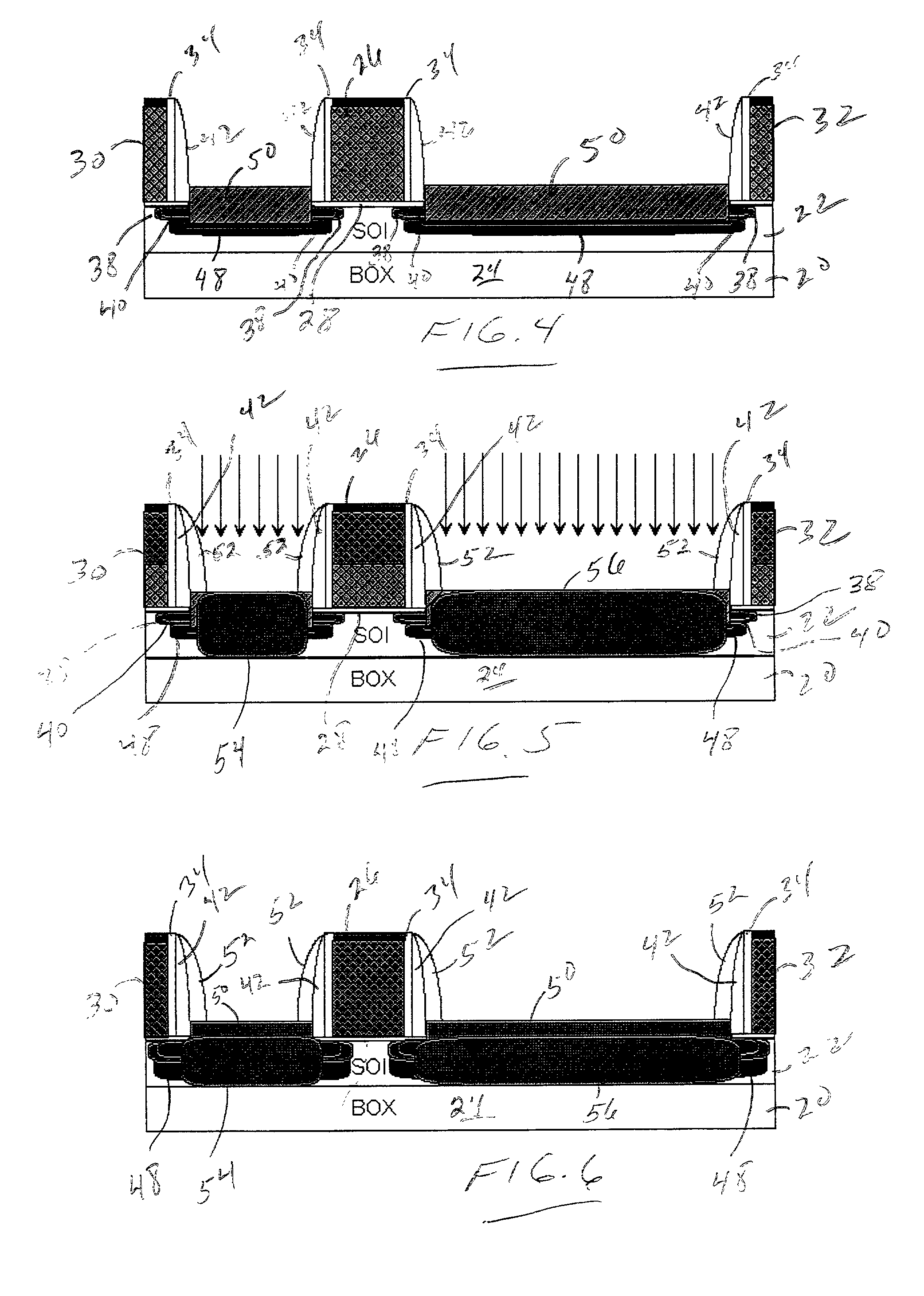

Process for fabricating an MOS device having highly-localized halo regions

InactiveUS20020072176A1Large diffusionEasy to makeTransistorSolid-state devicesBoronIon implantation

A process for fabricating an MOS device having a highly-localized halo region includes the formation of a first halo region at a first surface of a silicon substrate, and a second halo region at a second surface of the silicon substrate. The second surface of the silicon substrate is formed by anisotropically etching the first surface of the silicon substrate to remove a portion of the material from the substrate. Both the first and second halo regions are formed by low-energy ion implantation. For the fabrication of an n-channel device, boron is implanted at an energy of no more than about 1 keV. Upon implantation and a subsequent annealing process, the first and second halo regions form a continuous halo region within the semiconductor substrate.

Owner:IBM CORP

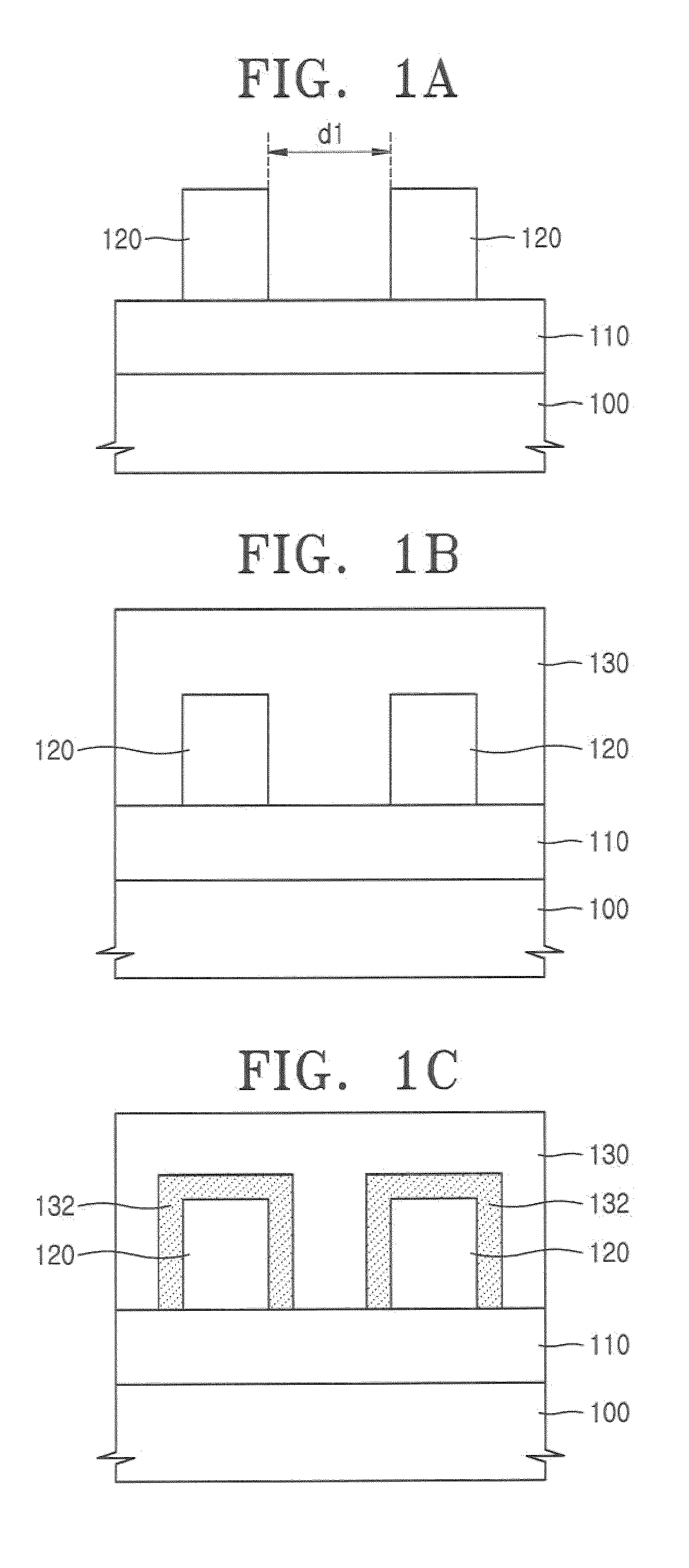

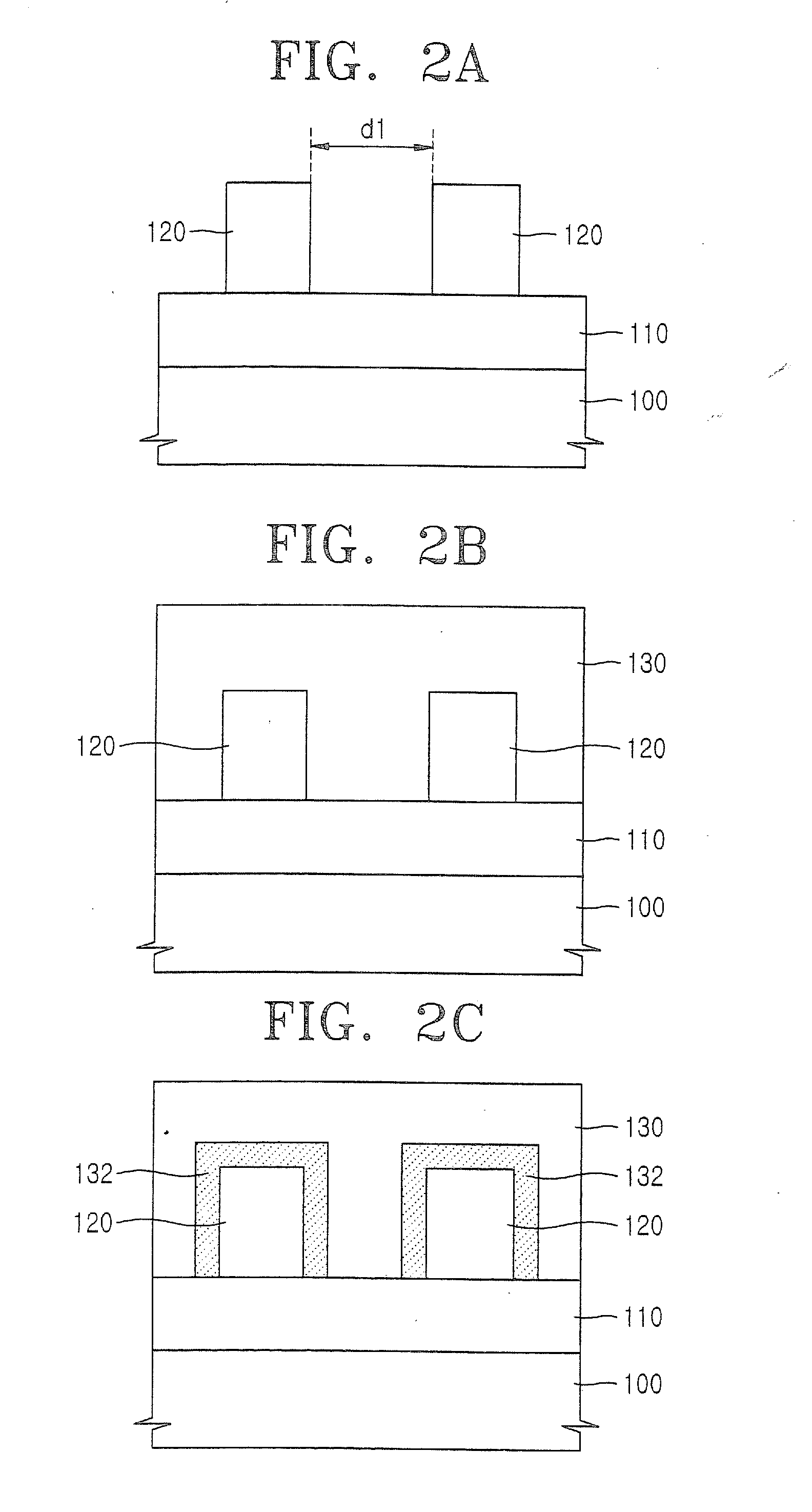

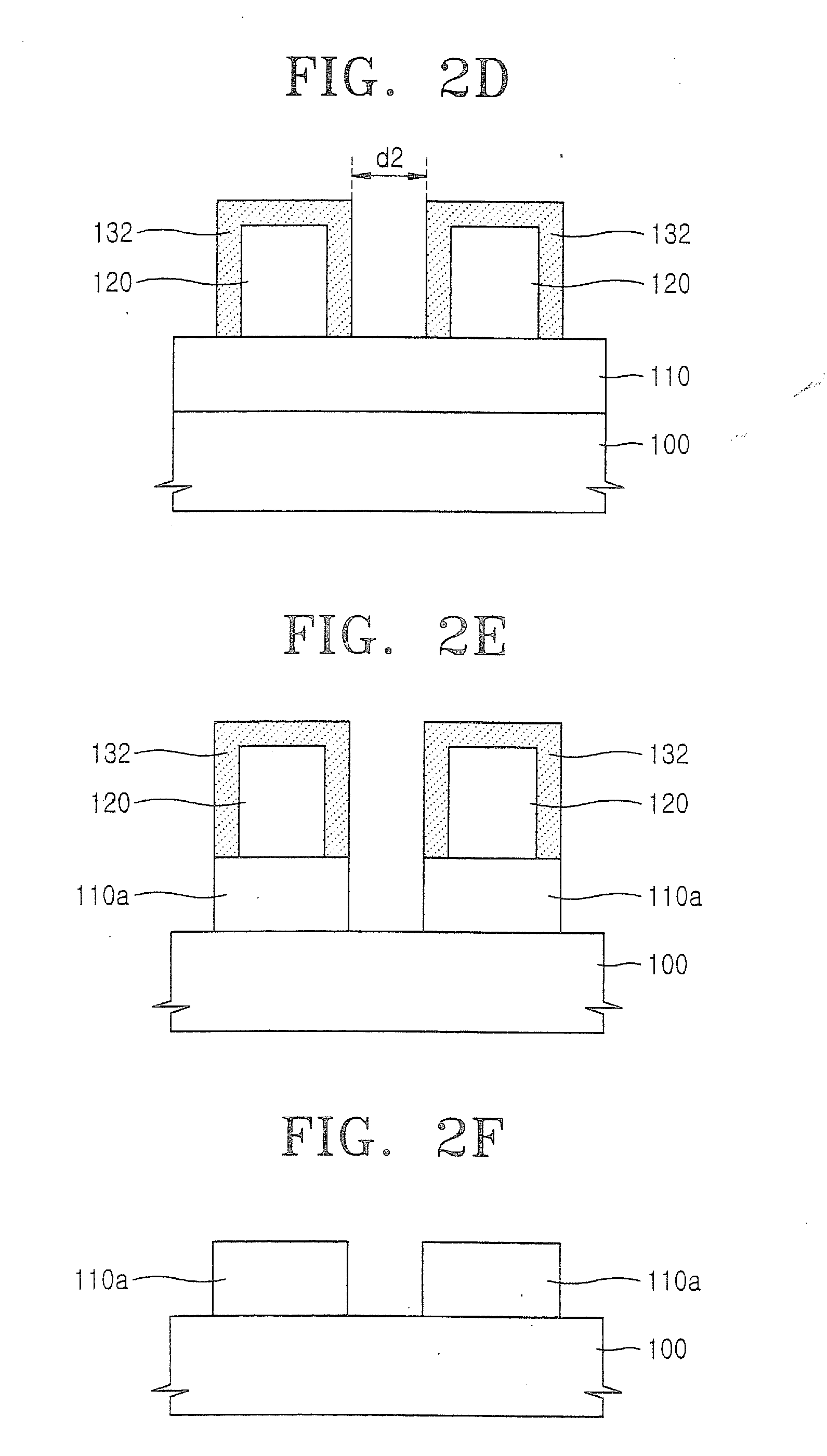

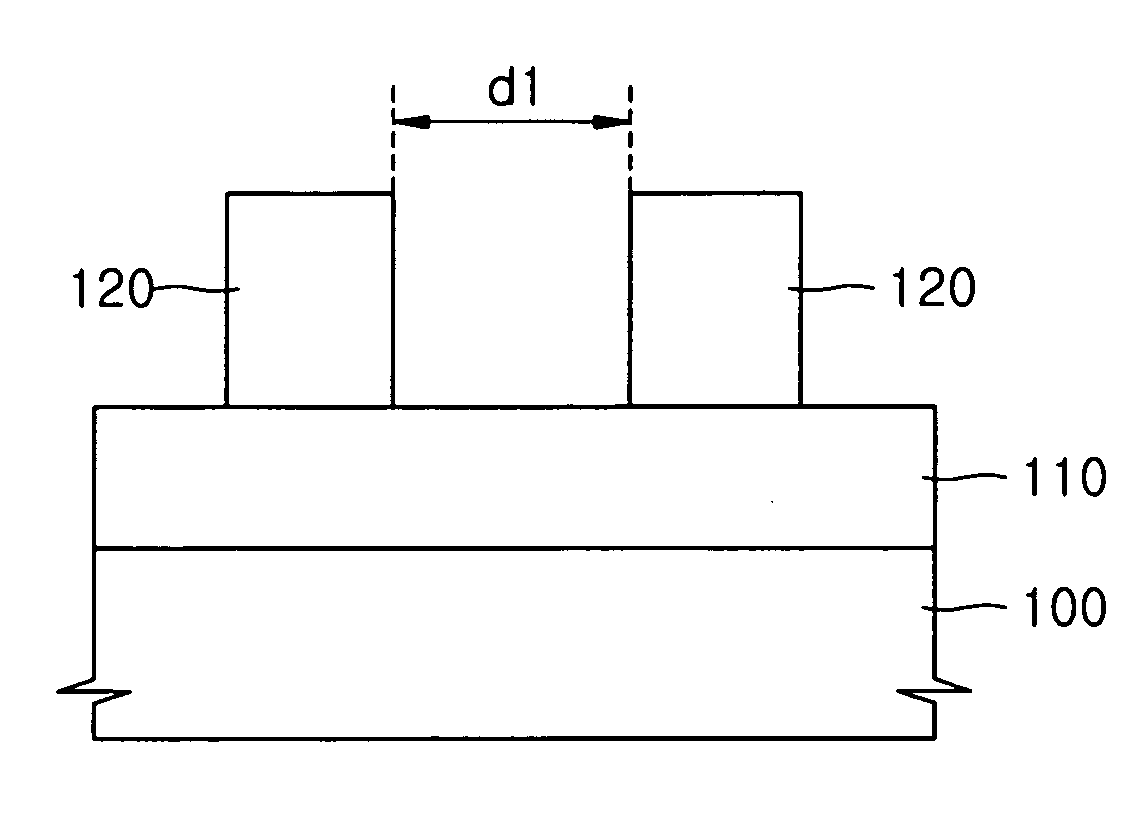

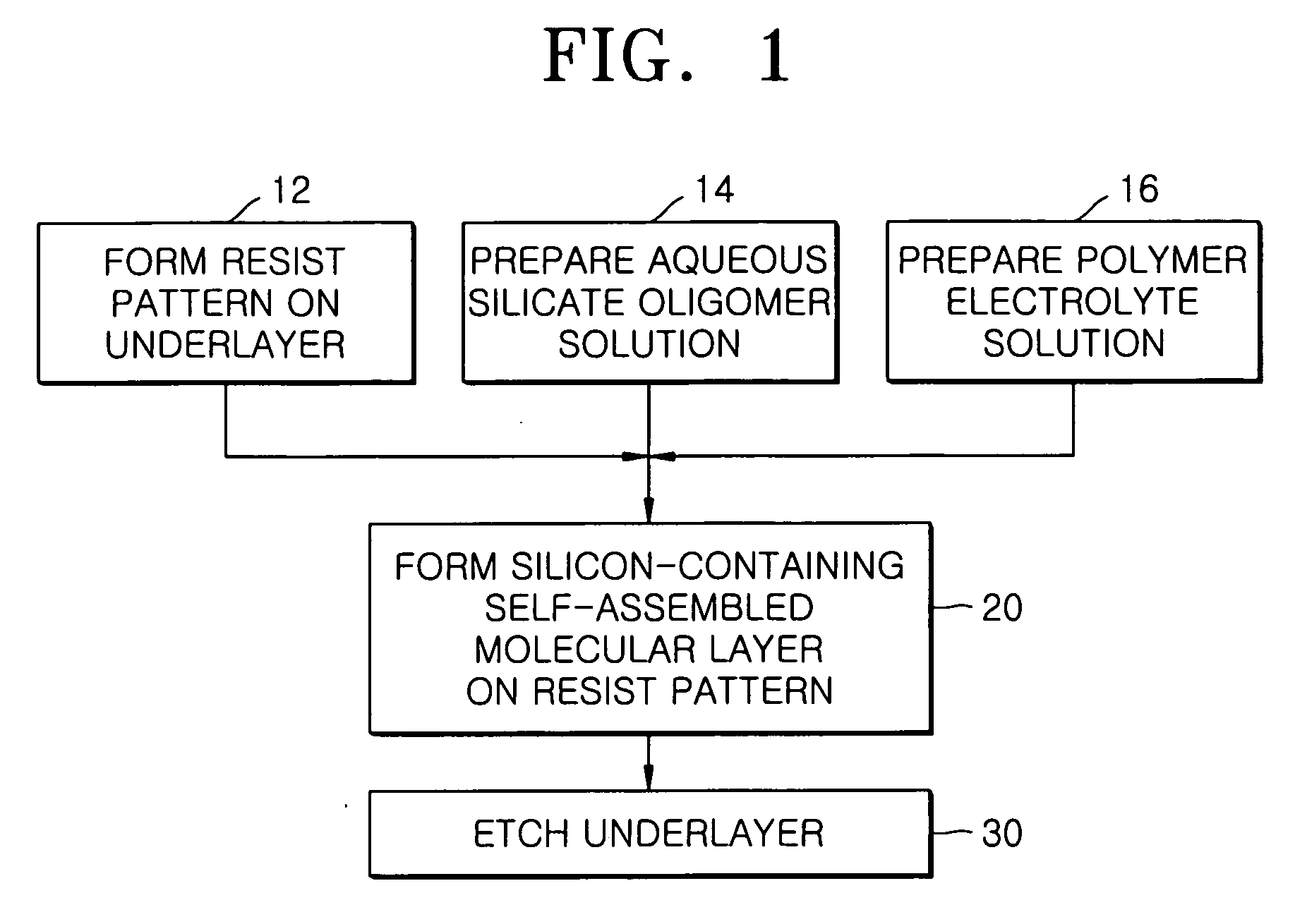

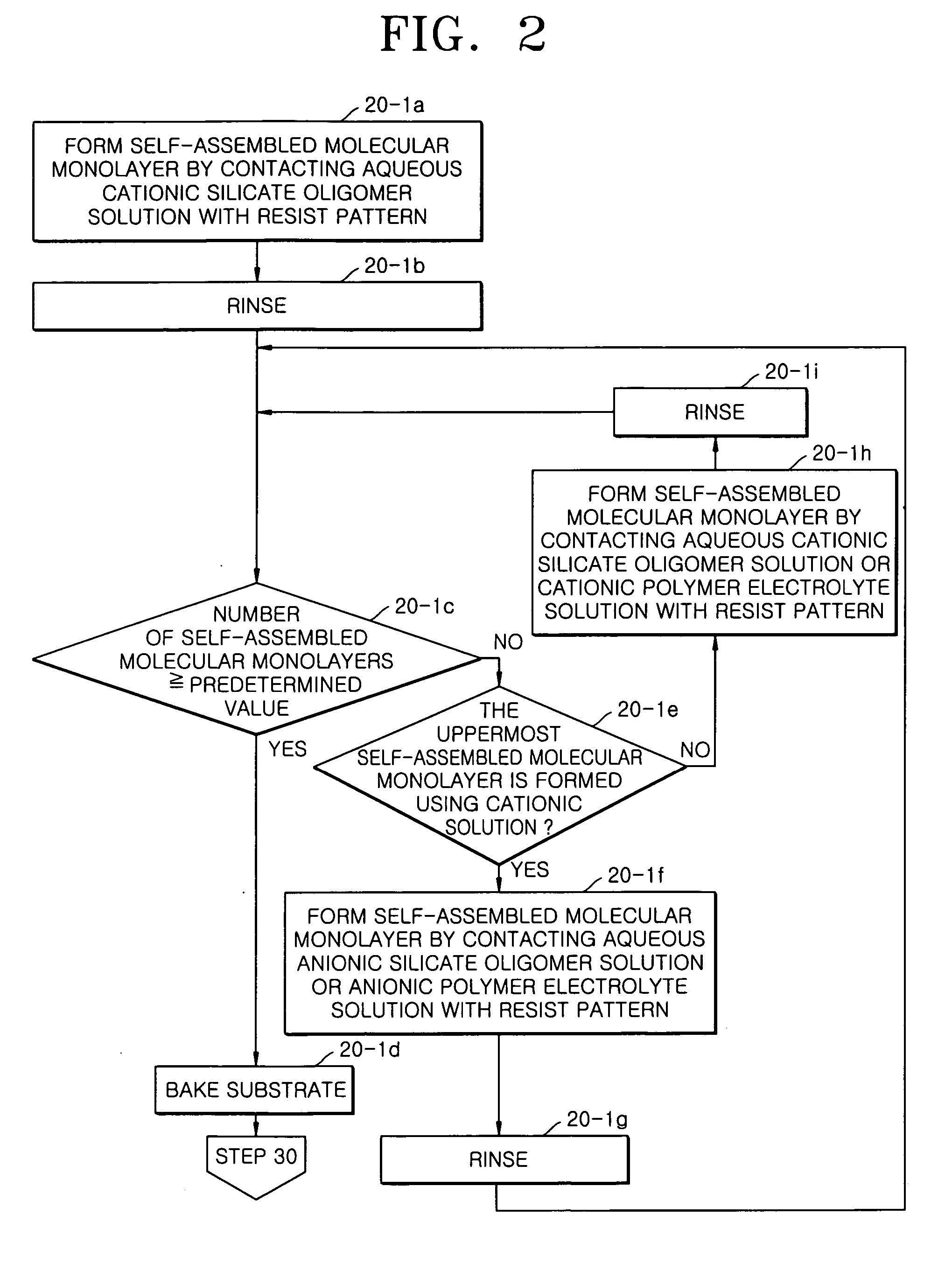

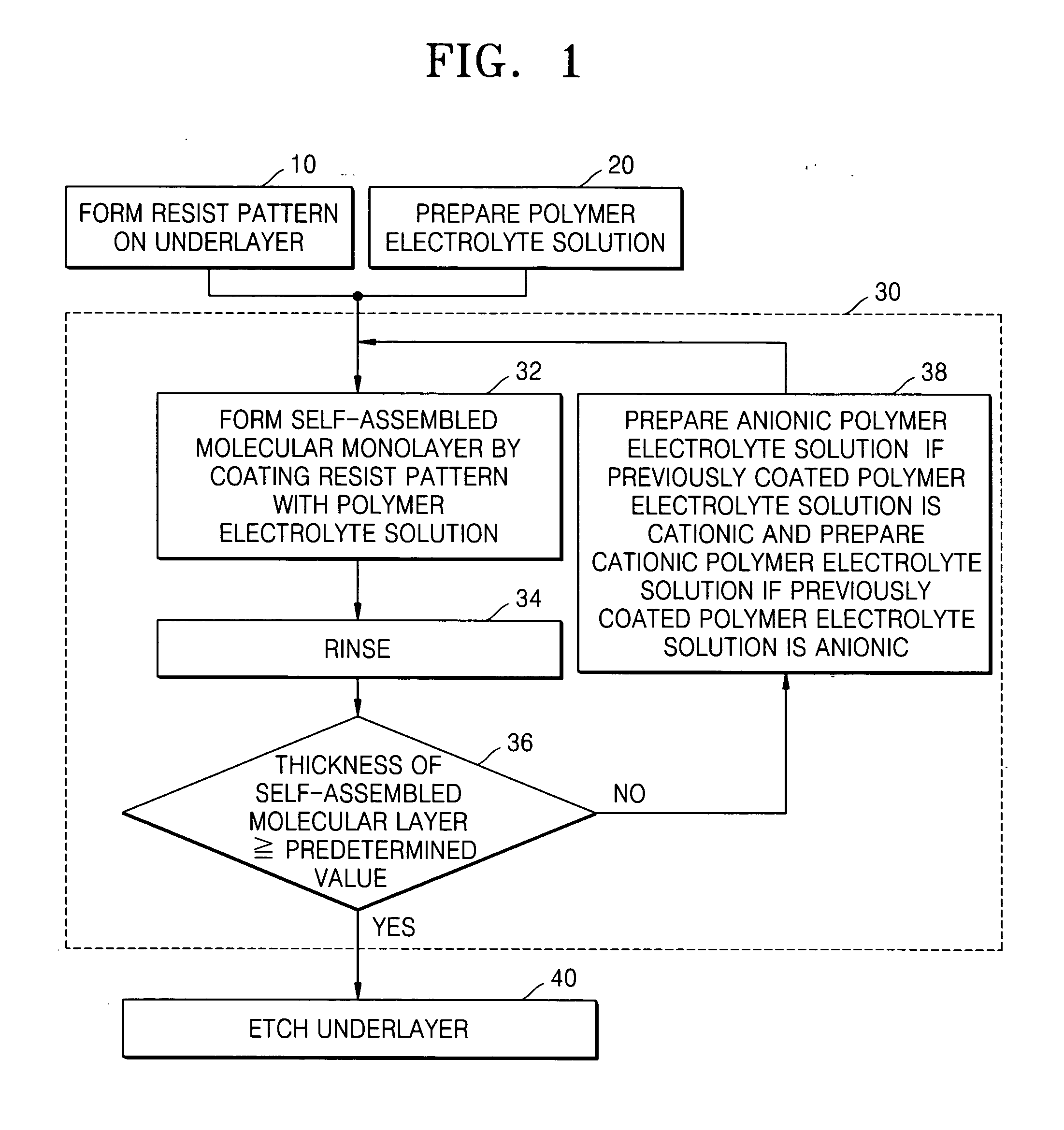

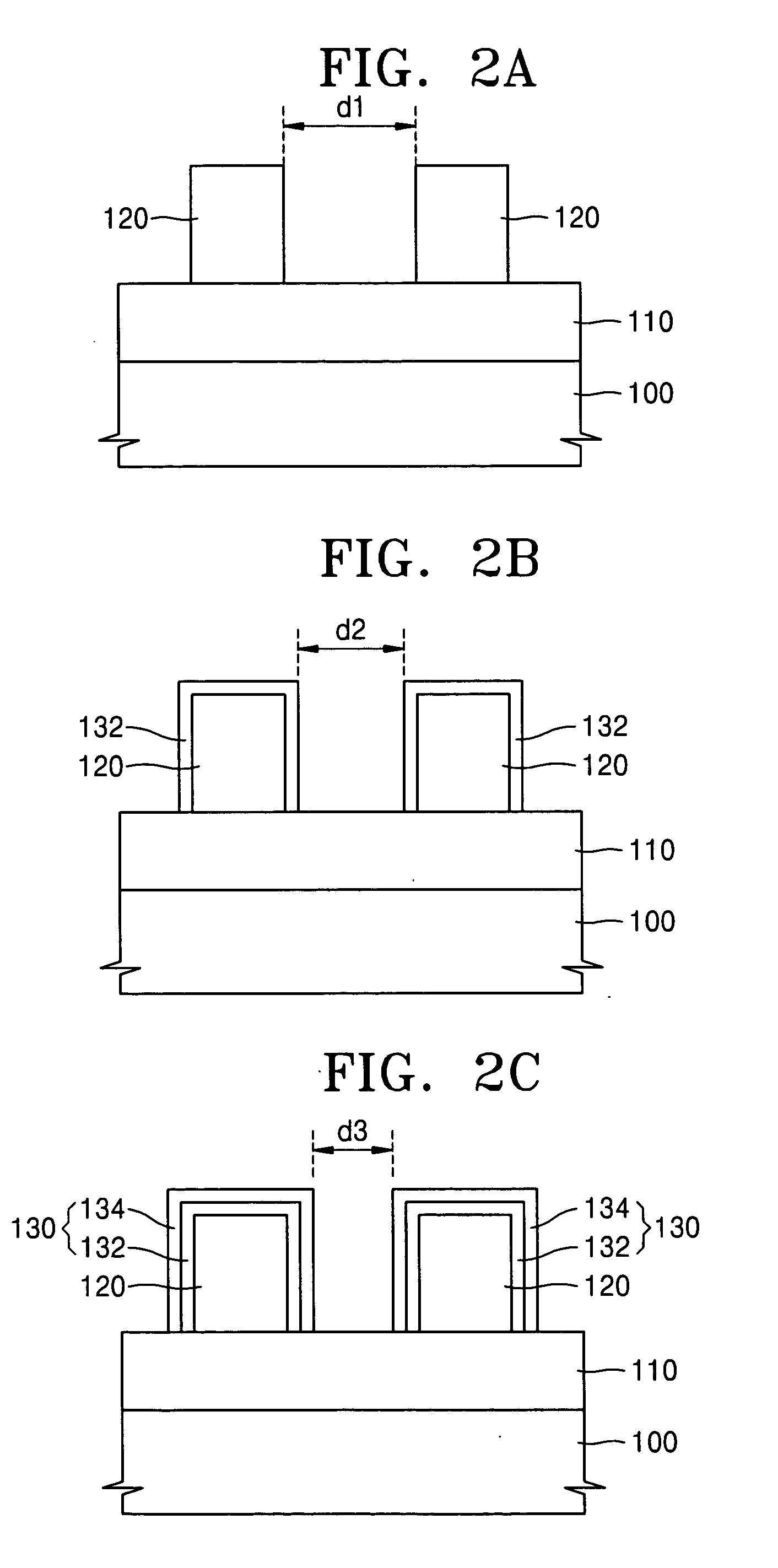

Mask pattern for semiconductor device fabrication, method of forming the same, and method of fabricating finely patterned semiconductor device

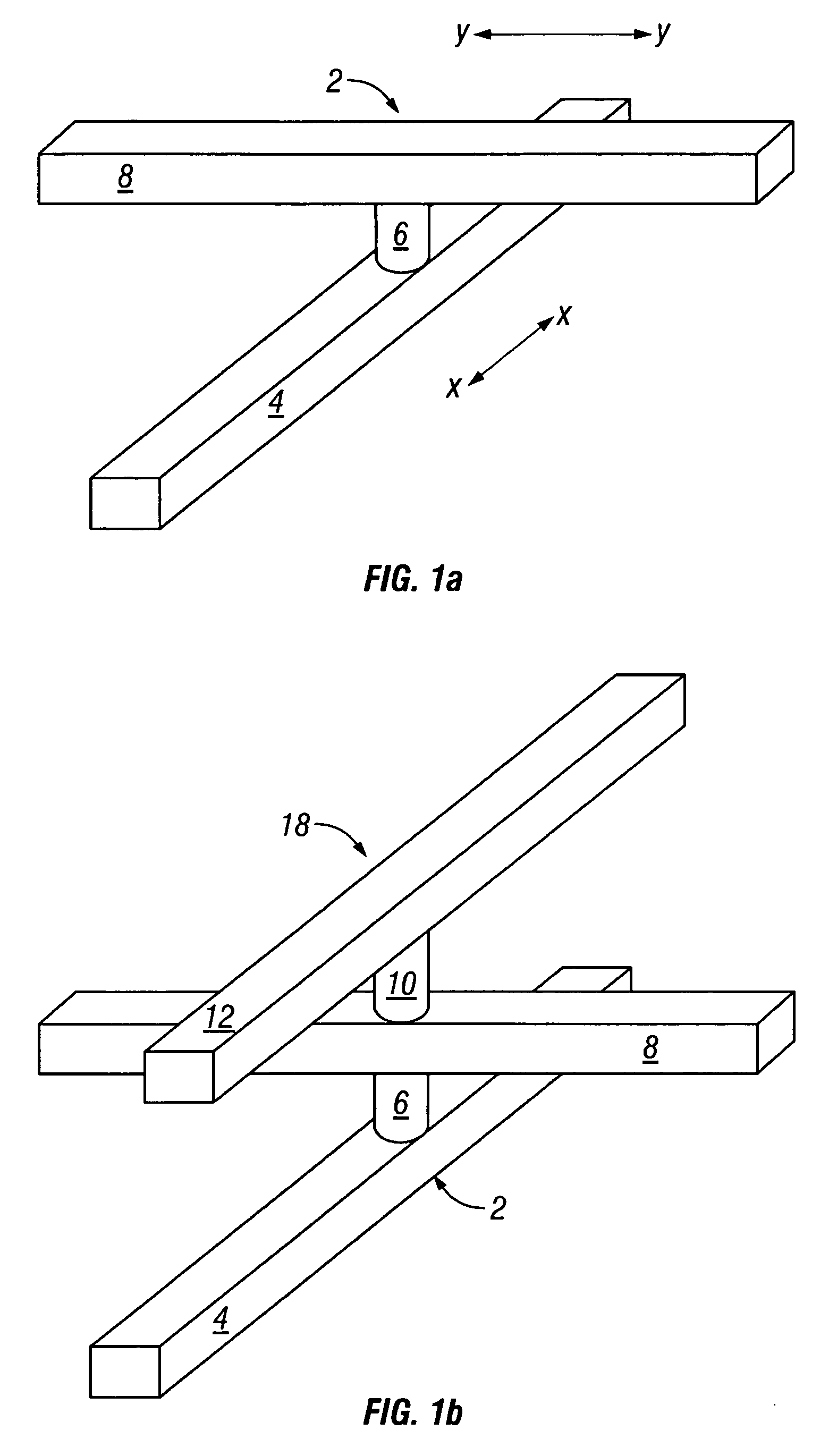

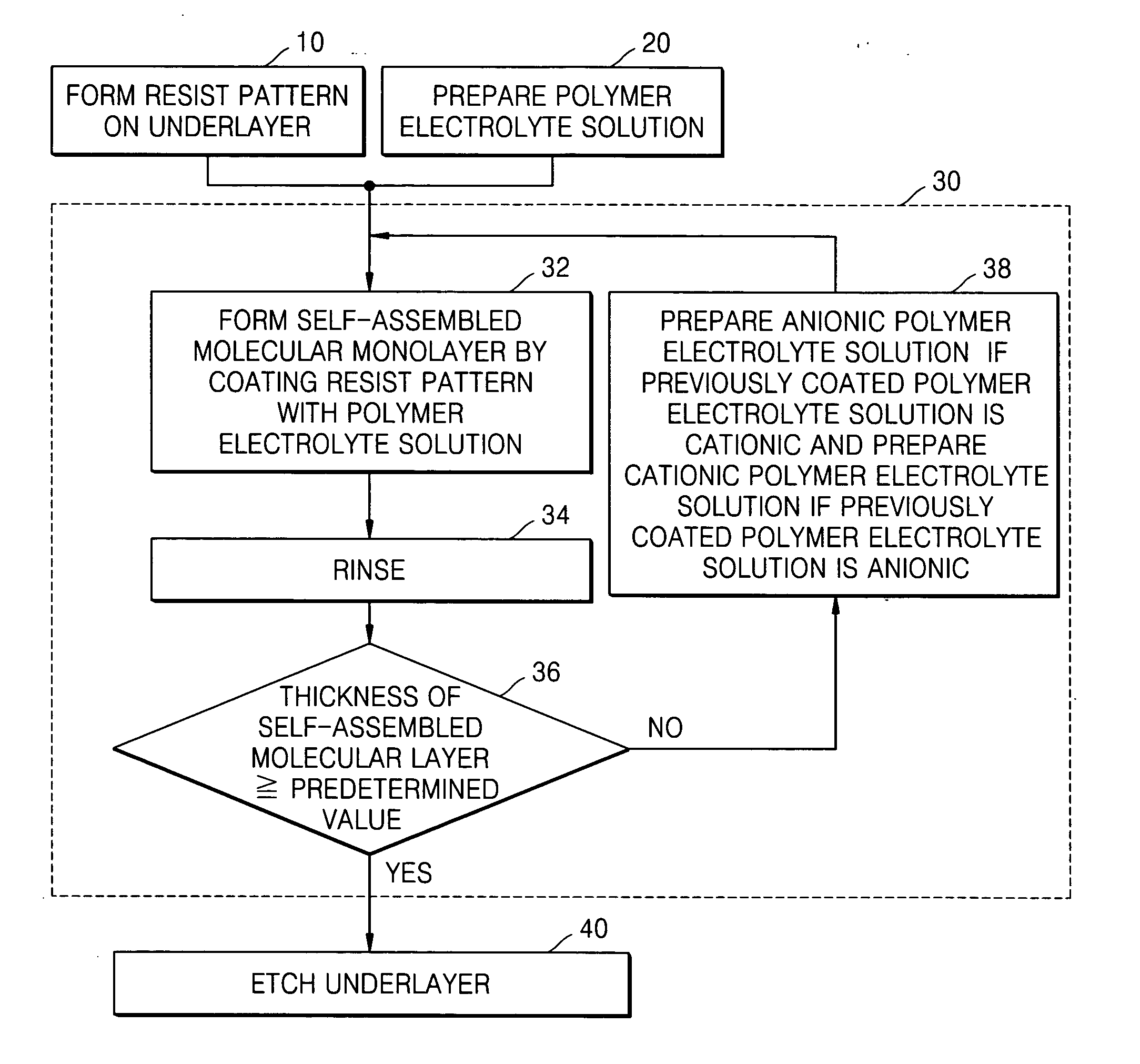

InactiveUS20060046205A1Simple and inexpensive processSimple methodMaterial nanotechnologyPhotosensitive materialsResistSilicon dioxide

Provided are a mask pattern including a silicon-containing self-assembled molecular layer, a method of forming the same, and a method of fabricating a semiconductor device. The mask pattern includes a resist pattern formed on a semiconductor substrate and the self-assembled molecular layer formed on the resist pattern. The self-assembled molecular layer has a silica network formed by a sol-gel reaction. To form the mask pattern, first, the resist pattern is formed with openings on an underlayer covering the substrate to expose the underlayer to a first width. Then, the self-assembled molecular layer is selectively formed only on a surface of the resist pattern to expose the underlayer to a second width smaller than the first width. The underlayer is etched by using the resist pattern and the self-assembled molecular layer as an etching mask to obtain a fine pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

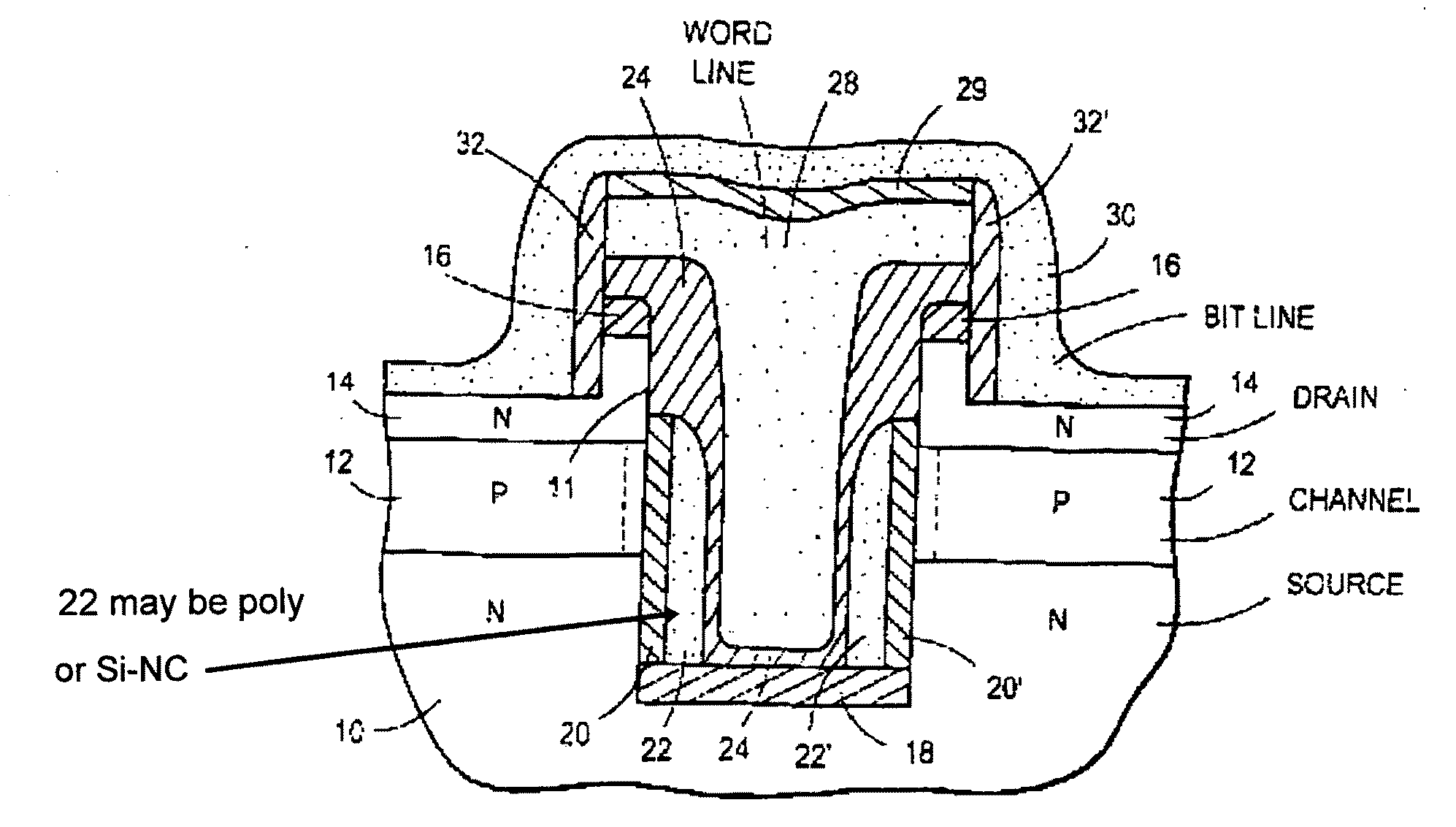

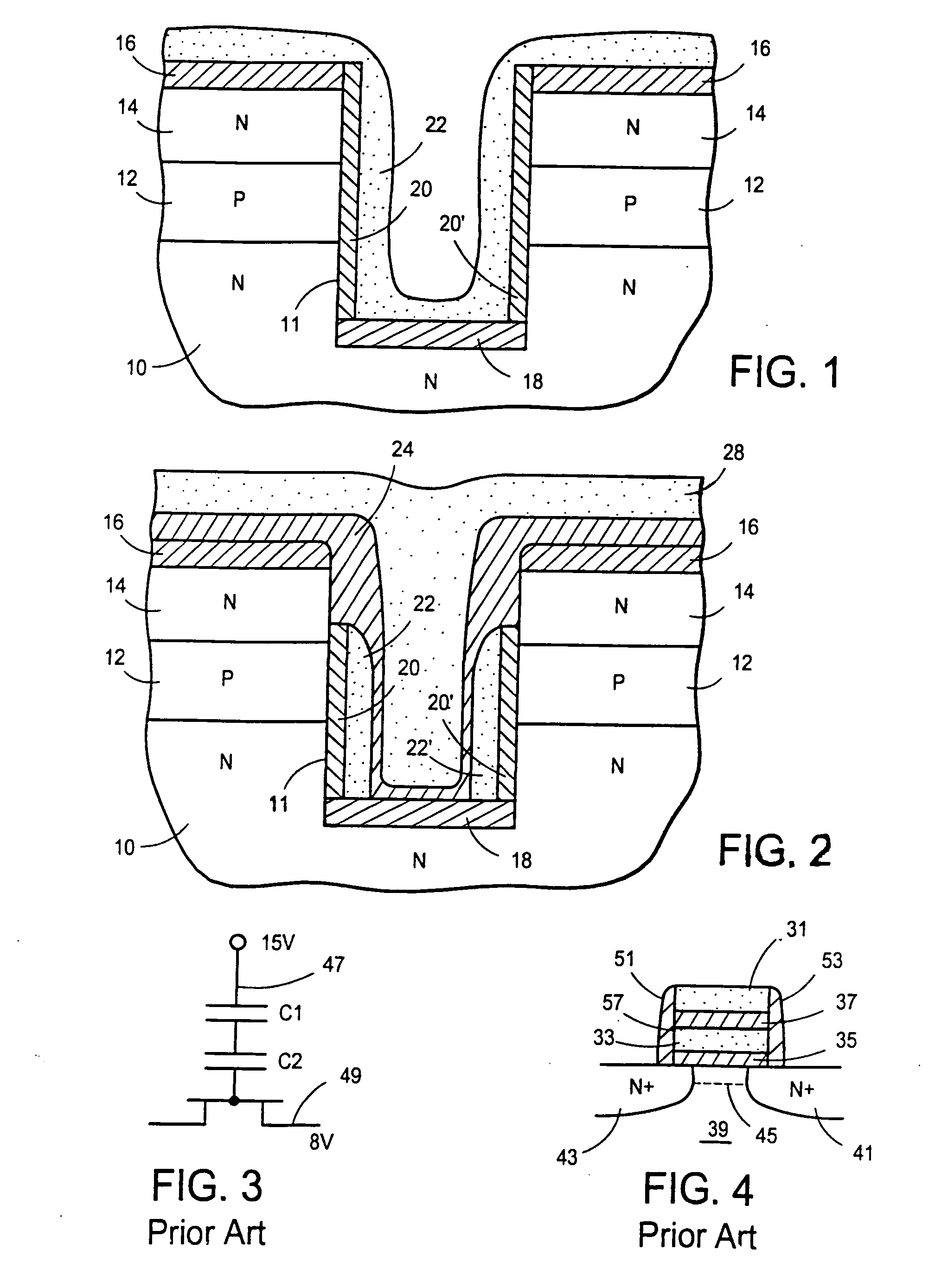

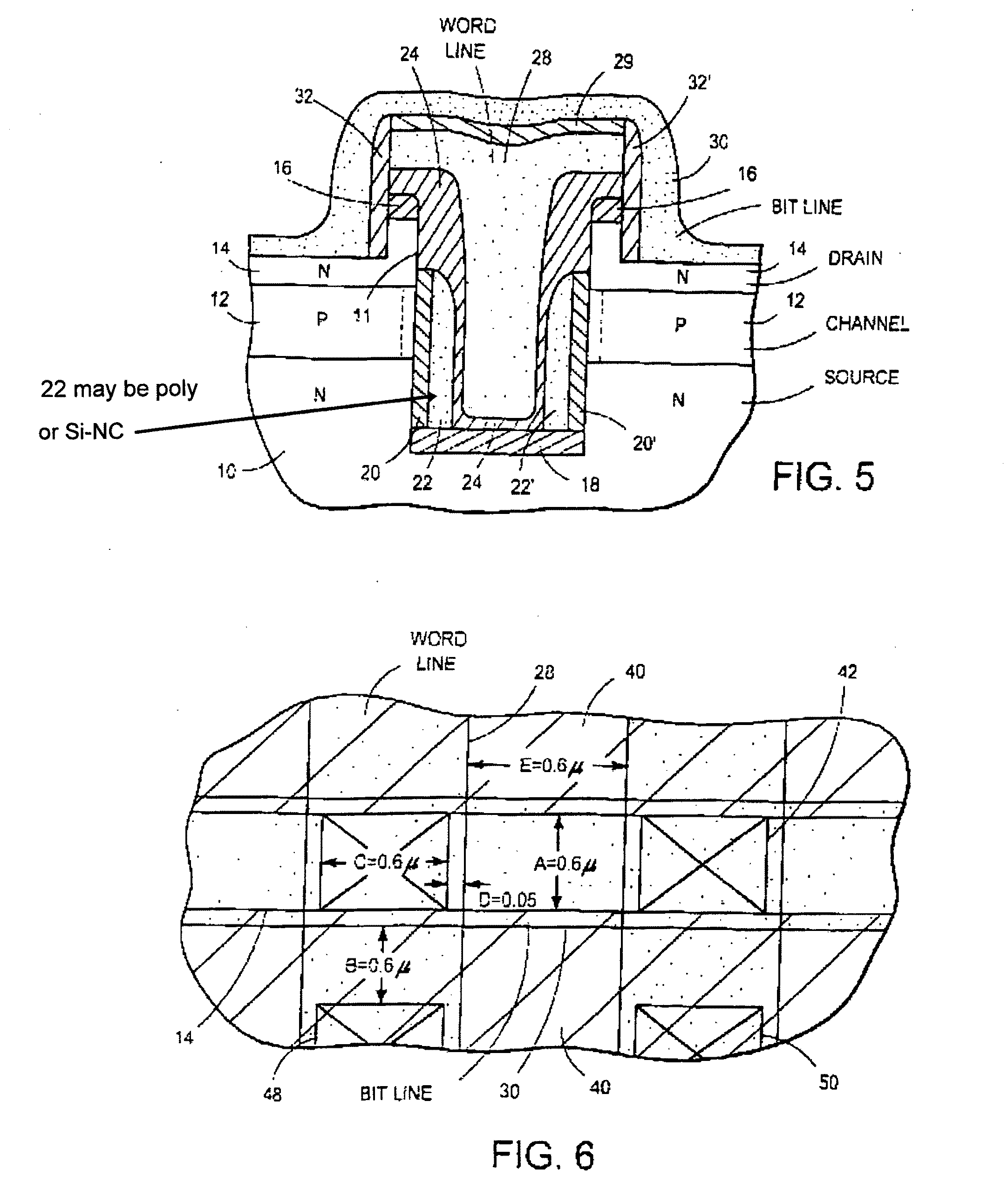

Vertically integrated flash EPROM for greater density and lower cost

InactiveUS20090039407A1Increase cell areaImprove the coupling ratioTransistorSolid-state devicesIon implantationPolycrystalline silicon

A nonvolative memory in the form of a vertical flash EPROM with high density and low cost. A vertical MOS transistor is formed in well etched into a semiconductor substrate, the substrate having source, body and drain regions formed by ion implantation. A thin gate oxide or oxide-nitride-oxide (ONO) layer is formed in the well and a self-aligned floating gate of polysilicon is formed over the gate oxide in the well to overlie the body region. An anisotropic etch is used to form the self aligned floating gate so as to remove all horizontal components and leave no portion of said floating gate extending beyond the perimeter of said well such that its lateral extents are determined by the anisotropic etch and not photolithography. Leff is determined by the energy of the implants used for form the source and drain regions and not by lithography. A deep field oxide bounding parts of said well keeps the coupling ratio good at all feature sizes. A vertically oriented NMOS and PMOS transistor are also disclosed.

Owner:VORA MADHUKAR B

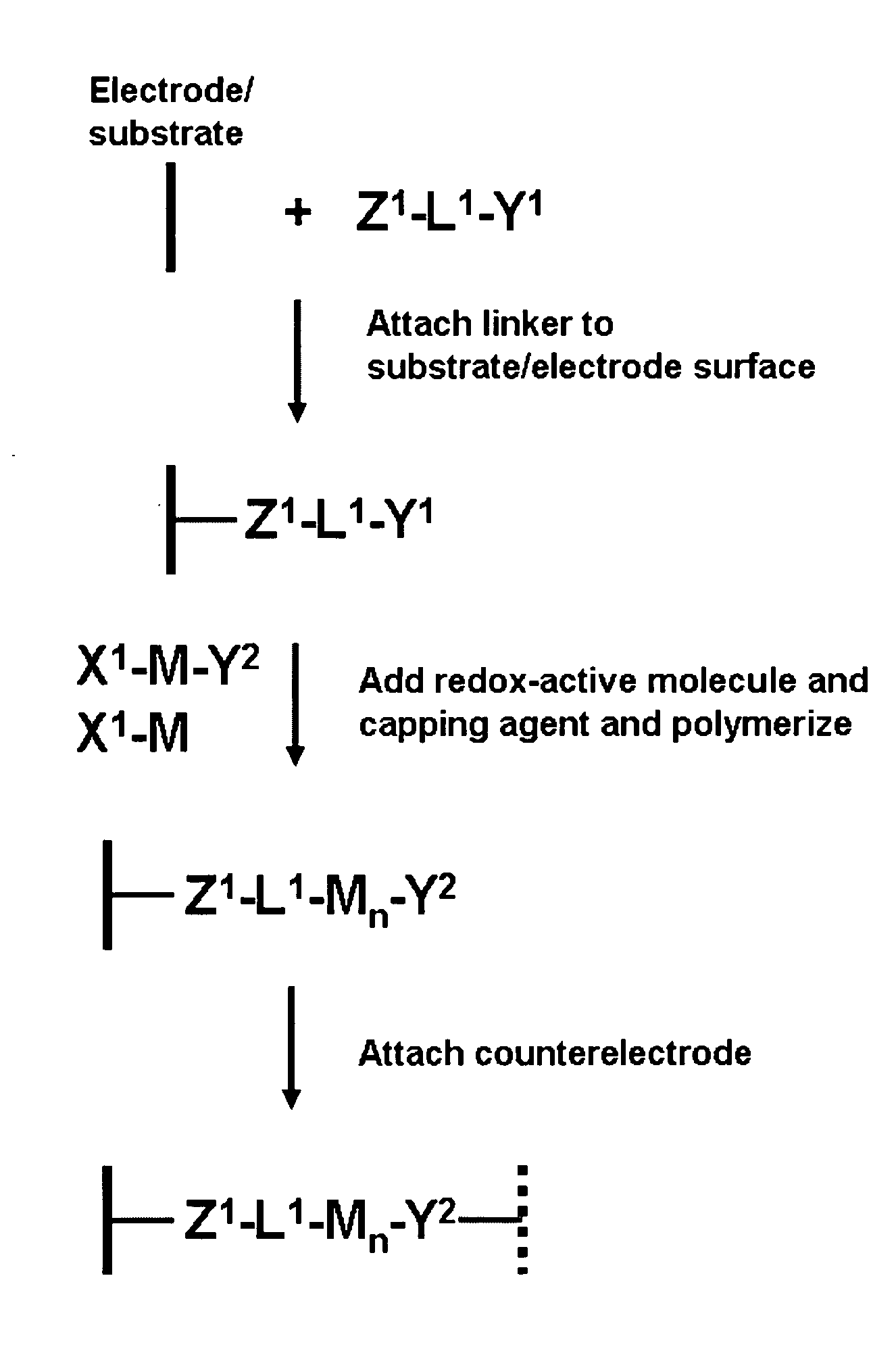

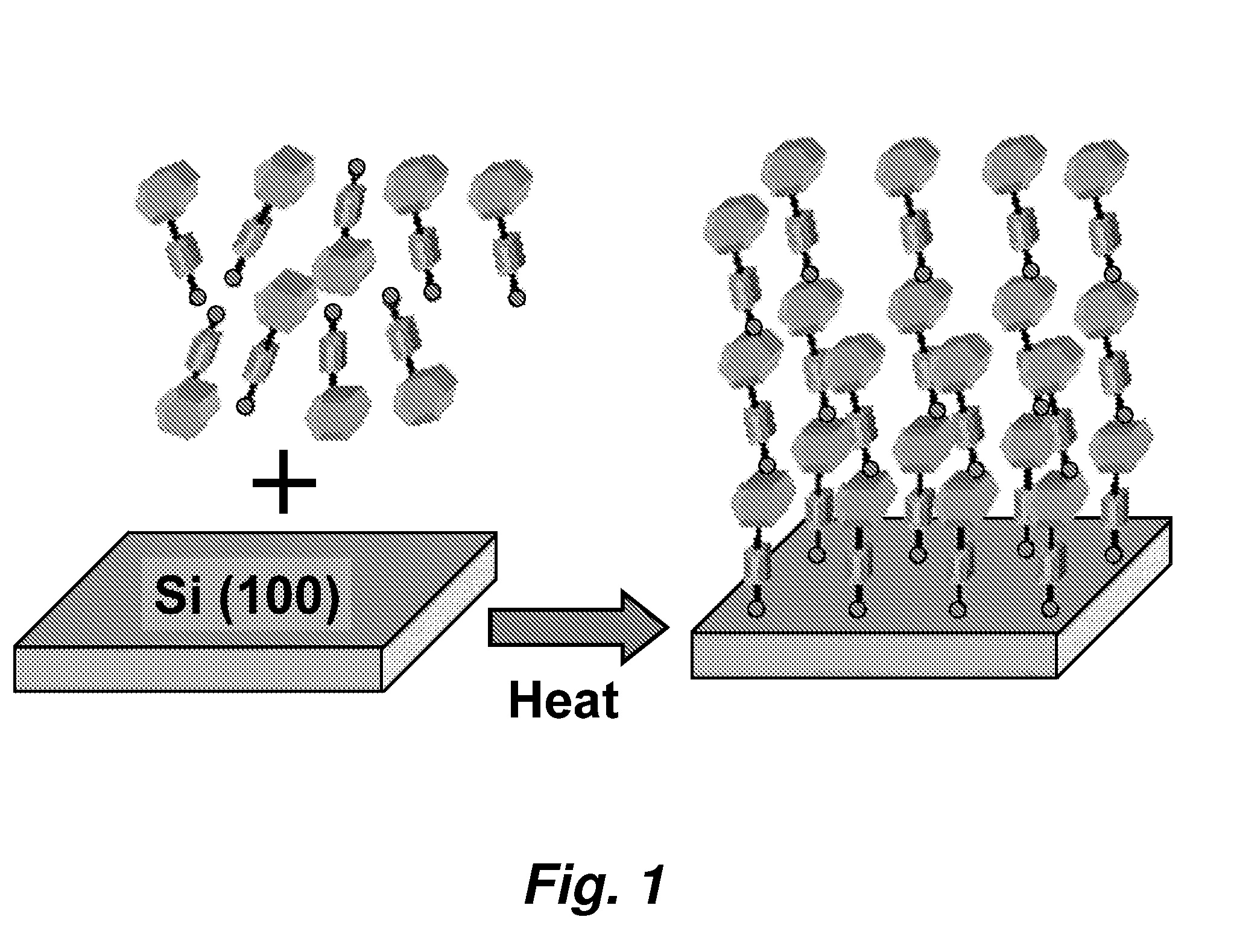

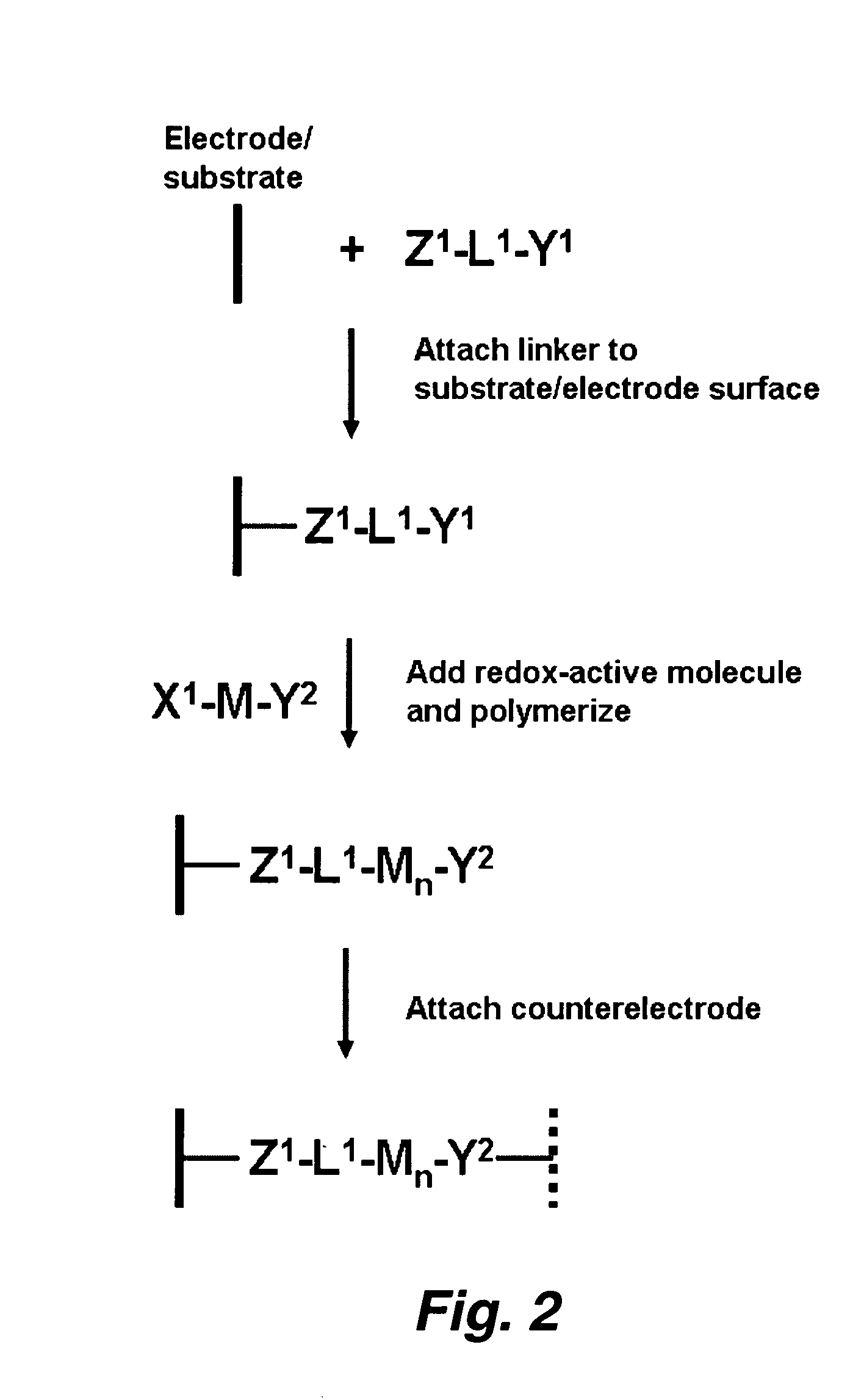

Procedure for preparing redox-active polymers on surfaces

InactiveUS20080280047A1Small feature sizeNanoinformaticsSolid-state devicesReactive sitePolymer chemistry

This invention provides novel methods for the formation of redox-active polymers attached to surfaces. In certain embodiments, the methods involve providing redox-active molecules bearing at least a first reactive site or group and a second reactive site or group; and contacting the surface with the redox-active molecules where the contacting is under conditions that result in attachment of said redox-active molecules to said surface via the first reactive site or group and attachment of redox-active molecules via the second reactive site or group, to the redox-active molecules attached to the surface thereby forming a polymer attached to said surface where the polymers comprise at least two of said redox-active molecules.

Owner:NORTH CAROLINA STATE UNIV +1

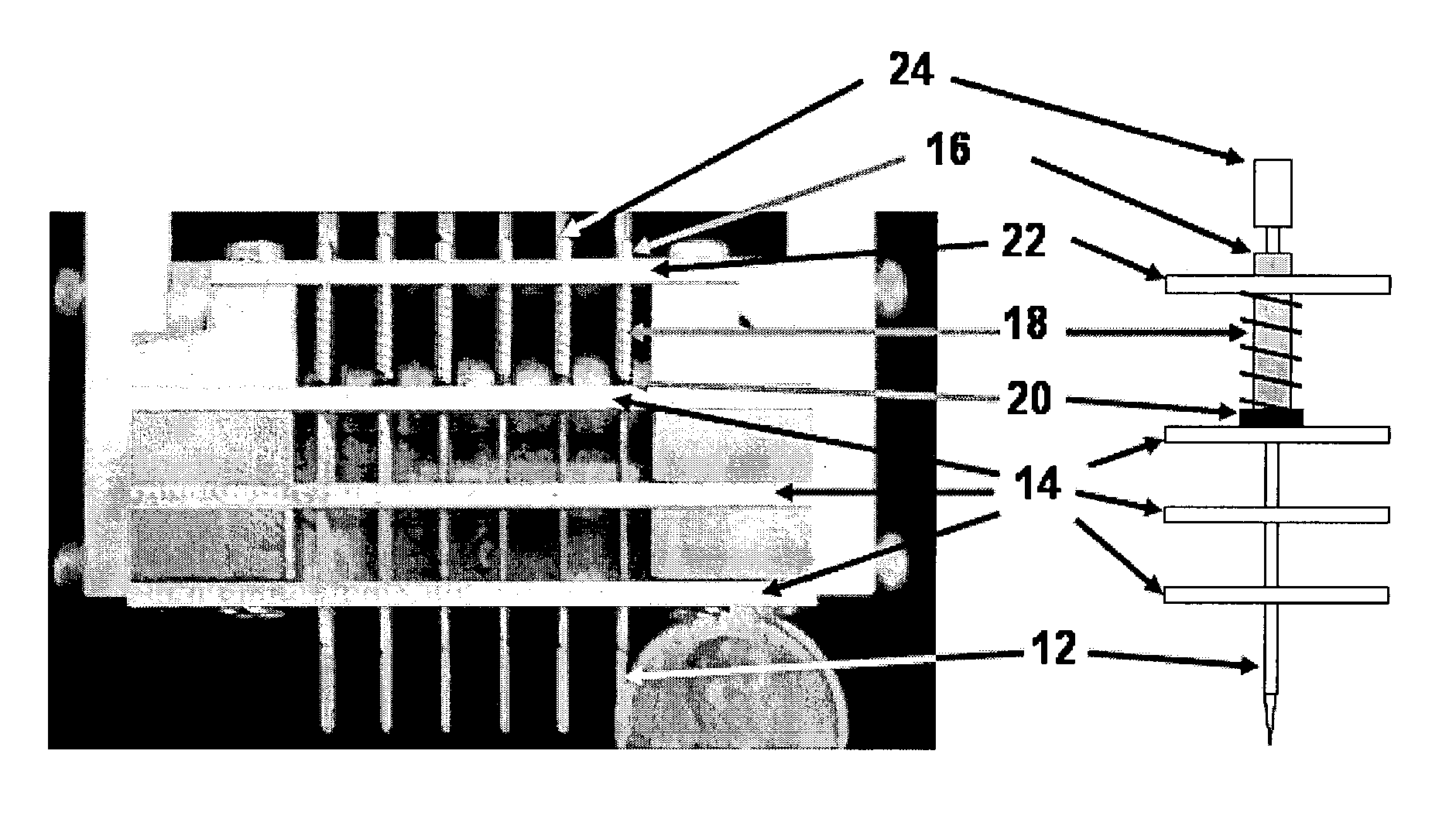

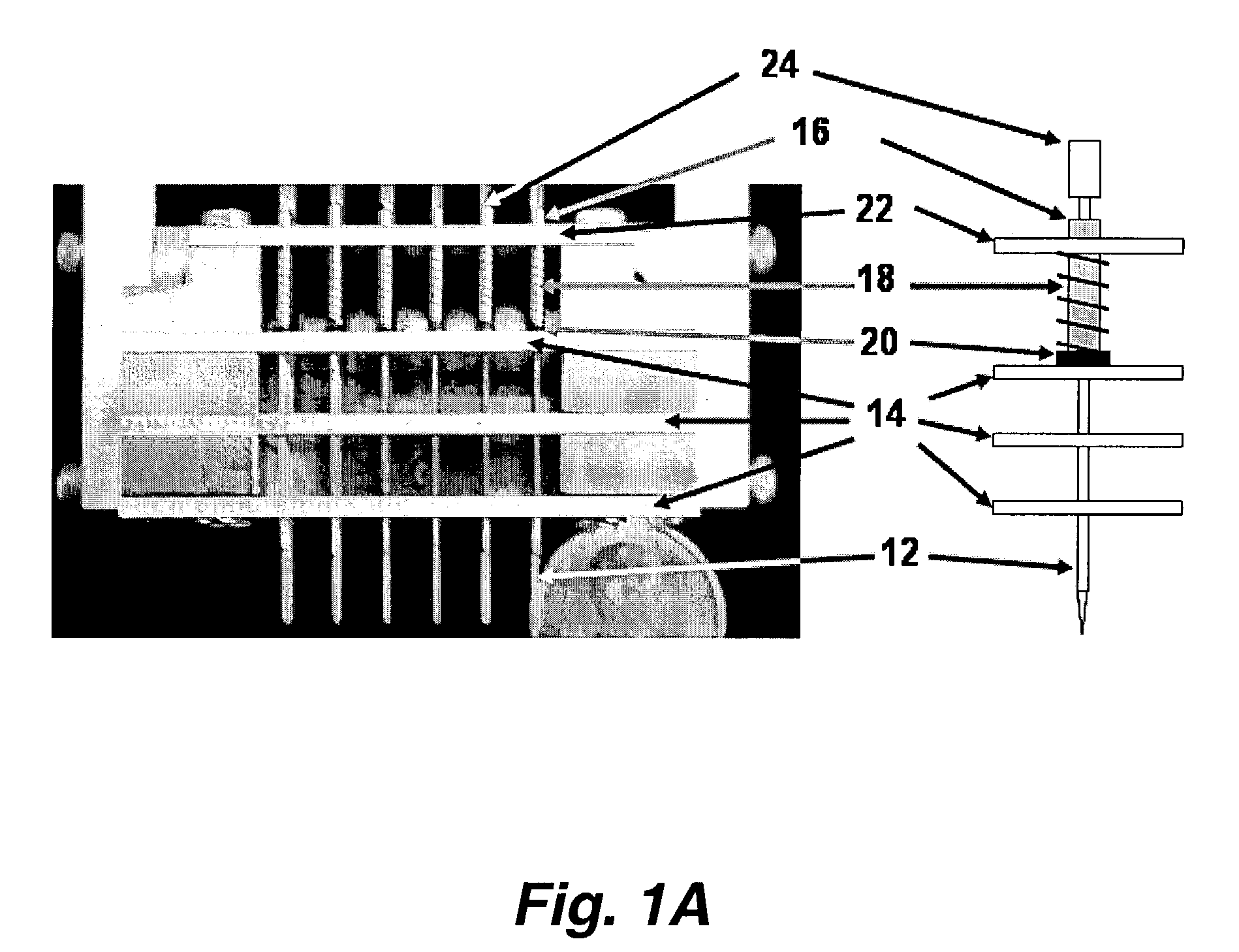

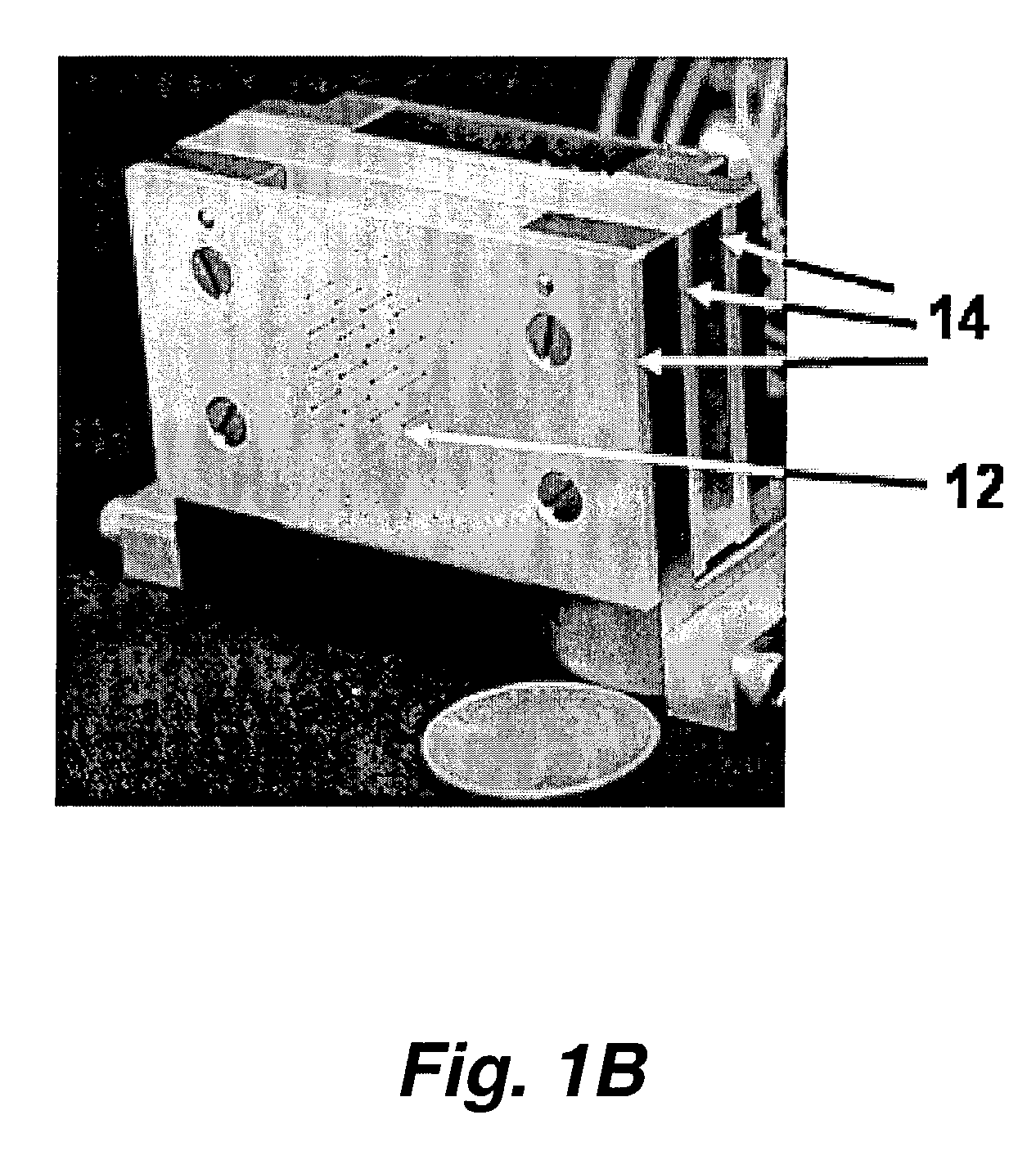

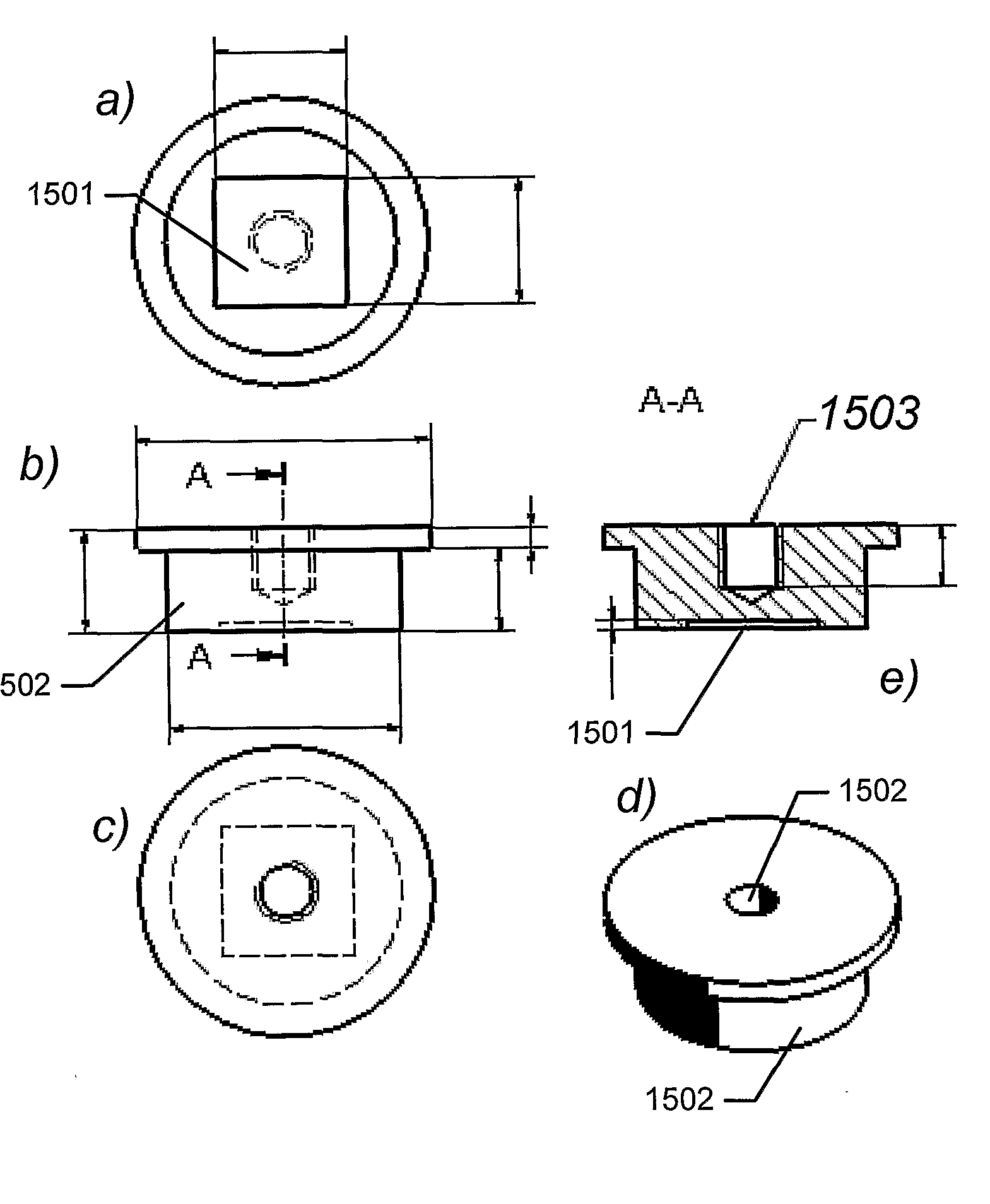

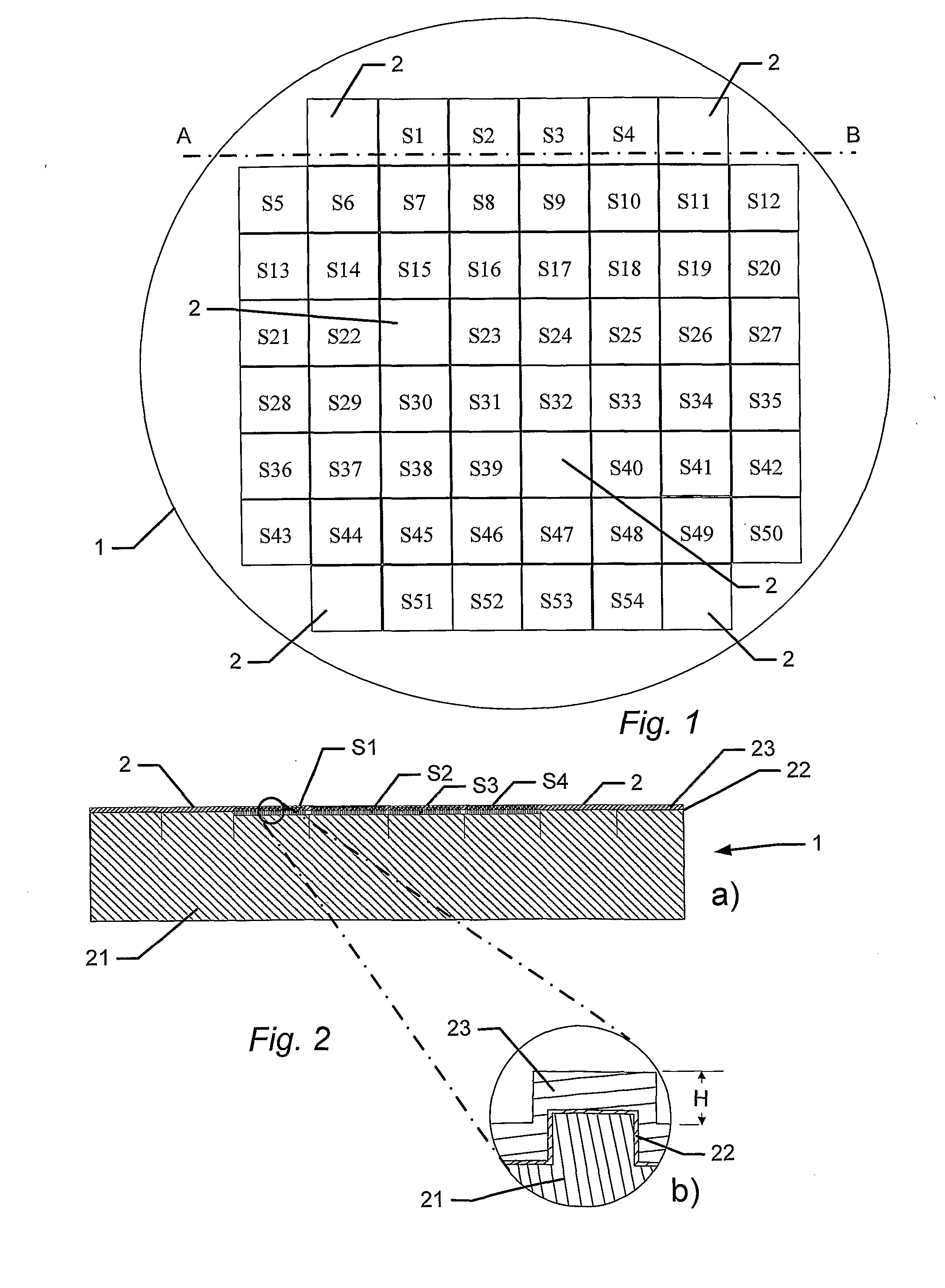

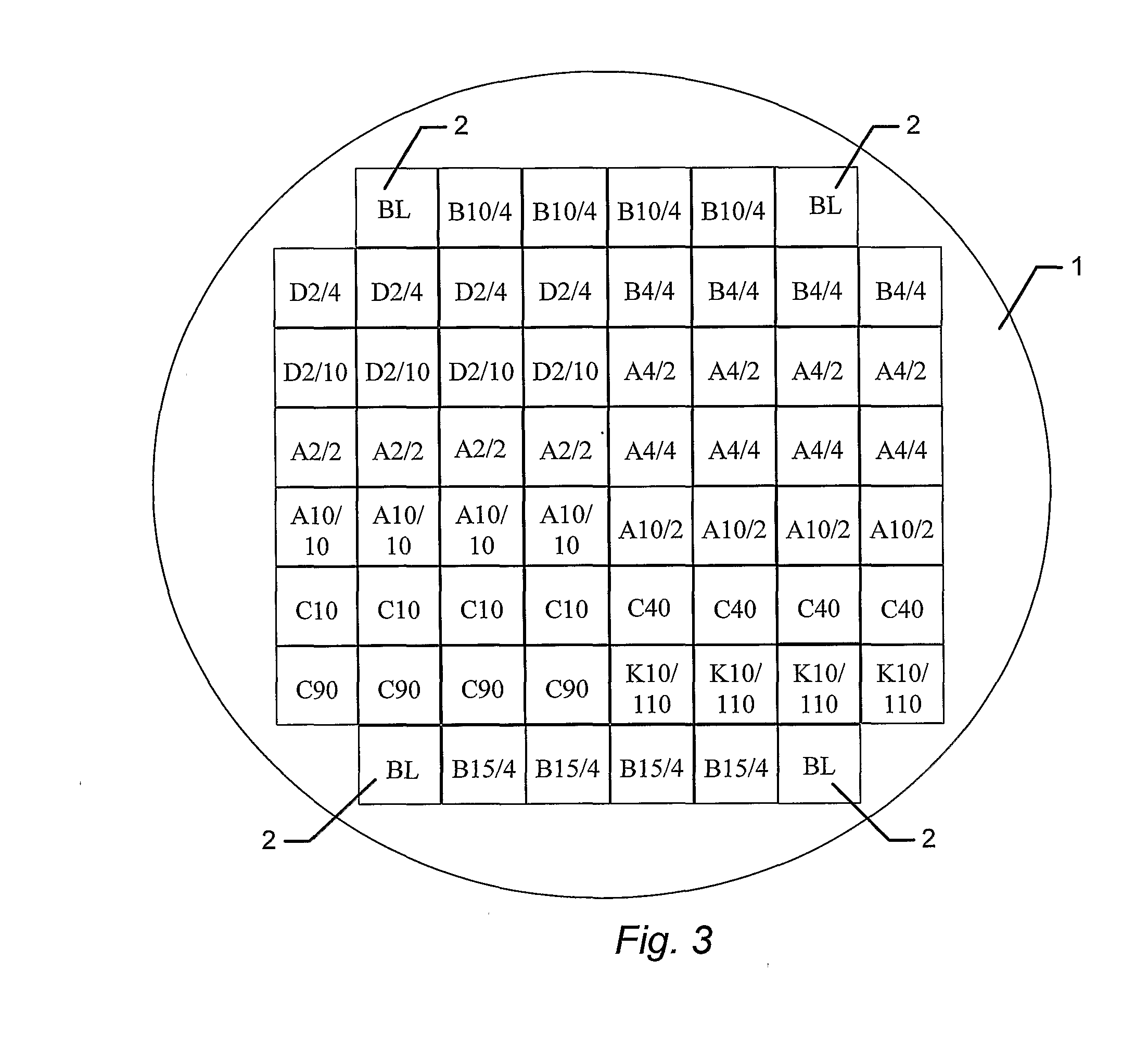

Capillary pins for high-efficiency microarray printing device

InactiveUS7312068B2Small feature sizeImproved-reagent usageBioreactor/fermenter combinationsBiological substance pretreatmentsLong axisQuartz

This invention provides improved components (e.g. array “pins”, print head, substrate platen, print head platen, and the like) for microarray printing devices as well as microarray printing devices incorporating such components. In one embodiment, this invention provides a microarray print head comprising a plurality of glass or quartz spotting capillaries disposed in a support that maintains a fixed spacing between the spotting capillaries and that permits the spotting capillaries to move in a direction parallel to the long axis of the capillaries.

Owner:RGT UNIV OF CALIFORNIA

Biocompatible Material for Surgical Implants and Cell Guiding Tissue Culture Surfaces

InactiveUS20080208351A1Promote resultsGood body shapeBone implantConfectioneryBiomedical engineeringTissue culture

A biocompatible material, wherein at least a part of a surface of the biocompatible material is characterized by a micro or nano-meter scale topographical structure comprising a plurality of features where the structure is selected to promote a predetermined cell function in vivo or ex vivo in cell or tissue culture.

Owner:AARHUS UNIV

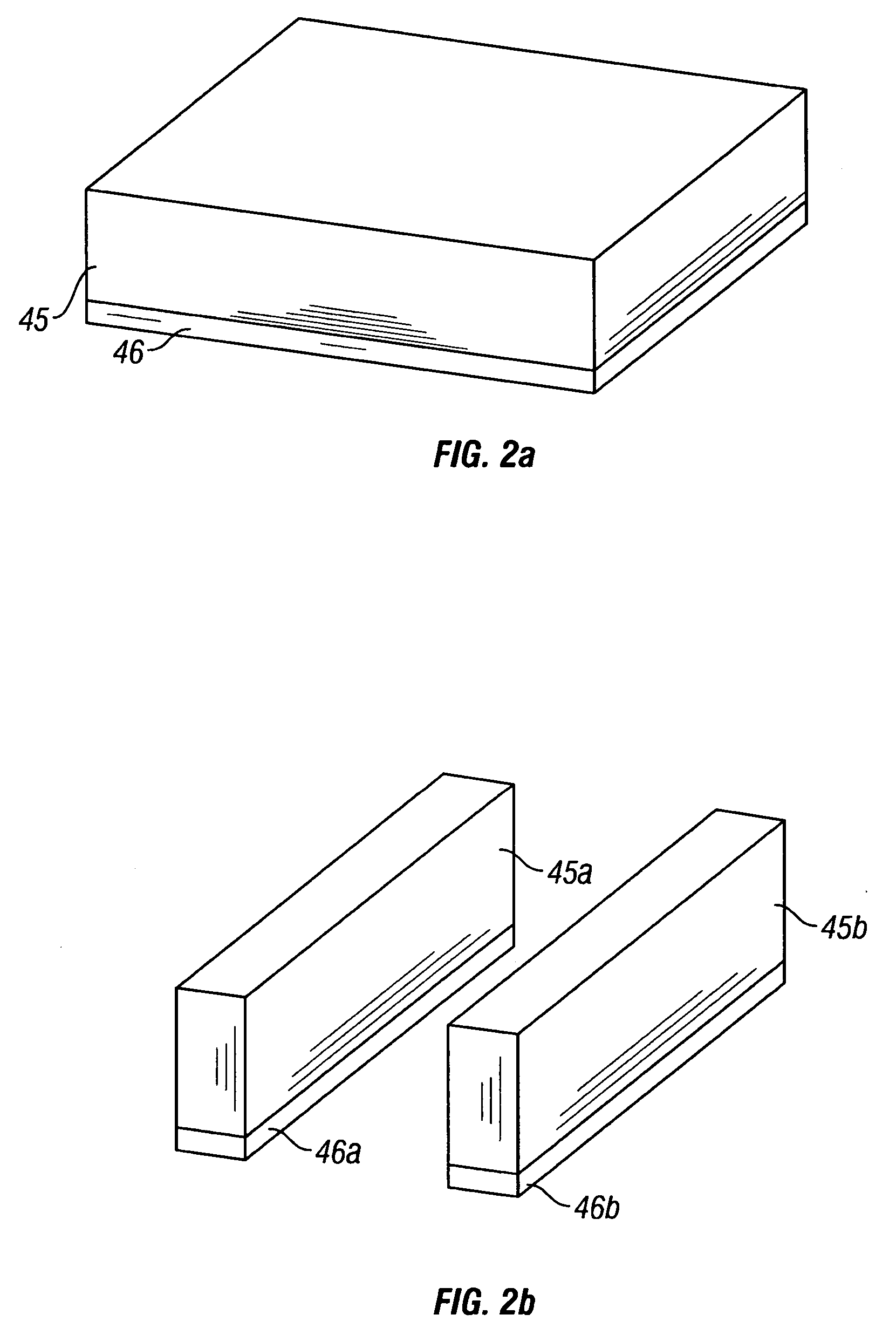

Contacts for an improved high-density nonvolatile memory

InactiveUS20050012220A1High densitySmall feature sizeTransistorSemiconductor/solid-state device detailsElectrical conductorHigh density

An improved method for fabricating a three dimensional monolithic memory with increased density. The method includes forming conductors preferably comprising tungsten, then filling and planarizing; above the conductors forming semiconductor elements preferably comprising two diode portions and an antifuse, then filling and planarizing; and continuing to form conductors and semiconductor elements in multiple stories of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

Mask pattern for semiconductor device fabrication, method of forming the same, and method of fabricating finely patterned semiconductor device

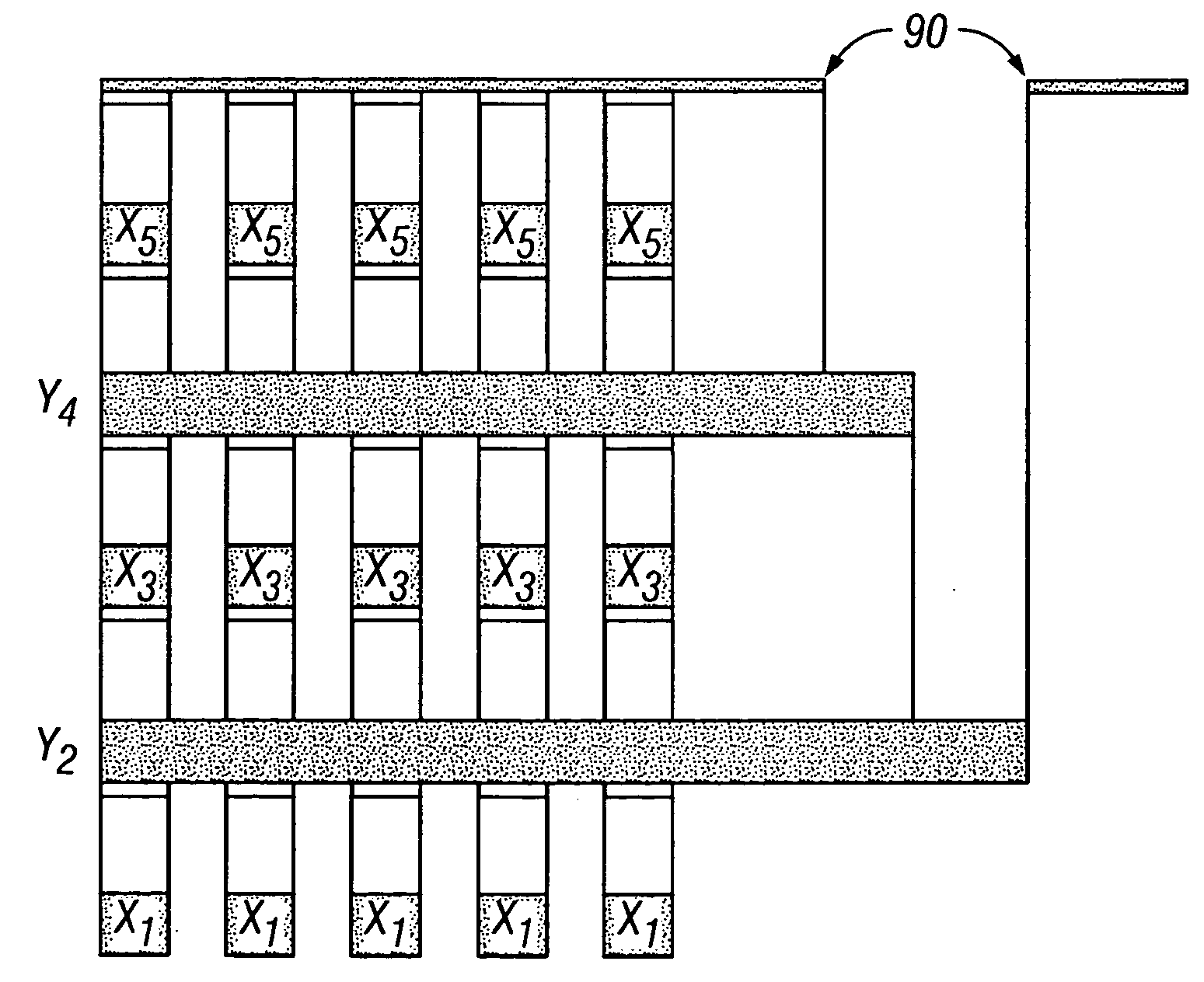

InactiveUS20050227492A1Small feature sizeMinimizing transformationMaterial nanotechnologySemiconductor/solid-state device manufacturingResistDevice material

Provided are a mask pattern including a self-assembled molecular layer, a method of forming the same, and a method of fabricating a semiconductor device. The mask pattern includes a resist pattern formed on a semiconductor substrate and the self-assembled molecular layer formed on at least a sidewall of the resist pattern. To form the mask pattern, first, the resist pattern is formed with openings on an underlayer covering the substrate to expose the underlayer to a first width. Then, the self-assembled molecular layer is selectively formed on a surface of the resist pattern to expose the underlayer to a second width smaller than the first width. The underlayer is etched using the resist pattern and the self-assembled molecular layer as an etching mask to obtain a fine pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

Wafer scale test interfact unit: low loss and high isolation devices and methods for high speed and high density mixed signal interconnects and contactors

InactiveUS20160341790A1Reduce lossGood precisionParticular array feeding systemsElectronic circuit testingHigh densityEngineering

Devices and methods for multilayer packages, antenna array feeds, test interface units, connectors, contactors, and large format substrates. The device comprising a 3D coaxial distribution network structure including a plurality of coaxial transmission lines separated by a first pitch at the input and a second, wider pitch at the output thereof.

Owner:CUBIC CORPORATION

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com