Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1456 results about "Field oxide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Field oxide, FOX. relatively thick oxide (typically 100 - 500 nm) formed to passivate and protect semiconductor surface outside of active device area; part of any semiconductor device, but does not participate in device operation.

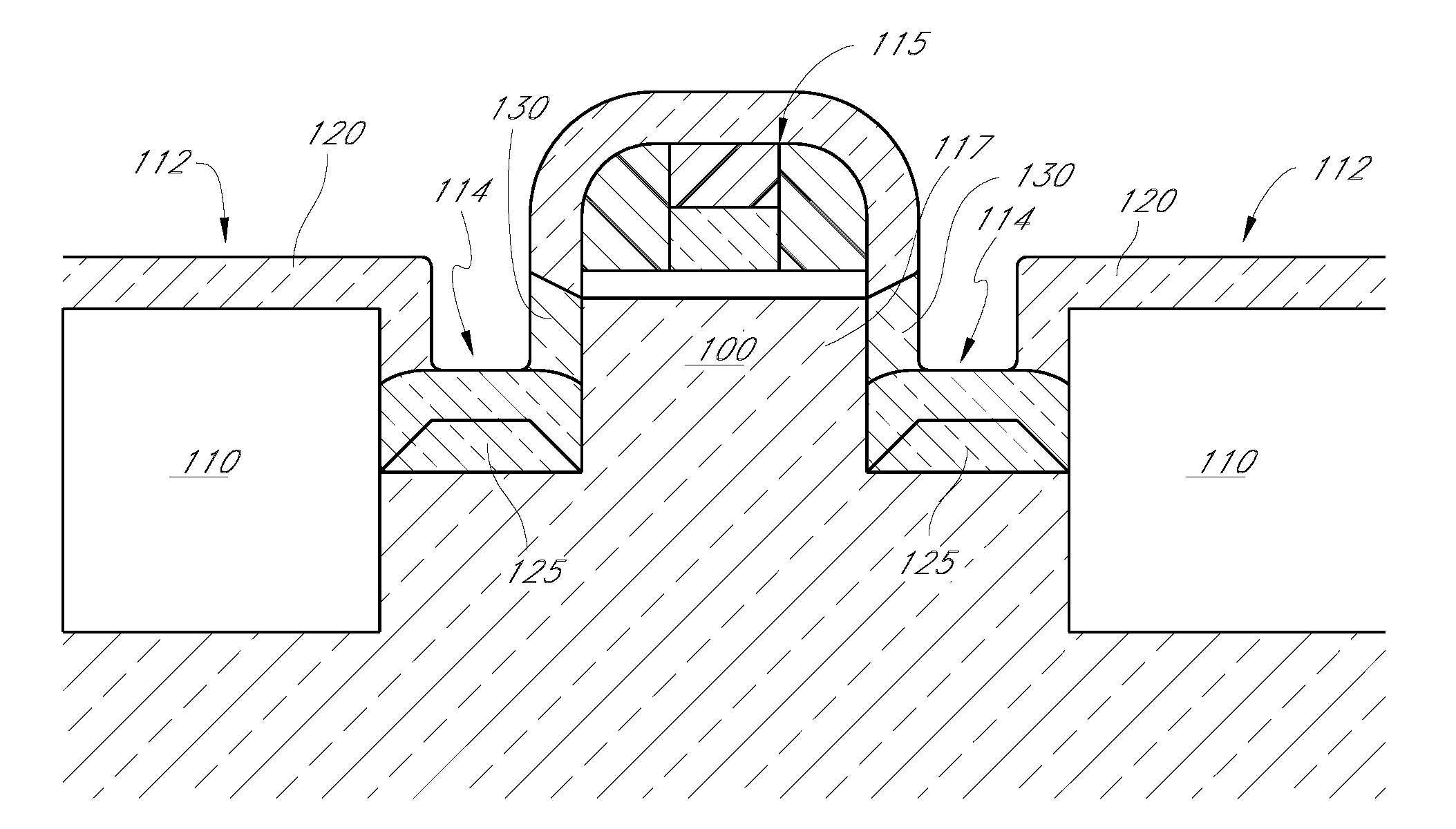

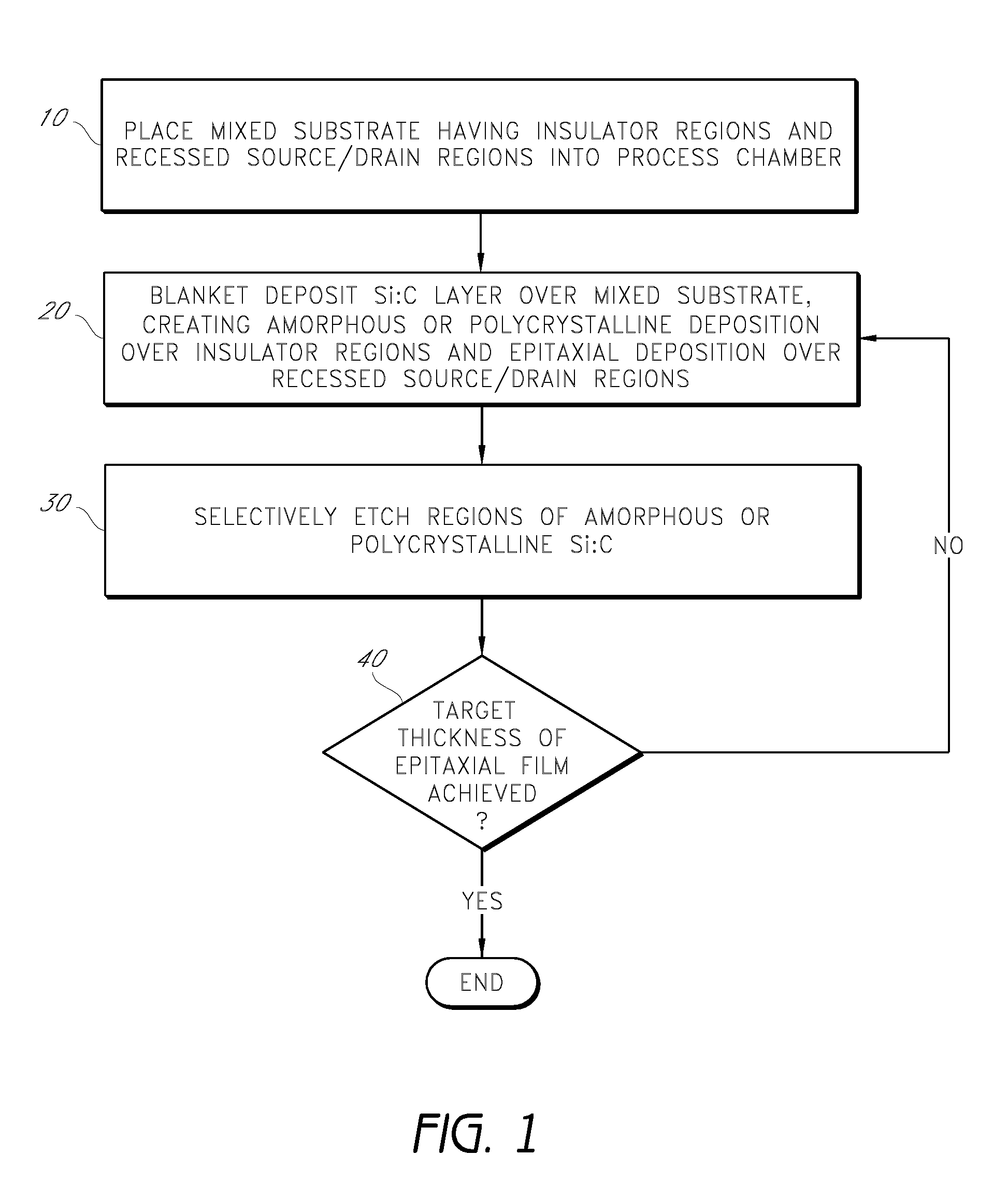

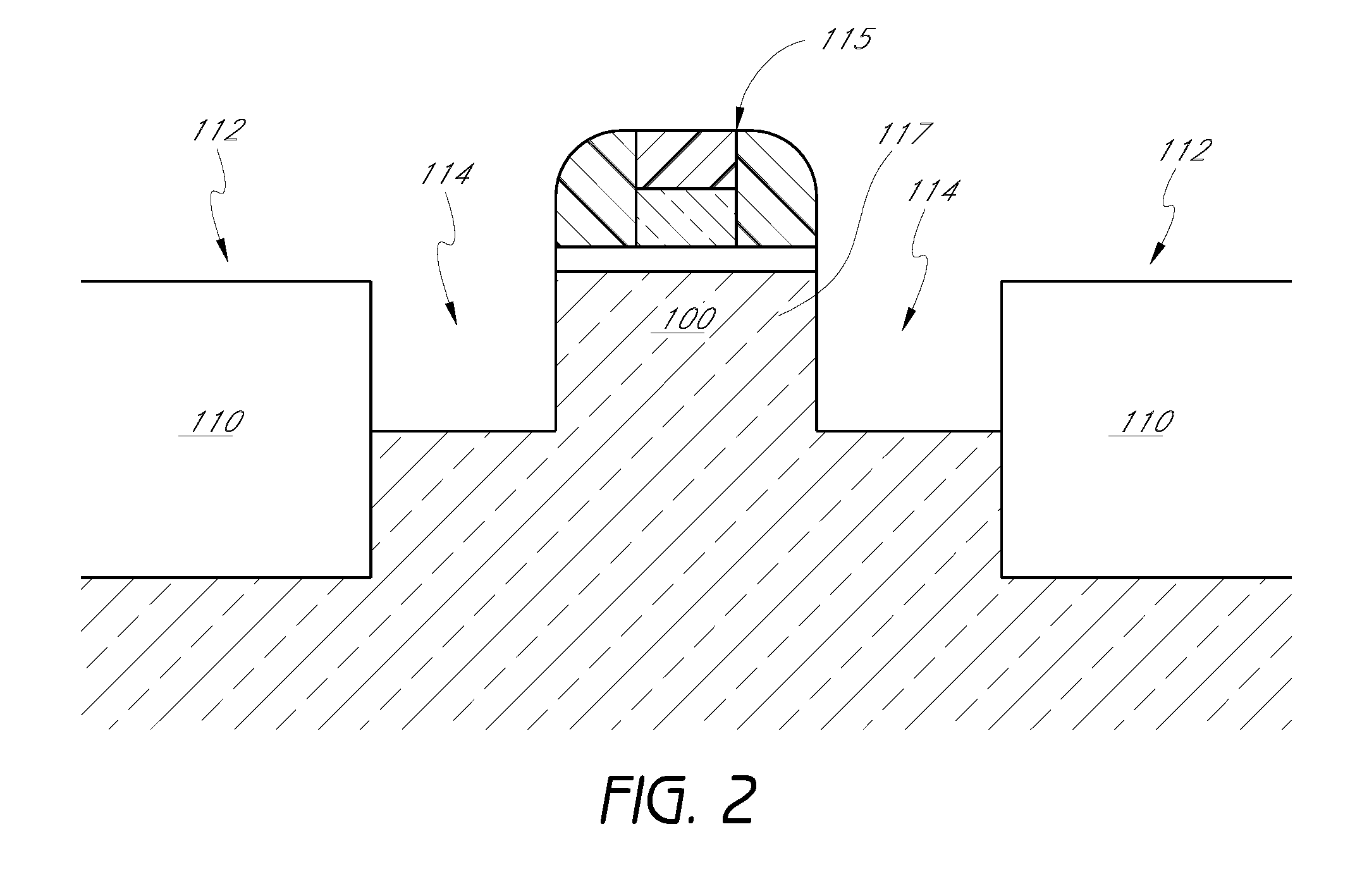

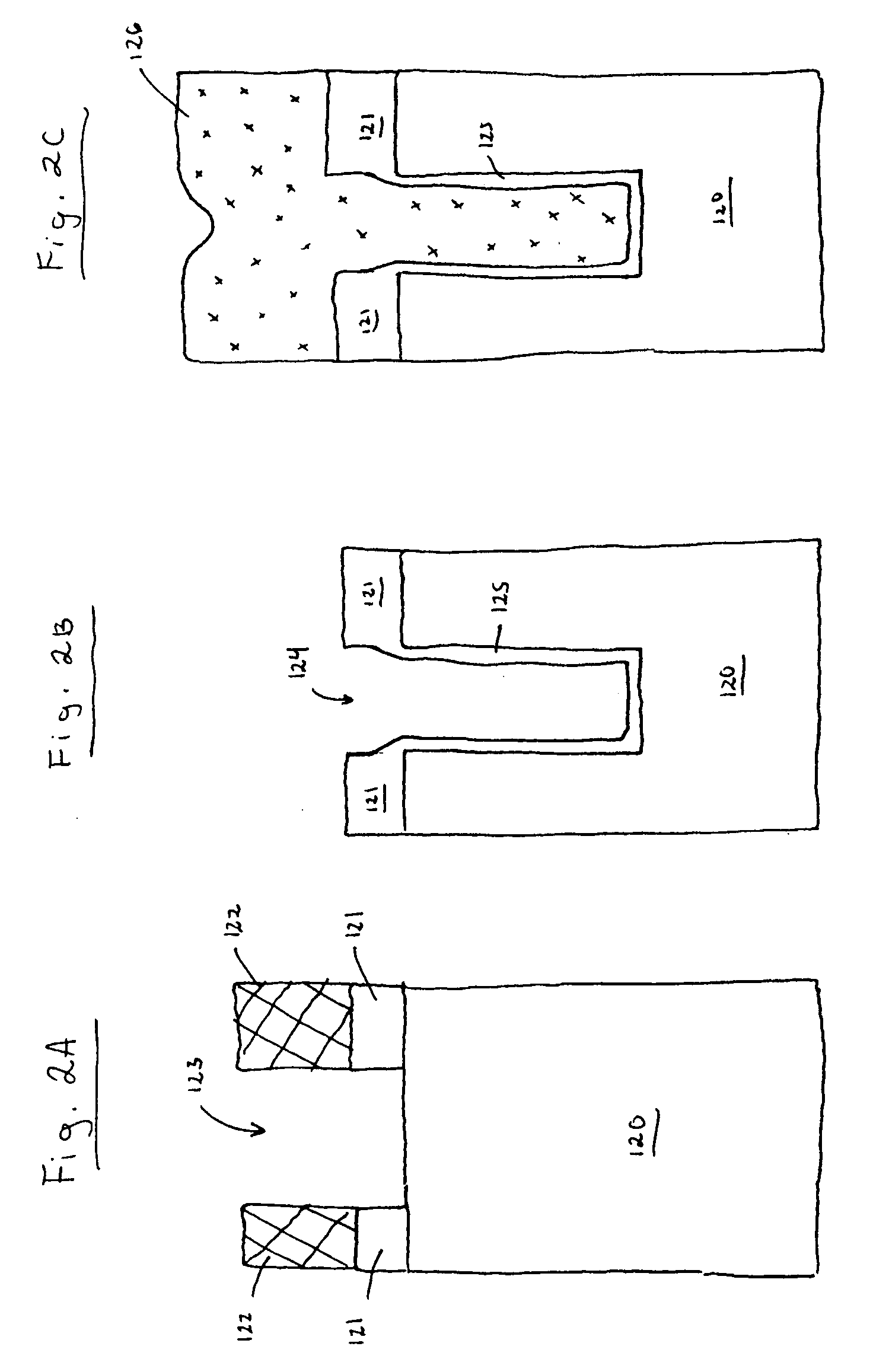

Selective epitaxial formation of semiconductor films

ActiveUS8278176B2Semiconductor/solid-state device manufacturingSemiconductor devicesCyclic processMetallurgy

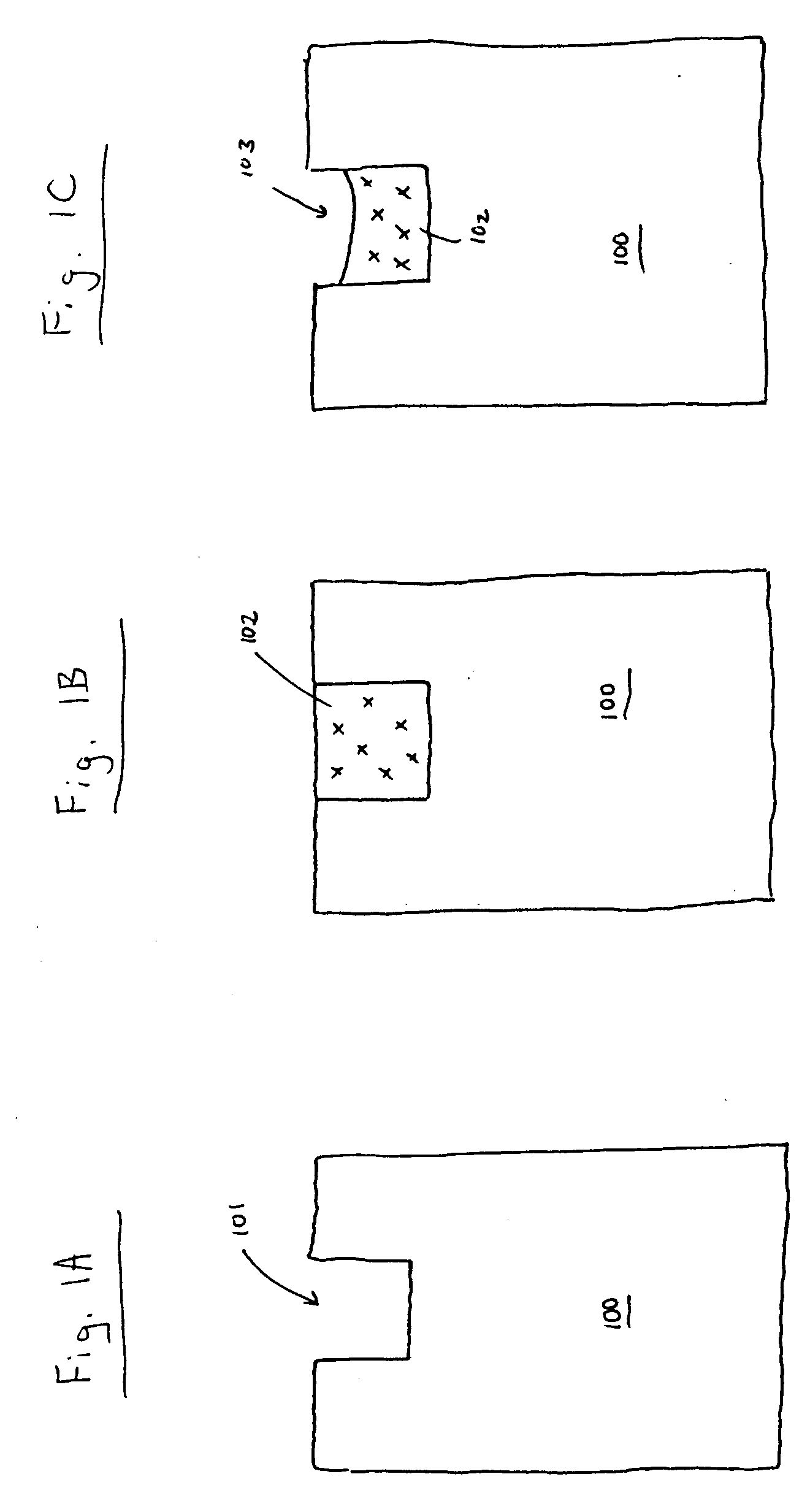

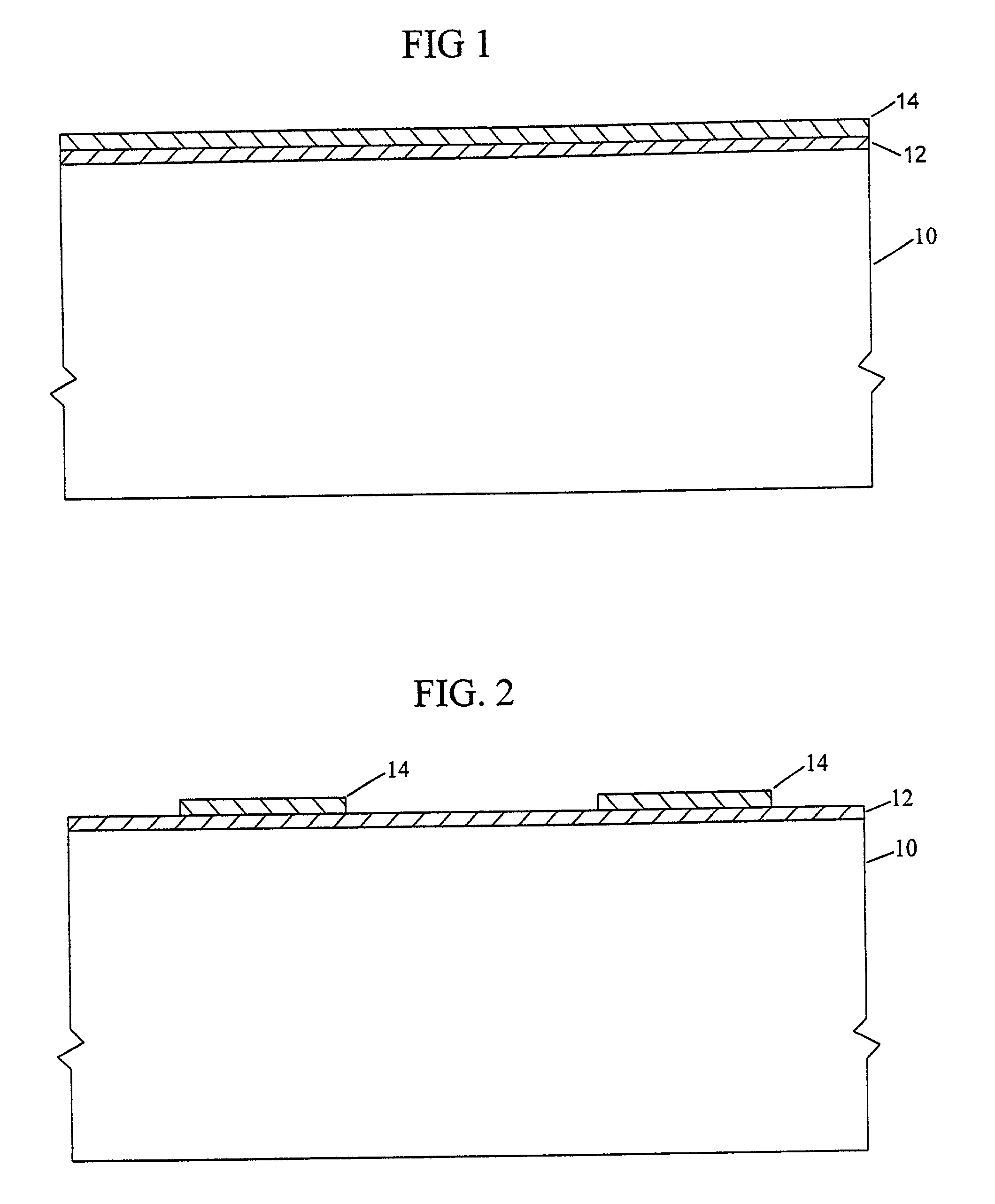

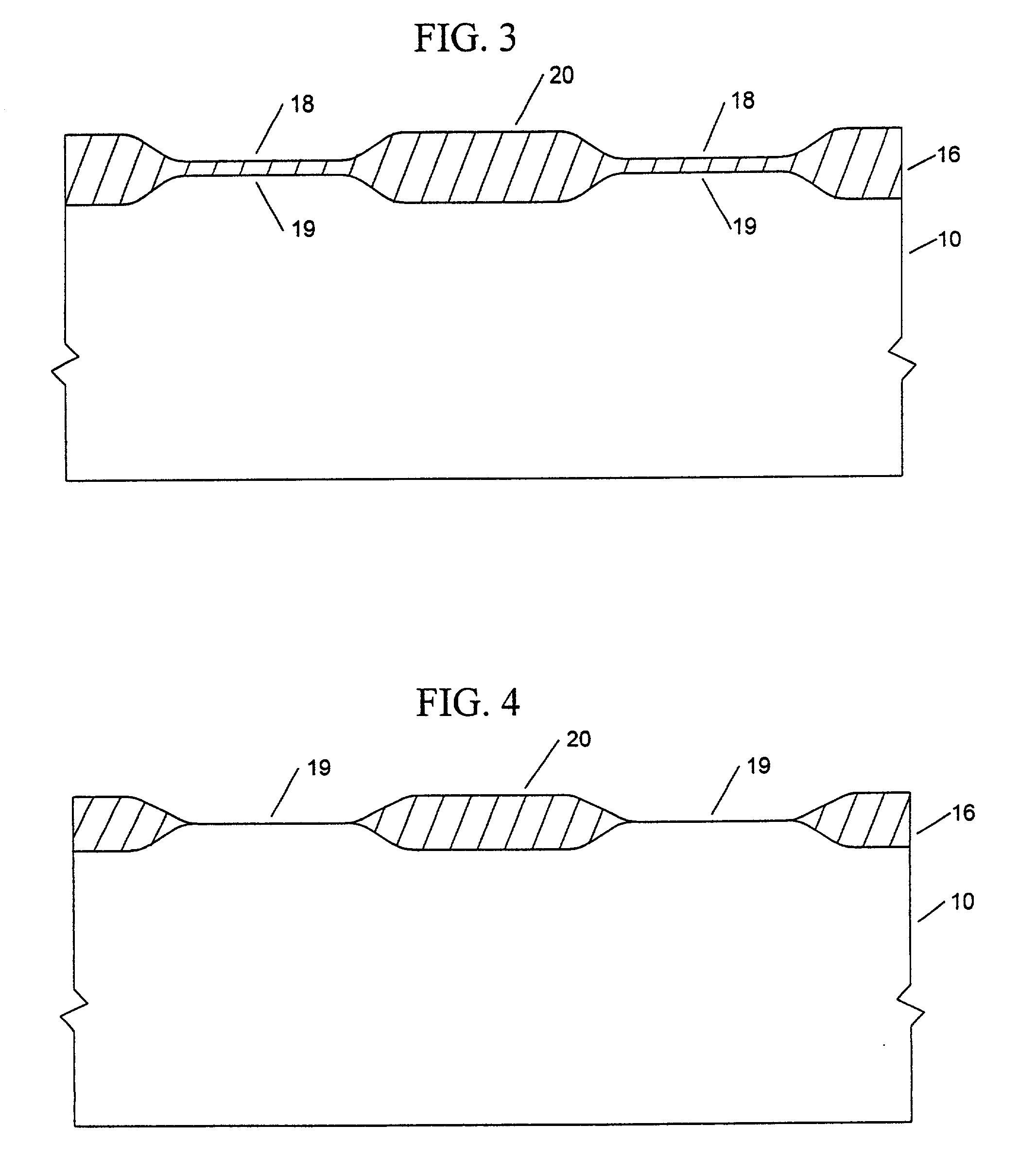

Epitaxial layers are selectively formed in semiconductor windows by a cyclical process of repeated blanket deposition and selective etching. The blanket deposition phases leave non-epitaxial material over insulating regions, such as field oxide, and the selective etch phases preferentially remove non-epitaxial material while deposited epitaxial material builds up cycle-by-cycle. Quality of the epitaxial material improves relative to selective processes where no deposition occurs on insulators. Use of a germanium catalyst during the etch phases of the process aid etch rates and facilitate economical maintenance of isothermal and / or isobaric conditions throughout the cycles. Throughput and quality are improved by use of trisilane, formation of amorphous material over the insulating regions and minimizing the thickness ratio of amorphous:epitaxial material in each deposition phase.

Owner:ASM IP HLDG BV

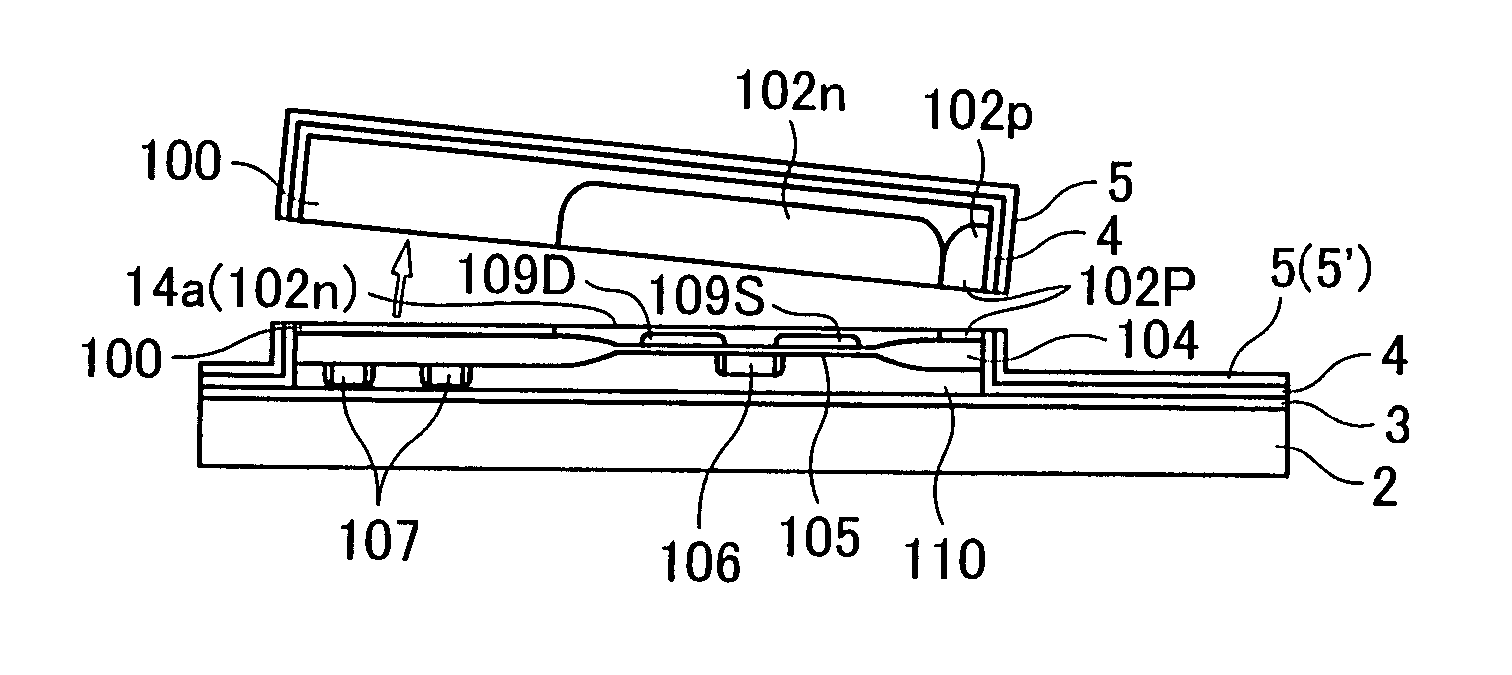

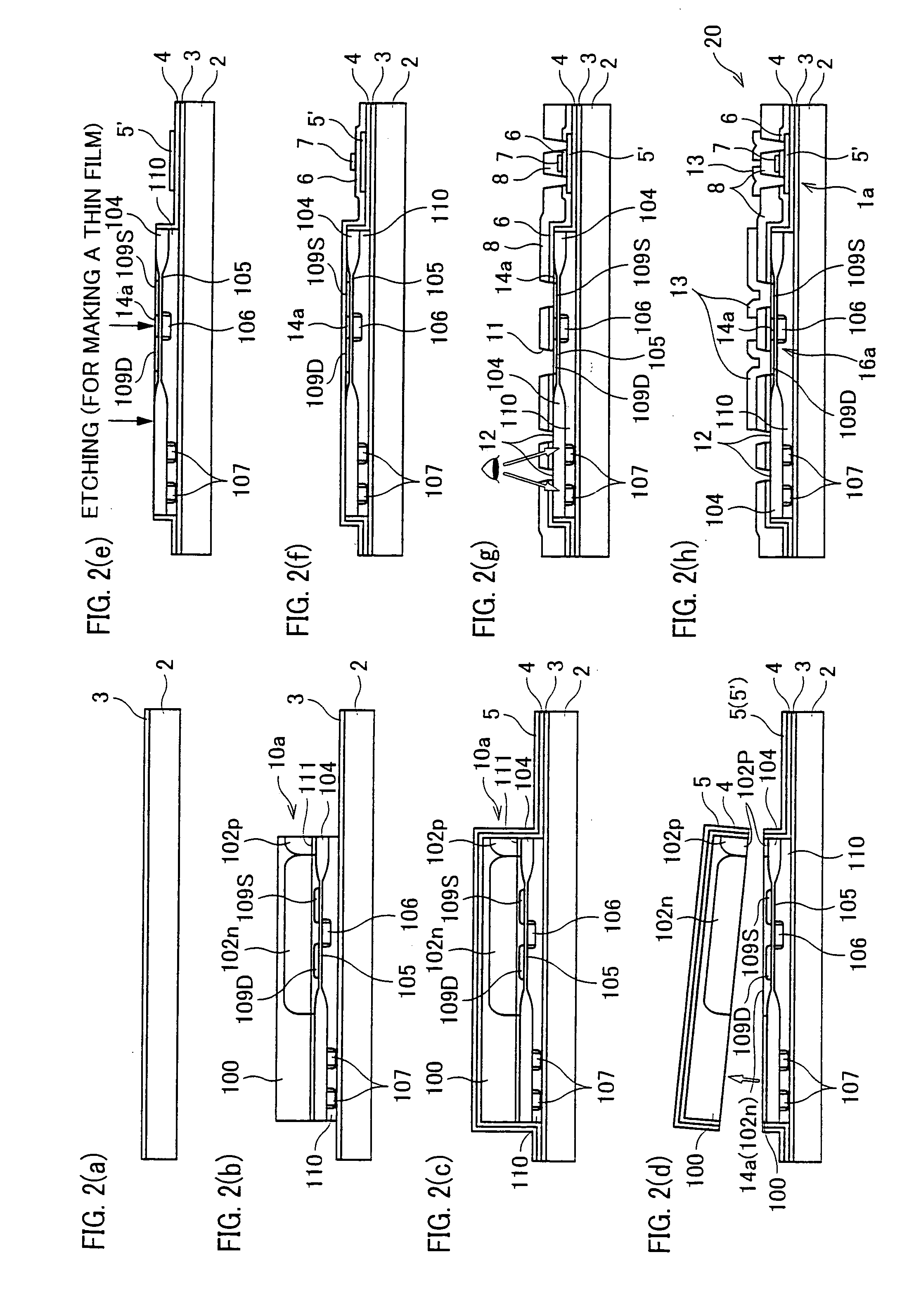

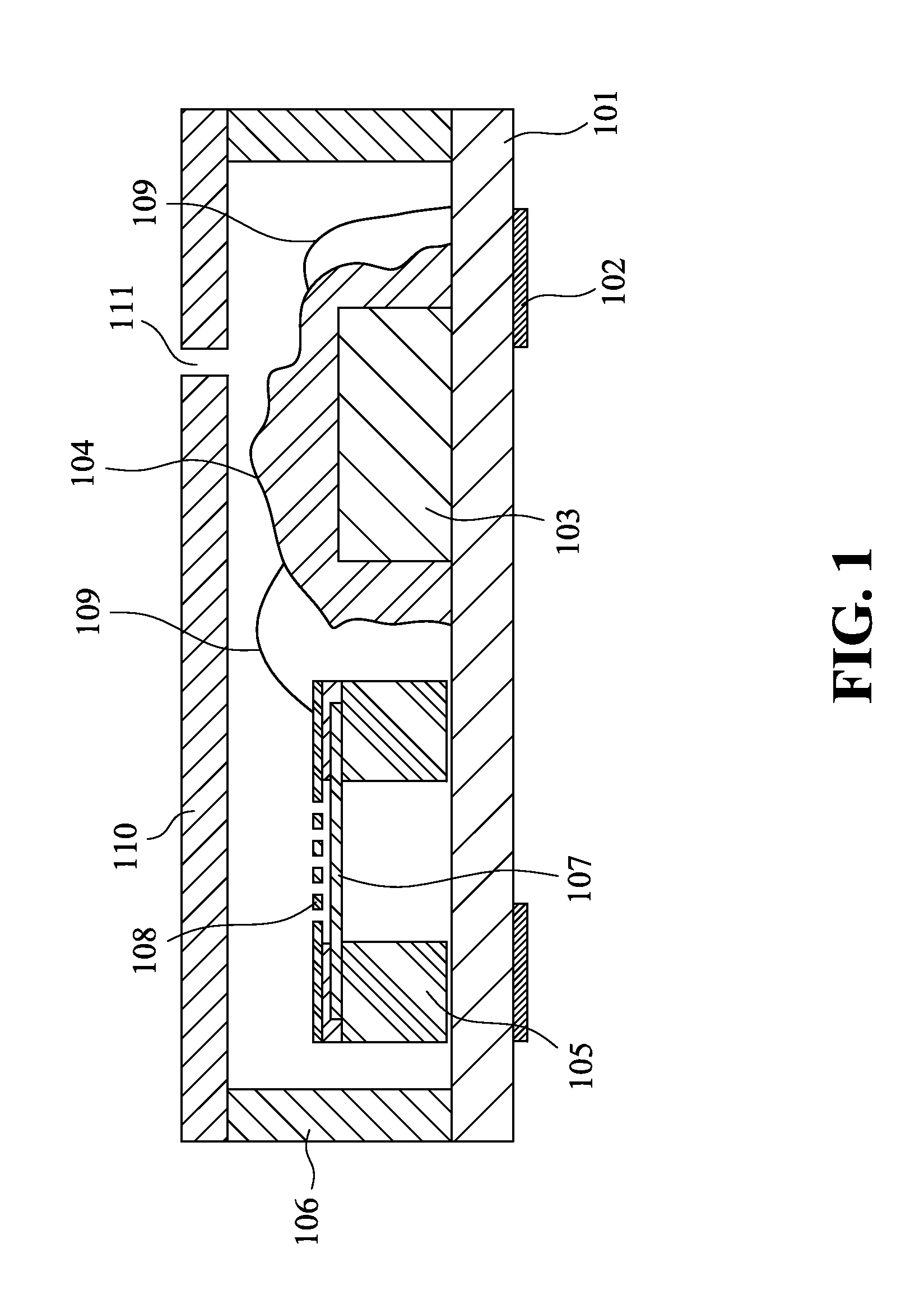

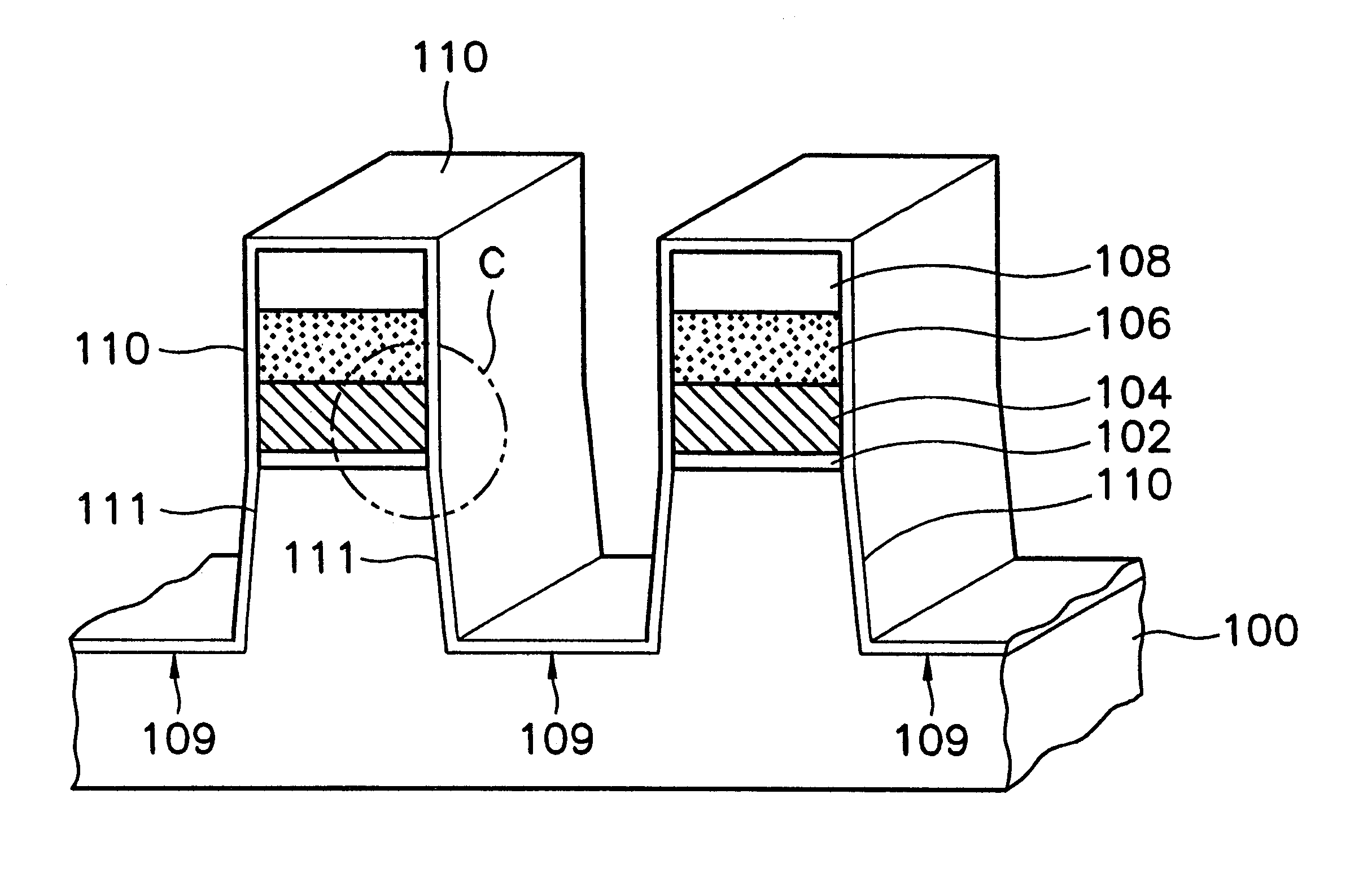

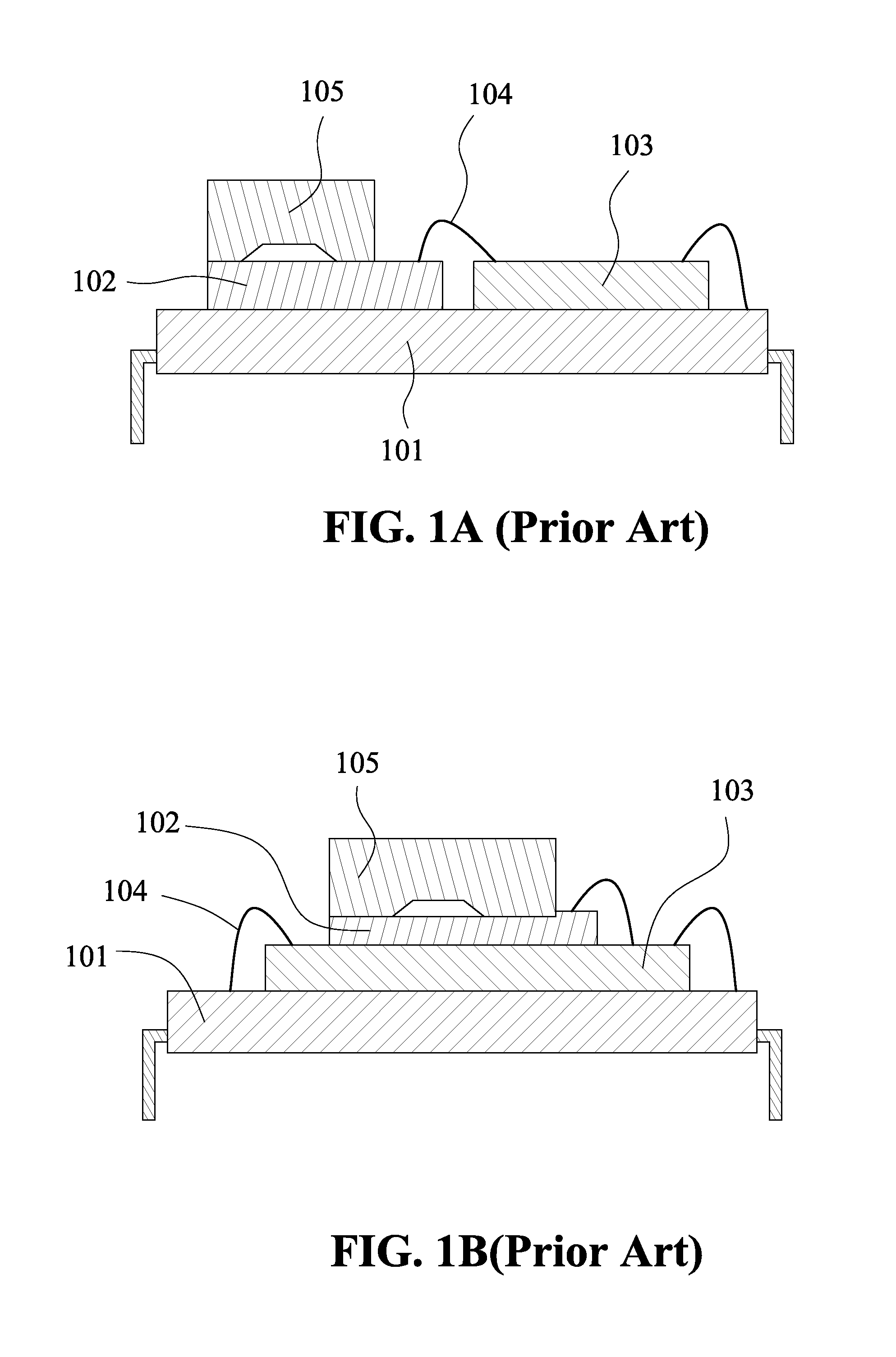

Semiconductor device and fabrication method for the same

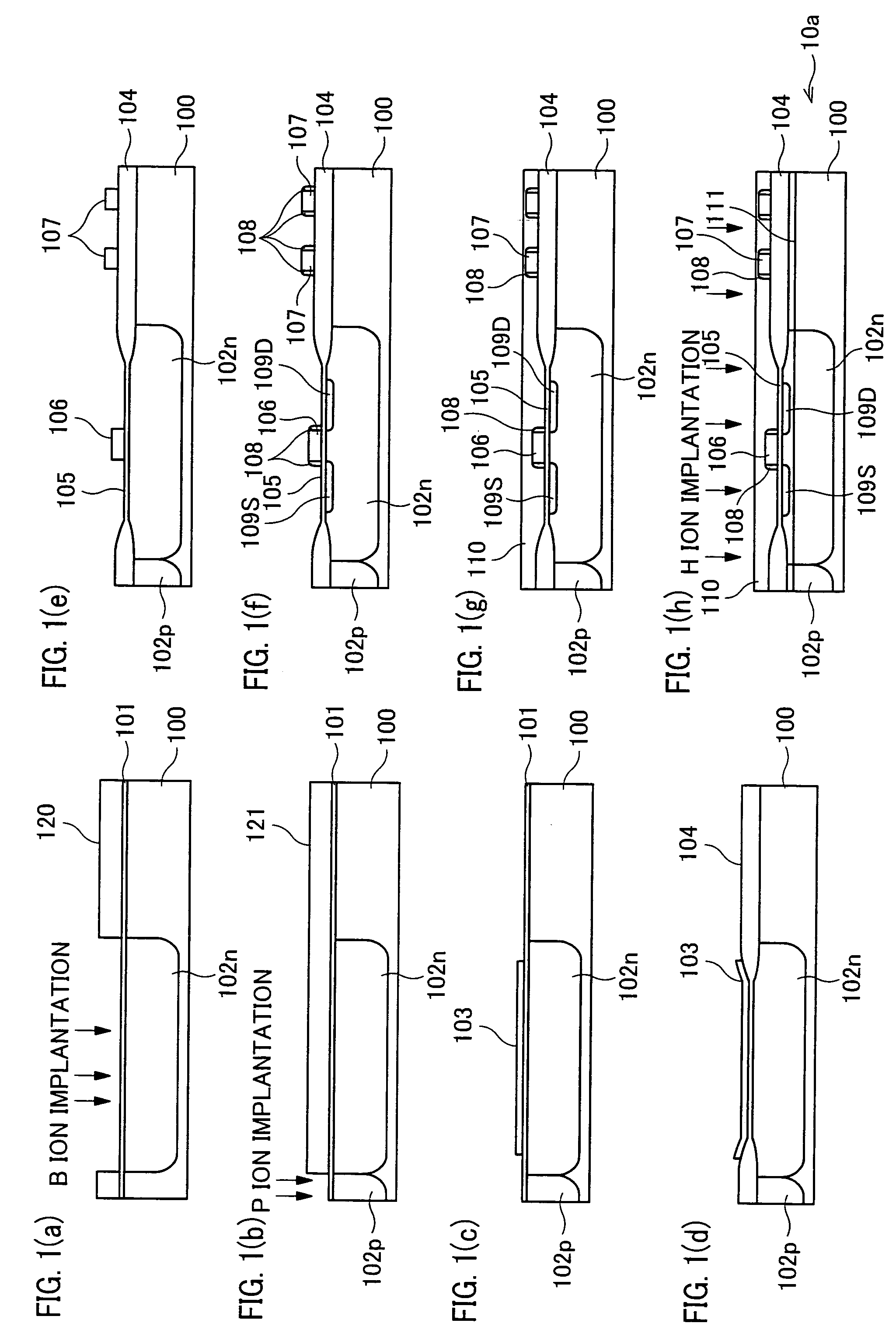

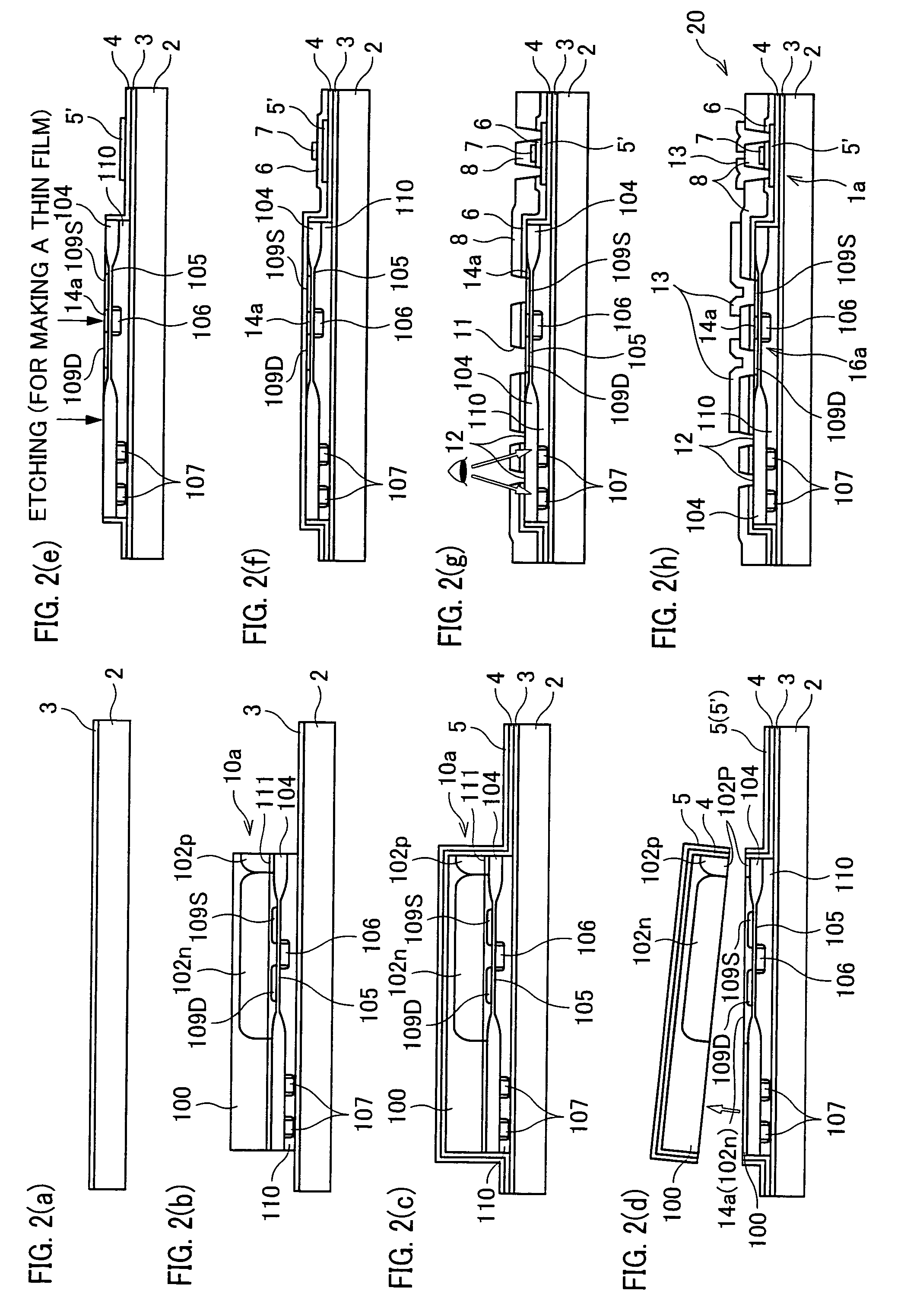

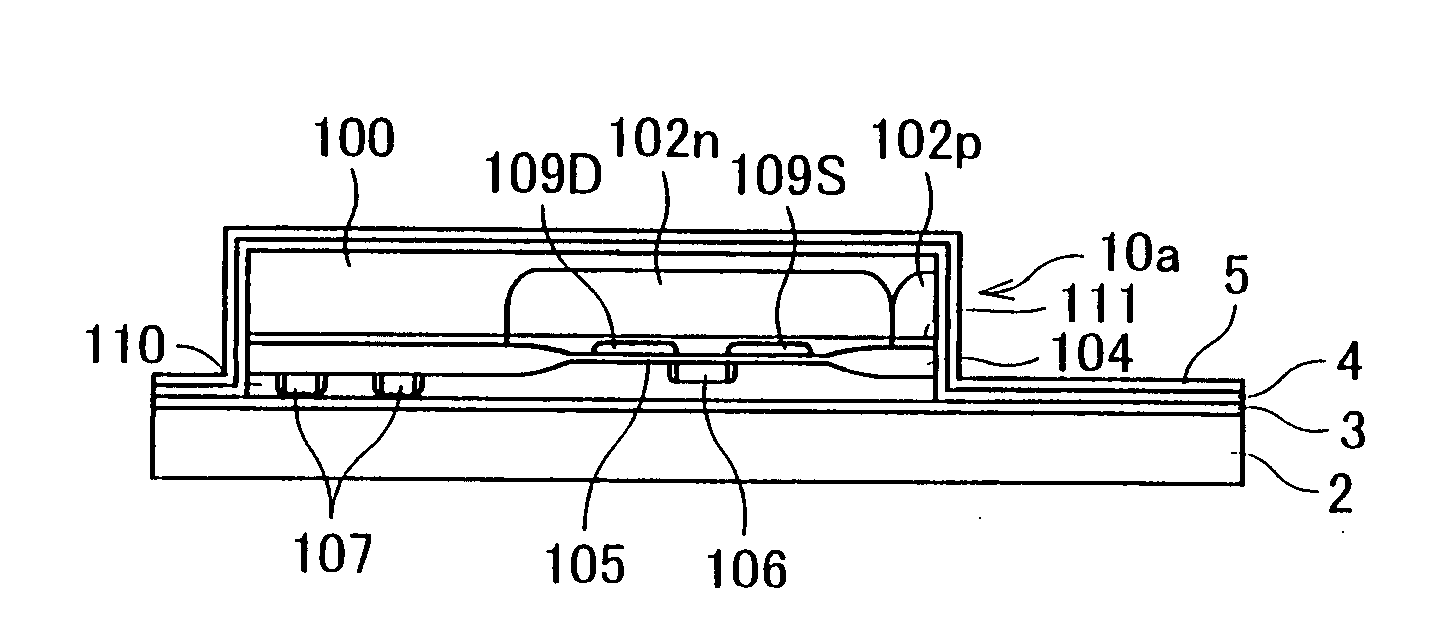

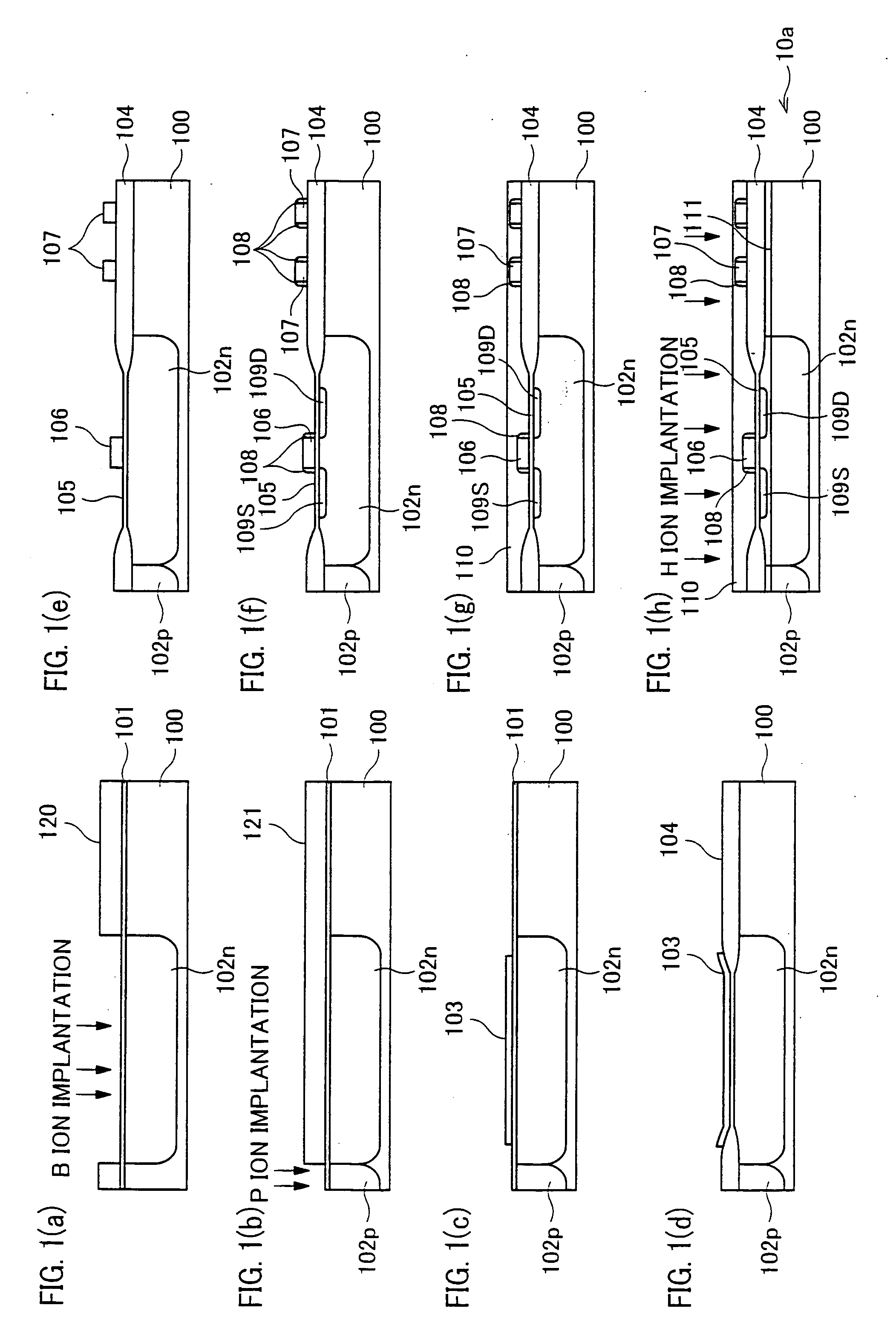

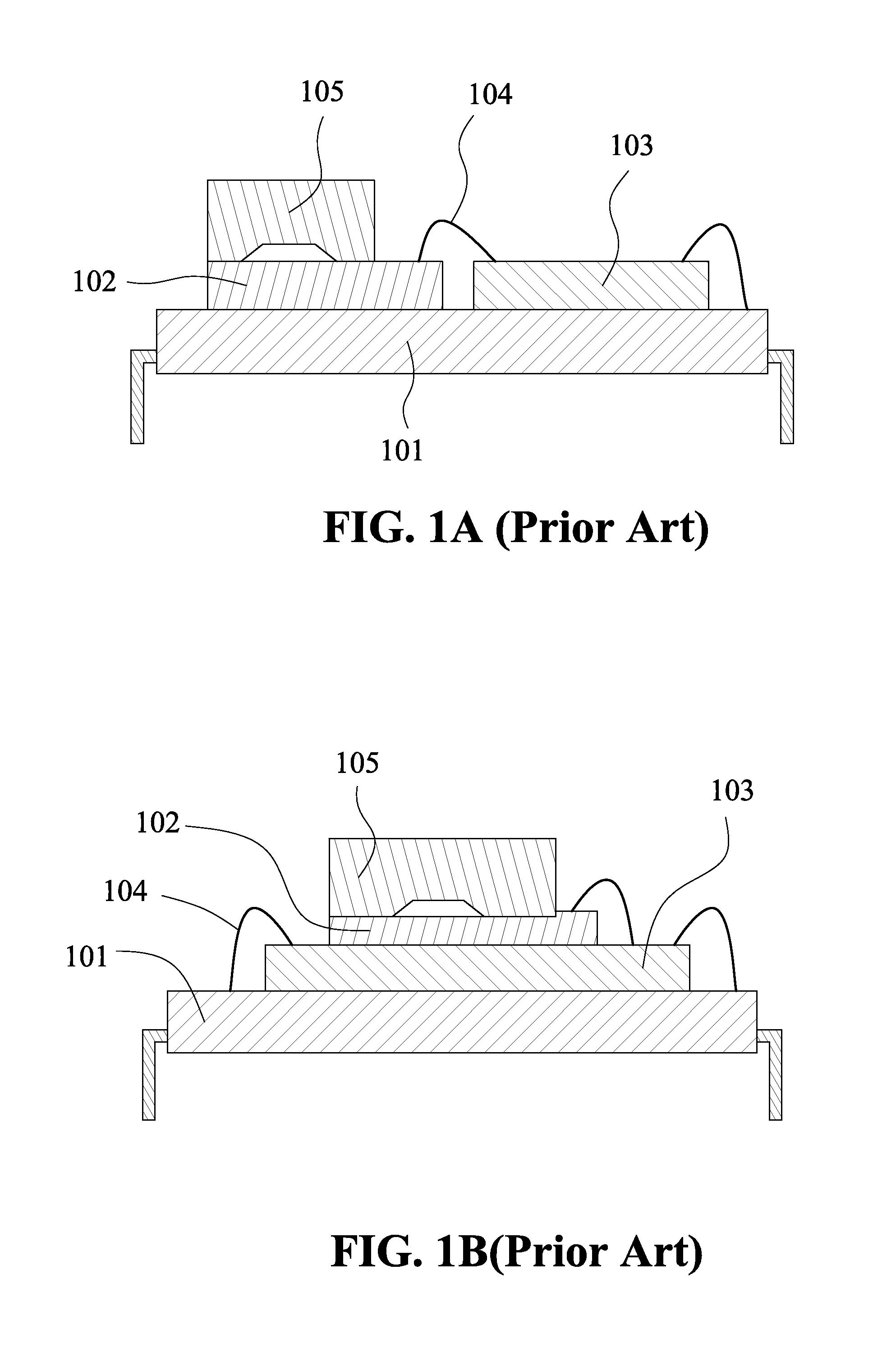

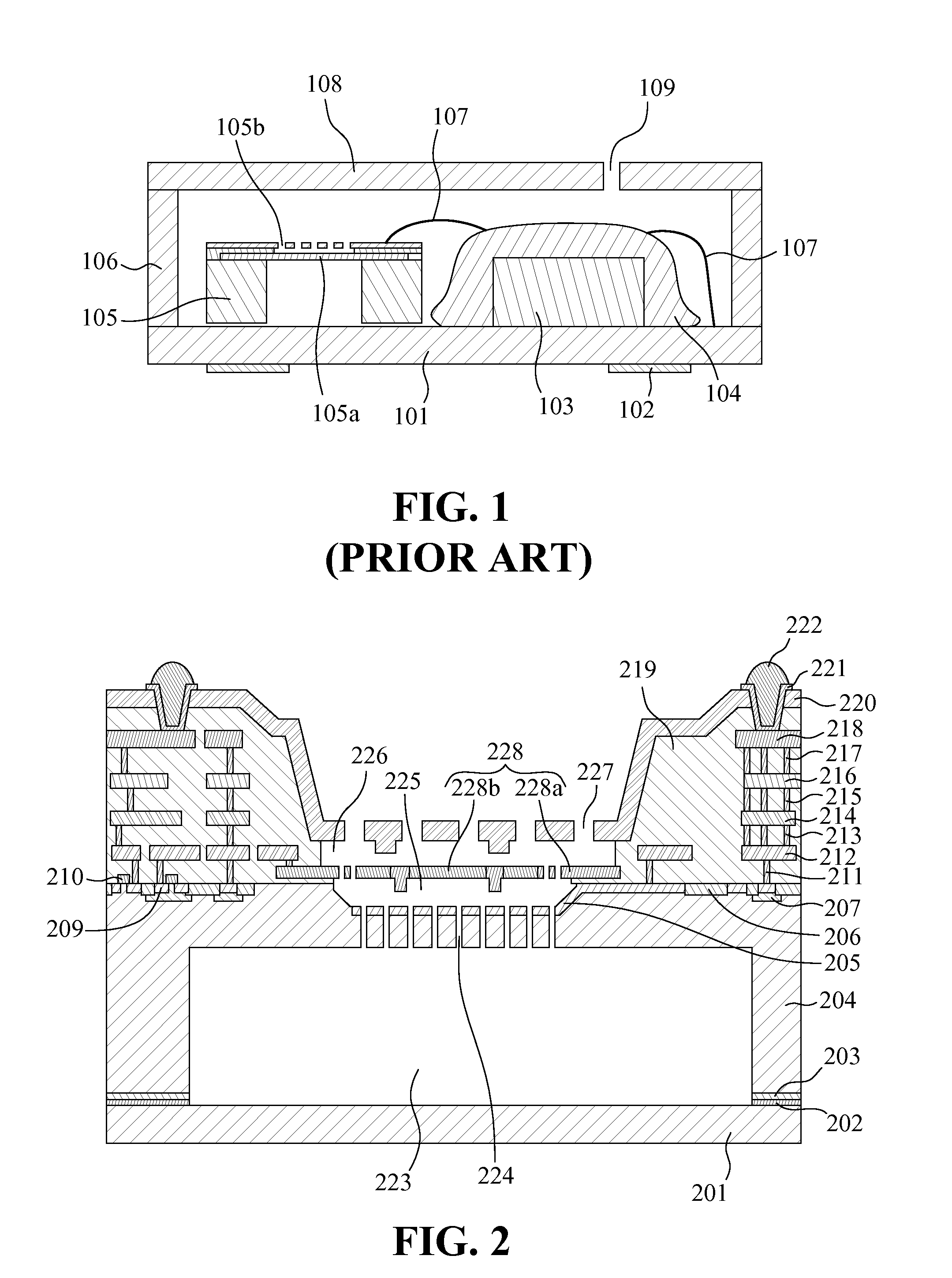

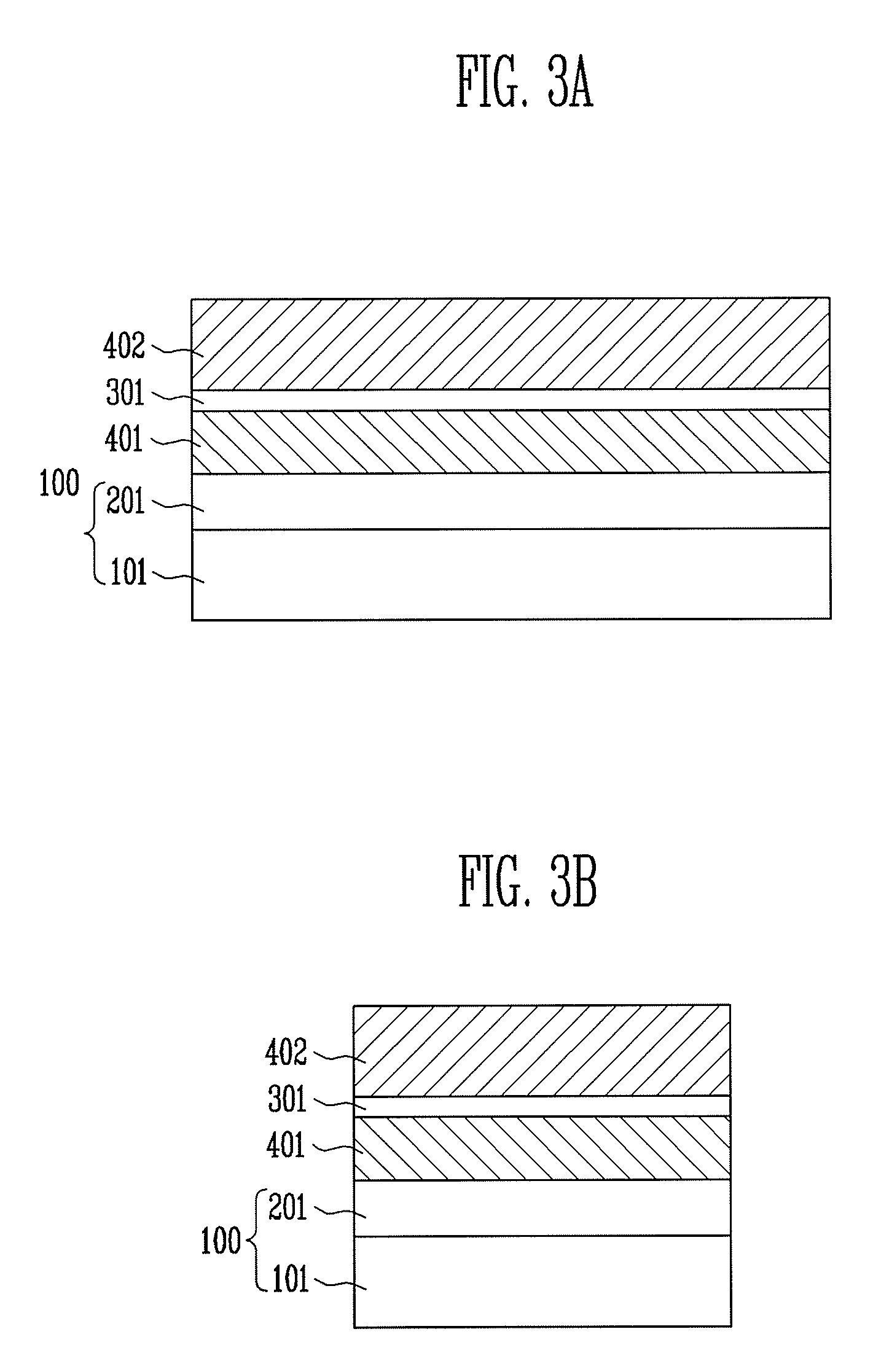

InactiveUS7205204B2Secure performanceImprove reliabilityTransistorSemiconductor/solid-state device detailsLOCOSSingle crystal

In a semiconductor device including a monocrystalline thin film transistor 16a that has been formed on a monocrystalline Si wafer 100 and then is transferred to a insulating substrate 2, LOCOS oxidization is performed with respect to the element-isolation region of the monocrystalline Si wafer 100 so as to create a field oxide film (SiO2 film) 104, and a marker 107 is formed on the field oxide film 104. With this structure, alignment of components may be performed based on a gate electrode 106 upon or after the transfer step.

Owner:SHARP KK

Semiconductor device and fabrication method for the same

InactiveUS20070108523A1Secure performanceImprove reliabilityTransistorSemiconductor/solid-state device detailsDevice materialLOCOS

In a semiconductor device including a monocrystalline thin film transistor 16a that has been formed on a monocrystalline Si wafer 100 and then is transferred to a insulating substrate 2, LOCOS oxidization is performed with respect to the element-isolation region of the monocrystalline Si wafer 100 so as to create a field oxide film (SiO2 film) 104, and a marker 107 is formed on the field oxide film 104. With this structure, alignment of components may be performed based on a gate electrode 106 upon or after the transfer step.

Owner:SHARP KK

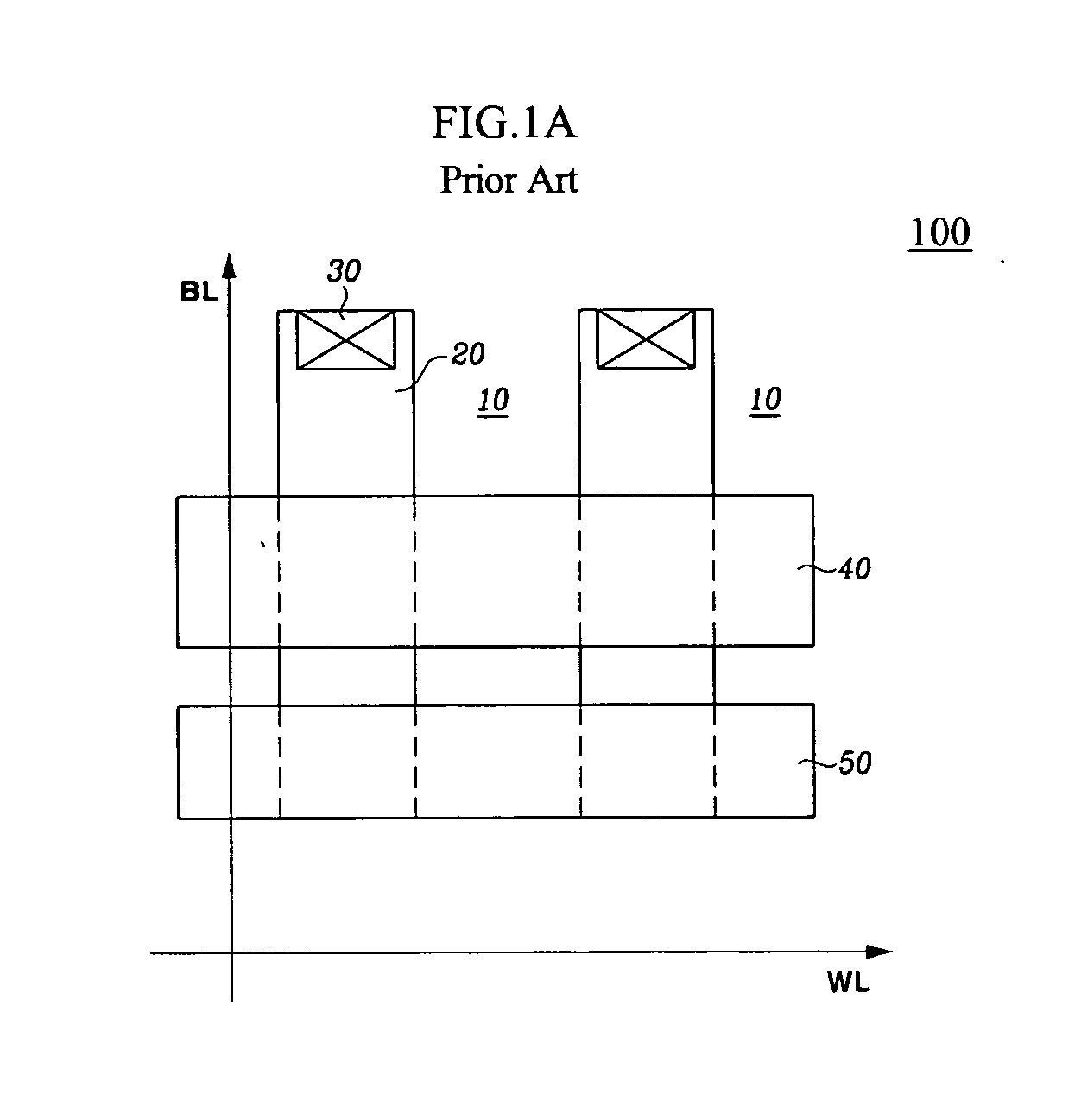

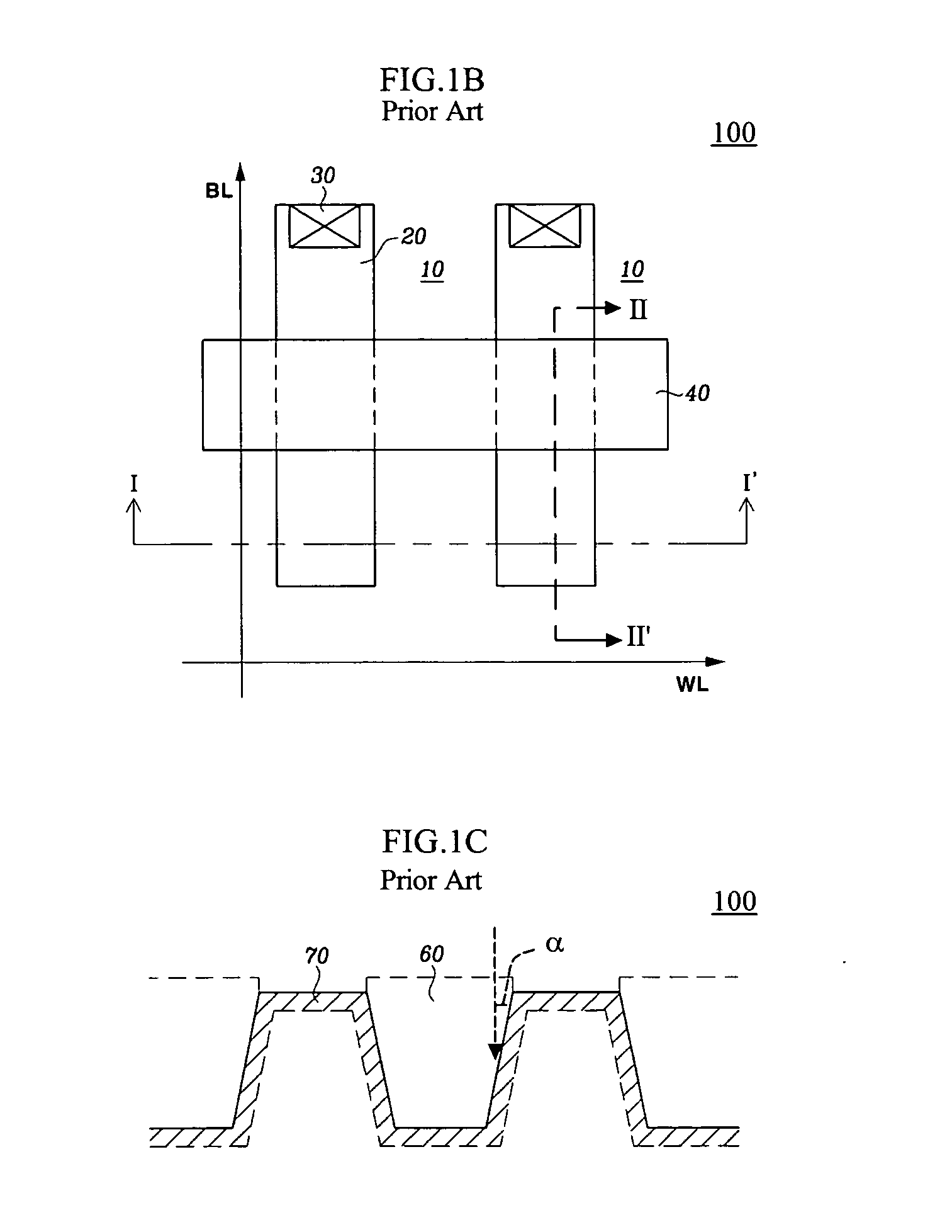

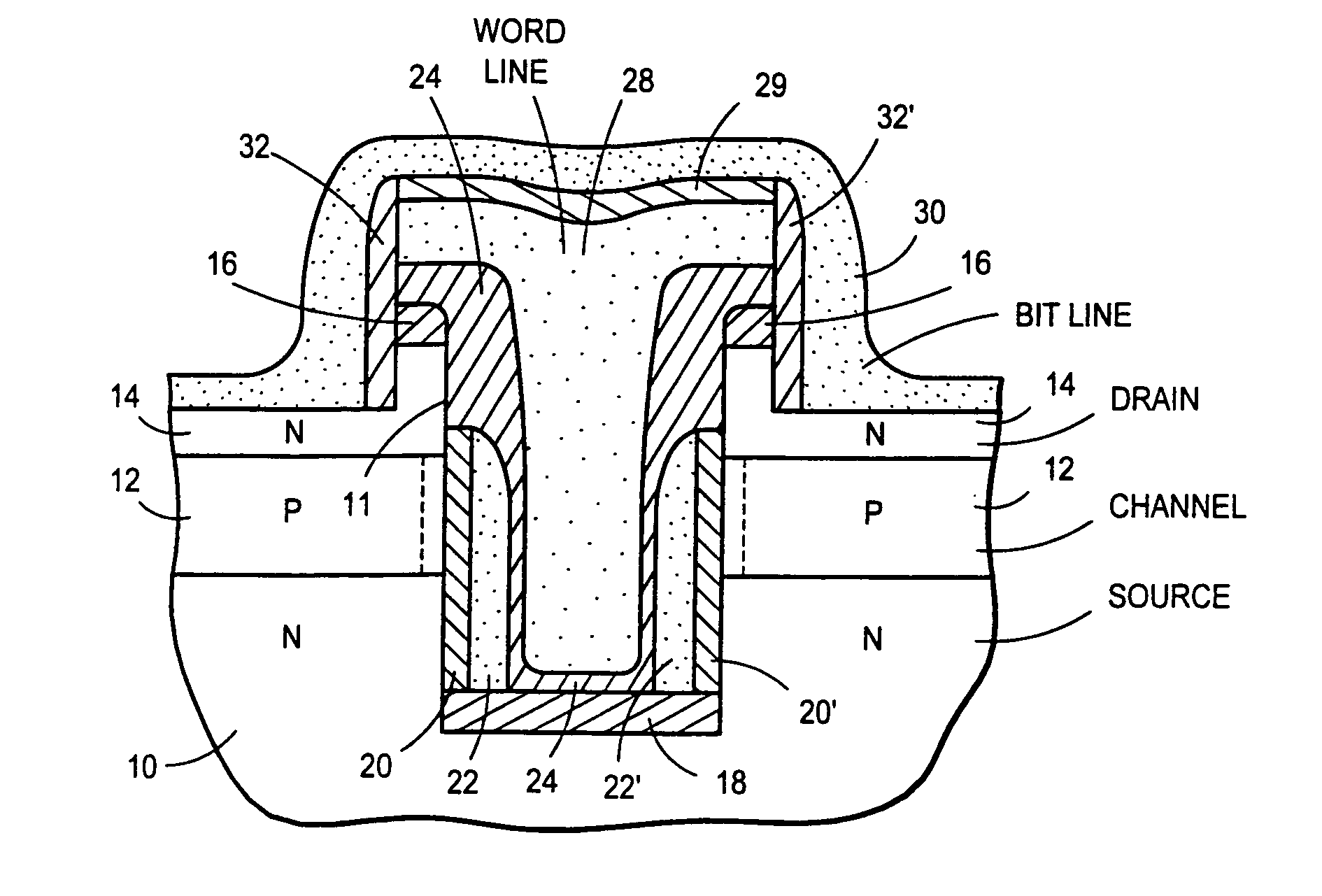

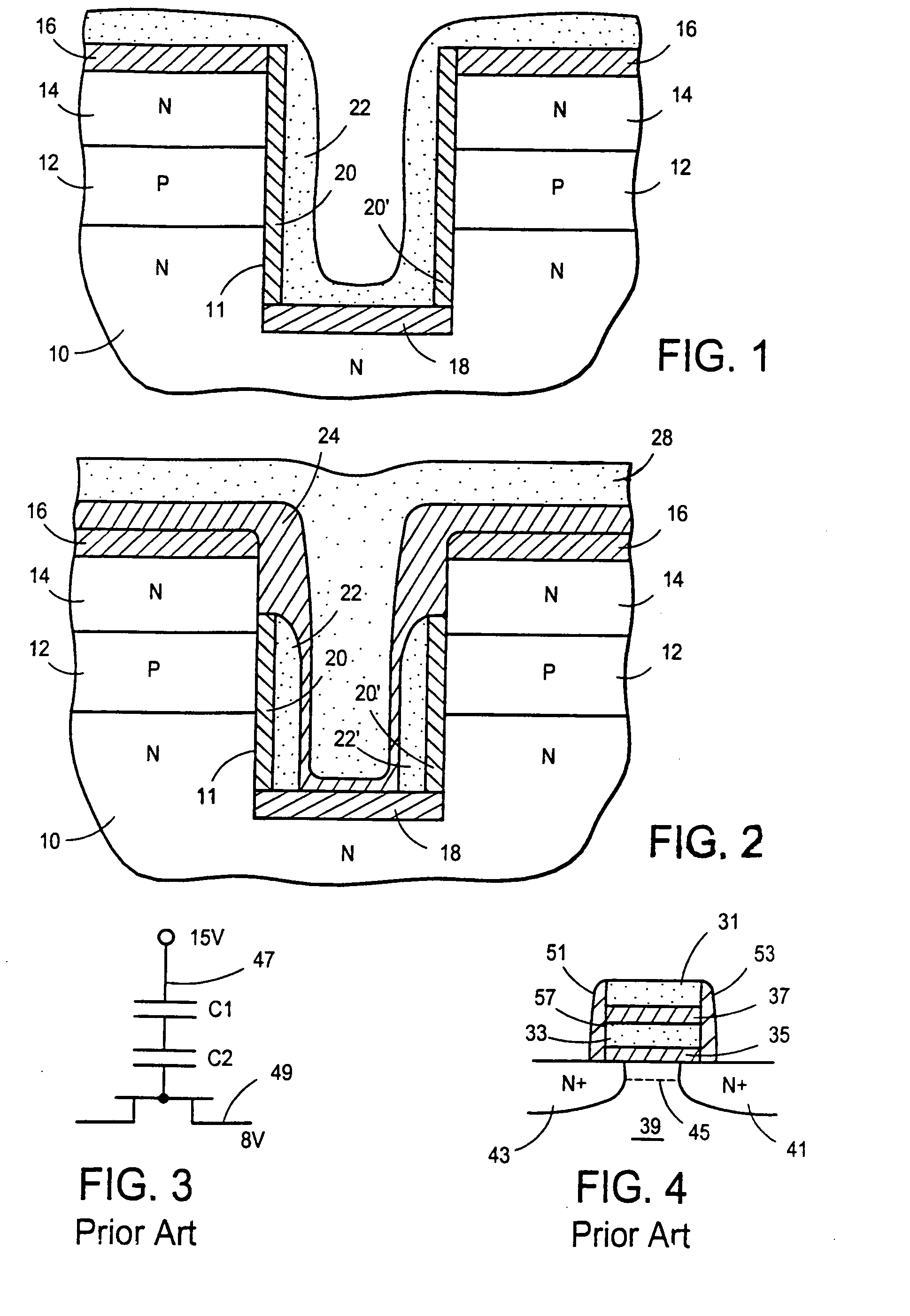

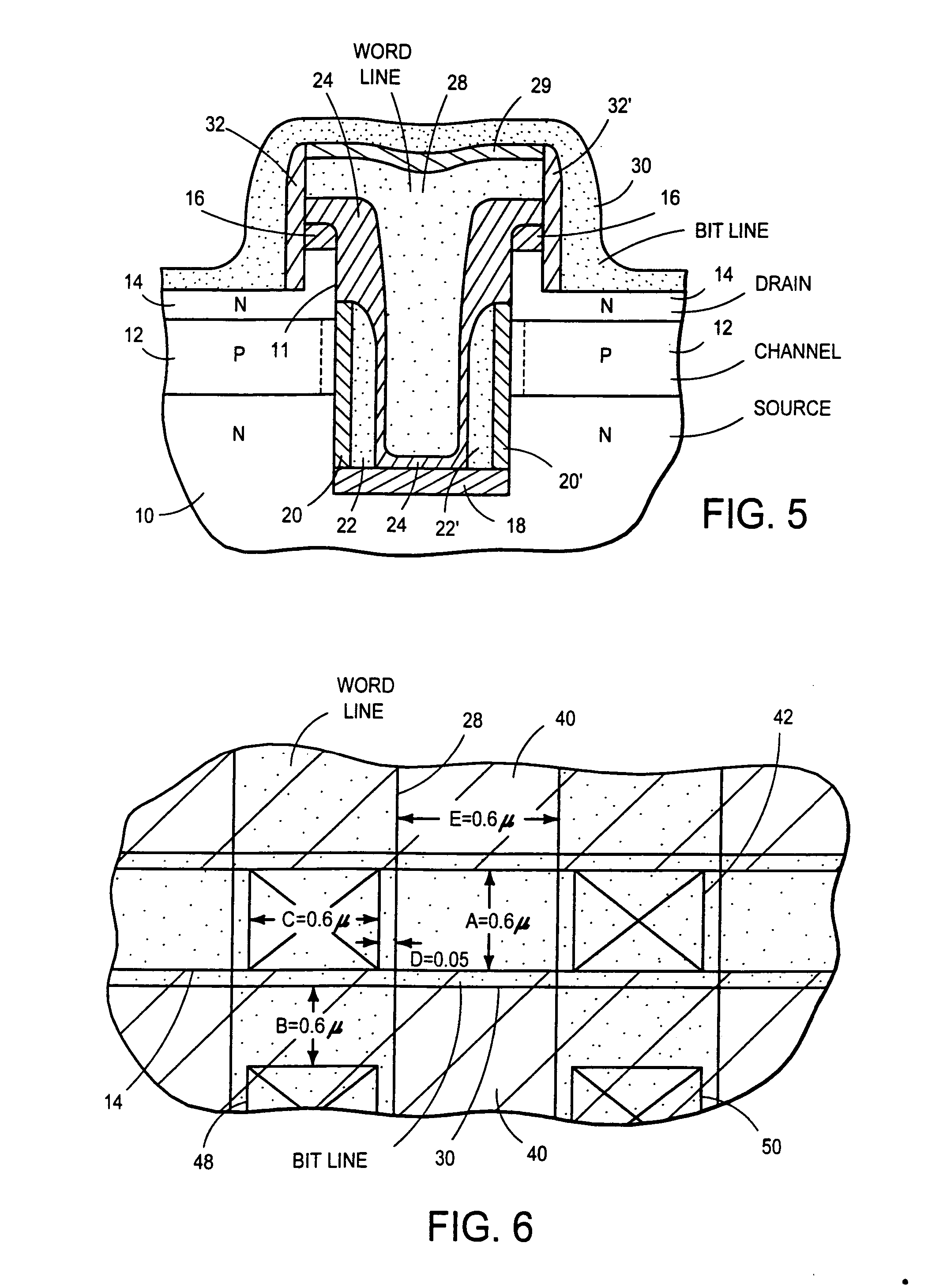

Method of forming DRAM access transistors

Owner:ROUND ROCK RES LLC

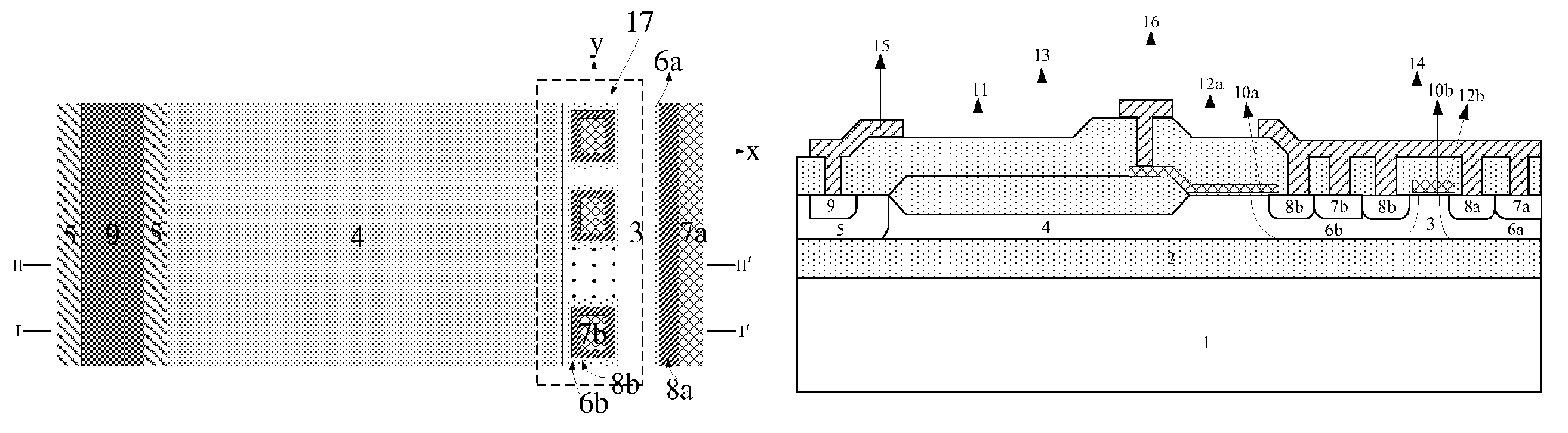

Semiconductor device and a method for fabricating the semiconductor device

InactiveUS20050074949A1Reduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialCondensed matter physics

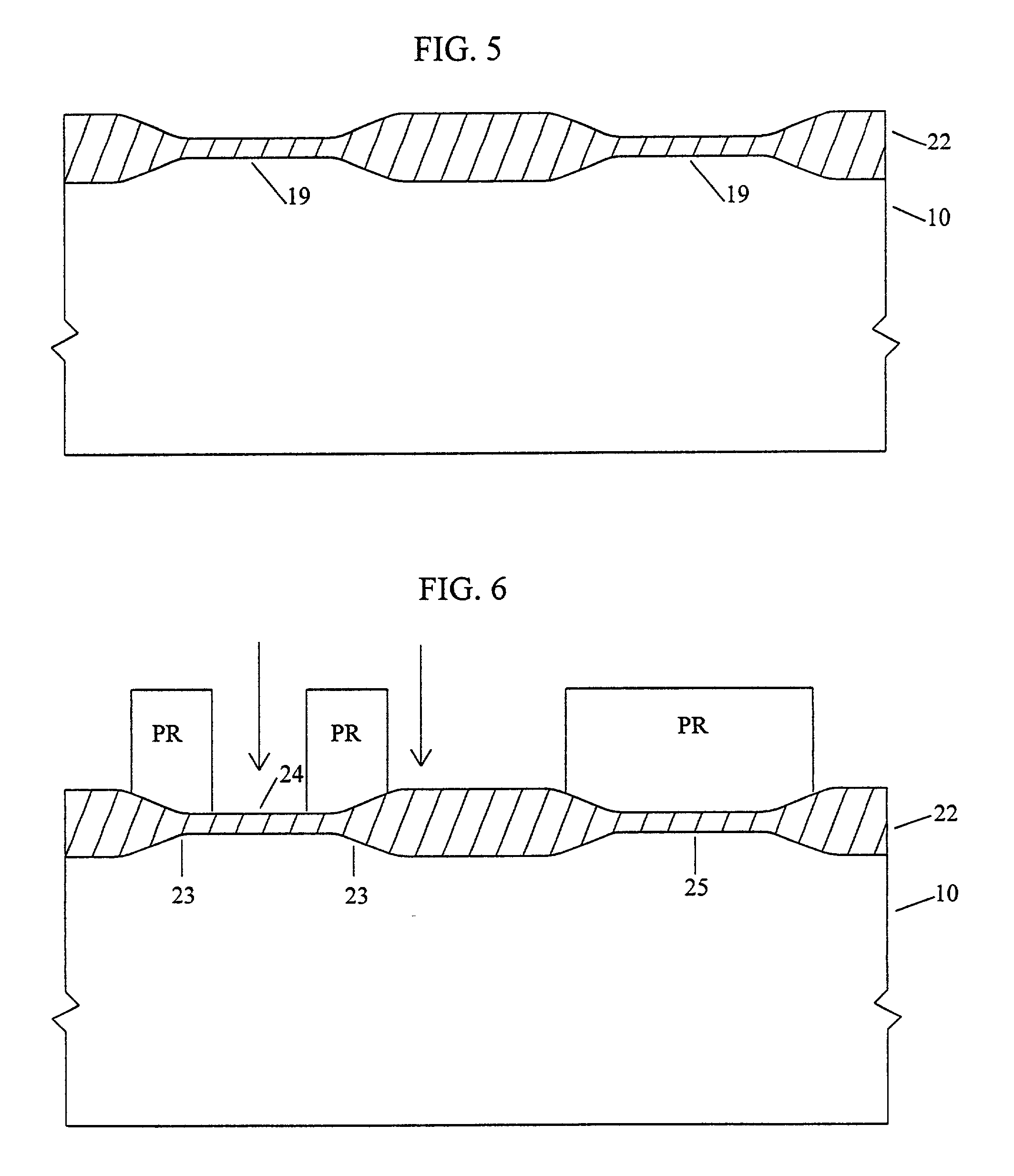

A method for fabricating the semiconductor device includes forming linear field oxide regions on a semiconductor substrate; forming gate oxide lines on the semiconductor substrate between the field oxide regions; and forming gate lines on the field oxide regions and the gate oxide lines, the gate lines being substantially perpendicular to the field oxide regions, wherein forming the gate lines also includes forming recesses in the semiconductor substrate between the gate lines, the recesses exposing portions of the semiconductor substrate.

Owner:DONGBU ELECTRONICS CO LTD

Transverse ultra-thin insulated gate bipolar transistor having high current density

ActiveUS9240469B2High densityIncrease the number ofSemiconductor/solid-state device detailsSolid-state devicesHigh current densityField oxide

A transverse ultra-thin insulated gate bipolar transistor having current density includes: a P substrate, where the P substrate is provided with a buried oxide layer thereon, the buried oxide layer is provided with an N epitaxial layer thereon, the N epitaxial layer is provided with an N well region and P base region therein, the P base region is provided with a first P contact region and an N source region therein, the N well region is provided with an N buffer region therein, the N well region is provided with a field oxide layer thereon, the N buffer region is provided with a P drain region therein, the N epitaxial layer is provided therein with a P base region array including a P annular base region, the P base region array is located between the N well region and the P base region, the P annular base region is provided with a second P contact region and an N annular source region therein, and the second P contact region is located in the N annular source region. The present invention greatly increases current density of a transverse ultra-thin insulated gate bipolar transistor, thus significantly improving the performance of an intelligent power module.

Owner:SOUTHEAST UNIV

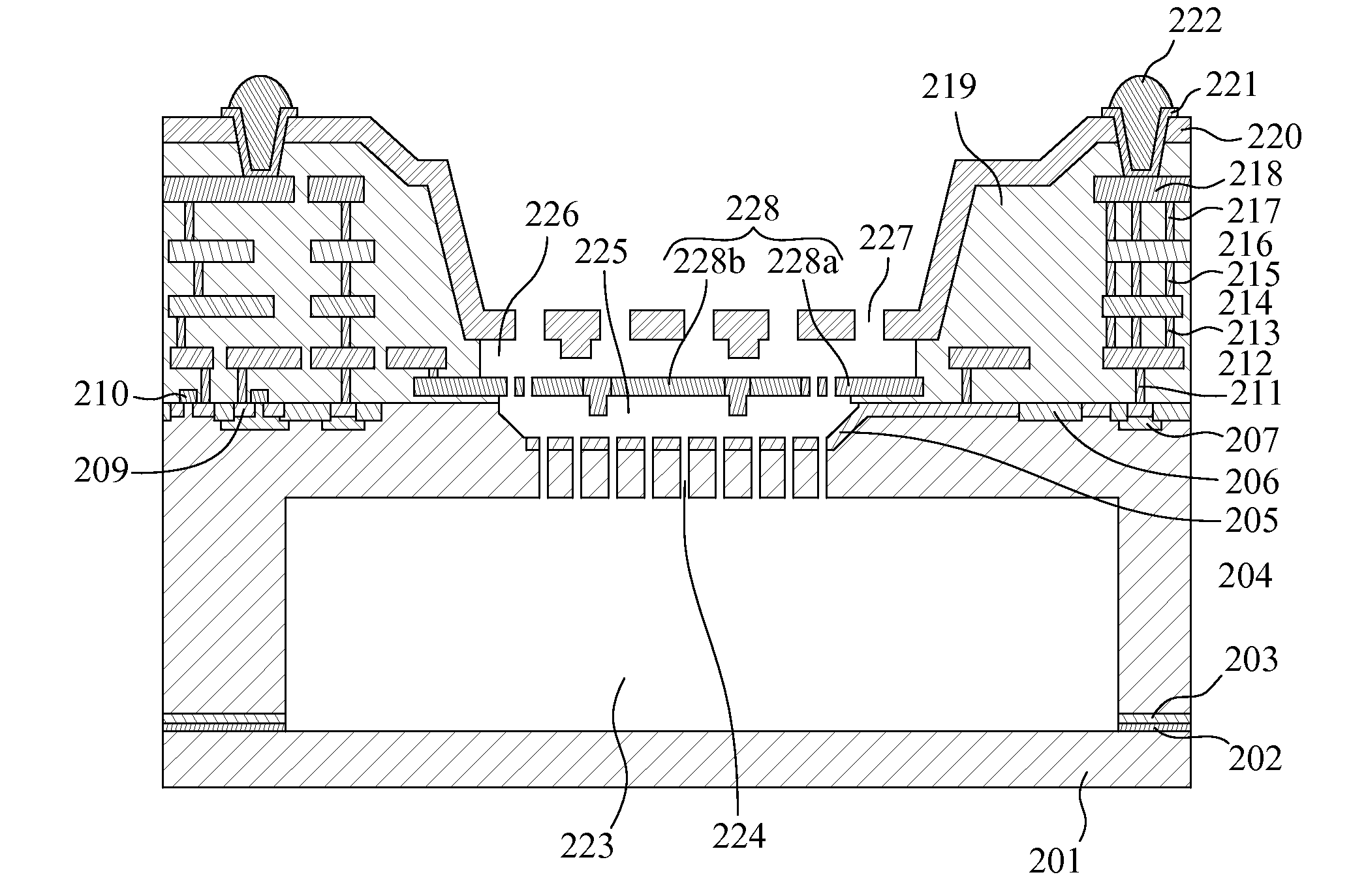

Integrated MEMS device

InactiveUS20130161702A1Improve reliabilityReduce manufacturing costMicrophonesLoudspeakersCMOSControl layer

An integrated MEMS device is provided, including, from bottom up, a bonding wafer layer, a bonding layer, an aluminum layer, a CMOS substrate layer defining a large back chamber area (LBCA), a small back chamber area (SBCA) and a sound damping path (SDP), a set of CMOS wells, a field oxide (FOX) layer, a set of CMOS transistor sources / drains, a first polysilicon layer forming CMOS transistor gates, a second polysilicon layer, said CMOS wells, said CMOS transistor sources / drains and said CMOS gates forming CMOS transistors, an oxide layer embedded with a plurality of metal layers interleaved with a plurality of via hole layers, and a gap control layer, an oxide layer, a first Nitride deposition layer, a metal deposition layer, a second Nitride deposition layer, an under bump metal (UBM) layer made of preferably Al / NiV / Cu and a plurality of solder spheres.

Owner:WINDTOP TECH CORP

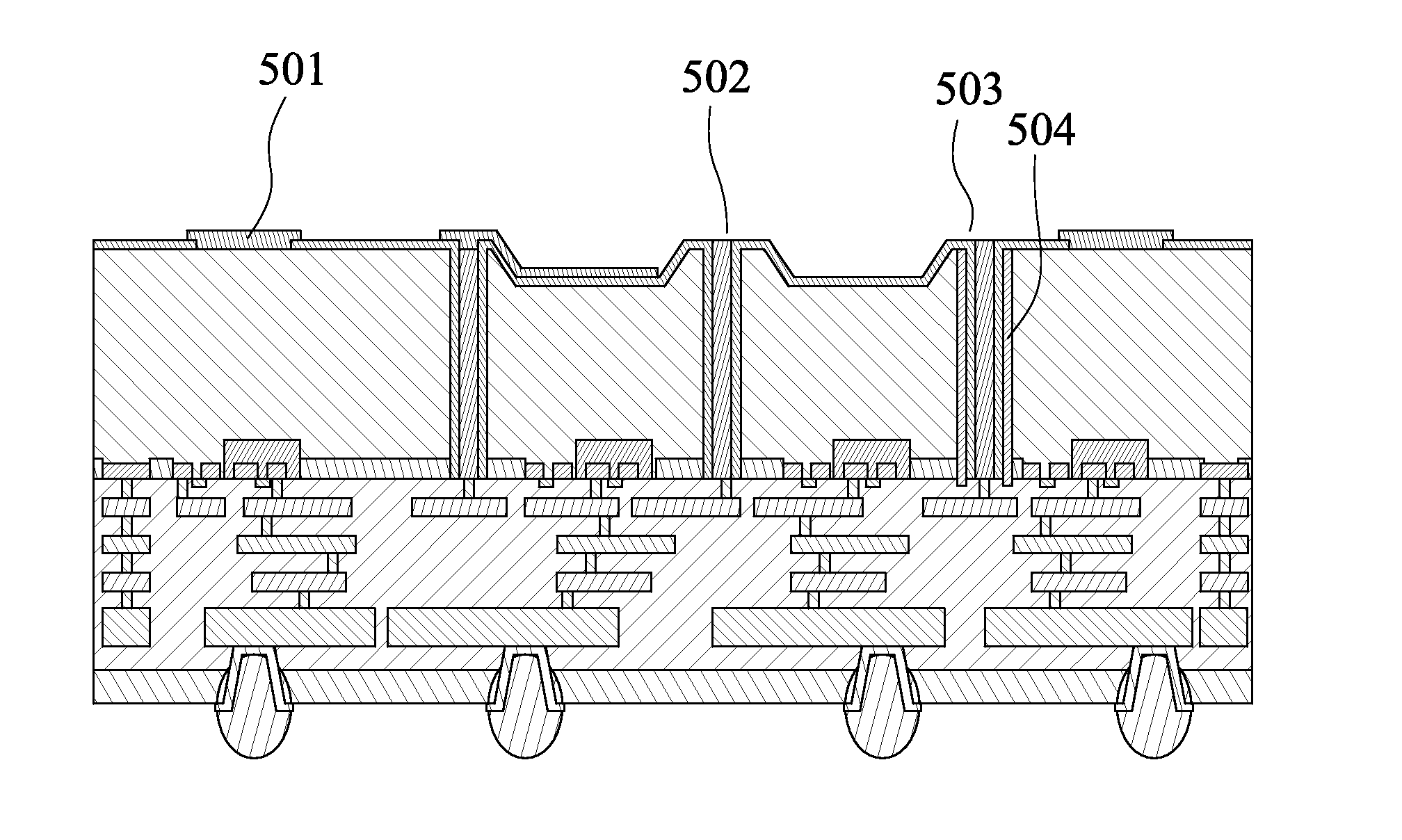

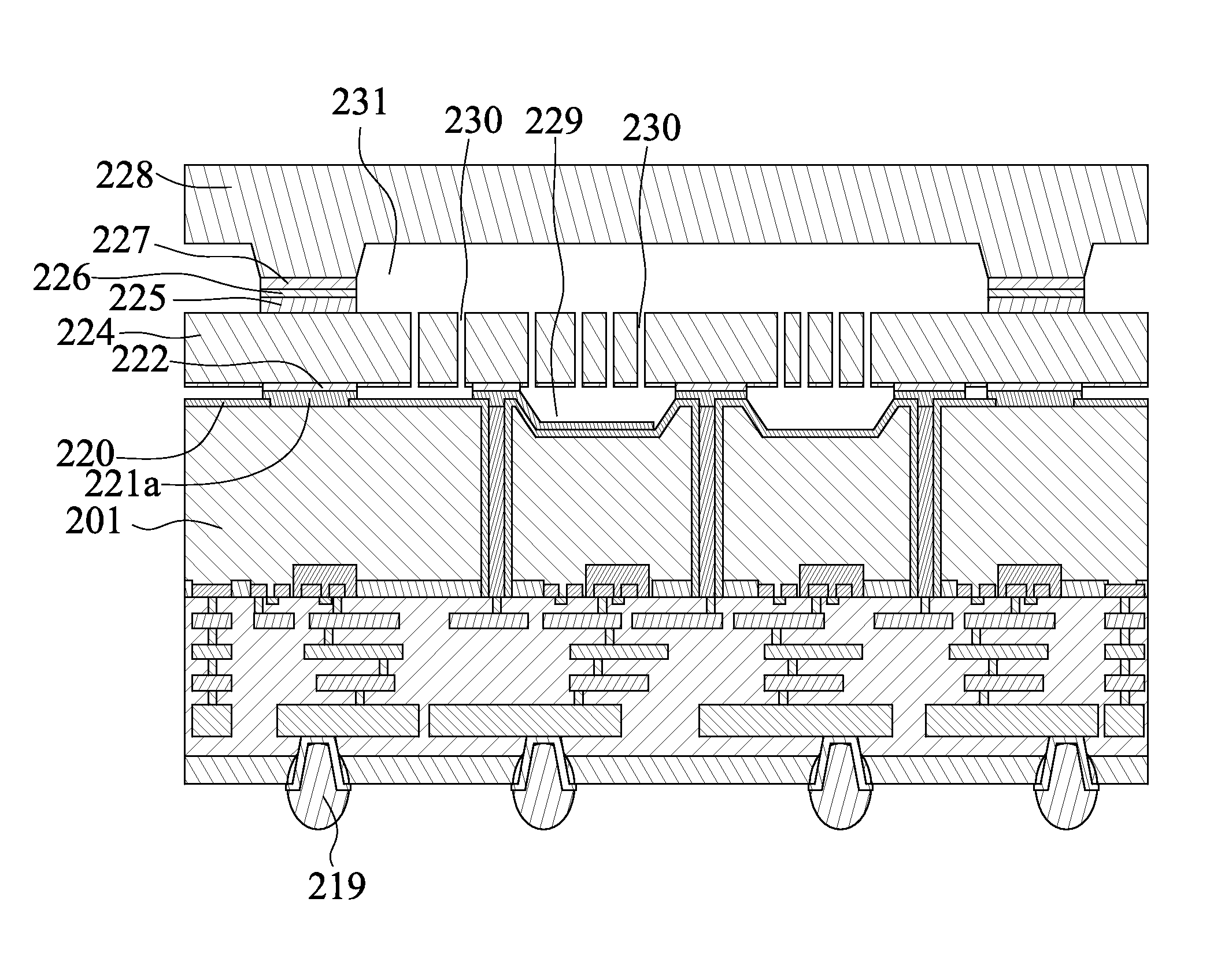

Integrated compact MEMS device with deep trench contacts

InactiveUS20130168740A1High aspect ratioIncrease contactSolid-state devicesSpeed/acceleration/shock instrument detailsCMOSSolder ball

A compact MEMS motion sensor device is provided, including a CMOS substrate layer, with plural anchor posts having an isolation oxide layer surrounding a conductive layer. On one side of CMOS substrate layer, the device further includes a field oxide (FOX) layer, a first set and a second set of implant doped silicon areas, a first polysilicon layer, an oxide layer embedded with plural metal layers interleaved with via hole layers, a Nitride deposition layer, an under bump metal (UBM) layer and a plurality of solder spheres. On the other side of CMOS substrate layer, the present invention further includes a backside interconnect isolation oxide layer, a first MEMS bonding layer, a first metal compound layer, a second MEMS bonding layer, a MEMS layer, a first MEMS eutectic bonding layer, a second metal compound layer, a second MEMS eutectic bonding layer, and a MEMS cap layer.

Owner:WINDTOP TECH CORP

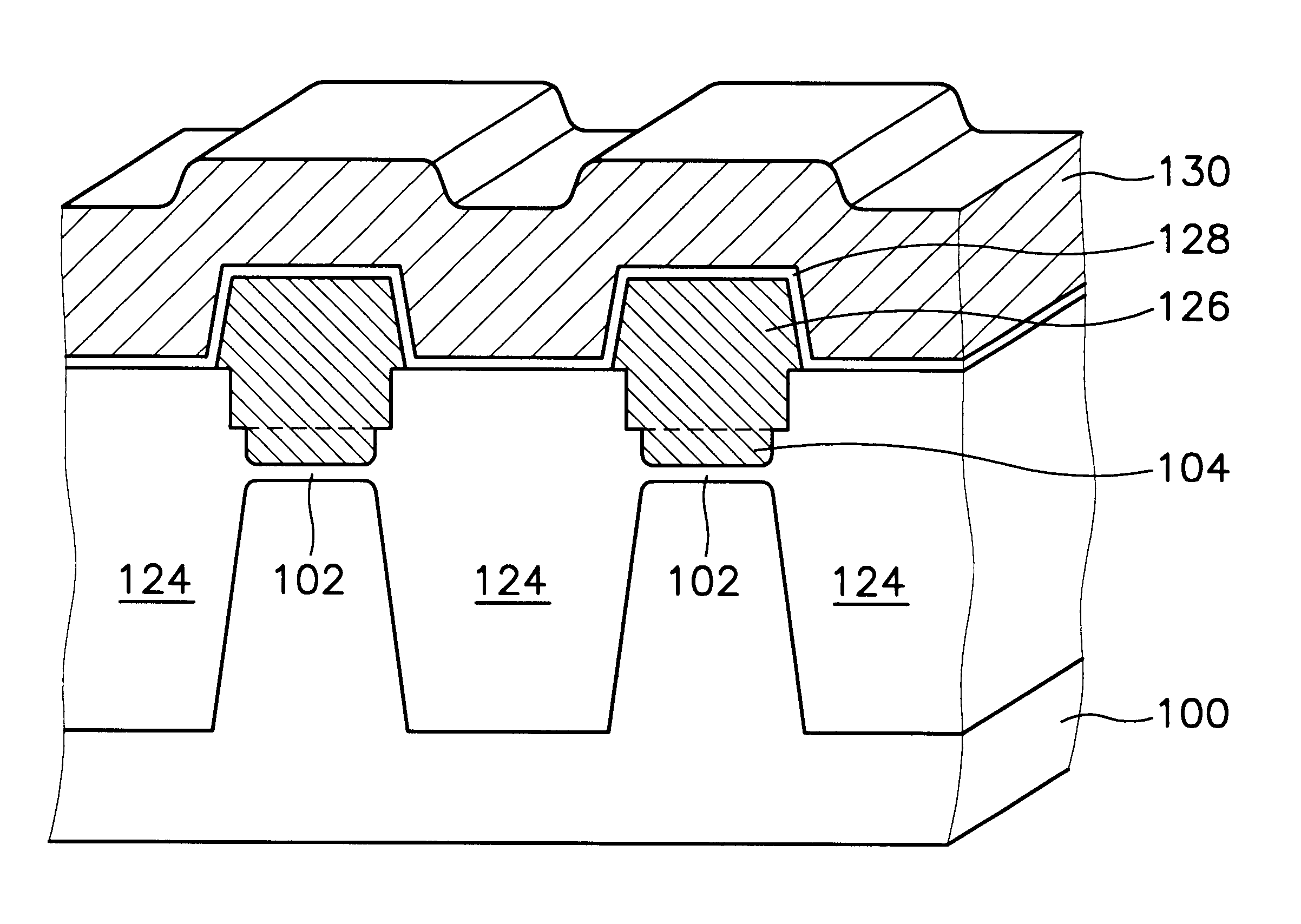

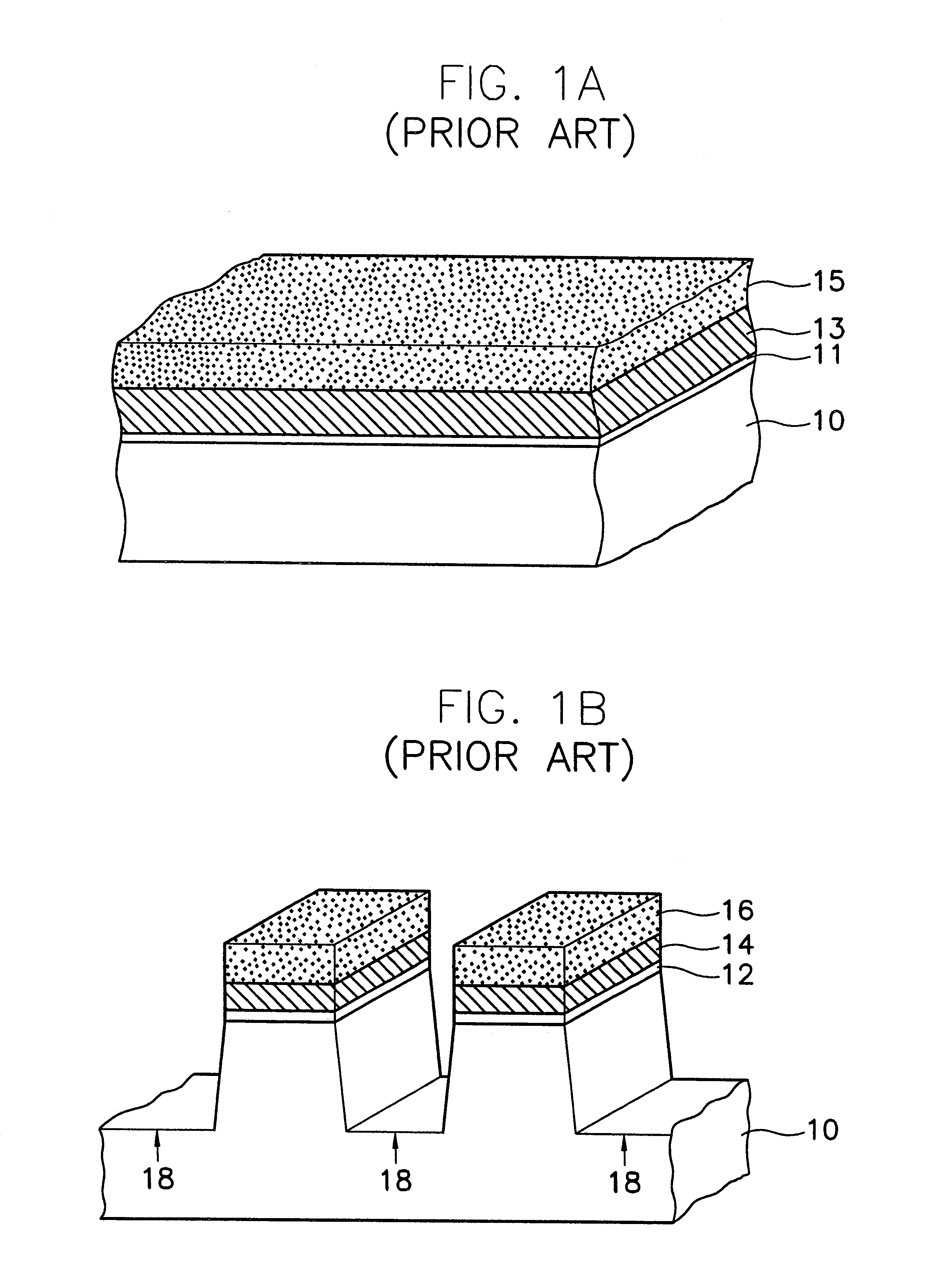

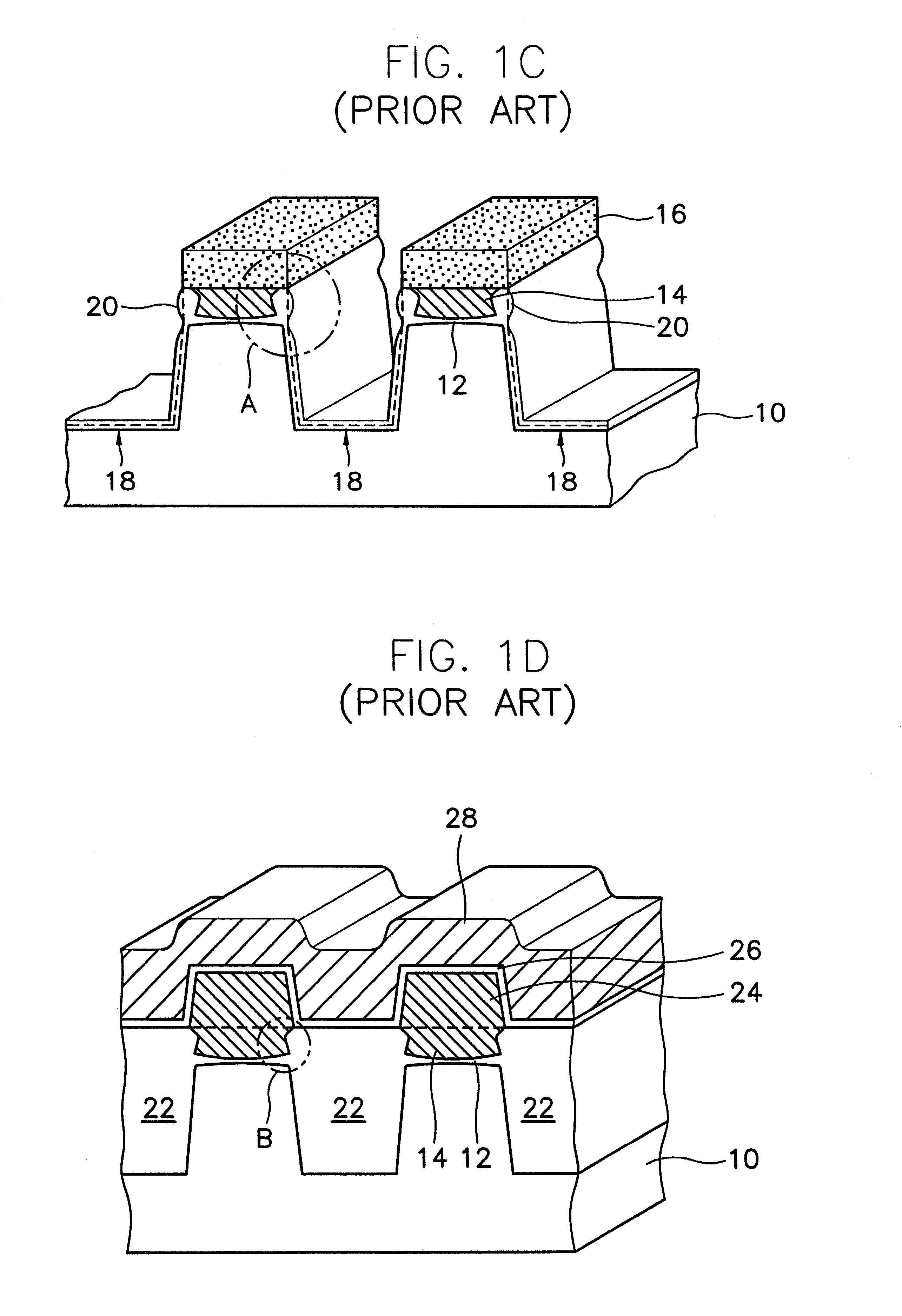

Semiconductor device having desired gate profile and method of making the same

InactiveUS6620681B1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialConductive materials

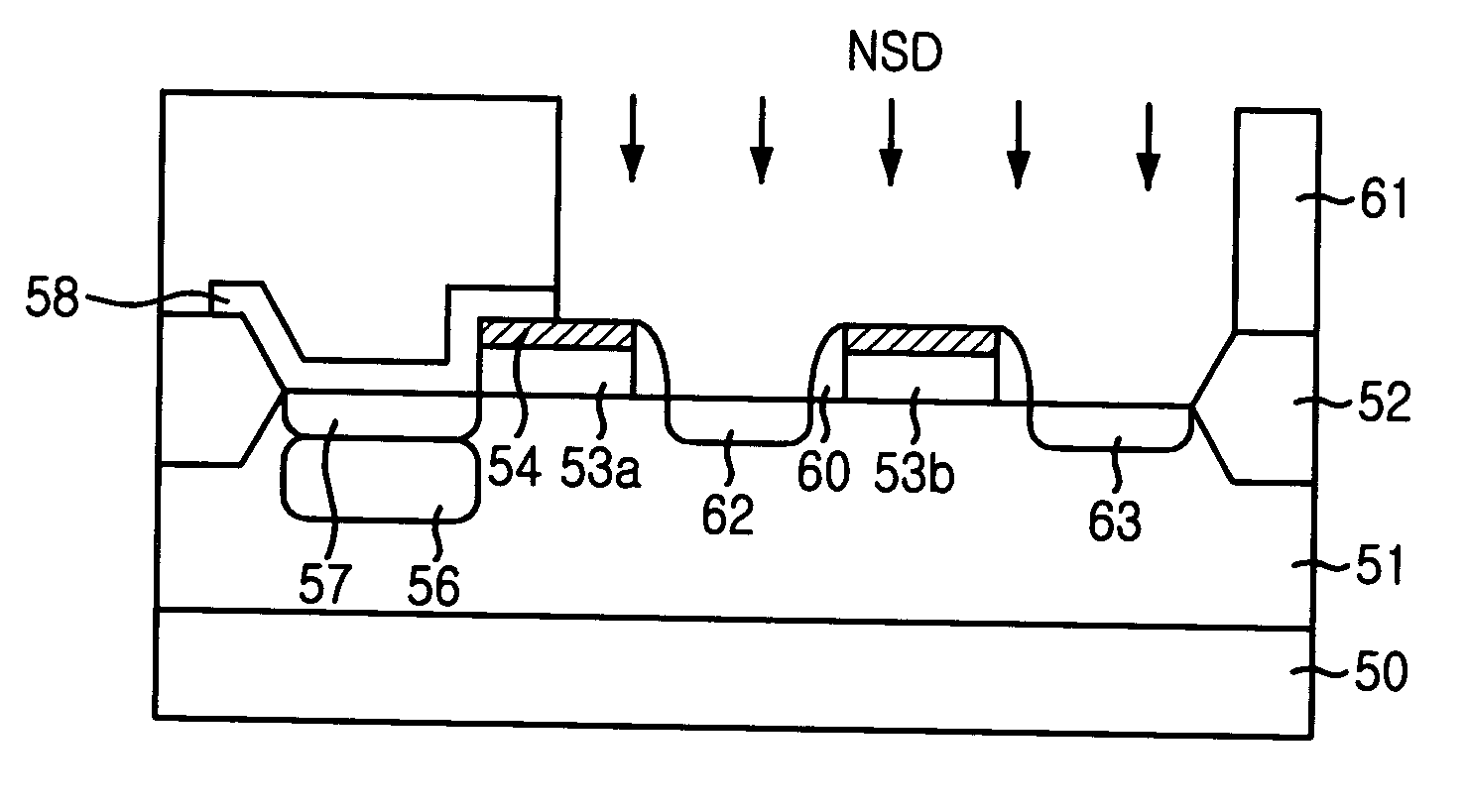

In a method of manufacturing a non-volatile memory or other semiconductor device, a control gate made of conductive material is formed in a more uniform fashion. The method includes forming a silicon layer on a buffer oxide layer on a semiconductor substrate. After forming the buffer oxide layer, a stopping layer is formed. The control gate of conductive material, such as a floating gate in an EEPROM memory device, is provided by patterning the silicon layer, gate oxide layer, and the substrate, and then, a trench is formed in the upper portion of the substrate. Uniformity is achieved by oxidizing the sidewalls of the trench to create bird's beaks at both upper and lower portions of the control gate material. Then, a field oxide layer that fills up the trench is formed. Because bird's beaks are evenly formed at both upper and lower portions of the control gate material during oxidation of the sidewalls of the trench, it is formed in a more uniform fashion since achieves uniformity is attained by preventing the sidewalls of the floating gate, for example, from having positive slopes.

Owner:SAMSUNG ELECTRONICS CO LTD

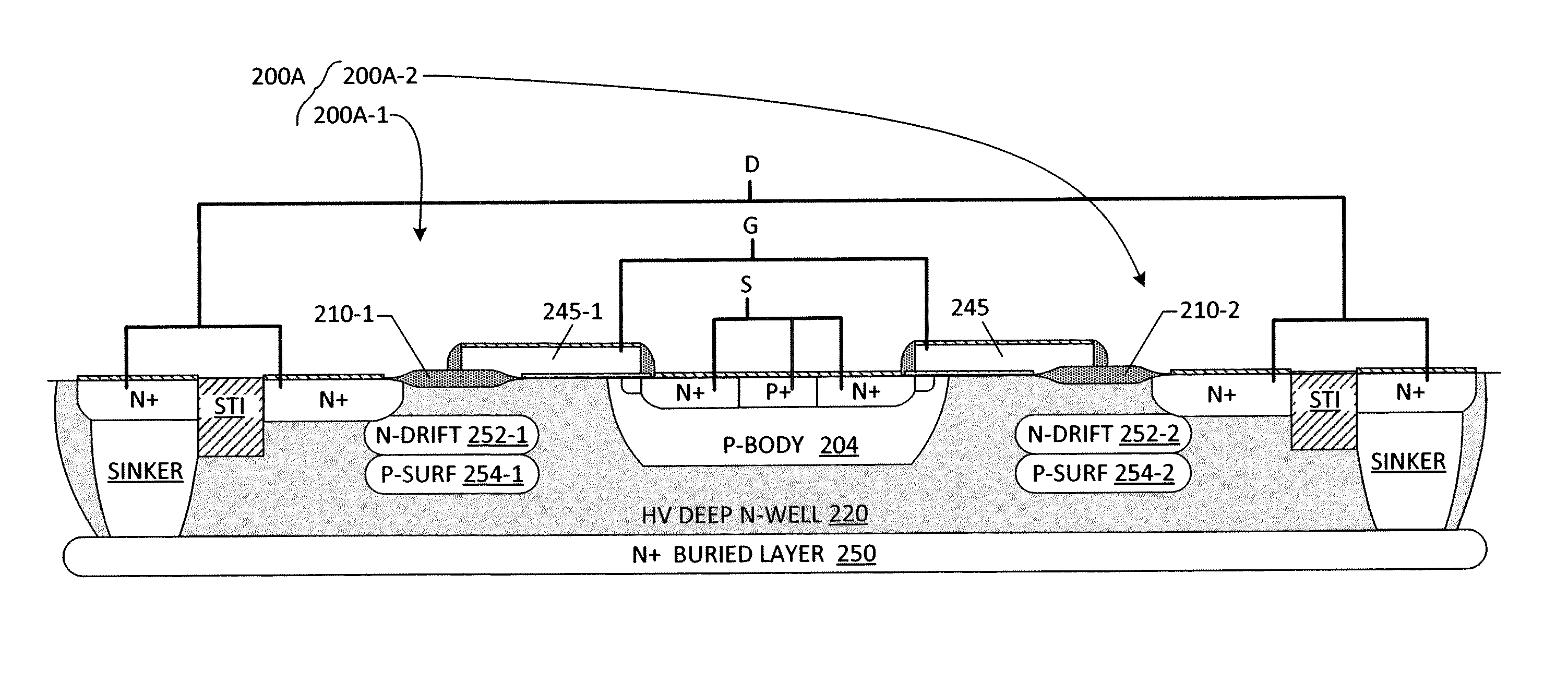

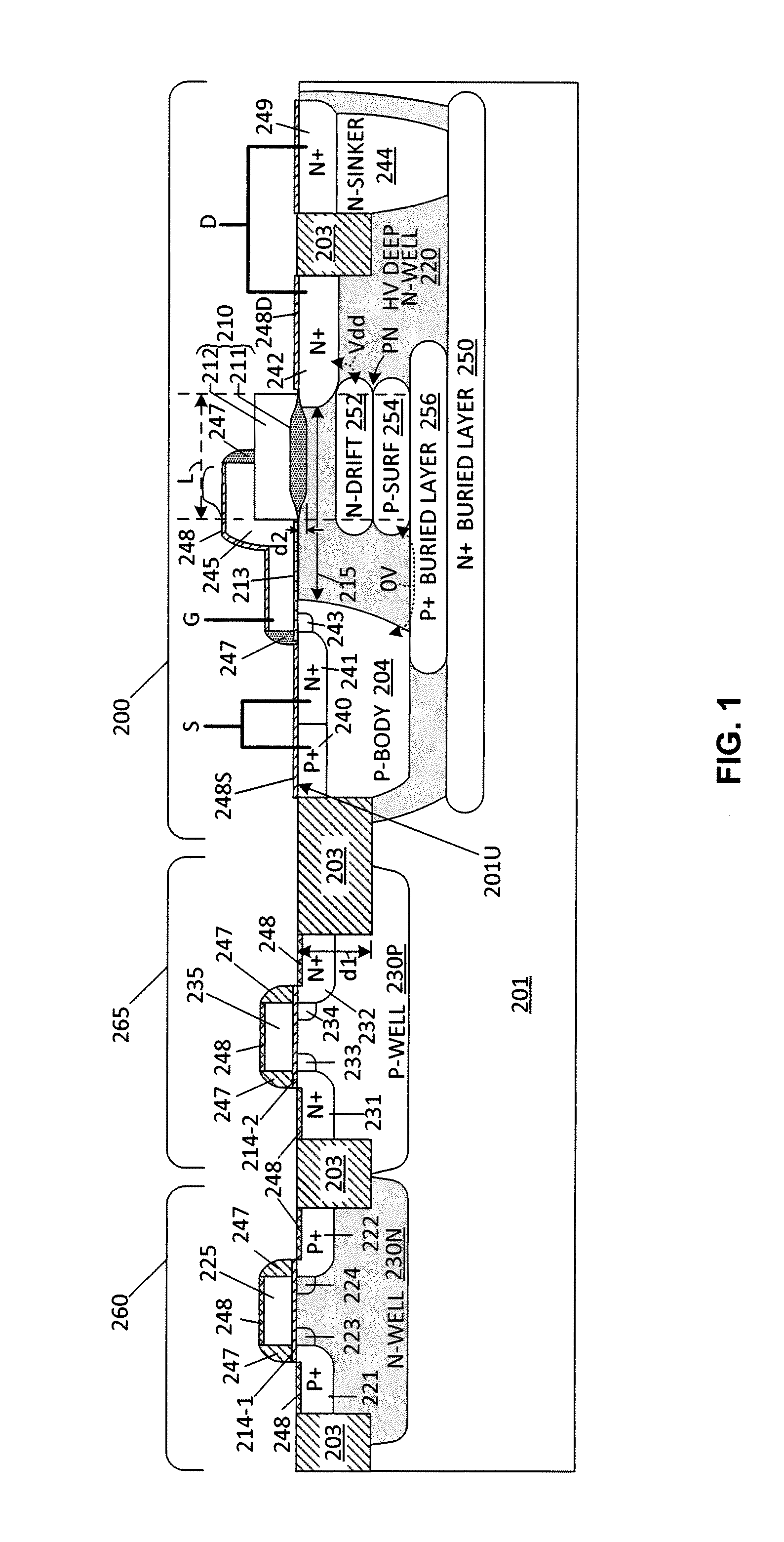

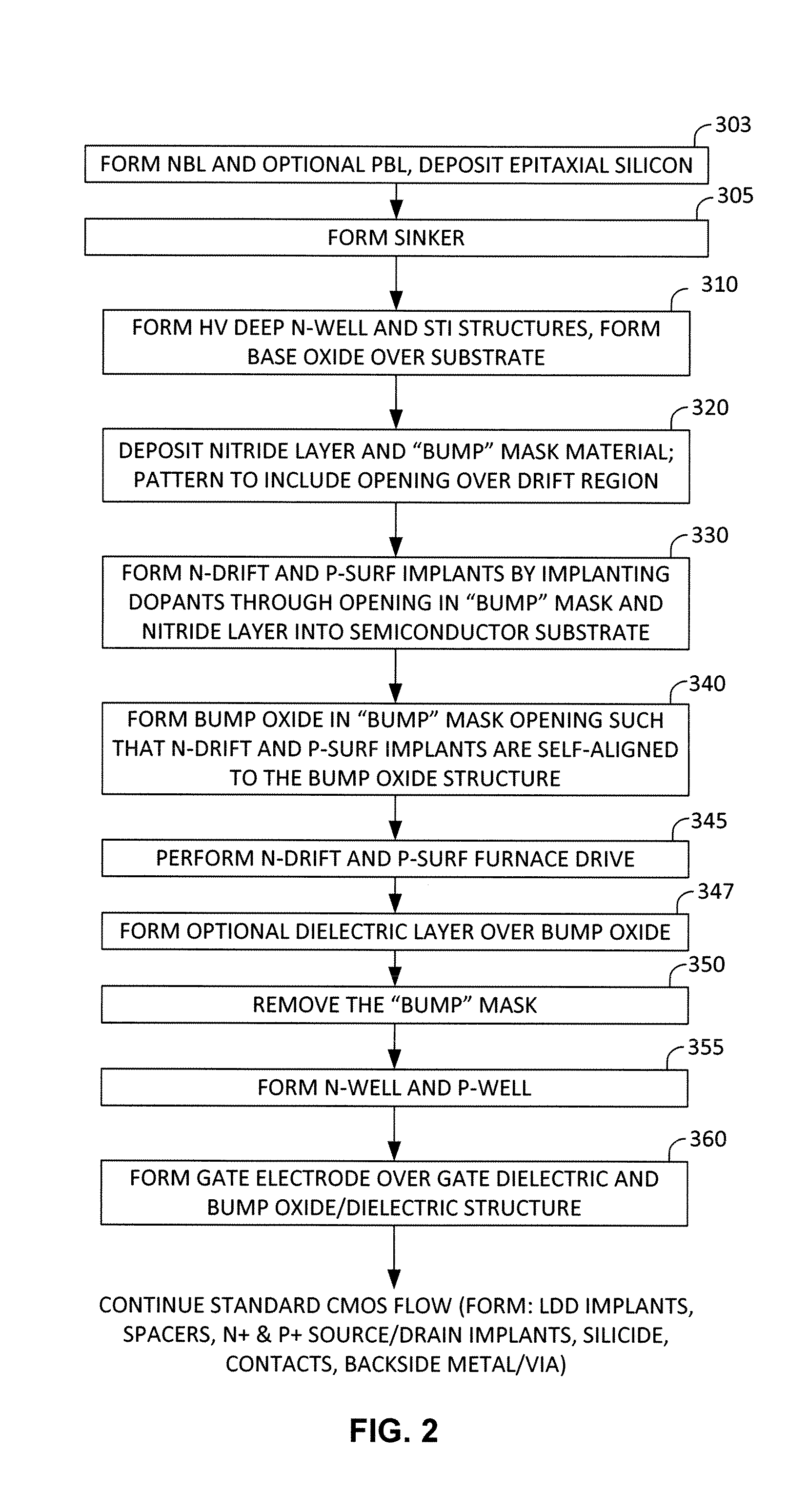

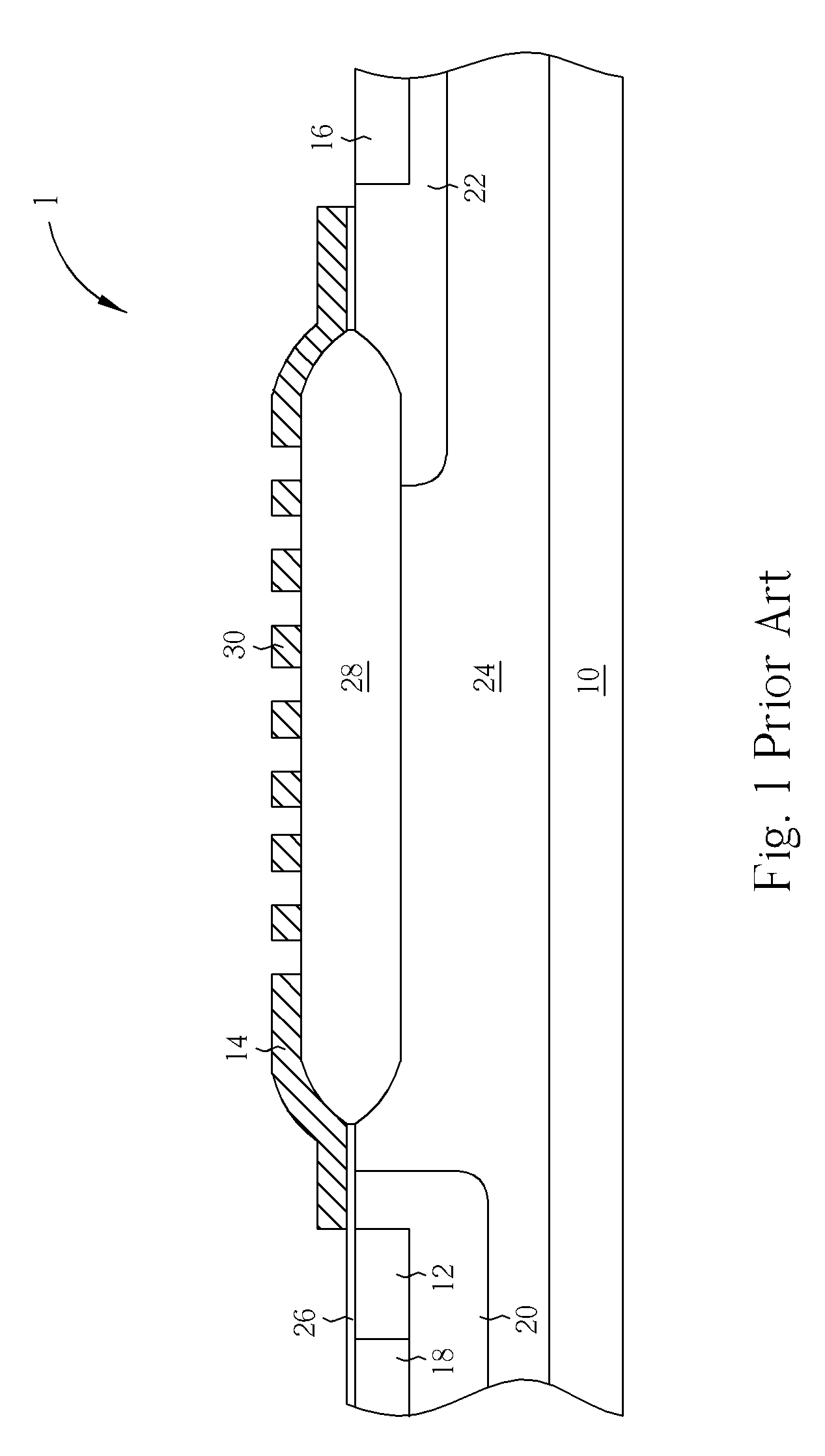

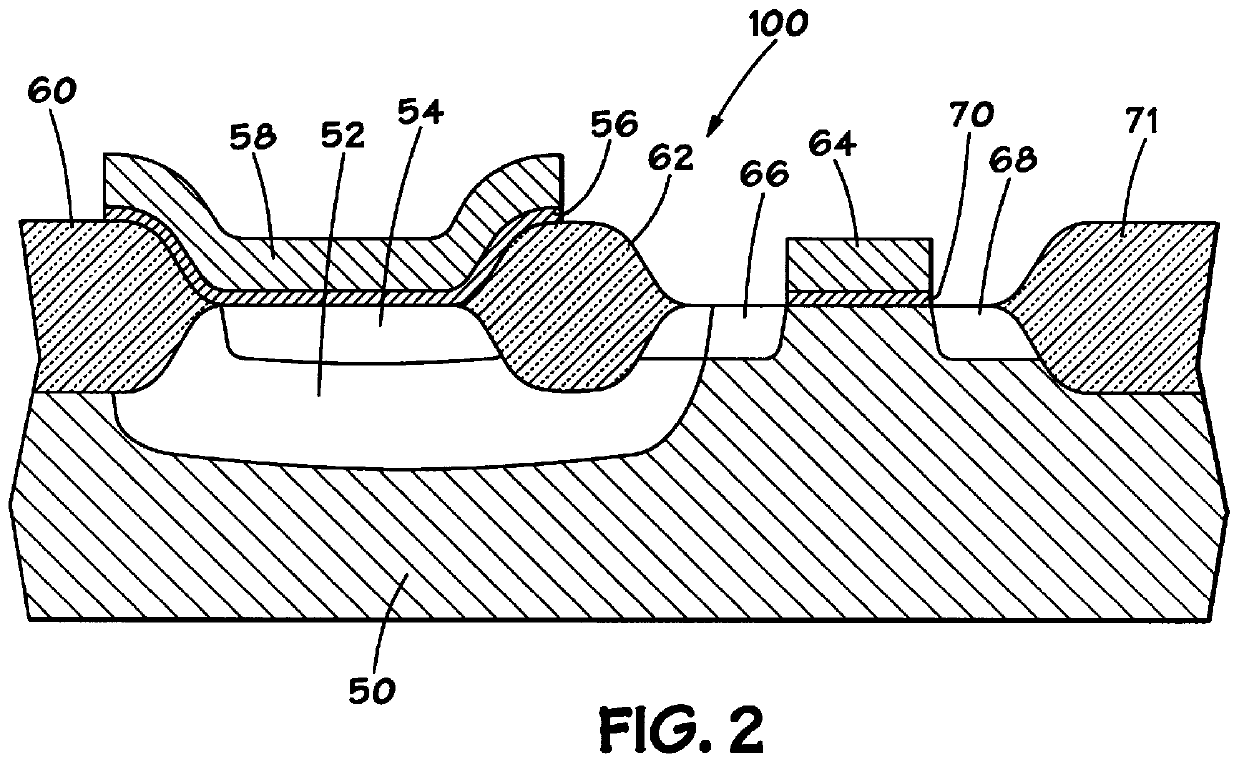

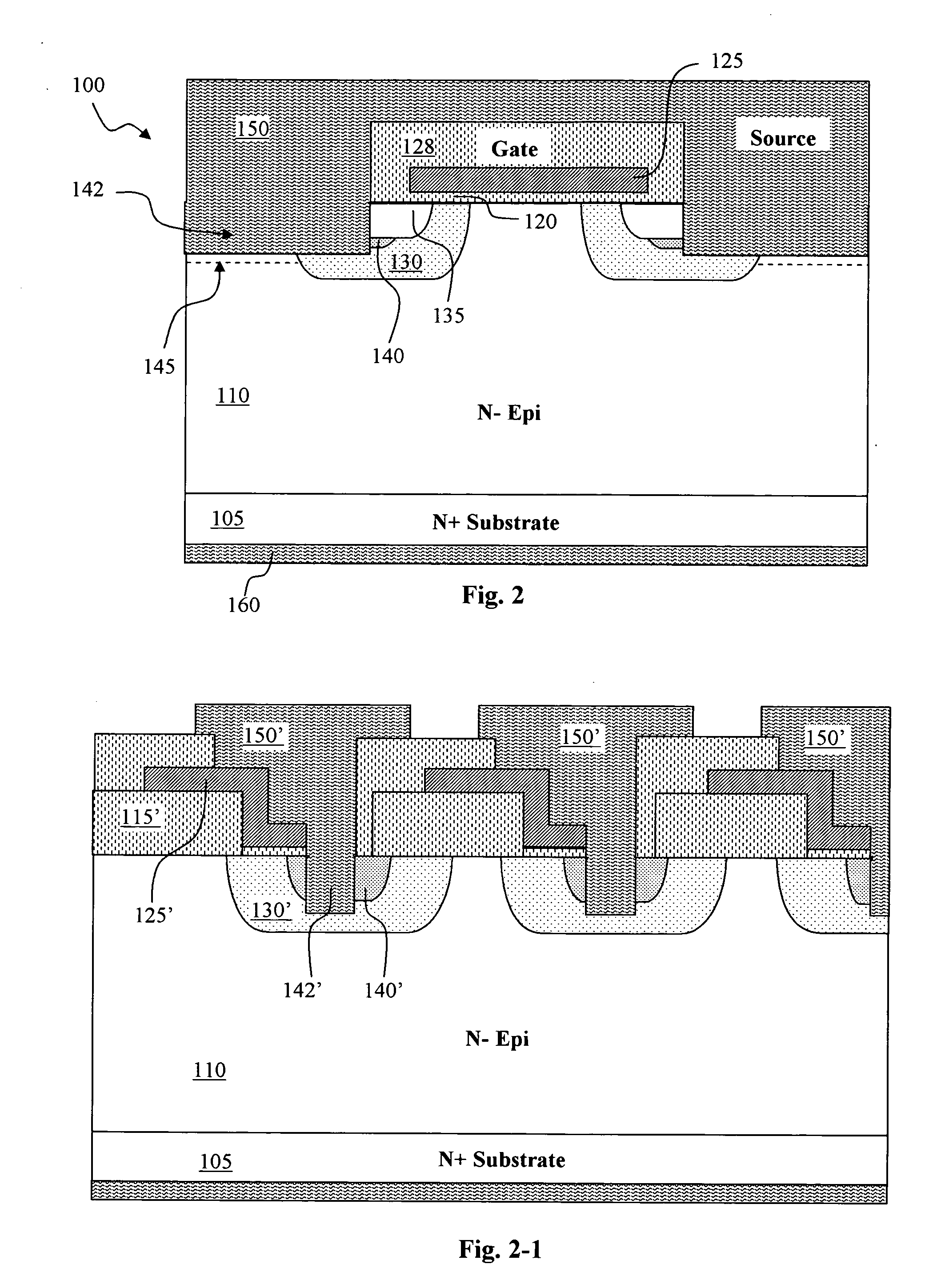

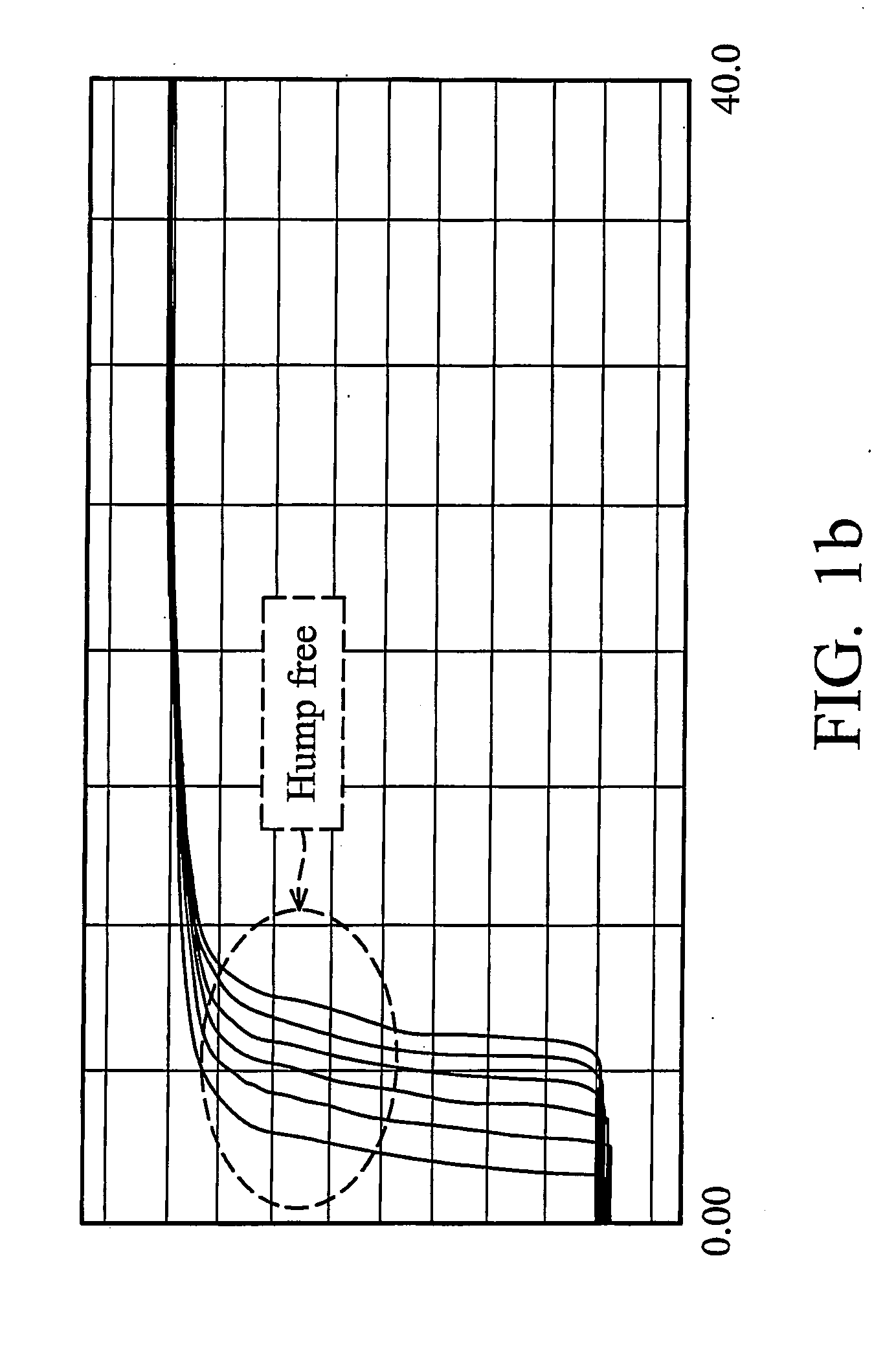

Double-Resurf LDMOS With Drift And PSURF Implants Self-Aligned To A Stacked Gate "BUMP" Structure

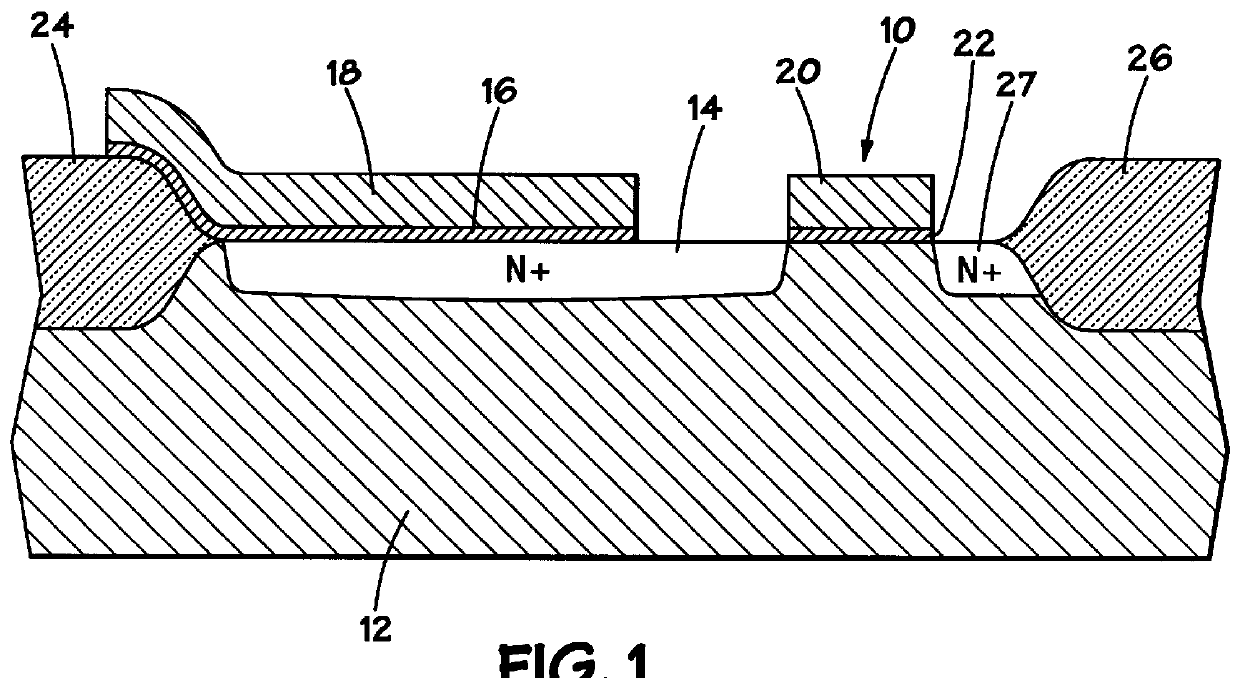

ActiveUS20140070315A1Ideal overall performanceHighest possible BVTransistorSolid-state devicesLDMOSGate dielectric

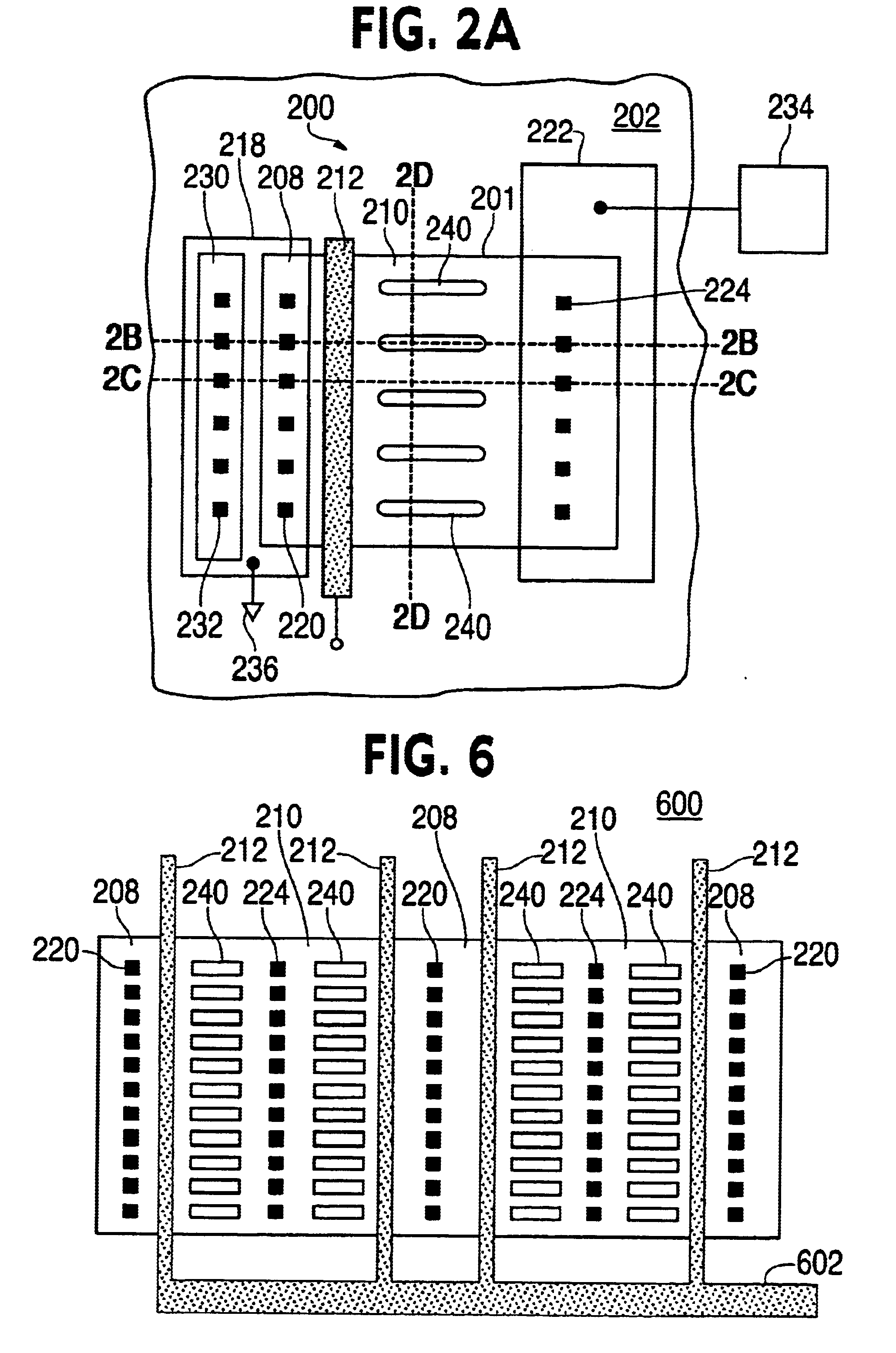

A double-RESURF LDMOS transistor has a gate dielectric structure including a shallow field “bump” oxide region and an optional raised dielectric structure that provides a raised support for the LDMOS transistor's polysilicon gate electrode. Fabrication of the shallow field oxide region is performed through a hard “bump” mask and controlled such that the bump oxide extends a minimal depth into the LDMOS transistor's drift (channel) region. The hard “bump” mask is also utilized to produce an N-type drift (N-drift) implant region and a P-type surface effect (P-surf) implant region, whereby these implants are “self-aligned” to the gate dielectric structure. The N-drift implant is maintained at Vdd by connection to the LDMOS transistor's drain diffusion. An additional Boron implant is utilized to form a P-type buried layer that connects the P-surf implant to the P-body region of the LDMOS transistor, whereby the P-surf implant is maintained at 0V.

Owner:TOWER SEMICONDUCTOR

Isolation structures for semiconductor integrated circuit substrates and methods of forming the same

InactiveUS20070132056A1Increase flexibilityCracking can be particularly problematicSemiconductor/solid-state device detailsSolid-state devicesDielectricCondensed matter physics

Isolation regions for semiconductor substrates include dielectric-filled trenches and field oxide regions. Protective caps of dielectric materials dissimilar from the dielectric materials in the main portions of the trenches and field oxide regions may be used to protect the structures from erosion during later process steps. The top surfaces of the isolation structures are coplanar with the surface of the substrate. Field doping regions may be formed beneath the field oxide regions. To meet the demands of different devices, the isolation structures may have varying widths and depths.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

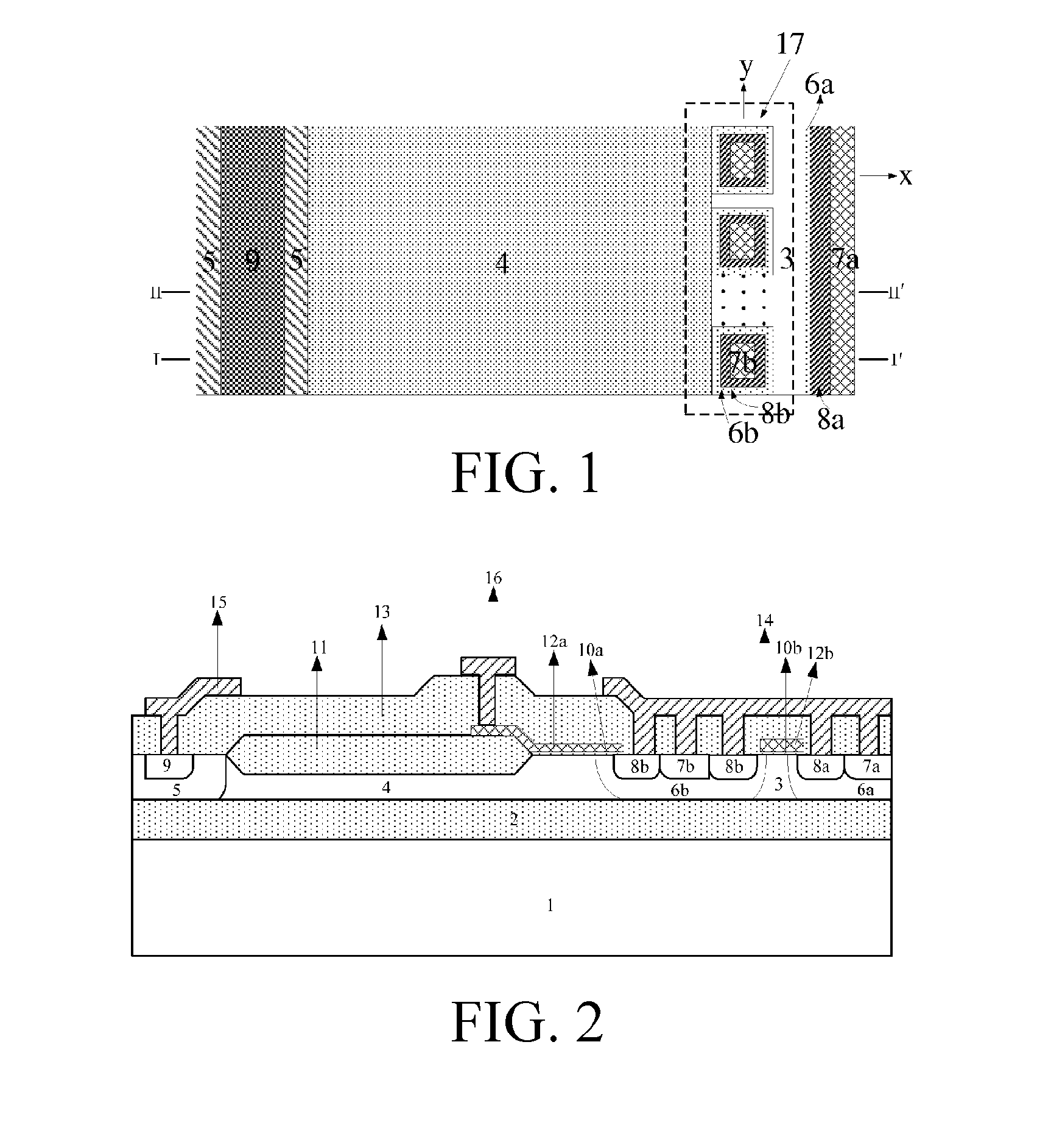

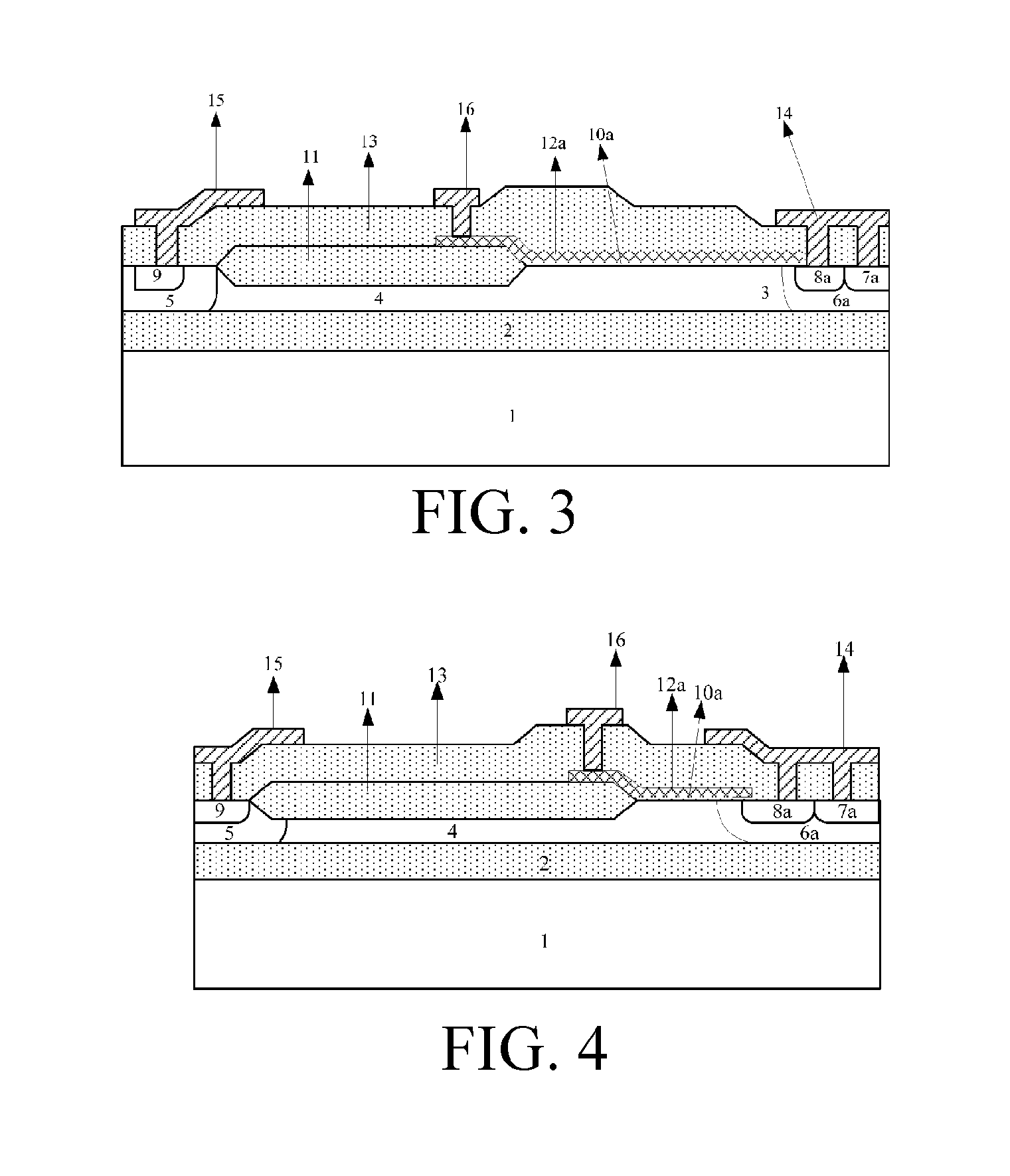

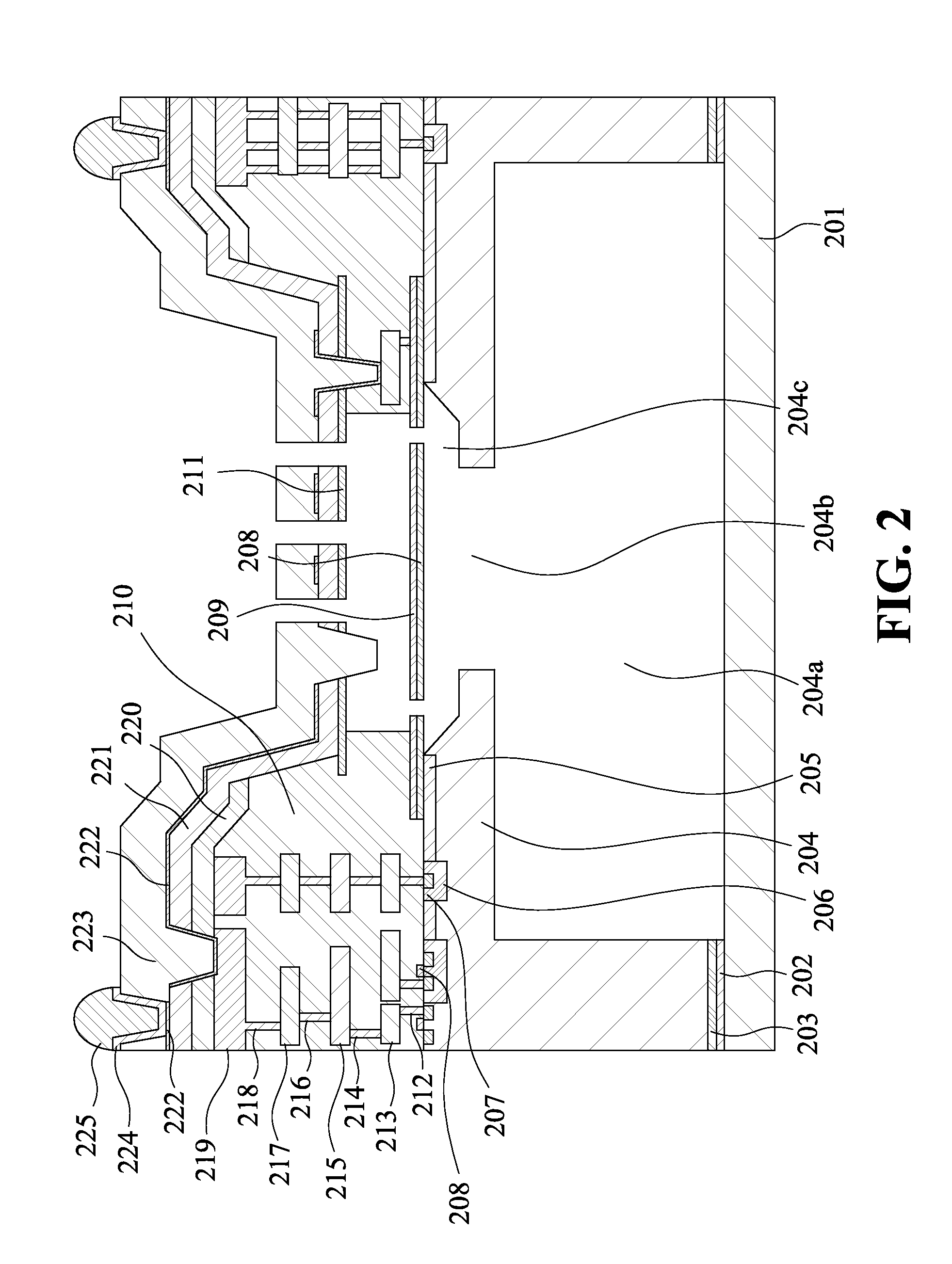

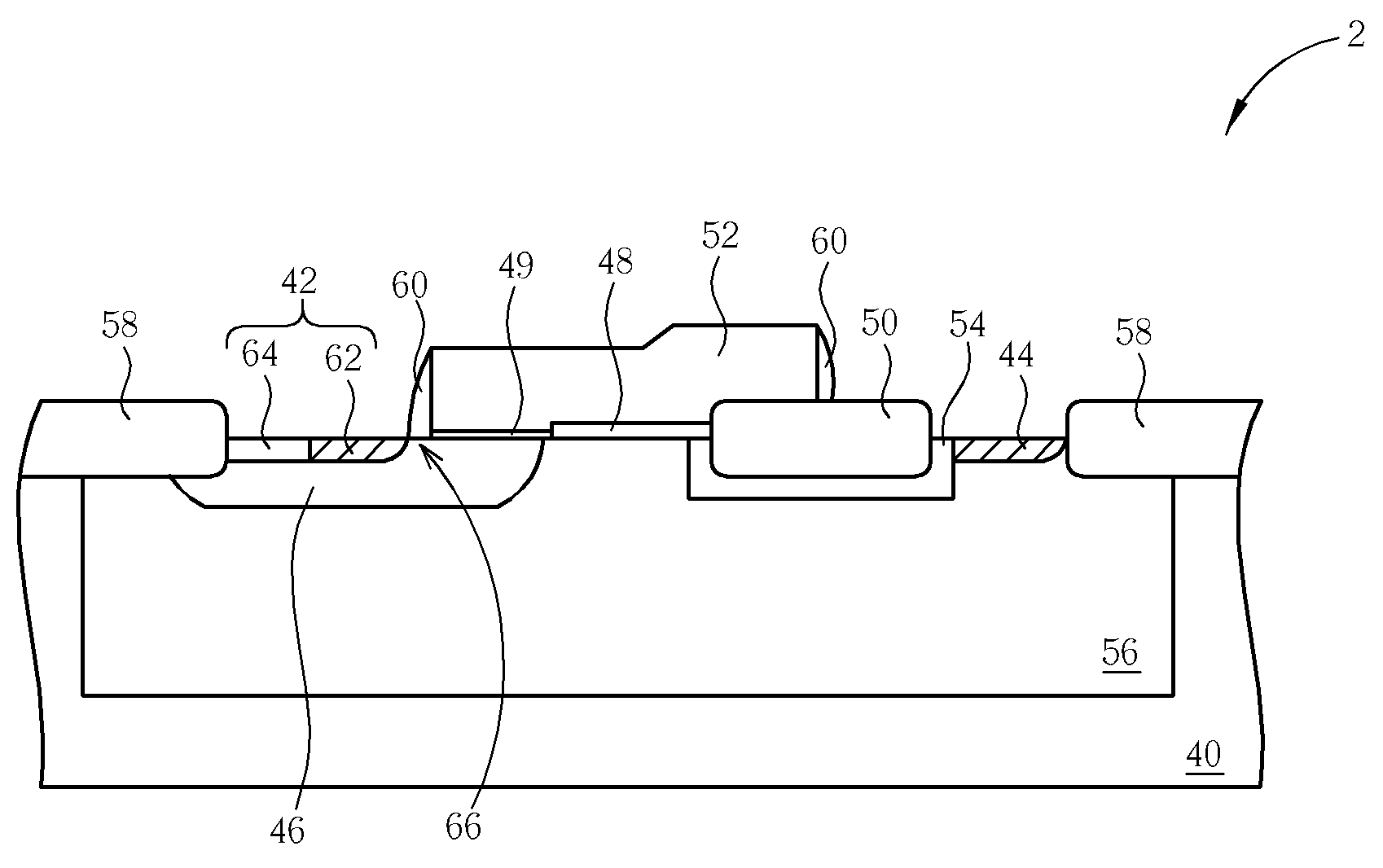

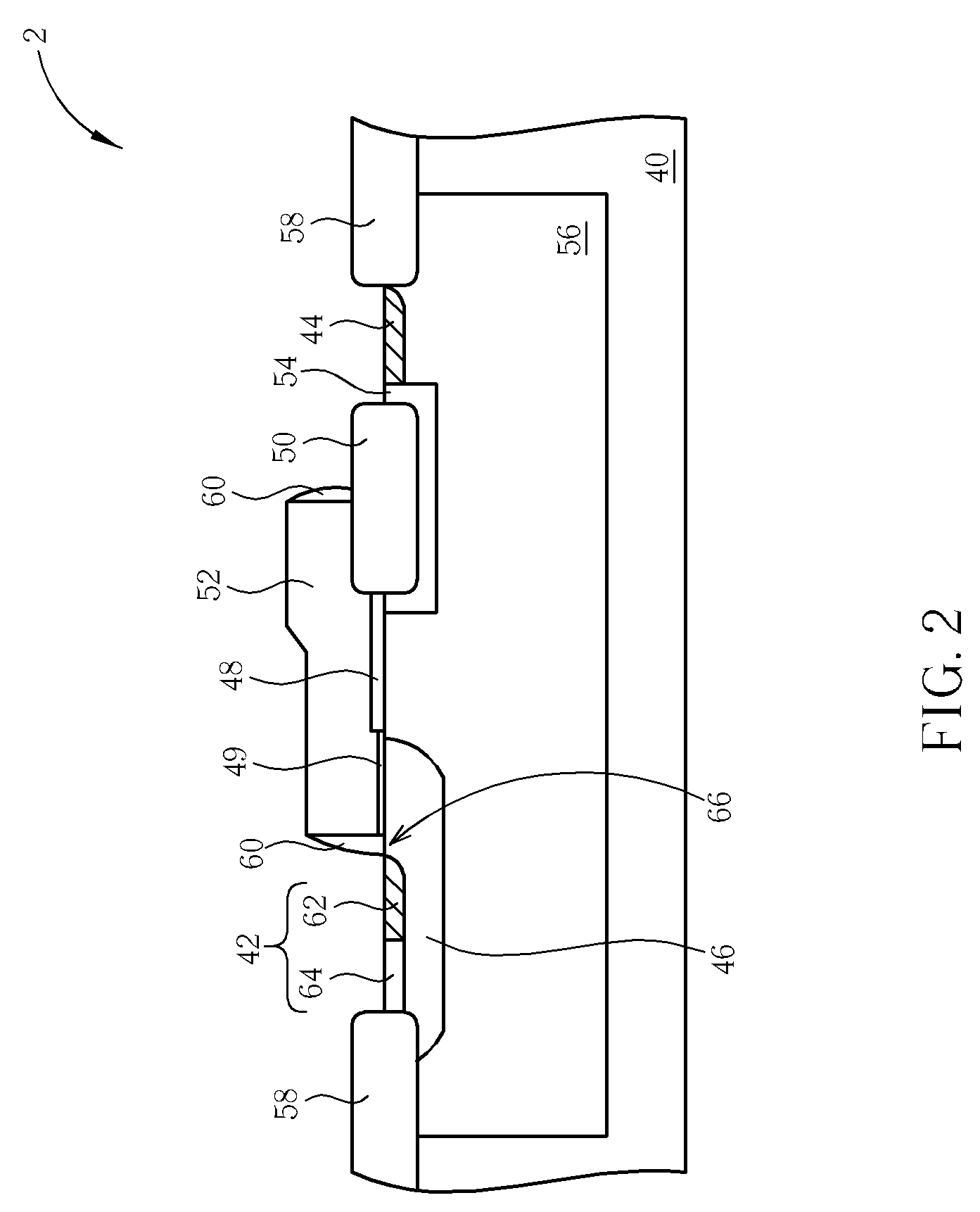

Laterally diffused metal-oxide-semiconductor device and method of making the same

ActiveUS20090072308A1Minimize impactSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate dielectric

A laterally diffused metal-oxide-semiconductor (LDMOS) device as well as a method of making the same is disclosed. A gate is formed on a semiconductor substrate between a source region and a drain region with one side laterally extending onto a part of a field oxide layer and the opposite side beside the source region. A gate dielectric layer is formed between the gate and the semiconductor substrate, wherein the gate dielectric layer comprises two or more portions having different thicknesses arranged laterally in a way that the thicknesses of the portions gradually increase from one side beside the source doping region to the opposite side bordering the field oxide layer. With such structure, the hot carrier impact is minimized and the gate length can be scaled down to gain Idlin.

Owner:UNITED MICROELECTRONICS CORP

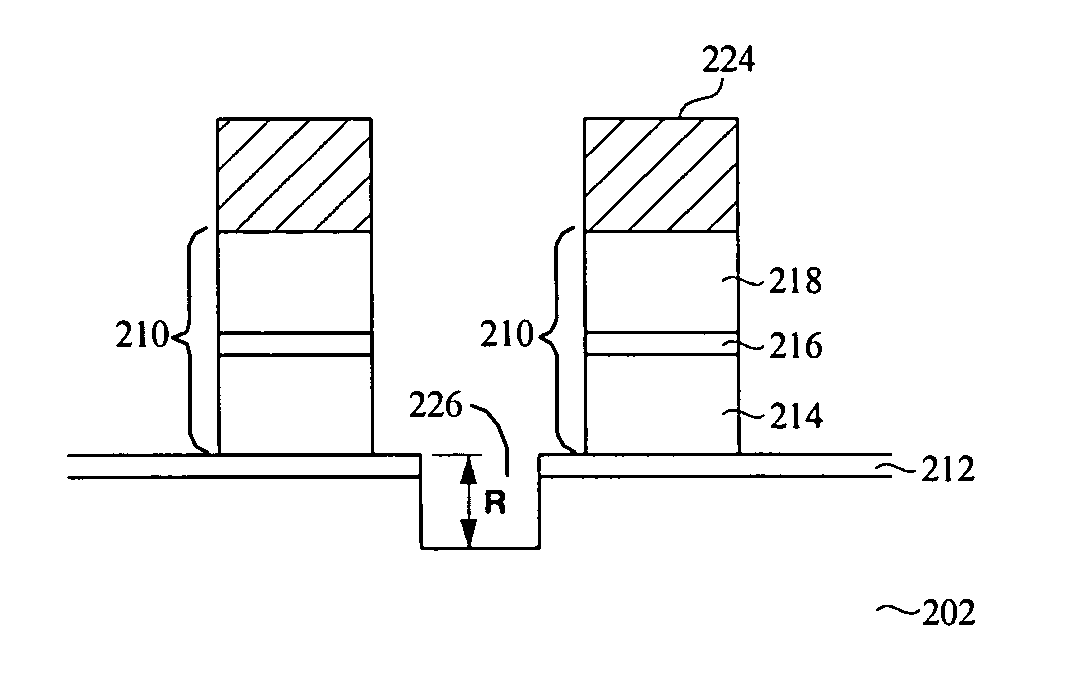

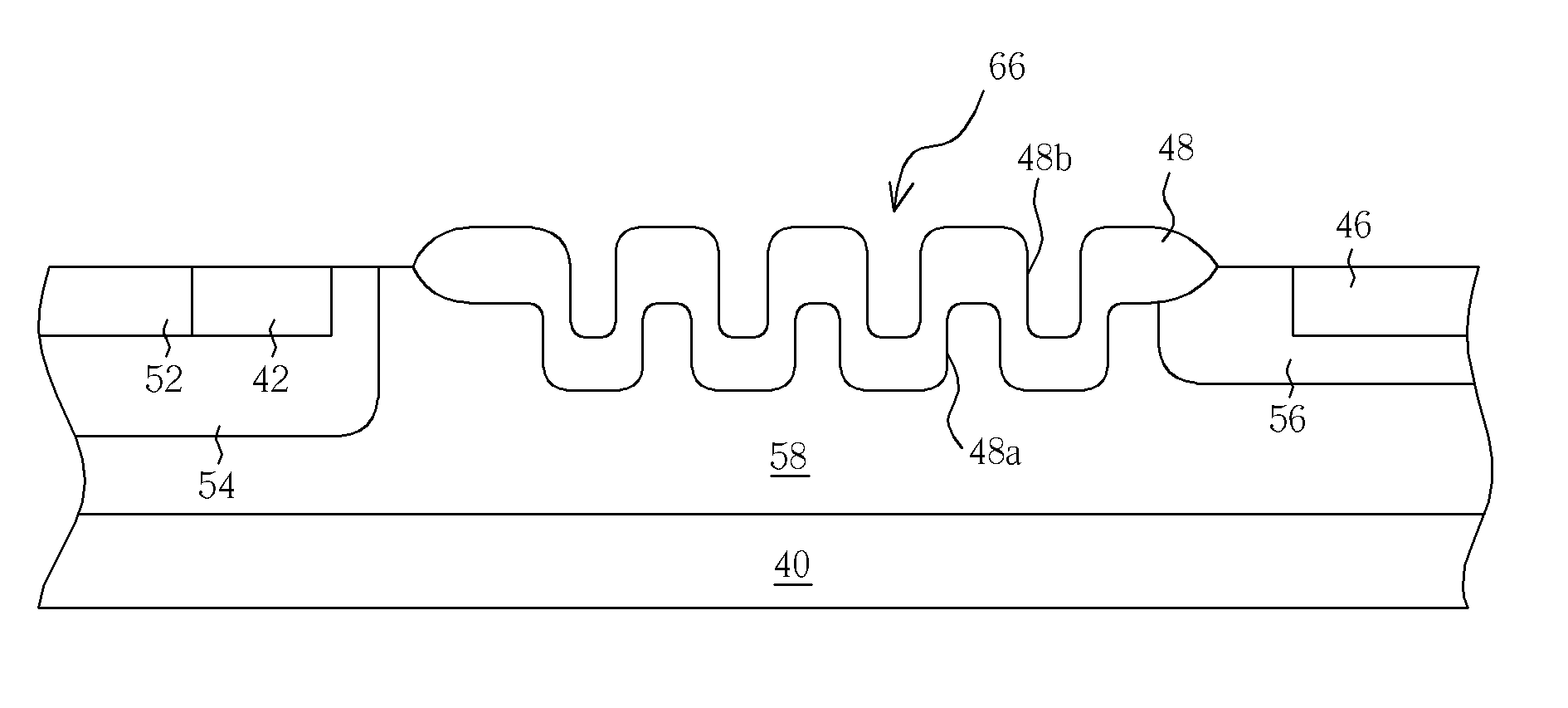

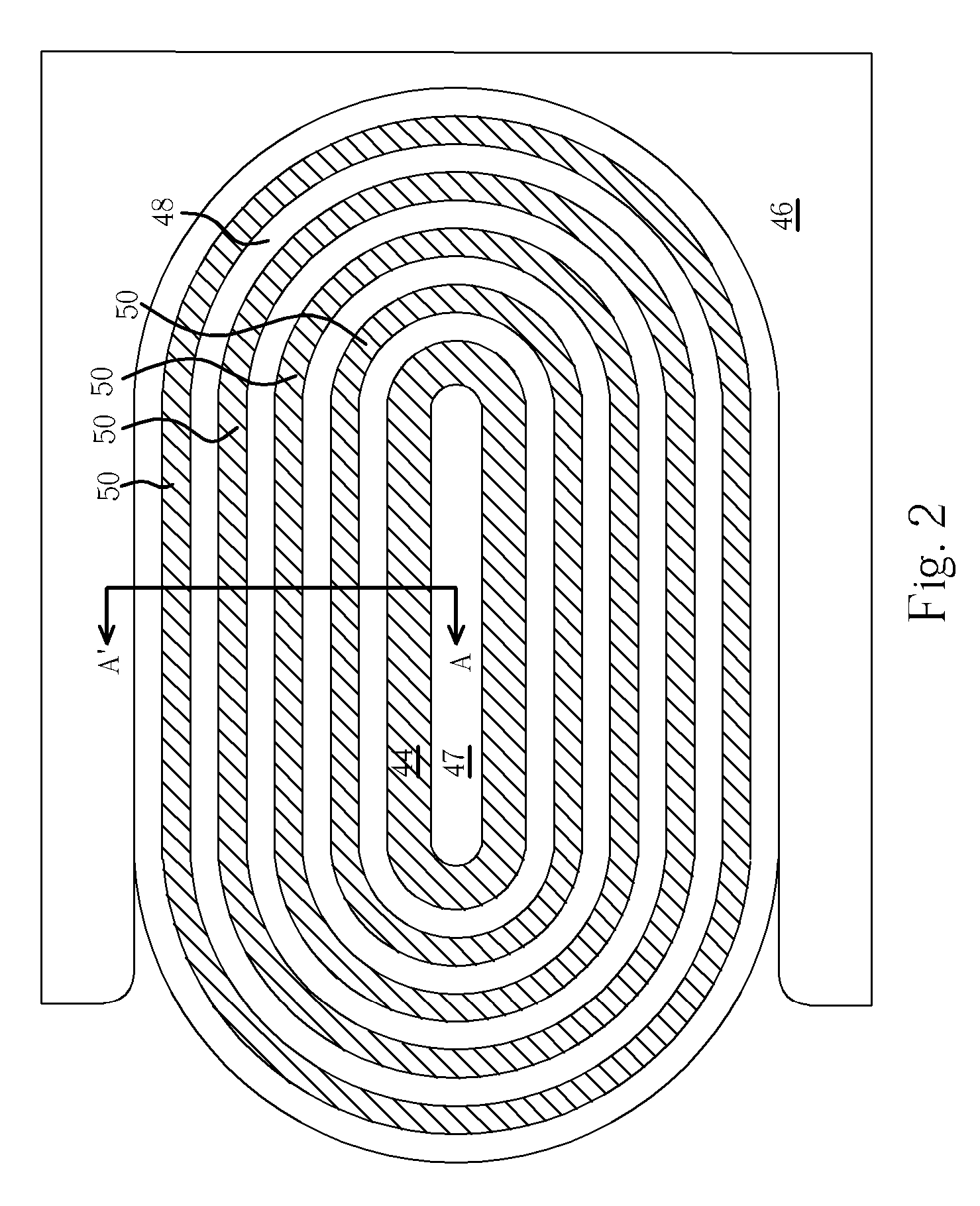

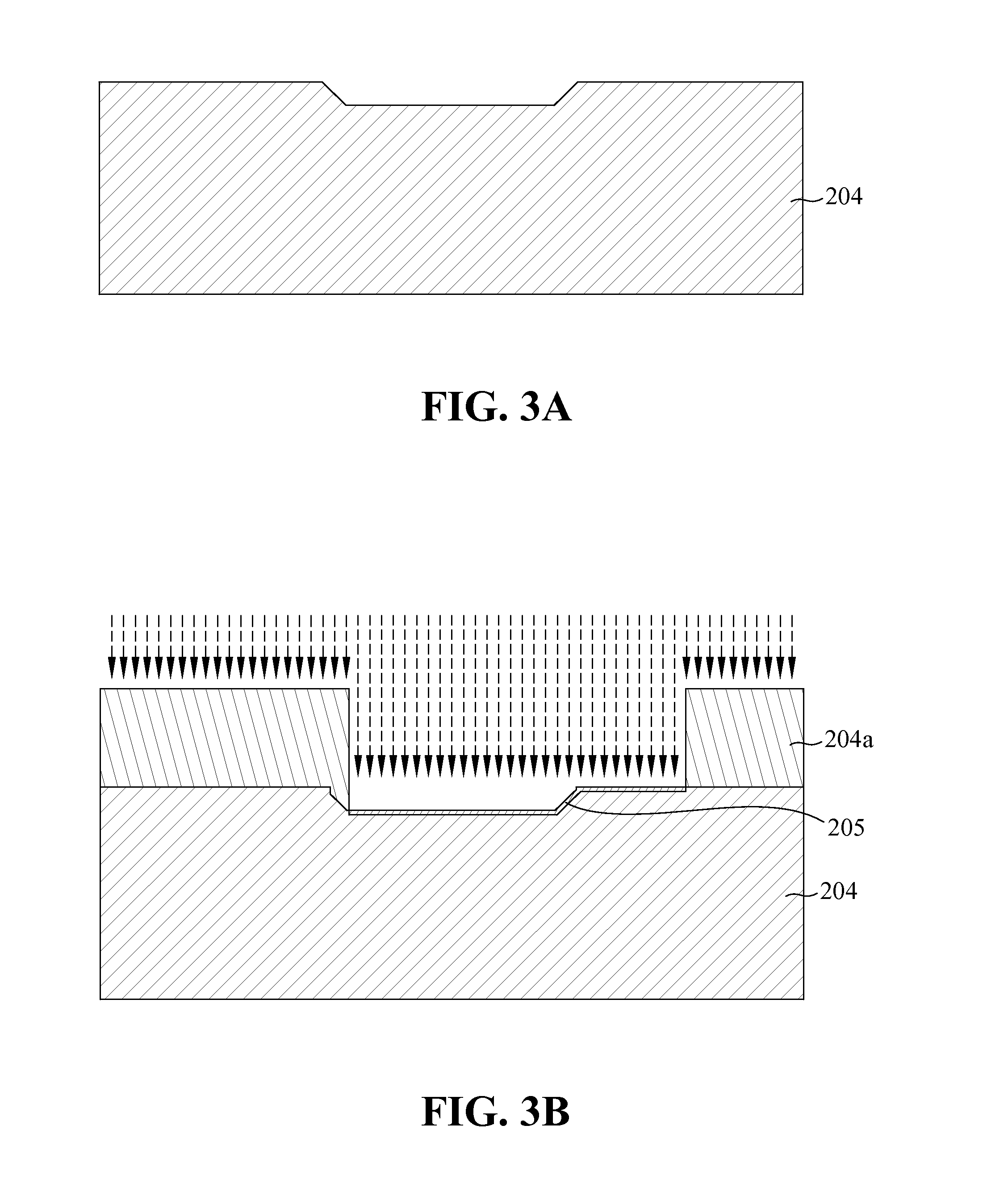

MOS transistor device structure combining Si-trench and field plate structures for high voltage device

ActiveUS20060270171A1Reduce device sizeSmall sizeTransistorSolid-state devicesHigh pressureSemiconductor

A metal-oxide-semiconductor transistor device for high voltage (HV MOS) and a method of manufacturing the same are disclosed. The HV MOS transistor device comprises a field oxide region with an indented lower surface combined with a plurality of field plates to elongate the path for disturbing the lateral electric field, therefore the transistor device has a relatively small size.

Owner:UNITED MICROELECTRONICS CORP

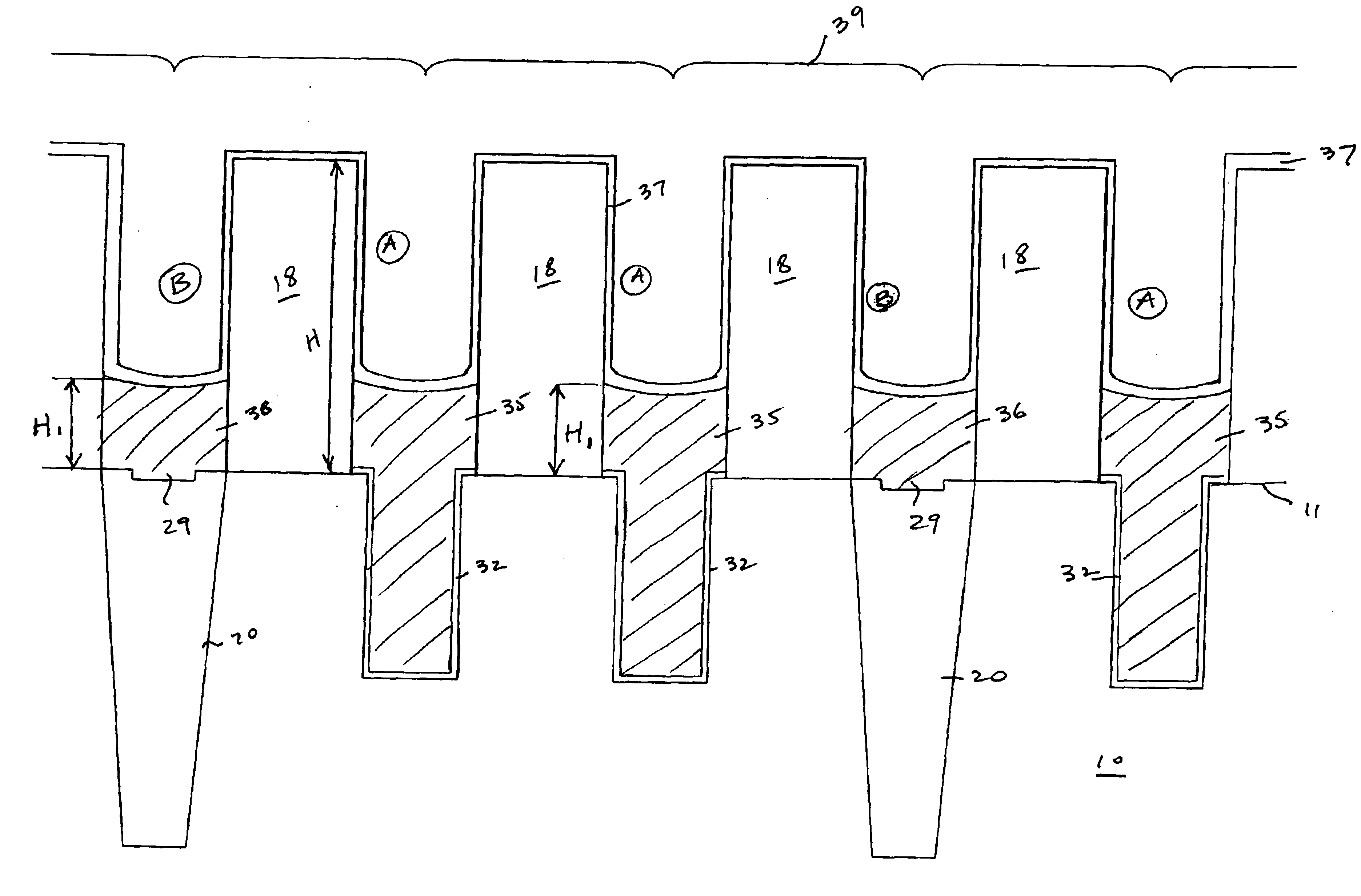

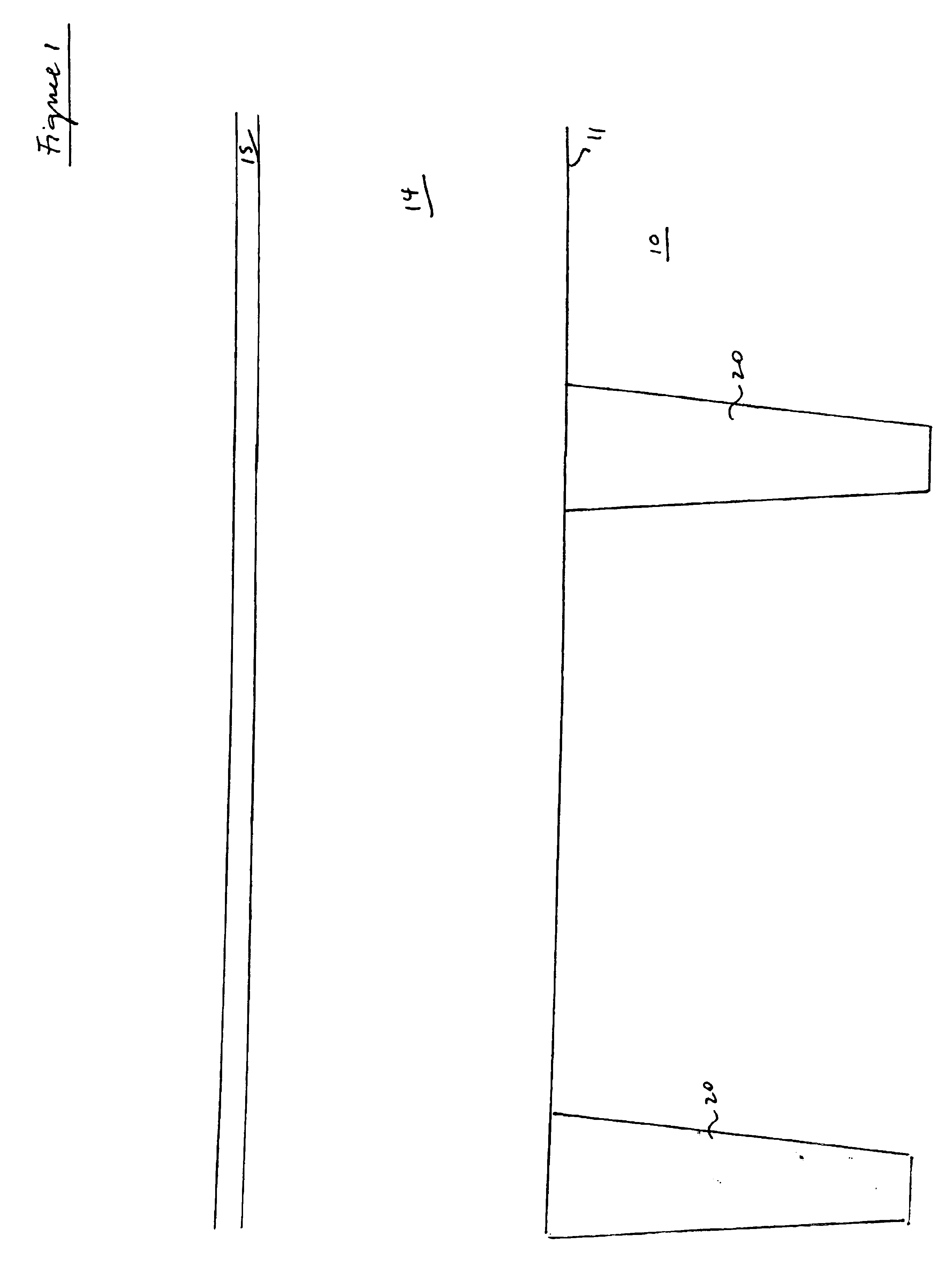

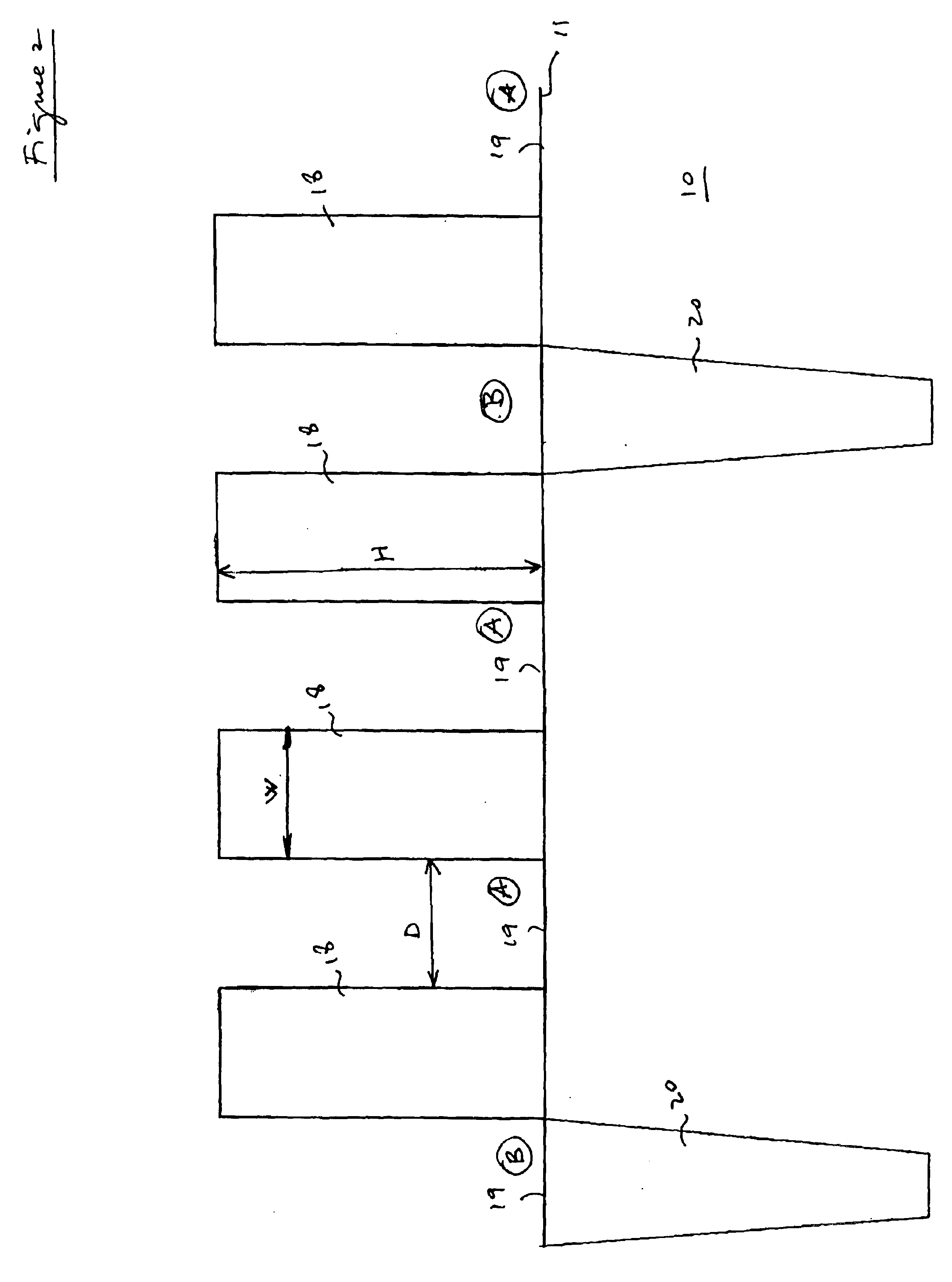

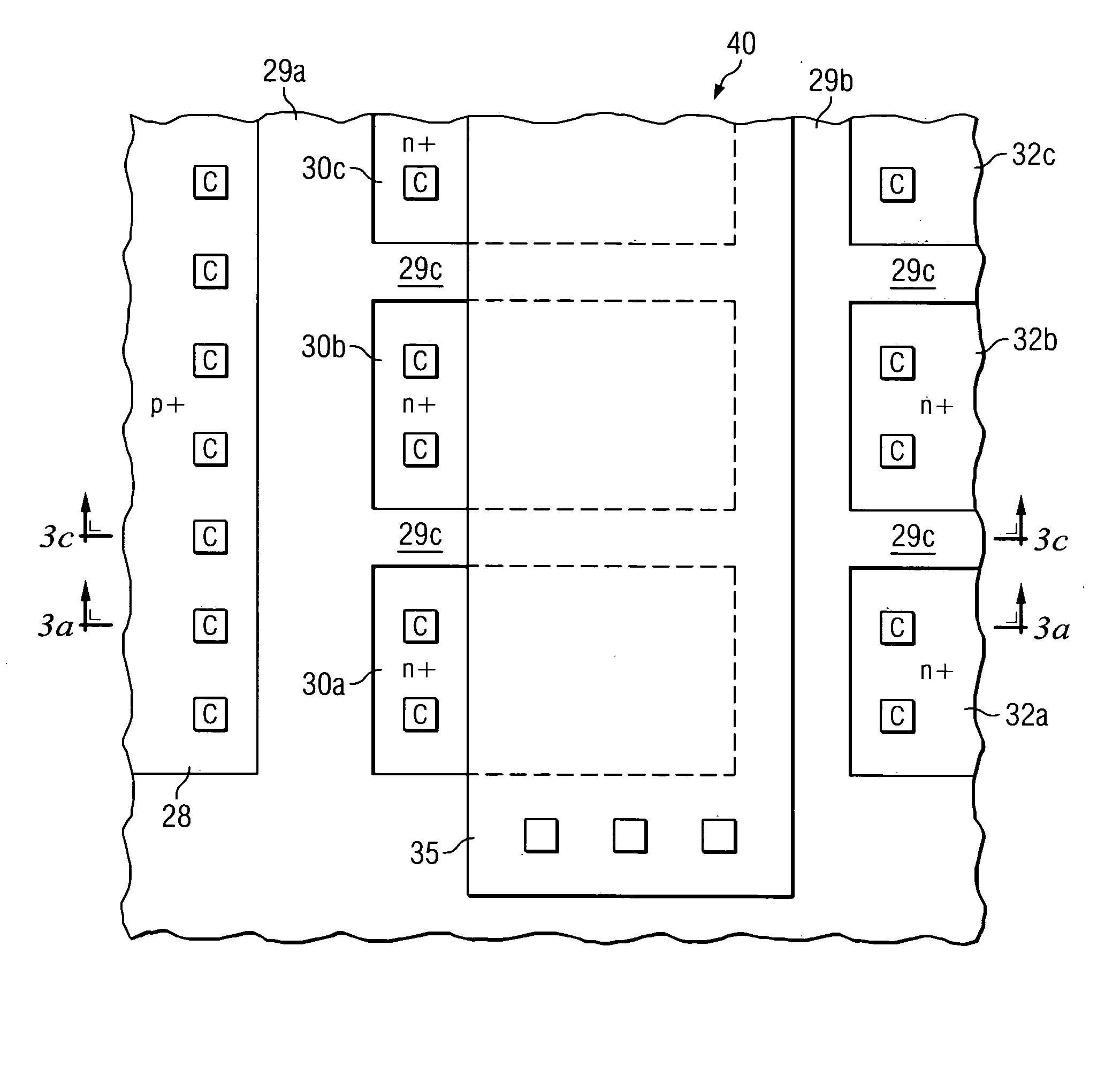

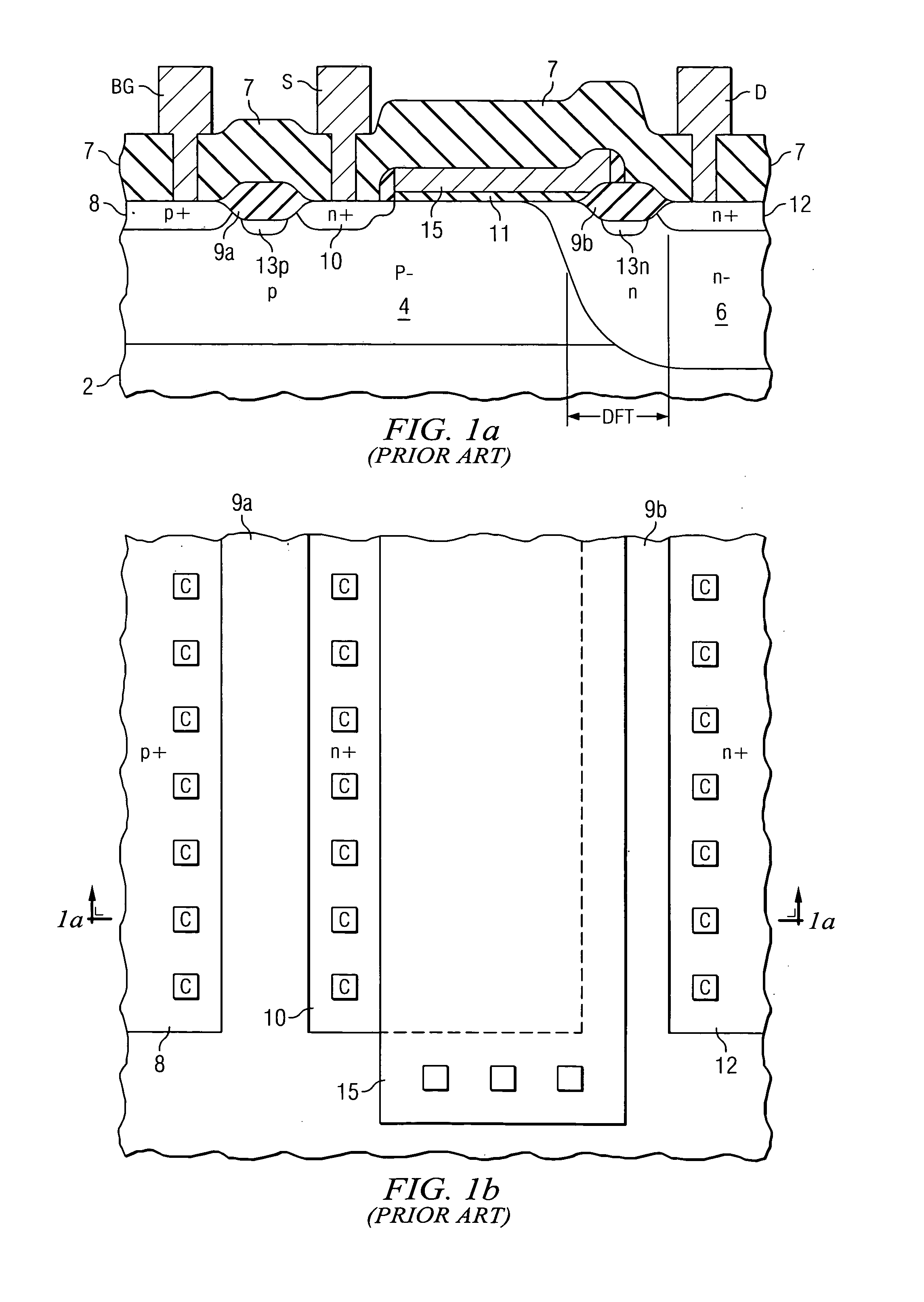

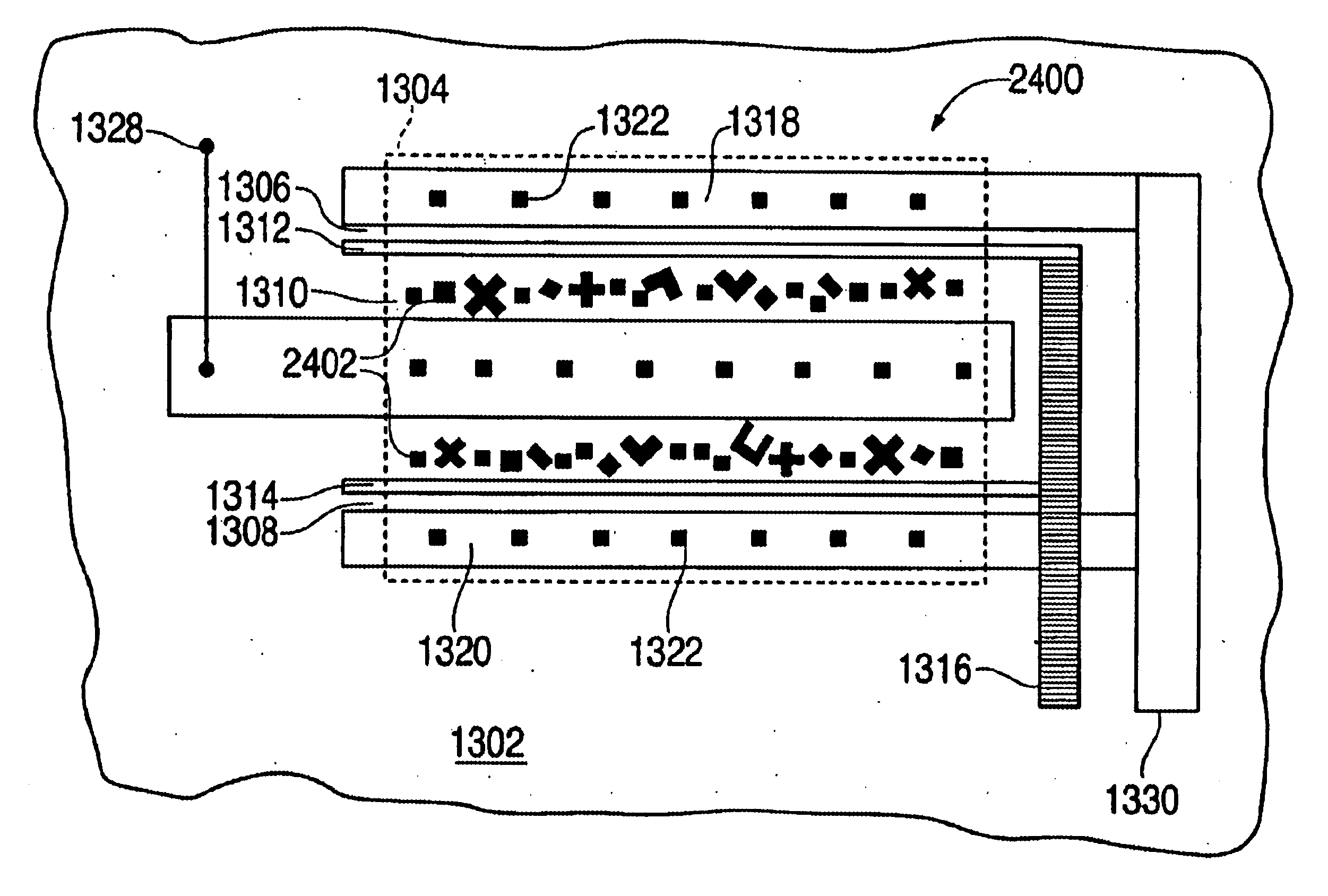

Drain extended MOS transistor with improved breakdown robustness

ActiveUS20050110081A1High currentLocalized damageTransistorSemiconductor/solid-state device manufacturingChannel widthSemiconductor

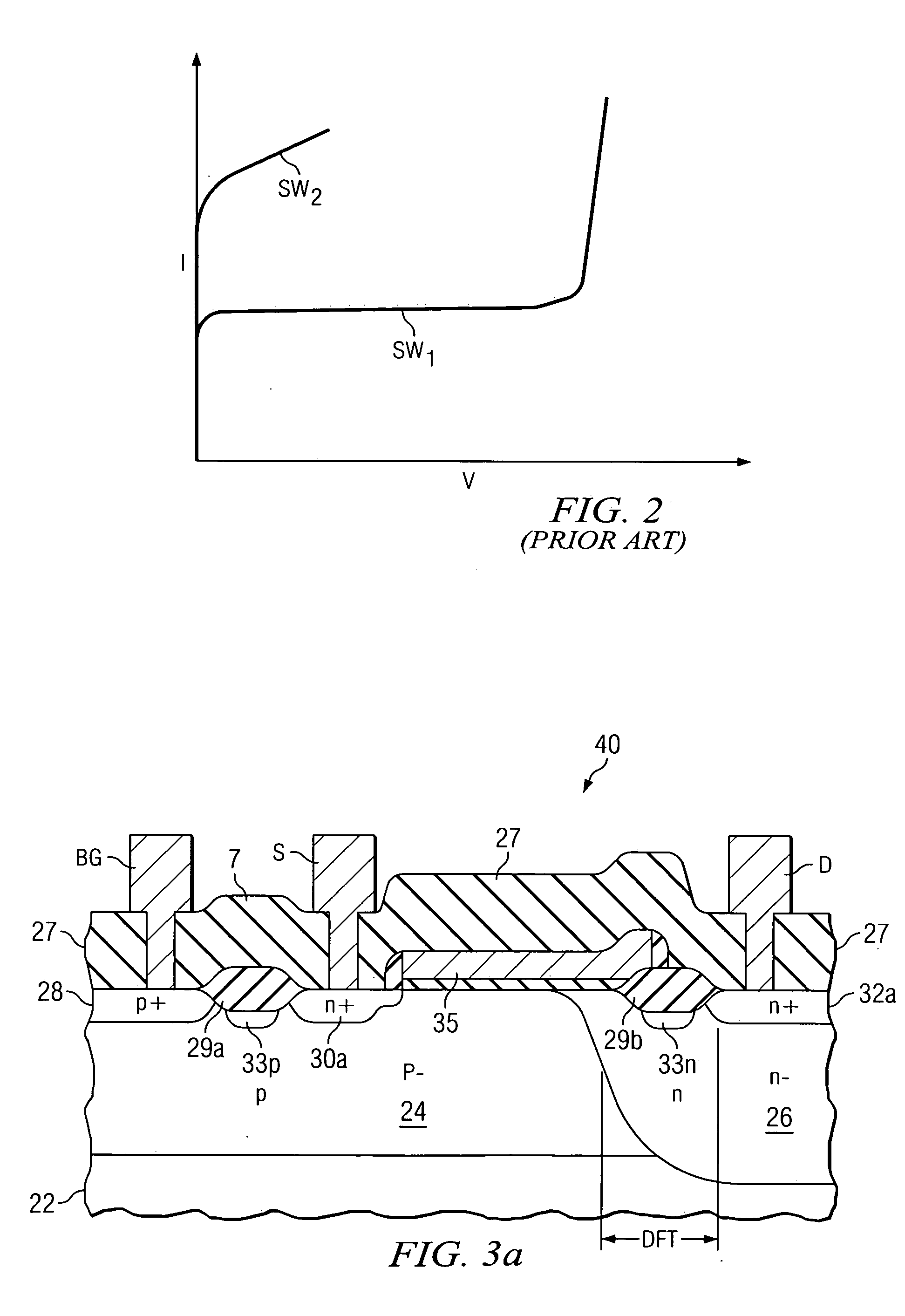

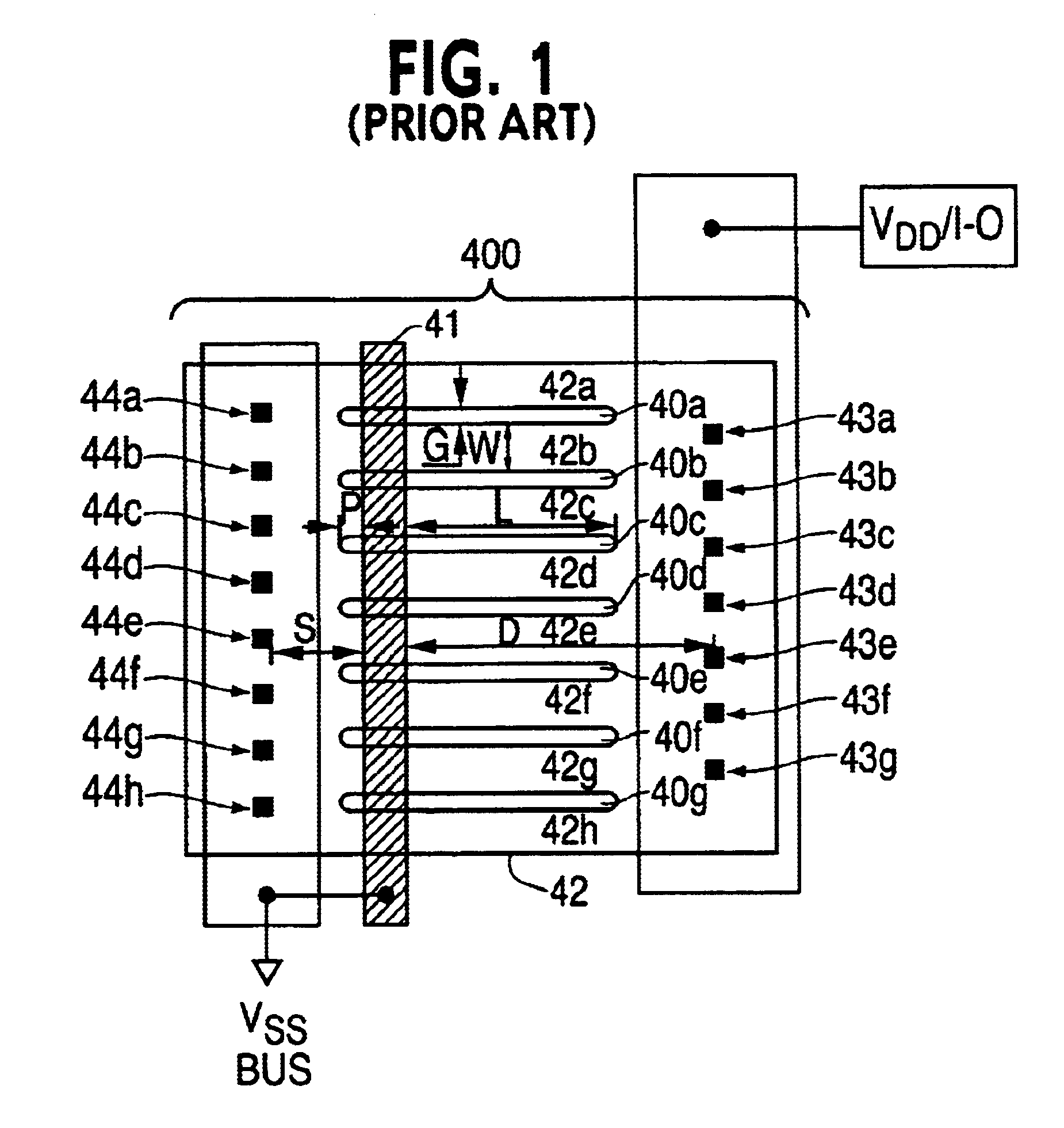

A drain-extended metal-oxide-semiconductor transistor (40) with improved robustness in breakdown characteristics is disclosed. Field oxide isolation structures (29c) are disposed between the source region (30) and drain contact regions (32a, 32b, 32c) to break the channel region of the transistor into parallel sections. The gate electrode (35) extends over the multiple channel regions, and the underlying well (26) and thus the drift region (DFT) of the transistor extends along the full channel width. Channel stop doped regions (33) underlie the field oxide isolation structures (29c), and provide conductive paths for carriers during breakdown. Parasitic bipolar conduction, and damage due to that conduction, is therefore avoided.

Owner:TEXAS INSTR INC

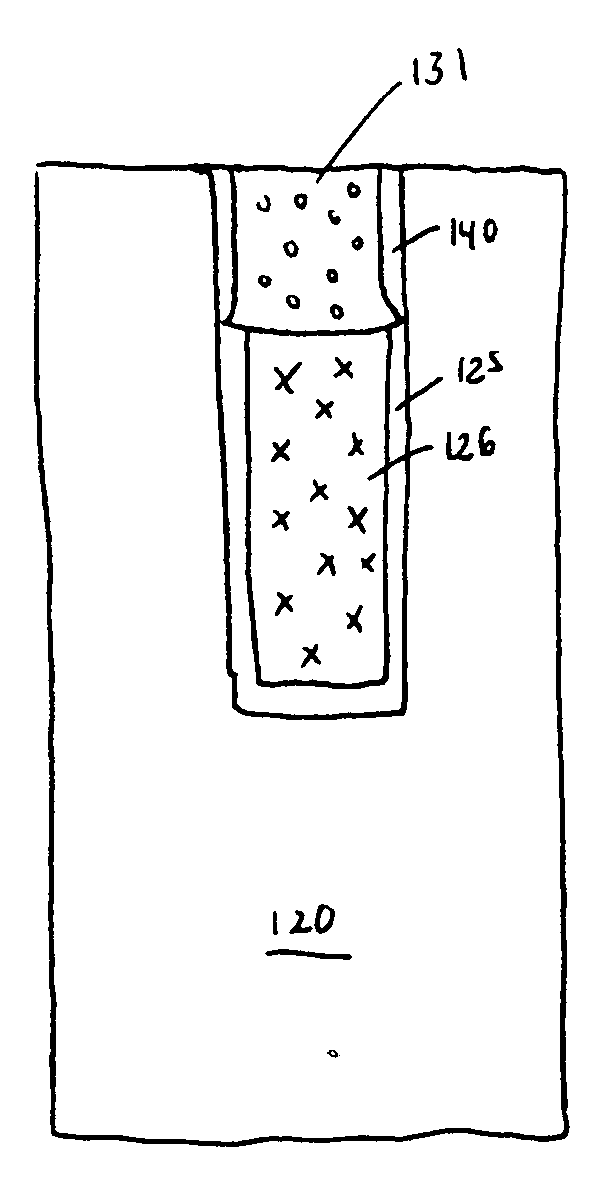

Self aligned gate JFET structure and method

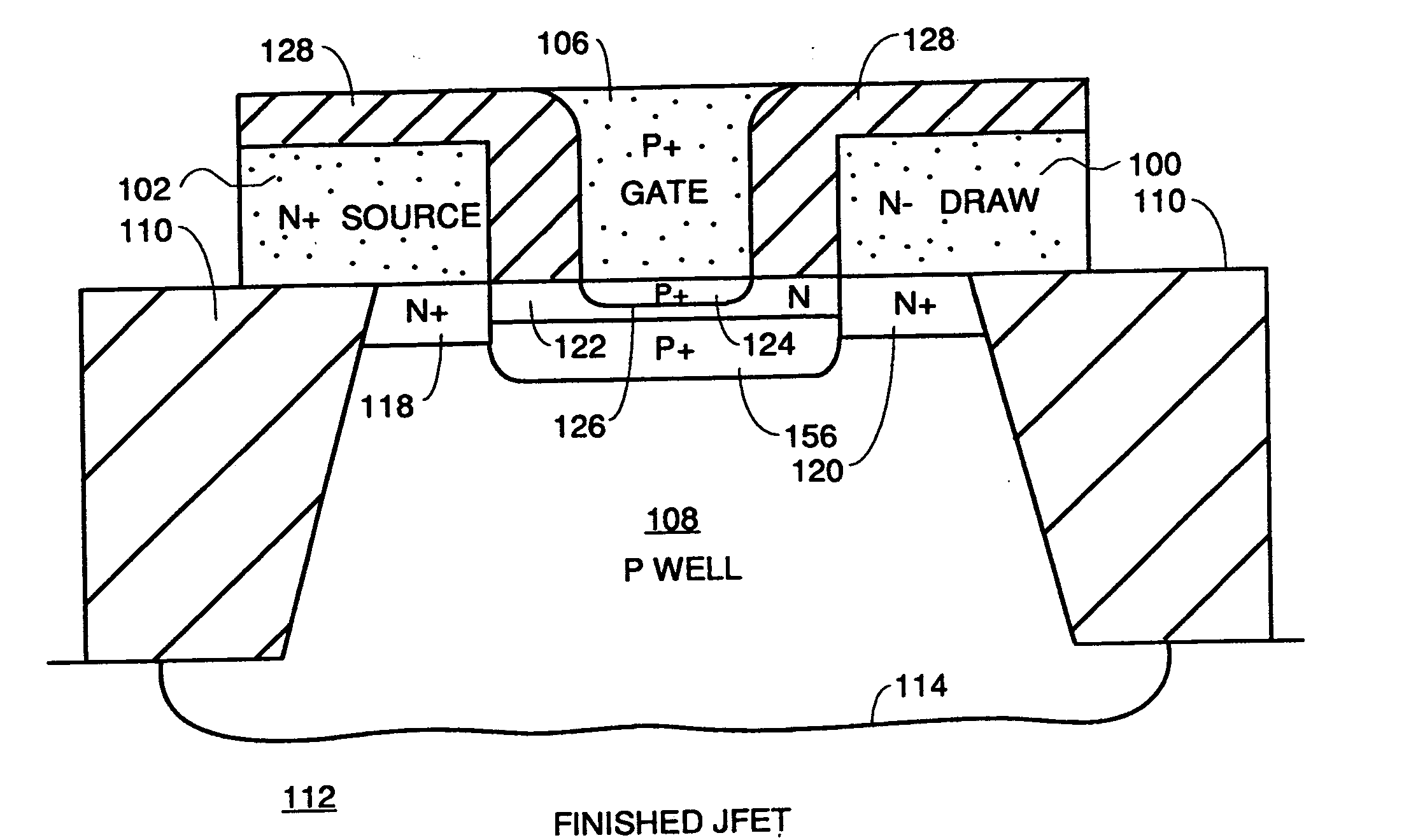

A JFET integrated onto a substrate having a semiconductor layer at least and having source and drain contacts over an active area and made of first polysilicon (or other conductors such as refractive metal or silicide) and a self-aligned gate contact made of second polysilicon which has been polished back to be flush with a top surface of a dielectric layer covering the tops of the source and drain contacts. The dielectric layer preferably has a nitride cap to act as a polish stop. In some embodiments, nitride covers the entire dielectric layer covering the source and drain contacts as well as the field oxide region defining an active area for said JFET. An embodiment with an epitaxially grown channel region formed on the surface of the substrate is also disclosed.

Owner:MIE FUJITSU SEMICON

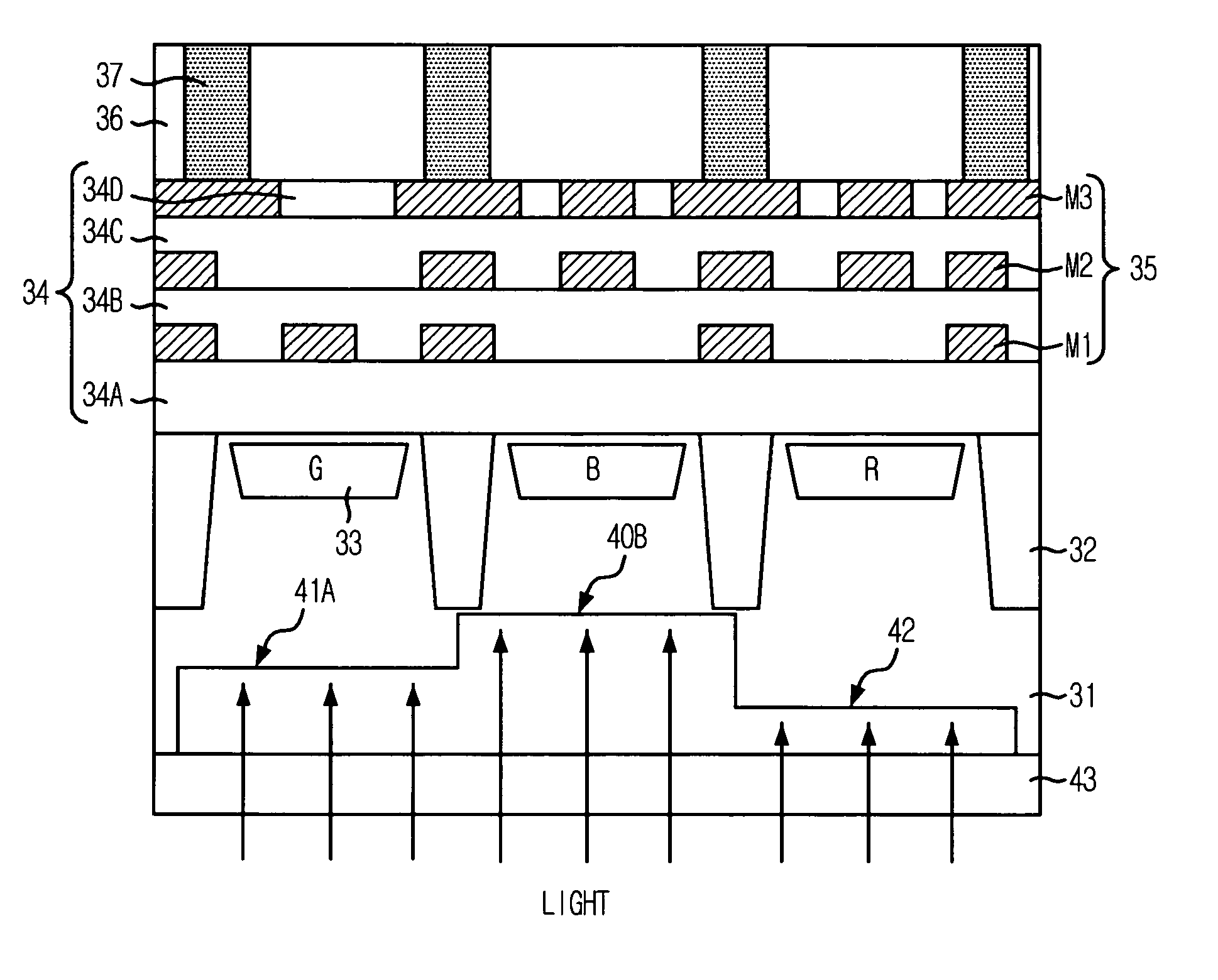

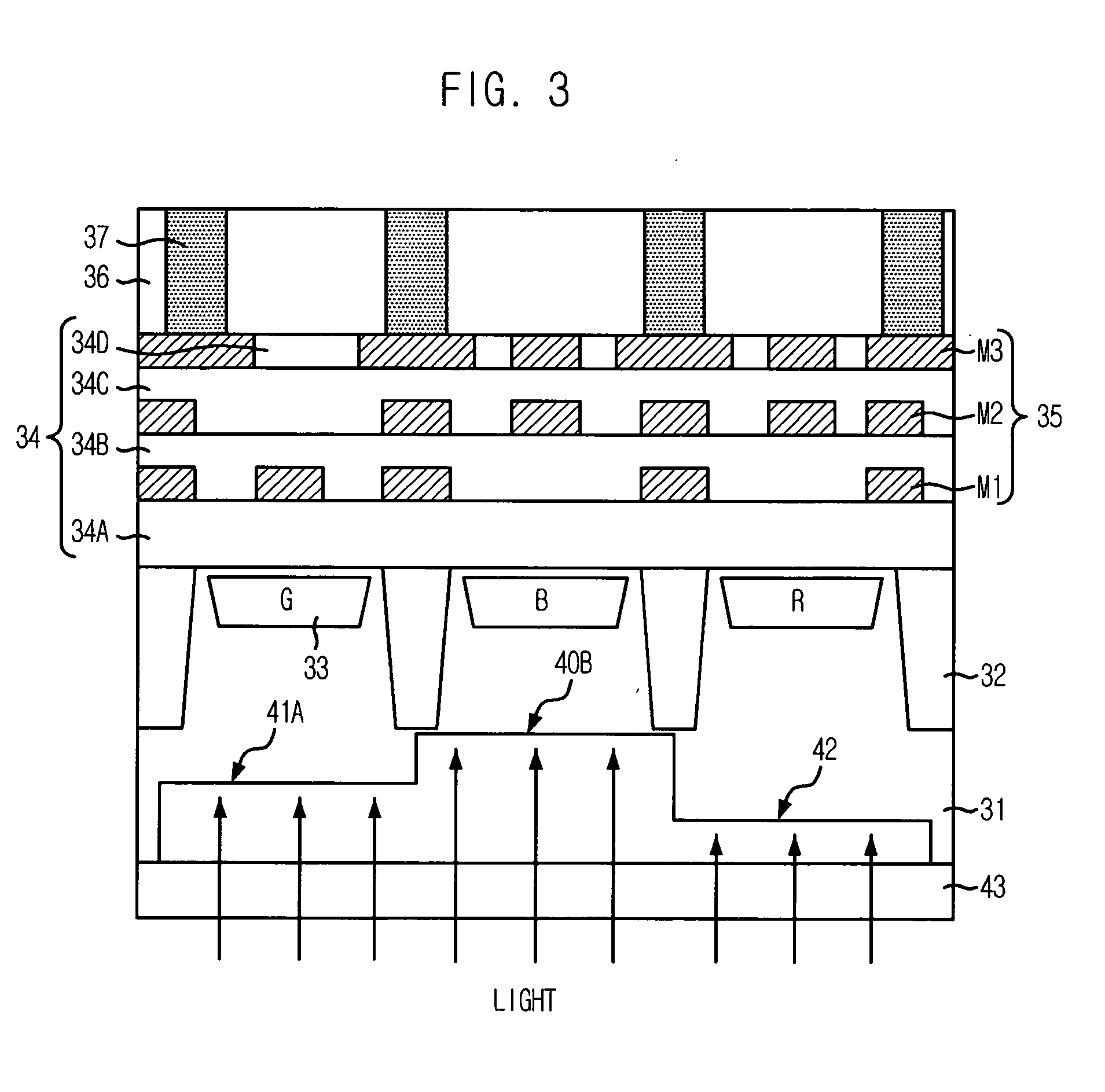

CMOS image sensor with backside illumination and method for manufacturing the same

A CMOS image sensor includes a plurality of pixel regions formed under a front surface of a substrate, and having photodiodes separated from each other by a field oxide, a multi-layered metal interconnection formed over the pixel regions of the front of the substrate, a bump connected to an uppermost metal interconnection of the multi-layered metal interconnection, a plurality of trenches formed in a backside of the substrate, wherein the trenches have different depths for each wavelength of light, and correspond to the respective pixel regions, and a glass covering the backside of the substrate.

Owner:INTELLECTUAL VENTURES II

Structure for an antifuse cell

A structure for an antifuse cell which comprises: (a) field oxide between the bottom plate of the antifuse element and its access transistor; and (b) an implanted region underlying the antifuse element to provide a conductive path between the source of the access transistor and the antifuse element.

Owner:MICRON TECH INC

A Method Of Fabricating A DRAM Transistor With A Dual Gate Oxide Technique

InactiveUS20010008808A1Solid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsPhotoresist

The process comprises the steps of growing a first oxide layer on the upper surface of a substrate; depositing a silicon nitride layer on top of the first oxide layer; patterning the silicon nitride layer with a photoresist mask to define field oxide areas; stripping the oxide layer and regrowing a pad oxide layer on the upper surfaces of the substrate not covered by the remnants of the silicon nitride layer; removing the remnants of the silicon nitride layer; stripping the pad oxide layer and growing a sacrificial oxide layer; masking the sacrificial oxide layer with a photoresist to protect the area where the memory array will be formed; stripping the sacrificial oxide not protected by the photoresist; stripping the photoresist; and growing a gate oxide layer which is thinner than the sacrificial oxide layer. Thereafter, fabrication of the memory device may be completed using any known prior art techniques.

Owner:ROUND ROCK RES LLC

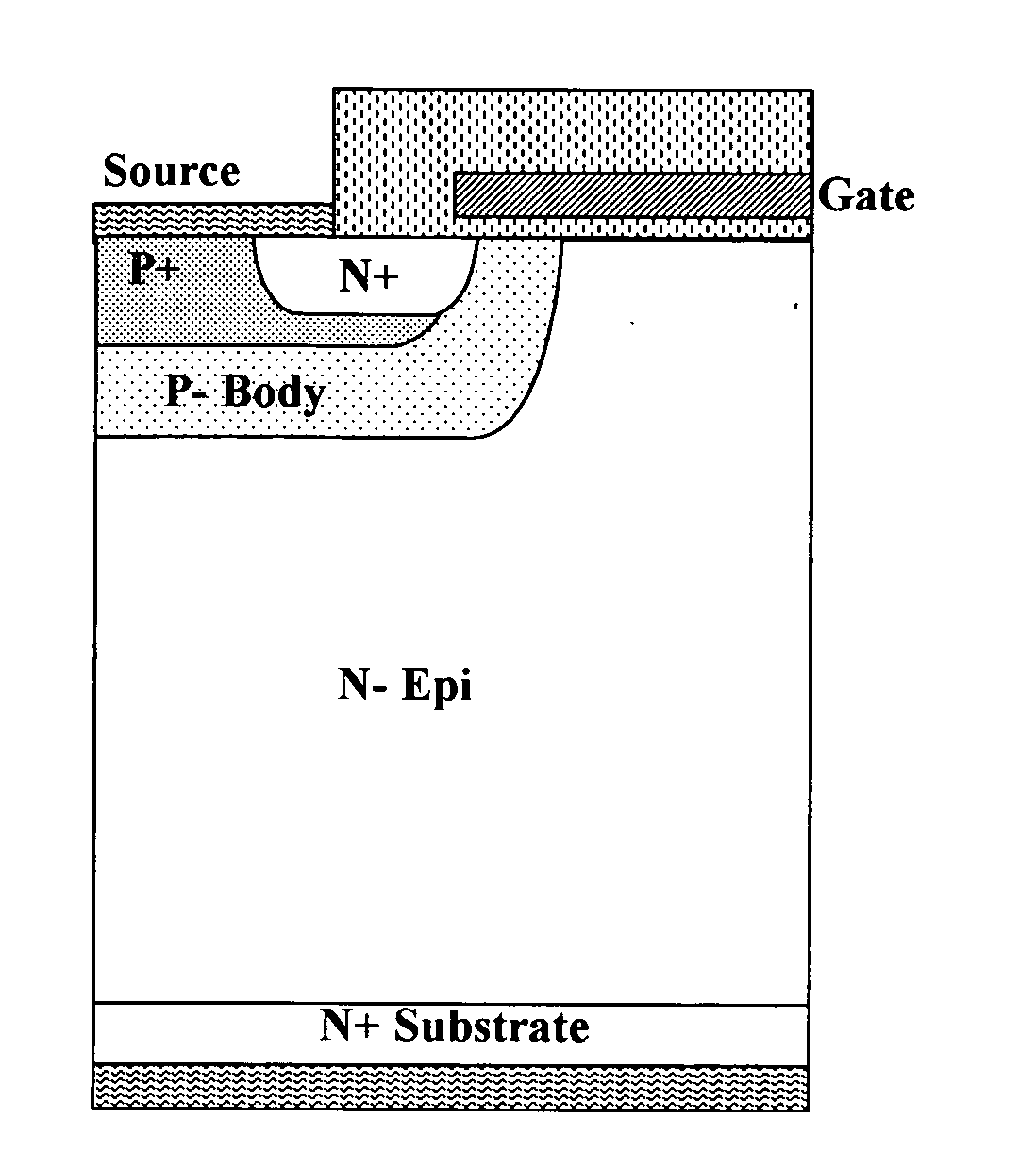

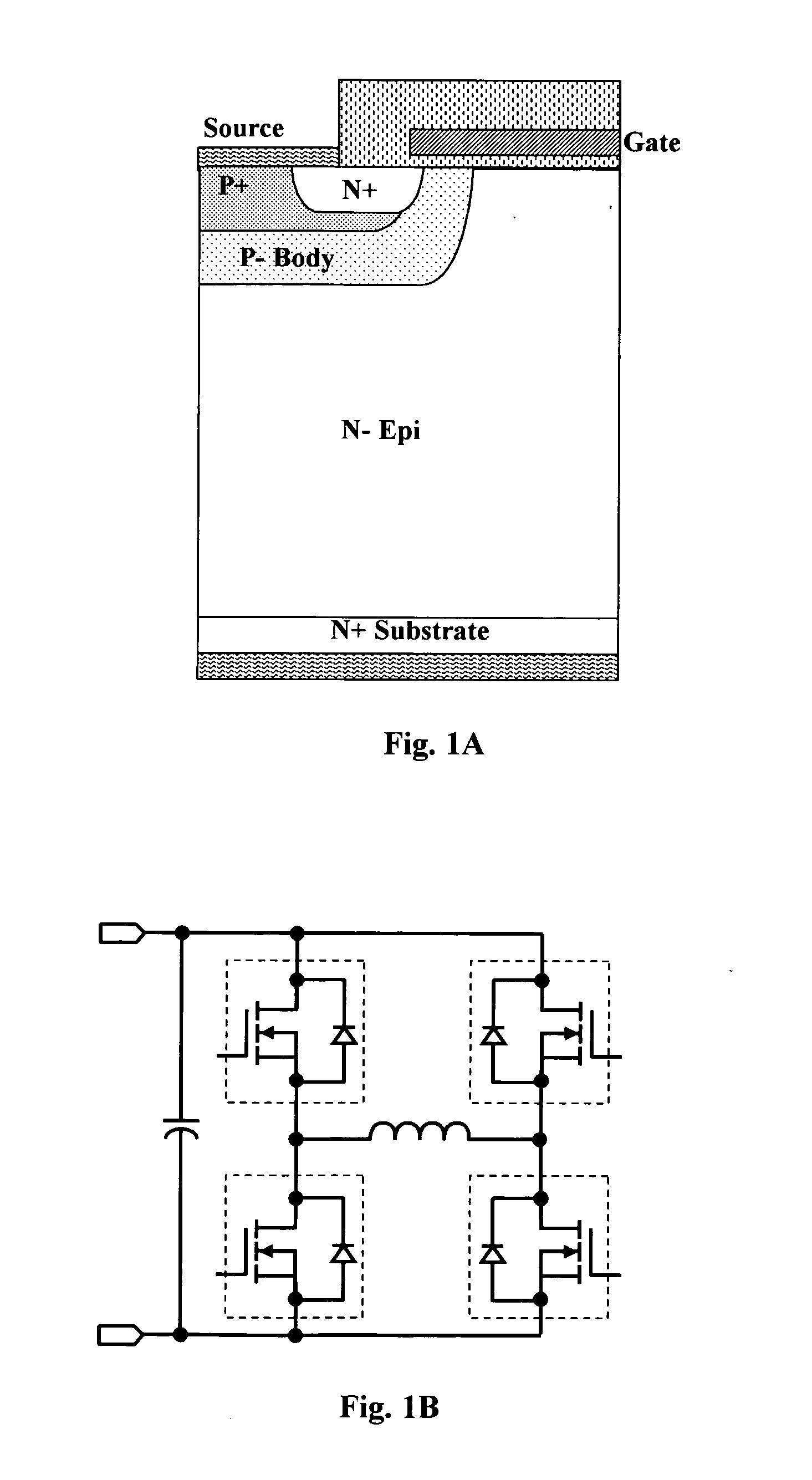

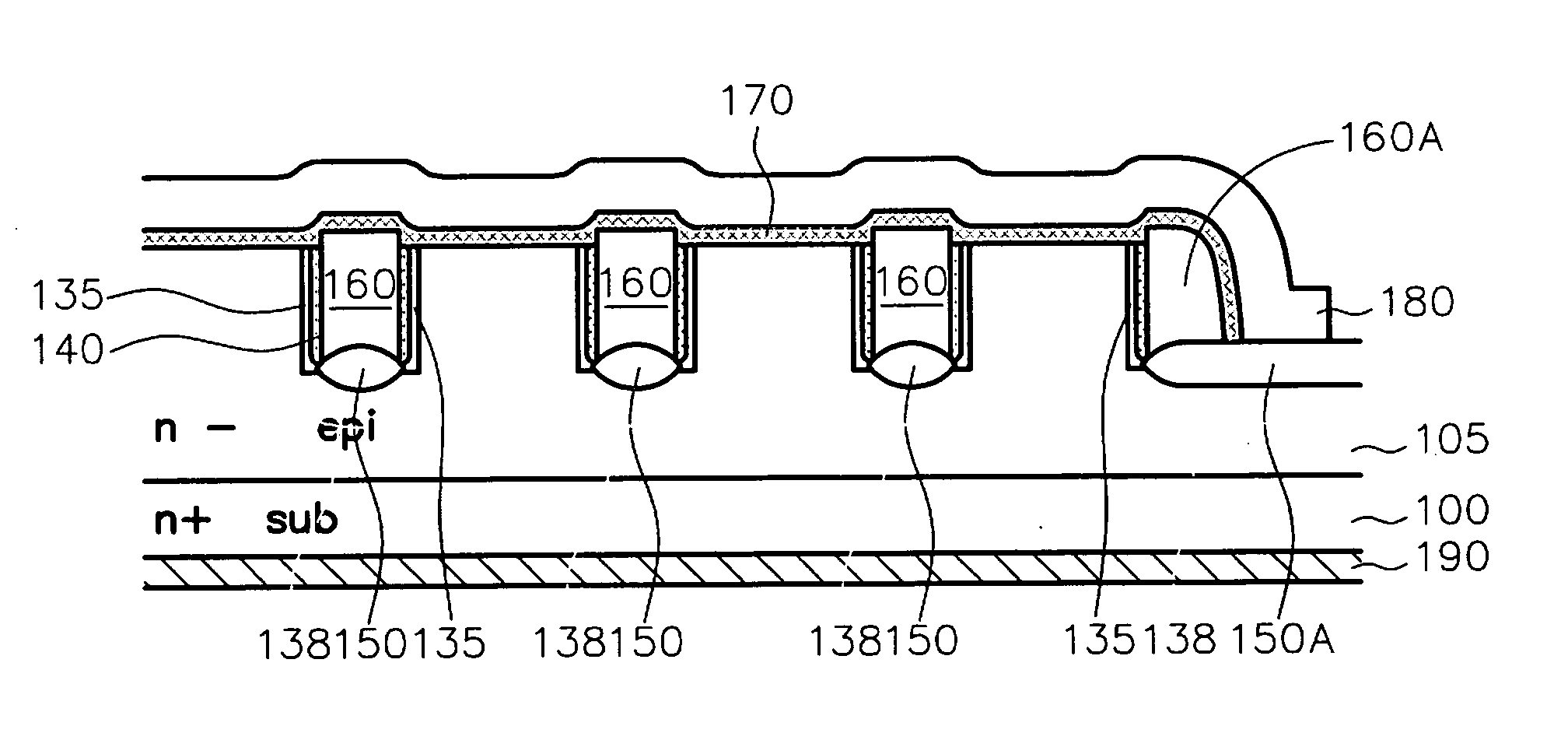

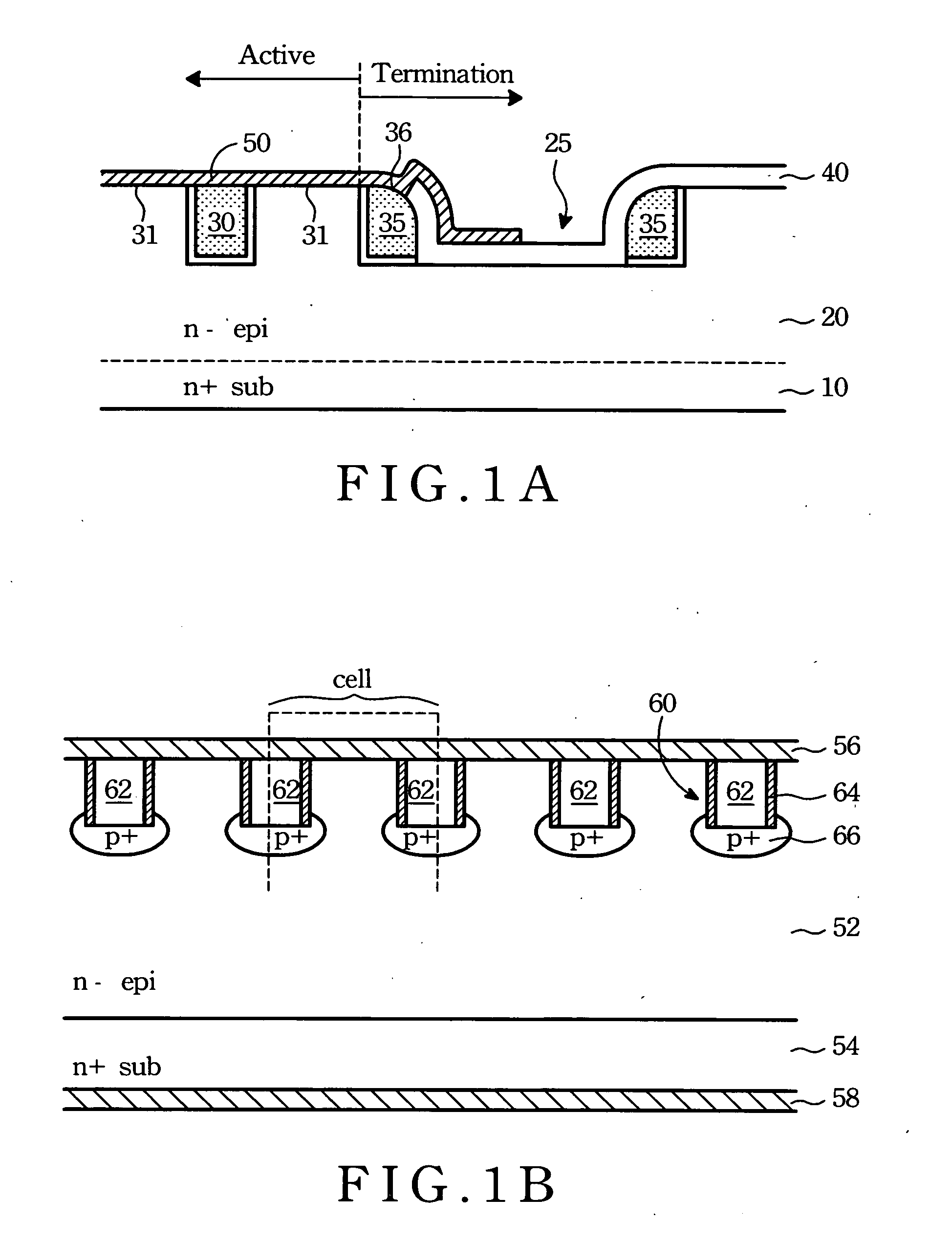

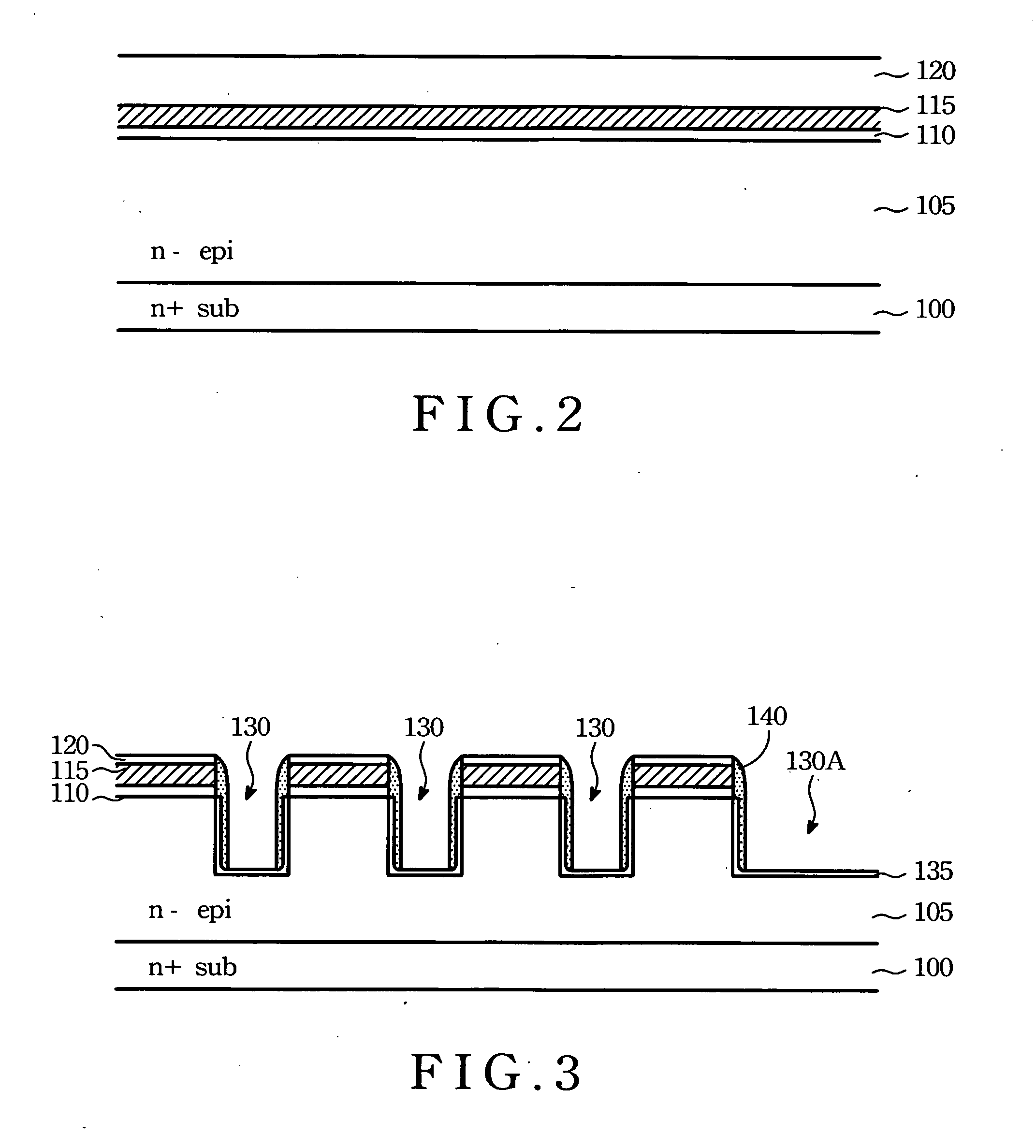

High voltage MOSFET diode reverse recovery by minimizing P-body charges

ActiveUS20110073906A1Improve configurationImprove methodSemiconductor/solid-state device manufacturingDiodeHigh concentrationDopant

This invention discloses a method for manufacturing a semiconductor power device in a semiconductor substrate comprises an active cell area and a termination area. The method comprises the steps of a) growing and patterning a field oxide layer in the termination area and also in the active cell area on a top surface of the semiconductor substrate b) depositing and patterning a polysilicon layer on the top surface of the semiconductor substrate at a gap distance away from the field oxide layer; c) performing a blank body dopant implant to form body dopant regions in the semiconductor substrate substantially aligned with the gap area followed by diffusing the body dopant regions into body regions in the semiconductor substrate; d) implanting high concentration body-dopant regions encompassed in and having a higher dopant concentration than the body regions e) applying a source mask to implant source regions having a conductivity opposite to the body region with the source regions encompassed in the body regions and surrounded by the high concentration body-dopant regions; and f) etching contact trenches into the source, body contact, and body regions.

Owner:ALPHA & OMEGA SEMICON INC

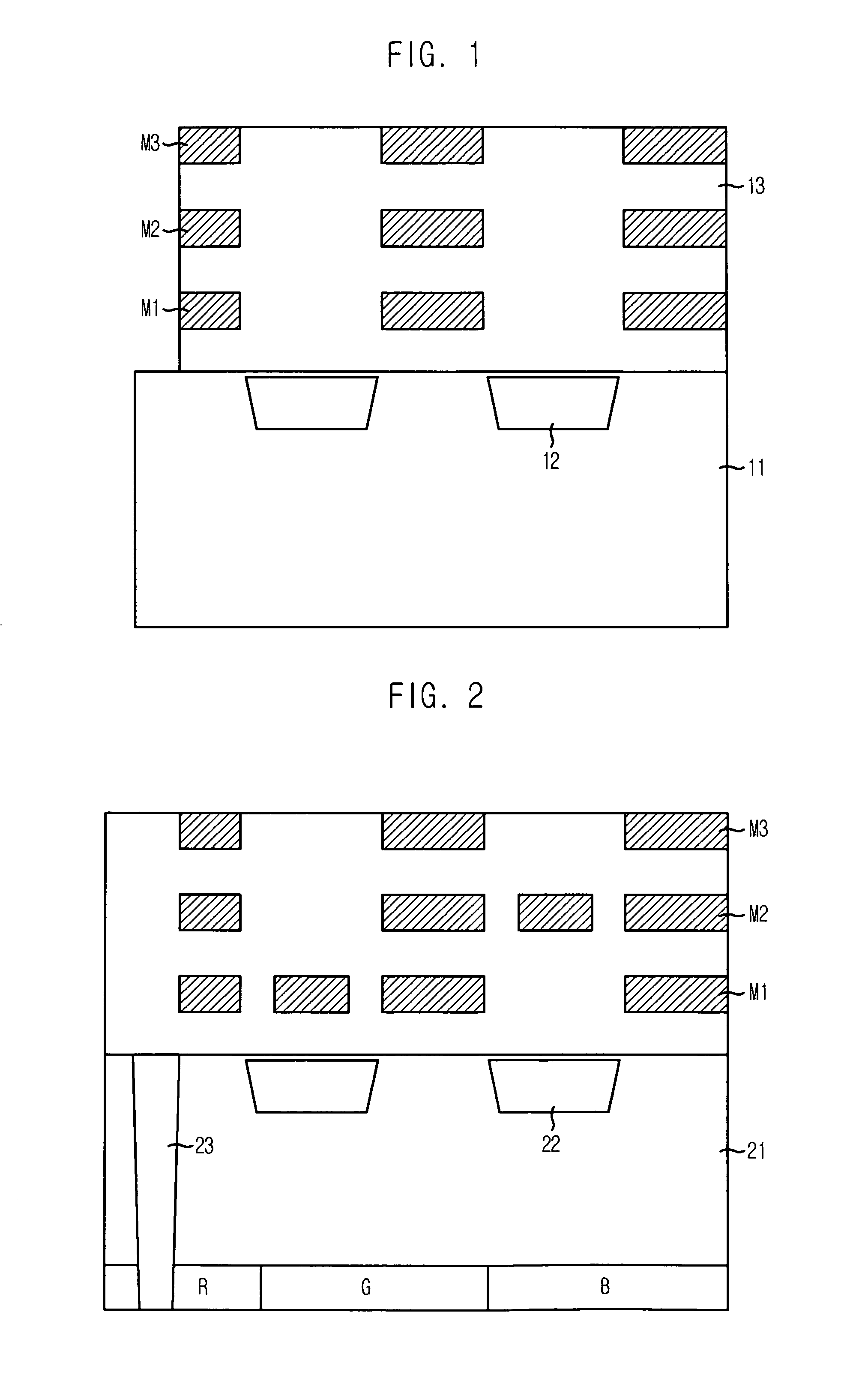

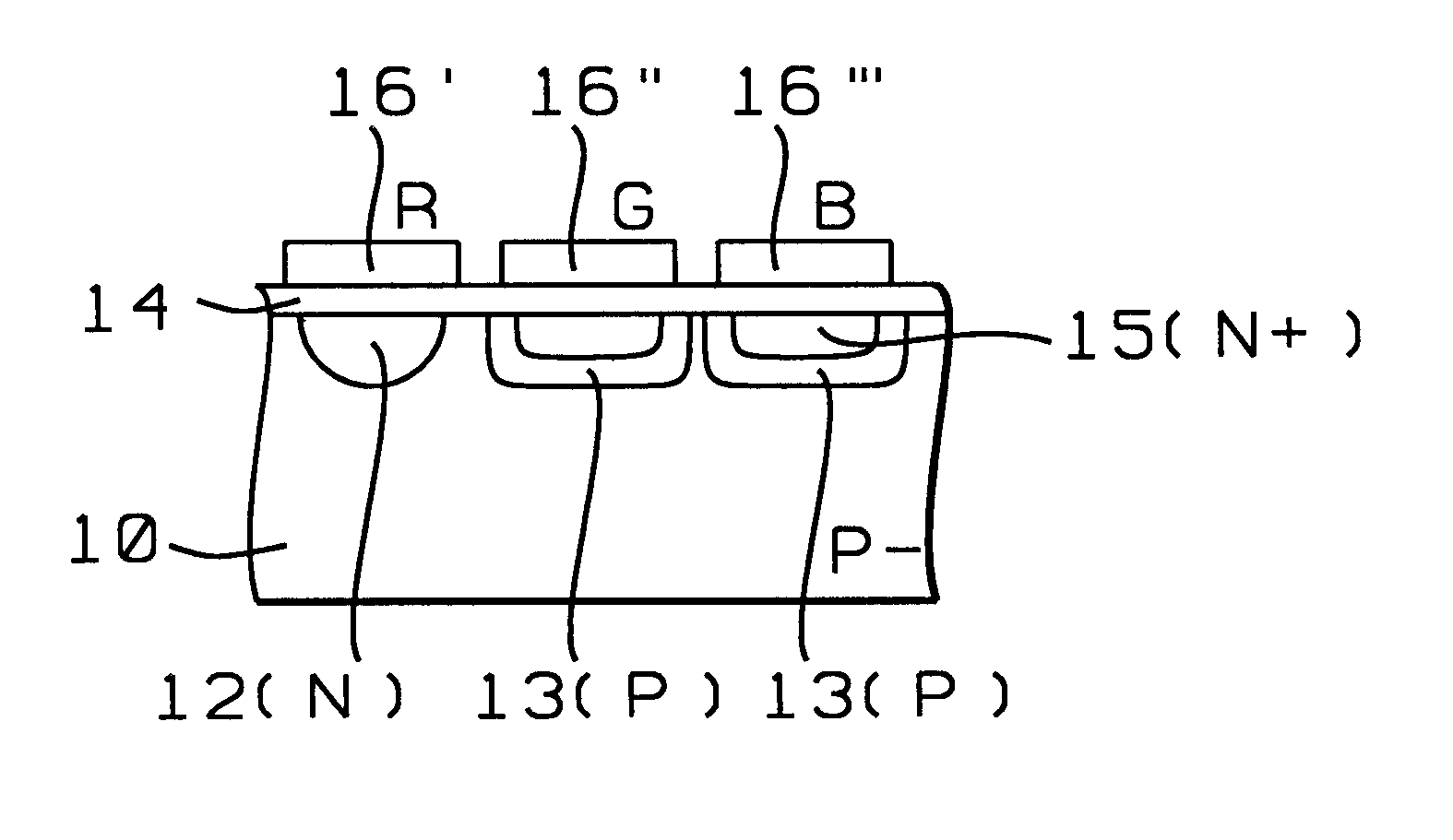

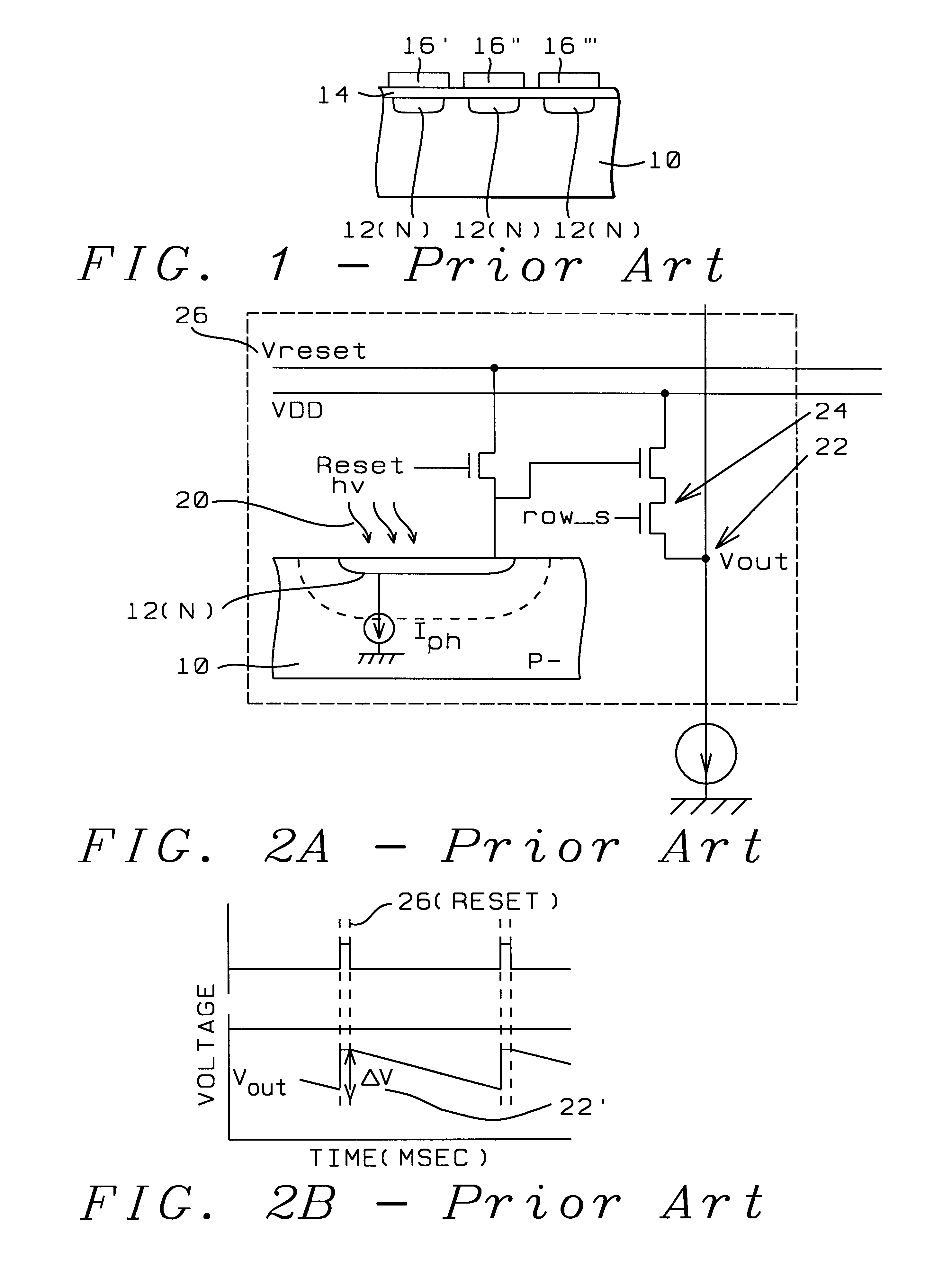

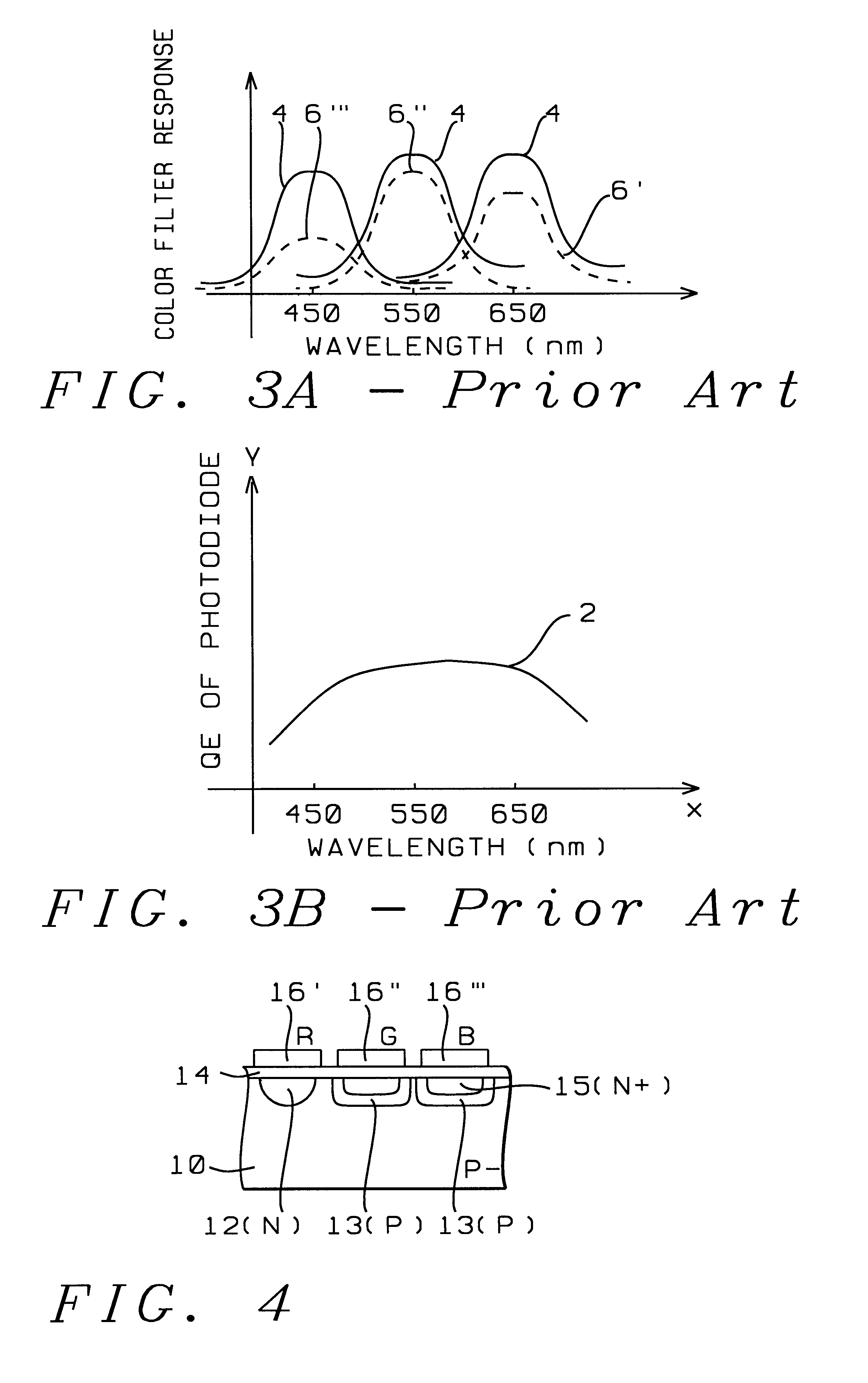

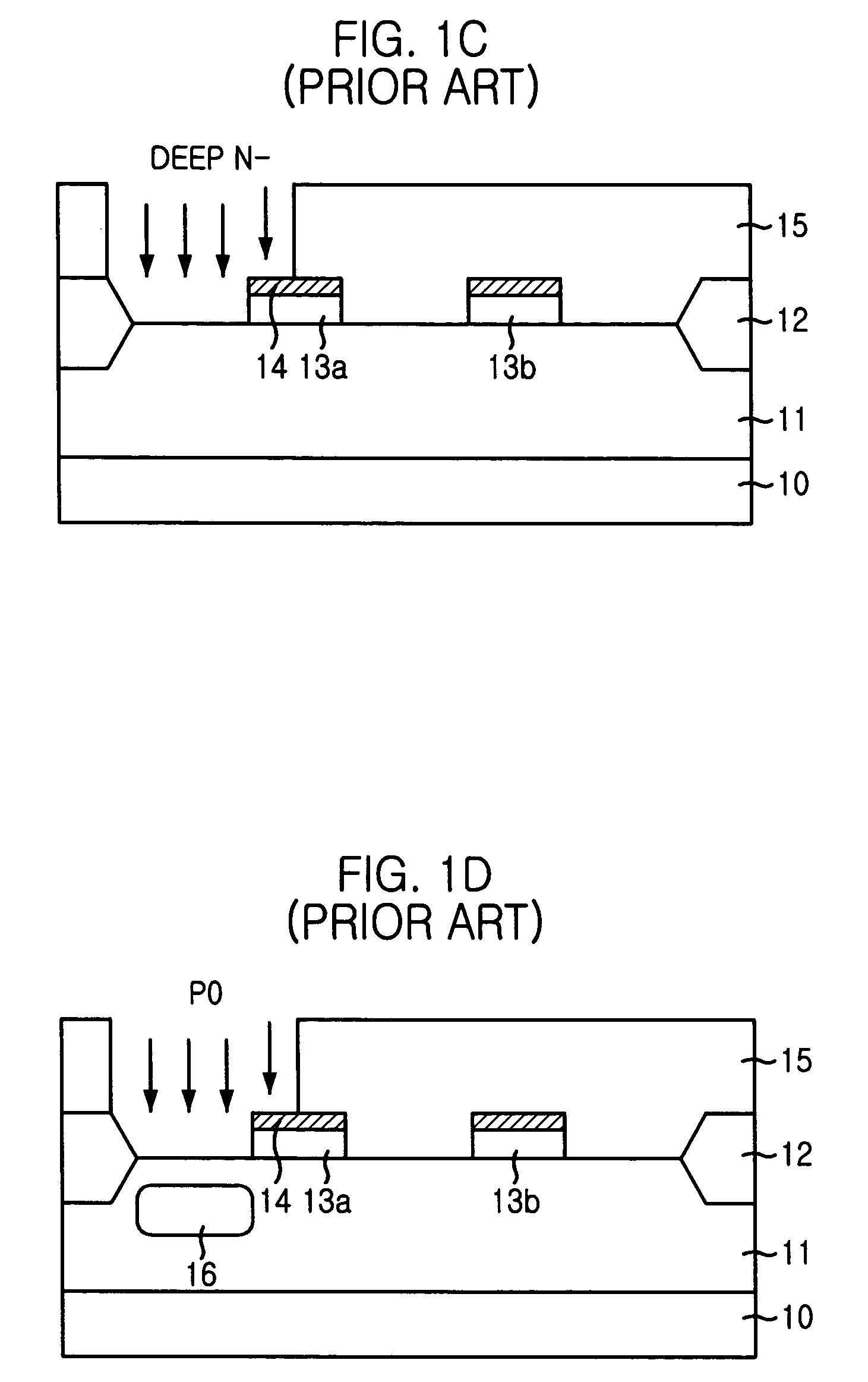

Method for making spectrally efficient photodiode structures for CMOS color imagers

InactiveUS6518085B1Solid-state devicesSemiconductor/solid-state device manufacturingQuantum efficiencyCMOS

A method for making an array of photodiodes with more uniform optical spectral response for the red, green, and blue pixel cells on a CMOS color imager is achieved. After forming a field oxide on a substrate to electrically isolate device areas for CMOS circuits, an array of deep N doped wells is formed for photodiodes for the long wavelength red pixel cells. An array of P doped well regions is formed adjacent to and interlaced with the N doped wells. Shallow diffused N+ regions are formed within the P doped wells for the shorter wavelength green and blue color pixels cells. The shallow diffused photodiodes improve the quantum efficiency (QE), and provide a color imager with improved color fidelity. An insulating layer and appropriate dye materials are deposited and patterned over the photodiodes to provide the array of color pixel cells. The N and P doped wells are also used for the supporting FET CMOS circuits to provide a cost-effective manufacturing process.

Owner:TAIWAN SEMICON MFG CO LTD

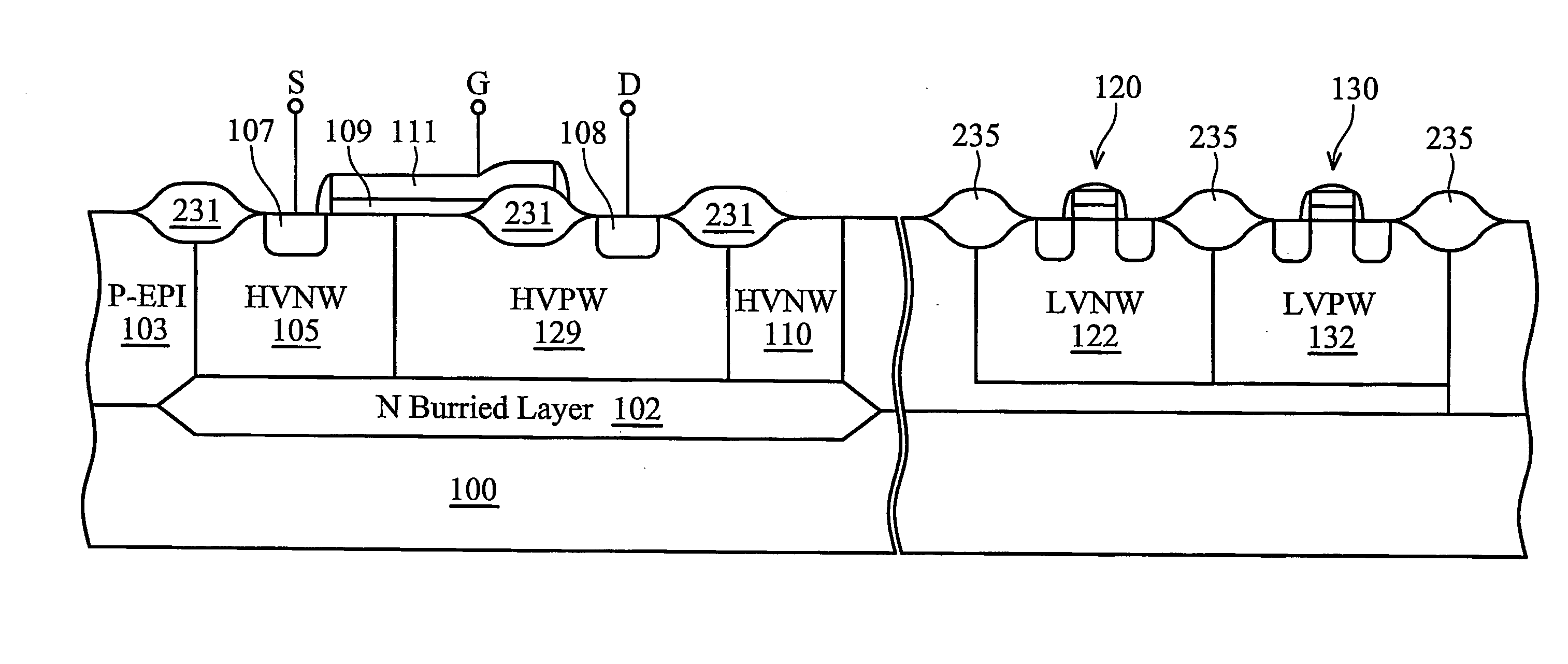

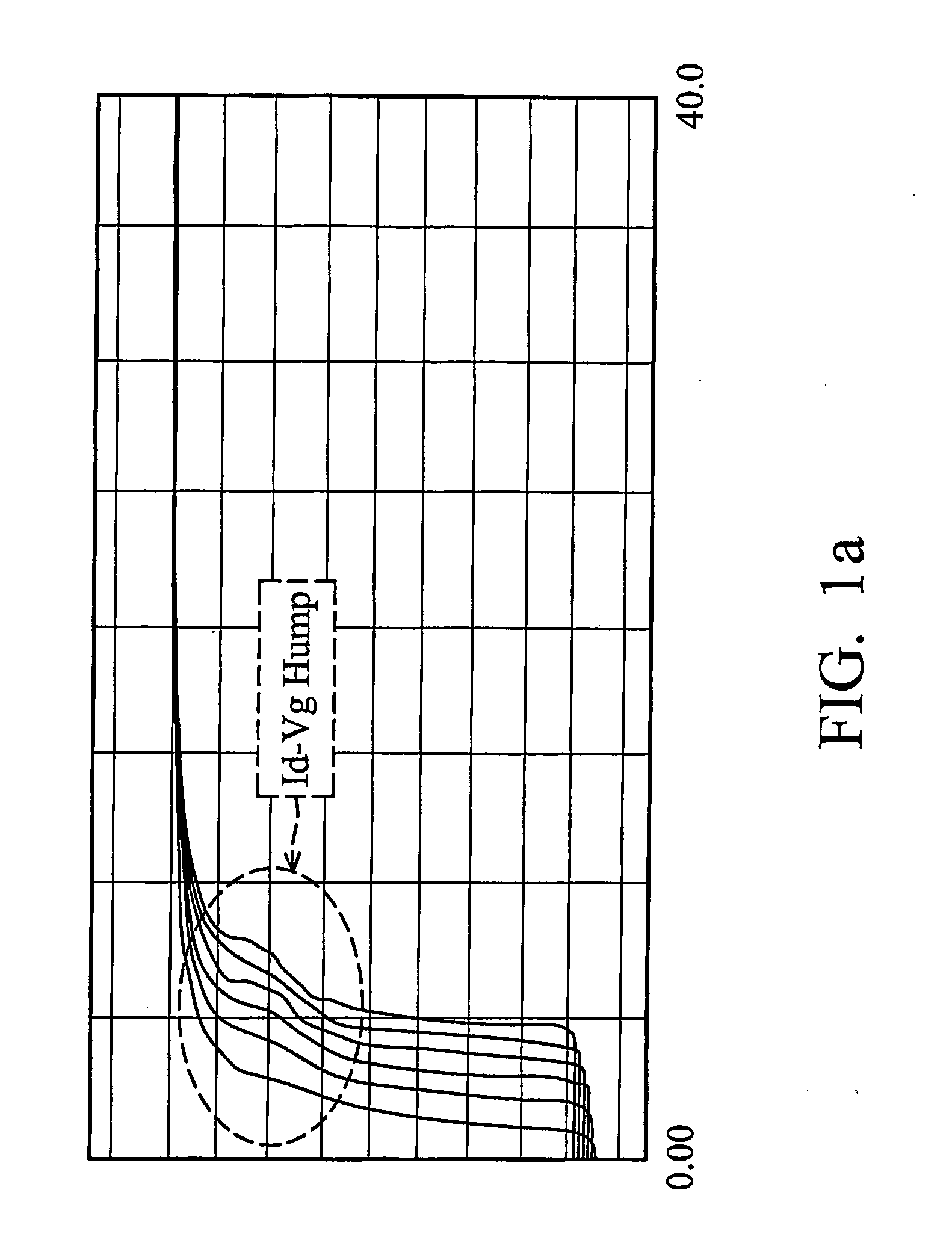

Method and apparatus for a semiconductor device having low and high voltage transistors

ActiveUS20060006462A1Semiconductor/solid-state device manufacturingSemiconductor devicesHigh voltage transistorsEngineering

Method and apparatus for a semiconductor device including high voltage MOS transistors is described. A substrate is provided with a low voltage and a high voltage region separated one from the other. Isolation regions containing an insulator are formed including at least one formed within one of said wells within the high voltage region. The angle of the transition from the active areas to the isolation regions in the high voltage device region is greater than a predetermined angle, in some embodiments it is greater than 40 degrees from vertical. In some embodiments the isolation regions are formed using shallow trench isolation techniques. In alternative embodiments the isolation regions are formed using field oxide formed by local oxidation of silicon techniques.

Owner:TAIWAN SEMICON MFG CO LTD

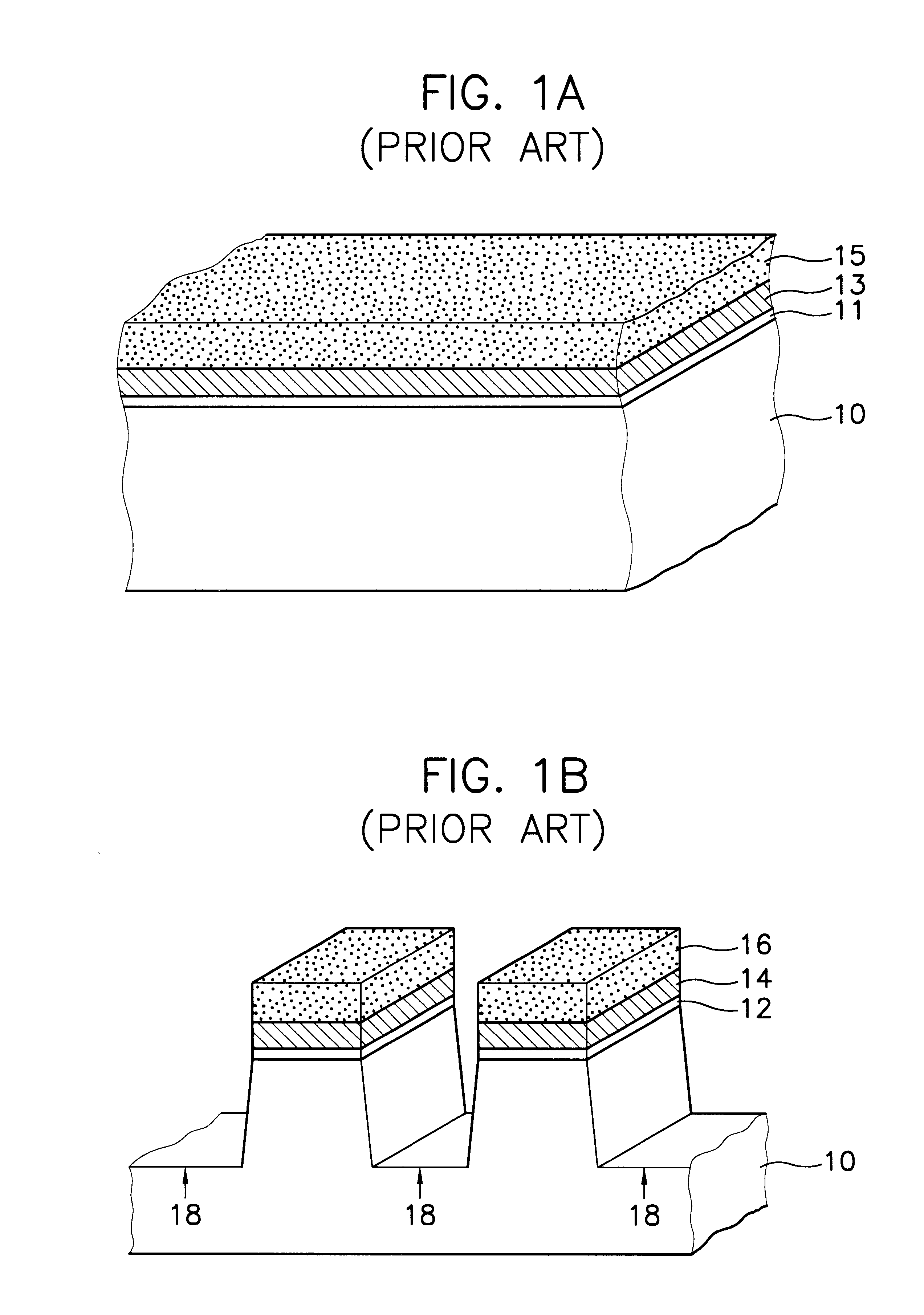

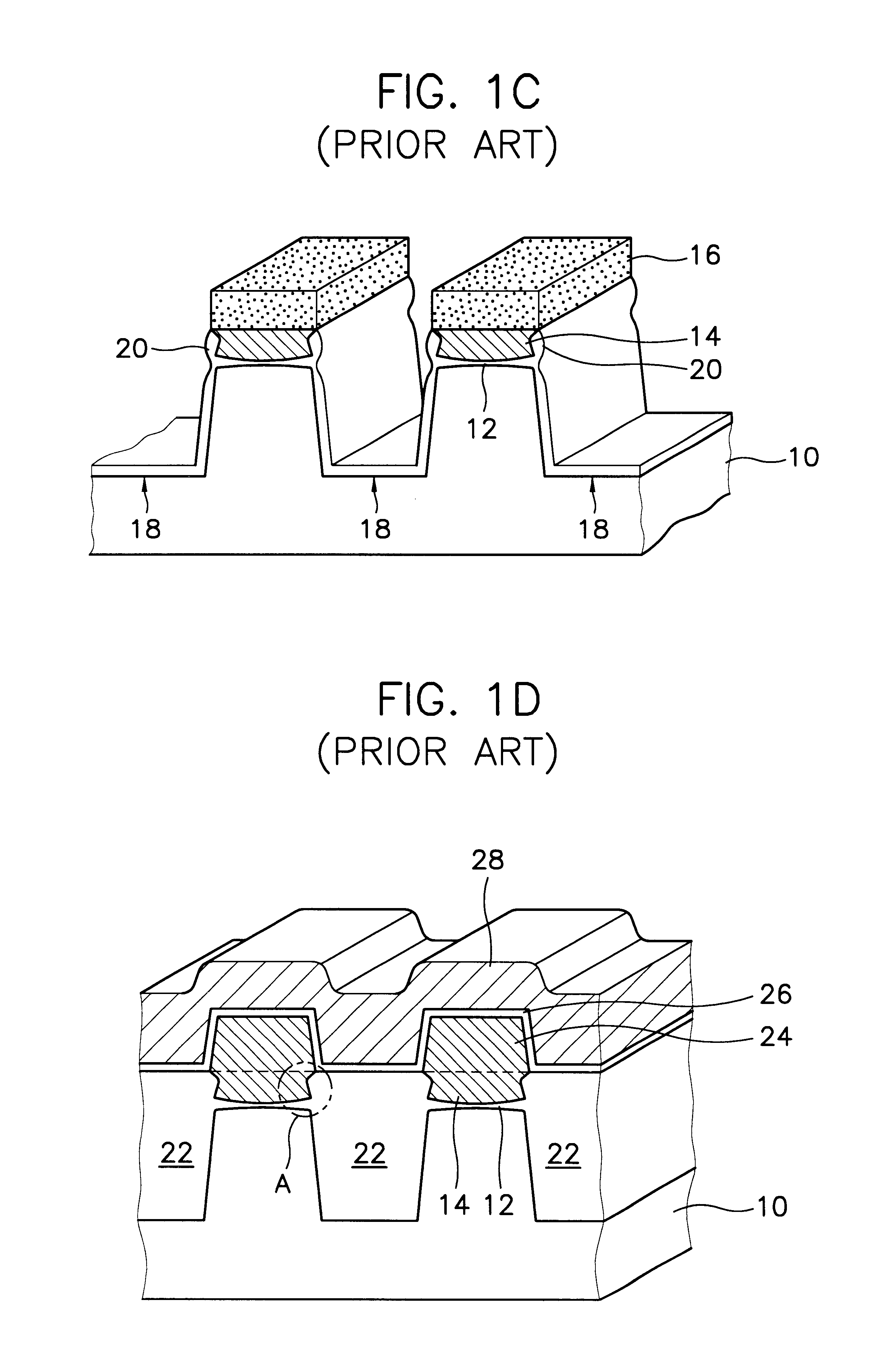

Method for self-aligned shallow trench isolation and method of manufacturing non-volatile memory device comprising the same

InactiveUS6548374B2Solid-state devicesSemiconductor/solid-state device manufacturingNitrideSemiconductor

A method of self-aligned shallow trench isolation and a method of manufacturing a non-volatile memory using the same are disclosed. An oxide layer, a first conductive layer and a nitride layer are successively formed on a semiconductor substrate. By using a single mask, the nitride layer, the first conductive layer and the oxide layer are etched to form an oxide layer pattern, a first conductive layer pattern and a nitride layer pattern. Subsequently, the upper portion of the substrate adjacent to the first conductive layer pattern is etched to form a trench. A CVD-oxide layer is deposited on the inner surface of the trench to form a trench inner-wall oxide layer, thereby preventing the formation of a positive profile at the sidewalls of the first conductive layer pattern. The trench inner-wall oxide layer is annealed in an N2O or NO atmosphere to form an oxynitride layer at the interface between the substrate and trench inner-wall oxide layer. Finally, a field oxide layer that fills up the trench is formed. Because the trench inner-wall oxide layer is formed by a CVD method to prevent the sidewalls of the first conductive layer pattern from having positive slopes, a conductive residue does not remain during a subsequent gate etching process.

Owner:SAMSUNG ELECTRONICS CO LTD

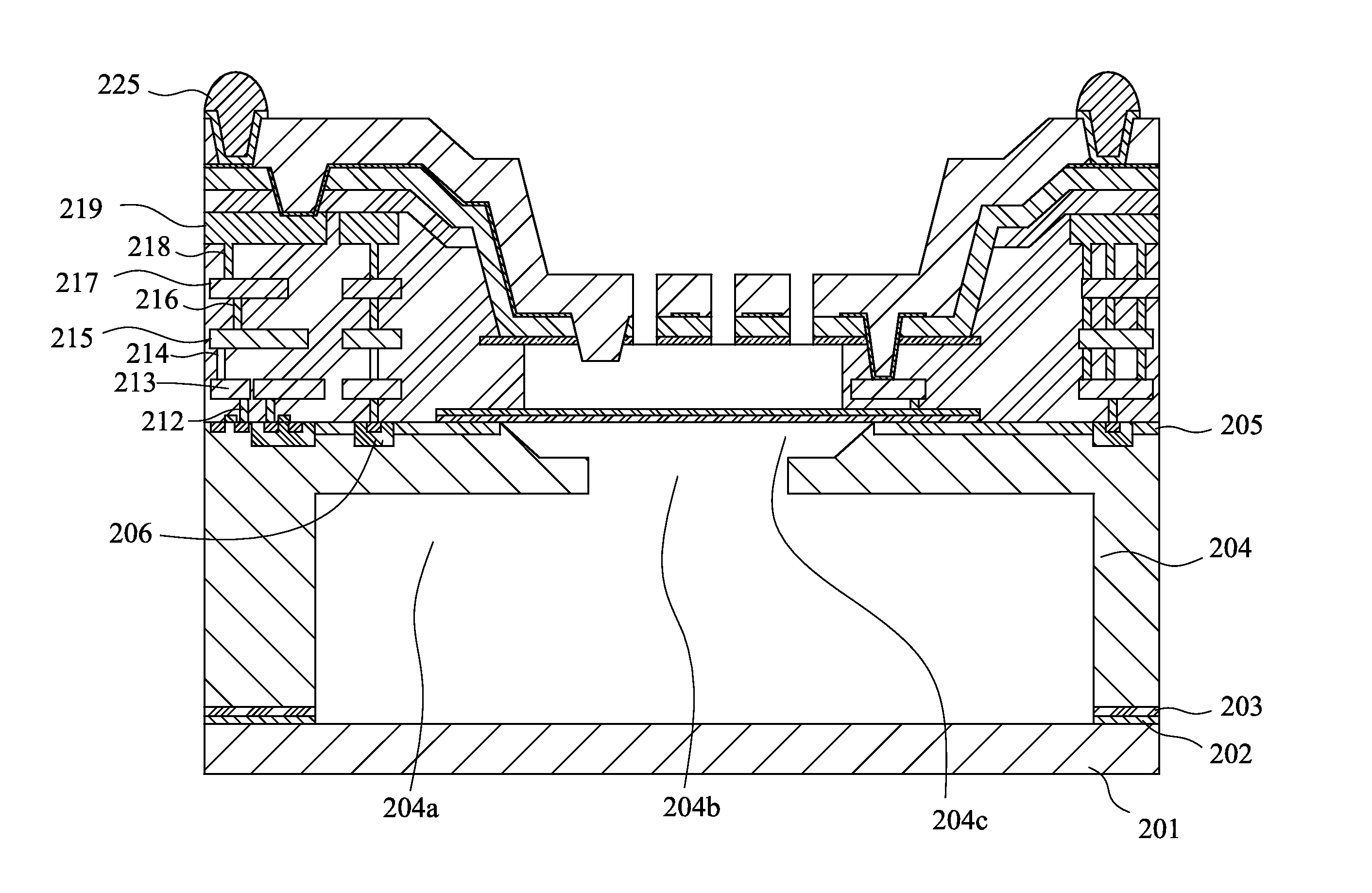

Integrated compact MEMS device with deep trench contacts

InactiveUS8587077B2Increase contactAvoid interferenceSolid-state devicesSpeed/acceleration/shock instrument detailsCMOSSolder ball

A compact MEMS motion sensor device is provided, including a CMOS substrate layer, with plural anchor posts having an isolation oxide layer surrounding a conductive layer. On one side of the CMOS substrate layer, the device further includes a field oxide (FOX) layer, a first set and a second set of implant doped silicon areas, a first polysilicon layer, an oxide layer embedded with plural metal layers interleaved with via hole layers, a Nitride deposition layer, an under bump metal (UBM) layer and a plurality of solder spheres. On the other side of the CMOS substrate layer, it further includes a backside interconnect isolation oxide layer, a first MEMS bonding layer, a first metal compound layer, a second MEMS bonding layer, a MEMS layer, a first MEMS eutectic bonding layer, a second metal compound layer, a second MEMS eutectic bonding layer, and a MEMS cap layer.

Owner:WINDTOP TECH CORP

Electrostatic discharge protection circuit

InactiveUS6864536B2Eliminate the problemTransistorSemiconductor/solid-state device detailsCurrent dividerEngineering

An electrostatic discharge (ESD) protection device includes a semiconductor layer, a source region formed in the layer, a drain region formed in the layer, a channel region in the layer between the source and drain regions, and a gate over the channel region. A plurality of current divider segments are distributed on the drain region and extend between the gate and drain contacts. The segments can be formed of polysilicon or a field oxide.

Owner:WINBOND ELECTRONICS CORP

Method for manufacturing CMOS image sensor using spacer etching barrier film

InactiveUS20040129990A1Good optical performanceTotal current dropTelevision system detailsSolid-state devicesCMOSInsulation layer

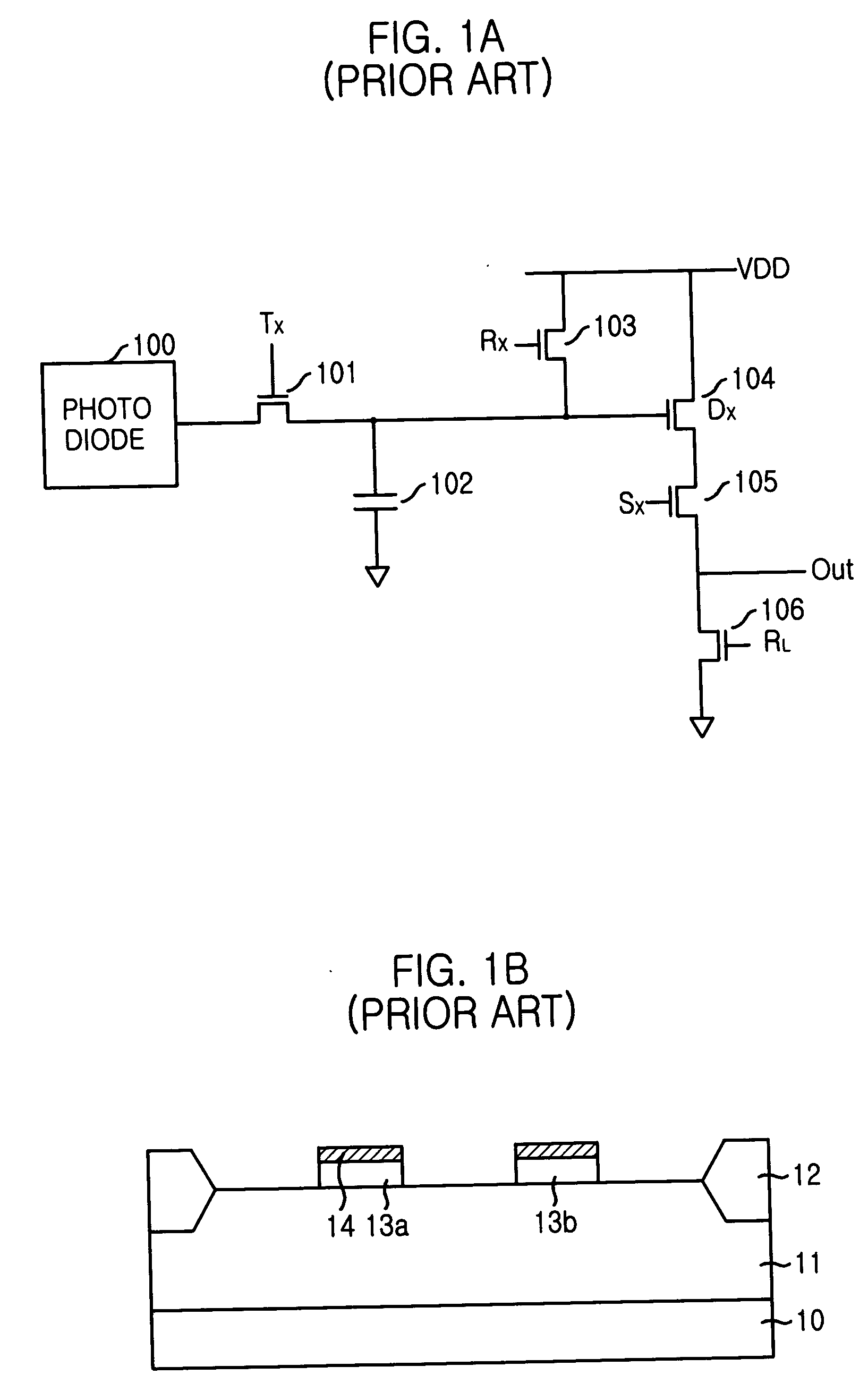

A method for fabricating a CMOS image sensor including a low voltage buried photodiode and a transfer transistor, includes the steps of: forming a field oxide for defining active area and field area on certain area of an epitaxial layer formed on a substrate, and forming a gate of transfer transistor on the epitaxial layer of the active area; forming the low voltage buried photodiode doping region in alignment with one side of the gate of transfer transistor and field oxide; forming a spacer insulation layer by stacking layers of oxide and nitride over the whole structure; forming a spacer block mask to open areas excluding doping region for the low voltage buried photodiode; and removing the spacer block mask, and forming a floating diffusion region on other side of the transfer transistor. Alternatively, the sacrificial nitride may be allowed to remain on the surface of the photodiode to improve optical properties for short wavelength lights.

Owner:CARL ZEISS SMT GMBH +1

Vertically integrated flash EPROM for greater density and lower cost

InactiveUS20070004134A1Increase cell areaImprove the coupling ratioSolid-state devicesSemiconductor/solid-state device manufacturingIon implantationPhotolithography

Owner:VORA MADHUKAR B

High switching speed two mask schottky diode with high field breakdown

InactiveUS20070290234A1Minimize current leakageImprove reverse breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesSchottky barrierLOCOS

A power Schottky rectifier device and method of making the same are disclosed. The Schottky rectifier device includes a LOCOS structure grown on the bottom of the trenches by using nitride spacer on the sidewall of the trenches as a thermal oxidation mask. A polycrystalline silicon layer is then filled the first trenches. Under LOCOS structure, a p doped region is optionally formed to minimize the current leakage when the device undergoes a reverse biased. A Schottky barrier silicide layer formed by sputtering and annealing steps is formed on the upper surfaces of the epi-layer and the polycrystalline silicon layer. A top metal layer served as anode is then formed on the Schottky barrier silicide layer and extended to cover a portion of field oxide region of the termination trench. A metal layer served as a cathode electrode is then formed on the backside surface of the substrate opposite to the top metal layer.

Owner:CHIP INTEGRATION TECH +1

Integrated MEMS microphone with mechanical electrical isolation

InactiveUS20150060955A1Improve reliabilityReduce manufacturing costDecorative surface effectsSemiconductor electrostatic transducersCMOSContact layer

An integrated MEMS microphone is provided, including, a bonding wafer layer, a bonding layer, an aluminum layer, CMOS substrate layer, an N+ implant doped silicon layer, a field oxide (FOX) layer, a plurality of implant doped silicon areas forming CMOS wells, a two-tier polysilicon layer with selective ion implantation forming a diaphragm, a plurality of implant doped silicon areas forming CMOS source / drain, a gate poly layer forming CMOS transistor gates, said CMOS wells, said CMOS transistor sources / drains and said CMOS gates forming CMOS transistors, an oxide layer embedded with an interconnect contact layer, a plurality of metal layers interleaved with a plurality of via hole layers, a Nitride deposition layer, an under bump metal (UBM) layer and a plurality of solder spheres. Diaphragm is sandwiched between a small top chamber and a small back chamber, and substrate layer includes a large back chamber.

Owner:WINDTOP TECH CORP

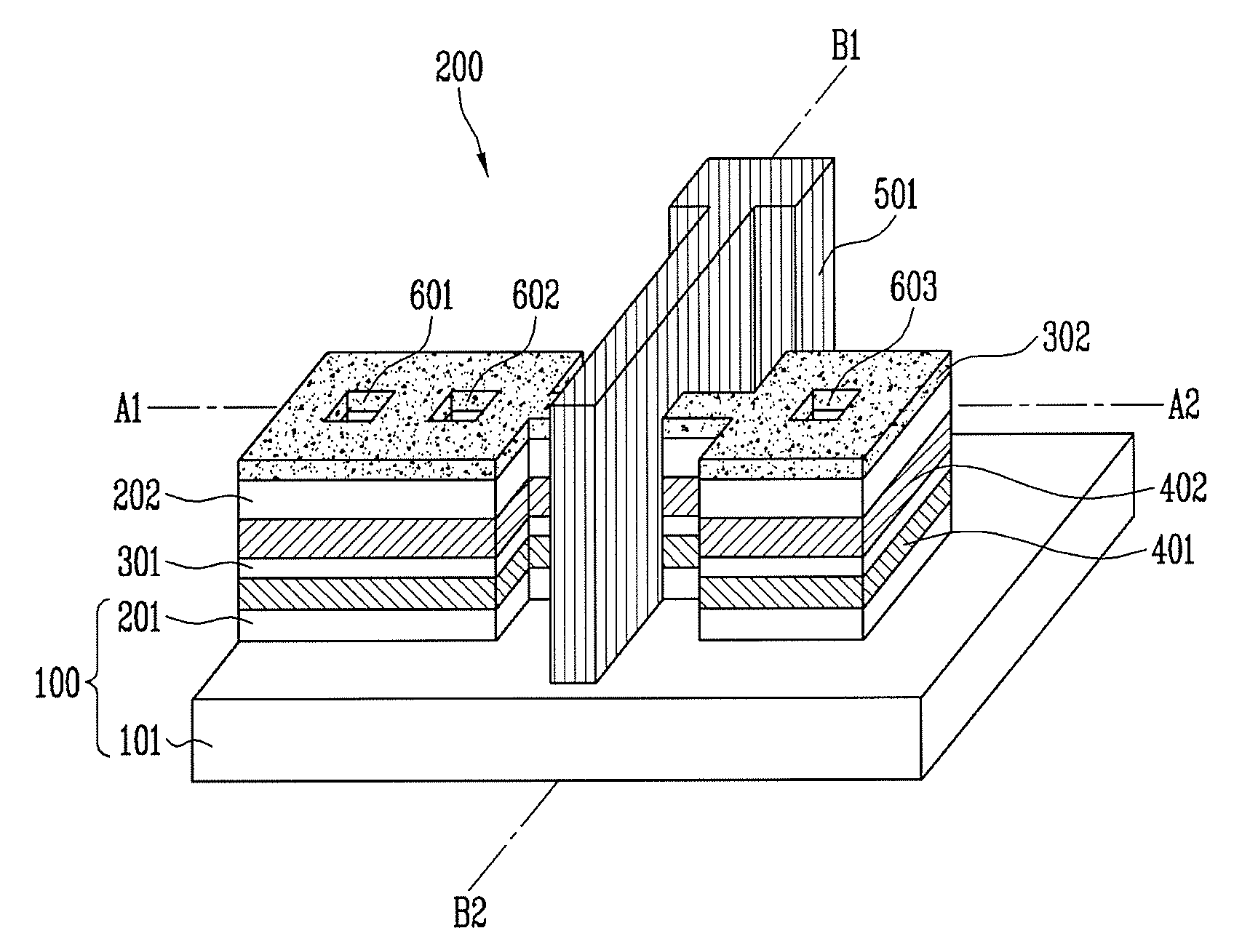

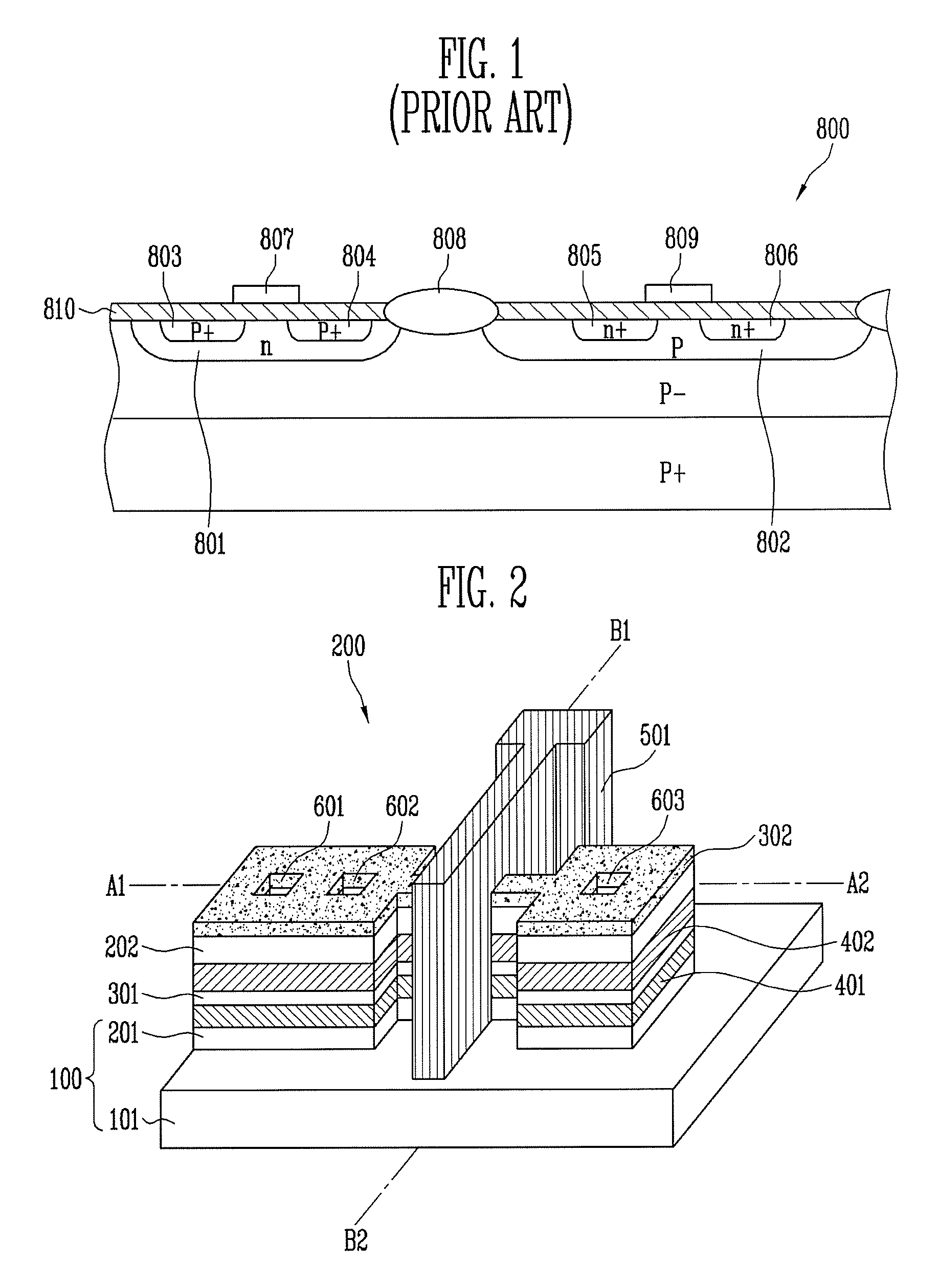

Dual structure finfet and method of manufacturing the same

ActiveUS20080135935A1High densityHigh carrier mobilityTransistorSolid-state devicesElectrical resistance and conductanceSource material

Provided are a dual structure FinFET and a method of fabricating the same. The FinFET includes: a lower device including a lower silicon layer formed on a substrate and a gate electrode vertically formed on the substrate; an upper device including an upper silicon layer formed on the lower device and the vertically formed gate electrode; and a first solid source material layer, a solid source material interlayer insulating layer, and a second solid source material layer sequentially formed between the lower silicon layer and the upper silicon layer. Therefore, the FinFET can be provided which enhances the density of integration of a circuit, suppresses thin film damages due to ion implantation using solid phase material layers, and has a stabilized characteristic by a simple and low-cost process. Also, mobility of an upper device can be improved to enhance current drivability of the upper device, isolation can be implemented through a buried oxide layer to reduce an effect due to a field oxide layer, and raised source and drain can be implemented to reduce serial resistance components of the source and drain to increase current drivability.

Owner:ELECTRONICS & TELECOMM RES INST

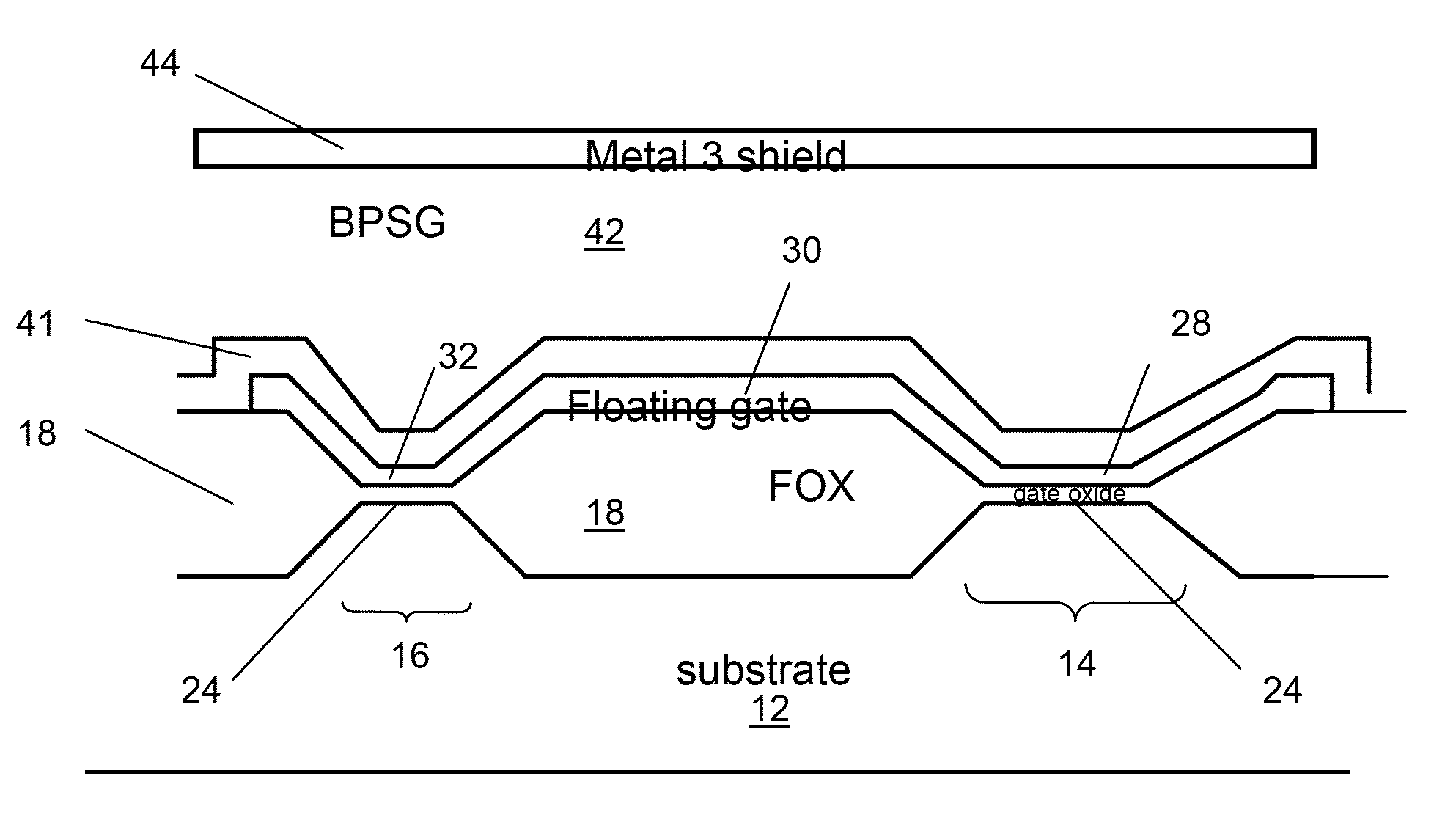

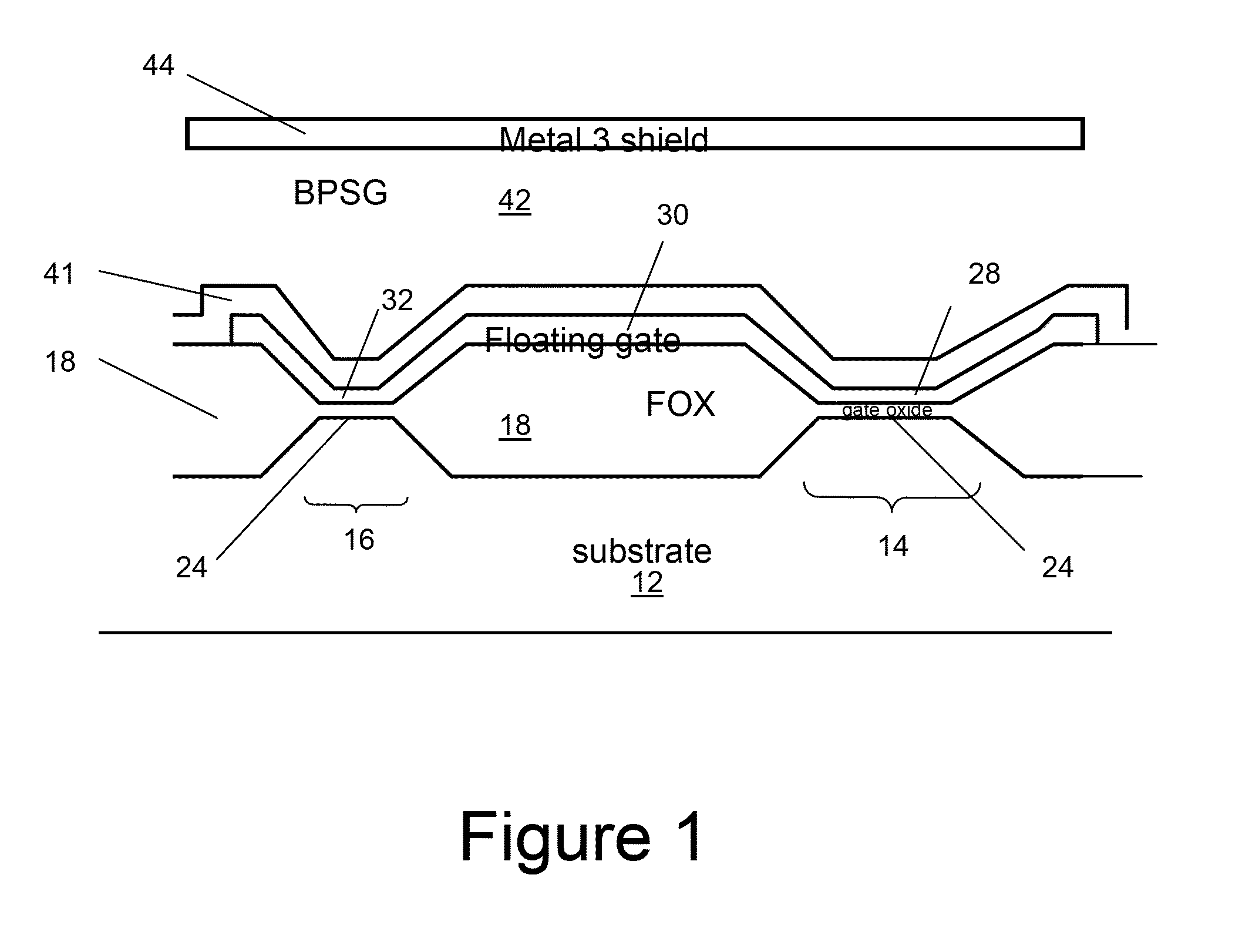

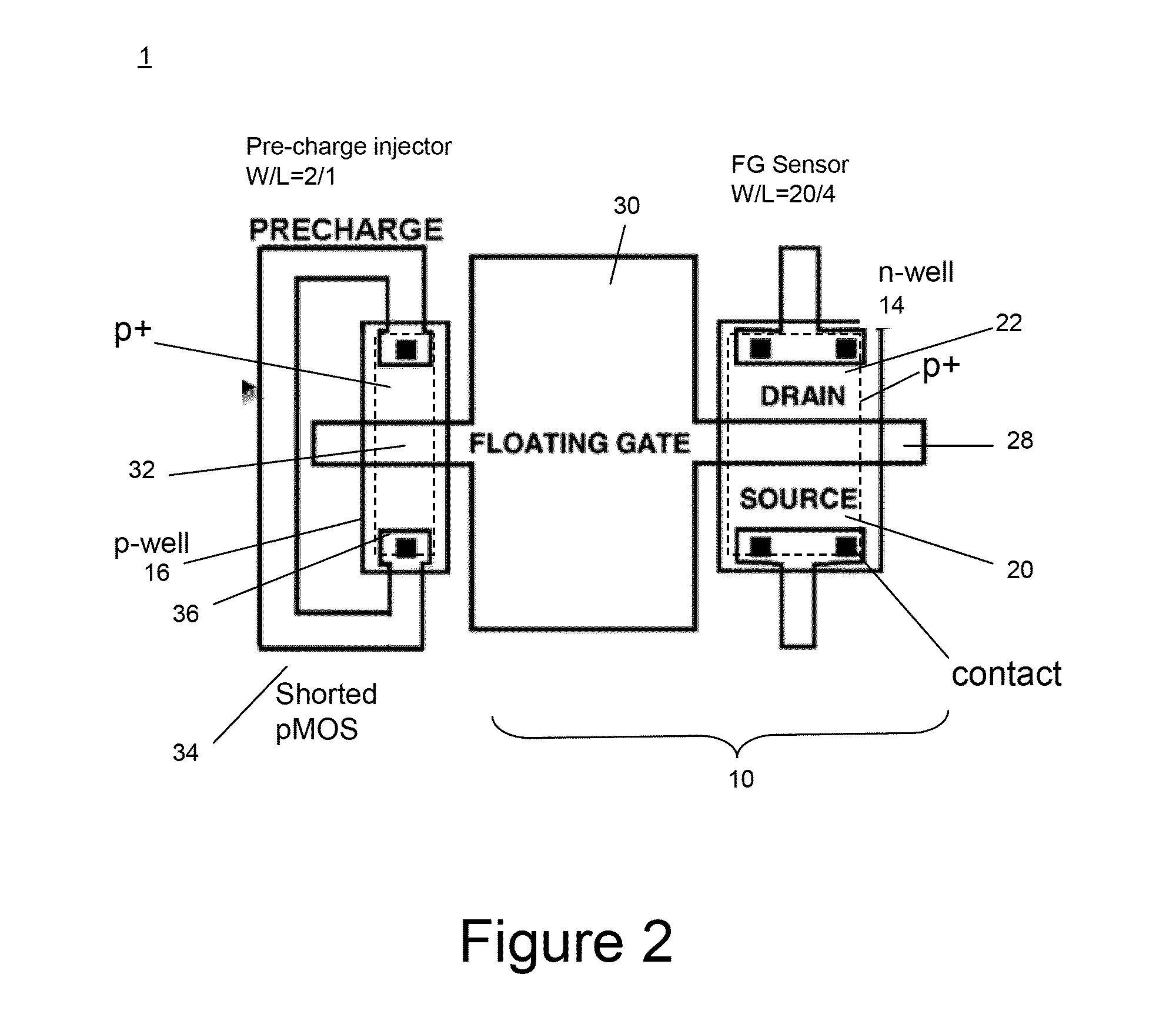

Miniaturized, low power fgmosfet radiation sensor and wireless dosimeter system

ActiveUS20100096556A1Reduce capacitanceHigh sensitivityDosimetersSolid-state devicesCapacitanceMOSFET

A miniaturized floating gate (FG) MOSFET radiation sensor system is disclosed, The sensor preferably comprises a matched pair of sensor and reference FGMOSFETs wherein the sensor FGMOSFET has a larger area floating gate with an extension over a field oxide layer, for accumulation of charge and increased sensitivity. Elimination of a conventional control gate and injector gate reduces capacitance, and increases sensitivity, and allows for fabrication using standard low cost CMOS technology. A sensor system may be provided with integrated signal processing electronics, for monitoring a change in differential channel current ID, indicative of radiation dose, and an integrated negative bias generator for automatic pre-charging from a low voltage power source. Optionally, the system may be coupled to a wireless transmitter. A compact wireless sensor System on Package solution is presented, suitable for dosimetry for radiotherapy or other biomedical applications.

Owner:KING ABDULLAH UNIV OF SCI & TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com