Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1574results about How to "Easily realized" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

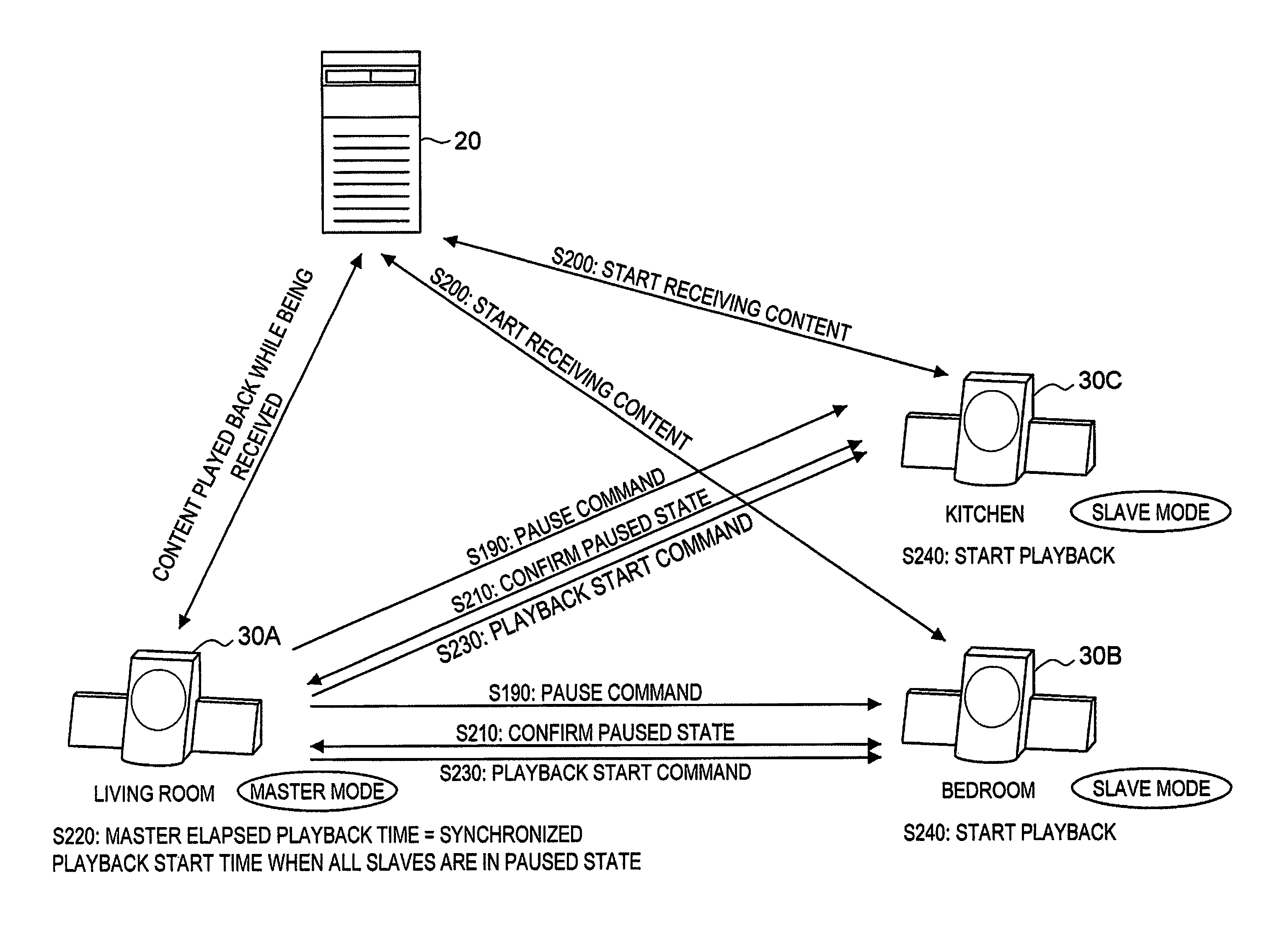

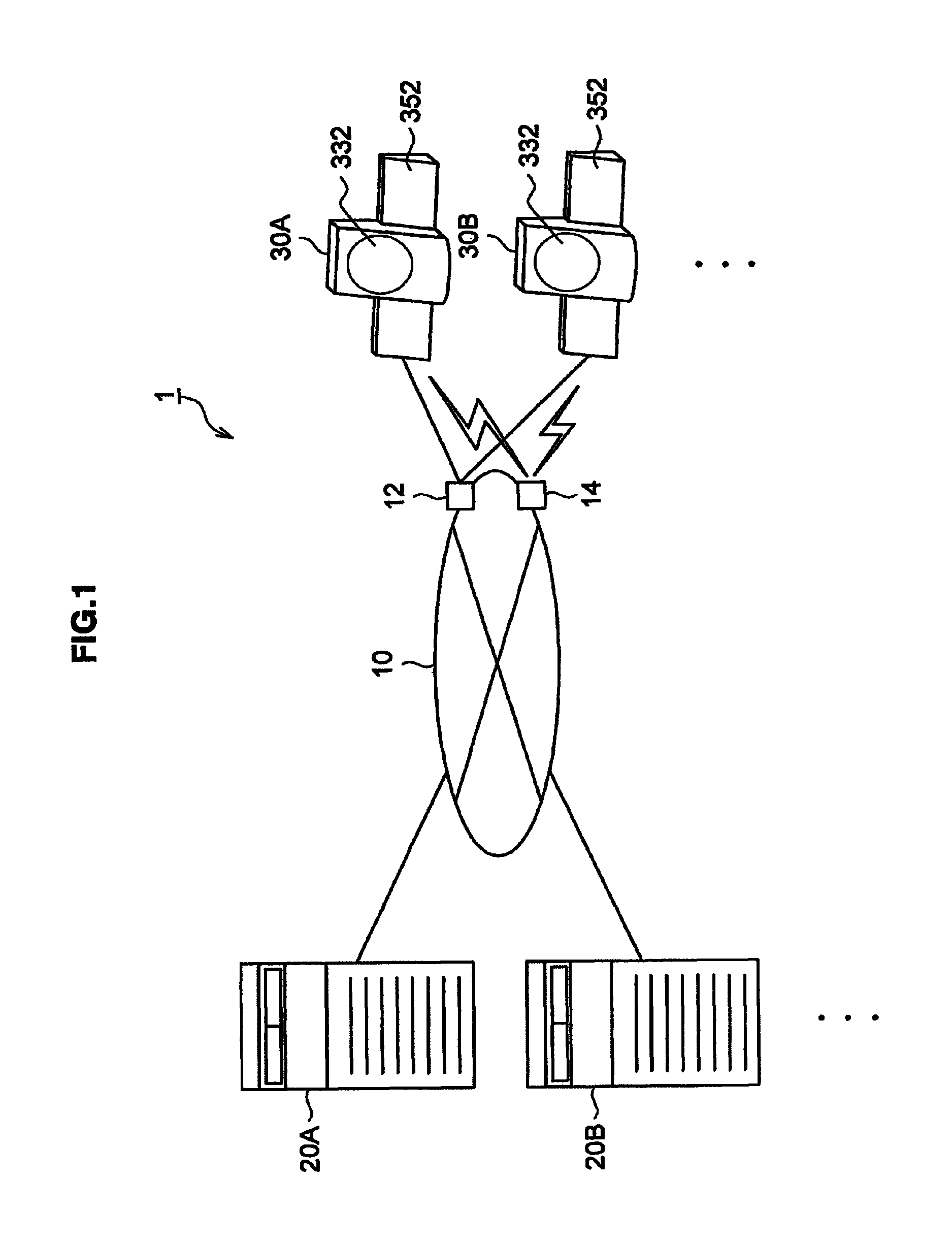

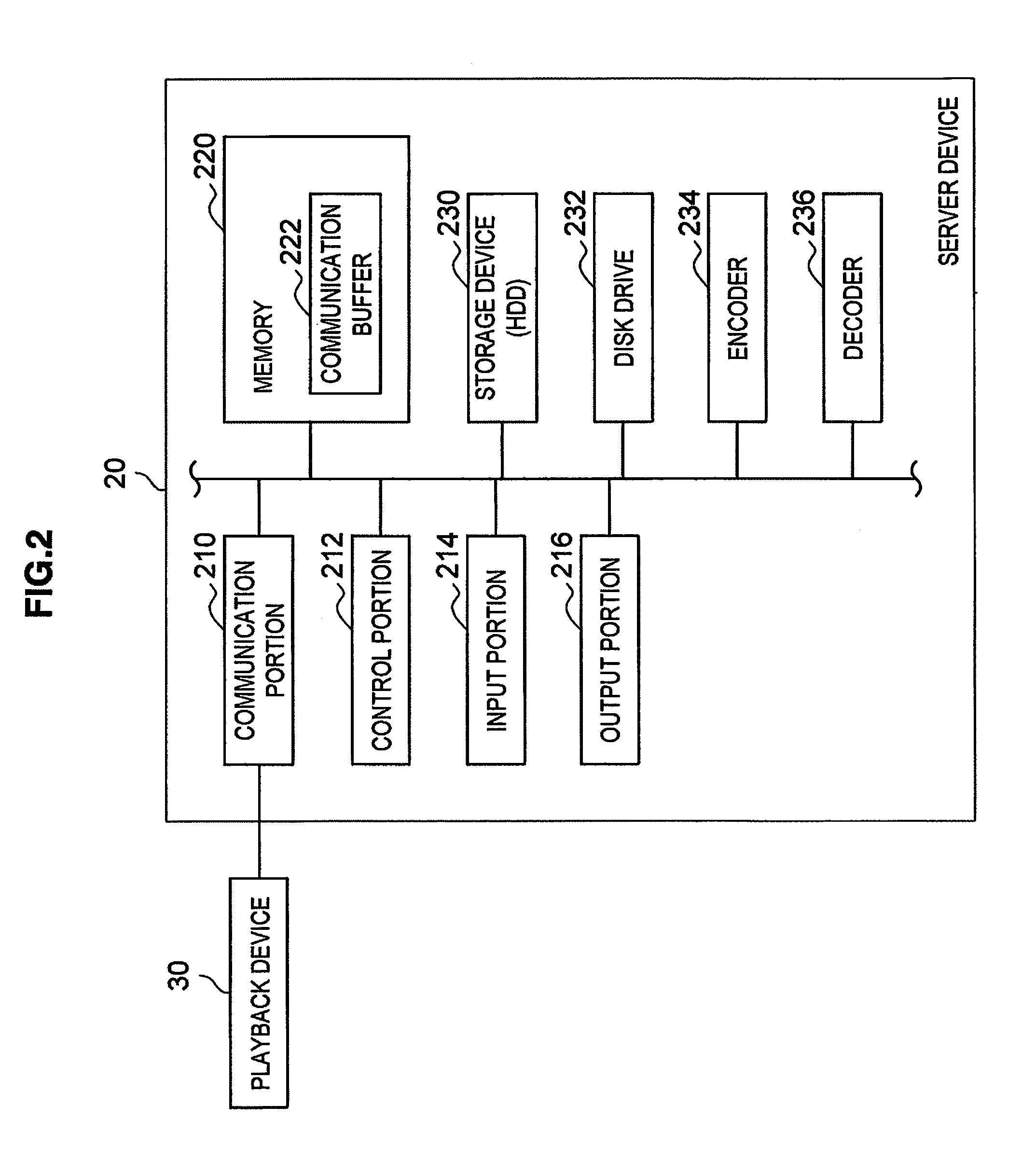

Content playback system, playback device, playback control method and program

ActiveUS20080177822A1The implementation process is simpleEasily realizedTelevision system detailsColor television detailsComputer hardwareStart time

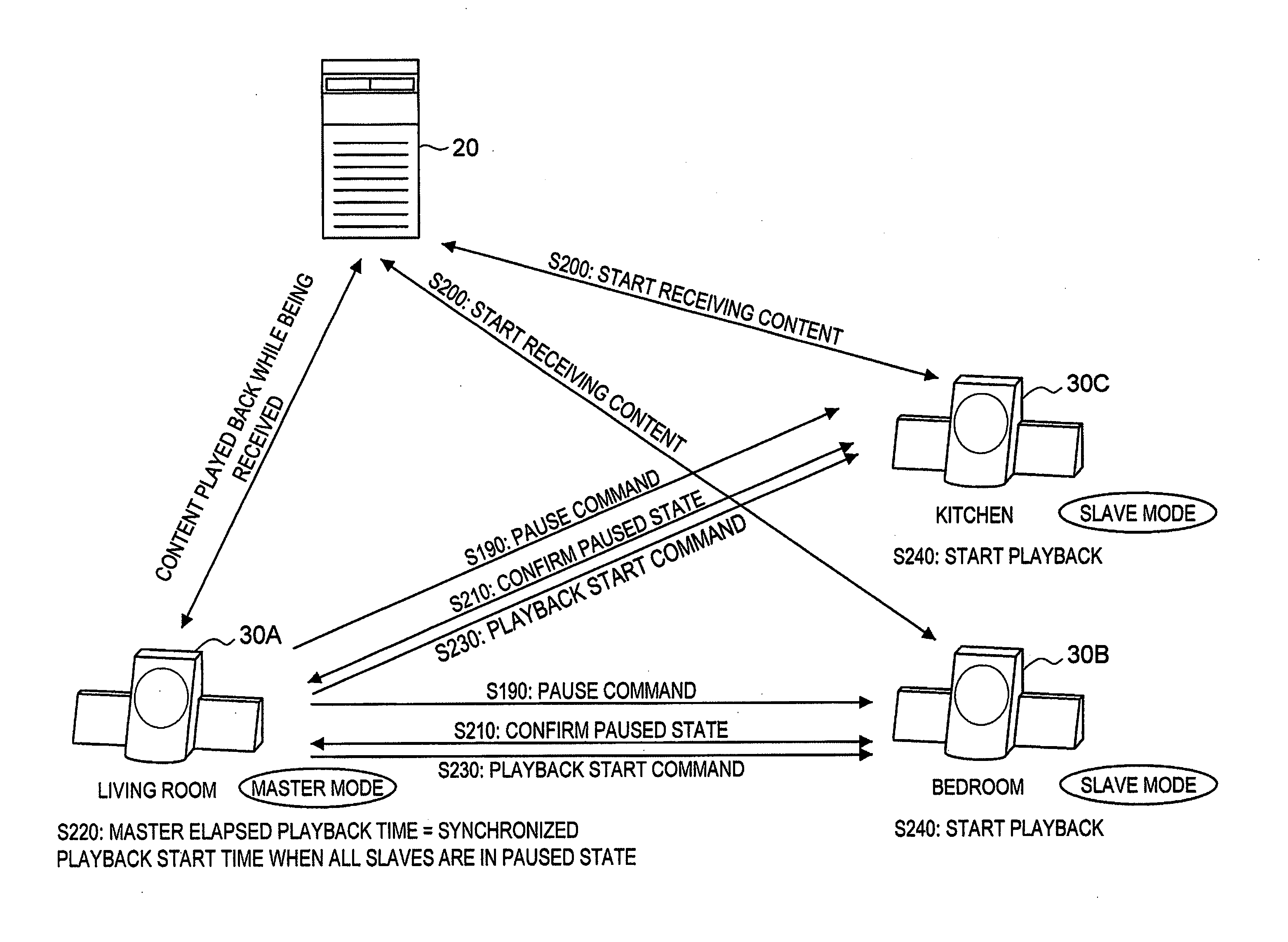

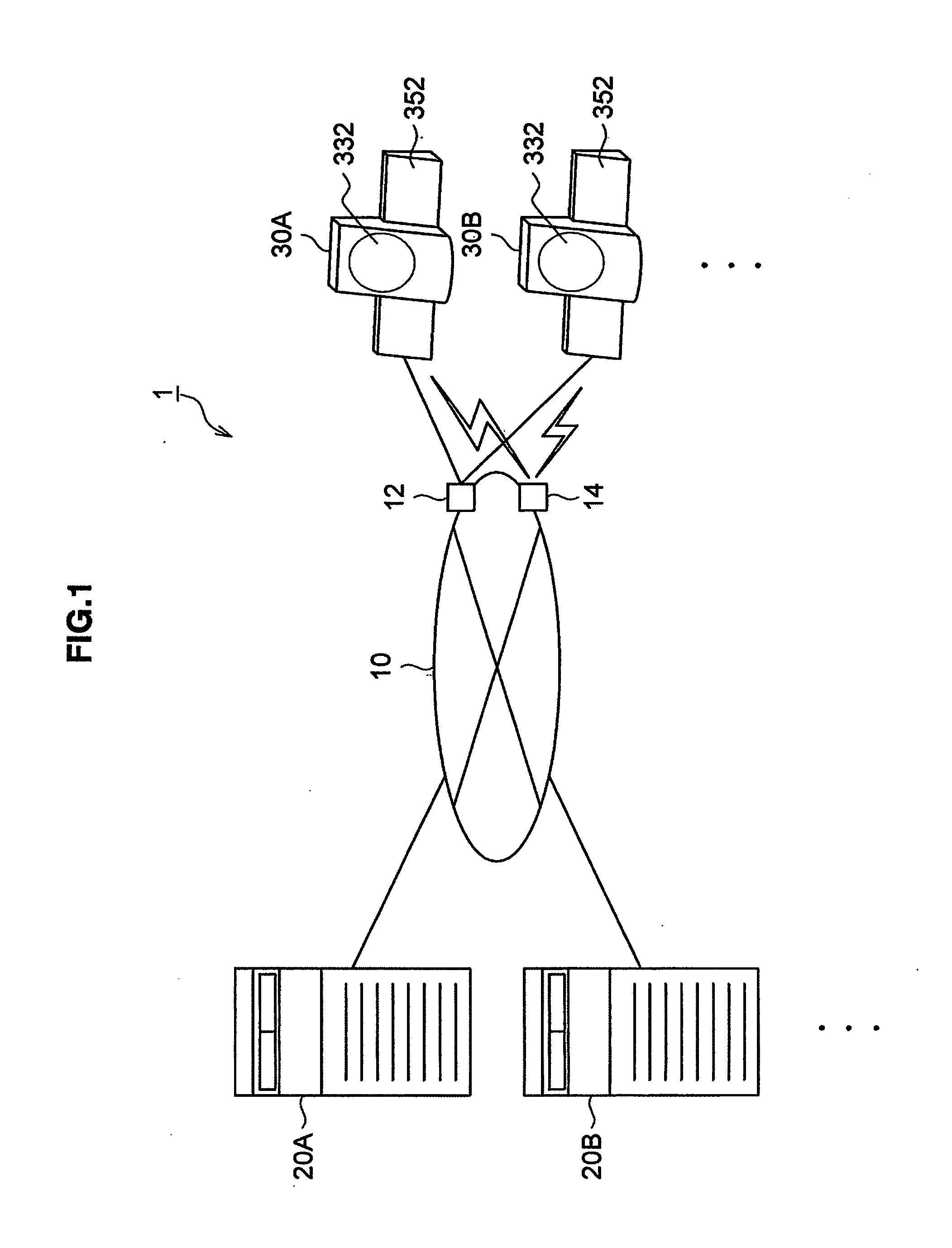

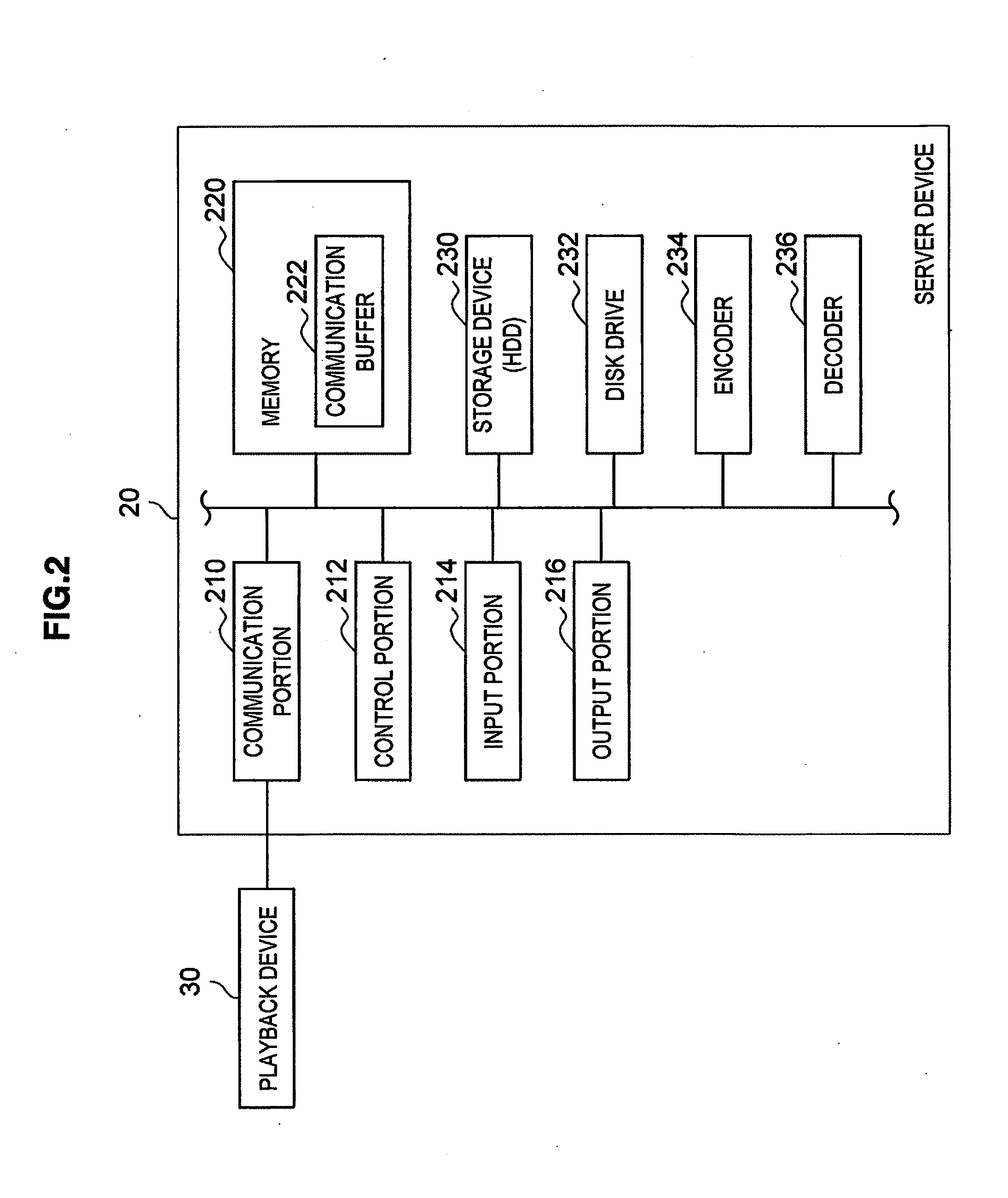

A first playback device, upon receiving a synchronized playback command while content playback is in progress, transmits, to a second playback device, information that pertains to the playback content and a synchronized playback start time obtained by adding a predetermined additional time to an elapsed playback time for the content. The second playback device starts receiving content data that begins from the synchronized playback start time from a server. After the data that is memorized in a memory reaches a specified volume, the second playback device transmits a playback preparation completion notification to the first playback device. Once the elapsed playback time for the content reaches the synchronized playback start time, the first playback device transmits a playback start command to the second playback device. Upon receiving this command, the second playback device starts playing back content data that begins from the synchronized playback start time.

Owner:SONY CORP

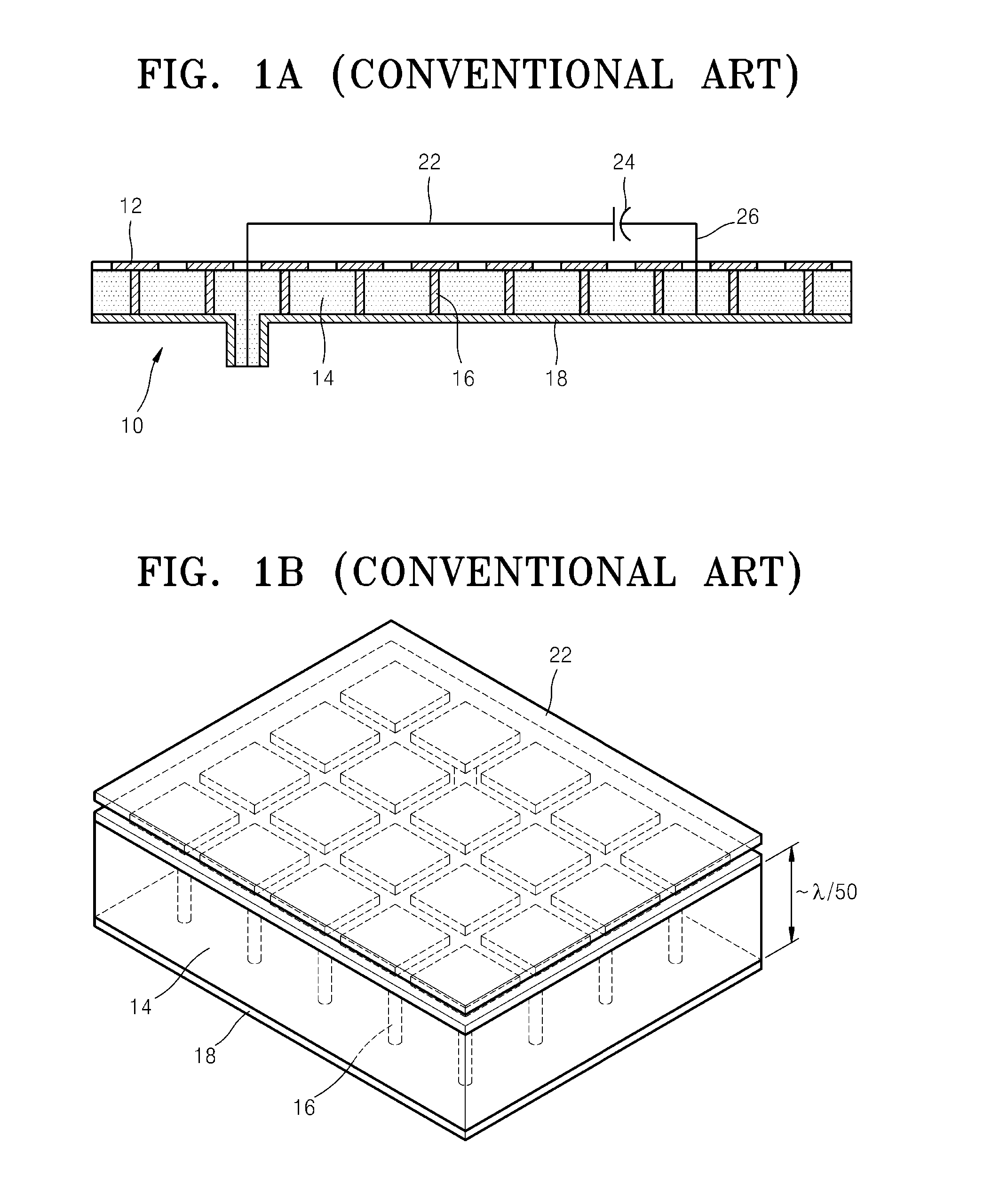

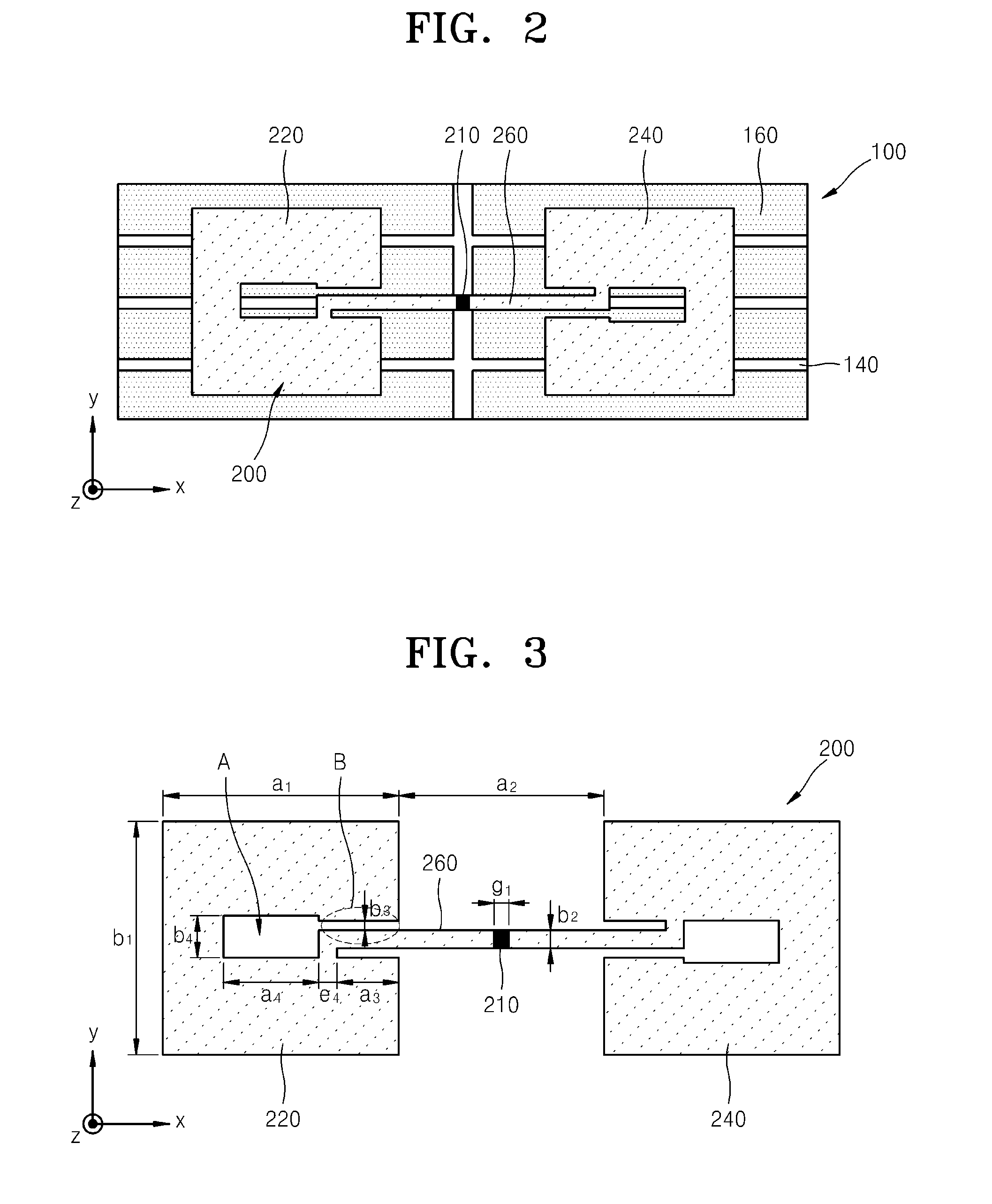

Dipole tag antenna structure mountable on metallic objects using artificial magnetic conductor for wireless identification and wireless identification system using the dipole tag antenna structure

InactiveUS20100007569A1Easy to manufactureEasy to installAntenna feed intermediatesRecord carriers used with machinesTag antennaElectrical conductor

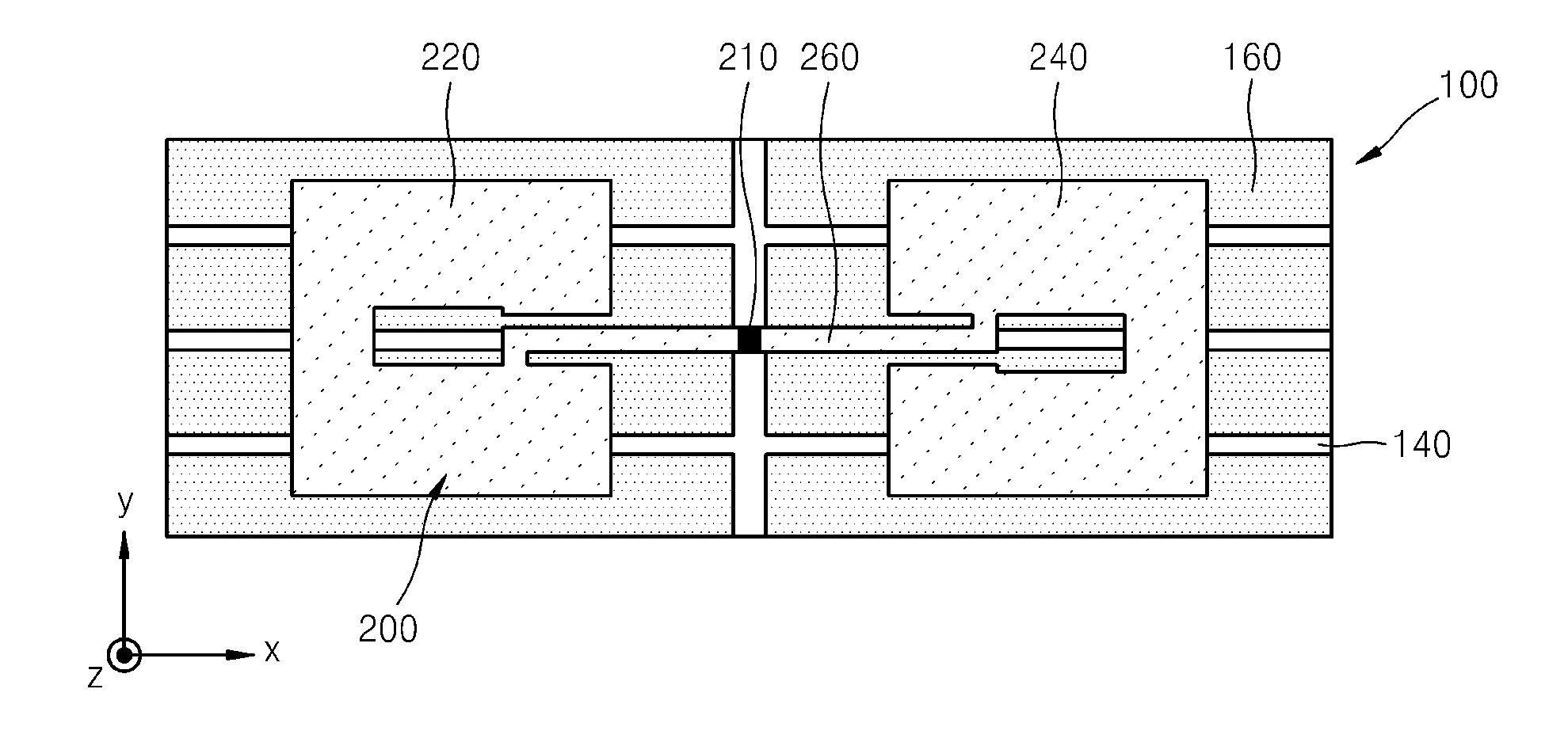

Provided are a dipole tag antenna using an artificial magnetic conductor (AMC) for wireless identification and a wireless identification system using the dipole tag antenna. The dipole tag antenna includes: a substrate formed of a first dielectric material; a conductive ground layer formed underneath the substrate; an AMC layer formed on the substrate; the dipole tag antenna mounted on the AMC layer and comprising a wireless identification chip; and the AMC directly mounted on a conductor.

Owner:ELECTRONICS & TELECOMM RES INST

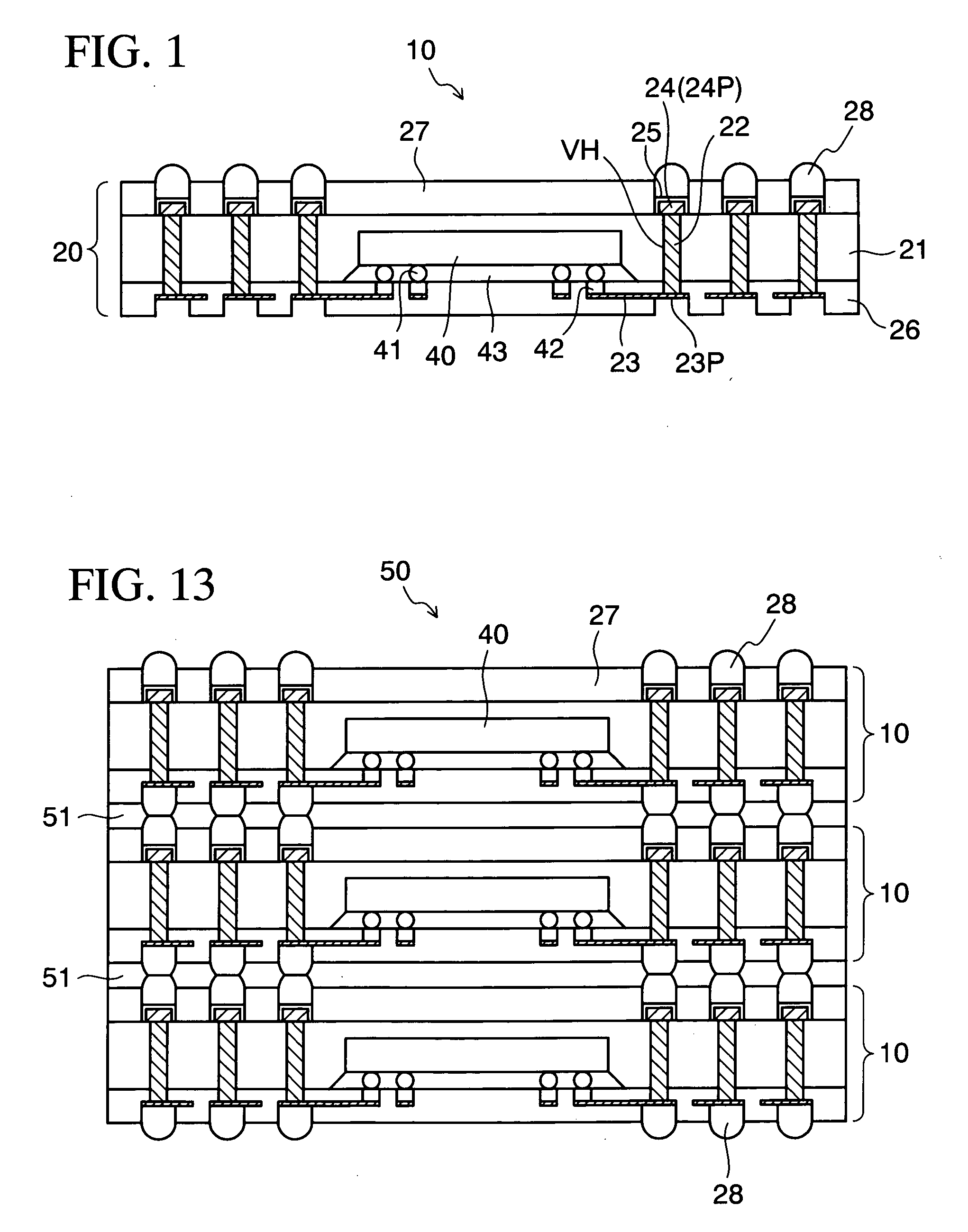

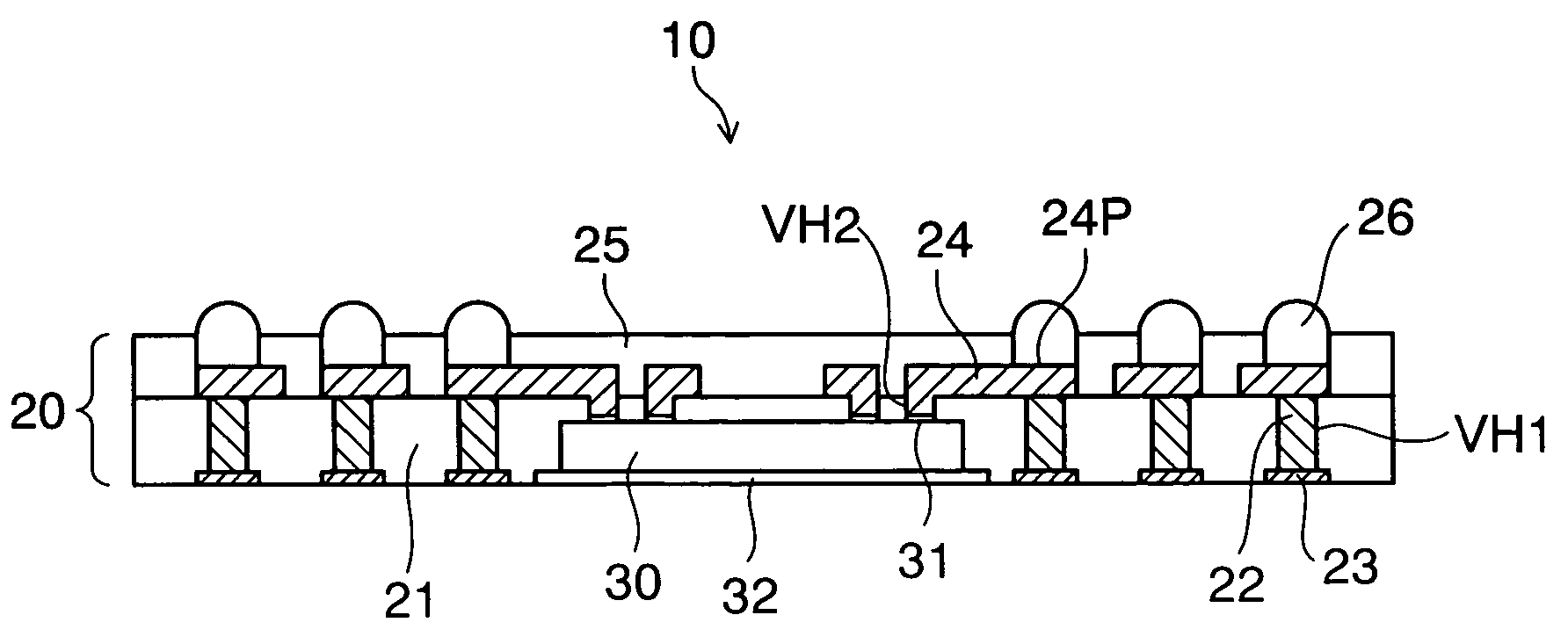

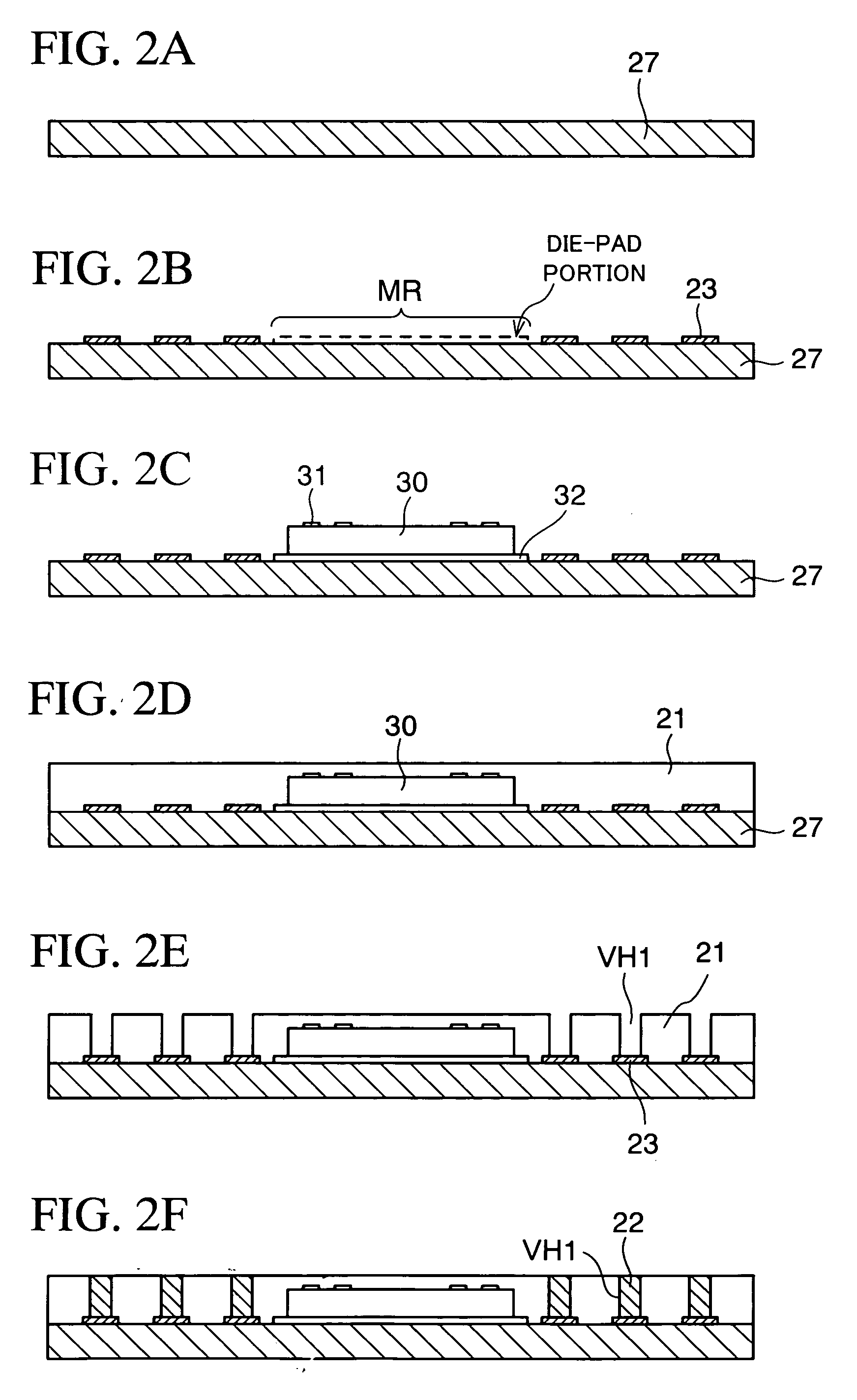

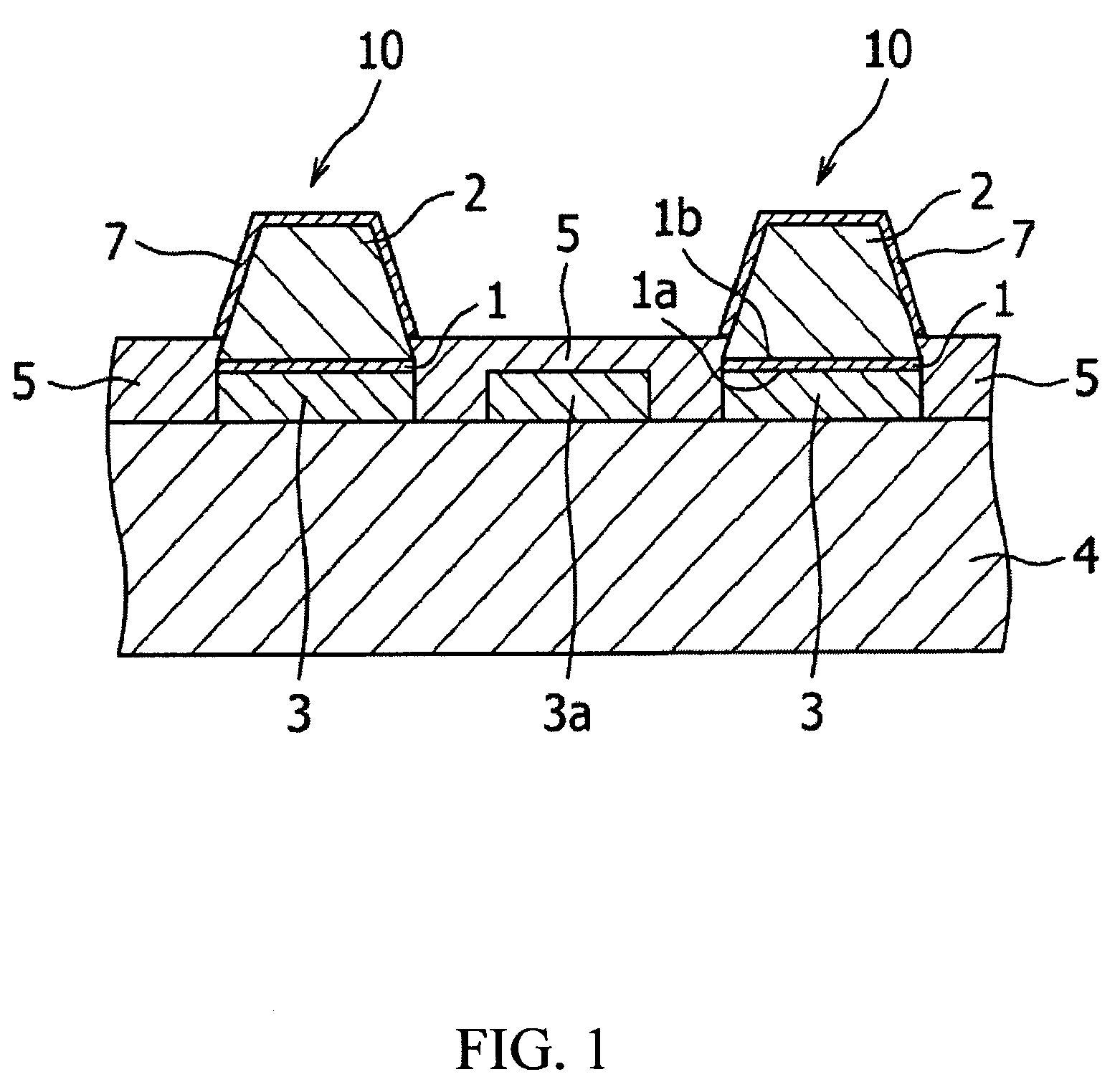

Semiconductor device and method of manufacturing the same

InactiveUS20050184377A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, and conductor layers are respectively formed to be connected to one end and another end of the conductor filled in the individual via hole. Portions (pad portions) of the conductor layers which correspond to the conductors are exposed from protective films, or external connection terminals are bonded to the pad portions. The chip is mounted with flip-chip technology so that at least some of electrode terminals thereof are electrically connected to the conductor layers.

Owner:SHINKO ELECTRIC IND CO LTD

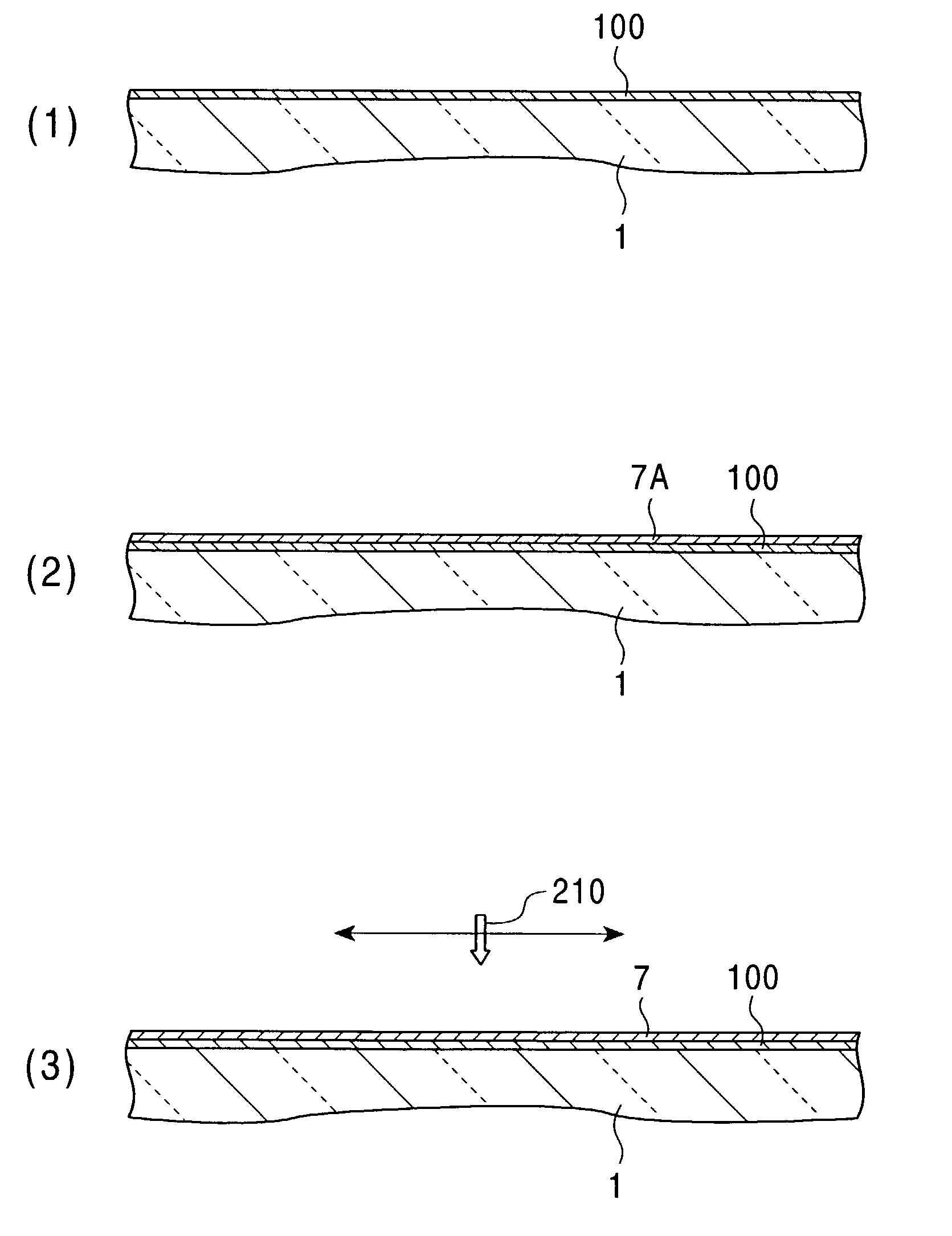

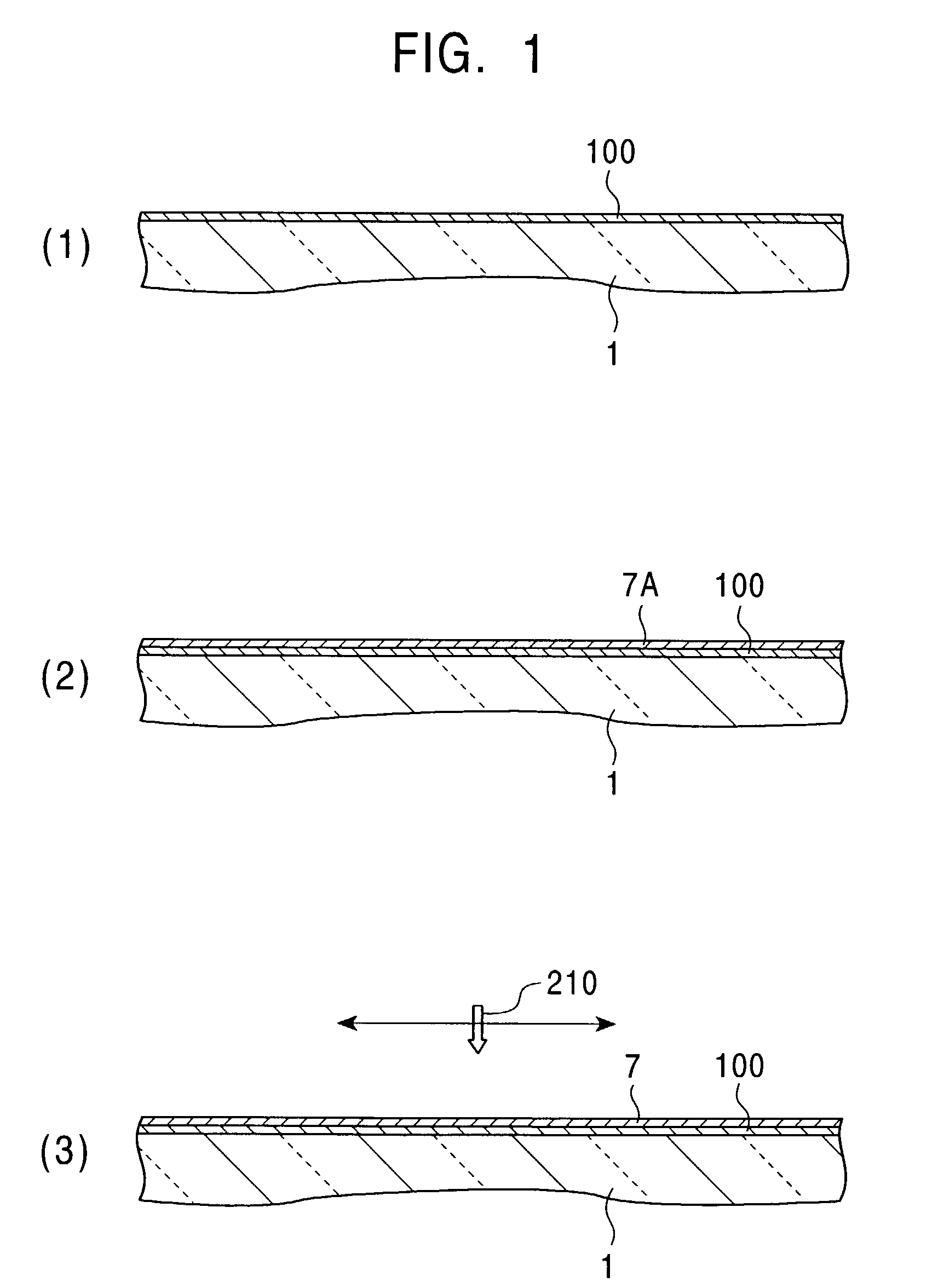

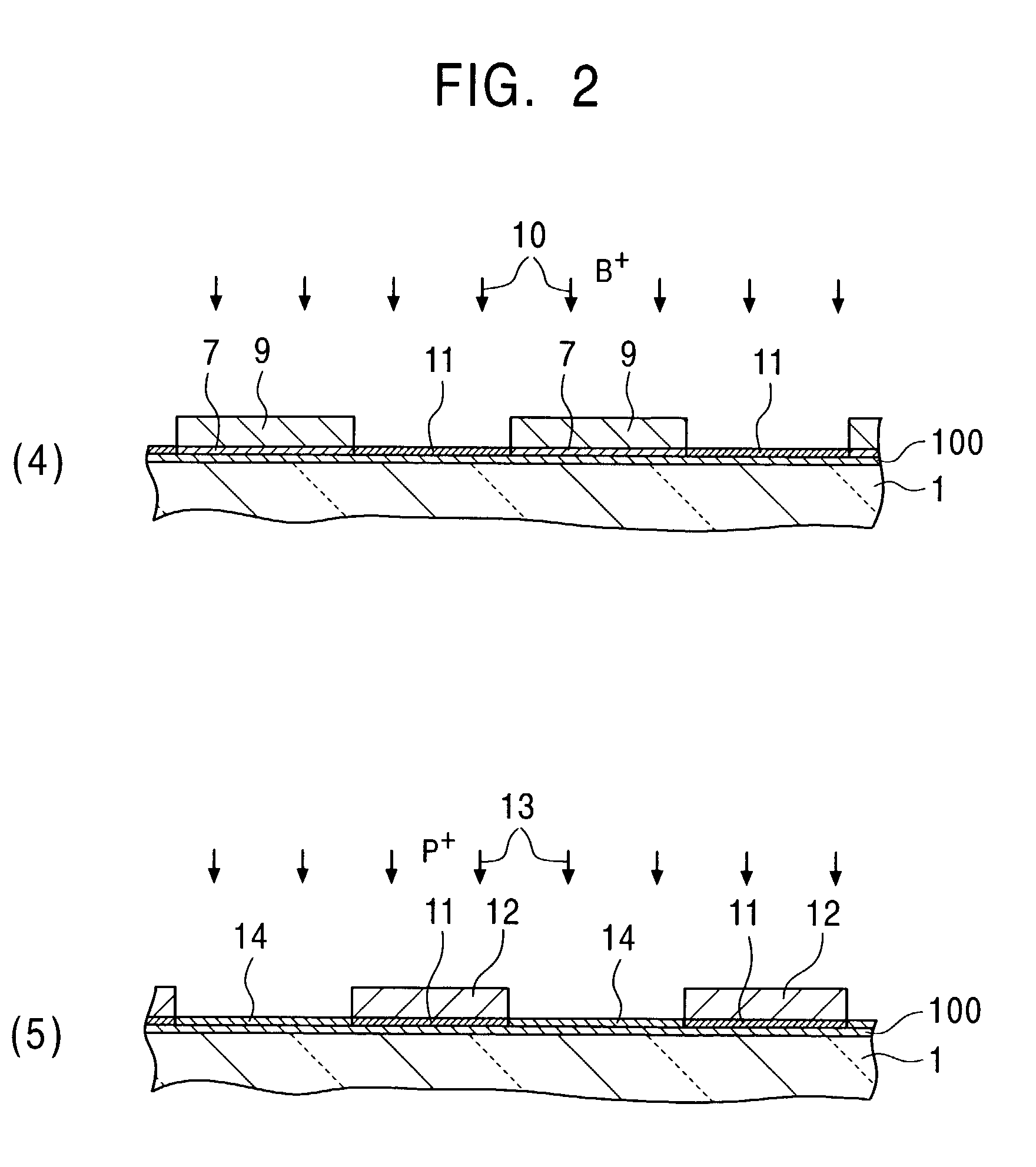

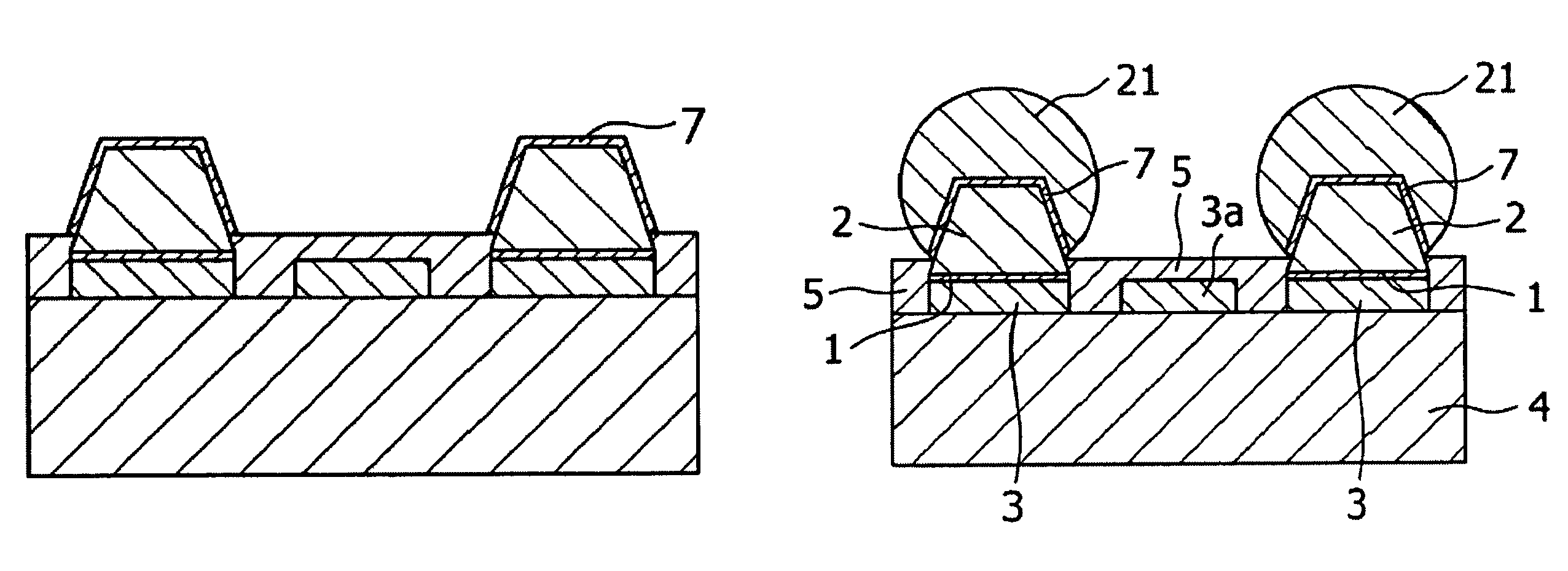

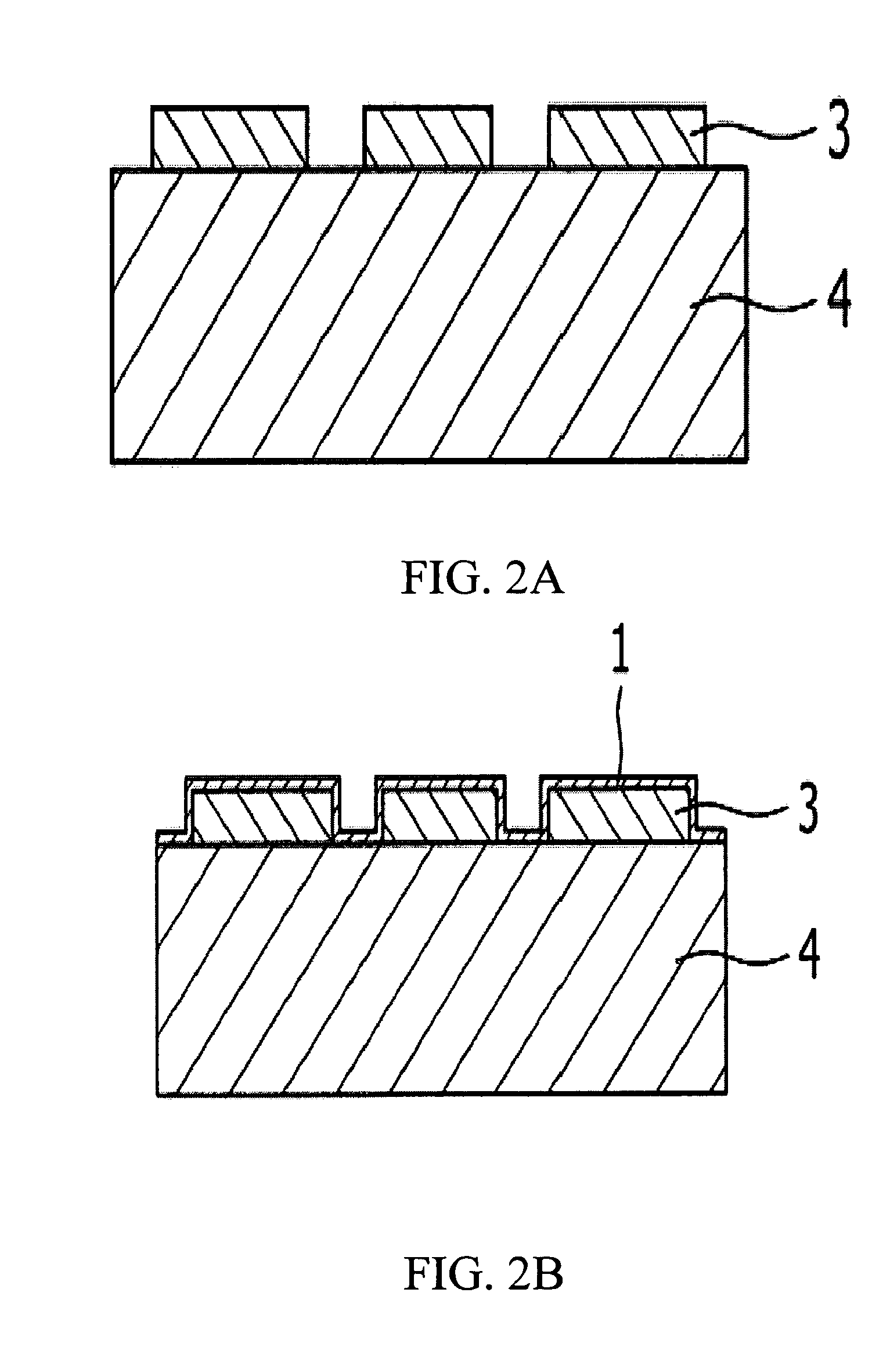

Method for forming thin semiconductor film, method for fabricating semiconductor device, system for executing these methods and electrooptic device

InactiveUS20030148565A1Promote crystallizationEasily realizedTransistorSolid-state devicesMolten stateUltraviolet

The present invention provides a method capable of easily forming a polycrystalline or monocrystalline semiconductor thin film of polycrystalline silicon with a high degree of crystallization and high quality at low cost, and an apparatus for carrying out the method. In a method of forming a polycrystalline (or monocrystalline) semiconductor thin film, a method of manufacturing a semiconductor device and an apparatus for carrying out these methods, in order to form a large-grain polycrystalline (or monocrystalline) semiconductor thin film (7) such as a polycrystalline silicon film with a high degree of crystallization on a substrate (1) or manufacturing a semiconductor device having the polycrystalline (or monocrystalline) semiconductor thin film (7), a low-crystalline semiconductor thin film (7A) is formed on the substrate (1), and then heated in a molten, semi-molten or non-molten state by laser annealing with ultraviolet rays (UV) or / and deep ultraviolet rays (DUV) and cooled to promote crystallization of the low-crystalline semiconductor thin film (7A), obtaining the polycrystalline (or monocrystalline) semiconductor thin film (7).

Owner:SONY CORP

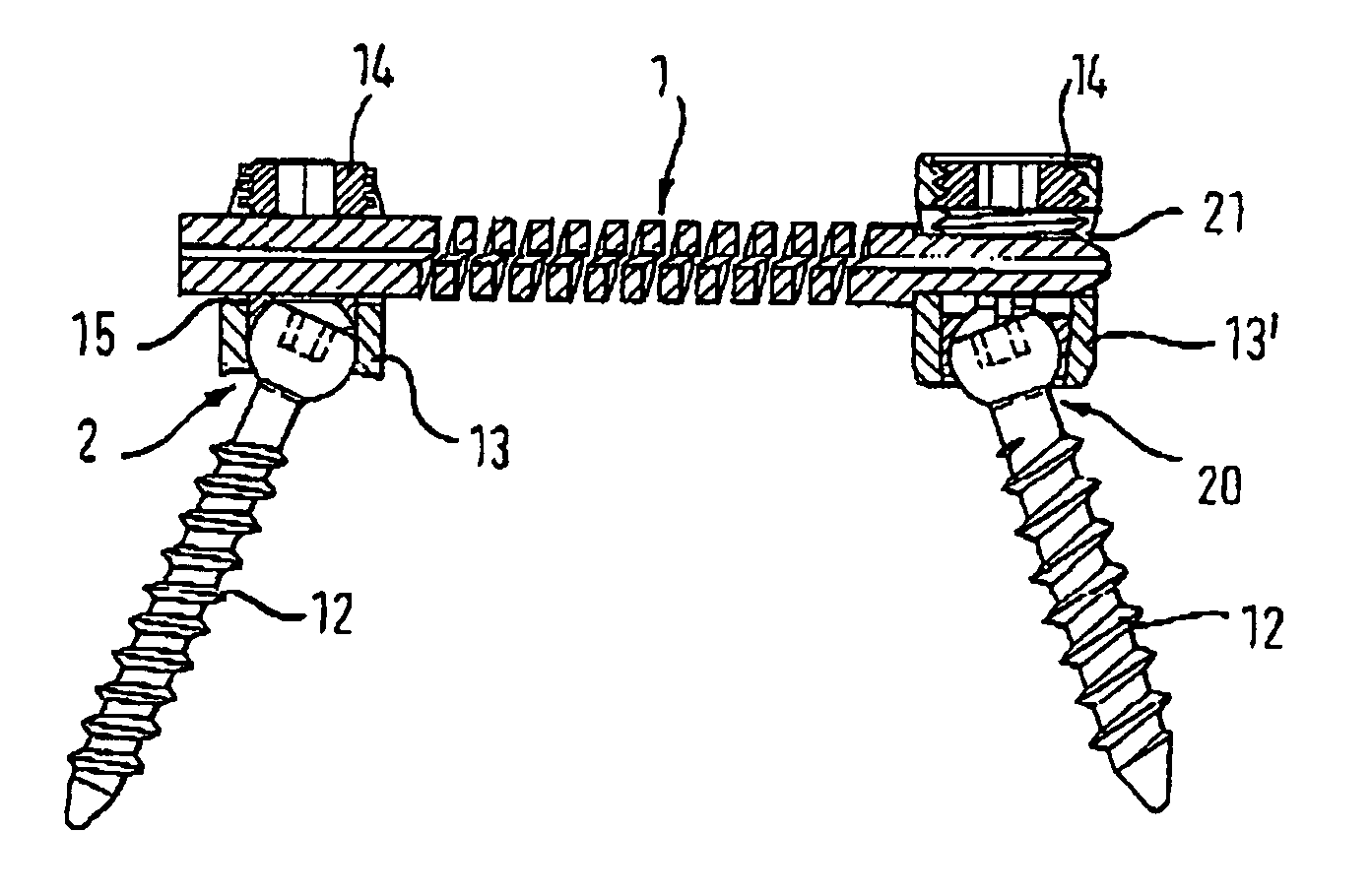

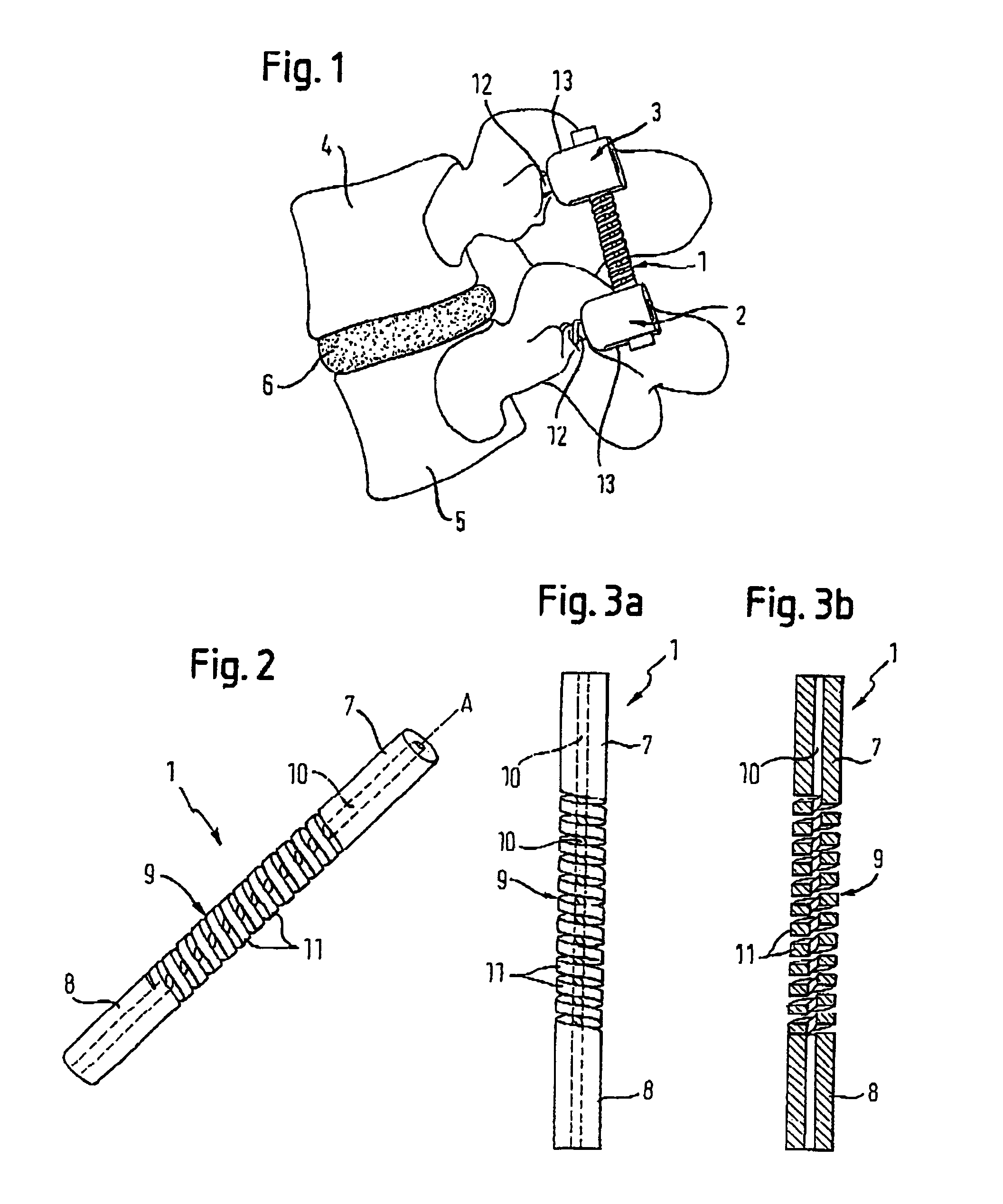

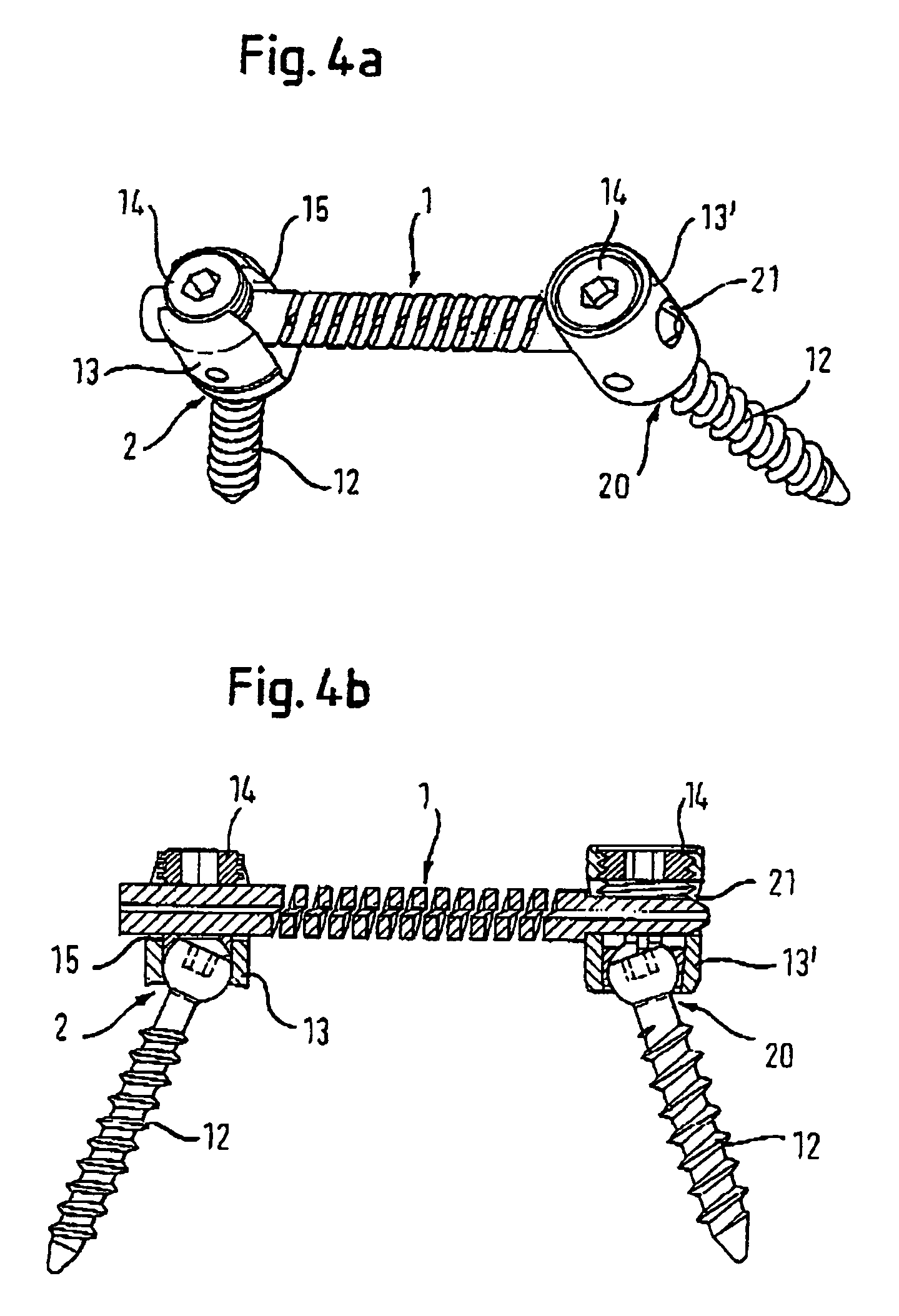

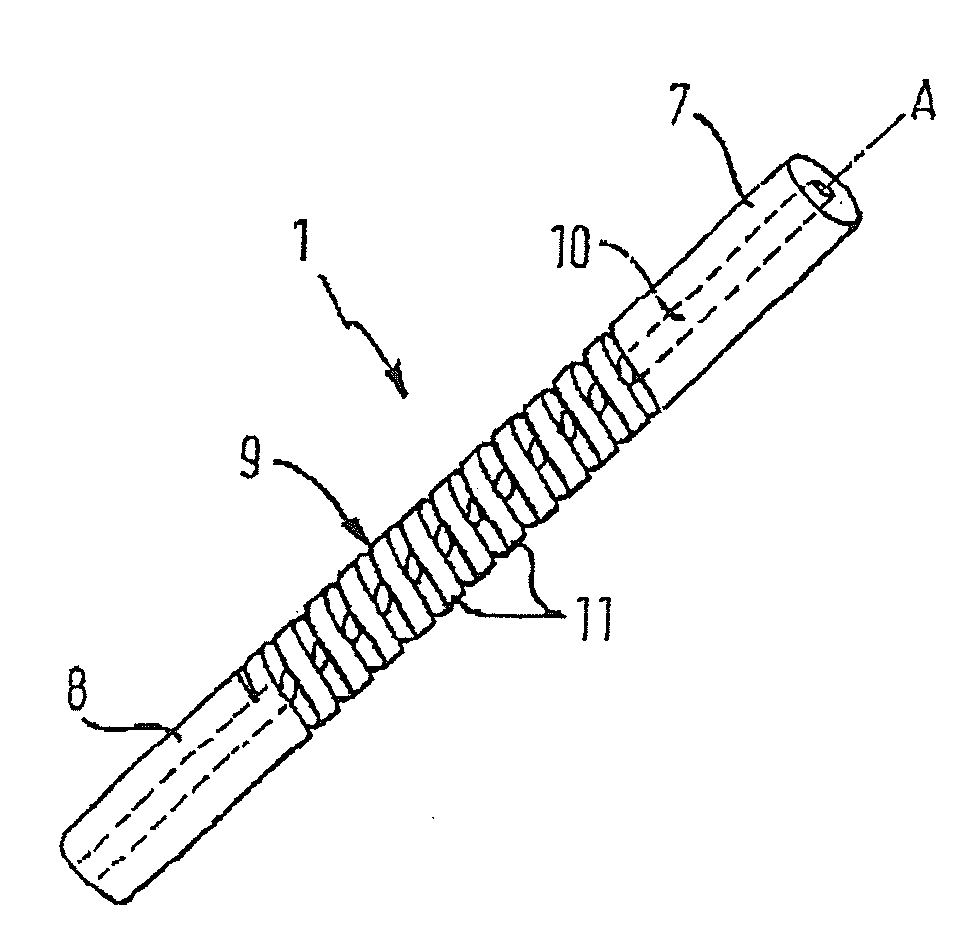

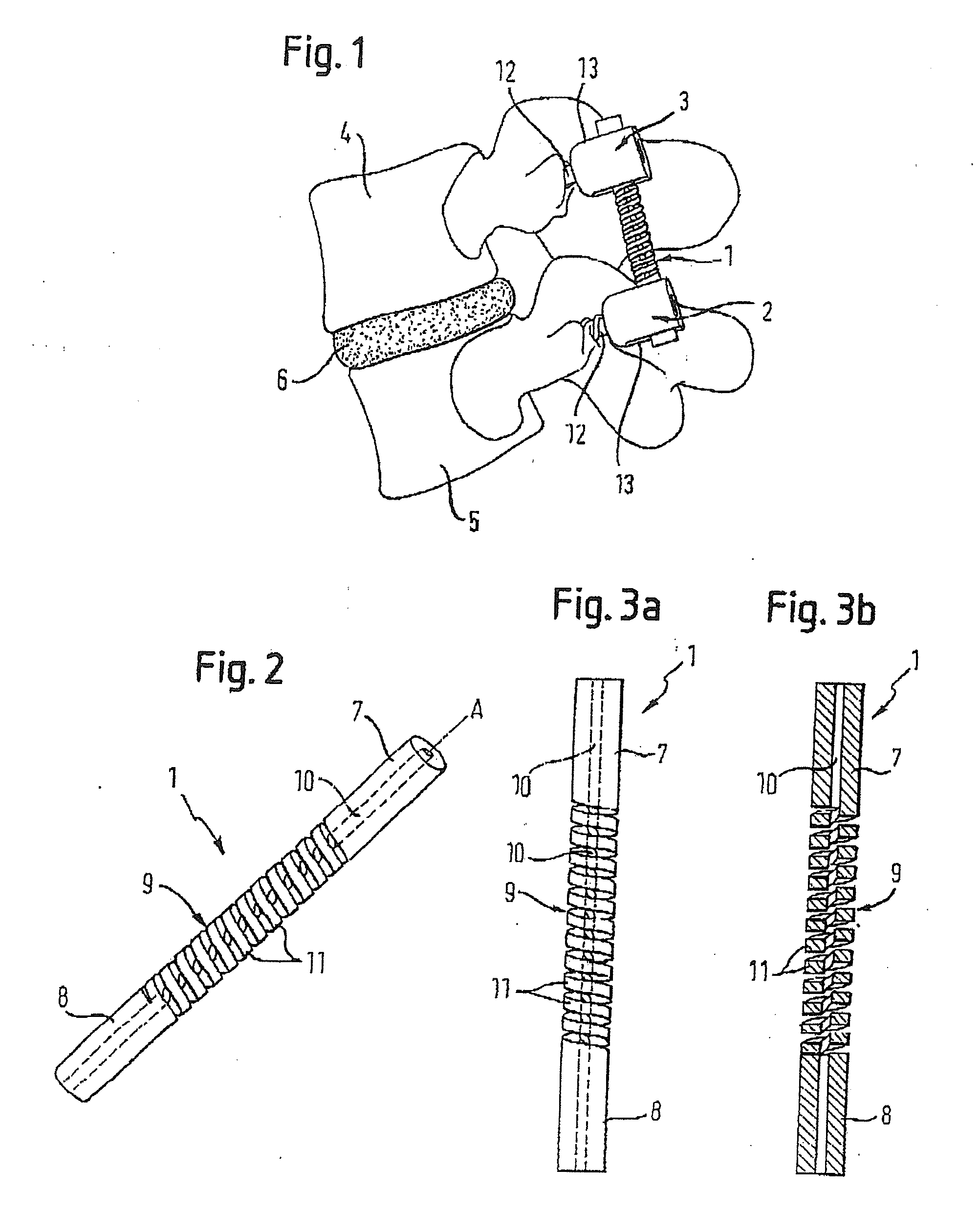

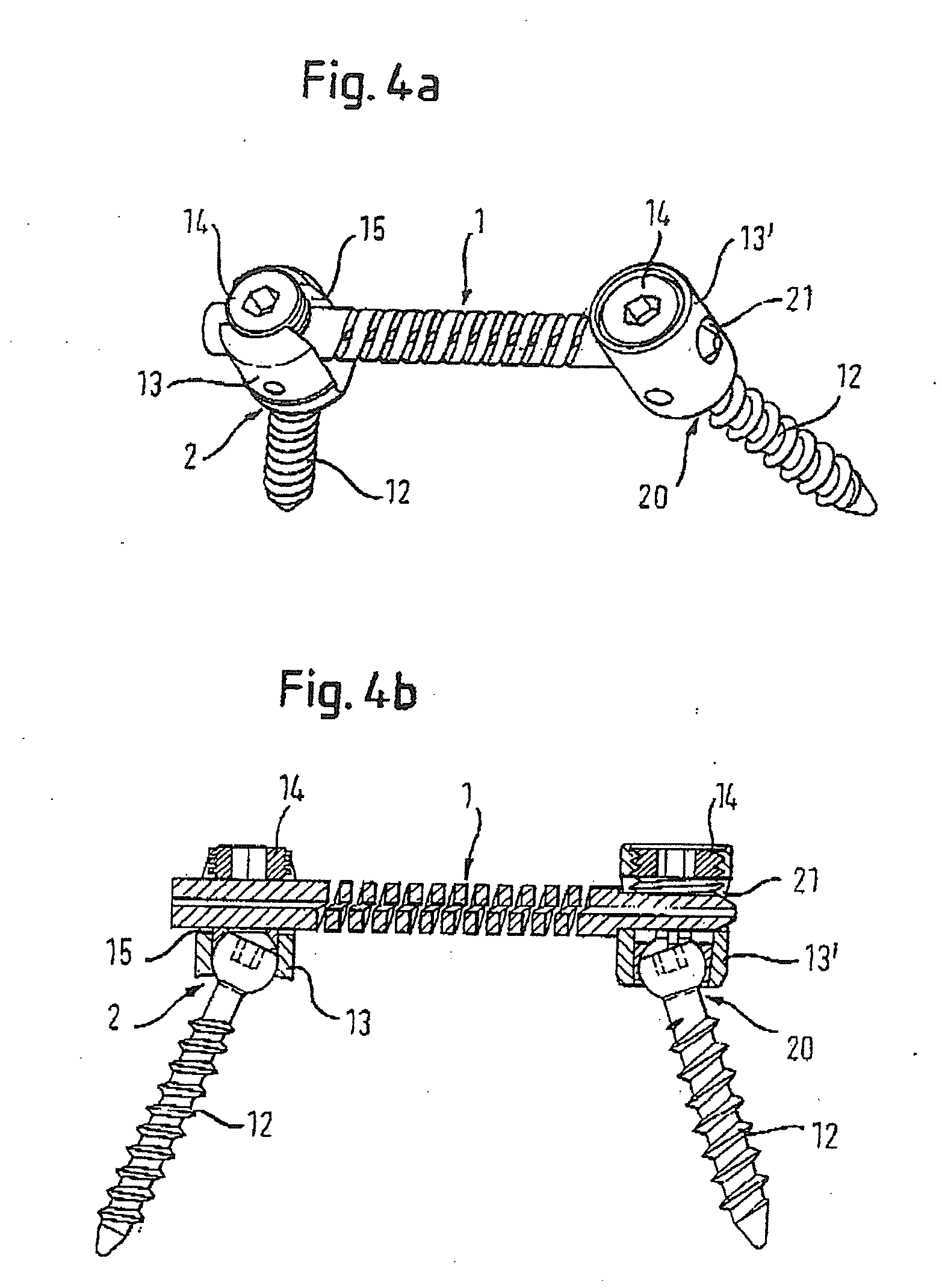

Rod-shaped implant element with flexible section

ActiveUS7621912B2Simple and compact designHigh reliability in useSuture equipmentsInternal osteosythesisBiomedical engineeringBone Anchors

A rod-shaped implant element for the connection of bone anchoring elements includes at least one rigid section that is configured to be placed in a receiver member of a bone anchoring element and a flexible section that is adjacent to the rigid section. The flexible section and the rigid section are formed as a continuous one-piece element.

Owner:BIEDERMANN TECH GMBH & CO KG

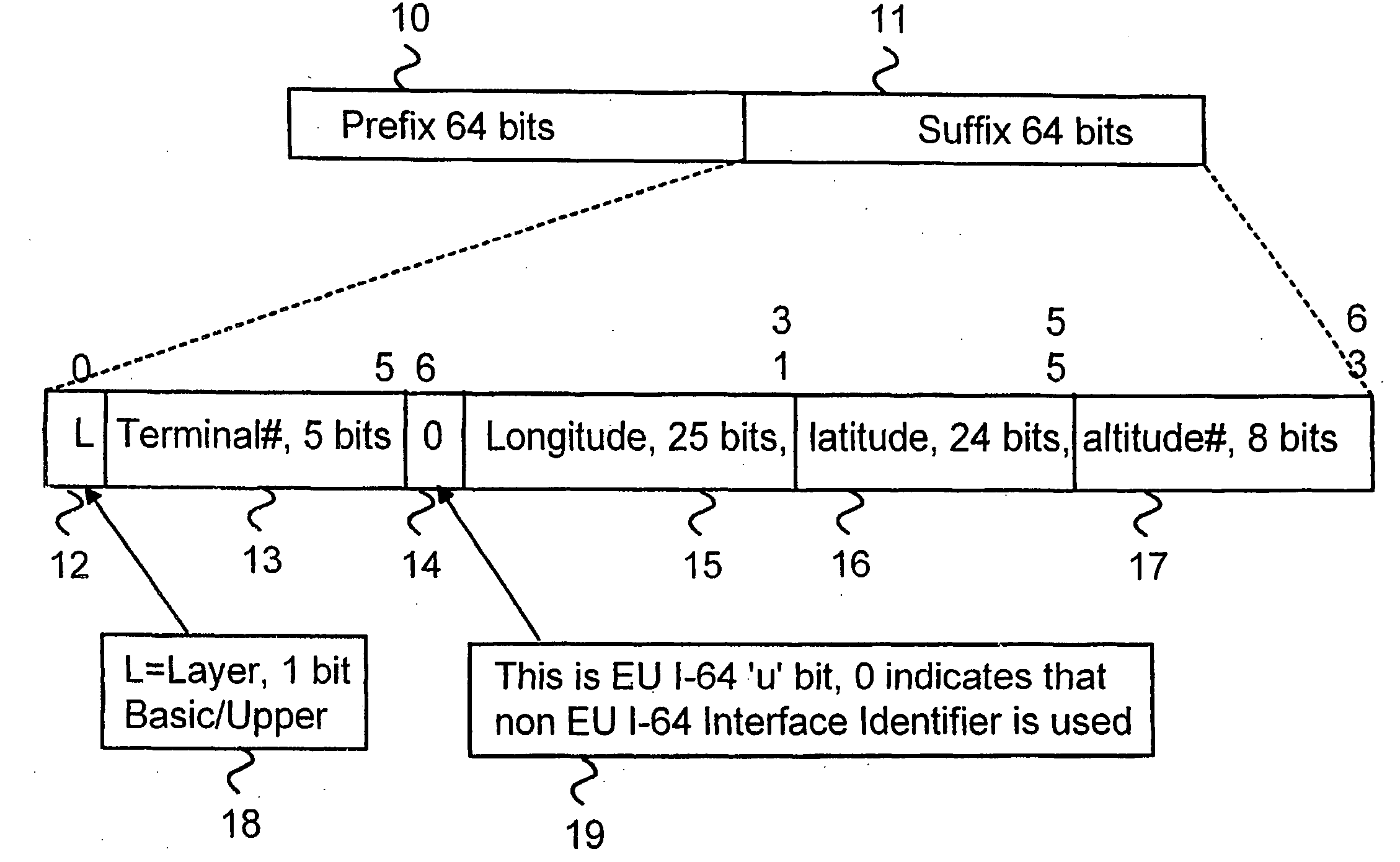

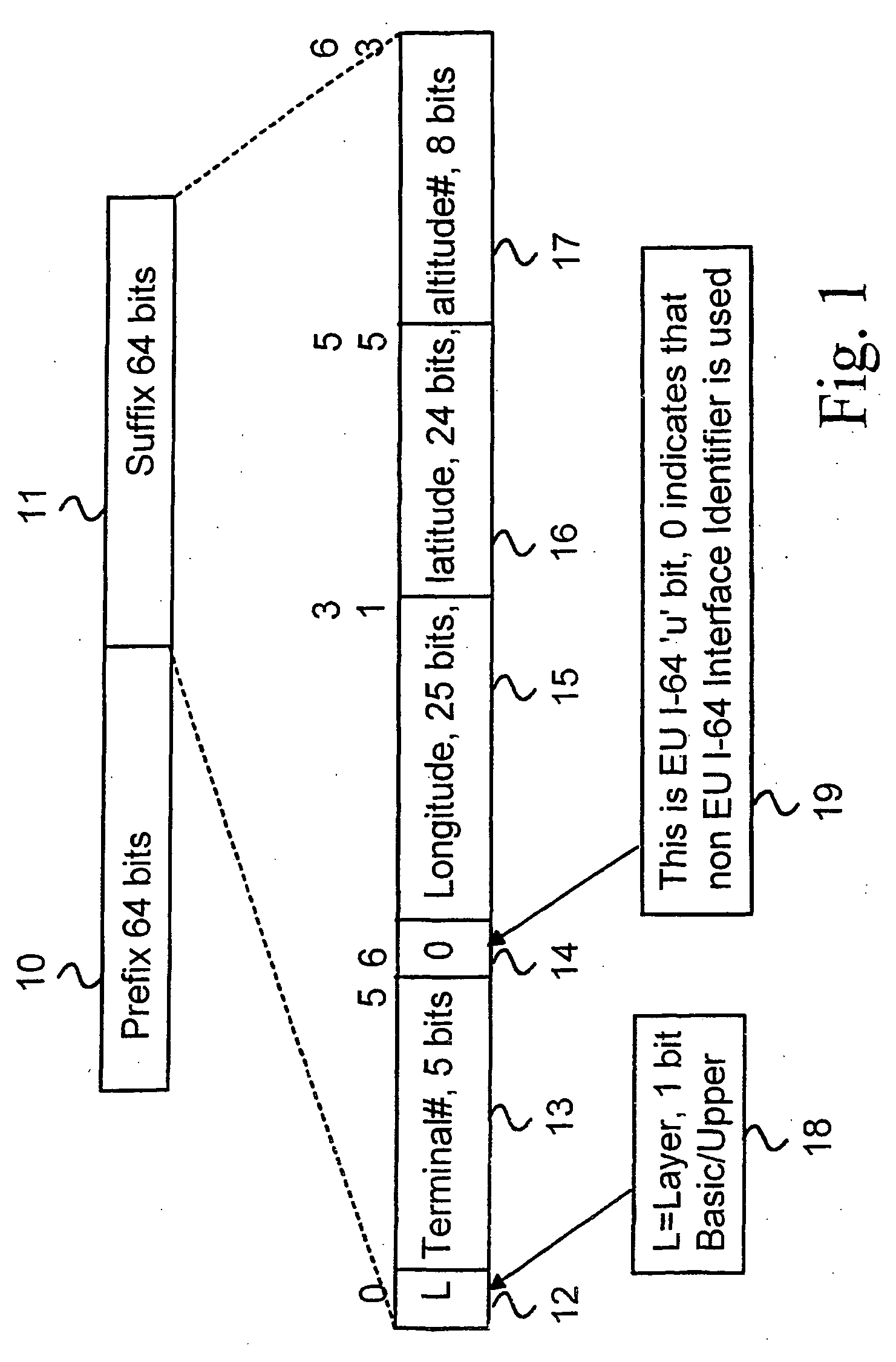

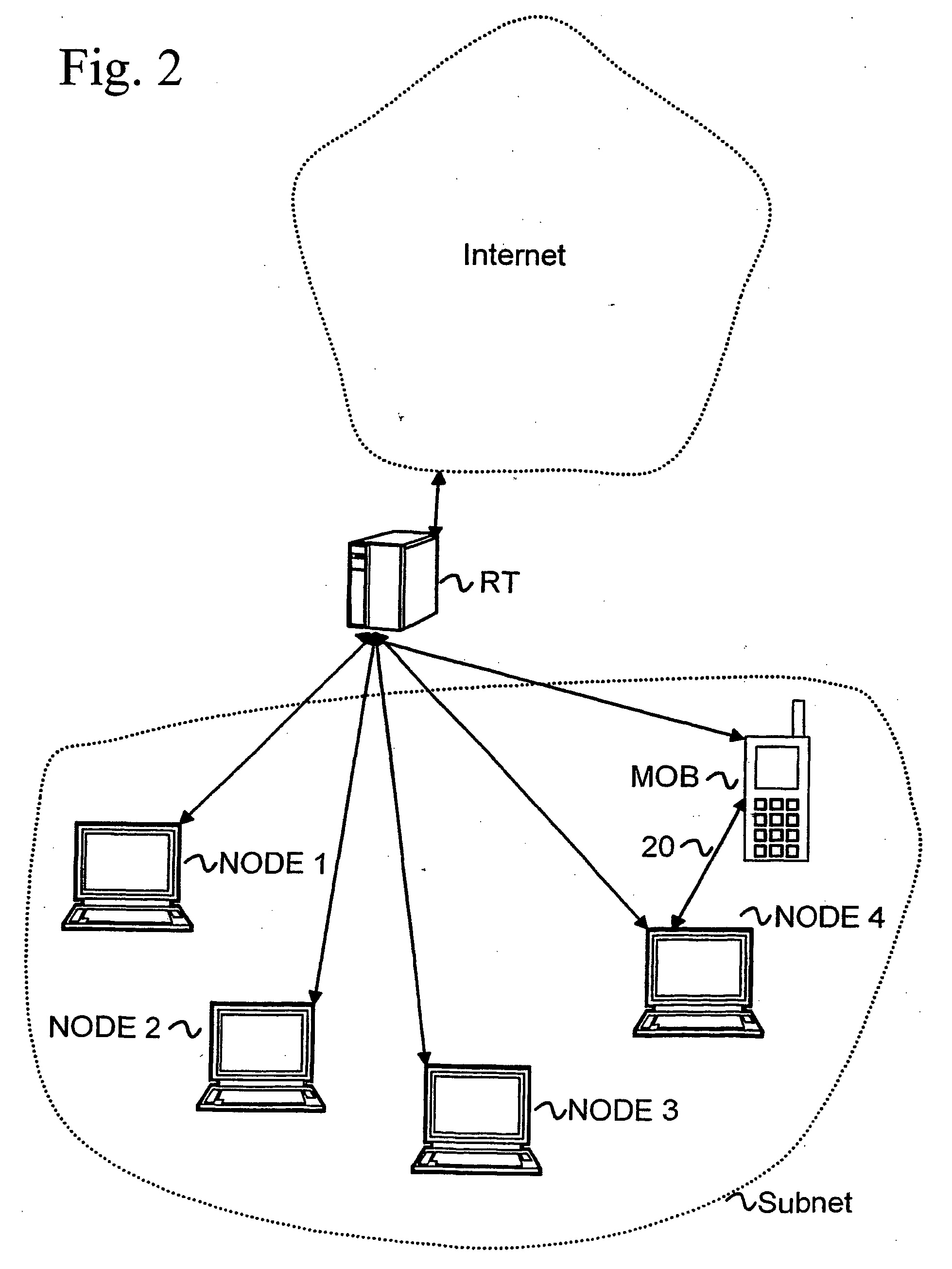

Utilization of geographic location information in IP addressing

InactiveUS20050018645A1Improve performanceConfiguring and routing table generation of the network can be fully automaticTime-division multiplexWireless network protocolsIp addressGeolocation

Owner:NOKIA CORP

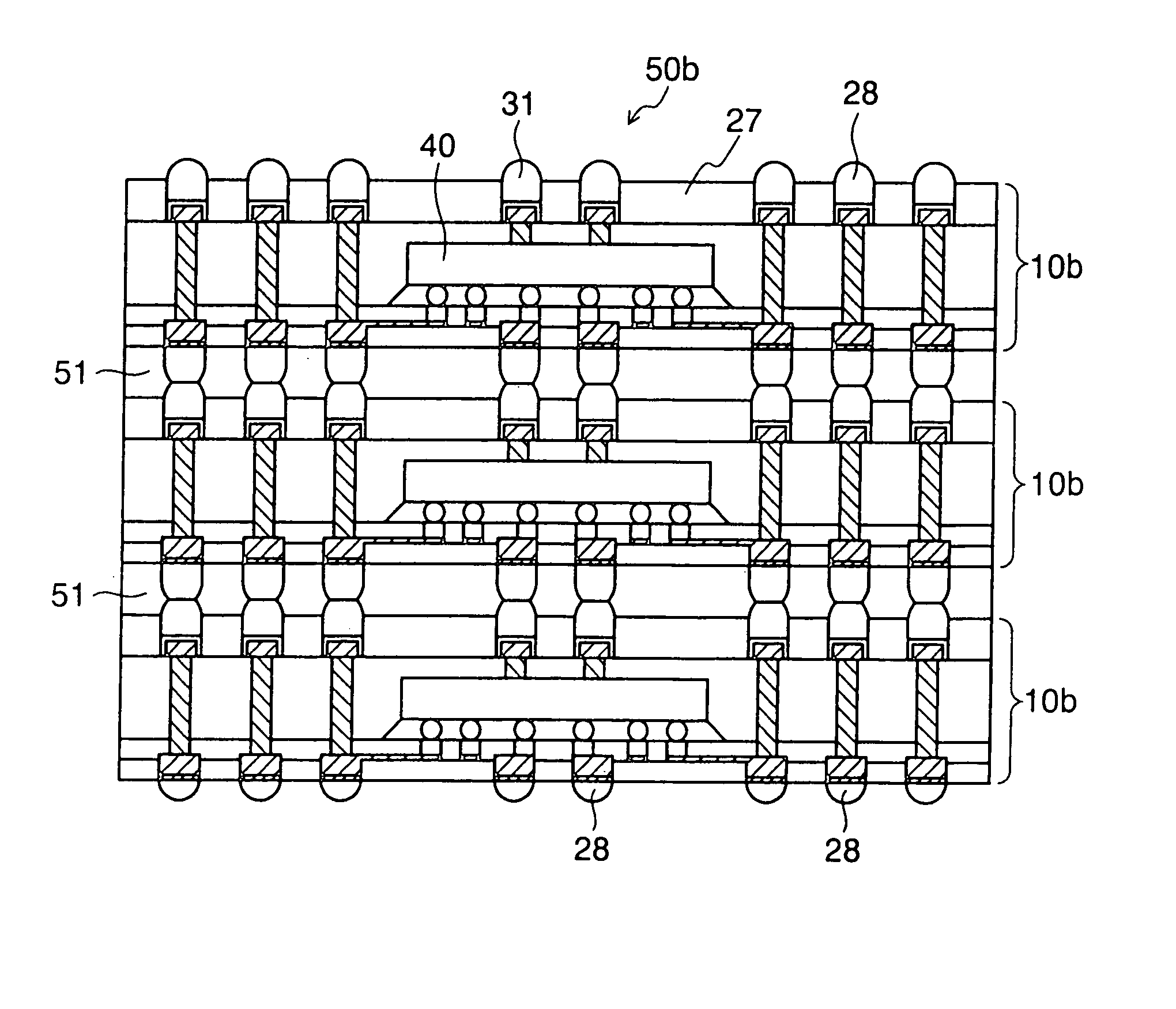

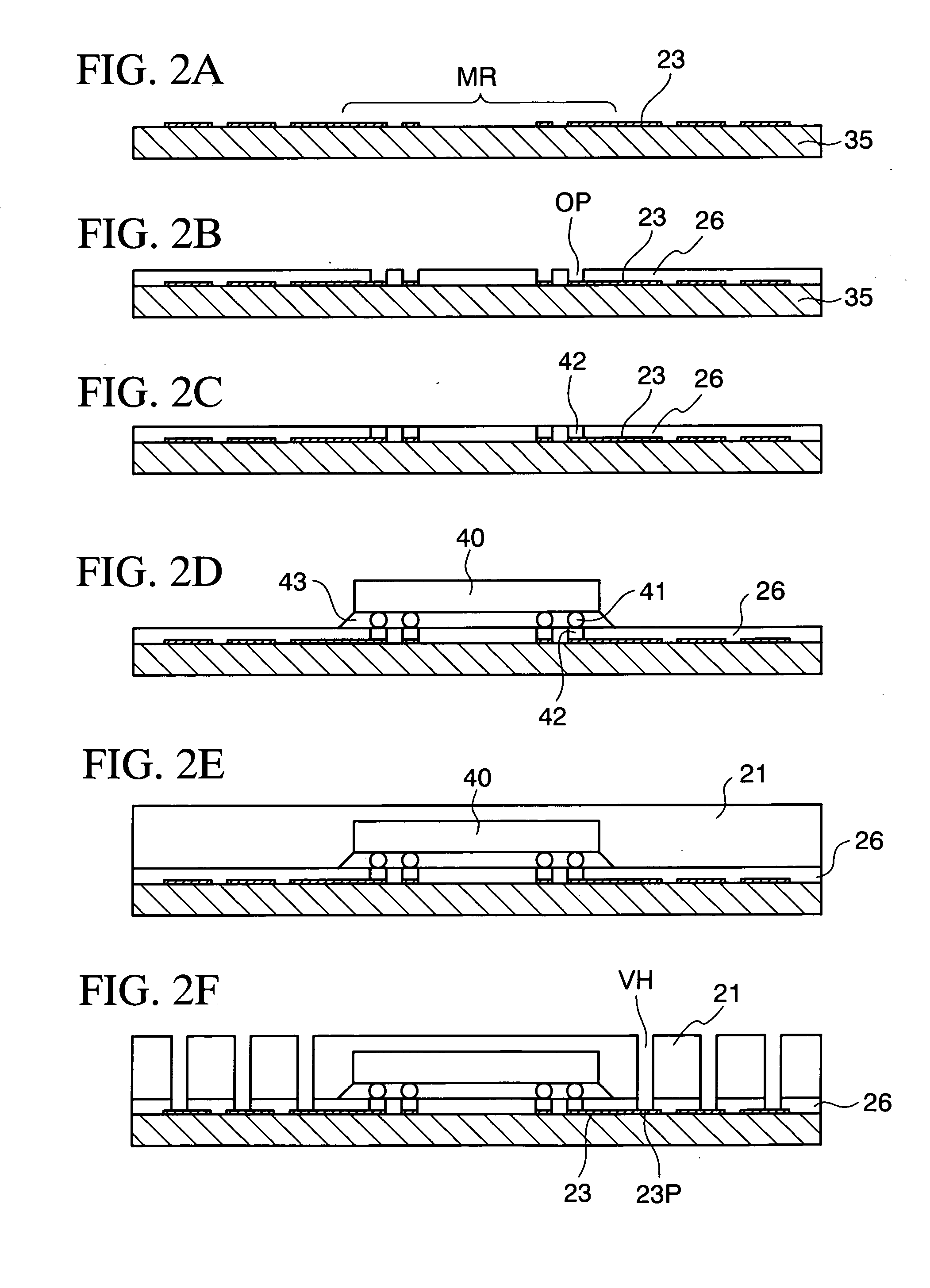

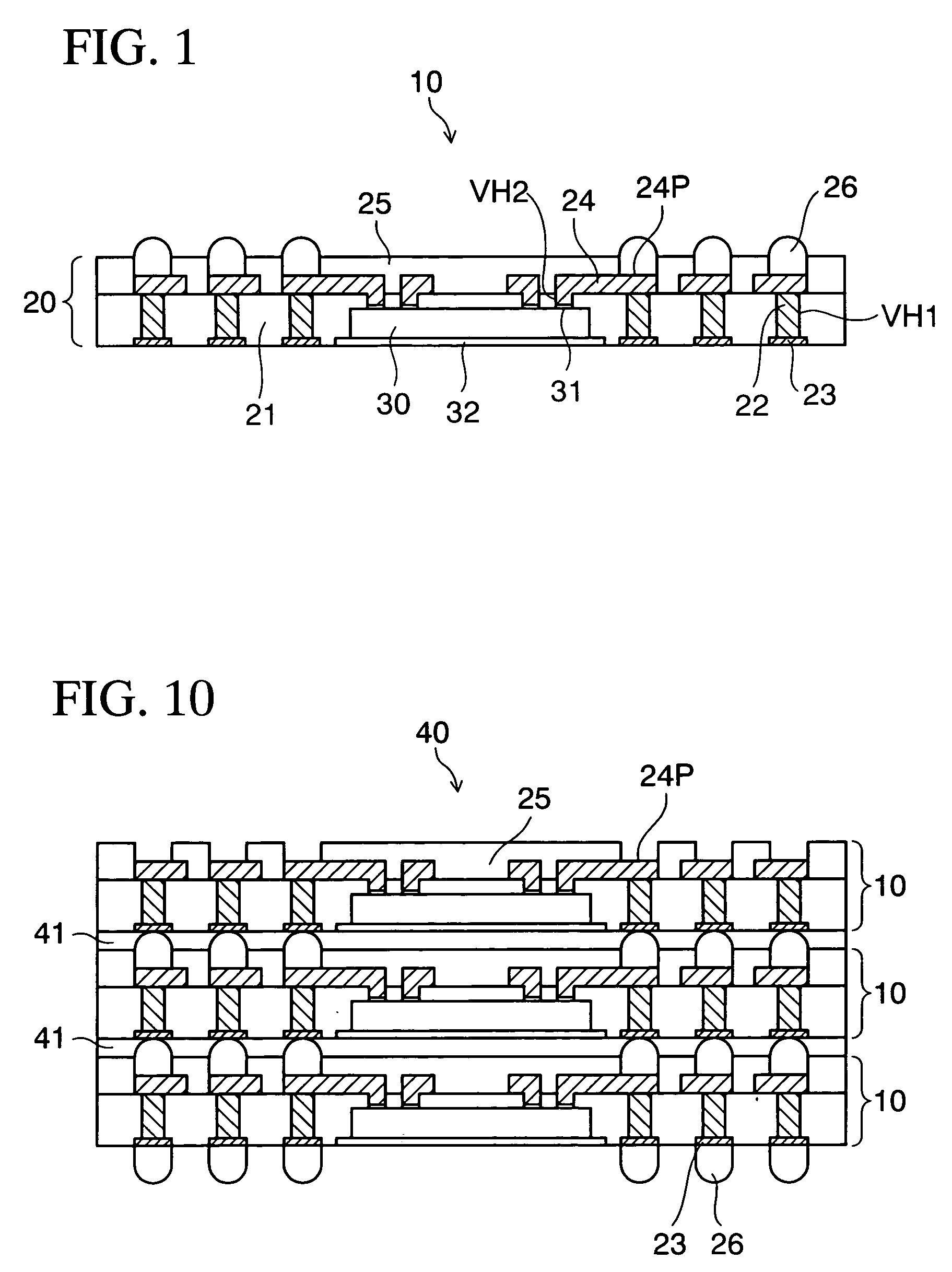

Semiconductor device and method of manufacturing the same

ActiveUS20050161833A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, one end of a conductor filled in the via hole is covered with a pad portion exposed to the outside, and a wiring layer connected to the other end of the conductor is formed. The portion (pad portion) of the wiring layer which correspond to the conductor is exposed from a protective film, or an external connection terminal is bonded to the top of the pad portion. Electrode terminals of the chip are connected to the wiring layer, and the opposite surface of the chip is exposed to the outside.

Owner:SHINKO ELECTRIC IND CO LTD

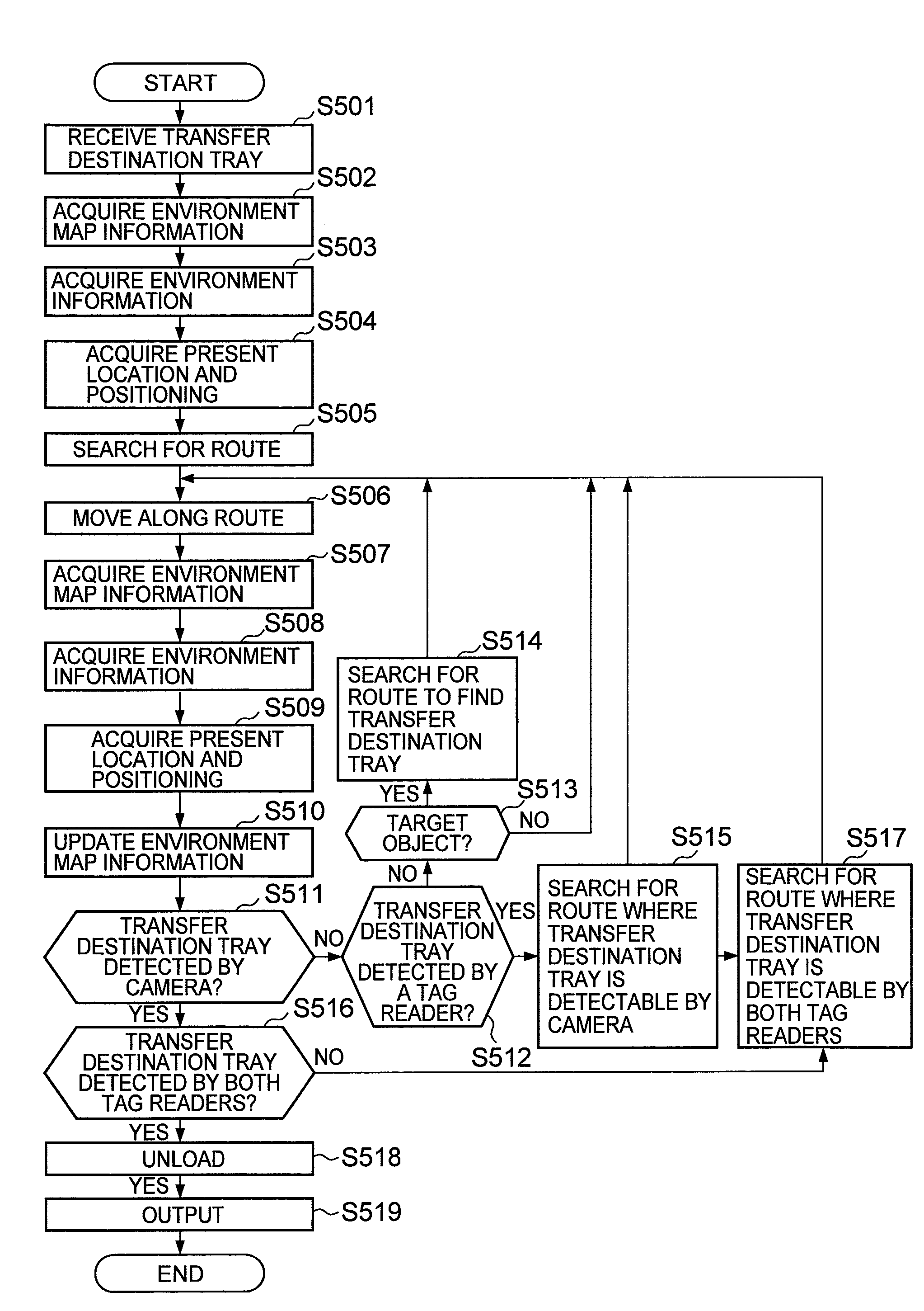

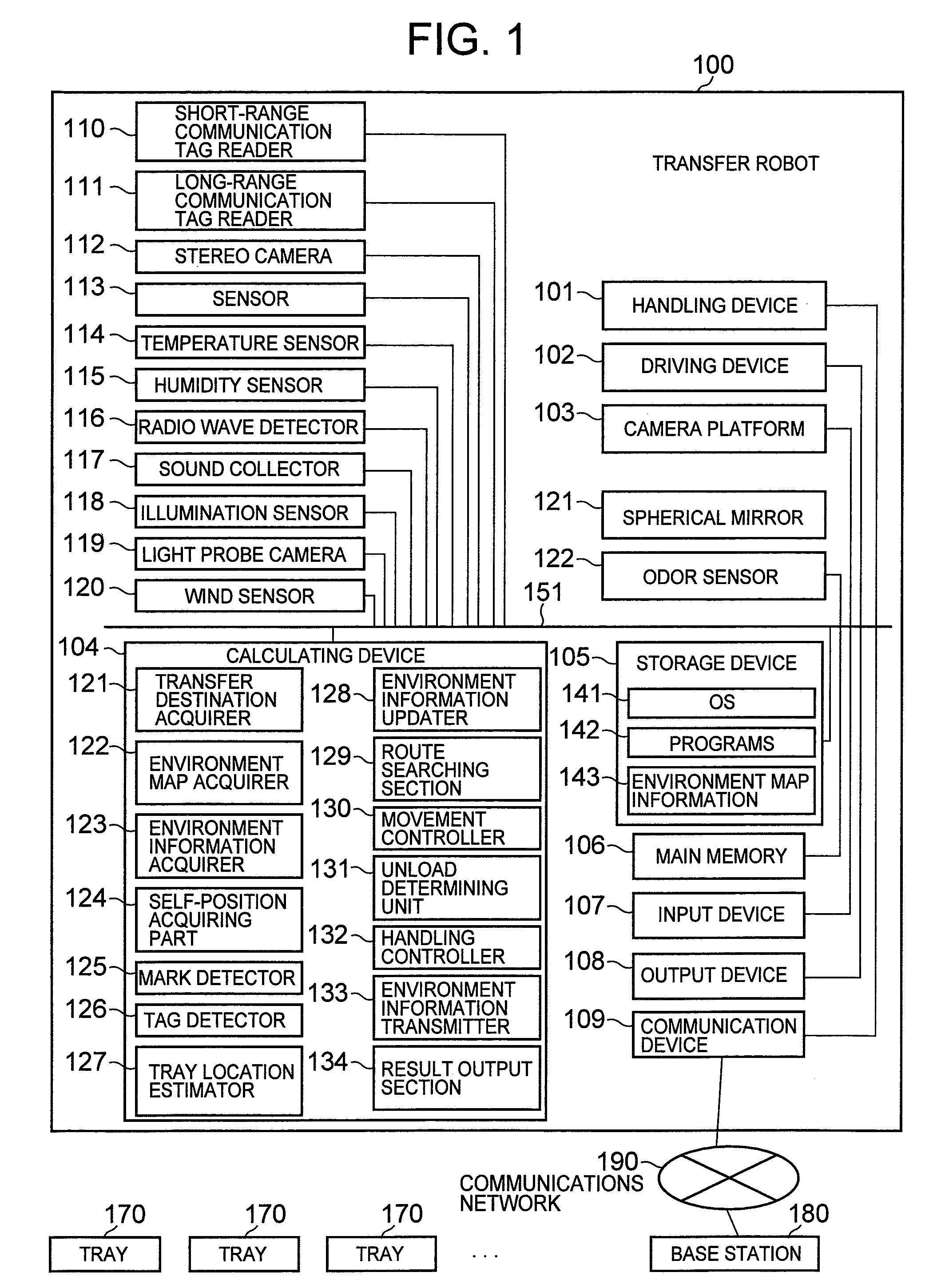

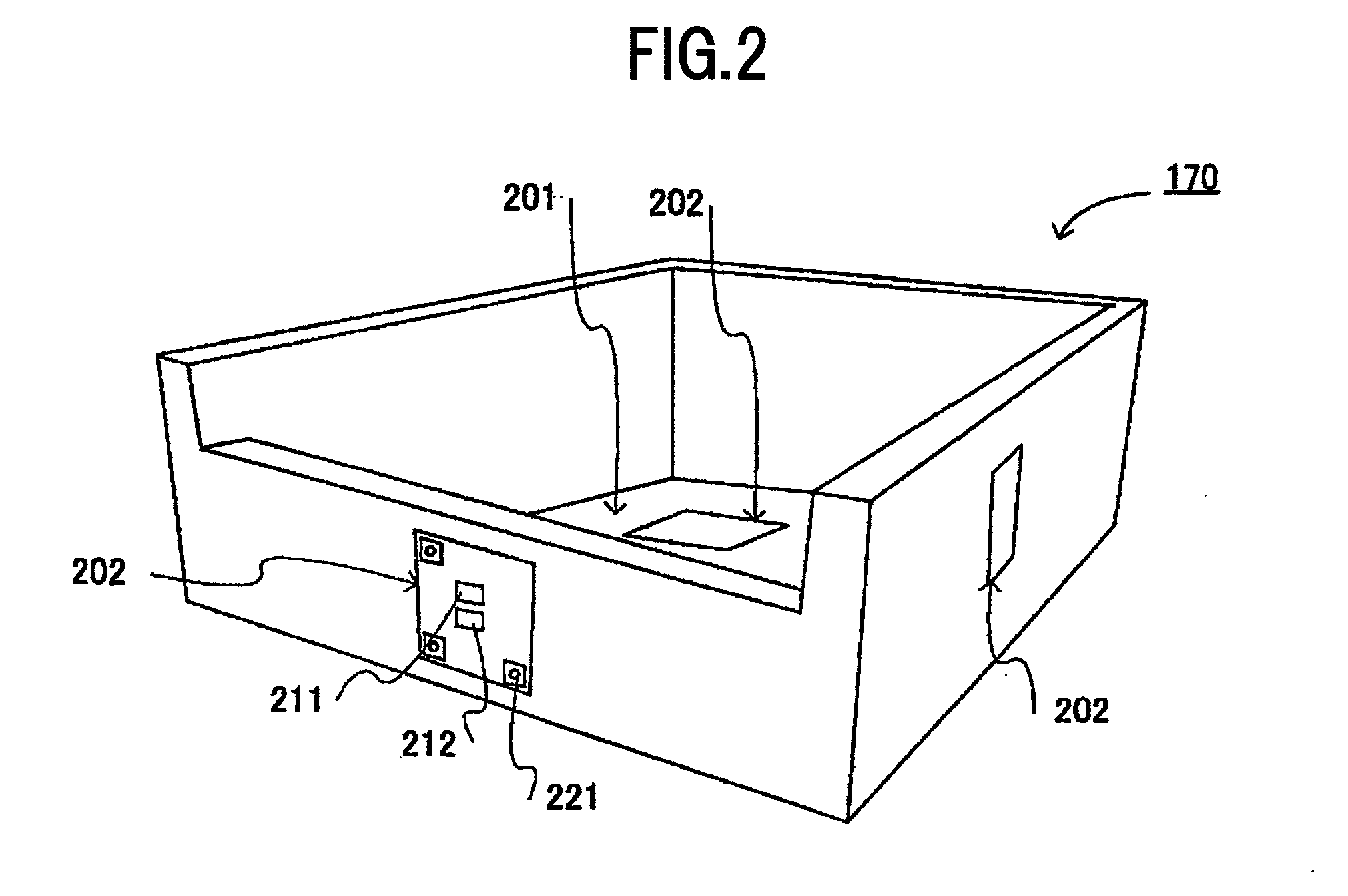

Mobile device, moving system, moving method, and moving program

InactiveUS20090012667A1Easily realizedVehicle position/course/altitude controlDistance measurementMobile deviceRemote sensing

A technology is provided that easily acquires the location where an article is placed and then moves to that location, even in cases where the article was originally placed in a location shielded from GPS radio wave, and subsequently moved to another location. Marks and RFID tags are affixed to a movable tray. A transfer robot includes a camera, a reader, and a sensor. The transfer robot detects the tray location from the location of a region in an image photographed by the camera that matches mark information. Furthermore, the reader in the transfer robot detects the tray location from the intensity of a radio wave whose information, when read, matches an ID retained in the RFID tag. The transfer robot moves with the camera and the reader, detecting the tray that is the target destination.

Owner:HITACHI LTD

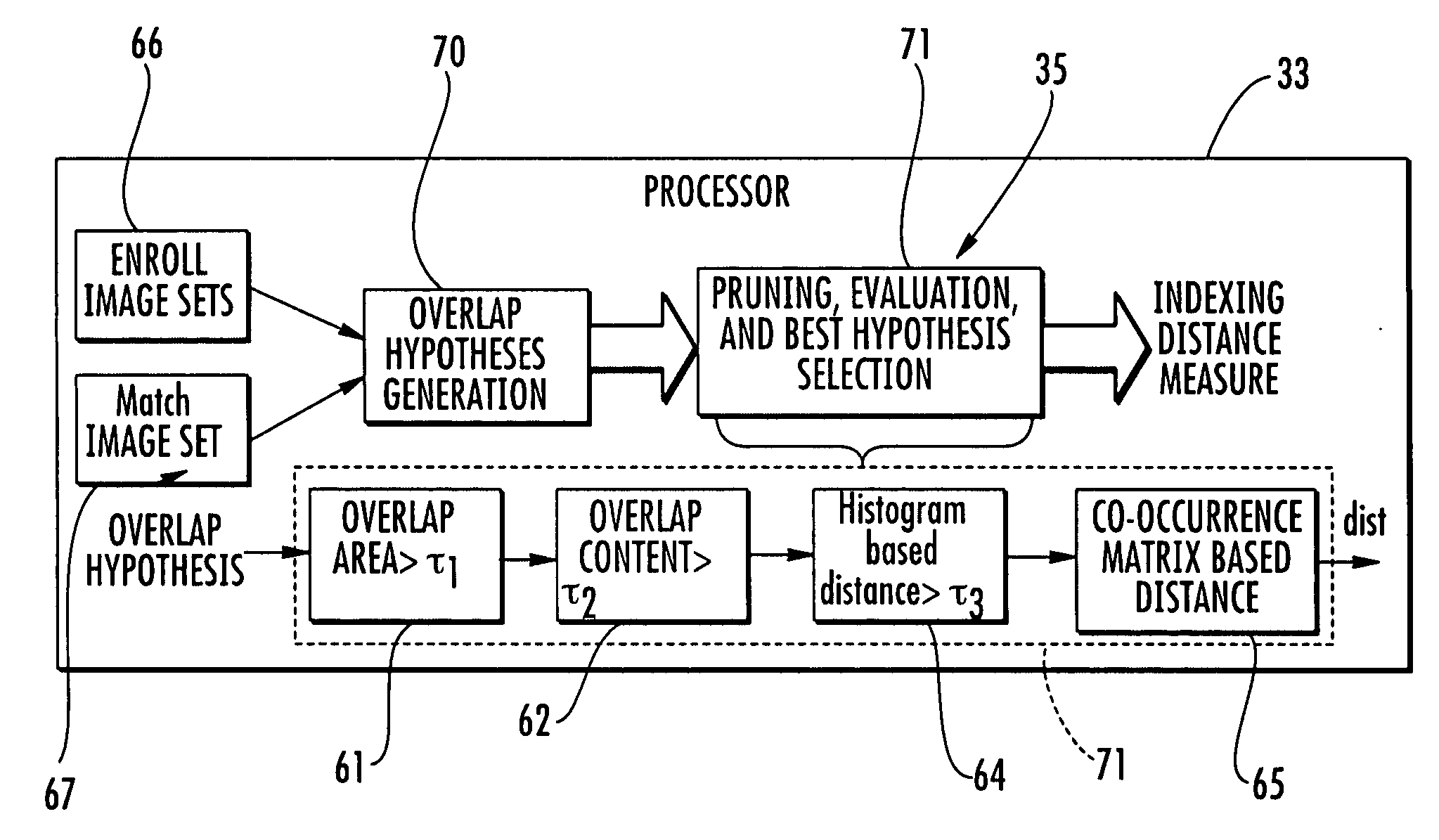

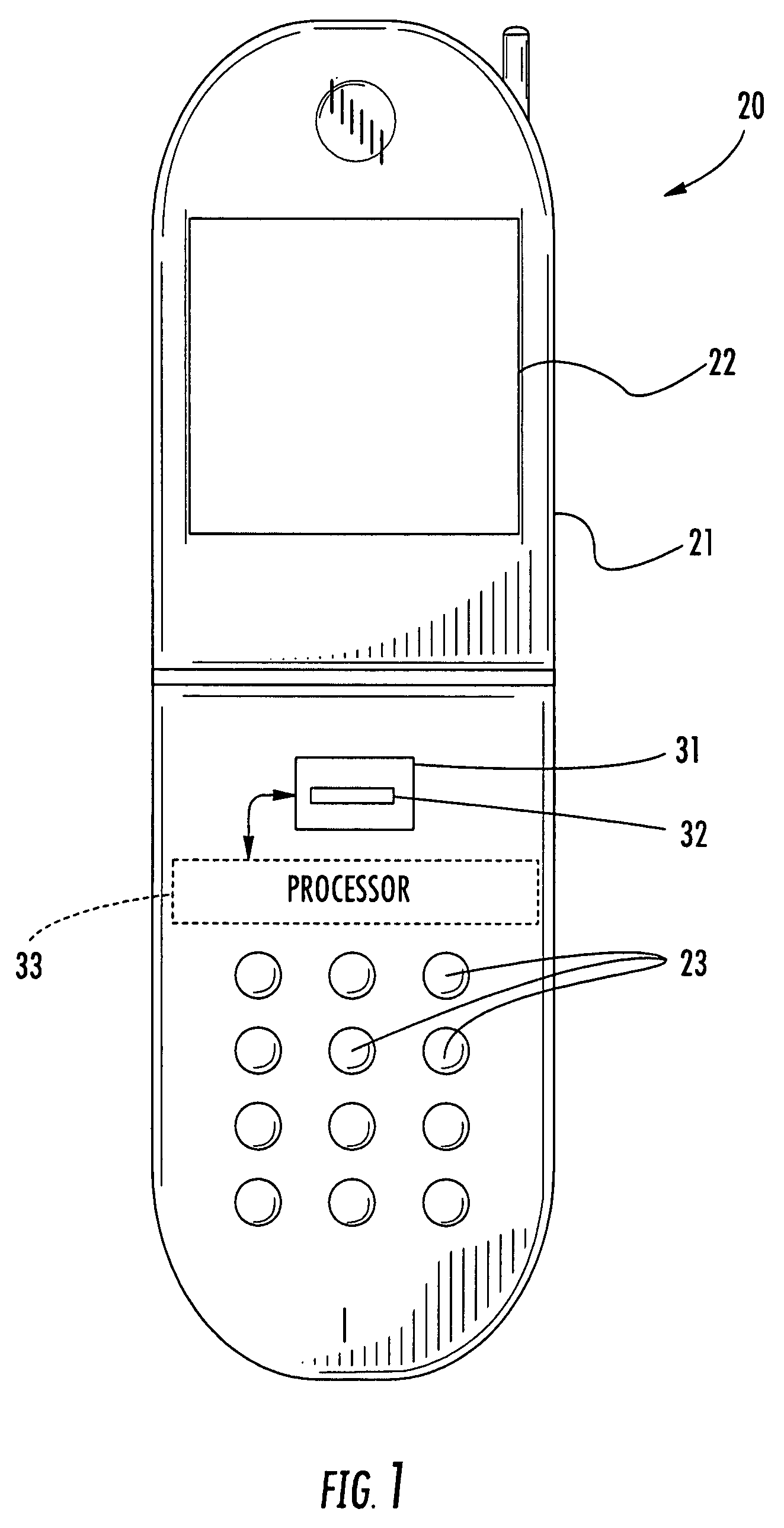

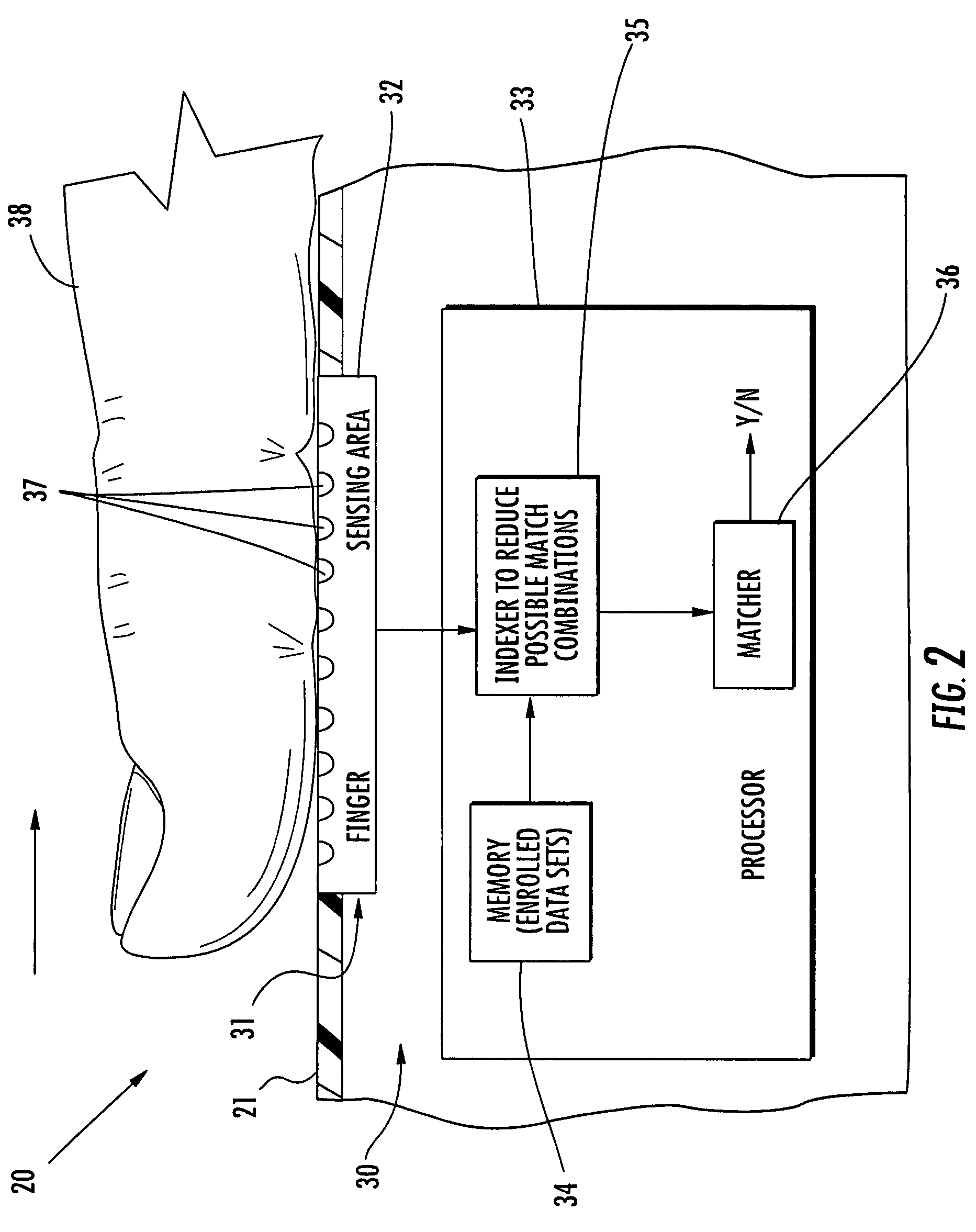

Finger sensing device using indexing and associated methods

InactiveUS20080013805A1Reduce in quantityEfficient indexingCharacter and pattern recognitionData setHypothesis

A finger sensing device includes a finger sensing area, and a processor cooperating therewith for reducing a number of possible match combinations between a sensed finger data set and each of a plurality of enrolled finger data sets. The processor may reduce the number of possible match combinations by generating a plurality of overlap hypotheses for each possible match combination, generating a co-occurrence matrix score based upon the plurality of overlap hypotheses for each possible match combination, and comparing the co-occurrence matrix scores to thereby reduce the number of possible match combinations. The processor may also perform a match operation for the sensed finger data set based upon the reduced number of possible match combinations. The sensed finger data set may include a sensed finger ridge flow data set, and each enrolled finger data set may include an enrolled finger ridge flow data set.

Owner:AUTHENTEC

Rod-shaped implant element with flexible section

ActiveUS20100042156A1Simple and compact designHigh reliability in useInternal osteosythesisJoint implantsEngineeringBiomedical engineering

Owner:BIEDERMANN TECH GMBH & CO KG

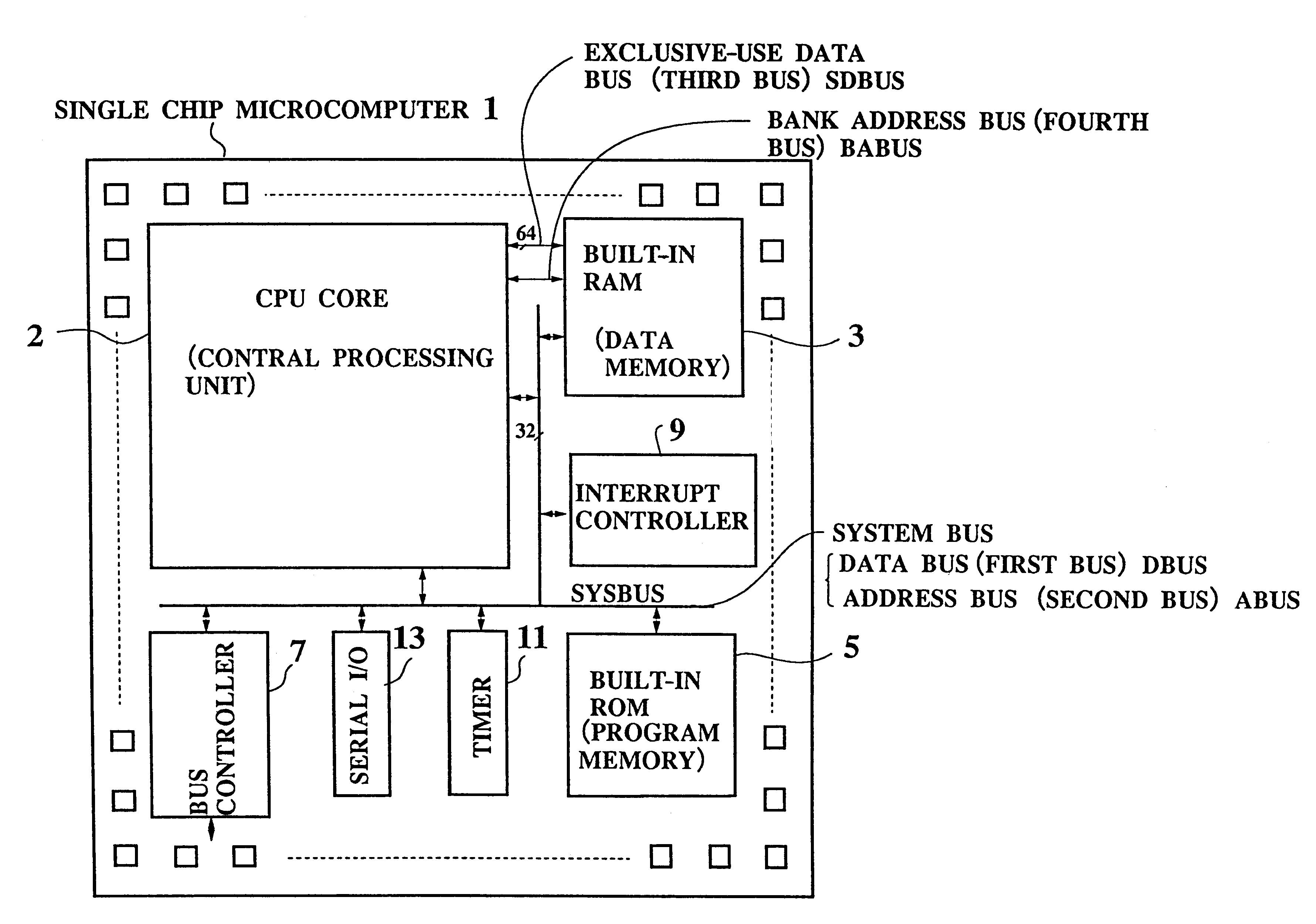

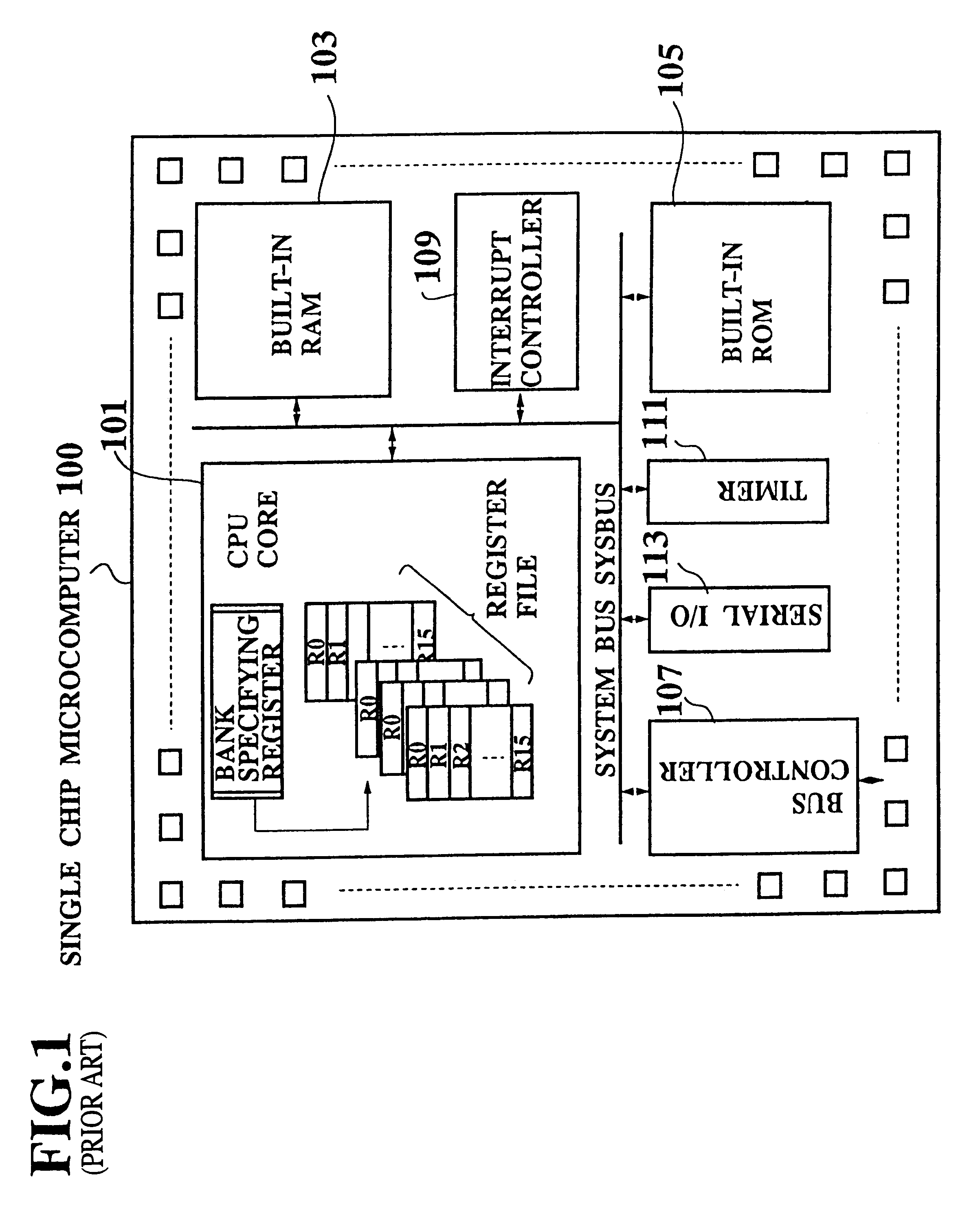

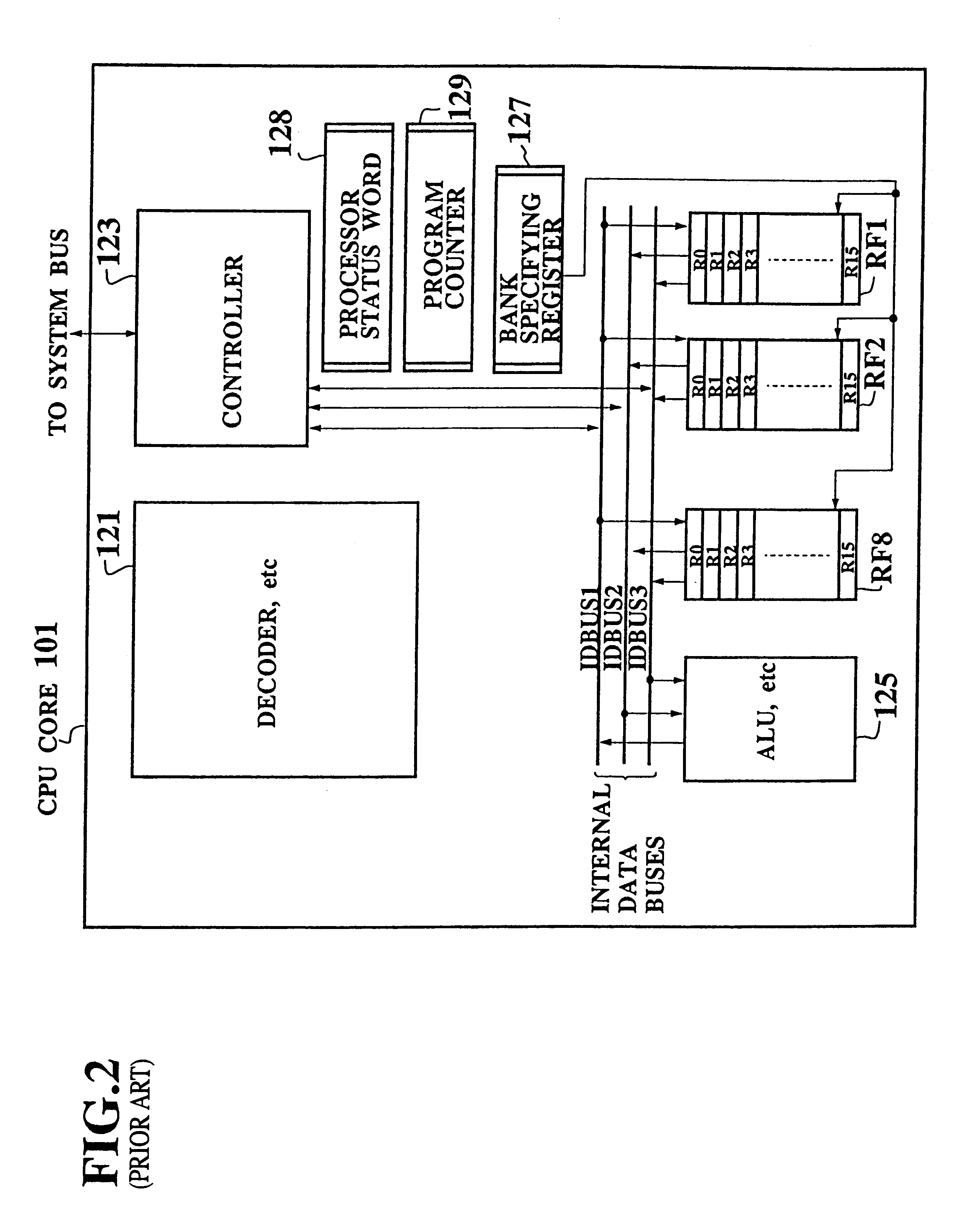

Single chip microcomputer having a dedicated address bus and dedicated data bus for transferring register bank data to and from an on-line RAM

InactiveUS6223279B1Efficiently chip spaceData transferArchitecture with single central processing unitSpecial data processing applicationsGeneral purposeProcessor register

A single chip microcomputer comprises a central processing unit (CPU) 2, a on-chip RAM 3, a on-chip ROM 5, a first bus DBUS for connecting the CPU, RAM, and ROM with one another and transferring data between them, a second bus ABUS for passing address data corresponding to the data passed through the first bus, a third bus SDBUS for connecting the CPU 2 with the RAM 3 and transferring data between them, the number of bits of the third bus SDBUS being larger than that of the first bus DBUS, and a fourth bus BABUS for connecting the CPU 2 with the RAM 3 and passing address data corresponding to the data passed through the third bus SDBUS. The CPU 2 has a data memory RF serving as general purpose registers for providing internal data to the third bus SDBUS, and a bank specifying register BP for holding positional data of a mapping region in the RAM 3 where the contents of the data memory RF are mapped and providing the positional data to the fourth bus BABUS. The RAM 3 has a memory cell array 31, a bank address control circuit 35 connected to the fourth bus BABUS, for generating a real address according to the contents of the bank specifying register BP (BP0, BP1), and a selection circuit 37 for selecting the real address generated by the bank address control circuit 35, or the address provided through the second bus ABUS.

Owner:KK TOSHIBA

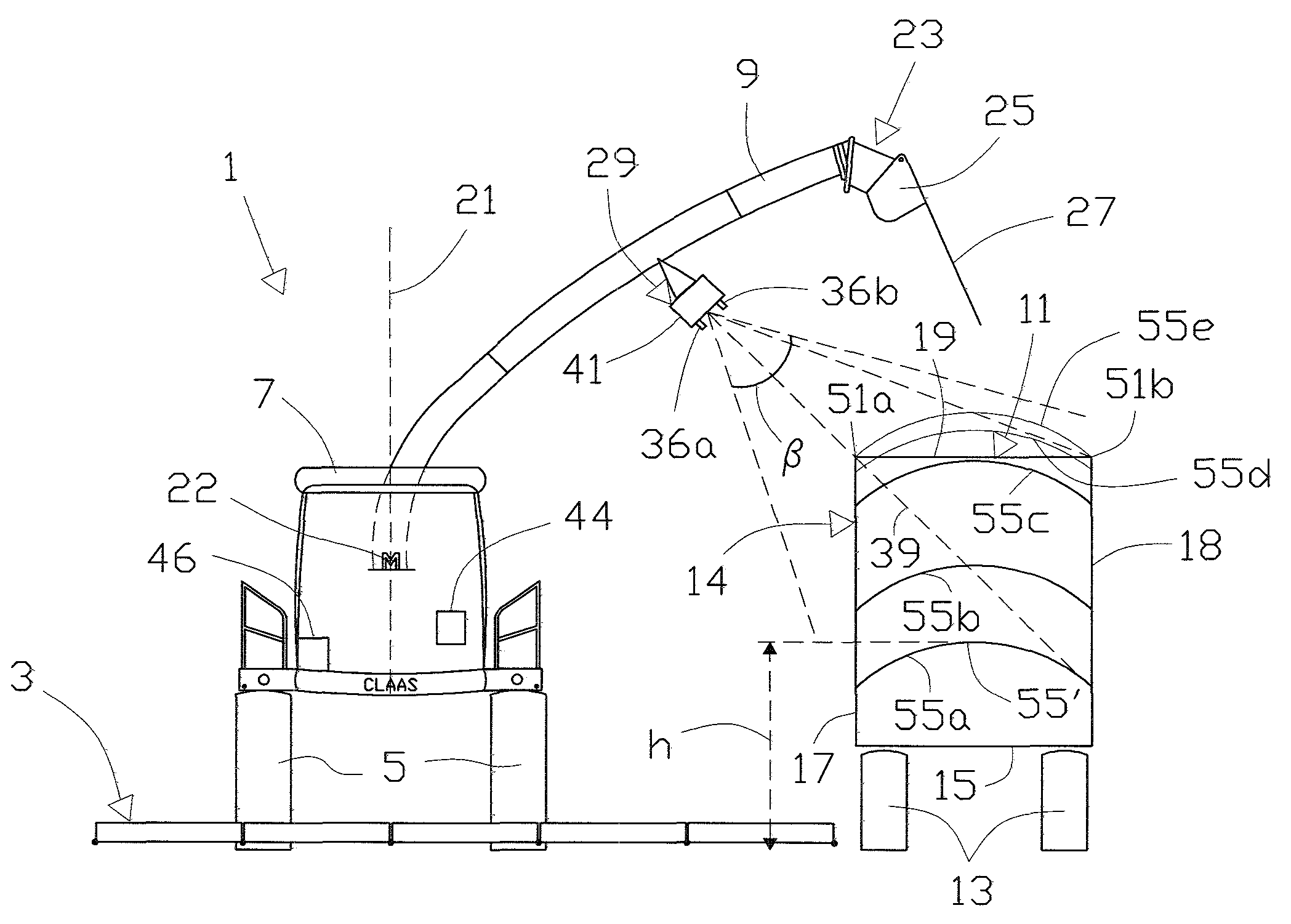

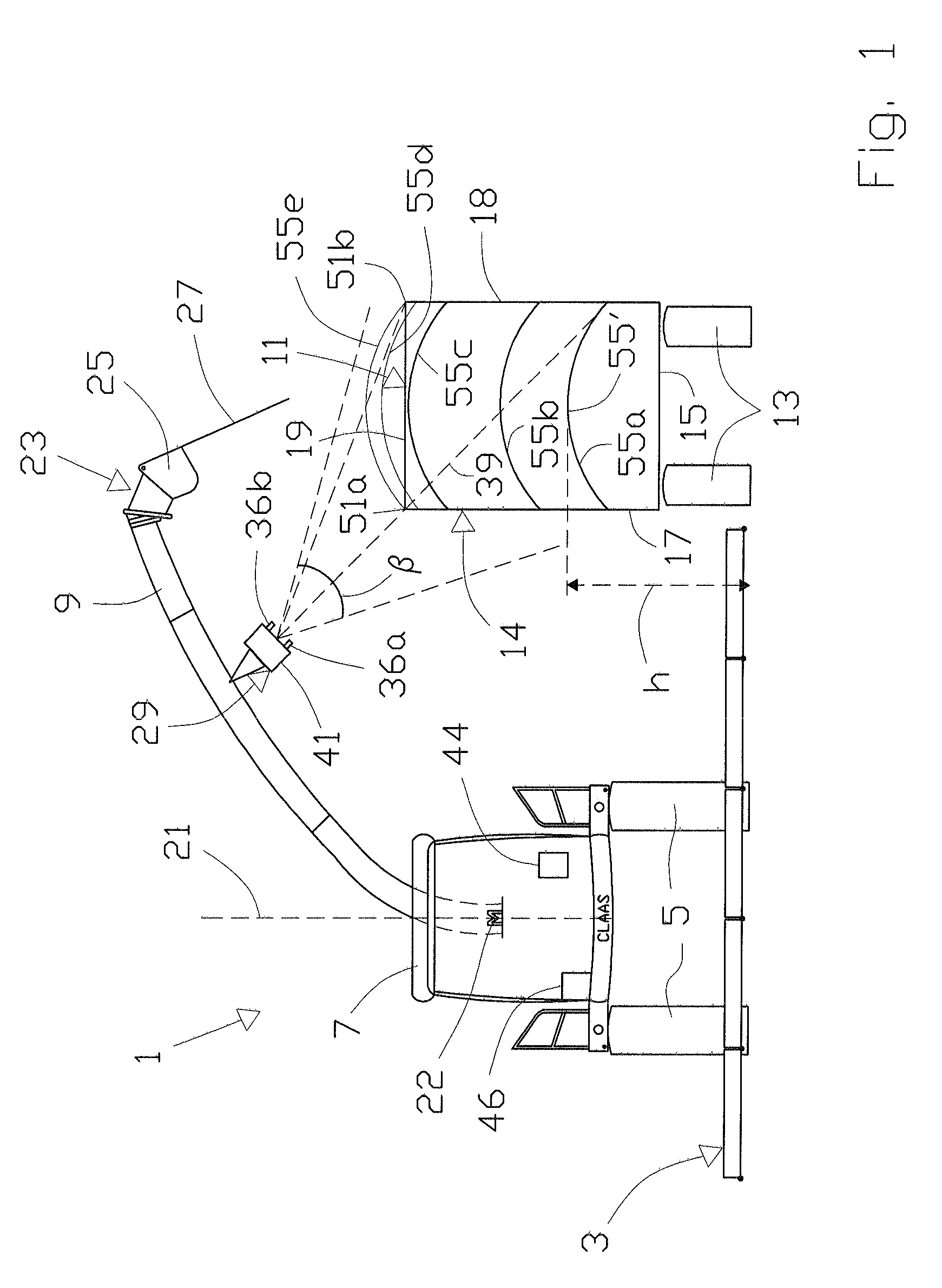

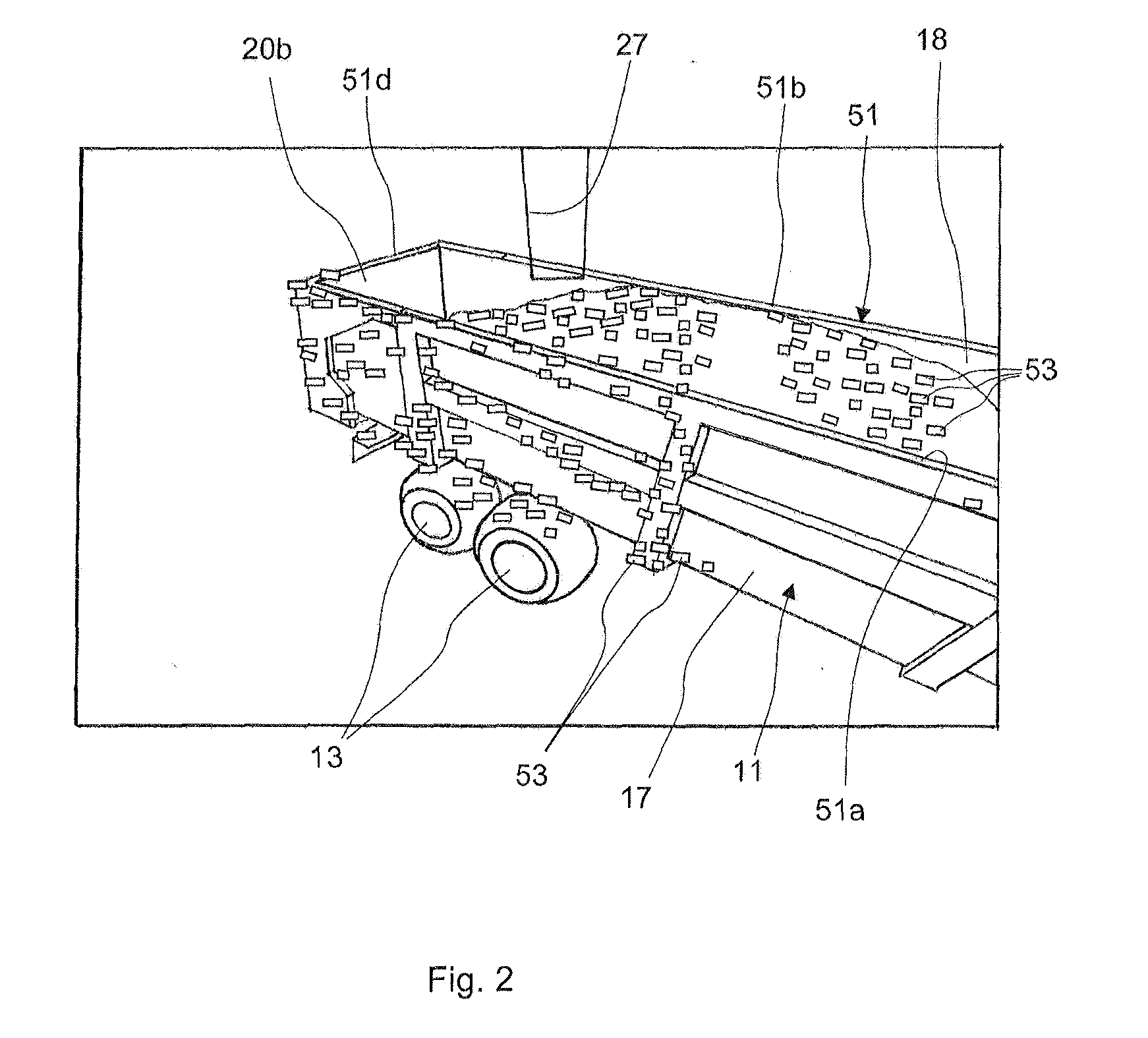

Filling degree gauge, agricultural vehicle with the gauge, and method of measuring and displaying residual filling potential of target area

ActiveUS20110061762A1Relieve pressureRaise the possibilityLiquid fillingConveyors3d sensorData control

A filling degree gauge for measuring and displaying a residual filling potential of a target area, such as a container, being filled through a target, such as an open top, with goods by a goods carrier, such as a discharge spout, of an agricultural vehicle, such as a harvester, has a 3D sensor for observing at least a part of the target area including at least a part of the target, a data control system and a visual display unit. The data control system operates to provide on the visual display unit a visual display indicating residual filling potential by indicating the current one of at least three different levels of residual filling potential.

Owner:CLAAS E SYST GMBH

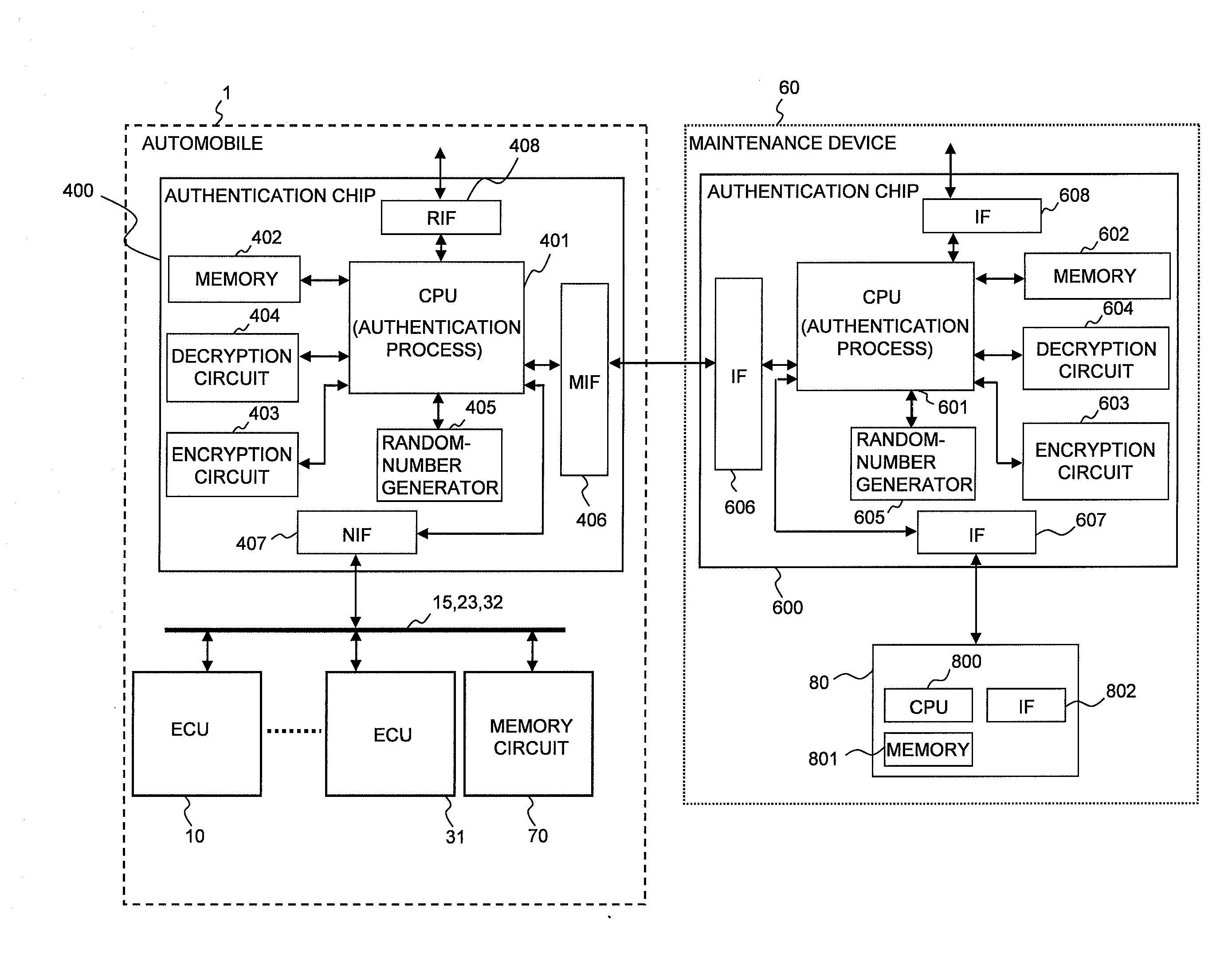

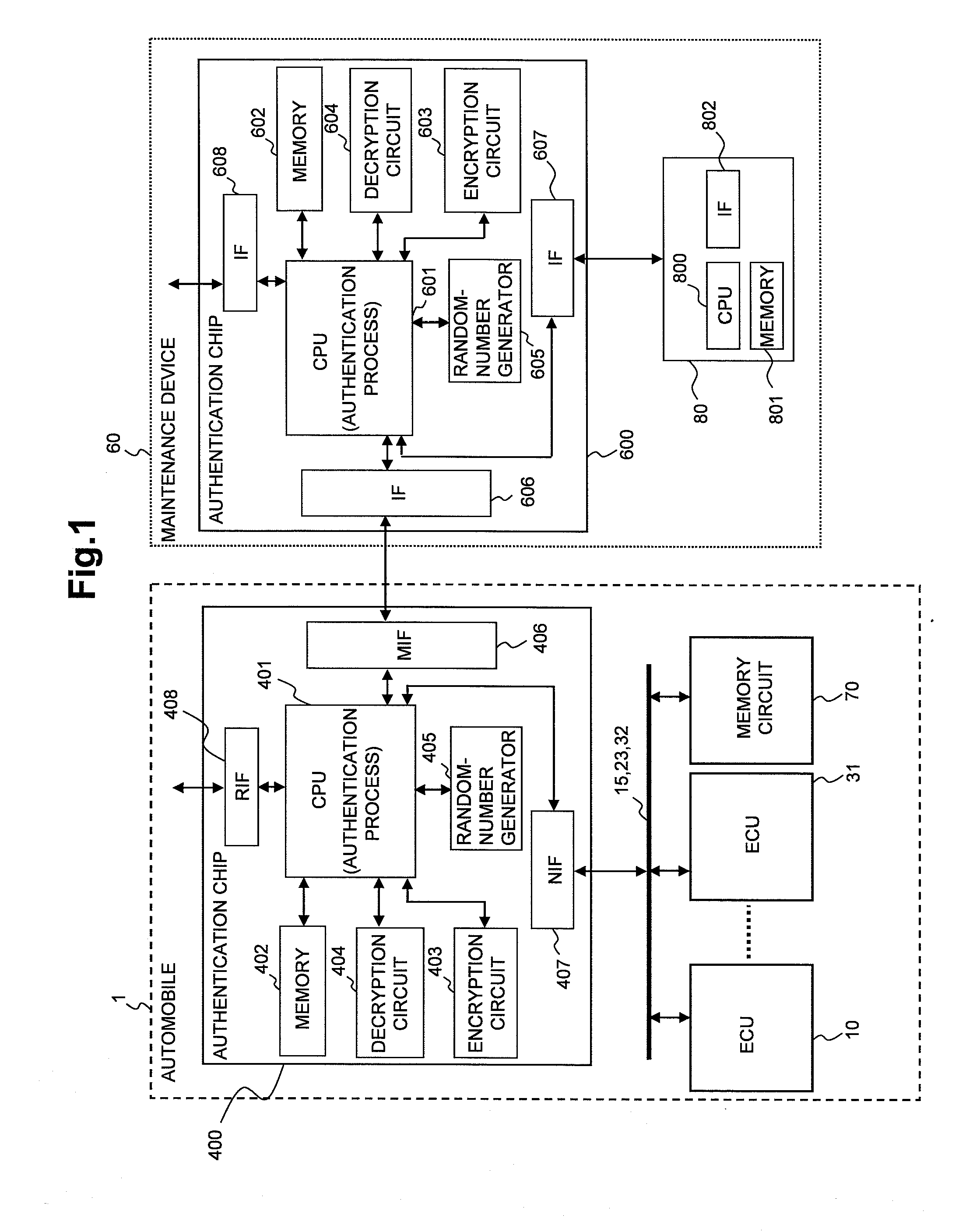

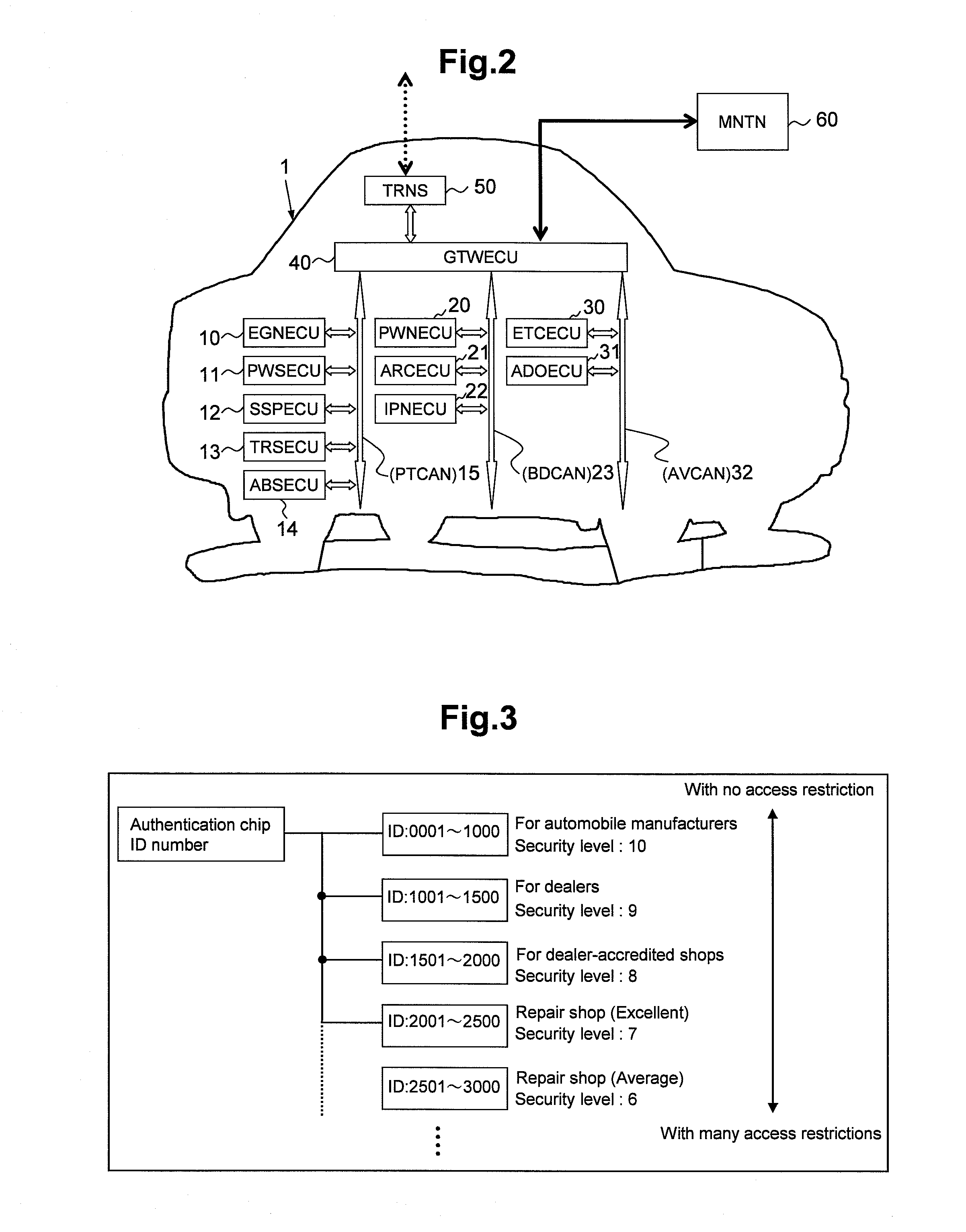

Vehicle, maintenance device, maintenance service system, and maintenance service method

InactiveUS20110083161A1Easily realizedDigital data processing detailsInternal/peripheral component protectionMicrocomputerEngineering

The vehicle includes electronic control units, and performs an authentication process to judge the validity of an external device outside the vehicle, e.g. a maintenance device, which tries accessing the electronic control unit. Based on the result of the judgment, the vehicle decides a range in which the maintenance device can access the electronic control unit. In the authentication, e.g. both the maintenance device and the vehicle use authentication microcomputers respectively. According to the invention, an external device outside the vehicle can be inhibited from making an unwanted access to the electronic control unit of the vehicle.

Owner:RENESAS ELECTRONICS CORP

Content playback system, playback device, playback control method and program

ActiveUS8316154B2The implementation process is simpleEasily realizedTelevision system detailsCarrier indexing/addressing/timing/synchronisingComputer hardwareStart time

A first playback device, upon receiving a synchronized playback command while content playback is in progress, transmits, to a second playback device, information that pertains to the playback content and a synchronized playback start time obtained by adding a predetermined additional time to an elapsed playback time for the content. The second playback device starts receiving content data that begins from the synchronized playback start time from a server. After the data that is memorized in a memory reaches a specified volume, the second playback device transmits a playback preparation completion notification to the first playback device. Once the elapsed playback time for the content reaches the synchronized playback start time, the first playback device transmits a playback start command to the second playback device. Upon receiving this command, the second playback device starts playing back content data that begins from the synchronized playback start time.

Owner:SONY CORP

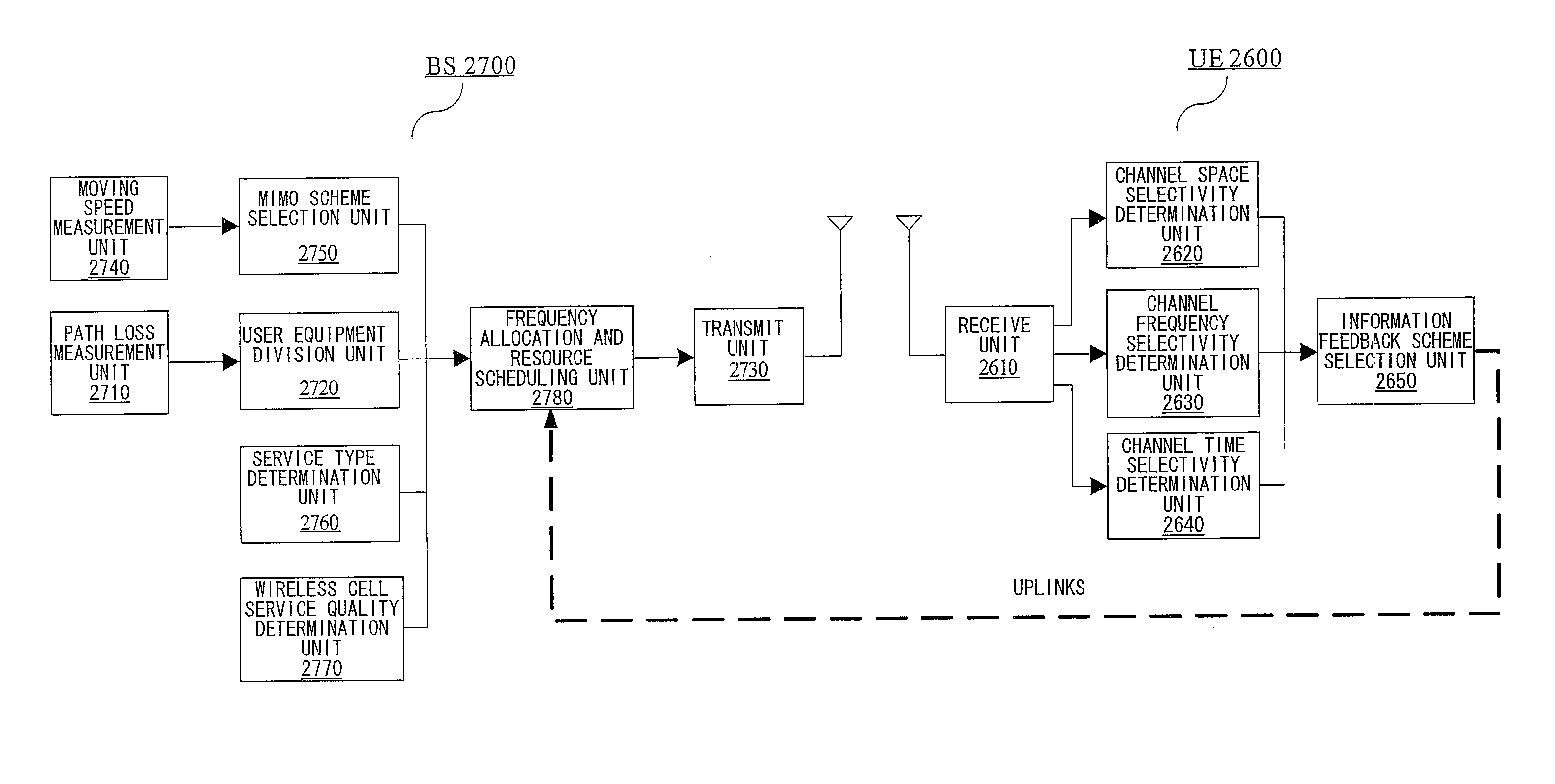

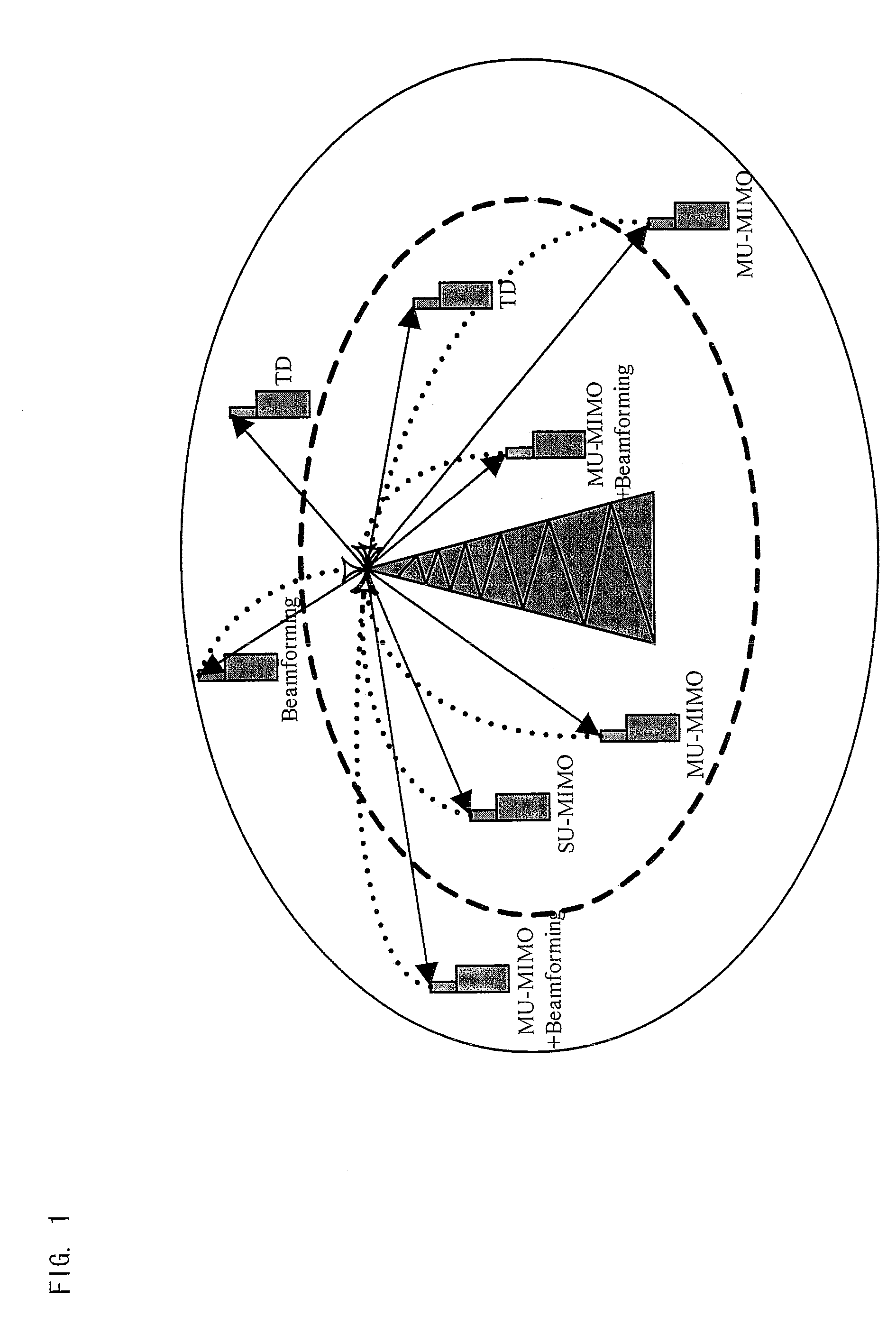

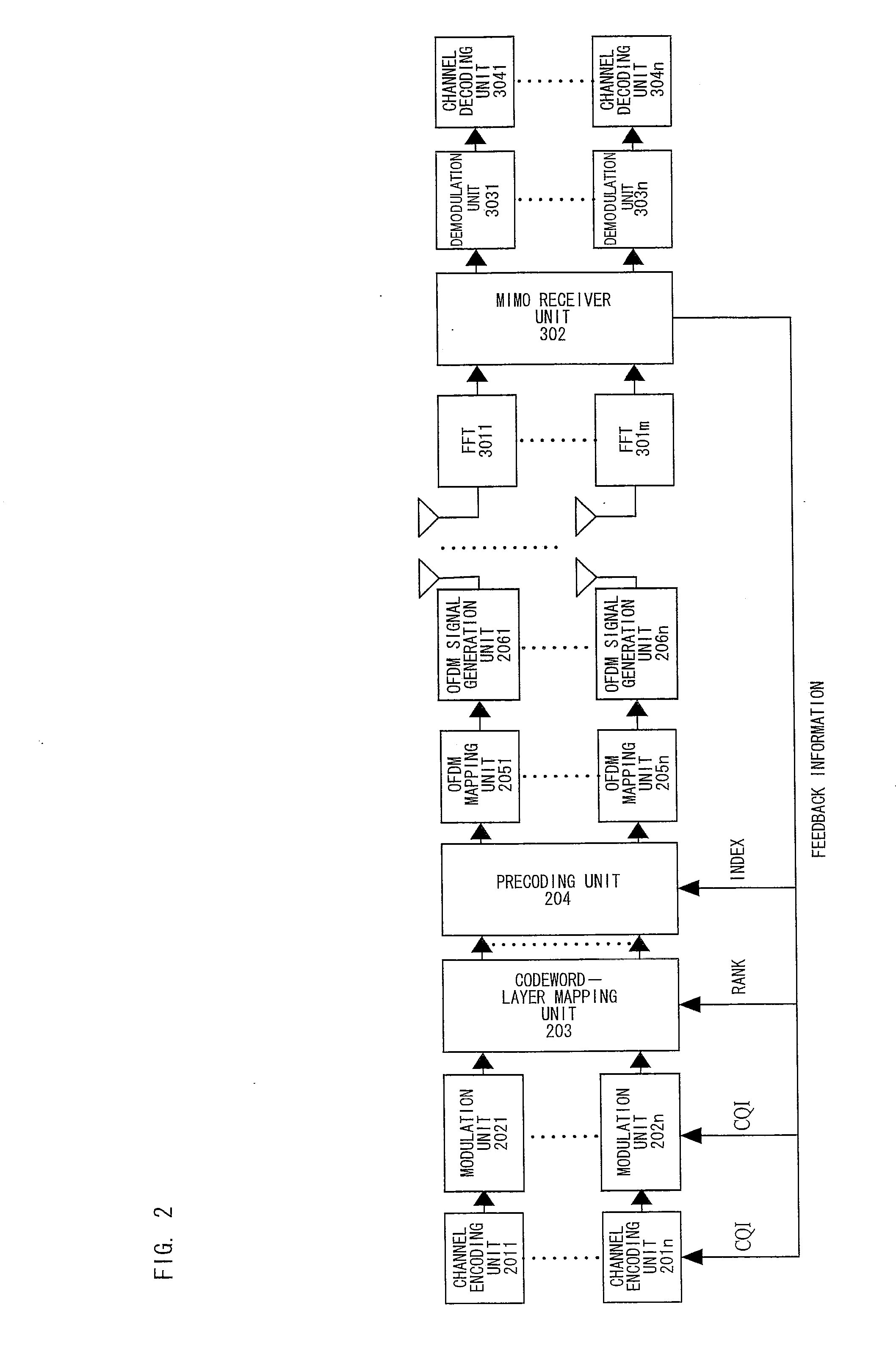

Space-time-frequency domain based information feedback method, user equipment and base station thereof

InactiveUS20100284351A1Reduce overheadImprove efficiencySecret communicationRadio transmissionSpace time frequencyFrequency domain

A space-time-frequency domain based information feedback method, system, user equipment and base station for wireless transmission technical fields is provided. The user equipment measures and evaluates quality of wireless transmission downlinks in MIMO system, obtains rank, precoding matrix index and channel quality indicator information in the wireless transmission downlinks, processes information of the wireless transmission downlink respectively in space domain, frequency domain and time domain by using space selectivity, frequency selectivity and time selectivity characteristics of a channel, and feeds back downlink information to the base station through uplinks by using feedback schemes. The base station optimizes a transmitter according to feedback information from the user equipment.

Owner:SHARP KK

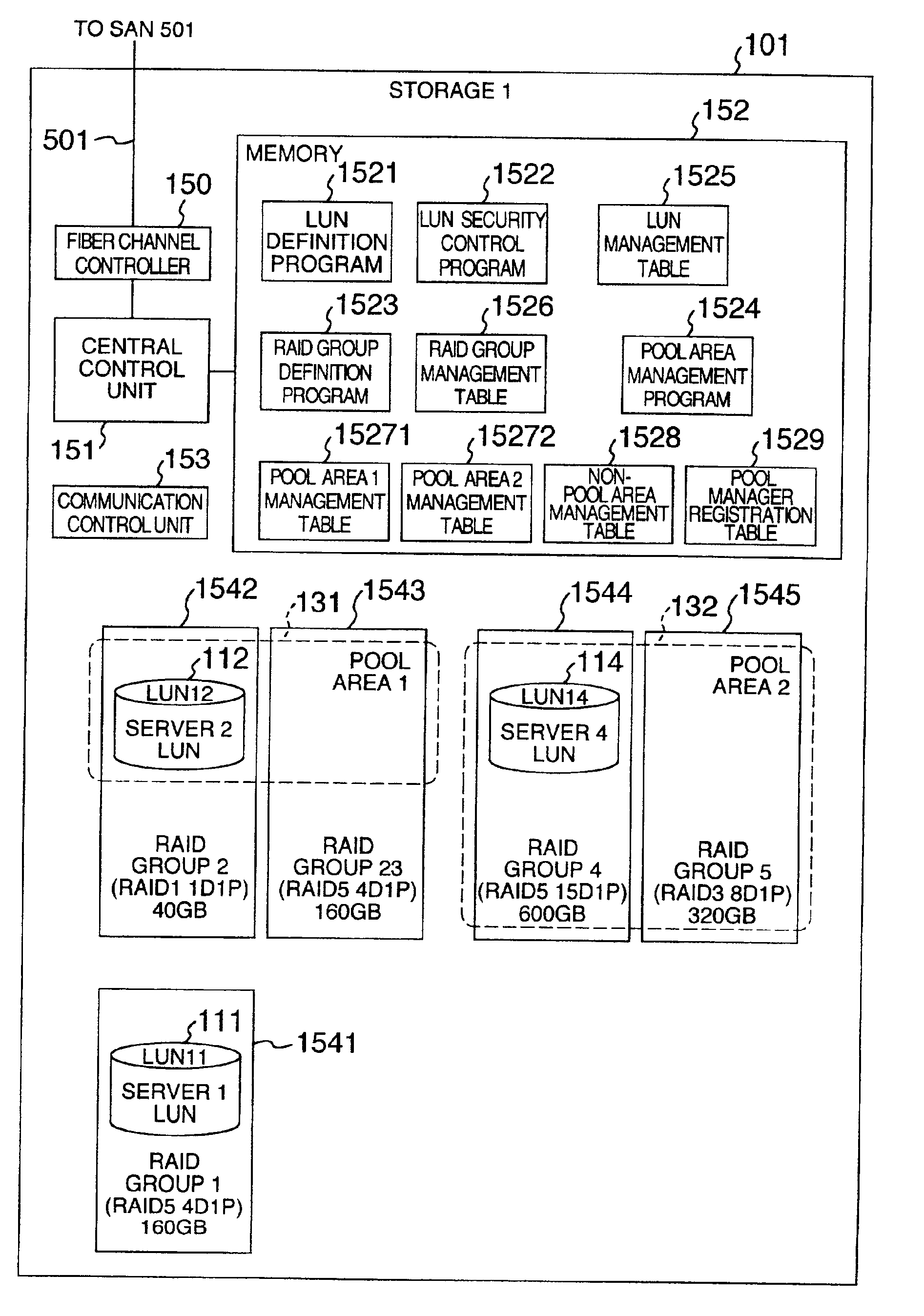

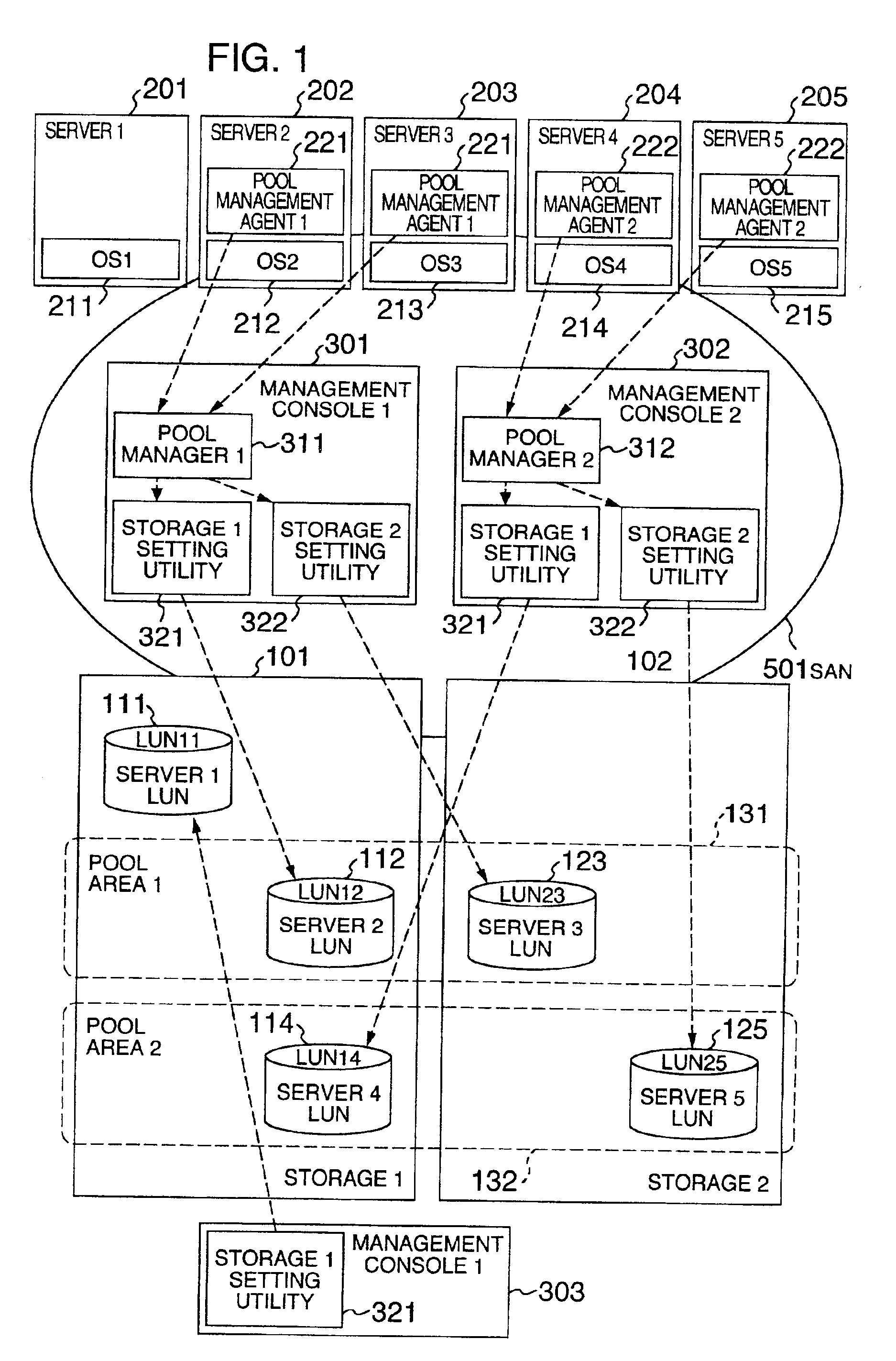

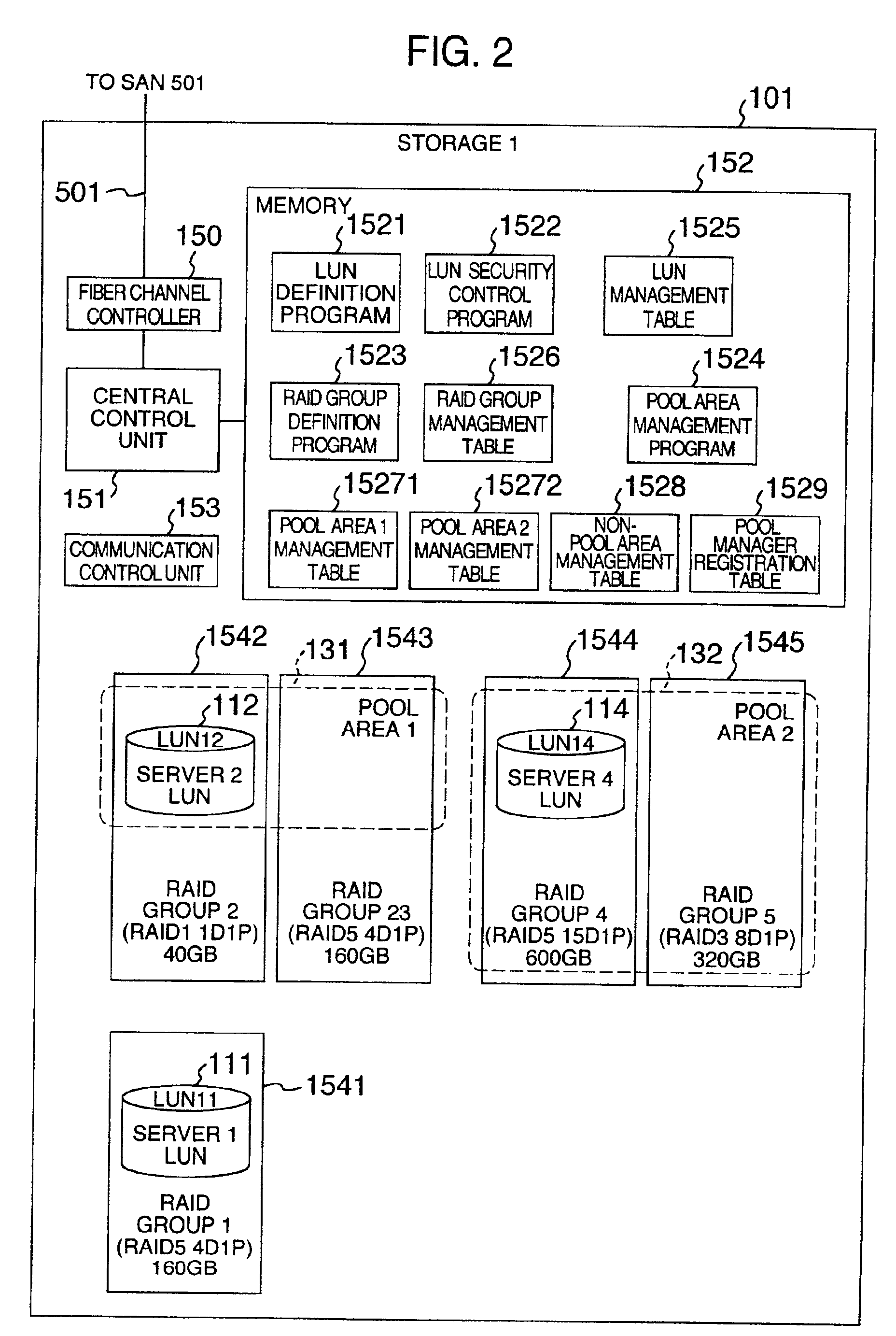

Method of creating a storage area & storage device

InactiveUS6912627B2Increase capacityEasily realizedInput/output to record carriersSafety arrangmentsOperating systemManagerial control

An administrator is required to prepare in advance LU as a pool area when a user storage area is set to a storage. LU configuration is generally cumbersome and it is not easy for a general user to configure it. A pool manager 1 and a storage 1 setting utility in a management console 1 communicate with a program in a storage 1. The storage 1 sets a pool area having a designated capacity. In response to a volume forming request from the management console 1, the storage 1 sets a designated volume by setting the designated volume as a used capacity of the set pool area. When a volume is formed, a policy is designated to select a storage area having a corresponding attribute from the pool area.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD

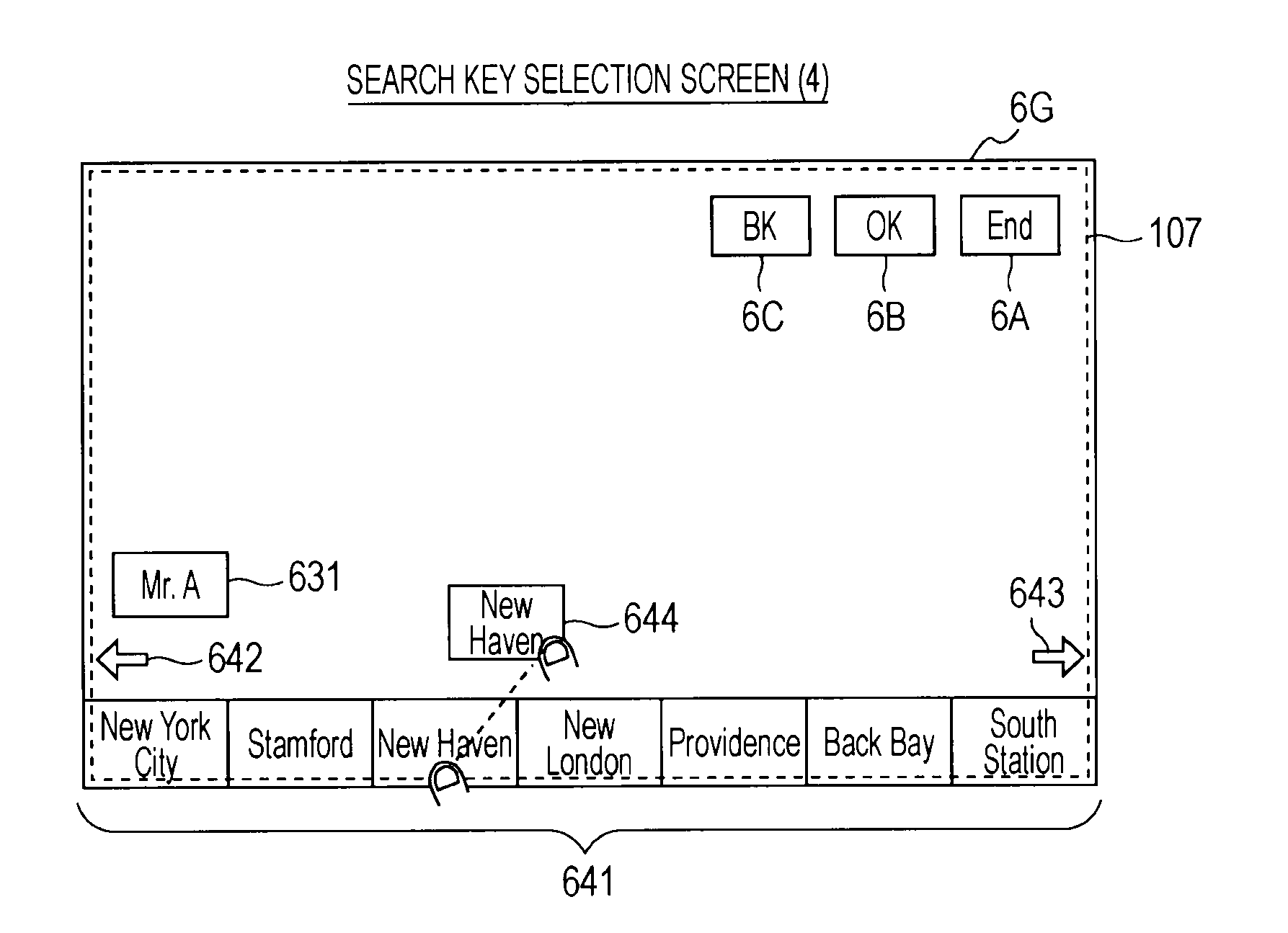

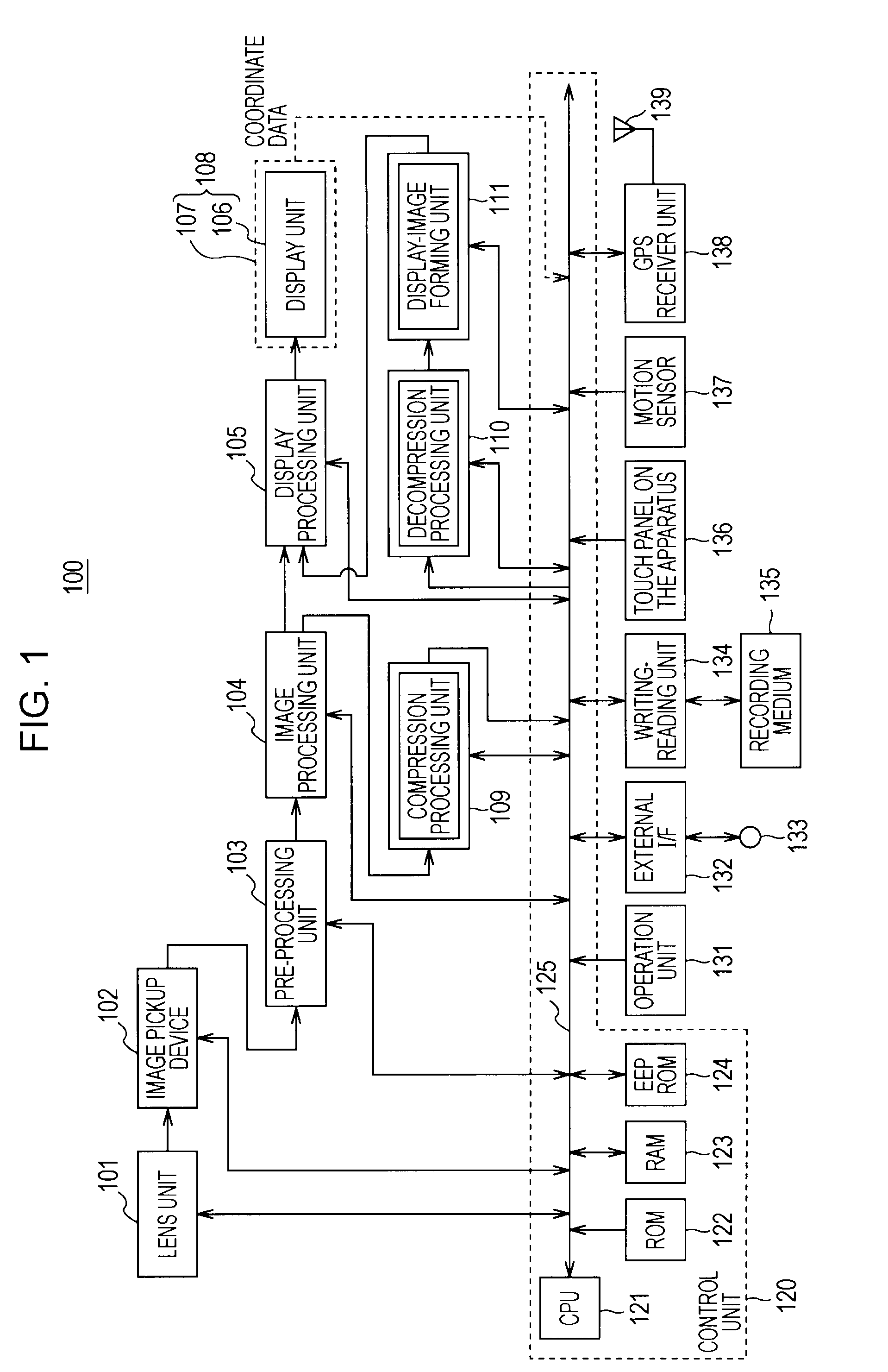

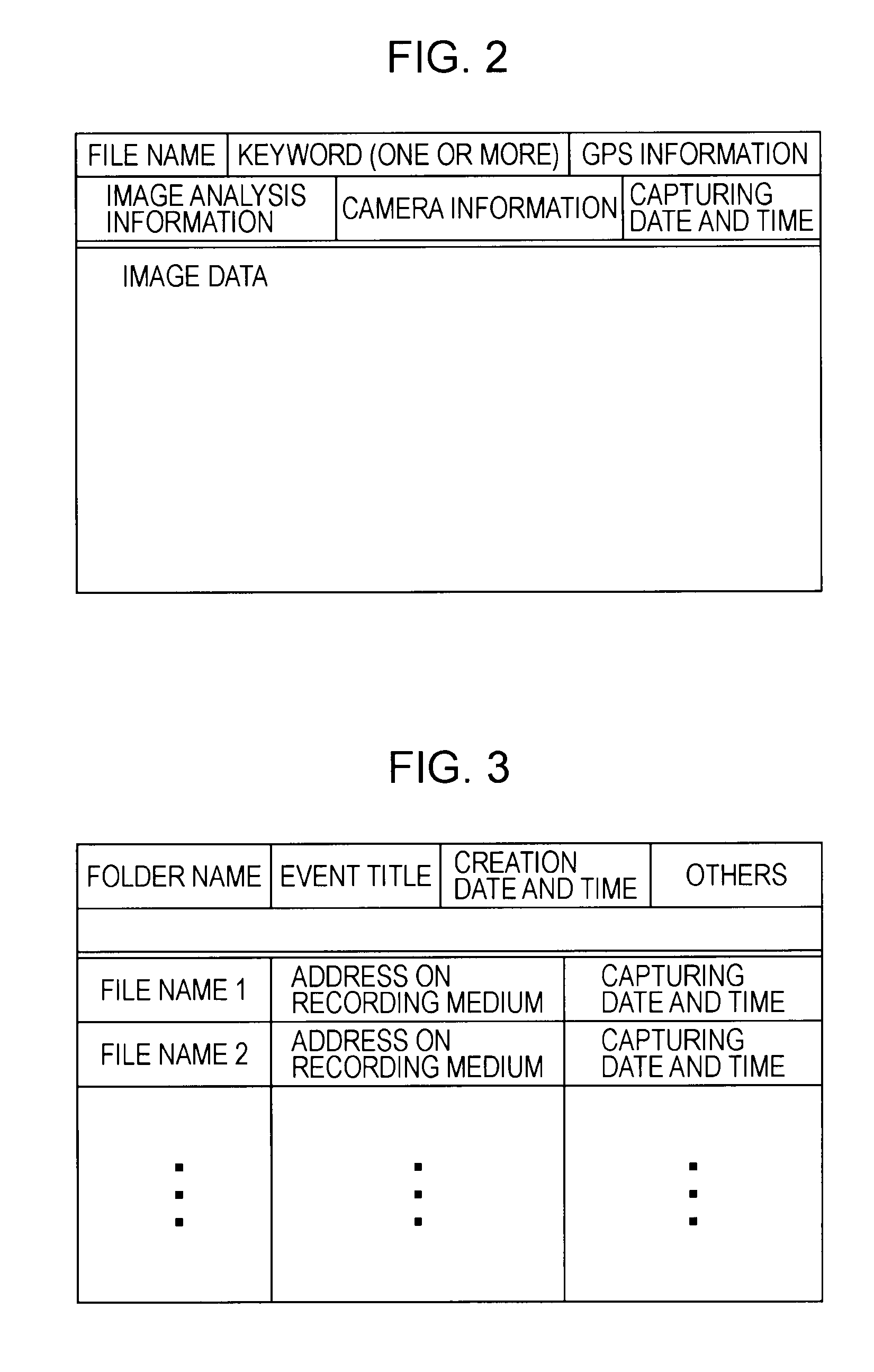

Image processing apparatus, image displaying method, and image displaying program

InactiveUS20100134415A1Flexible image searchEasily realizedTelevision system detailsDigital data processing detailsData displayImaging processing

An image processing apparatus includes an instructed-position detecting unit configured to receive an instruction operation by a user on a display screen of a display device and detect and output a position where the instruction operation is performed; a storing unit configured to store multiple image data items each including information corresponding to a search key; a search-key display controlling unit configured to cause at least one search key to be selectively displayed on the display screen of the display device; a searching unit configured to, if the search key displayed on the display screen is instructed by the search-key display controlling unit through the instructed-position detecting unit, search the storing unit for the image data corresponding to the search key to extract the image data; and a display controlling unit configured to collectively display images corresponding to the image data in a certain part on the display screen.

Owner:SONY CORP

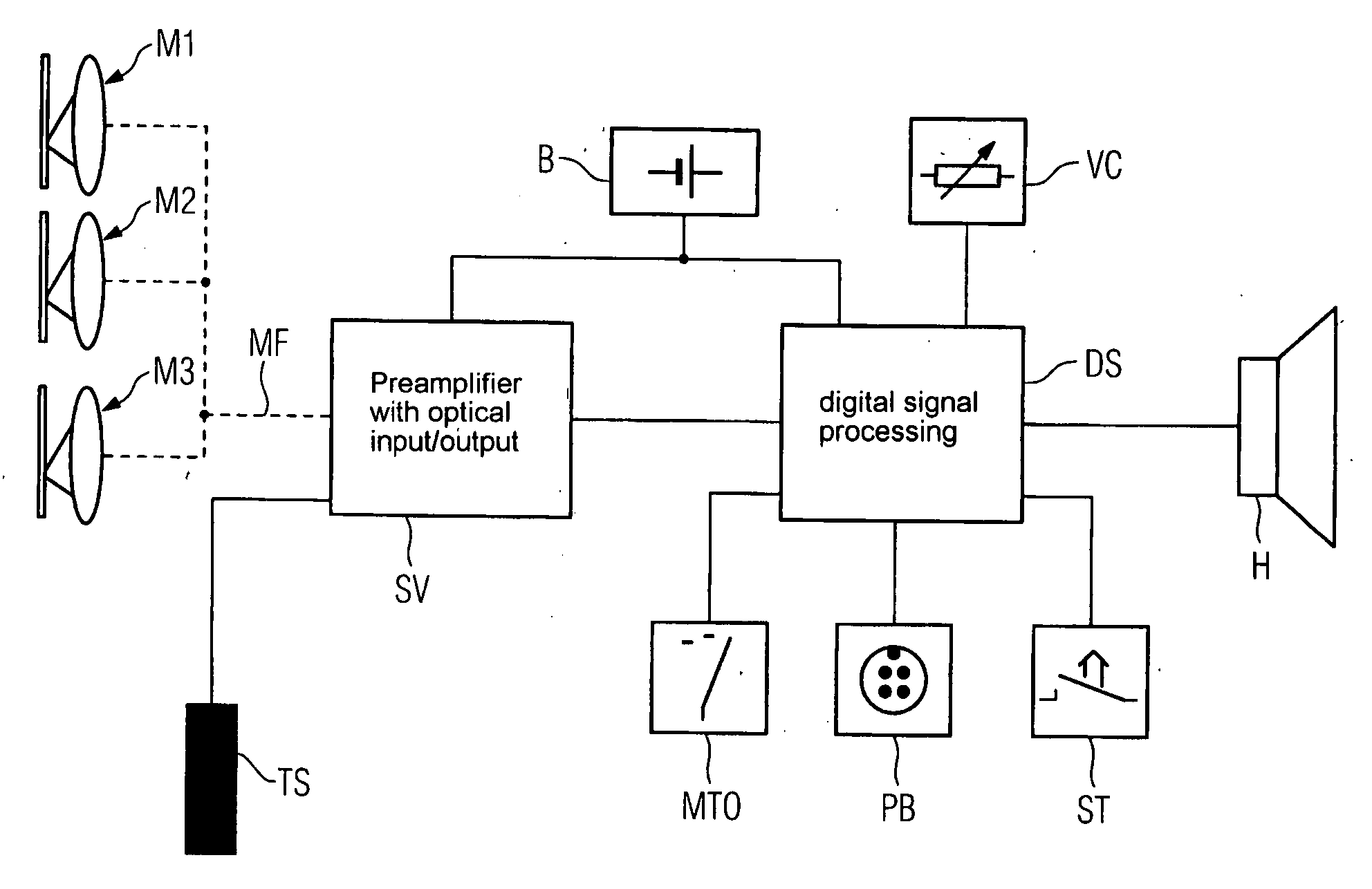

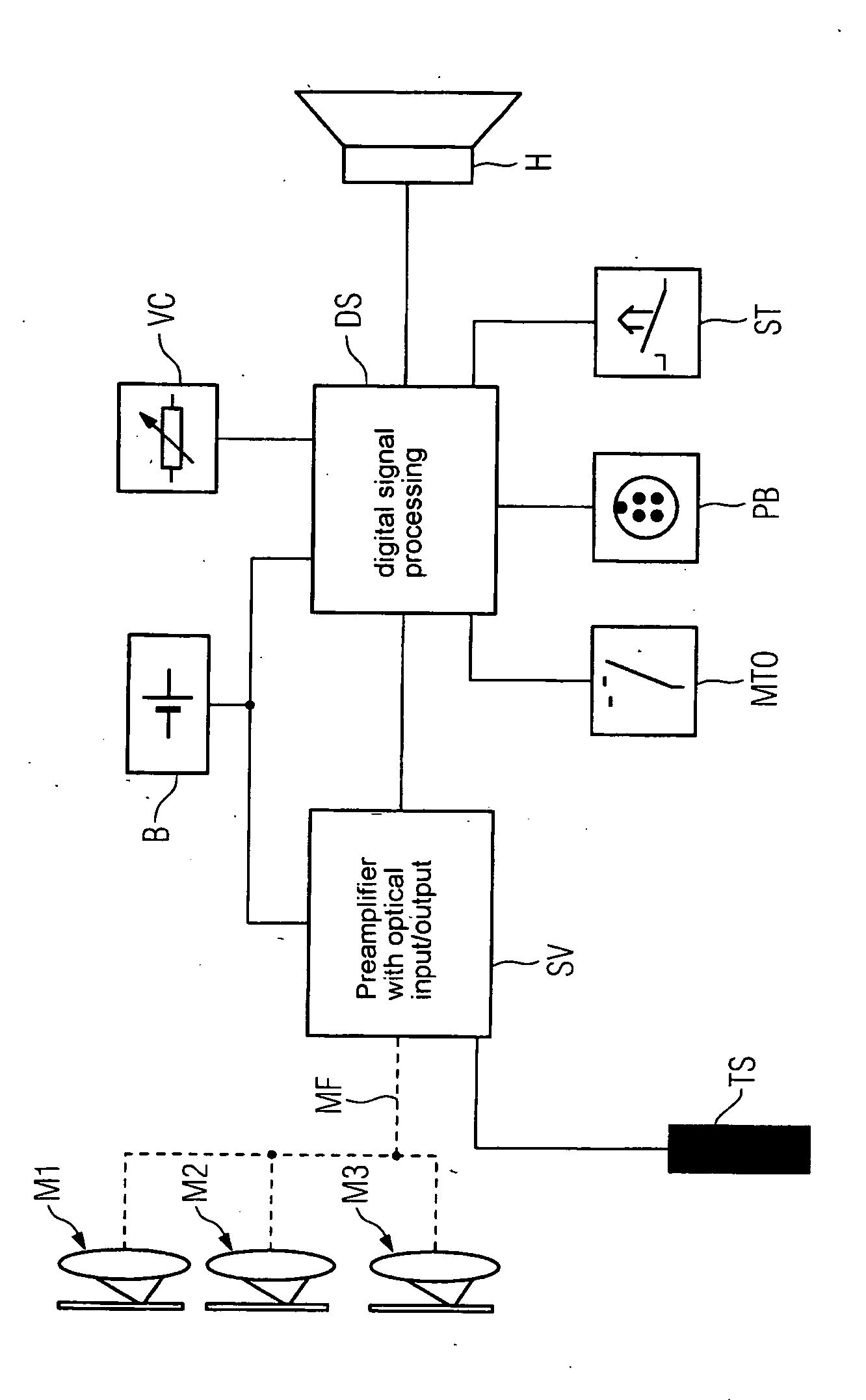

Hearing aid

InactiveUS20060233398A1Easy assessment processSimple designPiezoelectric/electrostrictive microphonesCompletely in canal hearing aidsElectromagnetic interferenceEMC problem

The robustness of hearing aid devices in terms of electromagnetic disturbances and chemically aggressive surroundings should be improved. For this purpose, provision is made to equip a hearing aid apparatus with optical microphones. Since no metal parts must be used for these optical micro-phones, corrosion can be largely excluded. Furthermore, no EMC problems occur as a result of the optical signal processing.

Owner:SIVANTOS PTE LTD

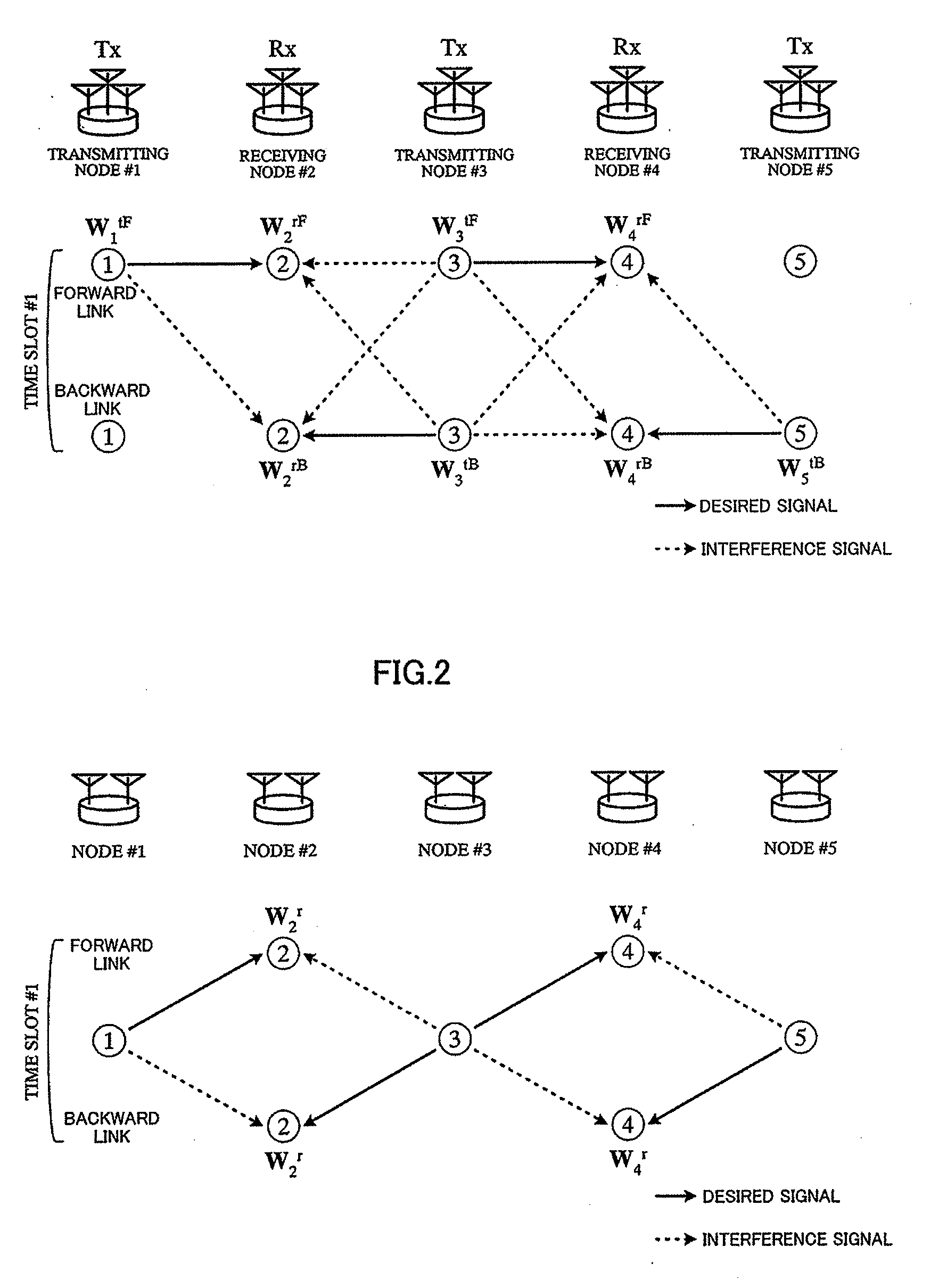

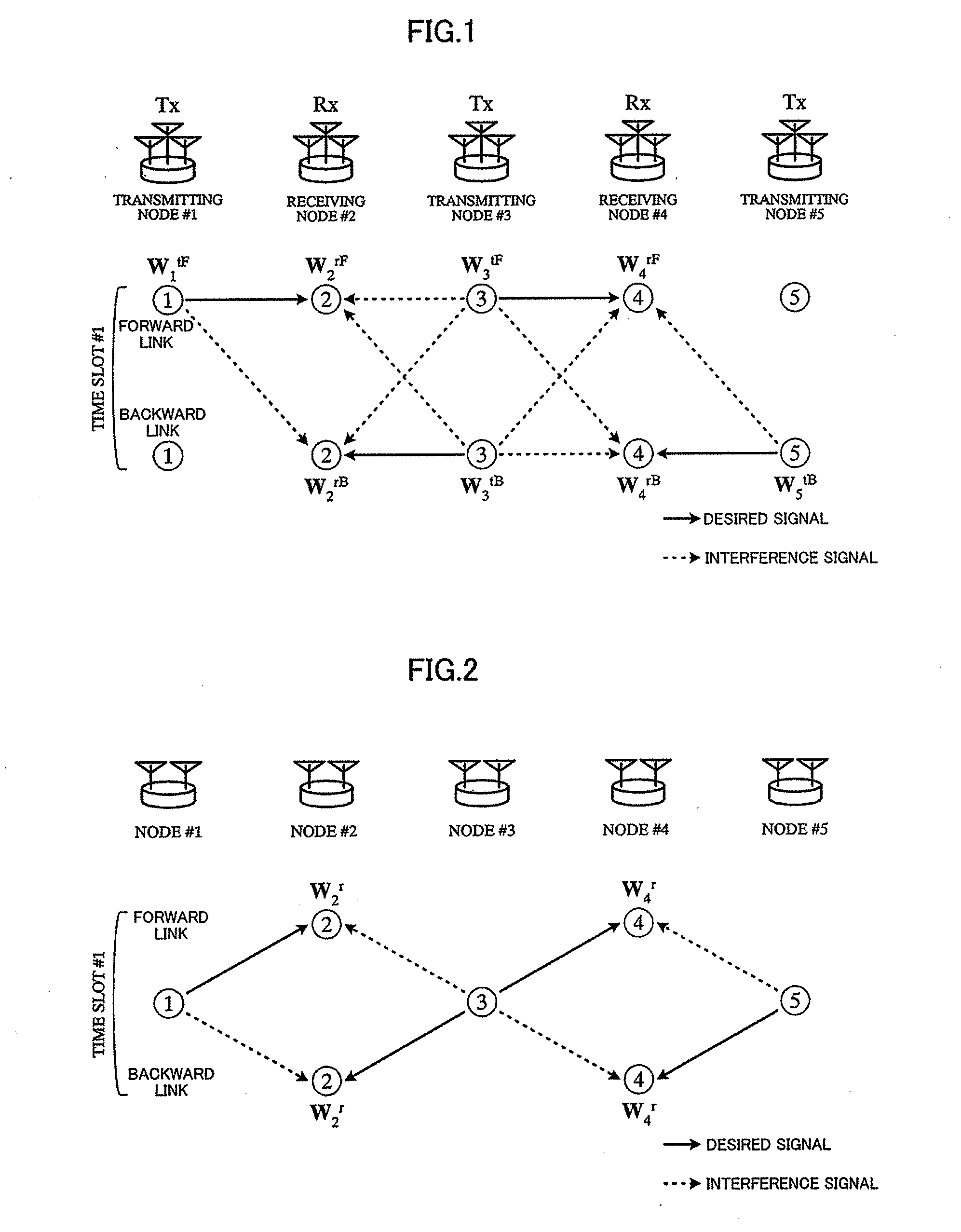

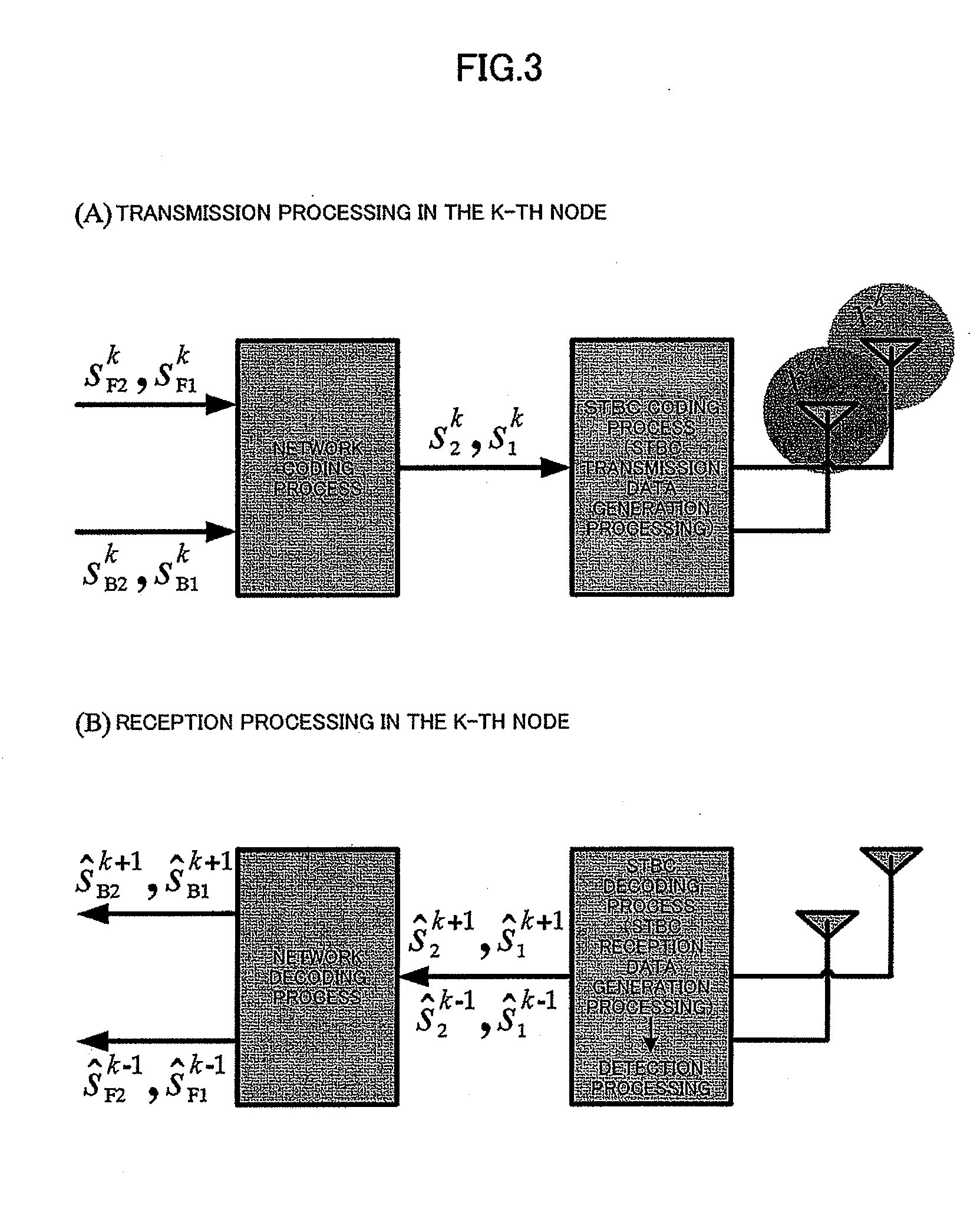

Multi-hop wireless communication system

InactiveUS20110149835A1Easily realizedSite diversityFrequency-division multiplex detailsNetwork codeTelecommunications

The present invention provides multi-hop wireless communication systems that easily realize a highly-efficient and highly reliable bi-directional wireless relay transmission by using MIMO network coding.A multi-hop wireless communication system with multiple node devices having a relay function in which each node device is equipped with multiple MIMO antennas and a wireless communication system is constructed by setting up wireless links between the node devices, the multi-hop wireless communication system characterized in that a multiple input multiple output (MIMO) scheme is applied to a transmission / reception scheme of network coding and a space time block coding (STBC) scheme is further applied, concretely, by combining STBC broadcast and MIMO multiple access into network coding, a bi-directional wireless relay transmission that multiplexs a forward link and a backward link in all wireless links is easily realized, each node device performs transmission / reception processing and the relay transmission of data.

Owner:NAT UNIV CORP YOKOHAMA NAT UNIV +1

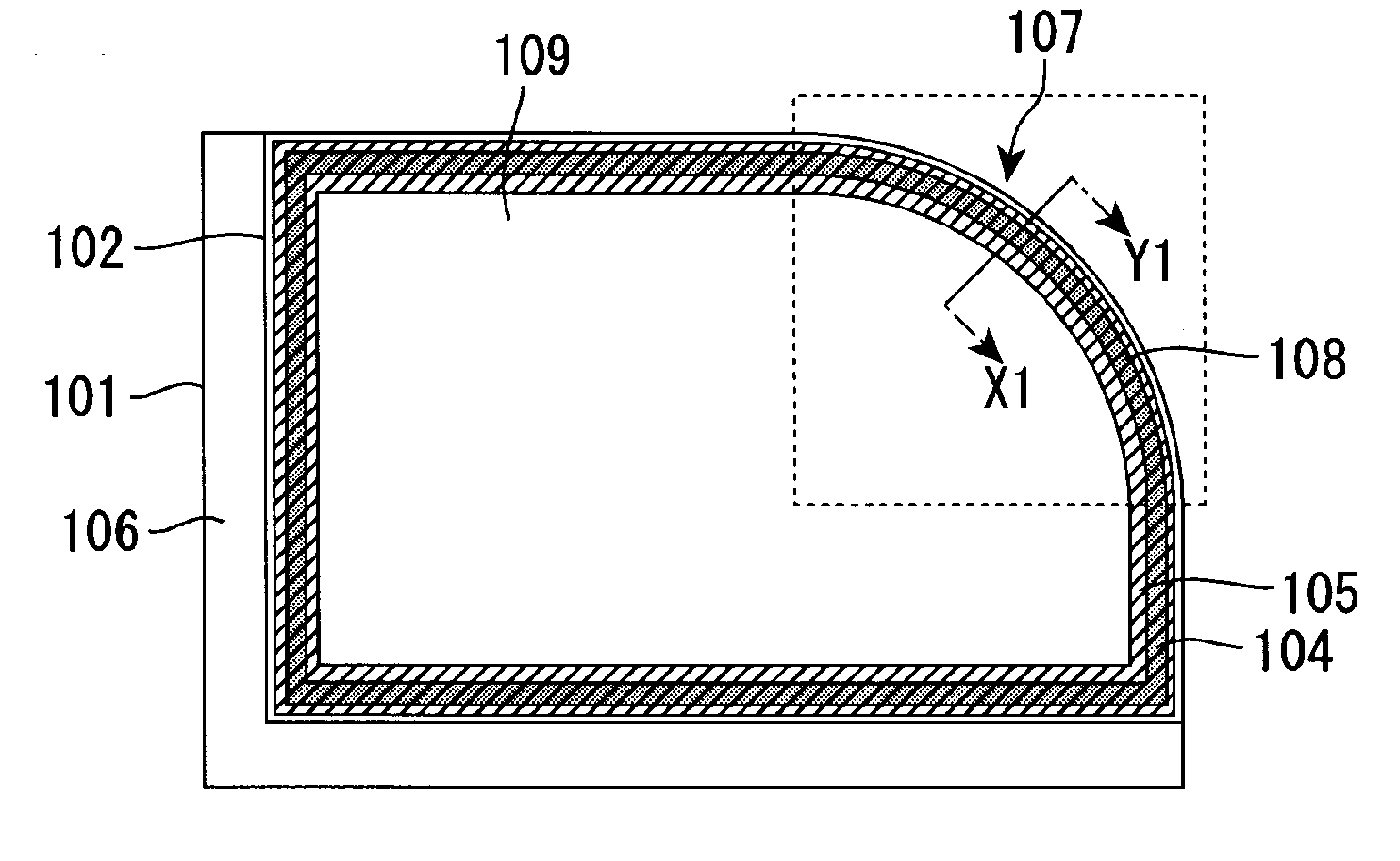

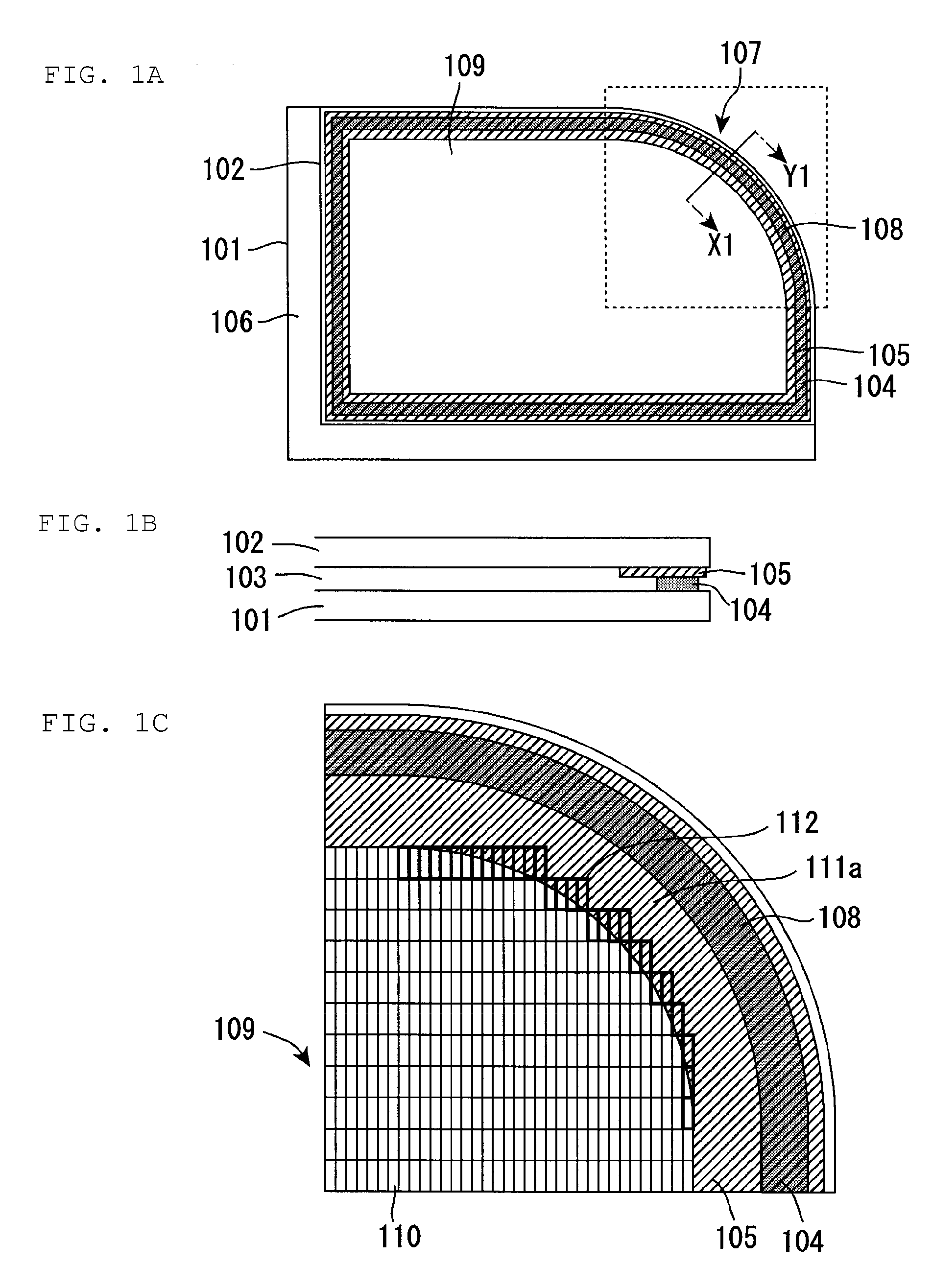

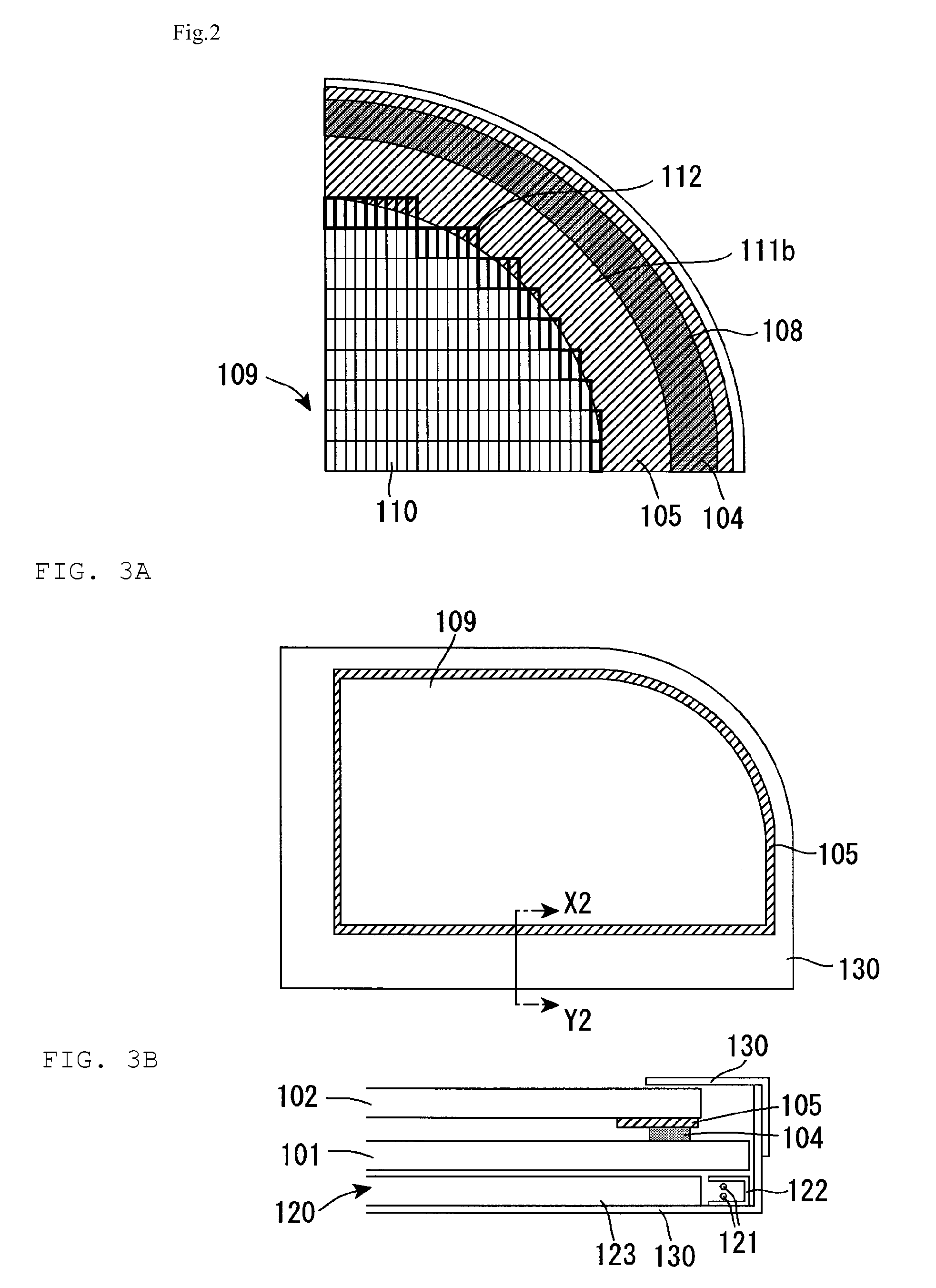

Display panel and display device

ActiveUS20090115933A1Suppress light leakageEasily realizedNon-linear opticsDisplay deviceEngineering

Each of a display panel and a display device includes a display region in which an image with uniform display quality is displayed and a curved line can be displayed in the contour. The display panel includes a shielding member and a plurality of pixels arrayed in a display region, wherein the shielding member includes a shielding curved portion having a curved planar shape, and the shielding curved portion shields the plurality of pixels to form a curved contour of the display region.

Owner:UNIFIED INNOVATIVE TECH

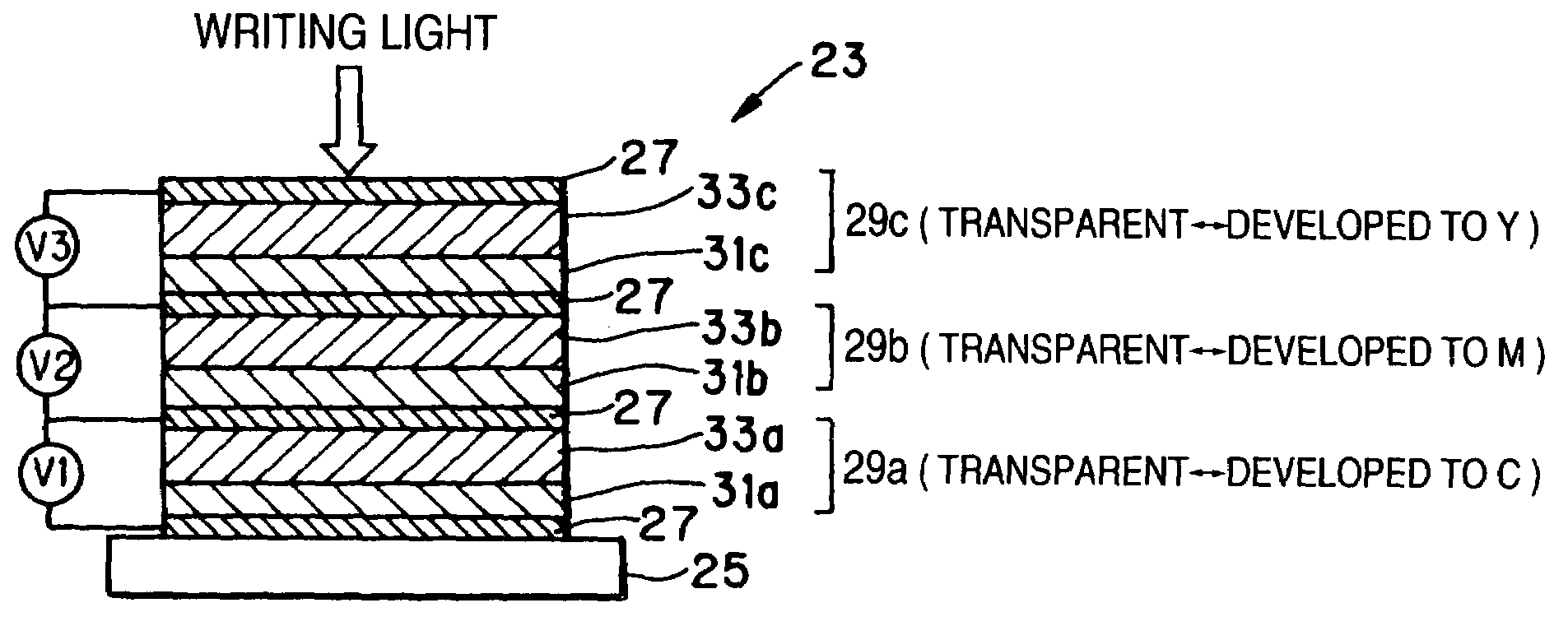

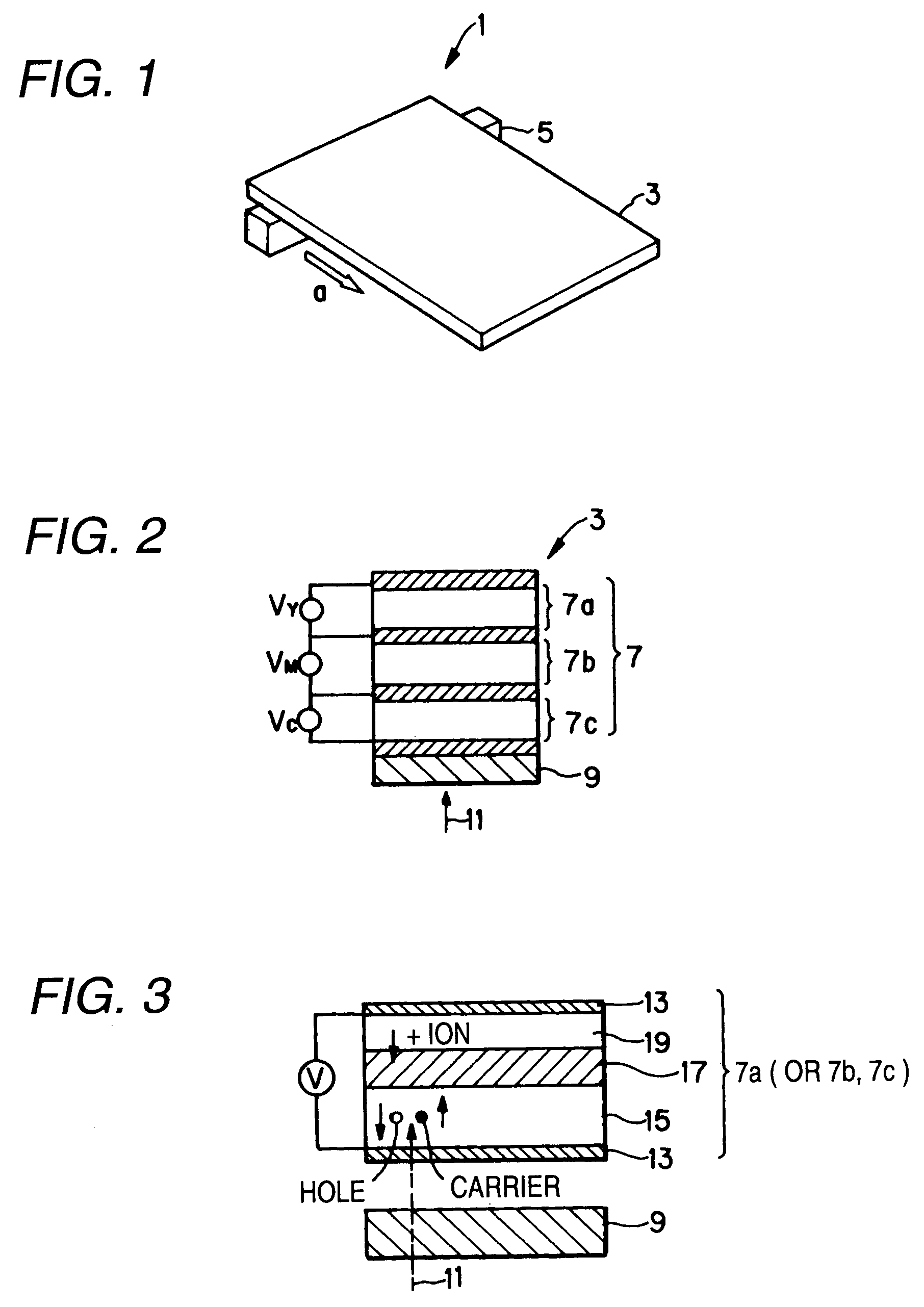

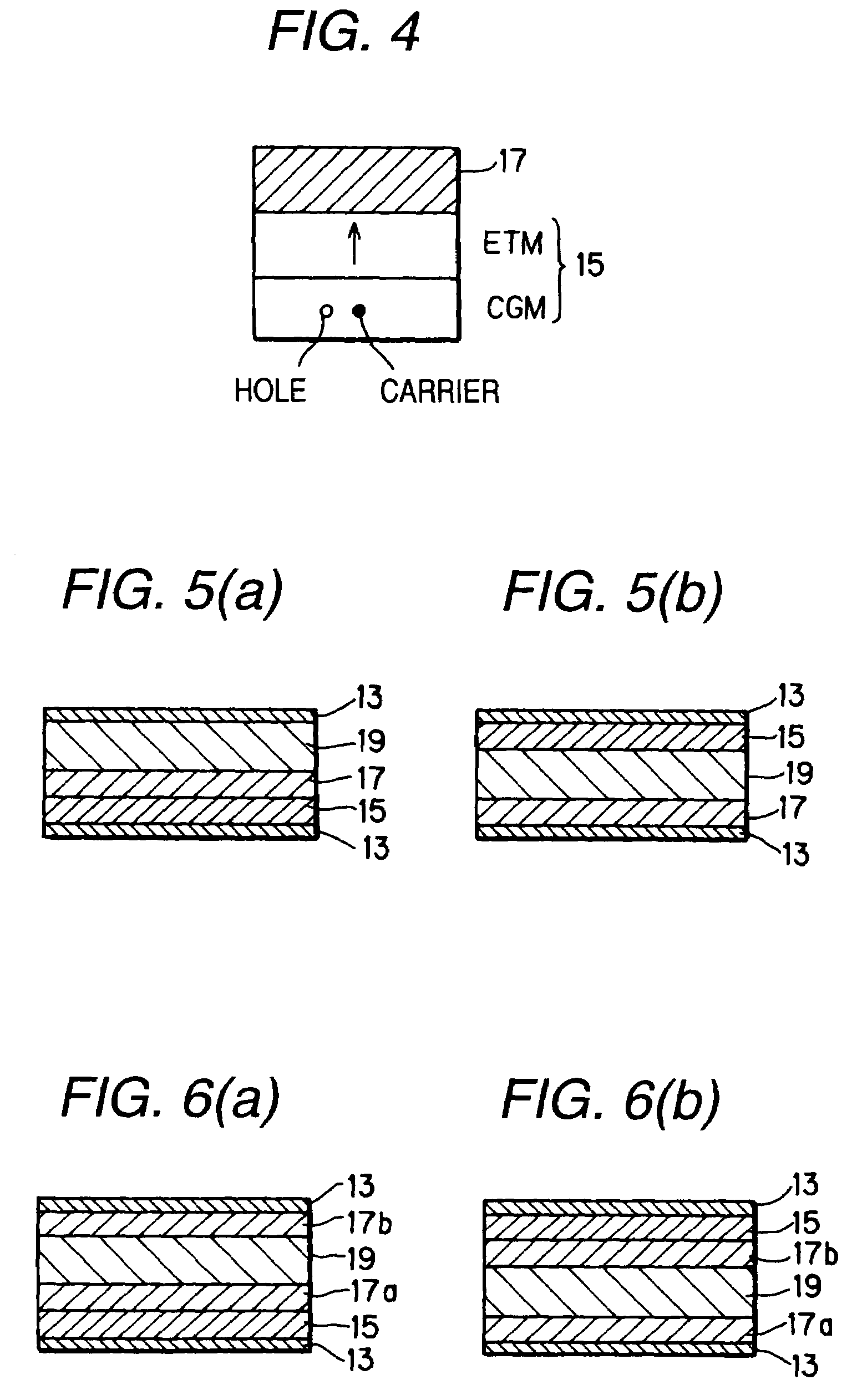

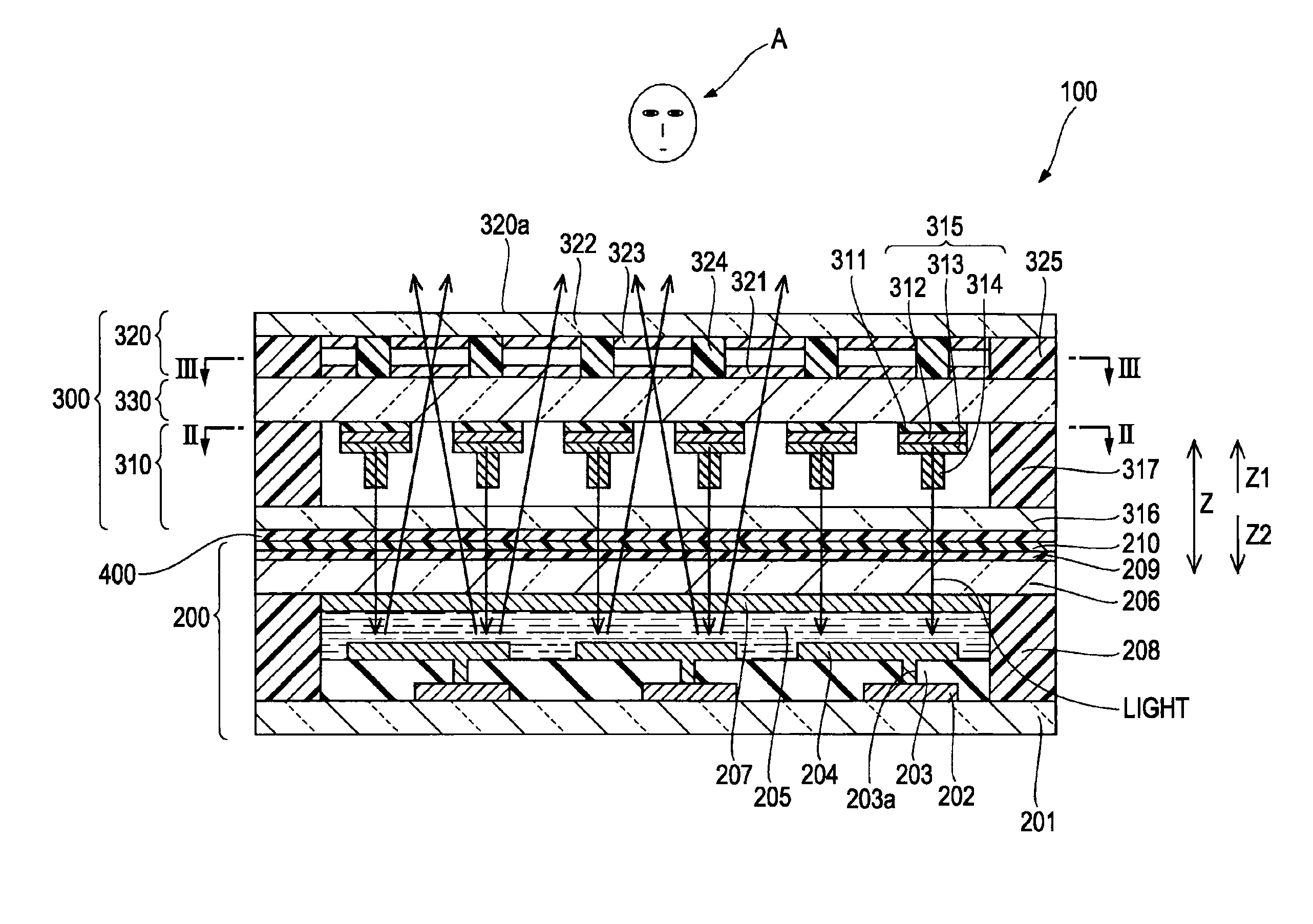

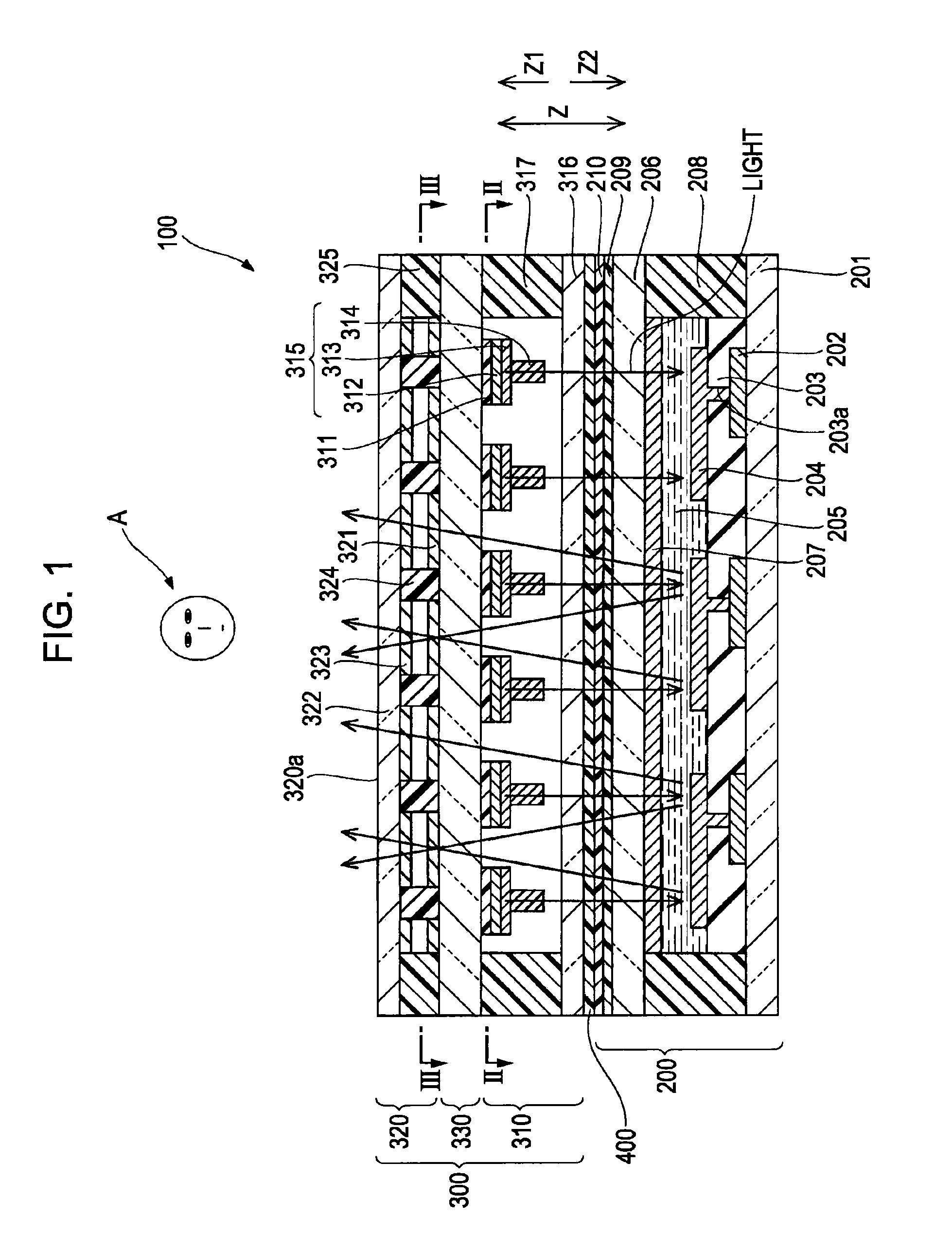

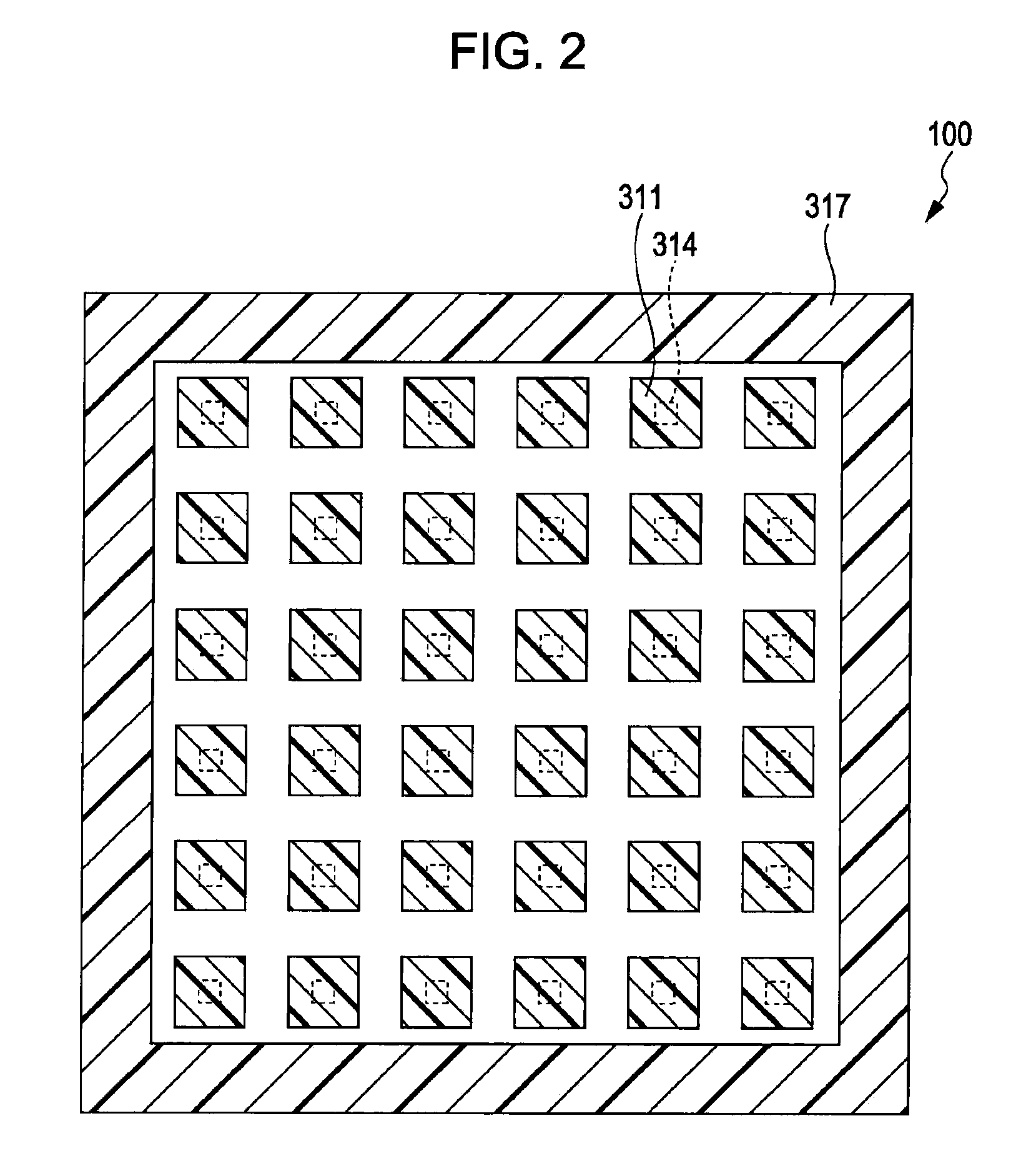

Photowriting display device and photowriting display unit incorporating the same

InactiveUS7116309B1Inhibited DiffusionClear boundariesStatic indicating devicesNon-linear opticsElectrical conductorCharge carrier

A photowriting display device which is capable of performing bright full color display and a photowriting display apparatus which incorporates the photowriting display device and on which the pen moving operation is directly reflected as information to be displayed. A photowriting display device is disclosed which incorporates: an electrochromic display member incorporating a photoconductor in which only regions irradiated with writing light generate carriers to realize conductivity; an electrochromic layer in which light absorption of the regions are reversibly changed owing to electrochemical oxidation and reduction reactions caused to occur due to the conductivity; an electrolyte in which the electrochromic layers are laminated or an electrochromic material is dissolved; and a pair of electrodes laminated through the photoconductor, the electrochromic layer and the electrolyte. A plurality of the electrochromic display members are laminated.

Owner:FUJIFILM CORP +1

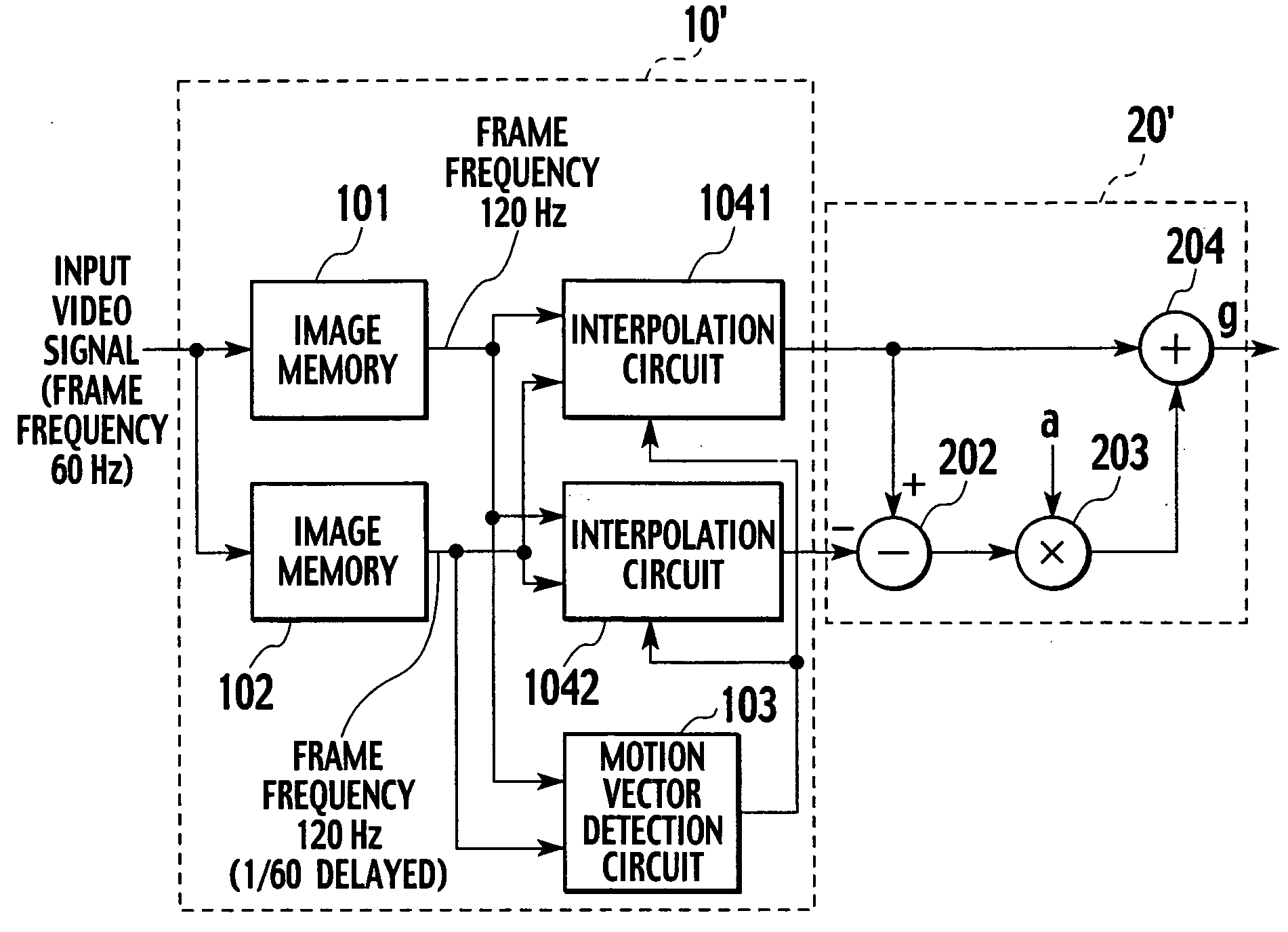

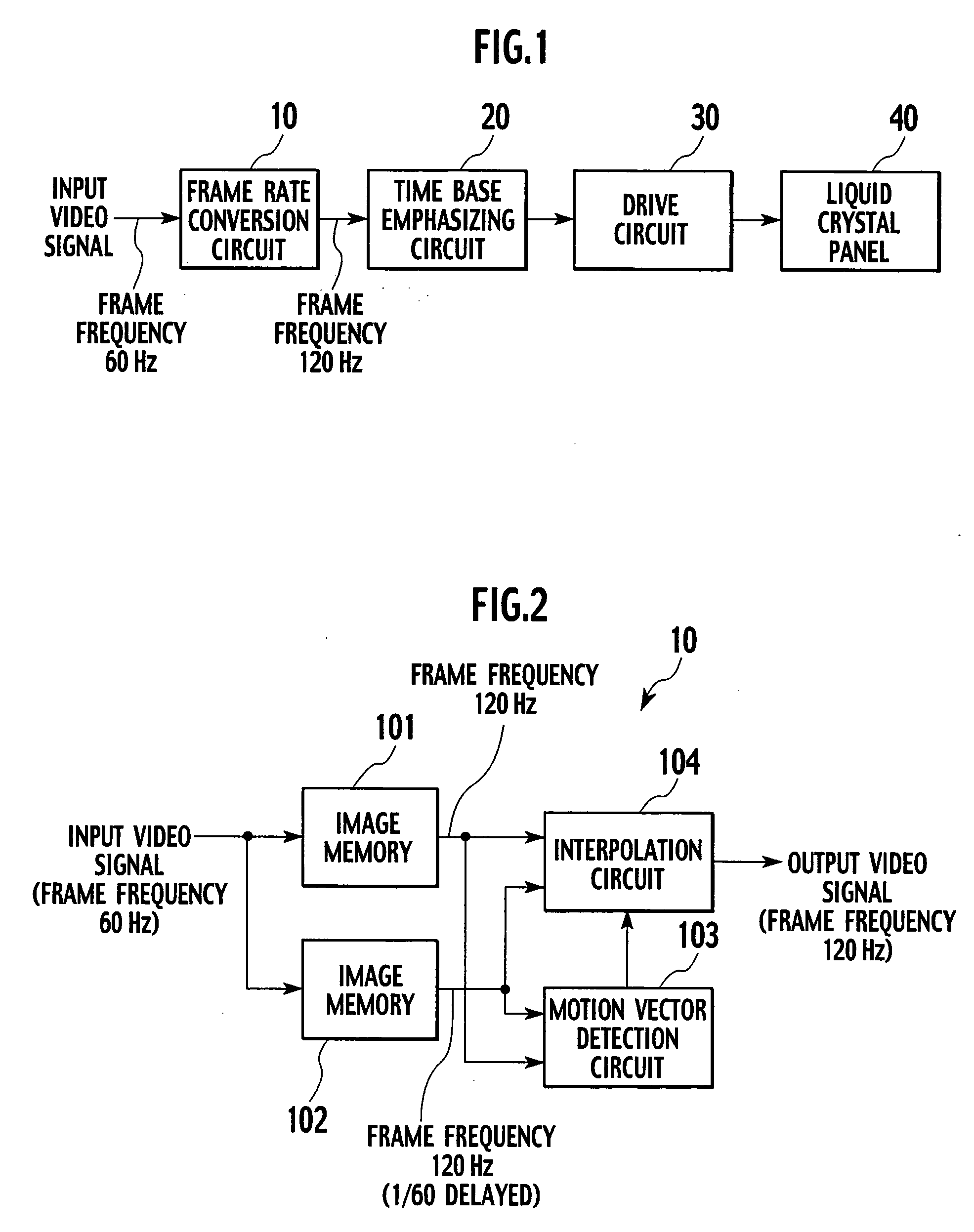

Image display unit

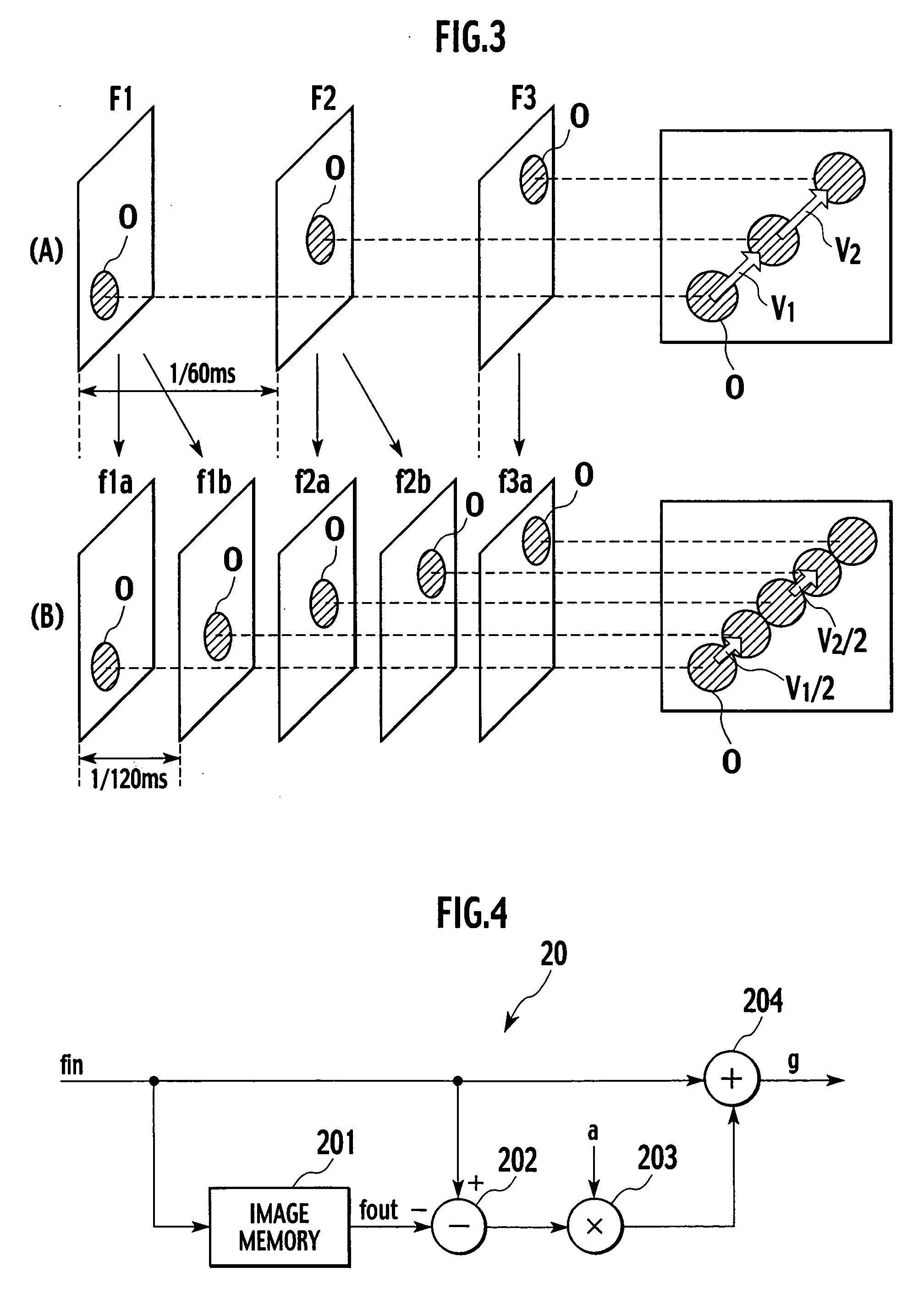

ActiveUS20050078069A1Reduce moving image blurrinessReduce blurTelevision system detailsTelevision system scanning detailsActive matrixComputer science

An active matrix type display panel is a hold type display panel which has a plurality of pixels arranged in a matrix form, and holds and displays an electrical signal pixel by pixel for a predetermined time. A frame rate conversion circuit converts a video signal having a first vertical frequency (60 Hz) into a video signal having a second vertical frequency (120 Hz) which is m / n-fold (wherein m is an integer of 2 or more, n is an integer of 1 or more, and conditions of m>n are satisfied) of the first vertical frequency. A time base emphasizing circuit subjects an output from the frame rate conversion circuit to time base emphasis. A drive circuit displays the video signal having the second vertical frequency in a display panel.

Owner:JVC KENWOOD CORP A CORP OF JAPAN

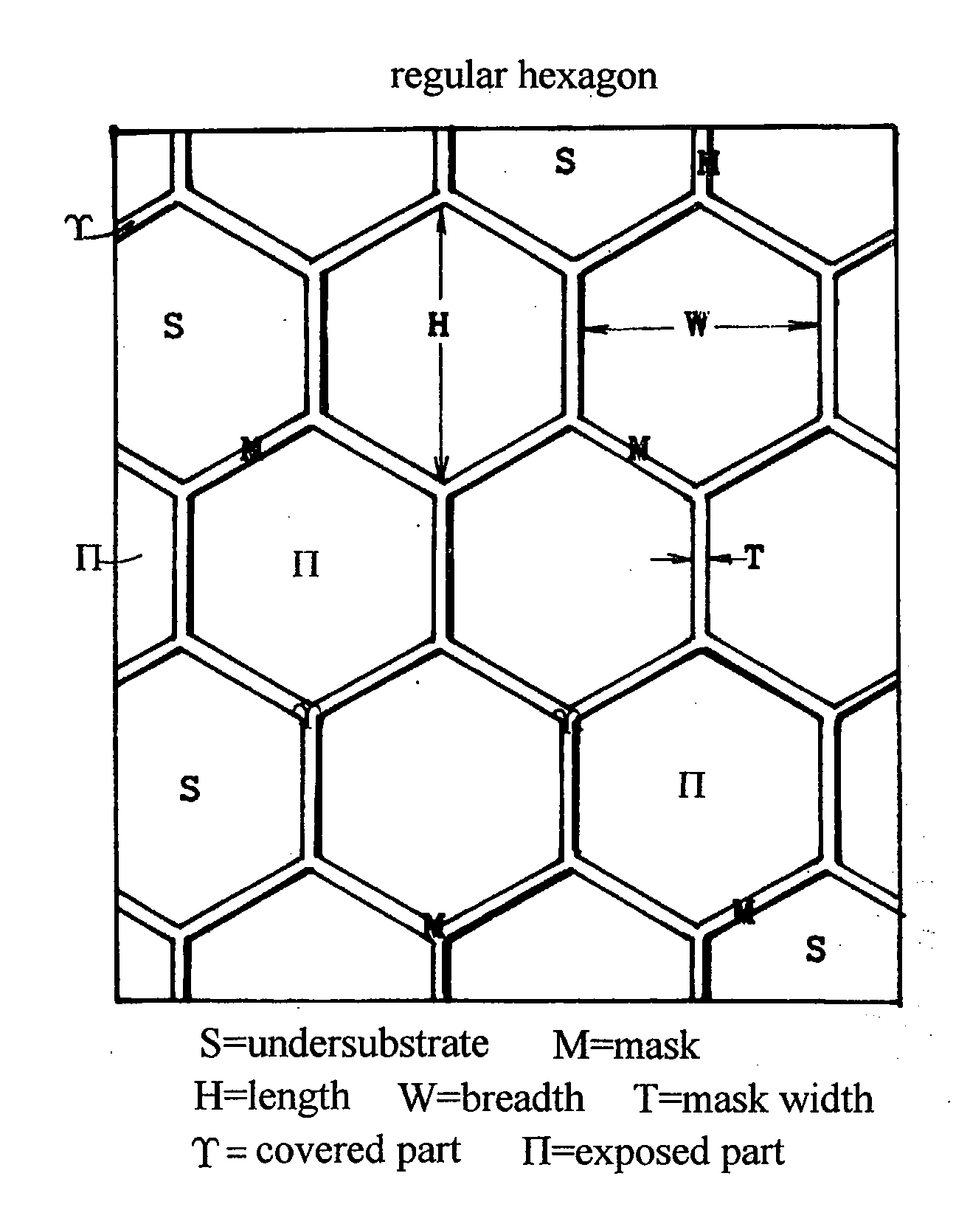

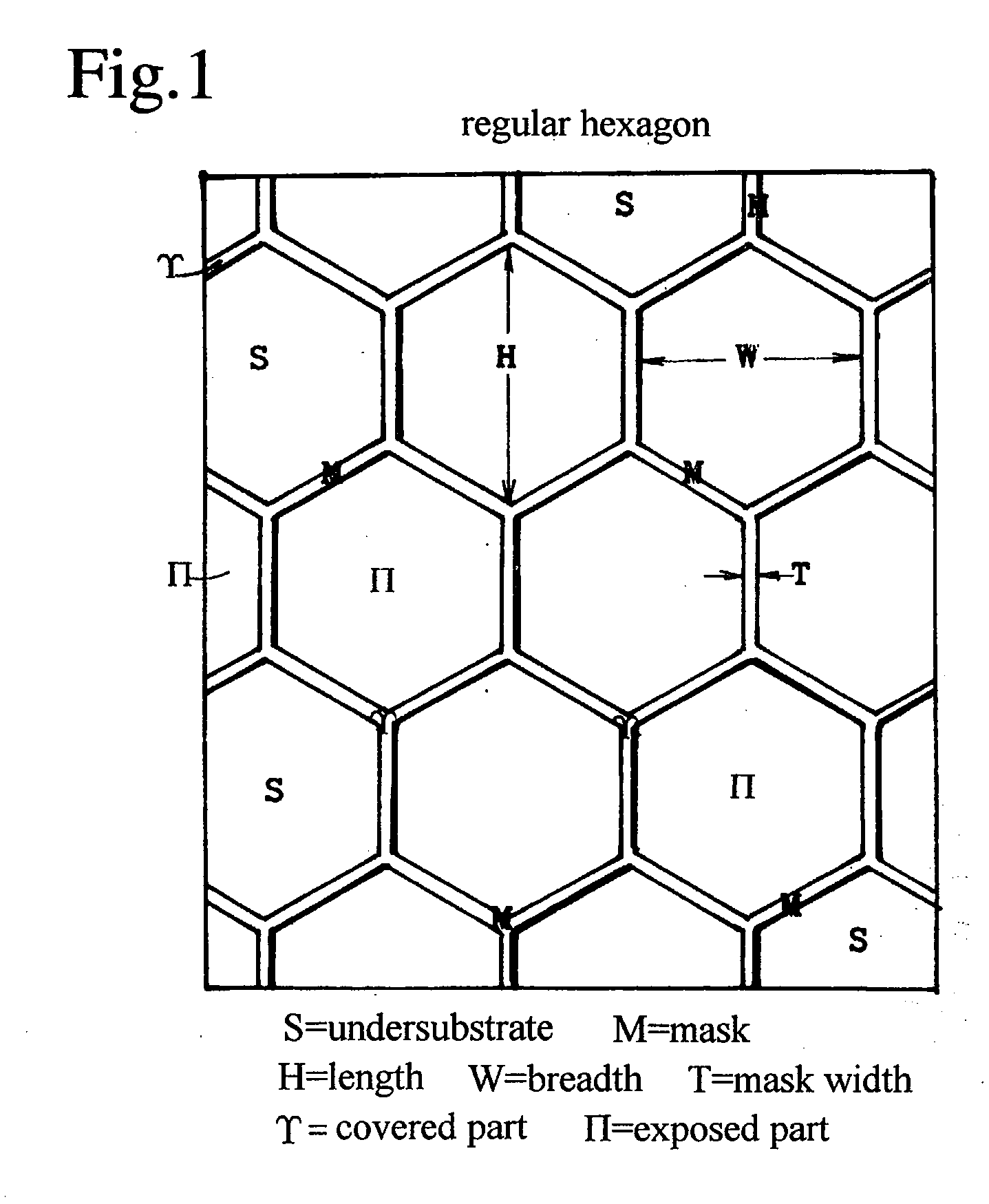

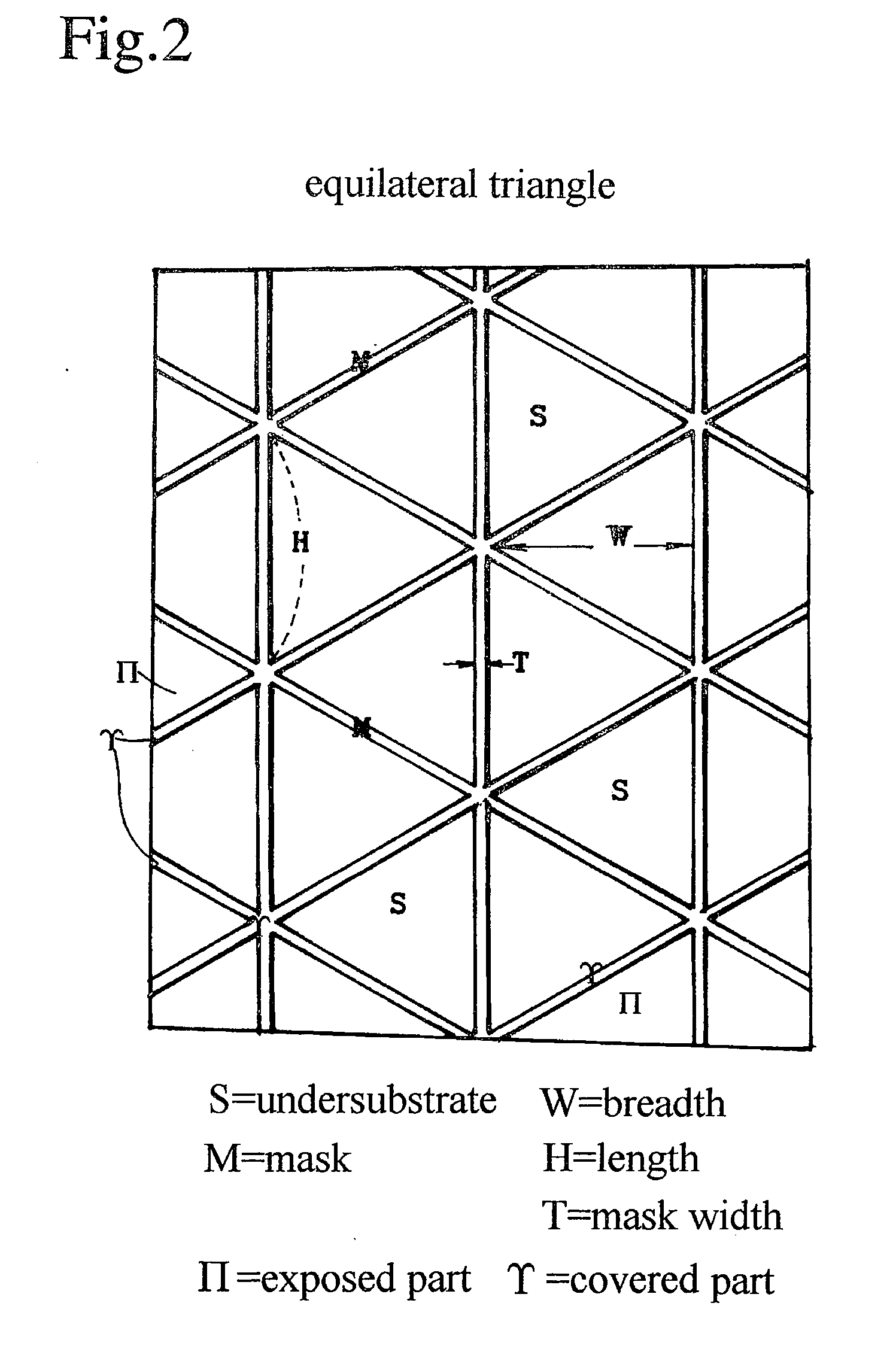

Nitride semiconductor substrate and method of producing same

ActiveUS20090155989A1Reduce dislocation densityEasily realizedPolycrystalline material growthSemiconductor/solid-state device manufacturingGas phaseClosed loop

A nitride semiconductor crystal substrate is produced by forming a network mask repeating a closed loop unit shape upon an undersubstrate, growing a nitride semiconductor crystal in vapor phase, producing convex facet hills covered with facets on exposed parts Π, forming outlining concavities on mask-covered parts not burying the facets, maintaining the convex facet hills on Π and the network concavities on excluding dislocations in the facet hills down to the outlining concavities on forming a defect accumulating region H on decreasing dislocations in the facet hills and improving the facet hills to low defect density single crystal regions Z, producing a rugged nitride crystal, and slicing and polishing the nitride crystal into mirror nitride crystal wafers. After the fabrication of devices on the nitride wafer, dry-etching or wet etching of hot KOH or NaOH divides the device-carrying wafer into chips by corroding the network defect accumulating region H.

Owner:SUMITOMO ELECTRIC IND LTD

Input apparatus, input display apparatus, and electronic device

InactiveUS20100214245A1Increasing the thicknessThinner configurationNon-linear opticsInput/output processes for data processingEngineeringElectronic equipment

Owner:SEIKO EPSON CORP

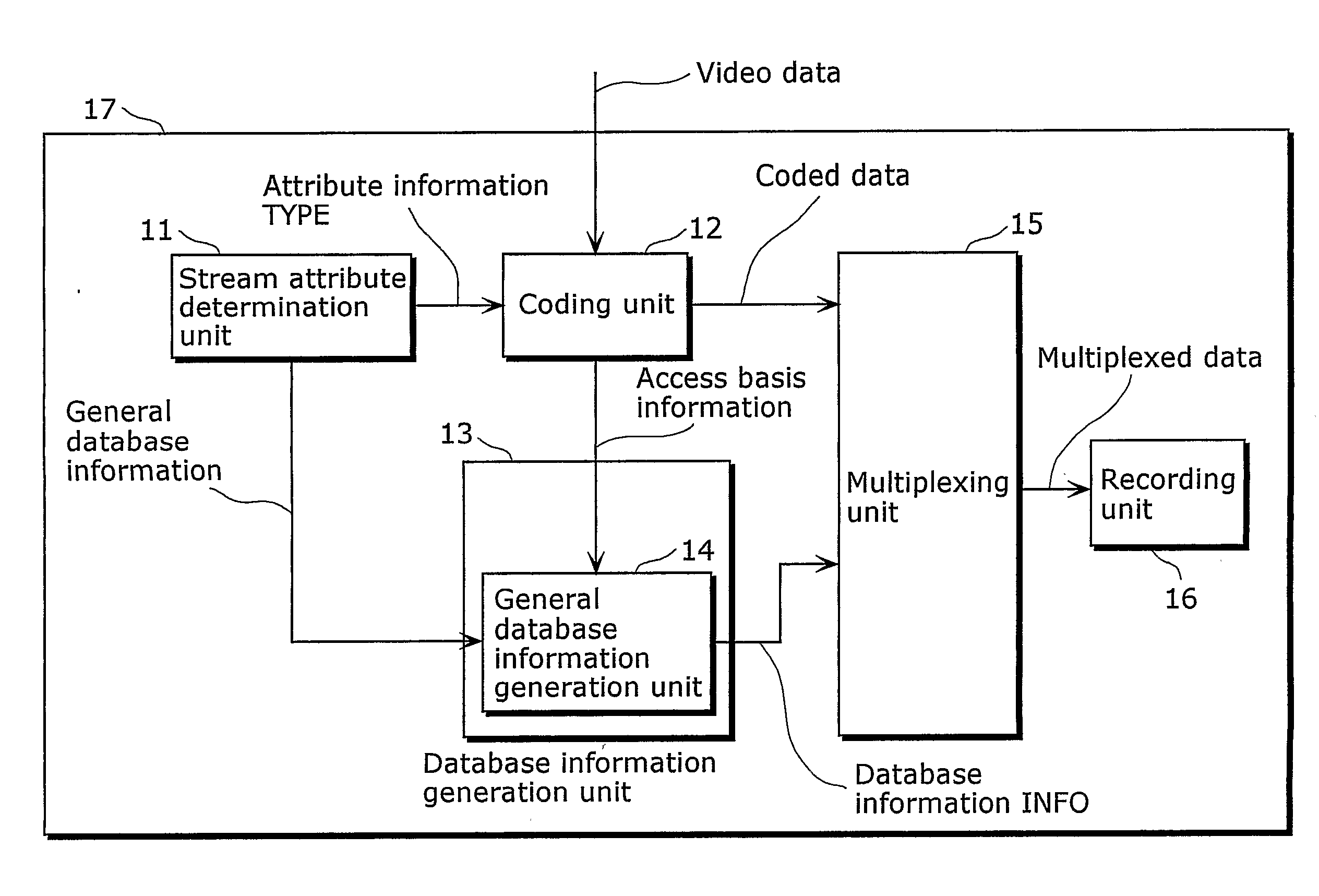

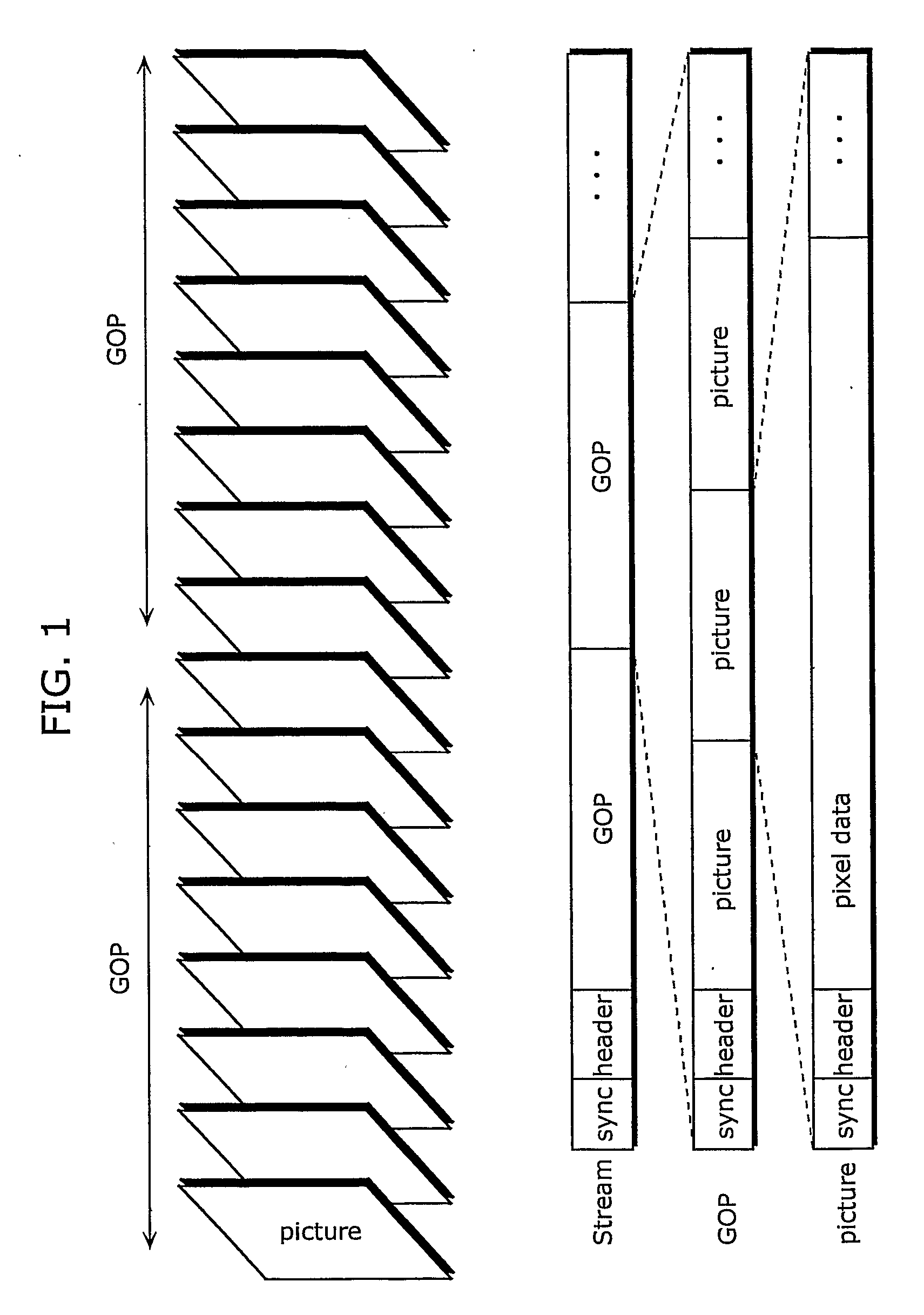

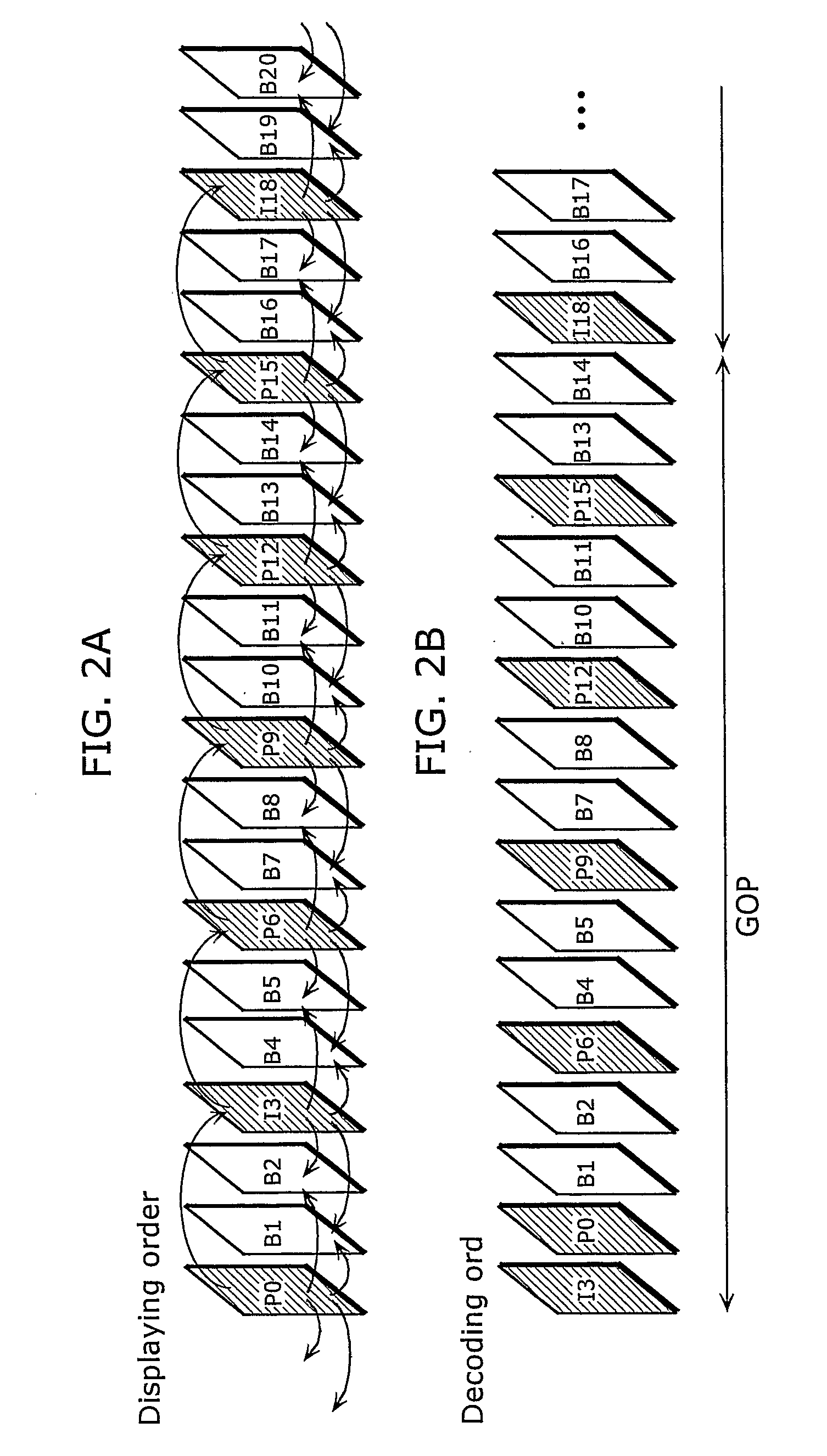

Stream generation apparatus, stream generation method, coding apparatus, coding method, recording medium and program thereof

ActiveUS20070116426A1Easily realizedAvoid failureTelevision system detailsPicture reproducers using cathode ray tubesComputer scienceRecording media

A stream generation apparatus of the present invention is a stream generation apparatus which generates a stream including coded pictures and a command for managing a buffer which holds a decoded picture, the command being added to one of the coded pictures as a reference picture. It includes a judging unit which judges whether or not the coded picture to which the command is added is skipped at the time of trick-play, an adding unit which adds, in the case where the coded picture is judged to be skipped, repetition information indicating the same contents as the command to another coded picture that follows, in decoding order, the coded picture judged to be skipped and that is not skipped at the time of the trick-play, and a generating unit which generates the stream including the coded pictures, the command and the repetition information.

Owner:PANASONIC CORP

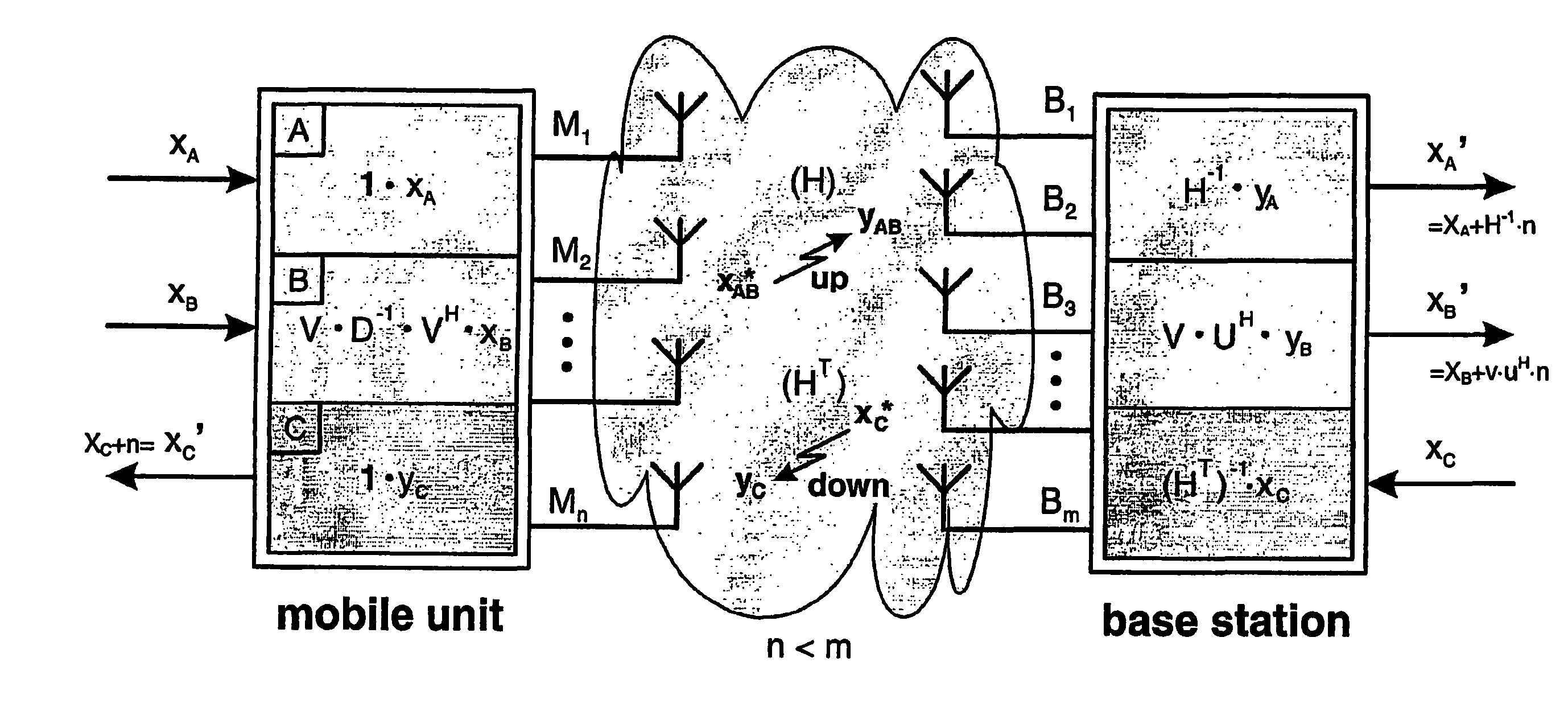

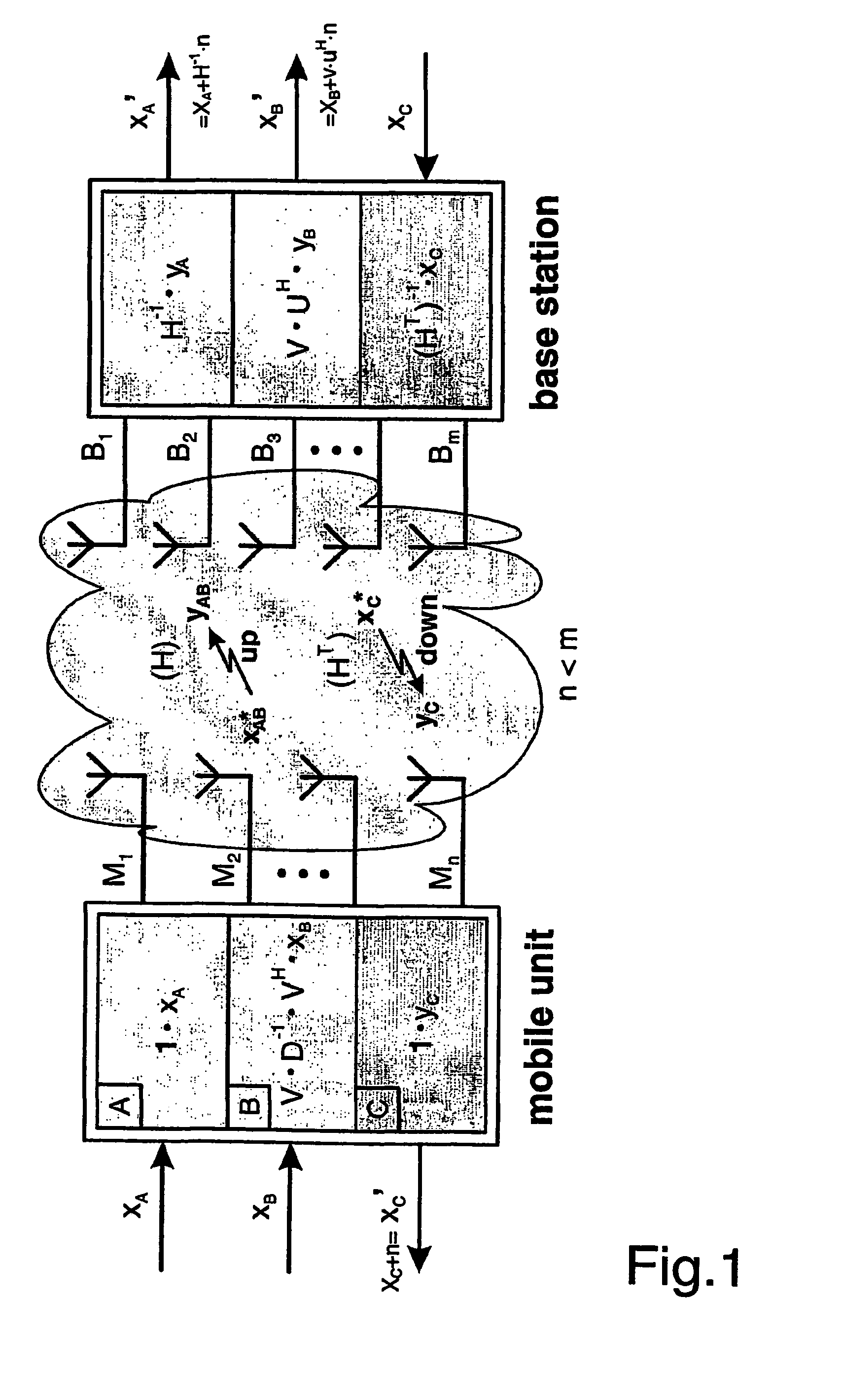

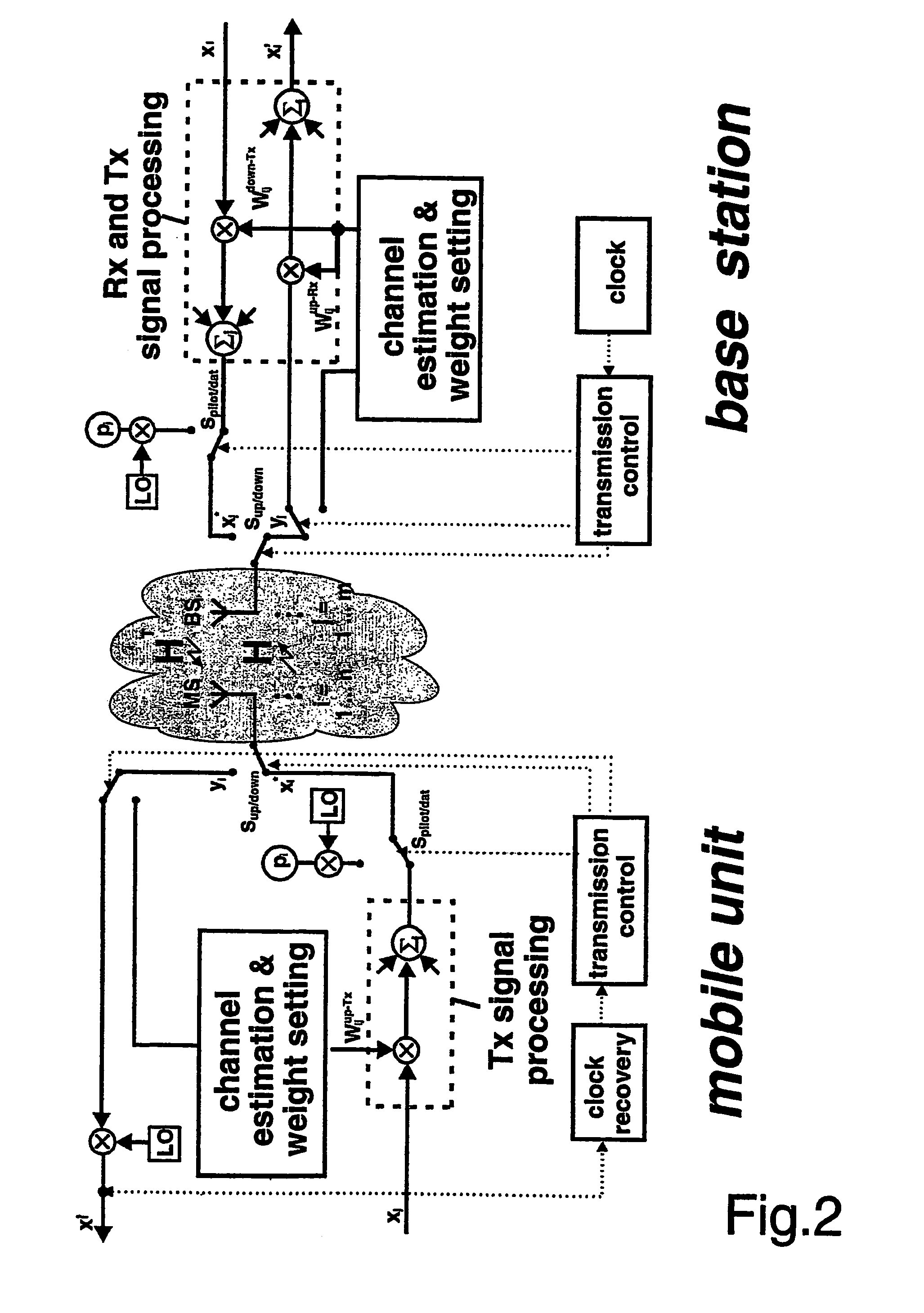

Adaptive signal processing method in a MIMO-system

ActiveUS7366520B2Improve efficiencyReduce transmit powerSpatial transmit diversityElectric discharge heatingData streamBidirectional transmission

The invention relates to a signal processing method which optimizes the bit error rate under pragmatic conditions. The signalling method is optimally matched to the radio channel, variable with time, in rapid sequence by means of linear operations. Uplink and downlink transmission sides are determined by an excess of antennae on the downlink transmission side. The estimations of the channel matrix in the one transmission direction, necessary for the matching of the transmitter, can, in the absence of common-channel distortions with the condition of channel reciprocity, be directly obtained from the estimations for the other transmission direction. By a suitable linear combination of the transmission signals and, optionally, also the received signals, an error-free bi-directional transmission of data streams can be achieved in Rayleigh and Rice channels with significantly lower transmission powers than in purely receiver-side linear signal processing.

Owner:SIEMENS AG

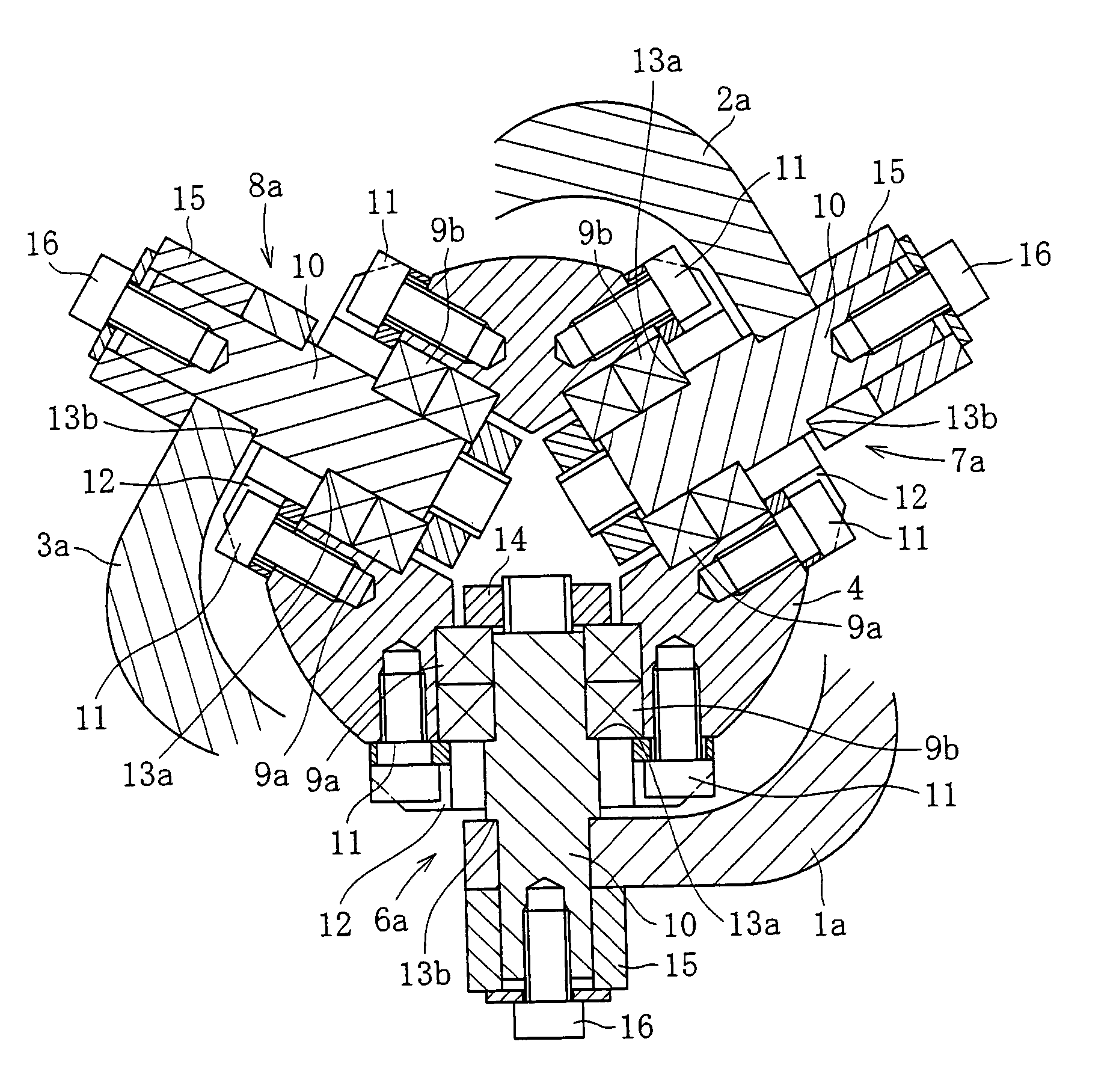

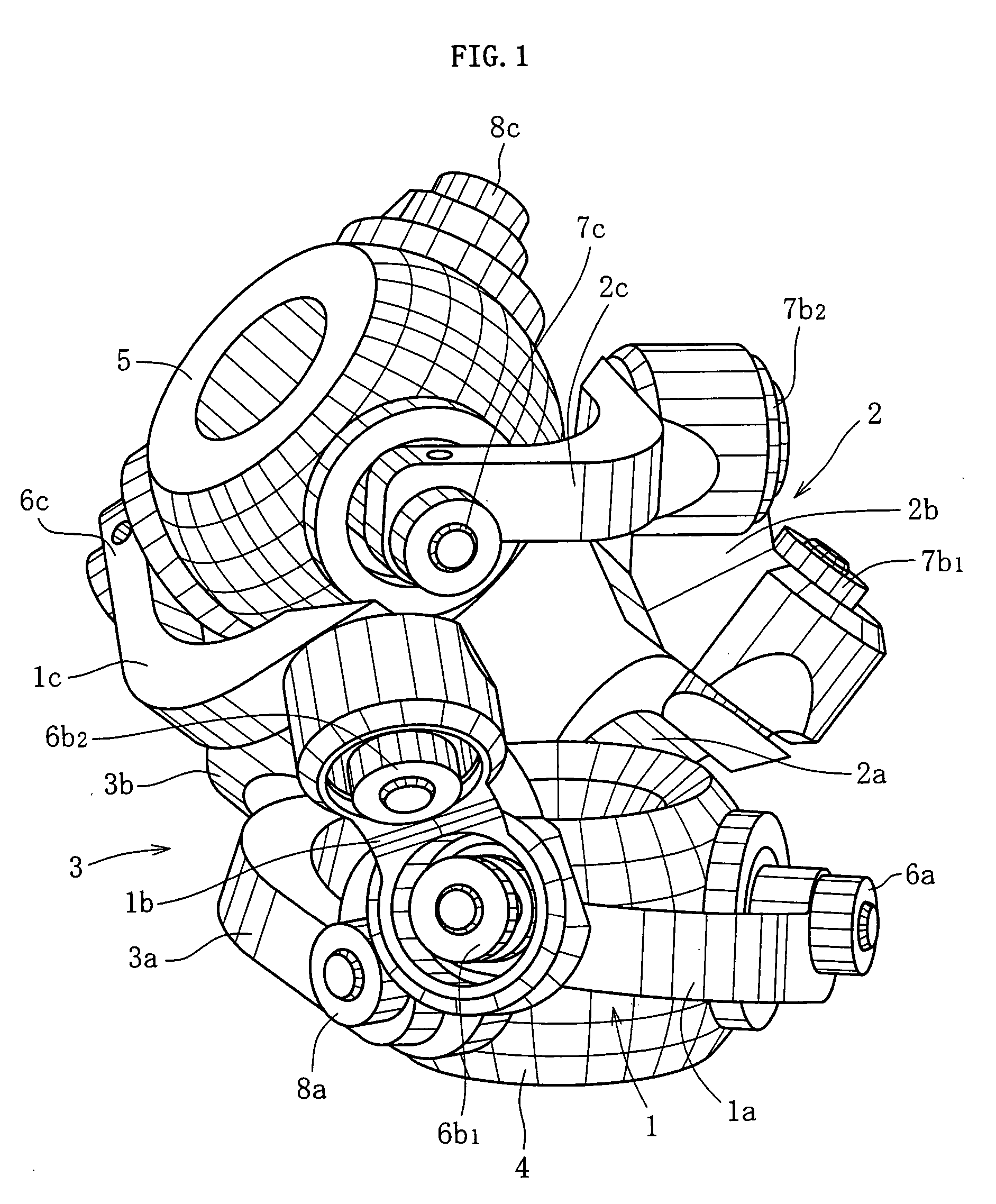

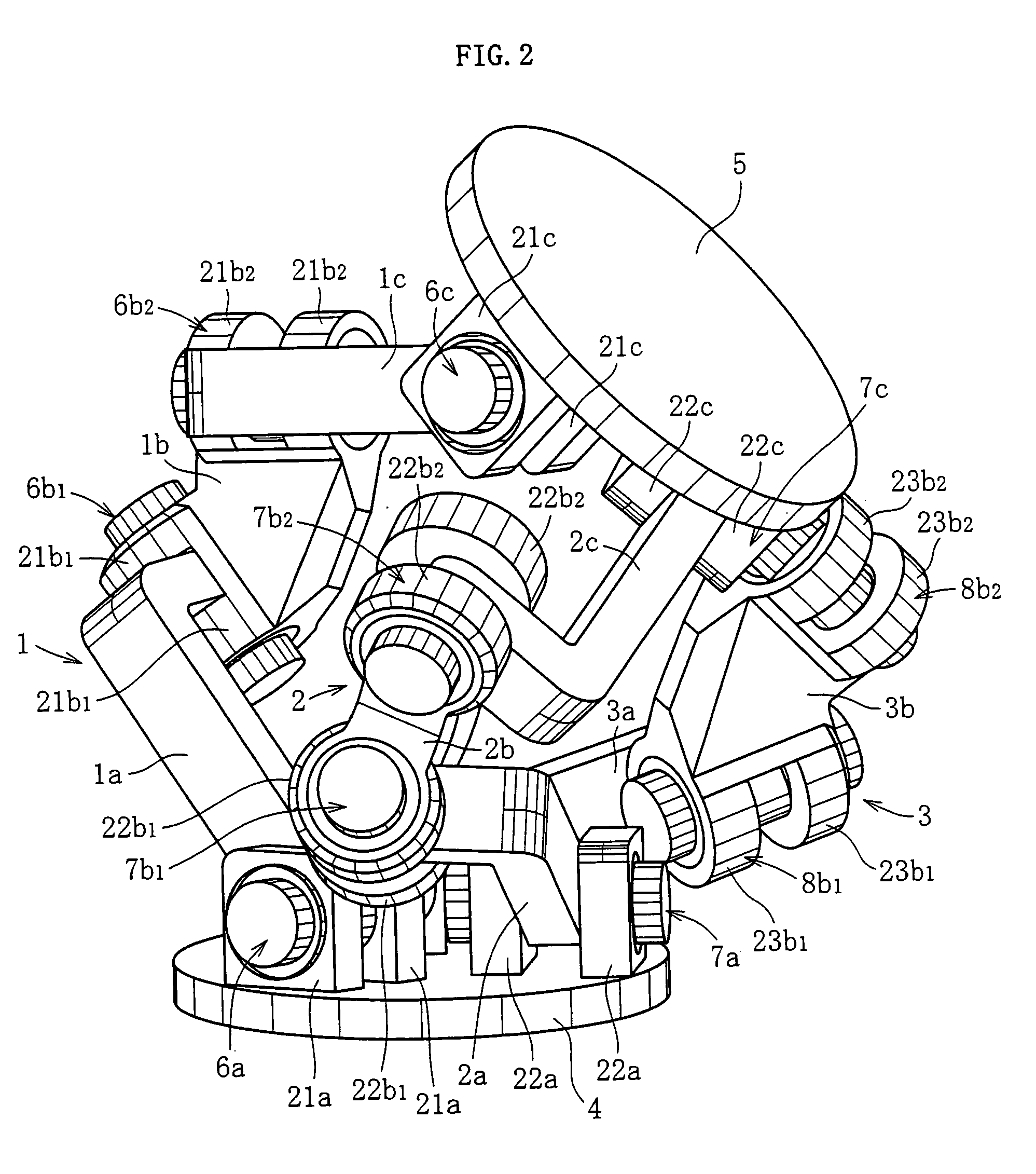

Link actuating device

ActiveUS20050199085A1Improvement in assembly propertyImprove workabilityProgramme-controlled manipulatorMechanical apparatusEngineeringMechanical engineering

In a bearing detachment prevention structure provided in a rotation pair portion of a link mechanism, play filling-up and pre-load adjustment for the bearing are realized with ease. As a means for therefor, there is provided a link actuating device having three or more sets of link mechanisms in each of which end link members are rotatably connected to input and output members respectively arranged on the input and output sides, the respective end link members on the input and output sides being rotatably connected to intermediate link members to form four rotation pair portions, the input and output sides being geometrically the same with respect to a cross section in a central portion of each link mechanism, in which each rotation pair portion of the link mechanisms has a bearing structure consisting of two bearings, with a play filling-up means for regulating axial movement of the two bearings being provided in the rotation pair portions. Further, by appropriately determining the configuration of each component forming the link mechanisms, interference between the components during operation of the link mechanisms is prevented. As a means therefor, a beveled portion is formed on the link side peripheral end edge portion of each input member, whereby interference between the end link member and the outer peripheral surface of the rotation pair portion of each intermediate link member is prevented.

Owner:NTN CORP

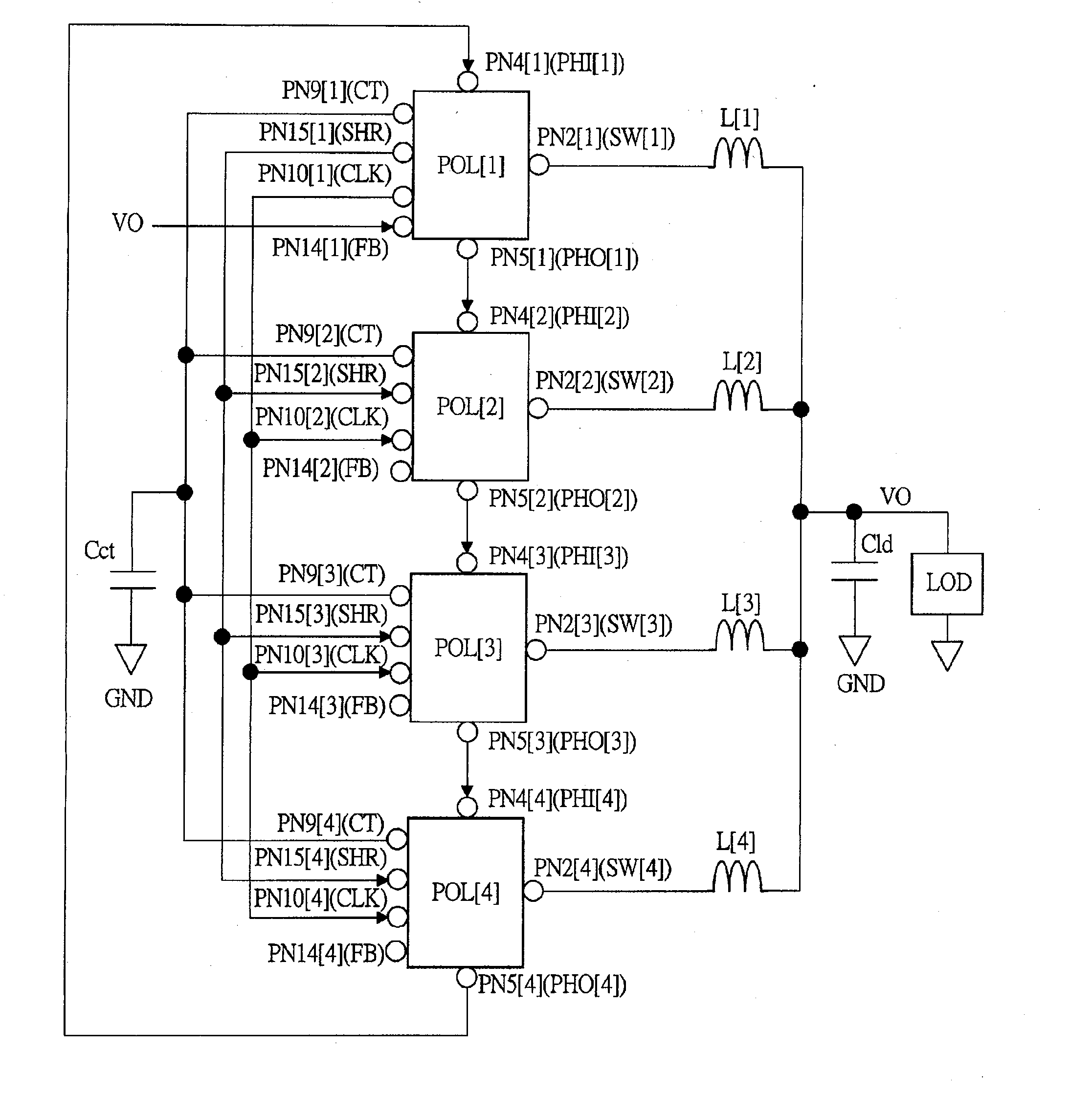

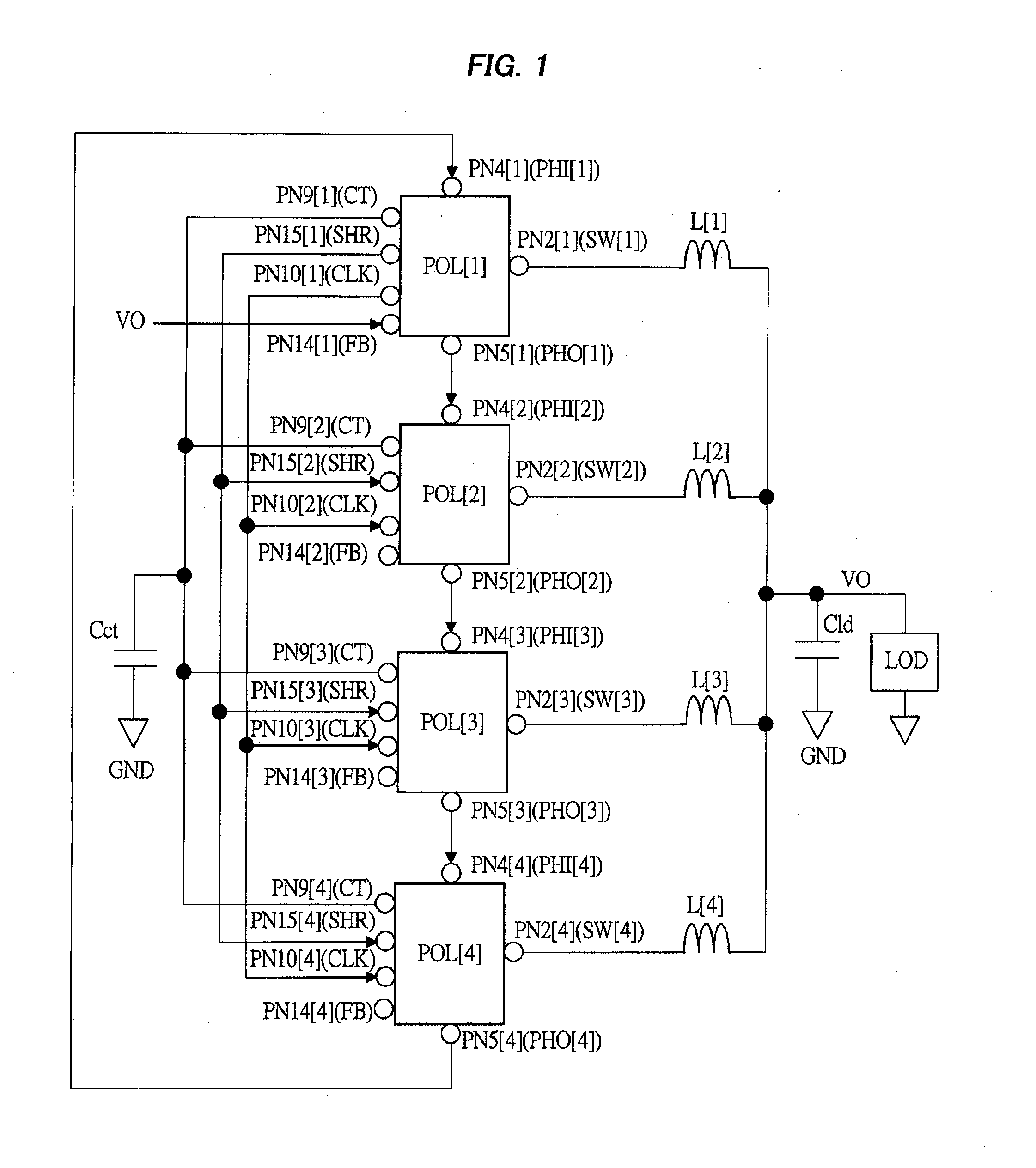

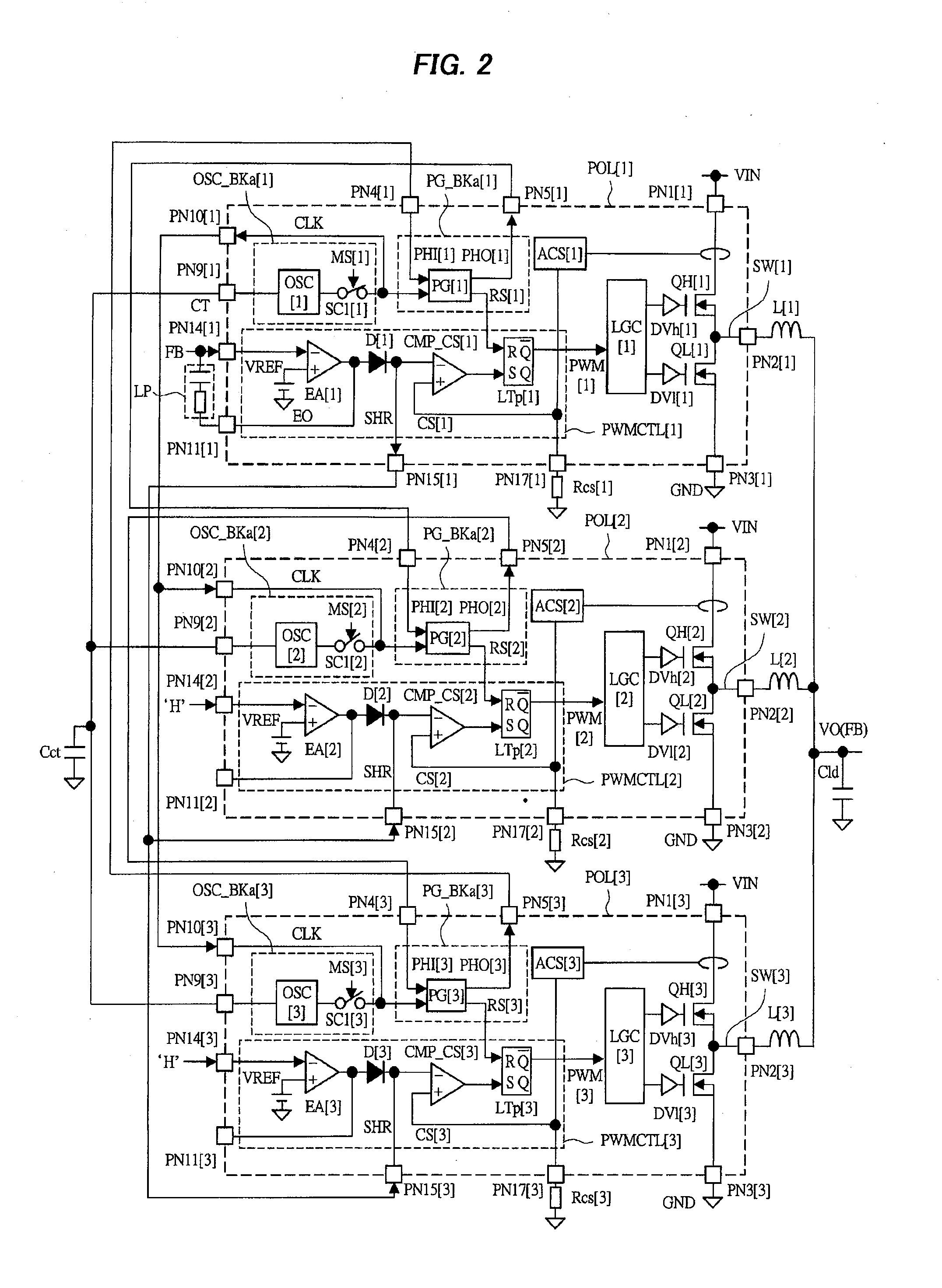

Semiconductor device and power source device

ActiveUS20110169471A1Improve power conversion efficiencyRange of fluctuation of consumptionDc-dc conversionSolid-state devicesAutomatic controlPhase number

A multi-phase power source device capable of easily changing the number of phases is realized. For example, a plurality of drive units POL[1]-POL[4] corresponding to the number of phases are provided, wherein each POL[n] receives a phase input signal PHI[n] serving as a pulse signal, and generates a phase output signal PHO[n] by delaying PHI[n] by a predetermined cycles of a clock signal CLK. PHI[n] and PHO[n] of each POL[n] are coupled in a ring, wherein each POL[n] performs a switching operation with PHI[n] or PHO[n] as a starting point. In this case, each POL[n] charges and discharges a capacitor Cct commonly coupled to each POL[n] with an equal current, and a frequency of CLK is determined based on this charge and discharge rate. That is, if the number of phases increases n times, the frequency of CLK will be automatically controlled to n times.

Owner:RENESAS ELECTRONICS CORP

Interconnection element for electric circuits

ActiveUS8299368B2Efficient heat transferImprove installation strengthLine/current collector detailsSemiconductor/solid-state device detailsElectrical conductorInterconnection

Owner:INVENSAS CORP

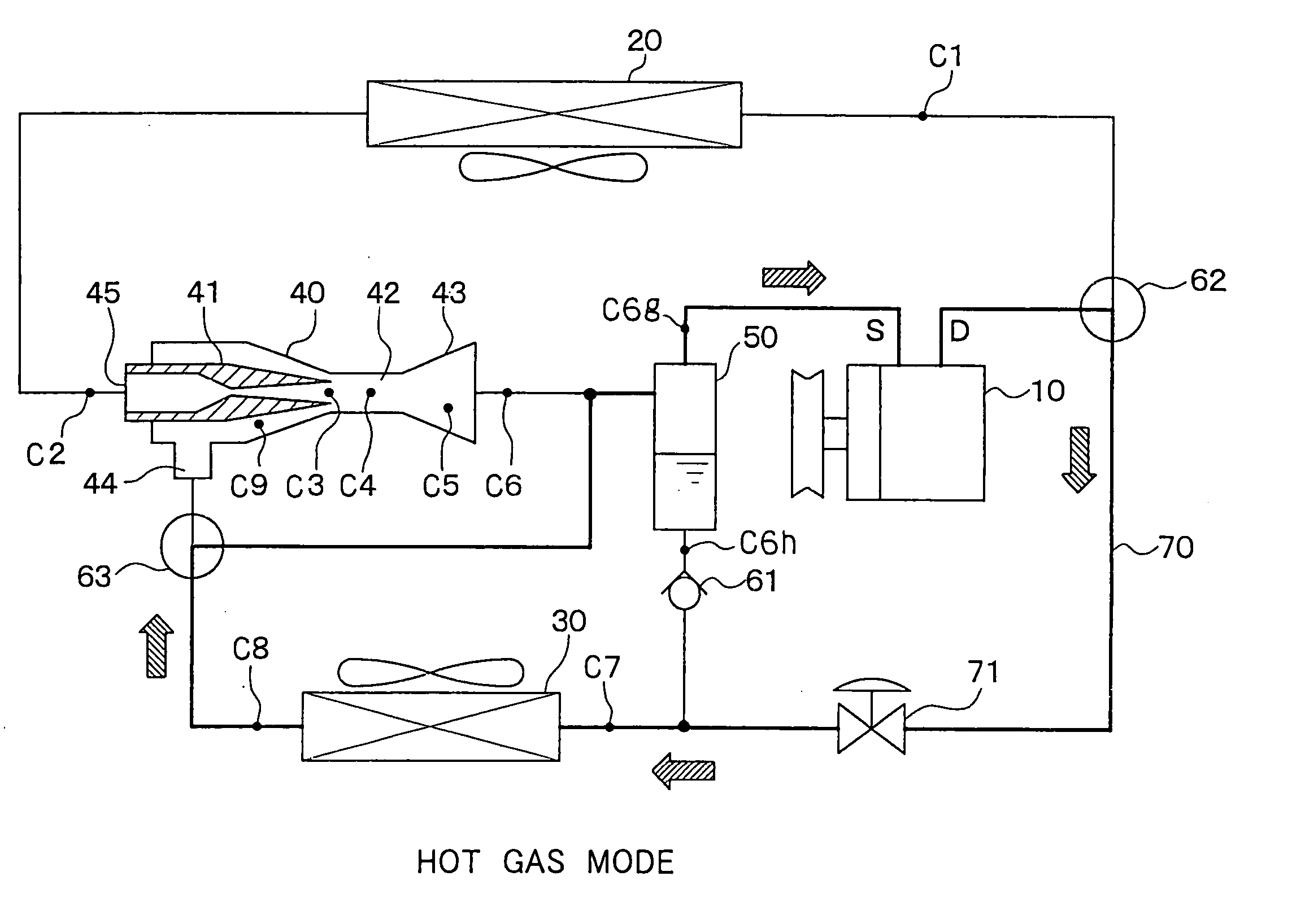

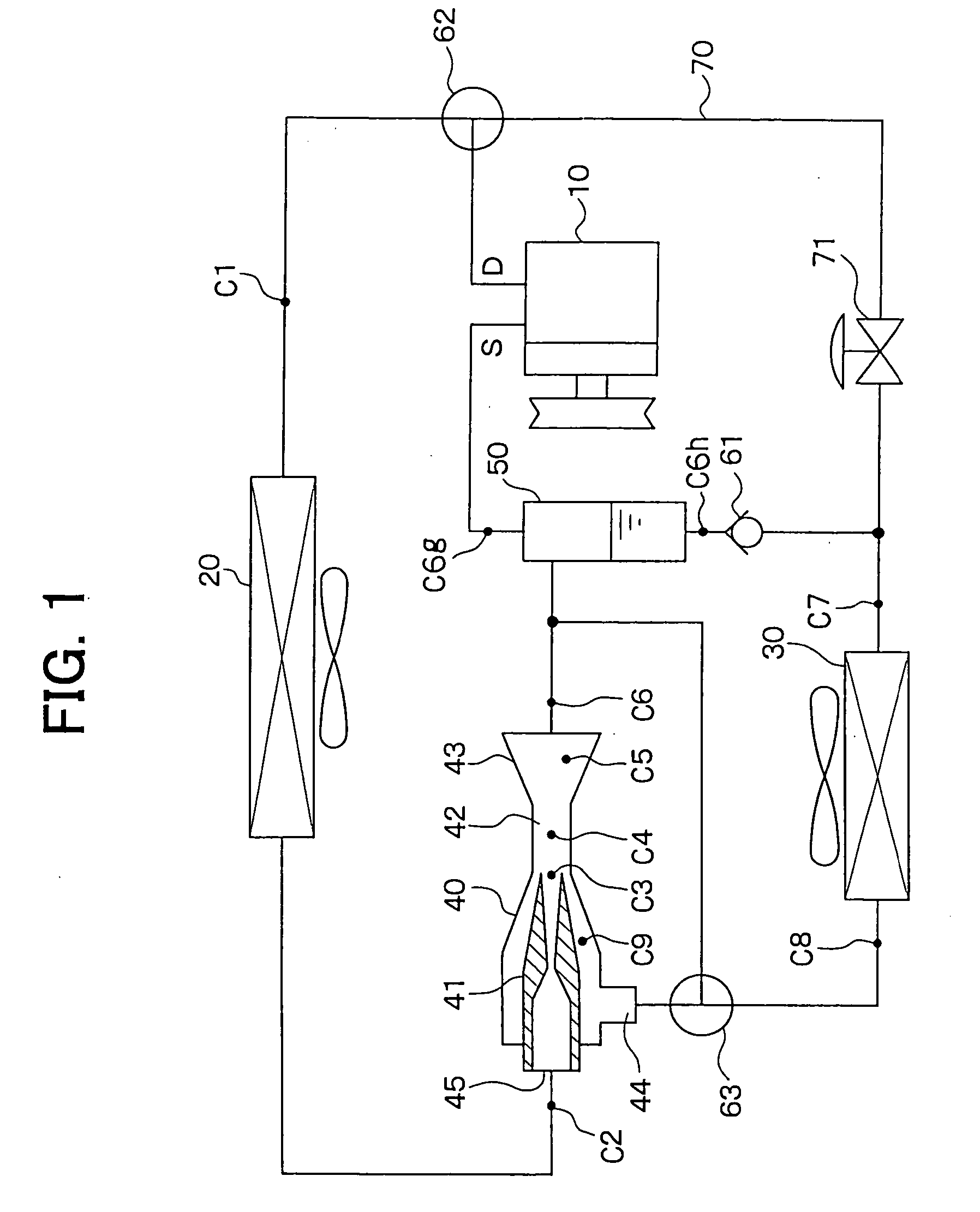

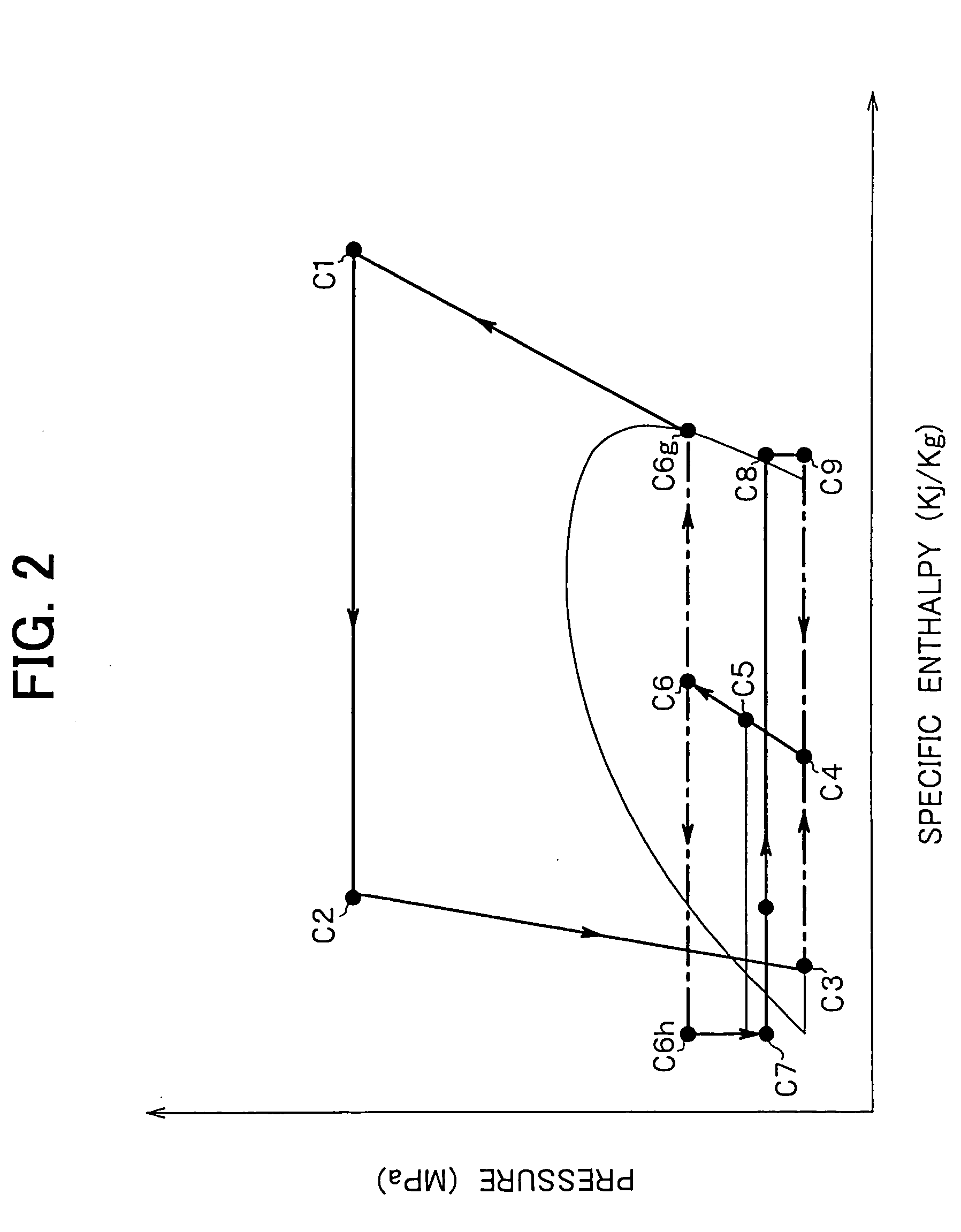

Ejector cycle system

InactiveUS20040103685A1Increase pressureEasy to set upAir-treating devicesCompression machines with non-reversible cycleRefrigerantInjector

In a hot gas heating mode of an ejector cycle system, hot gas refrigerant discharged from a compressor is introduced to an interior heat exchanger while bypassing an exterior heat exchanger. The refrigerant discharged from the interior heat exchanger can flow into an ejector from at least an inlet of a nozzle of the ejector, and flows into the gas-liquid separator, in the heating mode. Alternatively, refrigerant discharged from the compressor can be supplied to the interior heat exchanger through a clearance between an outer wall of the nozzle and an inner wall of a nozzle housing portion, while bypassing the exterior heat exchanger in the heating mode. Here, the nozzle is disposed in the nozzle housing portion, and a part of pressurizing portion is defined by the nozzle housing portion. Thus, the heating mode can be readily performed in the ejector cycle system.

Owner:DENSO CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com