Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1098results about How to "Reduce dislocation density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

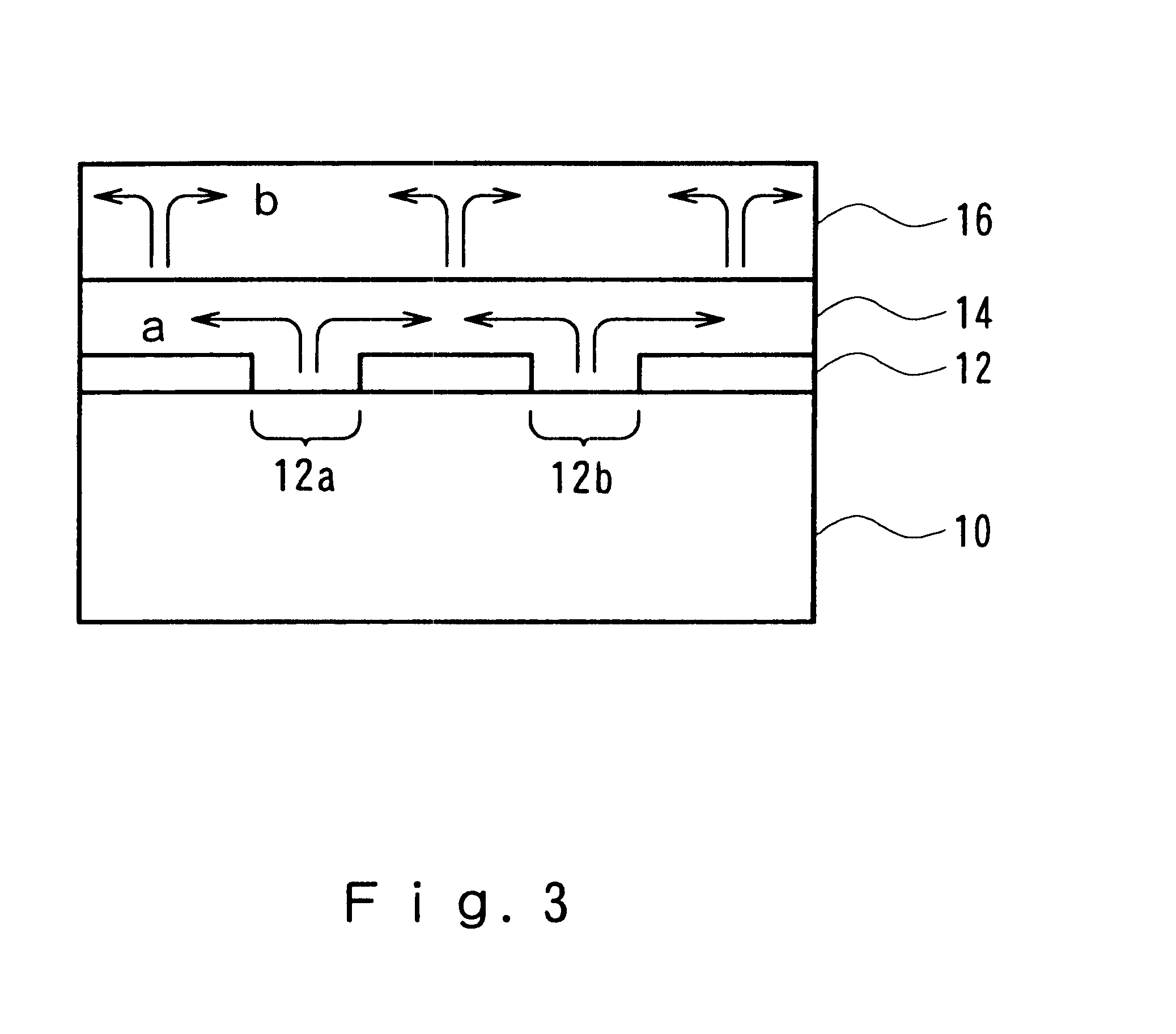

GaN field-effect transistor and method of manufacturing the same

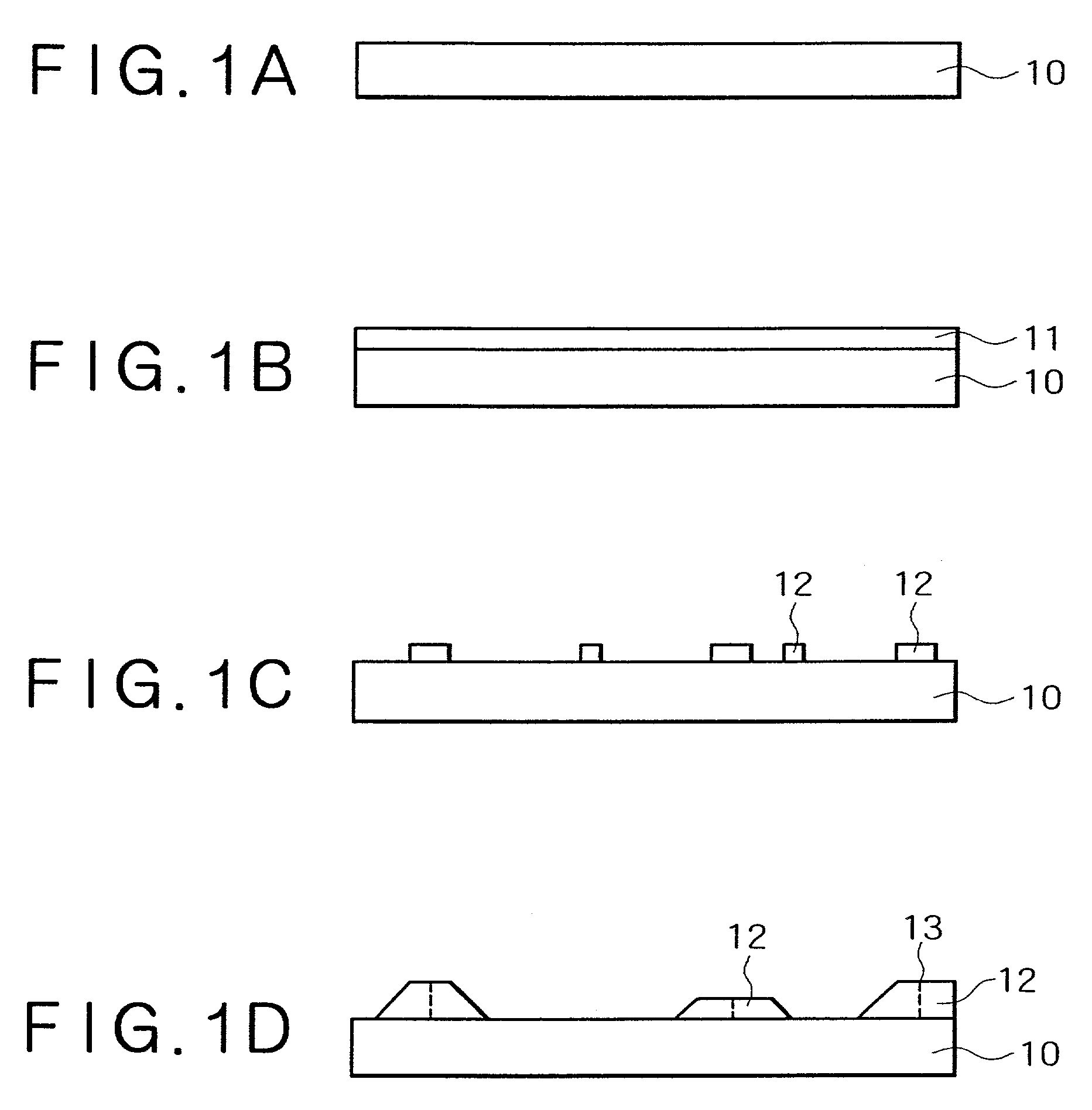

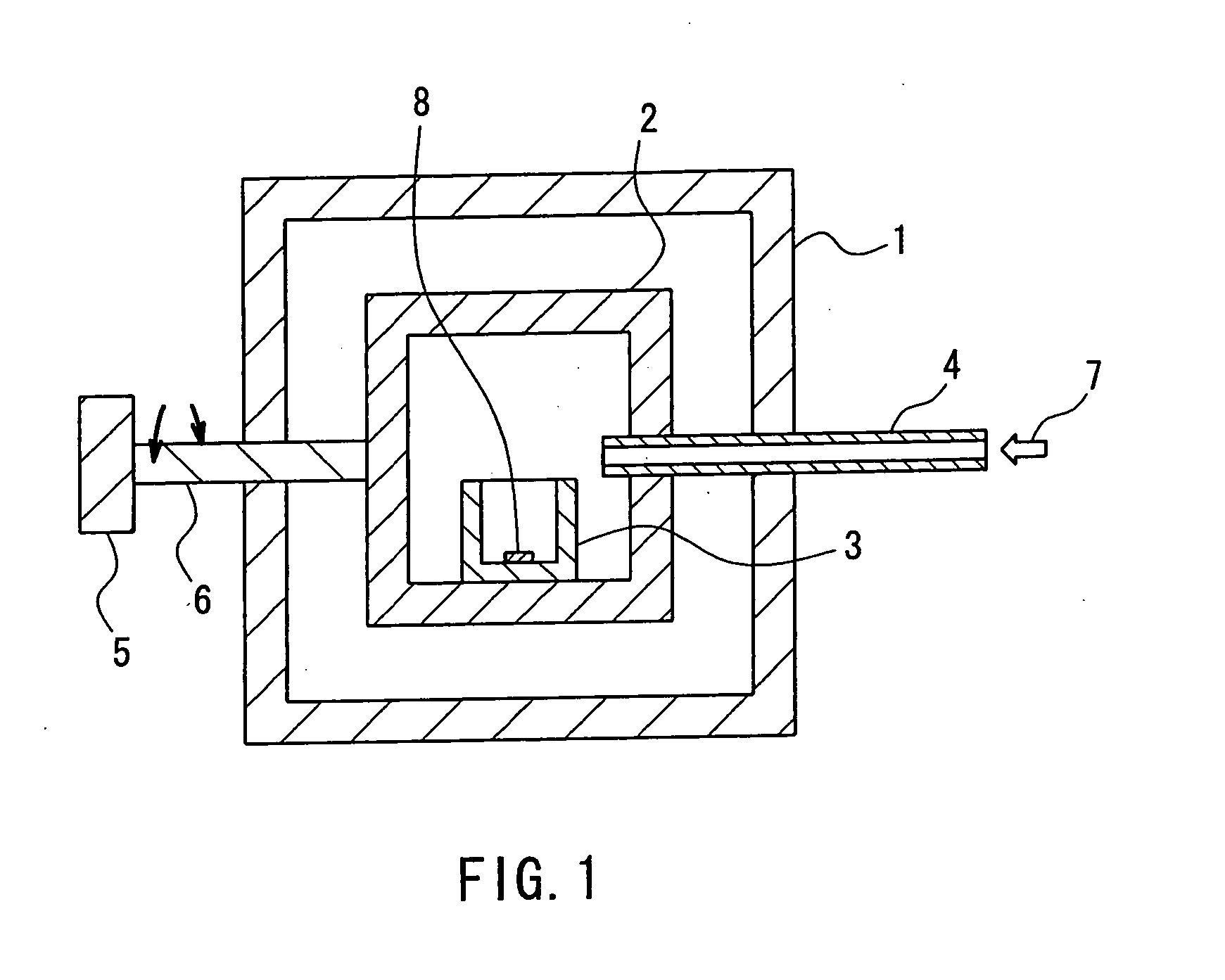

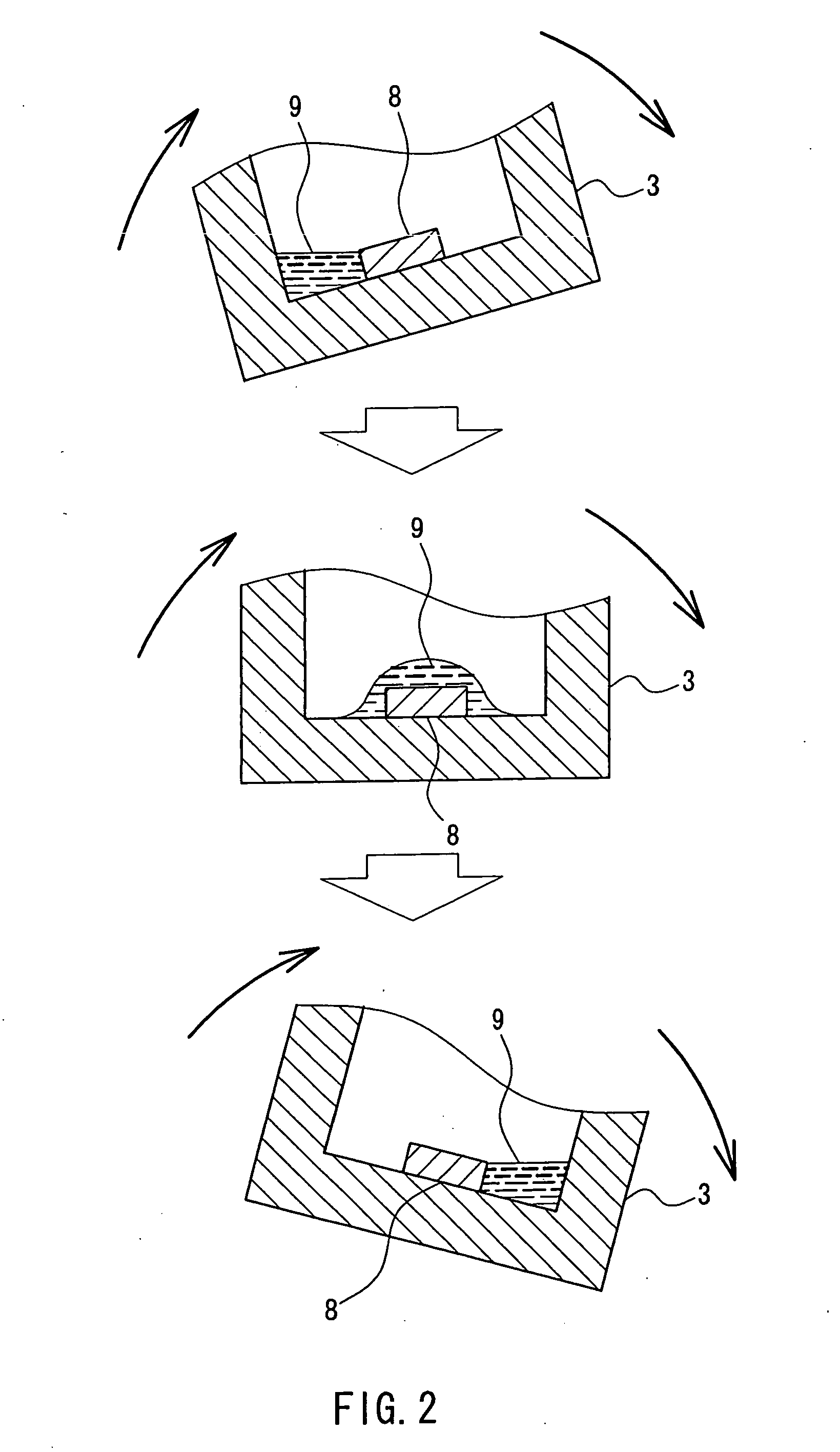

InactiveUS20010040246A1Reduce dislocation densityTransistorPolycrystalline material growthLateral overgrowthEngineering

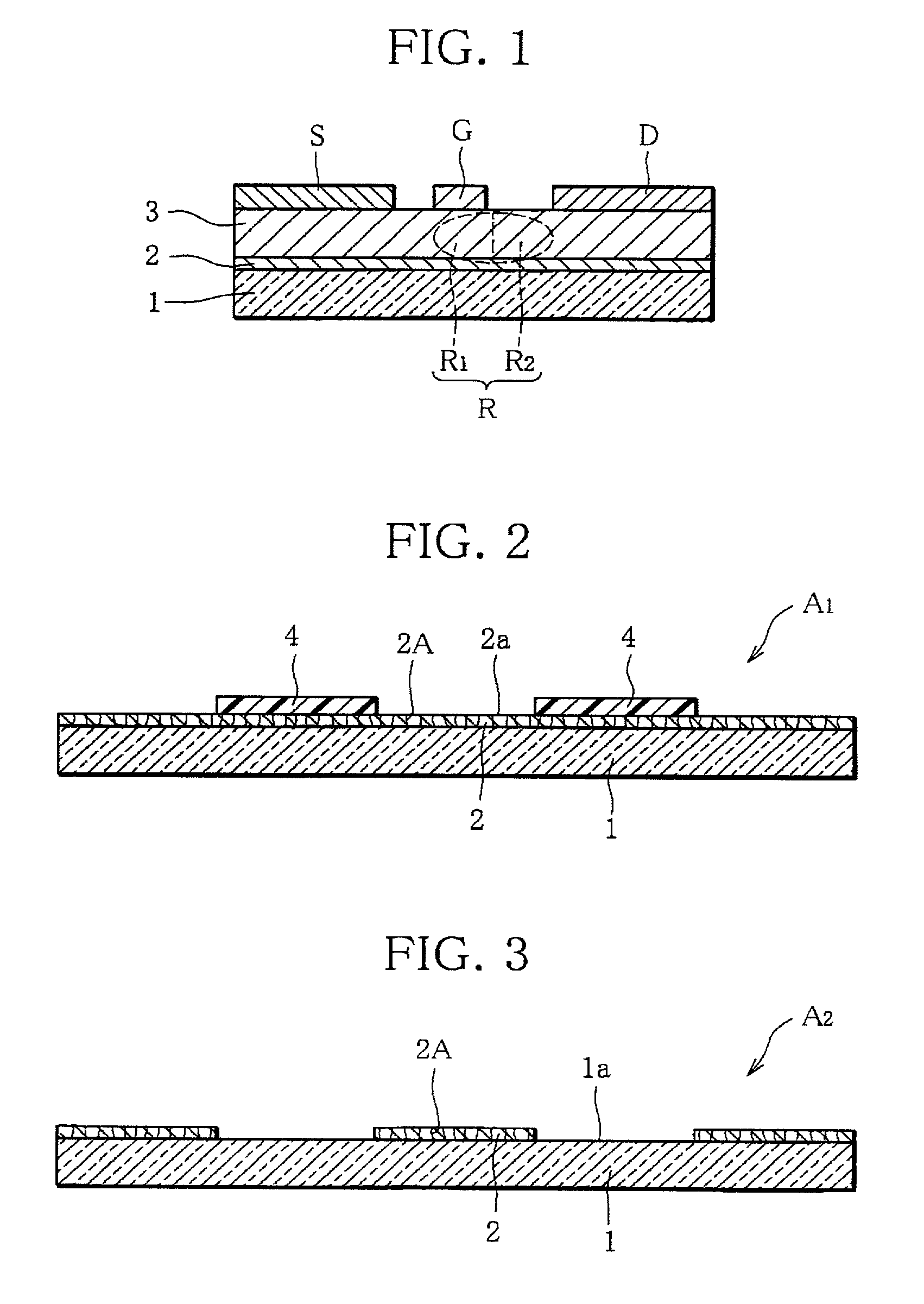

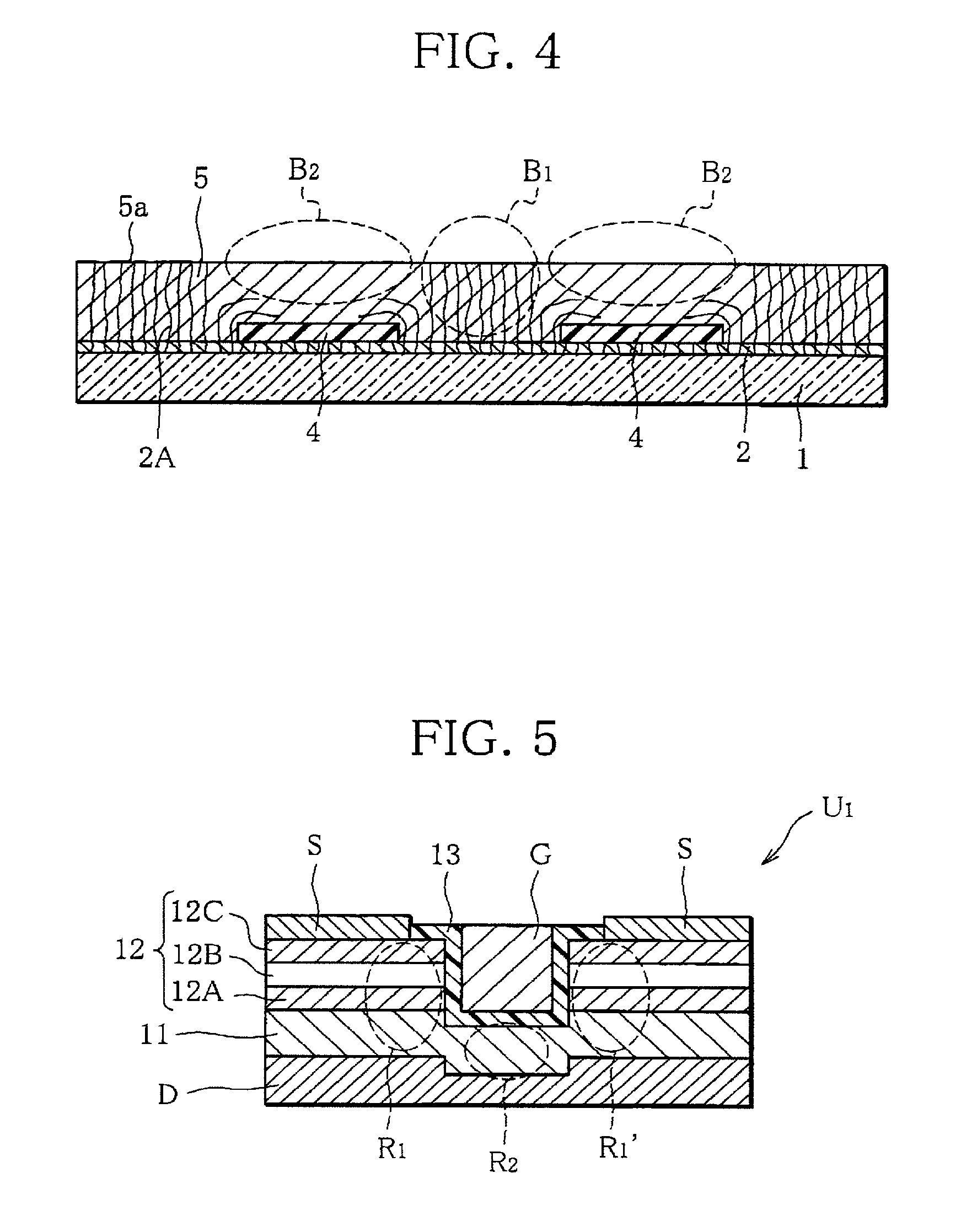

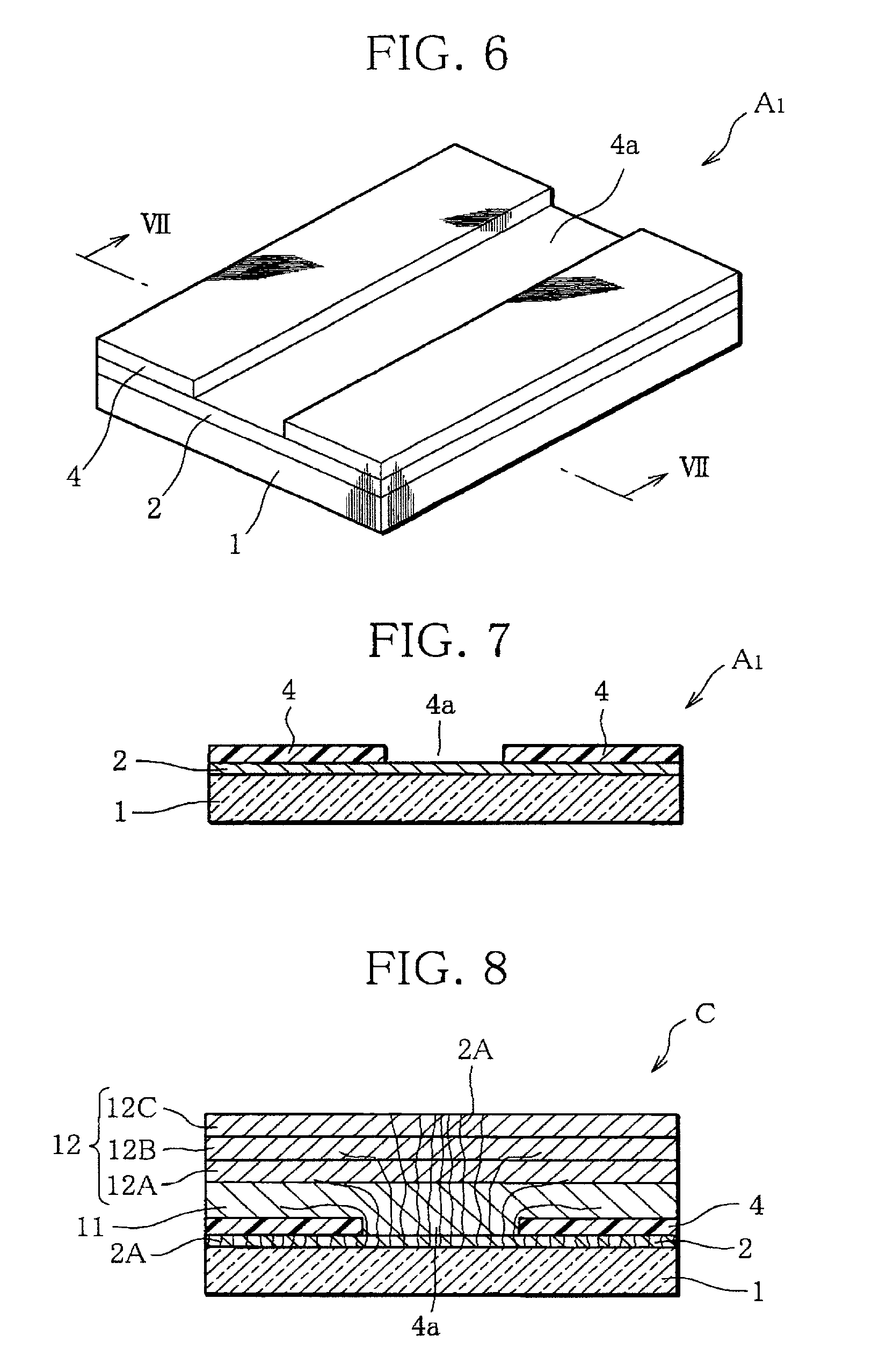

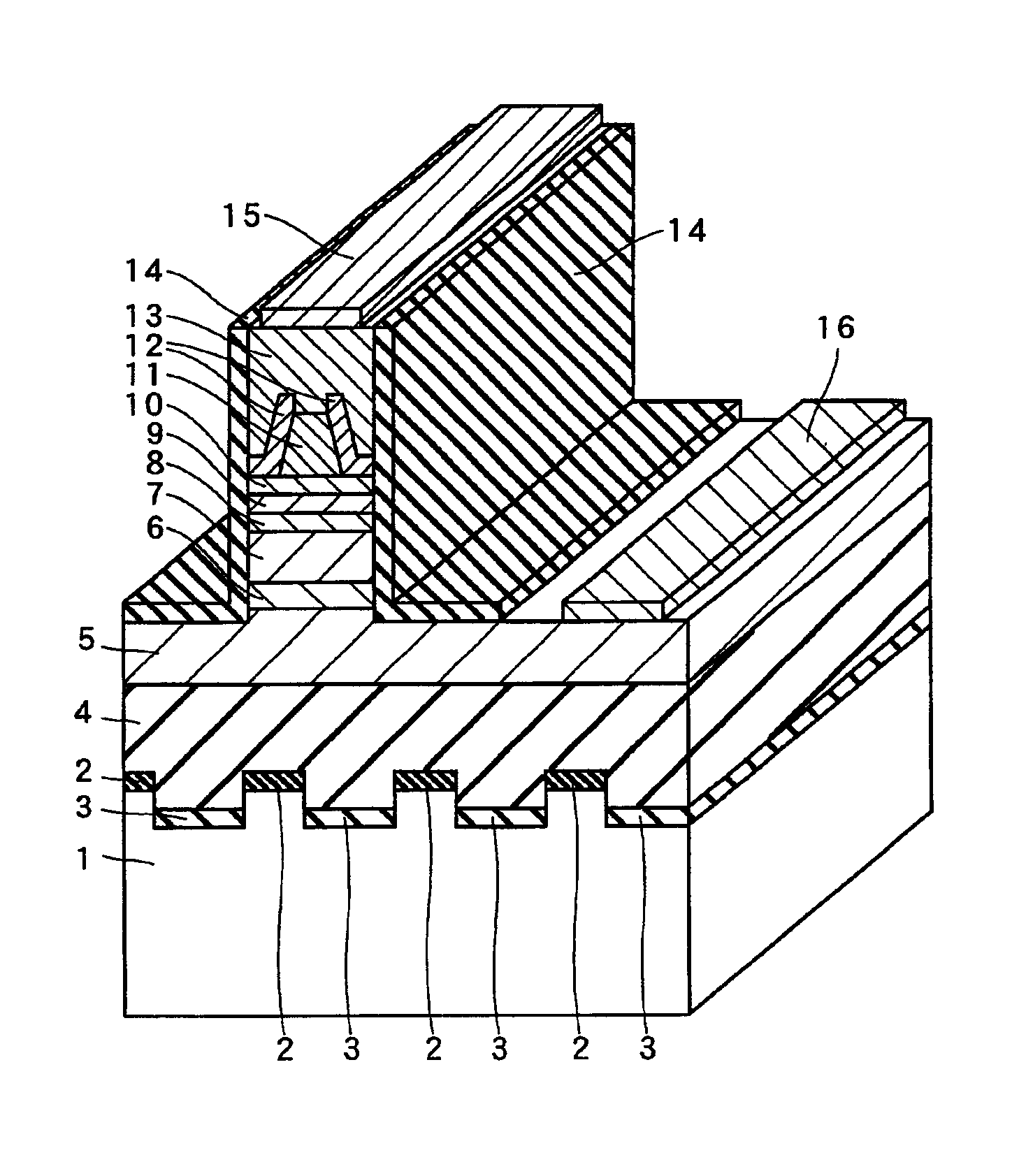

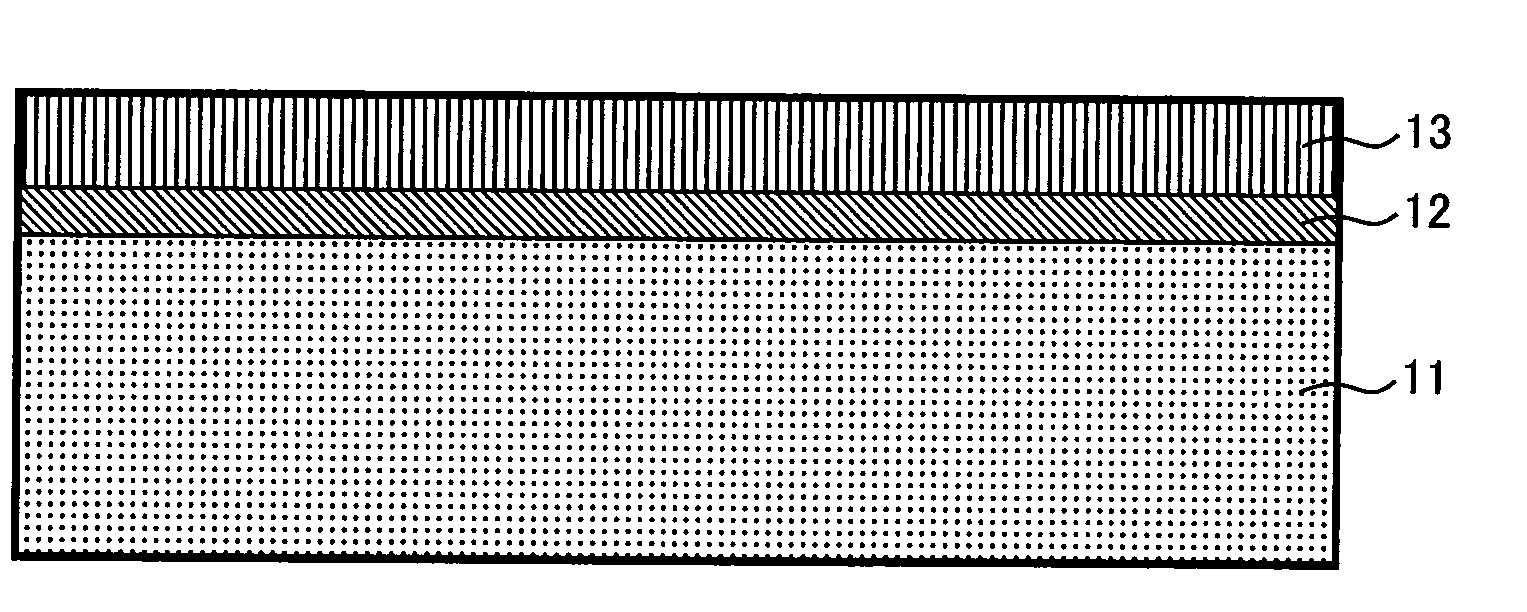

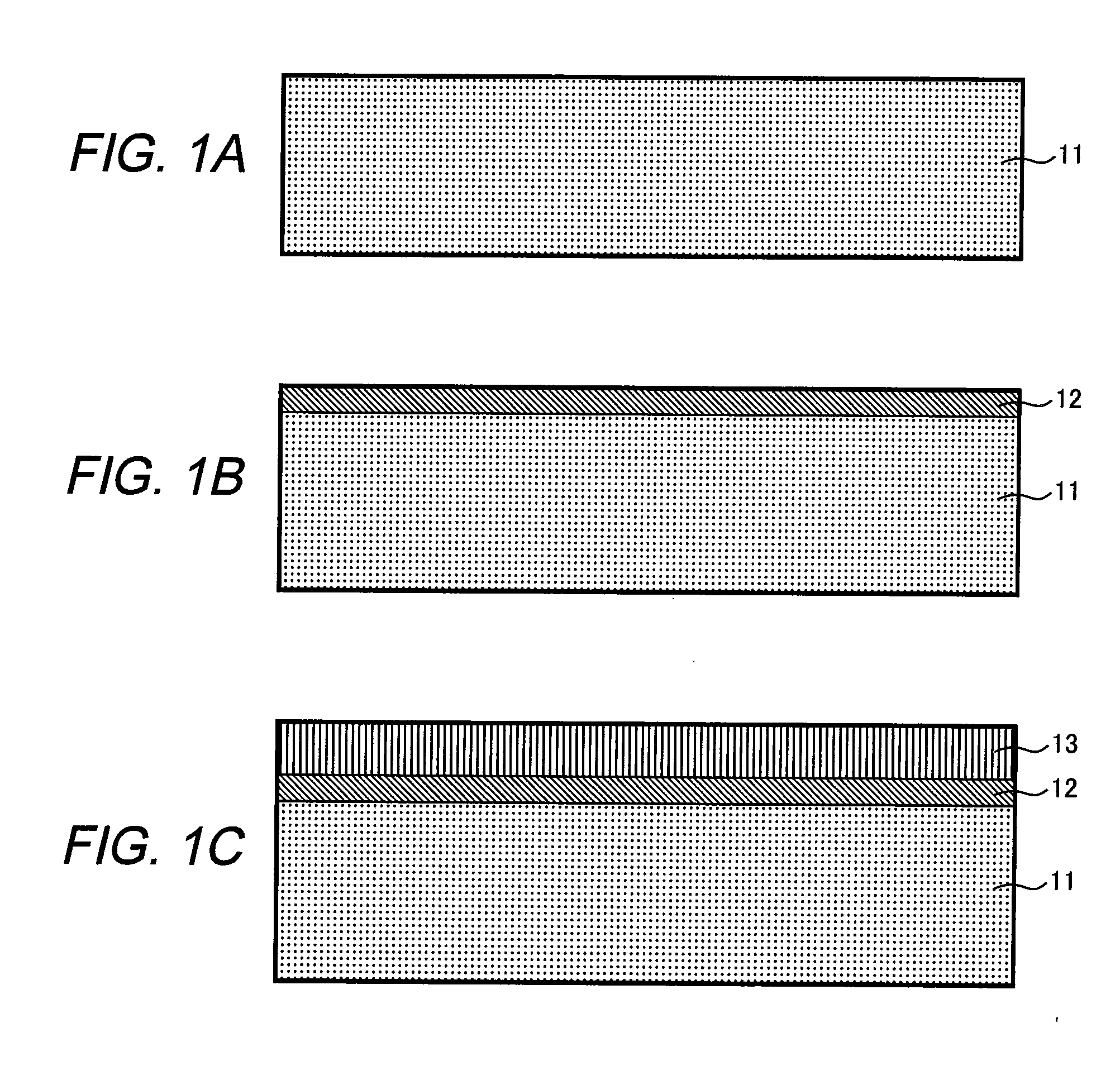

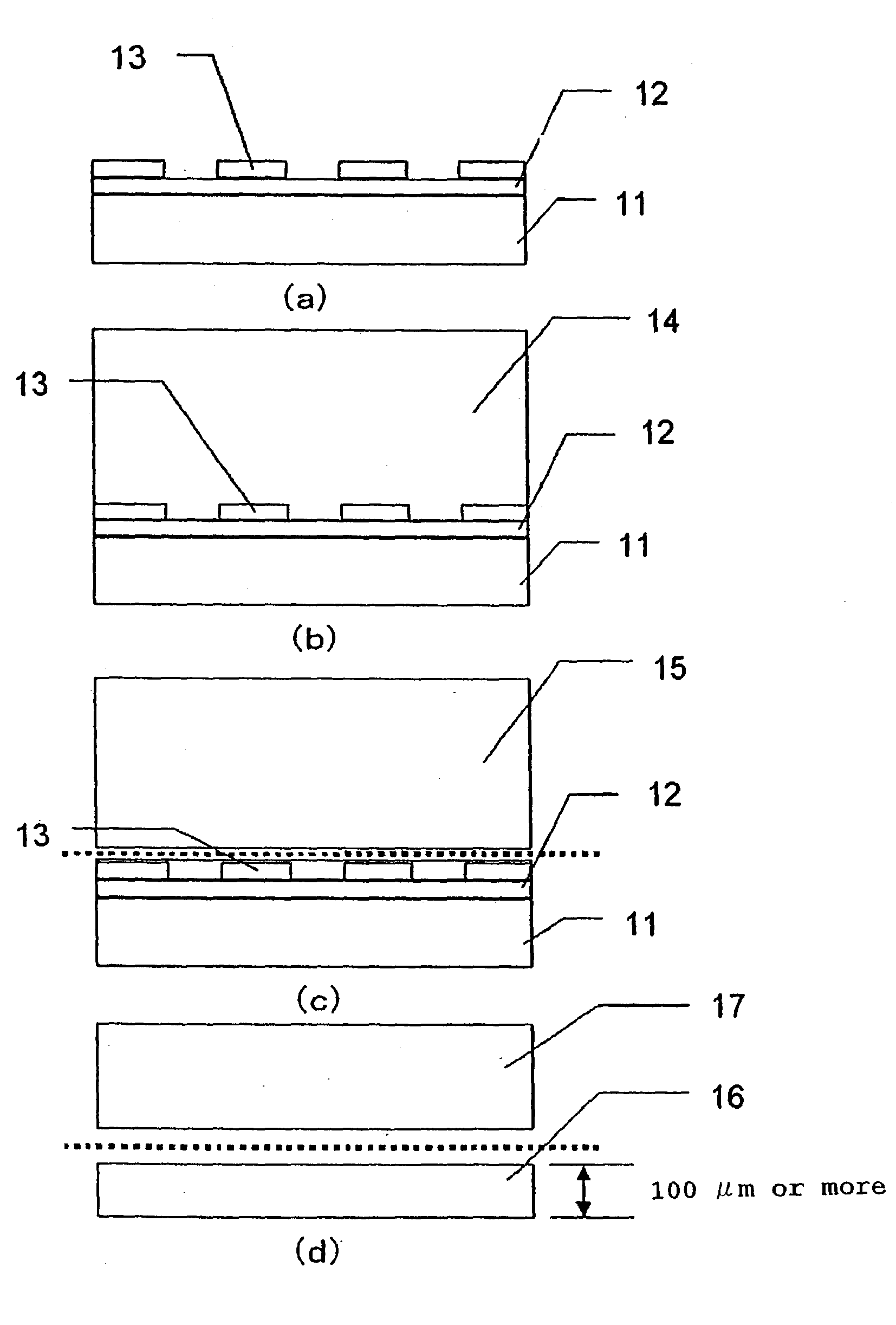

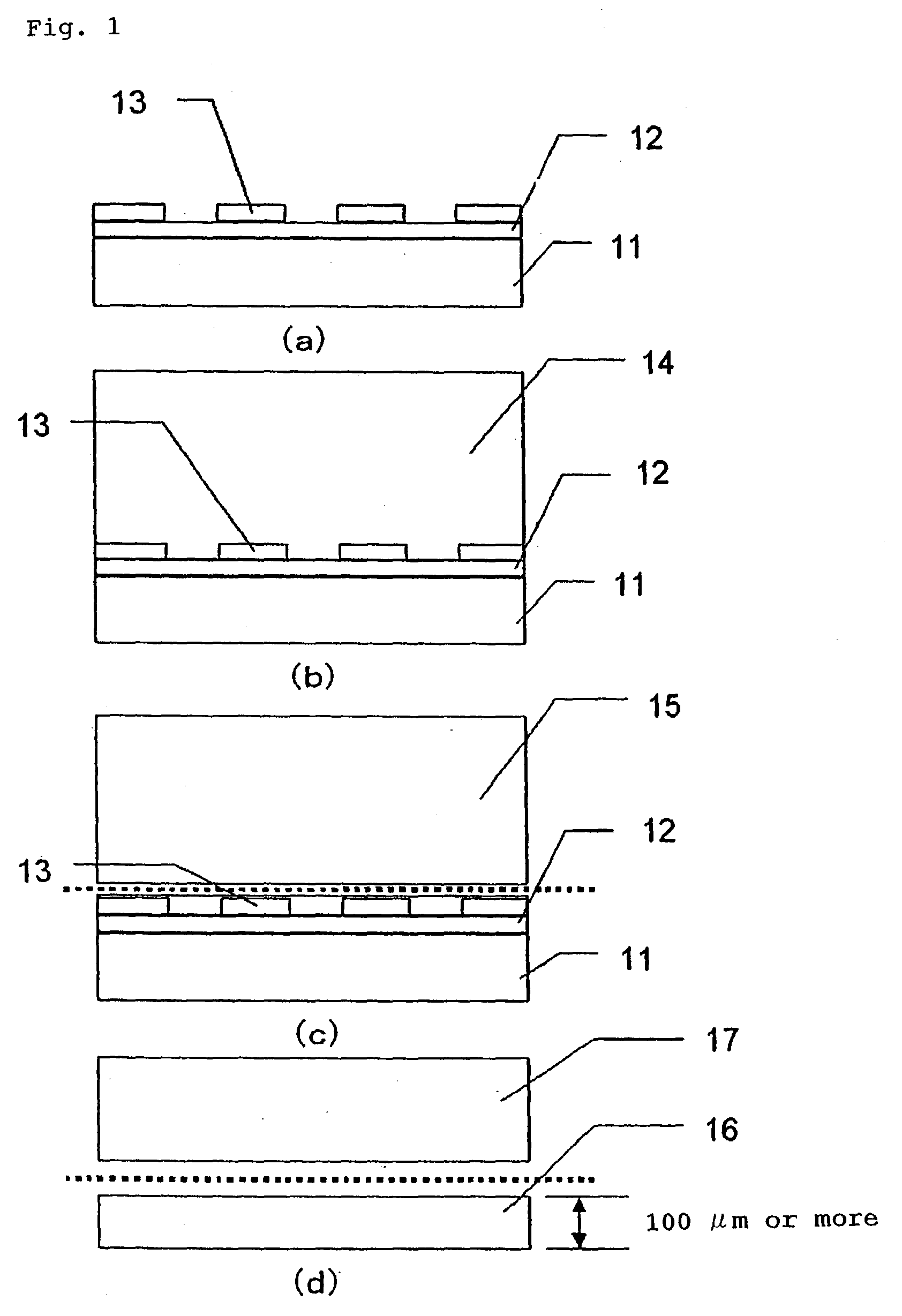

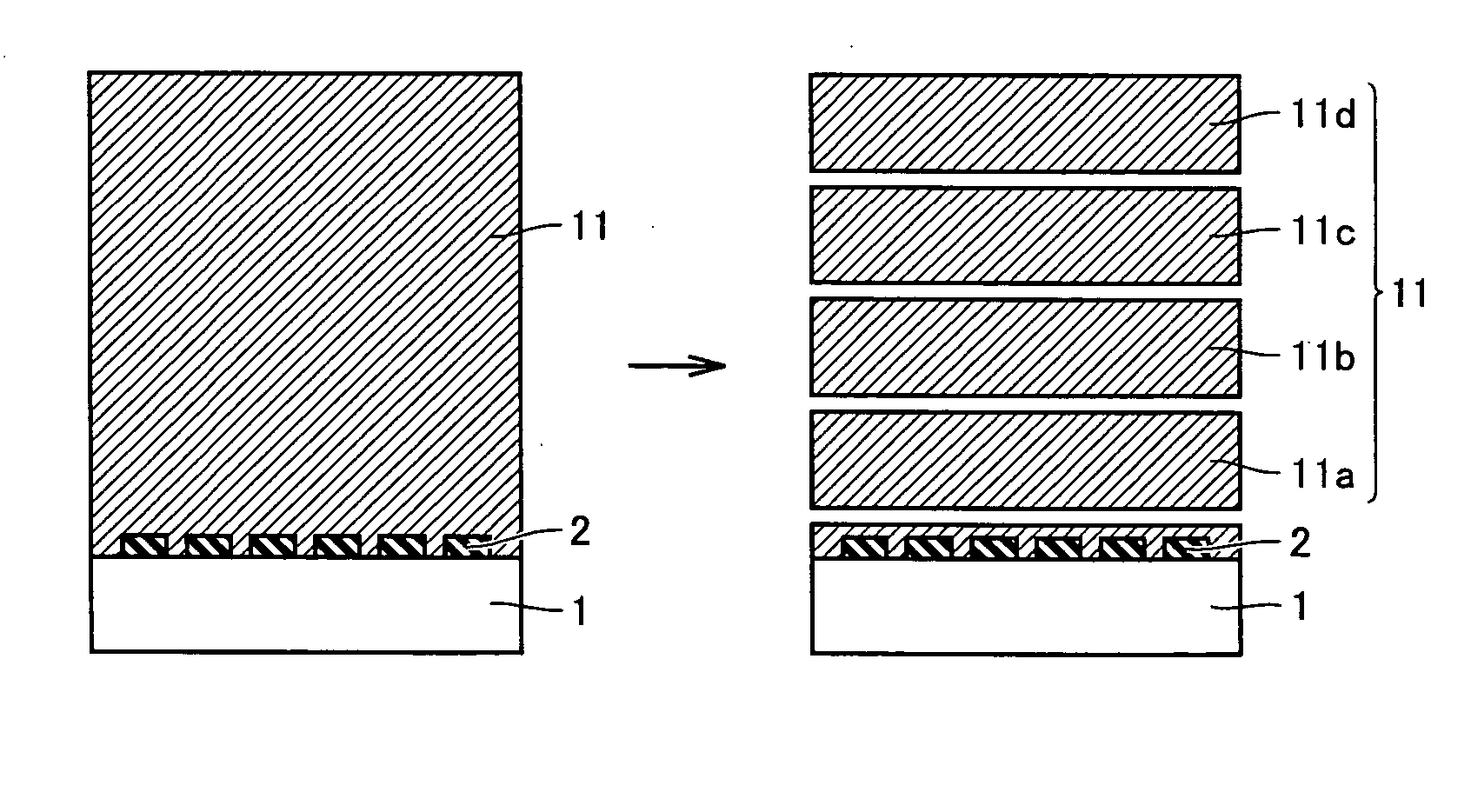

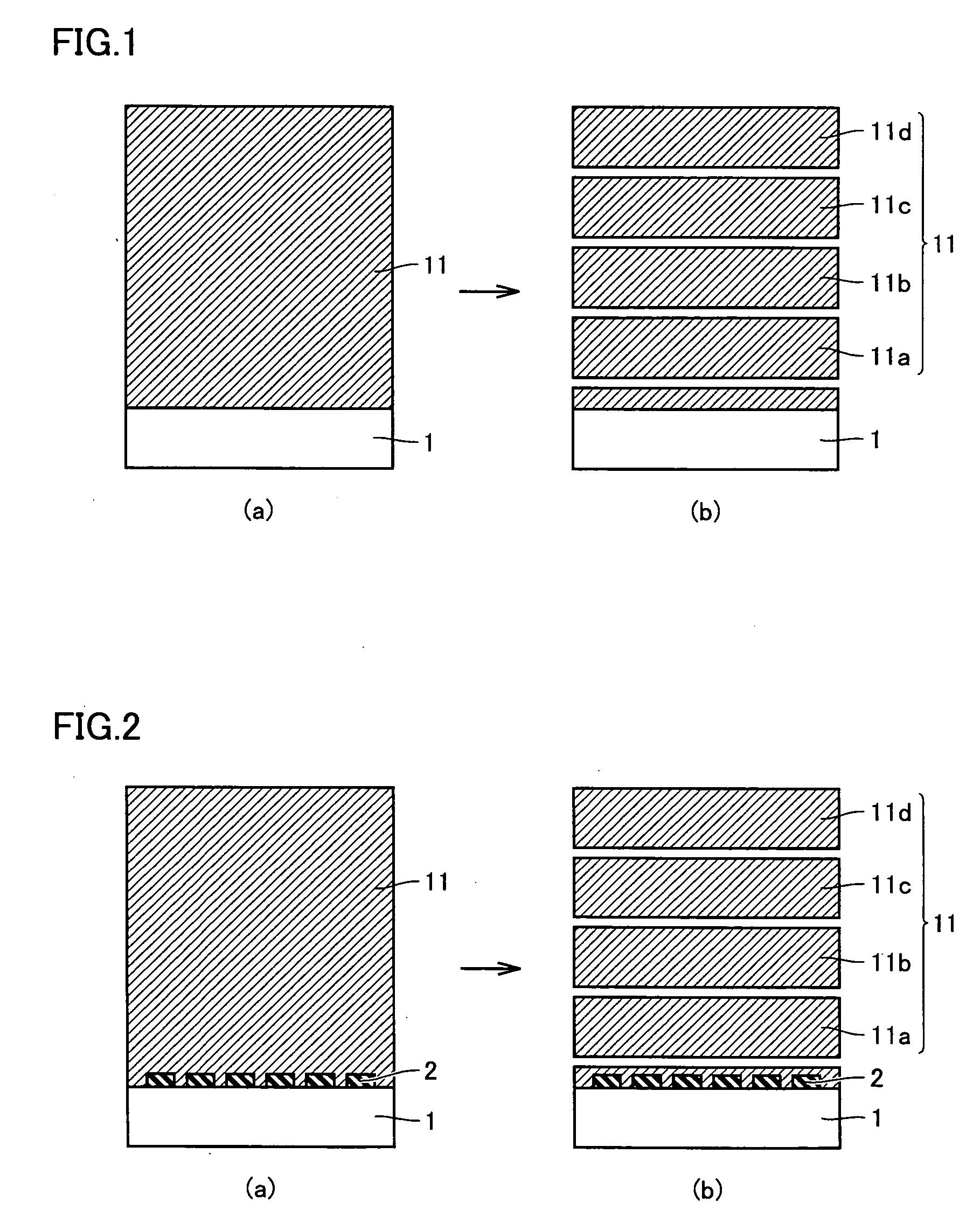

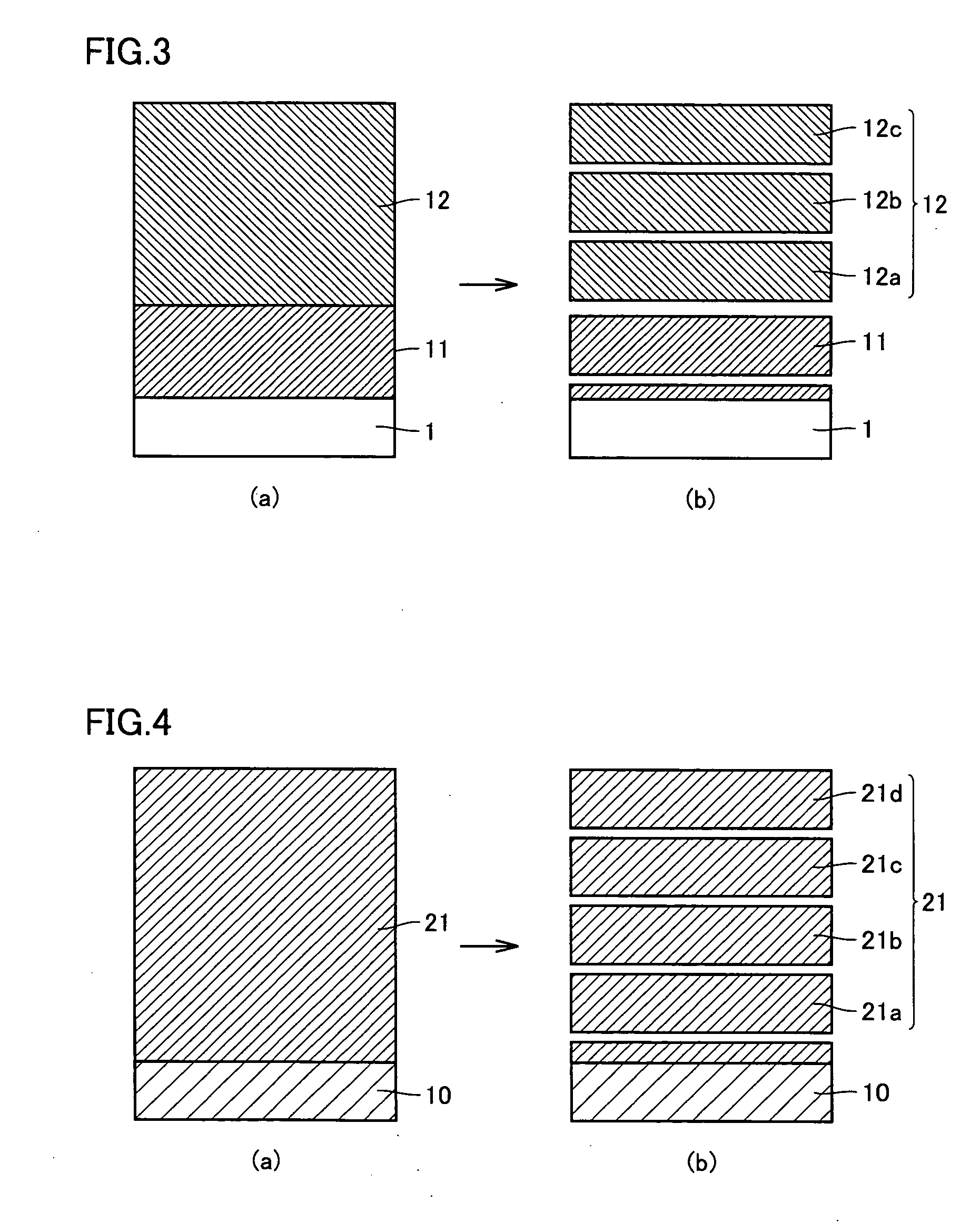

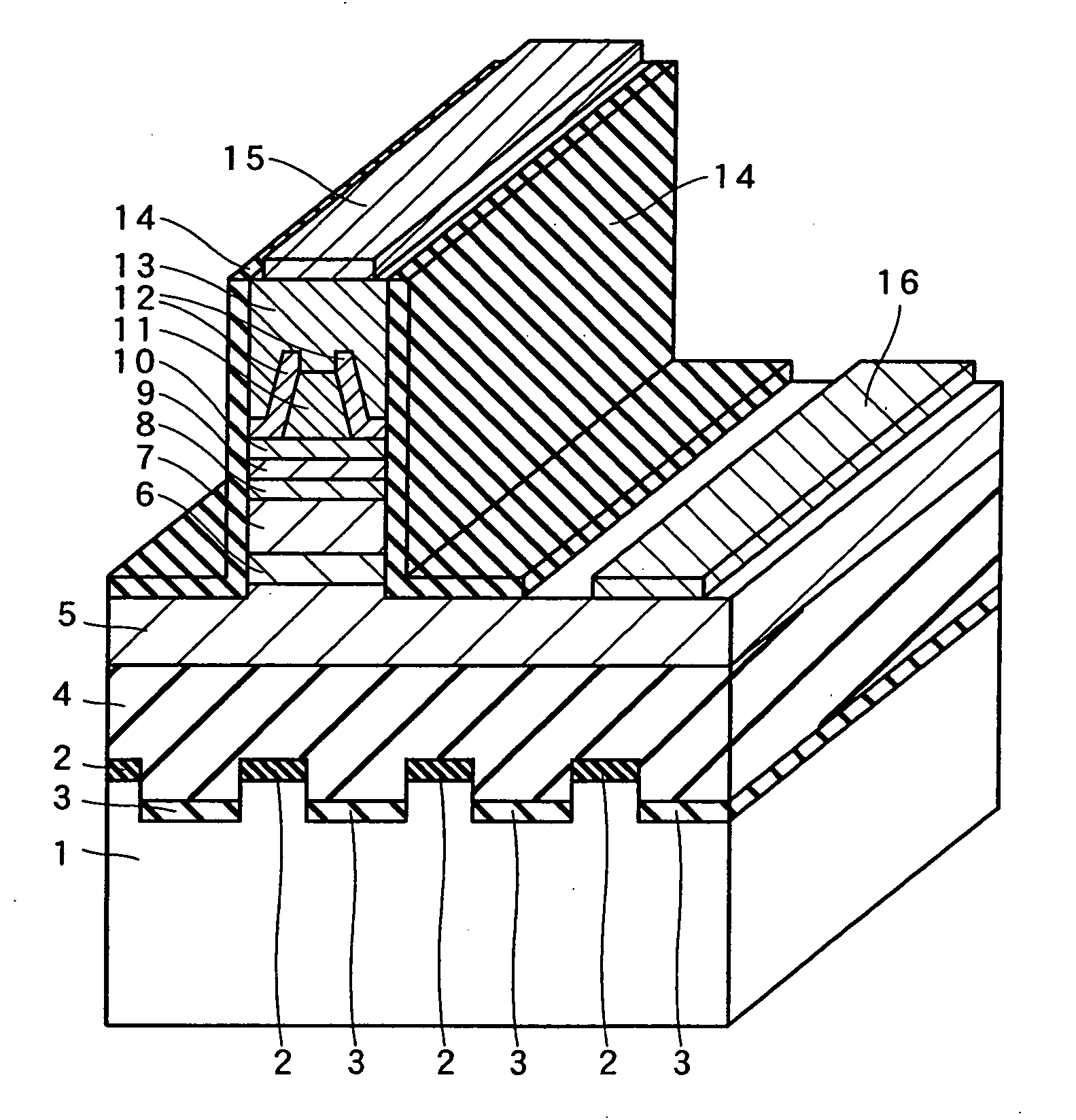

There are provided a GaN field effect transistor (FET) exhibiting an excellent breakdown voltage owing to the high quality of GaN crystal in a region where the electric lines of force concentrate during operation of the same, and a method of manufacturing the same. The FET has a layer structure formed of a plurality of GaN epitaxial layers. A gate electrode and a source electrode are disposed on the surface of the layer structure, and a drain electrode is disposed on the reverse surface of the same. A region of the layer structure in which the electric lines of force concentrate during operation of the FET has a reduced dislocation density compared with the other regions in the layer structure. The GaN FET is manufactured by forming, on a crystal-growing substrate having a surface formed with a plane pattern of a material other than a GaN-based material in an identical design to a plane pattern of an electrode determining the region in which the electric lines of force concentrate, a plurality of GaN epitaxial layers, one upon another, by using the epitaxial lateral overgrowth technique, thereby forming a layer structure, and then forming operational electrodes on the surface of the layer structure.

Owner:FURUKAWA ELECTRIC CO LTD

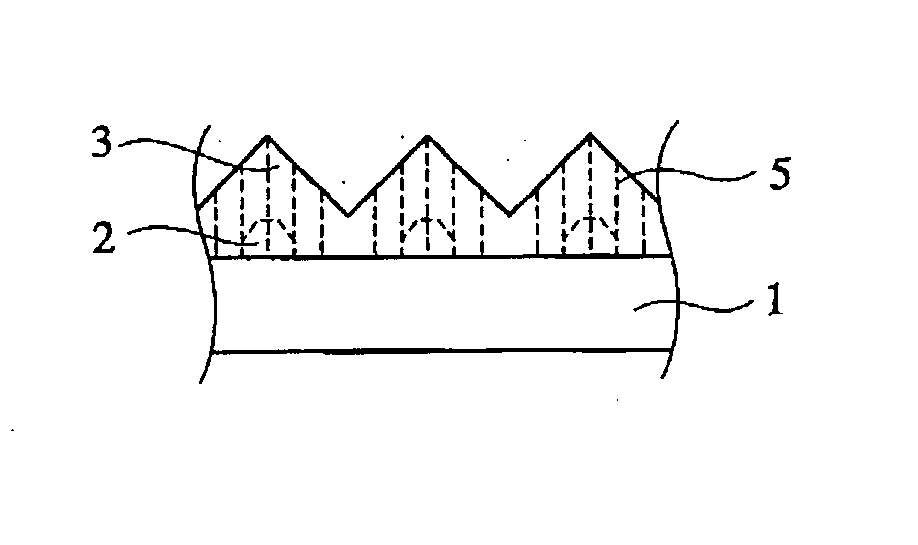

Light-emitting diode and method for manufacturing same, integrated light-emitting diode and method for manufacturing same, method for growing a nitride-based iii-v group compound semiconductor, substrate for growing a nitride-based iii-v group compound semiconductor, light source cell unit, light-emitting diode backlight, light-emitting diode illuminating device, light-emitting diode display and electronic instrument, electronic device and method for manufacturing same

InactiveUS20070085093A1Low luminous efficiencyLight extraction efficiencyPolycrystalline material growthSolid-state devicesDisplay deviceEngineering

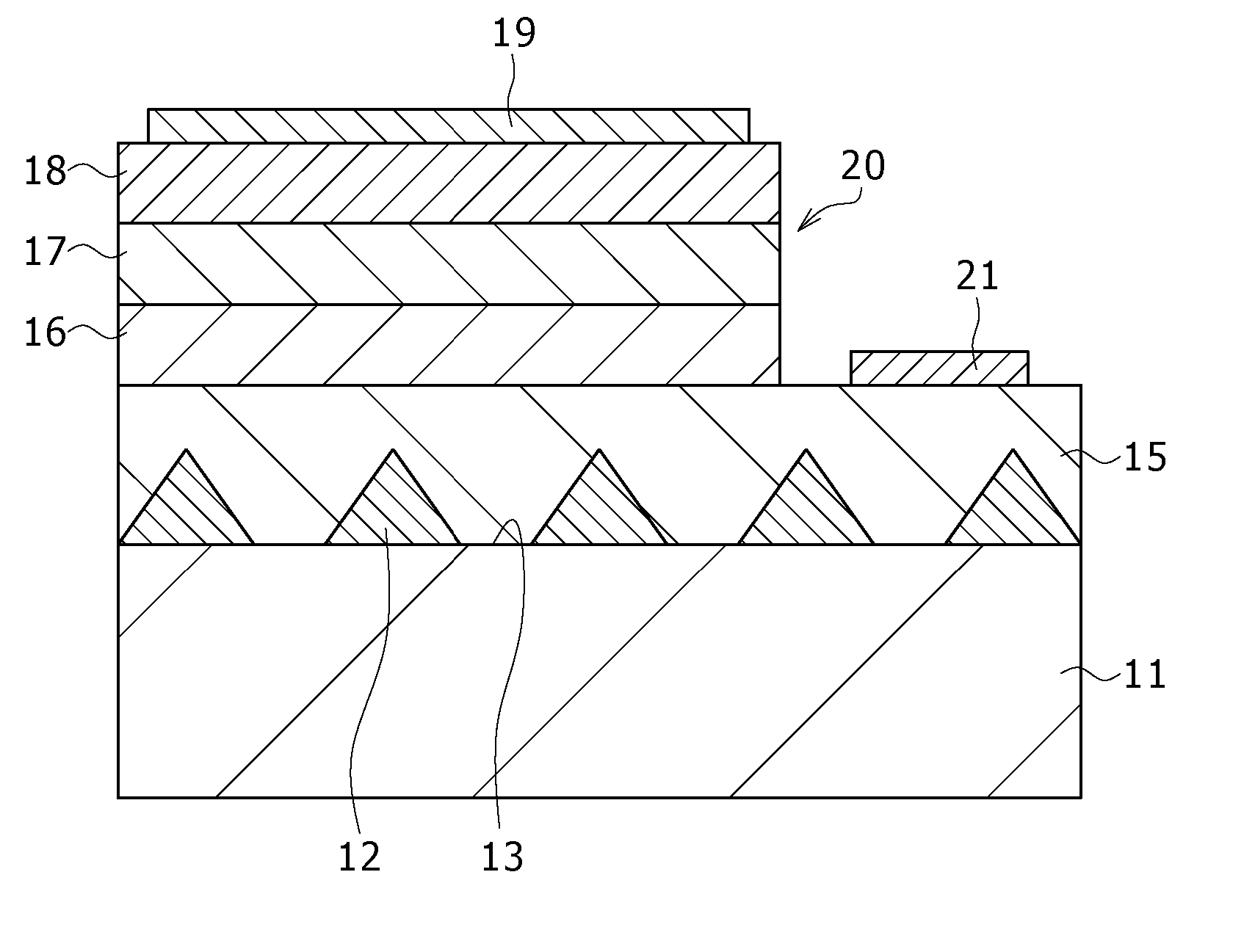

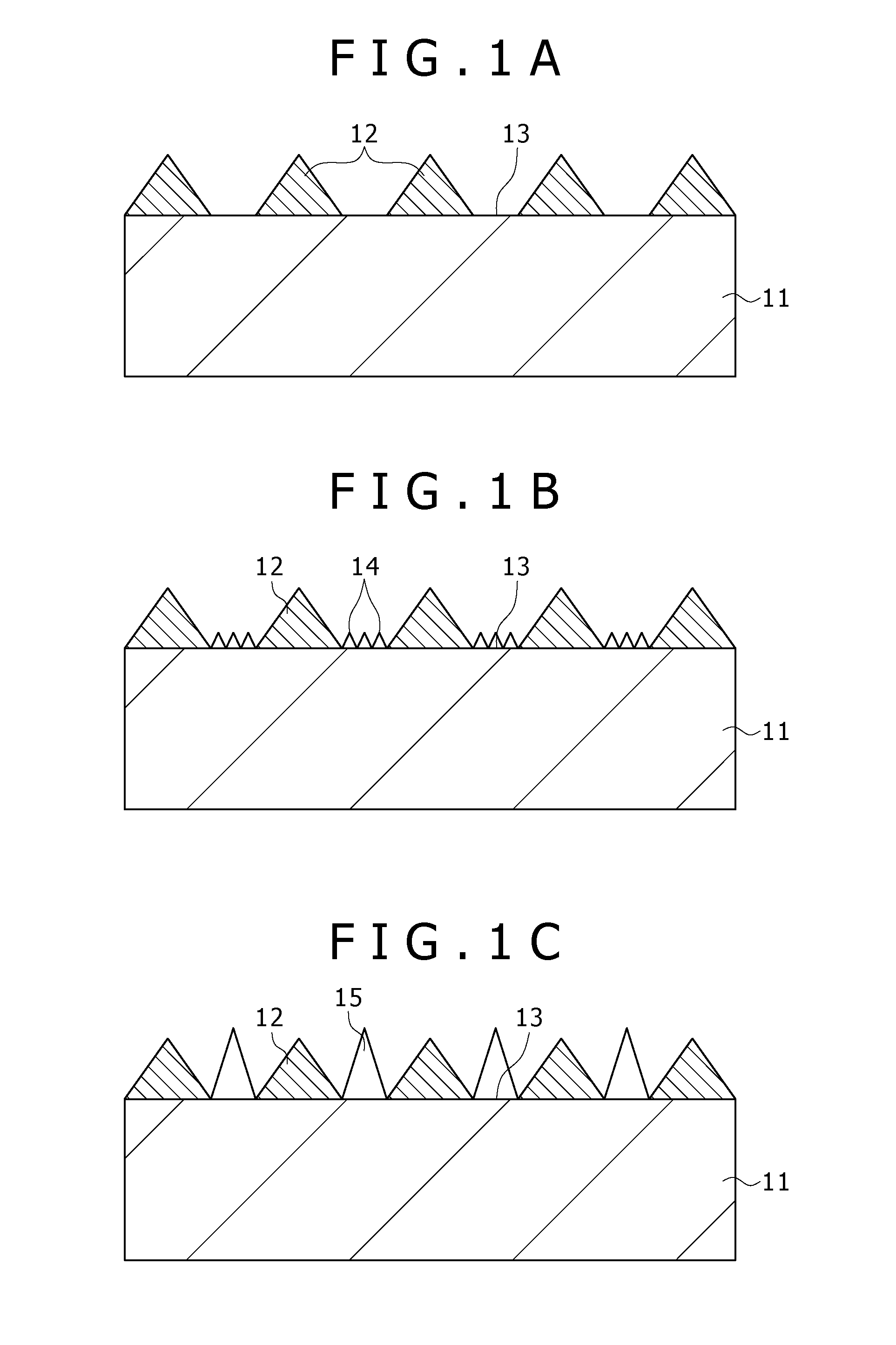

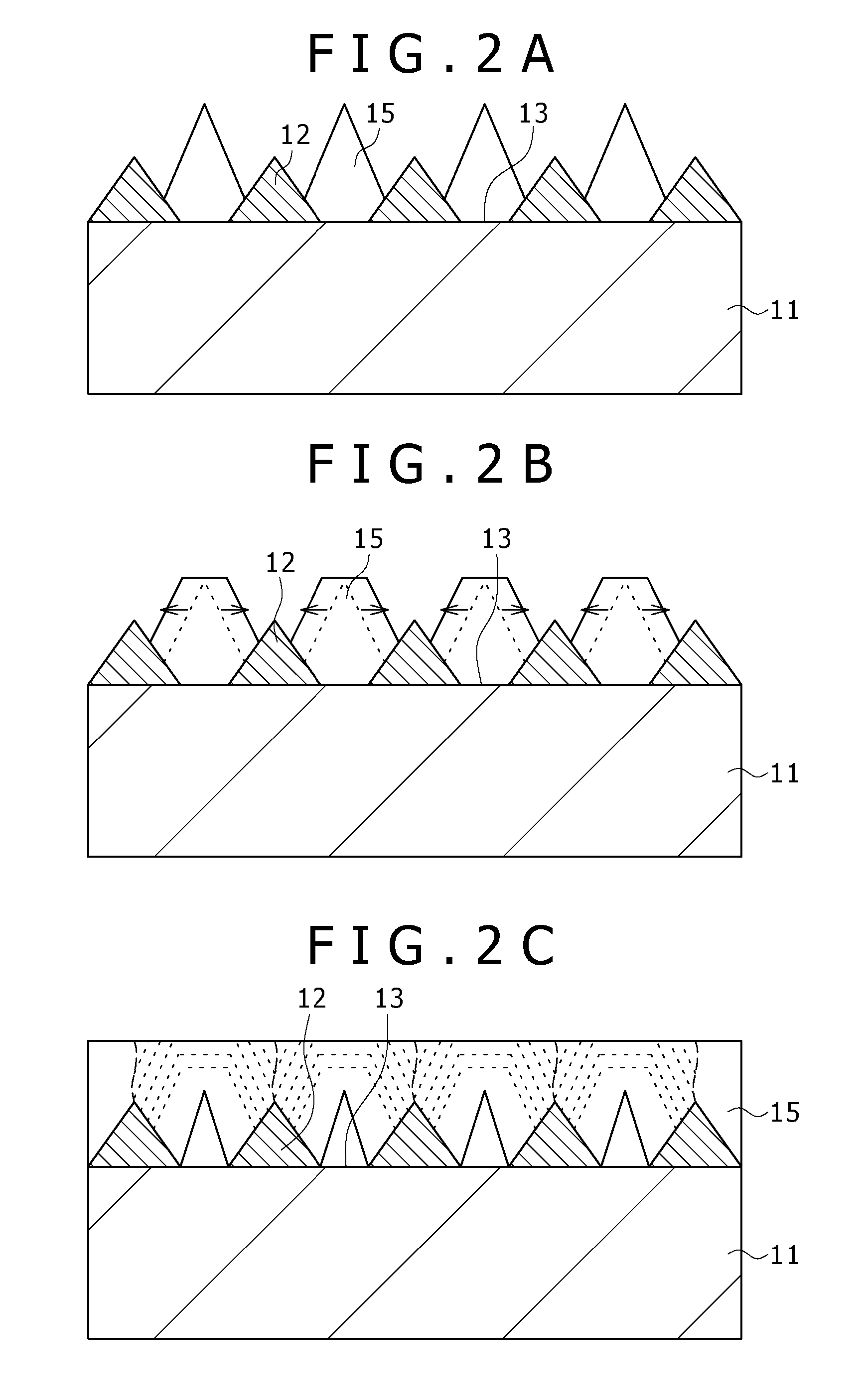

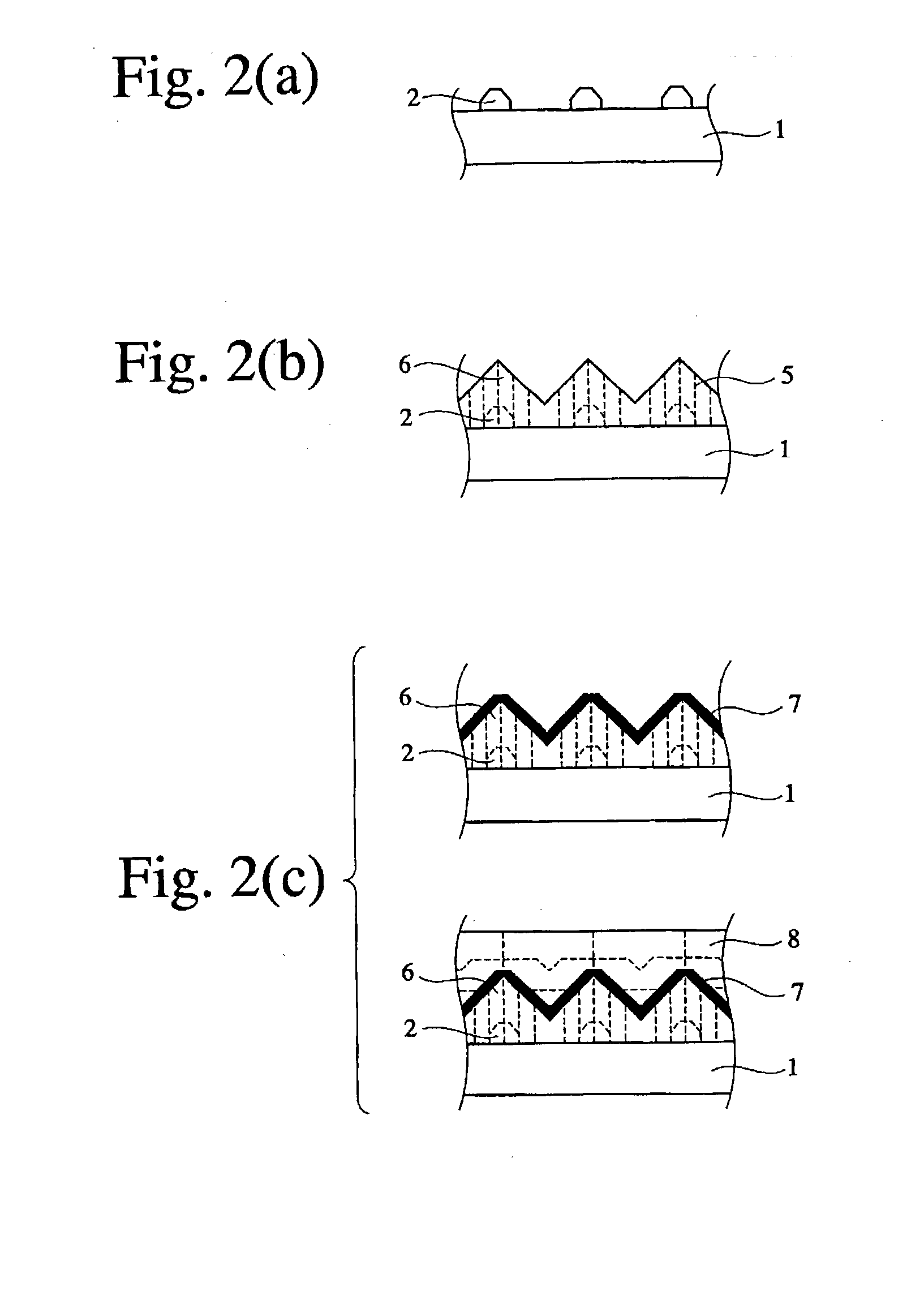

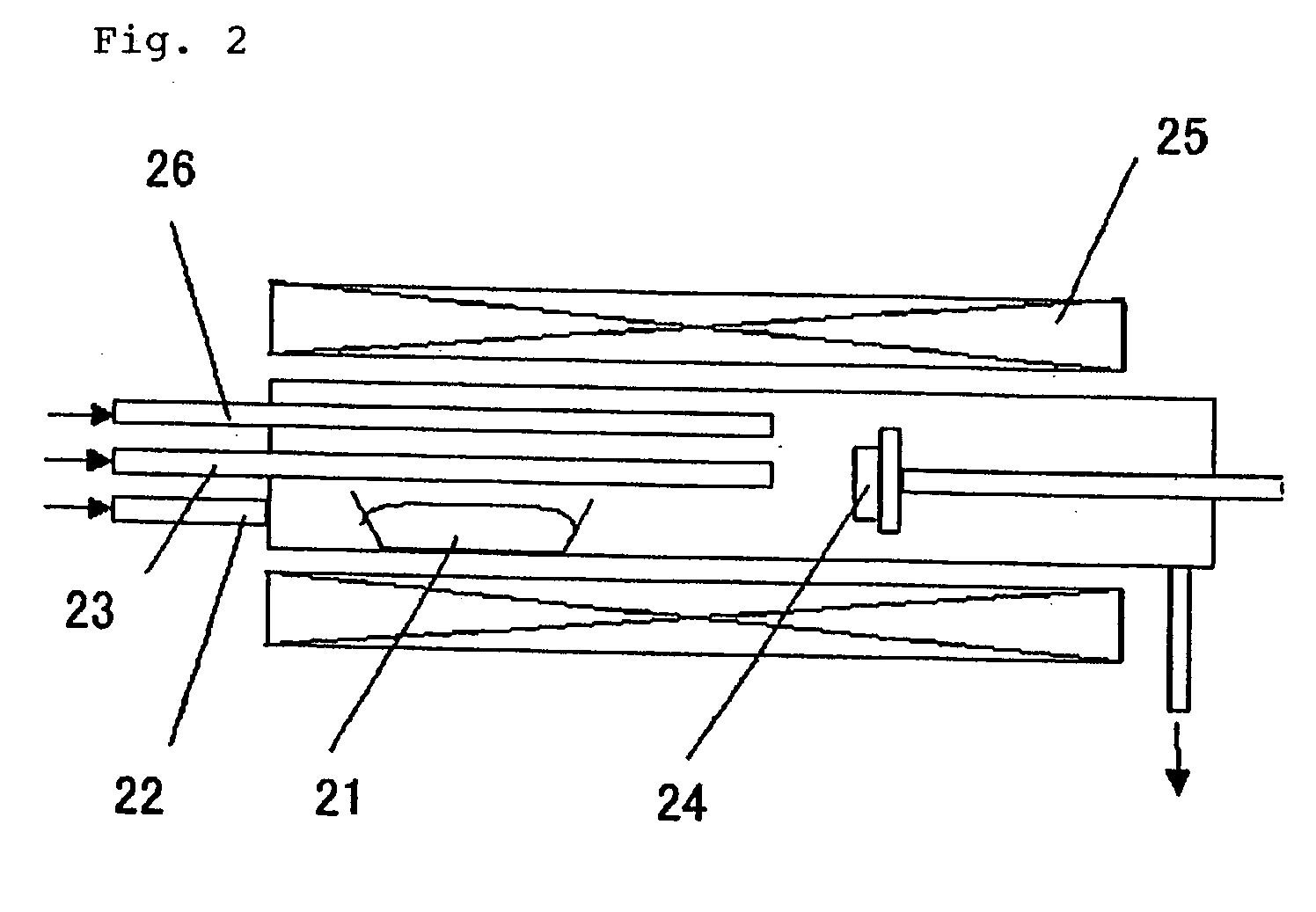

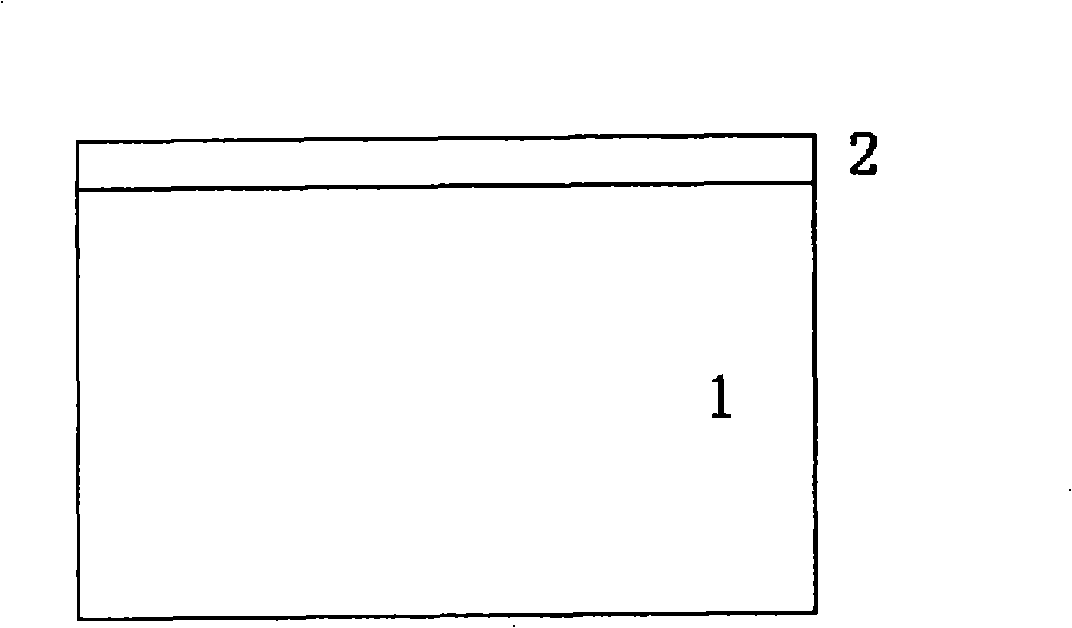

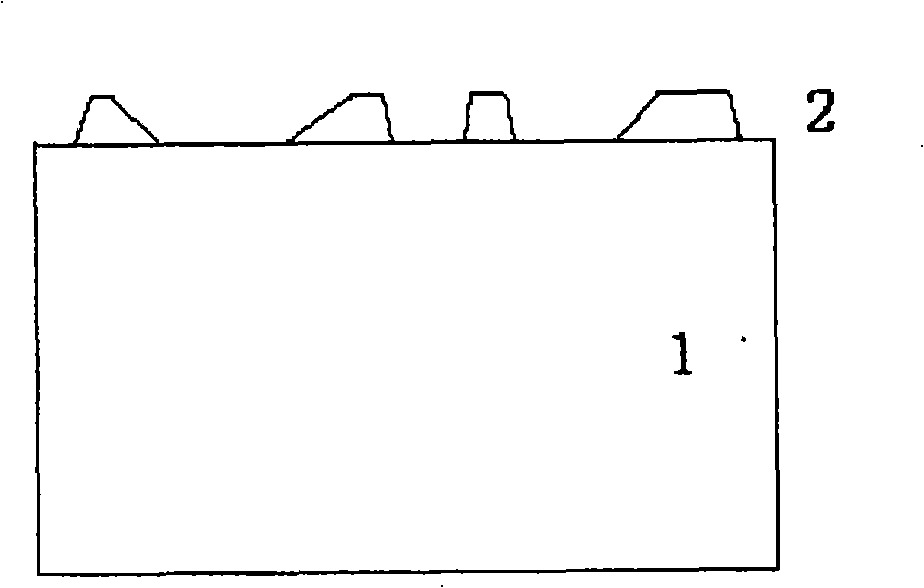

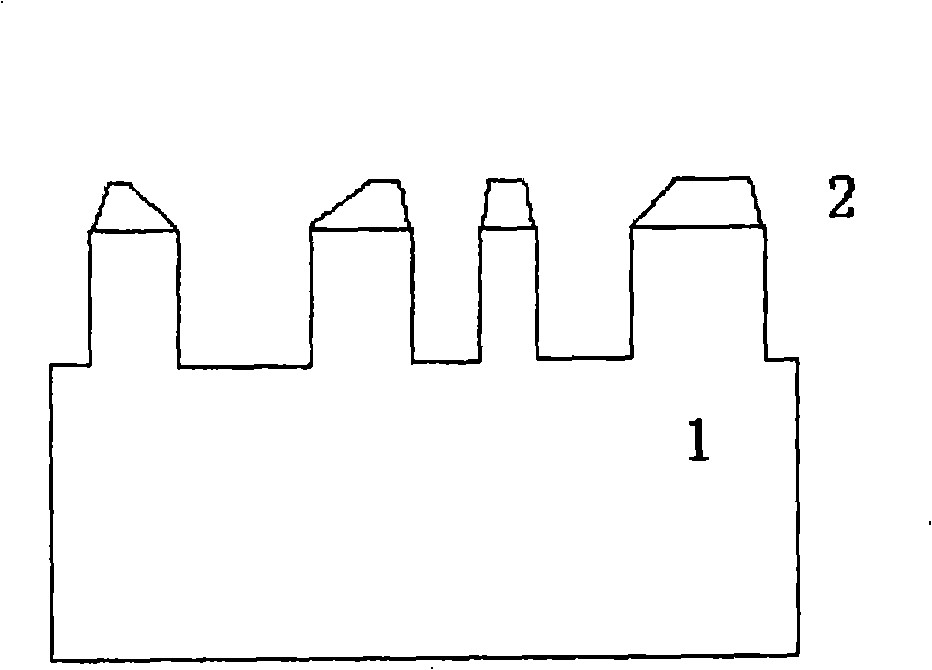

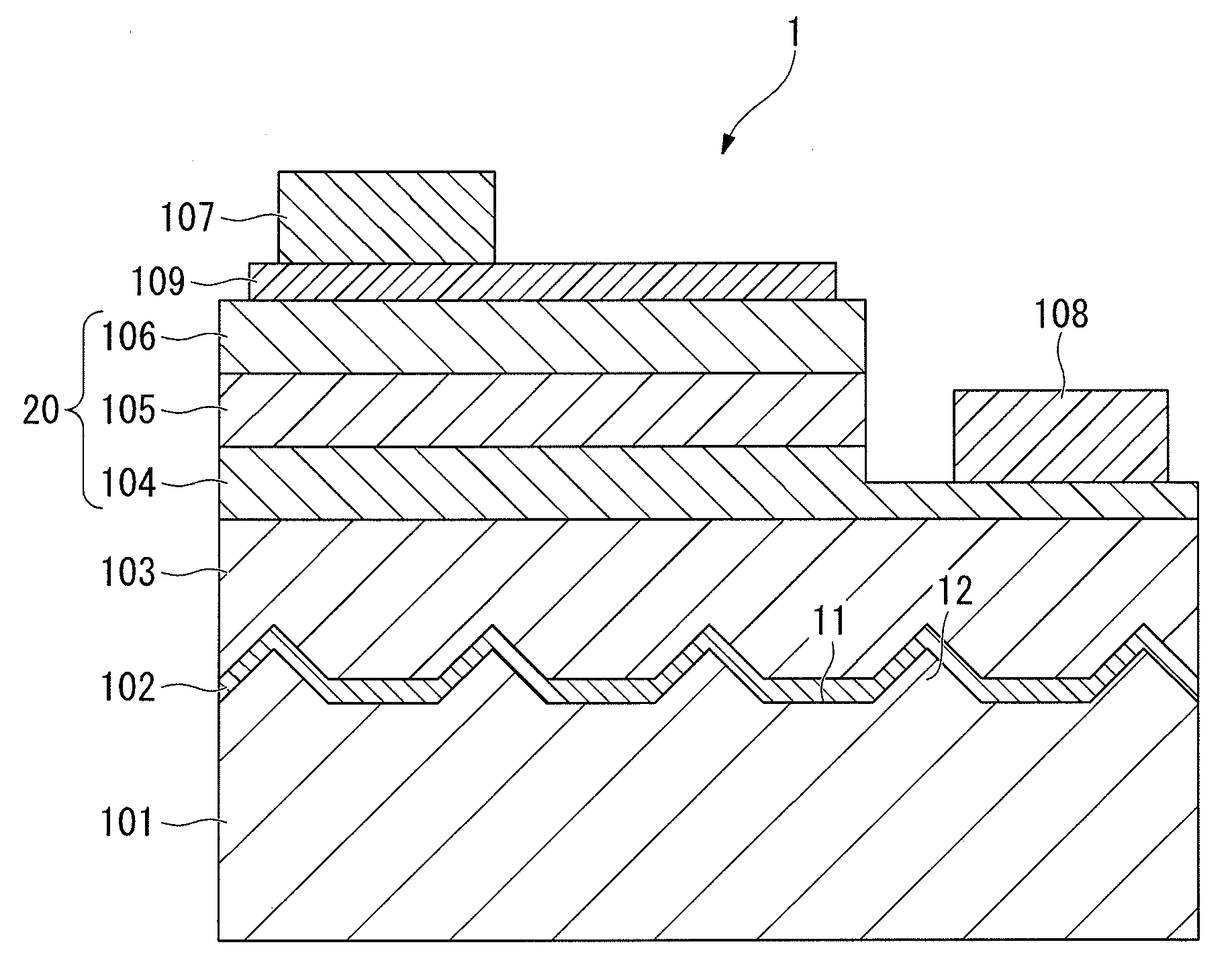

A method for manufacturing a light-emitting diode, which includes the steps of: providing a substrate having a plurality of protruded portions on one main surface thereof wherein the protruded portion is made of a material different in type from that of the substrate and growing a first nitride-based III-V Group compound semiconductor layer on each recess portion of the substrate through a state of making a triangle in section wherein a bottom surface of the recess portion becomes a base of the triangle; laterally growing a second nitride-based III-V Group compound semiconductor layer on the substrate from the first nitride-based III-V Group compound semiconductor layer; and successively growing, on the second nitride-based III-V Group compound semiconductor layer, a third nitride-based III-V Group compound semiconductor layer of a first conduction type, an active layer, and a fourth nitride-based III-V compound semiconductor layer of a second conduction type.

Owner:SONY CORP

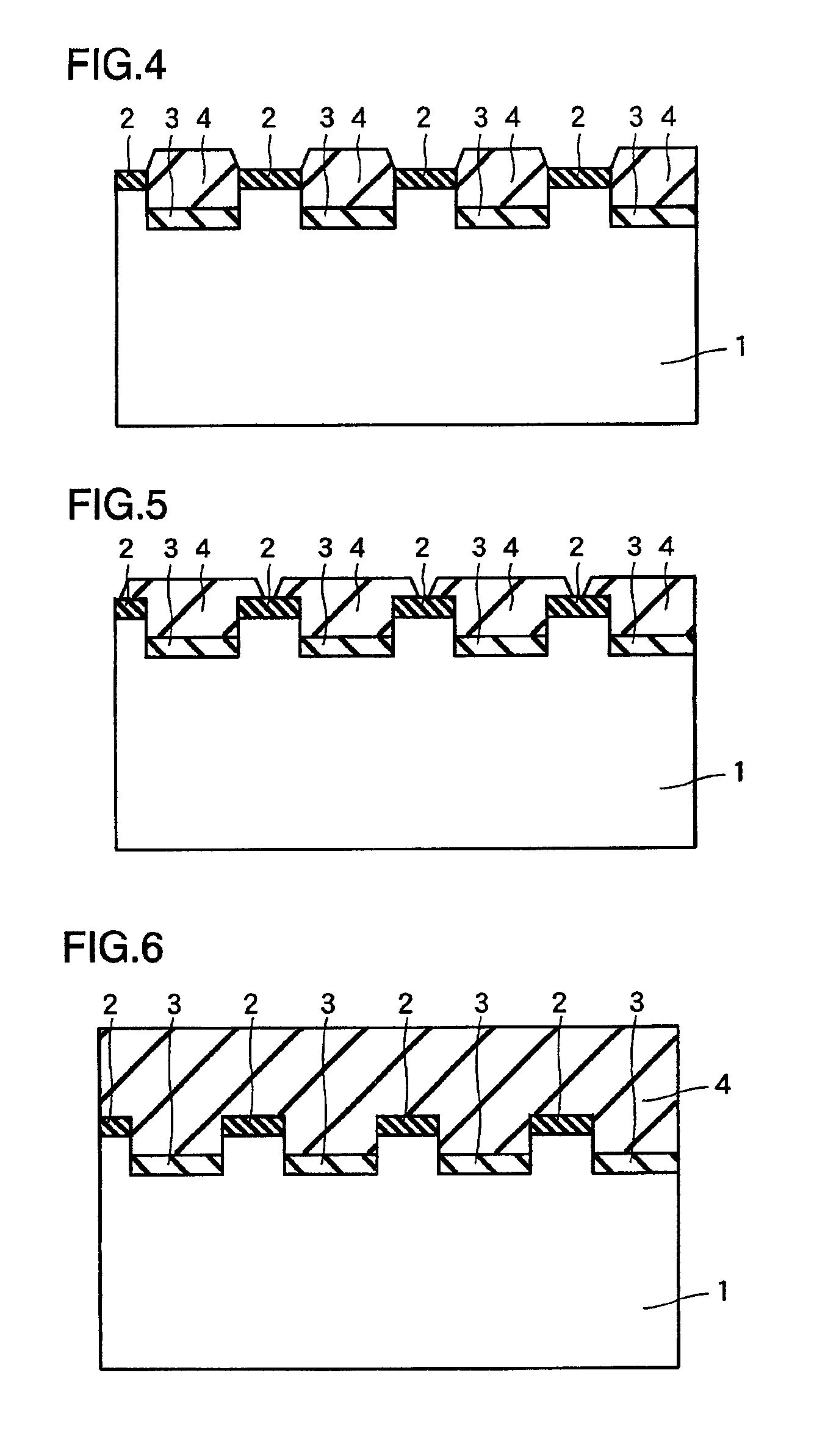

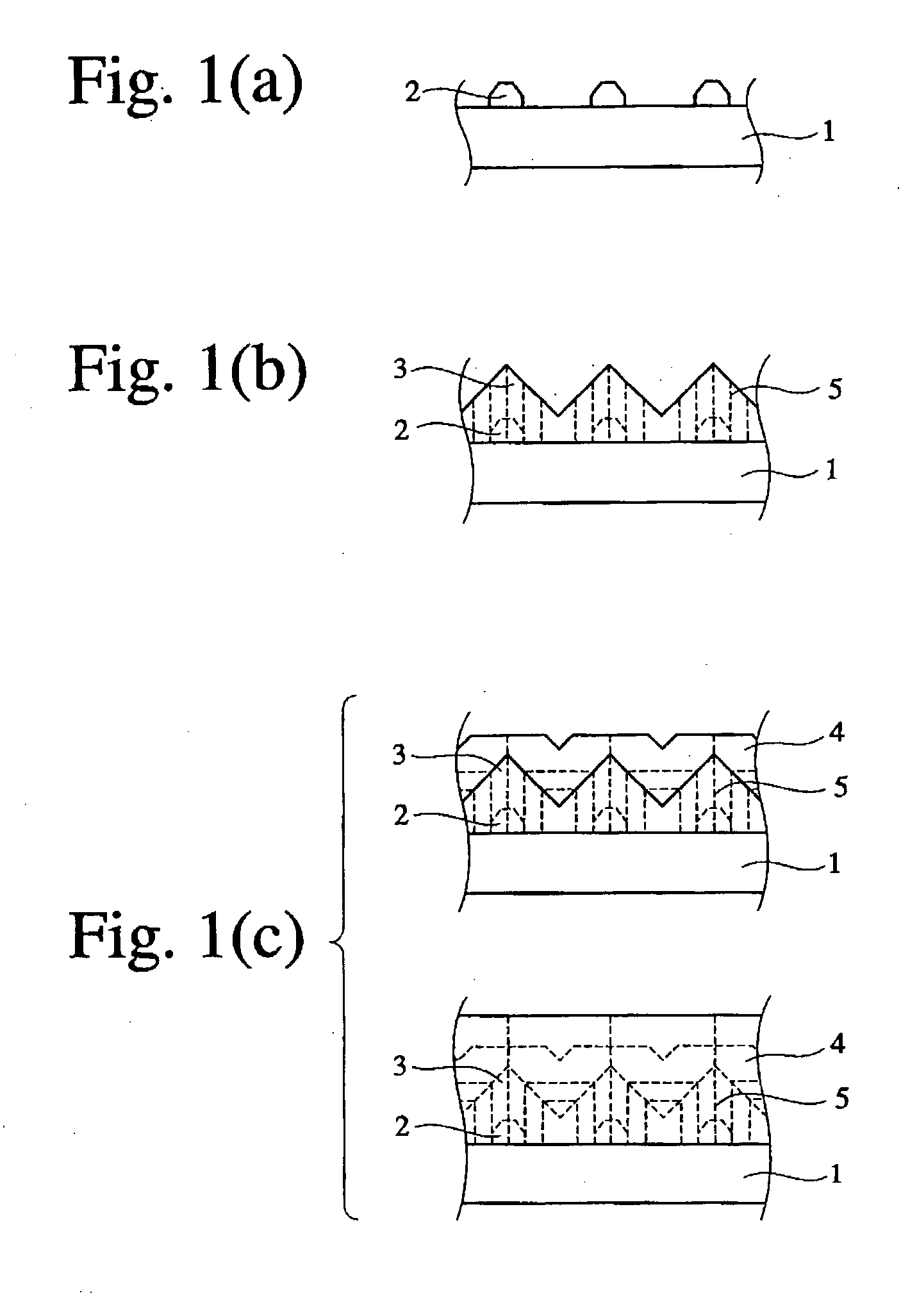

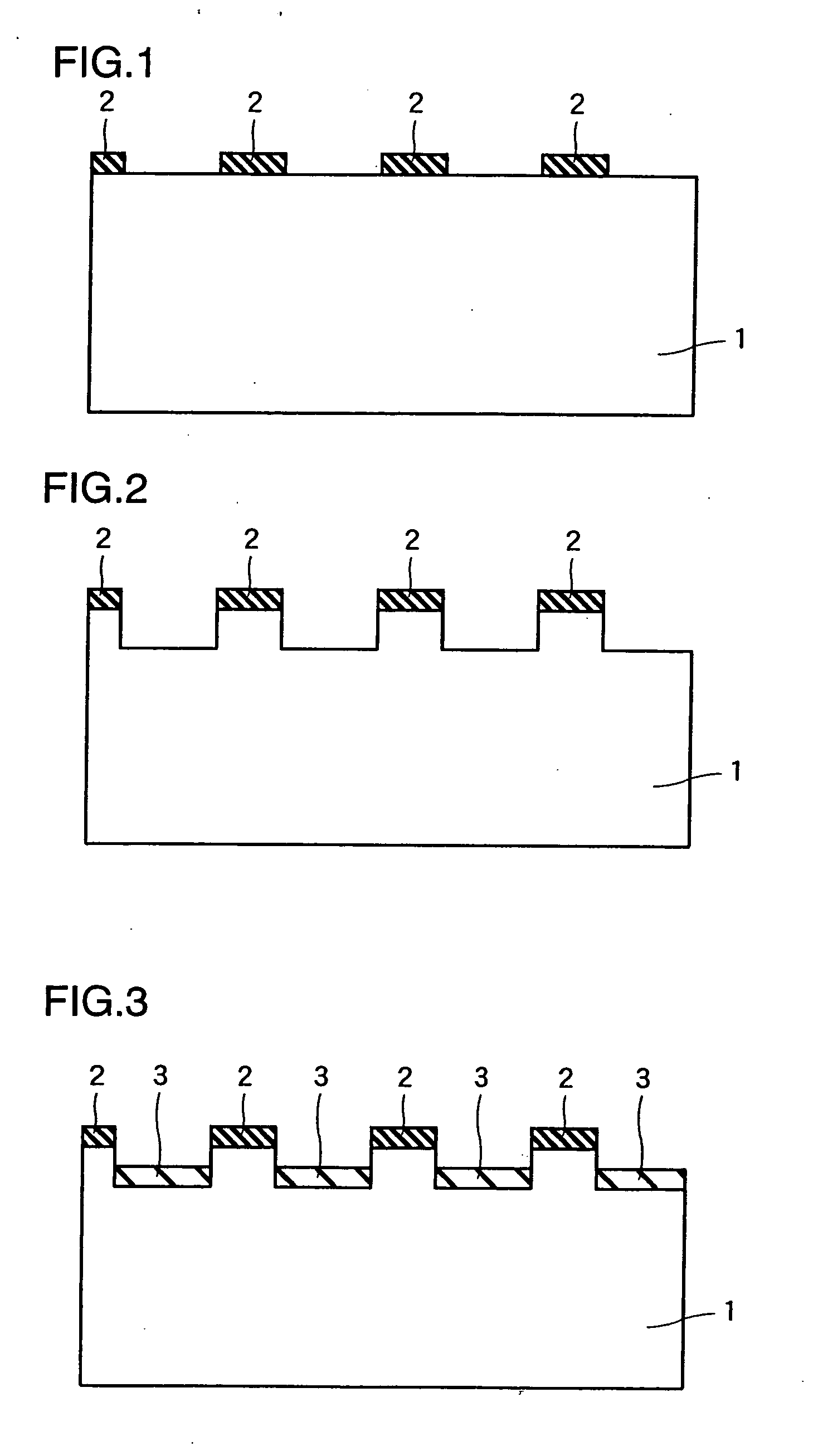

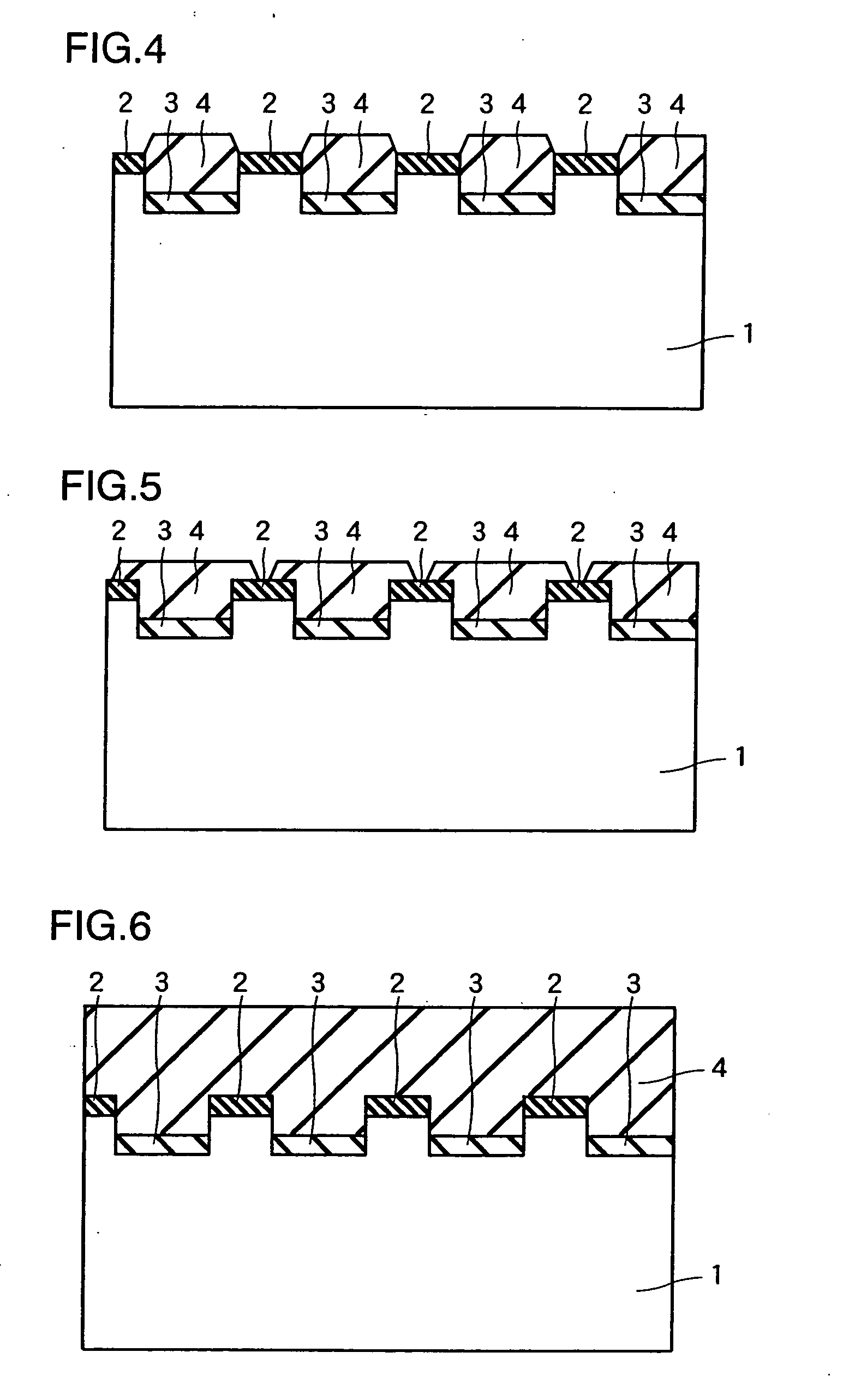

Nitride-based semiconductor element and method of forming nitride-based semiconductor

InactiveUS6994751B2Improve batch productivityExcellent element characteristicOptical wave guidancePolycrystalline material growthProduction rateDislocation

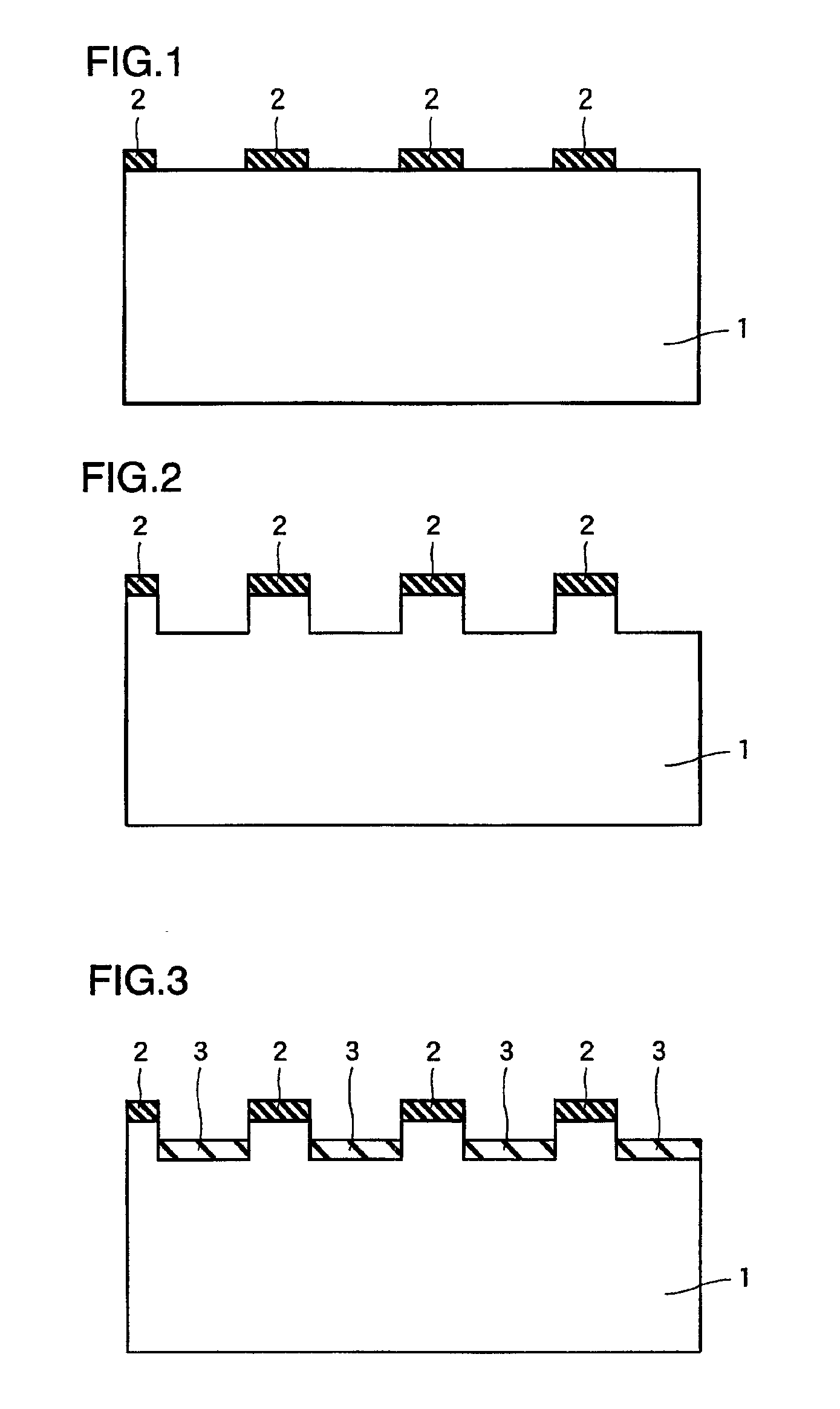

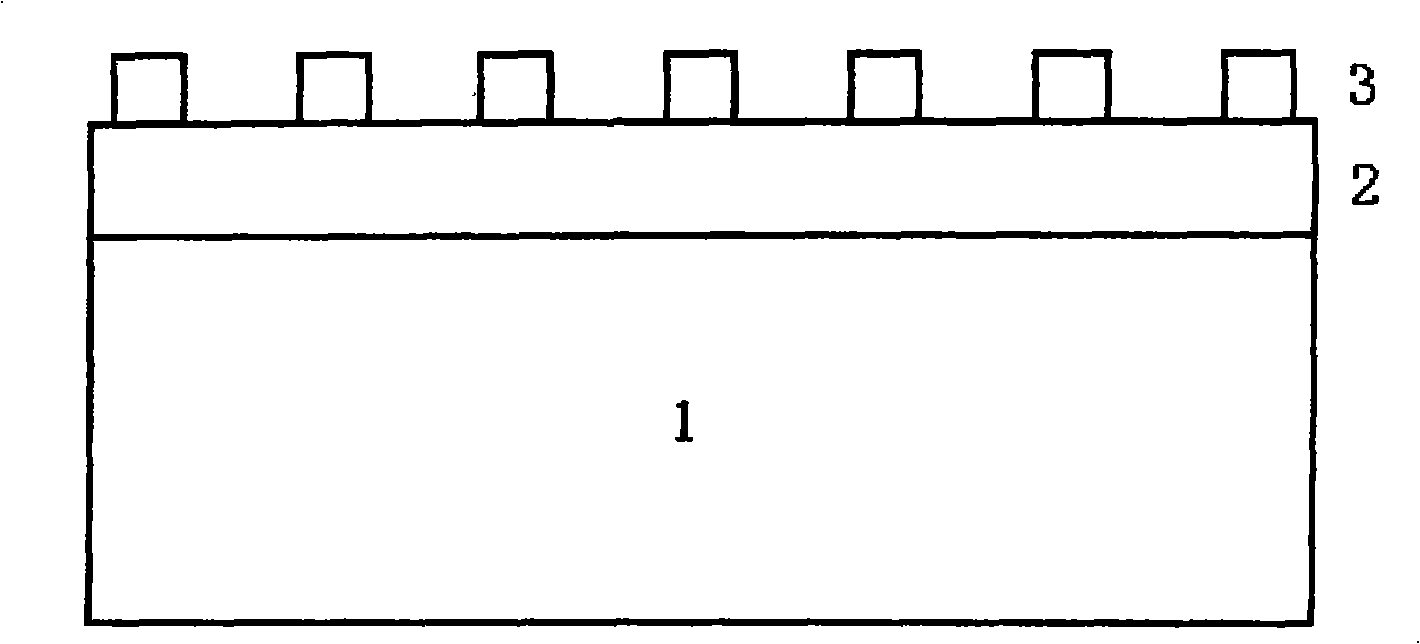

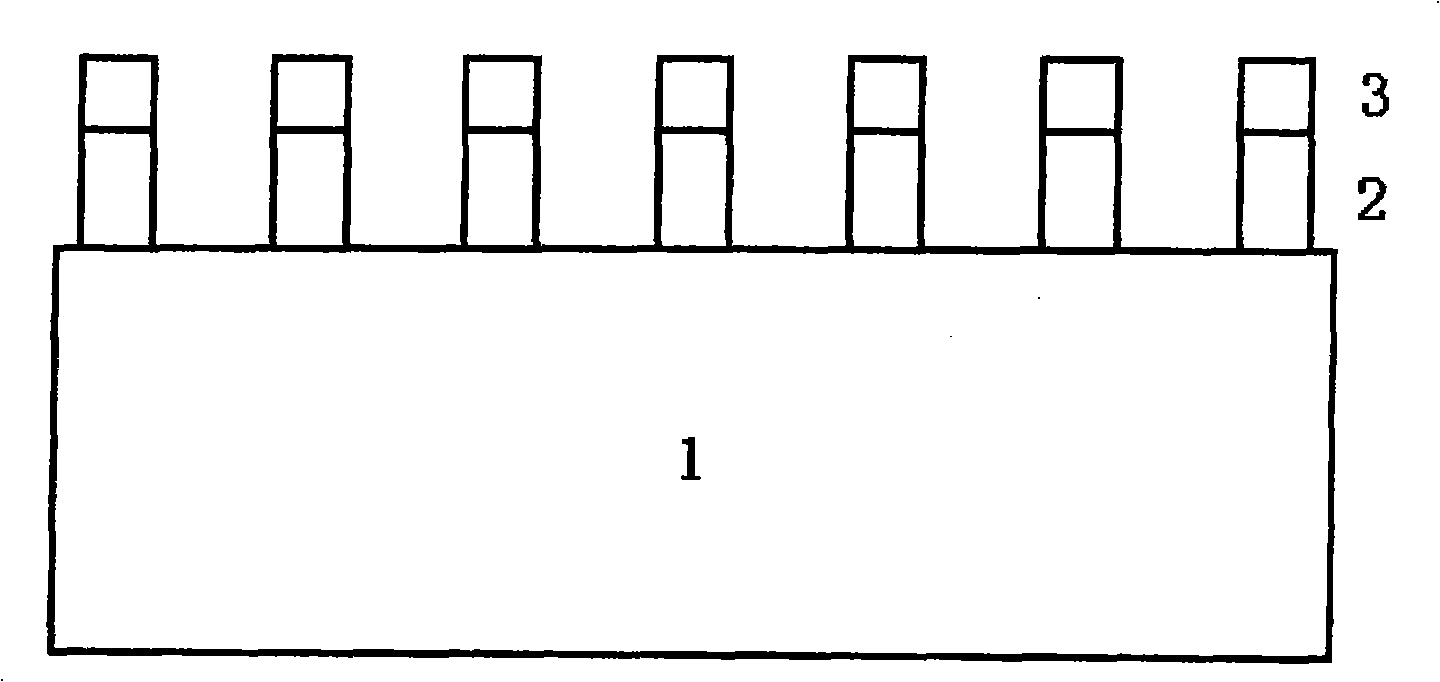

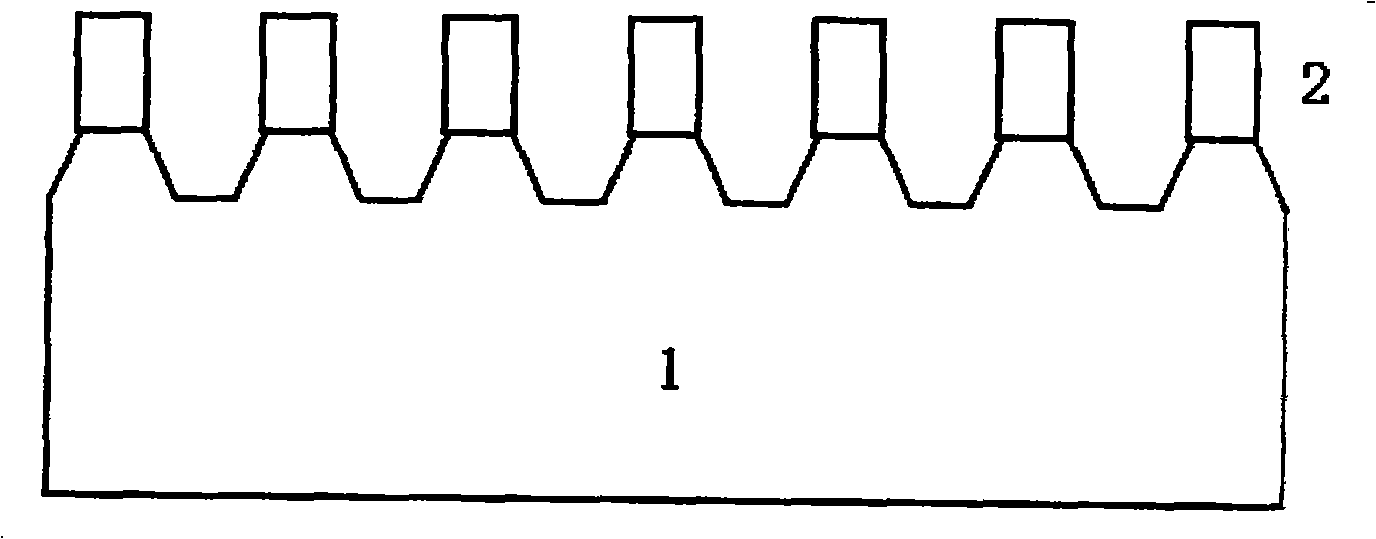

A nitride-based semiconductor element having superior mass productivity and excellent element characteristics is obtained. This nitride-based semiconductor element comprises a substrate comprising a surface having projection portions, a mask layer formed to be in contact with only the projection portions of the surface of the substrate, a first nitride-based semiconductor layer formed on recess portions of the substrate and the mask layer and a nitride-based semiconductor element layer, formed on the first nitride-based semiconductor layer, having an element region. Thus, the first nitride-based semiconductor layer having low dislocation density is readily formed on the projection portions of the substrate and the mask layer through the mask layer serving for selective growth. When the nitride-based semiconductor element layer having the element region is grown on the first nitride-based semiconductor layer having low dislocation density, a nitride-based semiconductor element having excellent element characteristics can be readily obtained. The first nitride-based semiconductor layer is formed through only single growth on the substrate, whereby a nitride-based semiconductor element having excellent mass productivity is obtained.

Owner:LEDVANCE GMBH

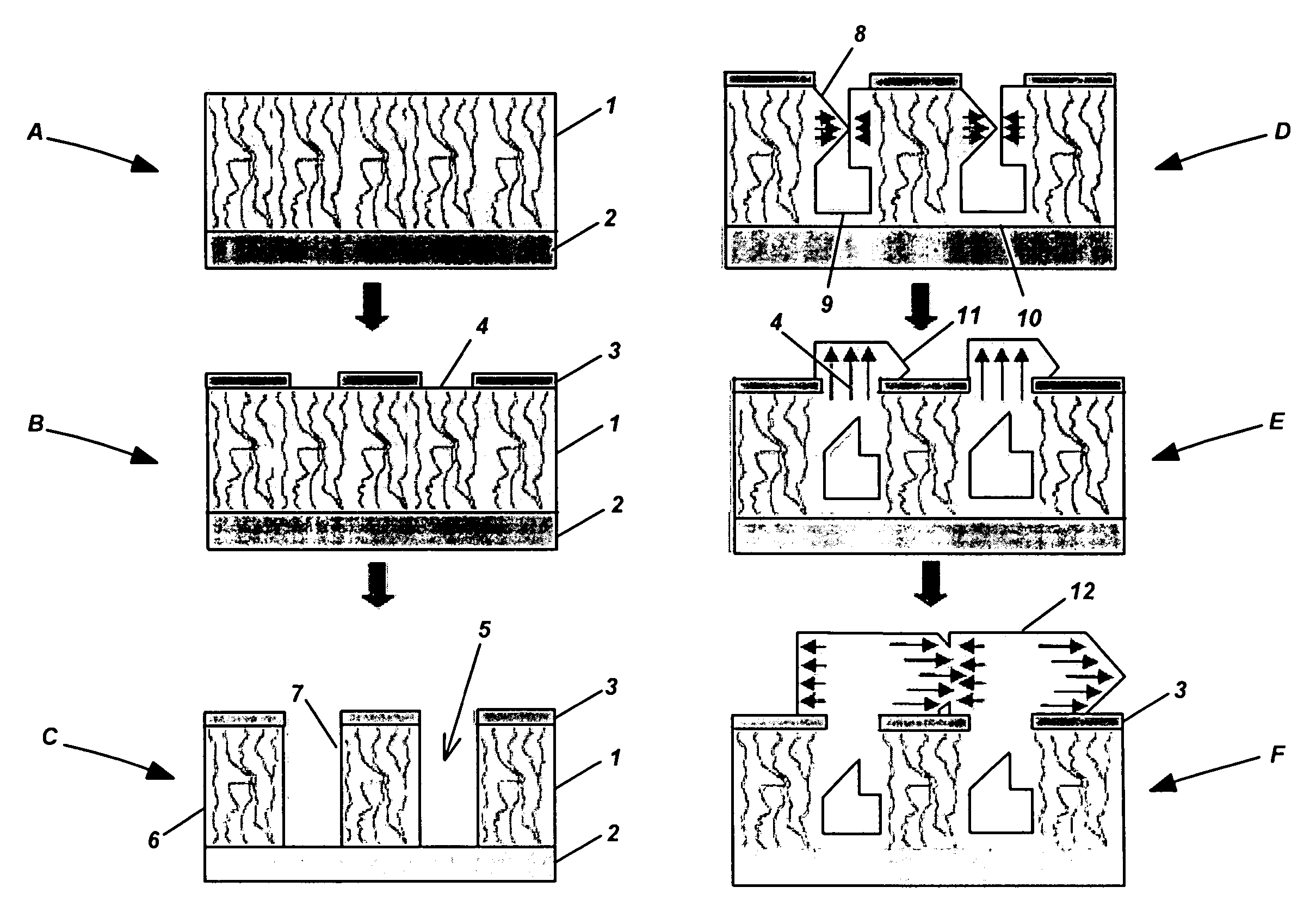

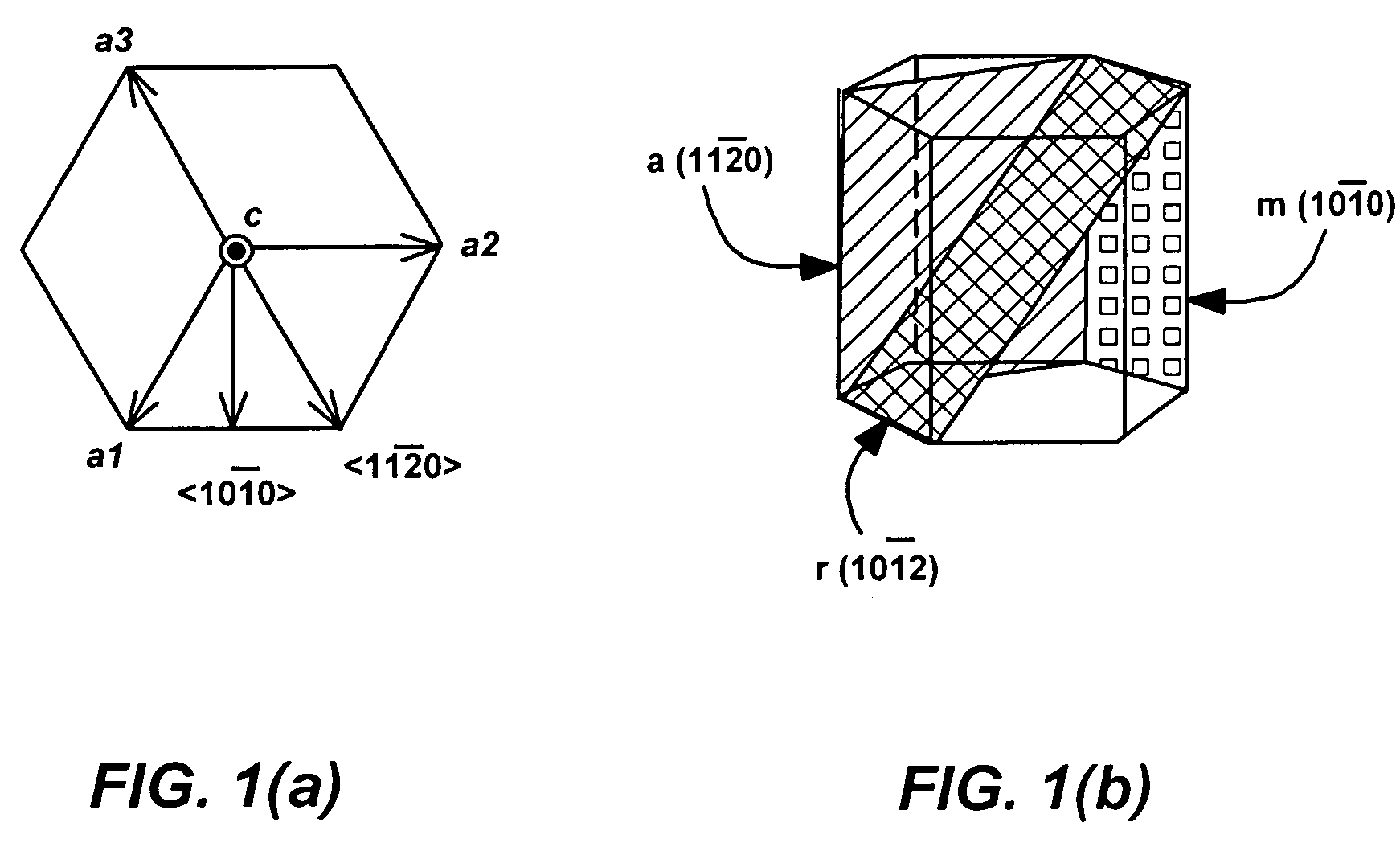

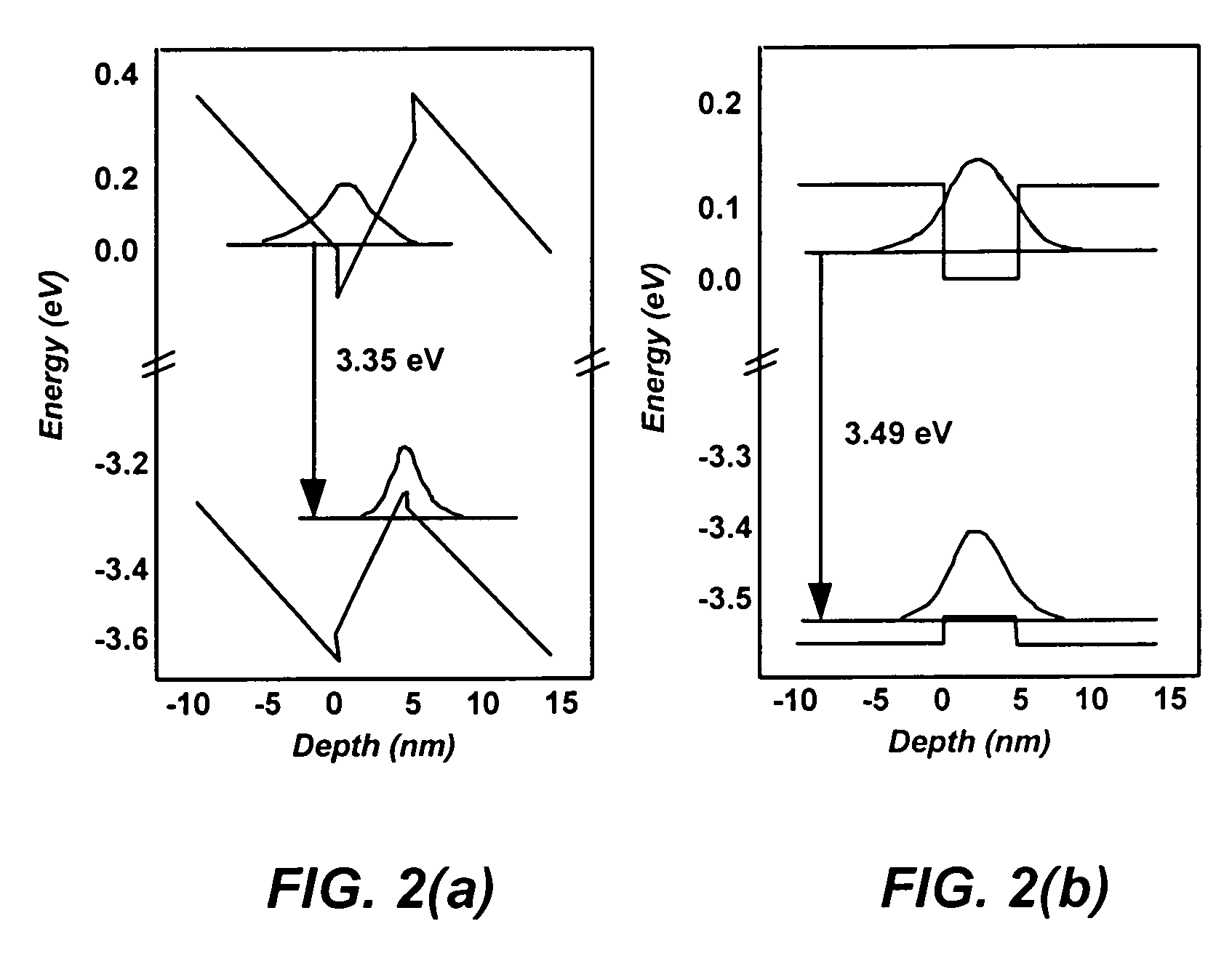

Defect reduction of non-polar and semi-polar III-Nitrides with sidewall lateral epitaxial overgrowth (SLEO)

ActiveUS7361576B2Quality improvementMinimum defect densitySemiconductor/solid-state device manufacturingSemiconductor devicesNitrideDislocation

A method of reducing threading dislocation densities in non-polar such as a-{11-20} plane and m-{1-100} plane or semi-polar such as {10-1n} plane III-Nitrides by employing lateral epitaxial overgrowth from sidewalls of etched template material through a patterned mask. The method includes depositing a patterned mask on a template material such as a non-polar or semi polar GaN template, etching the template material down to various depths through openings in the mask, and growing non-polar or semi-polar III-Nitride by coalescing laterally from the tops of the sidewalls before the vertically growing material from the trench bottoms reaches the tops of the sidewalls. The coalesced features grow through the openings of the mask, and grow laterally over the dielectric mask until a fully coalesced continuous film is achieved.

Owner:JAPAN SCI & TECH CORP

III-V Nitride homoepitaxial material of improved MOVPE epitaxial quality (surface texture and defect density) formed on free-standing (Al,In,Ga)N substrates, and opto-electronic and electronic devices comprising same

InactiveUS20030213964A1Improve material qualityReduce dislocation densityPolycrystalline material growthAfter-treatment detailsCelsius DegreeSource material

A III-V nitride homoepitaxial microelectronic device structure comprising a III-V nitride homoepitaxial epi layer of improved epitaxial quality deposited on a III-V nitride material substrate, e.g., of freestanding character. Various processing techniques are described, including a method of forming a III-V nitride homoepitaxial layer on a corresponding III-V nitride material substrate, by depositing the III-V nitride homoepitaxial layer by a VPE process using Group III source material and nitrogen source material under process conditions including V / III ratio in a range of from about 1 to about 10<5>, nitrogen source material partial pressure in a range of from about 1 to about 10<3 >torr, growth temperature in a range of from about 500 to about 1250 degrees Celsius, and growth rate in a range of from about 0.1 to about 10<2 >microns per hour. The III-V nitride homoepitaxial microelectronic device structures are usefully employed in device applications such as UV LEDs, high electron mobility transistors, and the like.

Owner:WOLFSPEED INC

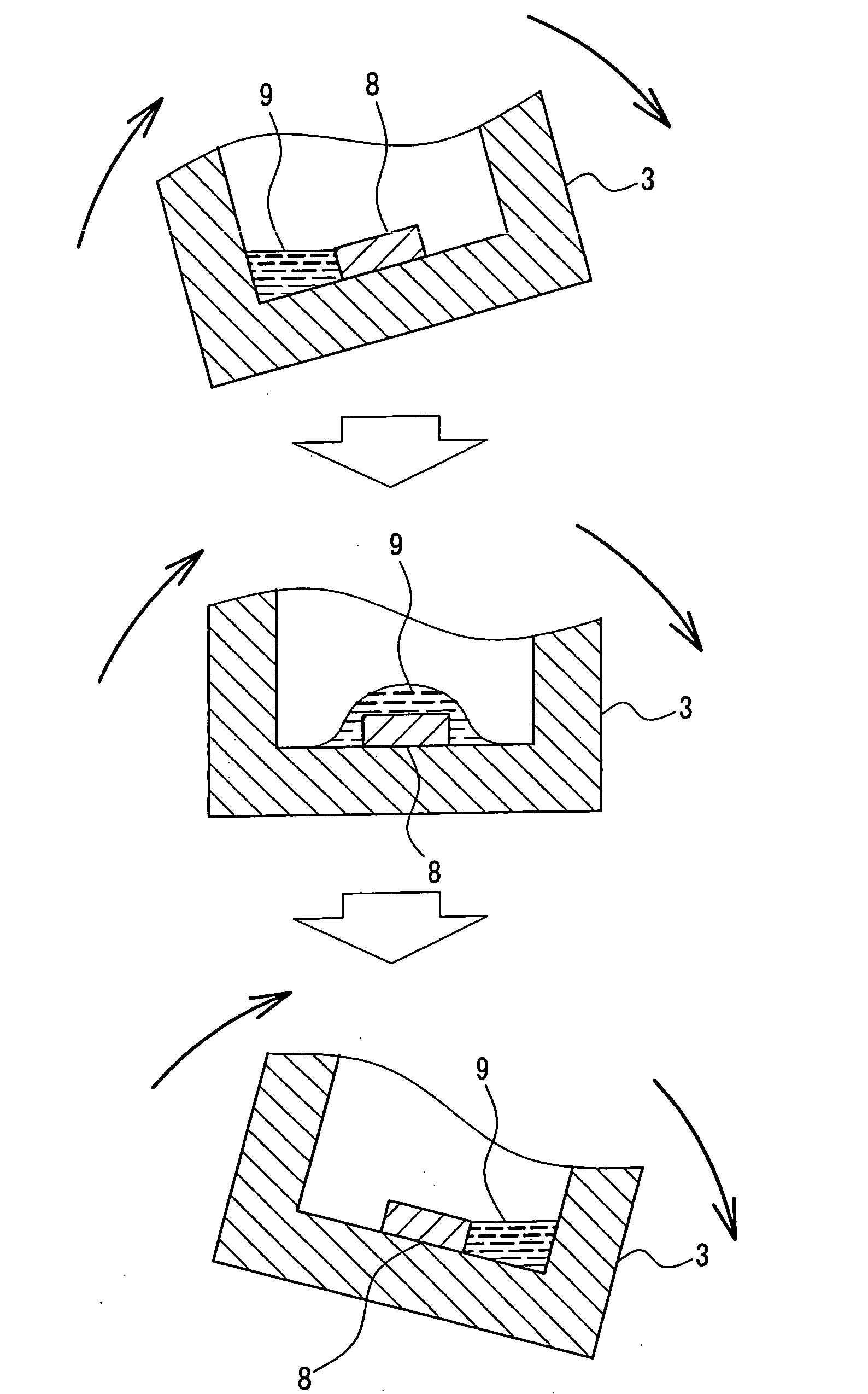

Crystal growth method for nitride semiconductor and formation method for semiconductor device

InactiveUS7033436B2Improving performance lifeExtended service lifePolycrystalline material growthLaser detailsSemiconductor materialsCrystal growth rate

Methods of crystal growth for semiconductor materials, such as nitride semiconductors, and methods of manufacturing semiconductor devices are provided. The method of crystal growth includes forming a number of island crystal regions during a first crystal growth phase and continuing growth of the island crystal regions during a second crystal growth phase while bonding of boundaries of the island crystal regions occurs. The second crystal growth phase can include a crystal growth rate that is higher than the crystal growth rate of the first crystal growth phase and / or a temperature that is lower than the first crystal growth phase. This can reduce the density of dislocations, thereby improving the performance and service life of a semiconductor device which is formed on a nitride semiconductor made in accordance with an embodiment of the present invention.

Owner:SONY CORP

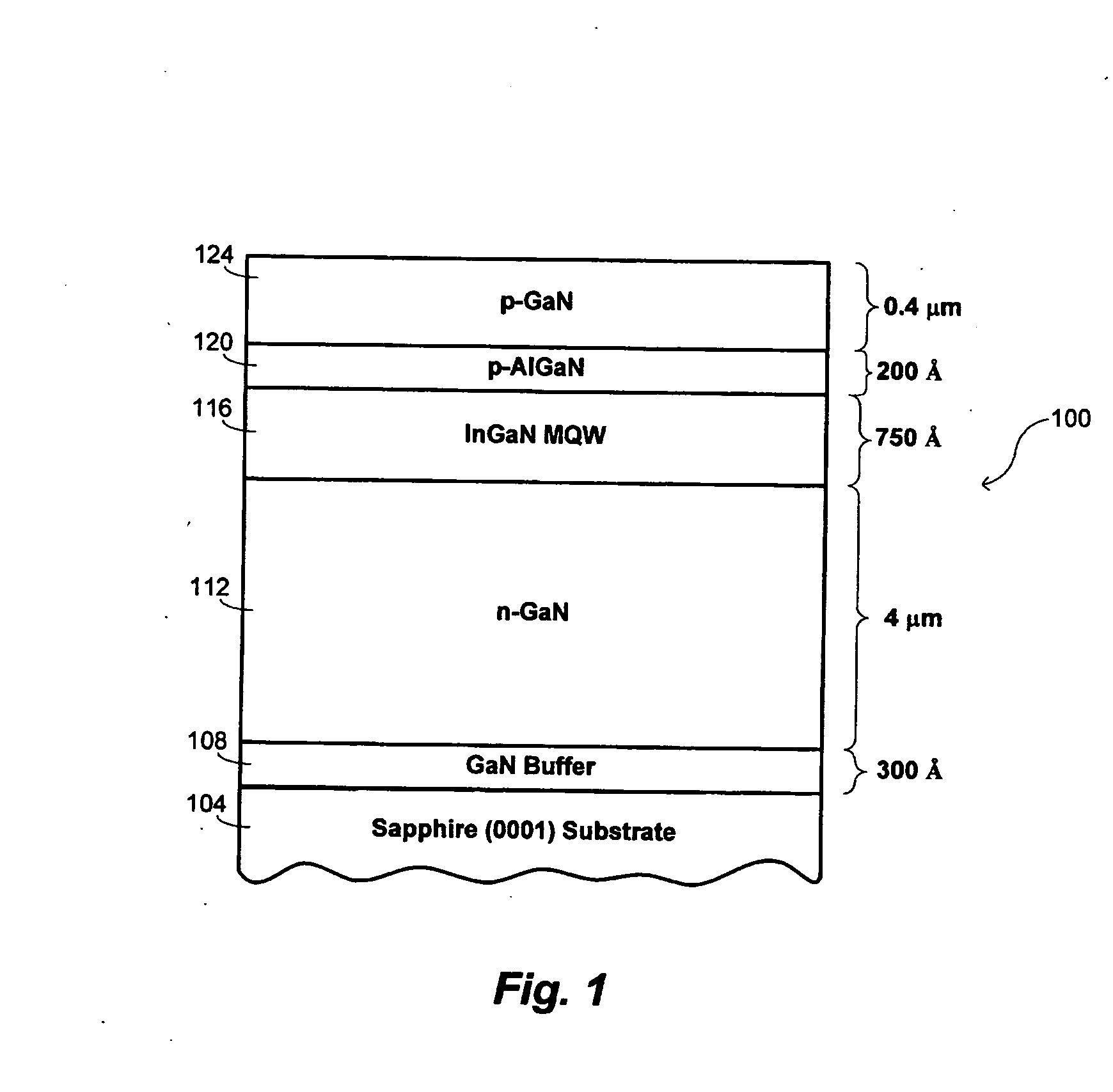

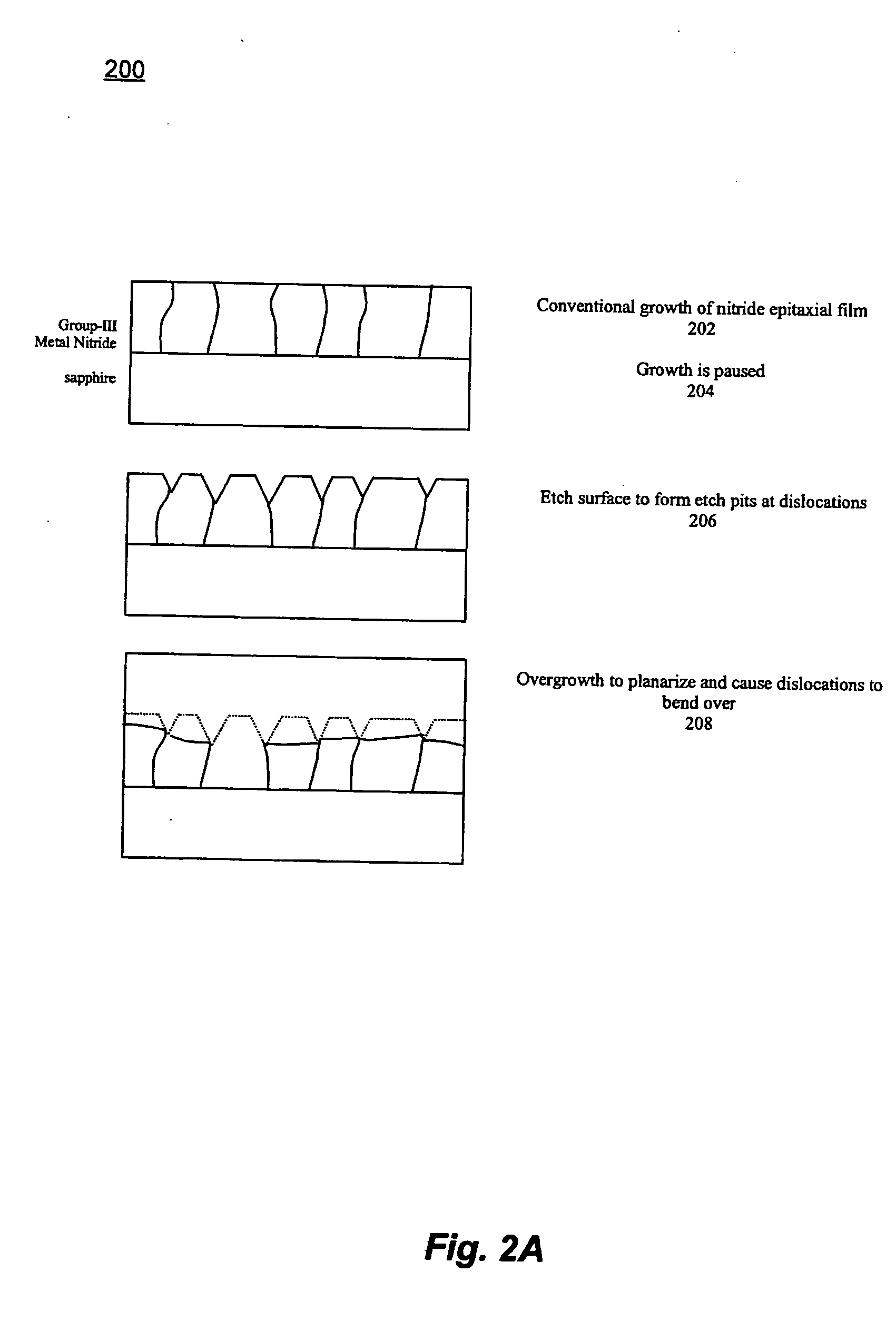

Dislocation-specific lateral epitaxial overgrowth to reduce dislocation density of nitride films

InactiveUS20070259504A1Reduce dislocation densityInhibit threading of the lattice mismatchPolycrystalline material growthBy zone-melting liquidsEtchingDislocation

In accordance with the present invention, improved methods for reducing the dislocation density of nitride epitaxial films are provided. Specifically, an in-situ etch treatment is provided to preferentially etch the dislocations of the nitride epitaxial layer to prevent threading of the dislocations through the nitride epitaxial layer. Subsequent to etching of the dislocations, an epitaxial layer overgrowth is performed. In certain embodiments, the etching of the dislocations occurs simultaneously with growth of the epitaxial layer. In other embodiments, a dielectric mask is deposited within the etch pits formed at the dislocations prior to the epitaxial layer overgrowth.

Owner:APPLIED MATERIALS INC

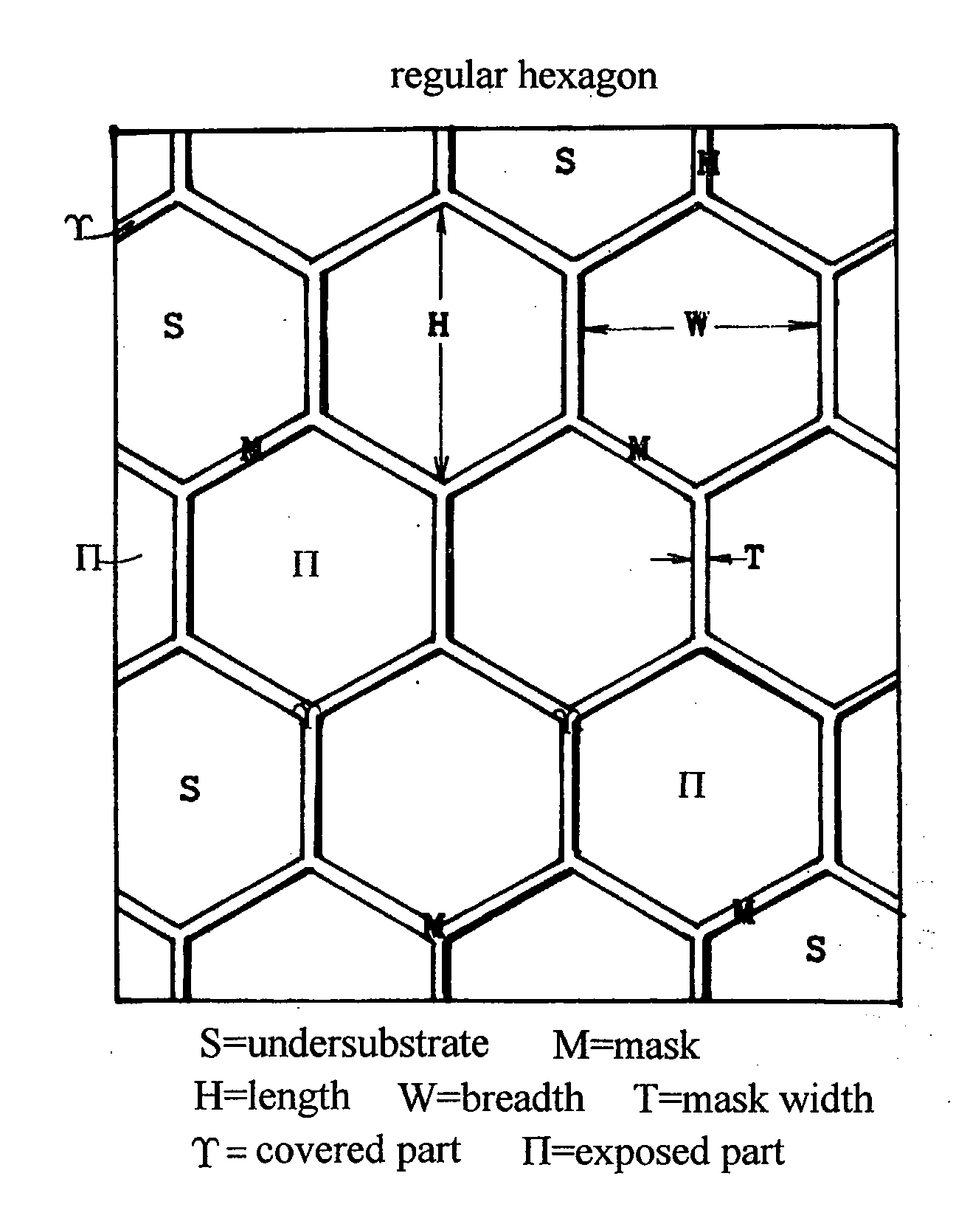

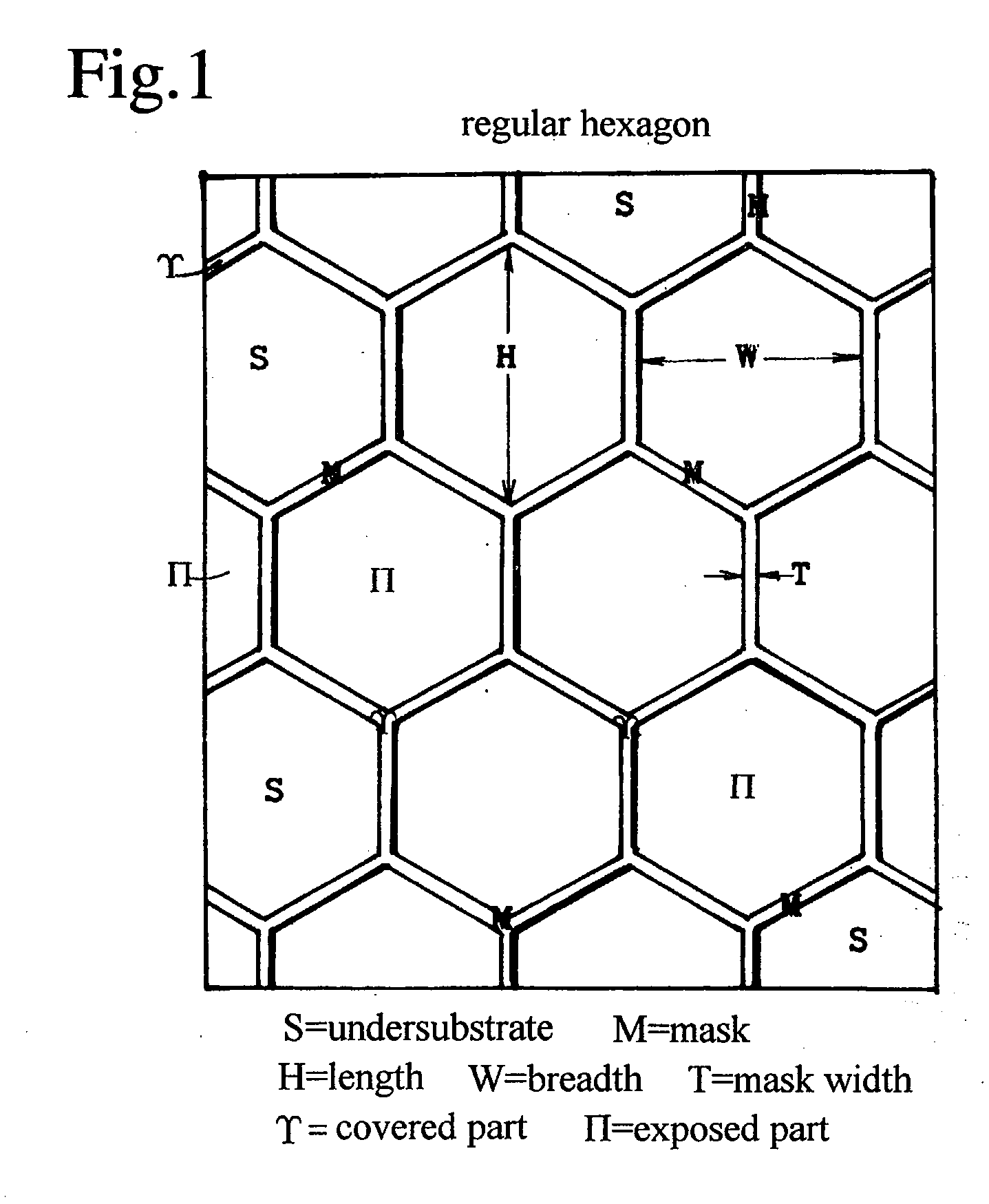

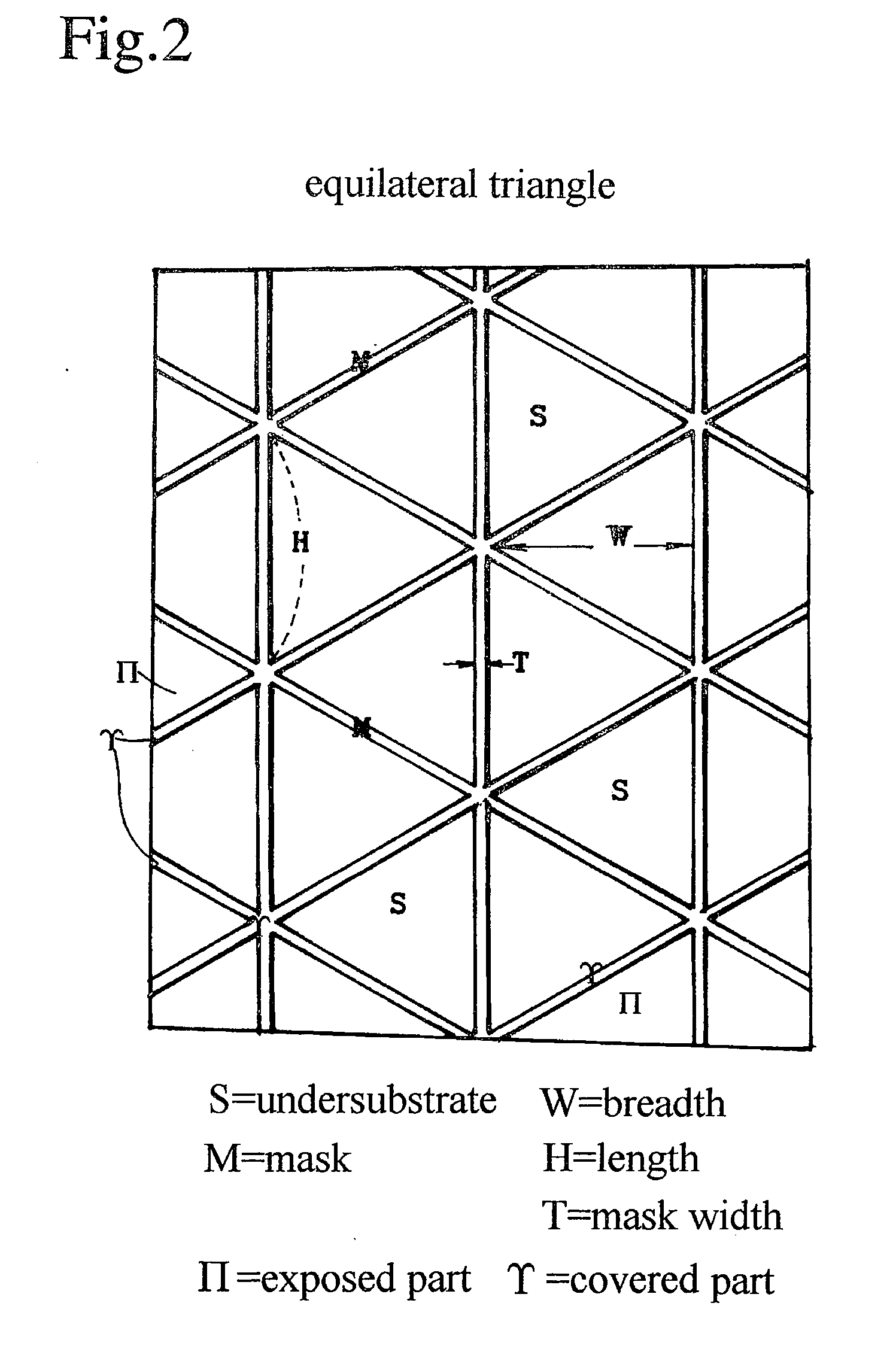

Nitride semiconductor substrate and method of producing same

ActiveUS20090155989A1Reduce dislocation densityEasily realizedPolycrystalline material growthSemiconductor/solid-state device manufacturingGas phaseClosed loop

A nitride semiconductor crystal substrate is produced by forming a network mask repeating a closed loop unit shape upon an undersubstrate, growing a nitride semiconductor crystal in vapor phase, producing convex facet hills covered with facets on exposed parts Π, forming outlining concavities on mask-covered parts not burying the facets, maintaining the convex facet hills on Π and the network concavities on excluding dislocations in the facet hills down to the outlining concavities on forming a defect accumulating region H on decreasing dislocations in the facet hills and improving the facet hills to low defect density single crystal regions Z, producing a rugged nitride crystal, and slicing and polishing the nitride crystal into mirror nitride crystal wafers. After the fabrication of devices on the nitride wafer, dry-etching or wet etching of hot KOH or NaOH divides the device-carrying wafer into chips by corroding the network defect accumulating region H.

Owner:SUMITOMO ELECTRIC IND LTD

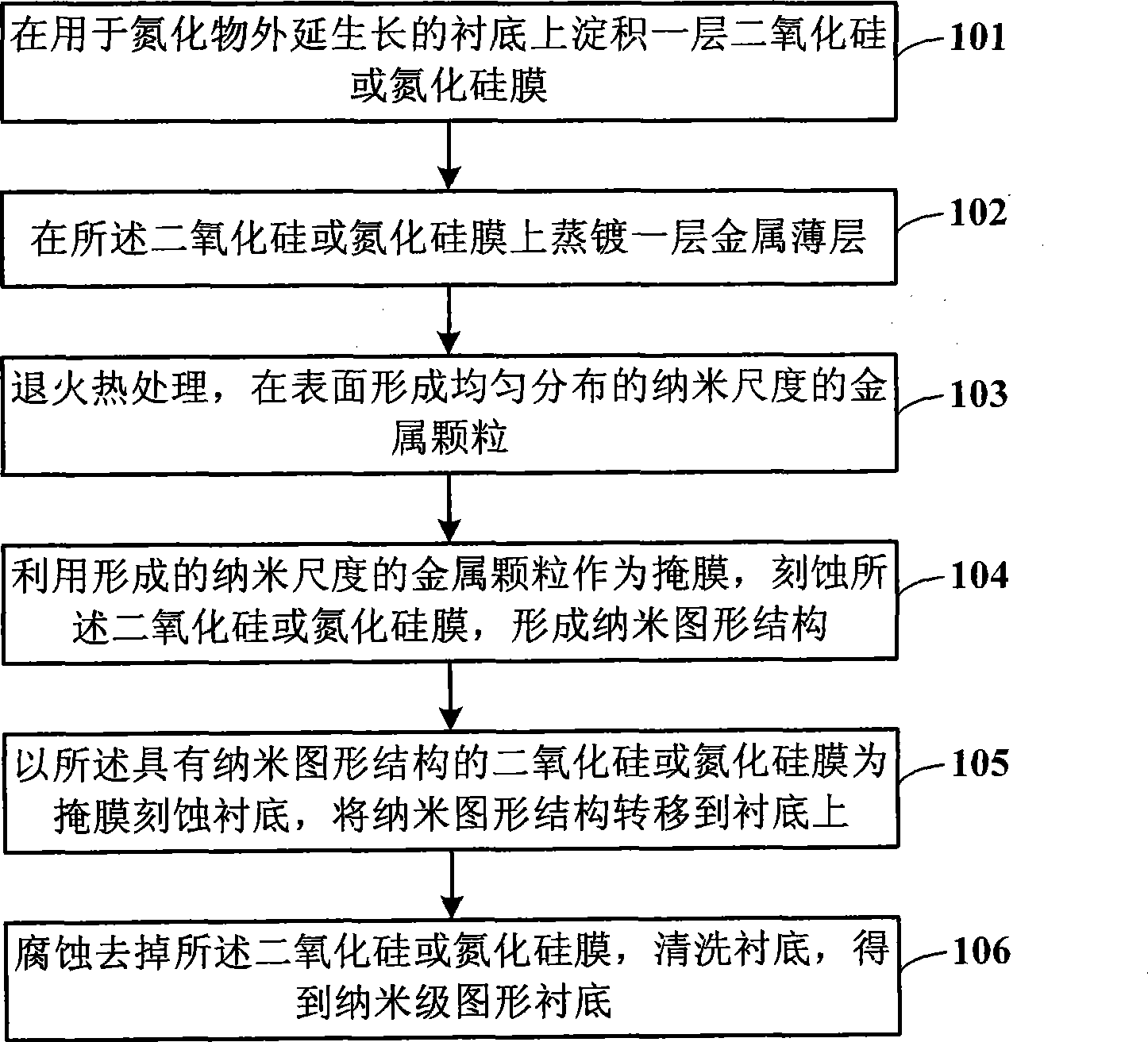

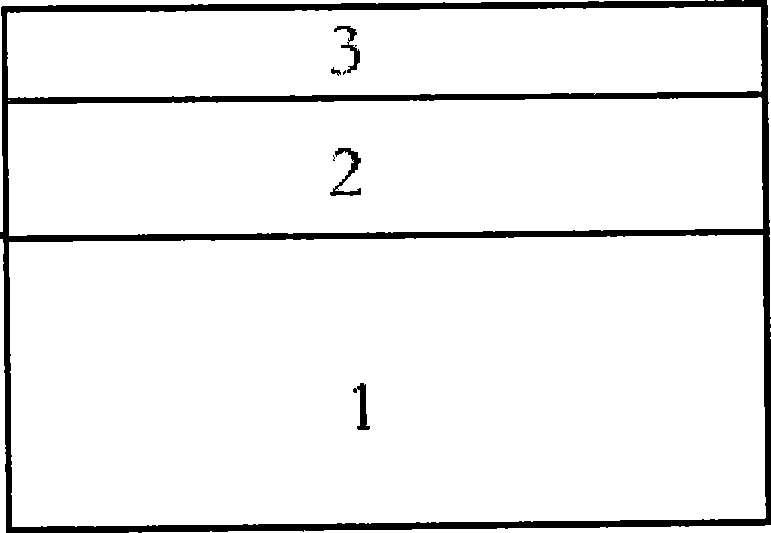

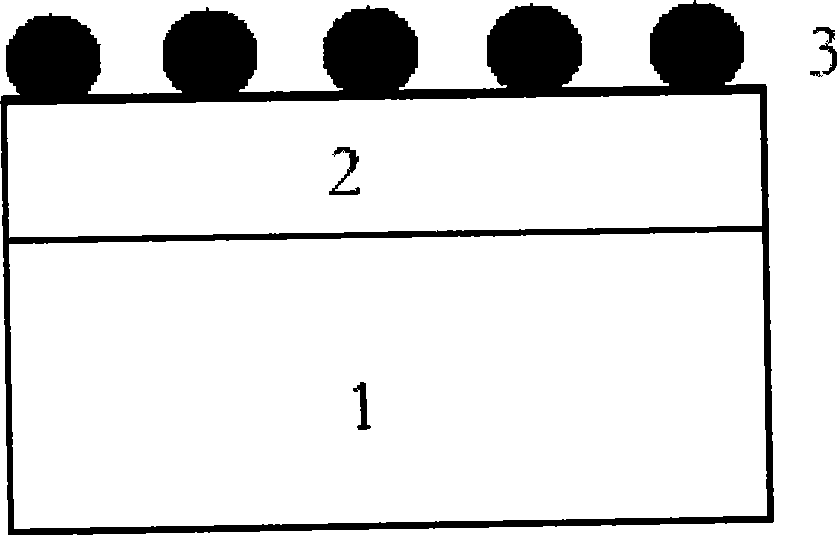

Method for preparing nano-scale pattern substrate for nitride epitaxial growth

InactiveCN101373714AReduce dislocation densityImprove crystal qualitySemiconductor/solid-state device manufacturingThin metalEpitaxial material

The invention relates to the semiconductor technical field and discloses a method for manufacturing a nanometer pattern substrate used for the epitaxial growth of a nitride. The method comprises the followings steps: settling a layer of silicon dioxide or silicon nitride film on a substrate used for the epitaxial growth of the nitride; the silicon dioxide or silicon nitride film is coated with a layer of thin metal layer through vapor deposition; conducting the annealing heat treatment, and forming uniformly distributed nano-scaled metal particles; utilizing the formed nano-scaled metal particles as masks to etch the silicon dioxide or silicon nitride film so as to form a nanometer pattern structure; using the silicon dioxide or silicon nitride film with the nanometer pattern structure as a mask etching substrate to transfer the nanometer pattern structure of the substrate; and etching to remove the silicon dioxide or silicon nitride film, cleaning the substrate, and obtaining the nanometer pattern substrate. The invention can reduce the dislocation density in the epitaxial layer of the nitride, improve the crystal quality of epitaxial materials, improve the performance of devices and help to realize the scaled and large area manufacture.

Owner:UNILUMIN GRP

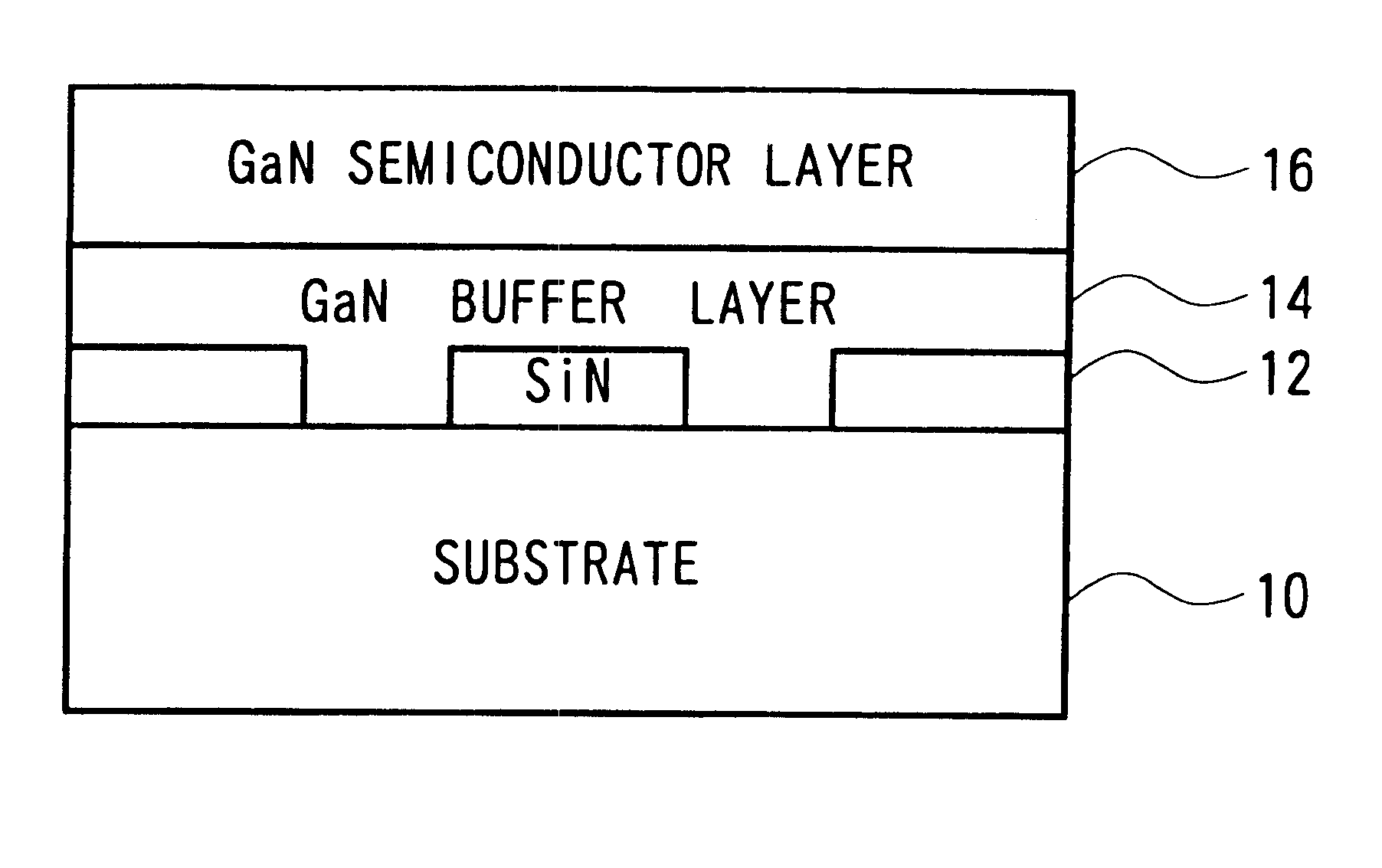

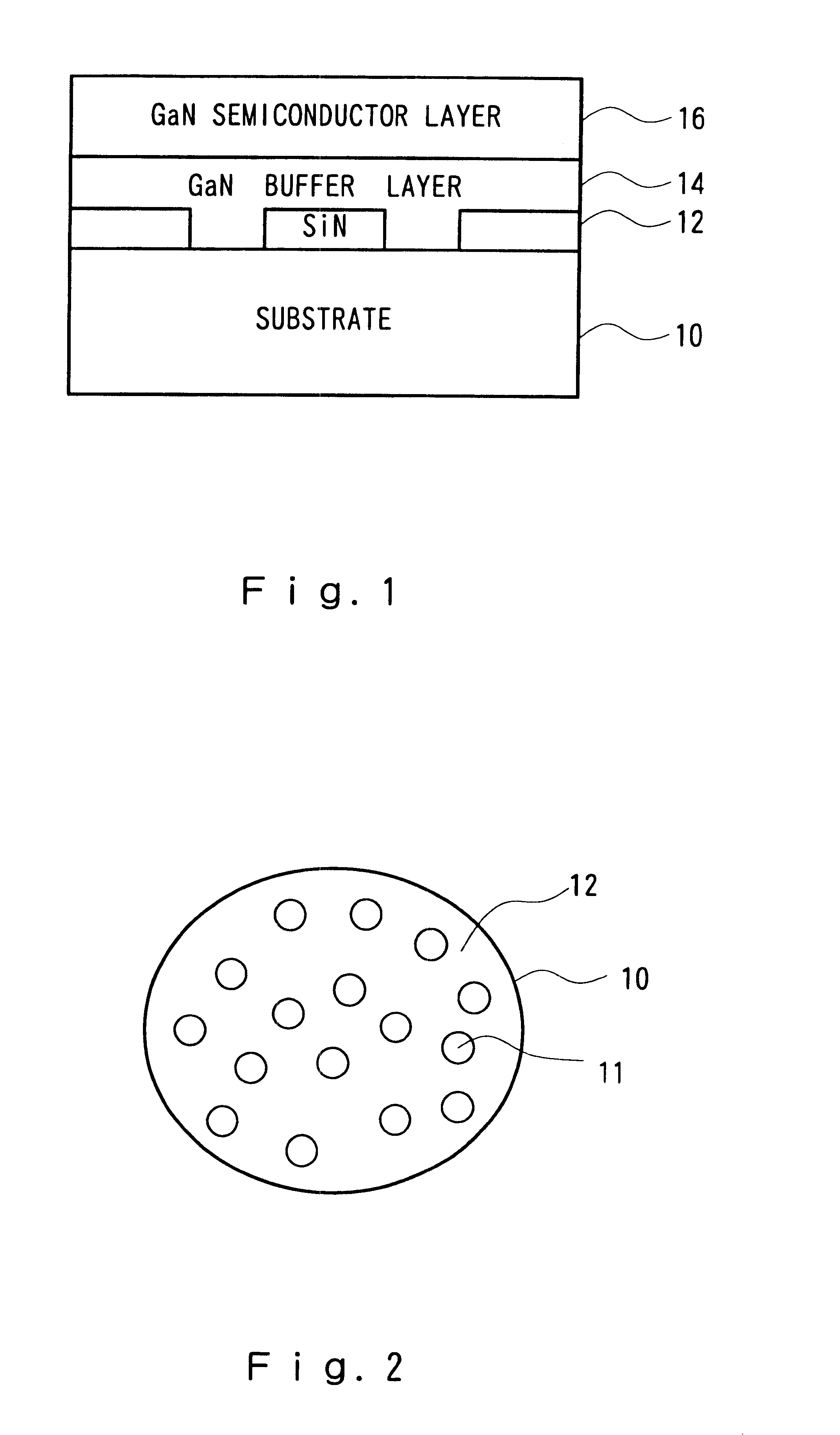

Method for producing GaN-based compound semiconductor and GaN-based compound semiconductor device

InactiveUS6475882B1Reduce dislocation densityInhibitionLaser detailsSemiconductor/solid-state device manufacturingSeed crystalSuperlattice

A production method of a GaN-based compound semiconductor having excellent crystallinity and a GaN-based semiconductor device produced therefrom. A discrete SiN buffer body is formed on a substrate, and a GaN buffer layer is formed thereon at low temperatures and a GaN semiconductor layer is then formed at high temperatures. By forming the discrete SiN buffer body, the crystal growth, which is dependent on the substrate, of the low-temperature buffer layer is inhibited and monocrystallization is promoted to generate seed crystals used at the time of growing the GaN buffer layer. Further, by forming SiO2 discretely between the substrate and the SiN buffer body or by forming InGaN or a superlattice layer on the GaN semiconductor layer, distortion of the GaN semiconductor layer is reduced.

Owner:NITRIDE SEMICON

Method for producing nitride semiconductor crystal, and nitride semiconductor wafer and nitride semiconductor device

InactiveUS20030183160A1Reduce dislocation densityPolycrystalline material growthLiquid-phase epitaxial-layer growthWaferingCondensed matter physics

A method for producing a nitride semiconductor crystal comprising a step (a) for forming fine crystal particles made of a nitride semiconductor on a substrate; a step (b) for forming a nitride semiconductor island structure having a plurality of facets inclined relative to a surface of the substrate with the fine crystal particles as nuclei; and a step (c) for causing the nitride semiconductor island structure to grow in a direction parallel with a surface of the substrate to merge a plurality of the nitride semiconductor island structures with each other, thereby forming a nitride semiconductor crystal layer having a flat surface; the steps (a)-(c) being continuously conducted in the same growing apparatus.

Owner:SUMITOMO CHEM CO LTD

Nitride semiconductor, nitride semiconductor crystal growth method, and nitride semiconductor light emitting element

ActiveUS20100244087A1Improve flatnessAvoid defectsPolycrystalline material growthSemiconductor/solid-state device manufacturingNitrogenCrystal growth

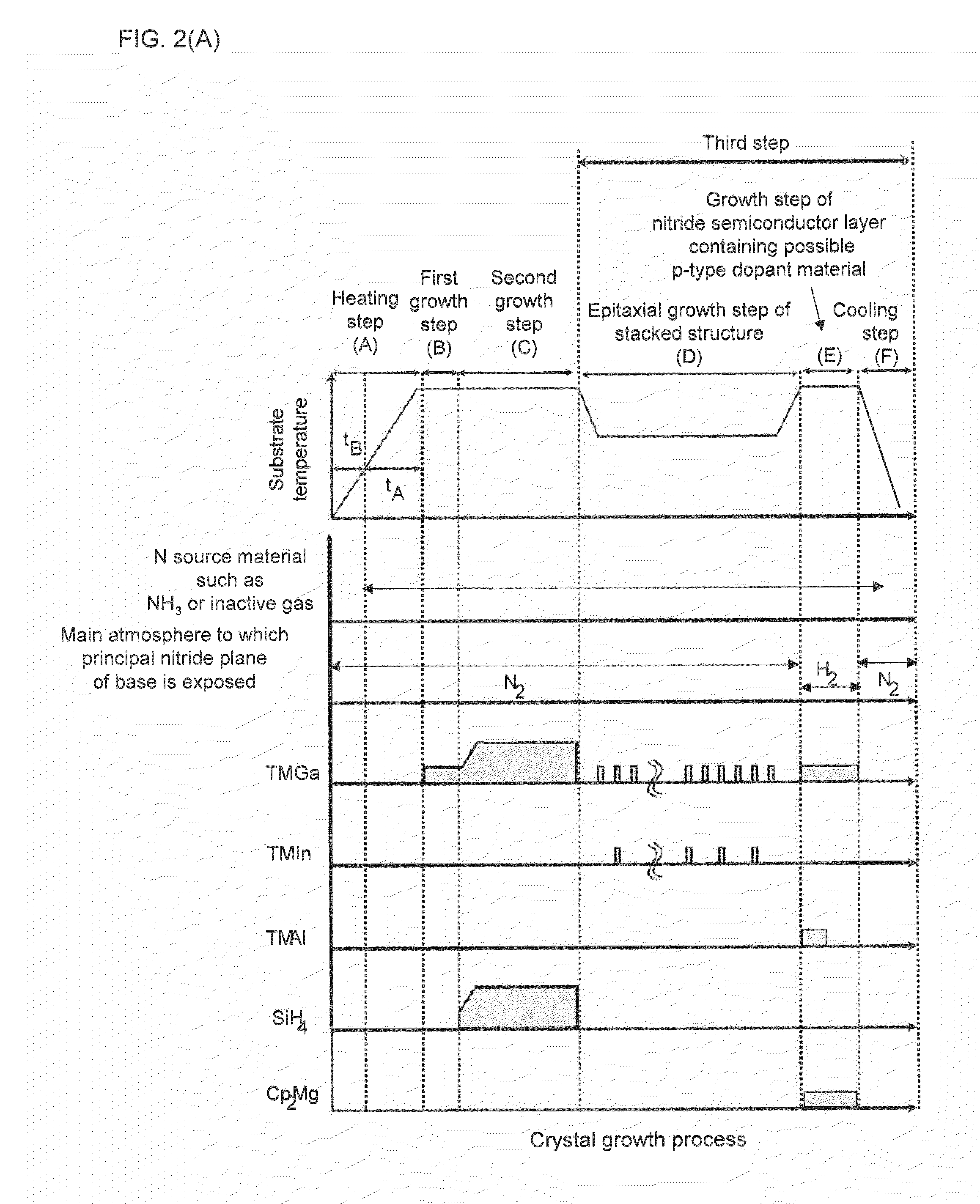

During the growth of a nitride semiconductor crystal on a nonpolar face nitride substrate, such as an m-face, the gas that constitutes the main flow in the process of heating up to a relatively high temperature range, before growth of the nitride semiconductor layer, (the atmosphere to which the main nitride face of the substrate is exposed) and the gas that constitutes the main flow until growth of first and second nitride semiconductor layers is completed (the atmosphere to which the main nitride face of the substrate is exposed) are primarily those that will not have an etching effect on the nitride, while no Si source is supplied at the beginning of growth of the nitride semiconductor layer. Therefore, nitrogen atoms are not desorbed from near the nitride surface of the epitaxial substrate, thus suppressing the introduction of defects into the epitaxial film. This also makes epitaxial growth possible with a surface morphology of excellent flatness.

Owner:MITSUBISHI CHEM CORP

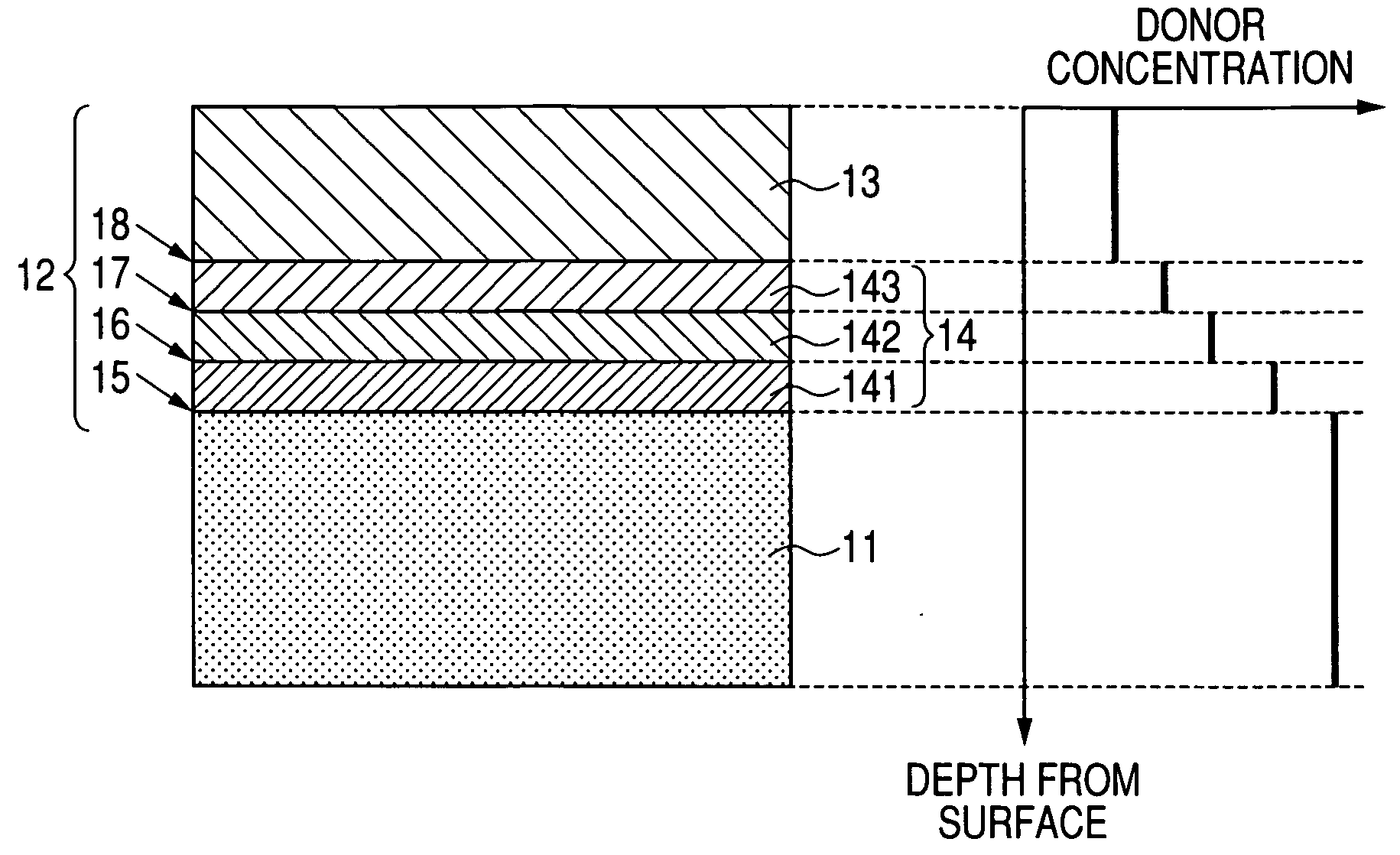

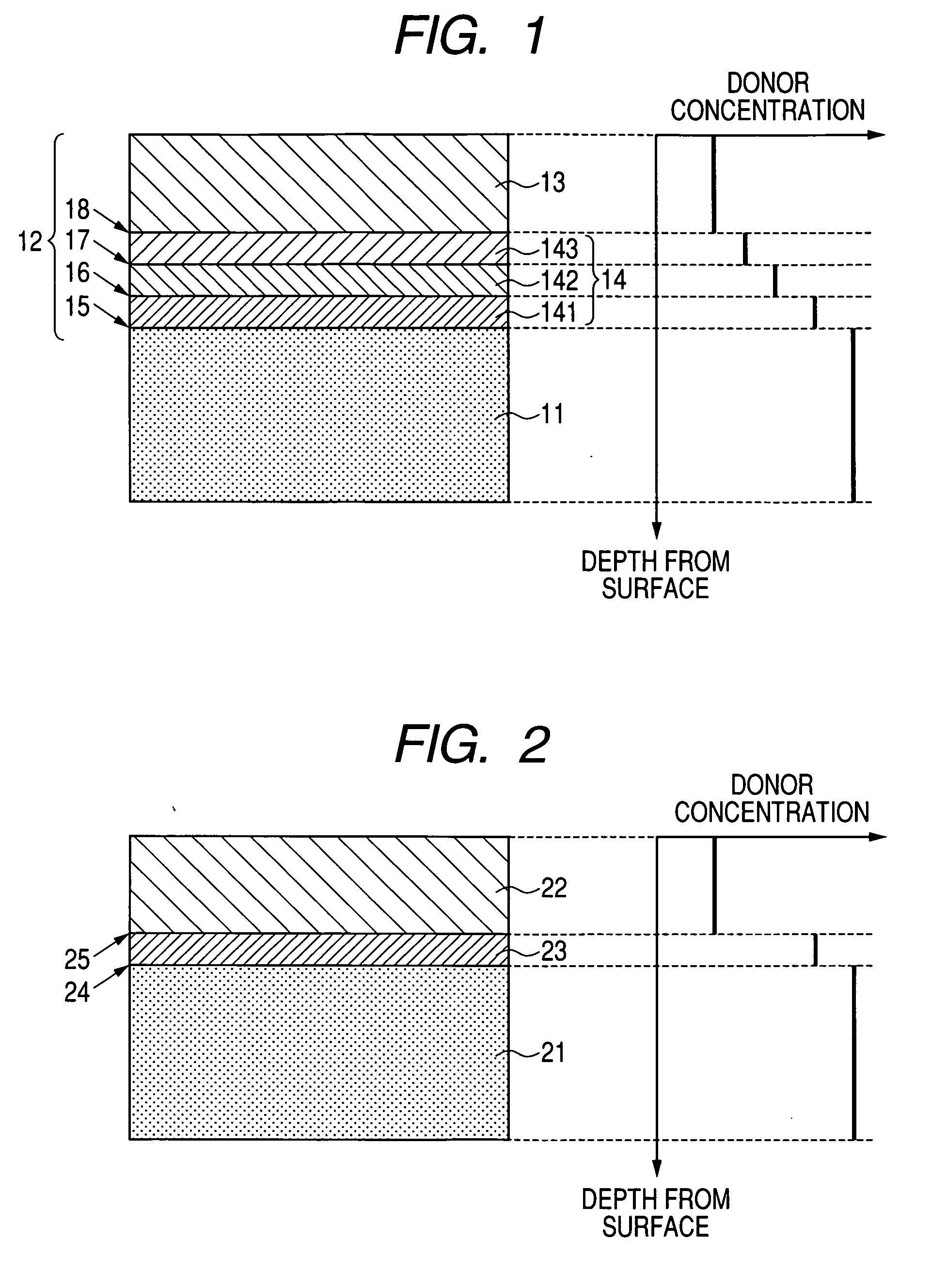

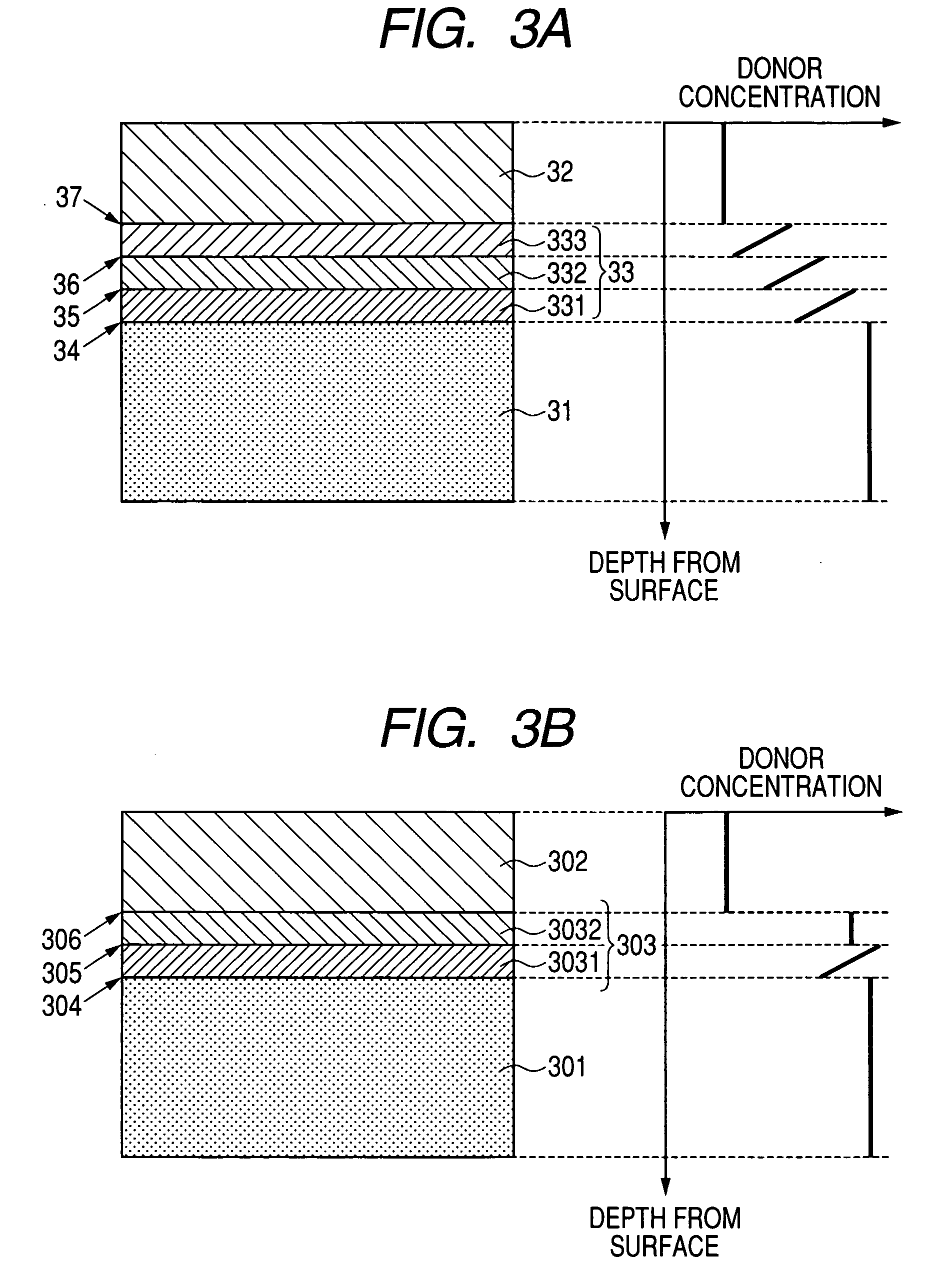

Silicon carbide semiconductor substrate and silicon carbide semiconductor device by using thereof

InactiveUS20090085044A1Reducing basal plane dislocation densityImprove conversion efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalDislocation

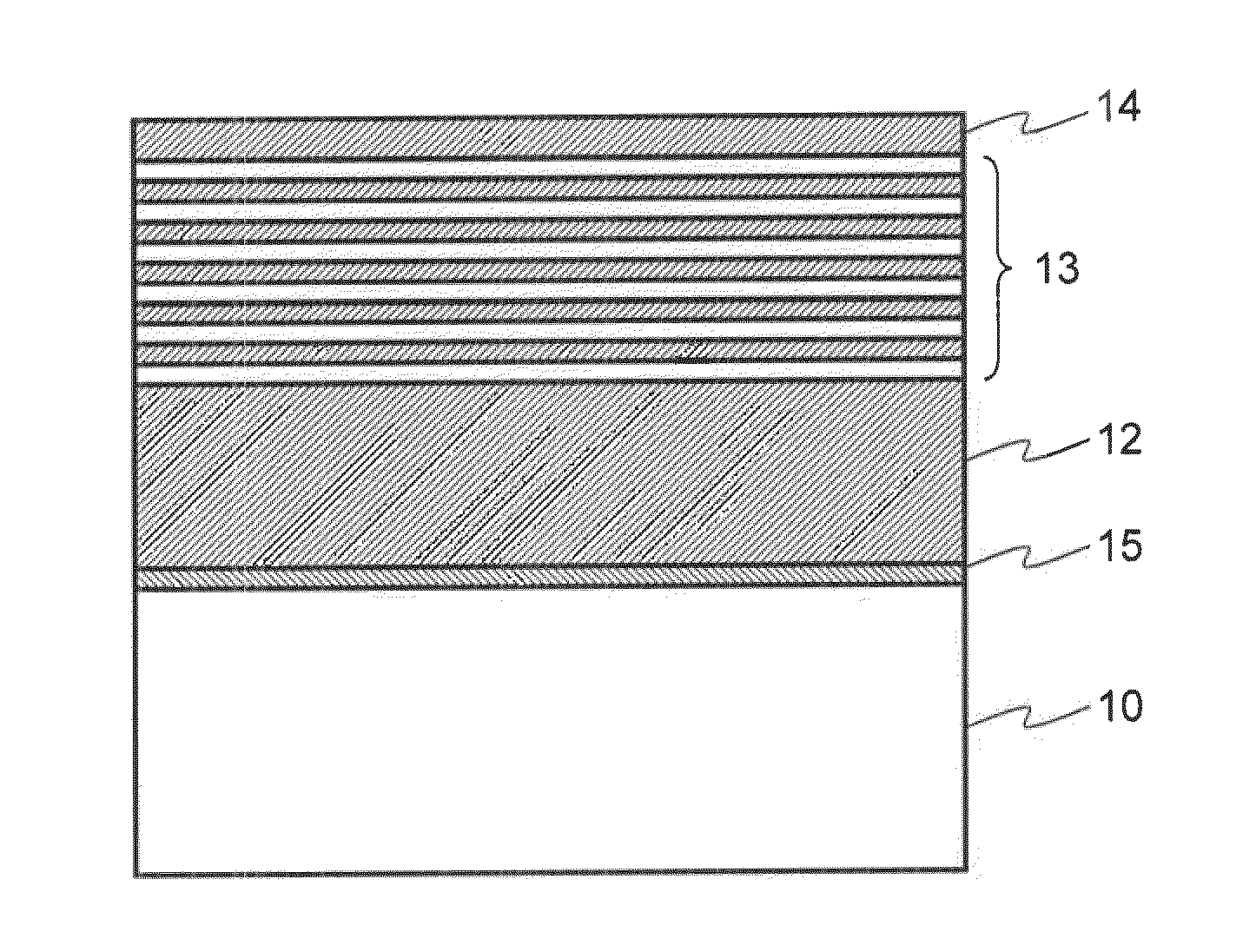

A manufacturing method is provided for a silicon carbide semiconductor substrate adapted for reduced basal plane dislocations in a silicon carbide epitaxial layer. Between a silicon carbide epitaxial layer for device fabrication (i.e., a drift layer) and a base substrate formed of a silicon carbide single-crystal wafer, a highly efficient dislocation conversion layer through which any basal plane dislocations in the silicon carbide single-crystal wafer are converted into threading edge dislocations very efficiently when the dislocations propagate into the layer epitaxially grown is provided by epitaxial growth. Assigning to the dislocation conversion layer a donor concentration lower than that of the drift layer, therefore, allows the above conversion of a larger number of basal plane dislocations than the case where the drift layer exists alone (without the dislocation conversion layer).

Owner:HITACHI CABLE

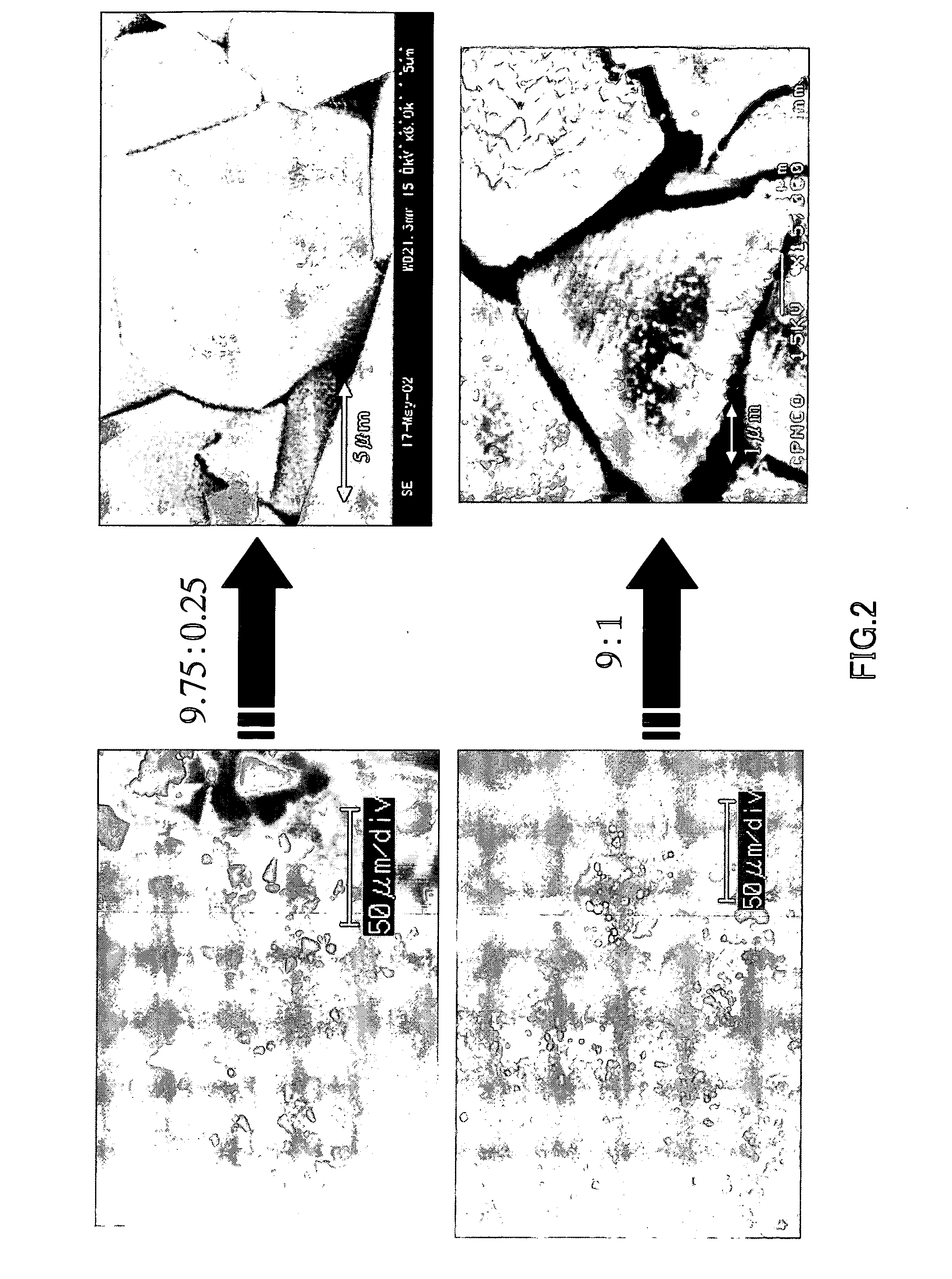

Group III nitride based semiconductor substrate and process for manufacture thereof

InactiveUS20030183157A1Quality improvementStable productionLaser detailsFrom solid stateDislocationNitride

To provide a semiconductor substrate of a group III nitride with a little warp, this invention provides a process comprising such steps of: epitaxial-growing a GaN layer 33 with a GaN low temperature grown buffer layer 32 upon a sapphire substrate 31; removing the sapphire substrate 31, the GaN buffer layer 32 and a small portion of the GaN layer 33 from the substrate taken out of a growth reactor to obtain a self-supporting GaN substrate 35; and after that, heat-treating the GaN substrate 35 by putting it into an electric furnace under the NH3 atmosphere at 1200° C. for 24 hours; which leads to a marked reduction of the warp of the self-supporting GaN substrate 35 such that dislocation densities of its obverse and reverse surface are 4x10<7 >cm<-2 >and 8x10<5 >cm<-2>, and thereby such a low ratio of dislocation densities of 50 is well-controlled.

Owner:SUMITOMO CHEM CO LTD

Deep-UV light-emitting diode and preparation method thereof

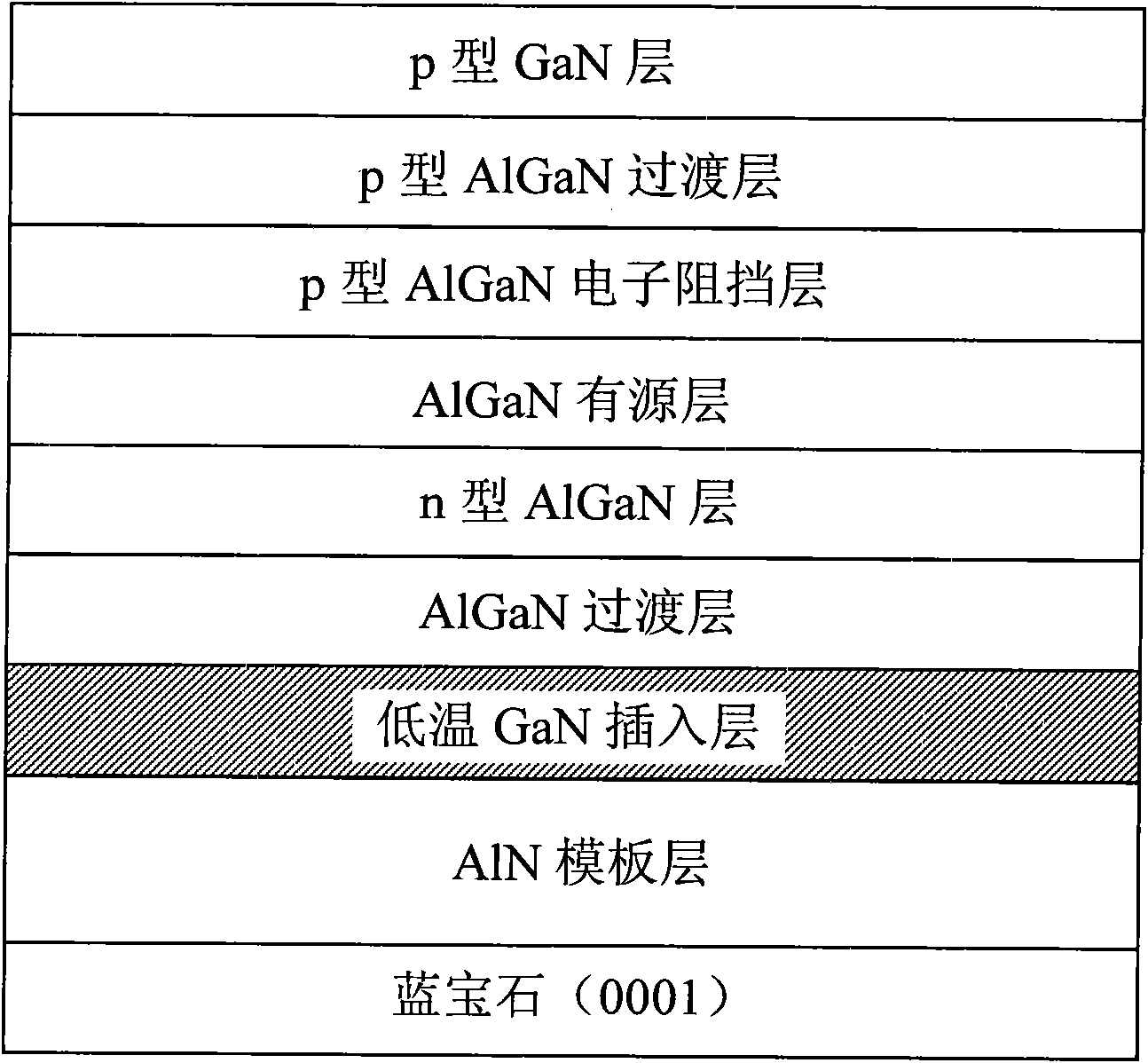

InactiveCN101604716AReduce dislocation densityImprove crystal qualitySemiconductor devicesDislocationSmooth surface

The invention provides a deep-UV light-emitting diode and a preparation method thereof. A low-temperature GaN insertion layer is used to replace an AlN / AlGaN superlattice or a high-temperature GaN insertion layer to grow the deep-UV light-emitting diode. The low-temperature GaN insertion layer is a GaN with thickness of 20-50nm under the conditions of temperature being 400-900 DEG C, pressure being 30-200torr, and V / III being 1500-2500. The method can effectively lower the dislocation density in an epitaxial AlGaN layer and a quantum well, and improves the surface planeness. The prepared LED component has smooth surface, better crystal quality, starting voltage reduction, and smaller serial resistances of the component; and the electroluminescene peak value is ranged from 300nm to 370nm.

Owner:PEKING UNIV

Method for improving luminous efficiency of GaN based LED by using graphic underlay

InactiveCN101345274AImprove luminous efficiencyQuality improvementSemiconductor devicesGraphicsNucleation

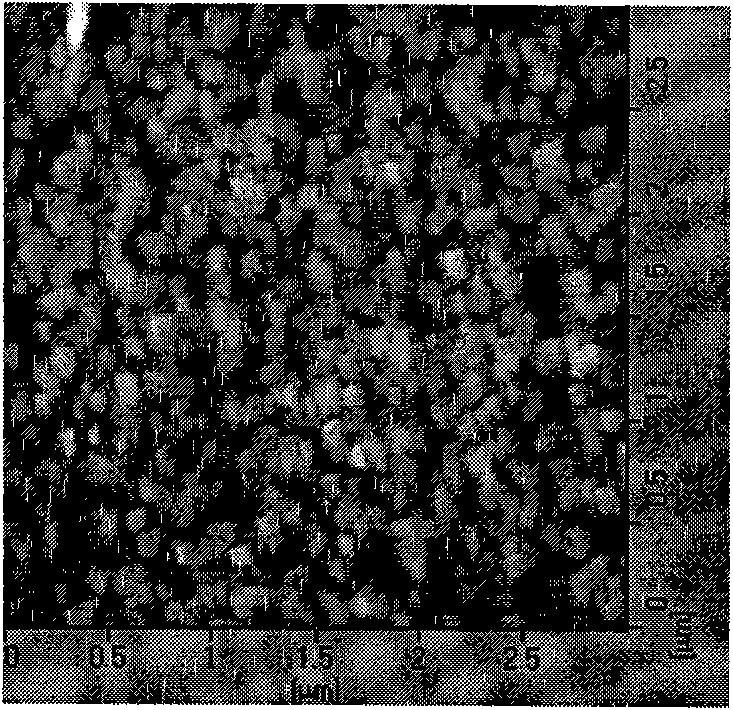

The invention provides a method which uses a graphic substrate to improve the illumination efficiency of a GaN-based efficiency, comprising the steps as follows: a silicon dioxide film is deposited on a sapphire substrate; a photoresist graphic array is optically etched; the photoresist graphic array is taken as a mask so as to etch the silicon dioxide film with the graphic structure; the silicon dioxide film with the graphic structure is taken as a mask so as to etch the sapphire substrate and the graphics is etched onto the sapphire substrate; the sapphire substrate is thoroughly cleaned so as to form a pyramid structure with triangular sections; a low-temperature nucleation layer grows on the graphic sapphire substrate; temperature is continuously increased on the low-temperature nucleation layer so as to grow an n-typed mixed GaN layer and an array structure which has low dislocation density and V-shaped holes on the surface; a multiple quantum well layer and a p-typed material layer required when the LED structure material grows continue to grow; furthermore, the final surface is led to still have the array structure with V-shaped holes.

Owner:YANGZHOU ZHONGKE SEMICON LIGHTING

Group III nitride semiconductor substrate and manufacturing method thereof

InactiveUS20070012943A1Controlled resistivityReduce dislocation densityPolycrystalline material growthSemiconductor/solid-state device manufacturingDislocationImpurity

A method of manufacturing a group III nitride semiconductor substrate includes the growth step of epitaxially growing a first group III nitride semiconductor layer on an underlying substrate, and the process step of forming a first group III nitride semiconductor substrate by cutting and / or surface-polishing the first group III nitride semiconductor layer. In the growth step, at least one element selected from the group consisting of C, Mg, Fe, Be, Zn, V, and Sb is added as an impurity element by at least 1×1017 cm−3 to the first group III nitride semiconductor layer. A group III nitride semiconductor substrate having controlled resistivity and low dislocation density and a manufacturing method thereof can thus be provided.

Owner:SUMITOMO ELECTRIC IND LTD

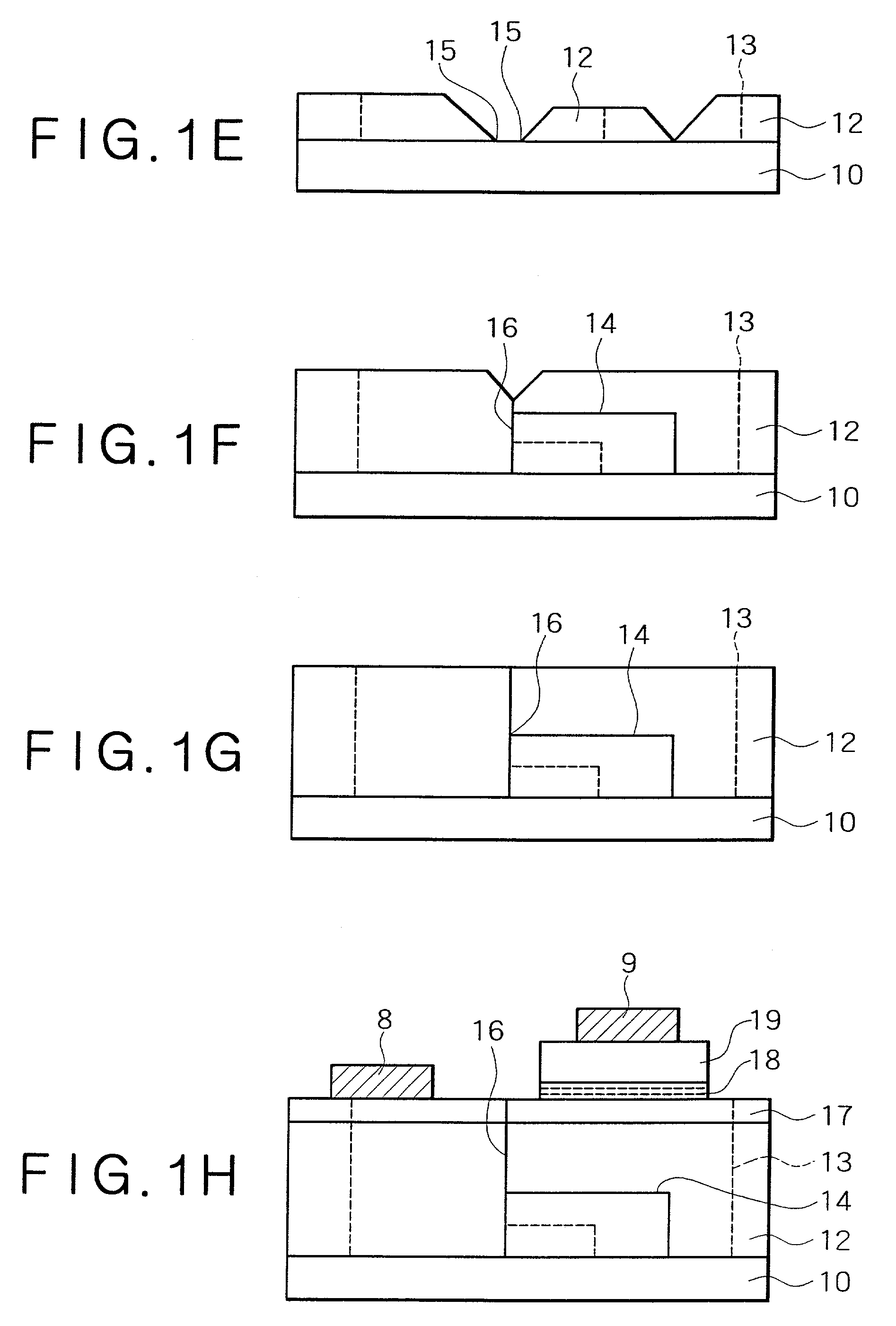

Nitride-based semiconductor element and method of forming nitride-based semiconductor

InactiveUS20050263778A1Improve batch productivityExcellent element characteristicOptical wave guidanceLaser detailsProduction rateNitride

A nitride-based semiconductor element having superior mass productivity and excellent element characteristics is obtained. This nitride-based semiconductor element comprises a substrate comprising a surface having projection portions, a mask layer formed to be in contact with only the projection portions of the surface of the substrate, a first nitride-based semiconductor layer formed on recess portions of the substrate and the mask layer and a nitride-based semiconductor element layer, formed on the first nitride-based semiconductor layer, having an element region. Thus, the first nitride-based semiconductor layer having low dislocation density is readily formed on the projection portions of the substrate and the mask layer through the mask layer serving for selective growth. When the nitride-based semiconductor element layer having the element region is grown on the first nitride-based semiconductor layer having low dislocation density, a nitride-based semiconductor element having excellent element characteristics can be readily obtained. The first nitride-based semiconductor layer is formed through only single growth on the substrate, whereby a nitride-based semiconductor element having excellent mass productivity is obtained.

Owner:EPISTAR CORP

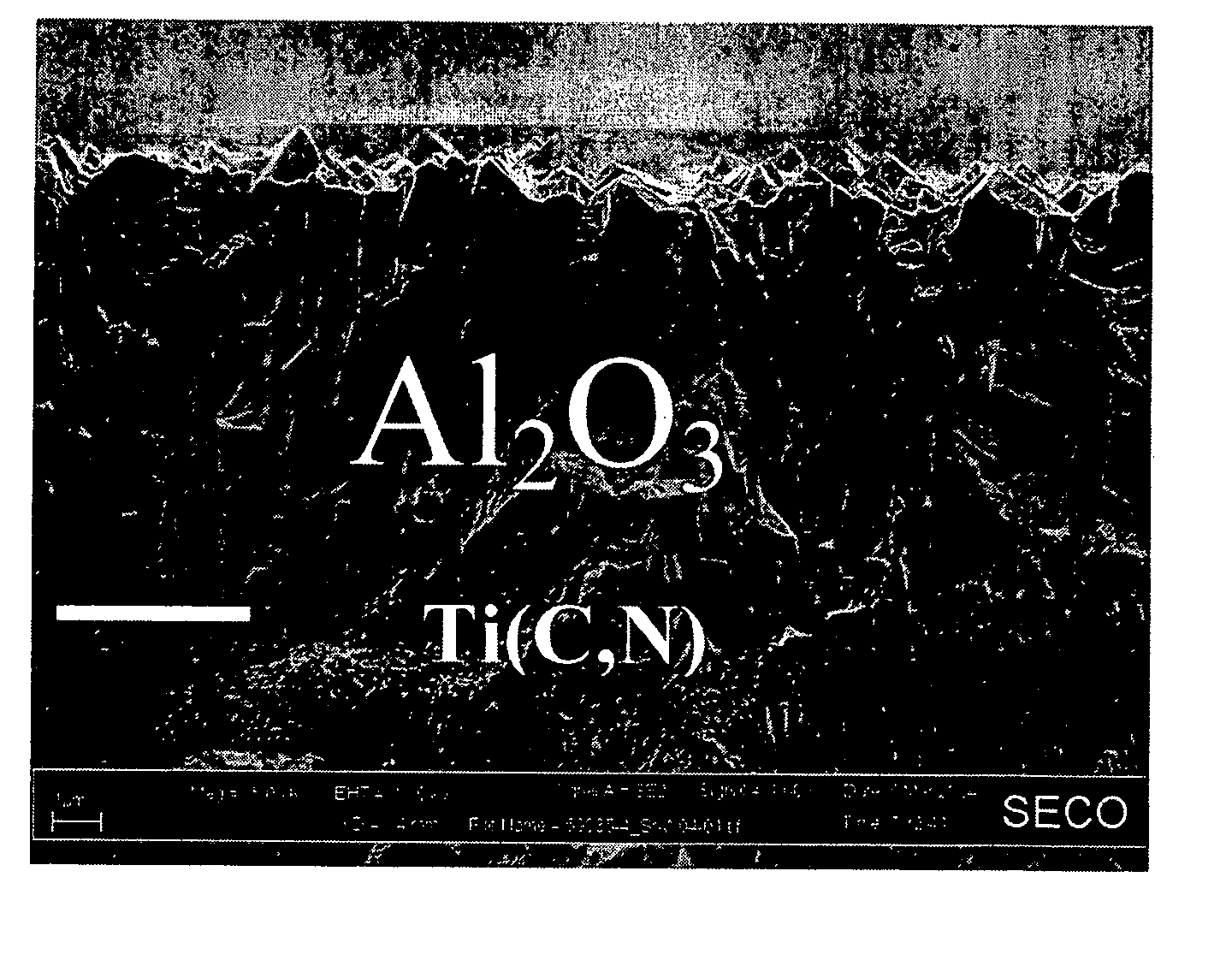

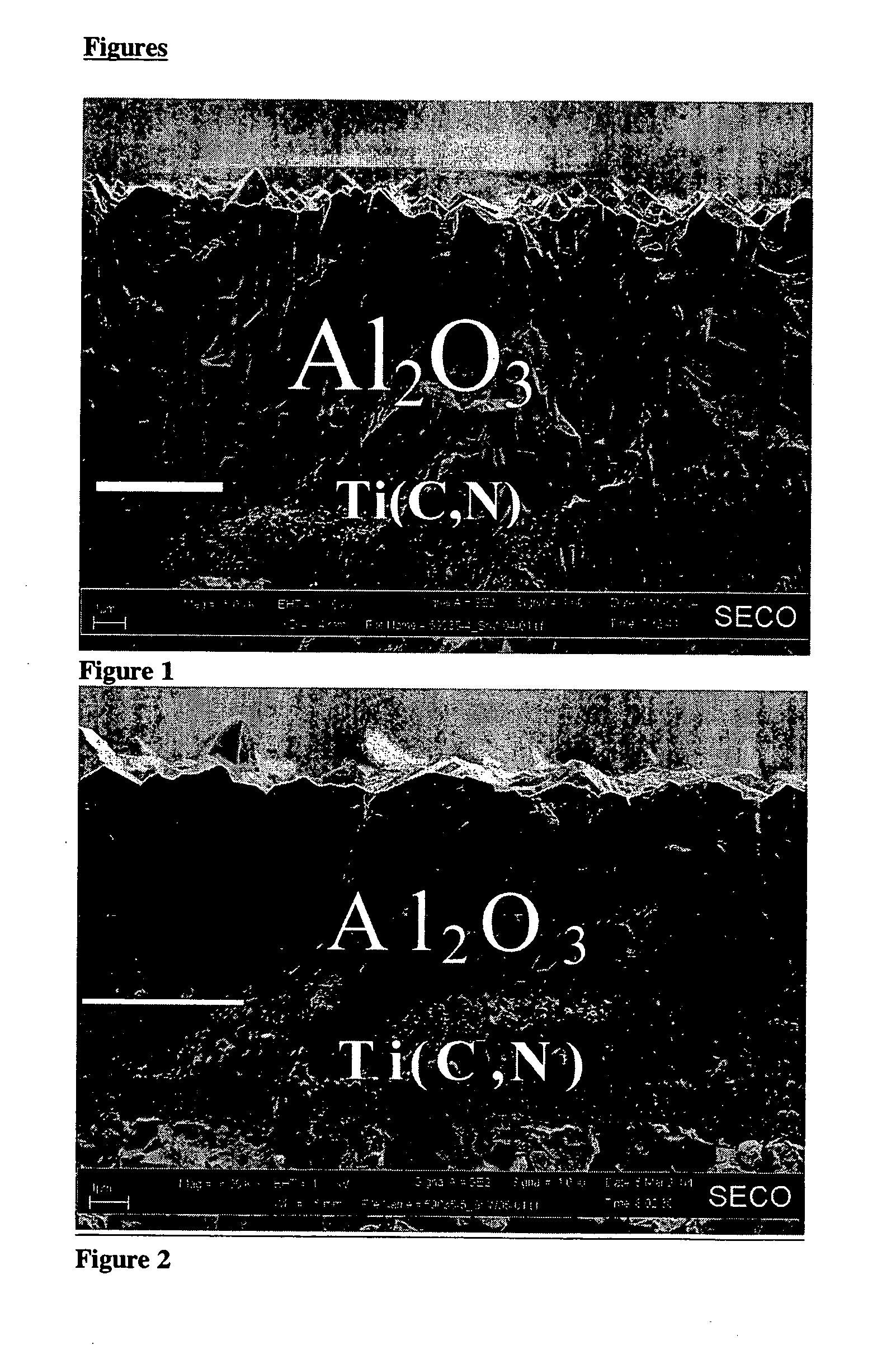

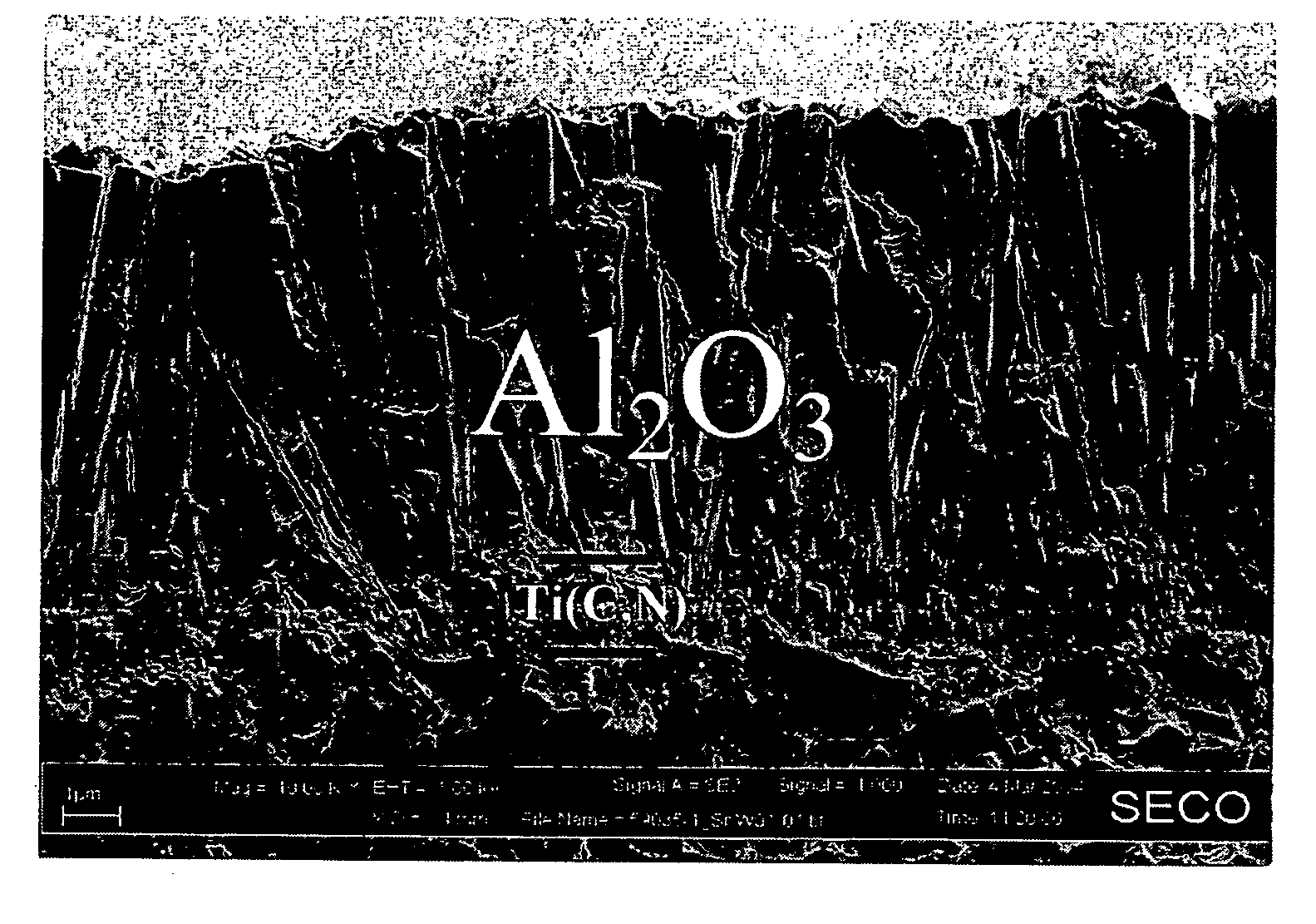

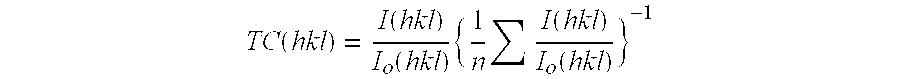

Alumina layer with controlled texture

InactiveUS20060199026A1Improve toughnessReduce dislocation densityPigmenting treatmentOther chemical processesNucleationWear resistance

A new and refined method to produce α-Al2O3 layers in a temperature range of from about 750 to about 1000° C. with a controlled growth texture and substantially enhanced wear resistance and toughness than the prior art is disclosed. The α-Al2O3 layer of the present invention is formed on a bonding layer of (Ti,Al)(C,O,N) with increasing aluminium content towards the outer surface. Nucleation of α-Al2O3 is obtained through a nucleation step being composed of short pulses and purges consisting of Ti / Al-containing pulses and oxidising pulses. The α-Al2O3 layer according to the present invention has a thickness ranging from about 1 to about 20 μm and is composed of columnar grains. The length / width ratio of the alumina grains is from about 2 to about 12, preferably from about 4 to about 8. The layer is characterized by a strong (104) growth texture, measured using XRD, and by low intensity of (012), (110), (113), (024) and (116) diffraction peaks.

Owner:SECO TOOLS AB

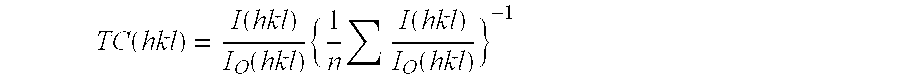

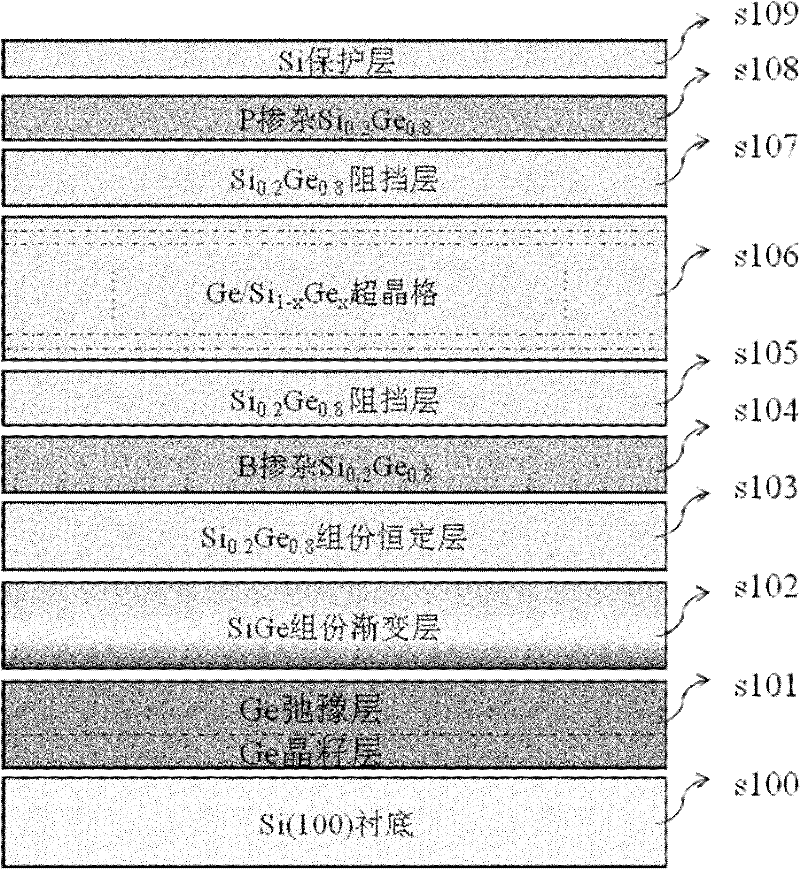

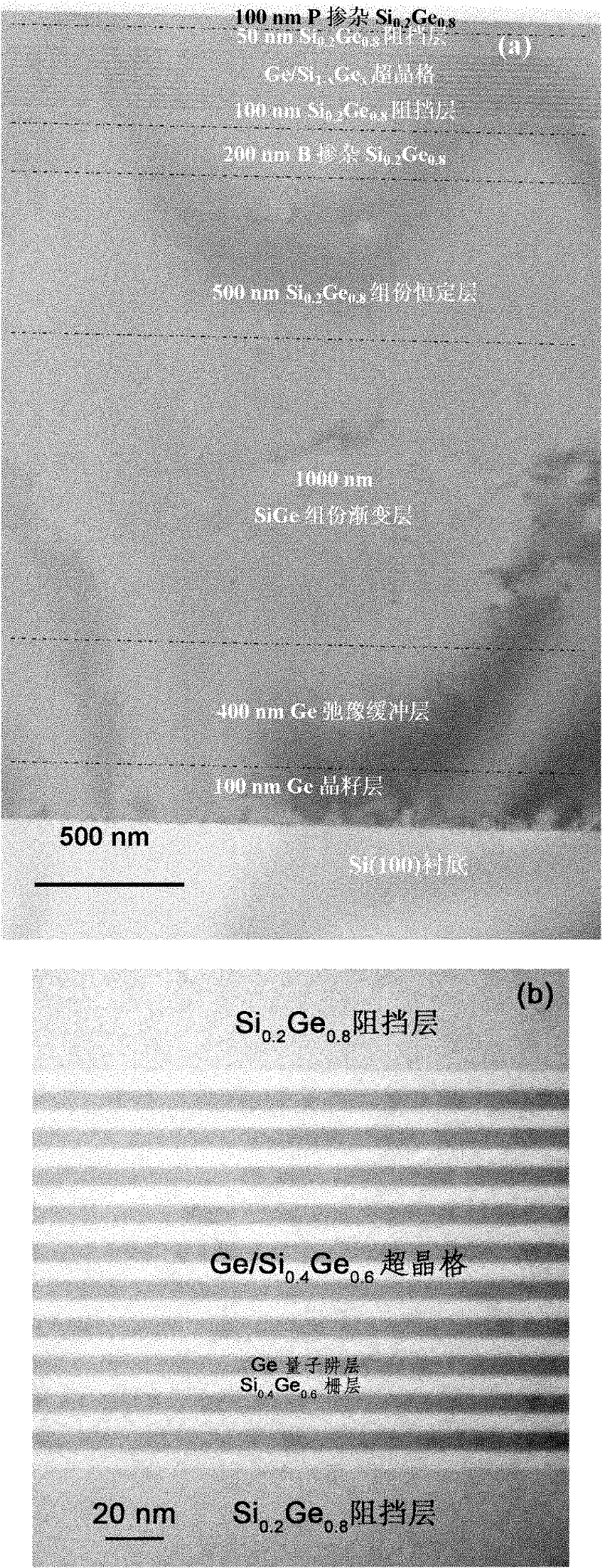

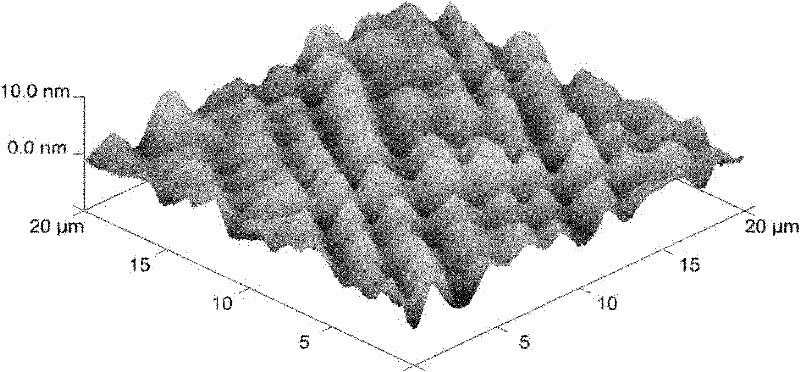

High quality strain Ge/SiGe super-lattice structure and preparation method thereof

InactiveCN102162137AHigh Ge contentReduce dislocation densityPolycrystalline material growthFrom chemically reactive gasesSemiconductor materialsReduced pressure chemical vapor deposition

The invention belongs to the technical field of semiconductor materials, and relates to a Ge / Si1-xGex super-lattice structure and preparation thereof. The high quality strain Ge / Si1-xGex super-lattice structure comprises a Si substrate, and a Si0.2Ge0.8 virtual substrate layer, a B-doped Si0.2Ge0.8 epitaxial layer, a Si0.2Ge0.8 blocking layer, a Ge / Si1-xGex super-lattice layer, a P-doped Si0.2Ge0.8 epitaxial layer, a Si0.2Ge0.8 blocking layer and a Si protective layer sequentially and epitaxially grown on the Si substrate, wherein x is more than or equal to 0.6 and less than or equal to 0.7. The epitaxial layers are sequentially grown on the Si substrate by adopting a reduced pressure chemical vapor deposition method; the obtained super-lattice structure has the properties of low dislocation defect density, low thickness and flat interface / surface, and the Ge / Si1-xGex super-lattice is in a strain state; and the super-lattice structure has high quality and is particularly suitable for manufacturing silicon-based laser devices and waveguide modulators.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

Silicon carbide semiconductor substrate and method of manufacturing the same

InactiveUS20090302328A1Reducing basal plane dislocation densityImprove conversion efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalDislocation

A buffer layer configured of the same conductive semiconductor layers of two or more layers as a drift layer is installed by epitaxial growth between a first semiconductor layer configuring the drift layer that is a layer in which components of the semiconductor device are made and a base substrate including a silicon carbide single crystal wafer. A step of donor concentration is provided at an interface between the drift layer and the buffer layer, an interface between the semiconductor layers configuring the buffer layer, and an interface between the buffer layer and the base substrate and the donor concentration of the drift layer side is lower than that of the base substrate side, thereby making it possible to convert most basal plane dislocations into threading edge dislocations as compared to the drift layer having one layer or the buffer layer configured of one layer.

Owner:HITACHI CABLE

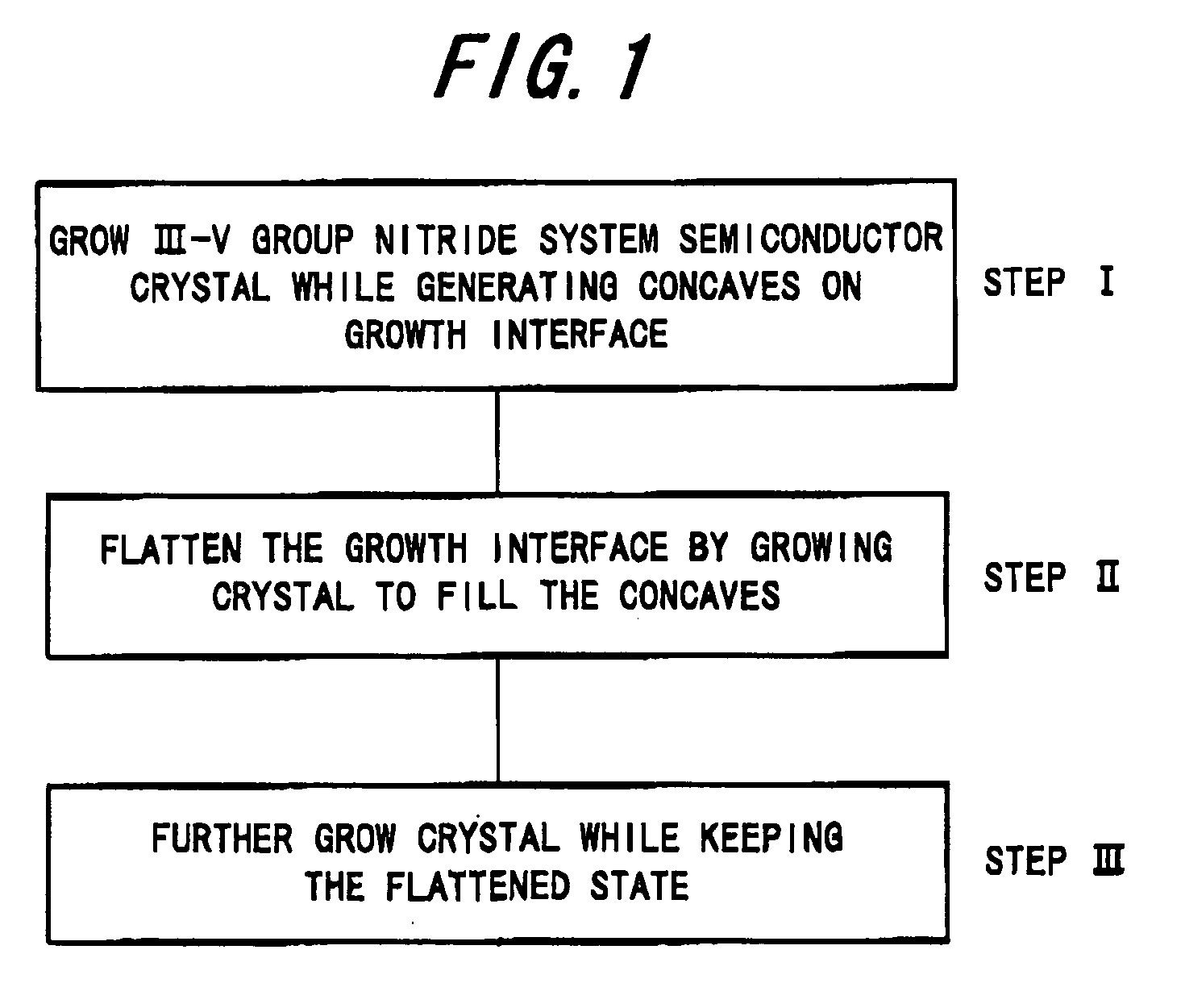

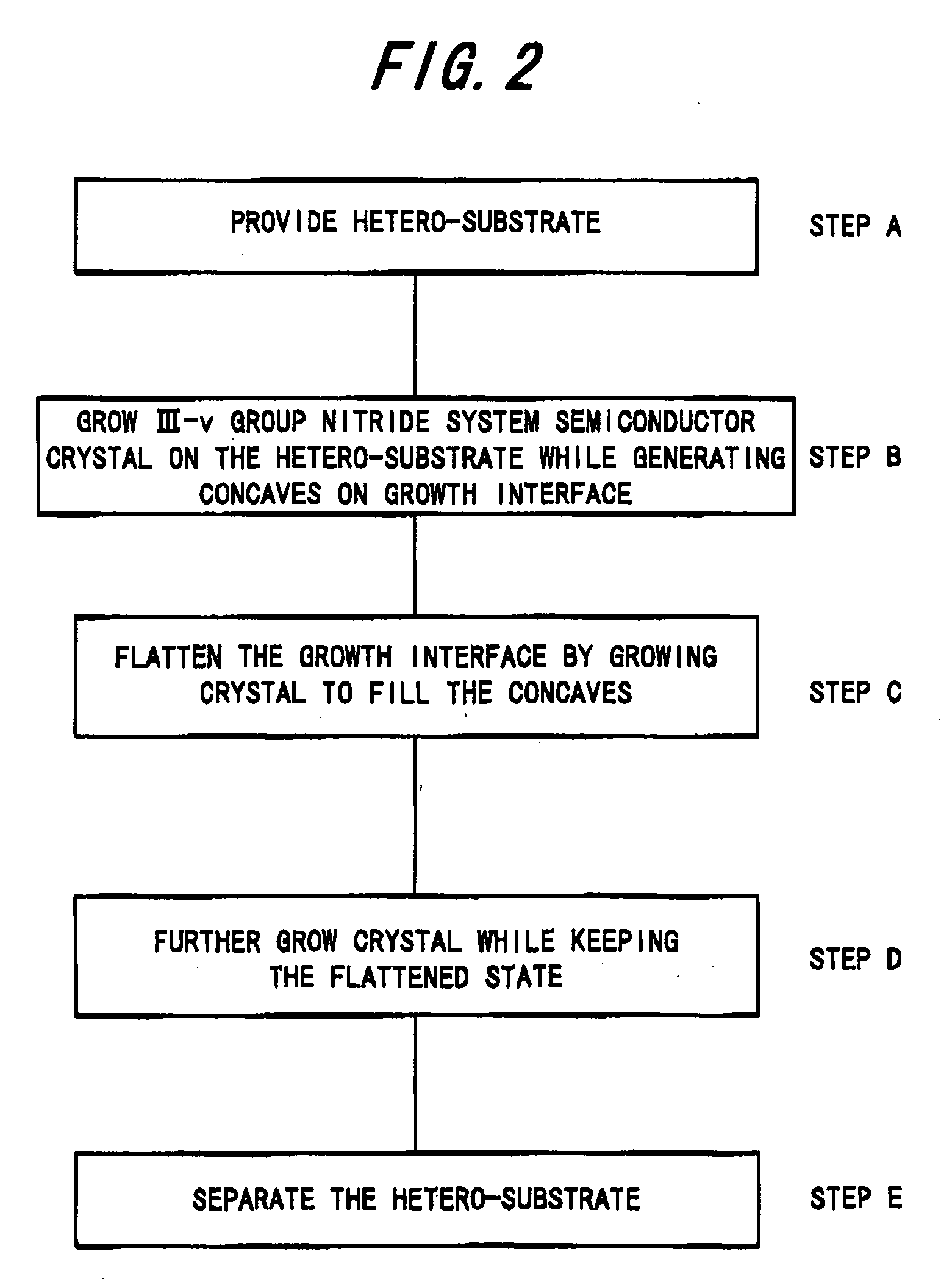

III-V nitride semiconductor substrate and its production method

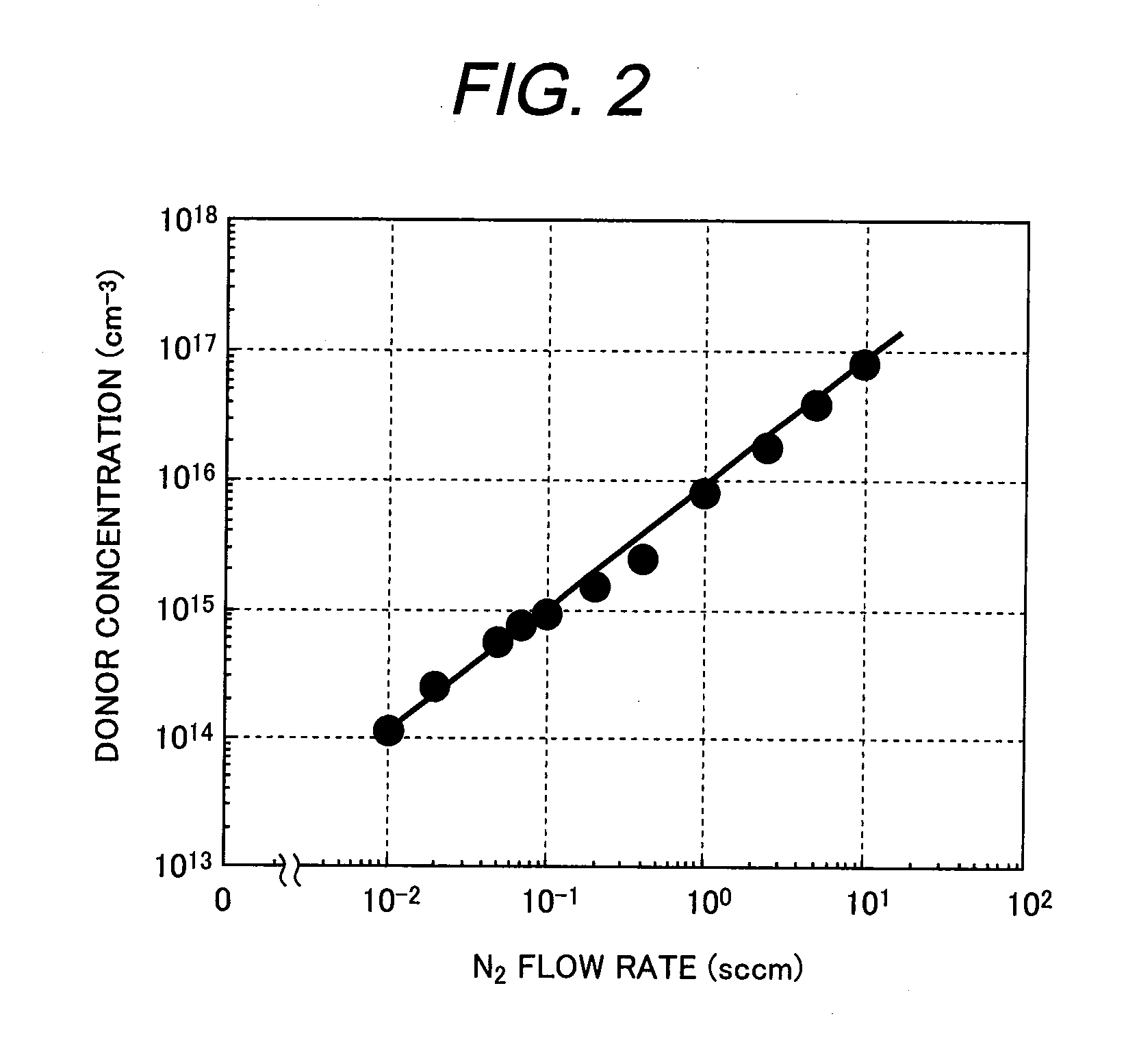

ActiveUS20050048685A1Low dislocation densityReduce variationPolycrystalline material growthFrom solid stateIntermediate stageCharge carrier

A self-supported III-V nitride semiconductor substrate having a substantially uniform carrier concentration distribution in a surface layer existing from a top surface to a depth of at least 10 μm is produced by growing a III-V nitride semiconductor crystal while forming a plurality of projections on a crystal growth interface at the initial or intermediate stage of crystal growth; conducting the crystal growth until recesses between the projections are buried, so that the crystal growth interface becomes flat; and continuing the crystal growth to a thickness of 10 μm or more while keeping the crystal growth interface flat.

Owner:SUMITOMO CHEM CO LTD

Method for producing group III element nitride single crystal and group III element nitride transparent single crystal prepared thereby

InactiveUS20060051942A1Quality improvementRapid productionPolycrystalline material growthFrom normal temperature solutionsIndiumAlkaline earth metal

A method for producing a Group III element nitride single crystal, which comprises reacting at least one Group III element selected from the group consisting of gallium(Ga), aluminum(Al) and indium(In) with nitrogen(N) in a mixed flux of sodium(Na) and at least one of an alkali metal (except Na) and an alkaline earth metal. The method allows the production, with a good yield, of the single crystal of a group III element nitride which is transparent, is reduced in the density of dislocation, has a bulk form, and is large. In particular, a gallium nitride single crystal produced by the method has high quality and takes a large and transparent bulk form, and thus has a high practical value.

Owner:OSAKA UNIV

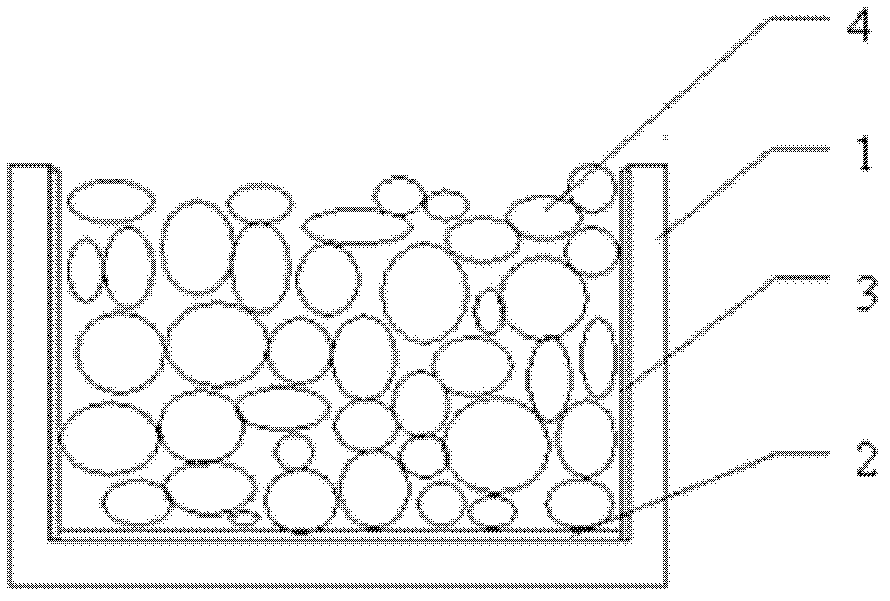

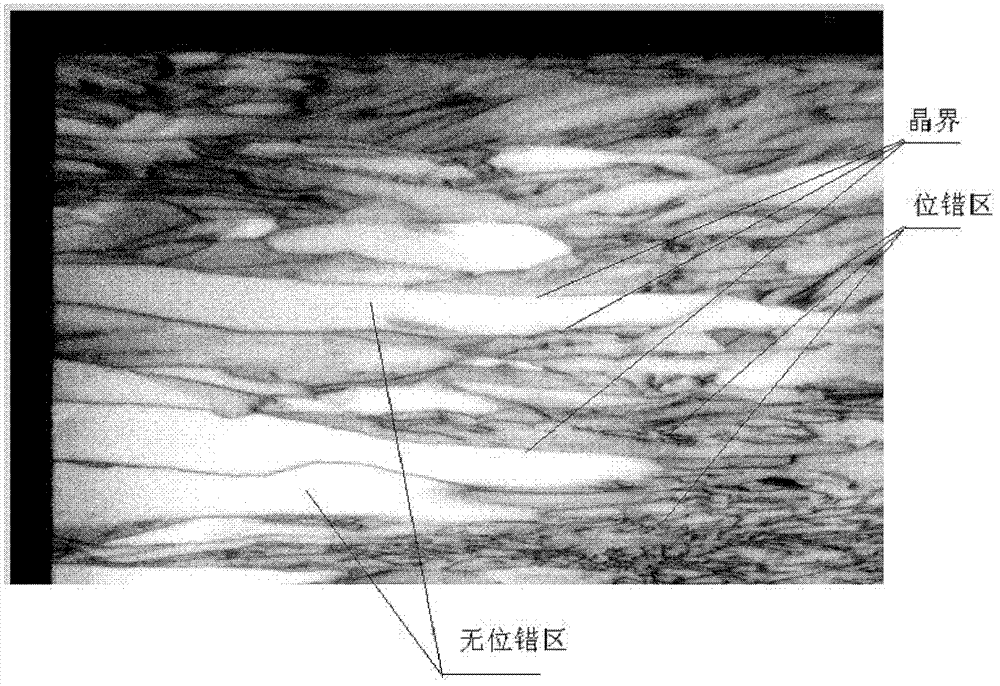

Polycrystalline silicon ingot, preparation method of polycrystalline silicon ingot, polycrystalline silicon slice and crucible for polycrystalline silicon ingot casting

ActiveCN102776561APromote nucleationUniform grainPolycrystalline material growthSingle crystal growth detailsMolten stateCrucible

The invention provides a preparation method of a polycrystalline silicon ingot. The preparation method comprises the following steps that a core source is arranged at the bottom of a crucible, and a core source layer is formed; silicon materials in a molten state are arranged on the core source layer; and the temperature in the crucible is controlled to gradually rise in a direction vertical to the upward direction form the bottom of the crucible, the temperature gradient is formed, the silicon materials in the molten state form core crystallization by utilizing the core source, and the polycrystalline silicon ingot is prepared. The invention also provides high-quality polycrystalline silicon ingot obtained by the preparation method, a polycrystalline silicon slice obtained through the preparation of the polycrystalline silicon ingot and the crucible for polycrystalline silicon ingot casting. The polycrystalline silicon ingot prepared by the preparation method has the advantages that the crystalline size is uniform and regular, the dislocation density is low, and in addition, no obvious pine-tree crystals or twin crystals exist.

Owner:JIANGXI SAI WEI LDK SOLAR HI TECH CO LTD

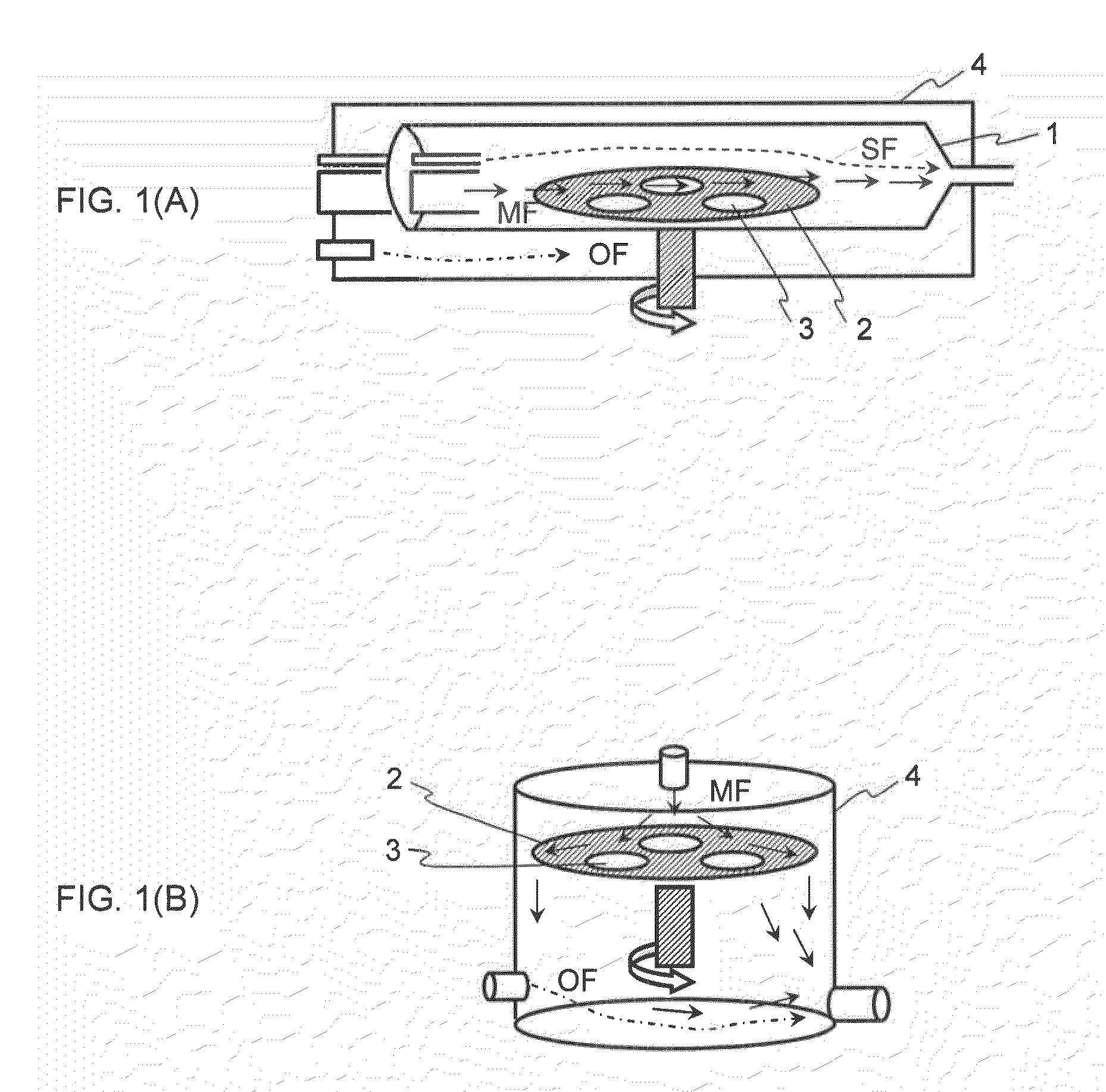

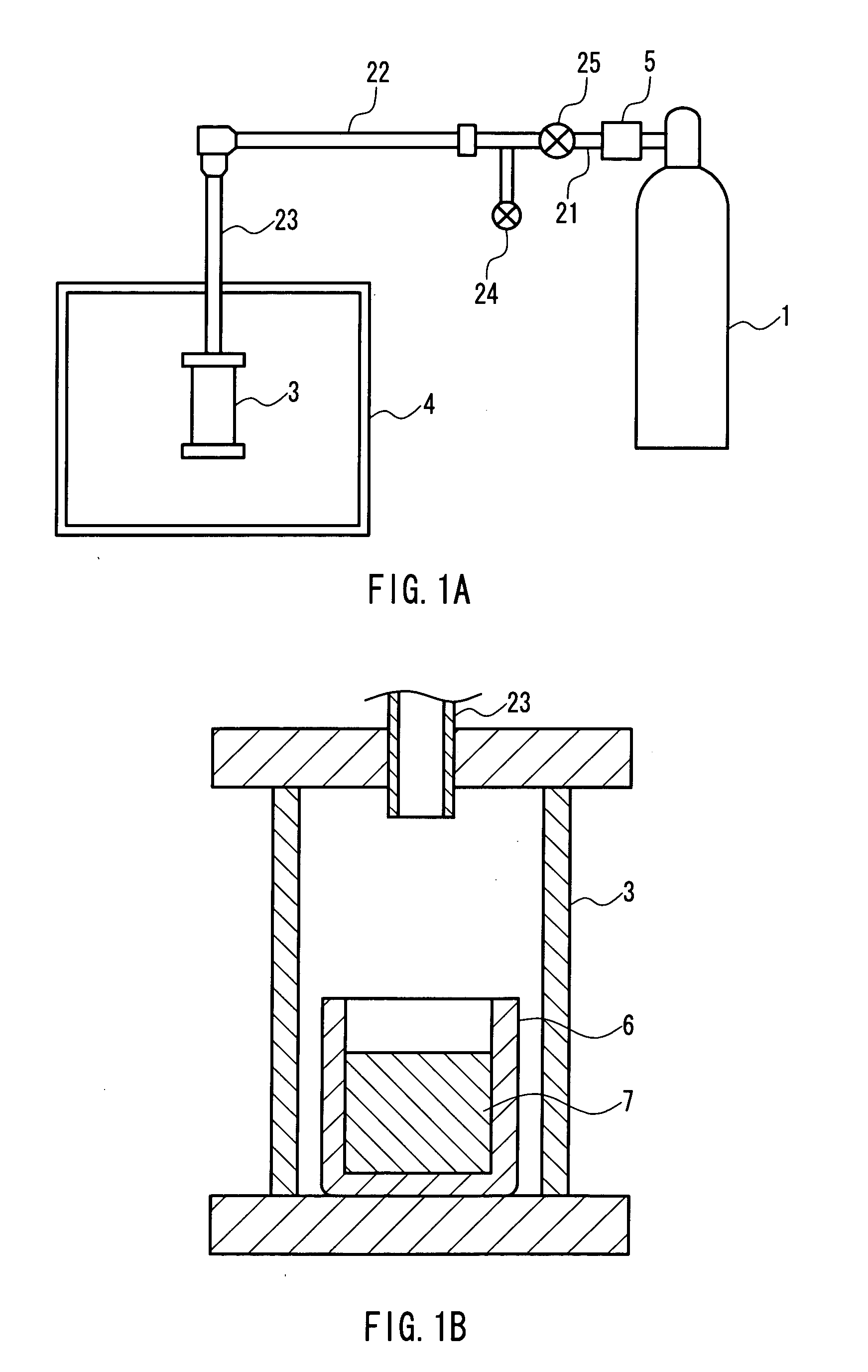

Method for producing group III nitride single crystal and apparatus used therefor

InactiveUS20060169197A1Reduce dislocation densityNon-uniform nitrogen distributionPolycrystalline material growthFrom normal temperature solutionsIndiumBulk crystal

A production method is provided in which Group-III-element nitride single crystals that have a lower dislocation density and a uniform thickness and are transparent, high quality, large, and bulk crystals can be produced with a high yield. The method for producing Group-III-element nitride single crystals includes: heating a reaction vessel containing at least one metal element selected from the group consisting of an alkali metal and an alkaline-earth metal and at least one Group III element selected from the group consisting of gallium (Ga), aluminum (Al), and indium (In) to prepare a flux of the metal element; and feeding nitrogen-containing gas into the reaction vessel and thereby allowing the Group III element and nitrogen to react with each other in the flux to grow Group-III-element nitride single crystals, wherein the single crystals are grown, with the flux being stirred by rocking the reaction vessel, for instance.

Owner:OSAKA UNIV

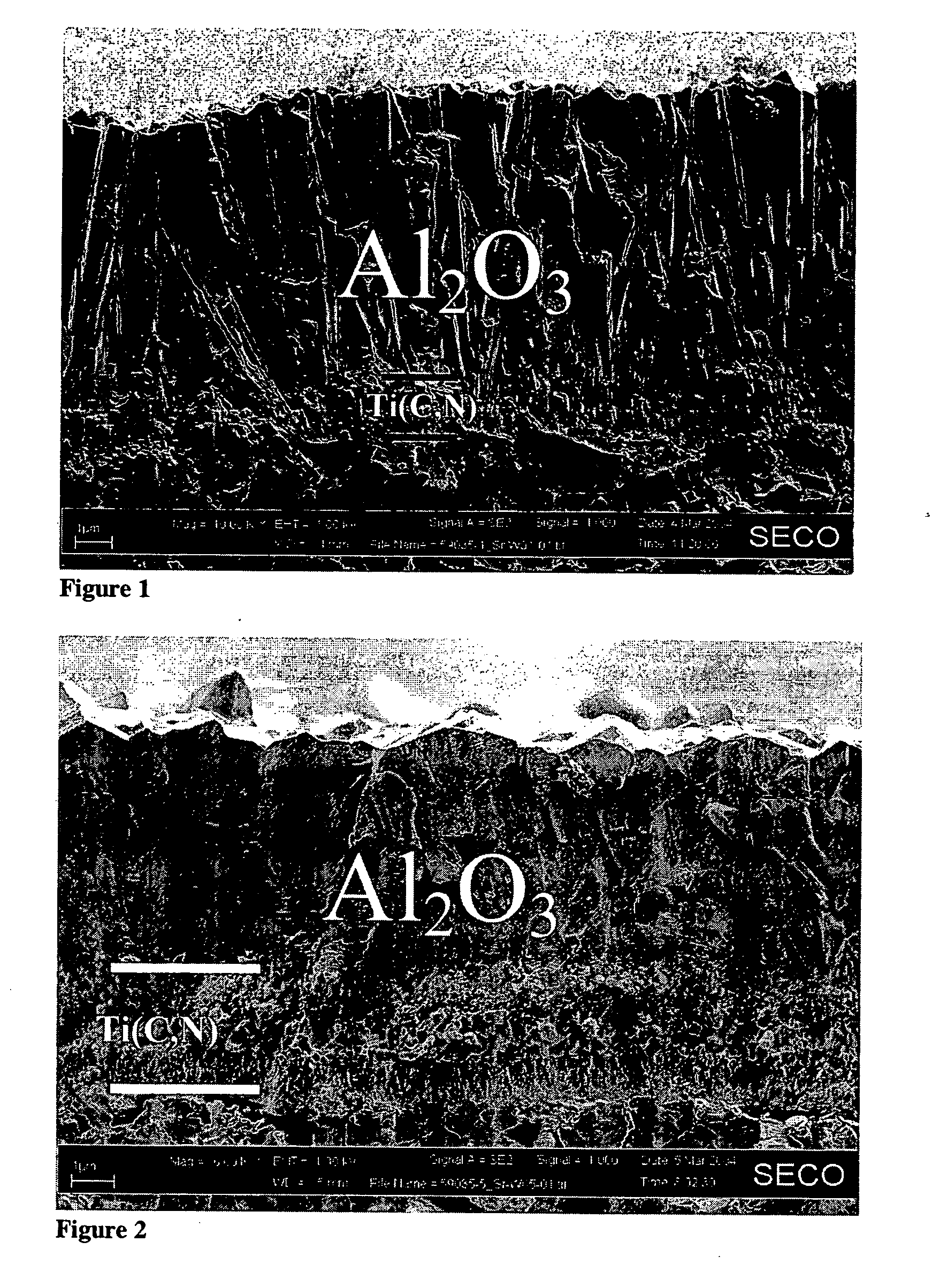

Enhanced alumina layer with texture

ActiveUS20060115662A1Improve toughnessReduce dislocation densityPigmenting treatmentRecord information storagePhysical chemistryTitanium

A refined method to produce textured α-Al2O3 layers in a temperature range of 750-1000° C. with a controlled texture and substantially enhanced wear resistance and toughness than the prior art is disclosed. The α-Al2O3 layer is formed on a bonding layer of (Ti,Al)(C,O,N) with increasing aluminium content towards the outer surface. Nucleation of α-Al2O3 is obtained through a nucleation step composed of short pulses and purges of Ti-containing and oxidizing steps. The α-Al2O3 layer has a thickness ranging from 1 to 20 μm and is composed of columnar grains. The length / width ratio of the alumina grains is from 2 to 15, preferably 6 to 10. The layer is characterised by a strong (110) growth texture, measured using XRD, and by the low intensity of (012), (104), (113), (024) and (116) diffraction peaks.

Owner:SECO TOOLS AB

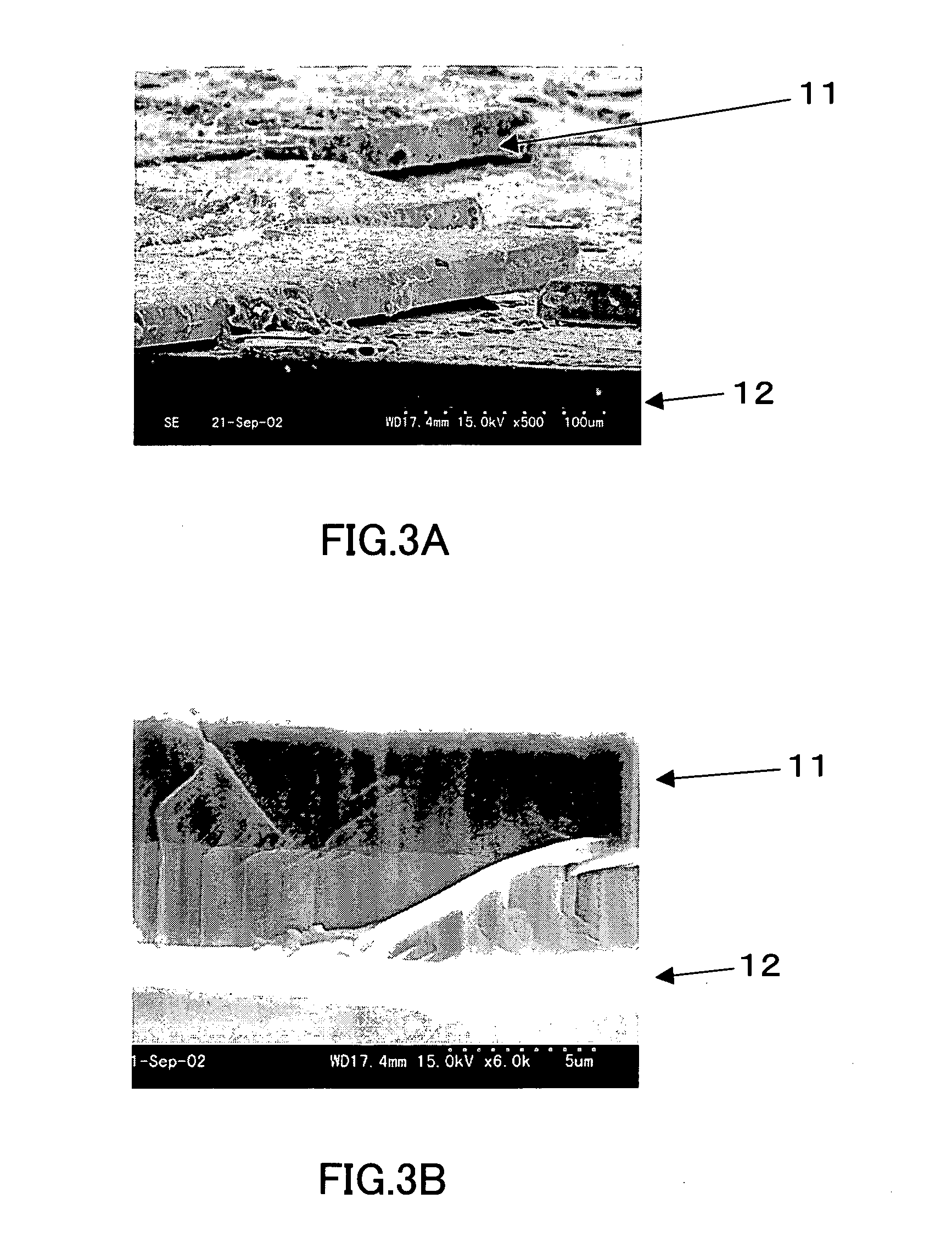

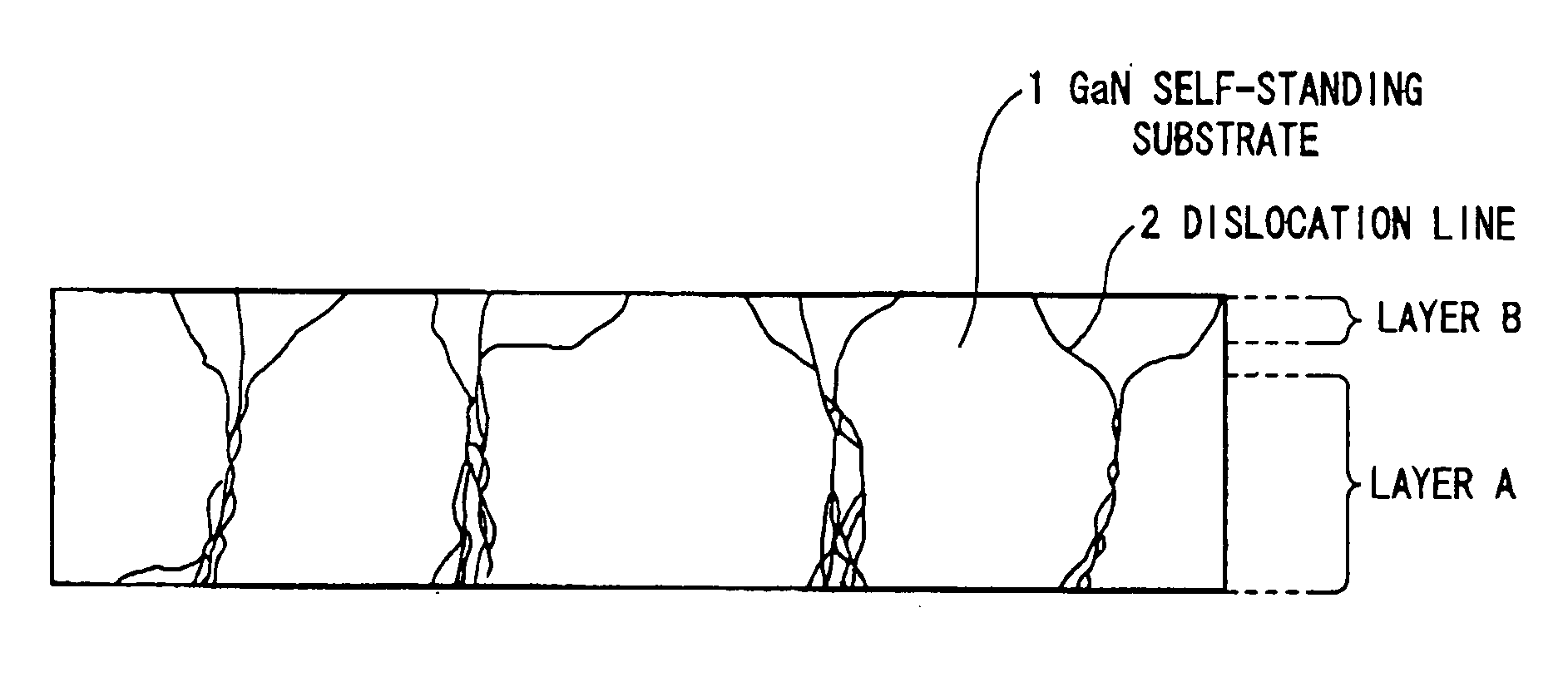

III-V group nitride system semiconductor self-standing substrate, method of making the same and III-V group nitride system semiconductor wafer

ActiveUS20060033119A1Improve crystal qualityLess distortionPolycrystalline material growthSemiconductor/solid-state device manufacturingWaferingDensity distribution

A III-V group nitride system semiconductor self-standing substrate has: a first III-V group nitride system semiconductor crystal layer that has a region with dislocation lines gathered densely, the dislocation lines being gathered substantially perpendicular to a surface of the substrate, and a region with dislocation lines gathered thinly; and a second III-V group nitride system semiconductor crystal layer that is formed up to 10 μm from the surface of the substrate on the first III-V group nitride system semiconductor crystal layer and that has a dislocation density distribution that is substantially uniform.

Owner:SUMITOMO CHEM CO LTD

Production method of pattern underlay for epitaxial growth of high-crystal quality nitride

InactiveCN101295636AReduce dislocation densityImprove crystal qualitySemiconductor/solid-state device manufacturingThin metalNitride

The invention relates to a preparation method for a graph underlay used for the epitaxial growth of a nitride with high crystal quality, which is characterized by including the steps of: step 1: depositing a layer of thin metal layer on the underlay; step 2: carrying out annealing treatment to lead the thin metal layer to form the amorphous graph of a metal mask with a micron dimension by self organizing; step 3: carrying out dry etching to transfer the graph of the metal mask to the underlay; step 4: removing the residual metal mask by adopting a method for wet corrosion and washing the underlay to prepare and finish the graph underlay.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

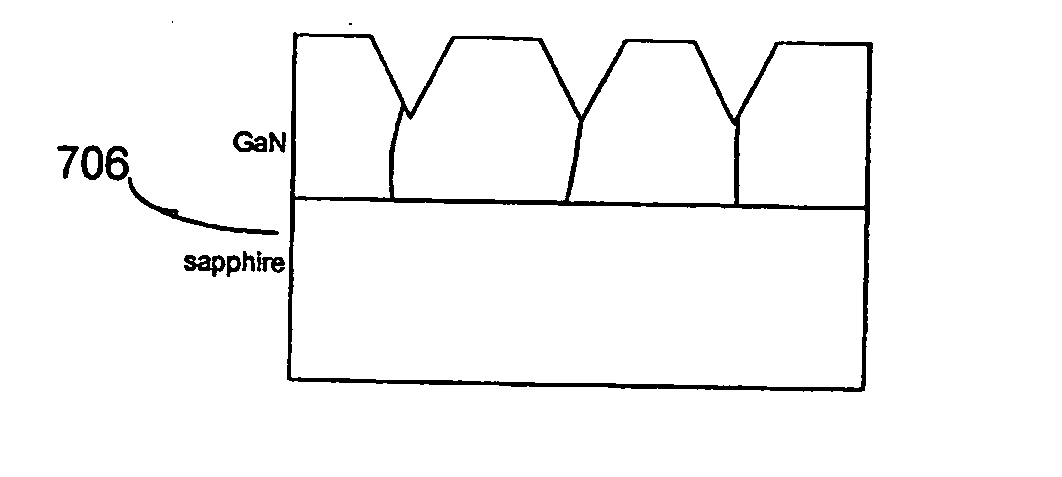

Semiconductor light-emitting device, manufacturing method thereof, and lamp

ActiveUS20120112188A1Solve the large outputHigh crystallinityRotary current collectorSolid-state devicesInter layerSingle crystal substrate

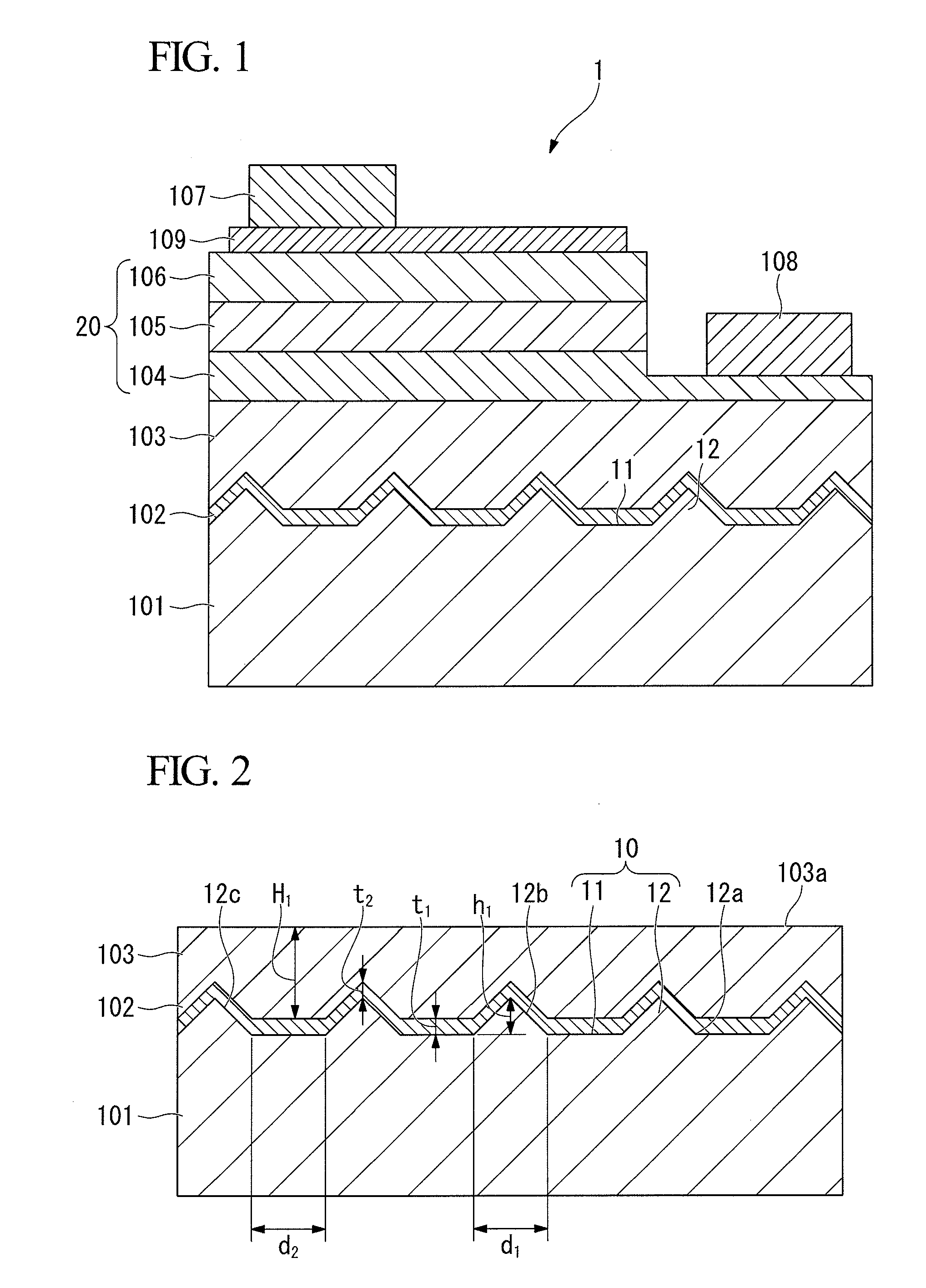

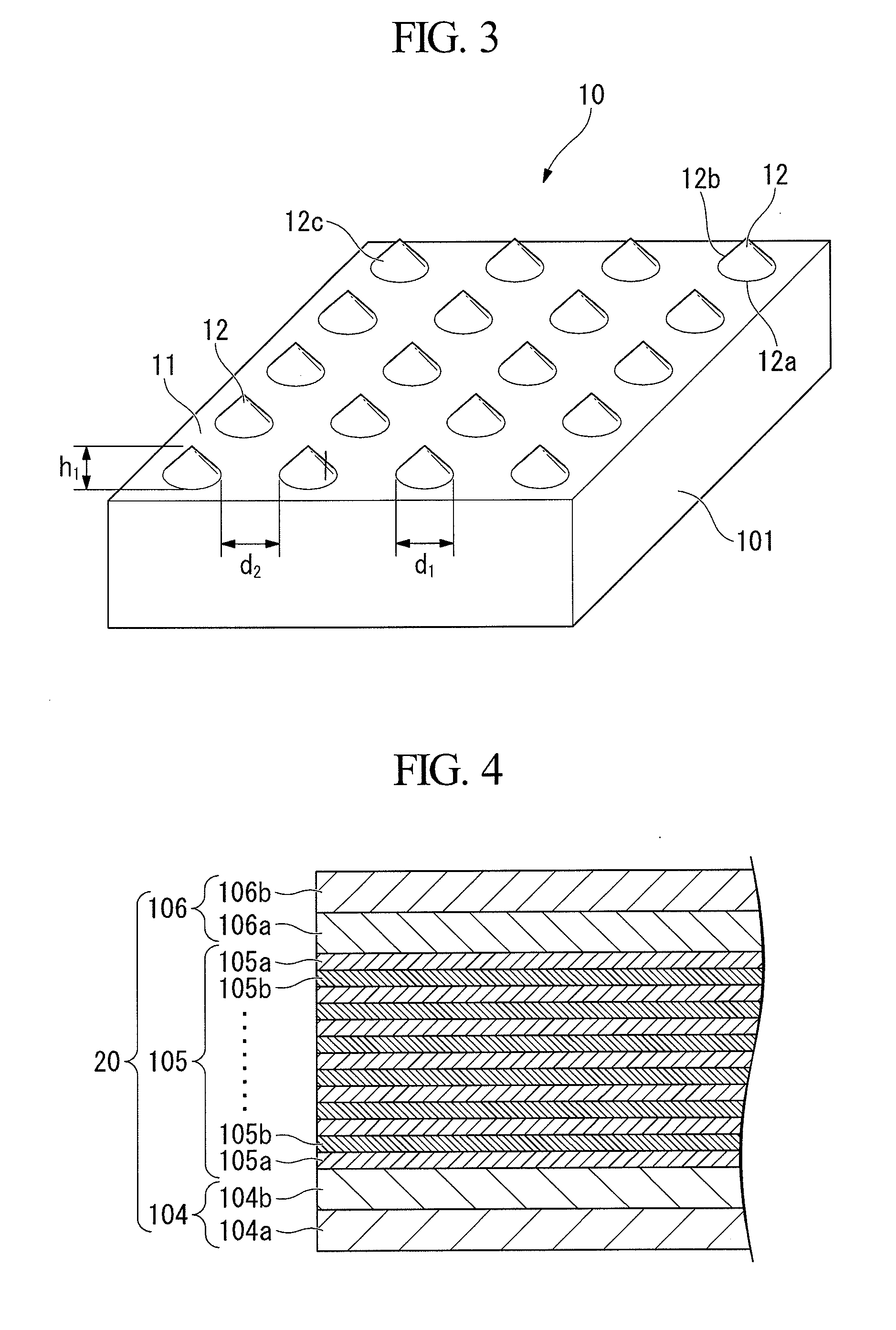

A semiconductor light-emitting device which includes: a single-crystal substrate formed with a plurality of projection portions on a c-plane main surface; an intermediate layer which is formed to cover the main surface of the single-crystal substrate, in which a film thickness t2 on the projection portion is smaller than a film thickness t1 on the c-plane surface, in which the film thickness t2 on the projection portion is 60% or more of the film thickness t1 on the c-plane surface, and which includes AlN having a single-crystal phase on the c-plane surface and a polycrystalline phase on the projection portion; and a semiconductor layer which is formed on the intermediate layer and includes a group III nitride semiconductor.

Owner:TOYODA GOSEI CO LTD

Method for preparing LED chip with separate crystal grain vertical structure

The invention presents a tube core shape design with high luminous efficiency, which comprises: epitaxial growing on island area LED chip with discrete grain; after laser peeling, packaging discrete chip into LED with vertical structure and high luminous efficiency. Wherein, the epitaxial growth improves crystal quality and internal quantum efficiency; the shape of island area increases LED light power; the island growth benefits to release stress, reduce stress on interface between GaN and sapphire substrate and the damage and spectral shift during peeling, thereby, it can obtain LED with high performance.

Owner:DONGGUAN INST OF OPTO ELECTRONICS PEKING UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com