Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2102 results about "Underlay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Underlay or underlayment generally refers to a thin layer of cushioning made of materials such as sponge rubber, foam, felt, or crumb rubber; this material is laid beneath carpeting to provide comfort underfoot, to reduce wear on the carpet, and to provide insulation against sound, moisture, and heat. In general, it is a layer which is underneath another layer, so underlay is thus also used to describe many different surface-covering products.

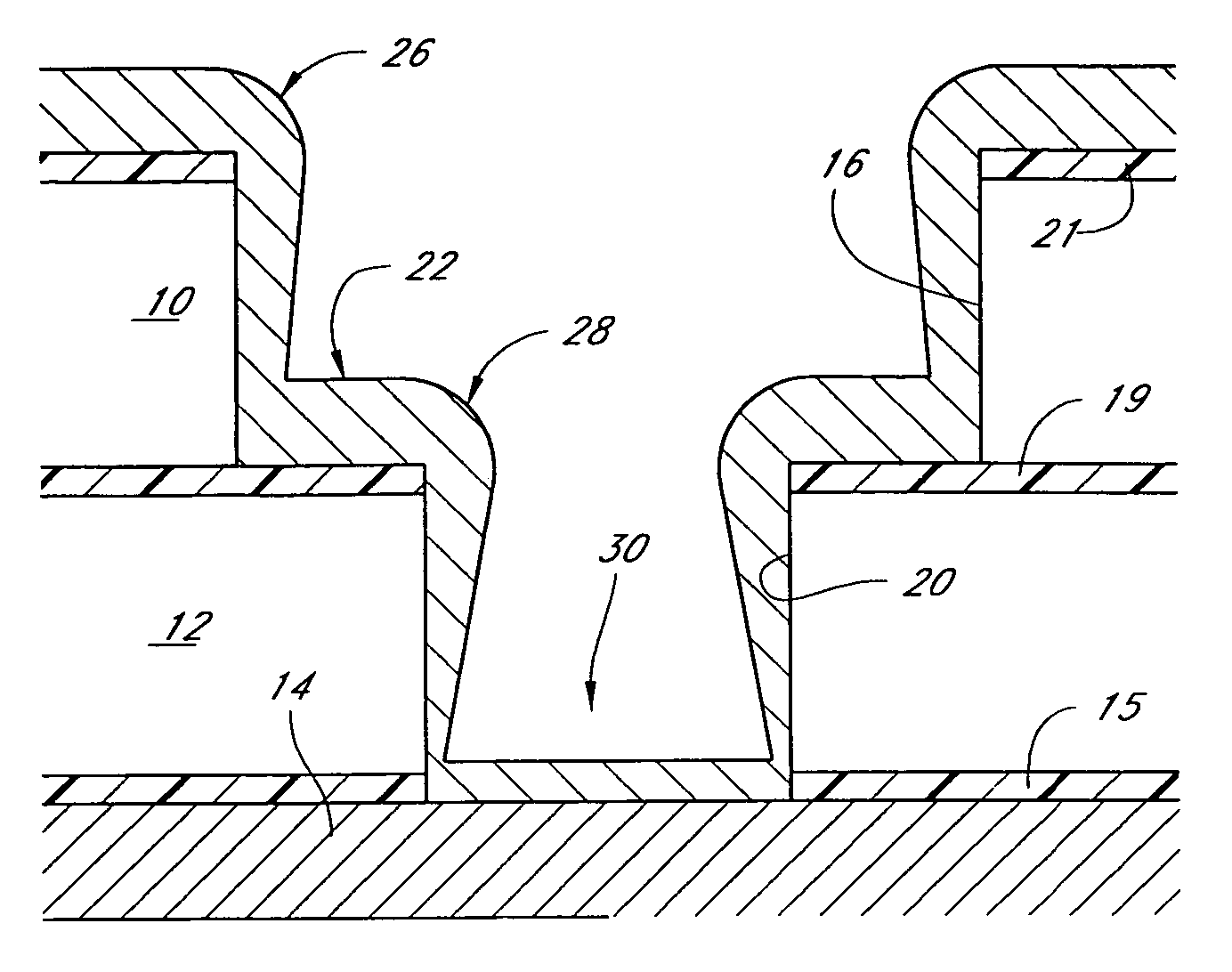

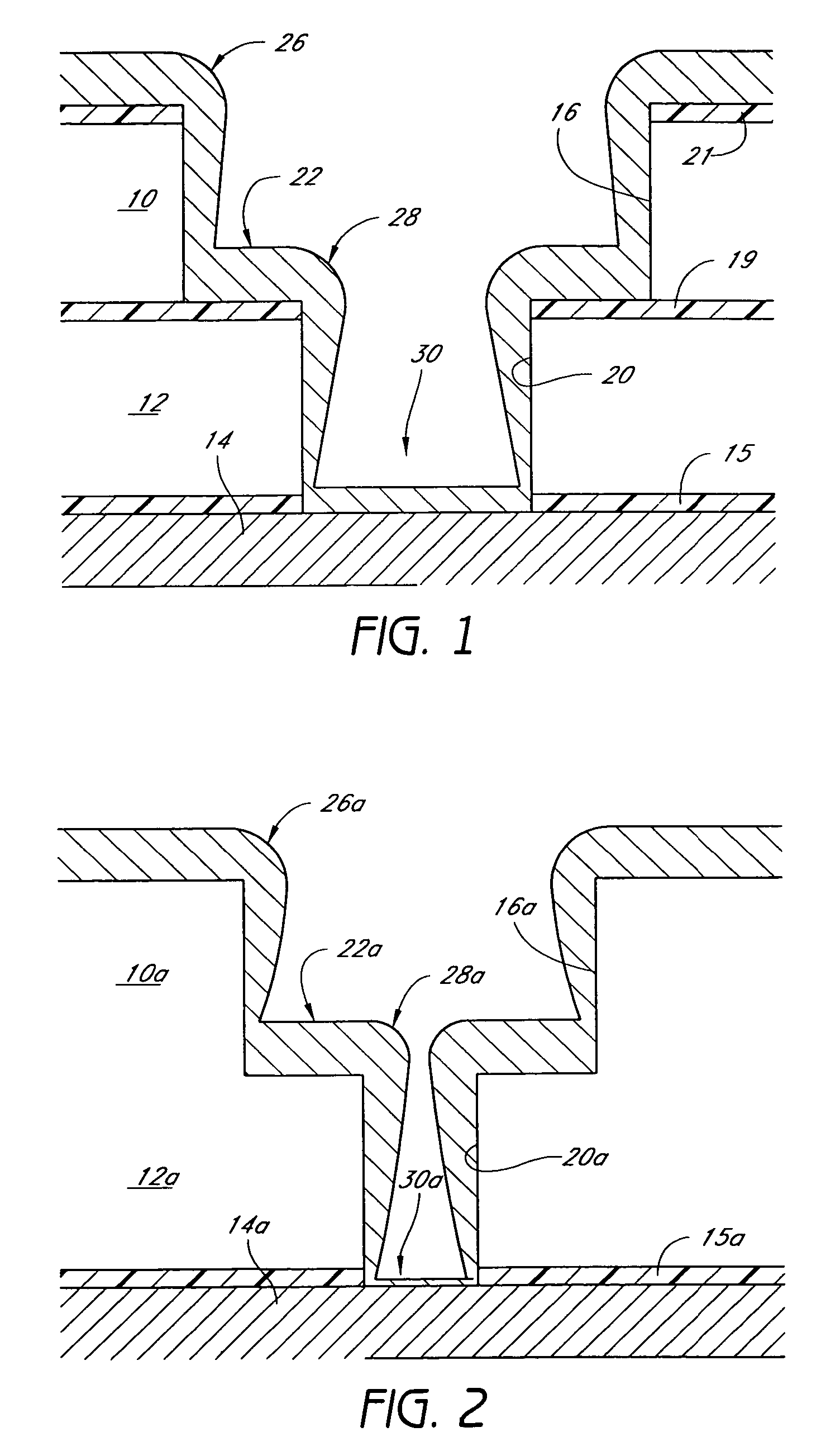

Plasma pre-treating surfaces for atomic layer deposition

ActiveUS7498242B2Improve barrier propertiesSemiconductor/solid-state device detailsVacuum evaporation coatingSelf limitingAtomic layer deposition

Owner:ASM IP HLDG BV

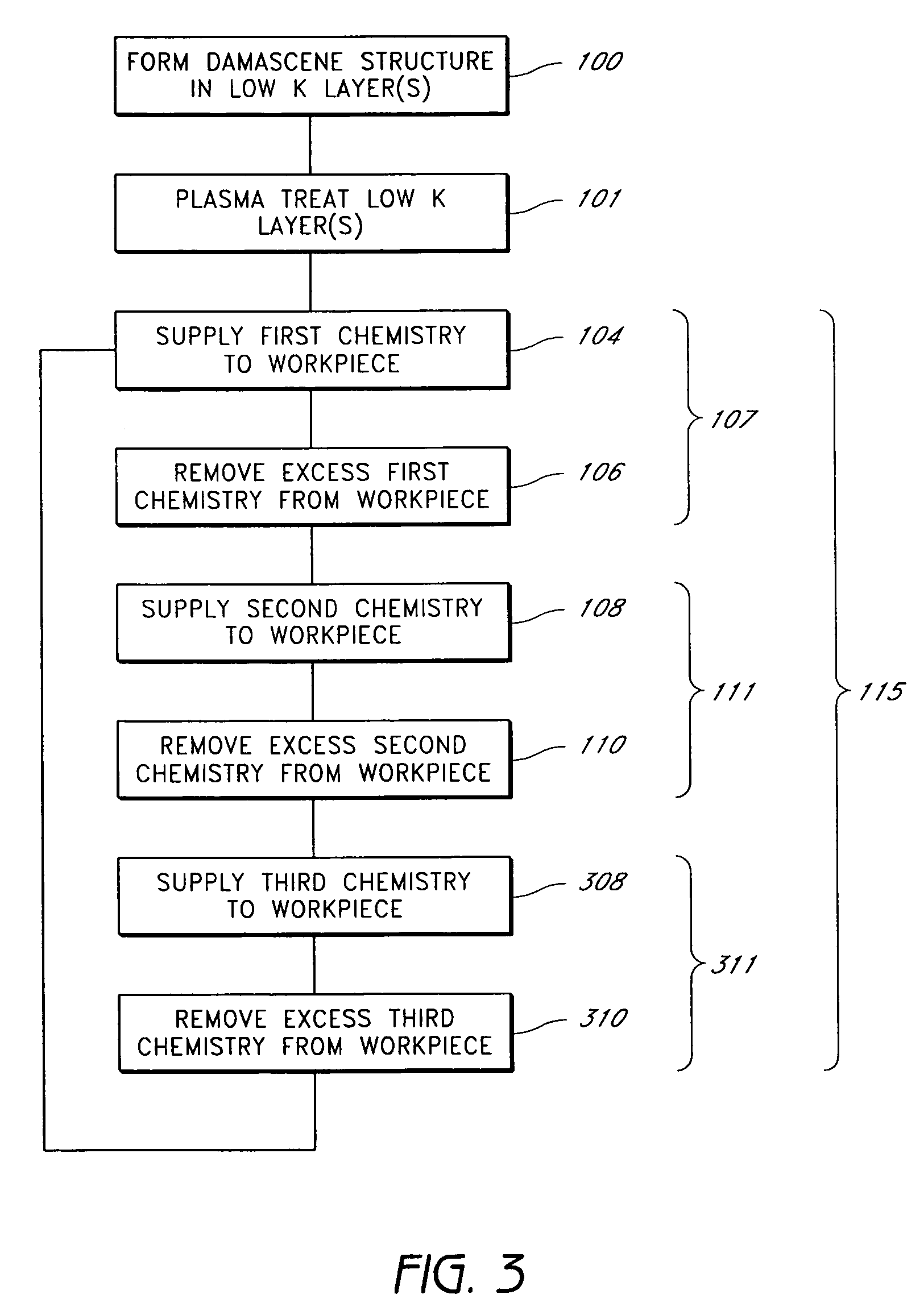

Method for fabricating an integrated circuit

InactiveUS20100055898A1Simple methodSemiconductor/solid-state device manufacturingEngineeringIntegrated circuit

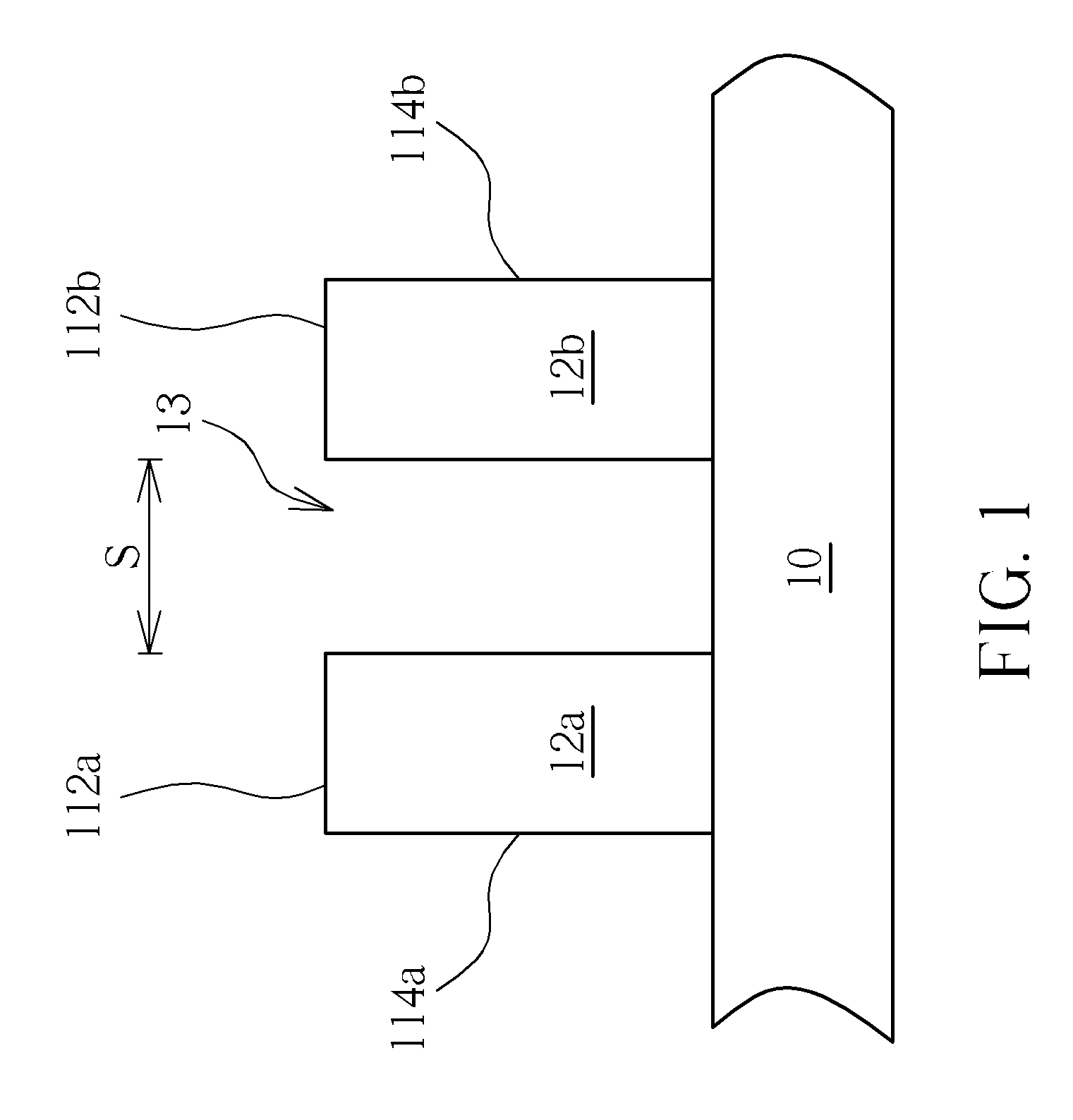

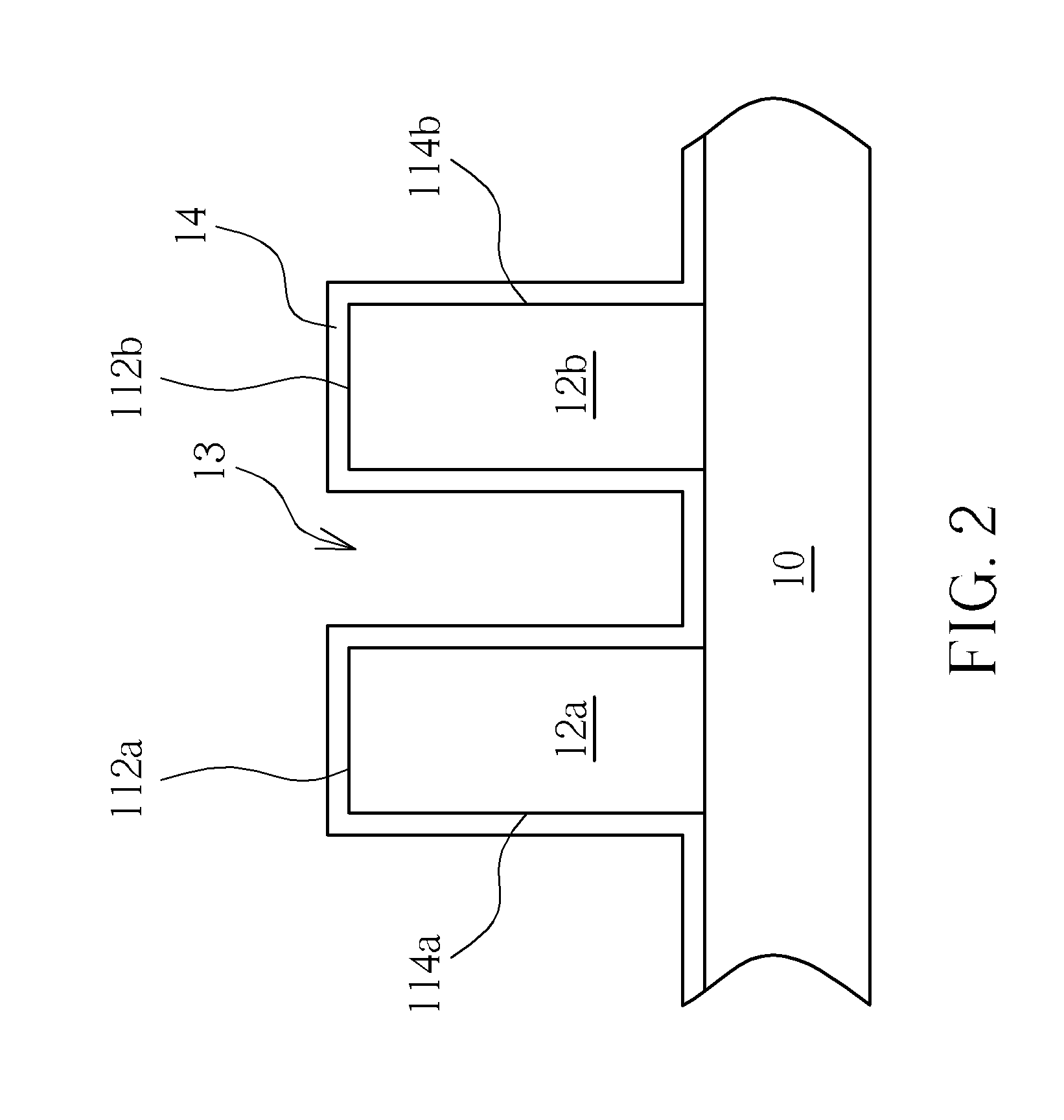

A method for fabricating an integrated circuit is provided. A substrate having thereon a first conductive wire and a second conductive wire is provided. A liner is formed on the first conductive wire and second conductive wire. An ashable material layer is filled into a gap between the first conductive wire and second conductive wire. The ashable material layer is then polished to expose a portion of the liner. A cap layer is formed on the ashable material layer and on the exposed liner. A through hole is etched into the cap layer to expose a portion of the ashable material layer. Thereafter, the ashable material layer is removed by way of the through hole.

Owner:NAN YA TECH

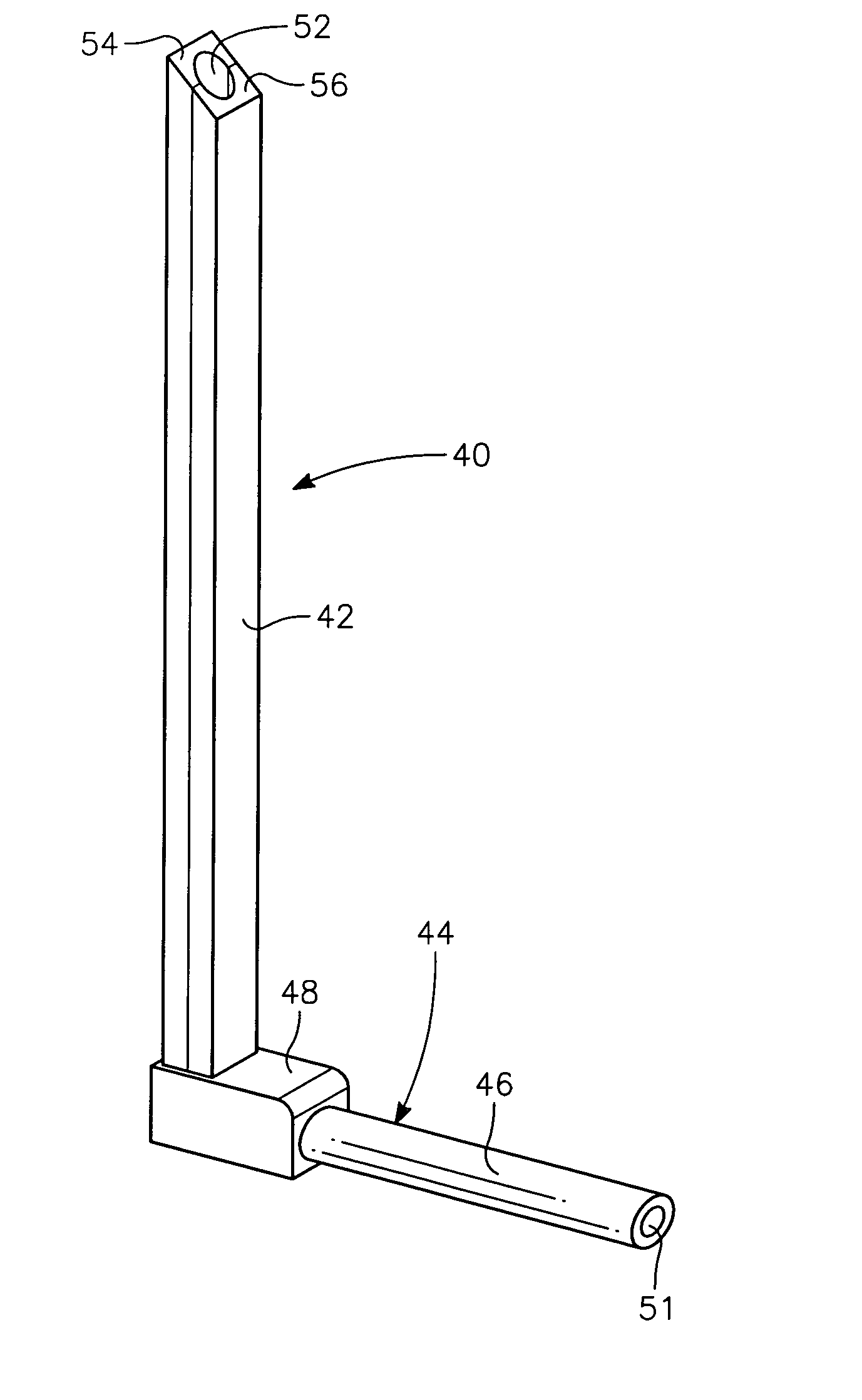

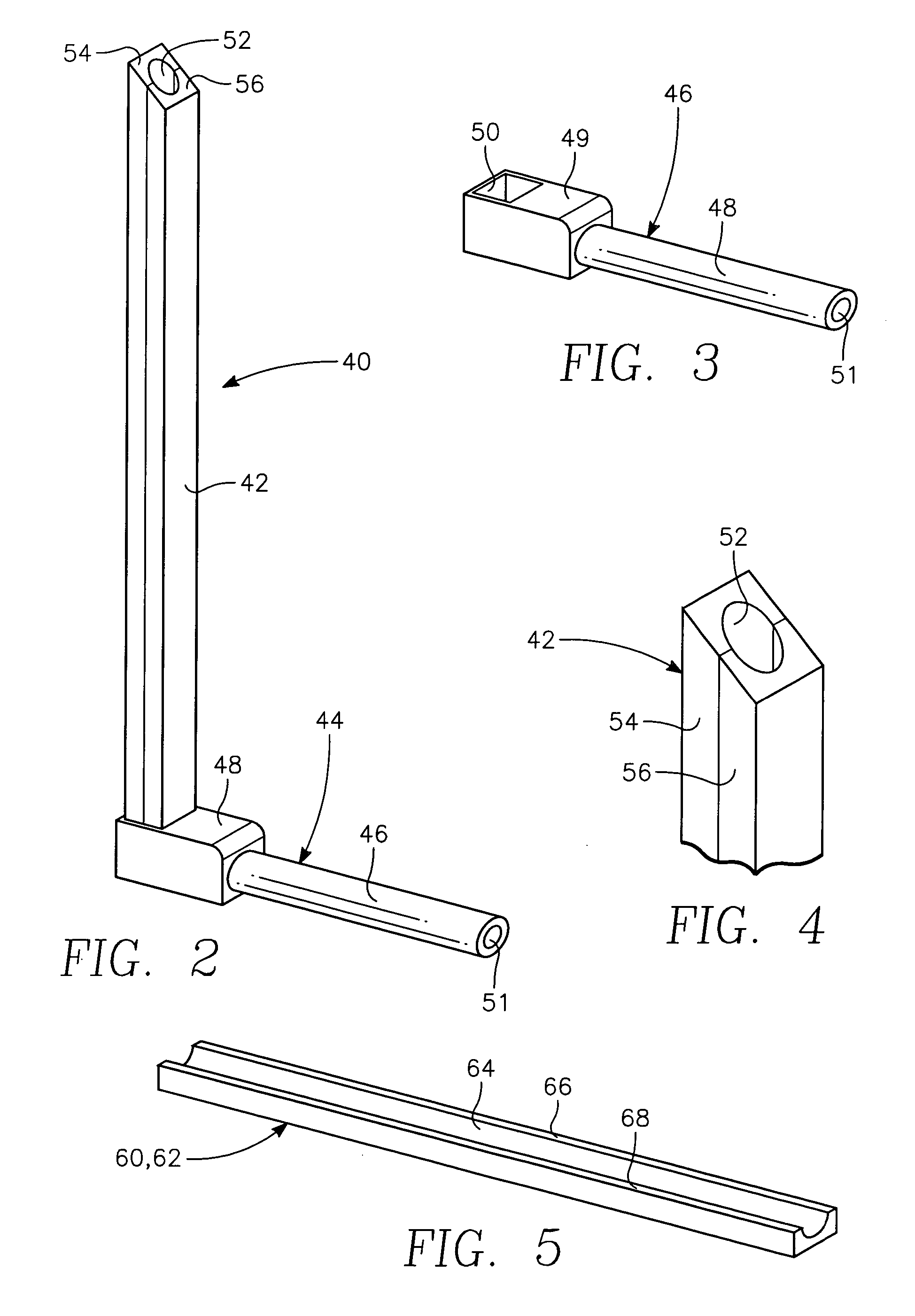

Silicon gas injector and method of making

A gas injector tube usable in a batch thermal treatment oven including two silicon shells joined together with an adhesive formed of a fine silicon powder and a curable silica-forming agent, such as a spin-on glass, which is ultrasonically homogenized. The tube may have a gas outlet on its distal end or be sealed with a silicon cap and have side outlet holes formed along its side. The silicon injector tube may be used in combination with a silicon tower and a silicon liner so that all bulk parts within the furnace hot zone are formed of silicon.

Owner:INTEGRATED MATERIALS

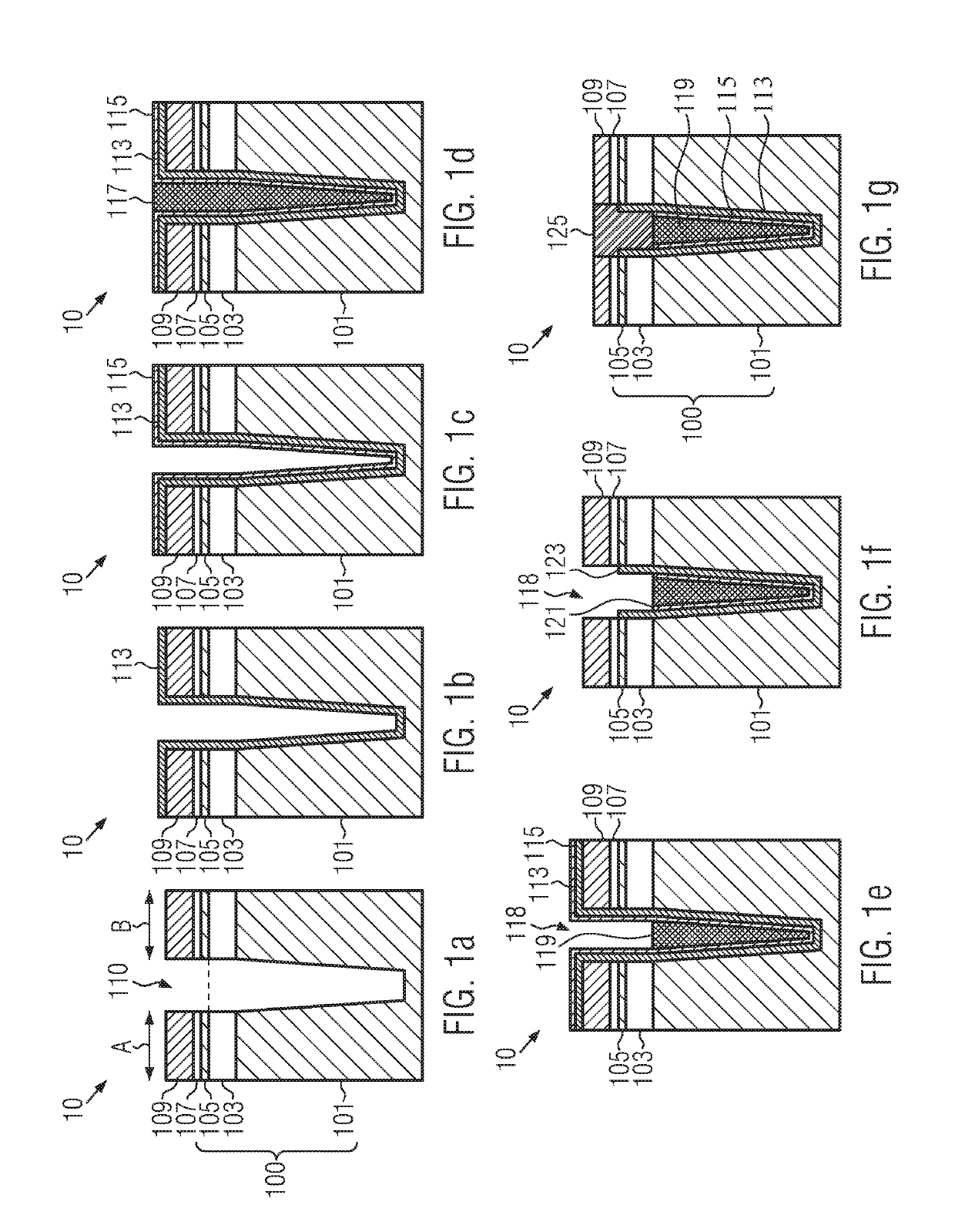

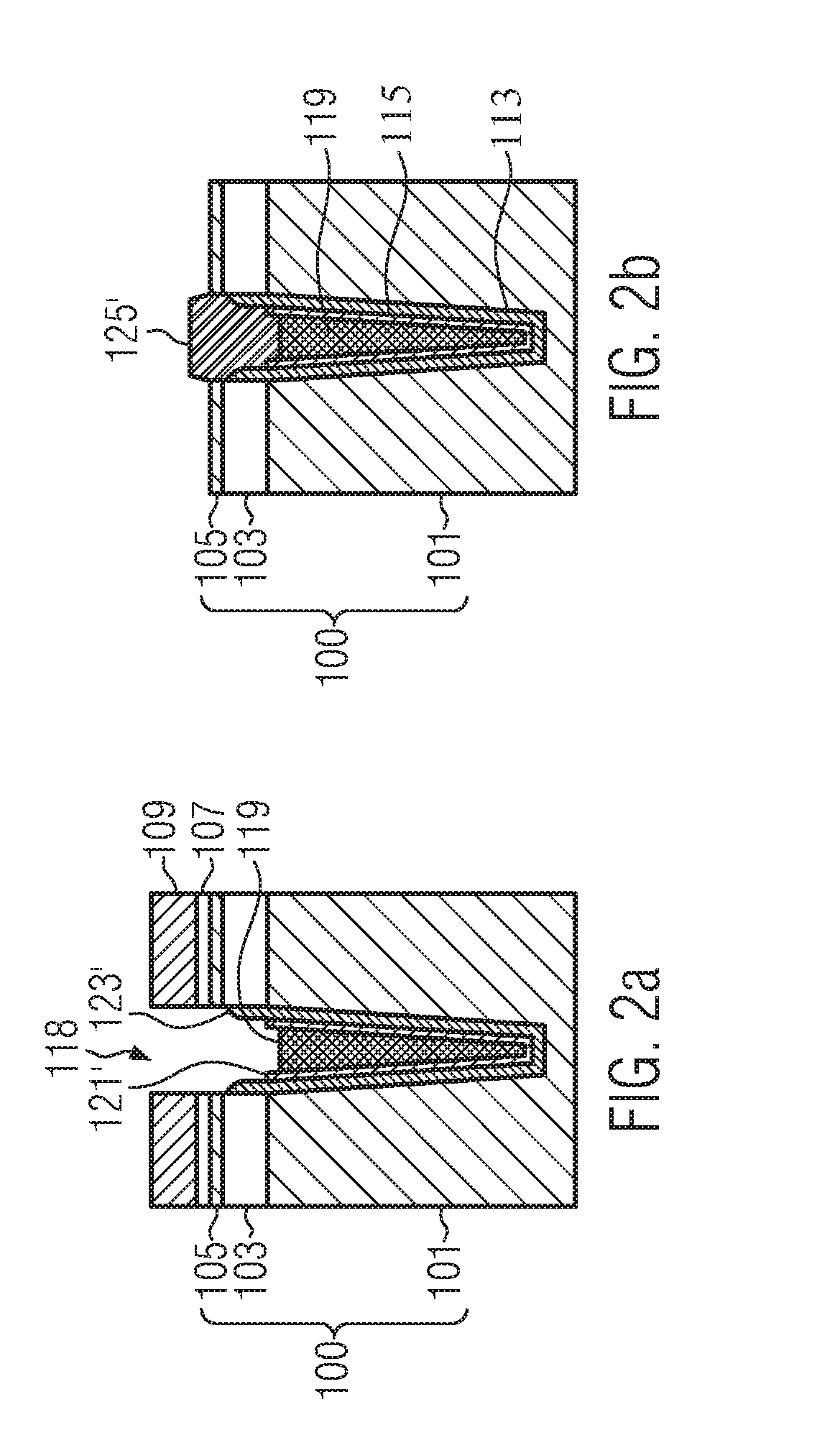

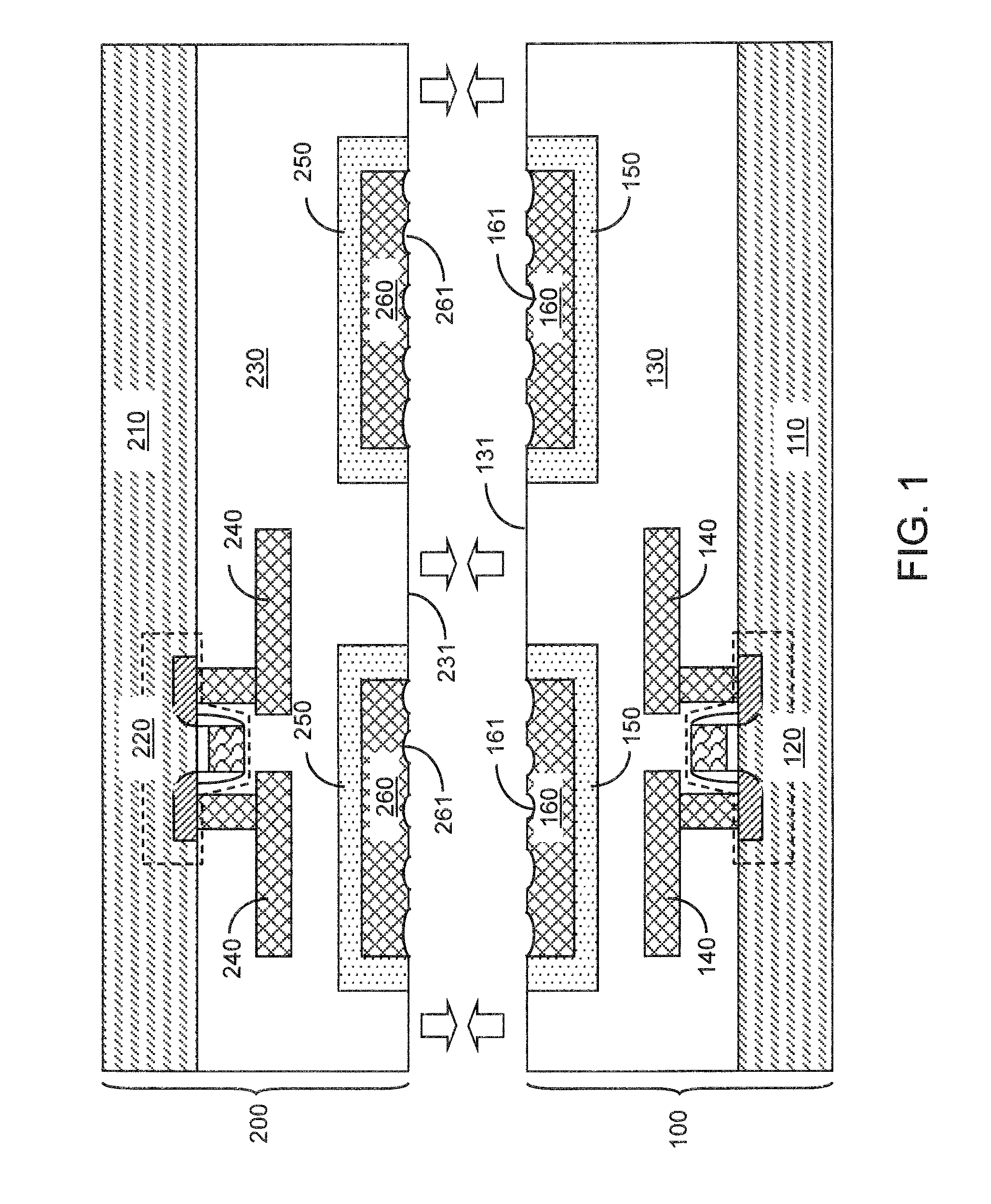

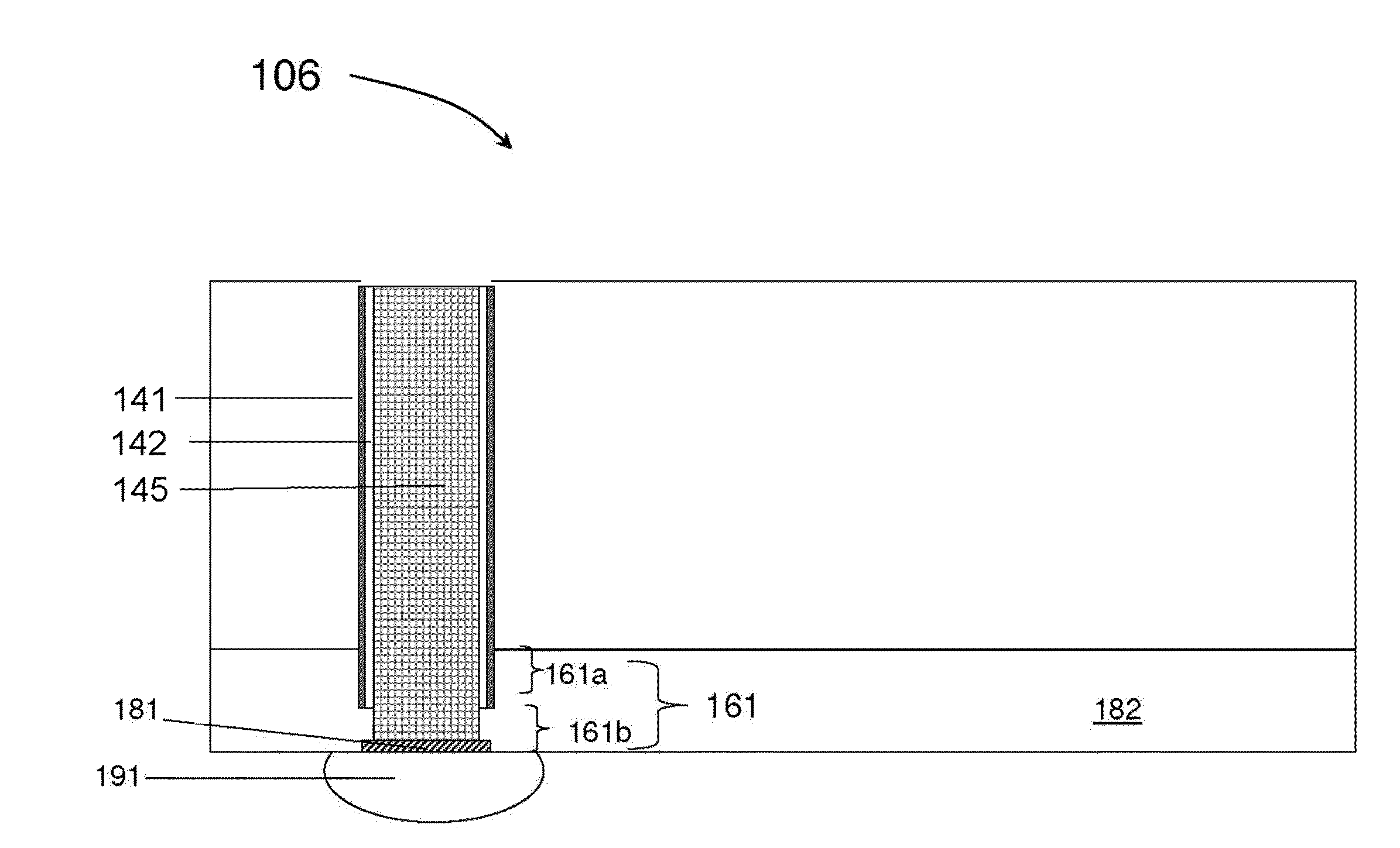

Front-end-of-line device structure and method of forming such a front-end-of-line device structure

ActiveUS10483154B1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesFilling materialsFront end of line

In various aspects, the present disclosure relates to device structures and a method of forming such a device structure. In some illustrative embodiments herein, a device is provided, including a semiconductor substrate having a first trench formed therein, and a first trench isolation structure formed in the first trench. The first trench isolation structure includes first and second insulating liners formed adjacent inner surfaces of the first trench, wherein the first insulating liner is in direct contact with inner surfaces of the first trench and the second insulating liner is formed directly on the first insulating liner, and a first insulating filling material which at least partially fills the first trench. In some aspects, a thickness of the first insulating liner is greater than a thickness of the second insulating liner.

Owner:GLOBALFOUNDRIES US INC

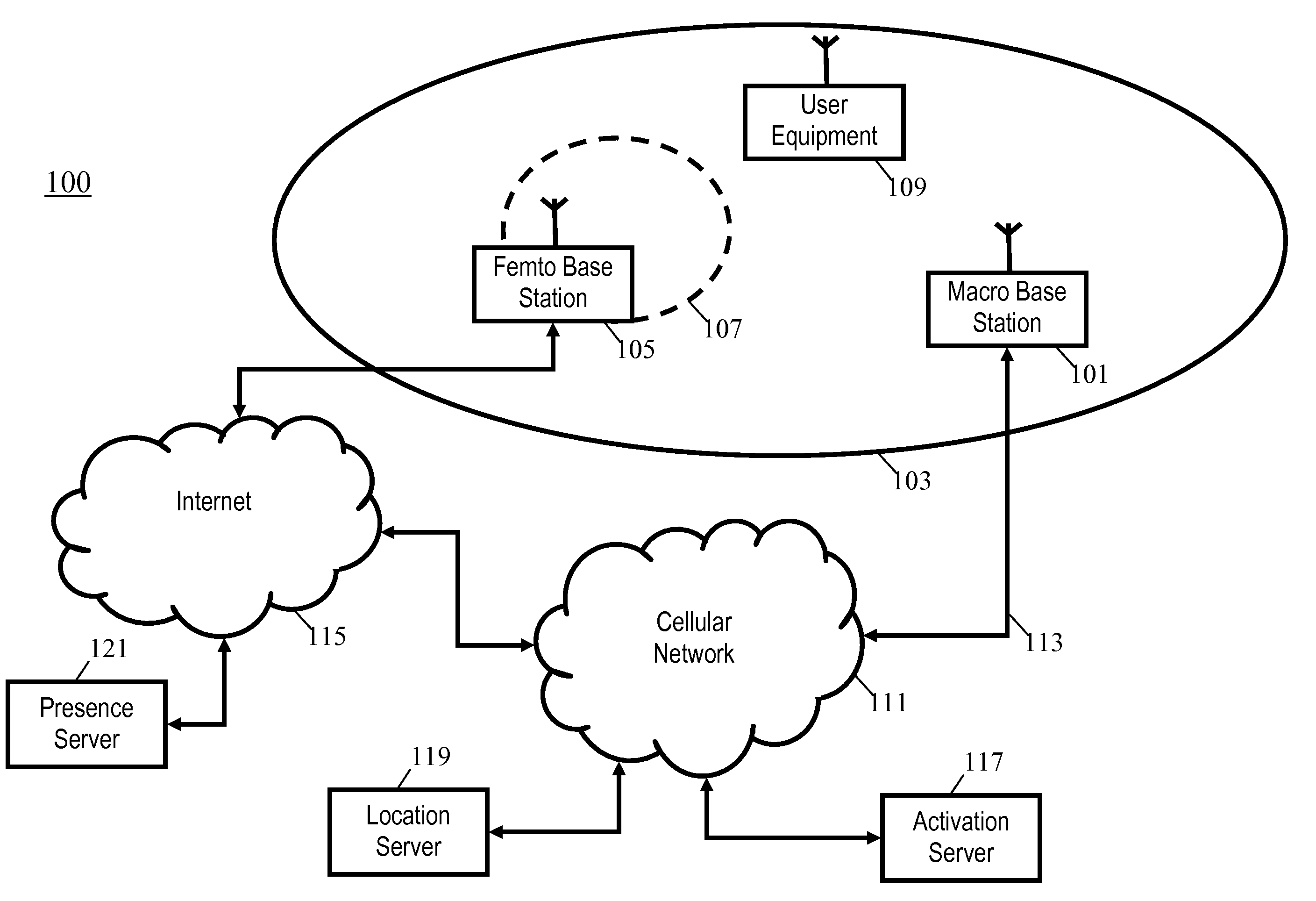

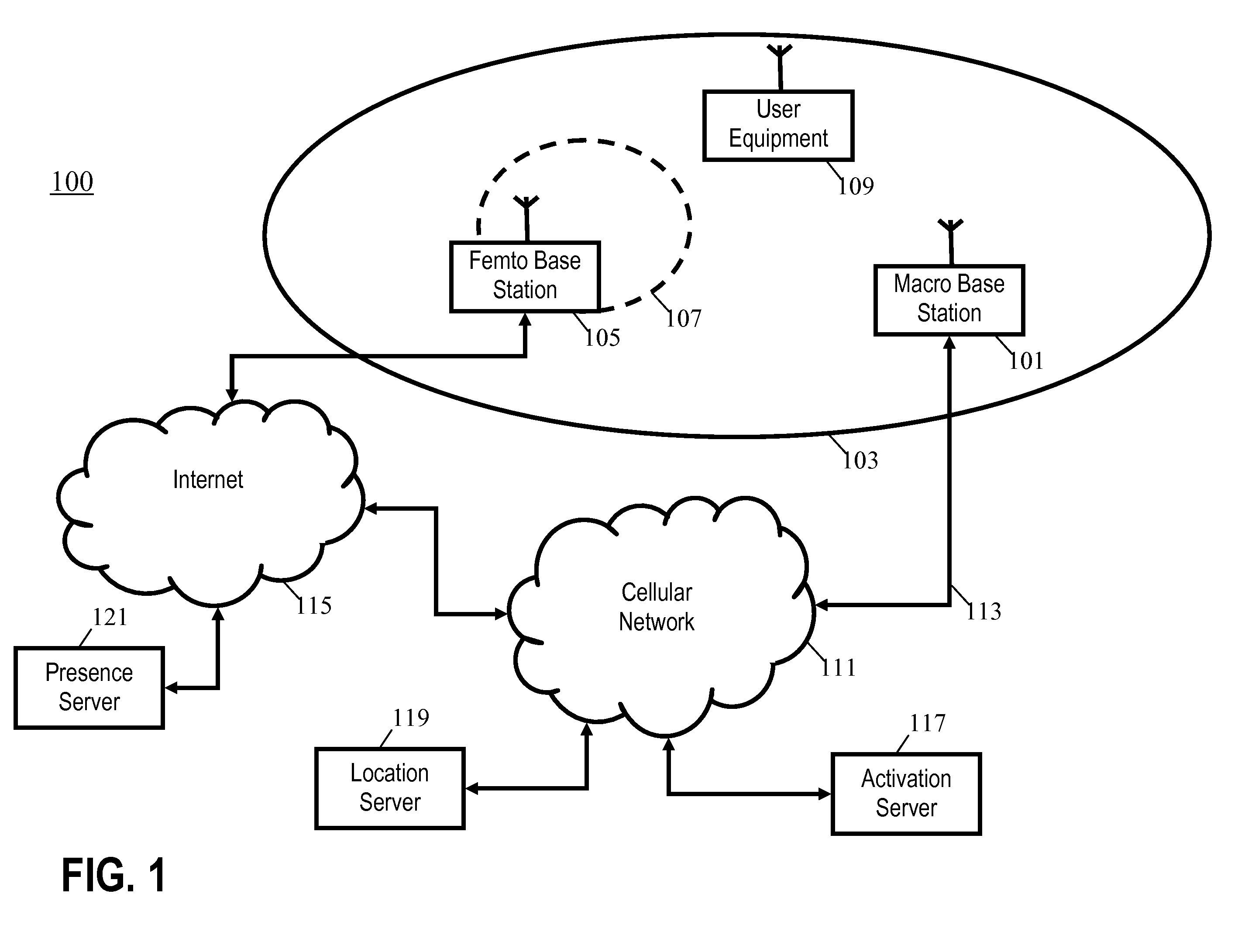

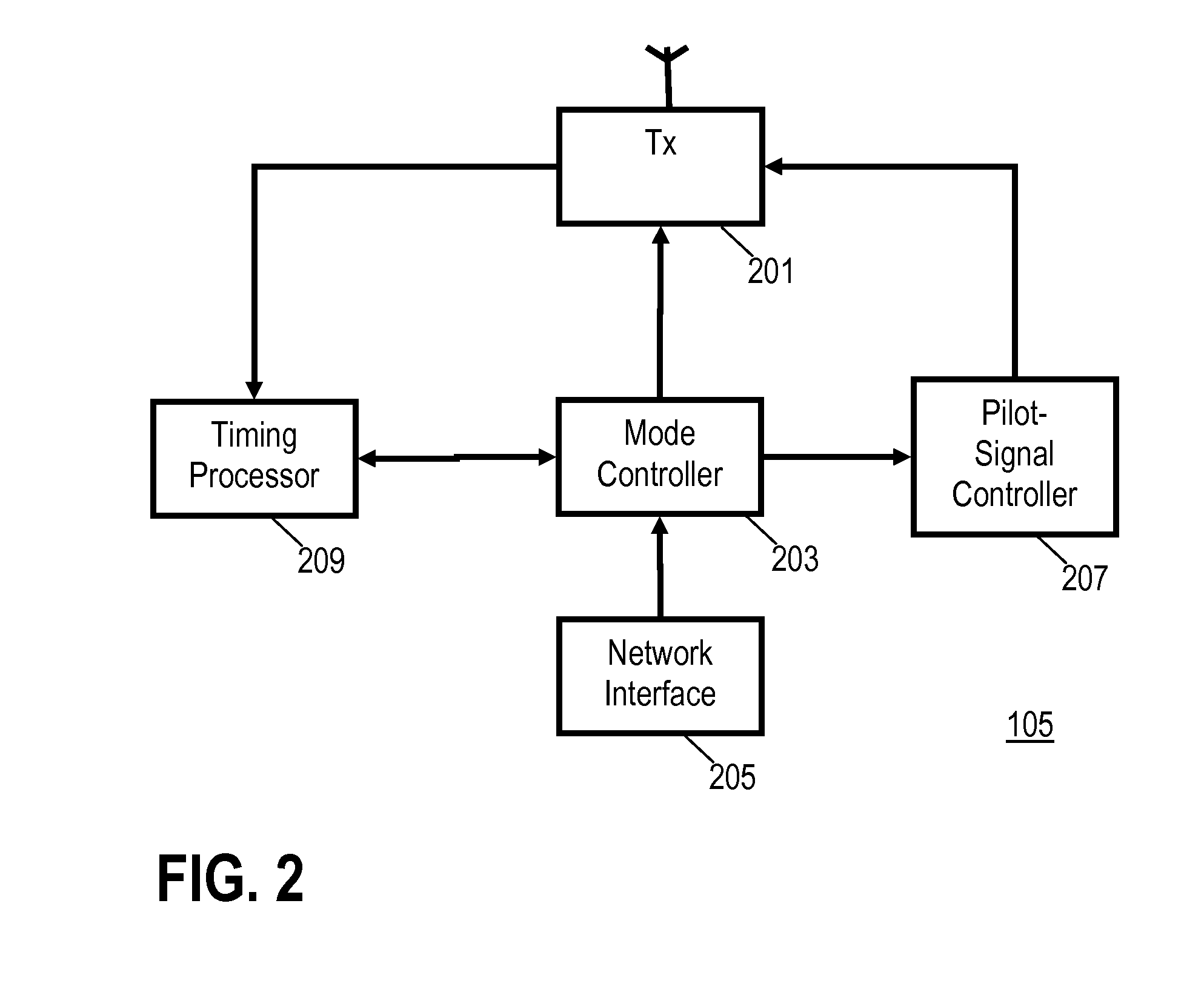

Presence-aware cellular communication system and method

InactiveUS20100056184A1Increase capacityReduce consumptionPower managementAssess restrictionAir interfaceCellular communication systems

A cellular communication system comprises a network supporting user equipment over an air interface, the network having a hierarchical cell arrangement with overlay cells and underlay cells. An underlay base station is associated with a subset of registered user equipment. An activation server switches the underlay base station between an inactive mode and an active mode in response to detecting that registered user equipment meets a location criterion. The underlay base station only supports user equipment when in the active mode, e.g., it may only transmit a pilot signal in this mode. Interference and power consumption may be substantially reduced by sending the base station into the inactive mode thereby resulting in increased capacity of the cellular communication system as a whole.

Owner:MOTOROLA MOBILITY LLC

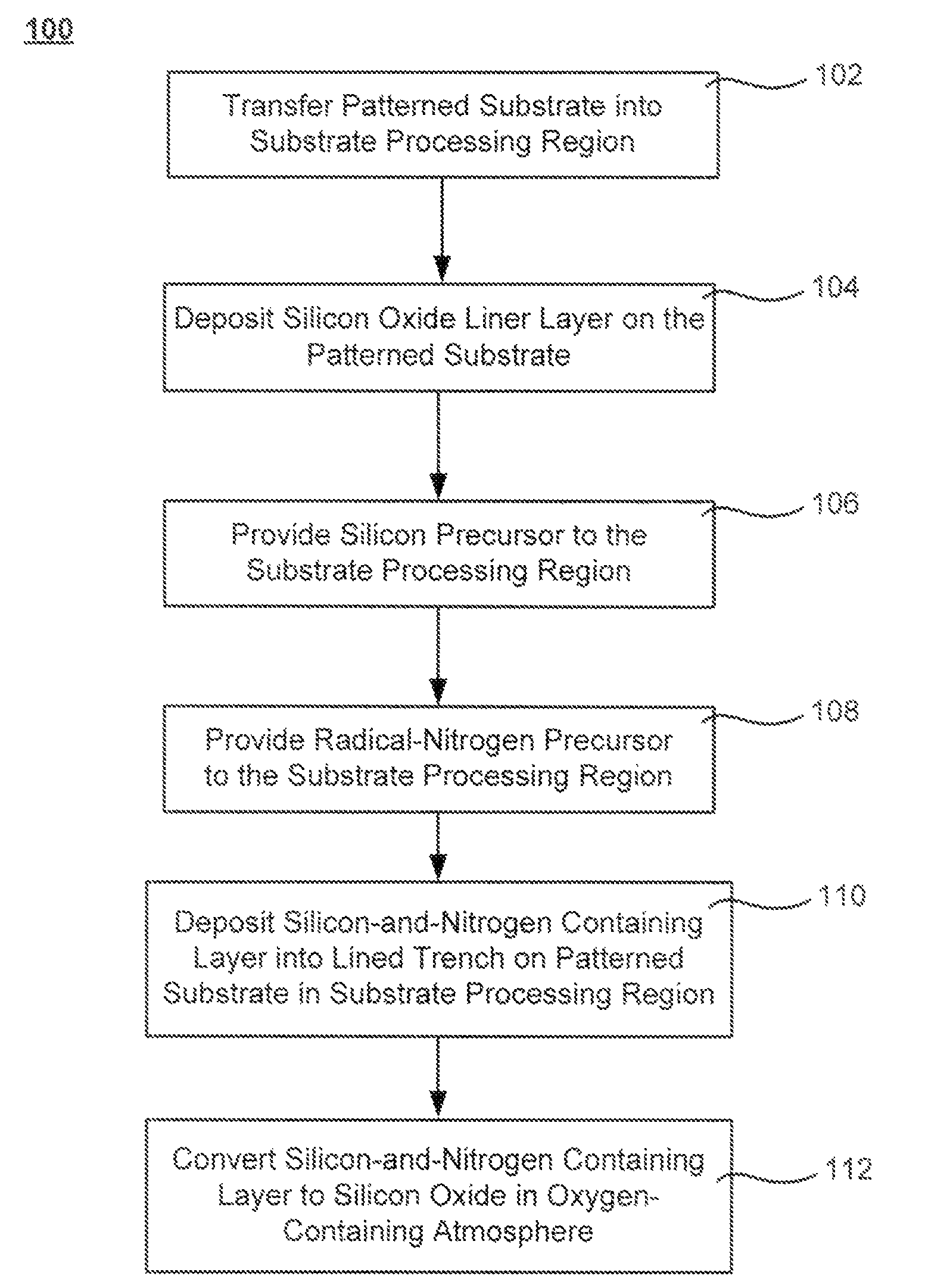

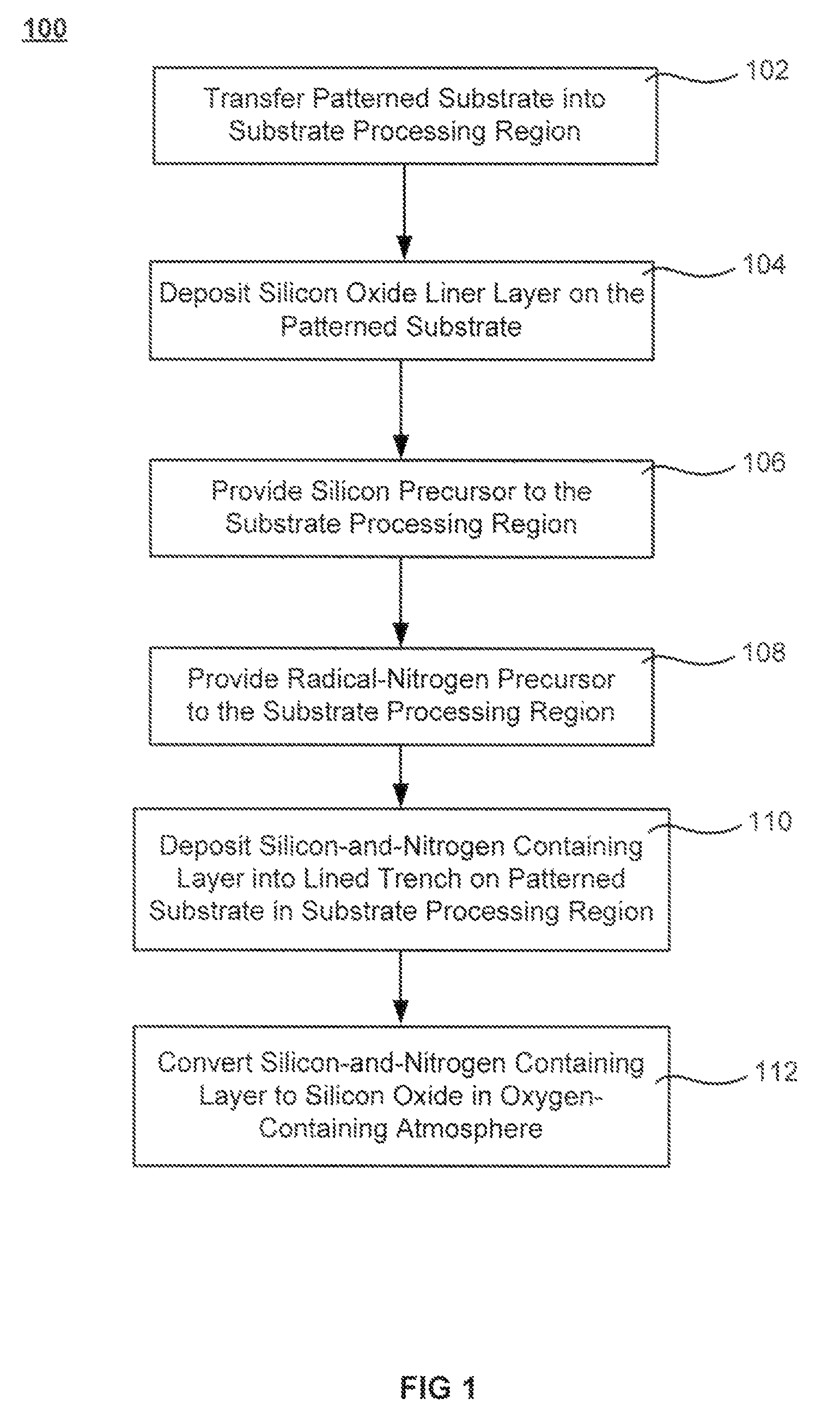

Oxide-rich liner layer for flowable CVD gapfill

The formation of a gap-filling silicon oxide layer with reduced volume fraction of voids is described. The deposition involves the formation of an oxygen-rich less-flowable liner layer before an oxygen-poor more-flowable gapfill layer. However, the liner layer is deposited within the same chamber as the gapfill layer. The liner layer and the gapfill layer may both be formed by combining a radical component with an unexcited silicon-containing precursor (i.e. not directly excited by application of plasma power). The liner layer has more oxygen content than the gapfill layer and deposits more conformally. The deposition rate of the gapfill layer may be increased by the presence of the liner layer. The gapfill layer may contain silicon, oxygen and nitrogen and be converted at elevated temperature to contain more oxygen and less nitrogen. The presence of the gapfill liner provides a source of oxygen underneath the gapfill layer to augment the gas phase oxygen introduced during the conversion.

Owner:APPLIED MATERIALS INC

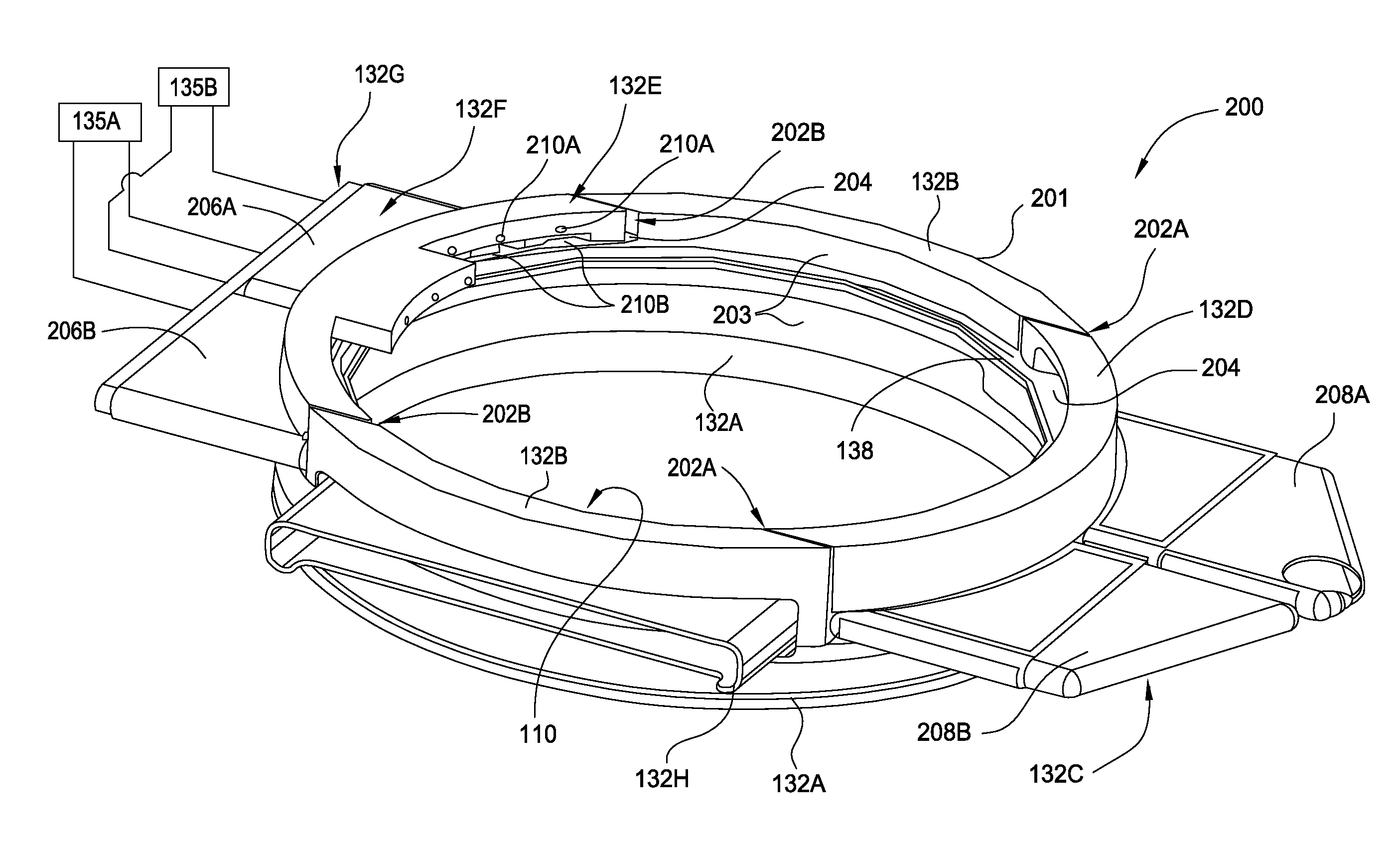

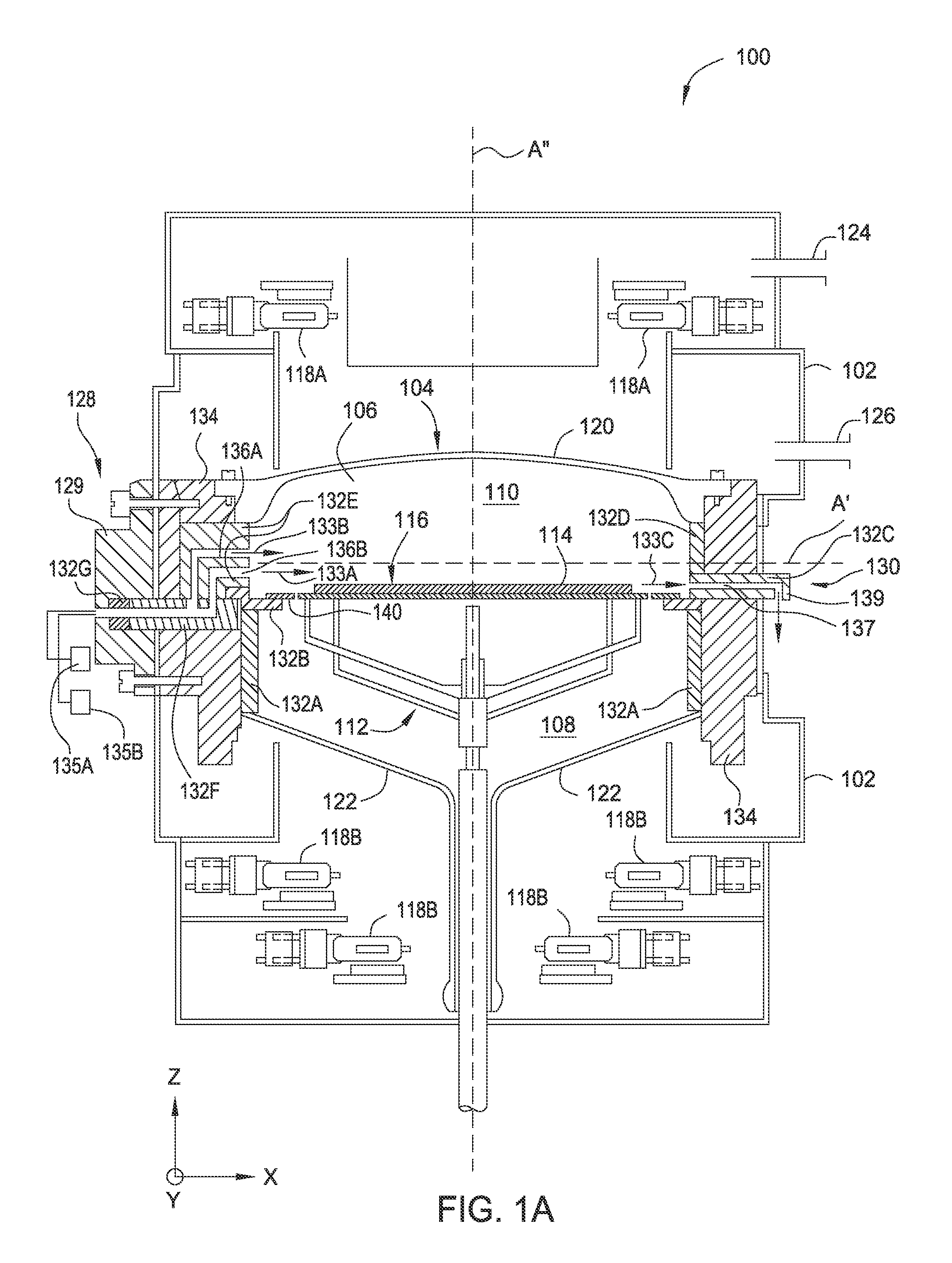

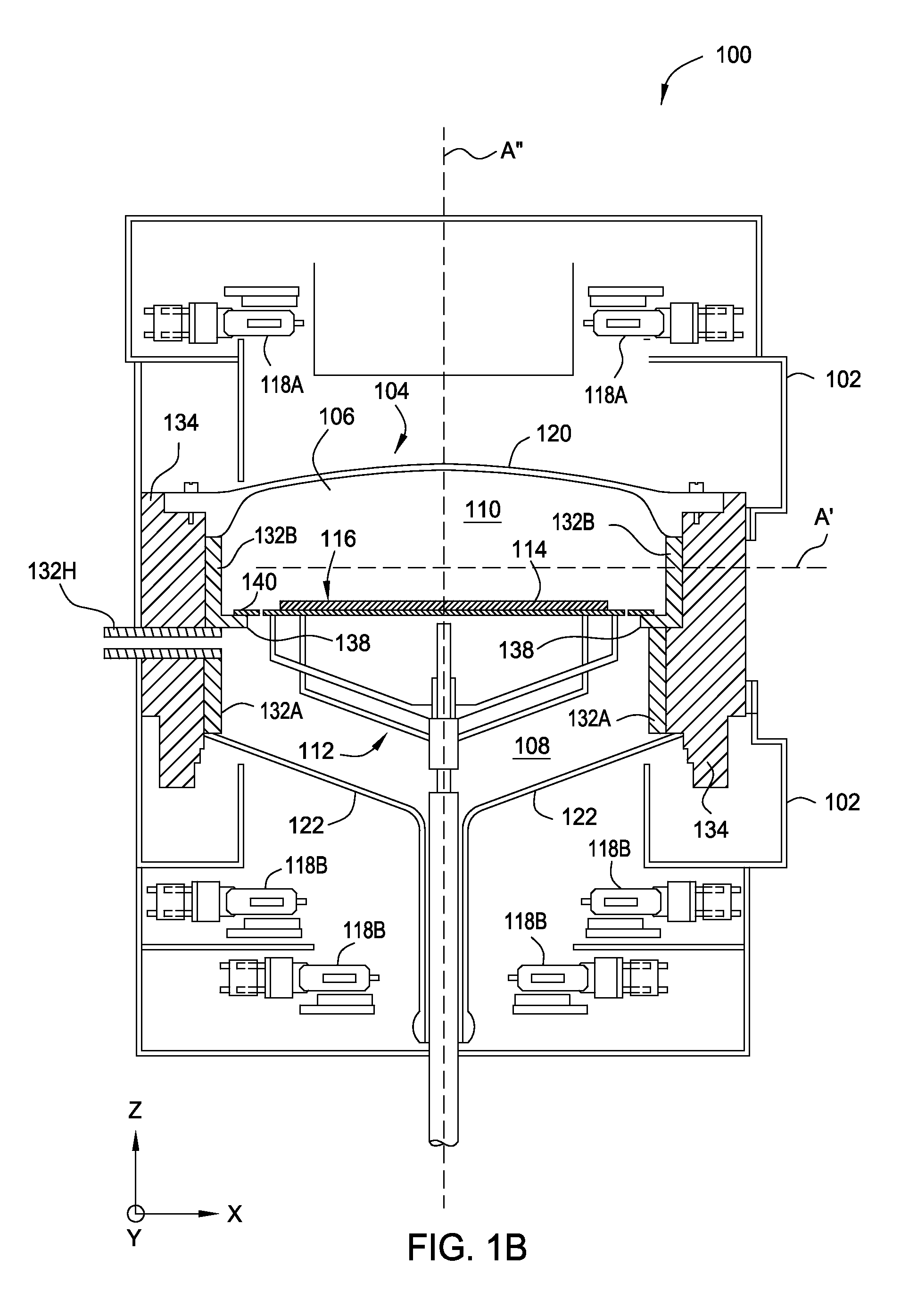

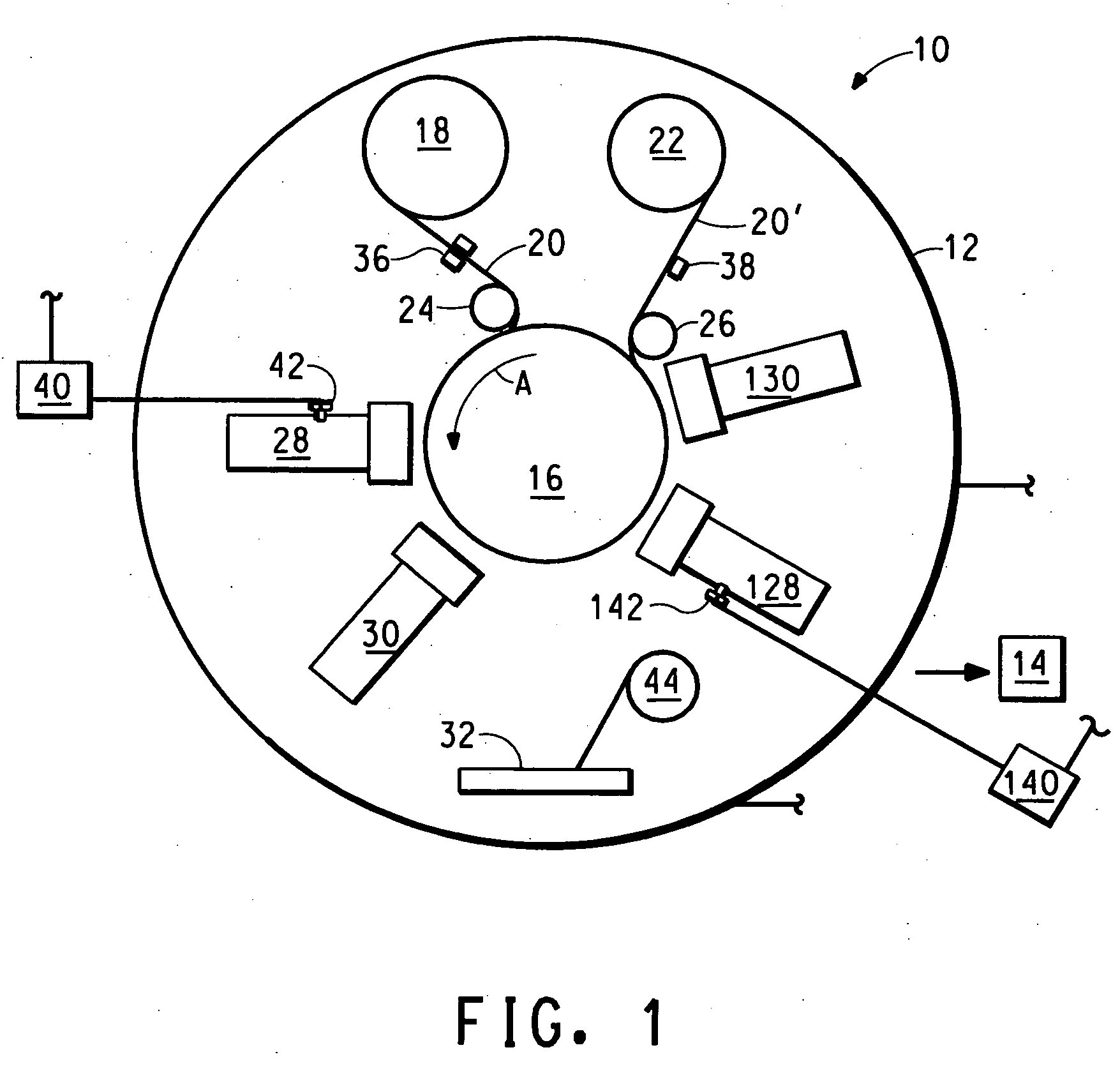

Liner assembly for chemical vapor deposition chamber

ActiveUS8980005B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingProcess regionBody size

Embodiments described herein relate to an apparatus and method for lining a processing region within a chamber. In one embodiment, a modular liner assembly for a substrate processing chamber is provided. The modular liner assembly includes a first liner and a second liner, each of the first liner and second liner comprising an annular body sized to be received in a processing volume of a chamber, and at least a third liner comprising a body that extends through the first liner and the second liner, the third liner having a first end disposed in the process volume and a second end disposed outside of the chamber.

Owner:APPLIED MATERIALS INC

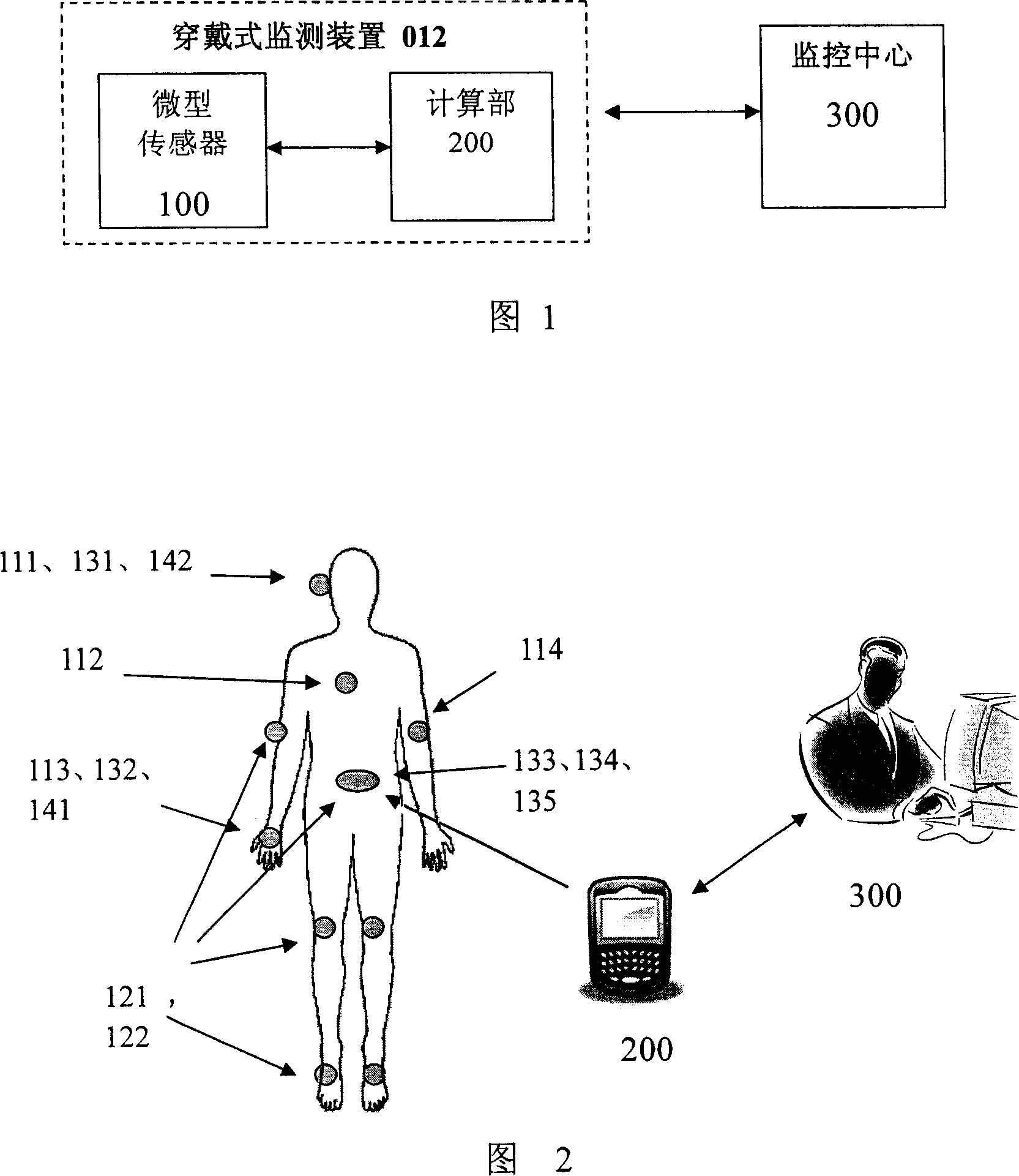

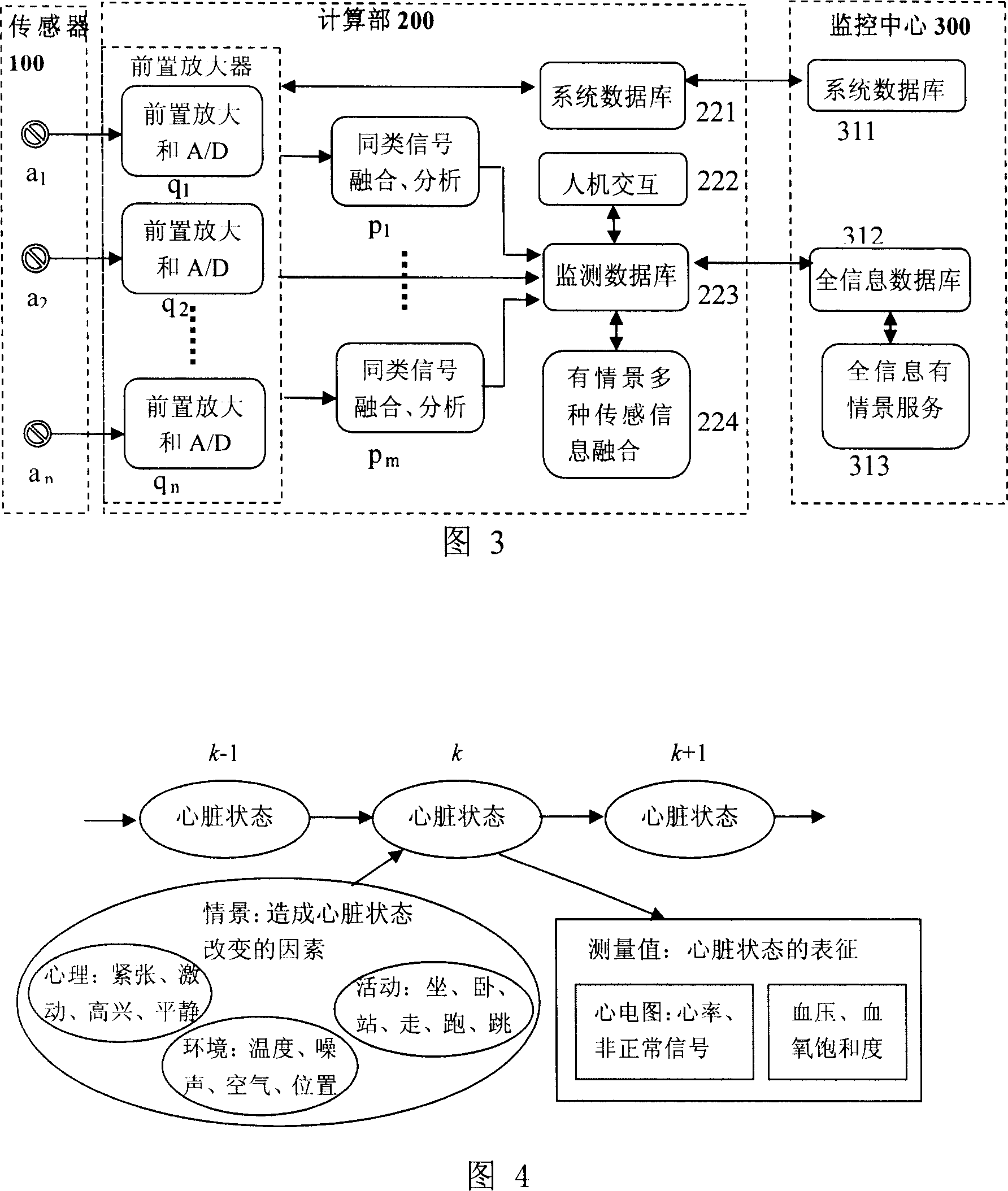

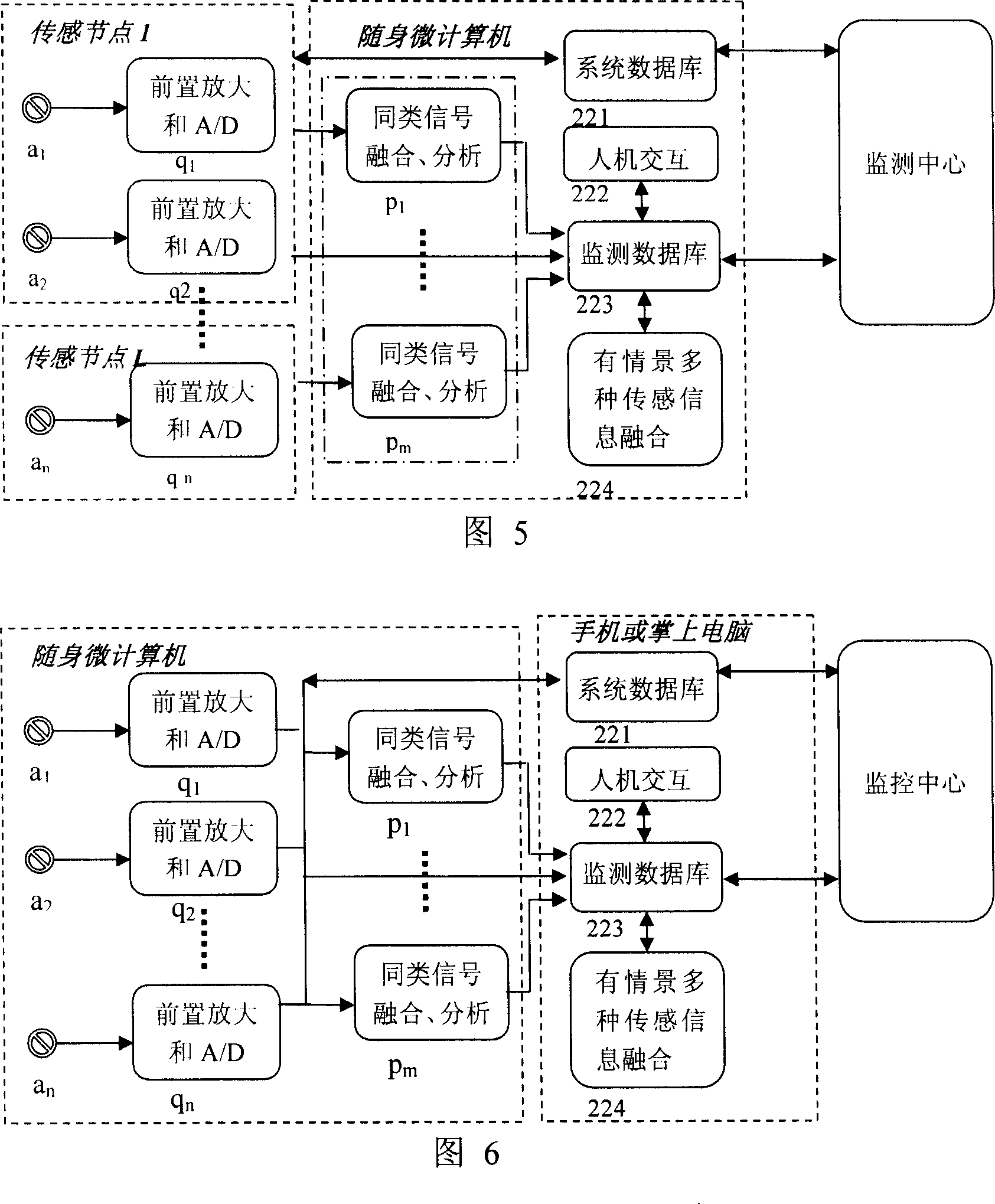

Dynamic monitoring system of body sign

The invention discloses a dynamic inspecting system for human body character, which comprises at least one or one set of minisize sensor on an underlay and a calculating part for each wearer. The calculating part is connected with the minisize sensor to jointly form the wearing type inspecting device. An inspecting and controlling center is provided, which is connected with the calculating part wirelessly or through cable communications. The invention, for continuously inspecting with a plurality kinds of sensors as physiology, activity, environment and psychology, etc, not only can collect affairs of low probability, but also can inspect the change of physiological reaction and physiological cadence during daily life such as activity, rest and sleeping and under environment condition and psychological factor, which is impossible for common inspecting equipment and method used for general surgery and hospital; on the other hand, by continuously inspecting the psychological signals and measuring the scene in daily life and then combining the two kinds of information, the invention is significantly for sport, health care and improvement of living quality.

Owner:WUXI MICROSENS

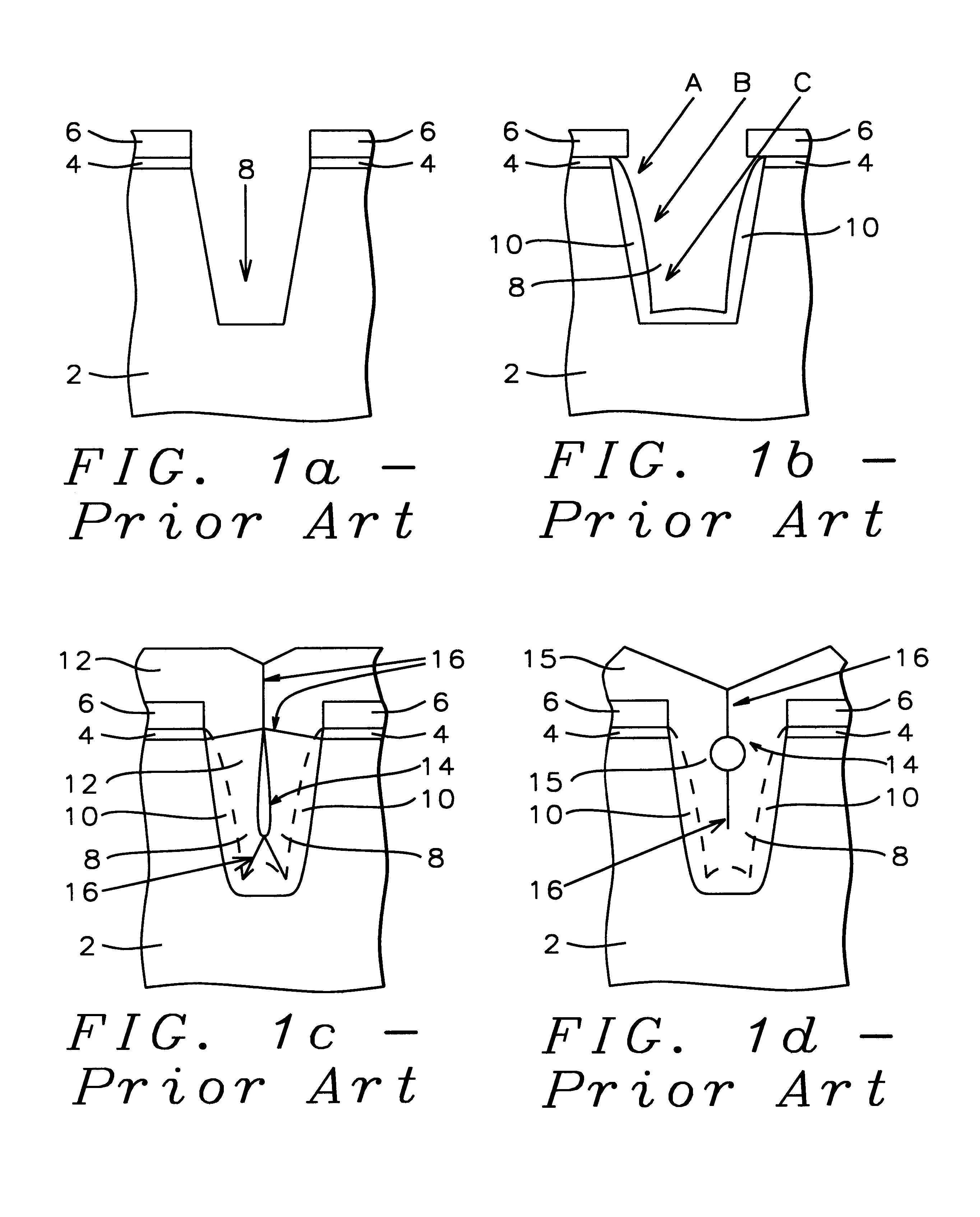

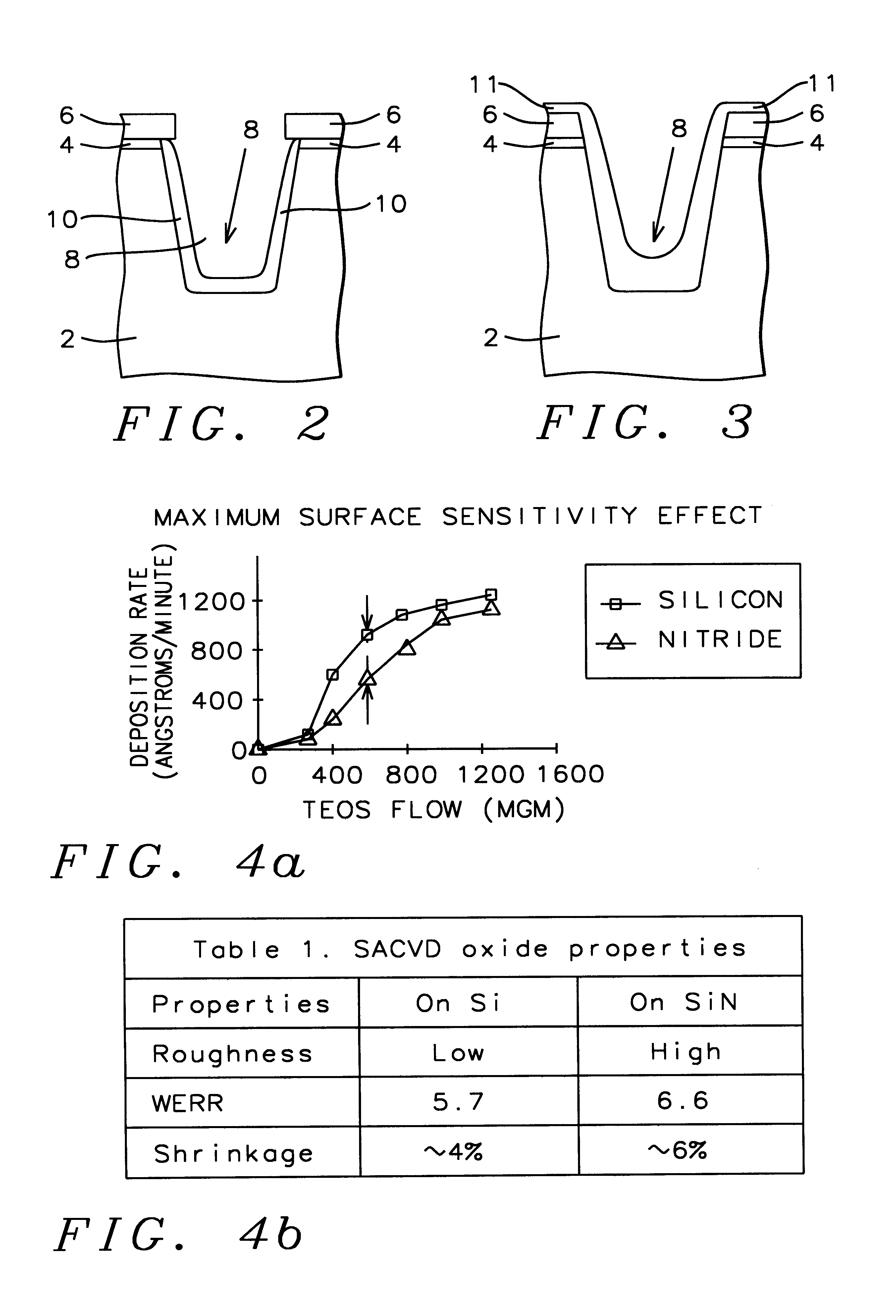

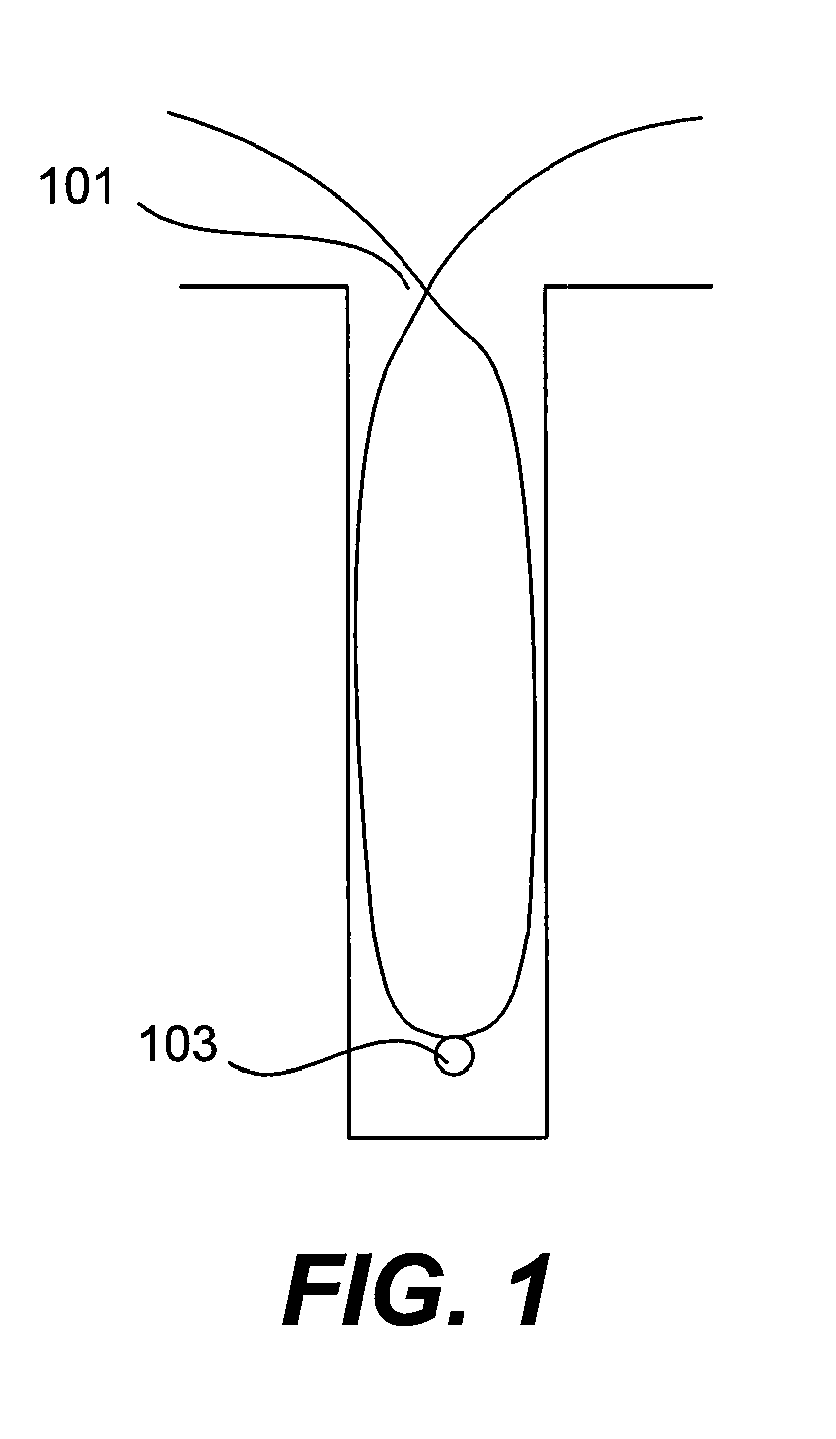

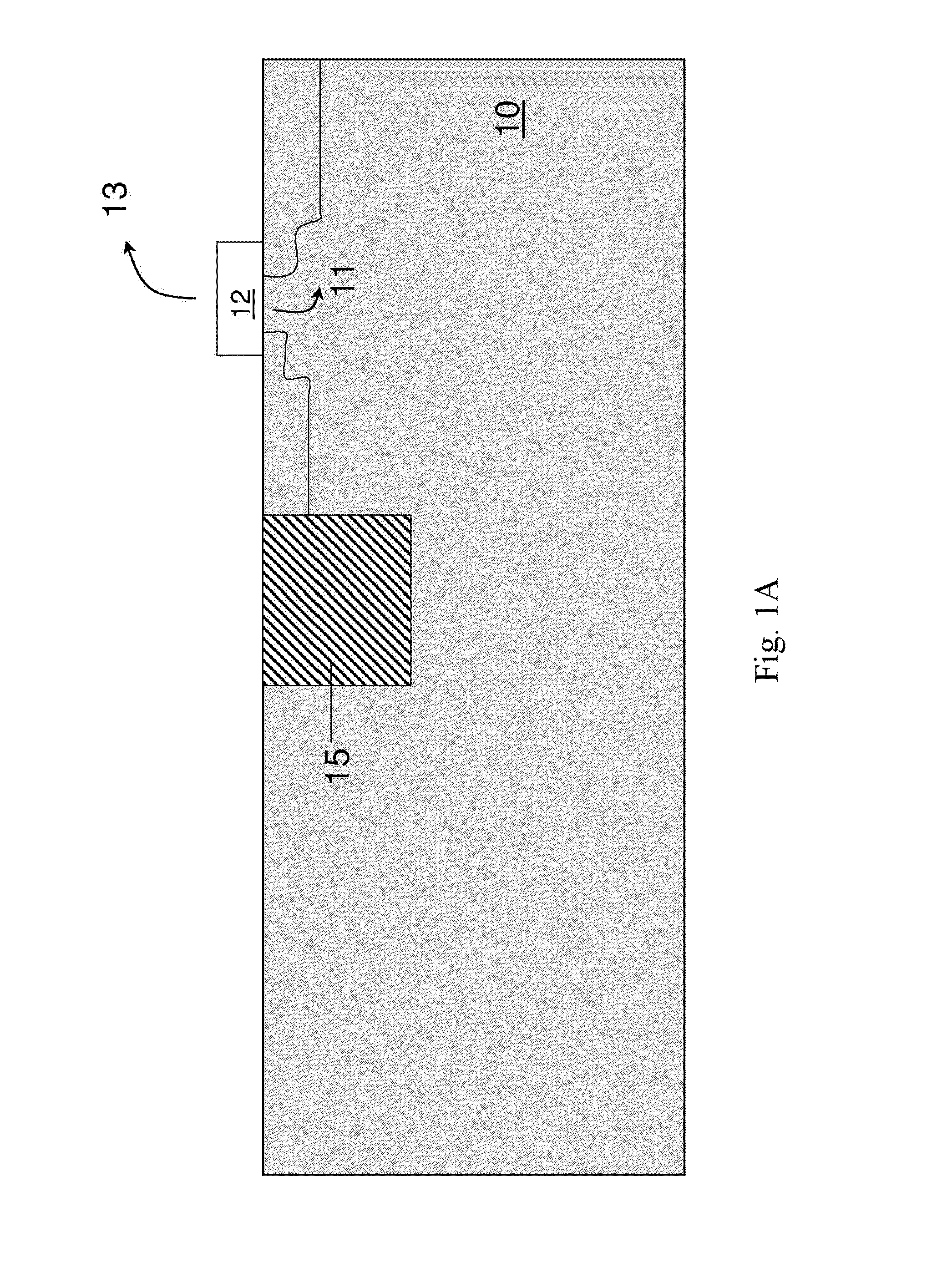

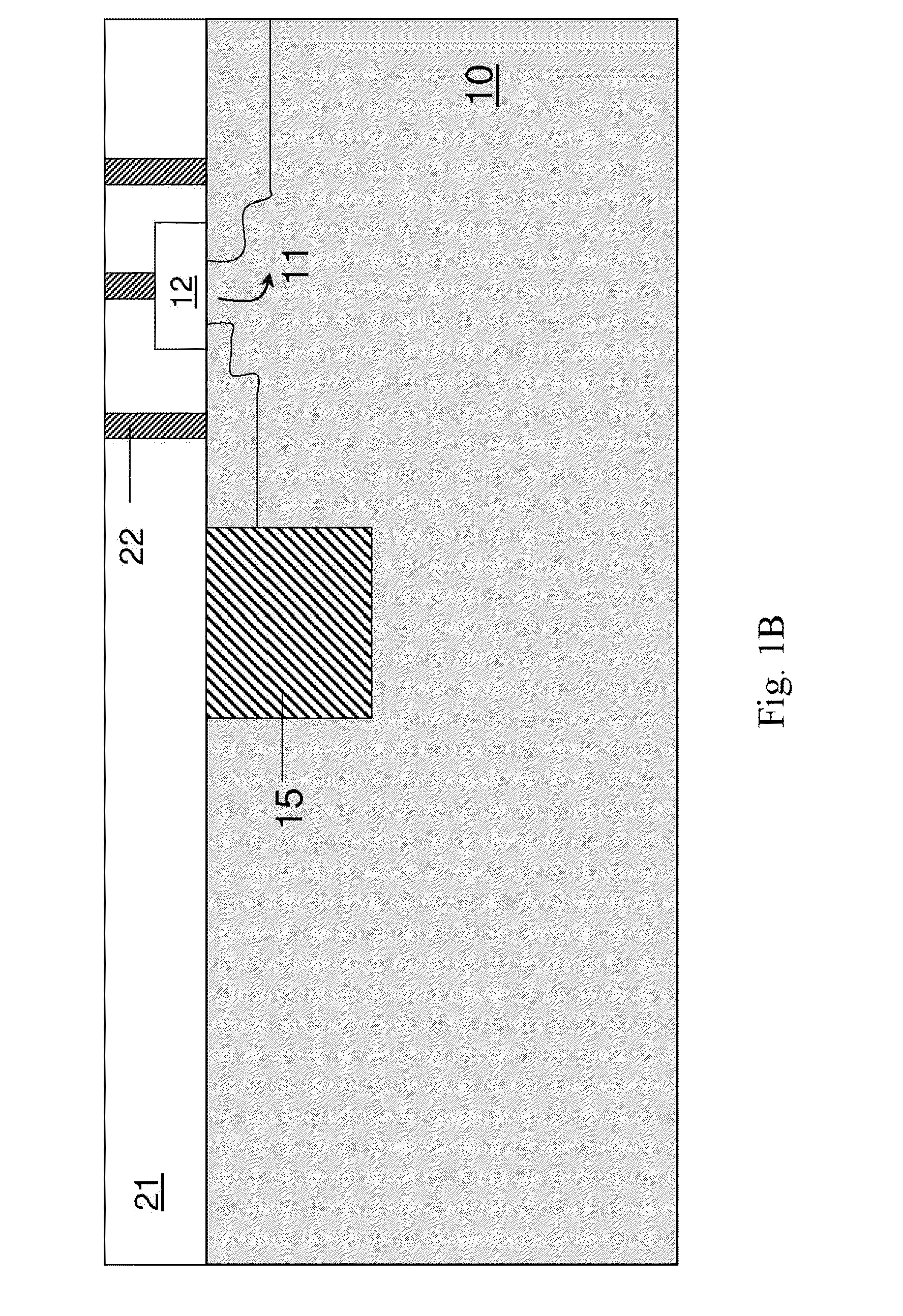

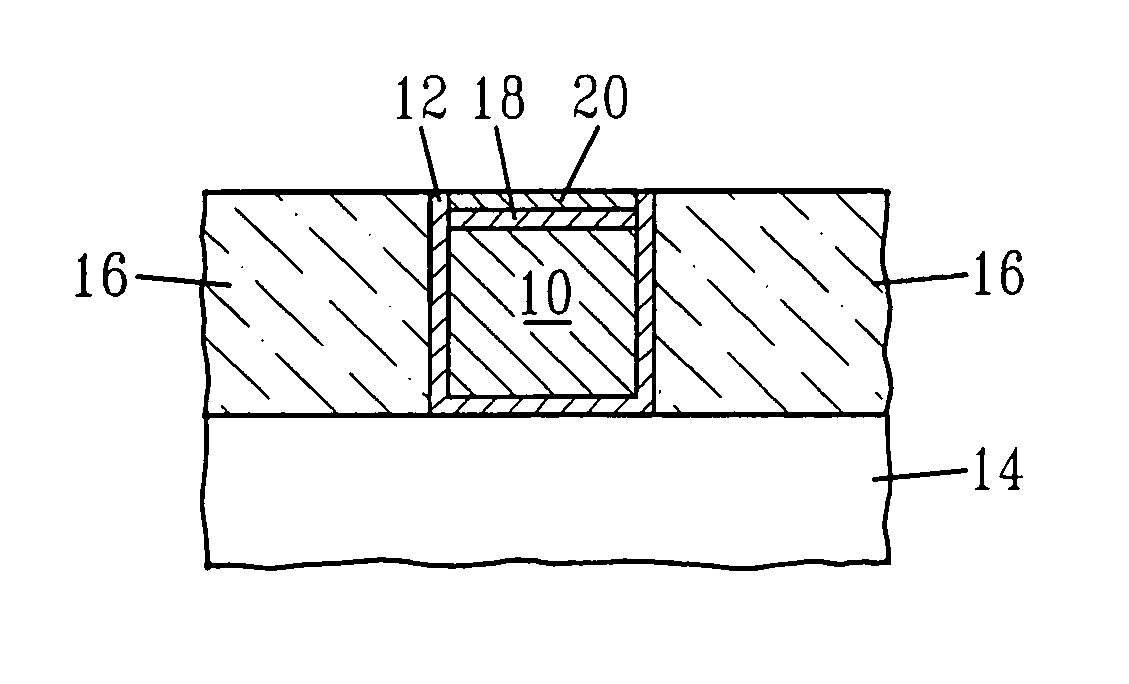

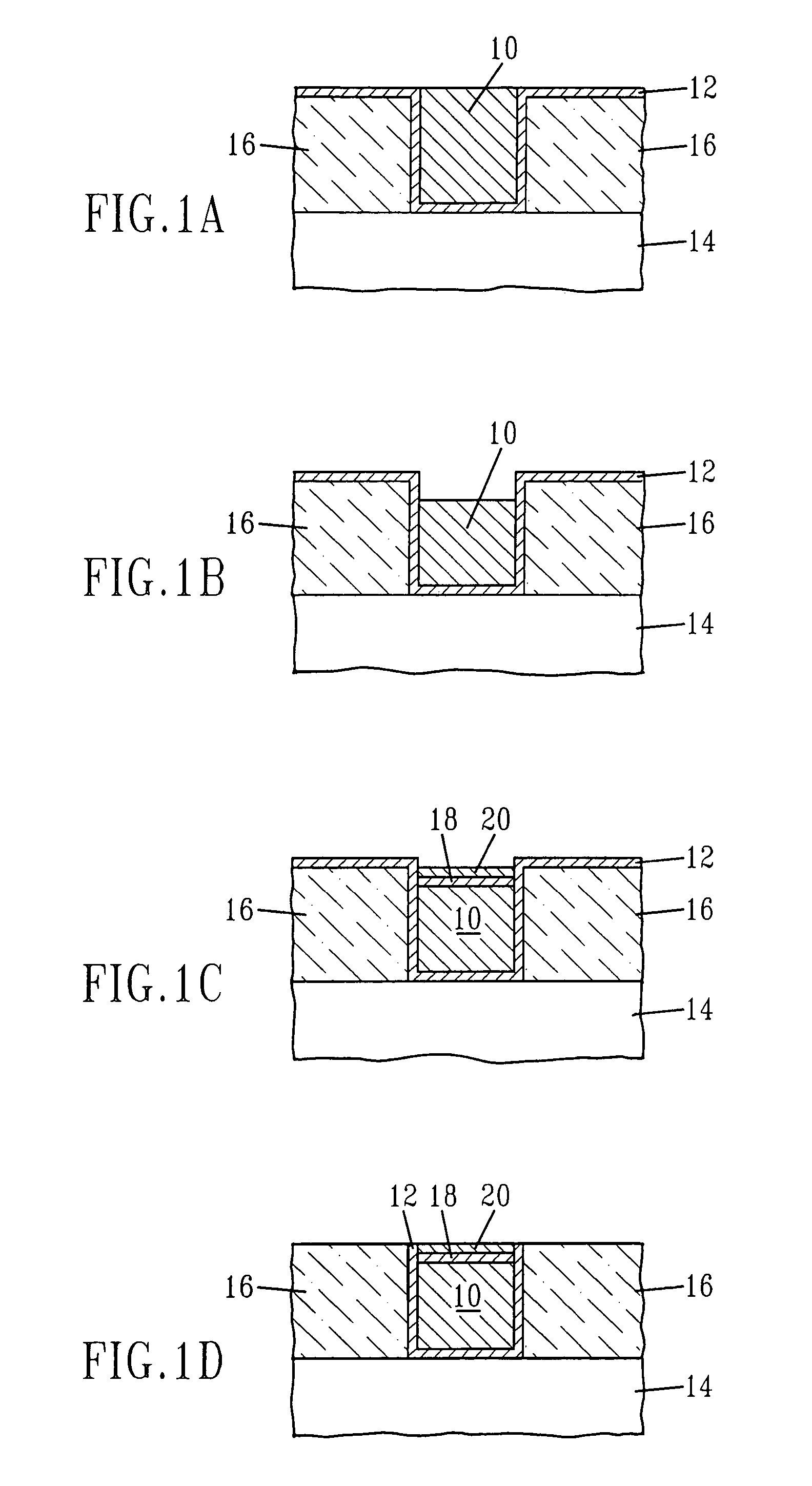

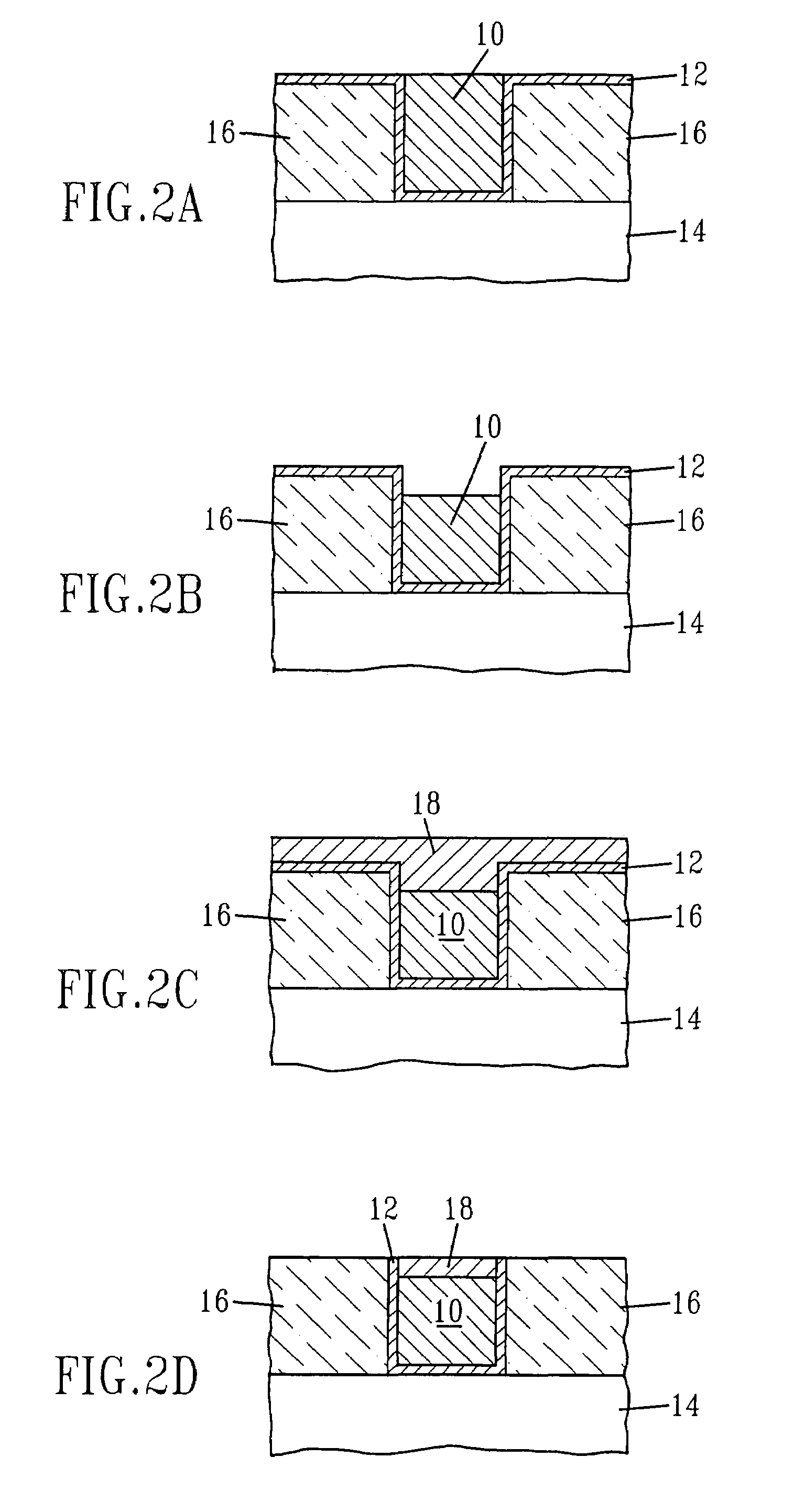

Method of filling shallow trenches

InactiveUS6180490B1Semiconductor/solid-state device manufacturingUnderlayIntegrated circuit fabrication

This invention relates to a method of fabrication used for semiconductor integrated circuit devices, and more specifically to an improved method of filling shallow trenches, in shallow trench isolation, STI sub-quarter micron technology. The present method relates to a process for forming trench gap filling with chemically vapor deposited (CVD) silicon dioxide layers within trenches within substrates employed in integrated circuit fabrication.There is first provided a silicon substrate having a trench formed therein. There is then formed a silicon dioxide layer through tetraethylorthosilicate (TEOS) and ozone reaction, at either sub-atmospheric, or atmospheric pressure, with enhanced surface sensitivity features, which lines the trench providing corner rounding. Then there is a thermal oxidation to form within the trench a thermal silicon dioxide layer underneath the TEOS-ozone trench silicon dioxide liner. Finally, there is formed on top of the trench a silicon dioxide layer formed by either low pressure CVD using TEOS, or non-surface sensitive TEOS ozone CVD, or a high-density plasma CVD process. All layers are further annealed to form a void-free trench fill.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

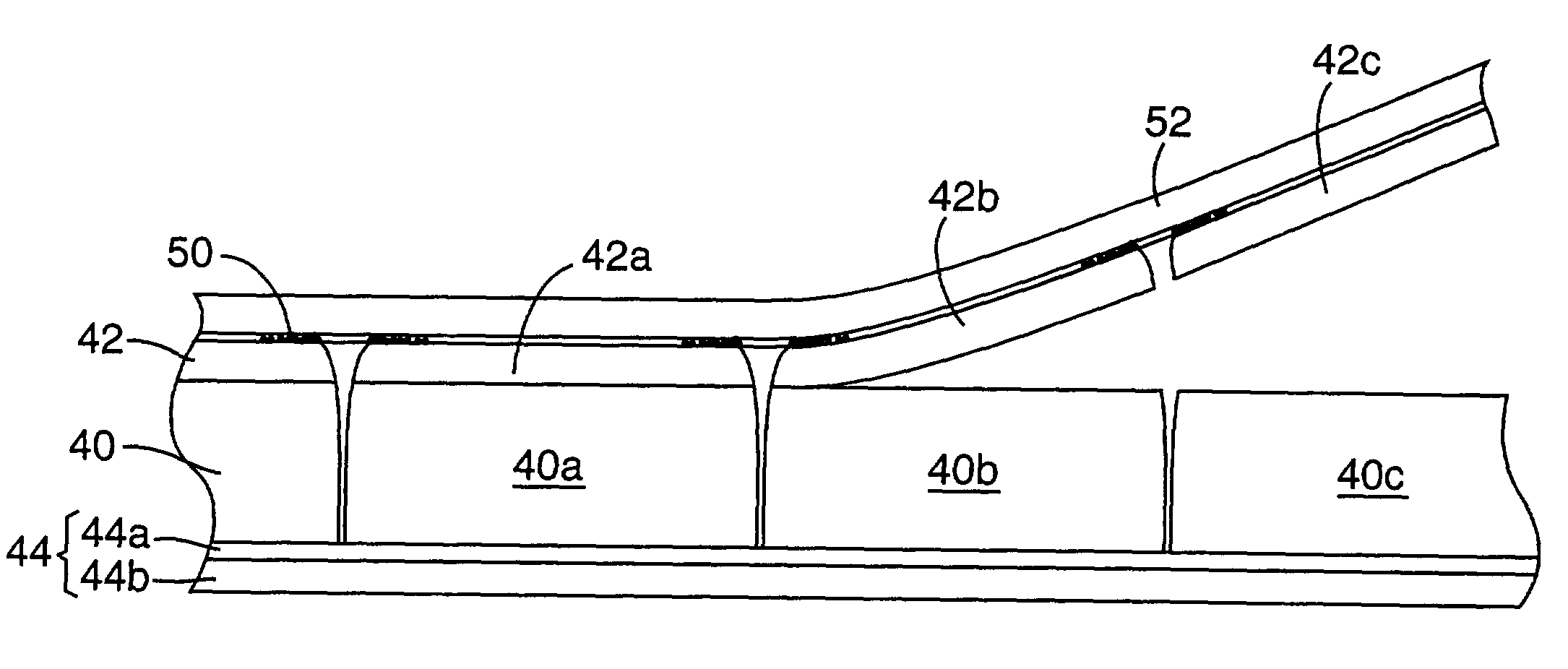

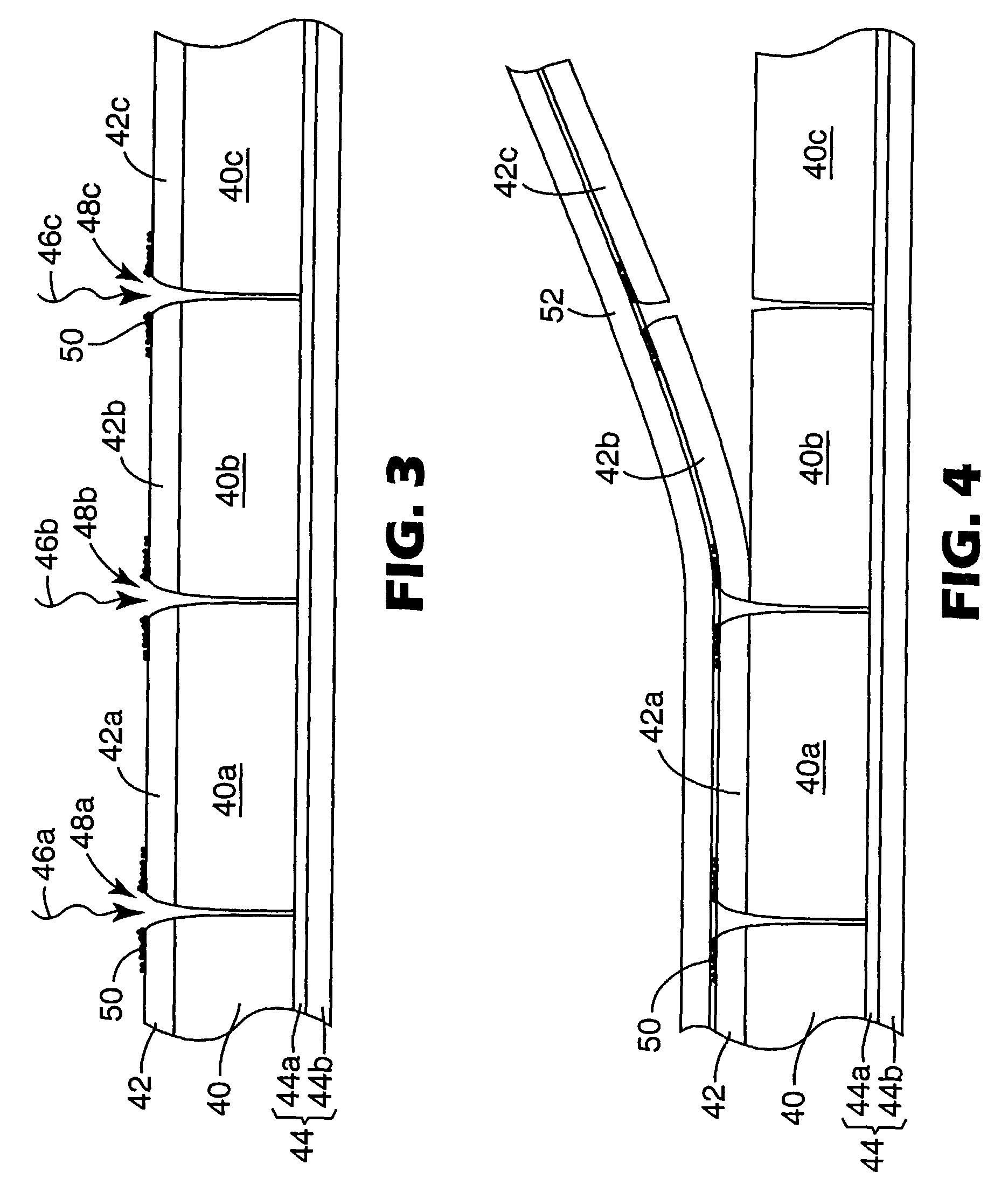

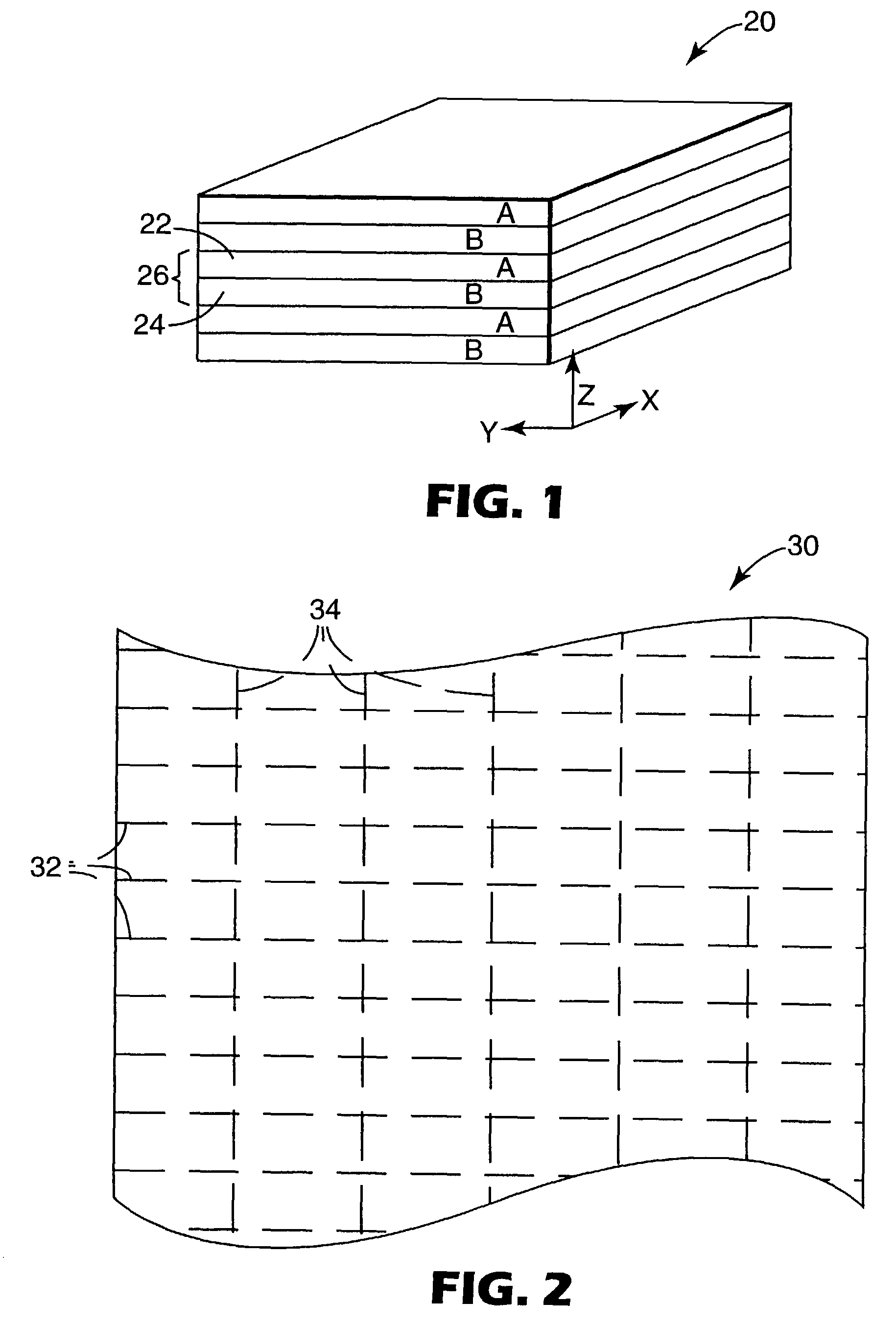

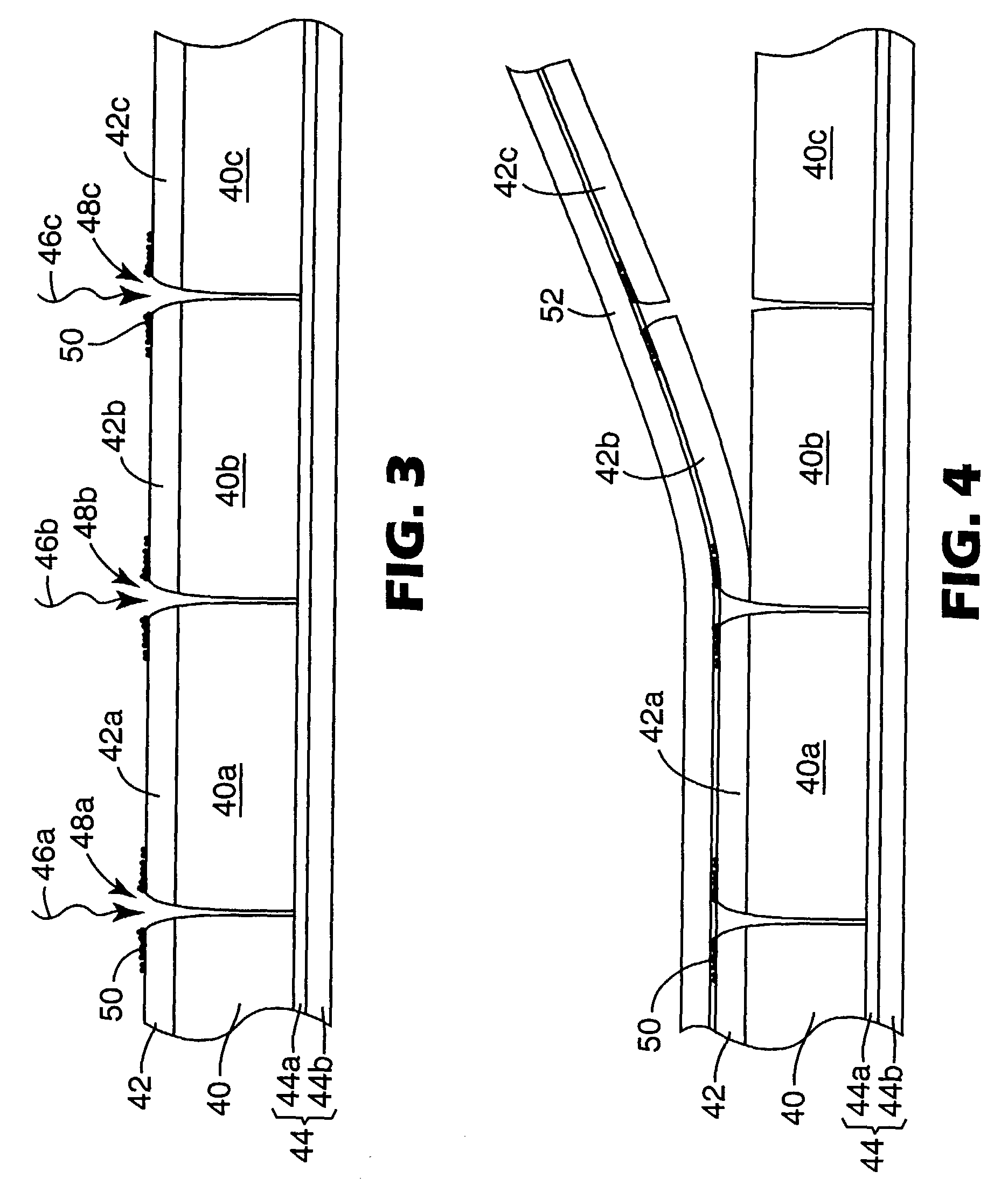

Method for subdividing multilayer optical film cleanly and rapidly

InactiveUS6991695B2Reduce electrostatic attractionPaper/cardboard articlesOptical articlesPolymerLaser

Owner:3M INNOVATIVE PROPERTIES CO

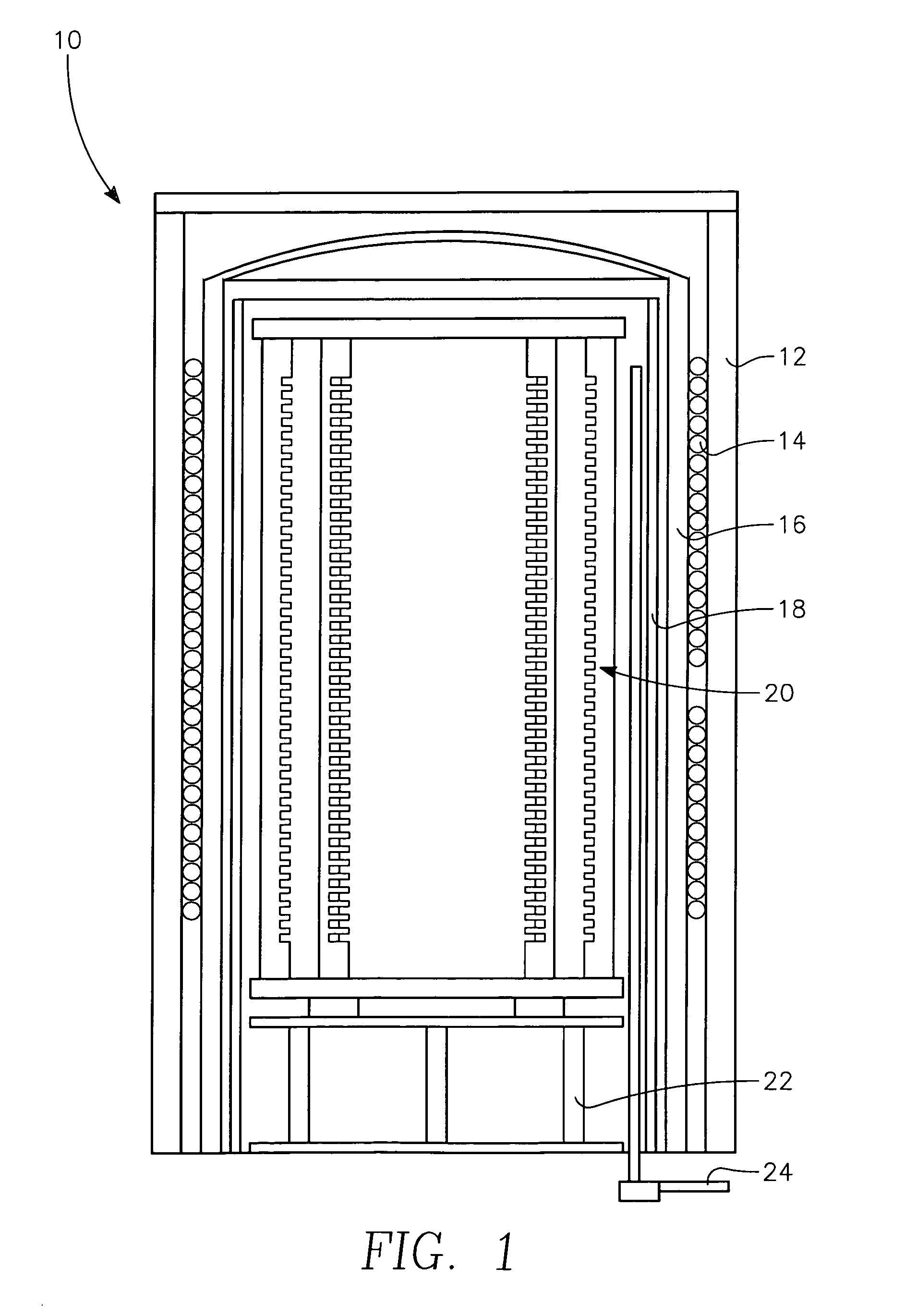

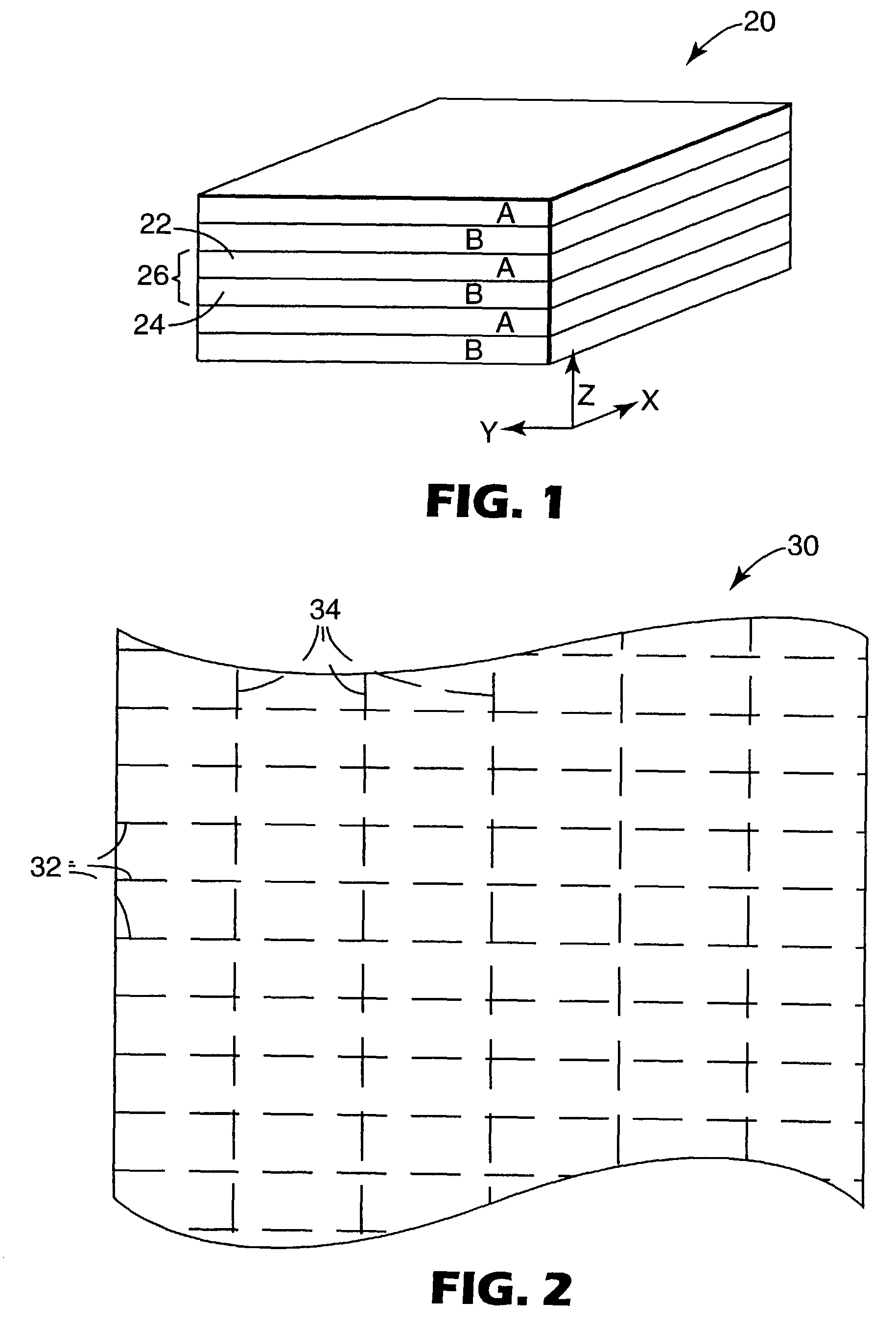

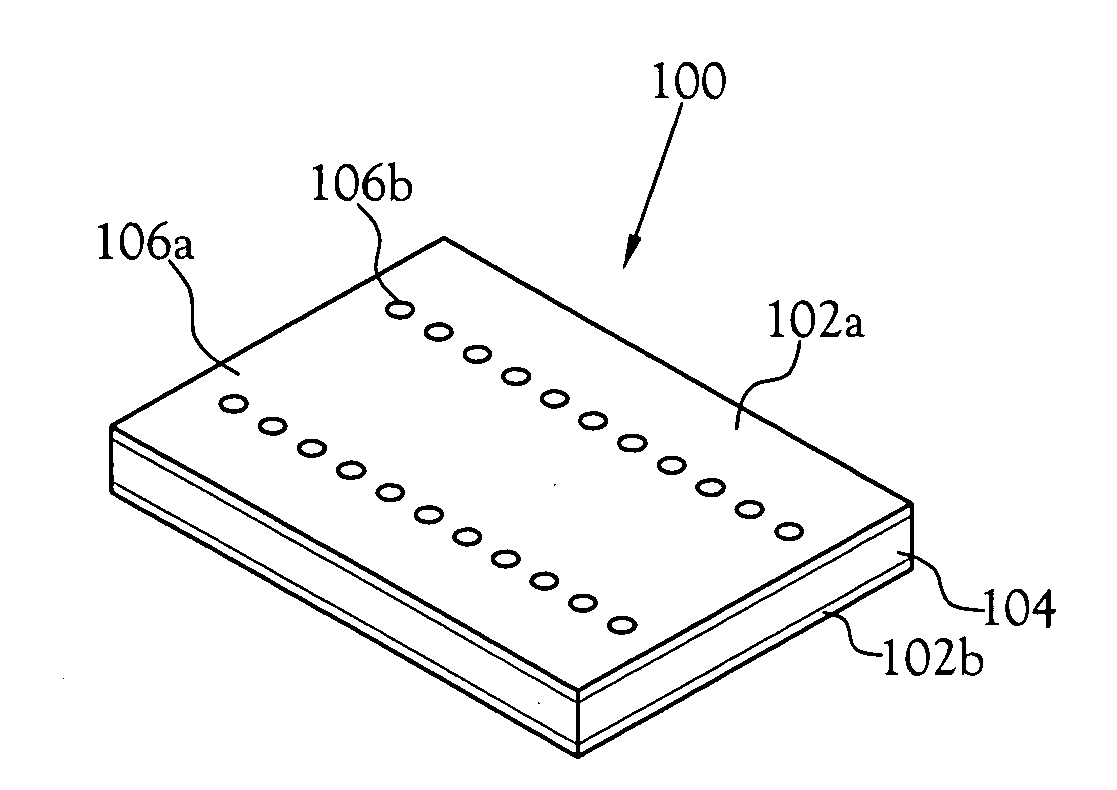

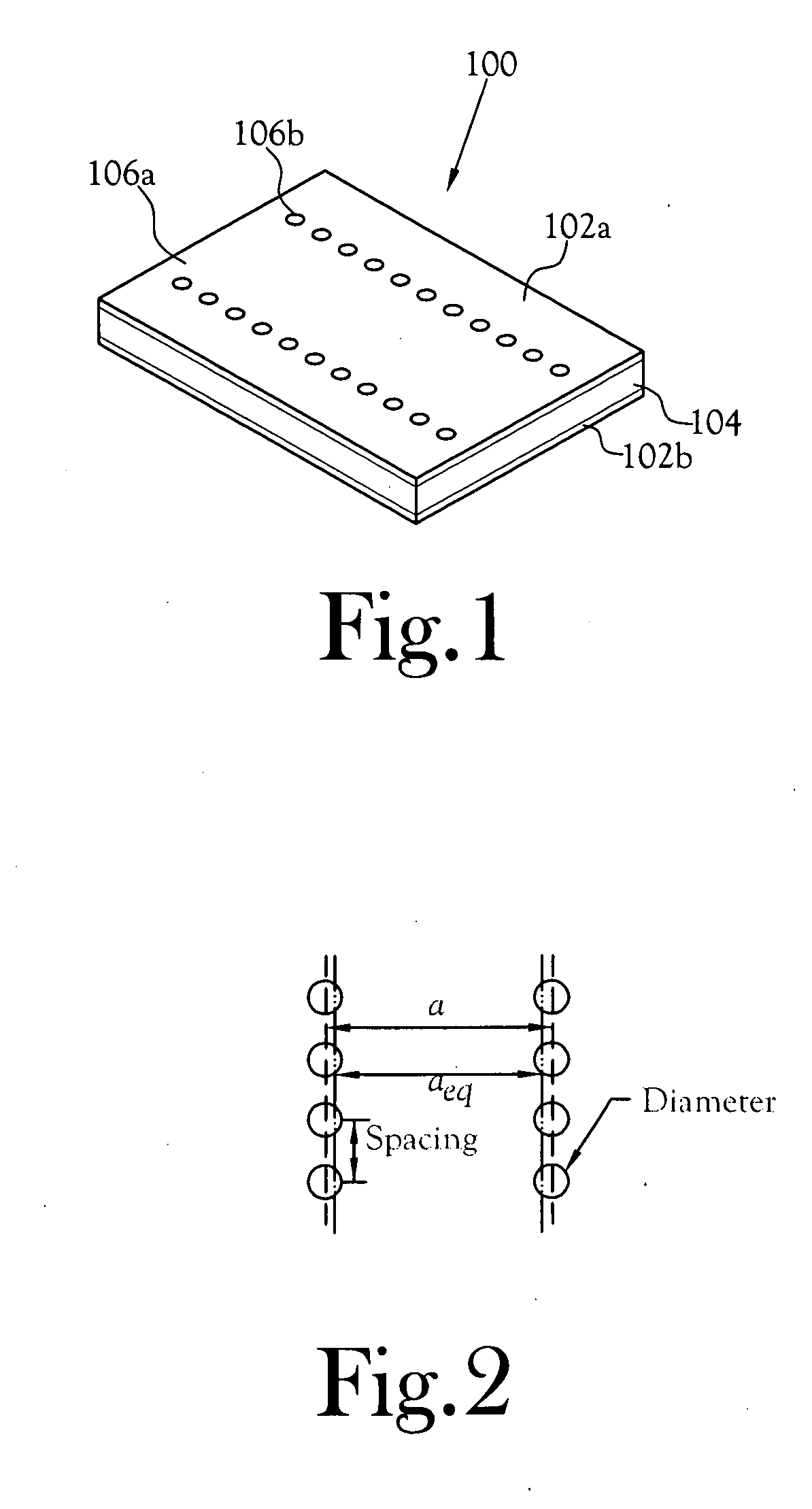

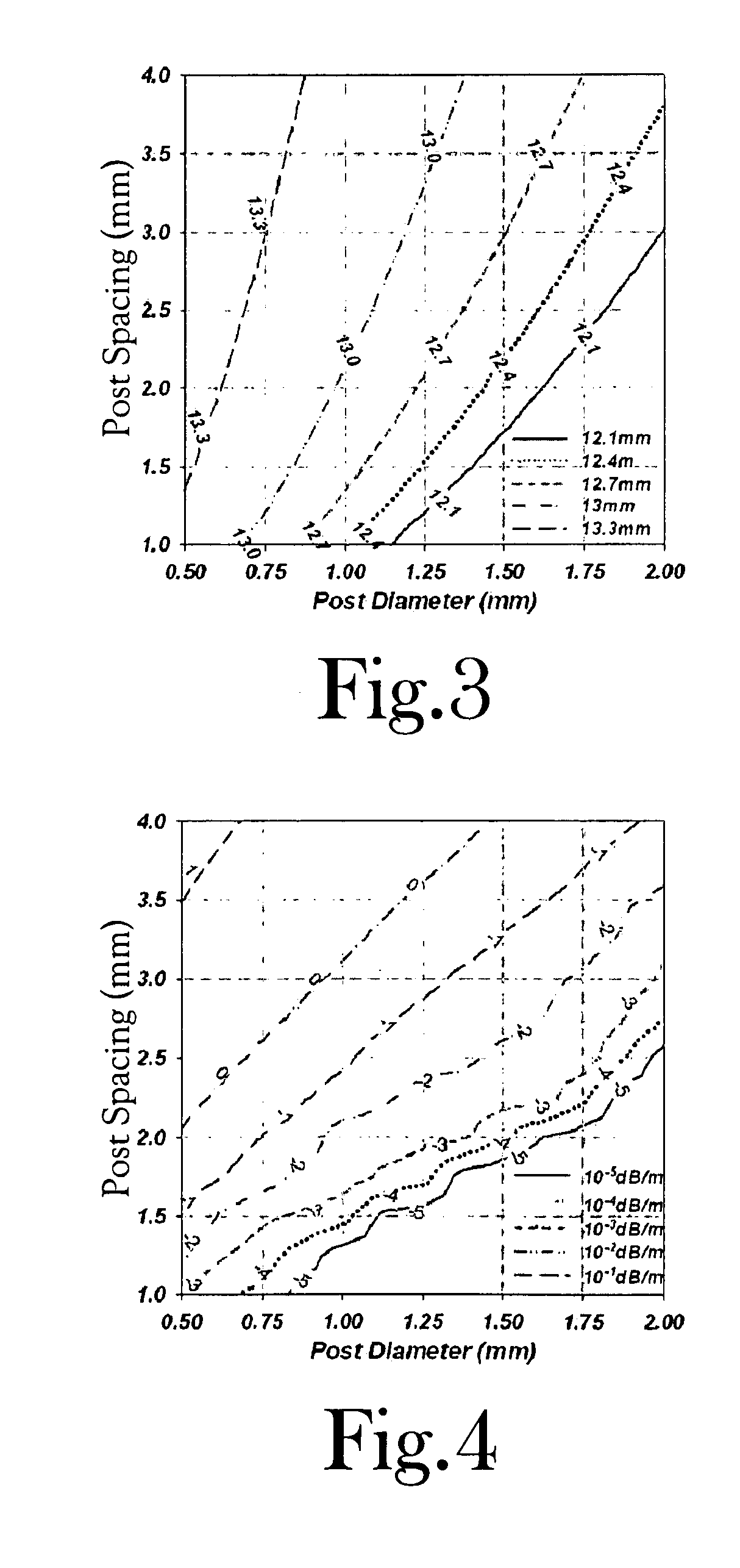

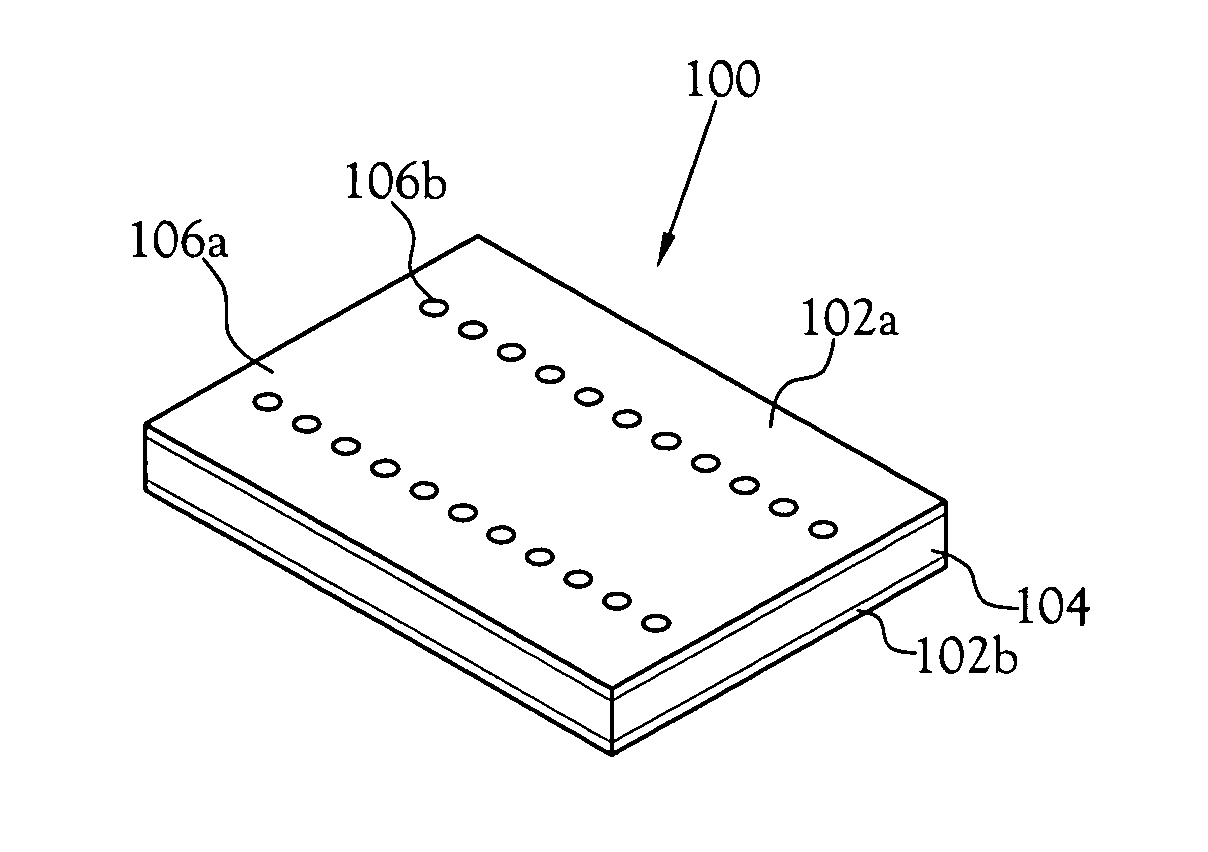

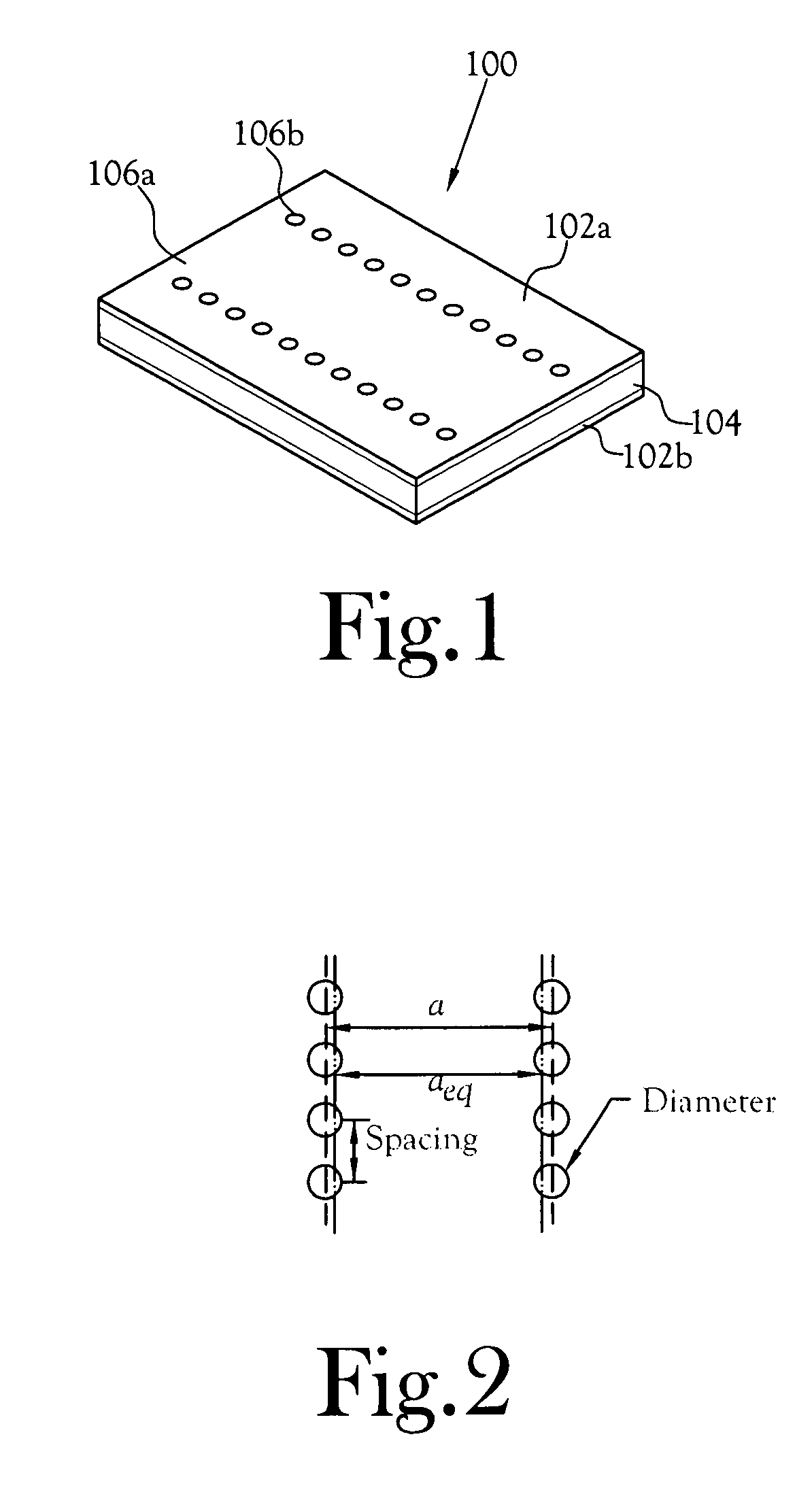

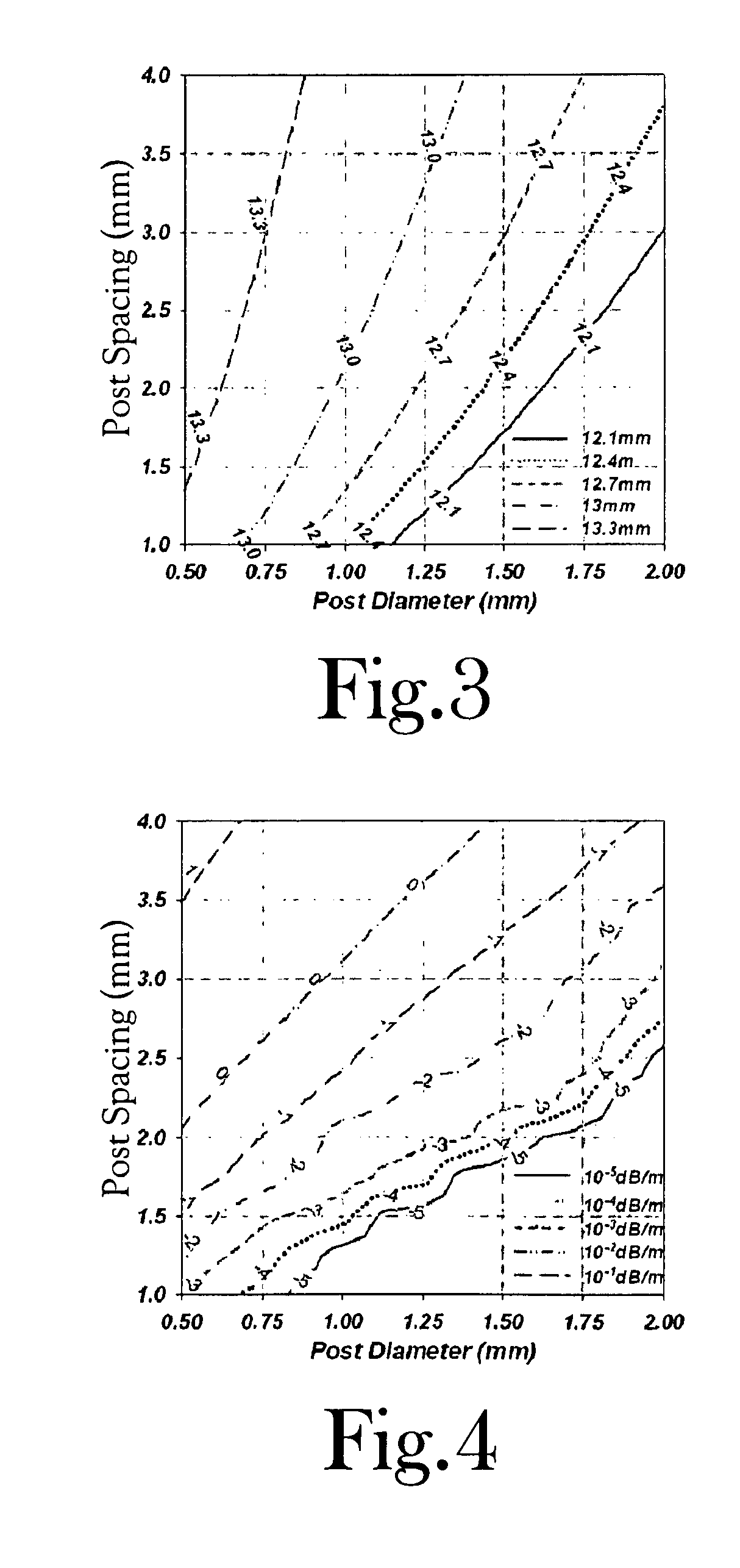

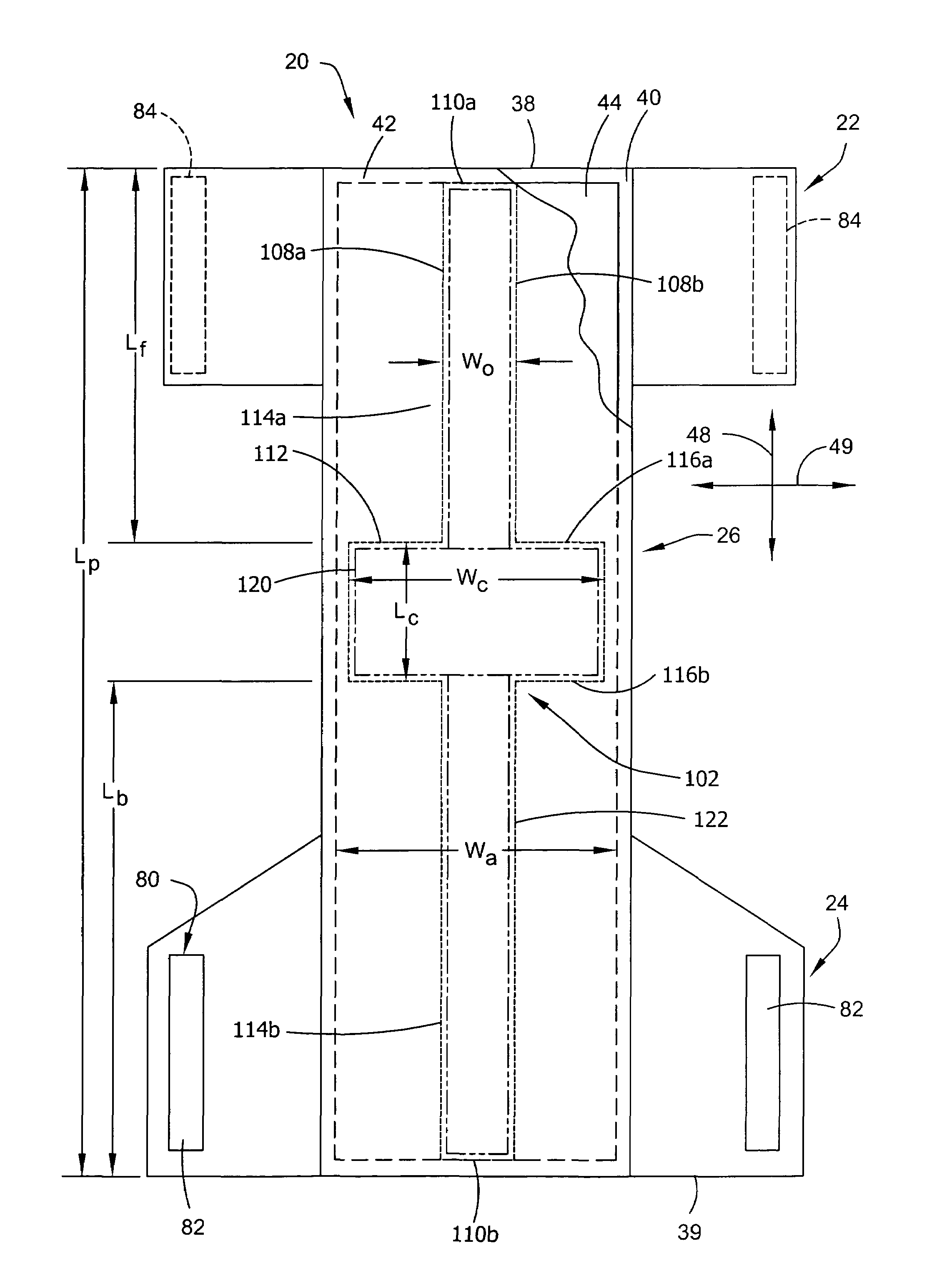

Substrate Integrated Waveguide Antenna Array

InactiveUS20090066597A1Reduce the overall heightMeet cutting requirementsLinear waveguide fed arraysWaveguidesMobile antennasDielectric substrate

A substrate integrated waveguide (SIW) slot full-array antenna fabricated employing printed circuit board technology. The SIW slot full-array antenna using either single or multi-layer structures greatly reduces the overall height and physical steering requirements of a mobile antenna when compared to a conventional metallic waveguide slot array antenna. The SIW slot full-array antenna is fabricated using a low-loss dielectric substrate with top and bottom metal plating. An array of radiating cross-slots is etched in to the top plating to produce circular polarization at a selected tilt-angle. Lines of spaced-apart, metal-lined vias form the sidewalls of the waveguides and feeding network. In multi-layer structures, the adjoining layers are coupled by transverse slots at the interface of the two layers.

Owner:UNIV OF TENNESSEE RES FOUND

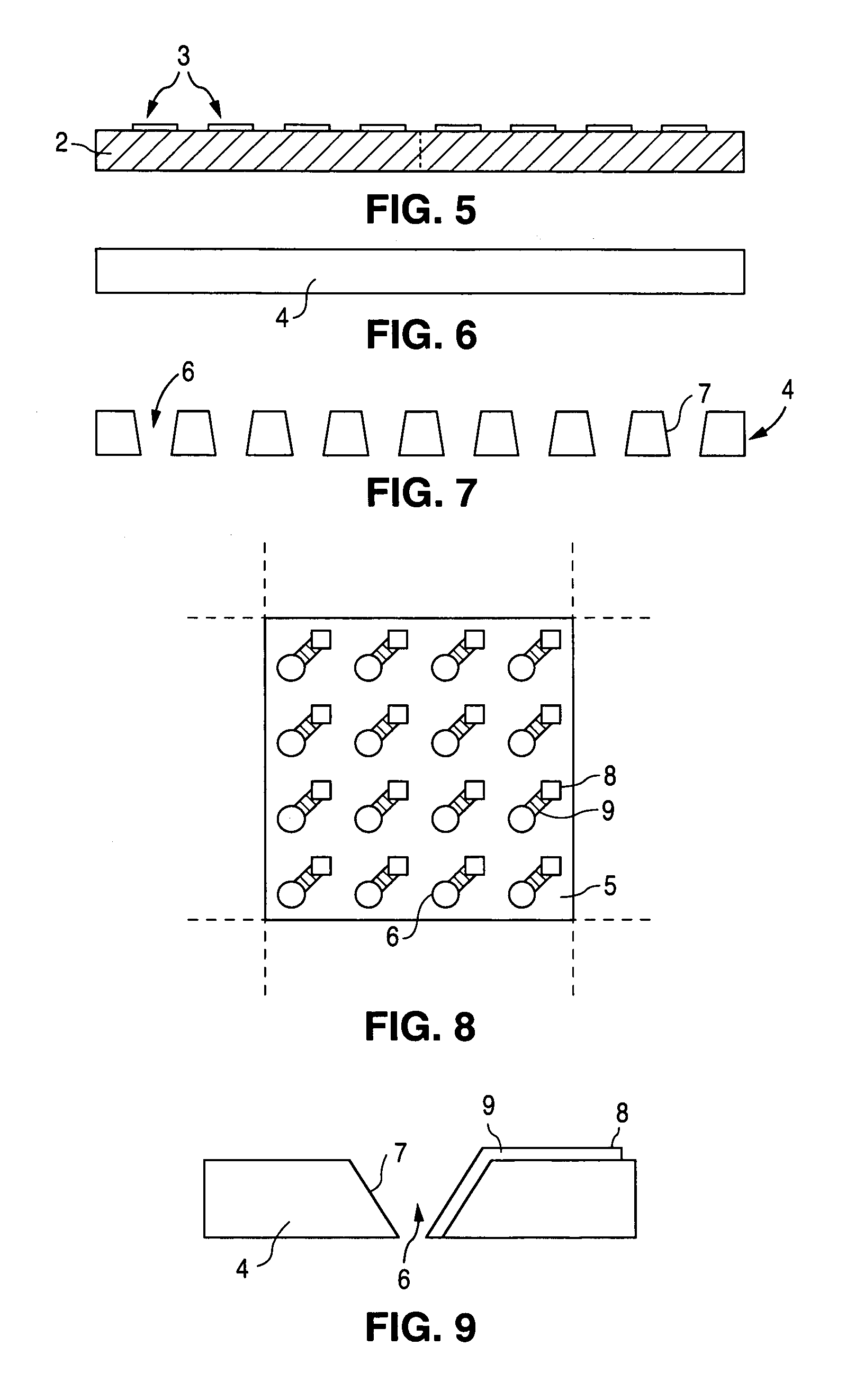

Method for subdividing multilayer optical film cleanly and rapidly

Polymeric multilayer optical films, and laminate bodies that include such films, are cut or subdivided into one or more discrete pieces by removably applying a first and second liner to opposed major surfaces of the multilayer optical film. Laser radiation is then directed at the multilayer optical film through the first liner in such a way as to produce cut lines that define a plurality of pieces of the first liner and of the multilayer optical film. Thereafter, the plurality of pieces of the first liner are removed from the plurality of pieces of the multilayer optical film while the pieces of multilayer optical film are supported by the second liner. Application of the first liner to the multilayer optical film can be accomplished with electrostatics.

Owner:3M INNOVATIVE PROPERTIES CO

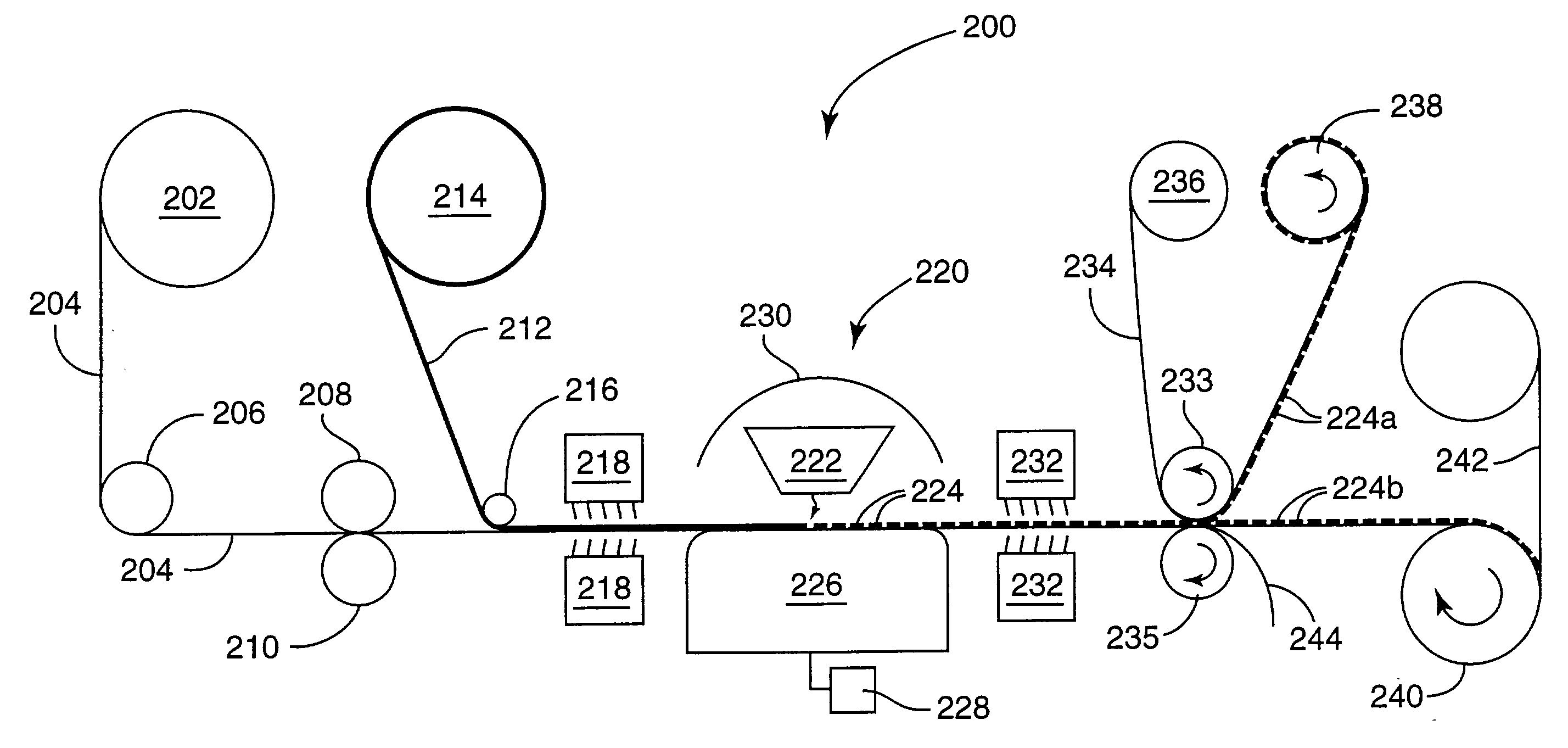

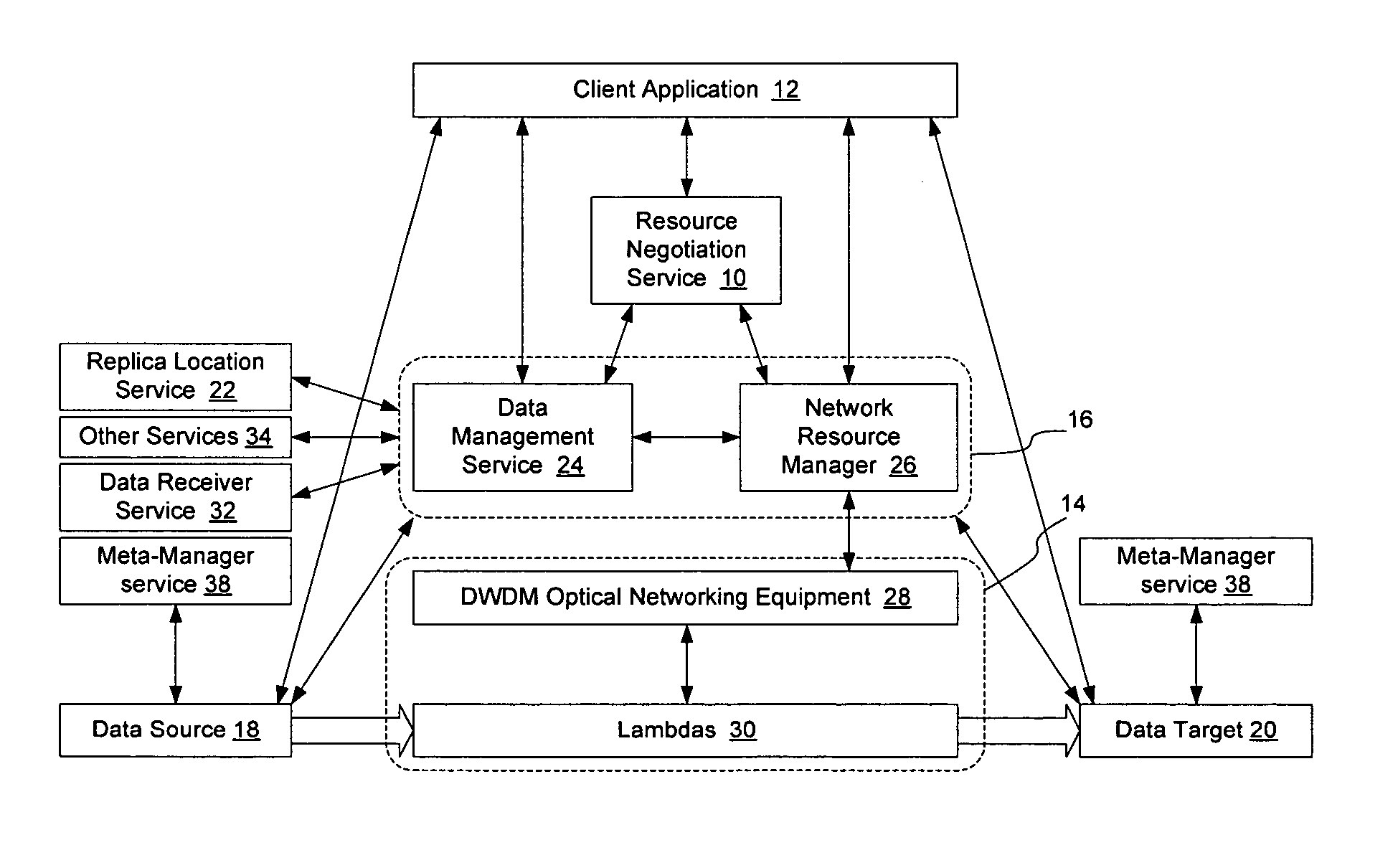

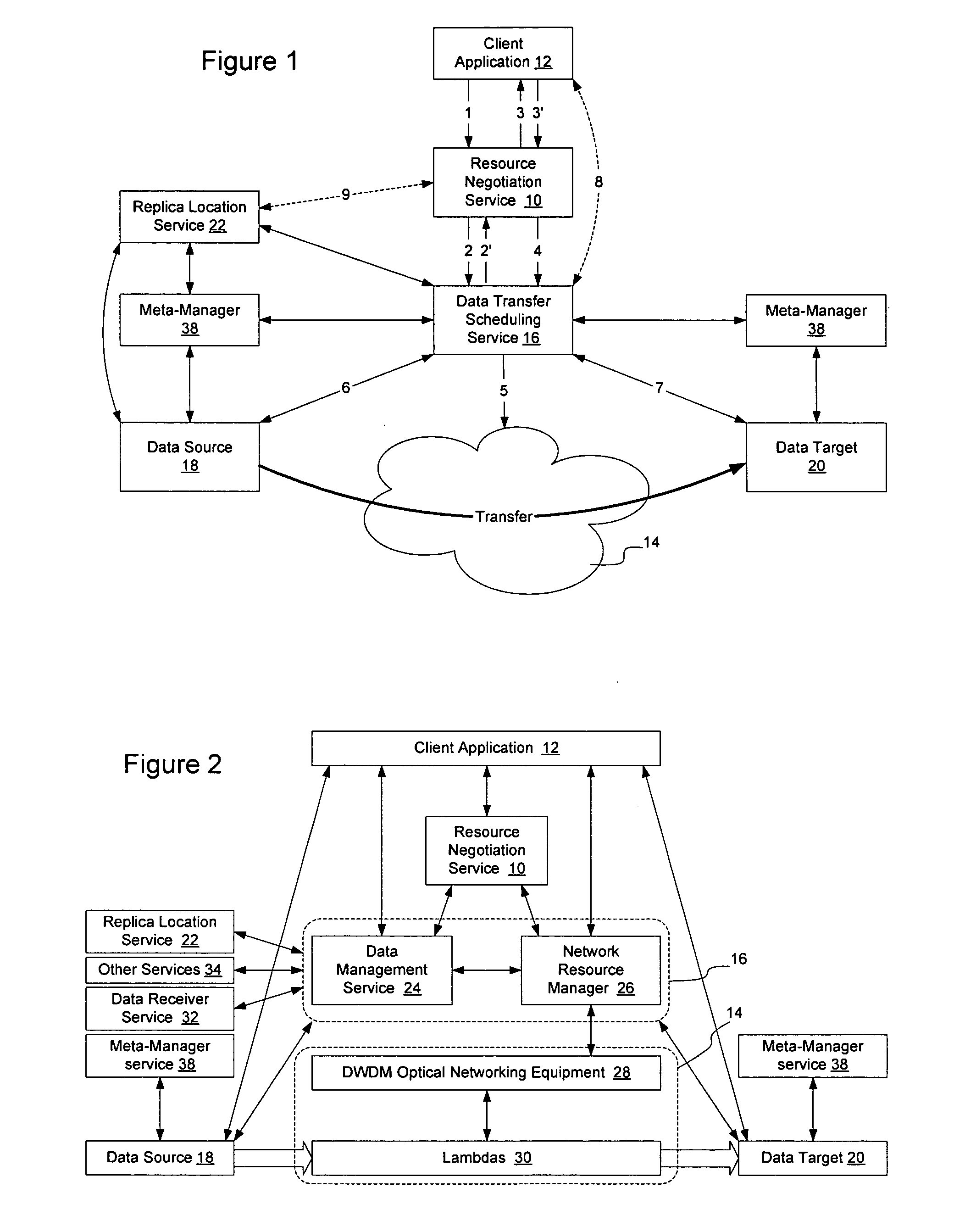

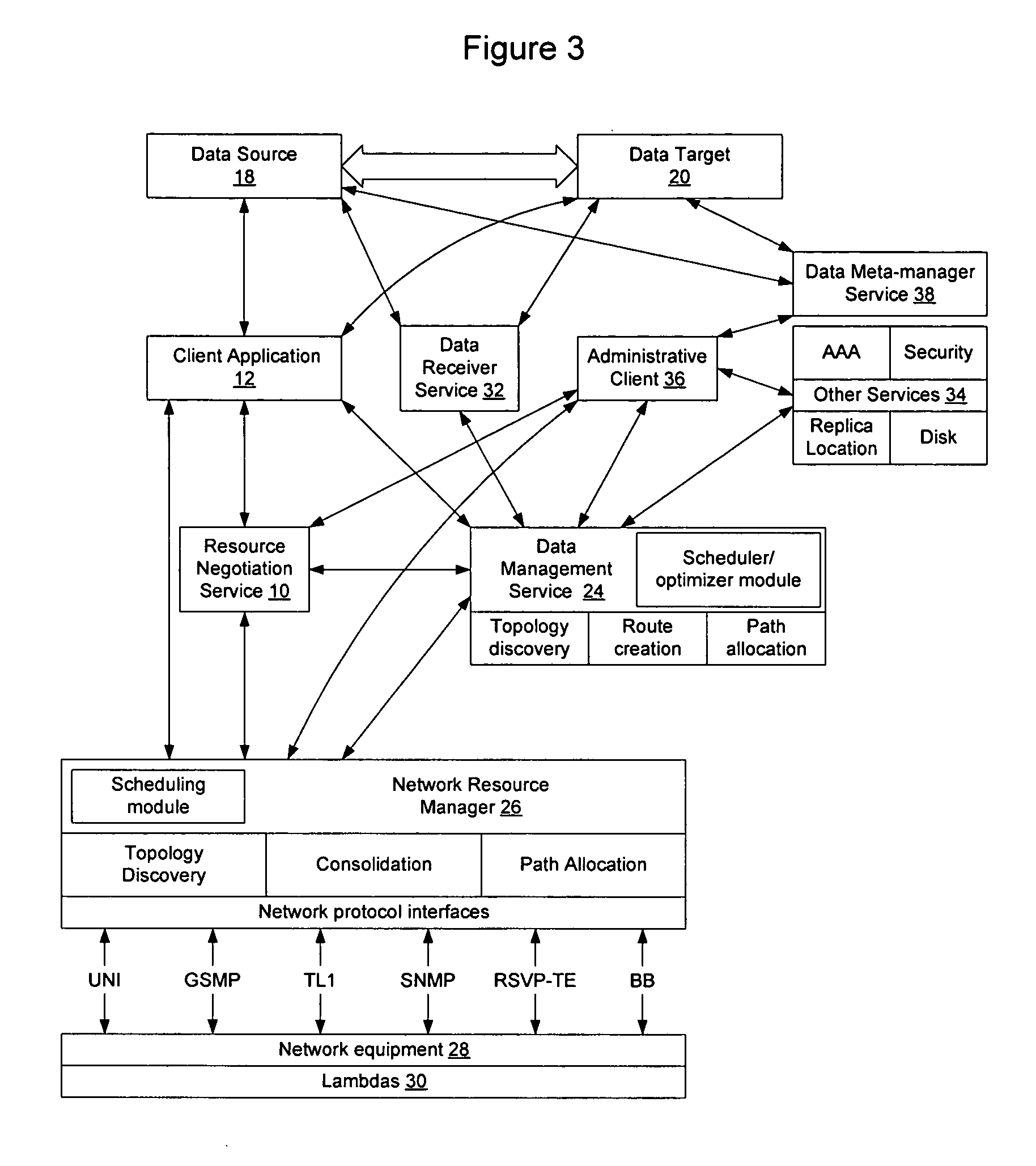

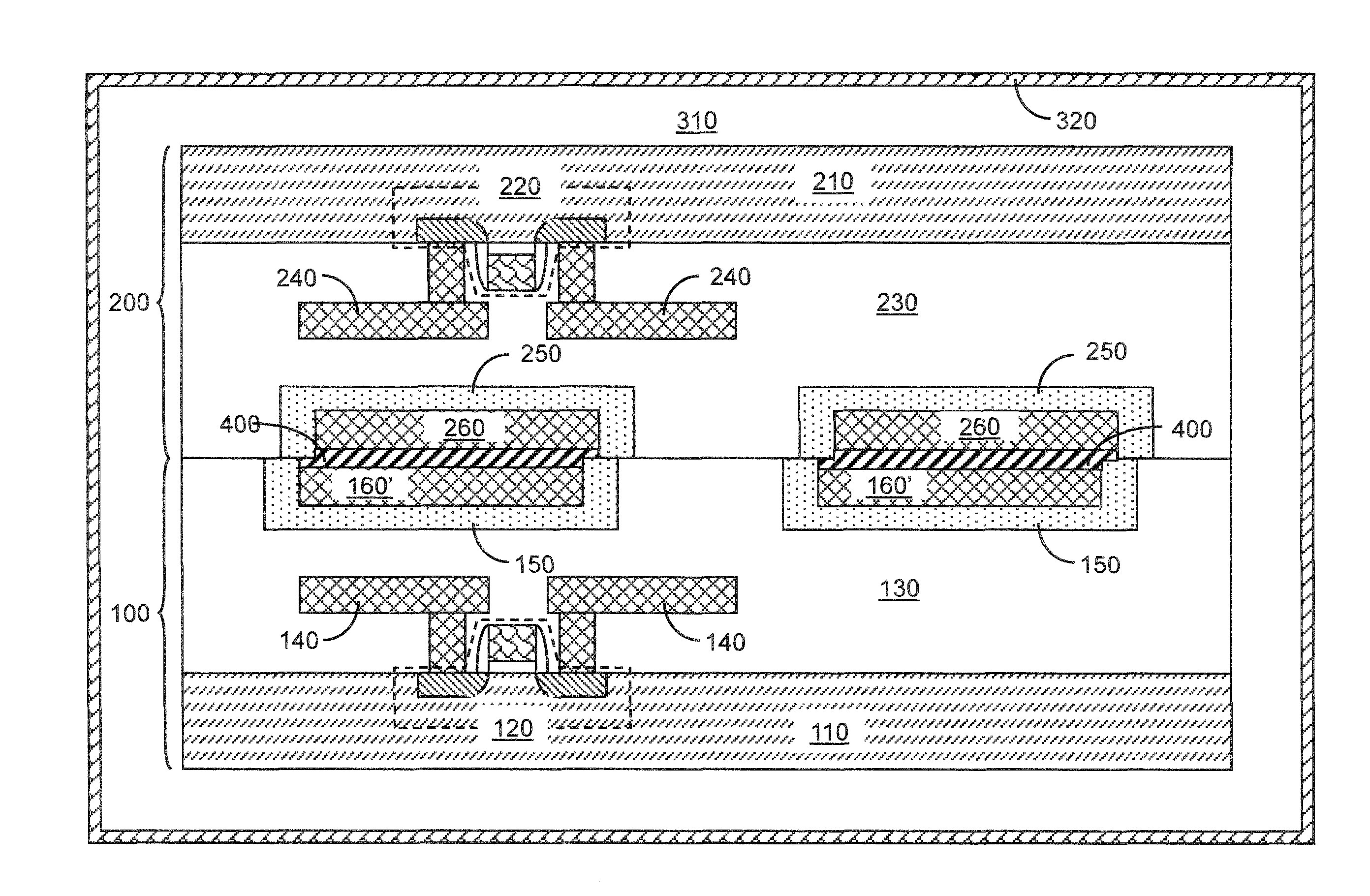

Method and apparatus for automated negotiation for resources on a switched underlay network

A resource negotiation service is provided to enable business logic decisions to be made when obtaining switched underlay network resources, to interface business logic with network conditions and schedules. The resource negotiation service may be implemented as a web service or other network service to enable business logic to be used in the selection of available network resources. This may allow policy to be used on both the subscriber side and the network provider side to optimize network resource allocations for a proposed transfer. The policy may include subscriber policy, network policy, and other factors such as current and expected network conditions. The resource negotiation service may include an interface to enable existing subscribers and new customers to obtain switched underlay resources.

Owner:NORTEL NETWORKS LTD

Pad bonding employing a self-aligned plated liner for adhesion enhancement

ActiveUS8482132B2Improve adhesionSemiconductor/solid-state device detailsSolid-state devicesDielectric surfaceConductive materials

Owner:TAIWAN SEMICON MFG CO LTD

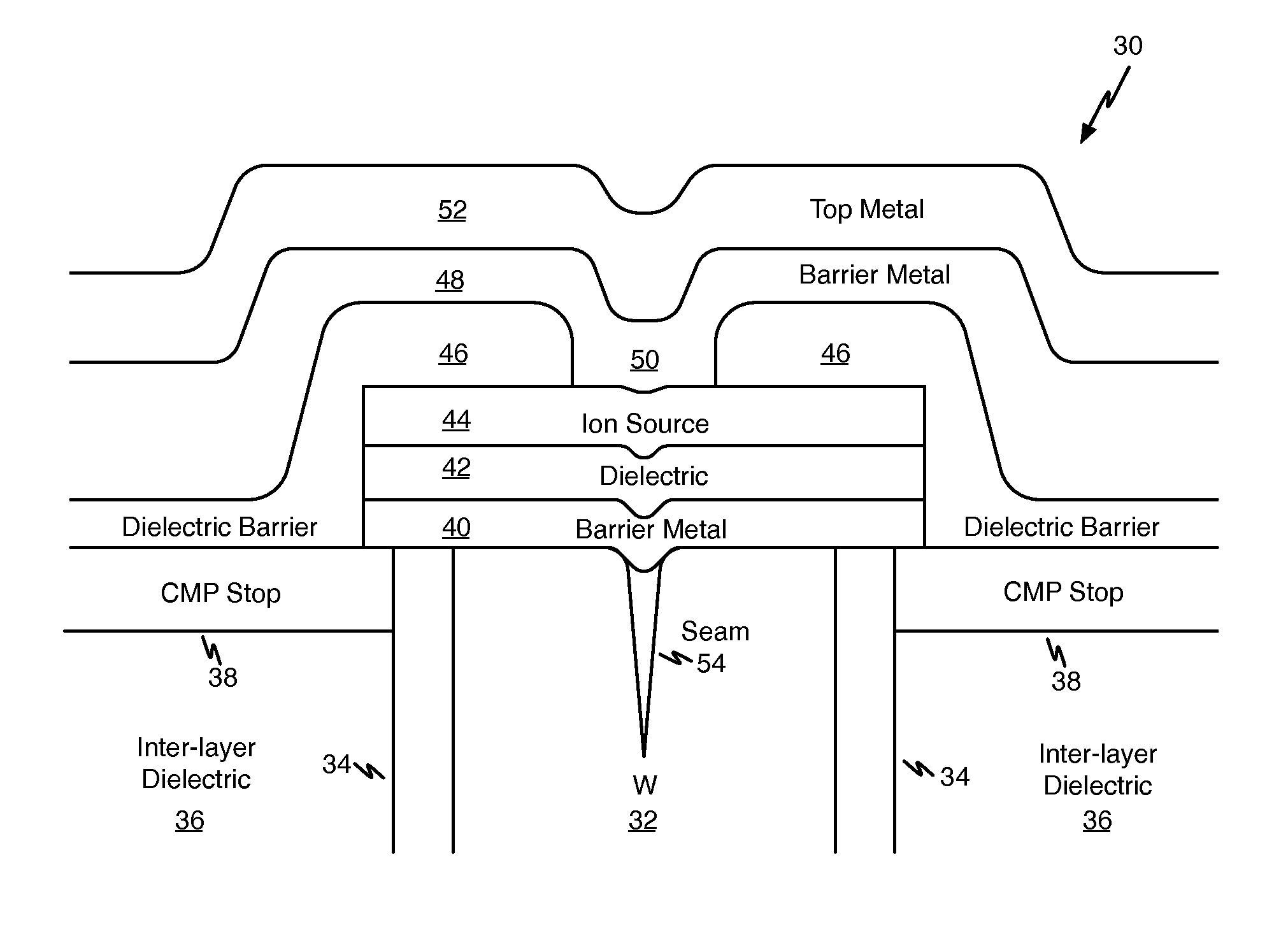

Front to back resistive random access memory cells

A resistive random access memory device formed on a semiconductor substrate comprises an interlayer dielectric having a via formed therethrough. A chemical-mechanical-polishing stop layer is formed over the interlayer dielectric. A barrier metal liner lines walls of the via. A conductive plug is formed in the via. A first barrier metal layer is formed over the chemical-mechanical-polishing stop layer and in electrical contact with the conductive plug. A dielectric layer is formed over the first barrier metal layer. An ion source layer is formed over the dielectric layer. A dielectric barrier layer is formed over the ion source layer, and includes a via formed therethrough communicating with the ion source layer. A second barrier metal layer is formed over the dielectric barrier layer and in electrical contact with the ion source layer. A metal interconnect layer is formed over the barrier metal layer.

Owner:MICROSEMI SOC

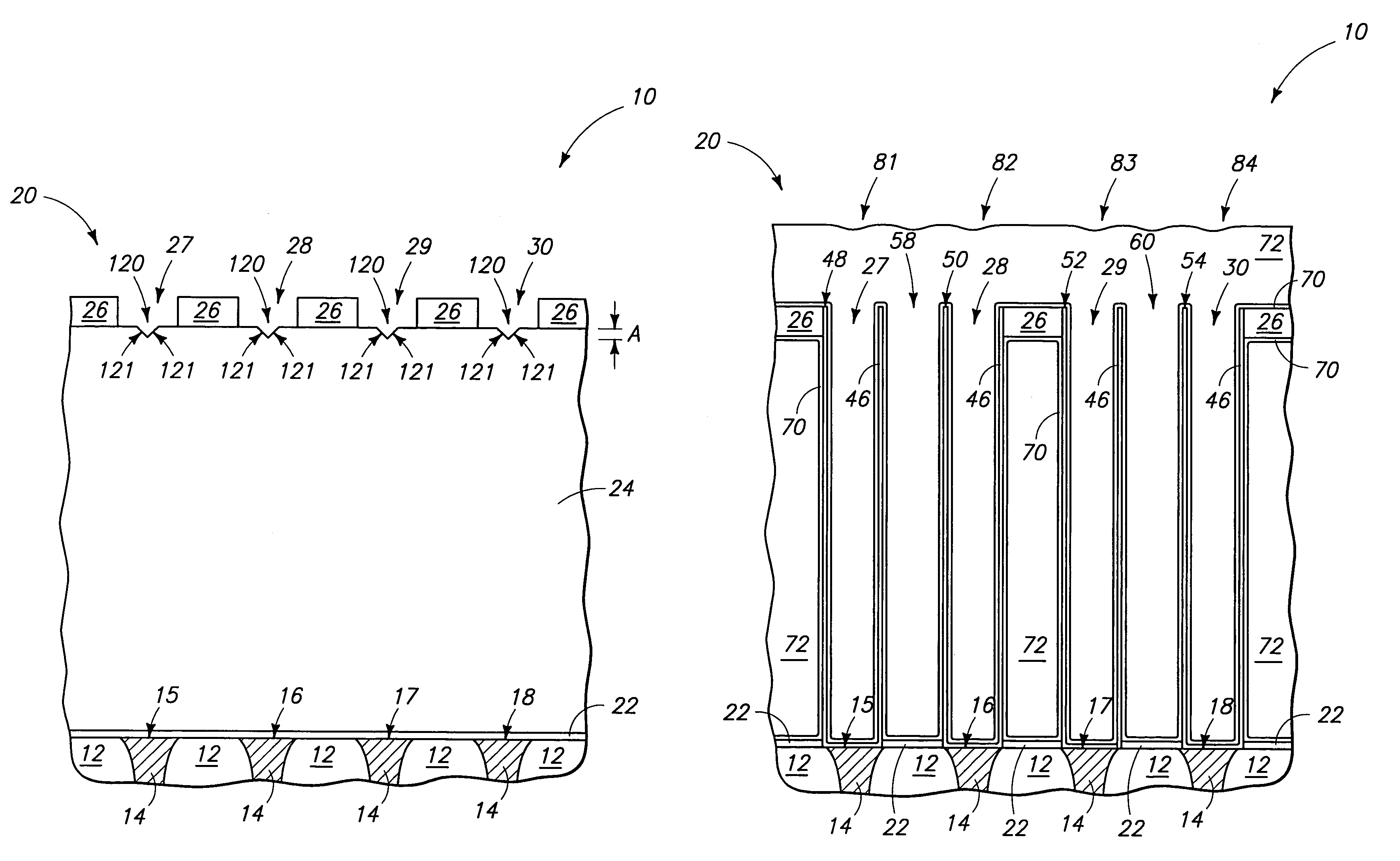

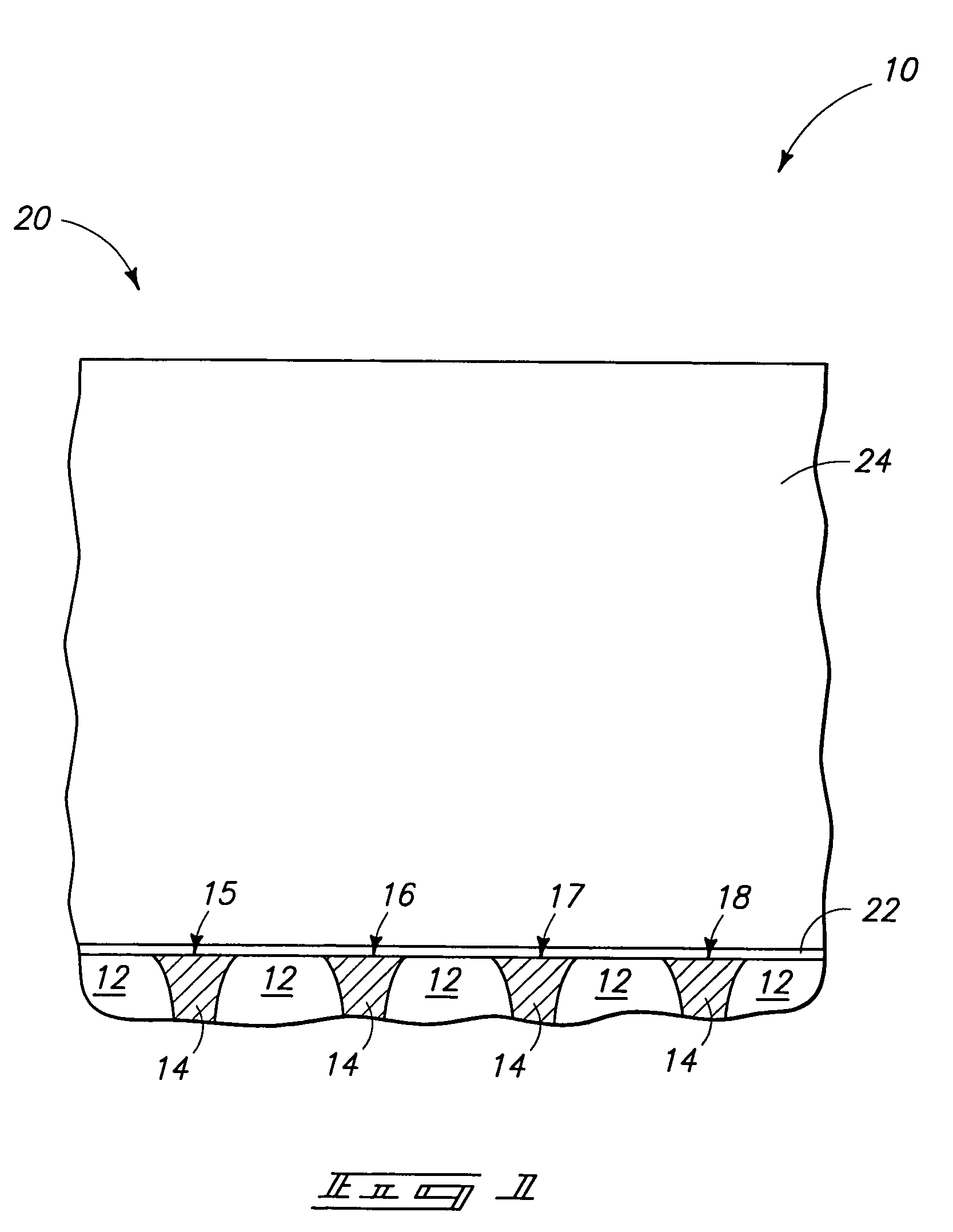

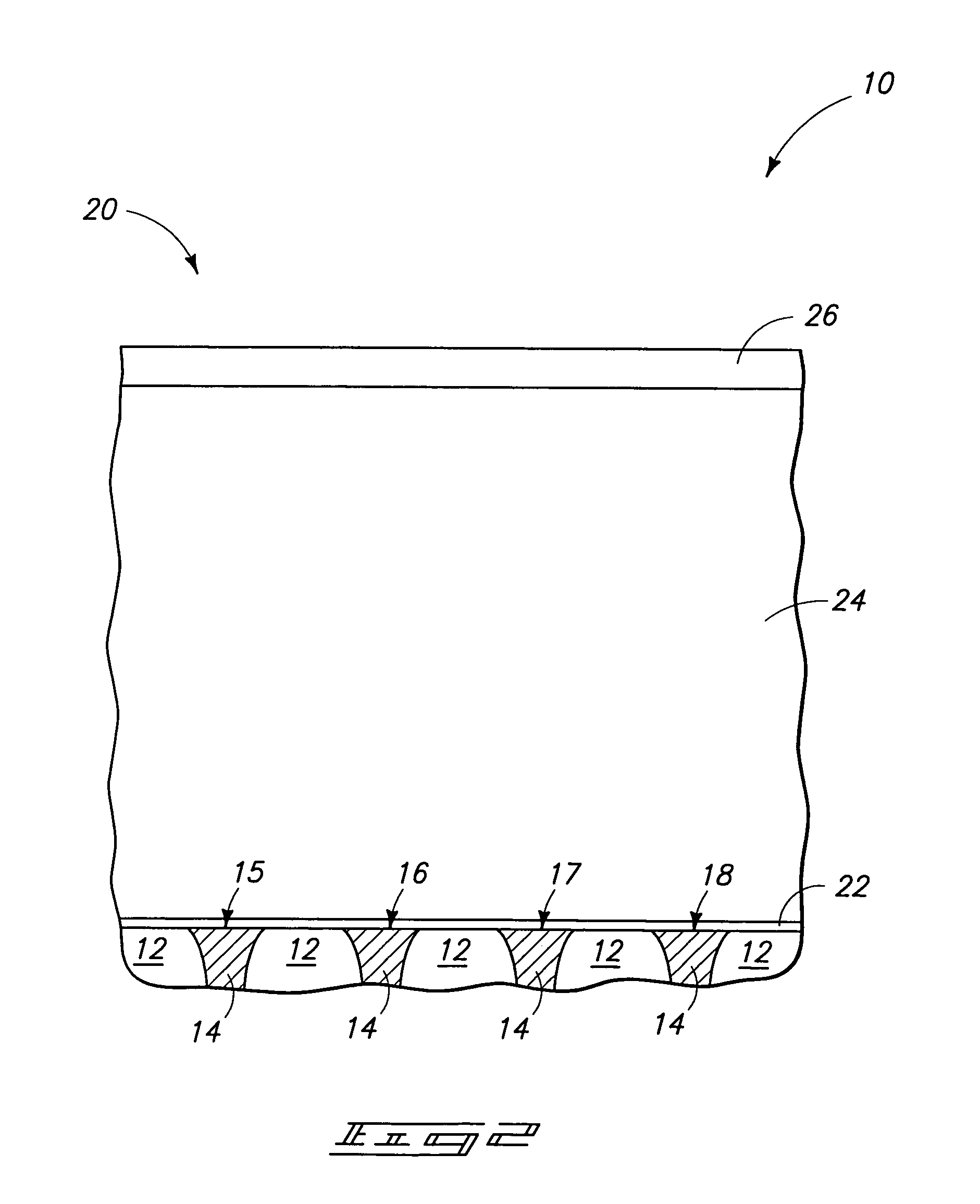

Methods of forming pluralities of capacitors

ActiveUS7199005B2Solid-state devicesSemiconductor/solid-state device manufacturingElectrical connectionCapacitor

The invention comprises methods of forming pluralities of capacitors. In one implementation, metal is formed over individual capacitor storage node locations on a substrate. A patterned masking layer is formed over the metal. The patterned masking layer comprises openings therethrough to an outer surface of the metal. Individual of the openings are received over individual of the capacitor storage node locations. A pit is formed in the metal outer surface within individual of the openings. After forming the pits, the metal is anodically oxidized through the openings effective to form a single metal oxide-lined channel in individual of the openings over the individual capacitor storage nodes. Individual capacitor electrodes are formed within the channels in electrical connection with the individual capacitor storage node locations. At least some of the metal oxide is removed from the substrate, and the individual capacitor electrodes are incorporated into a plurality of capacitors. Other aspects and implementations are contemplated.

Owner:MICRON TECH INC

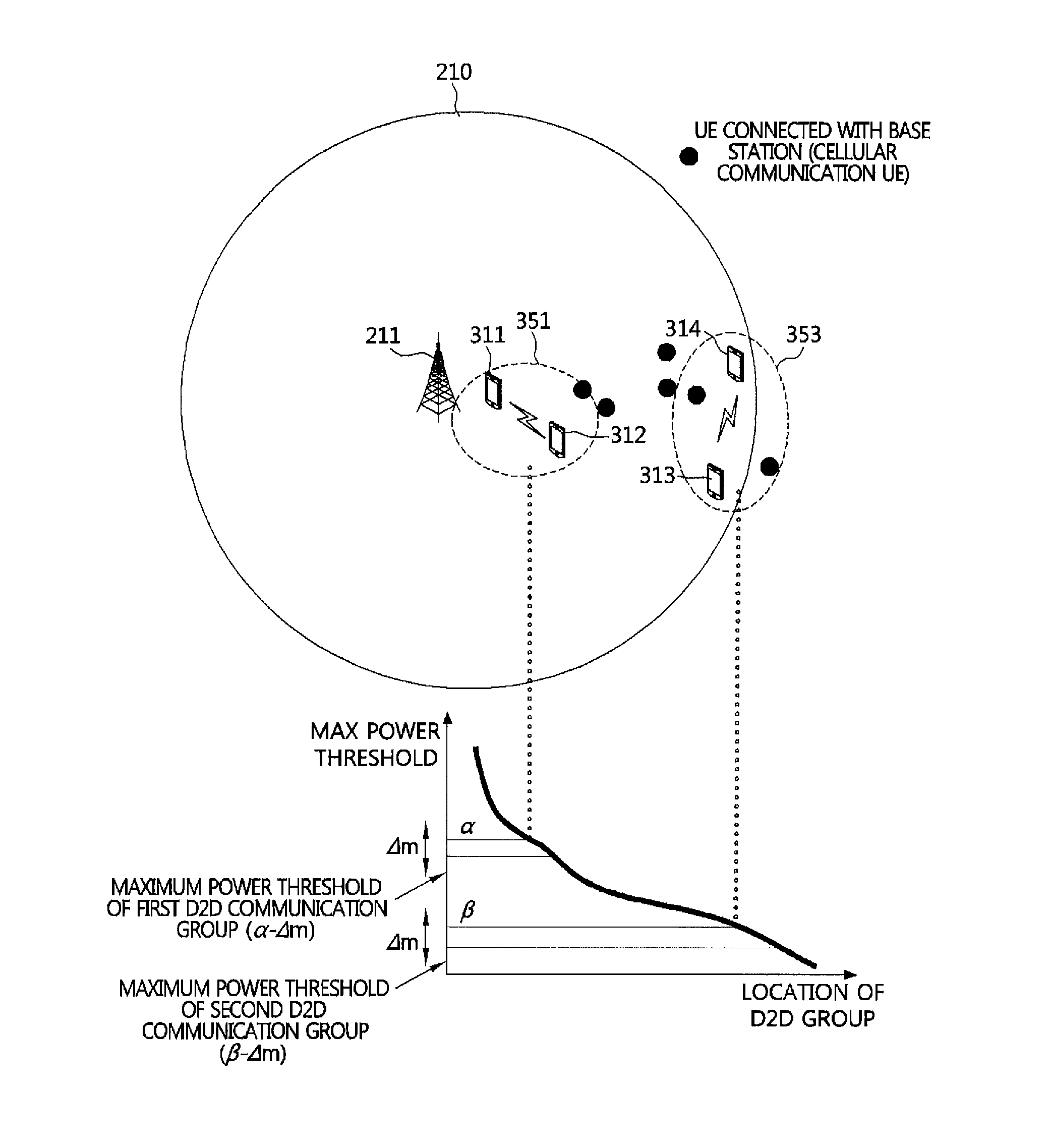

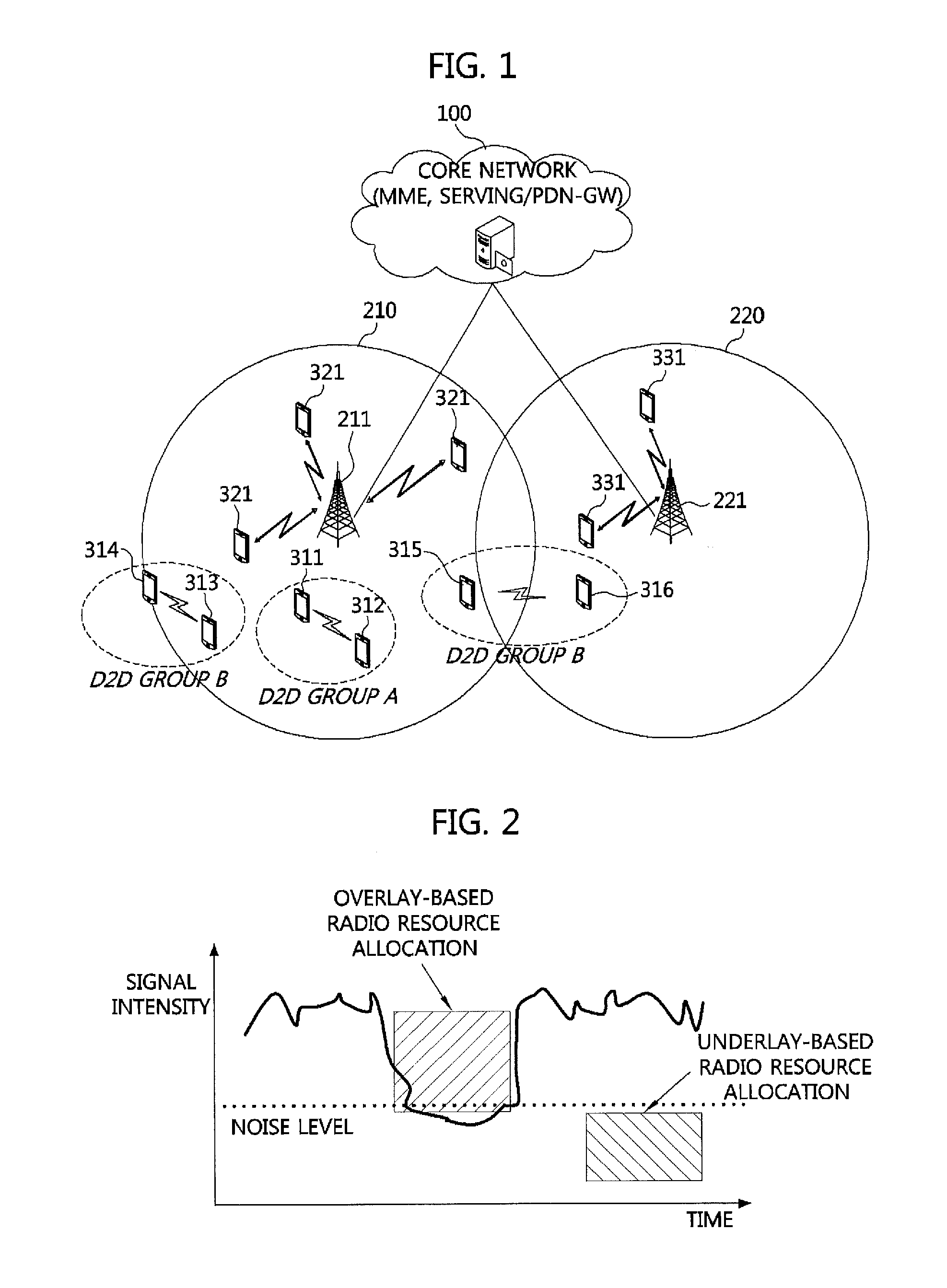

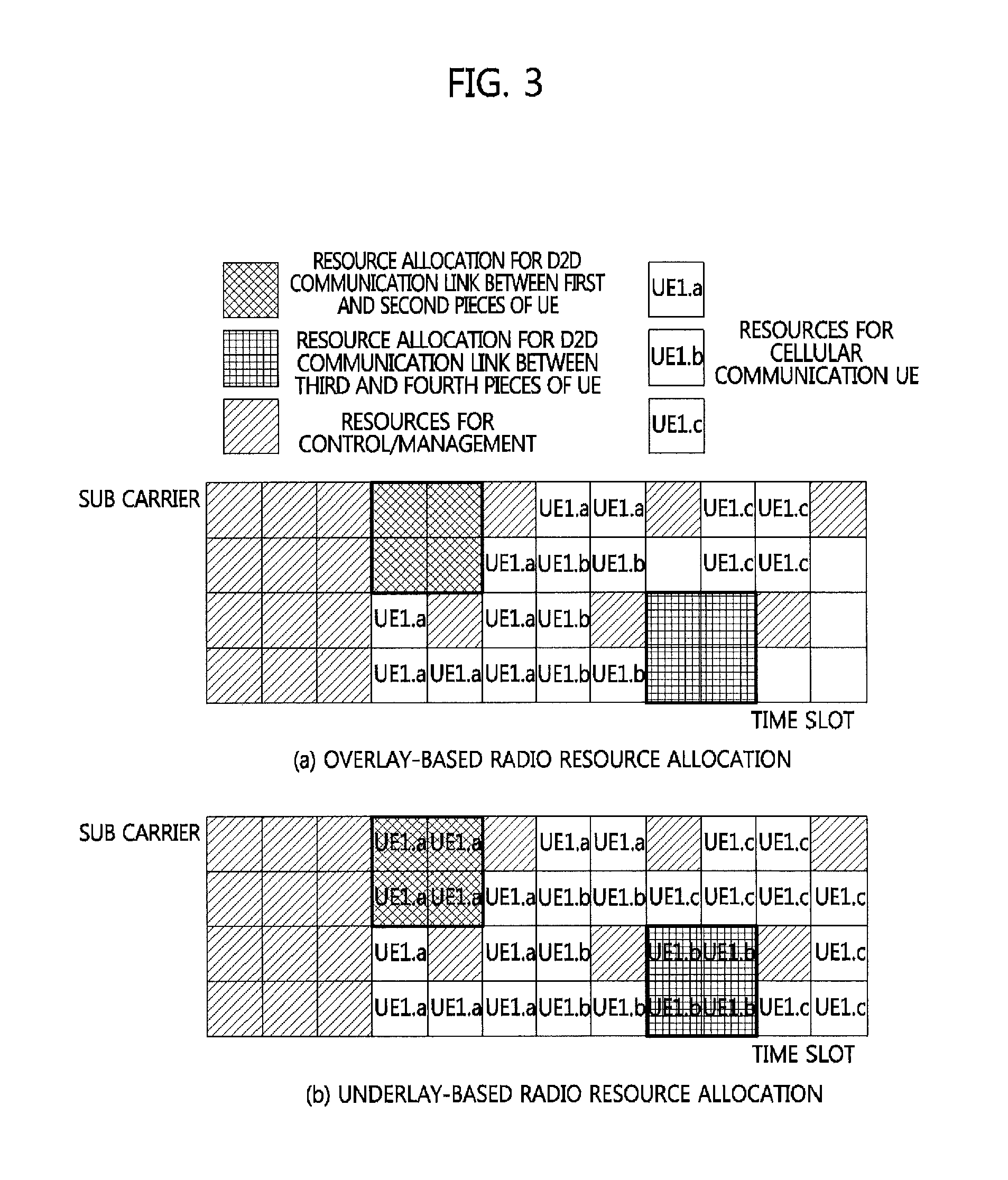

Control method for device-to-device communication

InactiveUS20130157676A1Effective distributionPower managementConnection managementControl powerUser equipment

Provided is a control method for device-to-device (D2D) communication. A base station measures a load of a cell, receives location information about each piece of user equipment (UE) from a plurality of pieces of UE, selects any one of an overlay-based resource allocation method and an underlay-based resource allocation method on the basis of the measured cell load and the location information about the respective pieces of UE, allocates resources for D2D communication on the basis of the selected resource allocation method, and controls power according to the locations of the pieces of UE and a density of pieces of cellular communication UE. Accordingly, it is possible to improve resource use efficiency and efficiently remove interference.

Owner:ELECTRONICS & TELECOMM RES INST

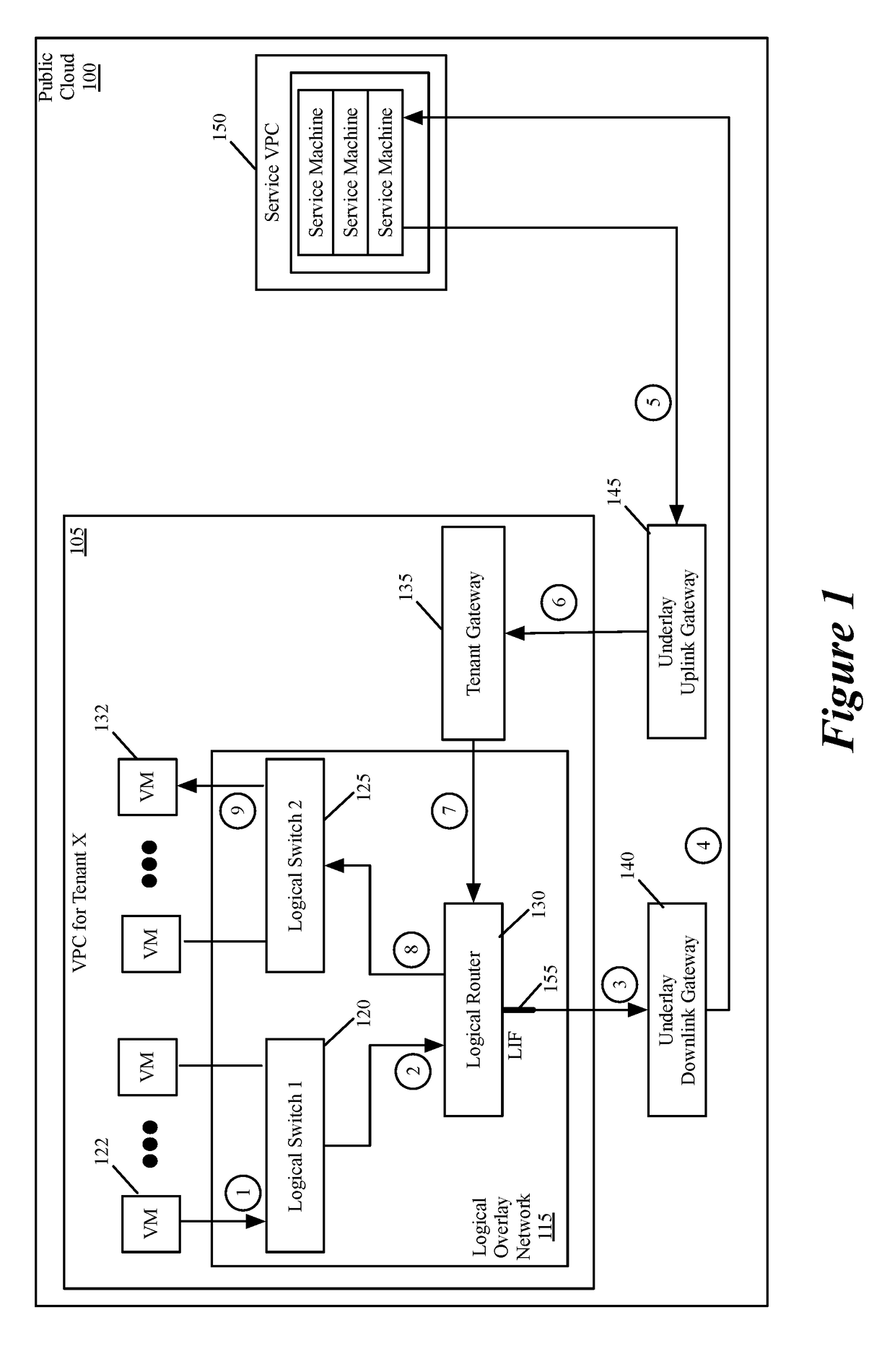

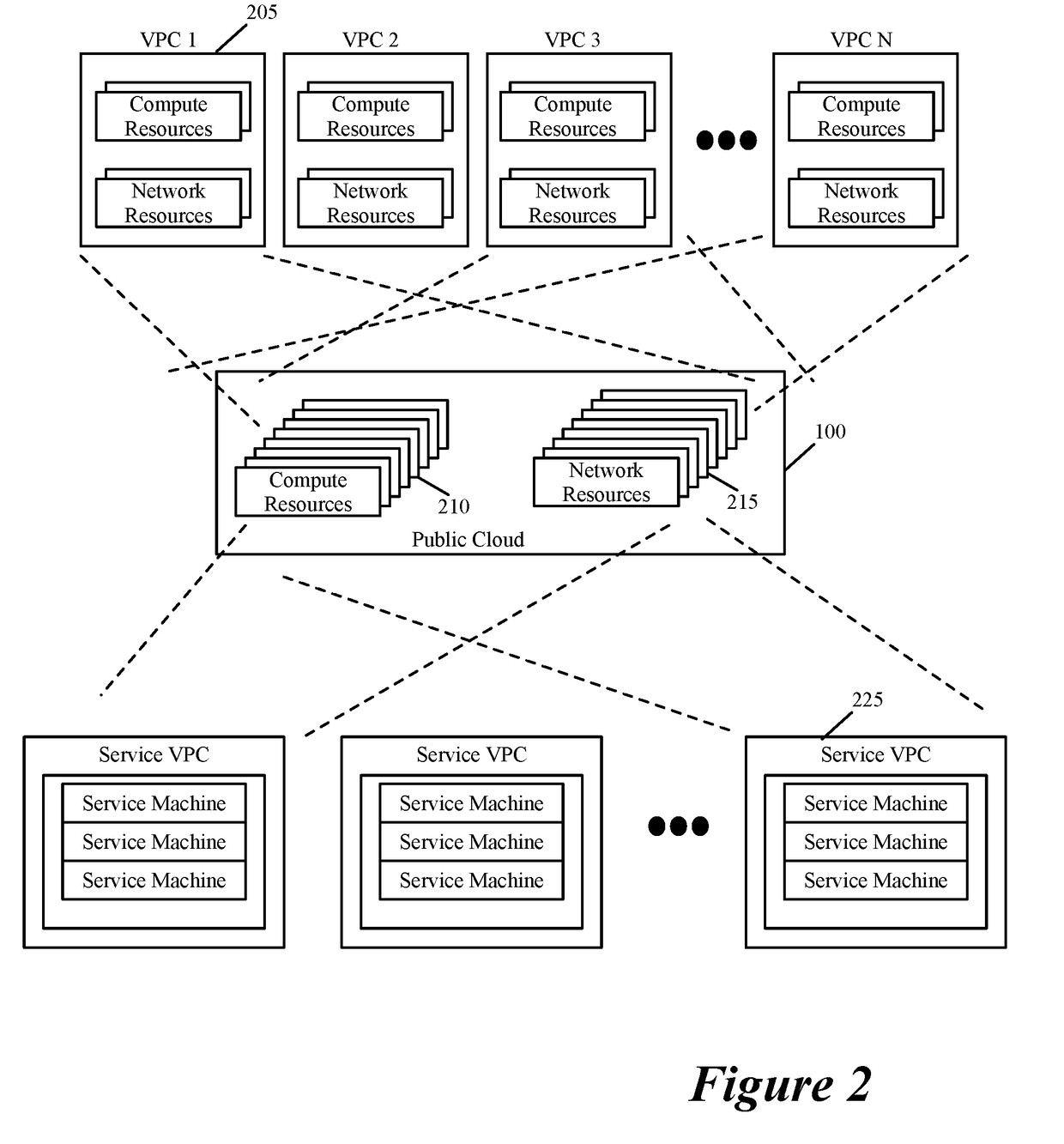

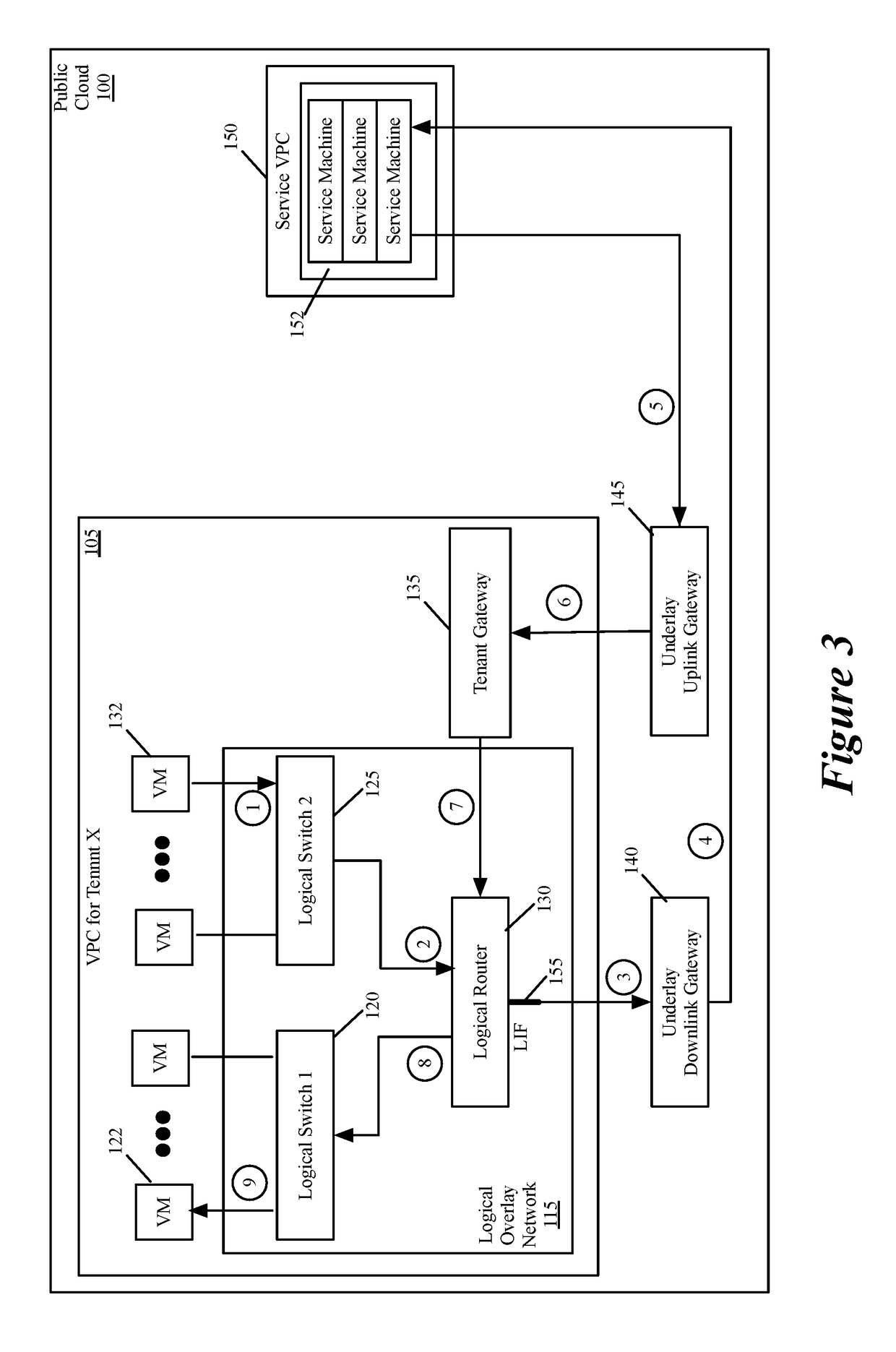

Performing in-line service in public cloud

Some embodiments provide a novel way to insert a service (e.g., a third party service) in the path of a data message flow, between two machines (e.g., two VMs, two containers, etc.) in a public cloud environment. For a particular tenant of the public cloud, some embodiments create an overlay logical network with a logical overlay address space. To perform a service on data messages of a flow between two machines, the logical overlay network passes to the public cloud's underlay network the data messages with their destination address (e.g., destination IP addresses) defined in the logical overlay network. The underlay network (e.g., an underlay default downlink gateway) is configured to pass data messages with such destination addresses (e.g., with logical overlay destination addresses) to a set of one or more service machines. The underlay network (e.g., an underlay default uplink gateway) is also configured to pass to the particular tenant's public cloud gateway the processed data messages that are received from the service machine set and that are addressed to logical overlay destination addresses. The tenant's public cloud gateway is configured to forward such data messages to a logical forwarding element of the logical network, which then handles the forwarding of the data messages to the correct destination machine.

Owner:NICIRA

Substrate integrated waveguide antenna array

InactiveUS7808439B2Reduce the overall heightMeet cutting requirementsLinear waveguide fed arraysWaveguidesMobile antennasDielectric substrate

A substrate integrated waveguide (SIW) slot full-array antenna fabricated employing printed circuit board technology. The SIW slot full-array antenna using either single or multi-layer structures greatly reduces the overall height and physical steering requirements of a mobile antenna when compared to a conventional metallic waveguide slot array antenna. The SIW slot full-array antenna is fabricated using a low-loss dielectric substrate with top and bottom metal plating. An array of radiating cross-slots is etched in to the top plating to produce circular polarization at a selected tilt-angle. Lines of spaced-apart, metal-lined vias form the sidewalls of the waveguides and feeding network. In multi-layer structures, the adjoining layers are coupled by transverse slots at the interface of the two layers.

Owner:UNIV OF TENNESSEE RES FOUND

Non polarity A side nitride film growing on the silicon(102) substrate and its making method and use

InactiveCN101009347AEasy to separateIncrease overlapLaser detailsFinal product manufactureSolar batteryLight-emitting diode

The invention relates to a nonpolar A side nitride film that comprises a silicon (102) underlay, metal layer which grows upon the silicon underlay sequentially, InGaAlN initial growth layer and the first InGaAlN buffer layer, it characterized in that: said silicon underlay is Si underlay which adopts the (102) side or offset angle. The nonpolar a side nitride film which grows on the silicon underlay can be used in LBD, laser, solar battery. The component extension configuration is adopted according to different component, for example the LBD and laser, and using the mature silicon craft further to produce relative diprosopia electrode component or peeling off component. The advantages of the invention are: the invention can increase the growth quality of nonpolar GaN base material, and decrease the cost; the craft of current component can be simplified greatly, the cost can be decreased, and increase the elimination efficiency and lightening efficiency greatly.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

Hermetic wafer scale integrated circuit structure

InactiveUS6982475B1Prevent surfaceDamaged and destroyedSemiconductor/solid-state device detailsSolid-state devicesScale structureHermetic seal

A wafer scale semiconductor integrated circuit packaging technique provides a hermetic seal for the individual integrated circuit die formed as part of the wafer scale structure. A semiconductor wafer is manufactured to include a number of individual semiconductor die. Each individual die formed on the wafer includes a number of bond pads that are exposed on the die surface in various locations to provide electrical connections to the circuitry created on the die. The wafer further includes a planar glass sheet that is substantially the same size as the wafer, the glass sheet being adhered to the wafer using a suitable adhesive. The glass sheet has a number of pre-formed holes in it, the arrangement of the pre-formed holes corresponding to the location of the bond pads at each of the individual semiconductor die formed as part of the wafer structure. Following adherence of the glass sheet to the semiconductor wafer utilizing the intermediate adhesive material, metal connections are made between pads formed on the glass sheet and the bond pads formed on the integrated circuit die. Solder balls are then attached to the pads on the glass sheet to provide a conductive flow between the solder balls and the bond pads. After the solder balls are attached, trenches are cut around each of the individual die on the wafer. The trenches are cut at an angle and extend through the glass sheet and the intermediate adhesive material and into the semiconductor substrate in which the integrated circuits are formed. After the trenches are cut around each individual semiconductor die, a noble metal is deposited on the sidewalls of the trench to extend over the interface between the glass sheet, the adhesive material and the semiconductor die. The wafer is then cut along the noble metal lined trenches to provide individual, hermetically sealed packaged integrated circuit die.

Owner:MICRO CHIP SCALE PACKAGING

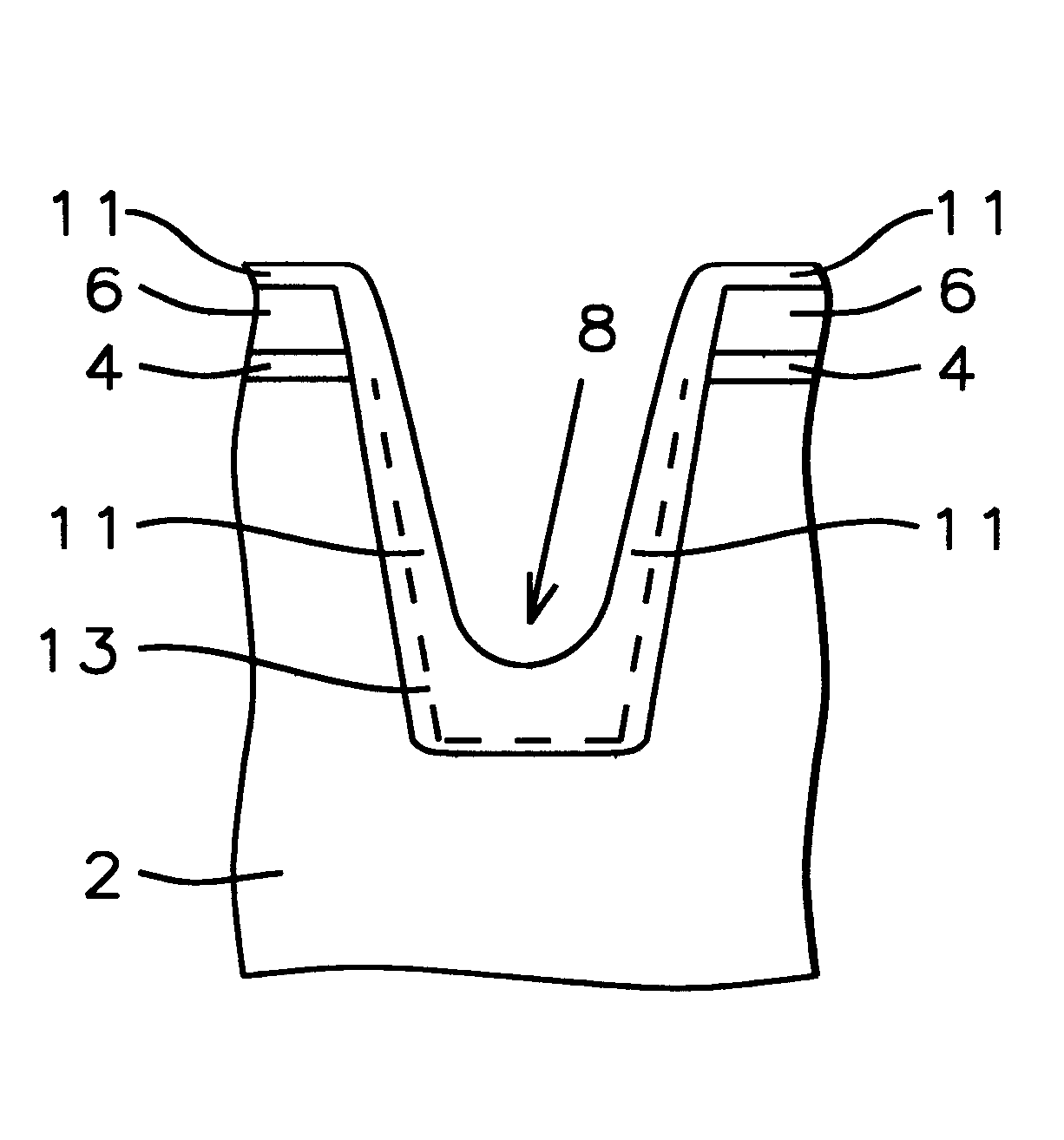

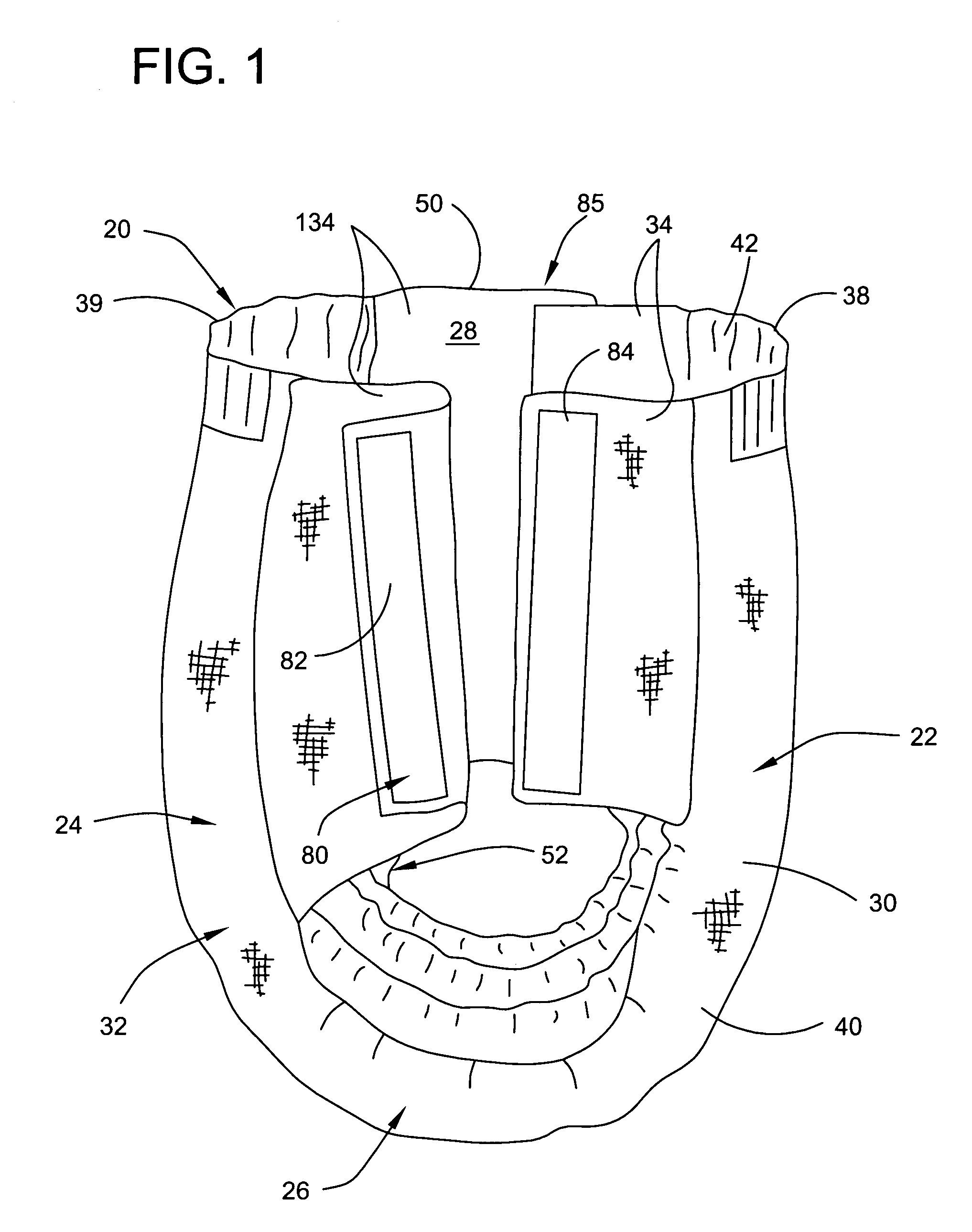

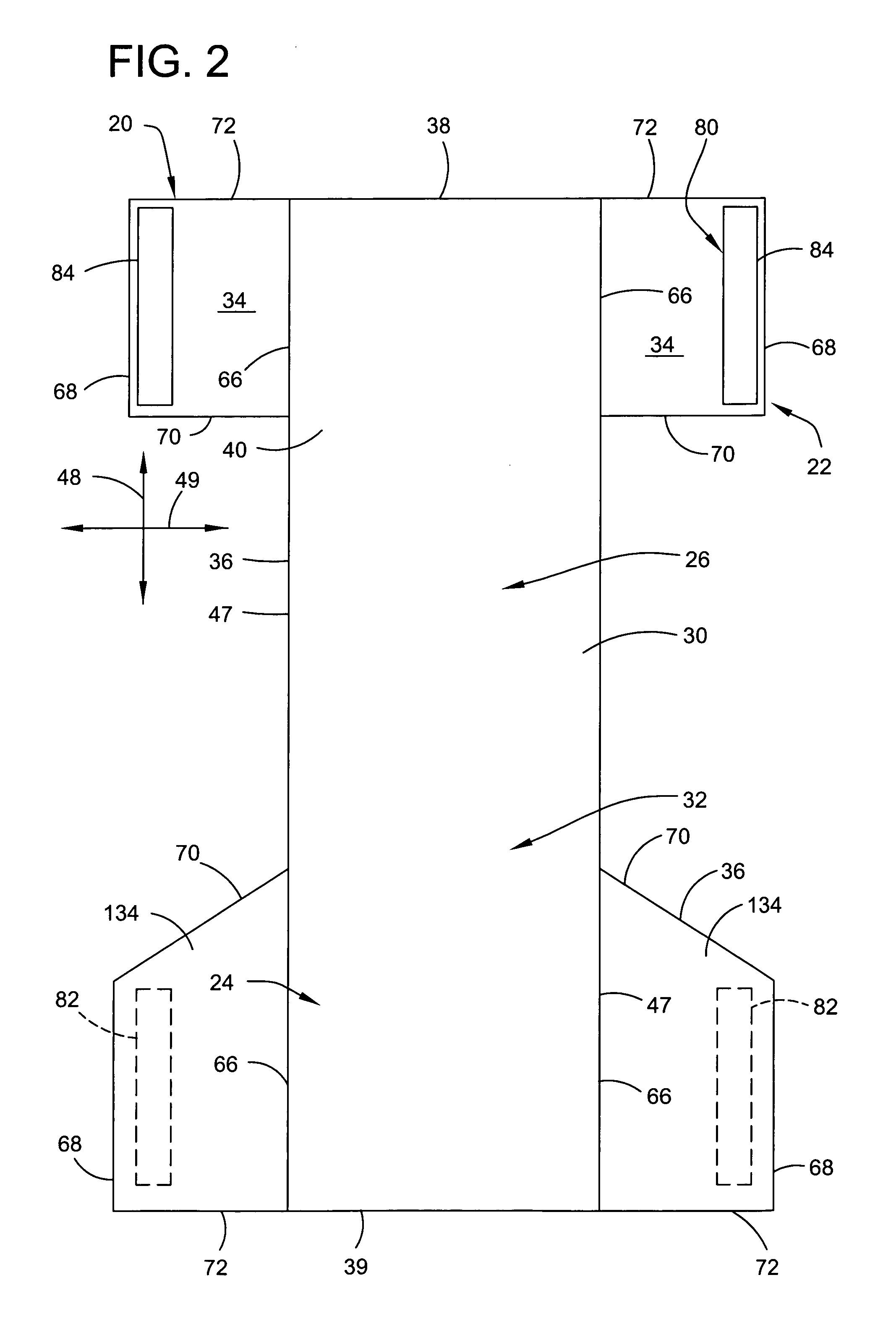

Absorbent article having an absorbent structure secured to a stretchable component of the article

Owner:KIMBERLY-CLARK WORLDWIDE INC

Current constricting phase change memory element structure

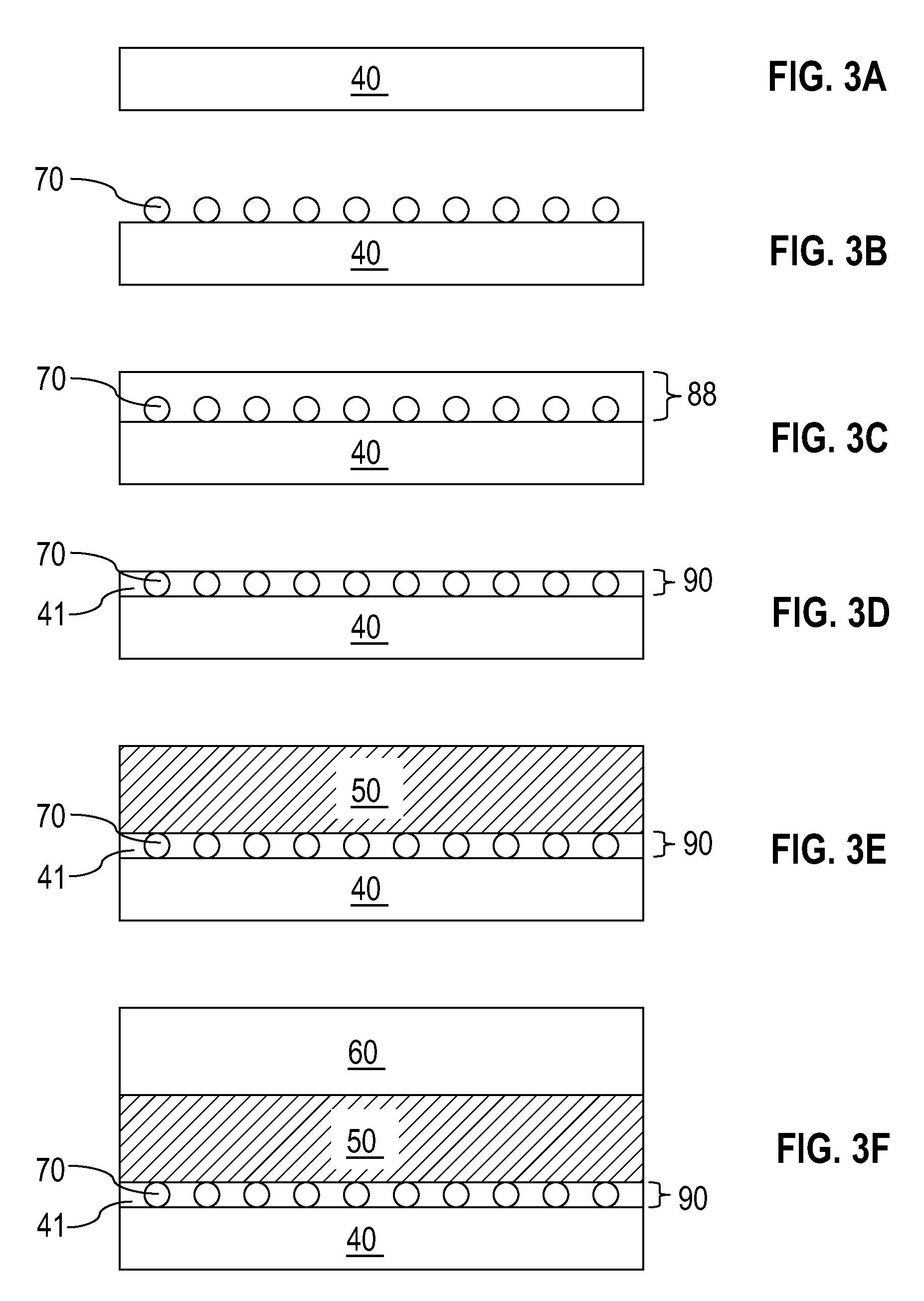

InactiveUS20090014704A1Small sizeHigh local temperatureNanoinformaticsBulk negative resistance effect devicesPhase-change memoryCurrent limiting

A layer of nanopaiticles having a dimension on the order of 10 nm is employed to form a current constricting layer or as a hardmask for forming a current constricting layer from an underlying insulator layer. The nanoparticles are preferably self-aligning and / or self-planarizing on the underlying surface. The current constricting layer may be formed within a bottom conductive plate, within a phase change material layer, within a top conductive plate, or within a tapered liner between a tapered via sidewall and a via plug contains either a phase change material or a top conductive material. The current density of the local structure around the current constricting layer is higher than the surrounding area, thus allowing local temperature to rise higher than surrounding material. The total current required to program the phase change memory device, and consequently the size of a programming transistor, is reduced due to the current constricting layer.

Owner:MACRONIX INT CO LTD +2

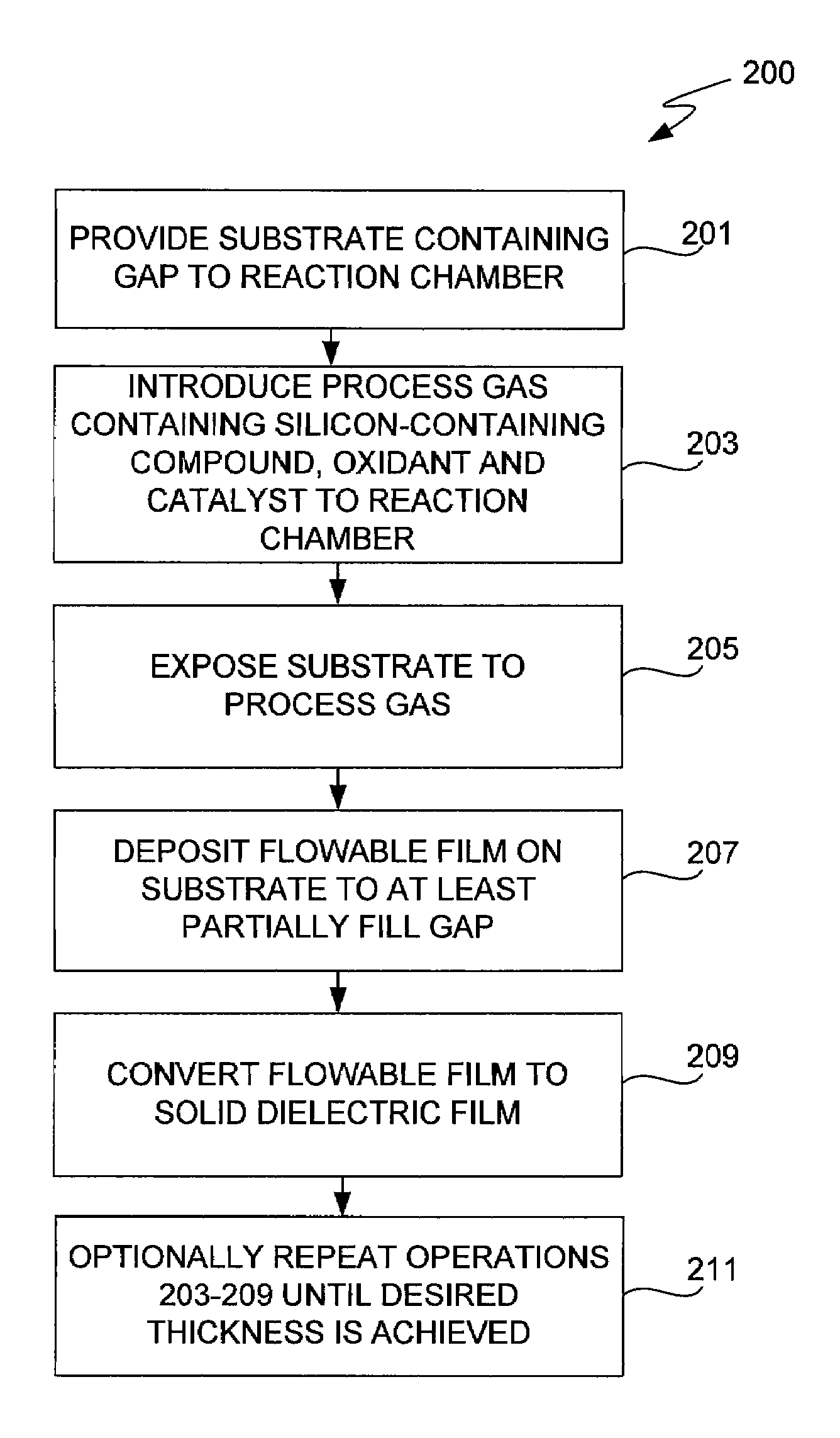

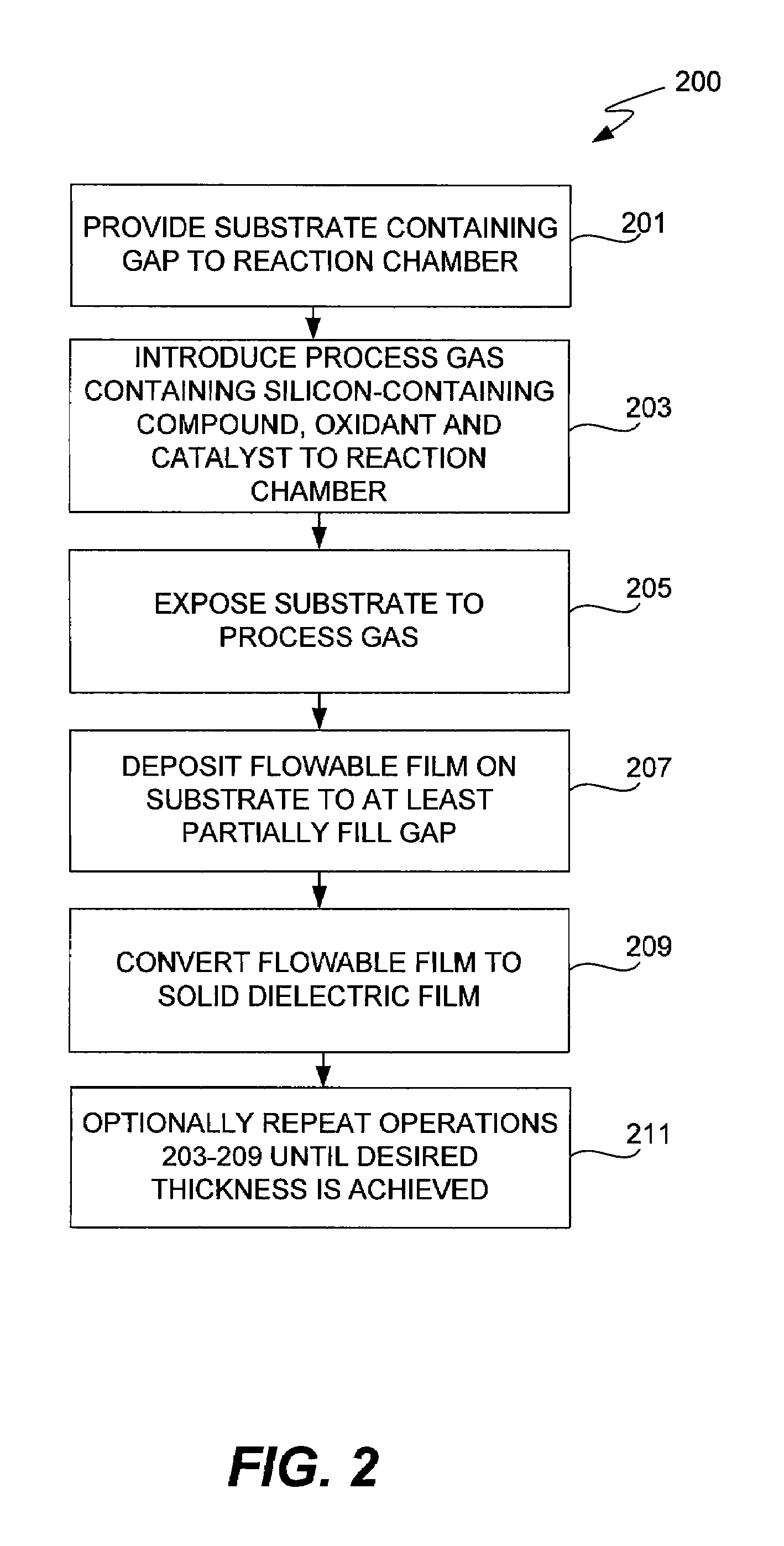

CVD flowable gap fill

Methods of lining and / or filling gaps on a substrate by creating flowable silicon oxide-containing films are provided. The methods involve introducing vapor-phase silicon-containing precursor and oxidant reactants into a reaction chamber containing the substrate under conditions such that a condensed flowable film is formed on the substrate. The flowable film at least partially fills gaps on the substrates and is then converted into a silicon oxide film. In certain embodiments, the methods involve using a catalyst, e.g., a nucleophile or onium catalyst, in the formation of the film. The catalyst may be incorporated into one of the reactants and / or introduced as a separate reactant. Also provided are methods of converting the flowable film to a solid dielectric film. The methods of this invention may be used to line or fill high aspect ratio gaps, including gaps having aspect ratios ranging from 3:1 to 10:1.

Owner:NOVELLUS SYSTEMS

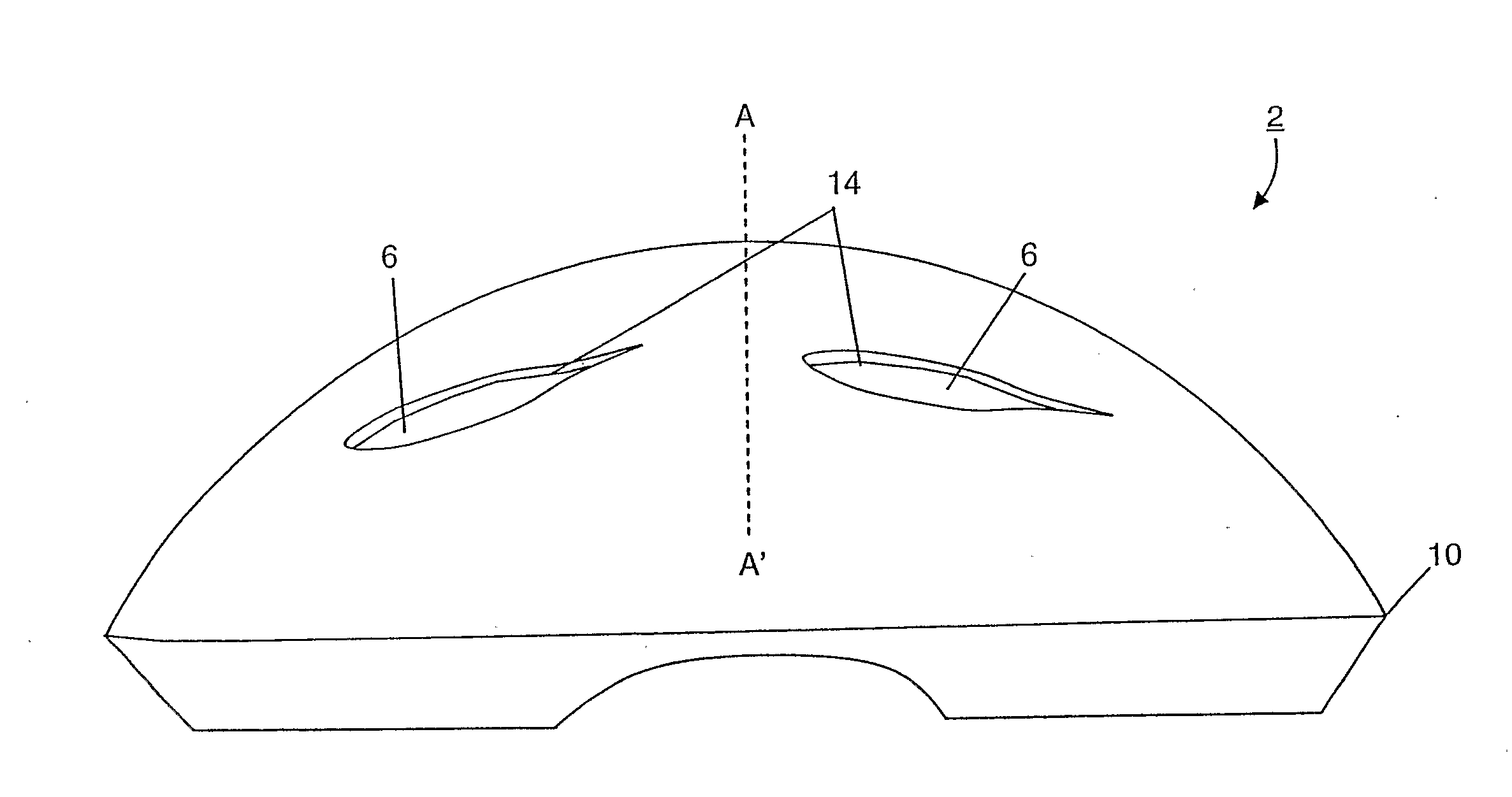

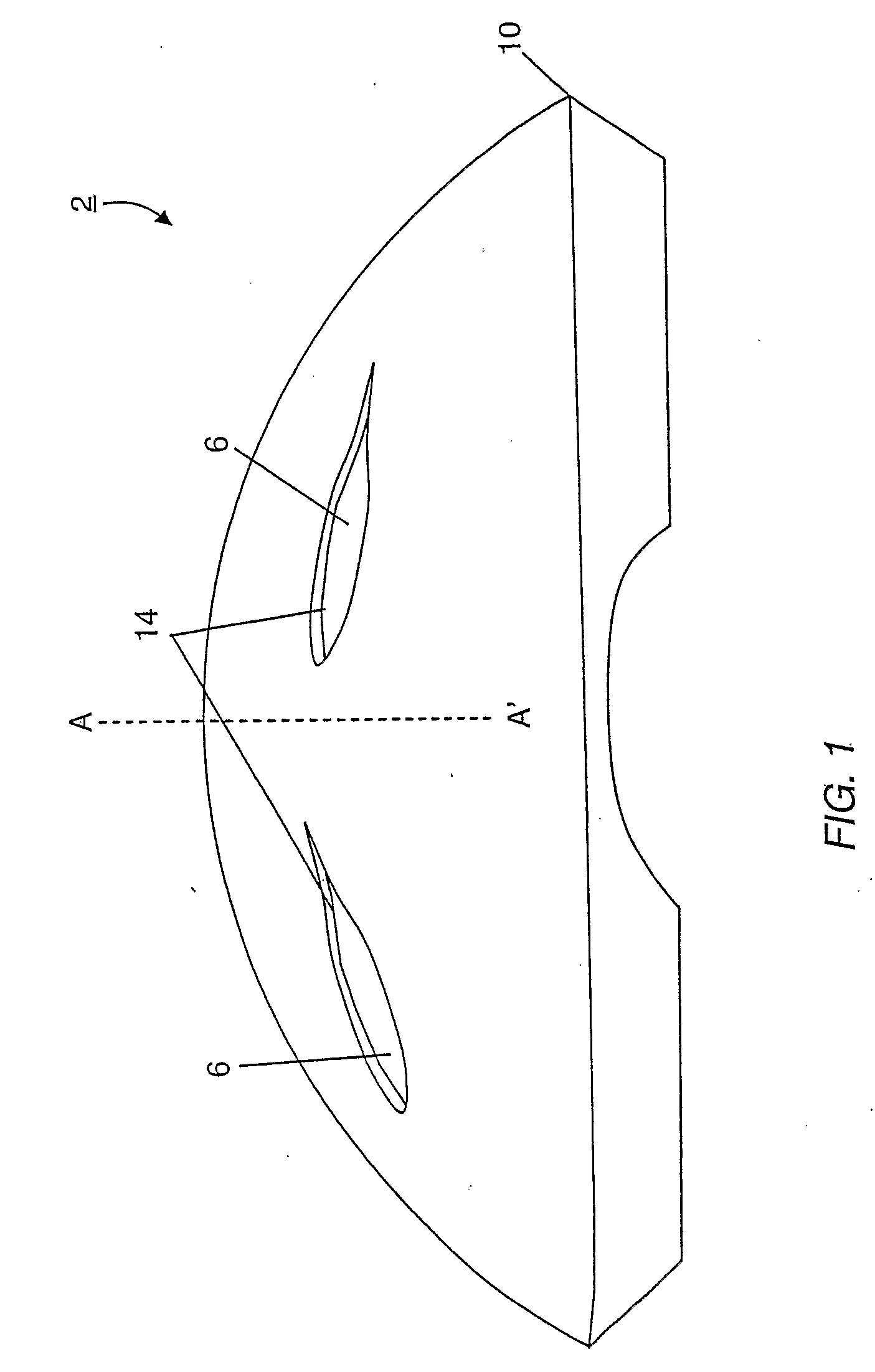

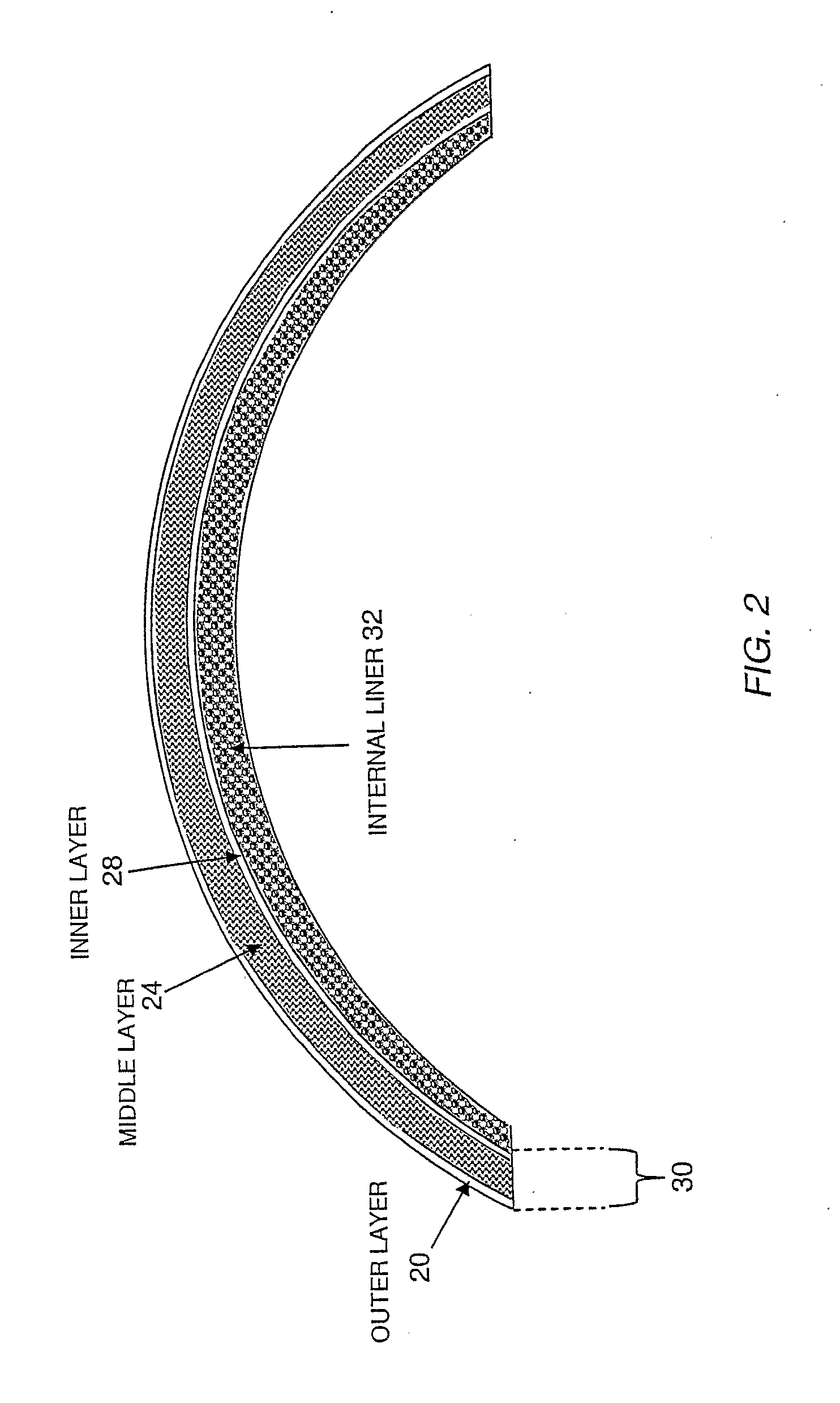

Energy-Absorbing Liners and Shape Conforming Layers for Use with Pro-Tective Headgear

InactiveUS20080155735A1Weight increaseEnhance user fit and comfortBiocideAnimal repellantsProtective headgearEnergy absorption

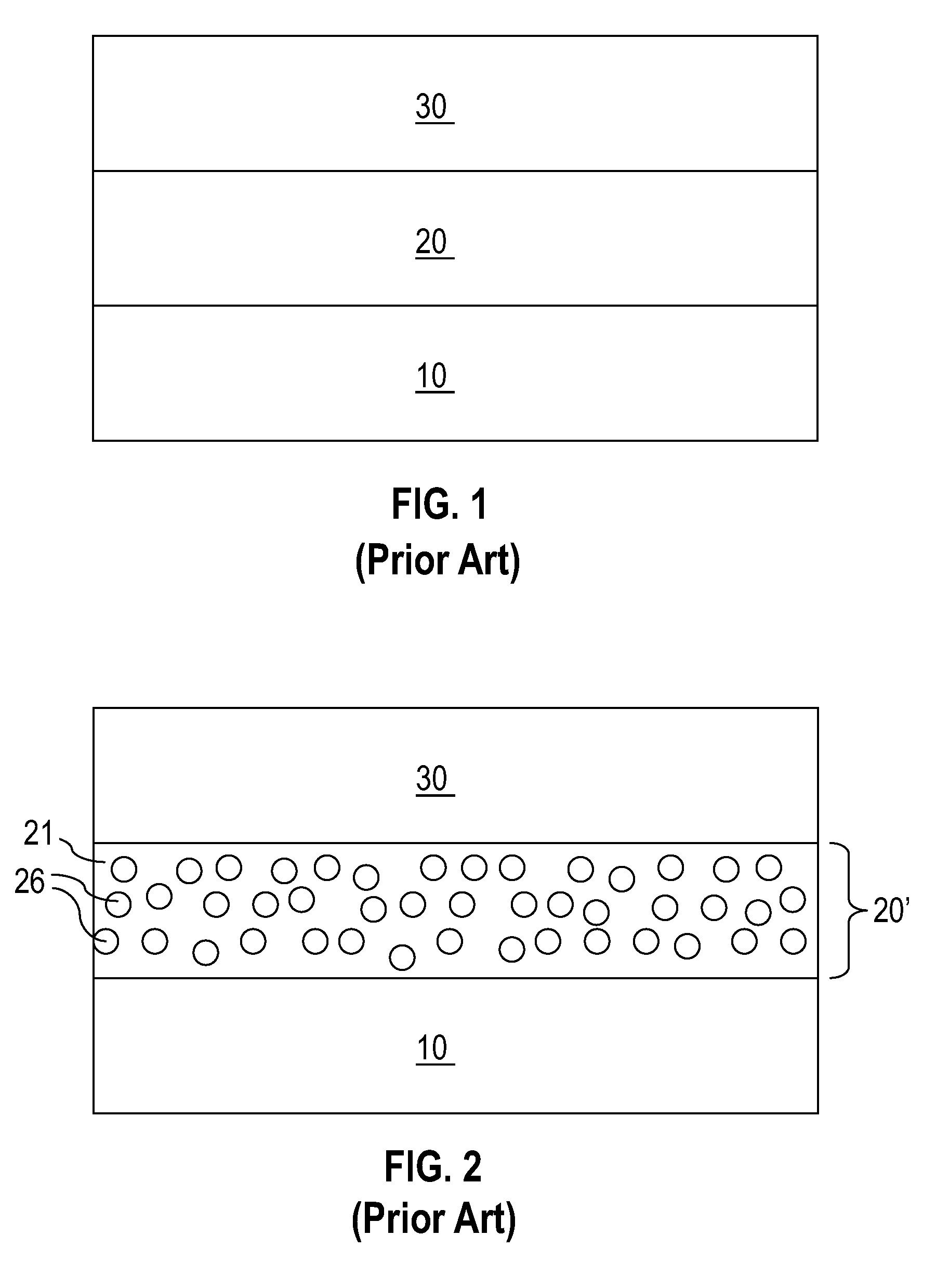

A multilayer shell for use in the construction of protective headgear, the shell including an outer layer, an inner layer, a middle layer disposed between the outer and inner layer which resiliently compresses in response to an impact to the outer layer, and an internal liner disposed inwardly of the inner layer. The middle layer includes a plurality of compressible members, which resiliently compress to absorb the energy of a direct impact to the outer layer and resiliently shear with respect to the inner layer in response to a tangential impact to the outer layer. The inner layer includes an open configuration, which reduces the weight of the shell, provides for greater heat ventilation from the head of the user, and permits for visualization of the compressible elements. The internal liner is formed from contourable materials which enhance user fit and comfort and reduce the weight of the protective headgear without compromising user safety.

Owner:XENITH

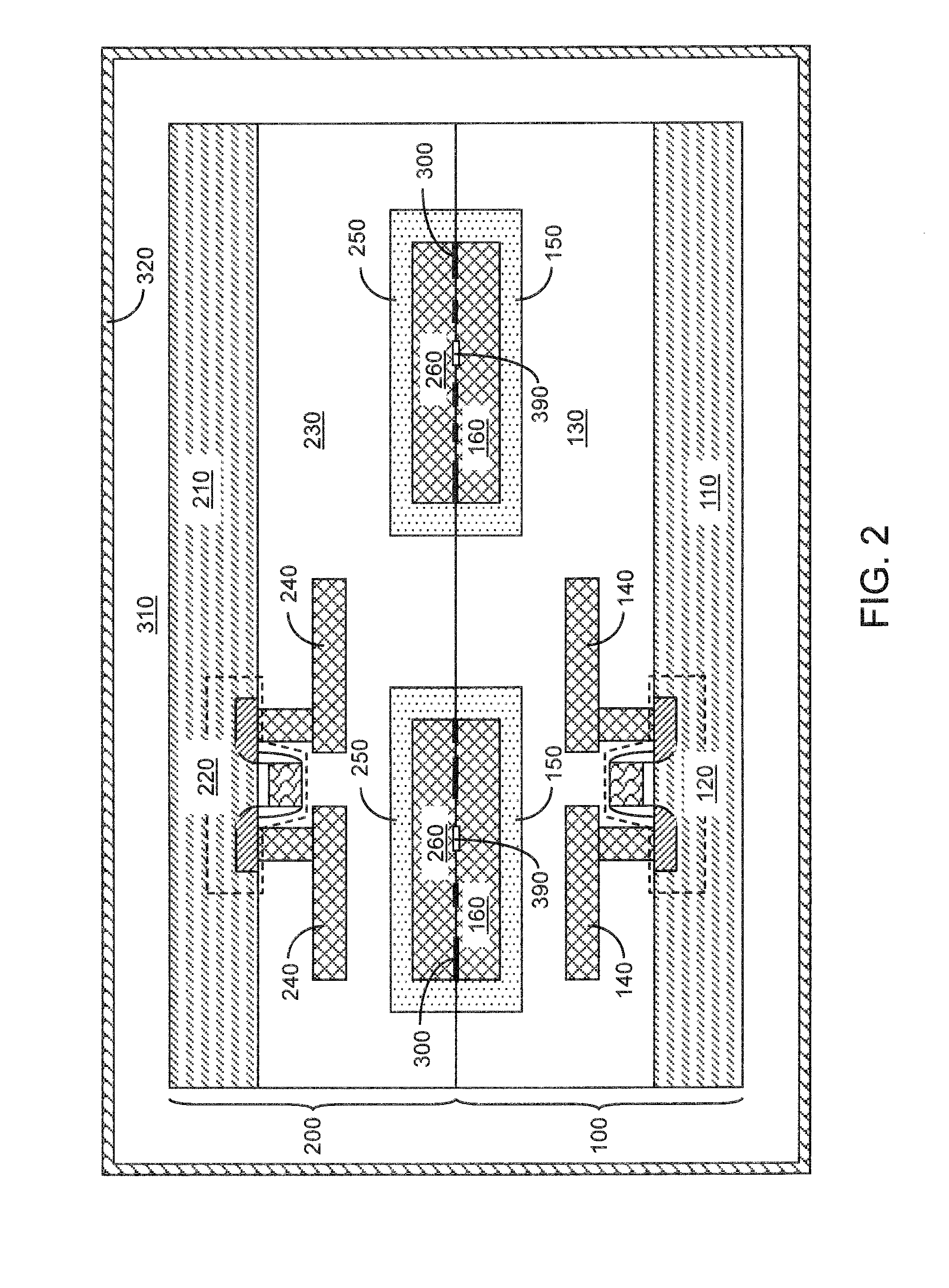

Stacked Integrated Chips and Methods of Fabrication Thereof

ActiveUS20100178761A1Easy to useSemiconductor/solid-state device detailsSolid-state devicesResistFilling materials

Structure and methods of forming stacked semiconductor chips are described. In one embodiment, a method of forming a semiconductor chip includes forming an opening for a through substrate via from a top surface of a first substrate. The sidewalls of the opening are lined with an insulating liner and the opened filled with a conductive fill material. The first substrate is etched from an opposite bottom surface to form a protrusion, the protrusion being covered with the insulating liner. A resist layer is deposited around the protrusion to expose a portion of the insulating liner. The exposed insulating liner is etched to form a sidewall spacer along the protrusion.

Owner:TAIWAN SEMICON MFG CO LTD

Breathable low-emissivity metalized sheets

A moisture vapor permeable metalized composite sheet is formed by coating a moisture vapor permeable sheet-with at least one metal layer and at least one outer organic coating layer. The moisture vapor permeability of the composite sheet is at least about 80% of the moisture vapor permeability of the starting sheet. The composite sheet provides a barrier to air and liquid water infiltration while having high moisture vapor permeability and good thermal barrier properties. The composite sheet material is suitable for use as a building construction wrap such as roof lining and house wrap.

Owner:EI DU PONT DE NEMOURS & CO

Selective capping of copper wiring

InactiveUS7008871B2Semiconductor/solid-state device detailsSolid-state devicesCopper-wiringElectroplating

Patterned copper structures are fabricated by selectively capping the copper employing selective etching and / or selective electroplating in the presence of a liner material. Apparatus for addressing the problem of an increased resistive path as electrolyte during electroetching and / or electroplating flows from the wafer edge inwards is provided.

Owner:TWITTER INC

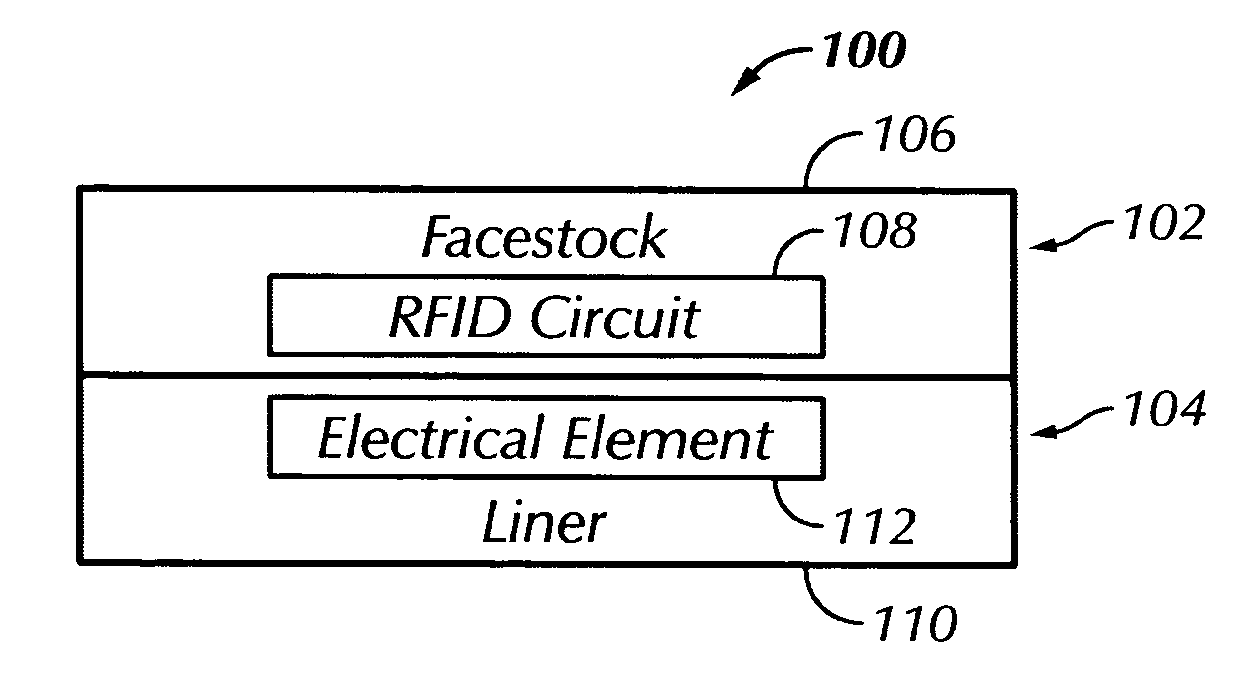

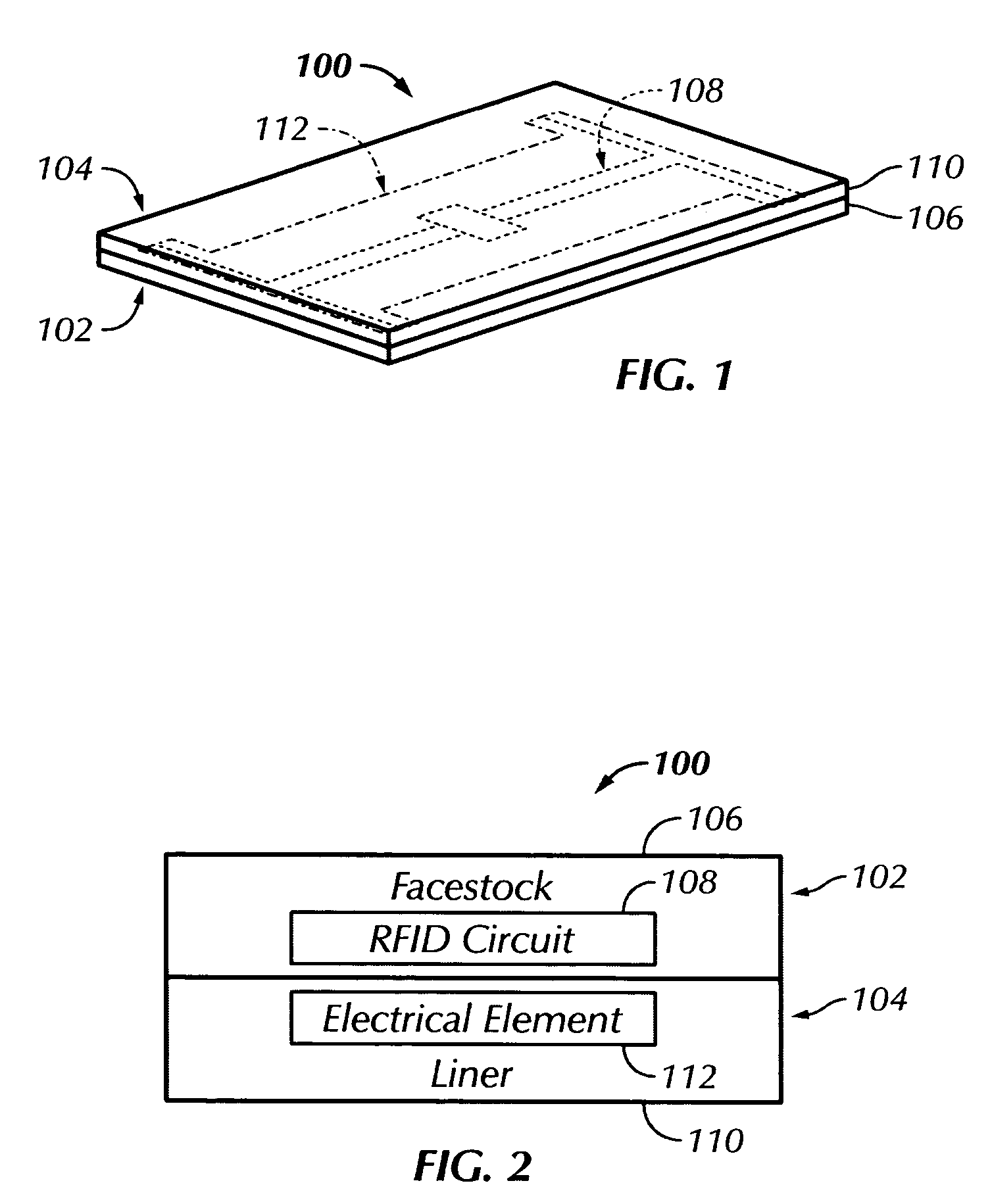

RFID tags with modifiable operating parameters

ActiveUS7170415B2Co-operative working arrangementsPrinted circuit manufactureEngineeringRadio frequency

Owner:AVERY DENNISON CORP

Polymer lined sealing member for a container

InactiveUS6866926B1High strengthIncreased durabilitySynthetic resin layered productsThin material handlingEngineeringBottle

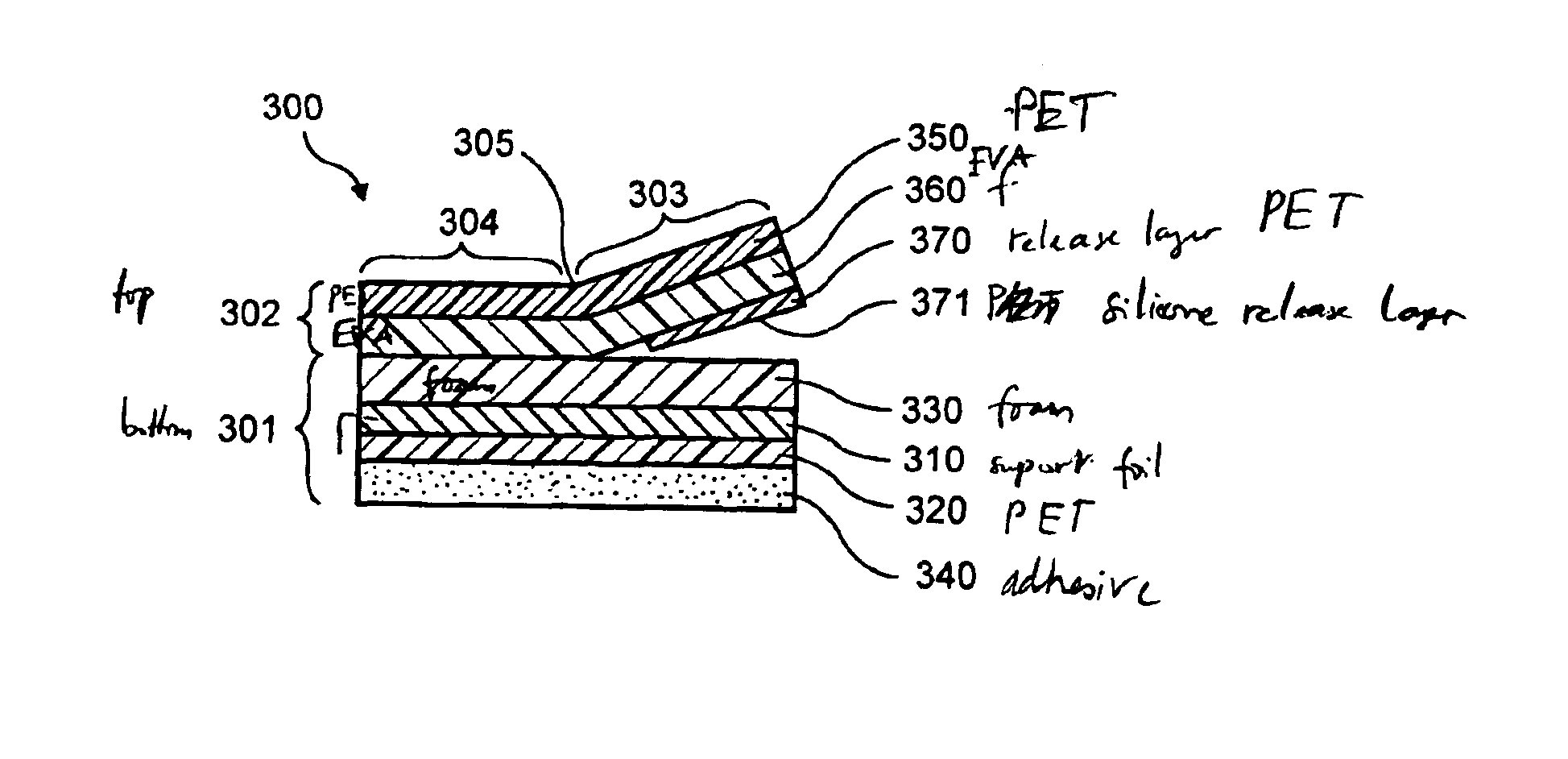

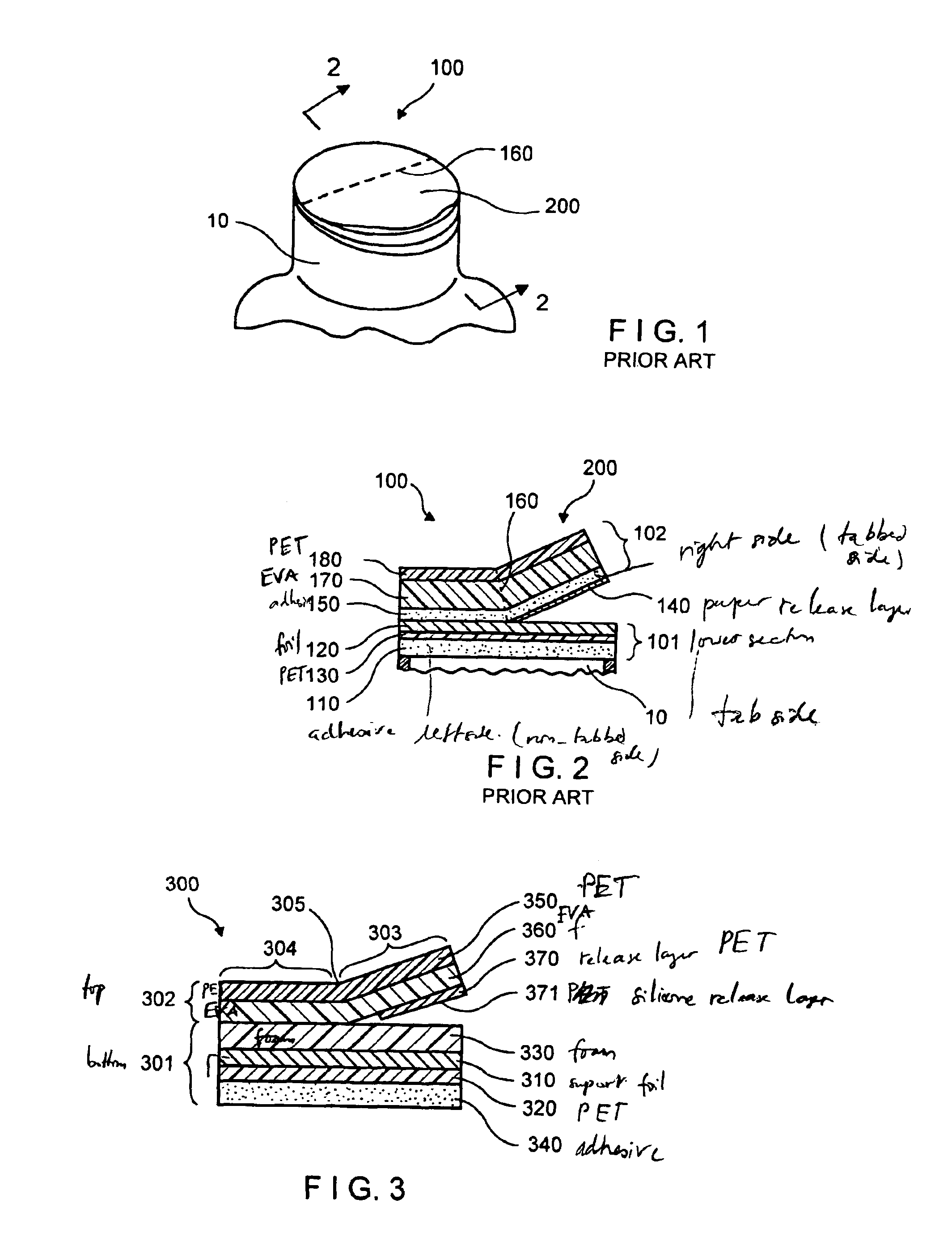

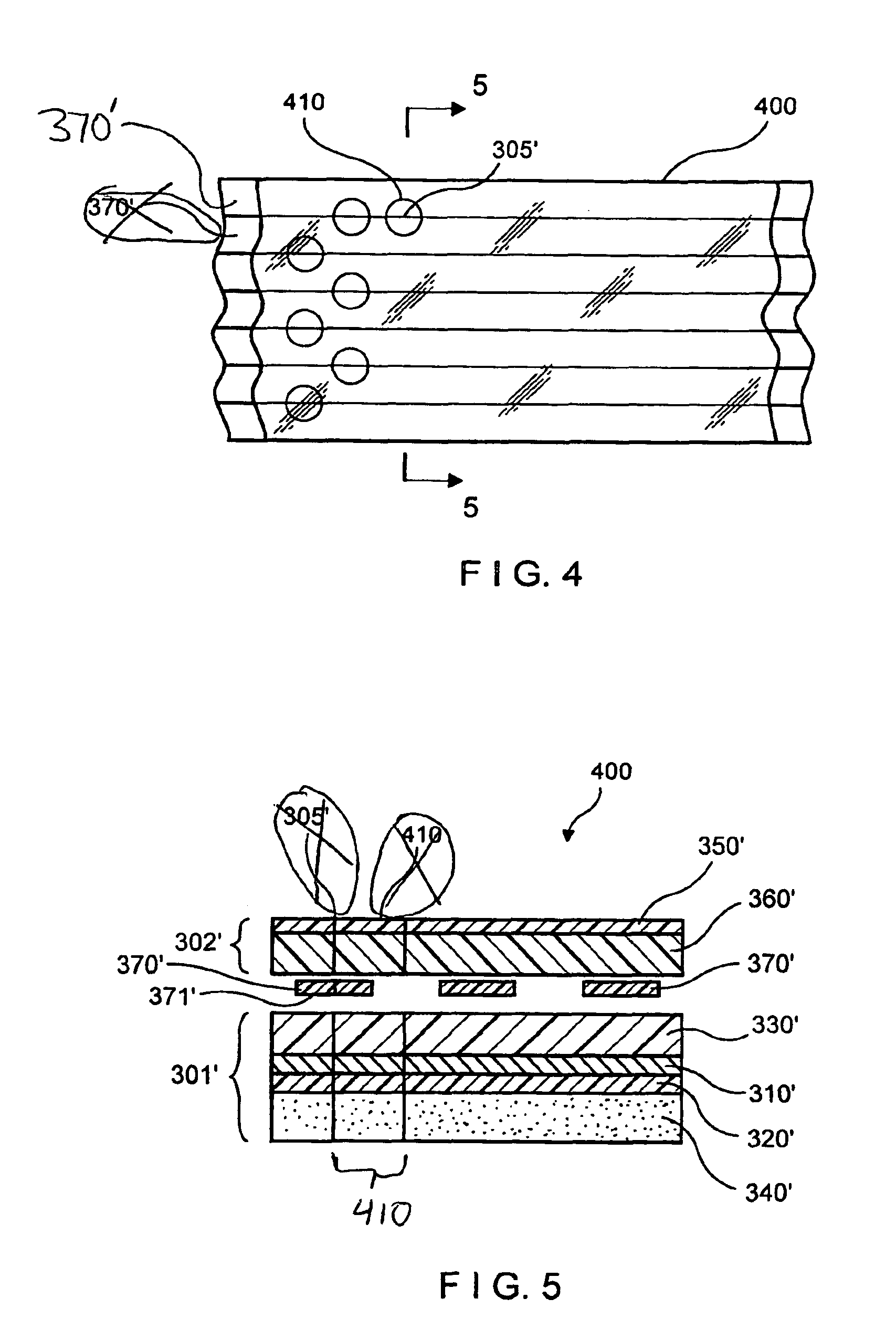

A seal and method of manufacture is provided for sealing containers such as bottles, jars and the like. The seal (closure) can be formed with a lower sheetlike structure having a foam layer thereon. The lower structure can include foil and have a polymer layer, such as a PET layer thereunder A sealant layer can be provided under the bottom surface of the PET layer to bond the seal to a container opening. The polymer foam is advantageously polyethylene foam. Seals in accordance with preferred embodiments of the invention also include a top portion, which can be only partially bonded (directly or indirectly) to the bottom portion, so as to leave a tab portion extended therefrom. The top portion is advantageously bonded from periphery to periphery of the bottom portion and at or slightly offset from the diameter (middle) of the bottom portion. The top portion is advantageously formed with polymer material, such as an ethylene vinyl acetate (EVA) layer, having a layer of PET bonded on the top thereof. A release strip, which can have a release layer coated on the bottom thereof can be adhered to the top or bottom structures and used to prevent the tab from adhering to the lower structure.

Owner:SELIG SEALING PROD INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com