Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2998 results about "Thermal oxidation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In microfabrication, thermal oxidation is a way to produce a thin layer of oxide (usually silicon dioxide) on the surface of a wafer. The technique forces an oxidizing agent to diffuse into the wafer at high temperature and react with it. The rate of oxide growth is often predicted by the Deal–Grove model. Thermal oxidation may be applied to different materials, but most commonly involves the oxidation of silicon substrates to produce silicon dioxide.

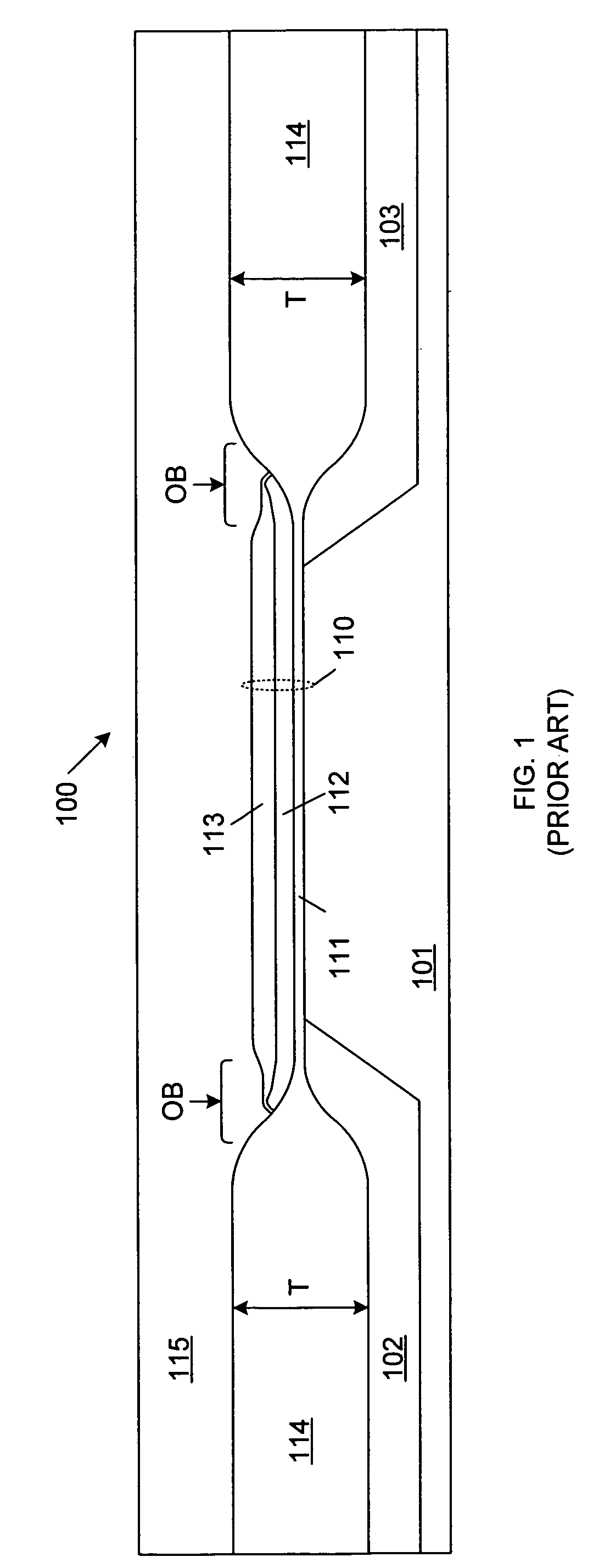

Method of manufacturing a semiconductor device

InactiveUS7199024B2Relaxation stressGuaranteed uptimeTransistorSolid-state devicesSmart CutSemiconductor

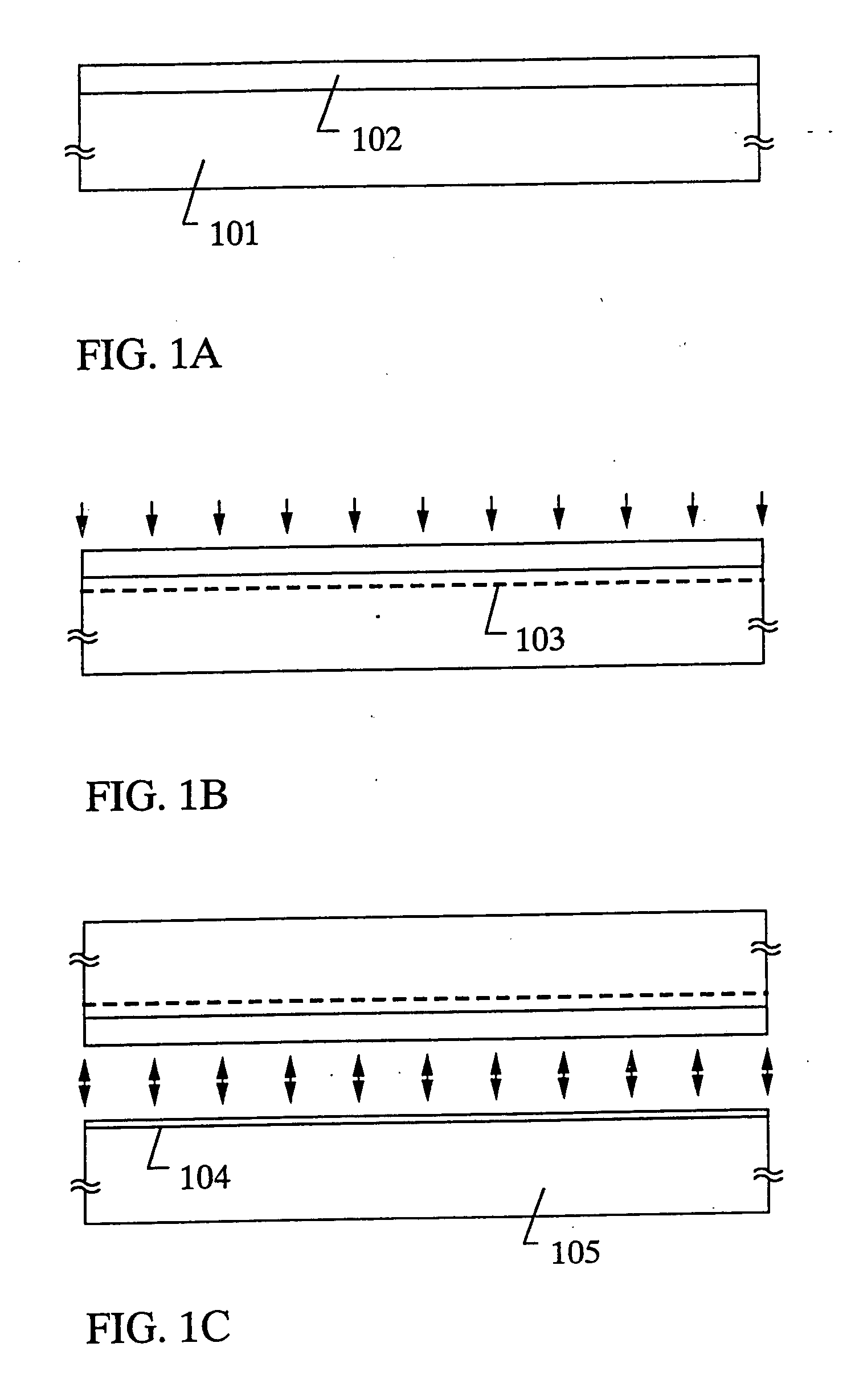

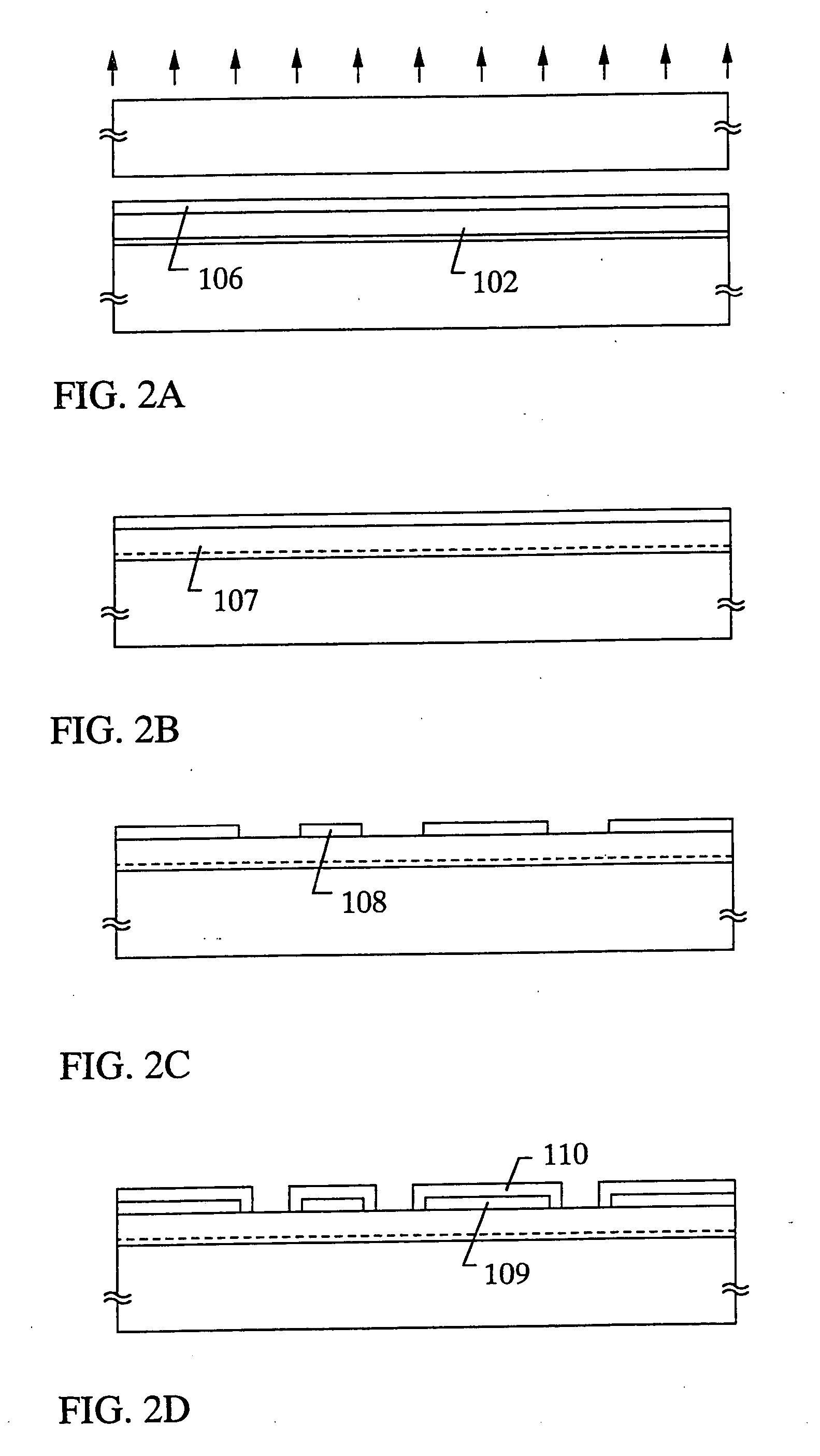

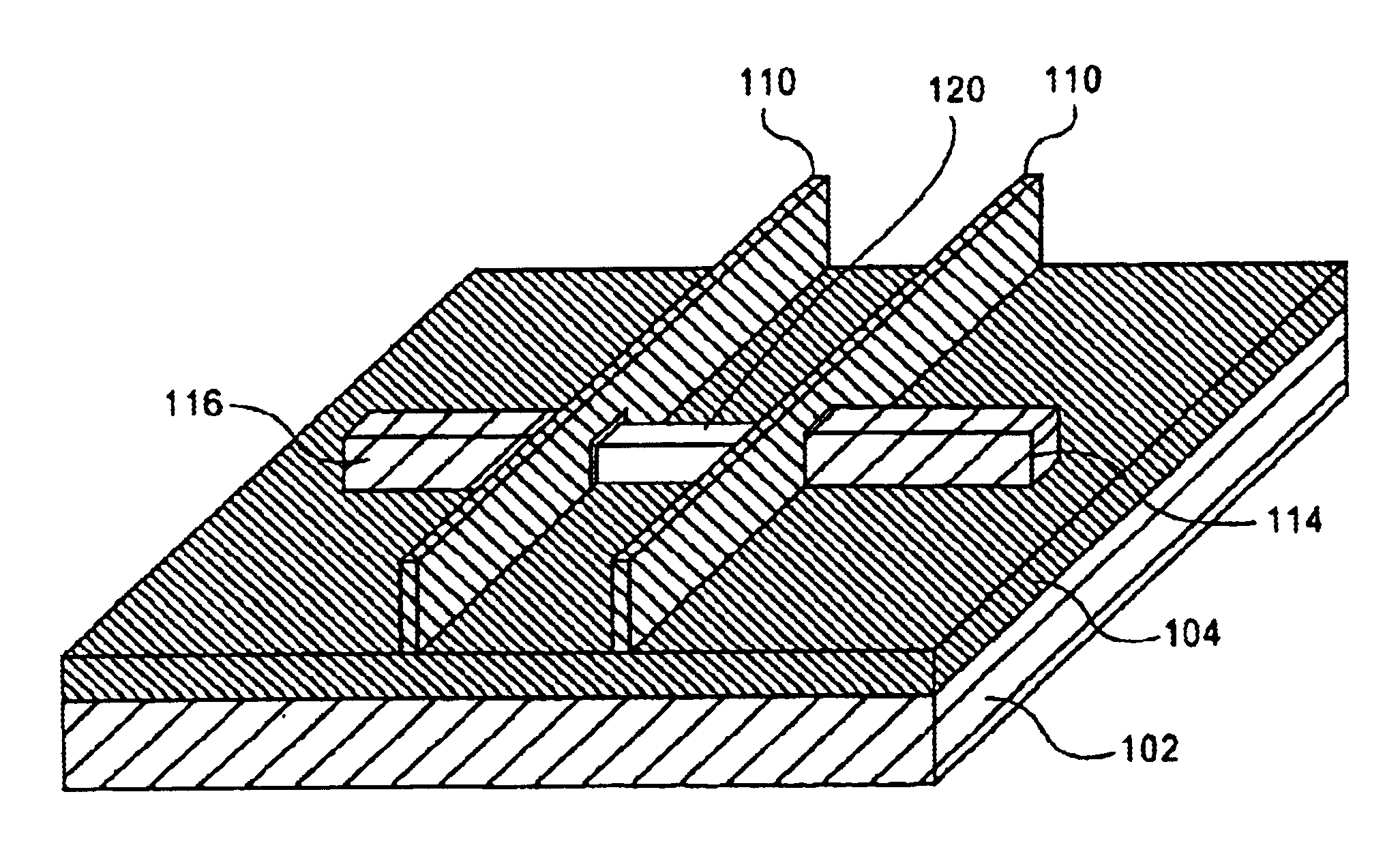

There is provided a method of removing trap levels and defects, which are caused by stress, from a single crystal silicon thin film formed by an SOI technique. First, a single crystal silicon film is formed by using a typical bonding SOI technique such as Smart-Cut or ELTRAN. Next, the single crystal silicon thin film is patterned to form an island-like silicon layer, and then, a thermal oxidation treatment is carried out in an oxidizing atmosphere containing a halogen element, so that an island-like silicon layer in which the trap levels and the defects are removed is obtained.

Owner:SEMICON ENERGY LAB CO LTD

Method of manufacturing a semiconductor device

InactiveUS20070173000A1Improve business performanceImprove performanceTransistorSolid-state devicesDevice materialSmart Cut

There is provided a method of removing trap levels and defects, which are caused by stress, from a single crystal silicon thin film formed by an SOI technique. First, a single crystal silicon film is formed by using a typical bonding SOI technique such as Smart-Cut or ELTRAN. Next, the single crystal silicon thin film is patterned to form an island-like silicon layer, and then, a thermal oxidation treatment is carried out in an oxidizing atmosphere containing a halogen element, so that an island-like silicon layer in which the trap levels and the defects are removed is obtained.

Owner:SEMICON ENERGY LAB CO LTD

Method of fabricating an ultra-narrow channel semiconductor device

A method of forming a nanowire is disclosed. A nanowire having a first dimension is deposited on a first dielectric layer that is formed on a substrate. A sacrificial gate stack having a sacrificial dielectric layer and a sacrificial gate electrode layer is deposited over a first region of the nanowire leaving exposed a second region and a third region of the nanowire. A first spacer is deposited on each side of the sacrificial gate stack. A second dielectric layer is deposited over the first dielectric layer to cover the second region and third region. The sacrificial gate stack is removed. The first region of the nanowire is thinned by at least one thermal oxidation process and oxide removal process to thin said first region from said first dimension to a second dimension.

Owner:TAHOE RES LTD

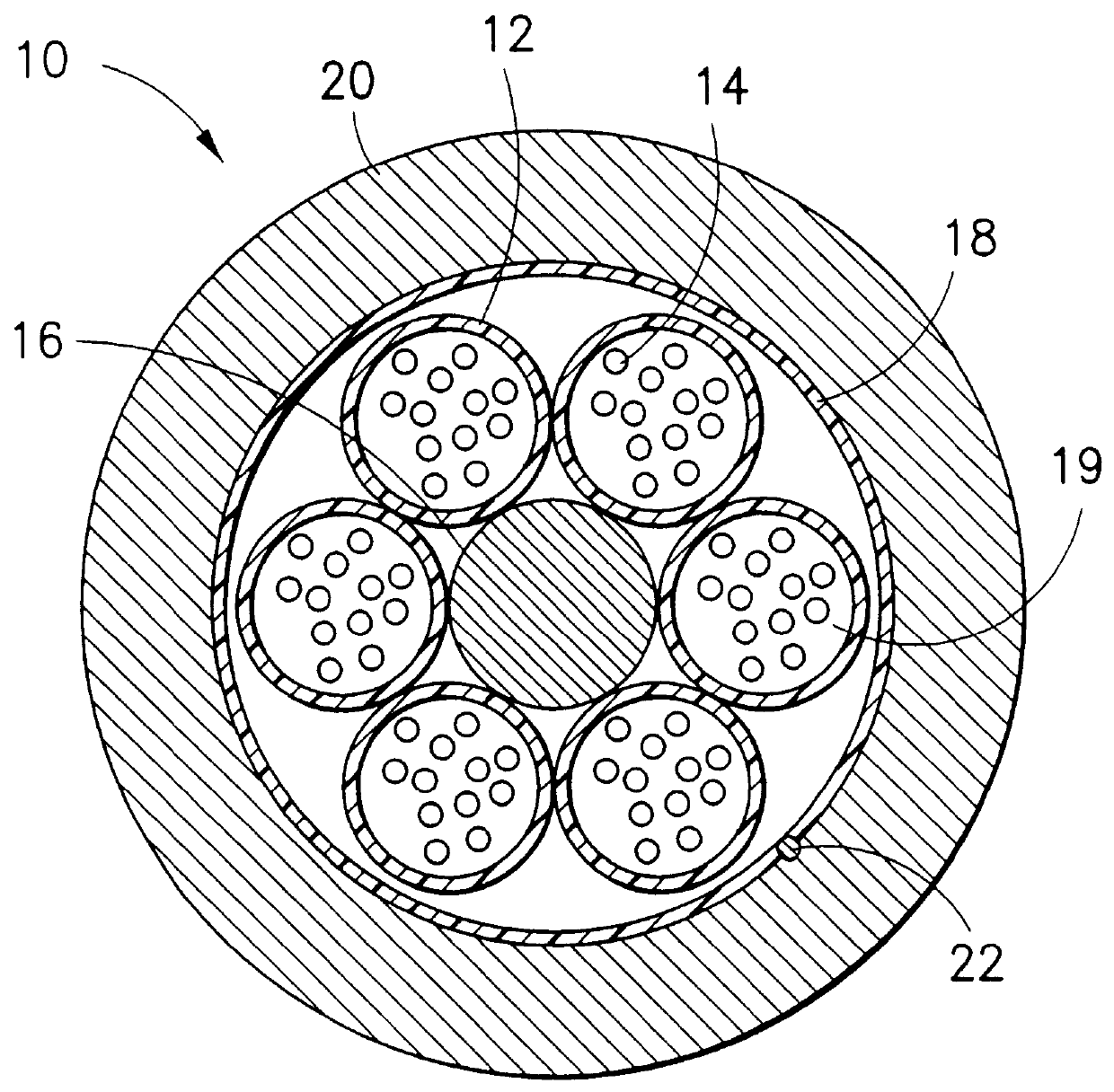

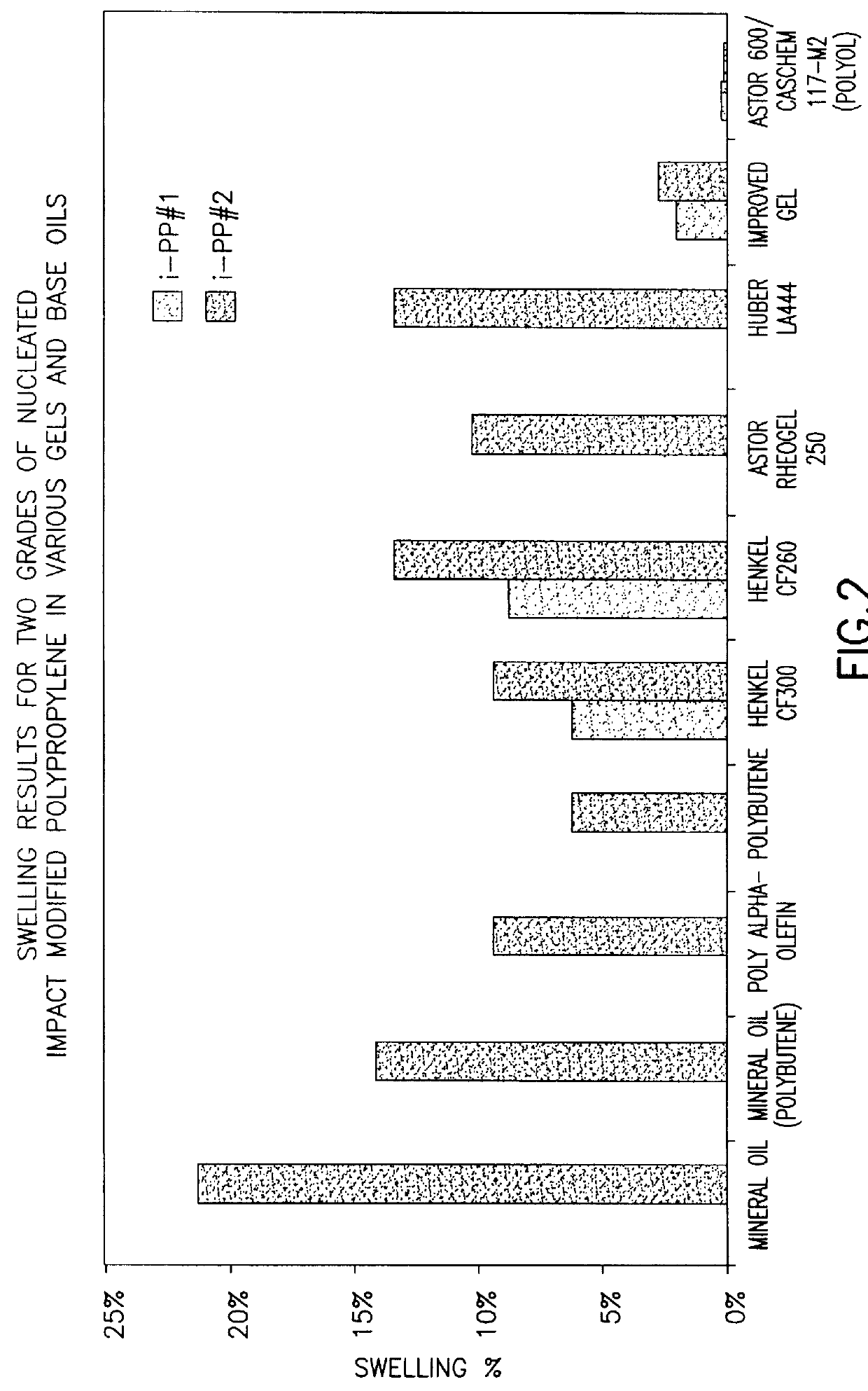

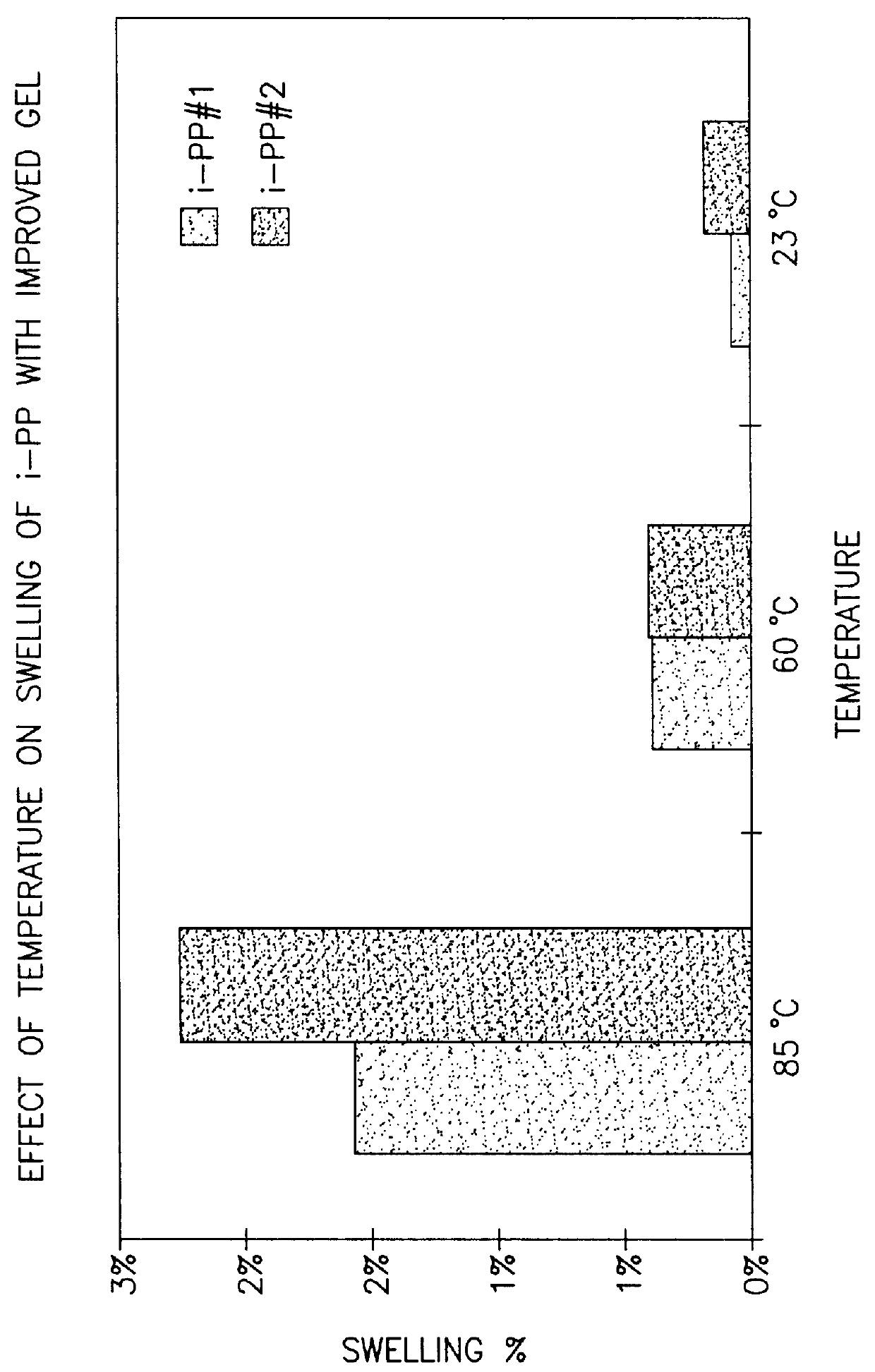

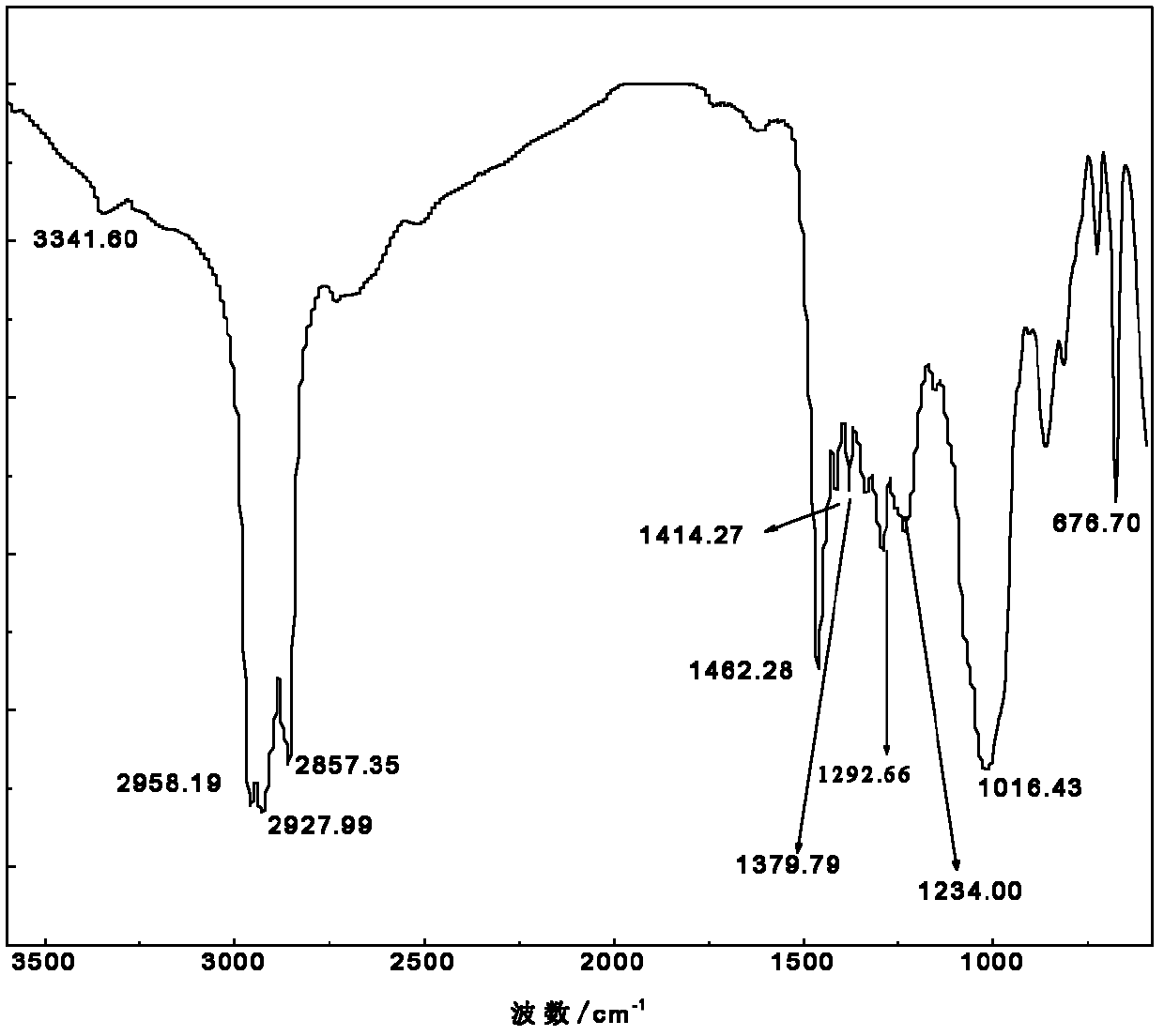

Water blocking gels compatible with polyolefin optical fiber cable buffer tubes and cables made therewith

A water blocking gel which is compatible with polyolefin optical fiber cable buffer tubes is disclosed. The water blocking gel comprises a polyolefin oil, wherein only a very small fraction of the polyolefin species have a molecular weight below about 2000. The gel also includes a thixotropic agent, and a thermal oxidation stabilizer. The gel is relatively low cost, does not cause substantially swelling of the polyolefin buffer tubes in contact therewith and does not degrade the buffer tube's physical properties.

Owner:ALCATEL LUCENT SAS

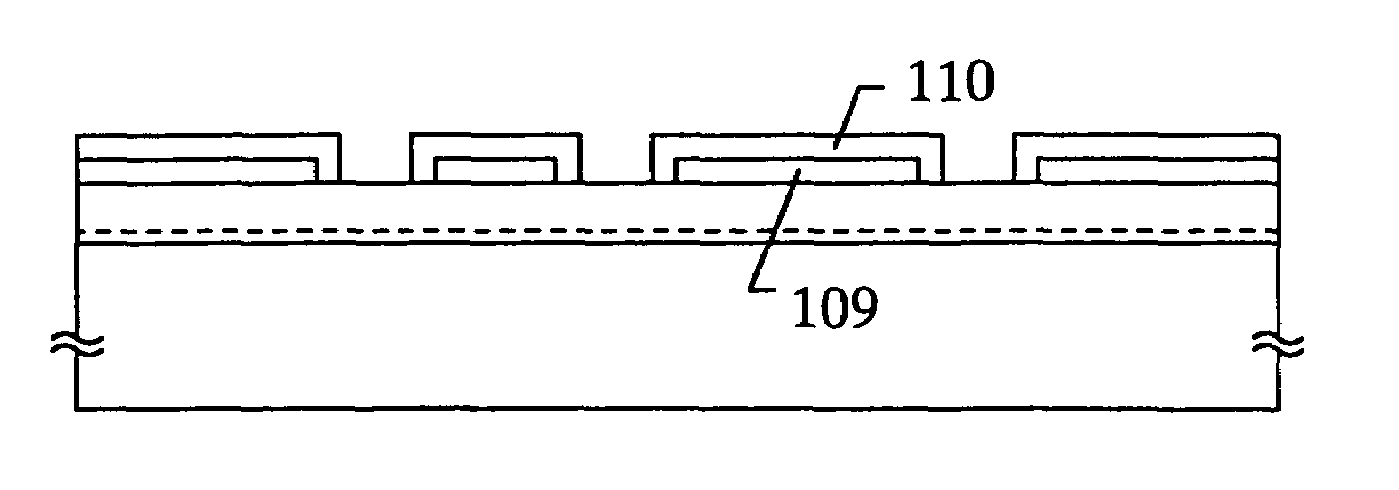

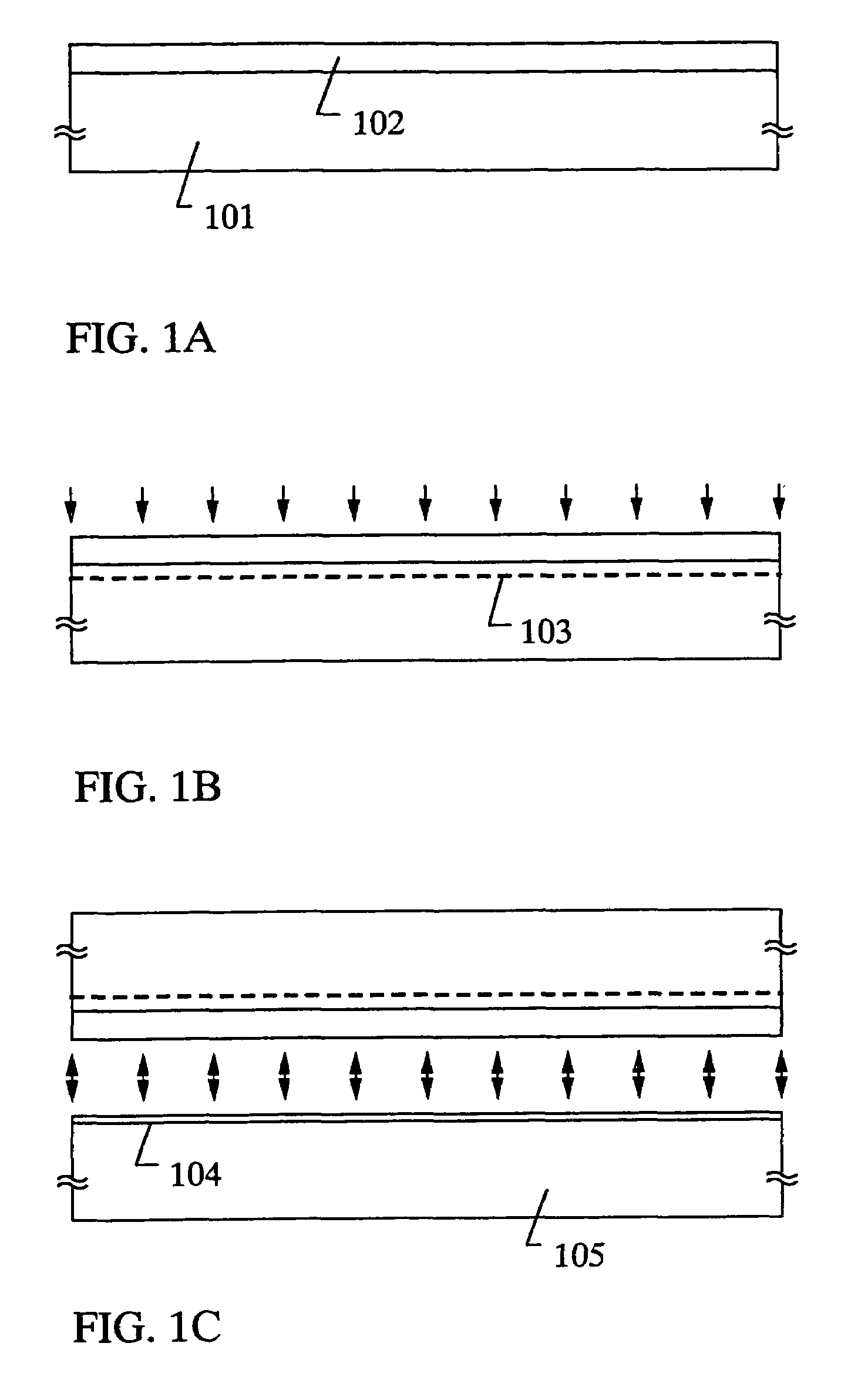

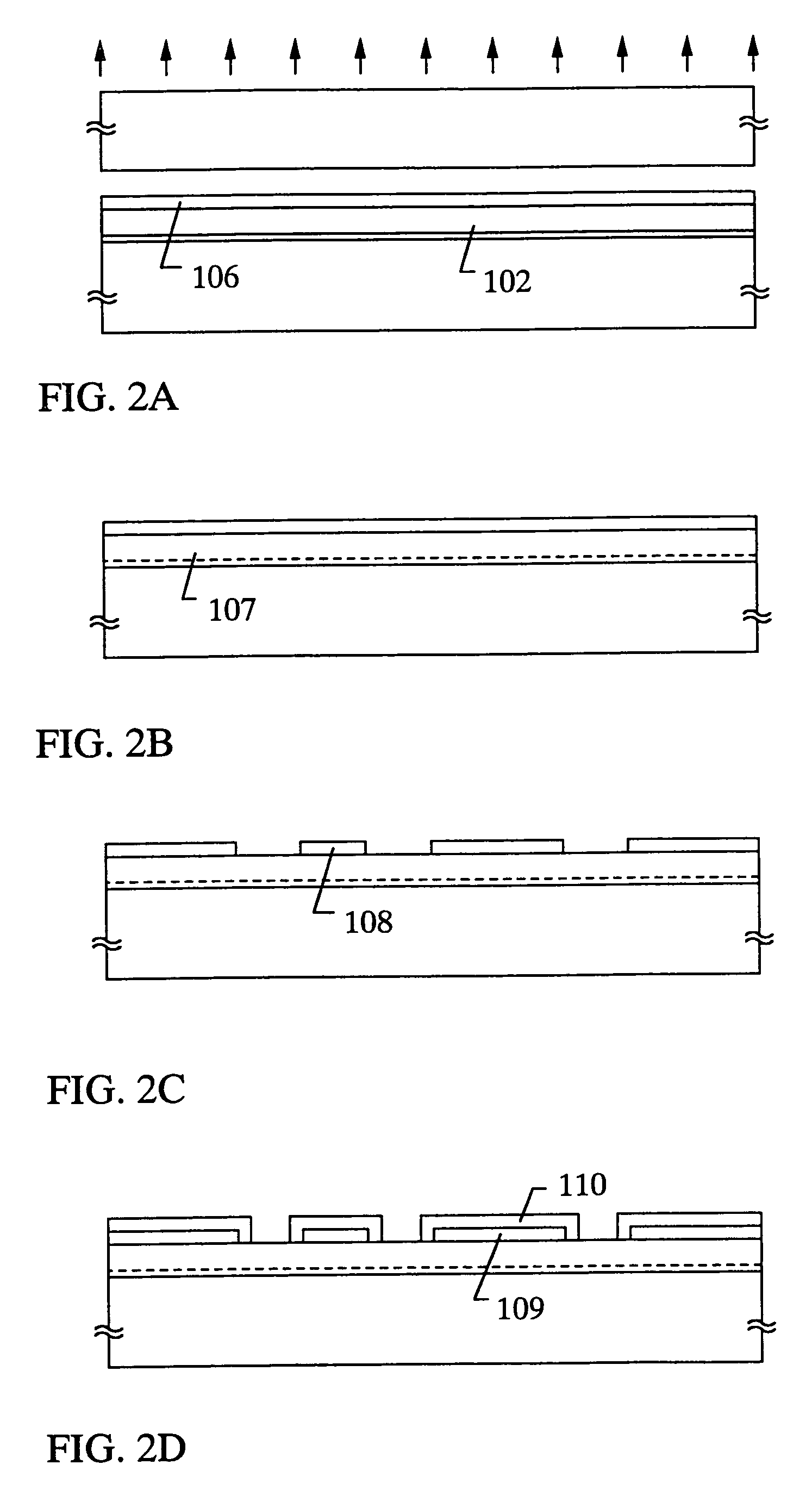

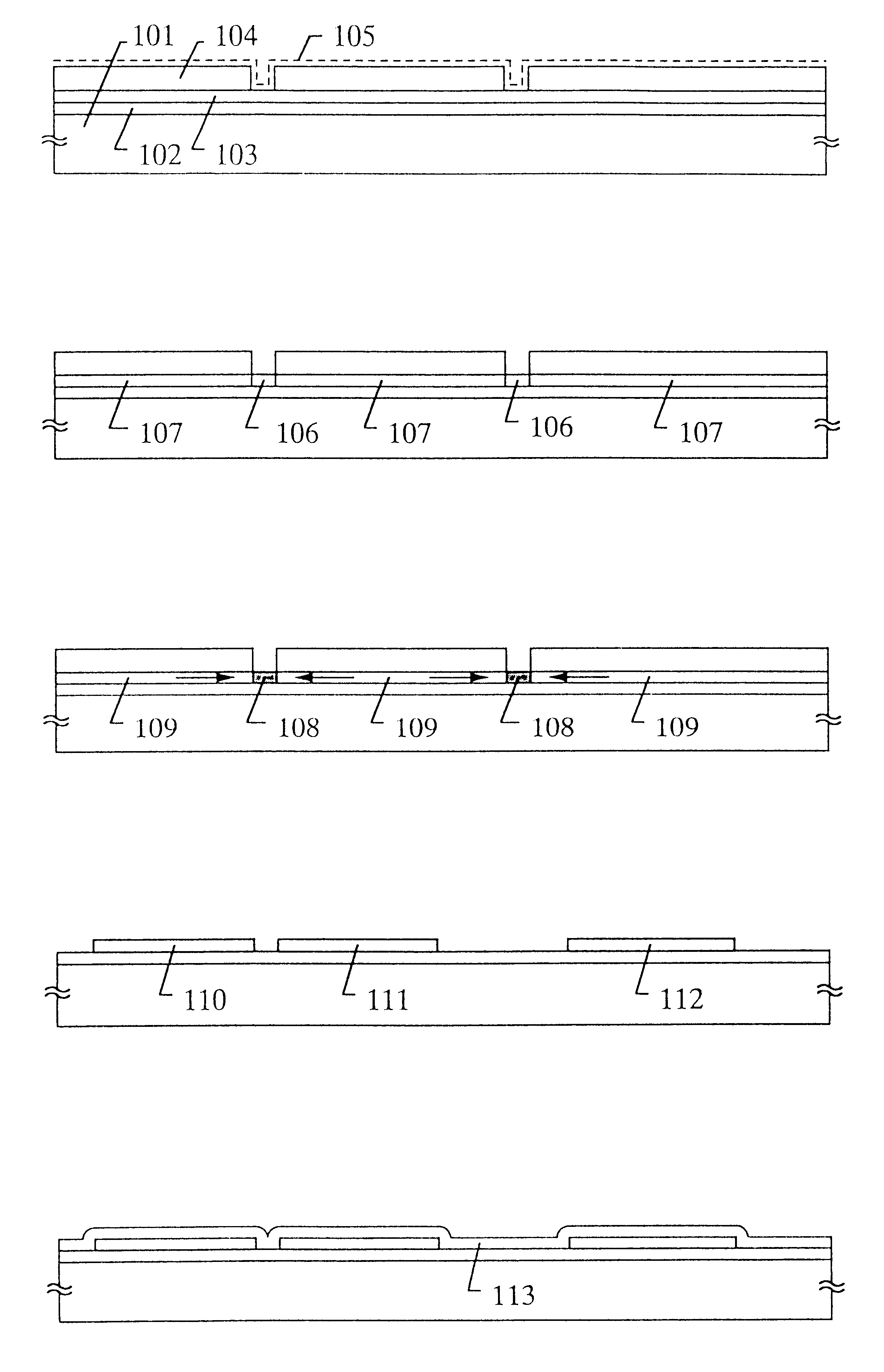

Introducing catalytic and gettering elements with a single mask when manufacturing a thin film semiconductor device

InactiveUS6348368B1TransistorSemiconductor/solid-state device manufacturingAbnormal growthsDevice material

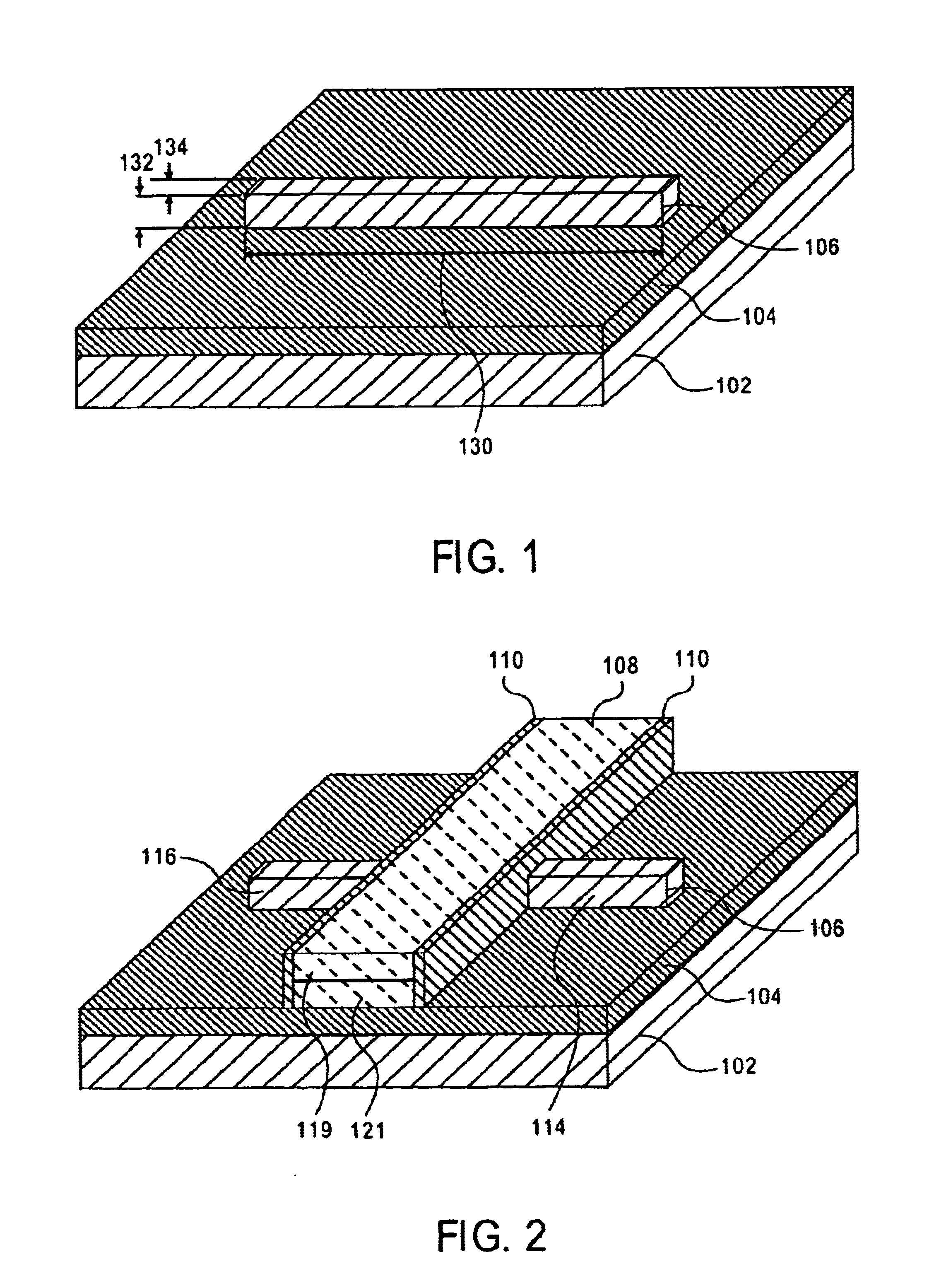

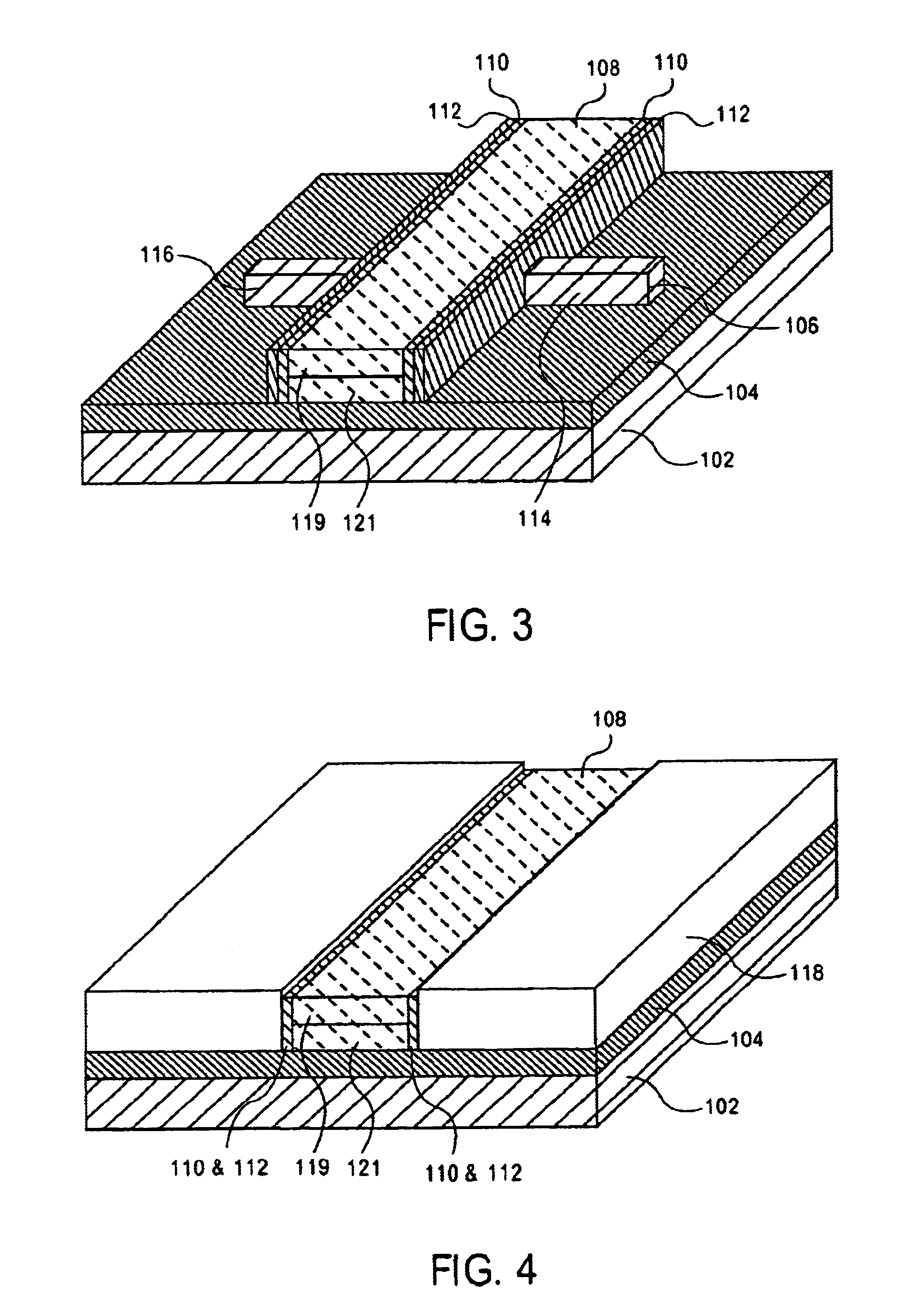

In a method of manufacturing a semiconductor device, after a lateral growth region 107 is formed by using a catalytic element 105 for facilitating crystallization of silicon, the catalytic element is gettered into a phosphorus added region 108 by a heat treatment. Thereafter, a gate insulating film 113 is formed to cover active layers 110 to 112 formed, and in this state, a thermal oxidation step is carried out. By this, the characteristics of an interface between the active layers and the gate insulating film can be improved while abnormal growth of a metal oxide is prevented.

Owner:SEMICON ENERGY LAB CO LTD

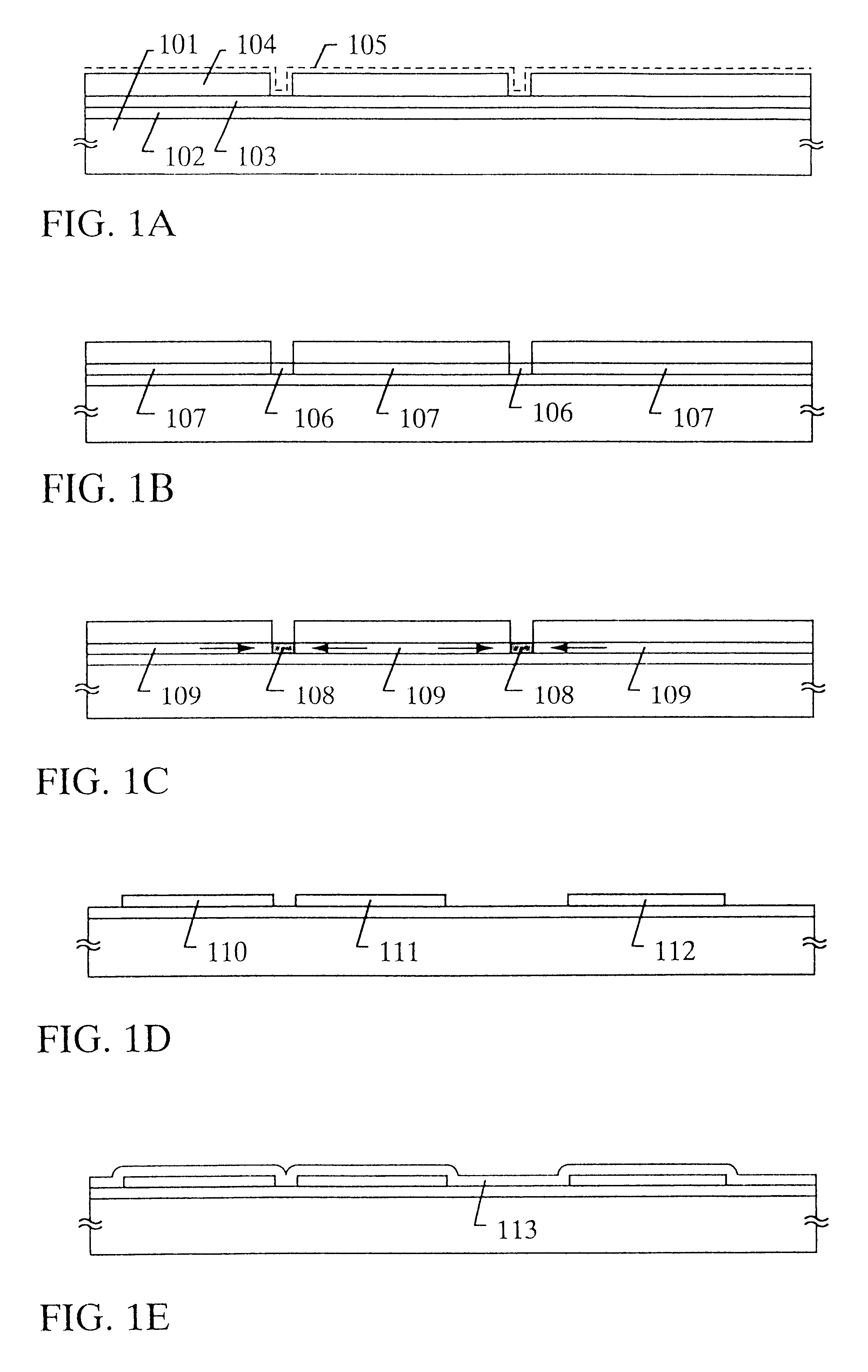

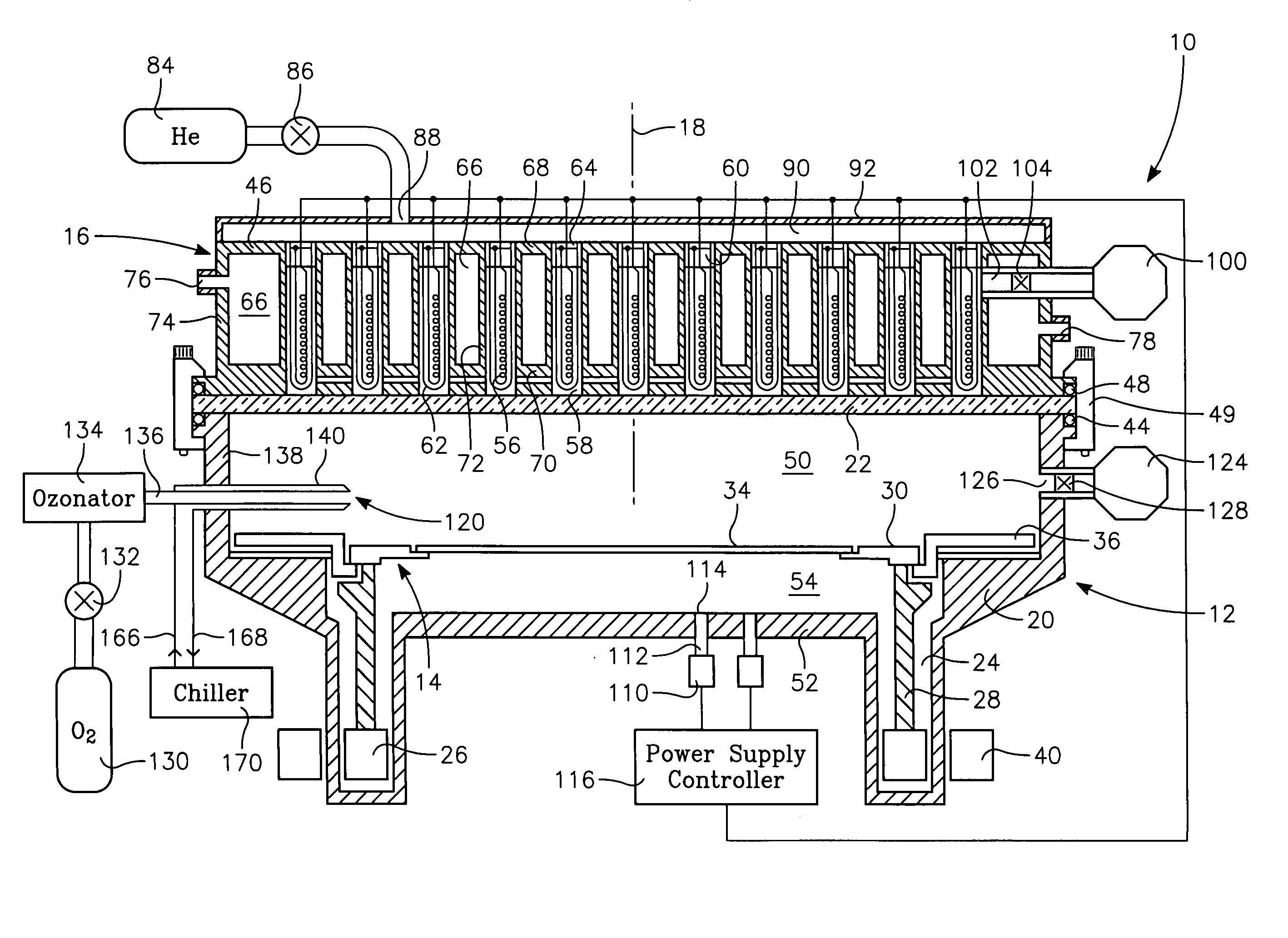

Thermal oxidation of silicon using ozone

A method and apparatus for oxidizing materials used in semiconductor integrated circuits, for example, for oxidizing silicon to form a dielectric gate. An ozonator is capable of producing a stream of least 70% ozone. The ozone passes into an RTP chamber through a water-cooled injector projecting into the chamber. Other gases such as hydrogen to increase oxidation rate, diluent gas such as nitrogen or O2, enter the chamber through another inlet. The chamber is maintained at a low pressure below 20 Torr and the substrate is advantageously maintained at a temperature less than 800° C. Alternatively, the oxidation may be performed in an LPCVD chamber including a pedestal heater and a showerhead gas injector in opposition to the pedestal.

Owner:APPLIED MATERIALS INC

Selective epitaxial growth for tunable channel thickness

ActiveUS7105399B1Increasing the thicknessReadily apparentSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSoi substrate

Gate electrodes with selectively tuned channel thicknesses are formed by selective epitaxial growth. Embodiments include forming shallow trench isolation regions in an SOI substrate, selectively removing the nitride stop layer and pad oxide layer in an exposed particular active region, and implementing selective epitaxial growth to increase the thickness of the semiconductor layer in the particular active region. Subsequently, the remaining nitride stop and pad oxide layers in other active regions are removed, gate dielectric layers formed, as by thermal oxidation, and the transistors completed.

Owner:GLOBALFOUNDRIES US INC

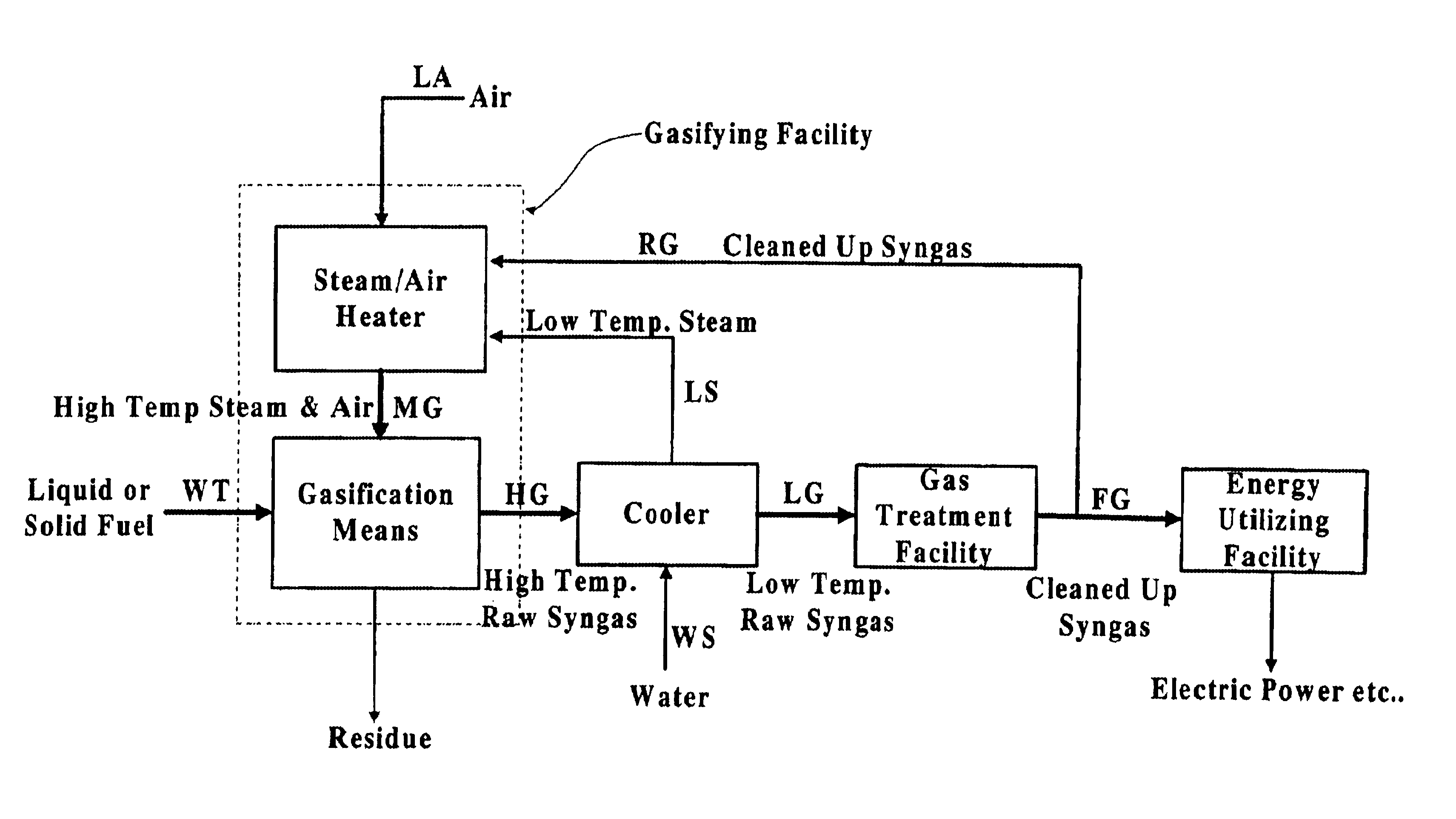

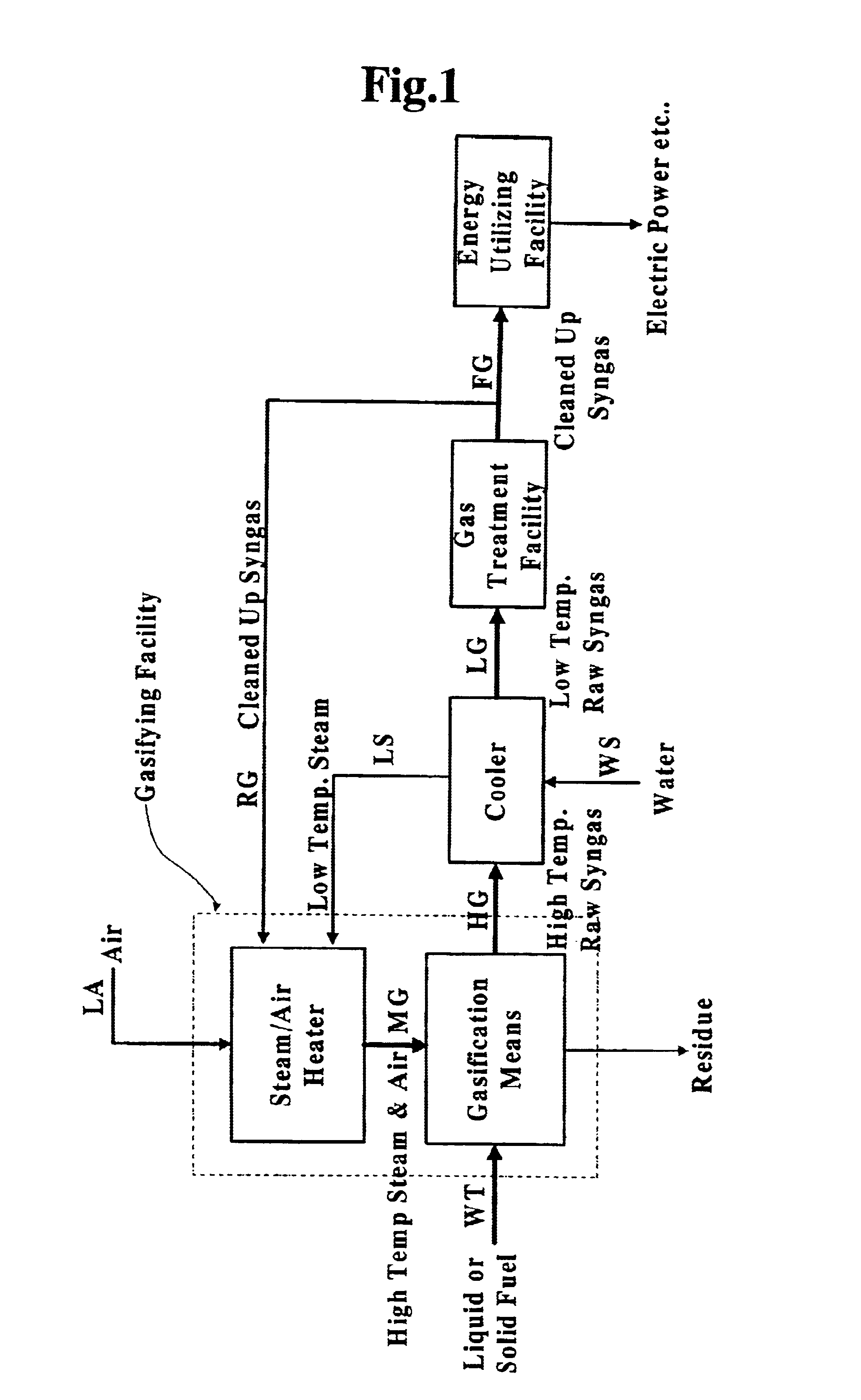

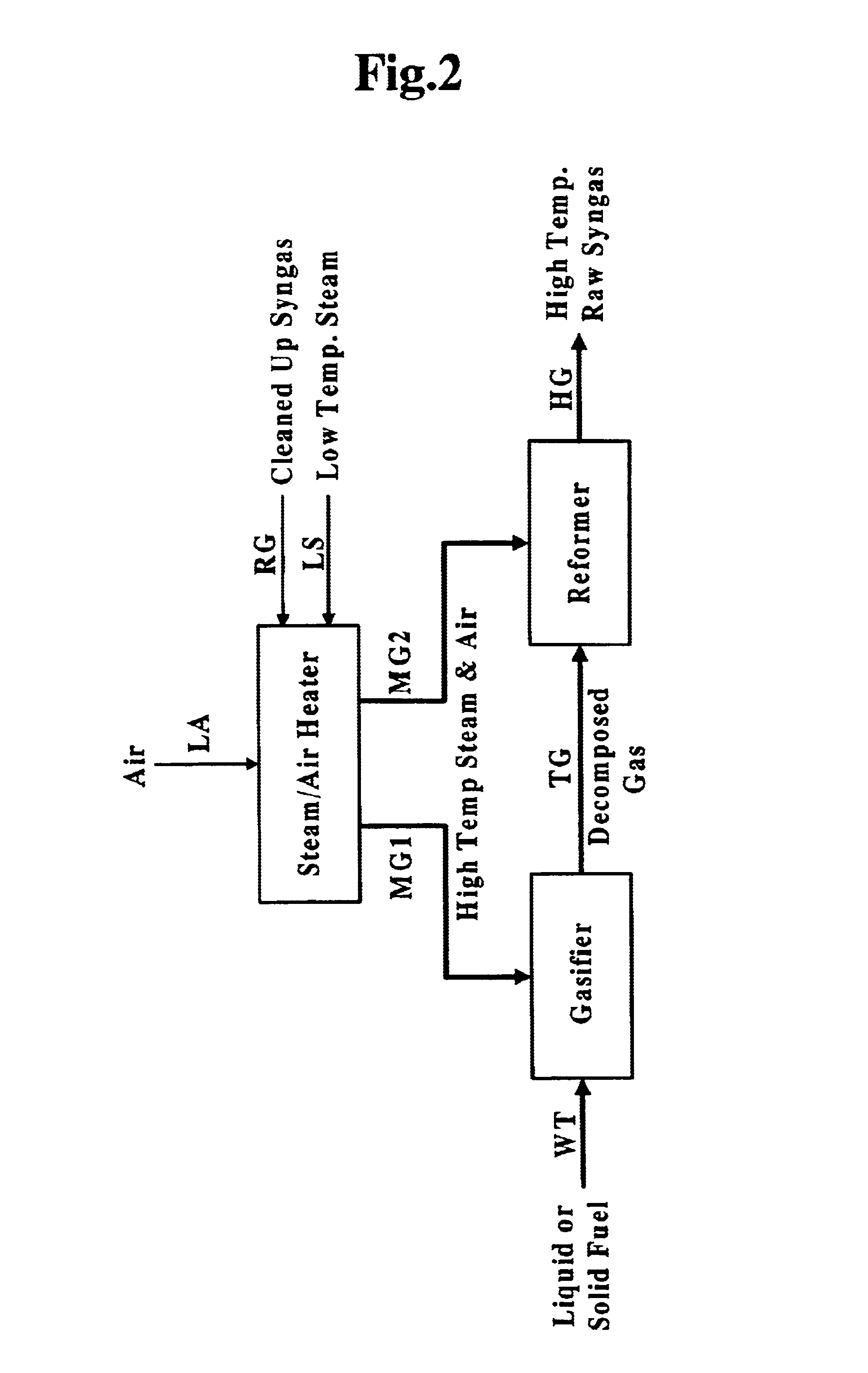

Apparatus and method for gasifying liquid or solid fuel

InactiveUS6837910B1Quality improvementAmount of heat can be ensuredHydrogenGaseous fuelsSyngasExothermic reaction

A gasifying apparatus comprises a gasifier, a reformer and a heating device. The gasifier produces a thermal decomposed gas with use of a thermal decomposition reaction of a liquid or solid fuel such as waste or coal, and the heating device heats a low-temperature steam and air so as to be a high-temperature steam and air, which have a temperature equal to or higher than 700 deg. C. The gasifying apparatus has feeding means including fluid passages for feeding the high-temperature steam and air to the gasifier and the reformer. In a thermal decomposition area of the gasifier, the liquid or solid fuel is thermally decomposed to produce the thermal decomposed gas with sensible heat of the high-temperature steam and air and with the heat generated by an exothermic oxidation reaction between the high-temperature air and the liquid or solid fuel. In the reformer, the thermal decomposed gas is reformed in the existence of the high-temperature steam so as to be a high-temperature syngas. The steam reforming reaction of the liquid or solid fuel is carried out with an exothermic reaction between the high-temperature air and hydrocarbon contained in the thermal decomposed gas and with an endothermic reaction between the hydrocarbon and the high-temperature steam.

Owner:NIPPON FURNANCE IND KAISHA +1

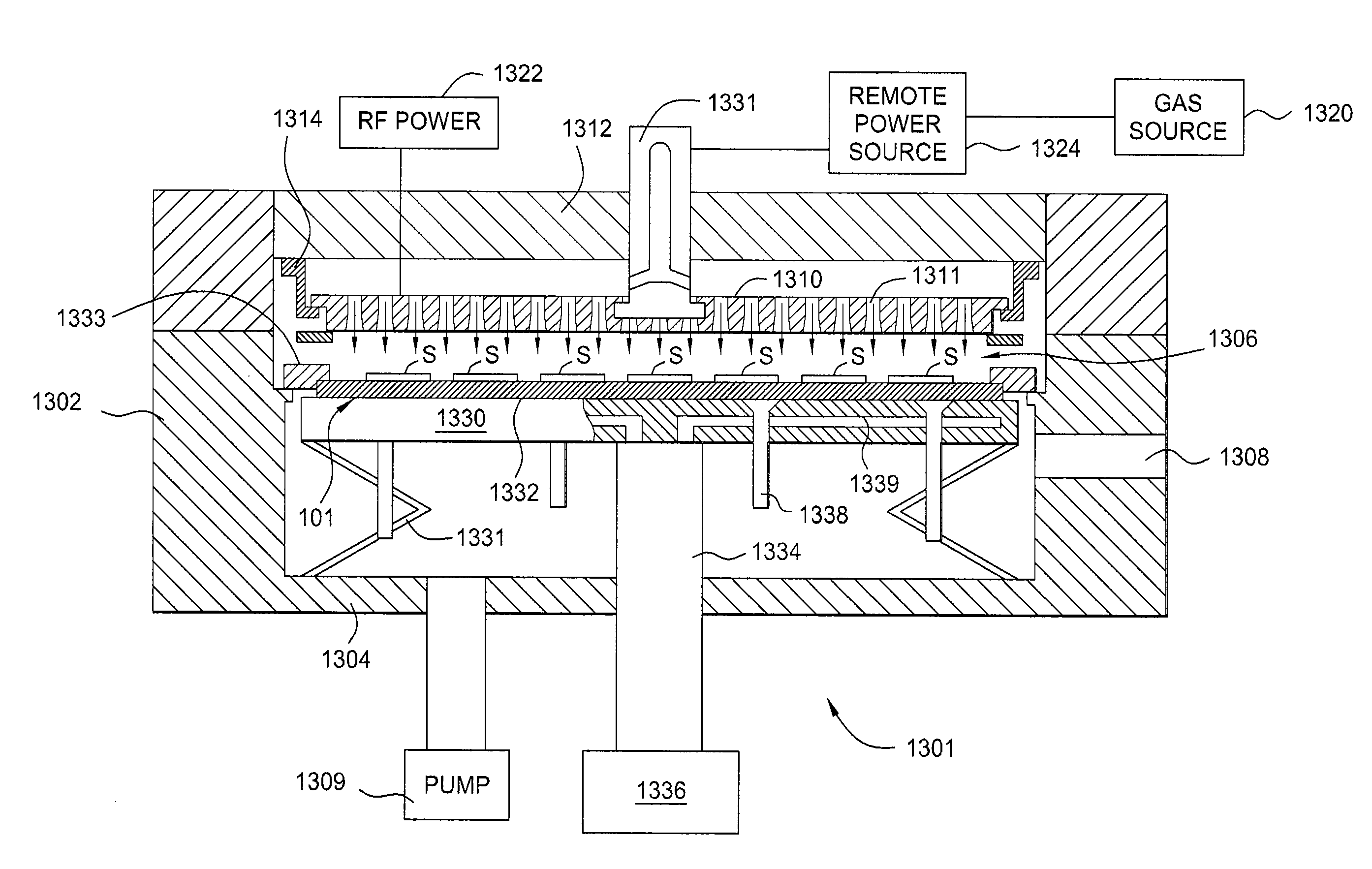

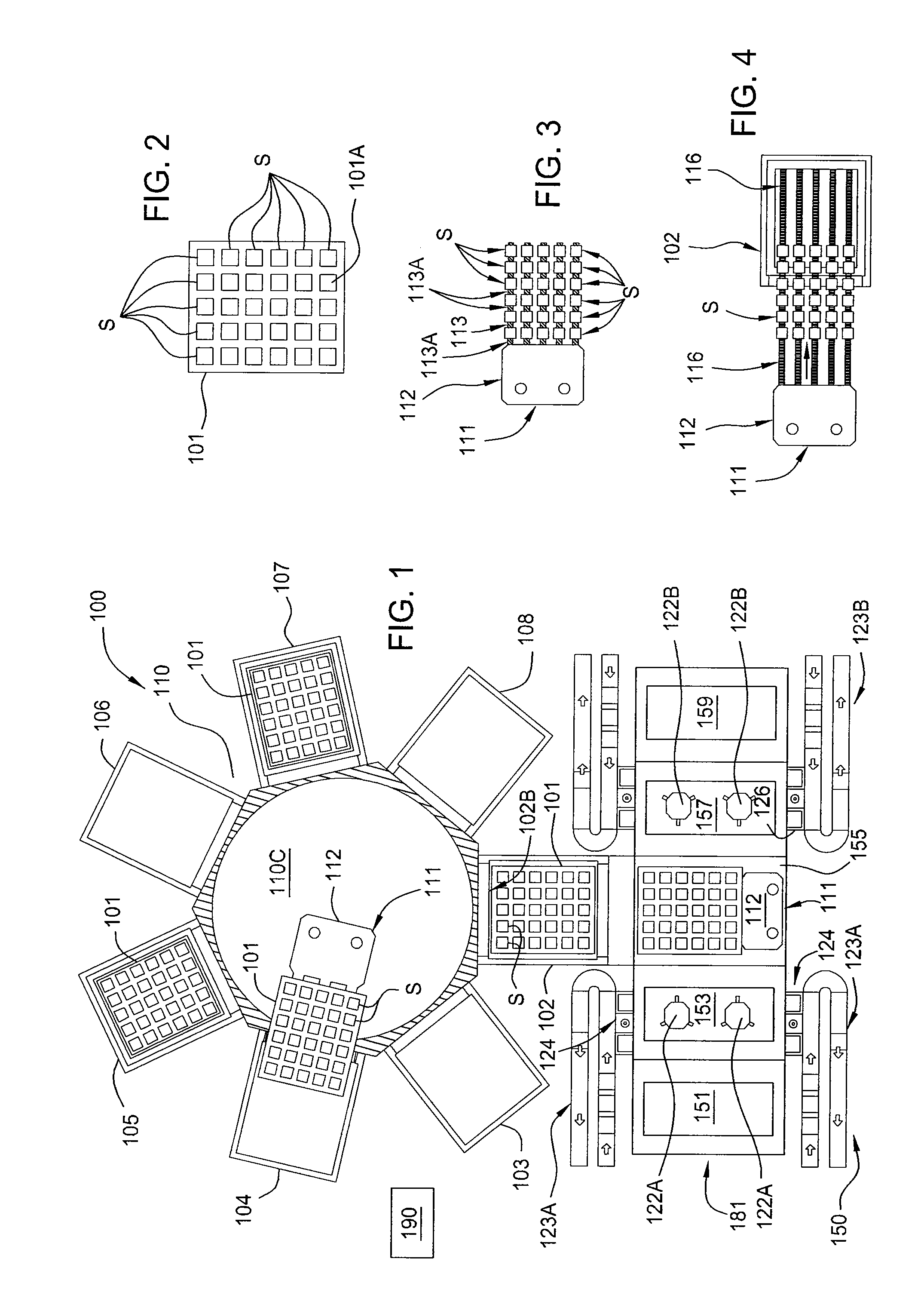

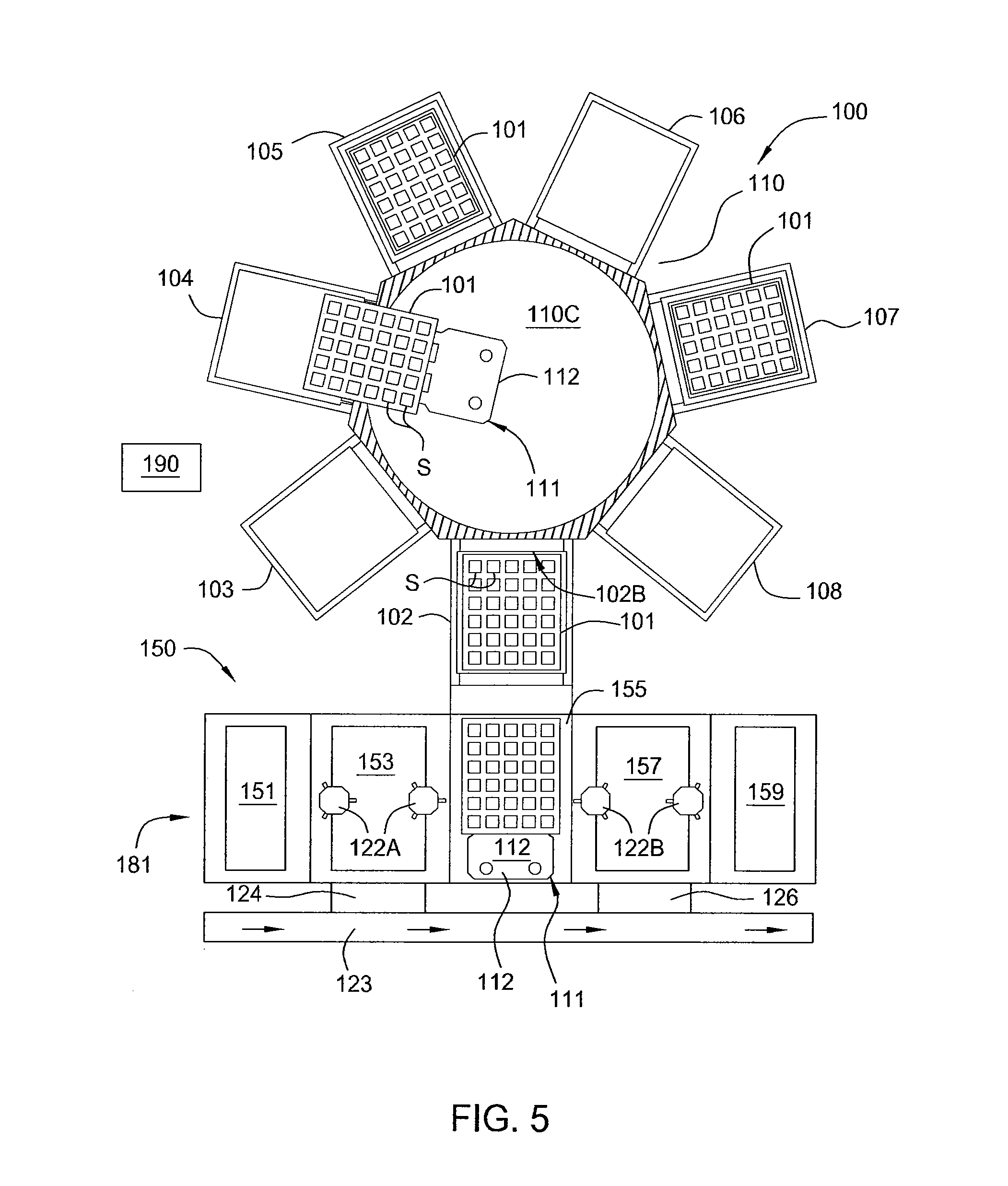

Advanced platform for processing crystalline silicon solar cells

InactiveUS20100087028A1Final product manufactureSemiconductor/solid-state device manufacturingGas phaseEngineering

The present invention generally provides a batch substrate processing system, or cluster tool, for in-situ processing of a film stack used to form regions of a solar cell device. In one configuration, the film stack formed on each of the substrates in the batch contains one or more silicon-containing layers and one or more metal layers that are deposited and further processed within the various chambers contained in the substrate processing system. The processing chambers may be, for example, physical vapor deposition (PVD) or sputtering chambers, plasma enhanced chemical vapor deposition (PECVD) chambers, low pressure chemical vapor deposition (LPCVD) chambers, hot wire chemical vapor deposition (HWCVD) chambers, plasma nitridation (DPN) chambers, ion implant / doping chambers, atomic layer deposition (ALD) chambers, plasma etching chambers, annealing chambers, rapid thermal oxidation (RTO) chambers, rapid thermal annealing (RTA) chambers, substrate reorientation chambers, laser annealing chambers, and / or plasma cleaning stations. In one embodiment, a batch of solar cell substrates is simultaneously transferred in a vacuum or inert environment to prevent contamination from affecting the solar cell formation process.

Owner:APPLIED MATERIALS INC

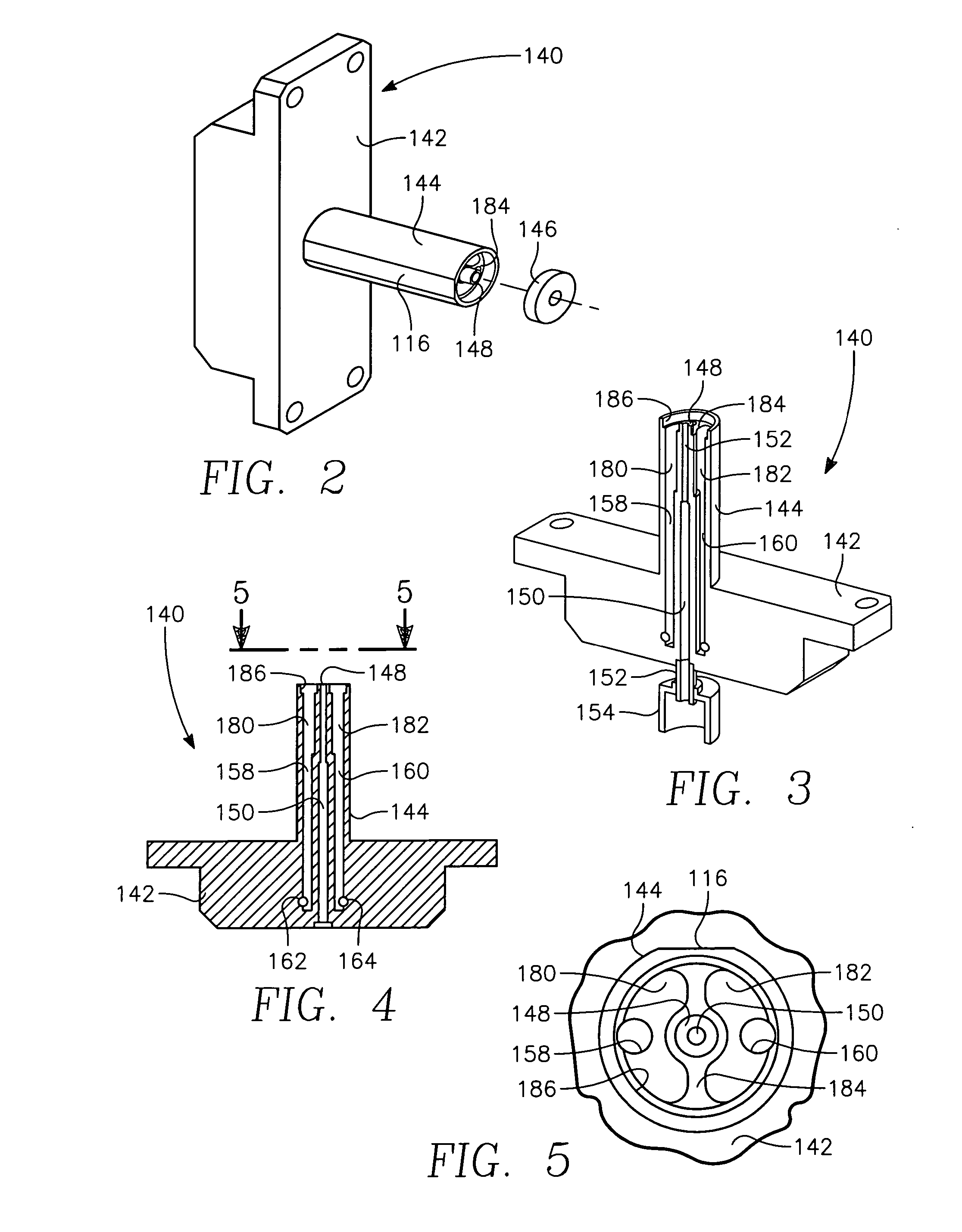

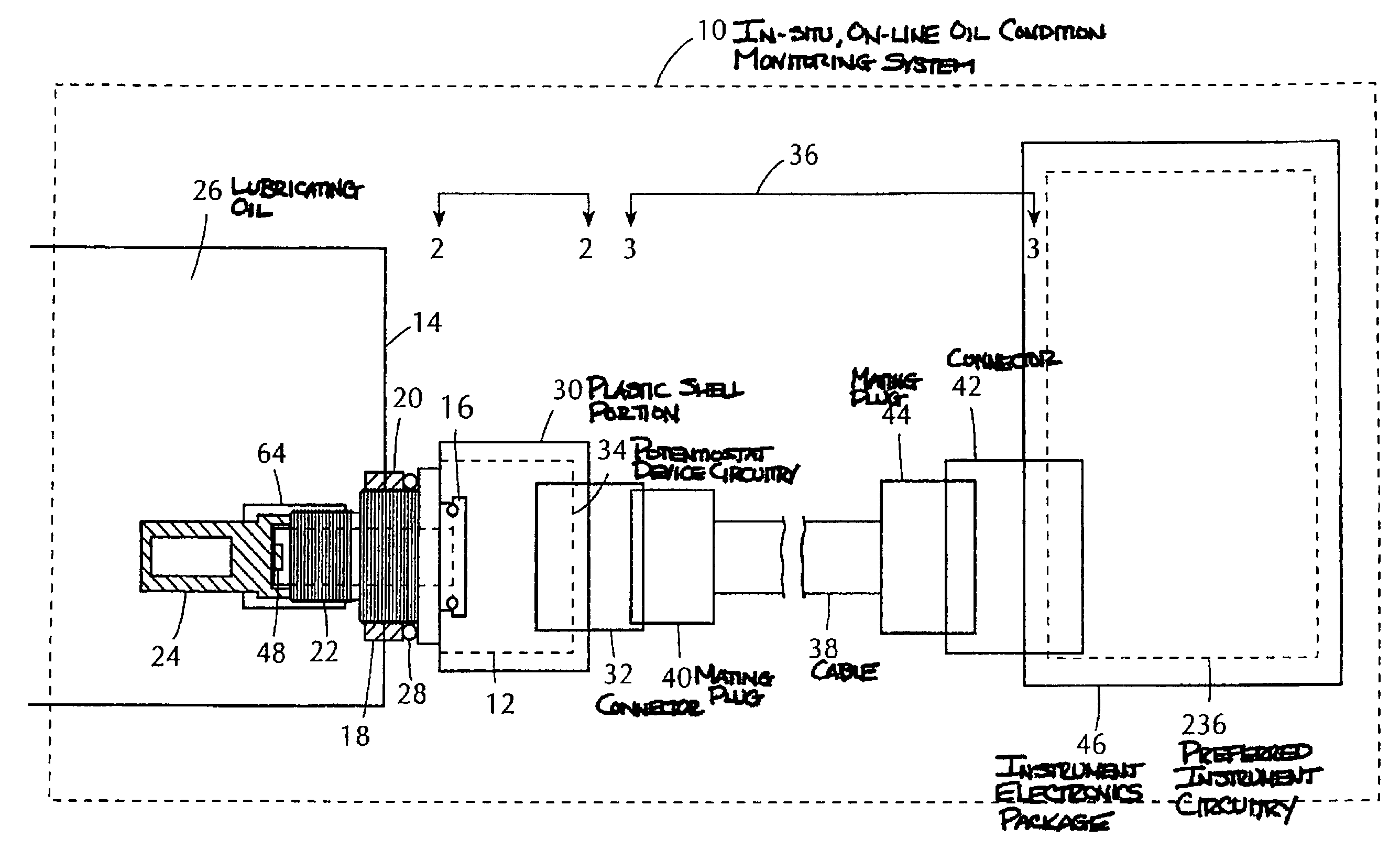

On-line oil condition sensor system for rotating and reciprocating machinery

InactiveUS7043402B2Improve performanceRepeatabilityFlow propertiesMachines/enginesElectrochemistryElectrode Contact

An on-line sensing system and method for monitoring in real-time thermal-oxidative breakdown, water contamination, and / or fuel dilution conditions in operational engine lubricating oils. The method of the invention includes an electrochemical impedance analysis technique specific to the particular oil to be monitored. Sensing devices having of at least two electrodes are configured for direct installation in an existing access port, or drain port, of a lubricating oil reservoir. An AC voltage waveform is applied to the sensing device (preferably less than 100 Hz) to produce voltage and current responses between the appropriate electrodes contacting the oil. The magnitude impedance |Z| and phase angle components of the complex impedance are used to characterize the quality and / or condition of the engine oil under test. The system also provides an electrical indication indicative of the percentage remaining useful life of the oil.

Owner:PHILLIPS INTPROP

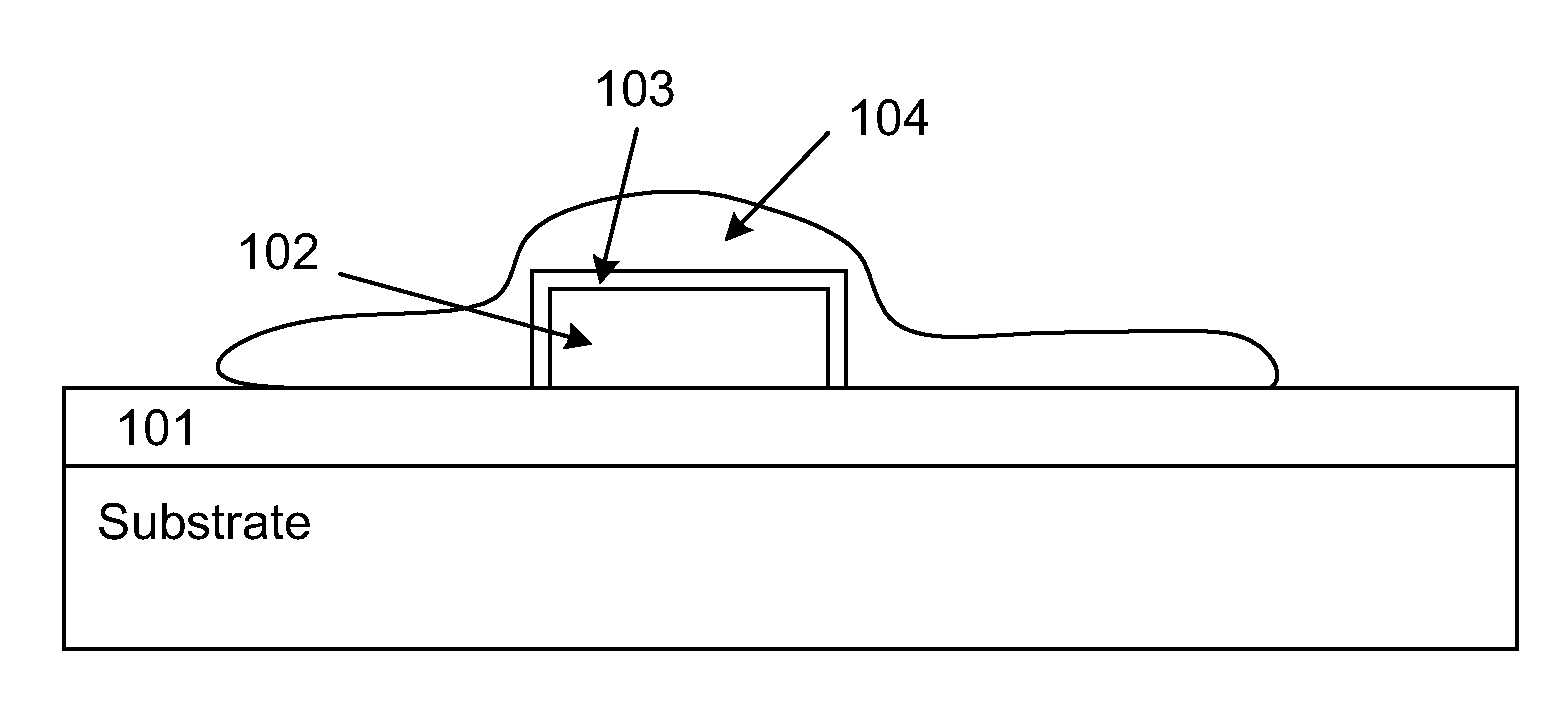

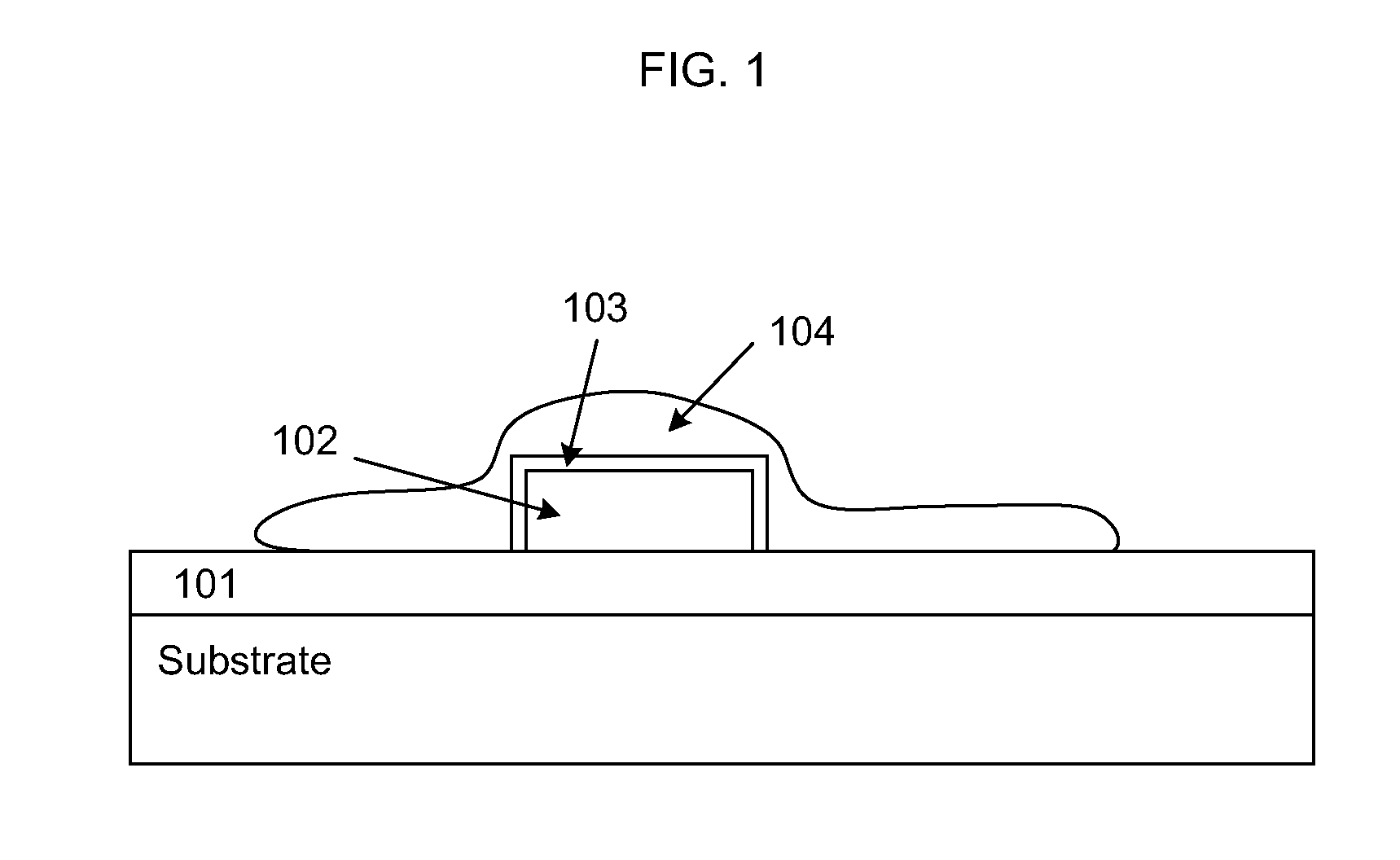

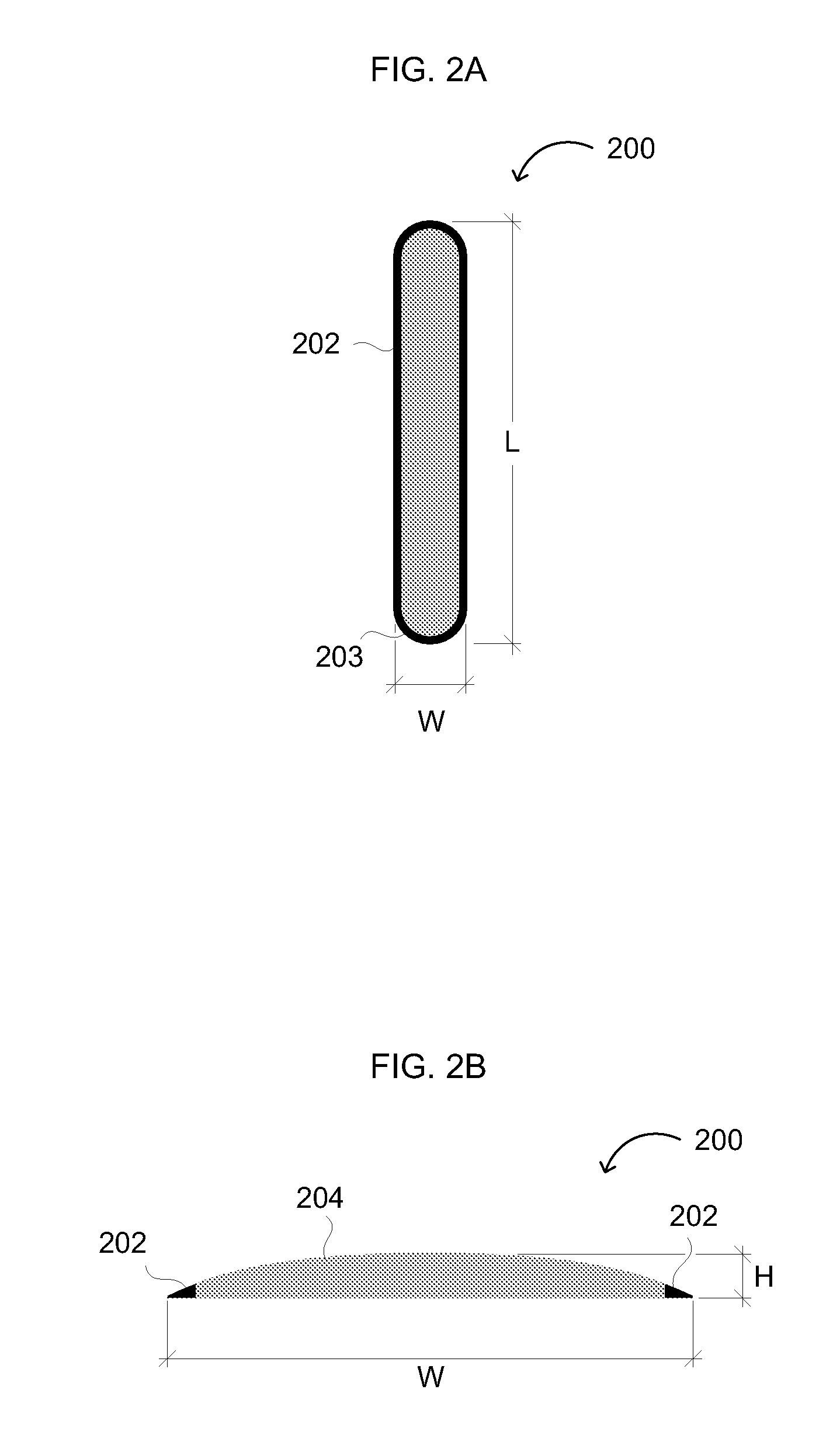

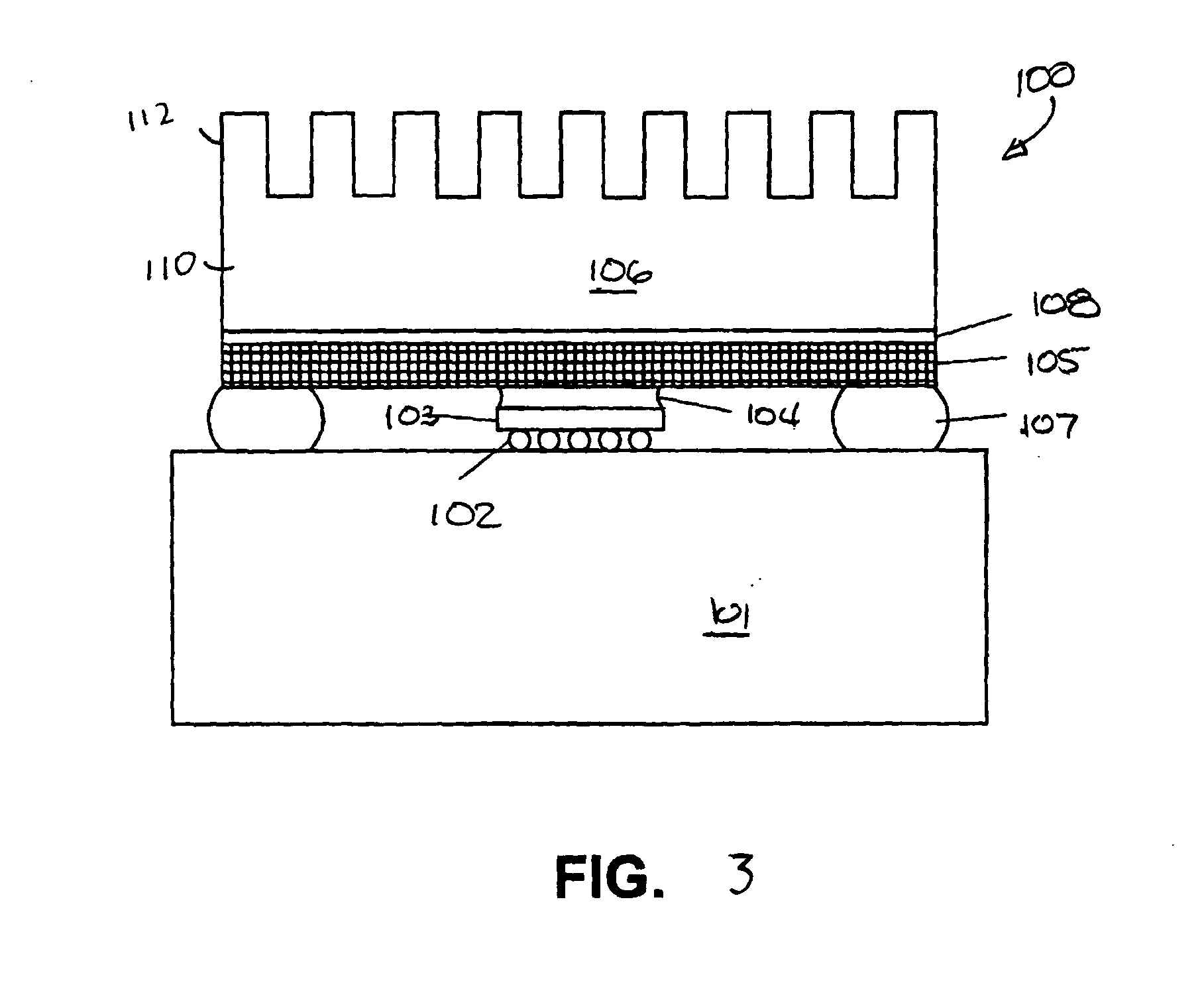

Profile Engineered Thin Film Devices and Structures

ActiveUS20090085095A1Improve performanceEasy to controlTransistorPrinted circuit aspectsDielectricElectrical conductor

The present invention relates to electrically active devices (e.g., capacitors, transistors, diodes, floating gate memory cells, etc.) having dielectric, conductor, and / or semiconductor layers with smooth and / or dome-shaped profiles and methods of forming such devices by depositing or printing (e.g., inkjet printing) an ink composition that includes a semiconductor, metal, or dielectric precursor. The smooth and / or dome-shaped cross-sectional profile allows for smooth topological transitions without sharp steps, preventing feature discontinuities during deposition and allowing for more complete step coverage of subsequently deposited structures. The inventive profile allows for both the uniform growth of oxide layers by thermal oxidation, and substantially uniform etching rates of the structures. Such oxide layers may have a uniform thickness and provide substantially complete coverage of the underlying electrically active feature. Uniform etching allows for an efficient method of reducing a critical dimension of an electrically active structure by simple isotropic etch.

Owner:ENSURGE MICROPOWER ASA

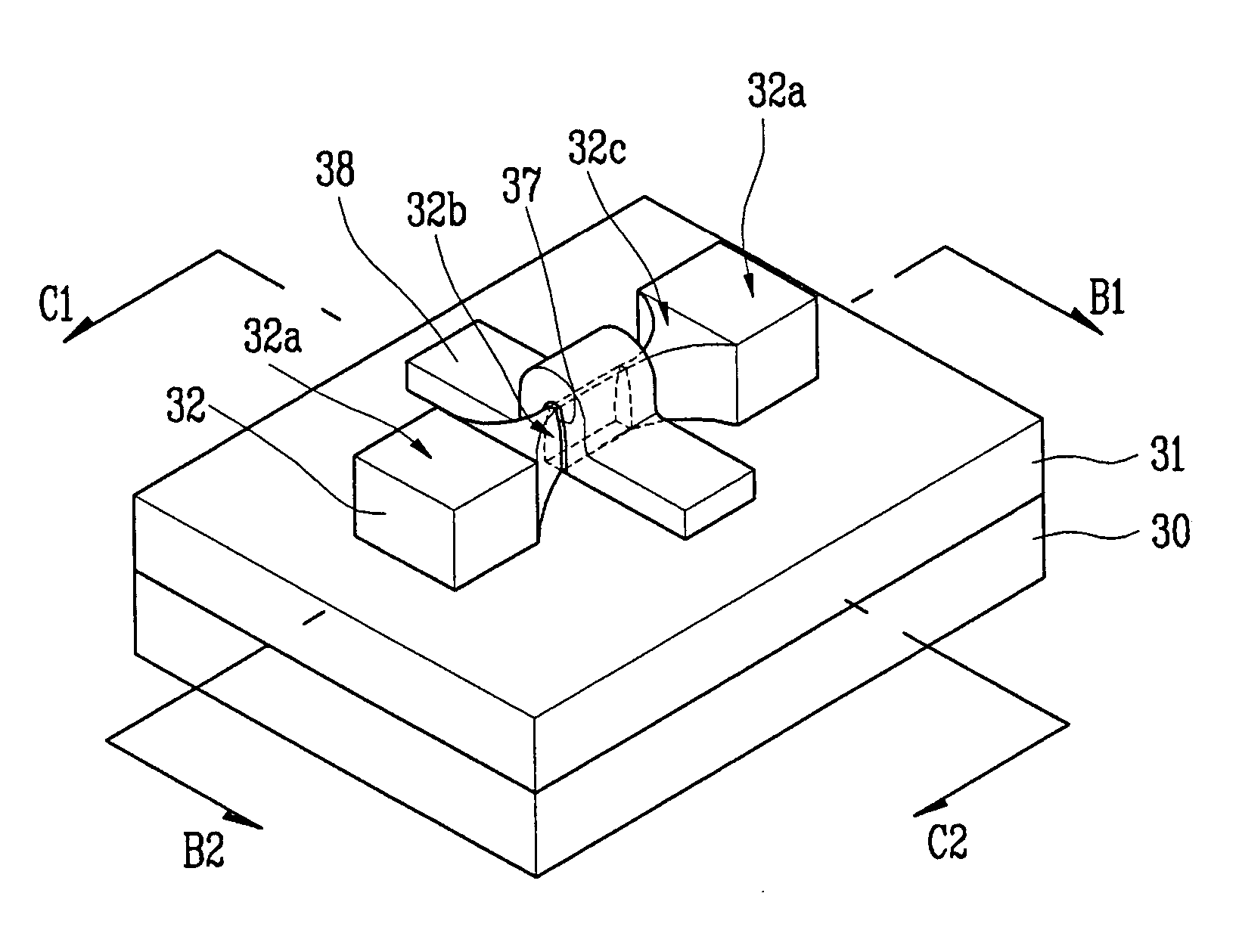

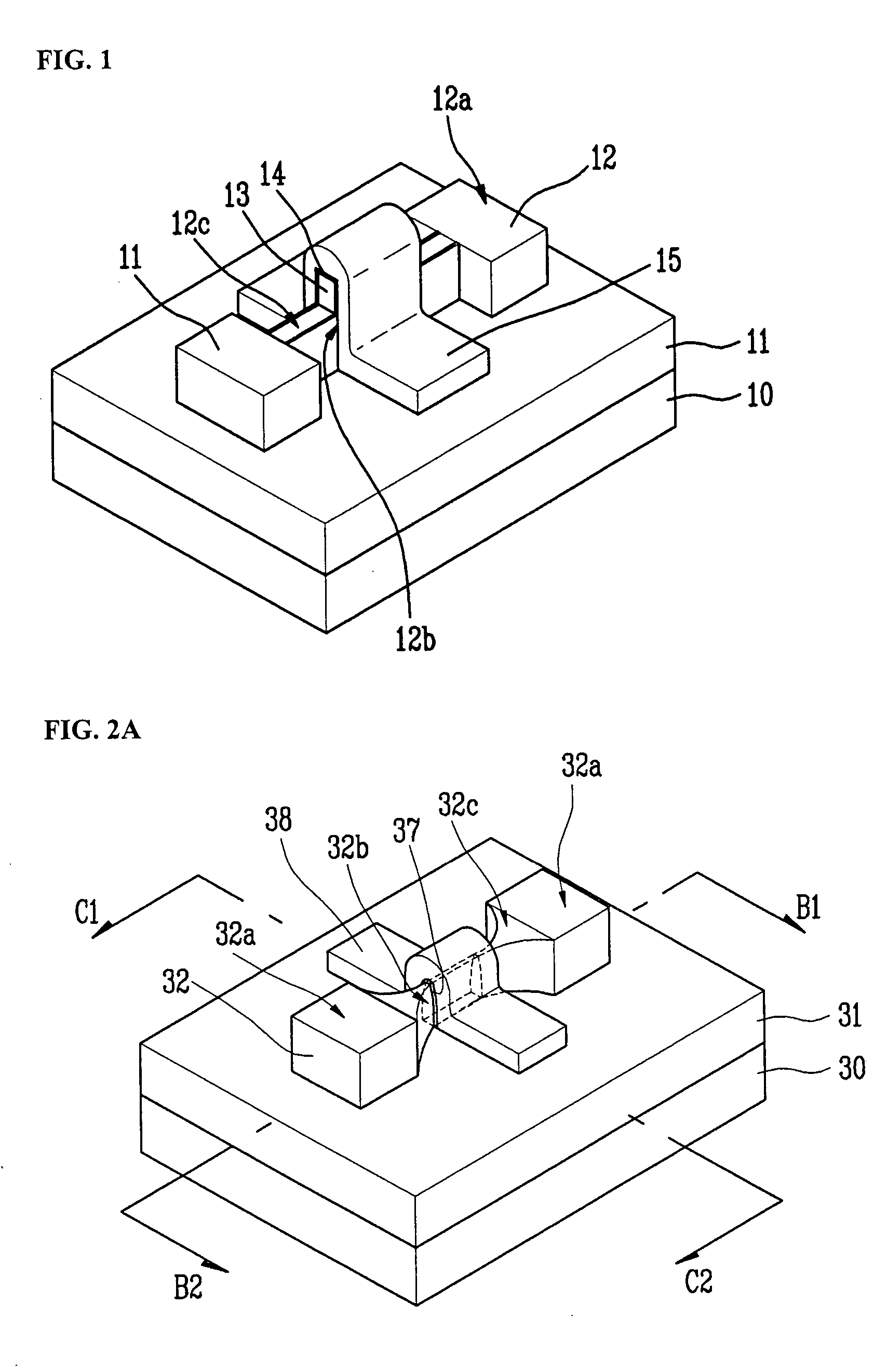

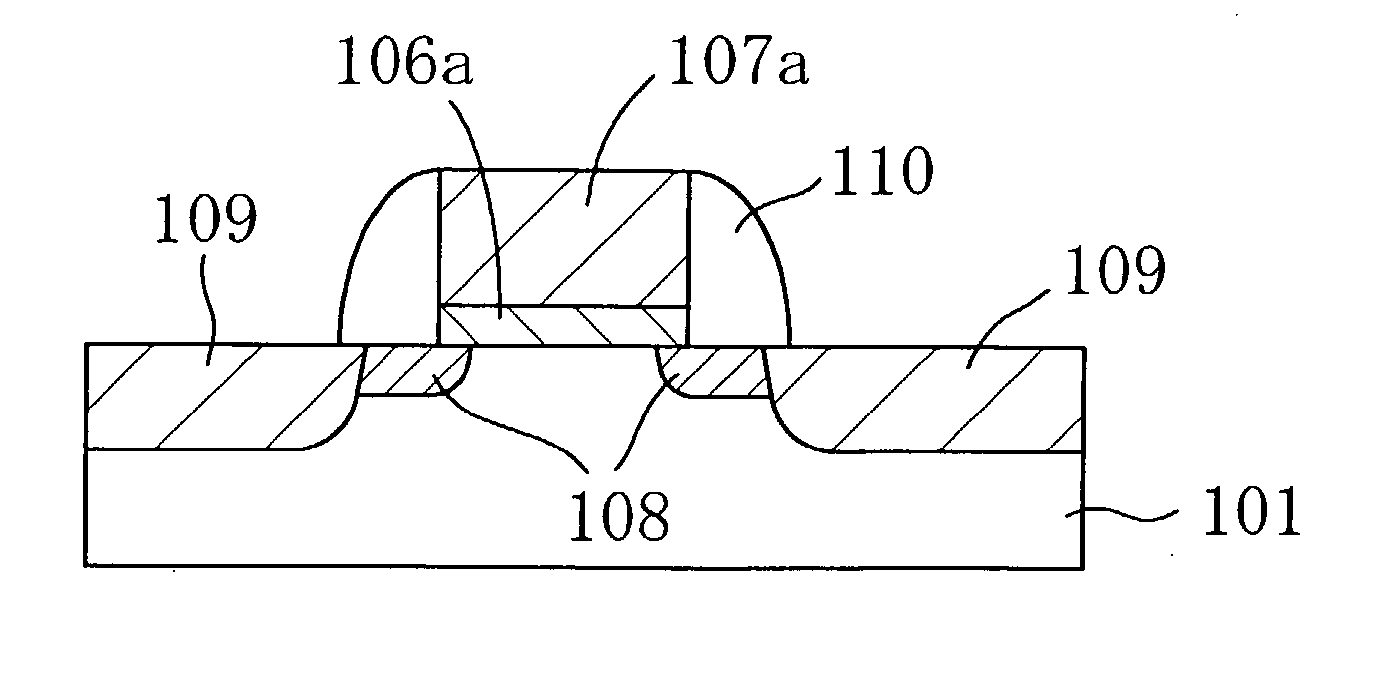

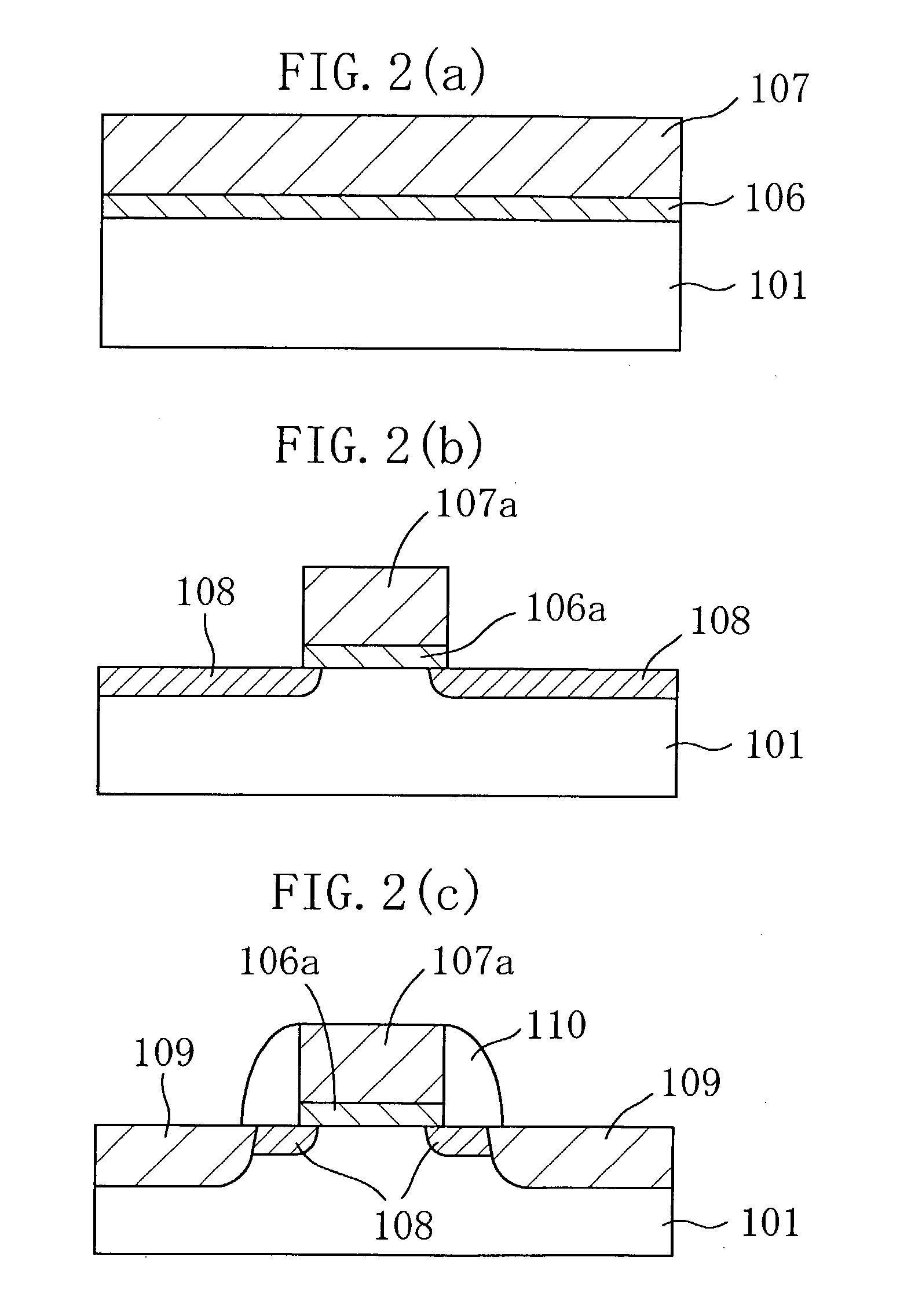

Multiple-gate MOS transistor and a method of manufacturing the same

InactiveUS20050263821A1Improve reliabilityImprove rendering capabilitiesTransistorGrinding drivesCrystal orientationGate voltage

Provided is a multiple-gate metal oxide semiconductor (MOS) transistor and a method for manufacturing the same, in which a channel is implemented in a streamline shape, an expansion region is implemented in a gradually increased form, and source and drain regions is implemented in an elevated structure by using a difference of a thermal oxidation rate depending on a crystal orientation of silicon and a geographical shape of the single-crystal silicon pattern. As the channel is formed in a streamline shape, it is possible to prevent the degradation of reliability due to concentration of an electric field and current driving capability by the gate voltage is improved because the upper portion and both sides of the channel are surrounded by the gate electrodes. In addition, a current crowding effect is prevented due to the expansion region increased in size and source and drain series resistance is reduced by elevated source and drain structures, thereby increasing the current driving capability.

Owner:III HLDG 2

Polydopamine-based biofunction modification method

InactiveCN102000658AImprove deformation resistanceImprove stabilityPretreated surfacesCoatingsAir atmosphereMetallic materials

The invention discloses a polydopamine-based biofunction modification method. The method comprises the following steps of: soaking clean inorganic / metal materials in dopamine alkaline aqueous solution with a pH value of 7.2 to 10, introducing oxygen to fully oxidize the clean inorganic / metal materials to obtain a monolayer polydopamine modification layer, drying, placing the material in the air atmosphere at 50 to 200 DEG C, performing thermal oxidation to obtain a multi-layer firmly-combined high-reactivity polydopamine layer, and soaking the treated material into the amino-containing and sulfydryl-containing biofunctional molecular solution to obtain a firmly combined biofunction simulate modification layer on the surface of the materials. The polydopamine modification layer obtained bythe method has excellent anti-deformation performance, stability and reactivity, can directly react with amino or the sulfydryl in the biomolecule to immobilize the bioactive molecule on the surface by covalent bonds; moreover, the process is simple, the condition is mild, and the method is easy to implement.

Owner:CO WITH LTD LIABILITY OF MEDICAL SCI +1

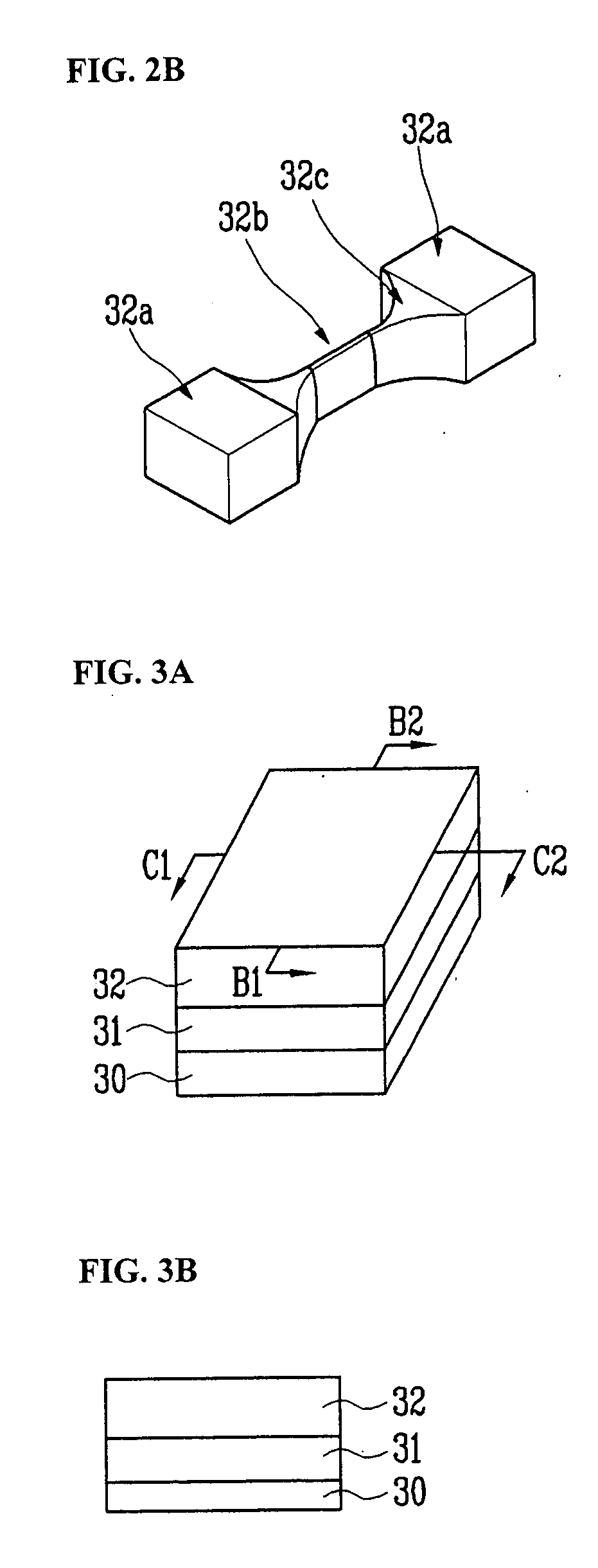

Process for manufacturing a semiconductor wafer integrating electronic devices and a structure for electromagnetic decoupling

InactiveUS6869856B2Improved electromagnetic decouplingSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

A process for manufacturing a semiconductor wafer integrating electronic devices and a structure for electromagnetic decoupling are disclosed. The method includes providing a wafer of semiconductor material having a substrate; forming a plurality of first mutually adjacent trenches, open on a first face of the wafer, which have a depth and a width and define walls); by thermal oxidation, completely oxidizing the walls and filling at least partially the first trenches, so as to form an insulating structure of dielectric material; and removing one portion of the substrate comprised between the insulating structure and a second face of the wafer, opposite to the first face of the wafer.

Owner:STMICROELECTRONICS SRL

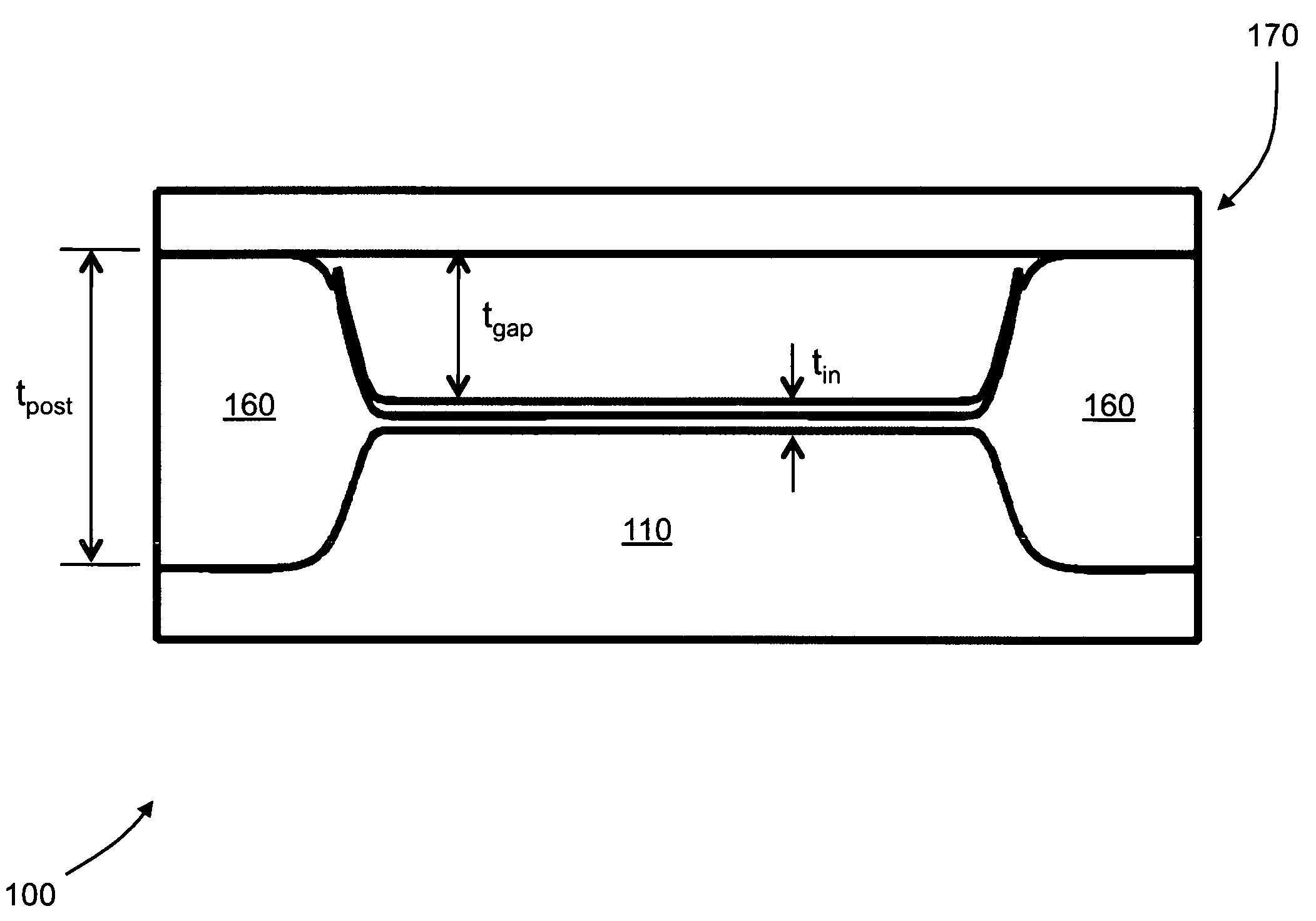

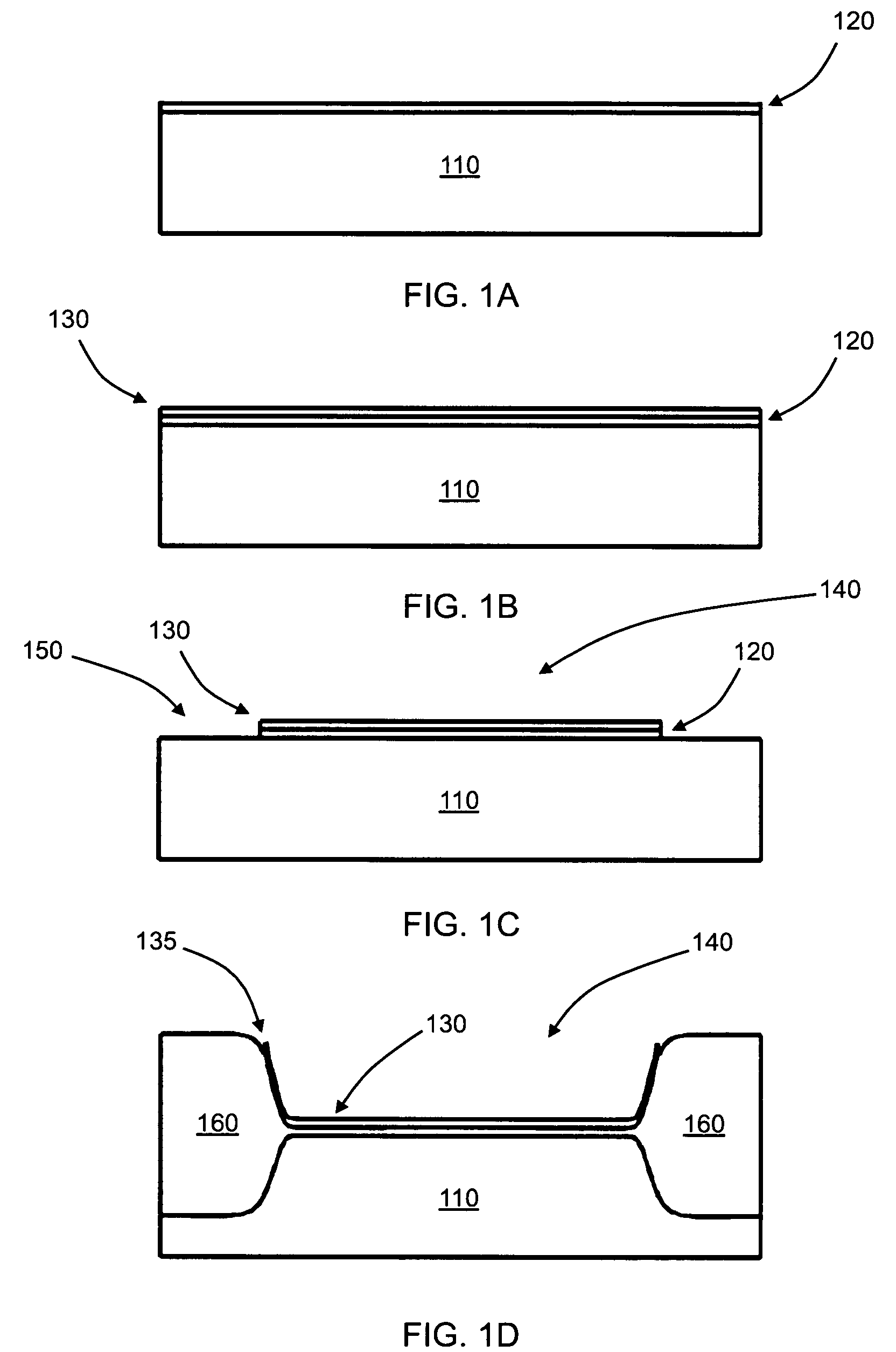

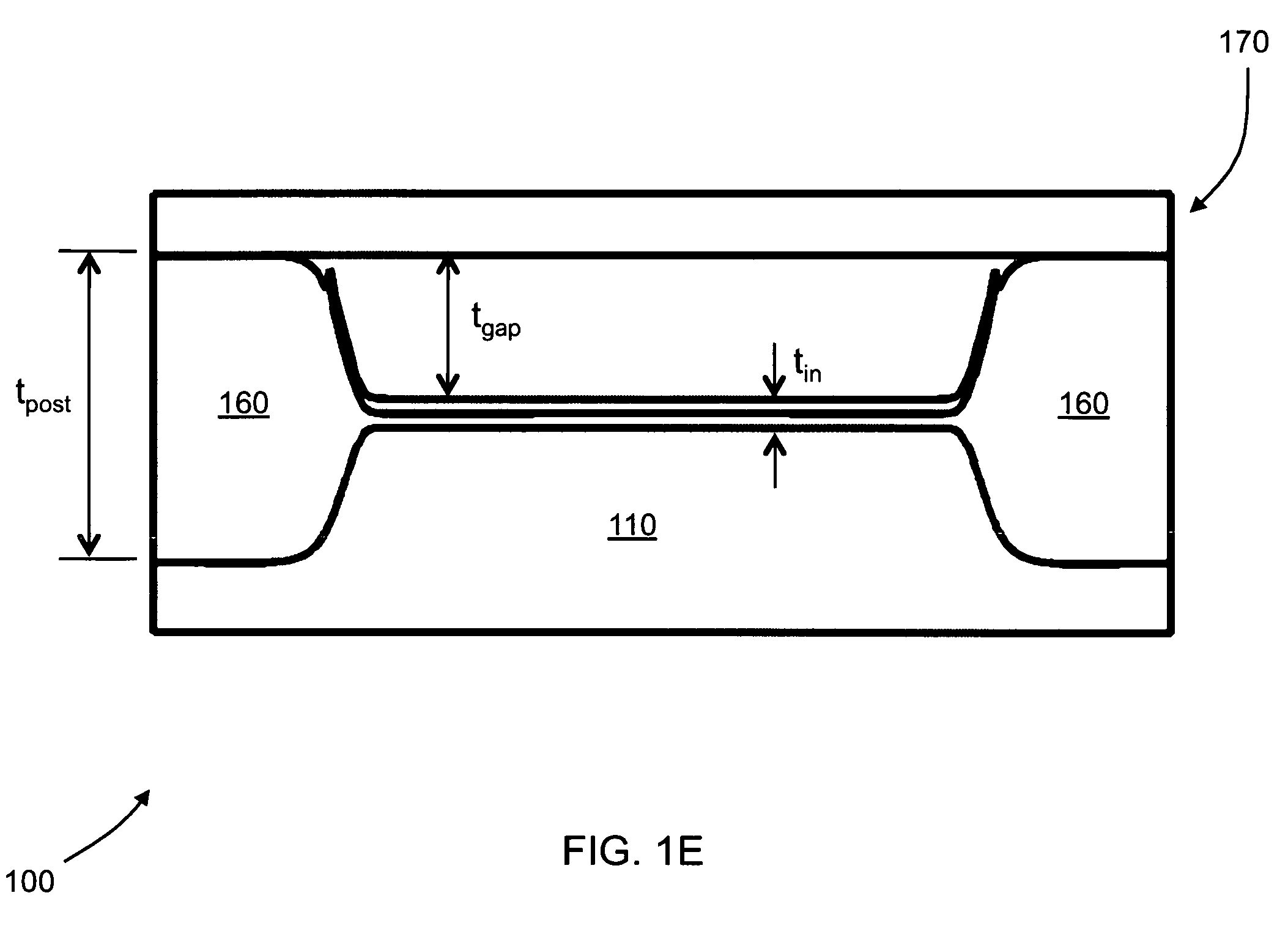

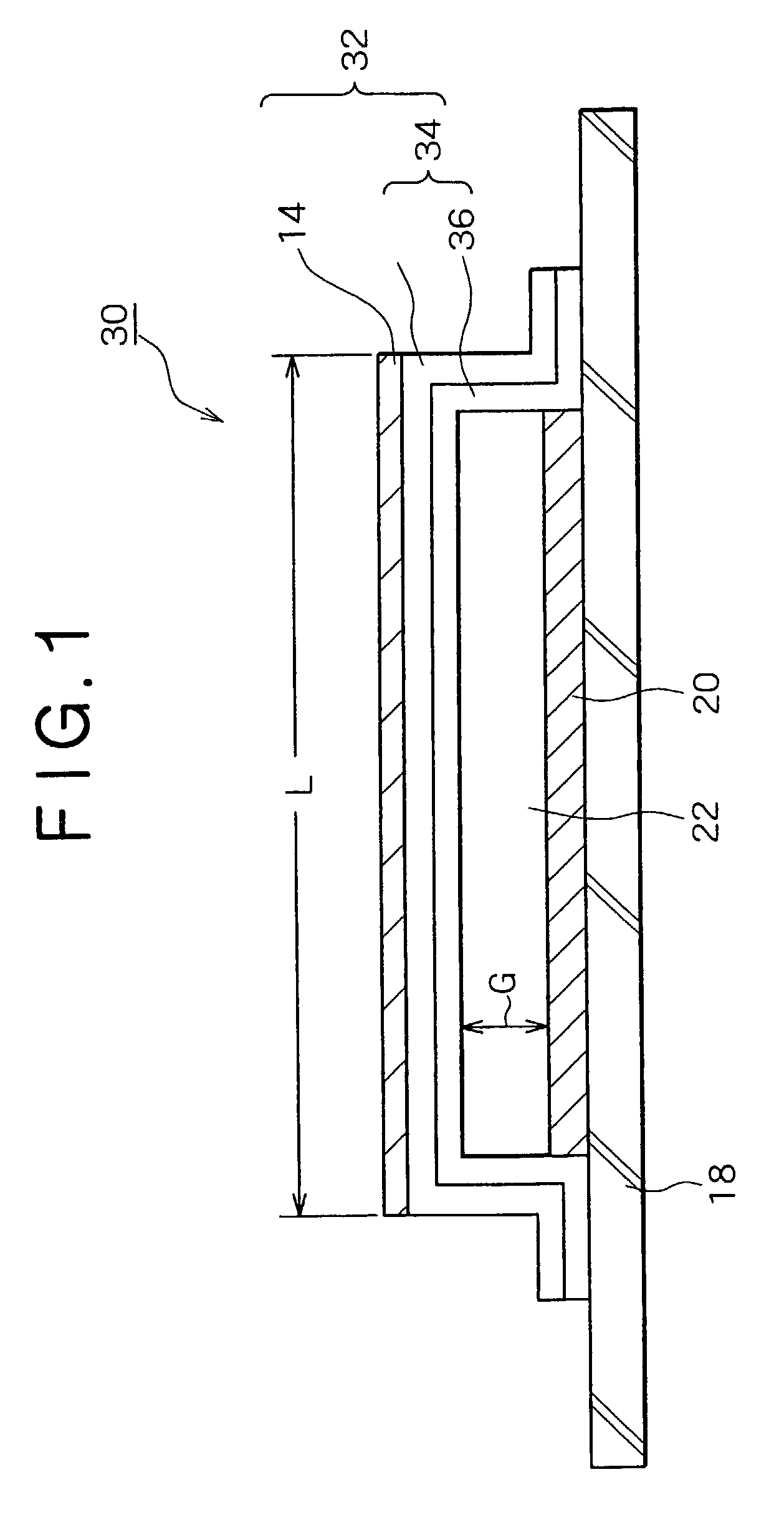

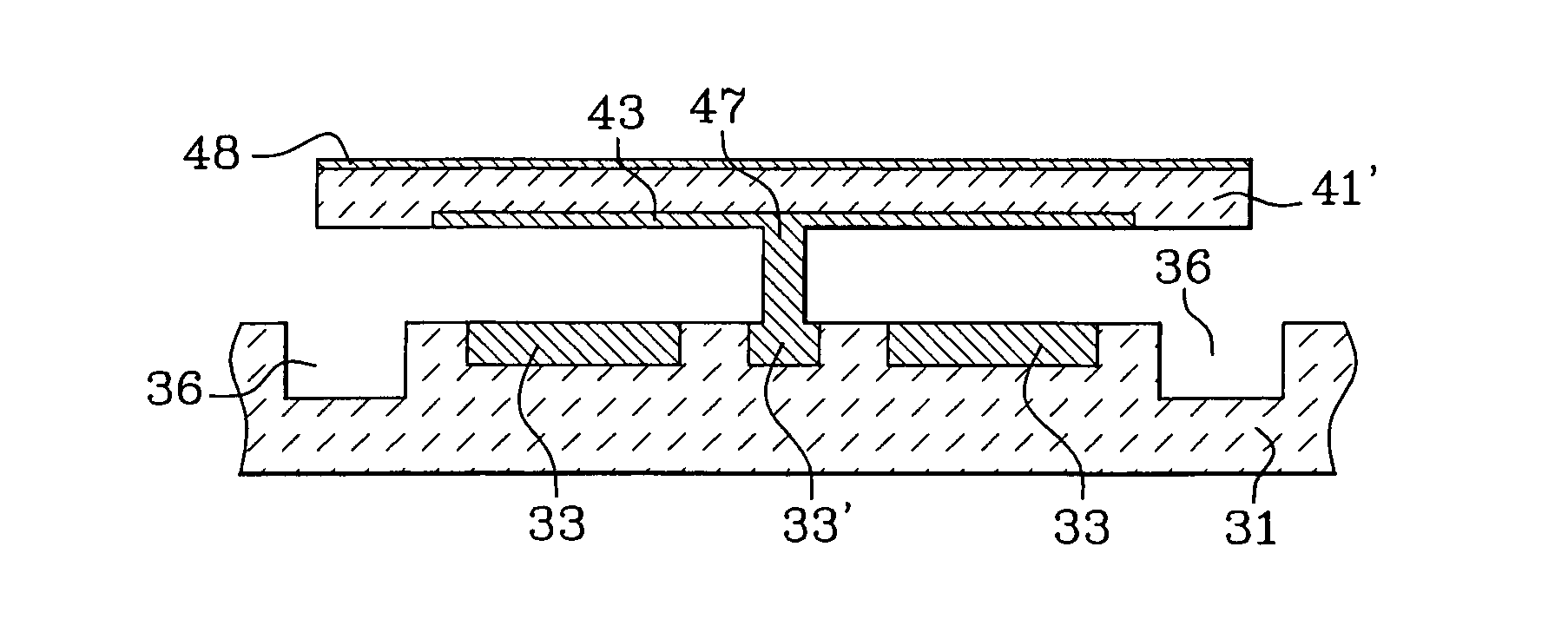

Fabrication of capacitive micromachined ultrasonic transducers by local oxidation

ActiveUS7745248B2Reduce parasitic capacitanceImprove breakdown voltageSemiconductor/solid-state device manufacturingMechanical vibrations separationCapacitanceCapacitive micromachined ultrasonic transducers

The current invention provides methods of fabricating a capacitive micromachined ultrasonic transducer (CMUT) that includes oxidizing a substrate to form an oxide layer on a surface of the substrate having an oxidation-enabling material, depositing and patterning an oxidation-blocking layer to form a post region and a cavity region on the substrate surface and remove the oxidation-blocking layer and oxide layer at the post region. The invention further includes thermally oxidizing the substrate to grow one or more oxide posts from the post region, where the post defines the vertical critical dimension of the device, and bonding a membrane layer onto the post to form a membrane of the device. A maximum allowed second oxidation thickness t2 can be determined, that is partially based on a desired step height and a device size, and a first oxidation thickness t1 can be determined that is partially based on the determined thickness t2.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

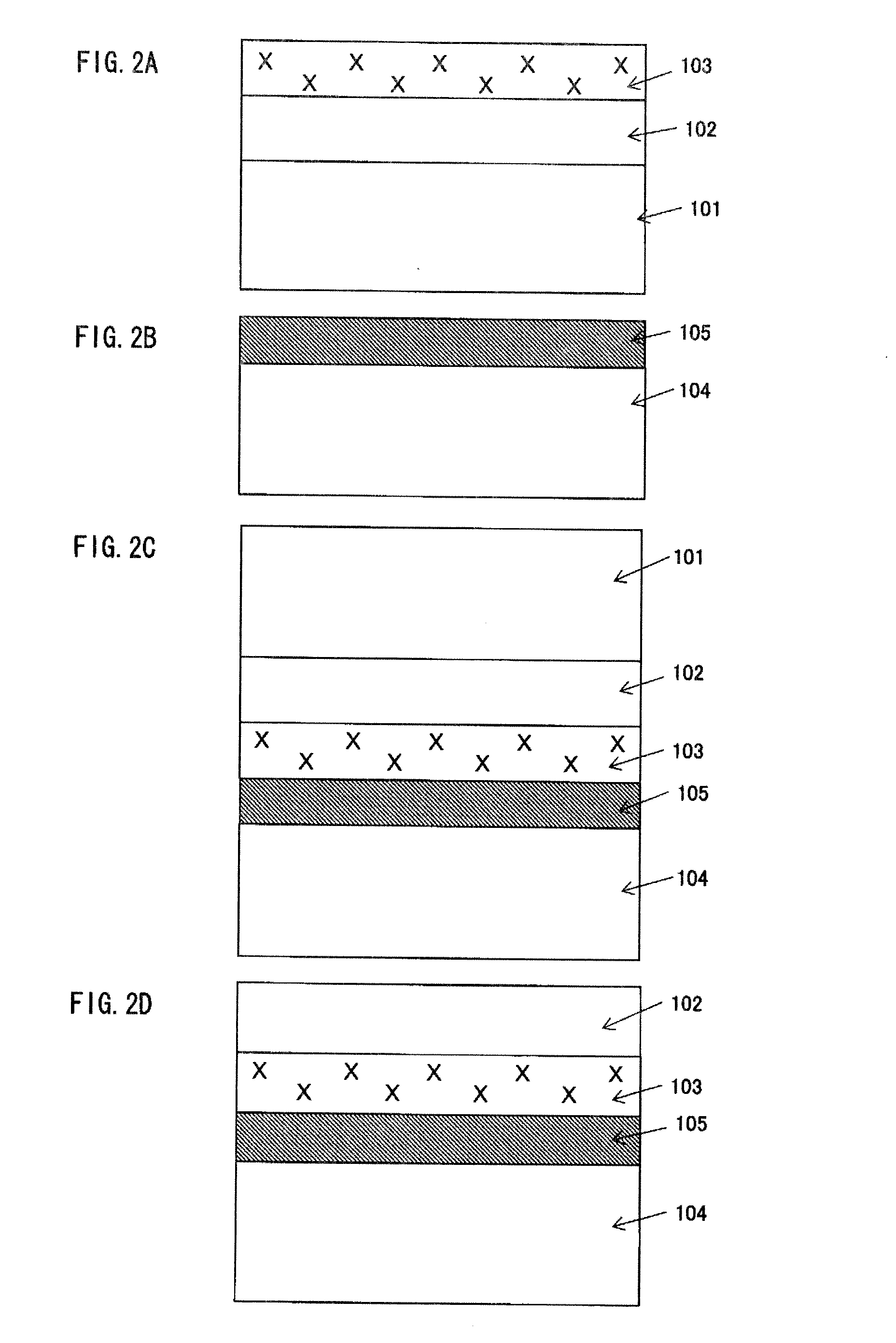

Soi wafer, method for producing same, and method for manufacturing semiconductor device

ActiveUS20110298083A1Promote precipitationImprove inhalation capacitySolid-state devicesSemiconductor/solid-state device manufacturingNitrogenOxygen

An SOI wafer including: a supporting substrate 1; a BOX layer 2 provided above the supporting substrate 1, the BOX layer 2 being formed by a thermal oxidization; a gettering layer 3 provided immediately on the BOX layer 2 and mainly composed of a silicon which contains one or more of oxygen, carbon and nitrogen and contains at least oxygen; and an S layer 4 in which semiconductor devices are to be formed, the S layer 4 being mainly composed of a monocrystalline silicon.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

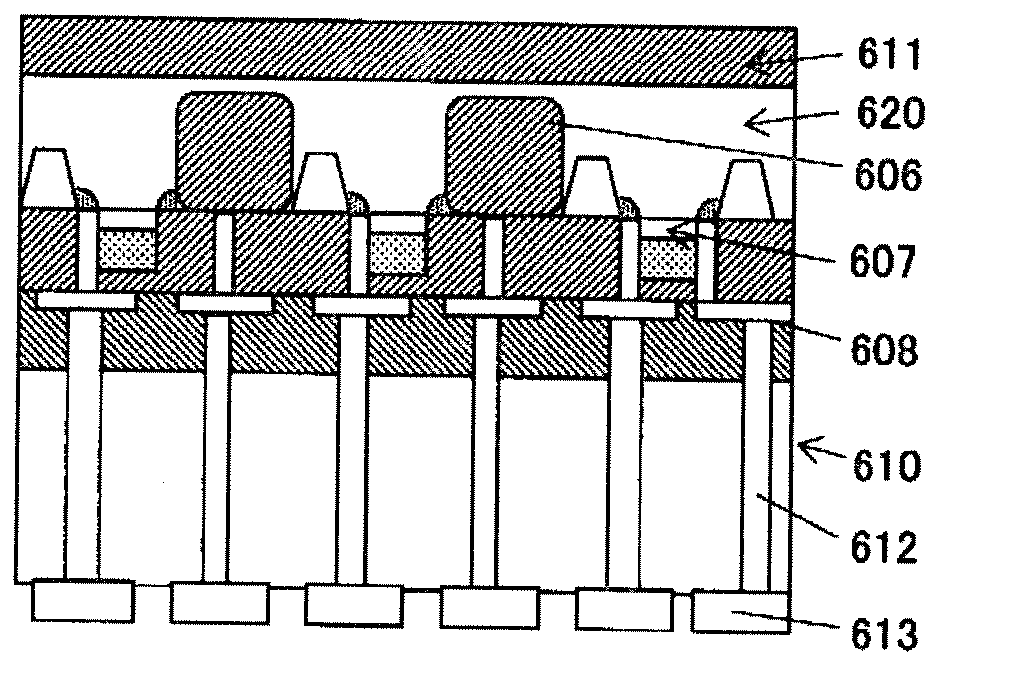

SONOS embedded memory with CVD dielectric

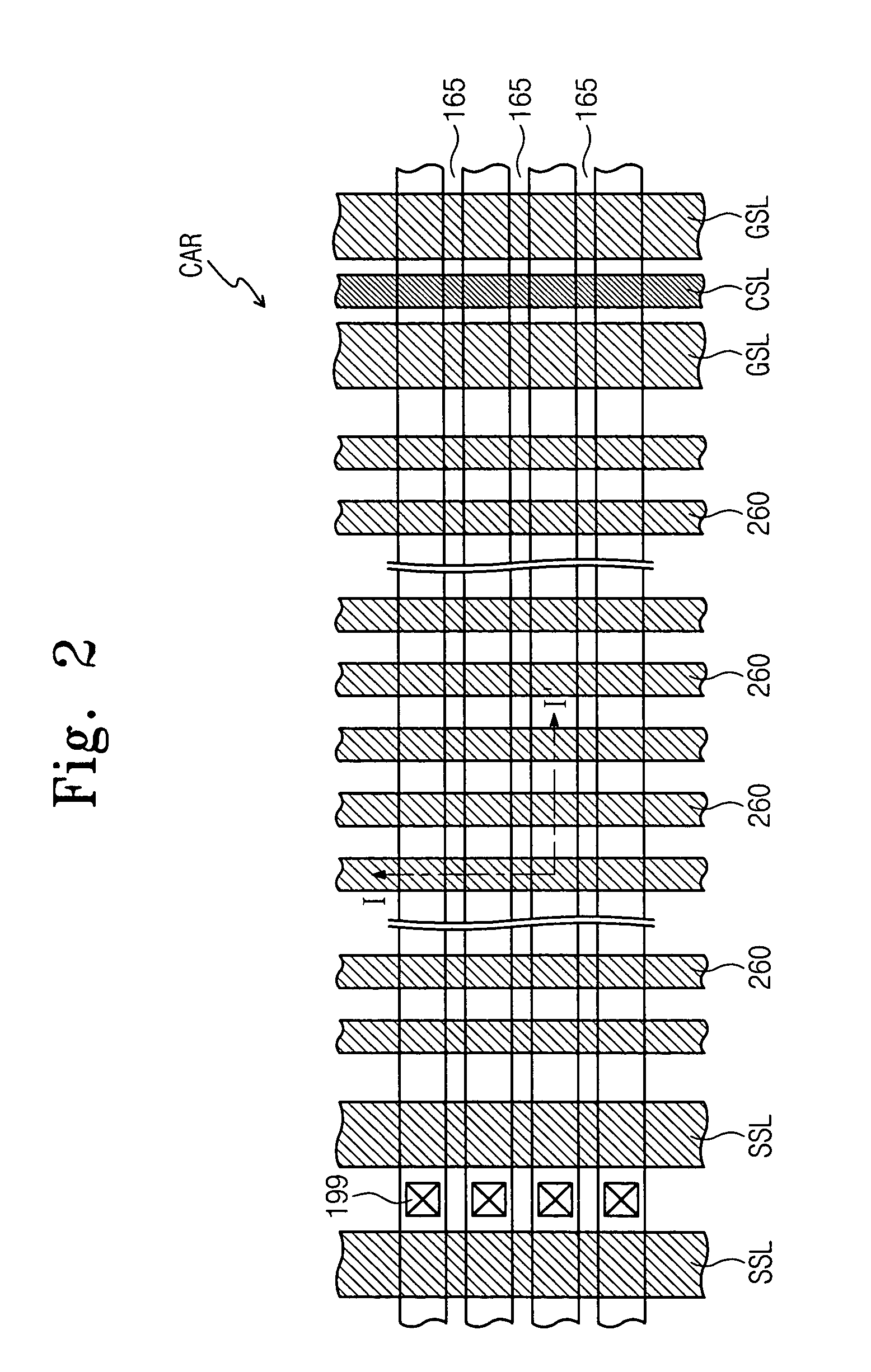

InactiveUS20050186741A1Faster rateRegion of becomes thinSolid-state devicesSemiconductor/solid-state device manufacturingCMOSBit line

An embedded semiconductor memory is fabricated by: forming diffusion bit line regions in a semiconductor substrate; then thermally oxidizing the upper surface of the substrate, thereby forming a bottom oxide layer over the substrate and simultaneously forming bit line oxide regions over each of the diffusion bit line regions; and then forming an intermediate dielectric layer (e.g., silicon nitride), over the bottom oxide layer and the bit line oxide regions. CMOS well implants are then performed in a CMOS section of the device through the silicon nitride layer and bottom oxide layer. The silicon nitride layer and bottom oxide layer are then removed in the CMOS section, and a top dielectric layer, such as a high-temperature oxide or a high-k dielectric, is deposited. The top dielectric layer completes a memory stack of the memory device, and forms a gate dielectric layer of a high voltage transistor in the CMOS section.

Owner:PS4 LUXCO SARL

Semiconductor devices having a convex active region and methods of forming the same

ActiveUS20080057644A1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

Methods of forming a semiconductor device include forming a trench mask pattern on a semiconductor substrate having active regions and device isolation regions. A thermal oxidation process is performed using the trench mask pattern as a diffusion mask to form a thermal oxide layer defining a convex upper surface of the active regions. The thermal oxide layer and the semiconductor substrate are etched using the trench mask pattern as an etch mask to form trenches defining convex upper surfaces of the active regions. The trench mask pattern is removed to expose the convex upper surfaces of the active regions. Gate patterns are formed extending over the active regions.

Owner:SAMSUNG ELECTRONICS CO LTD

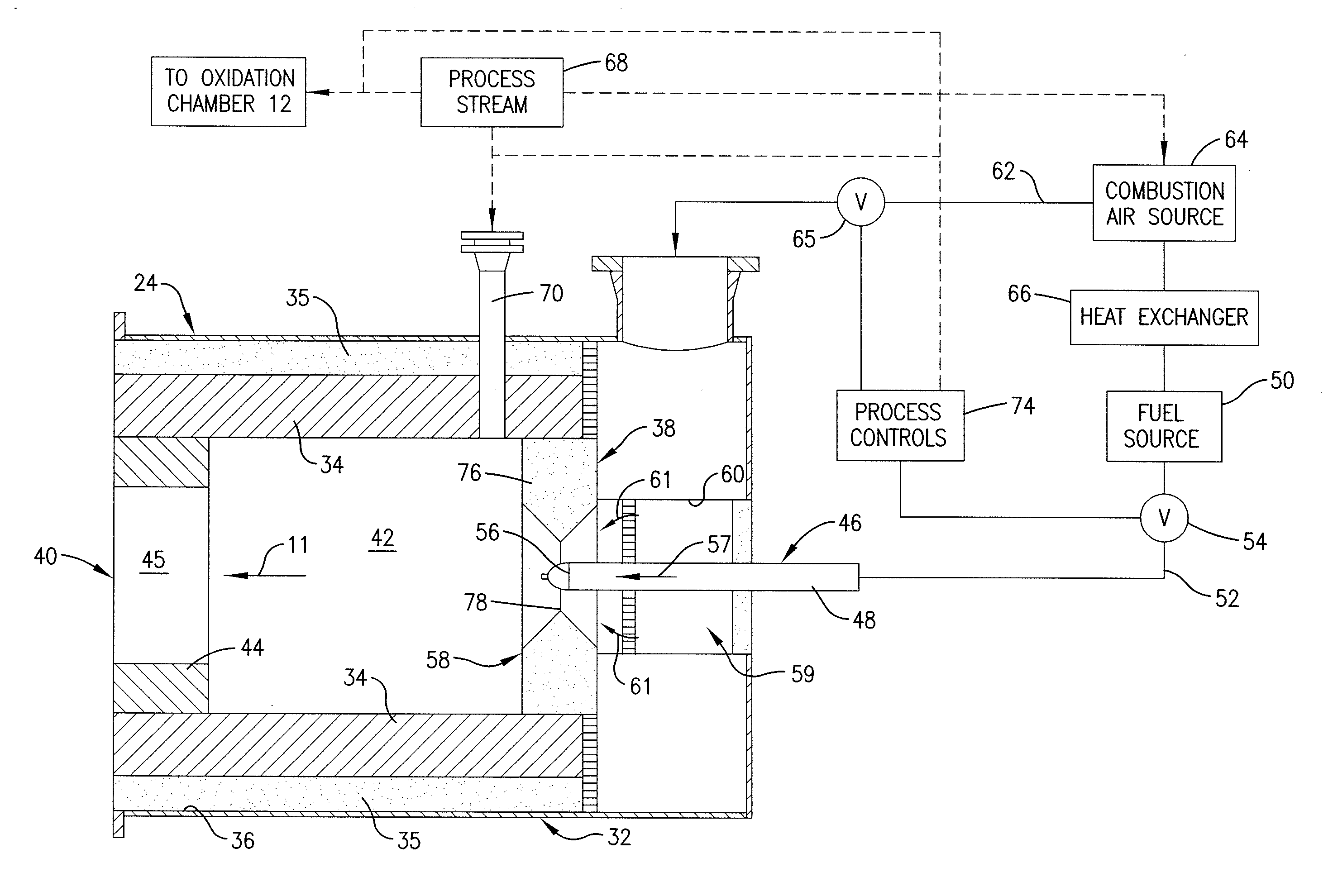

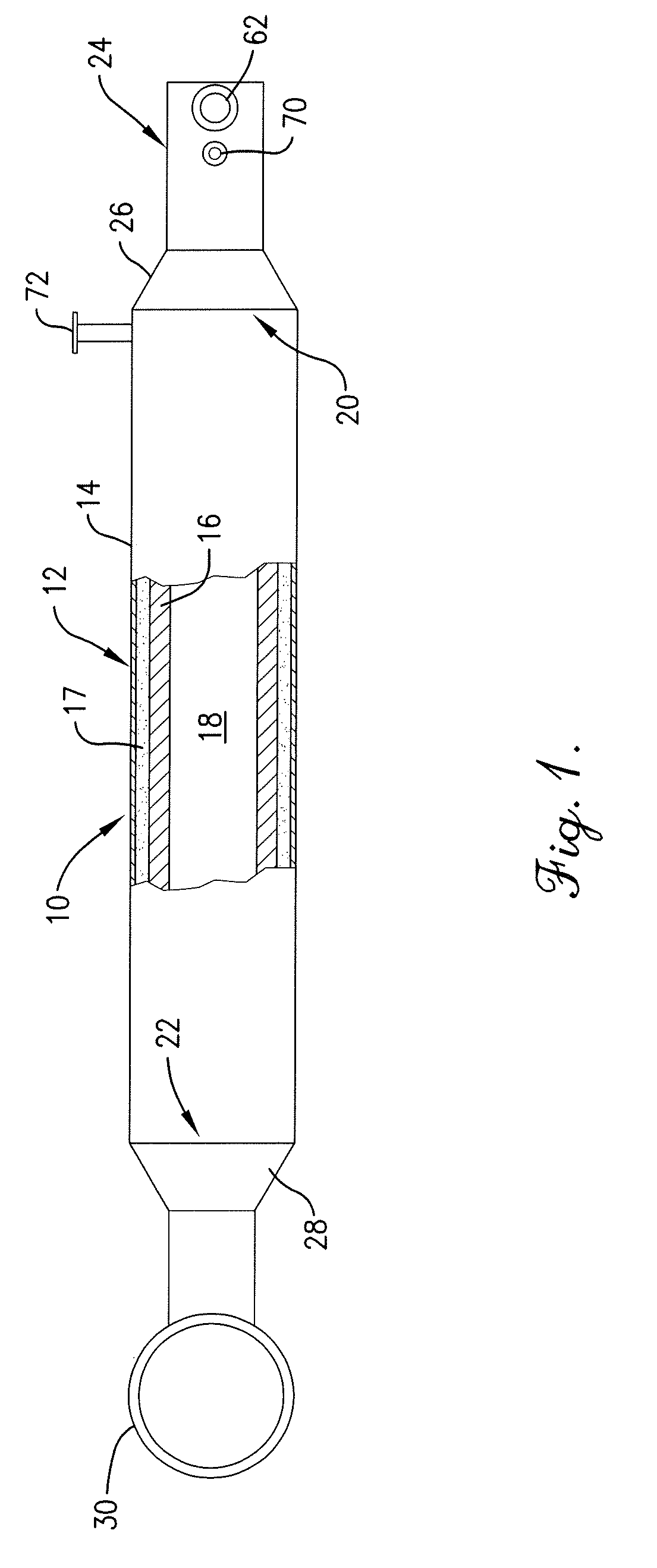

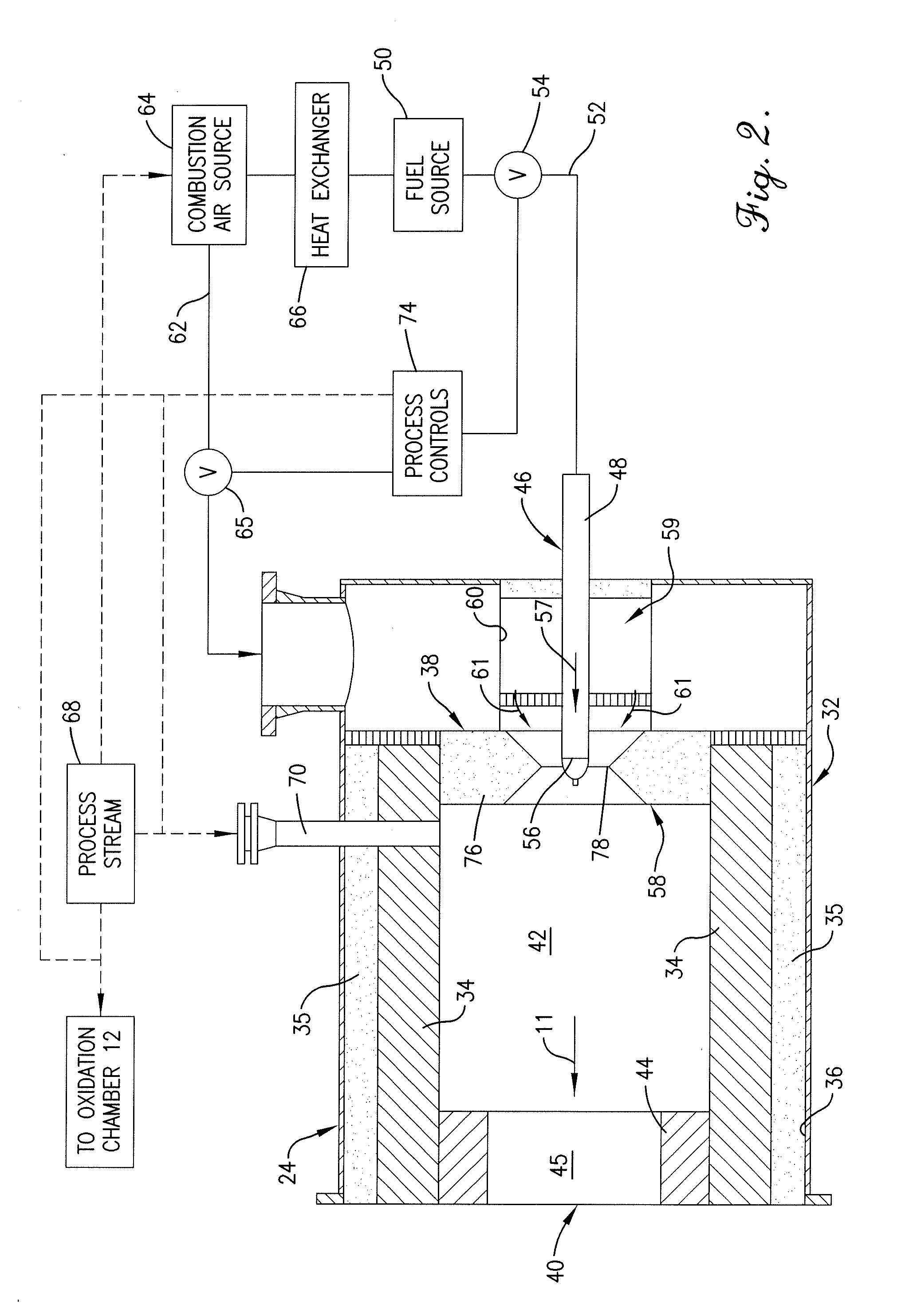

Method and apparatus for treatment of waste

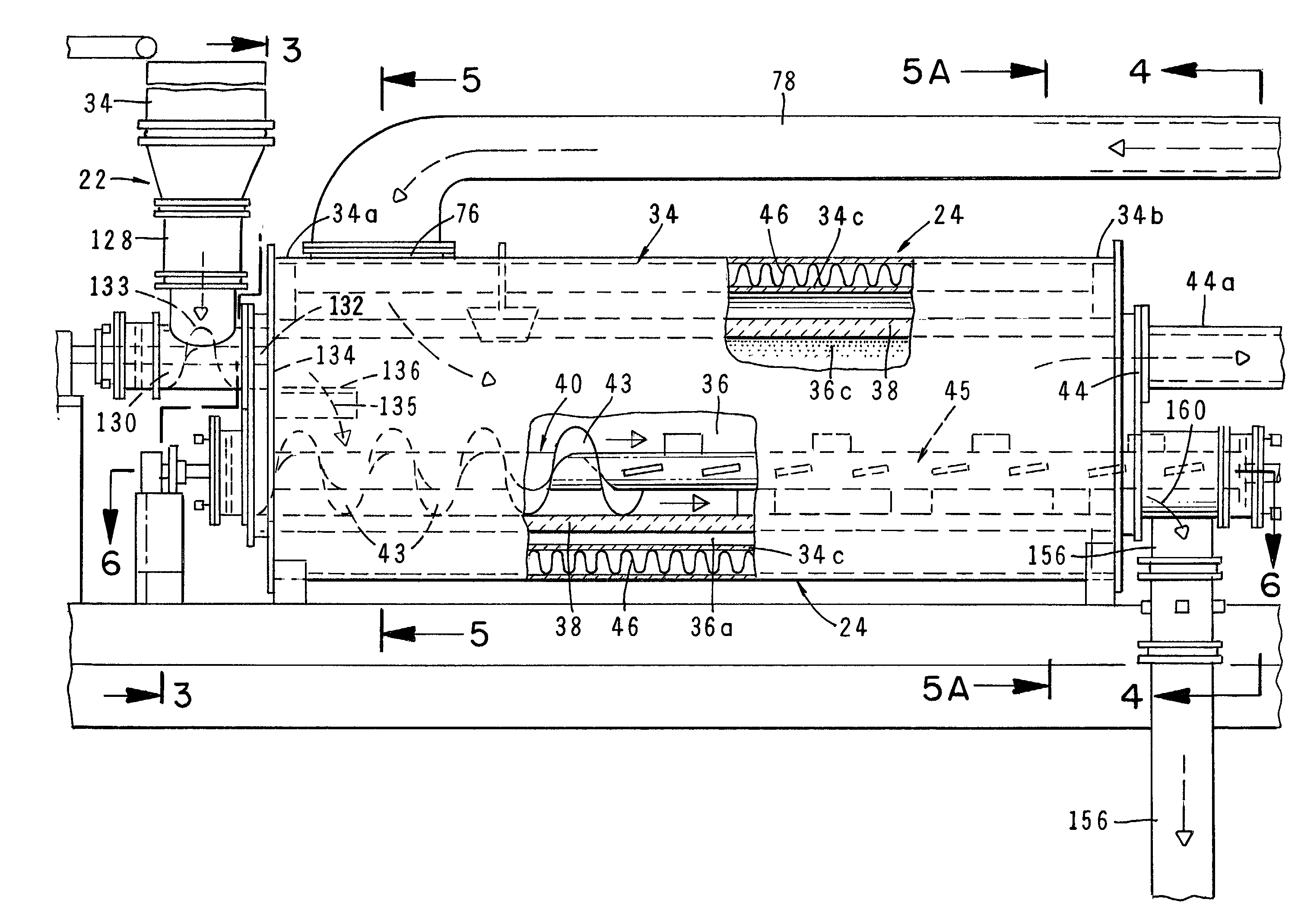

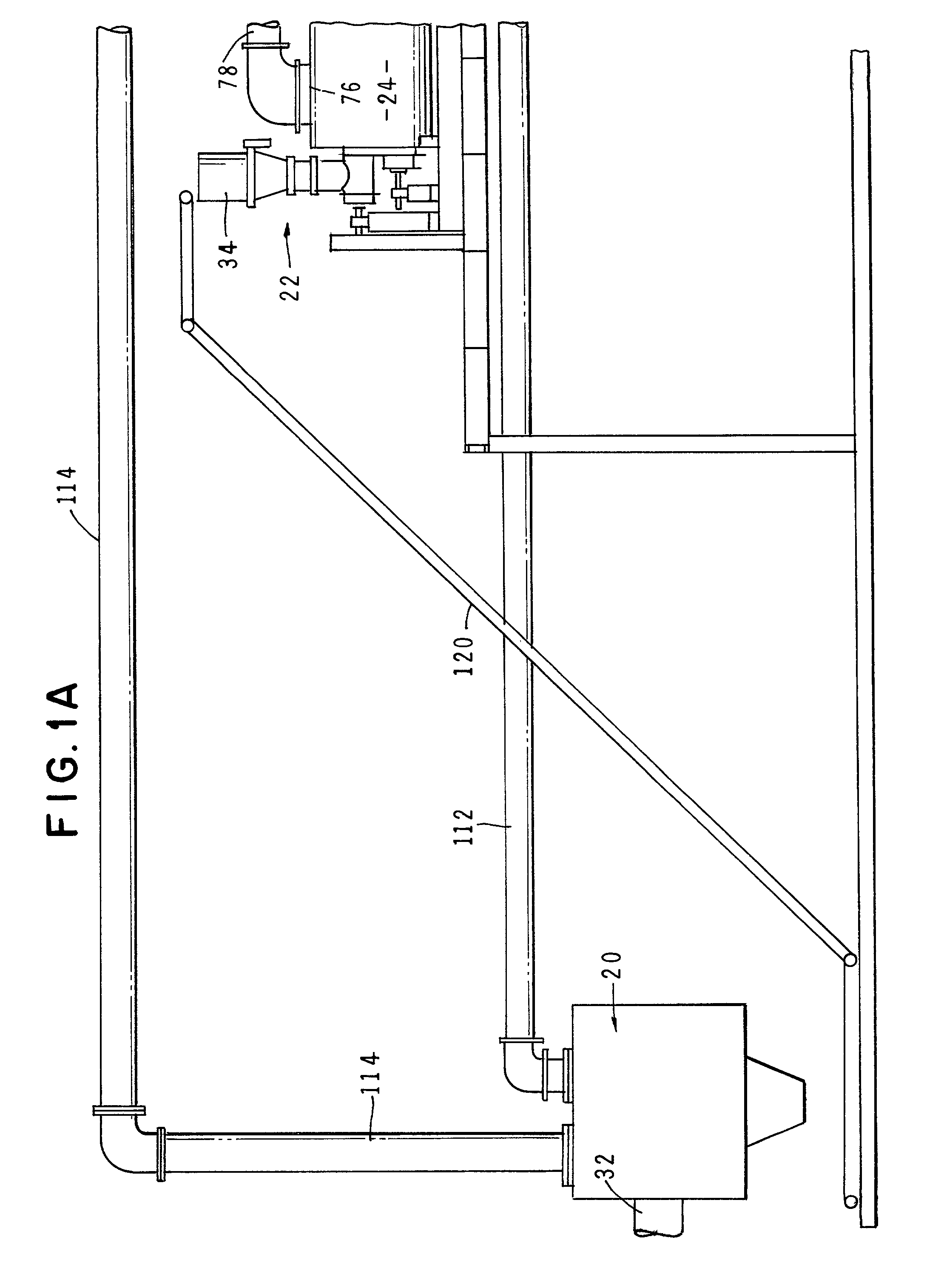

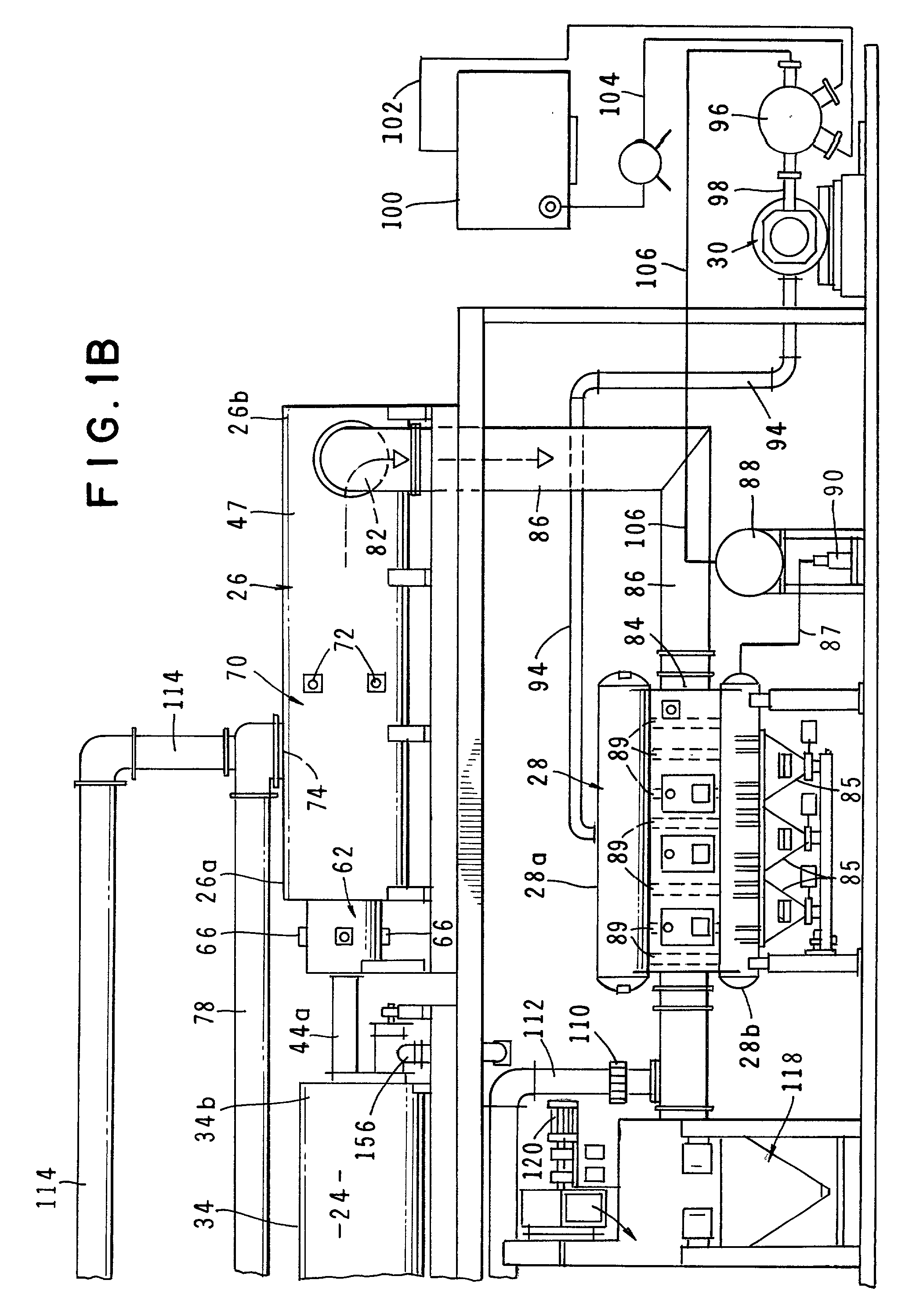

InactiveUS20020195031A1Efficient and reliable in operationEasy maintenanceSolid fuel combustionIncinerator apparatusEngineeringTransfer mechanism

An apparatus for treating waste material that comprises four major cooperating subsystems, namely a pyrolytic converter, a two-stage thermal oxidizer, a steam generator and a steam turbine driven by steam generated by the steam generator. In operation, the pyrolytic converter is uniquely heated without any flame impinging on the reactor component and the waste material to be pyrolyzed is transported through the reaction chamber of the pyrolytic converter by a pair of longitudinally extending, side-by-side material transfer mechanisms. Each of the transfer mechanisms includes a first screw conveyor section made up of a plurality of helical flights for conveying the heavier waste and a second paddle conveyor section interconnected with the first section for conveying the partially pyrolyzed waste, the second section comprising a plurality of paddle flights. Once operating, the apparatus is substantially self-sustaining and requires a minimum use of outside energy sources for pyrolyzing the waste materials.

Owner:APS IP HLDG

MEMS element, GLV device, and laser display

InactiveUS7016099B2No damageFacilitate control of elastic forceTelevision system detailsLaser detailsDisplay deviceOptoelectronics

A MEMS element is constituted as a light modulation element for constituting a GLV device, and it has the same constitution as a conventional MEMS element except for differing in the structure of a bridge member of a membrane. The membrane comprises SiN film of, for example, 100 nm in thickness laminated thereon, and a combined light reflective film and membrane-side electrode composed of an Al film of 100 nm in thickness provided on the bridge member. The SiO2 film may be a SiO2 film formed by thermal oxidation of a sacrificing layer formed of polysilicon or may be a SiO2 film formed by a CVD method or a PVD method.

Owner:SONY CORP

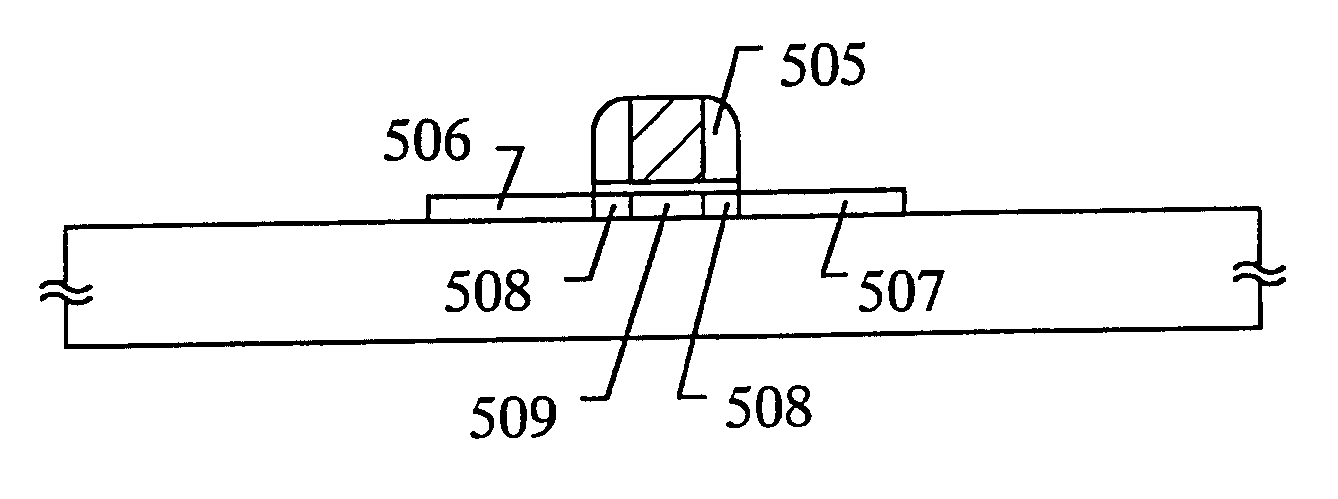

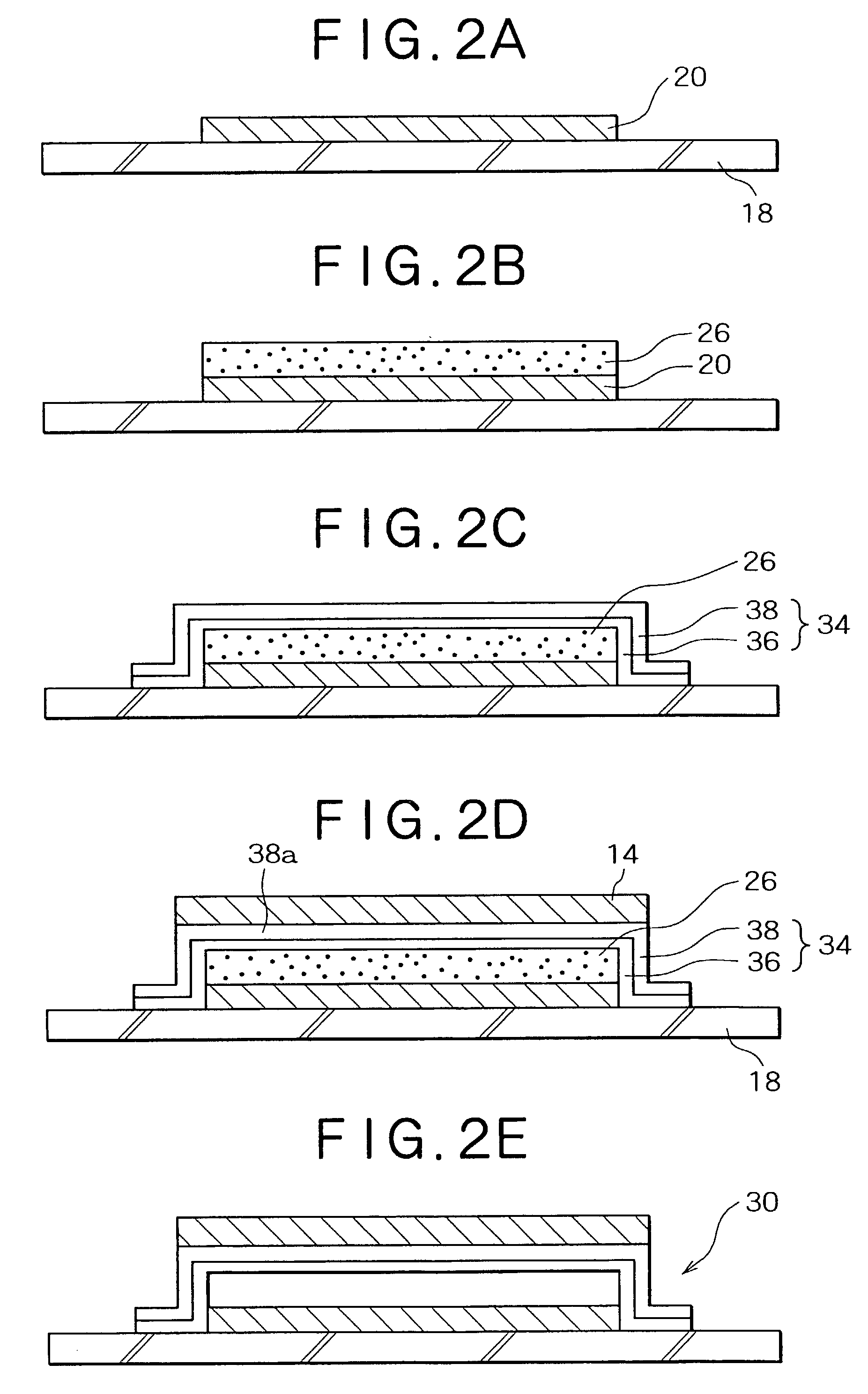

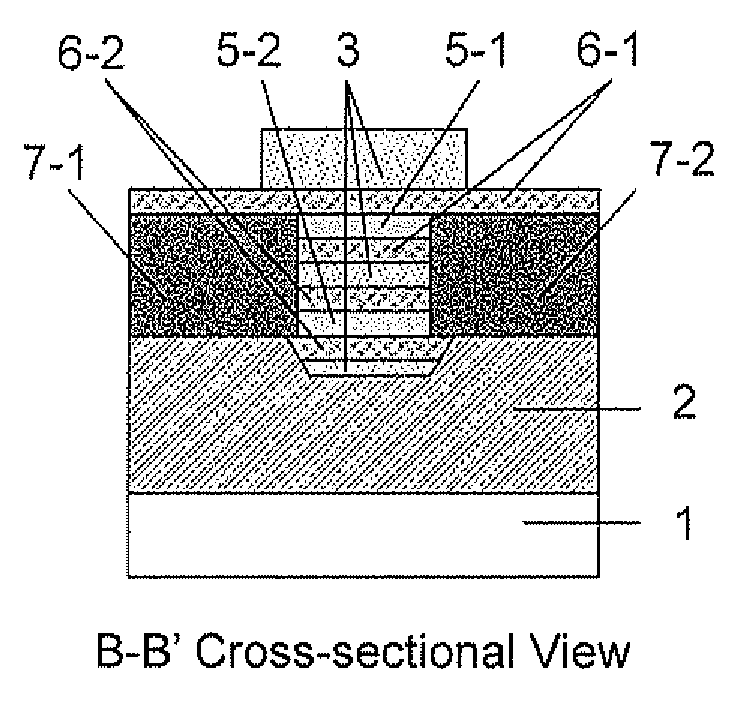

Nano-wire field effect transistor, method for manufacturing the transistor, and integrated circuit including the transistor

InactiveUS20110057163A1Superior in size reproducibility and uniformityNanoinformaticsSemiconductor/solid-state device manufacturingNanowireSoi substrate

Provided is a method for fabricating a nano-wire field effect transistor including steps of: preparing a nano-wire field effect transistor including two columnar members made of a silicon crystal configuring a nano-wire on a substrate are arranged on a substrate in parallel and one above the other, and an SOI substrate having a (100) surface orientation; processing a silicon crystal layer configuring the SOI substrate into a standing plate-shaped member having a rectangular cross-section; processing the silicon crystal by orientation dependent wet etching and thermal oxidation into a shape where two triangular columnar members are arranged one above the other with a spacing from each other as to face along the ridge lines of the triangular columnar members; and processing the triangular columnar member into a circular columnar member configuring a nano-wire by hydrogen-annealing or a thermal oxidation; and an integrated circuit including the transistor.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Methods of Forming a Dielectric Cap Layer on a Metal Gate Structure

ActiveUS20130181263A1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

Disclosed herein are various methods of forming isolation structures on FinFETs and other semiconductor devices, and the resulting devices that have such isolation structures. In one example, the method includes forming a plurality of spaced-apart trenches in a semiconducting substrate, wherein the trenches define a fin for a FinFET device, forming a layer of insulating material in the trenches, wherein the layer of insulating material covers a lower portion of the fin but not an upper portion of the fin, forming a protective material on the upper portion of the fin, and performing a heating process in an oxidizing ambient to form a thermal oxide region on the covered lower portion of the fin.

Owner:GLOBALFOUNDRIES US INC

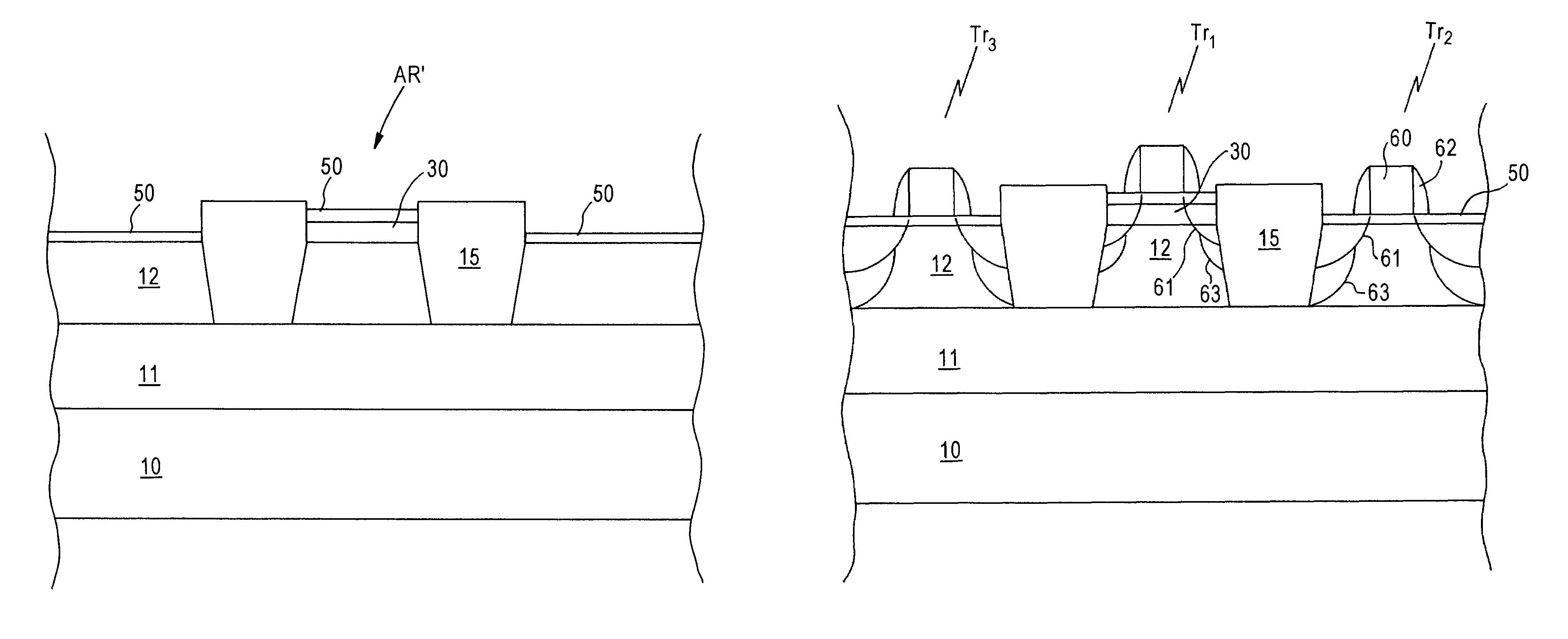

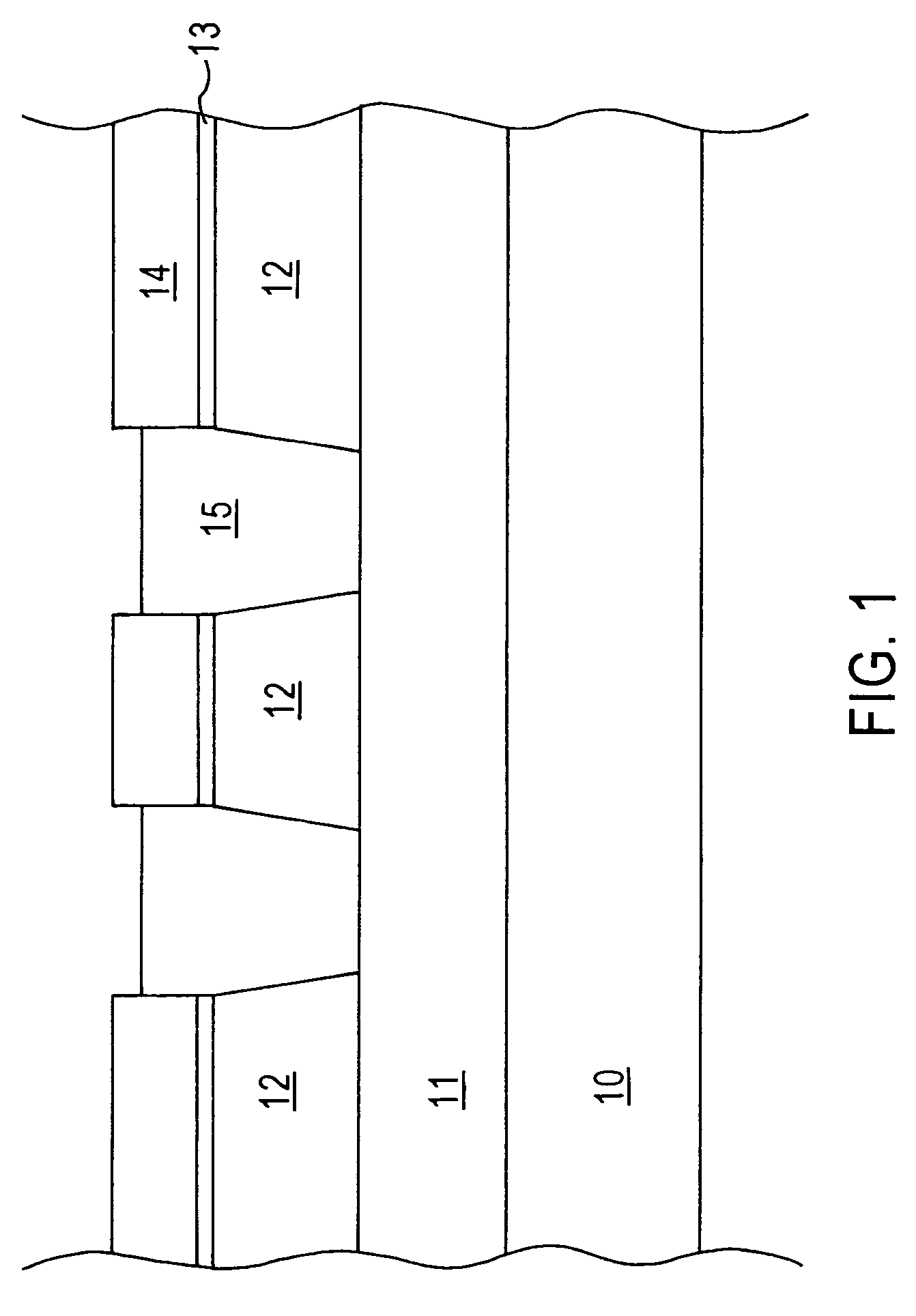

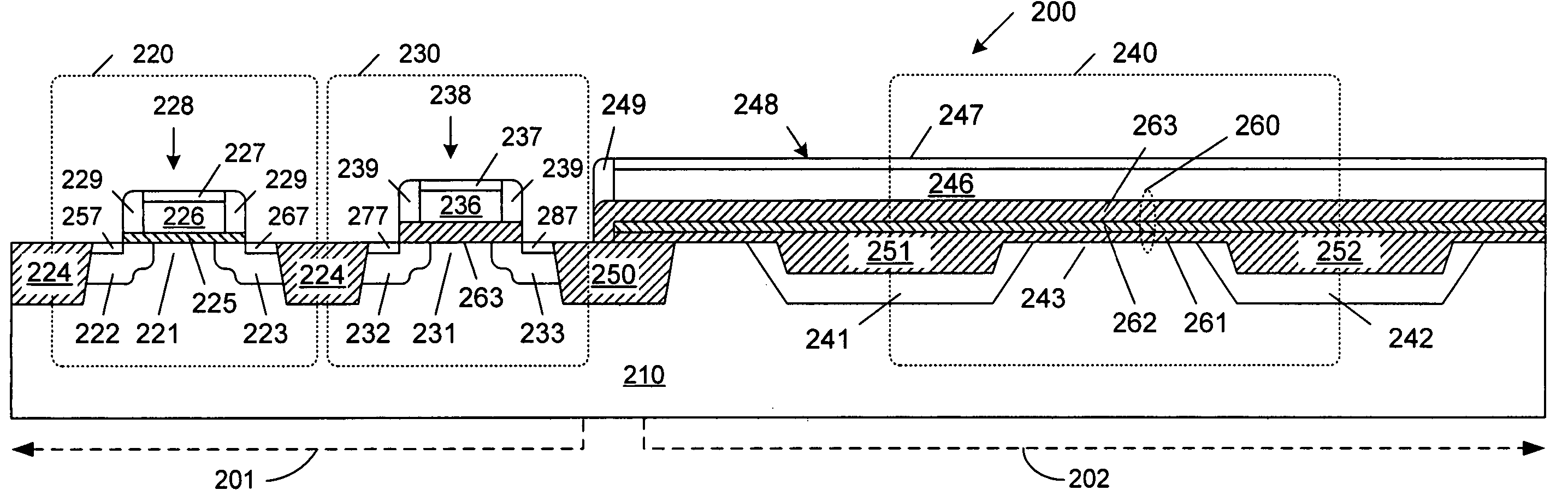

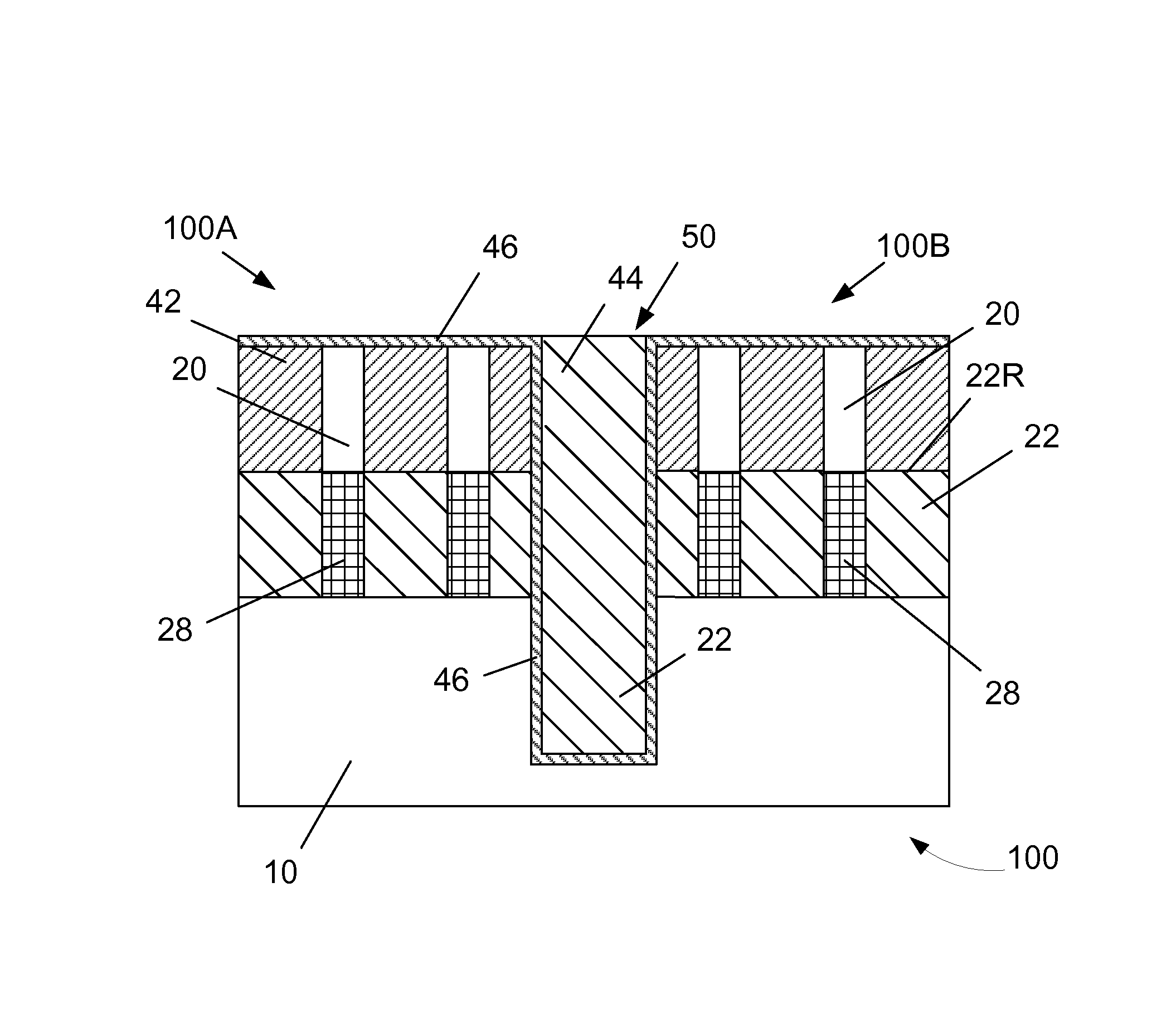

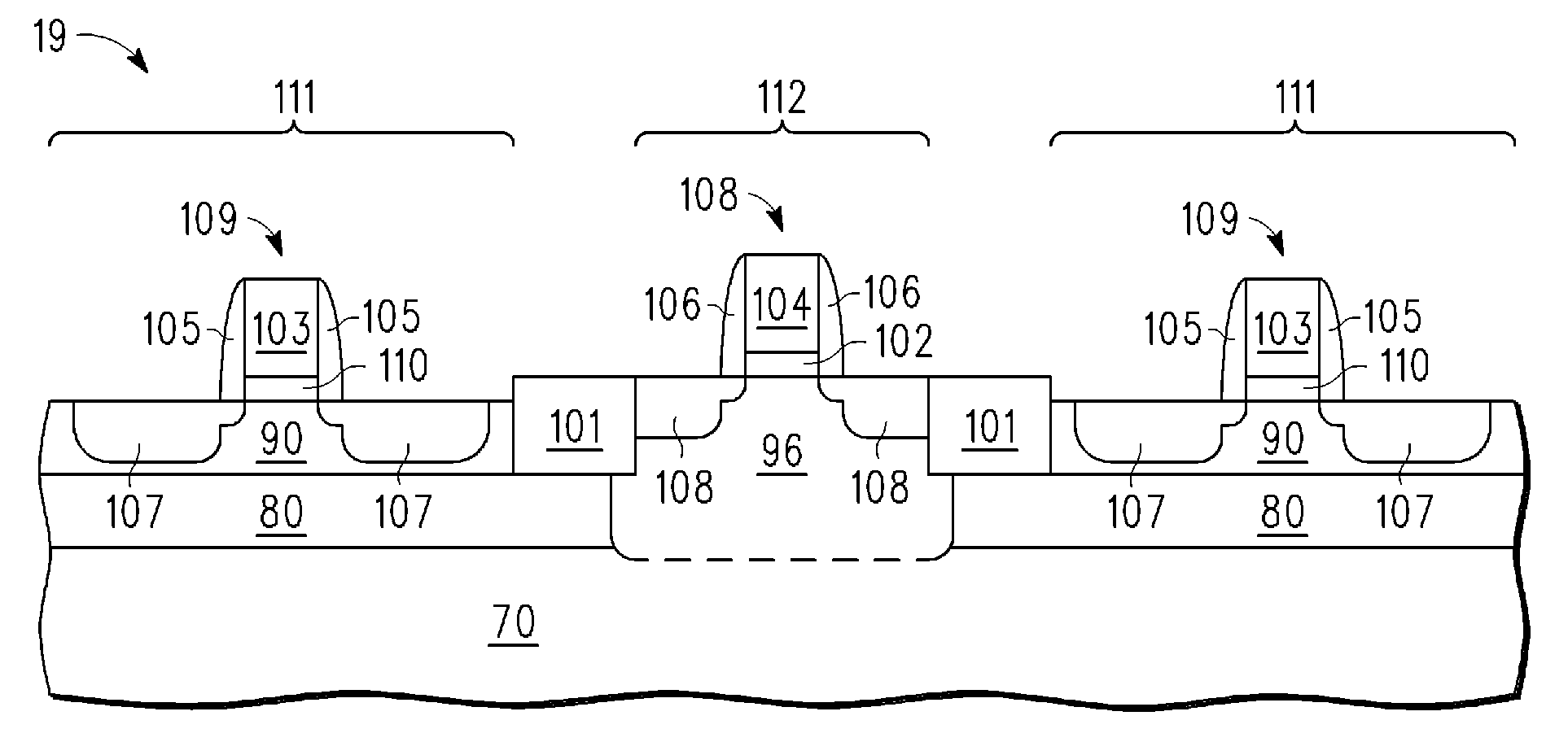

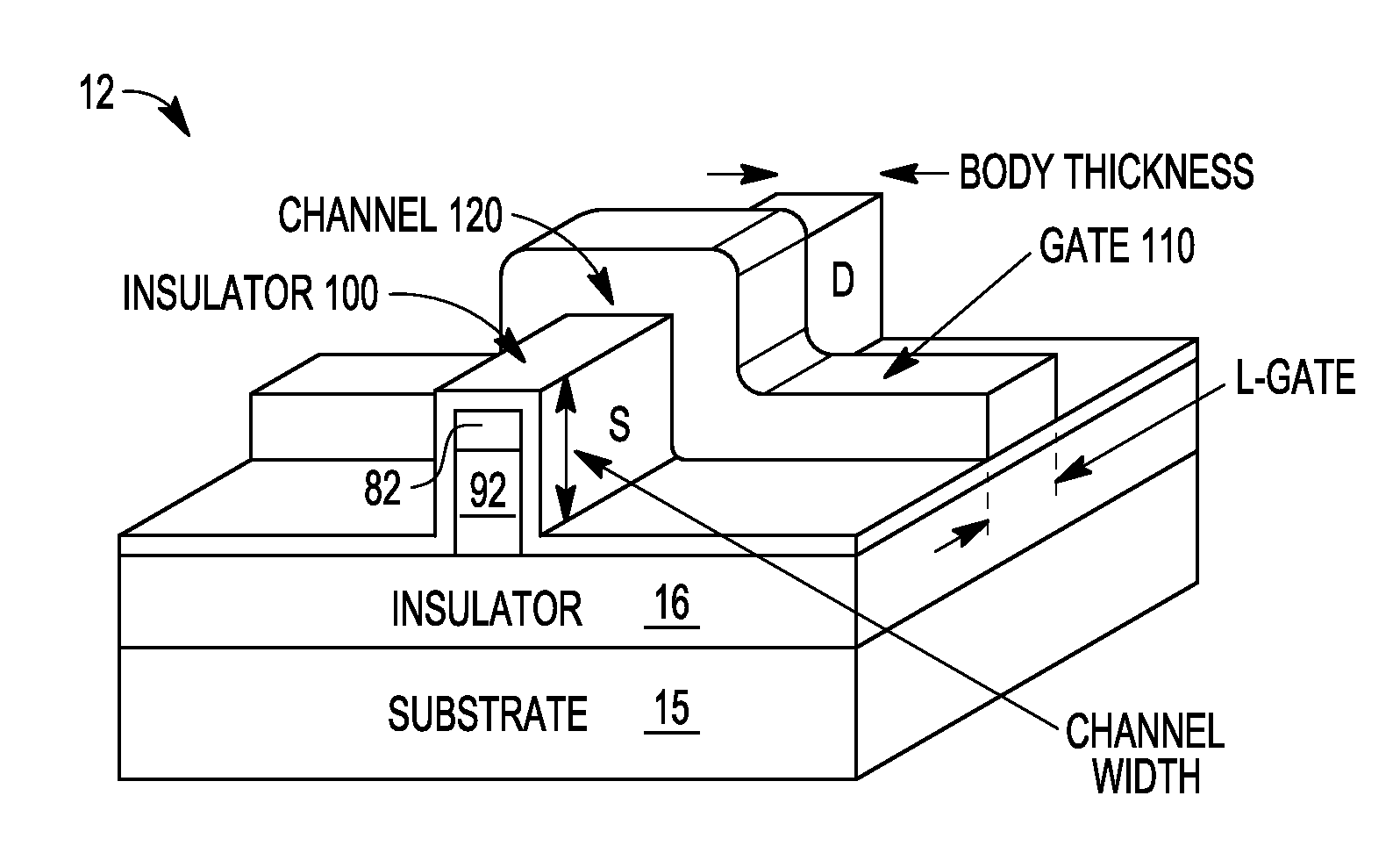

Dual substrate orientation or bulk on SOI integrations using oxidation for silicon epitaxy spacer formation

ActiveUS20080274595A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductorEpitaxy

A semiconductor process and apparatus provide a planarized hybrid substrate (15) by thermally oxidizing SOI sidewalls (90) in a trench opening (93) to form SOI sidewall oxide spacers (94) which are trimmed while etching through a buried oxide layer (80) to expose the underlying bulk substrate (70) for subsequent epitaxial growth of an epitaxial semiconductor layer (96). In this way, SOI sidewall oxide spacers (94) are formed that prevent epitaxial SOI sidewalls from being formed in the trench opening (93) during the epitaxial growth step, and that can be readily removed during any subsequent STI etch process

Owner:NXP USA INC

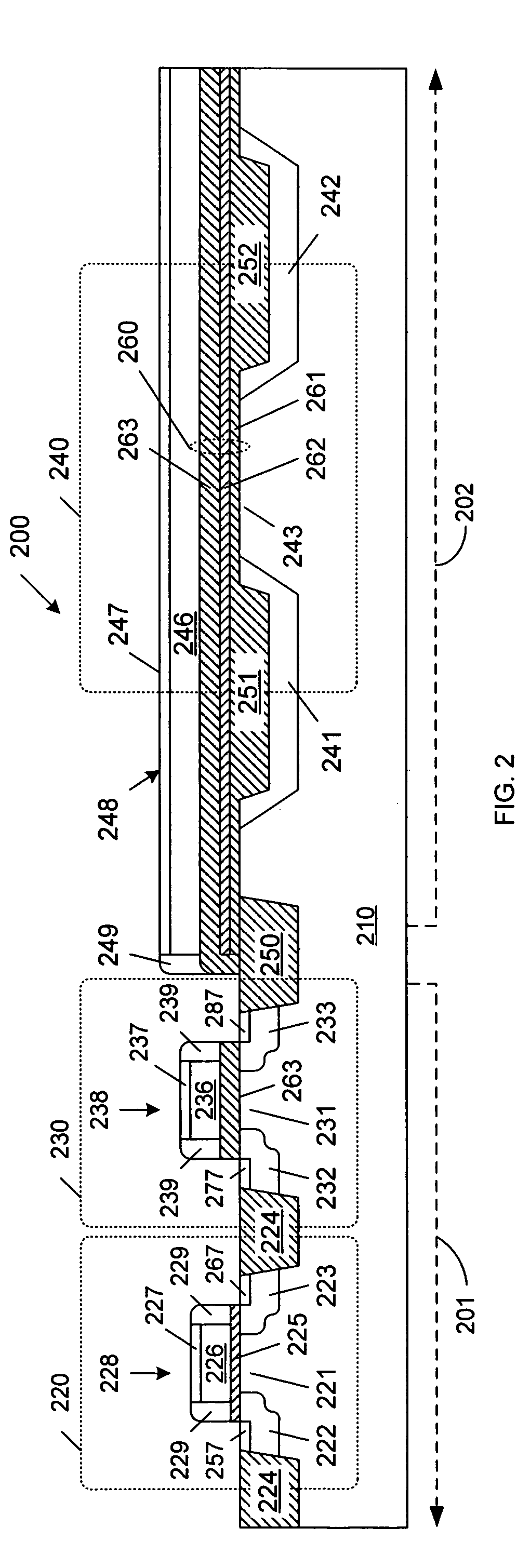

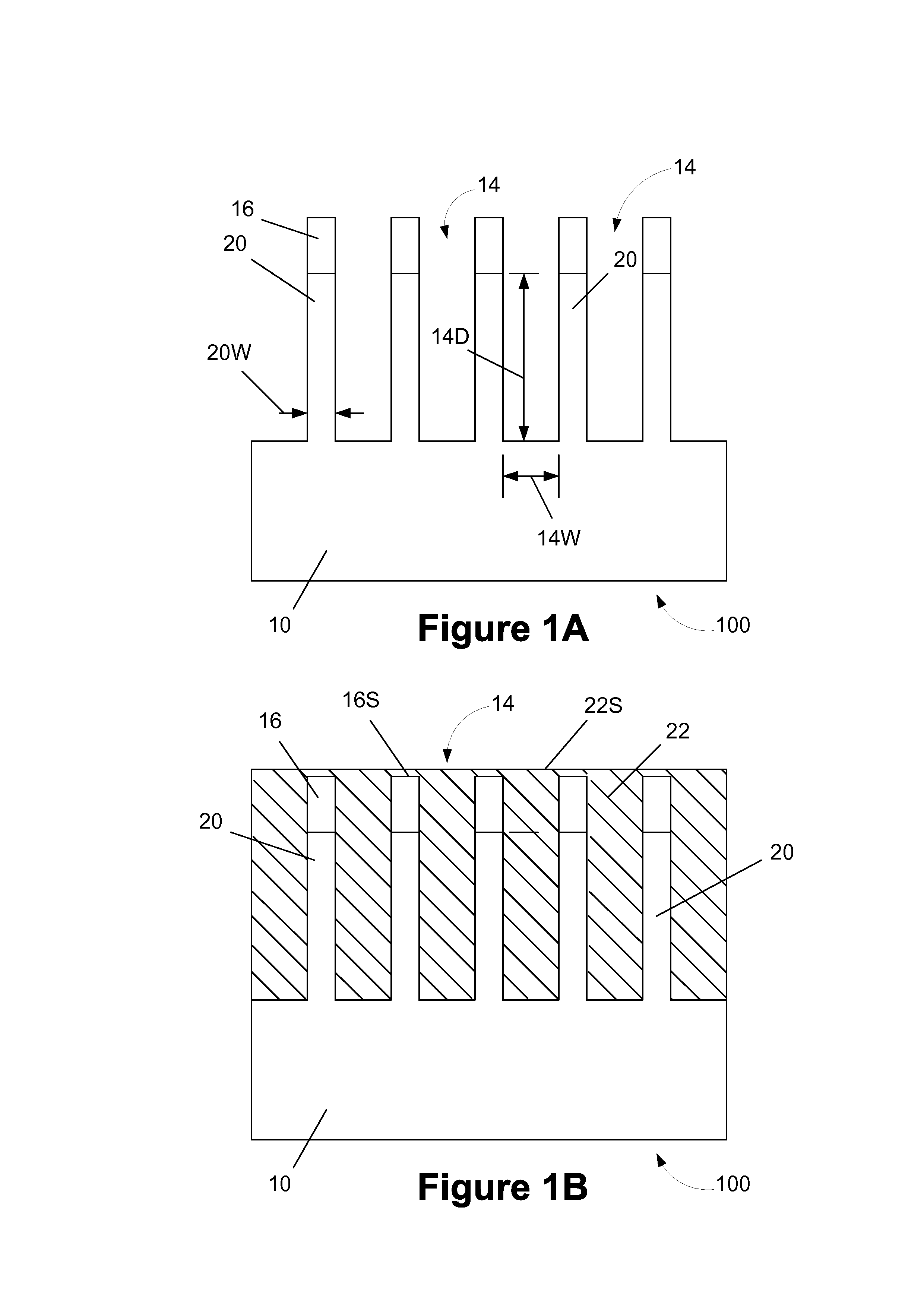

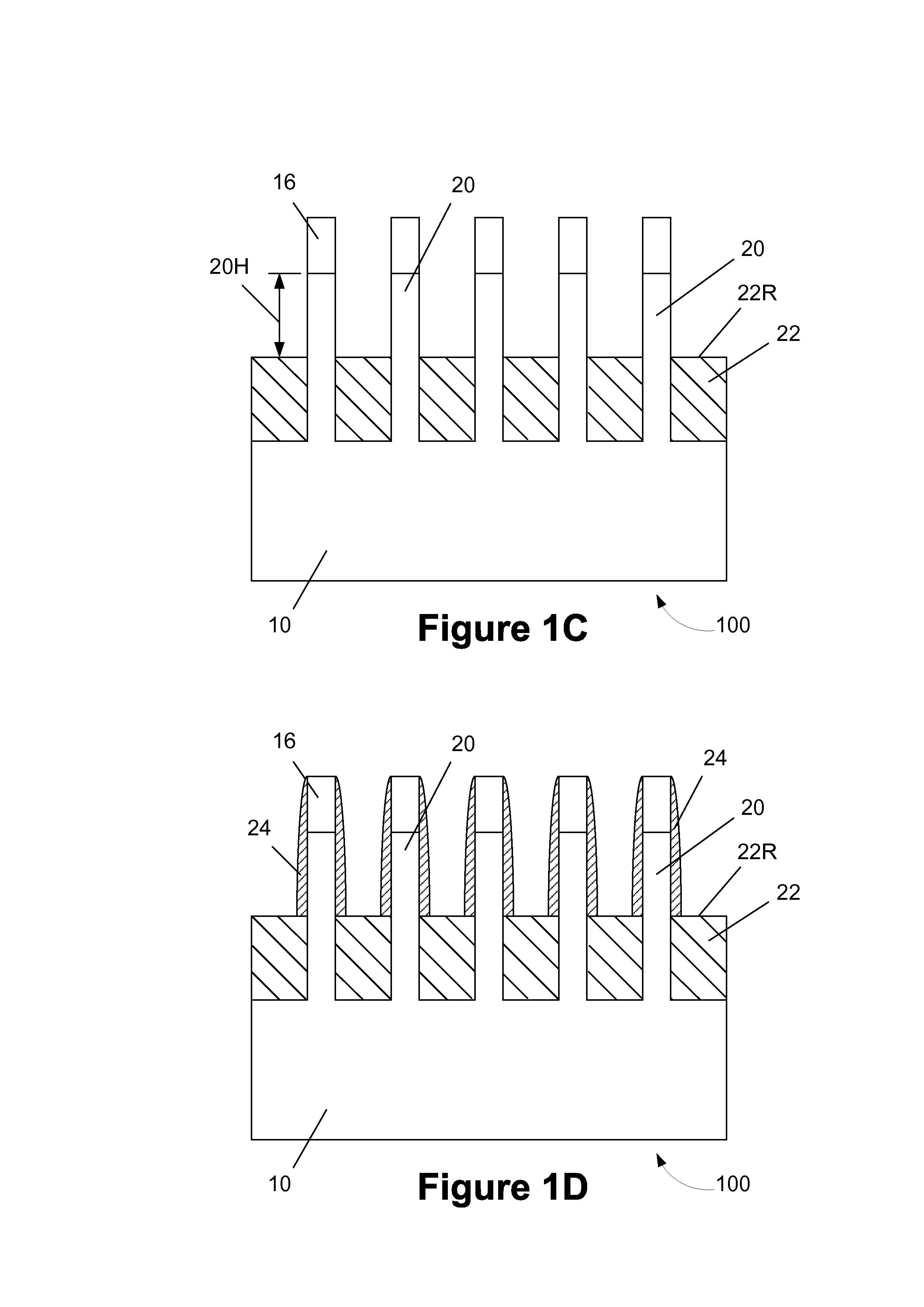

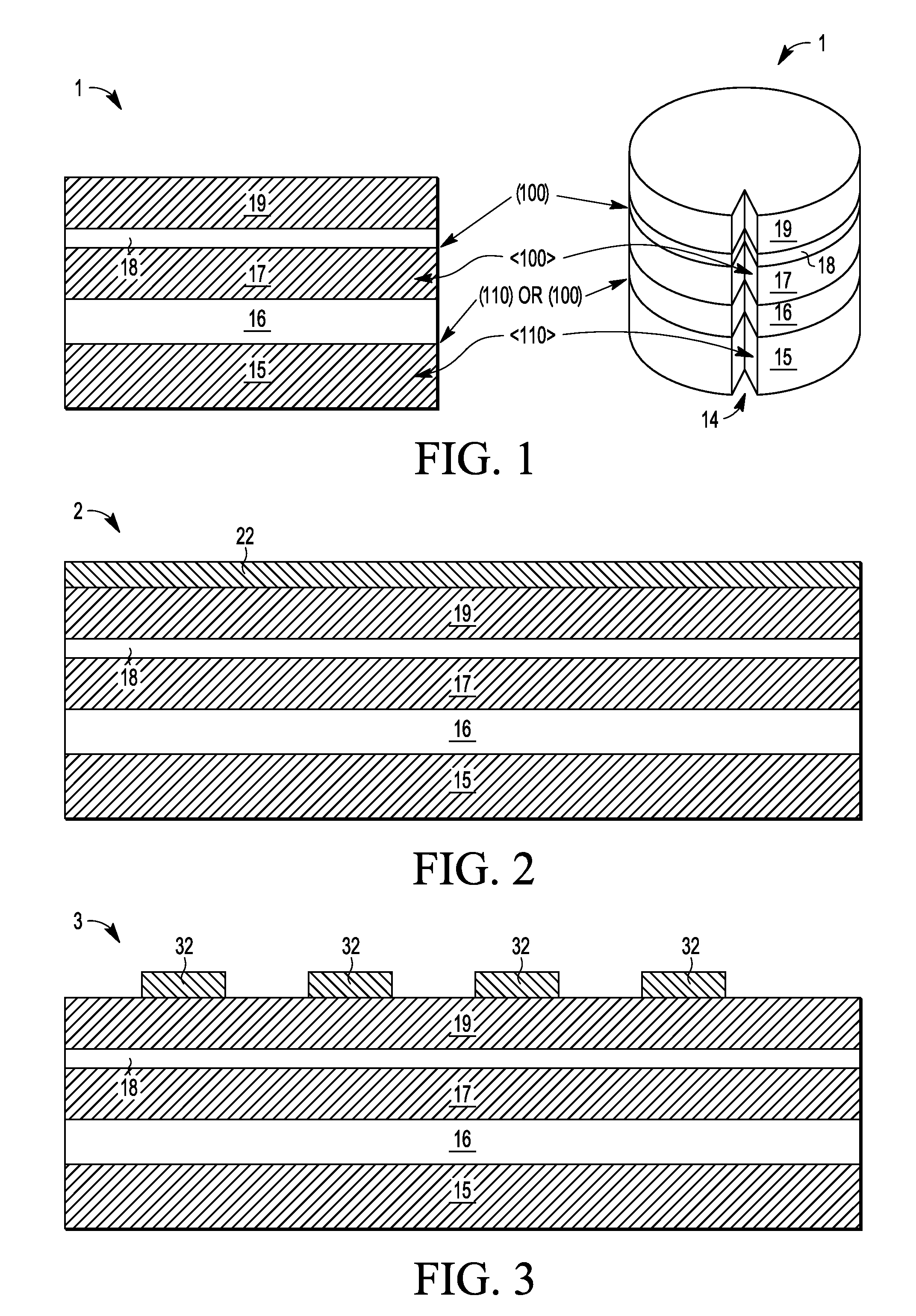

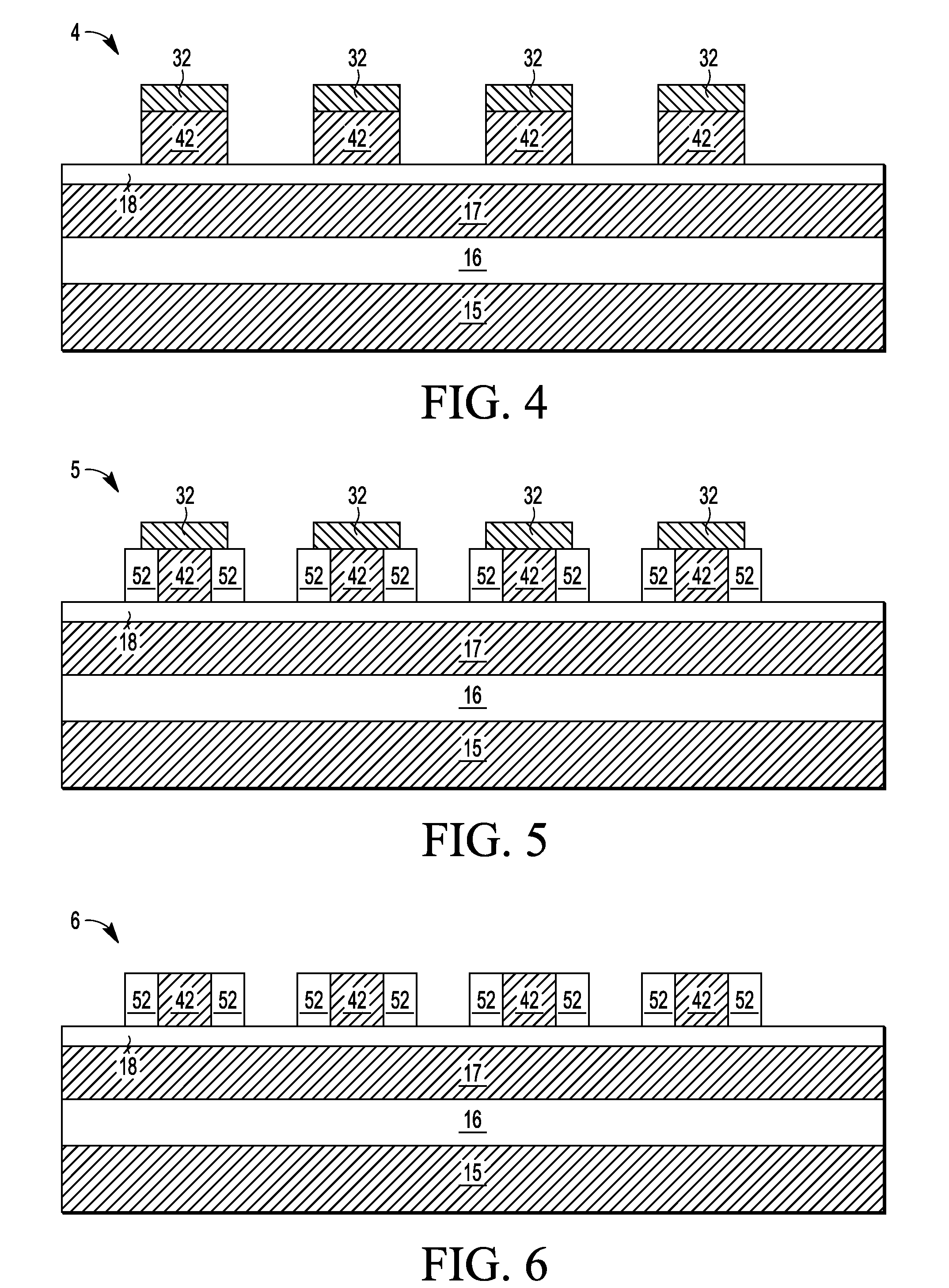

FinFET Formation with a Thermal Oxide Spacer Hard Mask Formed from Crystalline Silicon Layer

InactiveUS20110053361A1Decorative surface effectsSemiconductor/solid-state device manufacturingOptoelectronicsSingle crystal

A semiconductor process and apparatus provide a FinFET device by forming a second single crystal semiconductor layer (19) that is isolated from an underlying first single crystal semiconductor layer (17) by a buried insulator layer (18); patterning and etching the second single crystal semiconductor layer (19) to form a single crystal mandrel (42) having vertical sidewalls; thermally oxidizing the vertical sidewalls of the single crystal mandrel to grow oxide spacers (52) having a substantially uniform thickness; selectively removing any remaining portion of the single crystal mandrel (42) while substantially retaining the oxide spacers (52); and selectively etching the first single crystal semiconductor layer (17) using the oxide spacers (52) to form one or more FinFET channel regions (92).

Owner:NXP USA INC +1

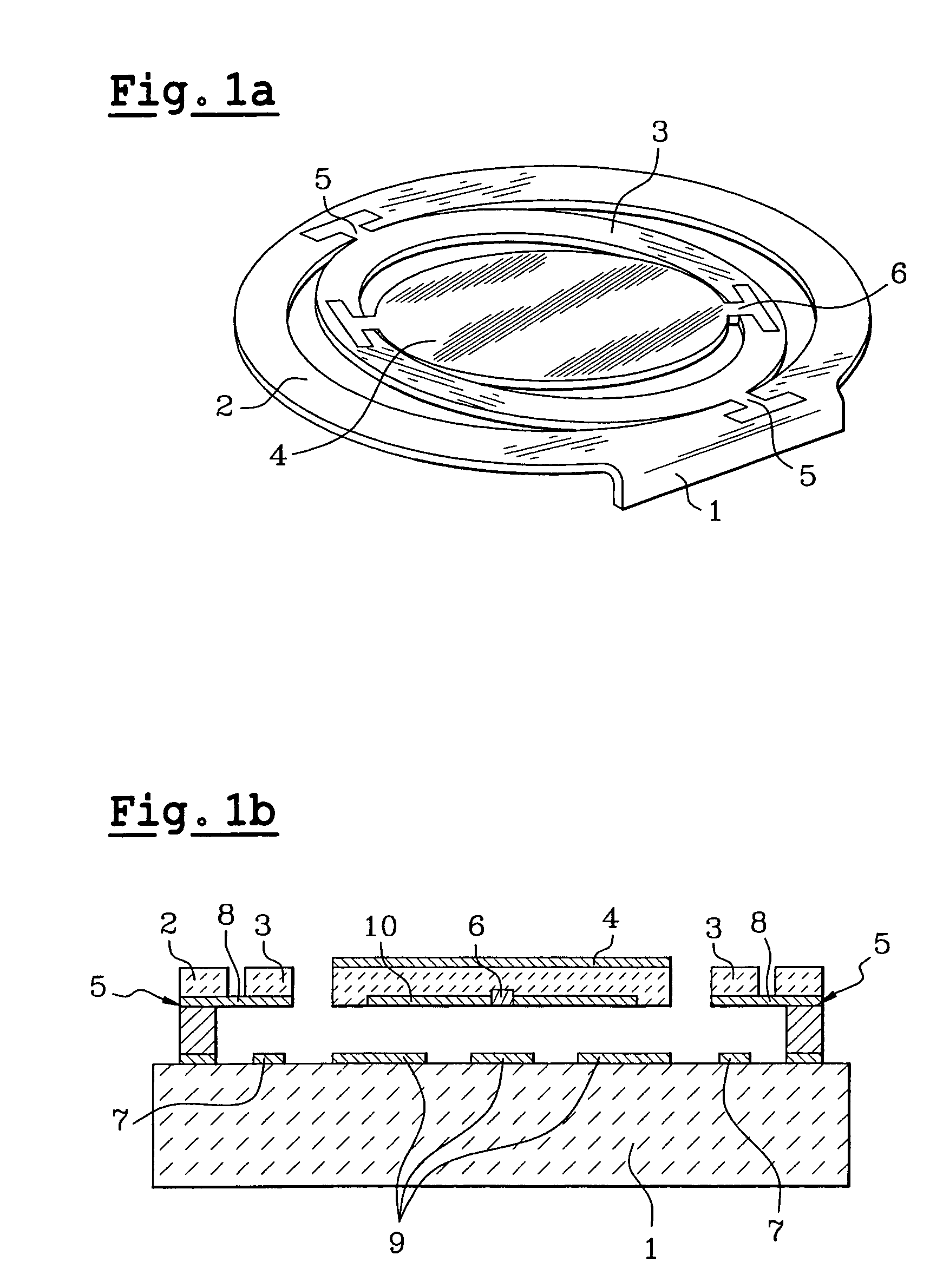

Method for making an optical micromirror and micromirror or array of micromirrors obtained by said method

InactiveUS7022249B2Overcome limitationsGreat freedomDecorative surface effectsOptical articlesProjection systemMicromirror array

A method for manufacturing an optical micro-mirror including a fixed part and a moveable part, with a reflection device connected to the fixed part by an articulation mechanism. This method realizes a stack including a mechanical substrate, a first layer of thermal oxidation material, and at least one second layer of material for forming the moveable part, realizes the articulation mechanism, realizes the reflection device on the second layer, realizes the moveable part by etching of at least the second layer of material, and eliminates the thermal oxidation layer to liberate the moveable part. Such an optical micro-mirror may find possible applications to optical routing or image projection systems.

Owner:TEEM PHOTONICS

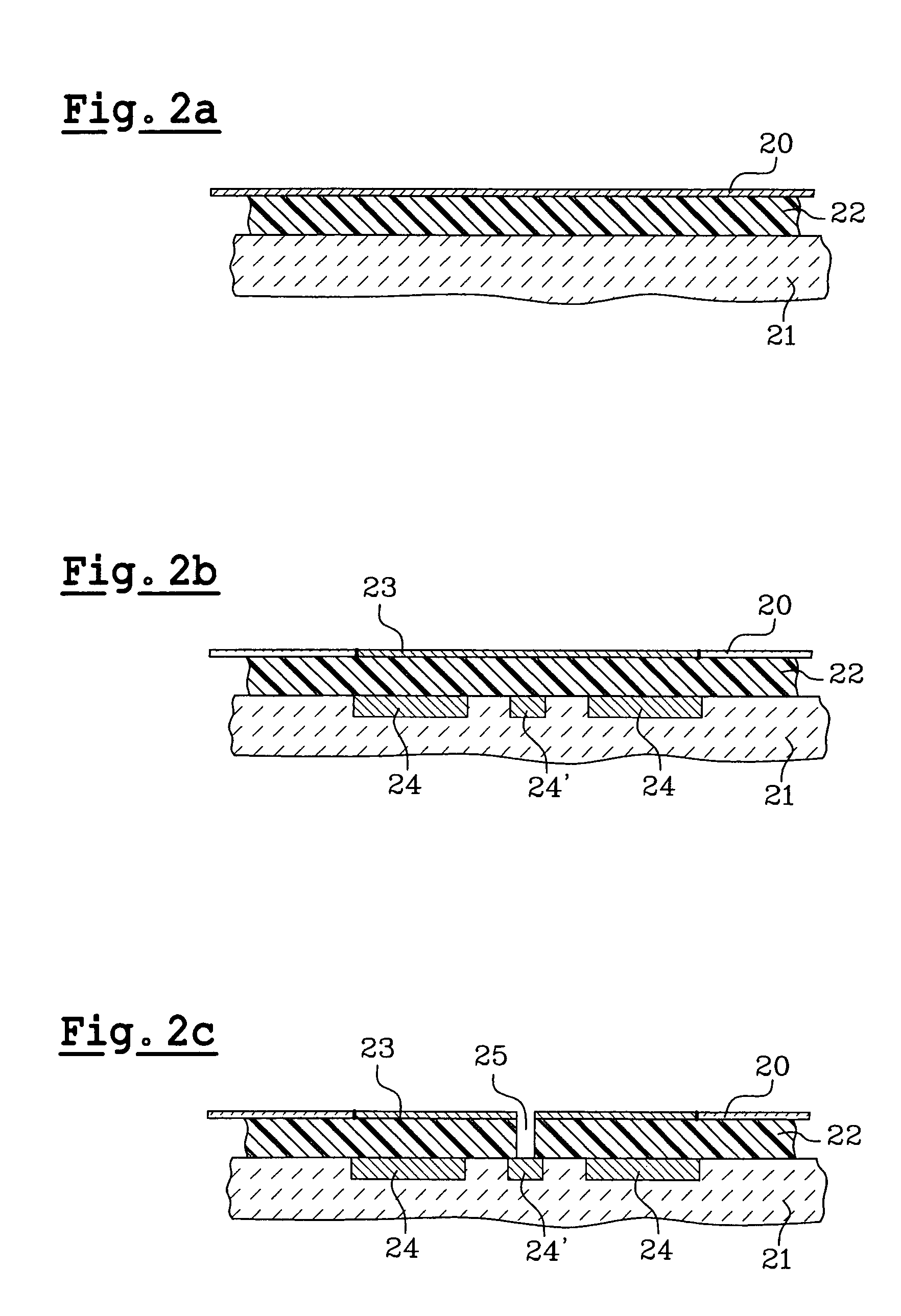

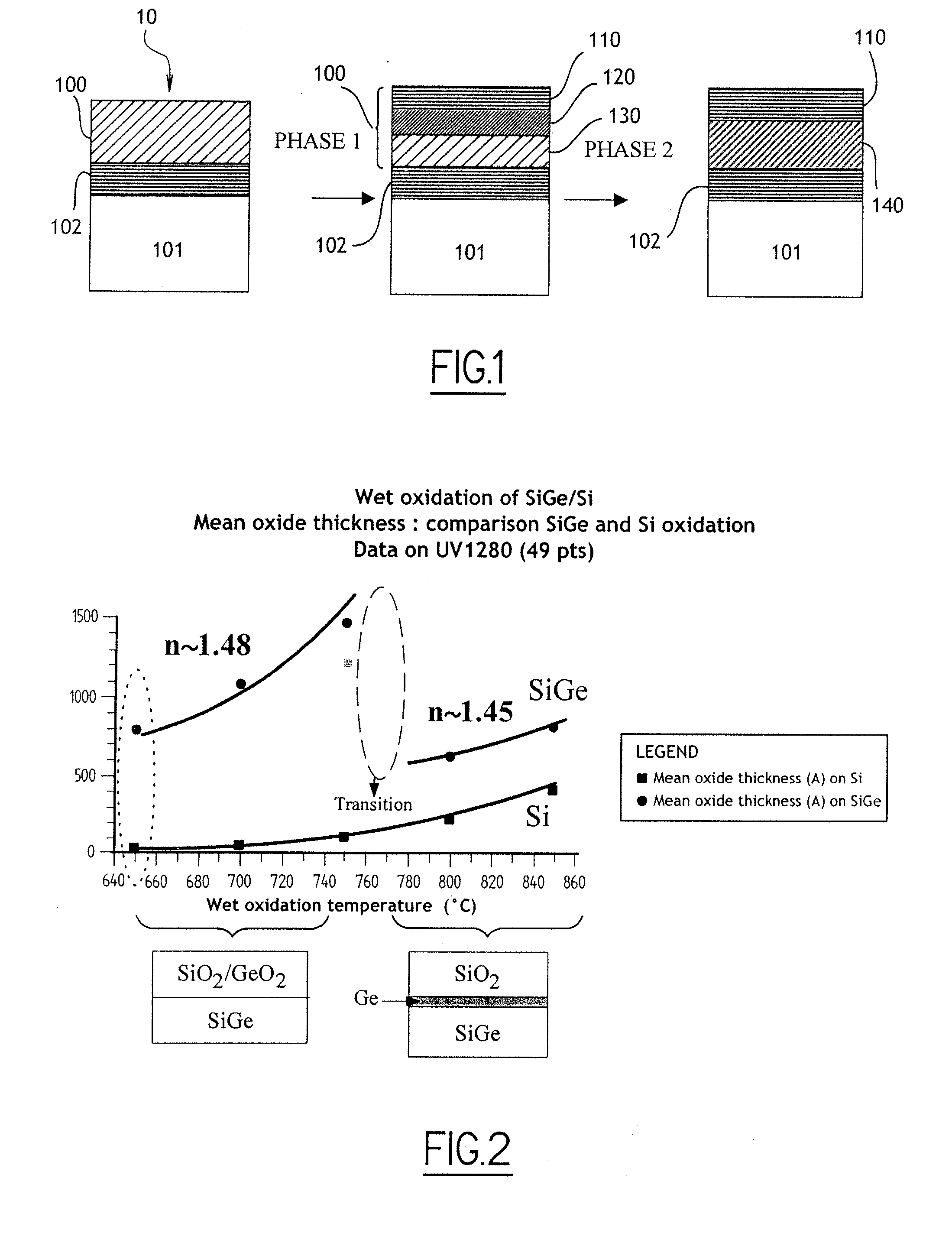

Thermal oxidation of a sige layer and applications thereof

ActiveUS20070254440A1Evenly distributedSemiconductor/solid-state device manufacturingThermal treatmentDislocation

The invention concerns a method for oxidizing a surface region of a SiGe layer that includes an oxidizing thermal treatment of the SiGe layer for oxidizing the surface region. The method includes two phases—a first phase of oxidizing thermal treatment, carried out directly on the SiGe layer, so as to obtain an oxidized region which is thick enough for forming a capping oxide which can protect the underlying SiGe from pitting during the subsequent second phase, but thin enough for keeping the thickness of the oxidized surface region under a threshold thickness range, corresponding to the generation of dislocations within the SiGe layer; and—a second phase of high temperature annealing in an inert atmosphere which is carried out on the SiGe layer after the first phase. The SiGe layer is capped with the oxidized region created during the first phase, and the high temperature annealing allows the diffusion of Ge from a Ge-enriched region into the underlying part of the SiGe layer.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

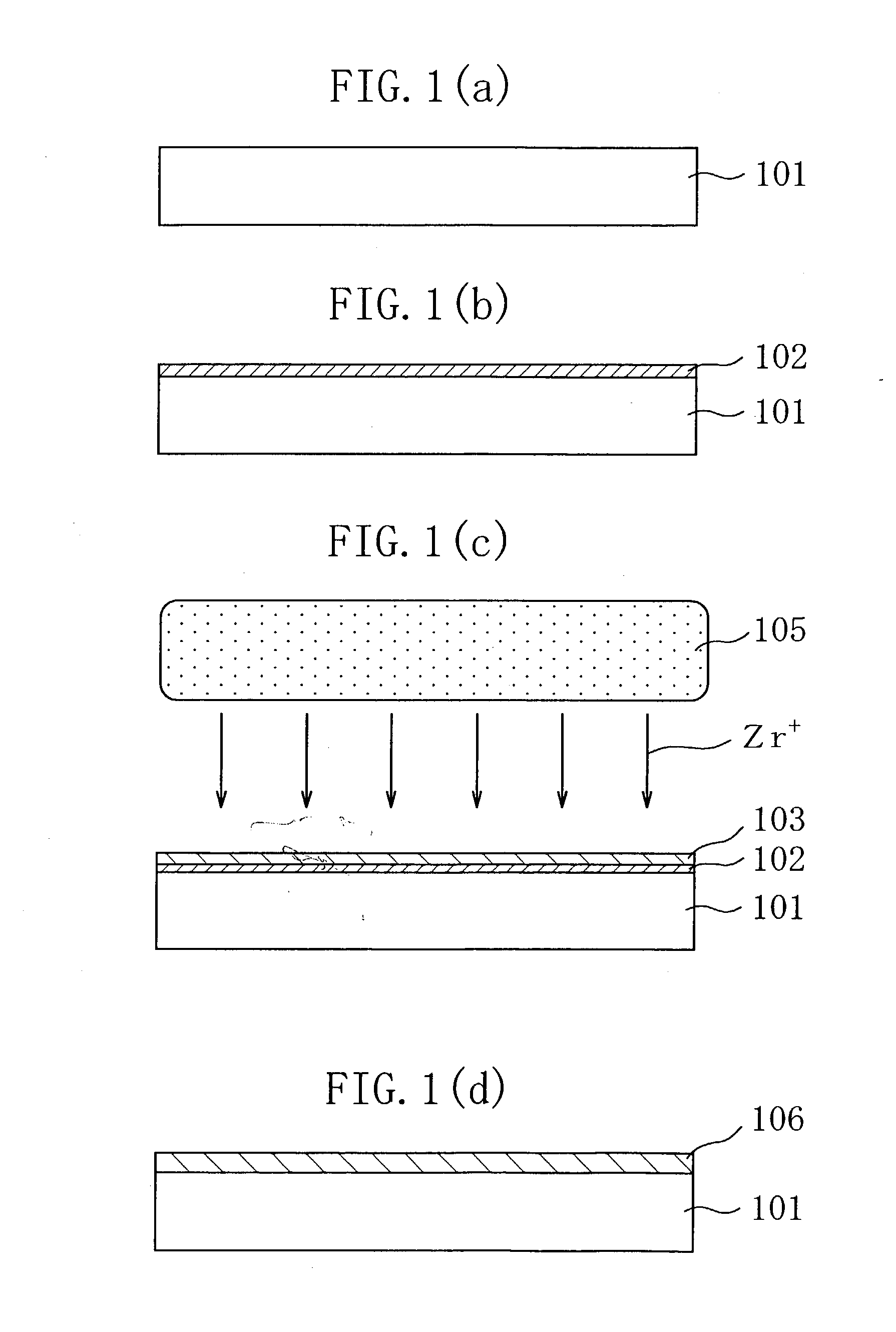

Method of forming insulating film and method of producing semiconductor device

InactiveUS20030092238A1Low reliabilityHigh-speed operation characteristicTransistorSemiconductor/solid-state device manufacturingHigh dielectric permittivitySemiconductor

A high dielectric film is formed by utilizing atom injection into a film through ion implantation or the like, and heat treatment. For example, an SiO2 film 102 which is a thermal oxide film is formed on a silicon substrate 101, and then Zr ions (Zr+) are injected from a plasma 105 into the SiO2 film 102. Thereafter, by annealing the SiO2 film 102 and a Zr injected layer 103, injected Zr is diffused in the Zr injected layer 103 and then the SiO2 film 102 and the Zr injected layer 103 are as a whole changed into a high dielectric film 106 of a high dielectric constant formed of Zr-Si-O (silicate). By using the high dielectric film 106 as an insulating film for an MISFET, an MISFET having excellent gate leakage properties can be achieved.

Owner:PANNOVA SEMIC

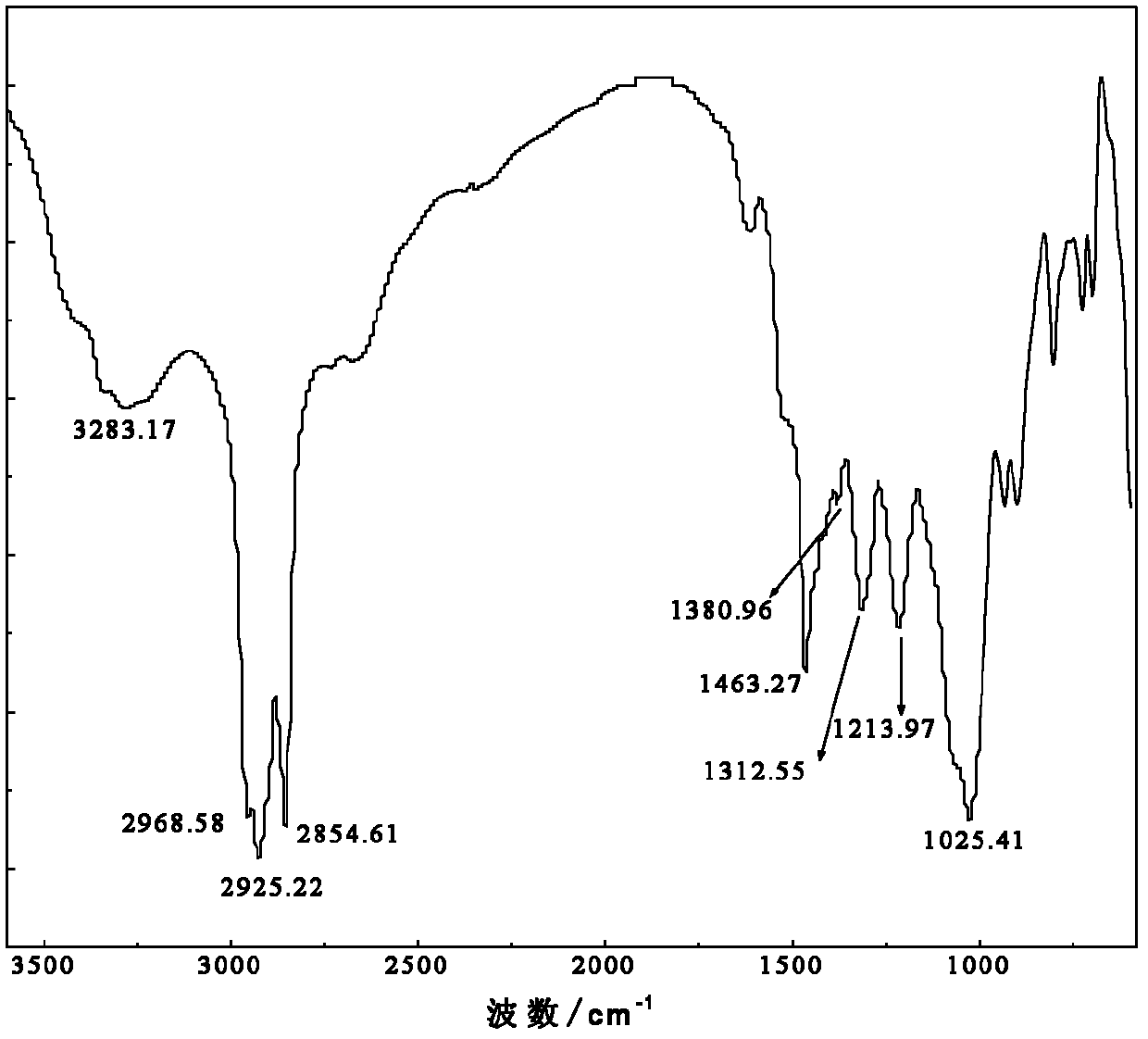

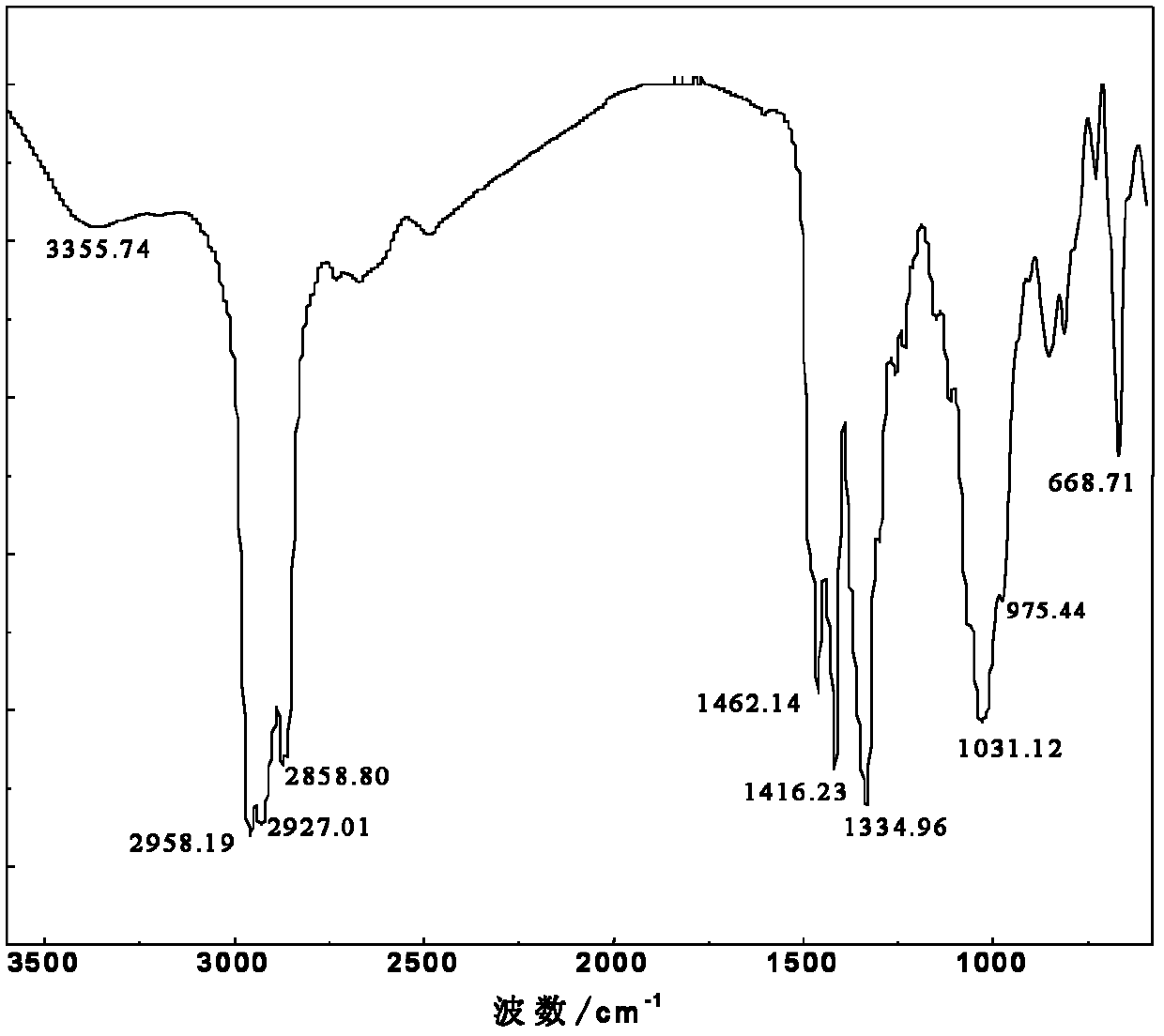

Extreme pressure antiwear additive and preparation method and application thereof

InactiveCN102504913AModerate chemical activityGood oil solubilityGroup 5/15 element organic compoundsAdditivesSolubilityOil sludge

The invention provides an extreme pressure antiwear additive and a preparation method and application thereof; the extreme pressure antiwear additive has a general formula structure as shown in the specification, wherein R1, R2 and R3 in the formula is respectively alkyl groups, aryl groups or aralkyl of a C4-C20 linear chain or branched chain. The extreme pressure antiwear additive provided by the invention is formed by reacting phosphorus oxychloride, C1-C20 alcohols, organic amine and benzotriazole. The extreme pressure antiwear additive provided by the invention can be applied to lubrication oil and lubricating grease with 0.1-2.0wt% of recommended dosage. The extreme pressure antiwear additive provided by the invention has moderate chemical activity, good oil solubility, very good compatibility with other addition agents, no peculiar smell and good thermal oxidation stability, and can effectively reduce the abrasion of devices and oil sedimentation as well as generation of oil sludge. After applied to gear oil, the extreme pressure antiwear additive has excellent antiwear performance and thermal oxidation stability; and simultaneously the extreme pressure antiwear additive can be applied to a lubricating grease and automatic transmission liquid and hydraulic oil of automobiles.

Owner:天津市金岛润滑科技股份有限公司

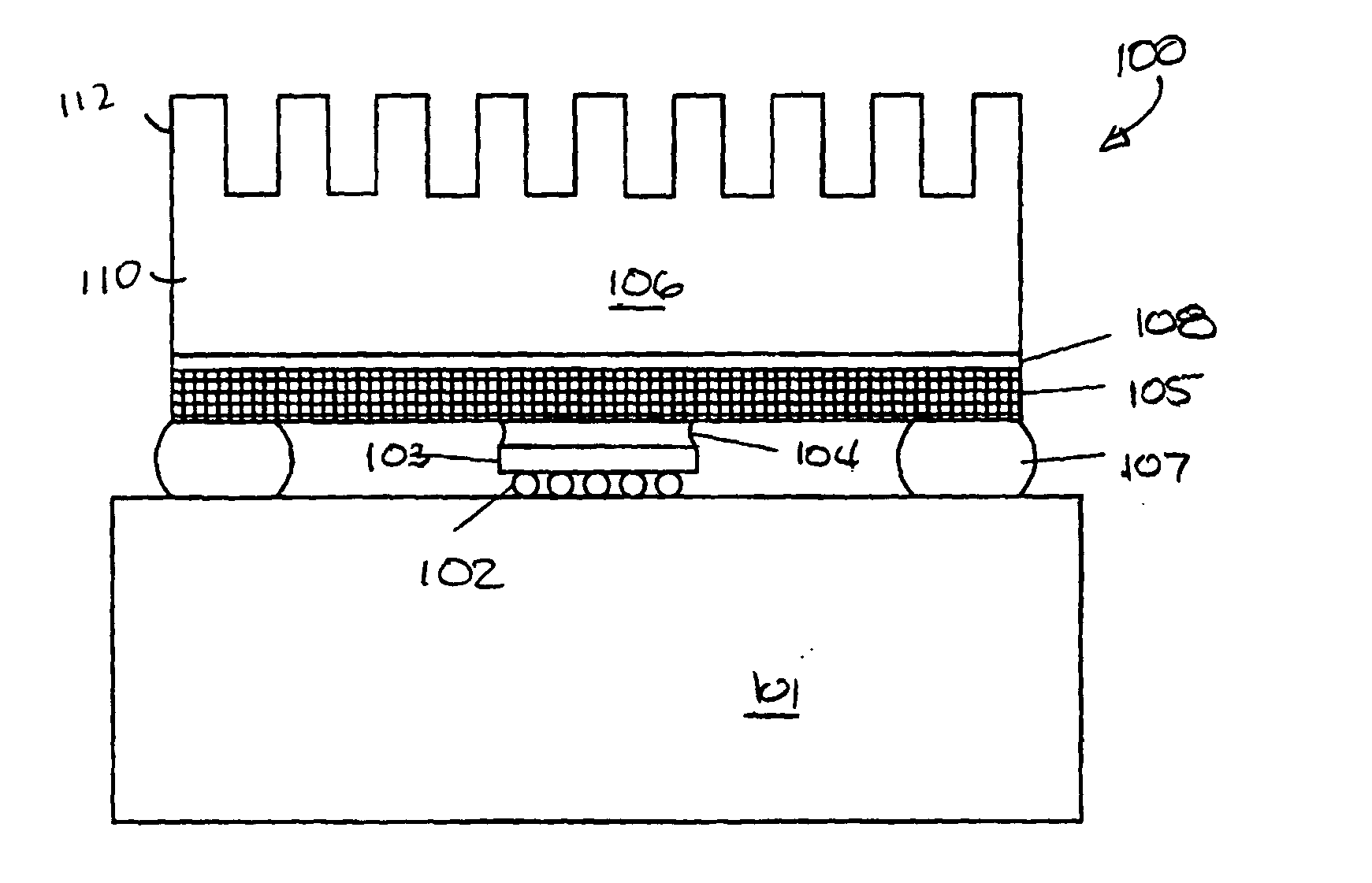

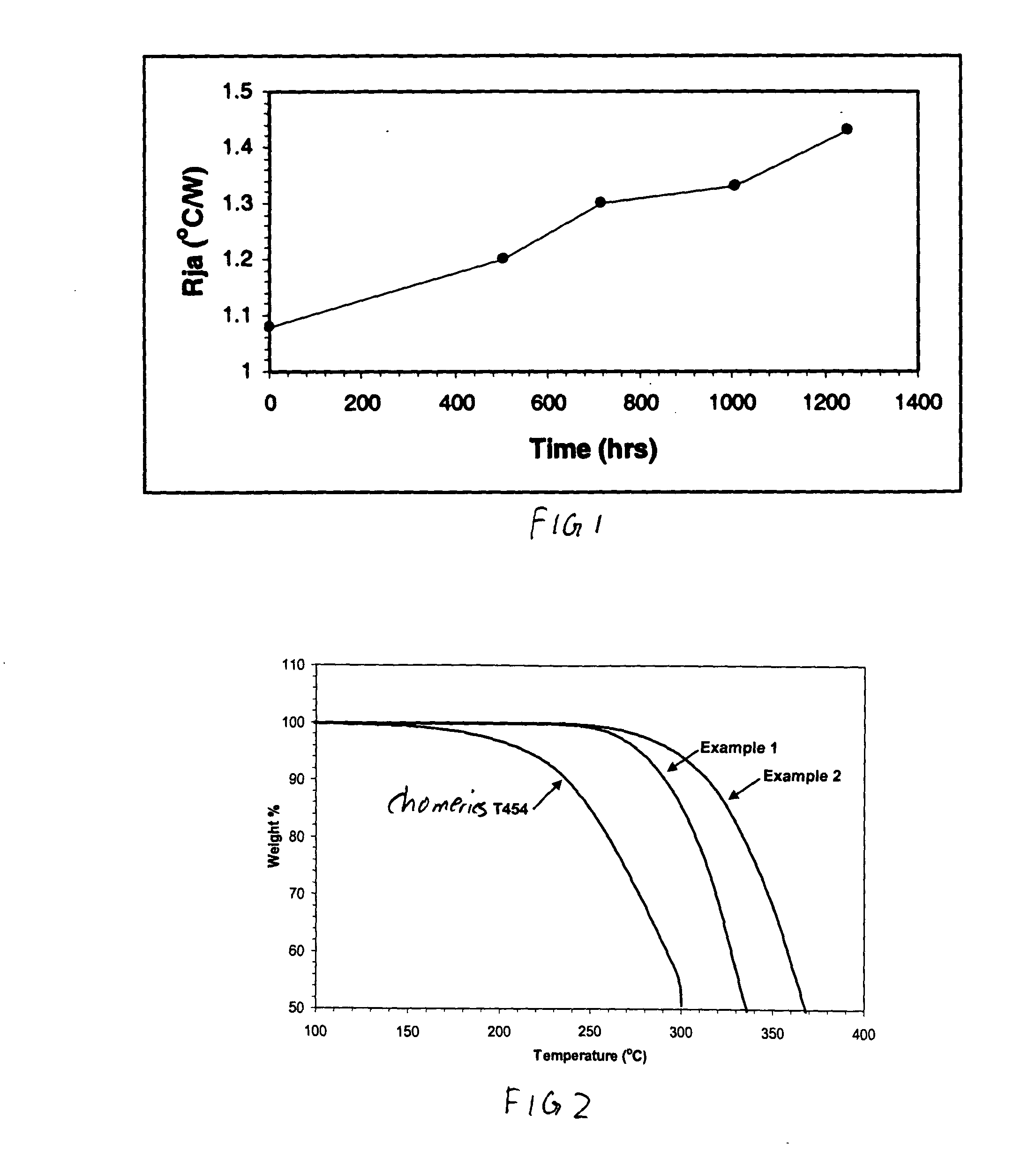

Phase change thermal interface materials including polyester resin

InactiveUS20050041406A1Improve thermo-oxidative stabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesPolyolefinPolyester resin

An embodiment of a phase change TIM of this invention comprises a polyester matrix with melting temperature near or below operating temperature (typically less than about 130° C.), thermally conductive filler with bulk thermal conductivity greater than about 50 W / mK, and optionally other additives. The polyester resin has improved thermo-oxidative stability compared to the polyolefin resins, thereby providing improved reliability performance during test.

Owner:INTEL CORP

Flameless thermal oxidation method

A thermal oxidizer is provided in which off-gases in a process stream are thermally oxidized within substantially the entire interior volume of an oxidation chamber. The thermal oxidation is conducted without the presence of a flame or with only a minor portion of the fuel being combusted in a flame.

Owner:JOHN ZINK CO LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com