Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1637 results about "Critical dimension" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In the renormalization group analysis of phase transitions in physics, a critical dimension is the dimensionality of space at which the character of the phase transition changes. Below the lower critical dimension there is no phase transition. Above the upper critical dimension the critical exponents of the theory become the same as that in mean field theory. An elegant criterion to obtain the critical dimension within mean field theory is due to V. Ginzburg.

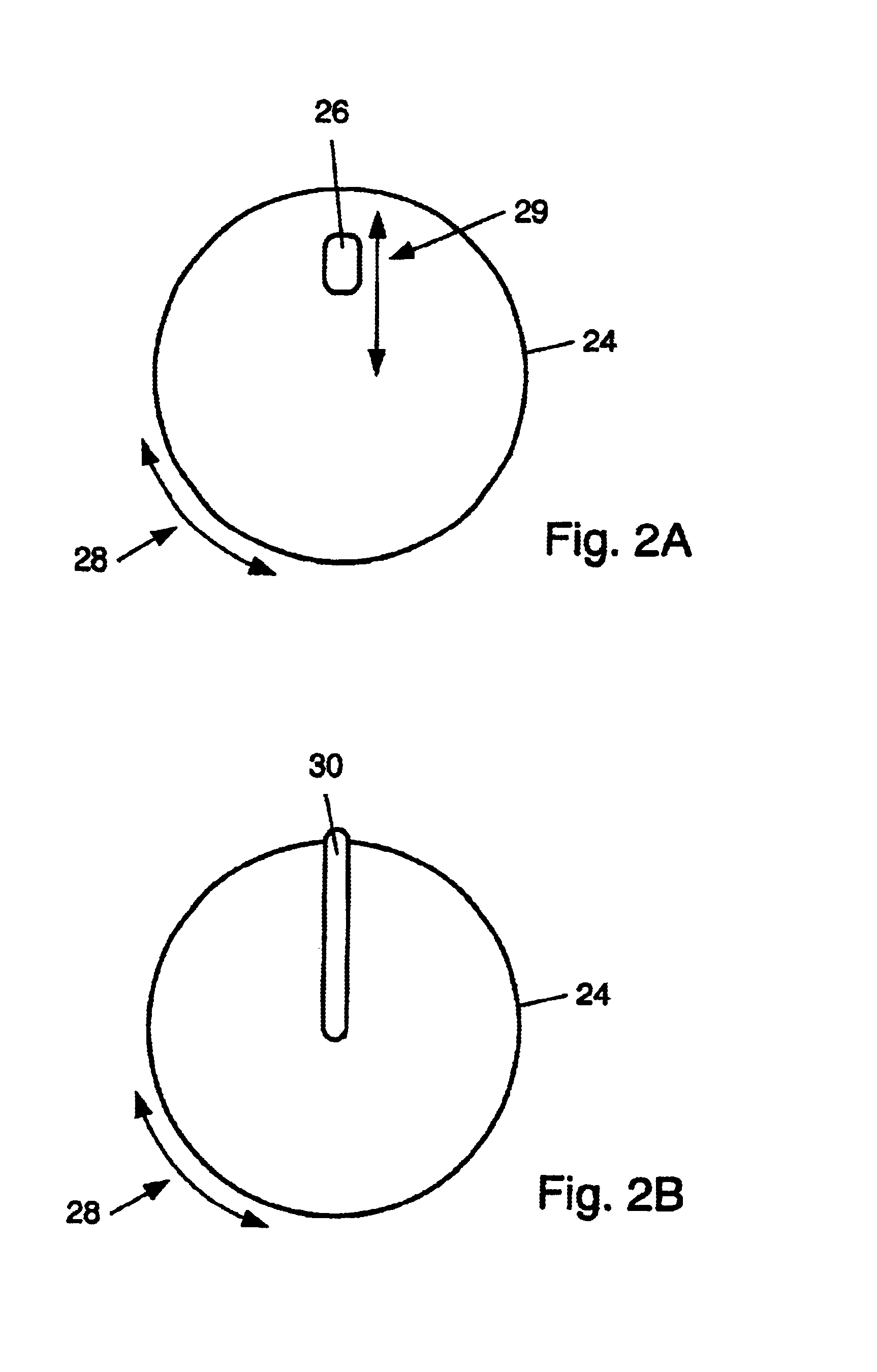

Method and system for drying a substrate

ActiveUS20050046934A1Good pattern uniformityImprove uniformityMicroscopesPhotomechanical exposure apparatusCooking & bakingThin membrane

A method and system is described for drying a thin film on a substrate following liquid immersion lithography. Drying the thin film to remove immersion fluid from the thin film is performed prior to baking the thin film, thereby reducing the likely hood for interaction of immersion fluid with the baking process. This interaction has been shown to cause non-uniformity in critical dimension for the pattern formed in the thin film following the developing process.

Owner:TOKYO ELECTRON LTD

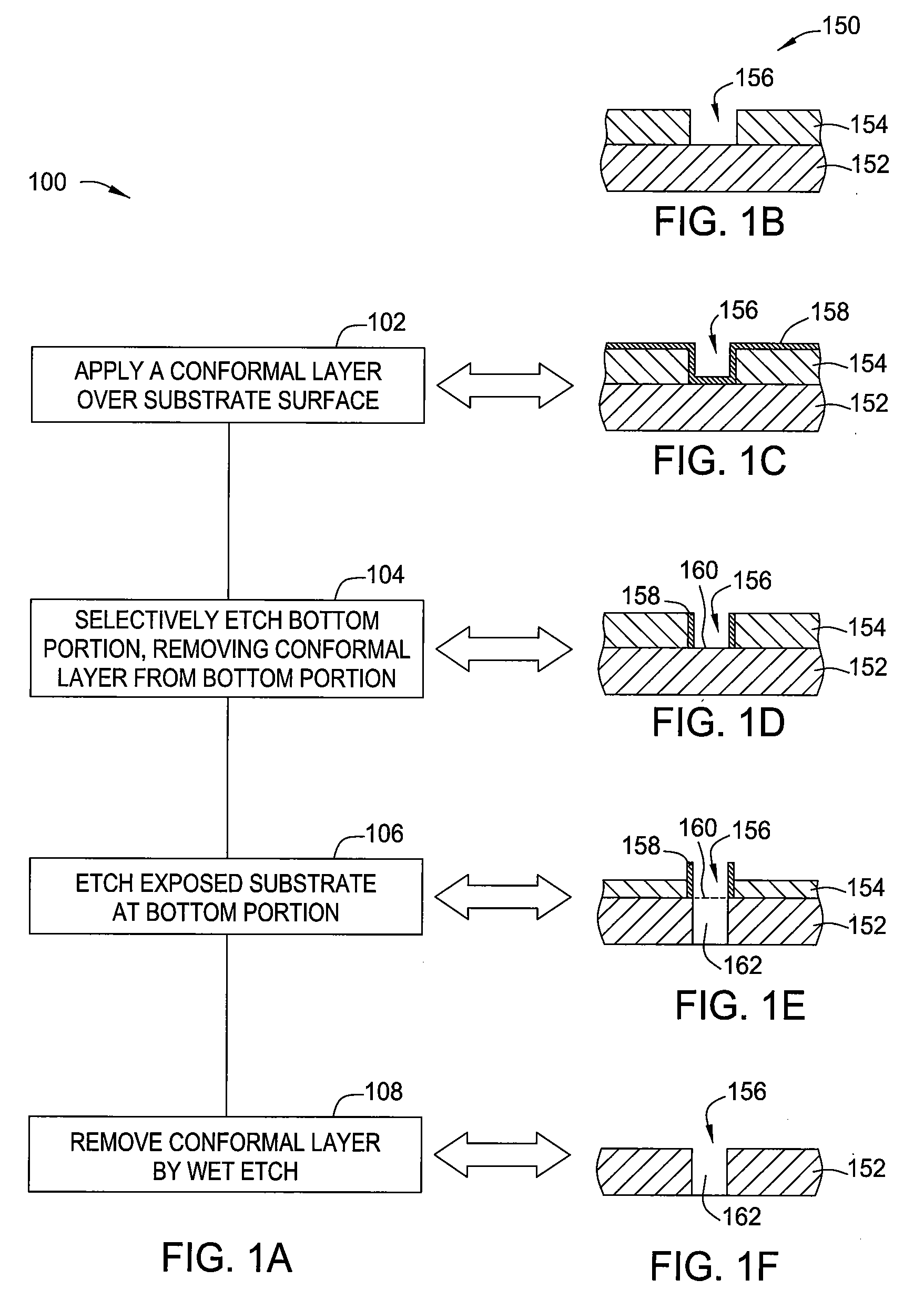

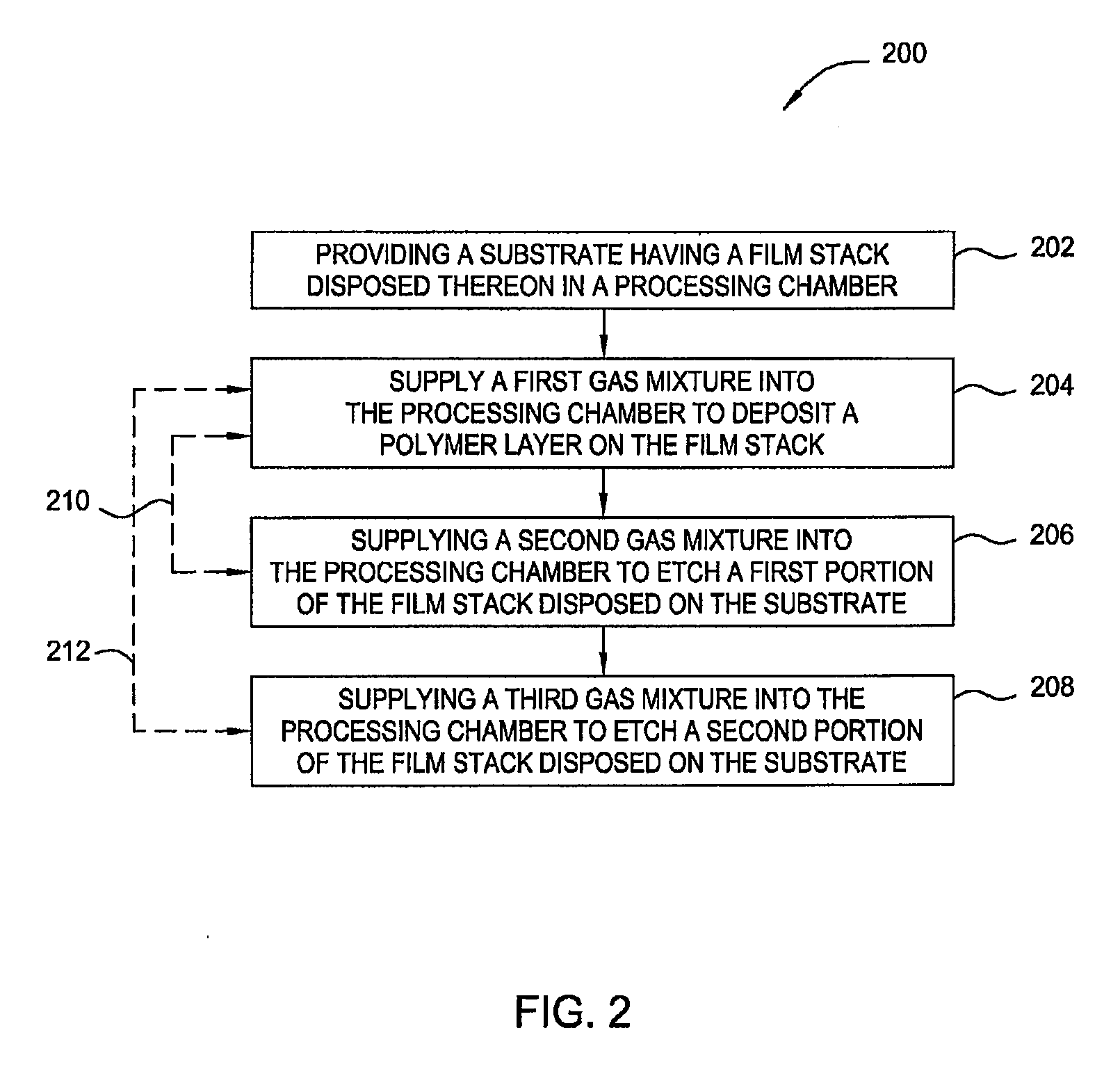

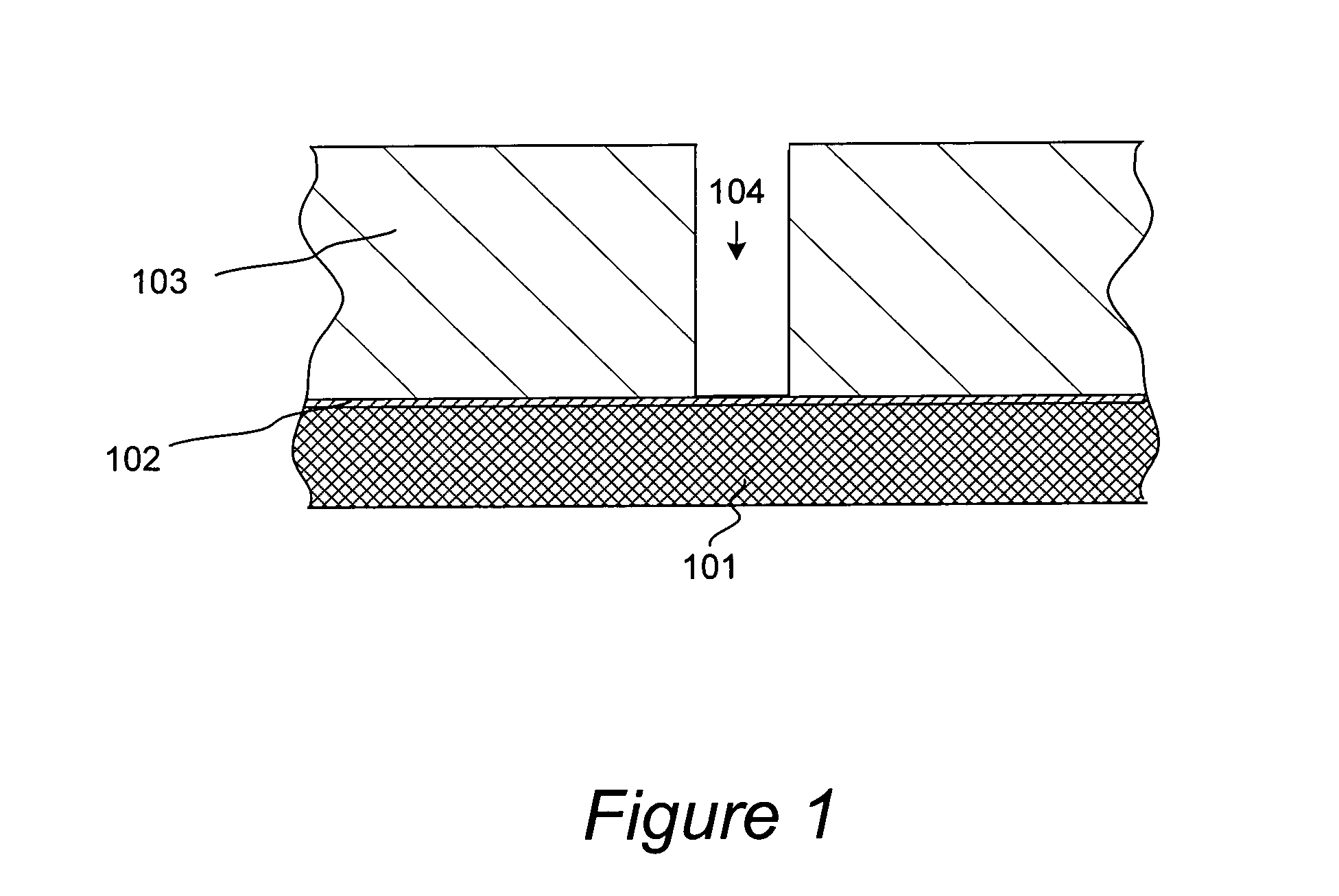

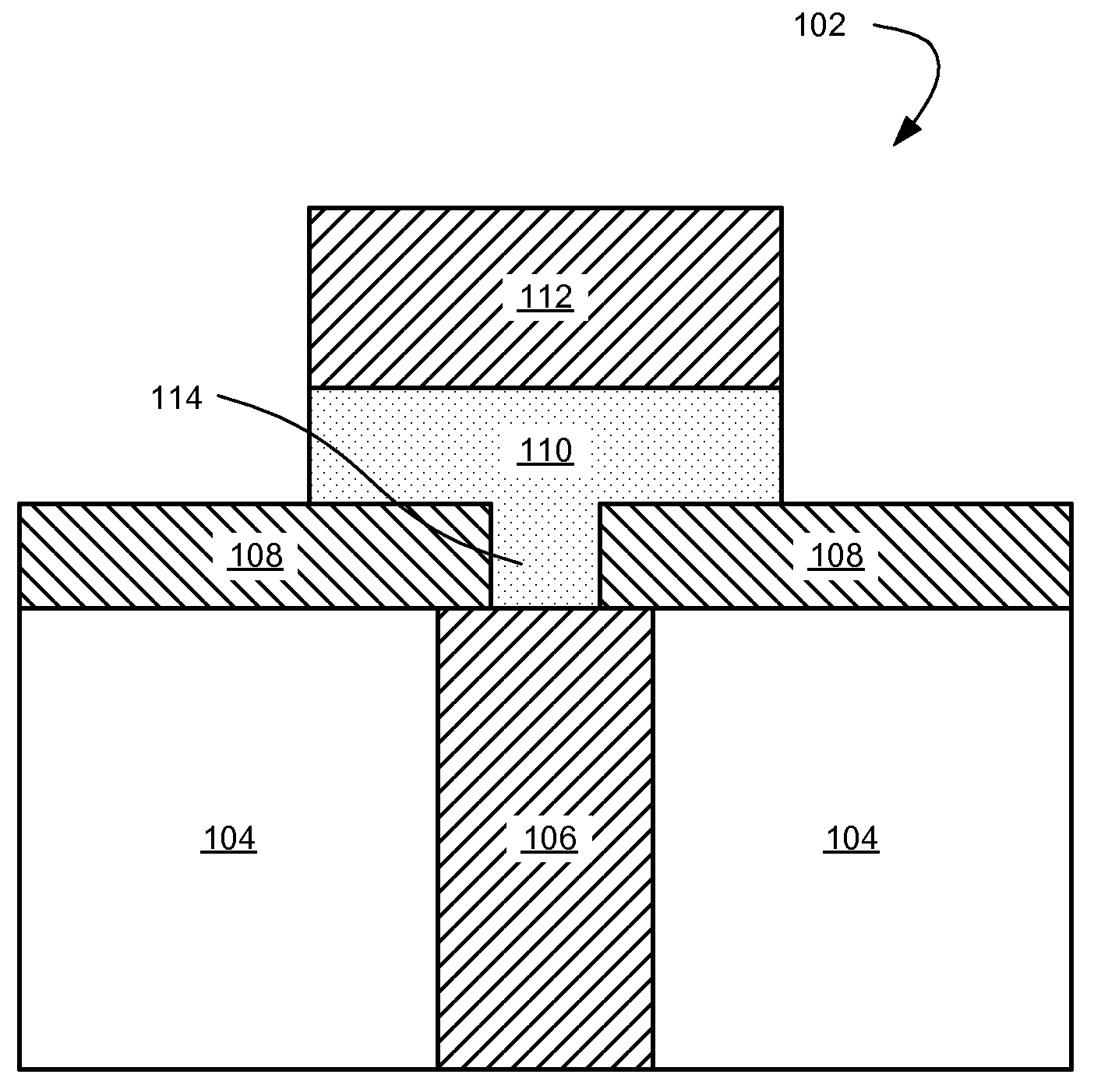

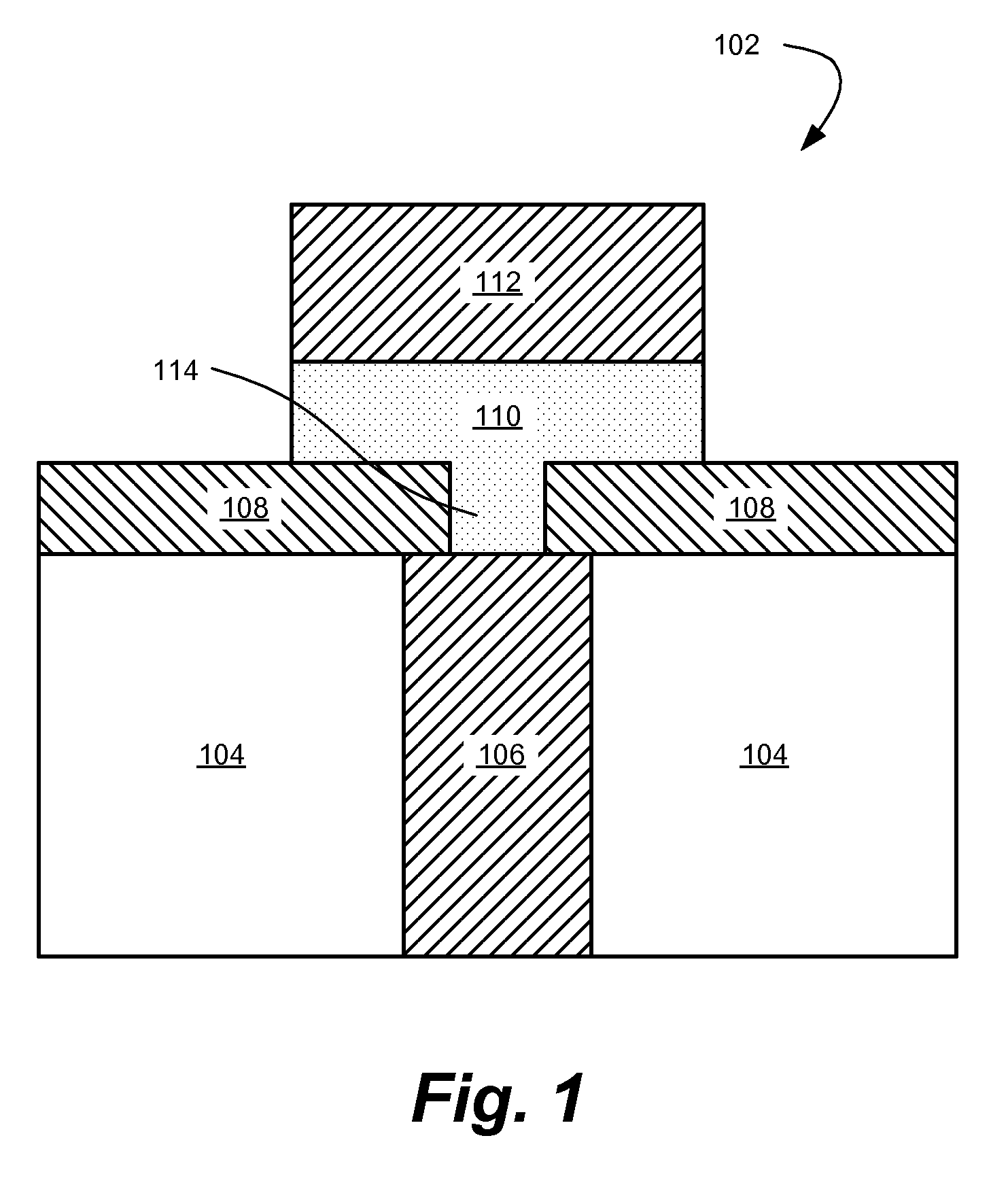

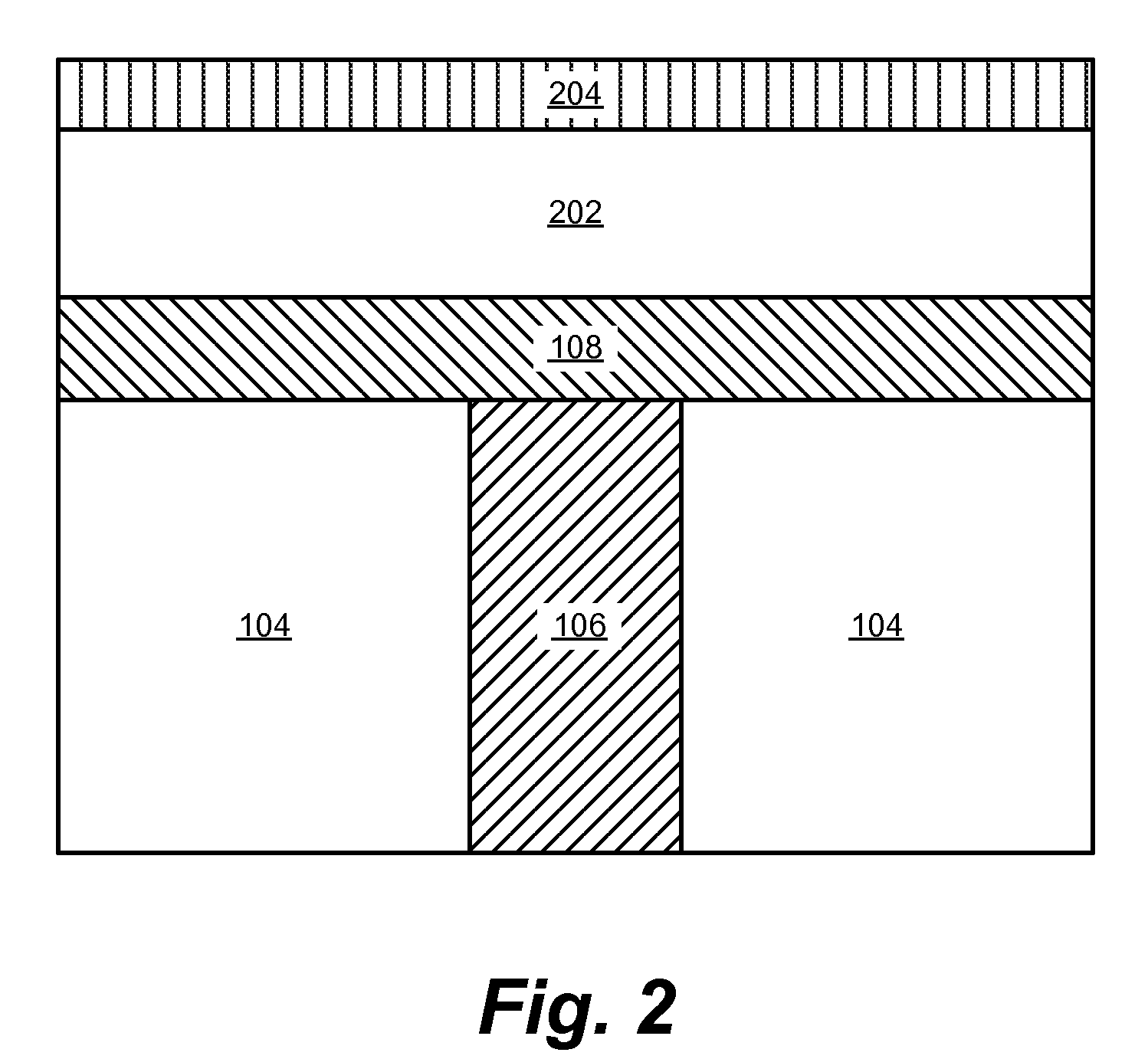

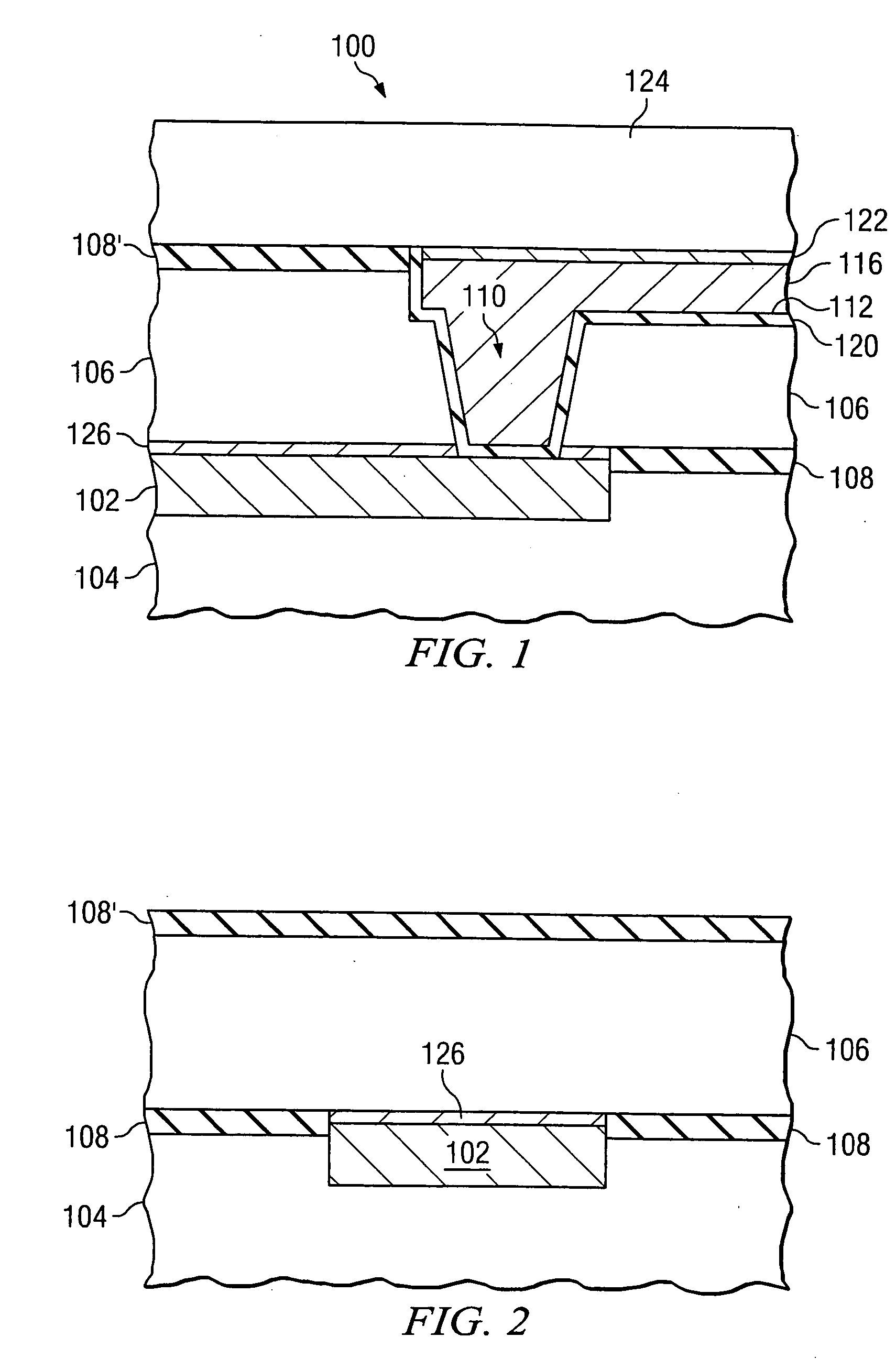

Method for critical dimension shrink using conformal pecvd films

InactiveUS20090286402A1Critical dimension reductionGood step coverageSemiconductor/solid-state device manufacturingLithographic artistAnisotropic etching

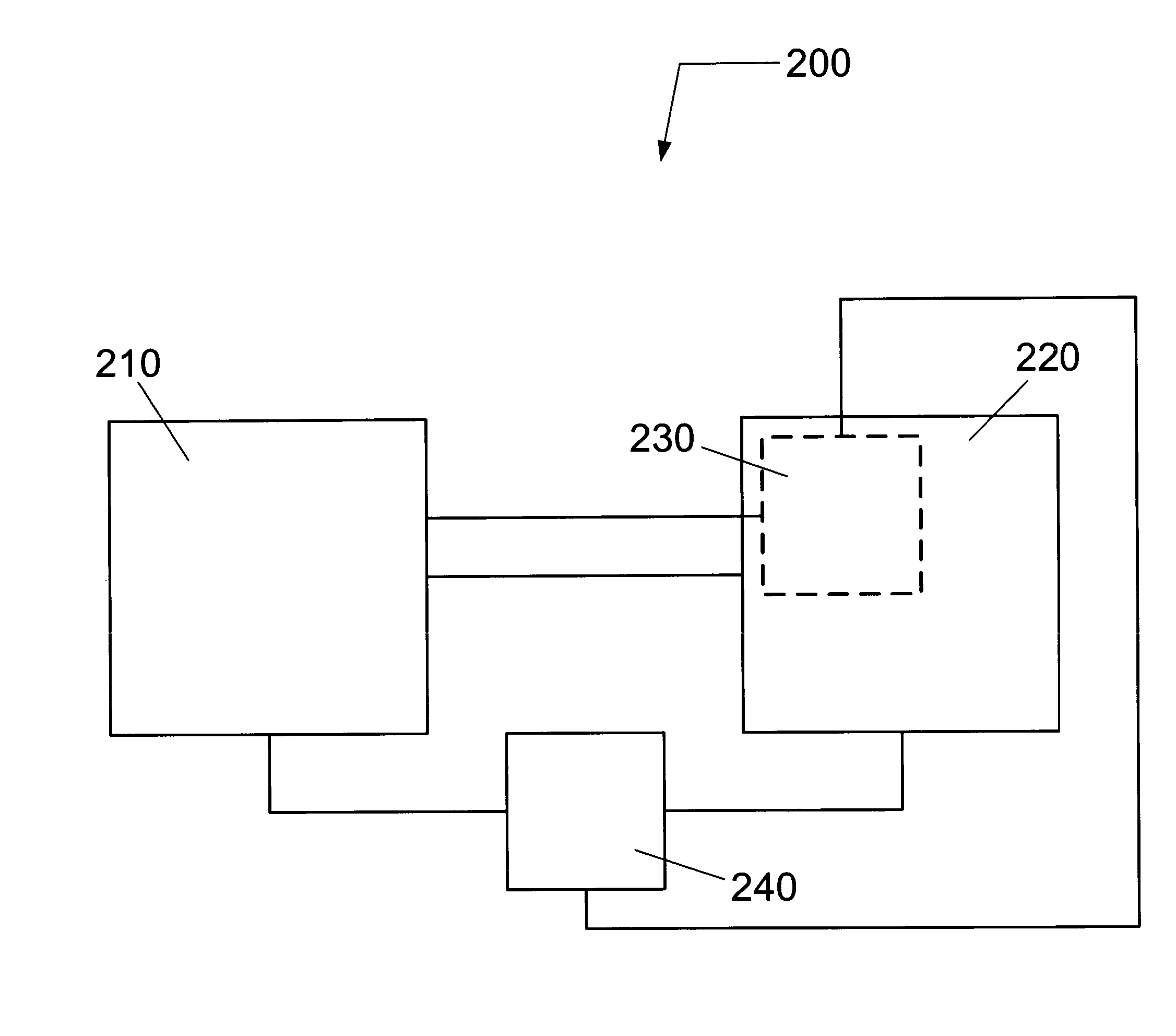

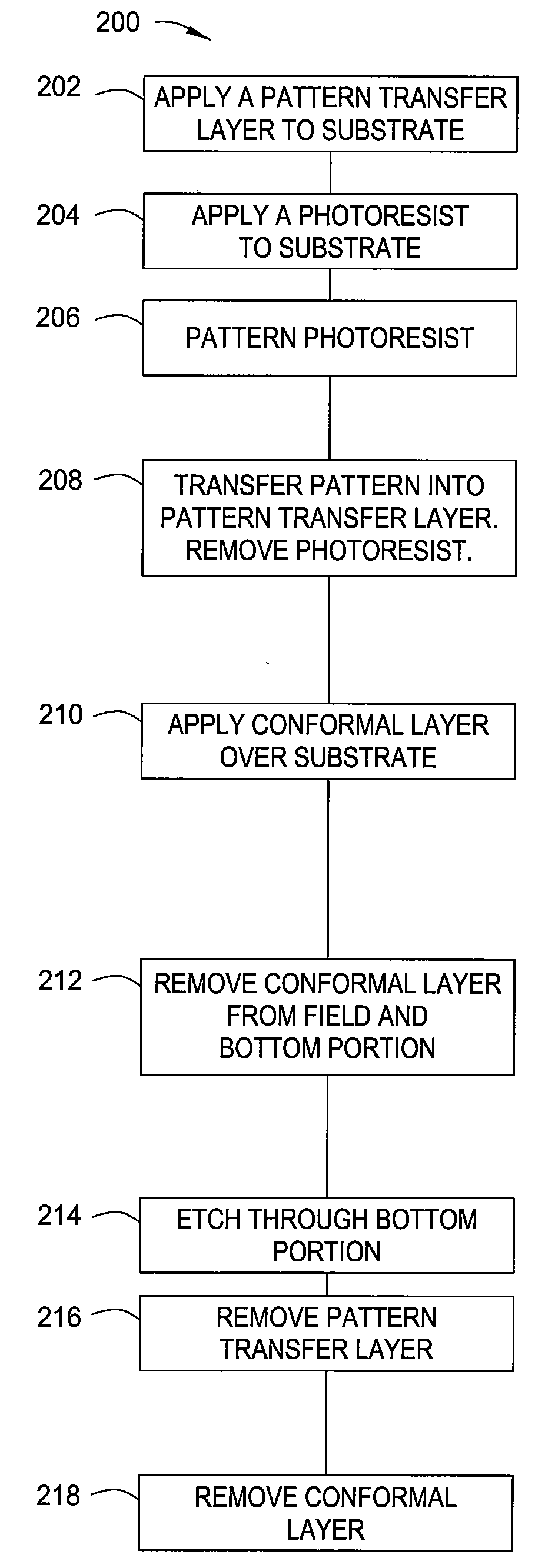

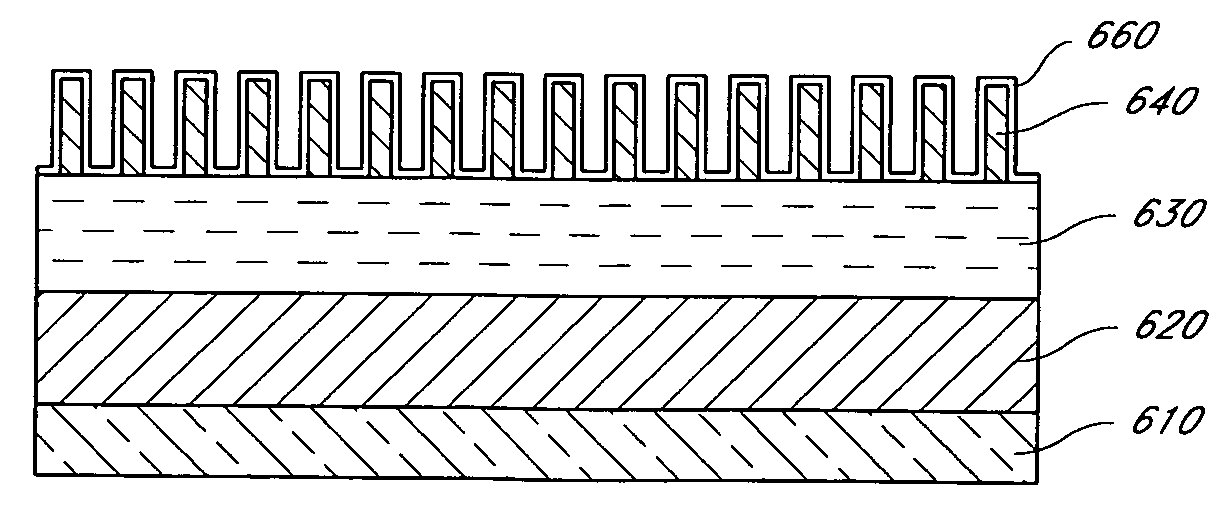

A method and apparatus for forming narrow vias in a substrate is provided. A pattern recess is etched into a substrate by conventional lithography. A thin conformal layer is formed over the surface of the substrate, including the sidewalls and bottom of the pattern recess. The thickness of the conformal layer reduces the effective width of the pattern recess. The conformal layer is removed from the bottom of the pattern recess by anisotropic etching to expose the substrate beneath. The substrate is then etched using the conformal layer covering the sidewalls of the pattern recess as a mask. The conformal layer is then removed using a wet etchant.

Owner:APPLIED MATERIALS INC

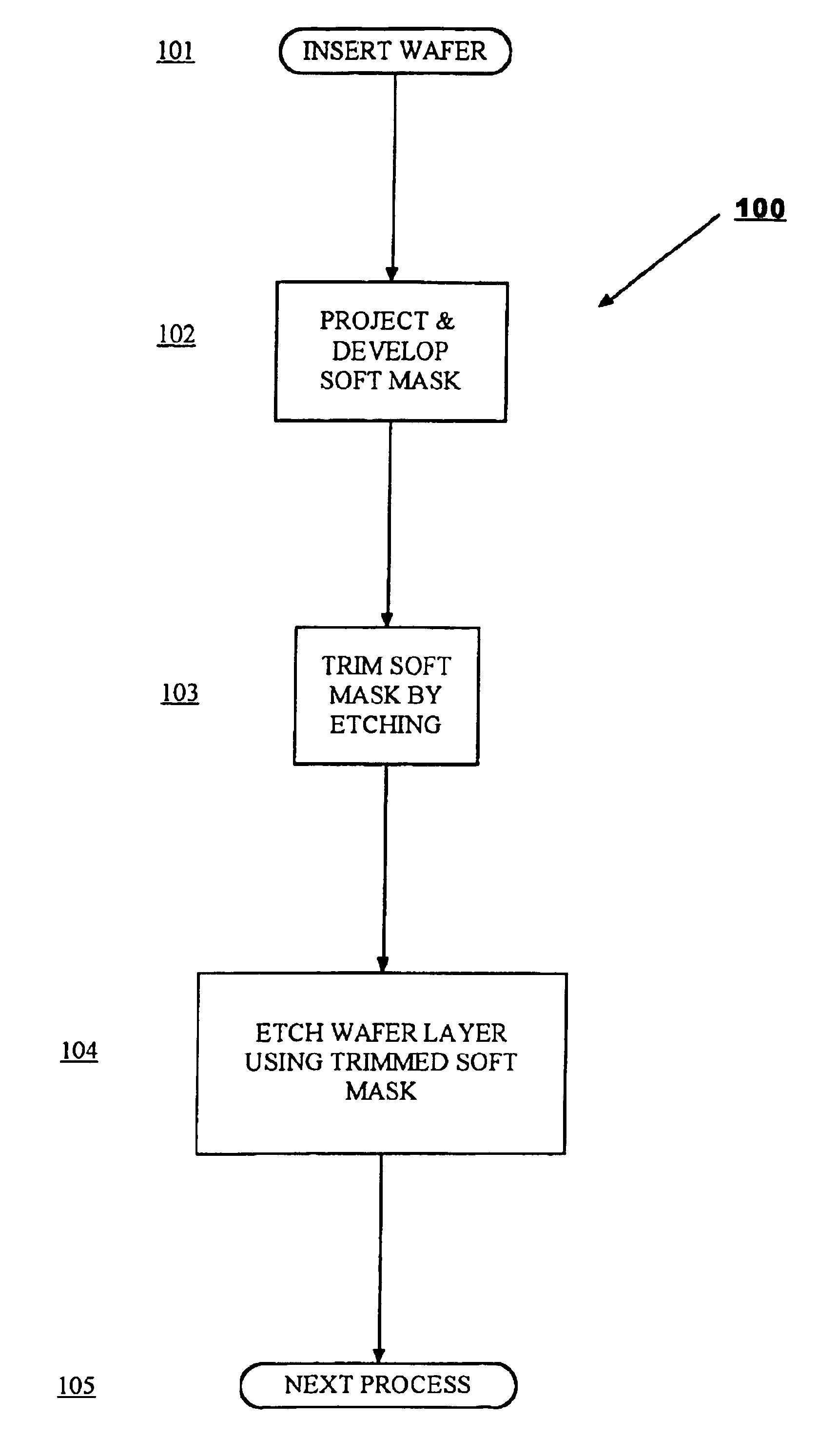

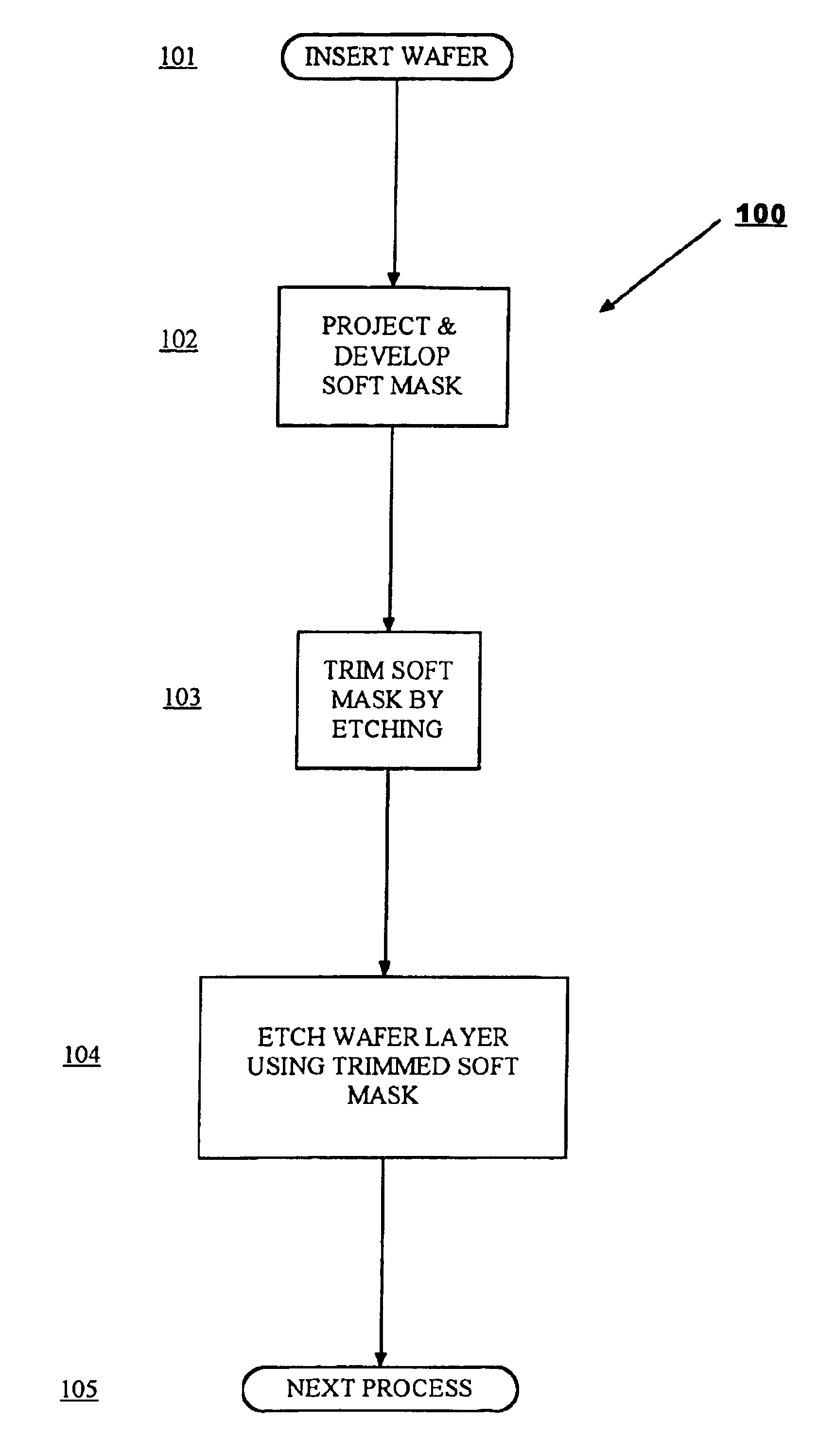

Gate linewidth tailoring and critical dimension control for sub-100 nm devices using plasma etching

InactiveUS6864041B2Tight tolerance variationMinimal variationVacuum gauge using ionisation effectsDecorative surface effectsImage resolutionLine width

A method of fabricating an electronic chip on a wafer in which a first mask at a predetermined lower resolution is developed on the wafer and then etched under a first set of conditions for a predetermined period to achieve a mask that is below the resolution limit of current lithography. The etched mask is then used as a hard mask for etching material on a lower layer.

Owner:INT BUSINESS MASCH CORP

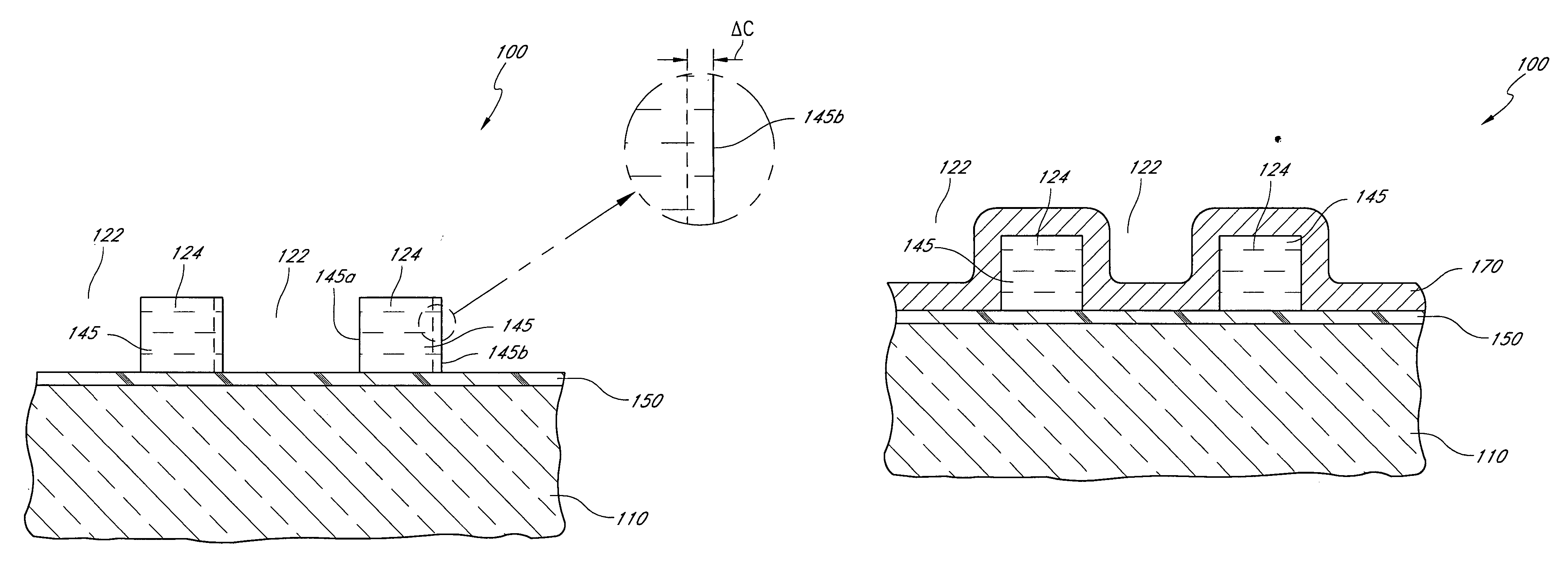

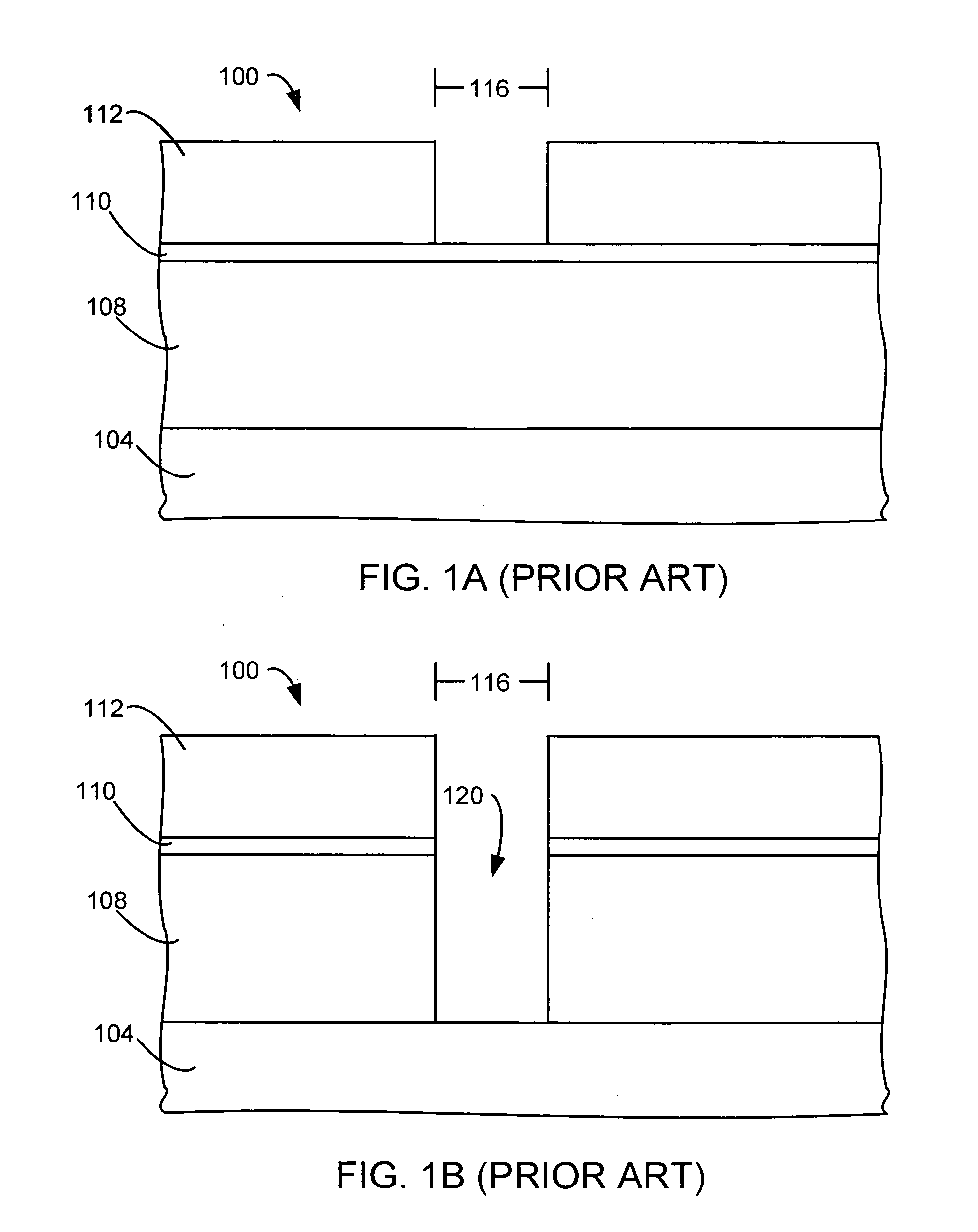

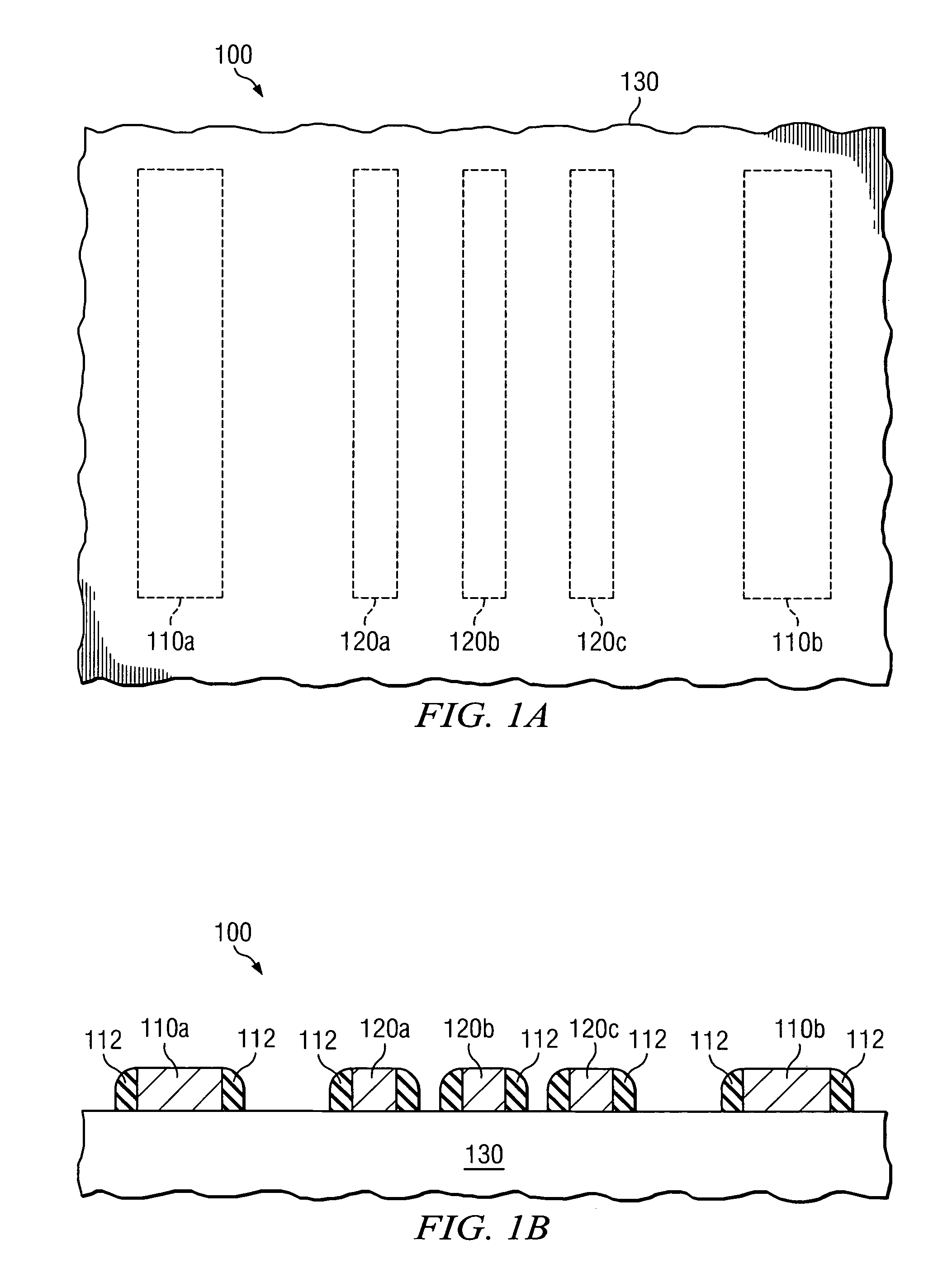

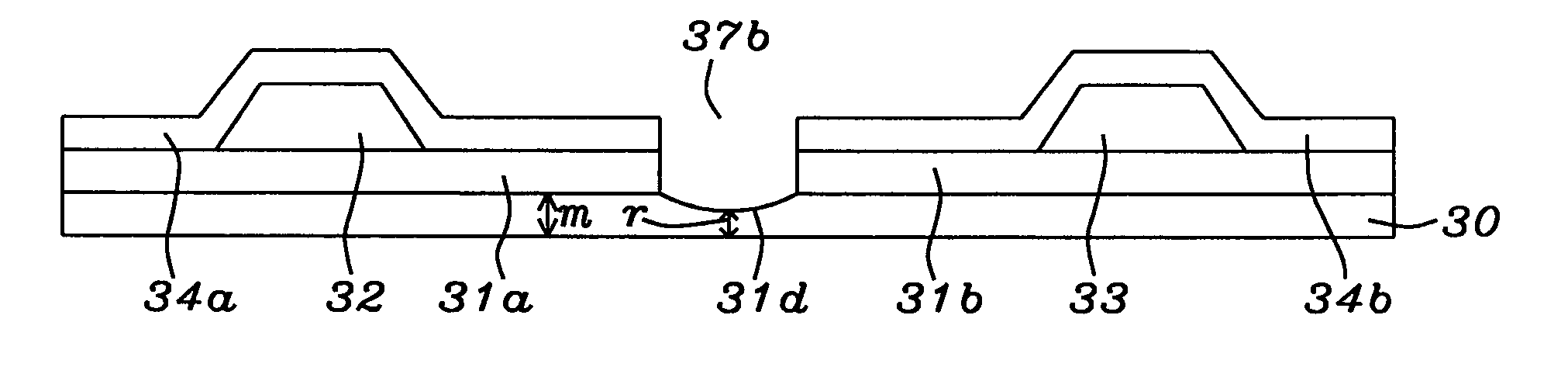

Method and apparatus for adjusting feature size and position

InactiveUS20060281266A1Minimum feature sizeSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCritical dimension

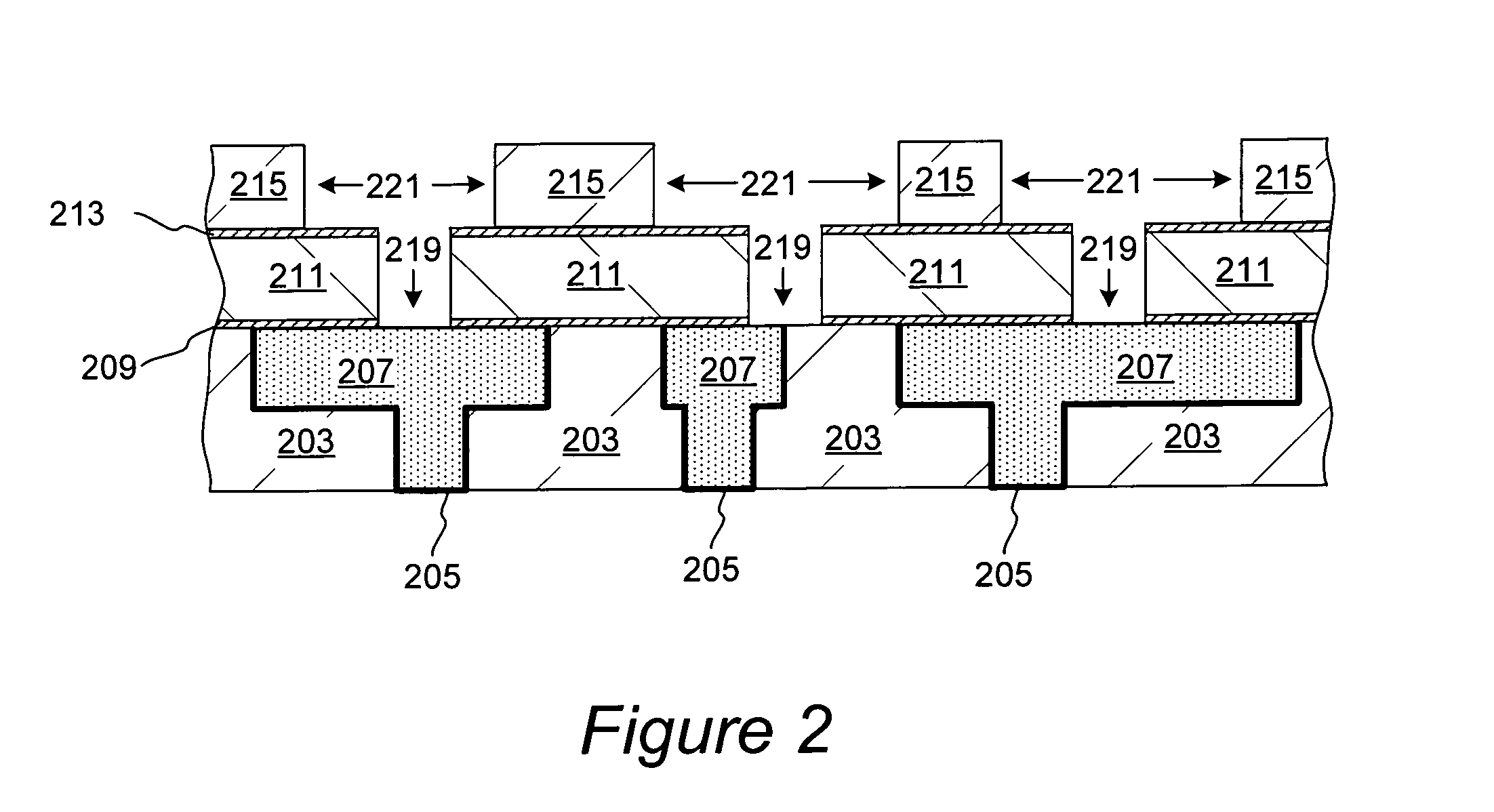

Variations in the pitch of features formed using pitch multiplication are minimized by separately forming at least two sets of spacers. Mandrels are formed and the positions of their sidewalls are measured. A first set of spacers is formed on the sideswalls. The critical dimension of the spacers is selected based upon the sidewall positions, so that the spacers are centered at desired positions. The mandrels are removed and the spacers are used as mandrels for a subsequent spacer formation. A second material is then deposited on the first set of spacers, with the critical dimensions of the second set of spacers chosen so that these spacers are also centered at their desired positions. The first set of spacers is removed and the second set is used as a mask for etching a substrate. By selecting the critical dimensions of spacers based partly on the measured position of mandrels, the pitch of the spacers can be finely controlled.

Owner:ROUND ROCK RES LLC

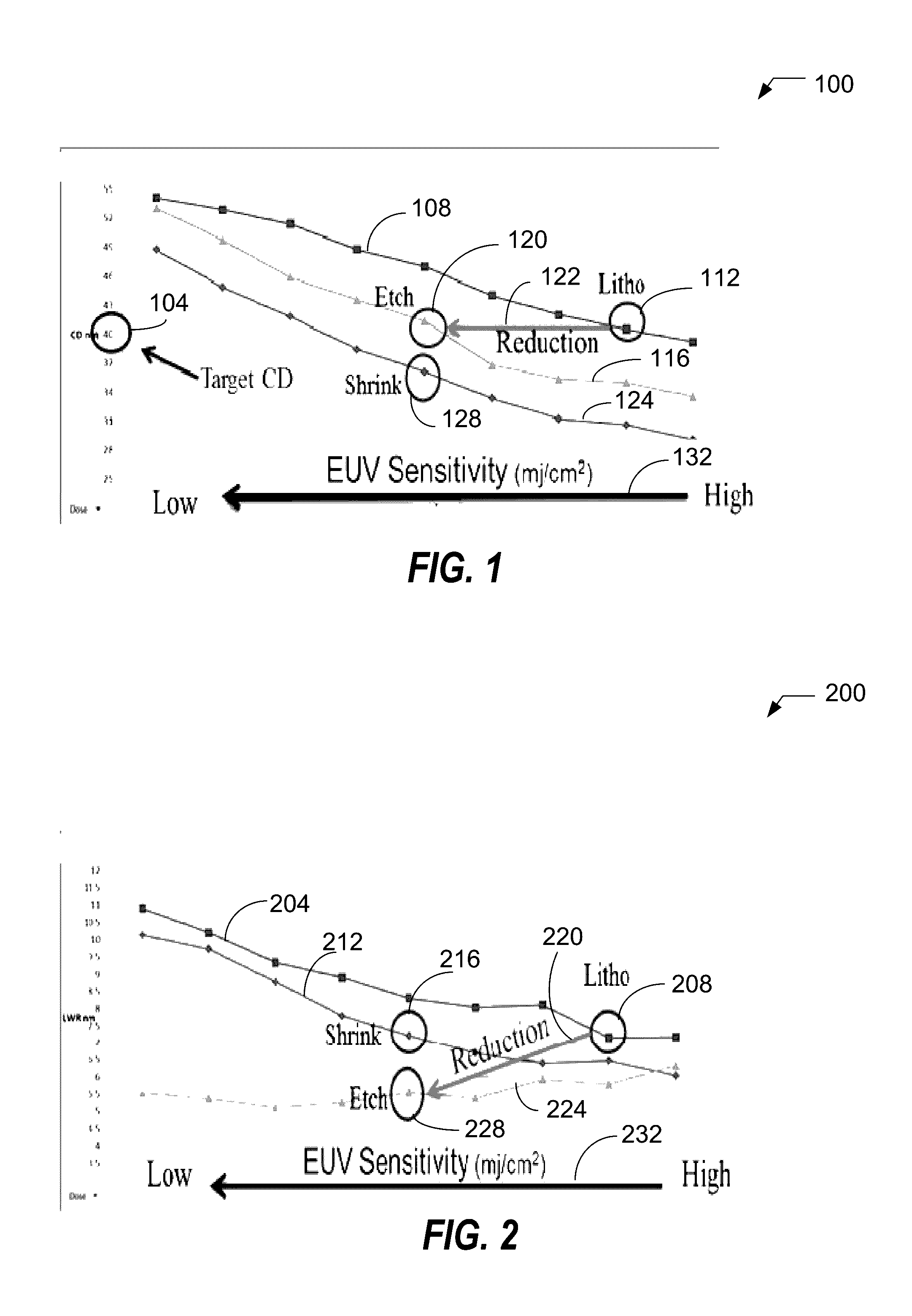

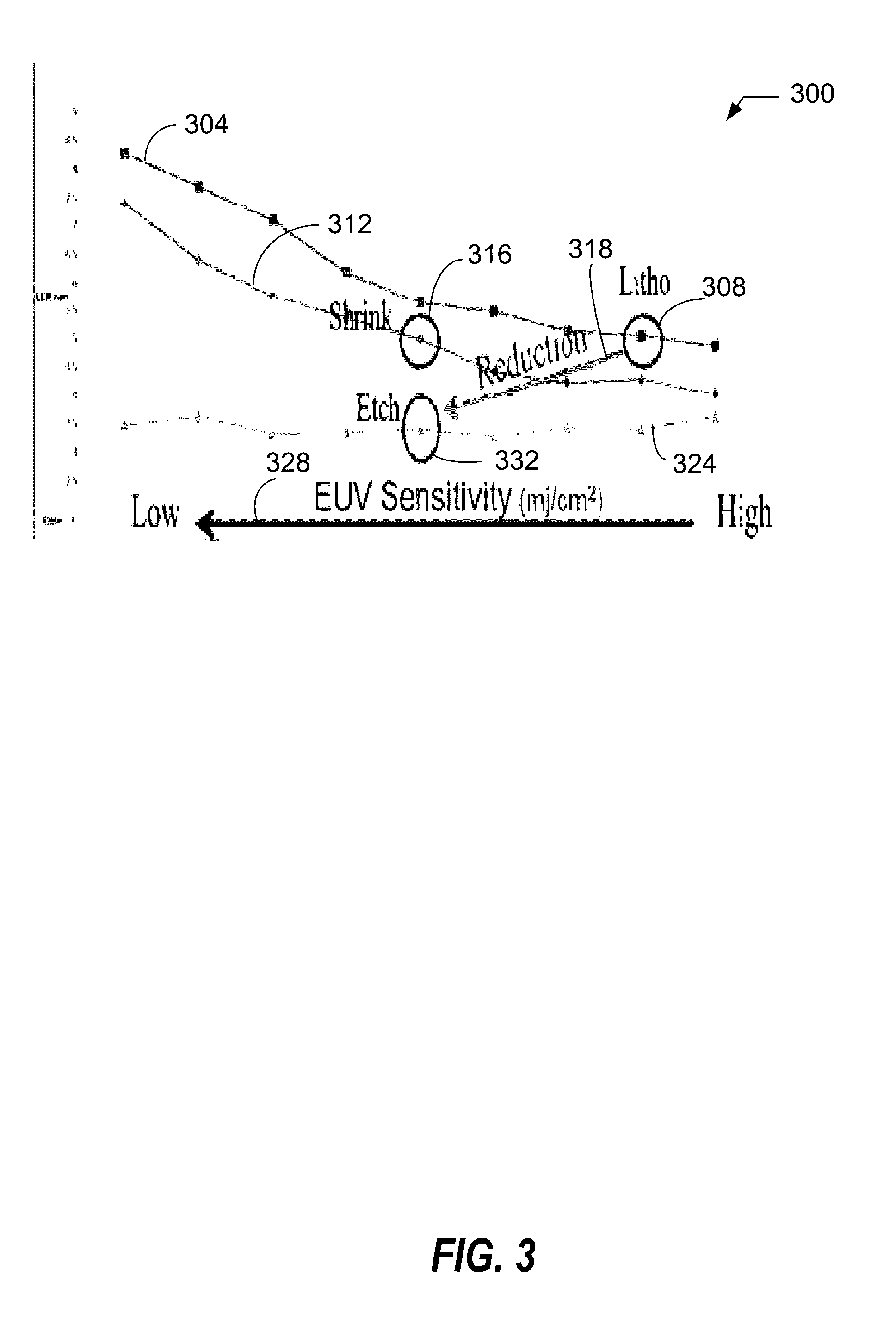

Extreme ultra-violet sensitivity reduction using shrink and growth method

ActiveUS20160334709A1Substrate throughput can be increasedImprove throughputPhotomechanical exposure apparatusPhotosensitive material processingCooking & bakingLine width

Provided is a method for patterning a substrate, comprising: forming a layer of radiation-sensitive material on a substrate; preparing a pattern in the layer of radiation-sensitive material using a lithographic process, the pattern being characterized by a critical dimension (CD) and a roughness; following the preparing the pattern, performing a CD shrink process to reduce the CD to a reduced CD; and performing a growth process to grow the reduced CD to a target CD. Roughness includes a line edge roughness (LER), a line width roughness (LWR), or both LER and LWR. Performing the CD shrink process comprises: coating the pattern with a hard mask, the coating generating a hard mask coated resist; baking the hard mask coated resist in a temperature range for a time period, the baking generating a baked coated resist; and developing the baked coated resist in deionized water.

Owner:TOKYO ELECTRON LTD

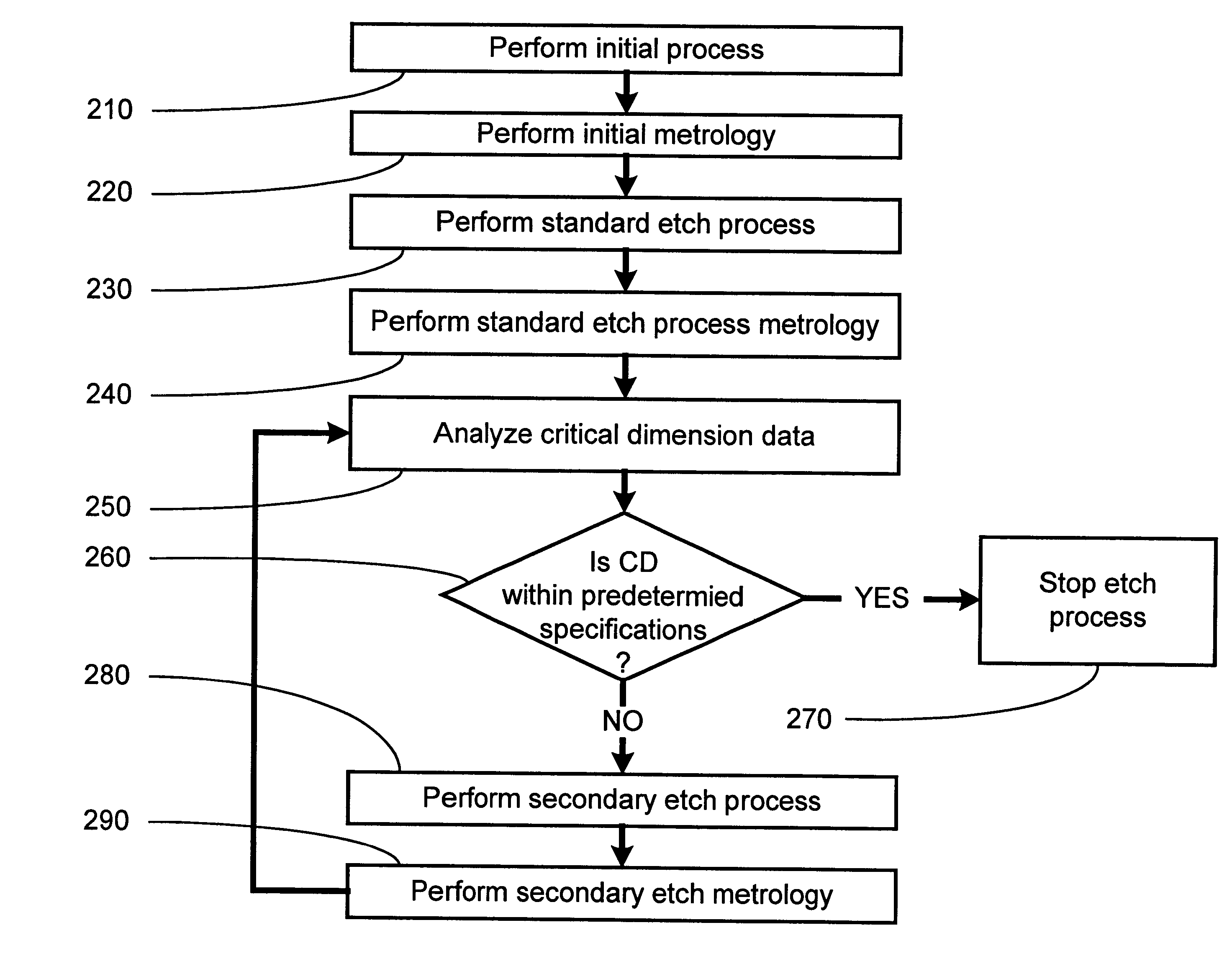

Method and apparatus for control of critical dimension using feedback etch control

InactiveUS6245581B1Semiconductor/solid-state device testing/measurementVacuum gauge using ionisation effectsEngineeringCritical dimension

The present invention provides for a method and an apparatus for controlling critical dimensions. At least one run of semiconductor devices is processed. A critical dimension measurement is performed upon at least one of the processed semiconductor device. An analysis of the critical dimension measurement is performed. A secondary process upon the semiconductor device in response to the critical dimension analysis is performed.

Owner:ADVANCED MICRO DEVICES INC

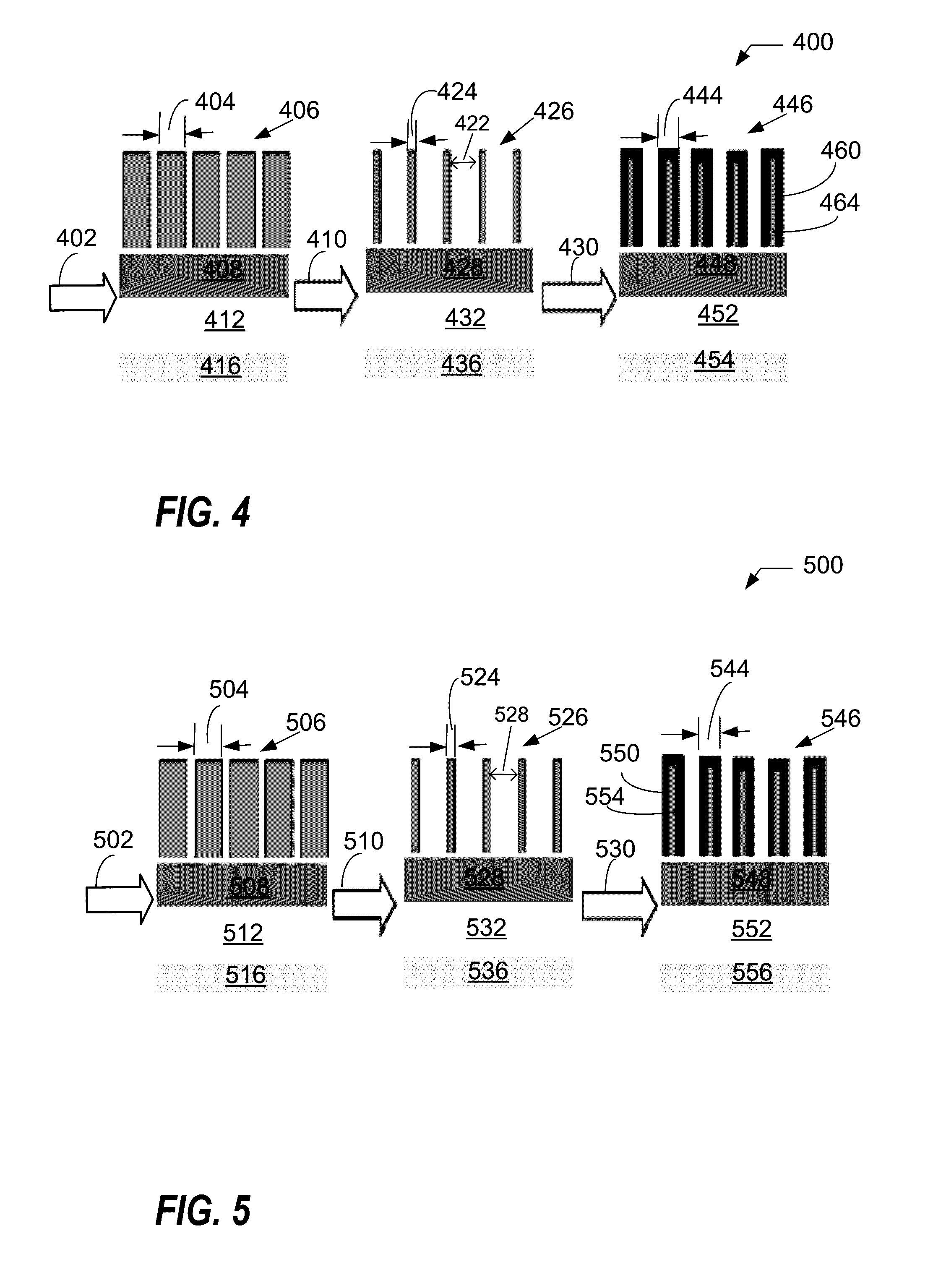

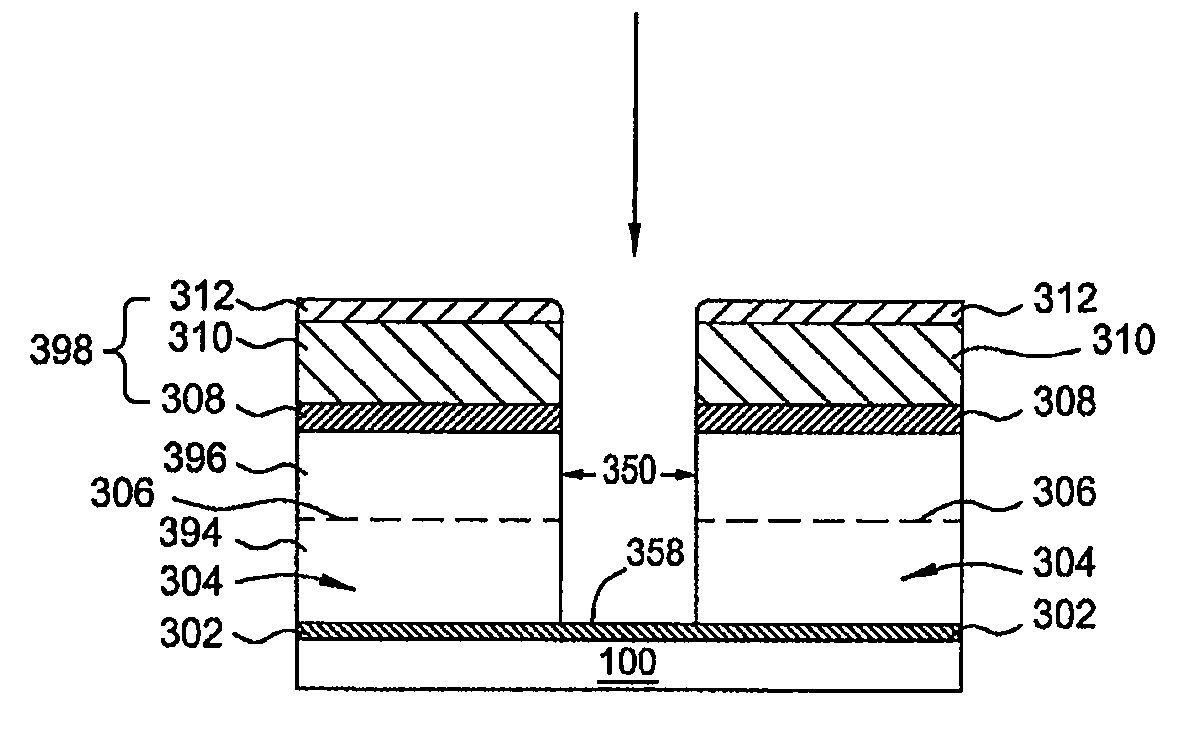

Hardmask open process with enhanced CD space shrink and reduction

InactiveUS20090191711A1Electric discharge tubesSemiconductor/solid-state device manufacturingResistCritical dimension

Methods for forming an ultra thin structure. The method includes a polymer deposition and etching process. In one embodiment, the methods may be utilized to form fabricate submicron structure having a critical dimension less than 30 nm and beyond. The method further includes a multiple etching processes. The processes may be varied to meet different process requirements. In one embodiment, the process gently etches the substrate while shrinking critical dimension of the structures formed within the substrate. The dimension of the structures may be shank by coating a photoresist like polymer to sidewalls of the formed structure, but substantially no polymer accumulation on the bottom surface of the formed structure on the substrate. The embodiments described herein also provide high selectivity in between each layers formed on the substrate during the fabricating process and preserving a good control of profile formed within the structure.

Owner:APPLIED MATERIALS INC

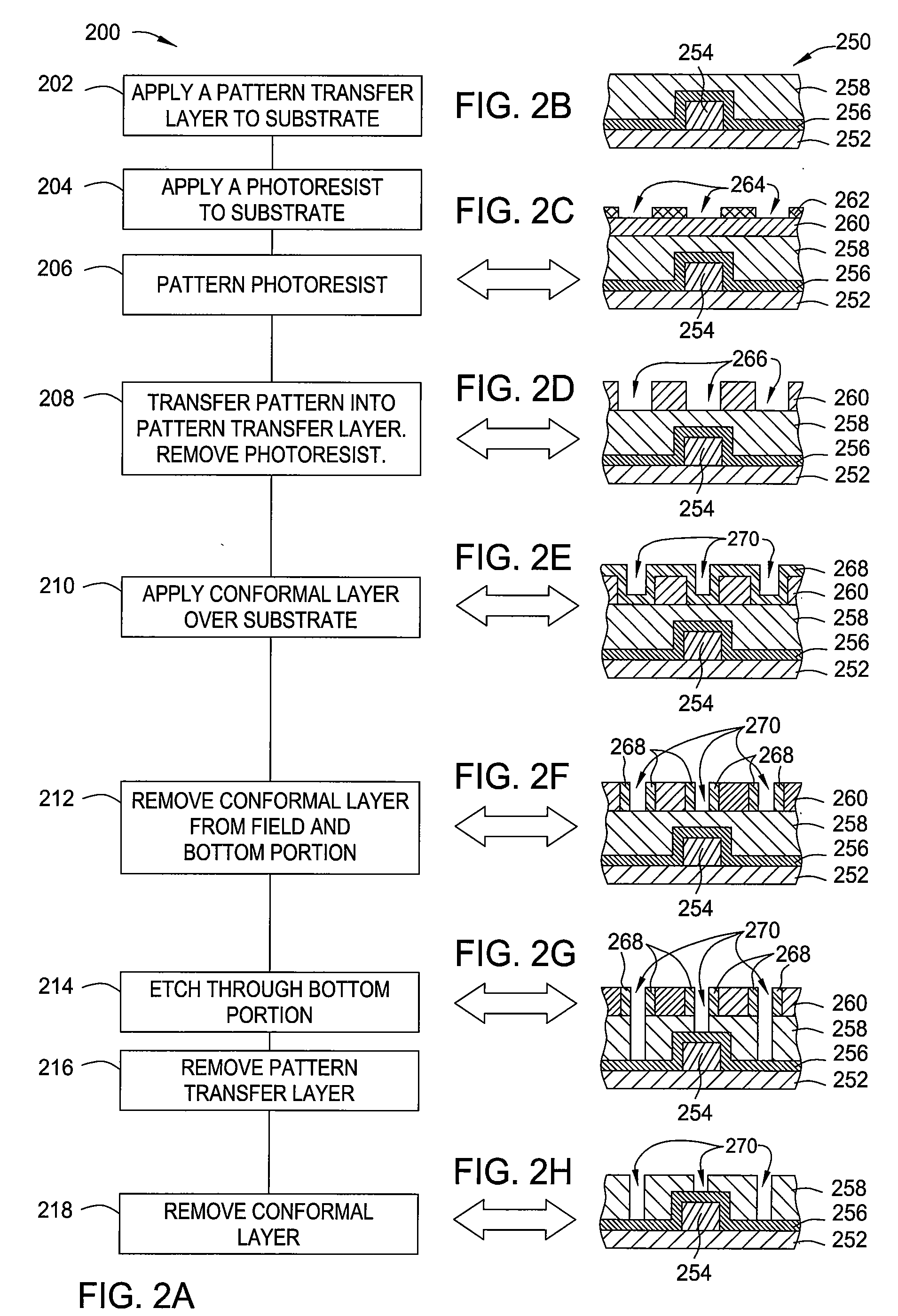

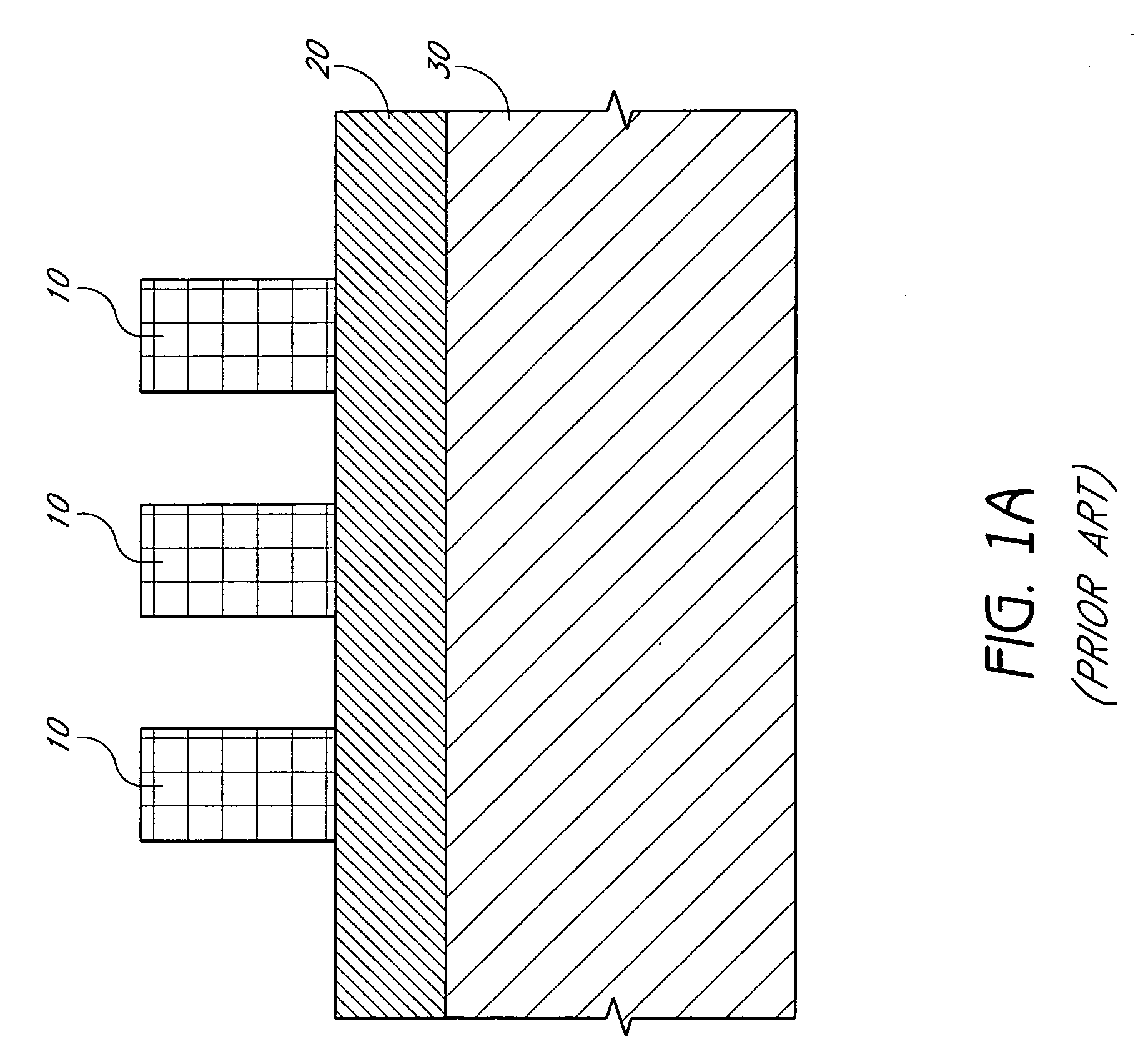

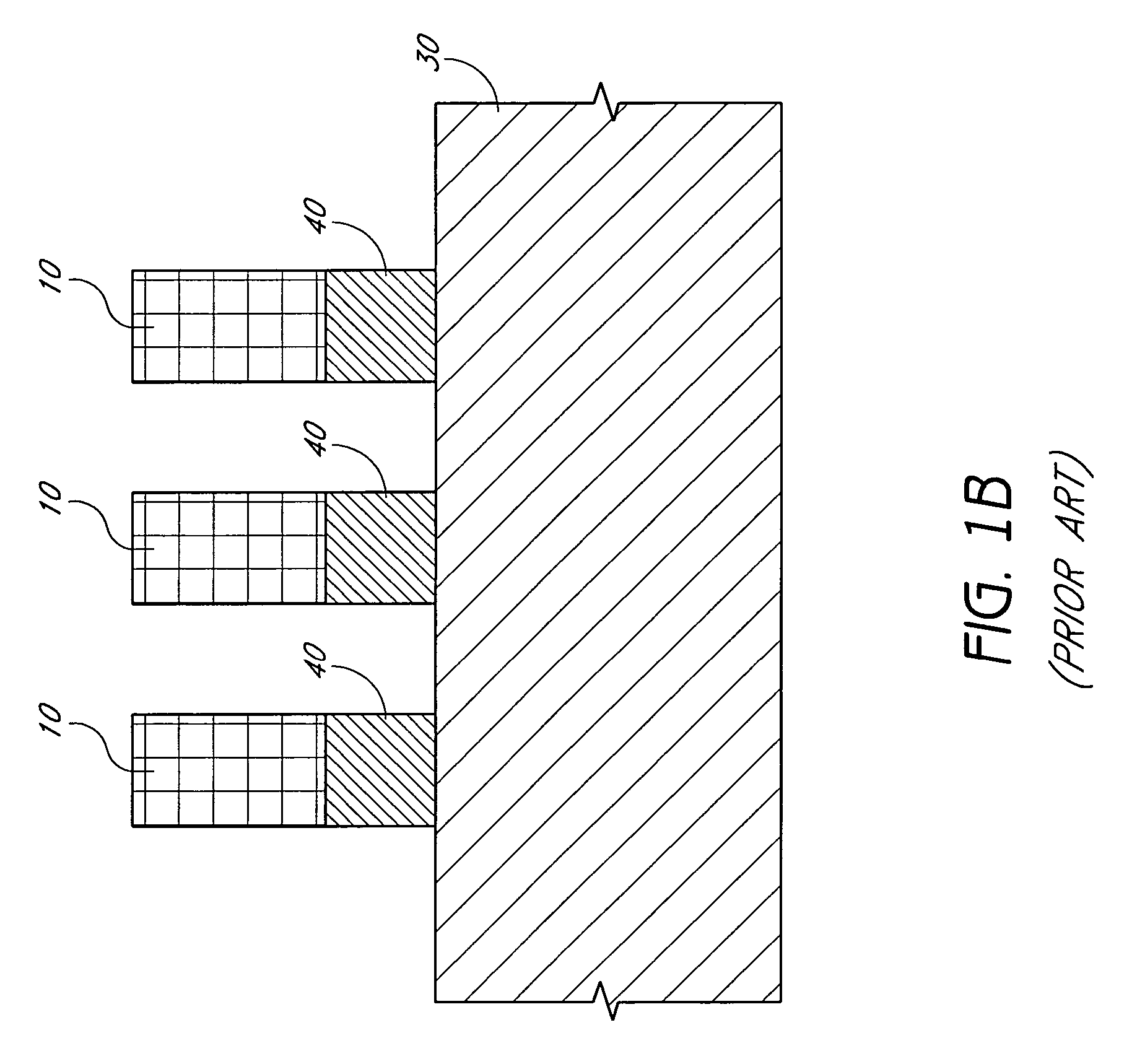

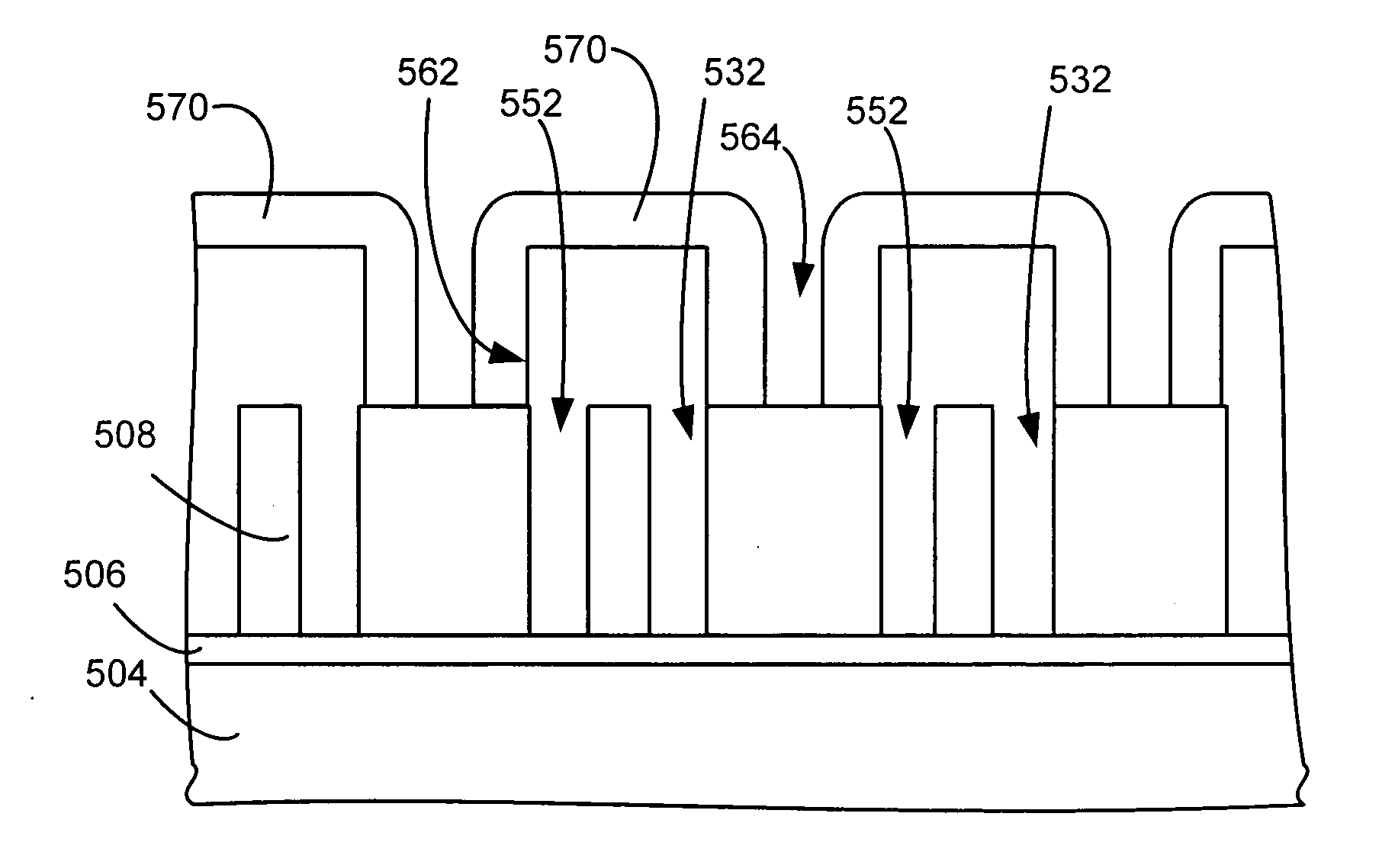

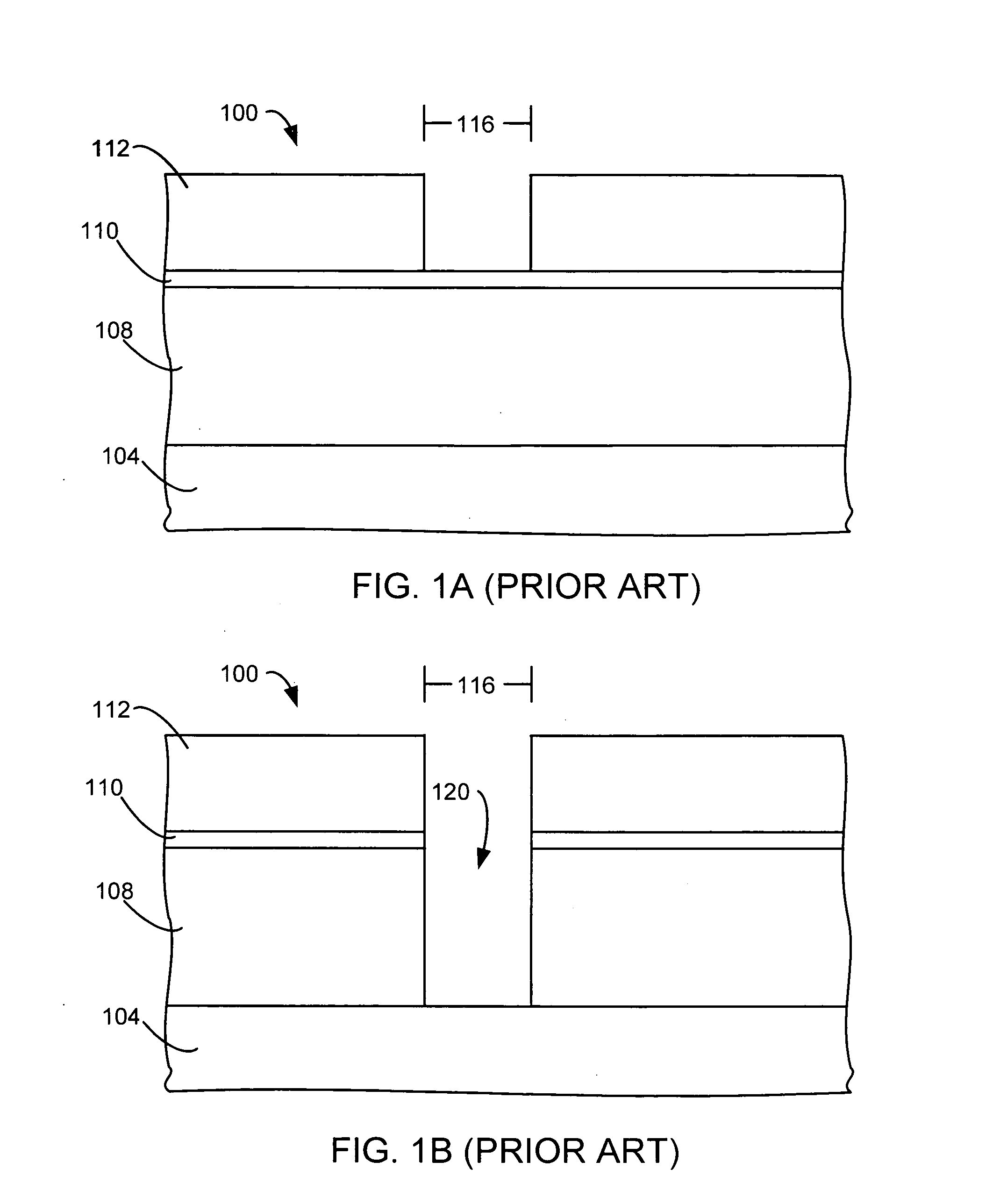

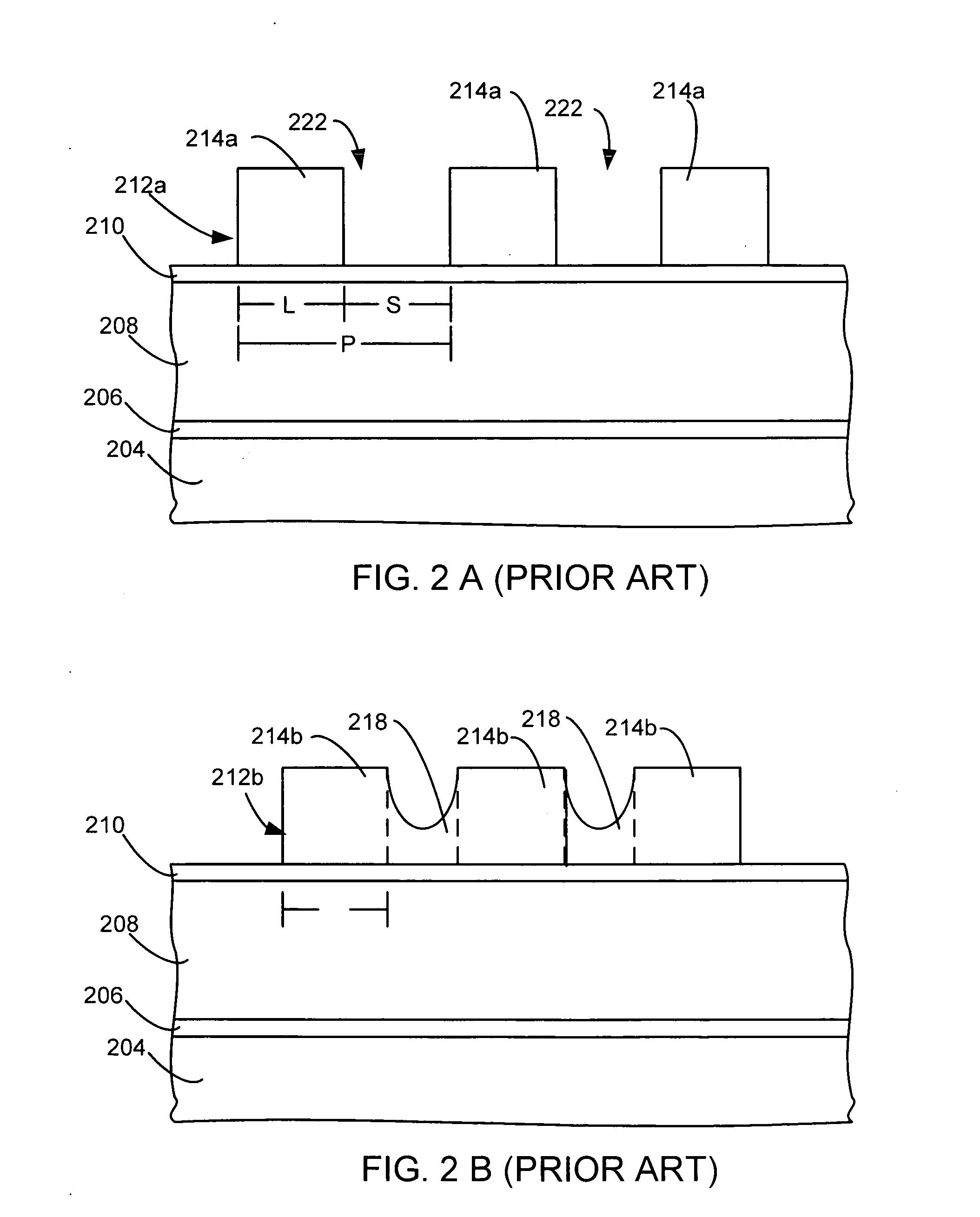

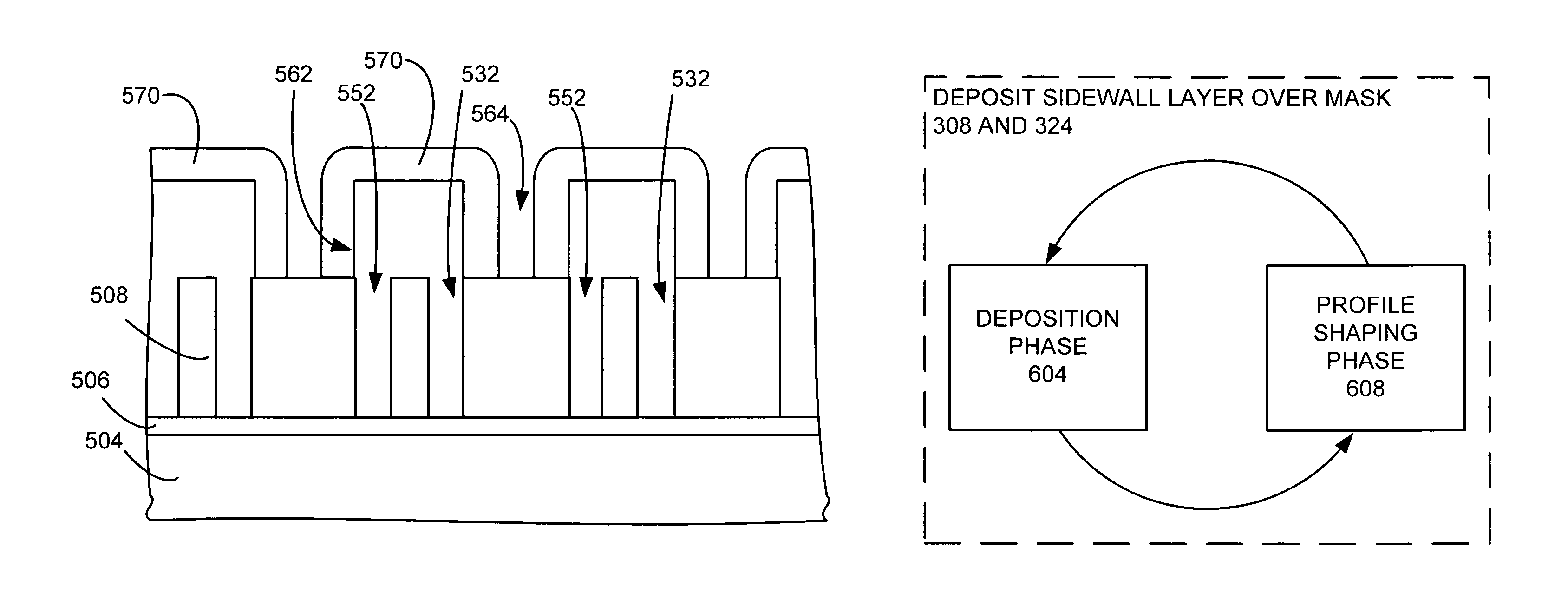

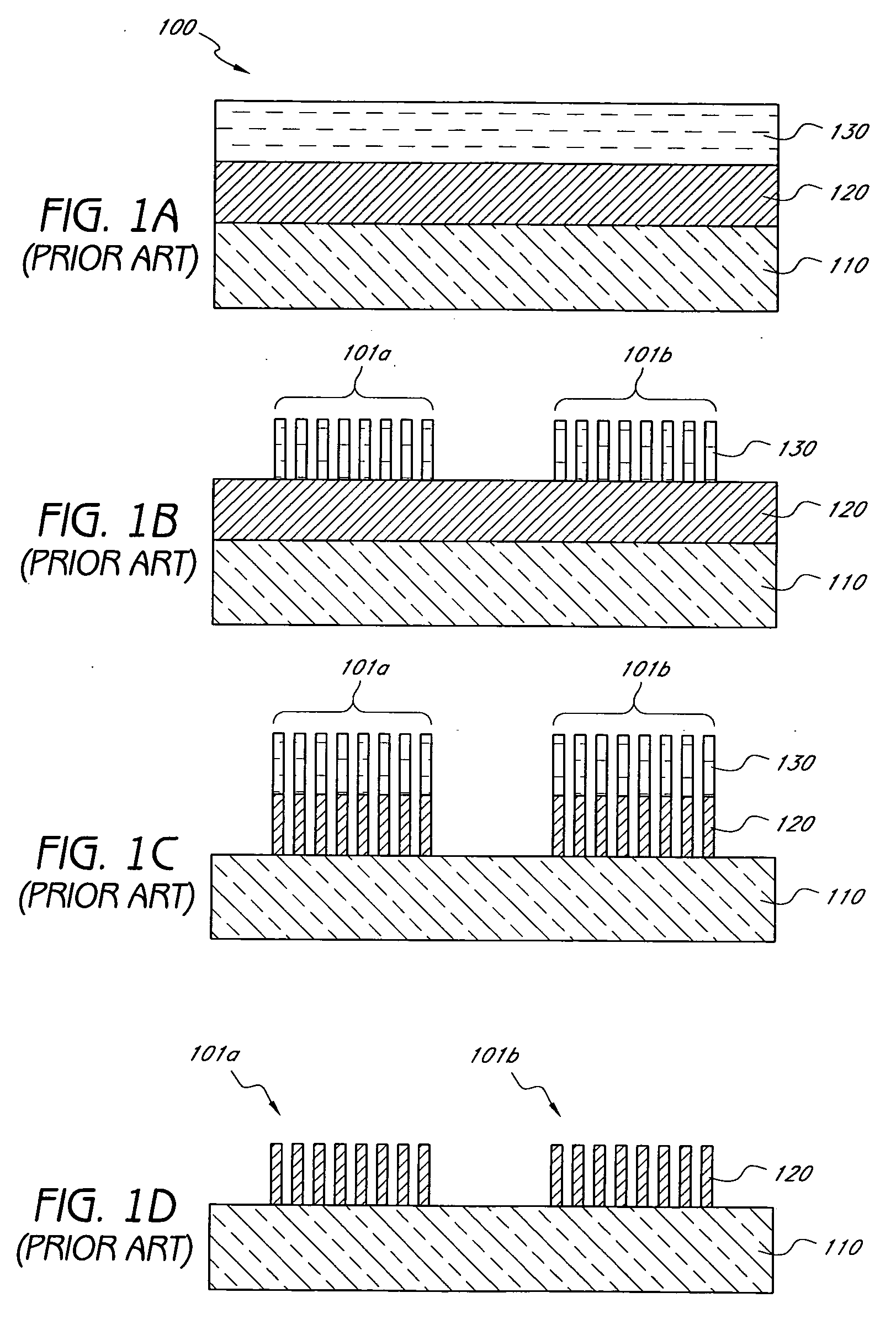

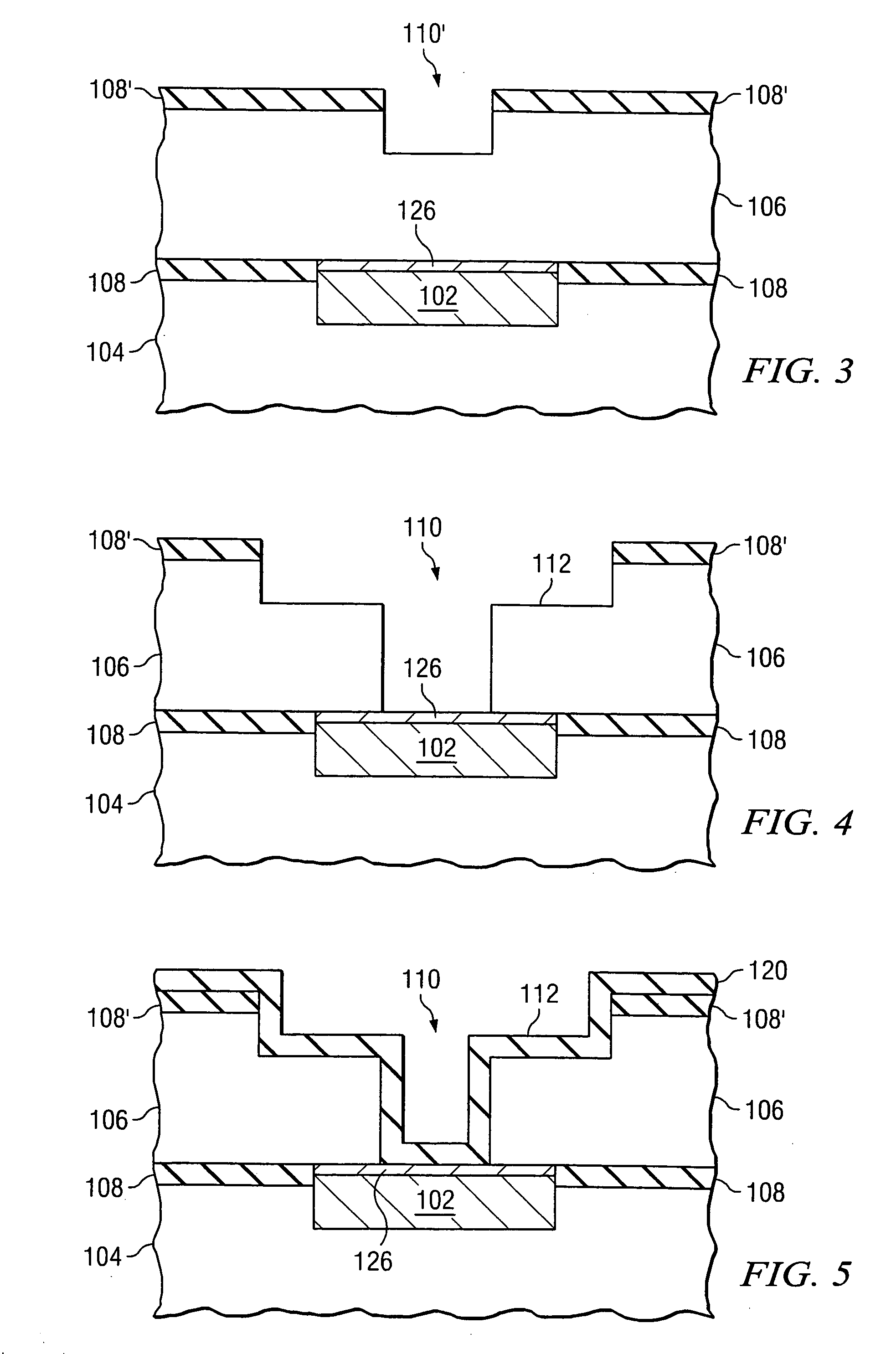

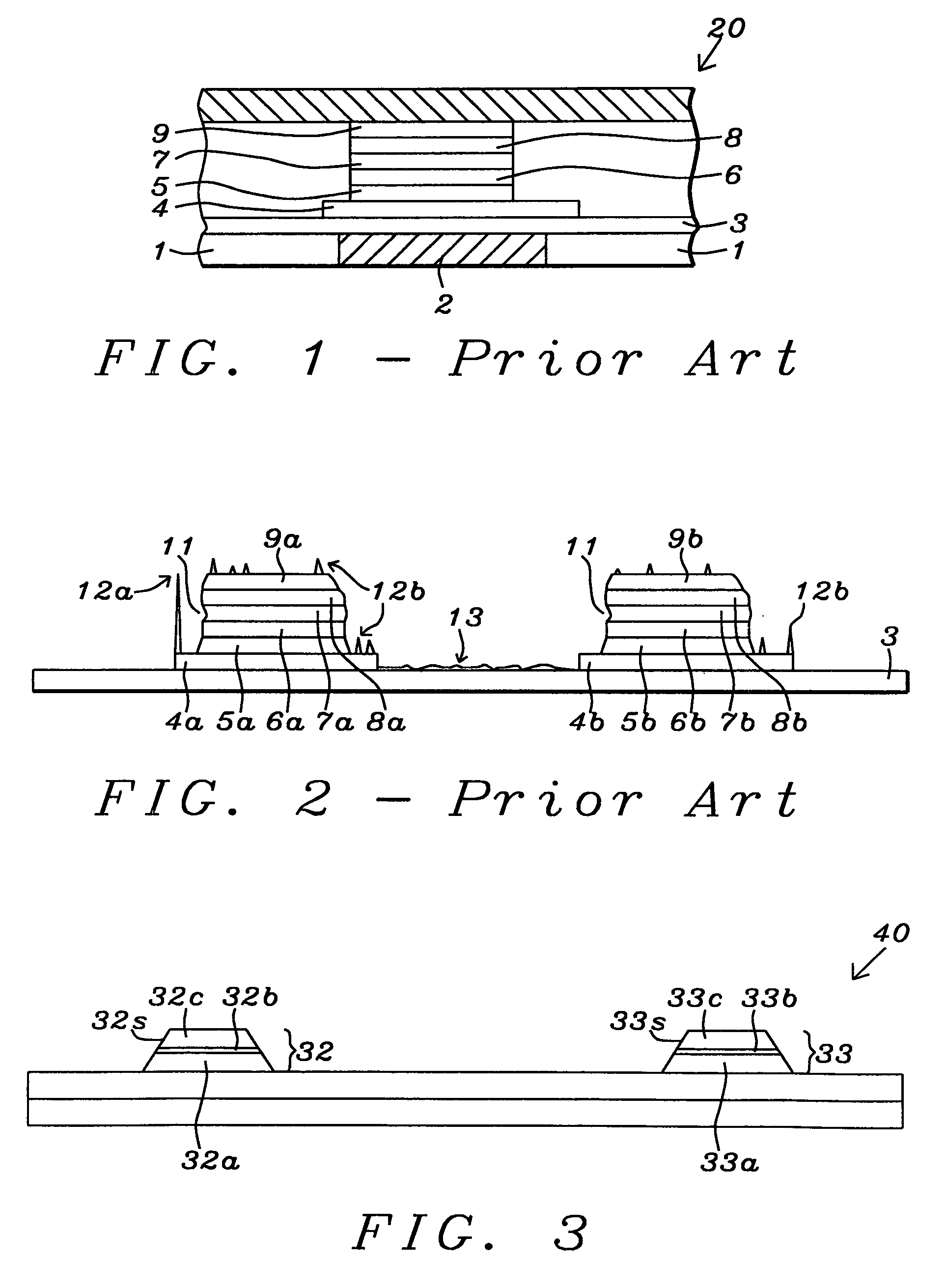

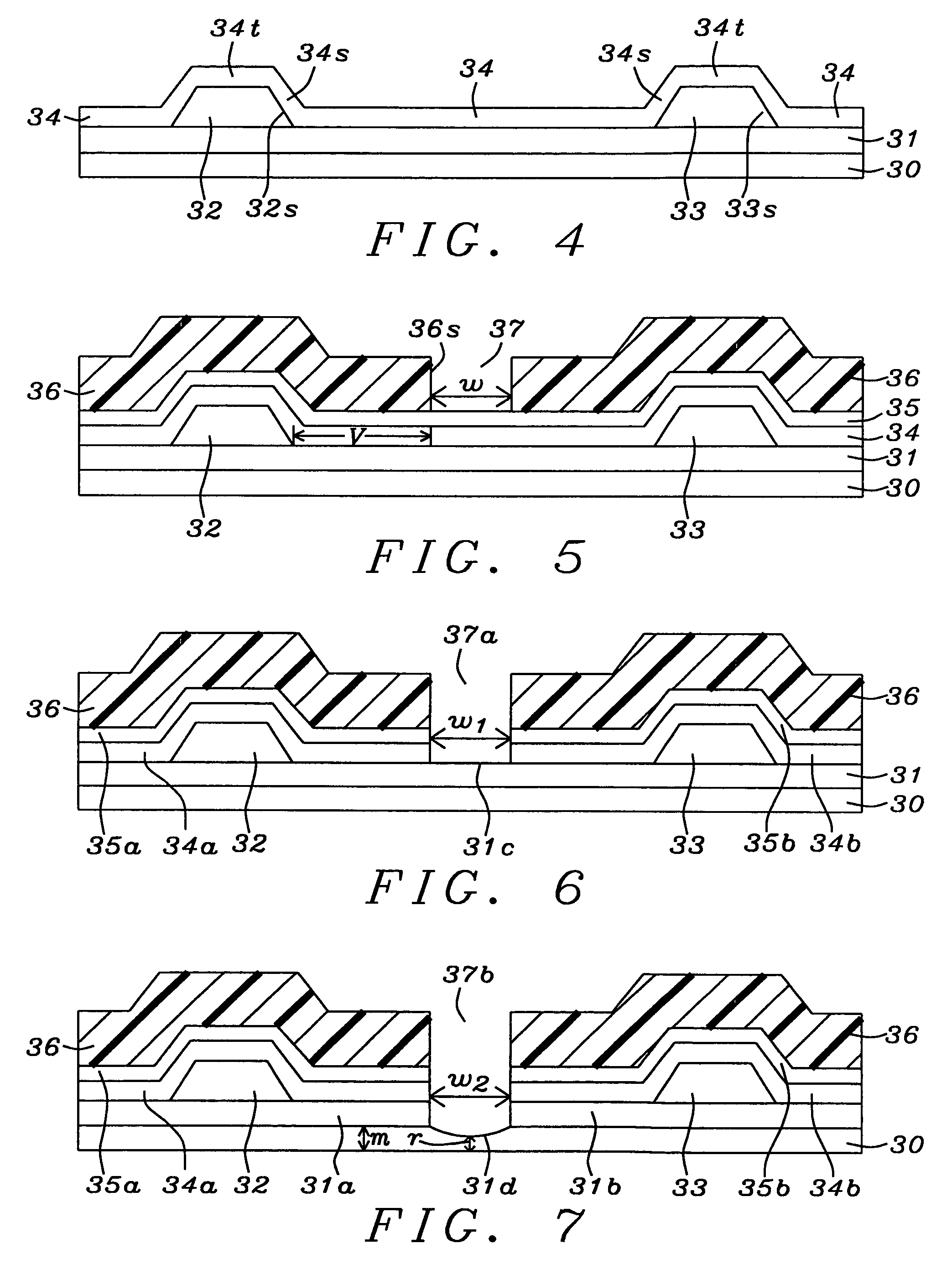

Reduction of feature critical dimensions using multiple masks

InactiveUS20060172540A1Reduce widthReduce space widthSemiconductor/solid-state device manufacturingCritical dimensionComputer science

A method for forming features in an etch layer is provided. A first mask is formed over the etch layer wherein the first mask defines a plurality of spaces with widths. A sidewall layer is formed over the first mask. Features are etched into the etch layer through the sidewall layer, wherein the features have widths that are smaller than the widths of the spaces defined by the first mask. The mask and sidewall layer are removed. An additional mask is formed over the etch layer wherein the additional mask defines a plurality of spaces with widths. A sidewall layer is formed over the additional mask. Features are etched into the etch layer through the sidewall layer, wherein the widths that are smaller than the widths of the spaces defined by the first mask. The mask and sidewall layer are removed.

Owner:LAM RES CORP

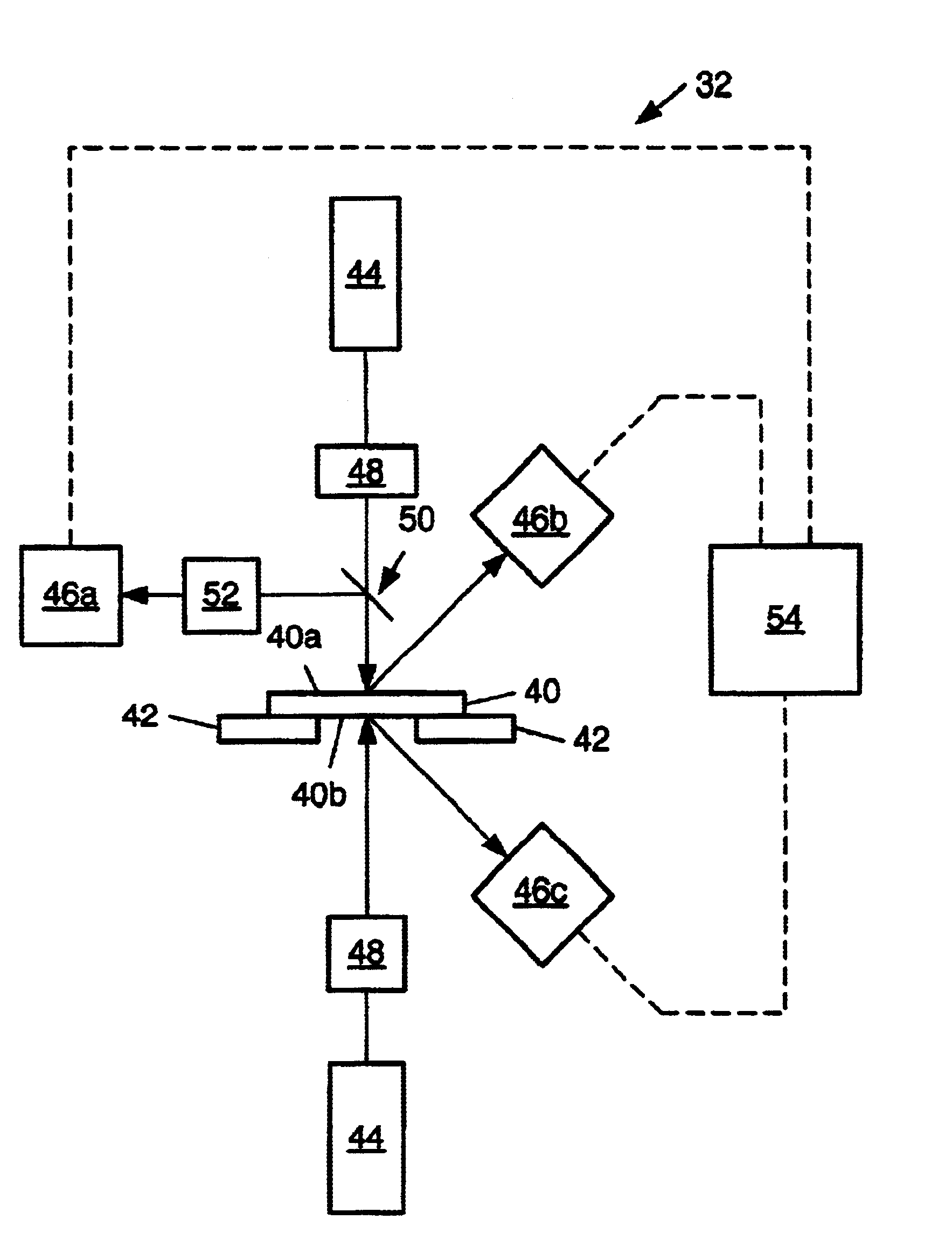

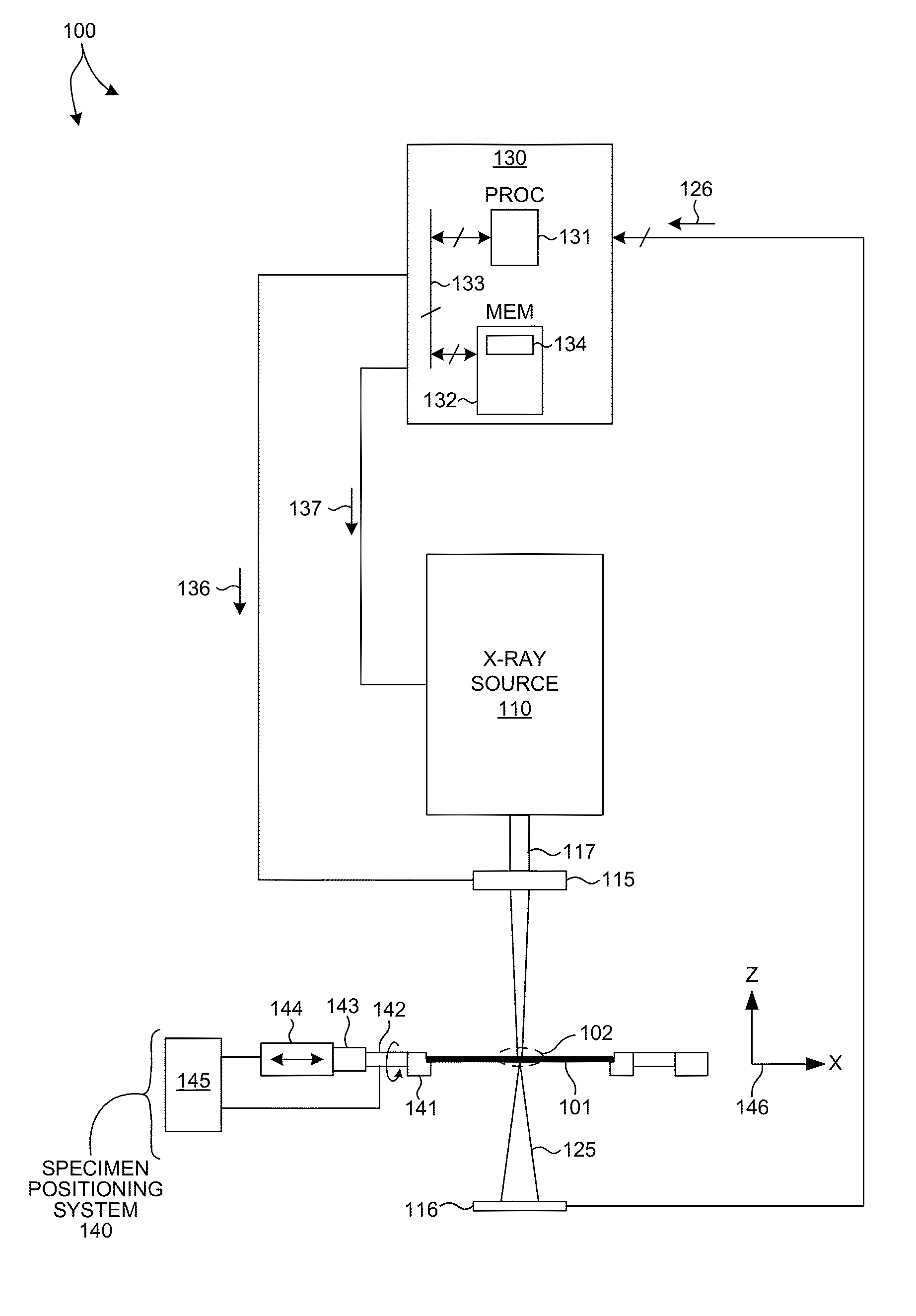

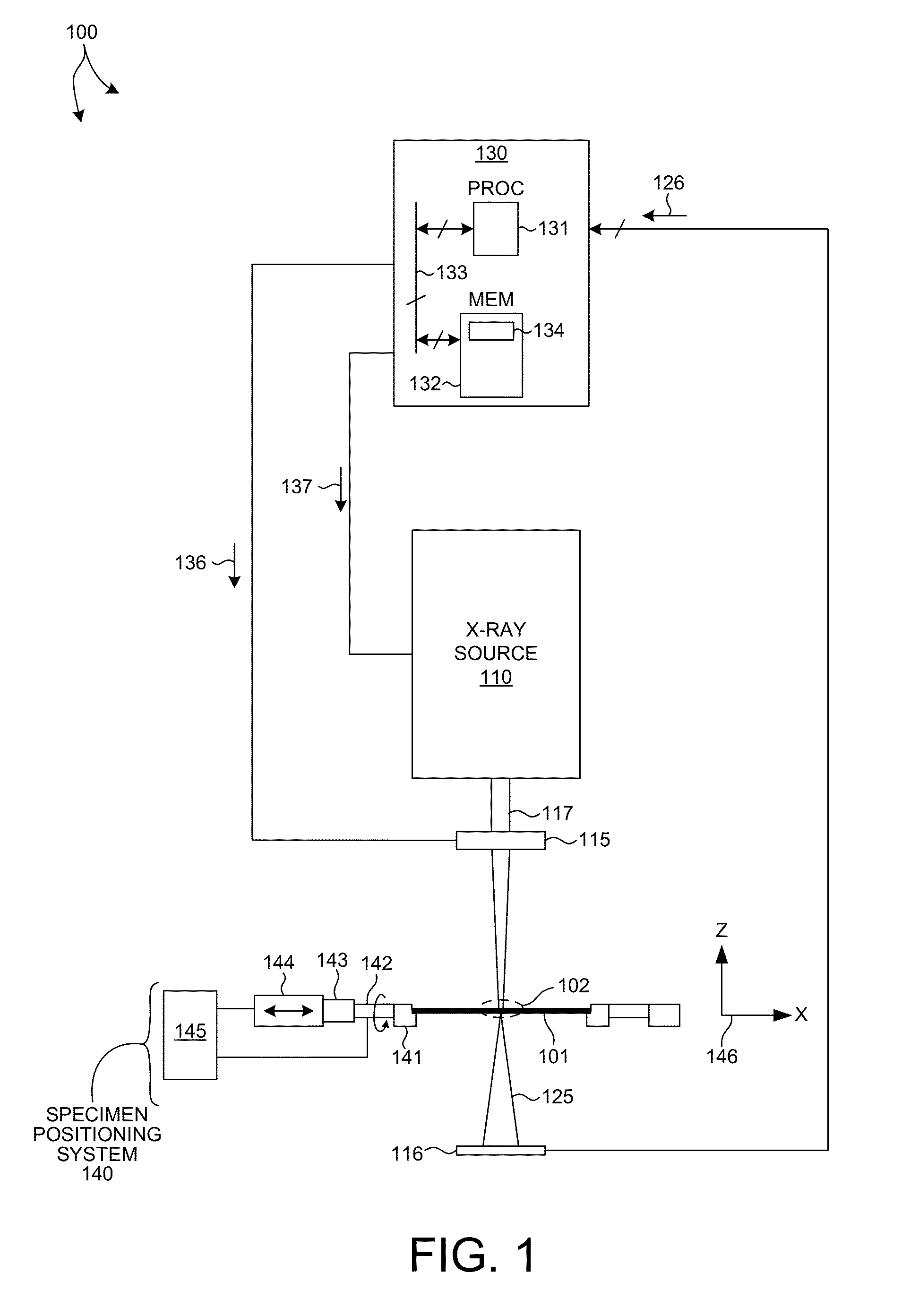

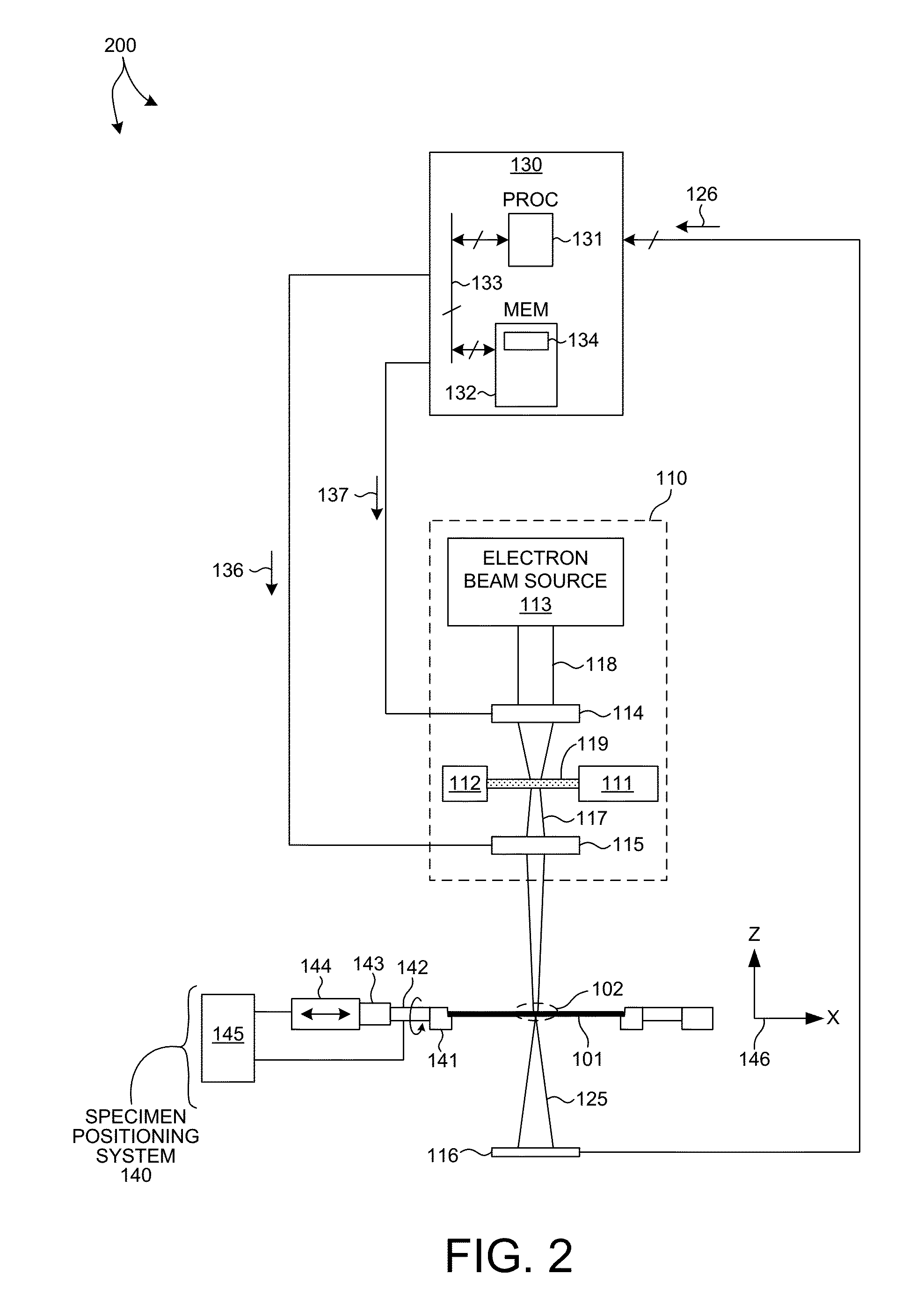

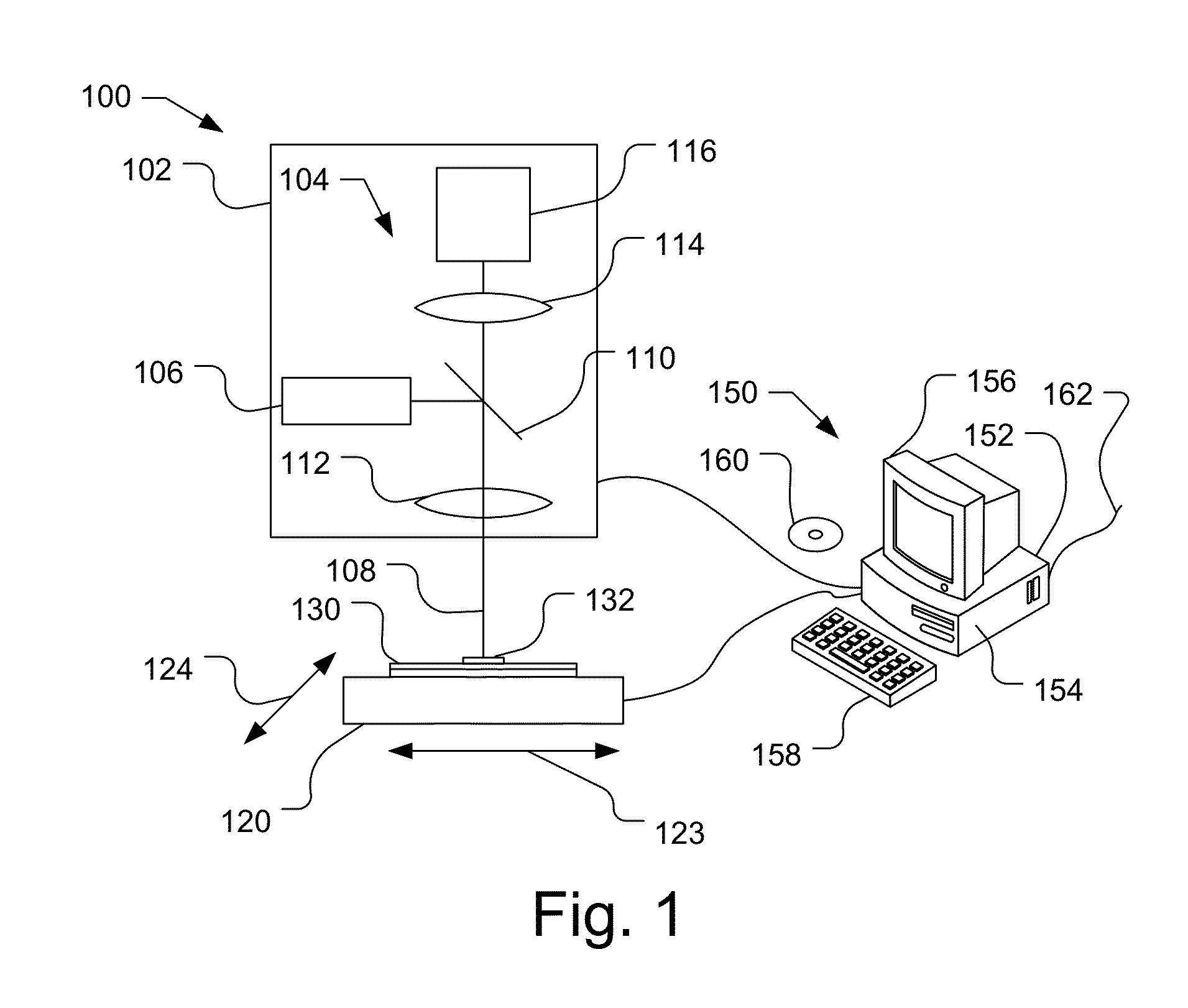

Methods and systems for determining a critical dimension and overlay of a specimen

InactiveUS6891627B1Speed up the processShorten the timeSemiconductor/solid-state device testing/measurementElectric discharge tubesMeasurement deviceEngineering

Methods and systems for monitoring semiconductor fabrication processes are provided. A system may include a stage configured to support a specimen and coupled to a measurement device. The measurement device may include an illumination system and a detection system. The illumination system and the detection system may be configured such that the system may be configured to determine multiple properties of the specimen. For example, the system may be configured to determine multiple properties of a specimen including, but not limited to, critical dimension and overlay misregistration. In this manner, a measurement device may perform multiple optical and / or non-optical metrology and / or inspection techniques.

Owner:KLA CORP

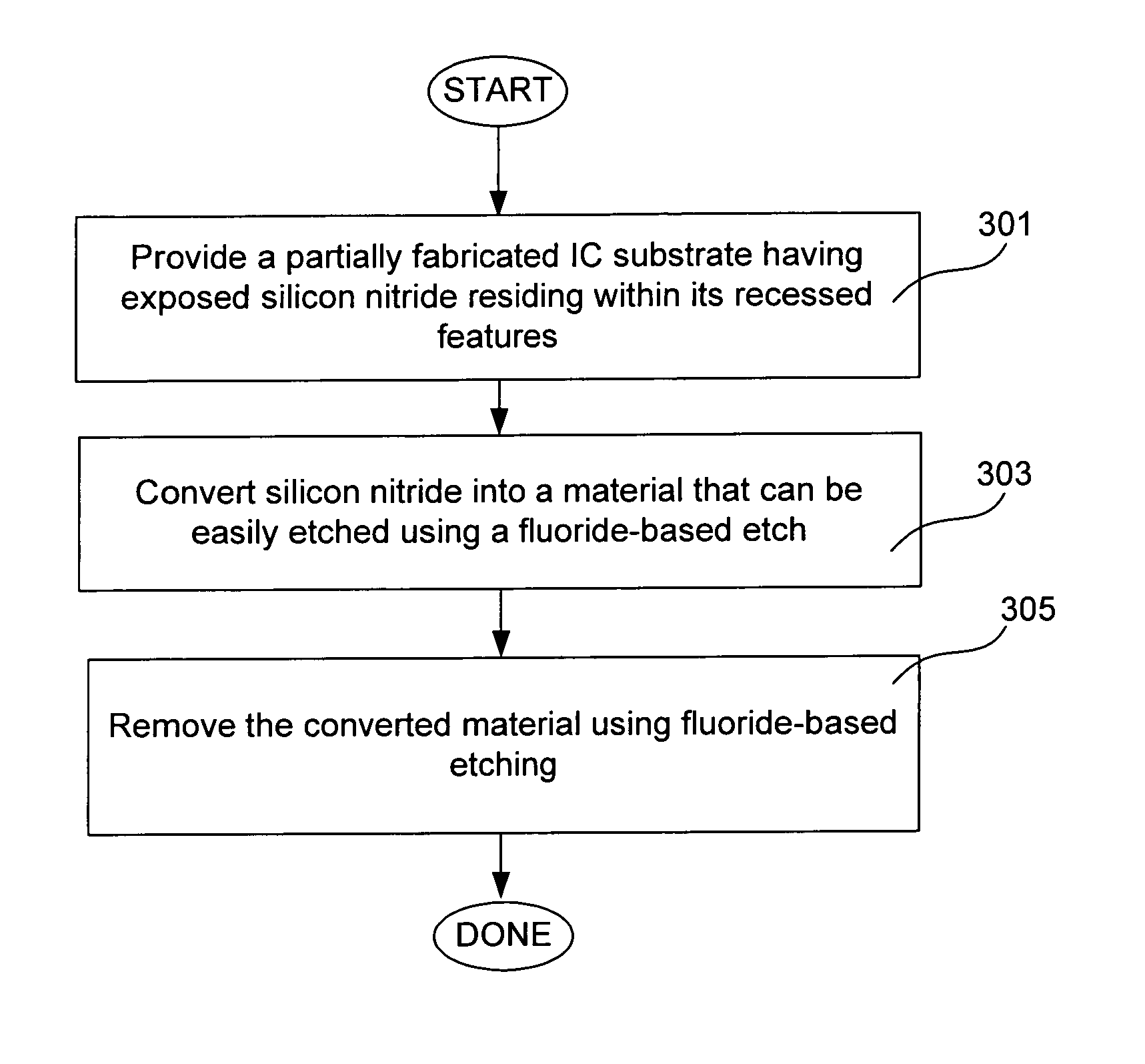

Methods for removing silicon nitride and other materials during fabrication of contacts

ActiveUS7977249B1Easy to etchMinimizes unwanted increaseDecorative surface effectsSemiconductor/solid-state device manufacturingHydrogenContact method

Methods for removing silicon nitride and elemental silicon during contact preclean process involve converting these materials to materials that are more readily etched by fluoride-based etching methods, and subsequently removing the converted materials by a fluoride-based etch. Specifically, silicon nitride and elemental silicon may be treated with an oxidizing agent, e.g., with an oxygen-containing gas in a plasma, or with O2 or O3 in the absence of plasma to produce a material that is more rich in Si—O bonds and is more easily etched with a fluoride-based etch. Alternatively, silicon nitride or elemental silicon may be doped with a number of doping elements, e.g., hydrogen, to form materials which are more easily etched by fluoride based etches. The methods are particularly useful for pre-cleaning contact vias residing in a layer of silicon oxide based material because they minimize the unwanted increase of critical dimension of contact vias.

Owner:NOVELLUS SYSTEMS

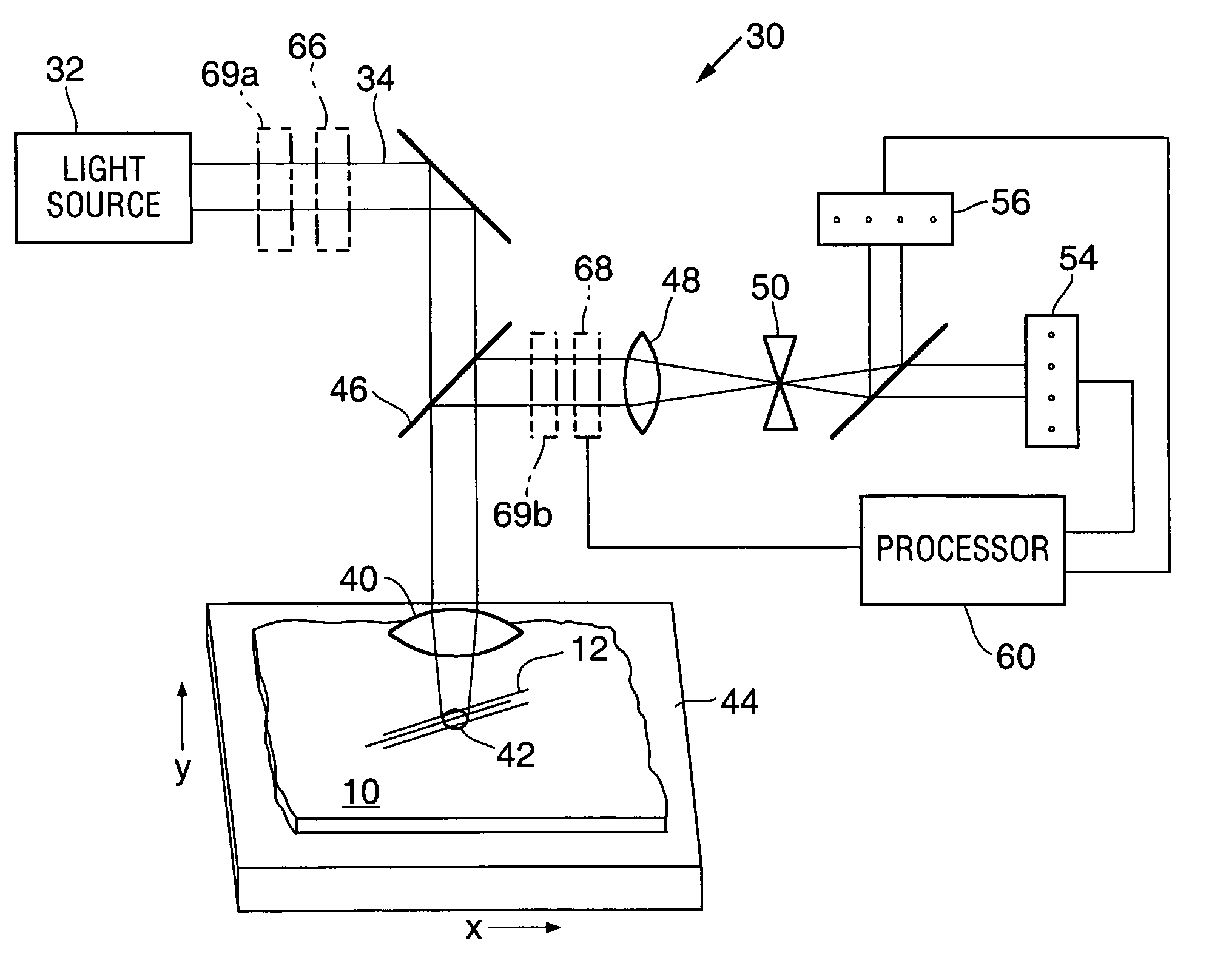

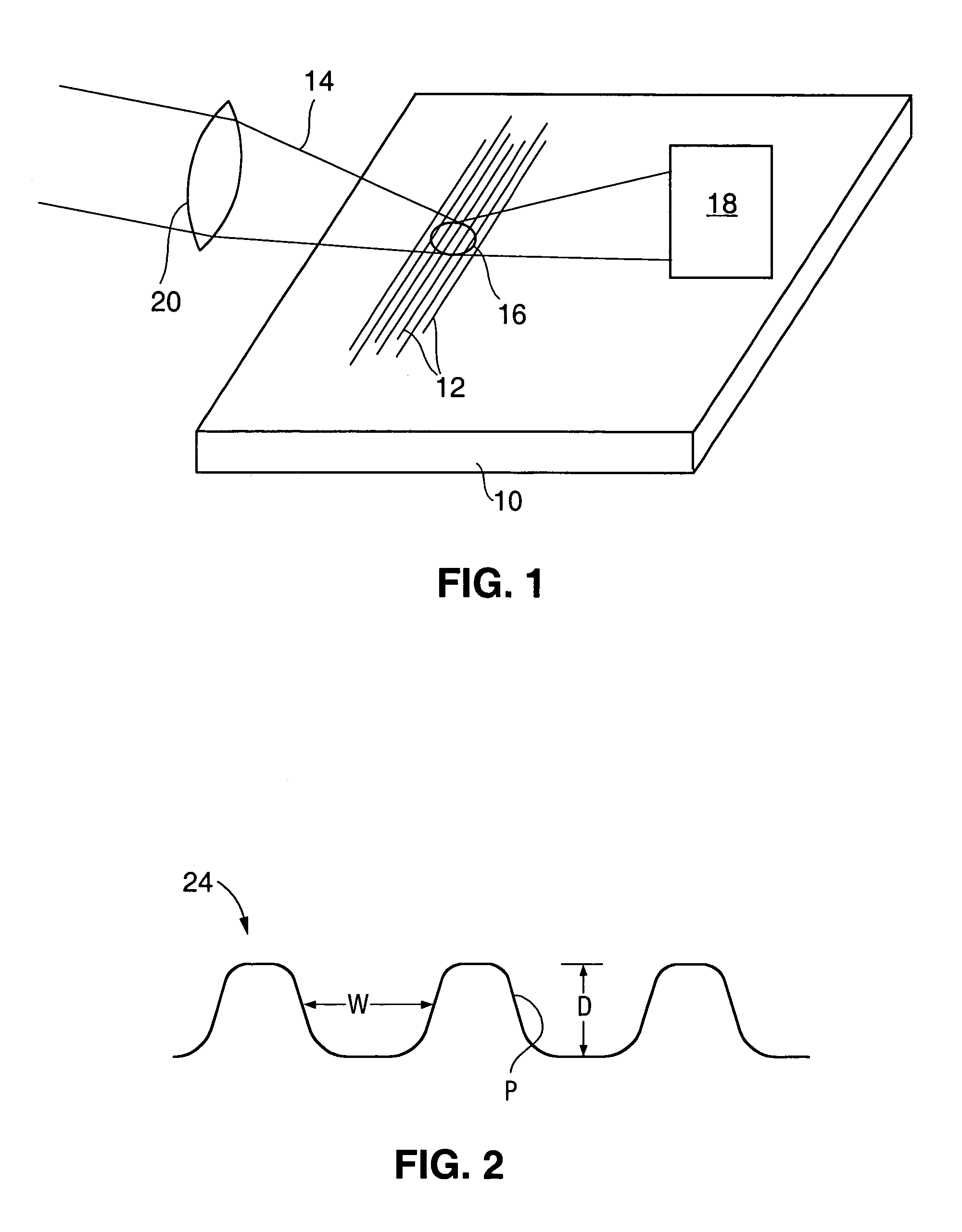

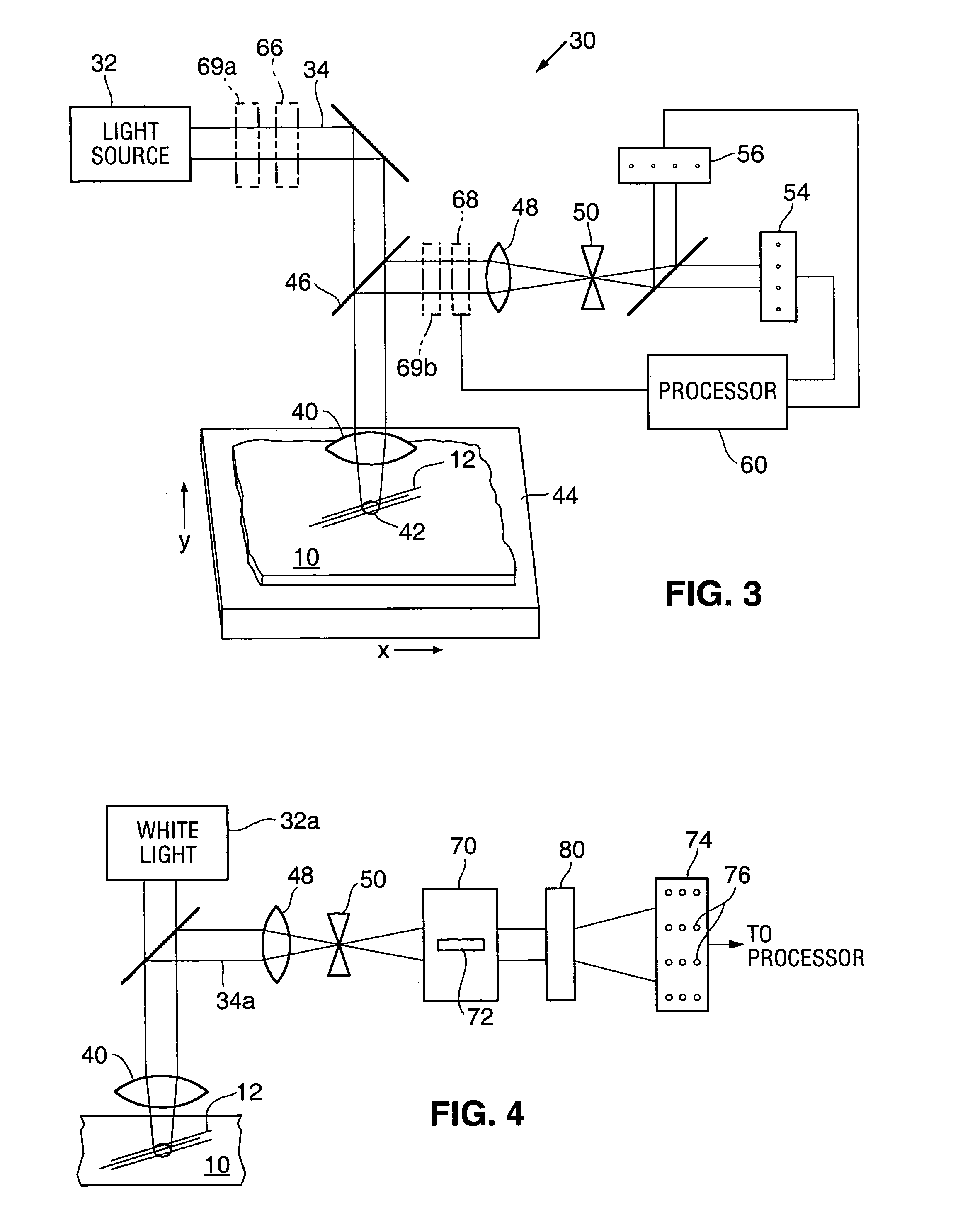

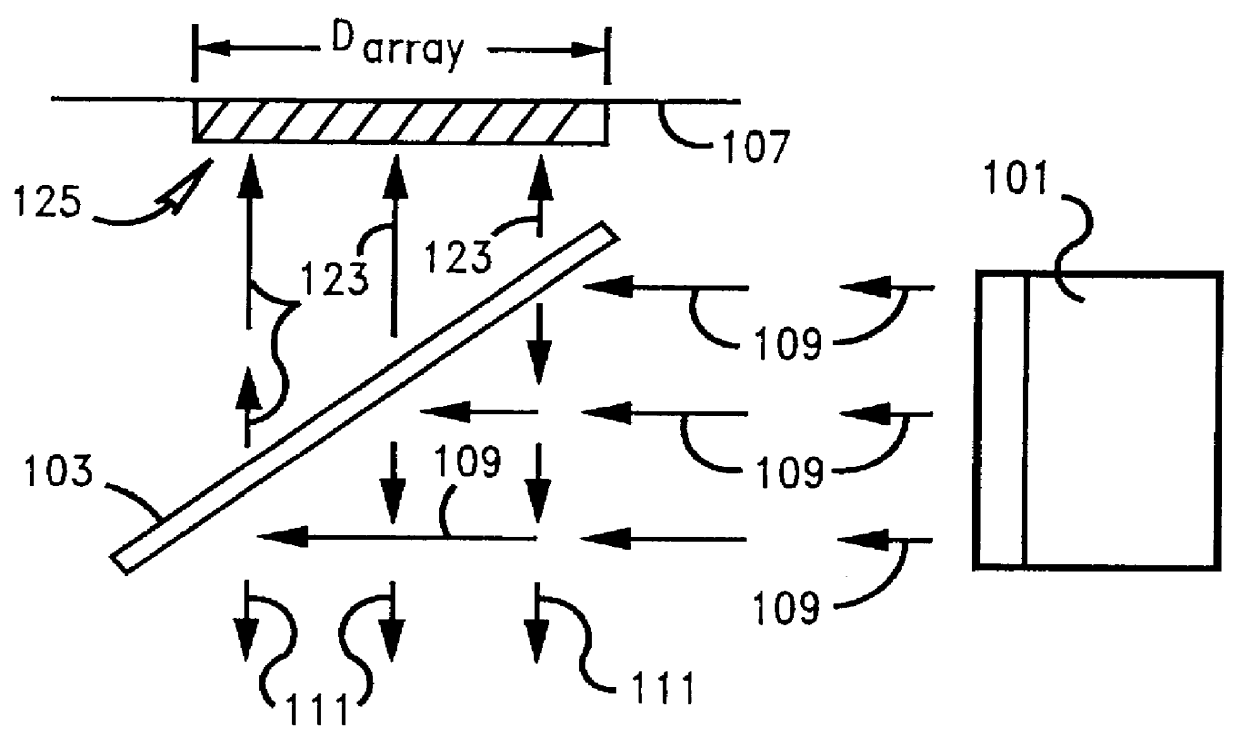

Critical dimension analysis with simultaneous multiple angle of incidence measurements

InactiveUS6972852B2Maximizes information contentImprove abilitiesPhotomechanical apparatusUsing optical meansAngle of incidenceLight beam

A method and apparatus are disclosed for evaluating relatively small periodic structures formed on semiconductor samples. In this approach, a light source generates a probe beam which is directed to the sample. In one preferred embodiment, an incoherent light source is used. A lens is used to focus the probe beam on the sample in a manner so that rays within the probe beam create a spread of angles of incidence. The size of the probe beam spot on the sample is larger than the spacing between the features of the periodic structure so some of the light is scattered from the structure. A detector is provided for monitoring the reflected and scattered light. The detector includes multiple detector elements arranged so that multiple output signals are generated simultaneously and correspond to multiple angles of incidence. The output signals are supplied to a processor which analyzes the signals according to a scattering model which permits evaluation of the geometry of the periodic structure. In one embodiment, the sample is scanned with respect to the probe beam and output signals are generated as a function of position of the probe beam spot.

Owner:THERMA WAVE INC

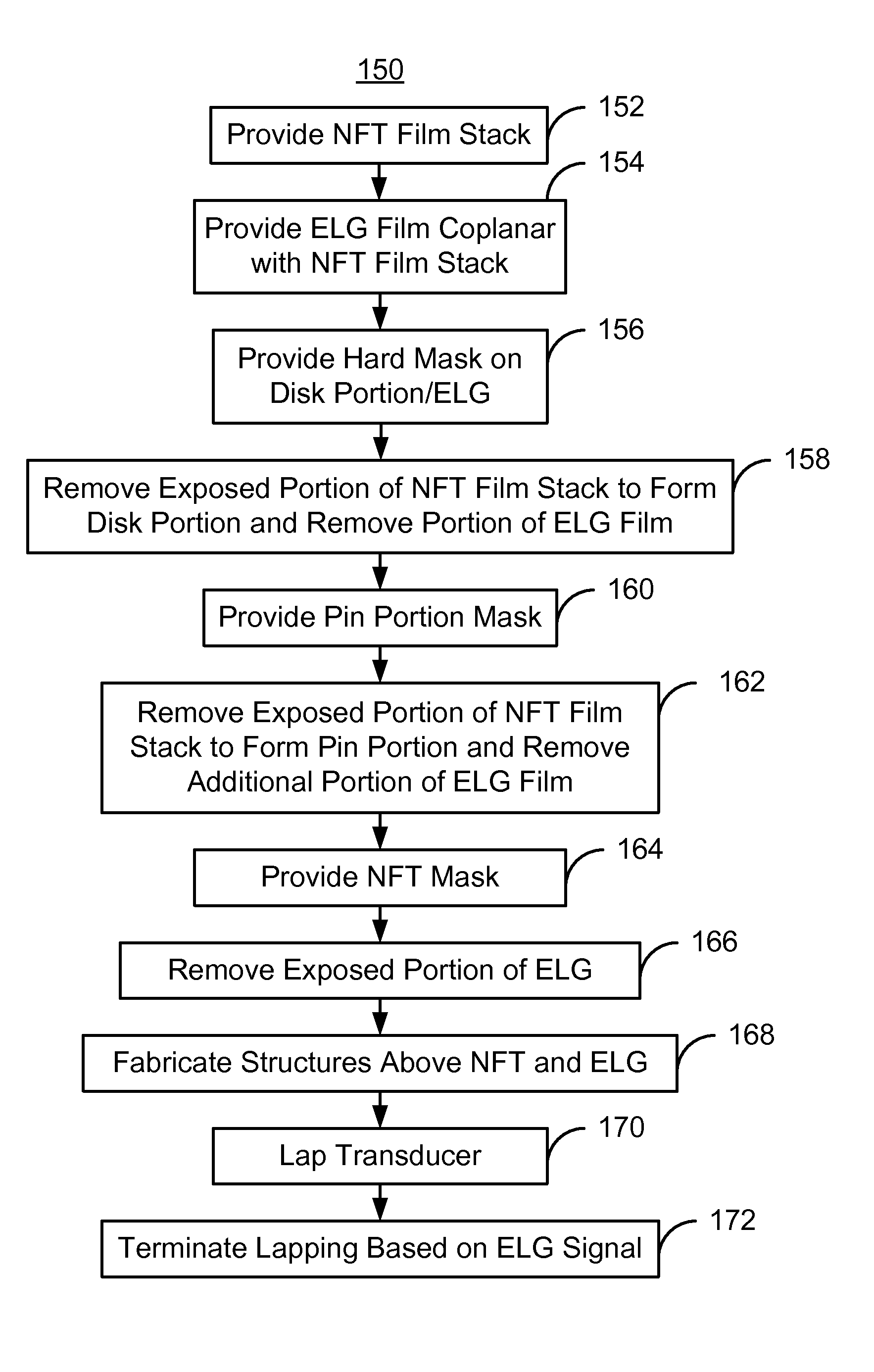

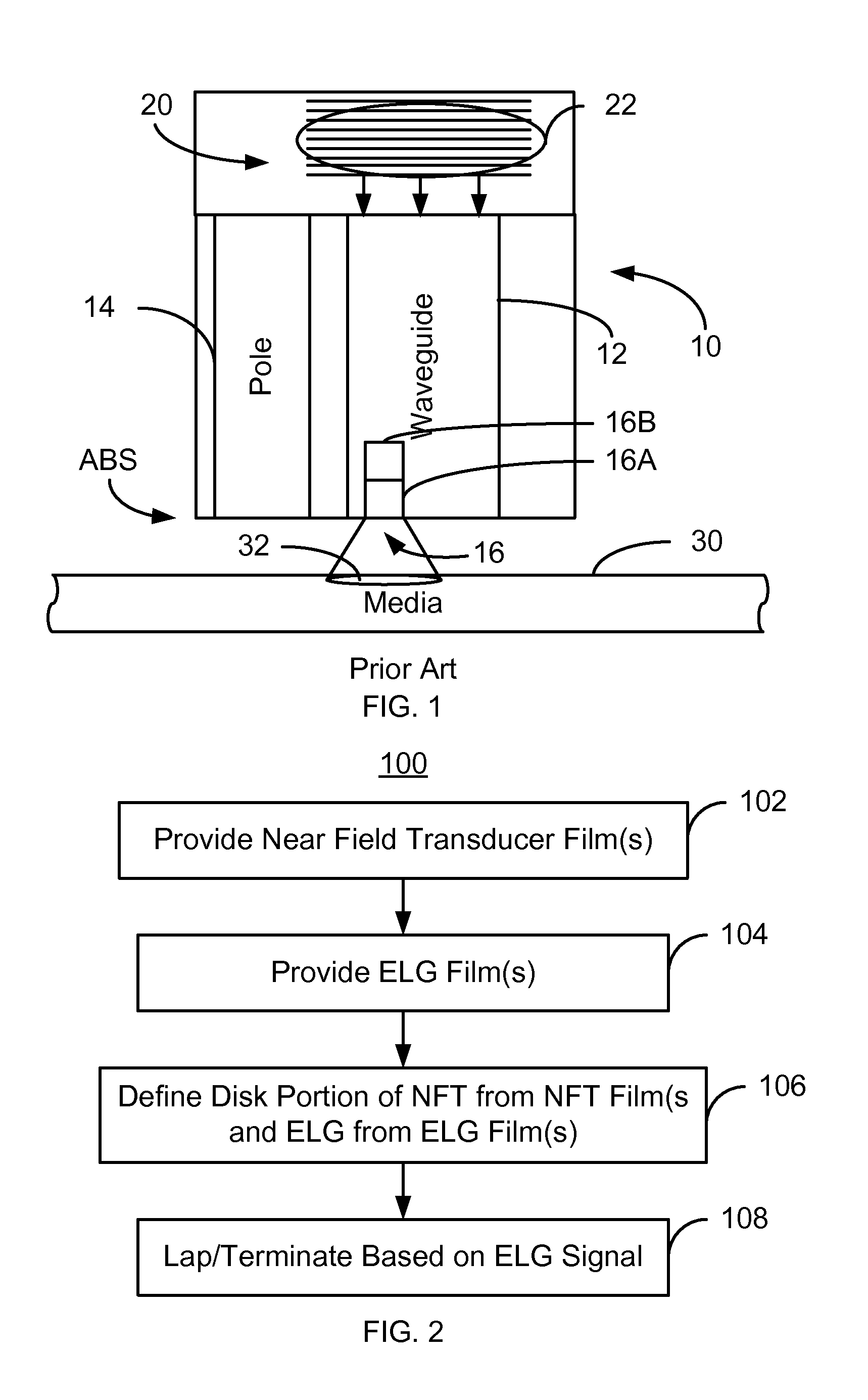

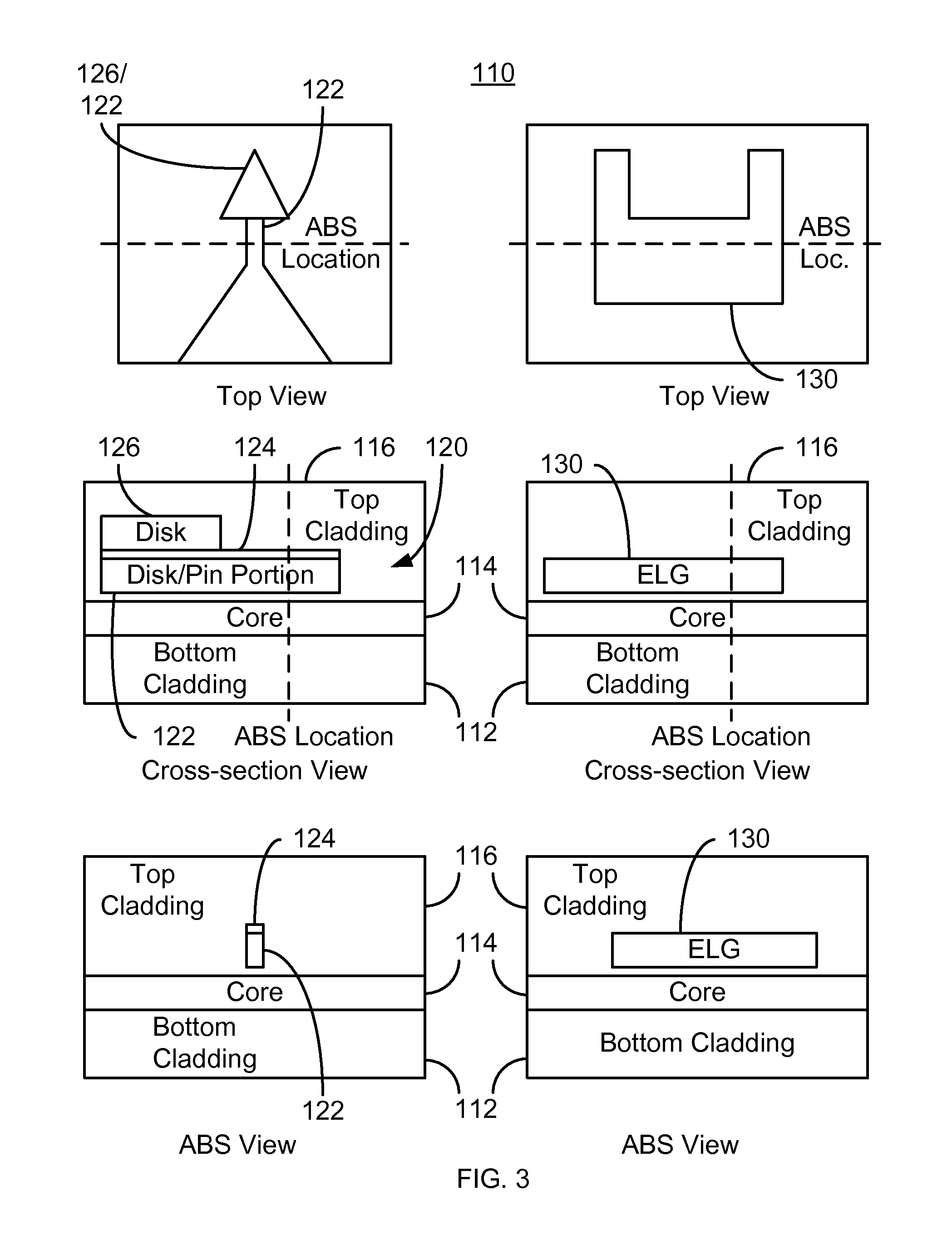

Method for providing an electronic lapping guide corresponding to a near-field transducer of an energy assisted magnetic recording transducer

A method fabricates a transducer having an air-bearing surface (ABS). The method includes providing at least one near-field transducer (NFT) film and providing an electronic lapping guide (ELG) film substantially coplanar with a portion of the at least one NFT film. The method also includes defining a disk portion of an NFT from the portion of the at least one NFT film and at least one ELG from the ELG film. The disk portion corresponds to a critical dimension of the NFT from an ABS location. The method also includes lapping the at least one transducer. The lapping is terminated based on a signal from the ELG.

Owner:WESTERN DIGITAL TECH INC

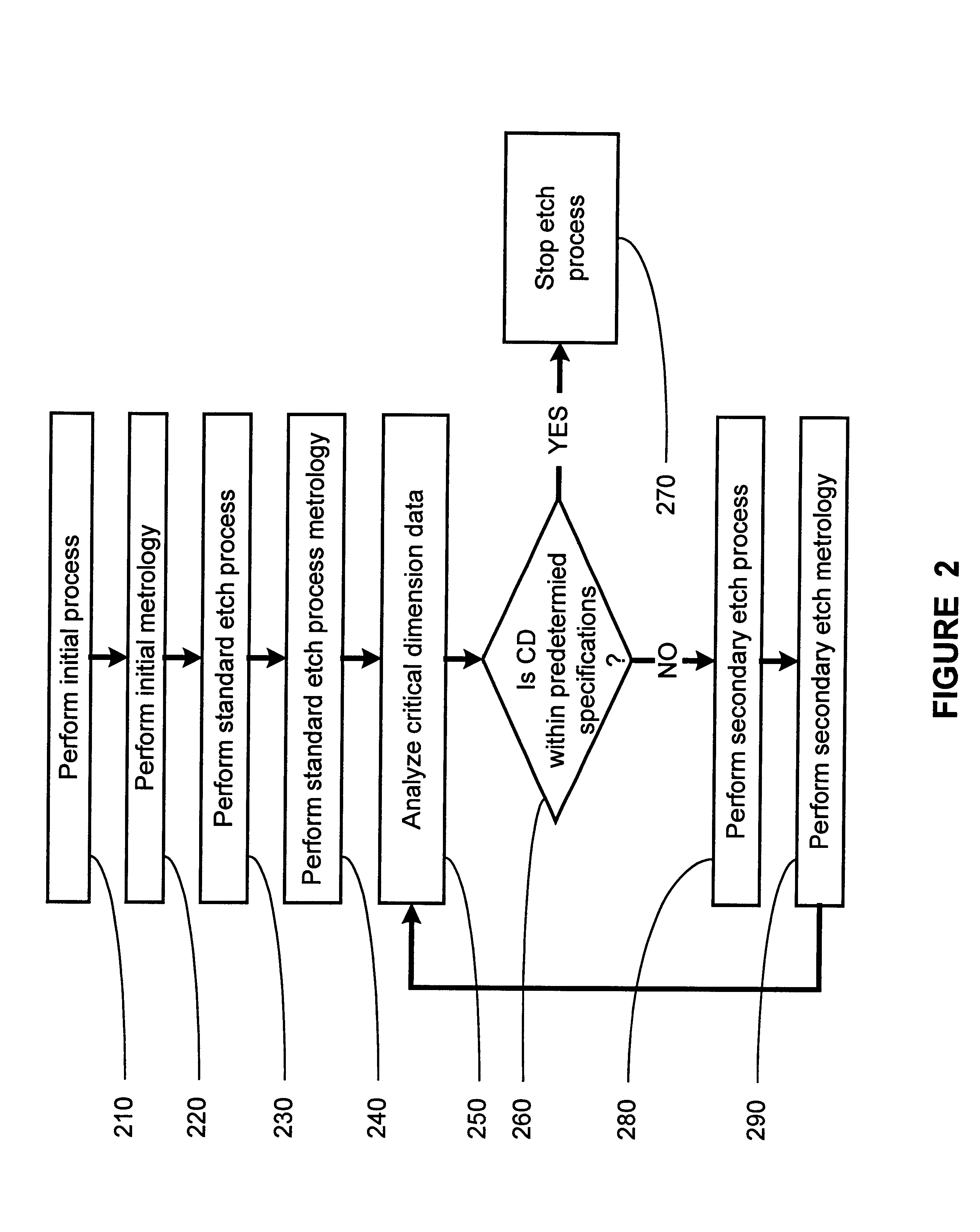

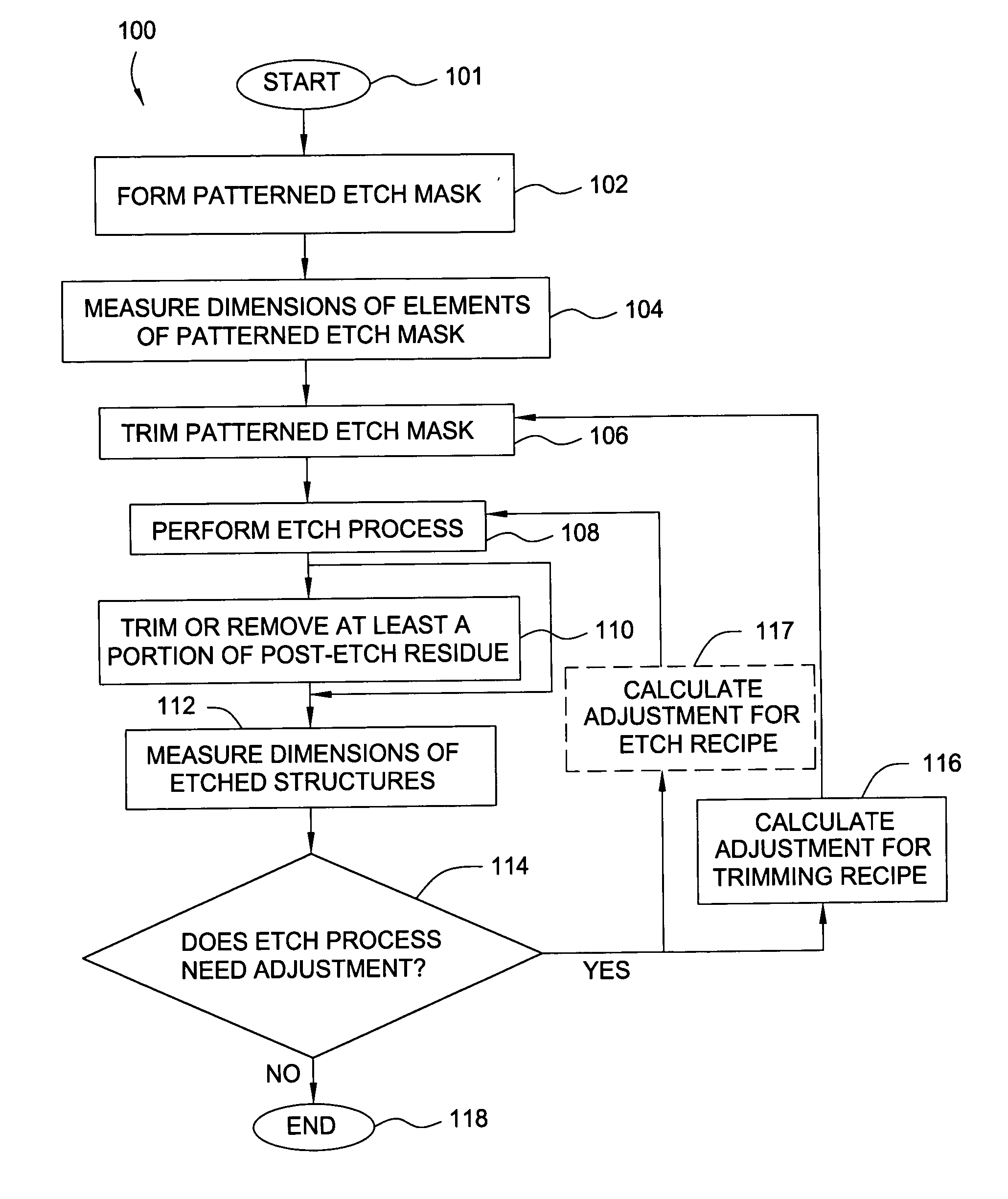

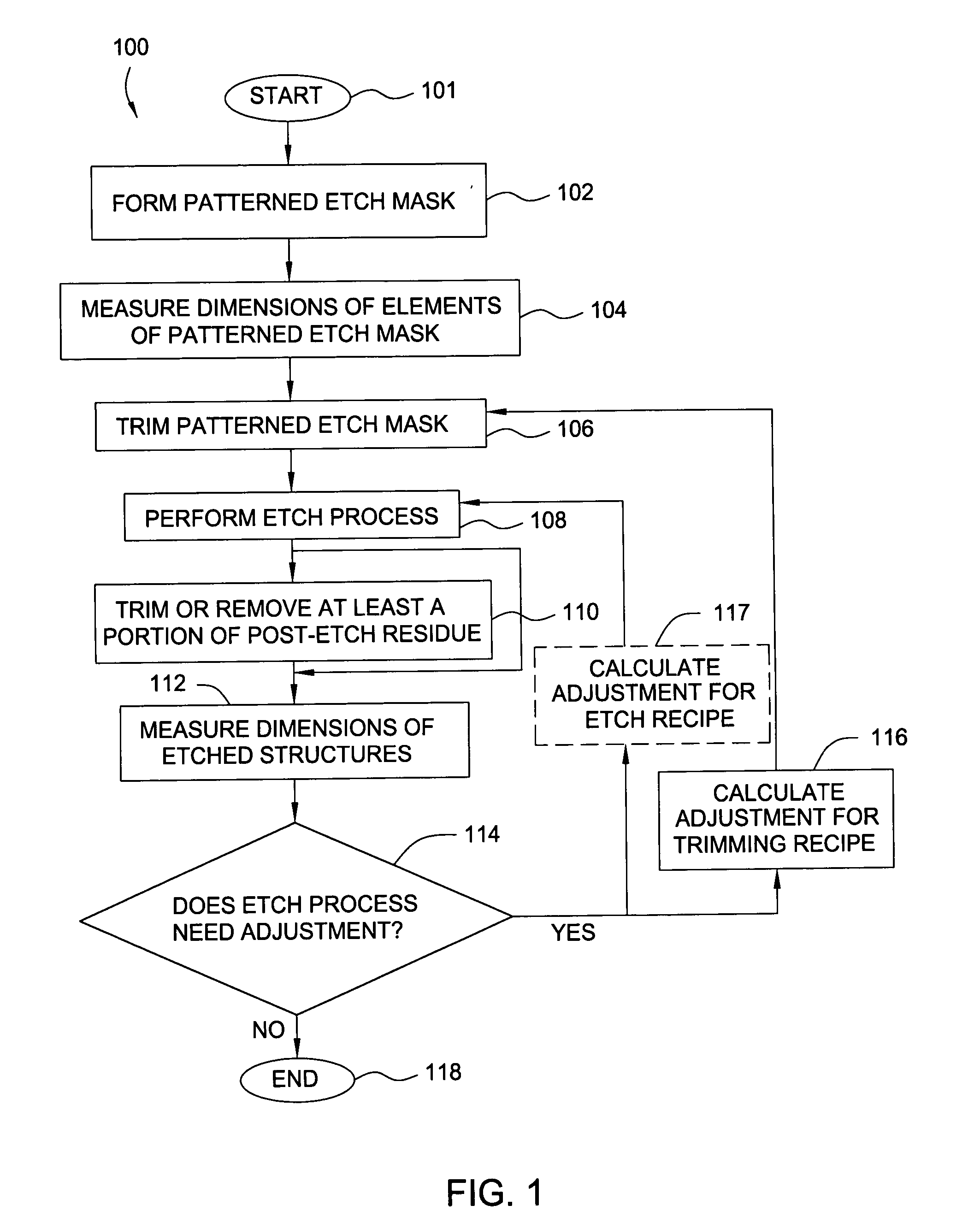

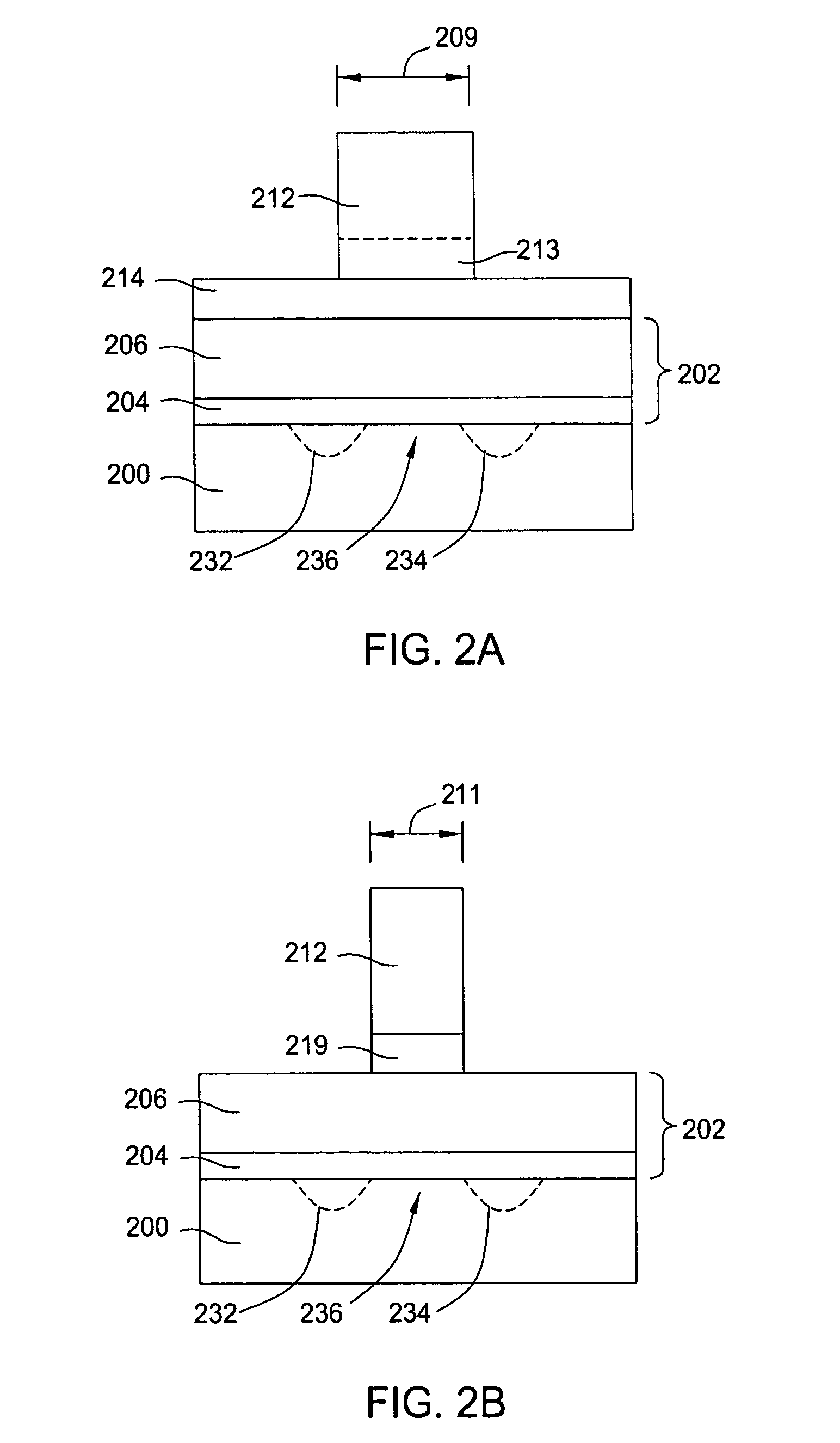

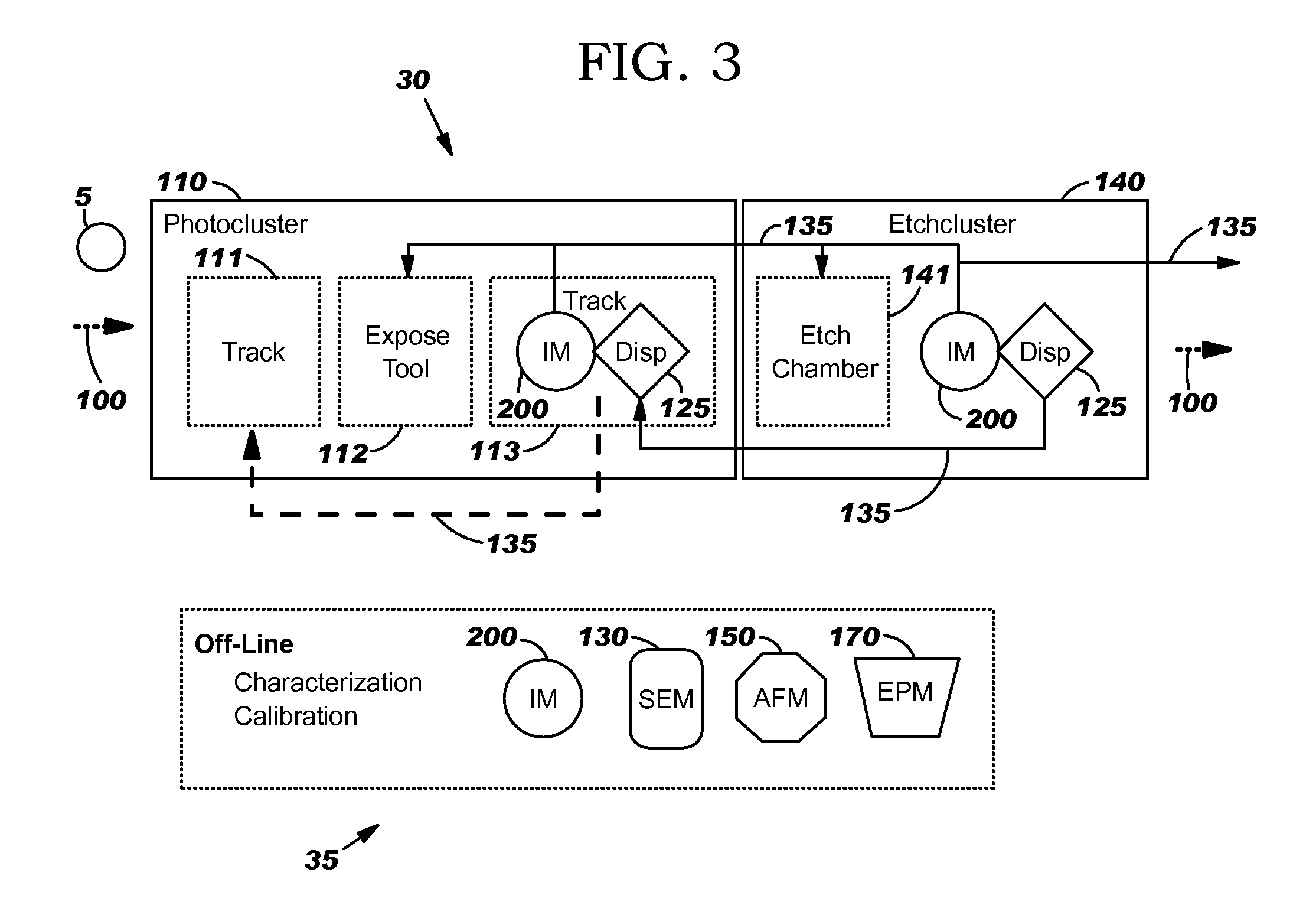

Method for controlling accuracy and repeatability of an etch process

InactiveUS20050085090A1Improve accuracyPoor repeatabilitySemiconductor/solid-state device testing/measurementVacuum gauge using ionisation effectsEngineeringRepeatability

Embodiments of the invention generally relate to a method for etching in a processing platform (e.g. a cluster tool) wherein robust pre-etch and post-etch data may be obtained in-situ. The method includes the steps of obtaining pre-etched critical dimension (CD) measurements of a feature on a substrate, etching the feature; treating the etched substrate to reduce and / or remove sidewall polymers deposited on the feature during etching, and obtaining post-etched CD measurements. The CD measurements may be utilized to adjust the etch process to improved the accuracy and repeatability of device fabrication.

Owner:APPLIED MATERIALS INC

Apparatus and Method for Improving Photoresist Properties

InactiveUS20100081285A1Harden radiation-sensitive materialsRemove roughnessSemiconductor/solid-state device manufacturingPhotosensitive material processingLine widthEngineering

The invention can provide apparatus and methods of processing a substrate in real-time using subsystems and processing sequences created to improve the etch resistance of photoresist materials. In addition, the improved photoresist layer can be used to more accurately control gate and / or spacer critical dimensions (CDs), to control gate and / or spacer CD uniformity, and to eliminate line edge roughness (LER) and line width roughness (LWR).

Owner:TOKYO ELECTRON LTD

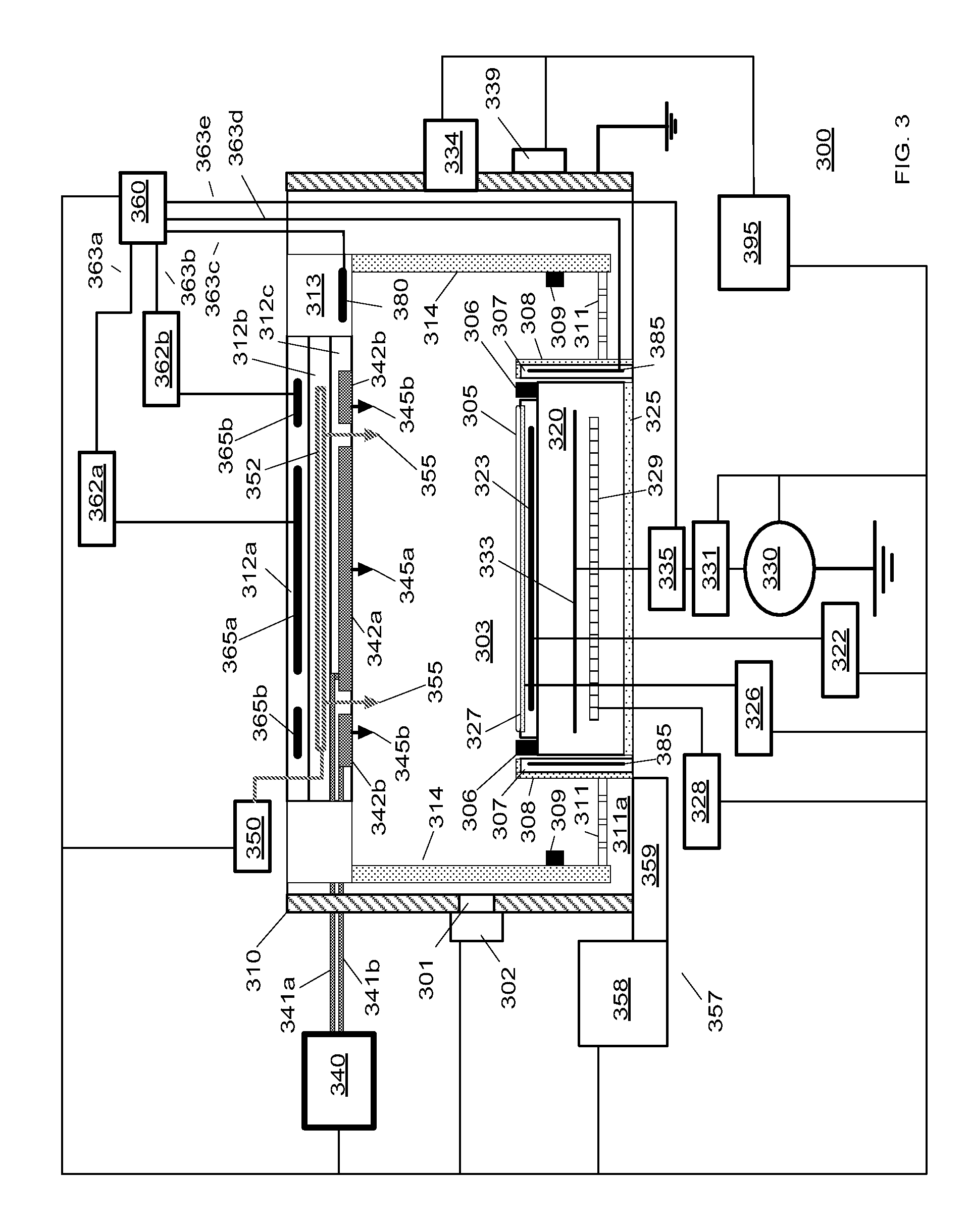

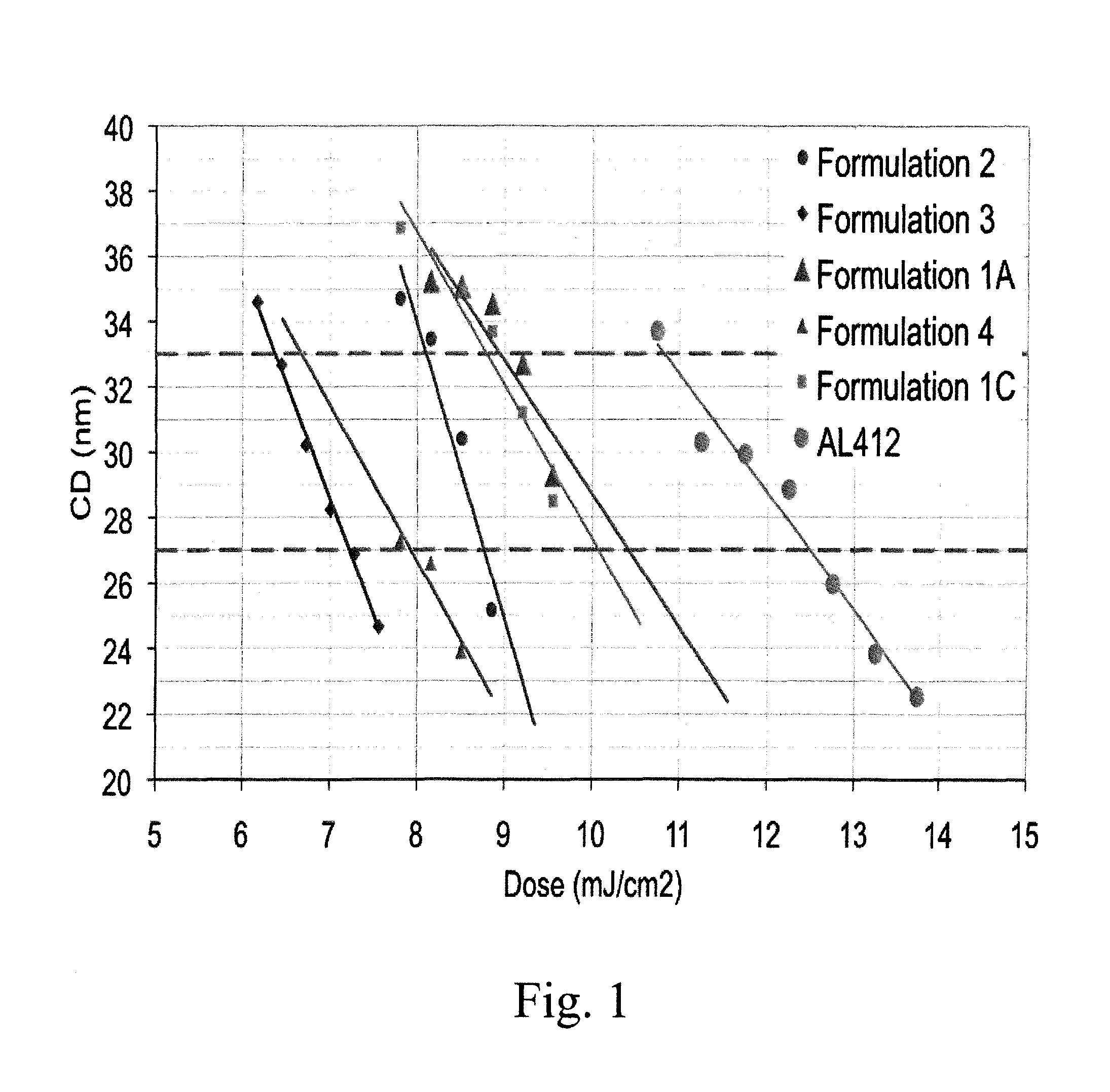

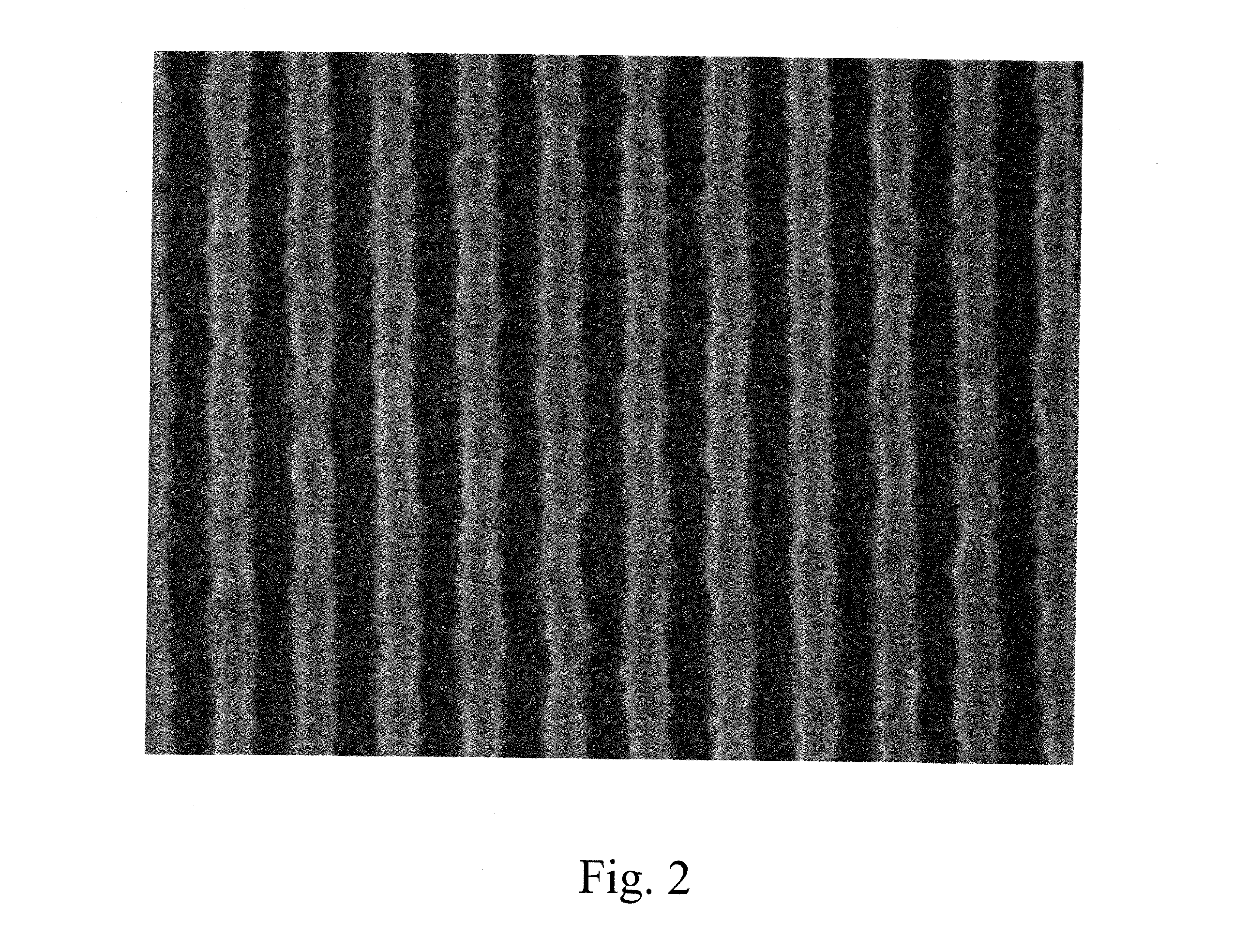

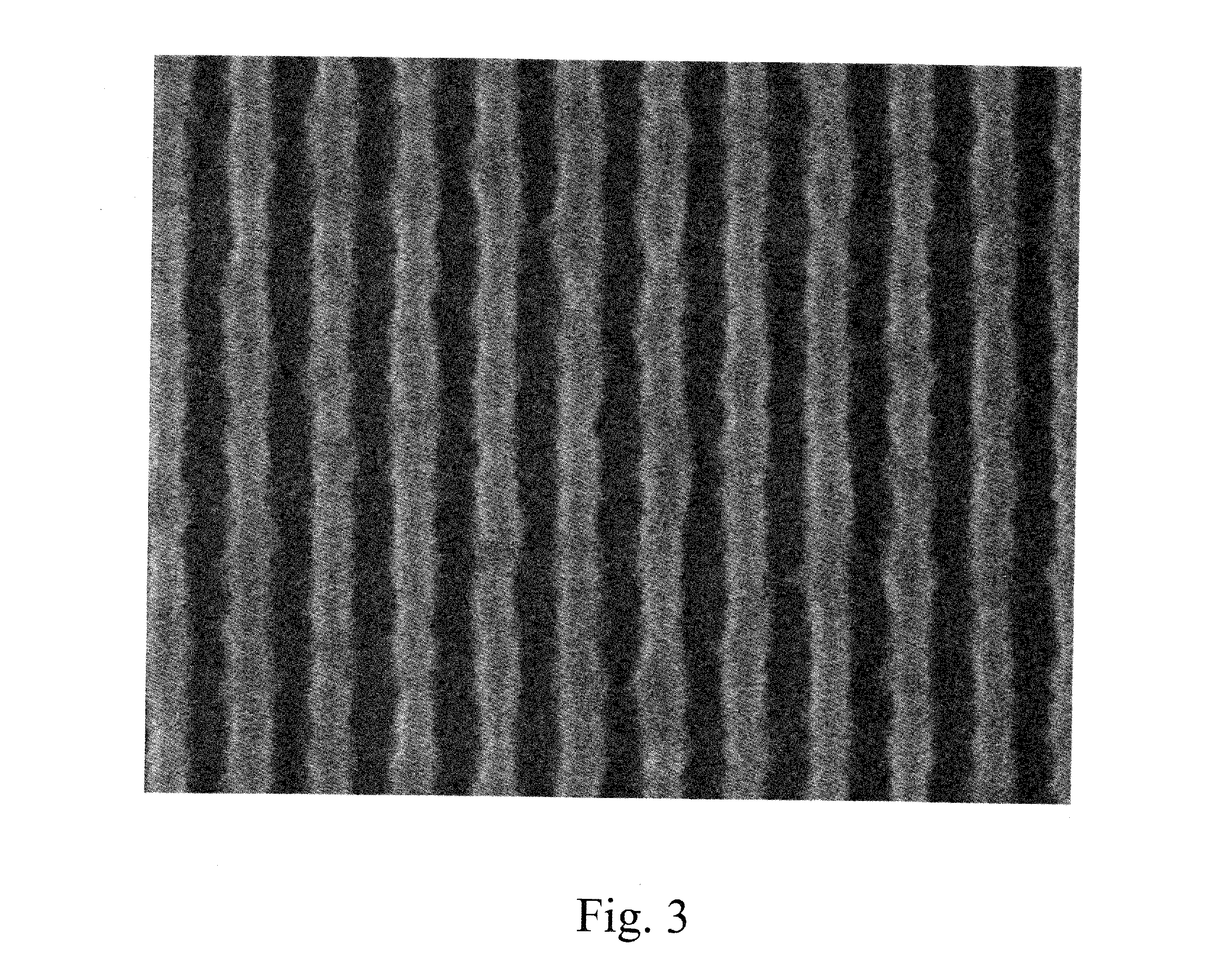

Assist layers for EUV lithography

ActiveUS8968989B2Reduce negative impactMaterial nanotechnologyPhotosensitive materialsElectronic structureLithographic artist

The present invention provides novel methods of fabricating microelectronics structures, and the resulting structures formed thereby, using EUV lithographic processes. The method involves utilizing an assist layer immediately below the photoresist layer. The assist layer can either be directly applied to the substrate, or it can be applied to any intermediate layer(s) that may be applied to the substrate. The preferred assist layers are formed from spin-coatable, polymeric compositions. The inventive method allows reduced critical dimensions to be achieved with improved dose-to-size ratios, while improving adhesion and reducing or eliminating pattern collapse issues.

Owner:BREWER SCI

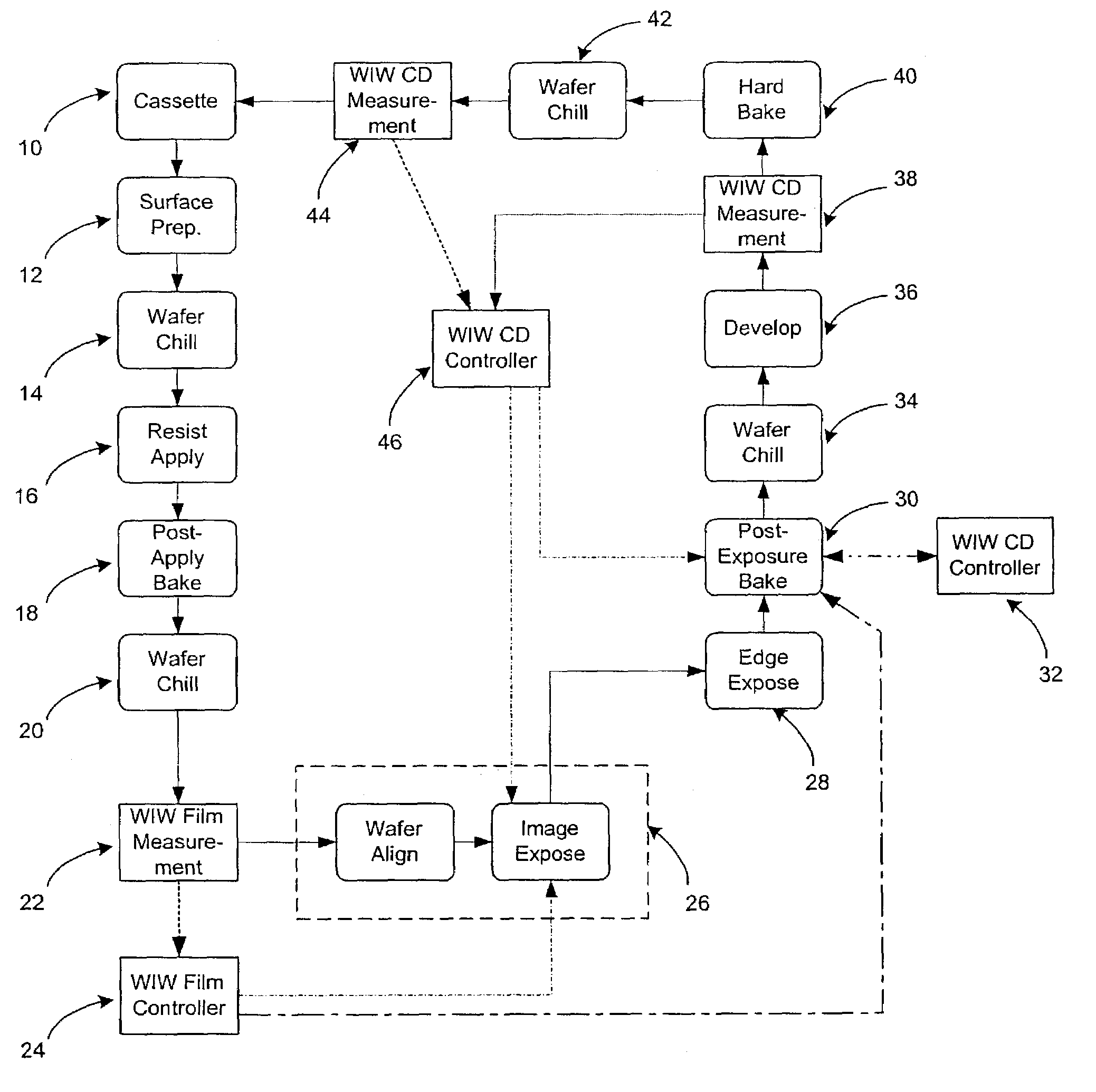

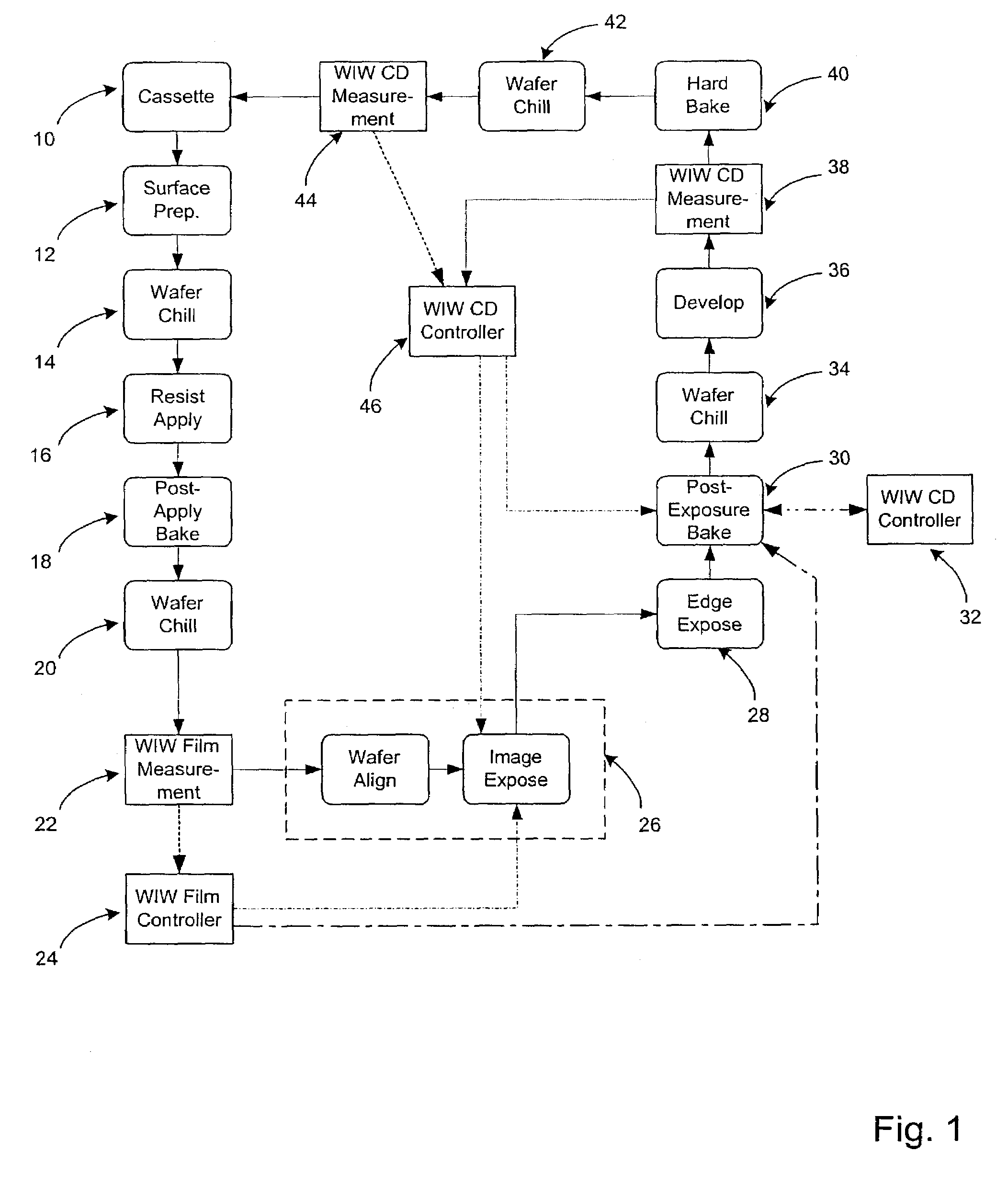

Methods and systems for lithography process control

InactiveUS6987572B2High performance bin distributionReduce yieldSemiconductor/solid-state device testing/measurementSolid-state devicesLithography processProcess module

Methods and systems for evaluating and controlling a lithography process are provided. For example, a method for reducing within wafer variation of a critical metric of a lithography process may include measuring at least one property of a resist disposed upon a wafer during the lithography process. A critical metric of a lithography process may include, but may not be limited to, a critical dimension of a feature formed during the lithography process. The method may also include altering at least one parameter of a process module configured to perform a step of the lithography process to reduce within wafer variation of the critical metric. The parameter of the process module may be altered in response to at least the one measured property of the resist.

Owner:KLA TENCOR TECH CORP

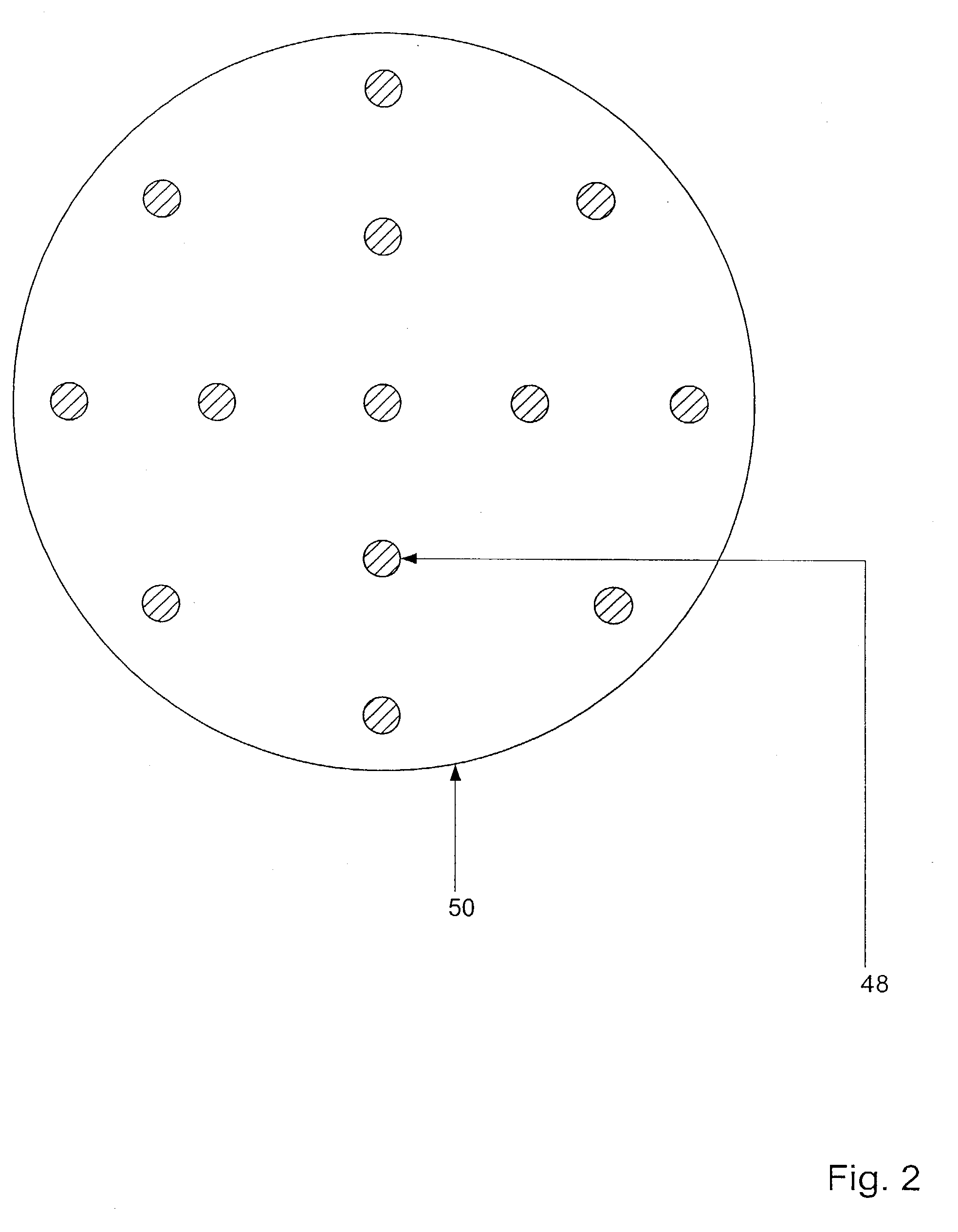

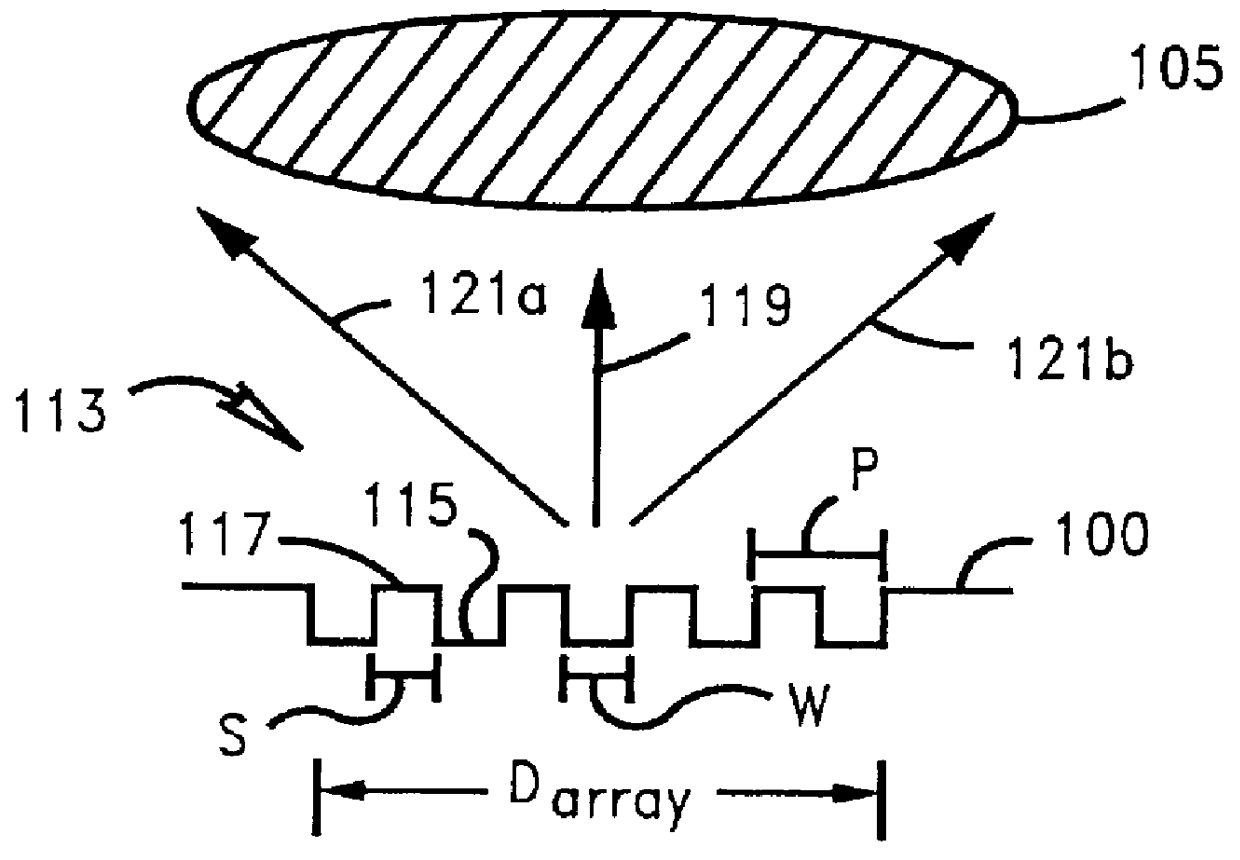

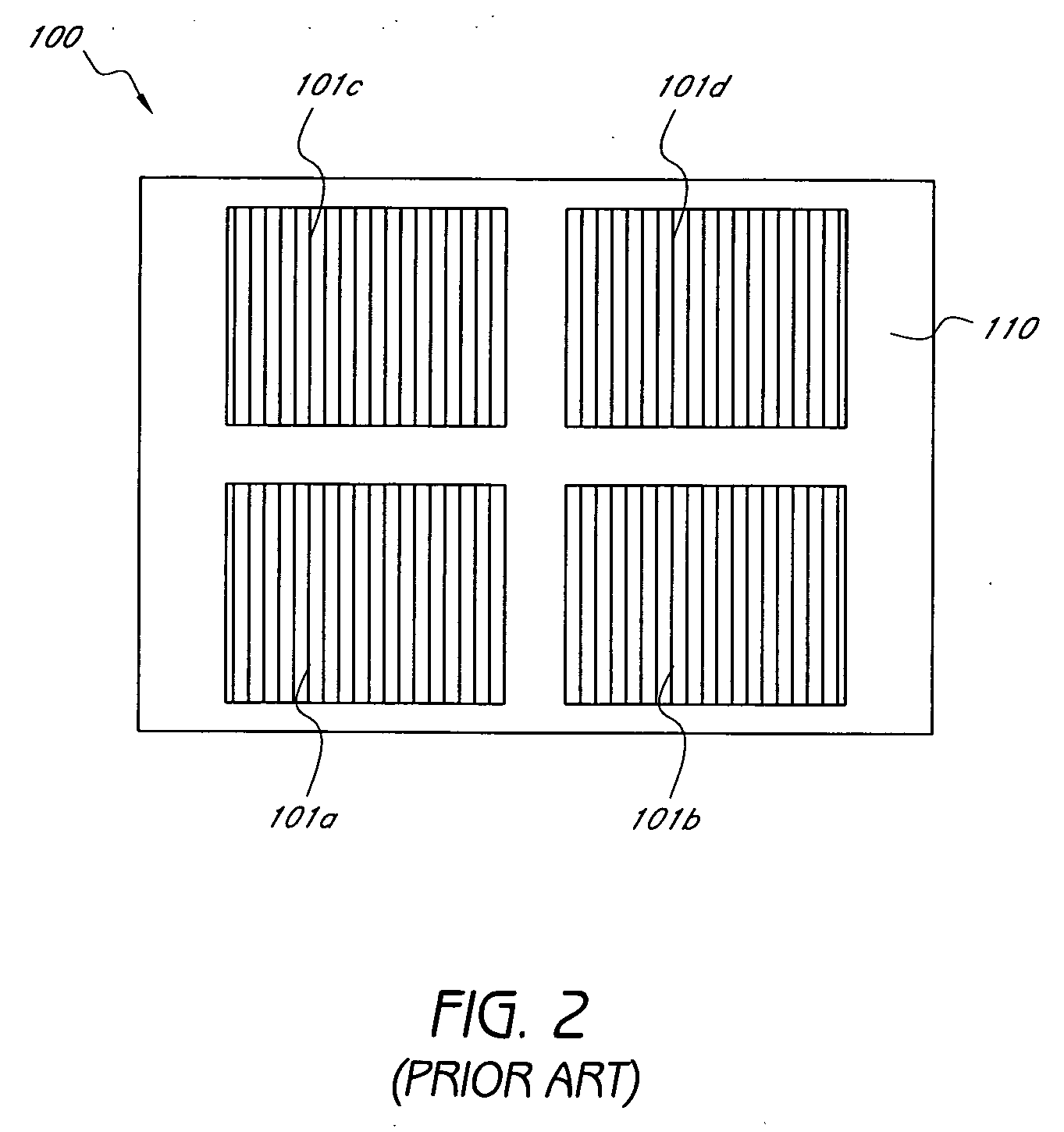

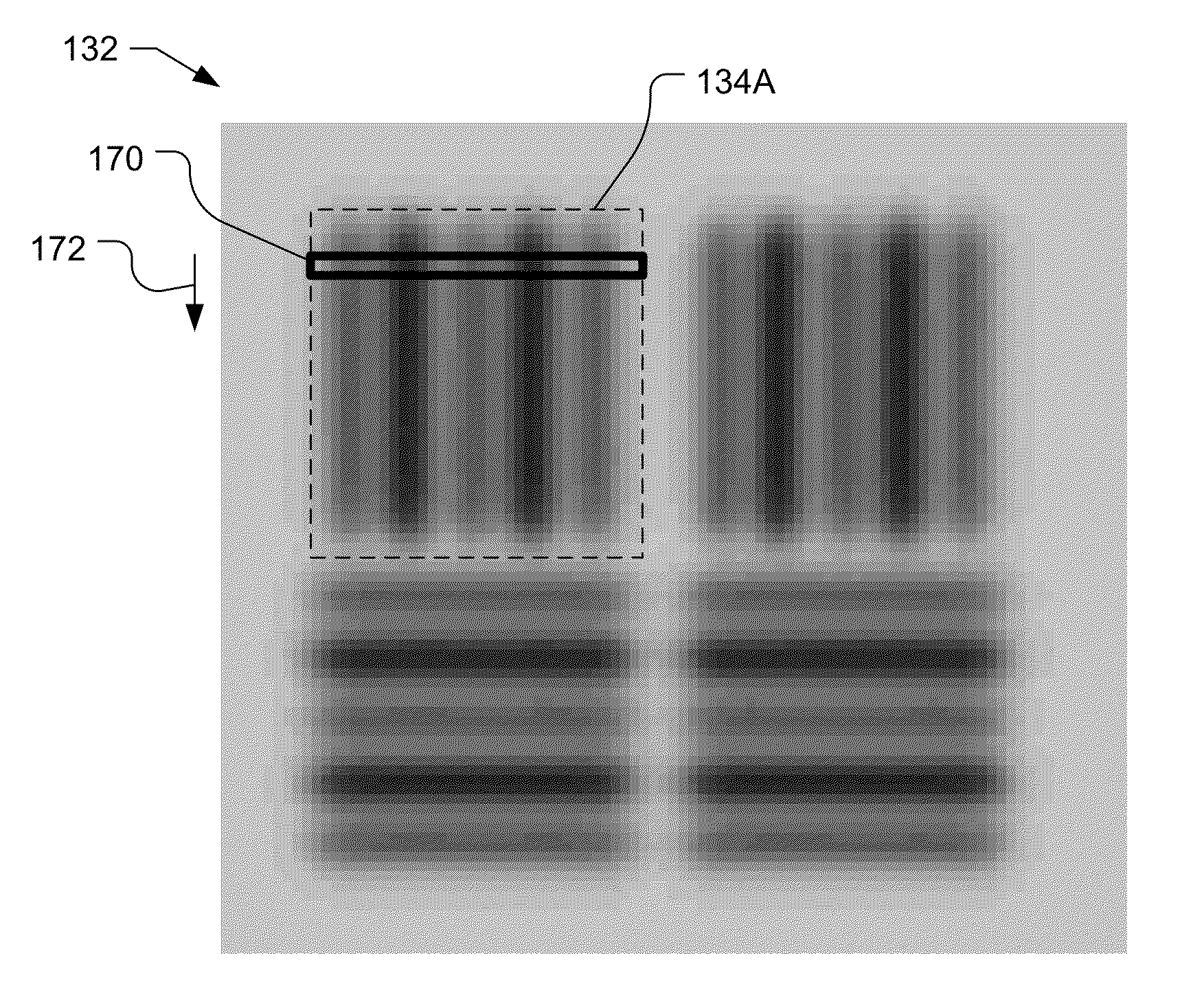

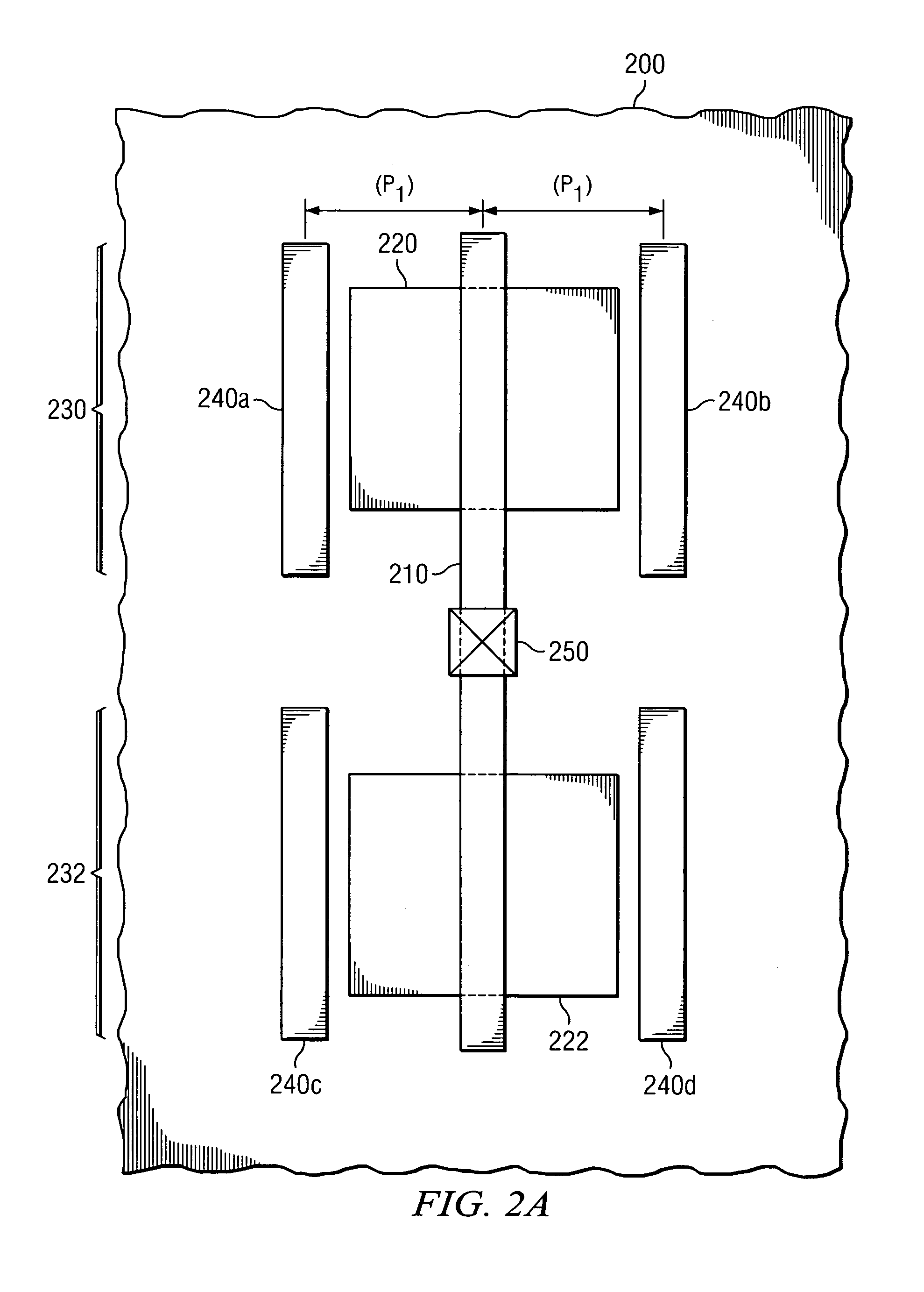

Segmented bar-in-bar target

InactiveUS6137578AEasy and inexpensive to utilizeUsing optical meansPhotomechanical exposure apparatusArray elementCritical dimension

A target for measurement of critical dimension bias on a substrate formed by a lithographic process comprises three sets of contrasting arrays of elements on the substrate. Each of the arrays has a plurality of spaced parallel elements contrasting with the substrate. Ends of the contrasting elements are aligned along parallel lines forming opposite array edges, with the length of the contrasting elements comprising the array width. The array edges are measurable by microscopy without resolution of individual elements of the array. The three arrays are spaced apart in the X- or Y-direction such that critical dimension bias may be measured by comparing the centerline of a first distance measured from one edge of the first array to one edge of the third array to the centerline of a second distance measured from one edge of the second array to one edge of the third array, with the centerlines being measured without resolution of the individual array elements.

Owner:IBM CORP

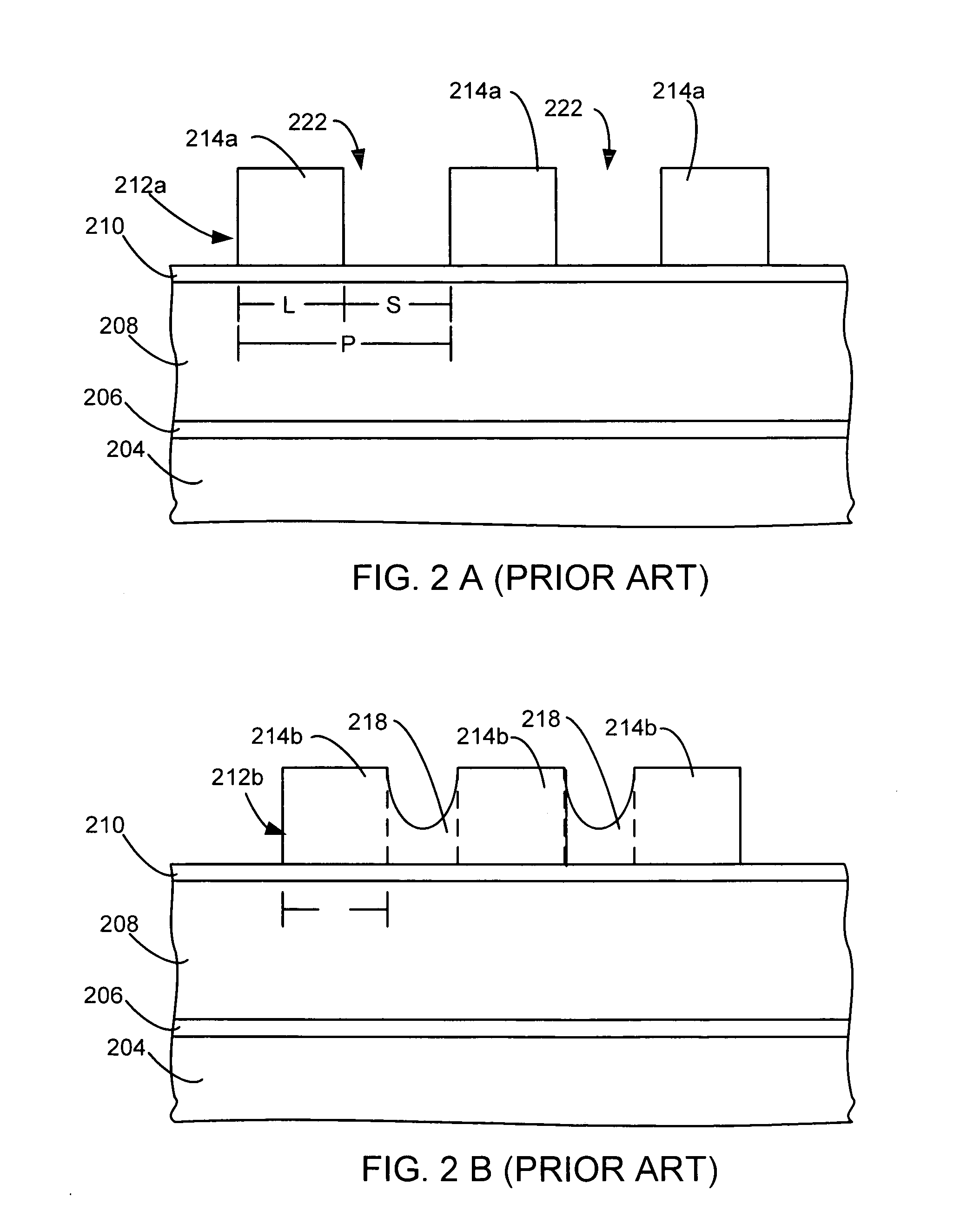

Reduction of feature critical dimensions using multiple masks

A method for forming features in an etch layer is provided. A first mask is formed over the etch layer wherein the first mask defines a plurality of spaces with widths. A sidewall layer is formed over the first mask. Features are etched into the etch layer through the sidewall layer, wherein the features have widths that are smaller than the widths of the spaces defined by the first mask. The mask and sidewall layer are removed. An additional mask is formed over the etch layer wherein the additional mask defines a plurality of spaces with widths. A sidewall layer is formed over the additional mask. Features are etched into the etch layer through the sidewall layer, wherein the widths that are smaller than the widths of the spaces defined by the first mask. The mask and sidewall layer are removed.

Owner:LAM RES CORP

Scatterometry-Based Imaging and Critical Dimension Metrology

ActiveUS20150300965A1Improve the measurement effectMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementDiffraction orderMetrology

Methods and systems for performing measurements of semiconductor structures and materials based on scatterometry measurement data are presented. Scatterometry measurement data is used to generate an image of a material property of a measured structure based on the measured intensities of the detected diffraction orders. In some examples, a value of a parameter of interest is determined directly from the map of the material property of the measurement target. In some other examples, the image is compared to structural characteristics estimated by a geometric, model-based parametric inversion of the same measurement data. Discrepancies are used to update the geometric model of the measured structure and improve measurement performance. This enables a metrology system to converge on an accurate parametric measurement model when there are significant deviations between the actual shape of a manufactured structure subject to model-based measurement and the modeled shape of the structure.

Owner:KLA TENCOR TECH CORP

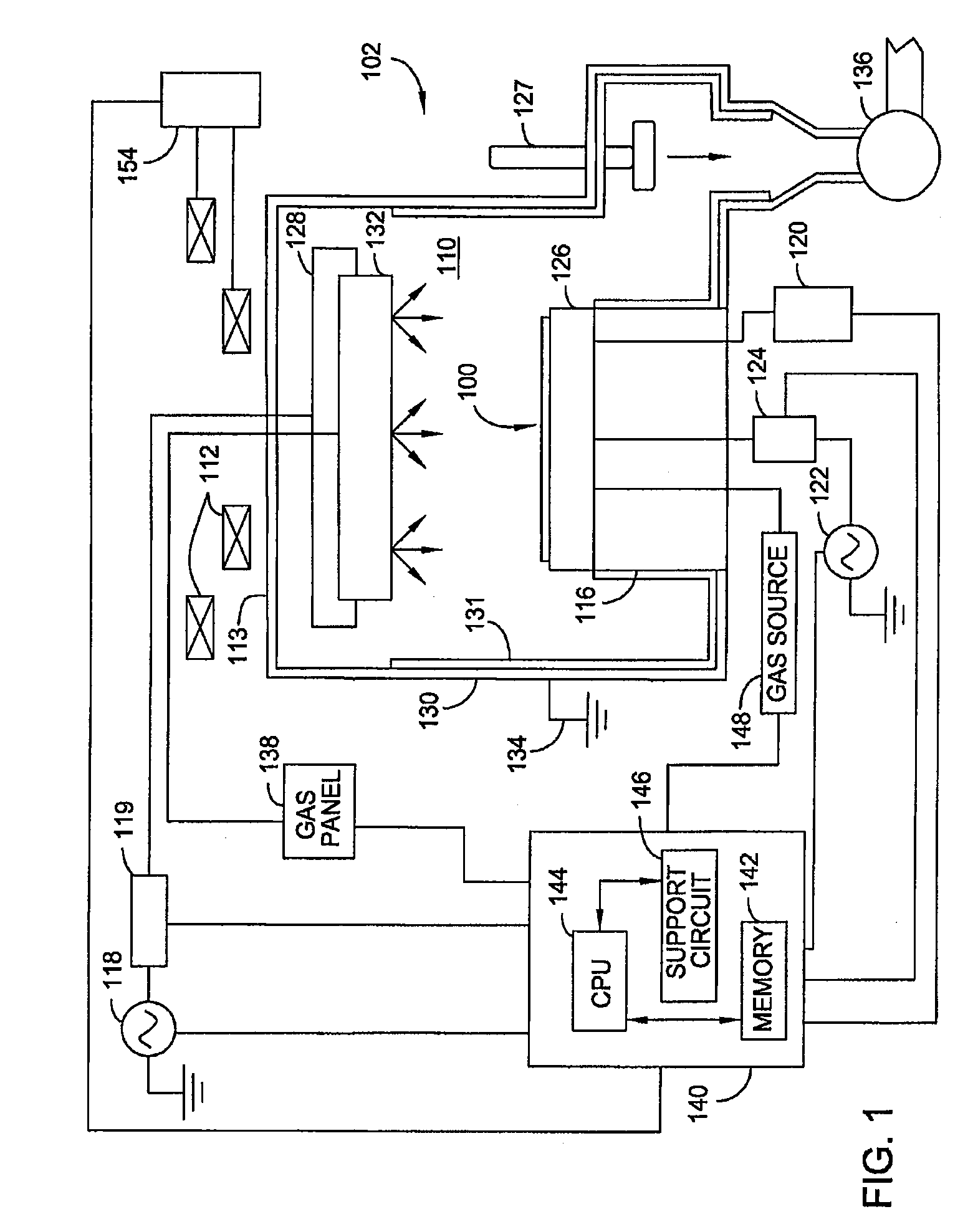

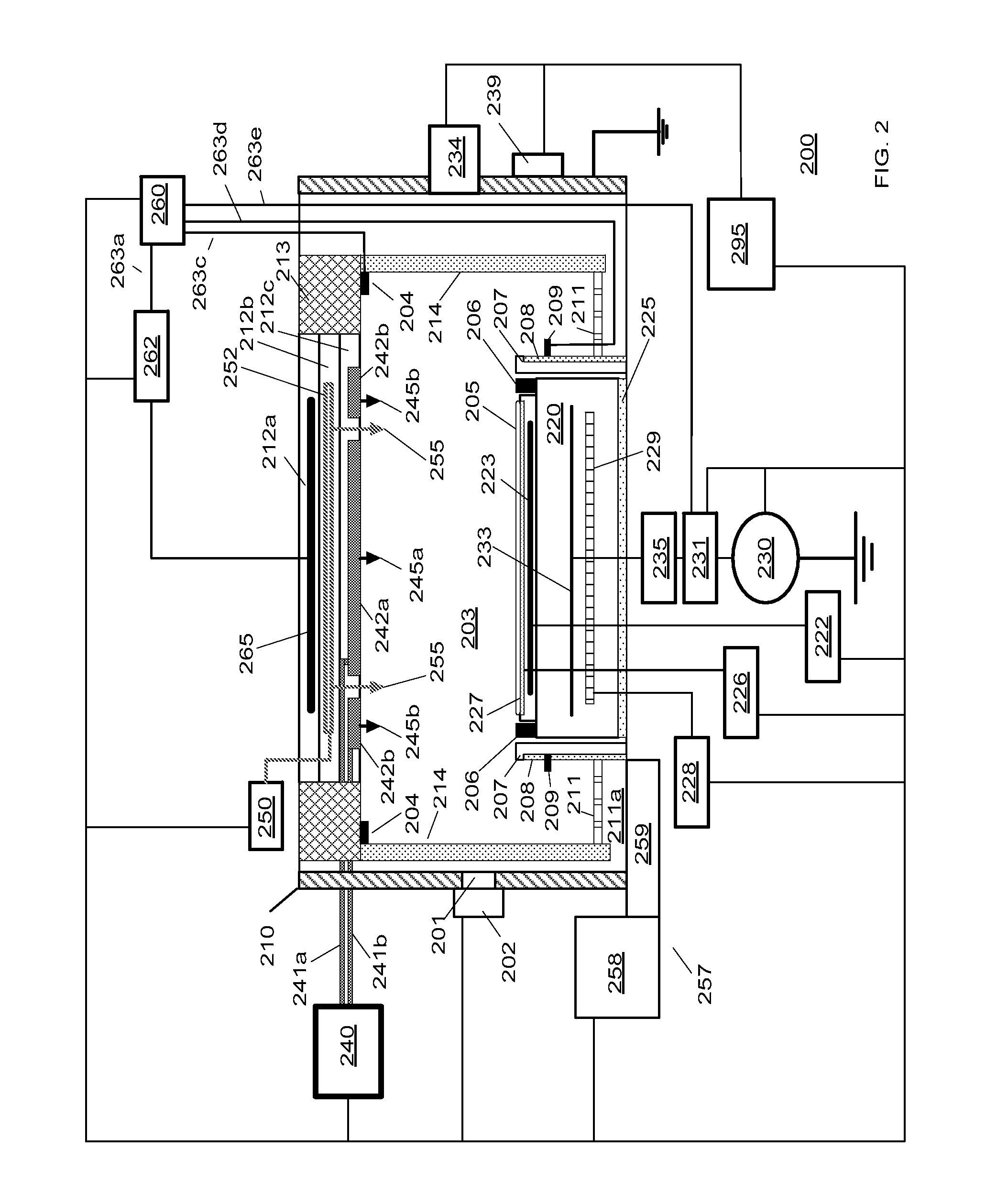

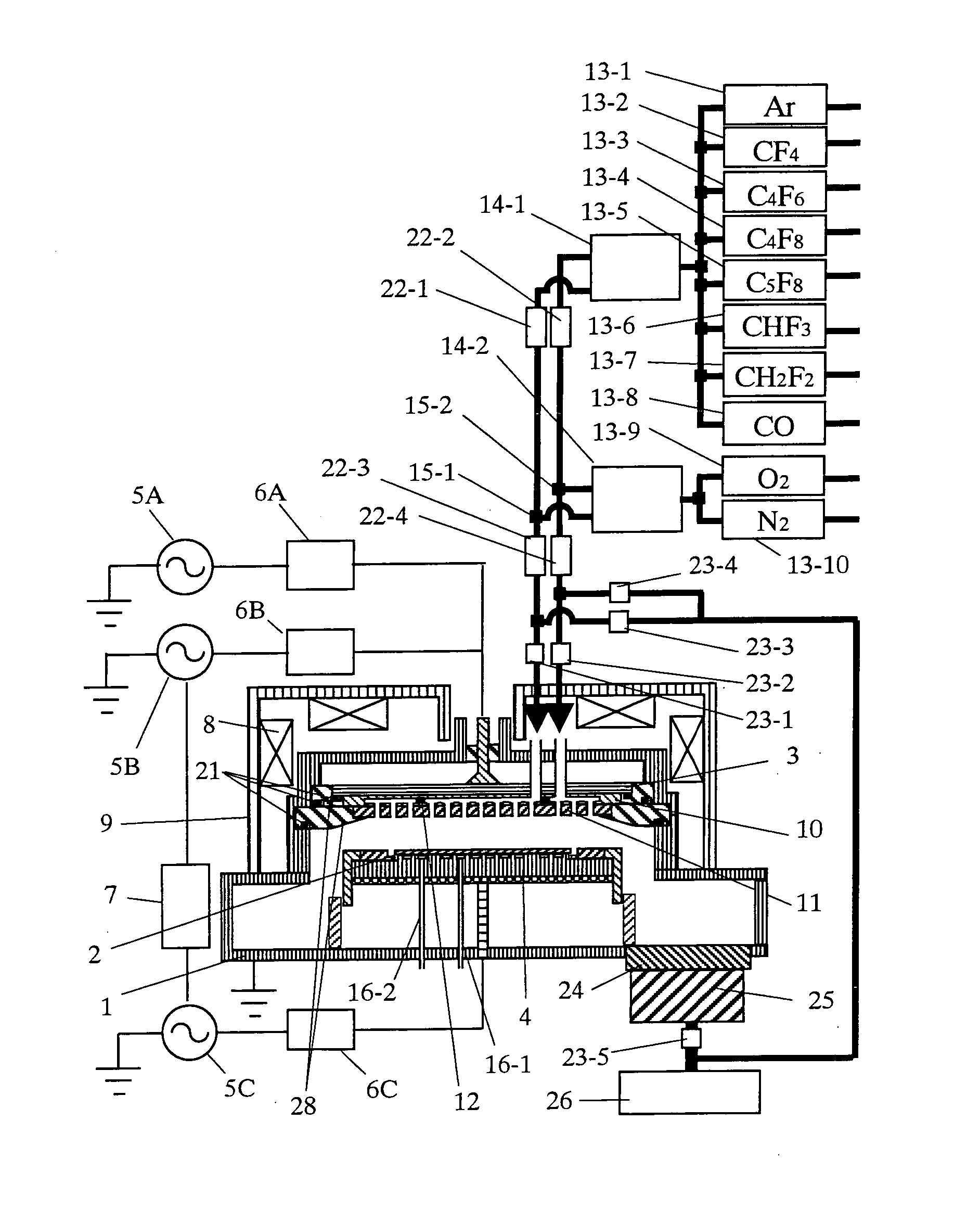

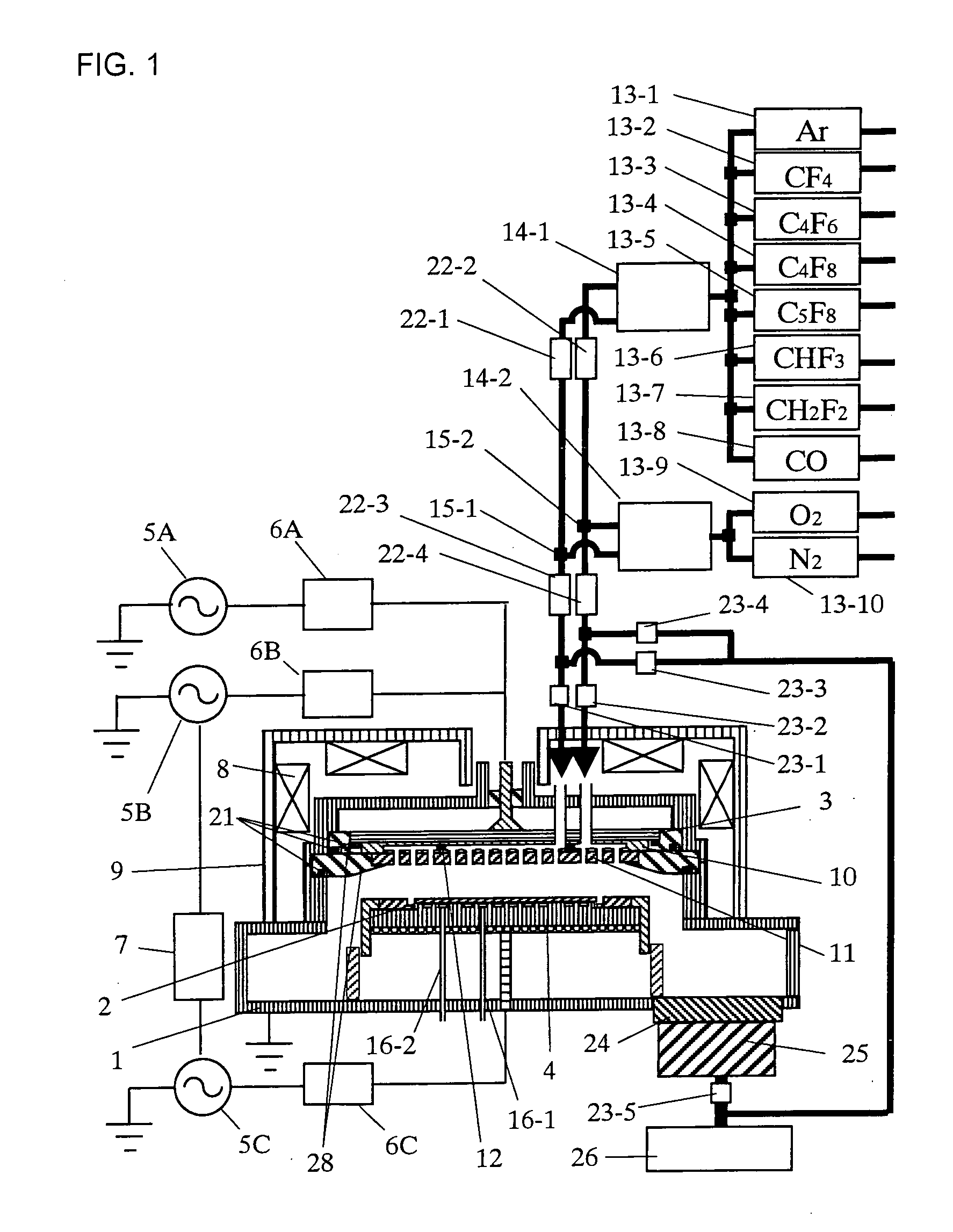

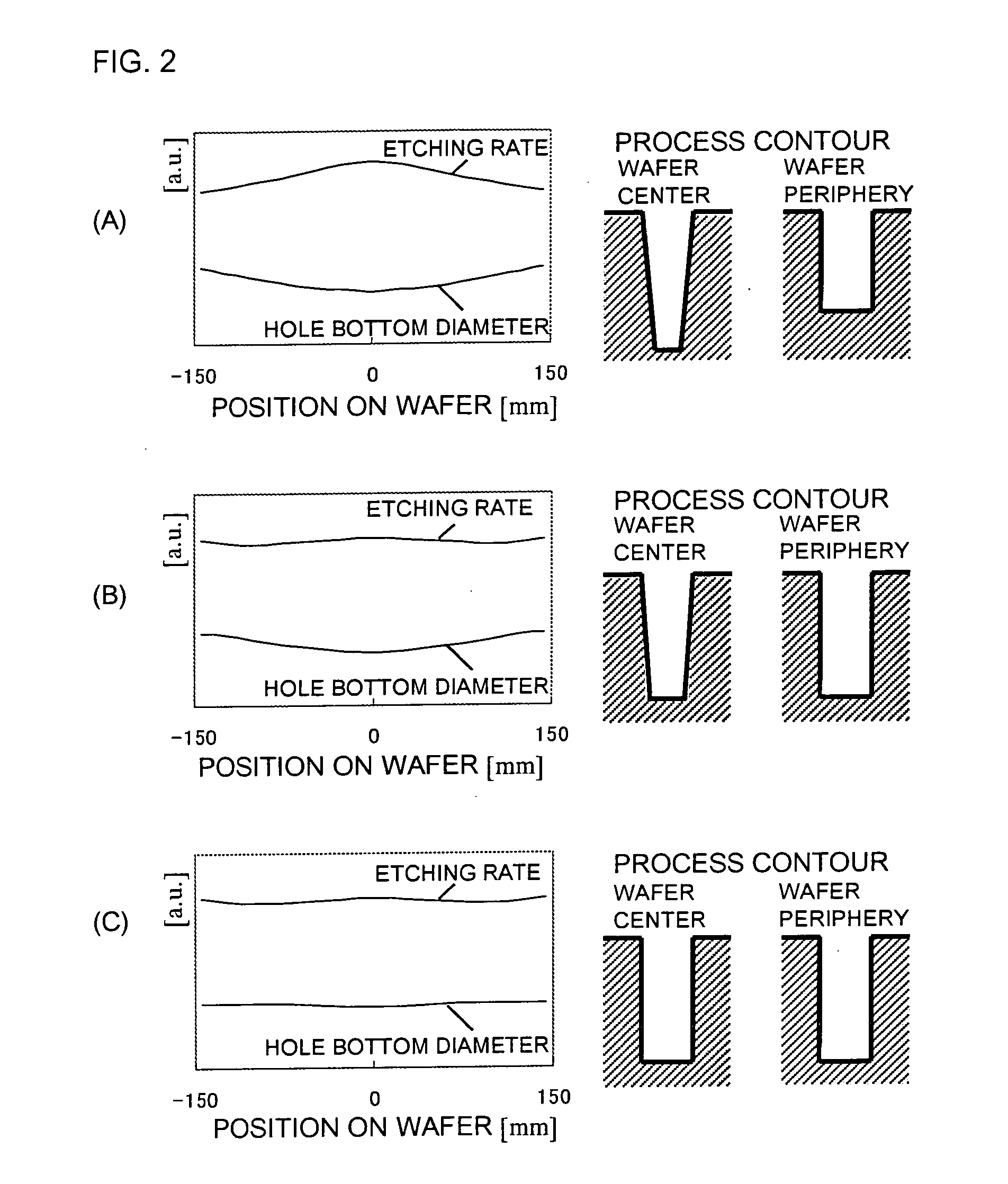

Plasma processing apparatus

InactiveUS20060016559A1Improve uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingIn planeEngineering

The object of the invention is to provide a plasma processing apparatus having enhanced plasma processing uniformity. The plasma processing apparatus comprises a processing chamber 1, means 13 and 14 for supplying processing gas into the processing chamber, evacuation means 25 and 26 for decompressing the processing chamber 1, an electrode 4 on which an object 2 to be processed such as a wafer is placed, and an electromagnetic radiation power supply 5A, wherein at least two kinds of processing gases having different composition ratios of O2 or N2 are introduced into the processing chamber through different gas inlets so as to control the in-plane uniformity of the critical dimension while maintaining the in-plane uniformity of the process depth.

Owner:HITACHI HIGH-TECH CORP +1

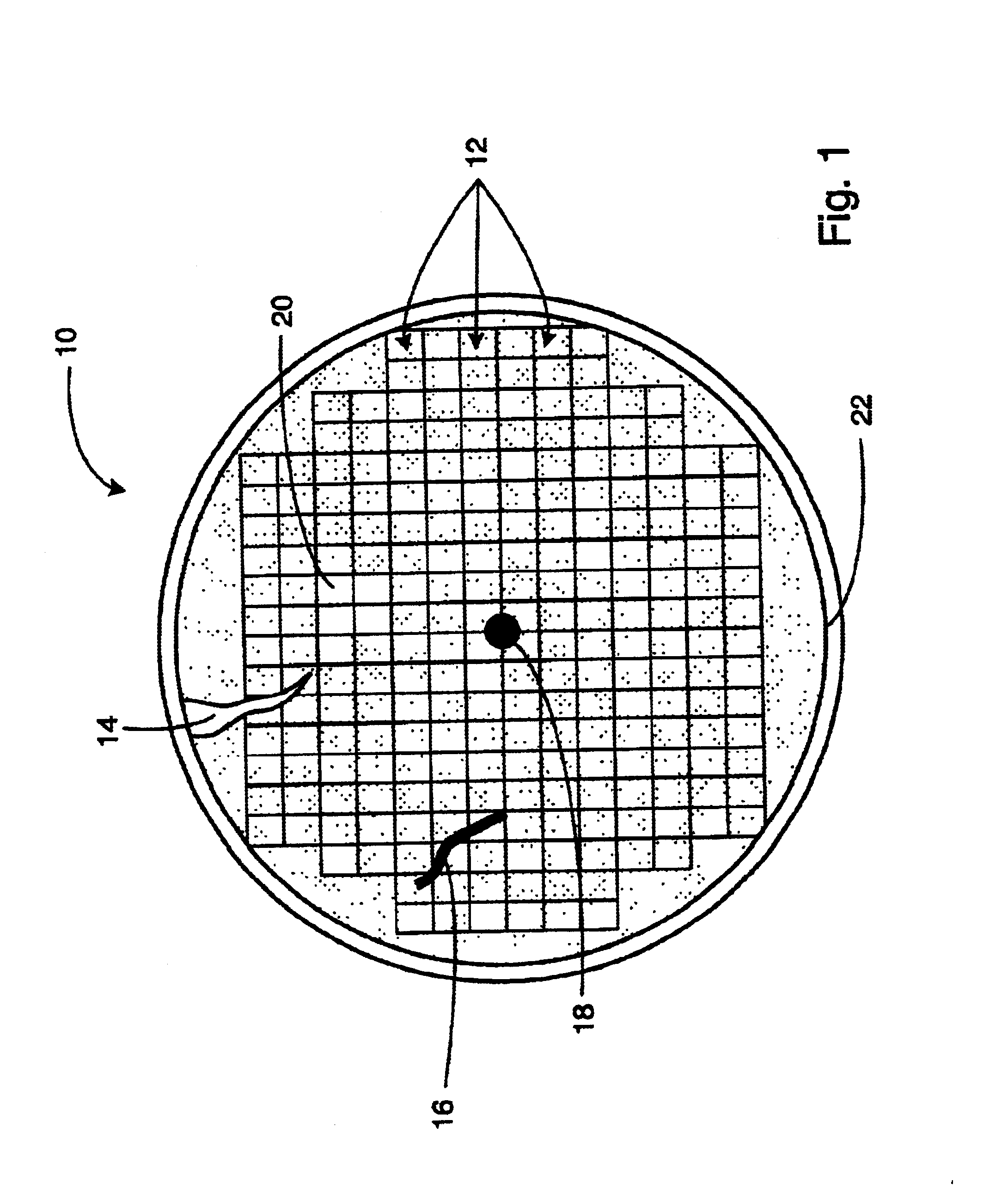

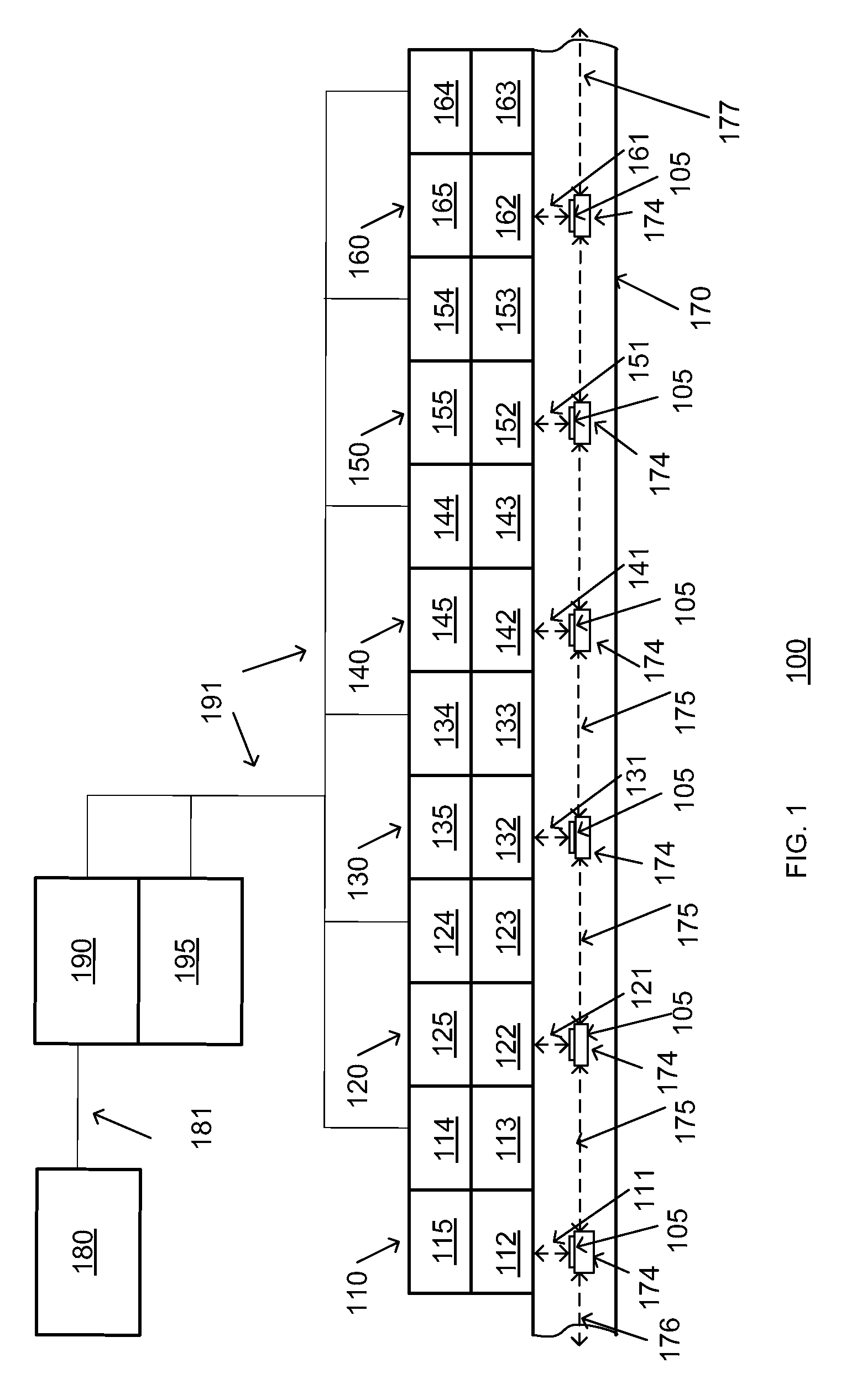

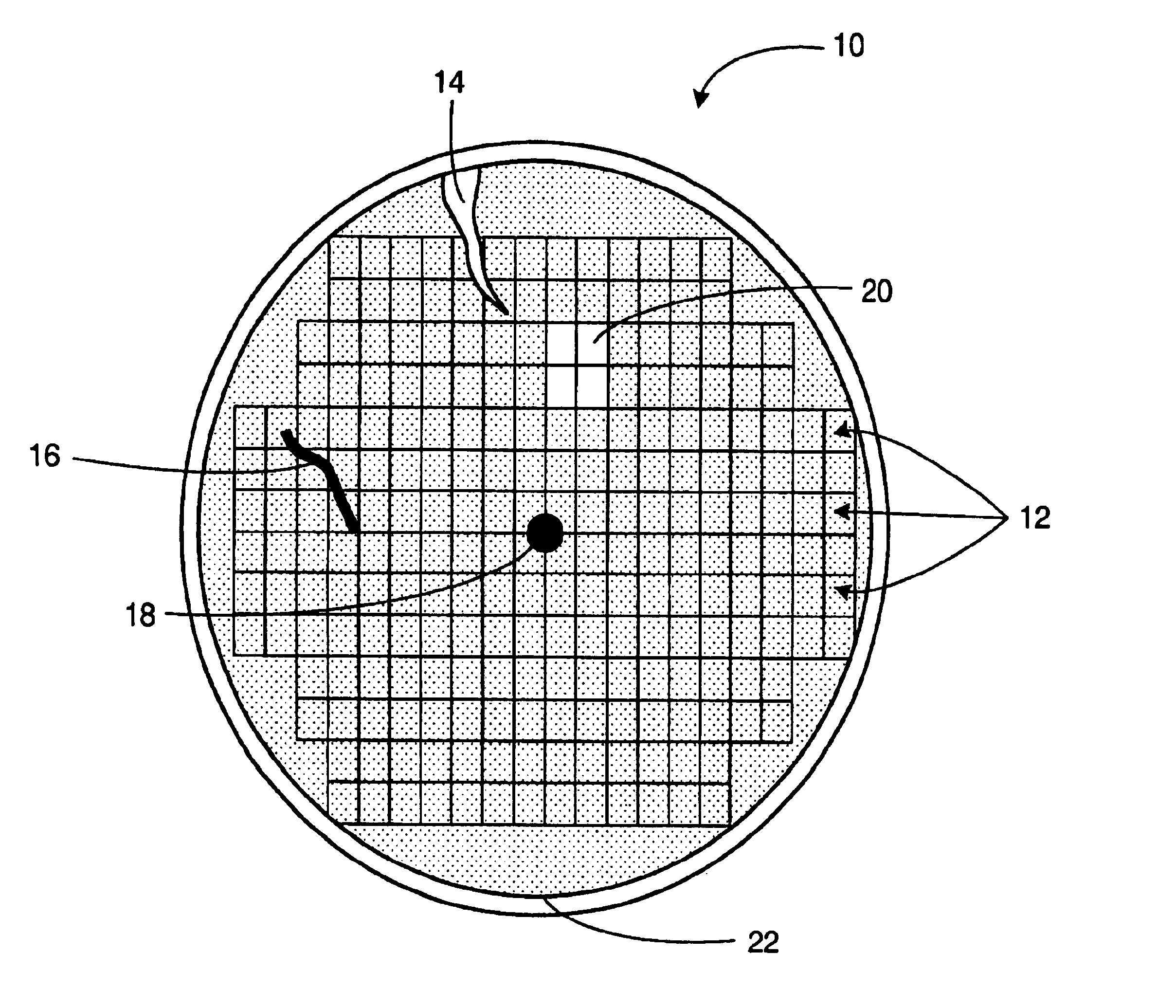

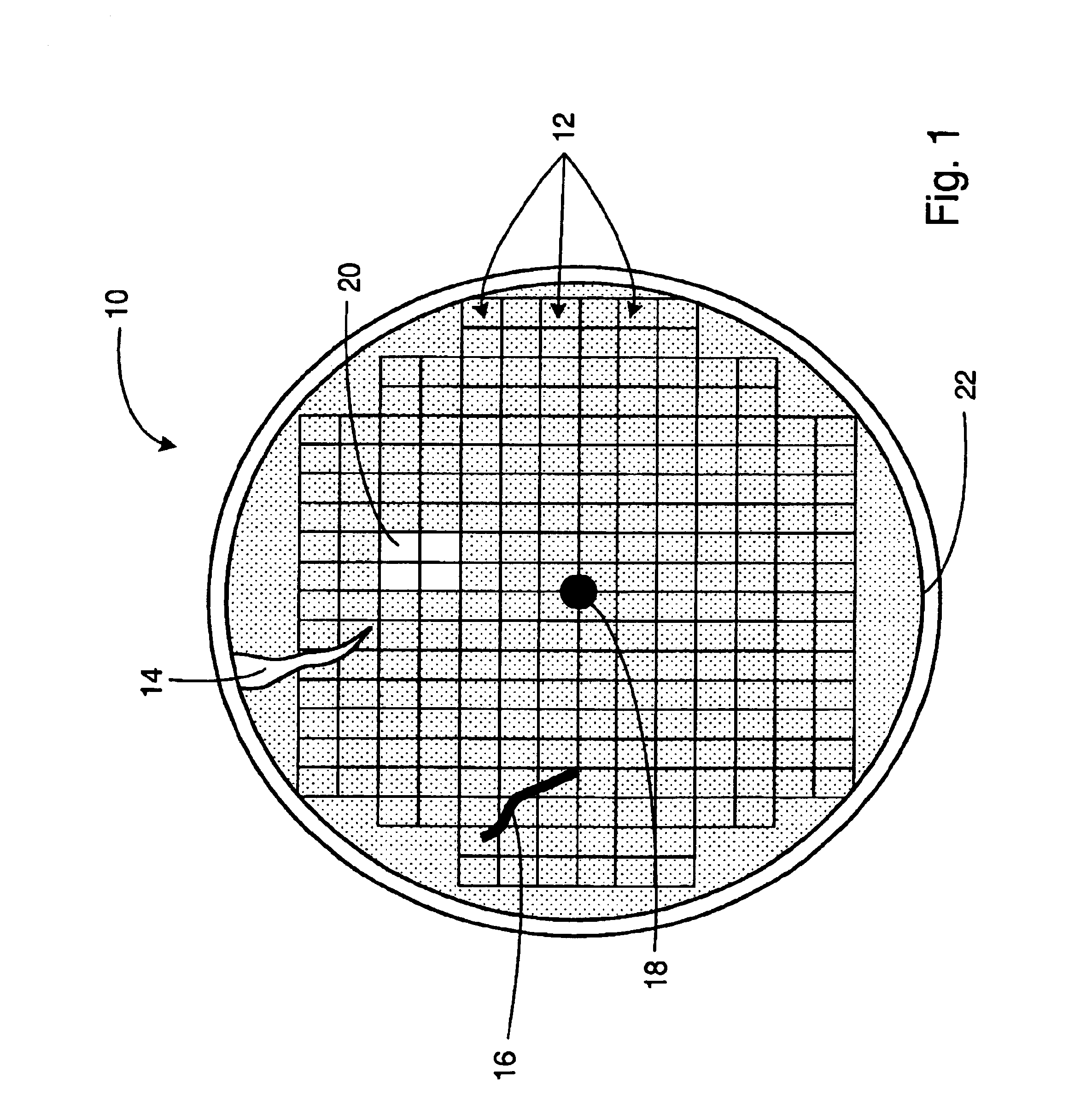

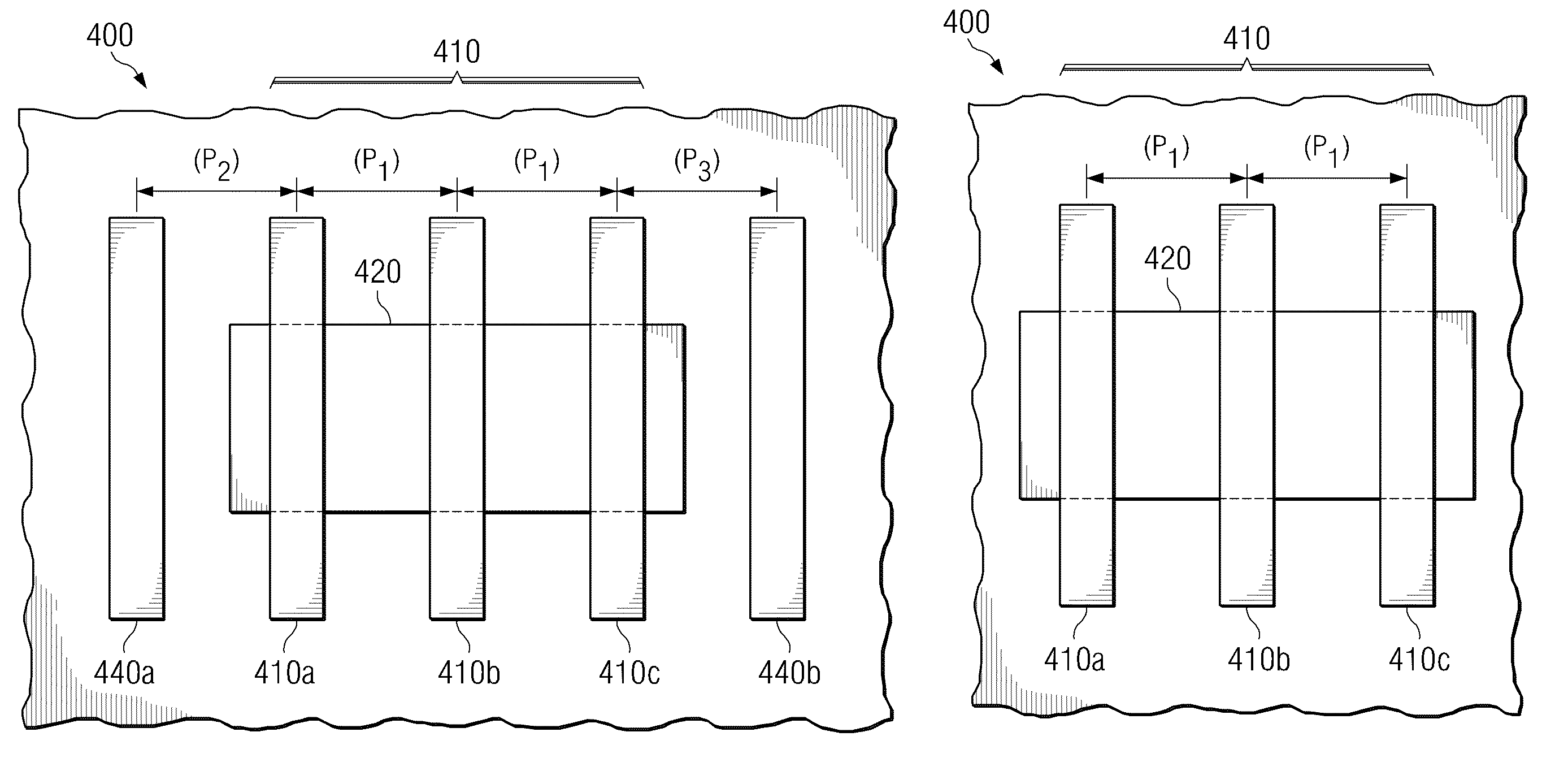

Process for improving critical dimension uniformity of integrated circuit arrays

ActiveUS20070249170A1Prevent such non-uniformityDecorative surface effectsSolid-state devicesEngineeringCritical dimension

Methods for patterning integrated circuit (IC) device arrays employing an additional mask process for improving center-to-edge CD uniformity are disclosed. In one embodiment, a repeating pattern of features is formed in a masking layer over a first region of a substrate. Then, a blocking mask is applied over the features in the masking layer. The blocking mask is configured to differentiate array regions of the first region from peripheral regions of the first region. Subsequently, the pattern of features in the array regions is transferred into the substrate. In the embodiment, an etchant can be uniformly introduced to the masking layer because there is no distinction of center / edge in the masking layer. Thus, CD uniformity can be achieved in arrays which are later defined.

Owner:MICRON TECH INC

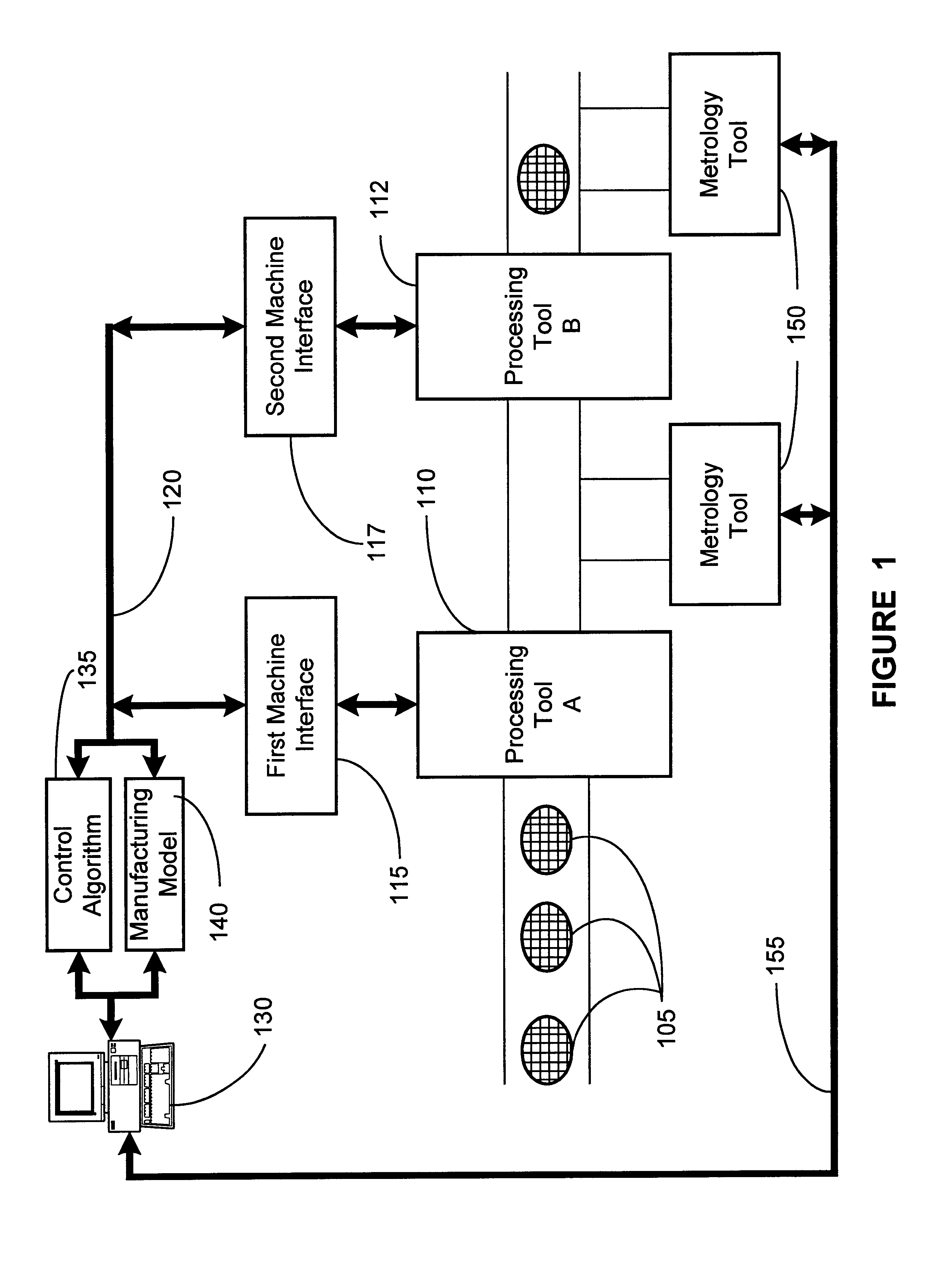

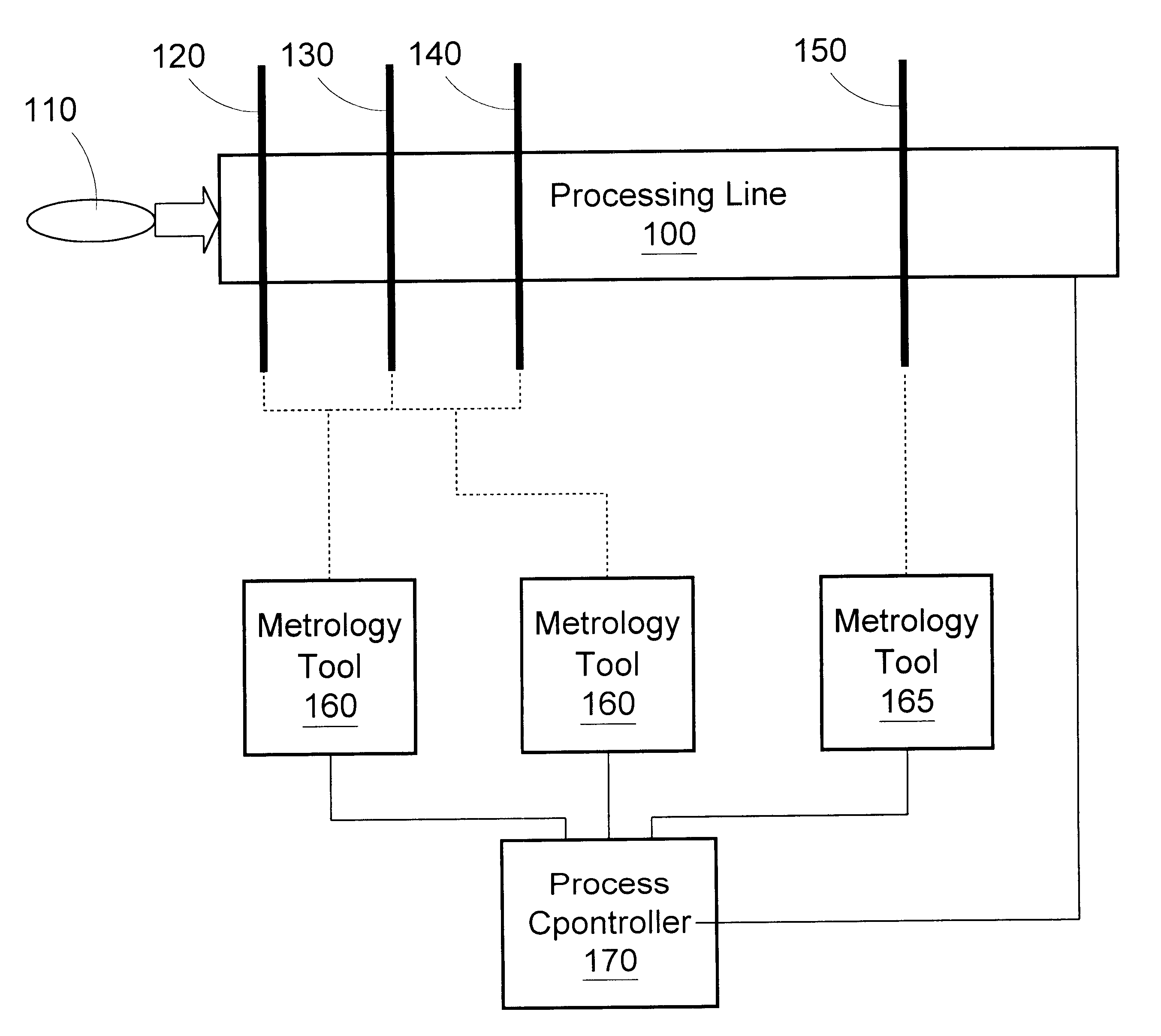

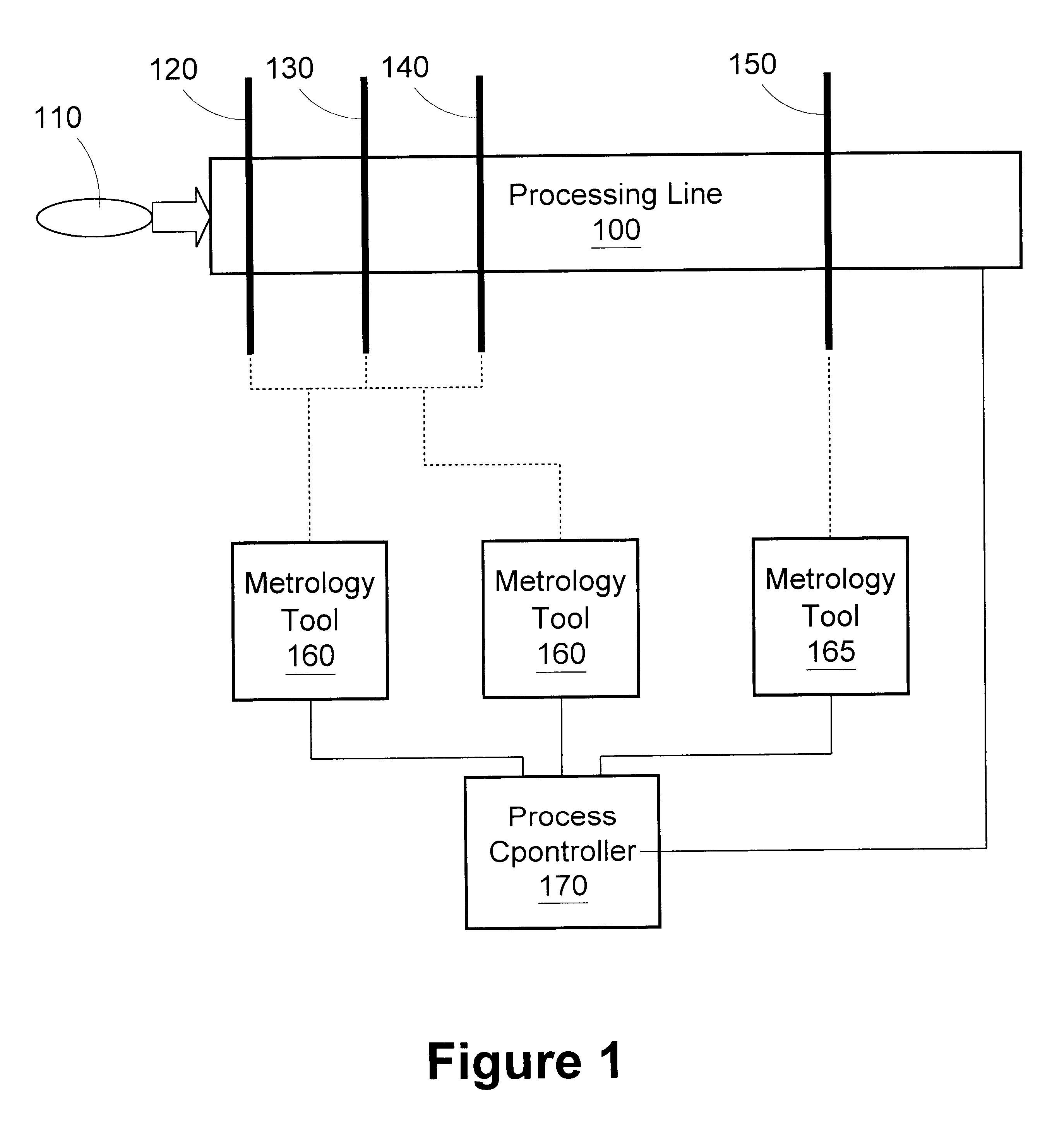

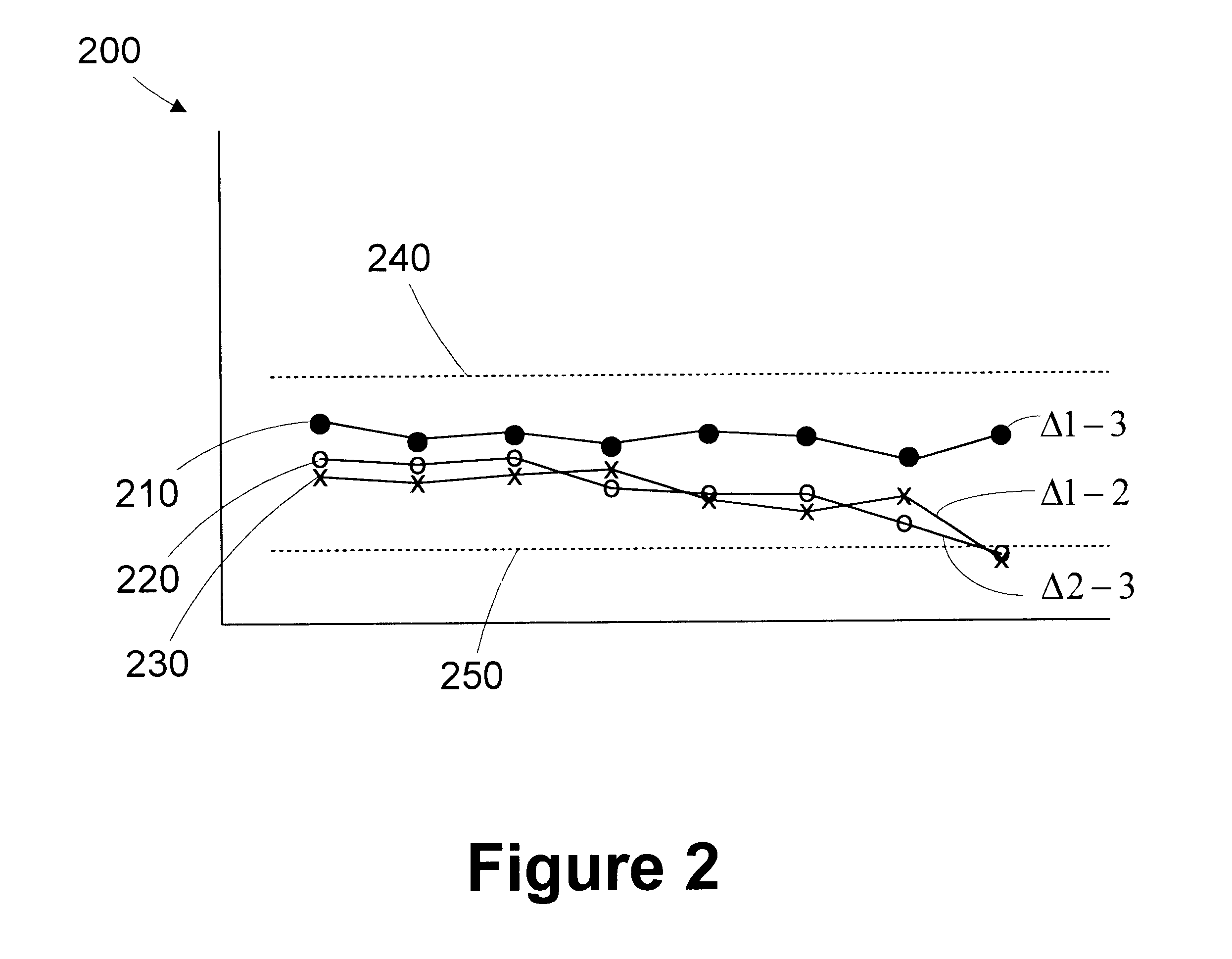

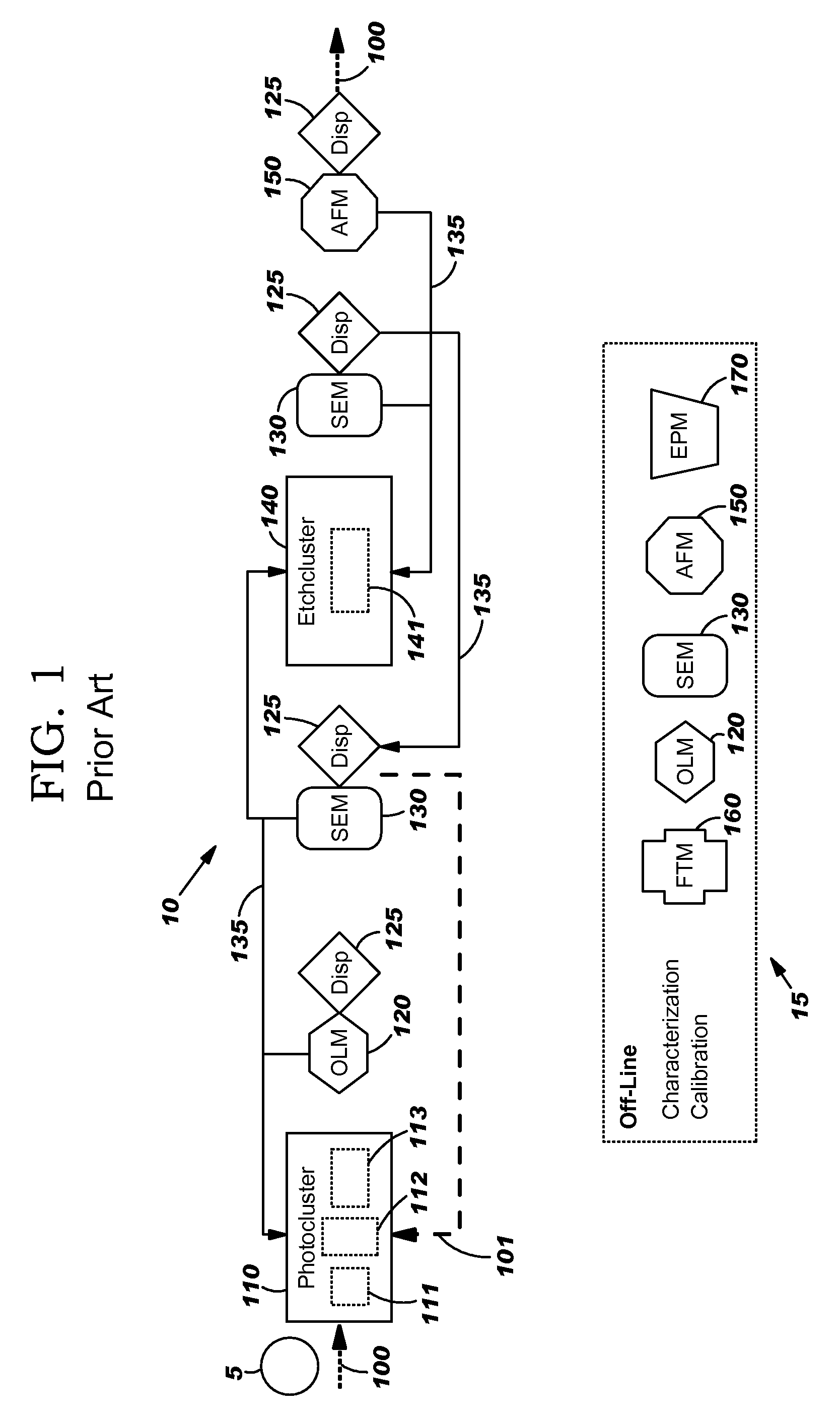

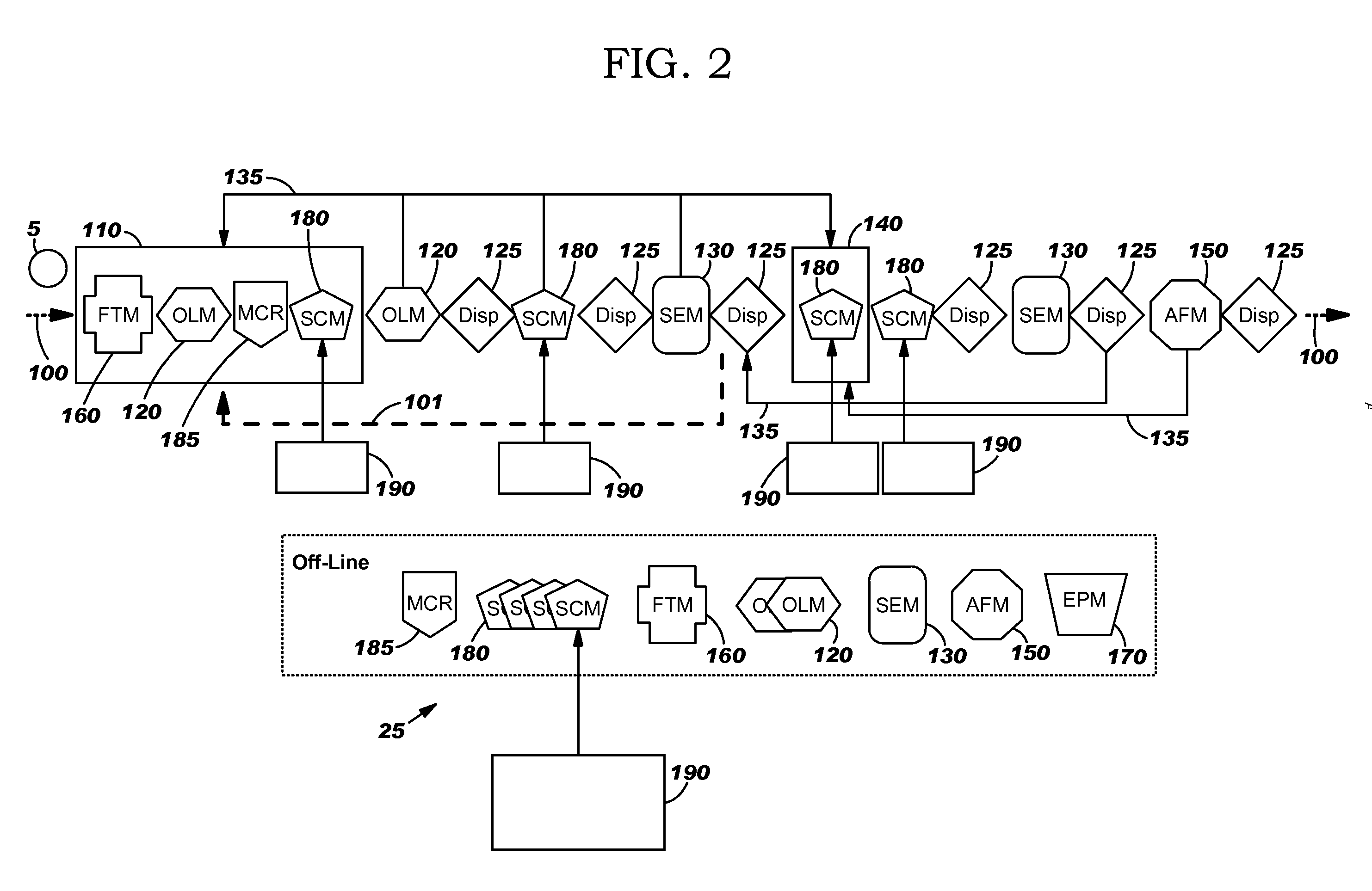

Method and apparatus for characterizing semiconductor device performance variations based on independent critical dimension measurements

InactiveUS6346426B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMetrologyEngineering

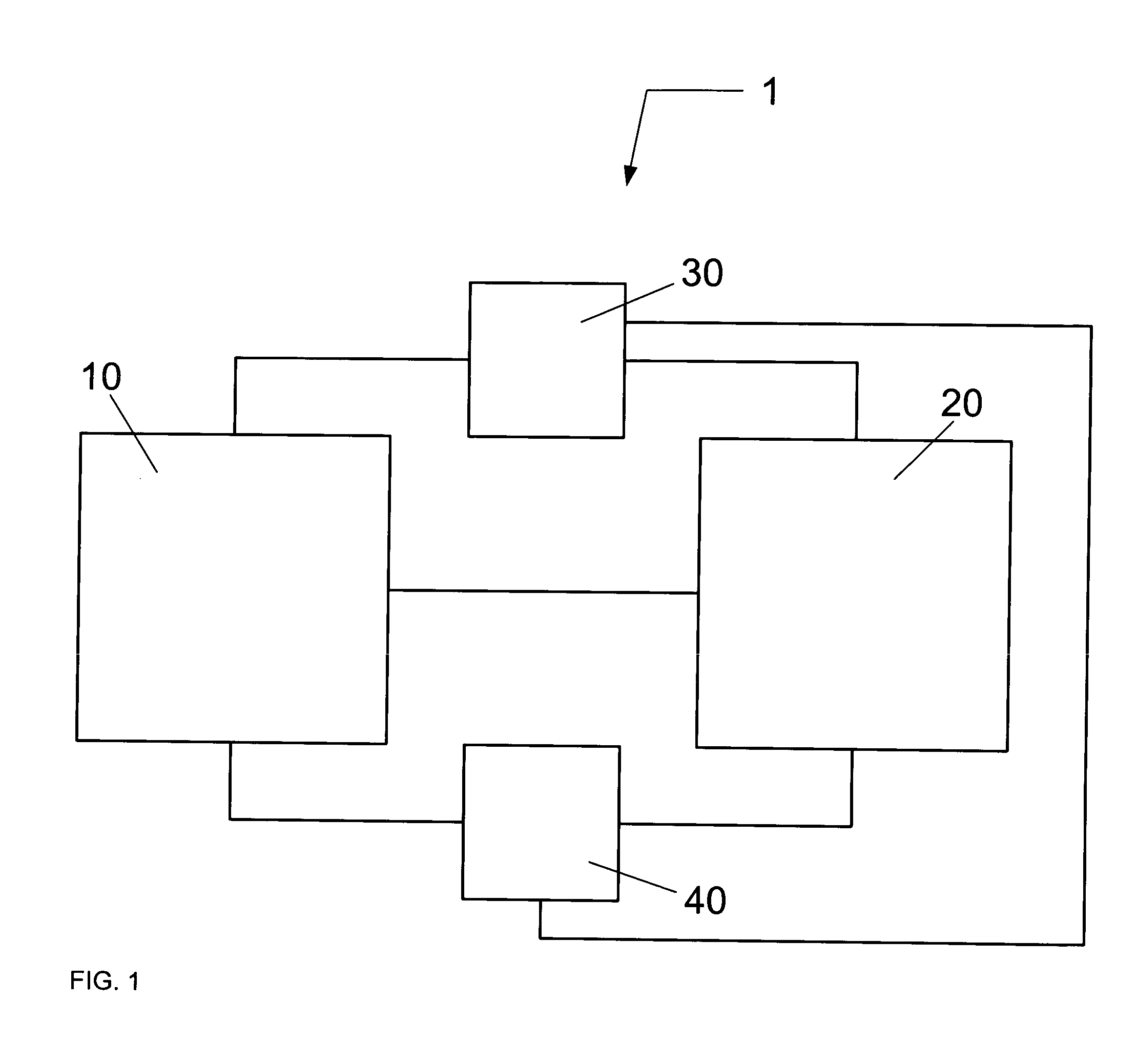

A method for characterizing semiconductor device performance variations includes processing a wafer in a processing line to form a feature on the wafer; measuring a physical critical dimension of the feature in a first metrology tool to generate a first critical dimension measurement; measuring the physical critical dimension of the feature in a second metrology tool to generate a second critical dimension measurement independent of the first critical dimension measurement; determining an effective critical dimension of the feature in a third metrology tool to generate a third critical dimension measurement; and comparing the first, second, and third critical dimension measurements to identify a metrology drift in one of the first and second metrology tools. A system for characterizing semiconductor device performance variations includes a processing line, first, second, and third metrology tools, and a process controller. The processing line is adapted to process a wafer to form a feature on the wafer. The first metrology tool is adapted to measure a physical critical dimension of the feature to generate a first critical dimension measurement. The second metrology tool is adapted to measure the physical critical dimension of the feature to generate a second critical dimension measurement independent of the first critical dimension measurement. The third metrology tool adapted to determine an effective critical dimension of the feature to generate a third critical dimension measurement. The process controller is adapted to compare the first, second, and third critical dimension measurements to identify a metrology drift in one of the first and second metrology tools.

Owner:ADVANCED MICRO DEVICES INC

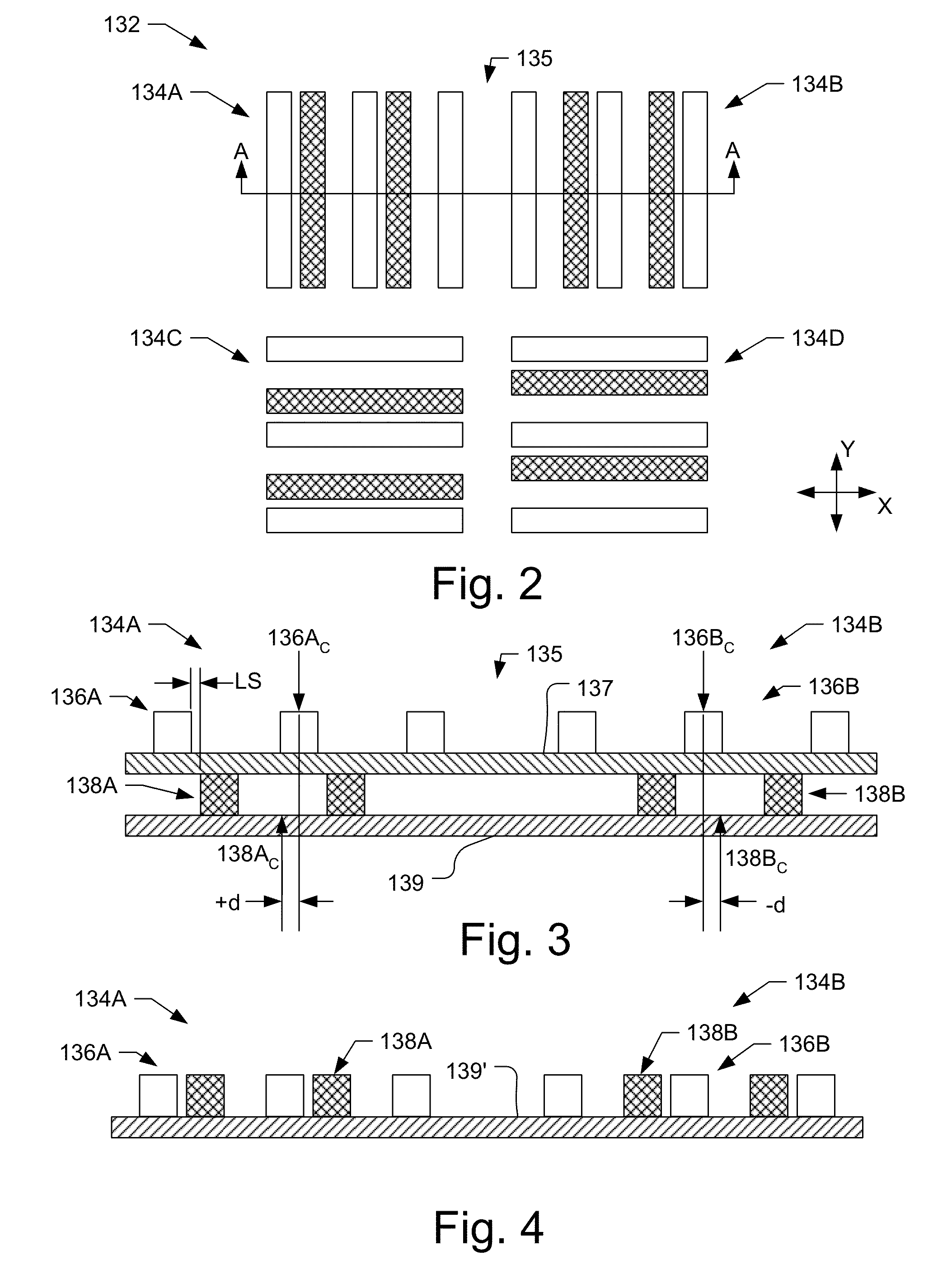

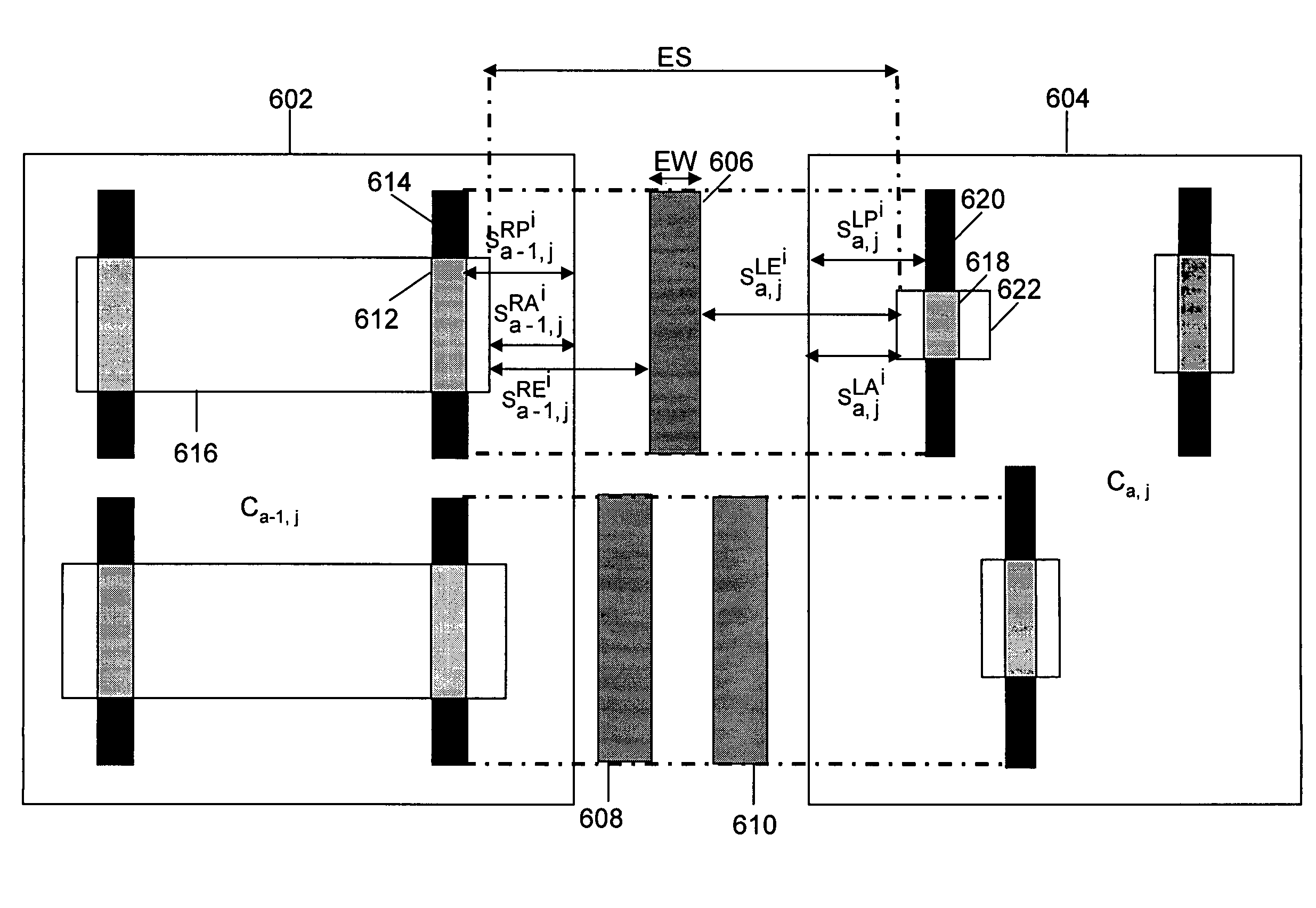

Differential critical dimension and overlay metrology apparatus and measurement method

InactiveUS20070105029A1Using optical meansPhotomechanical exposure apparatusMetrologyCritical dimension

A method is described for measuring a dimension on a substrate, wherein a target pattern is provided with a nominal characteristic dimension that repeats at a primary pitch of period P, and has a pre-determined variation orthogonal to the primary direction. The target pattern formed on the substrate is then illuminated so that at least one non-zero diffracted order is detected. The response of the non-zero diffracted order to variation in the printed characteristic dimension relative to nominal is used to determine the dimension of interest, such as critical dimension or overlay, on the substrate. An apparatus for performing the method of the present invention includes an illumination source, a detector for detecting a non-zero diffracted order, and means for positioning the source relative to the target so that one or more non-zero diffracted orders from the target are detected at the detector.

Owner:IBM CORP

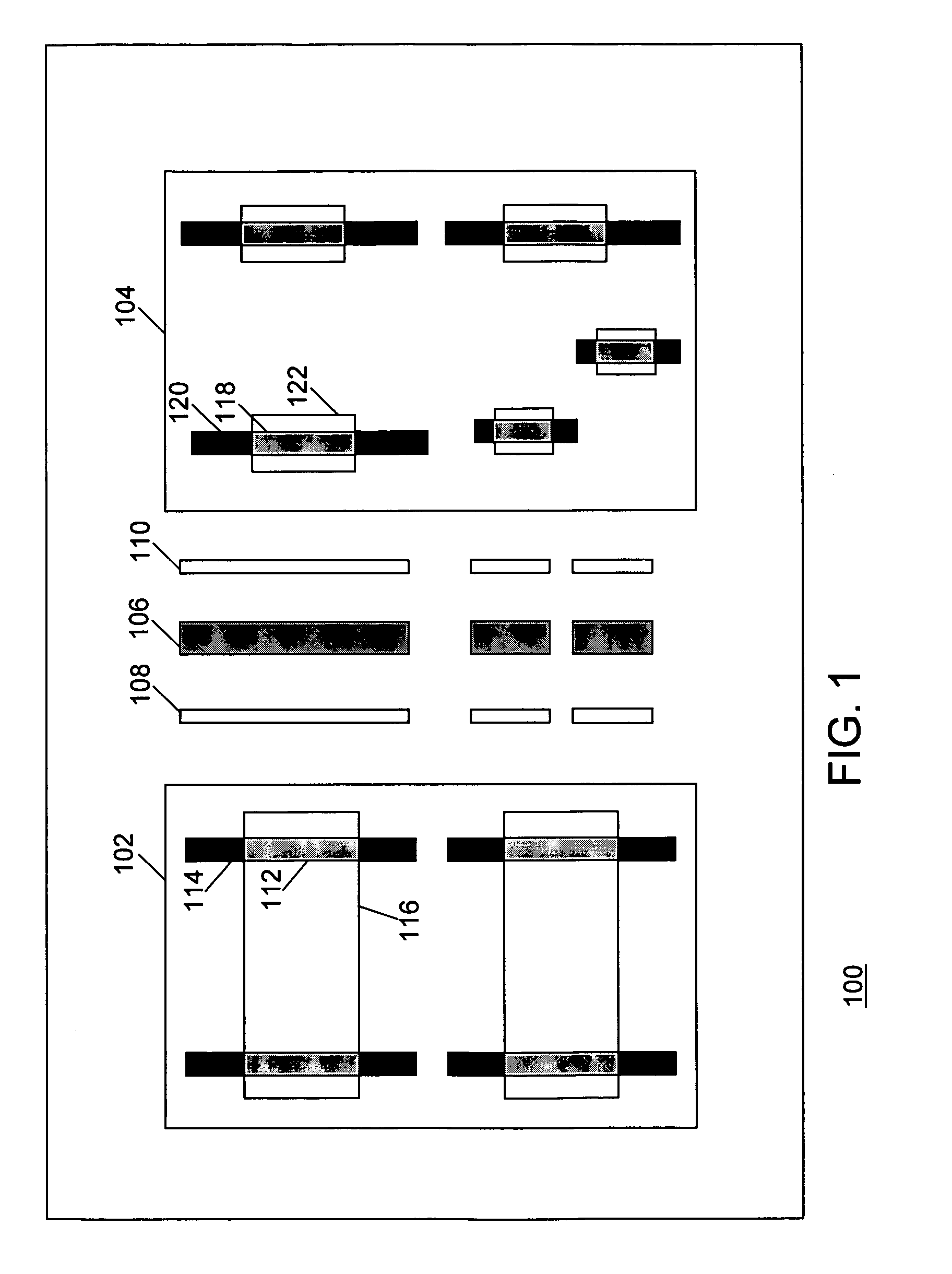

Image based overlay measurement with finite gratings

ActiveUS20130208279A1High sensitivityEasy to changePhotomechanical apparatusUsing optical meansMetrologyGrating

An image based overlay measurement is performed using an overlay target that includes shifted overlying gratings. The overlay target is imaged and an asymmetry is measured in the image of the overlaid gratings. The asymmetry is used to determine the overlay error. For each measurement direction, the overlay target may include two or more overlay measurement pads with different offsets between the top and bottom gratings. The measured asymmetries and offsets in the overlay measurement pads may be used to determine the overlay error, e.g., using self-calibration. The pitch and critical dimensions of the overlay target may be optimized to produce a greatest change of symmetry with overlay error for a numerical aperture and wavelength of light used by the image based metrology device.

Owner:ONTO INNOVATION INC

Methods and systems for determining a critical dimension, a presence of defects, and a thin film characteristic of a specimen

InactiveUS6919957B2Speed up the processShorten the timeSemiconductor/solid-state device testing/measurementPolarisation-affecting propertiesMeasurement deviceEngineering

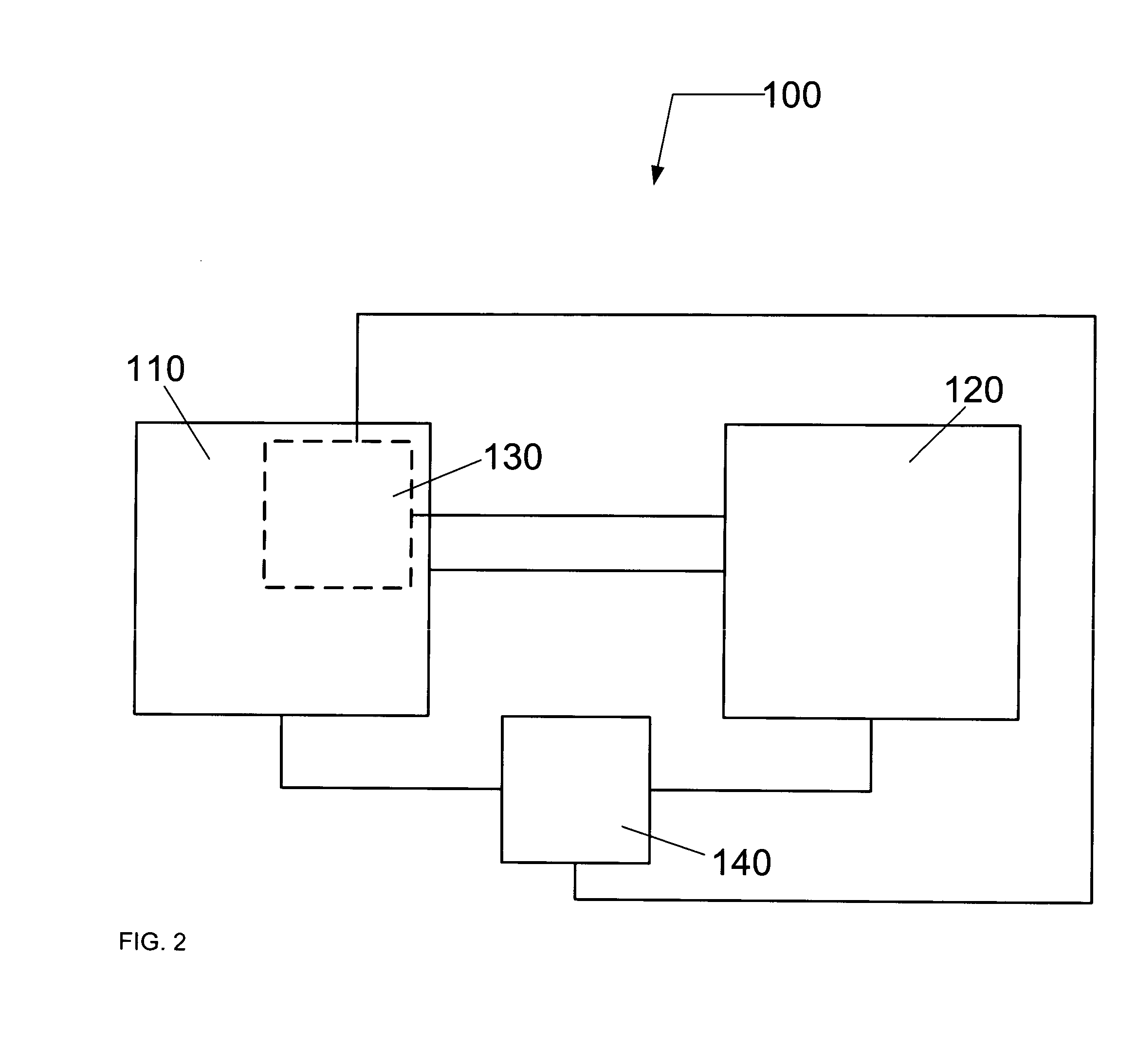

Methods and systems for monitoring semiconductor fabrication processes are provided. A system may include a stage configured to support a specimen and coupled to a measurement device. The measurement device may include an illumination system and a detection system. The illumination system and the detection system may be configured such that the system may be configured to determine multiple properties of the specimen. For example, the system may be configured to determine multiple properties of a specimen including, but not limited to, critical dimension, a presence of defects, and a thin film characteristic. In this manner, a measurement device may perform multiple optical and / or non-optical metrology and / or inspection techniques.

Owner:KLA TENCOR TECH CORP

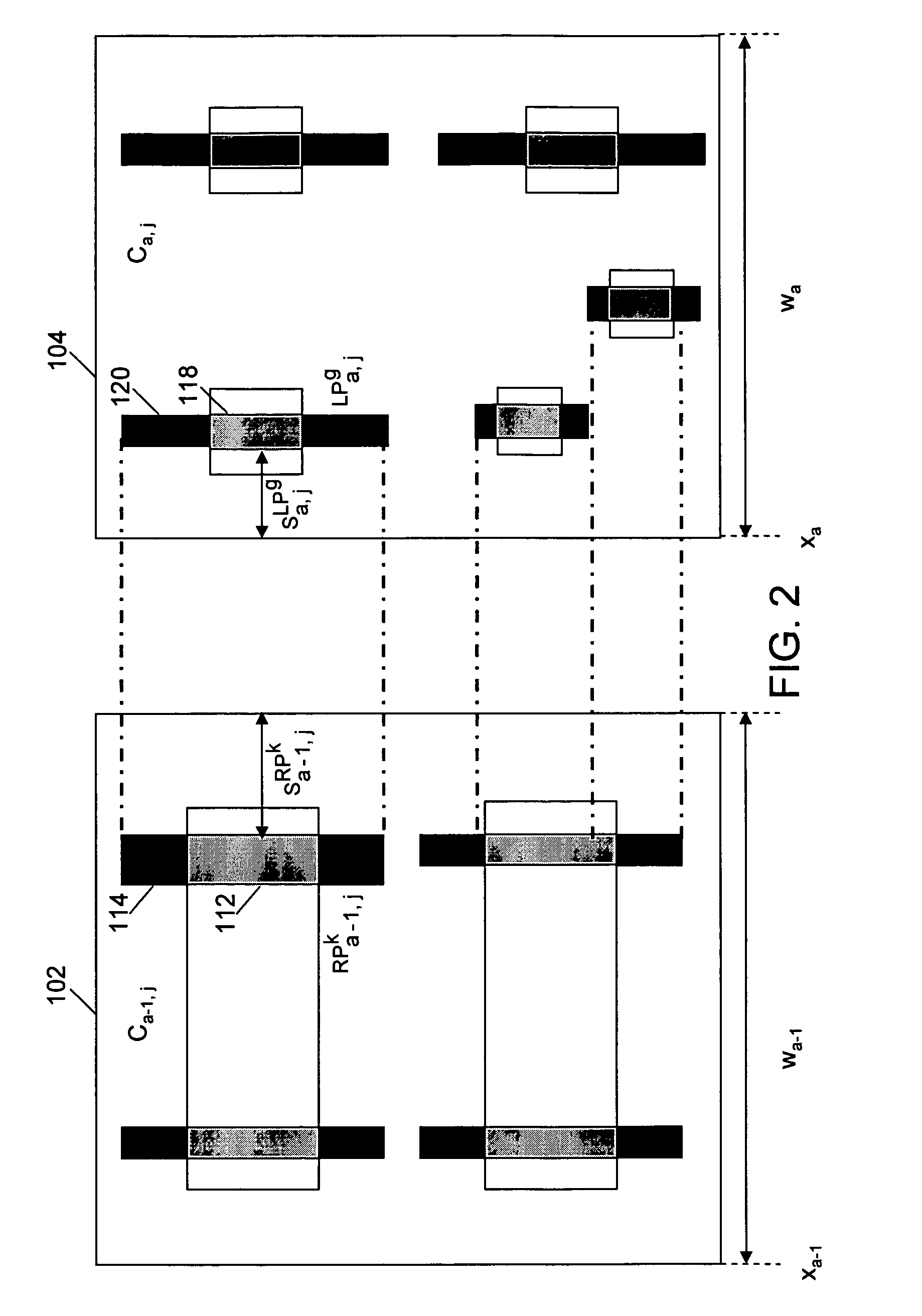

Method and system for placing layout objects in a standard-cell layout

InactiveUS7640522B2Reduce forbidden pitchesReduce CD skewCAD circuit designOriginals for photomechanical treatmentComputer architectureCritical dimension

A method and system for detailed placement of layout objects in a standard-cell layout design are disclosed. Layout objects comprise cells and etch dummies. The method includes a programming based technique to calculate layout object perturbation distances for the layout objects. The method includes adjusting the layout objects with their corresponding layout object perturbation distances. This leads to improved photolithographic characteristics such as reduced Critical Dimension (CD) errors and forbidden pitches in the standard-cell layout.

Owner:RPX CORP

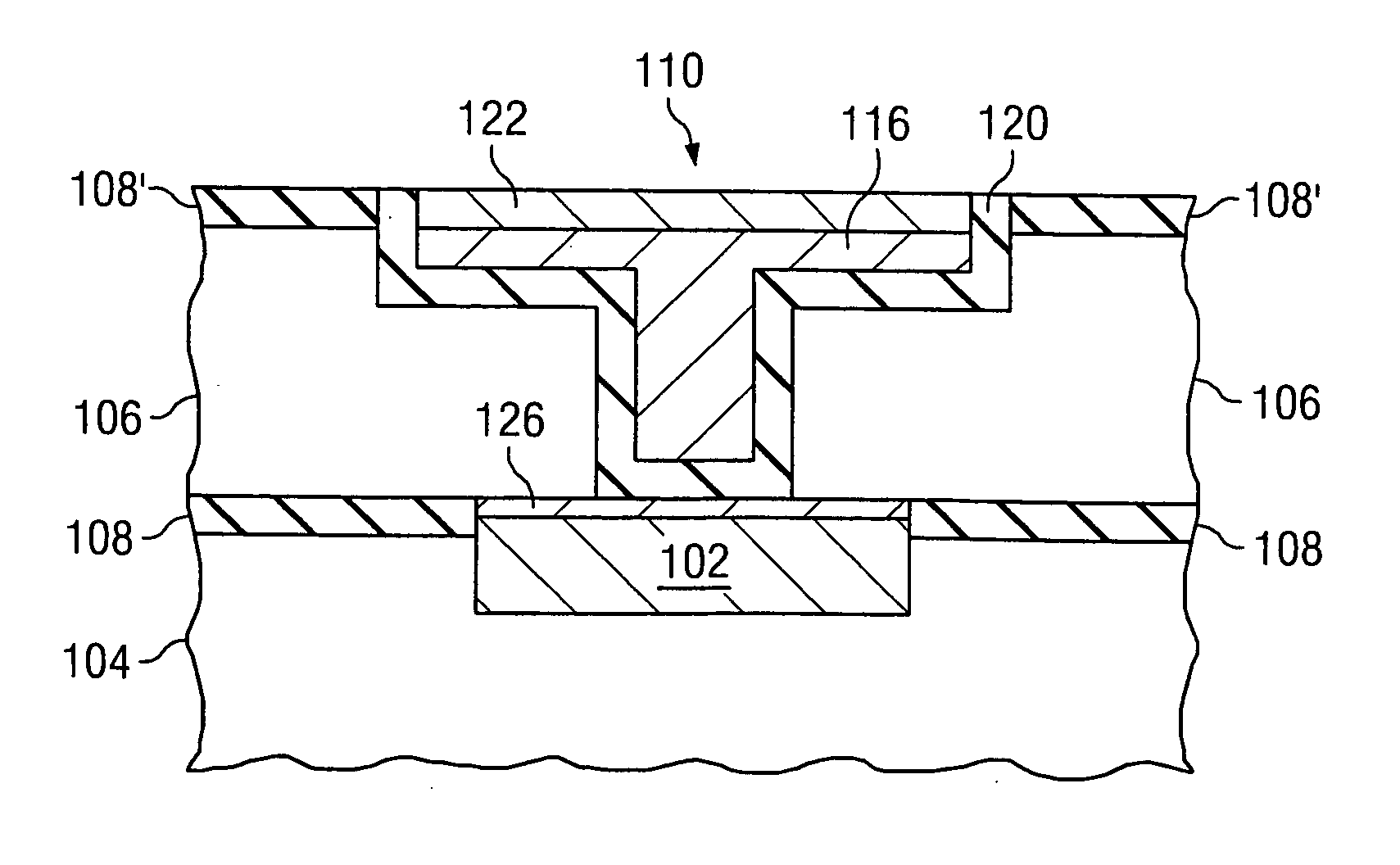

Uniform critical dimension size pore for pcram application

InactiveUS20080164453A1Semiconductor/solid-state device manufacturingBulk negative resistance effect devicesPhase-change materialCritical dimension

A memory cell and a method of making the same, that includes insulating material deposited on a substrate, a bottom electrode formed within the insulating material, a plurality of insulating layers deposited above the bottom electrode and at least one of which acts as an intermediate insulating layer. A via is defined in the insulating layers above the intermediate insulating layer. A channel is created for etch with a sacrificial spacer. A pore is defined in the intermediate insulating layer. All insulating layers above the intermediate insulating layer are removed, and the entirety of the remaining pore is filled with phase change material. An upper electrode is formed above the phase change material.

Owner:IBM CORP +1

Method of making a semiconductor interconnect with a metal cap

InactiveUS20060205204A1Improve capacitive delayEffective dielectric constantSemiconductor/solid-state device manufacturingConductive materialsCopper

A method for forming metallization is particularly useful for semiconductor devices having a critical dimension of less than 160 nm. A semiconductor wafer includes an insulating layer having an upper surface. First and second trenches are formed in the insulating layer. In one embodiment, the first trench is separated from the second trench by less than 160 nm. A barrier material is formed to line the trenches and also overlies the insulating layer between the trenches. A conductive material (e.g., copper) is formed within the trenches. The conductive material is then recessed within the trenches and a metal cap layer is selectively formed over the conductive material in the trenches. The barrier material overlying the insulating layer between the first trench and the second trench is then removed. This removal will further remove any residual portions of the metal cap layer from between the first trench and the second trench.

Owner:INFINEON TECH AG +1

Gate critical dimension variation by use of ghost features

ActiveUS7569309B2Photomechanical apparatusSemiconductor/solid-state device manufacturingCritical dimensionComputer science

According to various embodiments, the present teachings include various methods for forming a semiconductor device, computer readable medium for forming a semiconductor device, mask sets for forming a semiconductor device, and a semiconductor device made according to various methods. For example, a method can comprise forming a first feature and a second feature on a substrate by exposing a first mask to a first beam, wherein the second feature is disposed adjacent to the first feature, exposing a second mask to a second beam, and removing the second feature from the substrate.

Owner:TEXAS INSTR INC

Bottom electrode etching process in MRAM cell

ActiveUS8334213B2Not to damageImprove device yieldDecorative surface effectsSolid-state devicesBit lineWater based

A BE patterning scheme in a MRAM is disclosed that avoids damage to the MTJ array and underlying ILD layer while reducing BE-BE shorts and BE-bit line shorts. A protective dielectric layer is coated over a MTJ array before a photoresist layer is coated and patterned on the dielectric layer. The photoresist pattern is transferred through the dielectric layer with a dielectric etch process and then through the BE layer with a metal etch that includes a certain amount of overetch to remove metal residues. The photoresist is stripped with a sequence involving immersion or spraying with an organic solution followed by oxygen ashing to remove any other organic materials. Finally, a second wet strip is performed with a water based solution to provide a residue free substrate. In another embodiment, a bottom anti-reflective coating (BARC) is inserted between the photoresist and dielectric layer for improved critical dimension control.

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com