Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

63results about How to "Effective dielectric constant" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

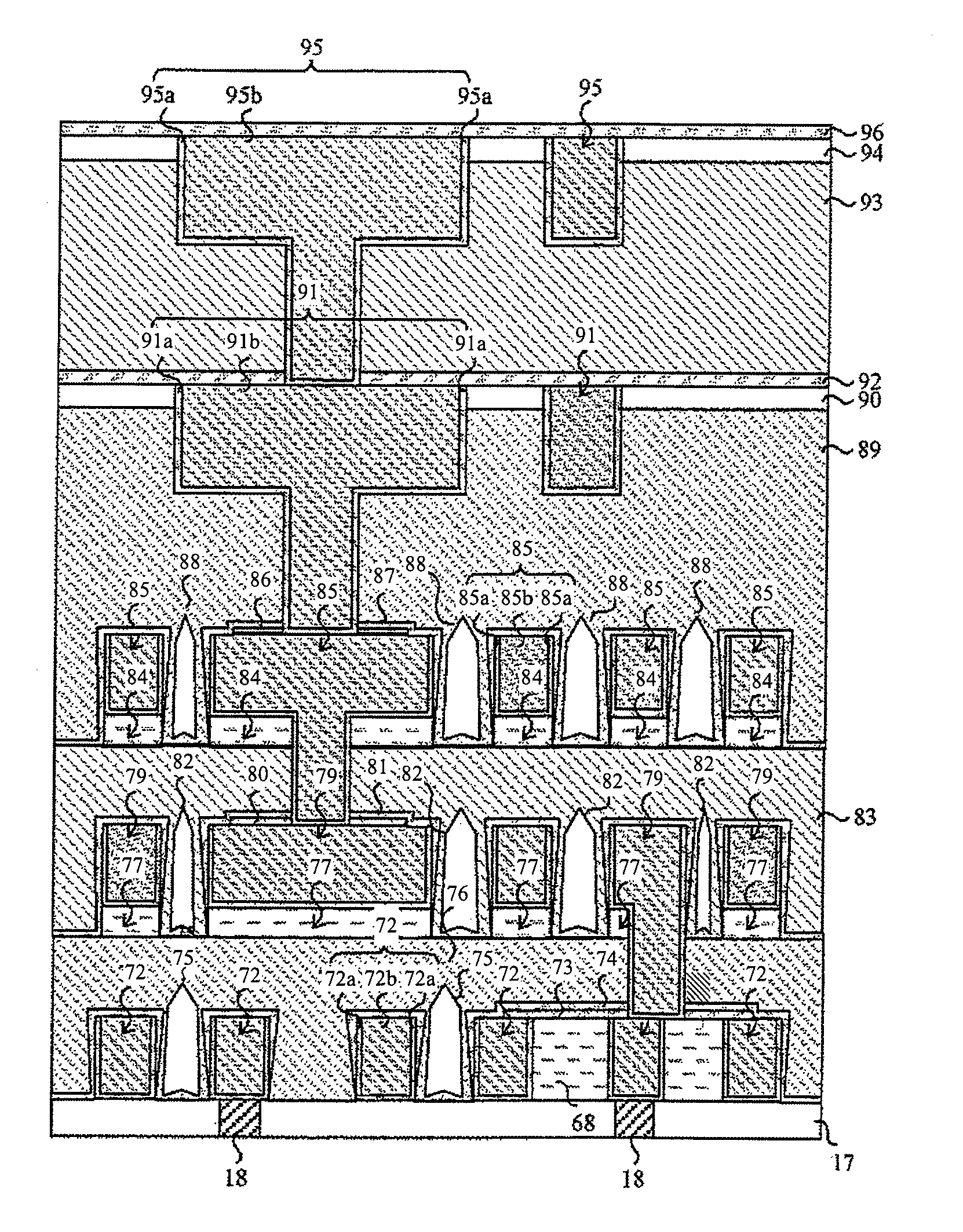

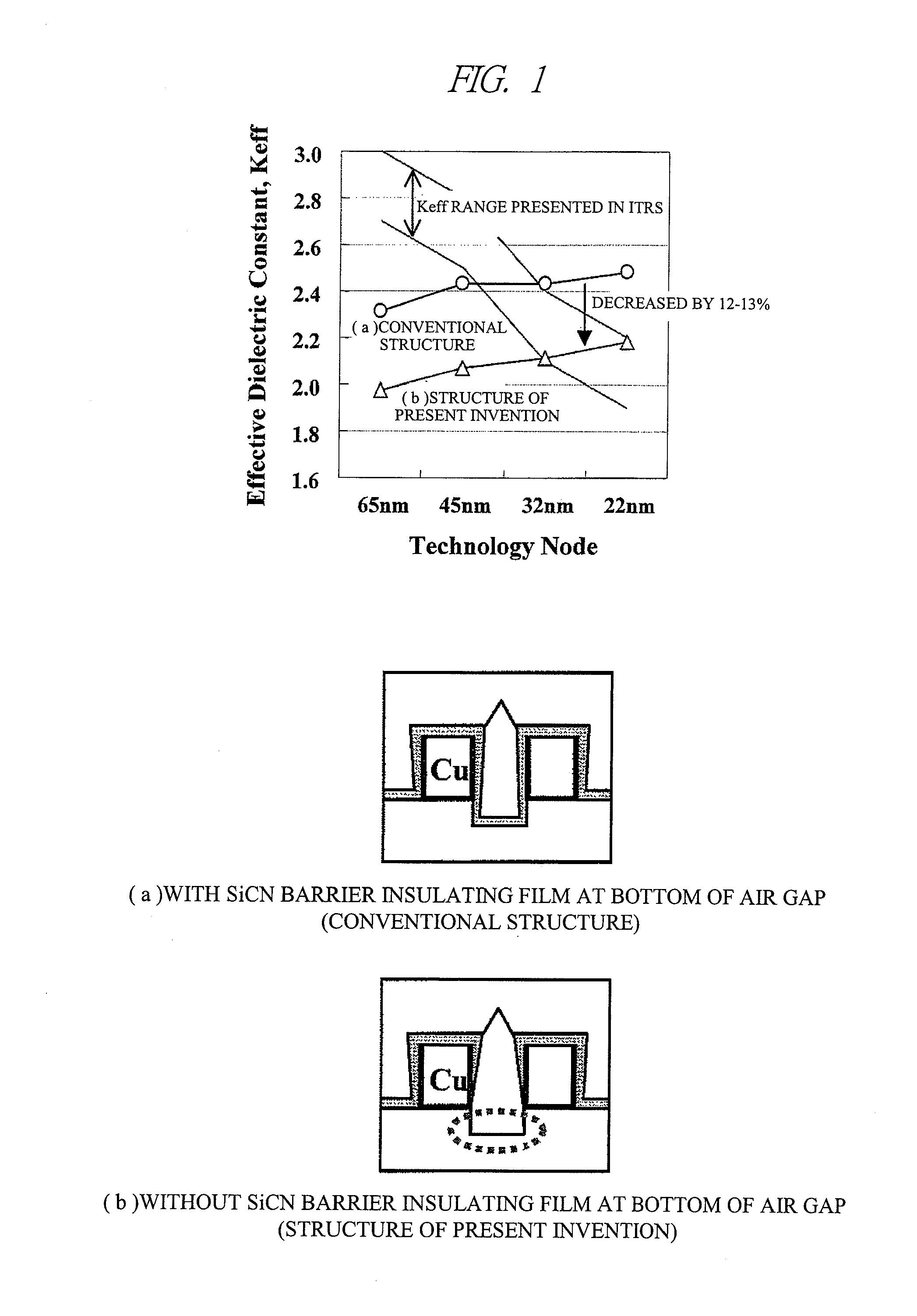

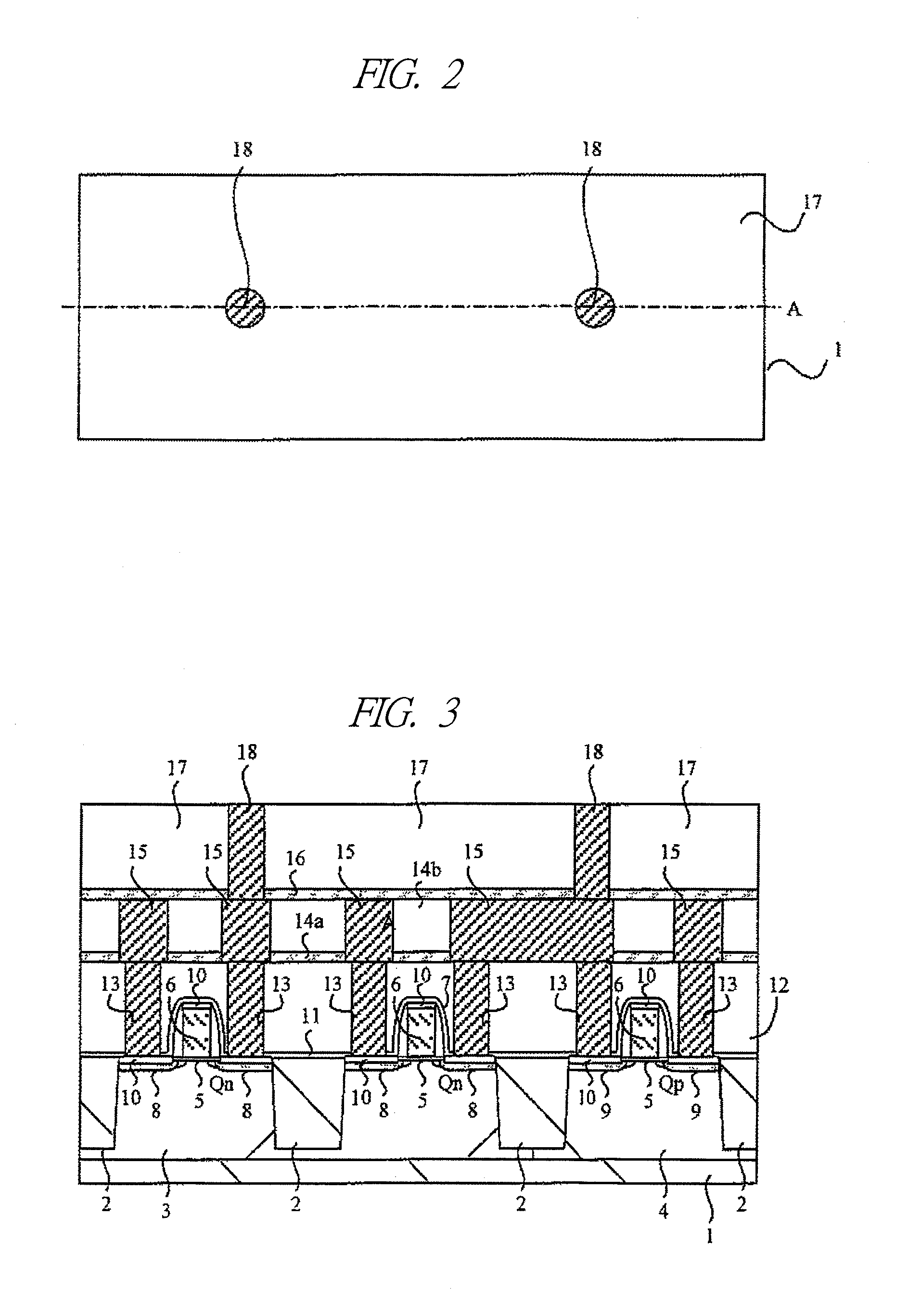

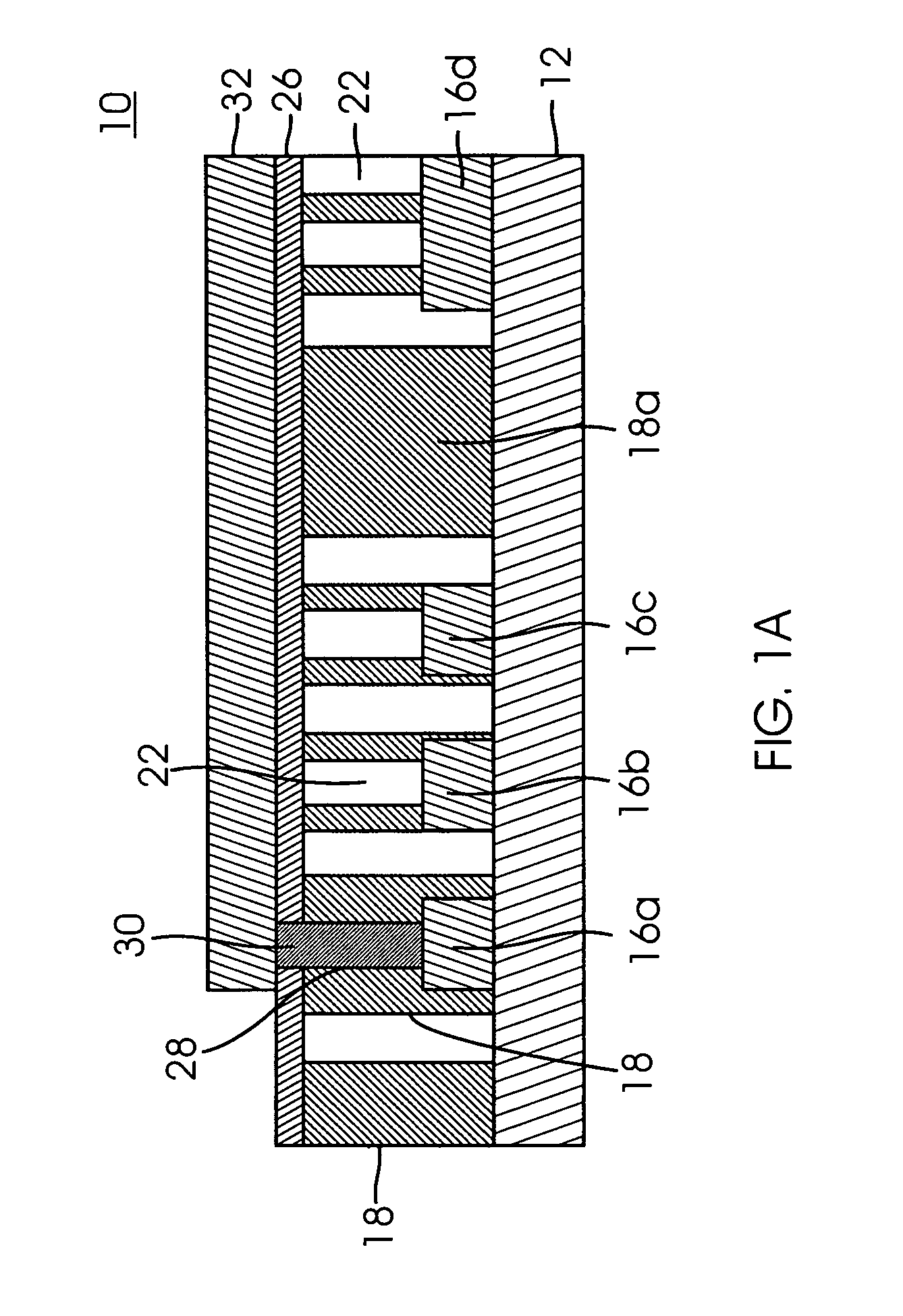

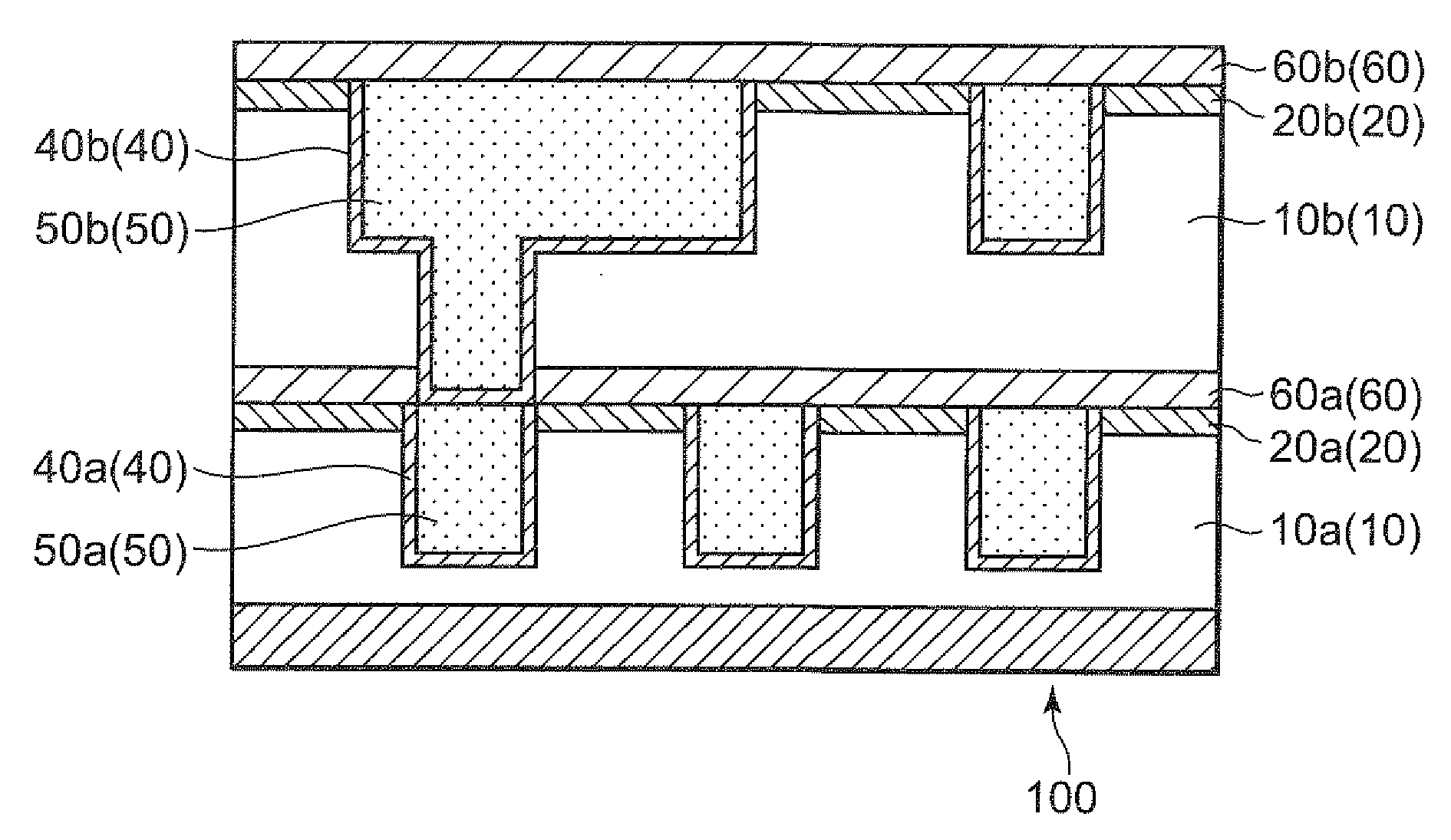

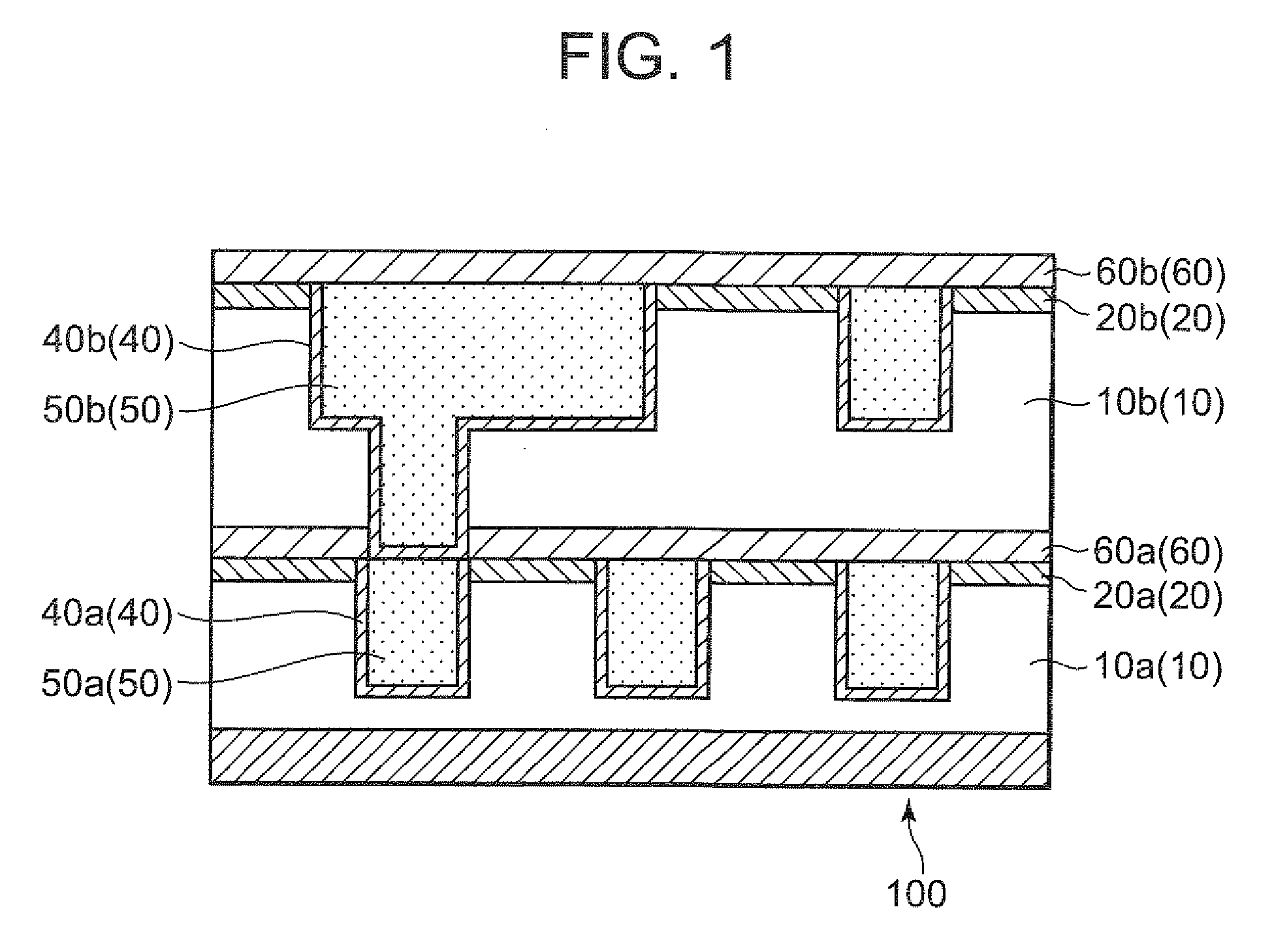

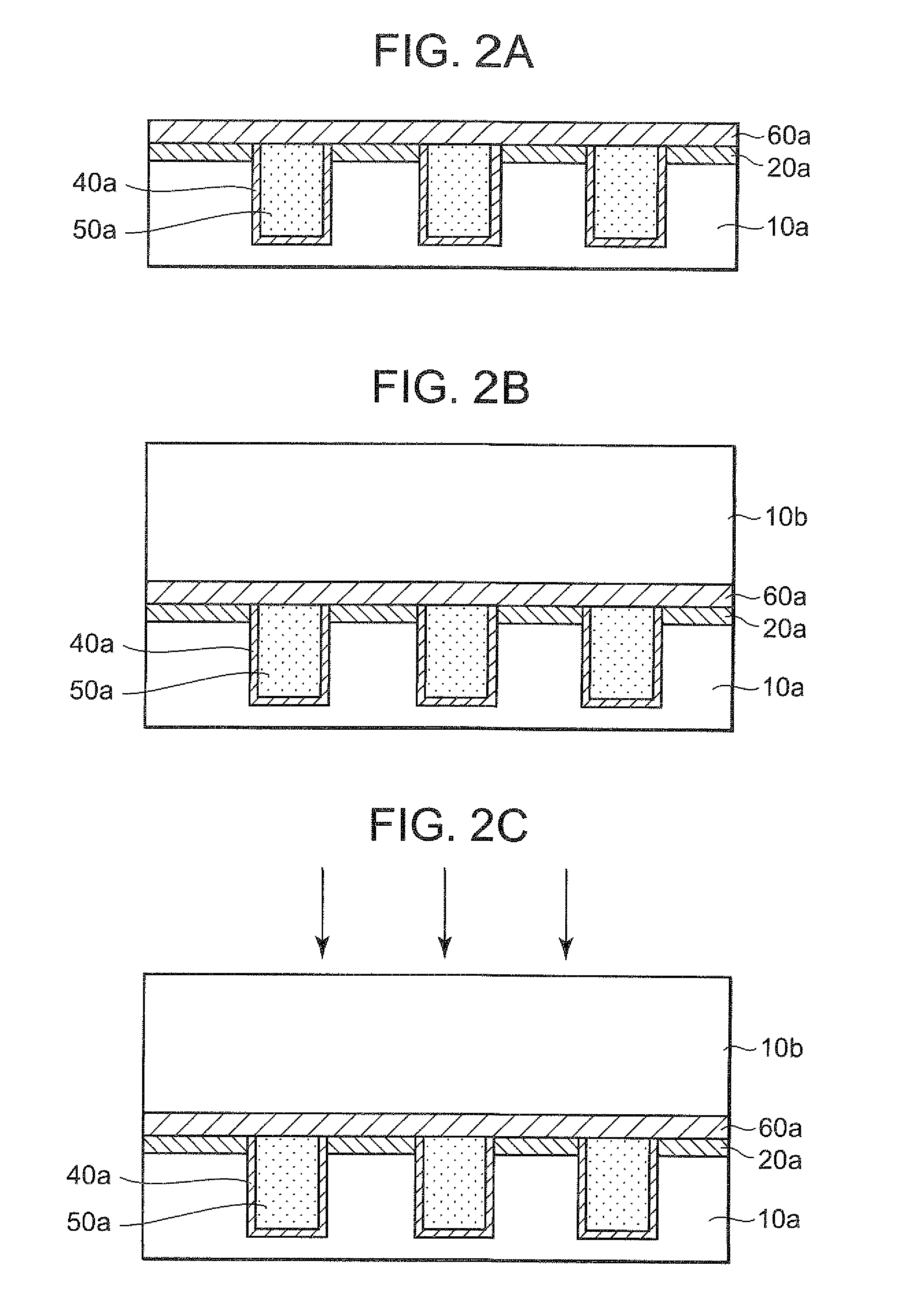

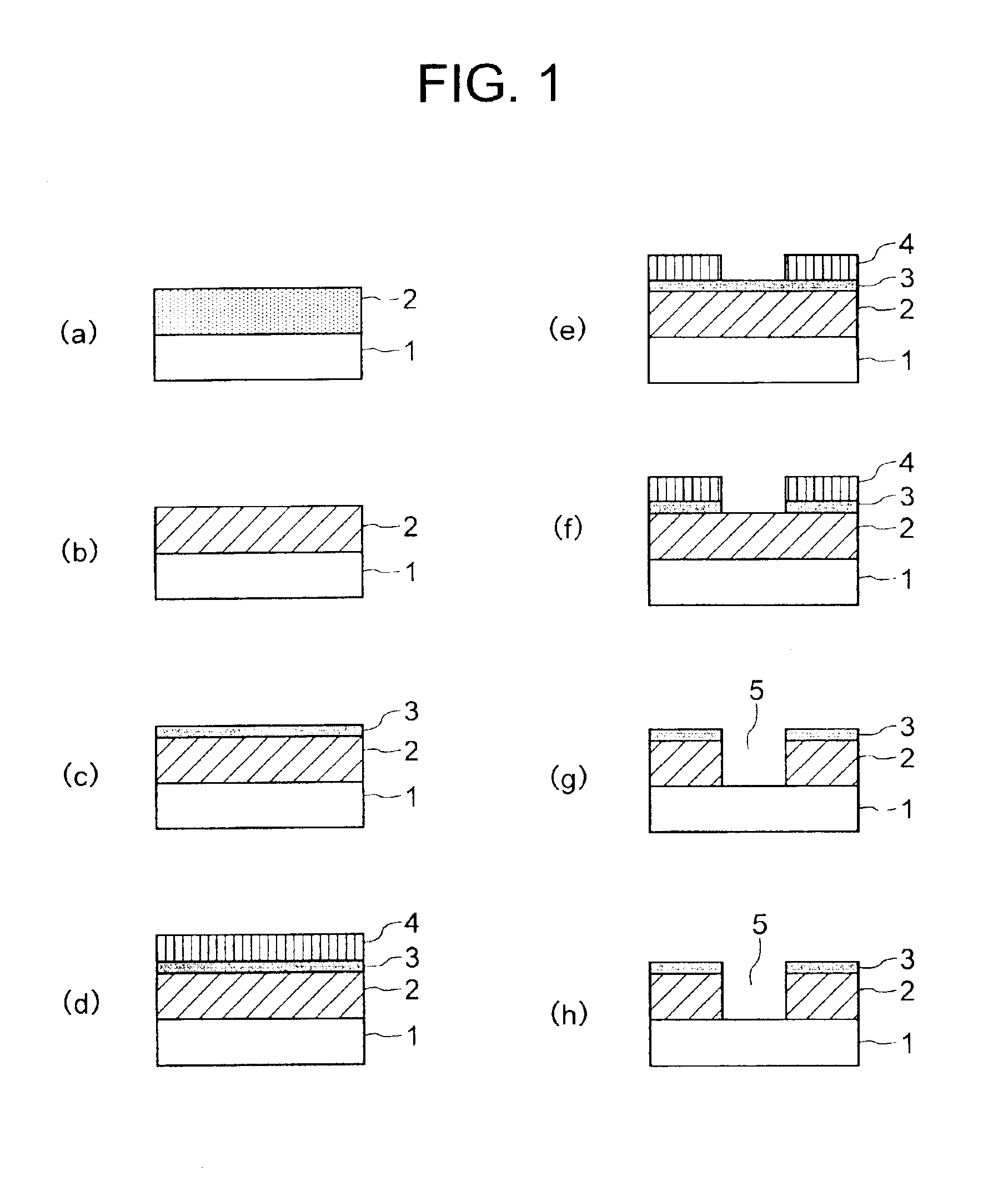

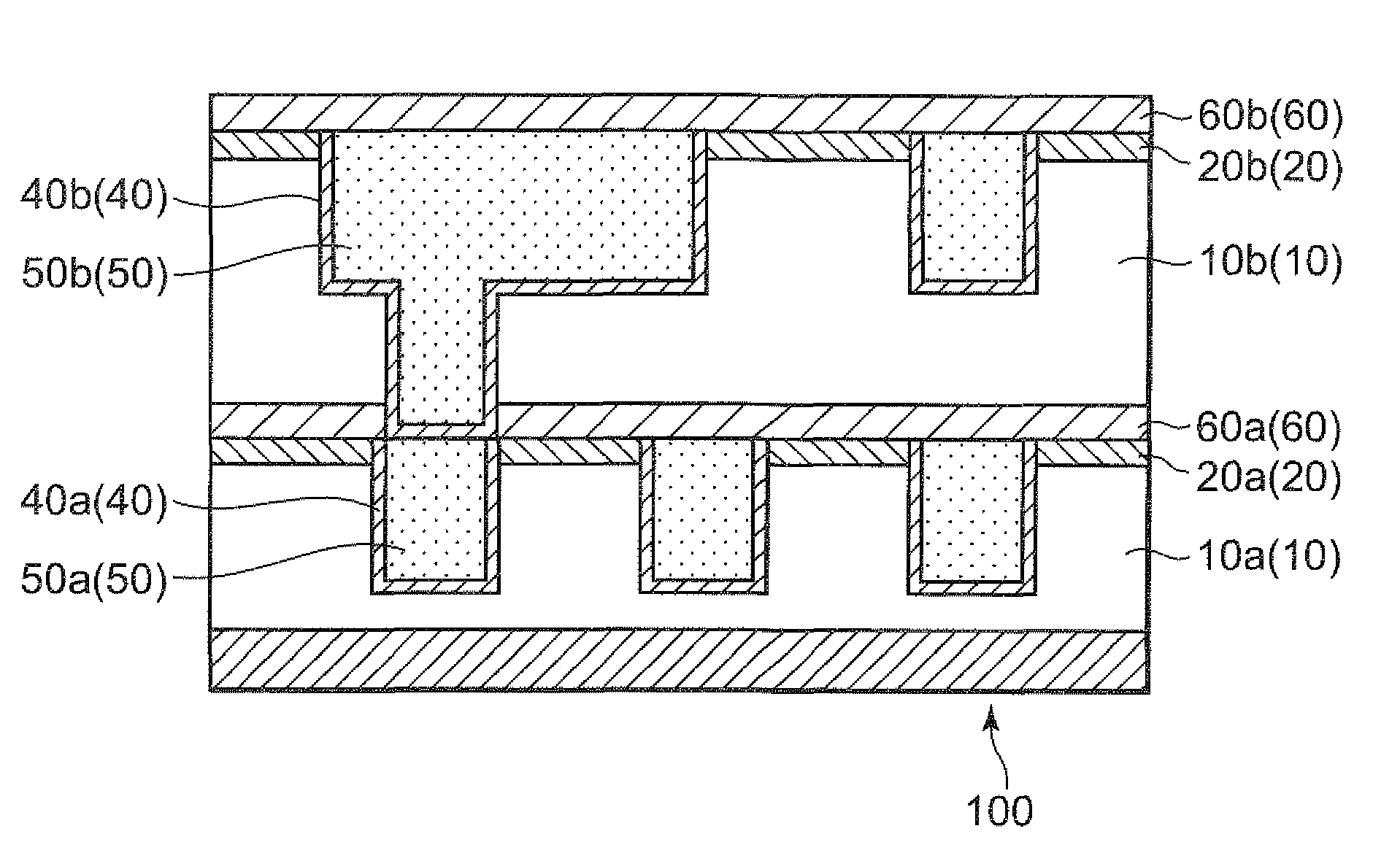

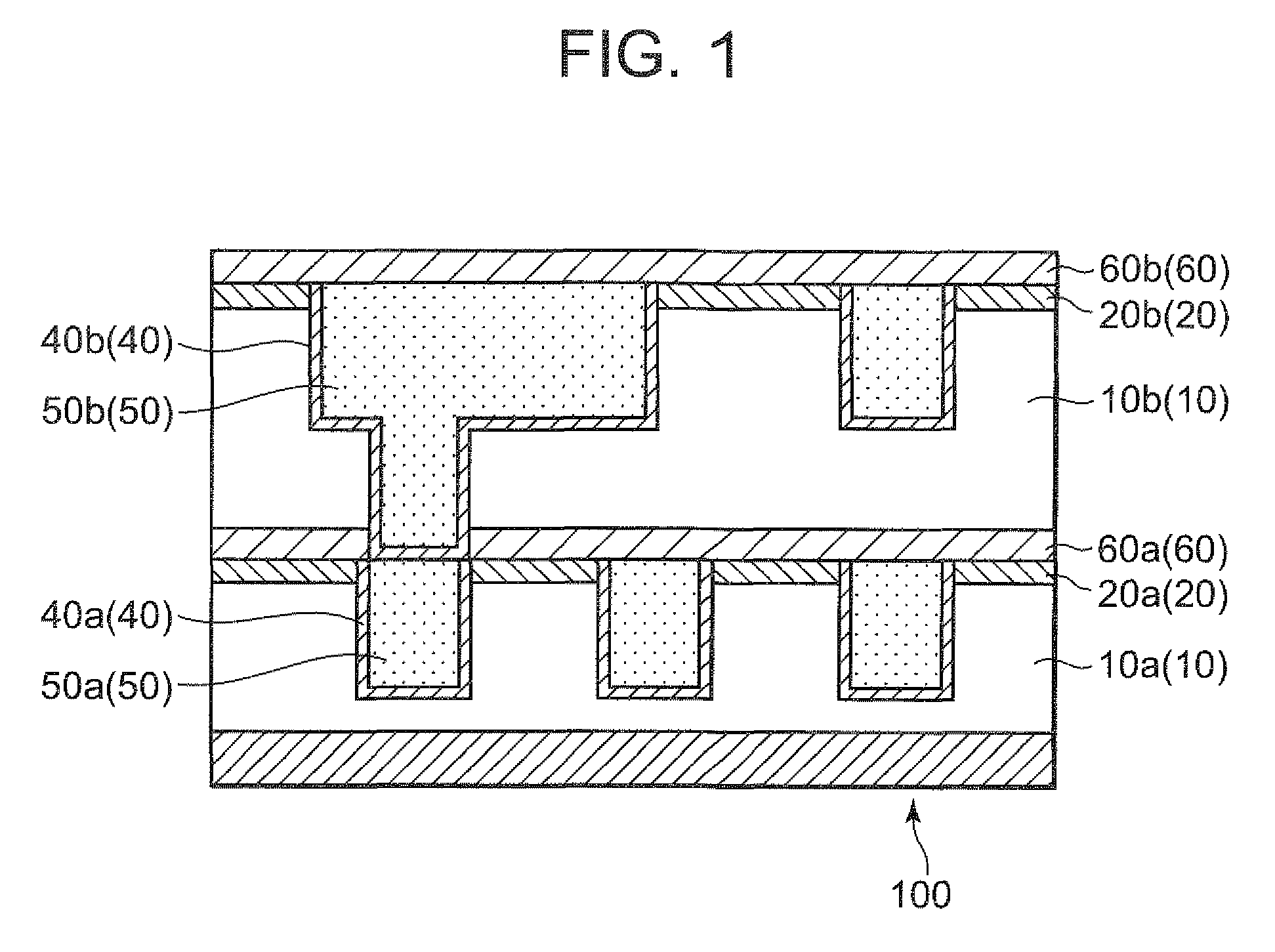

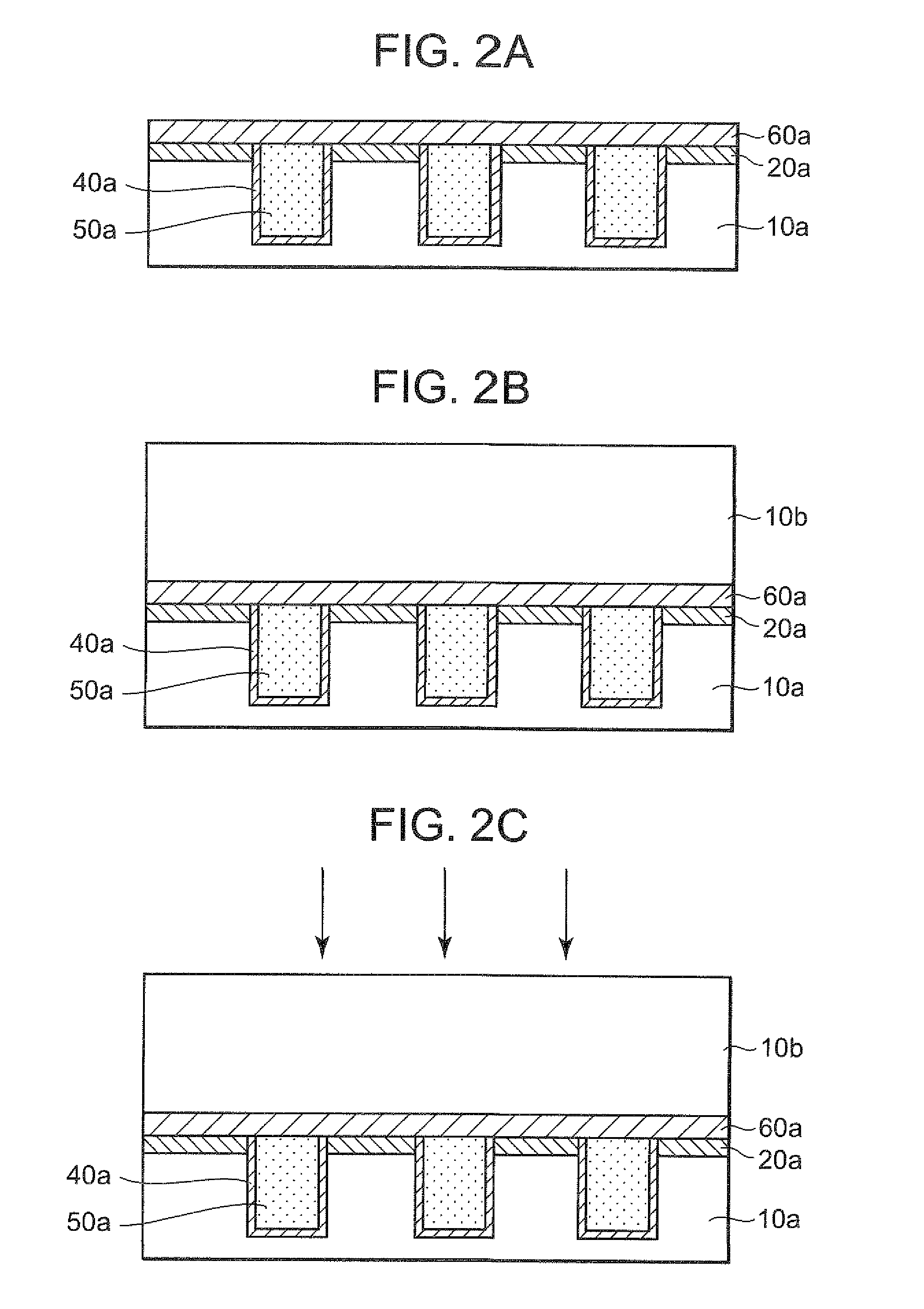

Semiconductor device and manufacturing method thereof

ActiveUS20100130001A1Reduce capacitanceEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesCapacitanceCopper

Wirings mainly containing copper are formed on an insulating film on a substrate. Then, after forming insulating films for reservoir pattern and a barrier insulating film, an insulating film for suppressing or preventing diffusion of copper is formed on upper and side surfaces of the wirings, the insulating film on the substrate, and the barrier insulating film. Here, thickness of the insulating film for suppressing or preventing diffusion of copper at the bottom of a narrow inter-wiring space is made smaller than that on the wirings, thereby efficiently reducing wiring capacitance of narrow-line pitches. Then, first and second low dielectric constant insulating films are formed. Here, a deposition rate of the first insulating film at an upper portion of the side surfaces of facing wirings is made higher than that at a lower portion thereof, thereby forming air gaps. Finally, the second insulating film is planarized by interlayer CMP.

Owner:KOKUSA ELECTRIC CO LTD

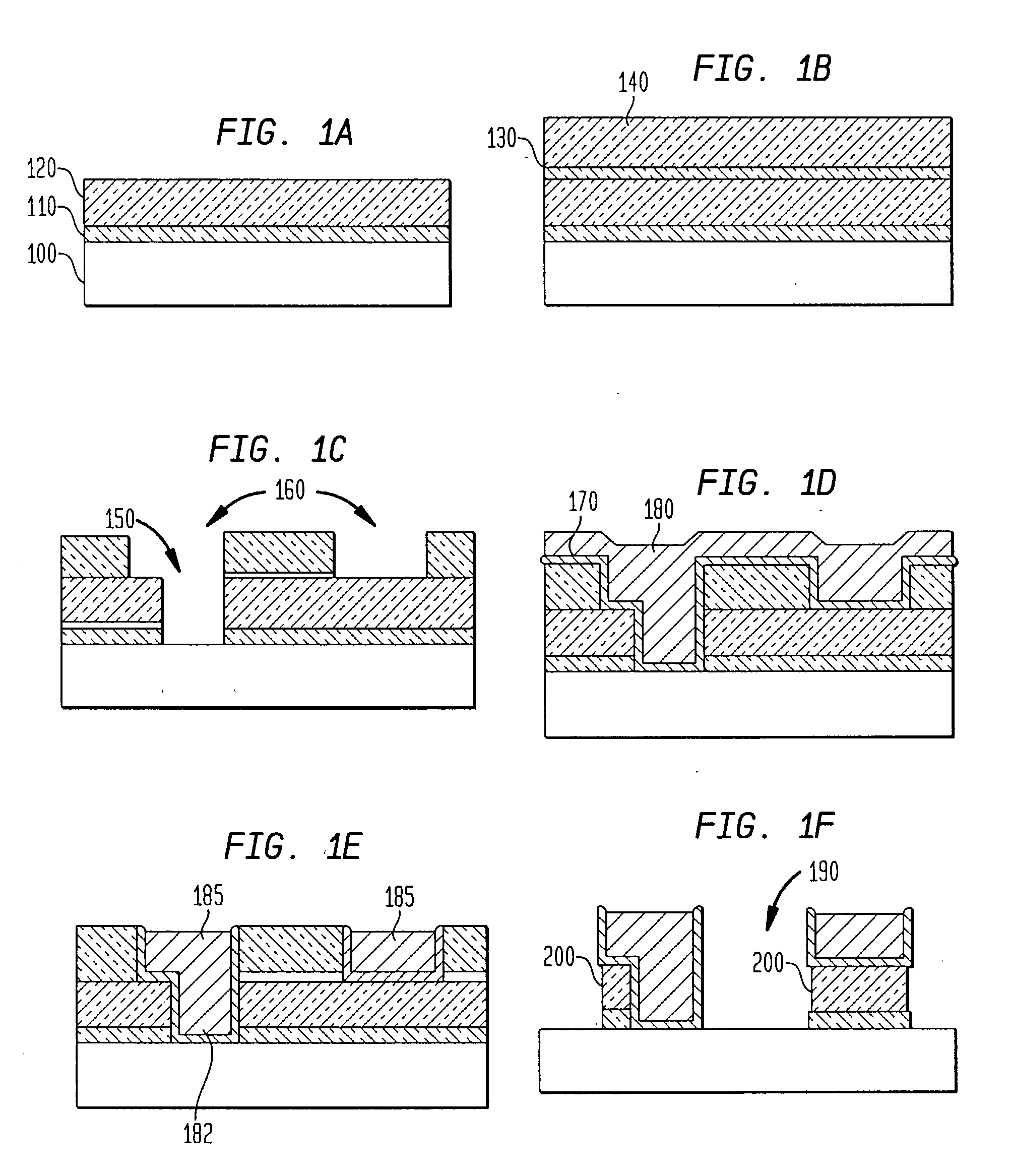

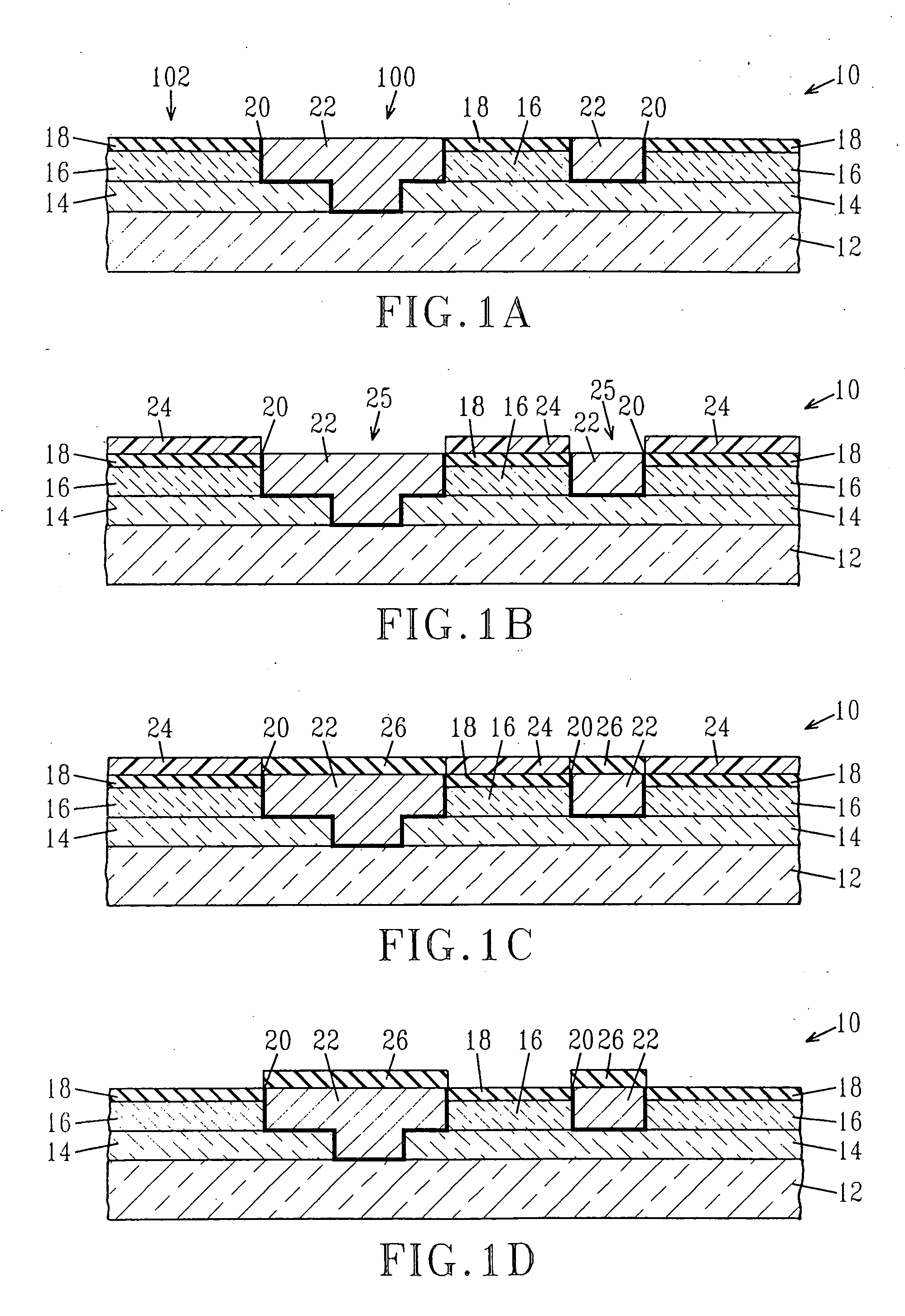

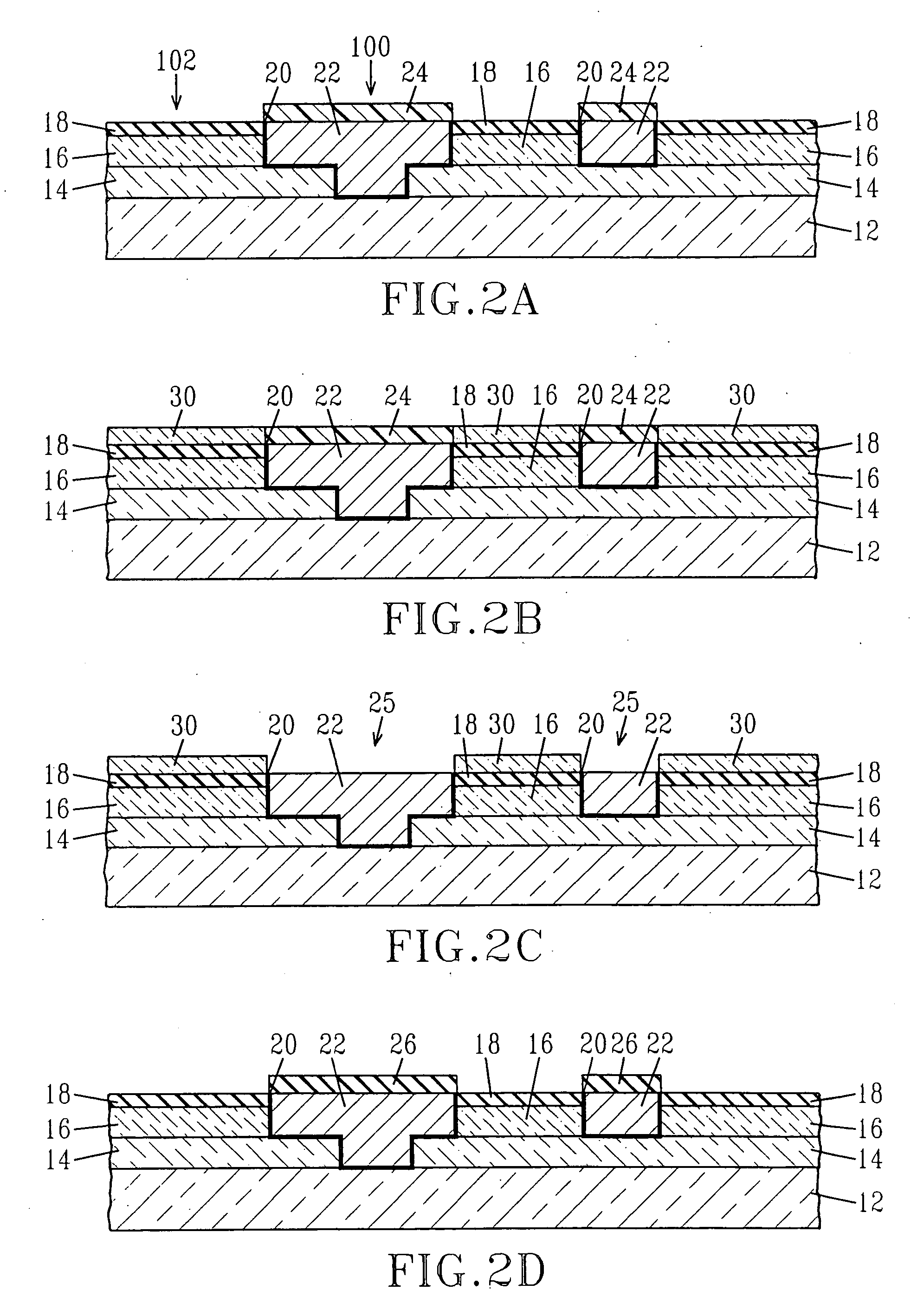

Multilevel interconnect structure containing air gaps and method for making

InactiveUS20020127844A1Maximizes air gap volume fractionQuantity minimizationSemiconductor/solid-state device detailsSolid-state devicesDielectric matrixEngineering

A method for forming a multilayer interconnect structure on a substrate that include interconnected conductive wiring and vias spaced apart by a combination of solid or gaseous dielectrics. The inventive method includes the steps of: (a) forming a first planar via plus line level pair embedded in a dielectric matrix formed from one or more solid dielectrics and comprising a via level dielectric and a line level dielectric on a substrate, wherein, at least one of said solid dielectrics is at least partially sacrificial; (b) etching back sacrificial portions of said at least partially sacrificial dielectrics are removed to leave cavities extending into and through said via level, while leaving, at least some of the original via level dielectric as a permanent dielectric under said lines; (c) partially filling or overfilling said cavities with a place-holder material which may or may not be sacrificial; (d) planarizing the structure by removing overfill of said place-holder material; (e) repeating, as necessary, steps (a)-(d); (f) forming a dielectric bridge layer over the planar structure; and (g) forming air gaps by at least partially extracting said place-holder material.

Owner:GLOBALFOUNDRIES US INC

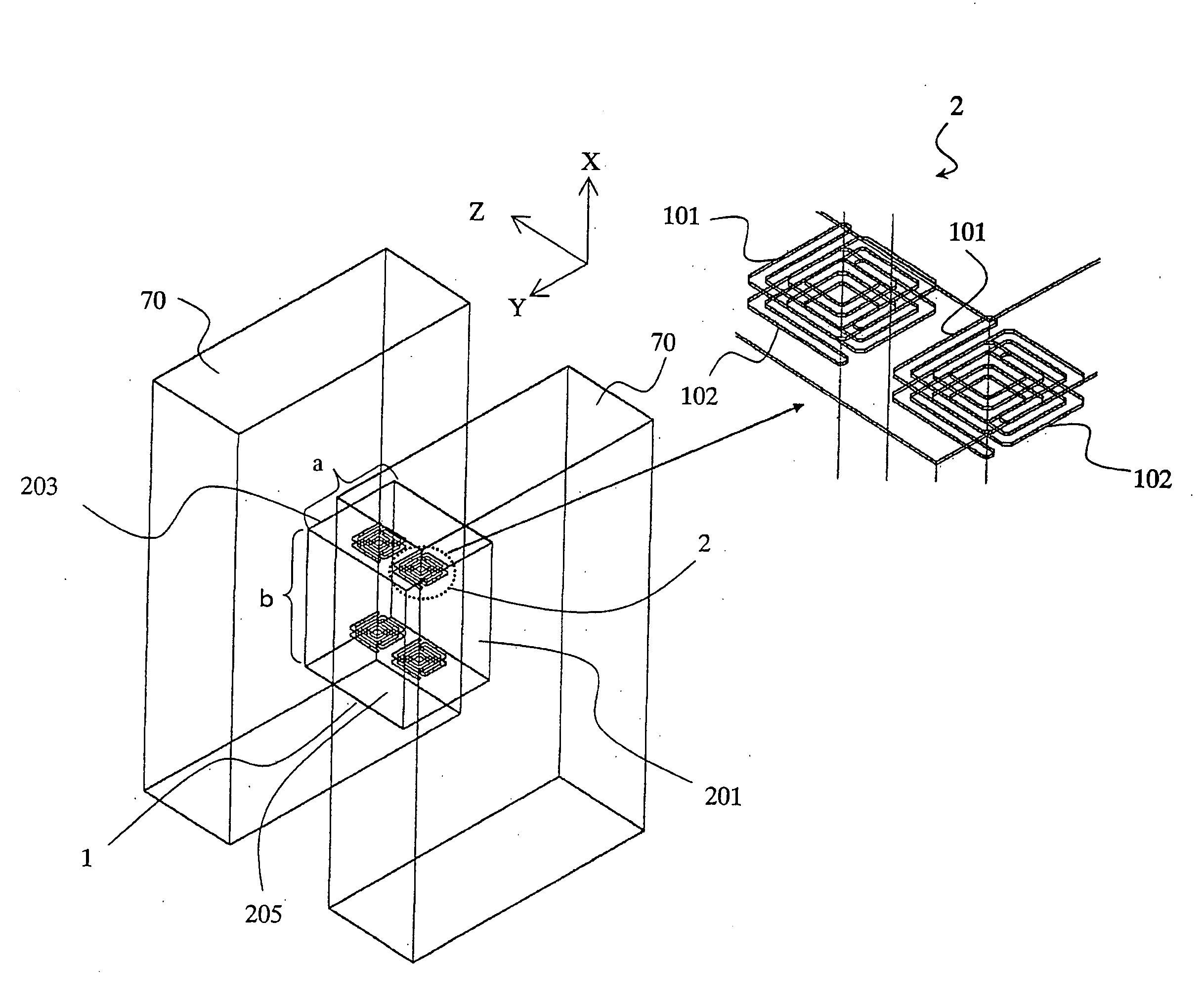

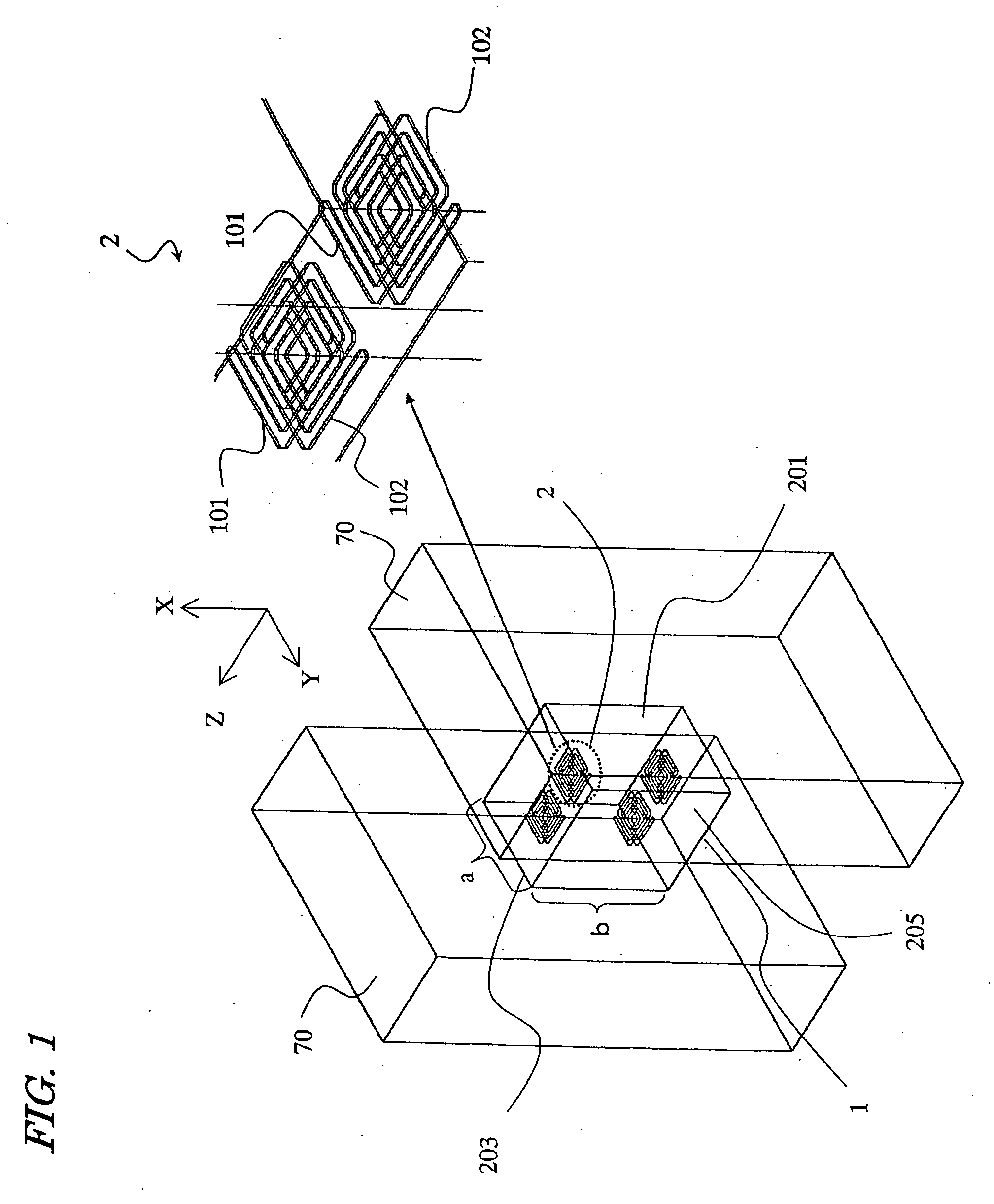

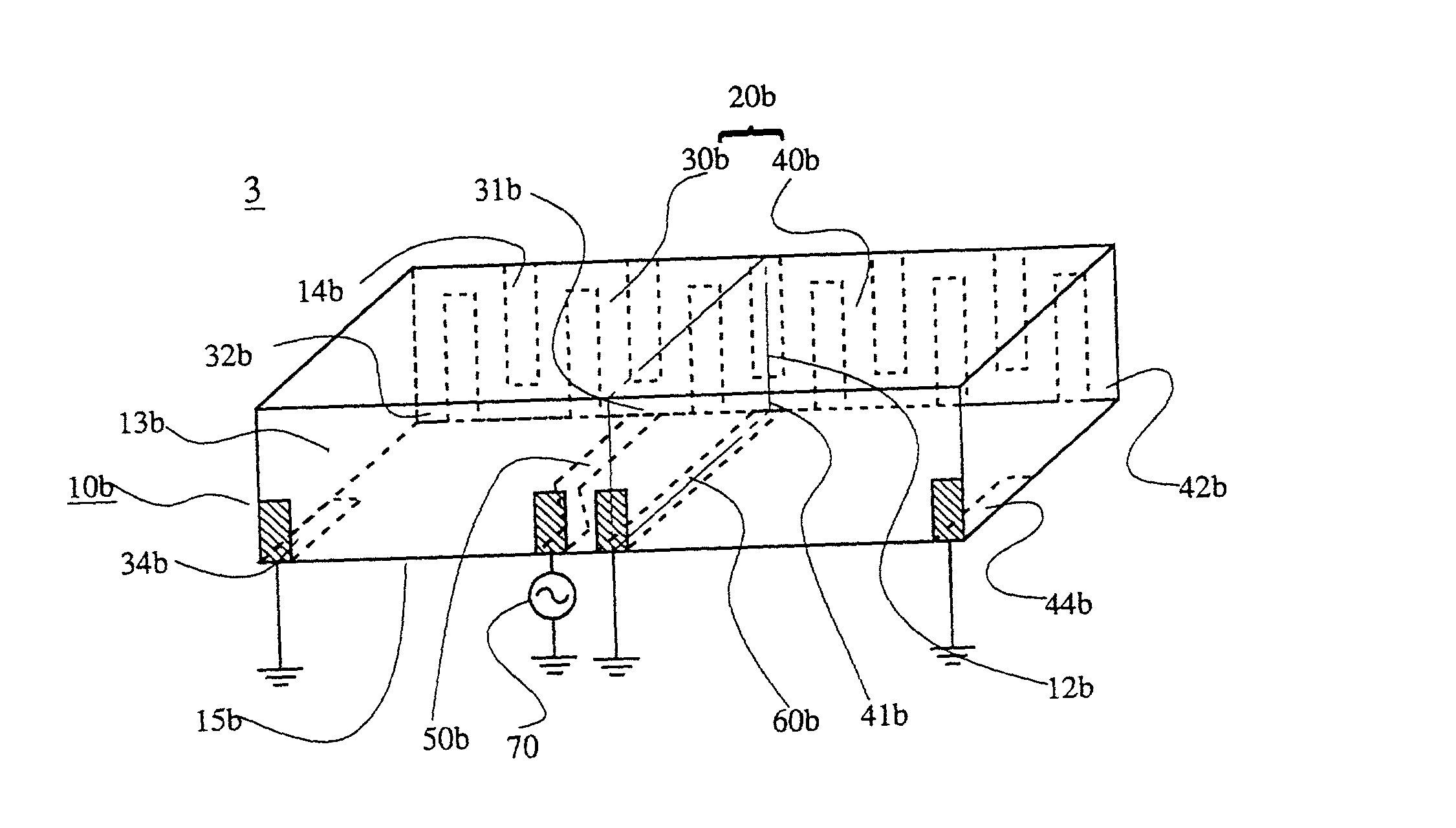

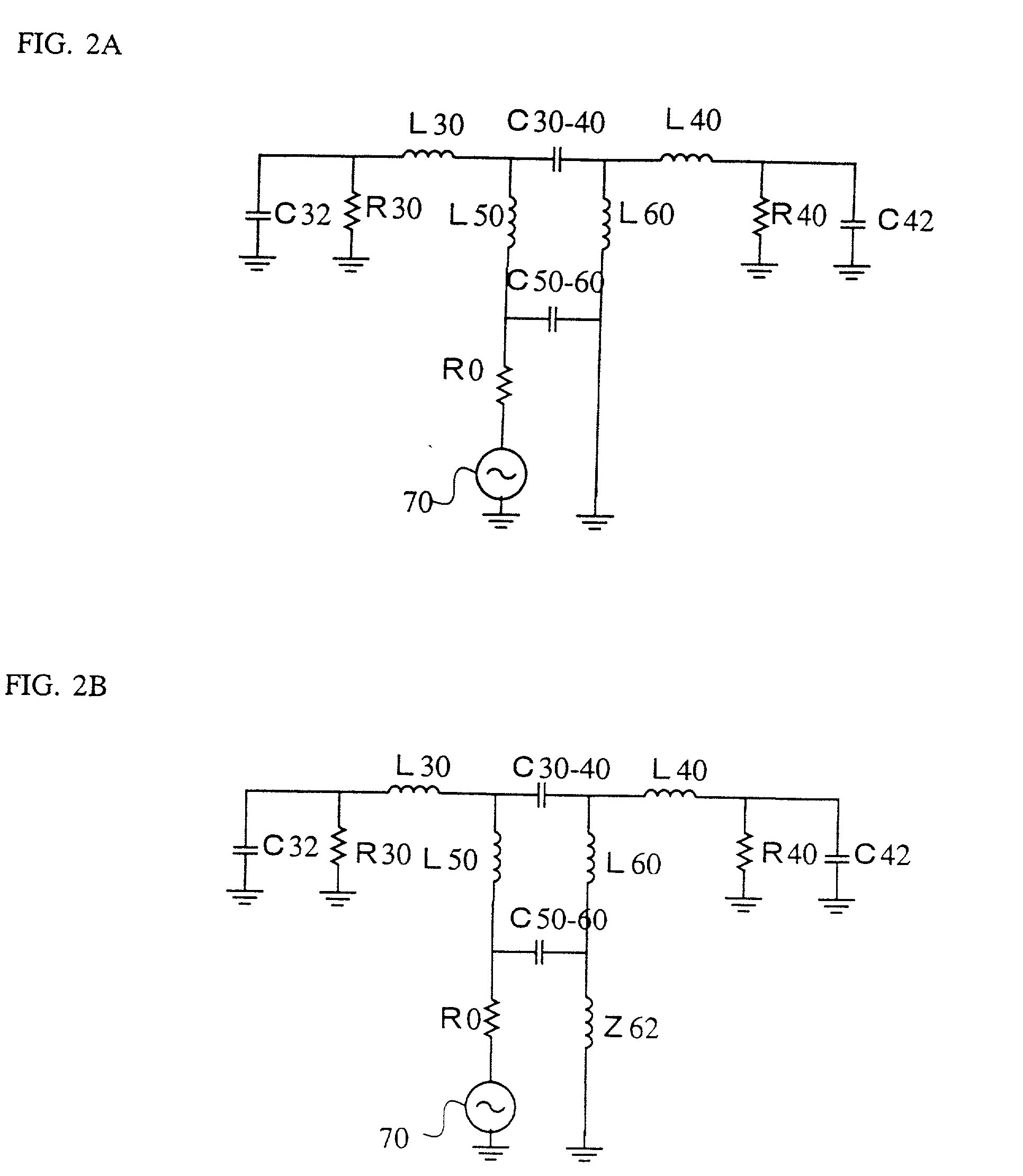

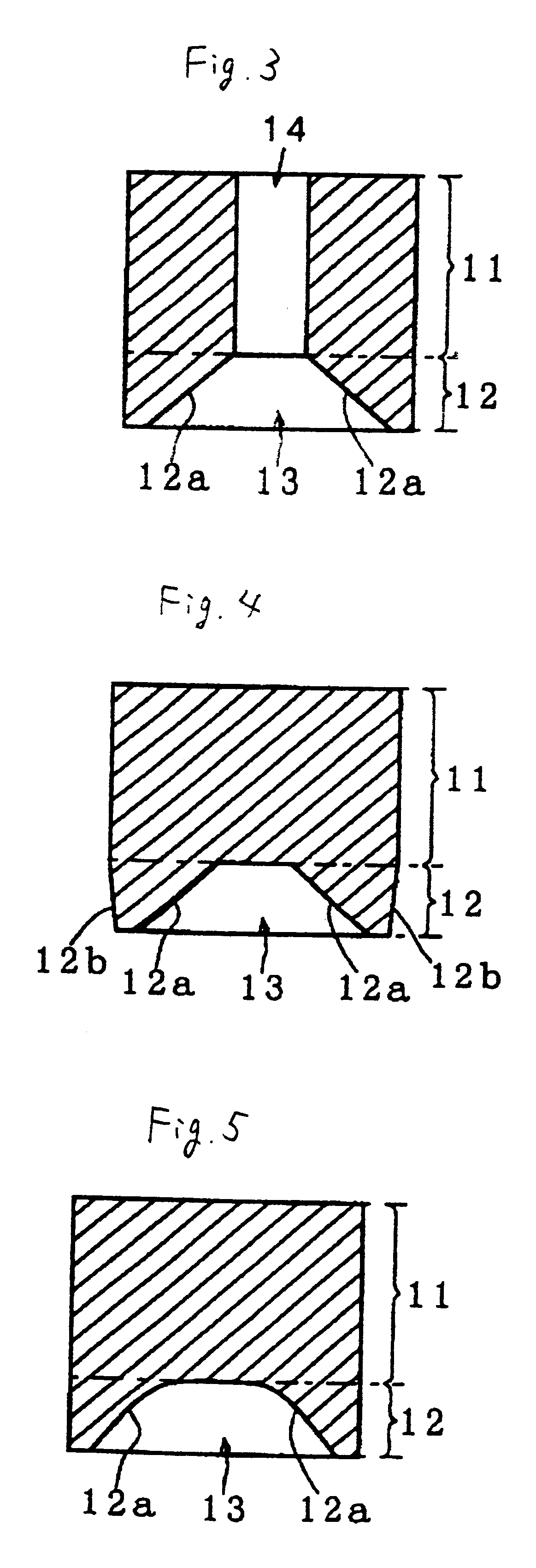

RF circuit component and RF circuit

ActiveUS20060022772A1Increase dielectric constantSufficient degree of couplingWaveguidesCoupling devicesPhysicsResonator

An RF circuit component according to the present invention includes a waveguide 1 and at least one resonator 2, which is arranged inside the waveguide 1. The resonator 2 includes at least one patterned conductor layer, which is parallel to a plane that crosses an H plane, and resonates at a lower frequency than a cutoff frequency, which is defined by the internal dielectric constant, shape and size of the waveguide 1, thereby letting an electromagnetic wave, having a lower frequency than the cutoff frequency, pass through the inside of the waveguide 1.

Owner:PANASONIC CORP

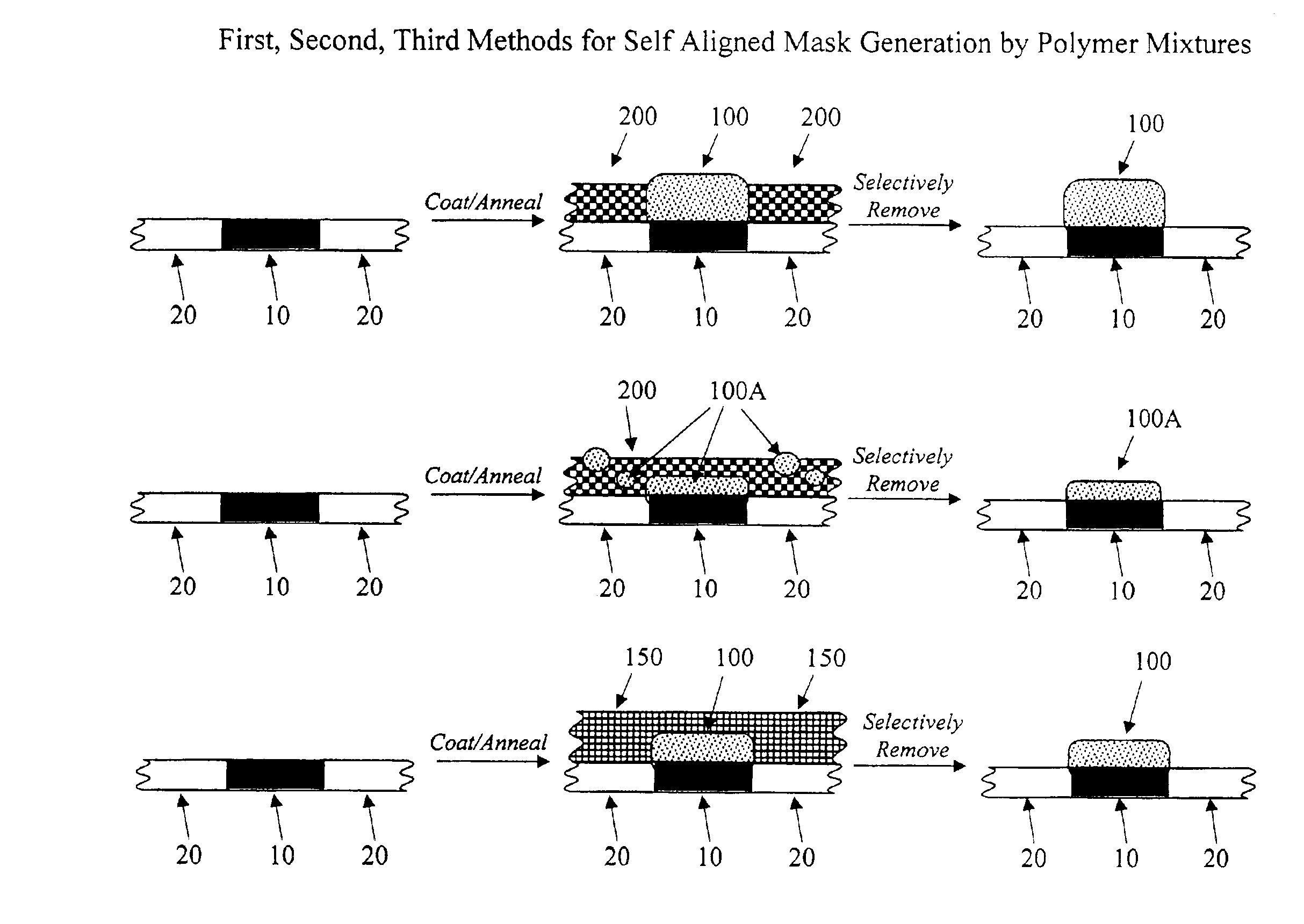

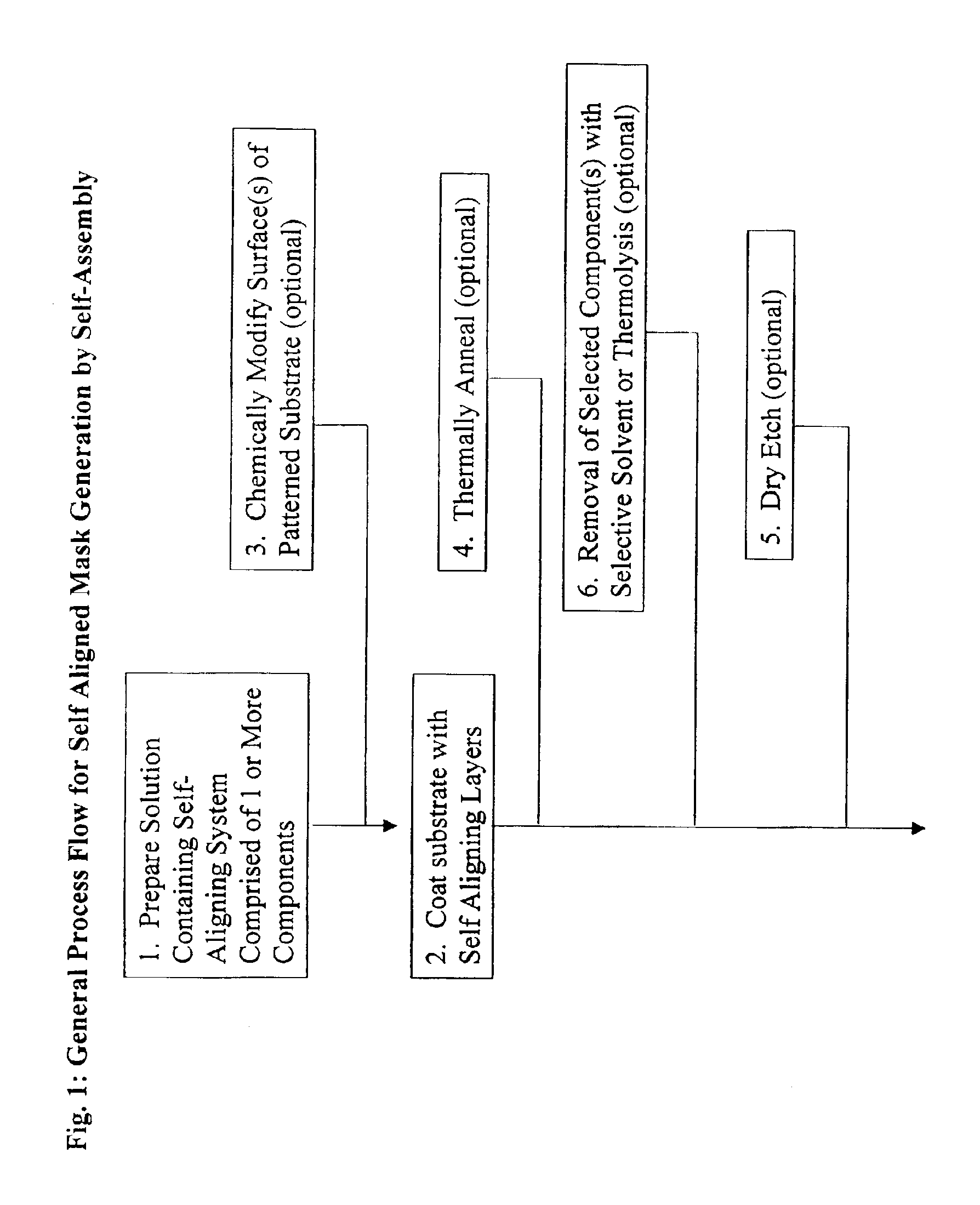

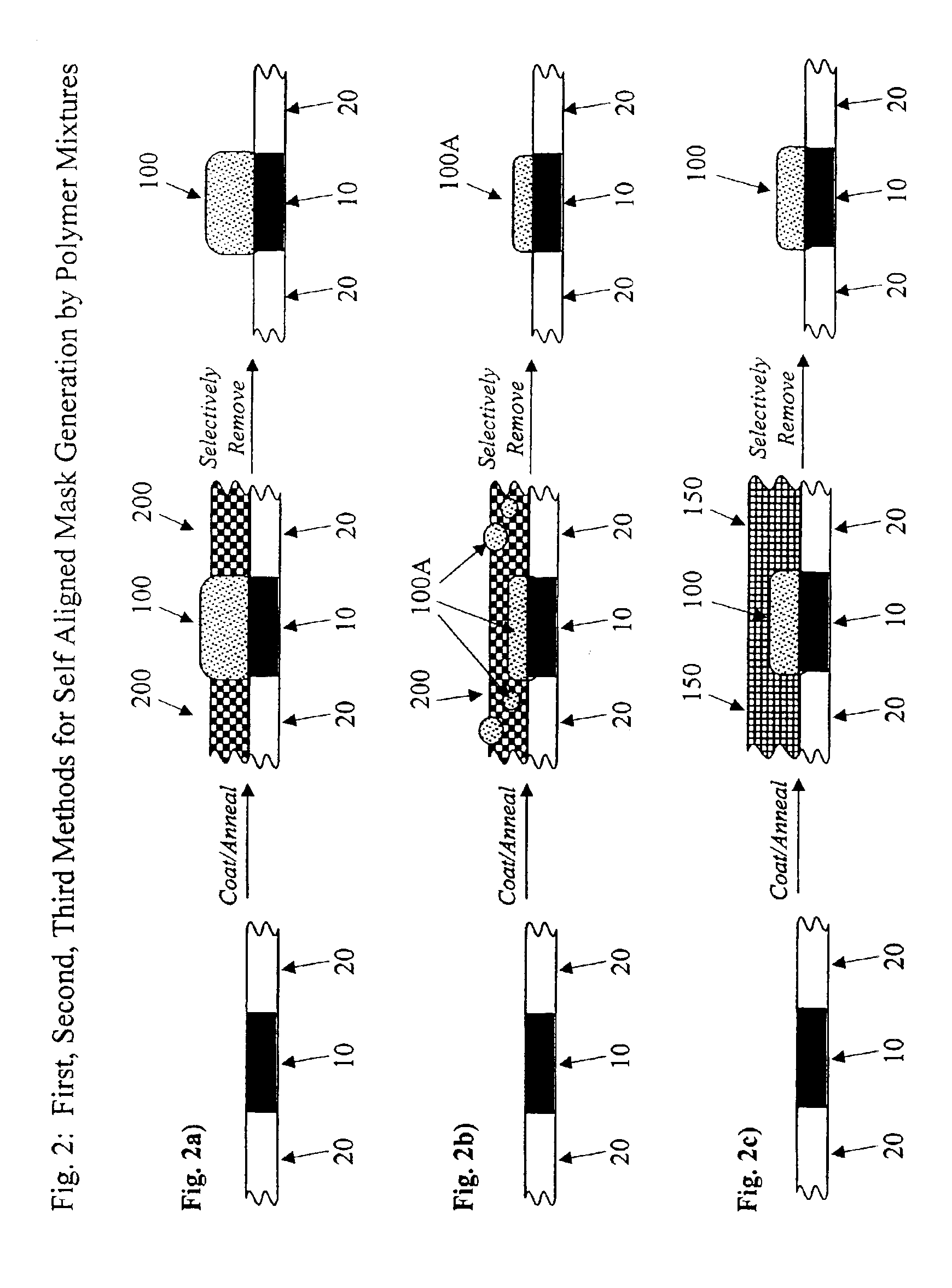

Nonlithographic method to produce self-aligned mask, articles produced by same and compositions for same

InactiveUS6911400B2Simple and robustSpeed maximizationLayered productsDecorative surface effectsAtomic compositionDielectric

A method for forming a self aligned pattern on an existing pattern on a substrate comprising applying a coating of a solution containing a masking material in a carrier, the masking material having an affinity for portions of the existing pattern; and allowing at least a portion of the masking material to preferentially assemble to the portions of the existing pattern. The pattern may be comprised of a first set of regions of the substrate having a first atomic composition and a second set of regions of the substrate having a second atomic composition different from the first composition. The first set of regions may include one or more metal elements and the second set of regions may include a dielectric. The first and second regions may be treated to have different surface properties. Structures made in accordance with the method. Compositions useful for practicing the method.

Owner:GLOBALFOUNDRIES INC

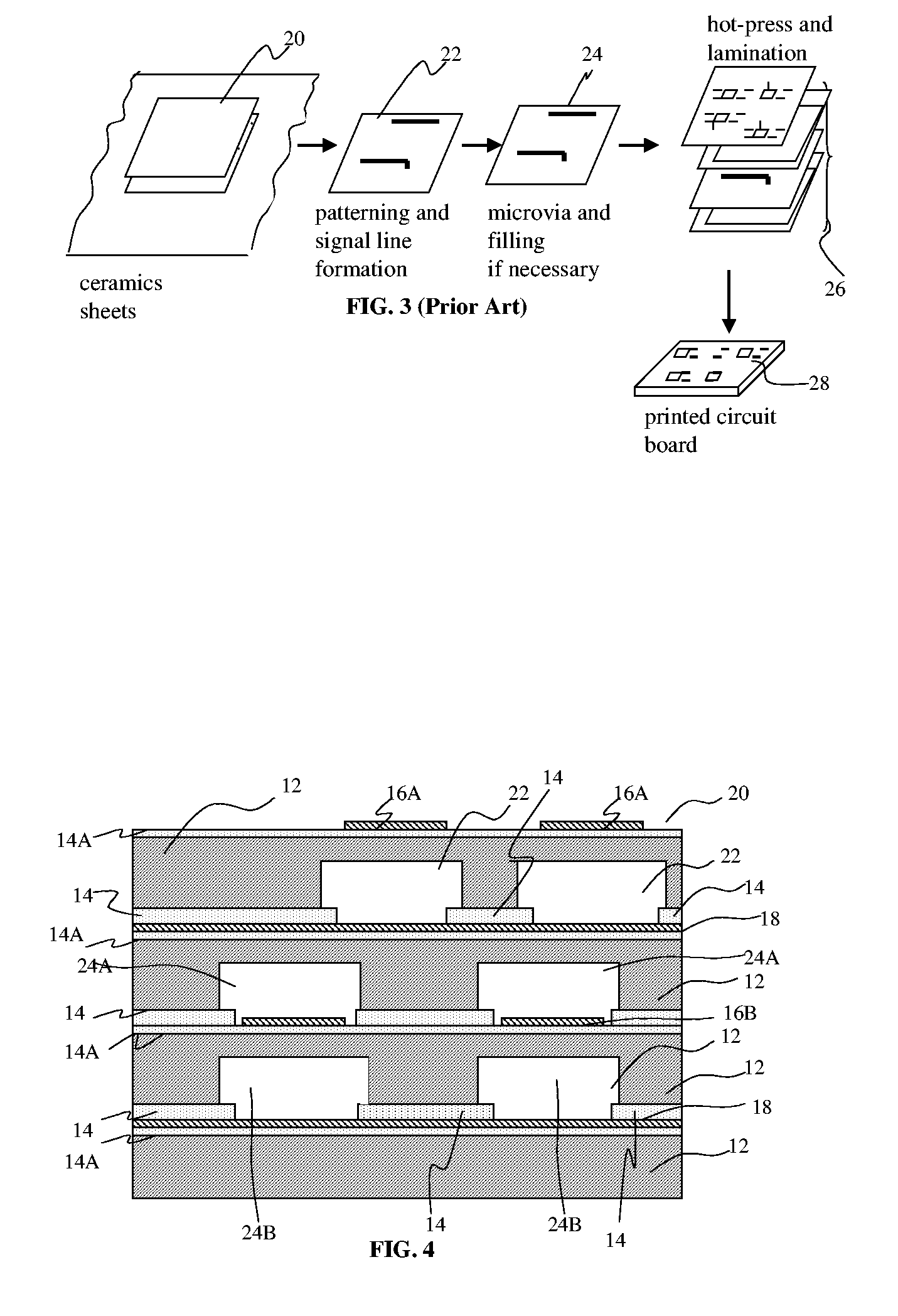

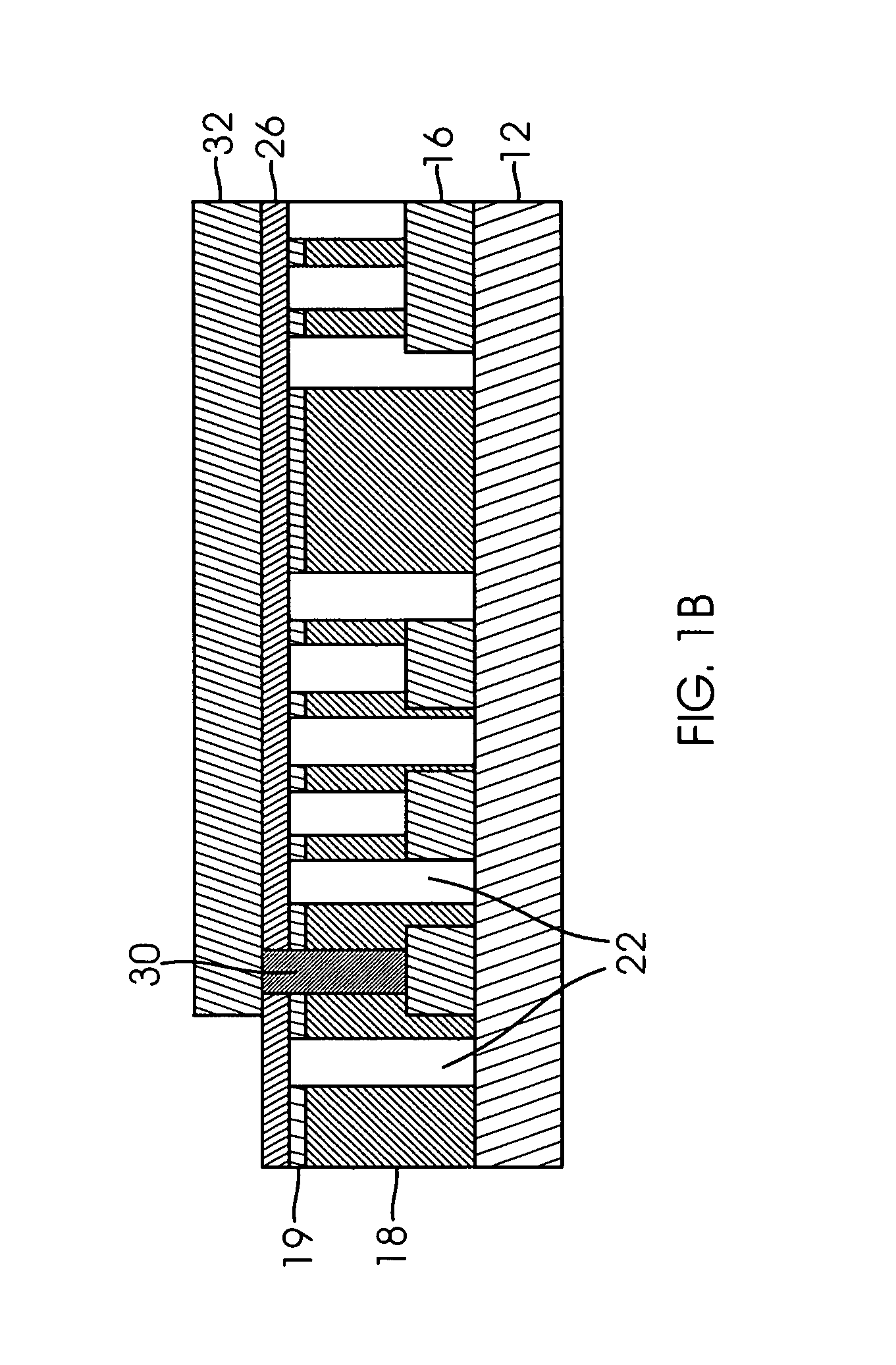

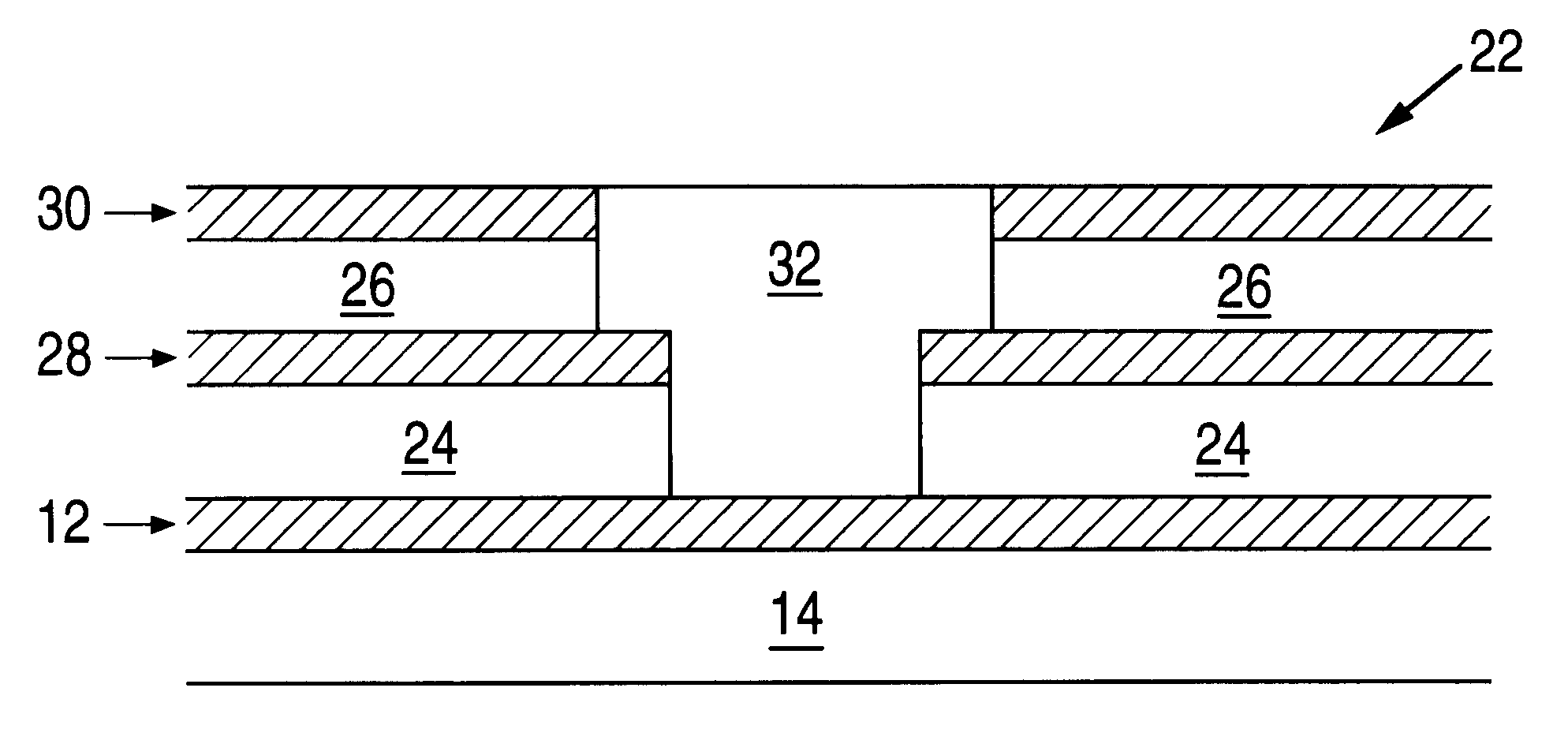

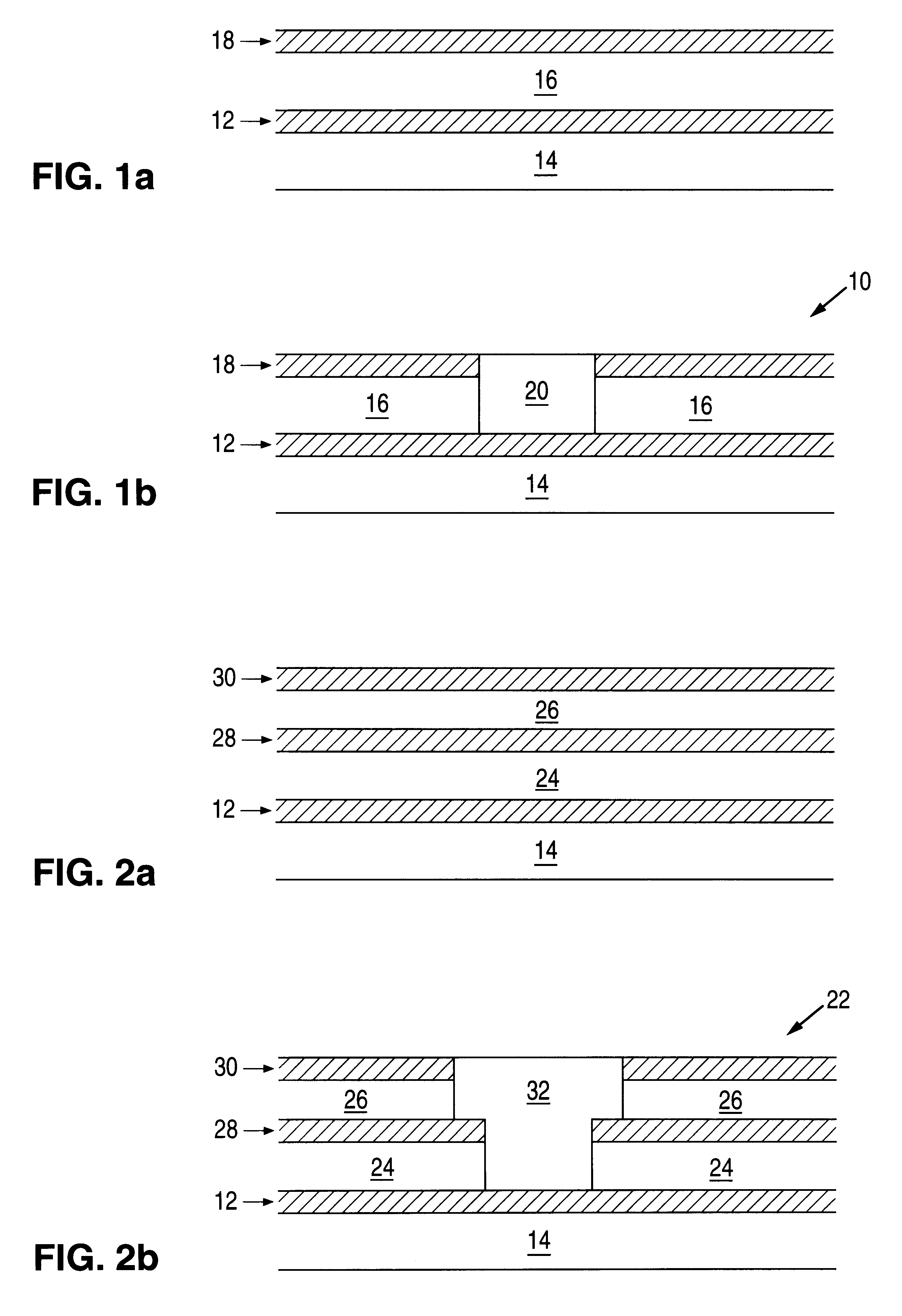

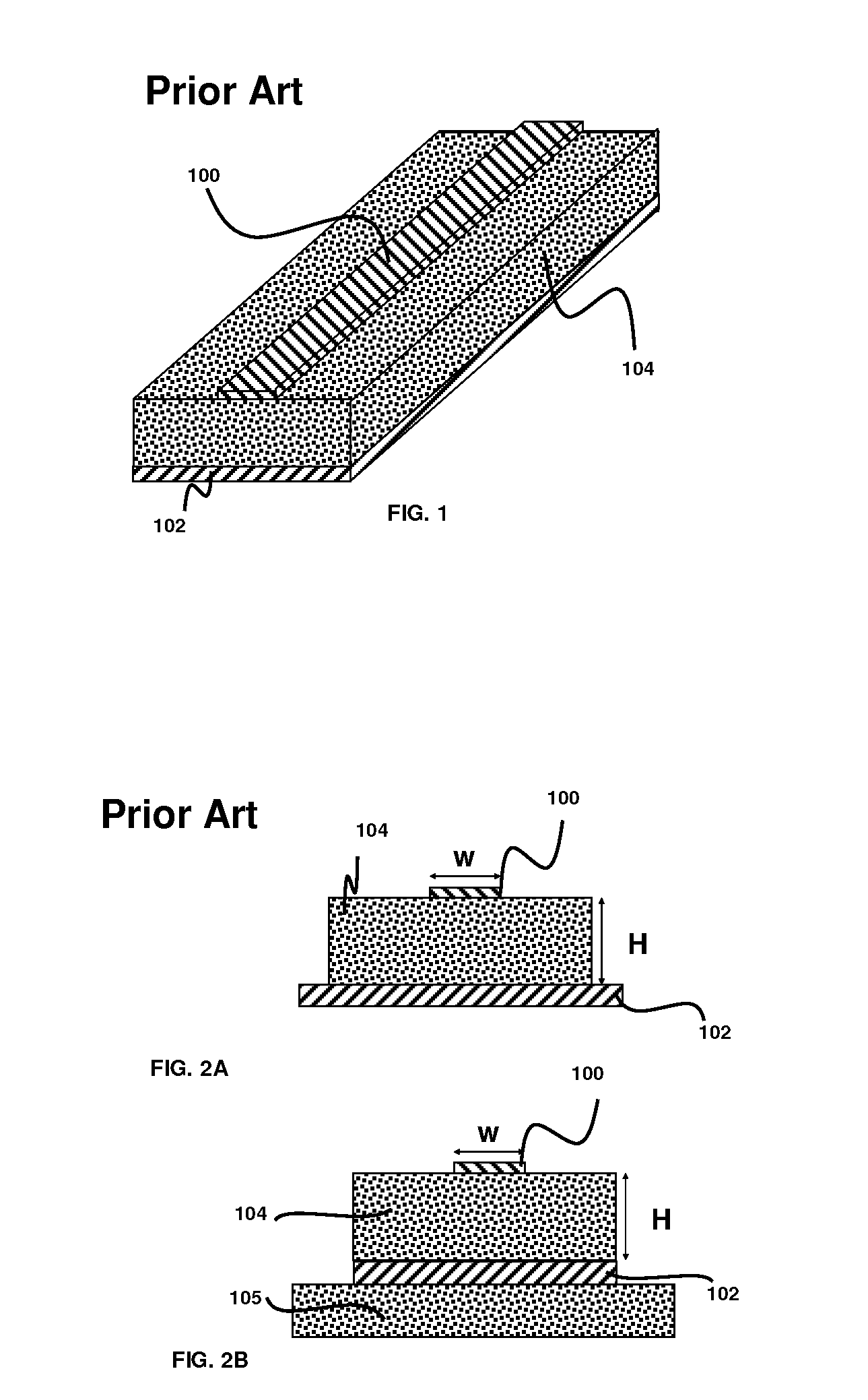

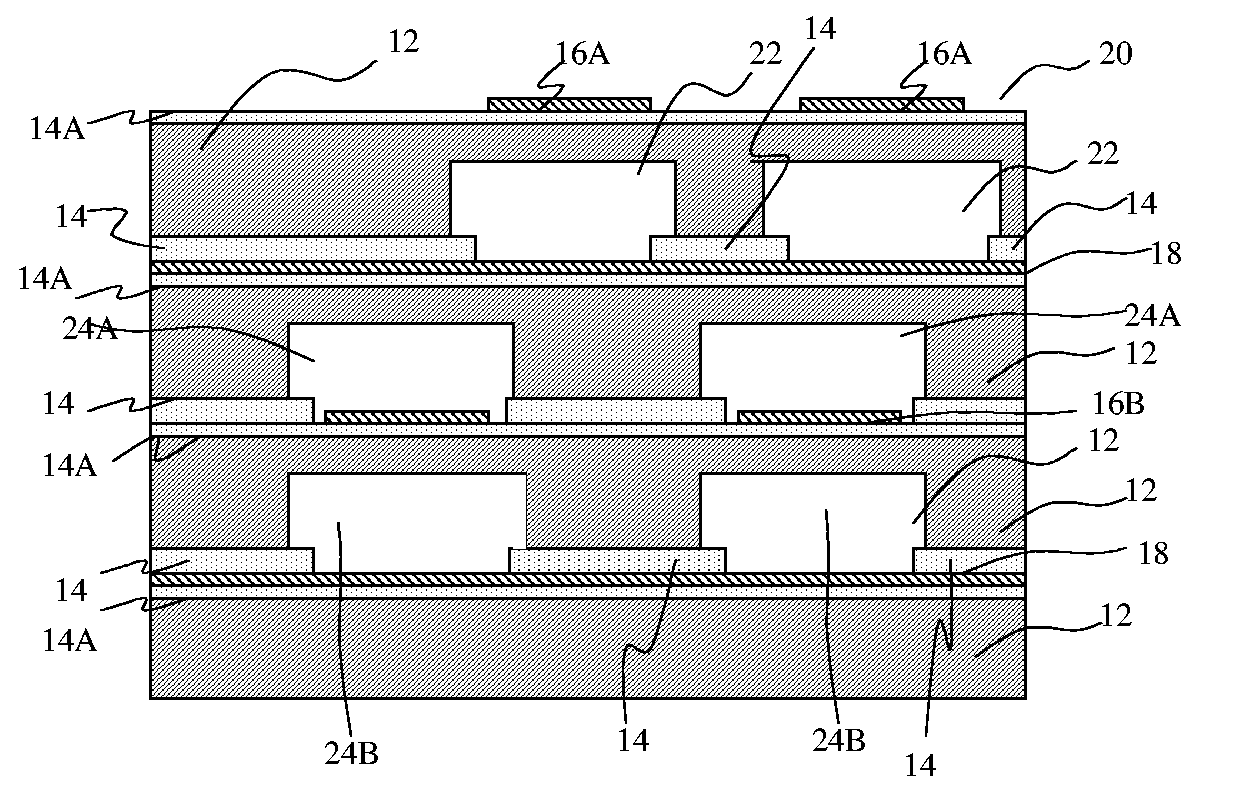

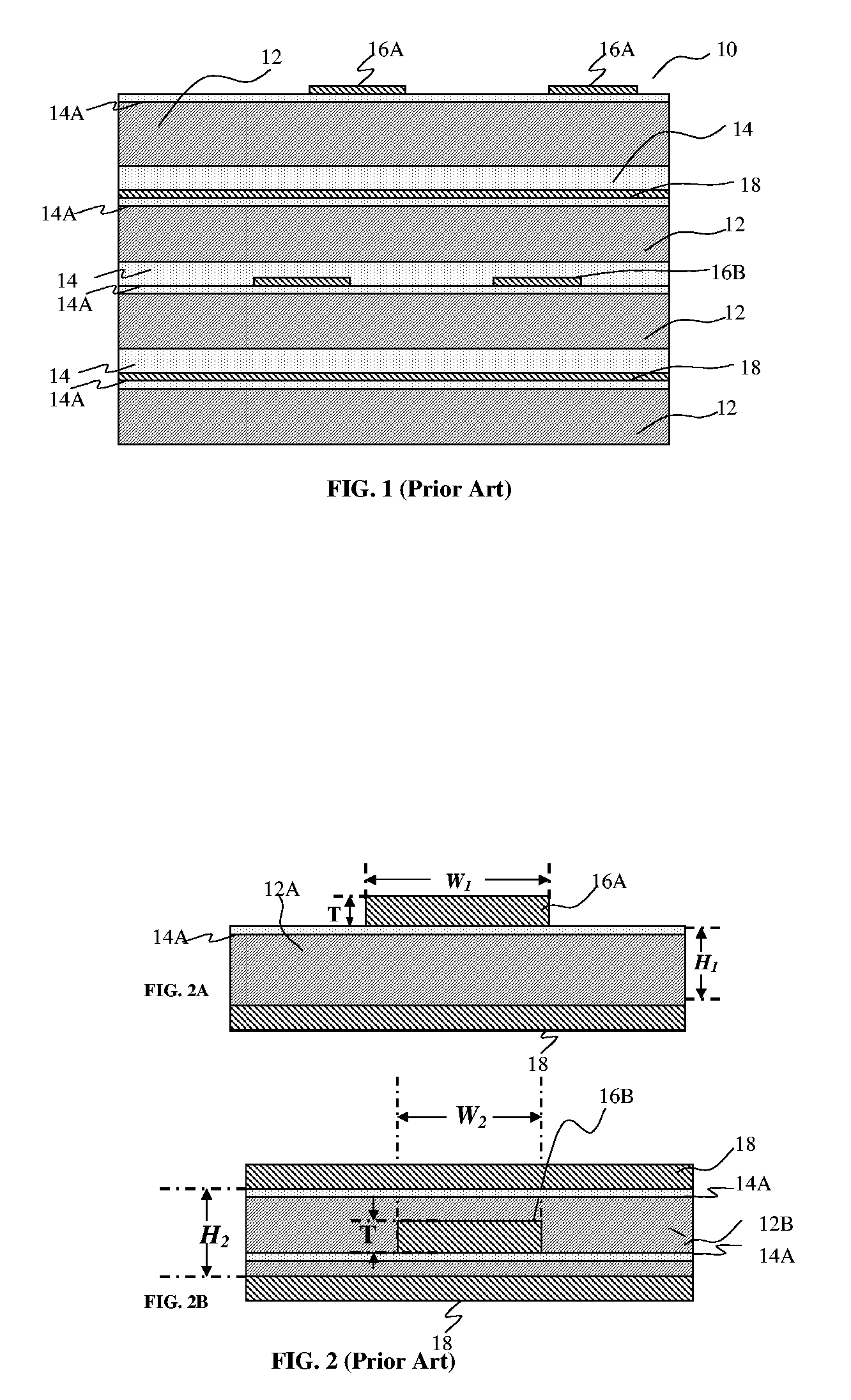

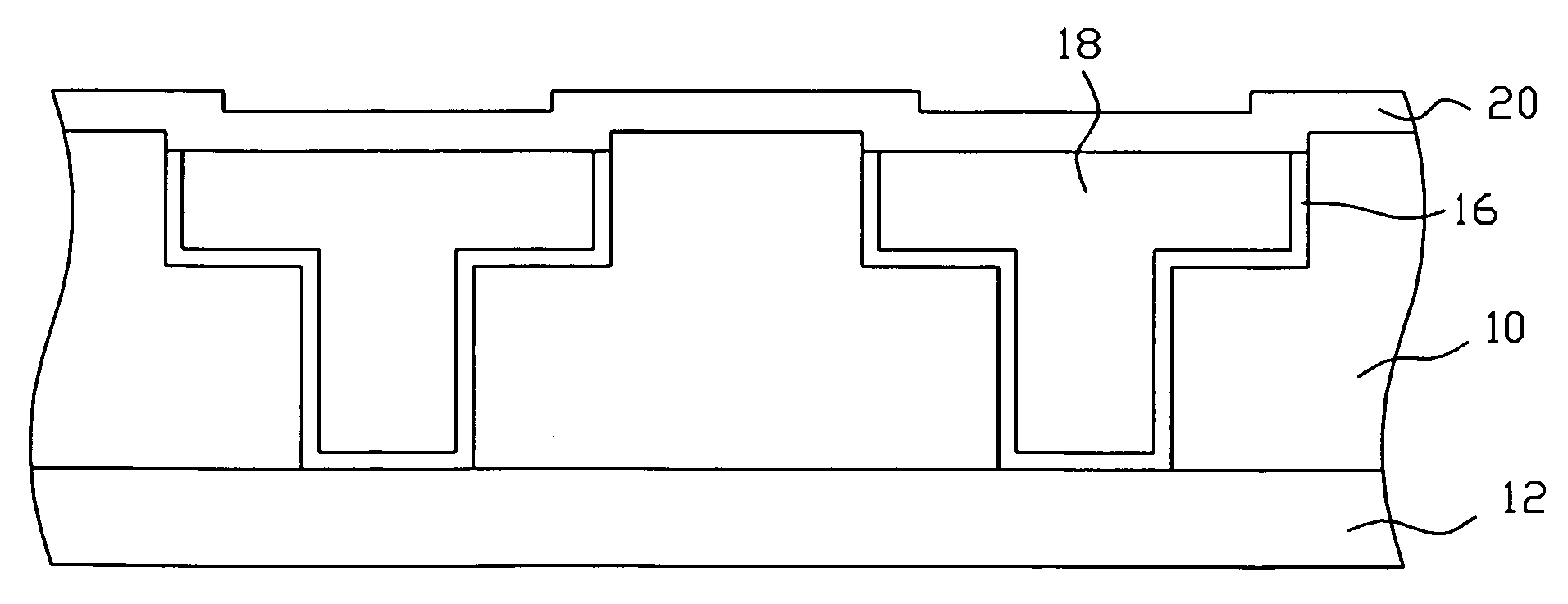

High-Speed Printed Circuit Boards (PCBs) and Manufacturing

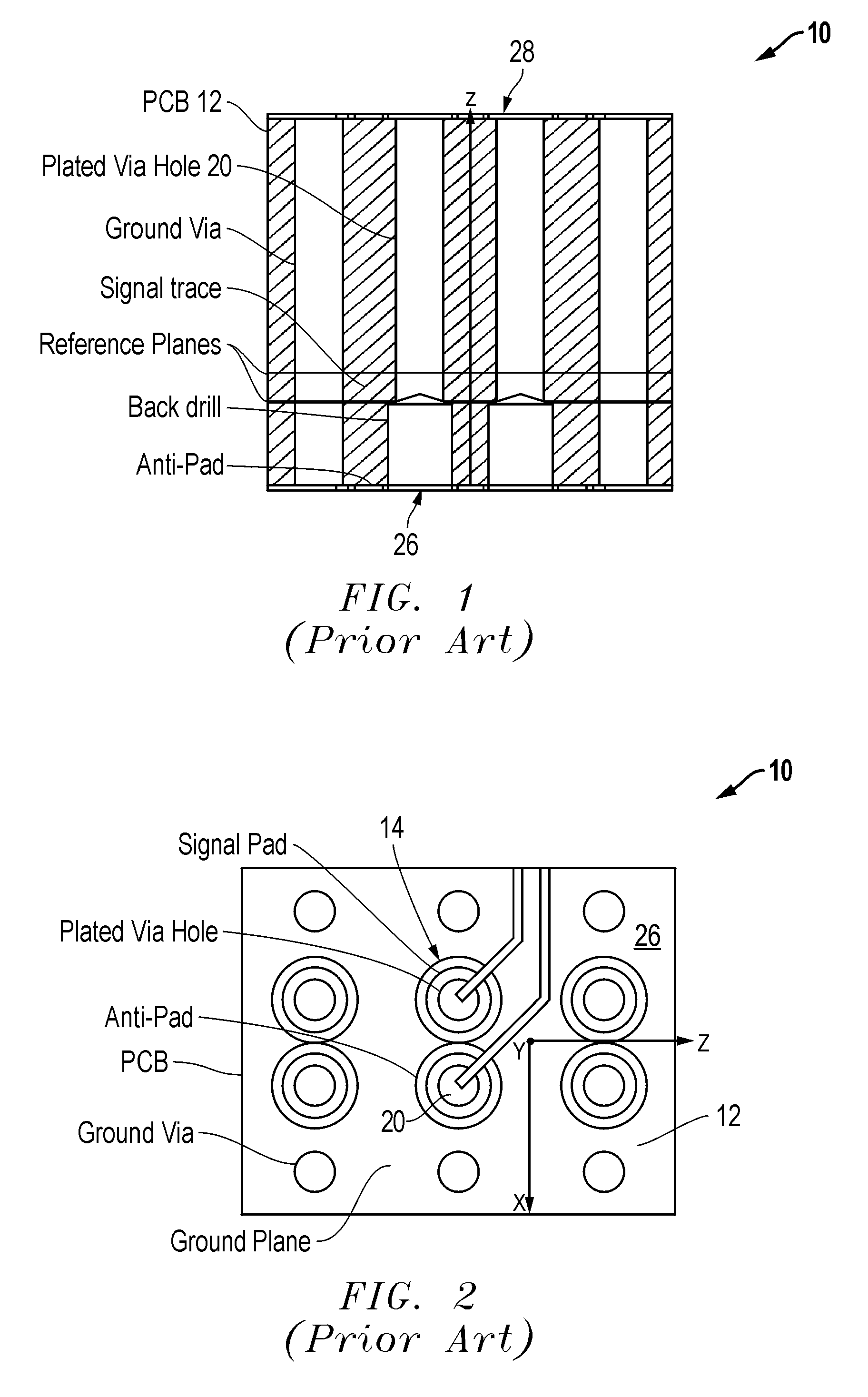

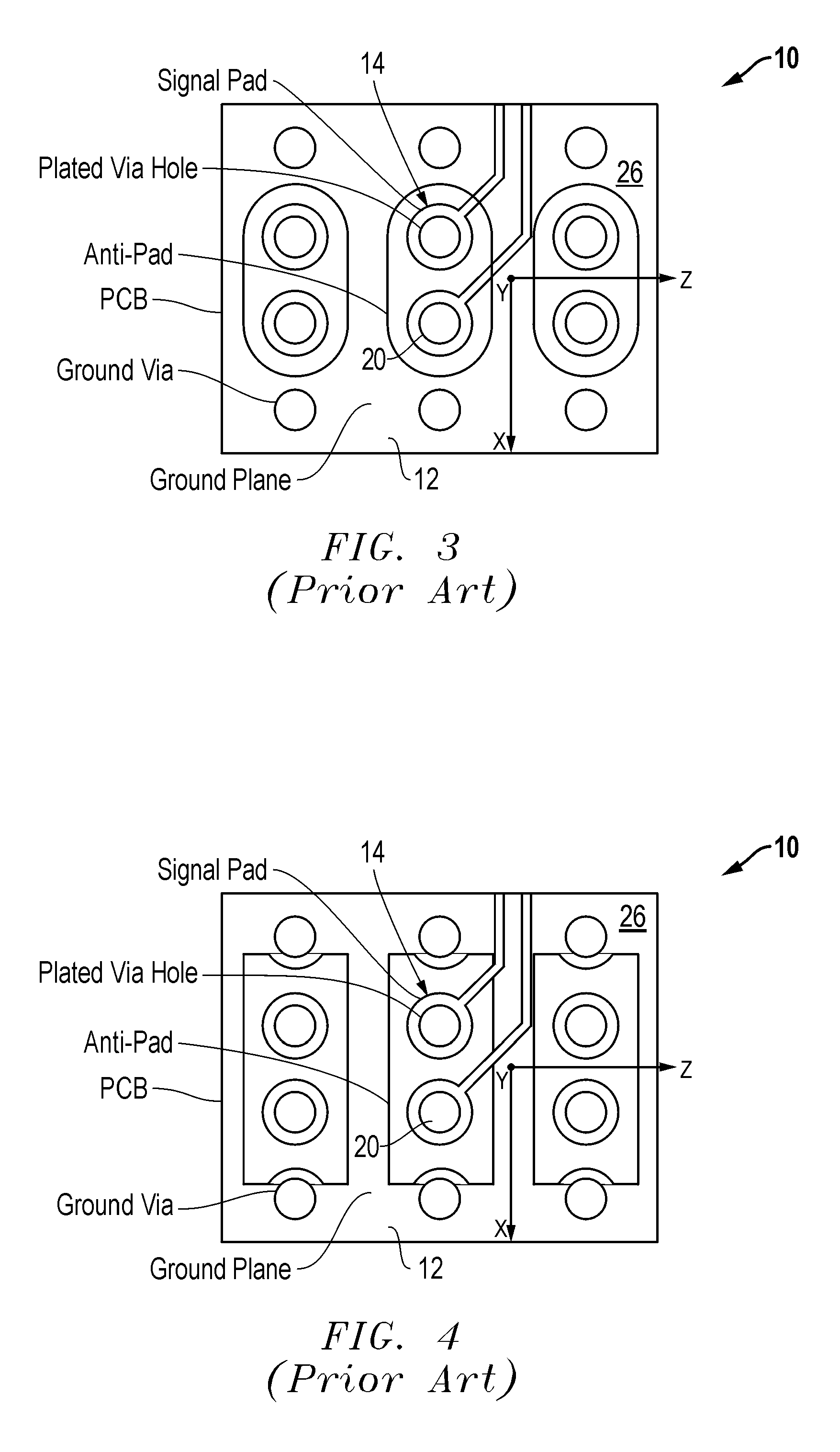

ActiveUS20060028305A1Reduce effective dielectric constant effective dielectricReduce effective dielectric effective dielectric lossMultiple-port networksHigh frequency circuit adaptationsDielectricEngineering

High speed printed circuit boards (PCBs) are disclosed comprising a dielectrics systems with the back-side trenches, prepregs, signal lines and ground-plans, wherein the signal line and ground-plan are located on the dielectrics. Using of the open trenches in the substrate help to reduce the microwave loss and dielectric constant and thus increasing the signal carrying speed of the interconnects. Thus, according to the present invention, it is possible to provide a simple high speed PCB using the conventional material and conventional PCB manufacturing which facilitates the design of circuits with controlled bandwidth based on the trench opening in the dielectrics, and affords excellent reliability. According to this present invention, high speed PCB with the interconnect system contains whole portion or portion of interconnects for high speed chips interconnects and that have have the dielectric system with opened trench or slot to reduce the microwave loss.

Owner:BANPIL PHOTONICS

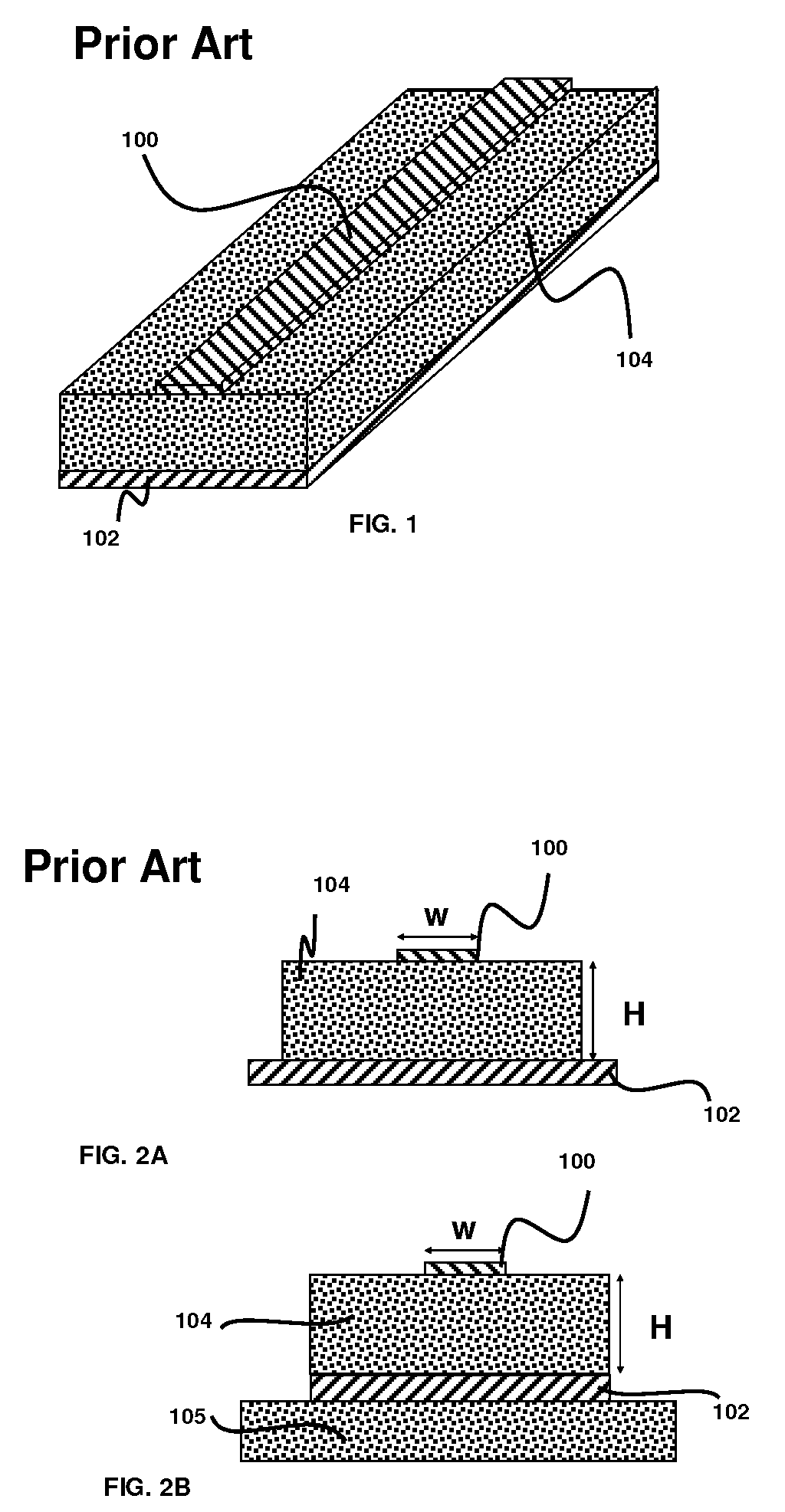

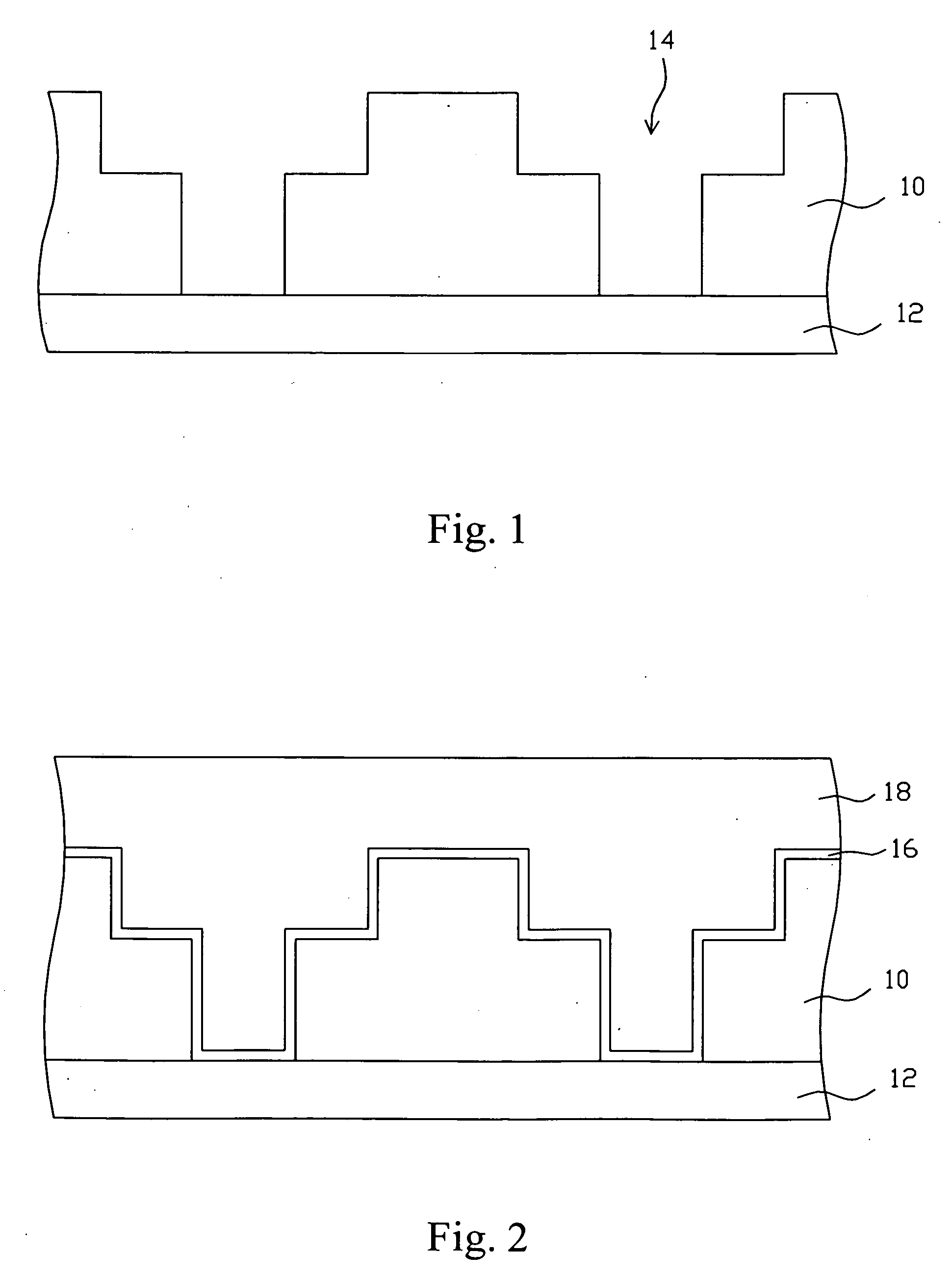

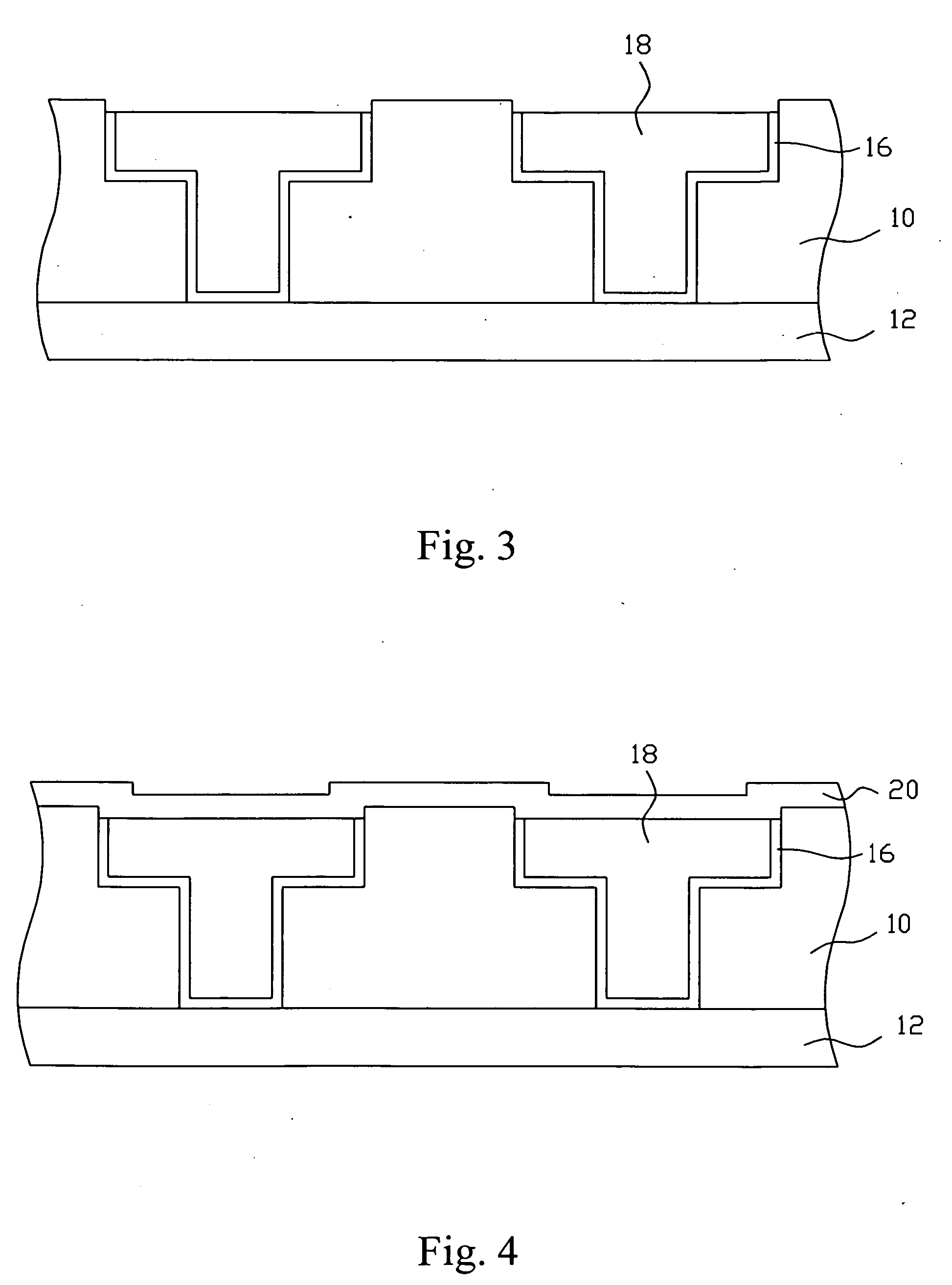

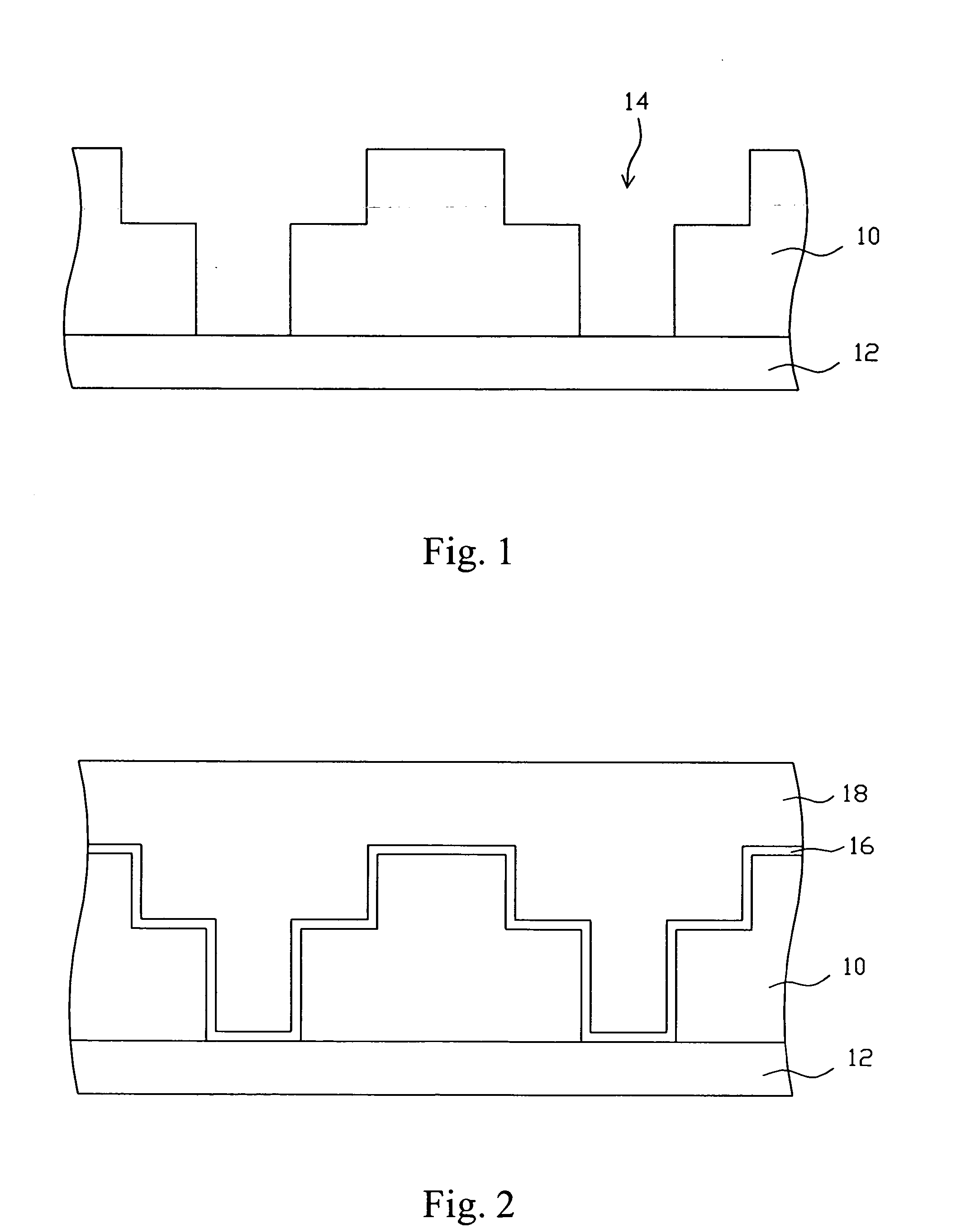

Air void via tuning

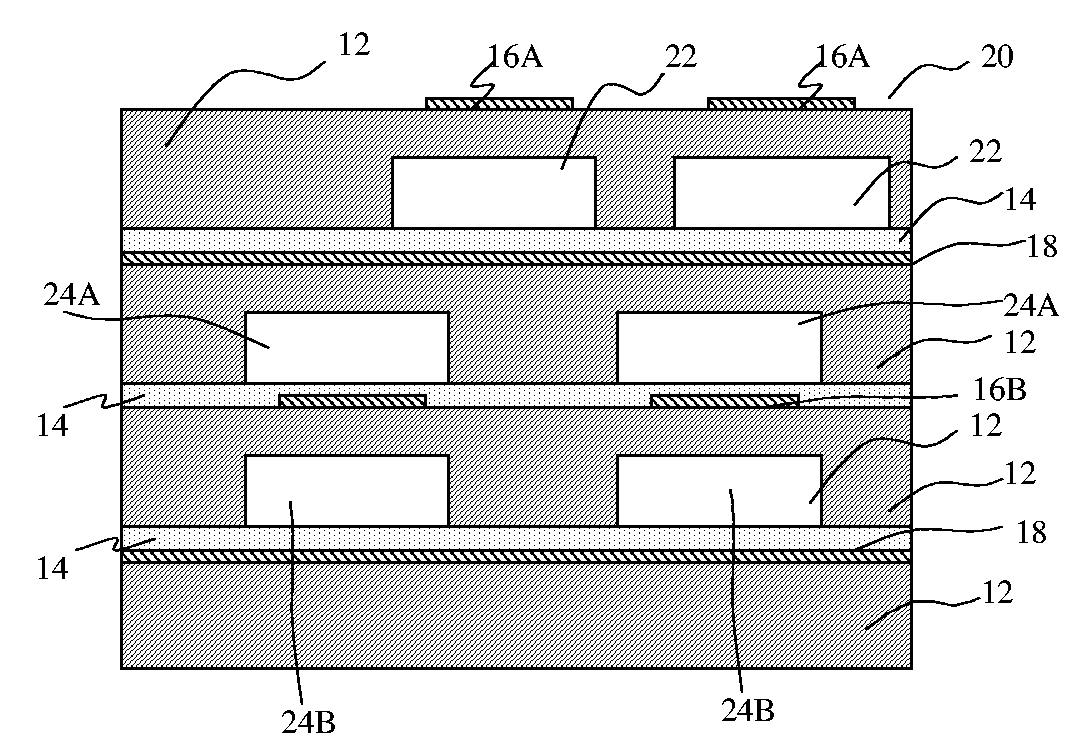

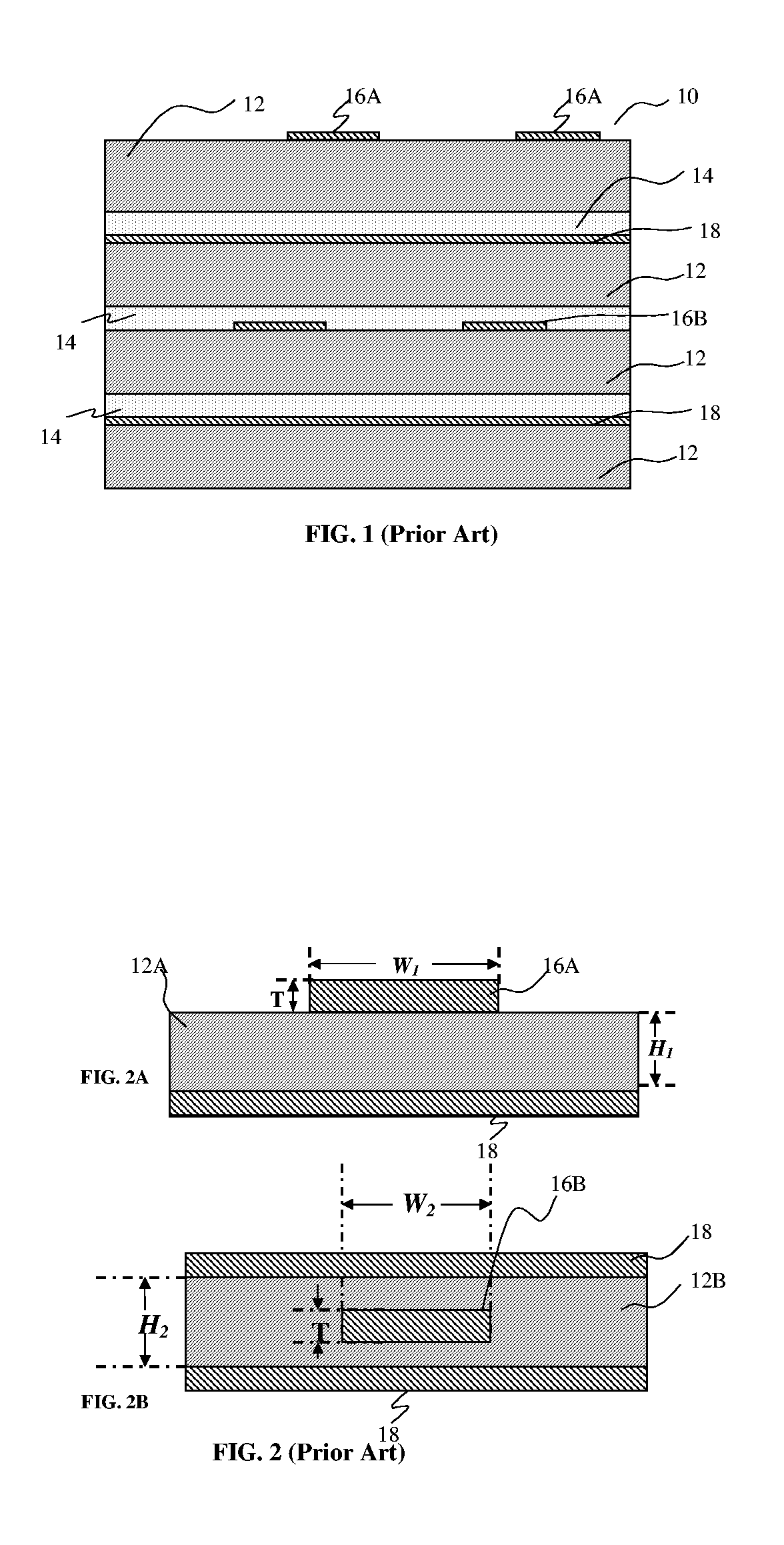

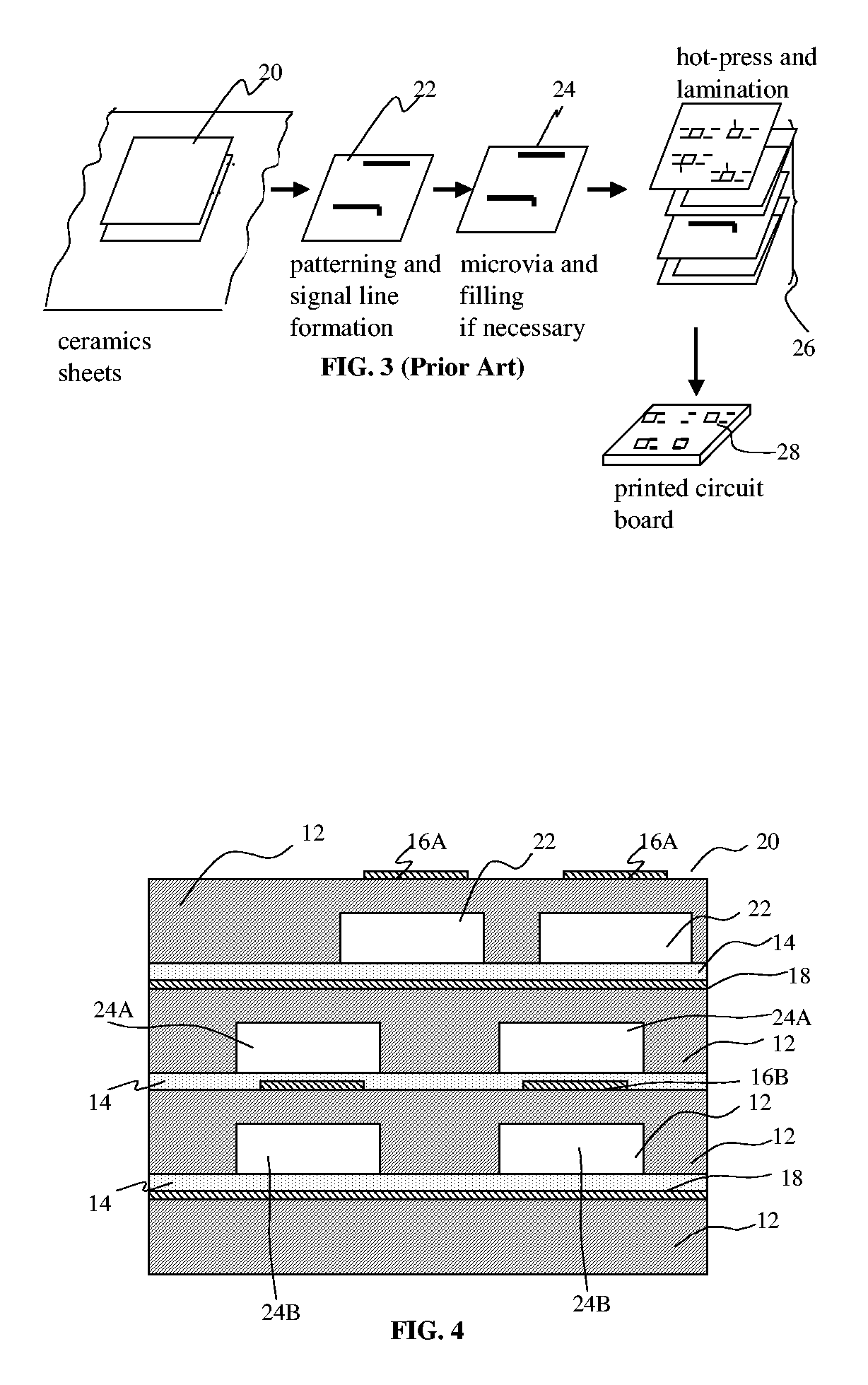

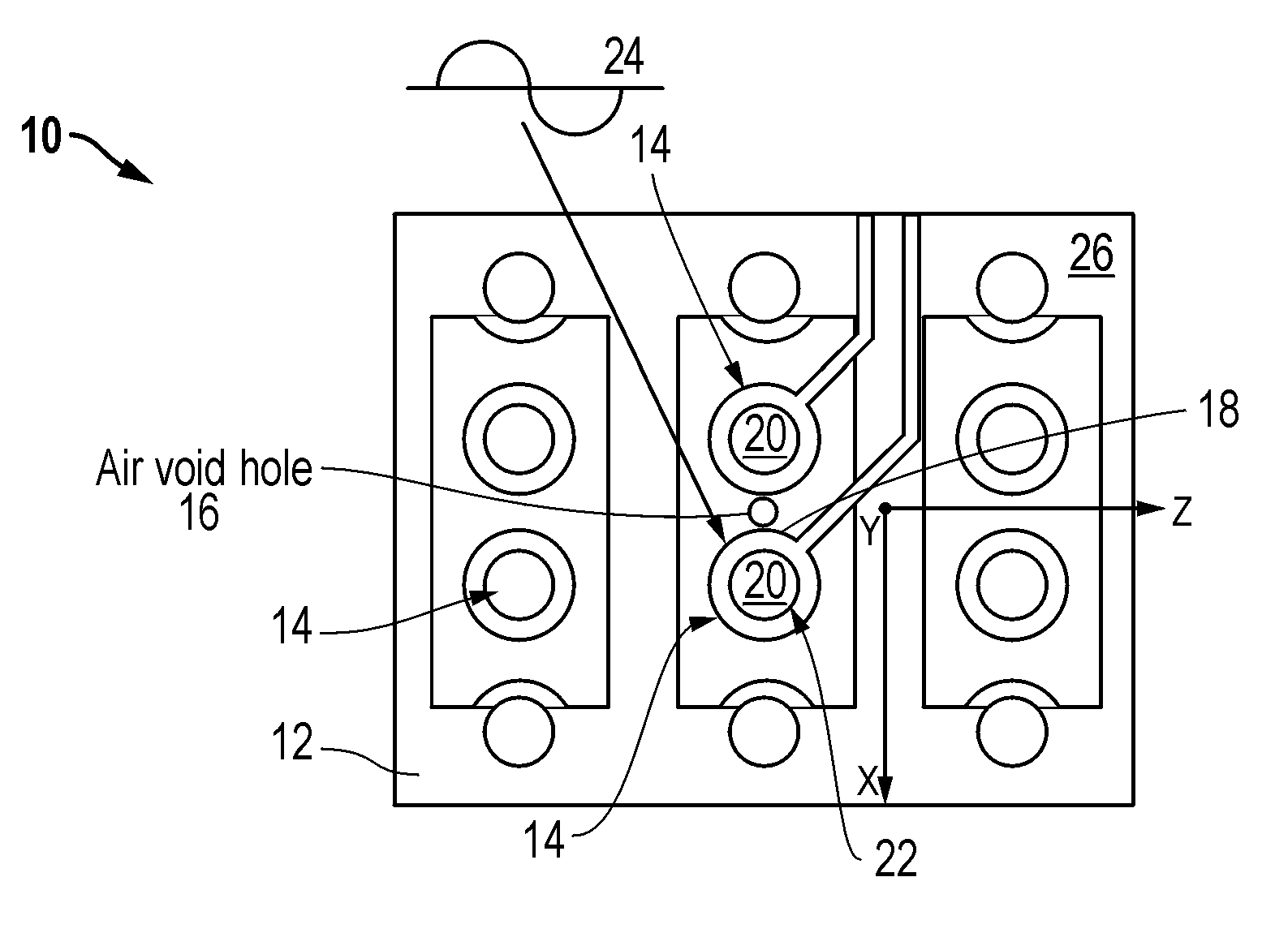

InactiveUS20060185890A1Improves main contributory factorImproves the main contributory factorsCross-talk/noise/interference reductionPrinted circuit aspectsElectromagnetic couplingEngineering

A wiring board (10) having reduced electromagnetic coupling between electronic devices includes a base board (12) that is adaptable to receive at least one electronic component (14) mounted on the base board (12). At least one hole or void (16) is formed in the base board (12). The hole (16) is separated from the selected electronic component (14) to be isolated against undesired electromagnetic radiation by a portion (18) of the base board (12).

Owner:SIMCLAR INTERCONNECT TECH

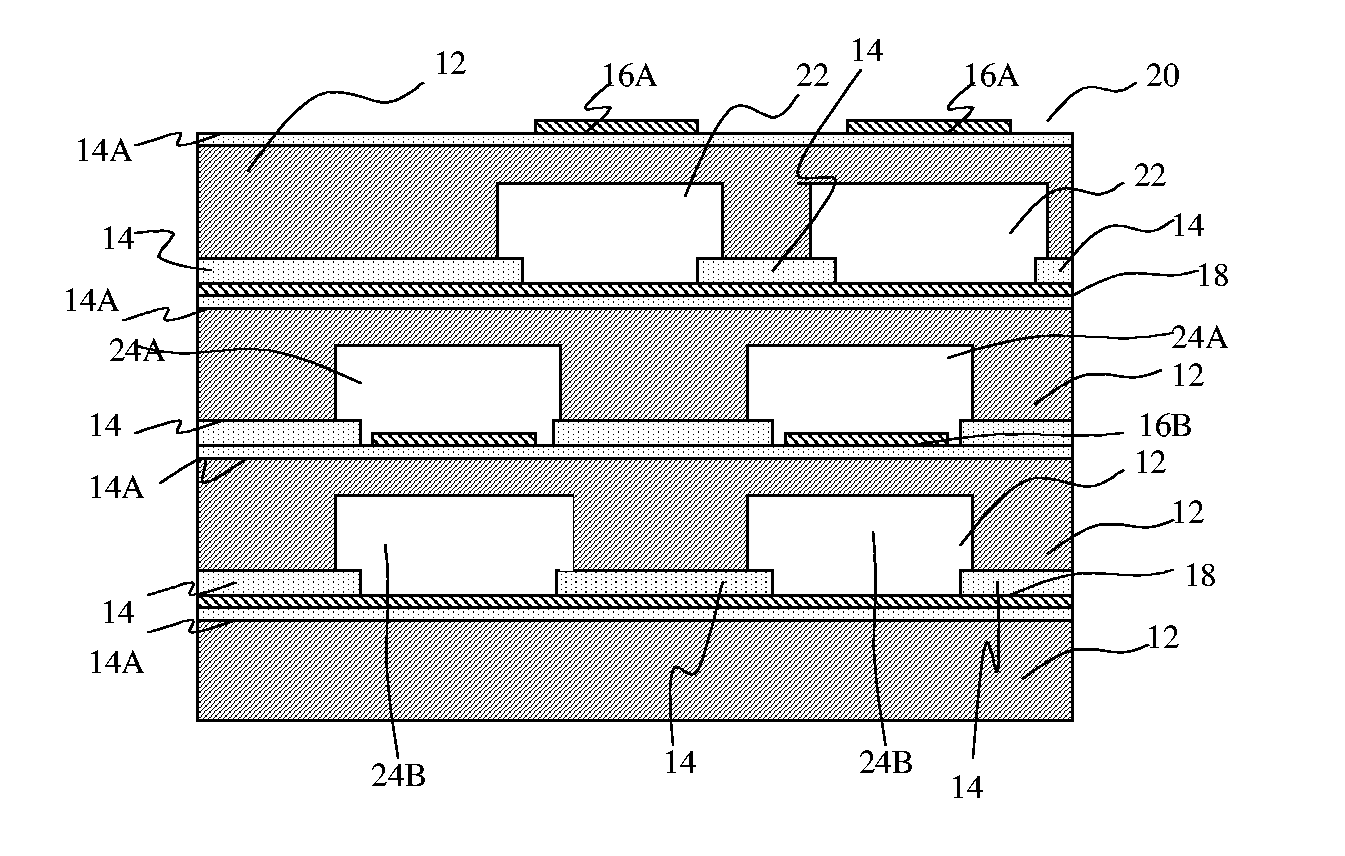

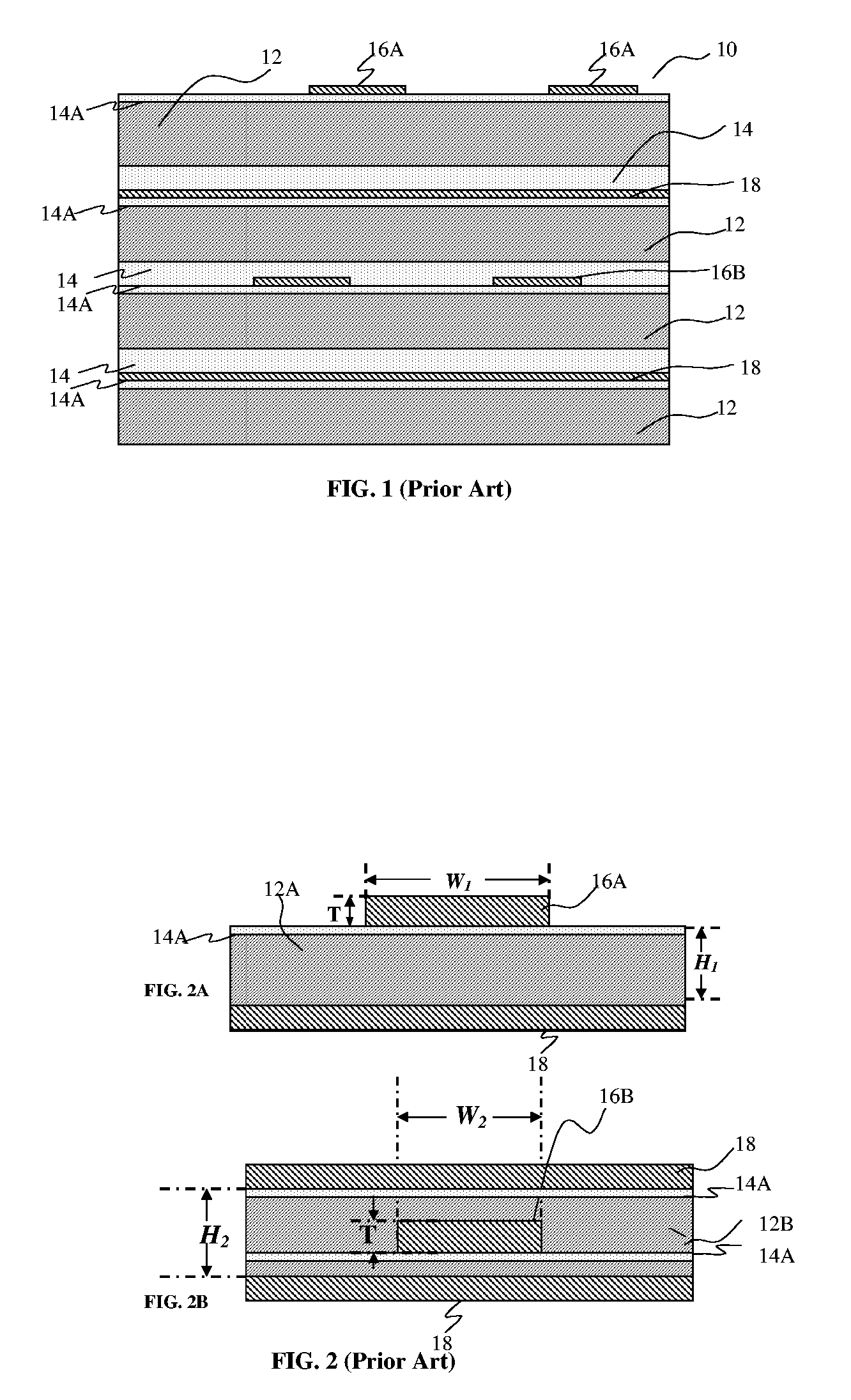

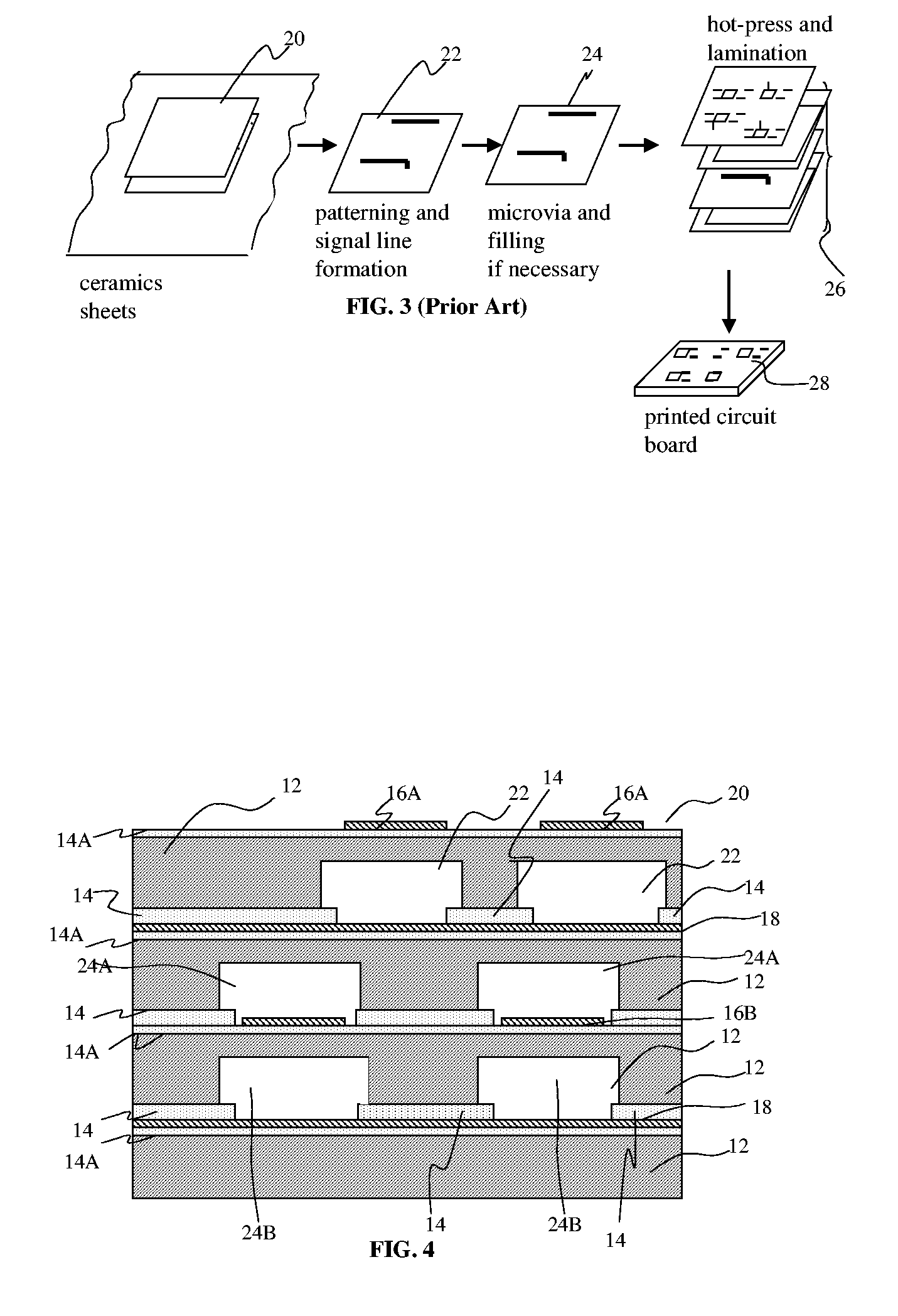

High-speed flex printed circuit and method of manufacturing

ActiveUS7663064B2Reduce effective dielectric constant and effective dielectric lossHigh bandwidthPrinted circuit assemblingPrinted circuit aspectsElectricityMicrowave

Multilayer high speed flex printed circuit boards (FLEX-PCBs) are disclosed including a dielectrics systems with the back-side trenches, adhesives, signal lines and ground planes, wherein the signal line and ground plane lane are located on the dielectrics. Using of the open trenches in the substrate help to reduce the microwave loss and dielectric constant and thus increasing the signal carrying speed of the interconnects. Thus, according to the present invention, it is possible to provide a simply constructed multiplayer high speed FLEX-PCB using the conventional material and conventional FLEX-PCB manufacturing which facilitates the design of circuits with controlled bandwidth based on the trench opening in the dielectrics, and affords excellent connection reliability. As the effective dielectric constant is reduced, the signal width is required to make wider or the dielectric thickness is required to make thinner keeping fixed characteristics impedance. The fundamental techniques disclosed here can also be used for high-speed packaging.

Owner:BANPIL PHOTONICS

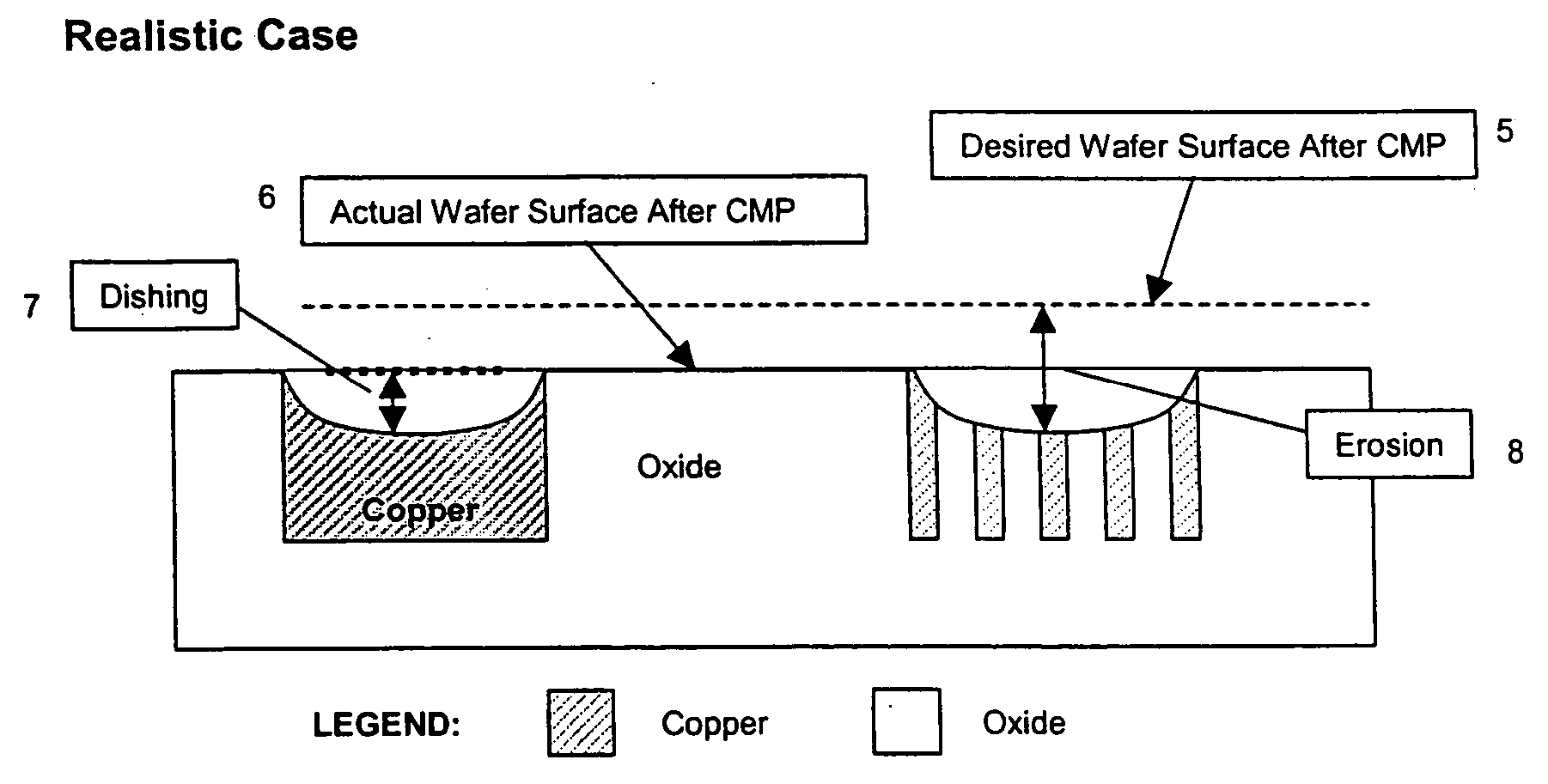

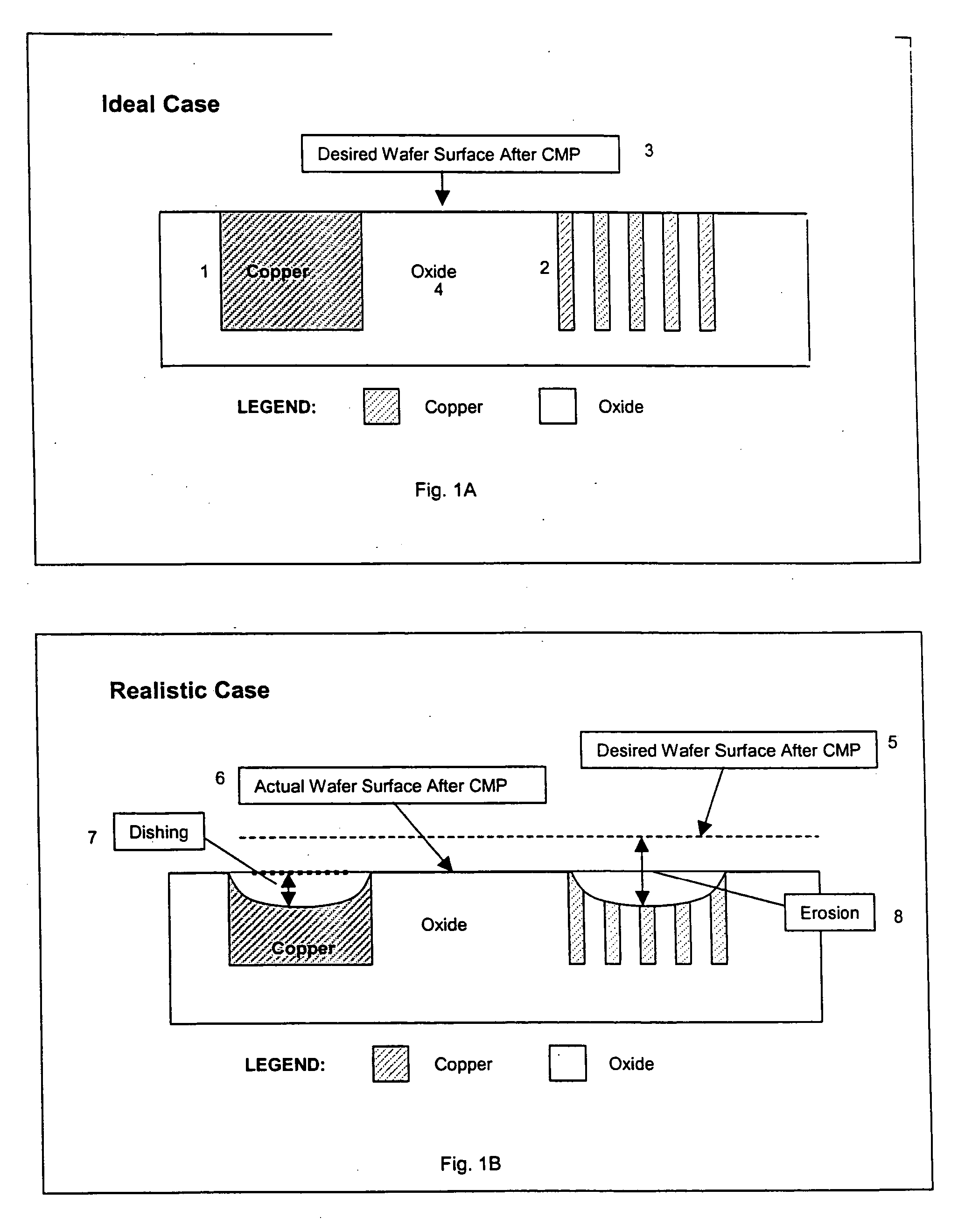

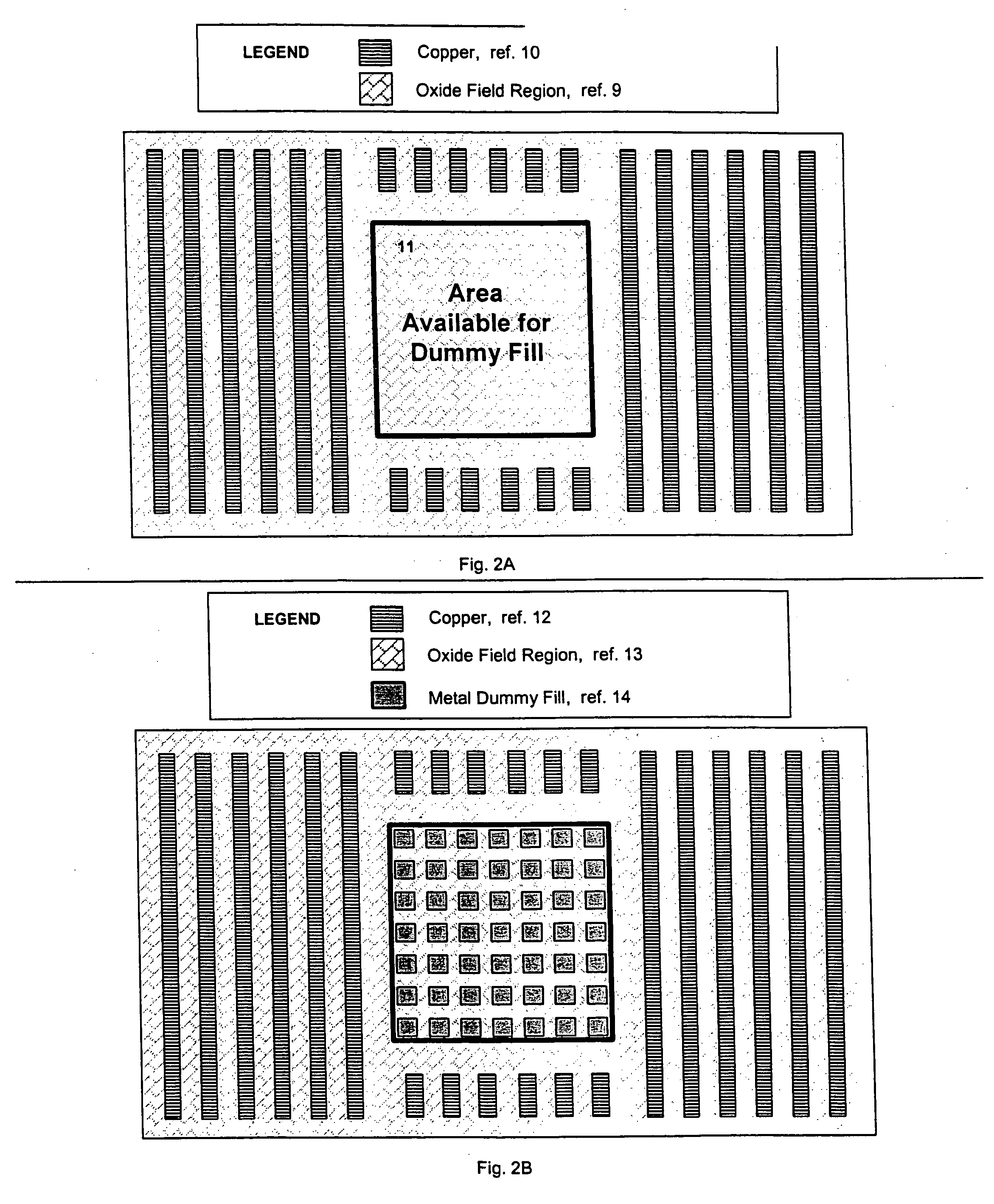

Dummy fill for integrated circuits

InactiveUS20050051809A1Speed up the processHigh densitySemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit manufacturingIntegrated circuit layout

A method and system are described to reduce process variation as a result of the electrochemical deposition (ECD), also referred to as electrochemical plating (ECP), and chemical mechanical polishing (CMP) processing of films in integrated circuit manufacturing processes. The described methods use process variation and electrical impact to direct the insertion of dummy fill into an integrated circuit.

Owner:CADENCE DESIGN SYST INC

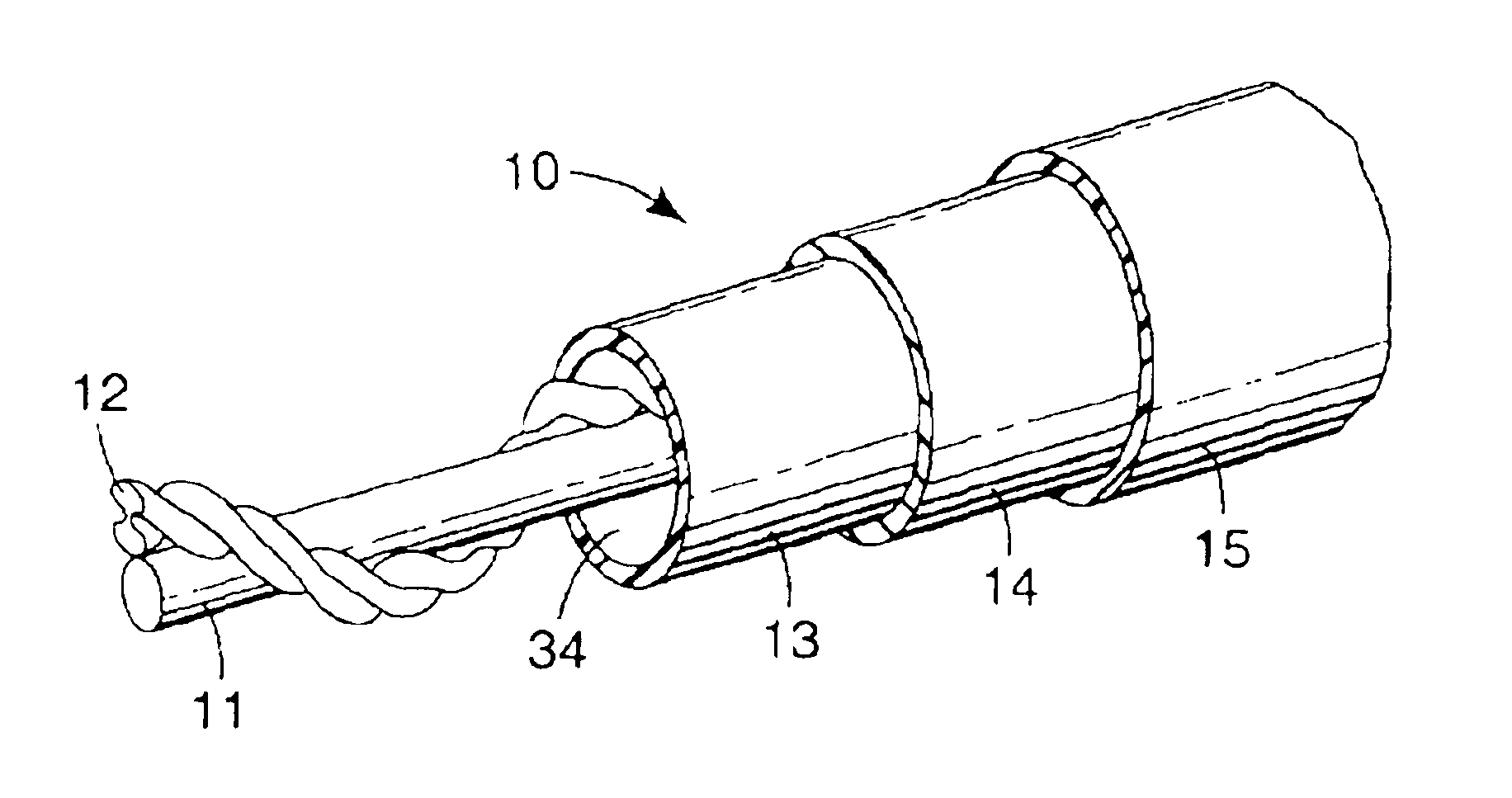

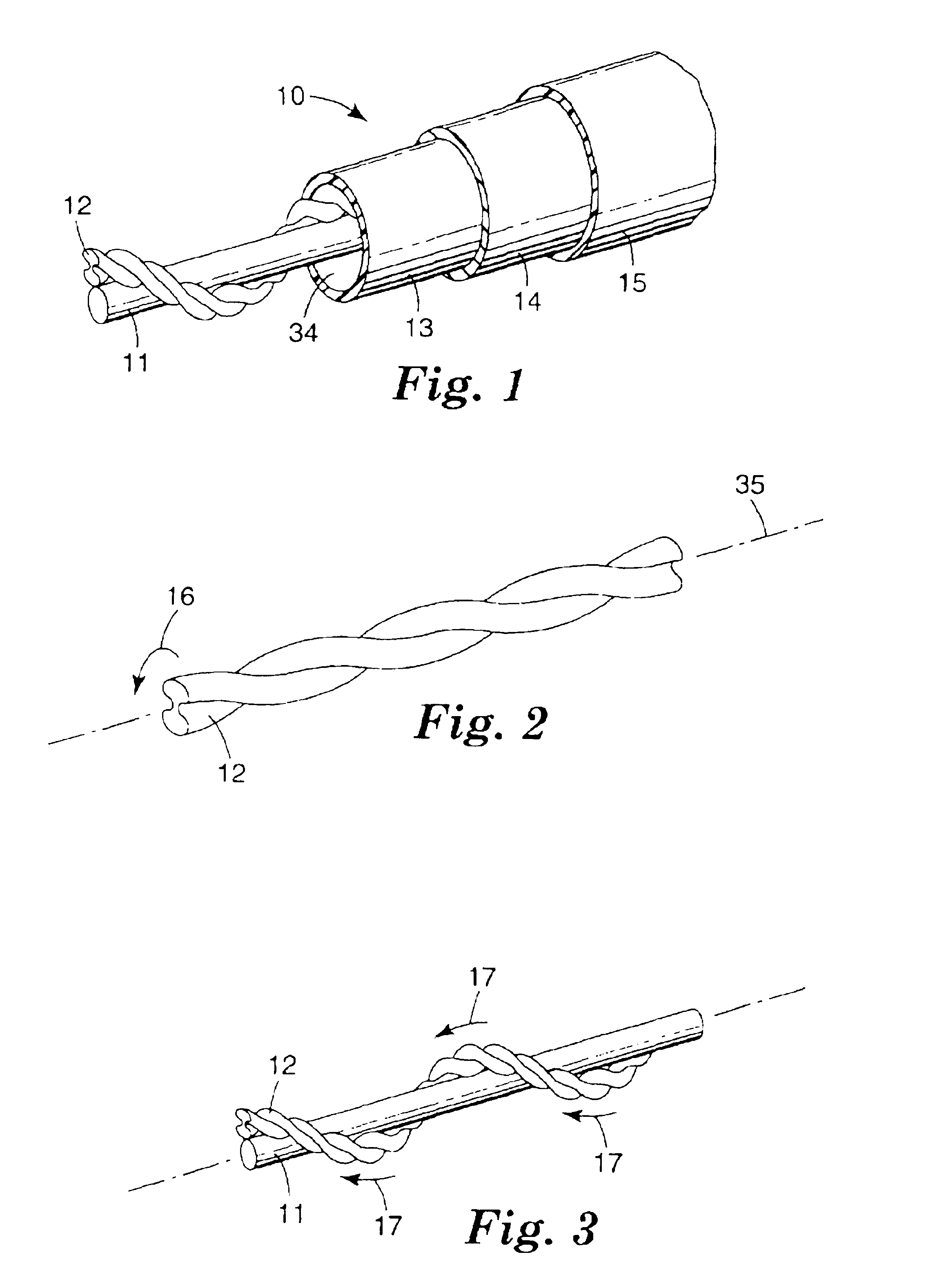

High propagation speed coaxial and twinaxial cable

InactiveUS6849799B2Low dielectric constantReduce morbidityCable insulation constructionInsulated cablesElectrical conductorEngineering

Owner:3M INNOVATIVE PROPERTIES CO

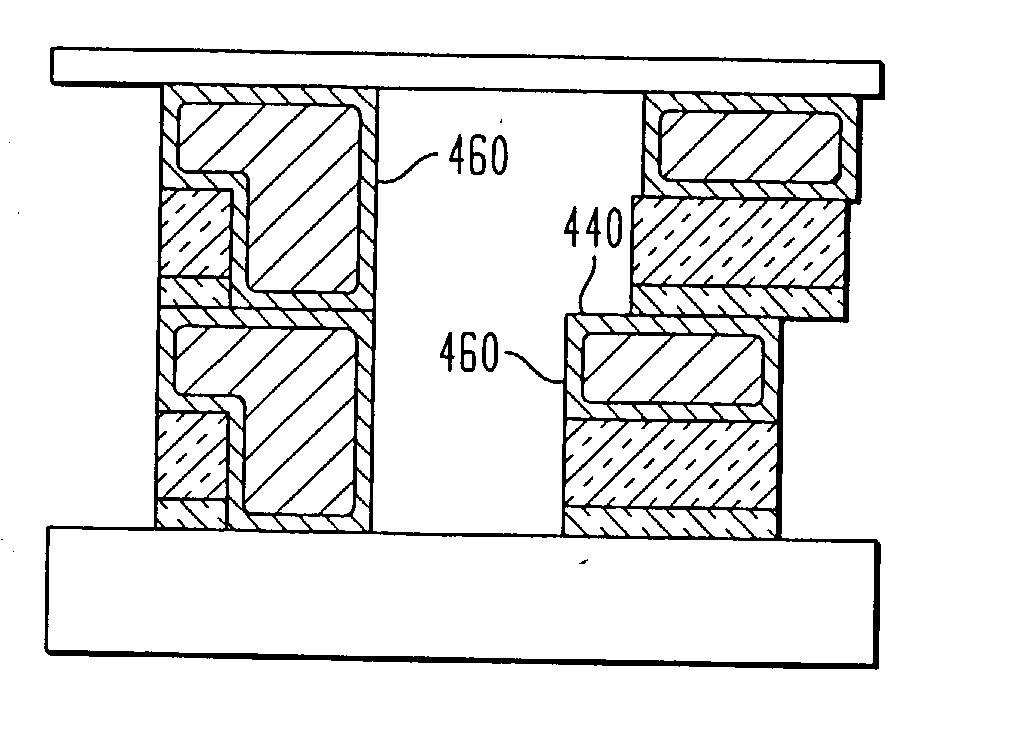

Method of fabricating an interconnect structure employing air gaps between metal lines and between metal layers

InactiveUS7056822B1Reduce parasitic capacitanceEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesCapacitanceInter layer

An interconnect structure and fabrication method are provided to form air gaps between interconnect lines and between interconnect layers. A conductive material is deposited and patterned to form a first level of interconnect lines. A first dielectric layer is deposited over the first level of interconnect lines. One or more air gaps are formed in the first dielectric layer to reduce inter-layer capacitance, intra-layer capacitance or both inter-layer and intra-layer capacitance. At least one support pillar remains in the first dielectric layer to promote mechanical strength and thermal conductivity. A sealing layer is deposited over the first insulative layer to seal the air gaps. Via holes are patterned and etched through the sealing layer and the first dielectric layer. A conductive material is deposited to fill the via holes and form conductive plugs therein. Thereafter, a conductive material is deposited and patterned to form a second level of interconnect lines.

Owner:NEWPORT FAB

Methylated oxide-type dielectric as a replacement for SiO2 hardmasks used in polymeric low K, dual damascene interconnect integration

InactiveUS6218317B1Shorten cycle timeEffective dielectric constantSemiconductor/solid-state device manufacturingDielectricCopper

Disclosed are multilevel interconnects for integrated circuit devices, especially copper / dual damascene devices, and methods of fabrication. Methylated-oxide type hardmasks are formed over polymeric interlayer dielectric materials. Preferably the hardmasks are materials having a dielectric constant of less than 3 and more preferably 2.7 or less. Advantageously, both the hardmask and the interlayer dielectric can be spincoated.

Owner:NAT SEMICON CORP

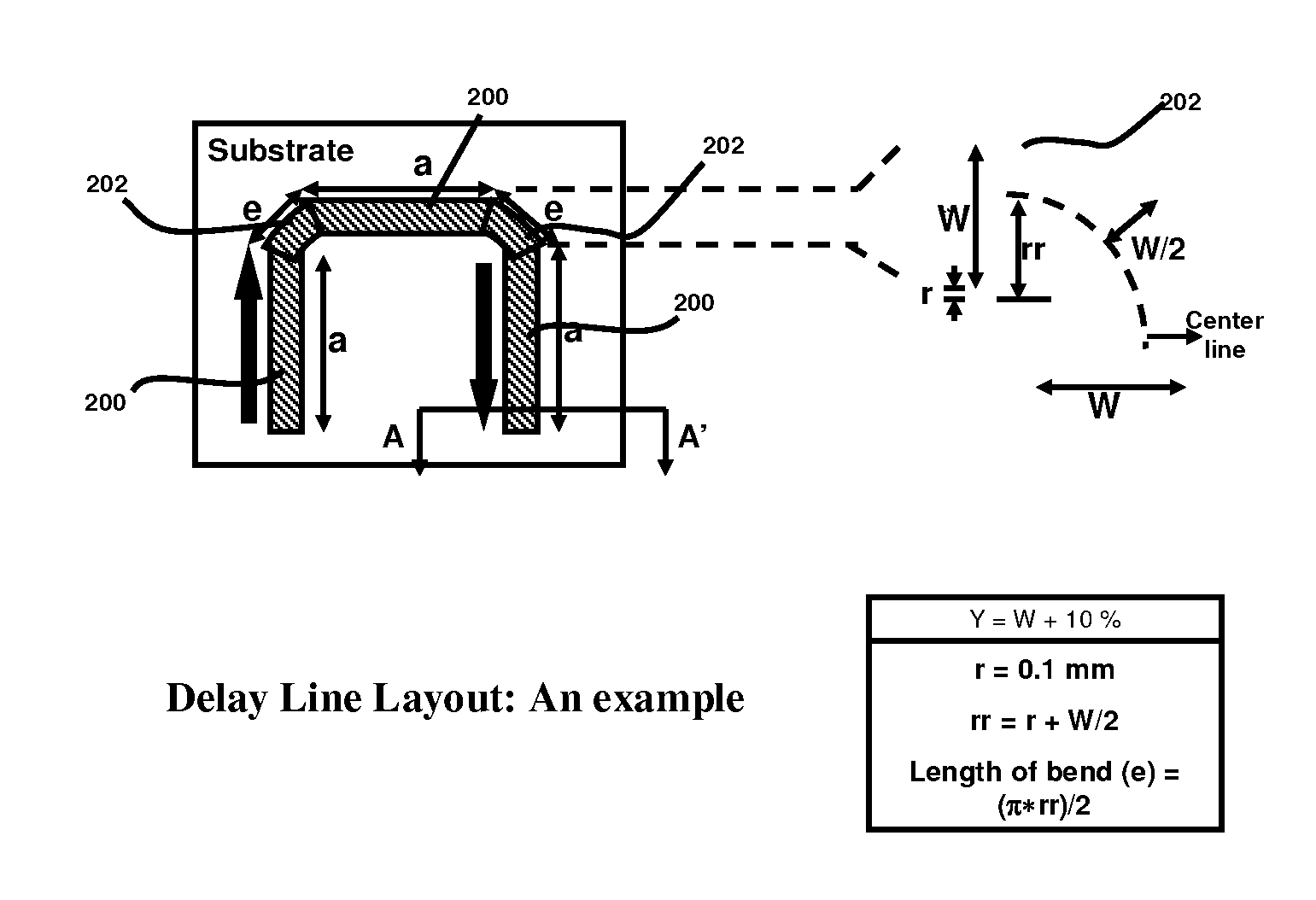

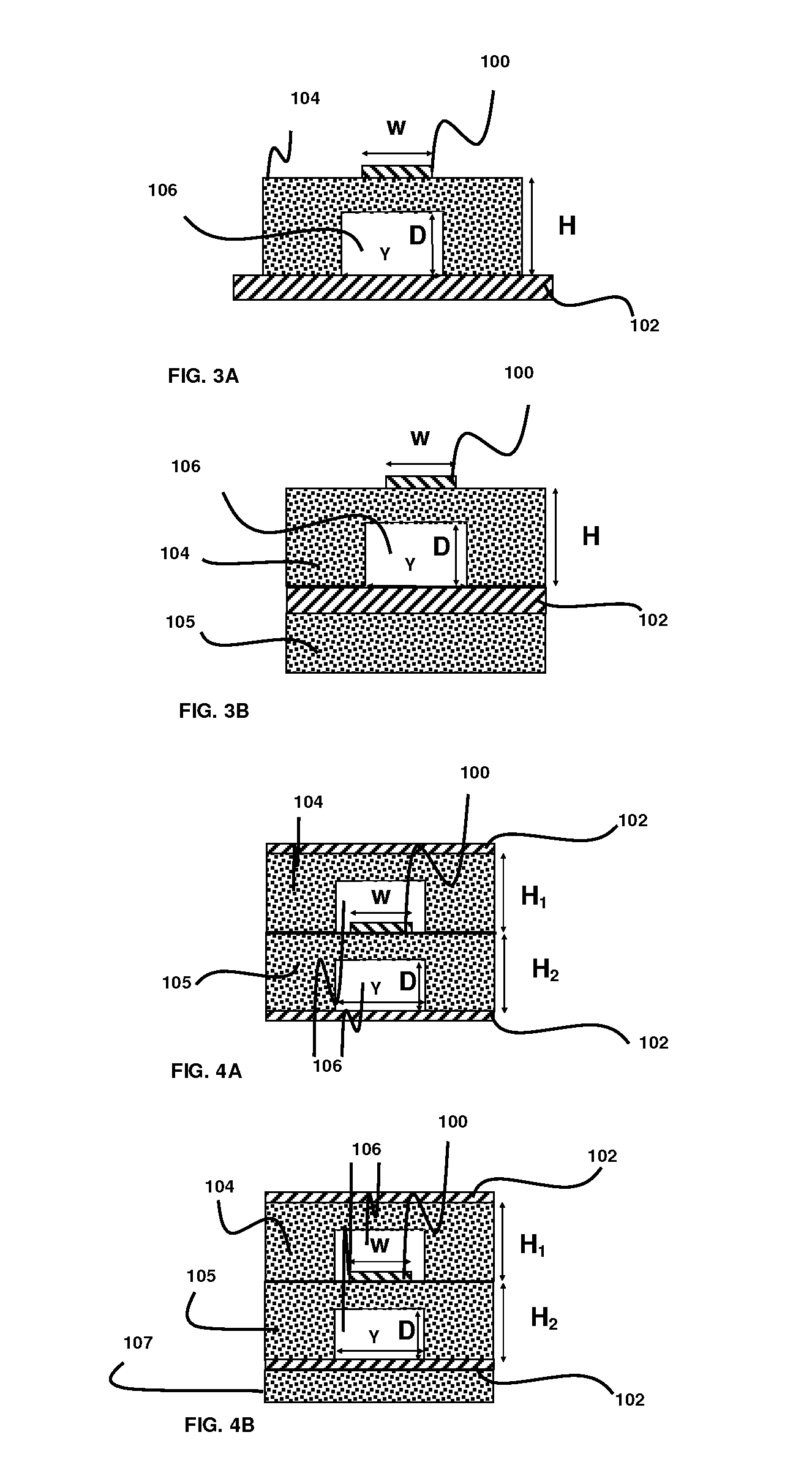

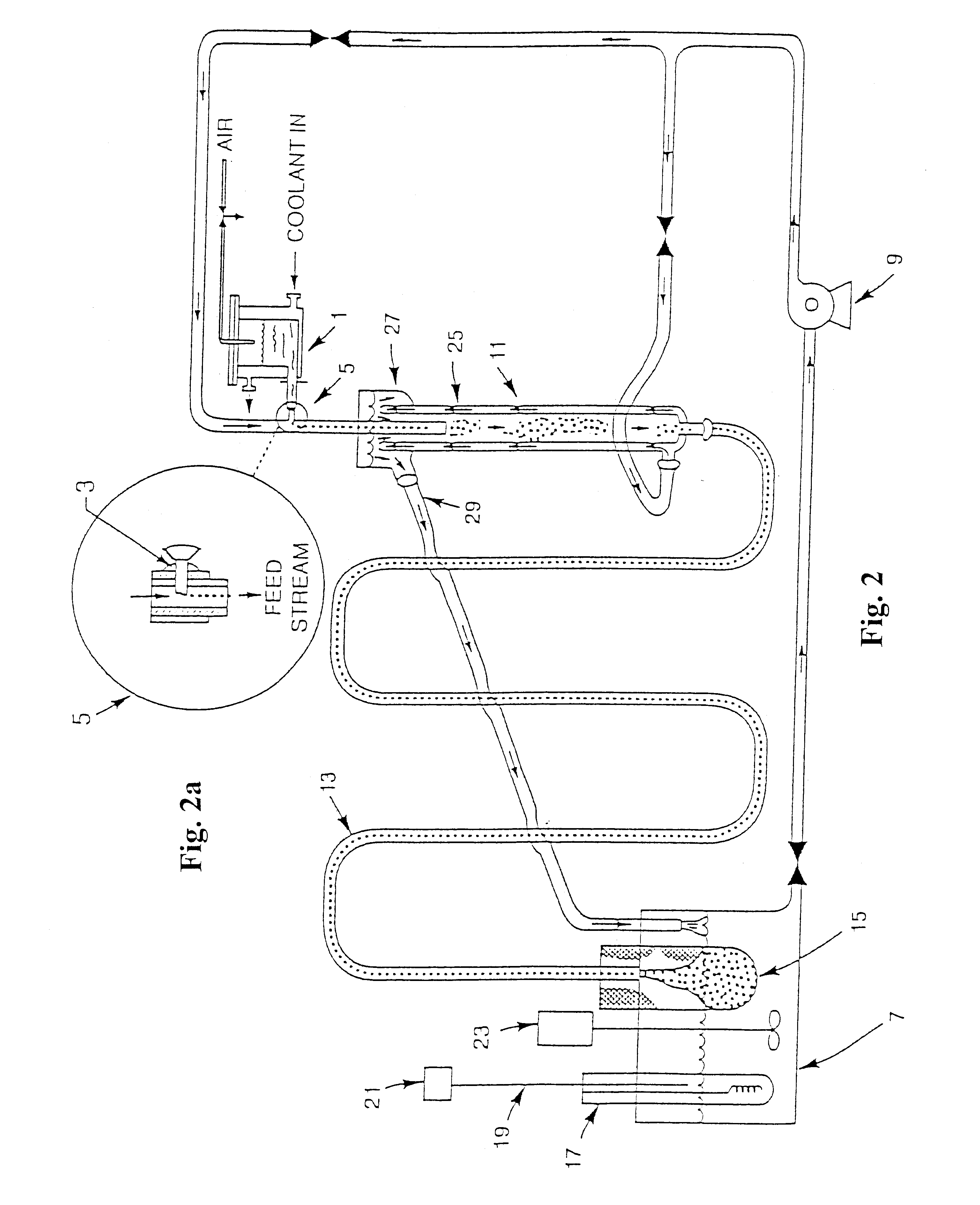

Low loss electrical delay line

ActiveUS20080048800A1Decrease dielectric lossSimplified delay line solutionSemiconductor/solid-state device detailsSolid-state devicesElectricityDielectric loss

A delay line system able to reduce the microwave loss by reducing the effective dielectric loss and dielectric constant of the system including a signal line, dielectric system with opened trench or slot filled up with the air or lower dielectric loss material, a ground plane, and a system of switches if the line is to be variable. The delay line proposed in this invention could be made of any type of signal line configuration, for example: micro-strip line, strip line, or coplanar line. The signal line can also be made as single ended or differential pairs of any configurations. The delay line systems based on the fundamental techniques provided in this invention can be used for on-chip devices where the delay line is laid on the oxide or dielectric material, or in a traditional PCB implementation such as FR4.

Owner:BANPIL PHOTONICS

Antenna element

InactiveUS20020126049A1Stable characteristicsHigh bandwidthSimultaneous aerial operationsAntenna supports/mountingsElectrical conductorResonance

To provide an antenna element having a radiation electrode formed mainly on one surface of a dielectric substrate. The radiation electrode is substantially symmetric in form with respect to the center thereof, and has a first half and a second half with the same direction of main polarization of radiation emitted therefrom. Each of the halves of the radiation electrode may be a quarter-wave antenna for a wavelength of the emitted radiation. A power supply conductor to be connected to a high frequency signal source is connected to the first half of the radiation electrode, and a ground conductor to be connected to a ground is connected to the second half. A total impedance of the first half of the radiation electrode and the power supply conductor and a total impedance of the second half of the radiation electrode and the ground conductor can substantially match to one another, so that resonance between the halves of the radiation electrode can be enhanced and a wider bandwidth can be realized.

Owner:HITACHI LTD +1

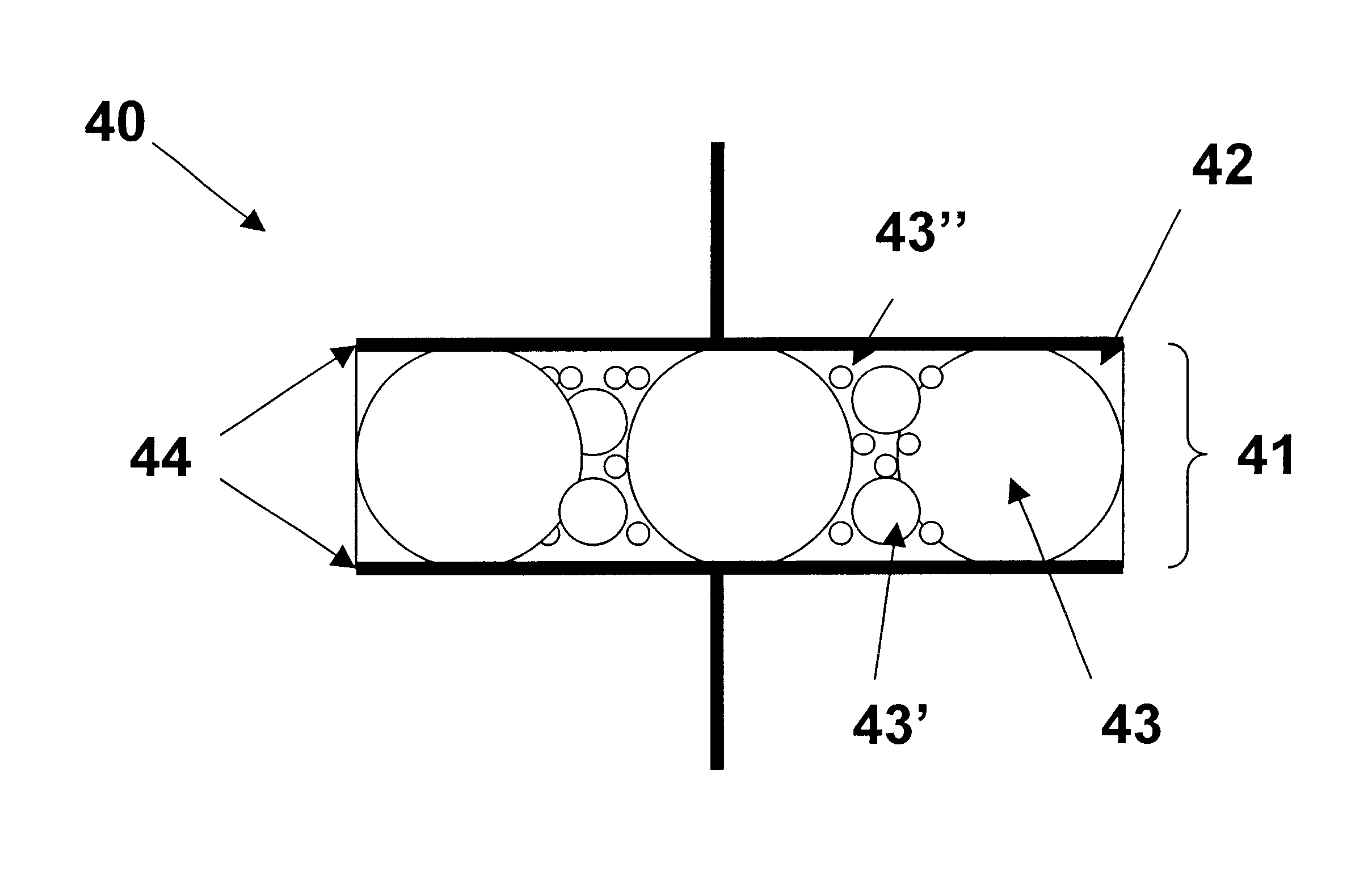

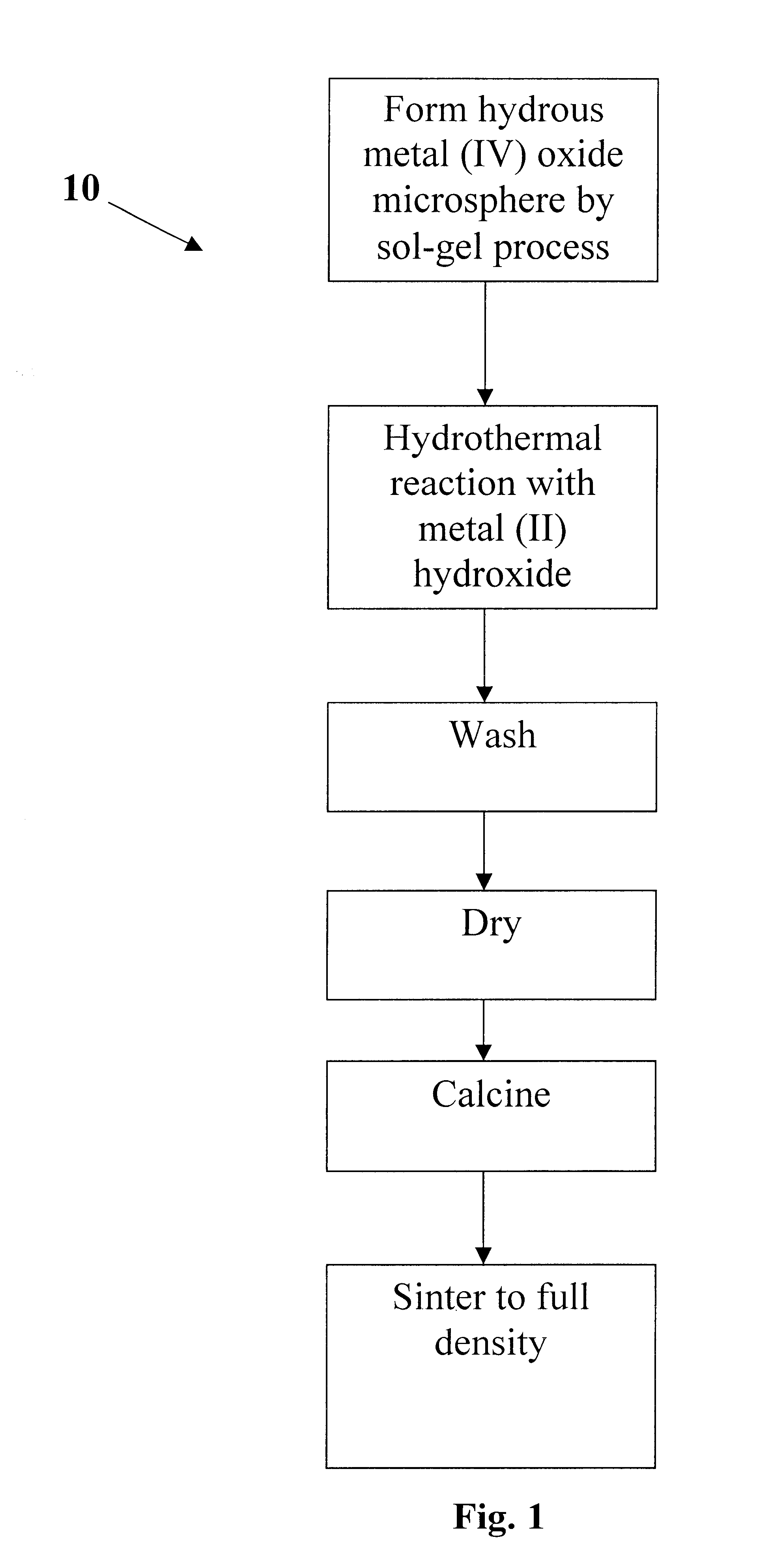

Dielectric composite materials and method for preparing

InactiveUS6600645B1Maximize volumetric packing densityQuantity maximizationAlkaline earth titanatesFixed capacitor dielectricPorositySpherical shaped

The invention allows the fabrication of small, dense beads of dielectric materials with selected compositions, which are incorporated into a polymeric matrix for use in capacitors, filters, and the like. A porous, generally spherical bead of hydrous metal oxide containing titanium or zirconium is made by a sol-gel process to form a substantially rigid bead having a generally fine crystallite size and correspondingly finely distributed internal porosity. The resulting gel bead may be washed and hydrothermally reacted with a soluble alkaline earth salt (typically Ba or Sr) at elevated temperature and pressure to convert the bead into a mixed hydrous titanium- or zirconium-alkaline earth oxide while retaining the generally spherical shape. Alternatively, the gel bead may be made by coprecipitation. This mixed oxide bead is then washed, dried and calcined to produce the desired (BaTiO3, PbTiO3, SrZrO3) structure. The sintered beads are incorporated into a selected polymer matrix. The resulting dielectric composite material may be electrically "poled" if desired.

Owner:EI DU PONT DE NEMOURS & CO +1

High-speed flex printed circuit and method of manufacturing

ActiveUS20070066126A1Reduce effective dielectric constant effective dielectricReduce effective dielectric effective dielectric lossPrinted circuit assemblingHigh frequency circuit adaptationsAdhesiveEngineering

High speed flex printed circuit boards (FLEX-PCBs) are disclosed comprising a dielectrics systems with the back-side trenches, adhesives, signal lines and ground-plans, wherein the signal line and ground-plan are located on the dielectrics. Using of the open trenches in the substrate help to reduce the microwave loss and dielectric constant and thus increasing the signal carrying speed of the interconnects. Thus, according to the present invention, it is possible to provide a simply constructed high speed FLEX-PCB using the conventional material and conventional FLEX-PCB manufacturing which facilitates the design of circuits with controlled bandwidth based on the trench opening in the dielectrics, and affords excellent connection reliability. As the effective dielectric constant is reduced, the signal width is required to make wider or the dielectric thickness is required to make thinner keeping fixed characteristics impedance. The fundamental techniques disclosed here can also be used for high-speed packaging.

Owner:BANPIL PHOTONICS

Low loss electrical delay line

ActiveUS7561006B2Reduce lossEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesElectricityDielectric loss

A delay line system able to reduce the microwave loss by reducing the effective dielectric loss and dielectric constant of the system including a signal line, dielectric system with opened trench or slot filled up with the air or lower dielectric loss material, a ground plane, and a system of switches if the line is to be variable. The delay line proposed in this invention could be made of any type of signal line configuration, for example: micro-strip line, strip line, or coplanar line. The signal line can also be made as single ended or differential pairs of any configurations. The delay line systems based on the fundamental techniques provided in this invention can be used for on-chip devices where the delay line is laid on the oxide or dielectric material, or in a traditional PCB implementation such as FR4.

Owner:BANPIL PHOTONICS

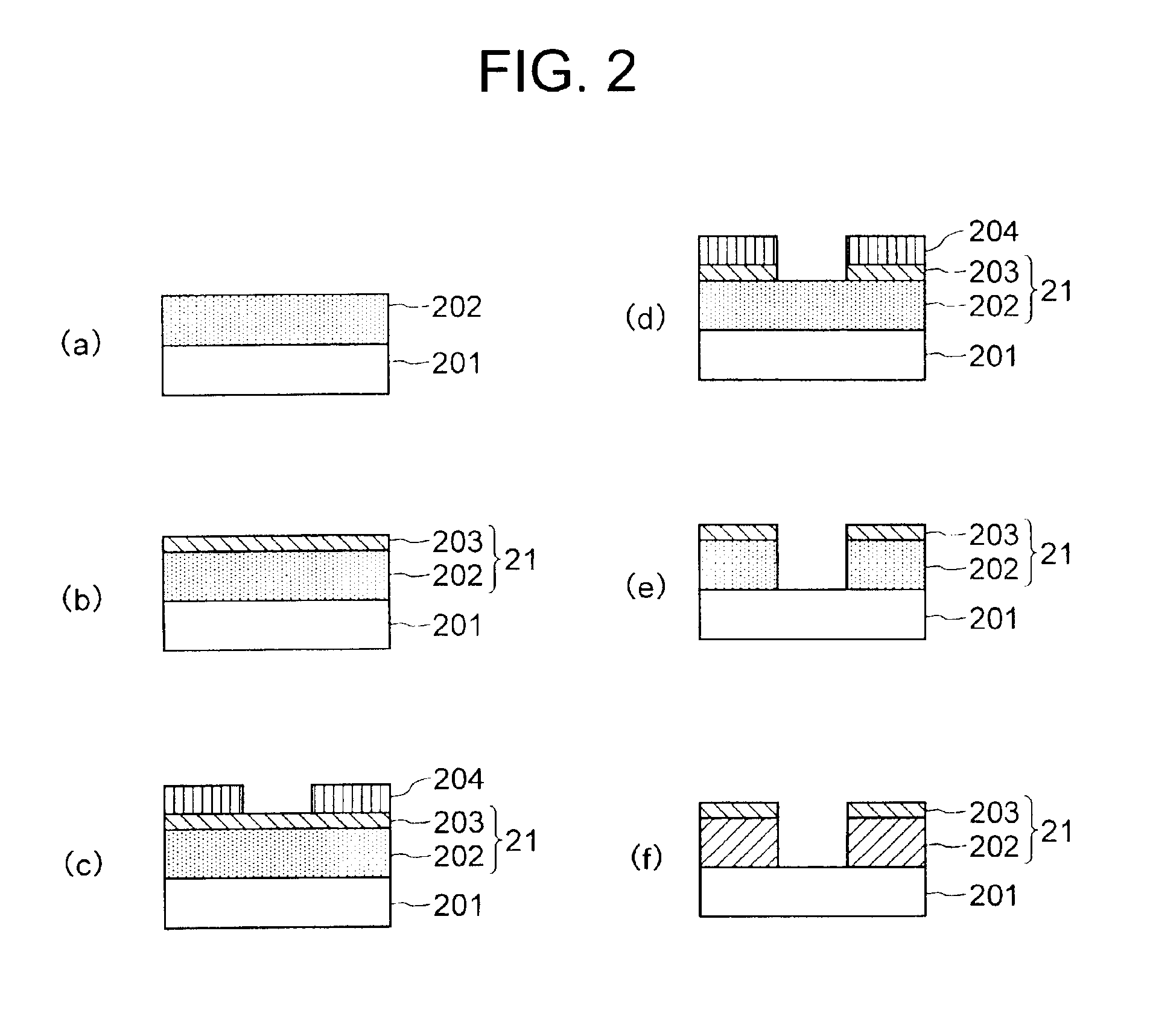

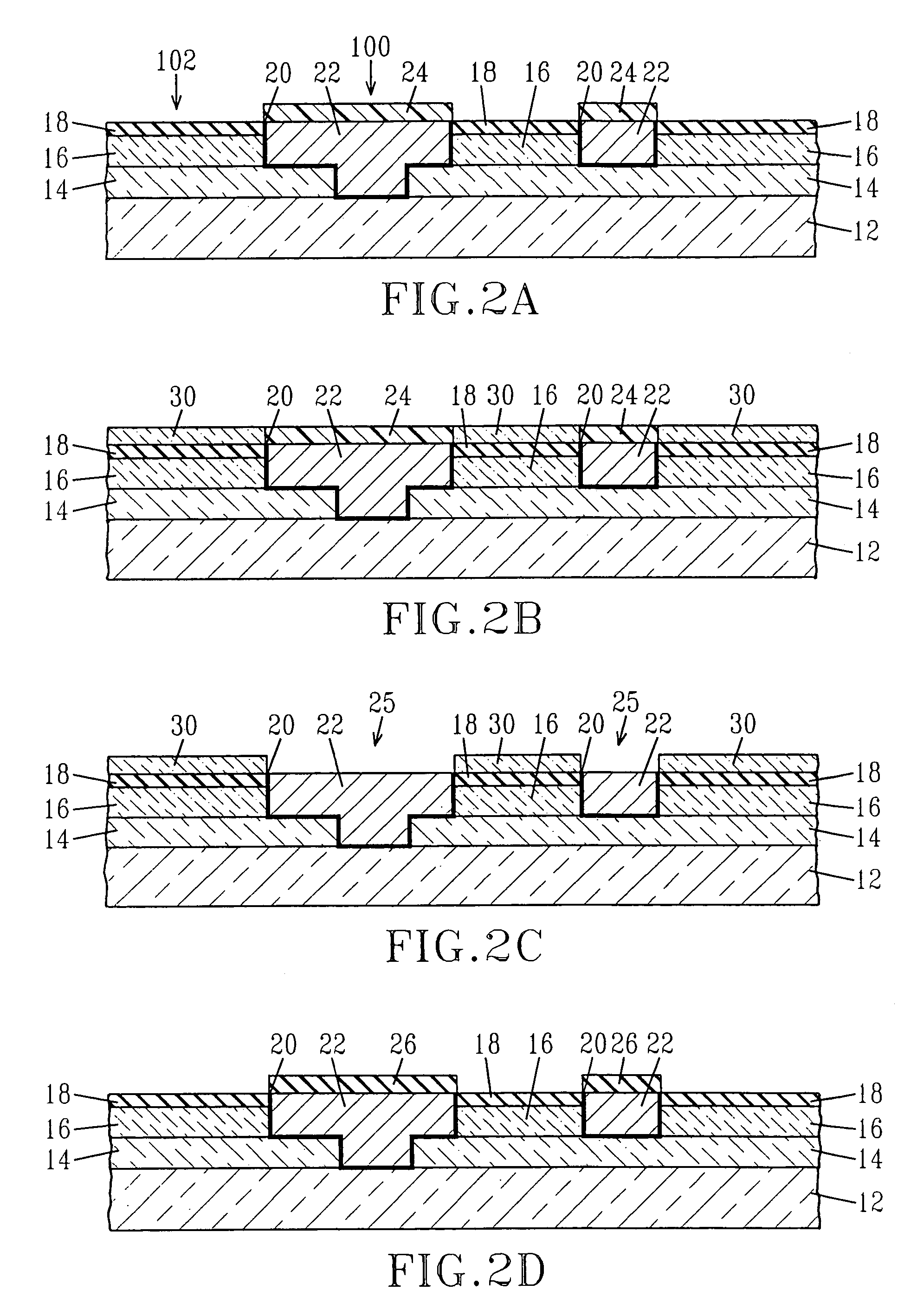

Dual damascene process for forming a multi-layer low-K dielectric interconnect

InactiveUS20050142853A1Effective dielectric constantShorten speedSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDielectric permittivity

In a dual damascene process for forming a multi-layer low-k dielectric interconnect, the formation of each layer of interconnect comprises deposition of a first low-k dielectric layer, etching of the first low-k dielectric layer to form two dual damascene vias, formation of two Cu conductor plugs enclosed with barrier layers in the two dual damascene vias, etching of the first low-k dielectric layer between the two dual damascene vias to form a trench, and spin-on of a second low-k dielectric layer filled in the trench. The spin-on low-k dielectric layer is selected to have a dielectric constant smaller than that of the first low-k dielectric layer to reduce the equivalent dielectric constant in the layer of interconnect.

Owner:MACRONIX INT CO LTD

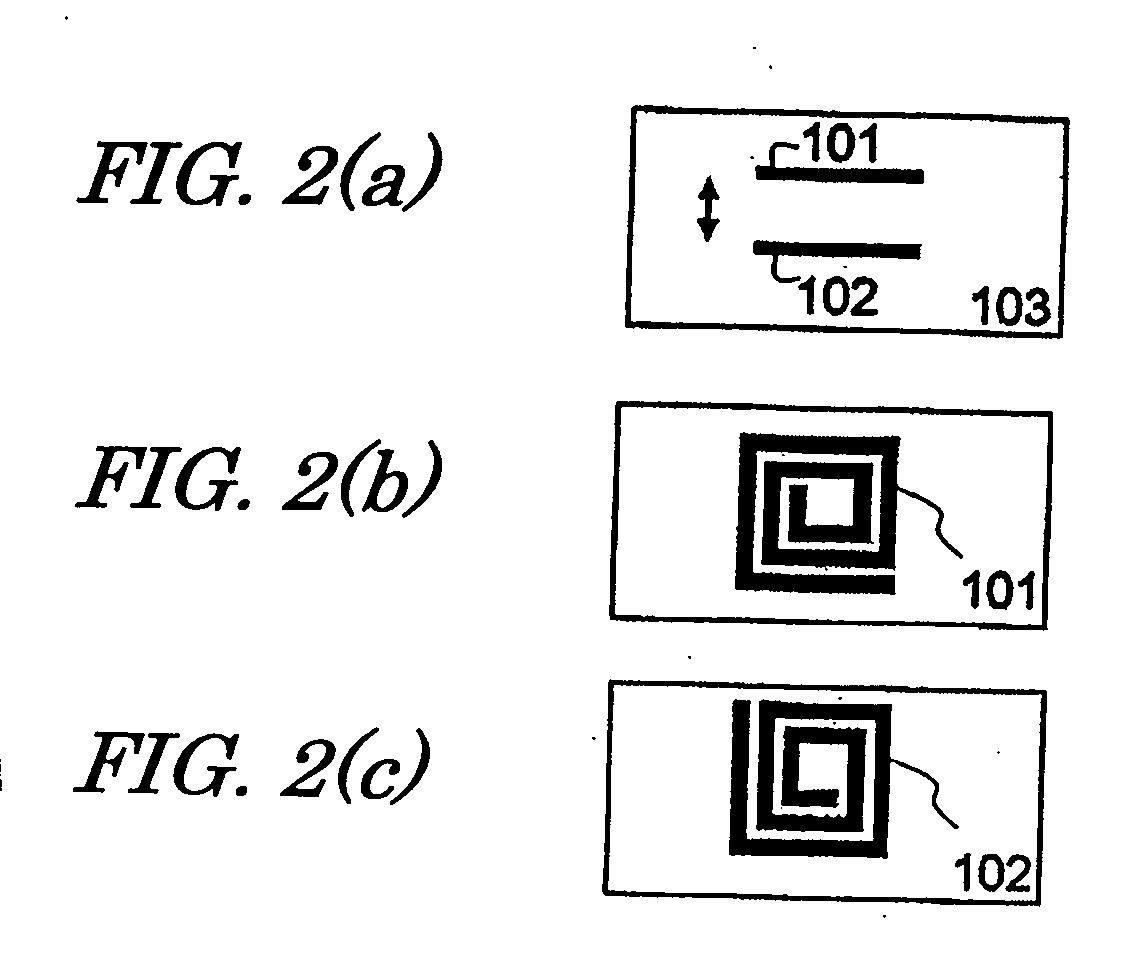

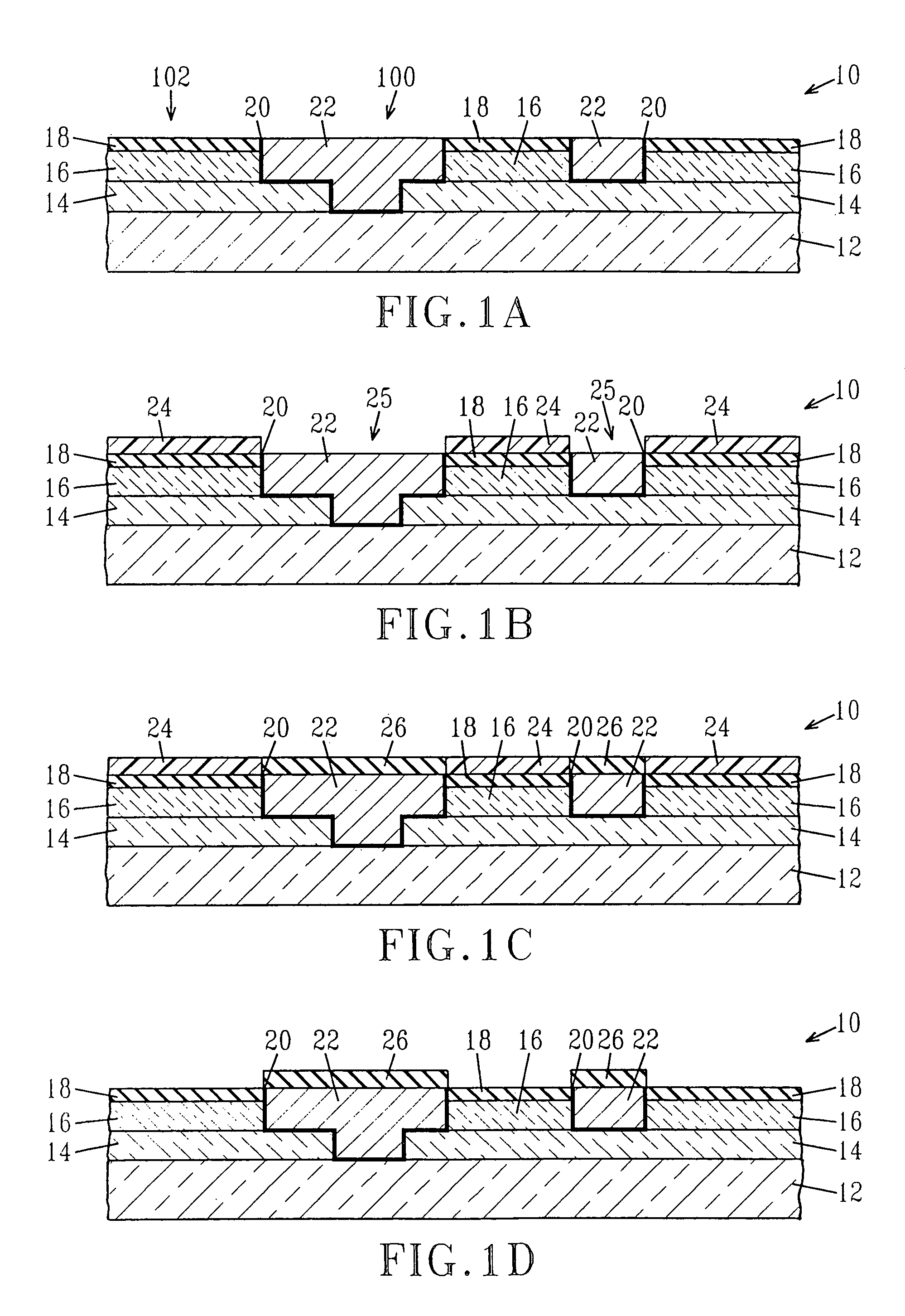

Method for producing self-aligned mask, articles produced by same and composition for same

InactiveUS20050045997A1Effective dielectric constant of be reduceMaximize propagation speedRadiation applicationsSemiconductor/solid-state device detailsReflectivityDielectric

A method for forming a self-aligned pattern on an existing pattern on a substrate comprising applying a coating of a solution containing a masking material in a carrier, the masking material being either photo or thermally sensitive; performing a blanket exposure of the substrate; and allowing at least a portion of the masking material to preferential develop in a fashion that is replicates the existing pattern of the substrate. The existing pattern may be comprised of a first set of regions of the substrate having a first reflectivity and a second set of regions of the substrate having a second reflectivity different from the first composition. The first set of regions may include one or more metal elements and the second set of regions may include a dielectric. Structures made in accordance with the method.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device having insulating film with surface modification layer and method for manufacturing the same

InactiveUS20100059887A1Shortening of CMP processCarbon concentration can be reducedSemiconductor/solid-state device detailsSolid-state devicesSurface layerEngineering

Provided is a semiconductor device, which includes an interlayer insulating film formed on a semiconductor substrate, a wiring layer filled in a recess formed in the interlayer insulating film, and a cap insulating film. The interlayer insulating film includes a first SiOCH film and a surface modification layer including an SiOCH film formed by modifying a surface layer of the first SiOCH film, the SiOCH film having a lower carbon concentration and a higher oxygen concentration than the first SiOCH film has. The cap insulating film contacts with surfaces of the metal wiring and the surface modification layer.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method of manufacturing the semiconductor device

InactiveUS6967407B2Run at high speedThe process steps are simpleSemiconductor/solid-state device detailsSolid-state devicesCapacitanceCooking & baking

A semiconductor device capable of high speed operation with a substantially small interlayer capacitance is produced by steps of using an insulating film comprising an organic insulating film and an insulating film composed of an organometallic polymer material as an interlayer insulating film formed by coating, patterning the insulating film in a semi-thermosetting state, etching the organic insulating film as the lower layer by means of the organometallic polymer as a mask, using a plasma gas containing oxygen as the main component, and then conducting ultimate baking treatment of these insulating films.

Owner:RENESAS ELECTRONICS CORP

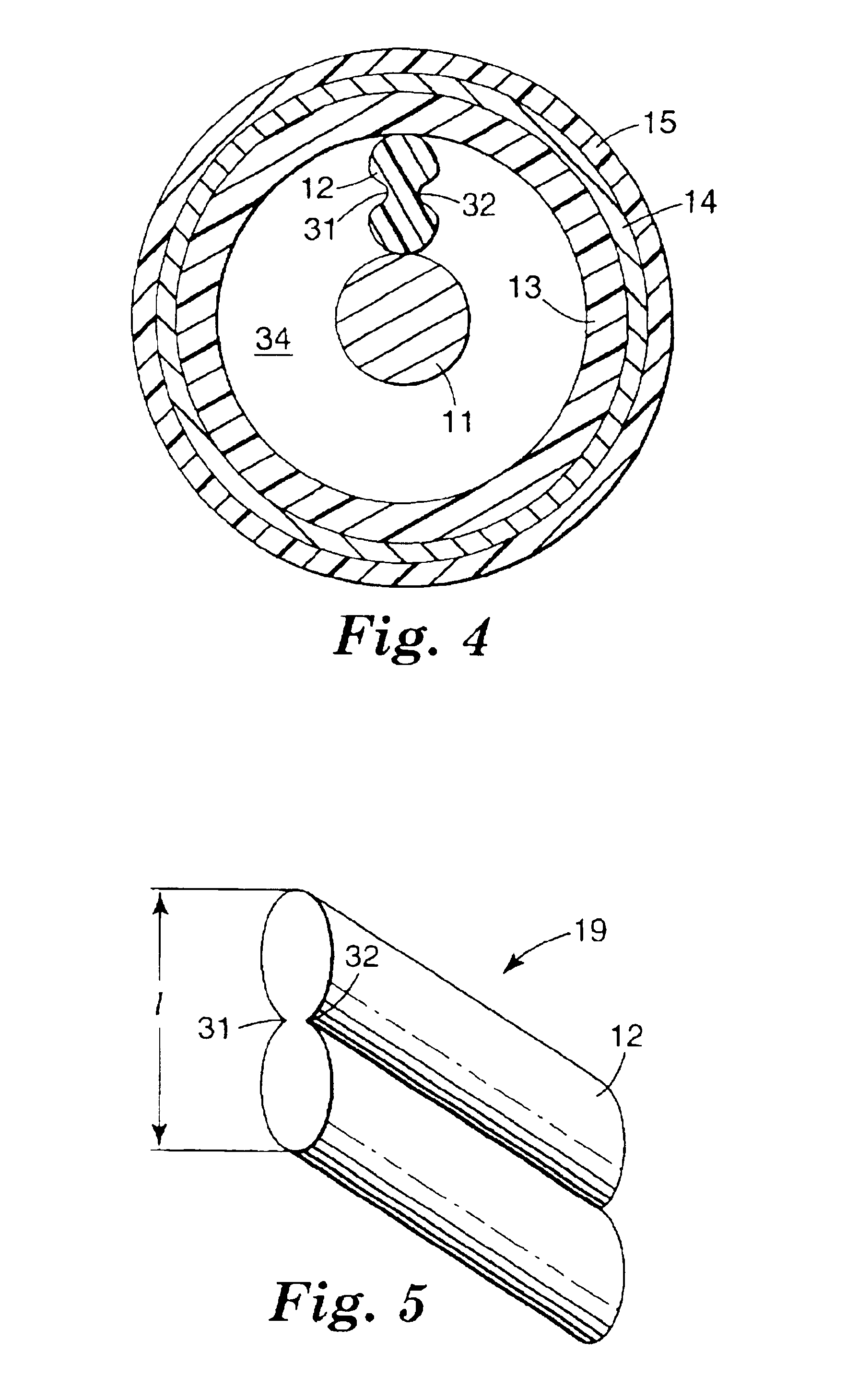

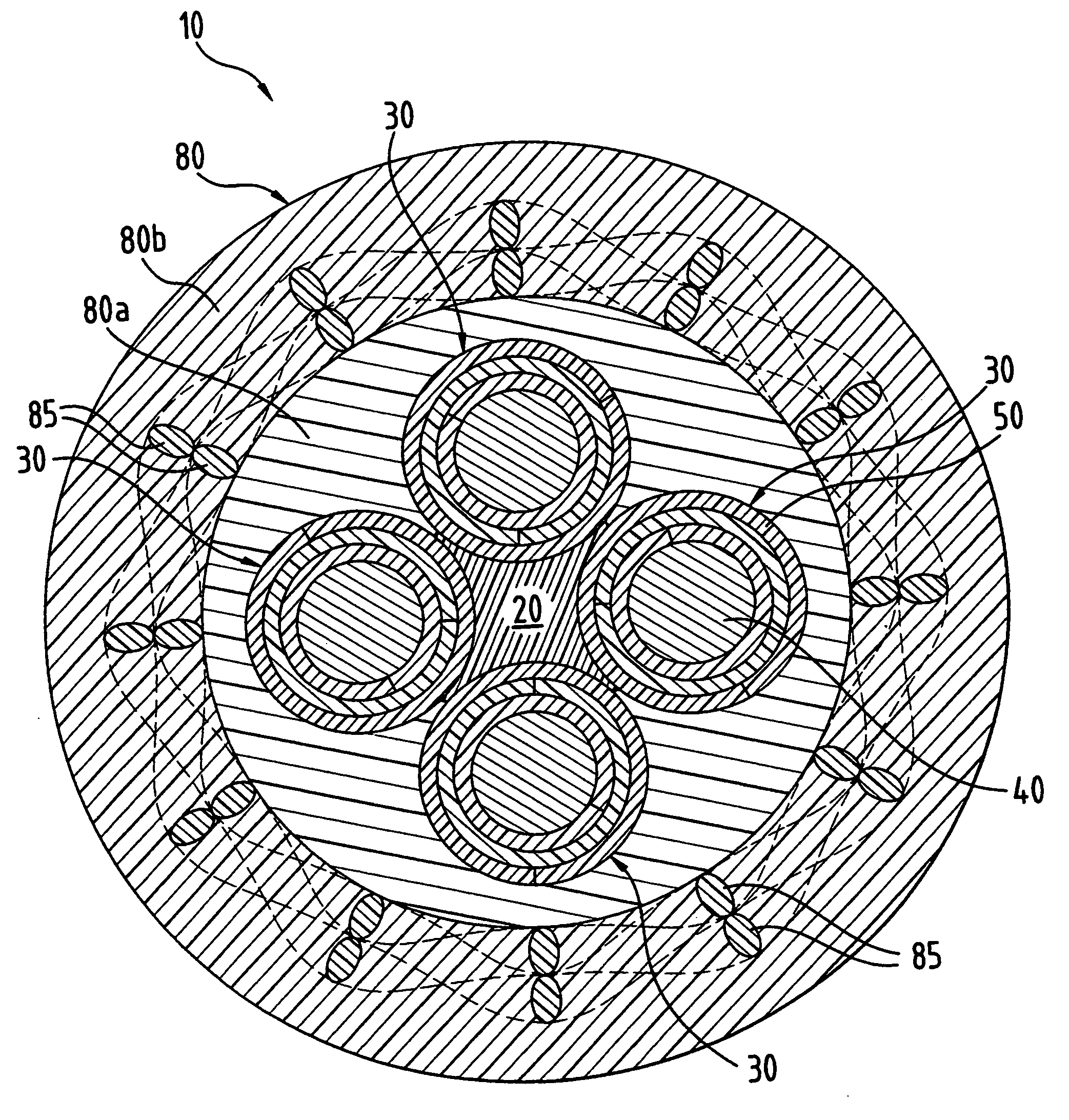

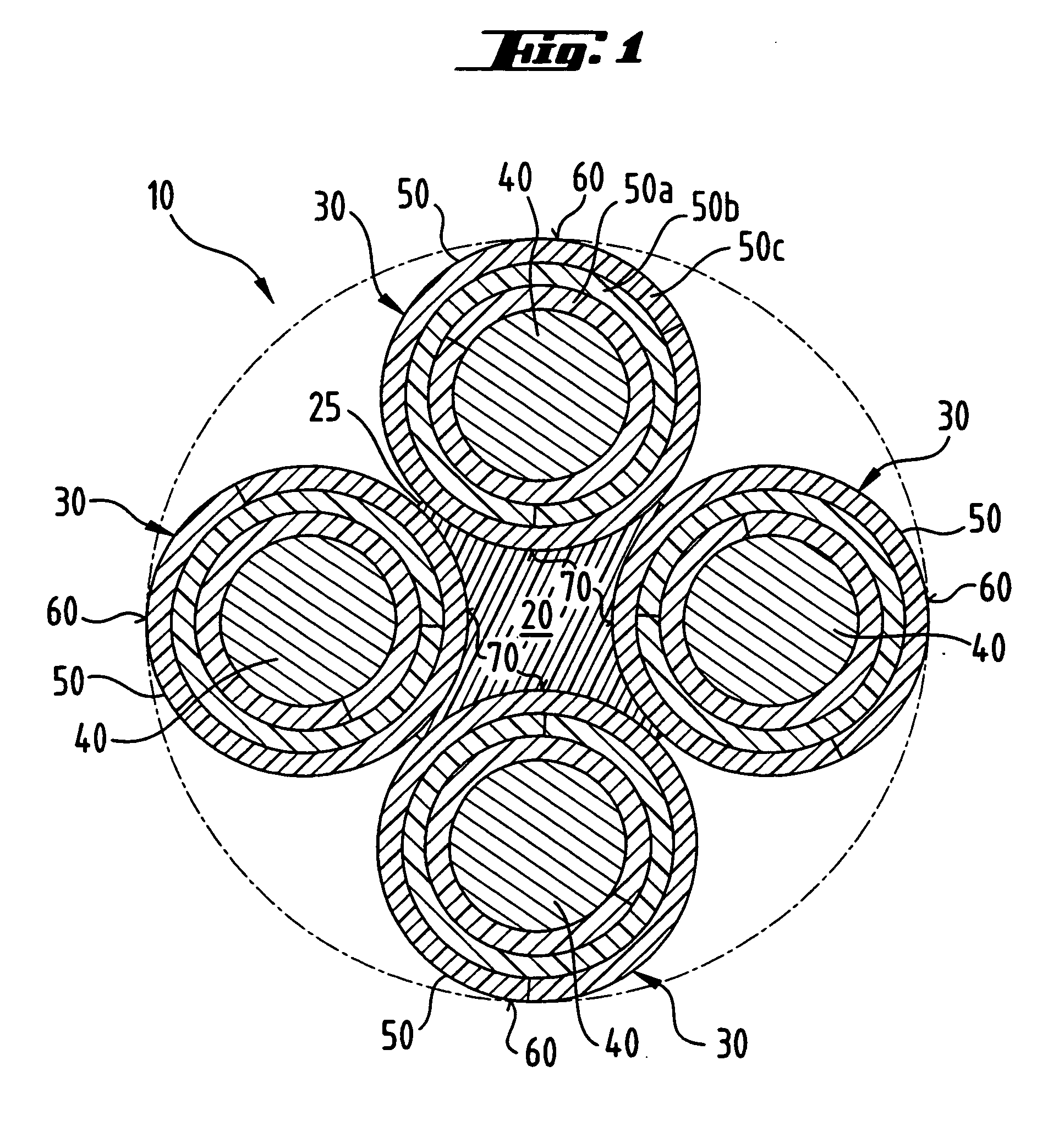

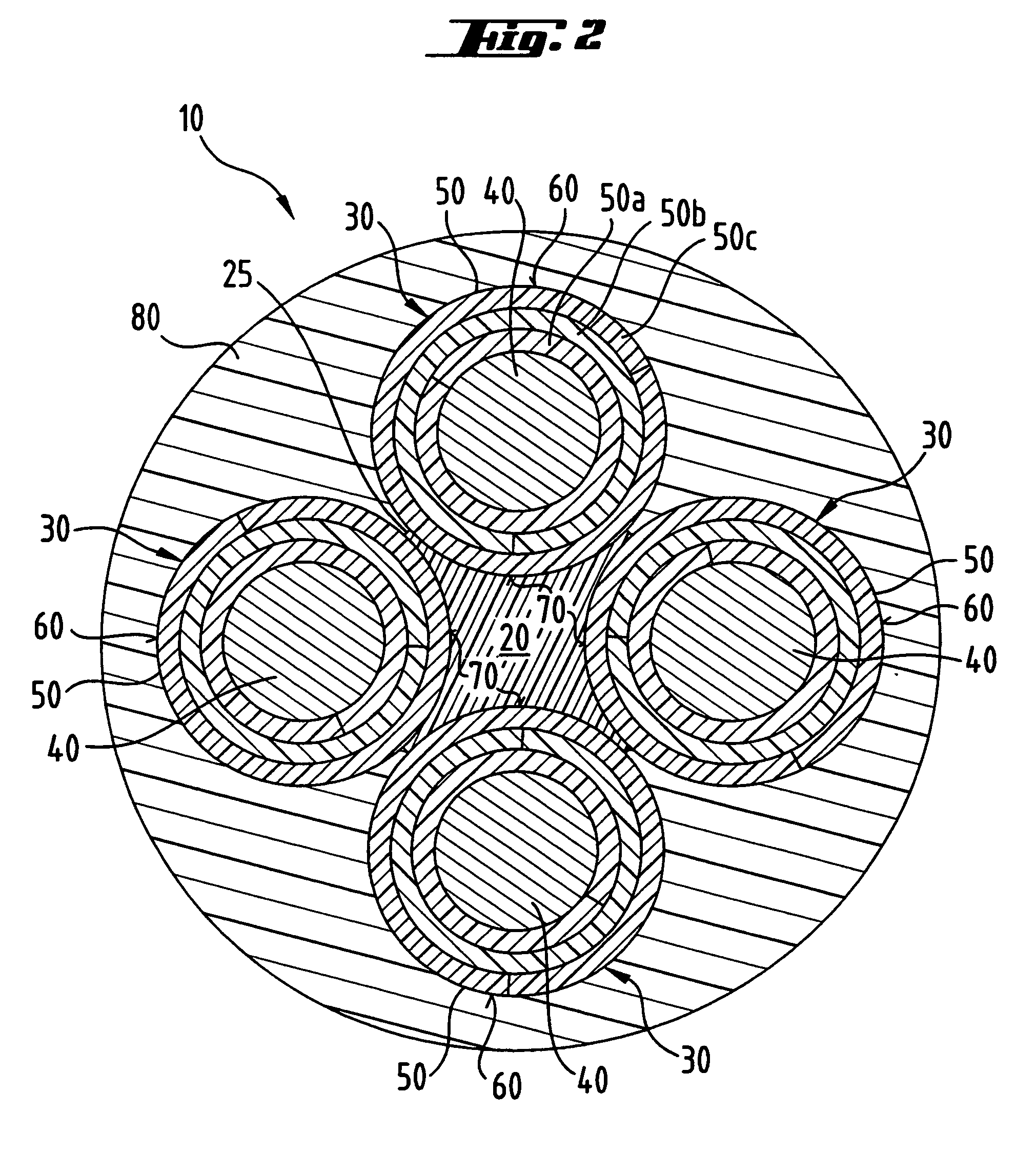

Quad cable

InactiveUS20110120745A1Improve electrical performanceIncrease flexibilityInsulated cablesSeismic signal receiversOcean bottomElectrical conductor

The invention relates to a cable (10) having an elongate core (20) made of a first dielectric material and having a core outer surface (25); and a plurality of elongate conducting elements (30) arranged about the elongate core (20). The elongate conducting elements (30) have an inner conductor (40) surrounded by an insulating layer (50) which is made of a second dielectric material. The outer surface of the inner conductor (40) is divided into a first outer surface area (60) and a second outer surface are a (70) and the first outer surface area (60) is attached, for example by sintering, to the core outer surface (25). The first and second dielectric materials are preferably expanded PTFE. The cable (10) finds application in a streamer (100) for use in seismographic surveys of the ocean bottom sub surface.

Owner:GORE ENTERPRISE HLDG INC

Method for producing self-aligned mask, articles produced by same and composition for same

InactiveUS7378738B2Reduce electromigrationEffective dielectric constantRadiation applicationsSemiconductor/solid-state device detailsDielectricMetal

A method for forming a self-aligned pattern on an existing pattern on a substrate comprising applying a coating of a solution containing a masking material in a carrier, the masking material being either photo or thermally sensitive; performing a blanket exposure of the substrate; and allowing at least a portion of the masking material to preferential develop in a fashion that is replicates the existing pattern of the substrate. The existing pattern may be comprised of a first set of regions of the substrate having a first reflectivity and a second set of regions of the substrate having a second reflectivity different from the first composition. The first set of regions may include one or more metal elements and the second set of regions may include a dielectric. Structures made in accordance with the method.

Owner:TAIWAN SEMICON MFG CO LTD

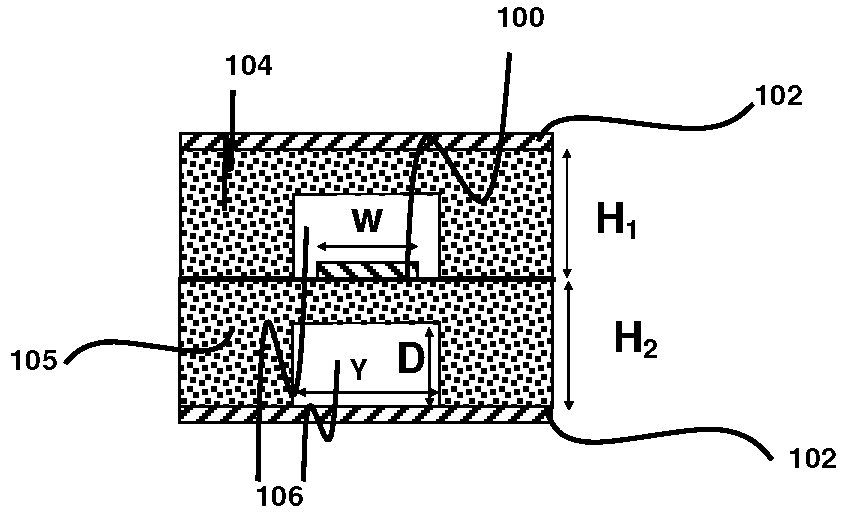

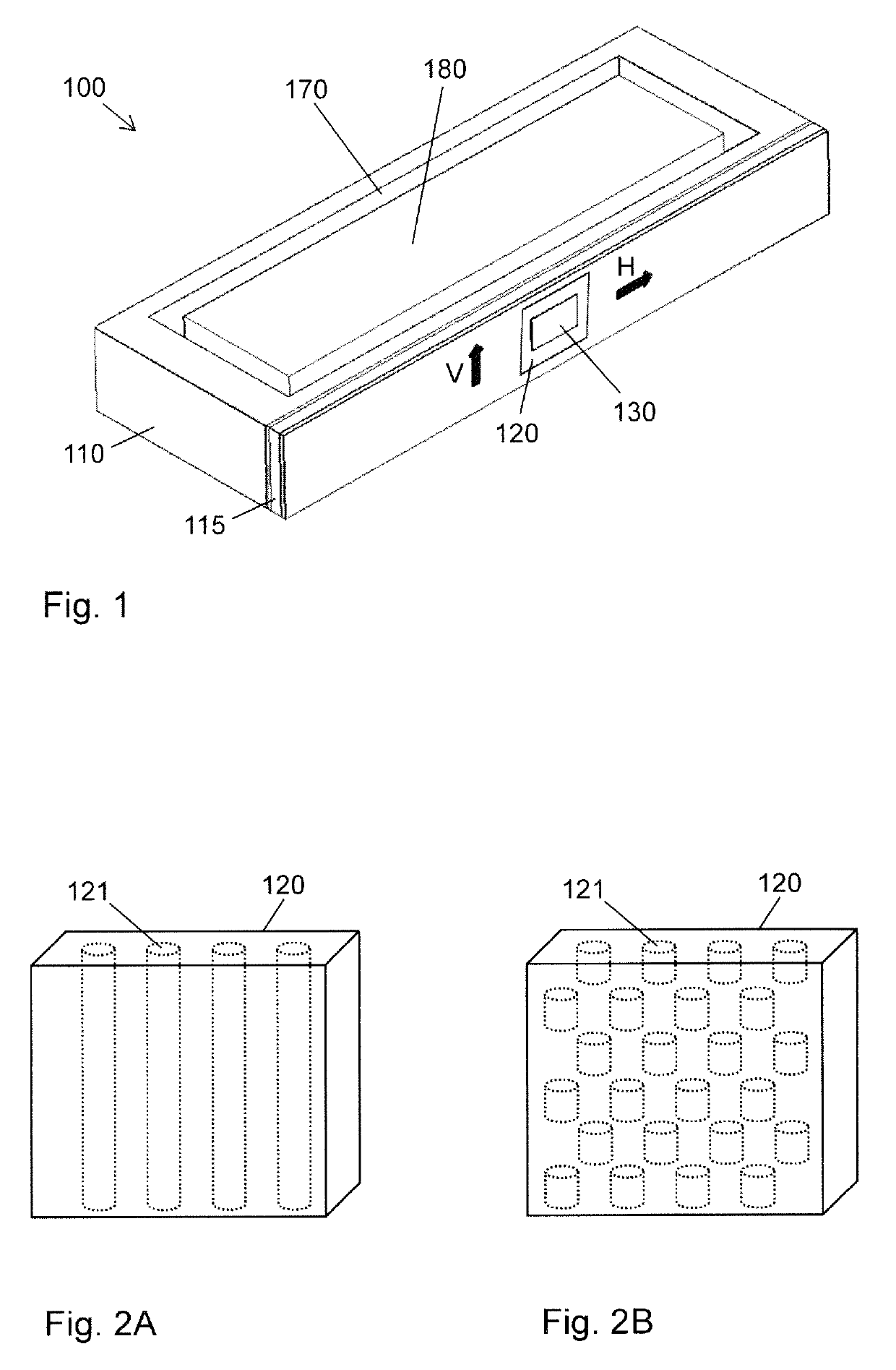

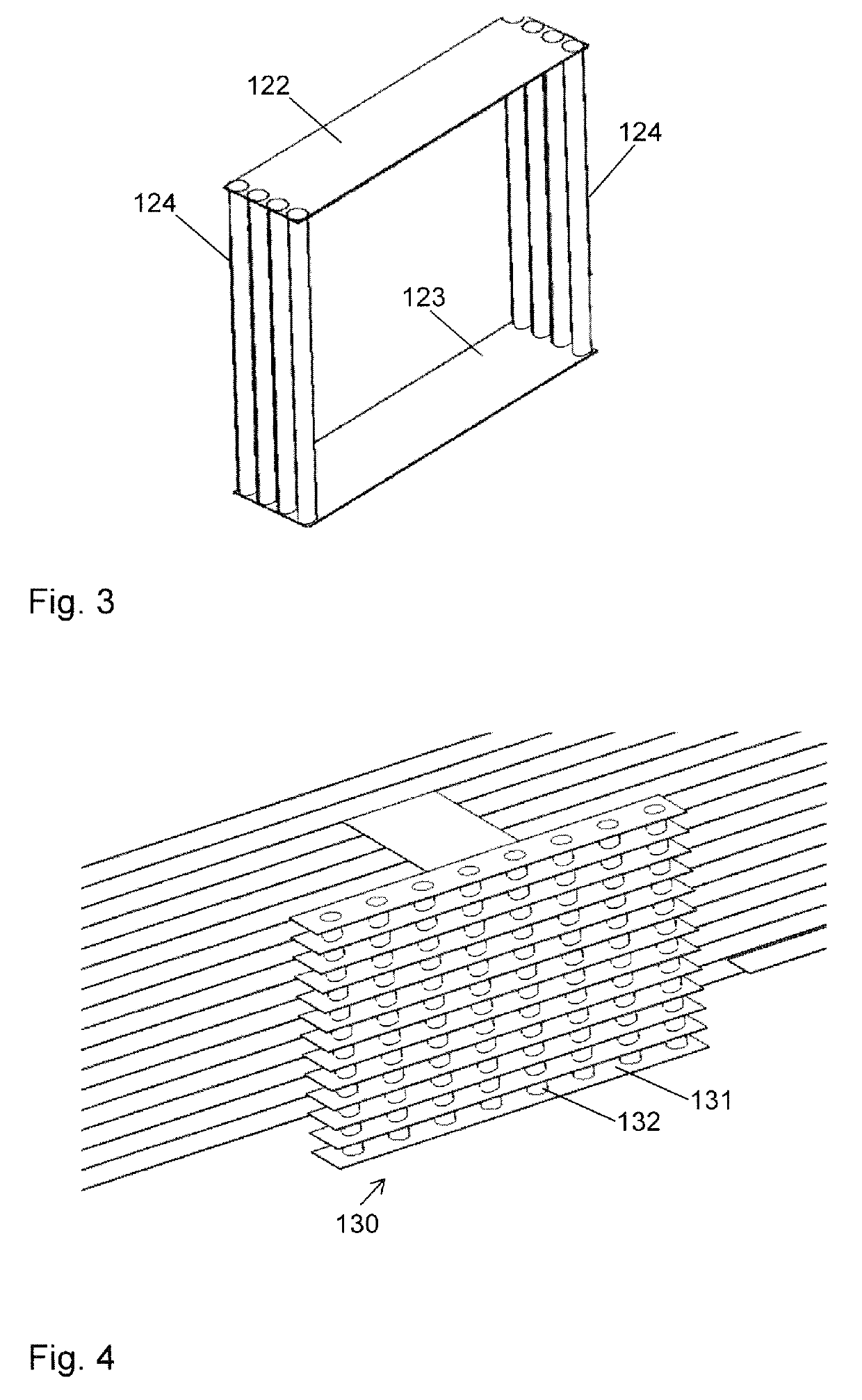

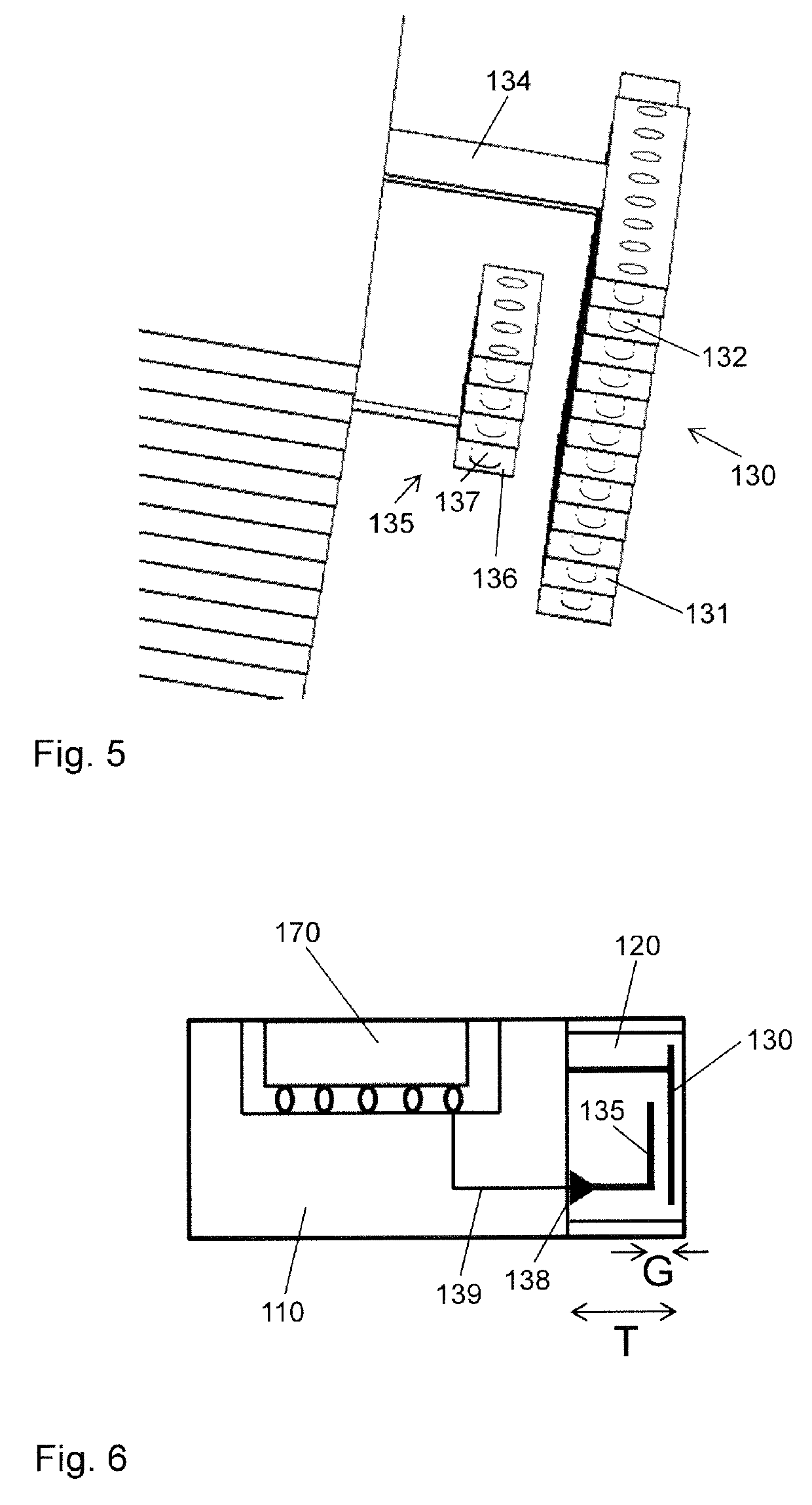

Vertical antenna patch in cavity region

ActiveUS20190288377A1Decrease their propagationReduce signalingAntenna supports/mountingsRadiating elements structural formsDielectric substrateEngineering

A multi-layer circuit structure (110) has multiple layers stacked along a vertical direction. Further, at least one cavity region (120) is formed at an edge of the multi-layer circuit structure (110). The at least one cavity region (120) is formed of multiple non-conductive vias from which a dielectric substrate material of the multi-layer circuit structure (120) is removed. Further, the device comprises at least one vertical antenna patch (130) arranged in the at least one cavity region (120).

Owner:SONY MOBILE COMM INC

Semiconductor device having insulating film with surface modification layer and method for manufacturing the same

InactiveUS8080878B2Reduce processReduce concentrationSemiconductor/solid-state device detailsSolid-state devicesSurface layerOxygen

Provided is a semiconductor device, which includes an interlayer insulating film formed on a semiconductor substrate, a wiring layer filled in a recess formed in the interlayer insulating film, and a cap insulating film. The interlayer insulating film includes a first SiOCH film and a surface modification layer including an SiOCH film formed by modifying a surface layer of the first SiOCH film, the SiOCH film having a lower carbon concentration and a higher oxygen concentration than the first SiOCH film has. The cap insulating film contacts with surfaces of the metal wiring and the surface modification layer.

Owner:RENESAS ELECTRONICS CORP

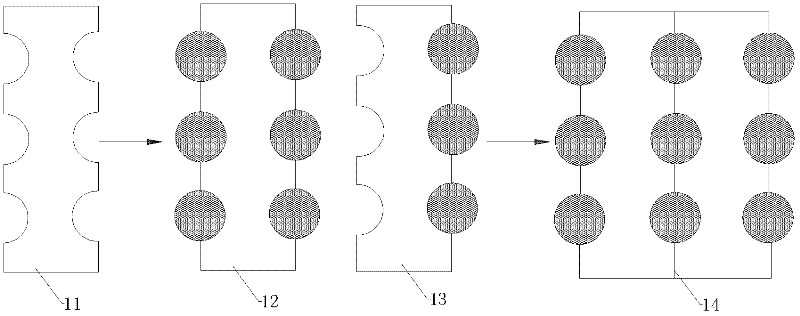

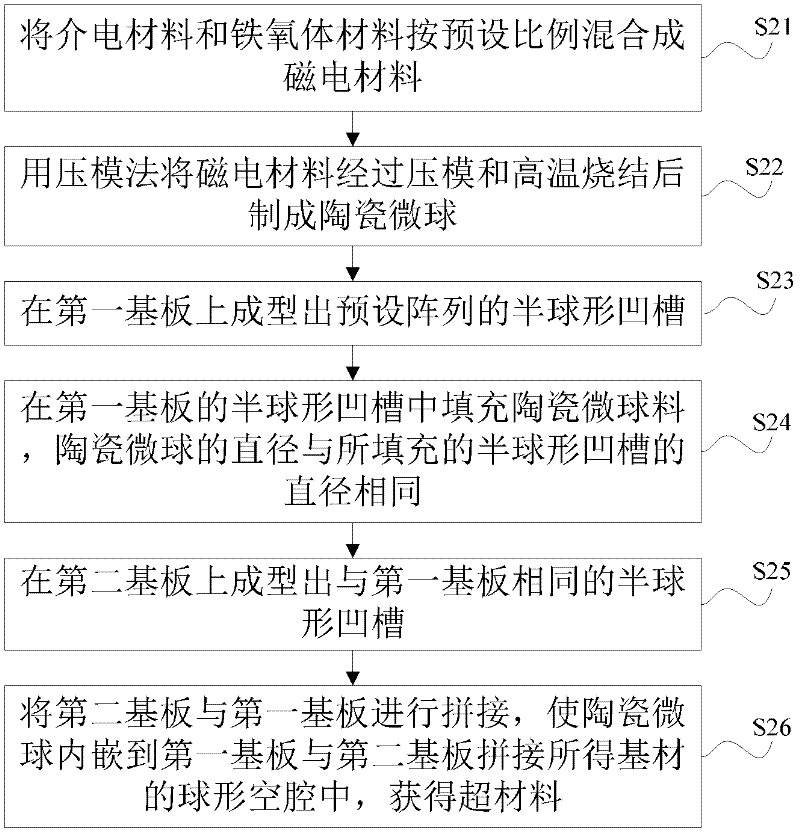

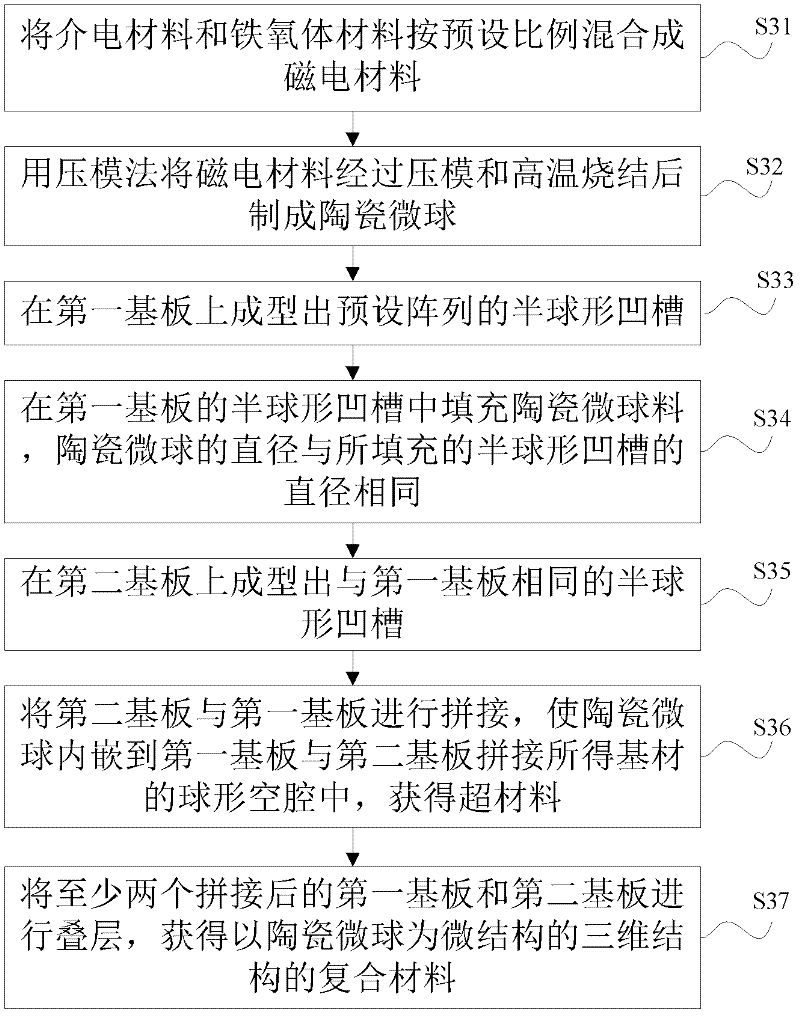

Preparing method of metamaterials

An embodiment of the invention provides a preparing method of metamaterials, which includes: mixing dielectric materials and ferrite materials in preset proportion to form magneto-electric materials, manufacturing the magneto-electric materials into ceramic microspheres through a stamping mode, and leading the ceramic microspheres to be embedded into preset base materials to obtain the metamaterials. In the preparing method, the ceramic microspheres made of the magneto-electric materials are filled in the base materials, dielectric constant and resonance of magnetic conductivity can be led to fall in the same frequency interval, and therefore negative refraction index is achieved.

Owner:KUANG CHI INST OF ADVANCED TECH +1

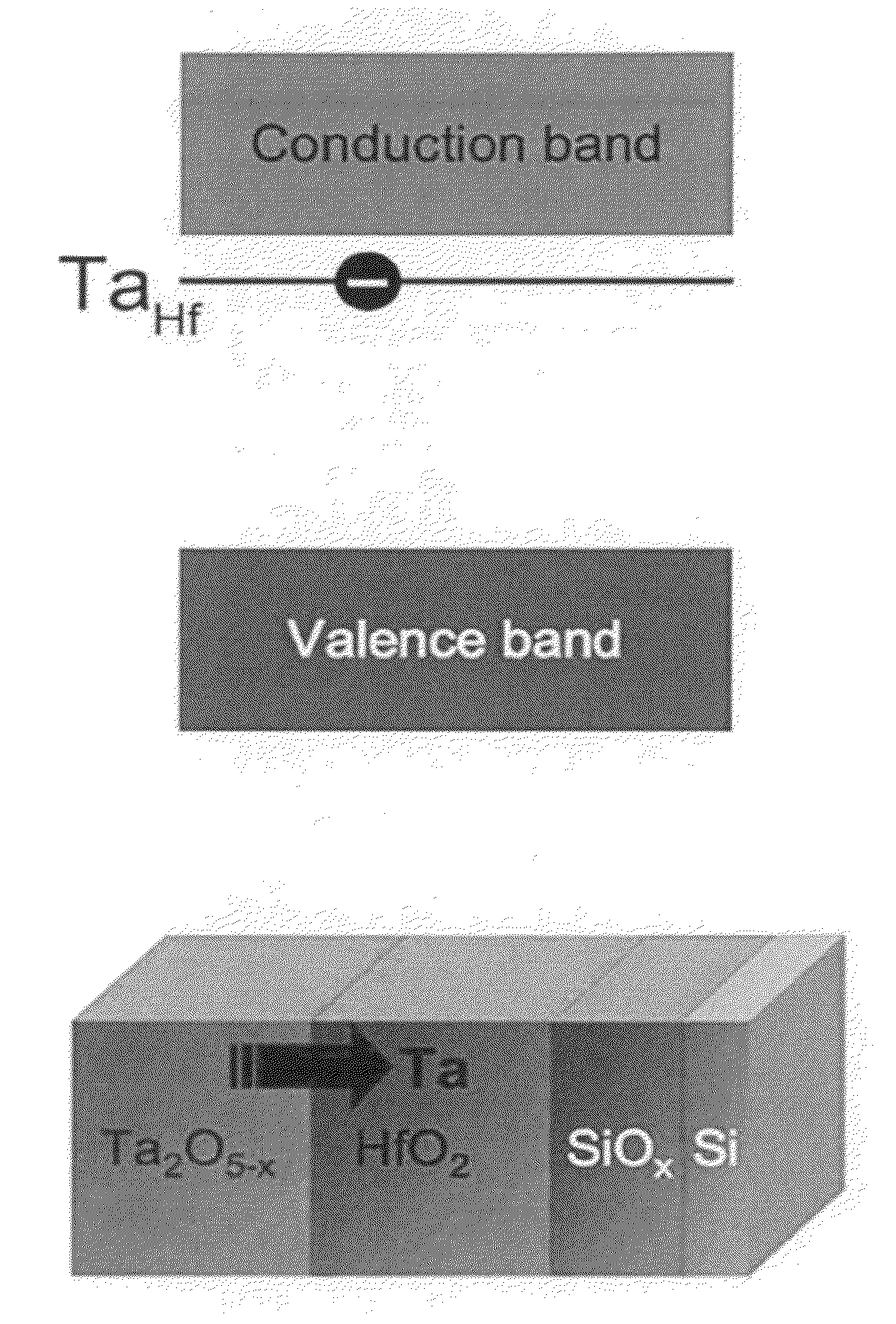

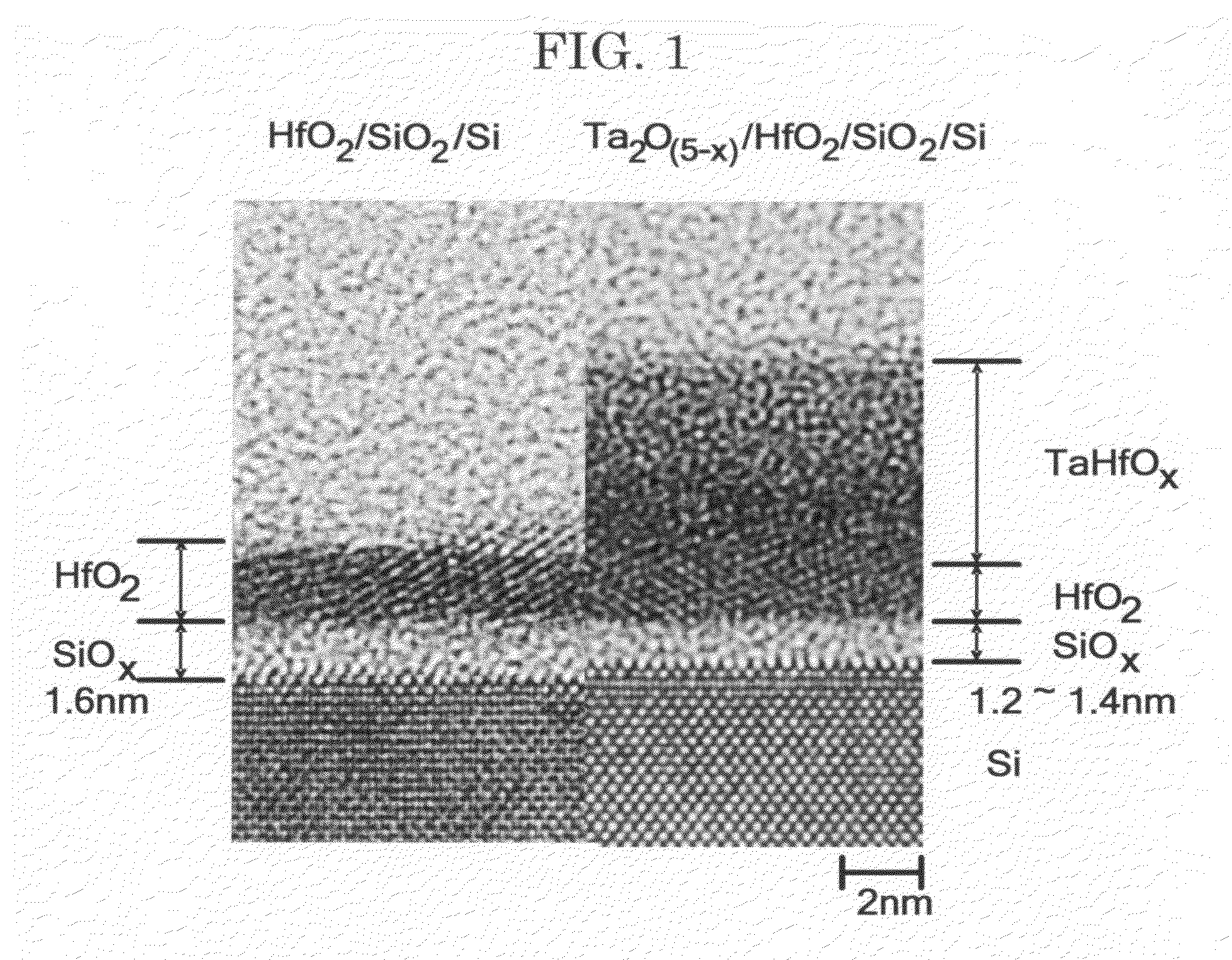

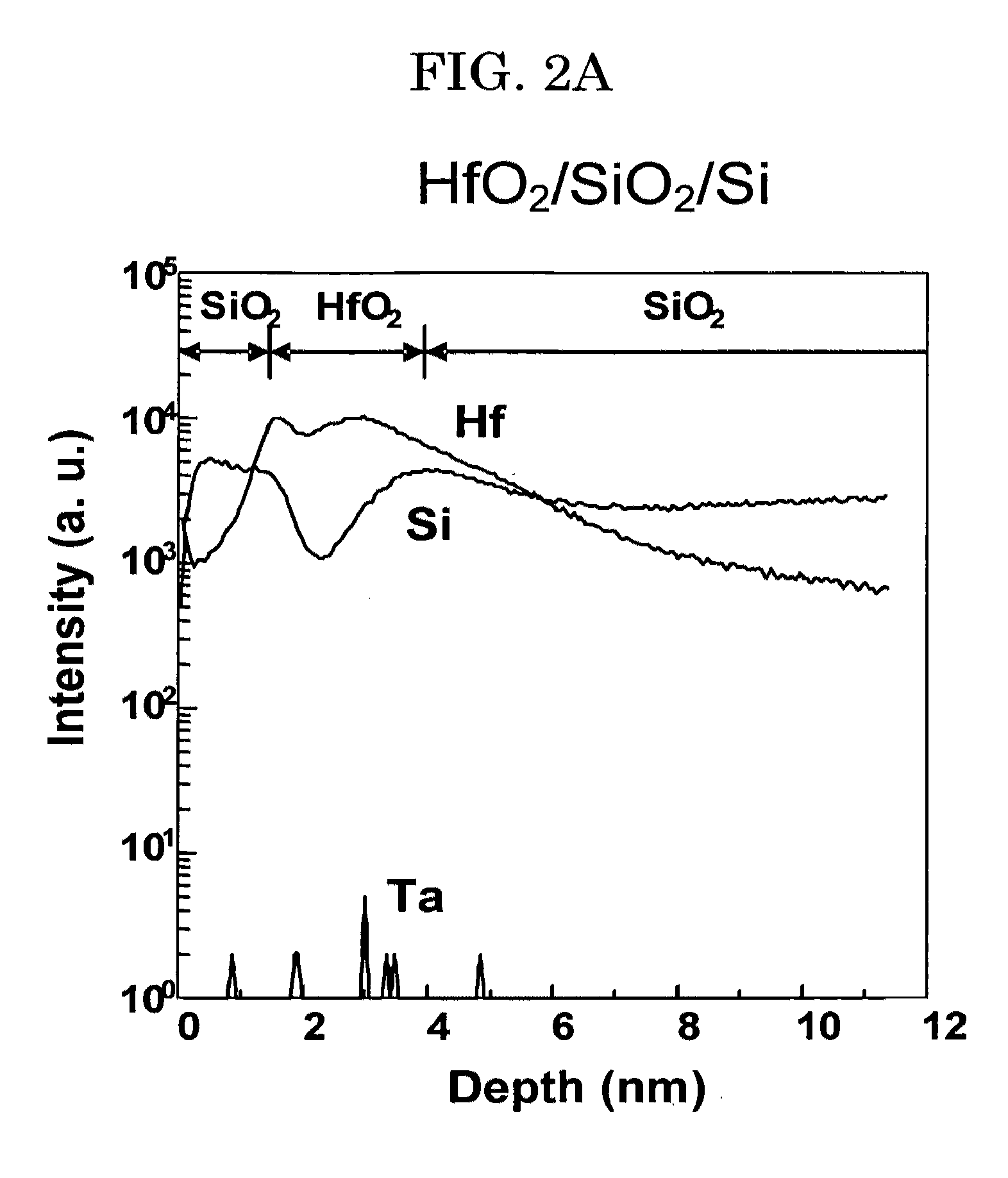

Method for Reducing Thickness of Interfacial Layer, Method for Forming High Dielectric Constant Gate Insulating Film, High Dielectric Constant Gate Insulating Film, High Dielectric Constant Gate Oxide Film, and Transistor Having High Dielectric Constant Gate Oxide Film

InactiveUS20120280372A1Reduce thicknessEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesDielectricGate oxide

To provide a method for reducing a thickness of an interfacial layer, which contains: (a) forming a film of an oxide of a first metal on a semiconductor layer via an oxide film of a semiconducdor serving as an interfacial layer; and (b) forming a film of an oxide of a second metal on the film of the oxide of the first metal, where the second metal has higher valency than that of the first metal.

Owner:NAT INST FOR MATERIALS SCI

Dual damascene process for forming a multi-layer low-k dielectric interconnect

InactiveUS20050130407A1Effective dielectric constantReduce speed delaySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDielectric permittivity

In a dual damascene process for forming a multi-layer low-k dielectric interconnect, the formation of each layer of interconnect comprises deposition of a first low-k dielectric layer, etching of the first low-k dielectric layer to form two dual damascene vias, formation of two Cu conductor plugs enclosed with barrier layers in the two dual damascene vias, etching of the first low-k dielectric layer between the two dual damascene vias to form a trench, and spin-on of a second low-k dielectric layer filled in the trench. The spin-on low-k dielectric layer is selected to have a dielectric constant smaller than that of the first low-k dielectric layer to reduce the equivalent dielectric constant in the layer of interconnect.

Owner:MACRONIX INT CO LTD

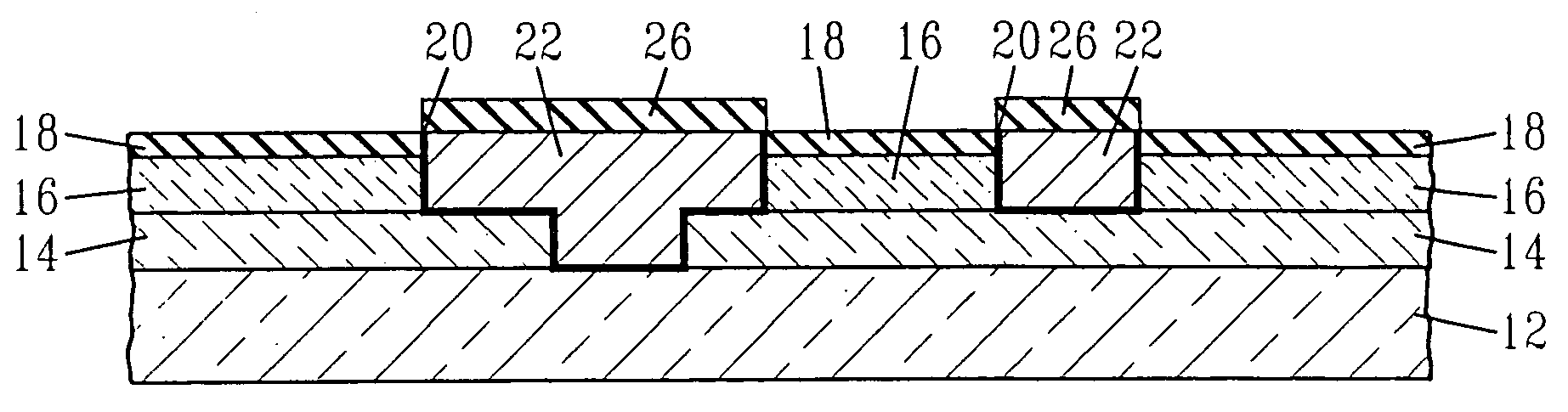

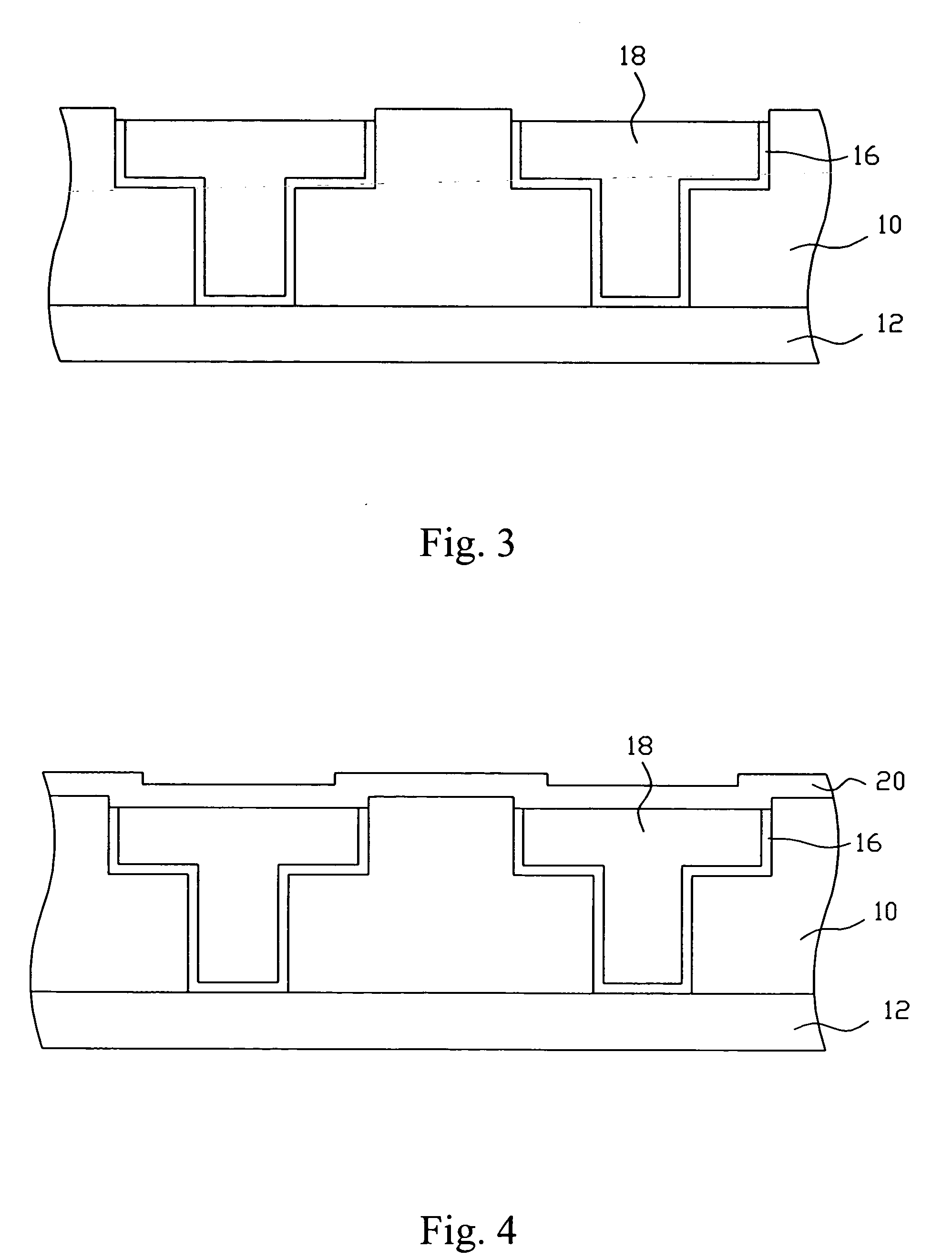

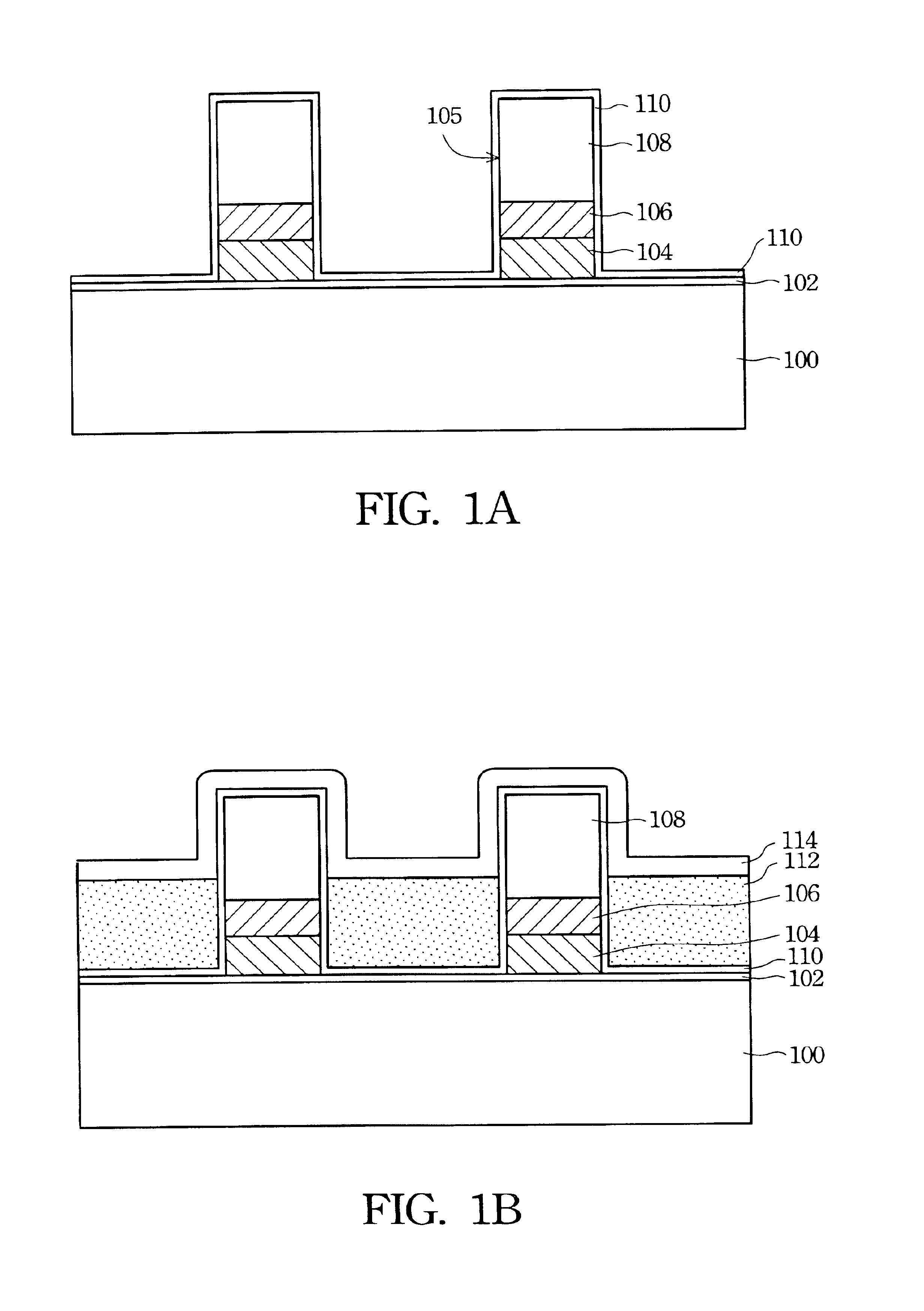

Stacked spacer structure and process

InactiveUS6828219B2Reduce widthReduce coupling capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDielectric layer

A stacked spacer structure and process adapted for a stacked layer on a semiconductor substrate is described. The stacked spacer structure is formed on the sidewalls of the stacked layer which comprise a conductive layer and a cap layer thereon. A dielectric layer made of a material with low dielectric constant lower than that of silicon nitride is formed on the semiconductor substrate. A first silicon nitride layer is then formed over the substrate. The first silicon nitride layer and dielectric layer are etched sequentially to form an inner spacer on the sidewalls of the stacked layer. A second silicon nitride layer is formed over the substrate and is etched to form an outer spacer on the sidewalls of the inner spacer. By forming the stacked spacer structure of the present invention embedded in low dielectric material, the coupling capacitance produced therein will be greatly reduced.

Owner:WINBOND ELECTRONICS CORP

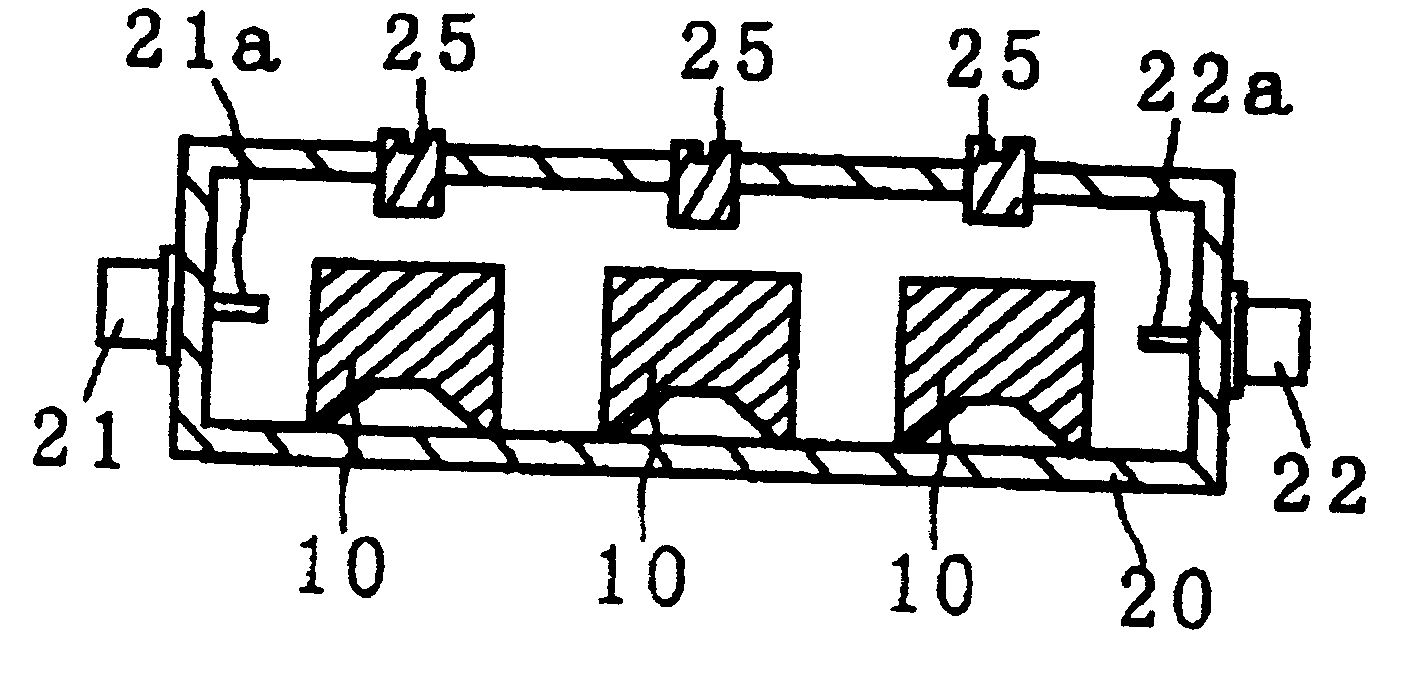

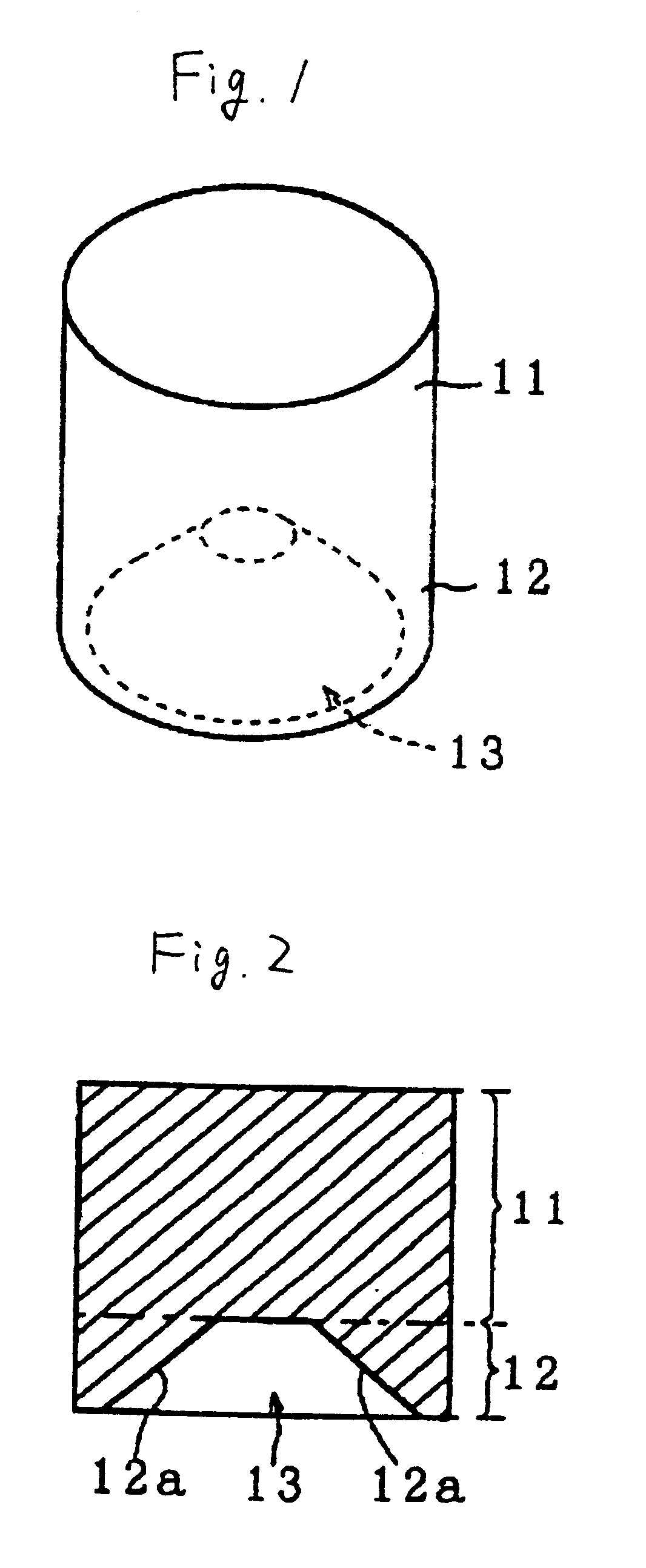

Dielectric resonator, filter, duplexer, oscillator and communication apparatus

InactiveUS6429756B1Reduce decreaseThickness of the dielectric constituting the supporting base sectionResonatorsCoupling devicesDielectric resonatorEngineering

A dielectric resonator comprising a resonator section and a supporting base section which are made of the same dielectric material as a single unit. The resonator section and the supporting base section have substantially the same outside diameter. A concave section having a trapezoidal cross-sectional shape is provided within the supporting base section such that the inside diameter of the supporting base section becomes smaller in the direction from the end face, which is used as a mounting face, and toward the resonator section.

Owner:MURATA MFG CO LTD

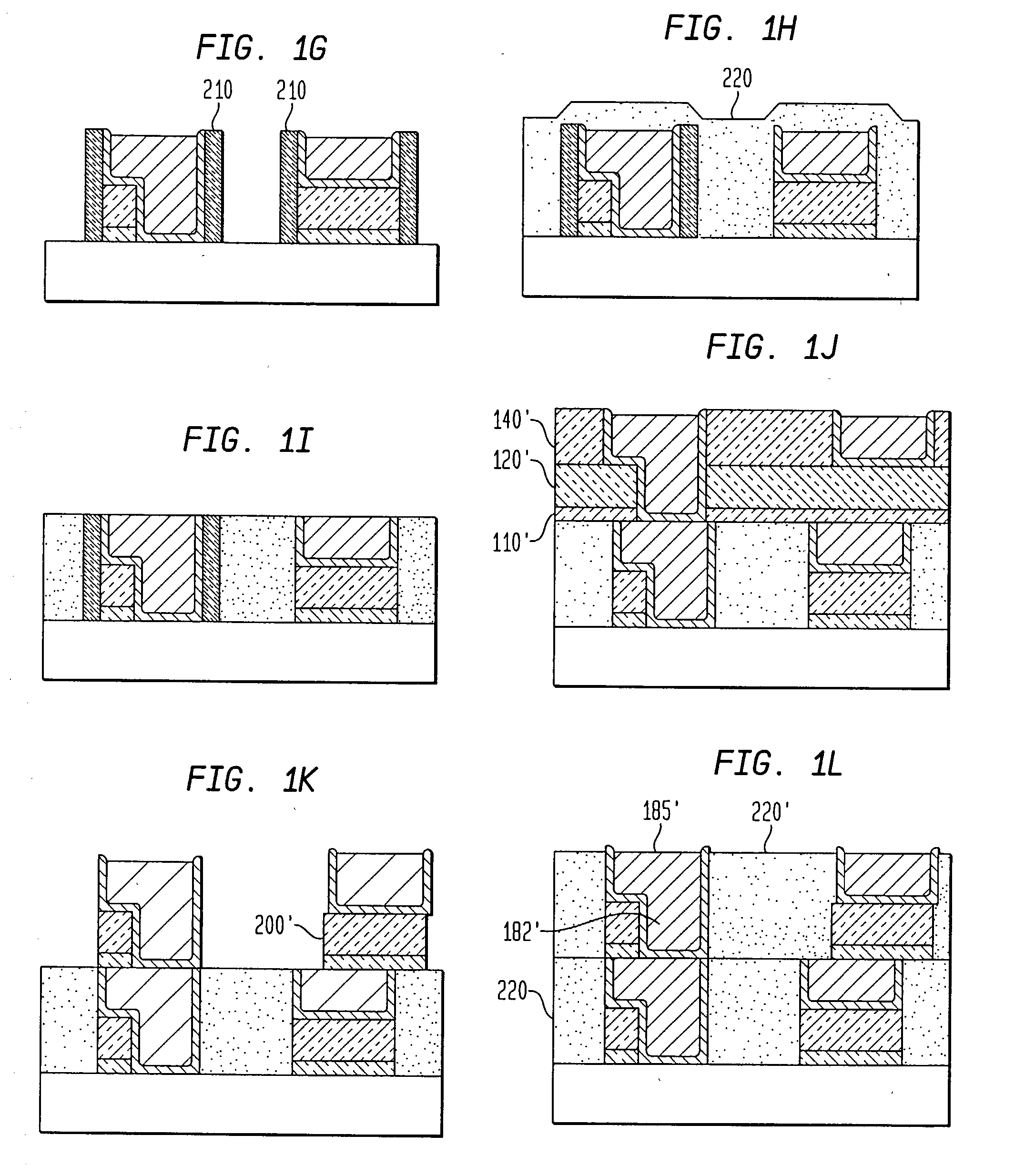

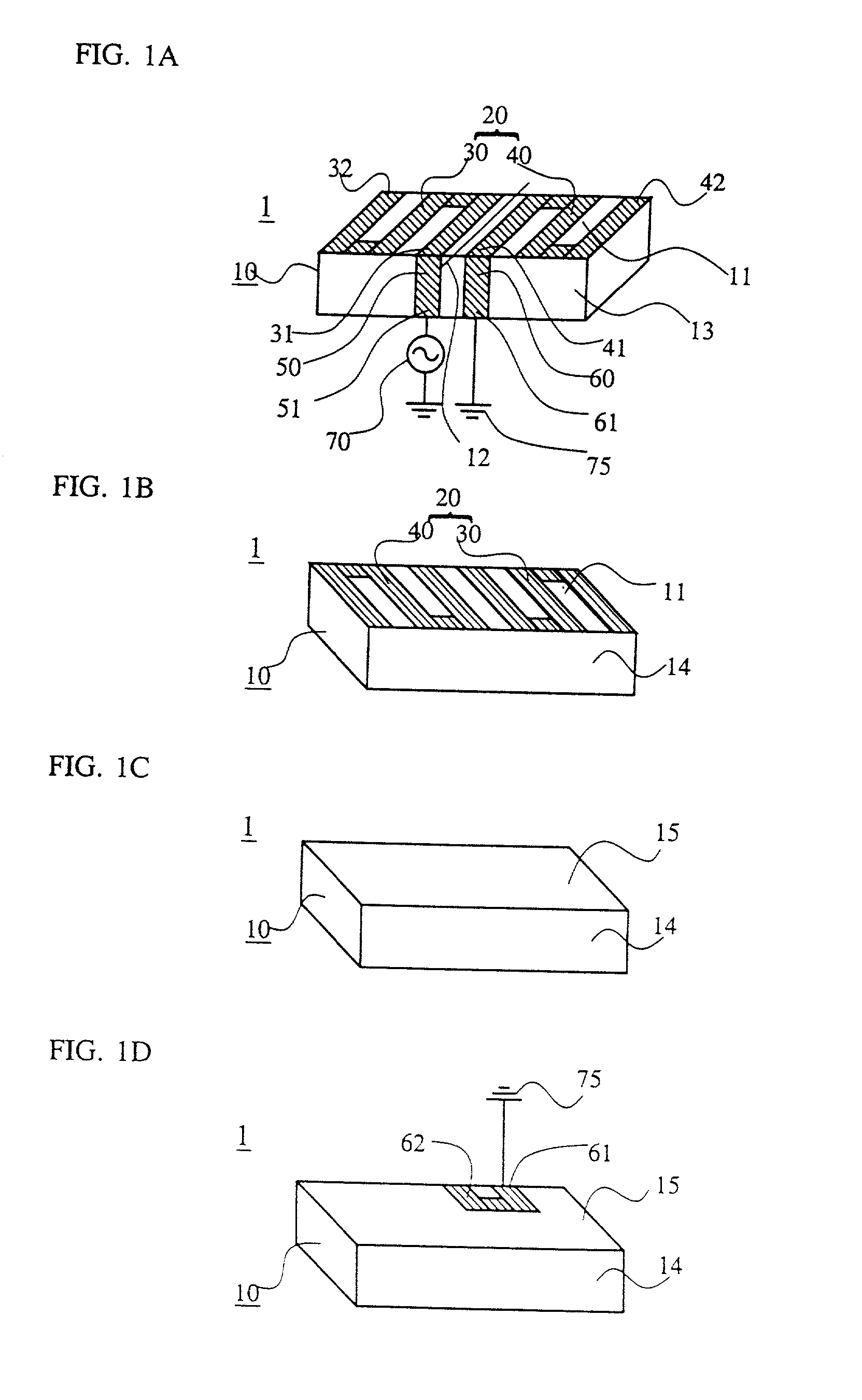

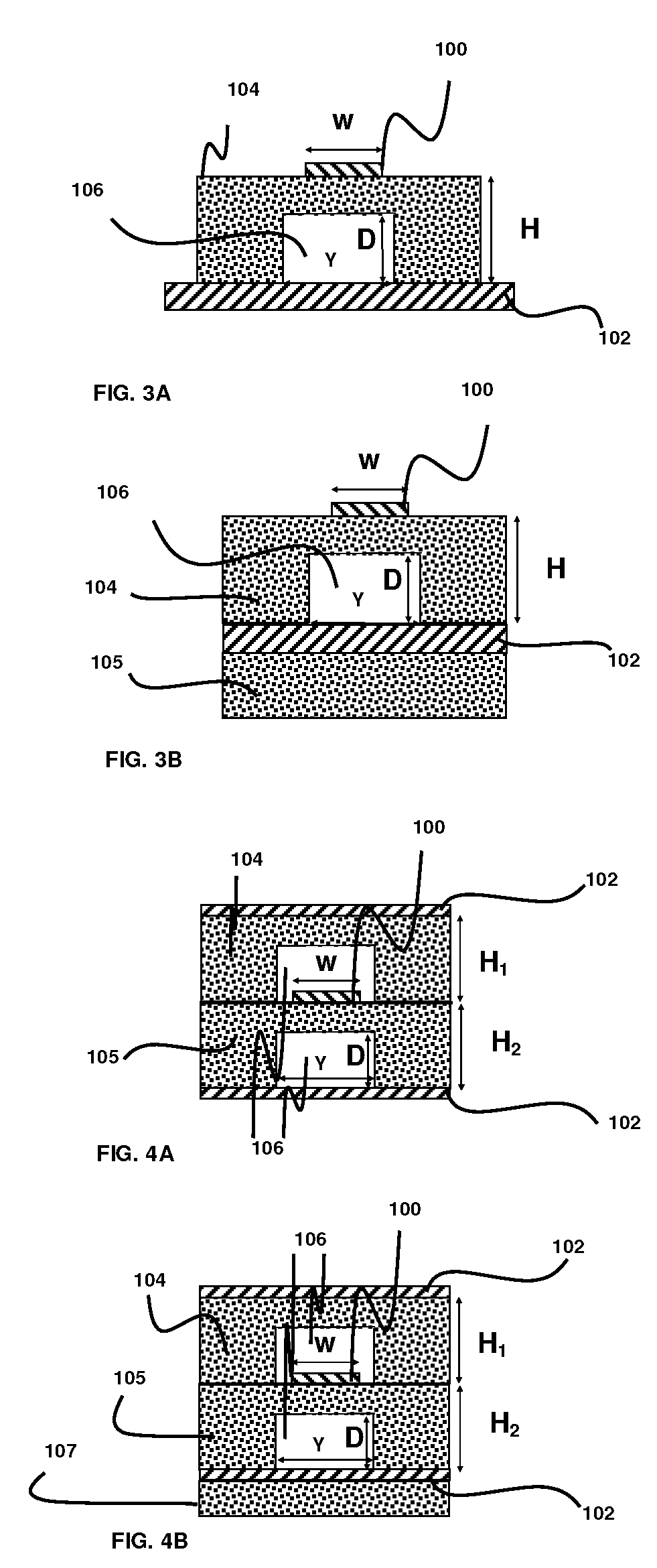

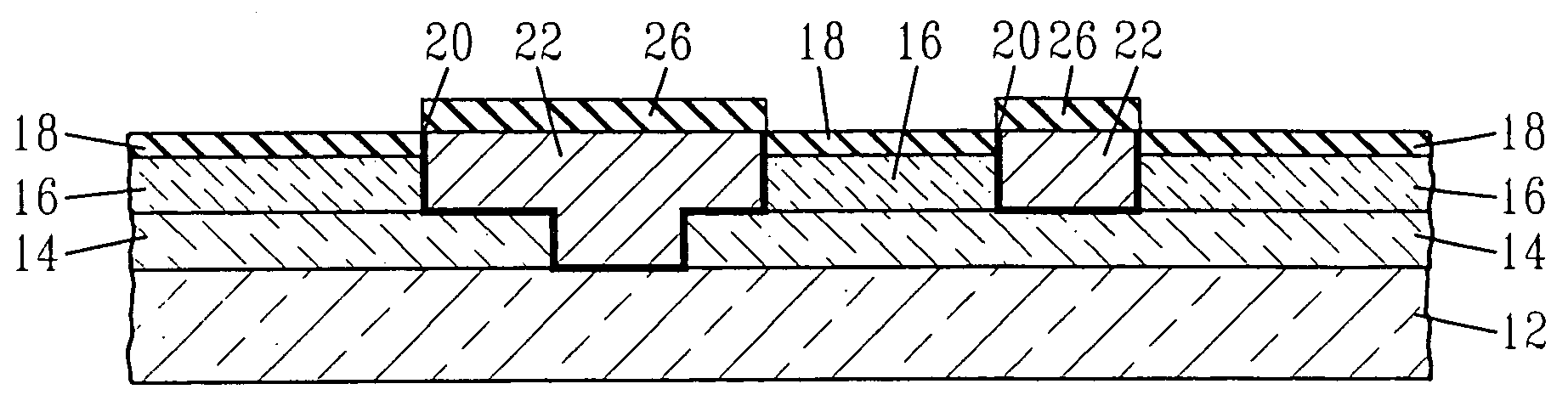

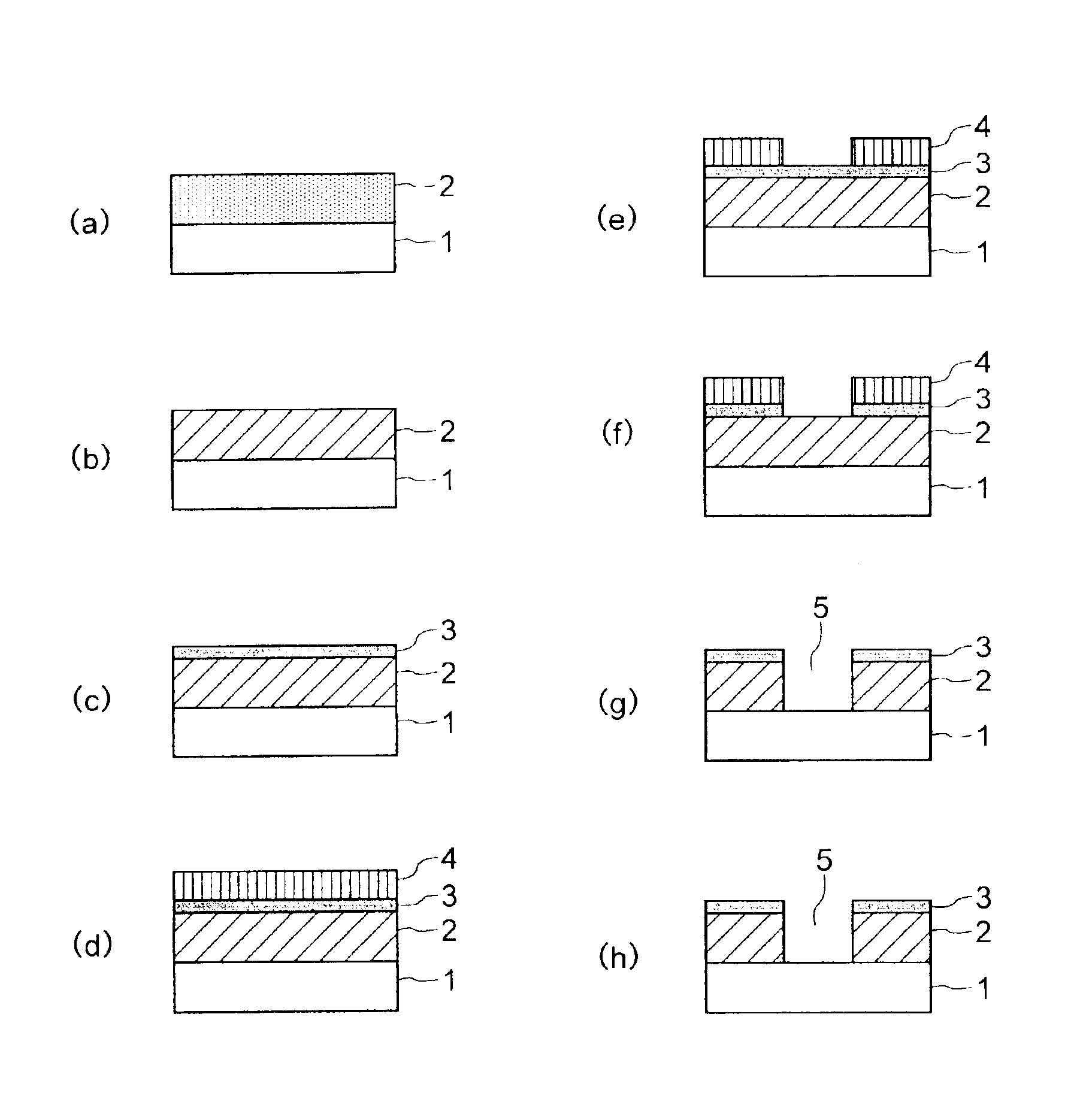

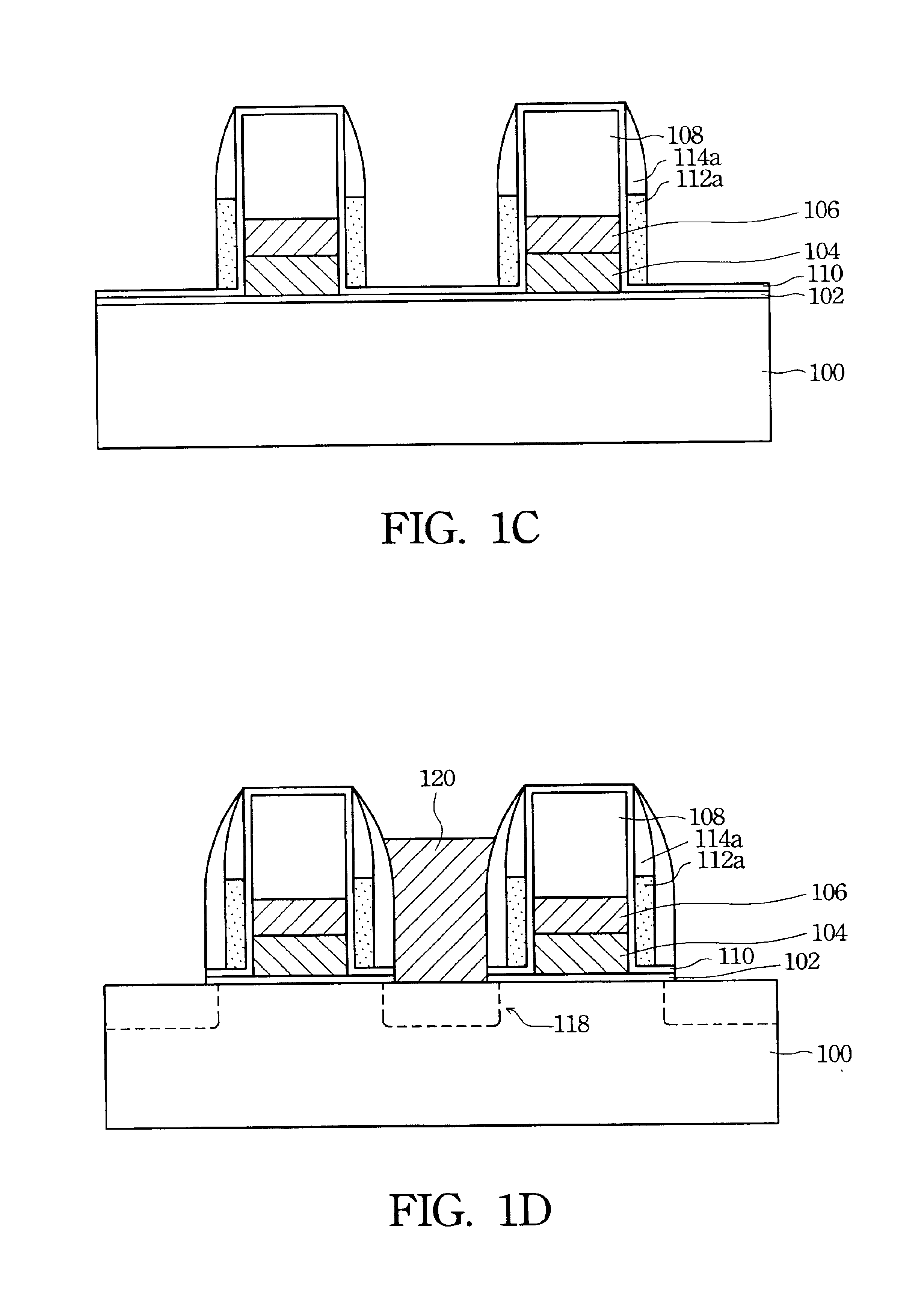

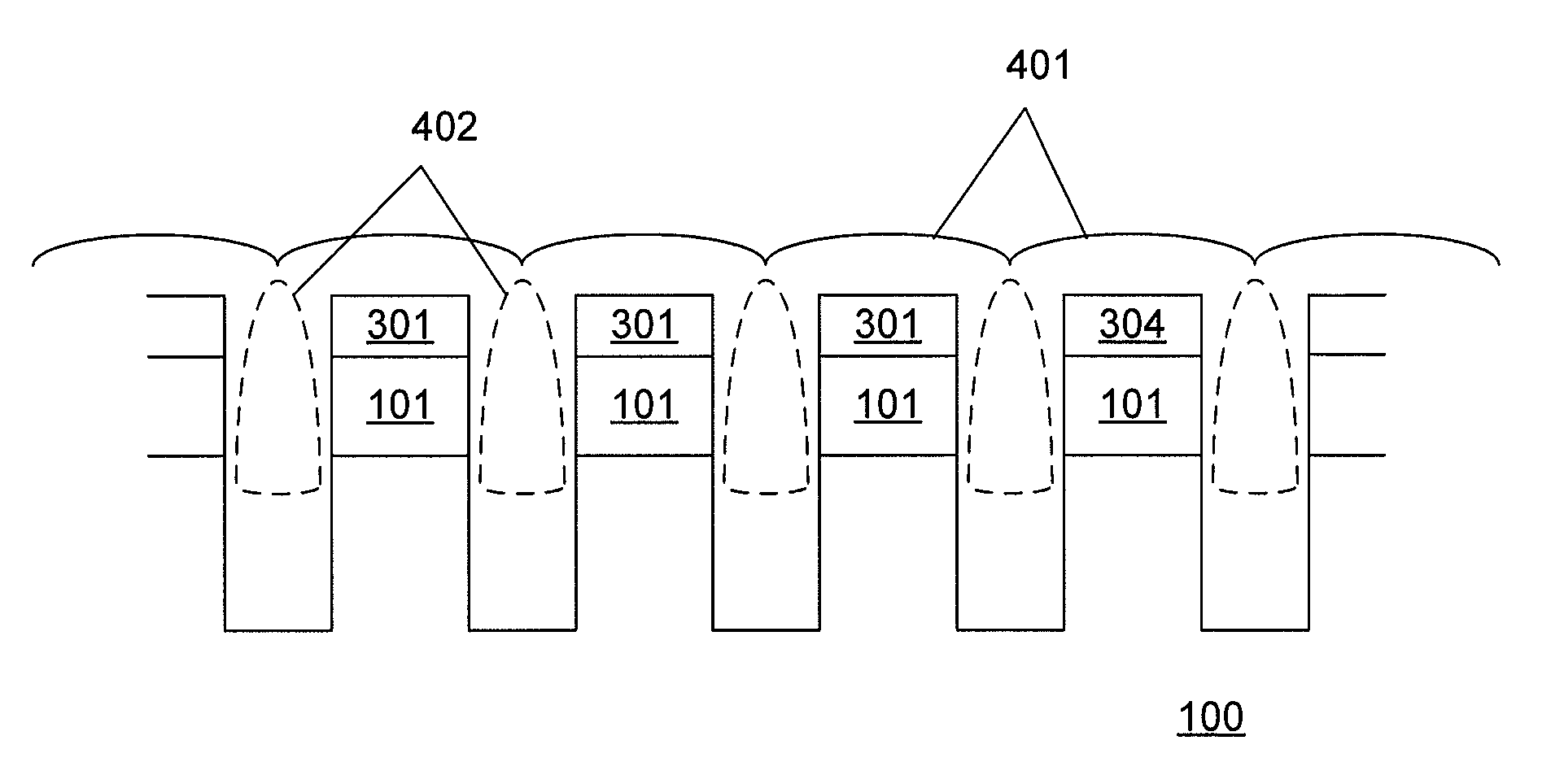

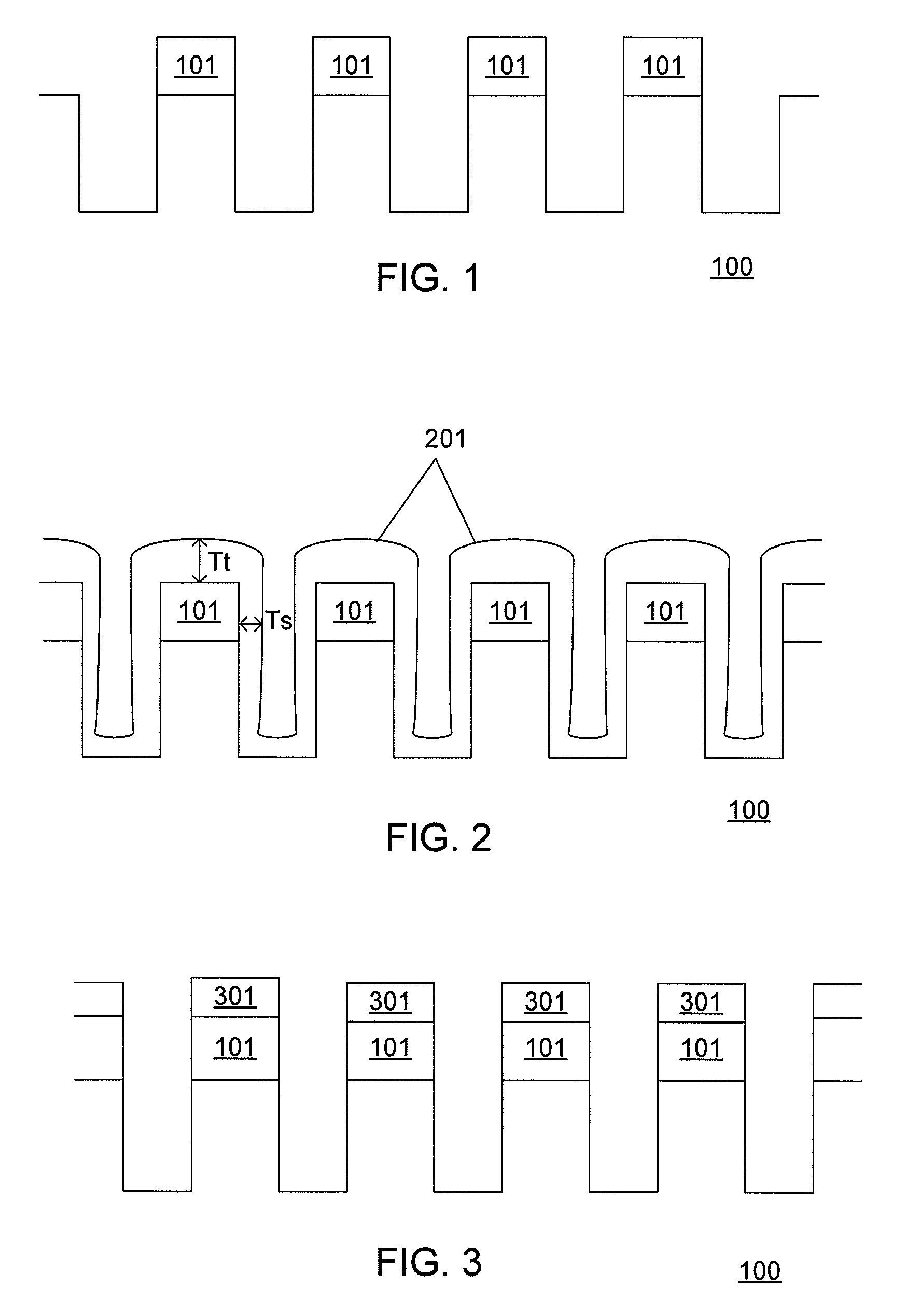

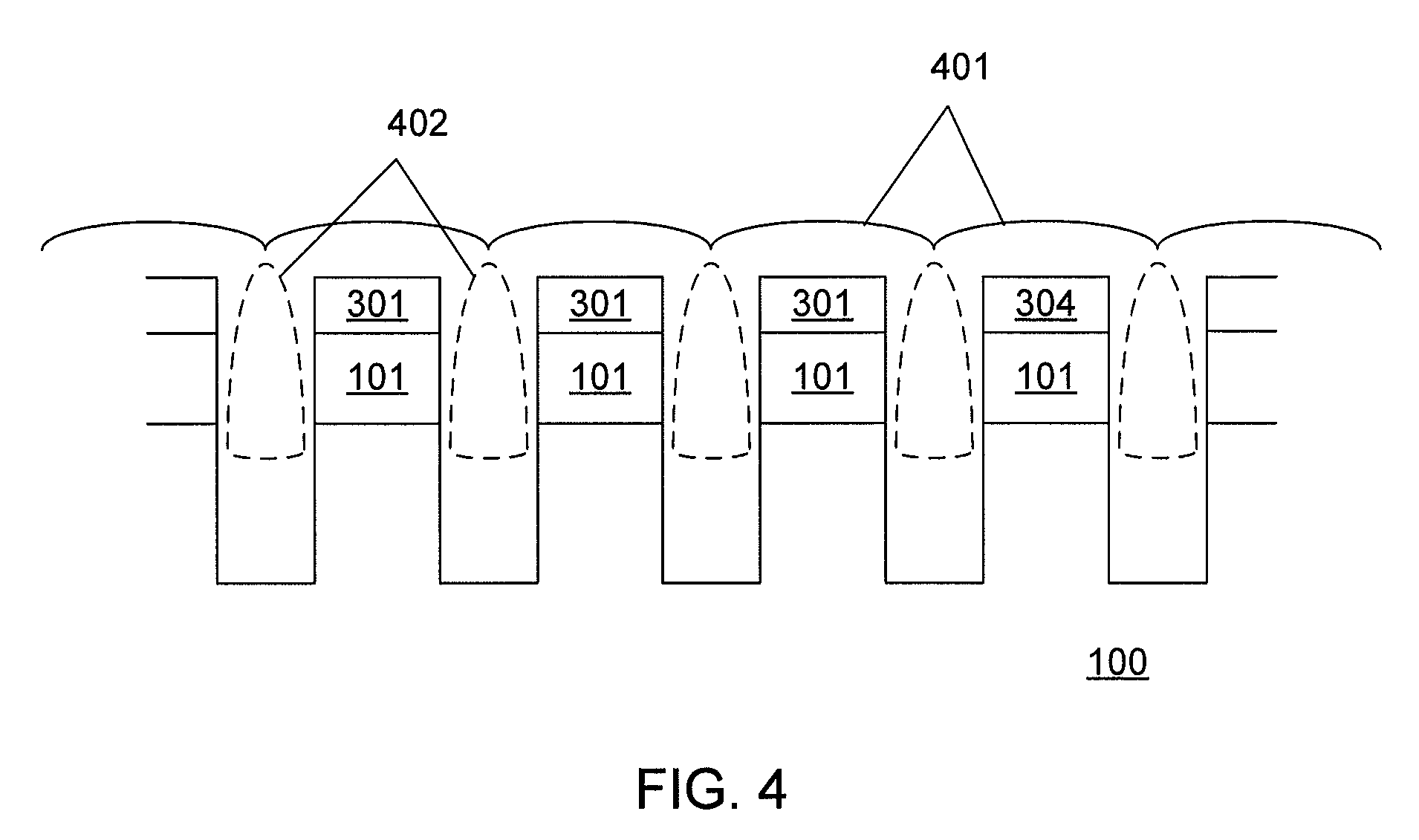

Systems and methods for controlling the effective dielectric constant of materials used in a semiconductor device

InactiveUS7855139B2Low effective capacitanceEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor

Systems and methods for controlling the effective dielectric constant of materials used in a semiconductor device are shown and described. In one embodiment, a method comprises providing a semiconductor substrate with a plurality of pillars formed thereon, depositing a first layer of dielectric material over a plurality of pillars, removing a portion of the first layer deposited over the plurality of pillars, and depositing a second layer of dielectric material over the plurality of pillars, where the second layer leaves a plurality of voids between the plurality of pillars.

Owner:SEMATECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com