Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32results about How to "Low effective capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

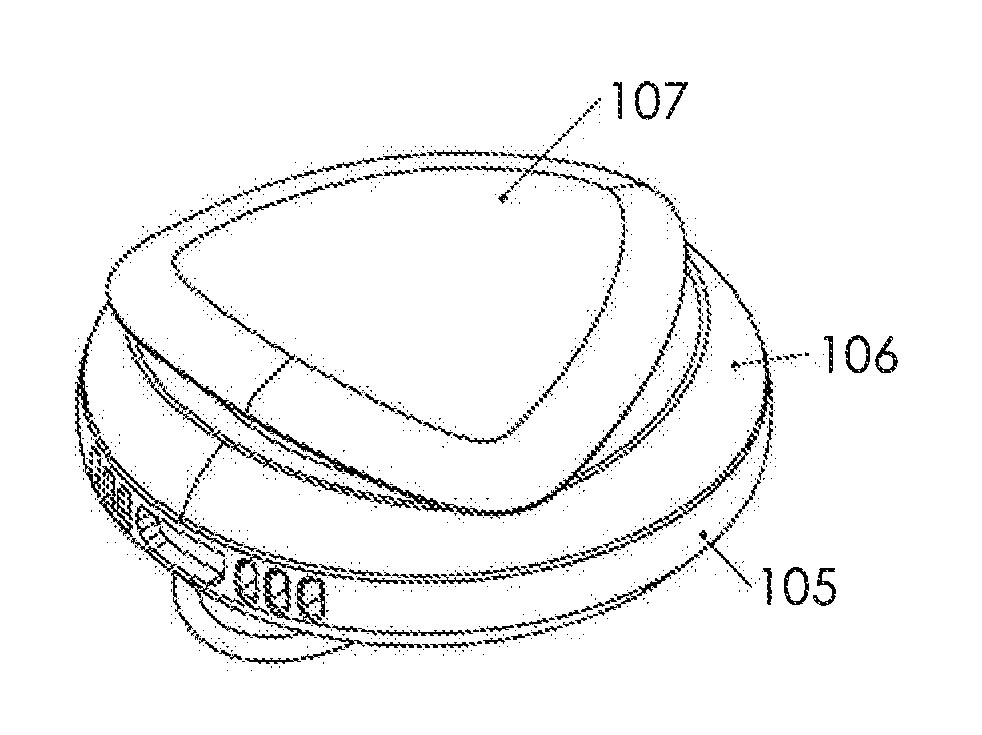

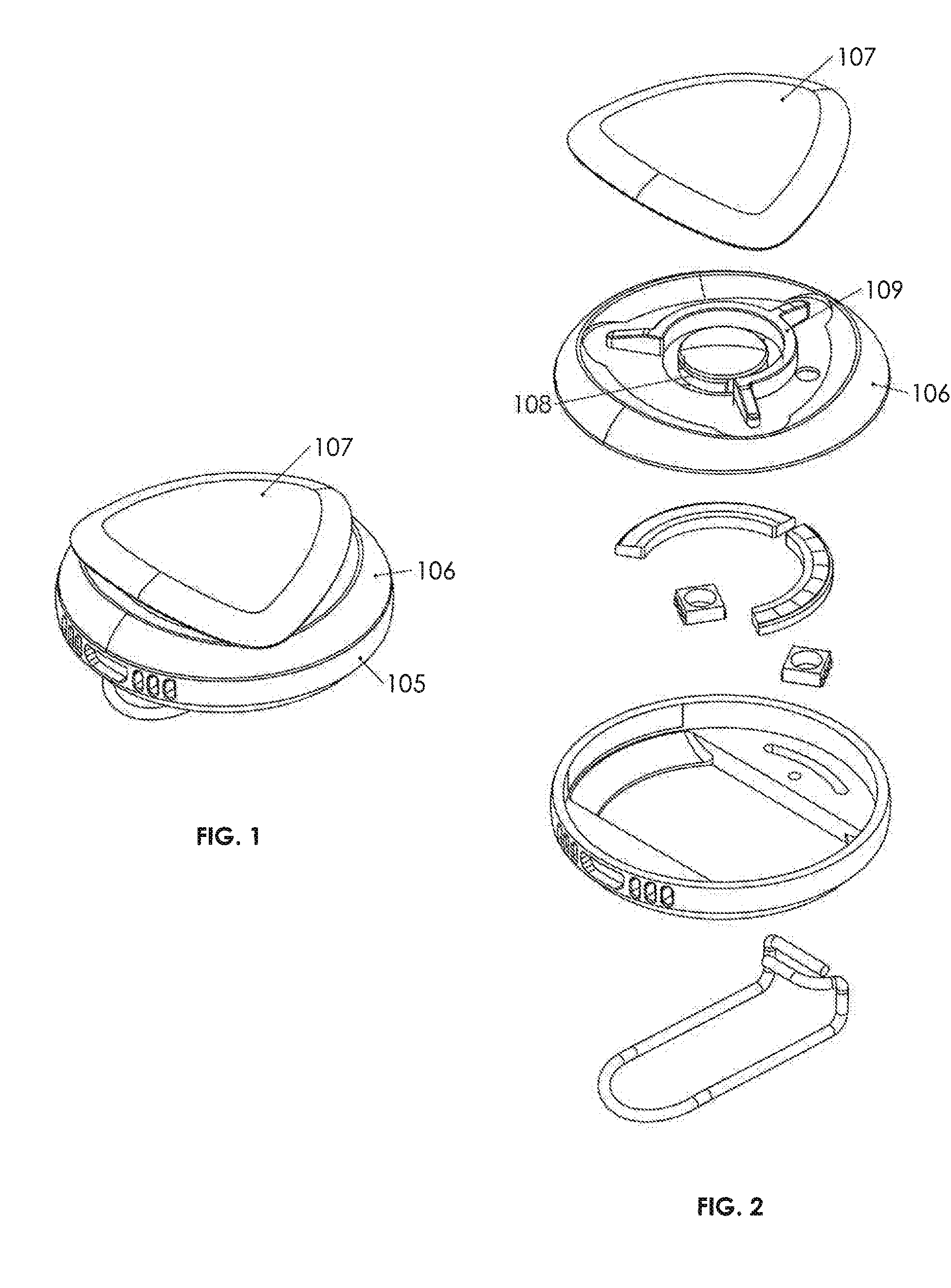

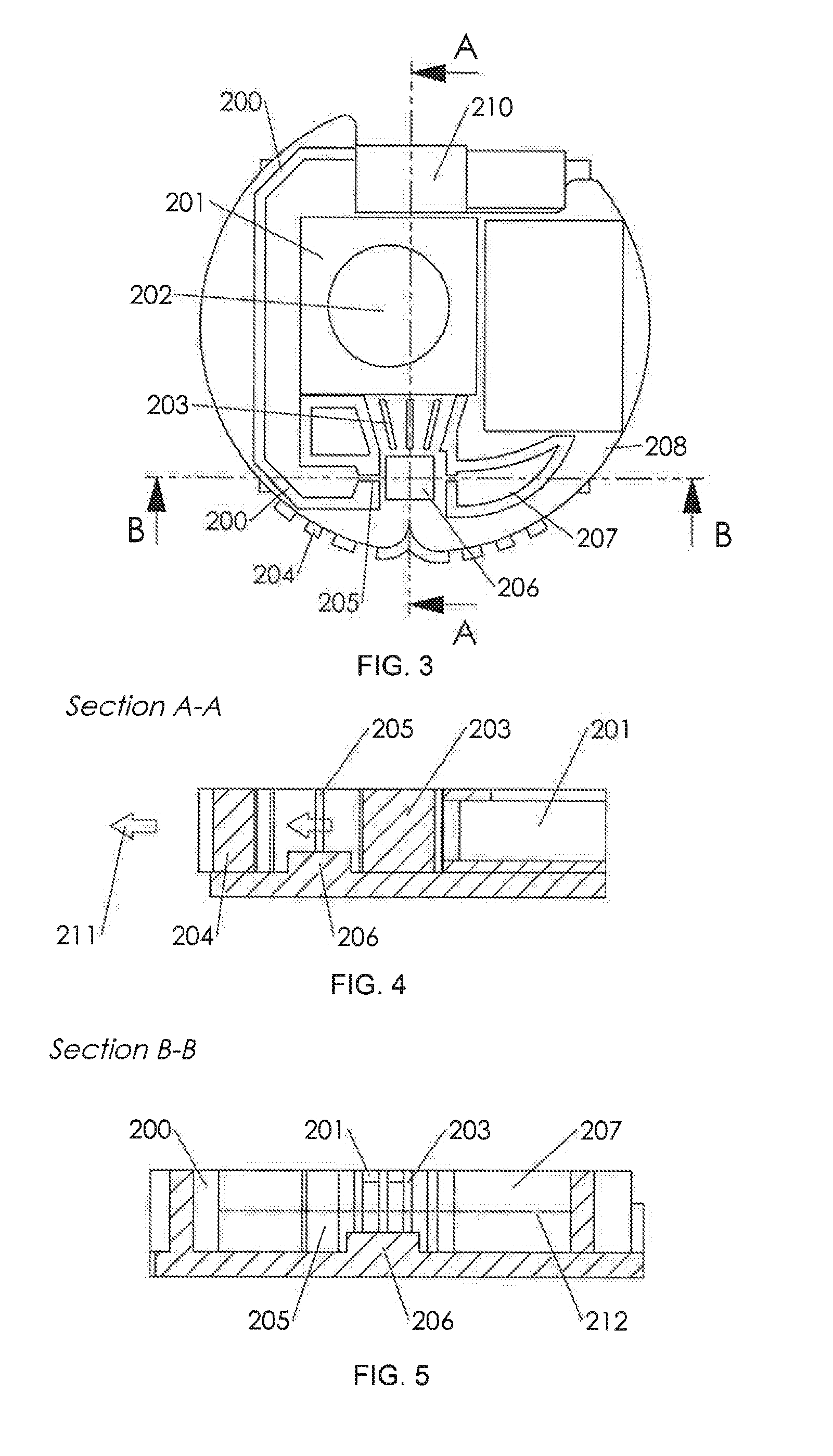

Portable device for detecting and measuring particles entrained in the air

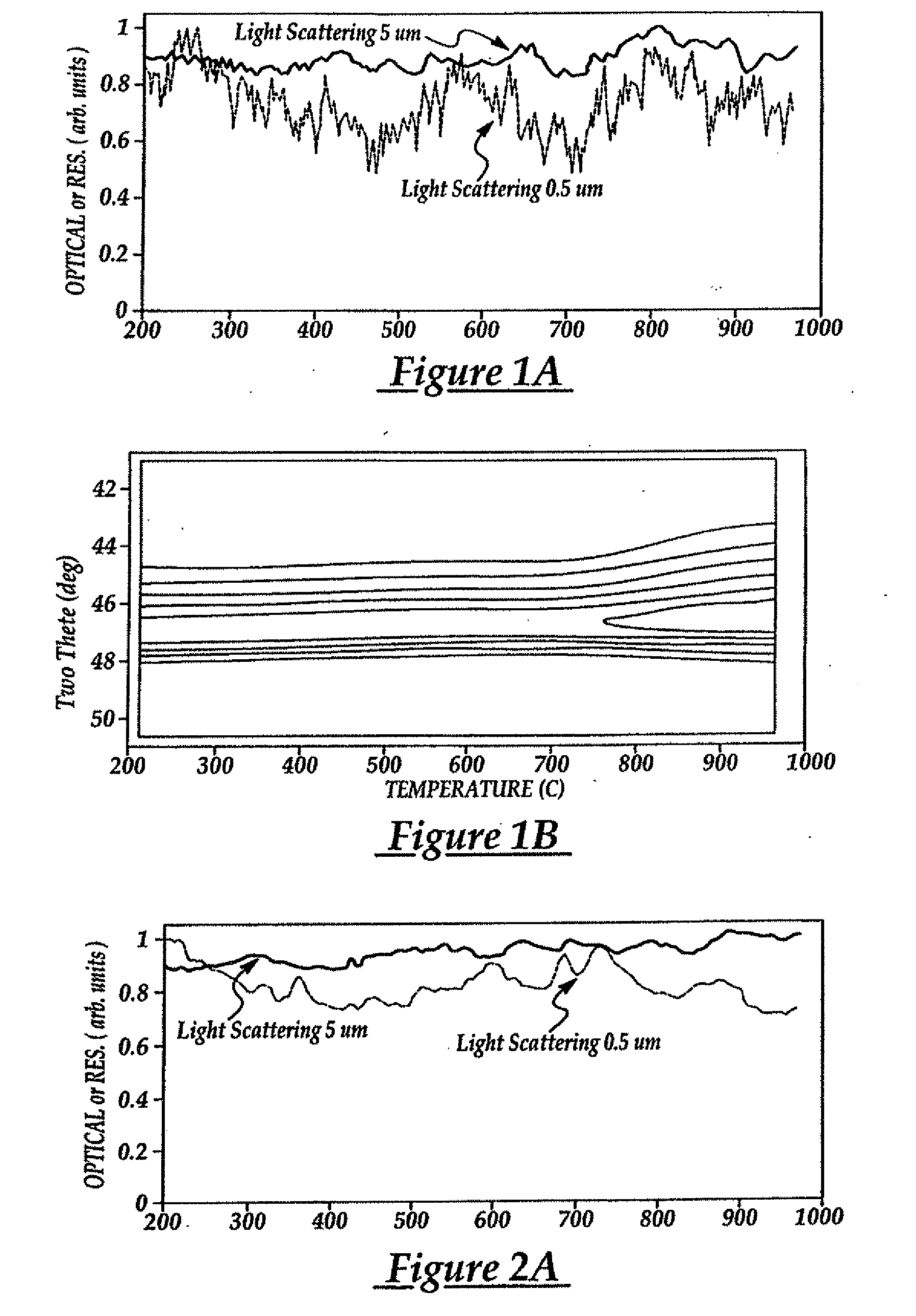

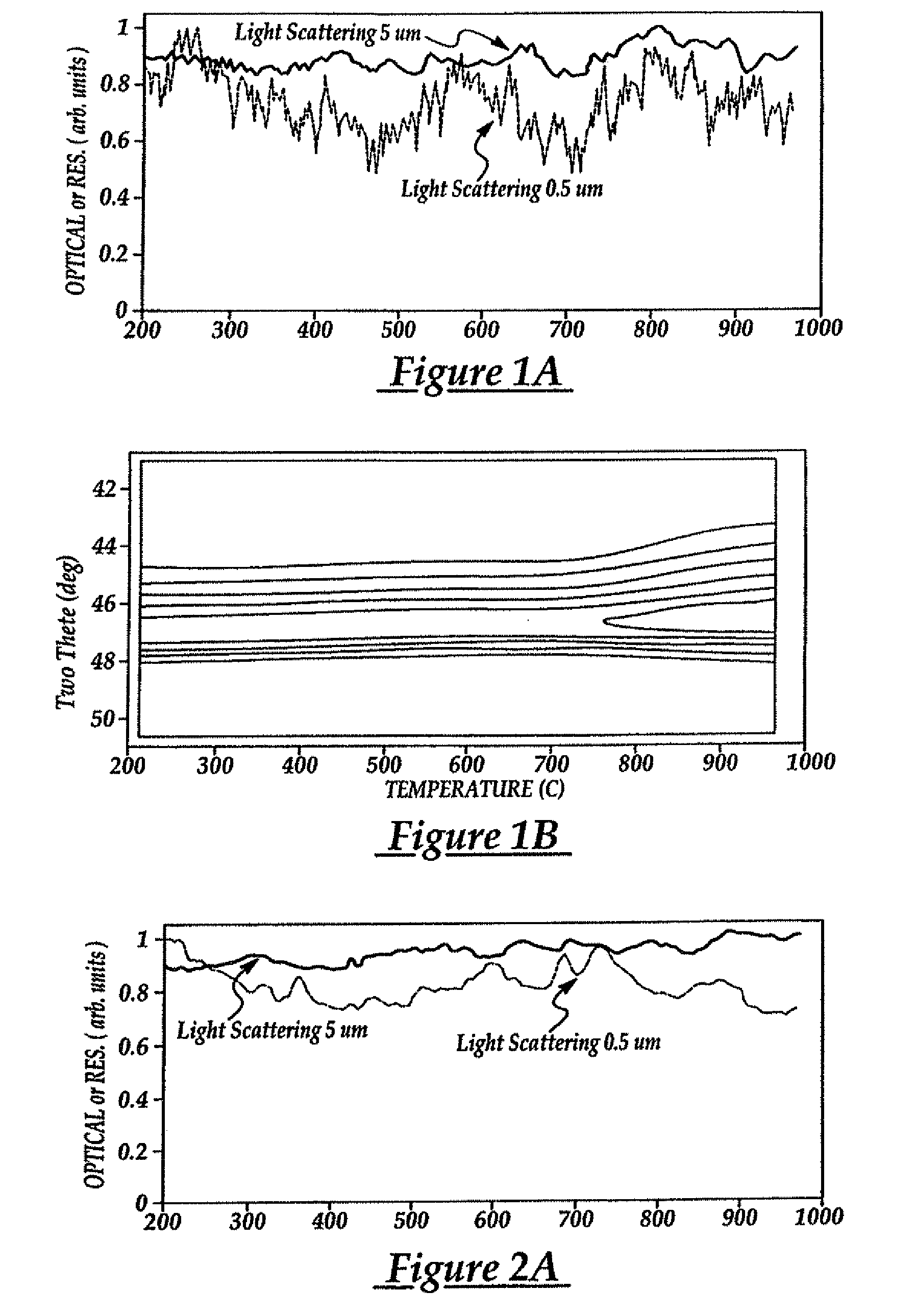

ActiveUS20170023457A1Reduce areaIncrease the areaScattering properties measurementsParticle suspension analysisLight beamEngineering

A portable ambient air quality monitor having an enclosure to enclose and protect the monitor from an ambient environment and an airflow intake for controllably allowing ambient air to enter the monitor. A photodiode is disposed at a location downstream from a fan. The airflow from the fan is laminarized by a mesh or baffle to allow a thin stream of air to flow over the photodiode. A sensing region is defined by an intersection of an airflow sampling path and an optical path. The sensing region is also disposed above the photodiode. The airflow sampling path is configured to receive laminar airflow from the airflow intake and for directing the laminar airflow into the sensing region. A light beam is generated from a laser to reflect the light beam for reducing the required area of the sensing region to detect and measure the particles floating in the ambient air.

Owner:TZOA CLAD INNOVATIONS LTD

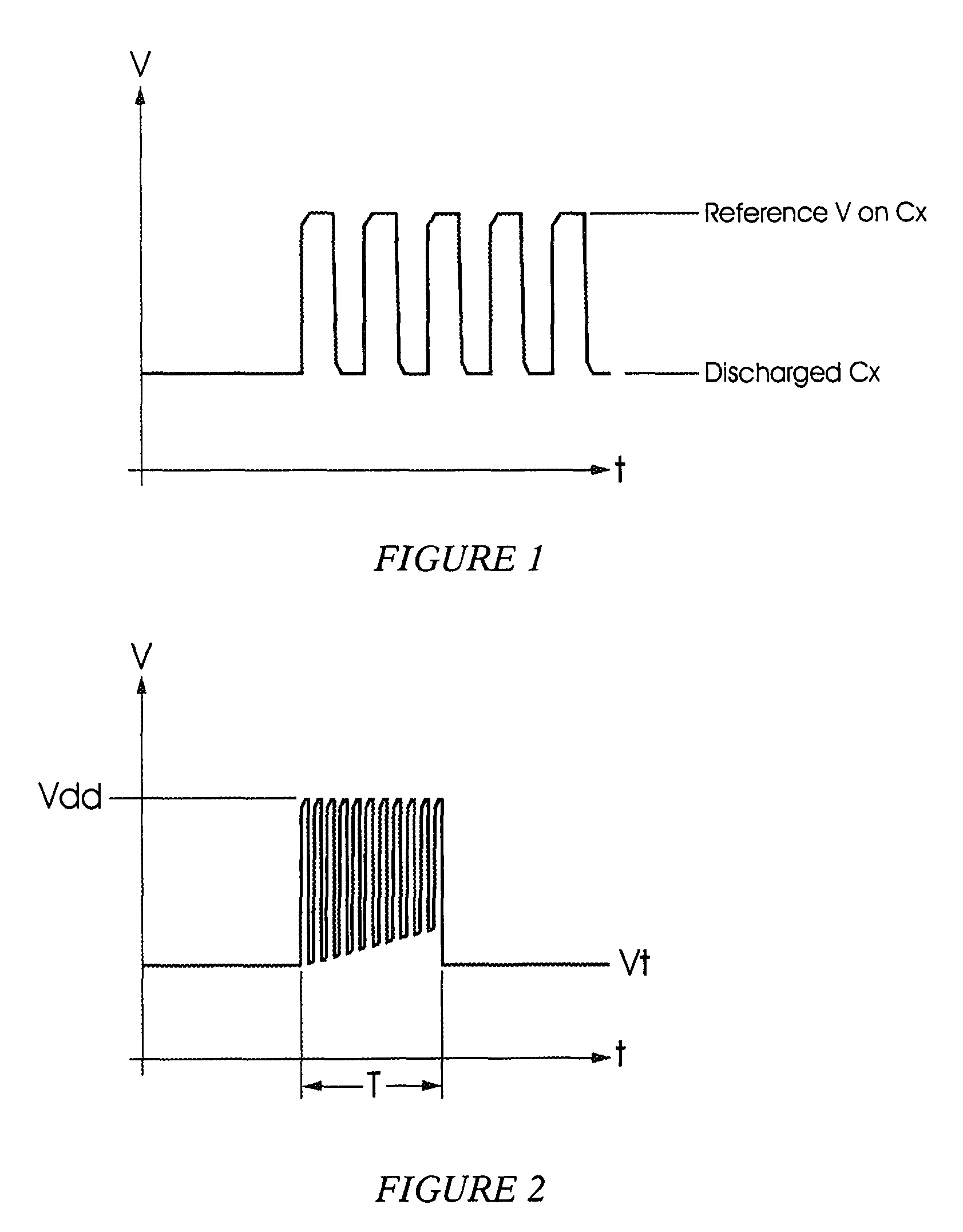

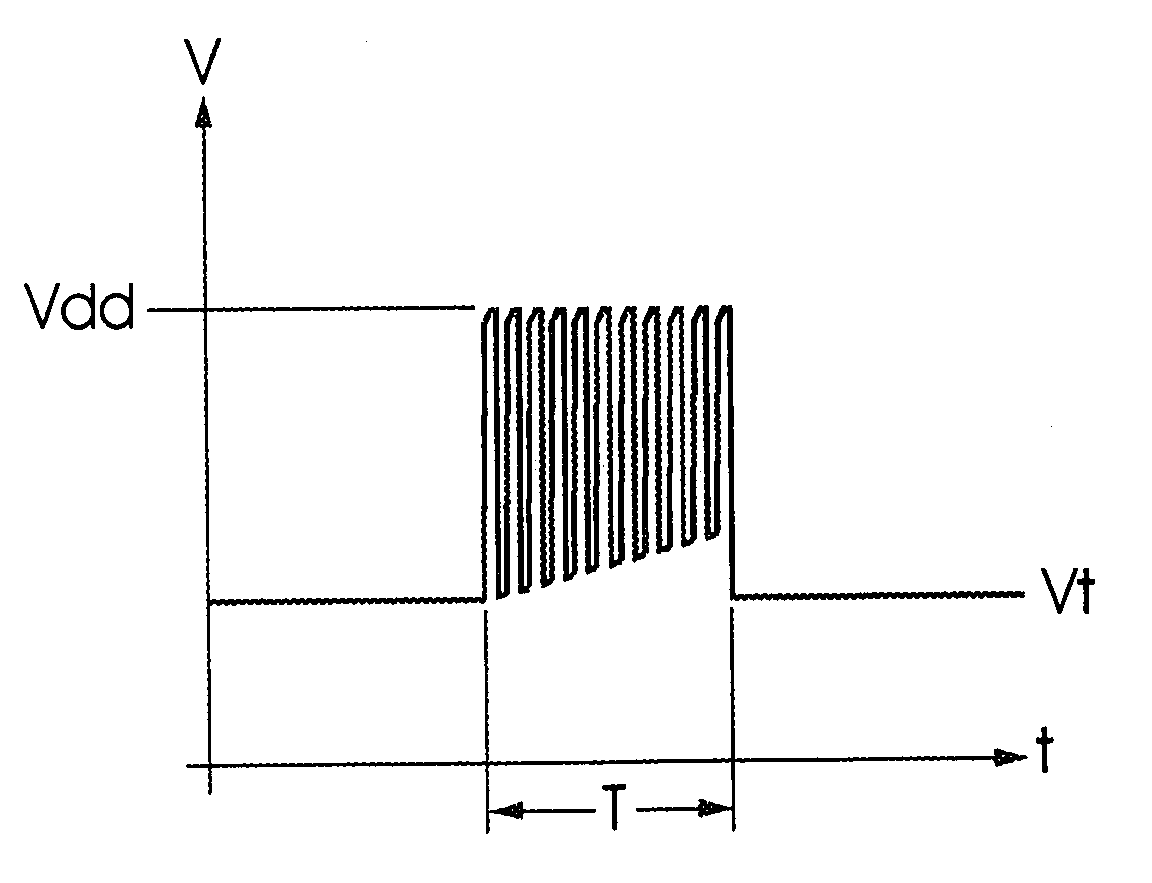

Noise rejection and parasitic capacitance removal implementations

ActiveUS8395395B2Accurate identificationLow effective capacitanceTransmission systemsResistance/reactance/impedenceSoftware engineeringParasitic capacitance

A capacitive sensing circuit including a microchip and a sense plate, wherein the microchip comprises a hardware Q RF noise detector module that provides a logical indication of when noise impacts on the integrated circuit.

Owner:AZOTEQ HLDG LTD

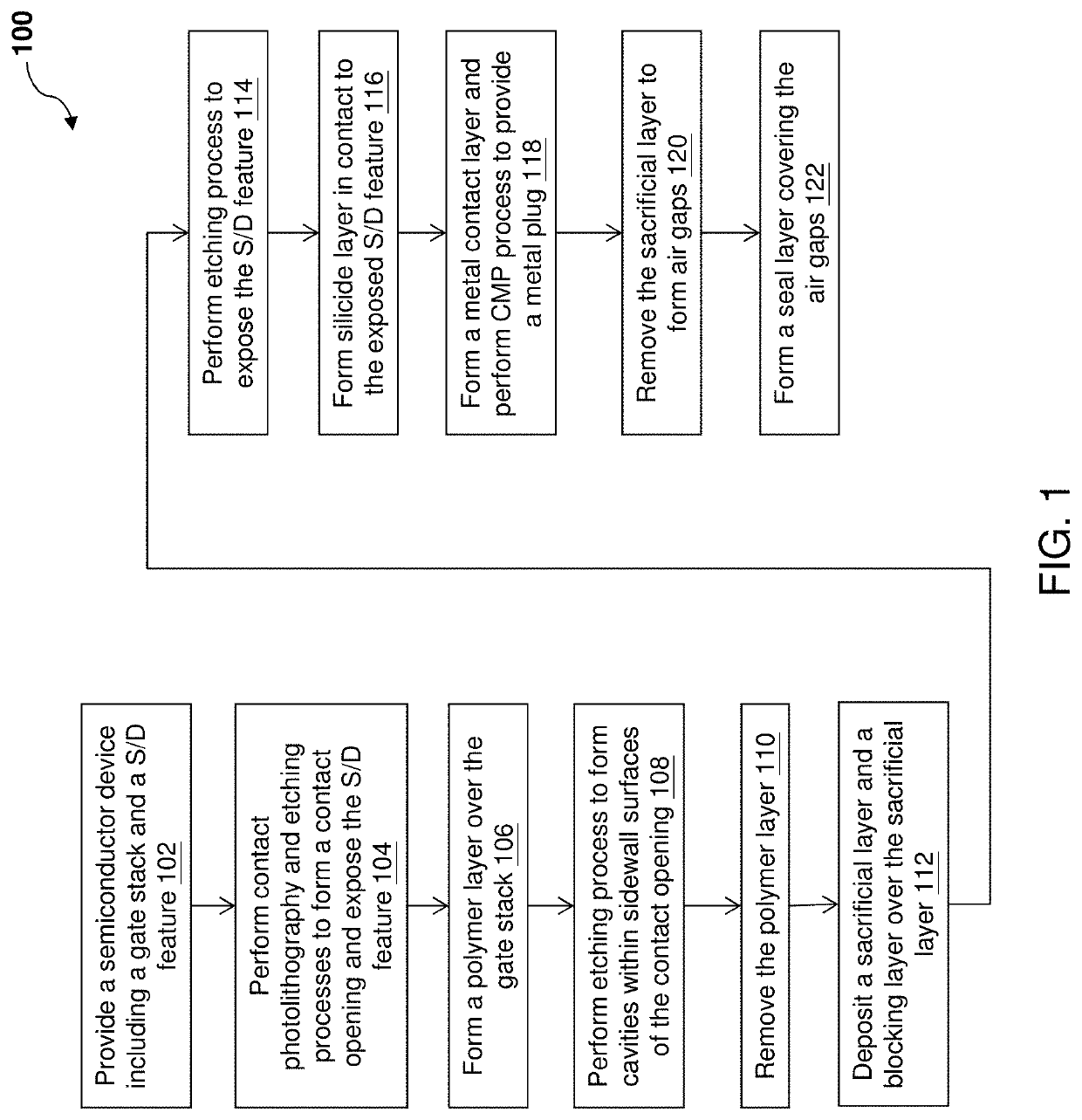

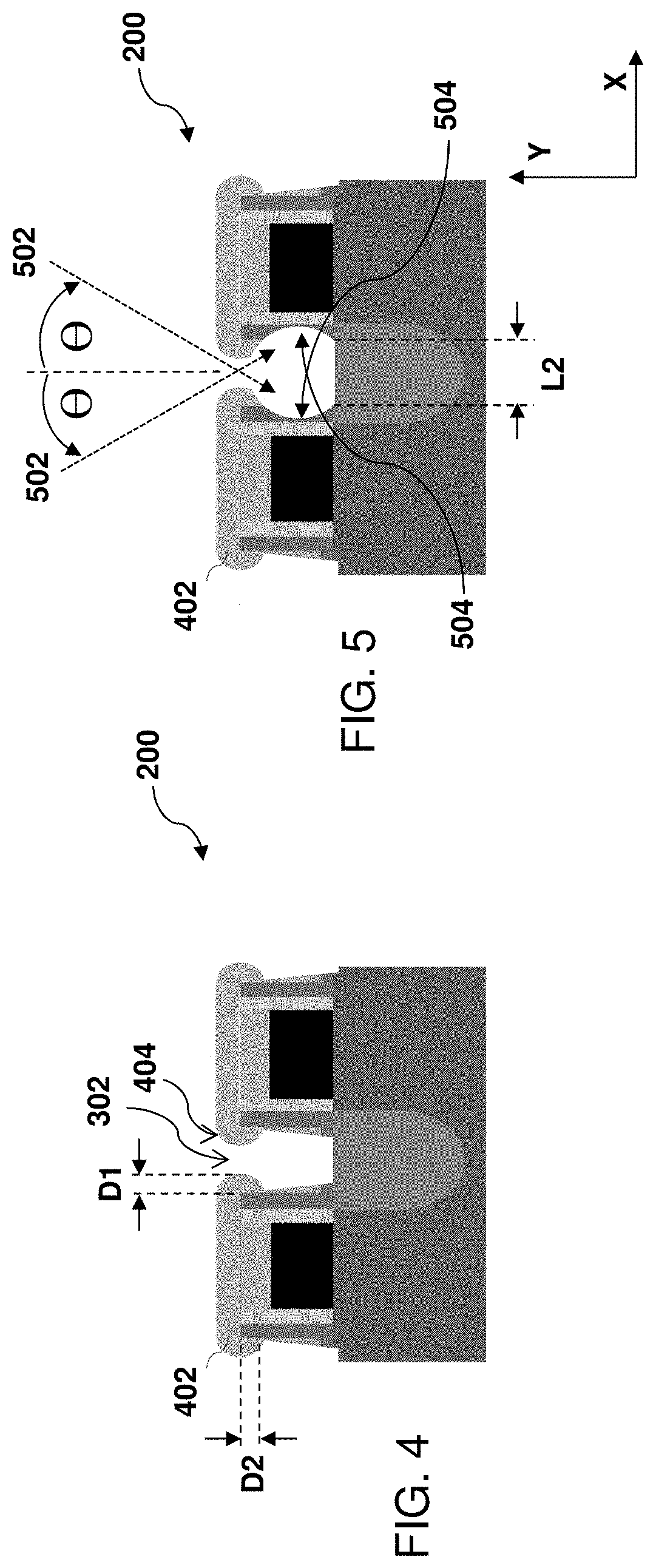

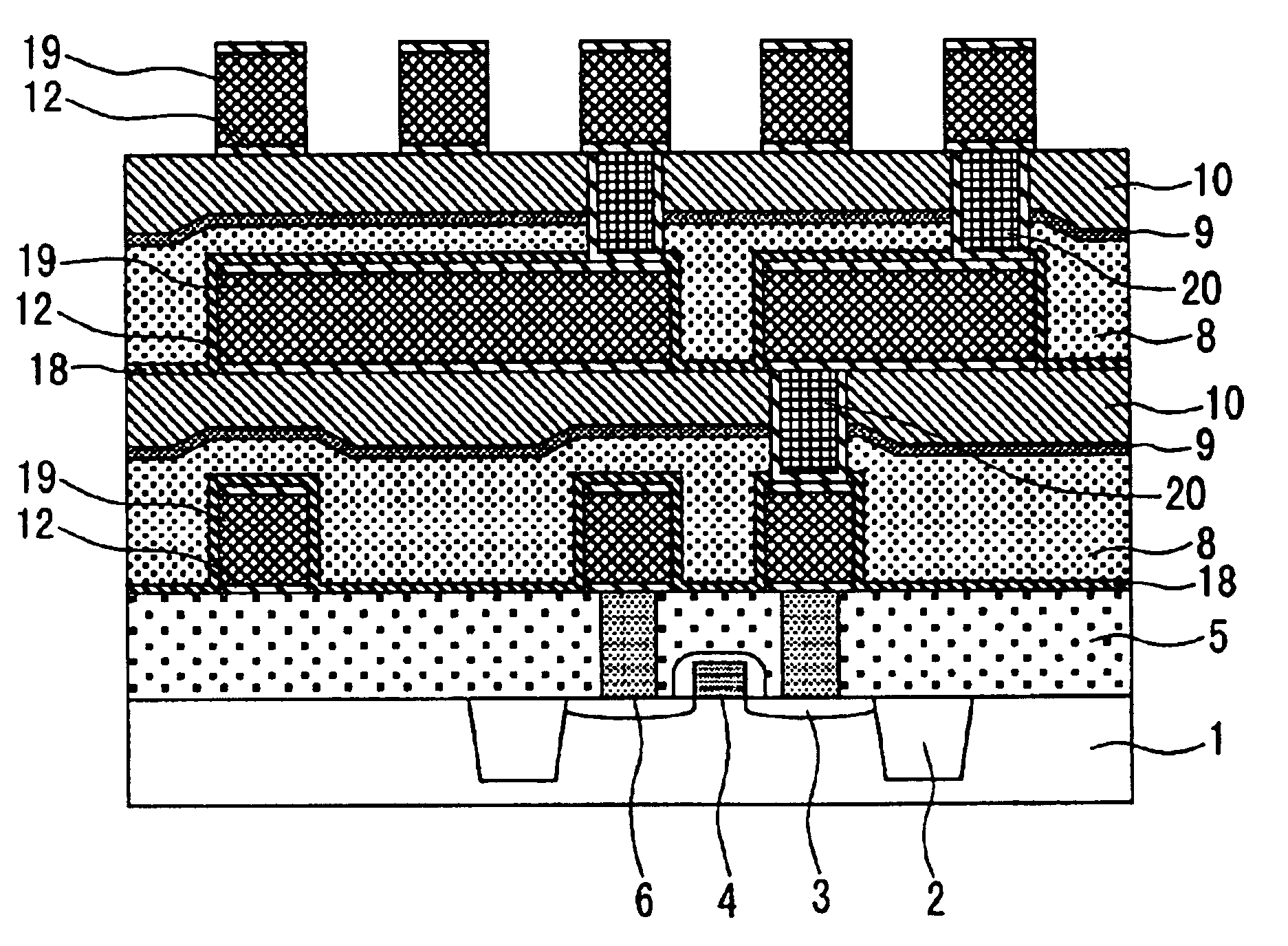

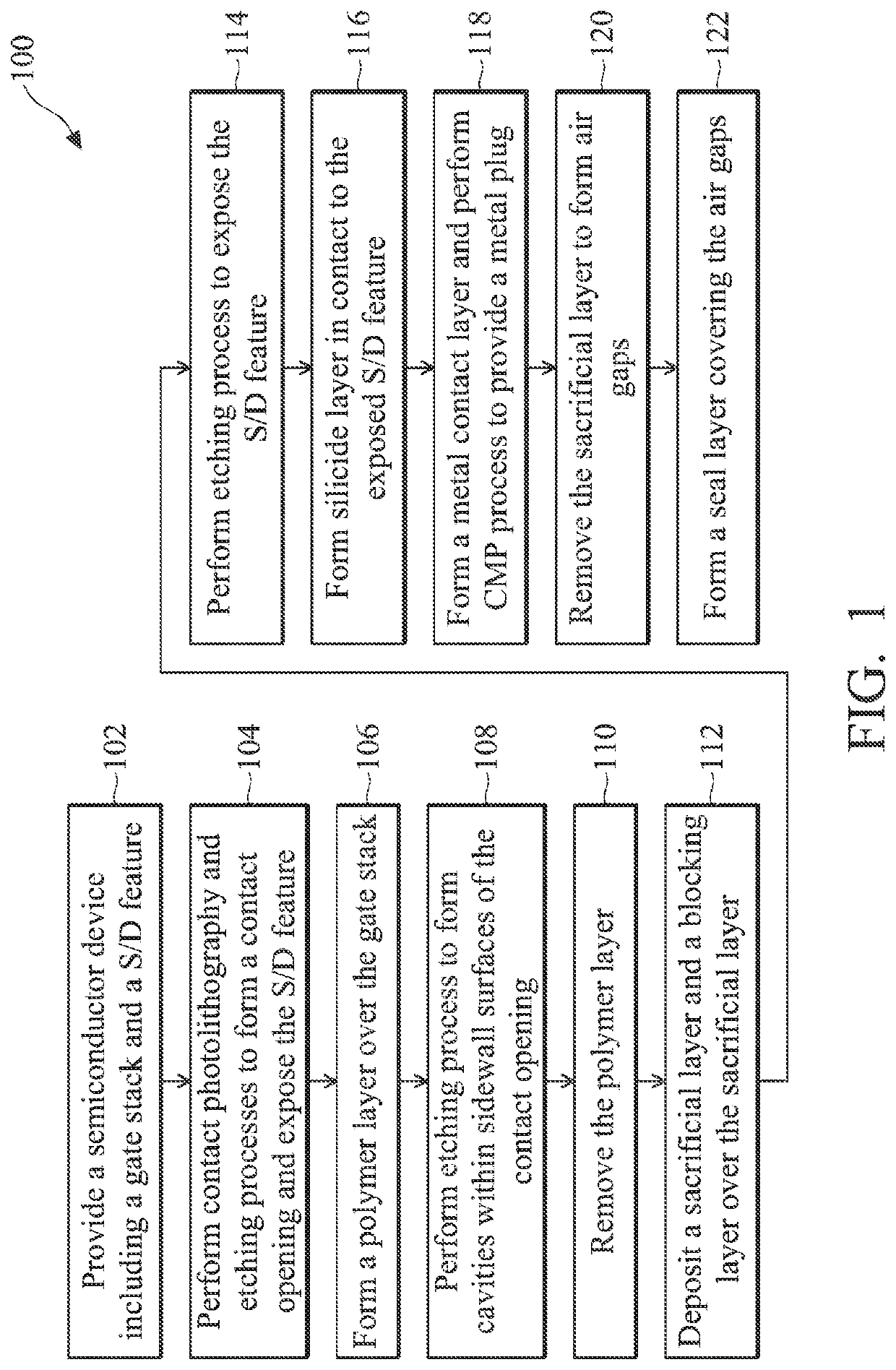

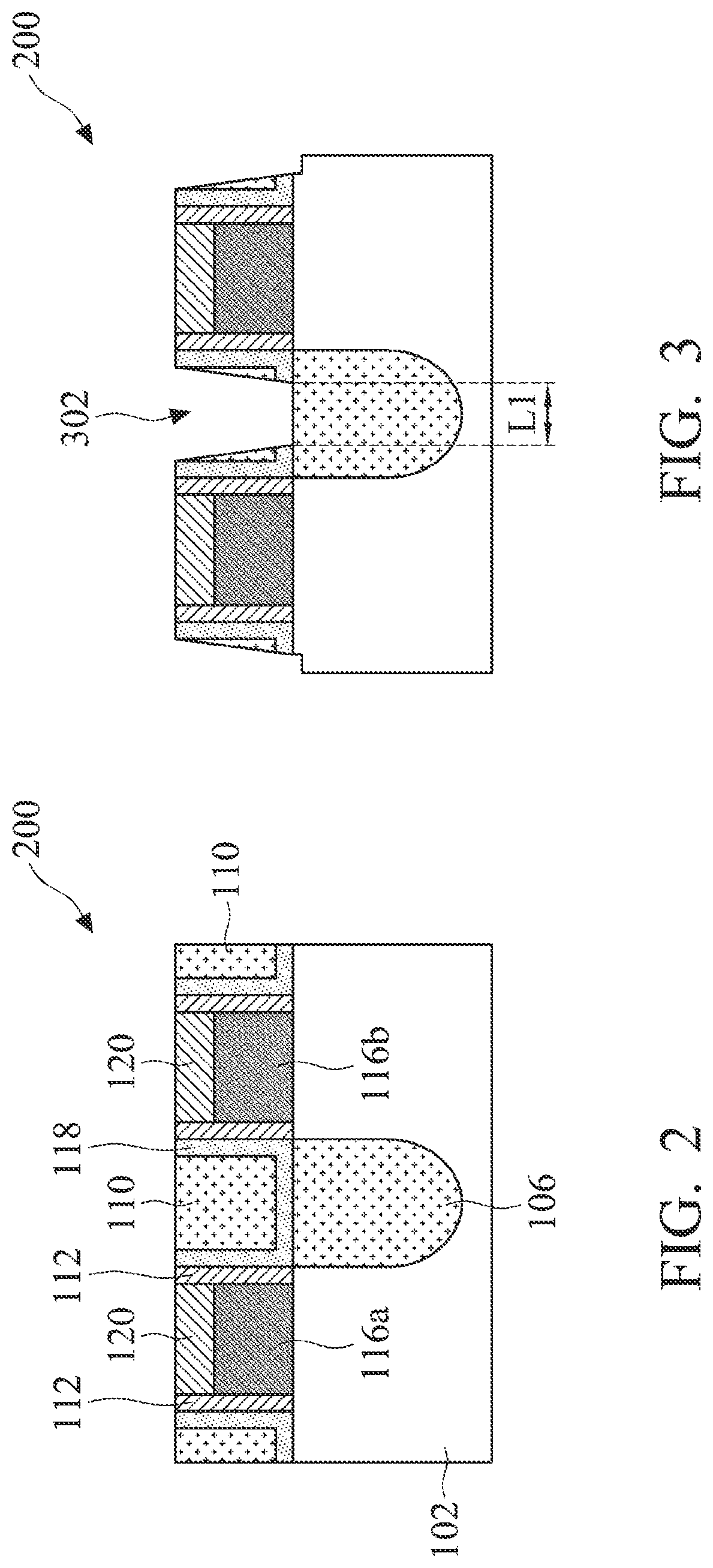

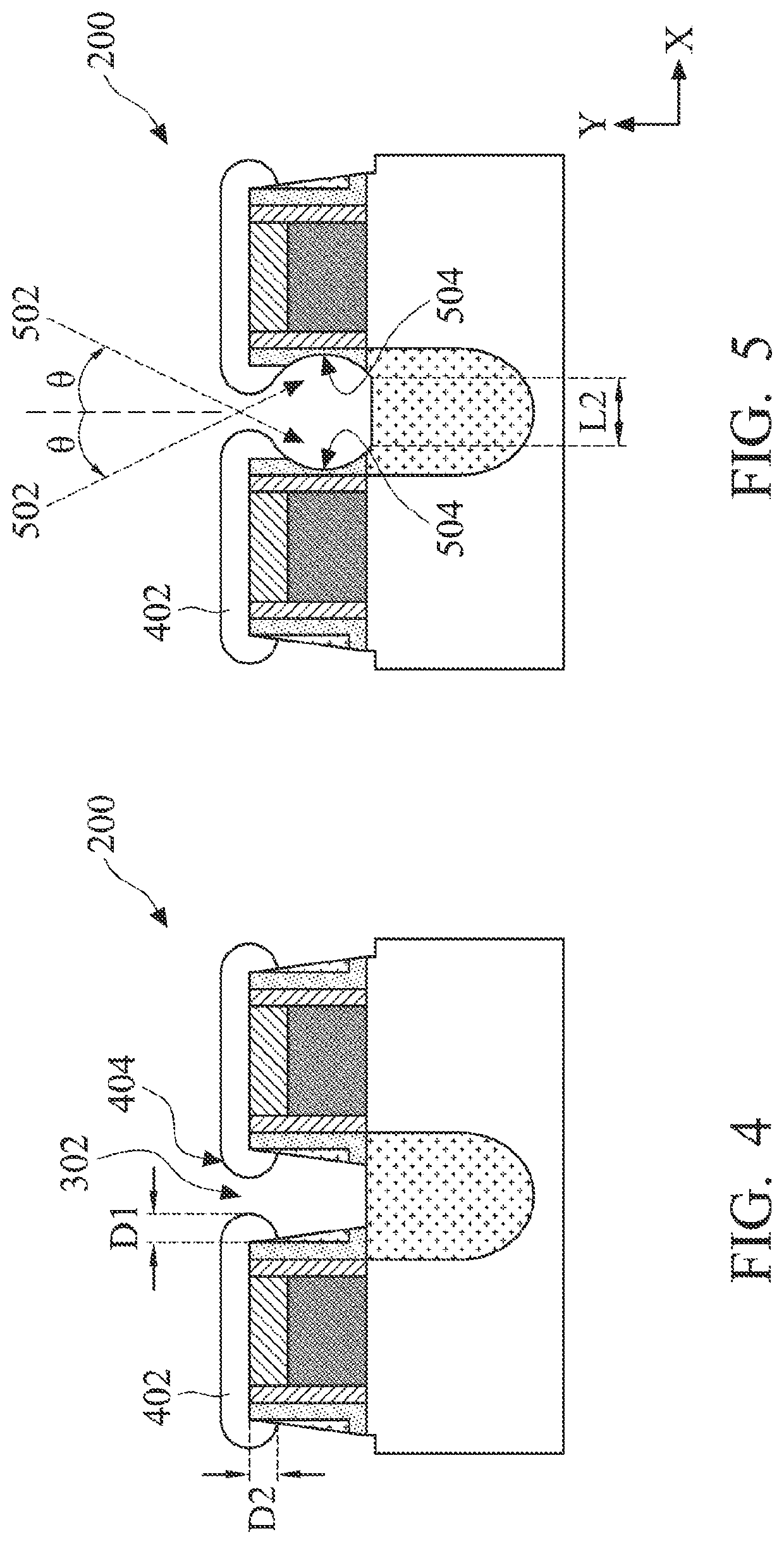

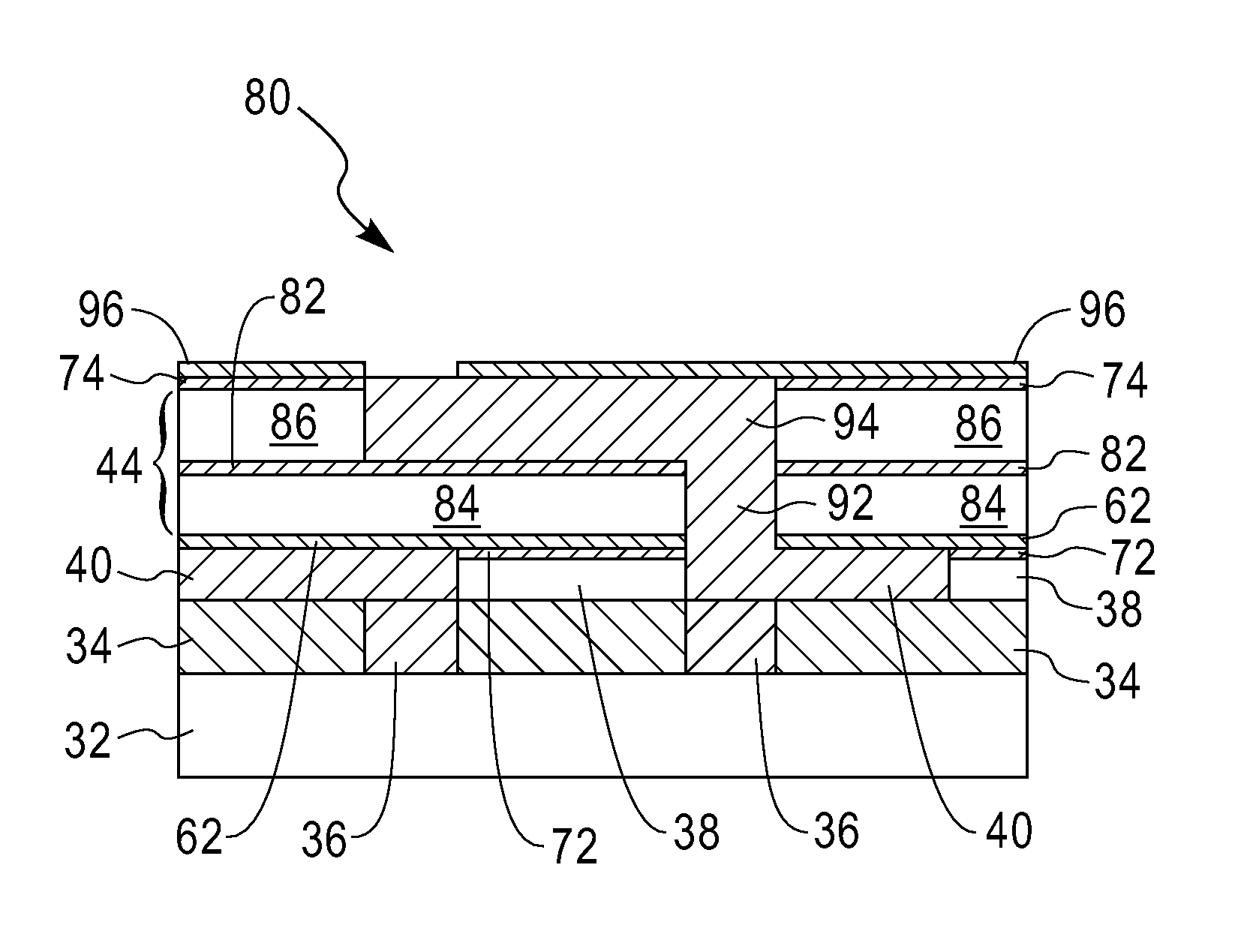

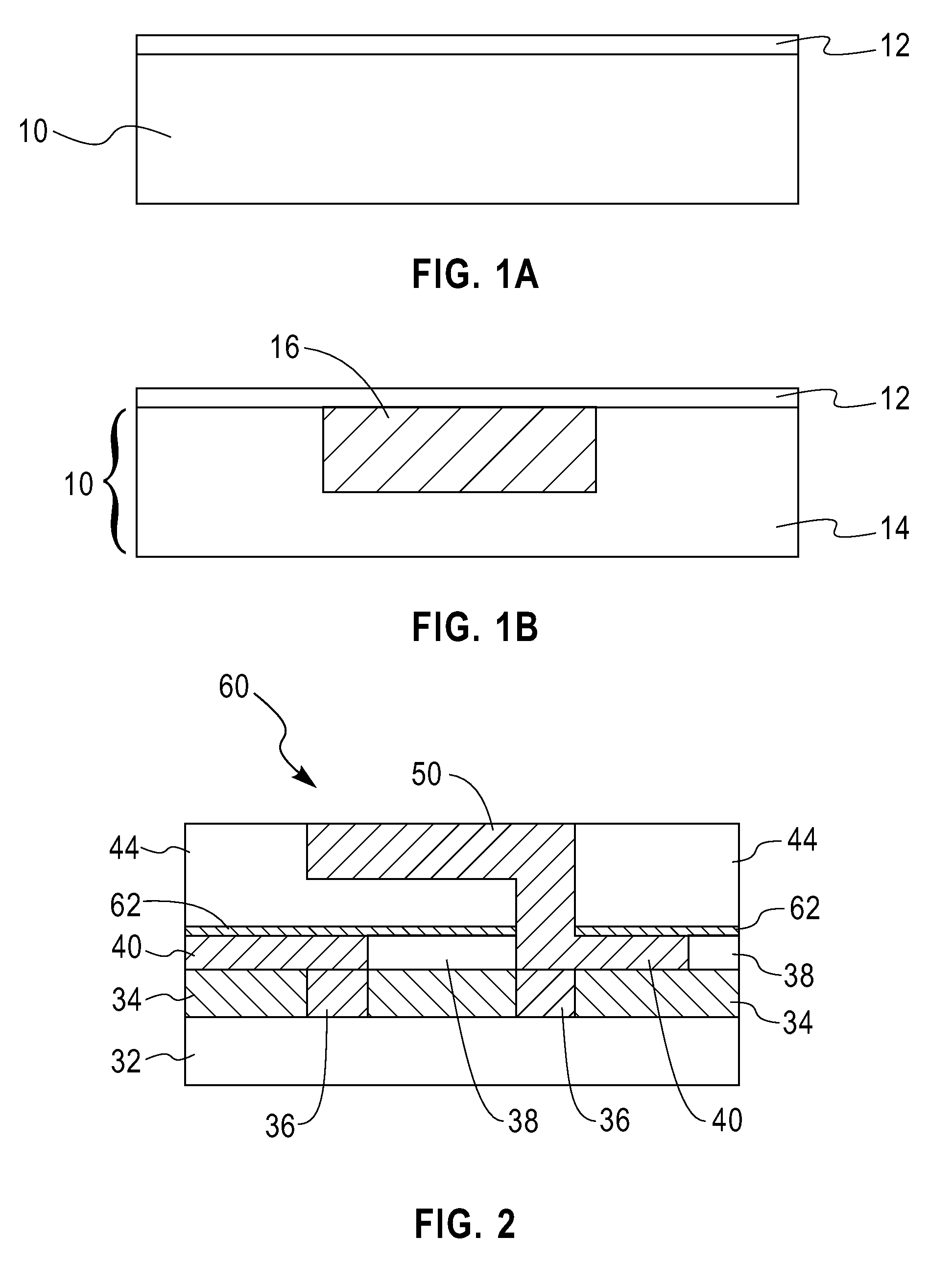

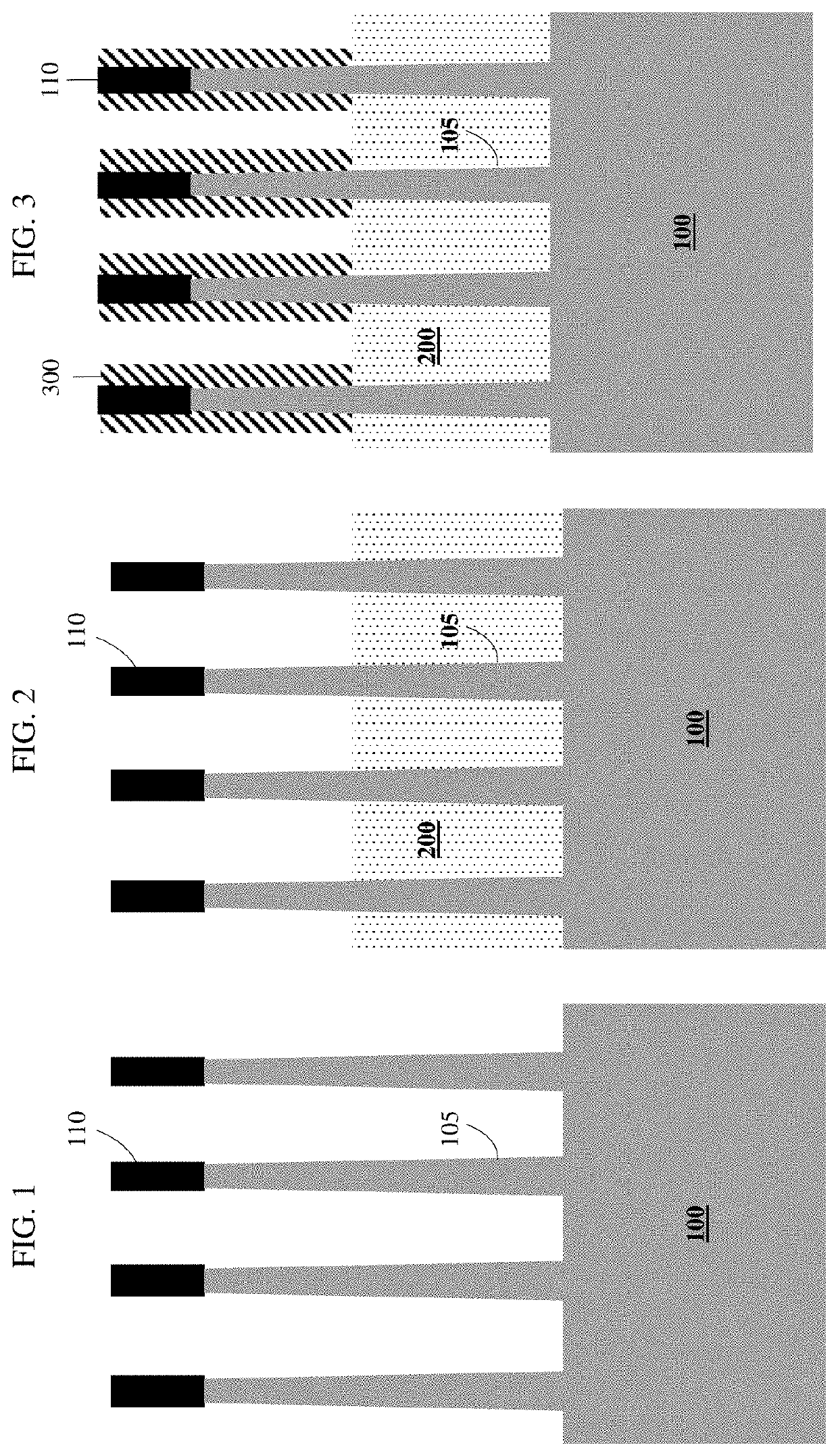

Contact air gap formation and structures thereof

ActiveUS20200135591A1Eliminate riskLow effective capacitanceTransistorSolid-state devicesEngineering physicsMaterials science

A method of forming a device includes providing a transistor having a gate structure and a source / drain structure adjacent to the gate structure. A cavity is formed along a sidewall surface of a contact opening over the source / drain structure. After forming the cavity, a sacrificial layer is deposited over a bottom surface and along the sidewall surface of the contact opening including within the cavity. A first portion of the sacrificial layer along the bottom surface of the contact opening is removed to expose a portion of the source / drain structure. A metal plug is then formed over the portion of the exposed source / drain structure. A remaining portion of the sacrificial layer is removed to form an air gap disposed between the metal plug and the gate structure. Thereafter, a seal layer is deposited over the air gap to form an air gap spacer.

Owner:TAIWAN SEMICON MFG CO LTD

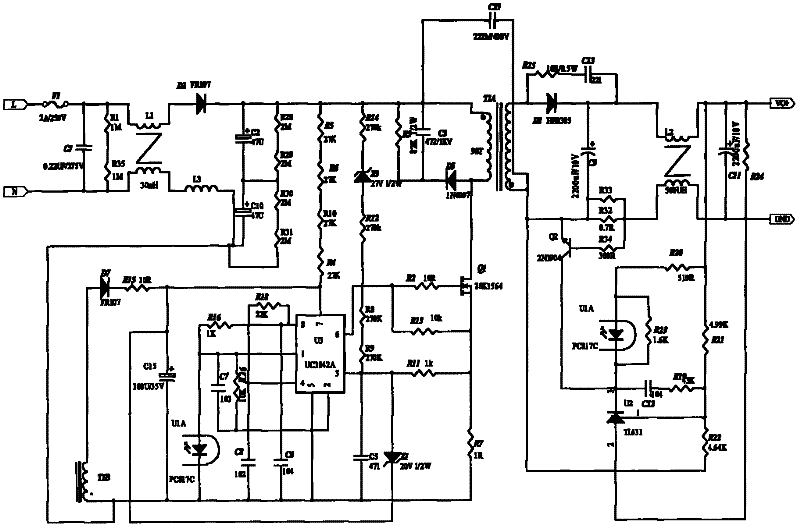

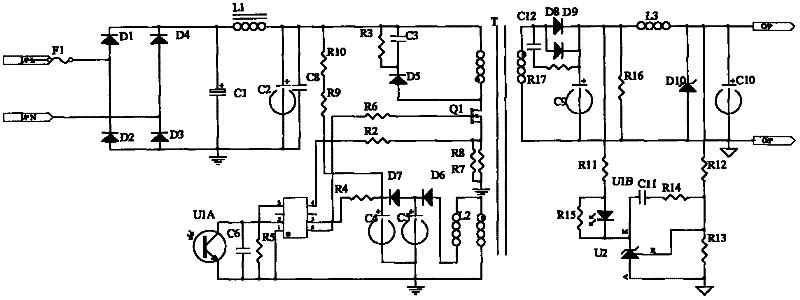

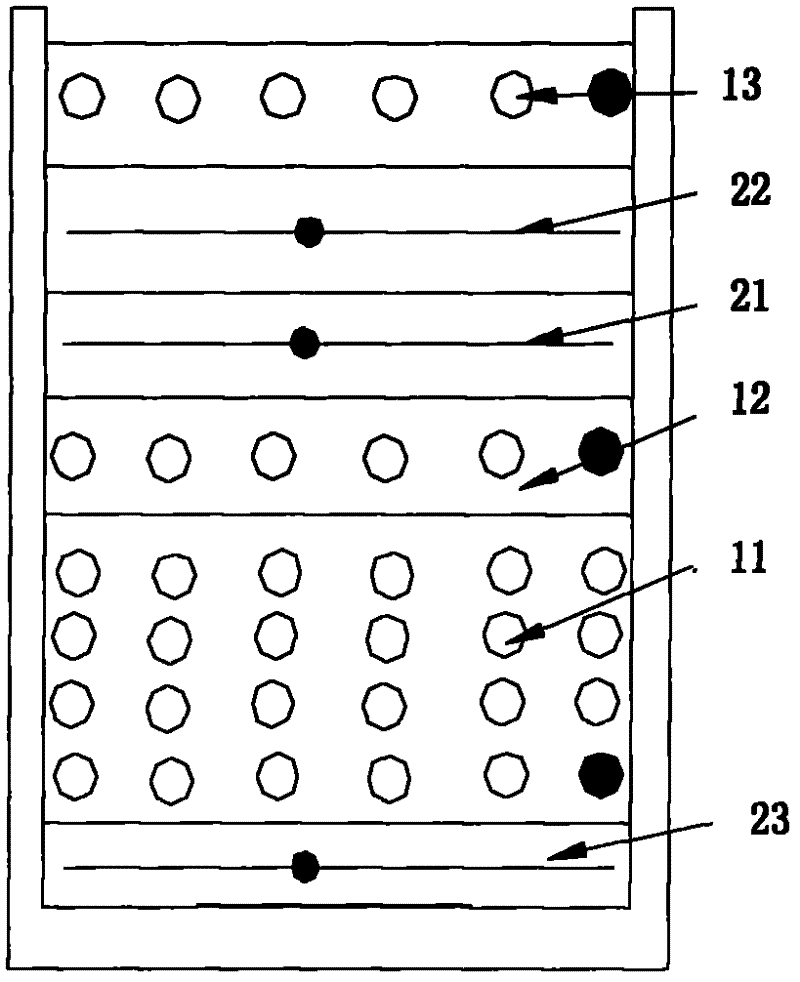

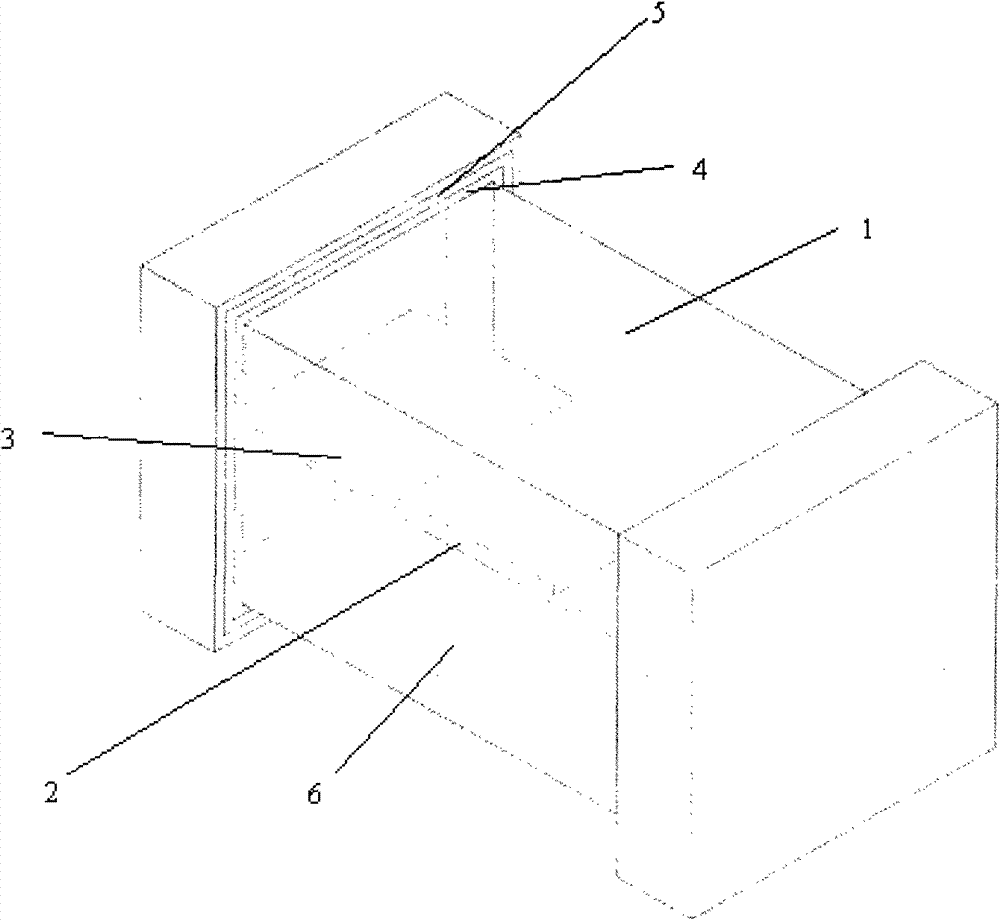

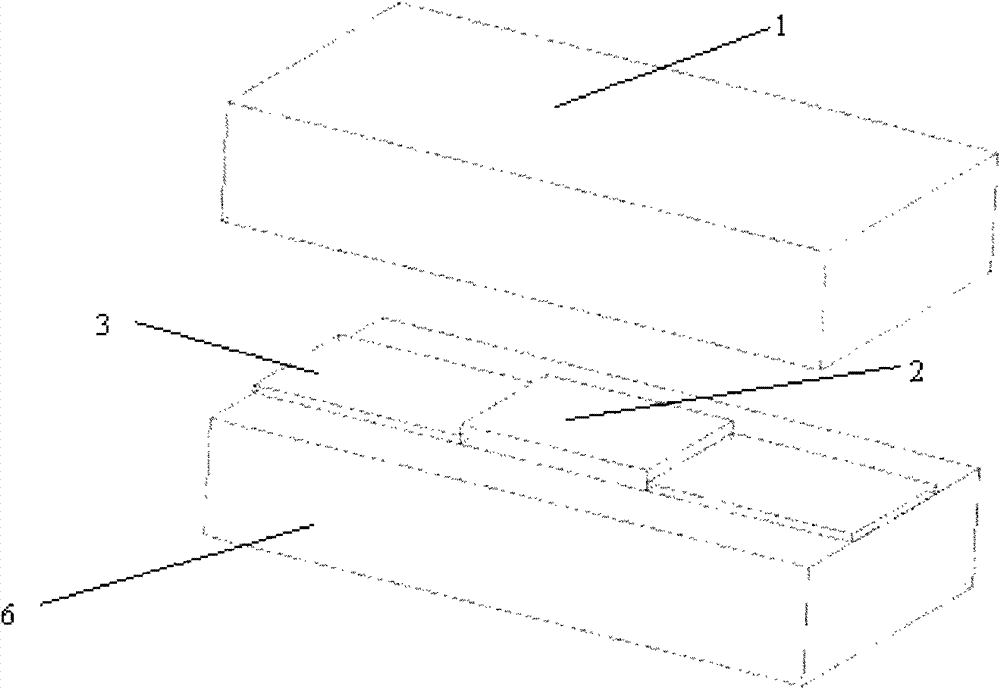

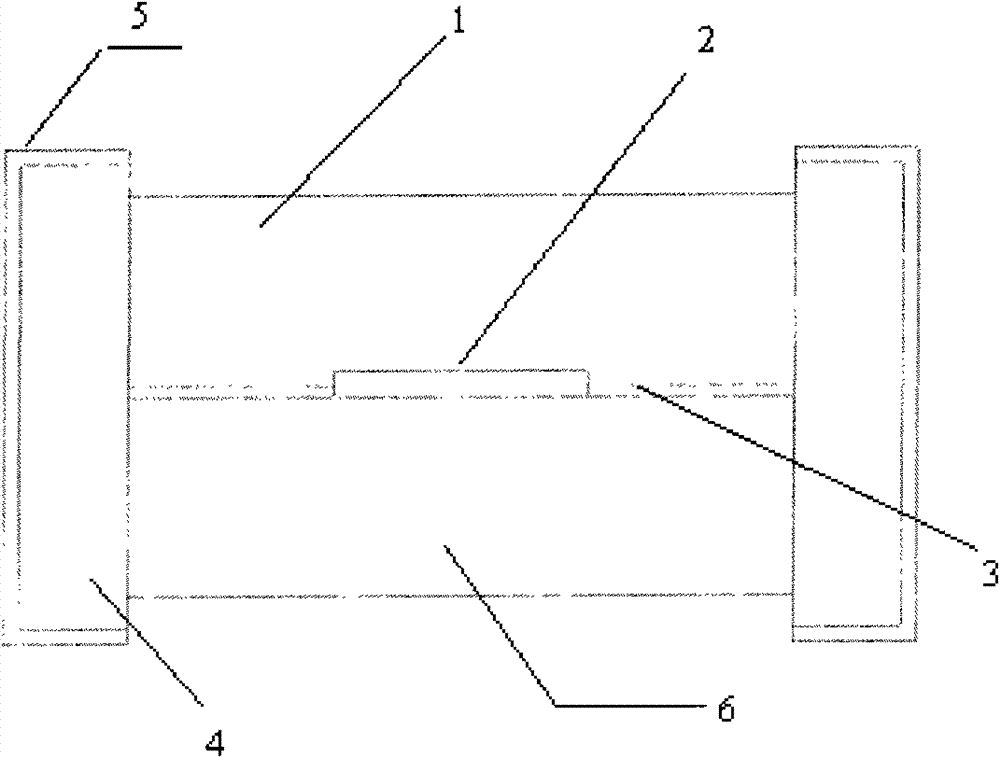

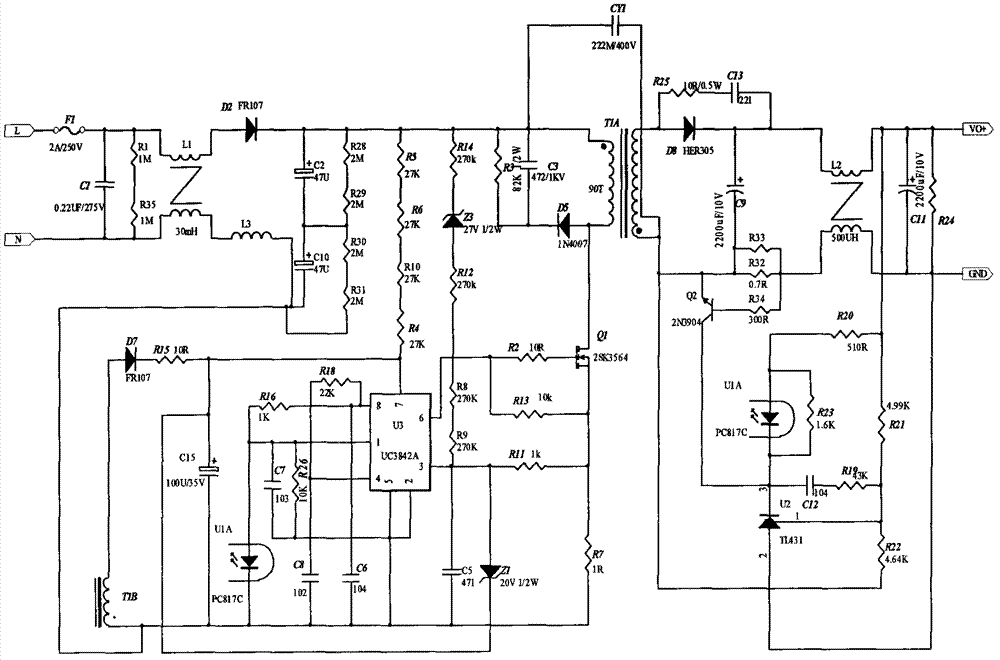

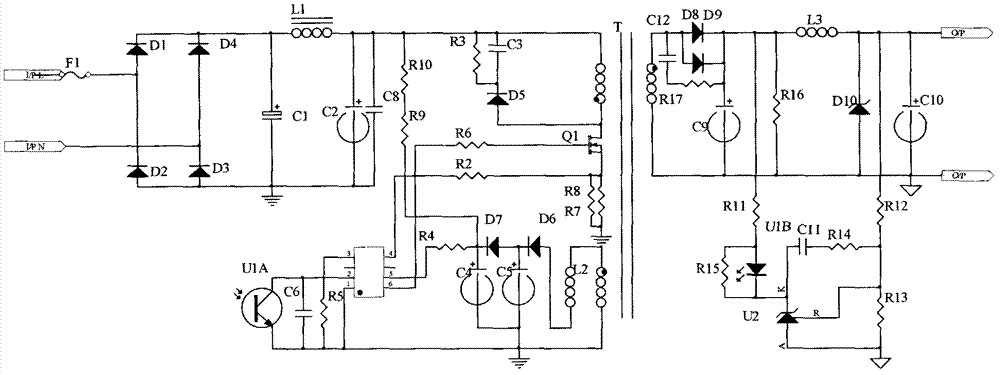

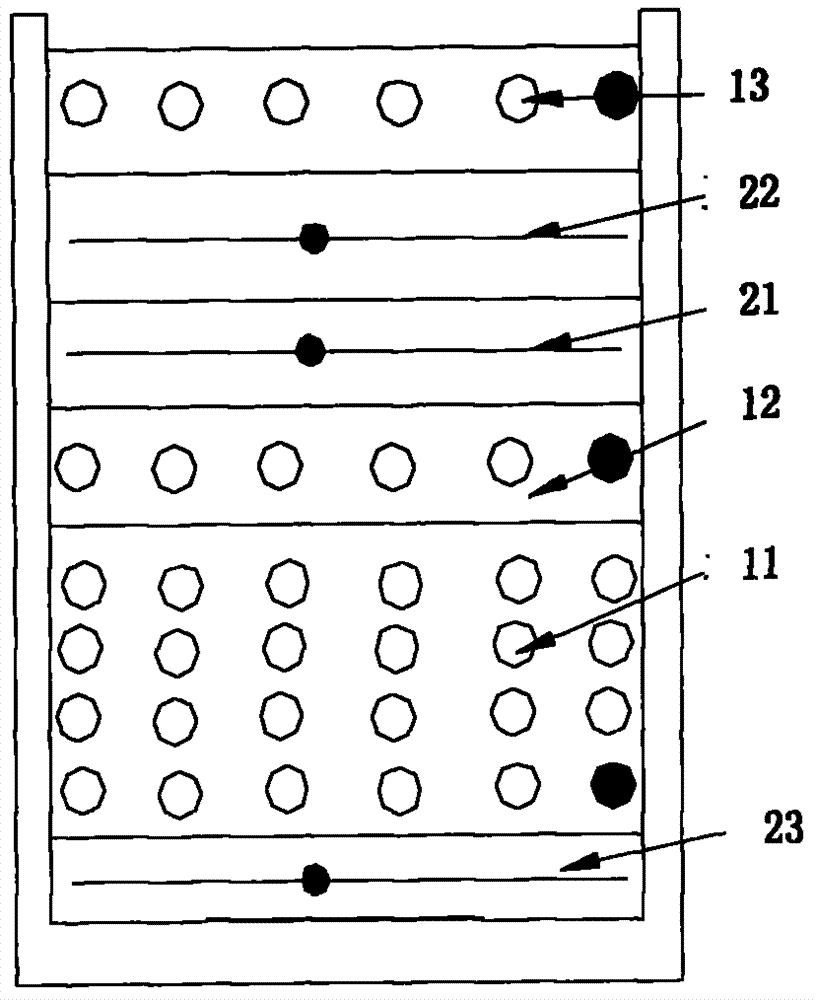

Transformer without Y capacitor and preparation method thereof

InactiveCN102163492AReduce interference currentLow effective capacitanceTransformers/inductances coils/windings/connectionsInductances/transformers/magnets manufactureCapacitanceTransformer

The invention discloses a transformer without Y capacitor, comprising a magnetic core, a primary main winding, a secondary winding and an auxiliary winding, wherein the primary main winding, the secondary winding and the auxiliary winding are successively winded on the magnetic core. The transformer further comprises a primary shielded winding connected with the primary main winding and a secondary shielded winding connected with the secondary winding, wherein the primary shielded winding and the secondary shielded winding have the same number of loops and the same phase. The invention solvestwo main problems of electromagnetic radiation and electric leakage in a switch power supply at the same time, realizes that the switch power supply can pass an electromagnetic radiation test withoutY capacitor, so the transformer is suitable for products fairly sensitive to leakage current, such as mobile phone chargers.

Owner:湖南崧顺科技有限公司

Portable device for detecting and measuring particles entrained in the air

ActiveUS9995667B2Reduce areaIncrease the areaScattering properties measurementsParticle size analysisLight beamEngineering

A portable ambient air quality monitor having an enclosure to enclose and protect the monitor from an ambient environment and an airflow intake for controllably allowing ambient air to enter the monitor. A photodiode is disposed at a location downstream from a fan. The airflow from the fan is laminarized by a mesh or baffle to allow a thin stream of air to flow over the photodiode. A sensing region is defined by an intersection of an airflow sampling path and an optical path. The sensing region is also disposed above the photodiode. The airflow sampling path is configured to receive laminar airflow from the airflow intake and for directing the laminar airflow into the sensing region. A light beam is generated from a laser to reflect the light beam for reducing the required area of the sensing region to detect and measure the particles floating in the ambient air.

Owner:TZOA CLAD INNOVATIONS LTD

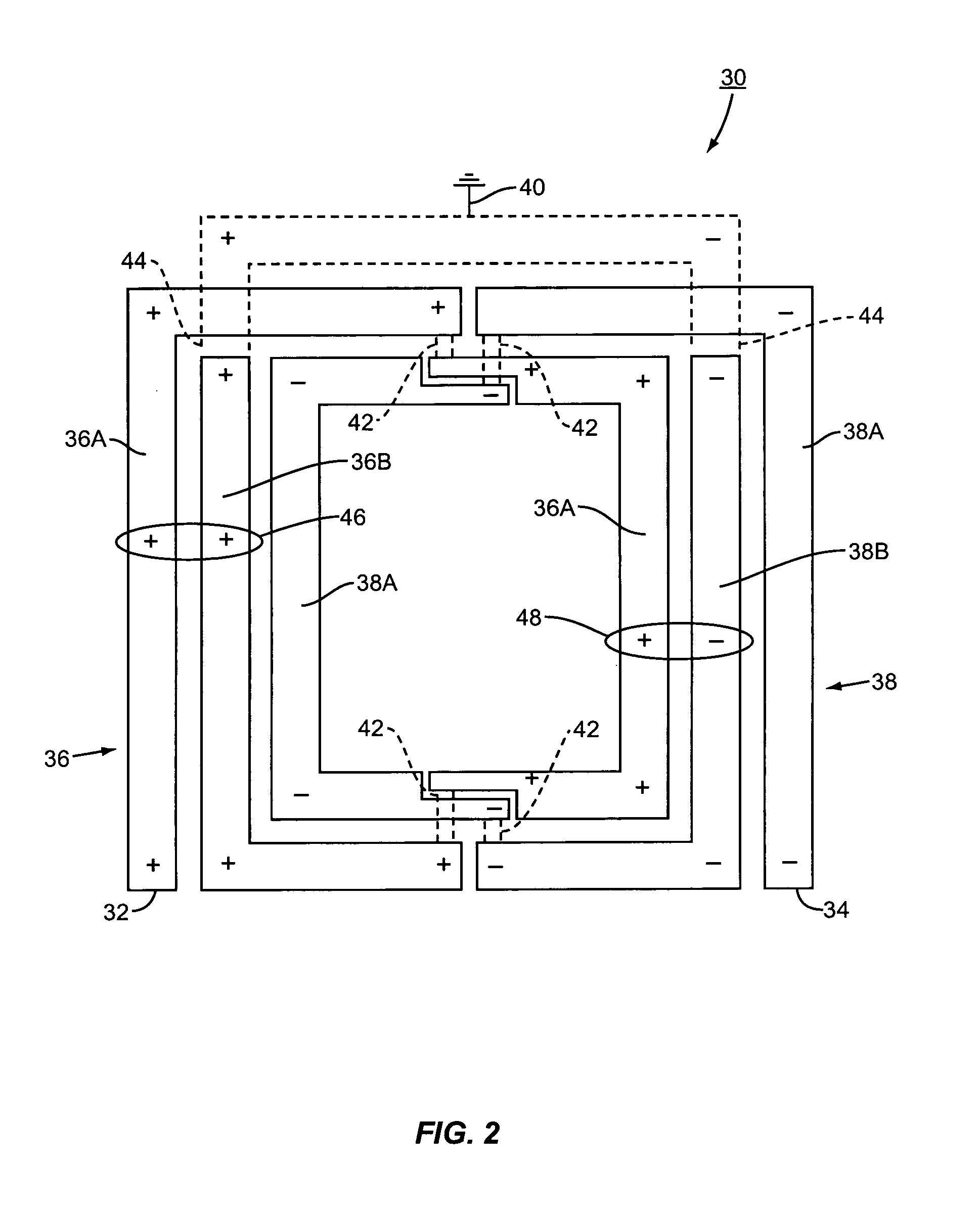

Method of constructing a differential inductor

ActiveUS8276259B1Low effective capacitanceLittle and voltage swingLine/current collector detailsElectrical transducersNear neighborEngineering

A method of constructing a differential inductor having a high self-resonance frequency is provided. In general, a ground point is identified. A first coil having a first and second loop is created such that the first loop is electrically further away from the ground point than the second loop. A second coil having a third and fourth loop are created such that the third loop is electrically further away from the ground point than the second loop. The first coil and the second coil are positioned such that the first loop is positioned as a near neighbor to said fourth loop and said second loop is positioned as a near neighbor to said third loop.

Owner:QORVO US INC

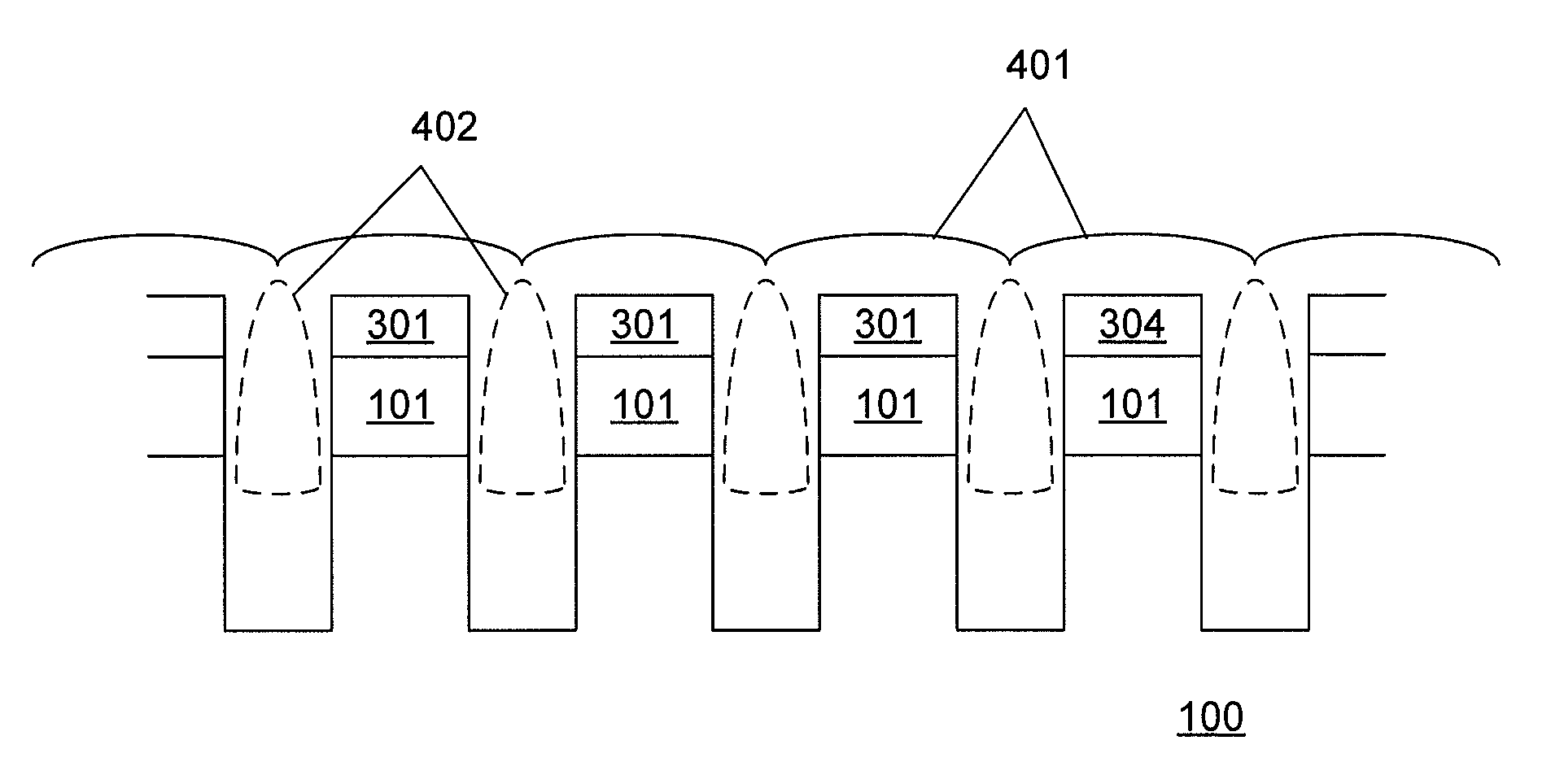

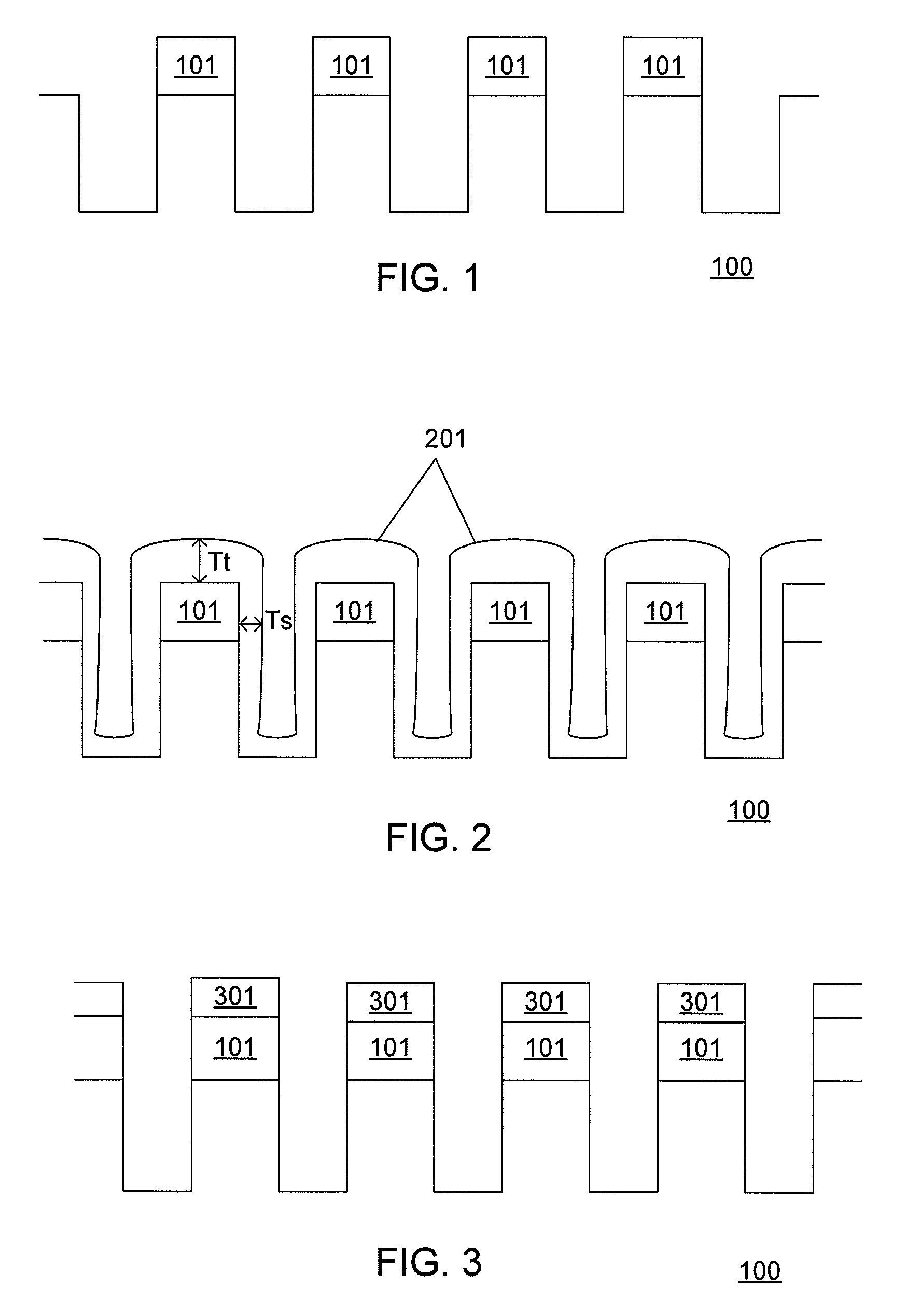

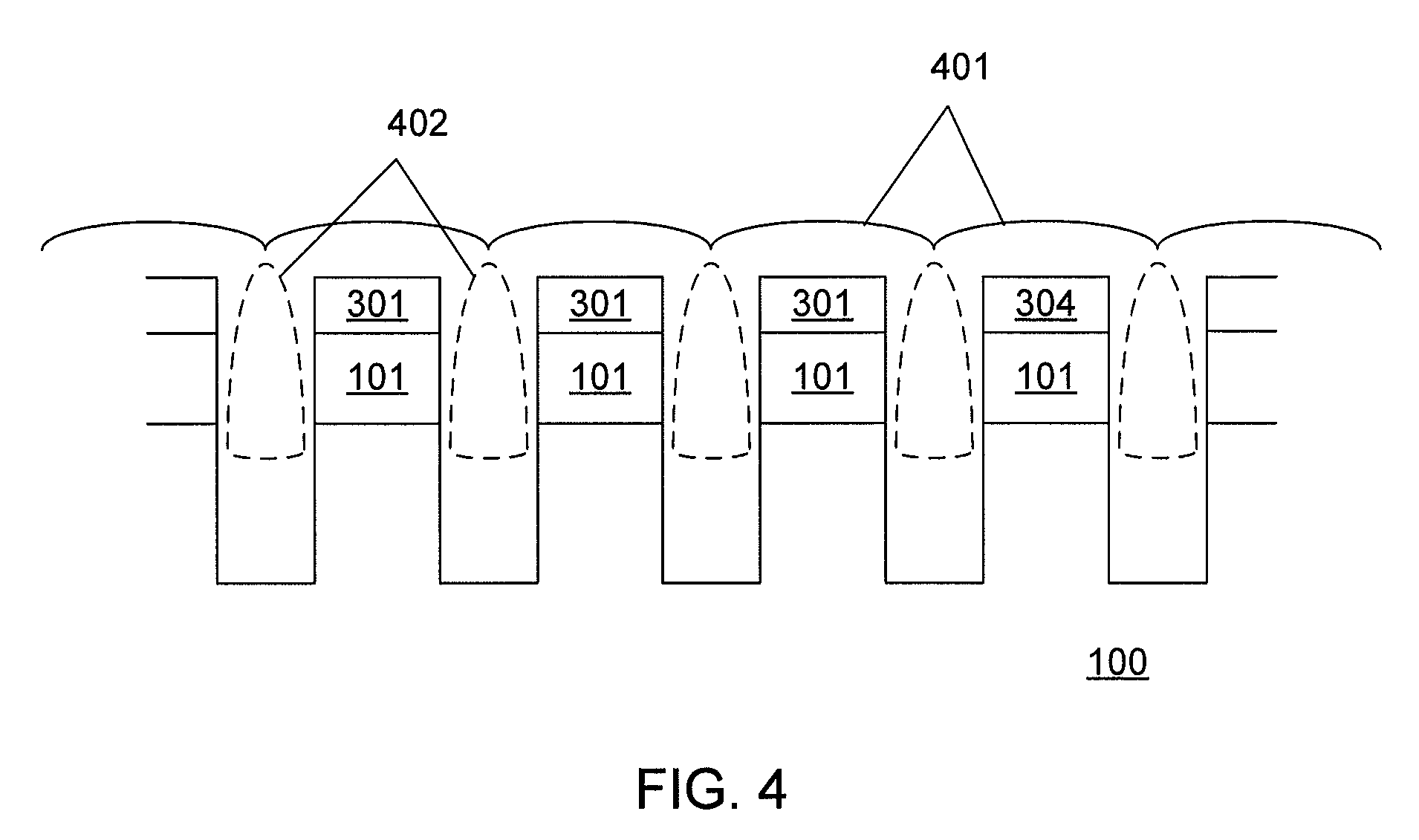

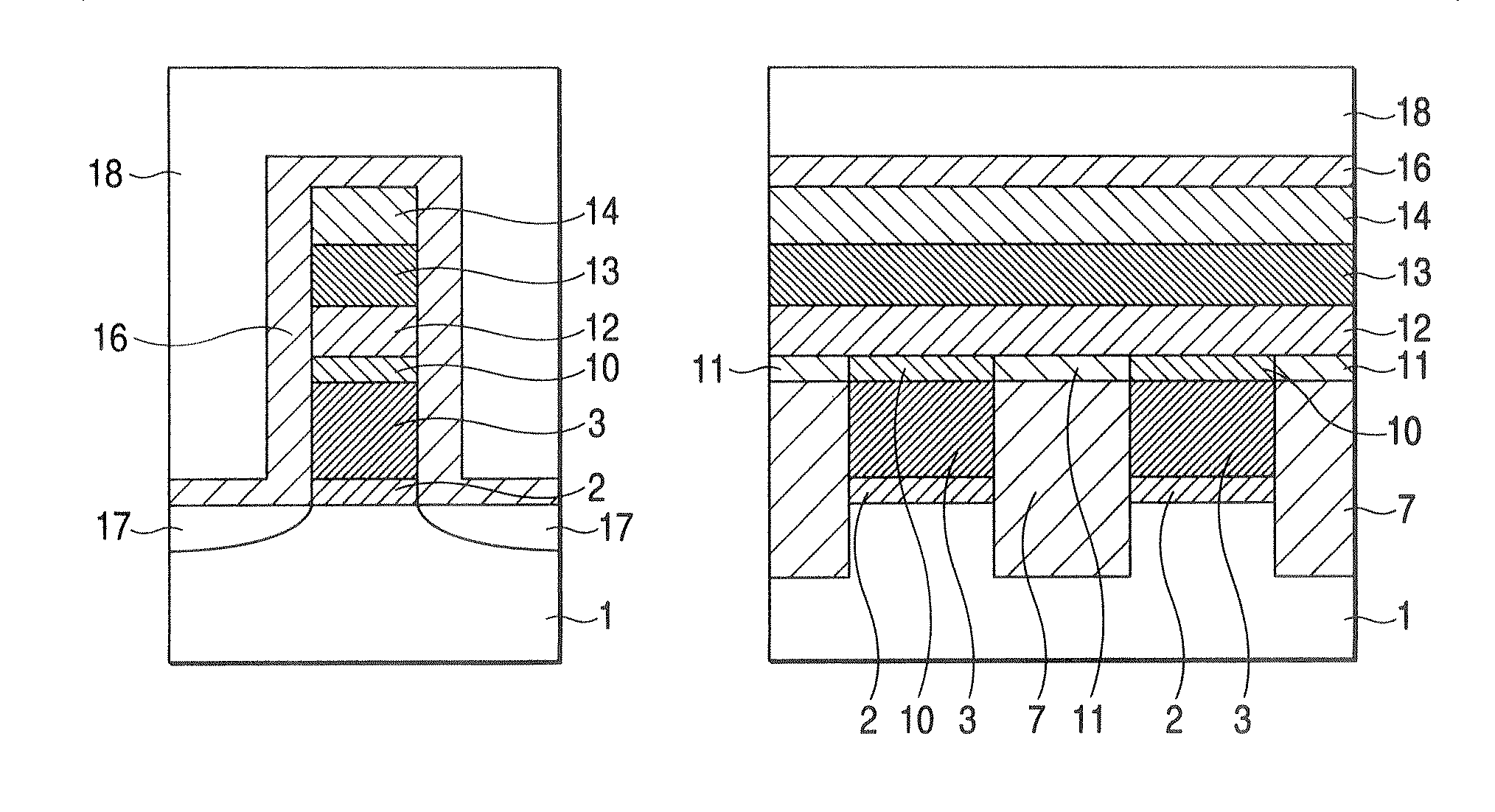

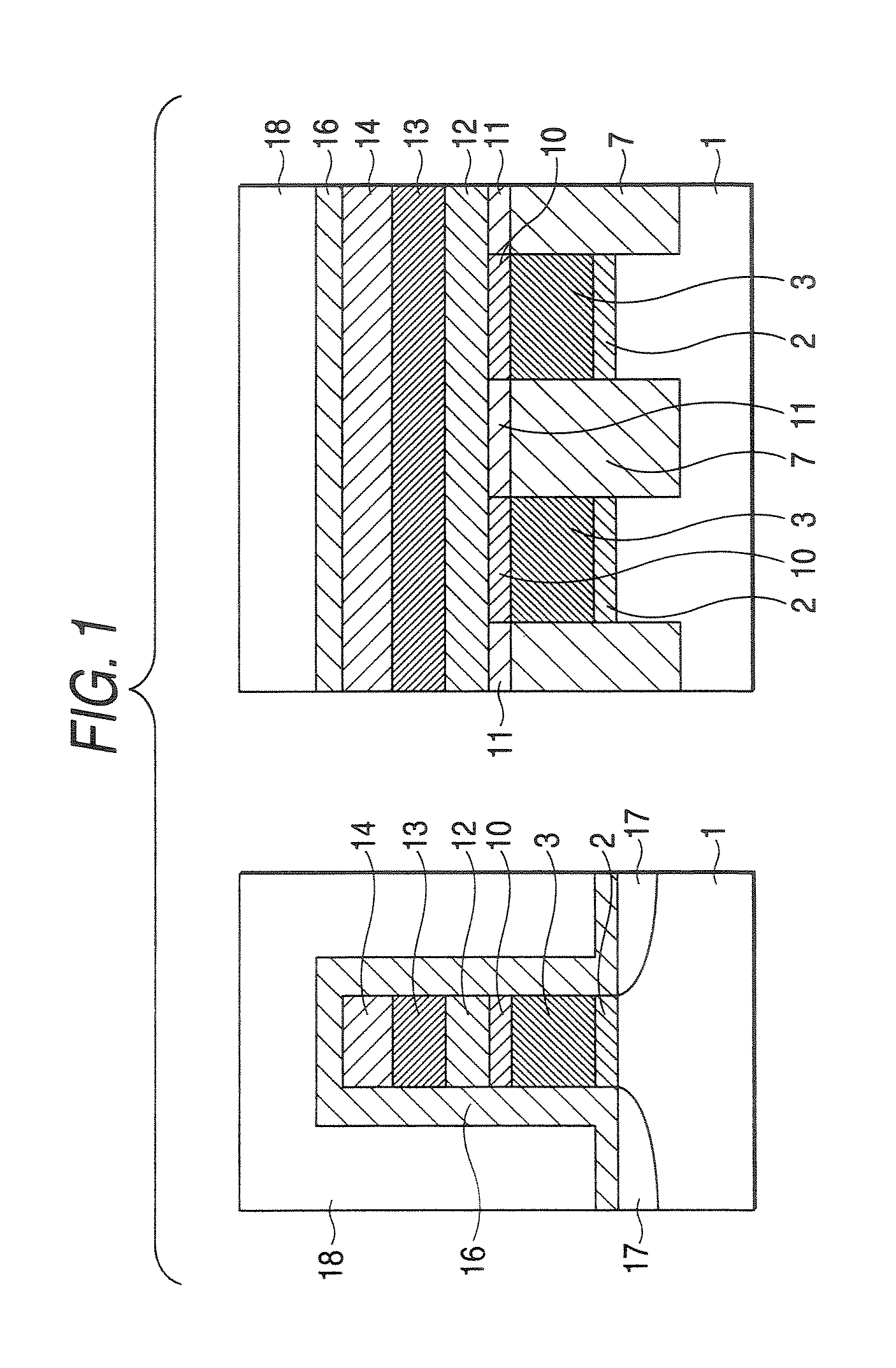

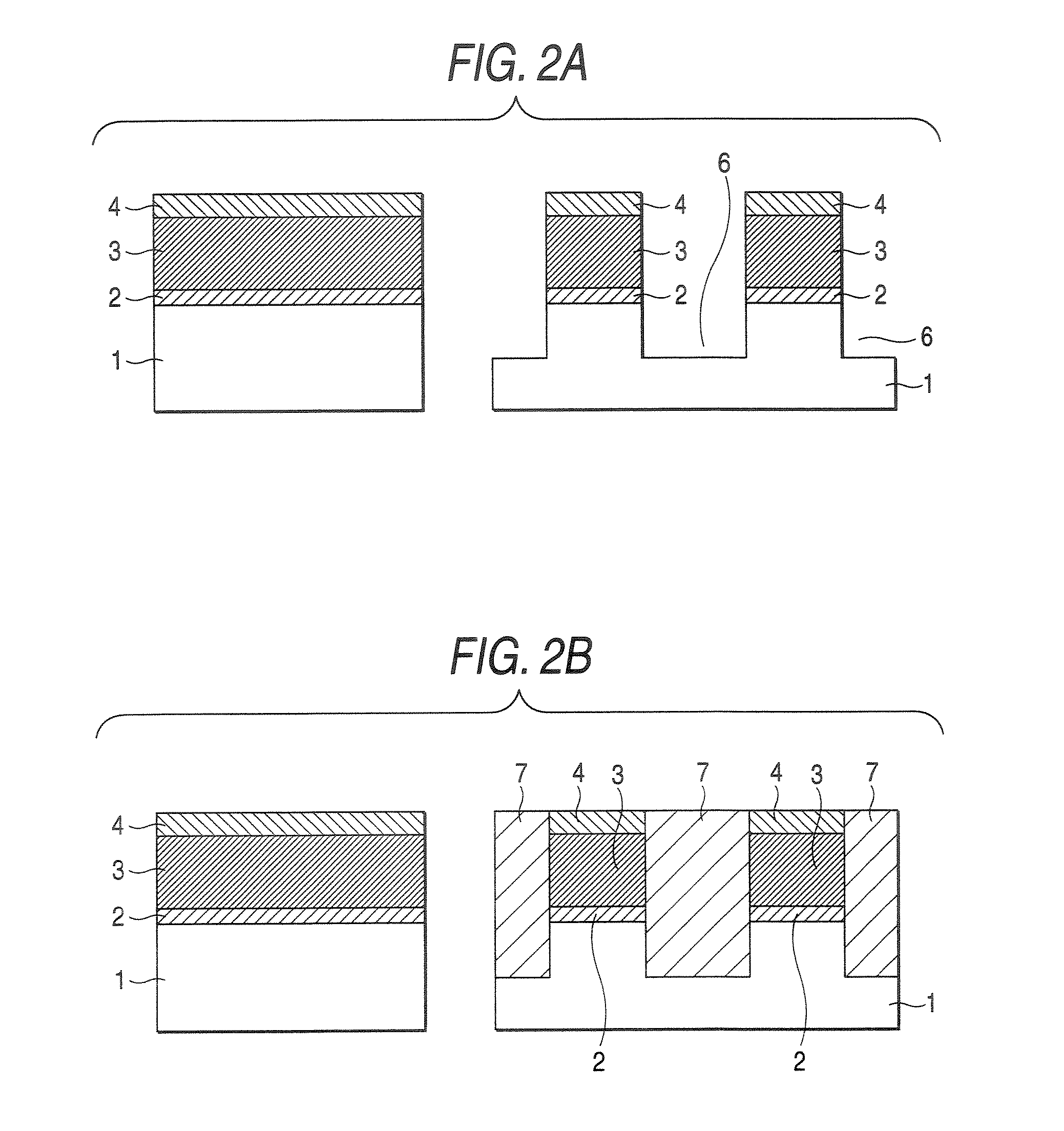

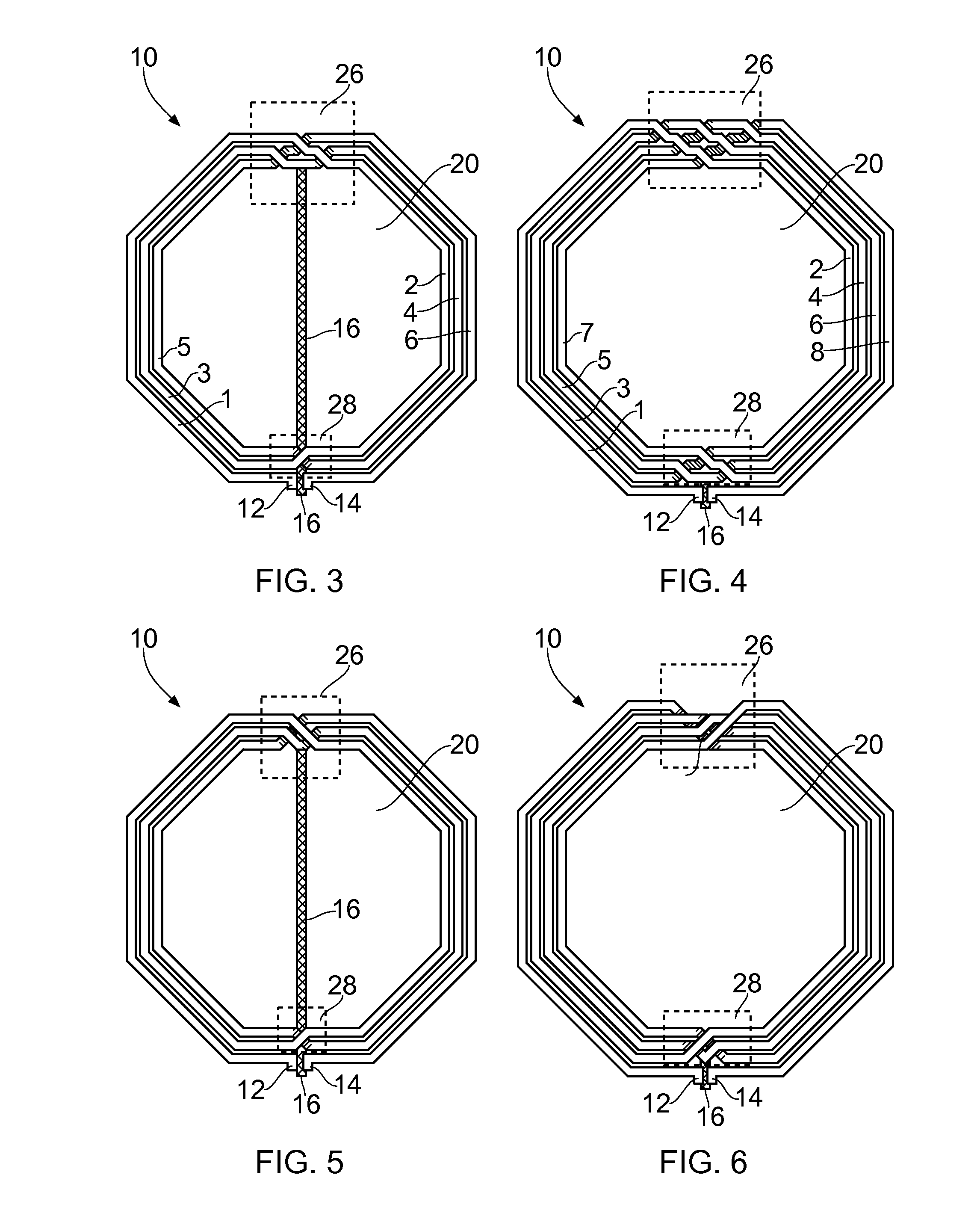

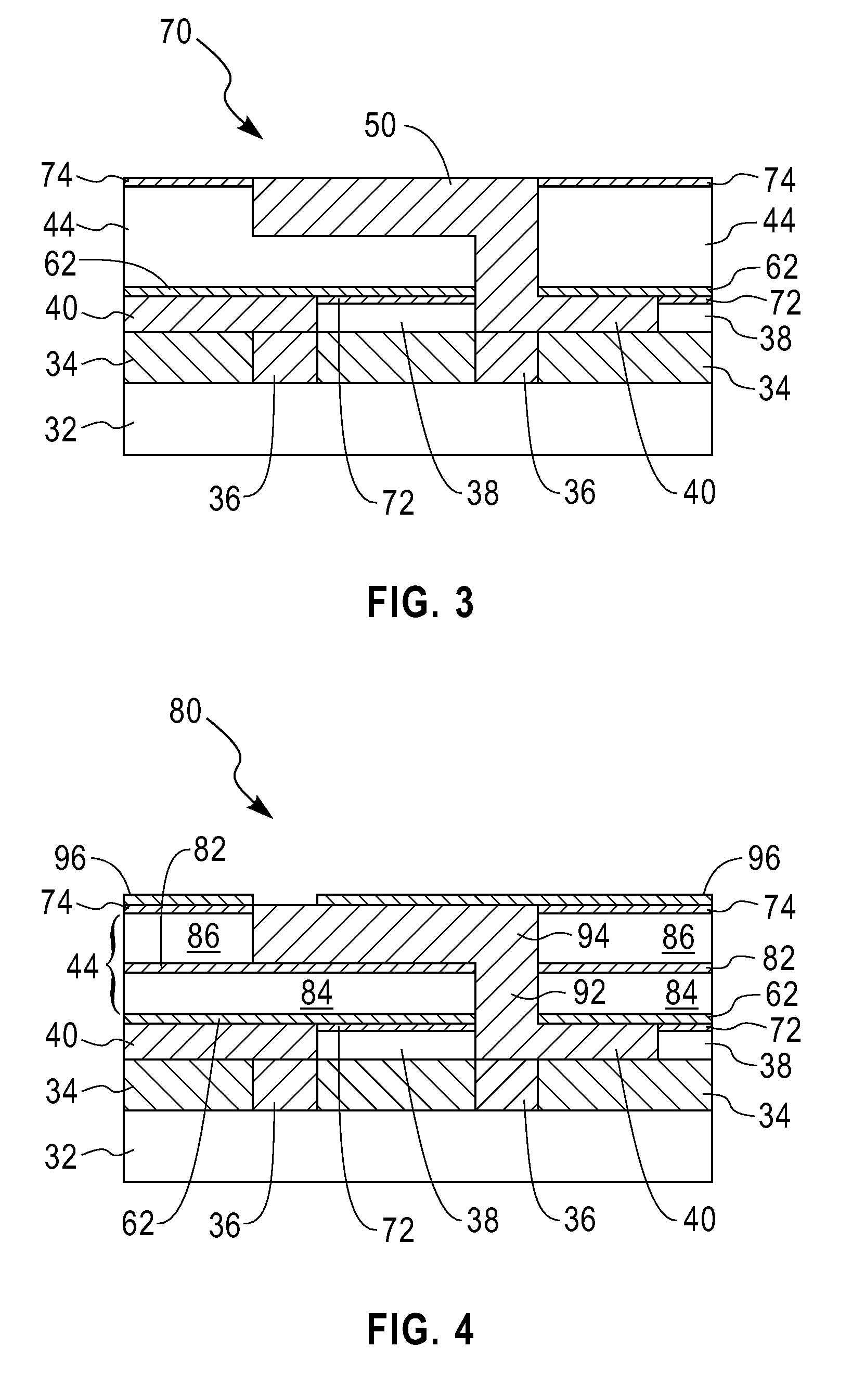

Systems and methods for controlling the effective dielectric constant of materials used in a semiconductor device

InactiveUS7855139B2Low effective capacitanceEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor

Systems and methods for controlling the effective dielectric constant of materials used in a semiconductor device are shown and described. In one embodiment, a method comprises providing a semiconductor substrate with a plurality of pillars formed thereon, depositing a first layer of dielectric material over a plurality of pillars, removing a portion of the first layer deposited over the plurality of pillars, and depositing a second layer of dielectric material over the plurality of pillars, where the second layer leaves a plurality of voids between the plurality of pillars.

Owner:SEMATECH

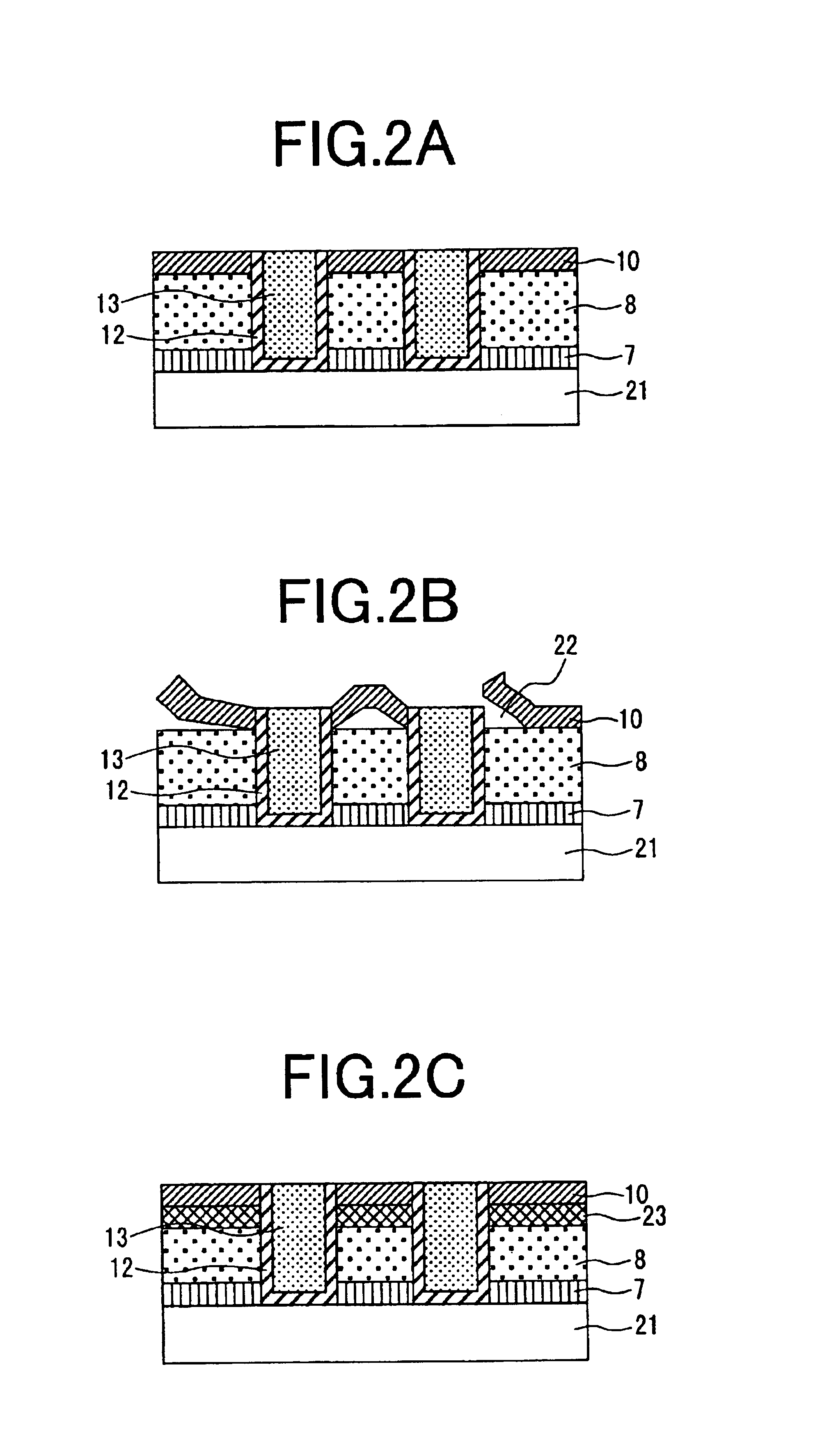

Nonvolatile semiconductor memory device and method of manufacturing the same

ActiveUS7755136B2Good cell operation characteristicInhibit deteriorationTransistorSolid-state devicesMetal silicideRare earth

A memory cell in a nonvolatile semiconductor memory device includes a tunneling insulating film, a floating gate electrode made of a Si containing conductive material, an inter-electrode insulating film made of rare-earth oxide, rare-earth nitride or rare-earth oxynitride, a control gate electrode, and a metal silicide film formed between the floating gate electrode and the inter-electrode insulating film.

Owner:KIOXIA CORP

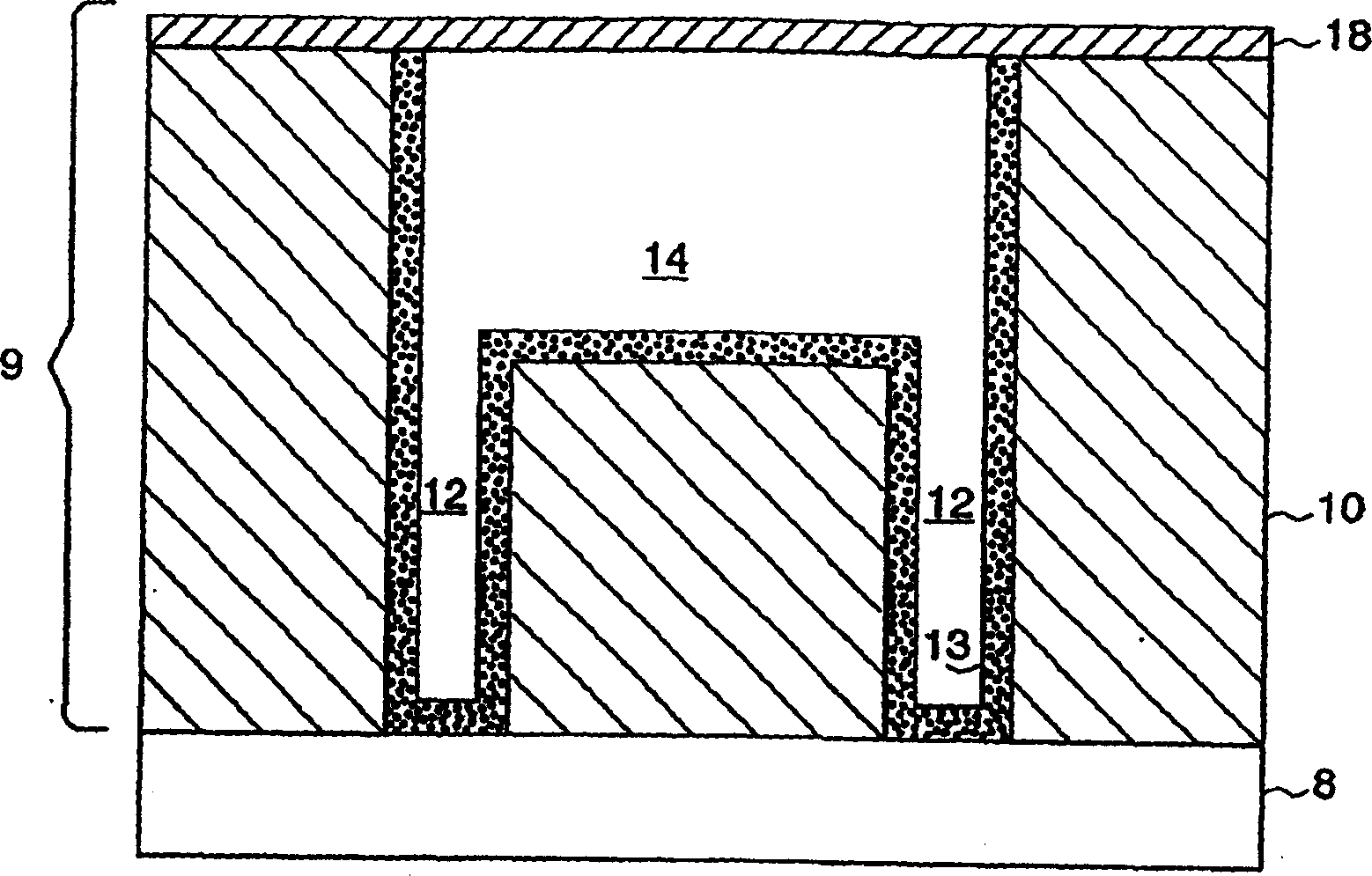

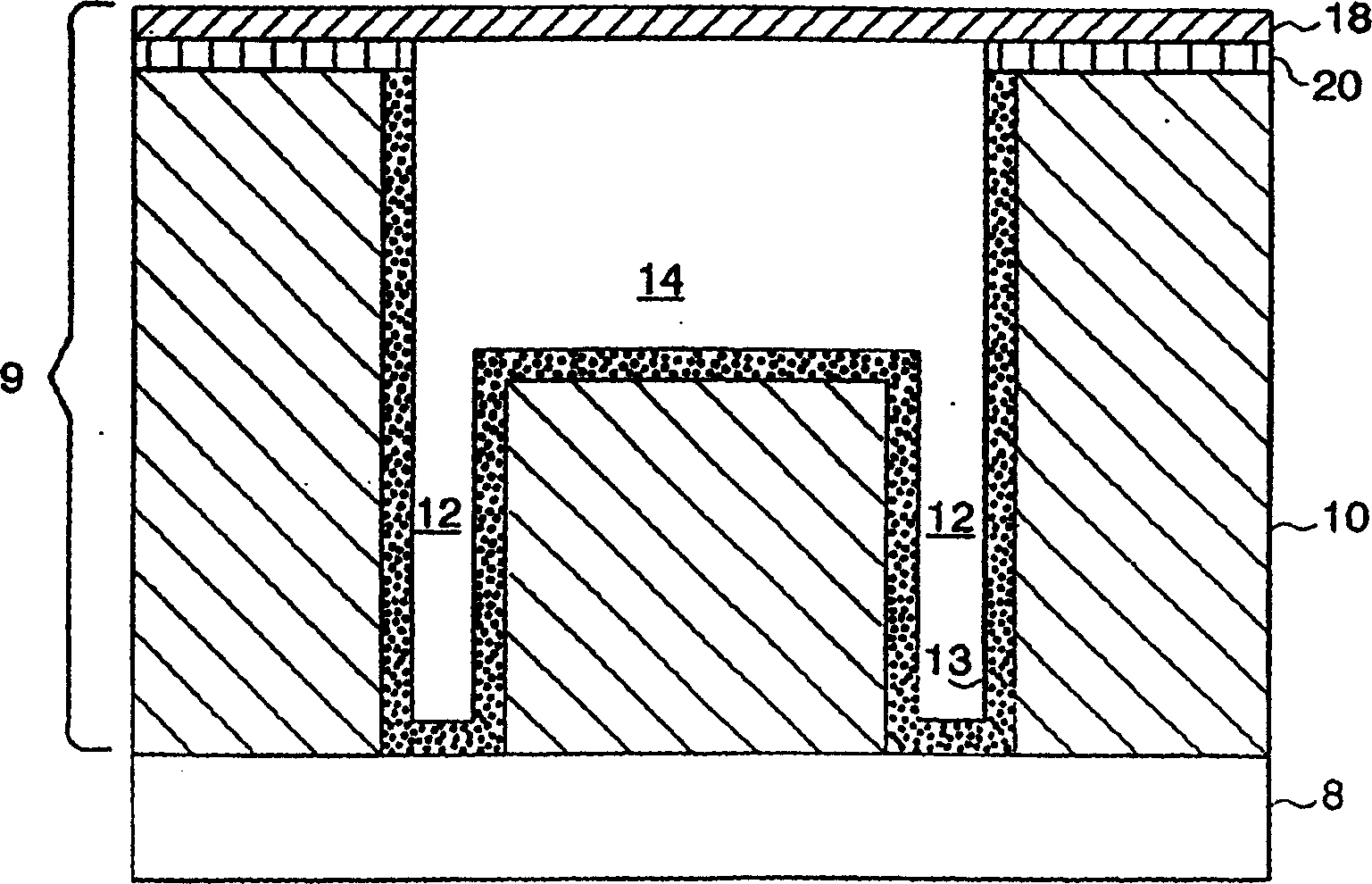

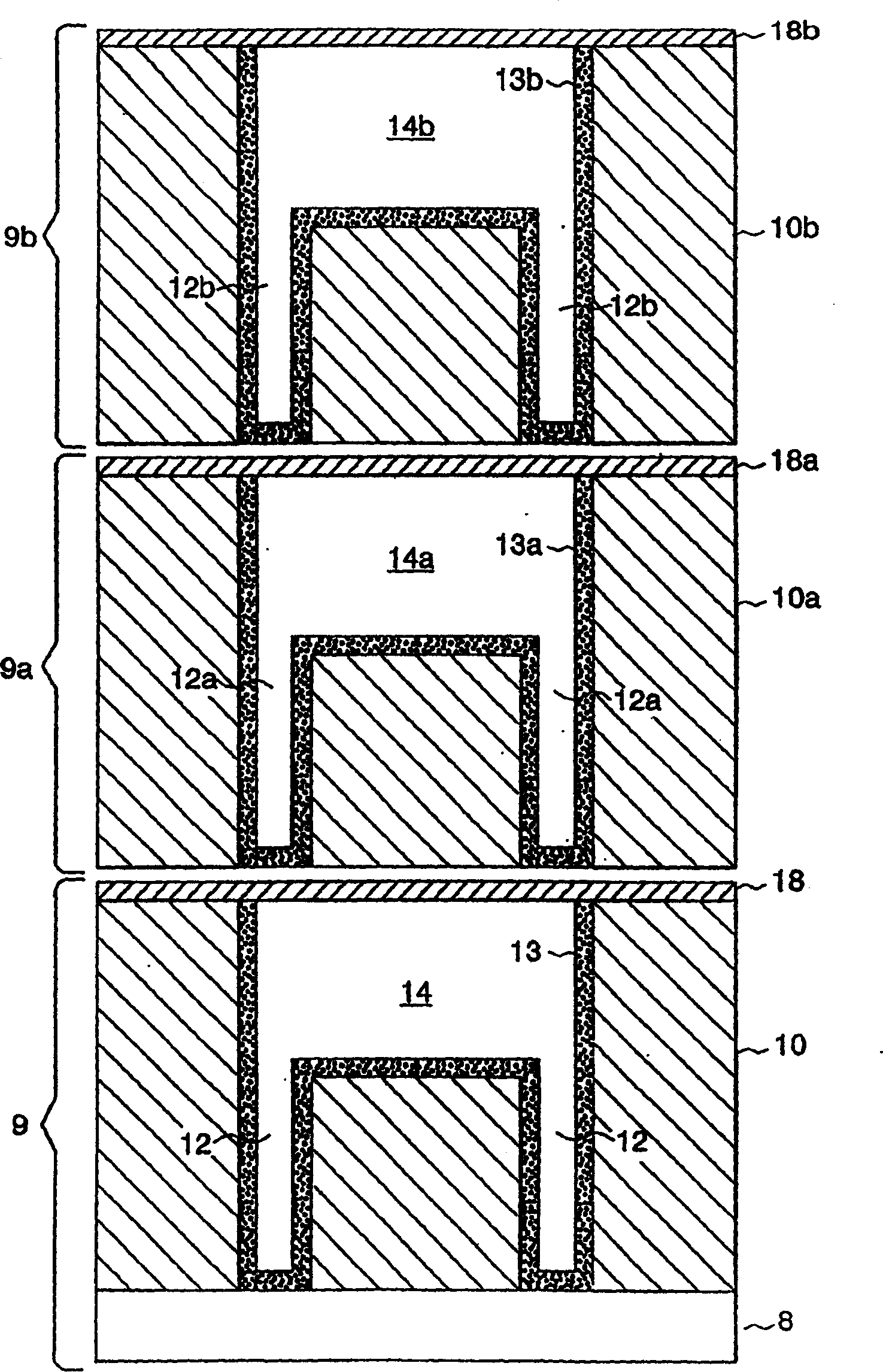

Interconnection structure containing stress regulating covering and its mfg. method

InactiveCN1477705ALow effective capacitanceImproved Stress Match StabilitySemiconductor/solid-state device detailsSolid-state devicesInternal stressSemiconductor

Novel interconnect structures possessing a relatively low internal stress and dielectric constant for use in semiconductor devices are provided herein. The novel interconnect structures comprise a first layer having a coefficient of thermal expansion greater than about 20 ppm and a first internal stress associated therewith, the first layer having a first set of metallic lines formed therein; a second layer having a coefficient of thermal expansion less than about 20 ppm and a second internal stress associated therewith, the second layer having a second set of metallic lines formed therein; and one or more stress adjustment cap layers formed between the first layer and the second layer, the cap layer(s) having a third internal stress to offset the first stress of the first layer and the second stress of the second layer and inducing a favorable relief of stress on the interconnect structure. Methods for making a semiconductor device having a substantially reduced internal stress are also provided.

Owner:格芯公司

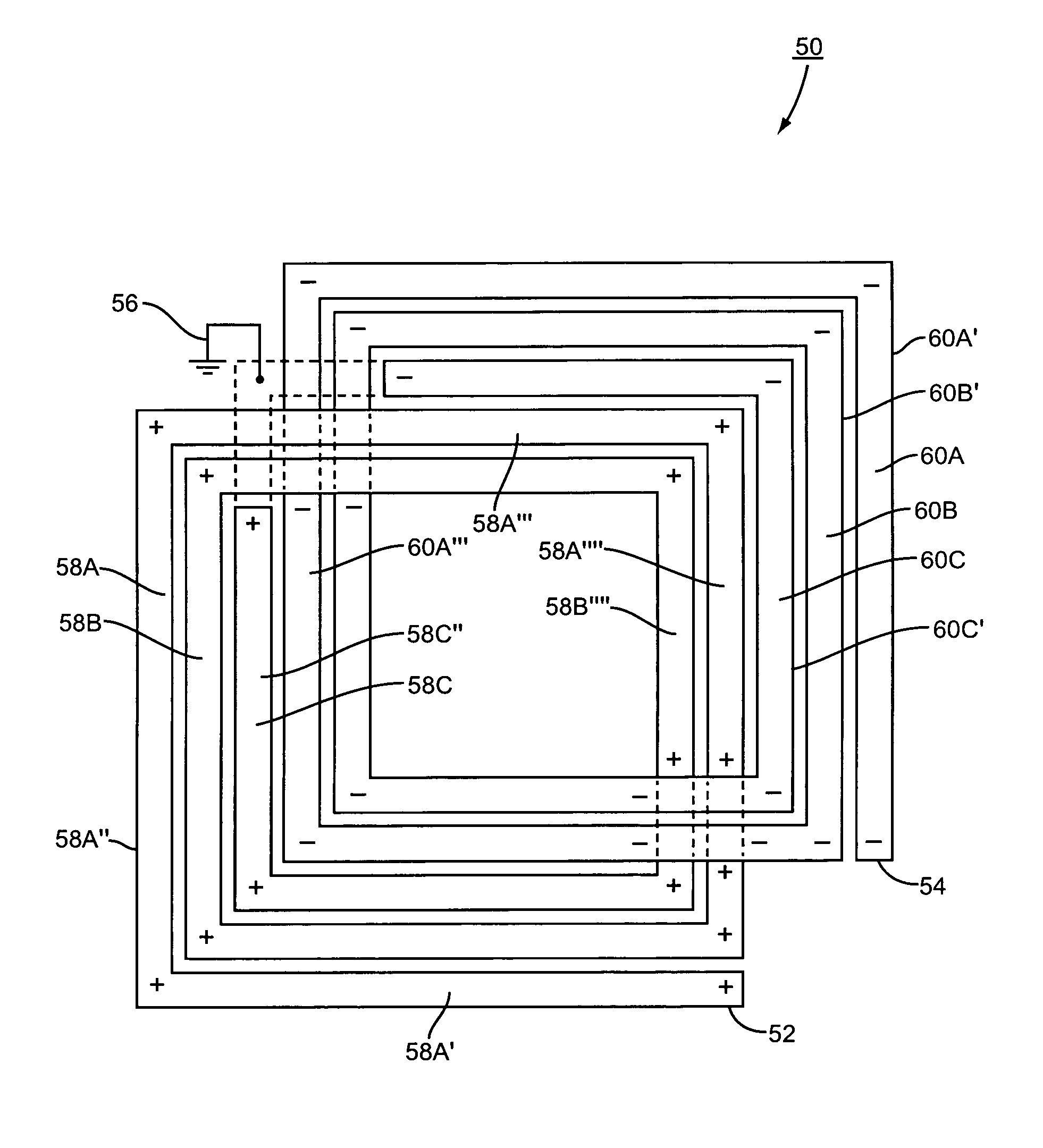

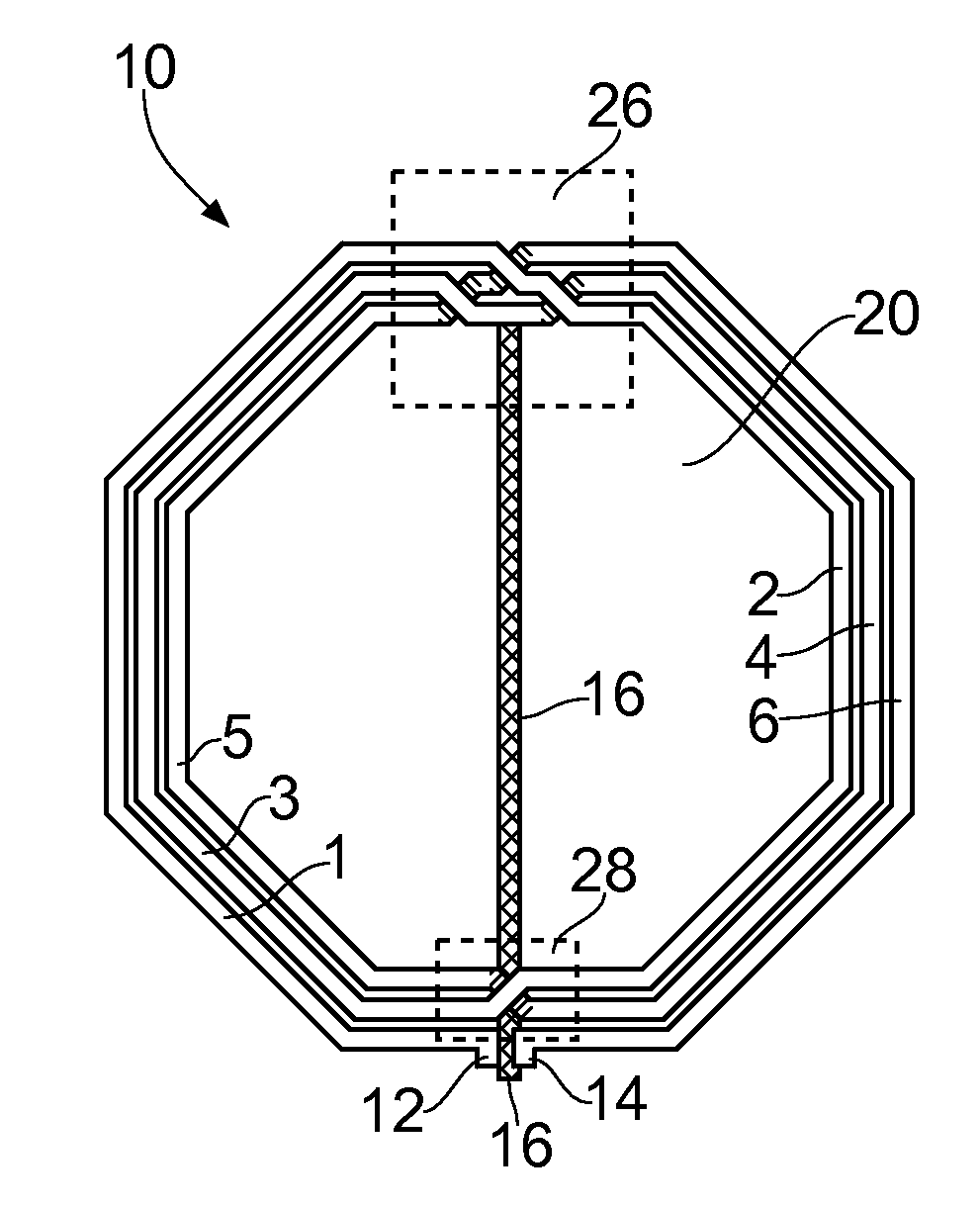

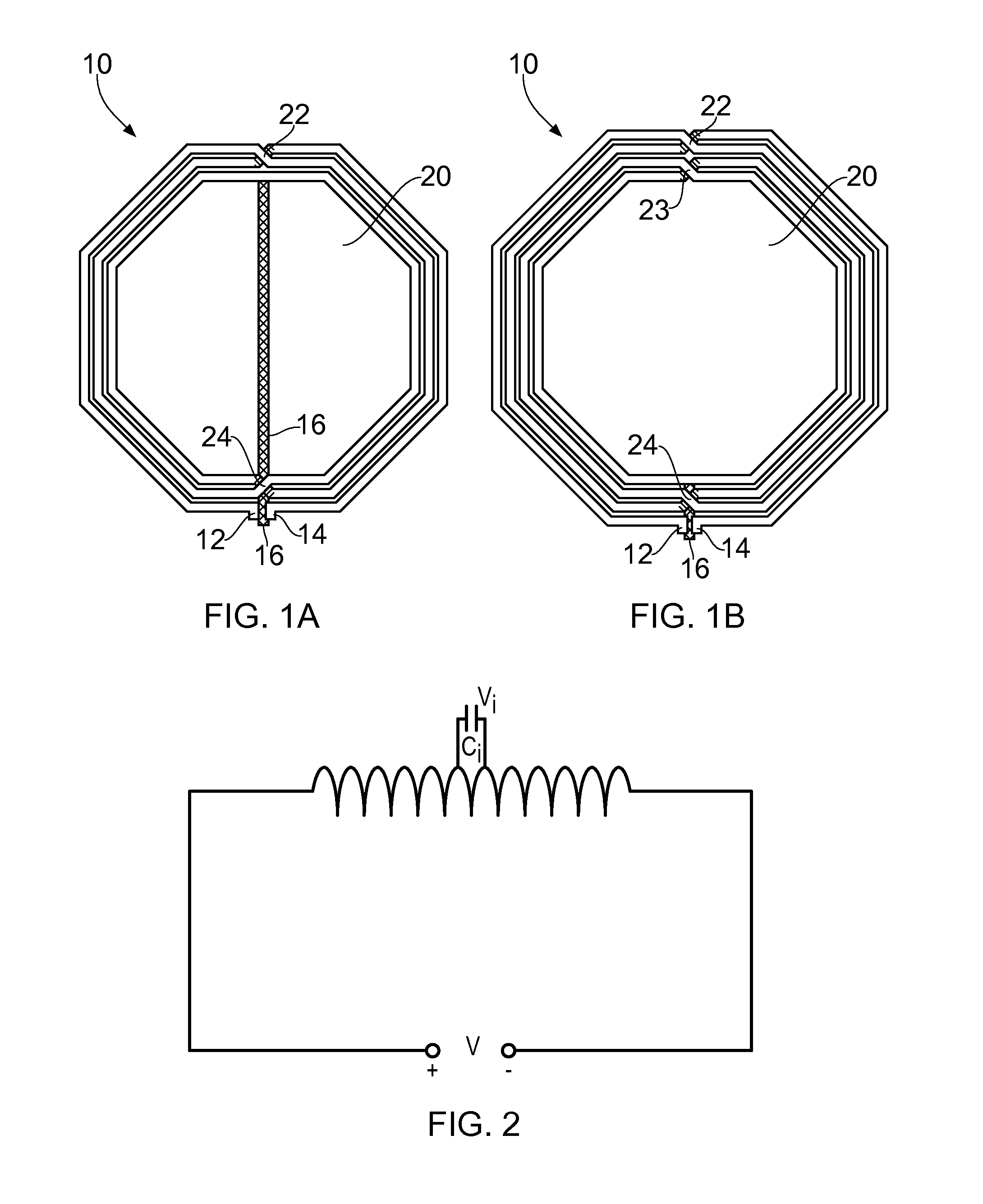

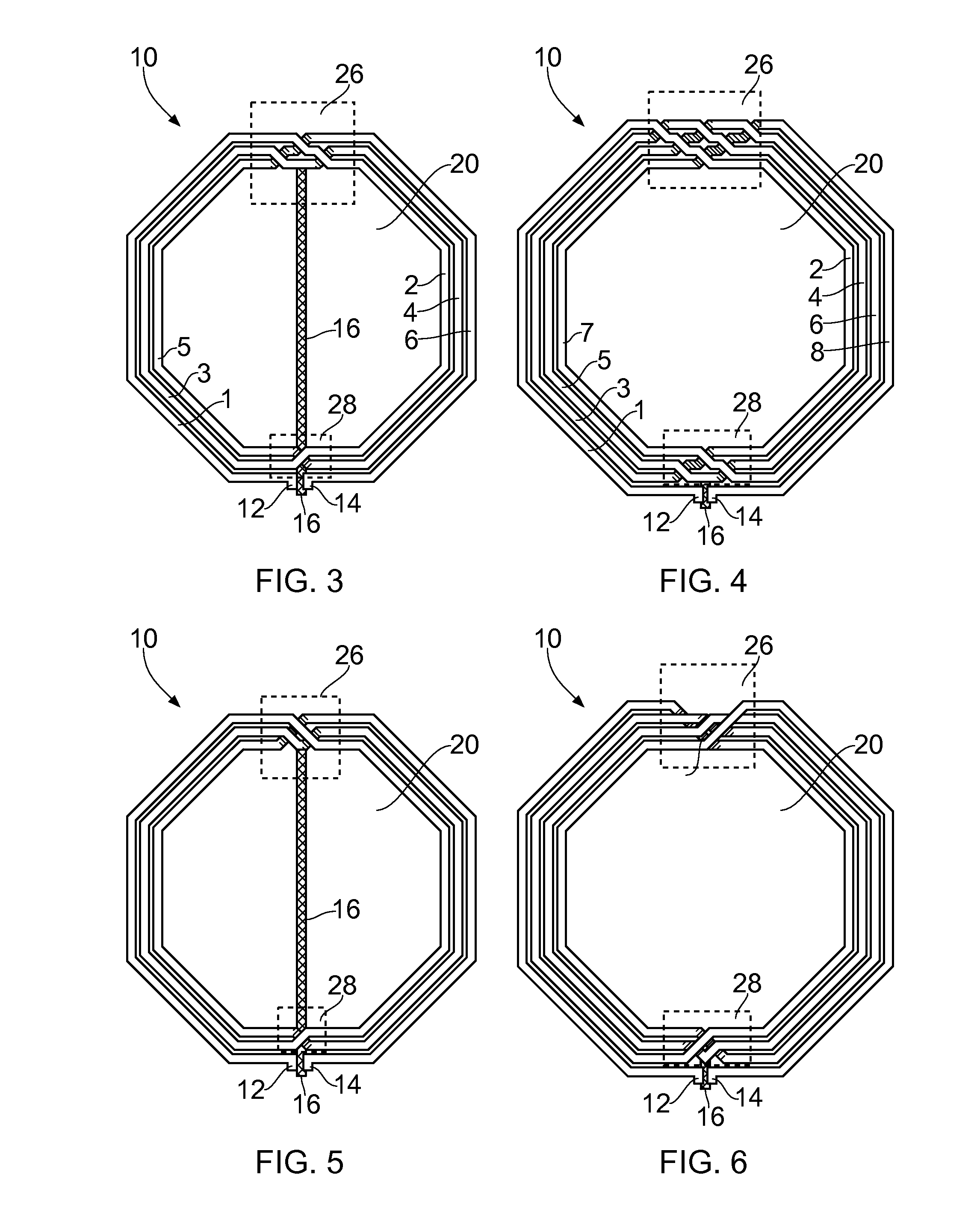

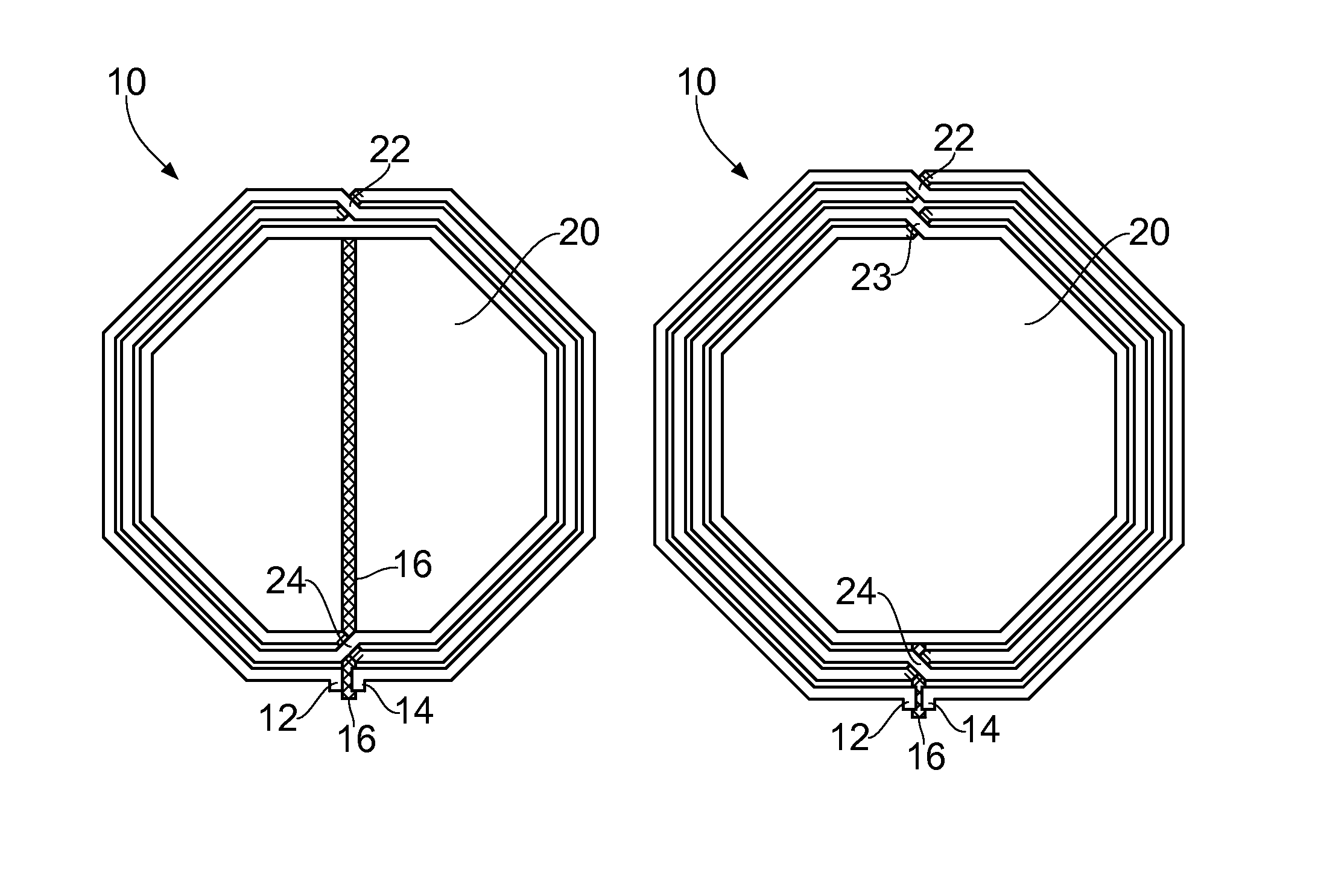

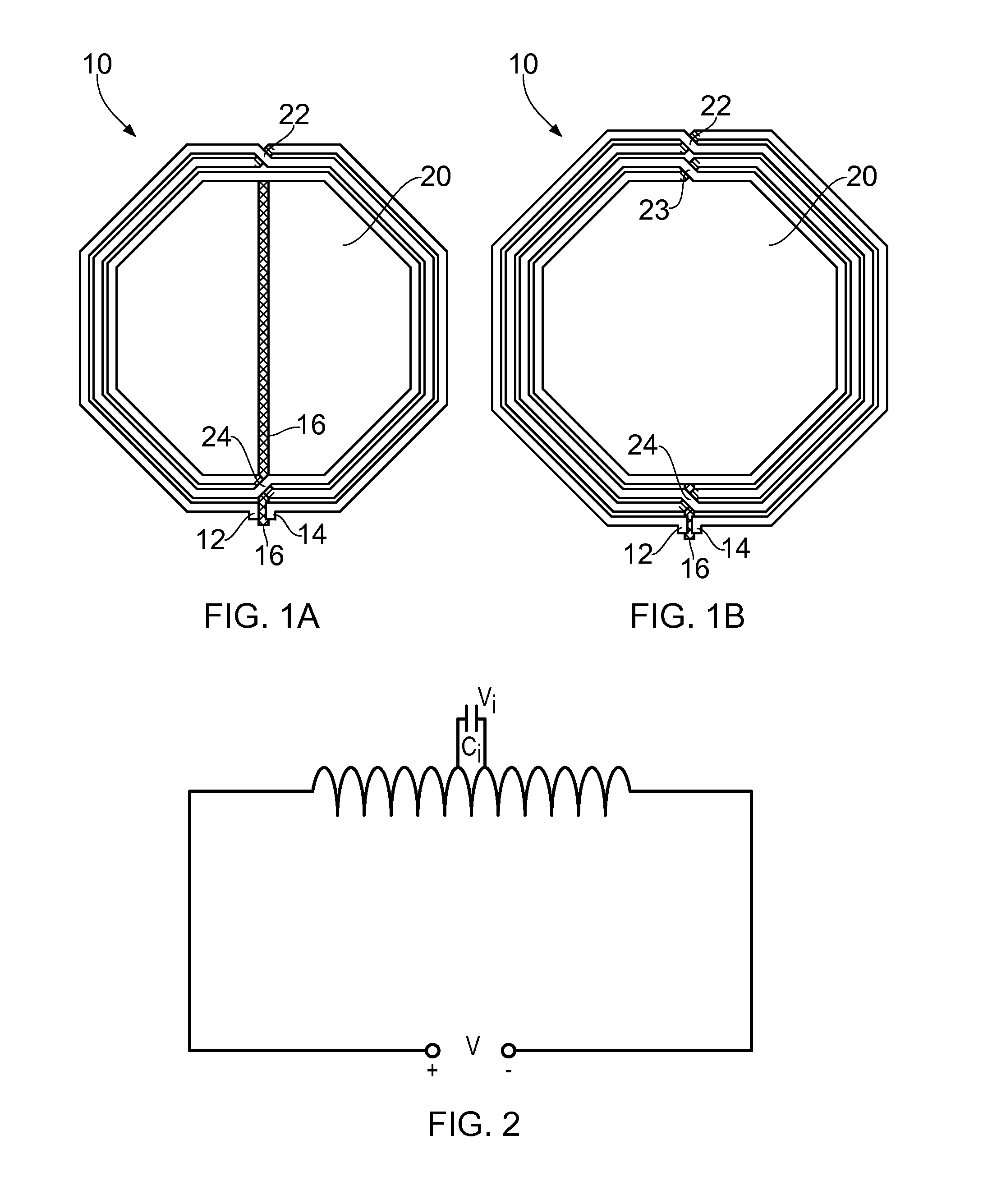

Inductor

ActiveUS20110148558A1Prevent electrical shortingReduce parasitic capacitanceTransformers/inductances coils/windings/connectionsUnwanted magnetic/electric effect reduction/preventionEngineeringInductor

An inductor includes a conductive track forming at least three inductor turns. The conductive track has a plurality of track sections. The inductor also includes at least two groups of crossing points, each crossing point comprising a location at which the conductive track crosses over itself. The crossing points of each group collectively reverse the order of at least some of the track sections in the inductor, such that inner track sections of the conductive track cross over to become respective outer track sections, and such that outer track sections of the conductive track cross over to become respective inner track sections.

Owner:NXP BV

Inductor

ActiveUS8203419B2Reduce parasitic capacitanceLow effective capacitanceTransformers/inductances coils/windings/connectionsUnwanted magnetic/electric effect reduction/preventionEngineeringInductor

An inductor includes a conductive track forming at least three inductor turns. The conductive track has a plurality of track sections. The inductor also includes at least two groups of crossing points, each crossing point comprising a location at which the conductive track crosses over itself. The crossing points of each group collectively reverse the order of at least some of the track sections in the inductor, such that inner track sections of the conductive track cross over to become respective outer track sections, and such that outer track sections of the conductive track cross over to become respective inner track sections.

Owner:NXP BV

Semiconductor device having low-K insulating film

InactiveUS6903445B2Improve adhesionAdhesivitySemiconductor/solid-state device detailsSolid-state devicesDevice materialOxygen

Disclosed is a semiconductor device having a dielectric film of a stacked structure, comprising a low dielectric constant film containing silicon, oxygen and carbon a modified layer for the low dielectric constant film containing silicon, oxygen, carbon and fluorine and a dielectric protection film formed successively on a semiconductor substrate, the semiconductor device being manufactured by applying a plasma treatment using a fluorine-containing gas to the surface of an organic siloxane film to form a modified layer and then forming a dielectric protection film, which can improve the adhesivity with the dielectric protection film without increasing the dielectric constant of the organic siloxane film to prevent delamination.

Owner:RENESAS ELECTRONICS CORP

Systems and methods for controlling the effective dielectric constant of materials used in a semiconductor device

InactiveUS20080299779A1Low effective capacitanceEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor

Systems and methods for controlling the effective dielectric constant of materials used in a semiconductor device are shown and described. In one embodiment, a method comprises providing a semiconductor substrate with a plurality of pillars formed thereon, depositing a first layer of dielectric material over a plurality of pillars, removing a portion of the first layer deposited over the plurality of pillars, and depositing a second layer of dielectric material over the plurality of pillars, where the second layer leaves a plurality of voids between the plurality of pillars.

Owner:SEMATECH

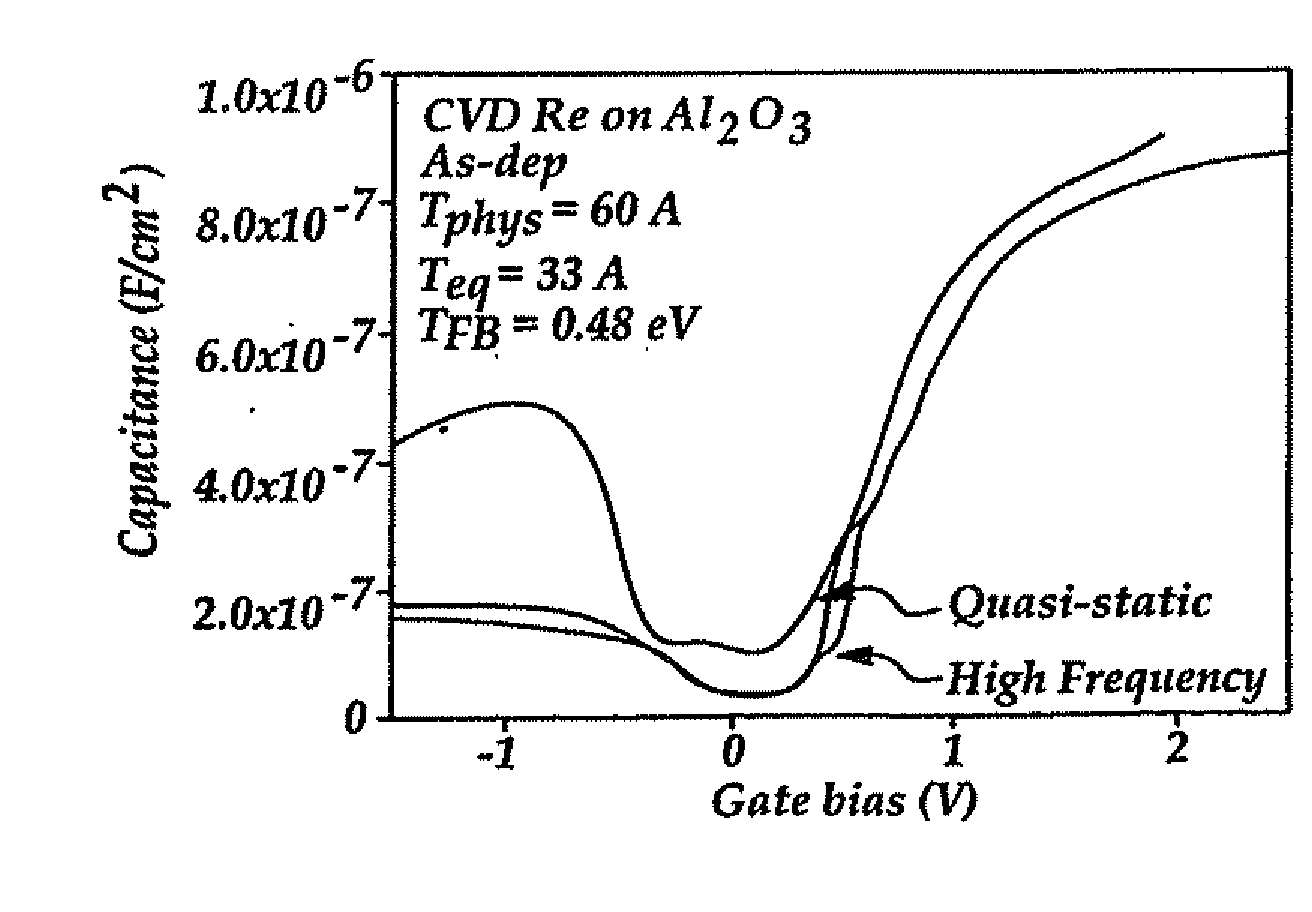

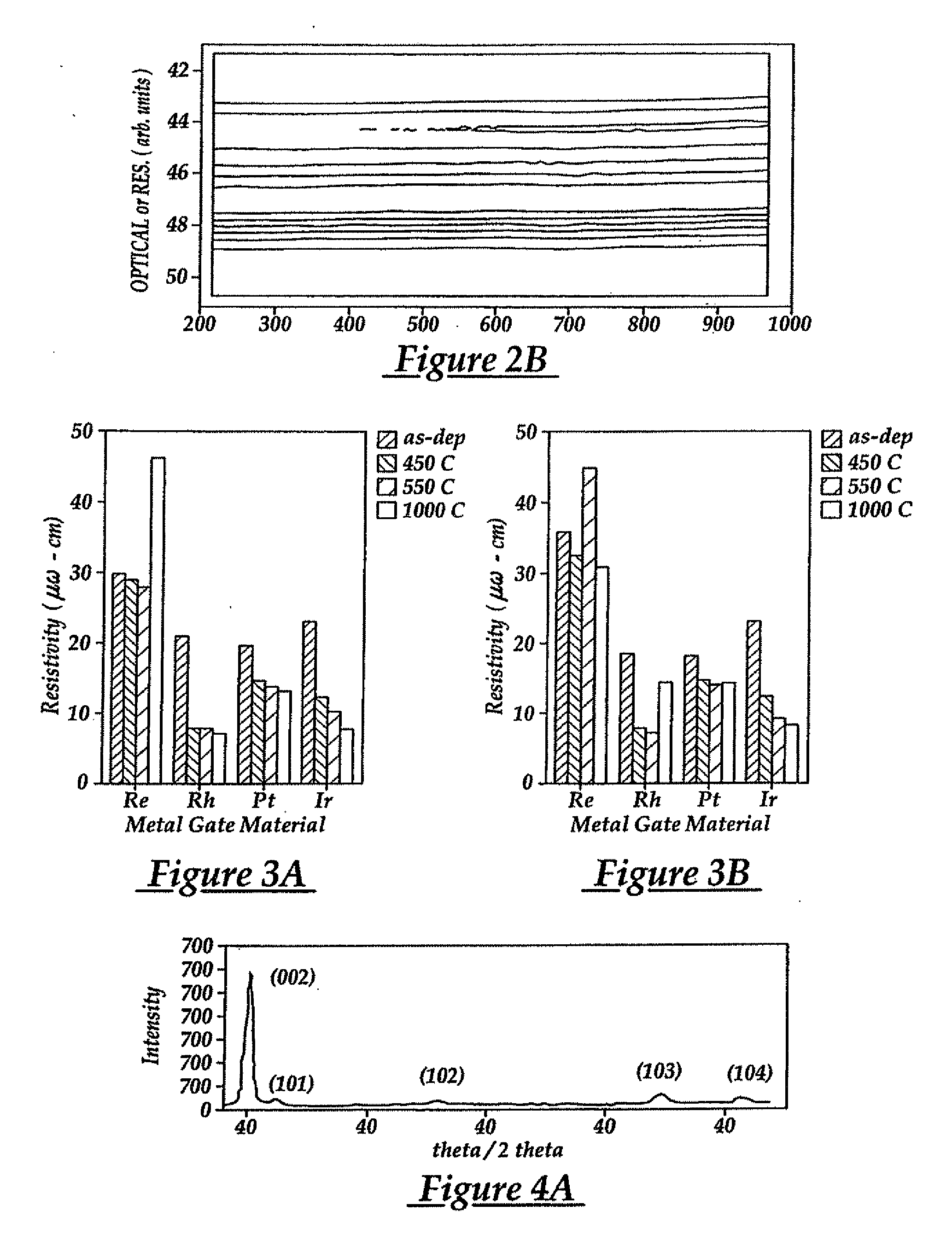

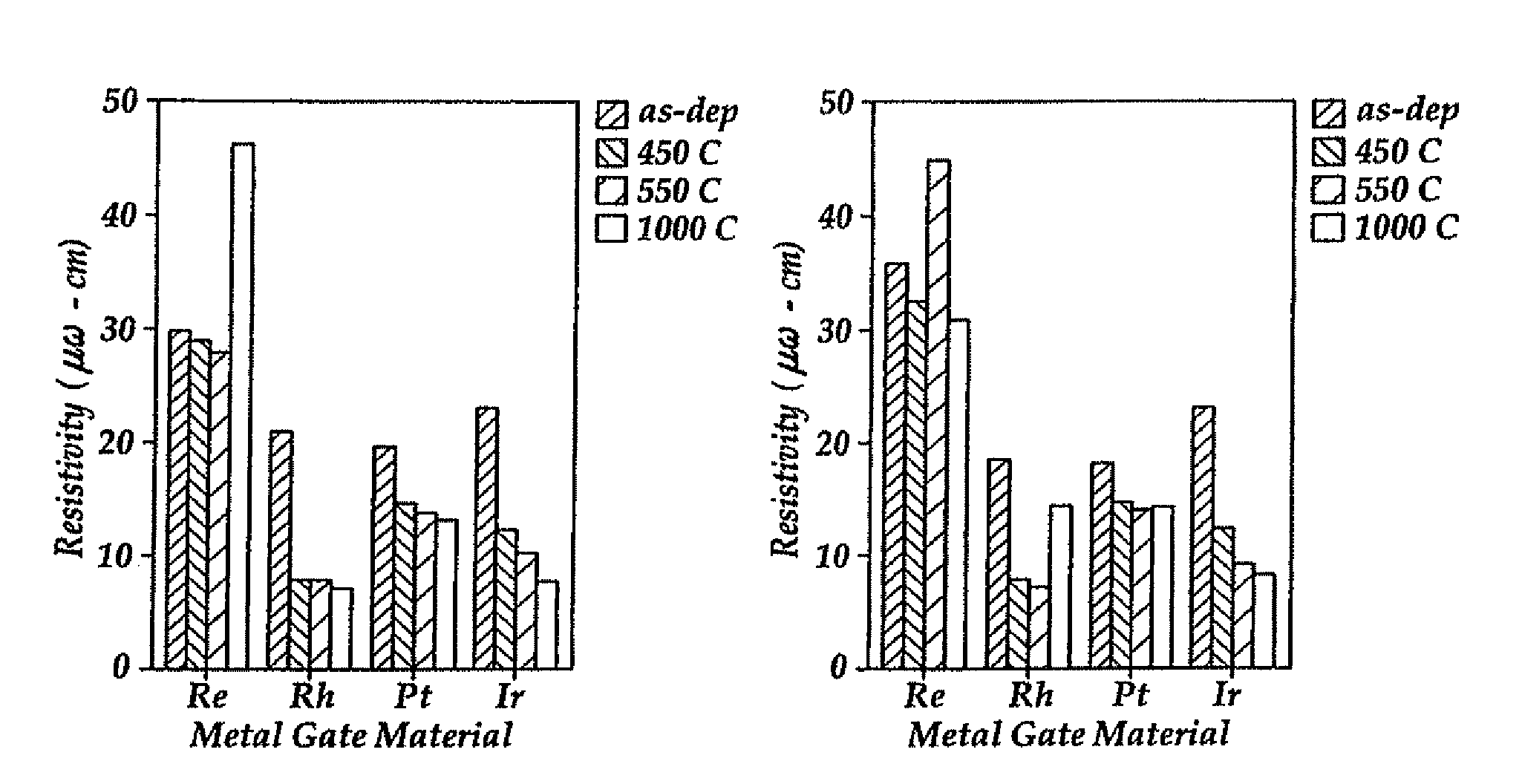

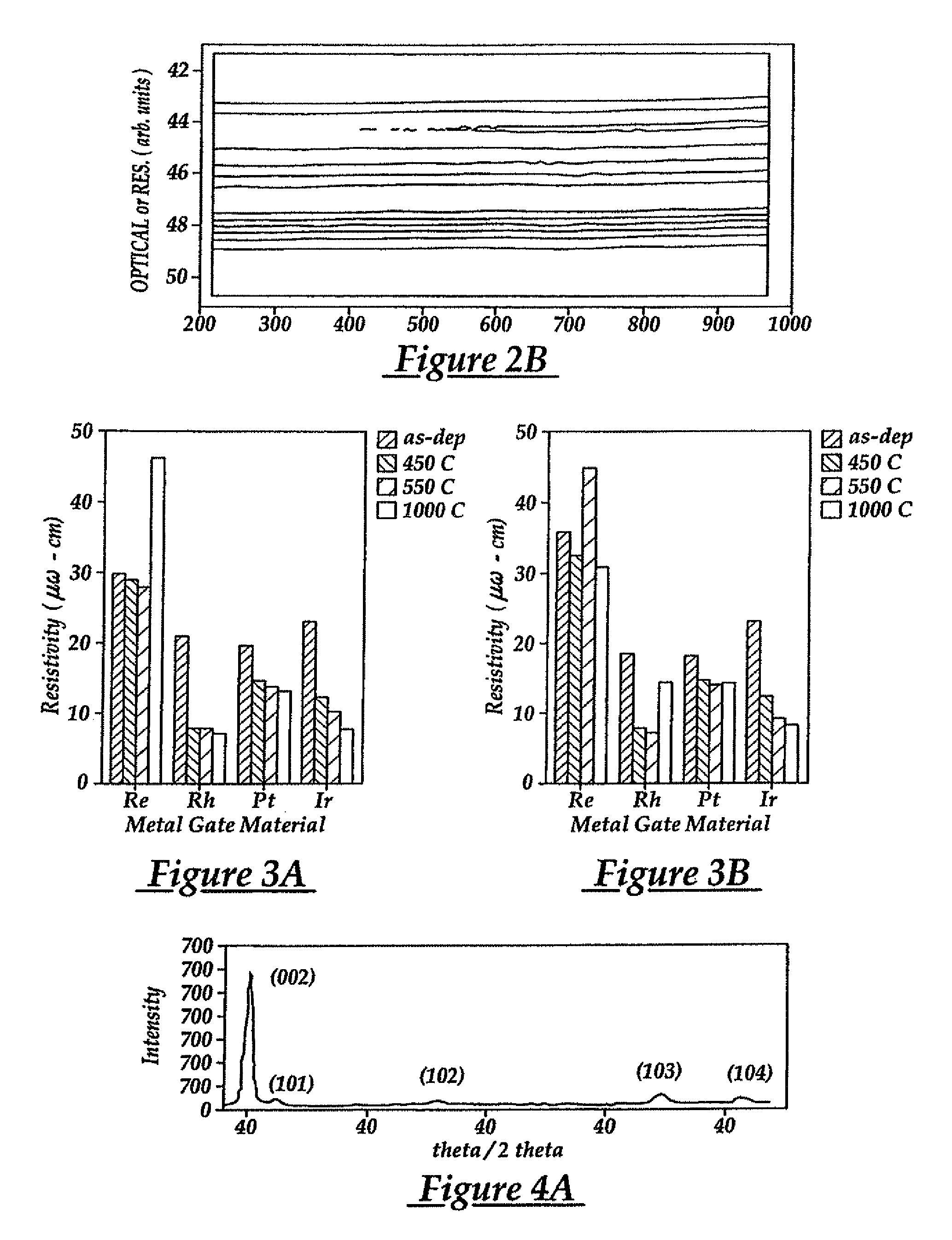

High Temperature Processing Compatible Metal Gate Electrode For pFETS and Methods For Fabrication

InactiveUS20080311745A1Improve pressure resistanceLow effective capacitanceTransistorSemiconductor/solid-state device manufacturingCMOSHydrogen pressure

A method for fabricating a CMOS gate electrode by using Re, Rh, Pt, Ir or Ru metal and a CMOS structure that contains such gate electrodes are described. The work functions of these metals make them compatible with current pFET requirements. For instance, the metal can withstand the high hydrogen pressures necessary to produce properly passivated interfaces without undergoing chemical changes. The thermal stability of the metal on dielectric layers such as SiO2, Al2O3 and other suitable dielectric materials makes it compatible with post-processing temperatures up to 1000° C. A low temperature / low pressure CVD technique with Re2(CO)10 as the source material is used when Re is to be deposited.

Owner:GLOBALFOUNDRIES INC

Contact air gap formation and structures thereof

ActiveUS10971408B2Eliminate riskLow effective capacitanceTransistorSolid-state devicesEngineering physicsMaterials science

A method of forming a device includes providing a transistor having a gate structure and a source / drain structure adjacent to the gate structure. A cavity is formed along a sidewall surface of a contact opening over the source / drain structure. After forming the cavity, a sacrificial layer is deposited over a bottom surface and along the sidewall surface of the contact opening including within the cavity. A first portion of the sacrificial layer along the bottom surface of the contact opening is removed to expose a portion of the source / drain structure. A metal plug is then formed over the portion of the exposed source / drain structure. A remaining portion of the sacrificial layer is removed to form an air gap disposed between the metal plug and the gate structure. Thereafter, a seal layer is deposited over the air gap to form an air gap spacer.

Owner:TAIWAN SEMICON MFG CO LTD

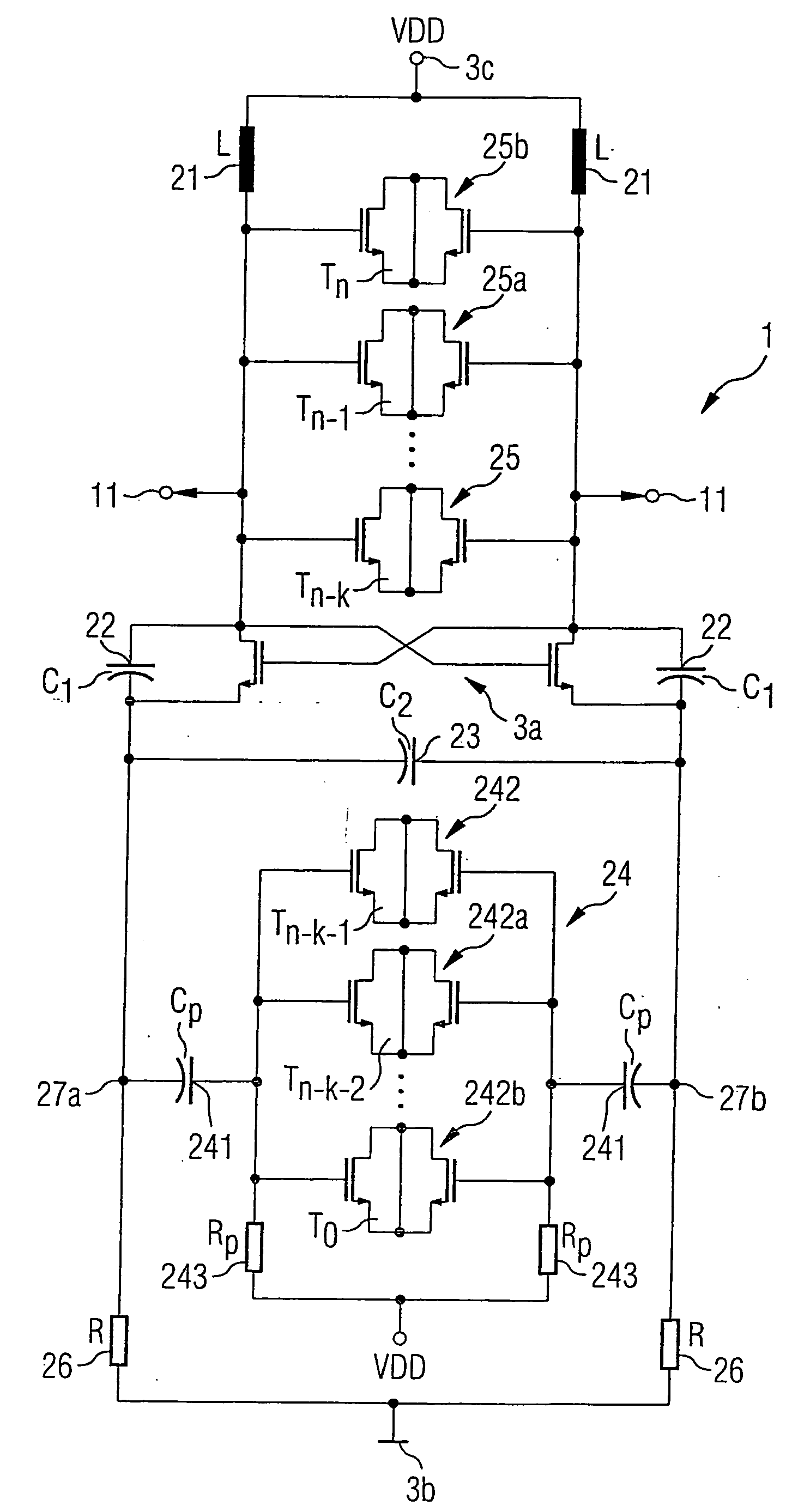

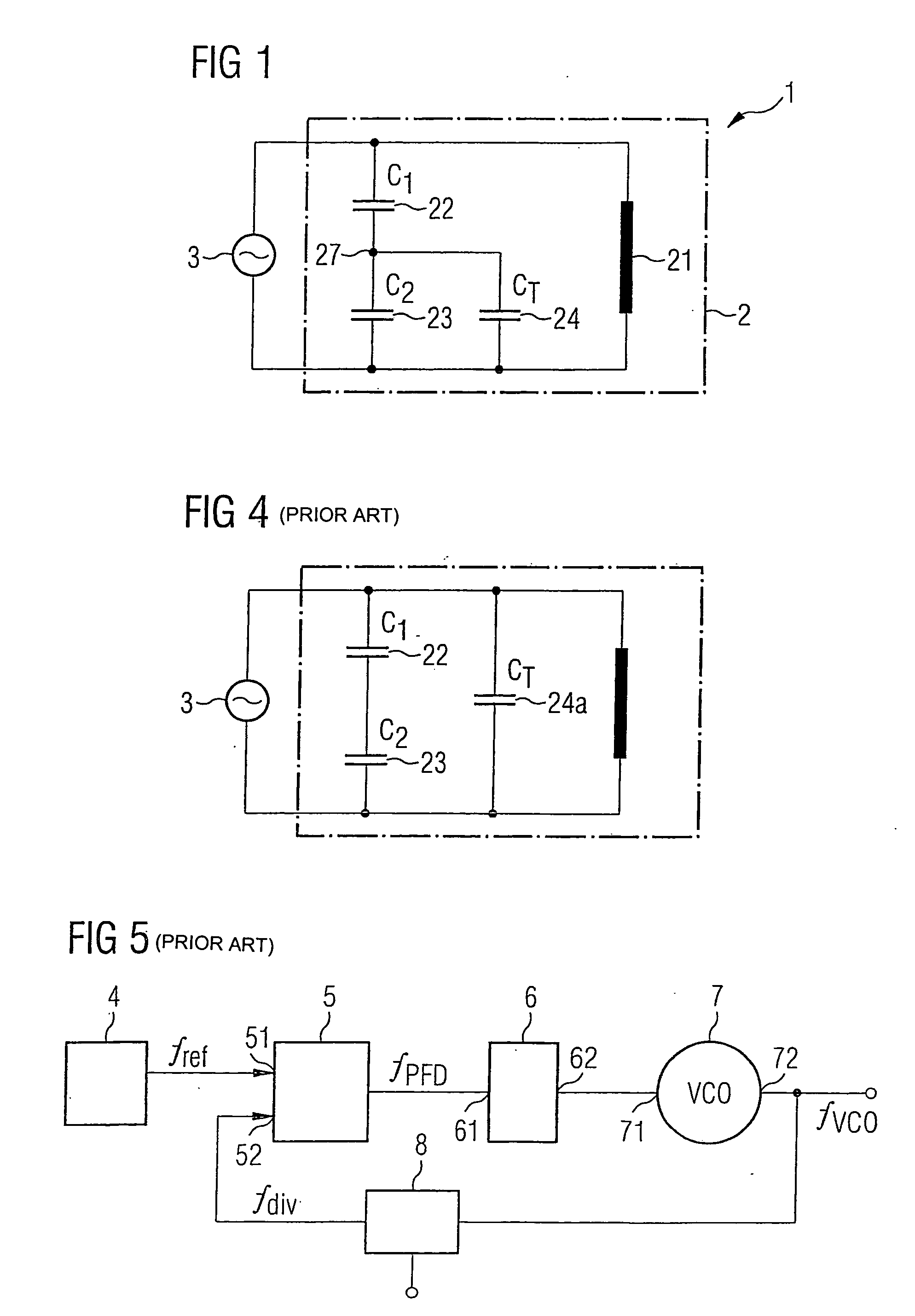

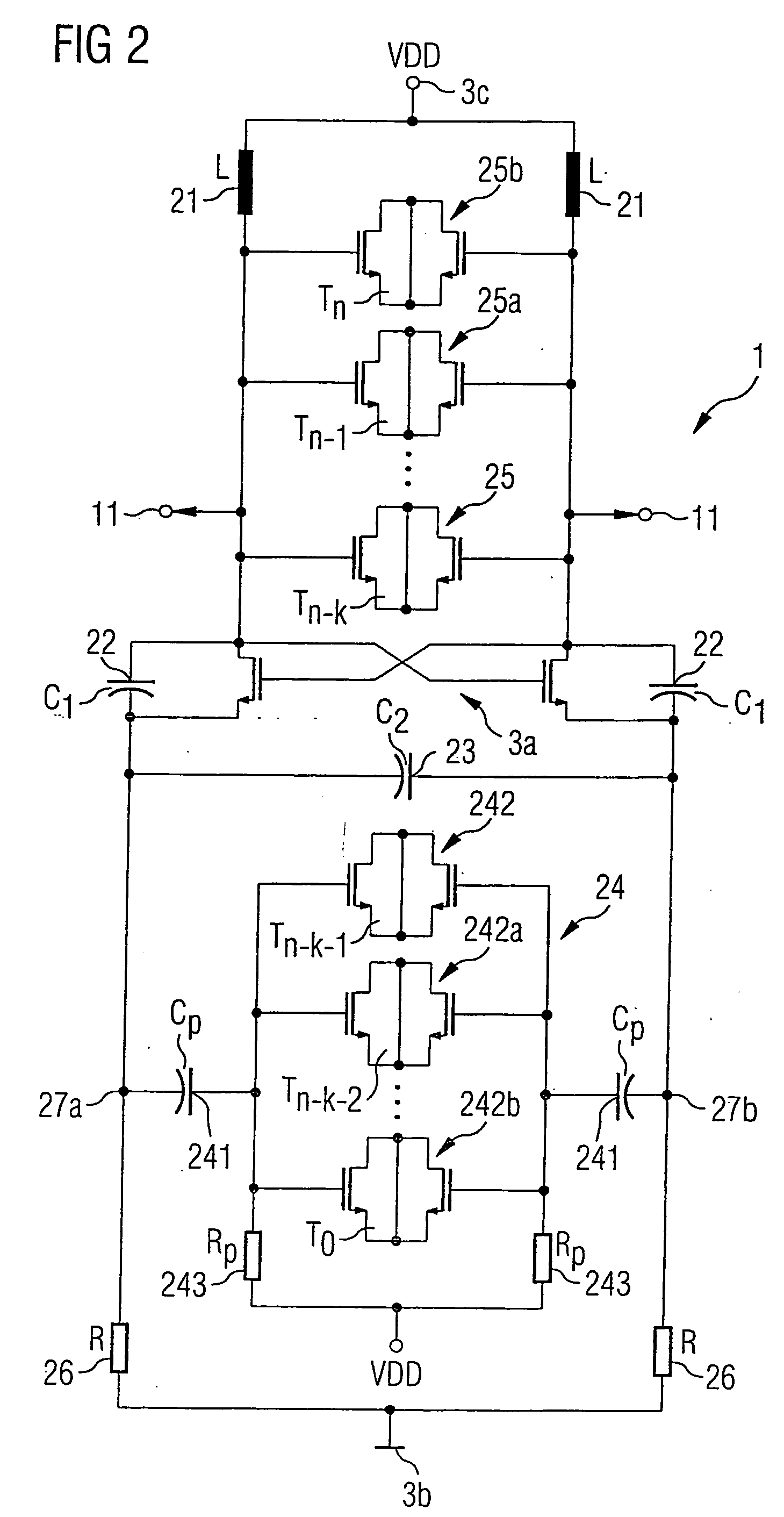

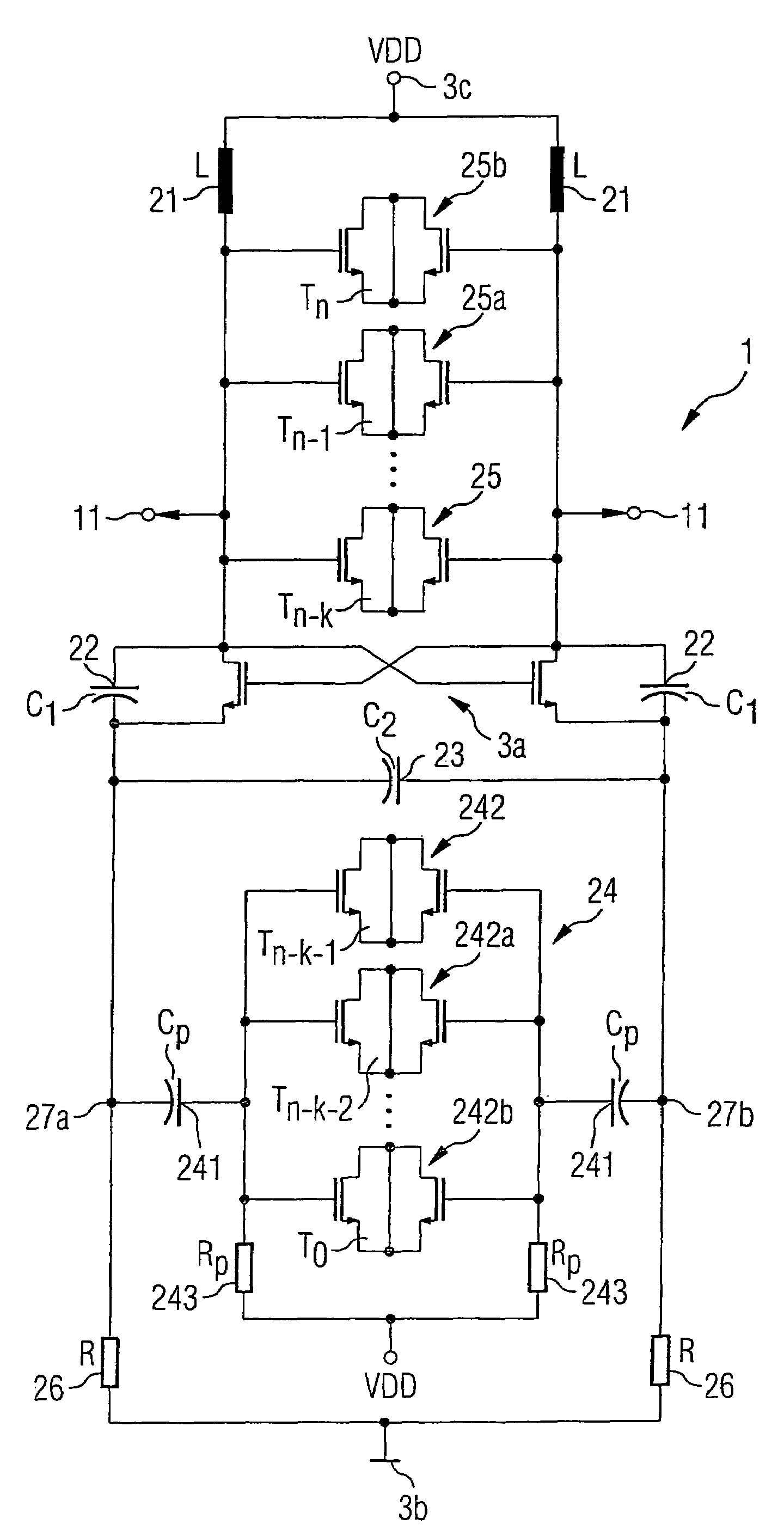

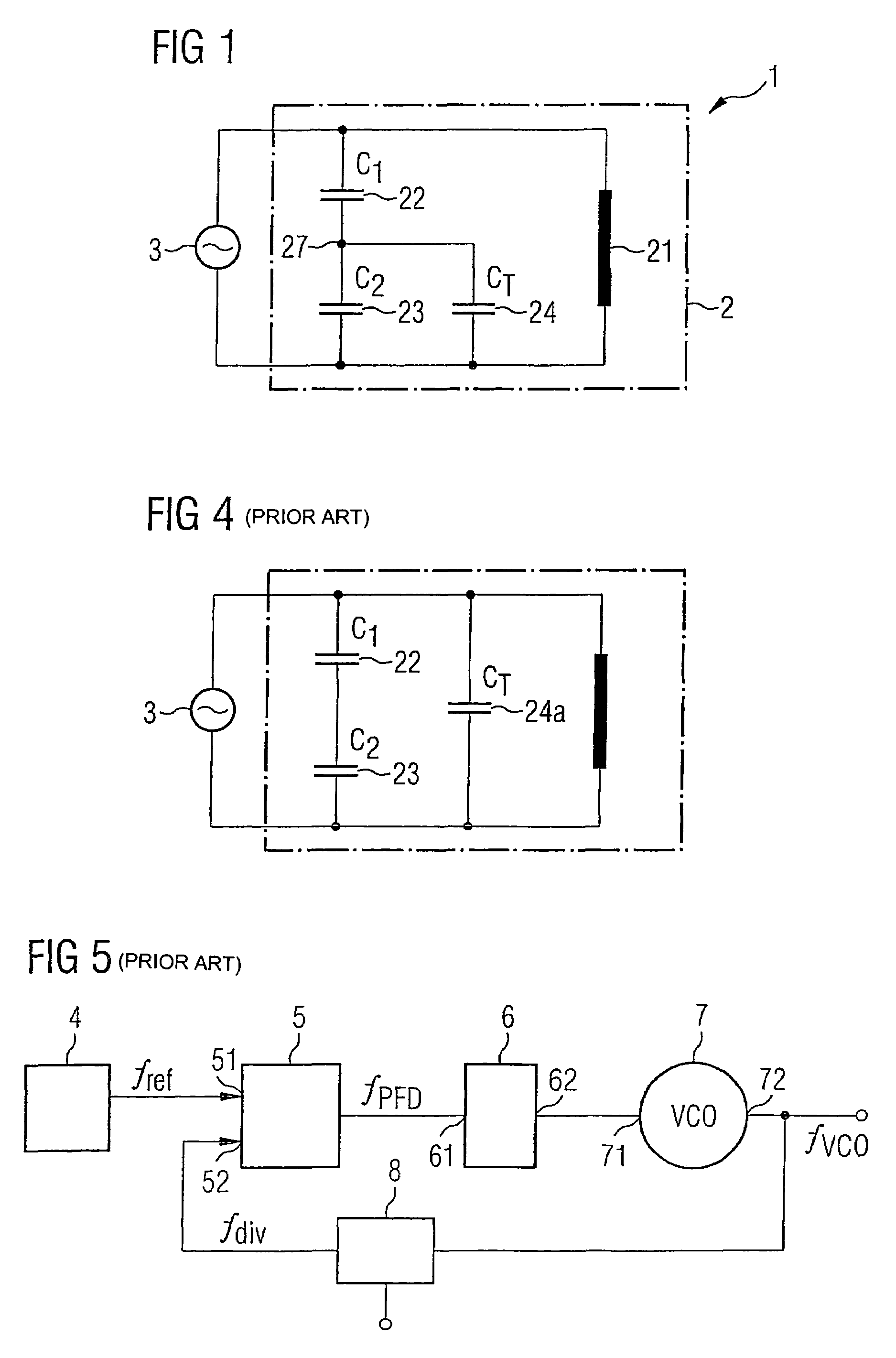

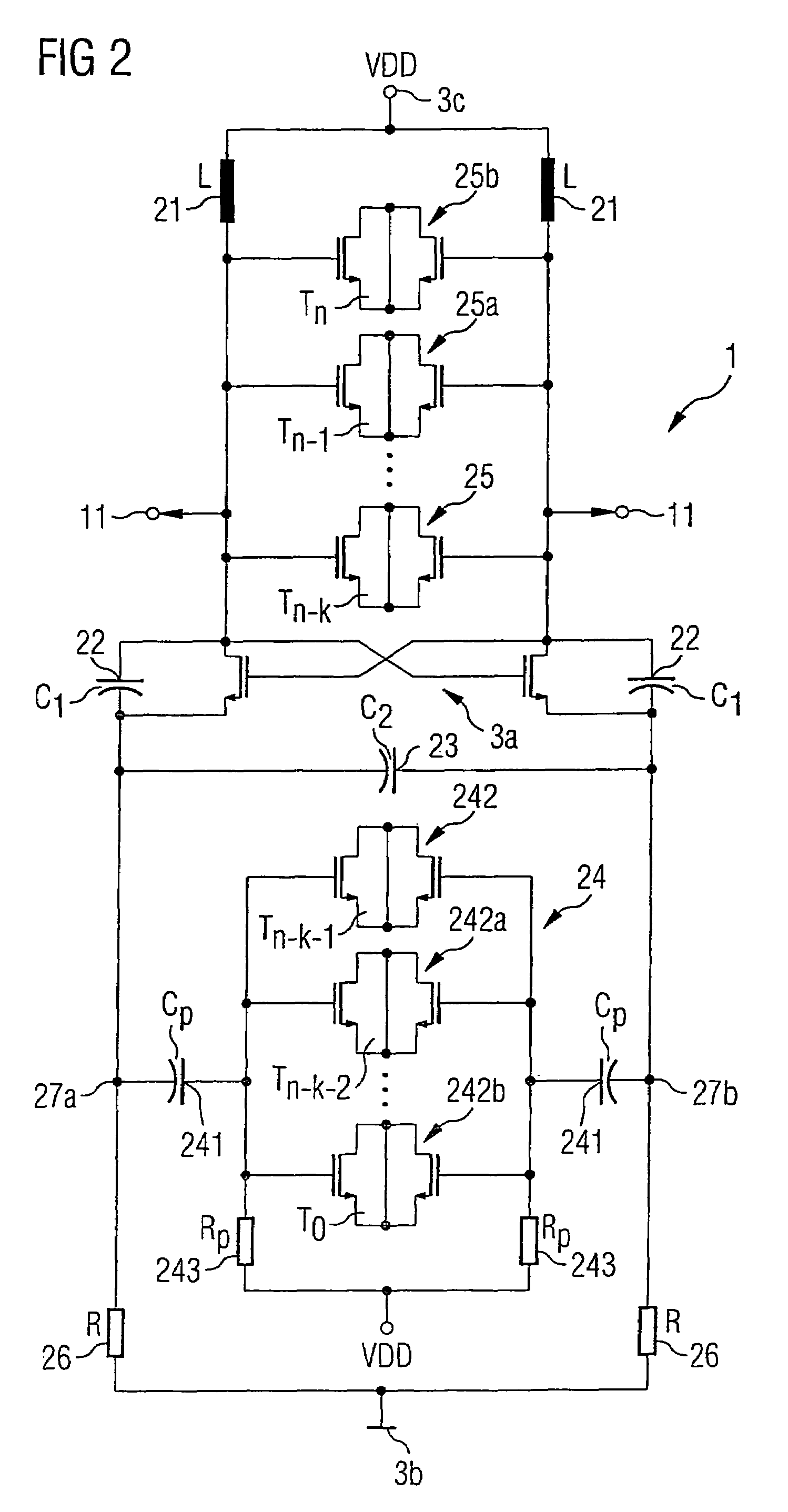

Oscillator circuit

The invention is directed to an oscillator circuit in which a frequency-determining resonant circuit includes an inductive element, a first capacitive element and at least one second capacitive element which is connected in series with the first capacitive element. A node is provided between the first capacitive element and at least one second capacitive element. The oscillator circuit contains a damping reduction amplifier which is arranged in parallel with the frequency-determining resonant circuit. In addition, the oscillator circuit has a first tuneable capacitive element, which is connected in parallel with the first capacitive element of the resonant circuit and has a connection connected to the node.

Owner:INFINEON TECH AG

Oscillator circuit

InactiveUS7372343B2Reduce impactLow effective capacitanceAngle modulation by variable impedenceAngle modulation detailsCapacitanceAudio power amplifier

The invention is directed to an oscillator circuit in which a frequency-determining resonant circuit includes an inductive element, a first capacitive element and at least one second capacitive element which is connected in series with the first capacitive element. A node is provided between the first capacitive element and at least one second capacitive element. The oscillator circuit contains a damping reduction amplifier which is arranged in parallel with the frequency-determining resonant circuit. In addition, the oscillator circuit has a first tuneable capacitive element, which is connected in parallel with the first capacitive element of the resonant circuit and has a connection connected to the node.

Owner:INFINEON TECH AG

Advanced low k cap film formation process for nano electronic devices

ActiveUS8212337B2Low costLow effective capacitanceSemiconductor/solid-state device detailsSolid-state devicesUV curingNitrogen

A carbon-rich silicon carbide-like dielectric film having a carbon concentration of greater than, or equal to, about 30 atomic % C and a dielectric constant of less than, or equal to, about 4.5 is provided. In some embodiments, the dielectric film may optionally include nitrogen. When nitrogen is present, the carbon-rich silicon carbide-like dielectric film has a concentration nitrogen that is less than, or equal, to about 5 atomic % nitrogen. The carbon-rich silicon carbide-like dielectric film can be used as a dielectric cap layer in an interconnect structure. The inventive dielectric film is highly robust to UV curing and remains compressively stressed after UV curing. Moreover, the inventive dielectric film has good oxidation resistance and prevents metal diffusion into an interconnect dielectric layer. The present invention also provides an interconnect structure including the inventive dielectric film as a dielectric cap. A method of fabricating the inventive dielectric film is also provided.

Owner:GLOBALFOUNDRIES INC

Noise rejection

ActiveUS20100060301A1Accurate identificationLow effective capacitanceResistance/reactance/impedenceElectronic switchingCapacitive sensingIntegrated circuit

A capacitive sensing circuit including a microchip and a sense plate, wherein the microchip comprises a hardware Q RF noise detector module that provides a logical indication of when noise impacts on the integrated circuit.

Owner:AZOTEQ HLDG LTD

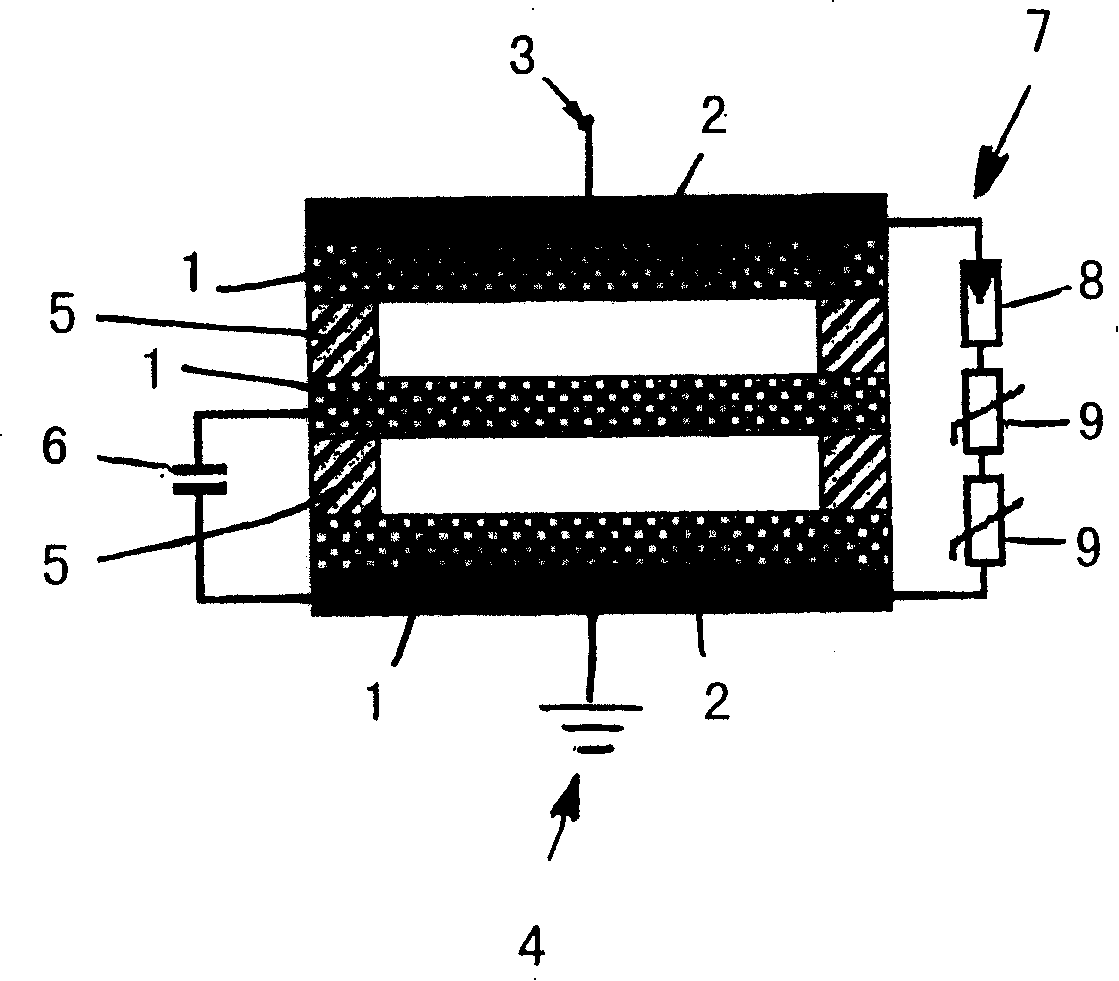

Arrester

InactiveCN100379107CDependence on reducing steepnessImproved action parameter propertiesSpark gaps with auxillary triggeringElectric lighting sourcesOvervoltageCapacitance

The spark clearance has as much possible partial spark clearances connected in series, in particular, these partial spark clearances are wired by capacitor (6) except the first spark clearance reacting in the case of overvoltage phenomenon, and, in particular, the second spark clearance and each spark clearance other than it are connected with common reference electric potential (4), particularly, ground potential through the capacity (6). To markedly improve reaction characteristic of a spark clearance, a bypass (7) composed of an auxiliary spark clearance (8) having a smaller reaction voltage than a reaction voltage of a single spark clearance or these partial spark clearances and at least one varistor (9) is connected in parallel with a multiple spark clearance composed of the single spark clearance or a plurality of partial spark clearances connected in series.

Owner:OBO BETTERMANN GMBH & CO KG

Major loop electric power cable for medium-voltage frequency converter

ActiveCN103794275AHigh tensile strengthImprove waterproof performanceClimate change adaptationPower cables with screens/conductive layersElectrical conductorPolyolefin

The invention provides a major loop electric power cable for a medium-voltage frequency converter. The cable comprises three power conductors, three control conductors and a central gap filler, wherein the cross section of the central gap filler is round, a cabled core is formed by stranding of the three power conductors and the three control conductors around the central gap filler, the control conductors are arranged between any two adjacent power conductors, the cabled core is sequentially coated with a third metal shielding layer, an electrostatic shielding layer, a water-blocking tape covering layer, a tin-plated steel wire winding armor layer and a polyolefin outer sheath, and water-blocking ropes with triangular cross sections are placed in gaps between the power conductors, the control conductors and the third metal shielding layer. According to the major loop electric power cable for the medium-voltage frequency converter, effective capacitance is low, transfer impedance is low, good electromagnetic compatibility is achievable, the tensile strength and water resistance of the cable are improved, and the service life of the cable is prolonged.

Owner:ANHUI HUAXI CABLE TECH

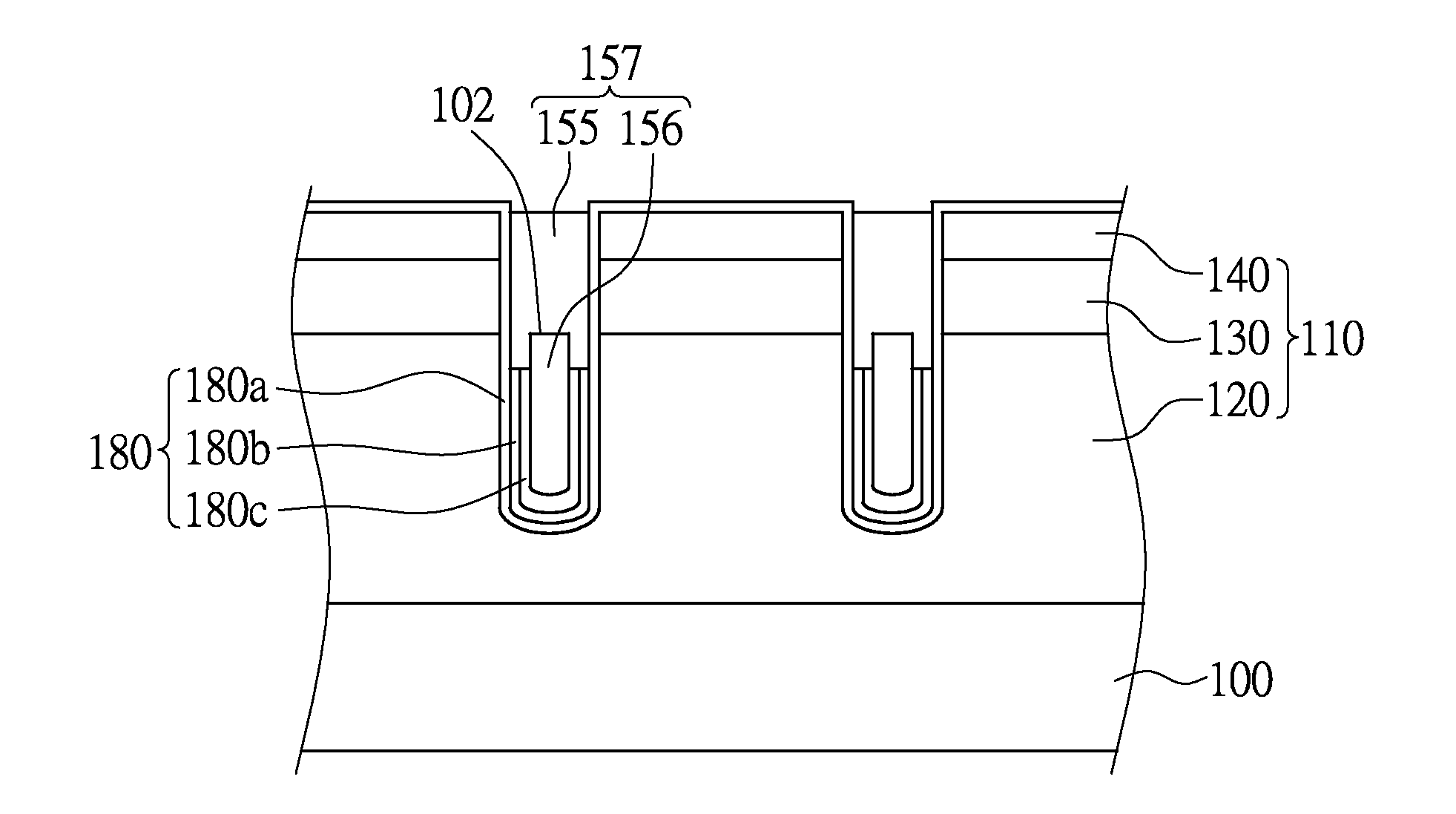

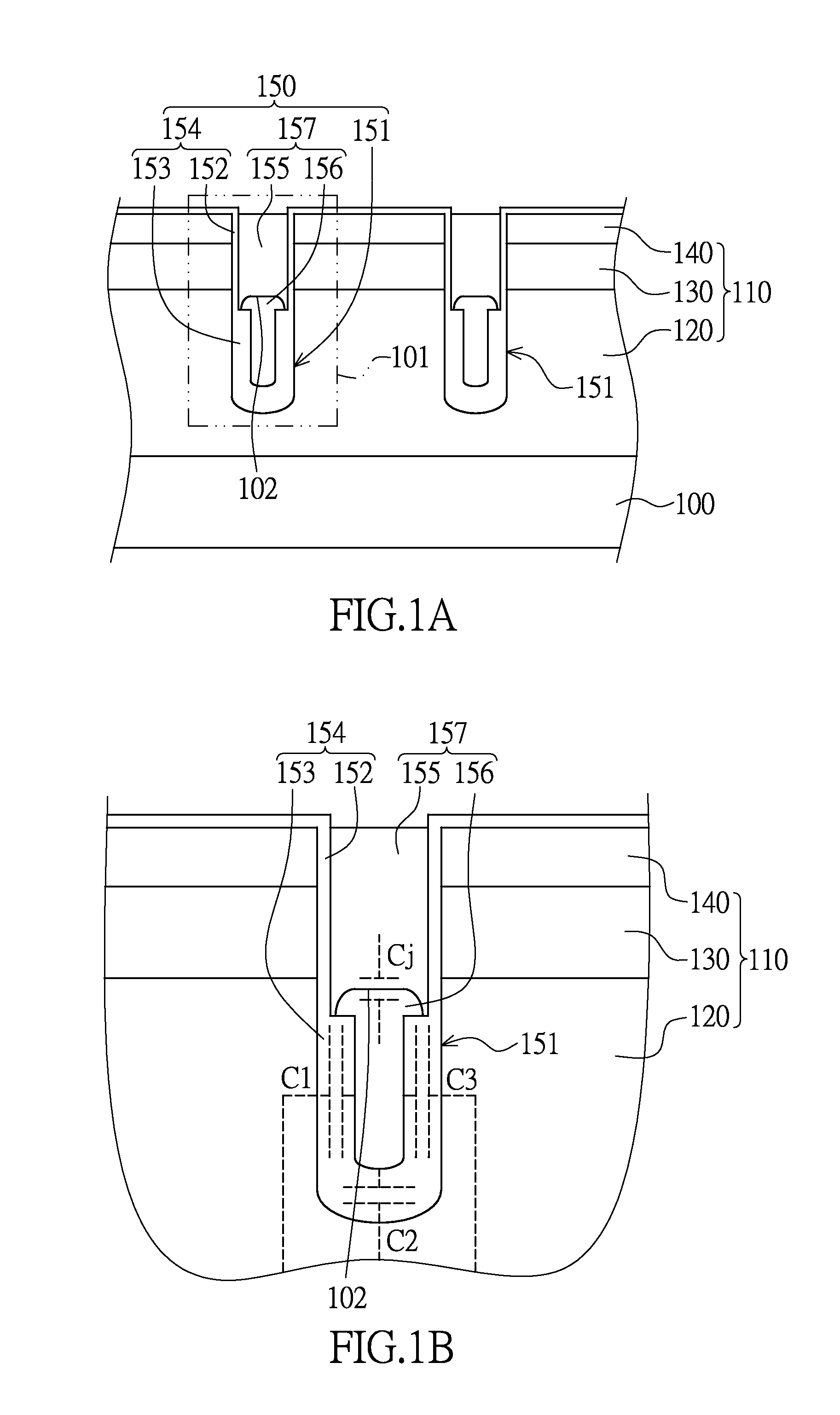

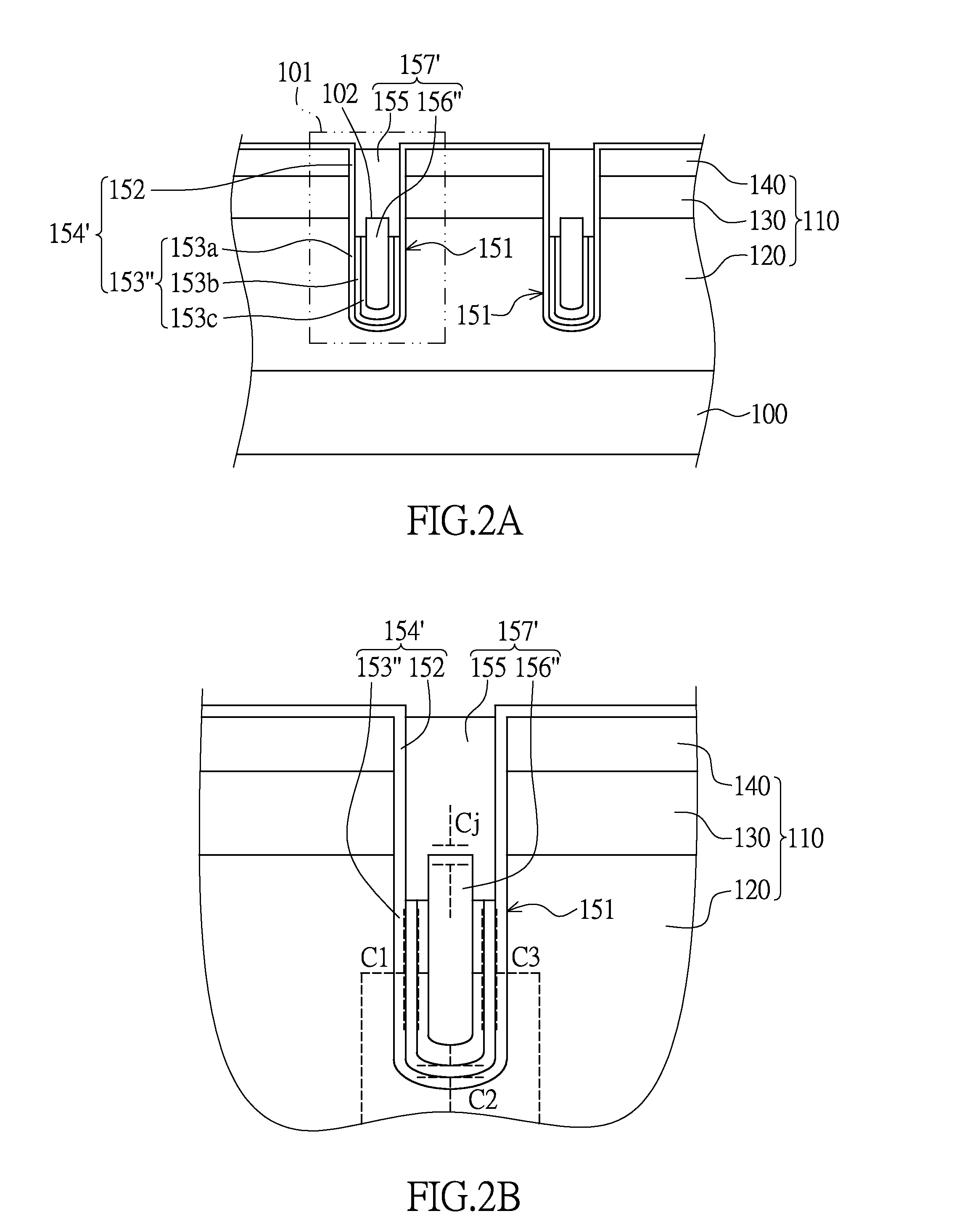

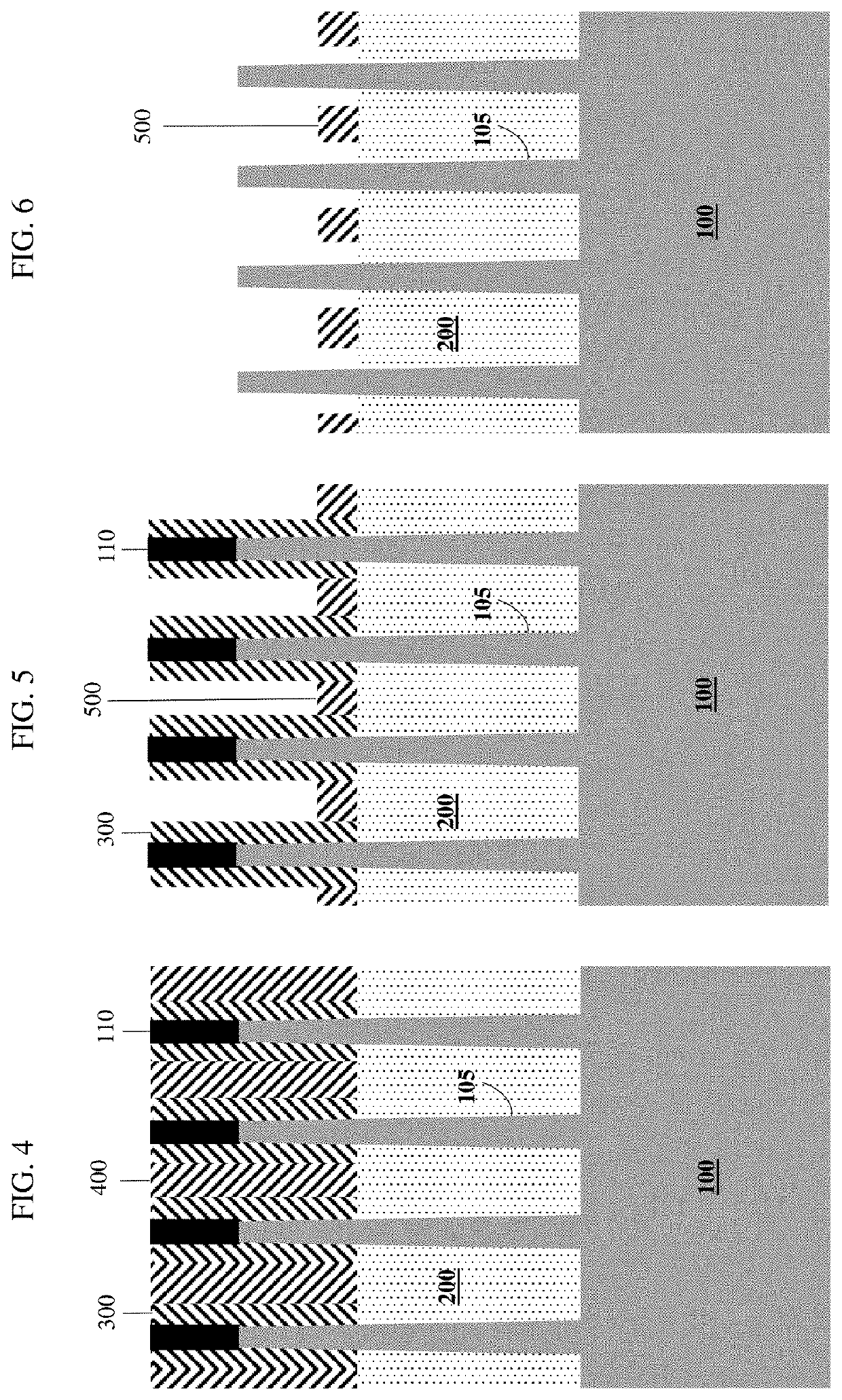

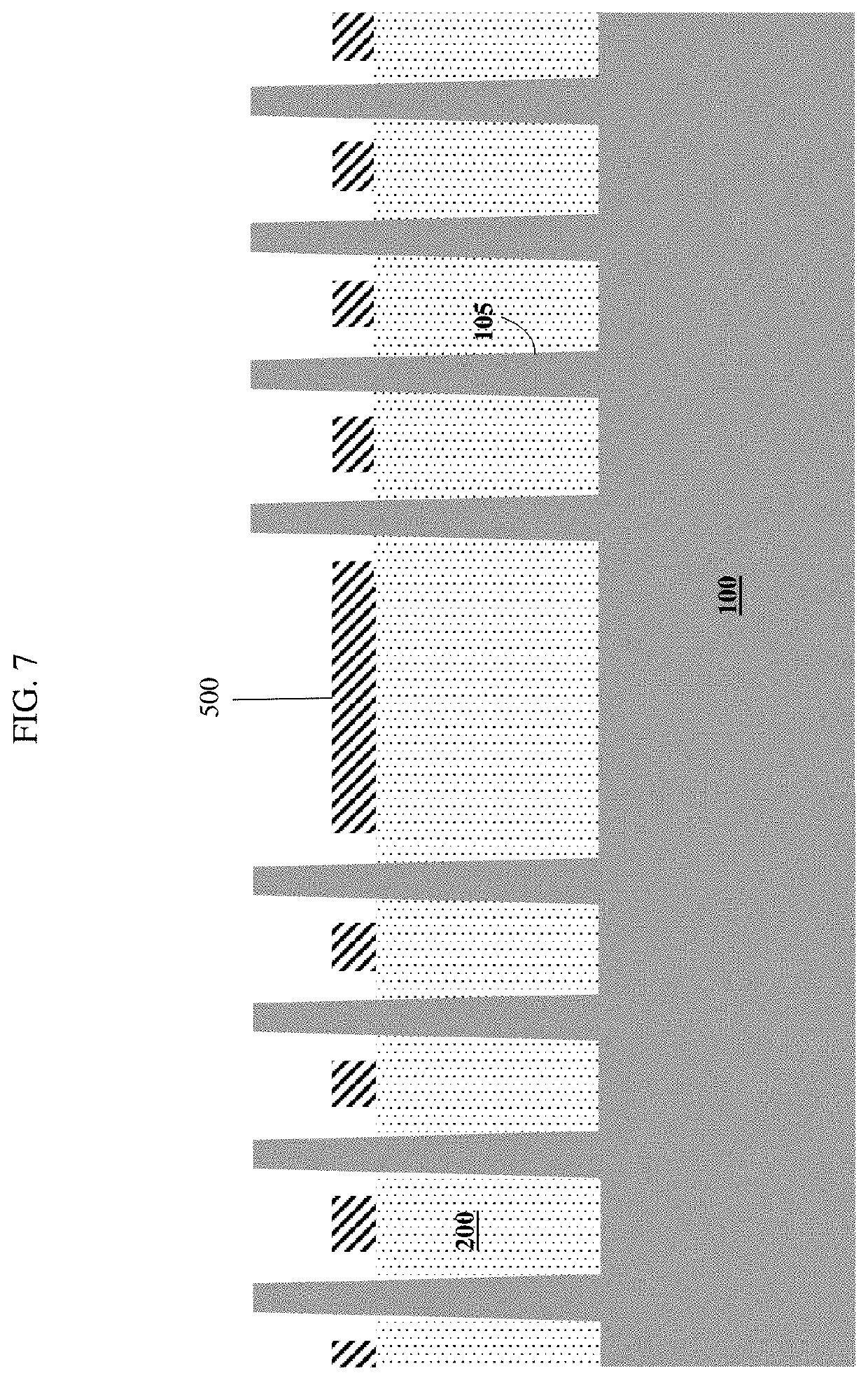

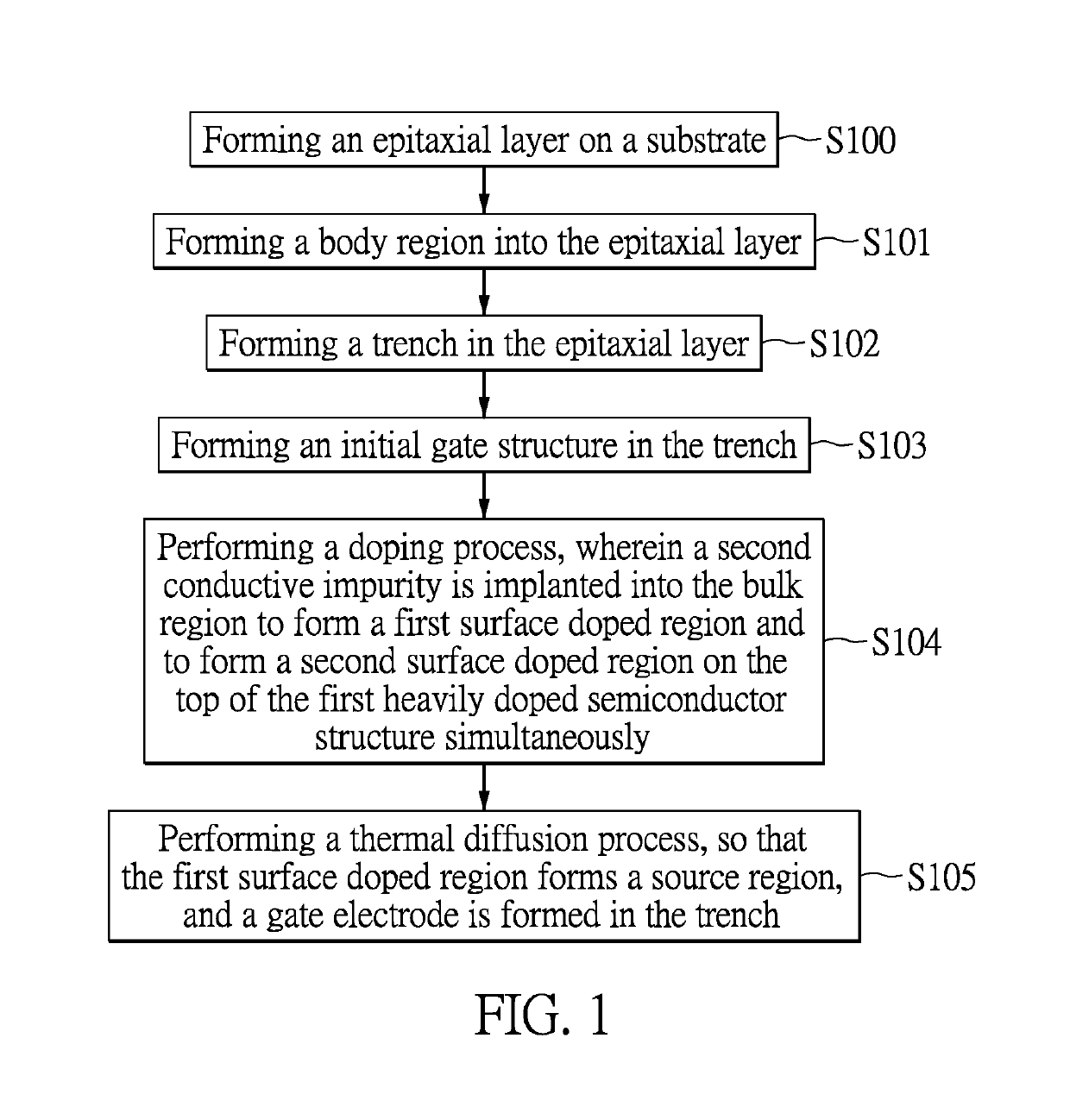

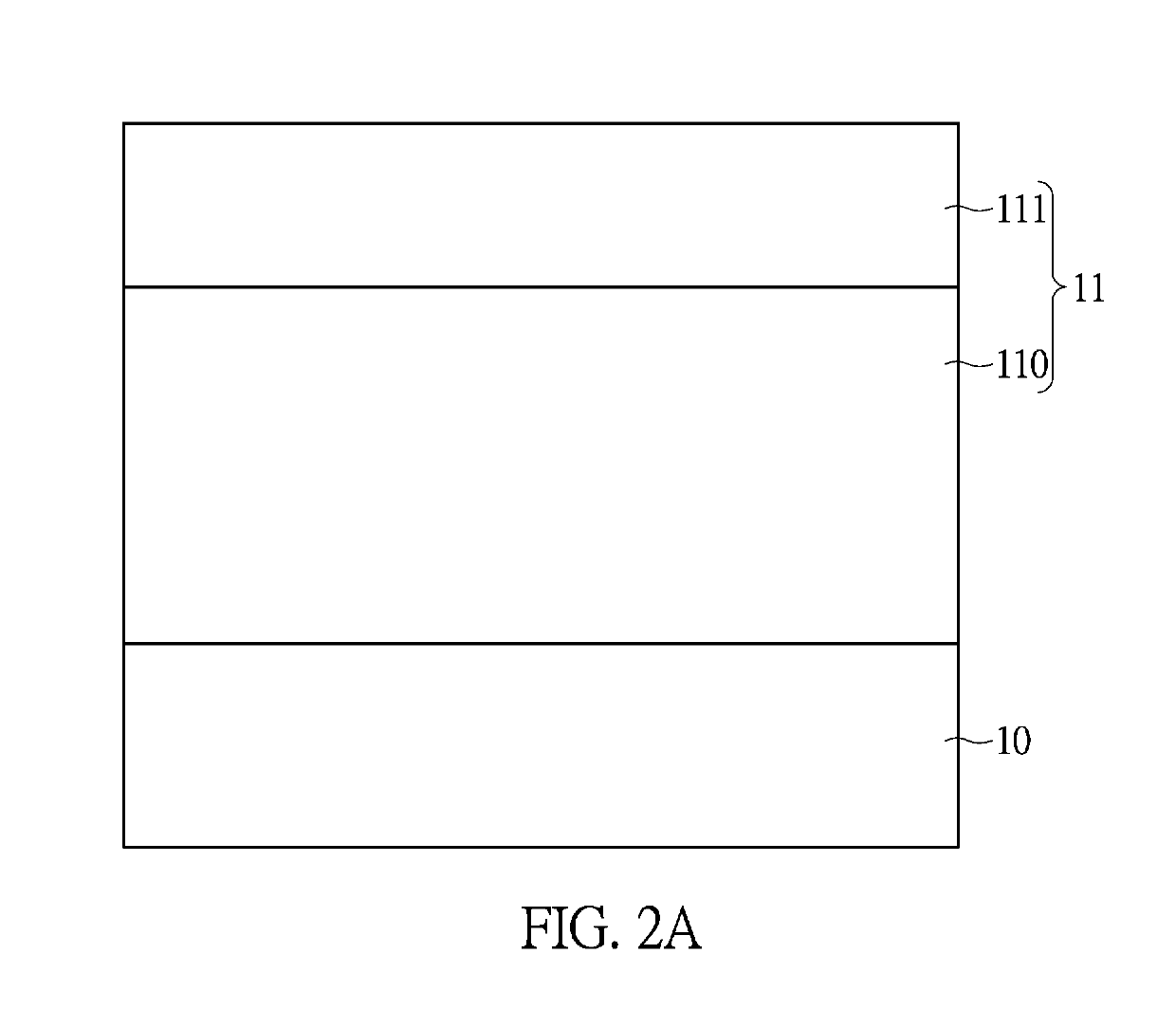

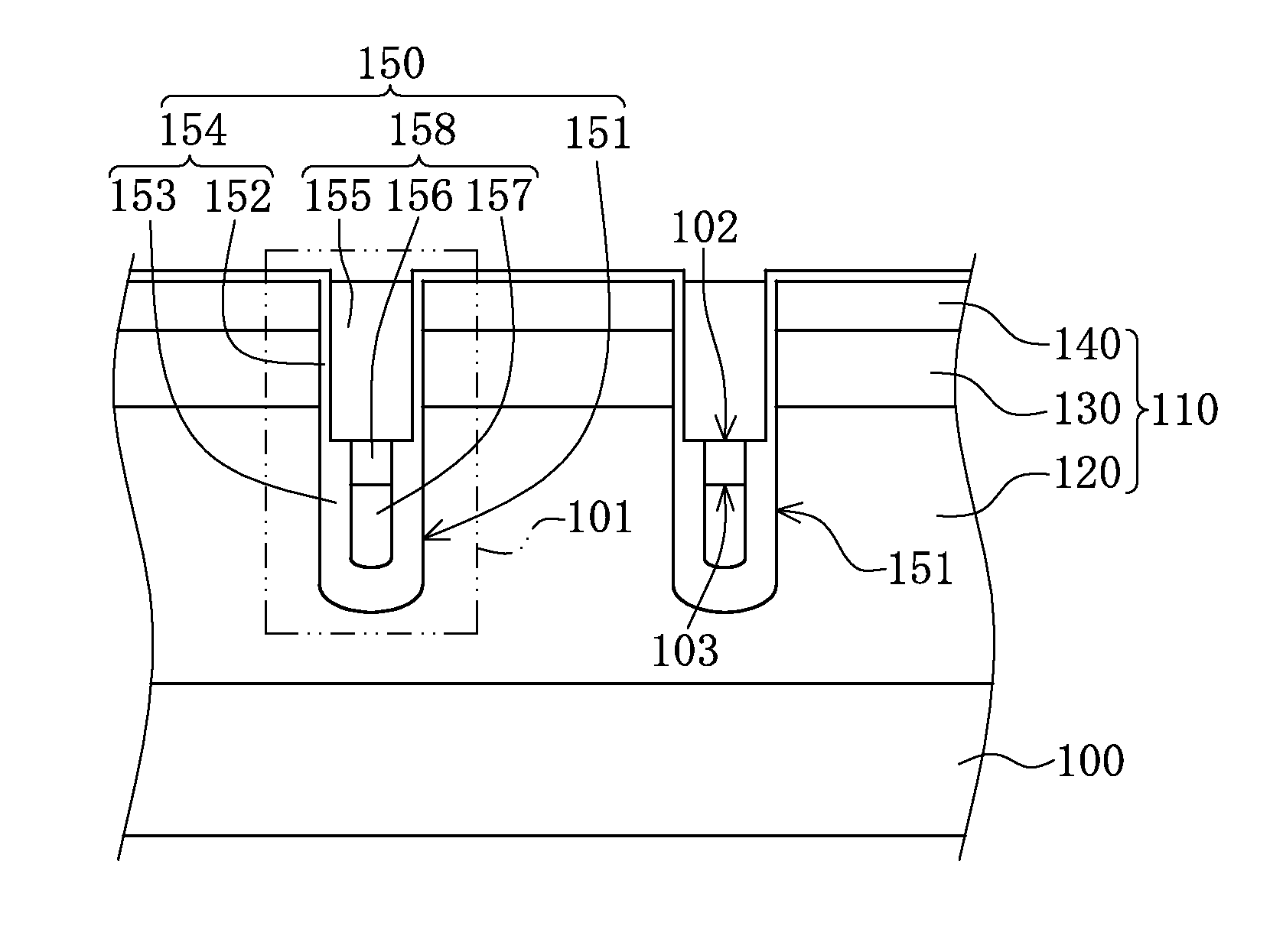

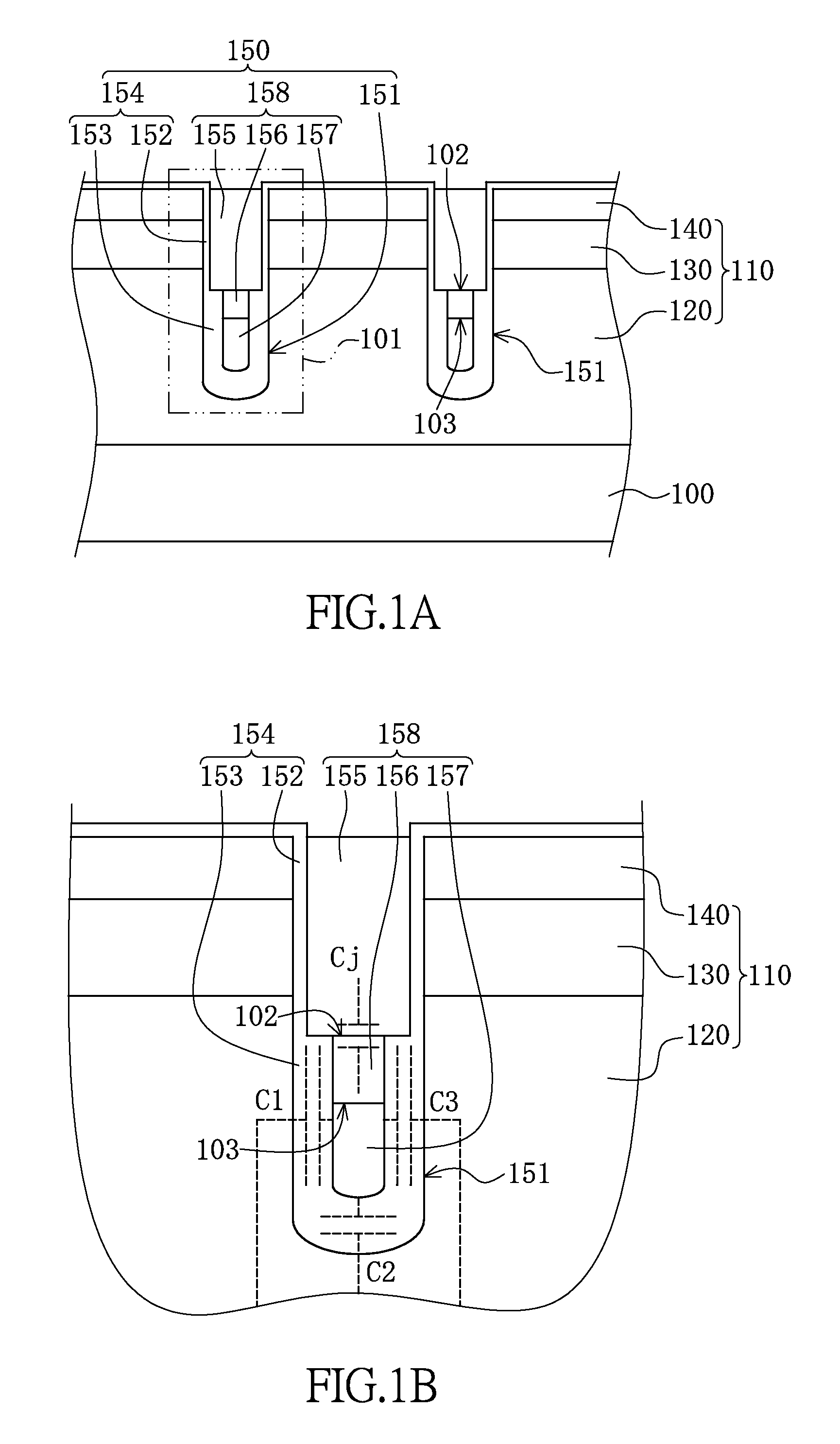

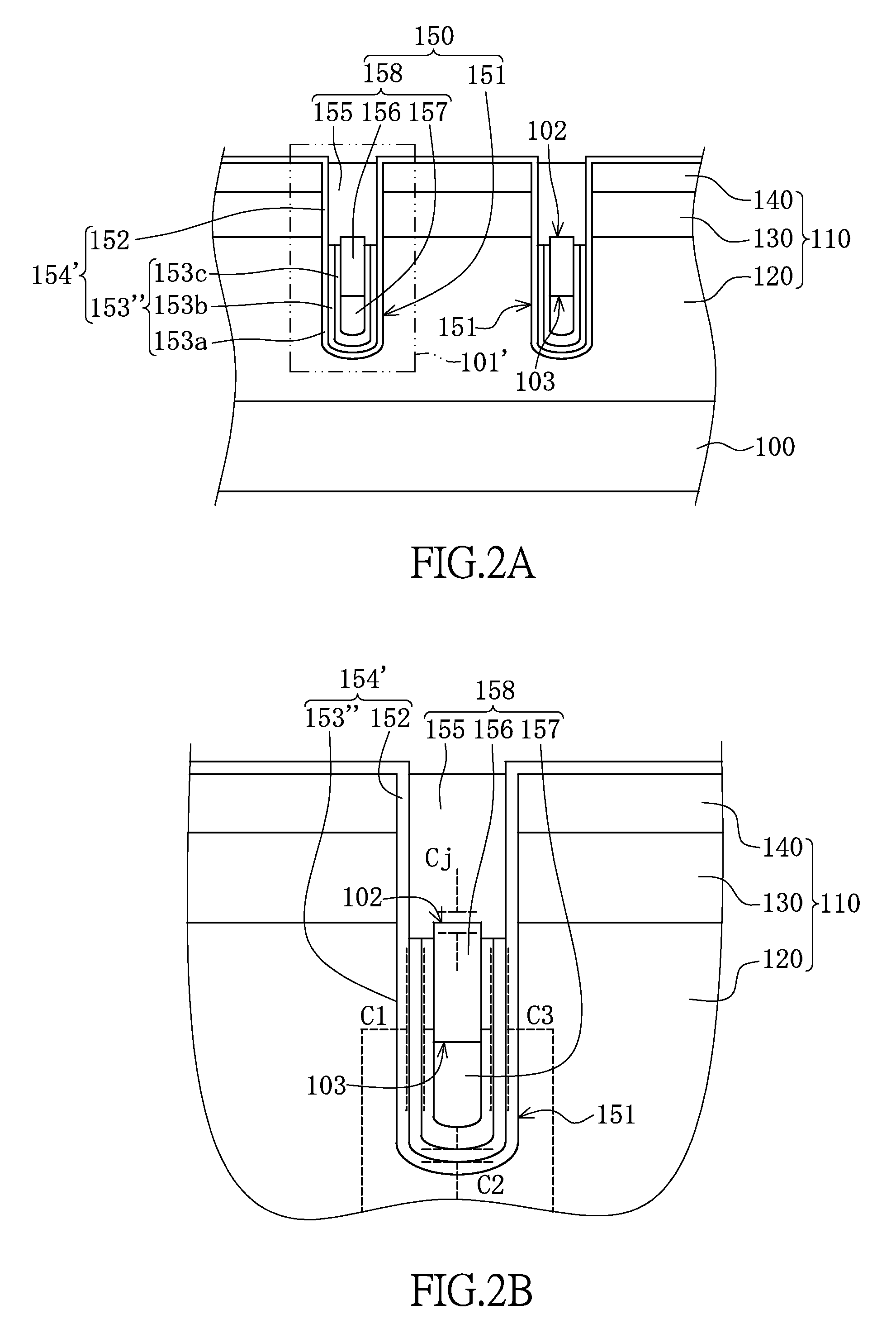

Trench power mosfet and manufacturing method thereof

ActiveUS20150270384A1Low effective capacitanceEffective capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceIntrinsics

A trench power MOSFET and a manufacturing method thereof are provided. The gate of the trench power MOSFET includes an upper doped region and a lower doped region which have different types of doping to form a PN junction. As such, when the trench power MOSFET is in operation, a junction capacitance formed at the PN junction is in series with the intrinsic gate-to-drain capacitance. Accordingly, the effective capacitance between the gate and the drain may be reduced.

Owner:SUPER GROUP SEMICON

High temperature processing compatible metal gate electrode for pFETS and methods for fabrication

InactiveUS7863083B2Improve pressure resistanceLow effective capacitanceTransistorSemiconductor/solid-state device manufacturingCMOSMetallurgy

A method for fabricating a CMOS gate electrode by using Re, Rh, Pt, Ir or Ru metal and a CMOS structure that contains such gate electrodes are described. The work functions of these metals make them compatible with current pFET requirements. For instance, the metal can withstand the high hydrogen pressures necessary to produce properly passivated interfaces without undergoing chemical changes. The thermal stability of the metal on dielectric layers such as SiO2, Al2O3 and other suitable dielectric materials makes it compatible with post-processing temperatures up to 1000° C. A low temperature / low pressure CVD technique with Re2(CO)10 as the source material is used when Re is to be deposited.

Owner:GLOBALFOUNDRIES INC

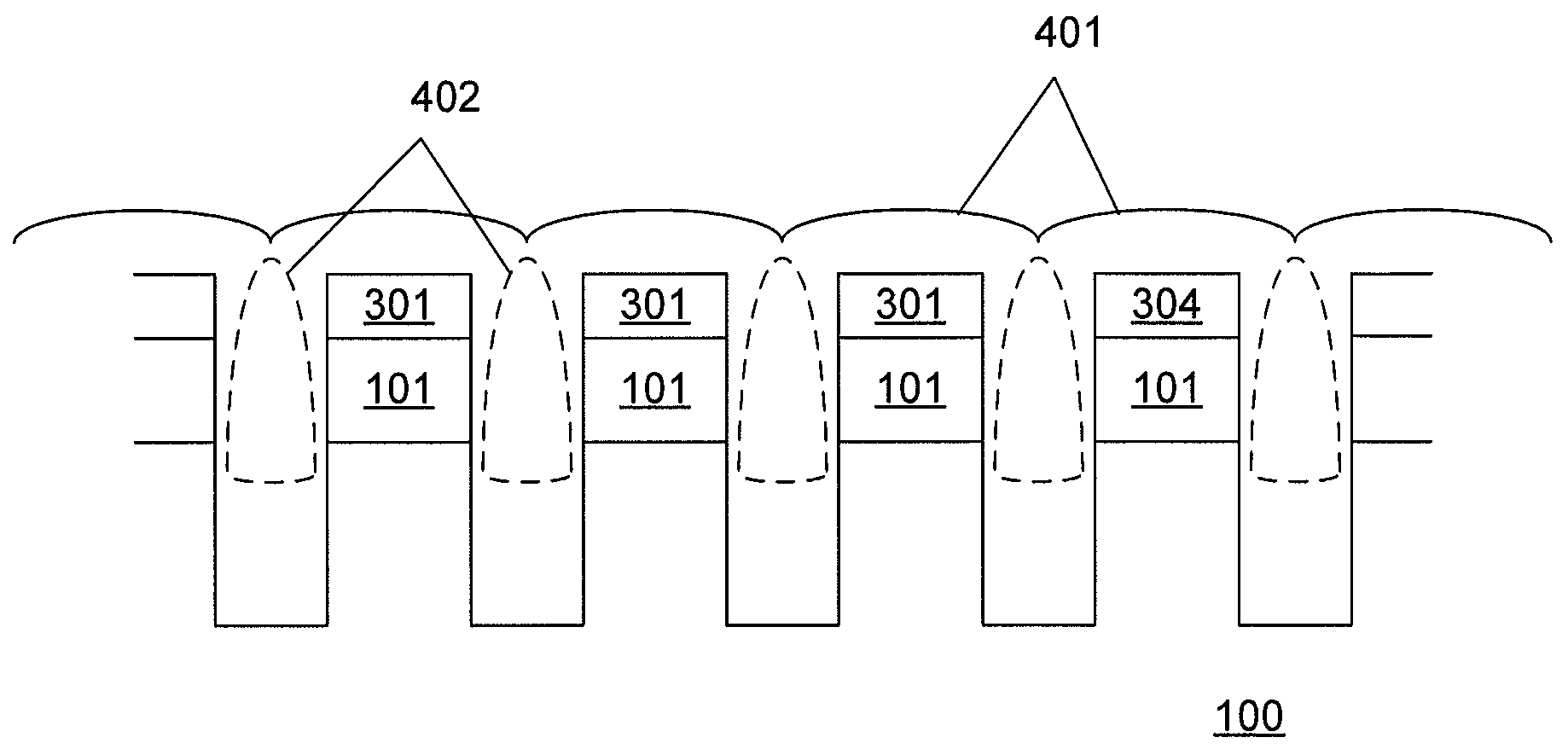

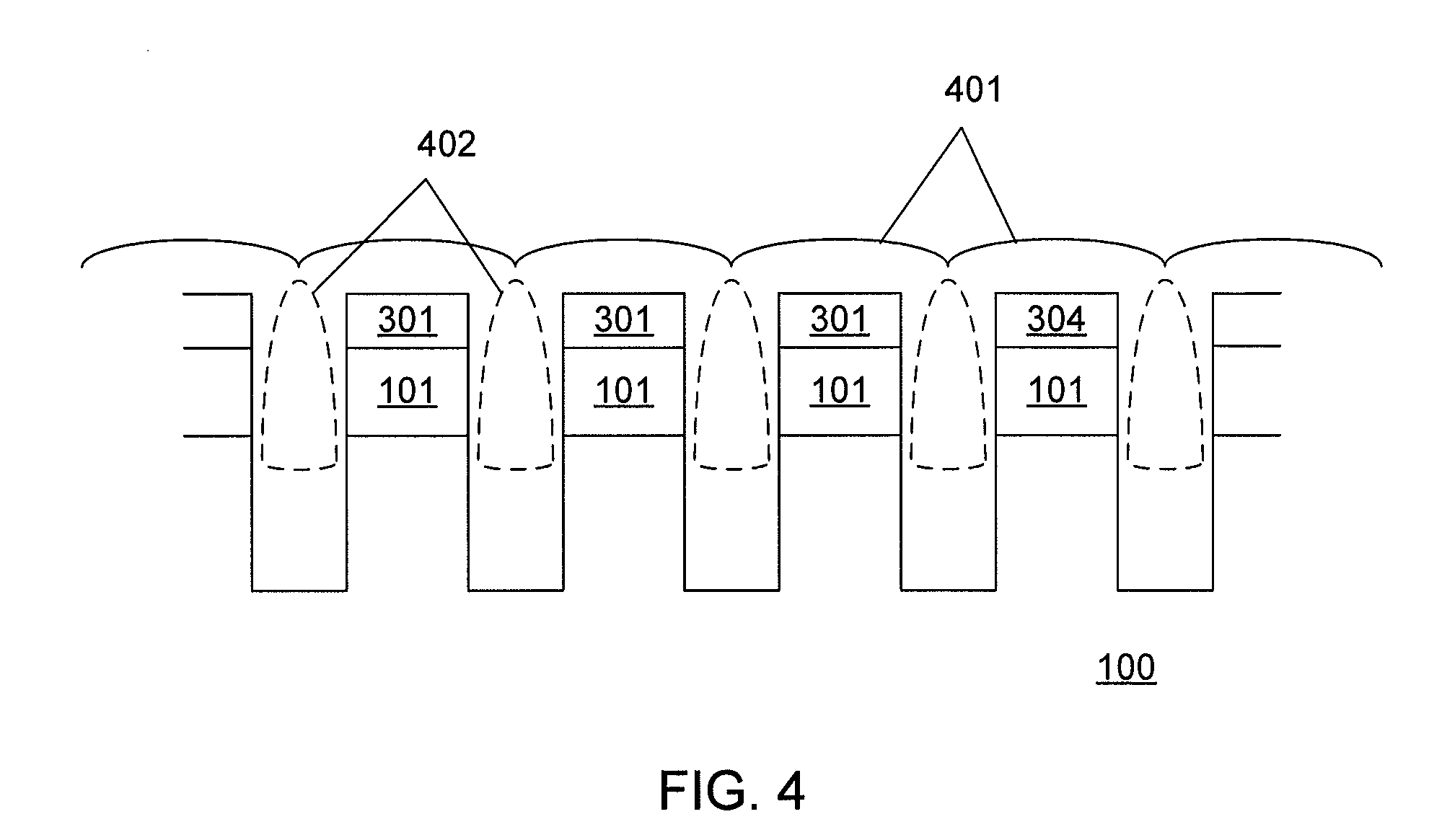

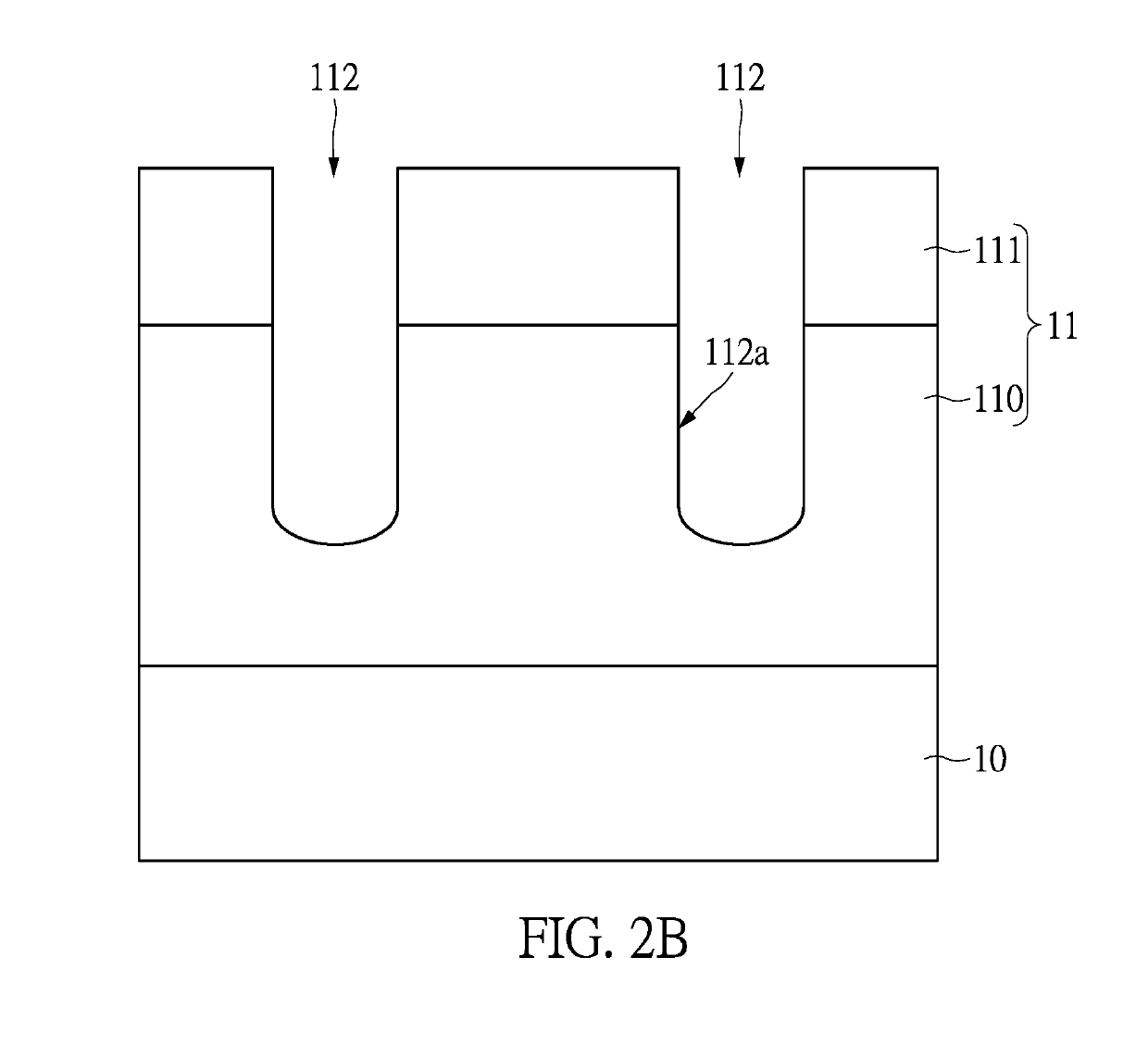

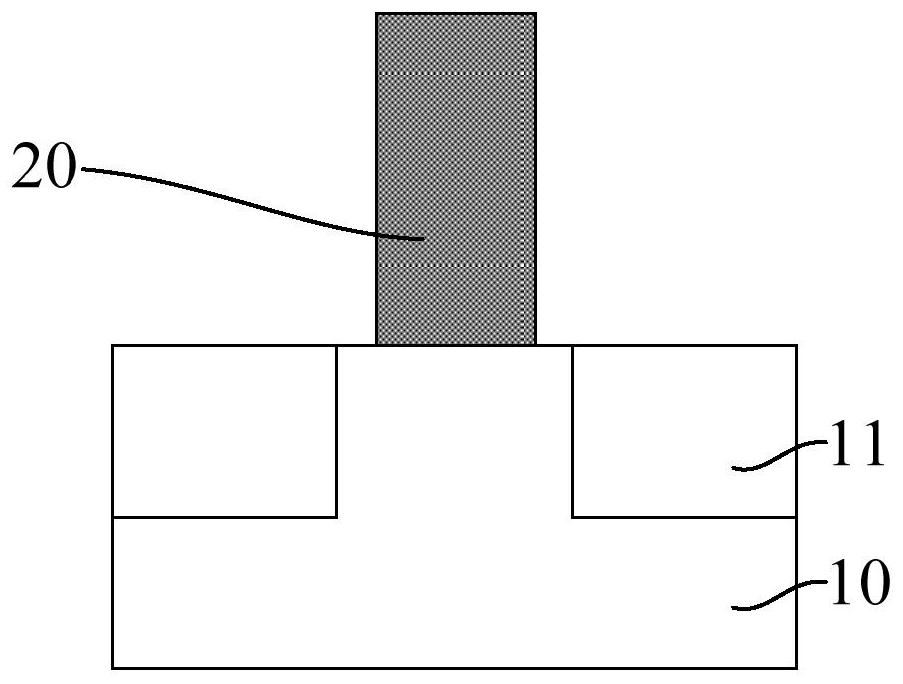

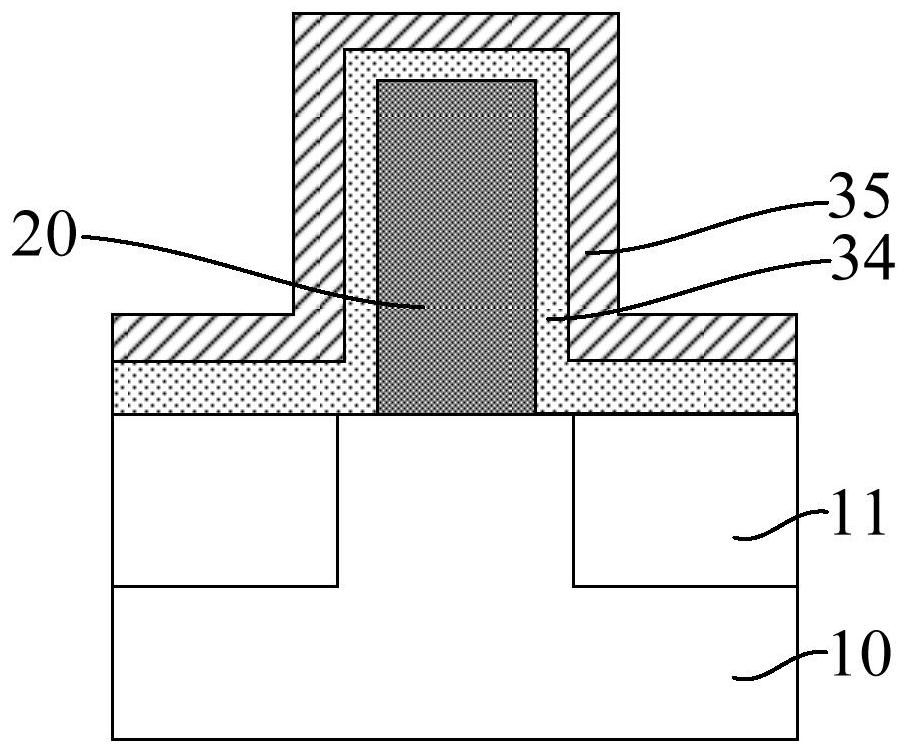

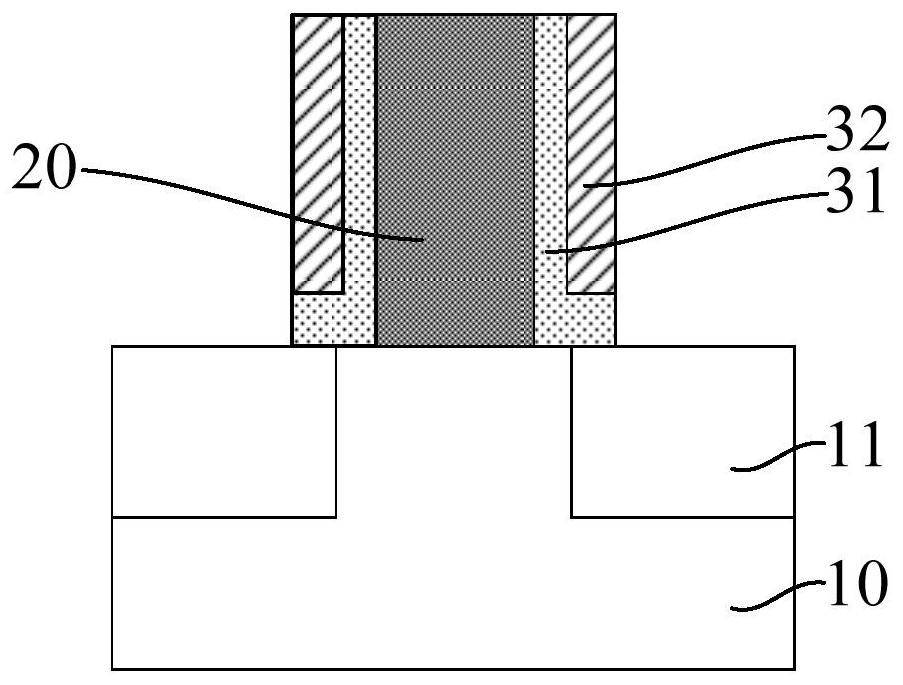

Finfet structure with dielectric bar containing gate to reduce effective capacitance, and method of forming same

A FinFET structure having reduced effective capacitance and including a substrate having at least two fins thereon laterally spaced from one another, a metal gate over fin tops of the fins and between sidewalls of upper portions of the fins, source / drain regions in each fin on opposing sides of the metal gate, and a dielectric bar within the metal gate located between the sidewalls of the upper portions of the fins, the dielectric bar being laterally spaced away from the sidewalls of the upper portions of the fins within the metal gate.

Owner:GLOBALFOUNDRIES US INC

Trench power semiconductor device and manufacturing method thereof

ActiveUS10446658B2Low effective capacitanceGood suppression characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

Owner:SUPER GROUP SEMICON

A main circuit power cable for a medium-voltage frequency converter

ActiveCN103794275BHigh tensile strengthImprove waterproof performanceClimate change adaptationPower cables with screens/conductive layersElectrical conductorPolyolefin

The invention provides a major loop electric power cable for a medium-voltage frequency converter. The cable comprises three power conductors, three control conductors and a central gap filler, wherein the cross section of the central gap filler is round, a cabled core is formed by stranding of the three power conductors and the three control conductors around the central gap filler, the control conductors are arranged between any two adjacent power conductors, the cabled core is sequentially coated with a third metal shielding layer, an electrostatic shielding layer, a water-blocking tape covering layer, a tin-plated steel wire winding armor layer and a polyolefin outer sheath, and water-blocking ropes with triangular cross sections are placed in gaps between the power conductors, the control conductors and the third metal shielding layer. According to the major loop electric power cable for the medium-voltage frequency converter, effective capacitance is low, transfer impedance is low, good electromagnetic compatibility is achievable, the tensile strength and water resistance of the cable are improved, and the service life of the cable is prolonged.

Owner:ANHUI HUAXI CABLE TECH

Semiconductor structure and forming method thereof

PendingCN114551597AImprove reliabilityImprove production yieldSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureContact layer

The invention discloses a semiconductor structure and a forming method thereof. The forming method comprises the steps of providing a substrate, a gate structure, a side wall located on the side wall of the gate structure, a source-drain doped region, a bottom dielectric layer and a source-drain contact layer; removing the side wall to form a gap; forming a protective layer covering the bottom and the side wall of the gap in a shape-preserving manner; and forming a top dielectric layer on the bottom dielectric layer, wherein the top dielectric layer seals the gap to form an air gap. According to the embodiment of the invention, after the substrate is provided, the side walls are removed to form the gap, the bottom and the side walls of the gap are covered with the protective layer in a shape-preserving manner, and then the top dielectric layer for sealing the gap is formed, so that the air gap and the protective layer are correspondingly of an integrated structure, and the protection effect of the protective layer on the bottom and the side walls of the gap is improved; the damage probability of the film layer structures (such as the gate structure and the substrate) at the bottom and the side wall of the gap is reduced, the integrity of the film layer structures at the bottom and the side wall of the gap is correspondingly improved, and then the reliability and the production yield of the semiconductor structure are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Trench power MOSFET and manufacturing method thereof

ActiveUS9536972B2Low effective capacitanceEffective capacitanceTransistorSemiconductor/solid-state device manufacturingParasitic capacitanceEngineering

A trench power MOSFET and a manufacturing method thereof are provided. The gate of the trench power MOSFET includes an upper doped region, a lower doped region and a middle region interposed therebetween. The upper has a conductive type reverse to that of the lower doped region, and the middle region is an intrinsic or lightly-doped region to form a PIN, P+ / N− or N+ / P− junction. As such, when the trench power MOSFET is in operation, a junction capacitance formed at the PIN, P+ / N− or N+ / P− junction is in series with the parasitic capacitance. Accordingly, the gate-to-drain effective capacitance may be reduced.

Owner:SUPER GROUP SEMICON

Chip type high polymer electrostatic discharge protecting element and manufacturing method thereof

ActiveCN102142430BSmall sizeLow effective capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

The invention provides a chip type high polymer electrostatic discharge protecting element. Inner electrodes are one of two inner electrodes opposite to each other in a length direction and two inner electrodes staggered with each other in the length direction; and a core material is one of a core material filled in a gap between the two inner electrodes opposite to each other in the length direction, a core material filled in a gap between the two inner electrodes staggered with each other in the length direction, and a core material filled in a through hole in the gap between the two inner electrodes opposite to each other in the length direction. The manufacturing method sequentially comprises the following steps: (1) the preparation of slurry of the core material; (2) the preparation of a lower substrate; (3) the preparation of the inner electrodes; (4) the preparation of the core material; (5) the preparation of an upper substrate; (6) cutting of a chip; (7) the preparation of terminal electrodes; and (8) electroplating. A chip type ESD (Electrostatic Discharge) protecting device which has small size and very small effective capacitance can be manufactured; the requirements of high-speed signal transmission equipment on the ESD protection can be sufficiently met; the inner electrodes and the terminal electrodes are easier to connect, and the terminal electrodes are easier to lead out, therefore, the chip type high polymer electrostatic discharge protecting element is easy to manufacture; moreover; and the gap between the inner electrodes can be correspondingly adjusted according to the value of a trigger voltage in the design.

Owner:SHENZHEN SUNLORD ELECTRONICS

Transformer without Y capacitor and preparation method thereof

InactiveCN102163492BReduce interference currentLow effective capacitanceTransformers/inductances coils/windings/connectionsInductances/transformers/magnets manufactureCapacitanceTransformer

The invention discloses a transformer without Y capacitor, comprising a magnetic core, a primary main winding, a secondary winding and an auxiliary winding, wherein the primary main winding, the secondary winding and the auxiliary winding are successively winded on the magnetic core. The transformer further comprises a primary shielded winding connected with the primary main winding and a secondary shielded winding connected with the secondary winding, wherein the primary shielded winding and the secondary shielded winding have the same number of loops and the same phase. The invention solvestwo main problems of electromagnetic radiation and electric leakage in a switch power supply at the same time, realizes that the switch power supply can pass an electromagnetic radiation test withoutY capacitor, so the transformer is suitable for products fairly sensitive to leakage current, such as mobile phone chargers.

Owner:湖南崧顺科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com