Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

315results about How to "Reduce coupling capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

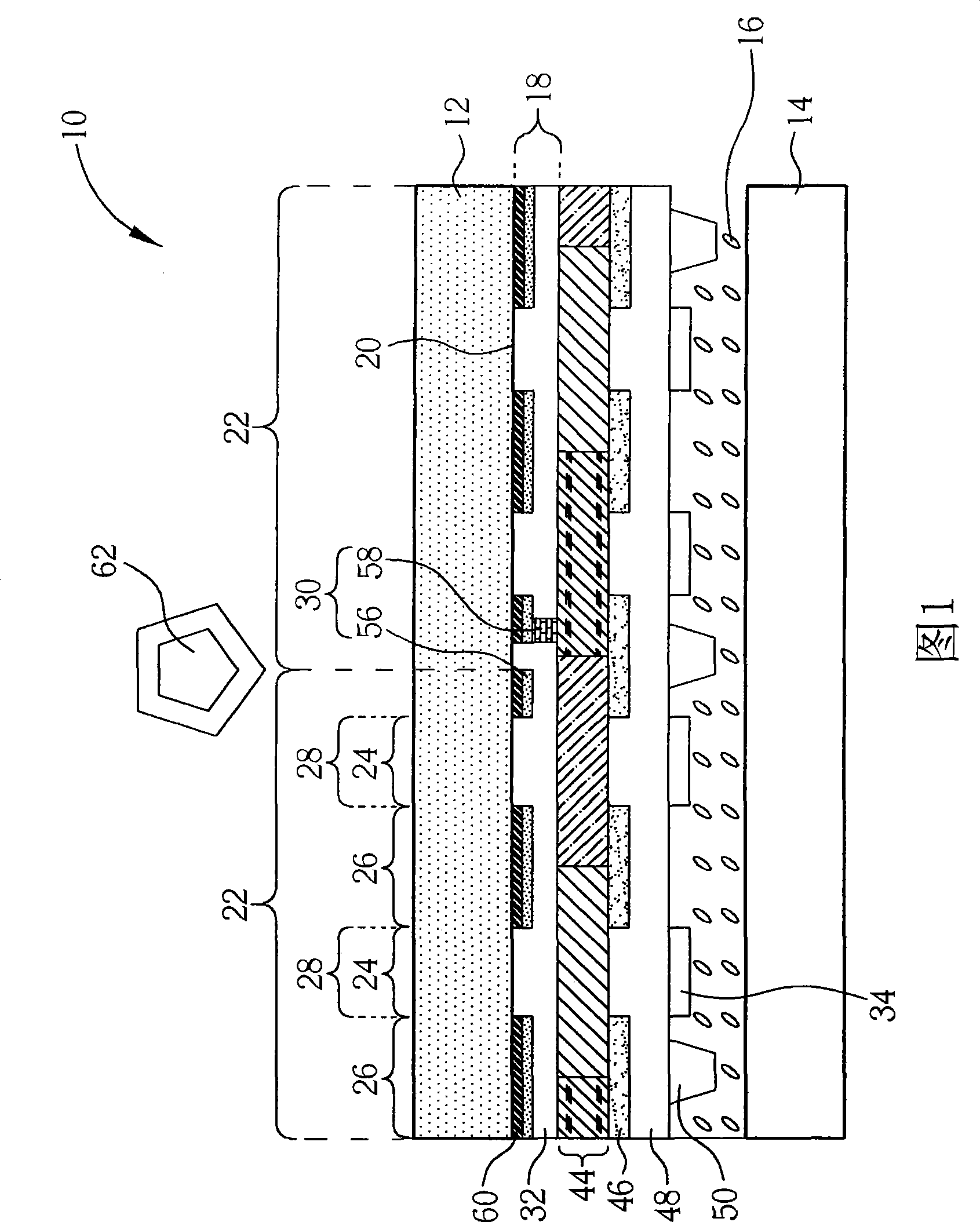

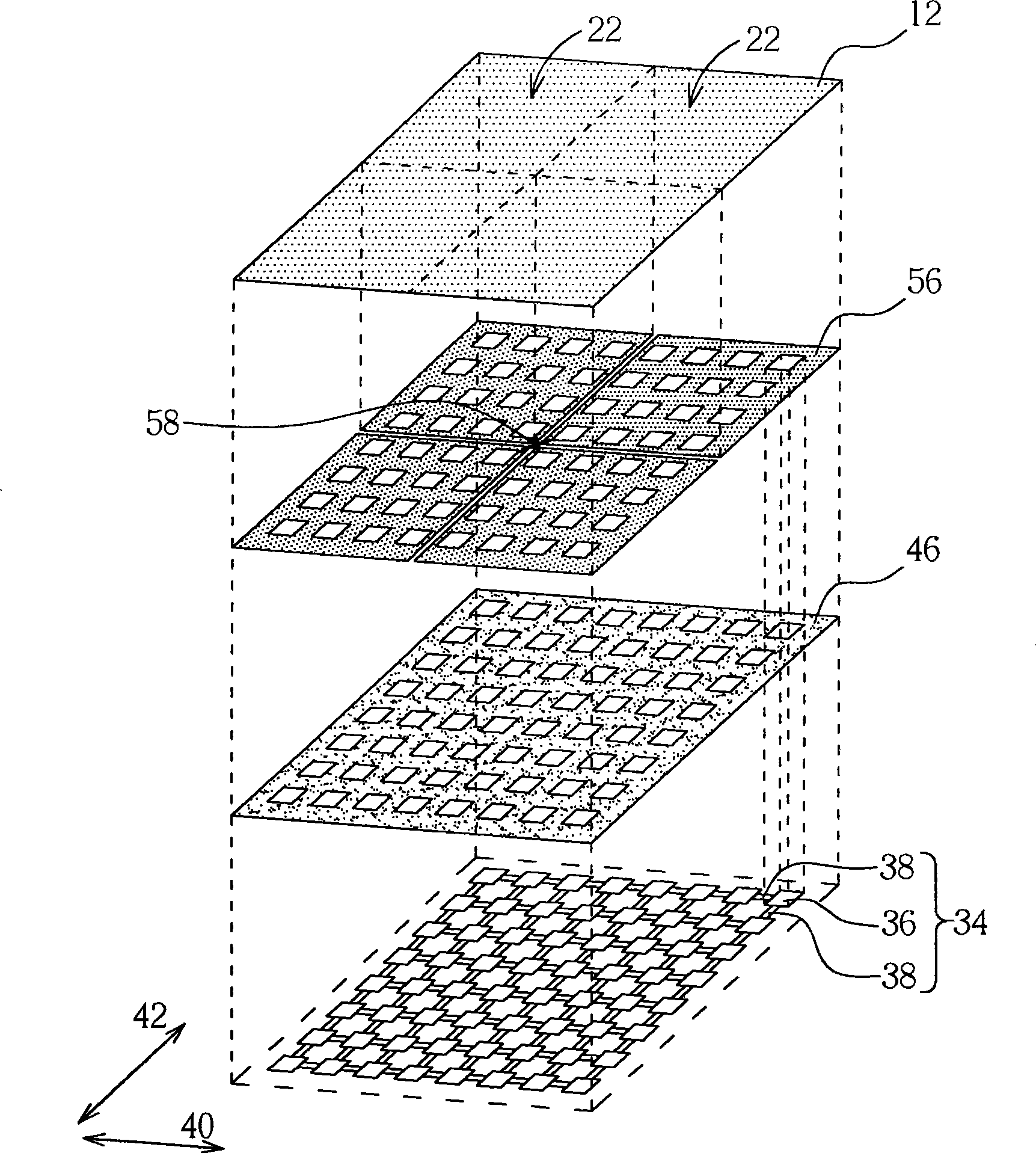

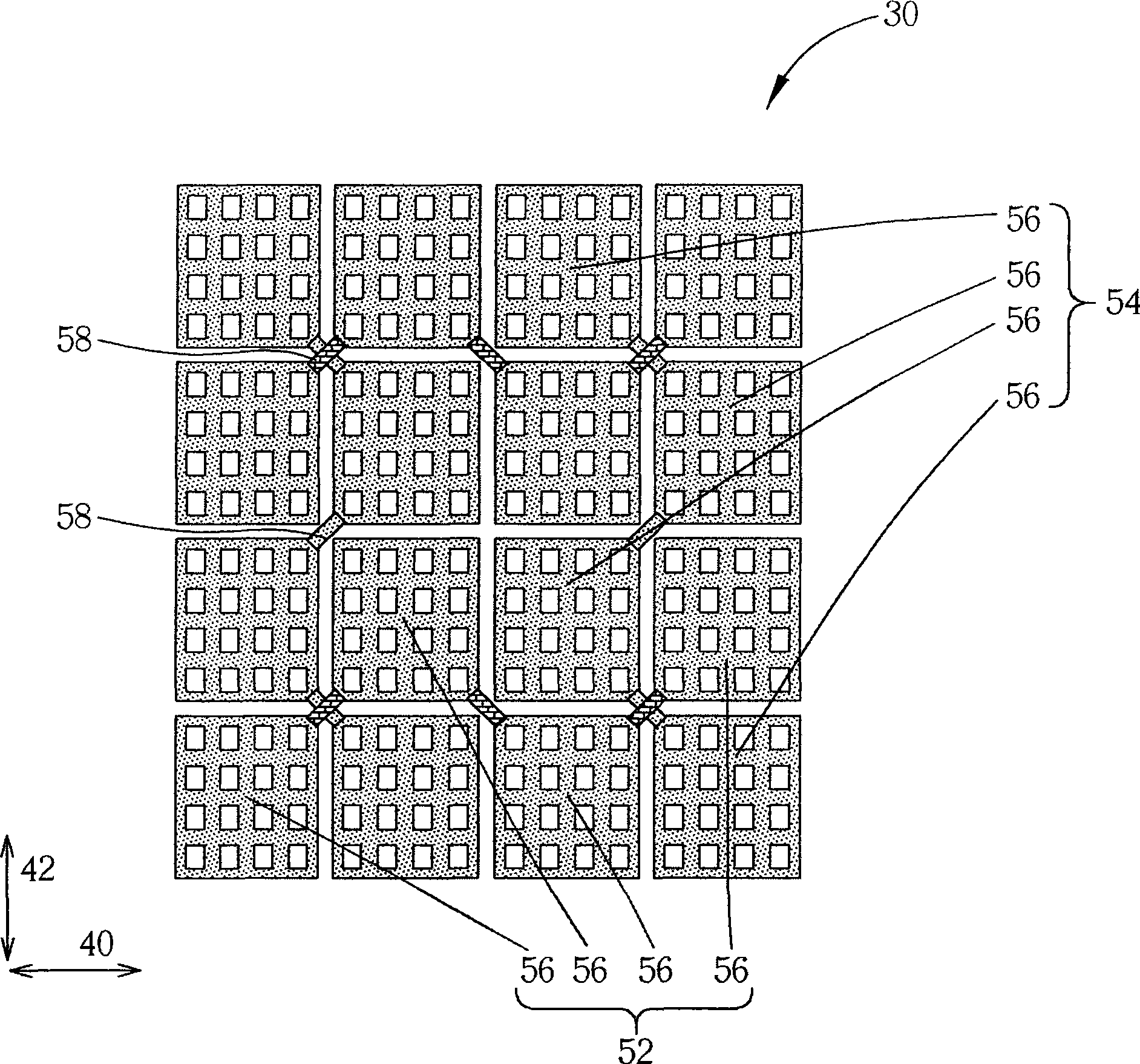

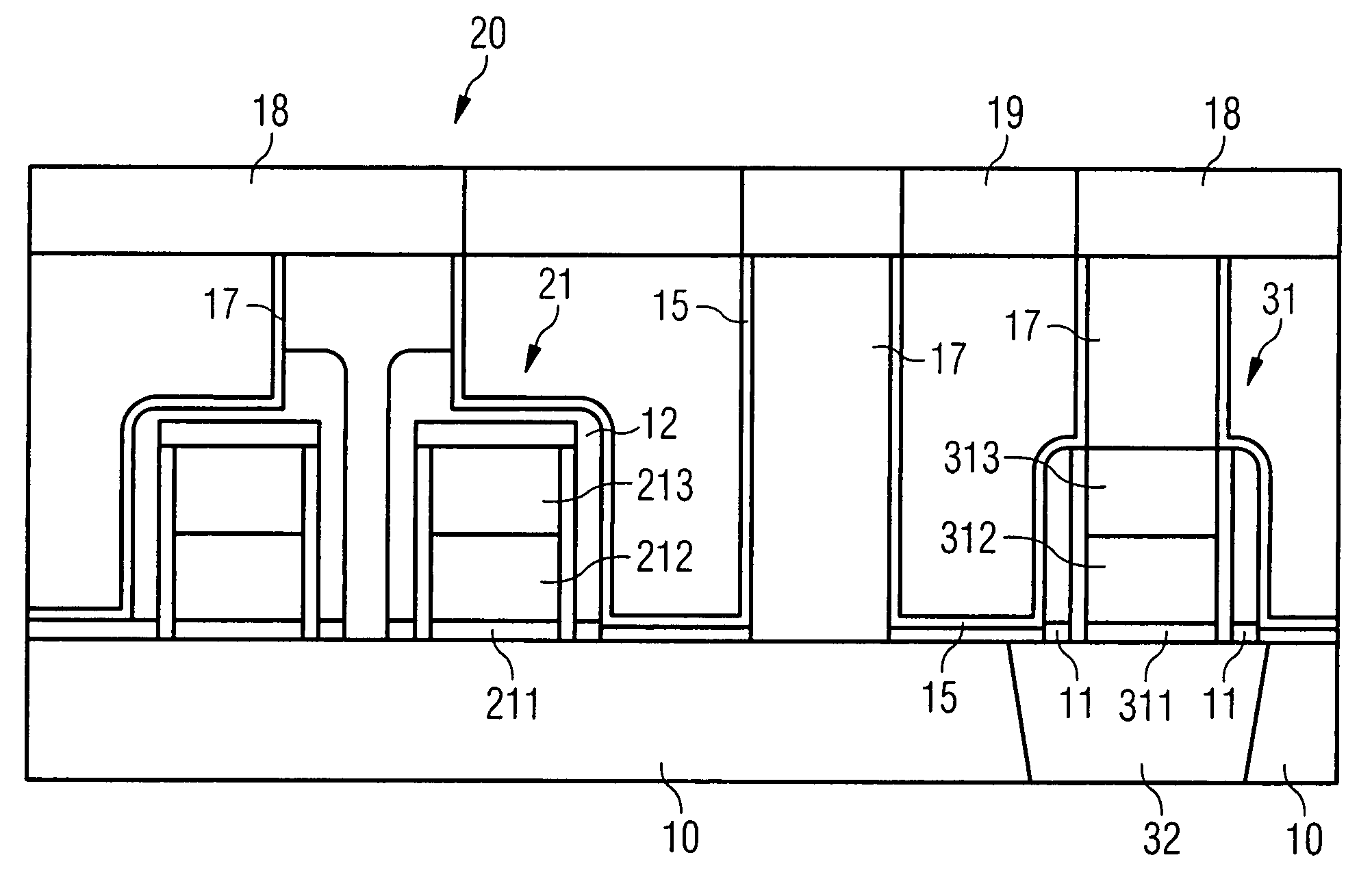

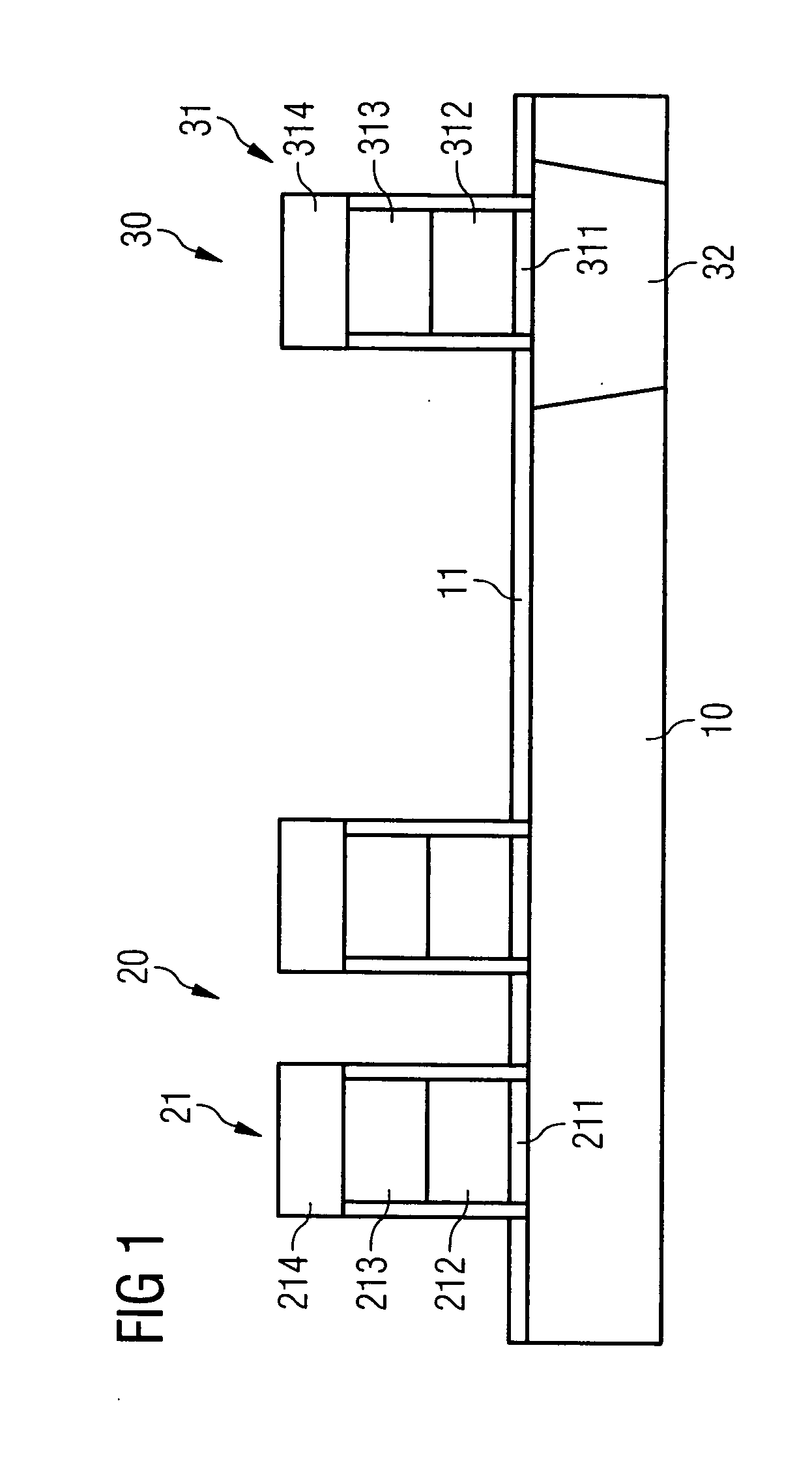

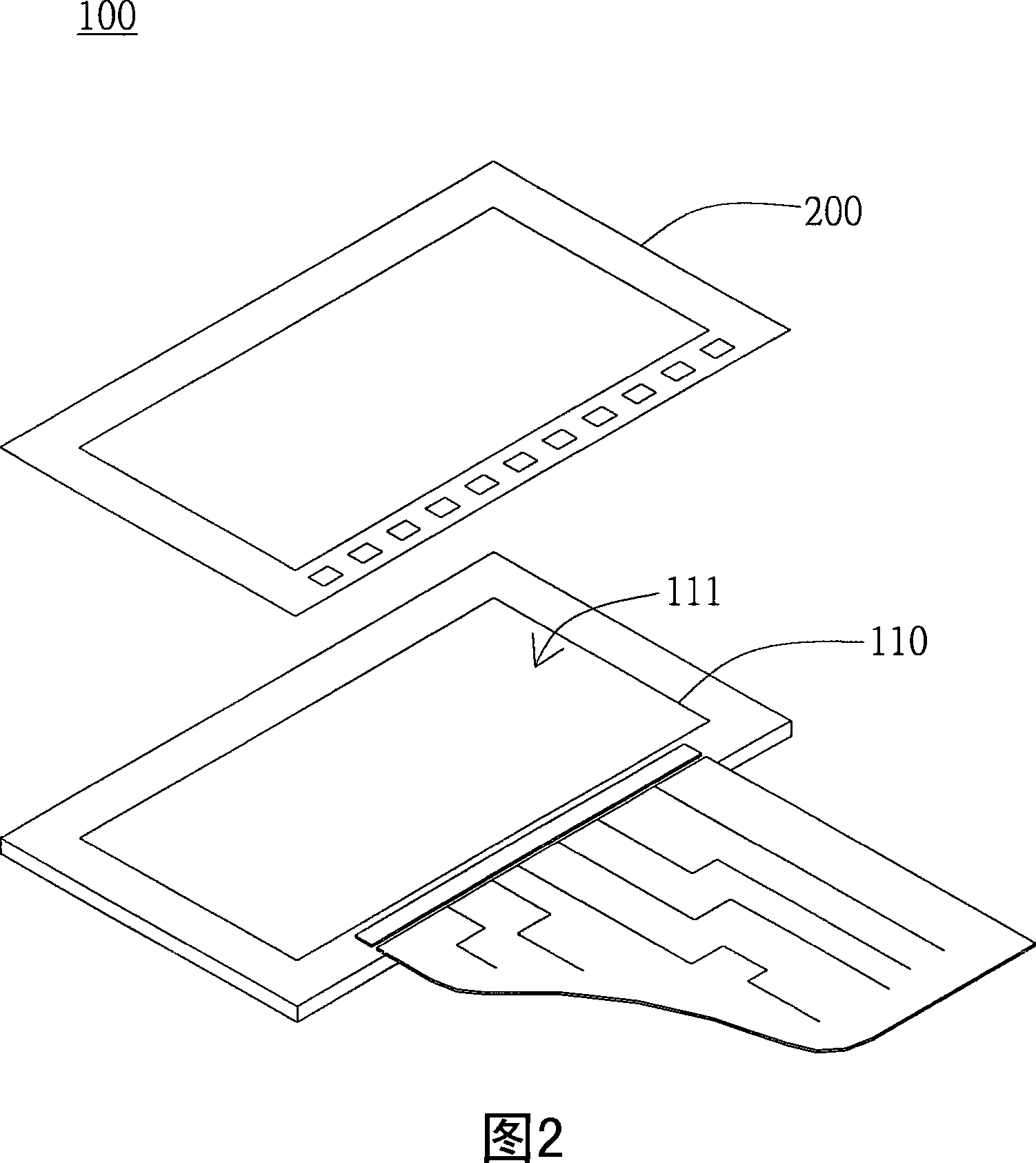

Touch device and touch display panel

InactiveUS20100149116A1Reduce couple capacitanceIncrease intensityStatic indicating devicesNon-linear opticsElectrical and Electronics engineeringElectrode

A touch device includes a patterned sensing electrode structure, an insulating layer and a patterned common electrode layer. The patterned sensing electrode structure is disposed on a surface of a substrate, defining a plurality of displaying regions and a light-shielding region. The patterned sensing electrode structure corresponds to the light-shielding region, and exposes the displaying regions. The insulating layer covers the patterned sensing electrode structure. The patterned common electrode layer is disposed on the insulating layer, and the patterned common electrode layer includes a plurality of electrode portions corresponding to the displaying regions and a plurality of connecting portions disposed between the adjacent electrode portions and electrically connected to the electrode portions.

Owner:AU OPTRONICS CORP

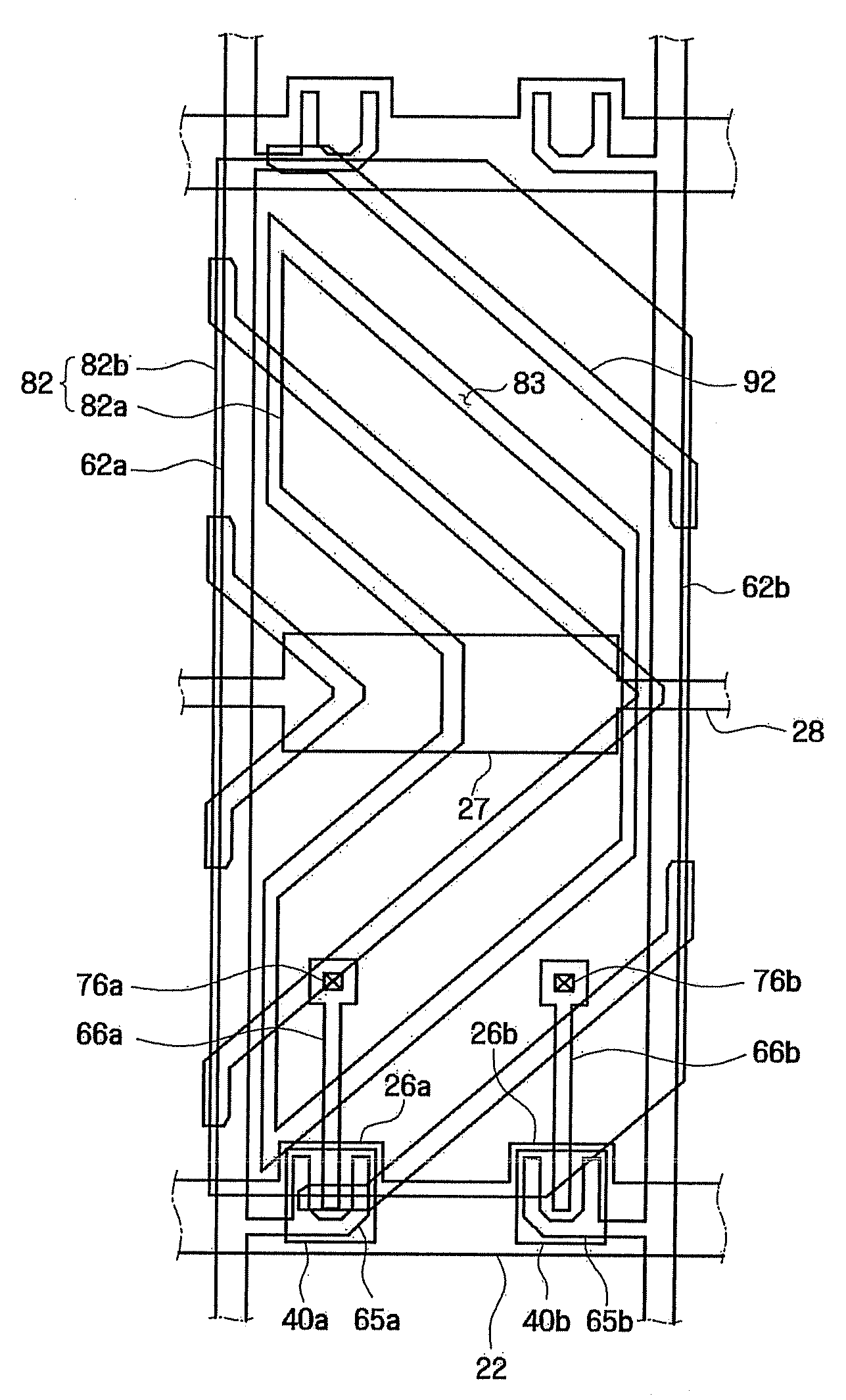

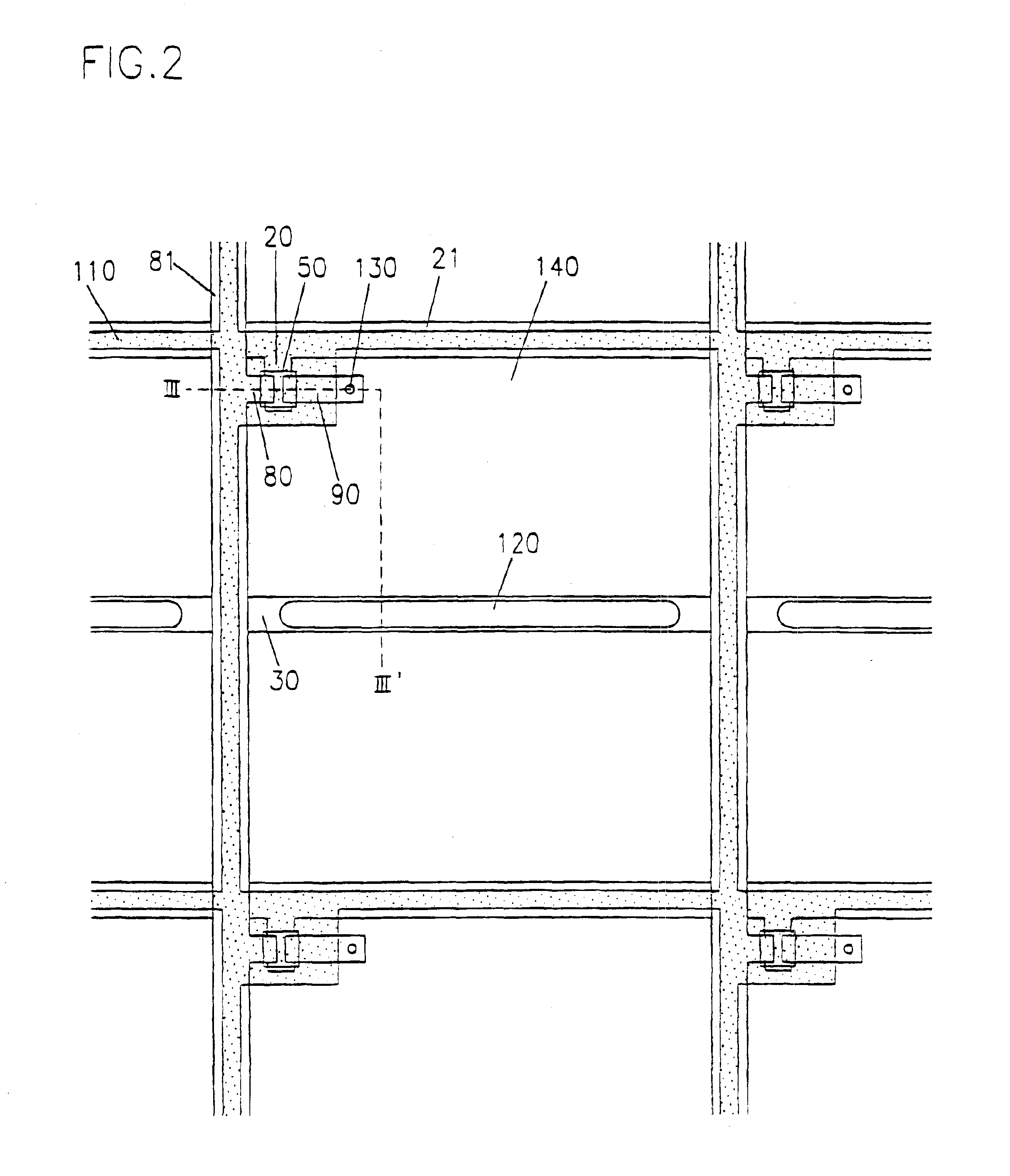

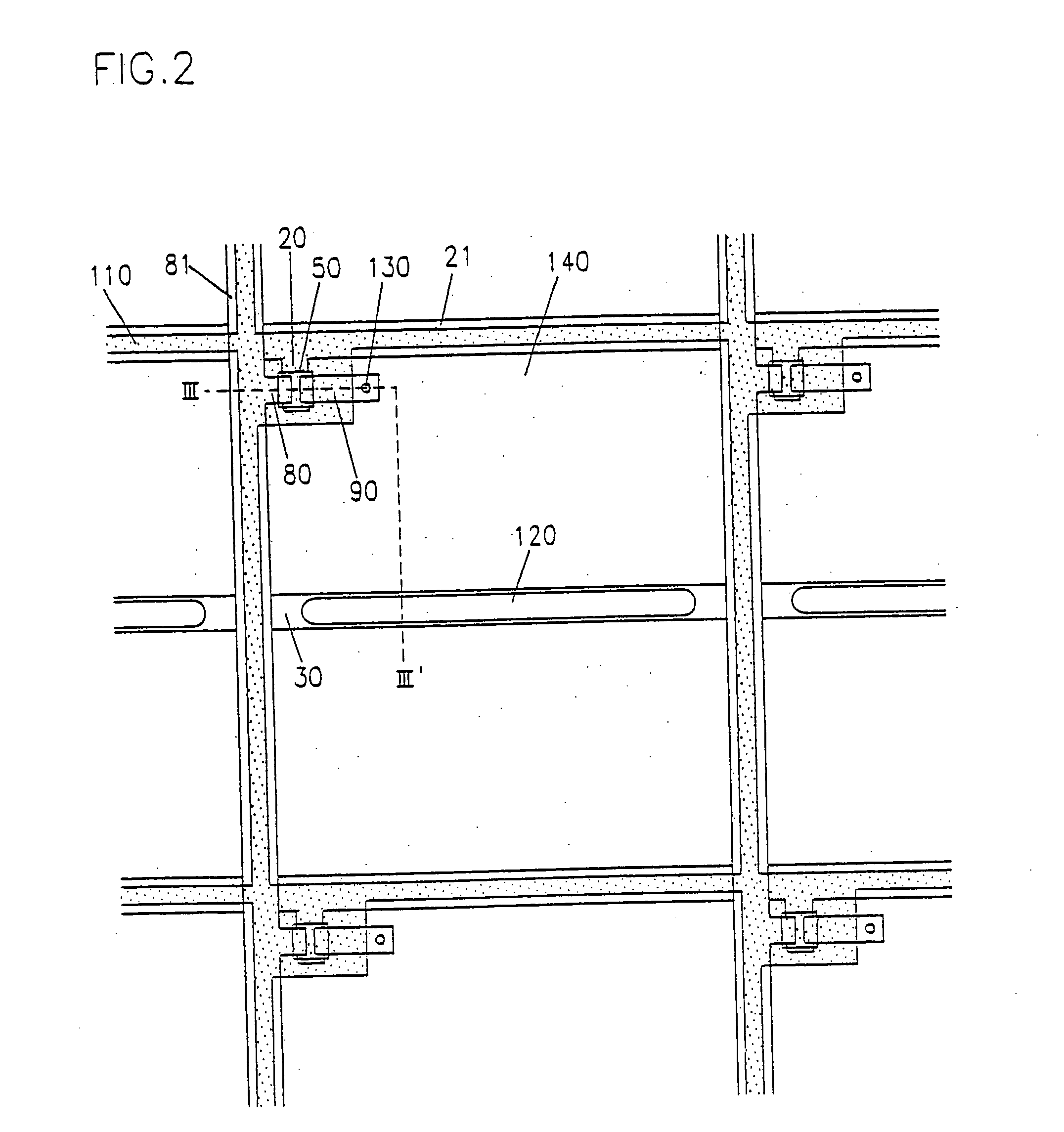

Liquid crystal display and method thereof

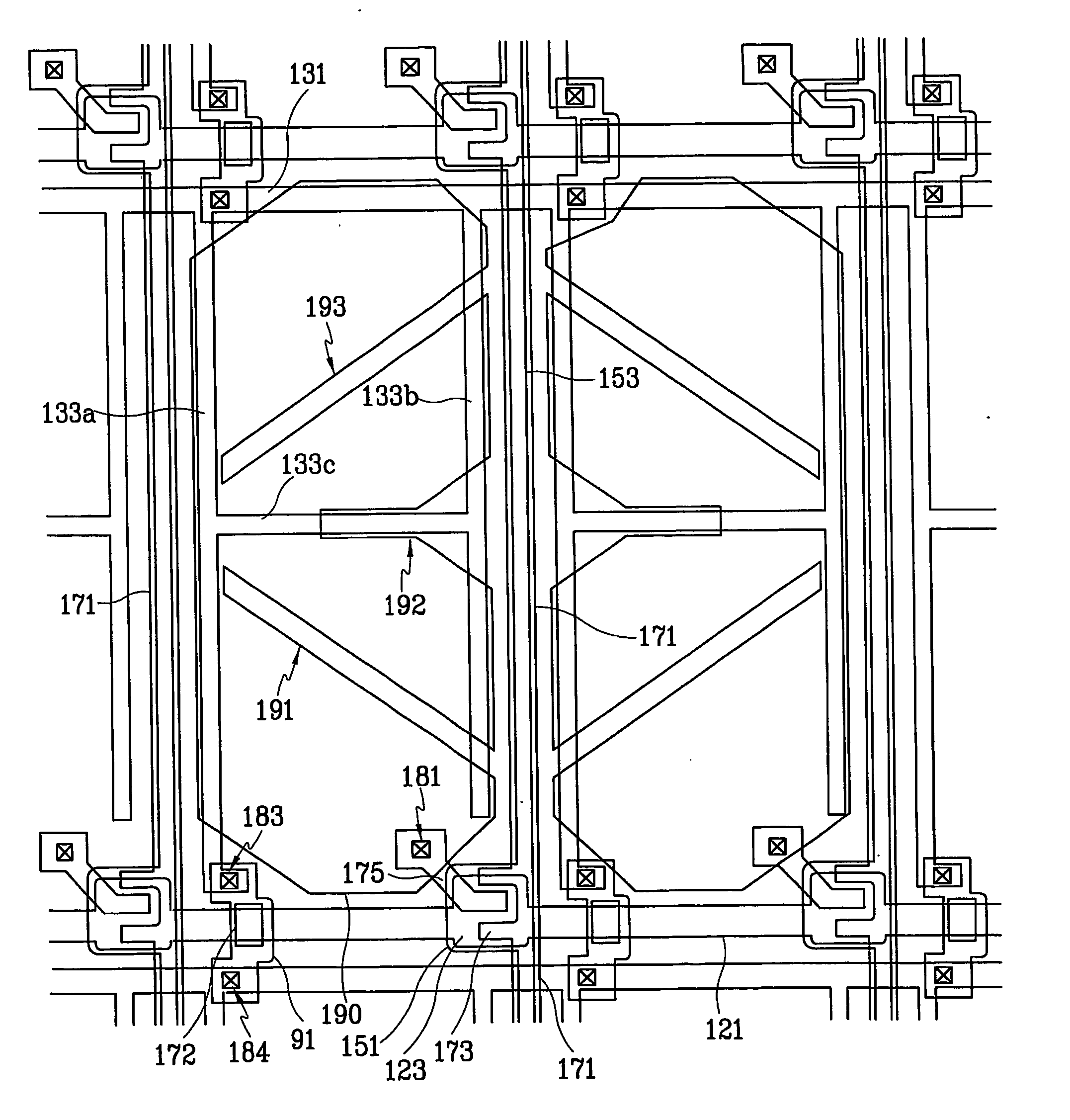

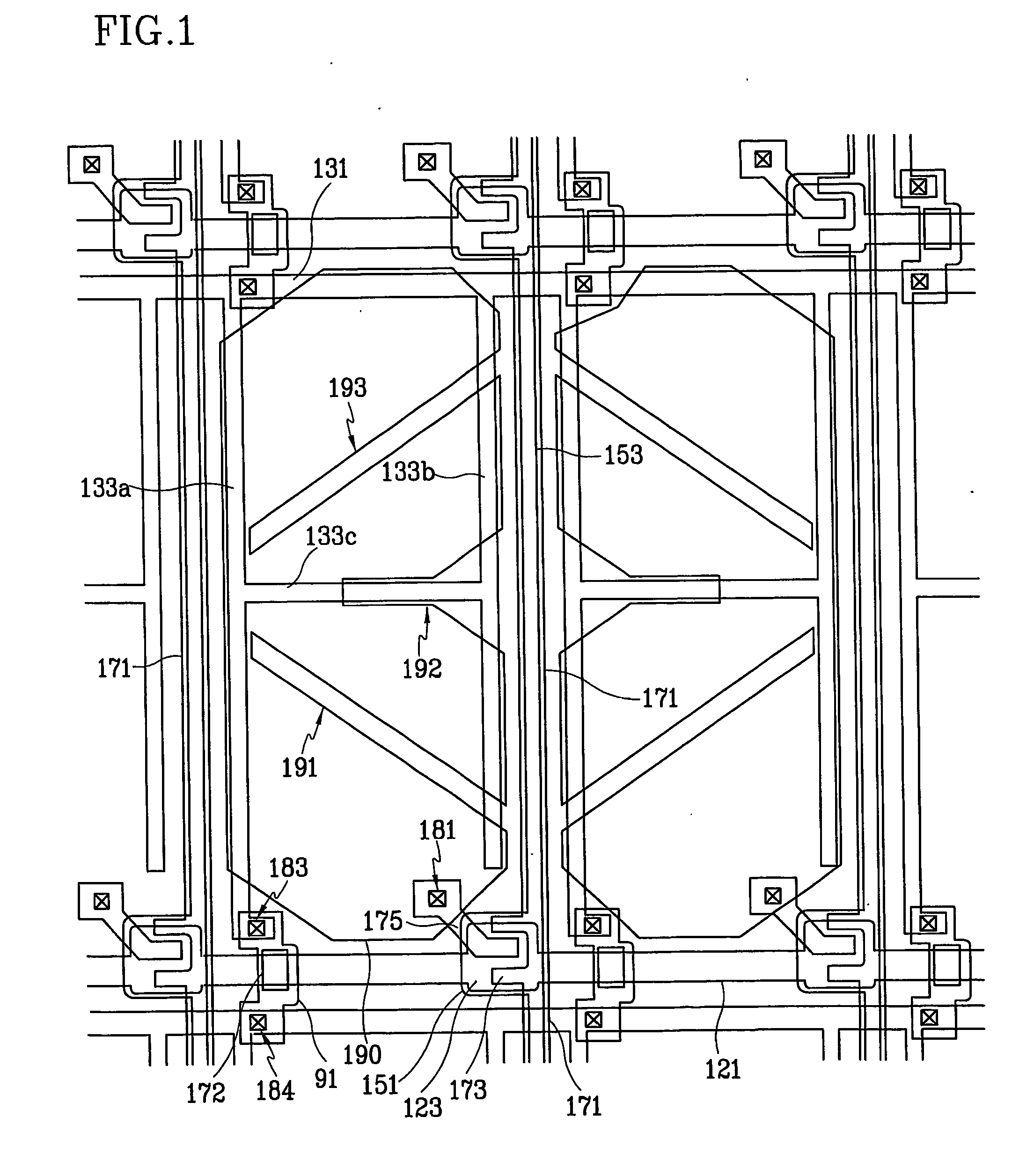

ActiveUS20080204613A1Improve display qualityReduce coupling capacitanceStatic indicating devicesSolid-state devicesLiquid-crystal displayVoltage

A liquid crystal display (“LCD”) capable of improving display quality includes a first insulating substrate, gate wiring lines formed on the first insulating substrate and extending in a first direction, data wiring lines insulated from and crossing the gate wiring lines and extending in a second direction, and pixel electrodes, each of which includes first and second sub-pixel electrodes that are applied with different data voltages from the data wiring lines, in which at least a part of the second sub-pixel electrode overlaps the data wiring lines.

Owner:SAMSUNG DISPLAY CO LTD

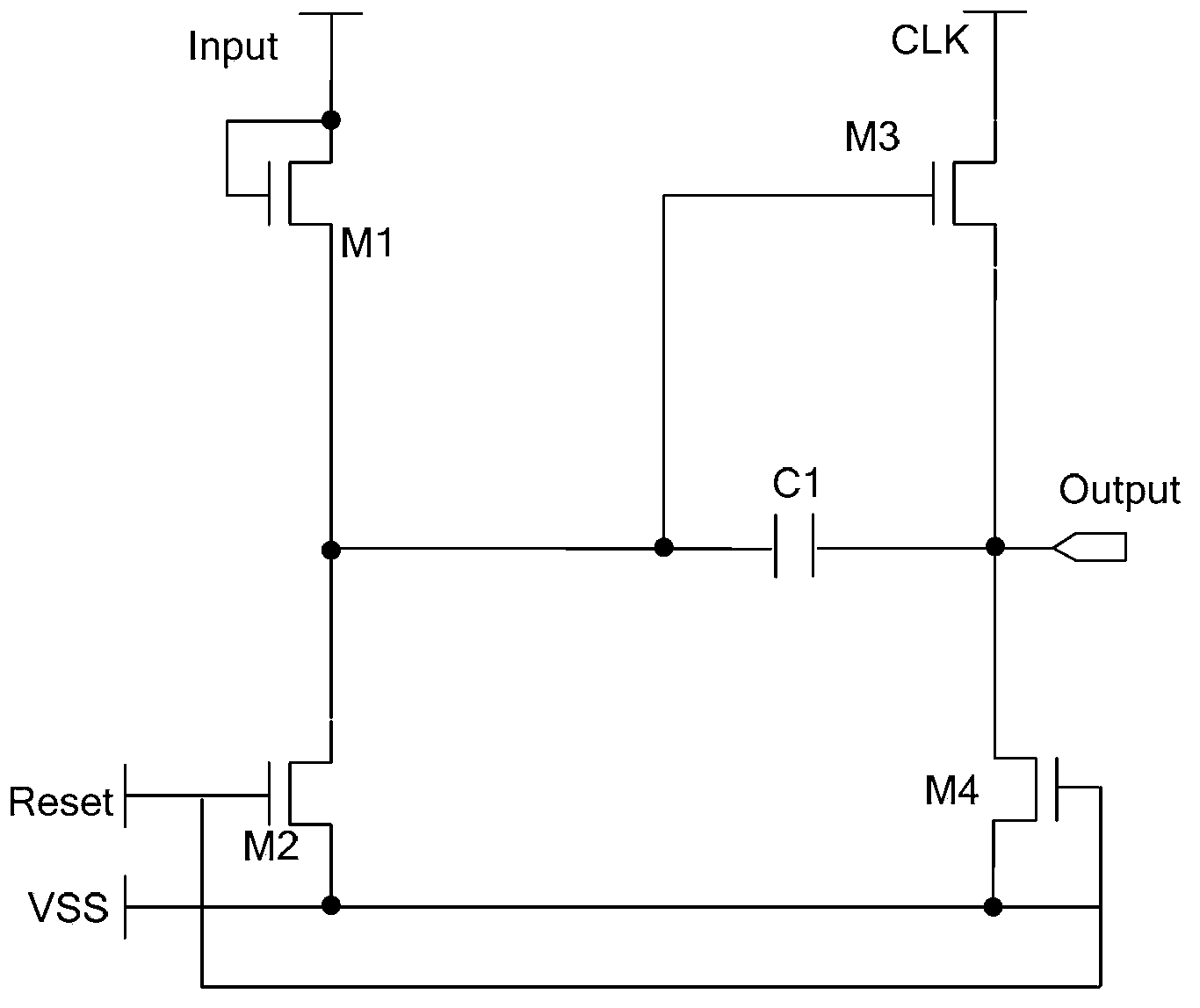

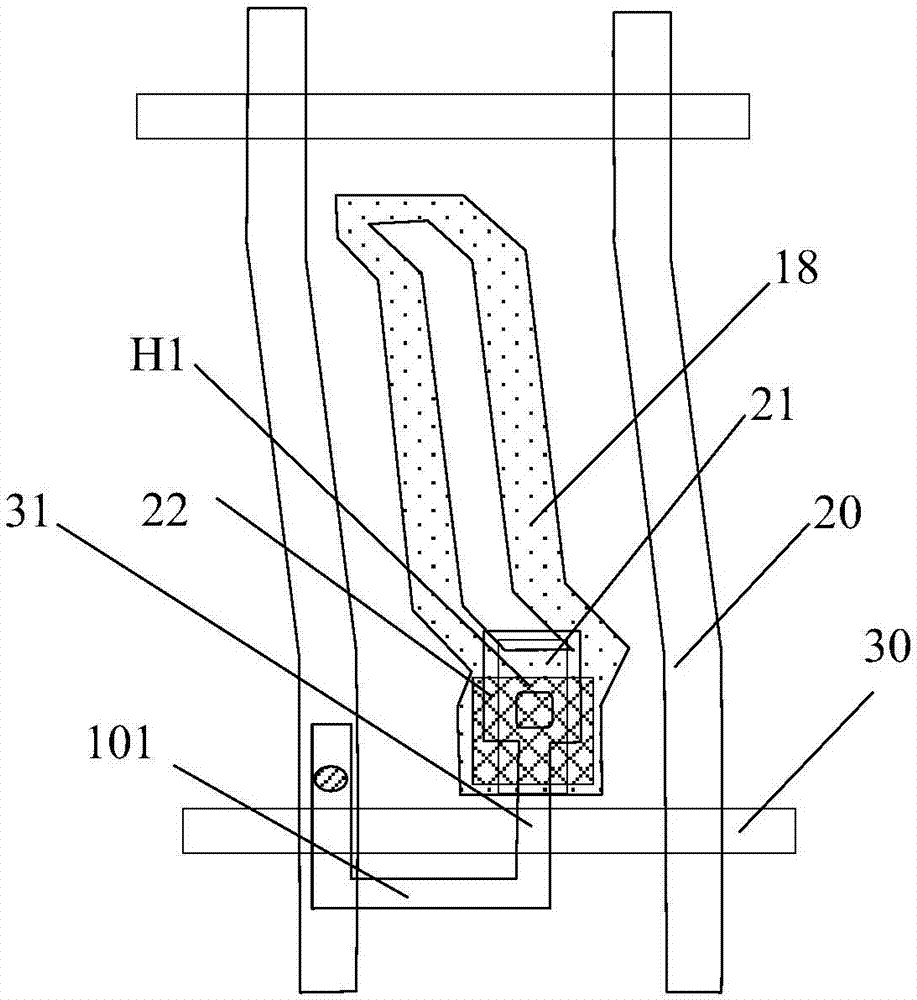

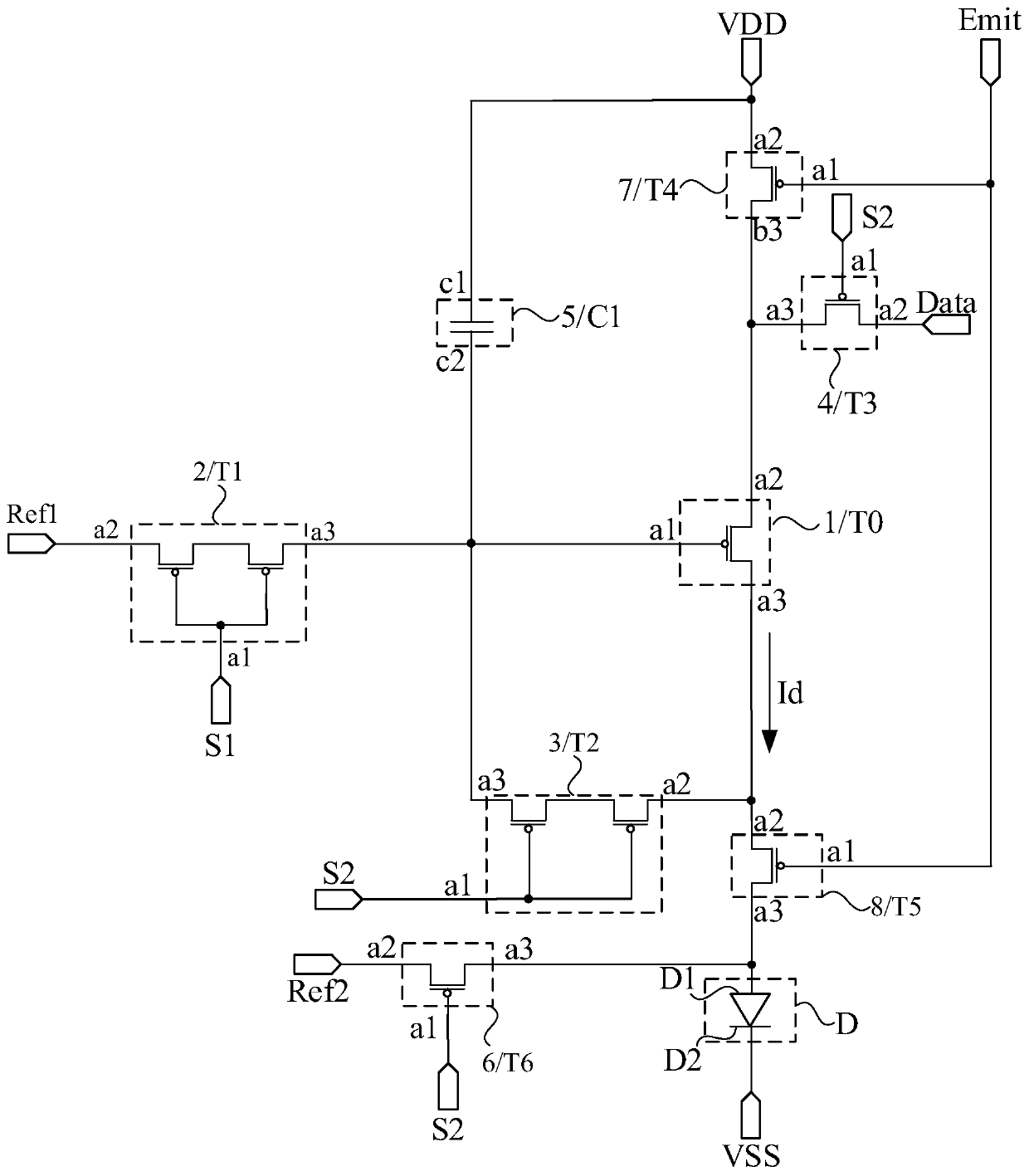

Shifting register unit, gate driving circuit and display device

ActiveCN103413531ASmall sizeReduce coupling capacitanceStatic indicating devicesDigital storageCapacitanceEngineering

The invention provides a shifting register unit, a gate driving circuit and a display device, and relates to the technical field of display. The coupling capacitance of a thin film transistor can be reduced. Noise of an output signal can be reduced. The shifting register unit comprises an input module, a control module, a restoration module, an upwards-pulling module, a downwards-pulling module and a noise reduction module. The shifting register unit, the gate driving circuit and the display device are used for achieving scanning driving.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

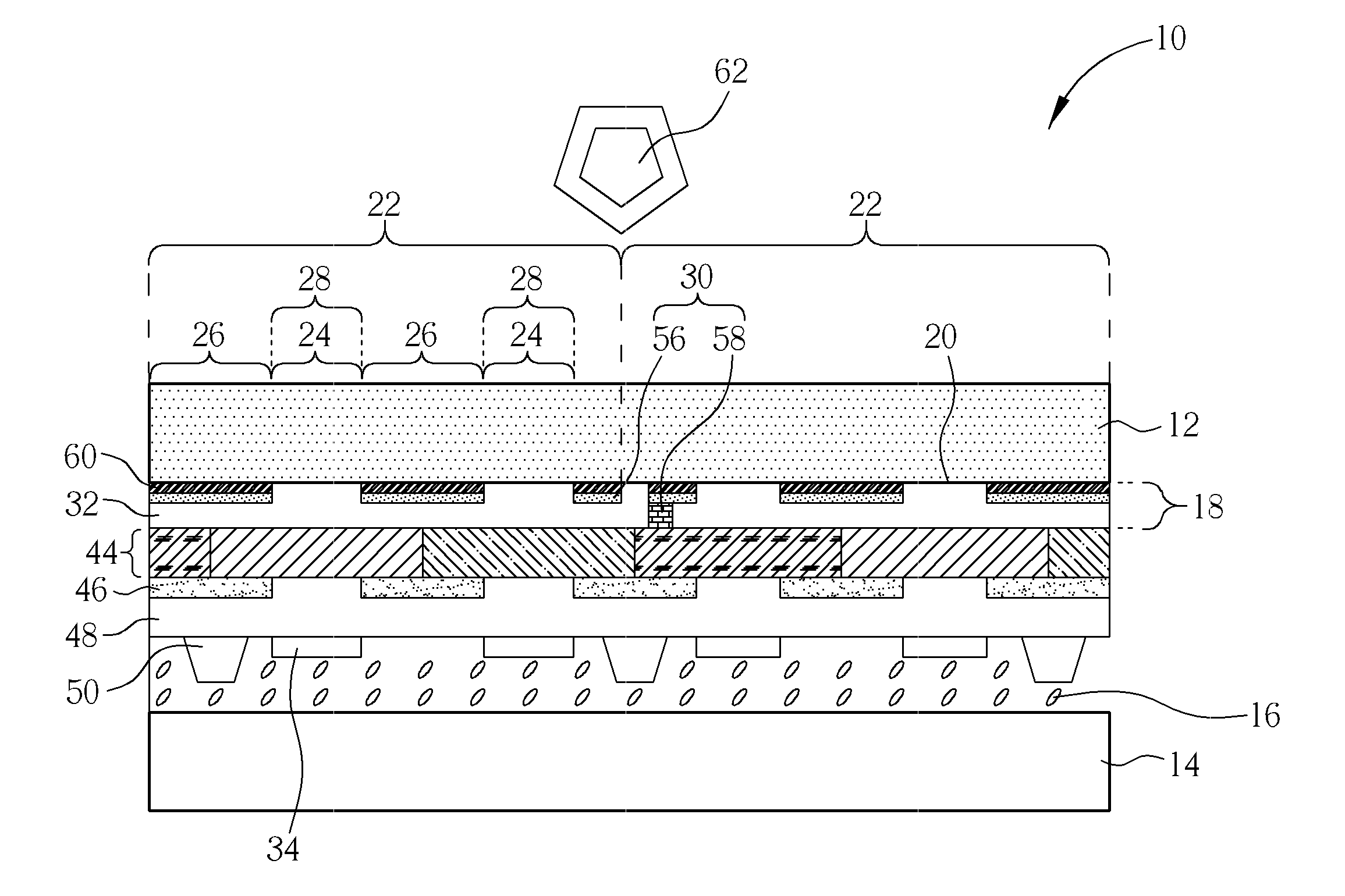

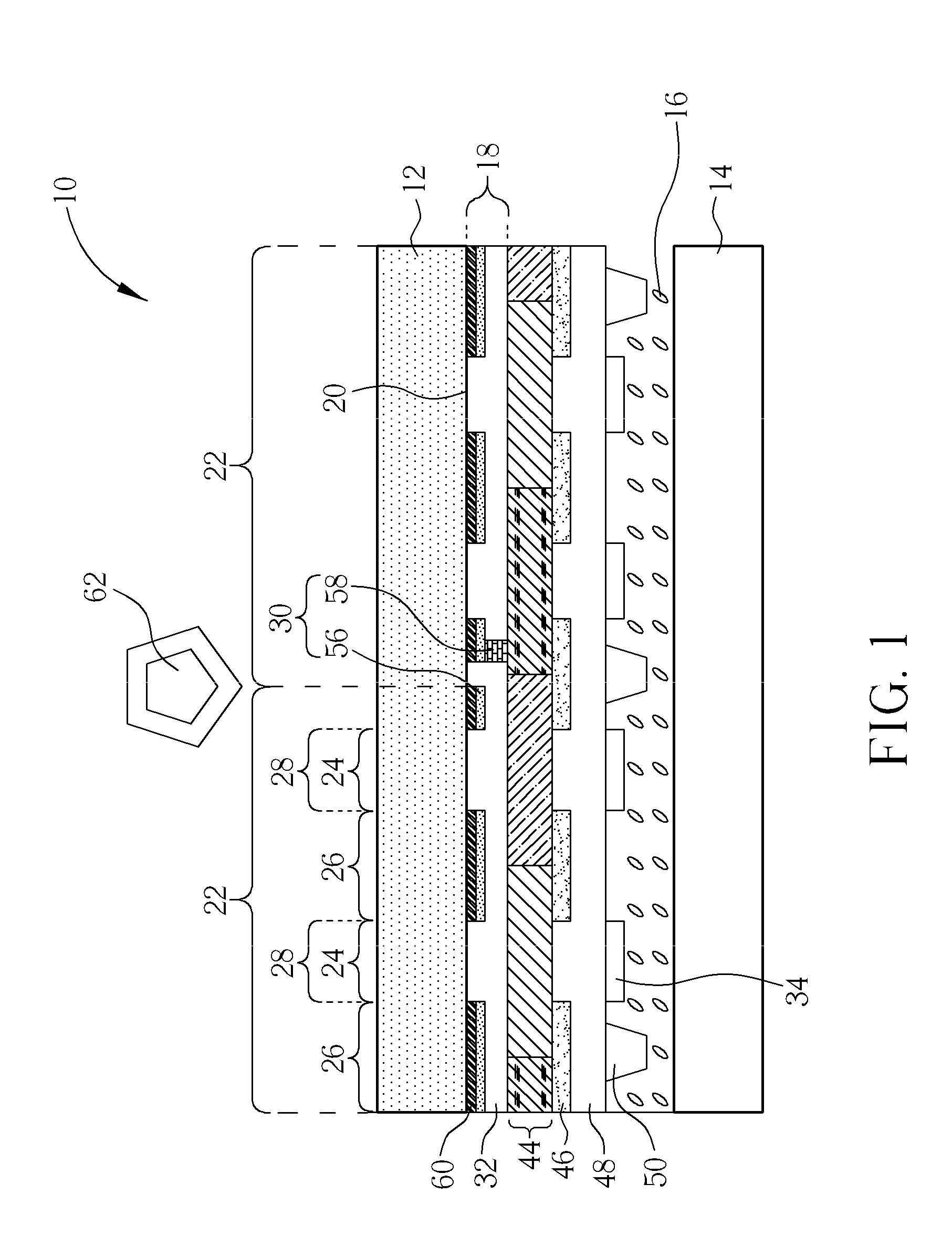

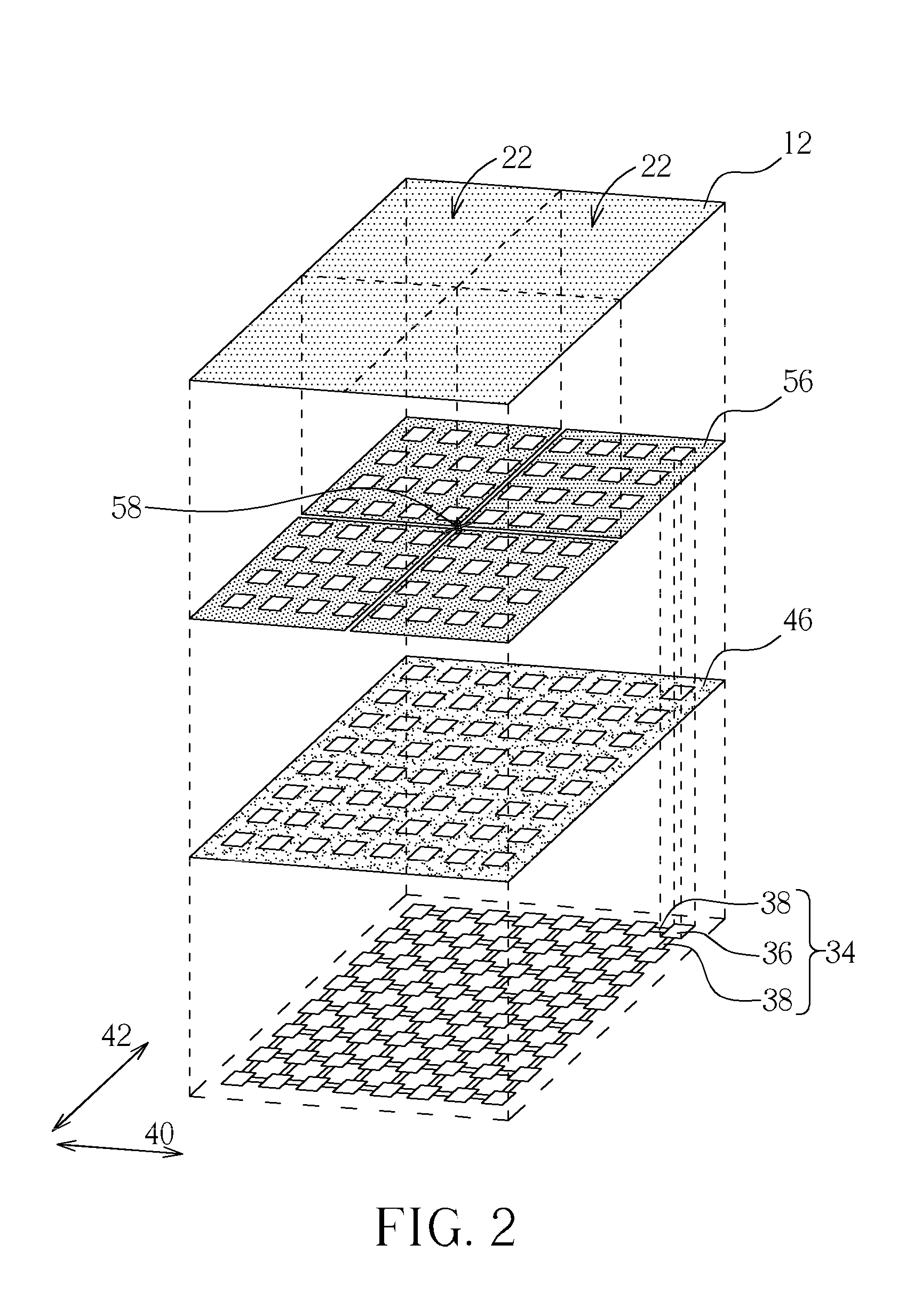

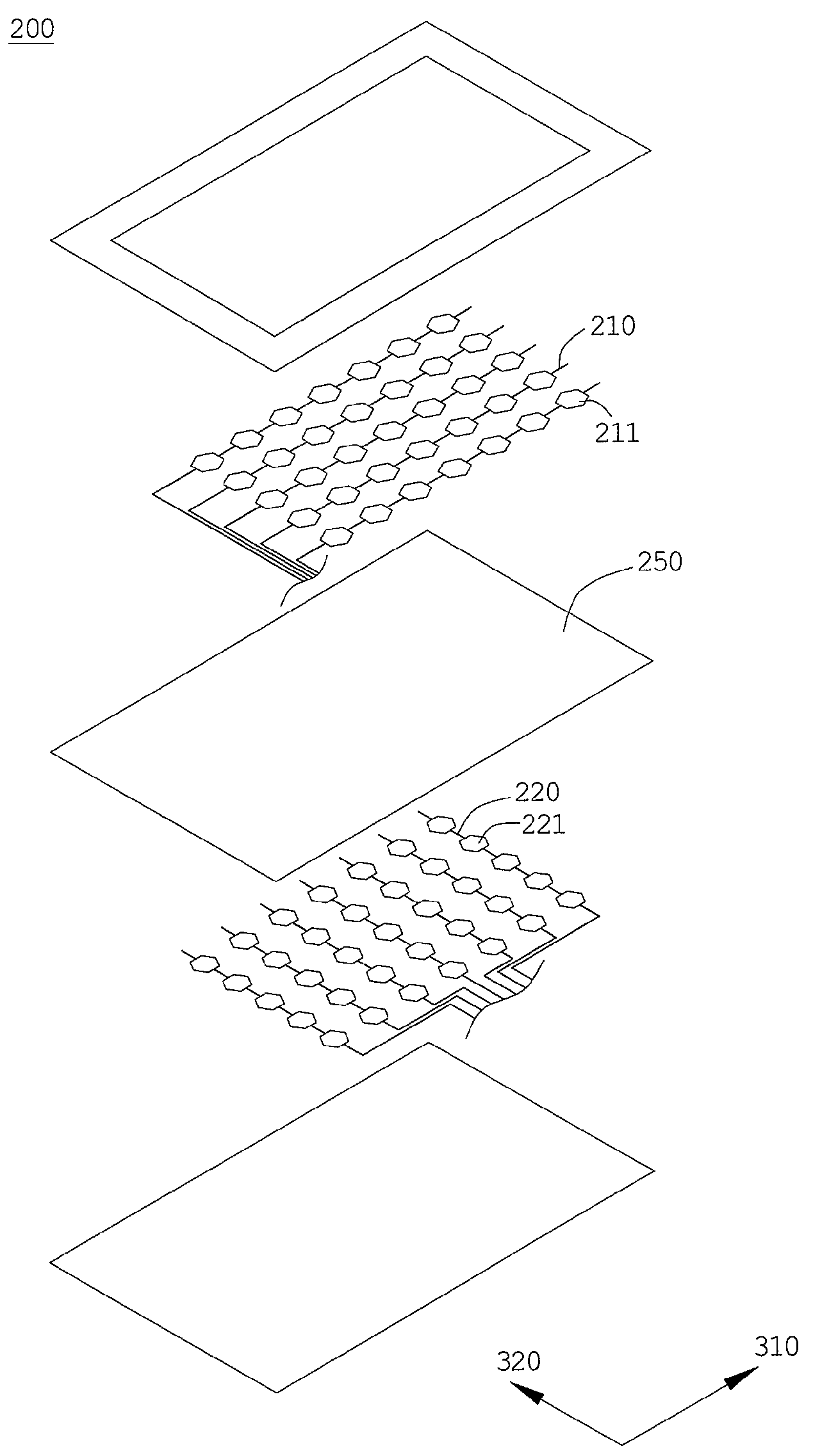

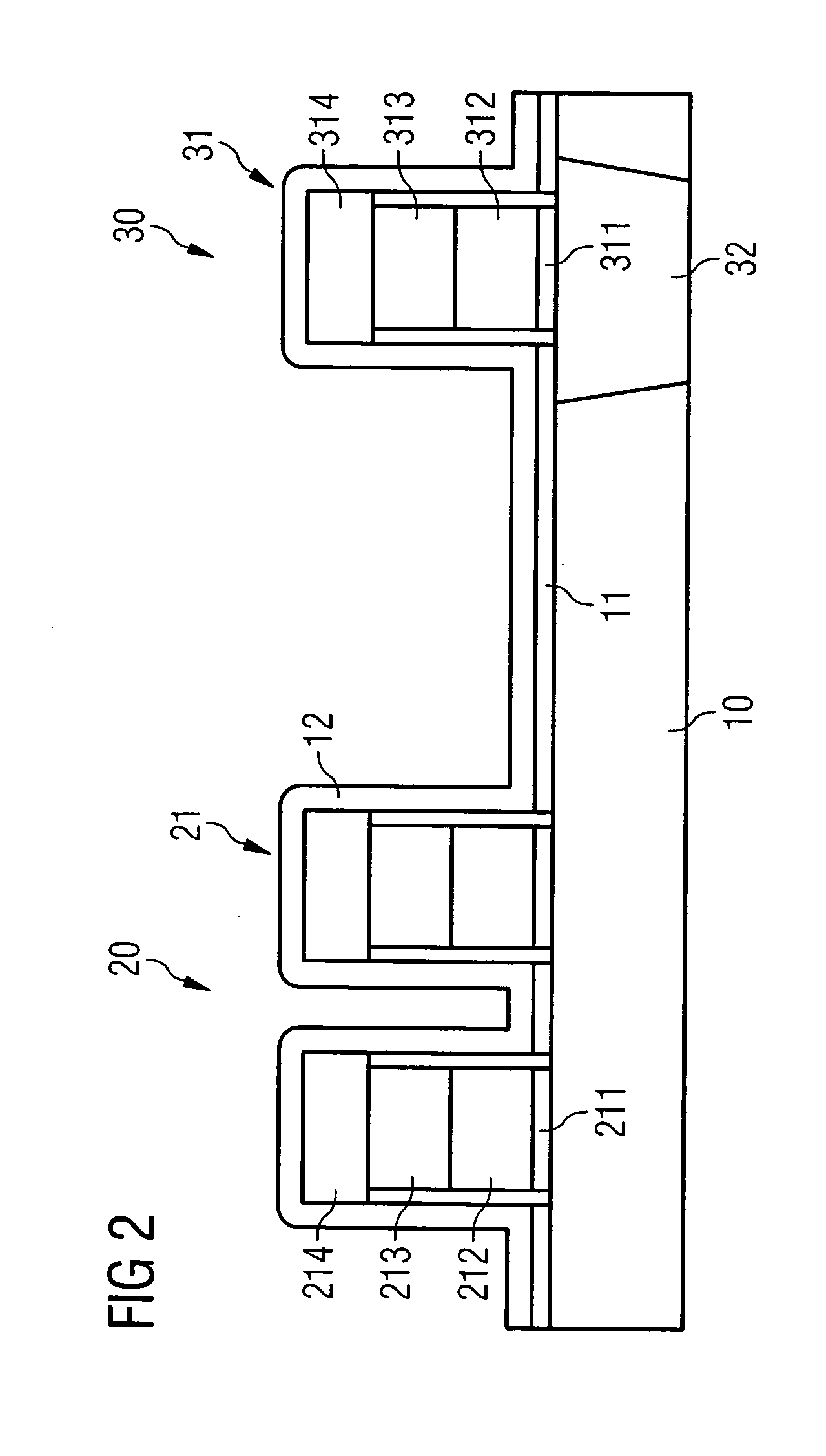

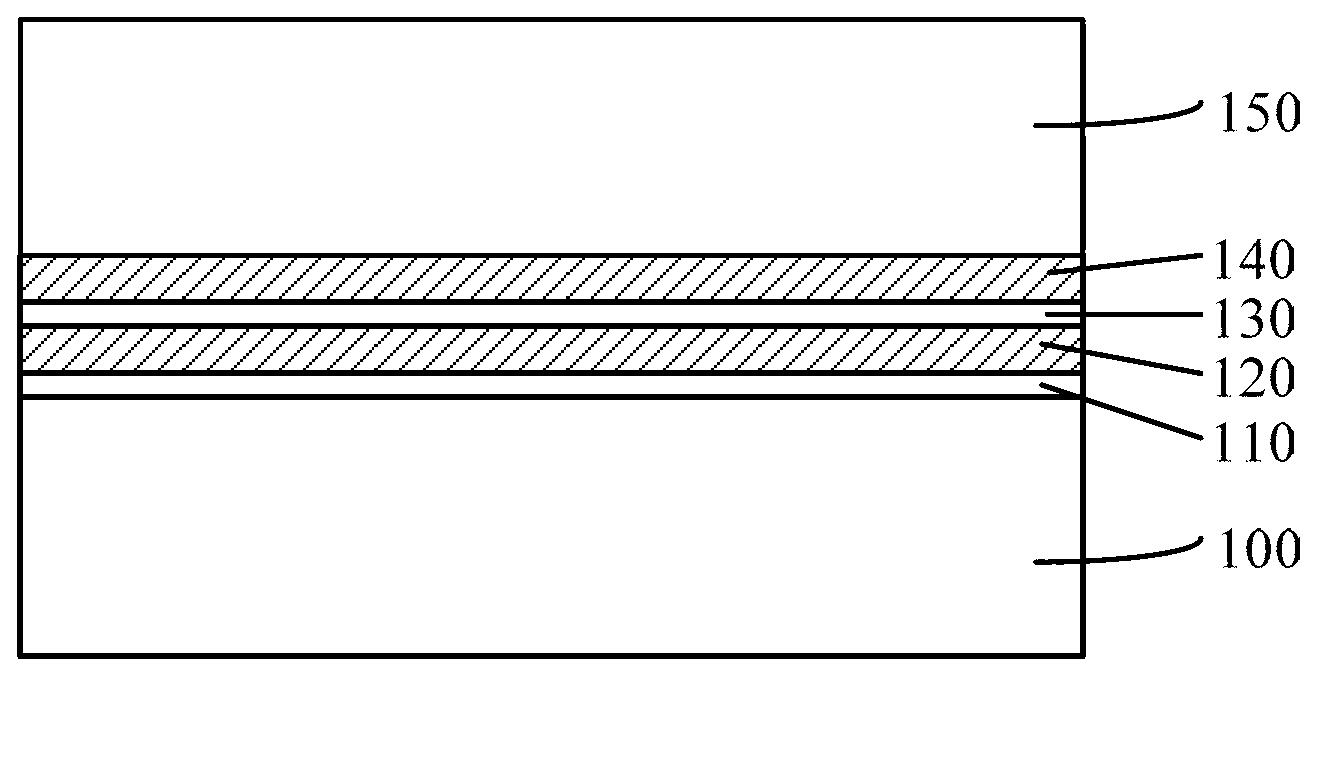

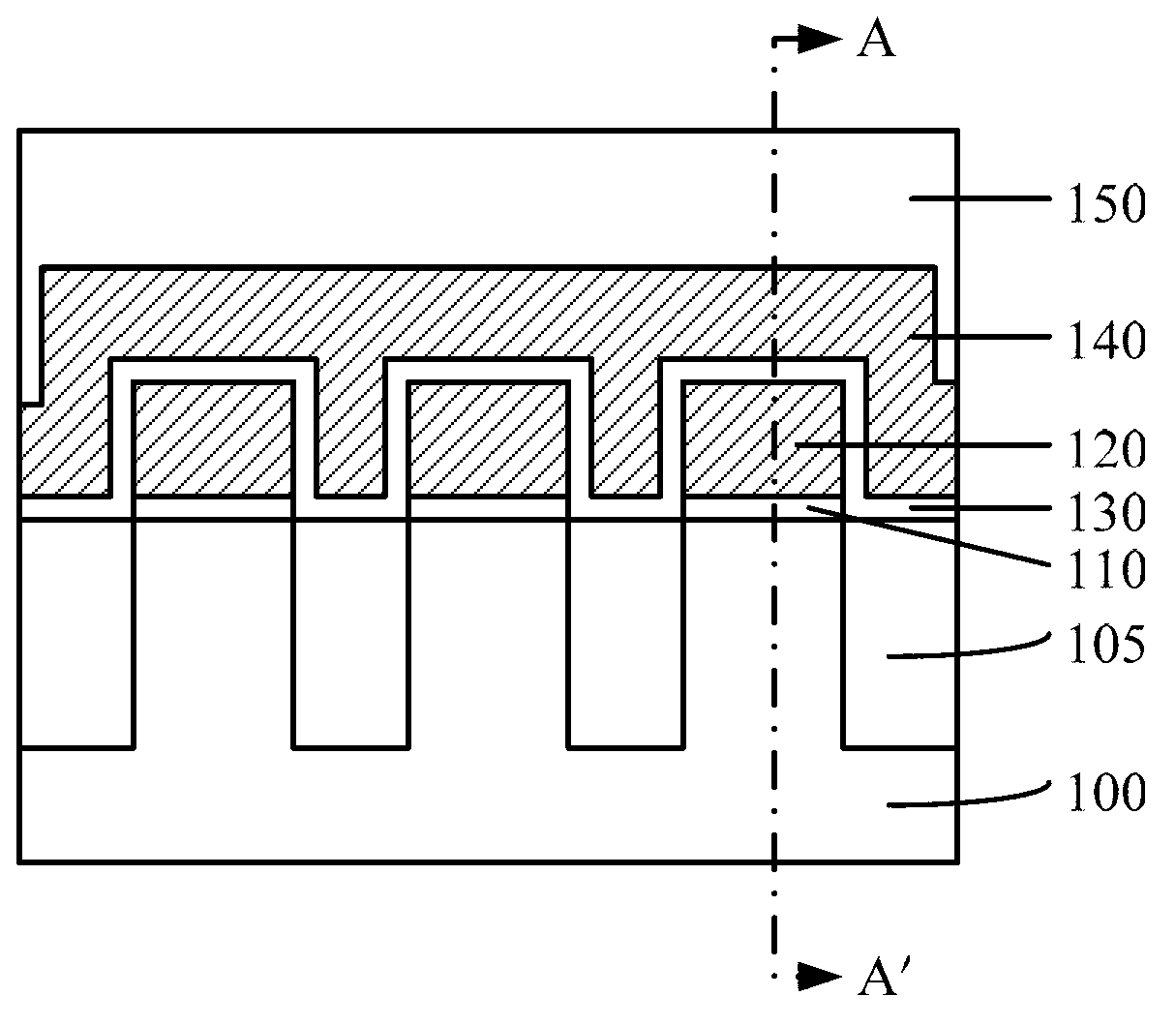

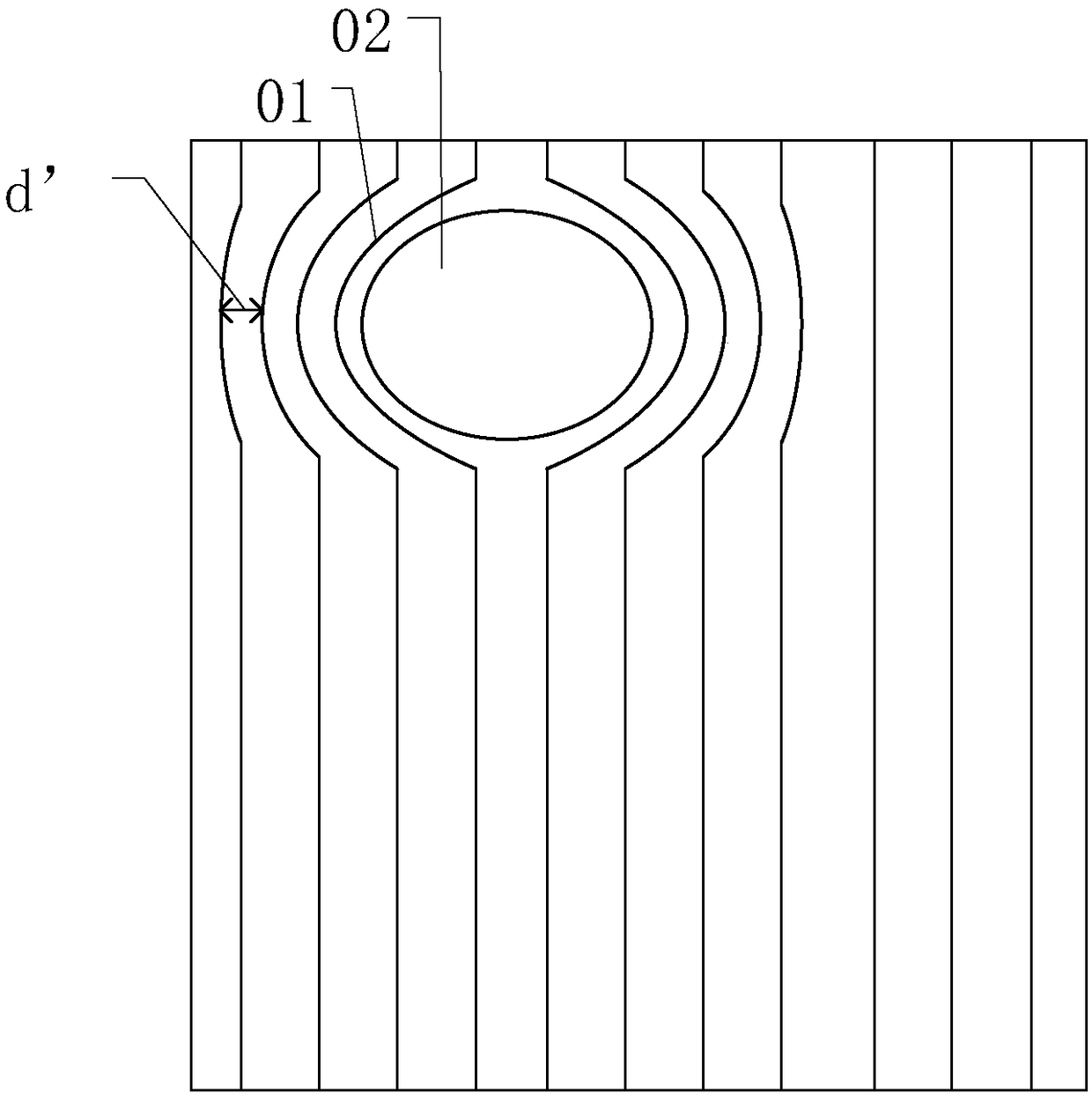

Structure of touch control type apparatus and touch control type display panel

ActiveCN101441538AIncrease the sensor signal strengthReduce overlap areaStatic indicating devicesInput/output processes for data processingCapacitanceCoupling

The invention discloses a structure for a touch control device and a touch control display panel. The touch control device comprises a patterned sensing electrode structure, an insulating layer and a patterned sharing electrode layer. The patterned sensing electrode structure is arranged on the surface of a substrate defined with a plurality of display areas and a shading area, wherein the display areas are exposed corresponding to the shading area. The insulating layer covers the patterned sensing electrode structure. The patterned sharing electrode layer is arranged on the surface of the insulating layer, and comprises a plurality of electrode parts corresponding to the display areas and a plurality of connecting parts arranged between adjacent electrode parts and electrically connected to the electrode parts. The touch control device provides the patterned sensing electrode structure corresponding to the shade area, coordinately provides the electrode parts of the patterned sharing electrode layer corresponding to the display areas, and reduces area of the connecting parts to reduce superposition area of the patterned sensing electrode structure and the patterned sharing electrode layer, so as to reduce coupling capacitance thereof and promote intensity of sensed signals sensed by the patterned sensing electrode structure.

Owner:AU OPTRONICS CORP

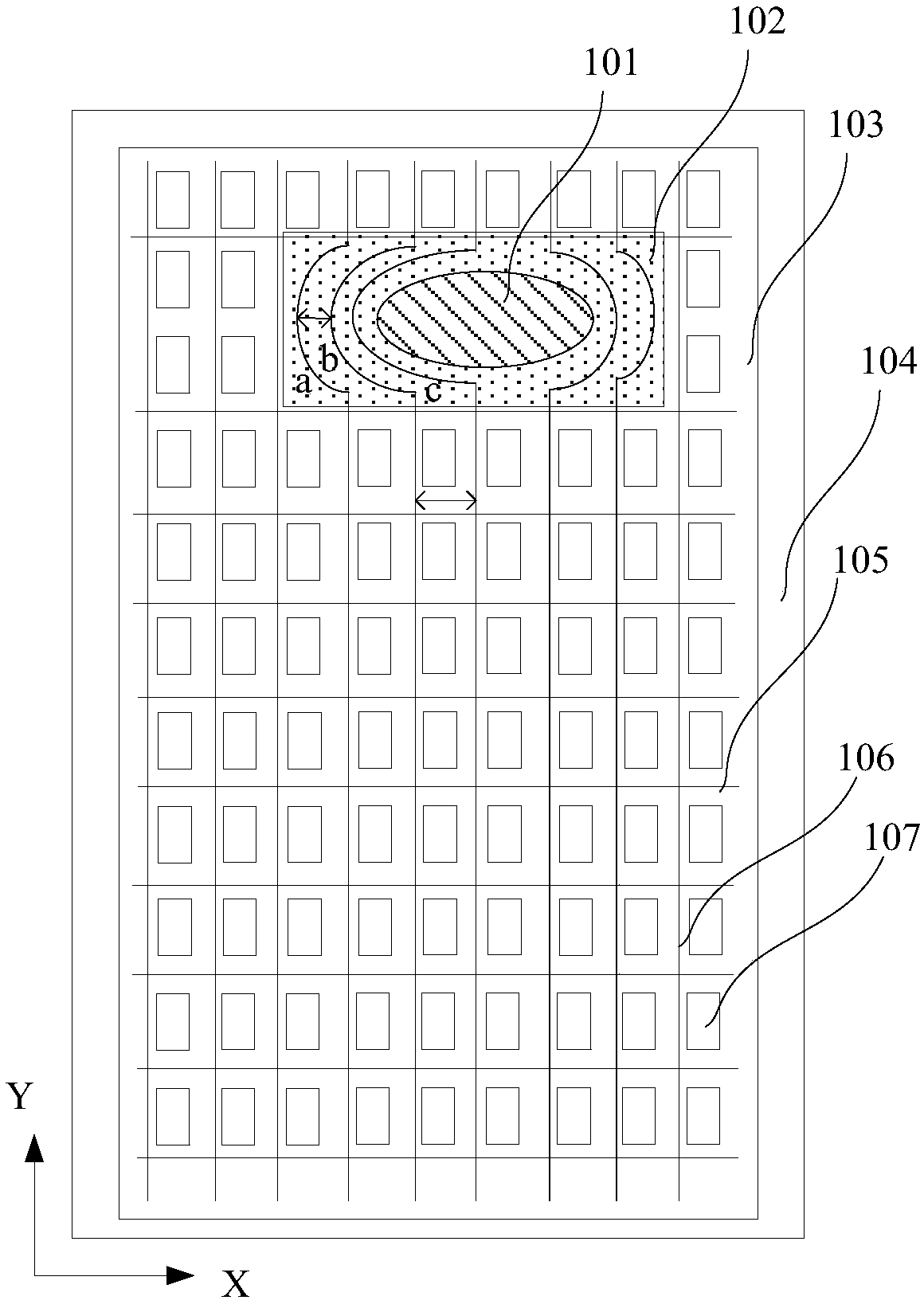

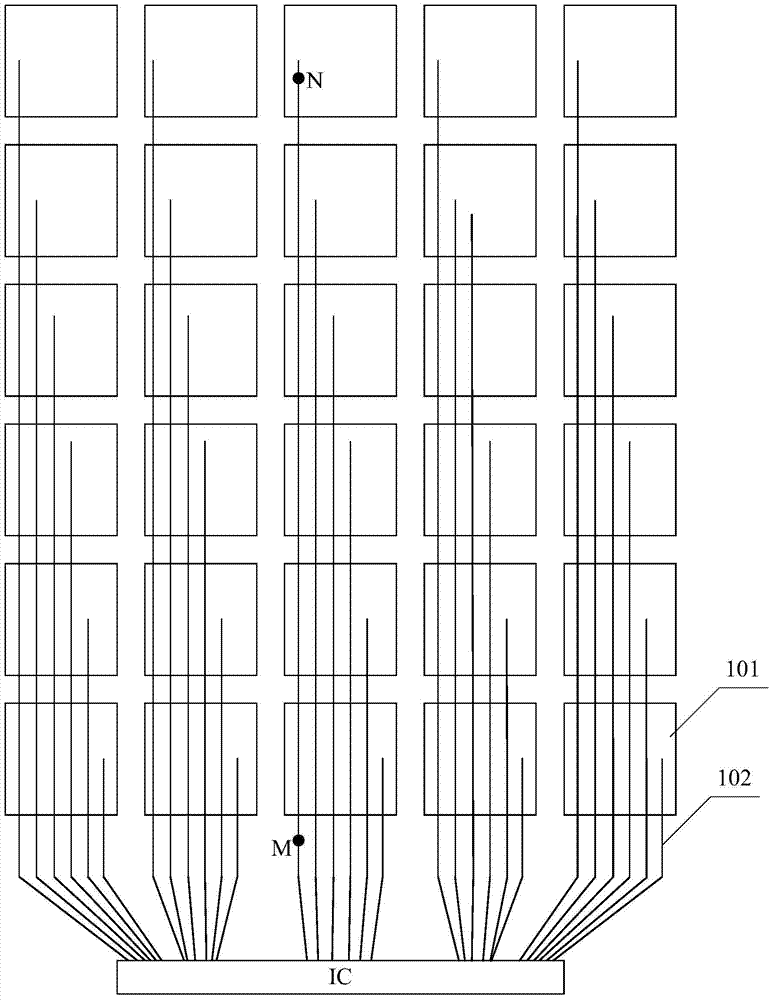

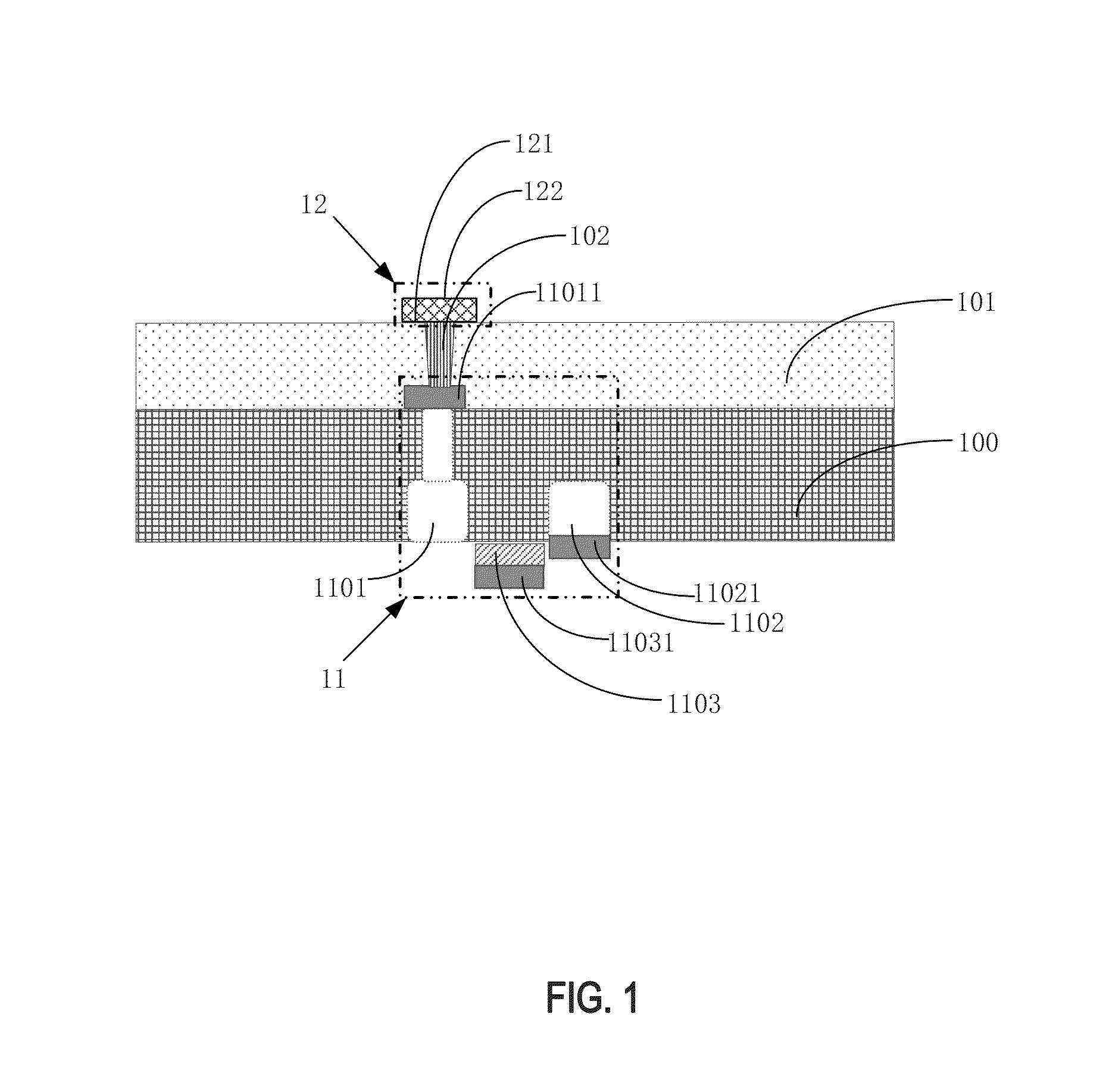

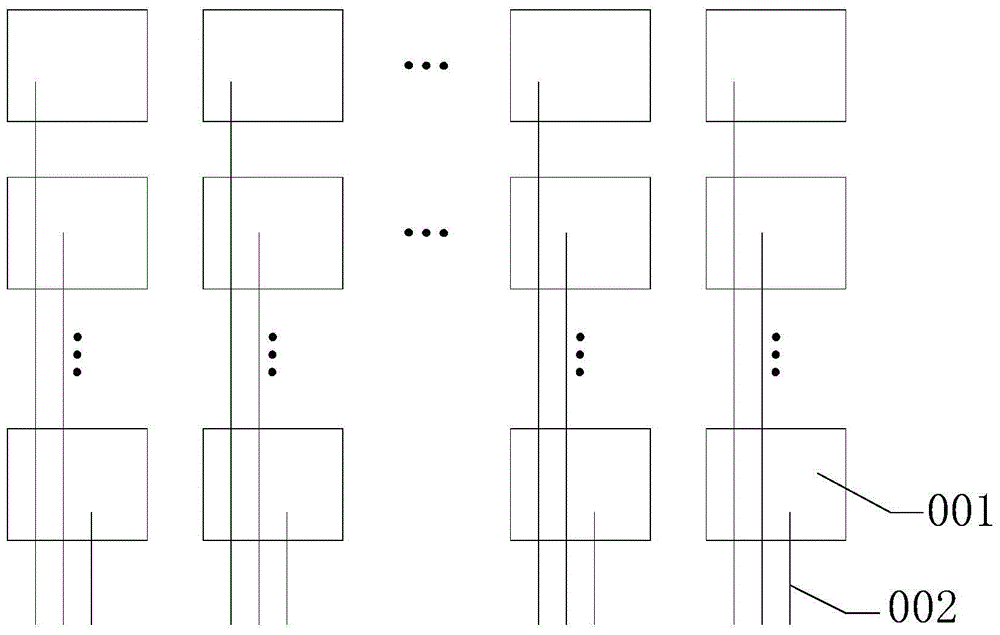

Array substrate and display panel

ActiveCN108807426AReduce in quantityIncreased line spacingStatic indicating devicesSolid-state devicesCapacitanceMaterial Perforation

The invention provides an array substrate and a display panel. The array substrate comprises a non-display area and a display area, wherein the non-display area comprises a first non-display area anda second non-display area, the display area comprises a normal display area and a wire distribution area; the first non-display area surrounds the normal display area, the normal display area surrounds the wire distribution area, the wire distribution area surrounds the second non-display area, and the second non-display area comprises a perforation area. According to the technical scheme, data leads corresponding to subpixels which are simultaneously charged are arranged in an overlapping manner, so that the number of the data leads arranged in a same layer of the wire distribution area is reduced, the area of the wire distribution area is reduced, and a narrow frame design between the second non-display area and the normal display area is realized. Moreover, since the number of the dataleads in the same layer of the wire distribution area is reduced, a linear distance between the adjacent data leads is increased, so that the coupling capacitance between the adjacent data leads arranged on the same layer is reduced.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Display panel, method for preparing same and display device

InactiveCN108732841ASolve the display exceptionMeets requirements for guaranteed optical claritySolid-state devicesNon-linear opticsCapacitanceDisplay device

The invention discloses a display panel, a method for preparing the same and a display device. The display panel comprises at least one first data line. The first data lines penetrate a functional device zone. The display panel, the method and the display device have the advantages that the portions, which penetrate the functional device zone, of the first data lines are first transparent electricconduction lines, arrangement regions for data lines which penetrate a second non-display zone can be increased, accordingly, the distances between the data lines which penetrate the second non-display zone can be increased, coupling resistance between the adjacent data lines can be lowered, and the problem of abnormal display of existing display panels due to the fact existing data lines are excessively densely arranged can be solved; the display panel is provided with the first transparent electric conduction lines, the quantities of data lines required to be arranged in a border zone can be reduced, accordingly, the purpose of reducing the areas occupied by the border zone can be achieved, and the screen-to-body ratio of the display panel further can be increased.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

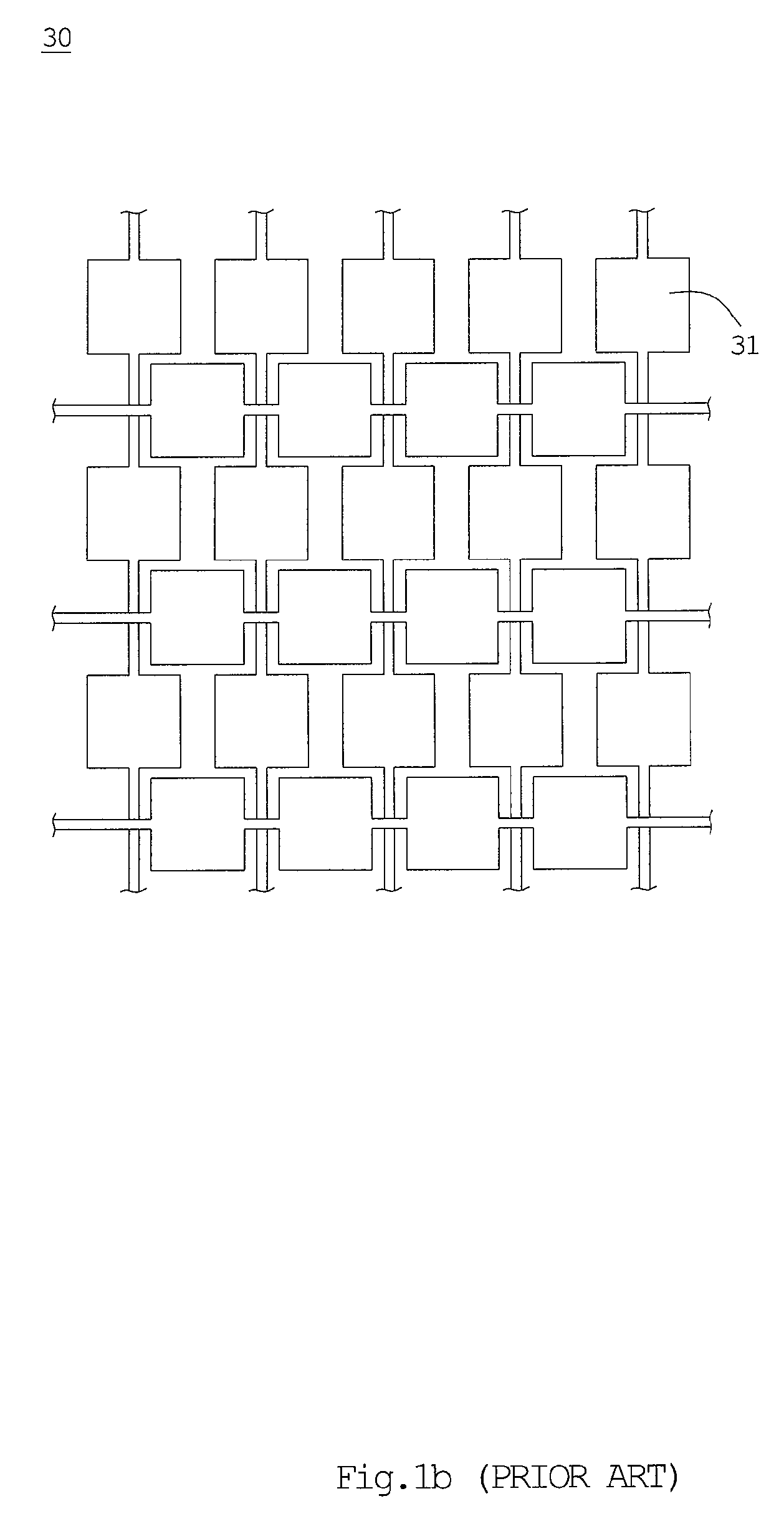

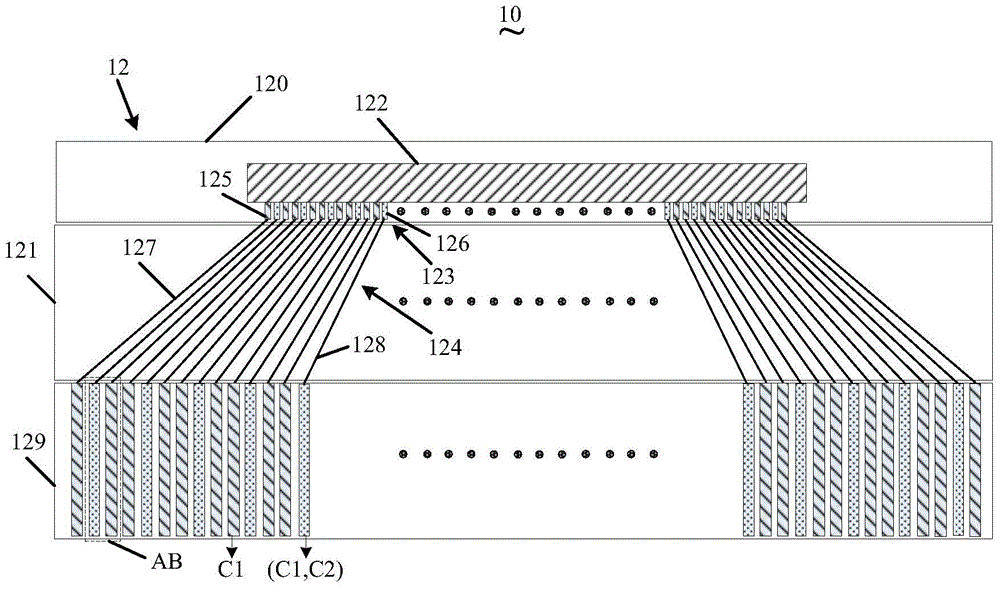

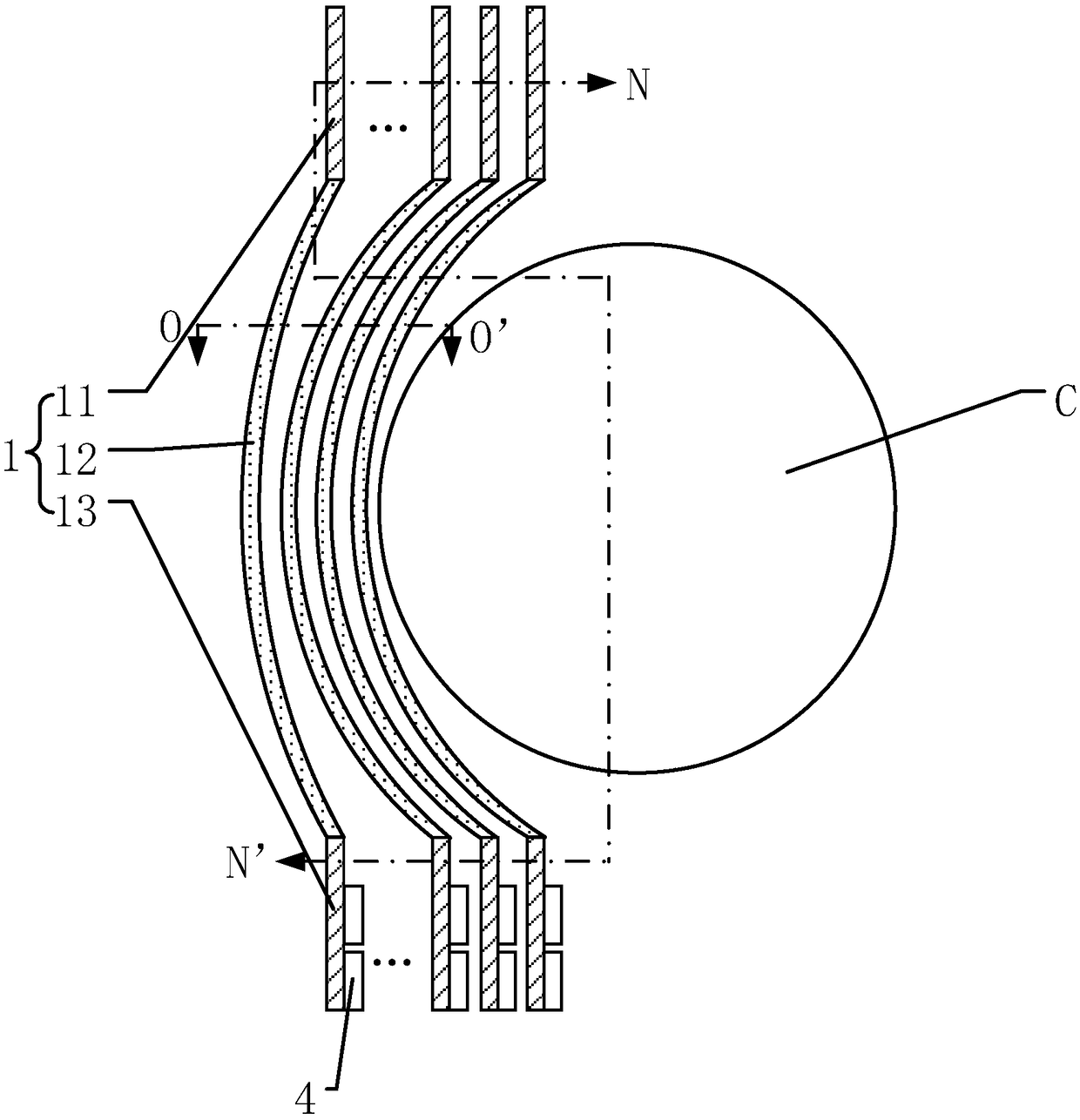

Capacitive Touch Panel with Low Coupling Capacitance and Display Device Using the Capacitive Touch Panel

ActiveUS20090084613A1Reduce lateral capacitanceReduces effective overlapping areaTransmission systemsInput/output processes for data processingTouch panelCapacitance

A capacitive touch panel and a display device using the capacitive touch panel are provided. The capacitive touch panel includes a plurality of first direction electrode strings and second direction electrode strings. Each first direction electrode string has a plurality of first electrodes while each second direction electrode has a plurality of second electrodes. In order to reduce the lateral capacitance between adjacent electrodes, width of the first electrode is reduced from the middle to two sides of the electrode along a second direction. In addition, the first electrode has a perimeter surrounding itself. Each quarter of the perimeter of the first electrode facing the adjacent second electrode has a first slope change rate and a different second slope change rate.

Owner:AU OPTRONICS CORP

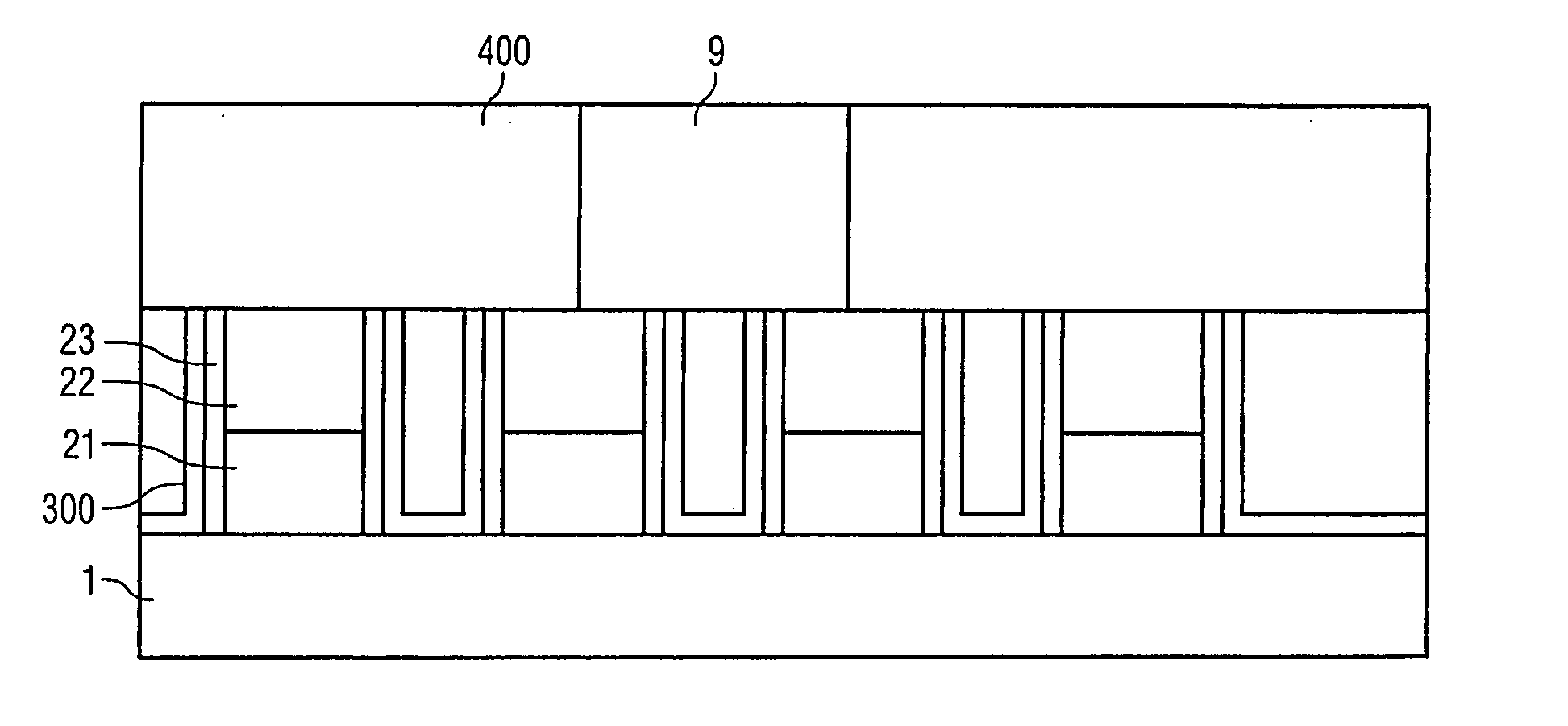

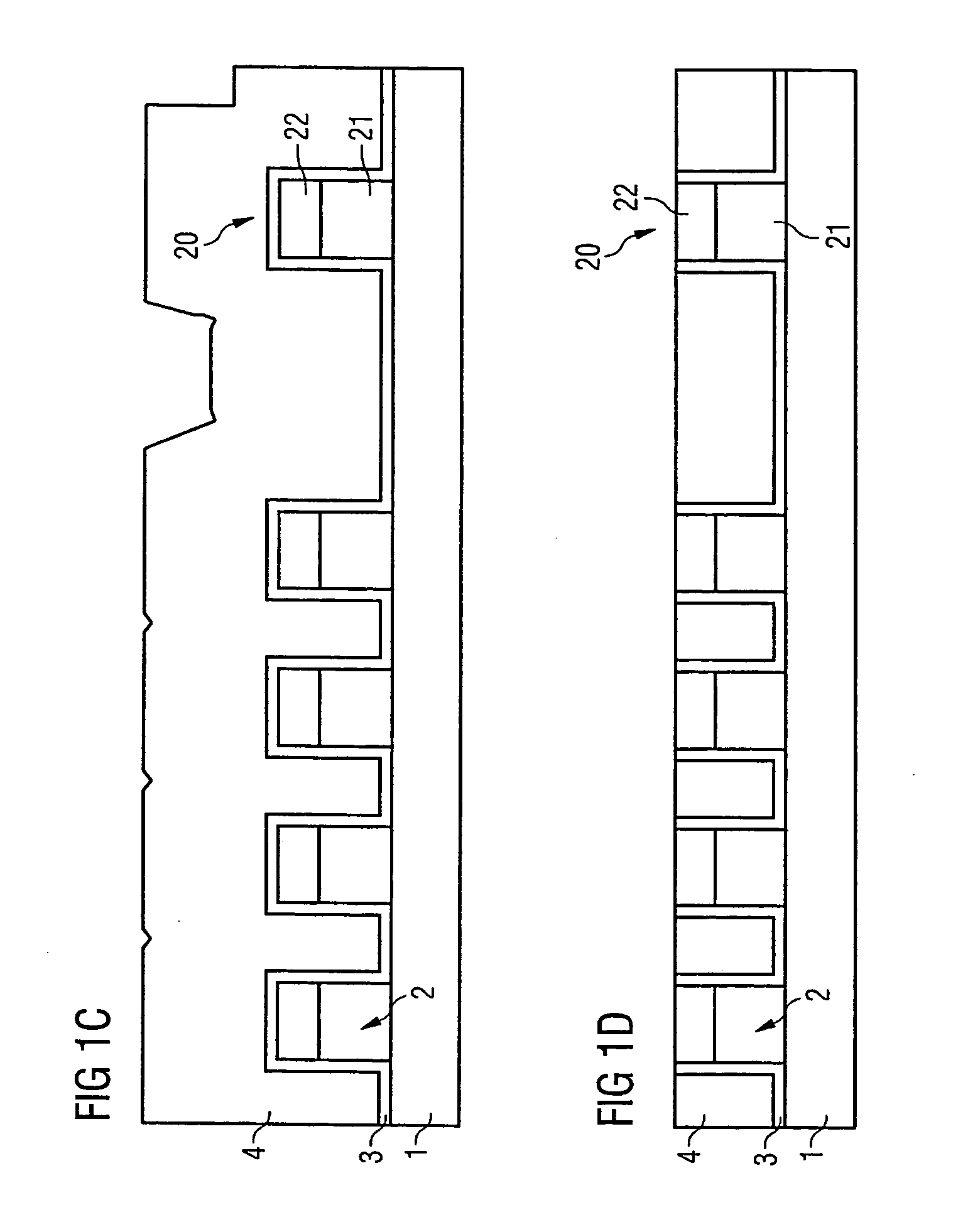

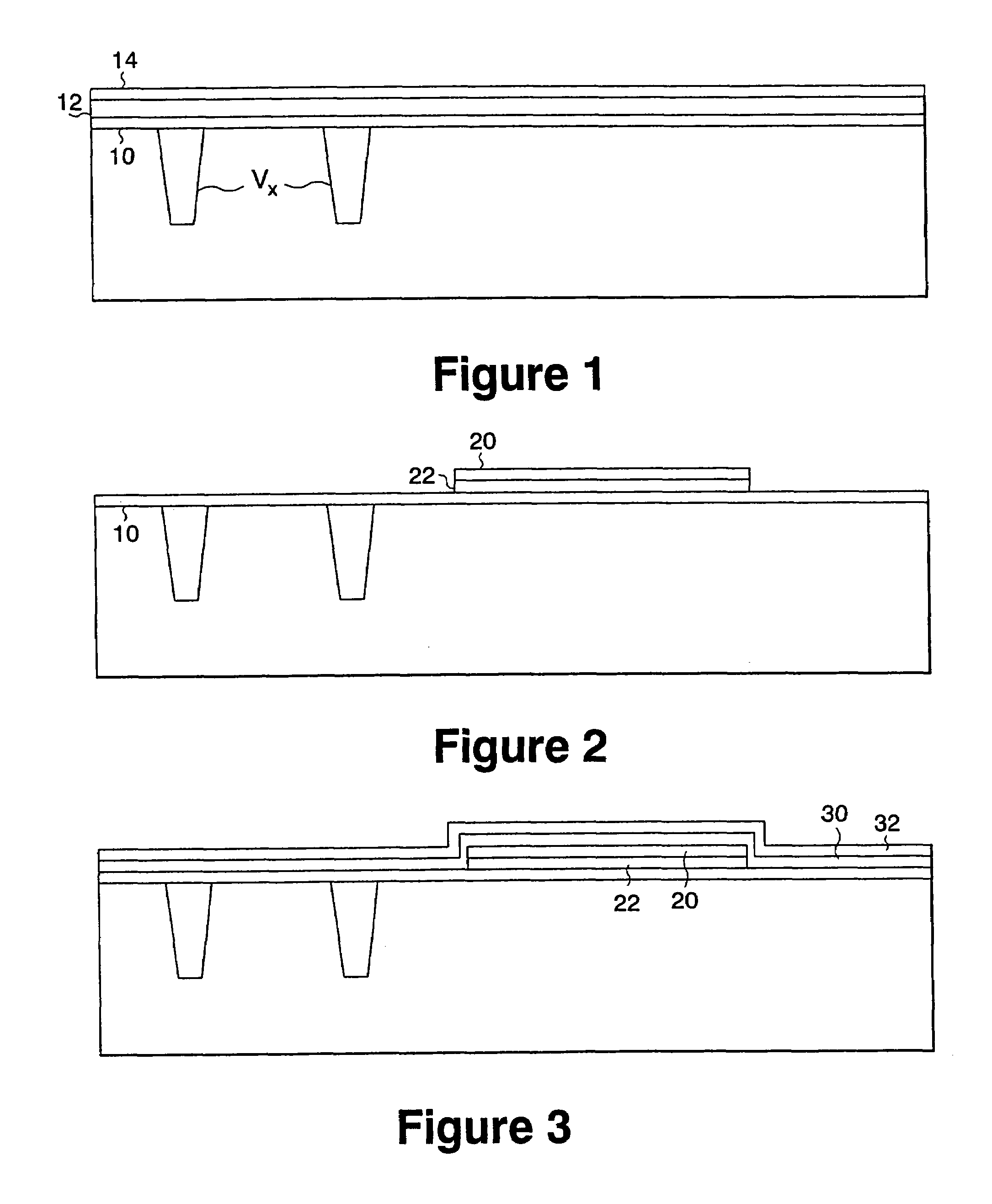

Method for fabricating a contact hole plane in a memory module

InactiveUS20050003308A1Reduce coupling capacitanceReliably fabricatedSolid-state devicesPhotomechanical apparatusConductive materialsSemiconductor

In order to fabricate a contact hole plane in a memory module with an arrangement of memory cells each having a selection transistor, on a semiconductor substrate with an arrangement of mutually adjacent gate electrode tracks on the semiconductor surface, an insulator layer is formed on the semiconductor surface and a sacrificial layer is subsequently formed on the insulator layer, then material plugs are produced on the sacrificial layer for the purpose of defining contact openings between the mutually adjacent gate electrode tracks, the sacrificial layer is etched to form material plugs with the underlying sacrificial layer blocks, after the production of the vitreous layer with uncovering of the sacrificial layer blocks above the contact openings between the mutually adjacent gate electrode tracks, an essentially planar surface being formed, then the sacrificial layer material is etched out from the vitreous layer and the uncovered insulator material is removed above the contact openings on the semiconductor surface and, finally, the contact opening regions are filled with a conductive material.

Owner:POLARIS INNOVATIONS LTD

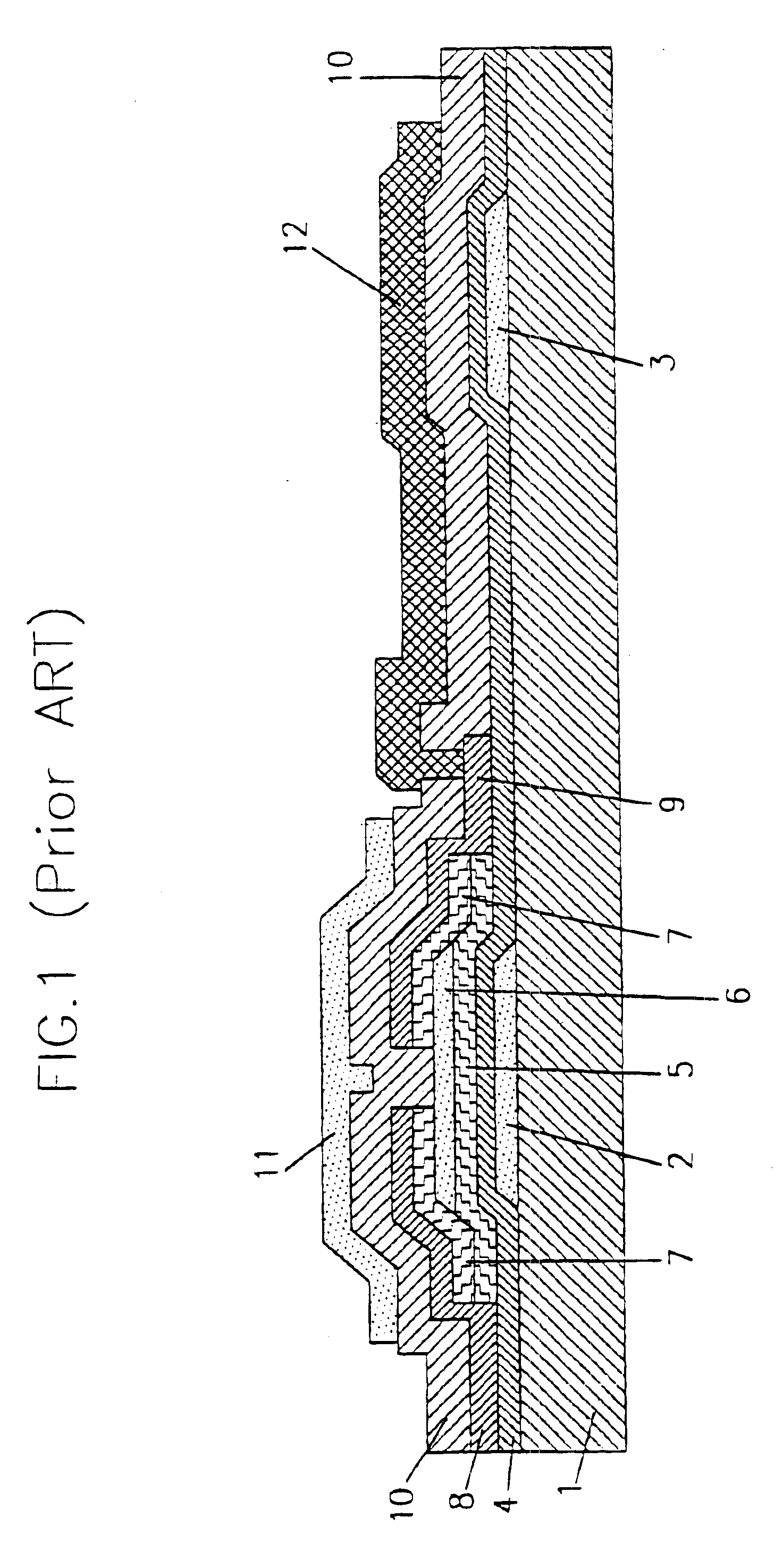

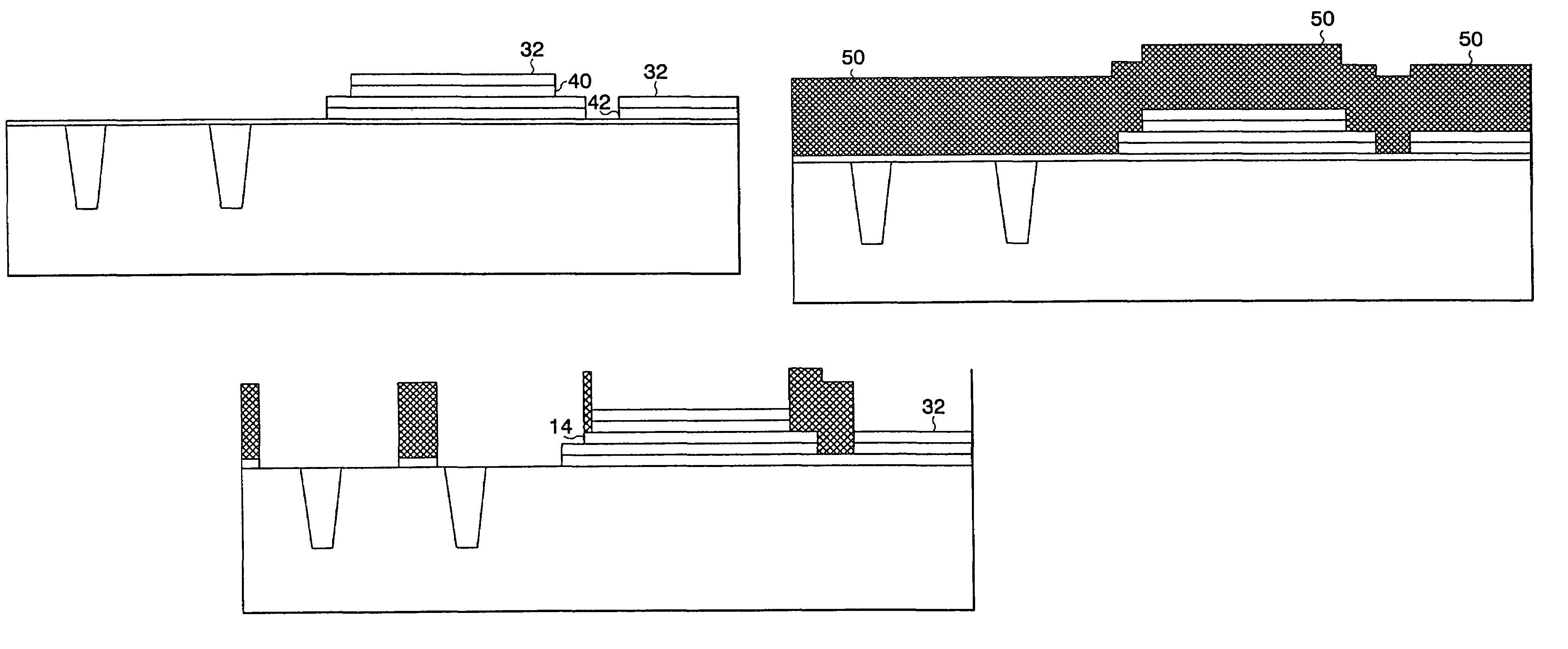

Liquid crystal displays including organic passivation layer contacting a portion of the semiconductor layer between source and drain regions

InactiveUS6940566B1Reduce coupling capacitanceReduce defectsNon-linear opticsSemiconductor devicesResistLiquid-crystal display

A passivation layer is formed by coating a flowable insulating material on the substrate where a thin film transistor and a storage capacitor electrode, and a pixel electrode is formed on the passivation layer. A portion of the passivation layer is etched using the pixel electrode as a mask to make a groove on the thin film transistor, and then a black matrix is formed by filling an organic black photoresist in the groove. To increase the storage capacitance, a portion of the passivation layer is removed or to form a metal pattern on the storage capacitor electrode. A flowable insulating material is used as a gate insulating layer to planarize the substrate. In this case of the etch stopper type thin film transistor, a photo definable material is used as the etch stopper layer to reduce the parasitic capacitance between the gate electrode and the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

Method for fabricating a first contact hole plane in a memory module

InactiveUS20060148227A1Simple and reliable processSimple processSolid-state devicesSemiconductor/solid-state device manufacturingBit lineConductive materials

A silicon dioxide layer is formed and a mask layer is deposited and then patterned to produce openings in the mask layer in the region around the gate contacts onto the gate electrode tracks in the logic region. The surface is uncovered around the gate contacts to the gate electrode tracks in the logic region, reducing the silicon dioxide layer. A sacrificial layer covering the gate electrode tracks is formed and patterned to form sacrificial layer blocks above the contact openings for the bit line contacts between the mutually adjacent gate electrode tracks in the cell array region and above the contact openings for the substrate contacts to the semiconductor surface and the gate contacts onto the gate electrode tracks in the logic region. A filling layer is formed between the sacrificial layer blocks, and the sacrificial layer blocks are removed. The contact opening regions are filled with conductive material.

Owner:INFINEON TECH AG

Touch control panel and driving method thereof

InactiveCN104914606AReduce in quantityReduce coupling capacitanceStatic indicating devicesNon-linear opticsCapacitanceTime-sharing

The invention discloses a touch control panel and a driving method thereof. A driving chip is arranged on a chip area of a non-display area, the driving chip comprises a plurality of pins, at least part of the pins in the pins are output a first driving signal used for controlling a pixel electrode and a second driving signal used for controlling a touch control sensor in a time-sharing mode, a plurality of wirings corresponding to the pins are arranged on a fan-shaped area, and the wirings are used for transmitting the first driving signal and the second driving signal. Through the mode, the touch control panel and the driving method thereof can reduce the difficulty of a bonding technique. Meanwhile, the coupling capacitance between the walking wires is reduced, and therefore the display quality and the touch control sensitivity of the touch control panel are improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD +1

Conductor track arrangement and associated production method

InactiveUS20070120263A1Simple manufacturing methodLow costSemiconductor/solid-state device detailsSolid-state devicesResistCapacitance

A conductor track arrangement includes a substrate, at least two conductor tracks, a cavity and a resist layer that covers the conductor tracks and closes off the cavity. By forming carrier tracks with a width less than a width of the conductor tracks, air gaps can also be formed laterally underneath the conductor tracks for reducing the coupling capacitances and the signal delays in a self-aligning manner.

Owner:INFINEON TECH AG

Low coupling capacitor condenser type touch control board

InactiveCN101126969ALow interelectrode lateral capacitanceReduce coupling capacitanceInput/output processes for data processingCapacitanceCoupling

The utility model provides a capacitive type touch panel with low coupling capacitance and a display unit with the capacitive type touch panel, comprising a plurality of first directional electrode strings and a plurality of second directional electrode strings. A plurality of A electrodes are arranged on the first directional electrode strings along the first direction; a plurality of B electrodes are arranged on the second directional electrode strings along the second direction. In order to reduce the lateral capacitor between the A electrode and the B electrode or the adjacent two A electrodes, the width of A electrode is reduced along the second direction from the middle part to the both sides. Furthermore, each A electrode has a circumference of A electrode form. Meanwhile, the quarter part of the circumference adjacent to the B electrode has the dissimilar first slope change rate and the second slope change rate.

Owner:AU OPTRONICS CORP

Vertically aligned mode liquid crystal display

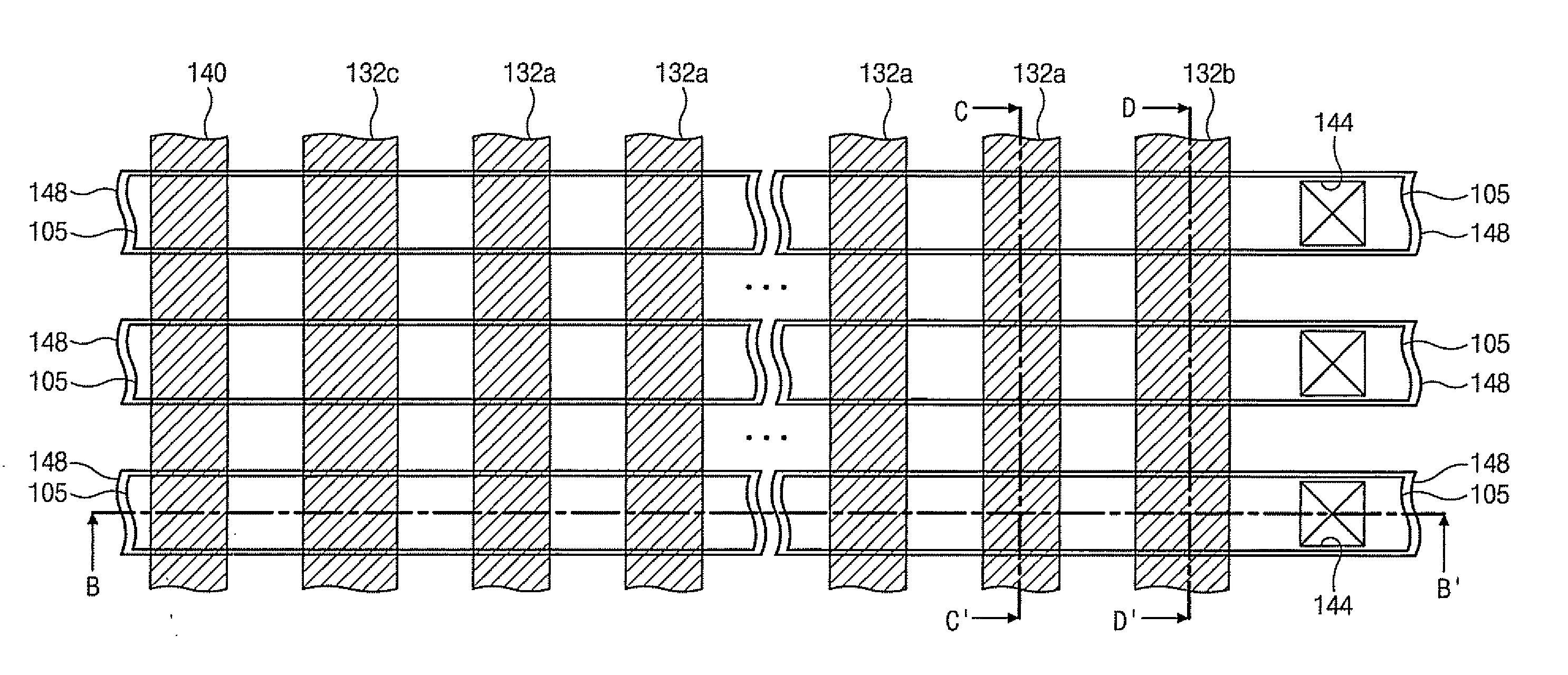

ActiveUS20050231671A1Improve image qualityReduce data loadTransistorSemiconductor/solid-state device manufacturingLiquid-crystal displayTransistor

A plurality of gate lines and a plurality of data lines intersecting each other are formed on a first insulating substrate having a plurality of first cutouts are formed on the respective pixel areas defined by the data lines and the gate lines. A thin film transistor is connected to each pixel electrode. A reference electrode having a plurality of second cutouts is formed on a second substrate opposite the first substrate. The first cutouts and the second cutouts in the adjacent two pixel areas opposite each other with respect to one data line have an inversion symmetry with respect to the data line.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

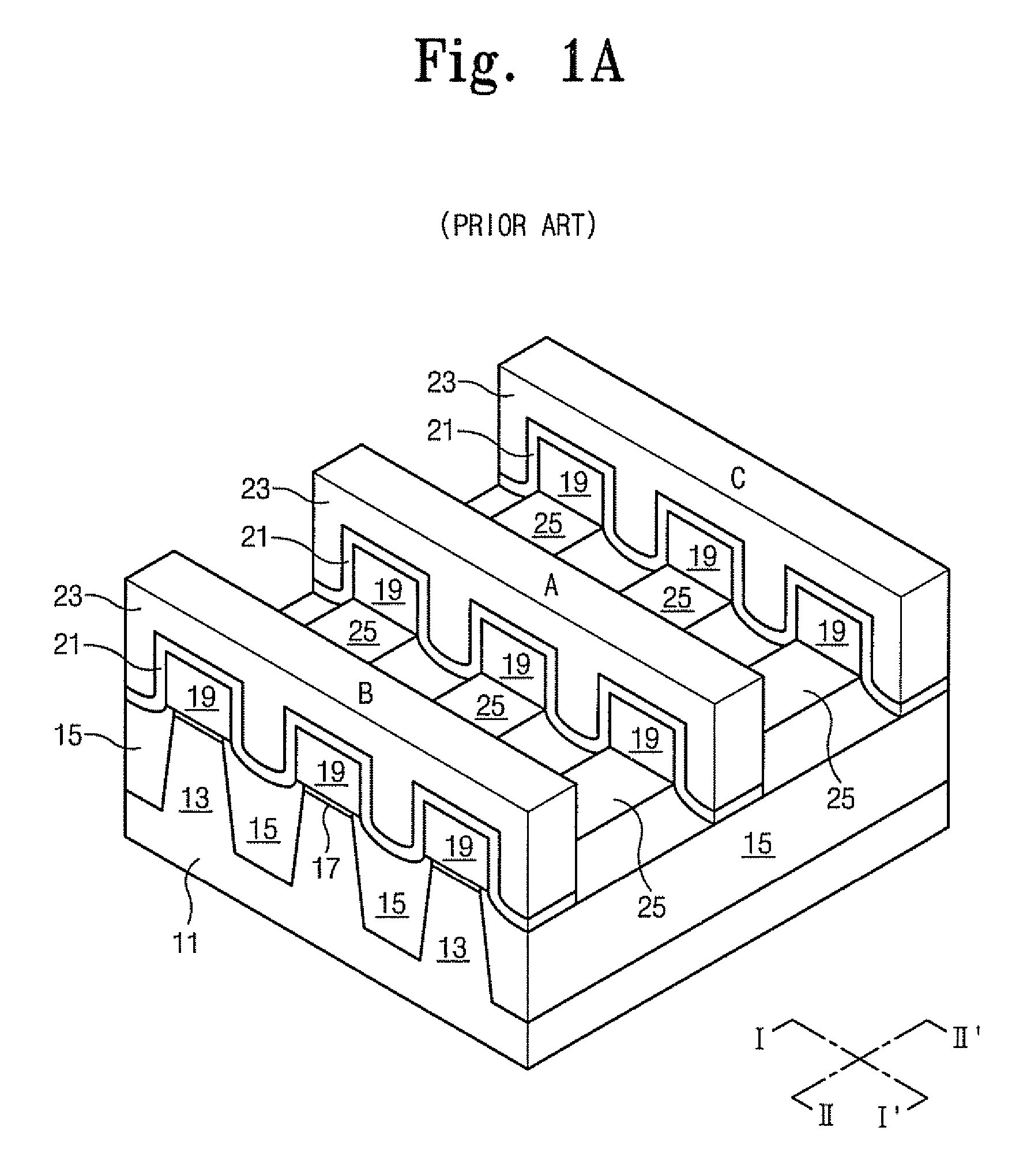

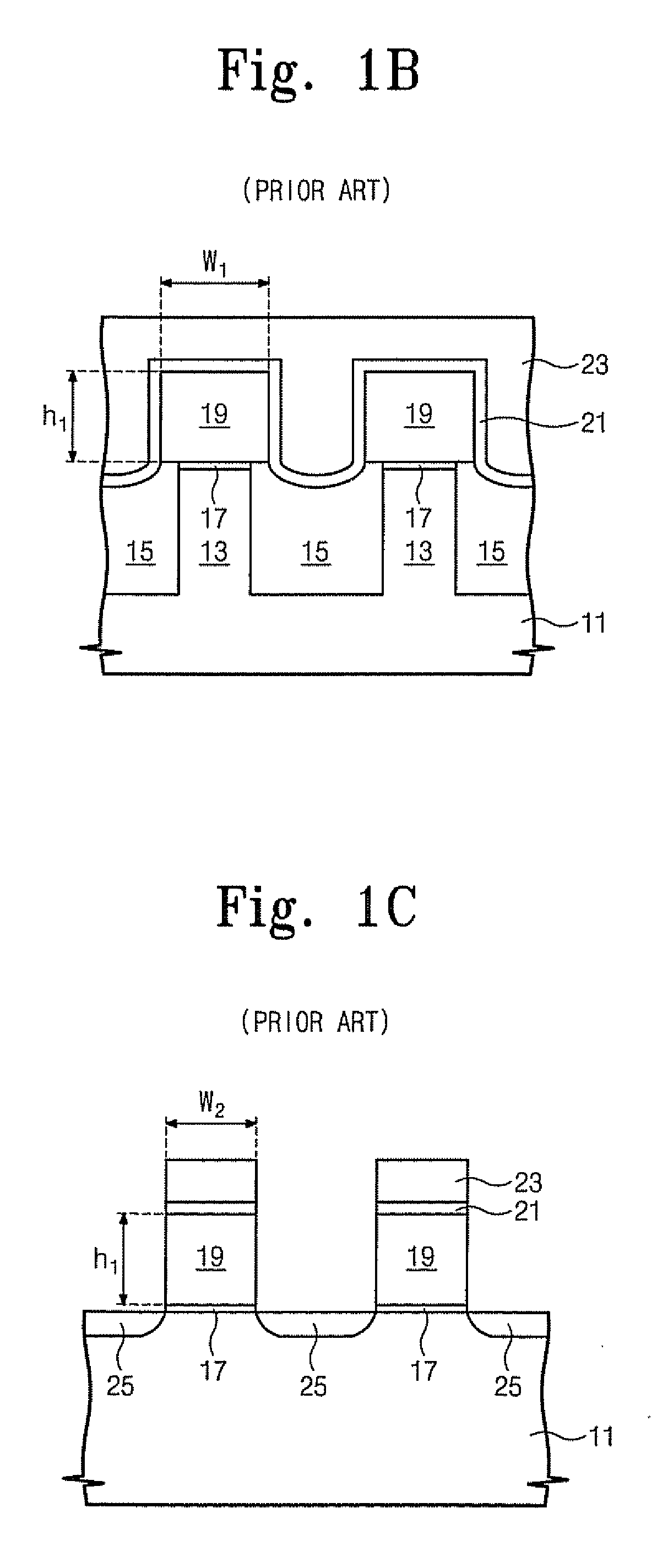

Non-Volatile Memory Devices Having L-Shaped Floating Gate Electrodes and Methods of Forming Same

InactiveUS20070053223A1Reduced cell-to-cell coupling capacitanceImprove the coupling ratioSolid-state devicesRead-only memoriesNon-volatile memoryVertical segment

A flash EEPROM array includes a first row of EEPROM cells having a first floating gate electrode therein and a second row of EEPROM cells having a second floating gate electrode therein. The first floating gate electrode includes at least one horizontal segment and at least one vertical segment, which collectively define a first L-shaped portion of the first floating gate electrode that faces a first direction. The second floating gate electrode includes at least one horizontal segment and at least one vertical segment that collectively define a second L-shaped portion of the second floating gate electrode that faces a second direction opposite the first direction.

Owner:SAMSUNG ELECTRONICS CO LTD

Array substrate, liquid crystal display panel and display device

ActiveCN107024813AImprove crosstalk phenomenonImprove yieldNon-linear opticsInput/output processes for data processingLiquid-crystal displayDisplay device

The invention provides an array substrate, a liquid crystal display panel and a display device. The array substrate comprises a substrate, a plurality of scanning lines, a plurality of thin film transistors arranged in a matrix form, a flattening layer, a filling electrode and a pixel electrode, wherein the scanning lines and multiple pieces of data are arranged in a cross manner; each thin film transistor comprises a gate, an active layer and a drain electrode; the flattening layer covers the gate, the active layer and the drain electrode; a through hole penetrating through the flattening layer is formed in a position, which corresponds to the drain electrode, of the flattening layer; the drain electrode is positioned inside the through hole; the filling electrode is positioned in the through hole, is connected with the drain electrode and covers the drain electrode; the pixel electrode is indirectly connected to the drain electrode through the filling electrode. According to the array substrate disclosed by the invention, the distance between the data line and the pixel electrode is enlarged, the influence of the data line on the pixel electrode is reduced, and a crosstalk phenomenon of the display device is improved; a segment gap of the drain electrode is compensated through the filling electrode, the line breakage problem of the pixel electrode is improved, and the yield of the display device is improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Liquid crystal displays using organic insulating material and manufacturing methods thereof

InactiveUS20050185109A1Reduce coupling capacitanceReduce defectsNon-linear opticsResistLiquid-crystal display

A passivation layer is formed by coating a flowable insulating material on the substrate where a thin film transistor and a storage capacitor electrode, and a pixel electrode is formed on the passivation layer. A portion of the passivation layer is etched using the pixel electrode as a mask to make a groove on the thin film transistor, and then a black matrix is formed by filling an organic black photoresist in the groove. To increase the storage capacitance, a portion of the passivation layer is removed or to form a metal pattern on the storage capacitor electrode. A flowable insulating material is used as a gate insulating layer to planarize the substrate. In the case of the etch stopper type thin film transistor, a photo definable material is used as the etch stopper layer to reduce the parasitic capacitance between the gate electrode and the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

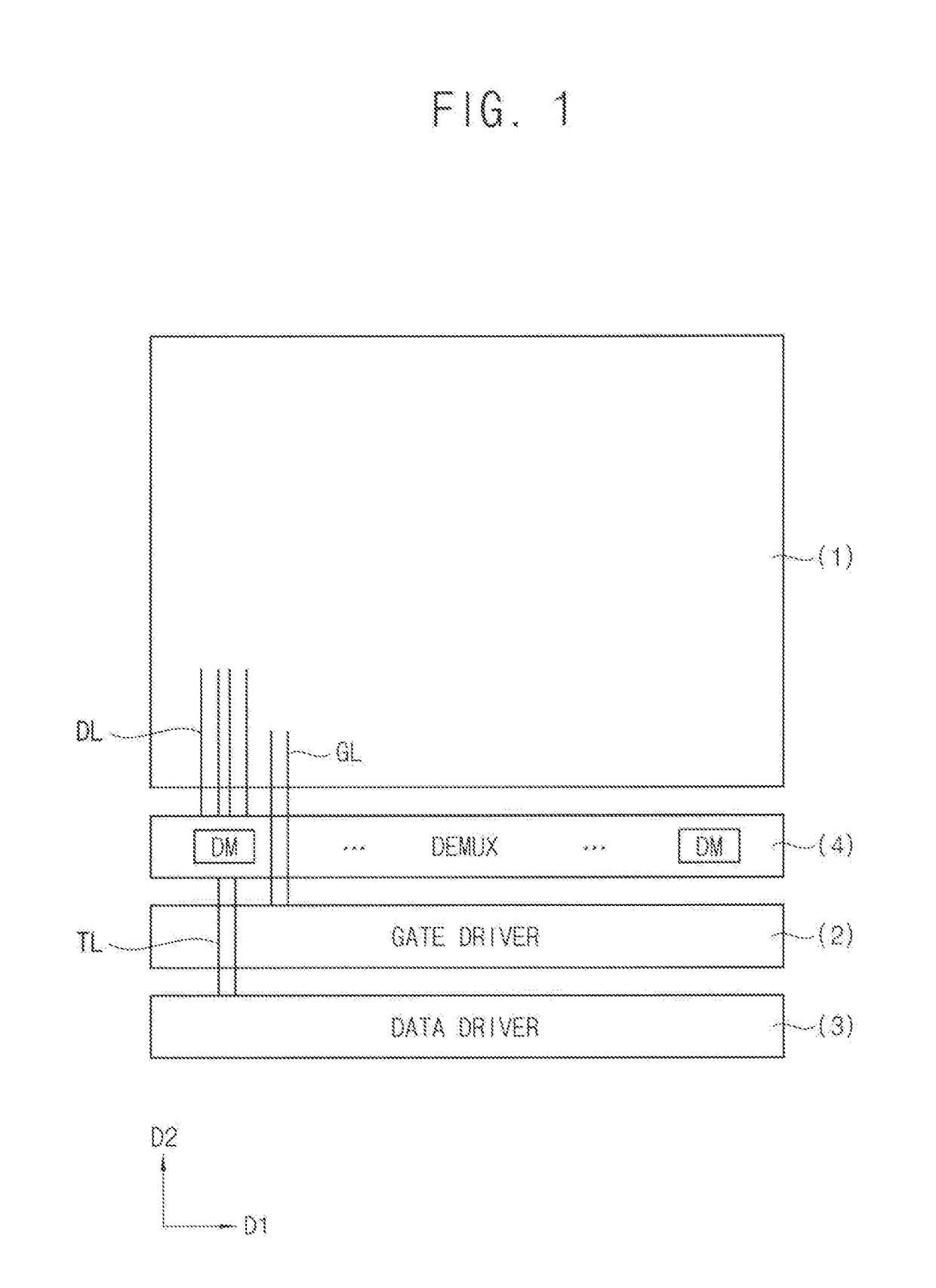

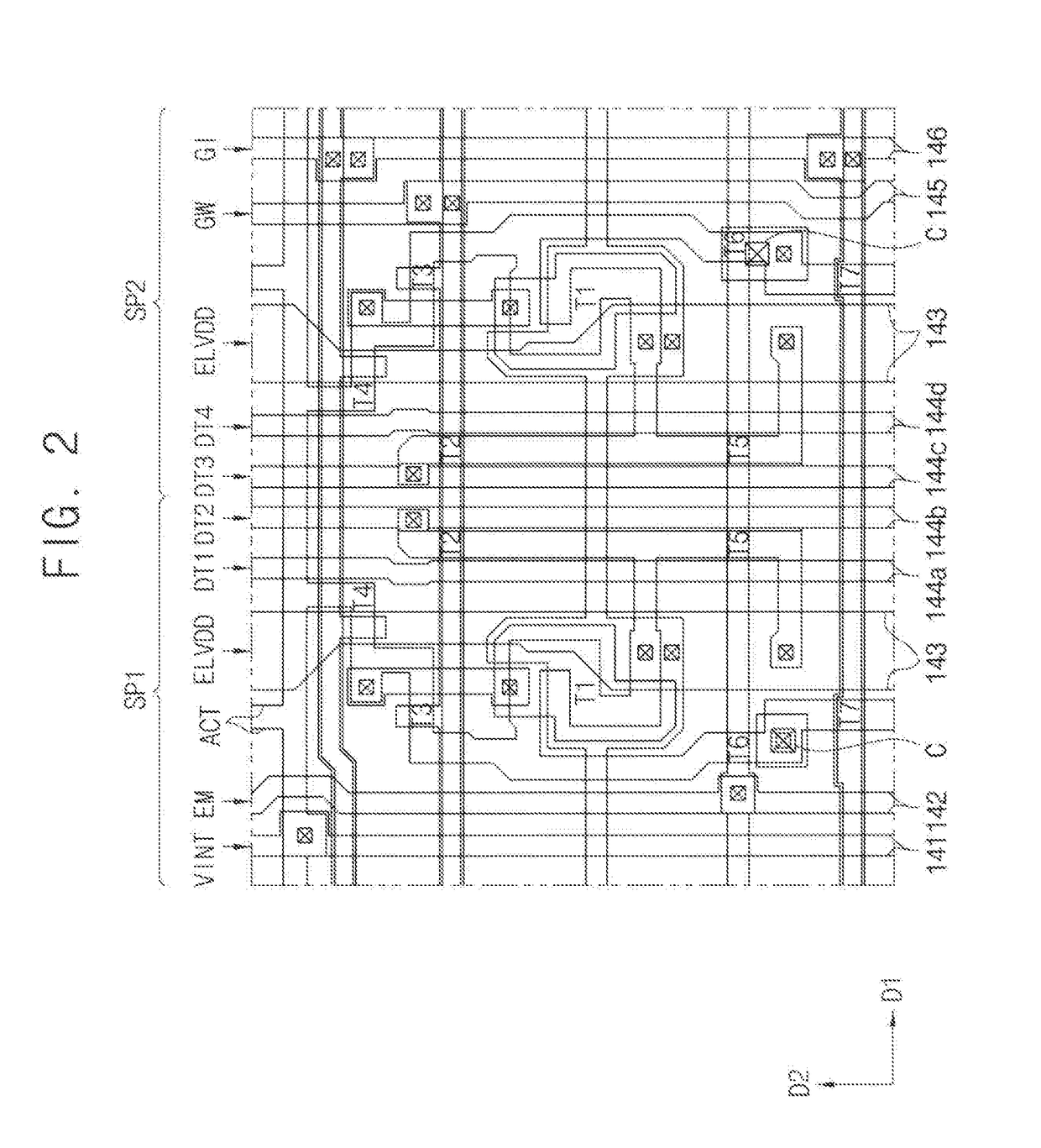

Display apparatus

InactiveUS20170069271A1Coupling capacitanceReduce coupling capacitanceStatic indicating devicesSolid-state devicesEngineeringData lines

Owner:SAMSUNG DISPLAY CO LTD

Array substrate, display panel and display device

ActiveCN104731412AIncrease distanceReduce coupling capacitanceNon-linear opticsInput/output processes for data processingCapacitanceDisplay device

The invention discloses an array substrate, a display panel and a display device. The array substrate comprises multiple gate lines, multiple data lines and multiple touch leads; the extension directions of the touch leads are parallel to the extension directions of the data lines, each touch lead comprises multiple lead portions and multiple connecting portions, the lead portions and the gate lines are arranged on the same layer, and each lead portion is arranged between two adjacent gate lines; the connecting portions and the lead portions are located at different conducting layers, and each connecting portion connects two lead portions through a via hole. Each touch lead is arranged to be a line provided with the multiple lead portions and the multiple connecting portions, the lead portions and the gate lines are arranged at the same layer, the two lead portions are in electric connection with each other through a via hole connection mode, the distance between the conducting layer of the lead portions and the conducting layer of touch electrodes are enlarged, and coupling capacitance between the lead portions and touch electrodes corresponding to positions of the lead portions is reduced, and it is guaranteed that the touch accuracy of the display device is high.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

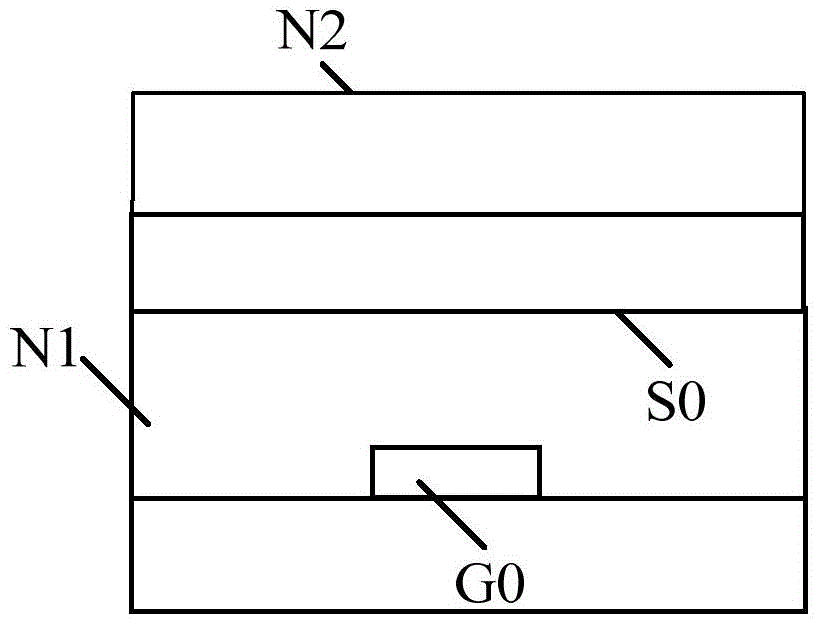

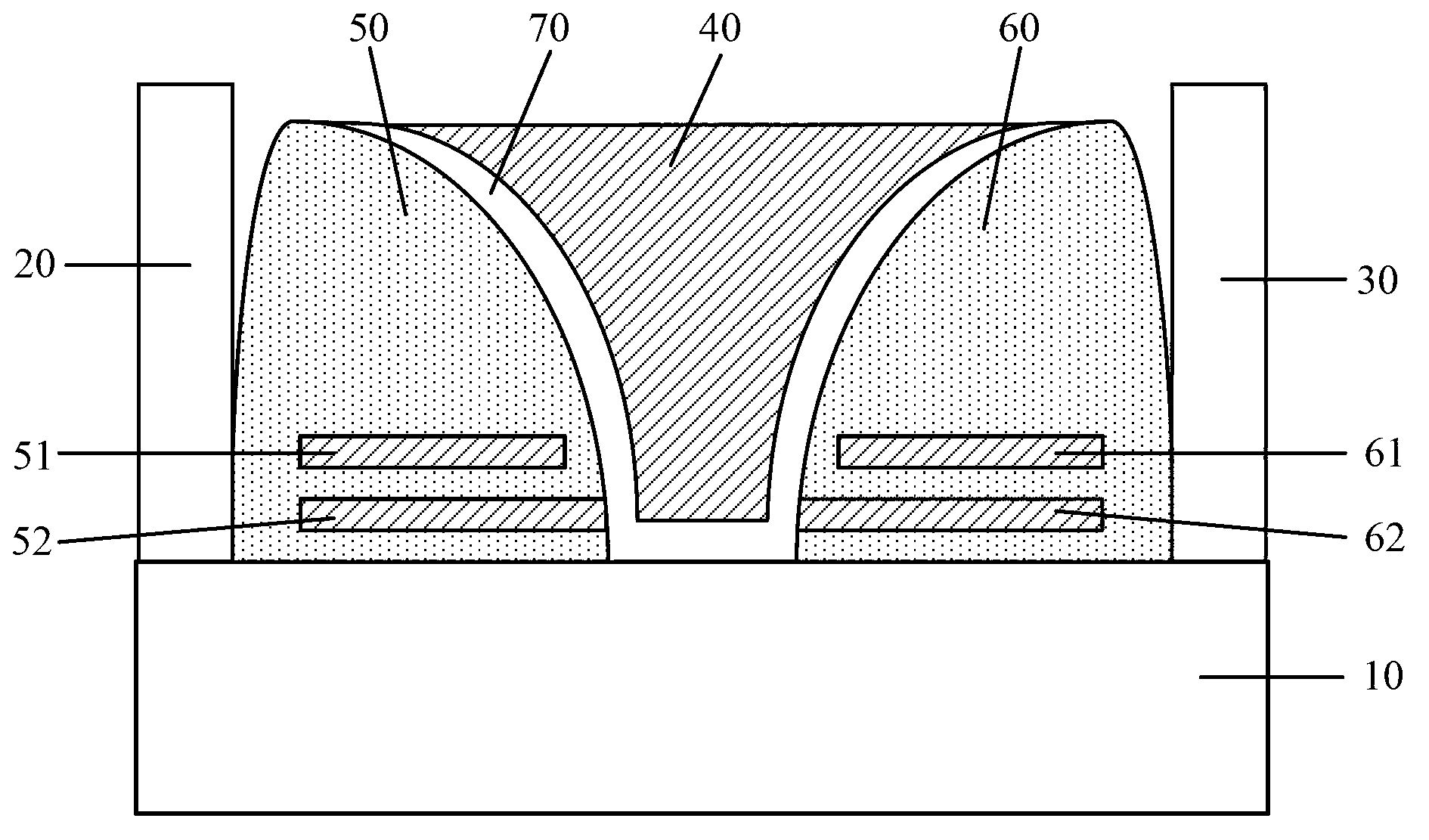

Split gate type flash memory and forming method thereof

ActiveCN102938406AImprove work efficiencyReduce coupling capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingState of artCapacitance

The invention discloses a split gate type flash memory which comprises a semiconductor substrate, a word line, two discrete storage bit units and oxidation layers, wherein the word line is located at the bottom surface of the semiconductor substrate; the two storage bit units are located at two sides of the word line; the oxidation layers are arranged between the two storage bit units and the word line; each storage bit unit comprises a first insulation layer which is located on the bottom surface of the semiconductor substrate, a floating gate which is located on the surface of the first insulation layer, a second insulation layer which is located on the surface of the floating gate, a control gate which is located on the surface of the second insulation layer and a side wall structure which covers the floating gate and the control gate; each floating gate comprises a first floating gate and a second floating gate; and the distance between each first floating gate and the word line is greater than the distance between each second floating gate and the word line. The distance between the first floating gates and the word line is greater than the distance in the prior art, so that the coupling capacitance between the floating gates and the word line is smaller than the capacitance in the prior art, the coupling capacitance between the word line and the floating gates is as small as possible and then the erasing efficiency and the read-write efficiency of the flash memory are improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

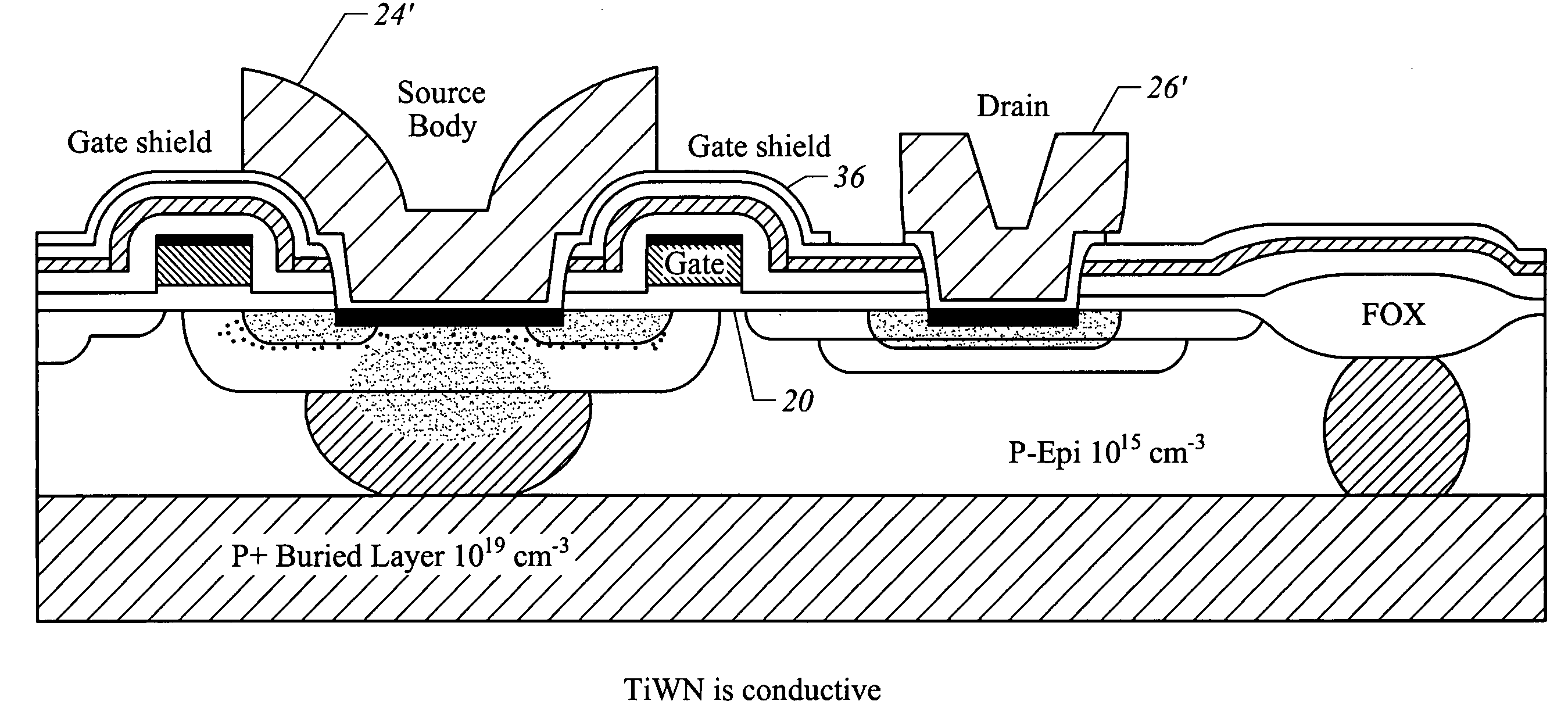

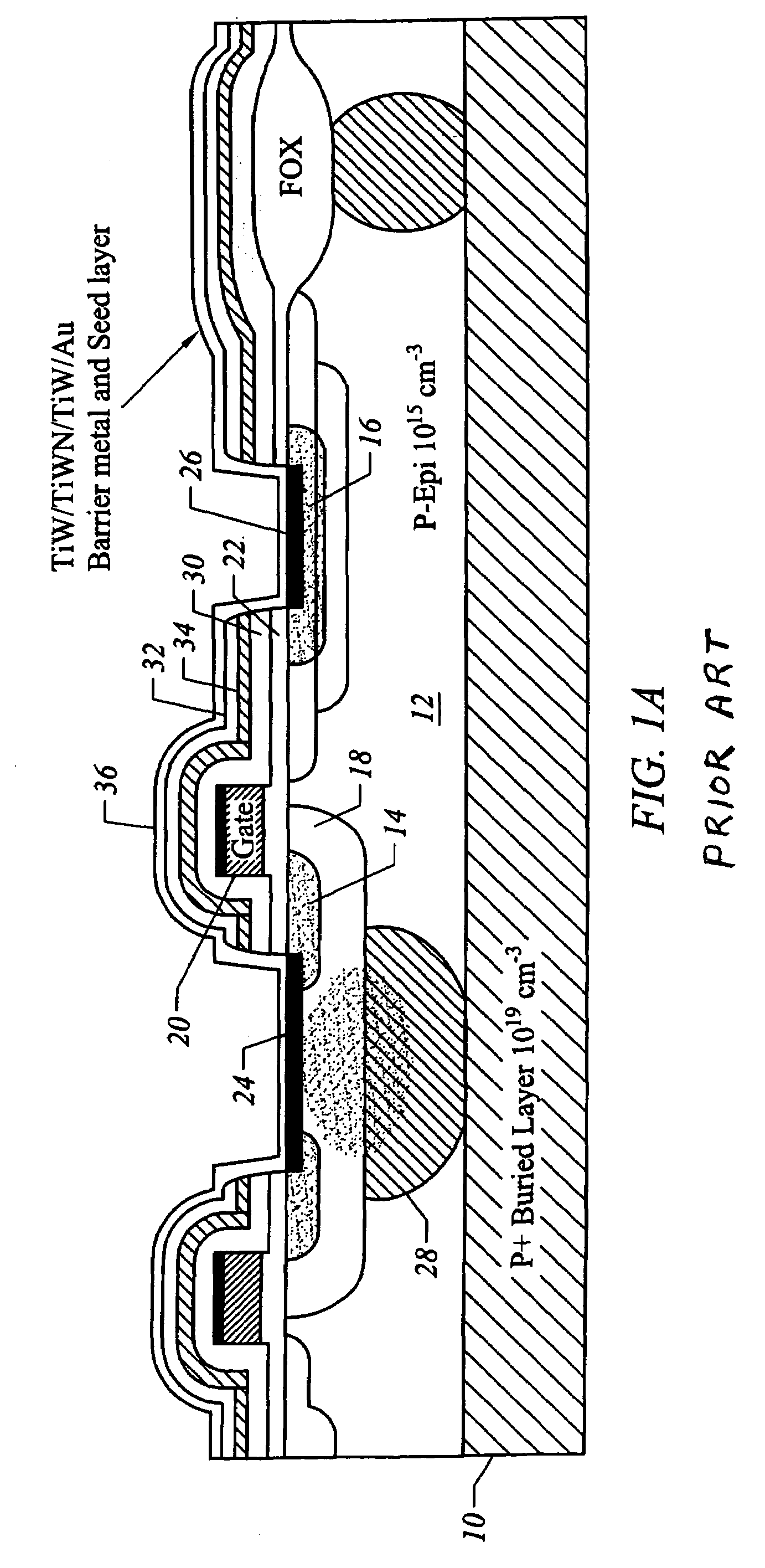

LDMOS transistor with improved gate shield

ActiveUS7307314B2Reduce coupling capacitanceEasy to makeSemiconductor/solid-state device detailsSolid-state devicesLDMOSCoupling

A LDMOS transistor having a gate shield provides reduced drain coupling to the gate shield and source by restricting the thickness of the gate shield and by confining a source contact to the source region without overlap of the gate.

Owner:F POSZAT HU

Resistor memory bit-cell and circuitry and method of making the same

ActiveUS20150090952A1Novel structureIncrease productionSolid-state devicesSemiconductor/solid-state device manufacturingMemory cellHemt circuits

A resistive memory cell control unit, integrated circuit, and method are described herein. The resistive memory cell control unit includes a switching transistor and a resistive memory cell. The switching transistor includes a gate disposed on a first surface of a semiconductor substrate, a source, and a drain each disposed in the semiconductor substrate, a gate terminal disposed on the first surface and connected to the gate, a source terminal disposed on the first surface and connected to the source, and a drain terminal connected to the drain and disposed on a second surface opposite the first surface. The resistive memory cell is disposed on the second surface and has a first end connected to the drain terminal. The structure provides a small area and simple manufacturing process for a resistive memory cell integrated circuit.

Owner:SEMICON MFG INT (SHANGHAI) CORP

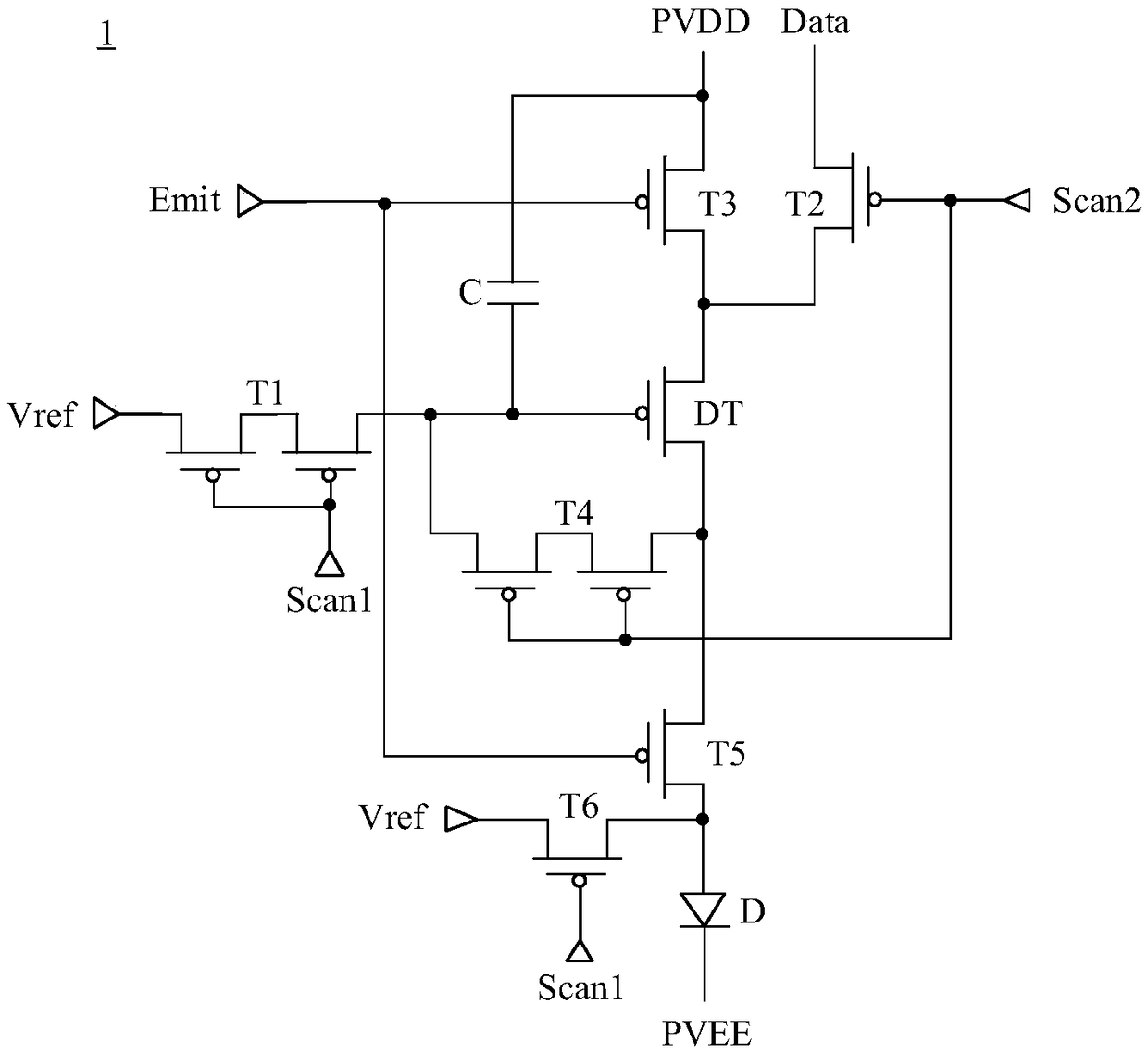

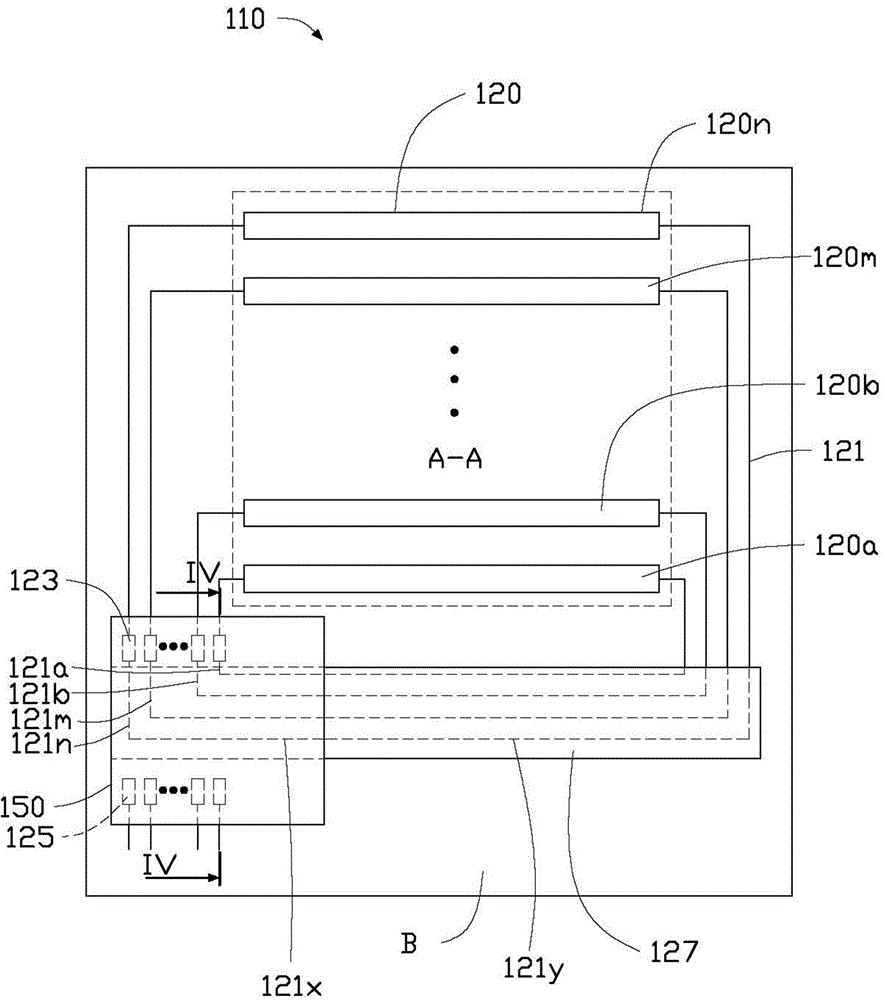

Display panel and display device

ActiveCN109272930ACoupled electric field reductionReduce coupling capacitanceStatic indicating devicesCapacitanceDisplay device

The embodiment of the invention provides a display panel and a display device, which relate to the technical field of display and reduce the coupling capacitance of a gate electrode of a driving transistor and a data line. The display panel includes a pixel circuit including a driving transistor; a first switching transistor having a first pole connected to a reference voltage signal line and a second pole connected to a gate of the driving transistor; a second switching transistor having a first pole connected to the data line and a second pole connected to the first pole of the driving transistor; a third switching transistor having a first pole connected to the power supply voltage signal line and a second pole connected to the first pole of the driving transistor; the display panel further includes a shielding unit for receiving a fixed potential signal, at least a part of the shield unit is located between the first semiconductor connection part and the second semiconductor connection part, the first semiconductor connection part is connected between the second pole of the first switching transistor and the gate of the driving transistor, and the second semiconductor connection part is connected between the first pole of the second switching transistor and the data line.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

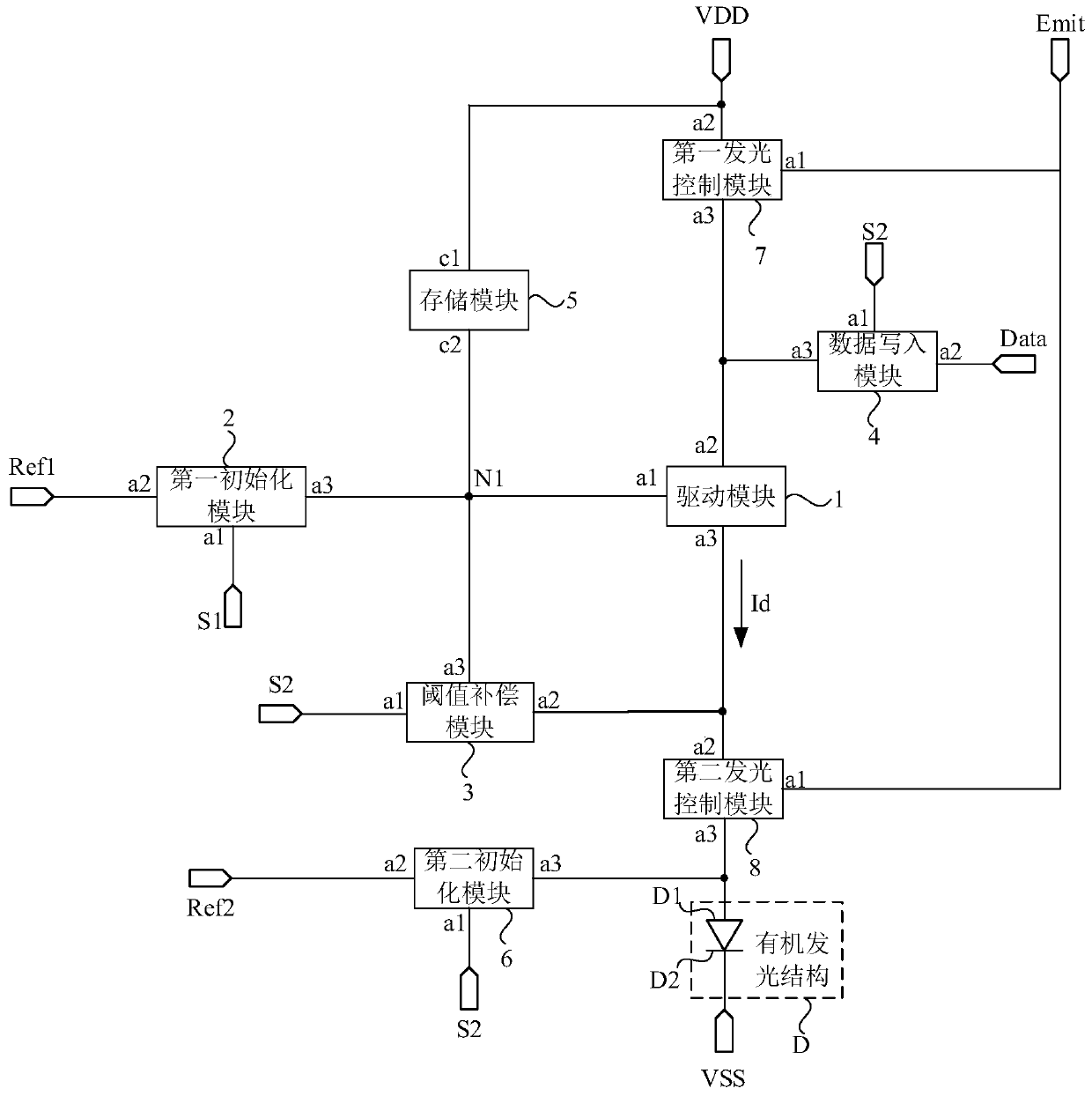

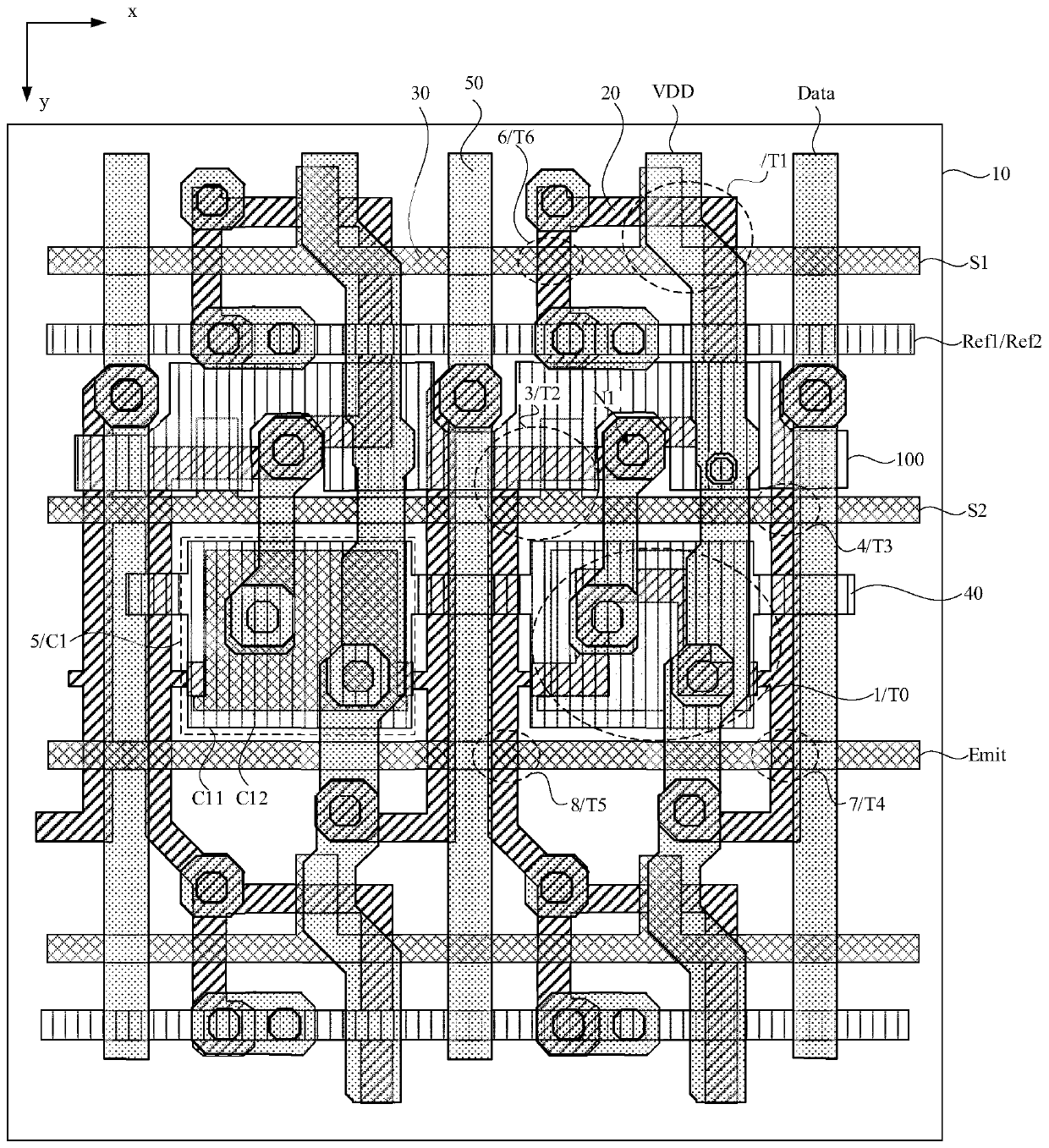

Array substrate, display panel and display device

InactiveCN110335564ASmall pressure dropReduce coupling capacitanceStatic indicating devicesSolid-state devicesElectricityCapacitance

The embodiment of the invention discloses an array substrate, a display panel and a display device. The array substrate comprises a pixel circuit, the pixel circuit comprises a driving module, and thecontrol end of the driving module is electrically connected with a first node; a first initialization module, wherein a second end of the first initialization module is electrically connected with the first node; a threshold compensation module, wherein the second end of the threshold compensation module is electrically connected with the first node; a data writing module which is used for writing the data signal into the first node; a storage module, wherein the first end of the storage module is electrically connected with the first power supply signal line, and a second end of the storagemodule is electrically connected with the first node; the array substrate further comprises a shielding layer, the shielding layer is electrically connected with the first power signal line, and in the signal lines electrically connected with the first node, at least part of the signal lines and the shielding layer are overlapped in an insulated mode in the direction perpendicular to the plane where the array substrate is located. According to the technical scheme, crosstalk caused by coupling capacitance in the pixel circuit can be reduced, and the display effect is improved.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

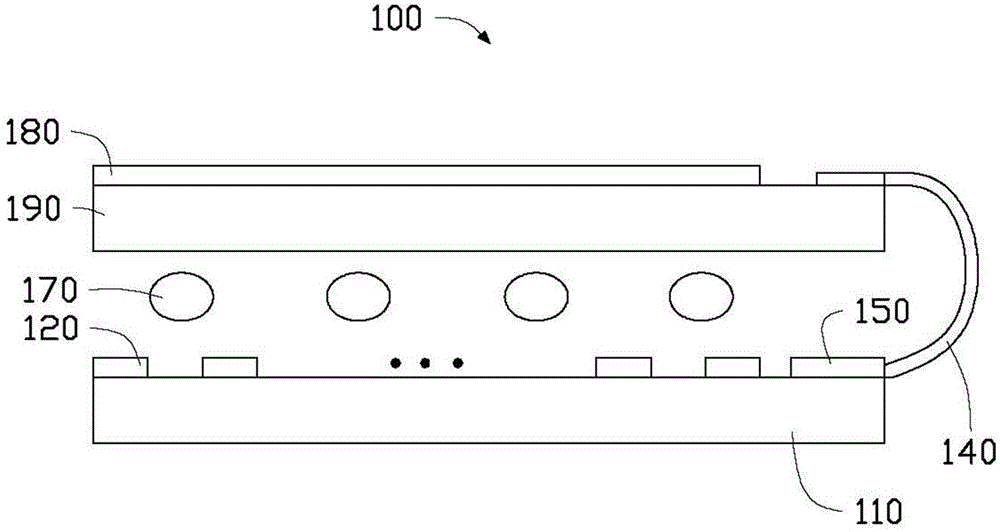

Touch display device

ActiveCN104571655AReduce coupling capacitanceImprove signal transmission performanceNon-linear opticsInput/output processes for data processingTouch SensesDisplay device

The invention relates to a touch display device. The touch display device comprises a first substrate and a second substrate which are oppositely arranged, first sensing electrodes and second sensing electrodes, wherein first pins transmit touch scanning signals, second pins transmit touch sensing signals, and the first substrate defines a touch display region and a non-touch display region; corresponding to the periphery of the non-touch display region, the first substrate is provided with the first pins, wires and the second pins; the first pins transmit the touch scanning signals and the second pins transmit the touch sensing signals; the wires are electrically connected with the corresponding sensing electrodes and the corresponding first pins, the second sensing electrodes are electrically connected with the corresponding second pins, the wires and the second pins are mutually insulated, a conductive layer is arranged at a part, close to the second pins, of the wires, and is located in a layer between the part, close to the second pins, of the wires and the second pins, and the conductive layer is grounded or is in direct electric signal connection with a constant potential. The touch display device is relatively high in touch precision.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

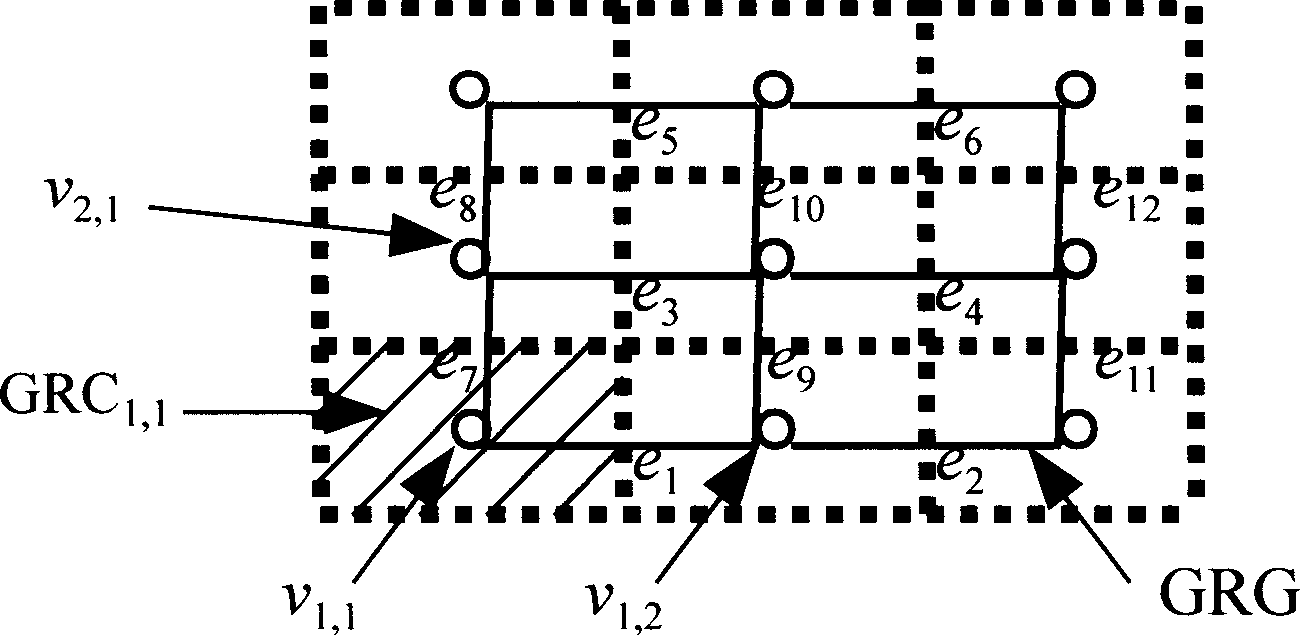

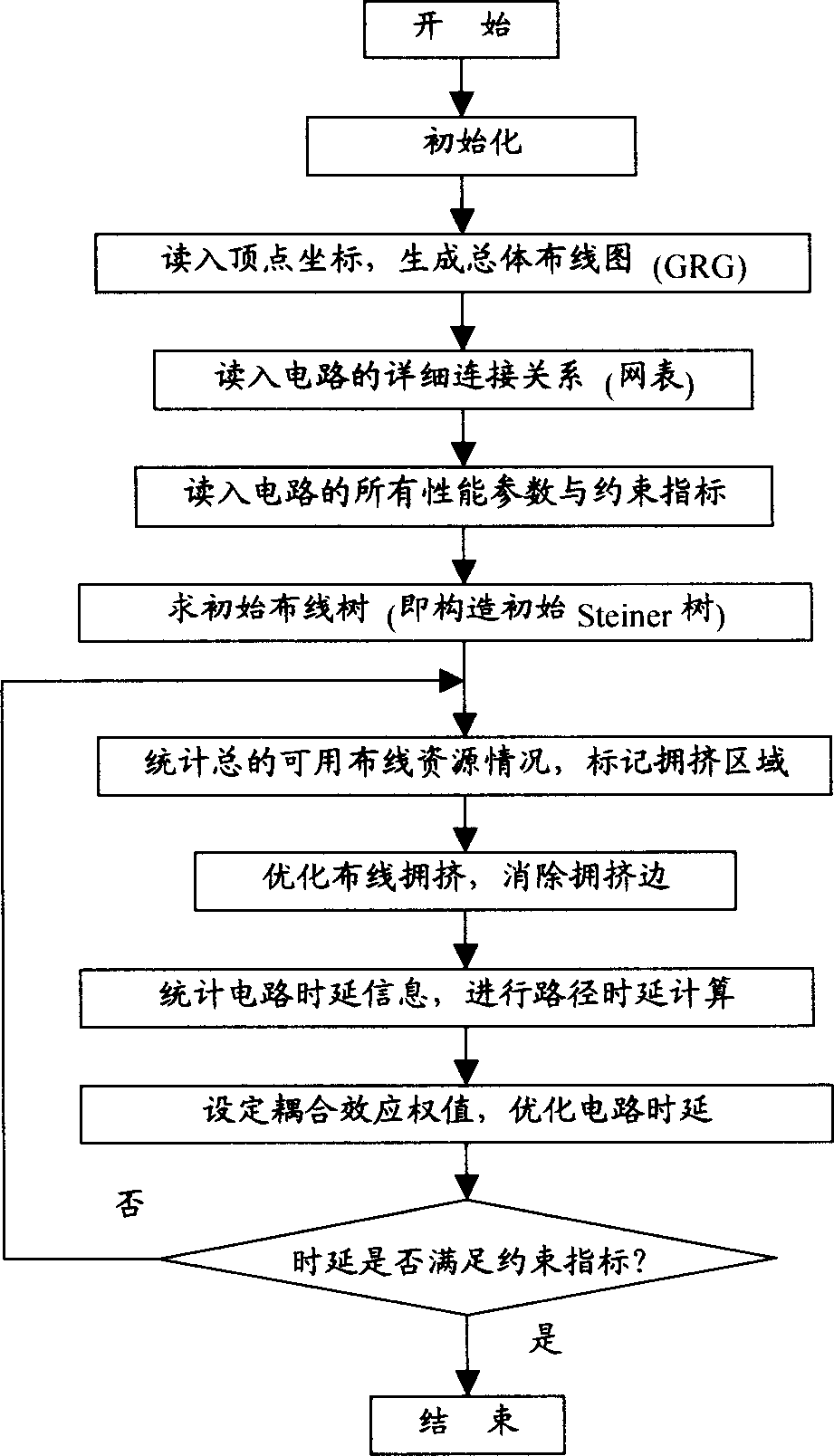

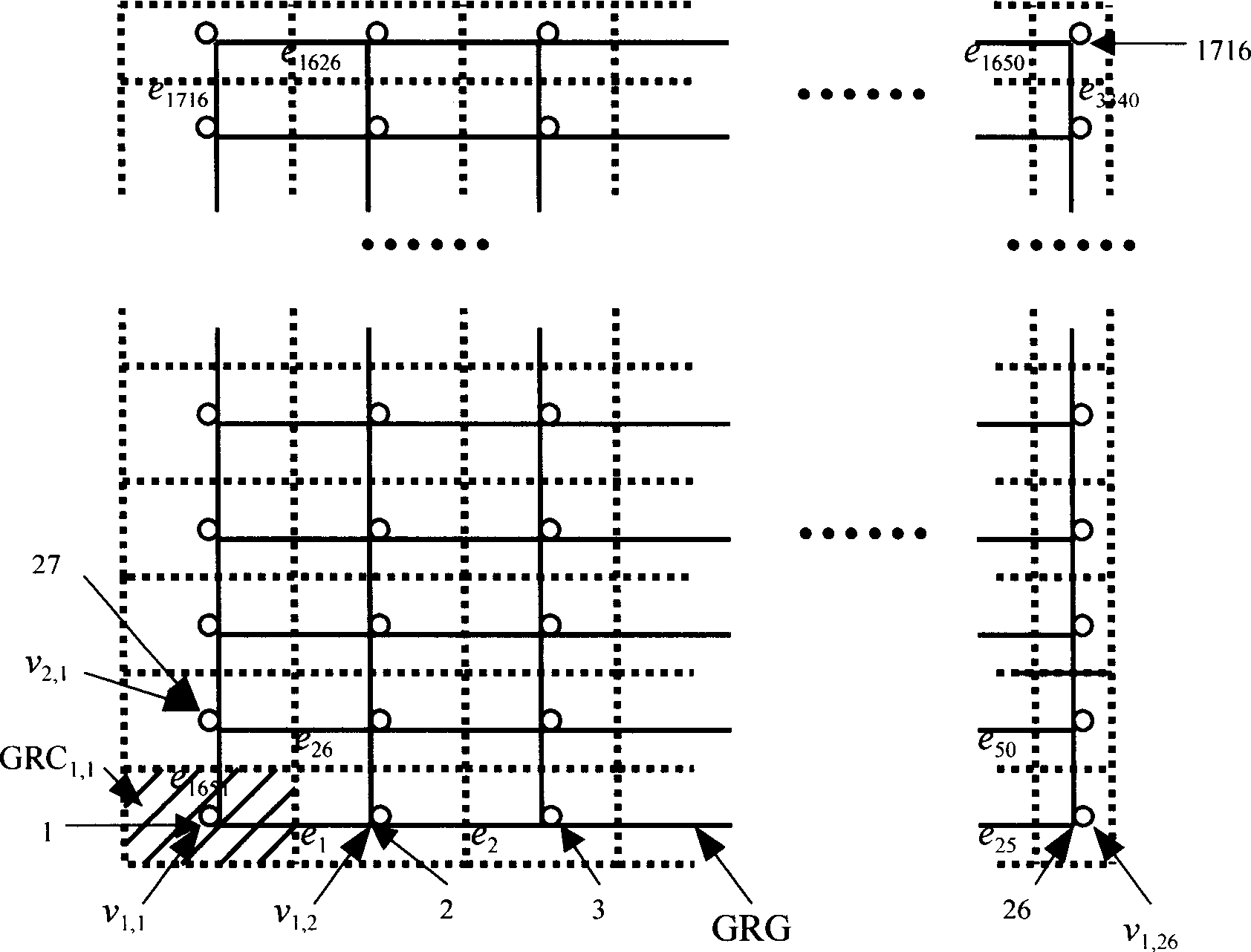

Integrated wiring method of standard units with carrying optimization of time delay based on considering coupling effect

InactiveCN1416082AReduce coupling capacitanceLower latencySpecial data processing applicationsPath delayTime delays

Standard unit general routing method of coupling effect in time delay optimization characterizes in making up time delay optimization routing tree under the condition that any of the wire nets is not restrained to further optimize outing congestion to estimated the link electricity parameter with successively connected linking load model based on empiric analog after elimianting congestion edge, to compute the link delay with congruence variation technology to compute gate delay etc. three steps to calculate the path general delay value with looking-up table+interpolation based on the delay information table given by user, then enhancing to considerate the key path up wire net weighted value of the couple effect to reduce routing density adjacent to the wire net, so as to reduce couple condenser and general path delay to optimize the circuit time delay.

Owner:TSINGHUA UNIV

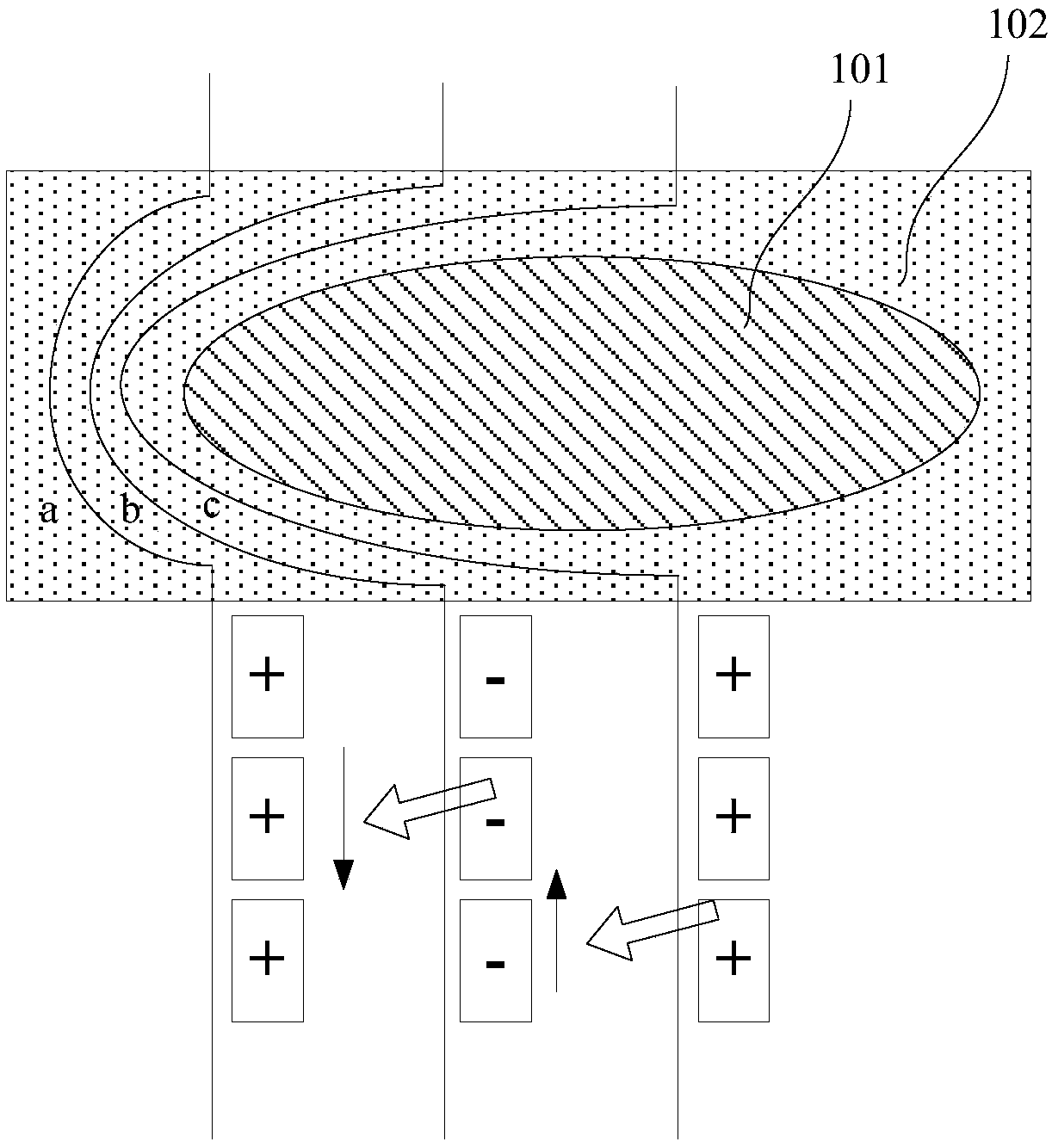

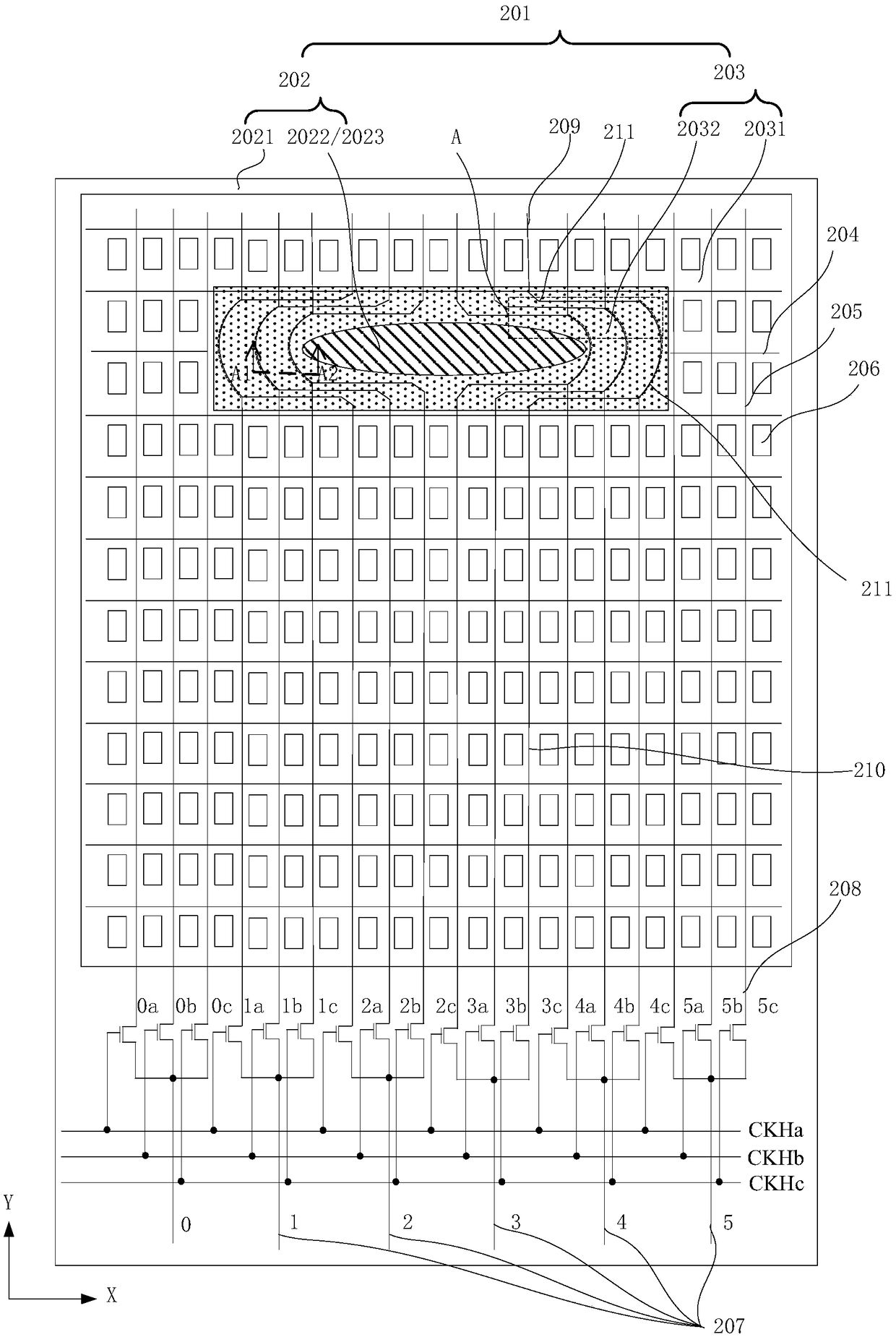

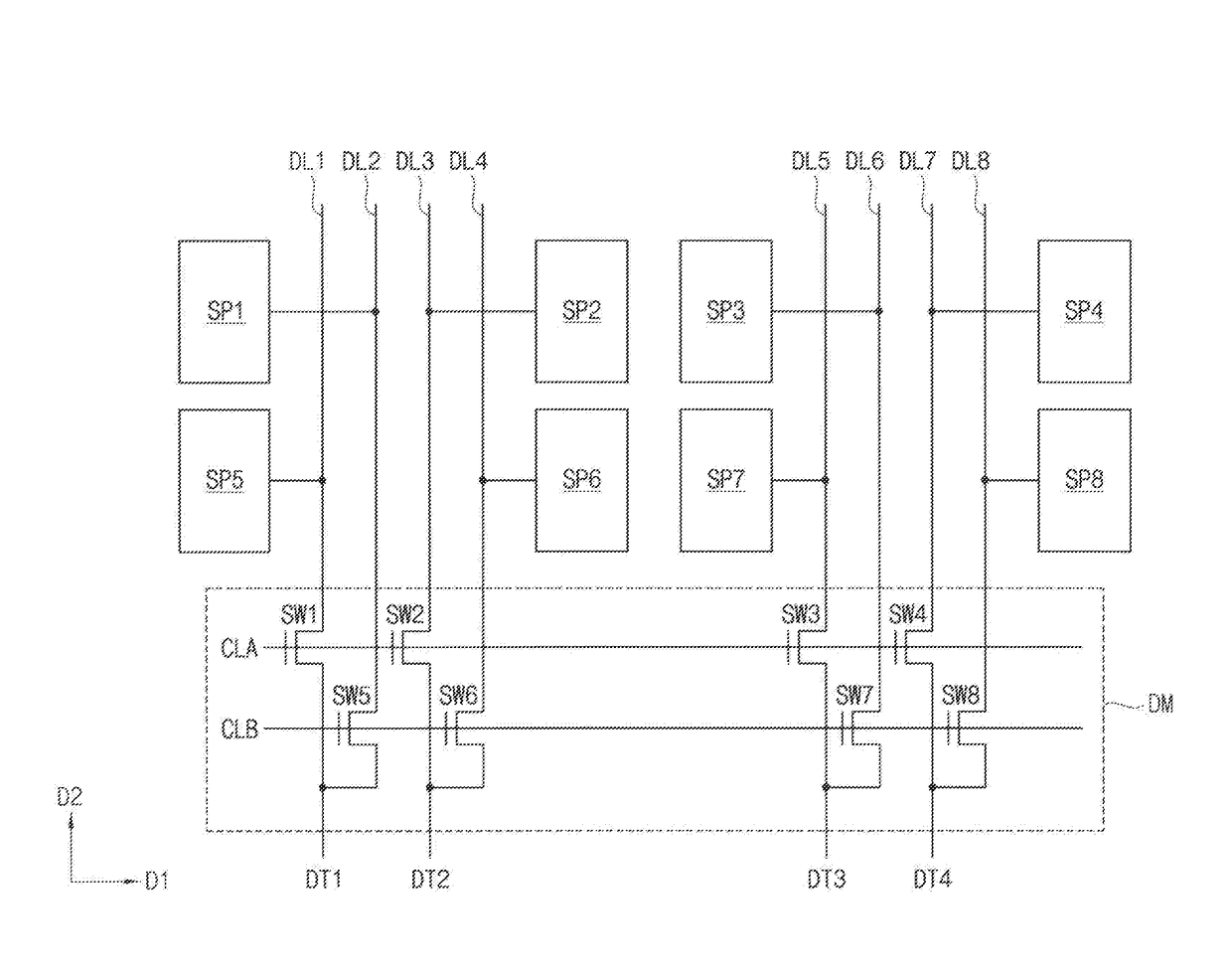

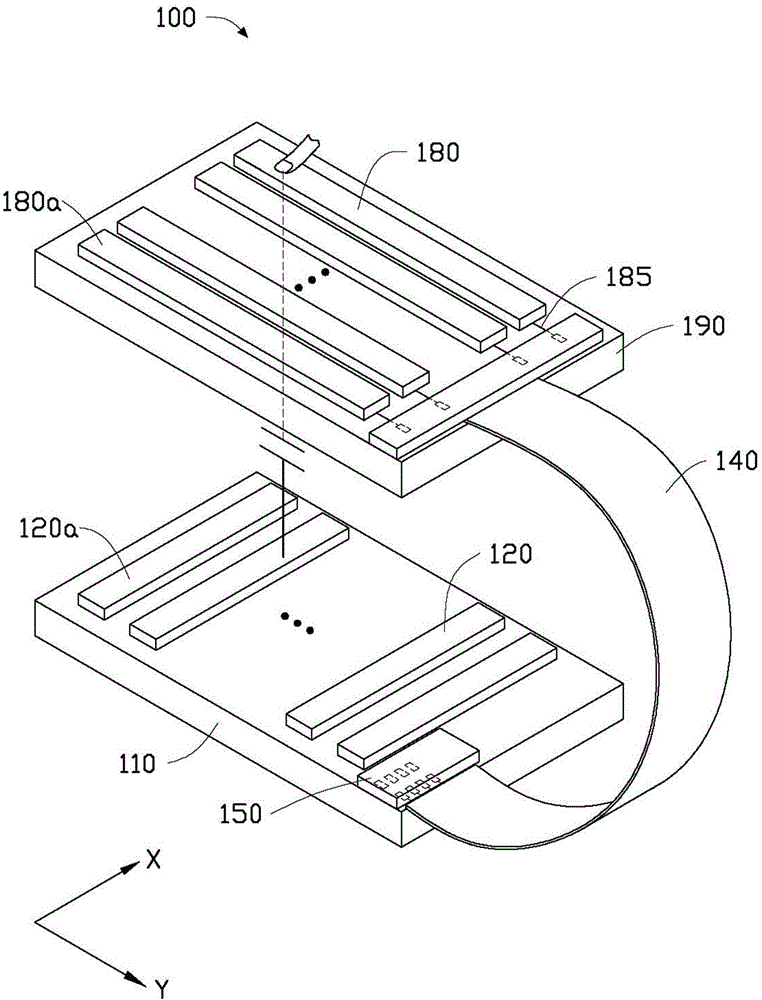

Touch display panel and manufacturing method and driving method thereof and display device

ActiveCN104991690AImprove touch performanceReduce coupling capacitanceInput/output processes for data processingCapacitanceDisplay device

The invention discloses a touch display panel and a manufacturing method and driving method thereof and a display device. According to the touch display panel, a plurality of pixel units are arranged in an array substrate in a matrix mode; the array substrate comprises a plurality of touch self-capacitance electrodes arranged in a matrix mode, and each touch self-capacitance electrode comprises a plurality of electrode blocks corresponding to the pixel units one to one; the array substrate further comprises touch leads corresponding to the touch self-capacitance electrodes one to one, the touch leads are arranged in clearances between the adjacent pixel units corresponding to the touch self-capacitance electrodes, and the touch self-capacitance electrodes are connected with touch chips through the touch leads. Due to the fact that the electrode blocks correspond to the pixel units one to one and are arranged in areas defined by adjacent grid lines and data lines, the electrode blocks are not overlapped with the grid lines or the data lines, coupling capacitance between the electrode blocks and the grid lines and between the electrode blocks and the data lines is lowered, loads are reduced, touch sensitivity is improved, and the excellent touch performance of the large-size display panel is achieved.

Owner:BOE TECH GRP CO LTD +1

Display panel and display device

ActiveCN108957890AUniform brightnessImprove the display effectNon-linear opticsDisplay deviceComputer science

The invention discloses a display panel and a display device, and belongs to the technical field of display. The display panel comprises a hollowed-out part, a first non-display area and a display area. Each data line passing through the first non-display area comprises a first sub-part, a first wire winding part and a second sub-part, the first sub-parts and the second sub-parts are located on the display area, the first wire winding parts are located on the first non-display area, and the first sub-part and the second sub-part of the same data line are electrically connected through the first wire winding part. A of m first wire winding parts and B of the m first wire winding parts are located on different film layers, the A first wire winding parts and the B first wire winding parts areoverlapped, and the overlapping area gradually changes. By arranging the overlapped first wire winding parts, the area occupied by the first non-display area is remarkably reduced, the display area of the display panel is increased, the load of the data lines is balanced, the coupling effect between the data lines is reduced, the display effect of the display panel is improved, and the display performance of the display panel is improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Method of fabrication of MIMCAP and resistor at same level

InactiveUS7022246B2Reduce parasitismEasy to useElectrolytic capacitorsDecorative surface effectsFront end of lineCapacitor

A method is disclosed of fabricating a MIMCAP (a capacitor (CAP) formed by successive layers of metal, insulator, metal (MIM)) and a thin film resistor at the same level. A method is also disclosed of fabricating a MIMCAP and a thin film resistor at the same level, and a novel integration scheme for BEOL (back-end-of-line processing) thin film resistors which positions them closer to FEOL (front-end-of-line processing) devices.

Owner:GLOBALFOUNDRIES US INC

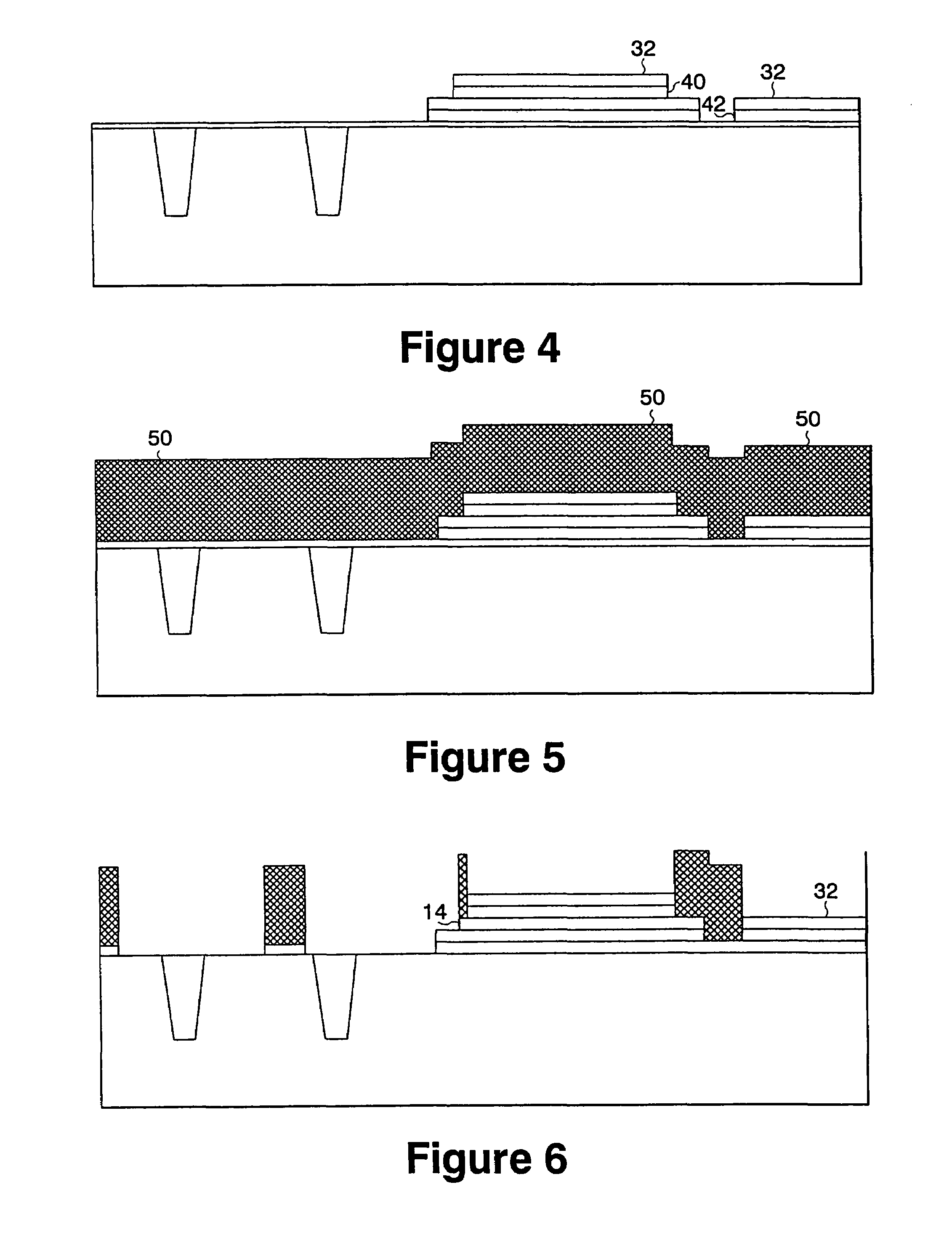

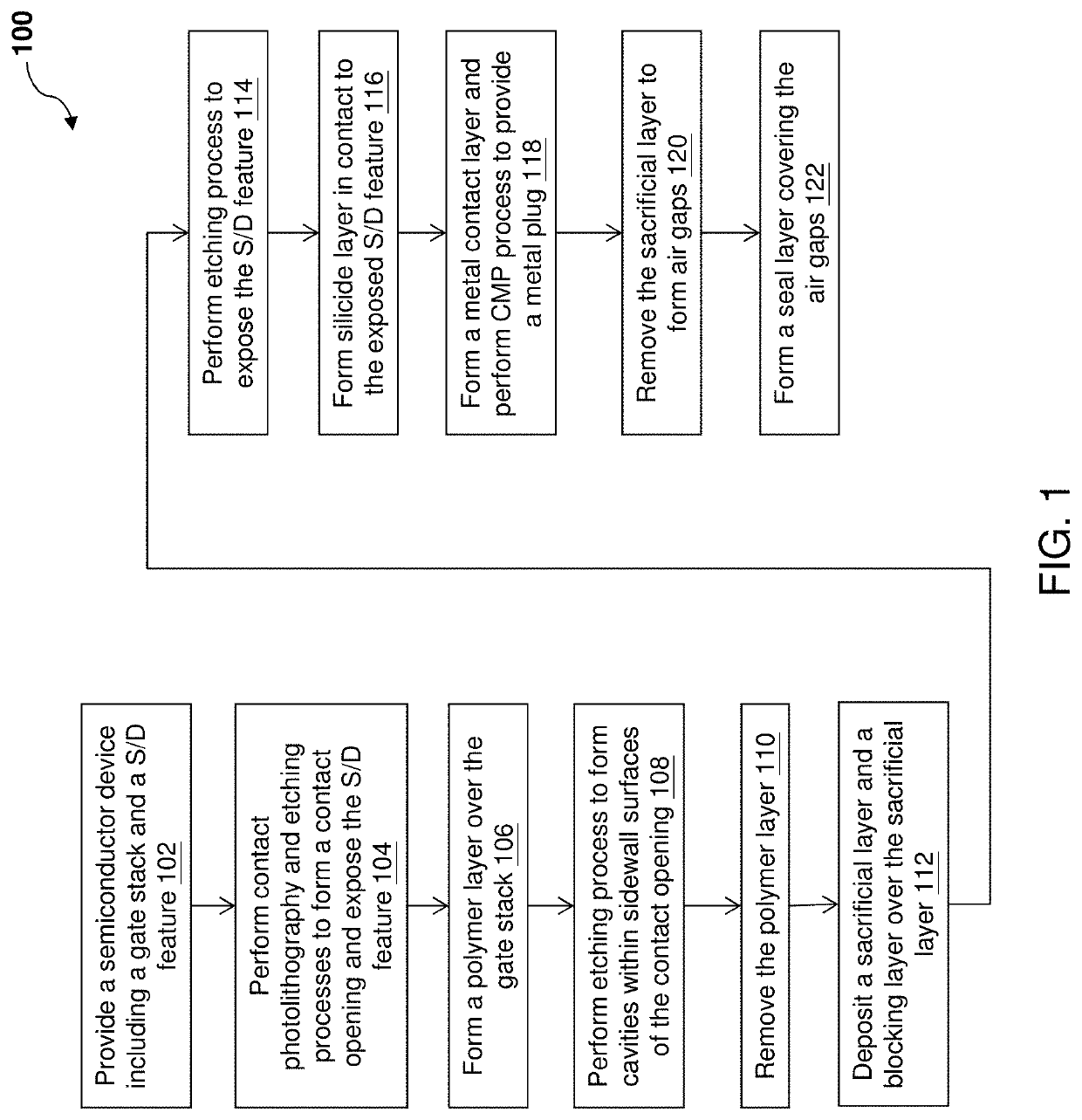

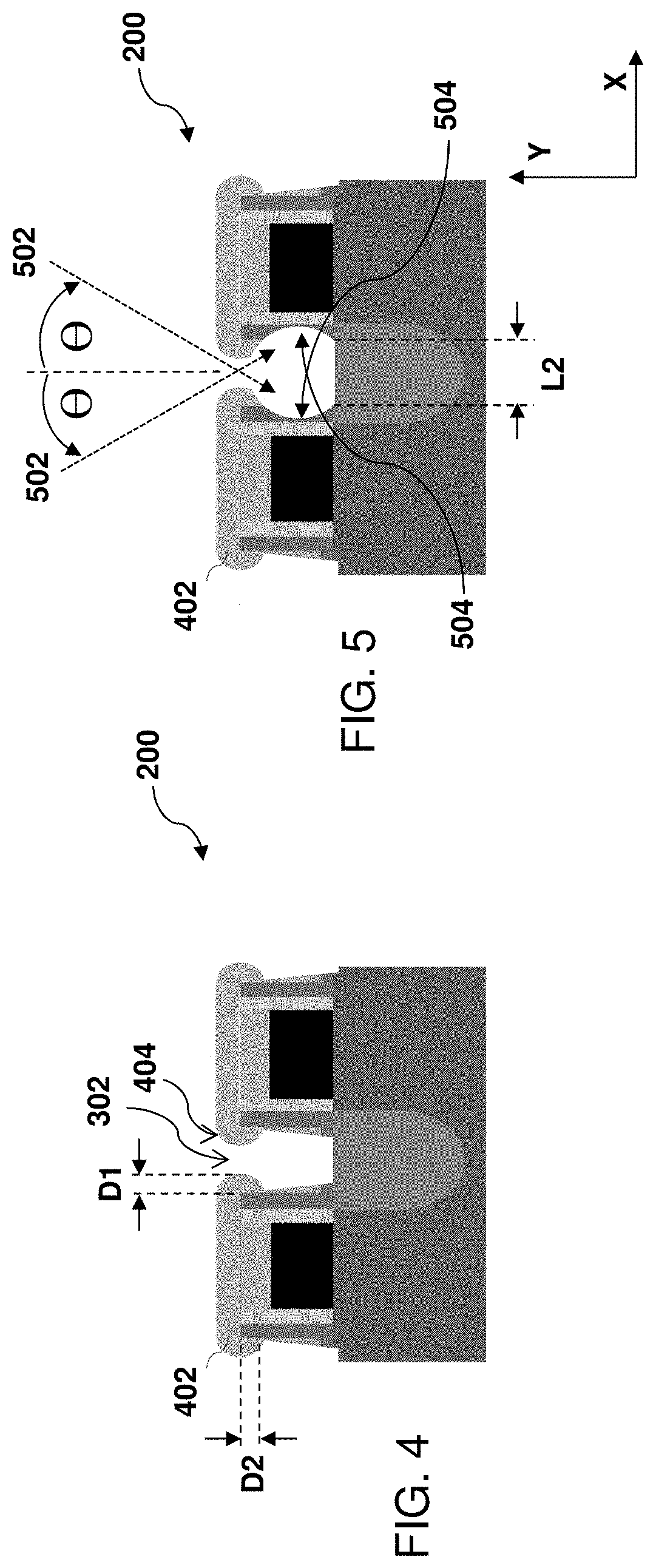

Contact air gap formation and structures thereof

ActiveUS20200135591A1Eliminate riskLow effective capacitanceTransistorSolid-state devicesEngineering physicsMaterials science

A method of forming a device includes providing a transistor having a gate structure and a source / drain structure adjacent to the gate structure. A cavity is formed along a sidewall surface of a contact opening over the source / drain structure. After forming the cavity, a sacrificial layer is deposited over a bottom surface and along the sidewall surface of the contact opening including within the cavity. A first portion of the sacrificial layer along the bottom surface of the contact opening is removed to expose a portion of the source / drain structure. A metal plug is then formed over the portion of the exposed source / drain structure. A remaining portion of the sacrificial layer is removed to form an air gap disposed between the metal plug and the gate structure. Thereafter, a seal layer is deposited over the air gap to form an air gap spacer.

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com