Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

8232 results about "Memory module" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

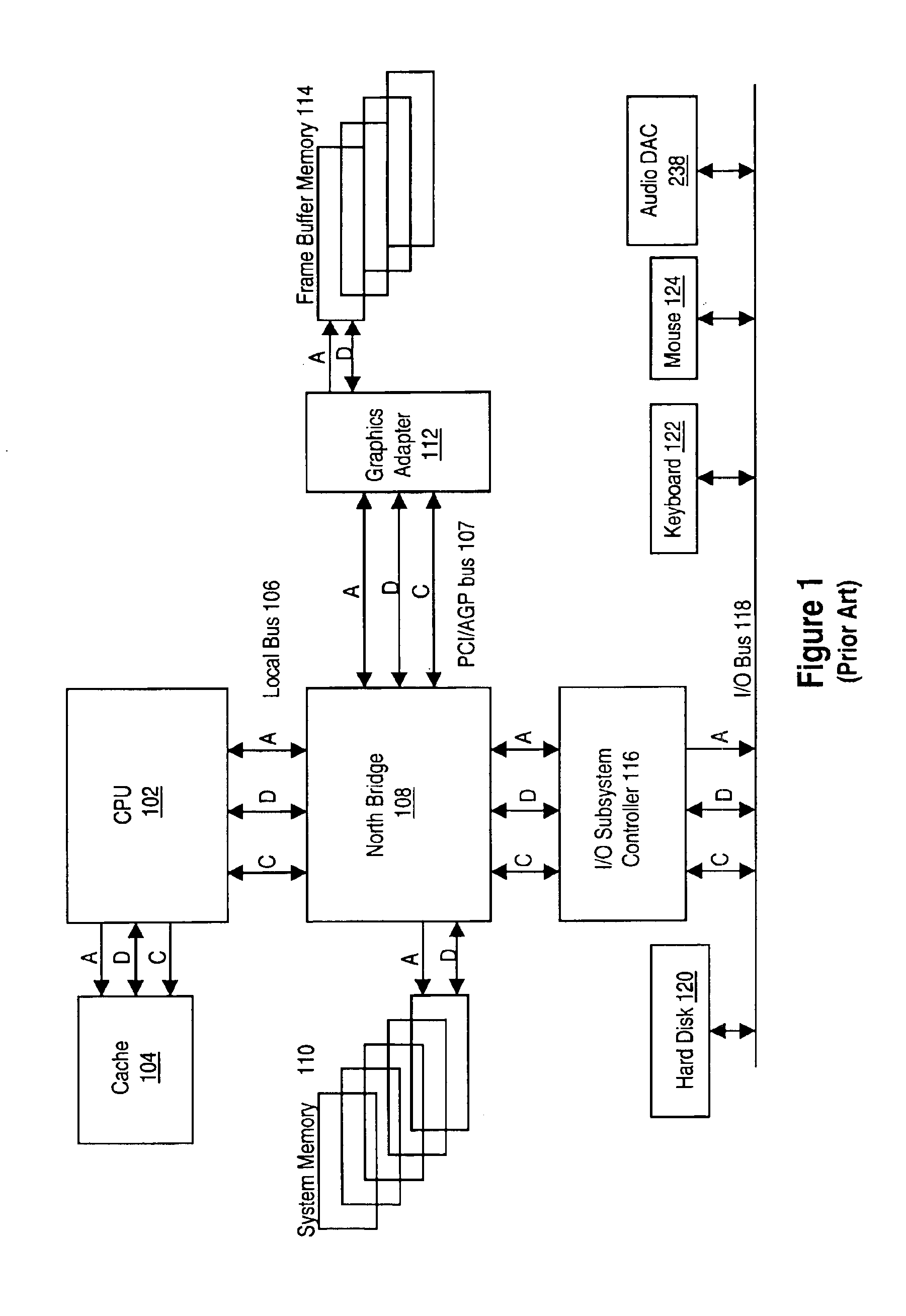

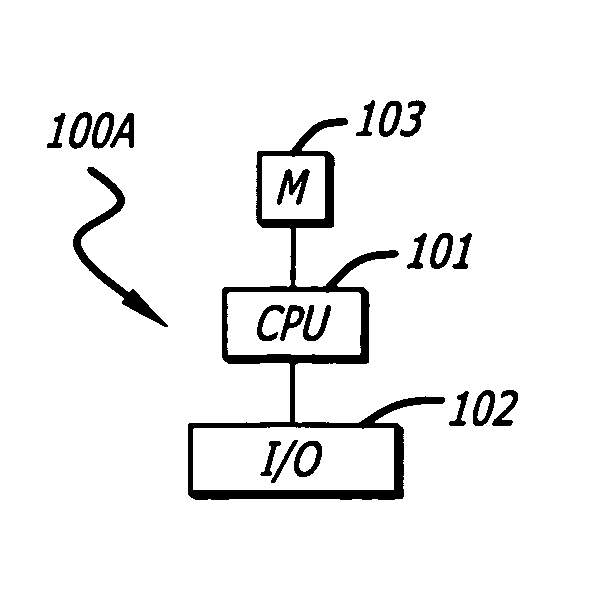

In computing, a memory module is a printed circuit board on which memory integrated circuits are mounted. Memory modules permit easy installation and replacement in electronic systems, especially computers such as personal computers, workstations, and servers. The first memory modules were proprietary designs that were specific to a model of computer from a specific manufacturer. Later, memory modules were standardized by organizations such as JEDEC and could be used in any system designed to use them.

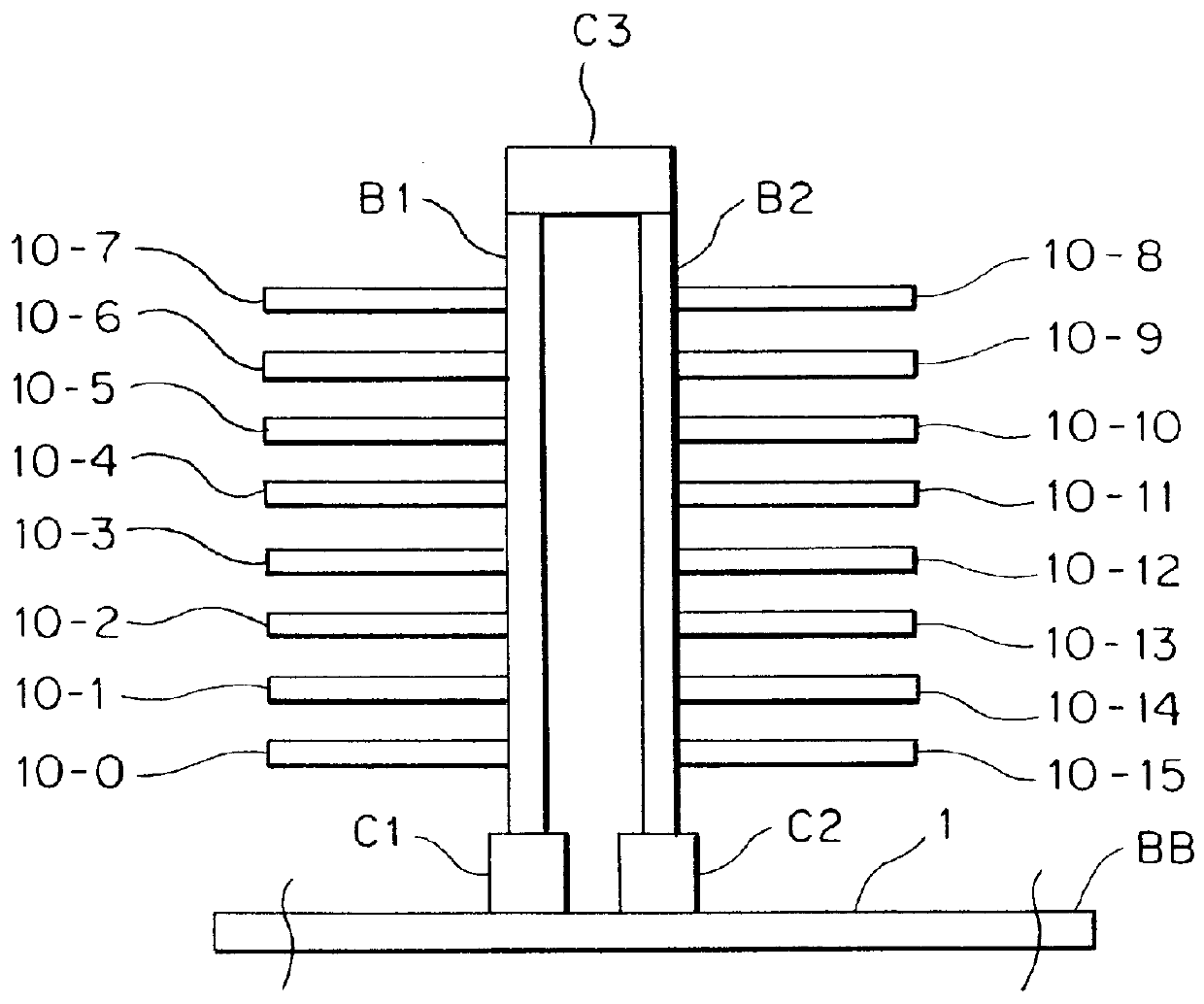

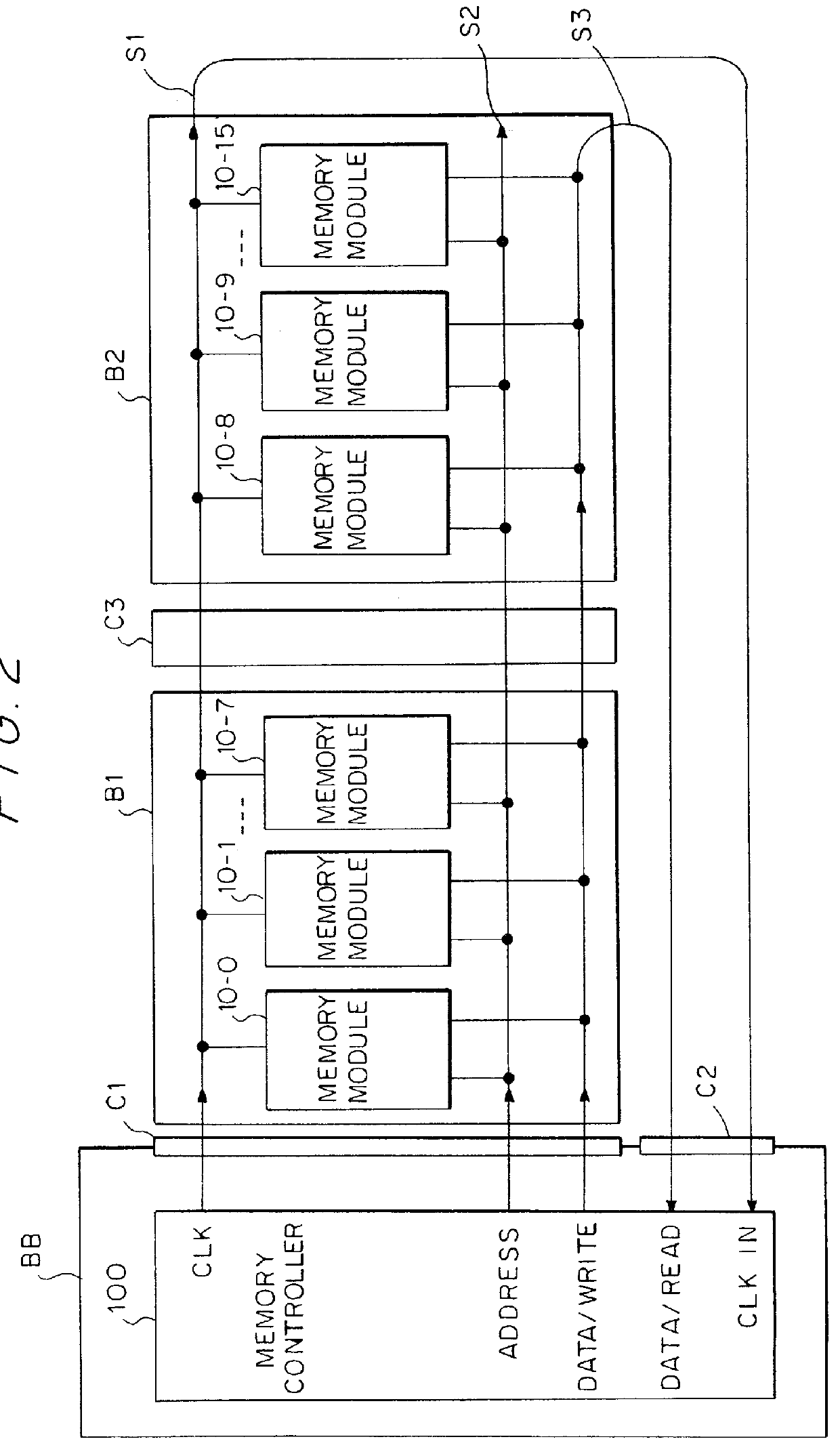

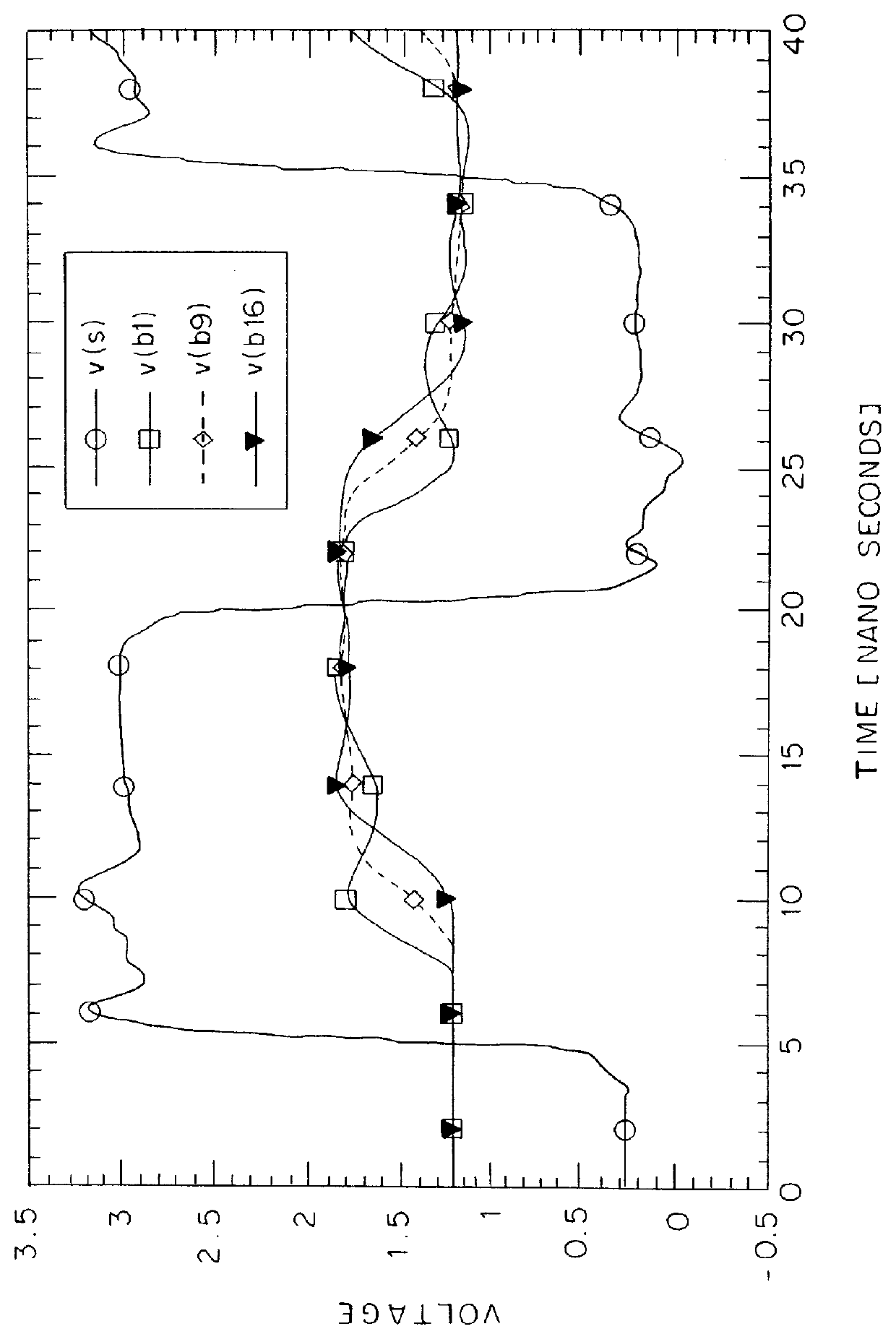

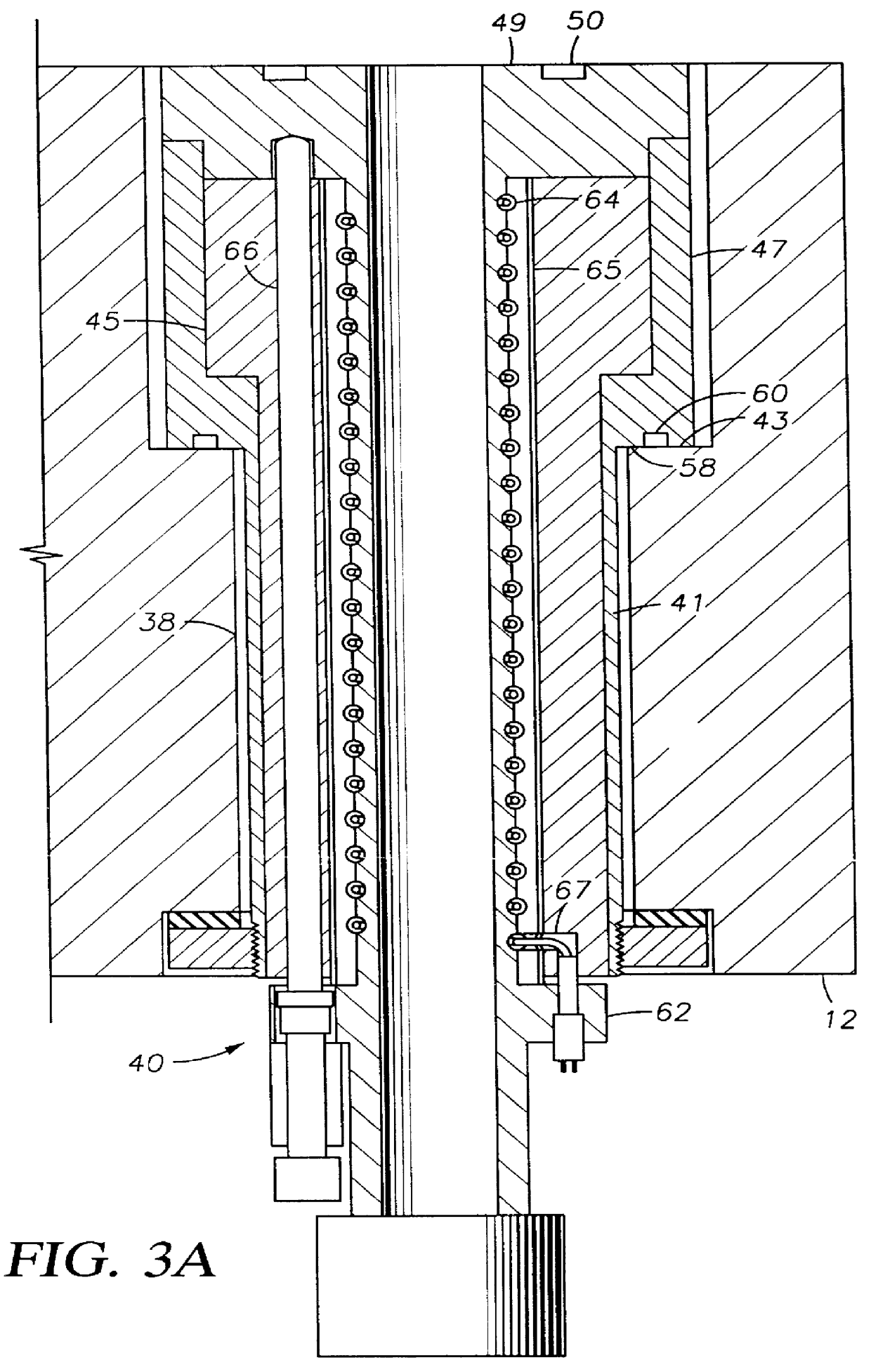

Source-clock-synchronized memory system and memory unit

InactiveUS6034878ALarge data storage capacity per memoryImprove installation densityMemory adressing/allocation/relocationDigital storageMemory bankComputer module

A source-clock-synchronized memory system having a large data storage capacity per memory bank and a high mounting density. The invention includes a memory unit having a first memory riser board B1 mounted on a base board through a first connector C1 and a second memory riser board B2 mounted on the base board BB through a second connector C2. The first memory riser board has a plurality of first memory modules mounted on the front surface thereof and the second memory riser board has a plurality of second memory modules mounted on the front surface thereof. The first and second memory riser boards are arranged in such a way that the back surface of the first memory riser board faces the back surface of the second memory riser board. The invention further includes a board linking connector for connecting signal lines on the first memory riser board to corresponding signal lines on the second memory riser board.

Owner:DELTA KOGYO CO LTD +1

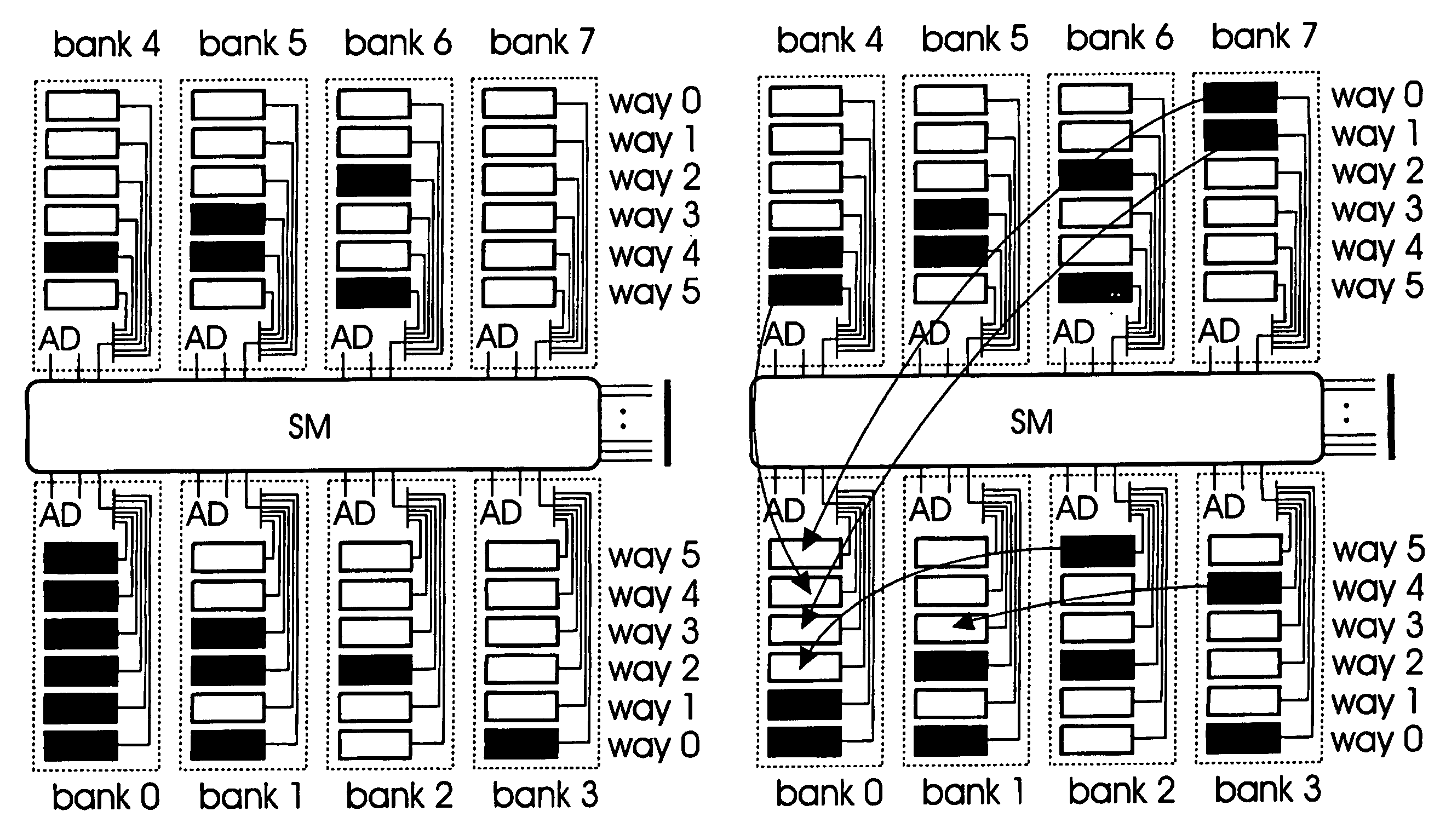

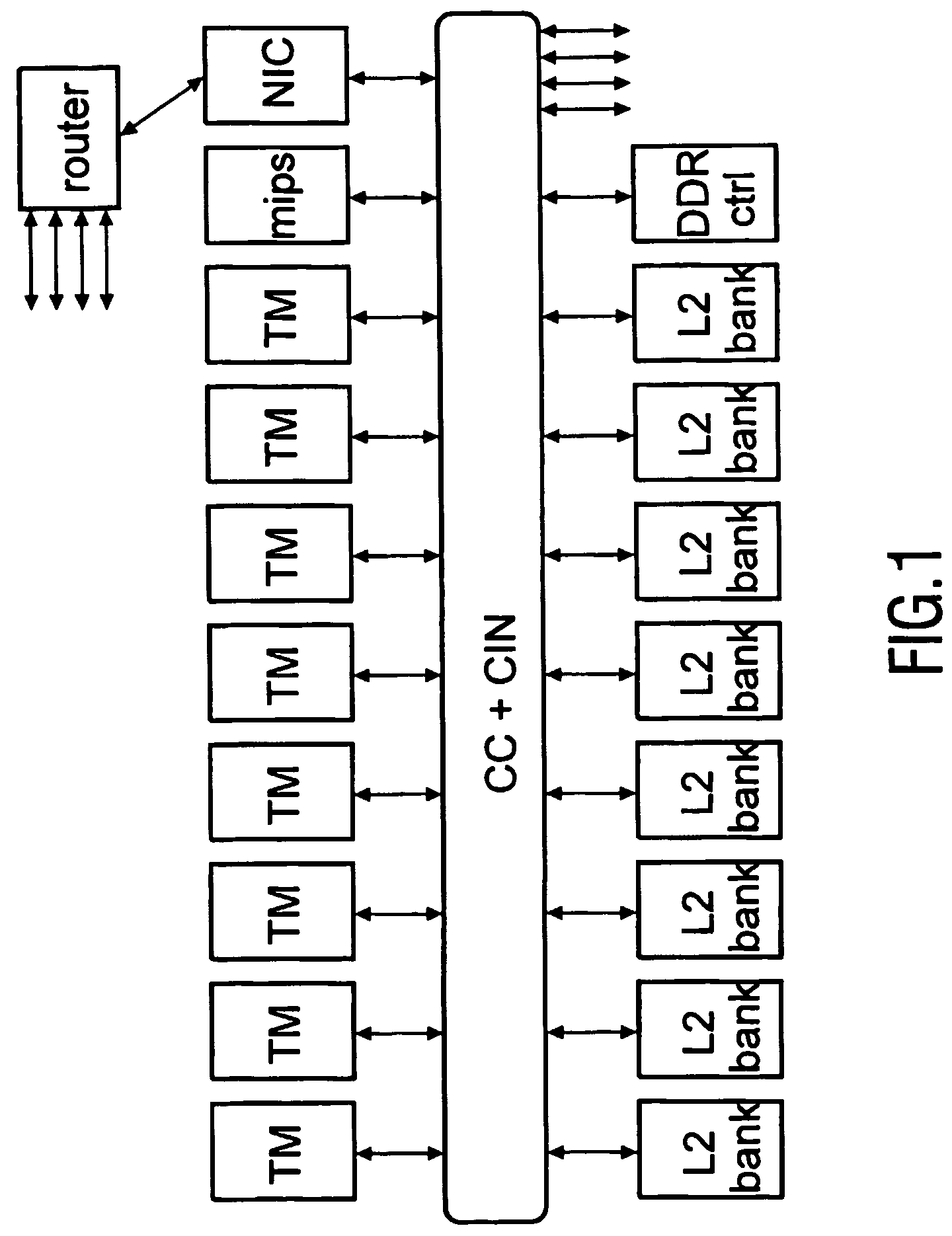

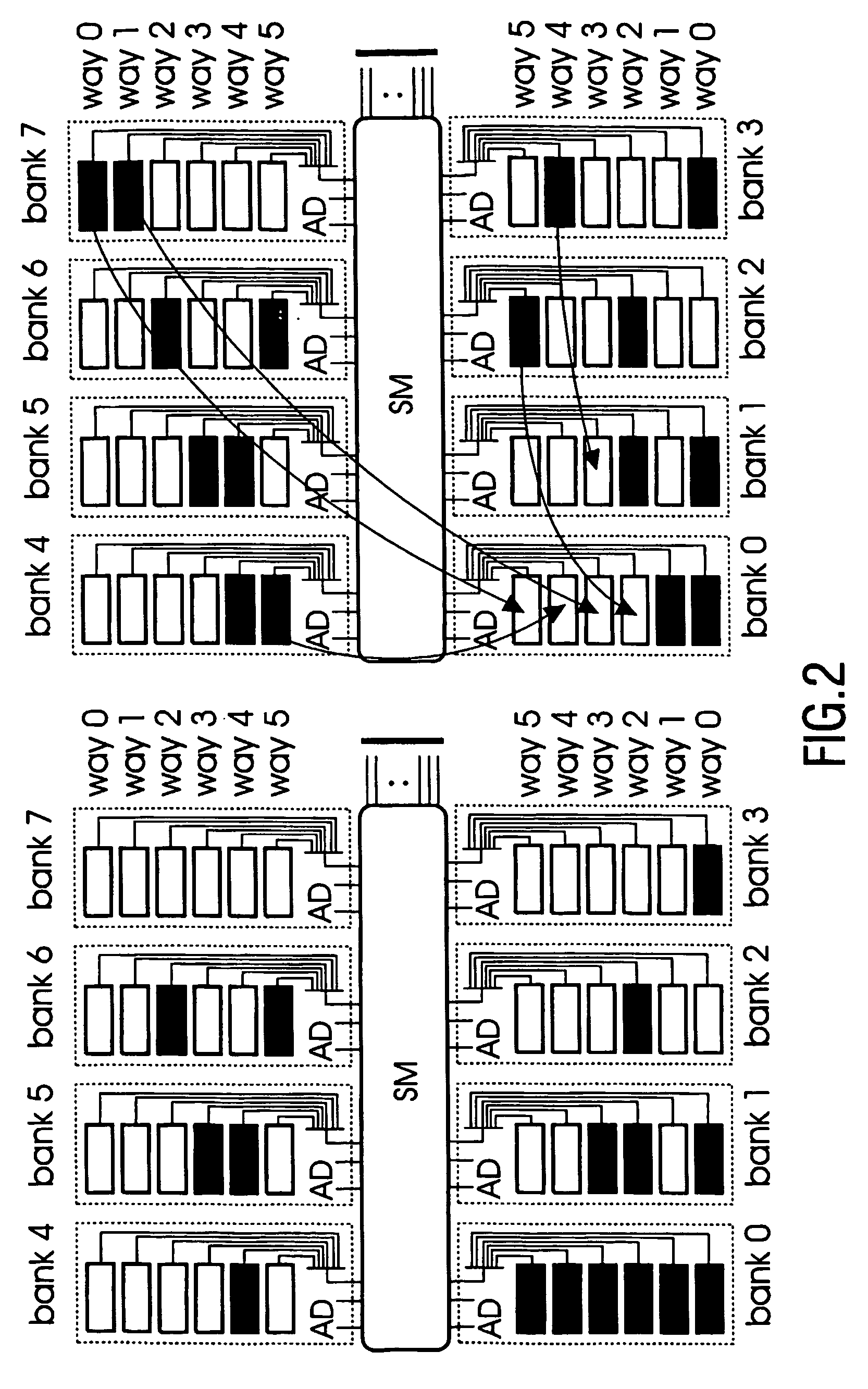

Intergrated circuit and a method of cache remapping

InactiveUS7827372B2Improve overall utilizationRapid cachingError detection/correctionMemory adressing/allocation/relocationParallel computingIntegrated circuit

An integrated circuit is provided with at least one processing unit (TM), a cache memory (L2 BANK) having a plurality of memory modules, and remapping means (RM) for performing an unrestricted remapping within said plurality of memory modules. Accordingly, faulty modules can be remapped without limitations in order to optimise the utilization of the memory modules by providing an even distribution of the faulty modules.

Owner:NYTELL SOFTWARE LLC

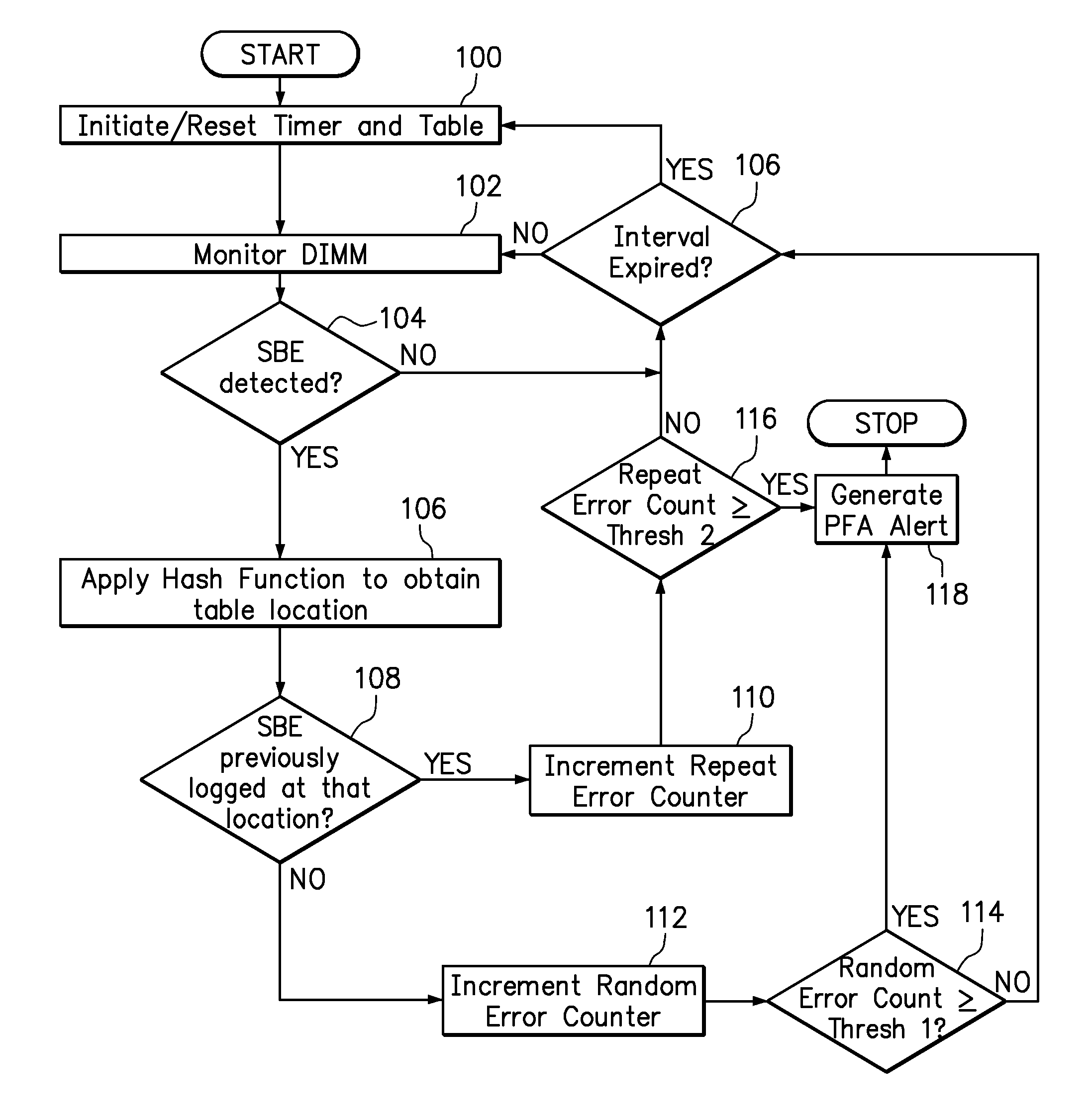

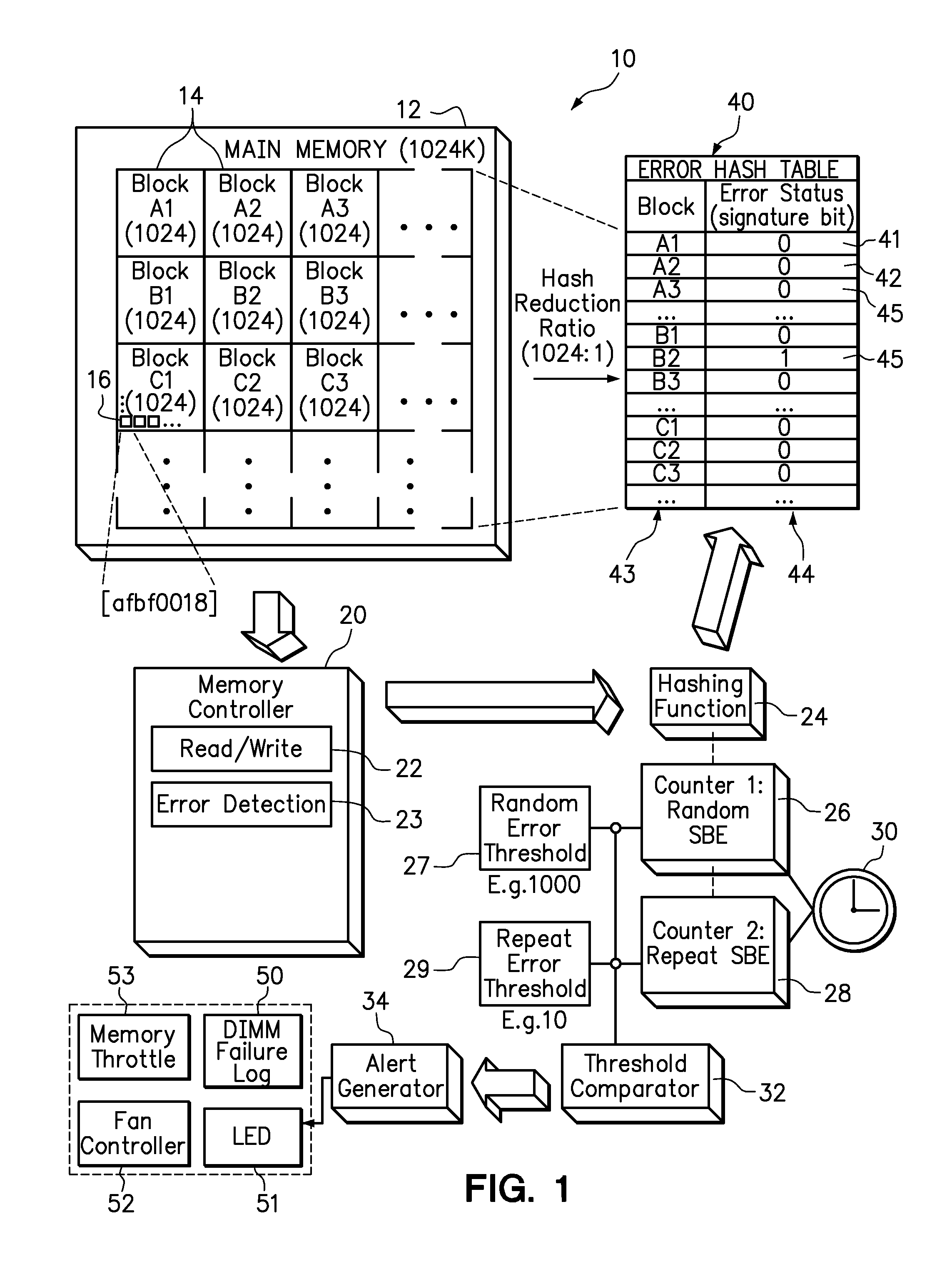

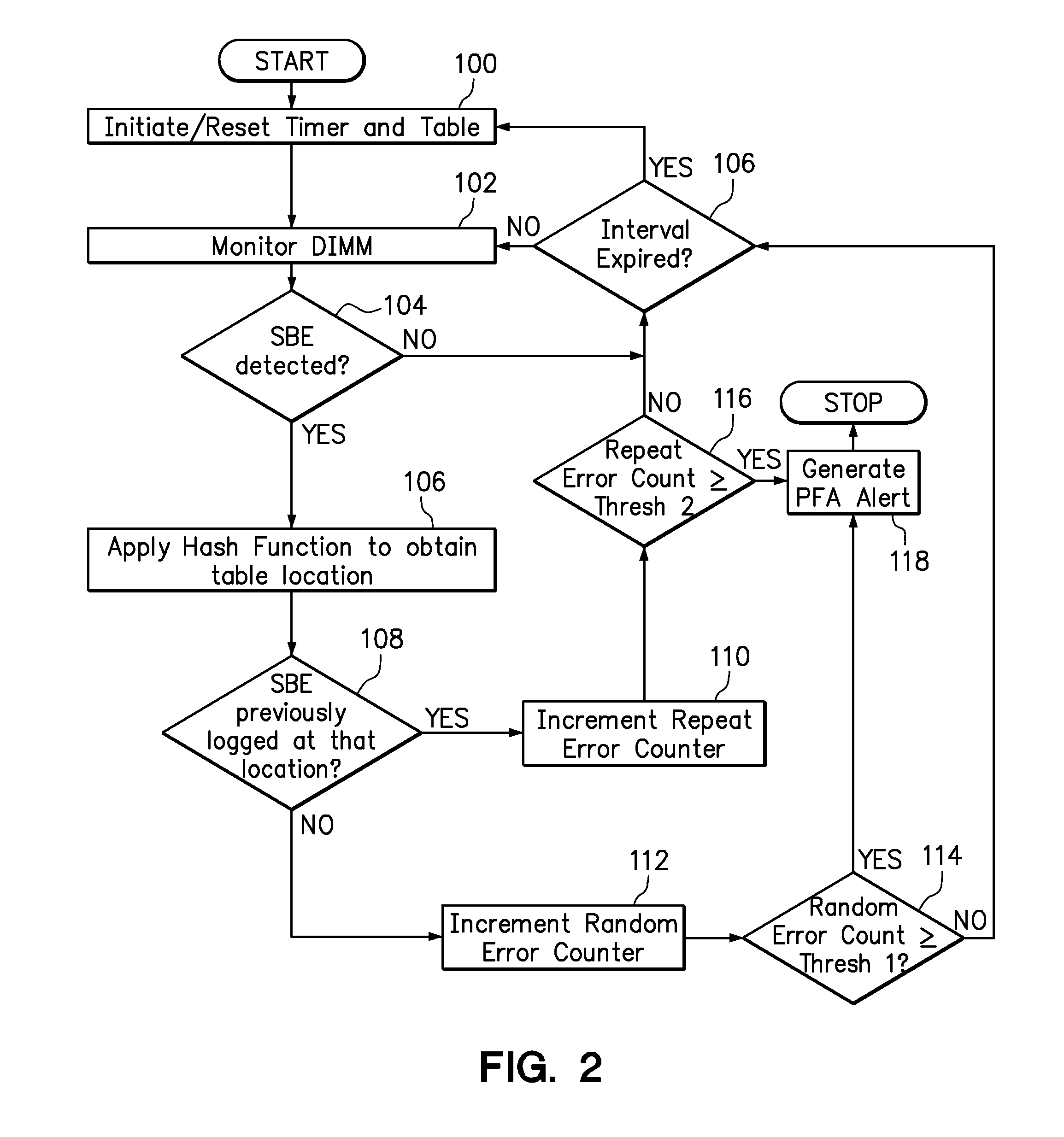

Use of hashing function to distinguish random and repeat errors in a memory system

One embodiment provides an error detection method wherein single-bit errors in a memory module are detected and identified as being a random error or a repeat error. Each identified random error and each identified repeat error occurring in a time interval is counted. An alert is generated in response to a number of identified random errors reaching a random-error threshold or a number of identified repeat errors reaching a repeat-error threshold during the predefined interval. The repeat-error threshold is set lower than the random-error threshold. A hashing process may be applied to the memory address of each detected error to map the location of the error in the memory system to a corresponding location in an electronic table.

Owner:LENOVO GLOBAL TECH INT LTD

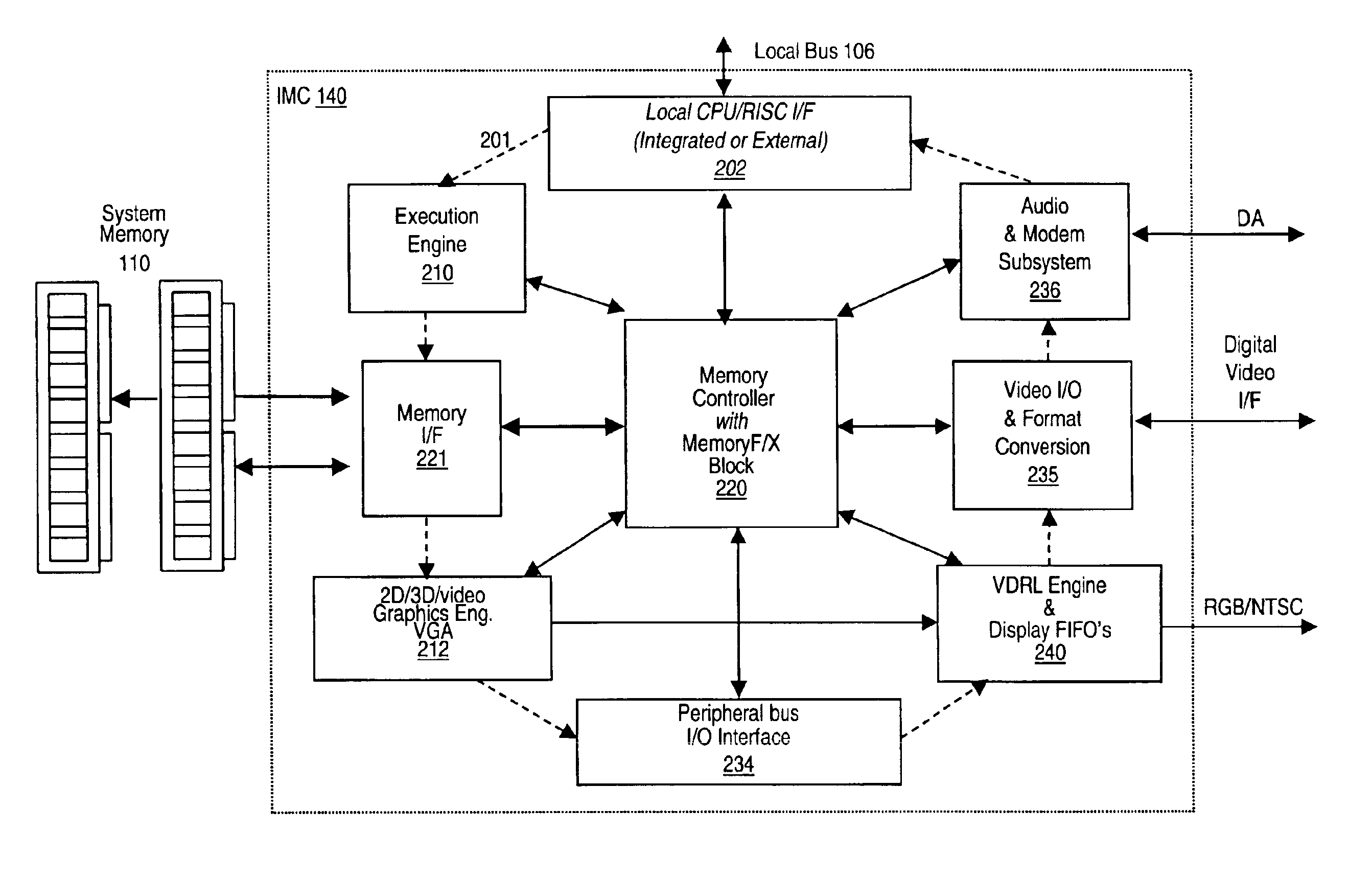

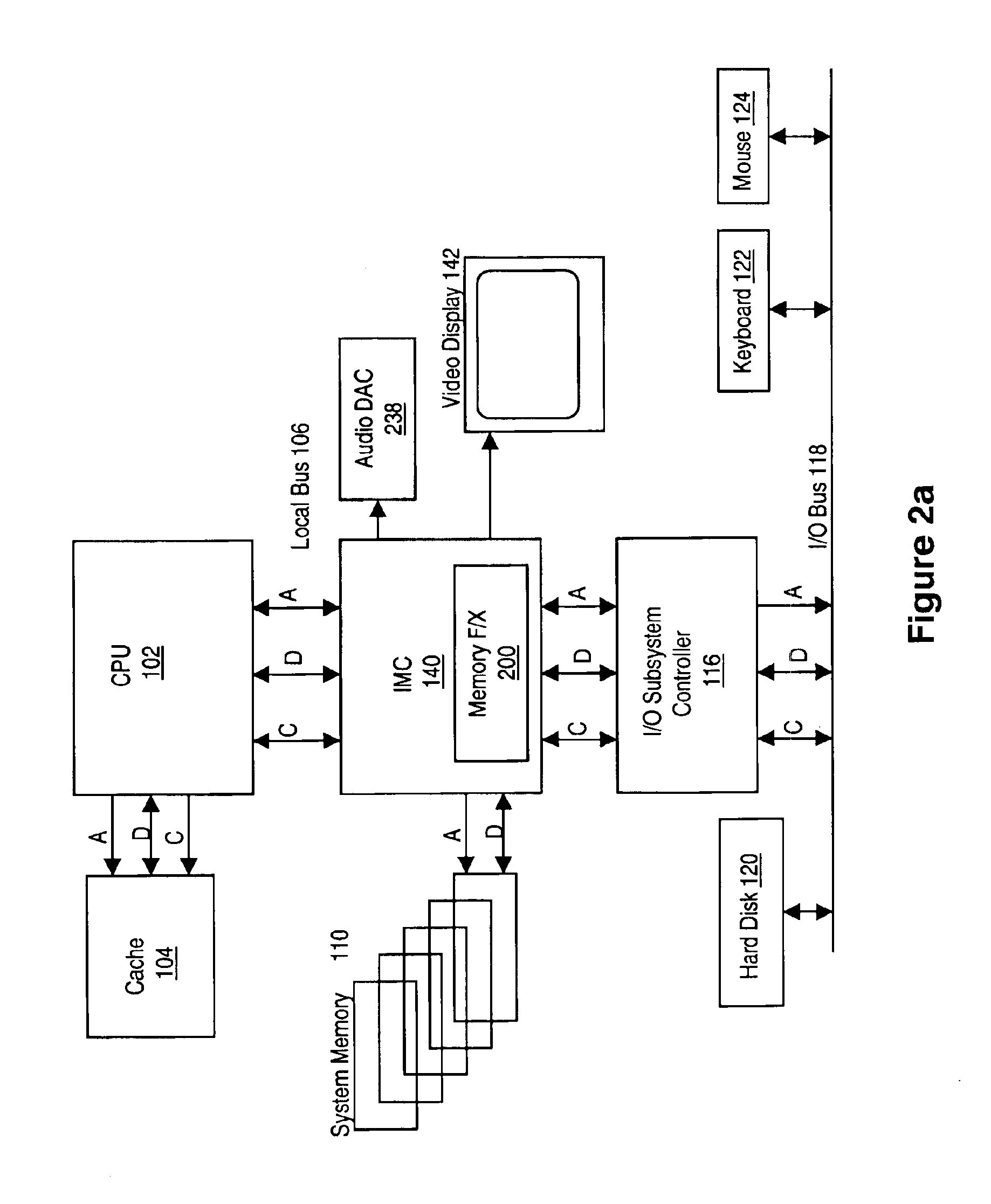

Memory module including scalable embedded parallel data compression and decompression engines

InactiveUS6879266B1Low costSmall data storage requirementMemory architecture accessing/allocationEnergy efficient ICTParallel compressionParallel computing

An memory module including parallel data compression and decompression engines for improved performance. The memory module includes MemoryF / X Technology. To improve latency and reduce performance degradations normally associated with compression and decompression techniques, the MemoryF / X Technology encompasses multiple novel techniques such as: 1) parallel lossless compression / decompression; 2) selectable compression modes such as lossless, lossy or no compression; 3) priority compression mode; 4) data cache techniques; 5) variable compression block sizes; 6) compression reordering; and 7) unique address translation, attribute, and address caches. The parallel compression and decompression algorithm allows high-speed parallel compression and high-speed parallel decompression operation. The memory module-integrated data compression and decompression capabilities remove system bottlenecks and increase performance. This allows lower cost systems due to smaller data storage, reduced bandwidth requirements, reduced power and noise.

Owner:INTELLECTUAL VENTURES I LLC

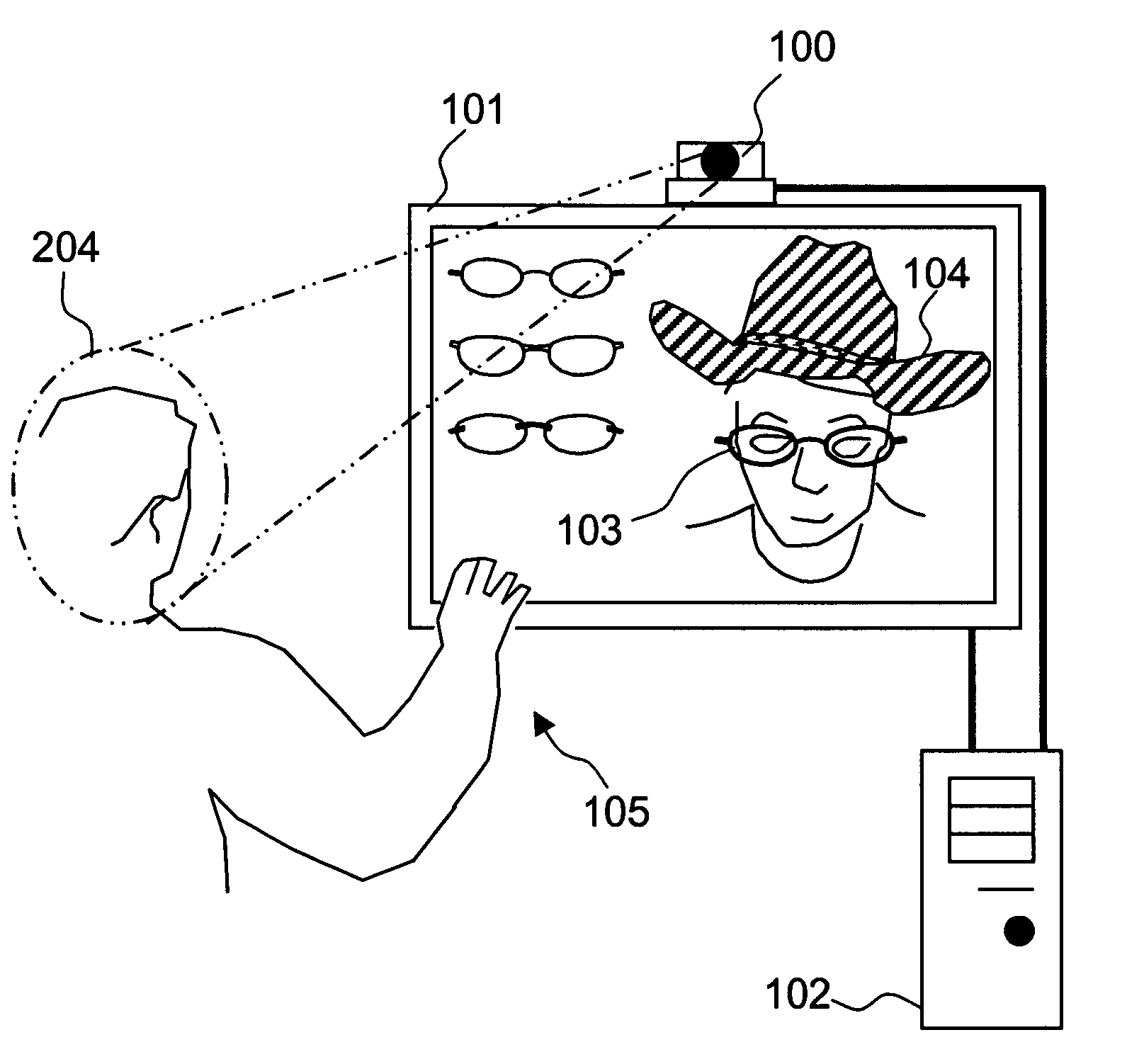

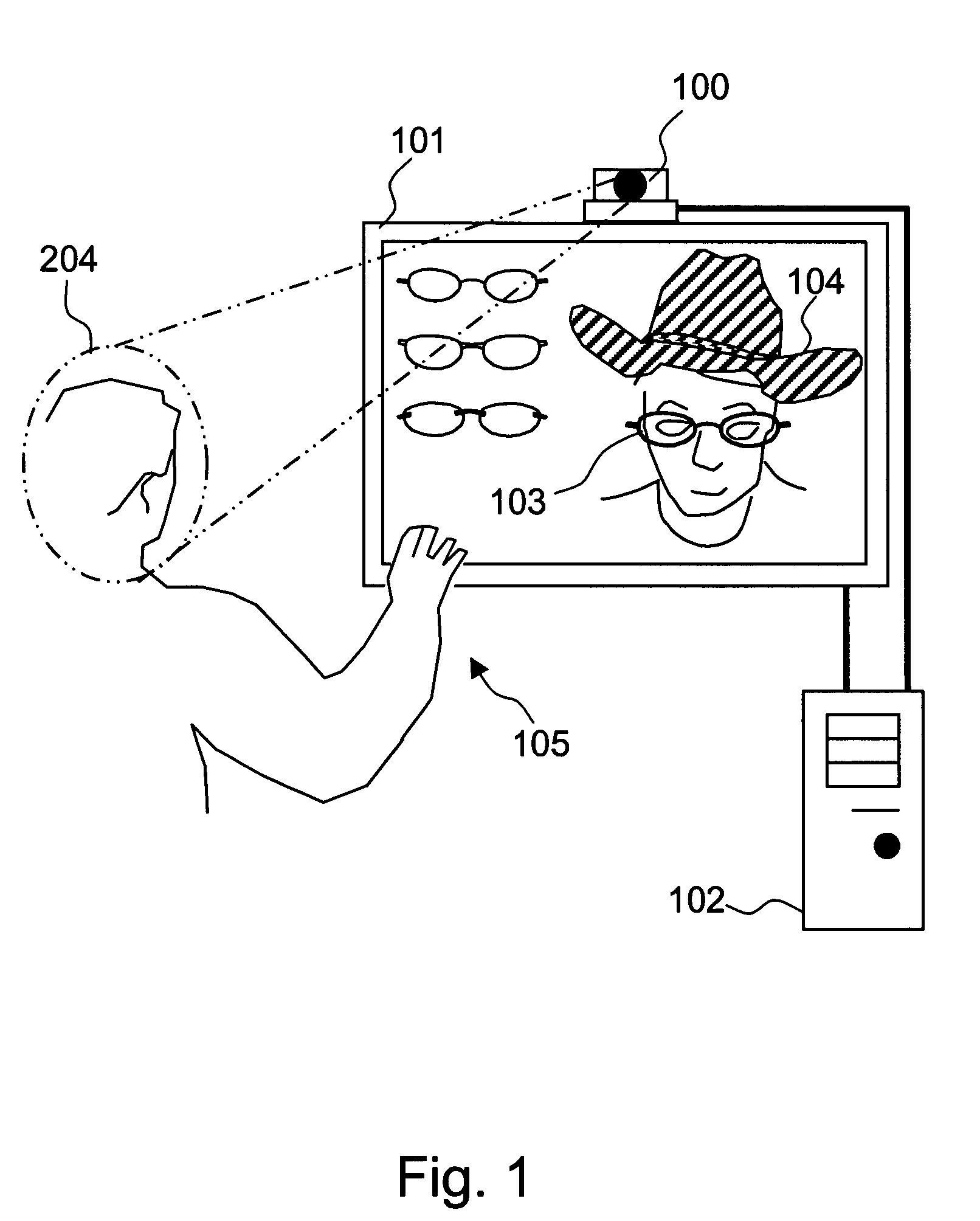

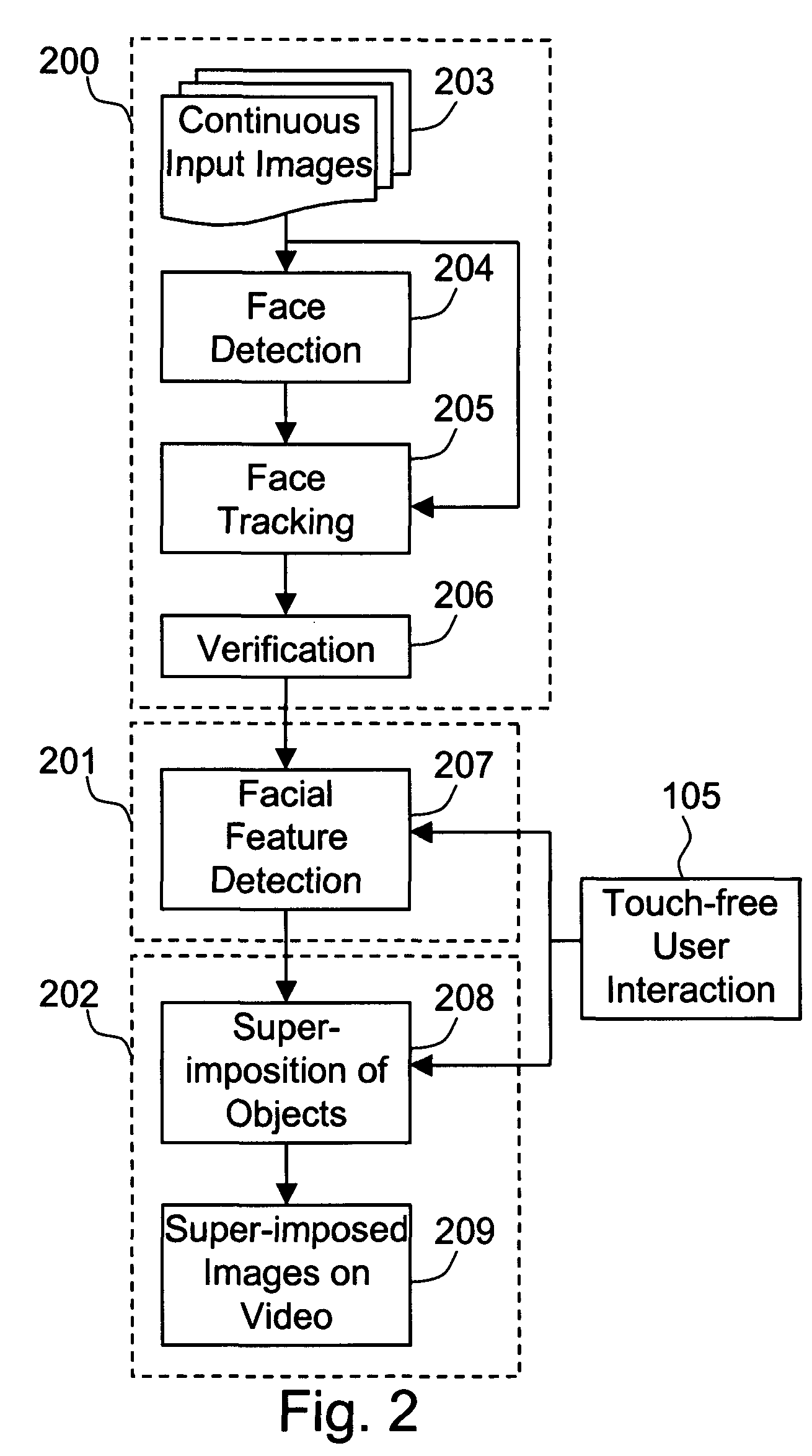

Method and system for real-time facial image enhancement

The present invention is a system and method for detecting facial features of humans in a continuous video and superimposing virtual objects onto the features automatically and dynamically in real-time. The suggested system is named Facial Enhancement Technology (FET). The FET system consists of three major modules, initialization module, facial feature detection module, and superimposition module. Each module requires demanding processing time and resources by nature, but the FET system integrates these modules in such a way that real time processing is possible. The users can interact with the system and select the objects on the screen. The superimposed image moves along with the user's random motion dynamically. The FET system enables the user to experience something that was not possible before by augmenting the person's facial images. The hardware of the FET system comprises the continuous image-capturing device, image processing and controlling system, and output display system.

Owner:F POSZAT HU

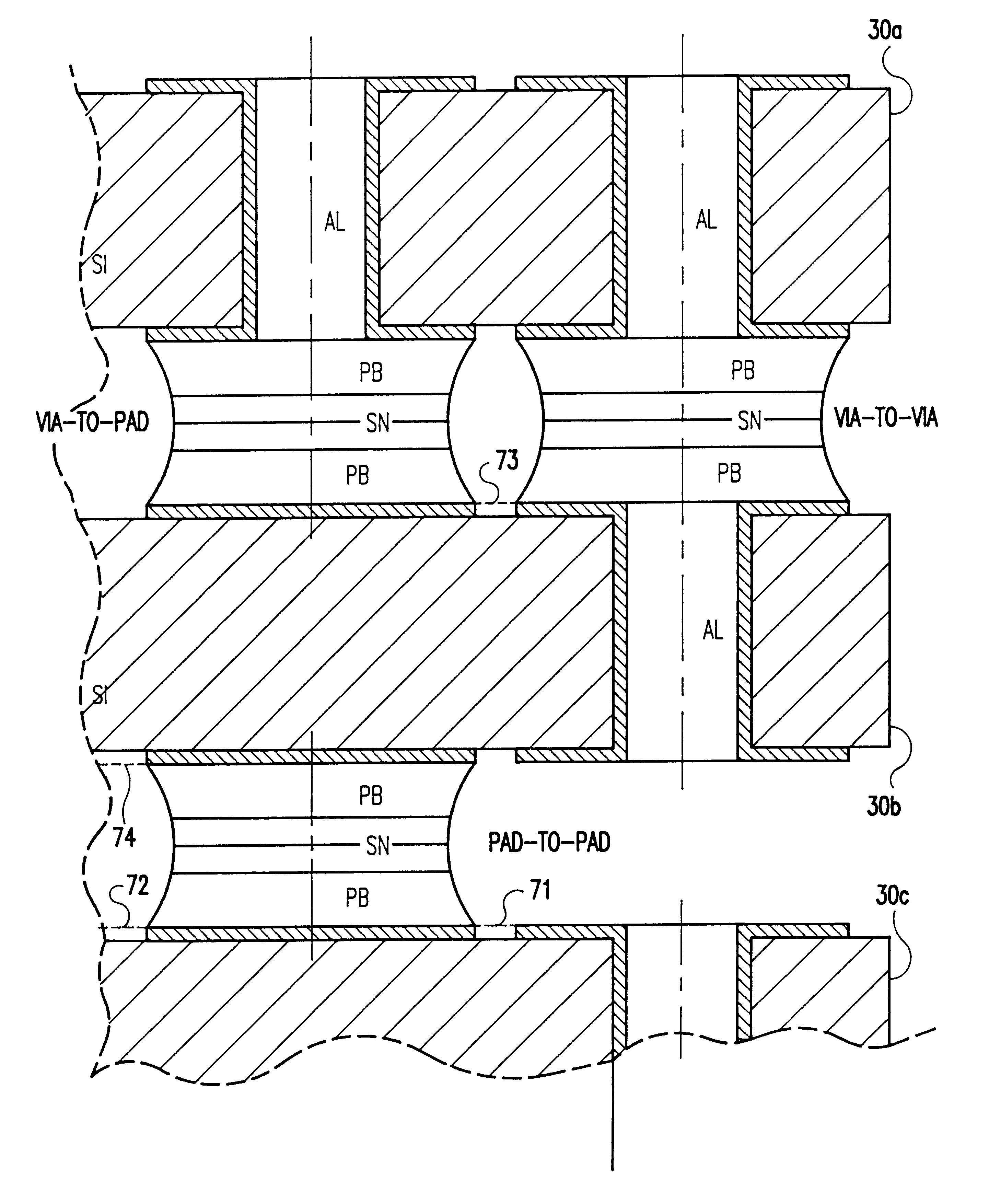

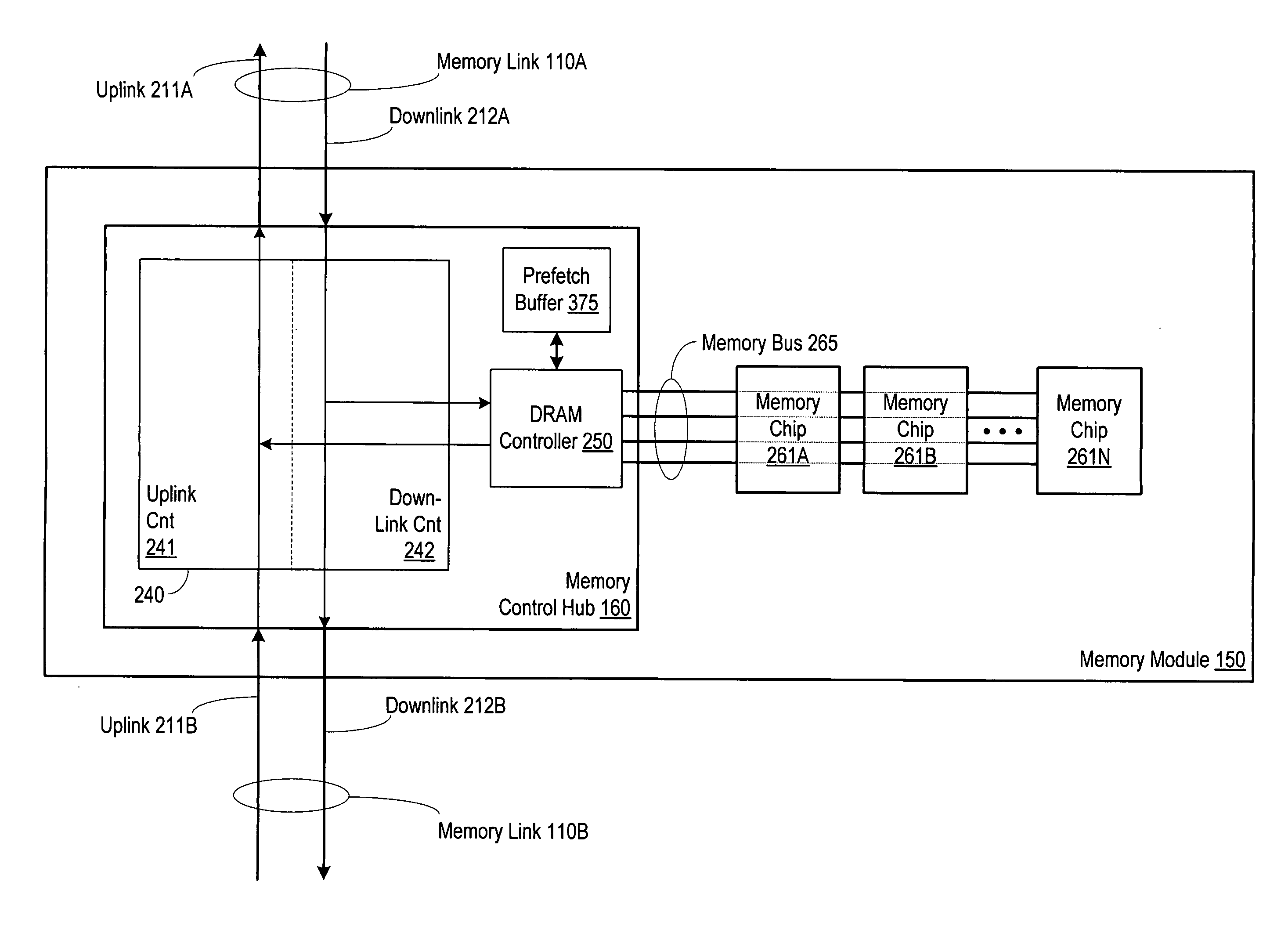

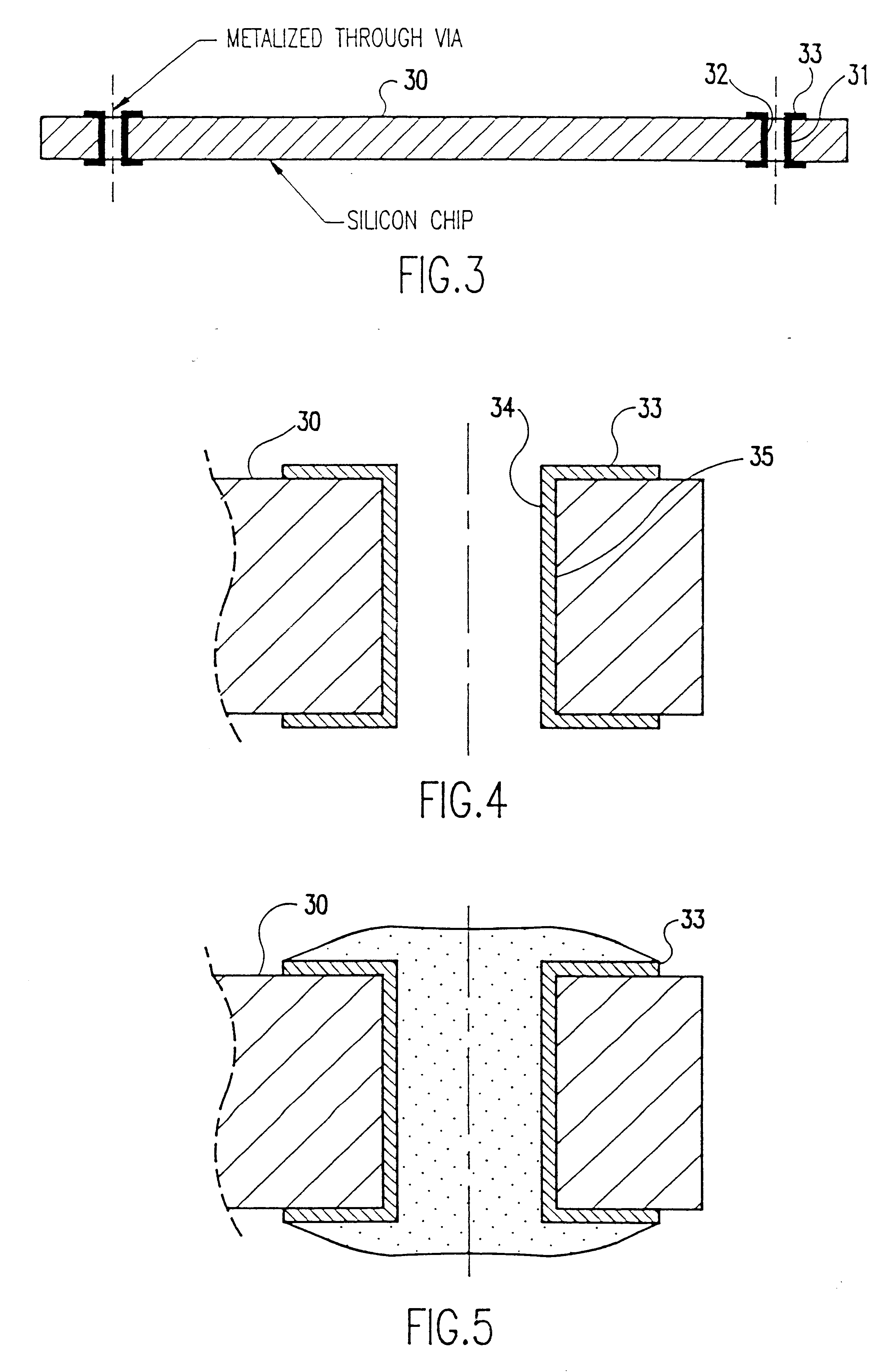

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6236115B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:INT BUSINESS MASCH CORP

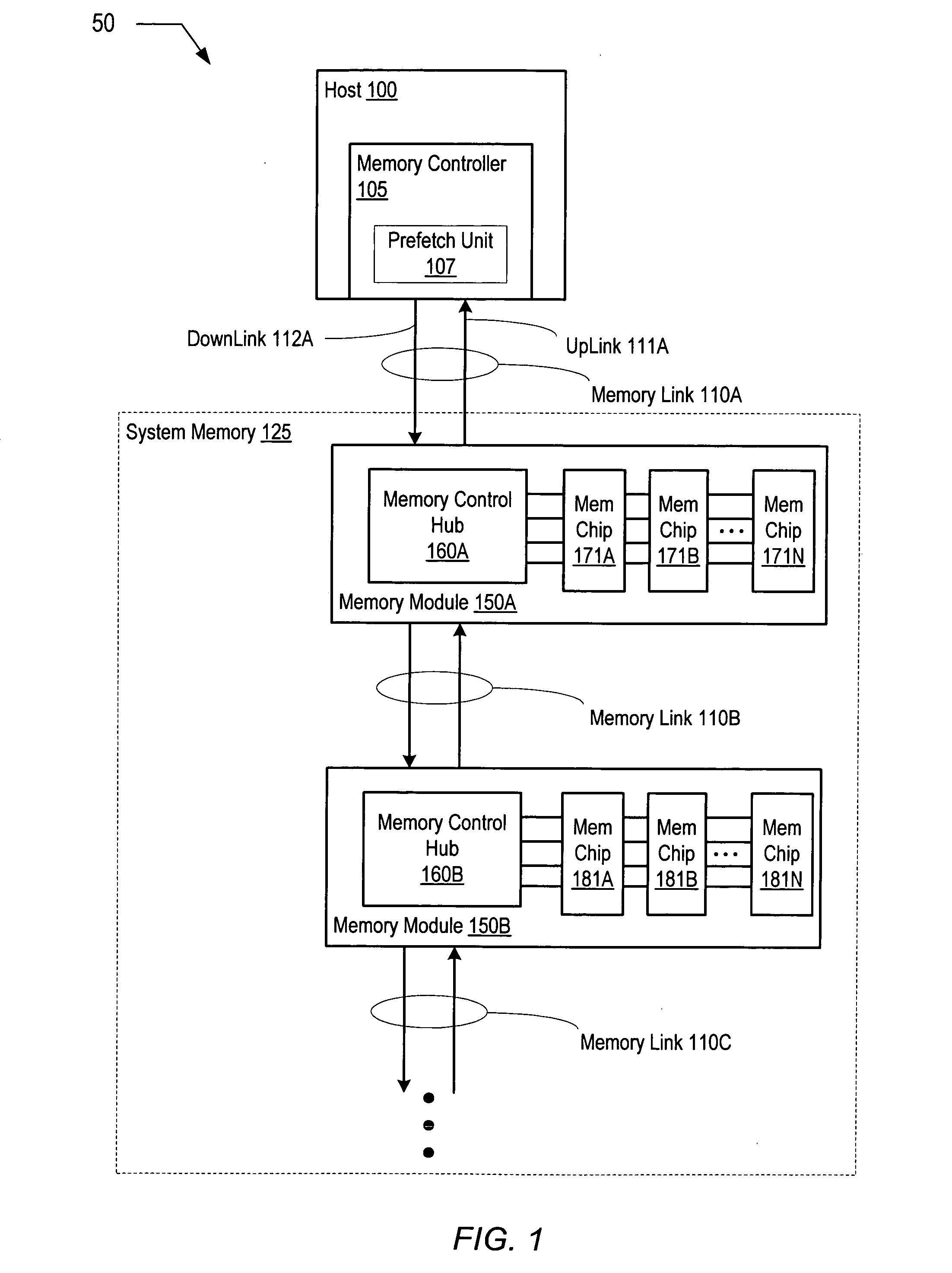

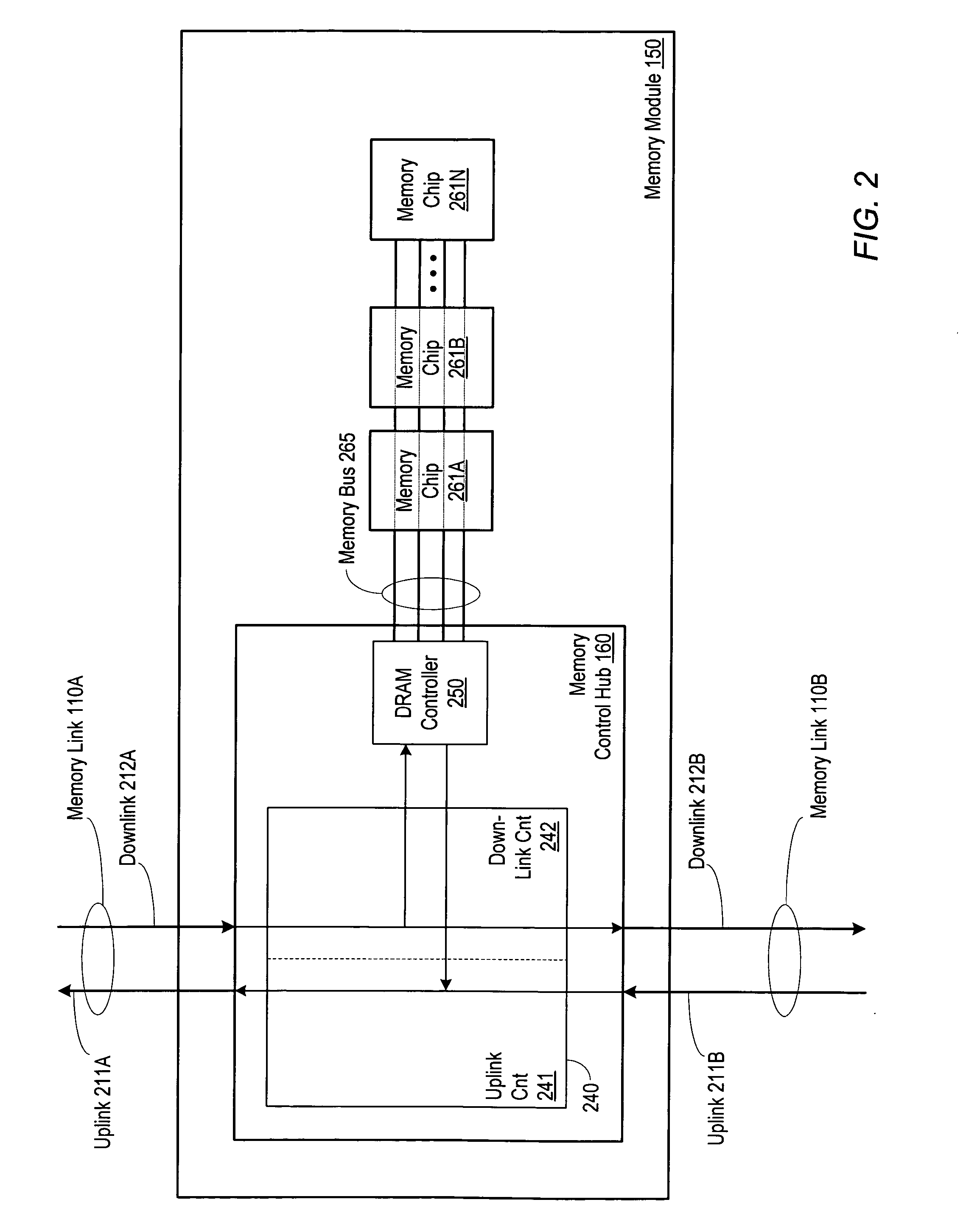

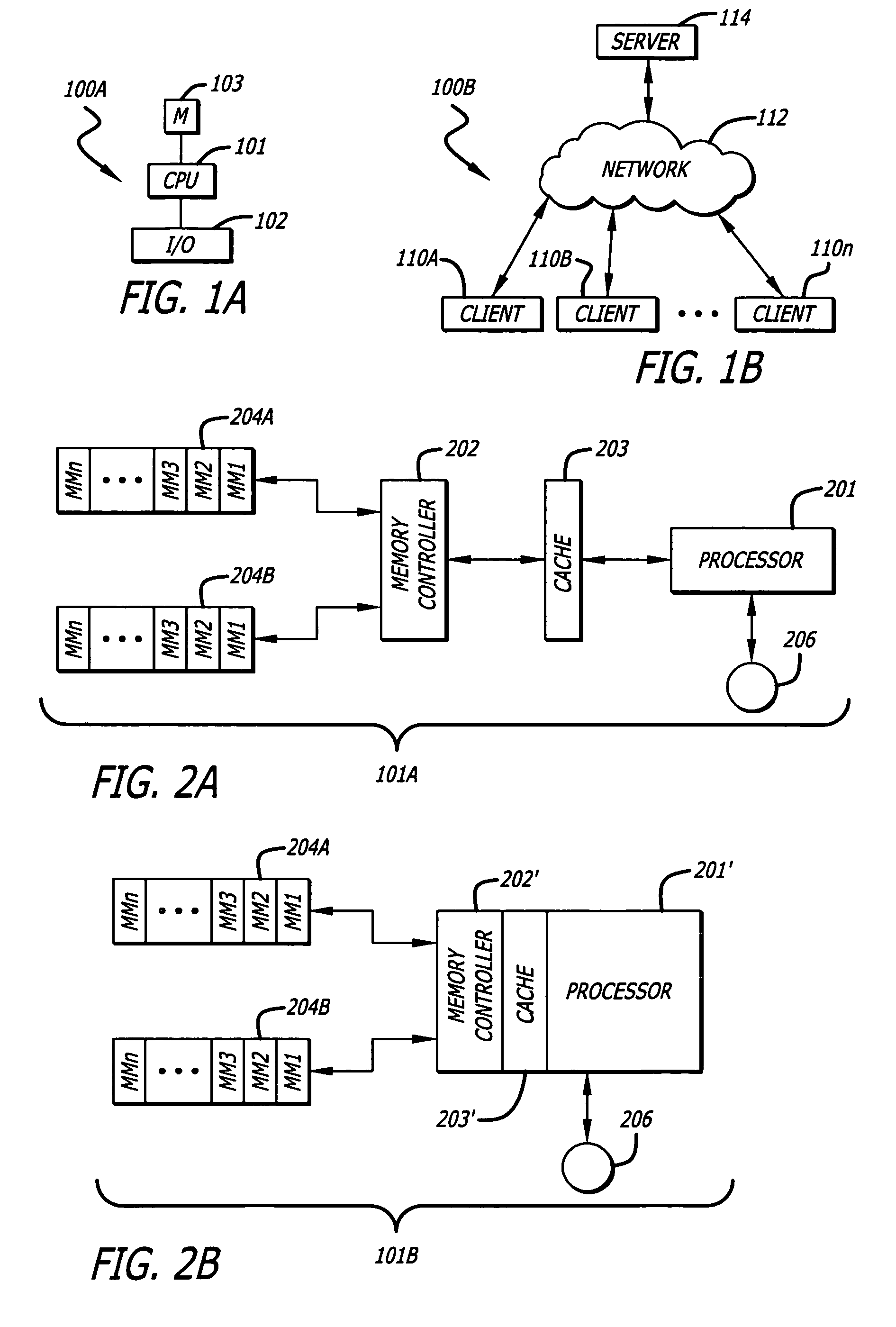

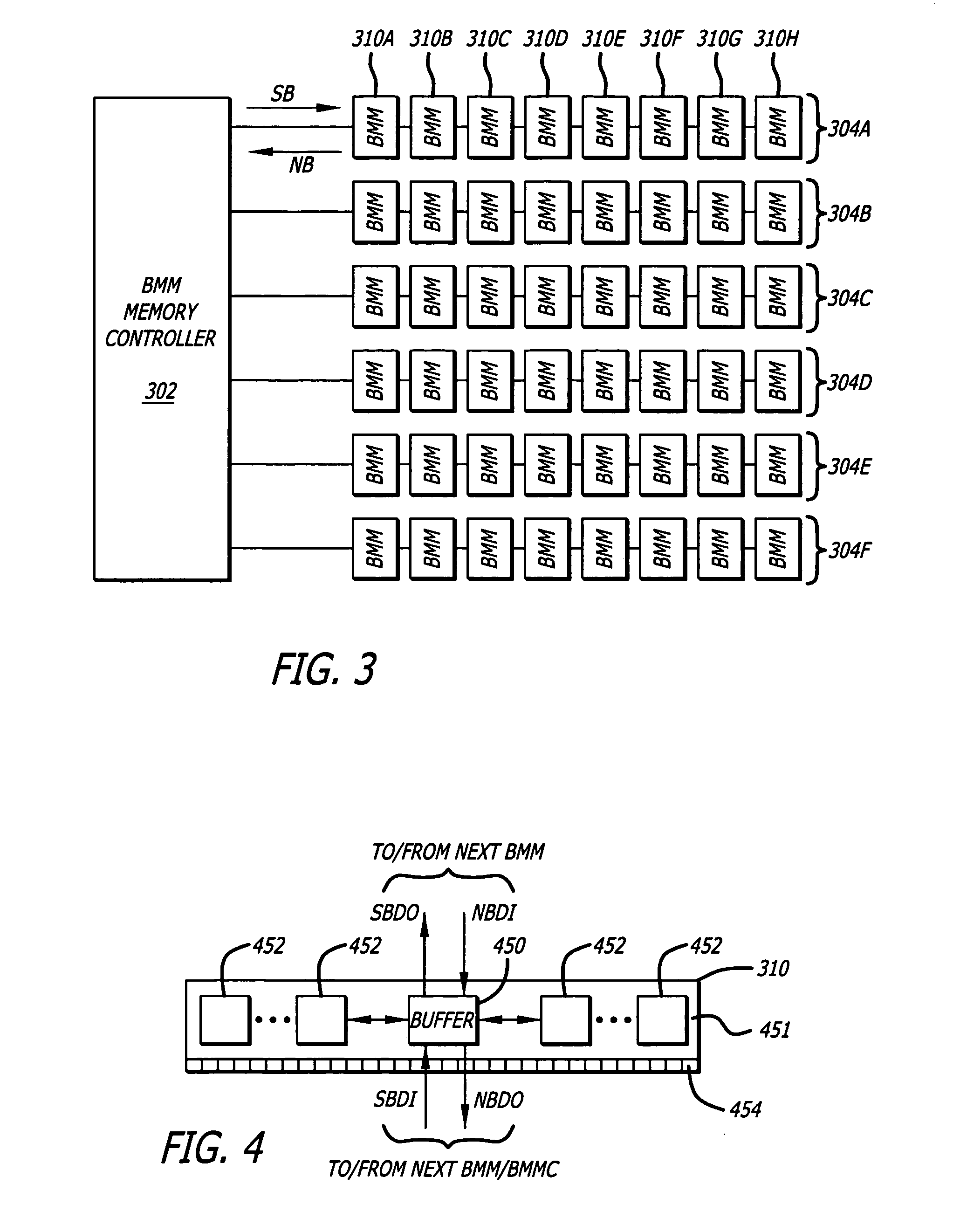

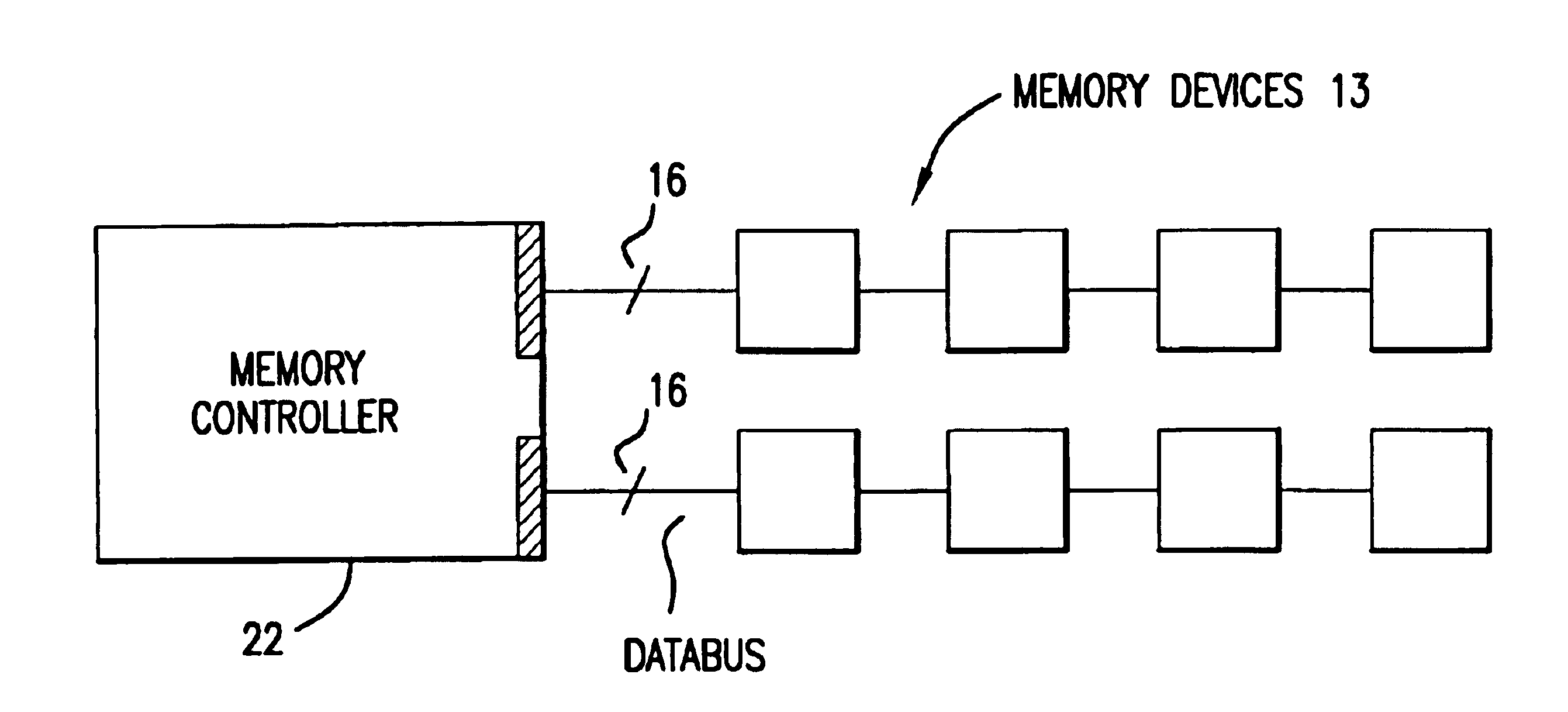

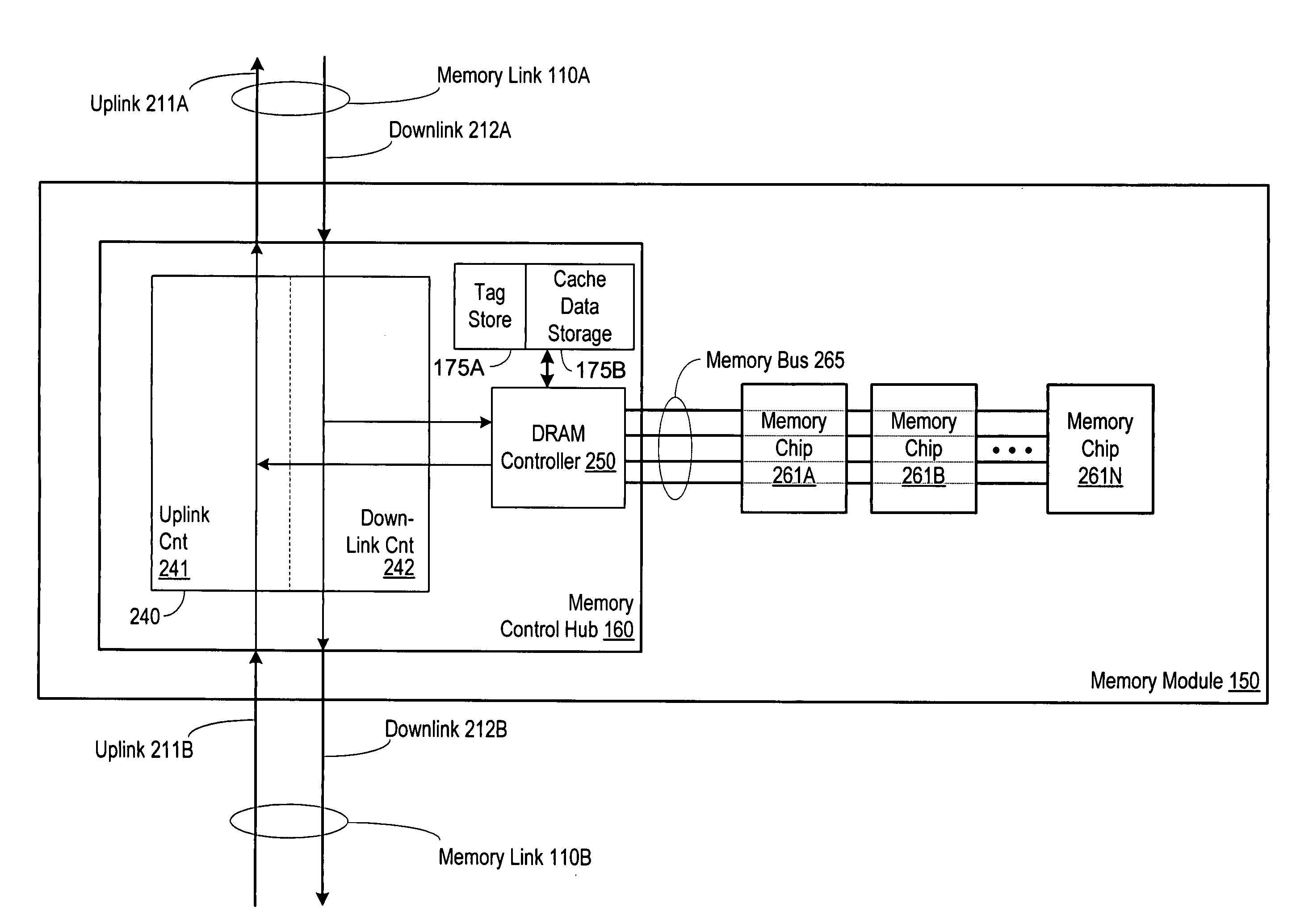

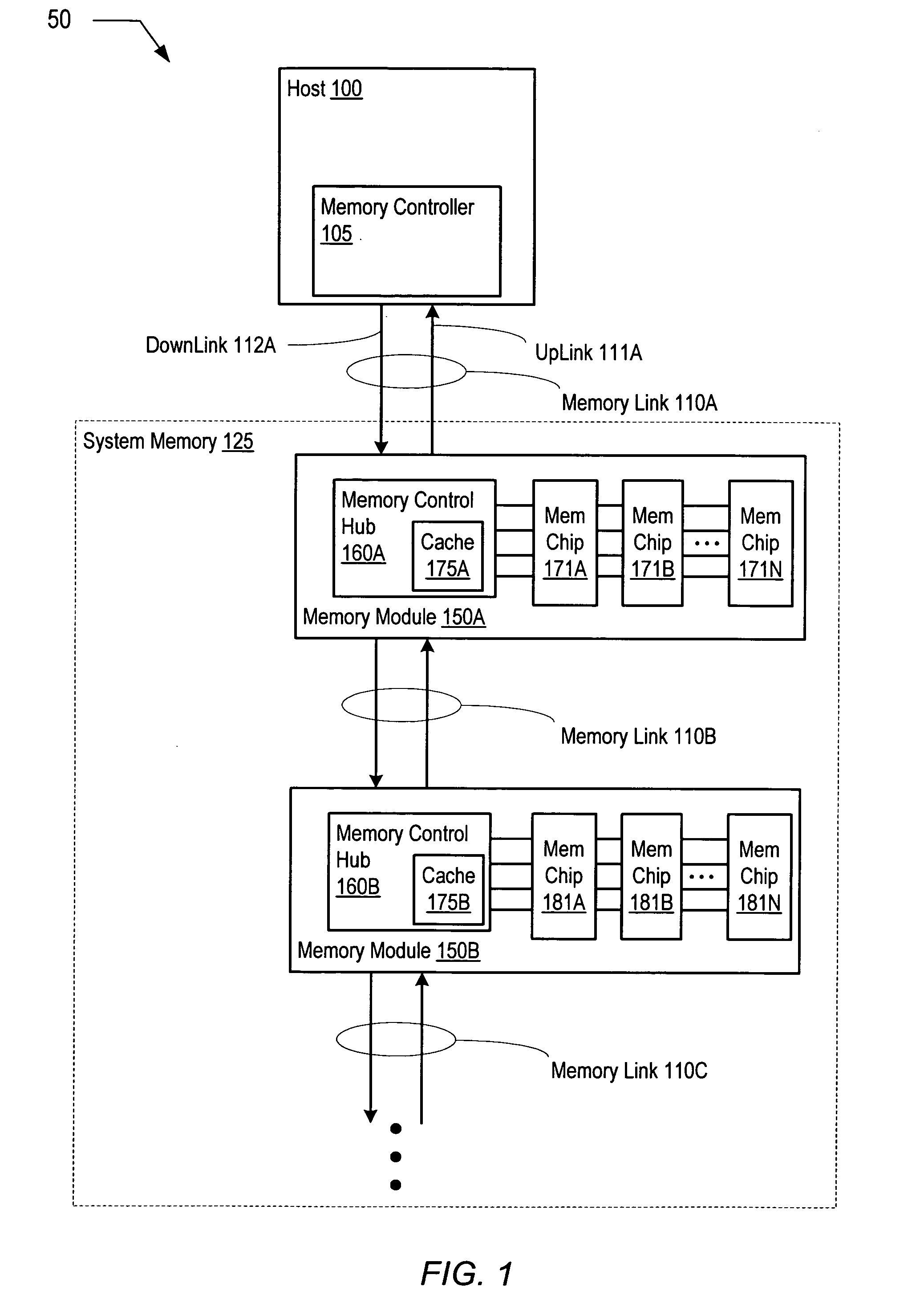

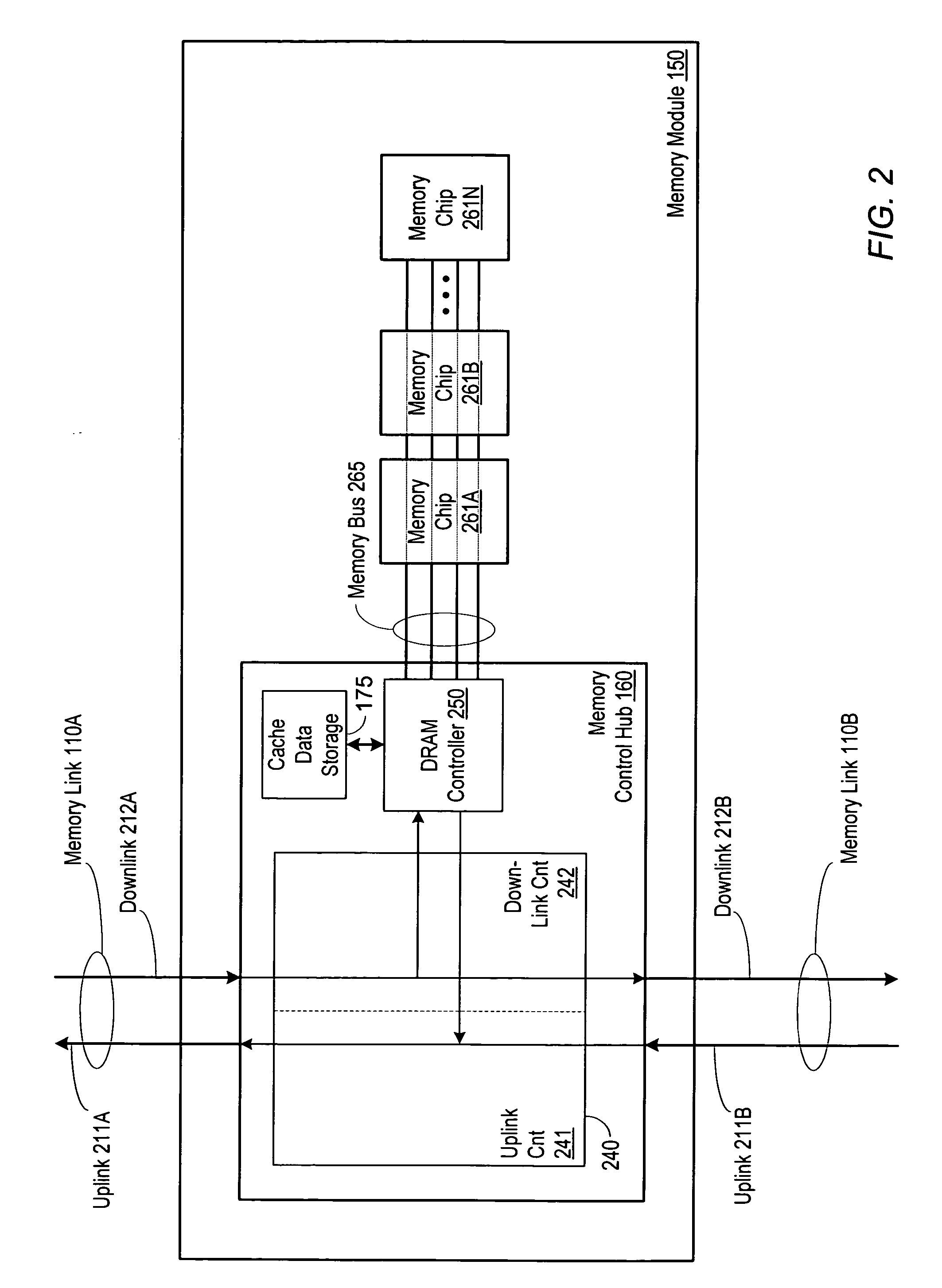

Prefetch mechanism for use in a system including a host connected to a plurality of memory modules via a serial memory interconnect

InactiveUS20050071542A1Memory architecture accessing/allocationStatic storageMemory controllerData storing

A system includes a host coupled to a serially connected chain of memory modules. In one embodiment, the host includes a memory controller that may be configured to issue a memory read request for data stored within the memory modules. The memory controller may further request that data be prefetched from the memory modules by encoding prefetch information within the memory read request. The memory controller may also be configured to issue a memory write request to write data to the memory modules and to selectively request that one or more pages of memory within a given one of the memory modules remain open by encoding the prefetch information within the memory write request.

Owner:ADVANCED MICRO DEVICES INC

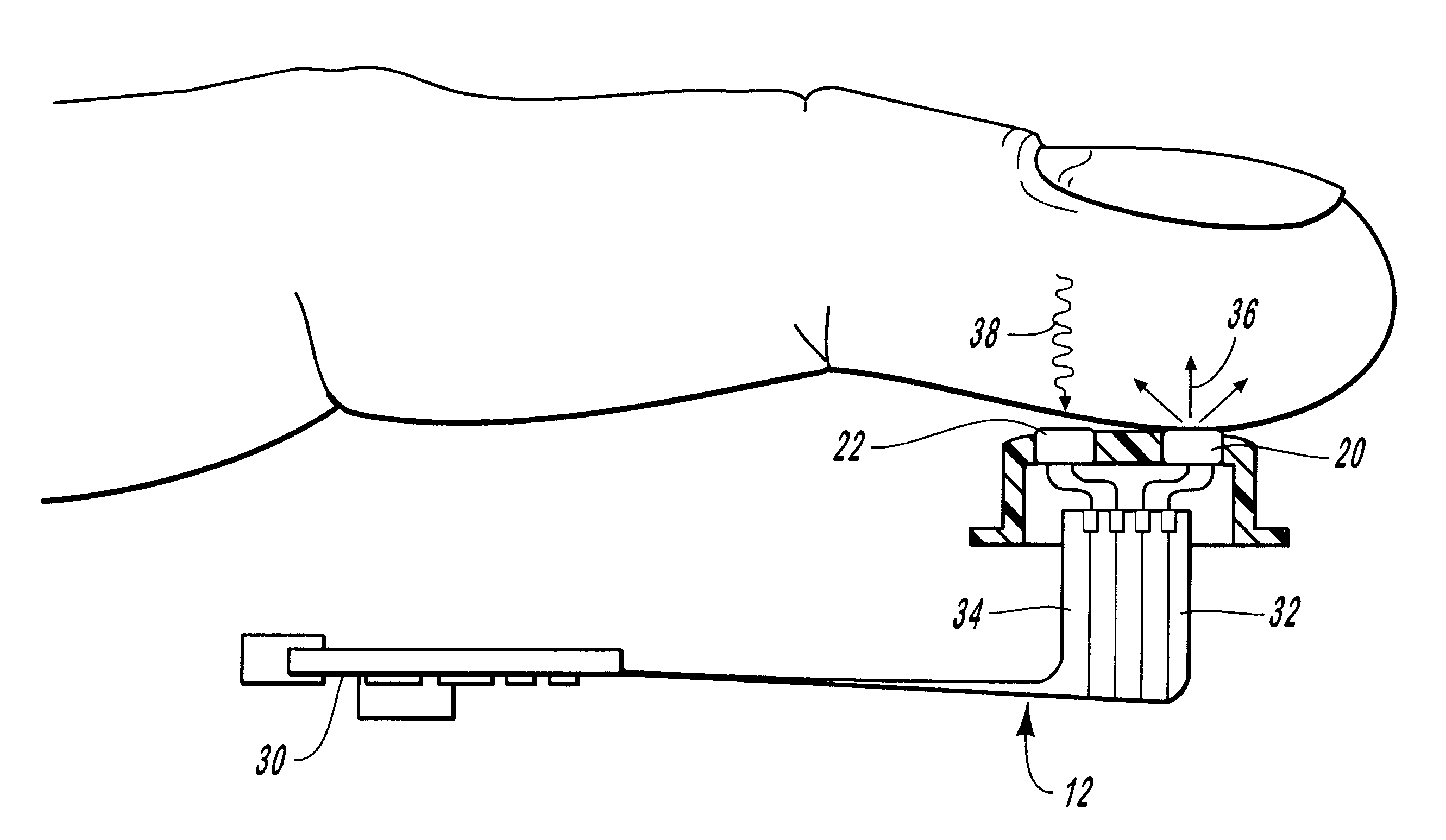

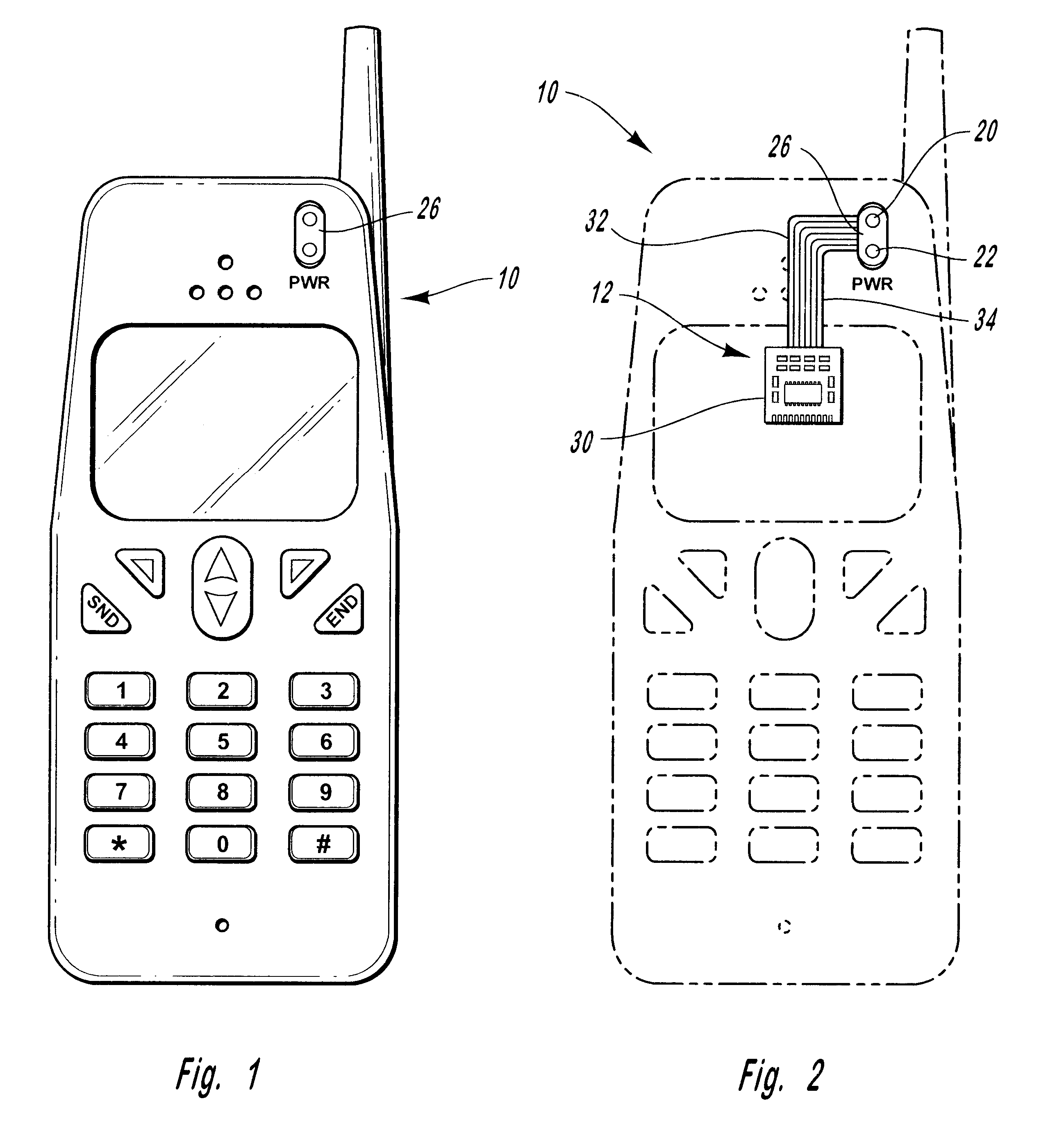

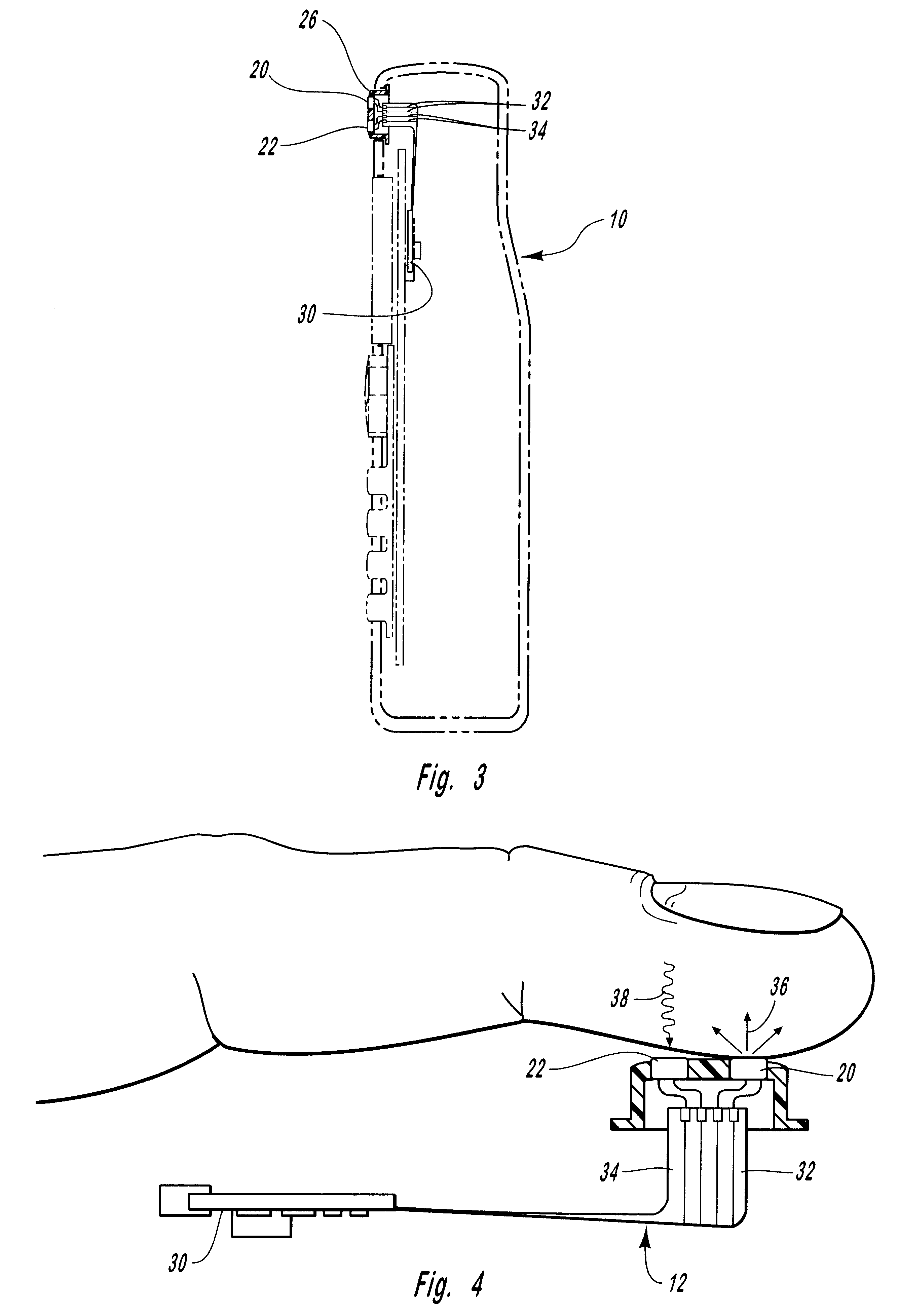

Method and apparatus for histological and physiological biometric operation and authentication

InactiveUS6483929B1Improve securityLow profileElectric signal transmission systemsImage analysisProcess moduleComputer science

The present invention is directed toward a device for biometric authentication. The device comprises an infra red signal transmitter, signal receiver, memory module, and processing module. The signal transmitter transmits infrared energy toward a user. The infrared energy is partly absorbed and partly reflected by the user's body. The infra red signal receiver collects partly reflected infrared energy. The memory module stores the data, and the processing module processes and compares the reflected infrared energy and stored data for use in biometric authentication.

Owner:HALO WEARABLES LLC

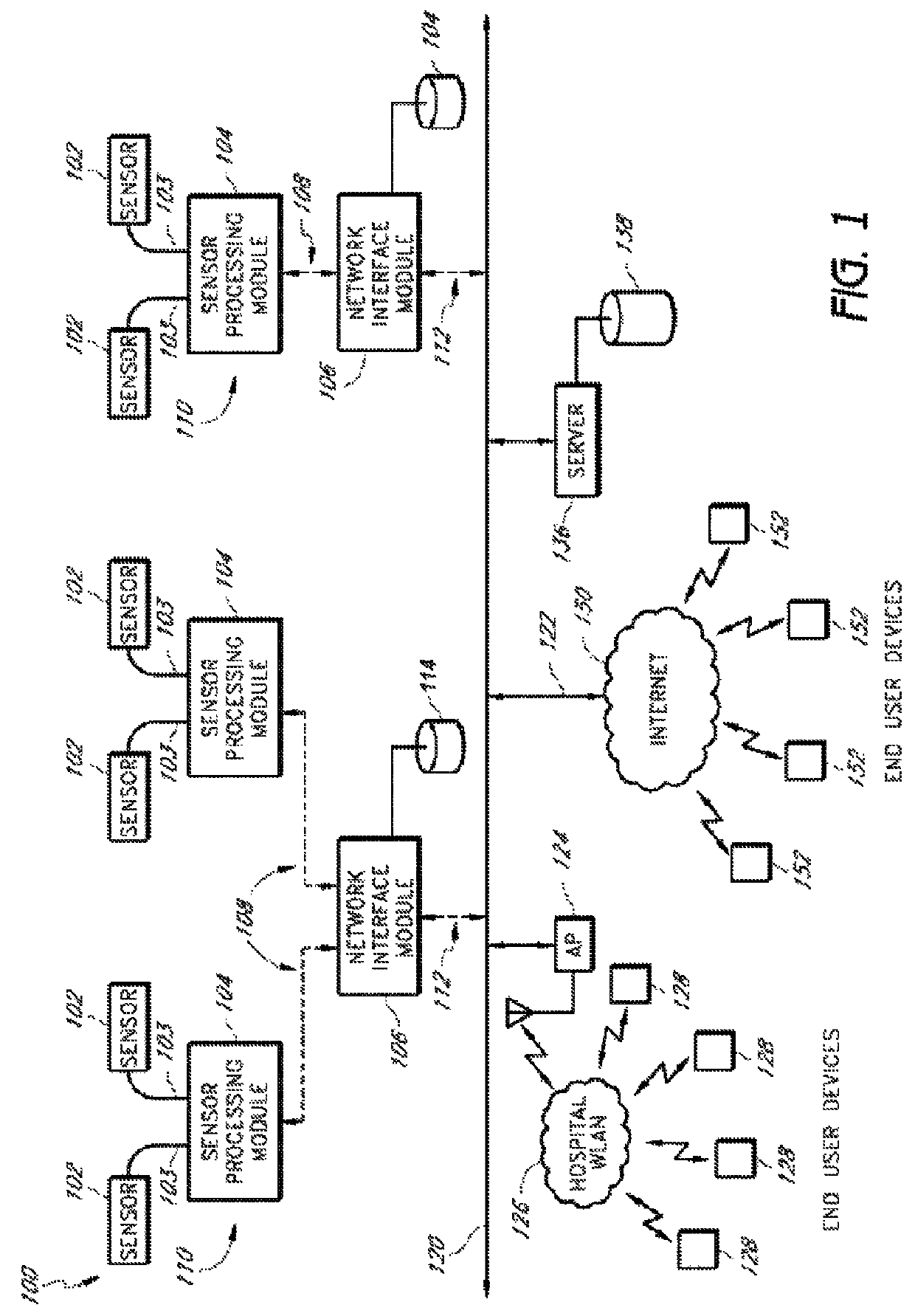

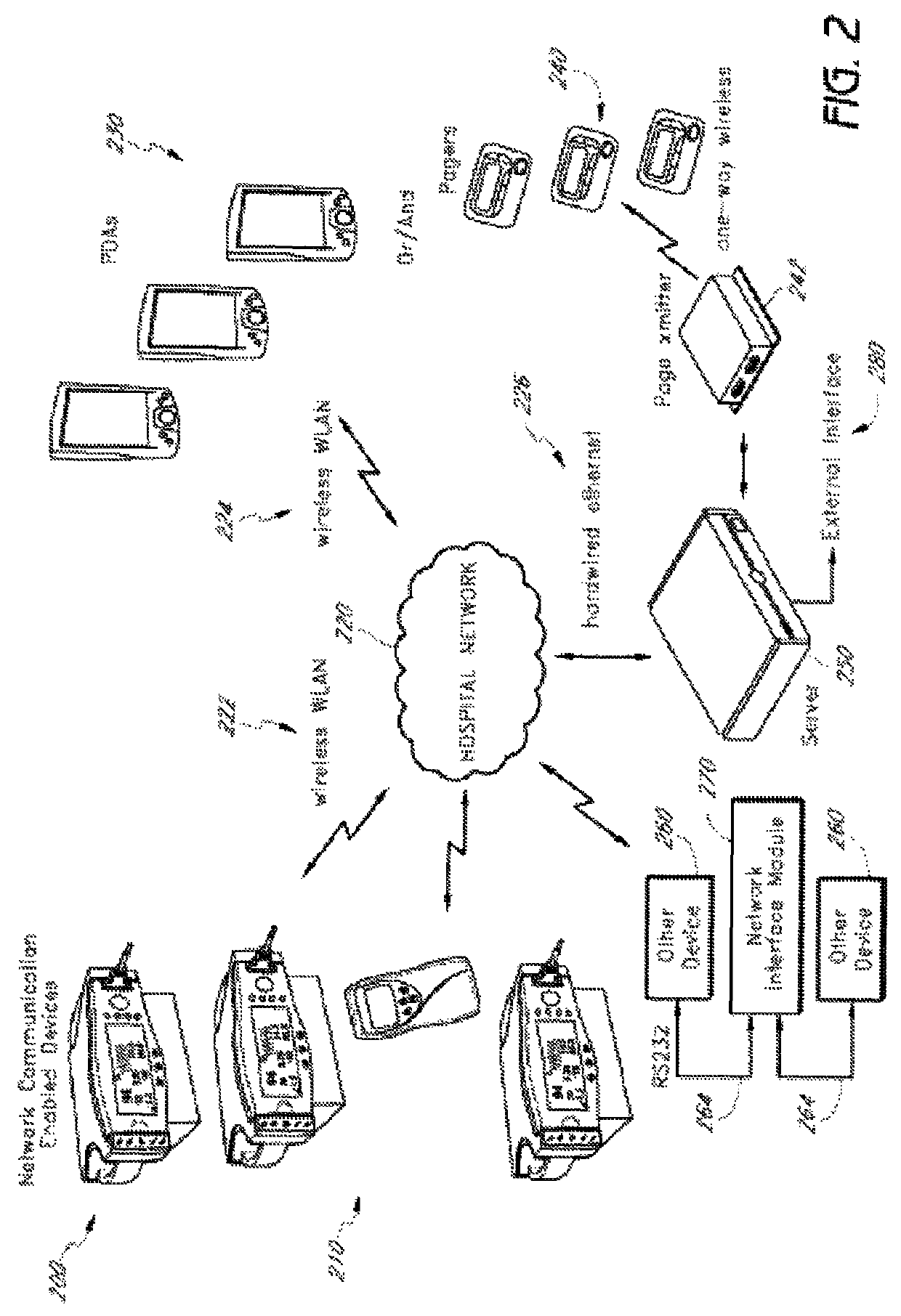

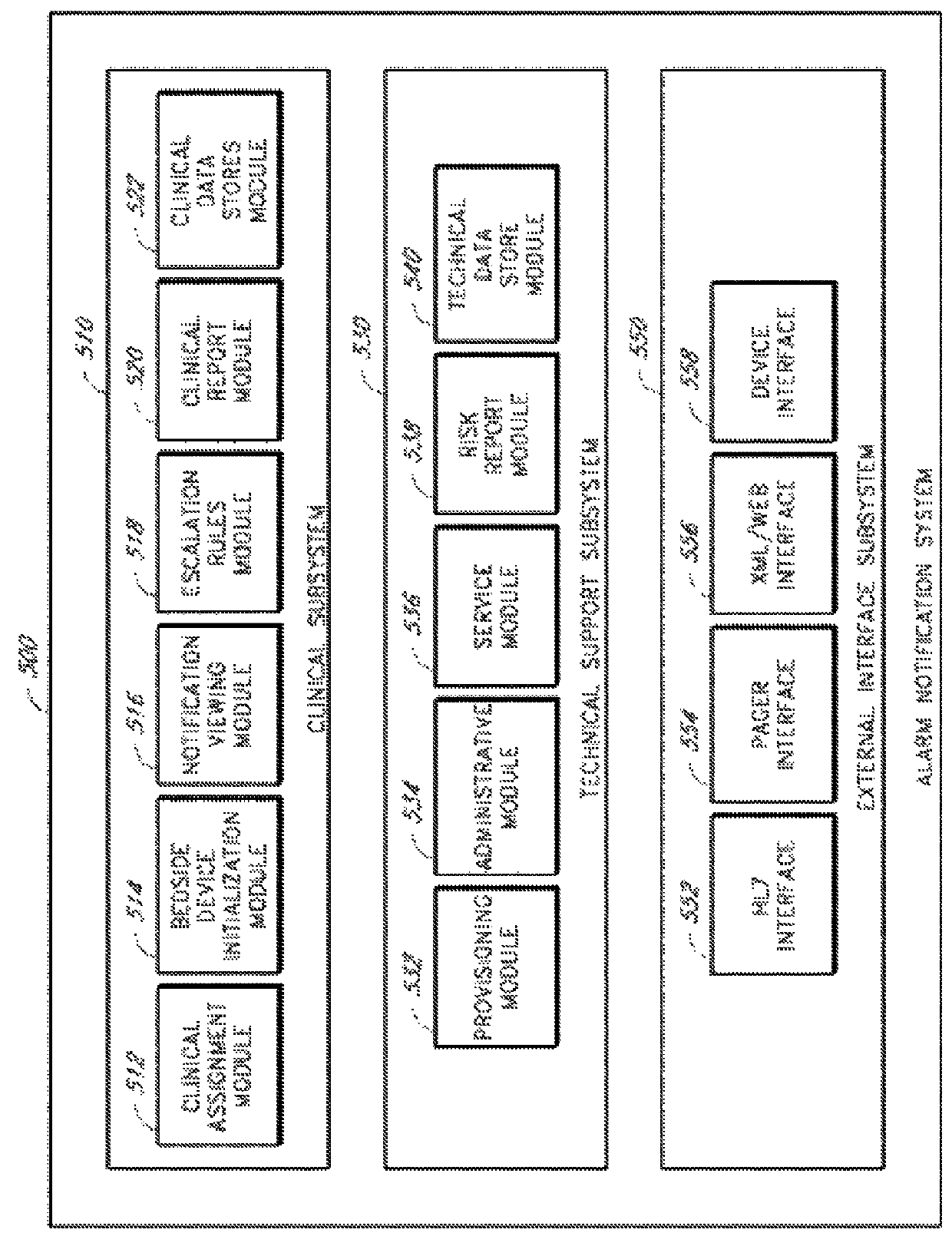

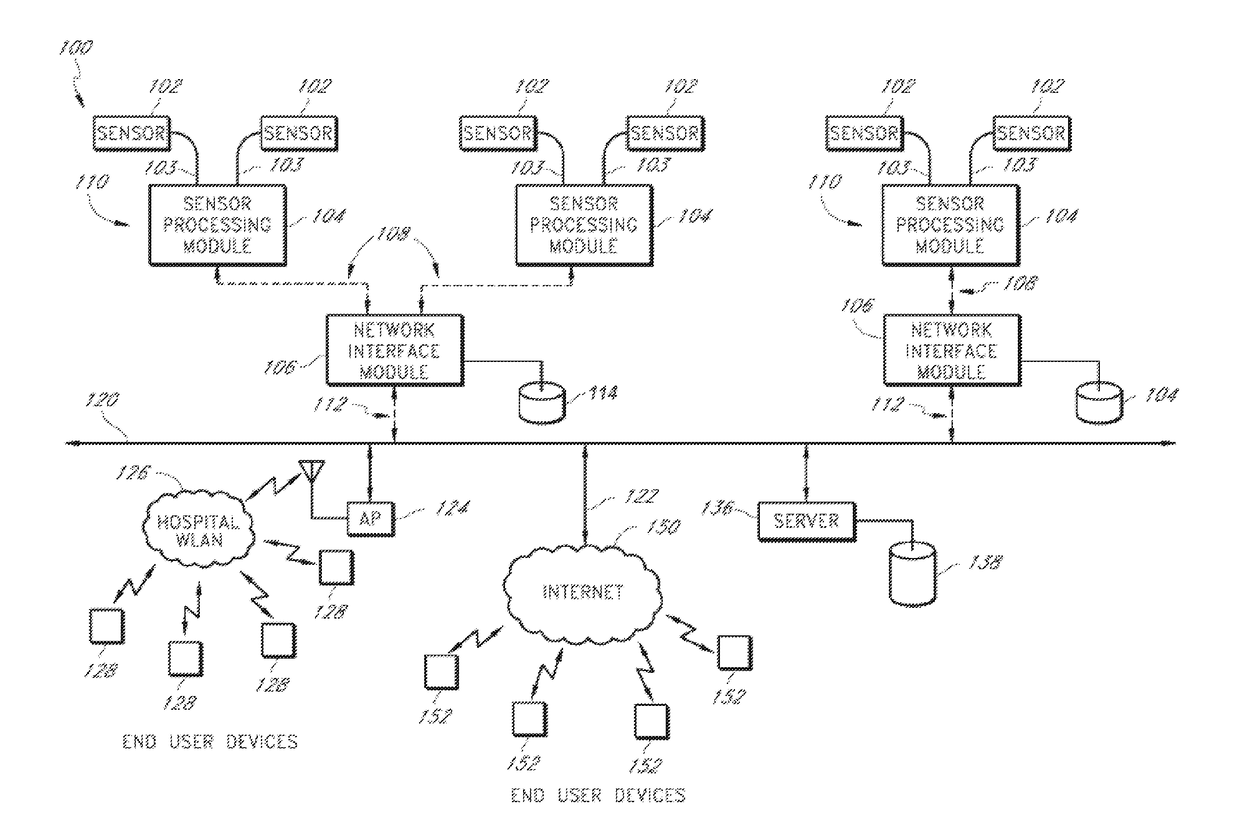

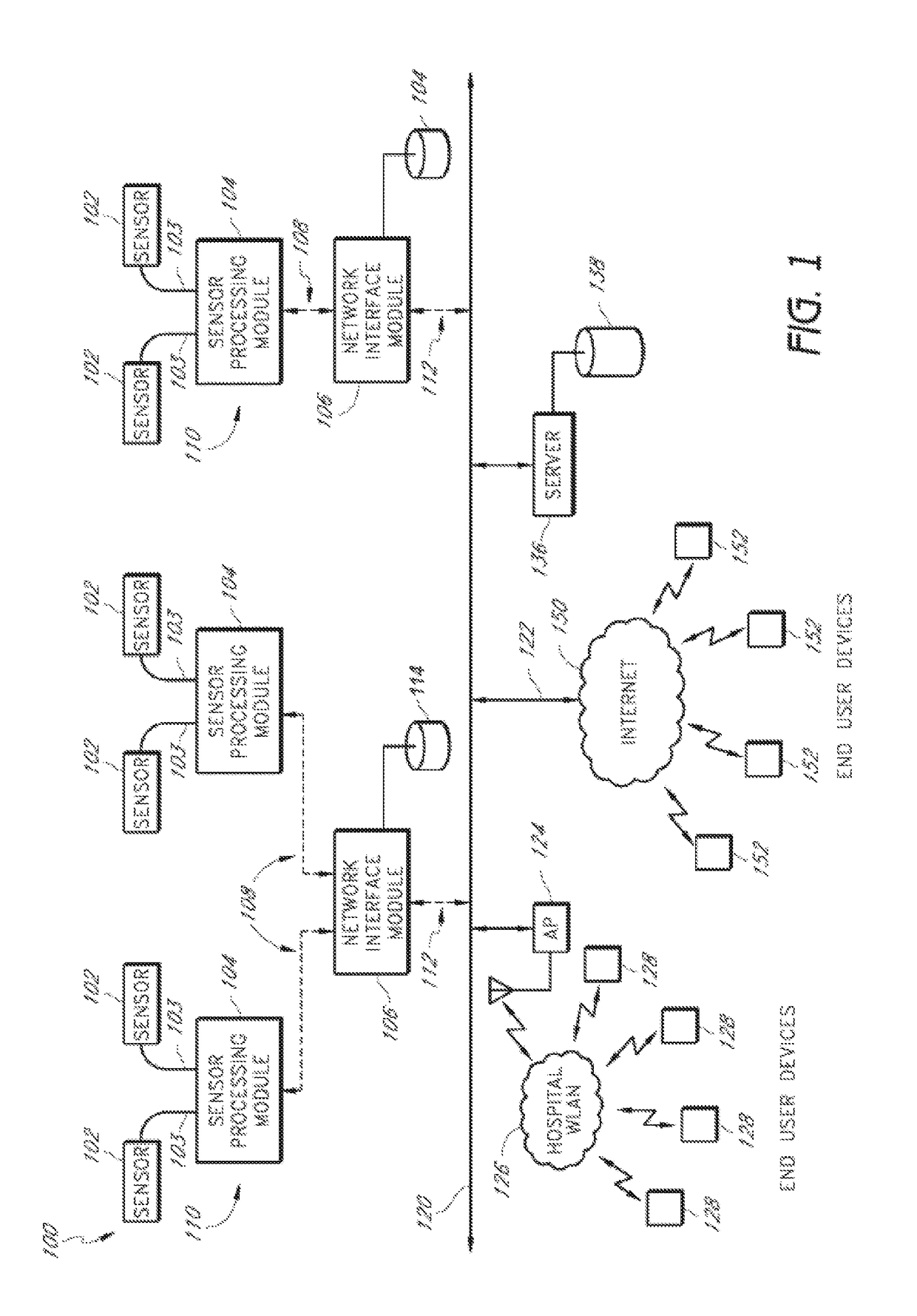

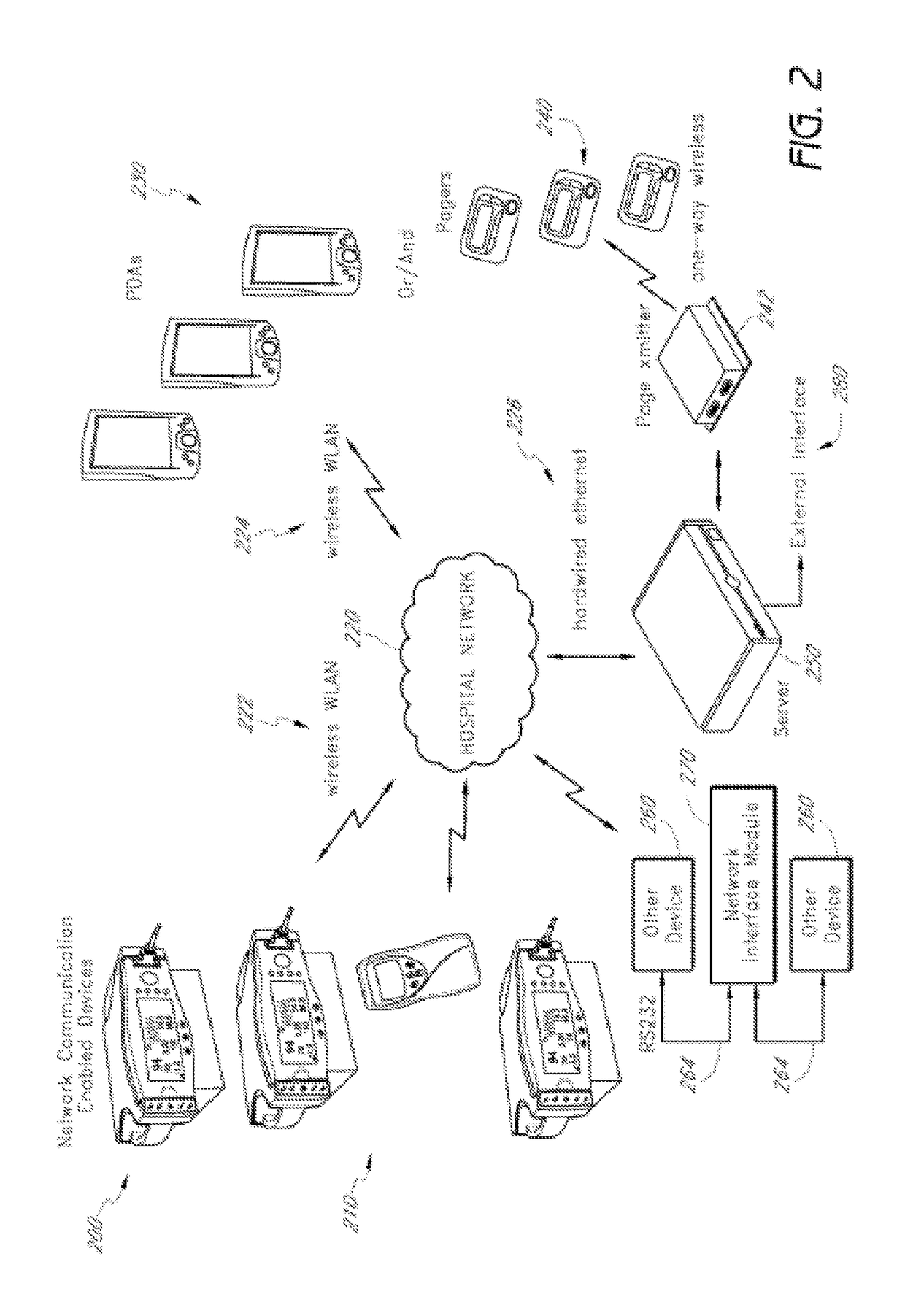

Systems and methods for monitoring a patient health network

ActiveUS9965946B2Transmission systemsTesting/monitoring control systemsCommunication interfacePhysiological monitoring

Systems and methods for monitoring physiological monitoring systems are described herein. A communication interface module can be configured to receive from a physiological monitoring system first data based on a snapshot taken of a status of the physiological monitoring system at a first time. A memory module can be configured to store the first data and a baseline associated with the physiological monitoring system. A processor module can be configured to compare the first data with the baseline and to generate a notification if the first data deviates from the baseline by a predetermined amount. A display module can be configured to display a physical location of a plurality of physiological monitoring systems and display the notification.

Owner:MASIMO CORP

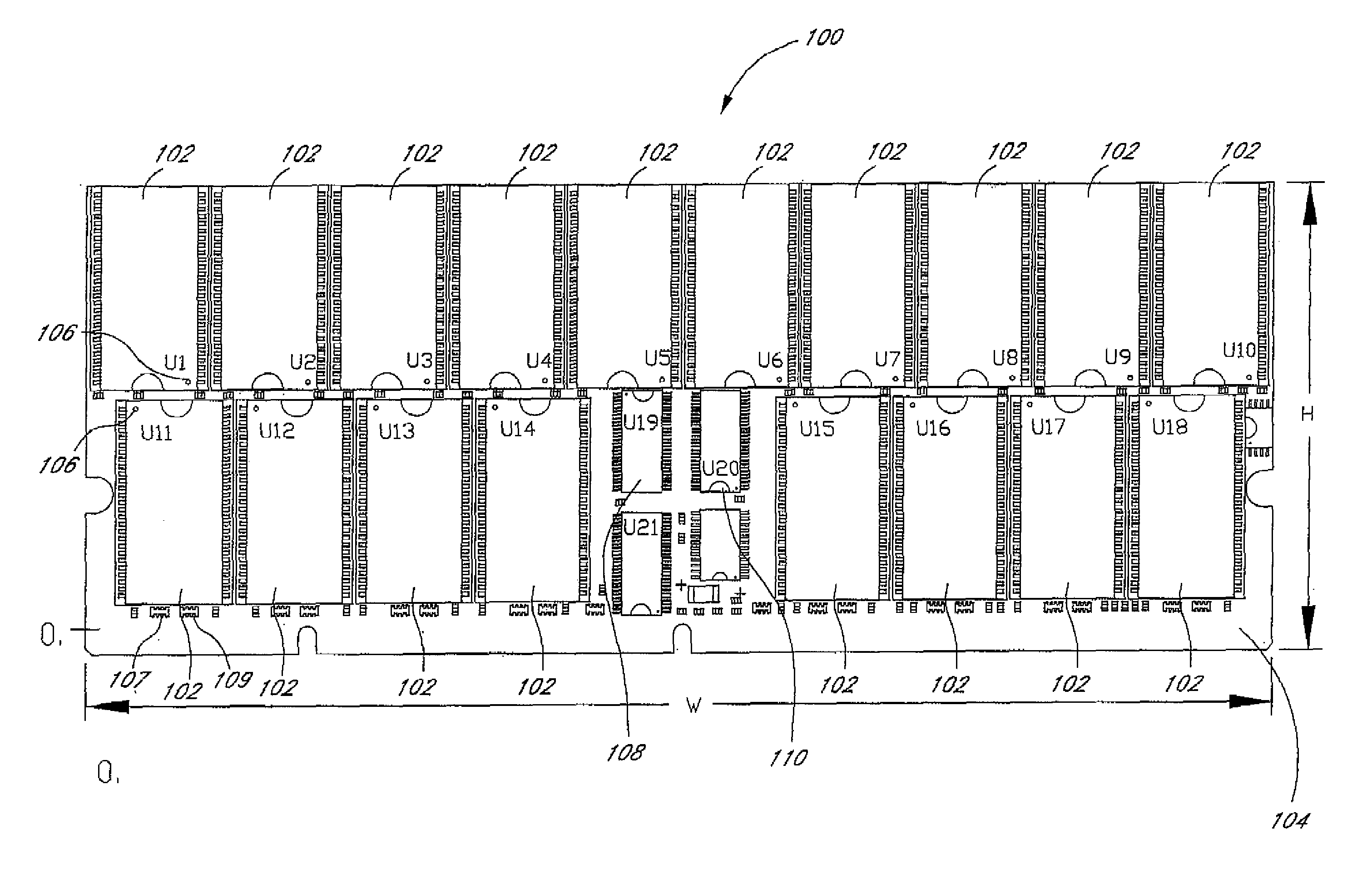

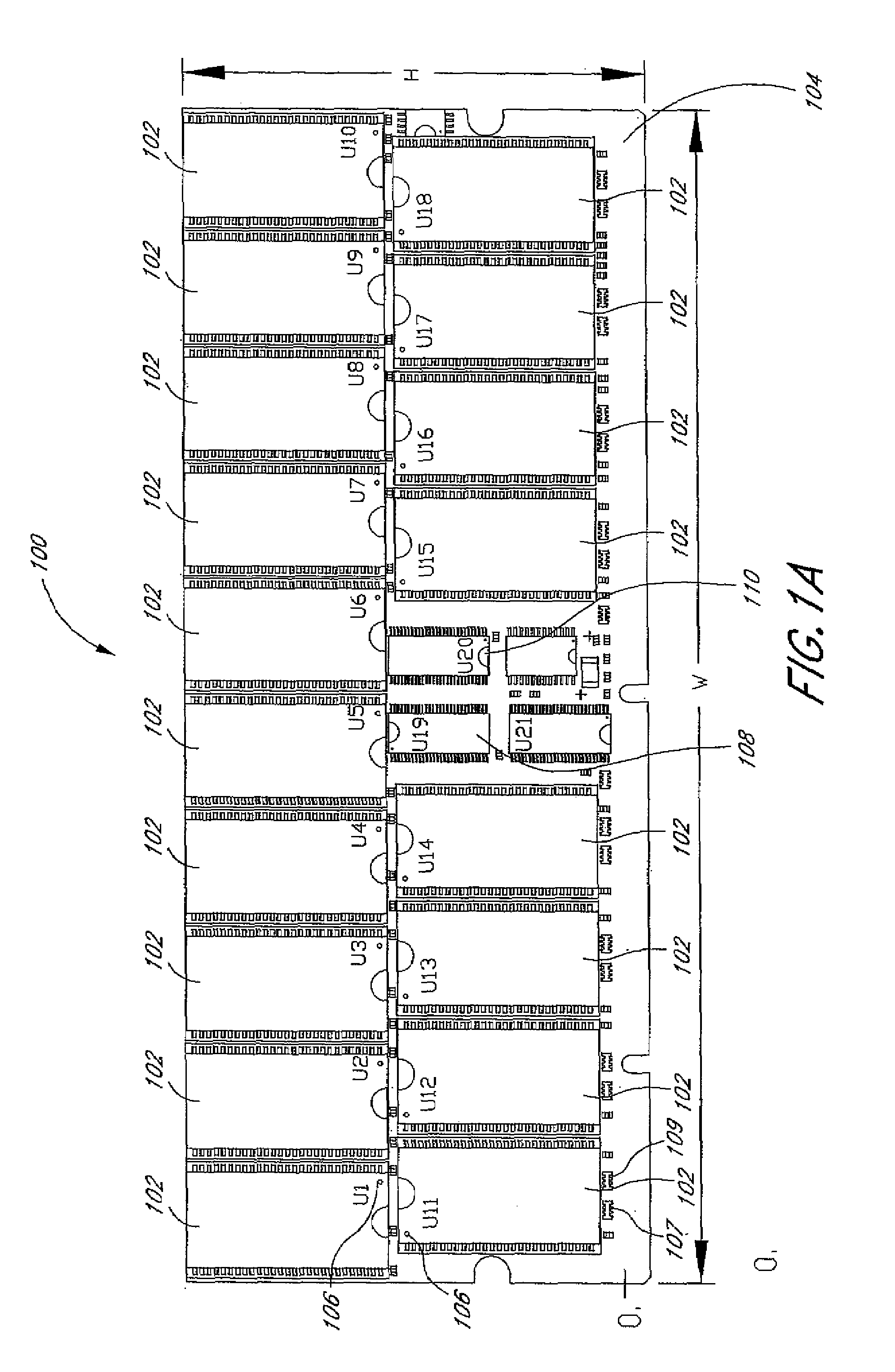

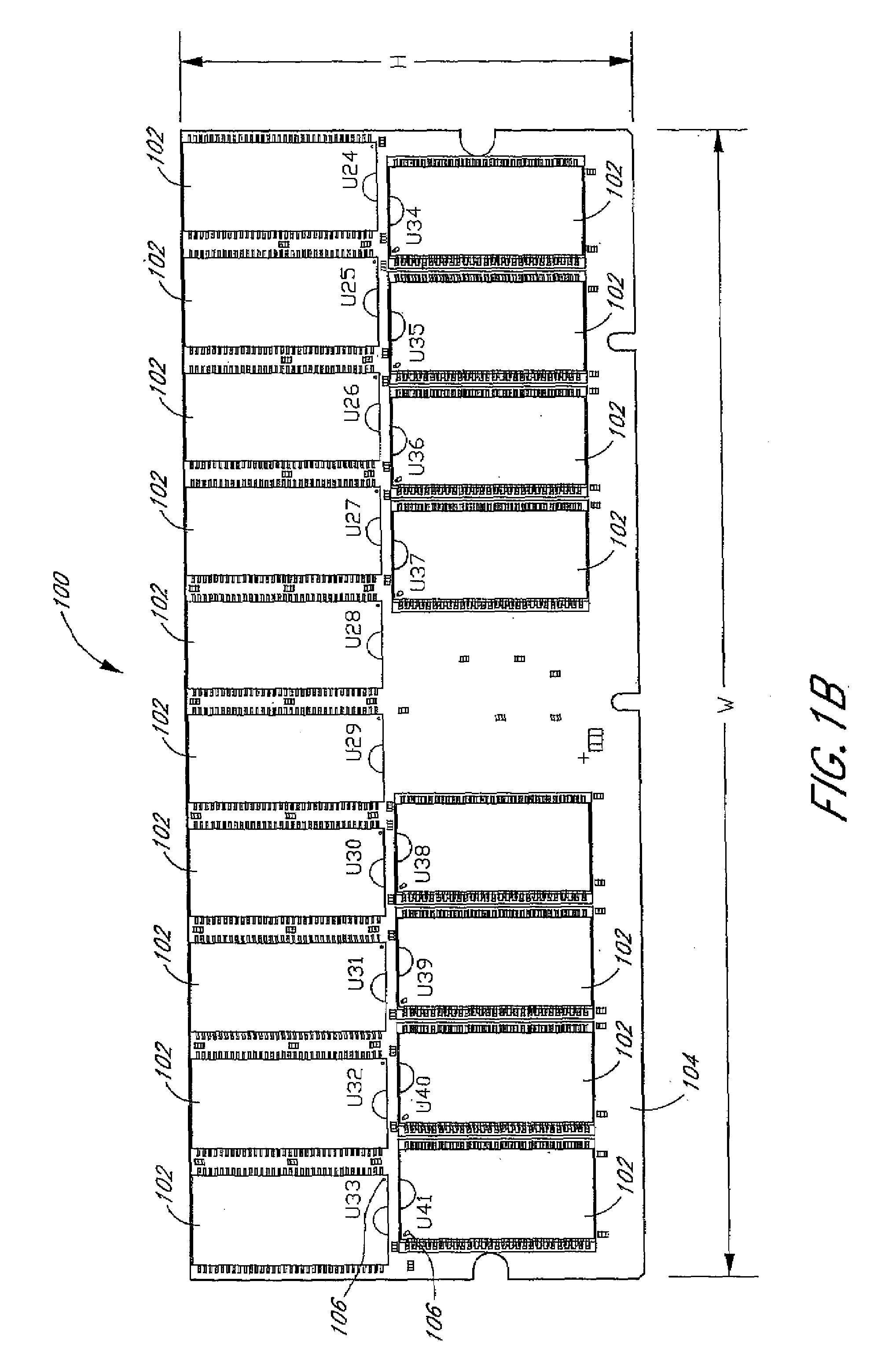

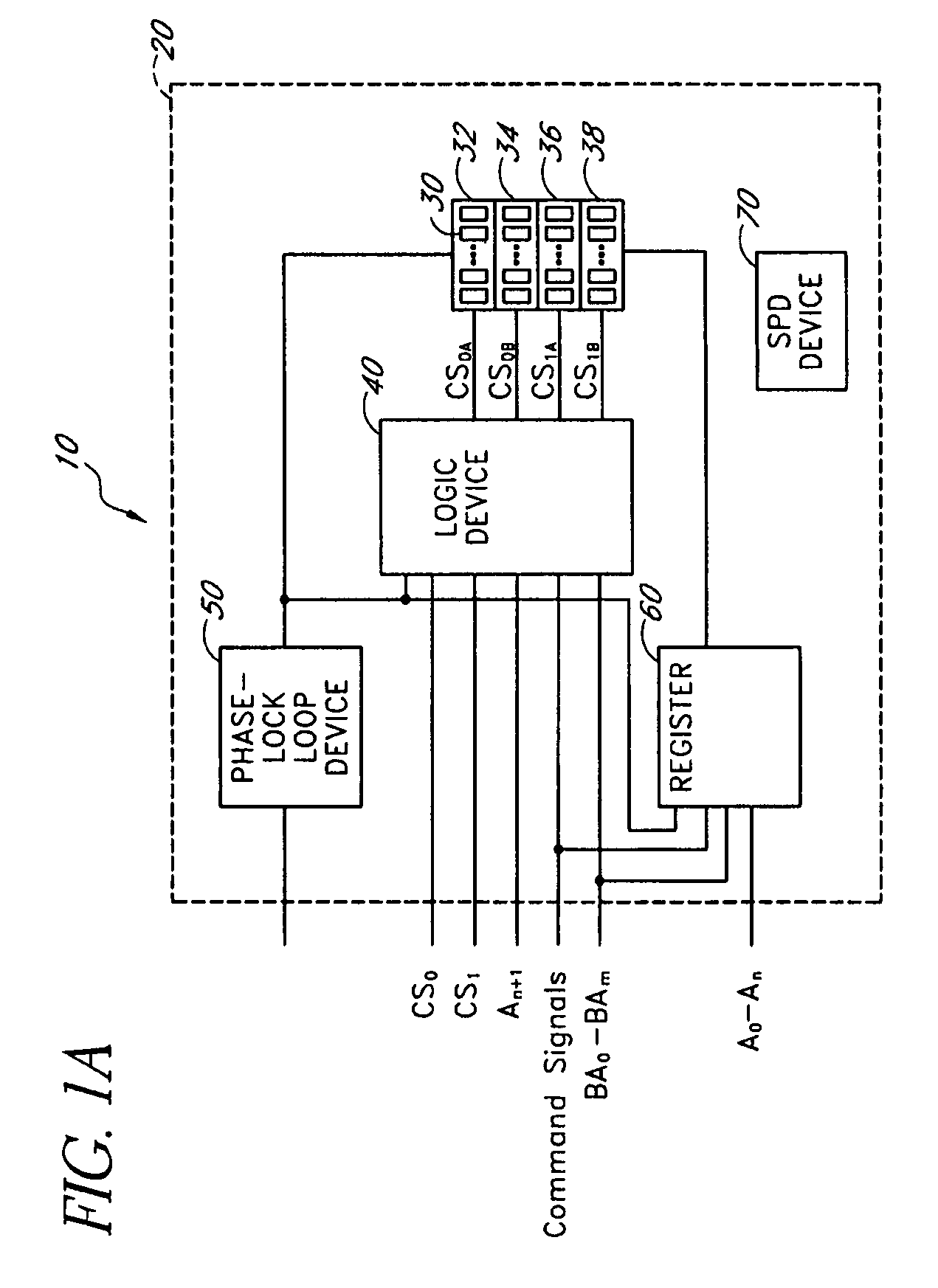

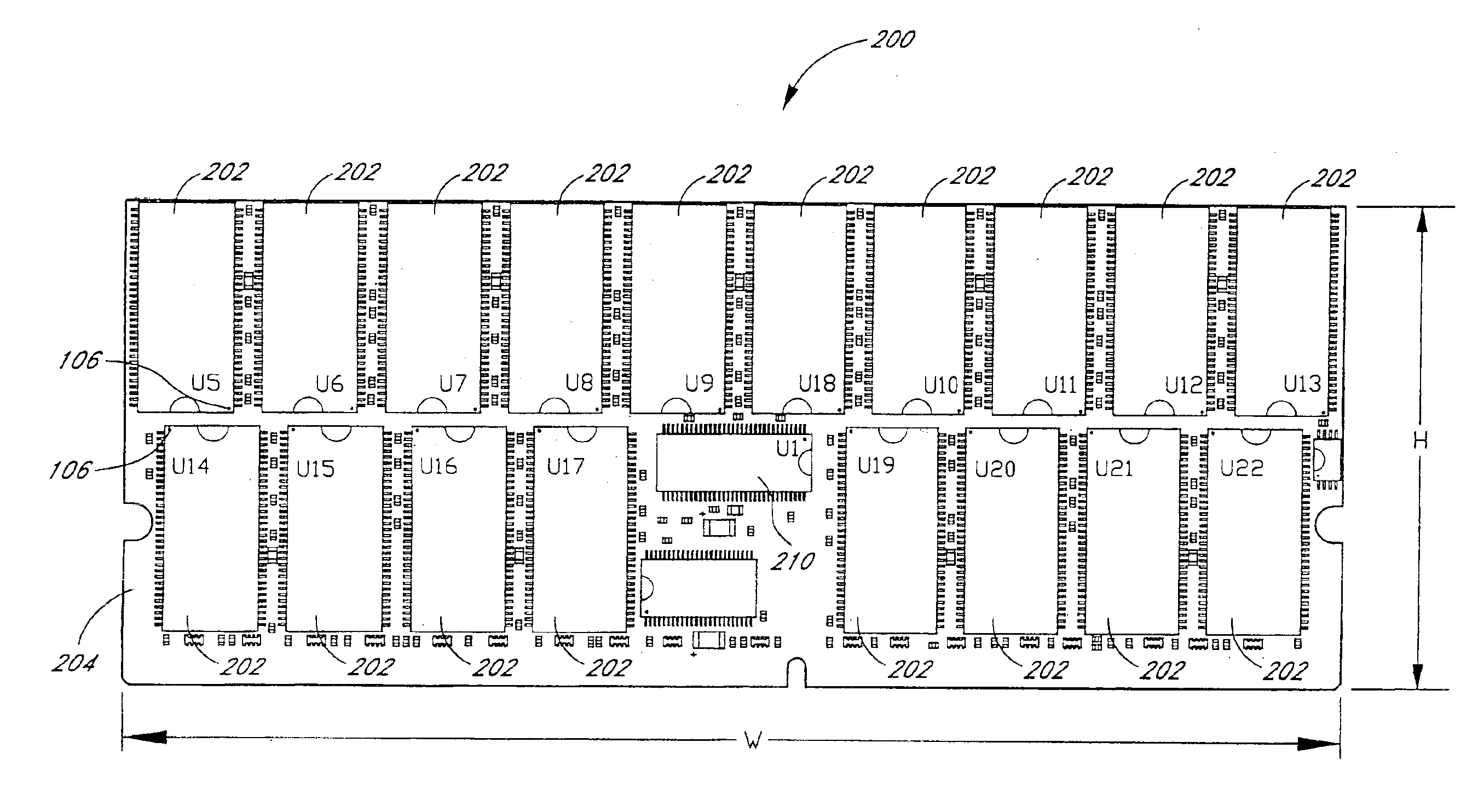

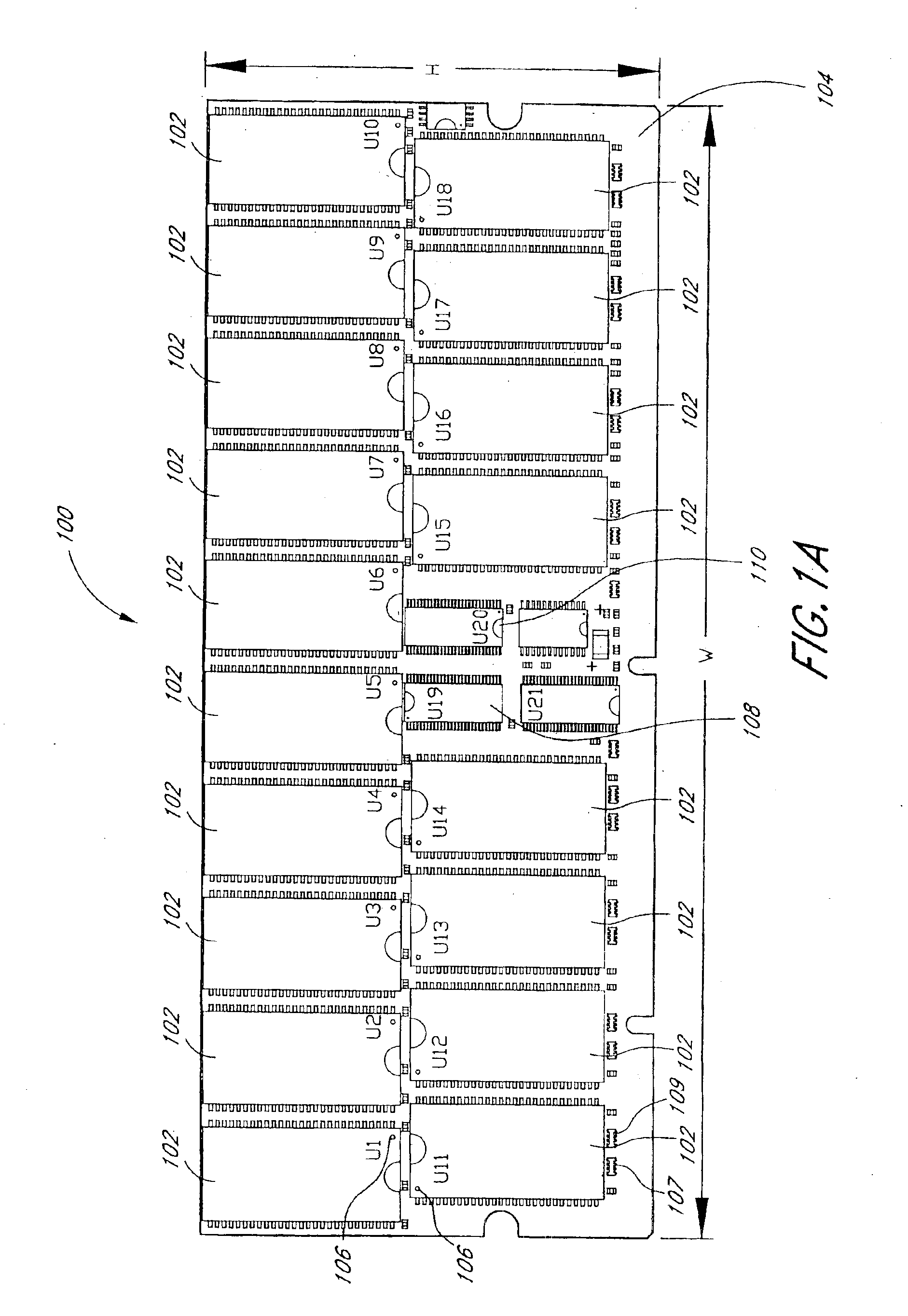

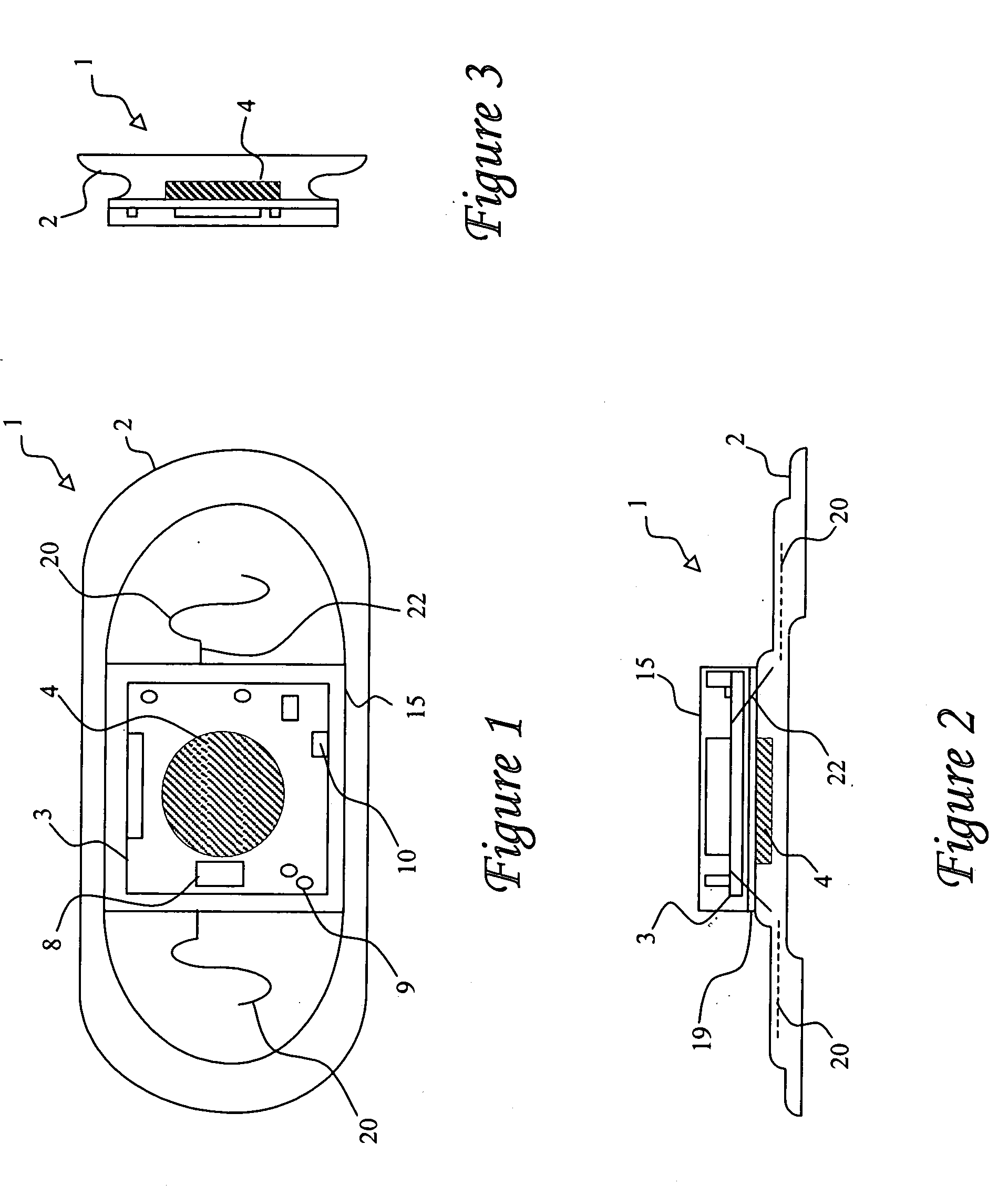

Arrangement of integrated circuits in a memory module

InactiveUS20050018495A1Final product manufactureCross-talk/noise/interference reductionGigabyteProcessor register

Abstract of the Disclosure Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of one-Gigabyte, two-Gigabyte, and four-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in the first row on a first lateral portion of the printed circuit board and in the second row on the first lateral portion are connected to a first addressing register with two register integrated circuits. The integrated circuits in the first row on the second lateral portion and in the second row on the second lateral portion are connected to a second addressing register with two register integrated circuits. Each addressing register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

High density integrated circuit packaging with chip stacking and via interconnections

InactiveUS6187678B1Reduced connection exposureLarge capacitySemiconductor/solid-state device detailsSolid-state devicesThermal expansionPrism

Chip stacks with decreased conductor length and improved noise immunity are formed by laser drilling of individual chips, such as memory chips, preferably near but within the periphery thereof, and forming conductors therethrough, preferably by metallization or filling with conductive paste which may be stabilized by transient liquid phase (TLP) processes and preferably with or during metallization of conductive pads, possibly including connector patterns on both sides of at least some of the chips in the stack. At least some of the chips in the stack then have electrical and mechanical connections made therebetween, preferably with electroplated solder preforms consistent with TLP processes. The connections may be contained by a layer of resilient material surrounding the connections and which may be formed in-situ. High density circuit packages thus obtained may be mounted on a carrier by surface mount techniques or separable connectors such as a plug and socket arrangement. The carrier may be of the same material as the chip stacks to match coefficients of thermal expansion. High-density circuit packages may also be in the form of removable memory modules in generally planar or prism shaped form similar to a pen or as a thermal conduction module.

Owner:IBM CORP

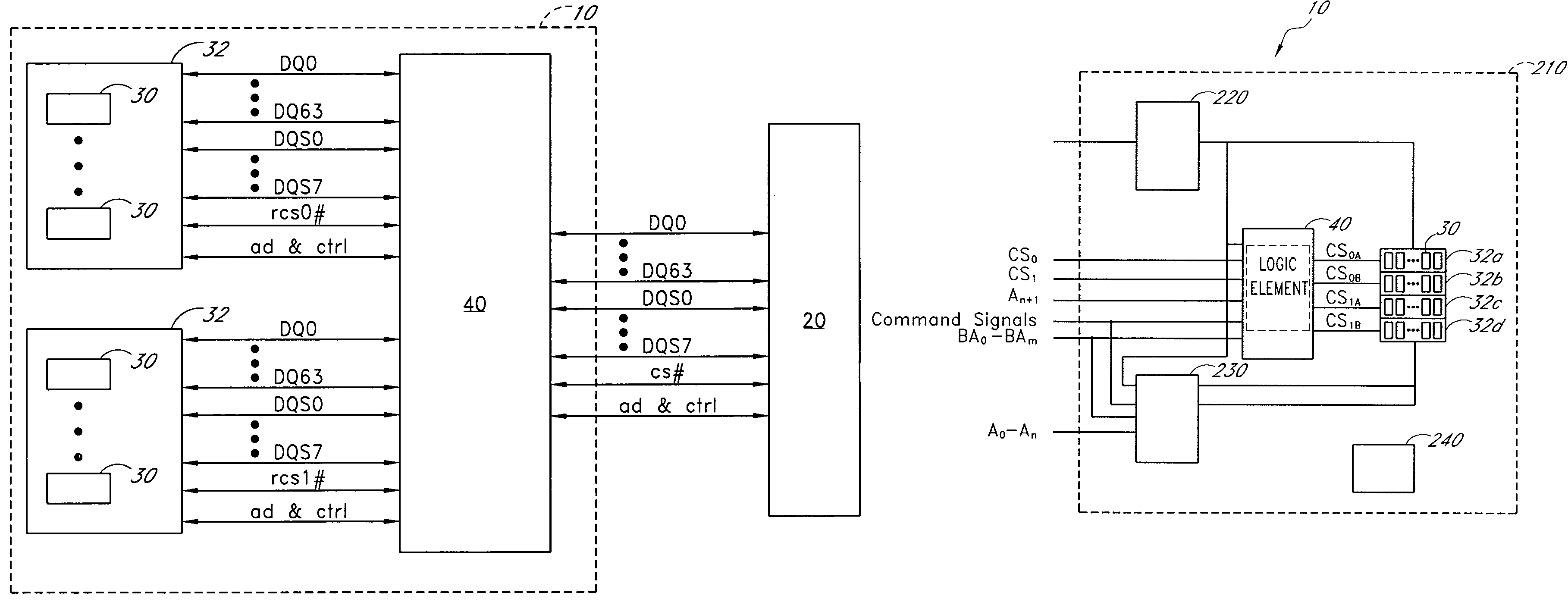

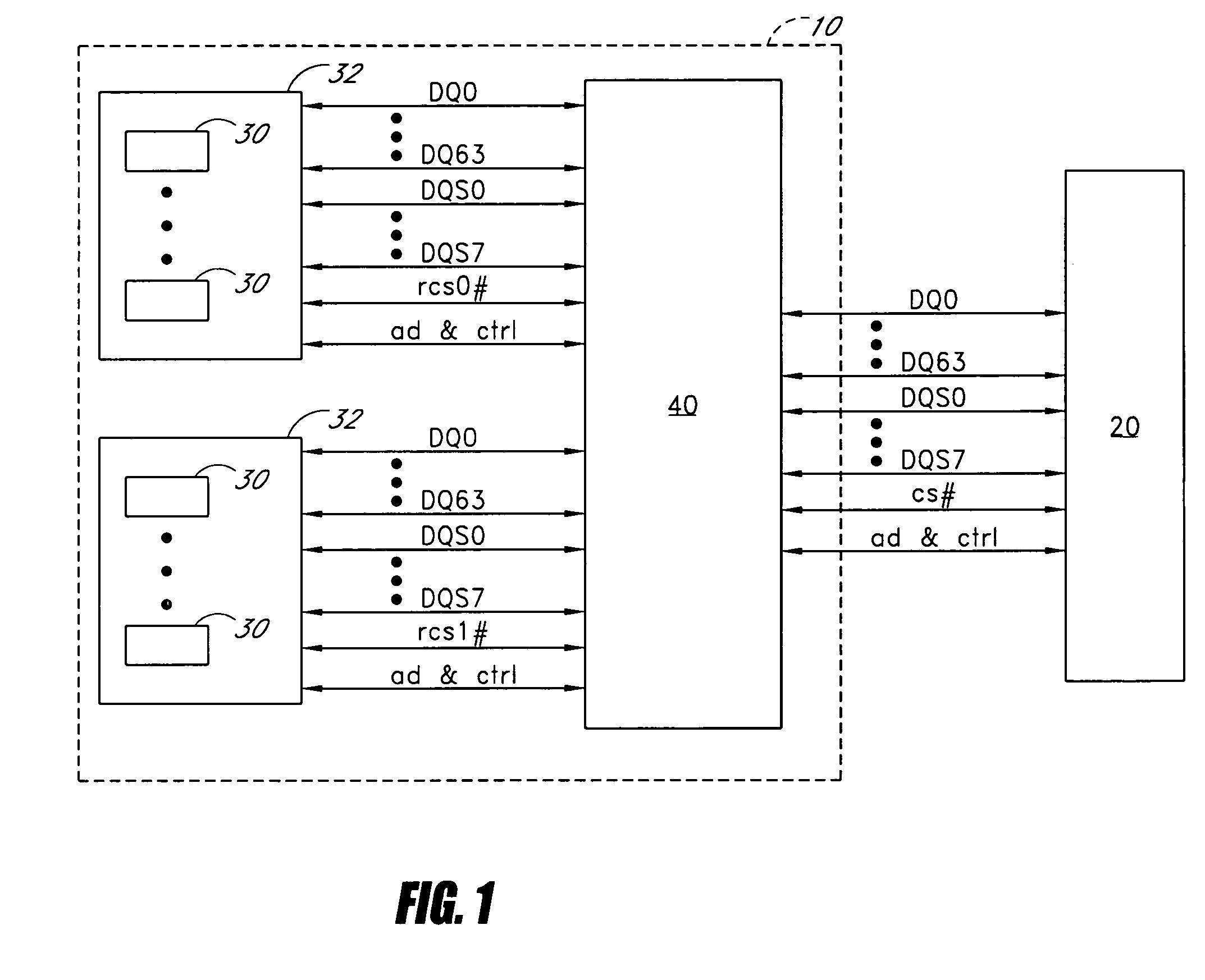

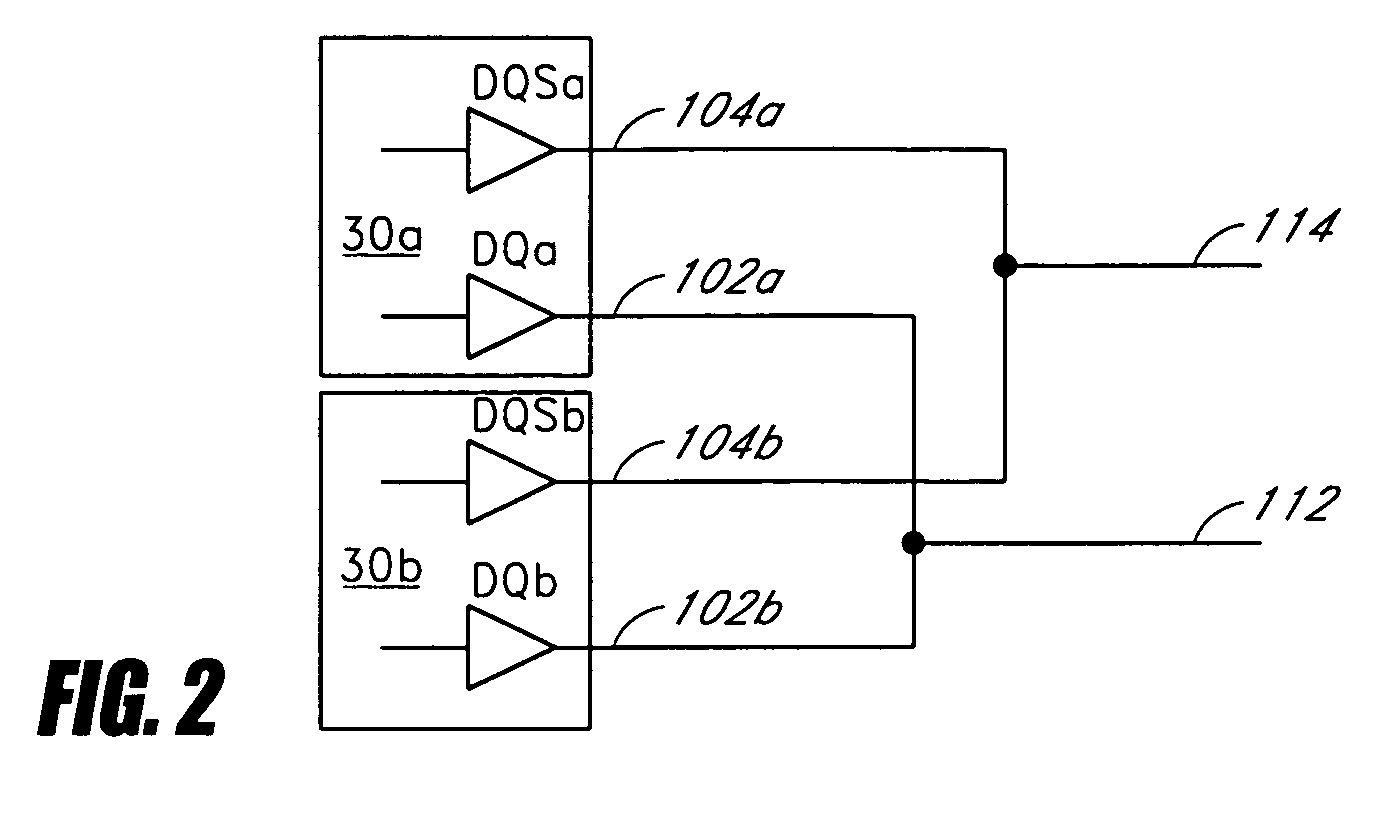

Memory module with a circuit providing load isolation and memory domain translation

A memory module includes a plurality of memory devices and a circuit. Each memory device has a corresponding load. The circuit is electrically coupled to the plurality of memory devices and is configured to be electrically coupled to a memory controller of a computer system. The circuit selectively isolates one or more of the loads of the memory devices from the computer system. The circuit comprises logic which translates between a system memory domain of the computer system and a physical memory domain of the memory module.

Owner:NETLIST INC

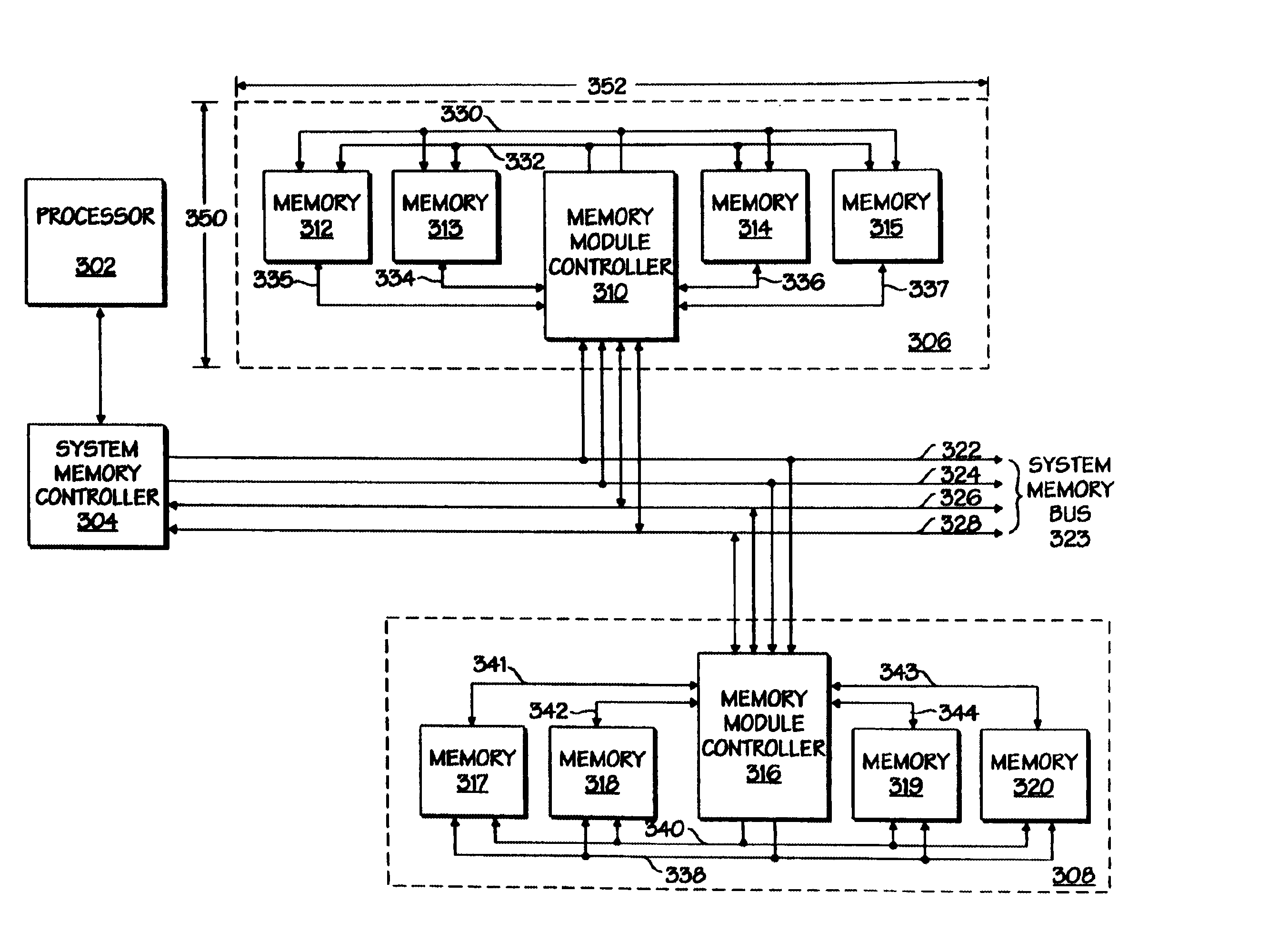

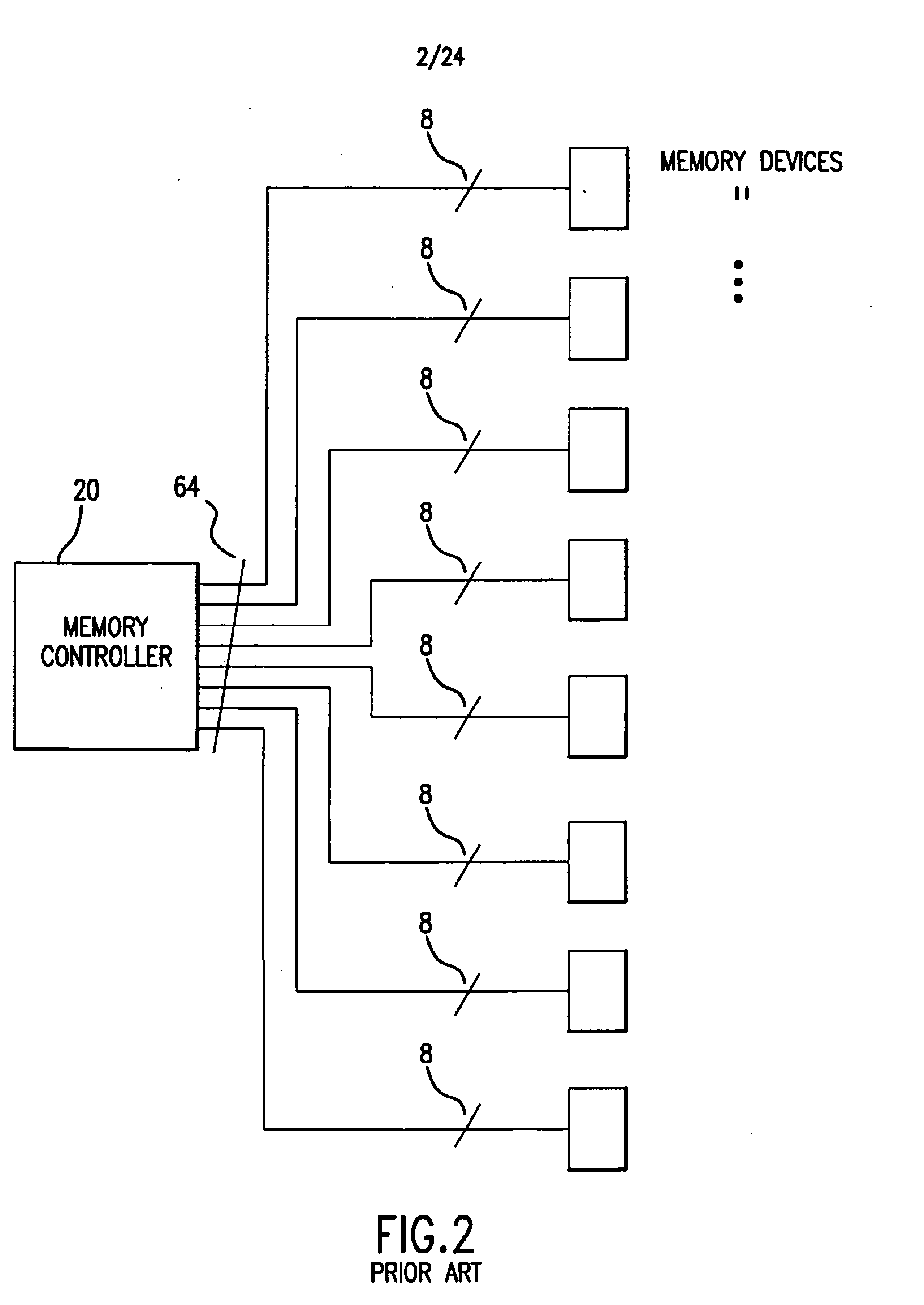

Memory module controller for providing an interface between a system memory controller and a plurality of memory devices on a memory module

A memory module controller for providing interface between a system memory controller and a plurality of memory devices on a memory module. The memory module includes first interface circuitry and control logic. The first interface circuitry is configured to receive from the system memory controller a first memory transaction in a first format. The control logic is coupled to the first interface circuitry and configured to convert the first memory transaction into a second memory transaction in a second format for the plurality of memory devices. The second format of the second memory transaction is different than the first format of the first memory transaction.

Owner:INTEL CORP

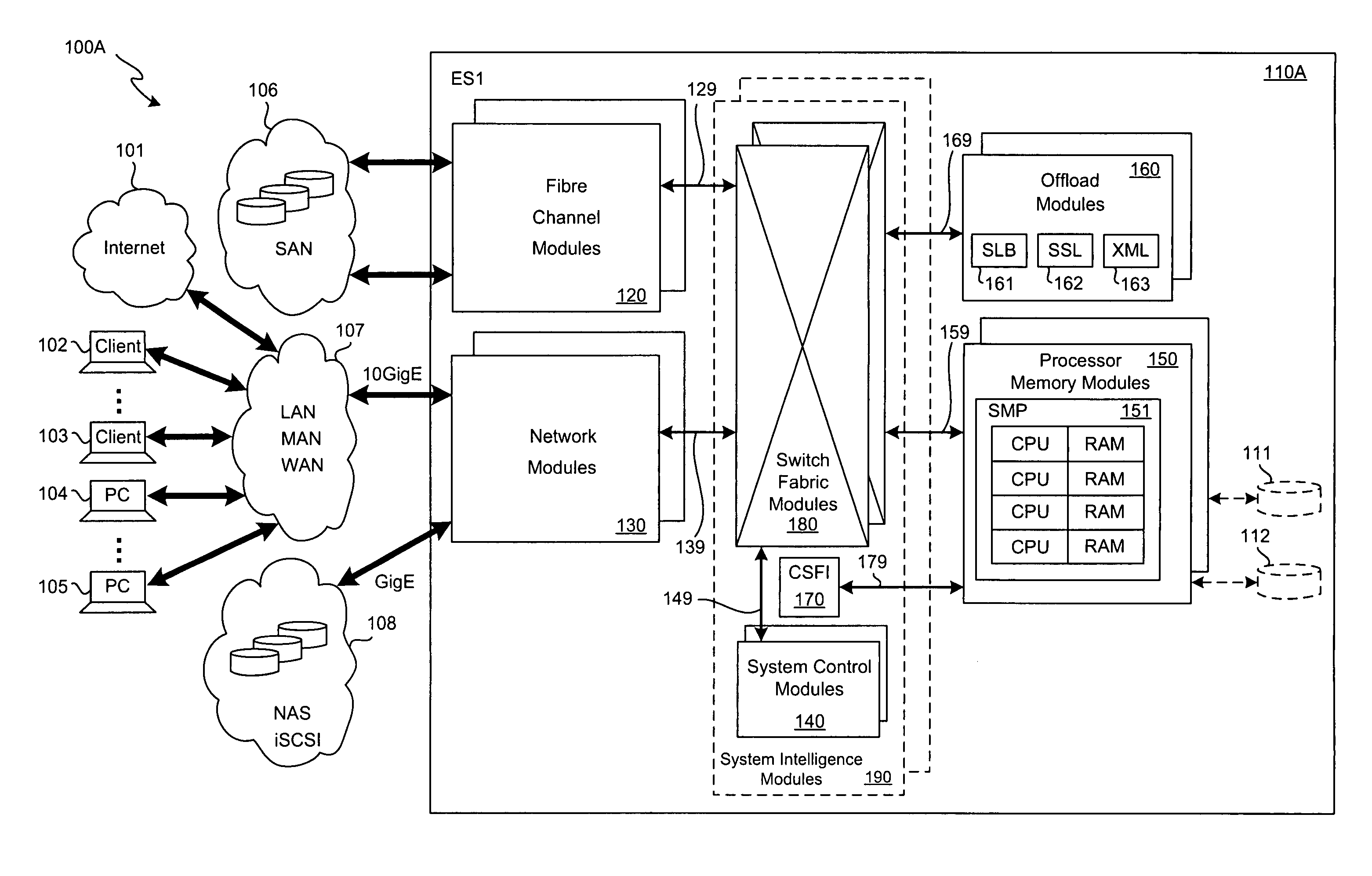

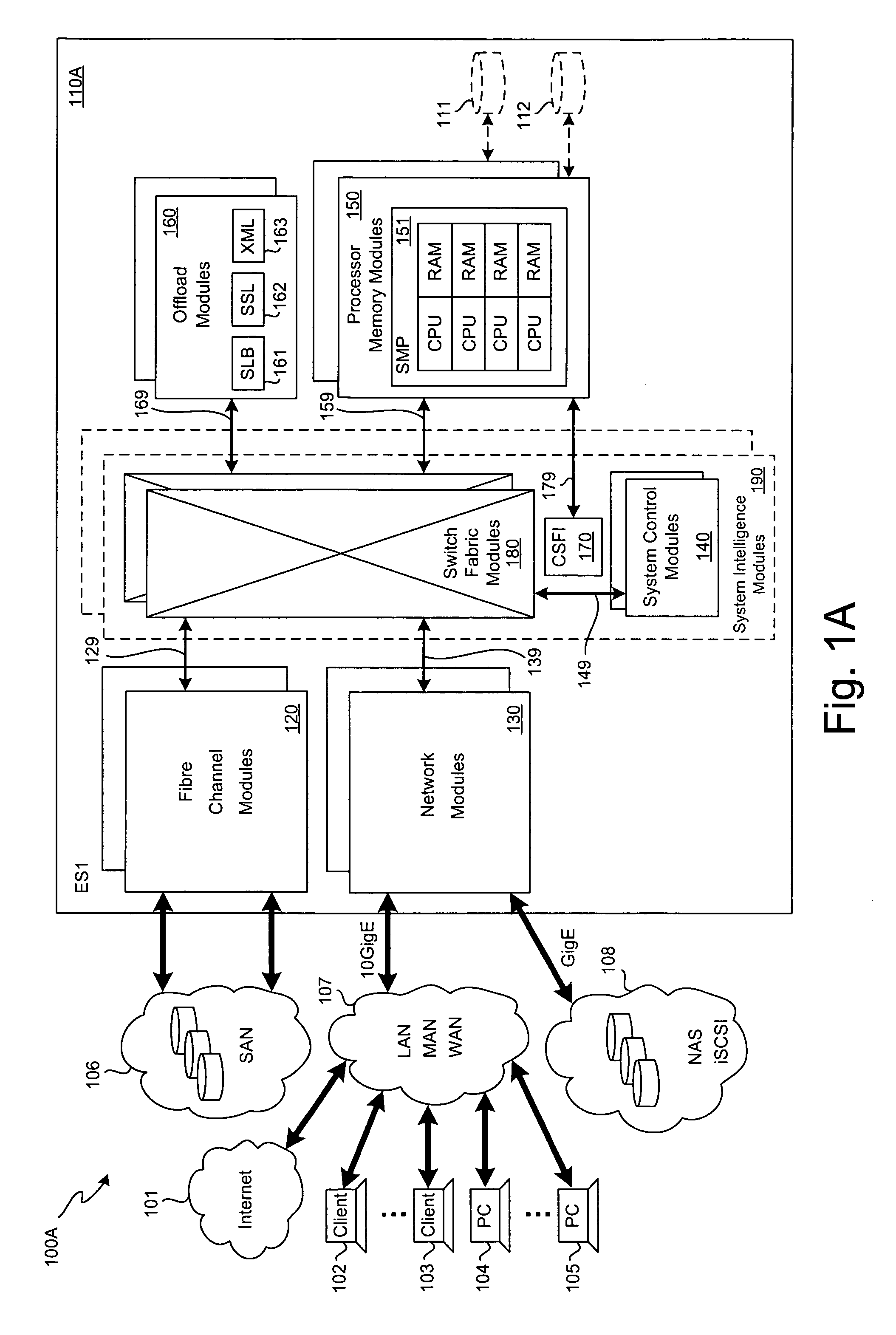

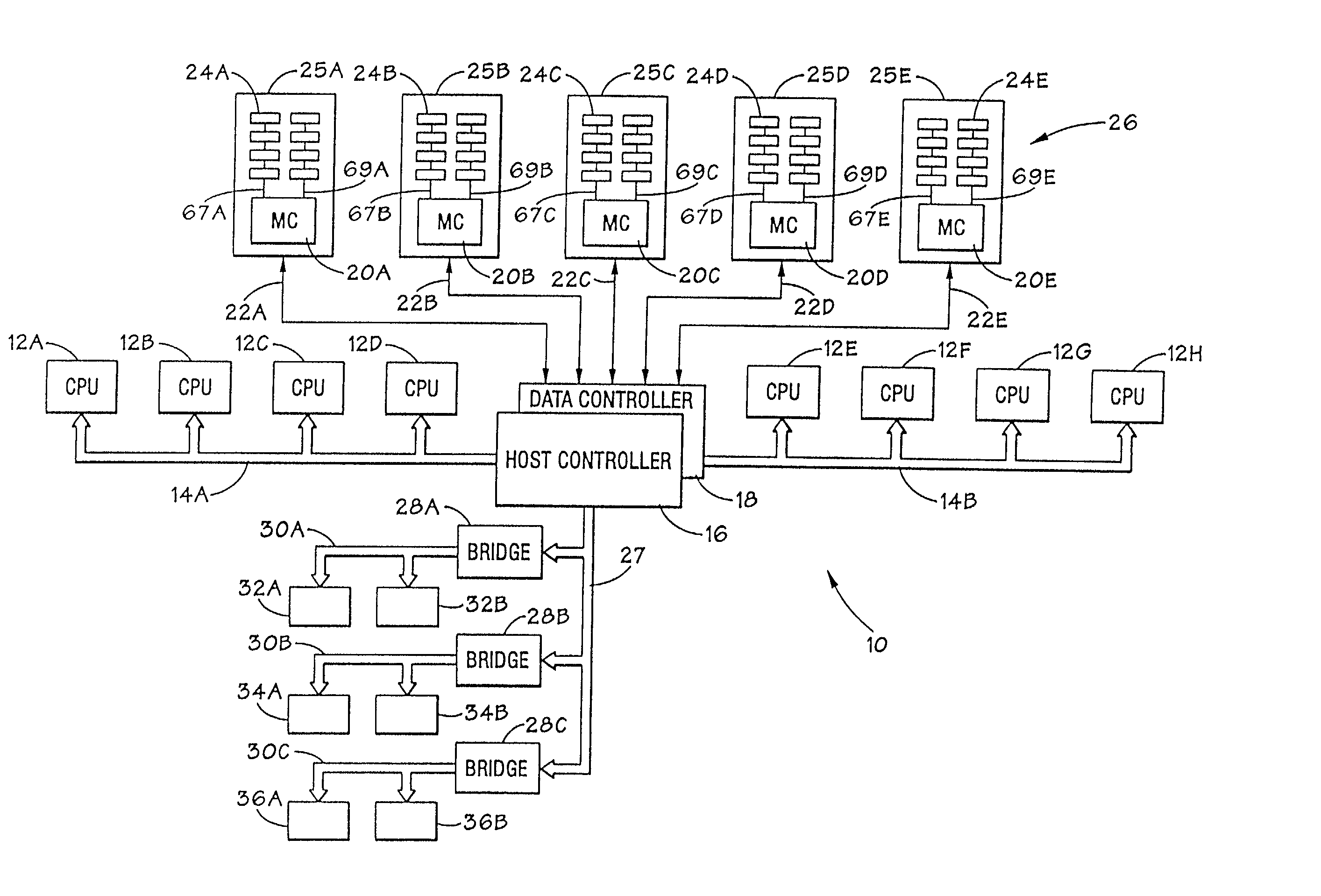

SCSI transport for fabric-backplane enterprise servers

ActiveUS7633955B1Improve performanceImprove efficiencyDigital computer detailsData switching by path configurationSCSI initiator and targetFiber

A Small Computer System Interface (SCSI) transport for fabric backplane enterprise servers provides for local and remote communication of storage system information between storage sub-system elements of an ES system and other elements of an ES system via a storage interface. The transport includes encapsulation of information for communication via a reliable transport implemented in part across a cellifying switch fabric. The transport may optionally include communication via Ethernet frames over any of a local network or the Internet. Remote Direct Memory Access (RDMA) and Direct Data Placement (DDP) protocols are used to communicate the information (commands, responses, and data) between SCSI initiator and target end-points. A Fibre Channel Module (FCM) may be operated as a SCSI target providing a storage interface to any of a Processor Memory Module (PMM), a System Control Module (SCM), and an OffLoad Module (OLM) operated as a SCSI initiator.

Owner:ORACLE INT CORP

Systems and methods for monitoring a patient health network

ActiveUS20180225960A1Transmission systemsTesting/monitoring control systemsCommunication interfacePhysiological monitoring

Systems and methods for monitoring physiological monitoring systems are described herein. A communication interface module can be configured to receive from a physiological monitoring system first data based on a snapshot taken of a status of the physiological monitoring system at a first time. A memory module can be configured to store the first data and a baseline associated with the physiological monitoring system. A processor module can be configured to compare the first data with the baseline and to generate a notification if the first data deviates from the baseline by a predetermined amount. A display module can be configured to display a physical location of a plurality of physiological monitoring systems and display the notification.

Owner:MASIMO CORP

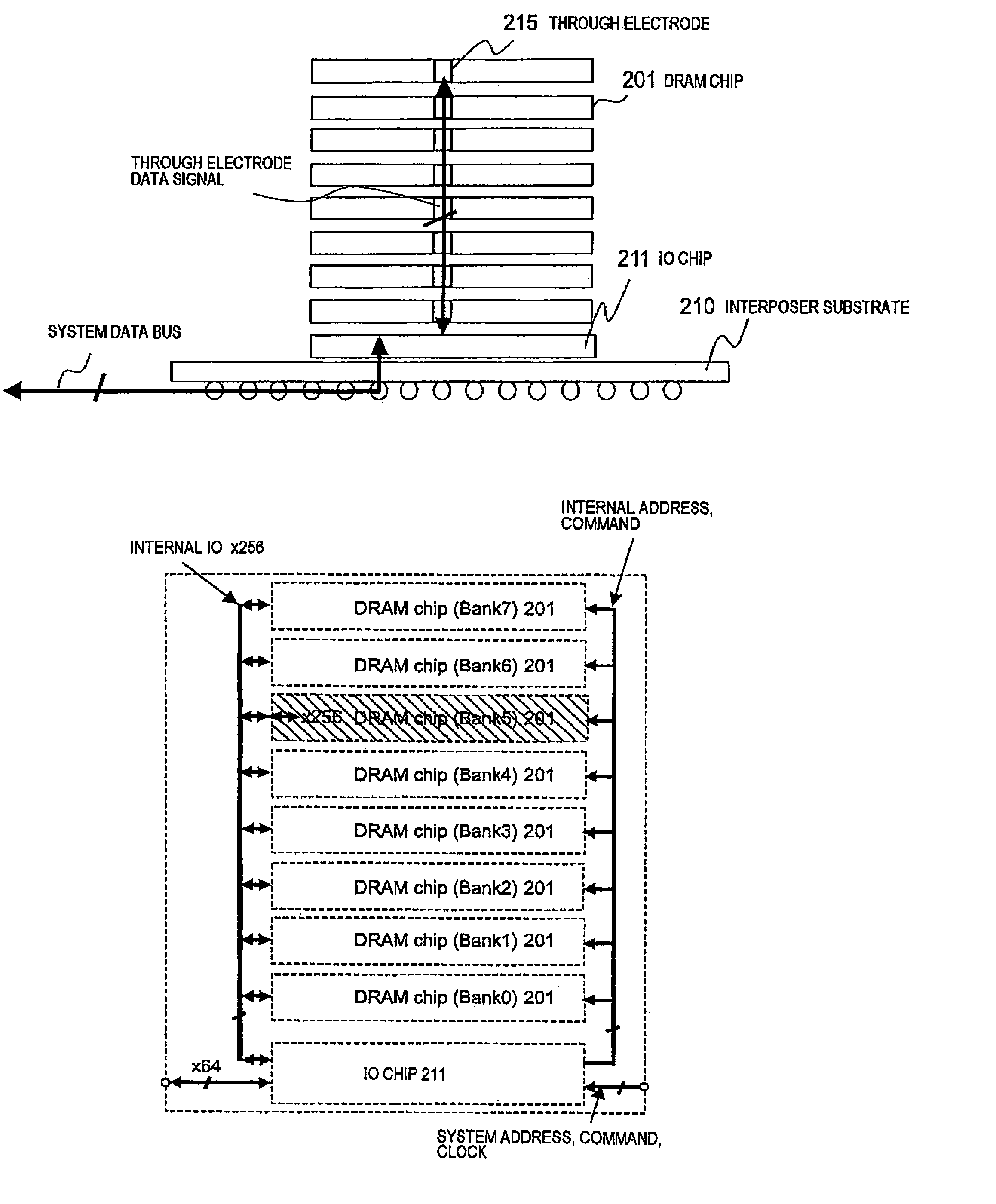

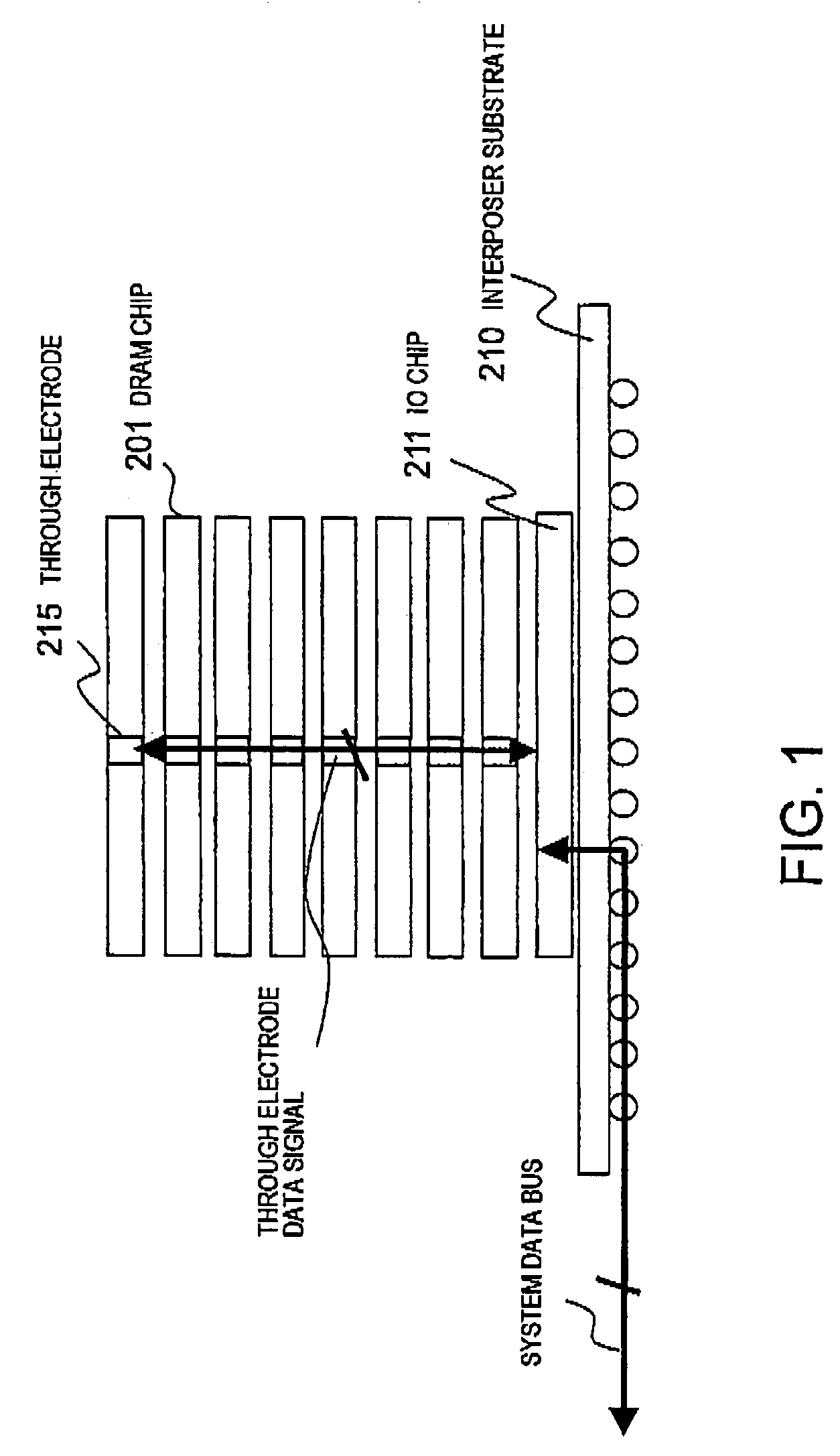

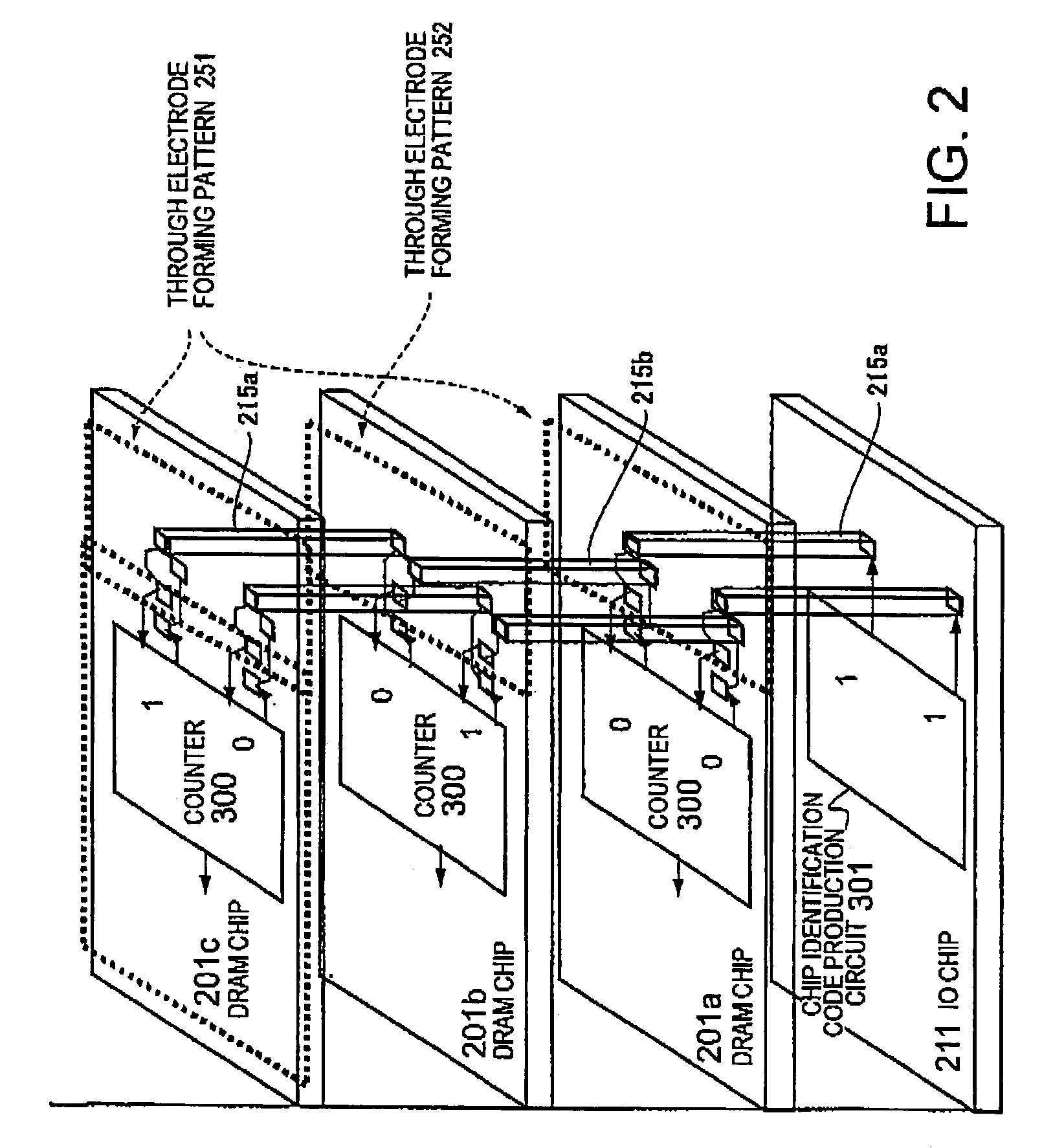

Memory module and memory system

ActiveUS7123497B2Increase chanceVarious problemDomestic stoves or rangesLighting and heating apparatusData signalComputer module

In a memory module including a plurality of DRAM chips which transmit / receive a system data signal with a predetermined data width and at a transfer rate and which transmit / receive an internal data signal having a larger data width and a lower transfer rate as compared with the system data signal, it has become clear that there is a restriction on the transfer rate of the system data signal and that speeding-up cannot be expected. A current consumption in a plurality of DRAMs constituting the memory module is large, and this is also a factor for hindering the speeding-up. There is obtained a memory module in which a plurality of DRAM chips are stacked on an IO chip and in which each DRAM chip is connected to the IO chip by a through electrode and which comprises a constitution for mutually converting the system data signal and the internal data signal in each DRAM chip by the IO chip. In this constitution, a wiring between the DRAM chips can be shortened, and DLL having a large current consumption may be disposed only on the IO chip.

Owner:LONGITUDE LICENSING LTD

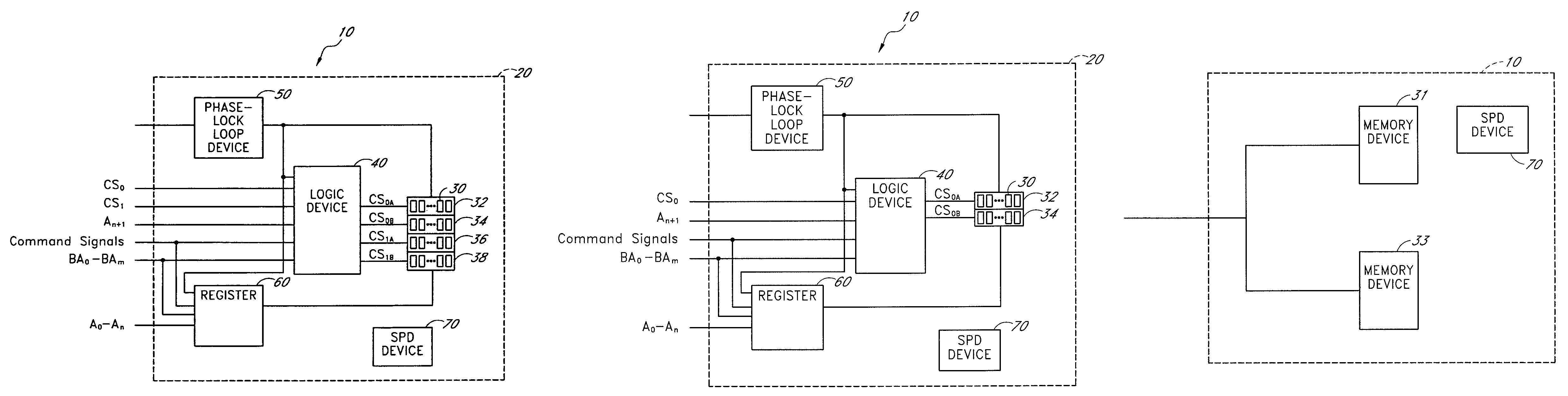

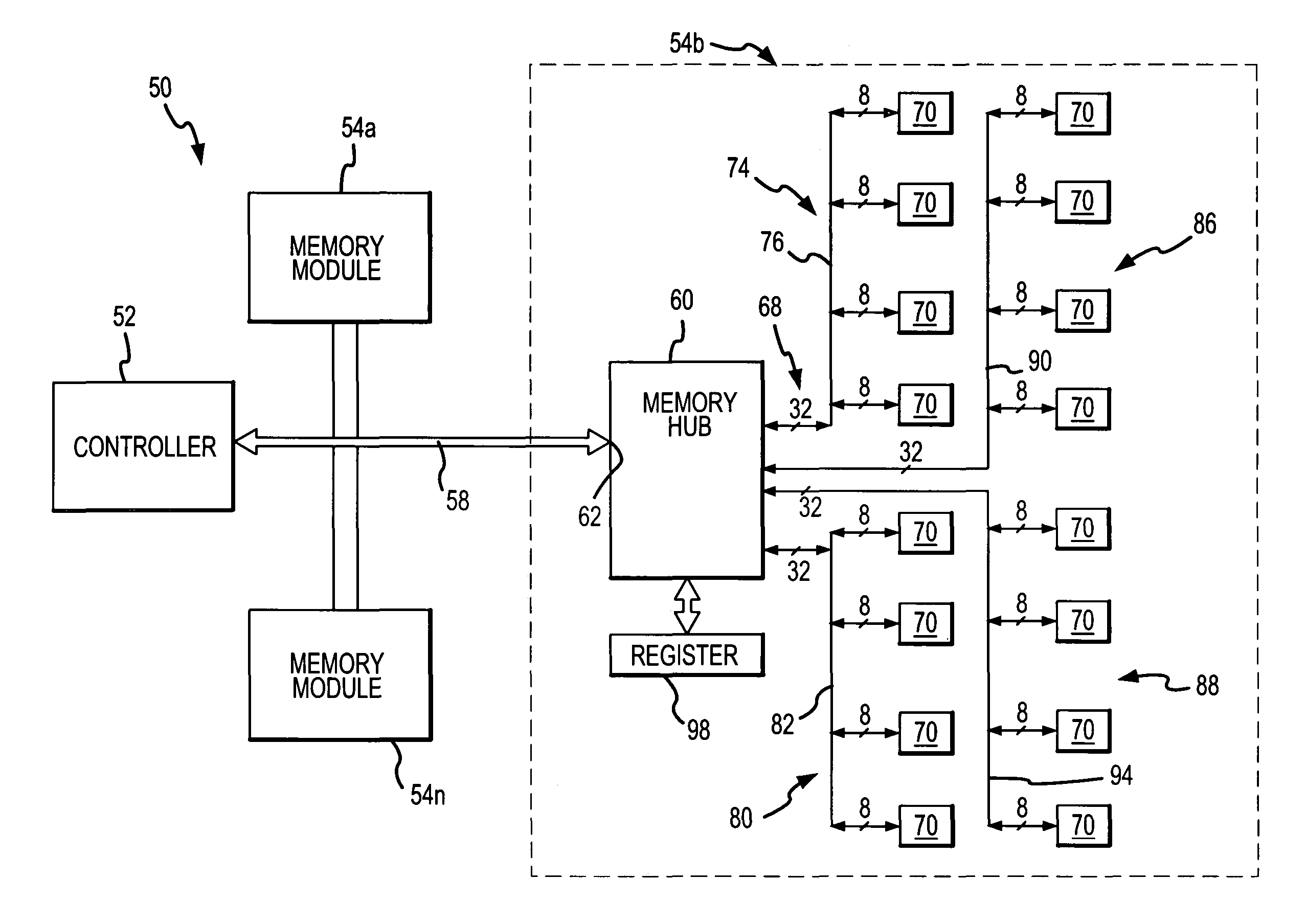

Memory module decoder

A memory module connectable to a computer system includes a printed circuit board, a plurality of memory devices coupled to the printed circuit board, and a logic element coupled to the printed circuit board. The plurality of memory devices has a first number of memory devices. The logic element receives a set of input control signals from the computer system. The set of input control signals corresponds to a second number of memory devices smaller than the first number of memory devices. The logic element generates a set of output control signals in response to the set of input control signals. The set of output control signals corresponds to the first number of memory devices.

Owner:NETLIST INC

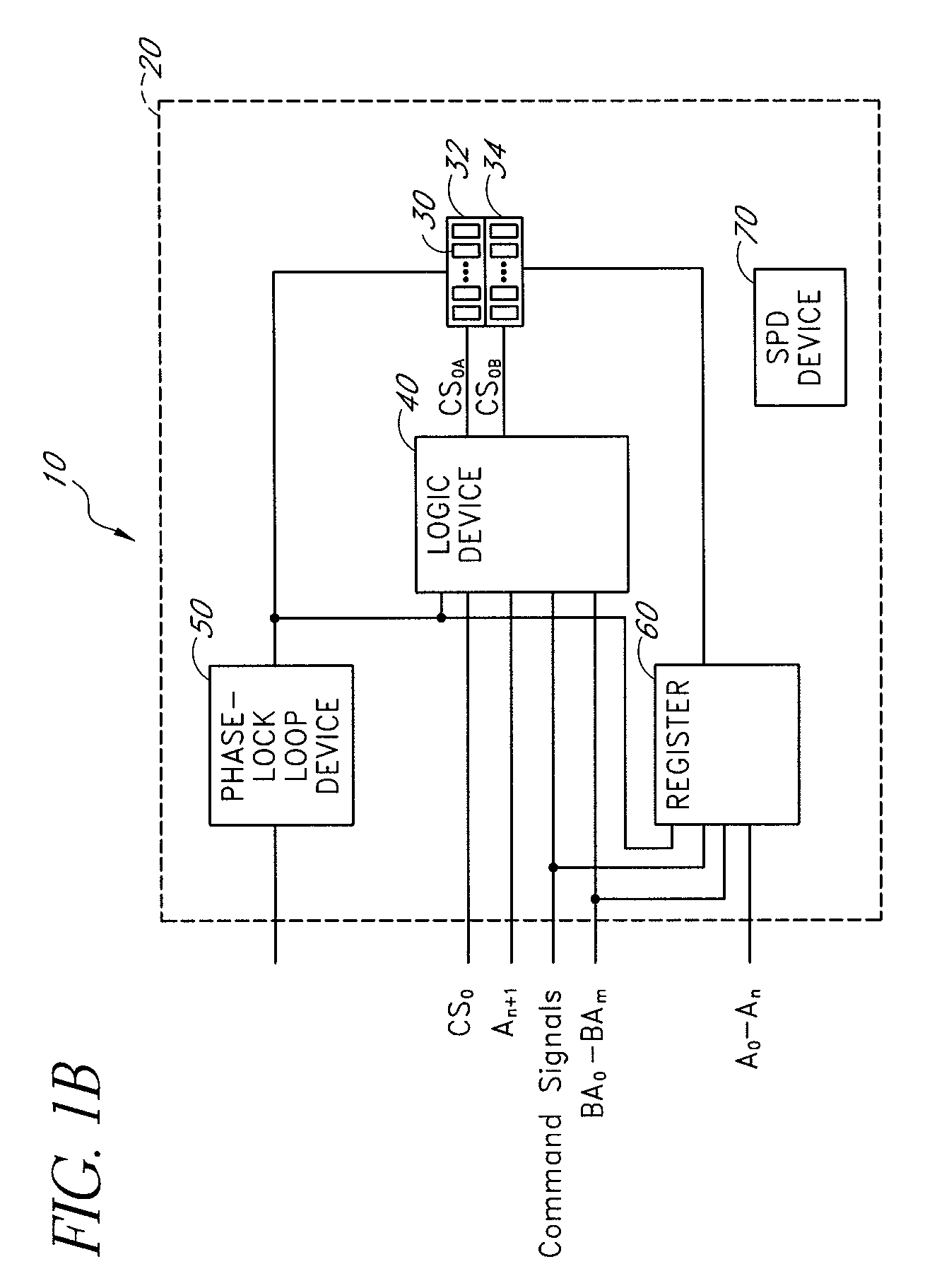

Reconfigurable memory module and method

InactiveUS7120727B2High bandwidthMemory adressing/allocation/relocationHigh bandwidthComputerized system

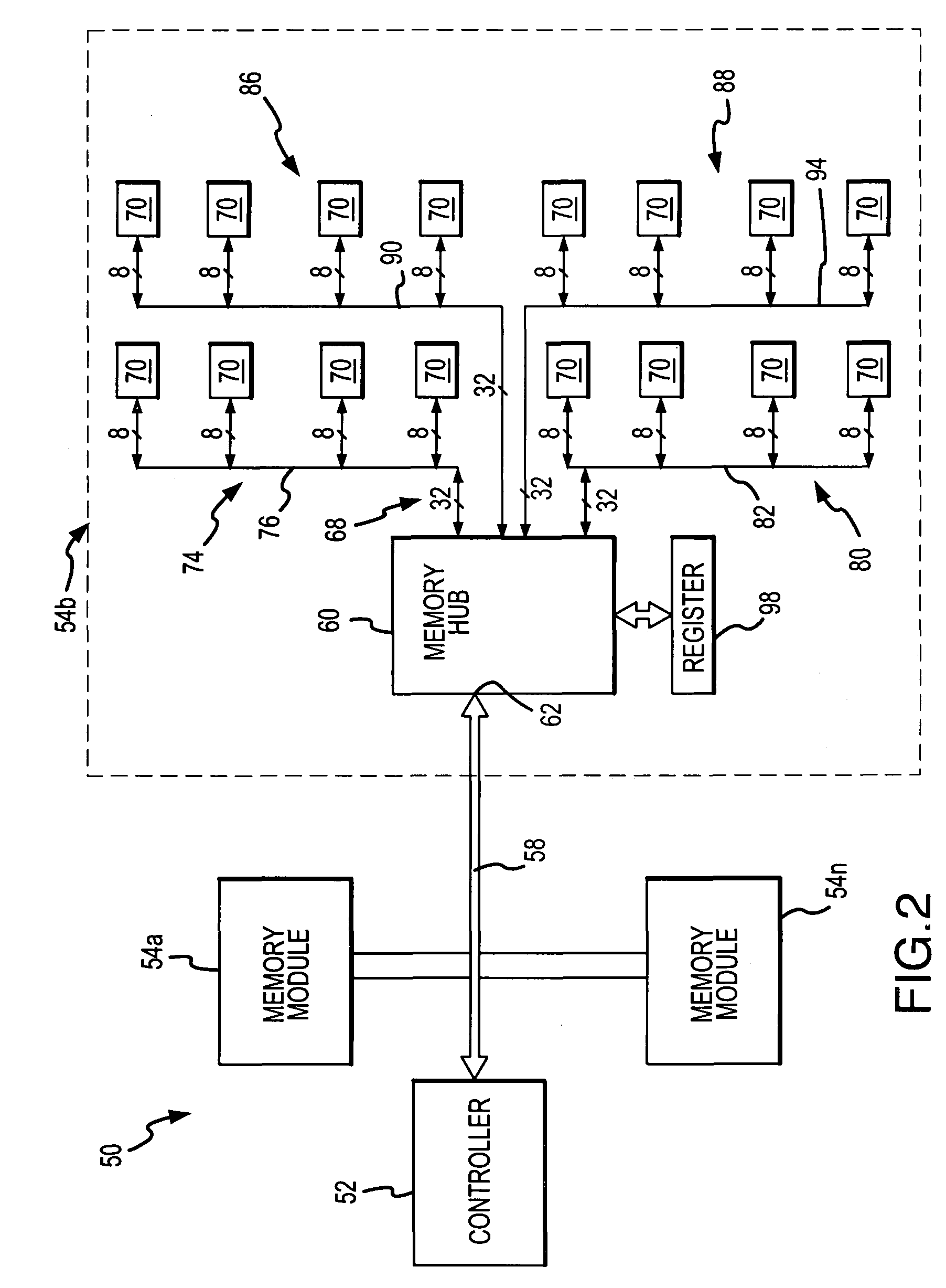

A computer system includes a controller coupled to a plurality of memory modules each of which includes a memory hub and a plurality of memory devices divided into a plurality of ranks. The memory hub is operable to configure the memory module to simultaneously address any number of ranks to operate in a high bandwidth mode, a high memory depth mode, or any combination of such modes.

Owner:ROUND ROCK RES LLC

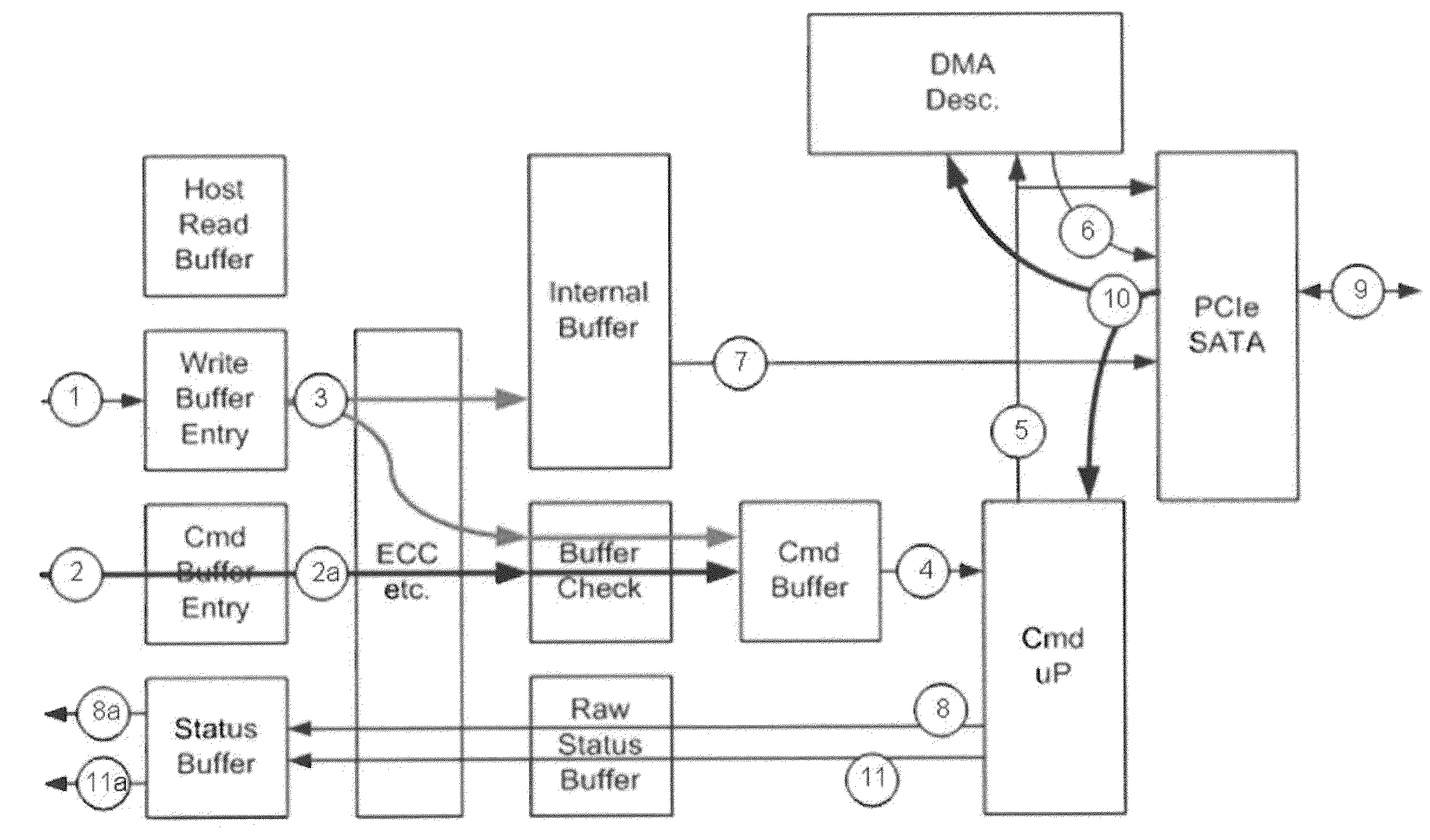

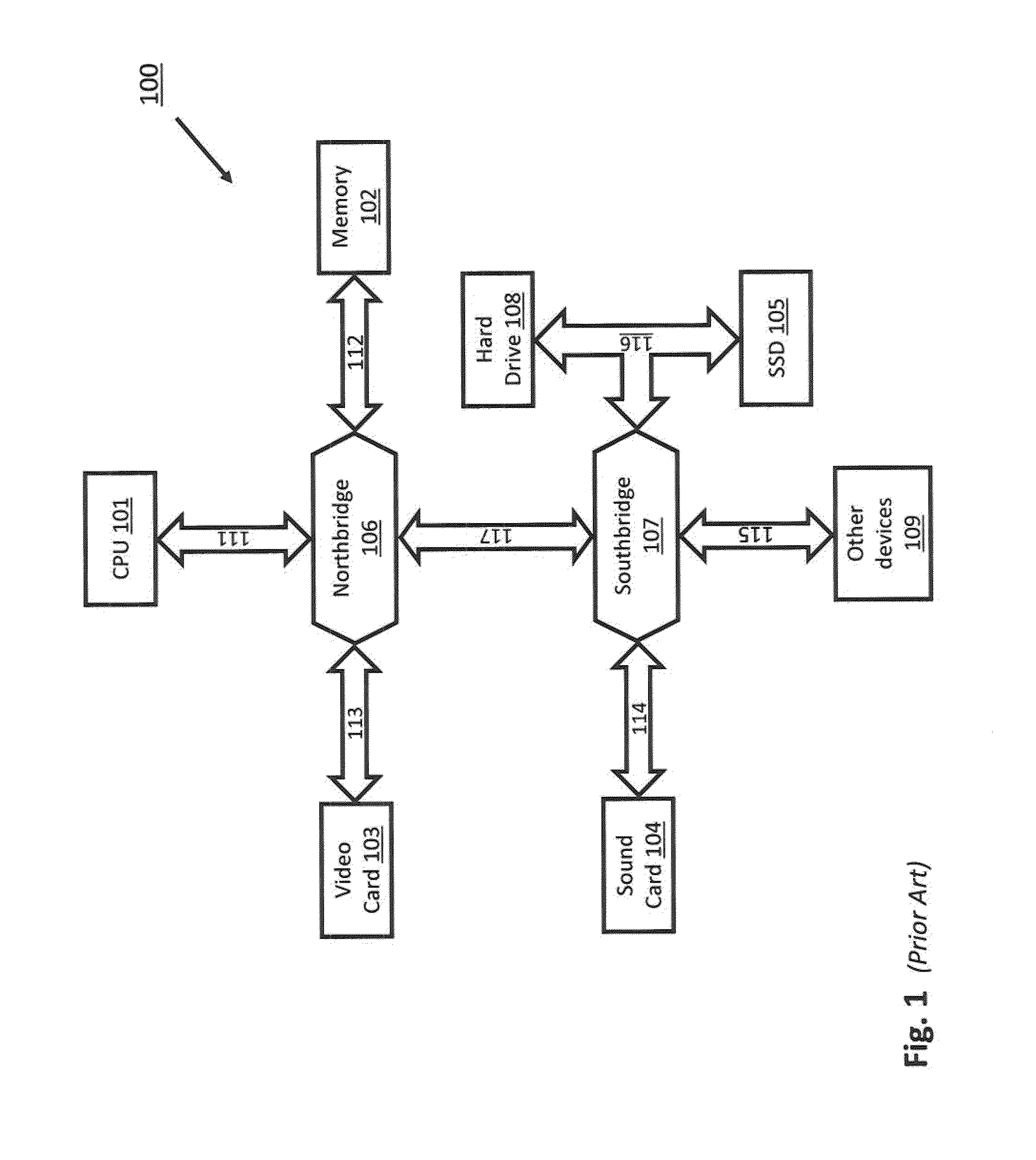

System and method of interfacing co-processors and input/output devices via a main memory system

ActiveUS20120204079A1Memory architecture accessing/allocationError detection/correctionComputer moduleMemory bus

A system for interfacing with a co-processor or input / output device is disclosed. According to one embodiment, the system includes a computer processing unit, a memory module, a memory bus that connects the computer processing unit and the memory module, and a co-processing unit or input / output device, wherein the memory bus also connects the co-processing unit or input / output device to the computer processing unit.

Owner:RAMBUS INC

Arrangement of integrated circuits in a memory module

Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of 1-Gigabyte and 2-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in a first half of the first row and in the corresponding half of the second row are connected via a signal trace to a first register. The integrated circuits in a second half of the first row and in the corresponding half of the second row are connected to a second register. Each register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

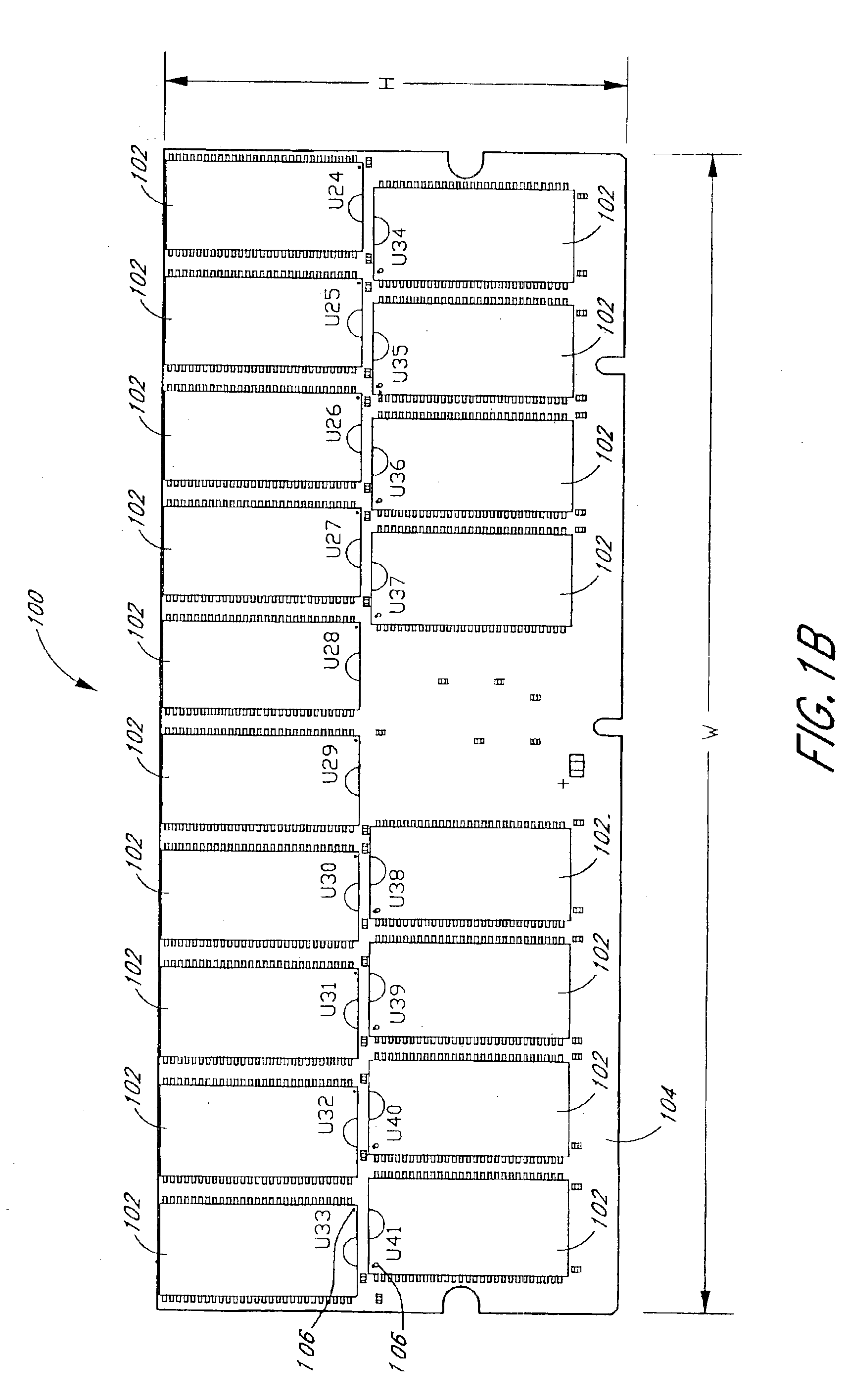

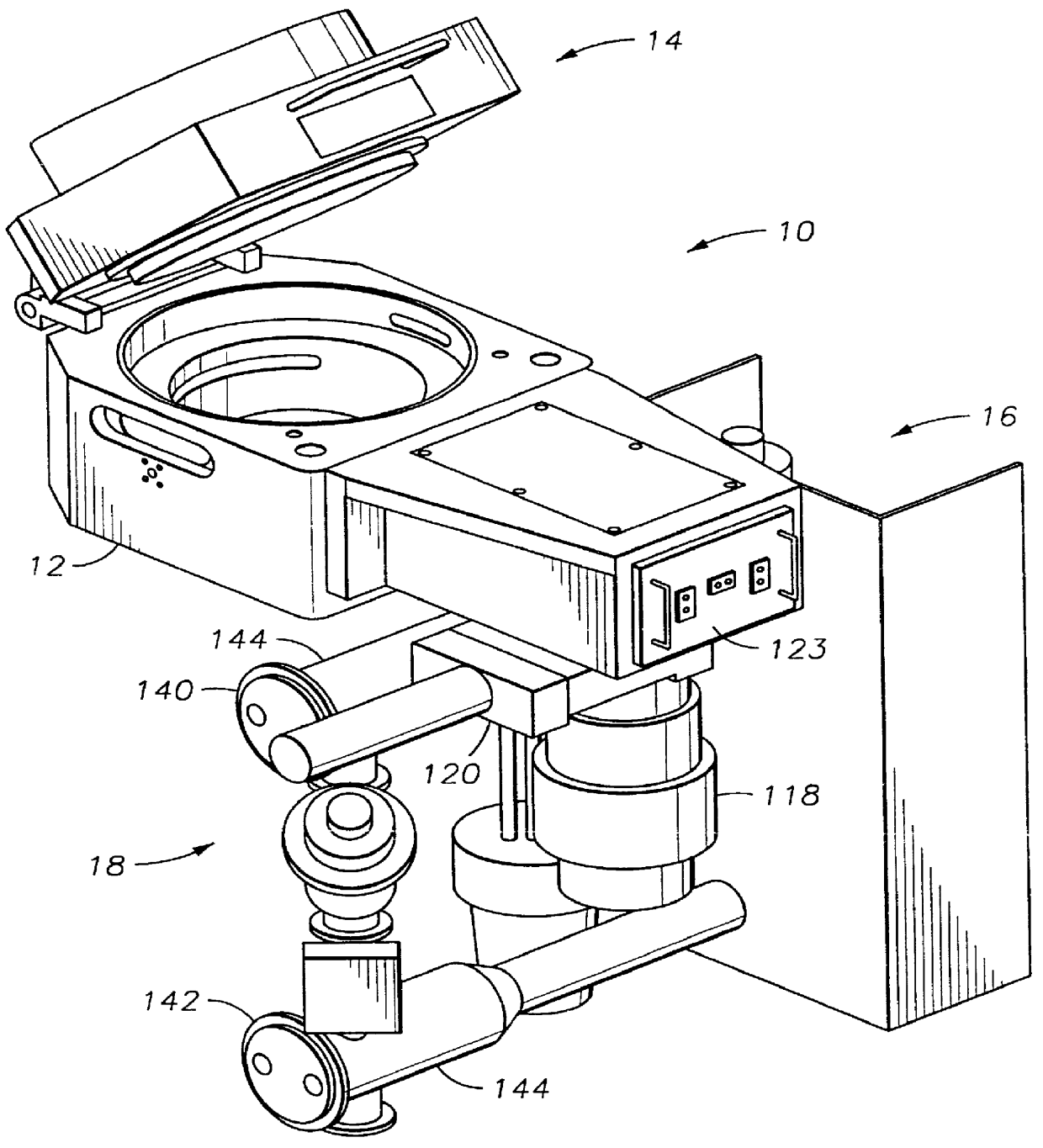

Temperature controlled chamber liner

InactiveUS6099651APrevent unwanted condensationPrevent decomposition and condensationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringTitanium oxide

The invention relates to an apparatus and process for the vaporization of liquid precursors and deposition of a film on a suitable substrate. Particularly contemplated is an apparatus and process for the deposition of a metal-oxide film, such as a barium, strontium, titanium oxide (BST) film, on a silicon wafer to make integrated circuit capacitors useful in high capacity dynamic memory modules.

Owner:APPLIED MATERIALS INC

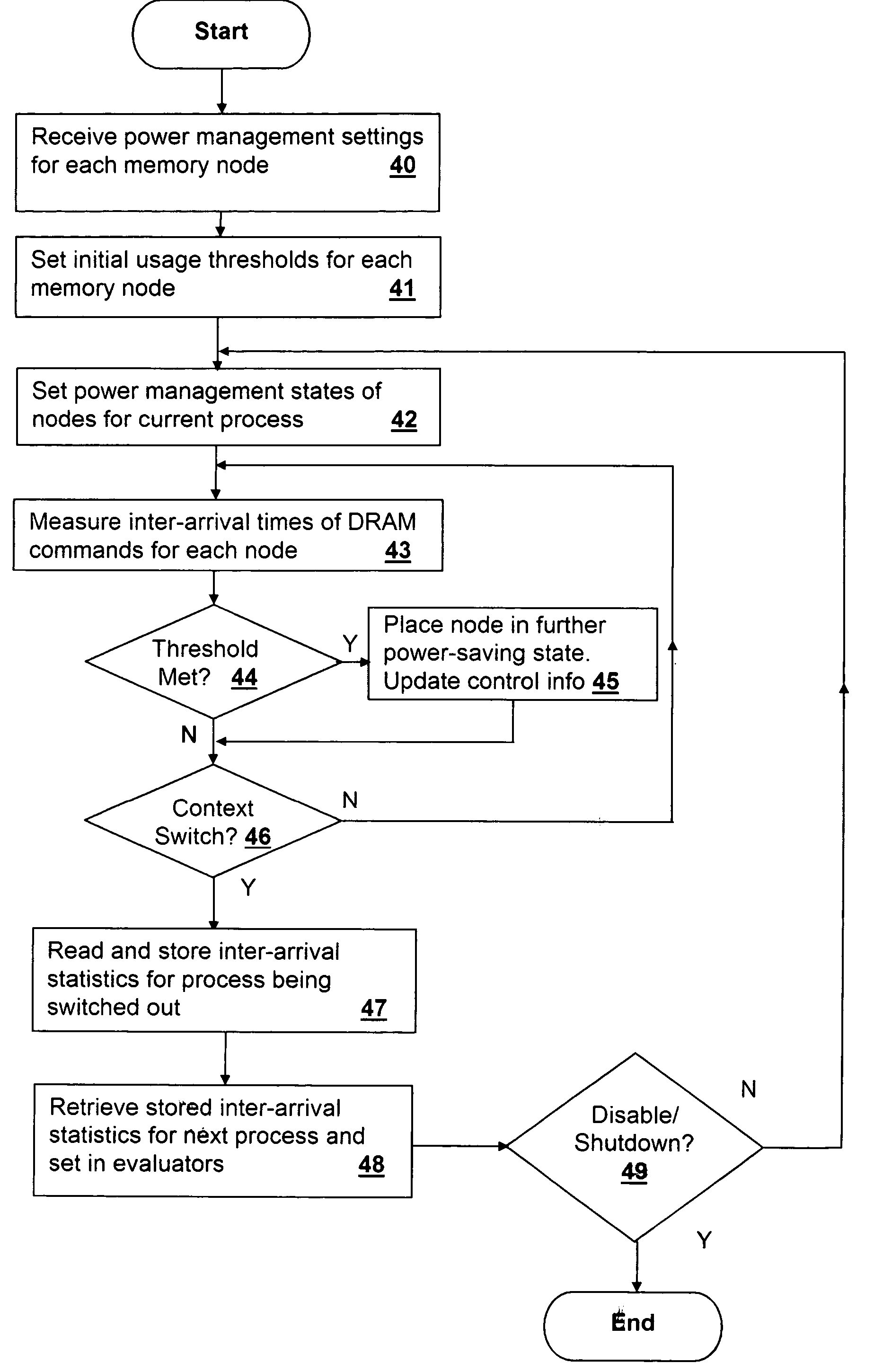

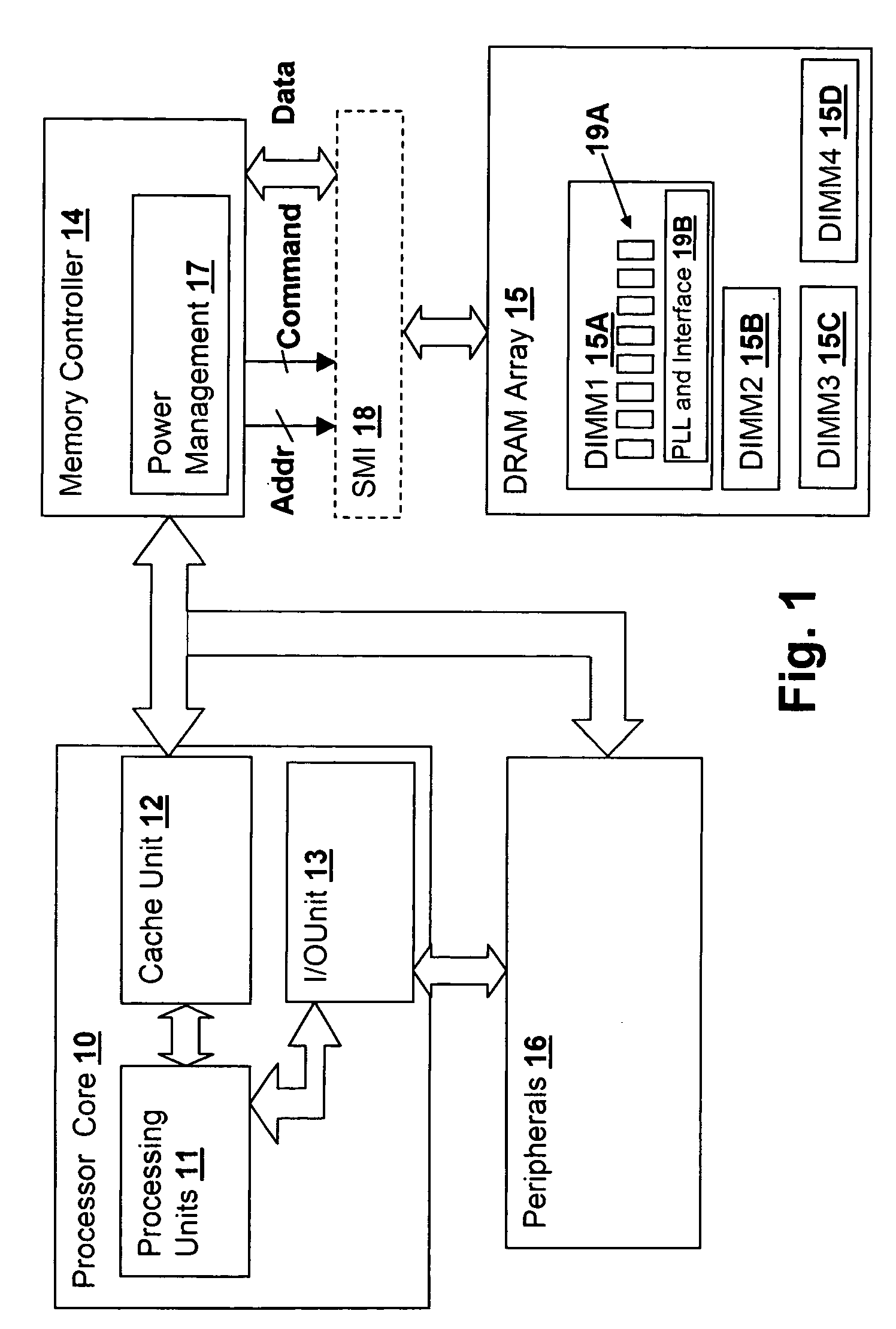

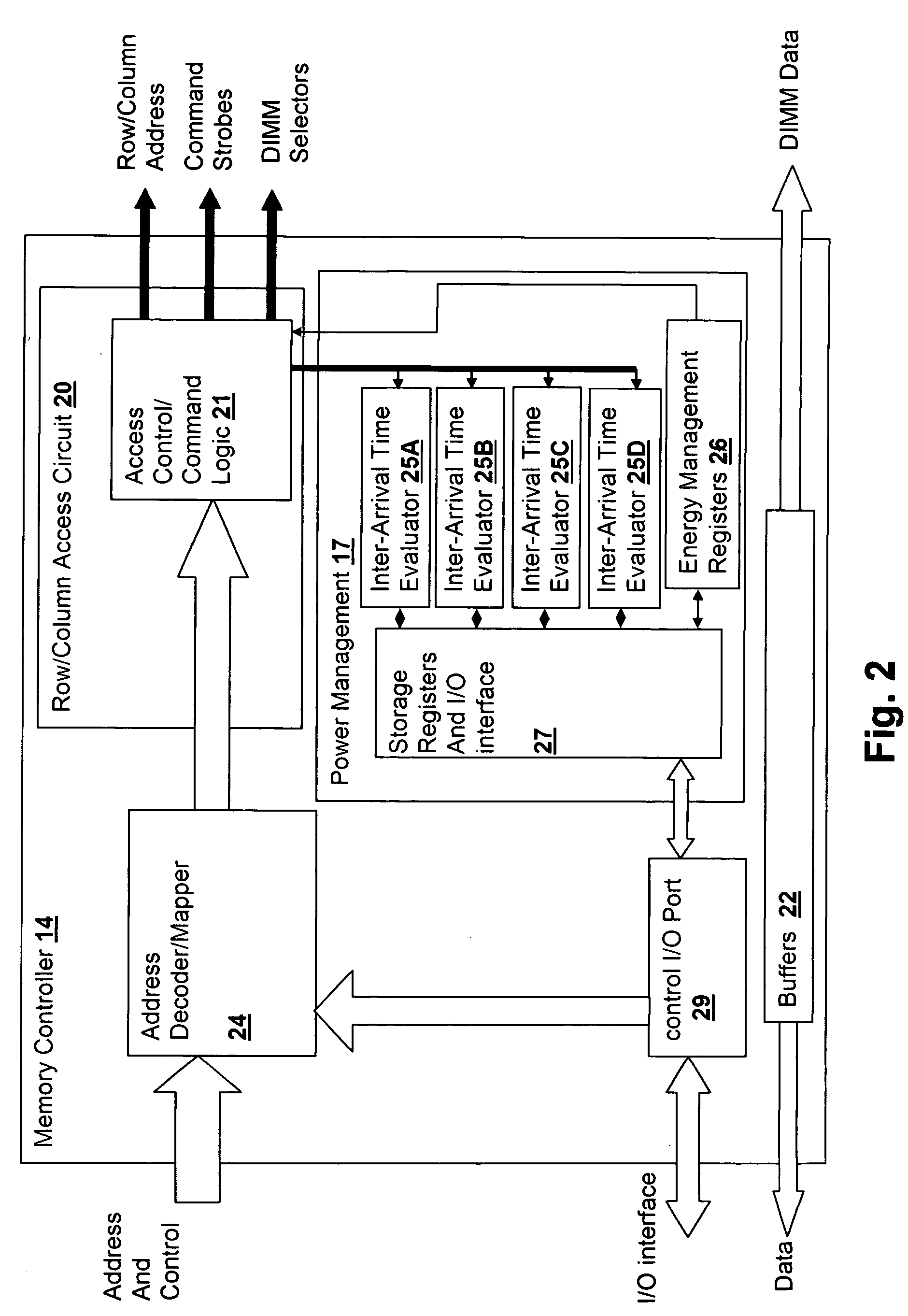

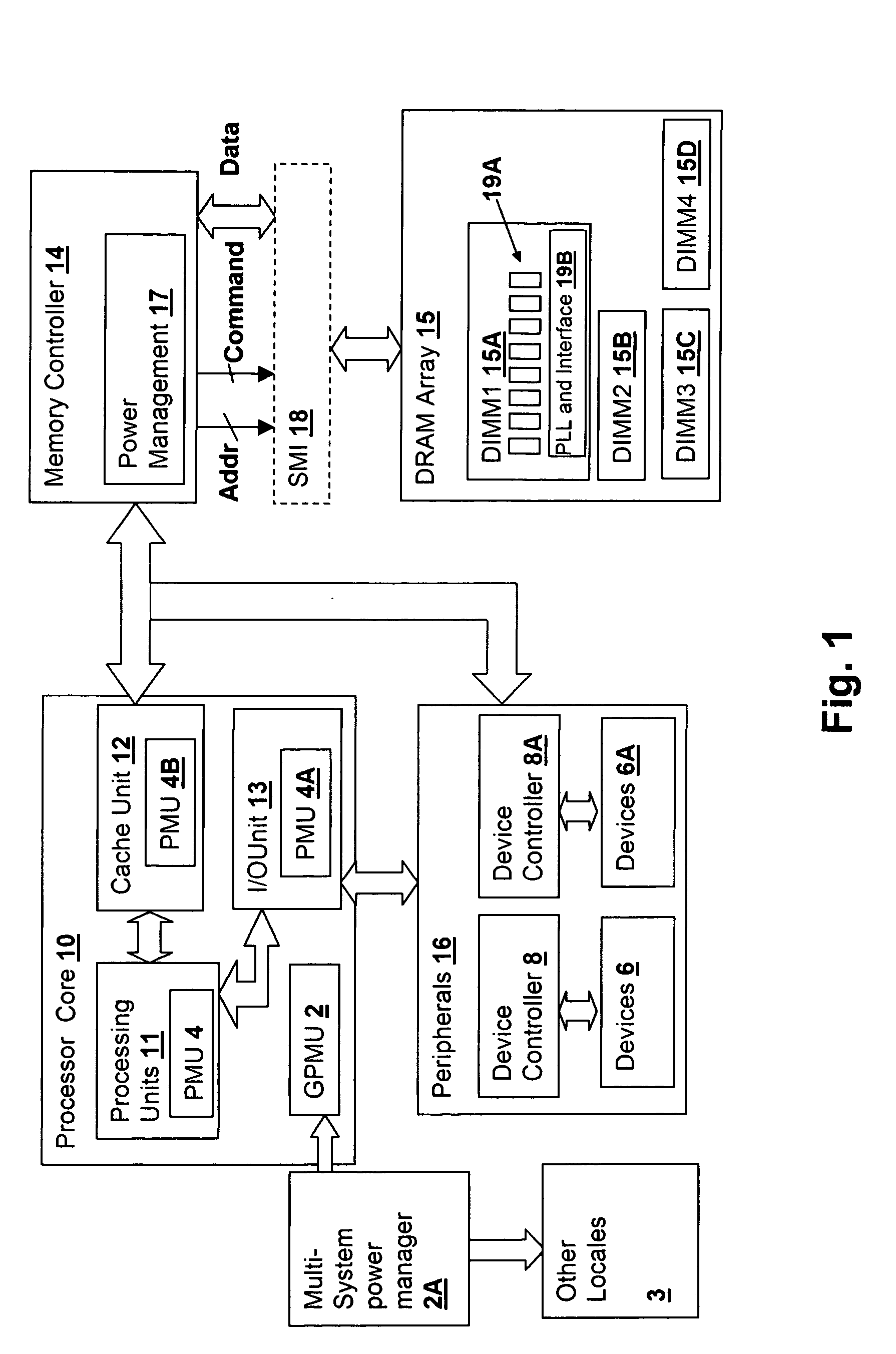

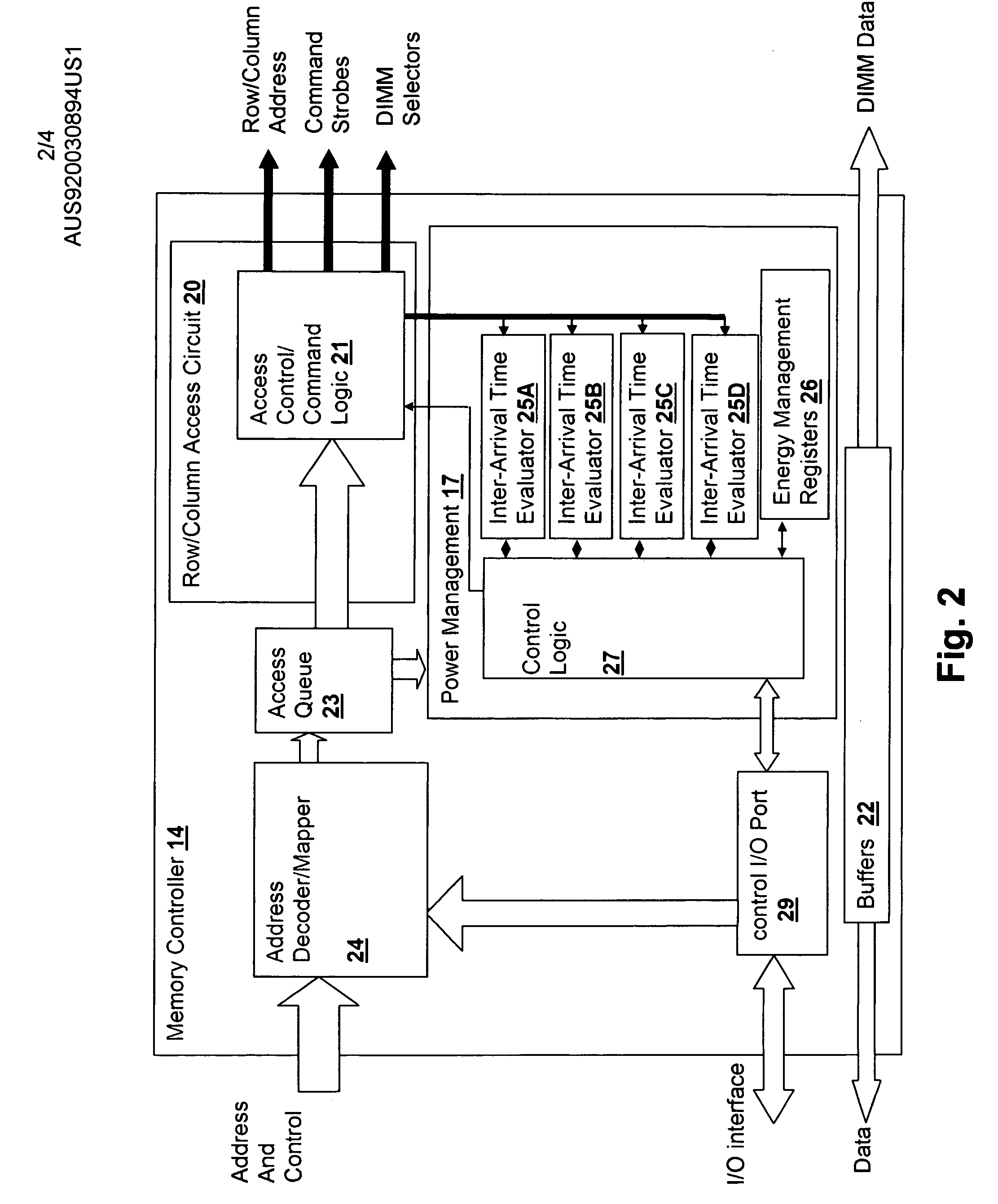

Method and system for power management including device controller-based device use evaluation and power-state control

InactiveUS20050125702A1Lower latencyReduce power consumptionEnergy efficient ICTVolume/mass flow measurementOperational systemDevice Usage

A method and system for power management including device controller-based device use evaluation and power-state control provides improved performance in a power-managed processing system. Per-device usage information is measured and evaluated during process execution and is retrieved from the device controller upon a context switch, so that upon reactivation of the process, the previous usage evaluation state can be restored. The device controller can then provide for per-process control of attached device power management states without intervention by the processor and without losing the historical evaluation state when a process is switched out. The device controller can control power-saving states of connected devices in conformity with the usage evaluation without processor intervention and across multiple process execution slices. The device controller may be a memory controller and the controlled devices memory modules or banks within modules if individual banks can be power-managed. Local thresholds provide the decision-making mechanism for each controlled device. The thresholds may be history-based, fixed or adaptive and are generally set initially by the operating system and may be updated by the memory controller adaptively or using historical collected usage evaluation counts or alternatively by the operating system via a system processor.

Owner:IBM CORP

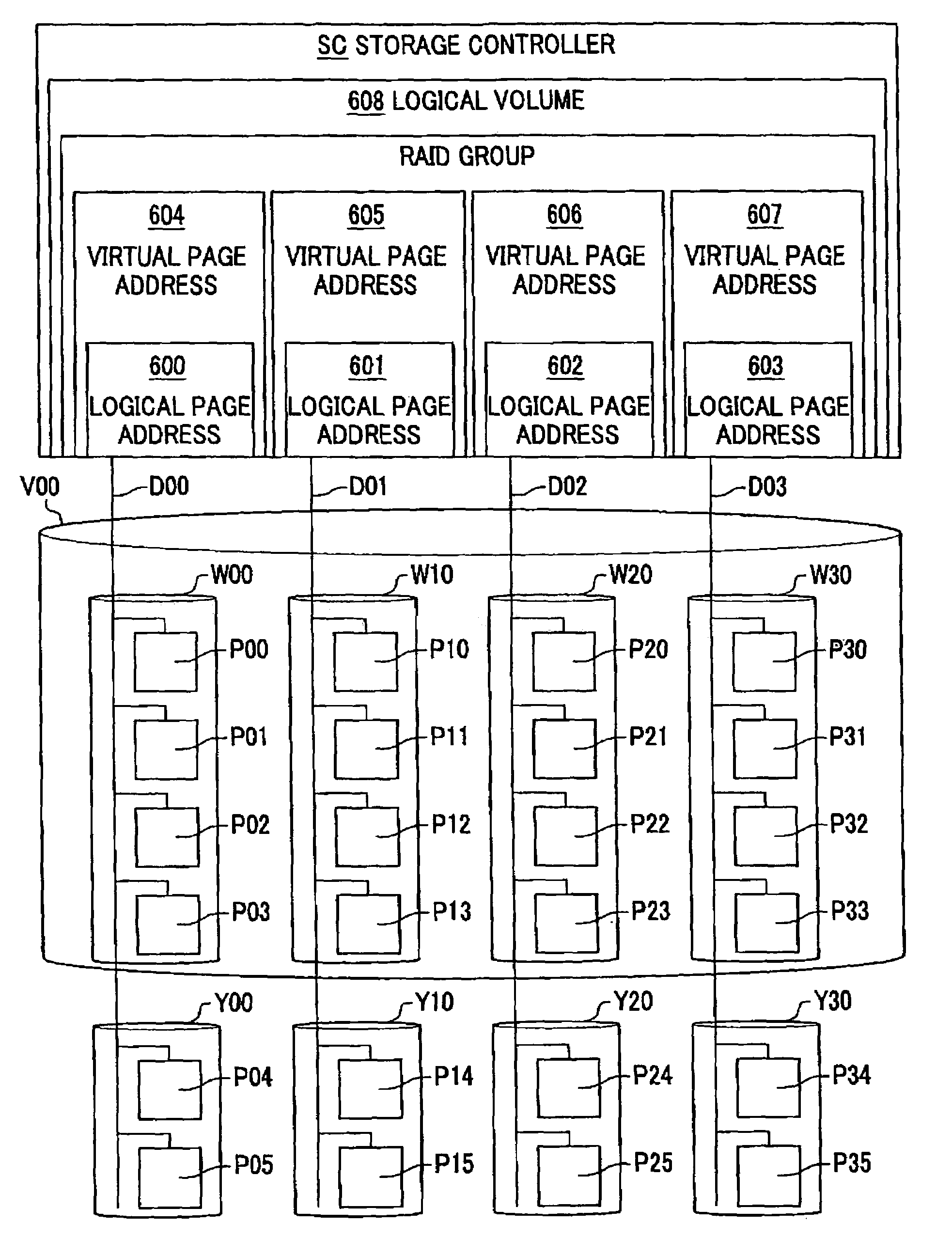

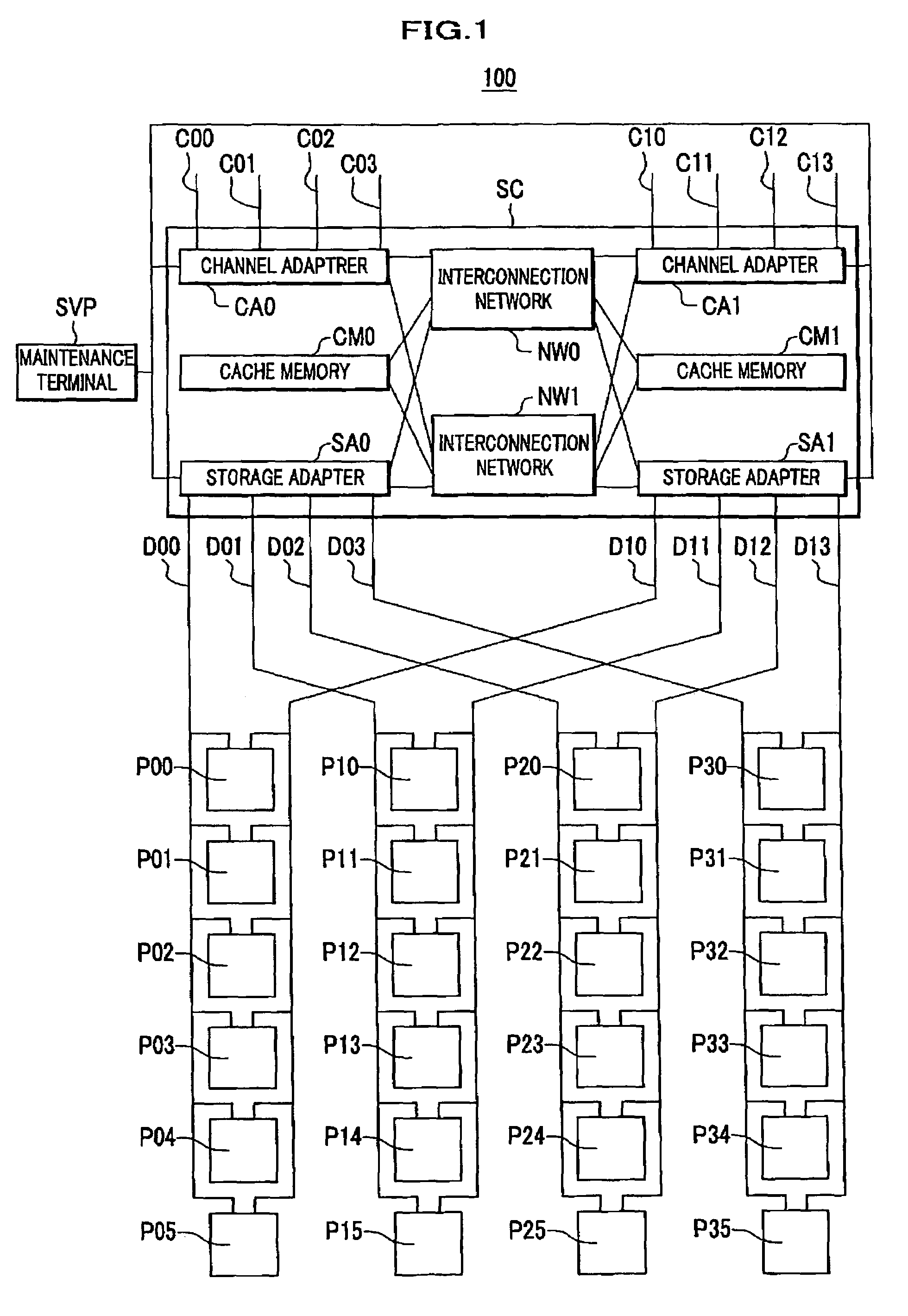

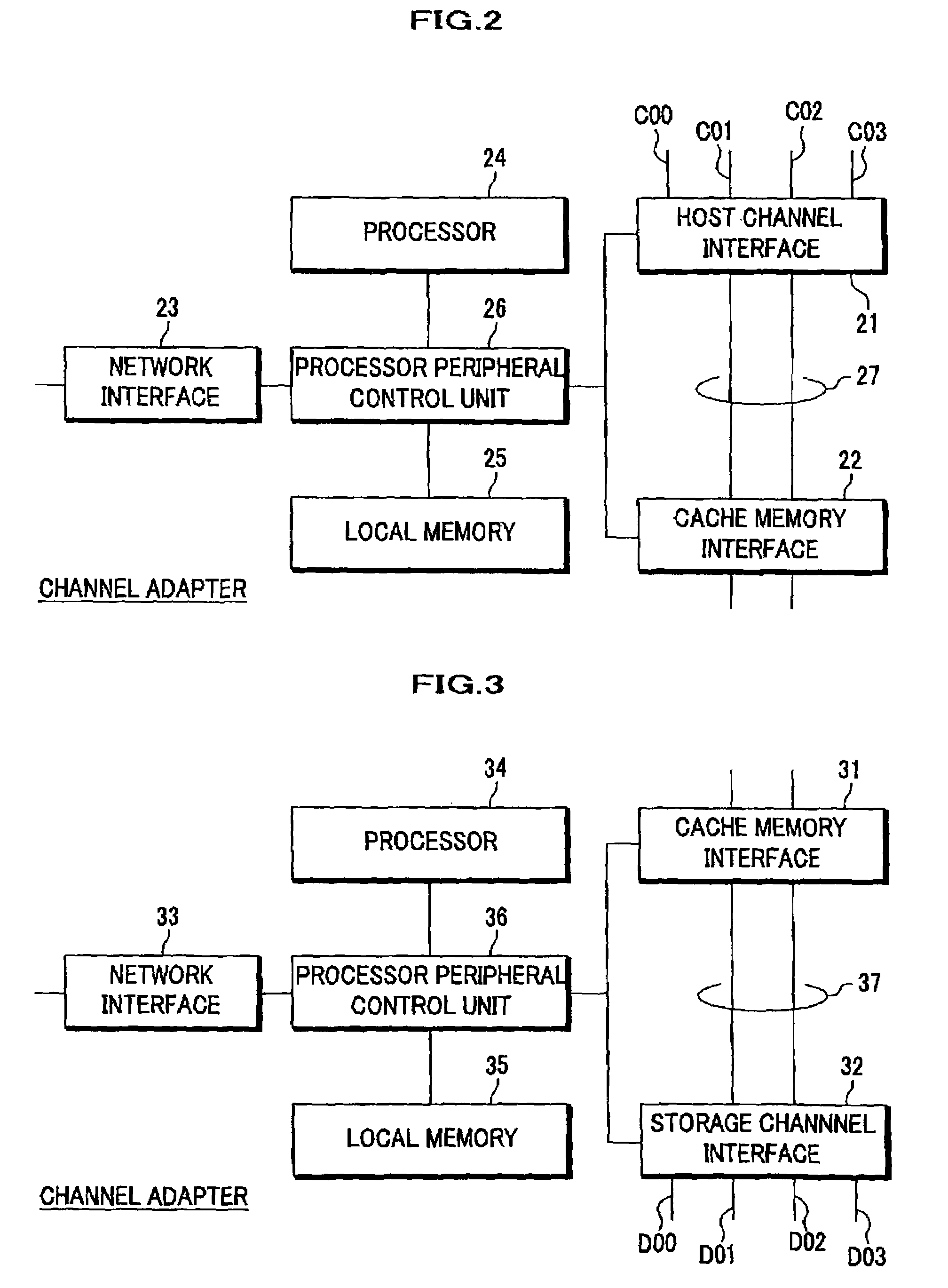

Storage system using flash memory modules logically grouped for wear-leveling and RAID

A storage system using flash memories includes a storage controller and plural flash memory modules as storage media. Each flash memory module includes at least one flash memory chip and a memory controller for leveling erase counts of blocks belonging to the flash memory chip. The storage controller combines the plural flash memory modules into a first logical group, translates a first address used for accessing the flash memory modules belonging to the first logical group to a second address used for handling the first address in the storage controller, and combines the plural first logical groups into a second logical group.

Owner:HITACHI LTD

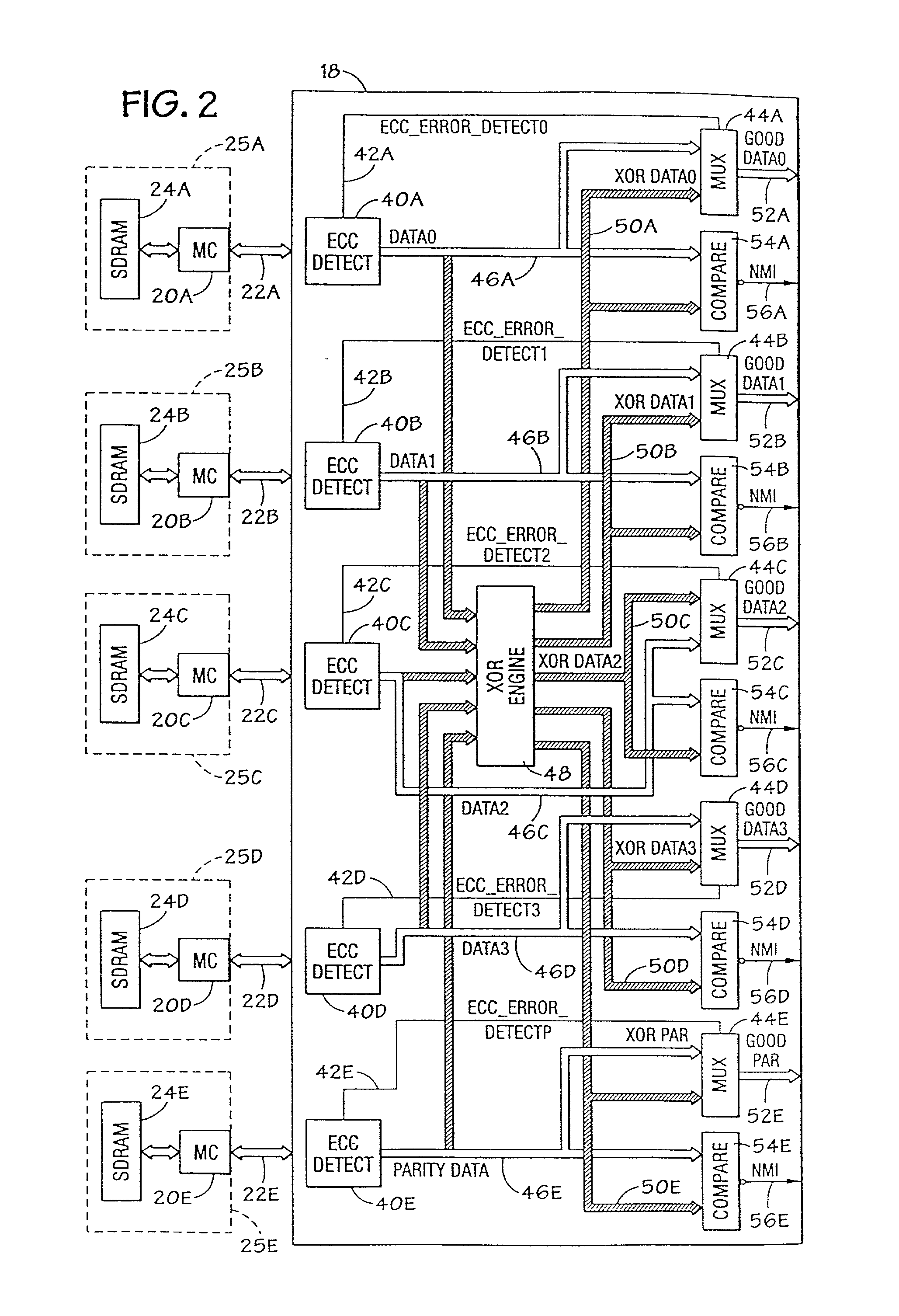

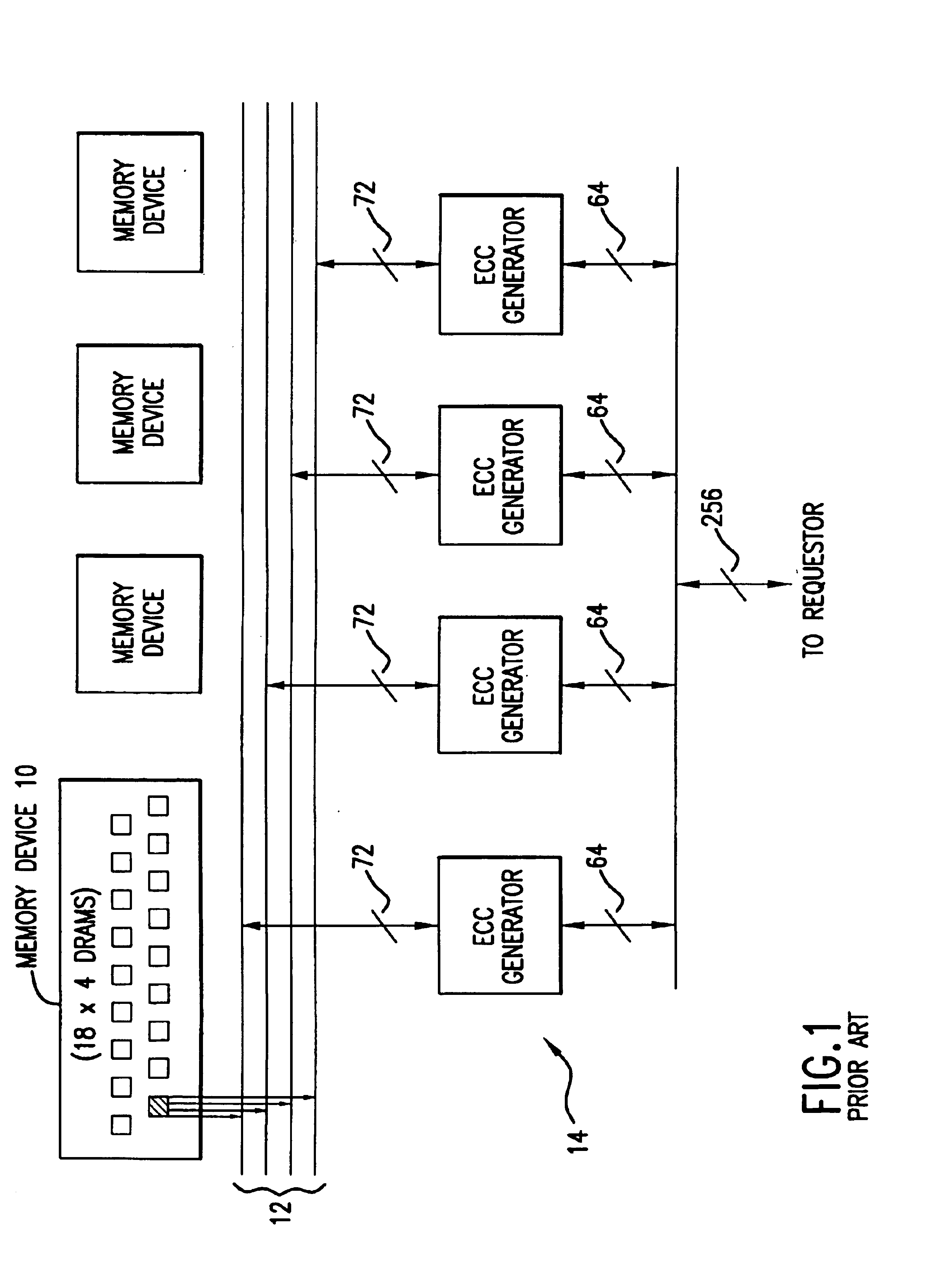

Error indication in a raid memory system

A computer system includes a plurality of memory modules that contain semiconductor memory, such as DIMMs. The system includes a host / data controller that utilizes an XOR engine to store data and parity information in a striped fashion on the plurality of memory modules to create a redundant array of industry standard DIMMs (RAID). The host / data controller also interleaves data on a plurality of channels associated with each of the plurality of memory modules. The system implements error interrupt control, ECC error reporting, cartridge error power down procedures in response to command errors, storage of error information in unused segments of each DIMM, hot-pug procedure indicator and remote tagging capabilities of memory cartridges and DIMMs.

Owner:SONRAI MEMORY LTD

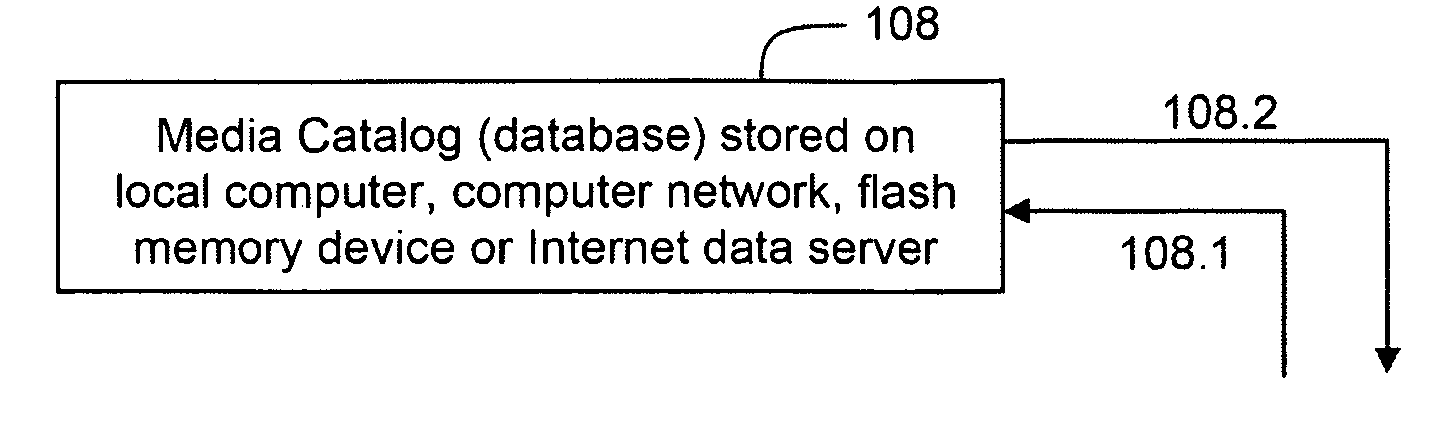

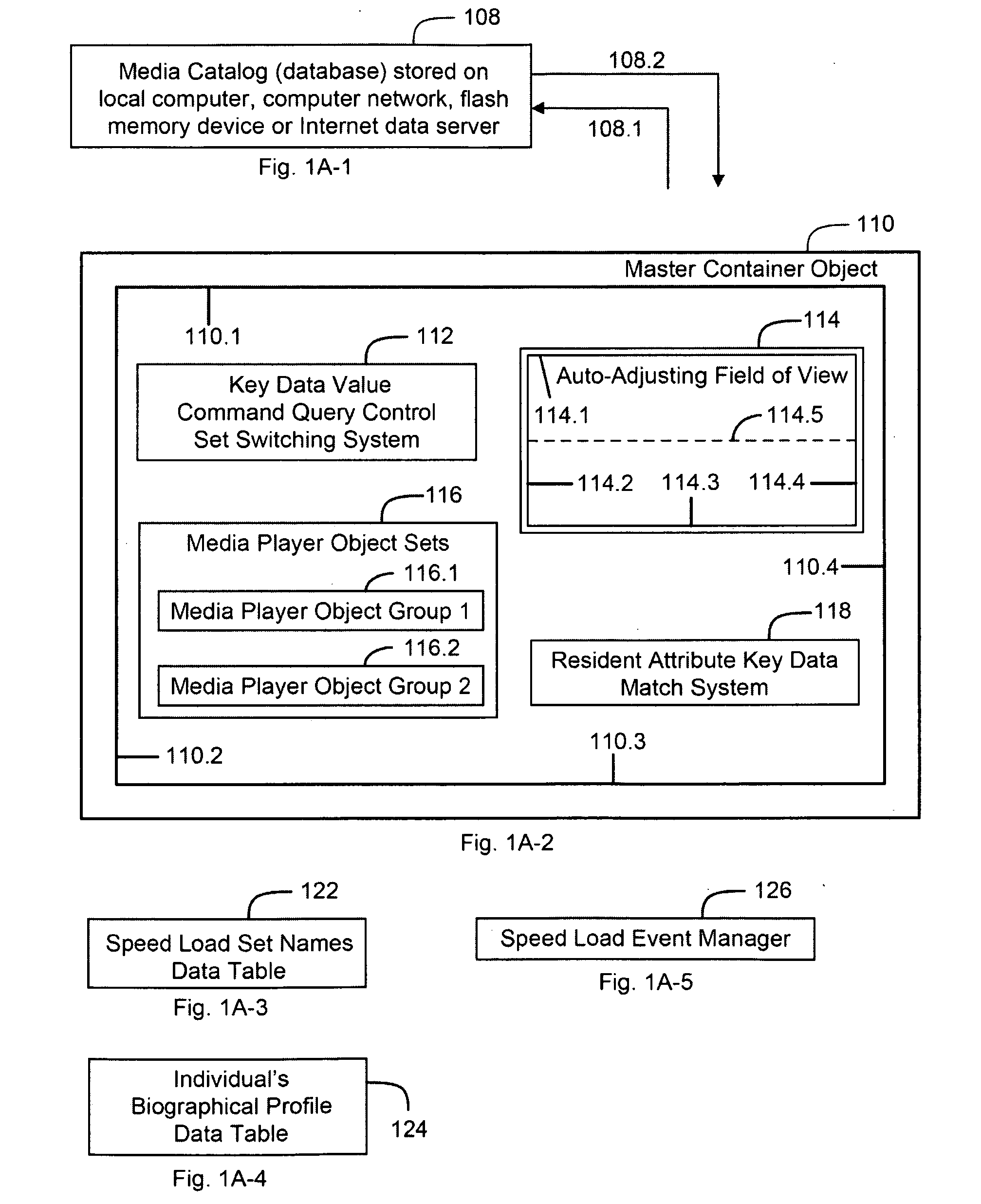

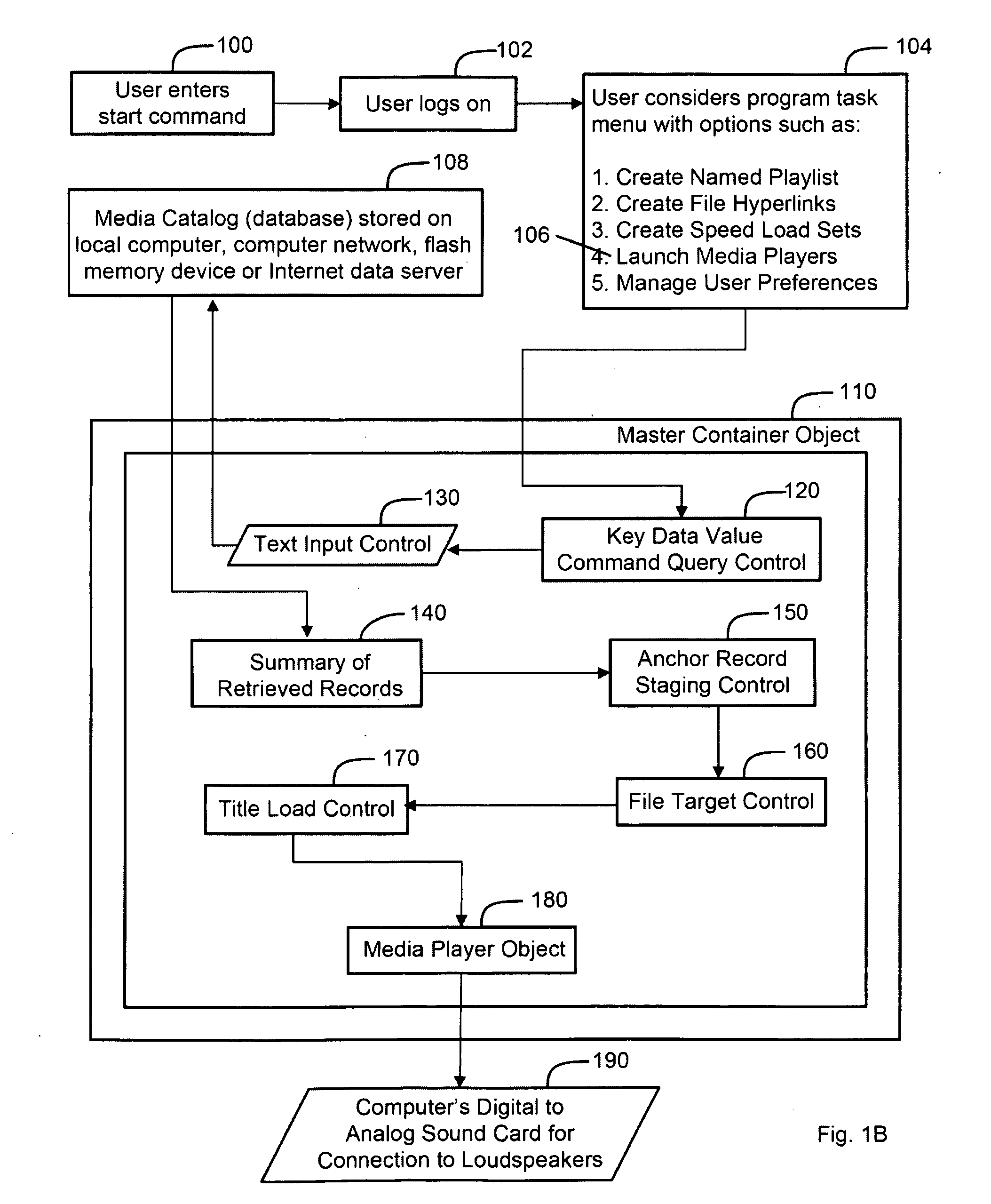

Scalable system and method for an integrated digital media catalog, management and reproduction system

InactiveUS20090177301A1Reduce stepsEfficient managementRecord information storageSpecial data processing applicationsScalable systemVisually guided

A system and method for creating an integrated digital media management and reproduction device comprised of a database with key data values for a plurality of records, and a module with search controls that include sets of compound parallel attribute queries that can execute instructions for a data category, and concurrently retrieve and display records across a plurality of related categories—thereby revealing the associations between discrete records. The invention also has a plurality of software instantiated media players which, through instructions managed by a “master container” design, function as if they were dynamically aware of user actions and the quantifiable states of each other player object—and respond according to logic rules, visually guiding event workflow. The system has a memory module for storing query information, a processor configured to retrieve data, a display unit for retrieved data and a digital-to-analog converter for providing capability for connection to loudspeakers.

Owner:CODENTITY

Memory buffers for merging local data from memory modules

InactiveUS20060195631A1Input/output for user-computer interactionDigital data processing detailsShift registerMultiplexing

An integrated circuit to serialize local data and selectively merge it with serialized feed-through data into a serial data stream output that includes a parallel-in-serial-out (PISO) shift register, a multiplexer, and a transmitter. The PISO shift register serializes parallel data on a local data bus into serialized local data. The multiplexer selectively merges serialized local data and feed-through data into a serial data stream. The transmitter drives the serial data stream onto a serial data link. In another embodiment of the invention, a method for a memory module includes receiving an input serial data stream; merging local frames of data and feed-through frames of data together into an output serial data stream in response to a merge enable signal; and transmitting the output serial data stream on a northbound data output to a next memory module or a memory controller. Other embodiments of the invention are disclosed and claimed.

Owner:INTEL CORP

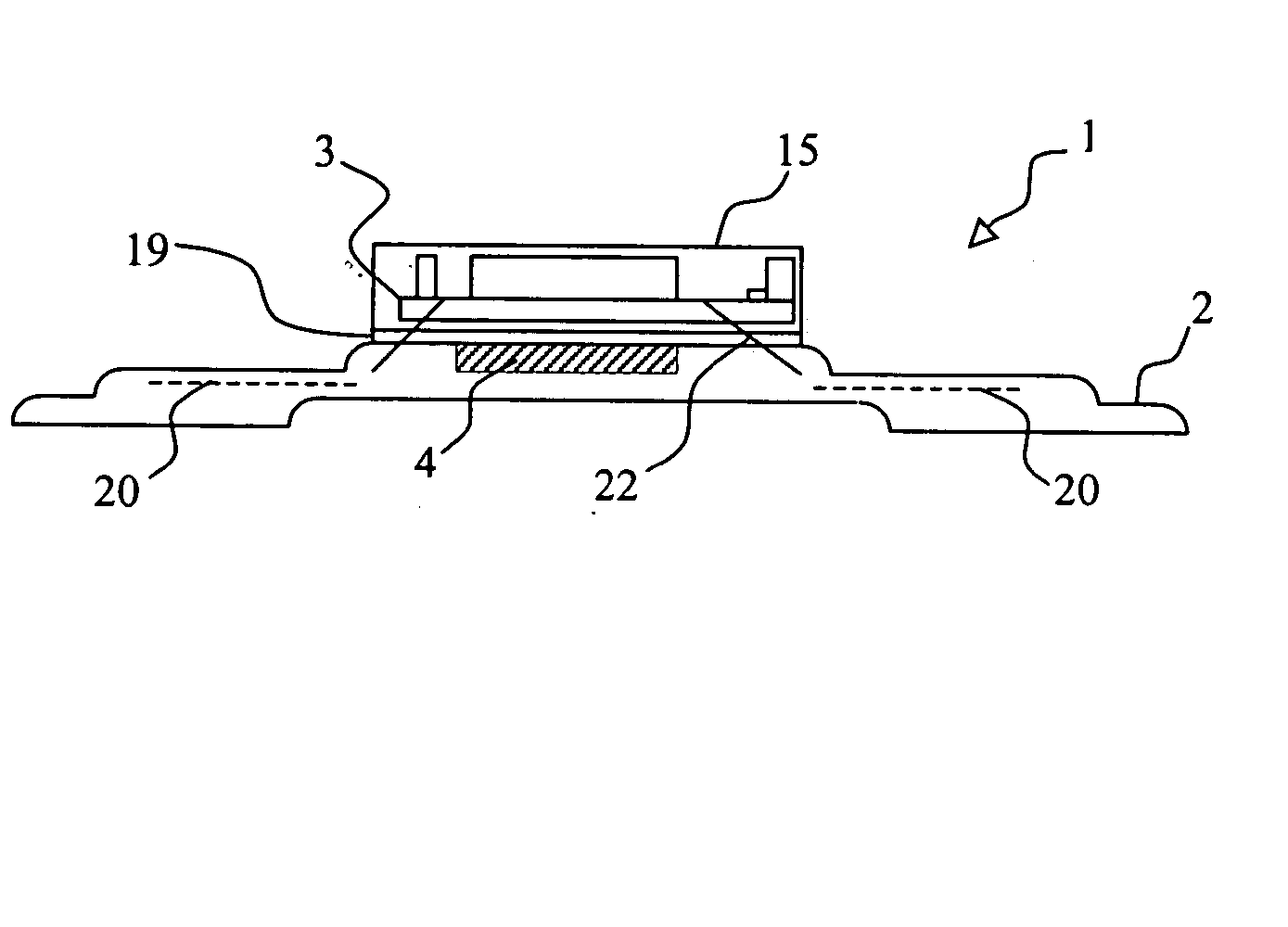

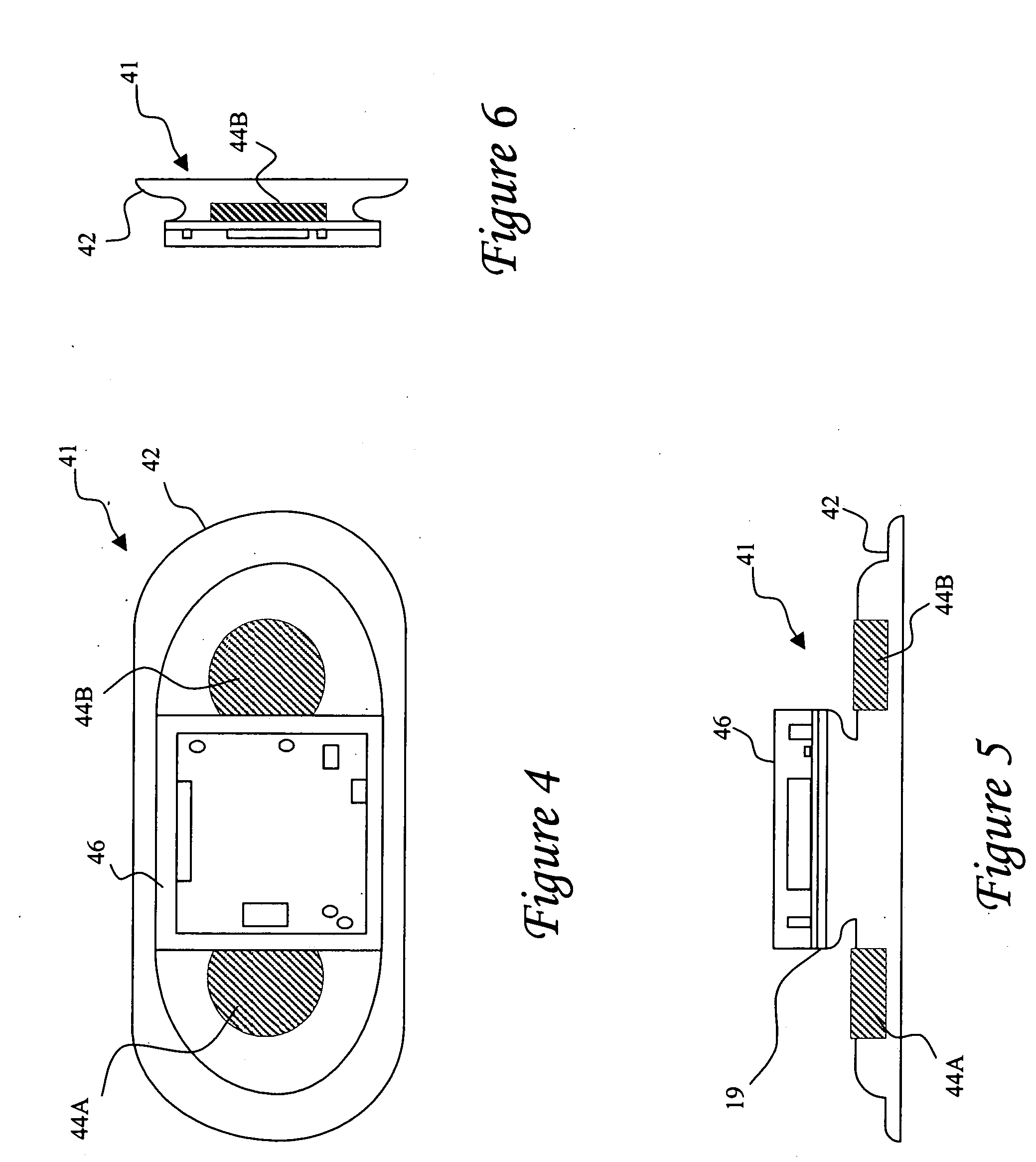

Post patch assembly for mounting devices in a tire interior

InactiveUS20050076982A1Lower center of gravityImprove mechanical stabilityInflatable tyresOptical signallingElastomerSurvivability

A modular electronic assembly for integration with a pneumatic tire includes a mounting patch, a power source, and at least one electronic device supported by a substrate. The mounting patch is preferably adapted for positioning on the inner liner of a pneumatic tire, and the power source is at least partially embedded in the mounting patch. Such embedded positioning of the battery results in an overall structure with a lower center of gravity than previous tire electronics assemblies, thus having increased mechanical stability and survivability in a tire environment. Electronic device(s) supported on the substrate may receive power from the power source, which in some embodiments corresponds to one or more batteries. The substrate supporting the at least one electronic device may be attached to the mounting patch by a variety of fashions. Exemplary attachment configurations may correspond to an adhesive layer, a hook and loop tape combination, or physical interconnection via terminals extending from the power source through the support substrate. Exemplary electronic devices may include such components as condition-responsive devices including transducers, acoustic devices, sensors, etc. for sensing certain environmental conditions such as temperature and / or pressure, tire revolution counters, vehicle speed sensors, sidewall deflection sensors, tire displacement sensors, microprocessors, memory modules, RFID transponders, light assemblies, data transmitters and / or receivers, and power, supply components. Selected of the electronic devices (including one or more antennas associated with any RF devices) may be encapsulated by a non-conductive rubber or elastic material to facilitate effective transmission characteristics. Conductive springs, flexible conductive elastomer or fatigue-resistance metal may be used to interconnect various electronic components (such as an RF device to an antenna).

Owner:MICHELIN RECH & TECH SA

Memory module with offset data lines and bit line swizzle configuration

InactiveUS6839266B1Simplified bus architectureIncrease data bandwidthMemory adressing/allocation/relocationRead-only memoriesBit lineComputer science

A memory module includes an array of N memory devices, each memory device having M data pins, where N is greater than M, and M and N are positive integers; and N bit lines traversing the array of N memory devices, such that each one of the N bit lines is connected to M of the N memory devices.

Owner:RAMBUS INC

System including a host connected serially in a chain to one or more memory modules that include a cache

InactiveUS20050166006A1Memory architecture accessing/allocationStatic storageComputer moduleData storing

Owner:ADVANCED MICRO DEVICES INC

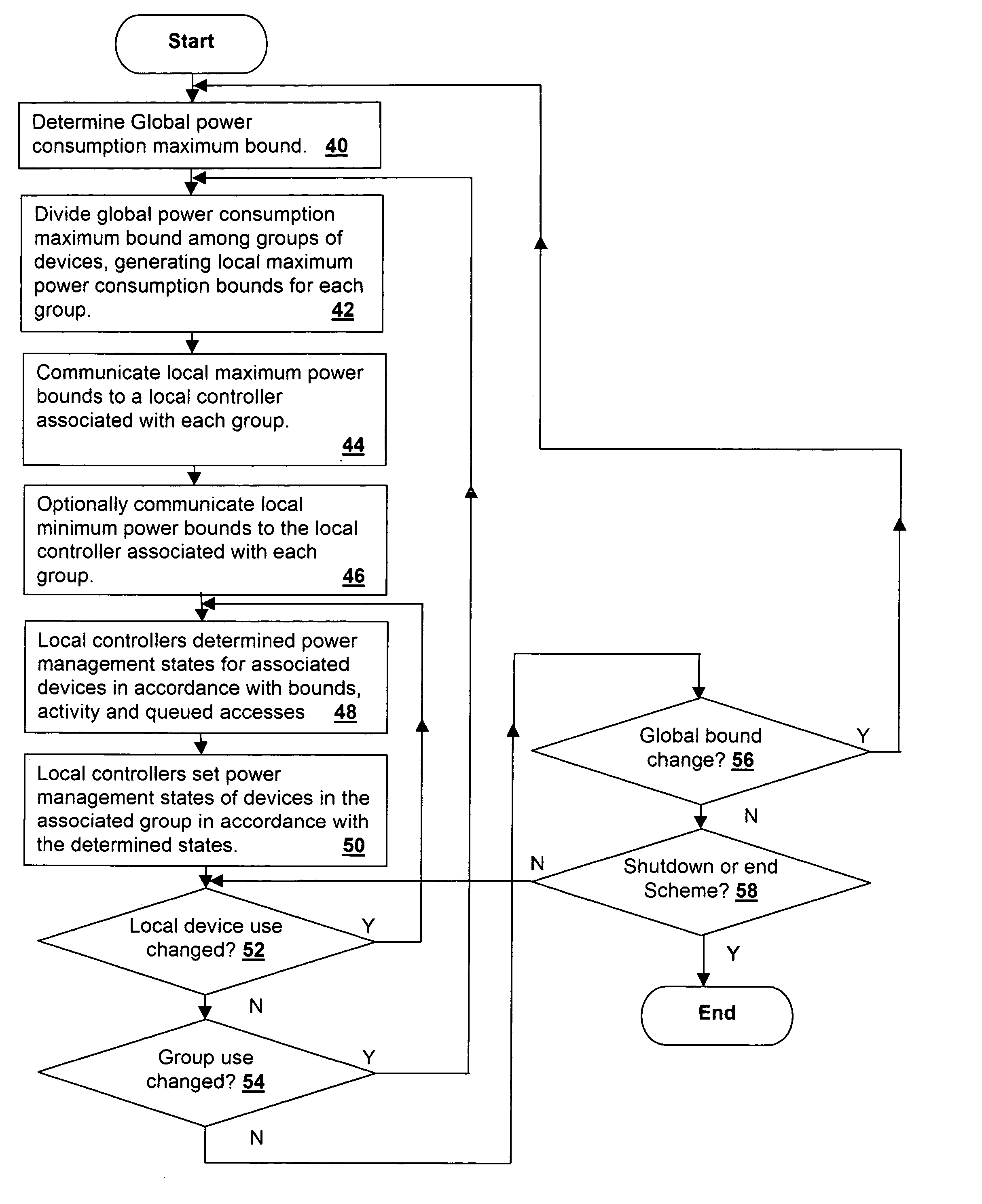

Method and system for power management including local bounding of device group power consumption

ActiveUS20050125703A1Inhibit currentSlow changeEnergy efficient ICTVolume/mass flow measurementMemory controllerGlobal system

A method and system for power management including local bounding of device group power consumption provides the responsiveness of local power control while meeting global system power consumption and power dissipation limits. At the system level, a global power bound is determined and divided among groups of devices in the system so that local bounds are determined that meet the global system bound. The local bounds are communicated to device controllers associated with each group of devices and the device controllers control the power management states of the associated devices in the group to meet the local bound. Thus, by action of all of the device controllers, the global bound is met. The controllers may be memory controllers and the devices memory modules, or the devices may be other devices within a processing system having associated local controllers. Alternatively or in concert, the devices may be entire processing systems and the associated controller a power management controller for associated processing systems, whereby multiple processing locales may be power-managed consistent with a global power consumption budget.

Owner:HUAWEI TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com